Patents

Literature

3474 results about "Physical vapor deposition" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Physical vapor deposition (PVD) describes a variety of vacuum deposition methods which can be used to produce thin films and coatings. PVD is characterized by a process in which the material goes from a condensed phase to a vapor phase and then back to a thin film condensed phase. The most common PVD processes are sputtering and evaporation. PVD is used in the manufacture of items which require thin films for mechanical, optical, chemical or electronic functions. Examples include semiconductor devices such as thin film solar panels, aluminized PET film for food packaging and balloons, and titanium nitride coated cutting tools for metalworking. Besides PVD tools for fabrication, special smaller tools (mainly for scientific purposes) have been developed.

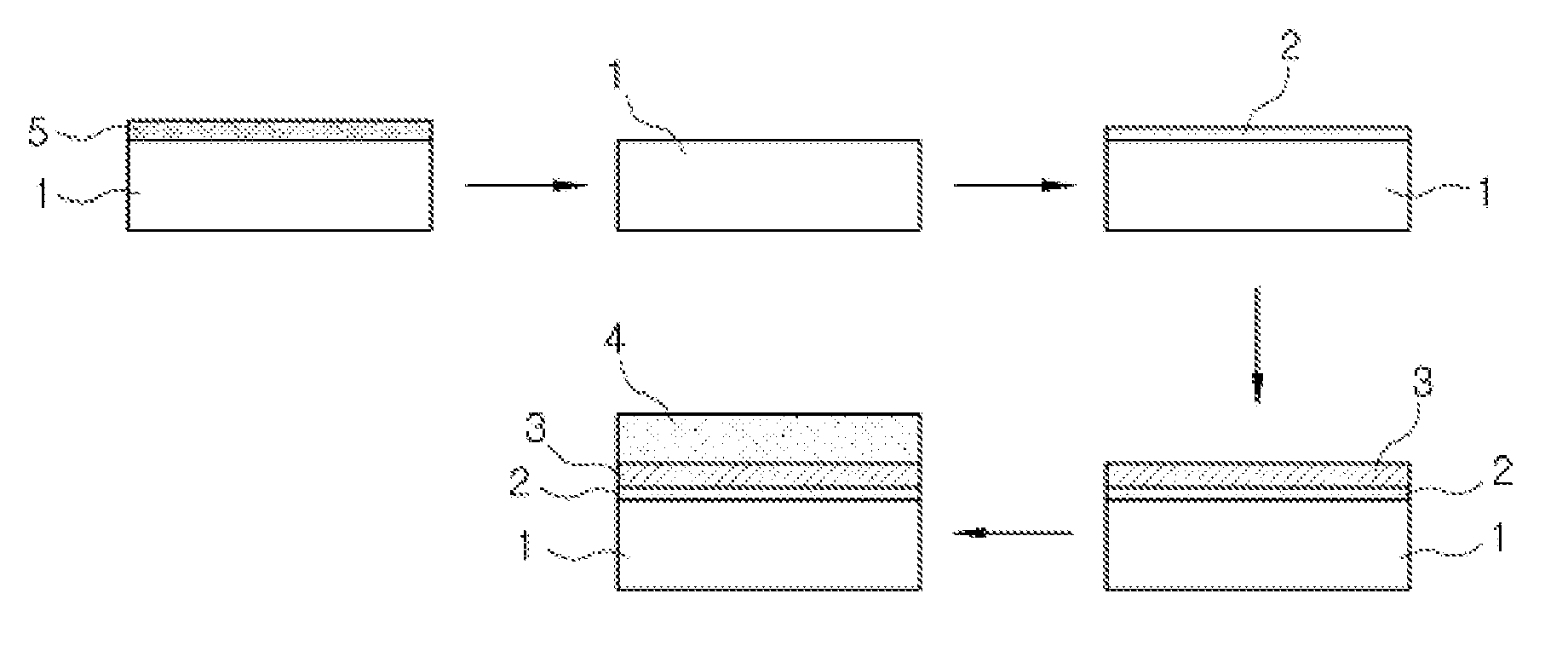

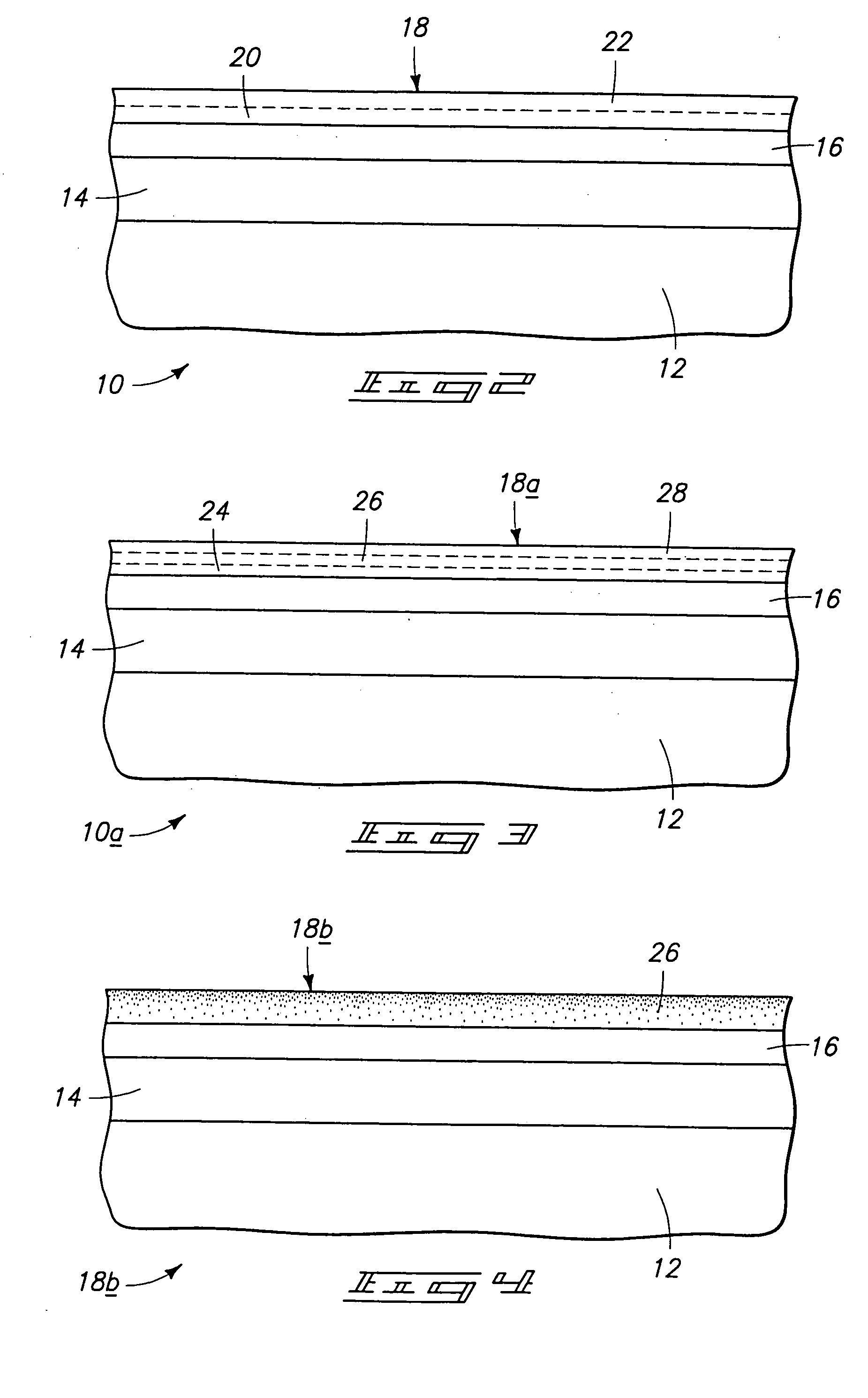

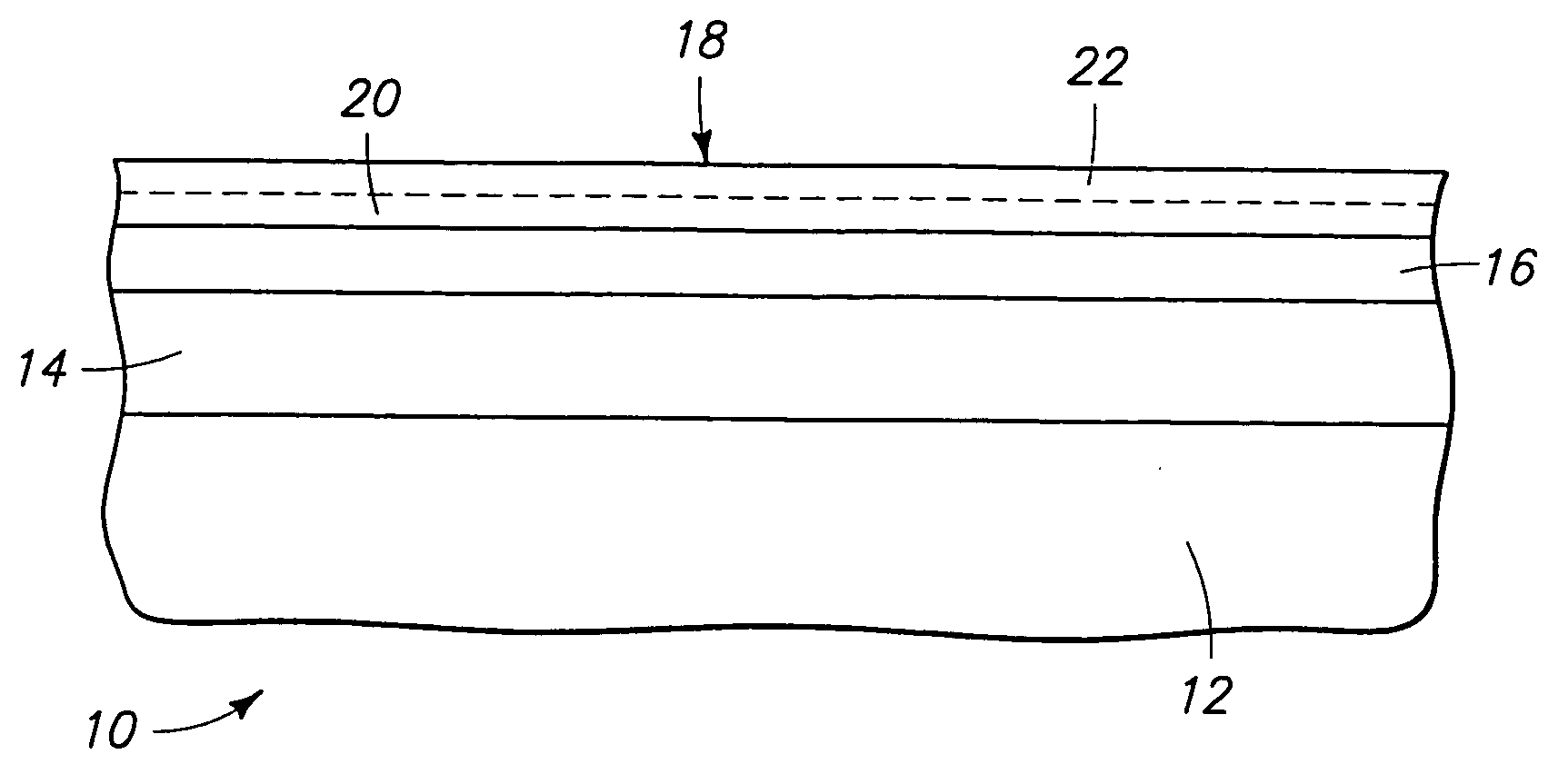

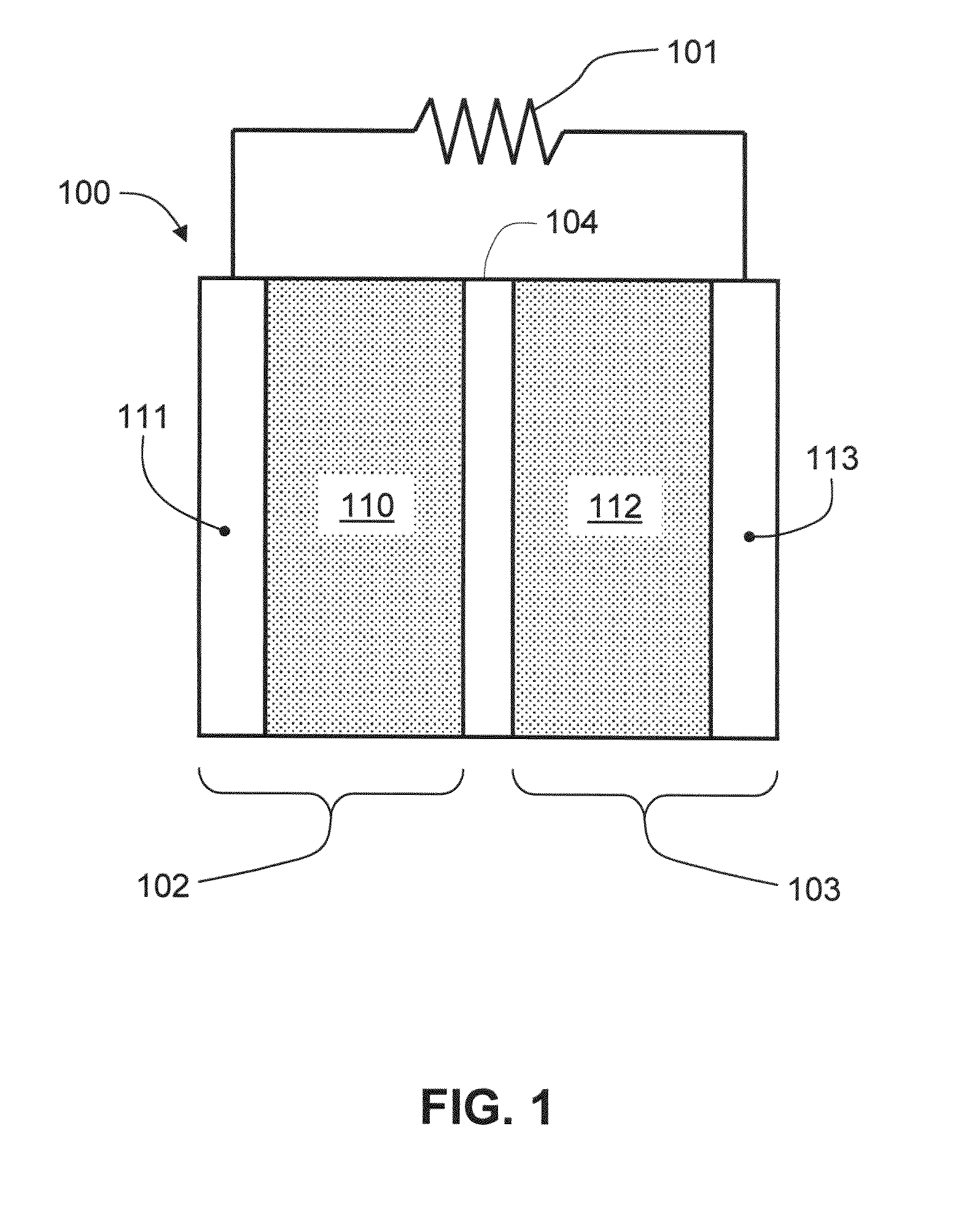

Fabrication of low defectivity electrochromic devices

ActiveUS20100243427A1High level of defectivityVacuum evaporation coatingSputtering coatingArchitectural glassGas phase

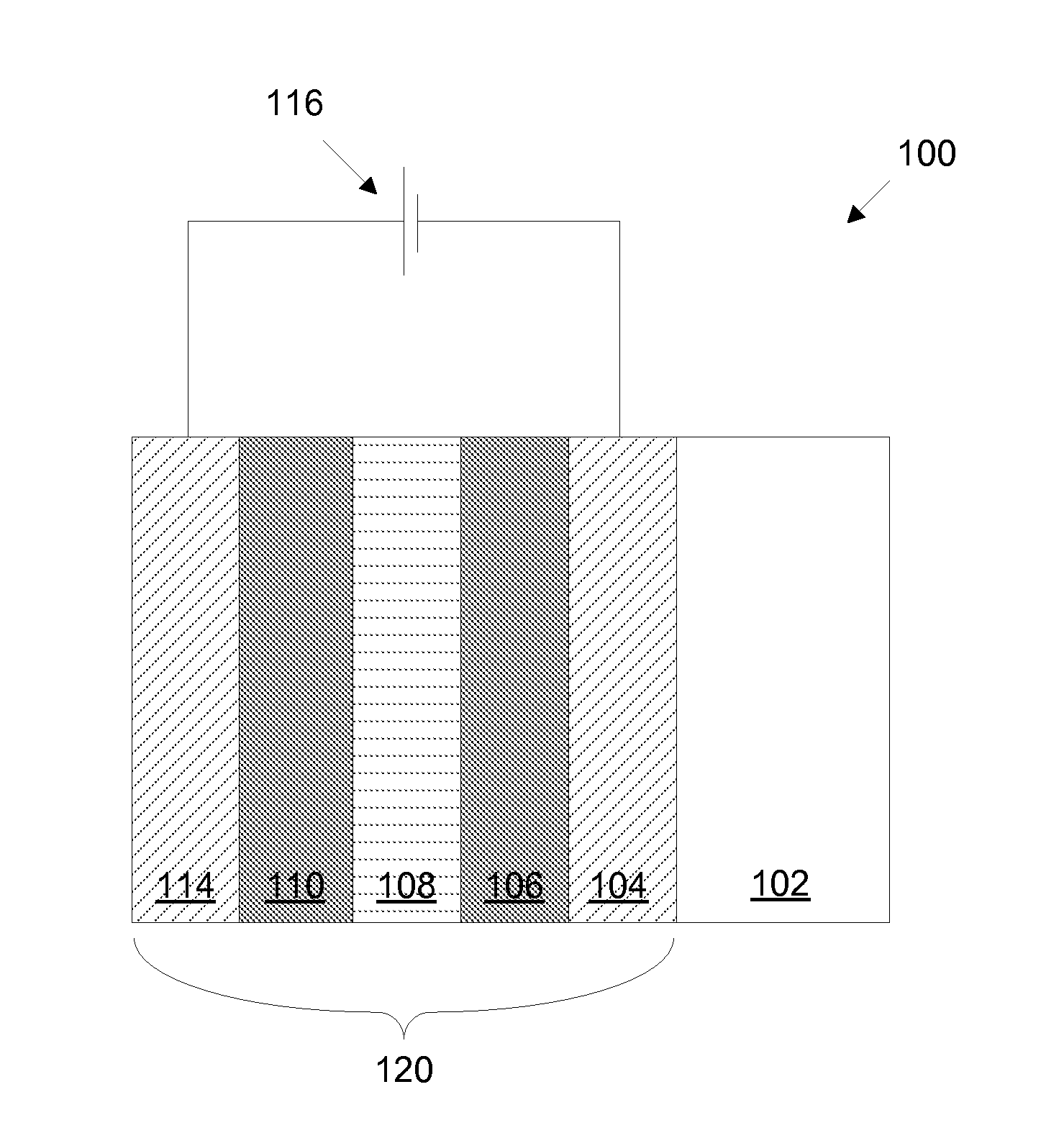

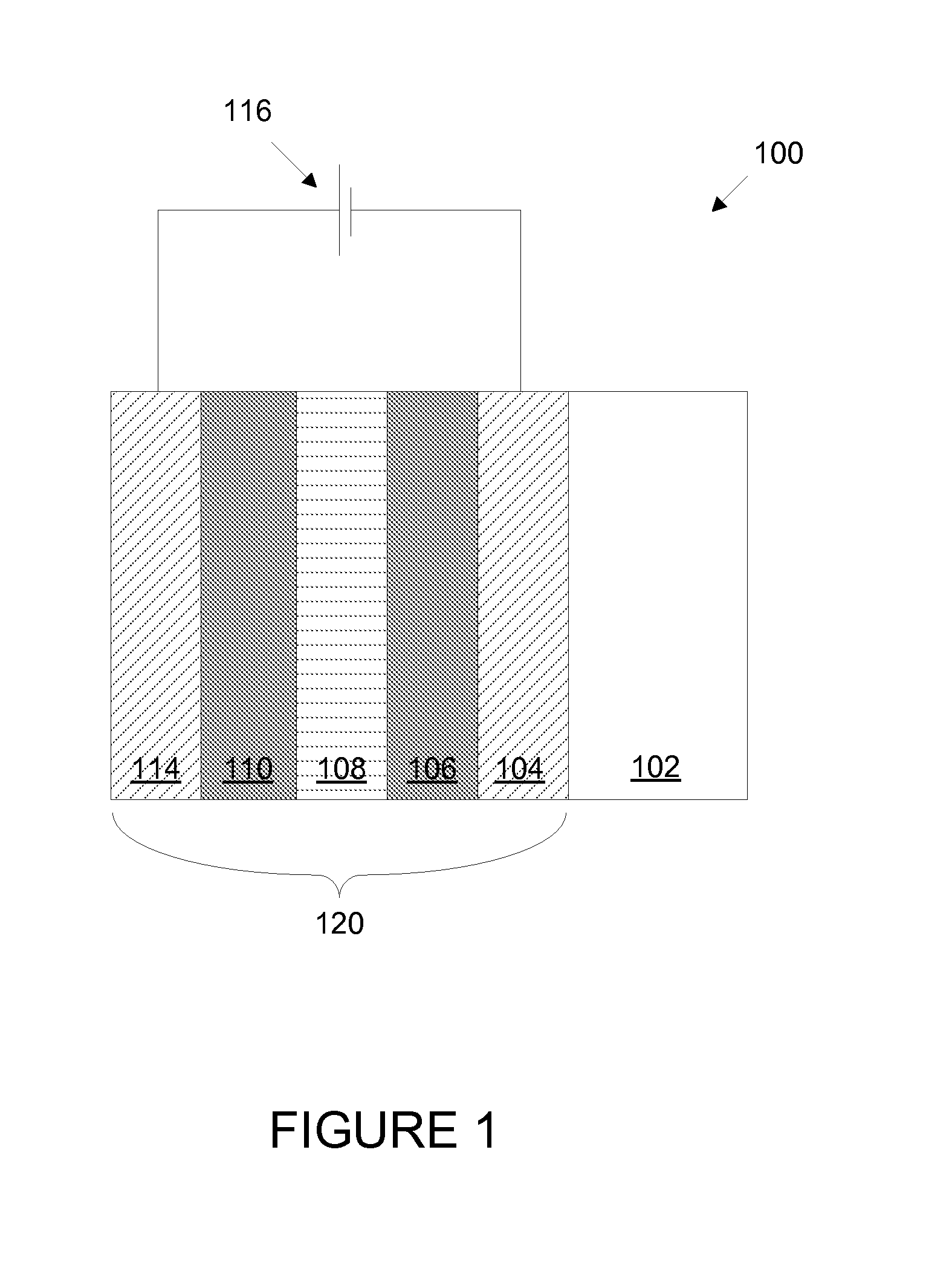

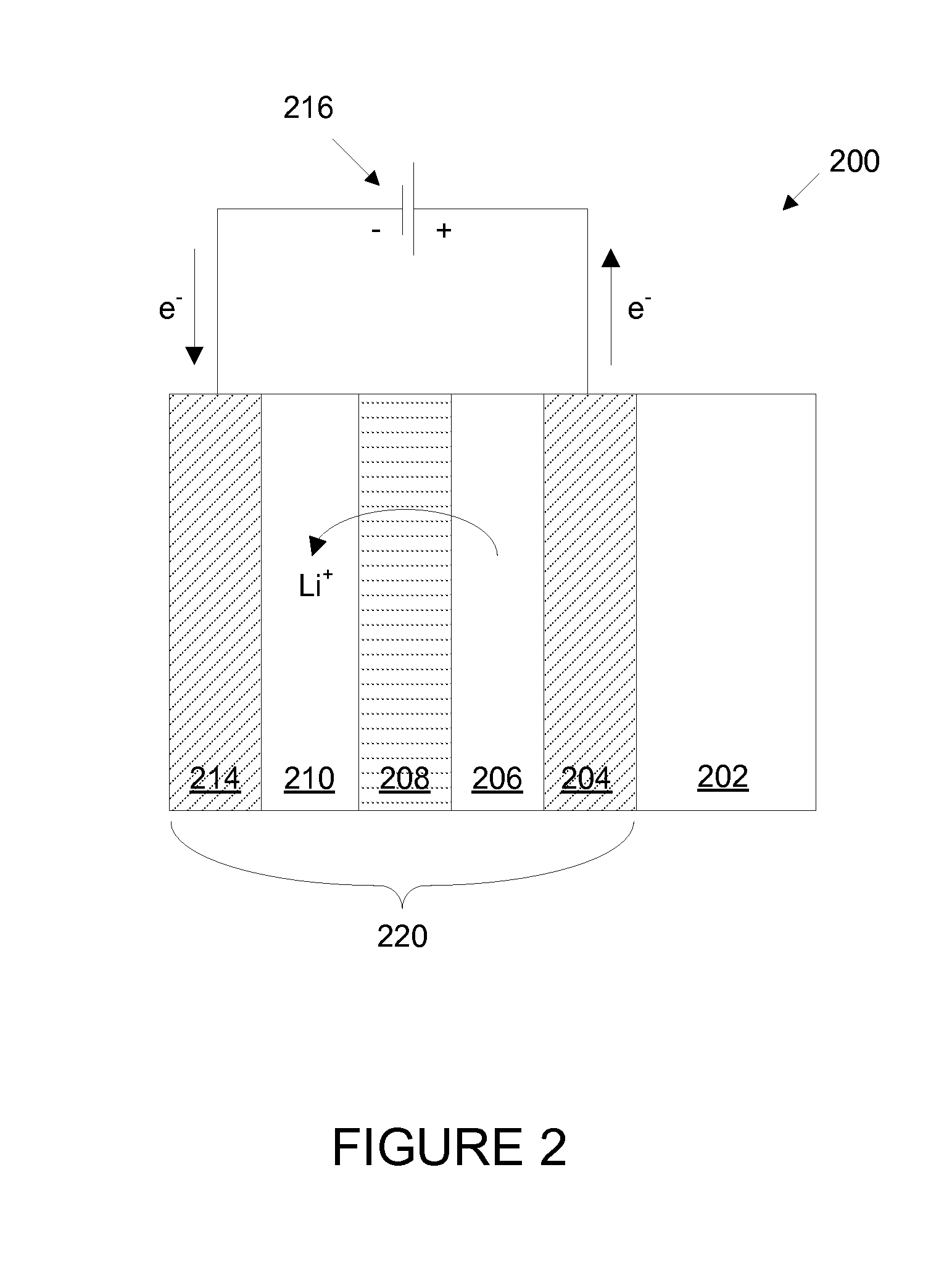

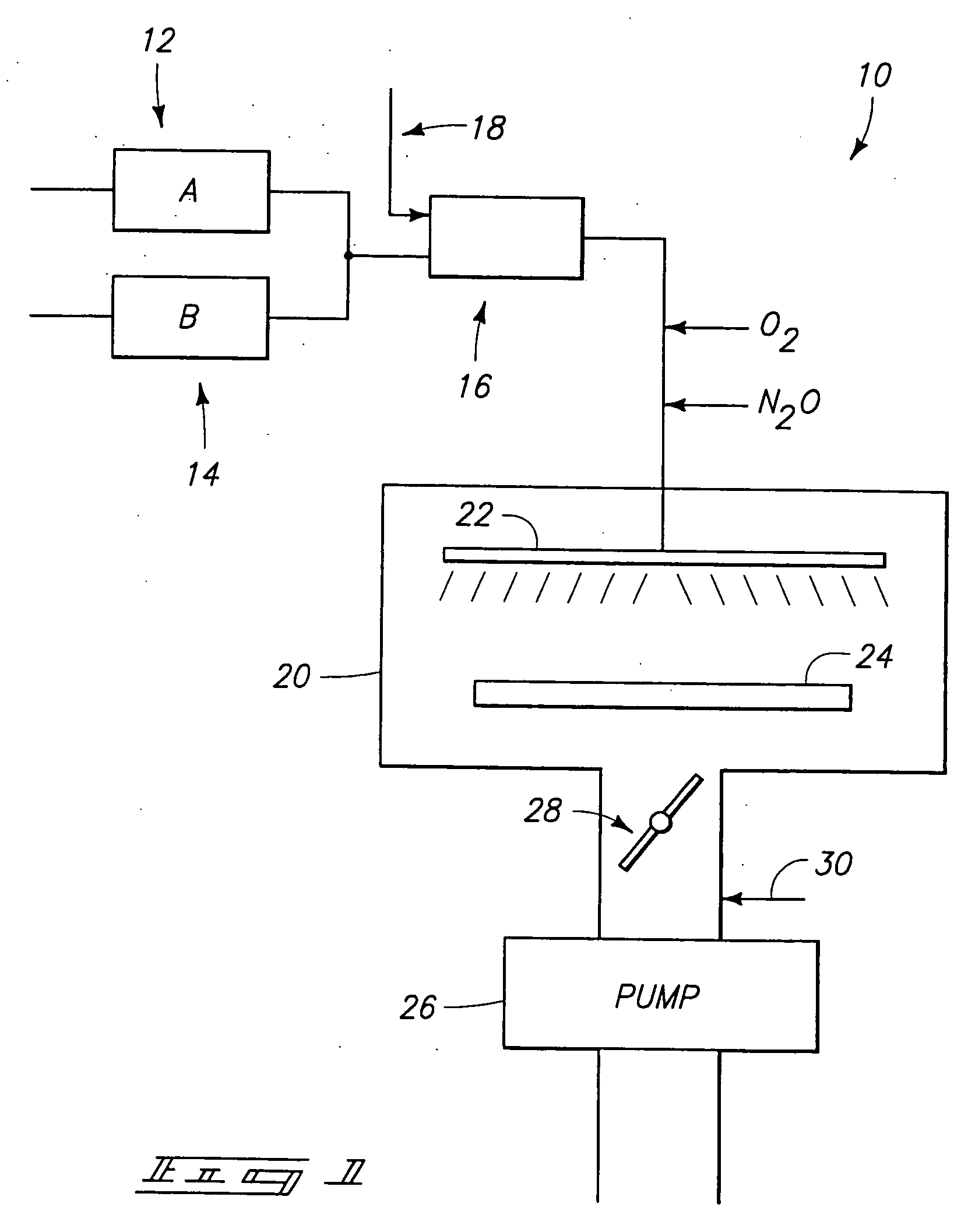

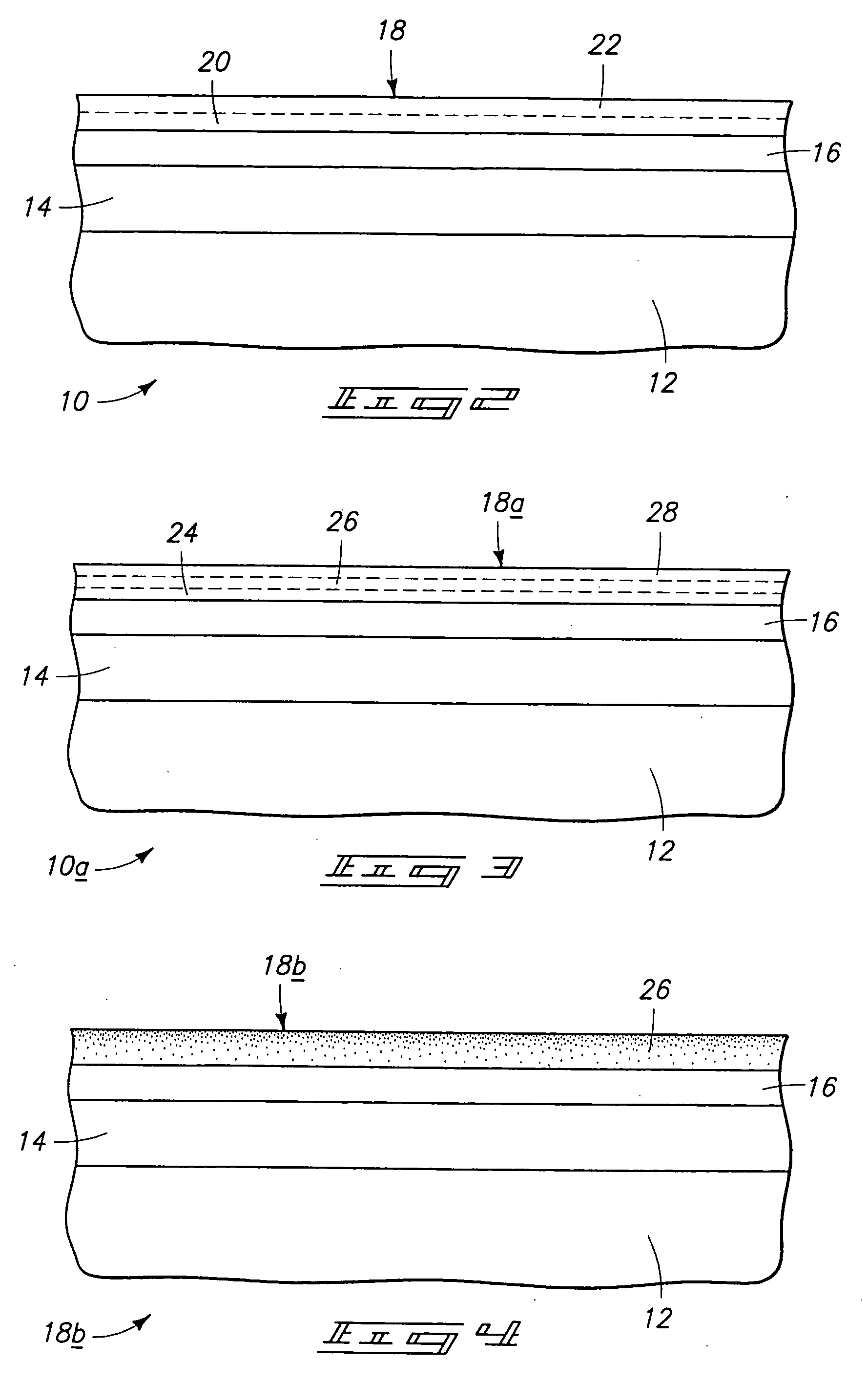

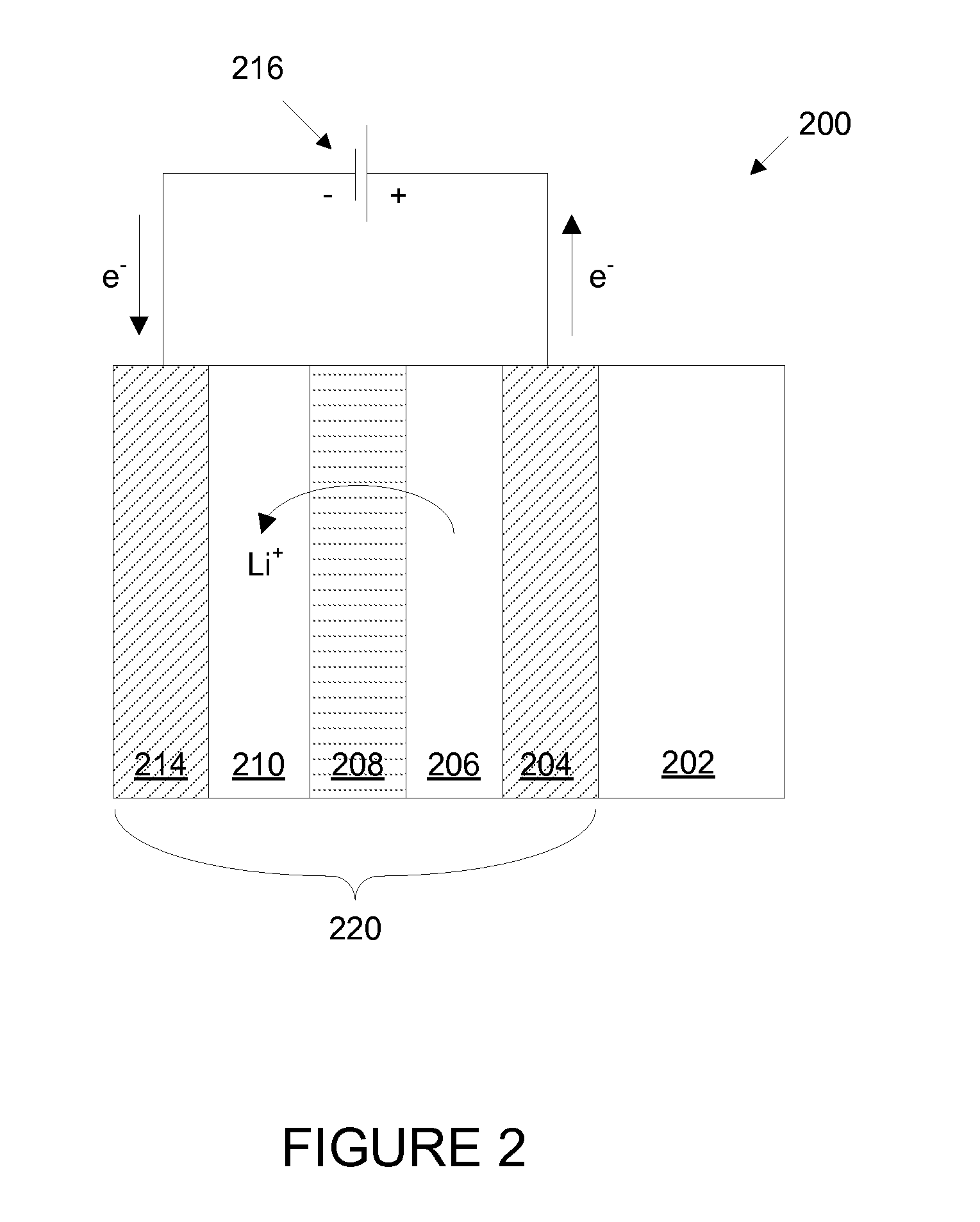

Prior electrochromic devices frequently suffer from high levels of defectivity. The defects may be manifest as pin holes or spots where the electrochromic transition is impaired. This is unacceptable for many applications such as electrochromic architectural glass. Improved electrochromic devices with low defectivity can be fabricated by depositing certain layered components of the electrochromic device in a single integrated deposition system. While these layers are being deposited and / or treated on a substrate, for example a glass window, the substrate never leaves a controlled ambient environment, for example a low pressure controlled atmosphere having very low levels of particles. These layers may be deposited using physical vapor deposition.

Owner:VIEW INC

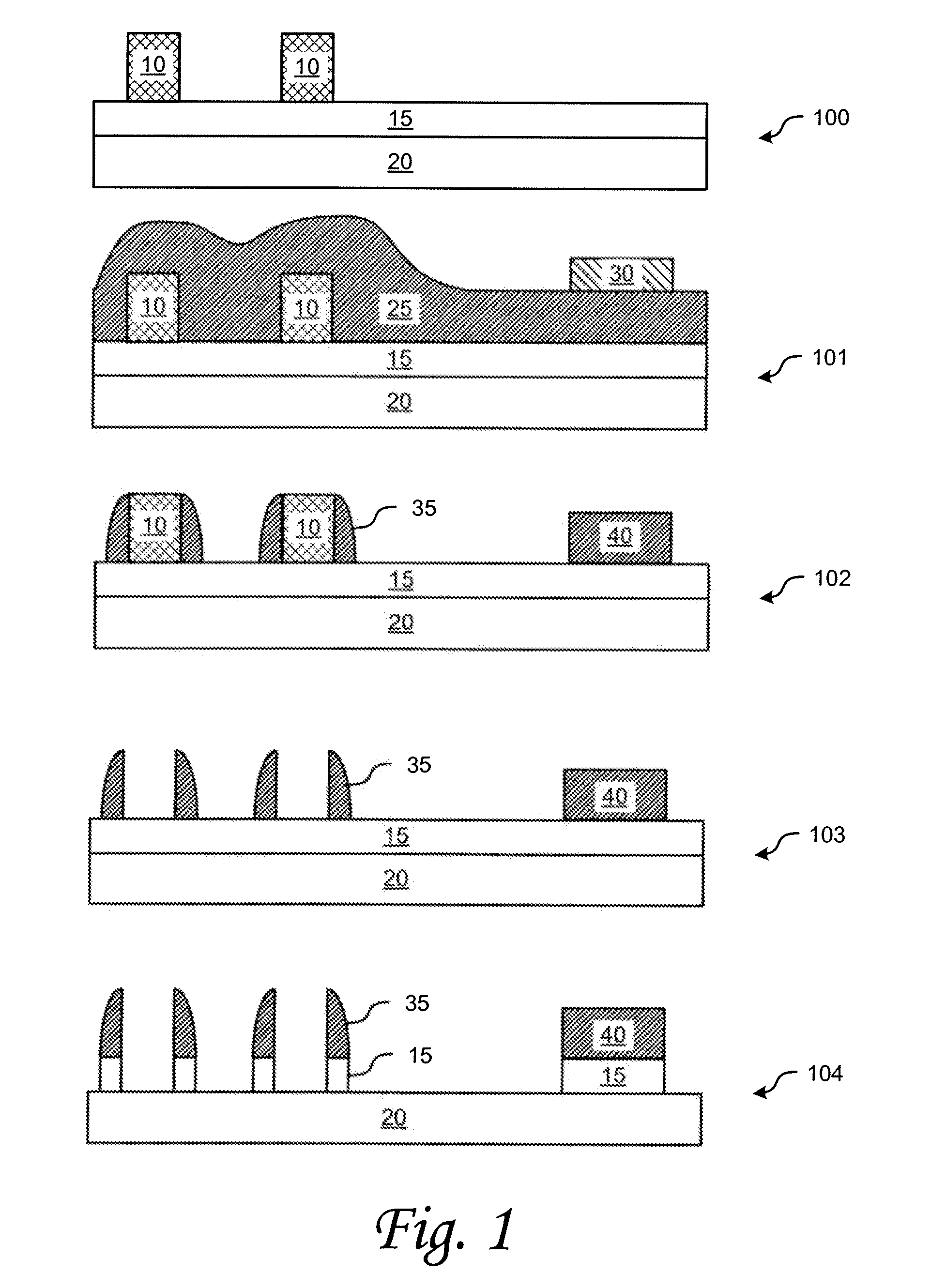

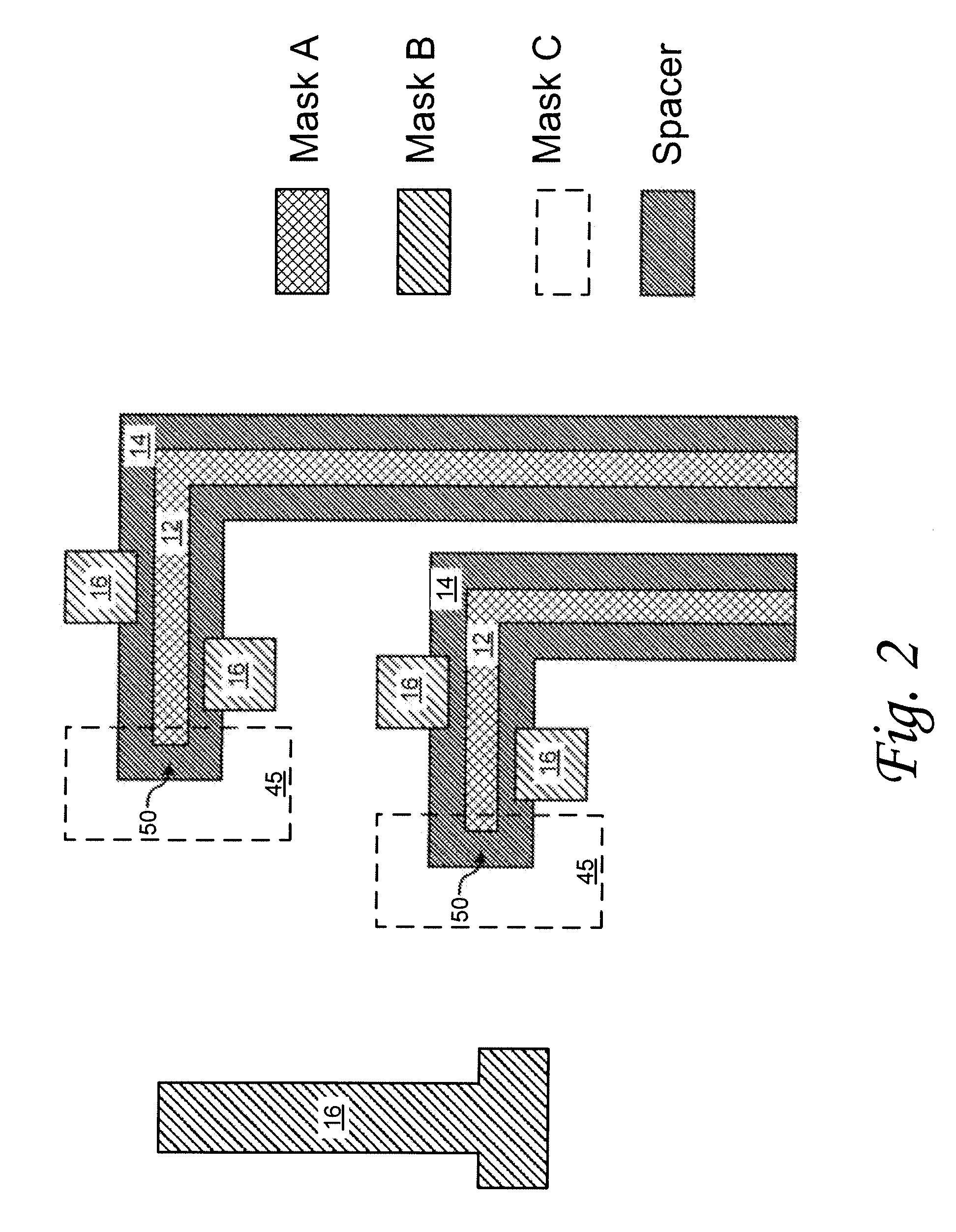

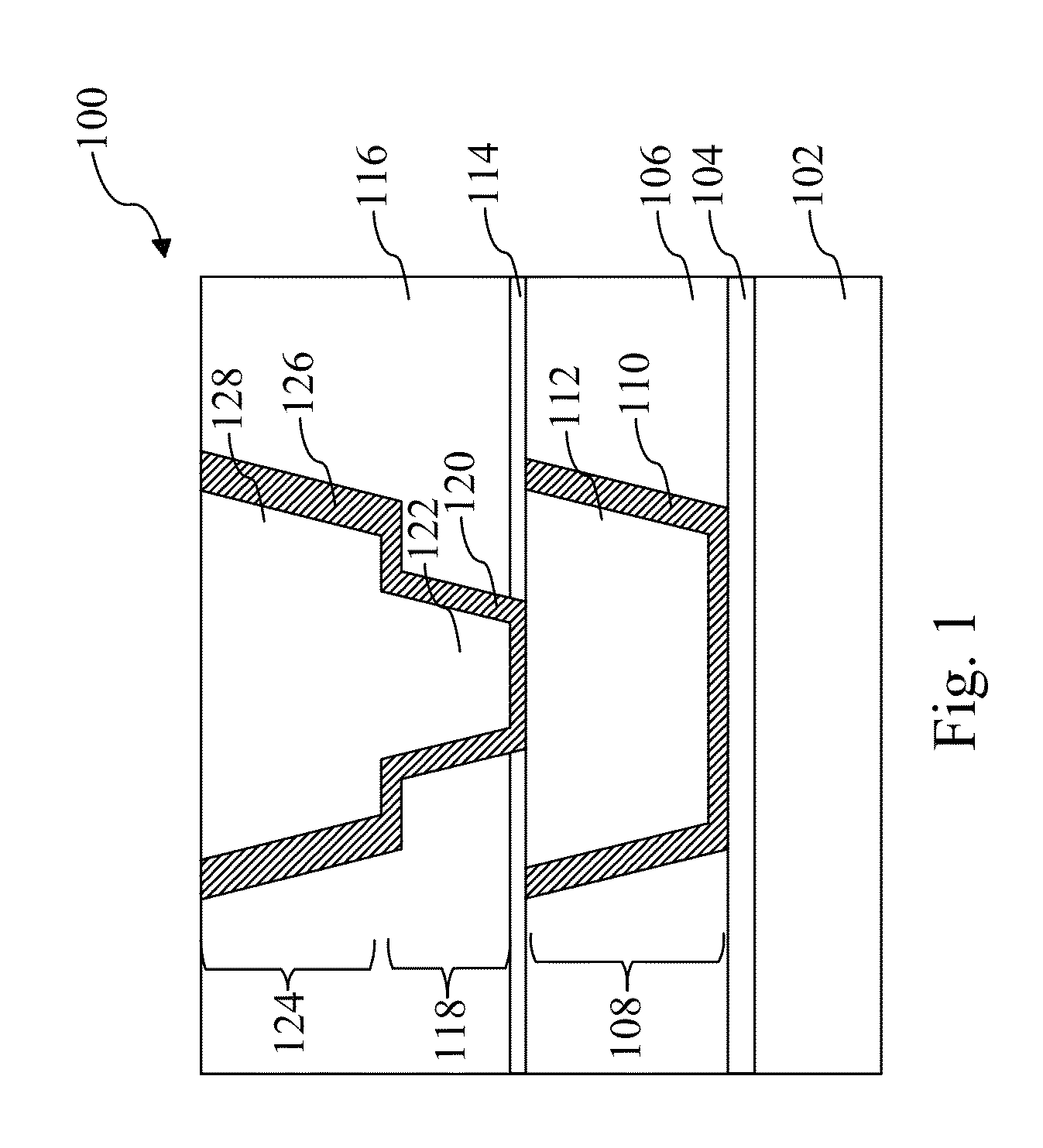

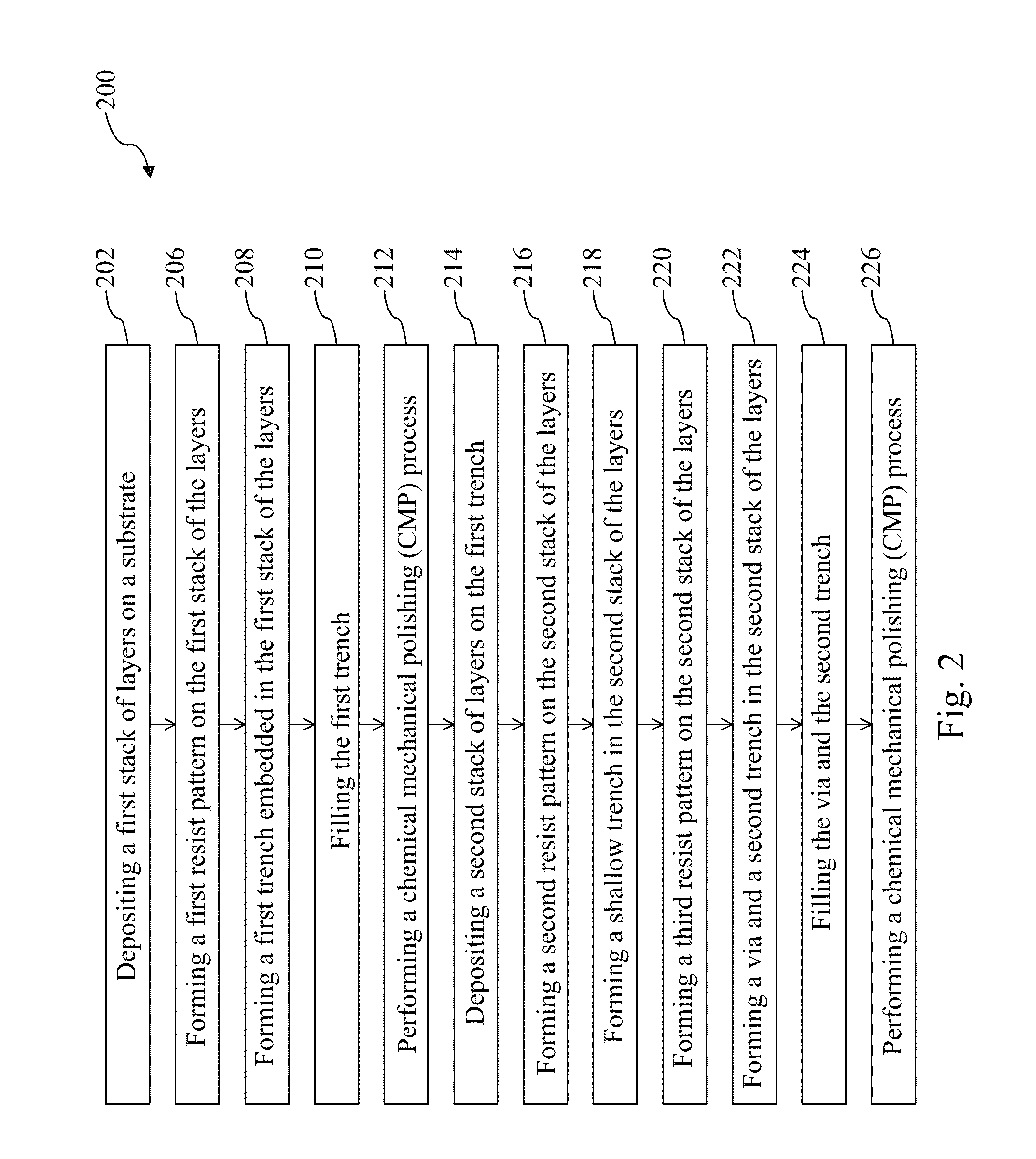

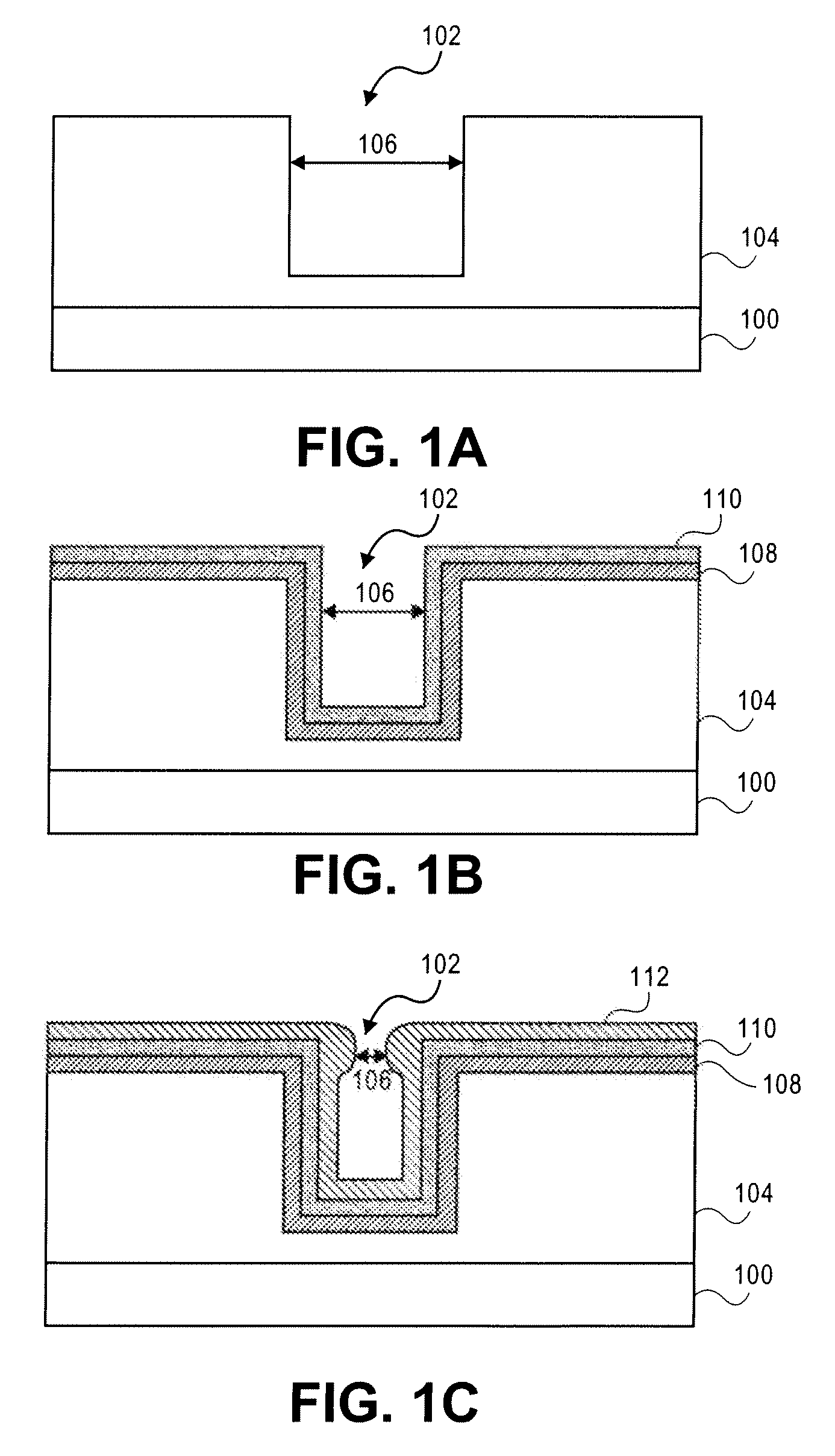

Method of eliminating a lithography operation

ActiveUS20090146322A1Semiconductor/solid-state device detailsSolid-state devicesLithographic artistEngineering

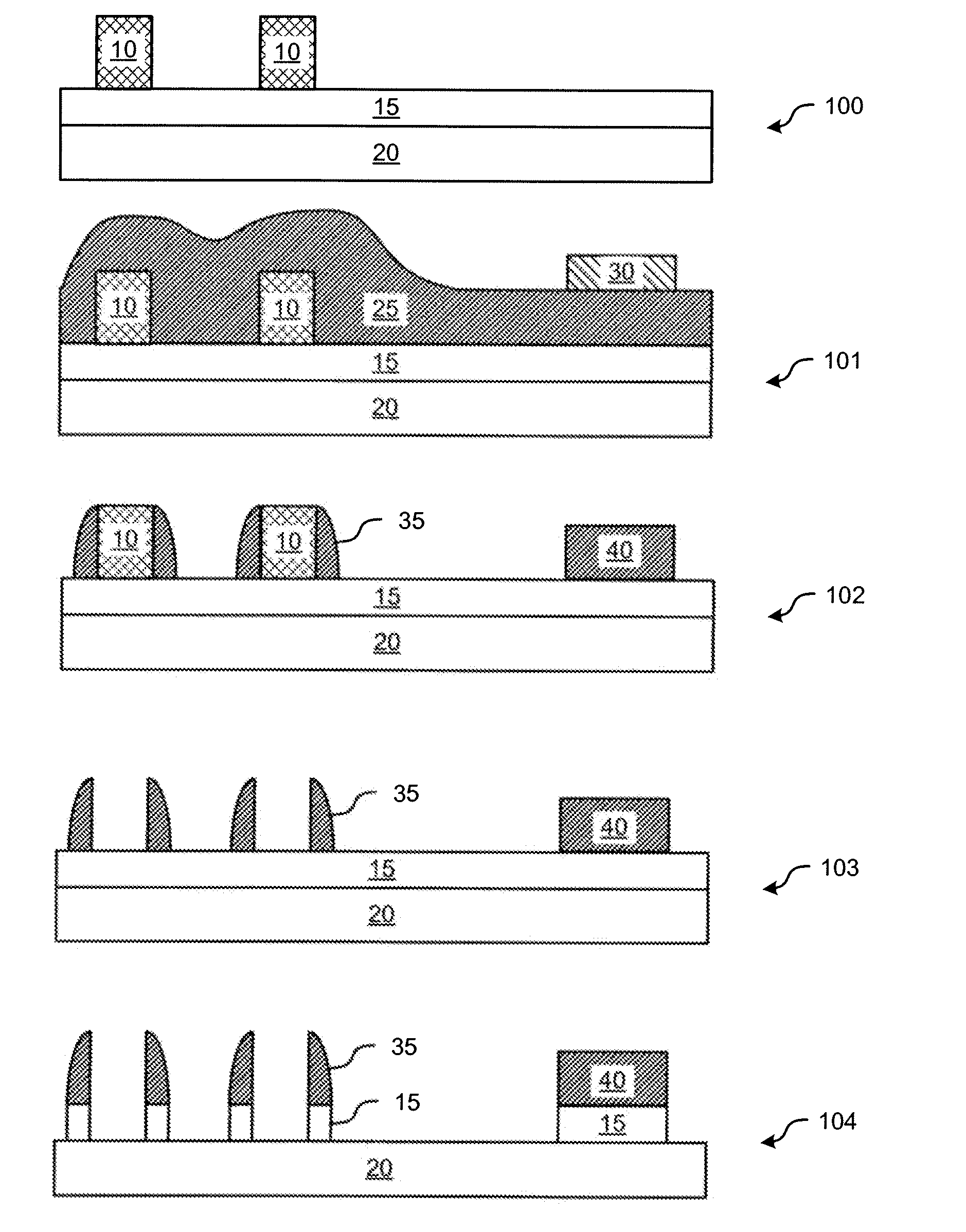

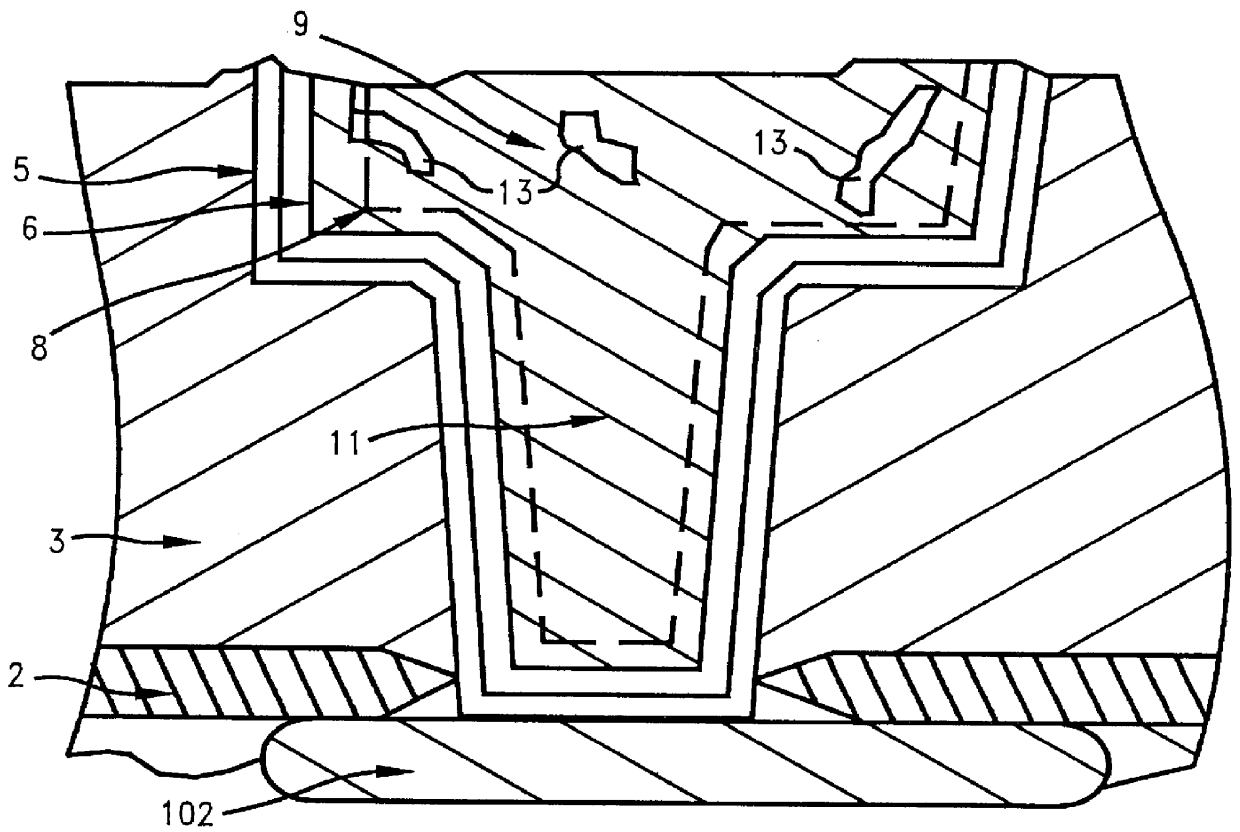

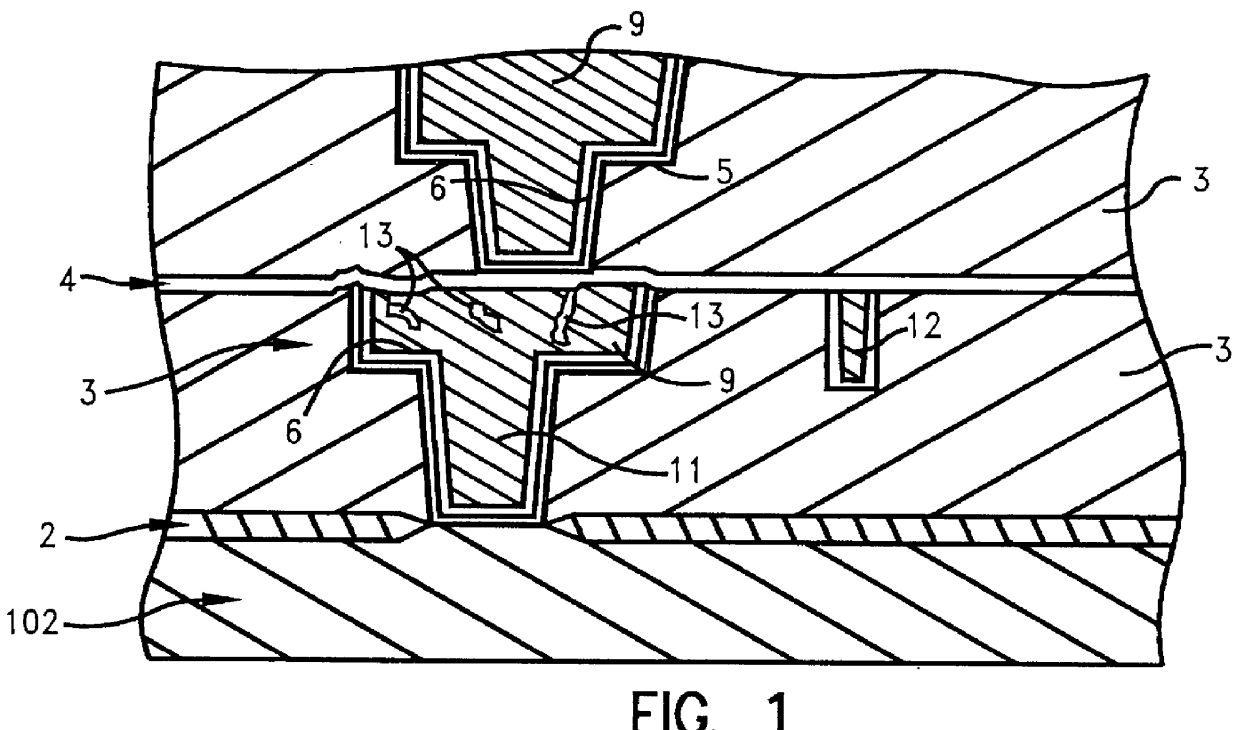

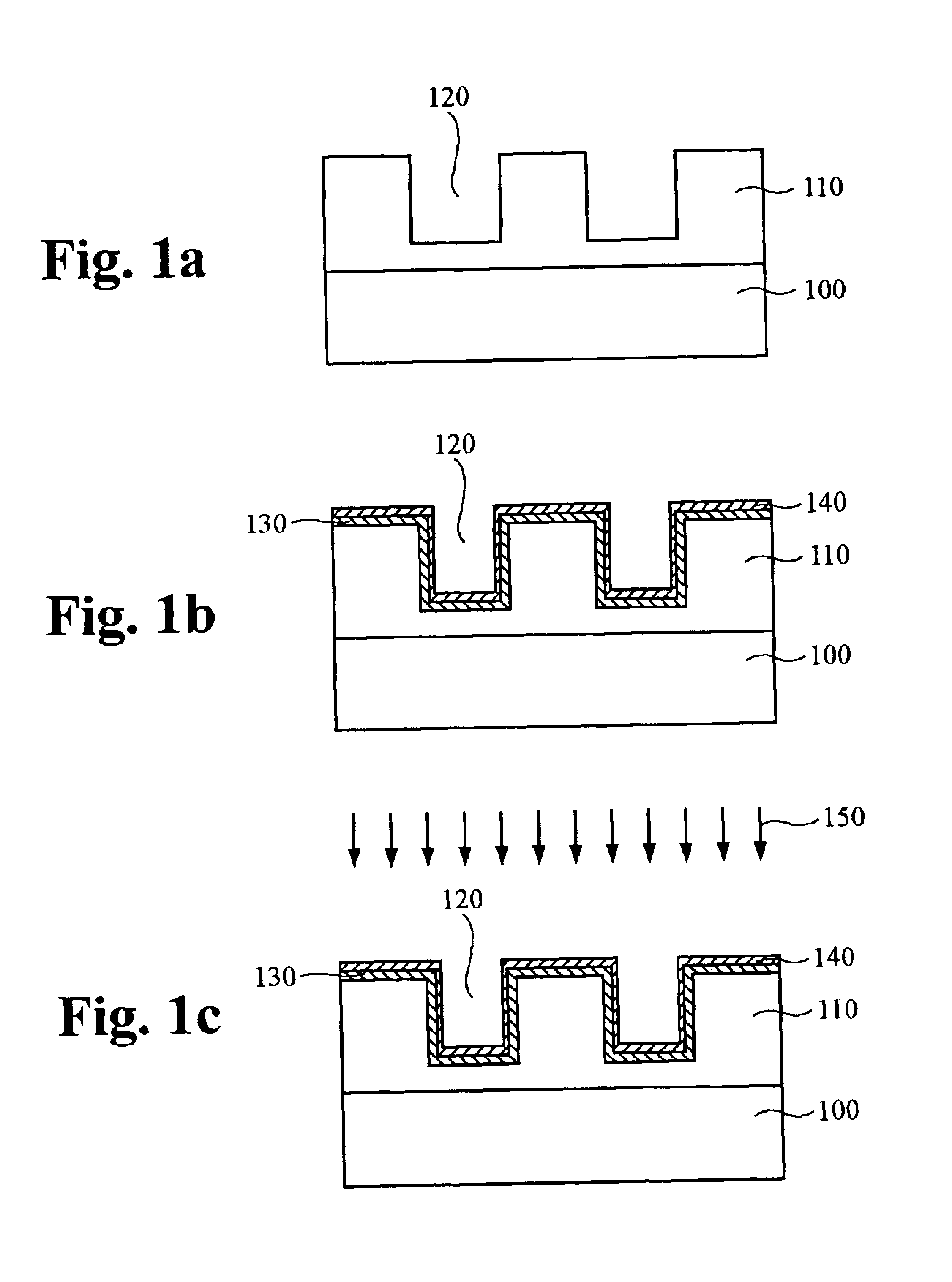

Methods of semiconductor device fabrication are disclosed. An exemplary method includes processes of depositing a first pattern on a semiconductor substrate, wherein the first pattern defines wide and narrow spaces; depositing spacer material over the first pattern on the substrate; etching the spacer material such that the spacer material is removed from horizontal surfaces of the substrate and the first pattern but remains adjacent to vertical surfaces of a wide space defined by the first pattern and remains within narrow a space defined by the first pattern; and removing the first pattern from the substrate. In one embodiment, the first pattern can comprise sacrificial material, which can include, for example, polysilicon material. The deposition can comprise physical vapor deposition, chemical vapor deposition, electrochemical deposition, molecular beam epitaxy, atomic layer deposition or other deposition techniques. According to another embodiment, features for lines and logic device components having a width greater than that of the lines are formed in the spacer material in the same mask layer.

Owner:CADENCE DESIGN SYST INC

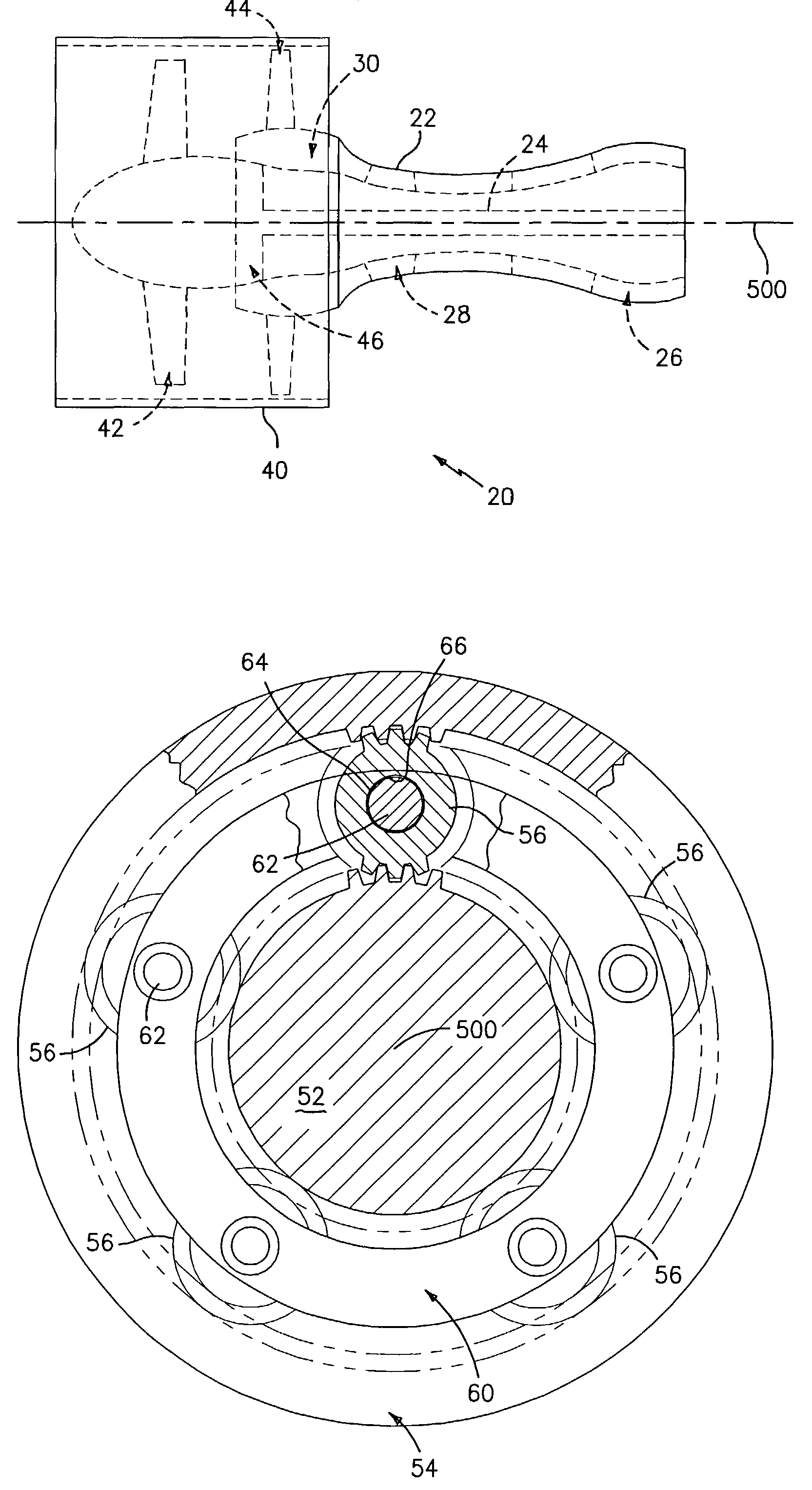

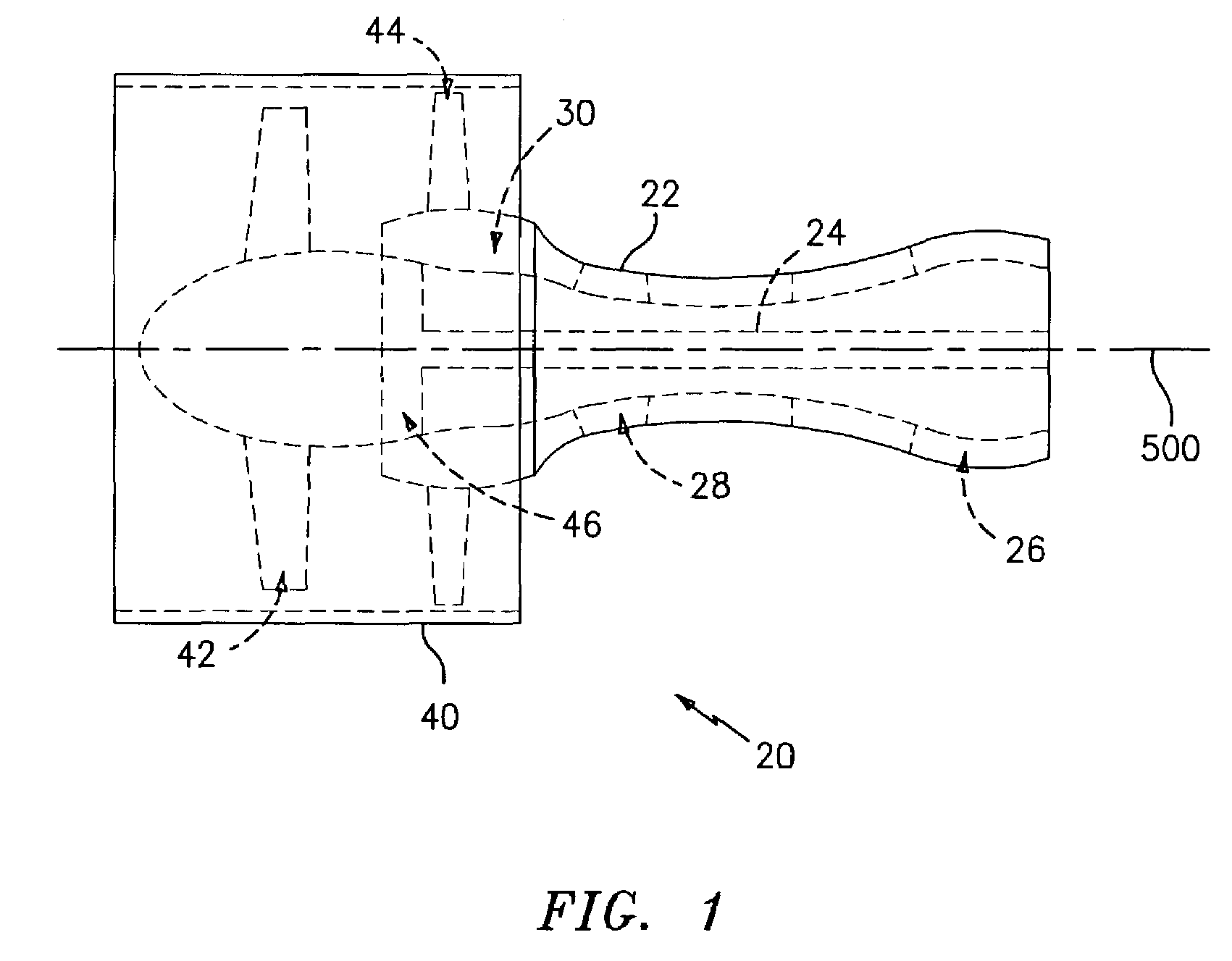

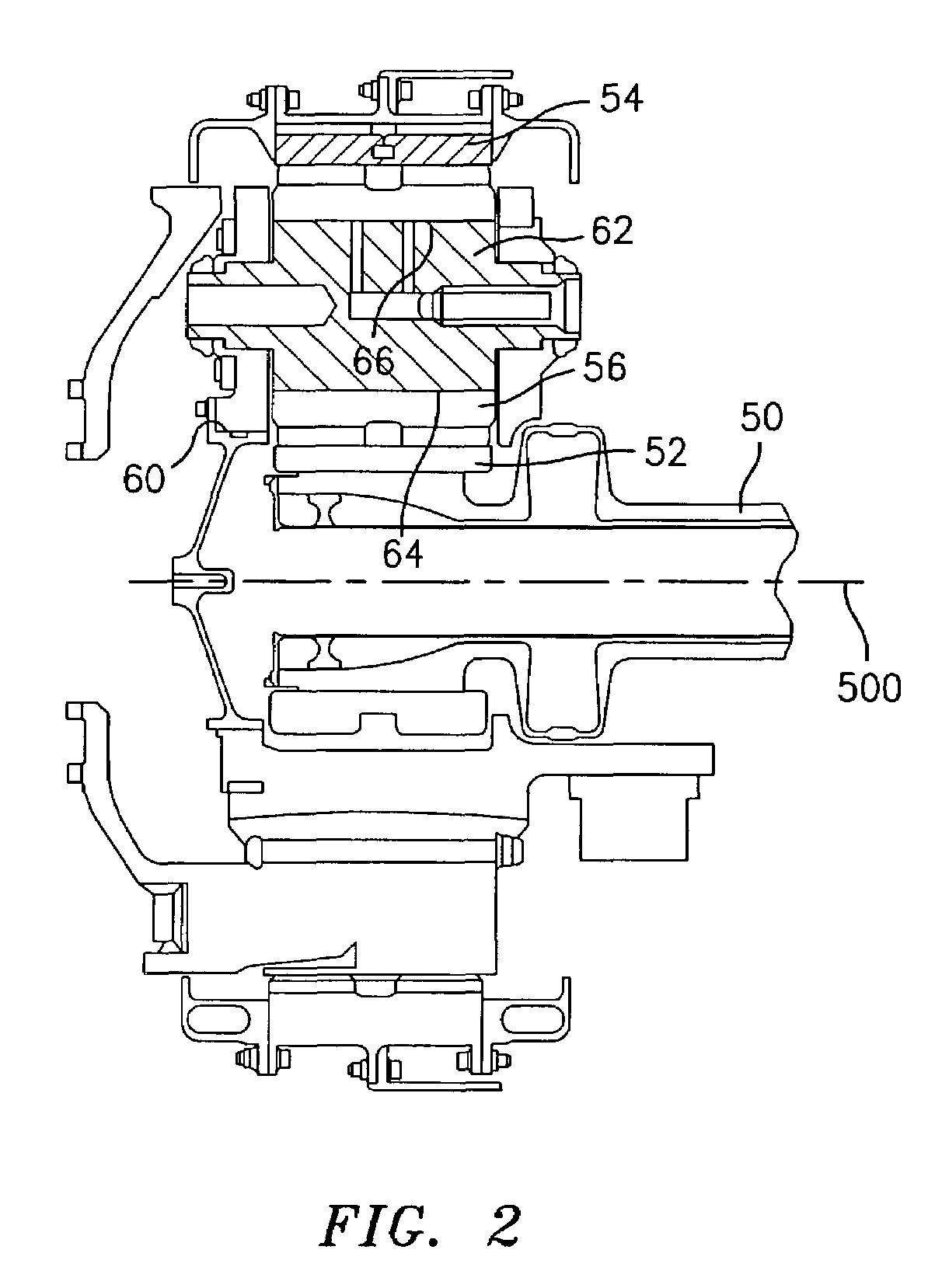

Geartrain coupling for a turbofan engine

Molybdenum disulfide (MoS2) is used as a journal coating for a gearing system. A particular application is the planetary gear system of a geared turbofan engine. Particularly advantageous coatings are deposited via physical vapor deposition (PVD) techniques.

Owner:RAYTHEON TECH CORP

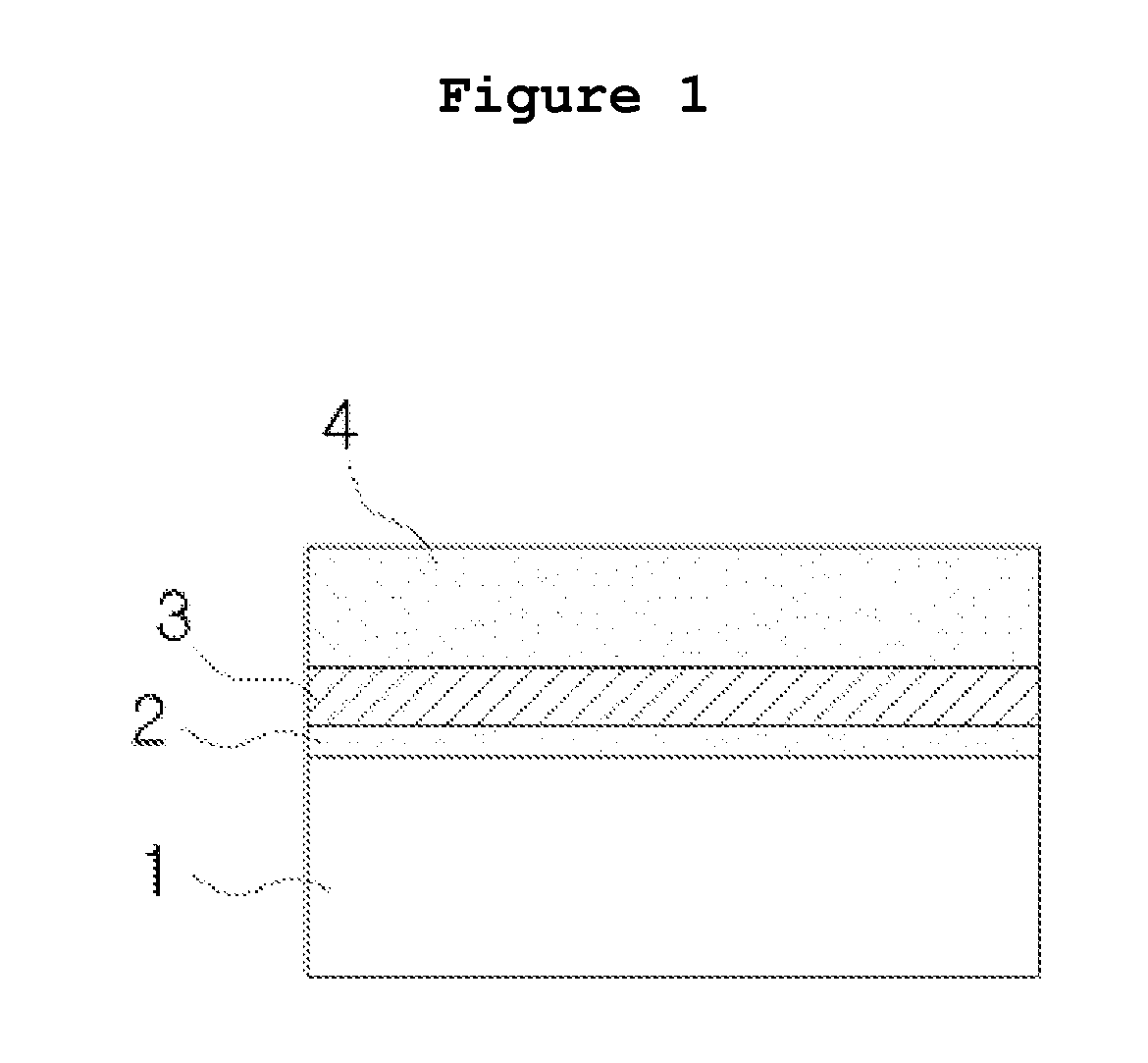

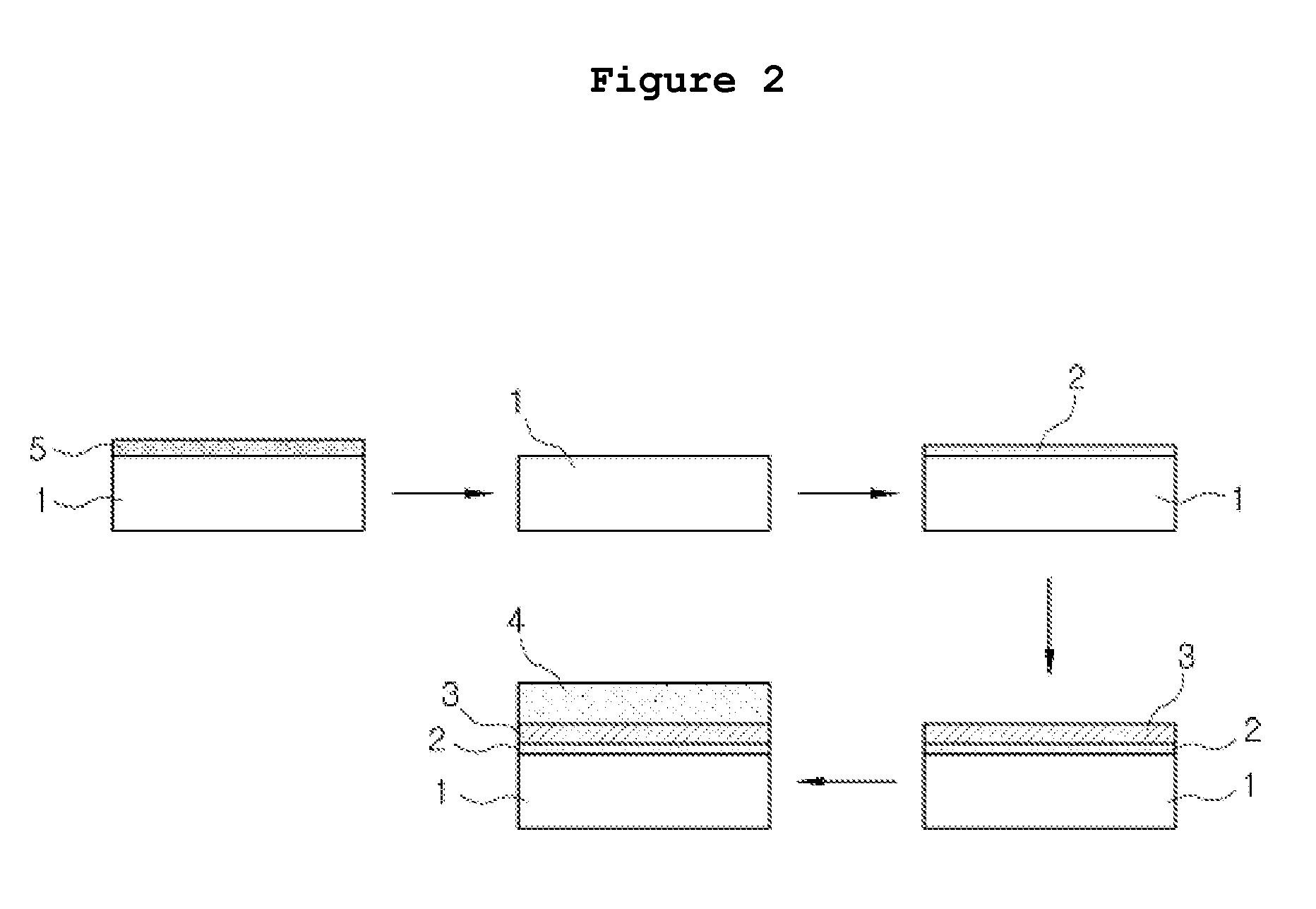

Method of depositing nanolaminate film for non-volatile floating gate memory devices by atomic layer deposition

Disclosed herein is a method of depositing a nanolaminate film for next-generation non-volatile floating gate memory devices by atomic layer deposition. The method includes the steps of: introducing a substrate into an atomic layer deposition reactor; forming on the substrate a first high-dielectric-constant layer by alternately supplying an oxygen source and a metal source selected from among an aluminum source, a zirconium source and a hafnium source; forming on the first high-dielectric-constant layer a nickel oxide layer by alternately supplying a nickel source and an oxygen source; and forming on the nickel oxide layer a second high-dielectric-constant layer by alternately supplying an oxygen source and a metal source selected from among an aluminum source, a zirconium source and a hafnium source. The nanolaminate film deposited according to the method shows good memory window characteristics compared to those of memory devices fabricated using nanocrystal floating gates according to the prior physical vapor deposition methods, and thus can be applied to non-volatile floating gate memory devices.

Owner:KOREA RES INST OF CHEM TECH

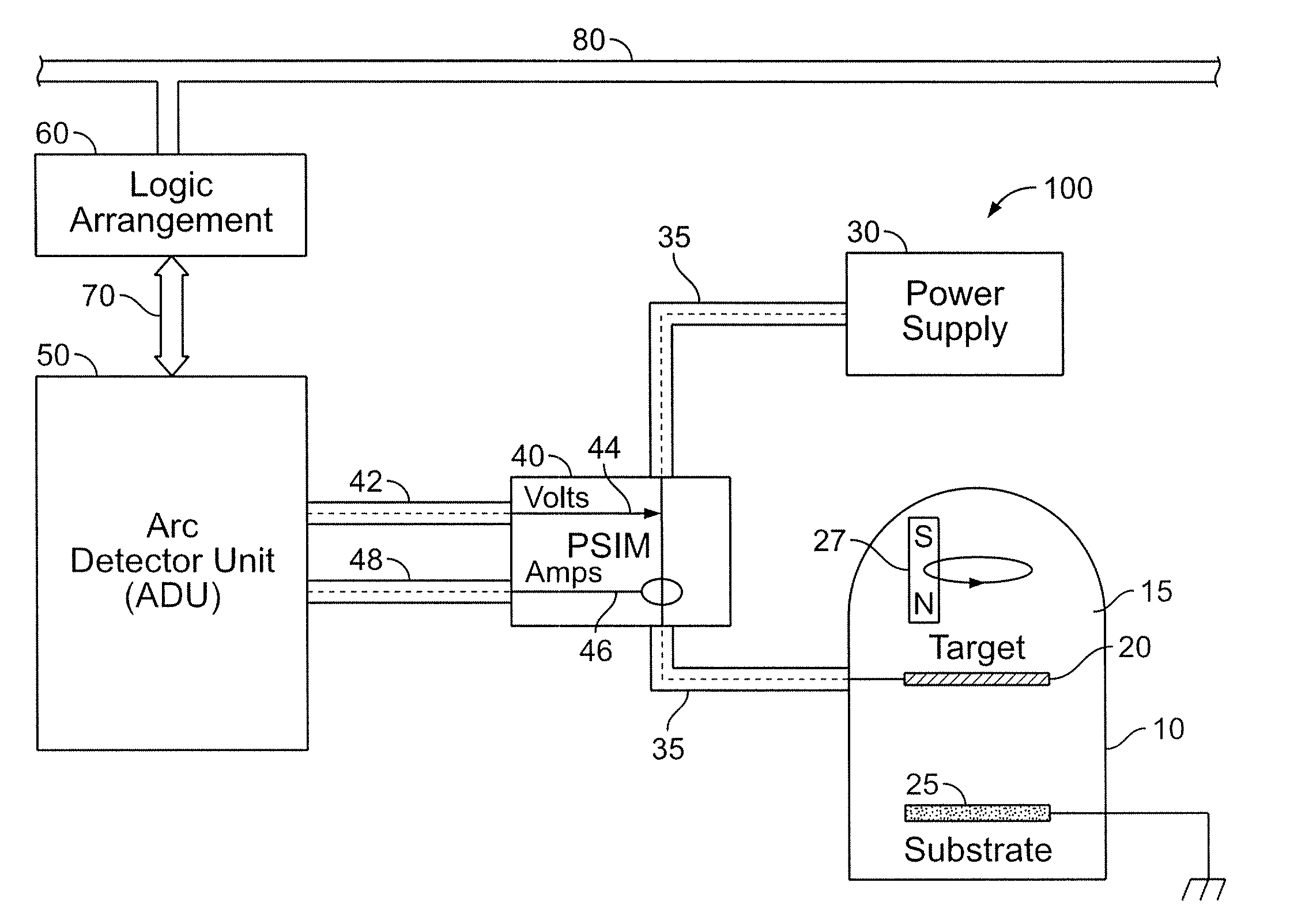

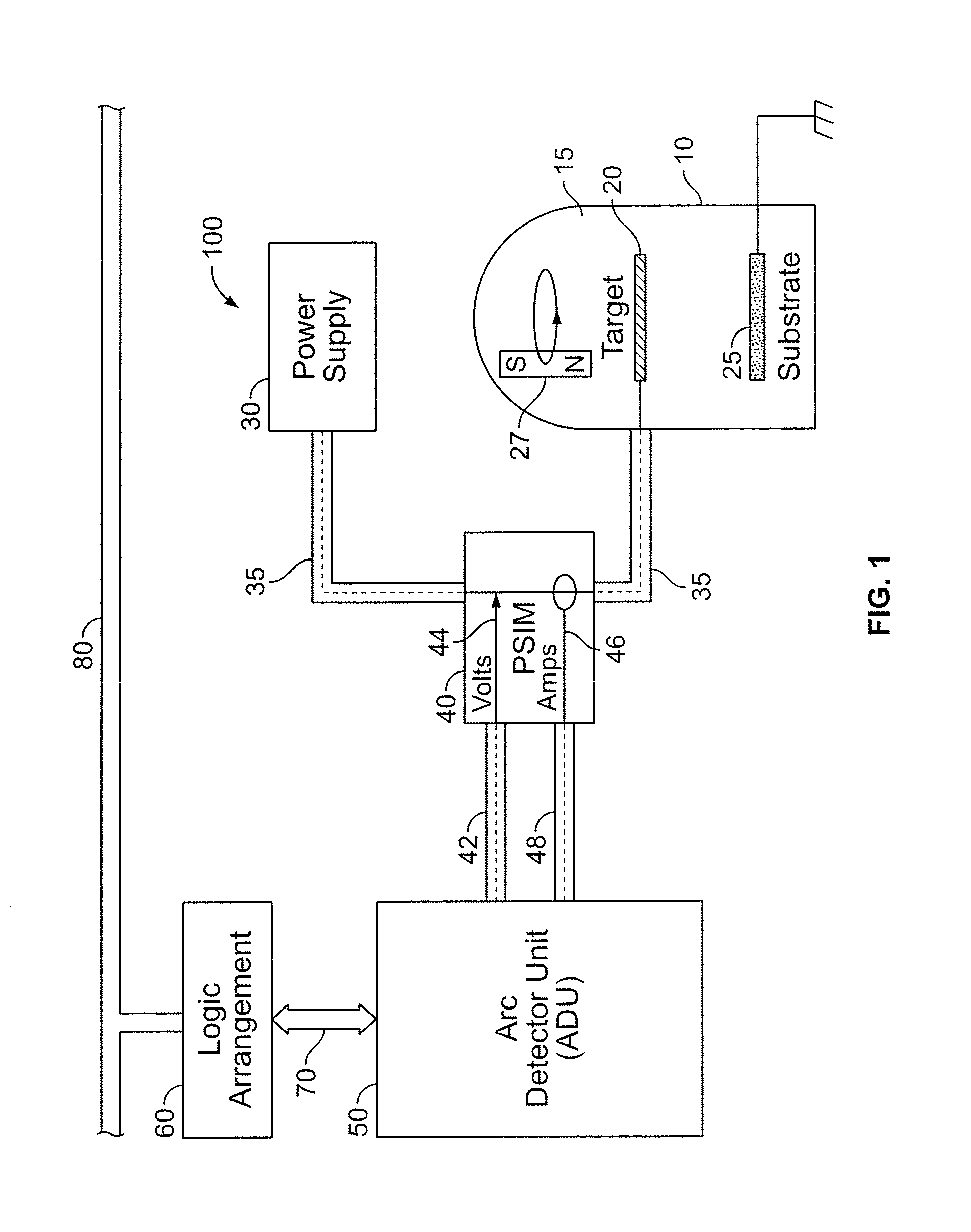

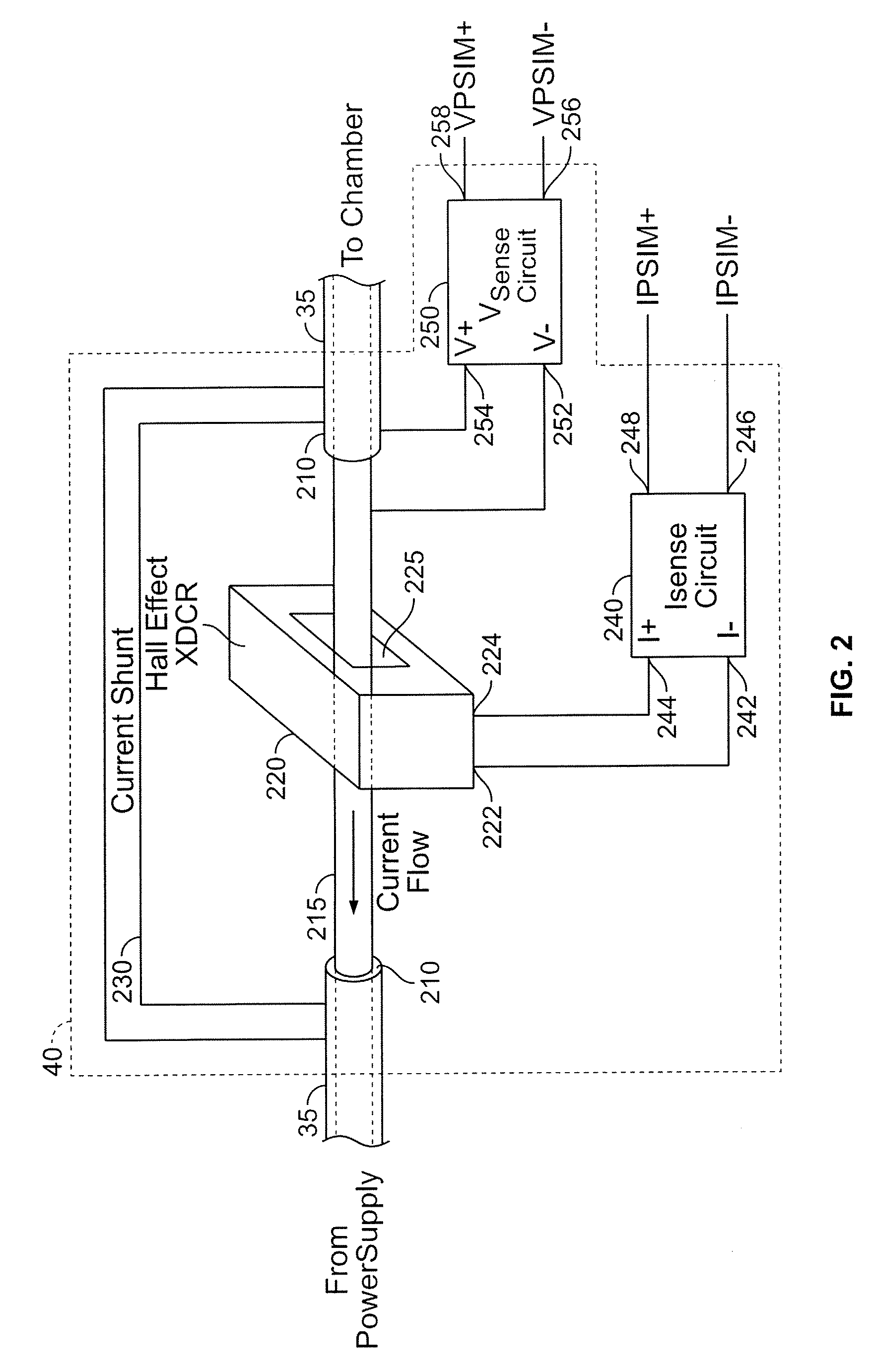

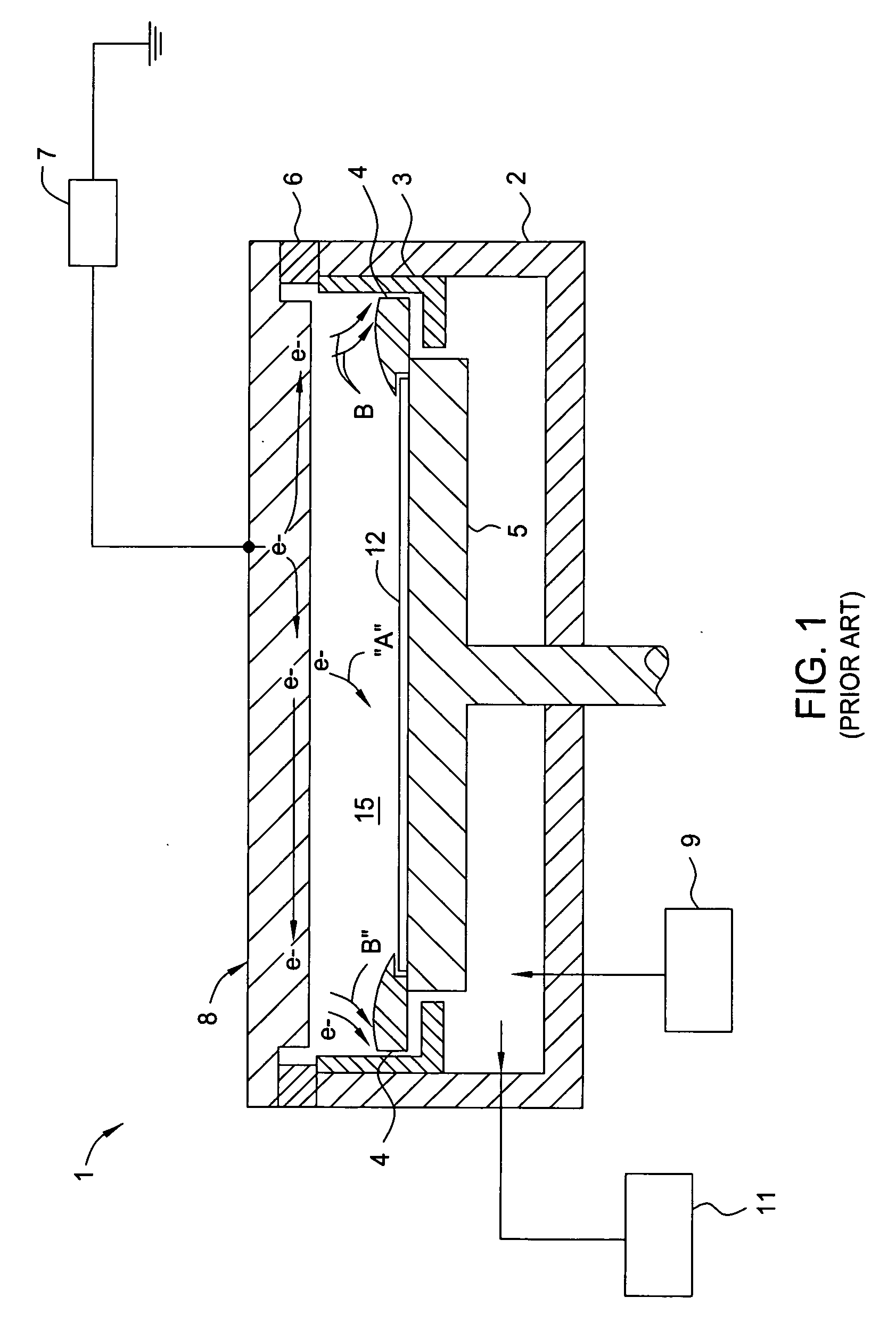

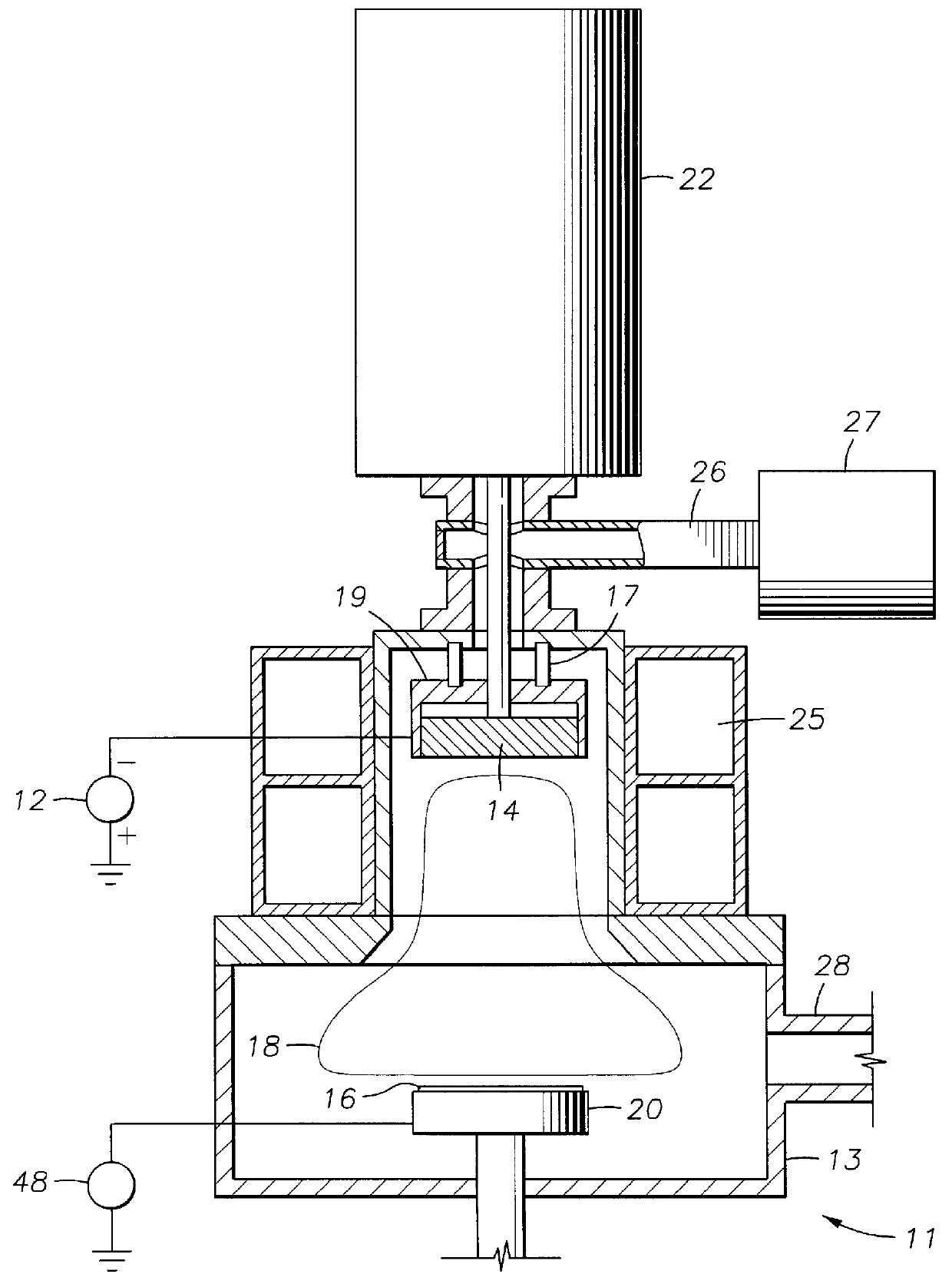

System and Method for Detecting Non-Cathode Arcing in a Plasma Generation Apparatus

ActiveUS20080133154A1Improve Wafer YieldReduce defectsTesting dielectric strengthElectric discharge tubesMoving averageEvent data

A system and method for detecting the potential of non-cathode arcing in a plasma generation apparatus, such as a physical vapor deposition chamber. The system and method involve computing a statistical parameter of cathode-arcing event data in the chamber and performing a pattern recognition technique to a moving average of the statistical parameter.

Owner:SCHNEIDER ELECTRIC USA INC

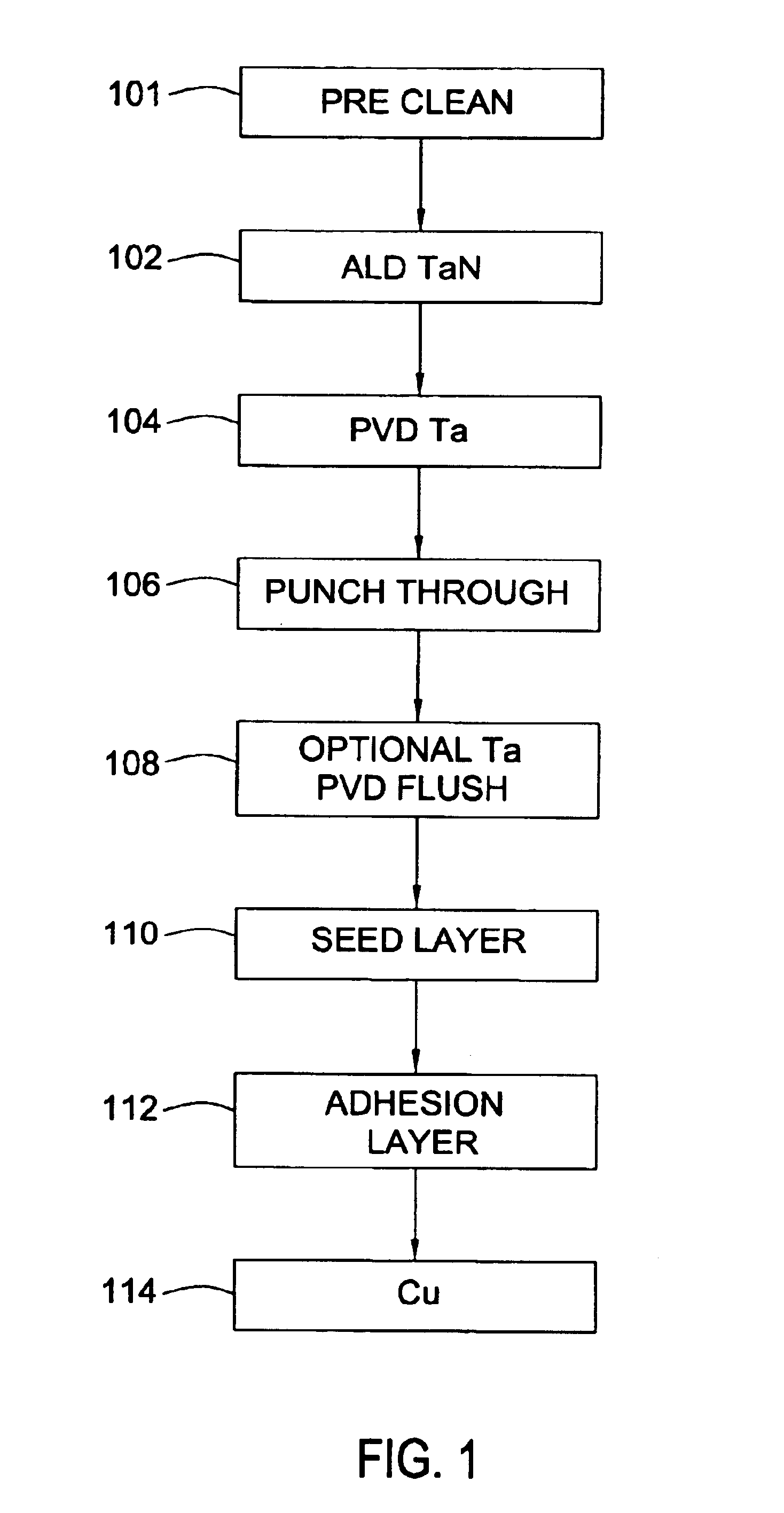

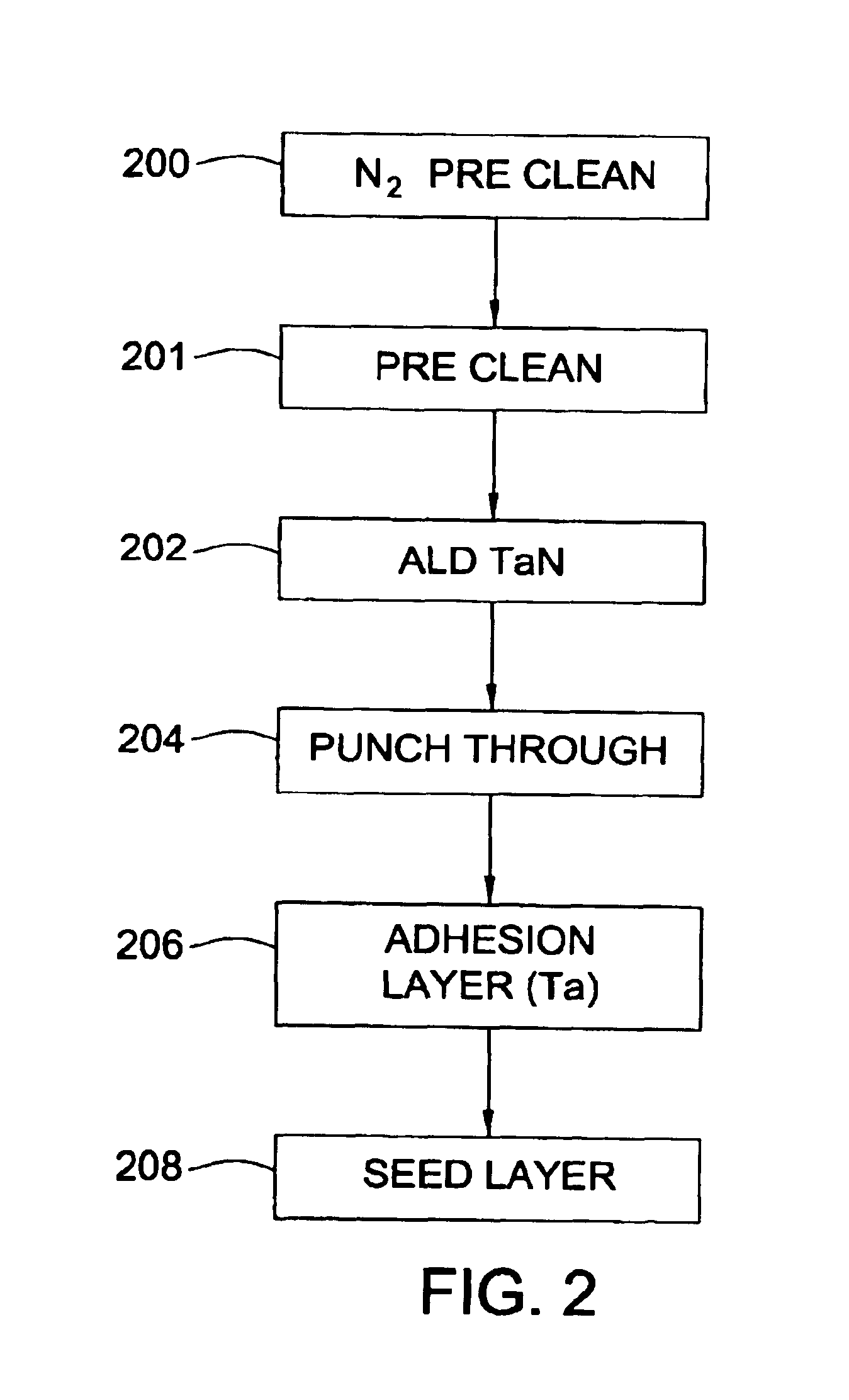

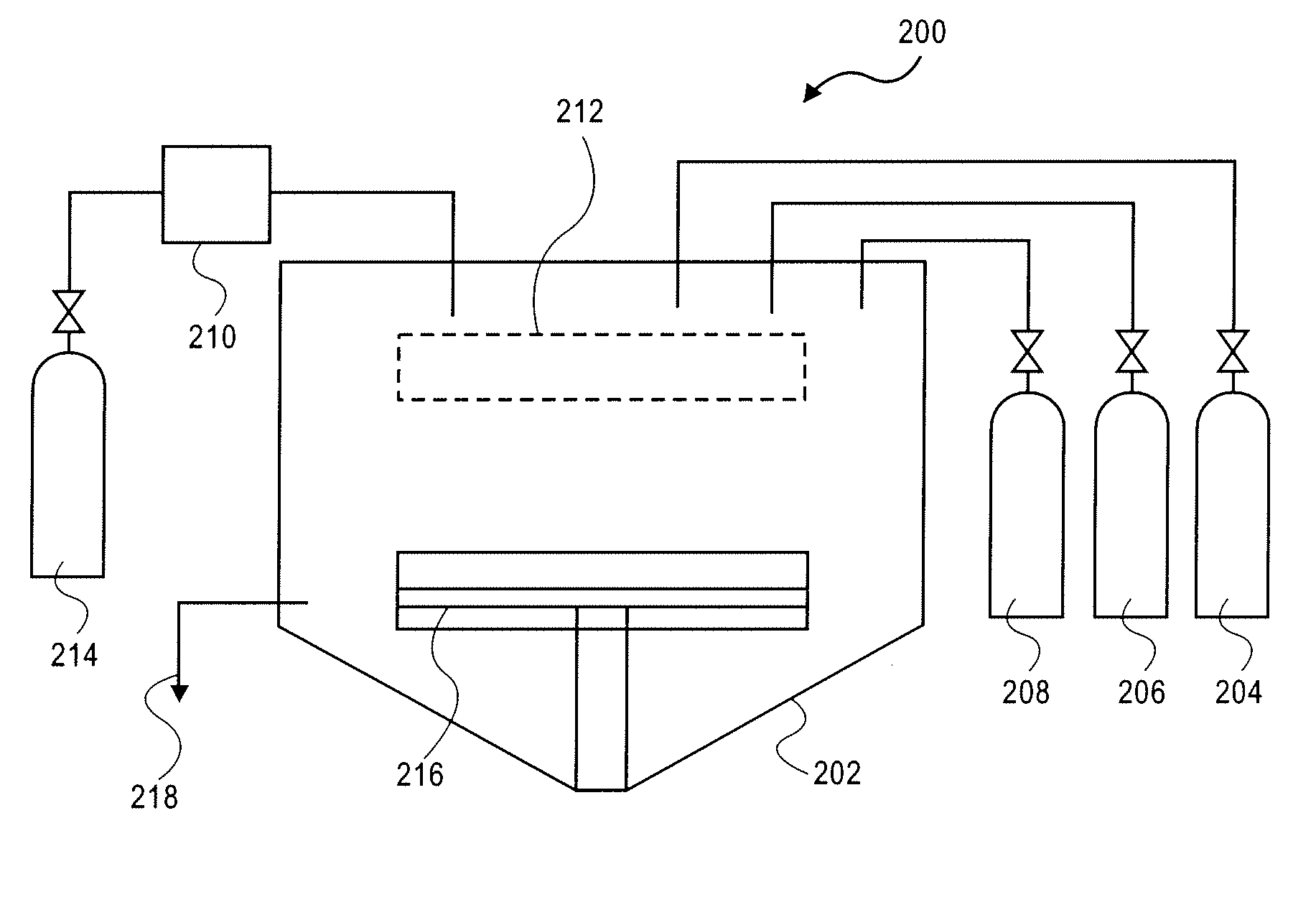

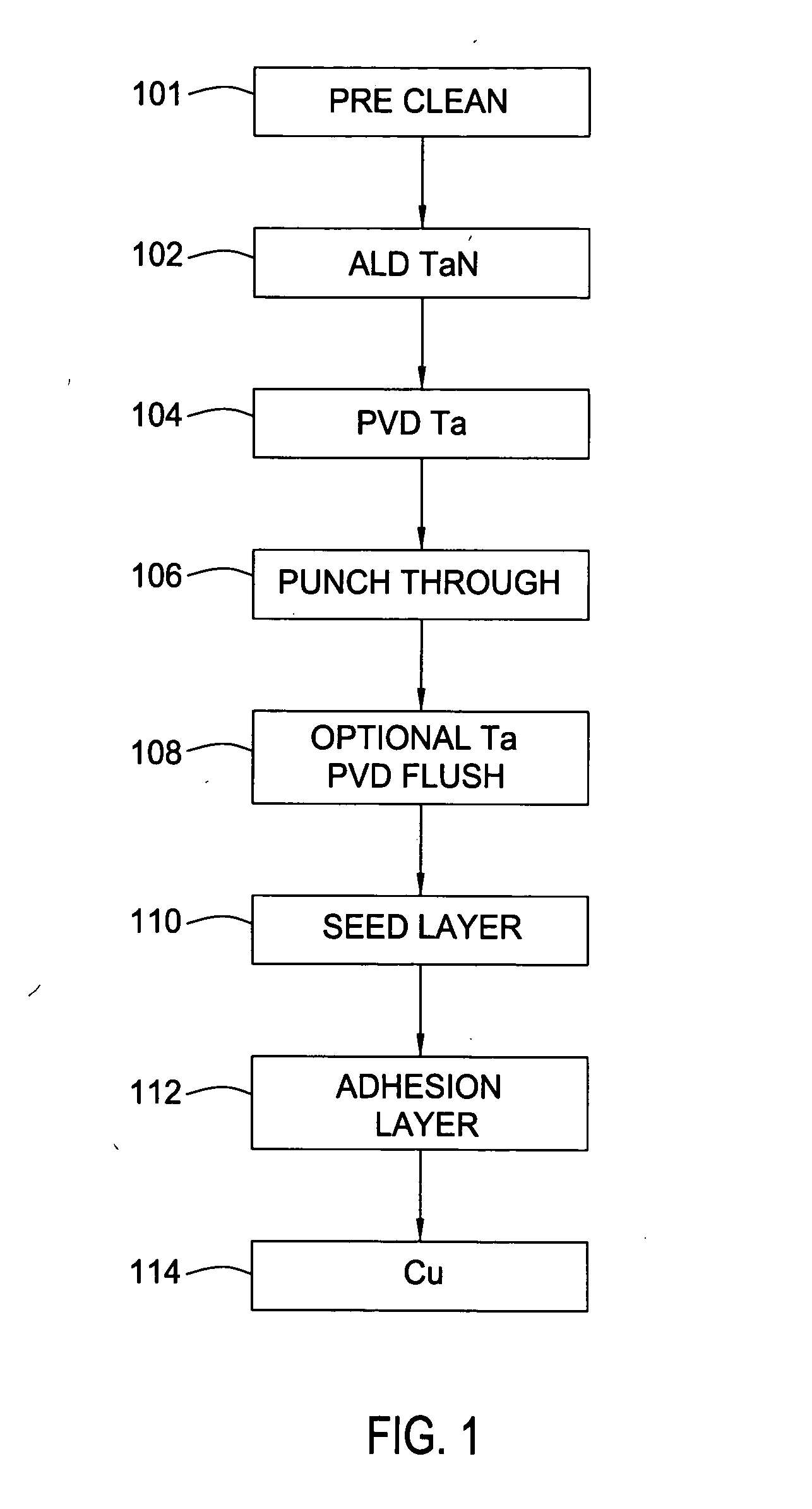

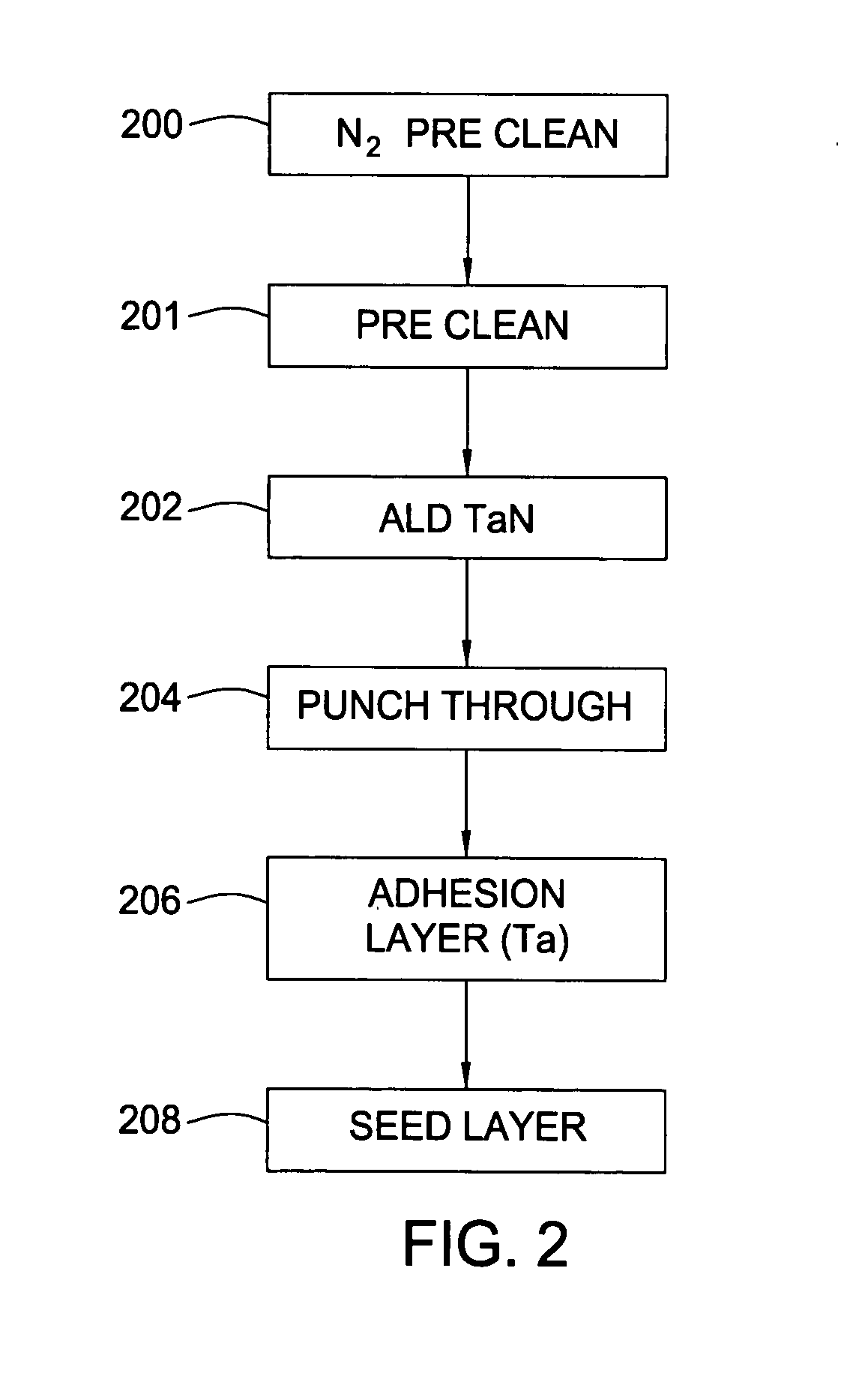

Integration of ALD tantalum nitride for copper metallization

InactiveUS7049226B2Semiconductor/solid-state device manufacturingChemical vapor deposition coatingTantalum nitrideConductive materials

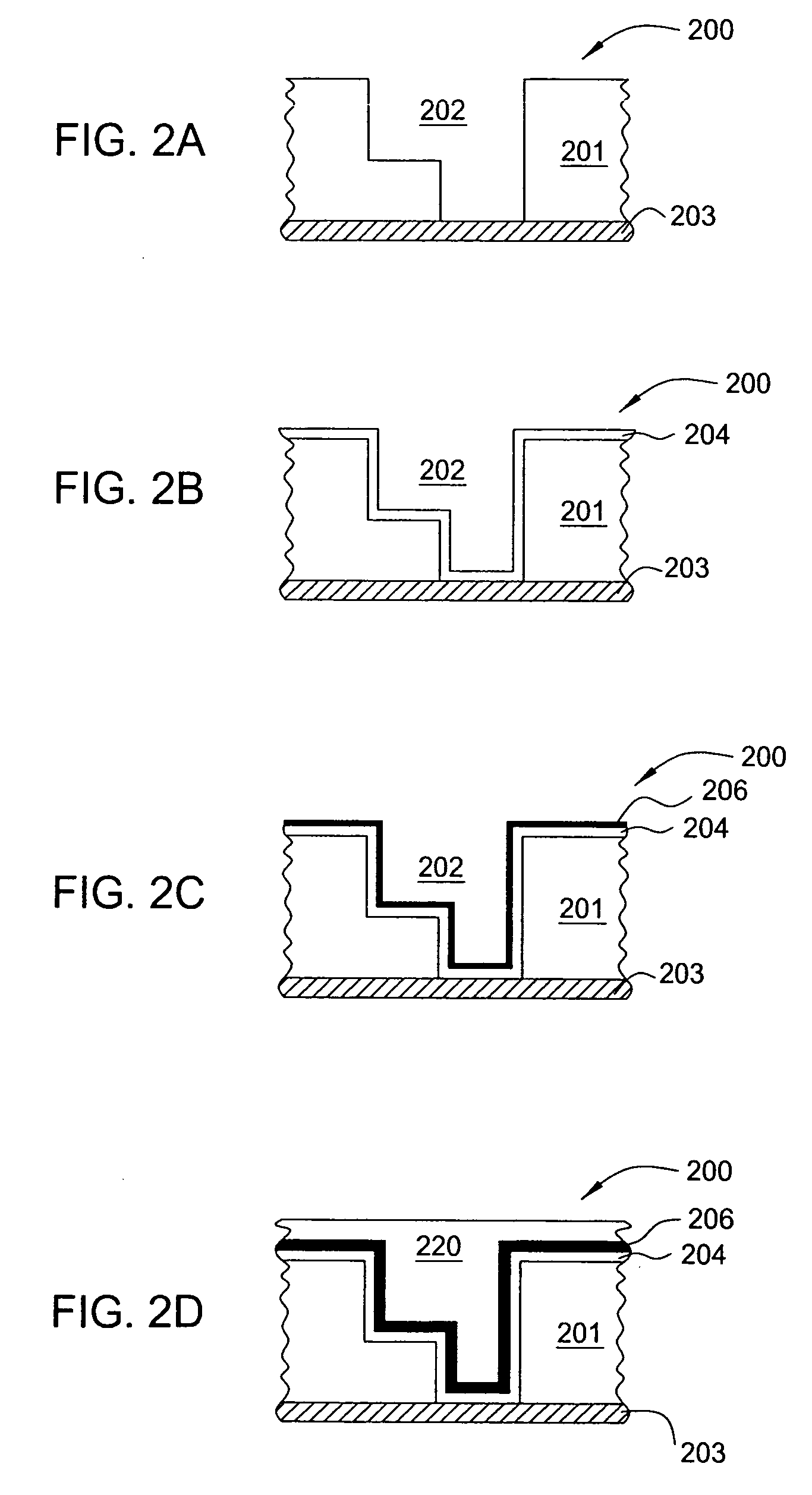

A method and apparatus for depositing a tantalum nitride barrier layer is provided for use in an integrated processing tool. The tantalum nitride is deposited by atomic layer deposition. The tantalum nitride is removed from the bottom of features in dielectric layers to reveal the conductive material under the deposited tantalum nitride. Optionally, a tantalum layer may be deposited by physical vapor deposition after the tantalum nitride deposition. Optionally, the tantalum nitride deposition and the tantalum deposition may occur in the same processing chamber.

Owner:APPLIED MATERIALS INC

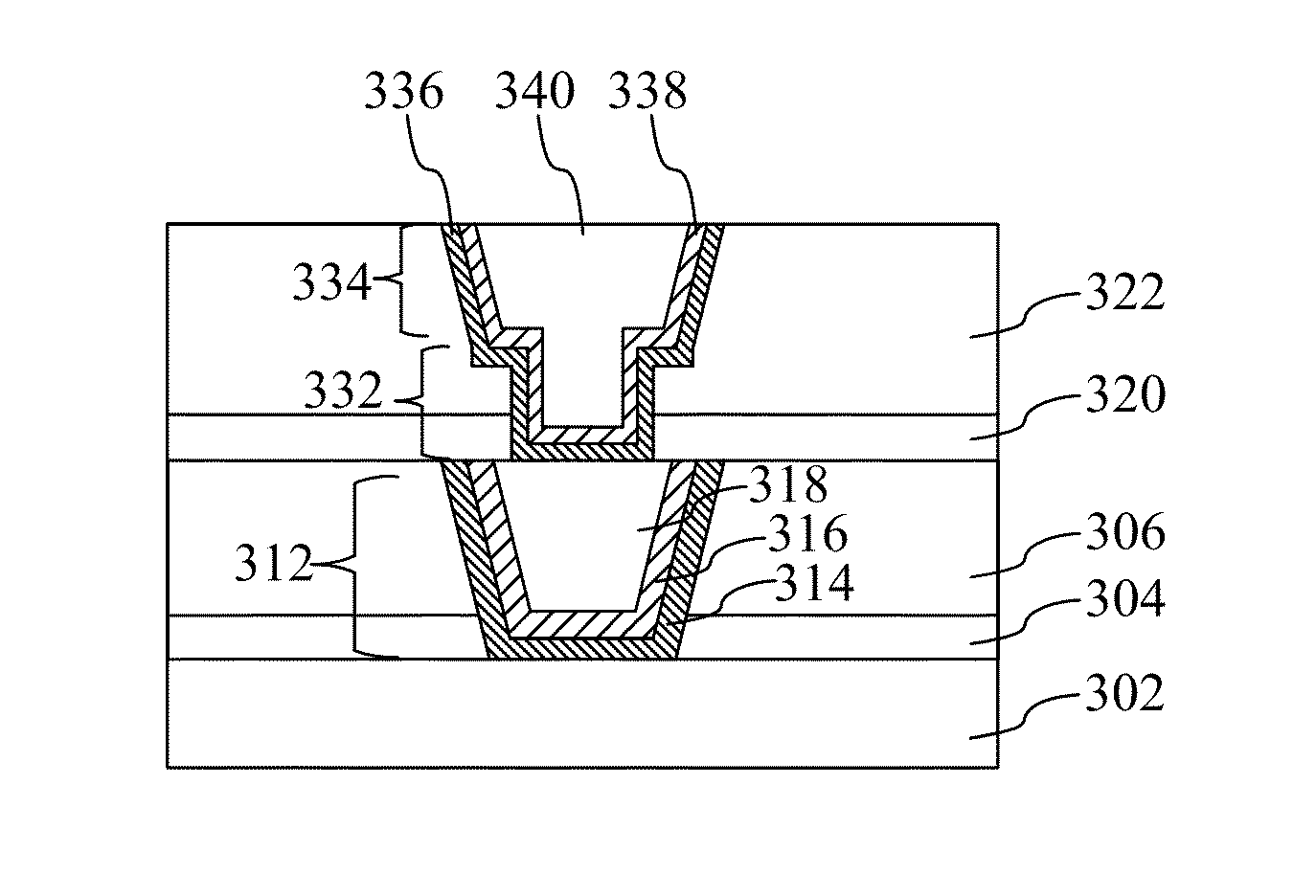

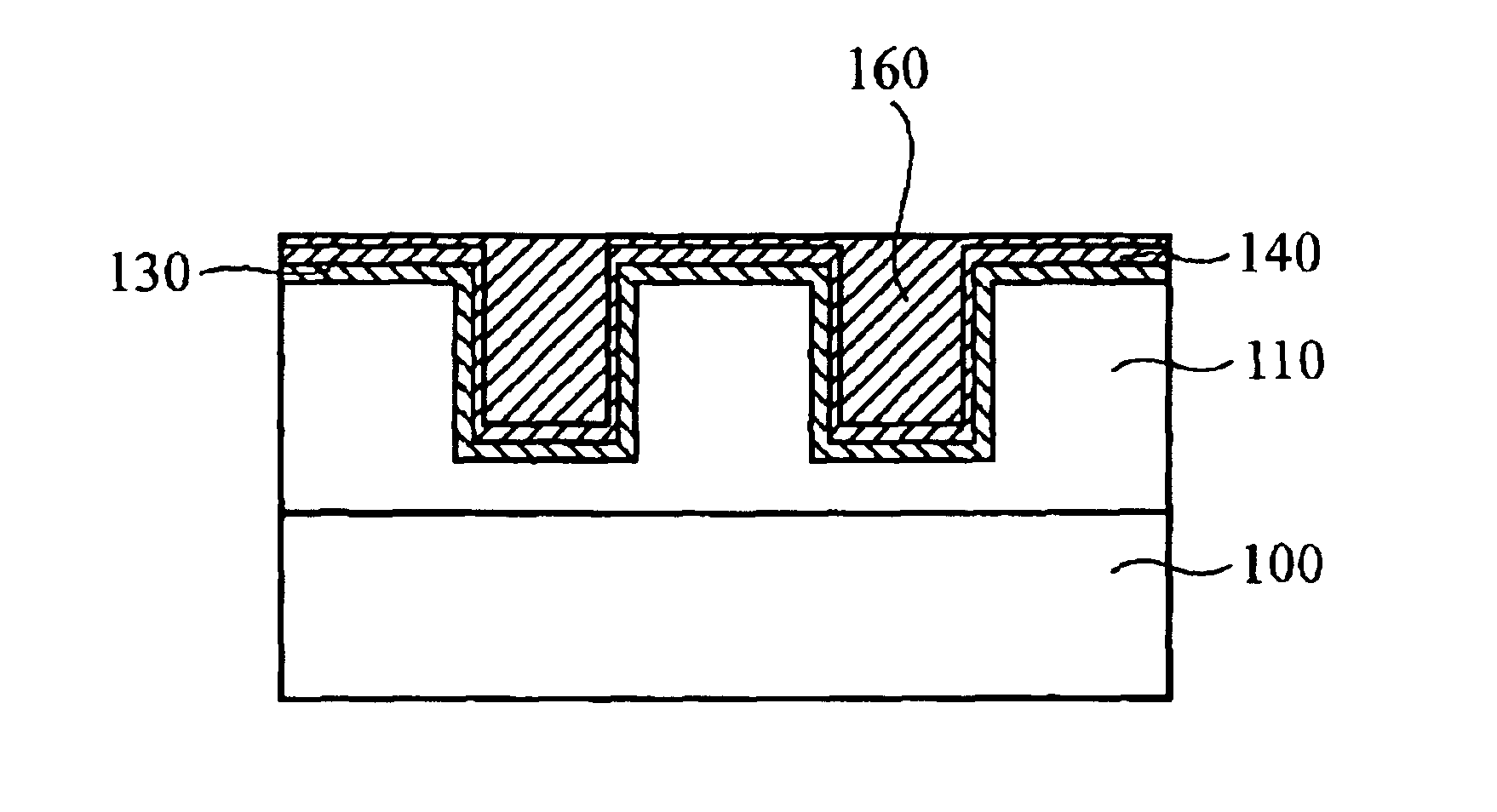

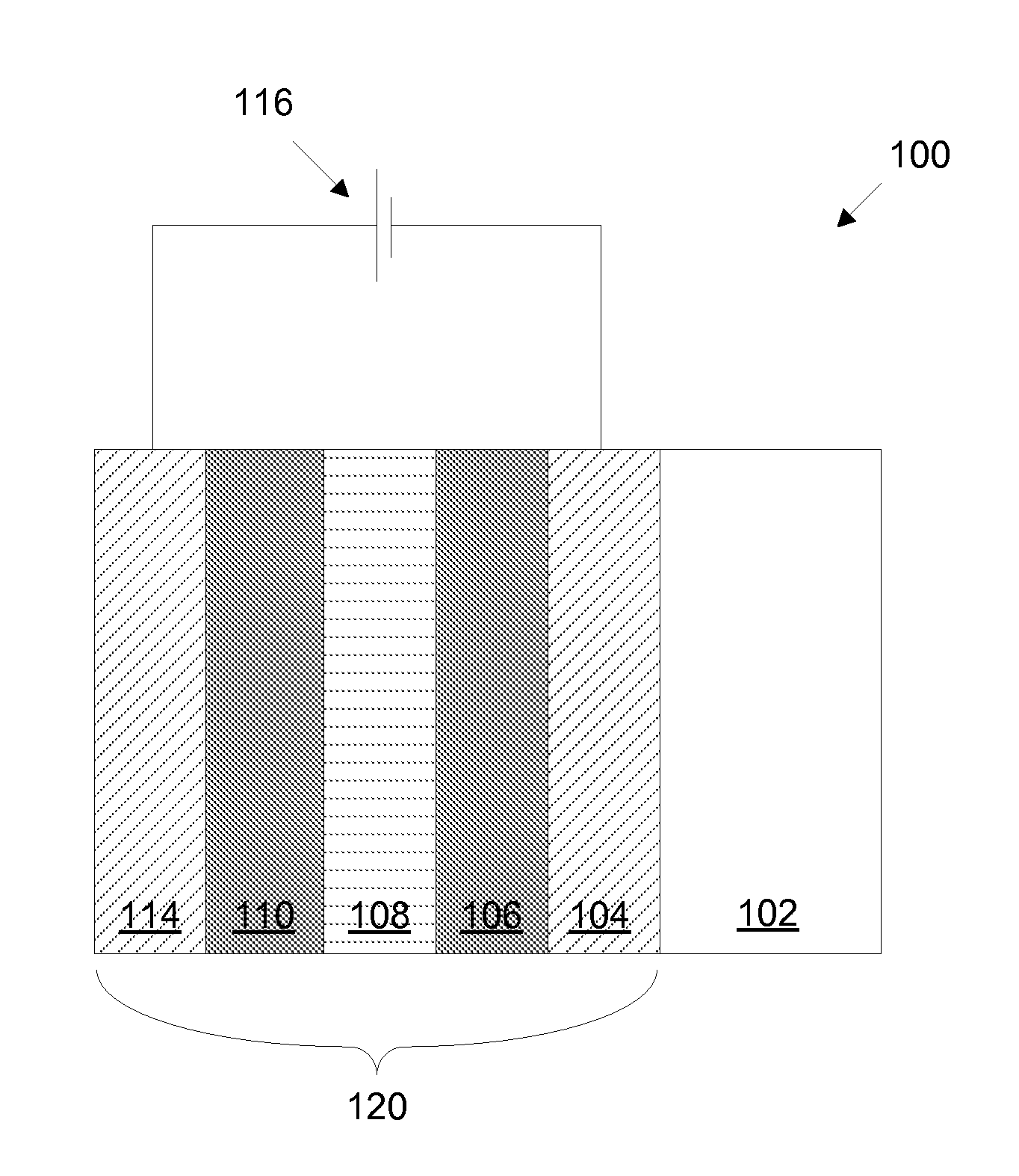

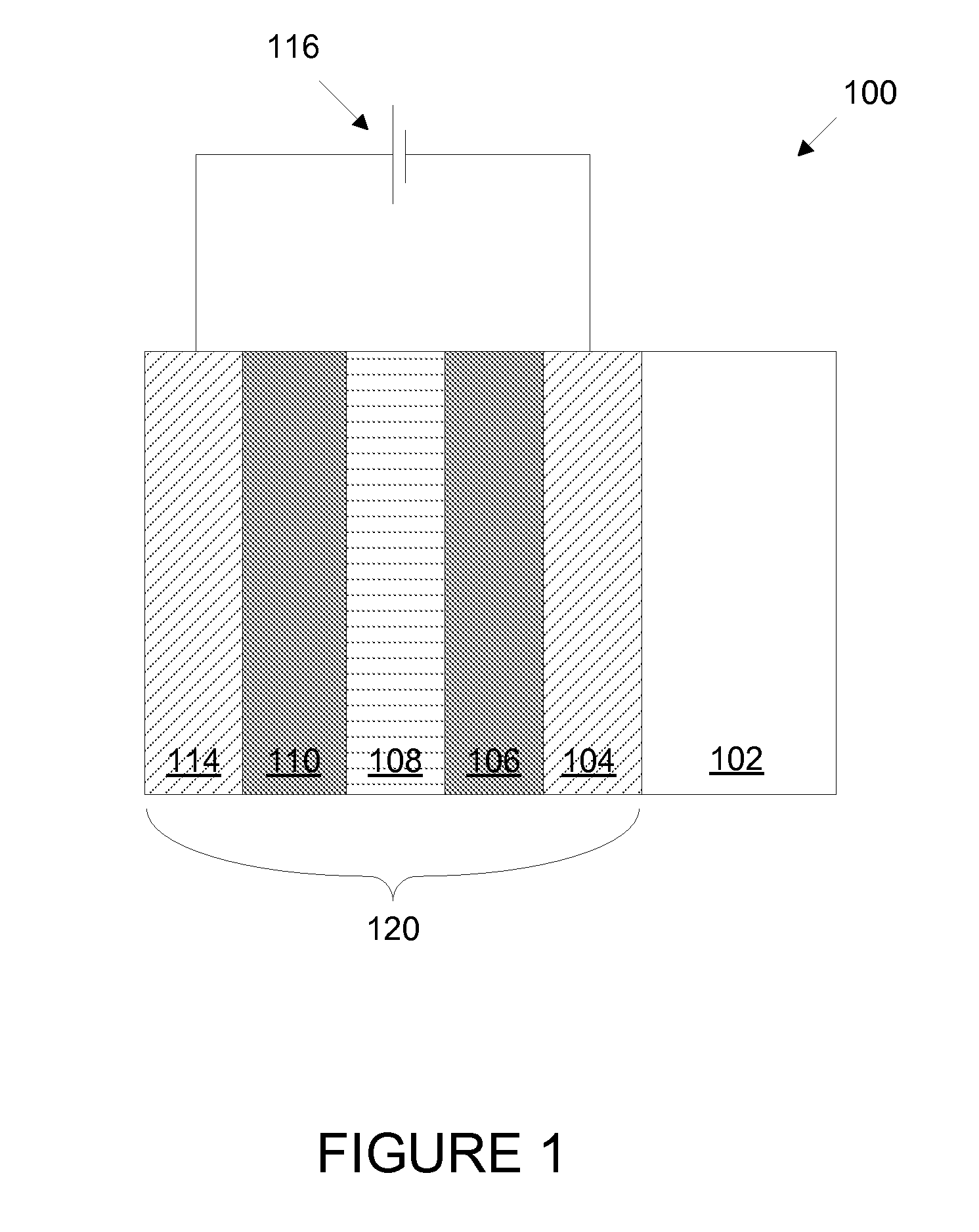

Device for reducing contact resistance of a metal

ActiveUS8736056B2Semiconductor/solid-state device detailsSolid-state devicesChemical vapor depositionAtomic layer deposition

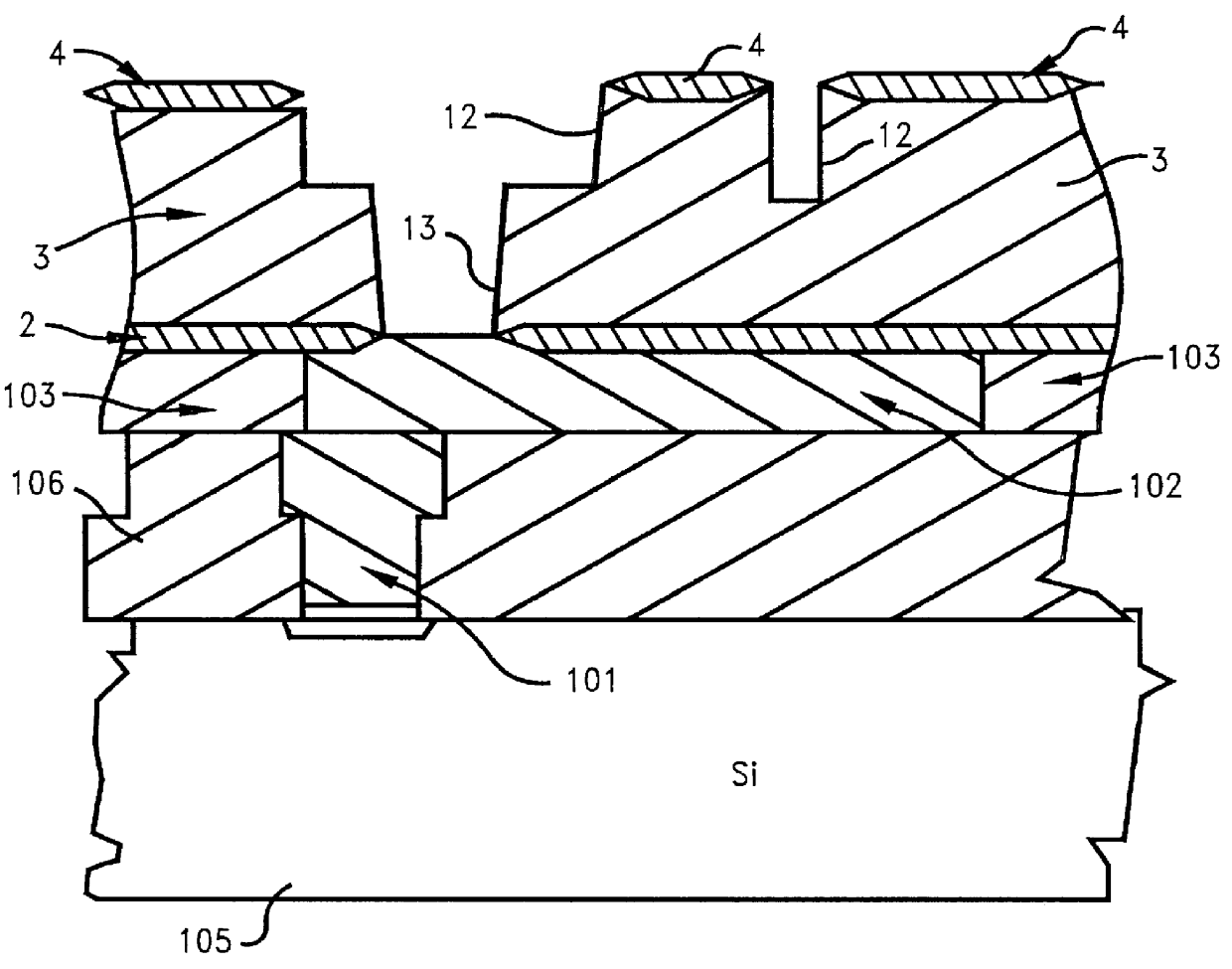

A structure for an integrated circuit with reduced contact resistance is disclosed. The structure includes a substrate, a cap layer deposited on the substrate, a dielectric layer deposited on the cap layer, and a trench embedded in the dielectric layer. The trench includes an atomic layer deposition (ALD) TaN or a chemical vapor deposition (CVD) TaN deposited on a side wall of the trench, a physical vapor deposition (PVD) Ta or a combination of the PVD Ta and a PVD TaN deposited on the ALD TaN or CVD TaN, and a Cu deposited on the PVD Ta or the combination of the PVD Ta and the PVD TaN deposited on the ALD TaN or the CVD TaN. The structure further includes a via integrated into the trench at bottom of the filled trench.

Owner:TAIWAN SEMICON MFG CO LTD

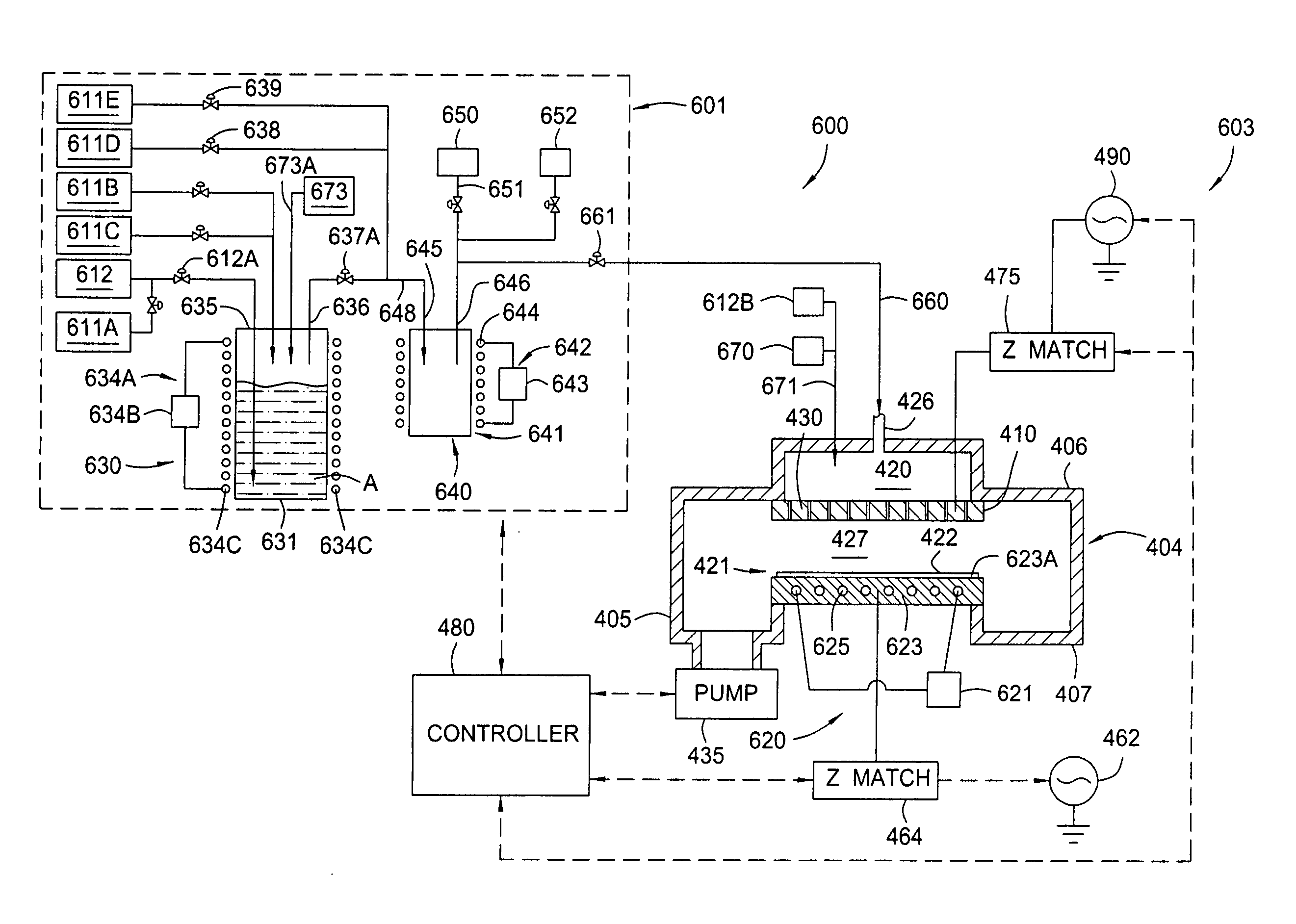

Ruthenium containing layer deposition method

ActiveUS20060165892A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingTemperature controlSource material

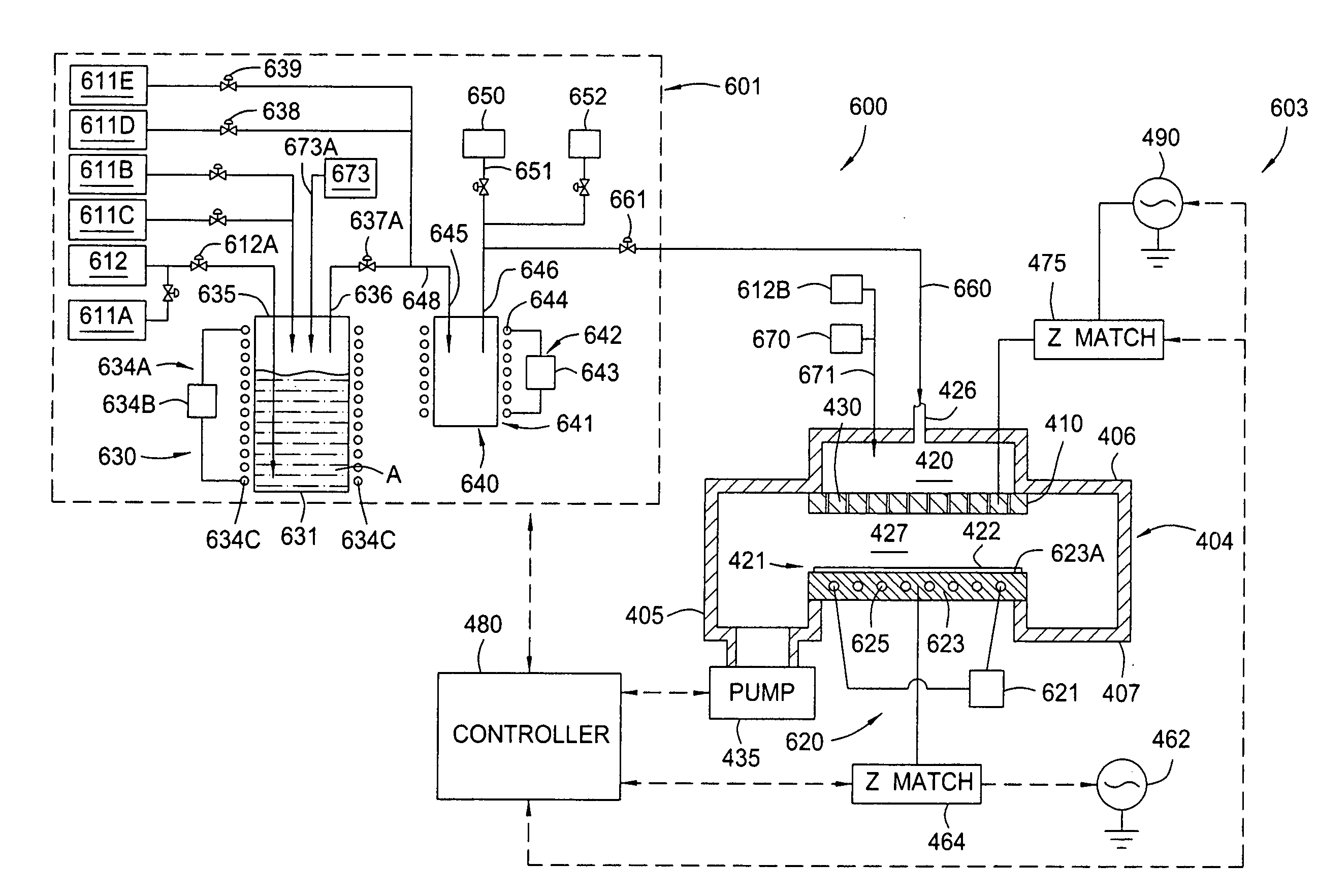

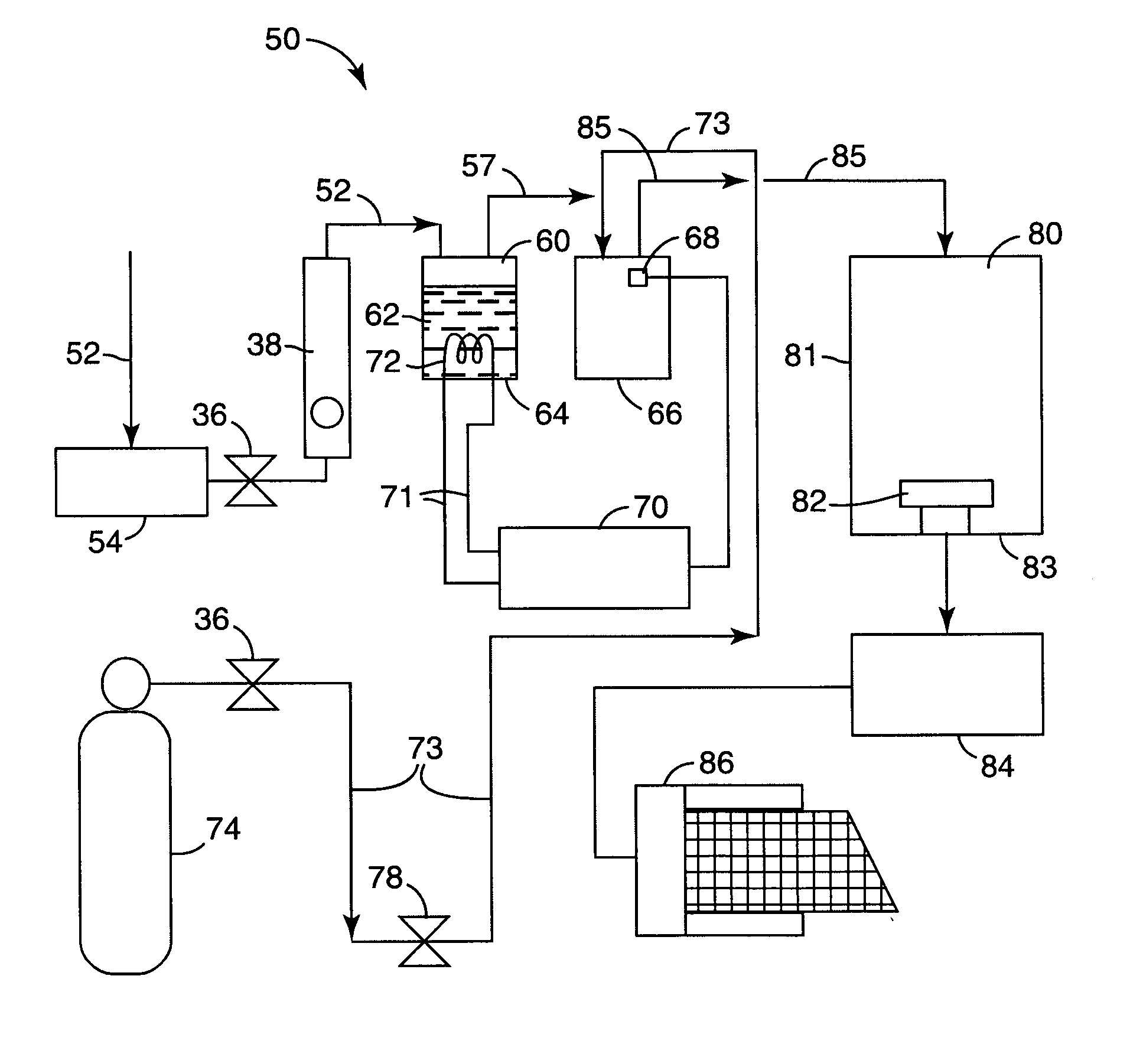

An exemplary apparatus and method of forming a ruthenium tetroxide containing gas to form a ruthenium containing layer on a surface of a substrate is described herein. The method and apparatus described herein may be especially useful for fabricating electronic devices that are formed on a surface of the substrate or wafer. Generally, the method includes exposing a surface of a substrate to a ruthenium tetroxide vapor to form a catalytic layer on the surface of a substrate and then filling the device structures by an electroless, electroplating, physical vapor deposition (PVD), chemical vapor deposition (CVD), plasma enhanced CVD (PECVD), atomic layer deposition (ALD) or plasma enhanced ALD (PE-ALD) processes. In one embodiment, the ruthenium containing layer is formed on a surface of a substrate by creating ruthenium tetroxide in an external vessel and then delivering the generated ruthenium tetroxide gas to a surface of a temperature controlled substrate positioned in a processing chamber. In one embodiment, a ruthenium tetroxide containing solvent formation process is used to form ruthenium tetroxide using a ruthenium tetroxide containing source material. In one embodiment, of a ruthenium containing layer is formed on a surface of a substrate, using the ruthenium tetroxide containing solvent. In another embodiment, the solvent is separated from the ruthenium tetroxide containing solvent mixture and the remaining ruthenium tetroxide is used to form a ruthenium containing layer on the surface of a substrate.

Owner:APPLIED MATERIALS INC

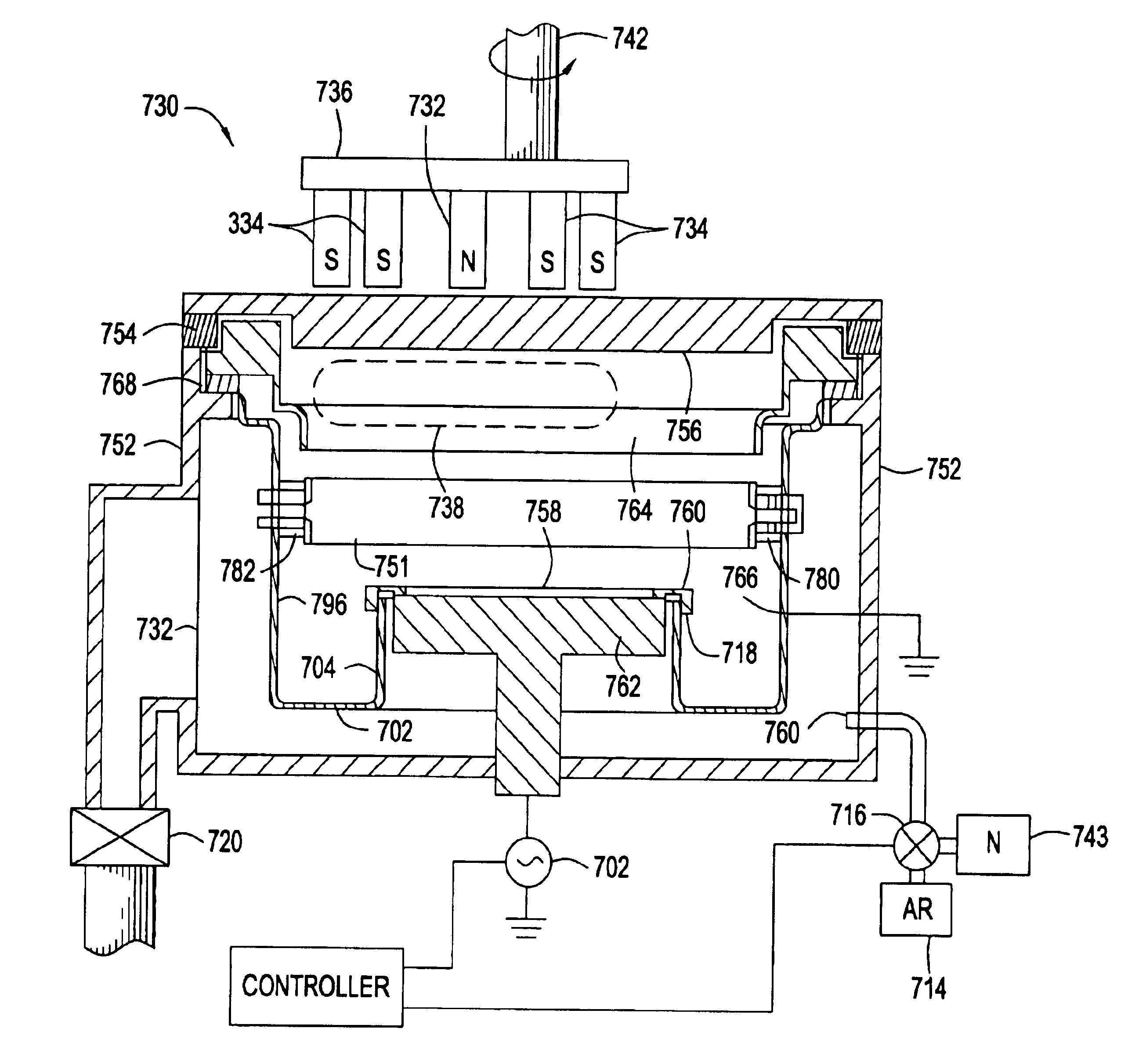

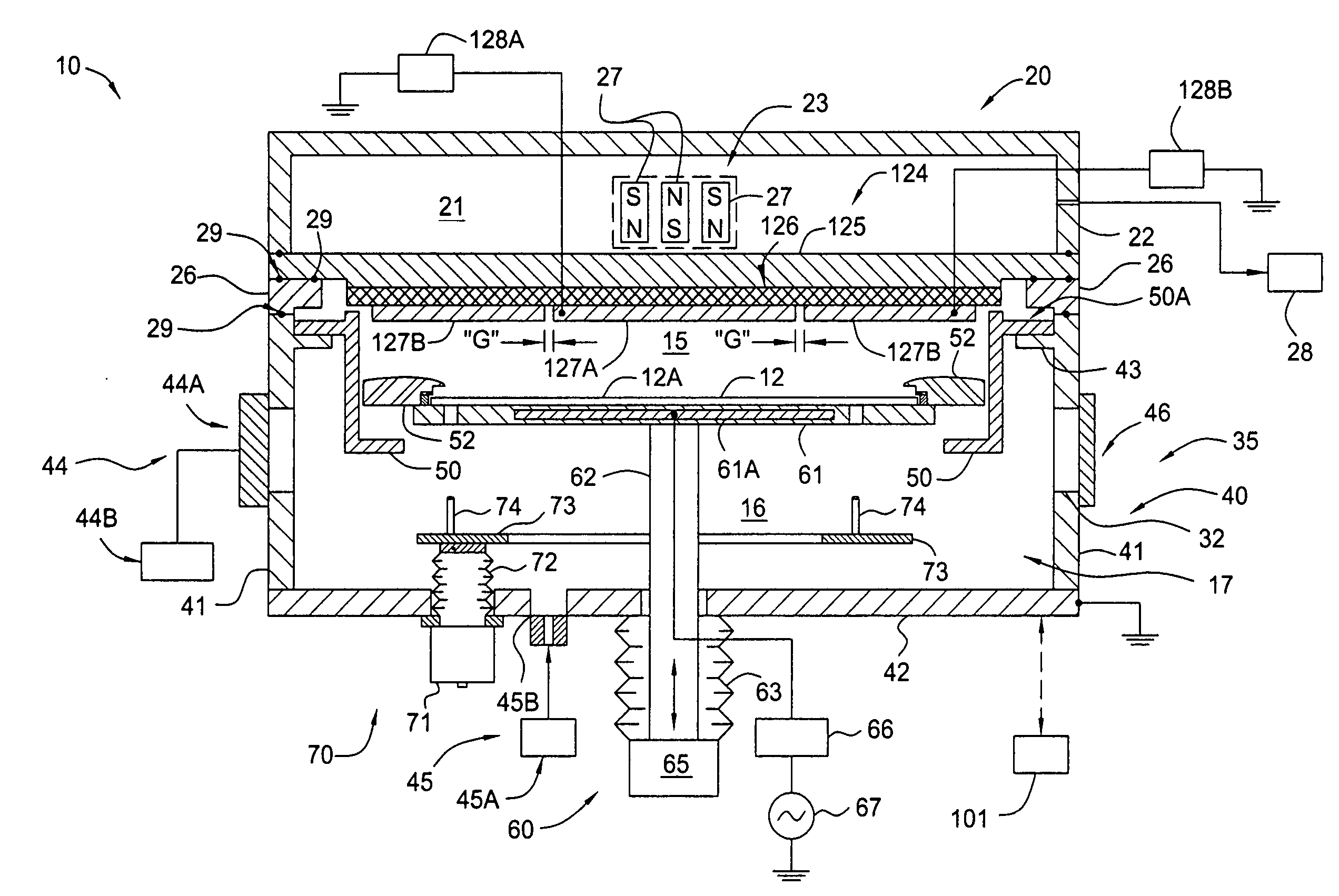

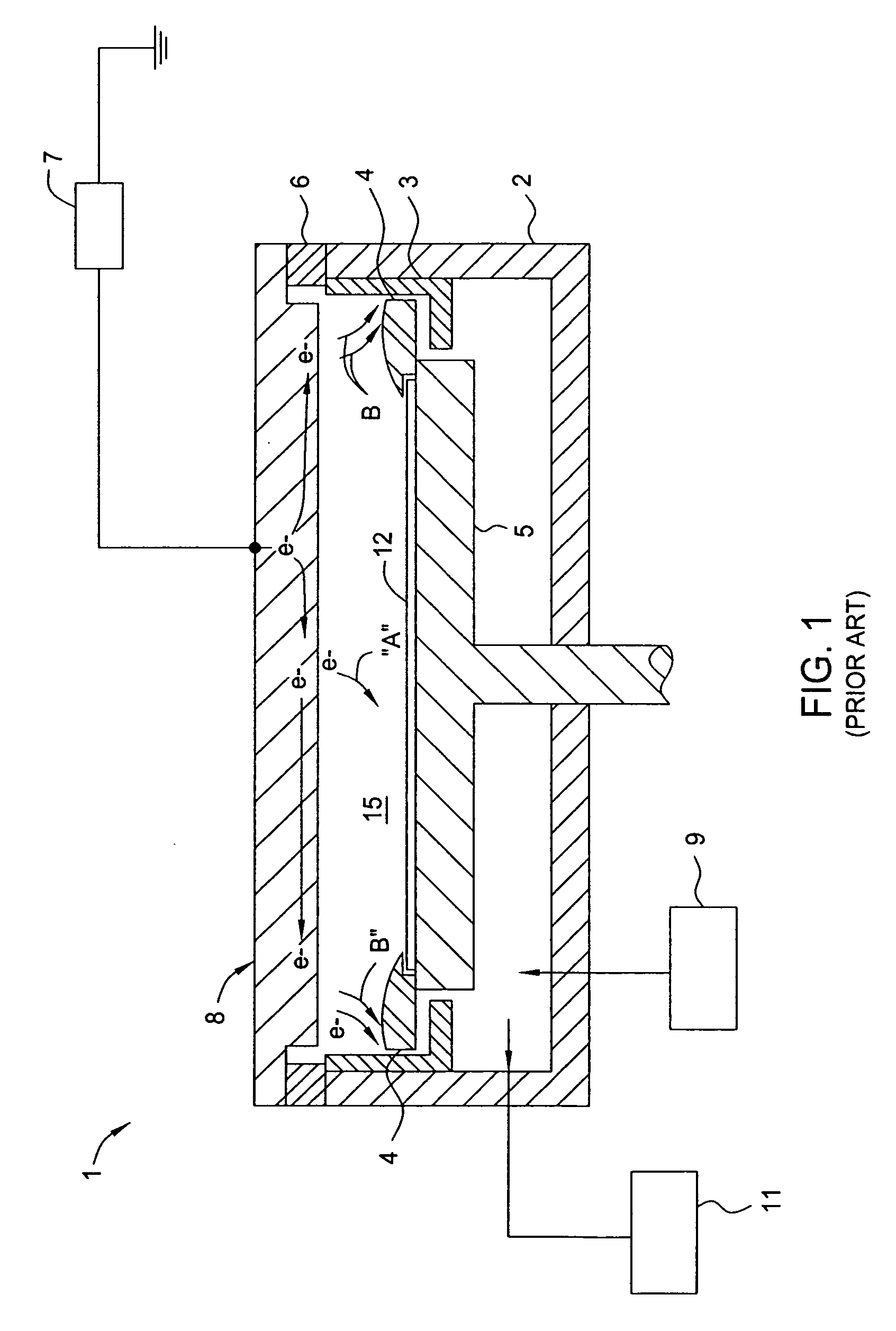

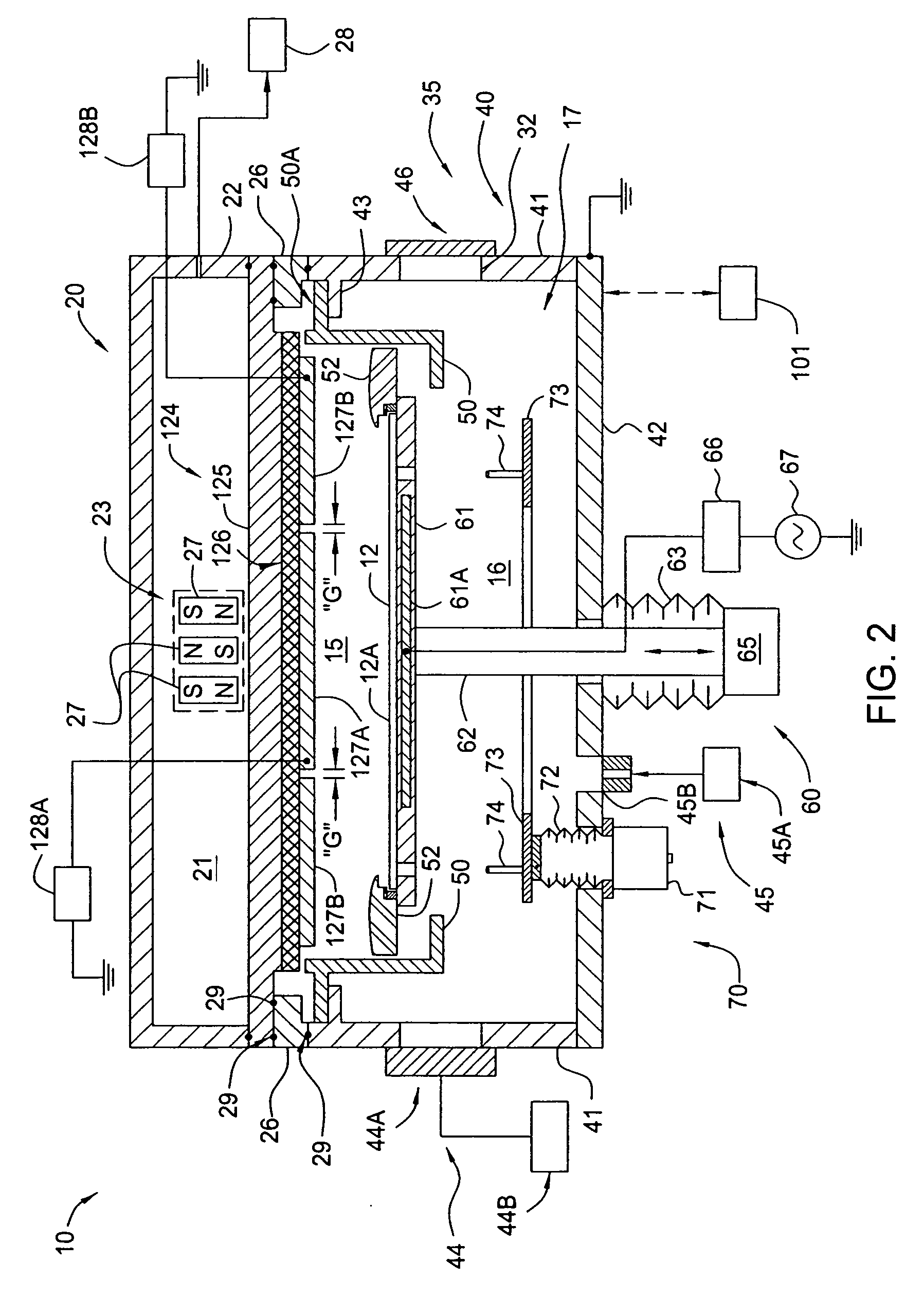

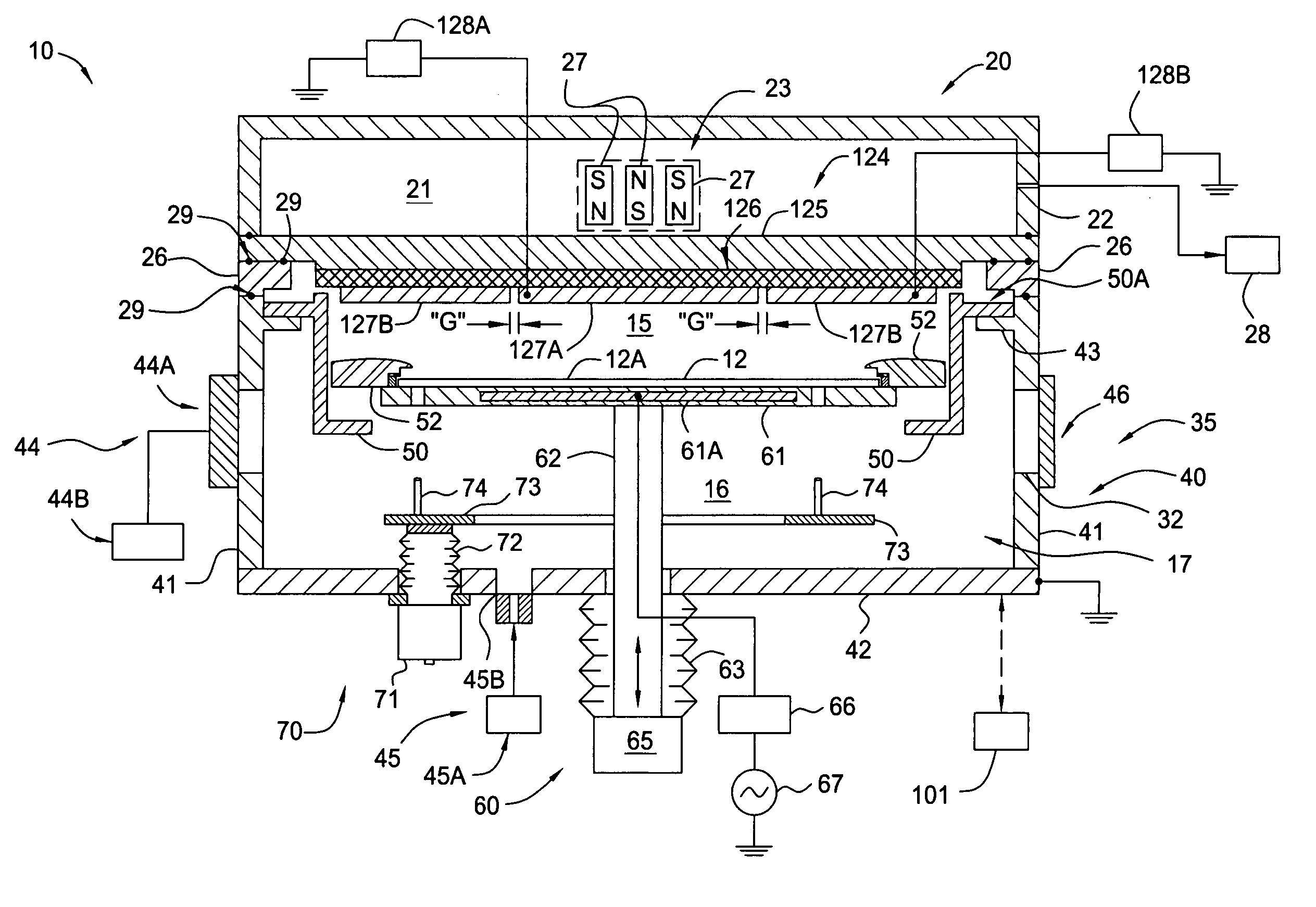

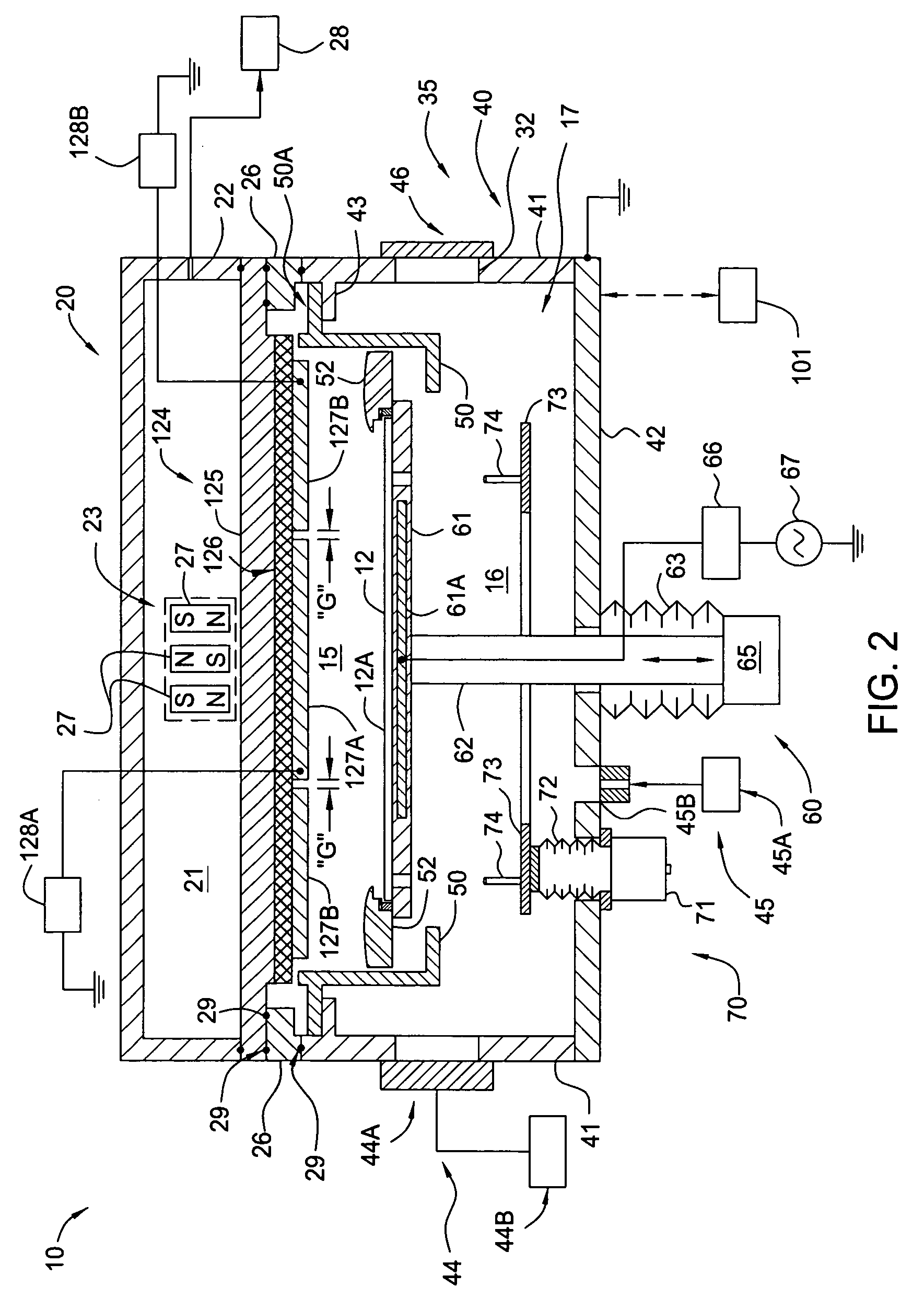

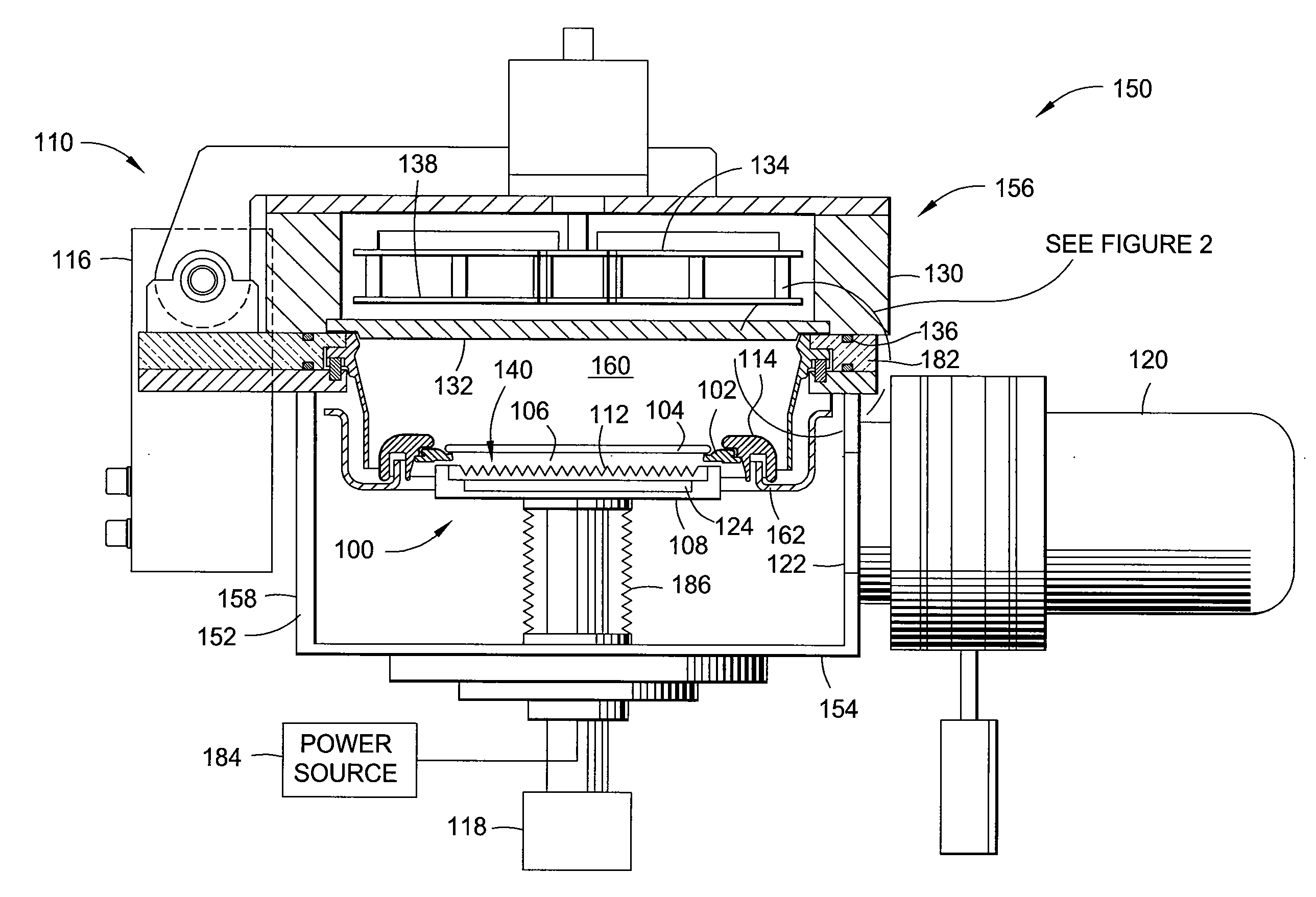

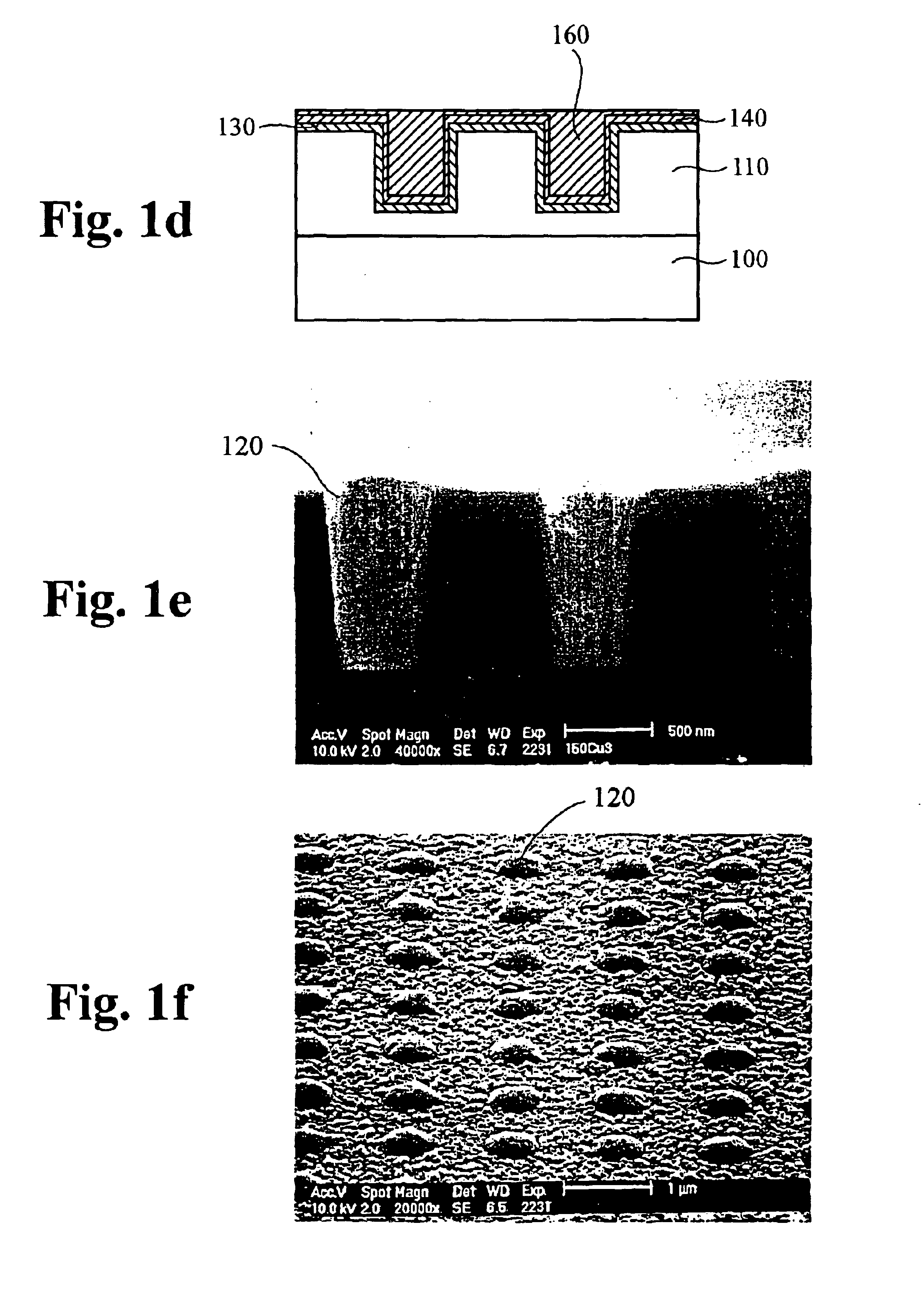

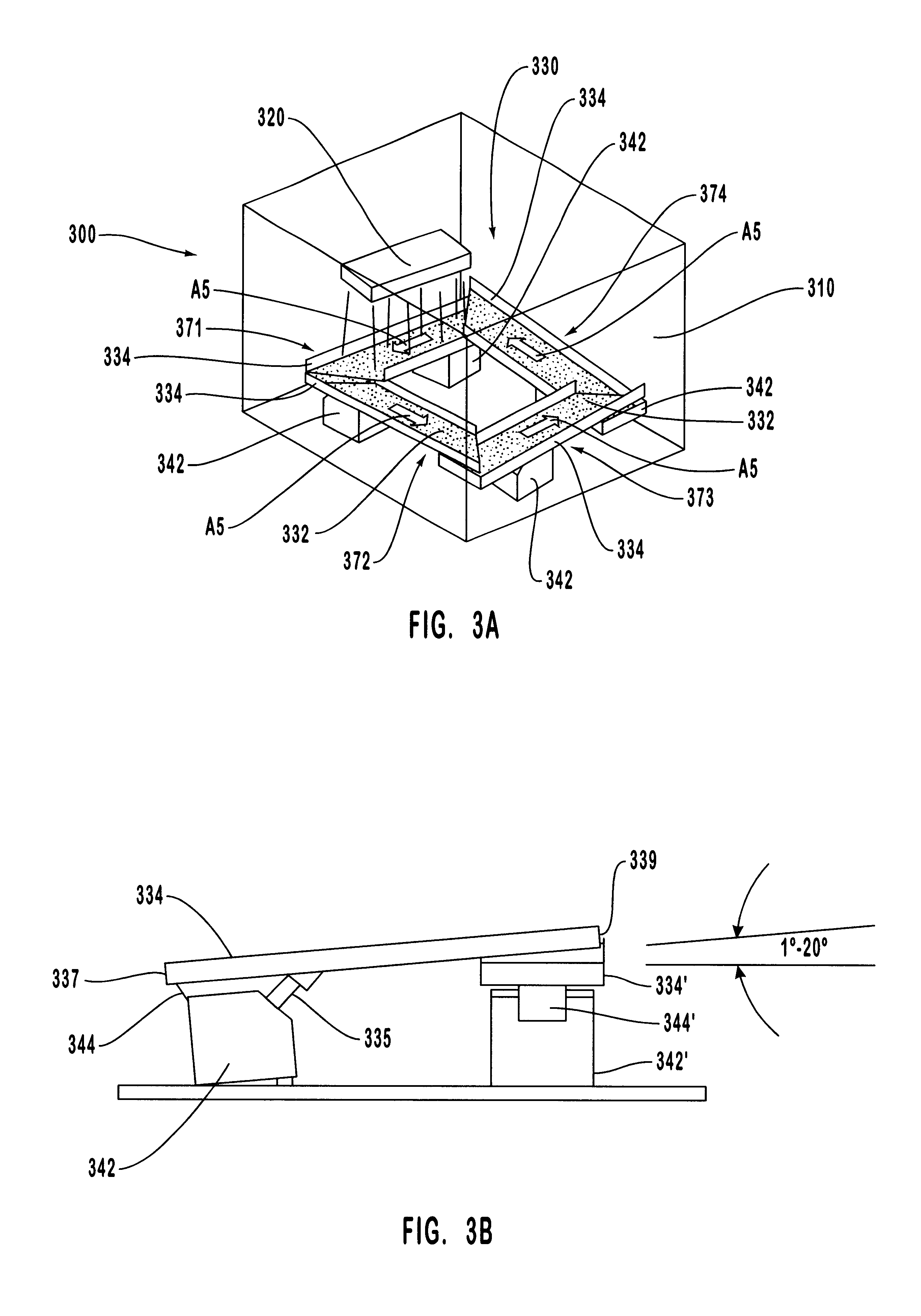

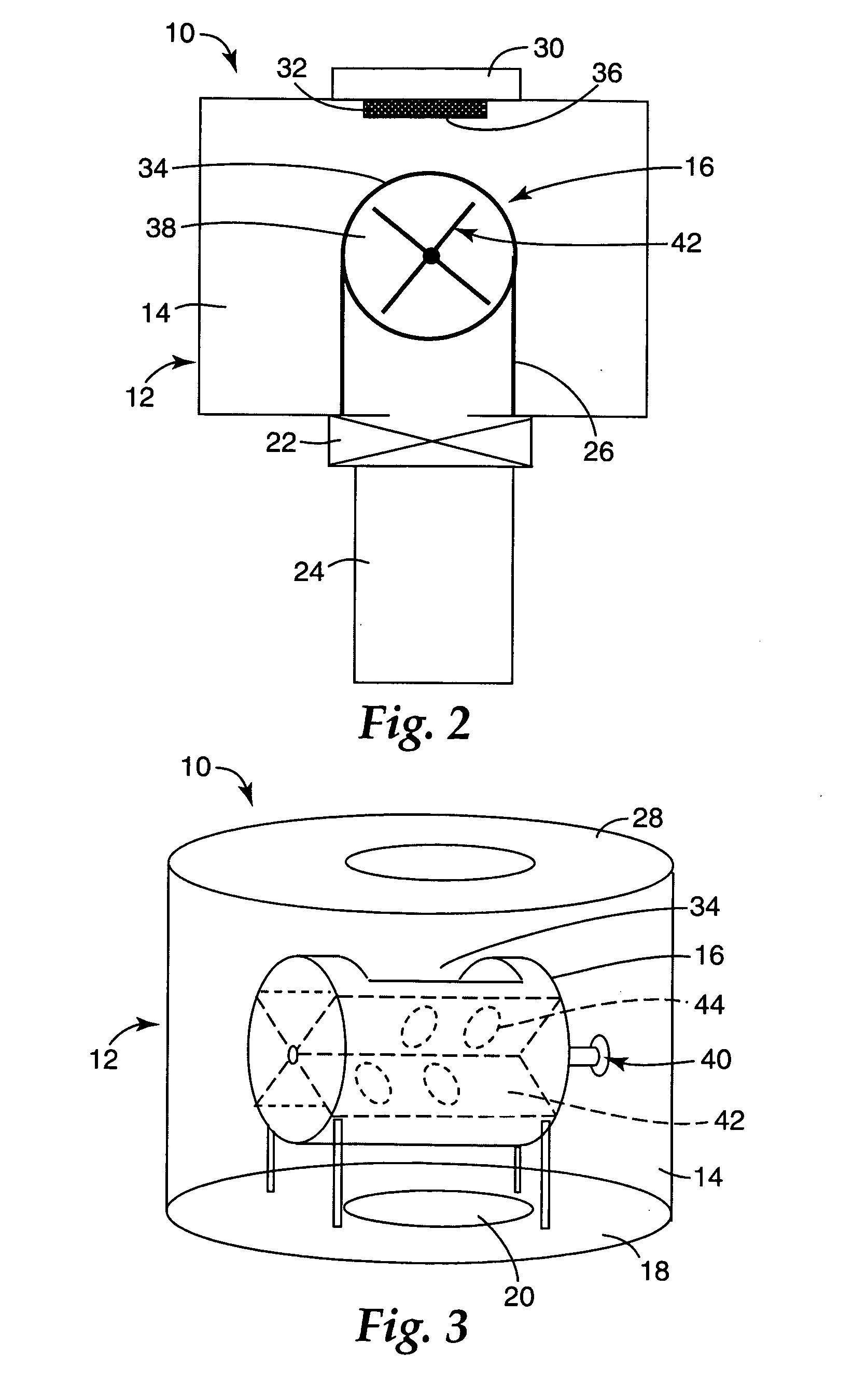

Method of processing a substrate using a large-area magnetron sputtering chamber with individually controlled sputtering zones

InactiveUS20070056843A1Vacuum evaporation coatingSputtering coatingCapacitanceElectrical resistance and conductance

The present invention generally provides a method for processing a surface of a substrate in a physical vapor deposition (PVD) chamber that has a sputtering target that has separately biasable sections, regions or zones to improve the deposition uniformity. In general, aspects of the present invention can be used for flat panel display processing, semiconductor processing, solar cell processing, or any other substrate processing. In one aspect, each of the target sections of the multizone target assembly are biased at a different cathodic biases by use of one or more DC or RF power sources. In one aspect, each of the target sections of the multizone target assembly are biased at a different cathodic biases by use of one power source and one or more resistive, capacitive and / or inductive elements. In one aspect, the processing chamber contains a multizone target assembly that has one or more ports that are adapted deliver a processing gas to the processing region of the PVD chamber. In one aspect, the processing chamber contains a multizone target assembly that has one or more magnetron assemblies positioned adjacent to one or more of the target sections.

Owner:APPLIED MATERIALS INC

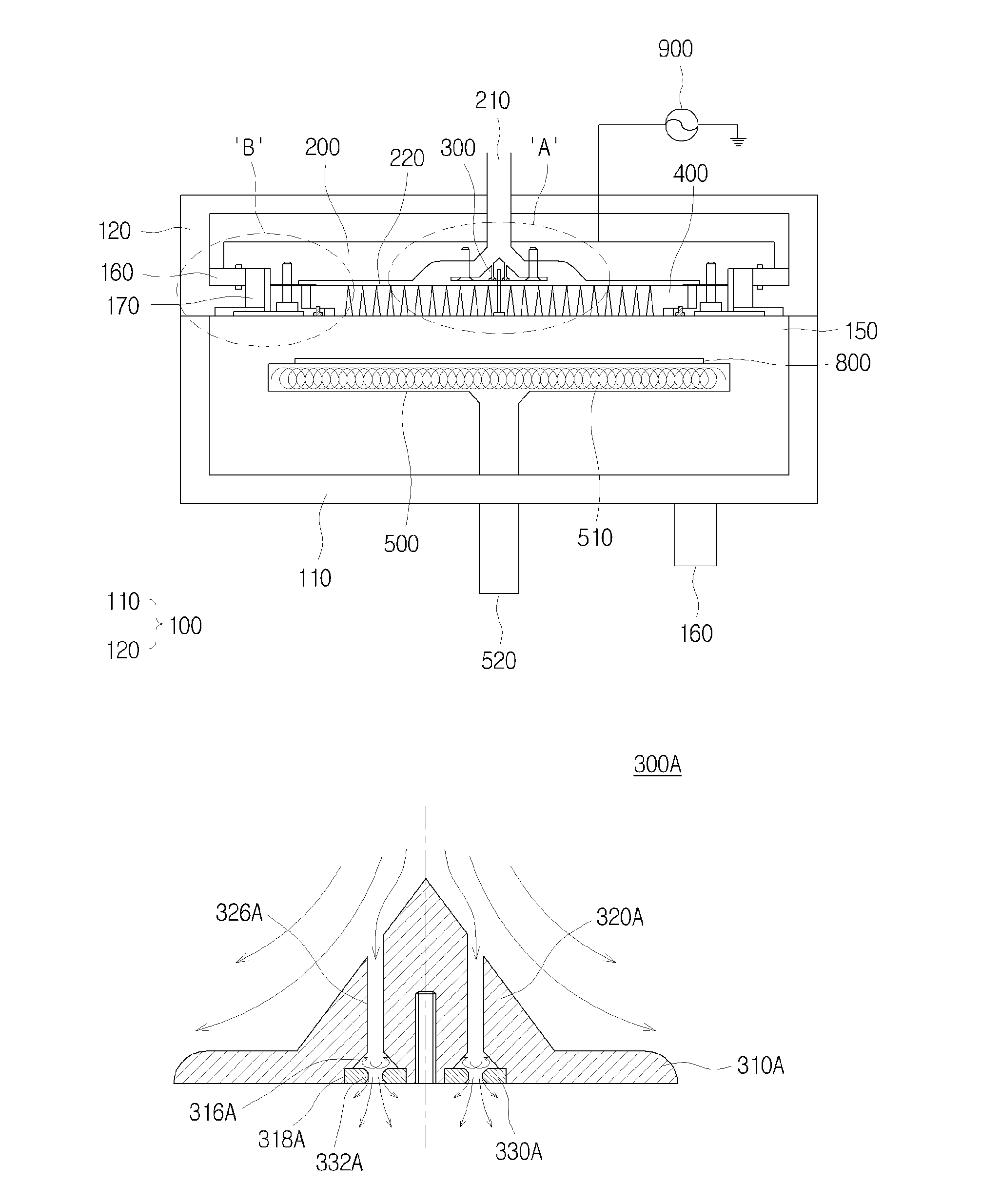

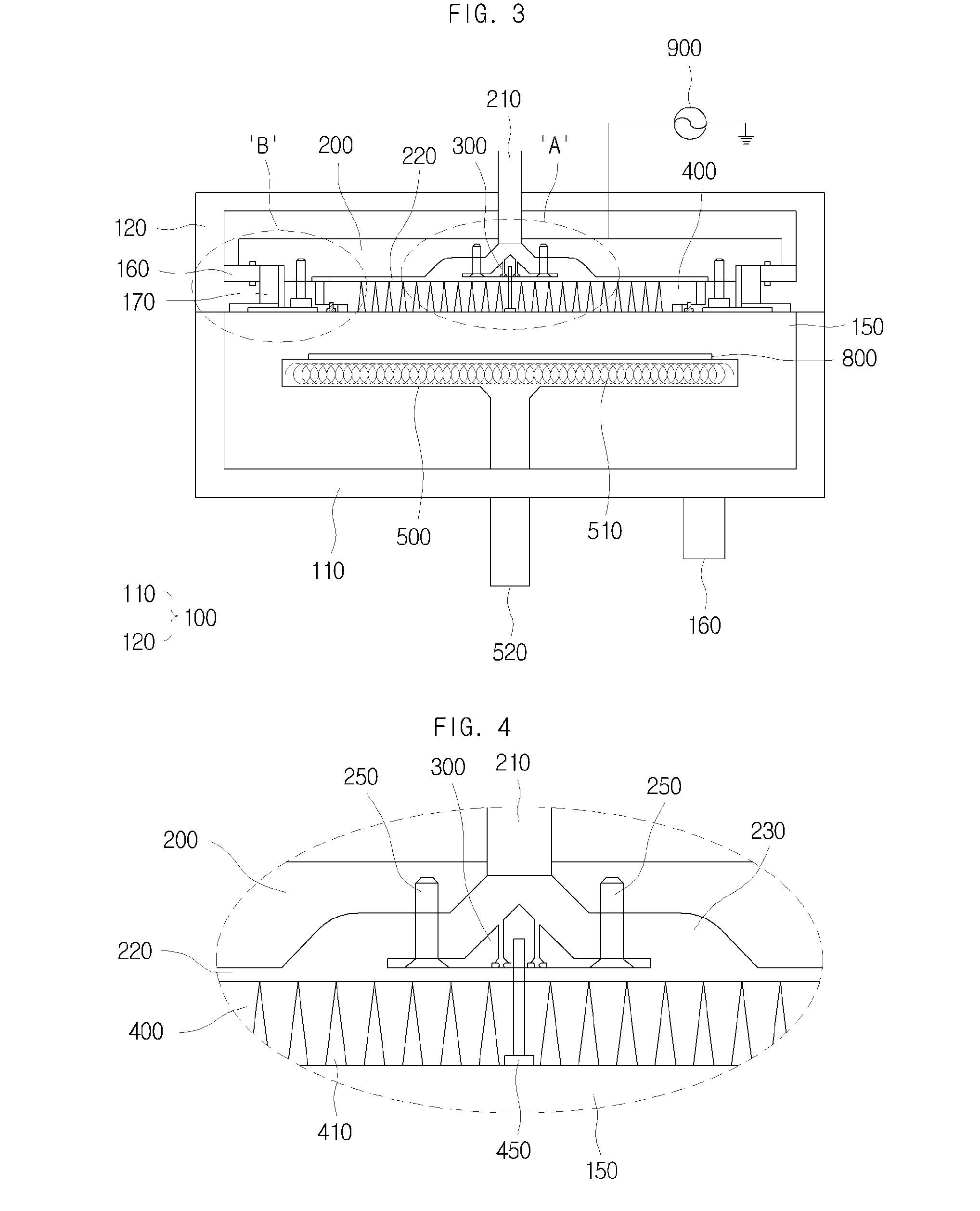

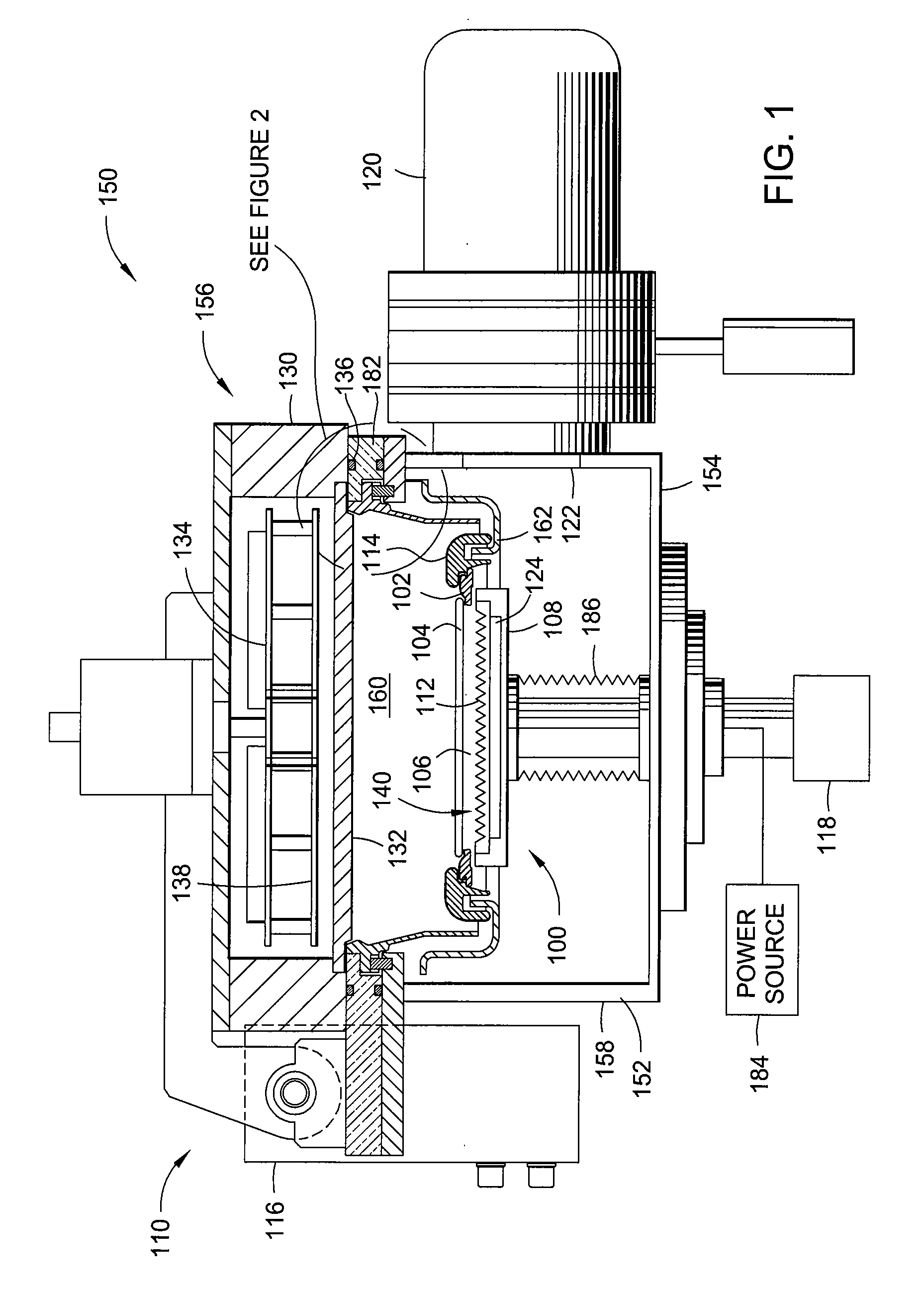

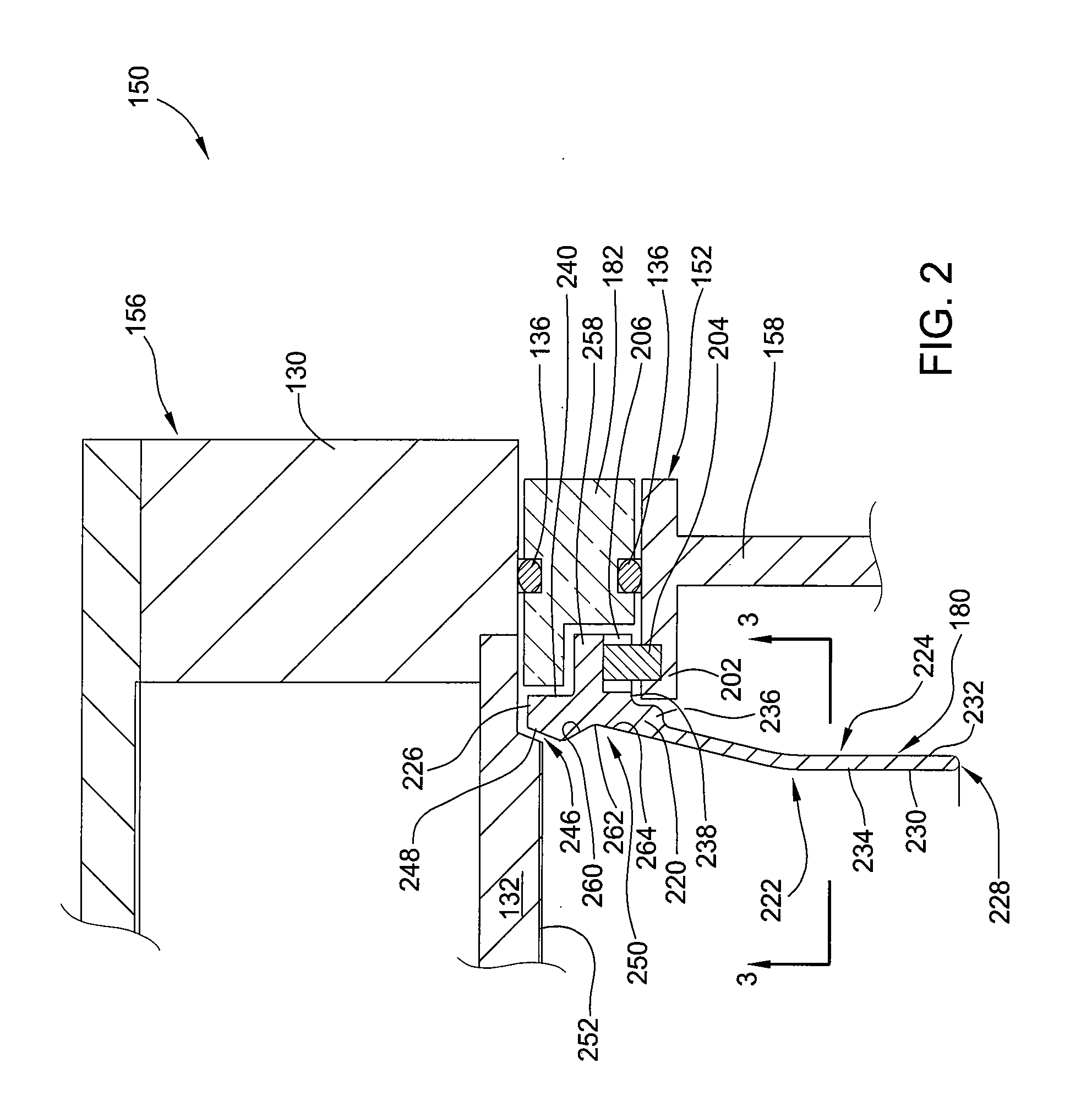

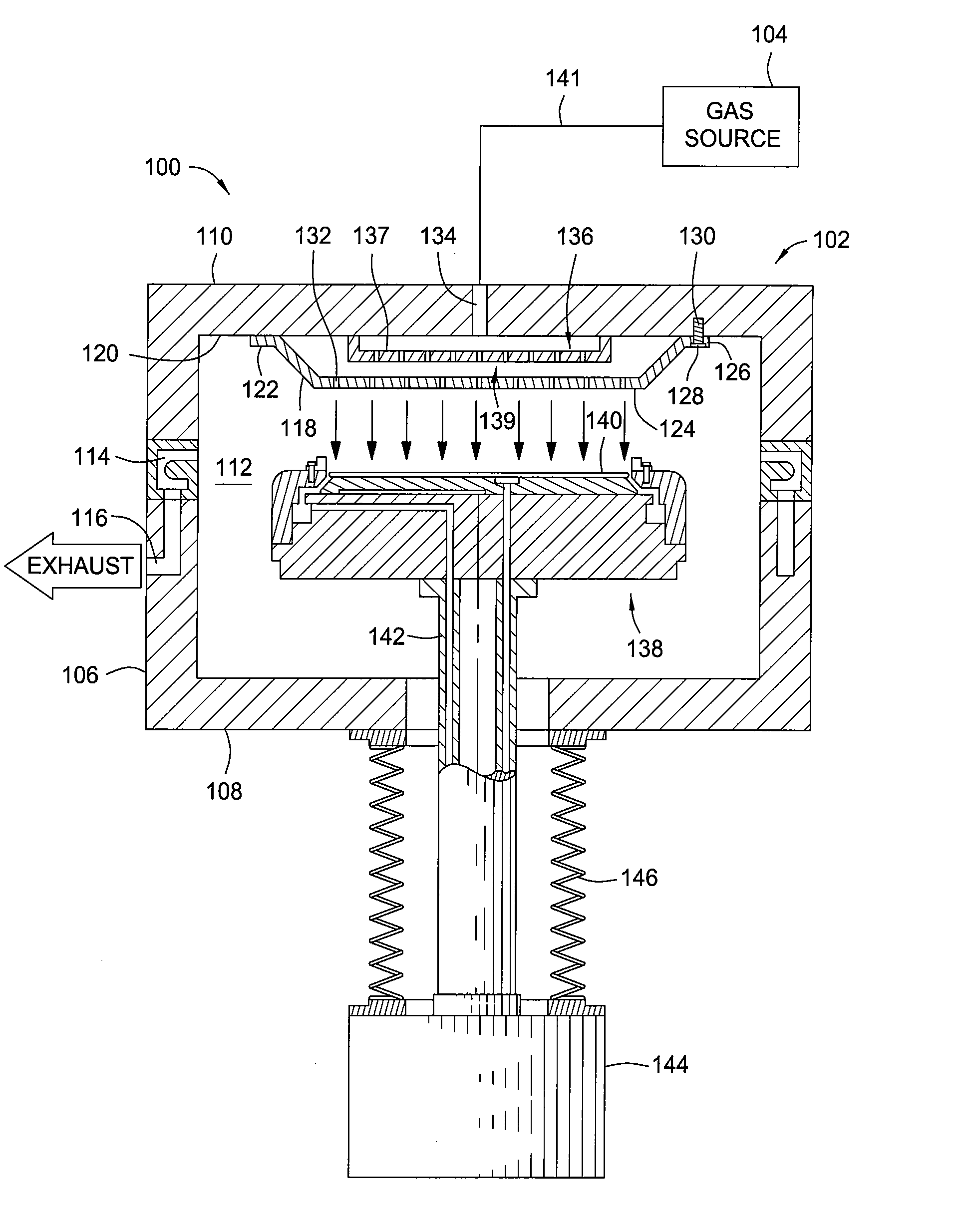

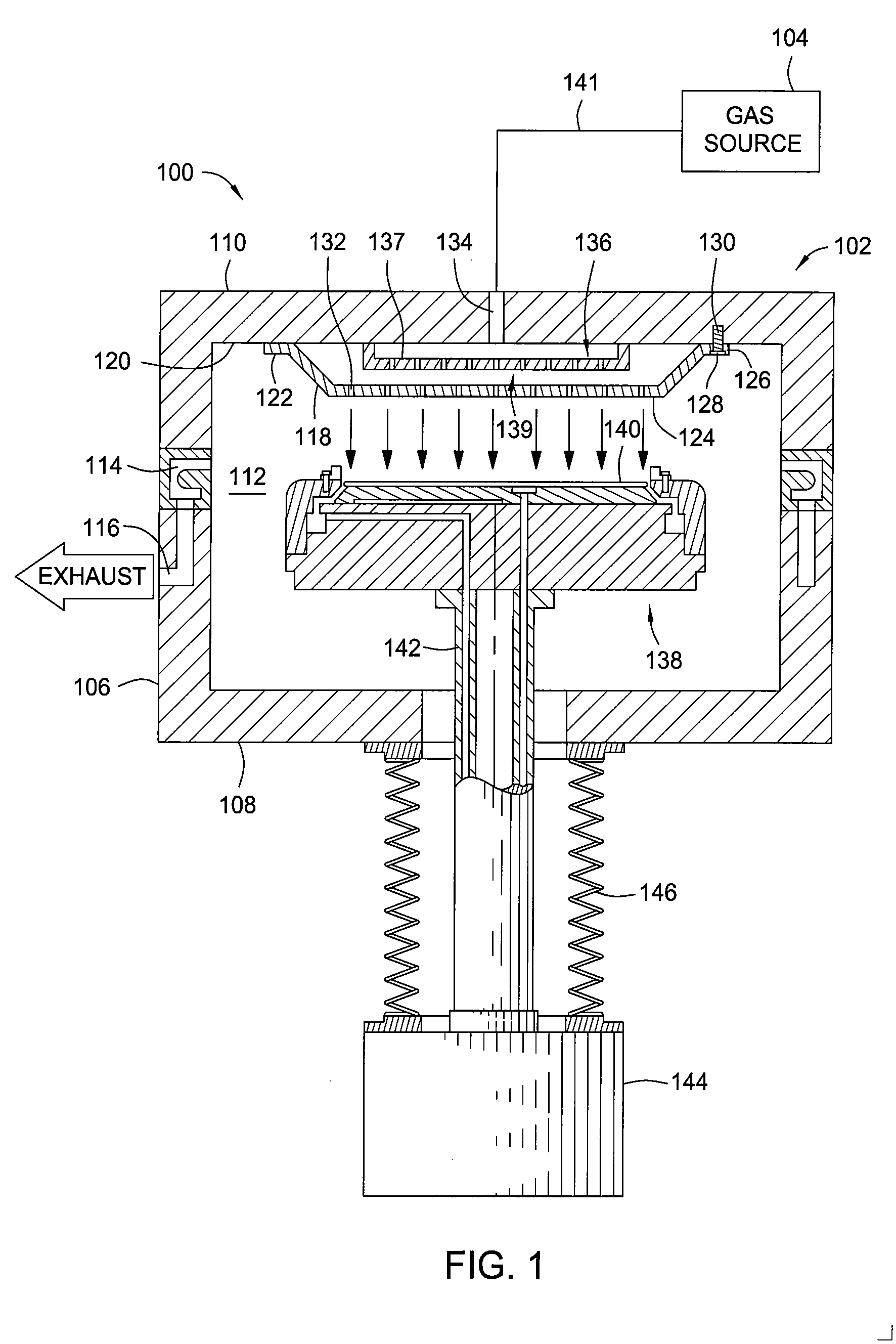

Large-area magnetron sputtering chamber with individually controlled sputtering zones

The present invention generally provides an apparatus for processing a surface of a substrate in a physical vapor deposition (PVD) chamber that has a sputtering target that has separately biasable sections, regions or zones to improve the deposition uniformity. In general, aspects of the present invention can be used for flat panel display processing, semiconductor processing, solar cell processing, or any other substrate processing. In one aspect, each of the target sections of the multizone target assembly are biased at a different cathodic biases by use of one or more DC or RF power sources. In one aspect, each of the target sections of the multizone target assembly are biased at a different cathodic biases by use of one power source and one or more resistive, capacitive and / or inductive elements. In one aspect, the processing chamber contains a multizone target assembly that has one or more ports that are adapted deliver a processing gas to the processing region of the PVD chamber. In one aspect, the processing chamber contains a multizone target assembly that has one or more magnetron assemblies positioned adjacent to one or more of the target sections.

Owner:APPLIED MATERIALS INC

Method of forming a capacitor

Owner:MICRON TECH INC

Organometallic precursors for seed/barrier processes and methods thereof

InactiveUS20080194105A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingGas phaseRuthenium

Organometallic precursors and methods for deposition on a substrate in seed / barrier applications are herein disclosed. In some embodiments, the organometallic precursor is a ruthenium-containing, tantalum-containing precursor or combination thereof and may be deposited by atomic layer deposition, chemical vapor deposition and / or physical vapor deposition.

Owner:INTEL CORP

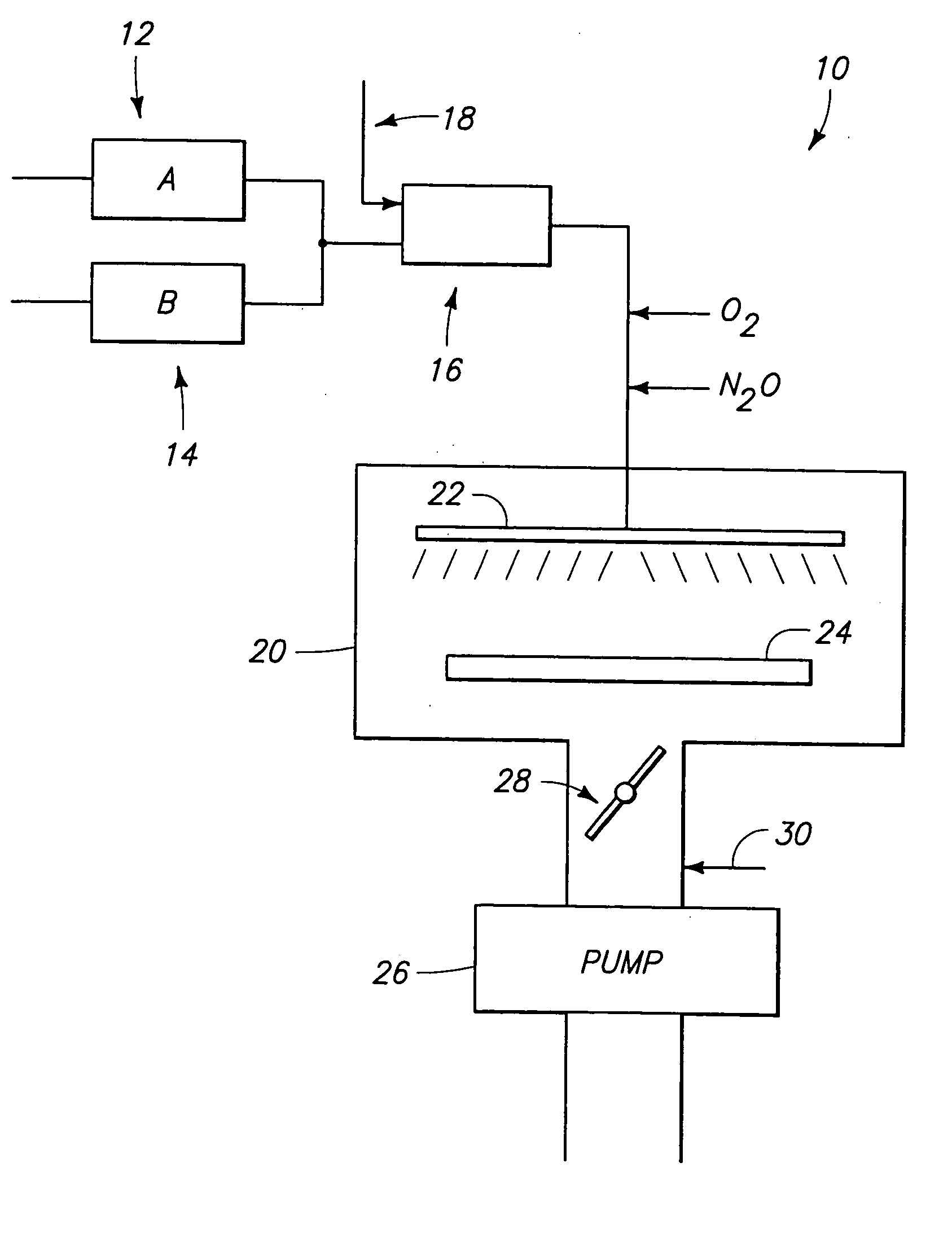

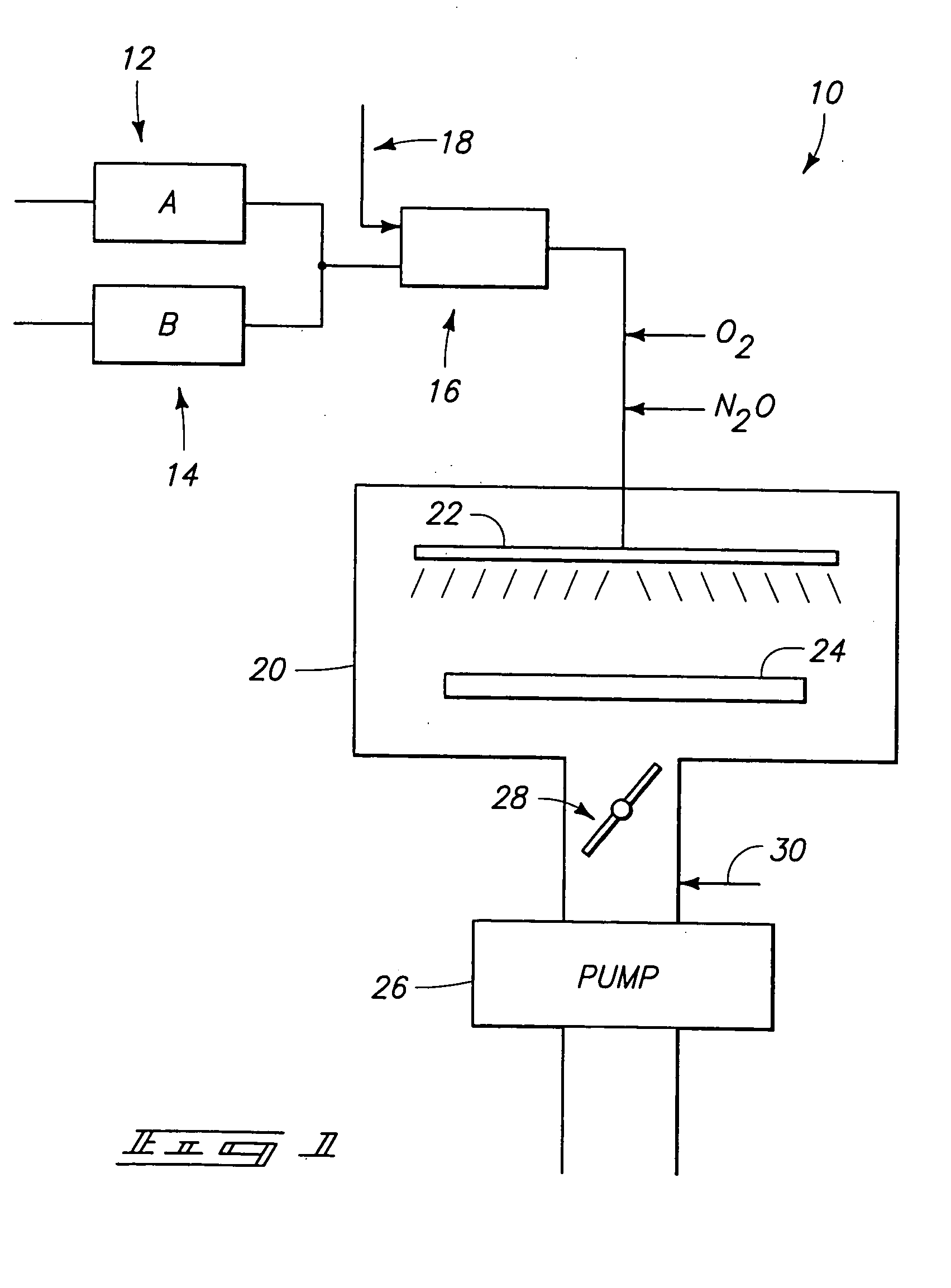

Chemical vapor deposition methods and physical vapor deposition methods

InactiveUS20050186688A1Vacuum evaporation coatingSemiconductor/solid-state device manufacturingSputteringGas phase

Owner:MICRON TECH INC

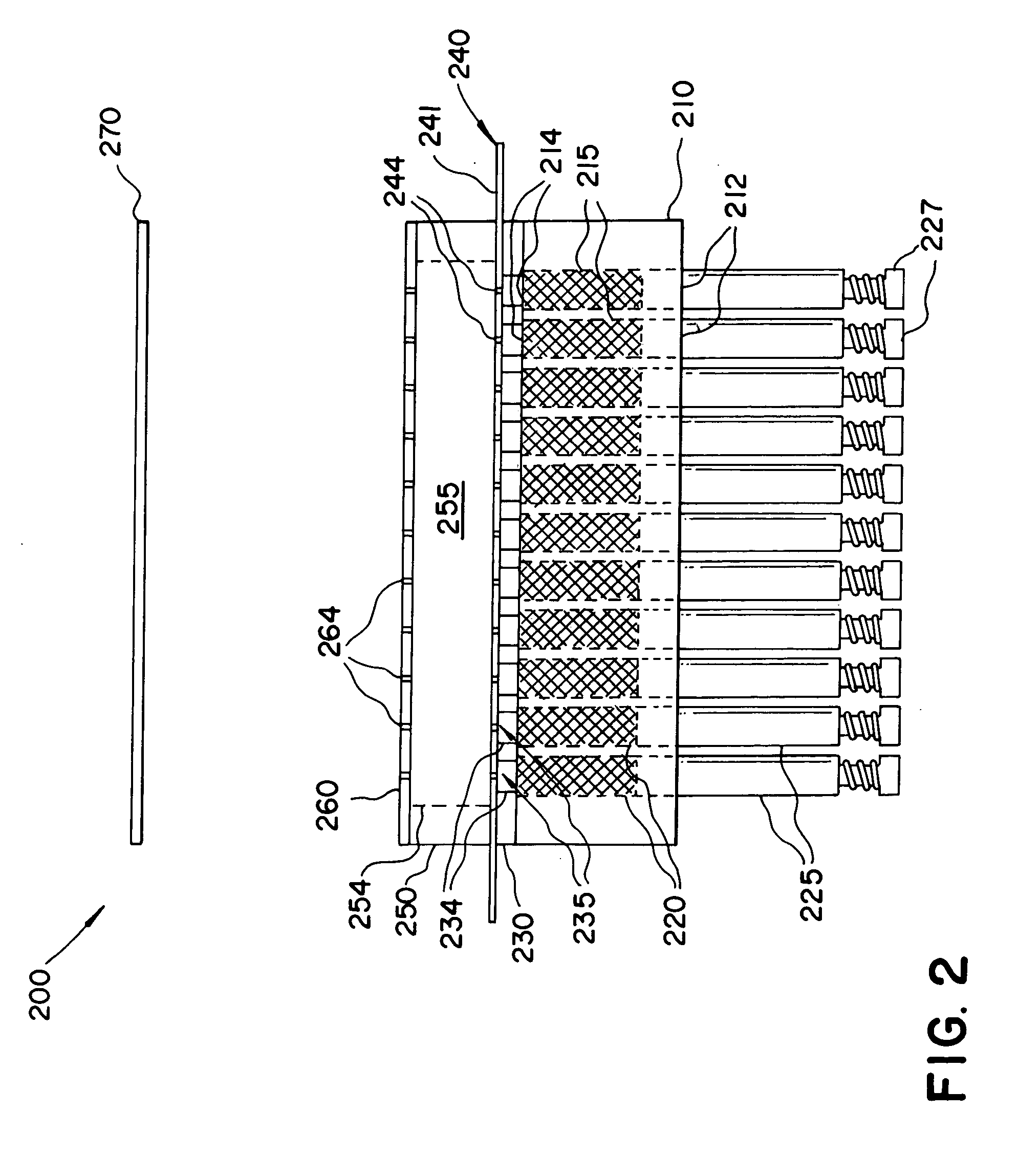

Apparatus for chemical vapor deposition

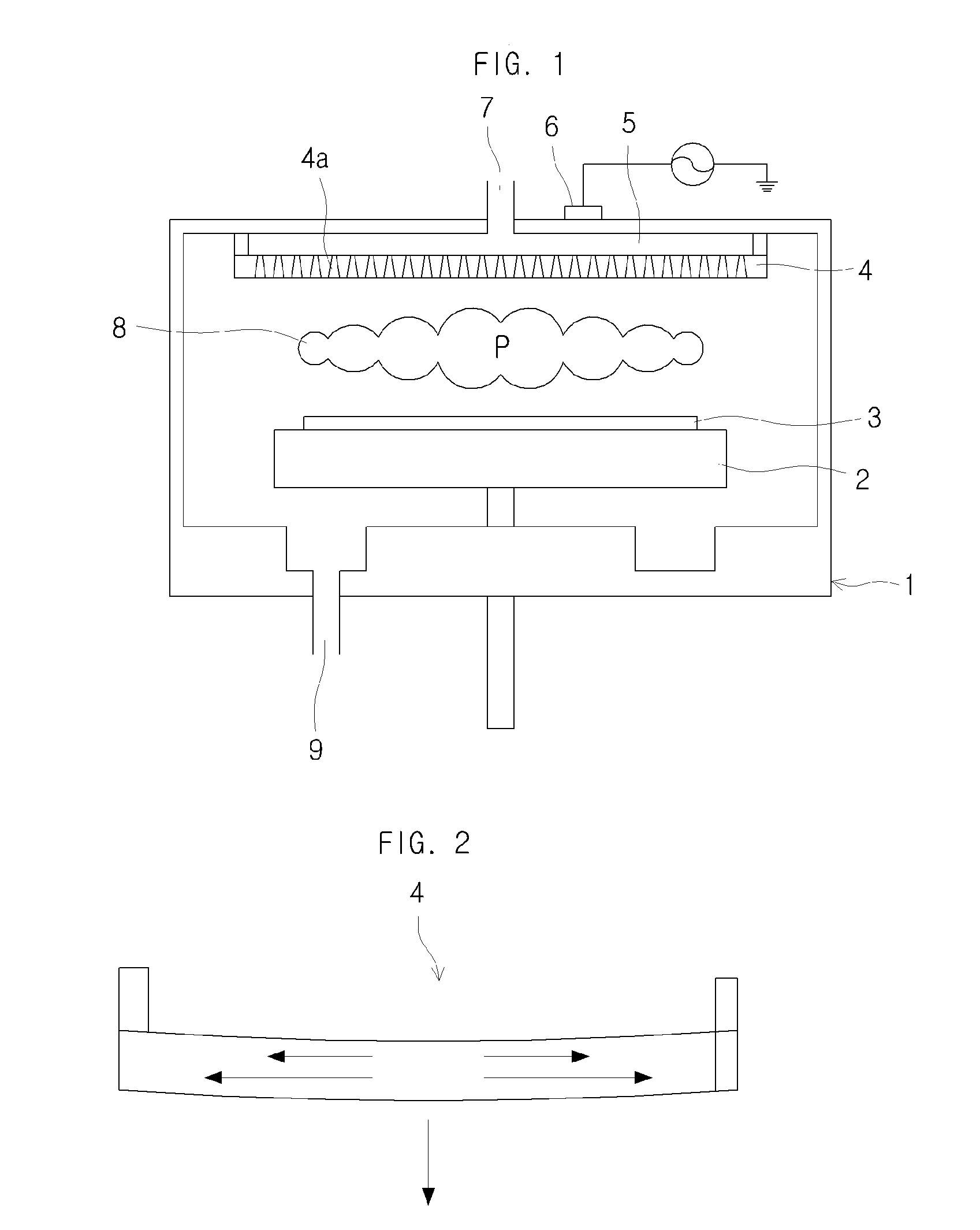

ActiveUS8980006B2Minimize thermal expansionUniform and good qualitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingSusceptorCoupling

An apparatus for chemical vapor deposition is disclosed. An aspect of the present invention provides an apparatus for chemical vapor deposition that includes: a process chamber configured to demarcate a reaction space; a back plate placed above the reaction space and having a gas inlet in a middle thereof; a gas diffusion member arranged below and separated from the gas inlet and coupled to the back plate by a first coupling member and configured to diffuse process gas supplied through the gas inlet; a shower head placed below and separated from the back plate and the gas diffusion member and having a middle part thereof coupled to the gas diffusion member by a second coupling member and having a plurality of spray holes perforated therein; and a susceptor arranged below and separated from the shower head and supporting a substrate. The gas diffusion member has a plurality of gas guiding holes that vertically penetrate the gas diffusion member such that the process gas supplied through the gas inlet is diffused toward a lower side of the gas diffusion member.

Owner:DMS CO LTD

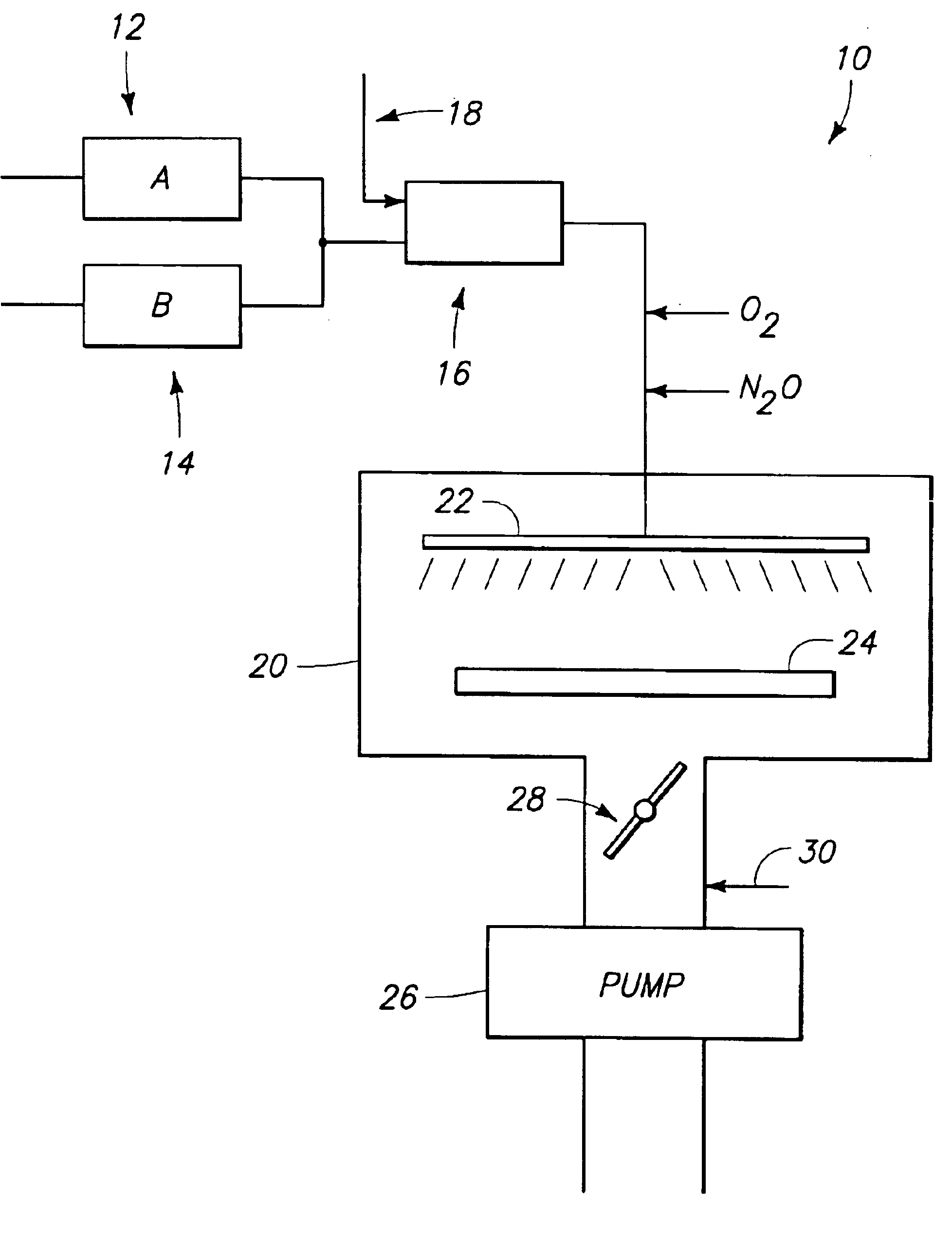

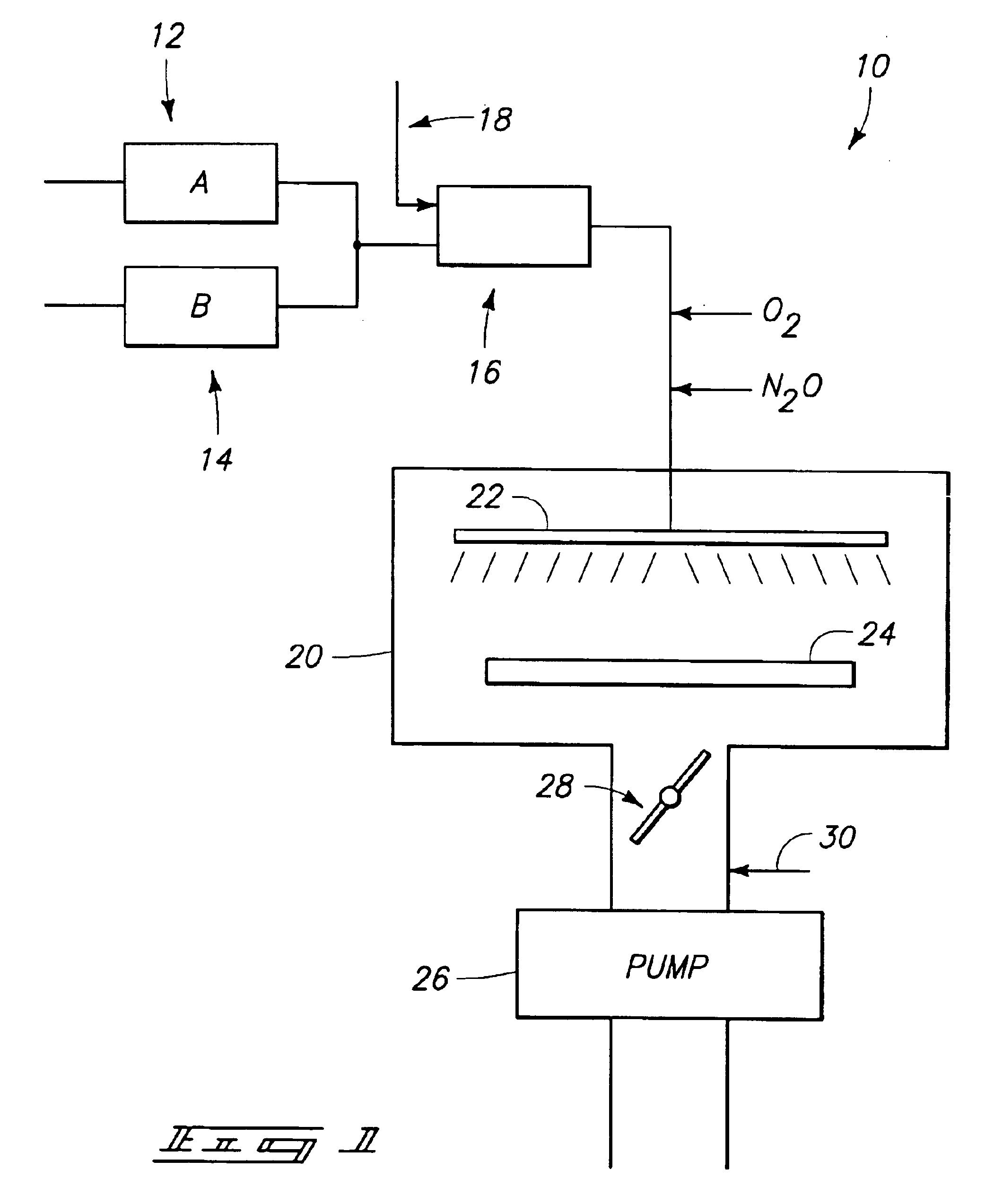

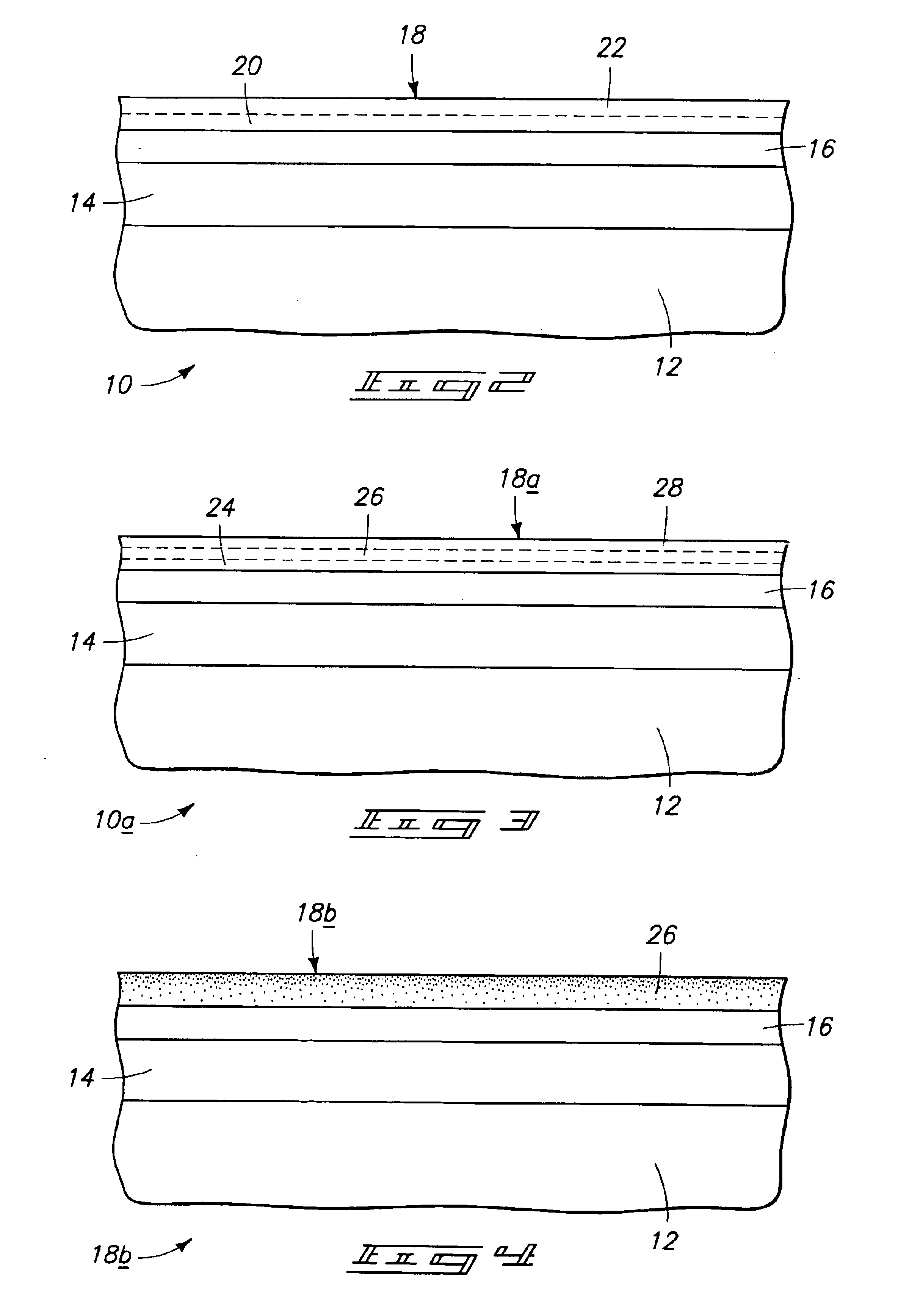

Chemical vapor deposition method for depositing a high k dielectric film

InactiveUS6884475B2FocusVacuum evaporation coatingSputtering coatingGas phaseChemical vapor deposition

The invention includes chemical vapor deposition and physical vapor deposition methods of forming high k ABO3 comprising dielectric layers on a substrate, where “A” is selected from the group consisting of Group IIA and Group IVB elements and mixtures thereof, and where “B” is selected from the group consisting of Group IVA metal elements and mixtures thereof. In one implementation, a plurality of precursors comprising A, B and O are fed to a chemical vapor deposition chamber having a substrate positioned therein under conditions effective to deposit a high k ABO3 comprising dielectric layer over the substrate. During the feeding, pressure within the chamber is varied effective to produce different concentrations of A at different elevations in the deposited layer and where higher comparative pressure produces greater concentration of B in the deposited layer. In one implementation, a subatmospheric physical vapor deposition method of forming a high k ABO3 comprising dielectric layer on a substrate includes providing a sputtering target comprising ABO3 and a substrate to be deposited upon within a physical vapor deposition chamber. A sputtering gas is fed to the chamber under conditions effective to sputter the target and deposit a high k ABO3 comprising dielectric layer over the substrate. During the feeding, pressure is varied within the chamber effective to produce different concentrations of B at different elevations in the deposited layer and where higher comparative pressure produces greater concentration of B in the deposited layer.

Owner:MICRON TECH INC

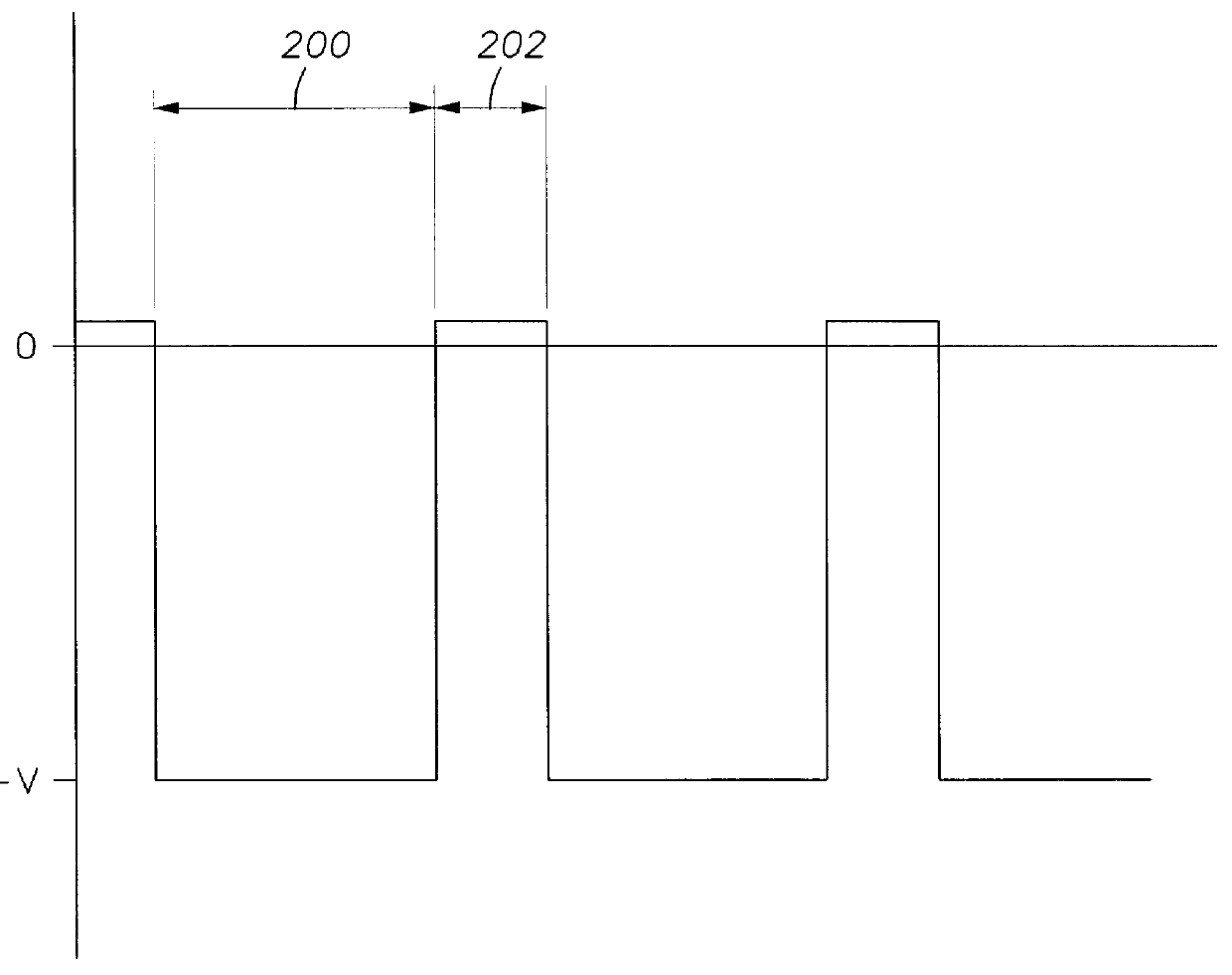

Use of pulsed-DC wafer bias for filling vias/trenches with metal in HDP physical vapor deposition

InactiveUS6051114AControl depositionPrevent openingCellsElectric discharge tubesCapacitanceIon current

The present invention provides a method and apparatus for preferential PVD conductor fill in an integrated circuit structure. The present invention utilizes a high density plasma for sputter deposition of a conductive layer on a patterned substrate, and a pulsed DC power source capacitively coupled to the substrate to generate an ion current at the surface of the substrate. The ion current prevents sticking of the deposited material to the field areas of the patterned substrate, or etches deposited material from the field areas to eliminate crowning or cusping problems associated with deposition of a conductive material in a trench, hole or via formed on the substrate.

Owner:APPLIED MATERIALS INC

Ground shield with reentrant feature

ActiveUS20070295602A1Good repeatabilityImprove uniformityCellsElectric discharge tubesEngineeringPhysical vapor deposition

The invention generally provides a ground shield for use in a physical vapor deposition (PVD) chamber. In one embodiment, a ground shield includes a generally cylindrical body comprising an outer wall, an inner upper wall, an inner lower wall having a diameter less than a diameter of the inner upper wall and a reentrant feature coupling the upper and inner lower walls. The reentrant feature advantageously prevents arching between the shield and target, which promotes greater process uniformity and repeatability along with longer chamber component service life.

Owner:APPLIED MATERIALS INC

Sub-quarter-micron copper interconnections with improved electromigration resistance and reduced defect sensitivity

InactiveUS6069068ASemiconductor/solid-state device detailsVacuum evaporation coatingGas phaseInterconnection

A method of providing sub-half-micron copper interconnections with improved electromigration and corrosion resistance. The method includes double damascene using electroplated copper, where the seed layer is deposited by chemical vapor deposition, or by physical vapor deposition in a layer less than about 800 angstroms.

Owner:GLOBALFOUNDRIES INC

Ruthenium layer deposition apparatus and method

InactiveUS20060162658A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingTemperature controlSource material

An exemplary apparatus and method of forming a ruthenium tetroxide containing gas to form a ruthenium containing layer on a surface of a substrate is described herein. The method and apparatus described herein may be especially useful for fabricating electronic devices that are formed on a surface of the substrate or wafer. Generally, the method includes exposing a surface of a substrate to a ruthenium tetroxide vapor to form a catalytic layer on the surface of a substrate and then filling the device structures by an electroless, electroplating, physical vapor deposition (PVD), chemical vapor deposition (CVD), plasma enhanced CVD (PECVD), atomic layer deposition (ALD) or plasma enhanced ALD (PE-ALD) processes. In one embodiment, the ruthenium containing layer is formed on a surface of a substrate by creating ruthenium tetroxide in an external vessel and then delivering the generated ruthenium tetroxide gas to a surface of a temperature controlled substrate positioned in a processing chamber. In one embodiment, a ruthenium tetroxide containing solvent formation process is used to form ruthenium tetroxide using a ruthenium tetroxide containing source material. In one embodiment, of a ruthenium containing layer is formed on a surface of a substrate, using the ruthenium tetroxide containing solvent. In another embodiment, the solvent is separated from the ruthenium tetroxide containing solvent mixture and the remaining ruthenium tetroxide is used to form a ruthenium containing layer on the surface of a substrate.

Owner:APPLIED MATERIALS INC

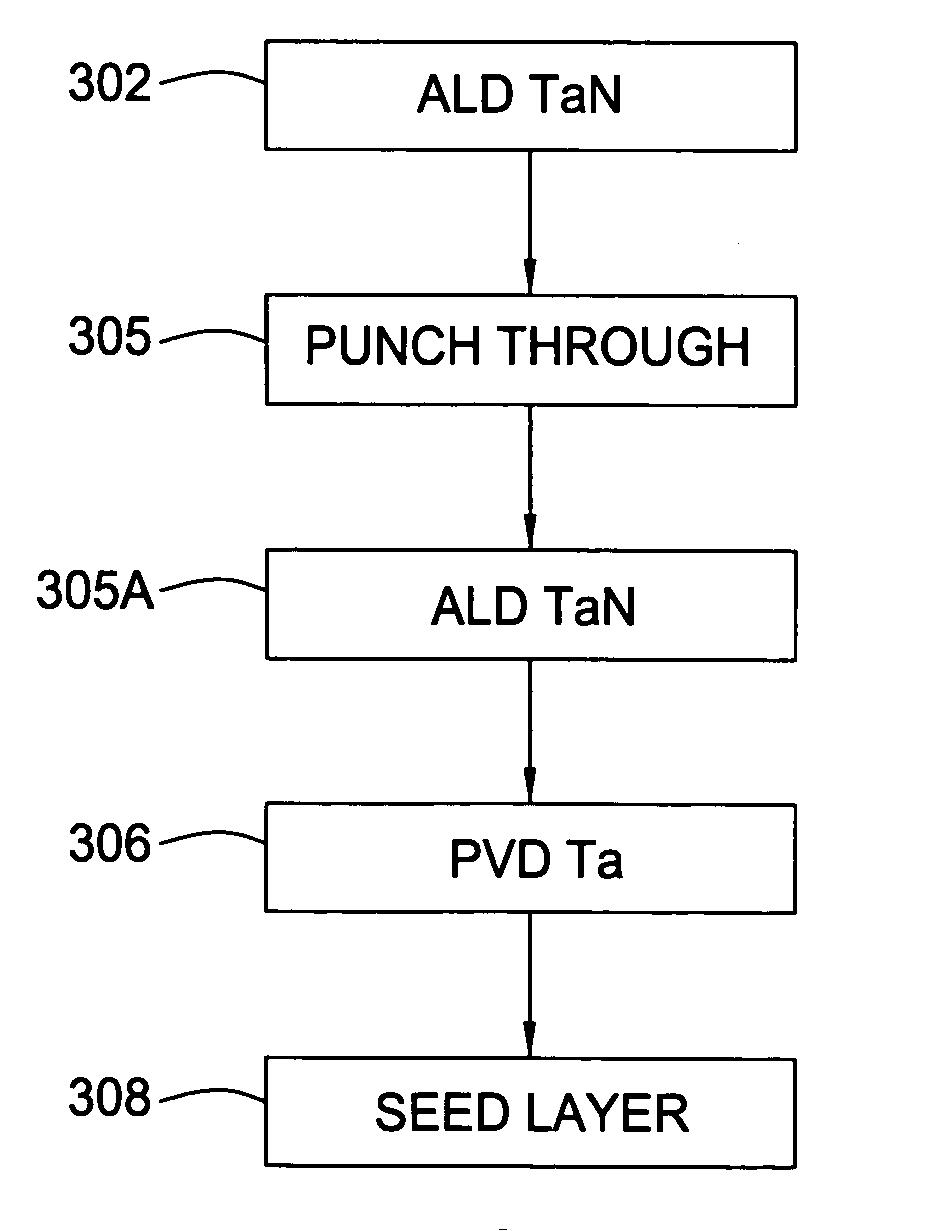

Integration of ALD tantalum nitride for copper metallization

InactiveUS20050106865A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingTantalum nitrideConductive materials

A method and apparatus for depositing a tantalum nitride barrier layer is provided for use in an integrated processing tool. The tantalum nitride is deposited by atomic layer deposition. The tantalum nitride is removed from the bottom of features in dielectric layers to reveal the conductive material under the deposited tantalum nitride. Optionally, a tantalum layer may be deposited by physical vapor deposition after the tantalum nitride deposition. Optionally, the tantalum nitride deposition and the tantalum deposition may occur in the same processing chamber.

Owner:APPLIED MATERIALS INC

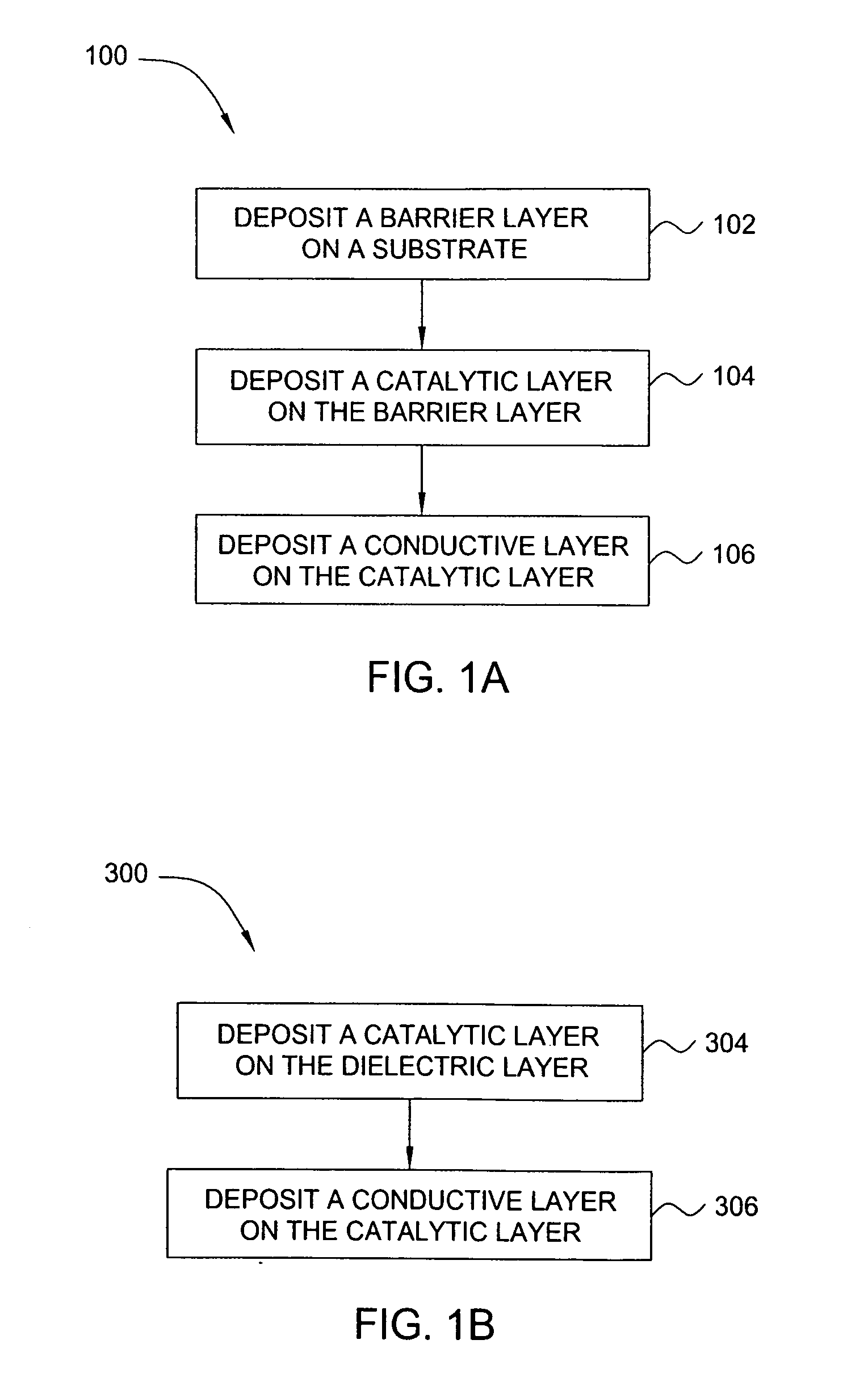

Method of forming copper interconnections and thin films using chemical vapor deposition with catalyst

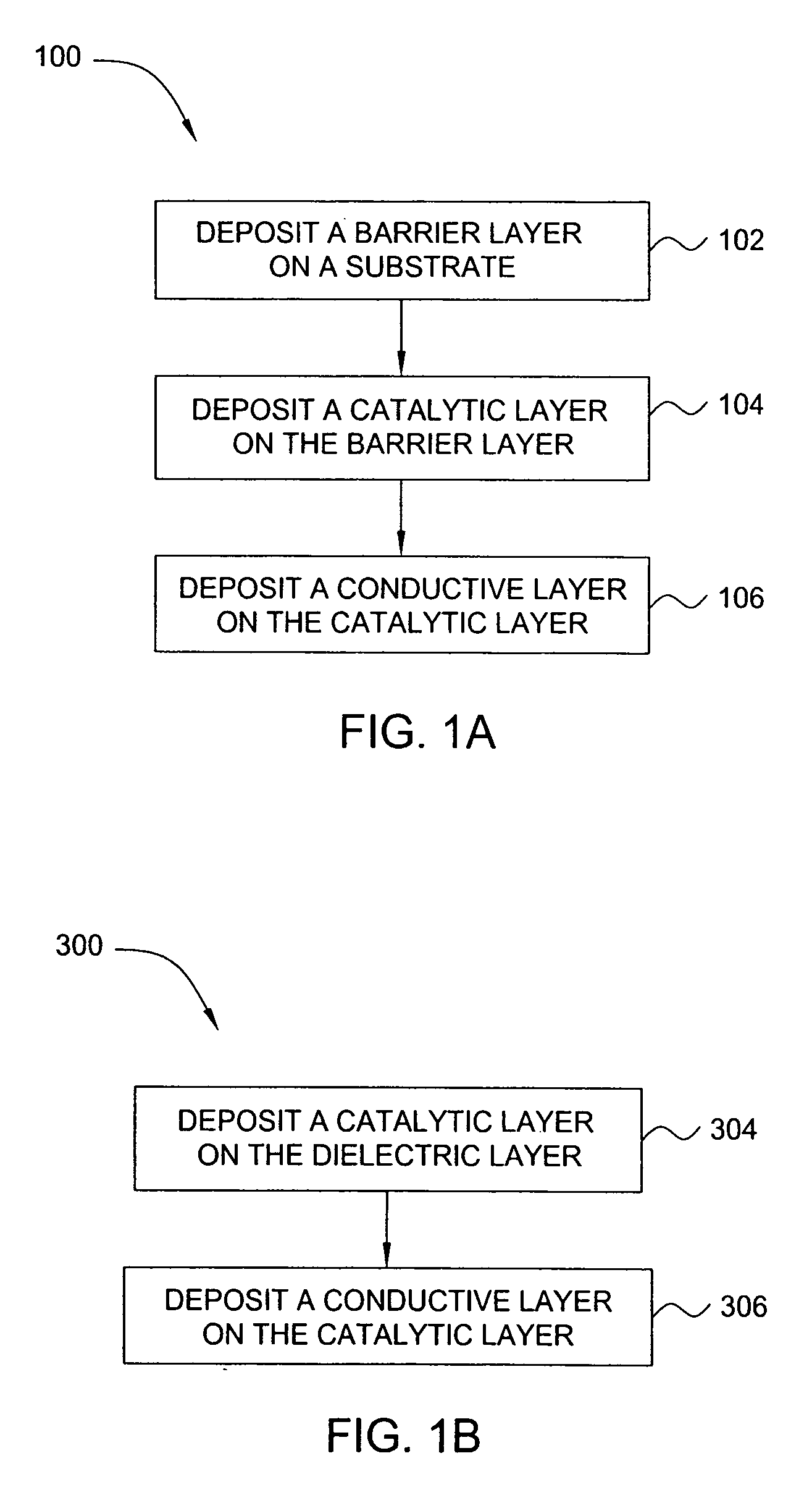

InactiveUS6720262B2Semiconductor/solid-state device detailsSolid-state devicesCopper conductorSource material

A method of forming copper conductors for interconnecting active and passive elements as well as signal and power lines for circuits and devices on silicon wafers is disclosed. The method disclosed herein involves with using catalysts in conjunction with a chemical vapor deposition(CVD) process with typically using copper as a source material for forming interconnecting conductors. Interconnecting method for filling trenches, via holes, contacts, large trenches and holes for power devices and lines as well as for forming large passive elements is also disclosed. Disclosed herein are also a method of filling narrow and deep trenches and small in diameter and deep holes, and a method of forming very thin film on the flat top surface so that an etchback process, such as wet or dry etchback as well as plasma etchback processes, can be used for removing a thin film in preparation for subsequent processing steps, thereby rather expensive chemical mechanical polishing(CMP) process need not be used.

Owner:ASM KOREA LTD

Methods and apparatus for producing enhanced interference pigments

InactiveUS6241858B1Interference be notGood effectElectric discharge heatingPigment preparation by PVD/CVD methodsGas phaseVaporization

Methods and apparatus are provided for uniformly depositing a coating material from a vaporization source onto a powdered substrate material to form a thin coalescence film of the coating material that smoothly replicates the surface microstructure of the substrate material. The coating material is uniformly deposited on the substrate material to form optical interference pigment particles. The thin film enhances the hiding power and color gamut of the substrate material. Physical vapor deposition processes are used for depositing the film on the substrate material. The apparatus and systems employed in forming the coated particles utilize vibrating bed coaters, vibrating conveyor coaters, or coating towers. These allow the powdered substrate material to be uniformly exposed to the coating material vapor during the coating process.

Owner:JDS UNIPHASE CORP

Thermal physical vapor deposition source using pellets of organic material for making OLED displays

Owner:GLOBAL OLED TECH

Catalysts, activating agents, support media, and related methodologies useful for making catalyst systems especially when the catalyst is deposited onto the support media using physical vapor deposition

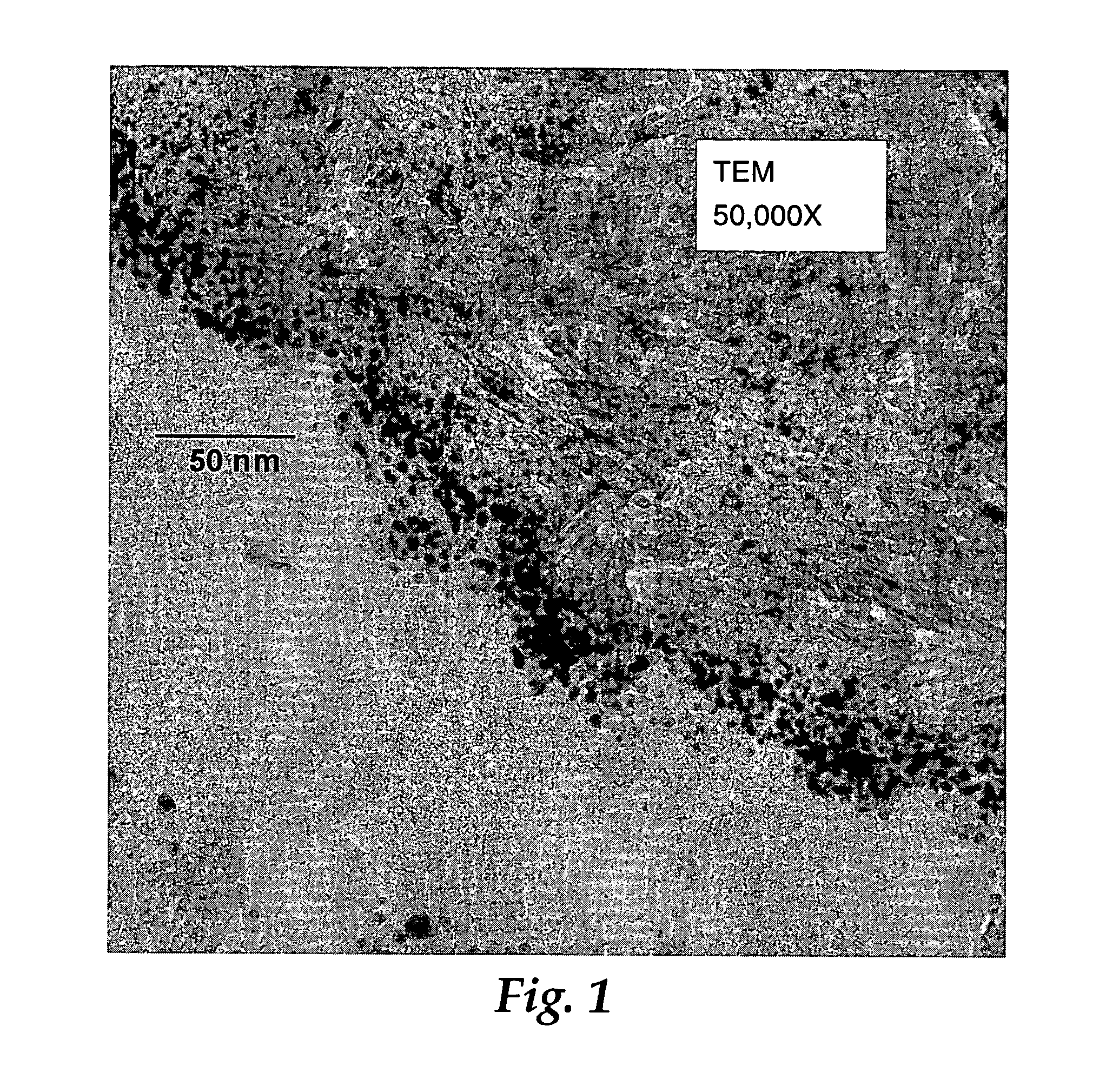

InactiveUS20050095189A1Improve performanceEasy to useMaterial nanotechnologyInternal combustion piston enginesGas phaseAdditive ingredient

Use of physical vapor deposition methodologies to deposit nanoscale gold on activating support media makes the use of catalytically active gold dramatically easier and opens the door to significant improvements associated with developing, making, and using gold-based, catalytic systems. The present invention, therefore, relates to novel features, ingredients, and formulations of gold-based, heterogeneous catalyst systems generally comprising nanoscale gold deposited onto a nanoporous support.

Owner:3M INNOVATIVE PROPERTIES CO

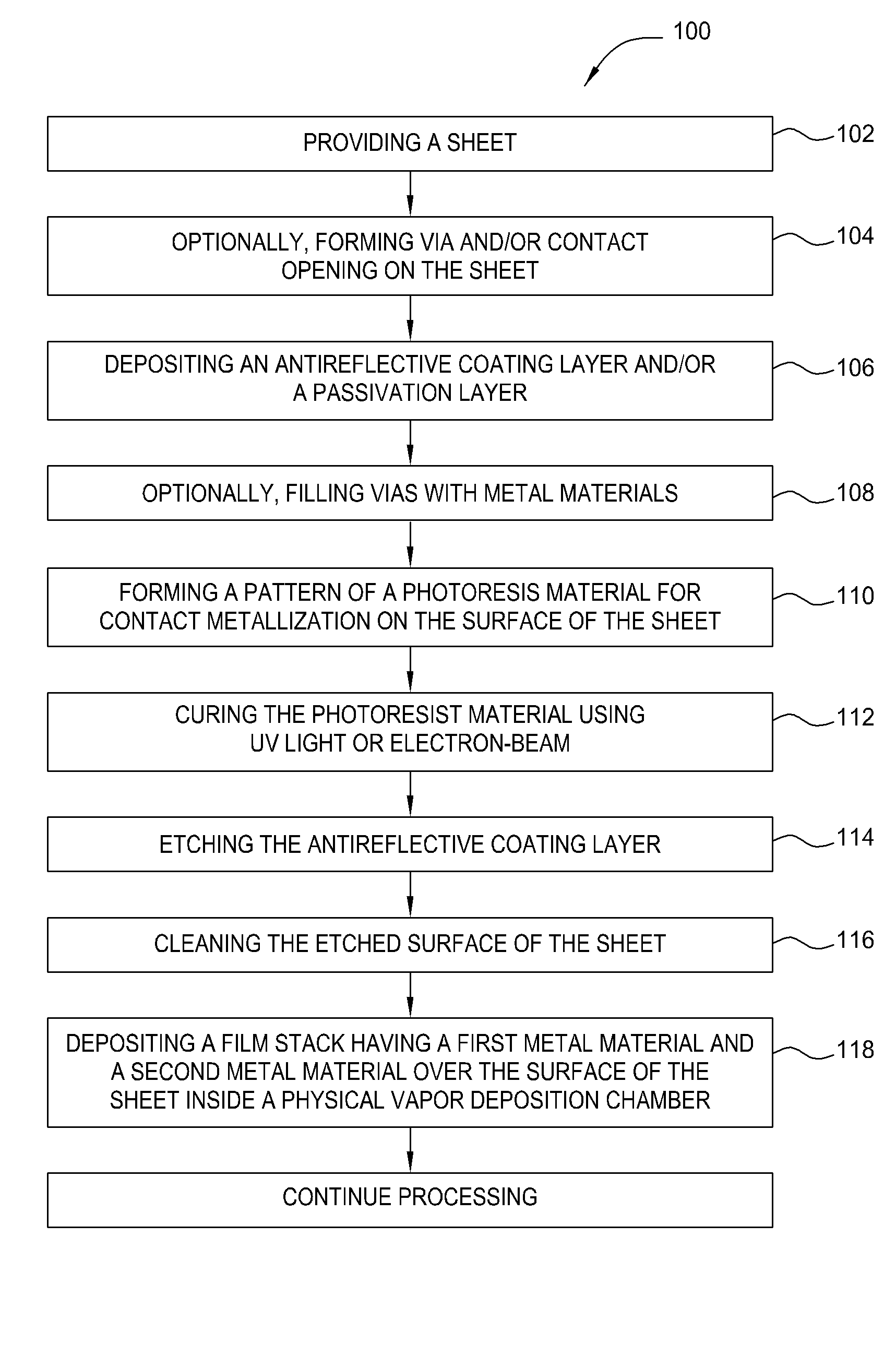

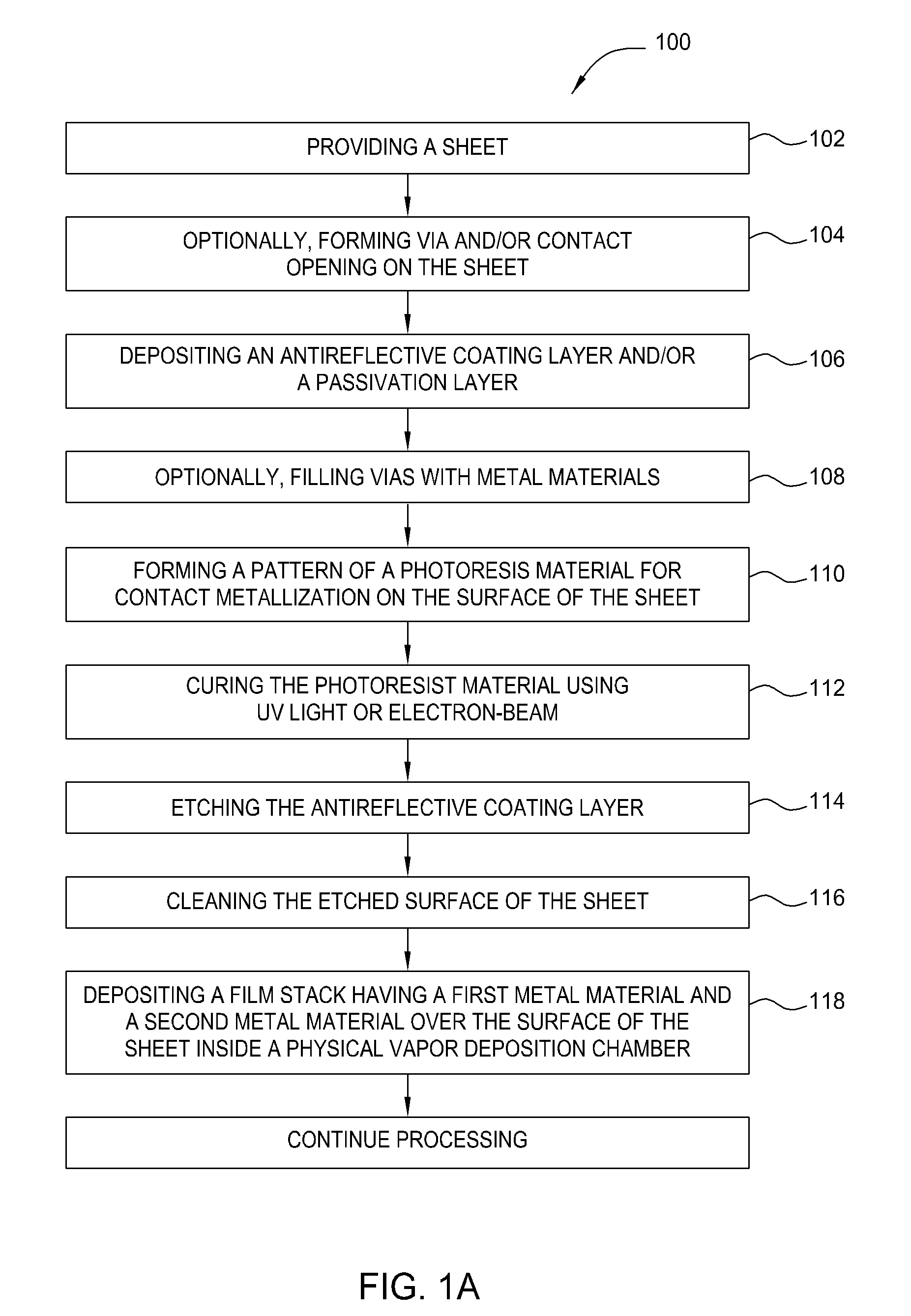

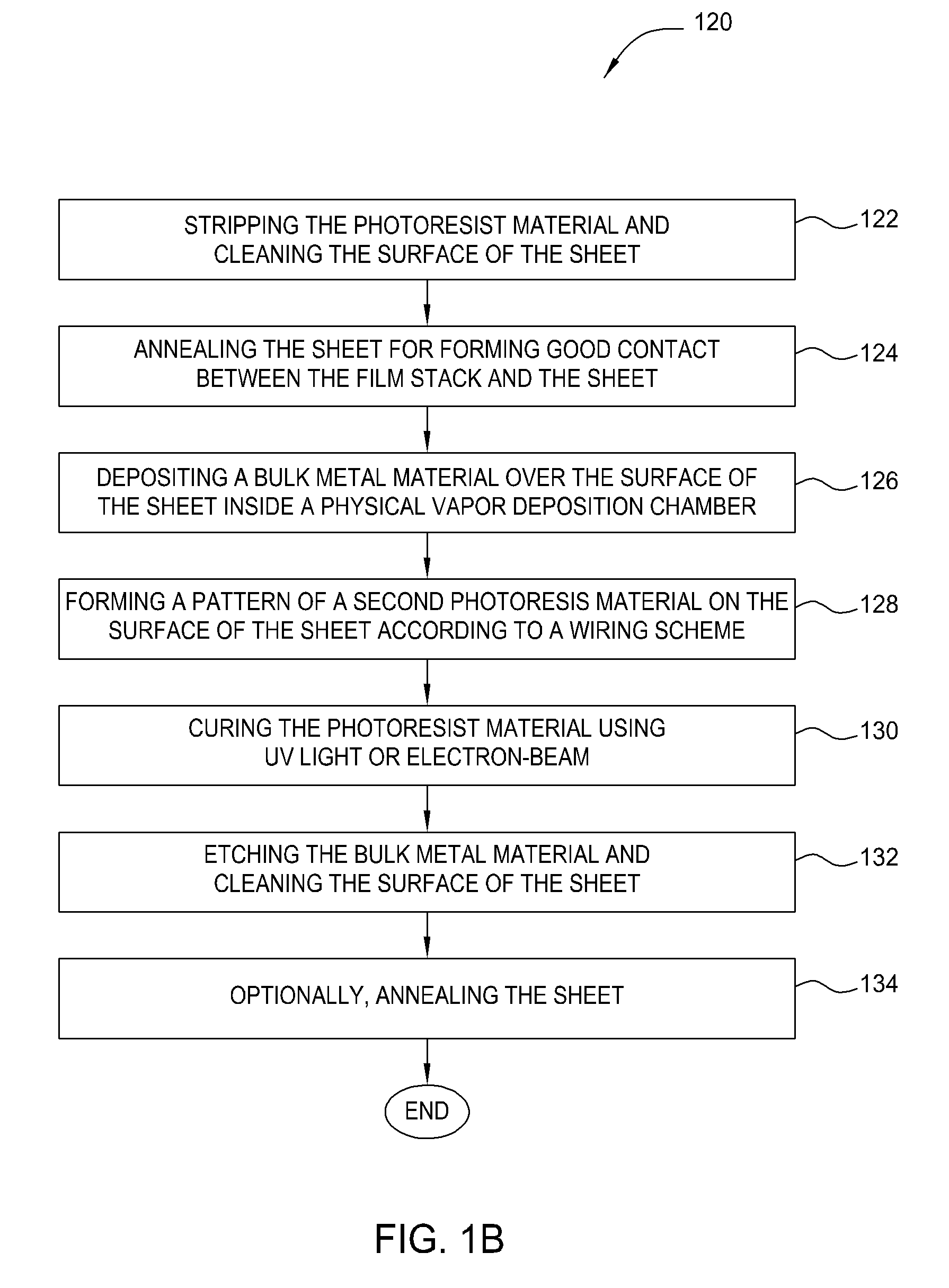

Photovoltaic contact and wiring formation

InactiveUS20070148336A1Reduce contact resistanceEnhanced vapor depositionVacuum evaporation coatingSputtering coatingEtchingGas phase

A method and apparatus for fabricating a solar cell and forming metal contact is disclosed. Solar cell contact and wiring is formed by depositing a thin film stack of a first metal material and a second metal material as an initiation layer or seed layer for depositing a bulk metal layer in conjunction with additional sheet processing, photolithography, etching, cleaning, and annealing processes. In one embodiment, the thin film stack for forming metal silicide with reduced contact resistance over the sheet is deposited by sputtering or physical vapor deposition. In another embodiment, the bulk metal layer for forming metal lines and wiring is deposited by sputtering or physical vapor deposition. In an alternative embodiment, electroplating or electroless deposition is used to deposit the bulk metal layer.

Owner:APPLIED MATERIALS INC

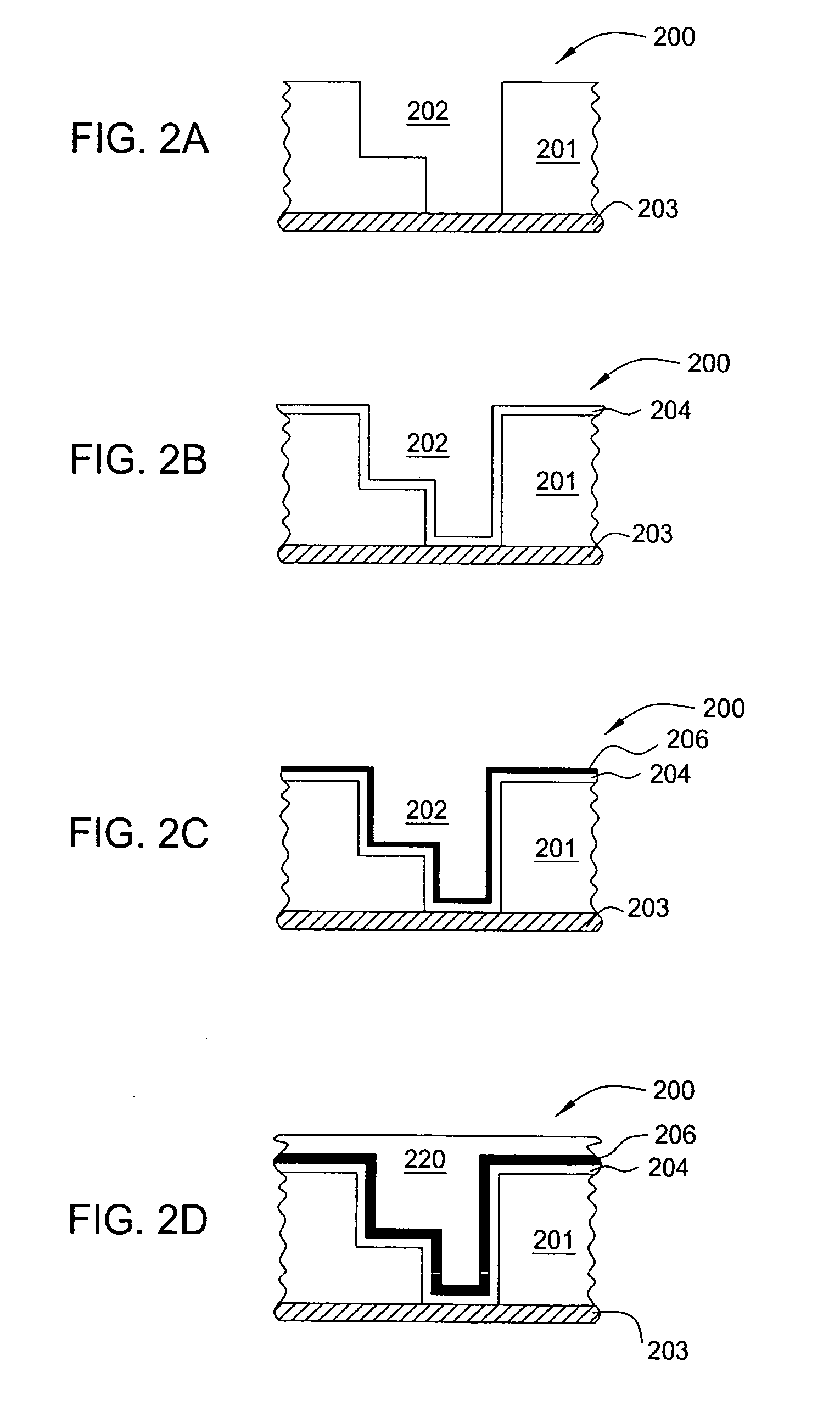

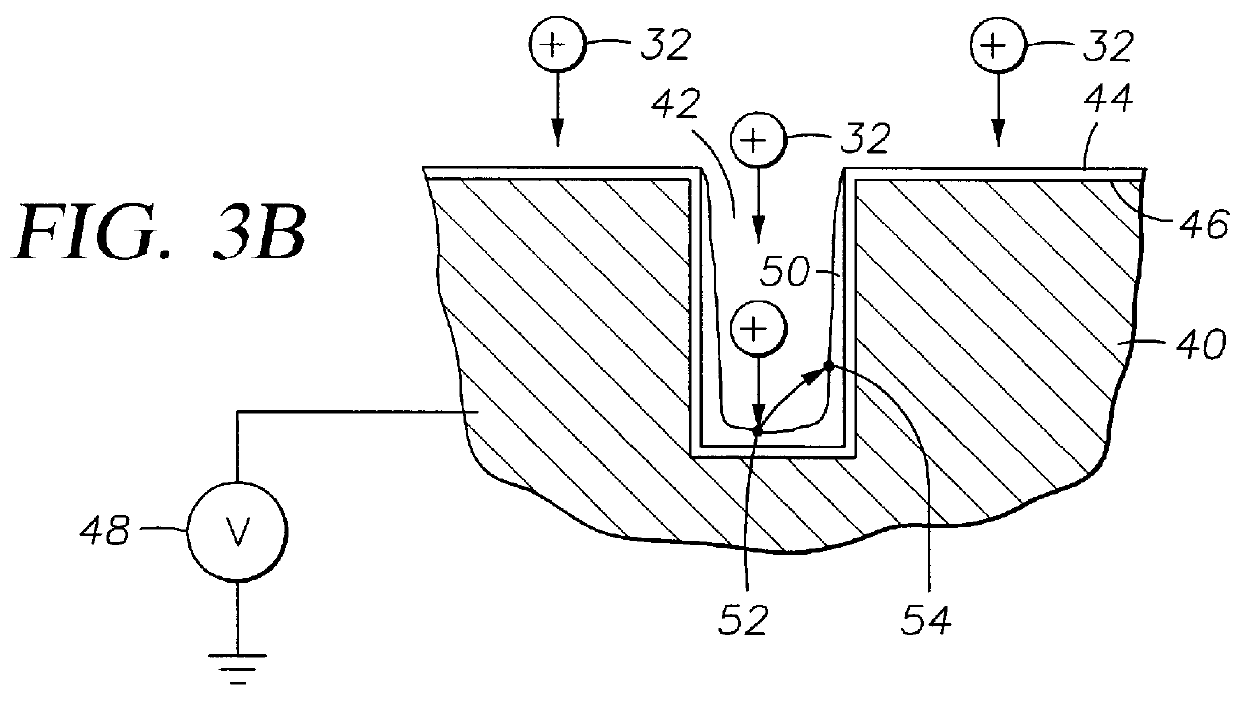

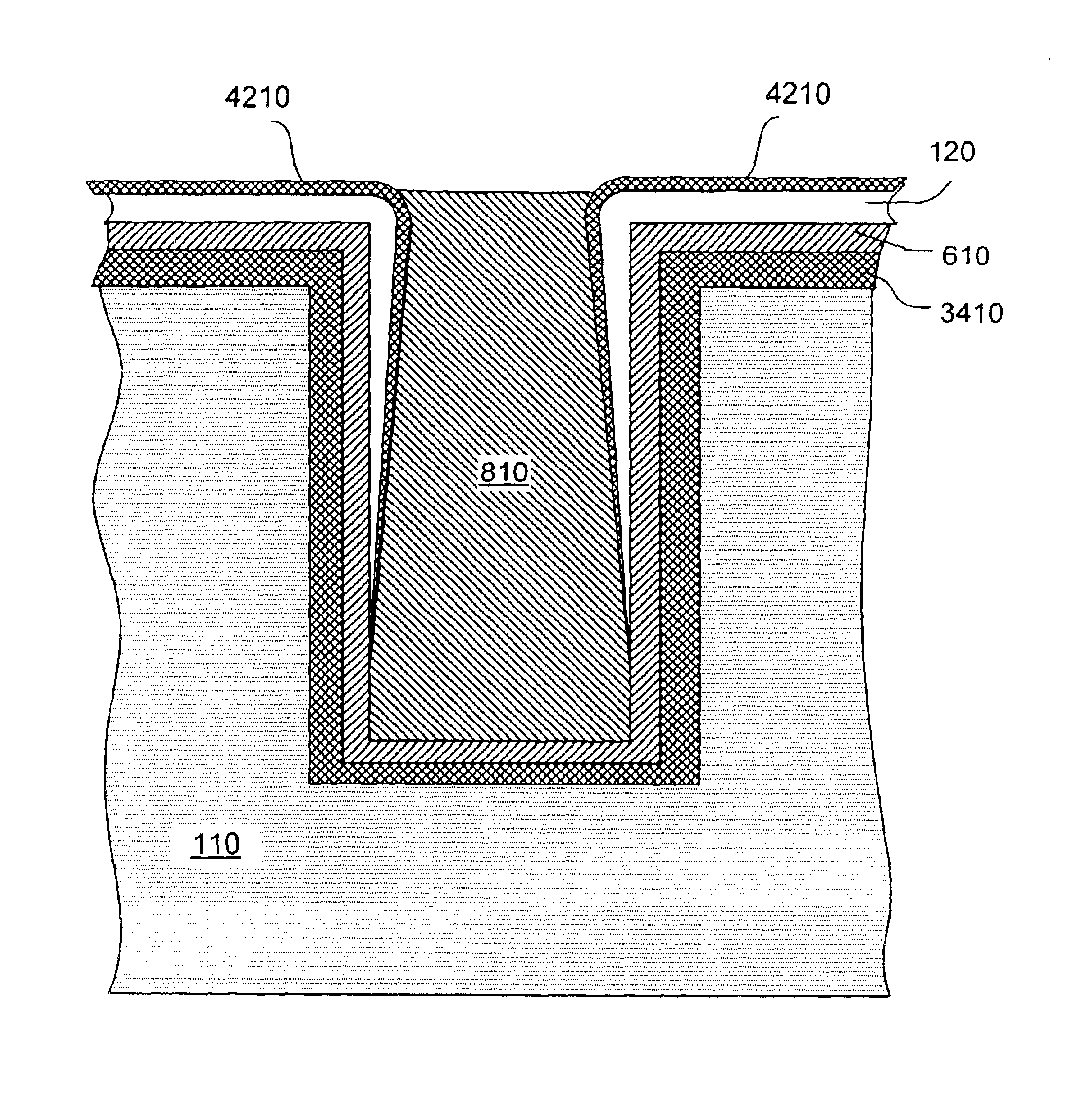

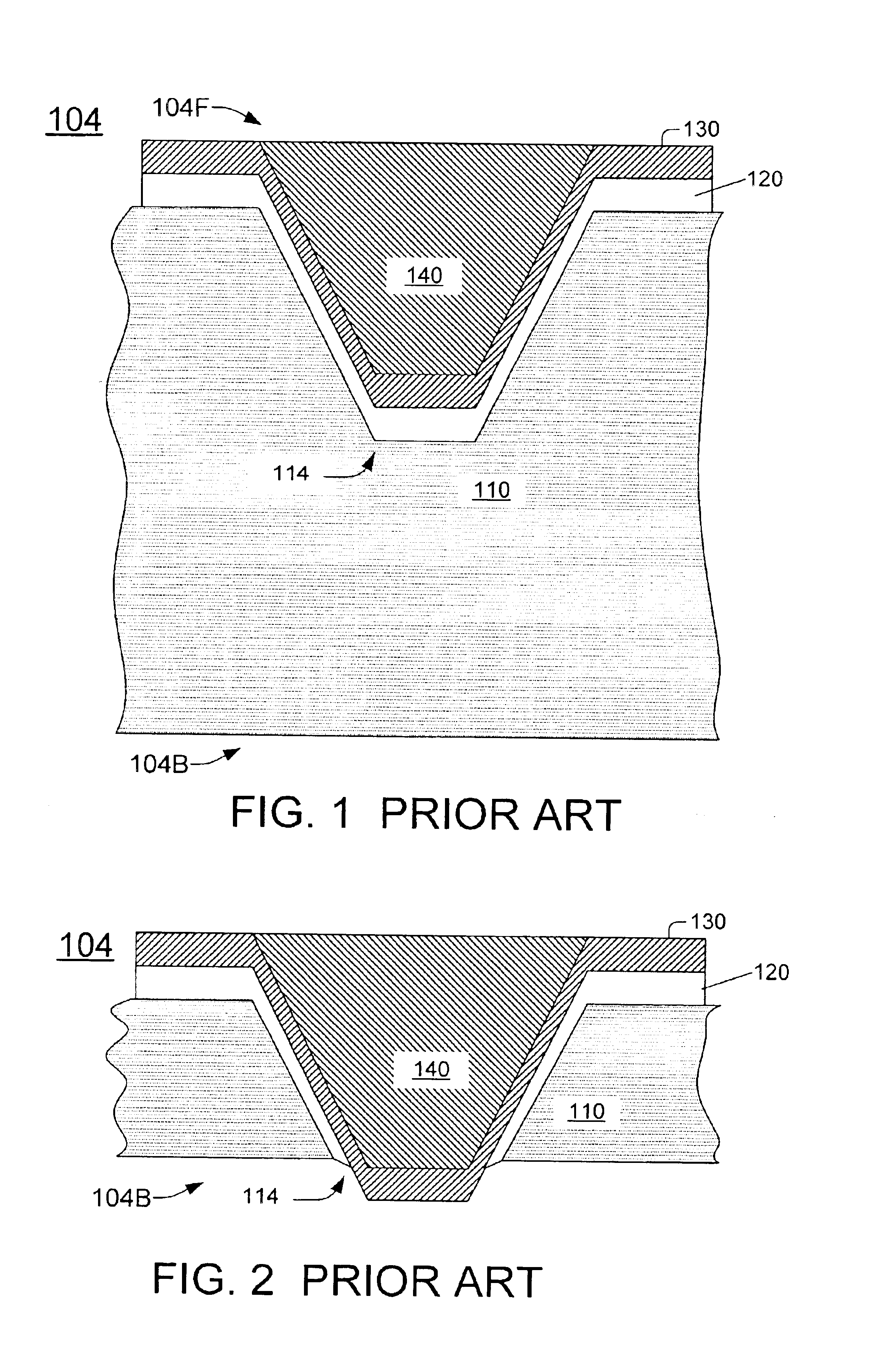

Electroplating and electroless plating of conductive materials into openings, and structures obtained thereby

InactiveUS6897148B2Improve throughputReduce tooling costsSemiconductor/solid-state device detailsSolid-state devicesResistDielectric

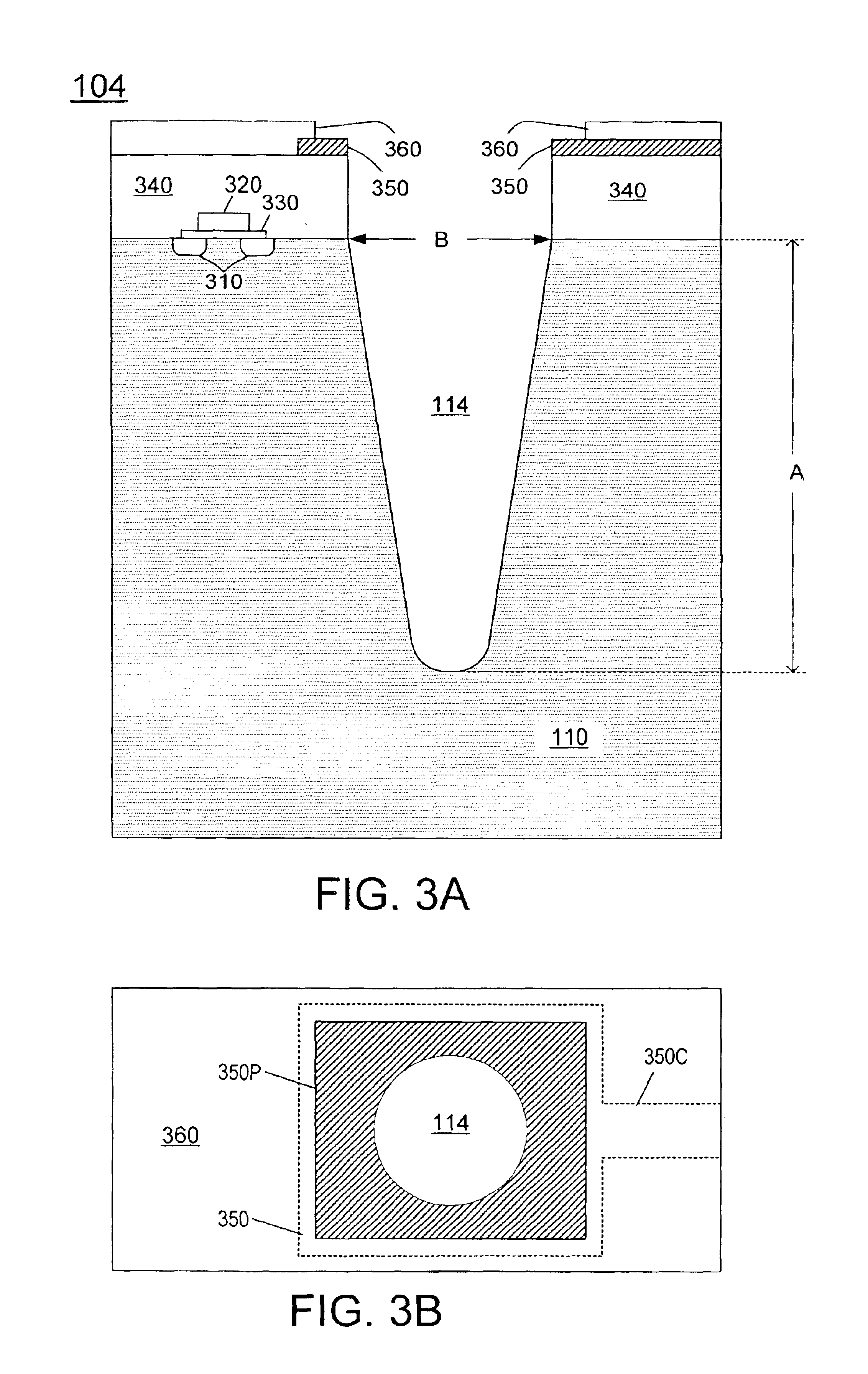

A through hole (114) is formed in a wafer (104) comprising a semiconductor substrate (110). A seed layer (610) is sputtered on the bottom surface of the wafer. The seed is not deposited over the through hole's sidewalls adjacent the top surface of the wafer. A conductor (810) is electroplated into the through hole. In another embodiment, a seed is deposited into an opening in a wafer through a dry film resist mask (1110). The dry film resist overhangs the edges of the opening, so the seed is not deposited over the opening's sidewalls adjacent the top surface of the wafer. In another embodiment, a dielectric (120) is formed in an opening in a semiconductor substrate (110) by a non-conformal physical vapor deposition (PVD) process that deposits the dielectric on the sidewalls but not the bottom of the opening. A seed (610) is formed on the bottom by electroless plating. A conductor (810) is electroplated on the seed. In another embodiment, a dielectric (2910) is formed in the opening to cover the entire surface of the opening. A non-conformal layer (120) is deposited by PVD over the sidewalls but not the bottom of the opening. The dielectric (2910) is etched off the bottom with the non-conformal layer (120) as a mask. A seed (610) is formed on the bottom by electroless plating. The non-conformal layer can be formed by electroplating. It can be tantalum deposited by electroplating, then anodized. Other embodiments are also provided.

Owner:INVENSAS CORP

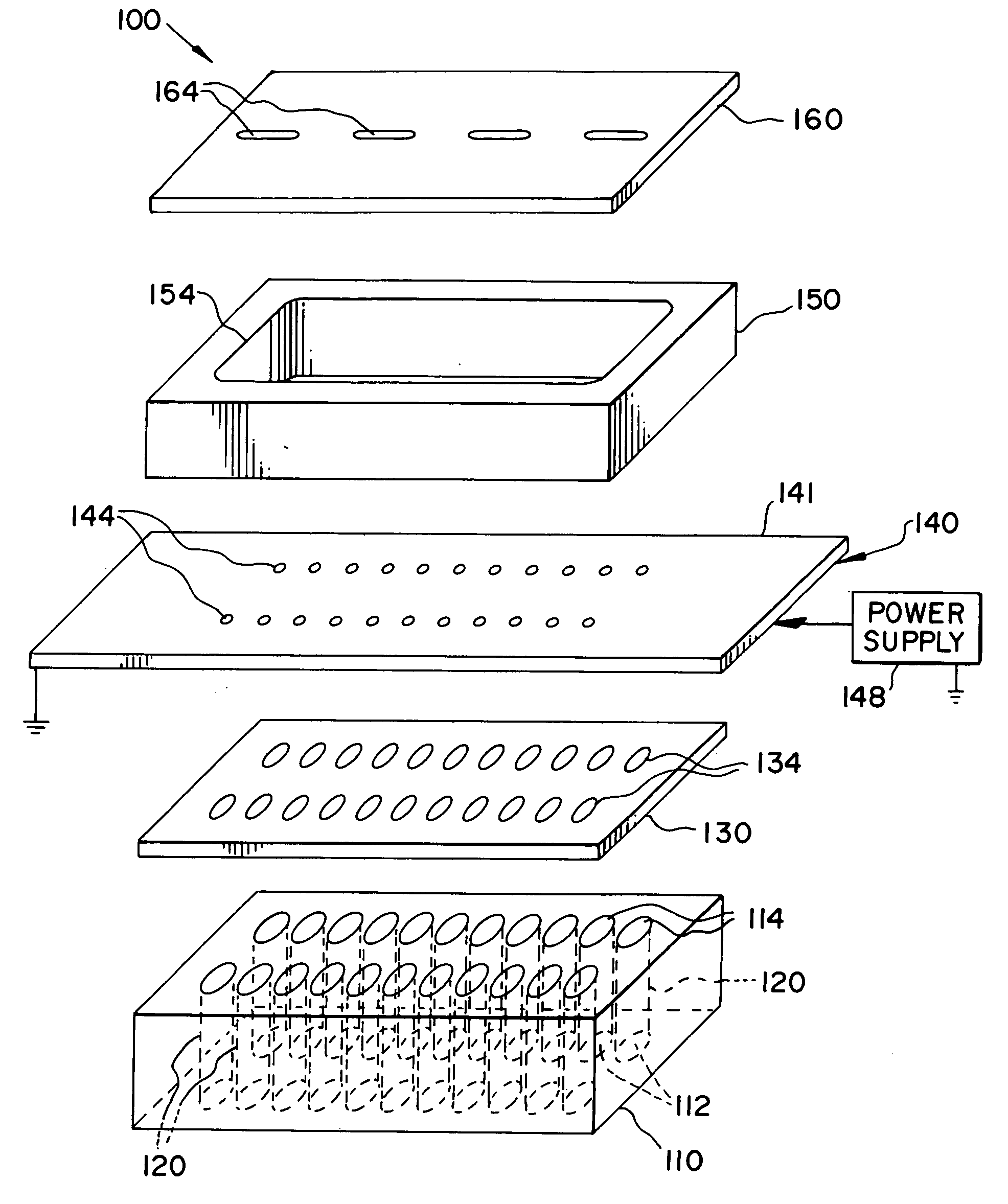

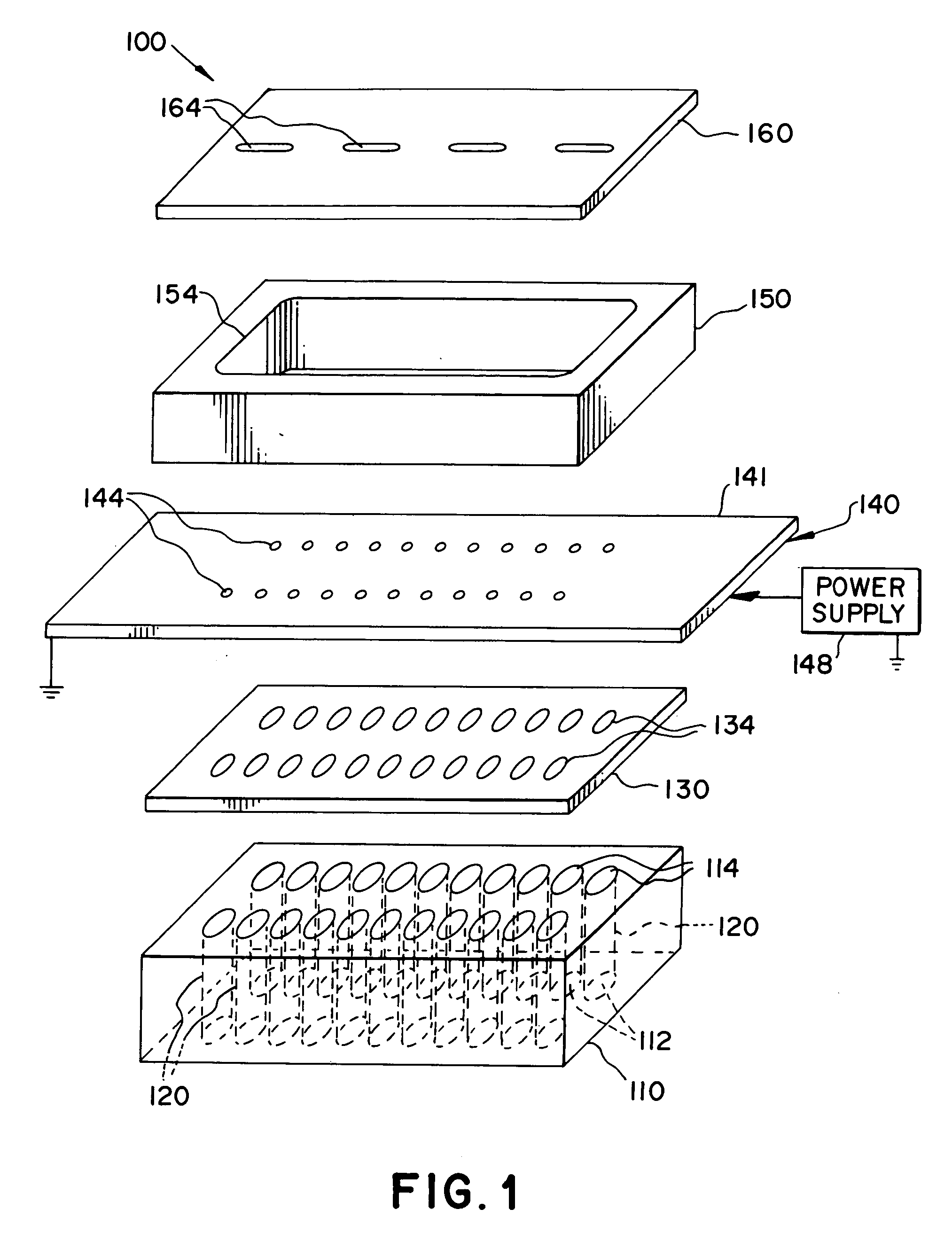

Unique passivation technique for a CVD blocker plate to prevent particle formation

InactiveUS20070022952A1Reduce particle pollutionEasily electropolishedVacuum evaporation coatingSemiconductor/solid-state device manufacturingGas phaseNucleation

Blocker plates for chemical vapor deposition chambers and methods of treating blocker plates are provided. The blocker plates define a plurality of holes therethrough and have an upper surface and a lower surface that are at least about 99.5% pure, which minimizes the nucleation of contaminating particles on the blocker plates. A physically vapor deposited coating, such as an aluminum physically vapor deposited coating, may be formed on the upper and lower surfaces of the blocker plates. Chemical vapor deposition chambers including blocker plates having a physically vapor deposited coating thereon are also provided.

Owner:APPLIED MATERIALS INC

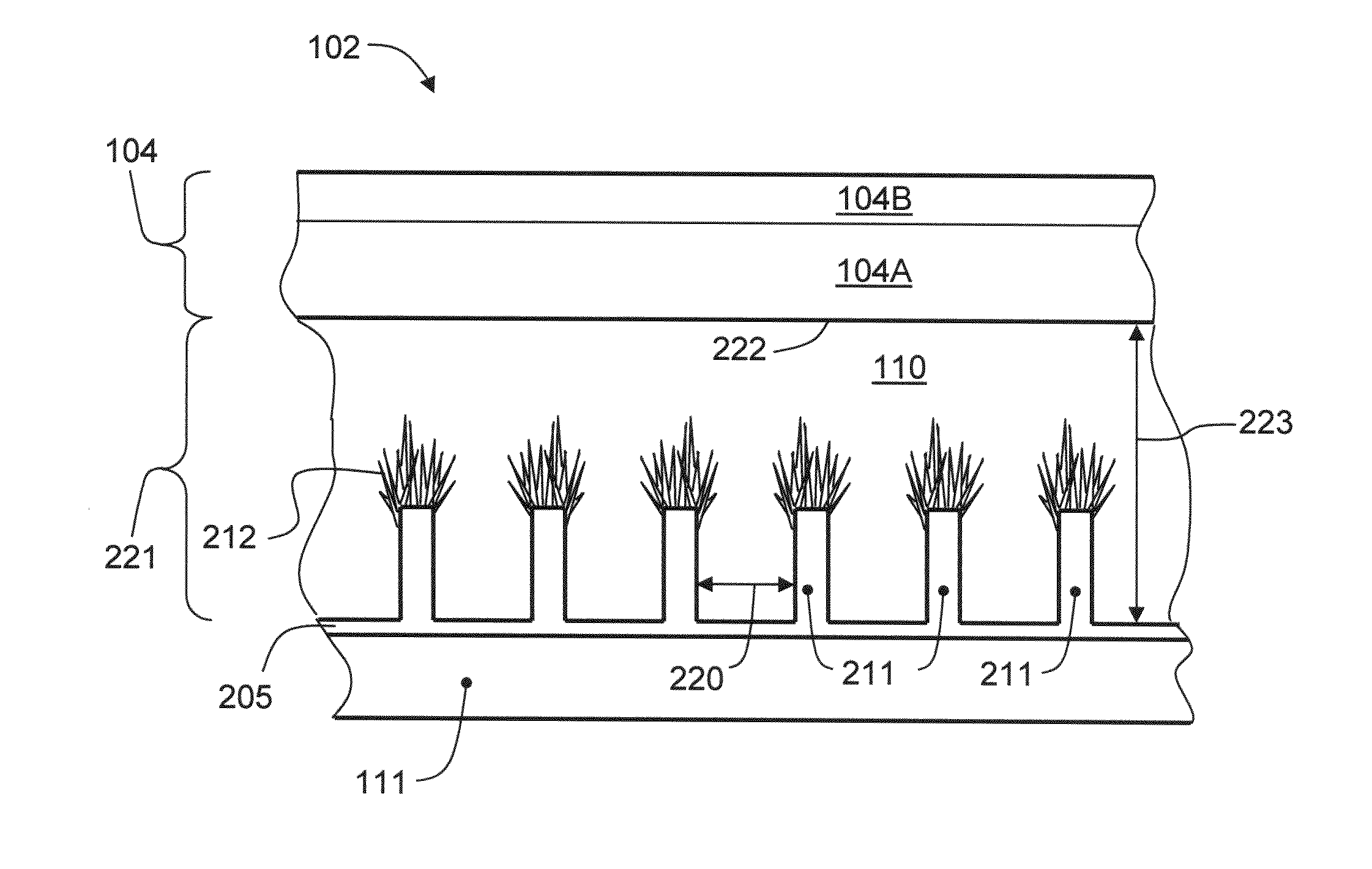

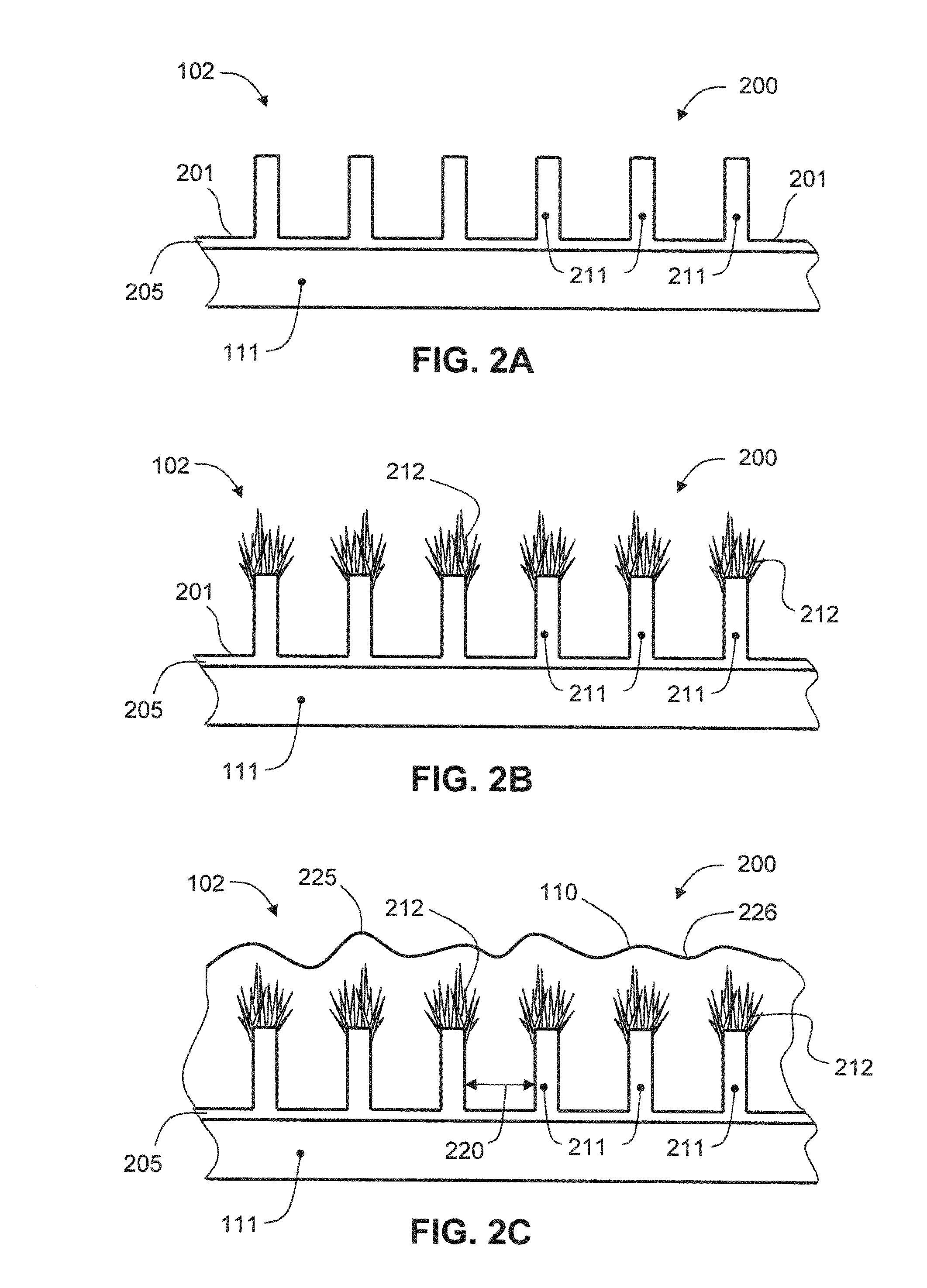

Thin film electrochemical energy storage device with three-dimensional anodic structure

InactiveUS20100216026A1Final product manufactureElectrode carriers/collectorsPorosityMicro structure

A method for forming a battery from via thin-film deposition processes is disclosed. A mesoporous carbon material is deposited onto a surface of a conductive substrate that has high surface area, conductive micro-structures formed thereon. A porous, dielectric separator layer is then deposited on the layer of mesoporous carbon material to form a half cell of an energy storage device. The mesoporous carbon material is made up of CVD-deposited carbon fullerene “onions” and carbon nano-tubes, and has a high porosity capable of retaining lithium ions in concentrations useful for storing significant quantities of electrical energy. Embodiments of the invention further provide for the formation of an electrode having a high surface area conductive region that is useful in a battery structure. In one configuration the electrode has a high surface area conductive region comprising a porous dendritic structure that can be formed by electroplating, physical vapor deposition, chemical vapor deposition, thermal spraying, and / or electroless plating techniques.

Owner:APPLIED MATERIALS INC

Fabrication of low defectivity electrochromic devices

Prior electrochromic devices frequently suffer from high levels of defectivity. The defects may be manifest as pin holes or spots where the electrochromic transition is impaired. This is unacceptable for many applications such as electrochromic architectural glass. Improved electrochromic devices with low defectivity can be fabricated by depositing certain layered components of the electrochromic device in a single integrated deposition system. While these layers are being deposited and / or treated on a substrate, for example a glass window, the substrate never leaves a controlled ambient environment, for example a low pressure controlled atmosphere having very low levels of particles. These layers may be deposited using physical vapor deposition.

Owner:VIEW INC

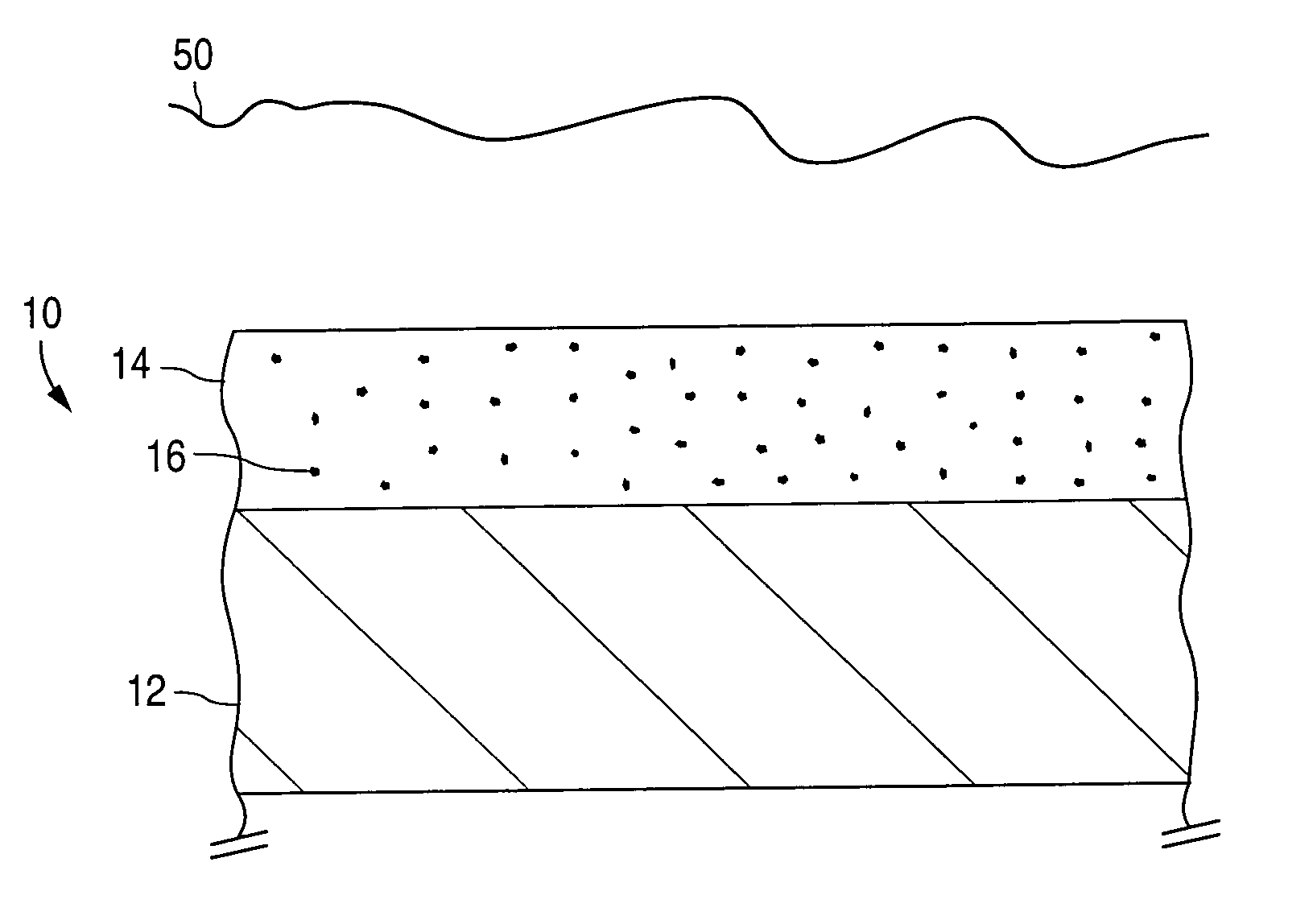

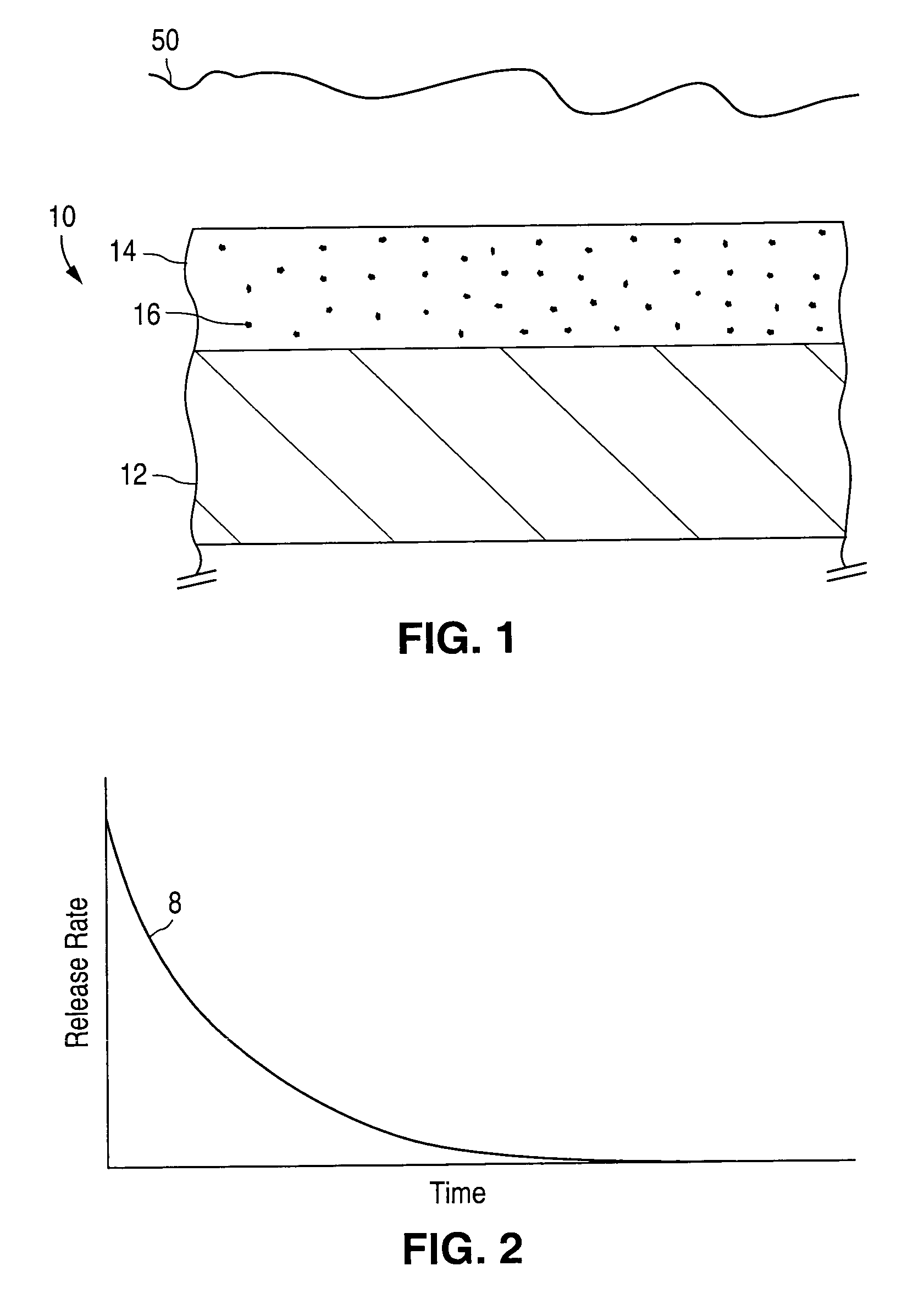

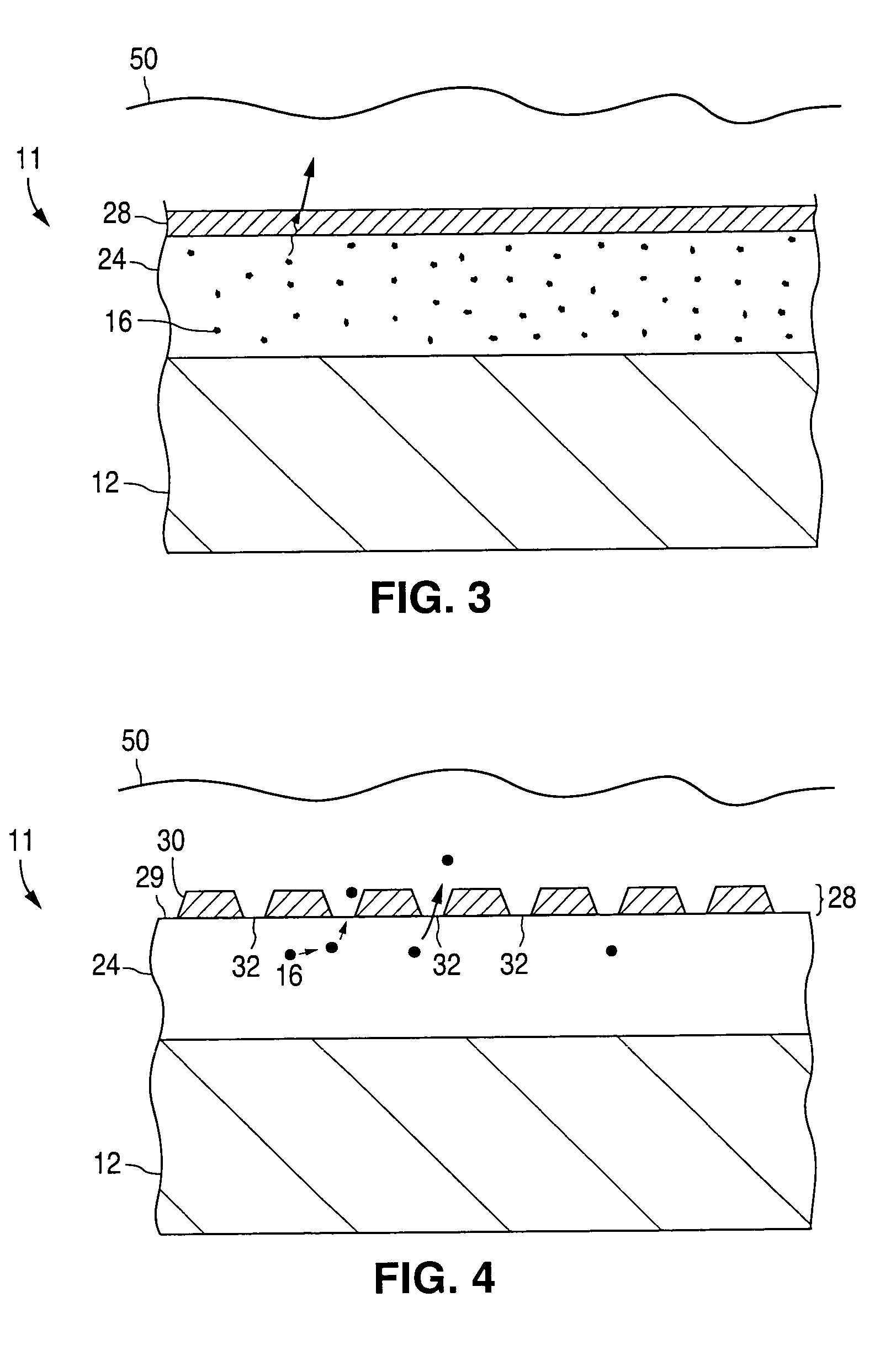

Barriers for polymer-coated implantable medical devices and methods for making the same

InactiveUS6953560B1Reduce and prevent and inflammationReduce and prevent proliferationStentsSurgeryHafniumPt element

An implantable medical device and methods for making the implantable medical device are disclosed. The implantable medical device includes a substrate. At least a portion of the substrate is coated with a first layer including a polymer containing a drug. A barrier overlies the first layer. The barrier significantly reduces the rate of release of the drug from the polymer, thereby sustaining release of the drug from the medical device for a longer time.The barrier may be a homogeneous layer overlying the first layer, or a number of discrete deposits over the first layer. Alternatively, the barrier may be intermixed with an outer portion of the first layer. The barrier material is biocompatible, and typically has a thickness ranging from about 50 angstroms to about 20,000 microns. Suitable materials for the barrier include, but are not limited to, inorganic compounds, such as inorganic silicides, oxides, nitrides, carbides, as well as pure metals such as aluminum, chromium, gold, hafnium, iridium, niobium, palladium, platinum, tantalum, titanium, tungsten, zirconium, and alloys of these metals. The barriers disclosed may be applied to the first layer by several techniques, depending on the material being applied. Exemplary deposition techniques include physical vapor deposition, alkoxide hydrolysis, and electroless plating.The implantable device may be a stent or a graft, among other possibilities.

Owner:ABBOTT CARDIOVASCULAR

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com