Patents

Literature

2635 results about "Diffusion barrier" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A diffusion barrier is a thin layer (usually micrometres thick) of metal usually placed between two other metals. It is done to act as a barrier to protect either one of the metals from corrupting the other.

Barrier material and process for Cu interconnect

InactiveUS20060113675A1Improved electromigration performanceImprove performanceSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorDiffusion barrier

A semiconductor diffusion barrier layer and its method of manufacture is described. The barrier layer includes of at least one layer of TaN, TiN, WN, TbN, VN, ZrN, CrN, WC, WN, WCN, NbN, AlN, and combinations thereof. The barrier layer may further include a metal rich surface. Embodiments preferably include a glue layer about 10 to 500 Angstroms thick, the glue layer consisting of Ru, Ta, Ti, W, Co, Ni, Al, Nb, AlCu, and a metal-rich nitride, and combinations thereof. The ratio of the glue layer thickness to the barrier layer thickness is preferably about 1 to 50. Other alternative preferred embodiments further include a conductor annealing step. The various layers may be deposited using PVD, CVD, PECVD, PEALD and / or ALD methods including nitridation and silicidation methods.

Owner:TAIWAN SEMICON MFG CO LTD

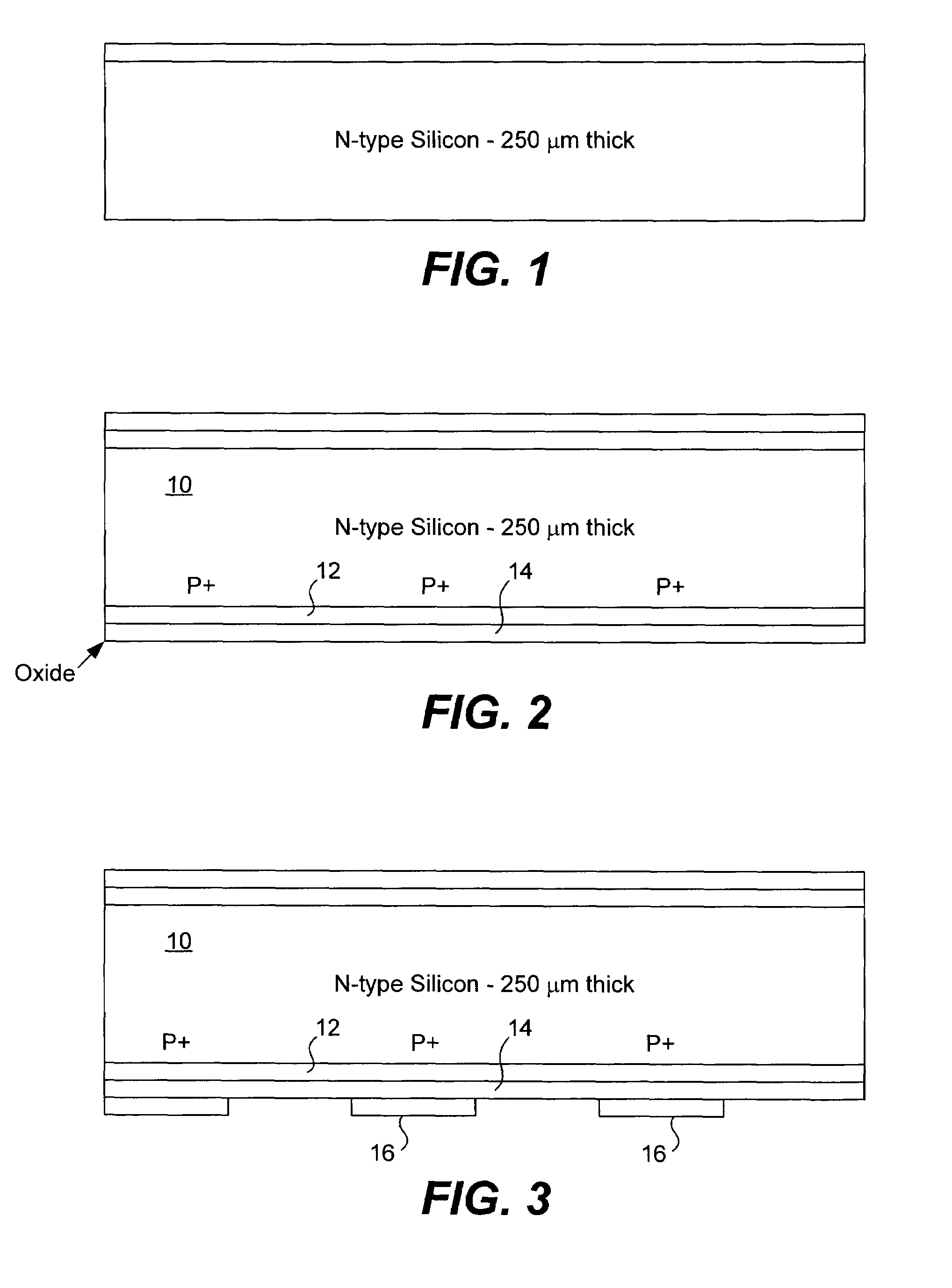

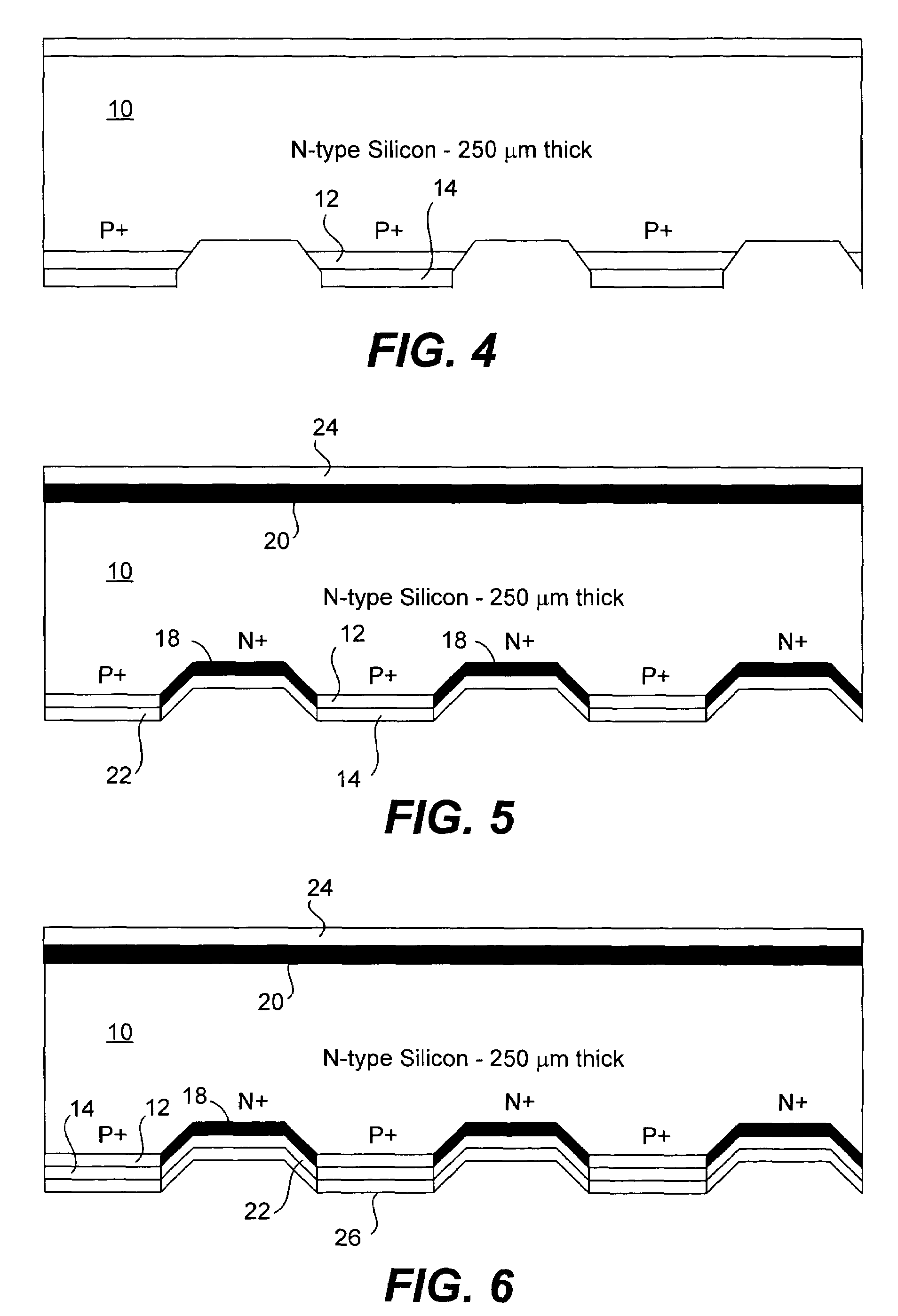

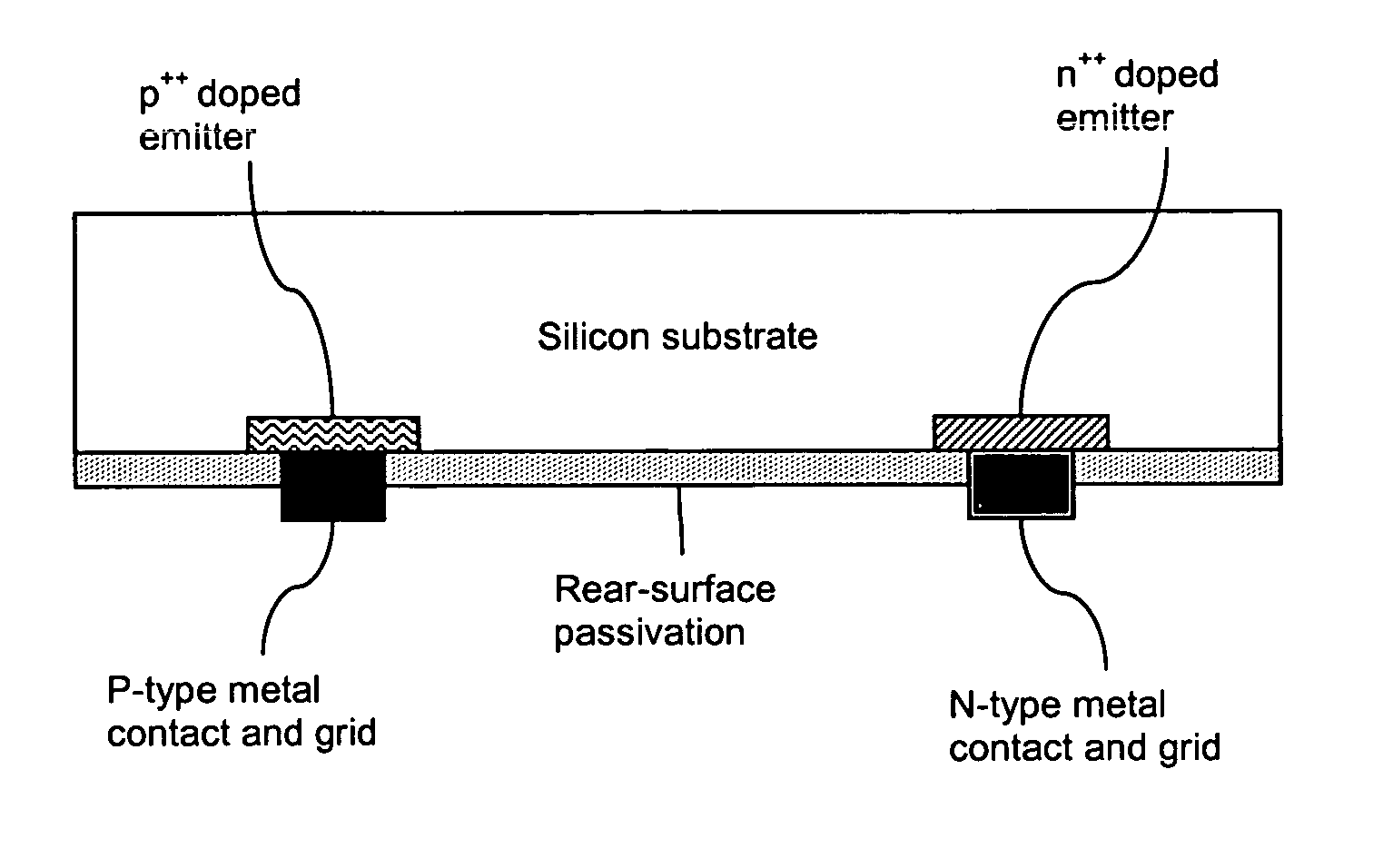

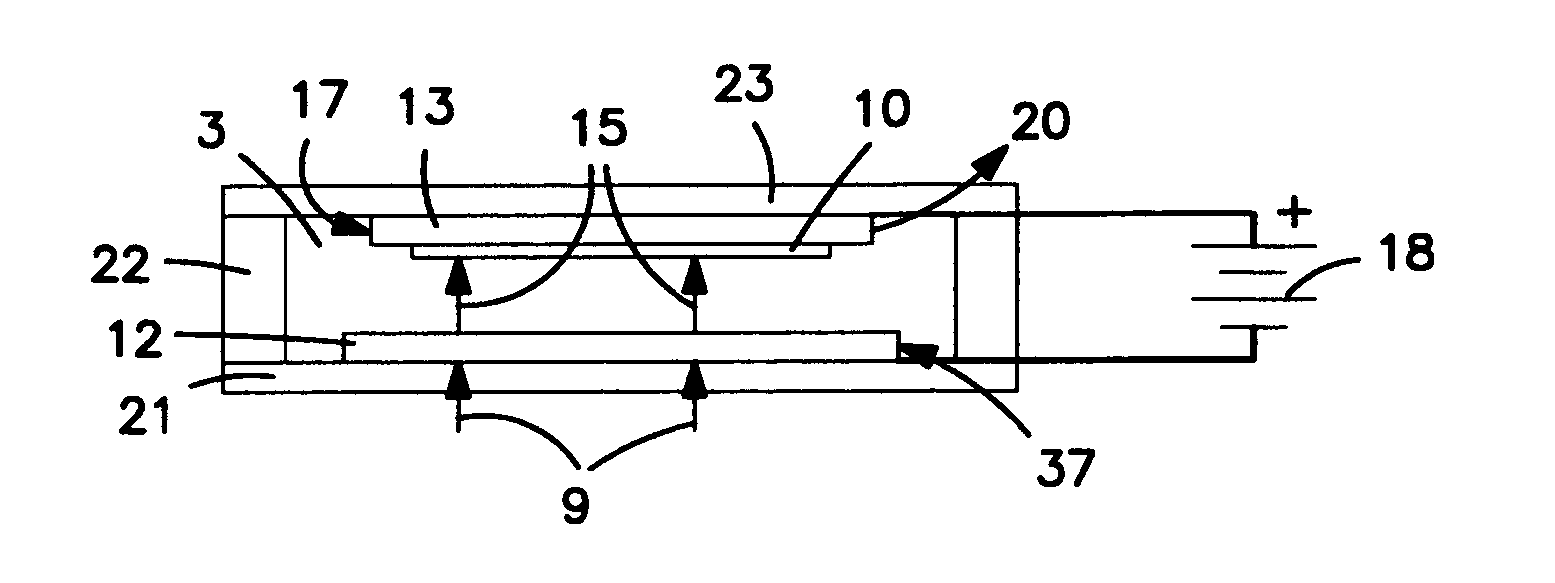

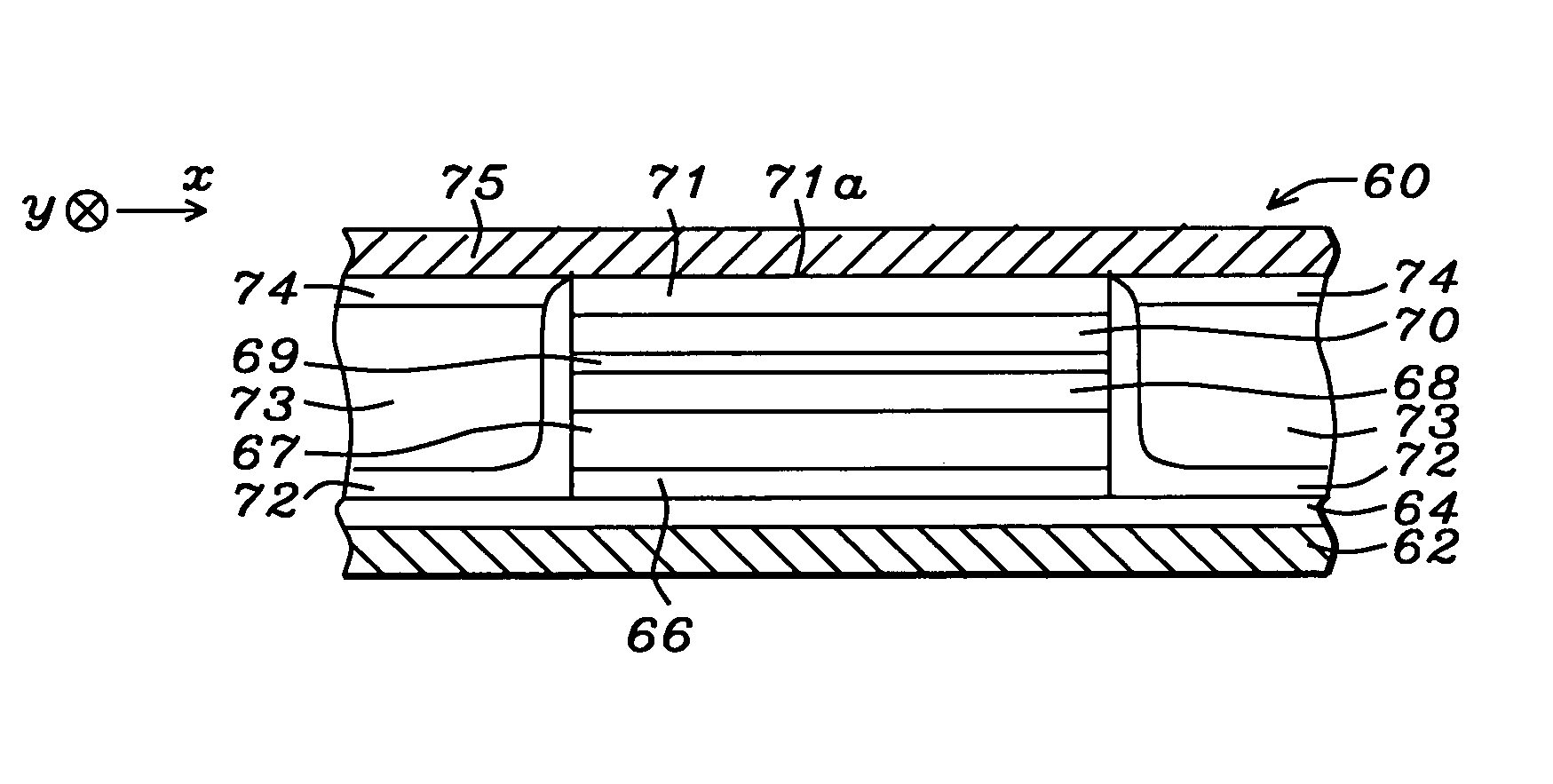

Solar cell and method of manufacture

ActiveUS7339110B1Easy to manufactureLess expensiveFinal product manufacturePhotovoltaic energy generationEngineeringSilicon oxide

A solar cell that is readily manufactured using processing techniques which are less expensive than microelectronic circuit processing. In preferred embodiments, printing techniques are utilized in selectively forming masks for use in etching of silicon oxide and diffusing dopants and in forming metal contacts to diffused regions. In a preferred embodiment, p-doped regions and n-doped regions are alternately formed in a surface of the wafer in offset levels through use of masking and etching techniques. Metal contacts are made to the p-regions and n-regions by first forming a seed layer stack that comprises a first layer such as aluminum that contacts silicon and functions as an infrared reflector, second layer such titanium tungsten that acts as diffusion barrier, and a third layer functions as a plating base. A thick conductive layer such as copper is then plated over the seed layer, and the seed layer between plated lines is removed. A front surface of the wafer is preferably textured by etching or mechanical abrasion with an antireflection layer provided over the textured surface. A field layer can be provided in the textured surface with the combined effect being a very low surface recombination velocity.

Owner:MAXEON SOLAR PTE LTD +1

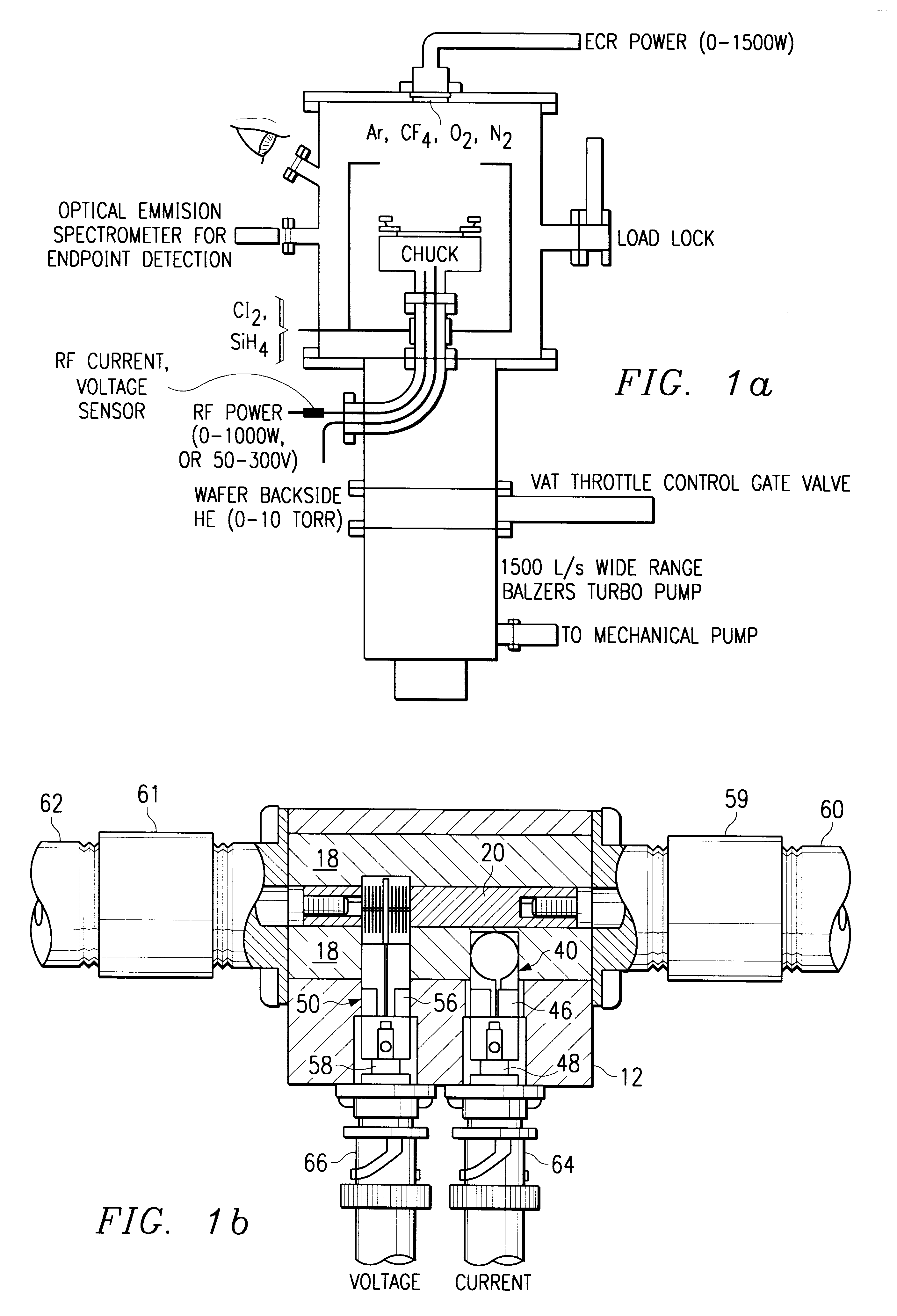

Reaction system for growing a thin film

ActiveUS20050241176A1Extension of timeLong stepDrying using combination processesDrying solid materials with heatControl systemDiffusion barrier

A reactor defines a reaction chamber for processing a substrate. The reactor comprises a first inlet for providing a first reactant and to the reaction chamber and a second inlet for a second reactant to the reaction chamber. A first exhaust outlet removes gases from the reaction chamber. A second exhaust outlet removes gases from the reaction chamber. A flow control system is configured to alternately constrict flow through the first and second exhaust outlets. The reactor chamber is configured to for a diffusion barrier within the reaction chamber.

Owner:ASM IP HLDG BV

Integrated circuit and method

InactiveUS6211035B1Solid-state devicesSemiconductor/solid-state device manufacturingDielectricDiffusion barrier

A via etch to contact a capacitor with ferroelectric between electrodes together with dielectric on an insulating diffusion barrier includes two-step etch with F-based dielectric etch and Cl- and F-based barrier etch.

Owner:TEXAS INSTR INC

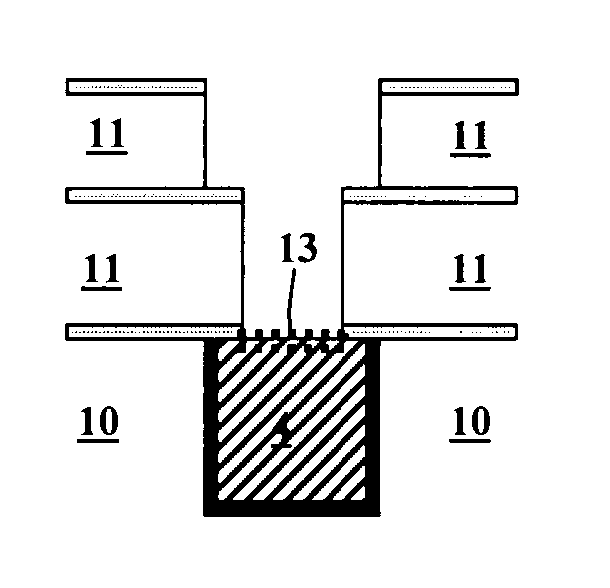

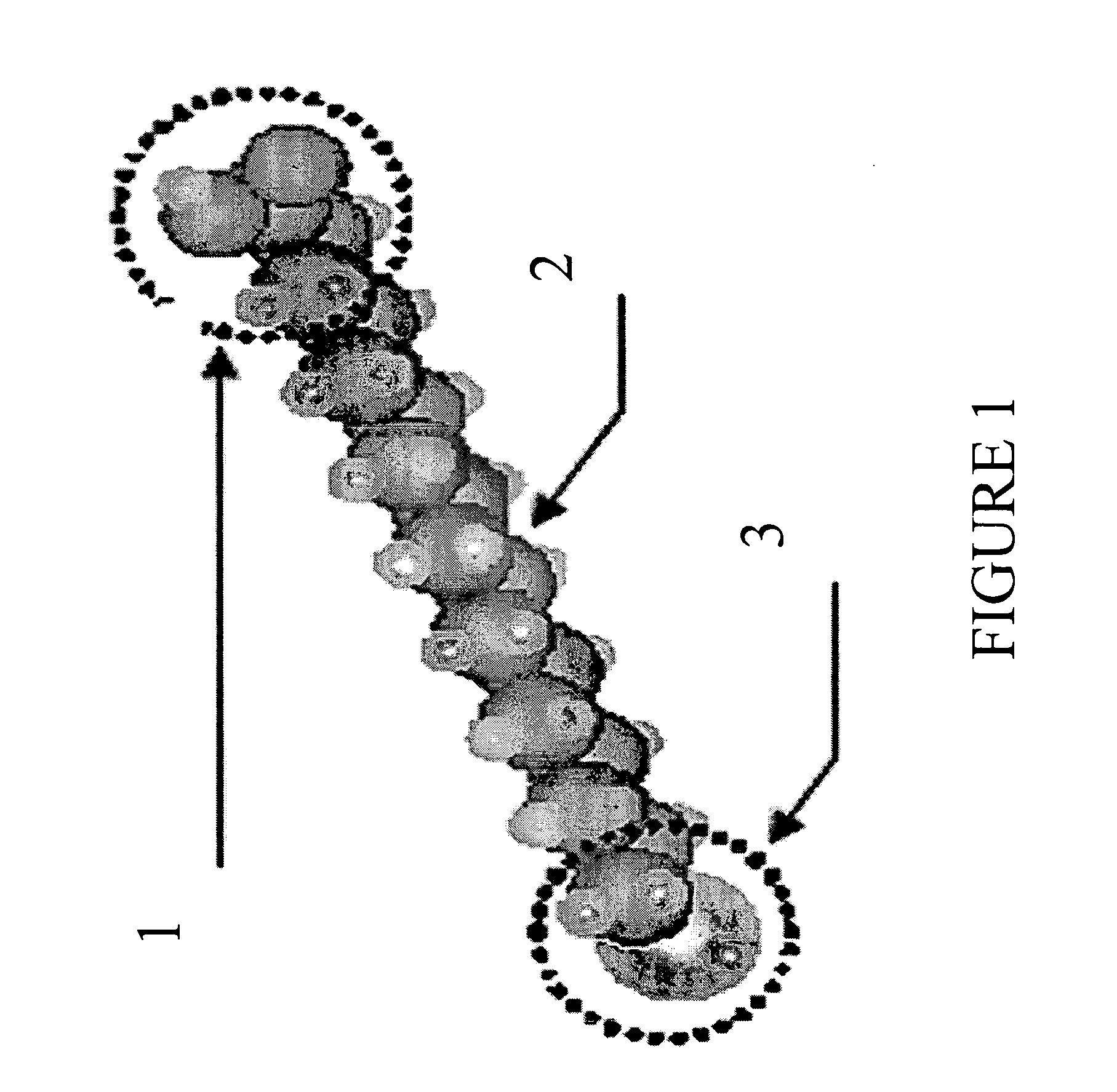

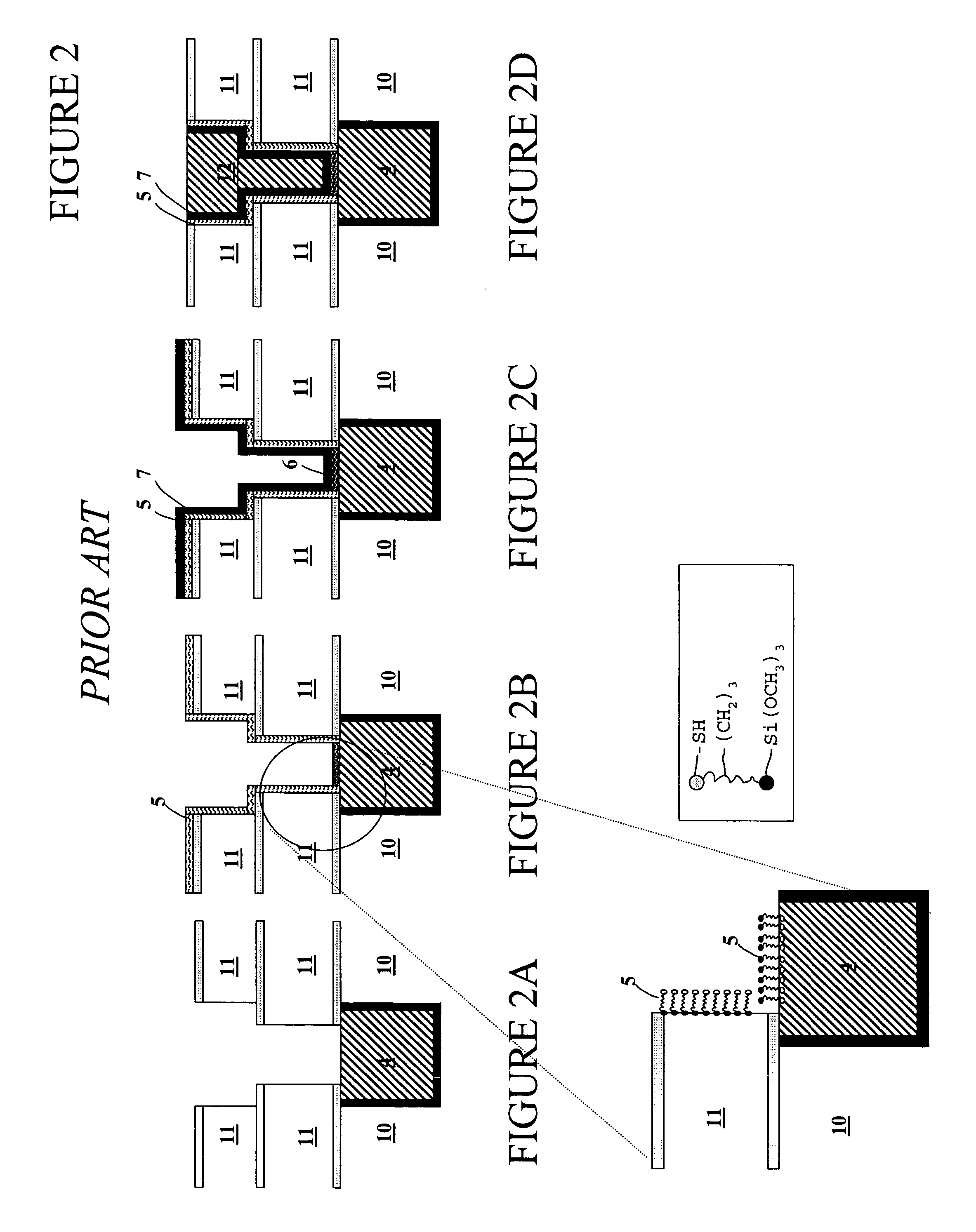

Method for selective deposition of a thin self-assembled monolayer

ActiveUS20060128142A1Material nanotechnologySemiconductor/solid-state device manufacturingSelf-assembled monolayerSelf assemble

A method for selective deposition of self-assembled monolayers to the surface of a substrate for use as a diffusion barrier layer in interconnect structures is provided comprising the steps of depositing a first self-assembled monolayer to said surface, depositing a second self-assembled monolayer to the non-covered parts of said surface and subsequently heating said substrate to remove the first self-assembled monolayer. The method of selective deposition of self-assembled monolayers is applied for the use as diffusion barrier layers in a (dual) damascene structure for integrated circuits.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW) +1

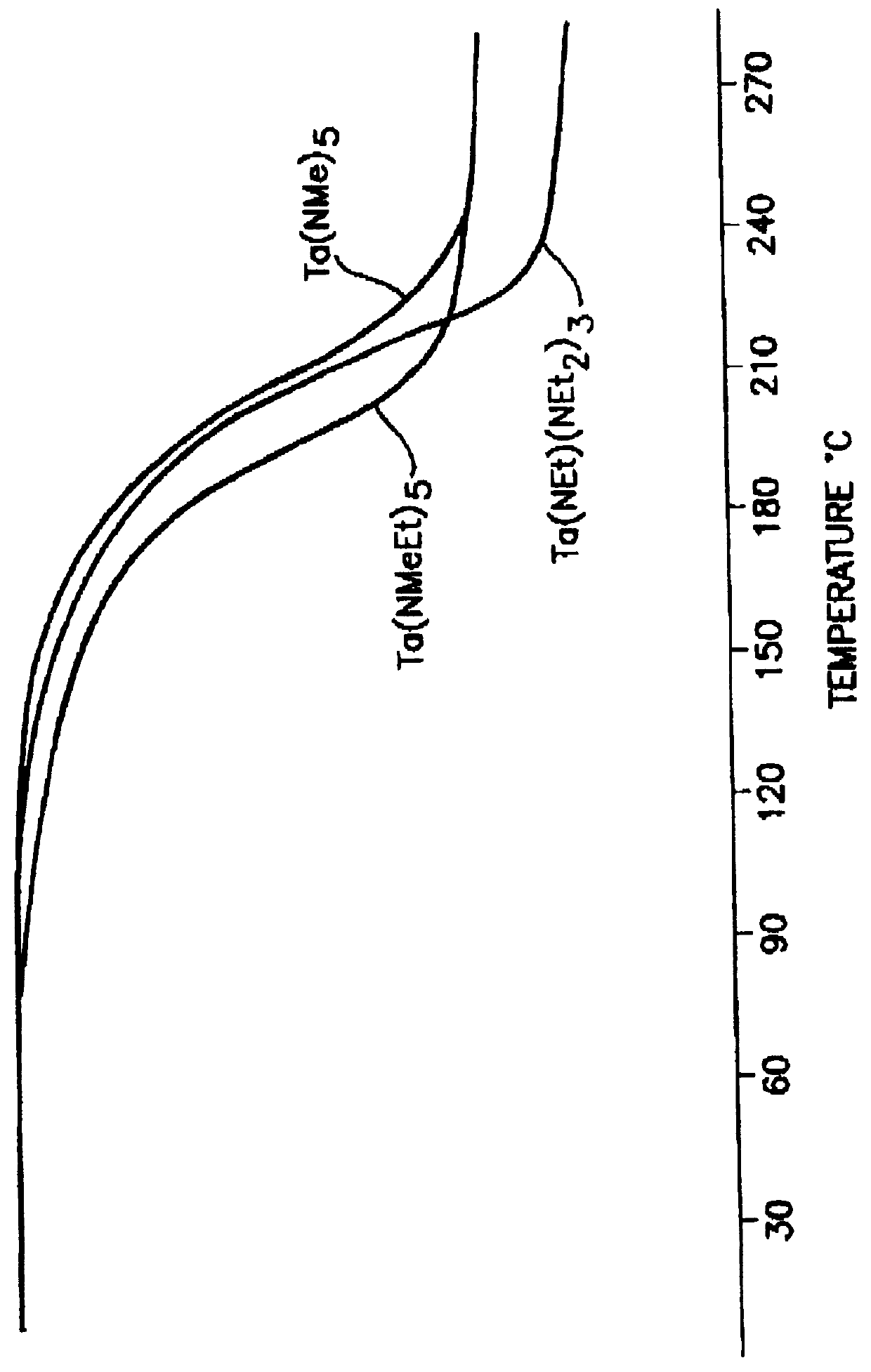

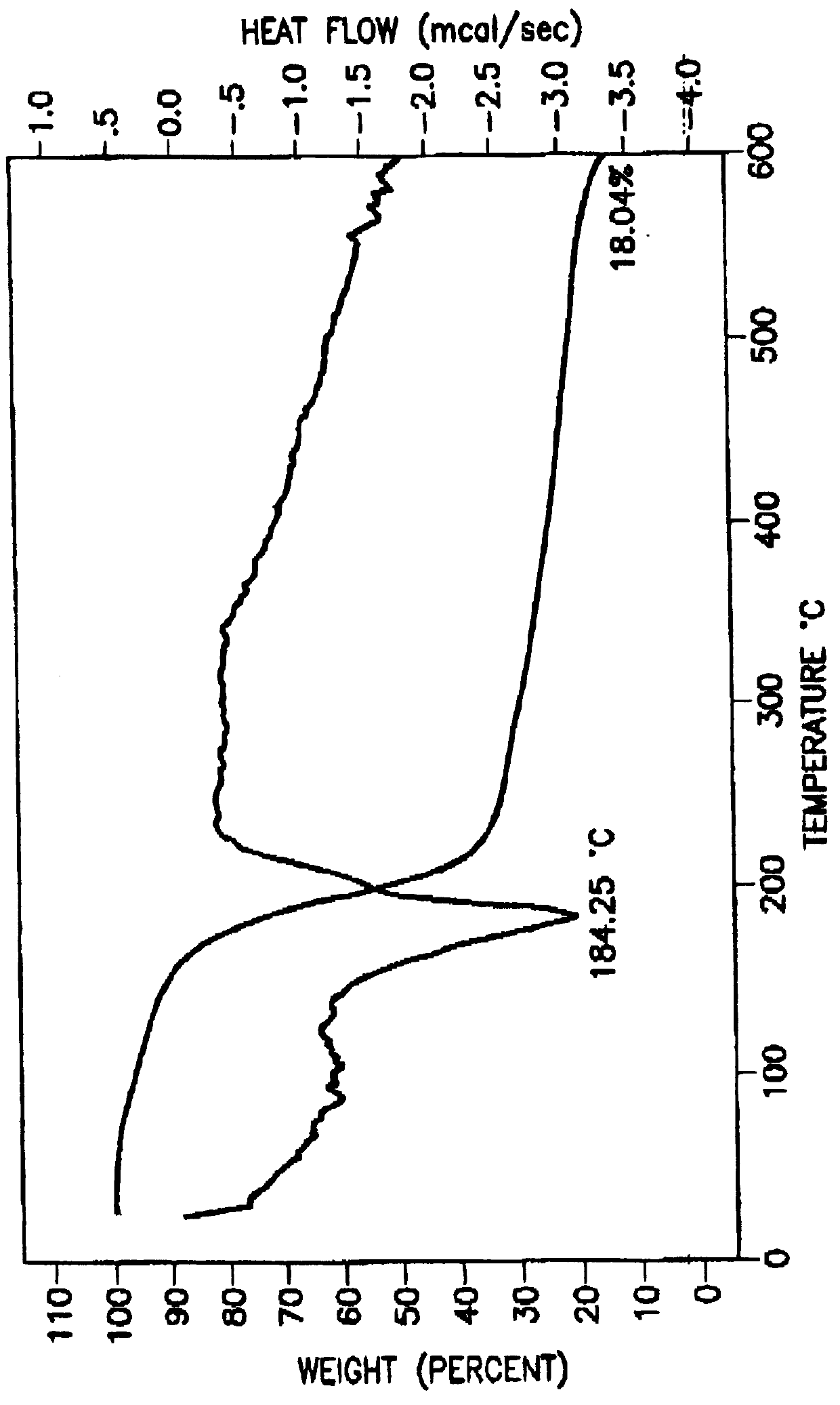

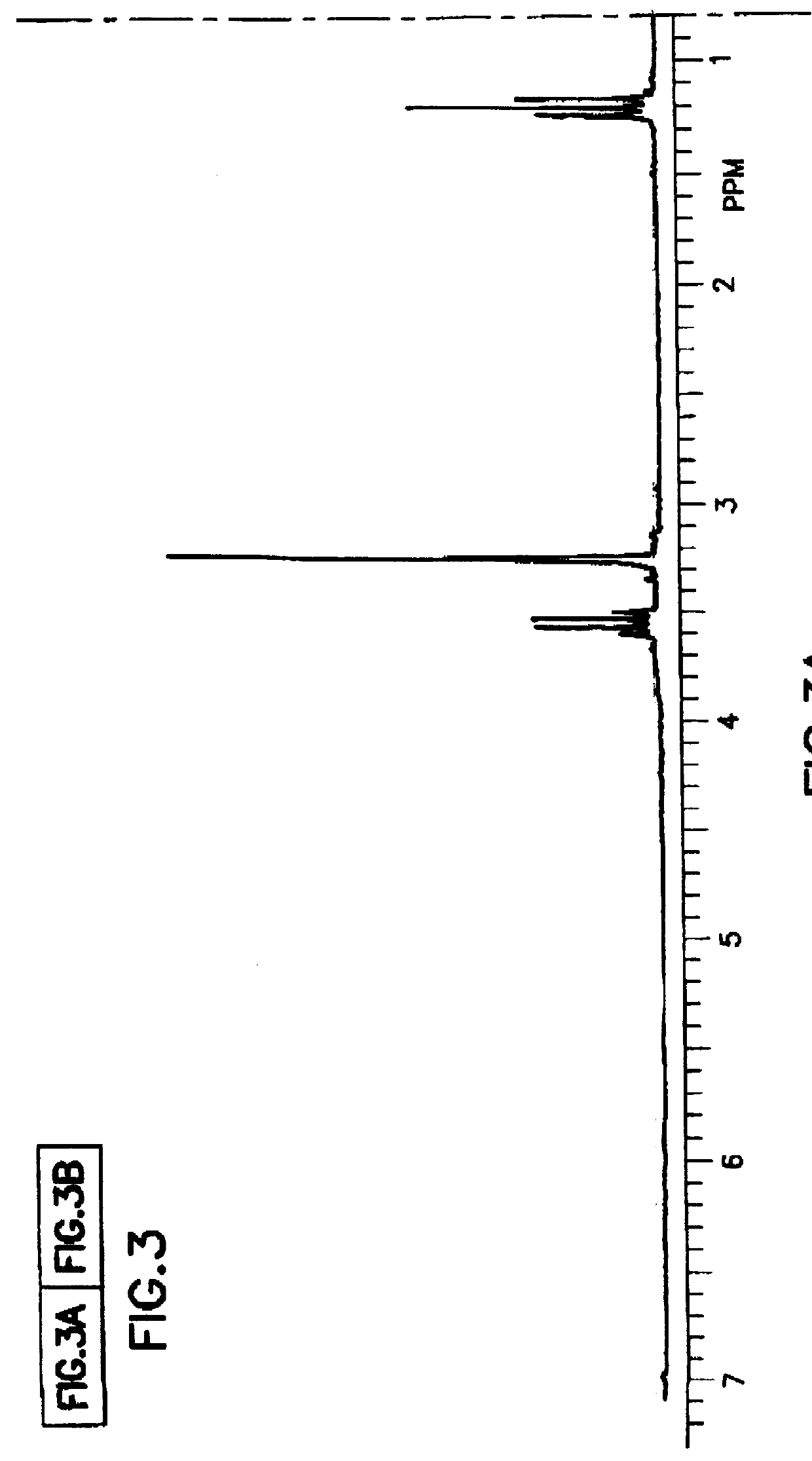

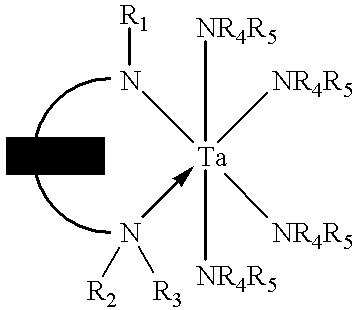

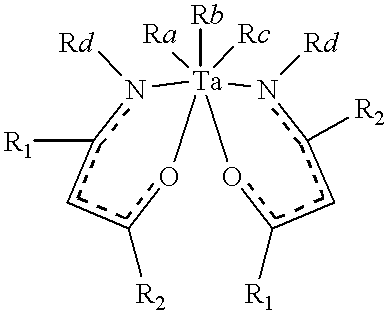

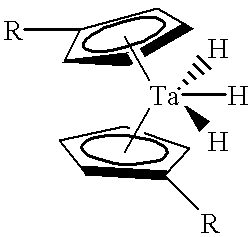

Tantalum amide precursors for deposition of tantalum nitride on a substrate

InactiveUS6015917ARapid heat treatmentSilicon organic compoundsPolycrystalline material growthFerroelectric thin filmsChemical vapor deposition

Tantalum and titanium source reagents are described, including tantalum amide and tantalum silicon nitride precursors for the deposition of tantalum nitride material on a substrate by processes such as chemical vapor deposition, assisted chemical vapor deposition, ion implantation, molecular beam epitaxy and rapid thermal processing. The precursors may be employed to form diffusion barrier layers on microlectronic device structures enabling the use of copper metallization and ferroelectric thin films in device construction.

Owner:ENTEGRIS INC

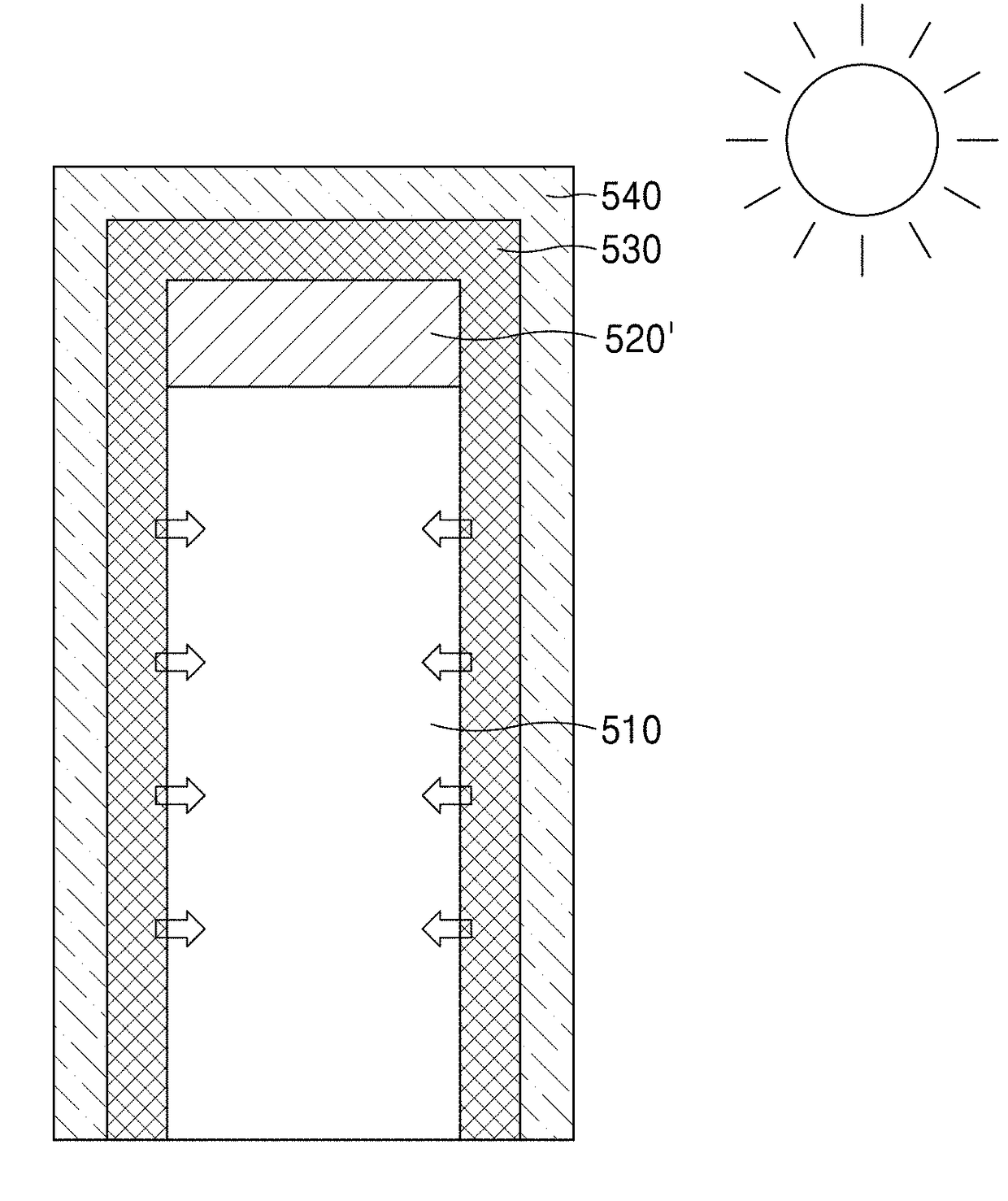

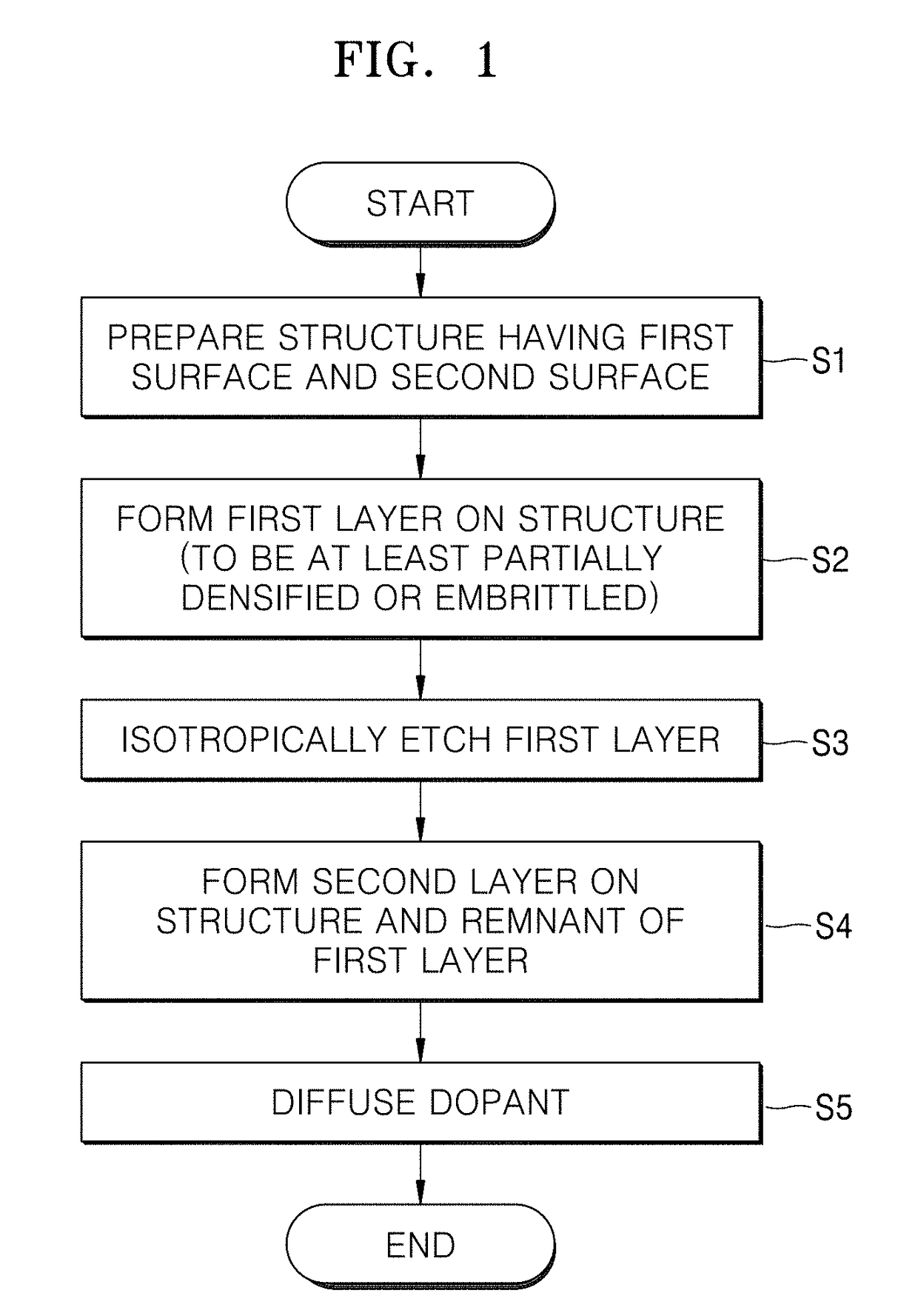

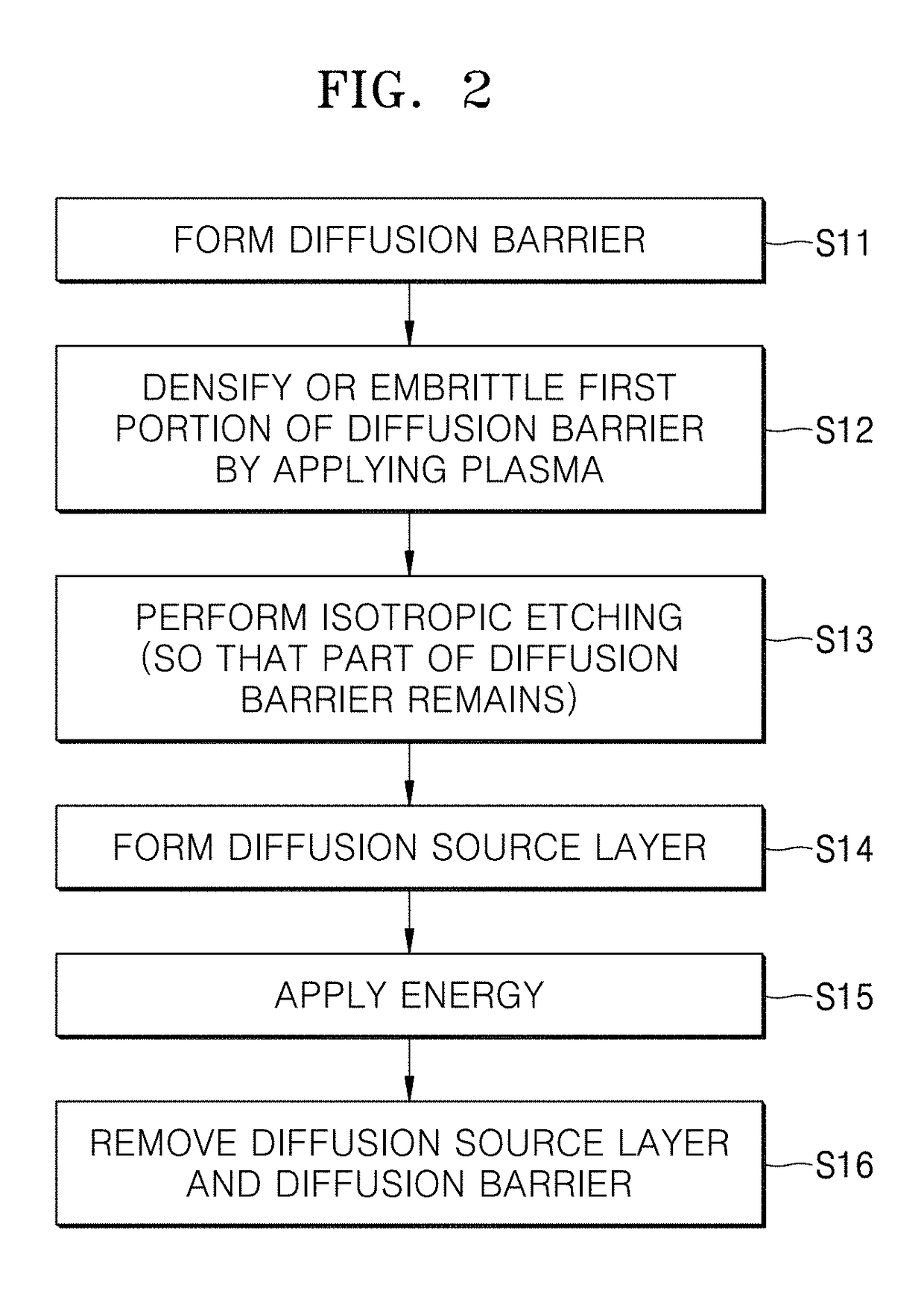

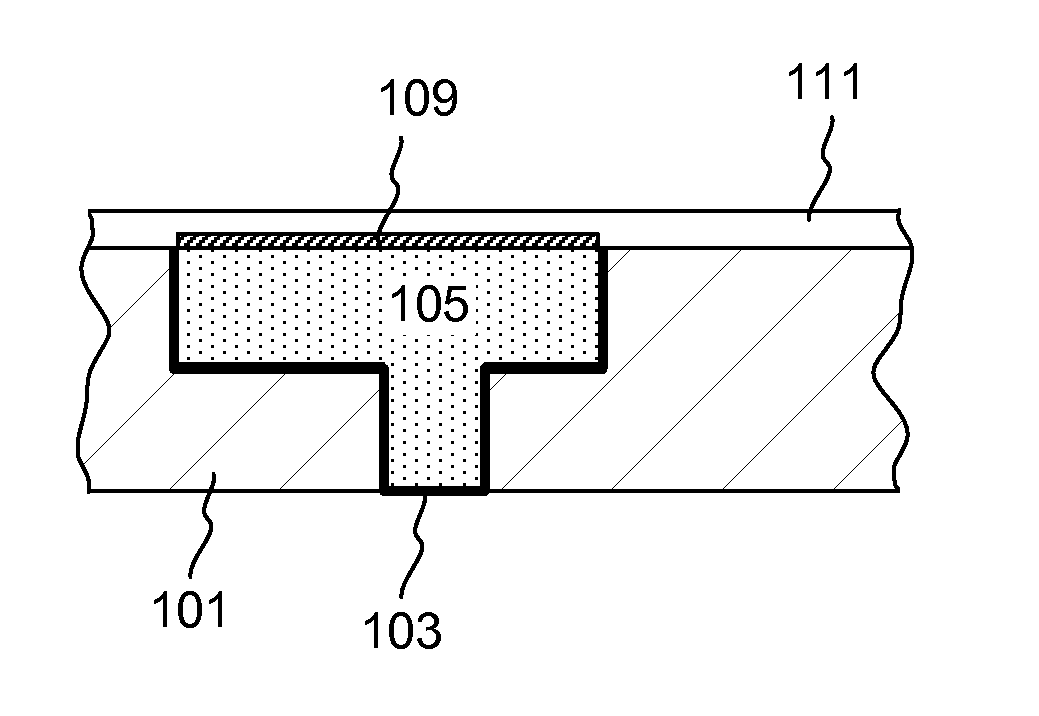

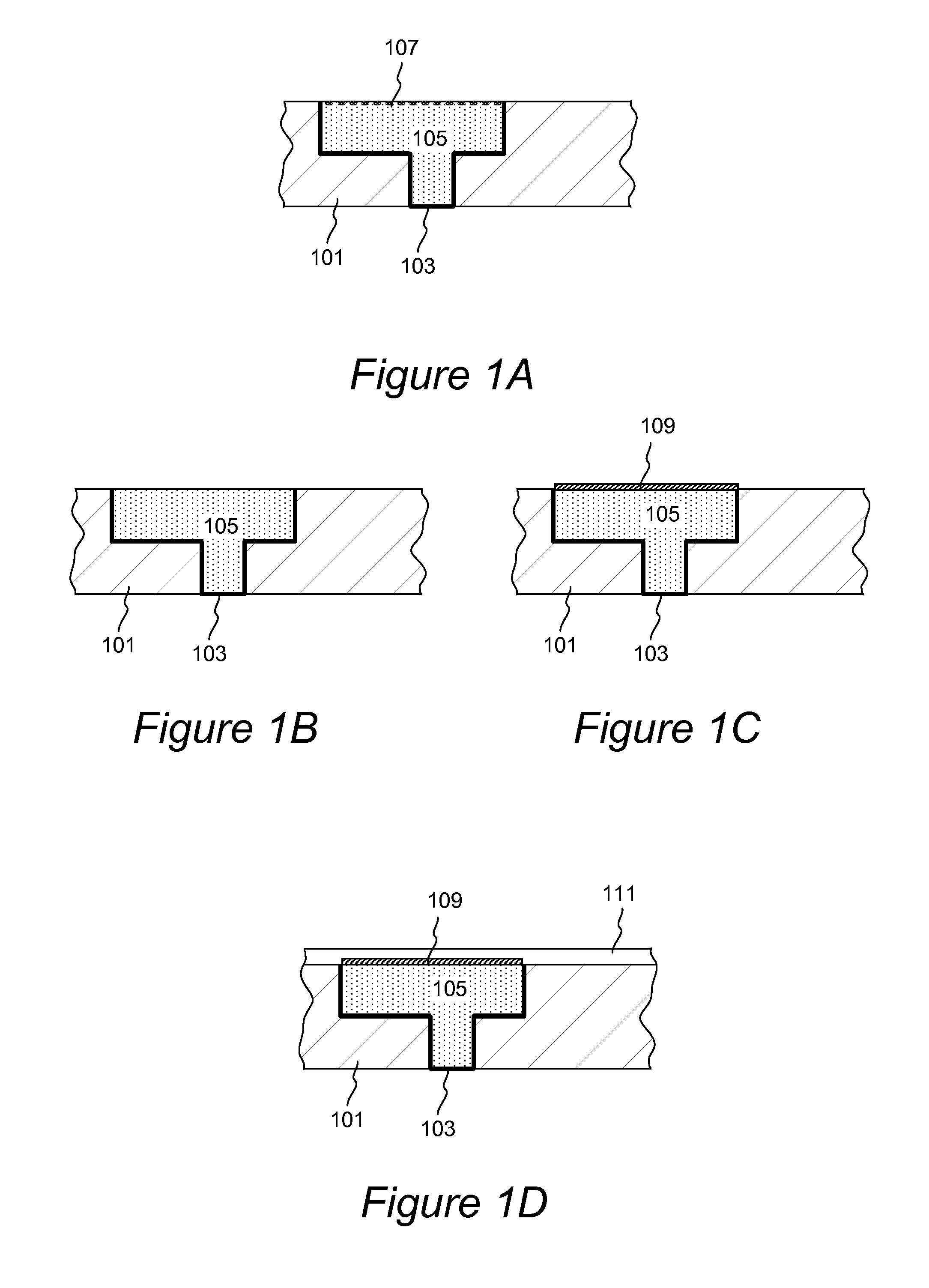

Method of processing substrate

A method of processing a substrate to enable selective doping without a photolithography process is provided. The method includes forming a diffusion barrier on the substrate having a patterned structure using plasma deposition method, removing the diffusion barrier except for part of the diffusion barrier using wet etching, forming a diffusion source layer on the patterned structure and the part of the diffusion barrier, and applying energy to the diffusion source layer.

Owner:ASM IP HLDG BV

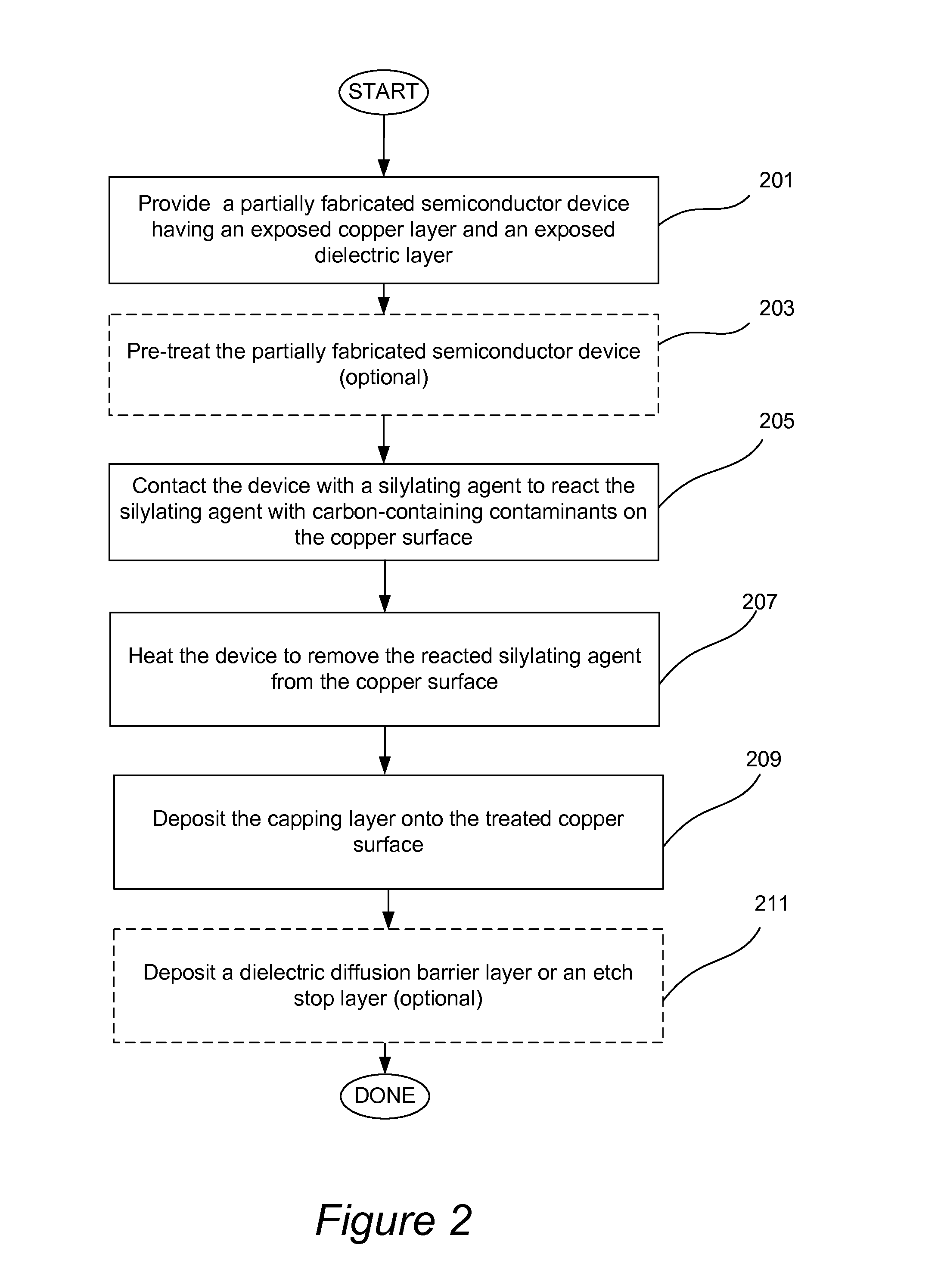

Cleaning of carbon-based contaminants in metal interconnects for interconnect capping applications

InactiveUS20150380296A1Avoid depositionLow deposition rateLiquid surface applicatorsSemiconductor/solid-state device manufacturingMetal interconnectSilylation

Protective caps residing at an interface between copper lines and dielectric diffusion barrier layers are used to improve various performance characteristics of interconnects. The caps, such as cobalt-containing caps or manganese-containing caps, are selectively deposited onto exposed copper lines in a presence of exposed dielectric using CVD or ALD methods. The deposition of the capping material is affected by the presence of carbon-containing contaminants on the surface of copper, which may lead to poor or uneven growth of the capping layer. A method of removing carbon-containing contaminants from the copper surface prior to deposition of caps involves contacting the substrate containing the exposed copper surface with a silylating agent at a first temperature to form a layer of reacted silylating agent on the copper surface, followed by heating the substrate at a higher temperature to release the reacted silylating agent from the copper surface.

Owner:LAM RES CORP

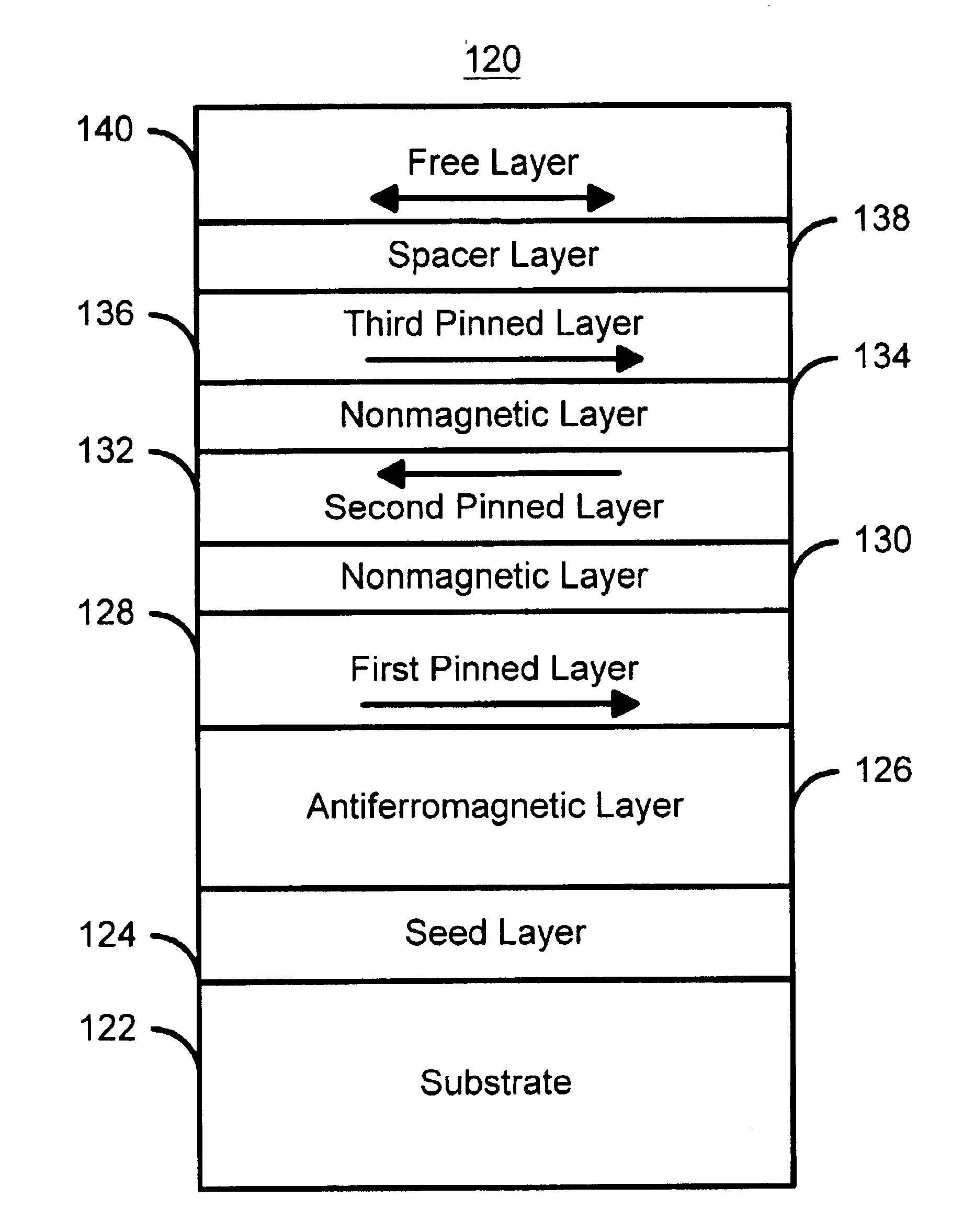

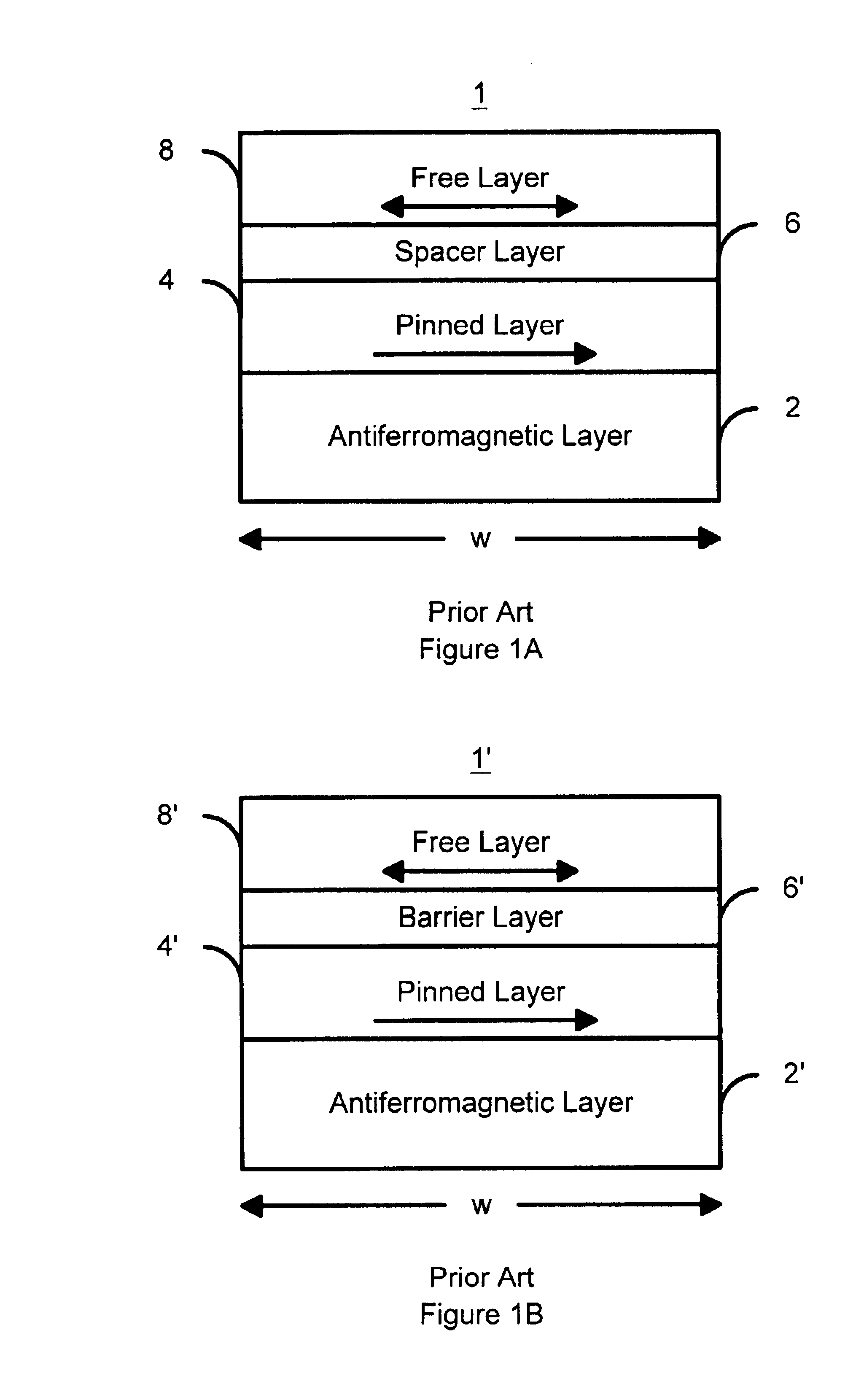

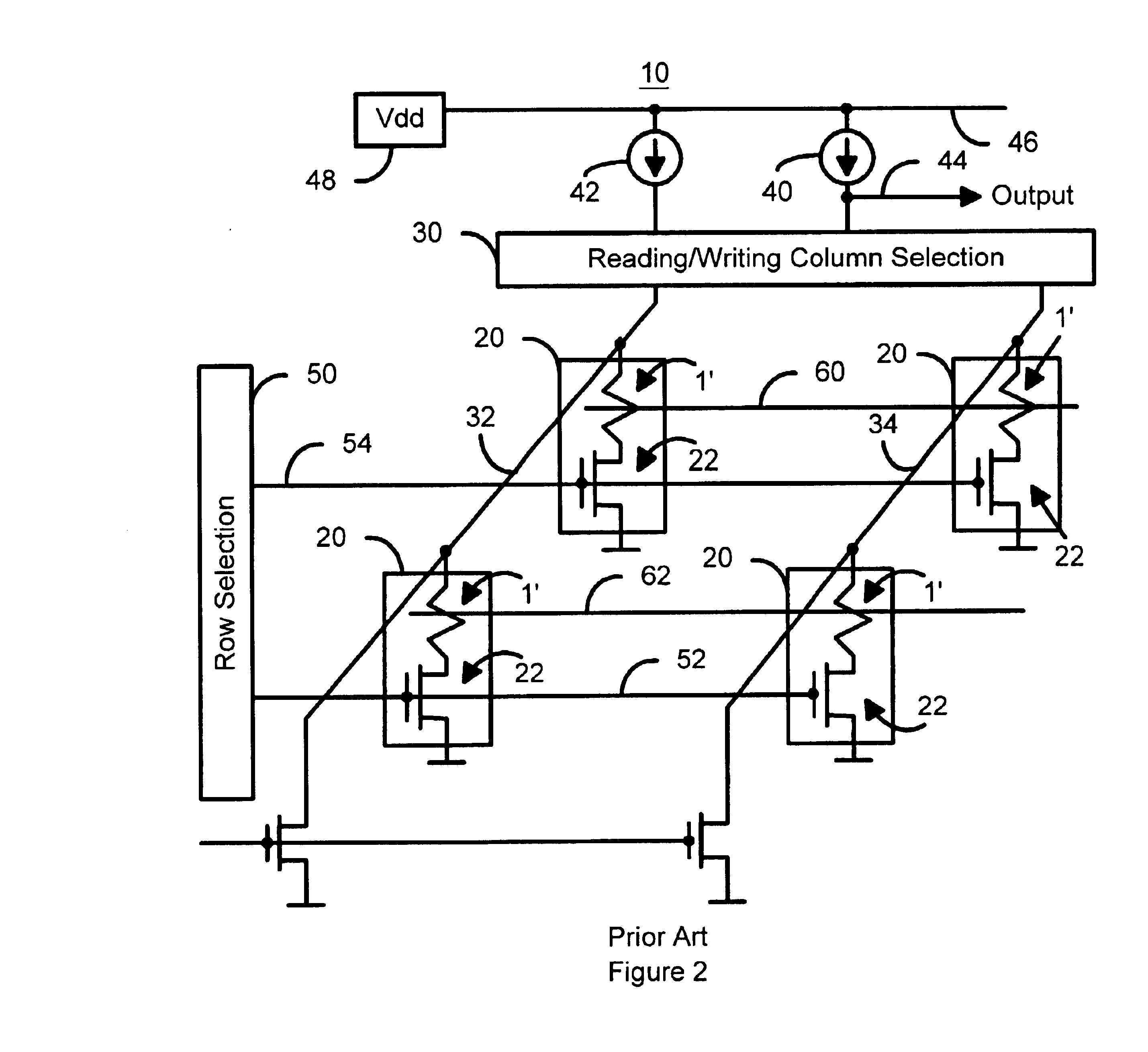

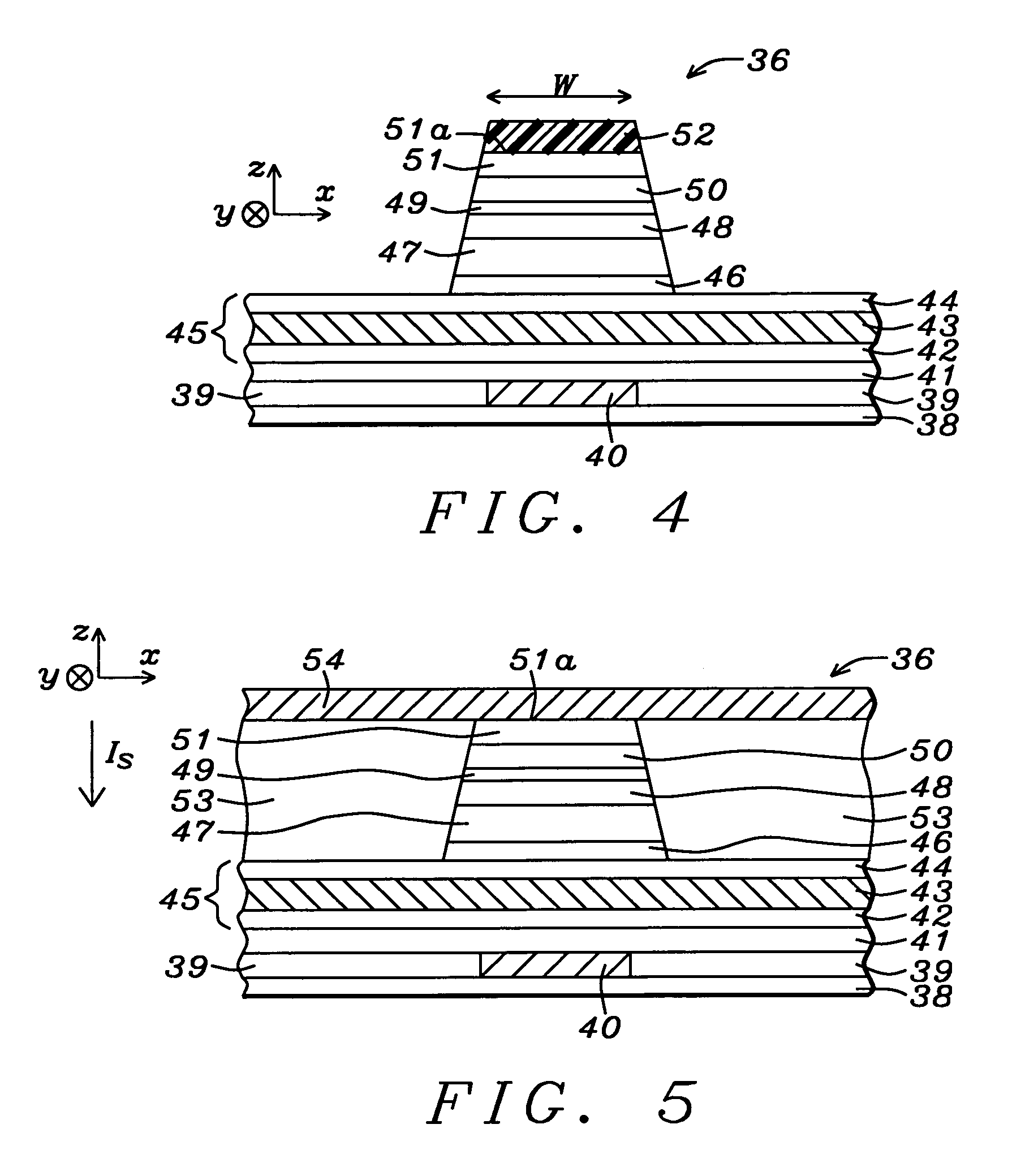

Thermally stable magnetic elements utilizing spin transfer and an MRAM device using the magnetic element

InactiveUS6838740B2Improve performanceImprove thermal stabilityTransistorNanomagnetismAntiferromagnetic couplingMagnetic memory

A method and system for providing a magnetic element capable of being written using spin-transfer effect while being thermally stable and a magnetic memory using the magnetic element are disclosed. The magnetic element includes a first, second and third pinned layers, first and second nonmagnetic layers, a free layer and a nonmagnetic spacer layers. The first, second and third pinned layers are ferromagnetic and have first, second and third magnetizations pinned in first, second and third directions. The first and second nonmagnetic layers include first and second diffusion barriers, respectively. The first and second nonmagnetic layers are between the first and second pinned layers and the second and third pinned layers, respectively. The first and second pinned layers and the second and third pinned layers are antiferromagnetically coupled. The nonmagnetic spacer layer is conductive and resides between the free layer and the third pinned layer. In addition, performance can be further improved by doping Co containing ferromagnetic layers with Cr and / or Pt.

Owner:SAMSUNG SEMICON

Novel film for copper diffusion barrier

InactiveUS20060019486A1Semiconductor/solid-state device detailsSolid-state devicesAtmospheric airBoron nitride

The present invention provides a low dielectric constant copper diffusion barrier film suitable for use in a semiconductor device and methods for fabricating such a film. Some embodiments of the film are formed of a silicon-based material doped with boron. Other embodiments are formed, at least in part, of boron nitride. Some such embodiments include a moisture barrier film that includes oxygen and / or carbon. Preferred embodiments of the copper diffusion barrier maintain a stable dielectric constant of less than 4.5 in the presence of atmospheric moisture.

Owner:NOVELLUS SYSTEMS

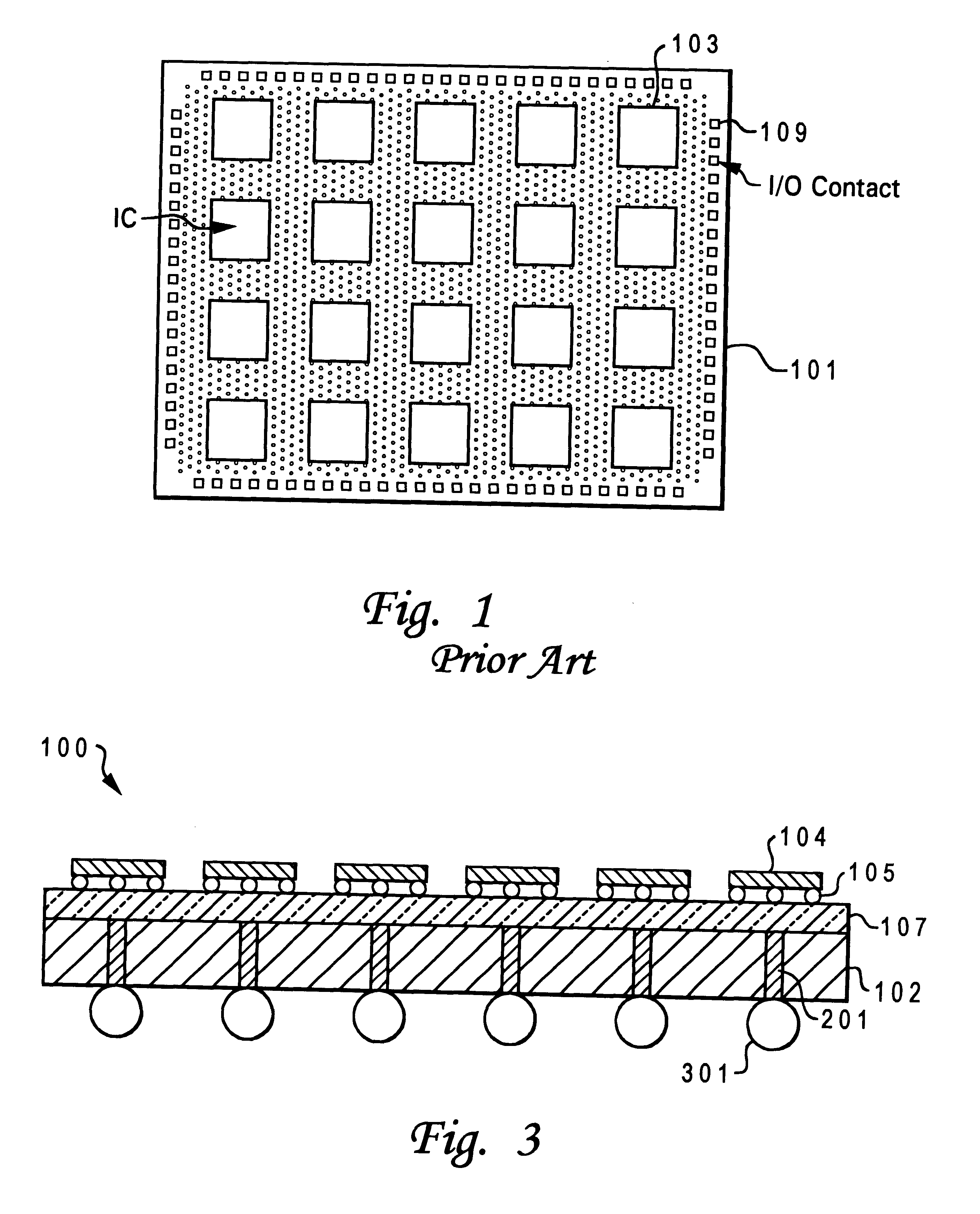

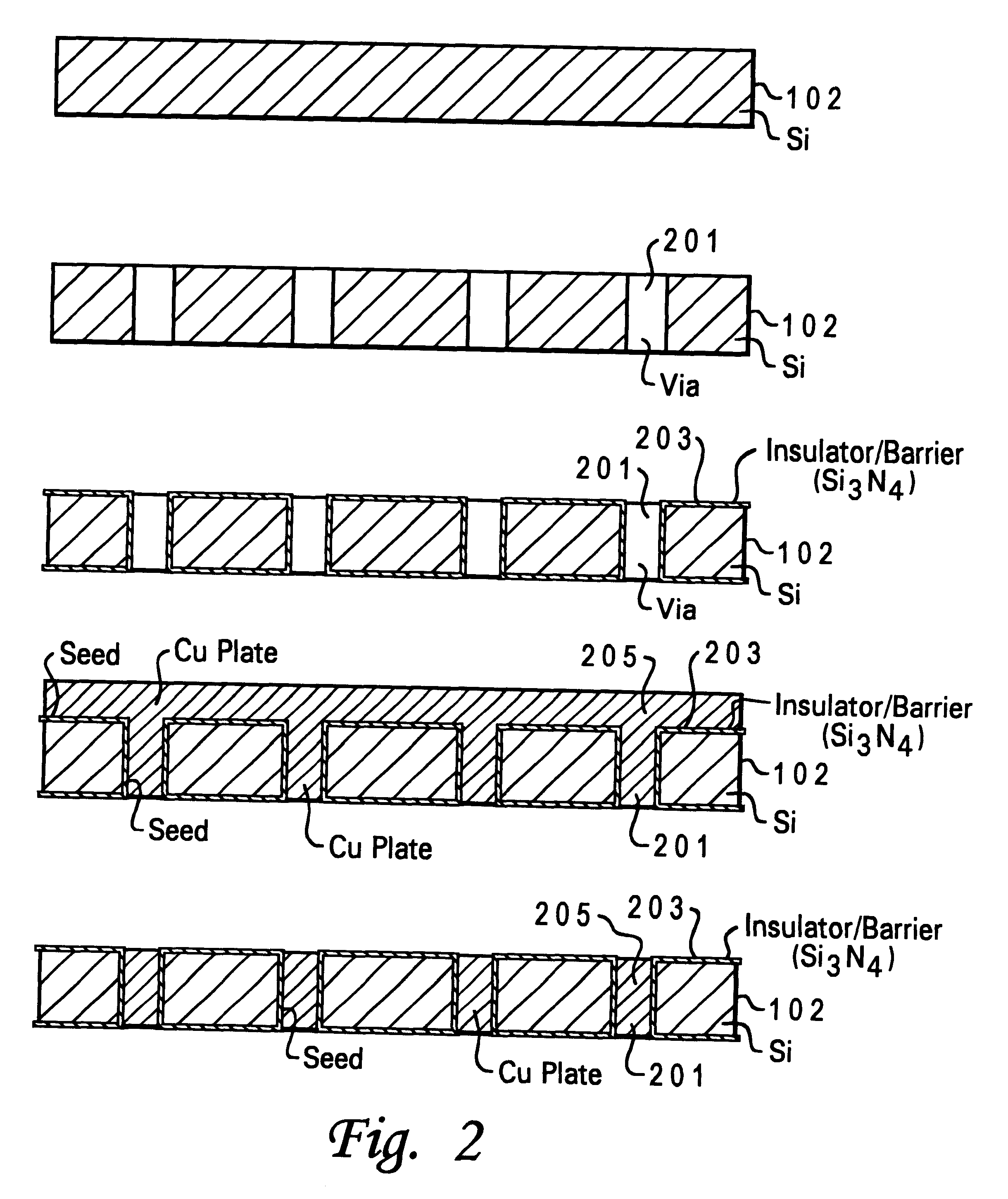

Method for integrated circuit power and electrical connections via through-wafer interconnects

InactiveUS6221769B1Solid-state devicesSemiconductor/solid-state device manufacturingHigh rateElectrical connection

A method for providing a through wafer connection to an integrated circuit silicon package. A hole is first created in the silicon package with an inner surface area extending from the bottom surface of the silicon package to the top surface of the silicon package. The hole is created by one of two methods. The first involves mechanical drilling with a diamond bit rotated at a high rate of speed. The second involves ultrasonically milling utilizing a slurry and steel fingers. The inner surface area of the hole is covered with an insulating material to insulate the conductive material which is later deposited and to serve as a diffusion barrier, then a seed material is placed in the hole. Finally, the hole is filled with a conductive material which is utilized to provide large power inputs or signaling connections to the integrated circuit chips.

Owner:IBM CORP

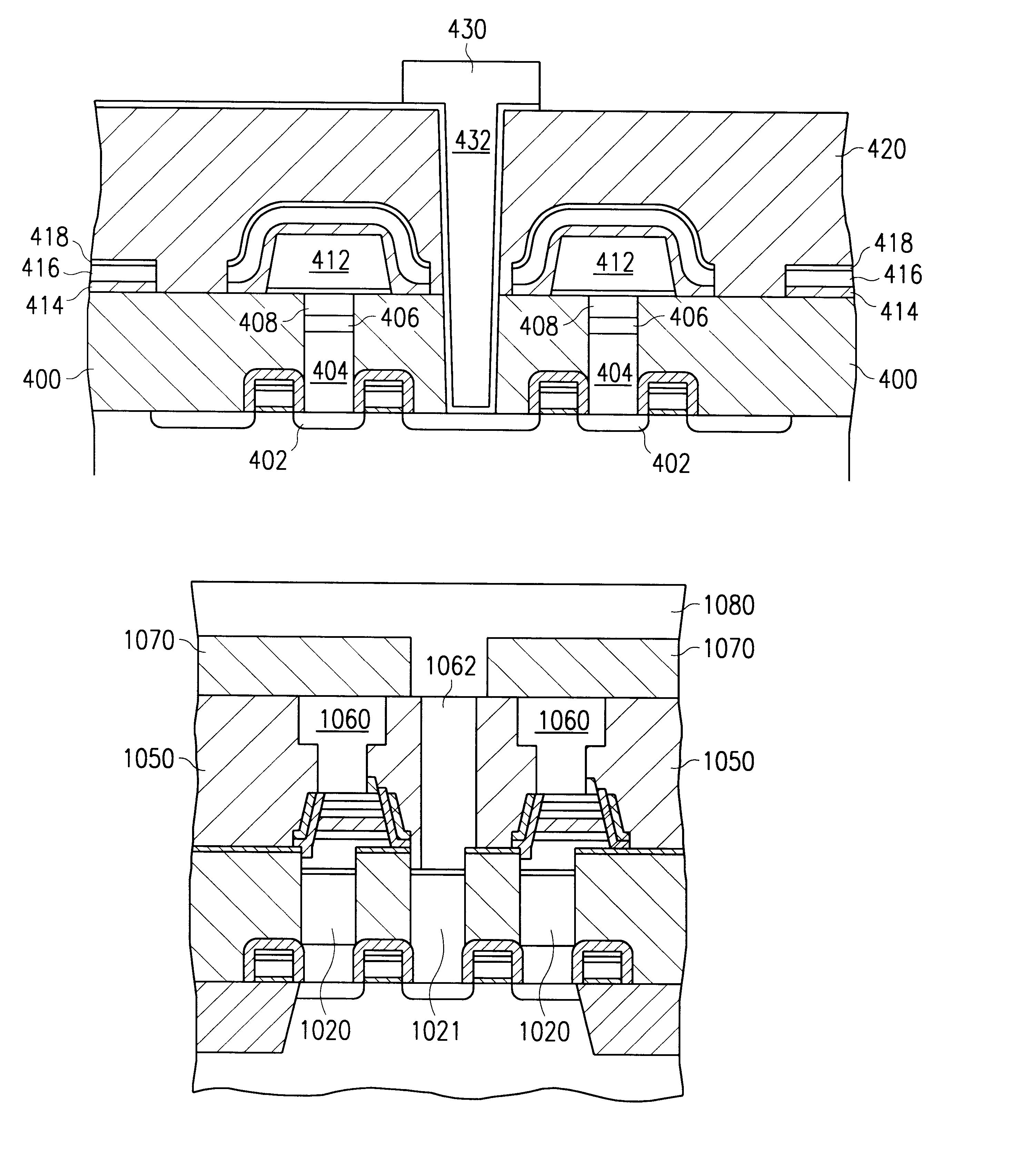

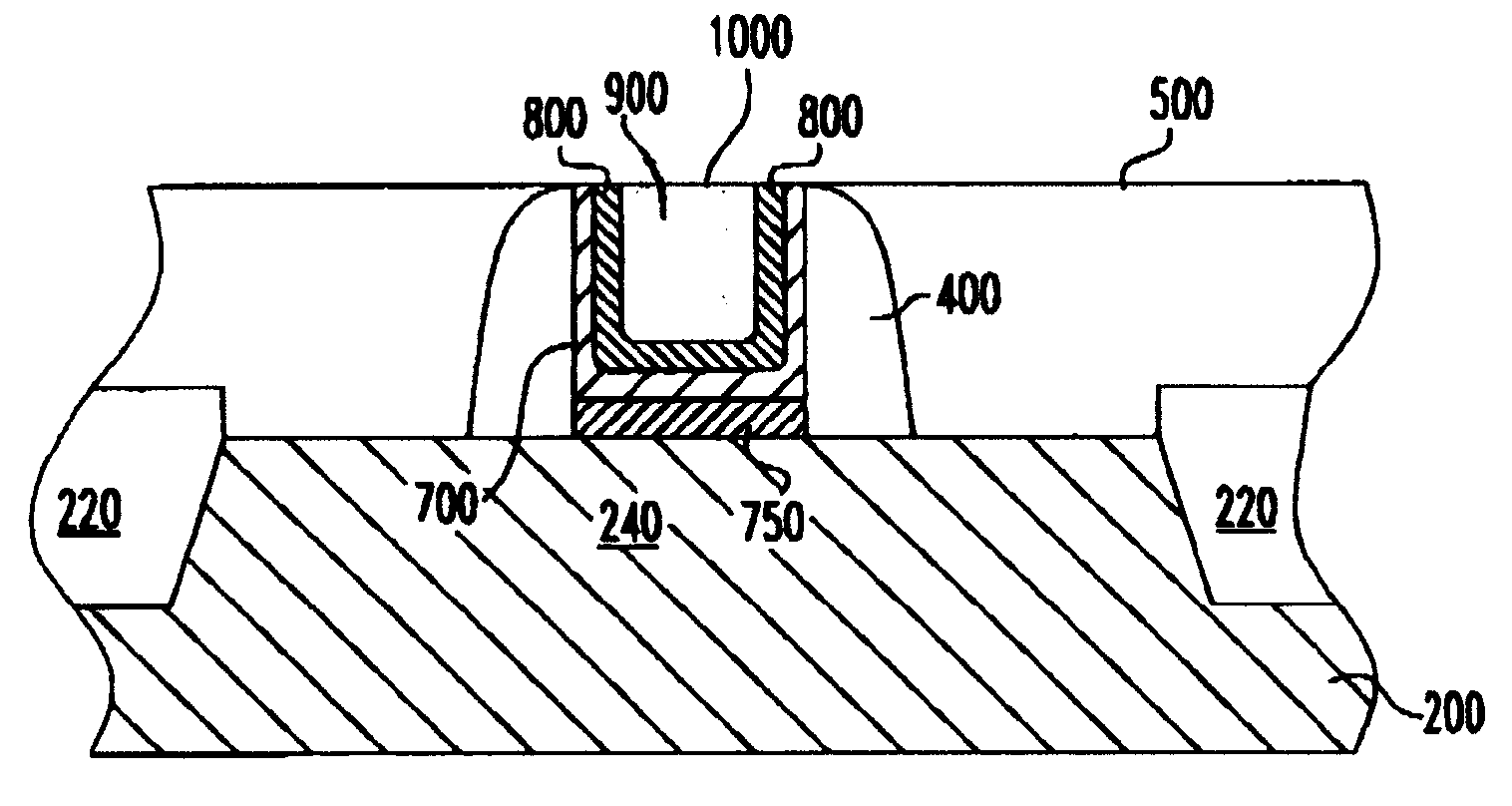

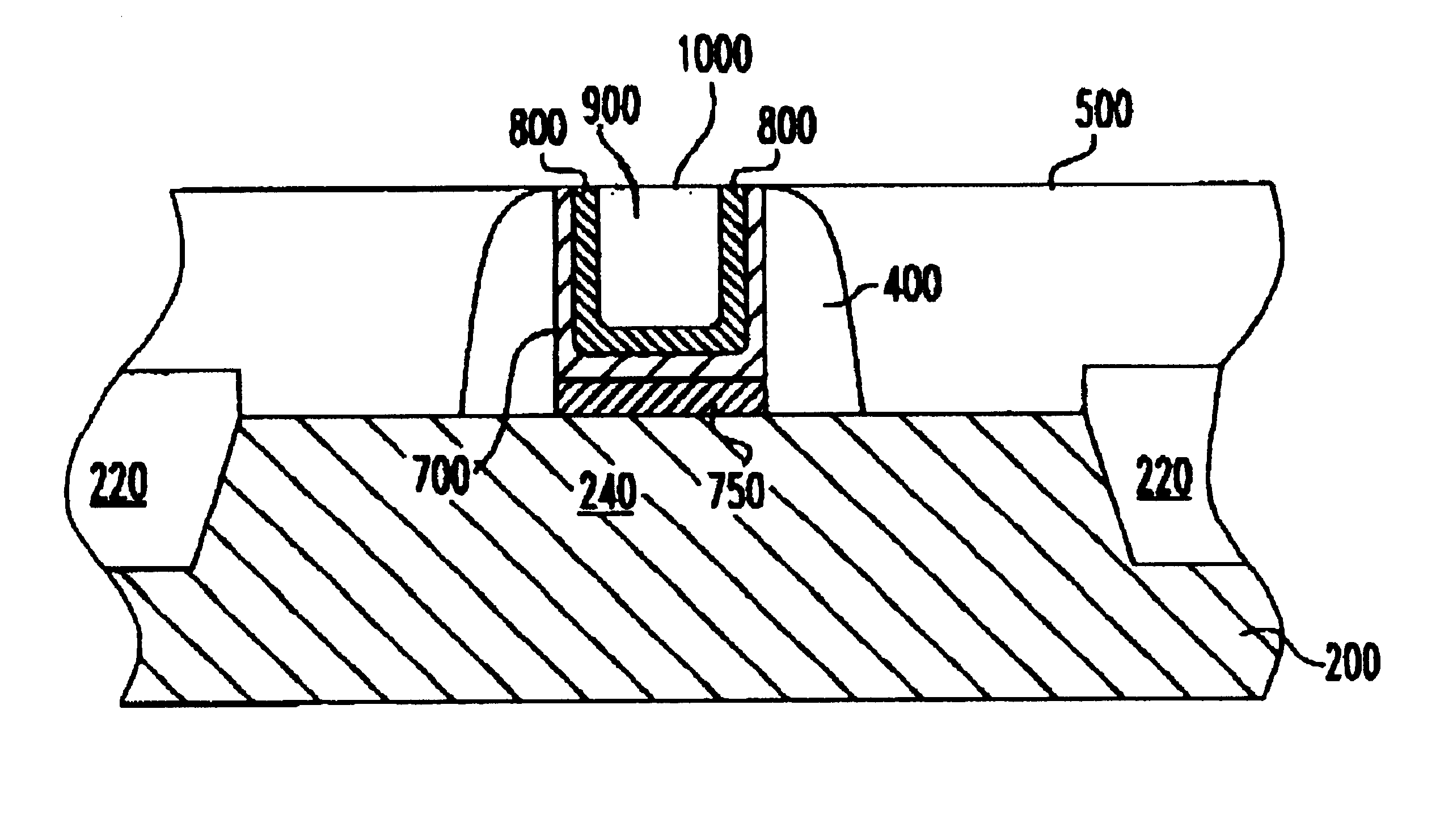

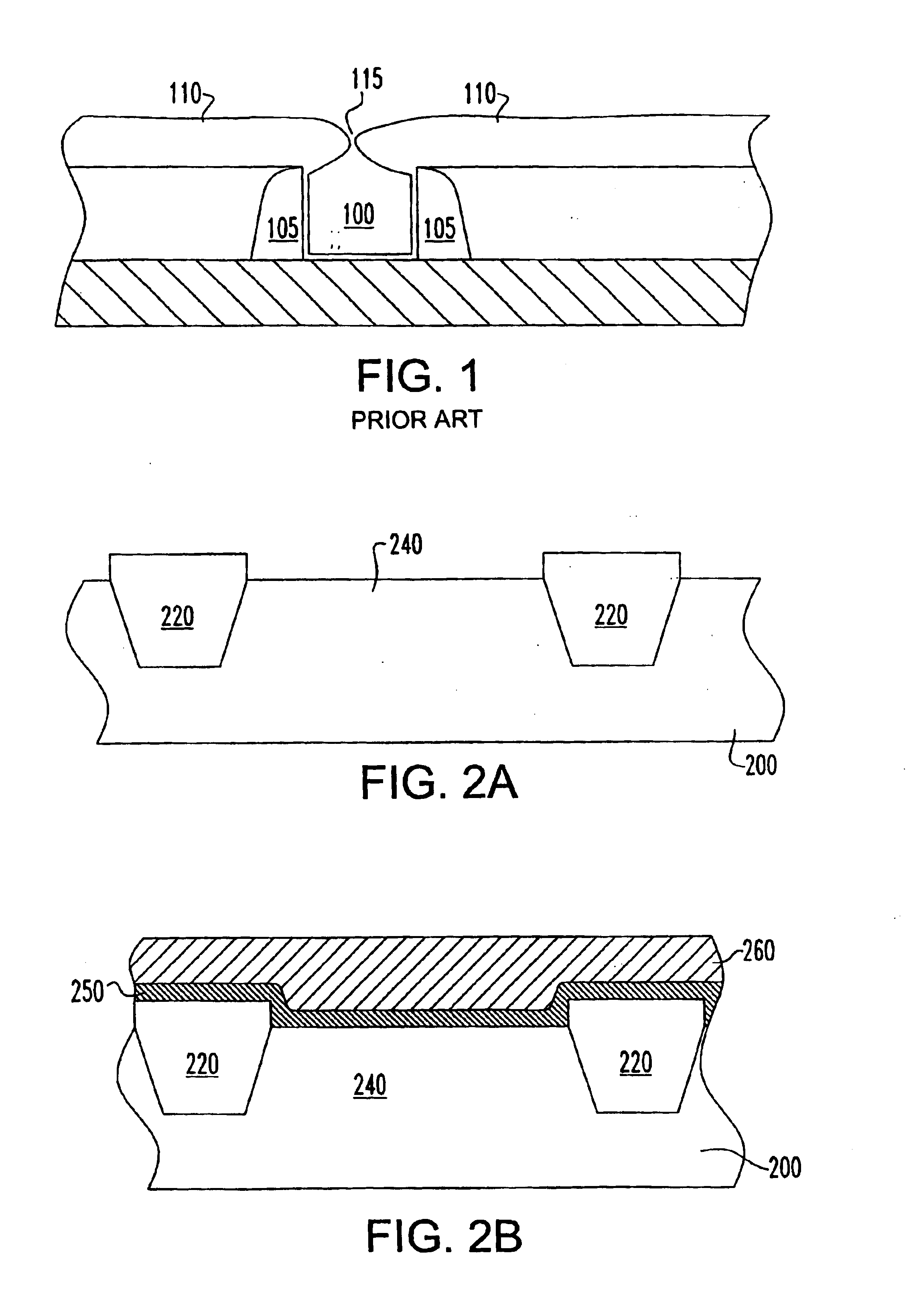

Structure and method for metal replacement gate of high performance

ActiveUS20050051854A1Improve performanceSemiconductor/solid-state device manufacturingSemiconductor devicesTitanium nitrideDiffusion barrier

A structure and method for a metal replacement gate of a high performance device is provided. A sacrificial gate structure is first formed on an etch stop layer provided on a semiconductor substrate. A pair of spacers is provided on sidewalls of the sacrificial gate structure. The sacrificial gate structure is then removed, forming an opening. Subsequently, a metal gate including an first layer of metal such as tungsten, a diffusion barrier such as titanium nitride, and a second layer of metal such as tungsten is formed in the opening between the spacers.

Owner:GLOBALFOUNDRIES US INC

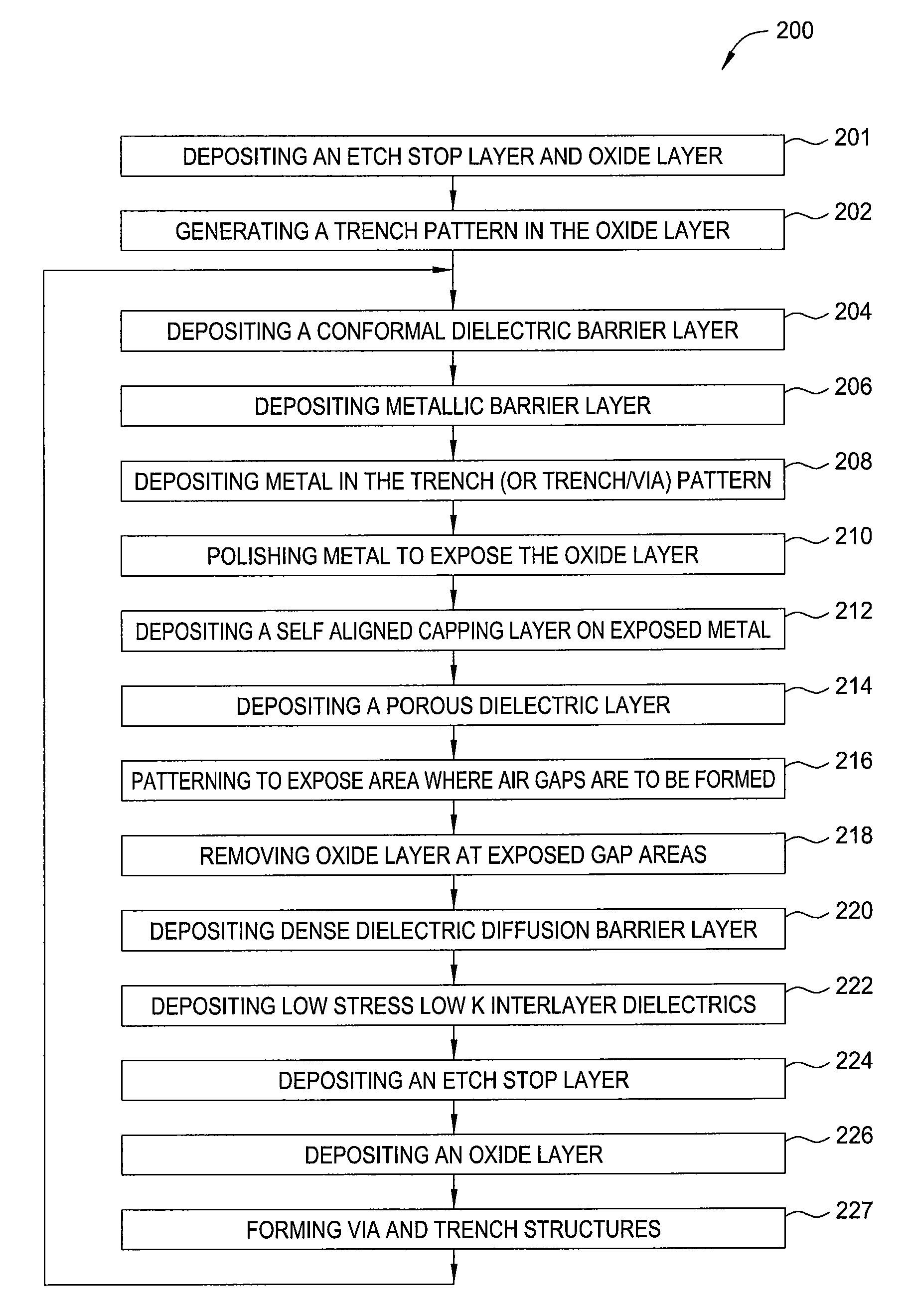

Method for forming an air gap in multilevel interconnect structure

InactiveUS20090093100A1Solid-state devicesSemiconductor/solid-state device manufacturingSemiconductor structureEngineering

The present invention generally provides a method for forming multilevel interconnect structures, including multilevel interconnect structures that include an air gap. One embodiment provides a method for forming conductive lines in a semiconductor structure comprising forming trenches in a first dielectric layer, wherein air gaps are to be formed in the first dielectric layer, depositing a conformal dielectric barrier film in the trenches, wherein the conformal dielectric barrier film comprises a low k dielectric material configured to serve as a barrier against a wet etching chemistry used in forming the air gaps in the first dielectric layer, depositing a metallic diffusion barrier film over the conformal low k dielectric layer, and depositing a conductive material to fill the trenches.

Owner:APPLIED MATERIALS INC

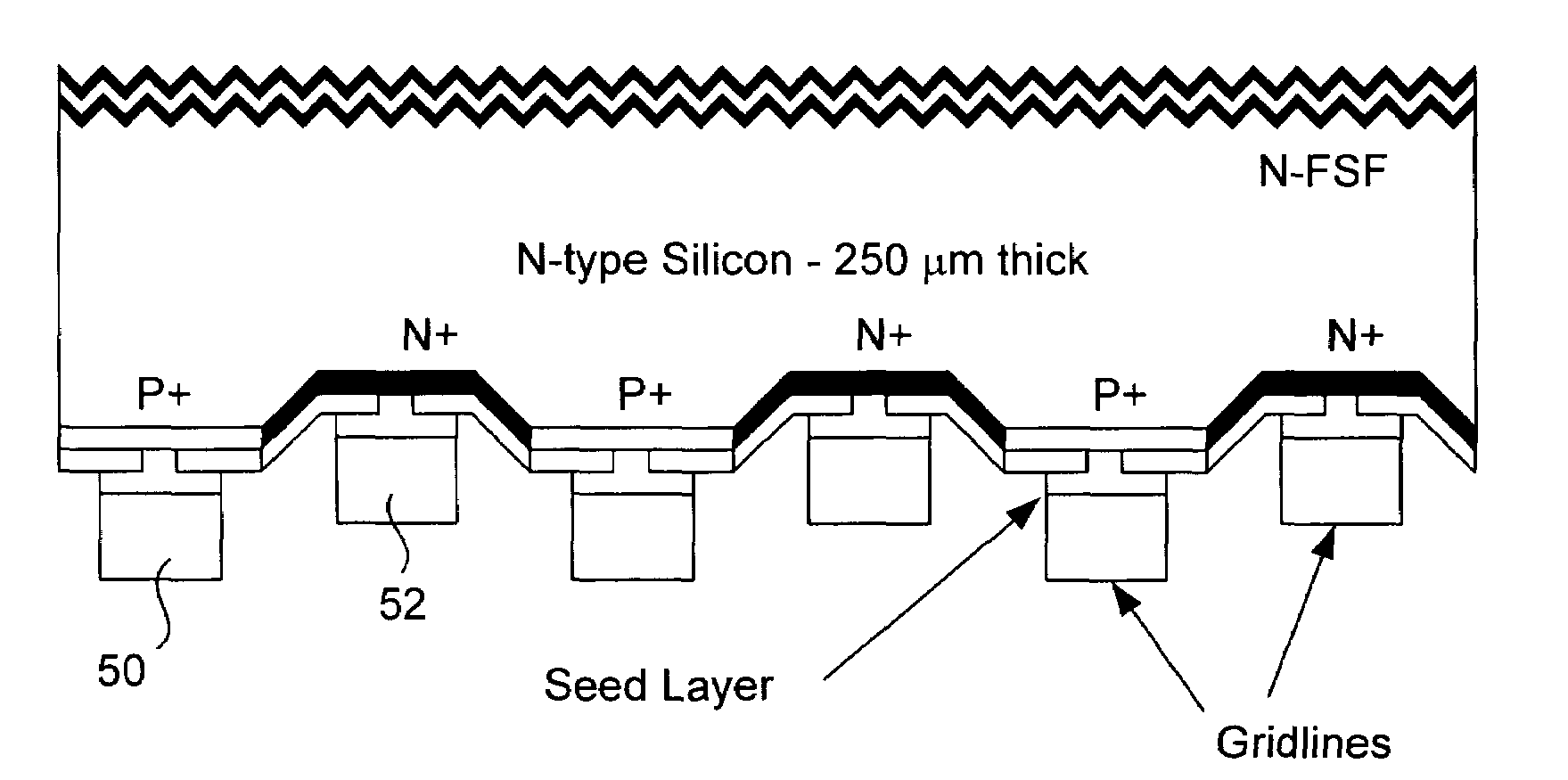

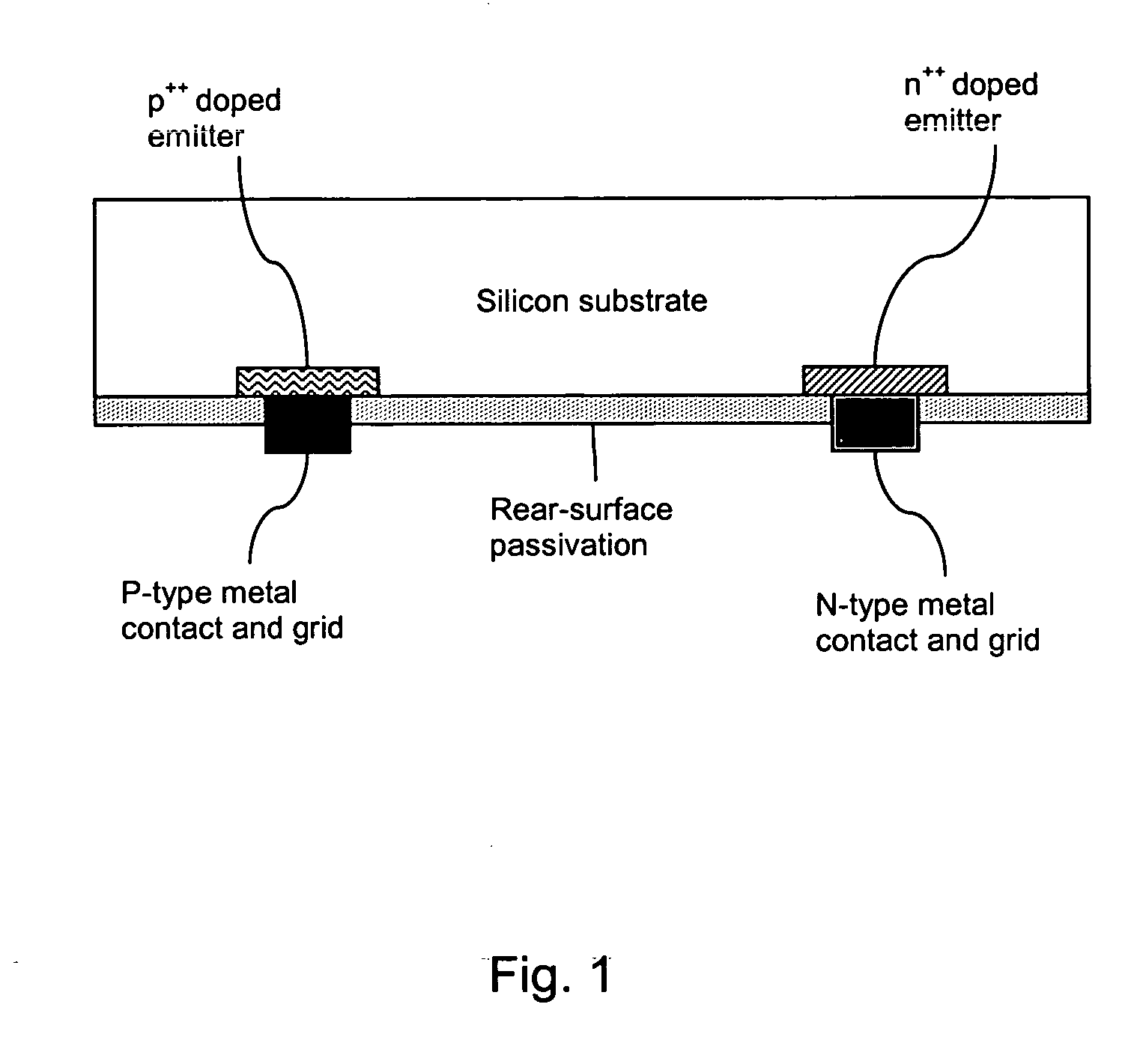

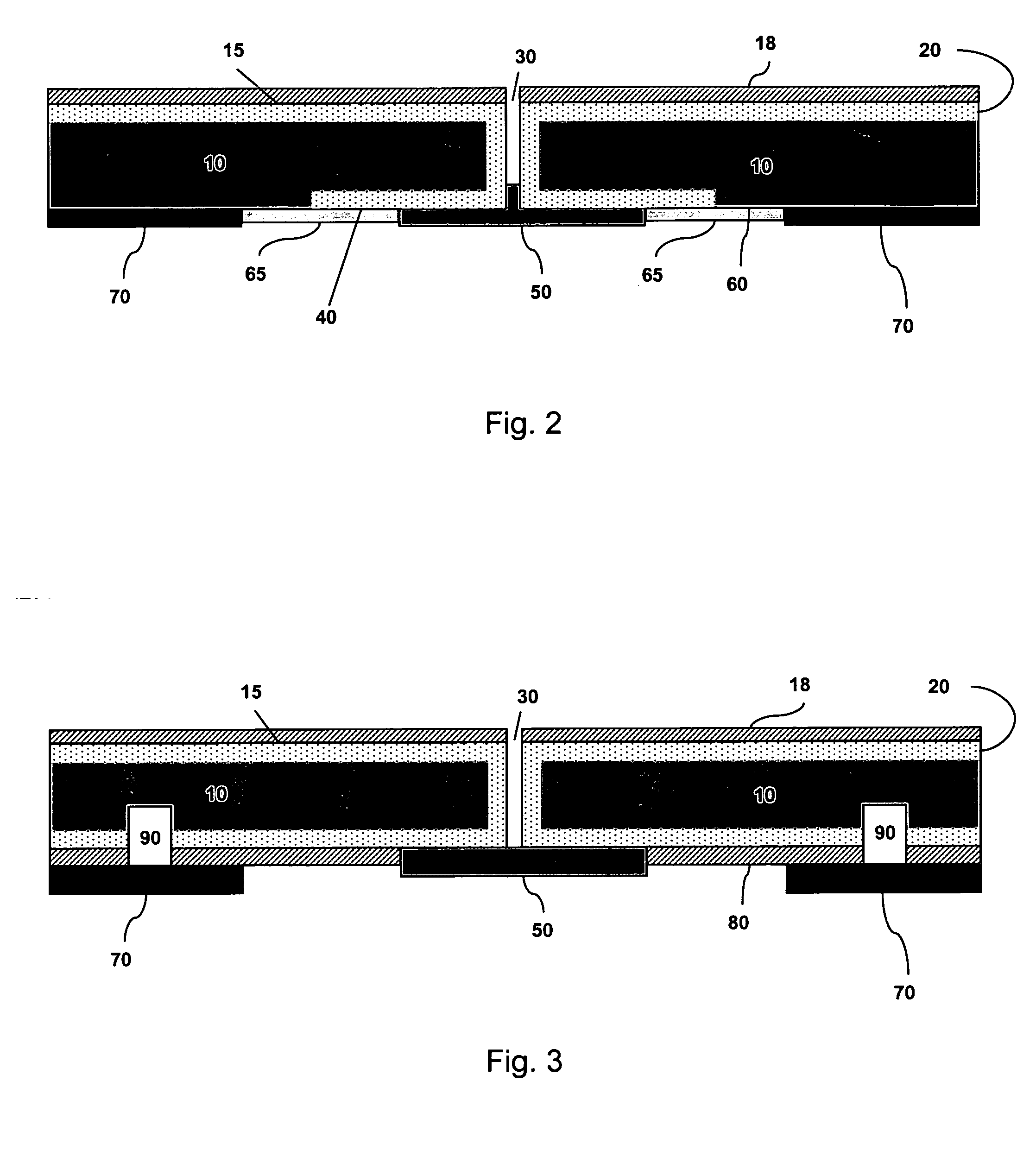

Contact fabrication of emitter wrap-through back contact silicon solar cells

InactiveUS20050172996A1Few and economical process stepImprove efficiencyFinal product manufactureSemiconductor/solid-state device manufacturingEngineeringSilicon solar cell

Back contact solar cells including rear surface structures and methods for making same. The rear surface has small contact areas through at least one dielectric layer, including but not limited to a passivation layer, a nitride layer, a diffusion barrier, and / or a metallization barrier. The dielectric layer is preferably screen printed. Large grid areas overlay the dielectric layer. The methods provide for increasing efficiency by minimizing p-type contact areas and maximizing n-type doped regions on the rear surface of a p-type substrate.

Owner:APPLIED MATERIALS INC

Tantalum amide precursors for deposition of tantalum nitride on a substrate

InactiveUS6379748B1Rapid heat treatmentSilicon organic compoundsPolycrystalline material growthFerroelectric thin filmsChemical vapor deposition

Tantalum and titanium source reagents are described, including tantalum amide and tantalum silicon nitride precursors for the deposition of tantalum nitride material on a substrate by processes such as chemical vapor deposition, assisted chemical vapor deposition, ion implantation, molecular beam epitaxy and rapid thermal processing. The precursors may be employed to form diffusion barrier layers on microelectronic device structures enabling the use of copper metallization and ferroelectric thin films in device construction.

Owner:ADVANCED TECH MATERIALS INC

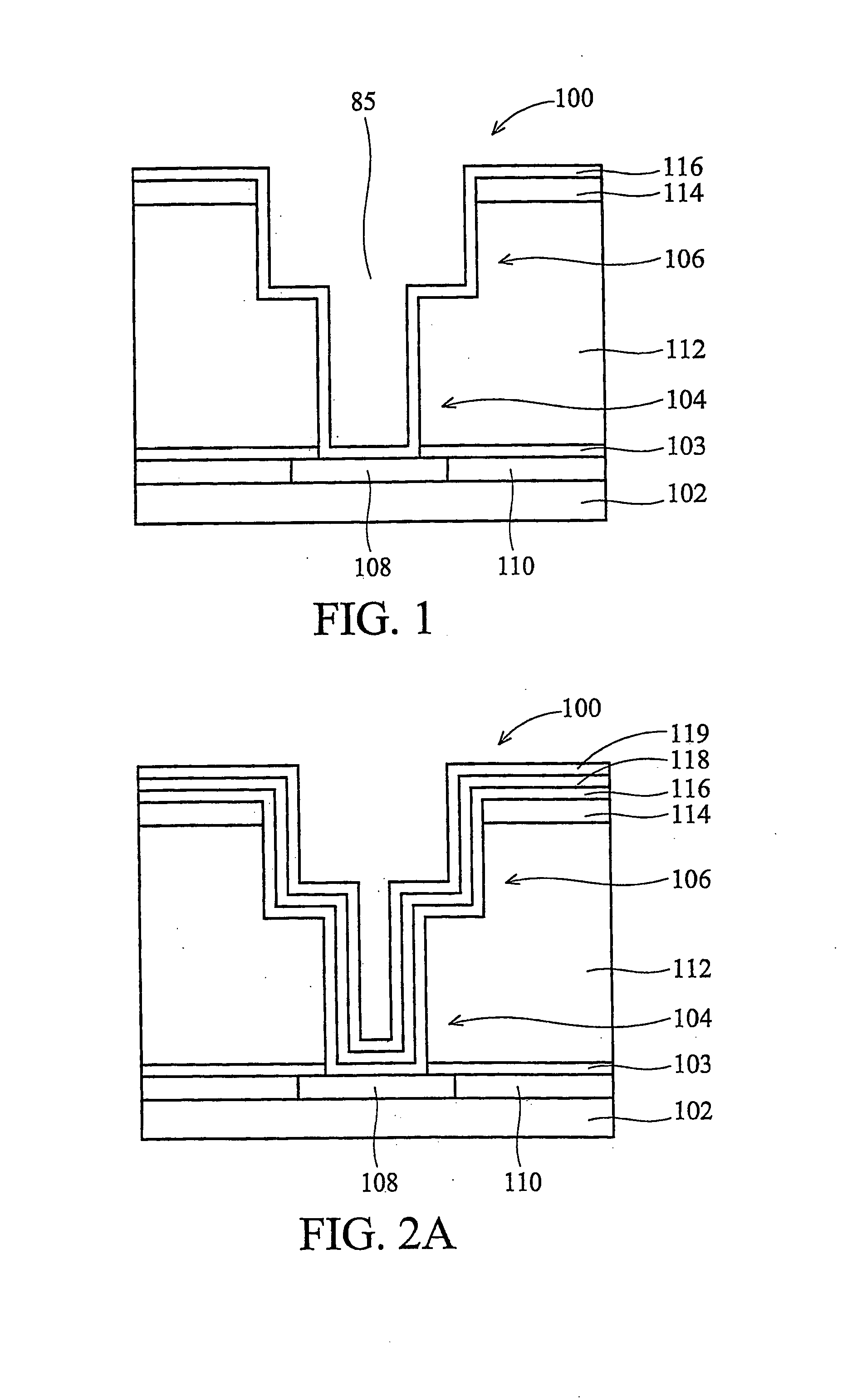

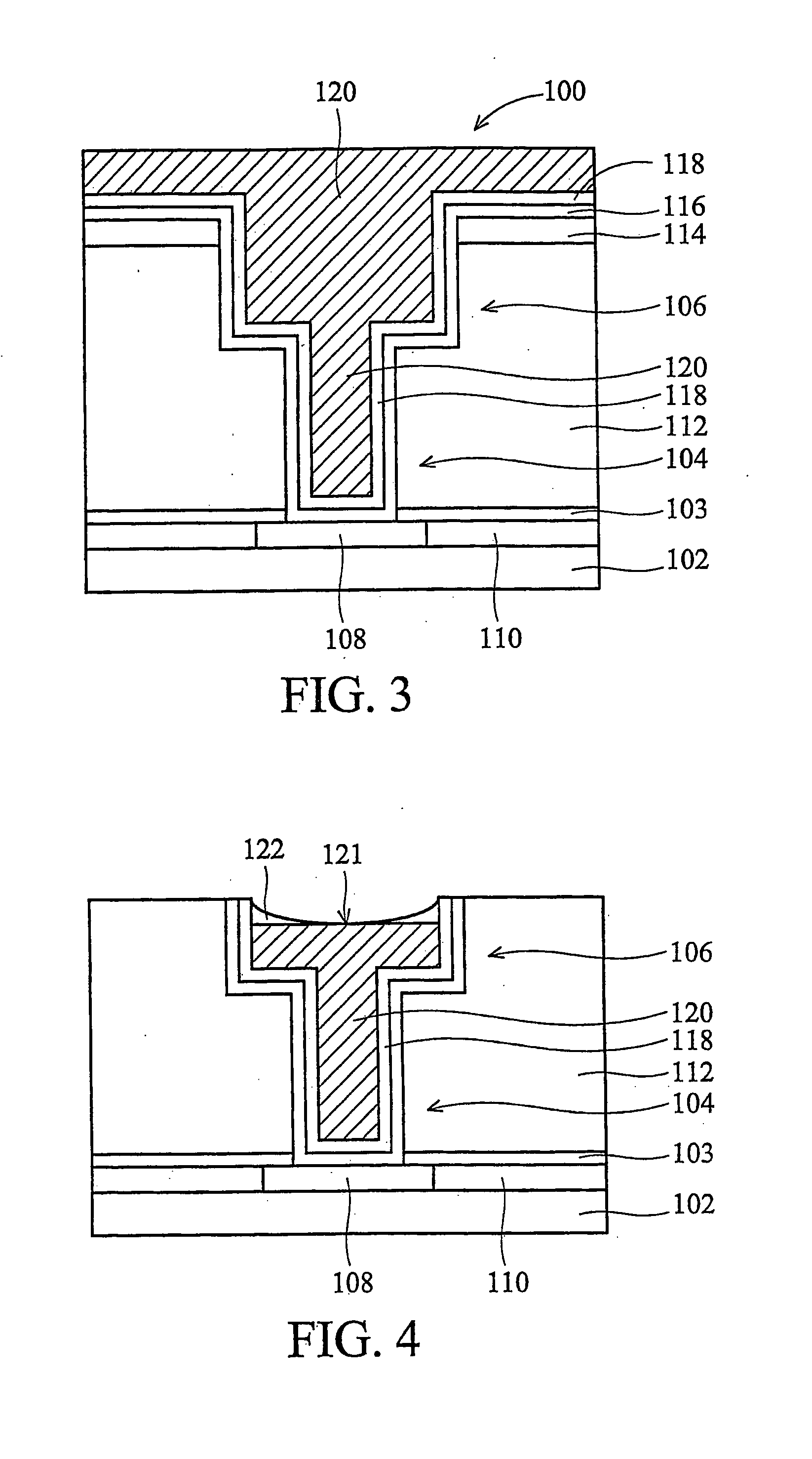

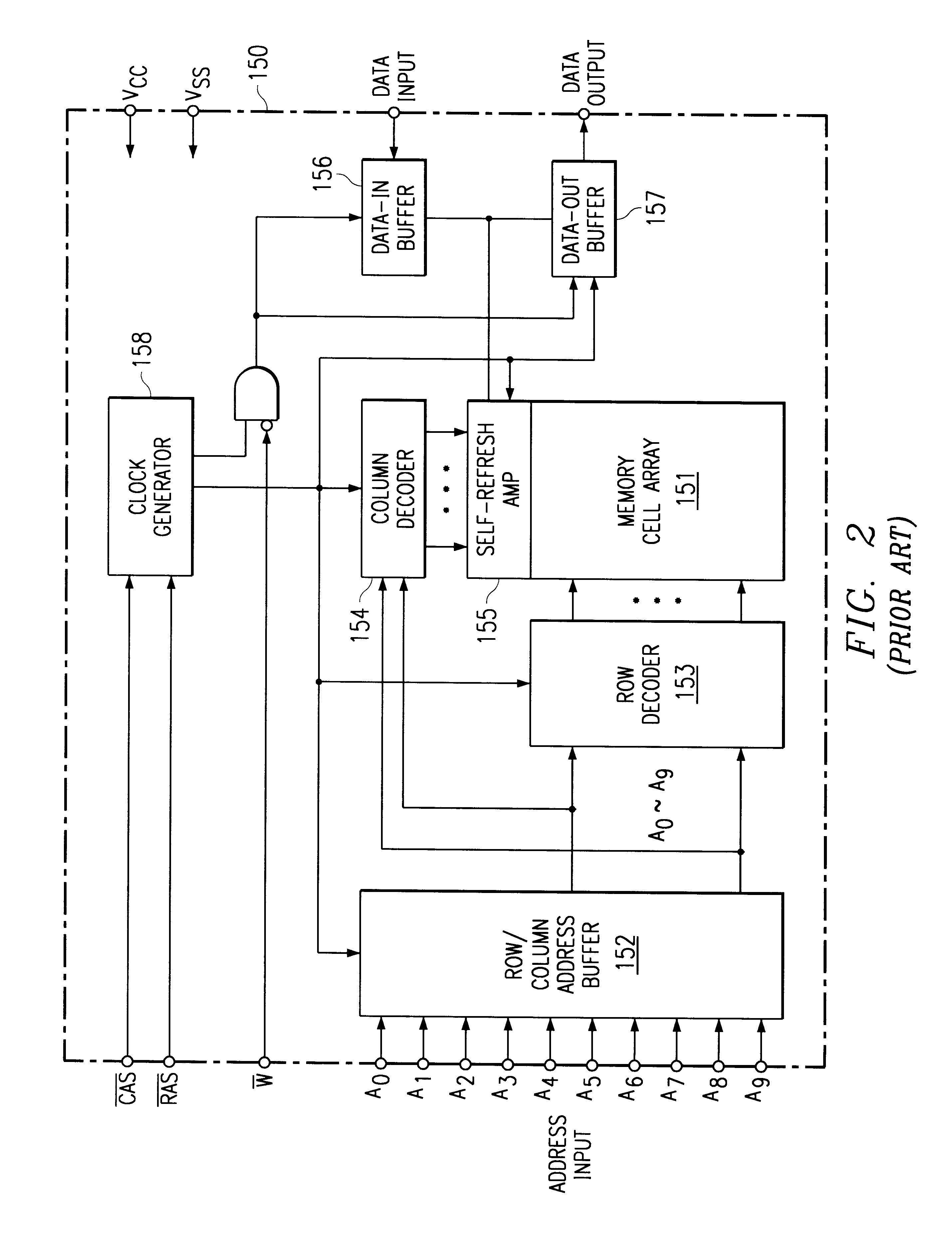

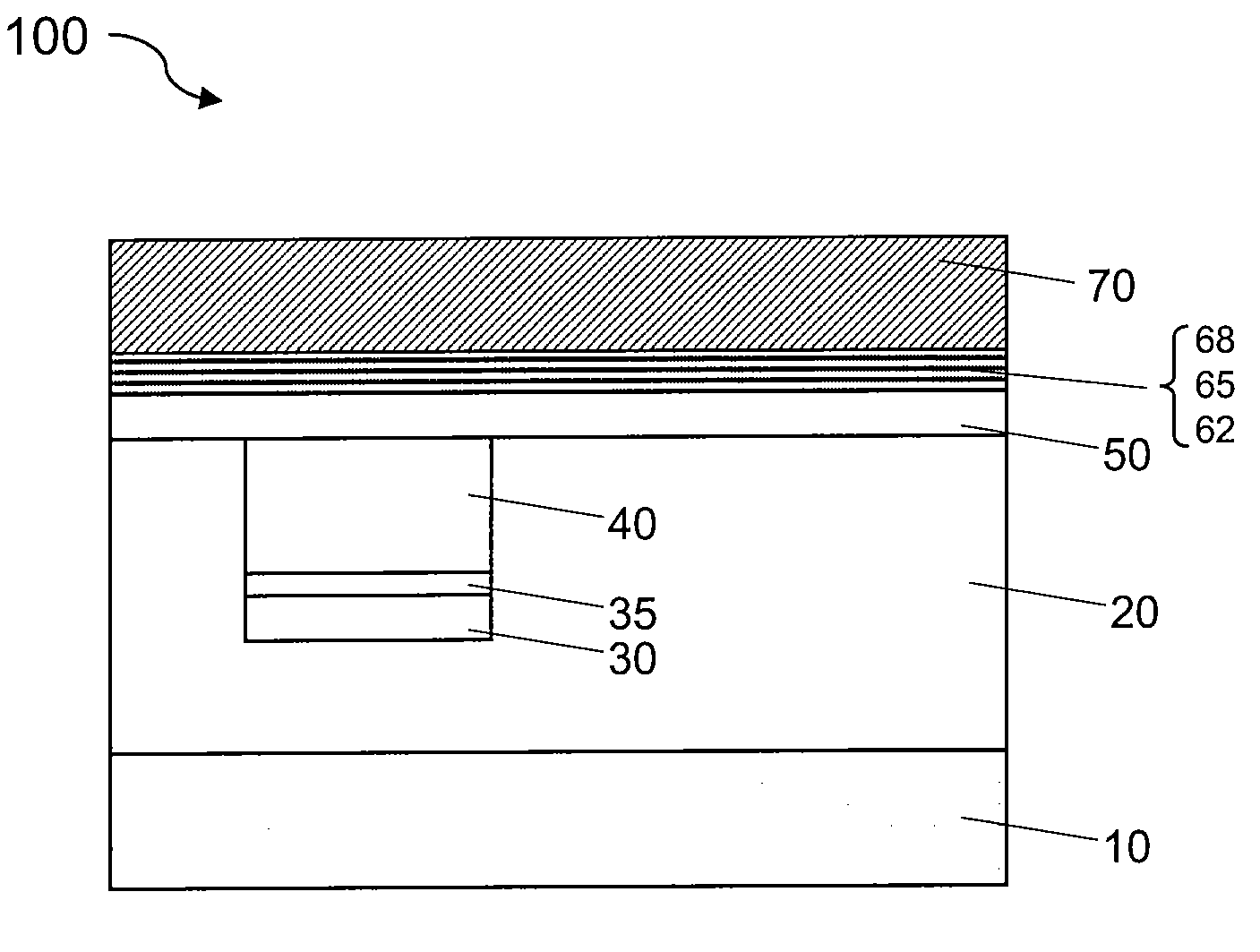

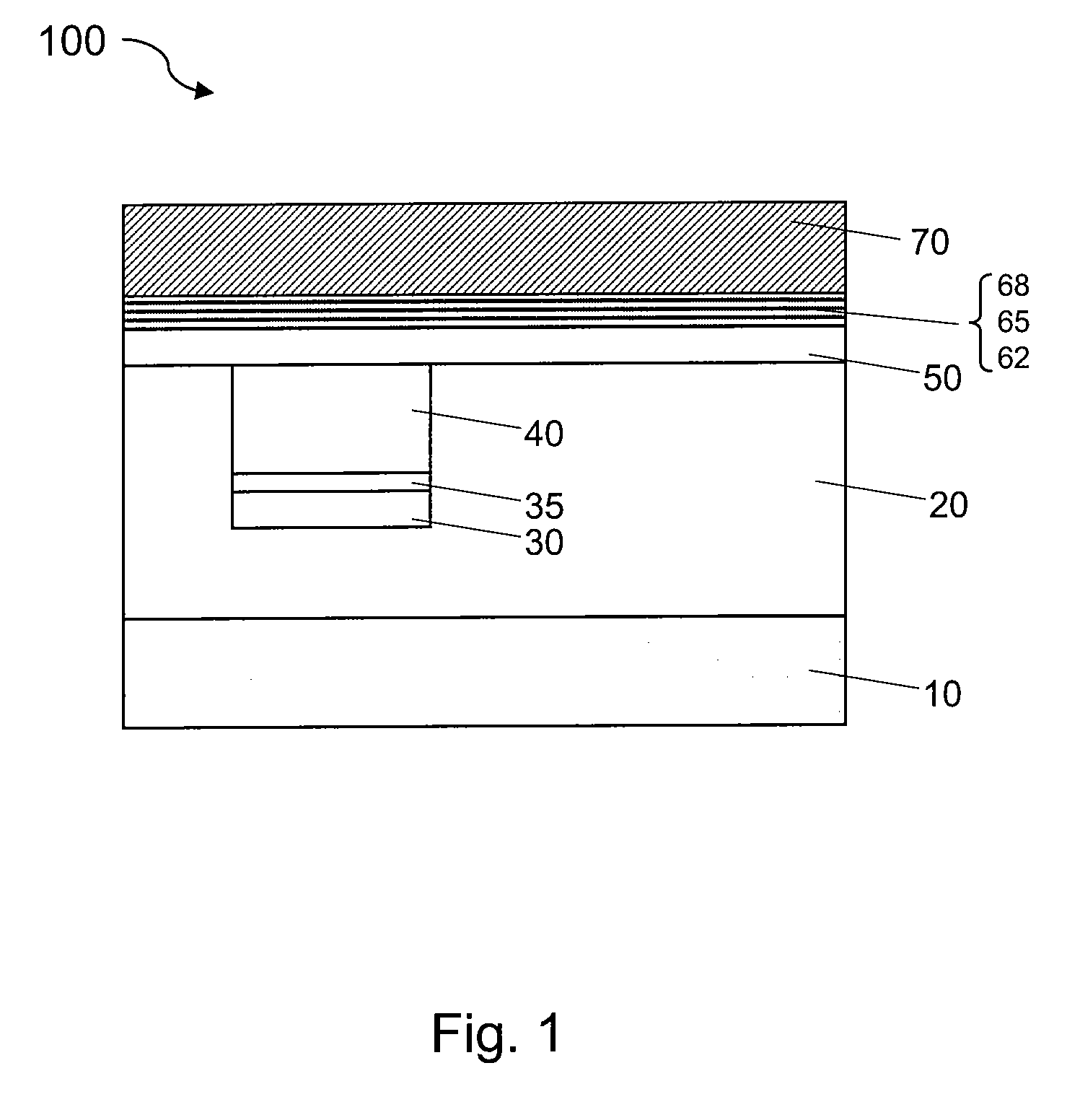

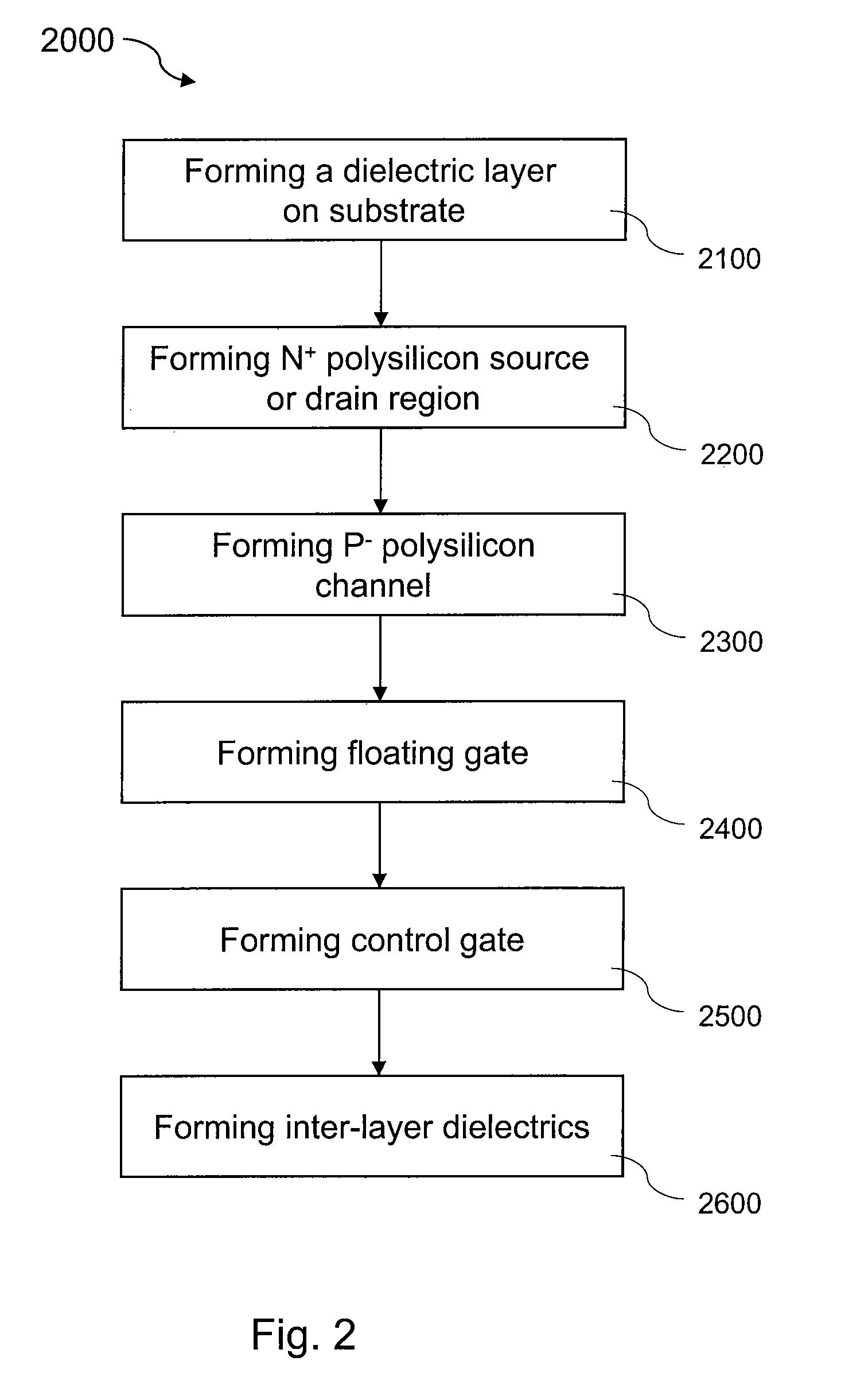

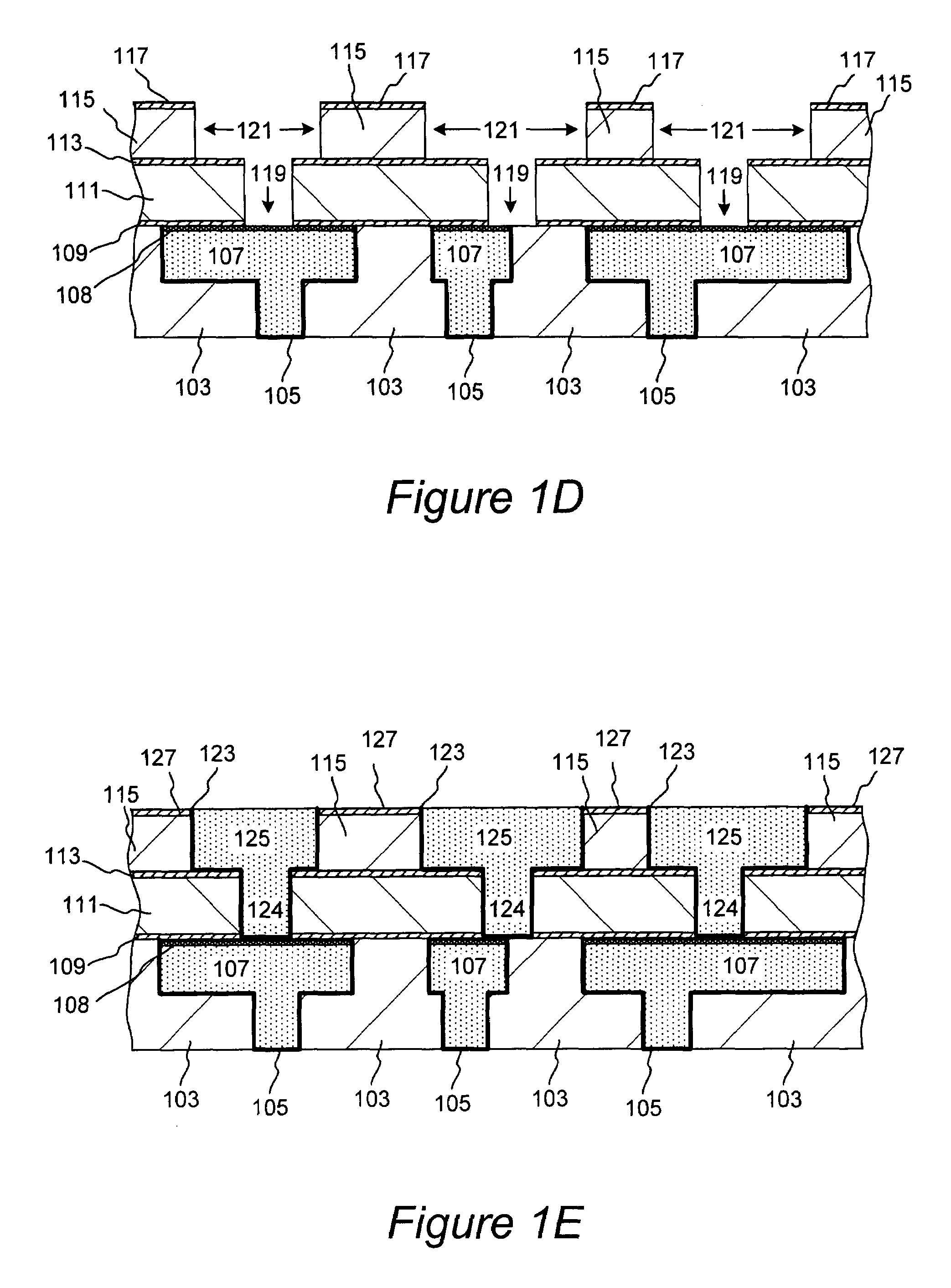

TFT floating gate memory cell structures

ActiveUS20100001282A1Improve reliabilitySmall geometric cell sizeTransistorSemiconductor/solid-state device manufacturingDiffusion barrierDielectric layer

A device having thin-film transistor (TFT) floating gate memory cell structures is provided. The device includes a substrate, a dielectric layer on the substrate, and one or more source or drain regions being embedded in the dielectric layer. the dielectric layer being associated with a first surface. Each of the one or more source or drain regions includes an N+ polysilicon layer on a diffusion barrier layer which is on a first conductive layer. The N+ polysilicon layer has a second surface substantially co-planar with the first surface. Additionally, the device includes a P− polysilicon layer overlying the co-planar surface and a floating gate on the P− polysilicon layer. The floating gate is a low-pressure CVD-deposited silicon layer sandwiched by a bottom oxide tunnel layer and an upper oxide block layer. Moreover, the device includes at least one control gate made of a P+ polysilicon layer overlying the upper oxide block layer. A method of making the same memory cell structure is provided and can be repeated to integrate the structure three-dimensionally.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

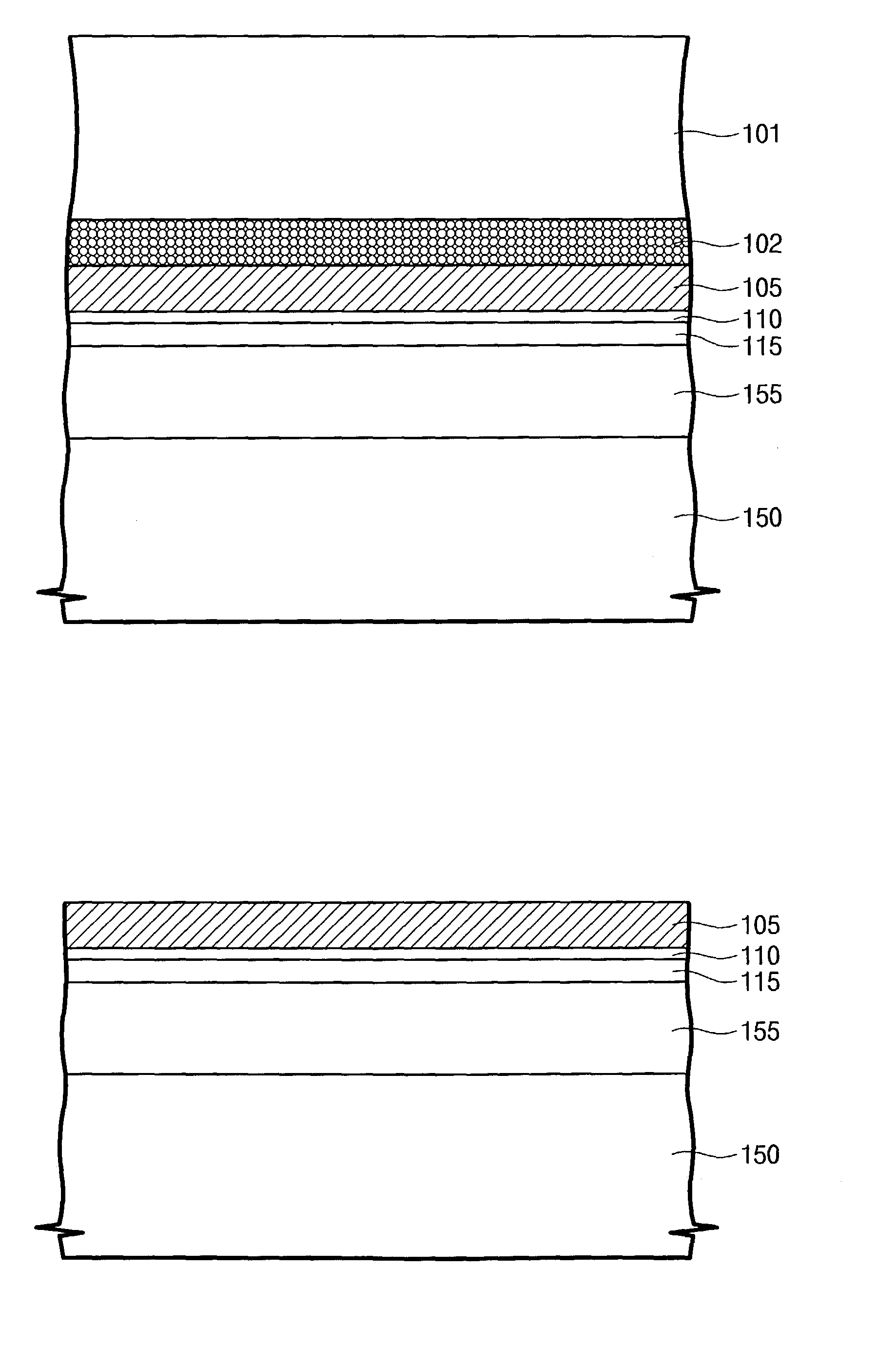

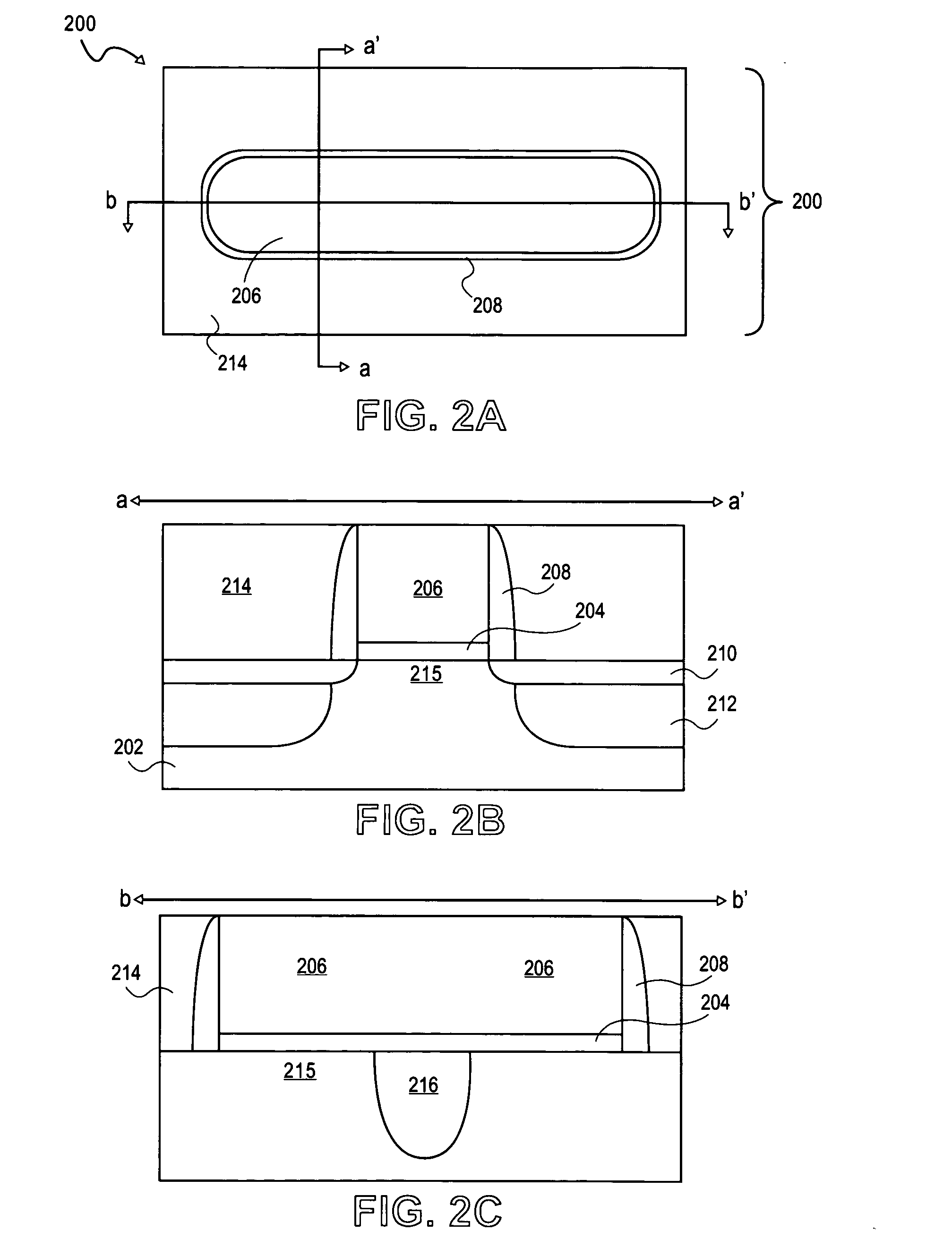

Method of forming silicon-on-insulator (SOI) semiconductor substrate and SOI semiconductor substrate formed thereby

InactiveUS7183172B2Inhibited DiffusionImpurity diffusion coefficientSolid-state devicesSemiconductor/solid-state device manufacturingImpurity diffusionDiffusion barrier

A method of forming an SOI semiconductor substrate and the SOI semiconductor substrate formed thereby, is provided. The method includes forming sequentially buried oxide, diffusion barrier and SOI layers on a semiconductor substrate. The diffusion barrier layer is formed by an insulating layer having a lower impurity diffusion coefficient as compared with the buried oxide layer. The diffusion barrier layer serves to prevent impurities implanted into the SOI layer from being diffused into the buried oxide layer or the semiconductor substrate.

Owner:SAMSUNG ELECTRONICS CO LTD

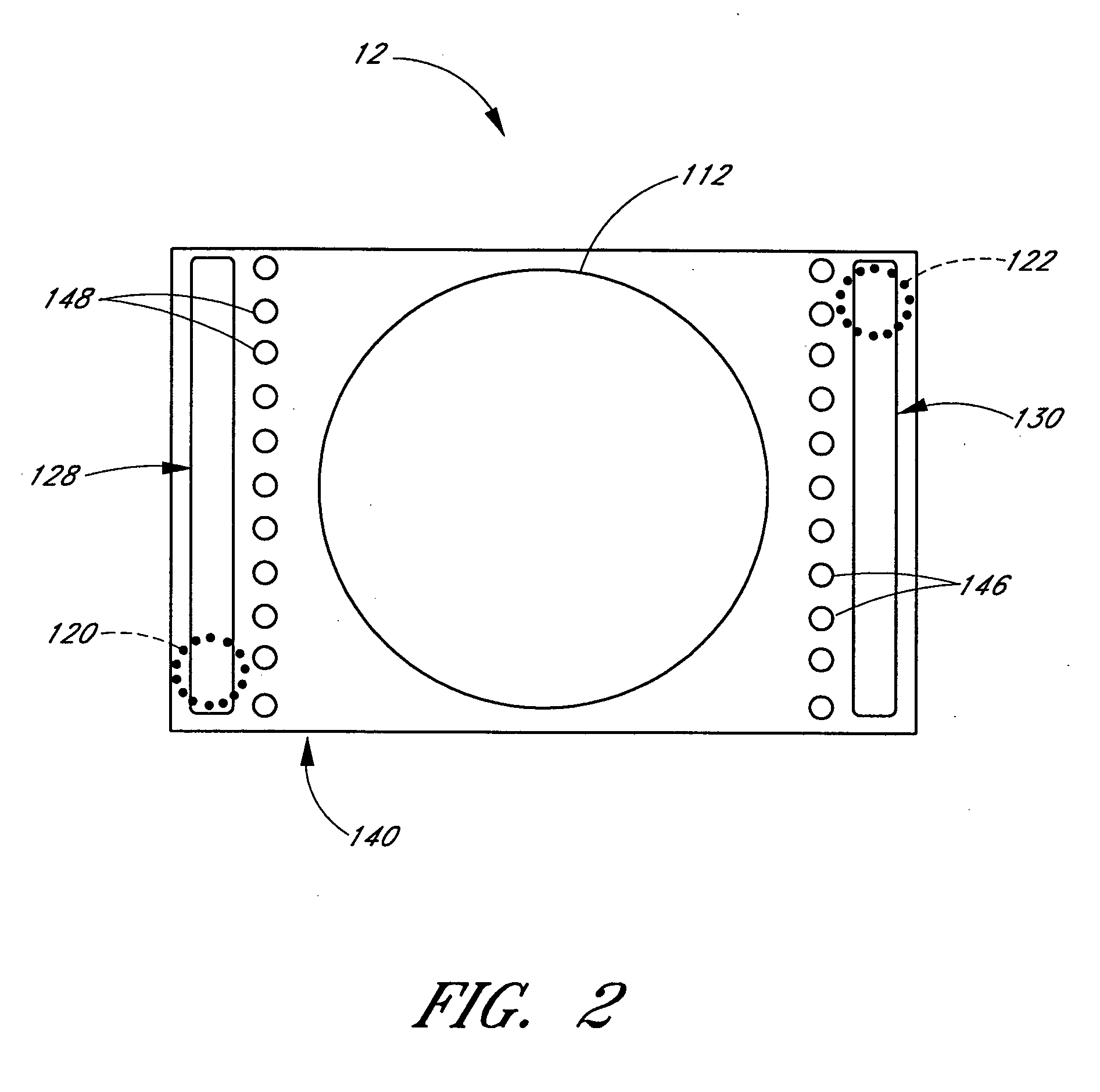

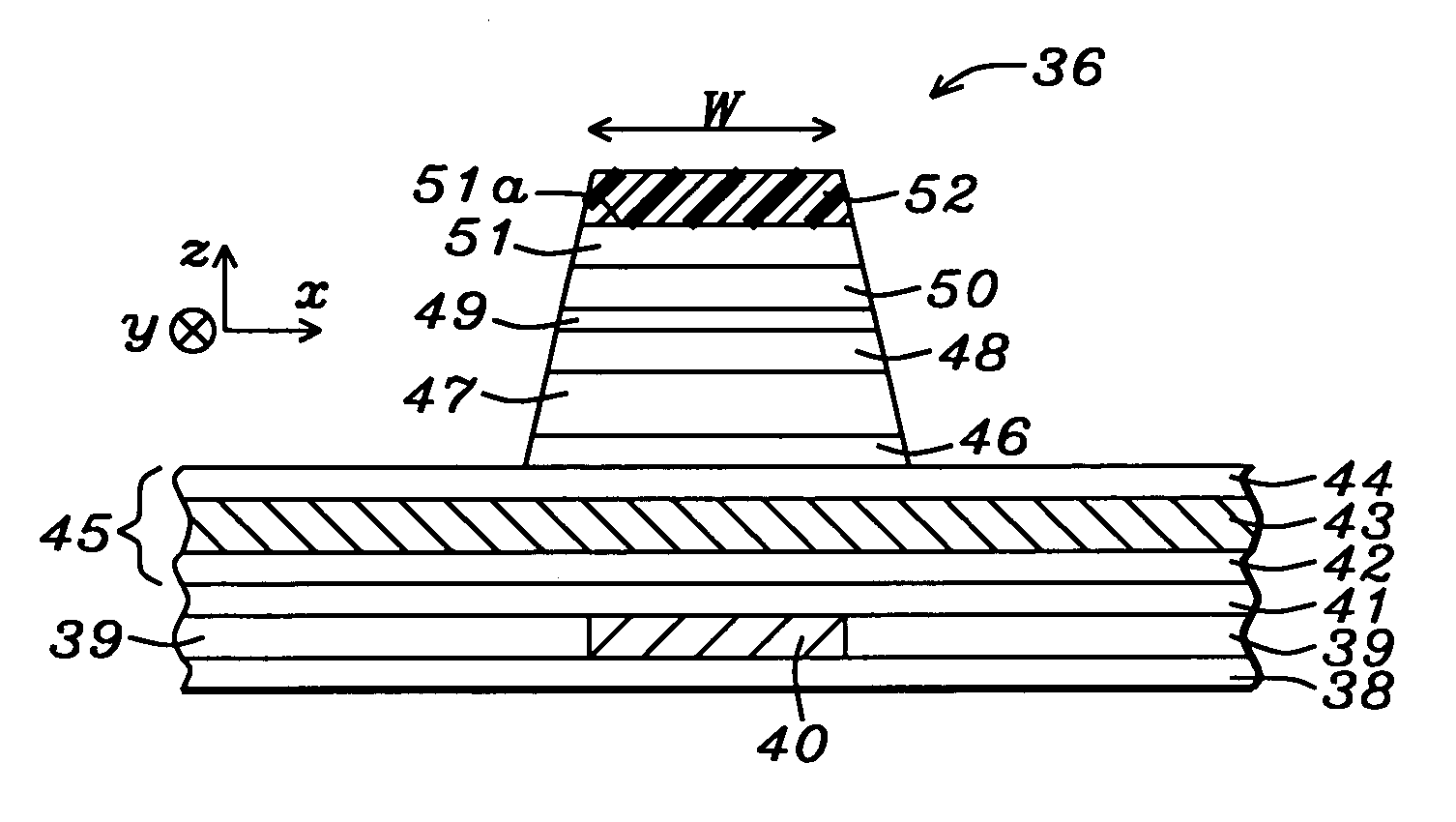

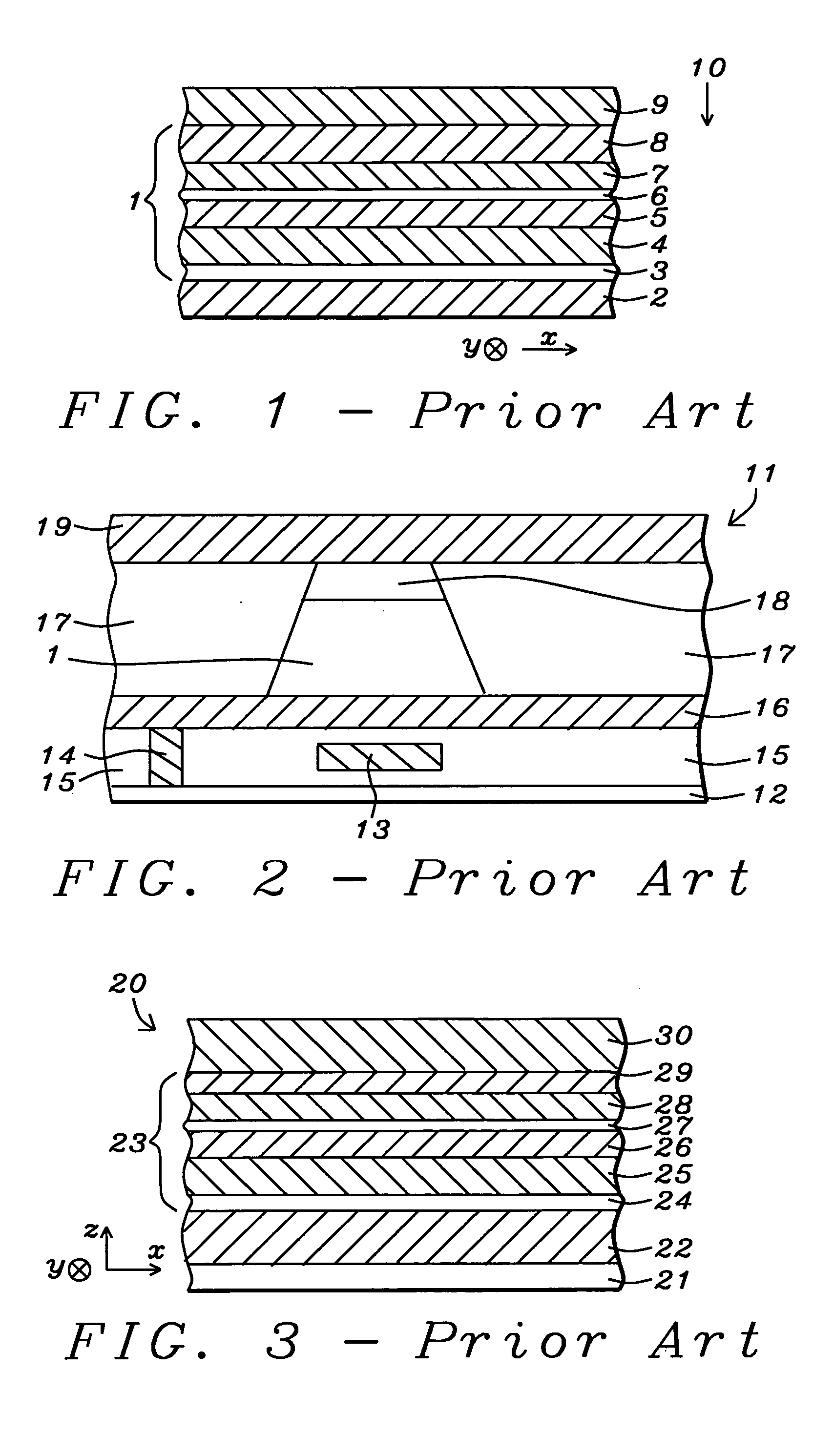

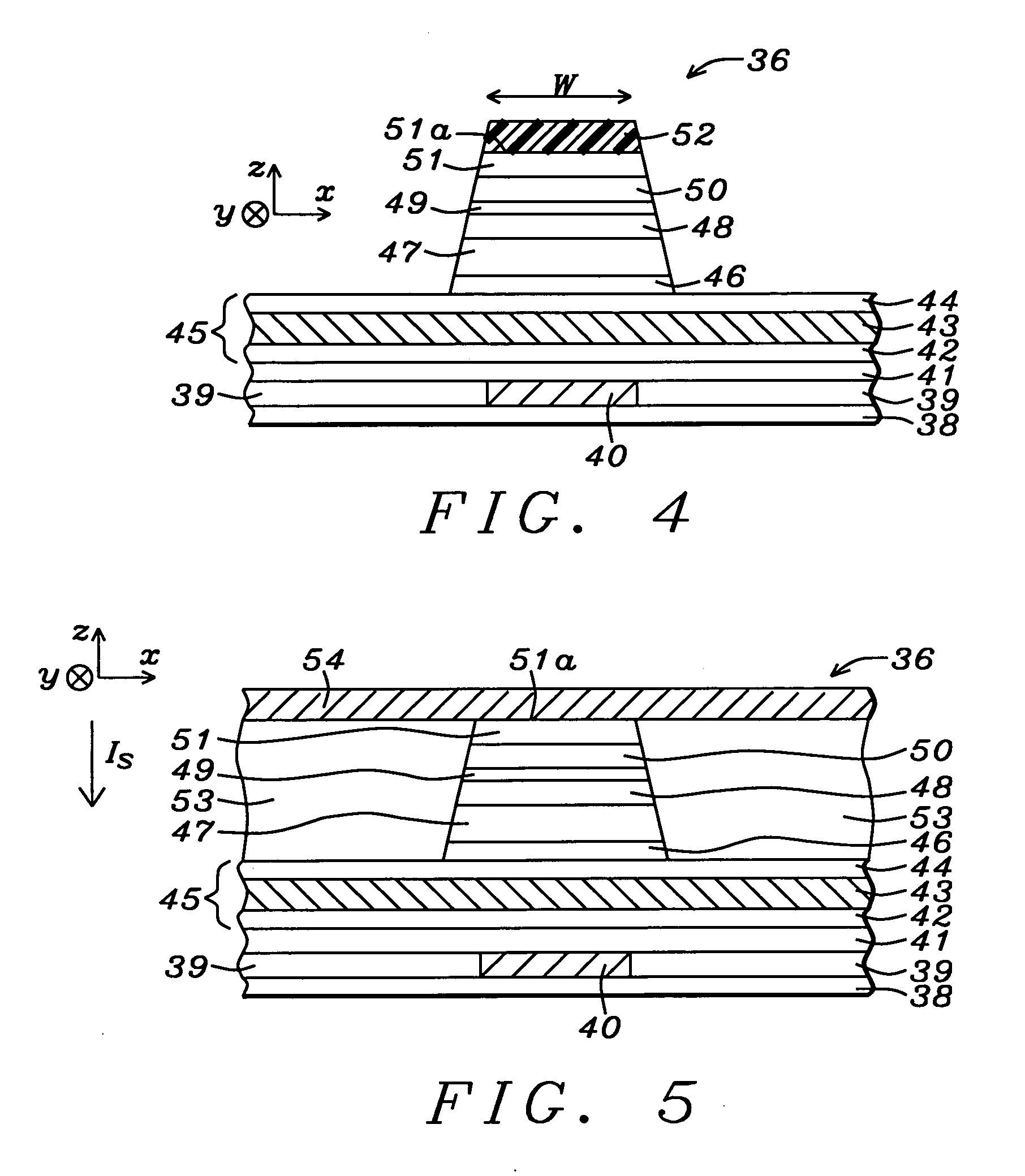

Backside imaging through a doped layer

ActiveUS20060138322A1Improve imaging effectImprove device yieldSolid-state devicesMaterial analysis by optical meansCMOSImage resolution

Backthinning in an area selective manner is applied to CMOS imaging sensors 12 for use in electron bombarded active pixel array devices. A further arrangement results in an array of collimators 51 aligned with pixels 42 or groups of pixels of an active pixel array providing improved image contrast of such image sensor. Provision of a thin P-doped layer 52 on the illuminated rear surface provides both a diffusion barrier resulting in improved resolution and a functional shield for reference pixels. A gradient in concentration of P-doped layer 52 optimizes electron collection at the pixel array.

Owner:EOTECH LLC

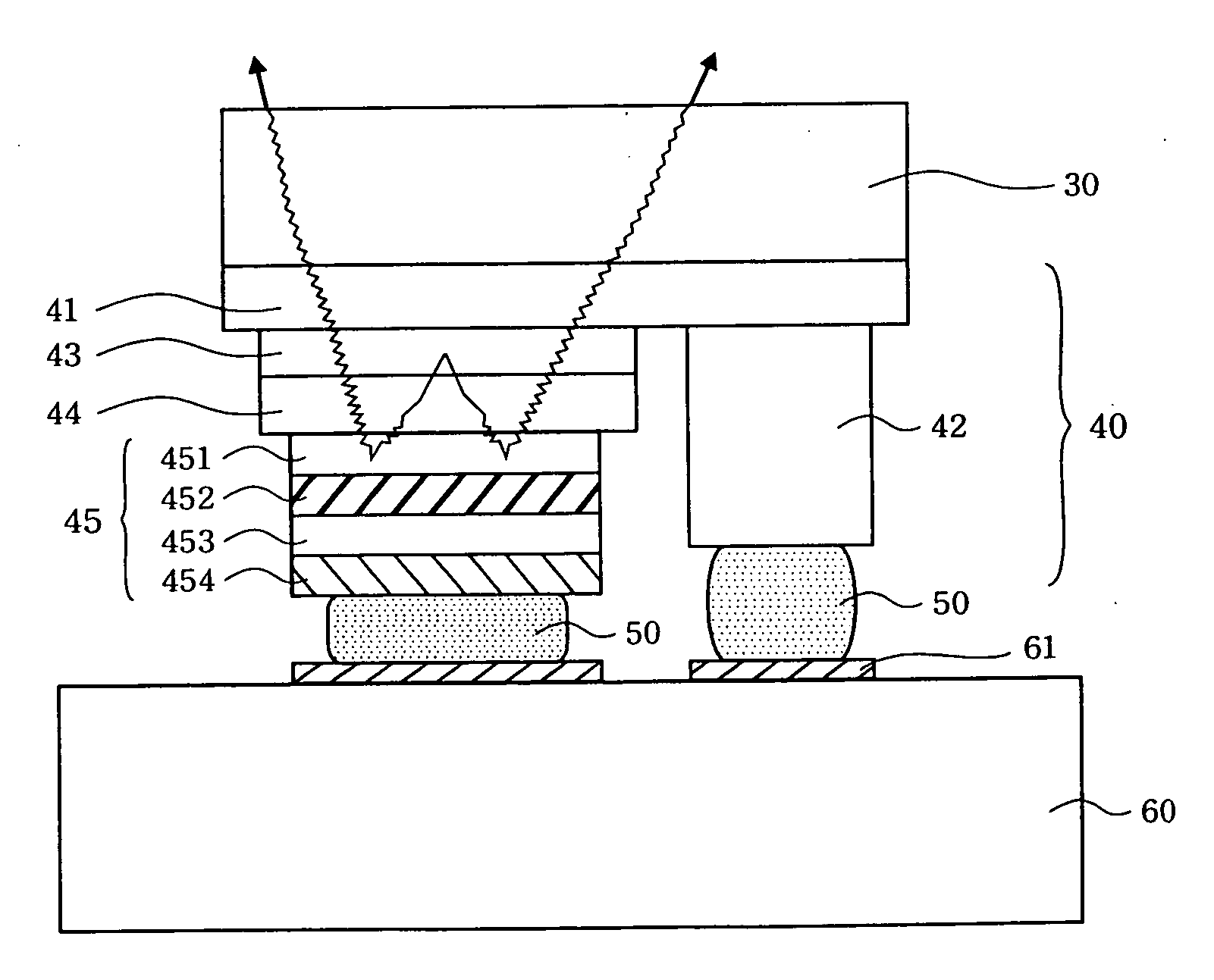

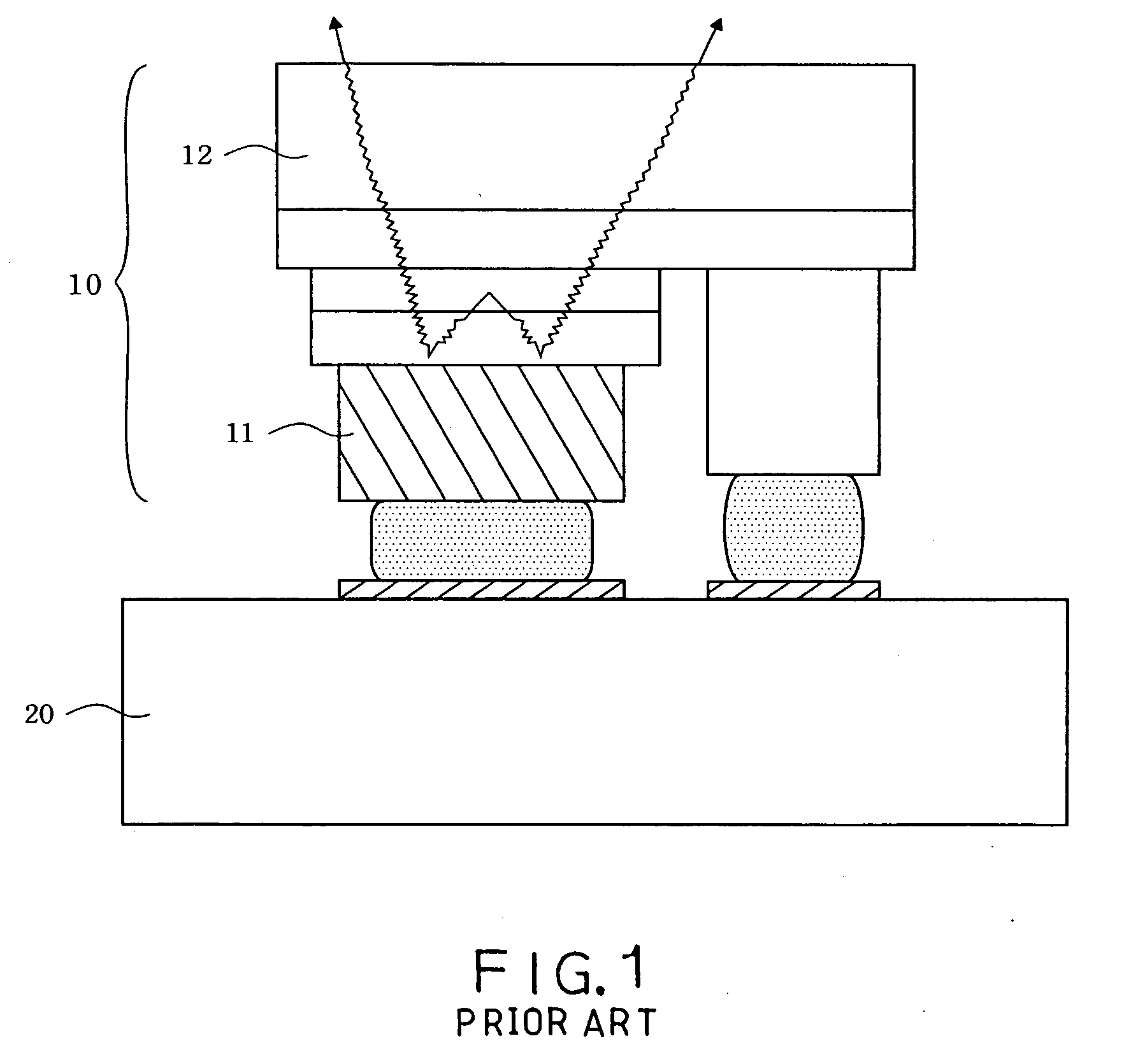

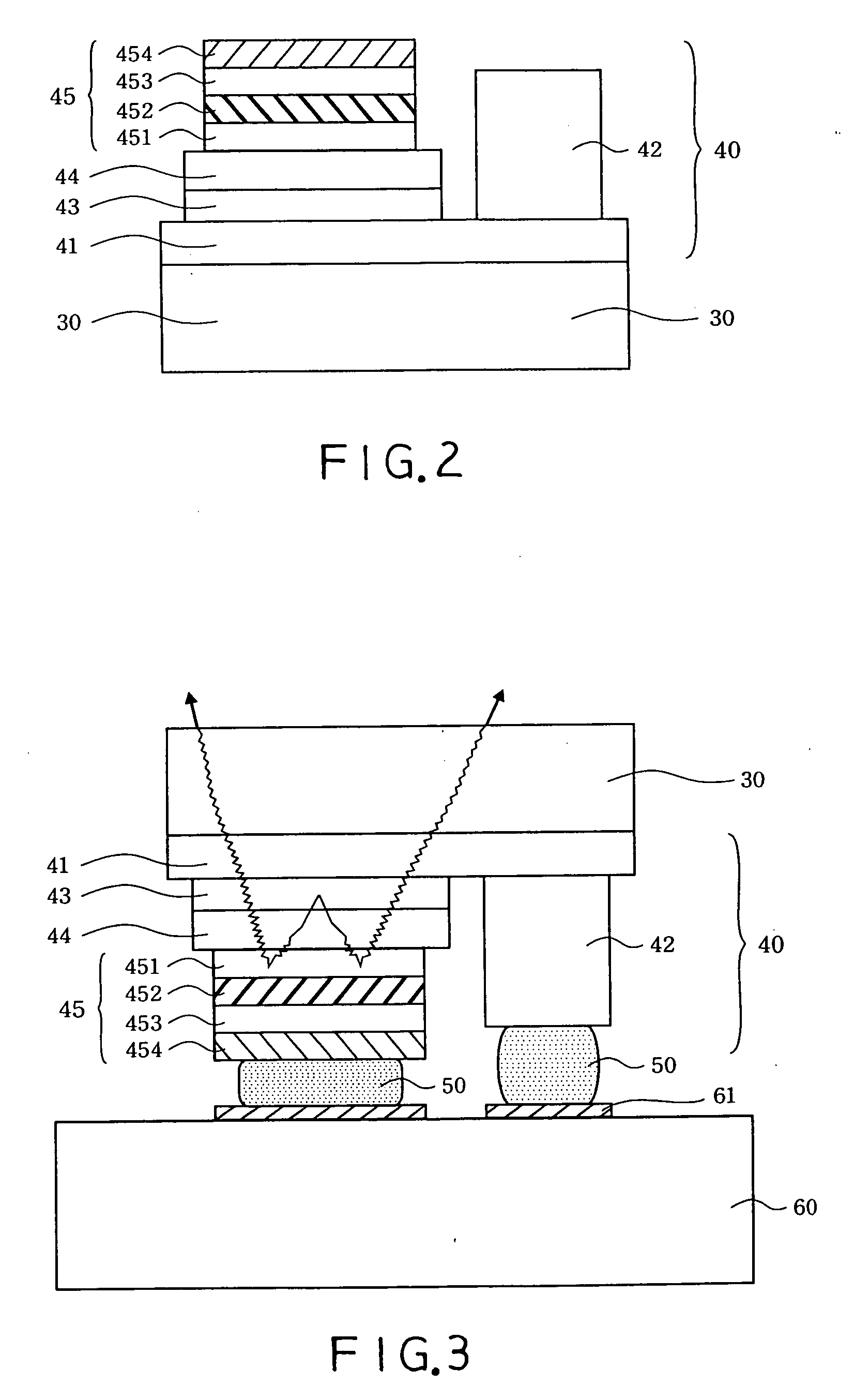

Flip-chip electrode light-emitting element formed by multilayer coatings

InactiveUS20060081869A1High reflective functionLuminous efficiencySolid-state devicesSemiconductor devicesInter layerOhmic contact

A flip-chip electrode light-emitting element formed by multilayer coatings where a translucent conducting layer and a highly reflective metal layer acts as flip-chip electrode for enhancing the LED luminous efficiency. The flip-chip electrode light-emitting element includes a translucent substrate, a semiconductor die structure attached on the translucent substrate and made of group III nitride compounds, and an intermediate layer adapted to support the inverted semiconductor die structure on a submount. The flip-chip electrode formed by multiplayer coatings includes a current-spreading transparent conducting layer formed on a top side of the second type semiconductor layer, a highly reflective metal layer formed on a top side of the transparent conducting layer, a metallic diffusion barrier layer formed on a top side of the highly reflective metal layer, and a bonding layer electrically coupled to the intermediate layer and formed on a top side of the barrier layer. Moreover, an ohmic contact layer is formed on the transparent conducting layer. And a passivation layer encloses the die structure for insulating p / n interface and for avoiding the creation of the leakage current.

Owner:ARIMA OPTOELECTRONICS

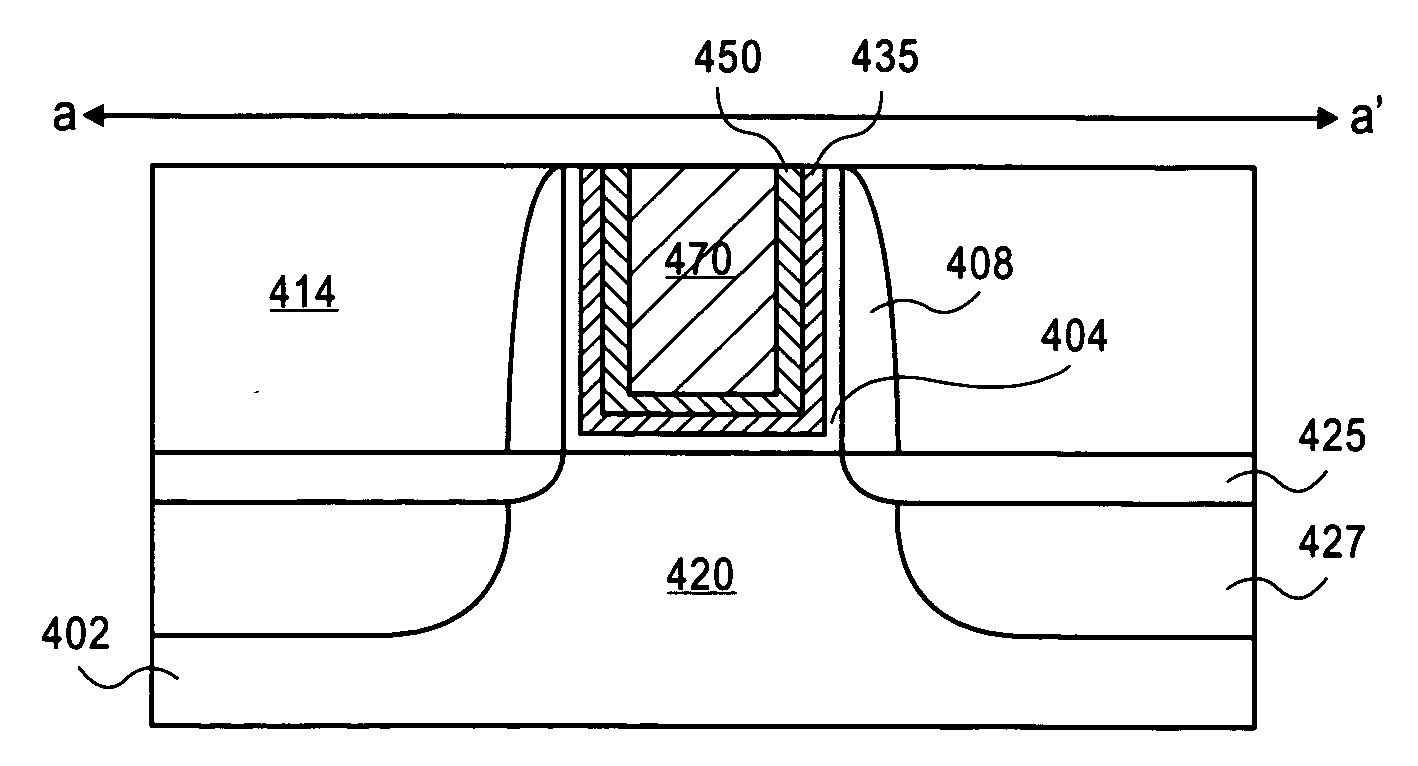

Tunable gate electrode work function material for transistor applications

Described herein are metal gate electrode stacks including a low resistance metal cap in contact with a metal carbonitride diffusion barrier layer, wherein the metal carbonitride diffusion barrier layer is tuned to a particular work function to also serve as a work function metal for a pMOS transistor. In an embodiment, the work function-tuned metal carbonitride diffusion barrier prohibits a low resistance metal cap layer of the gate electrode stack from migrating into the MOS junction. In a further embodiment of the present invention, the work function of the metal carbonitride barrier film is modulated to be p-type with a pre-selected work function by altering a nitrogen concentration in the film.

Owner:TAHOE RES LTD

Novel capping structure for enhancing dR/R of the MTJ device

InactiveUS20050276099A1Well controlled magnetizationWell controlled switching characteristicNanomagnetismNanoinformaticsElectrical conductorOxygen

Owner:HEADWAY TECH INC +1

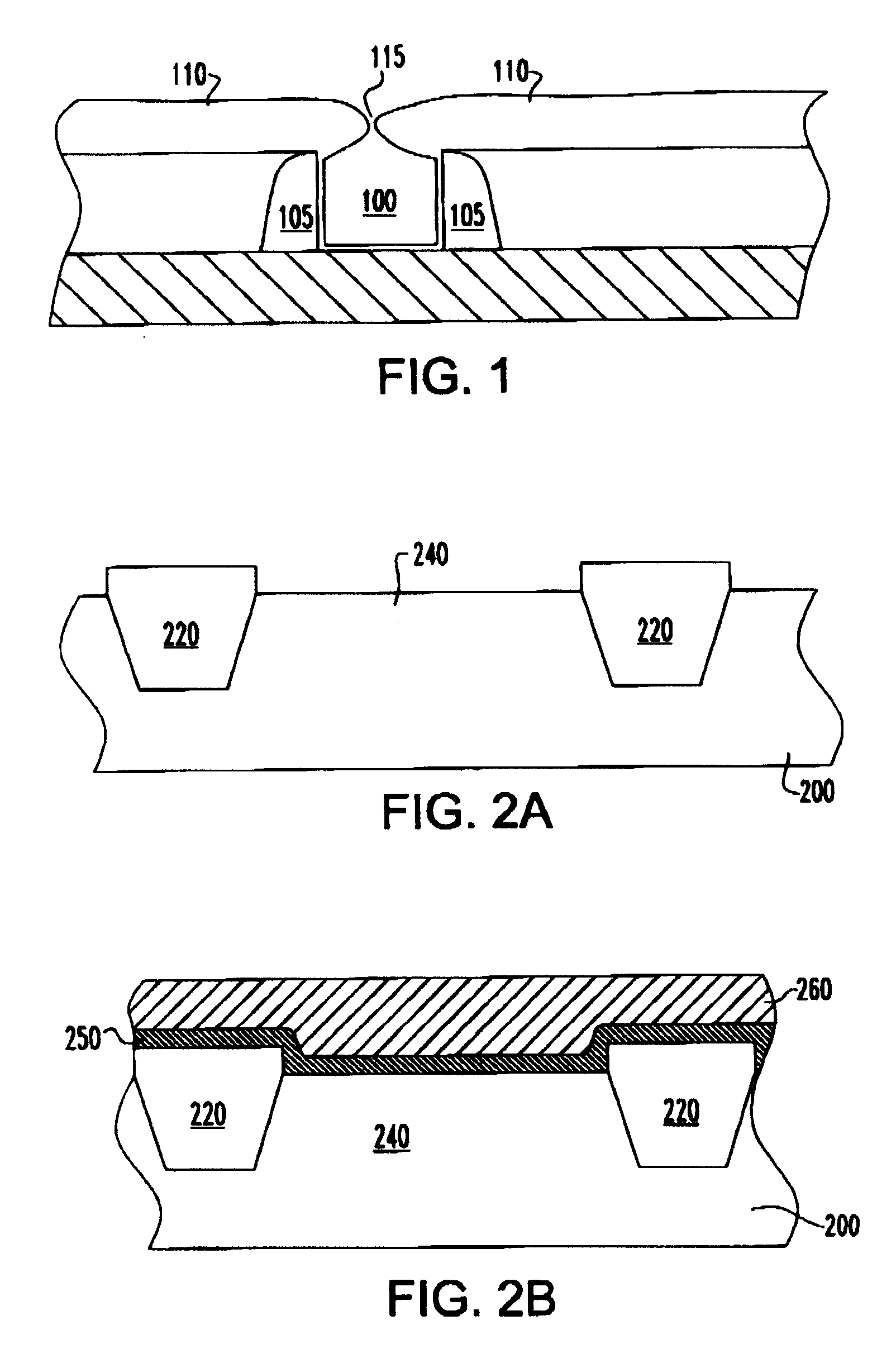

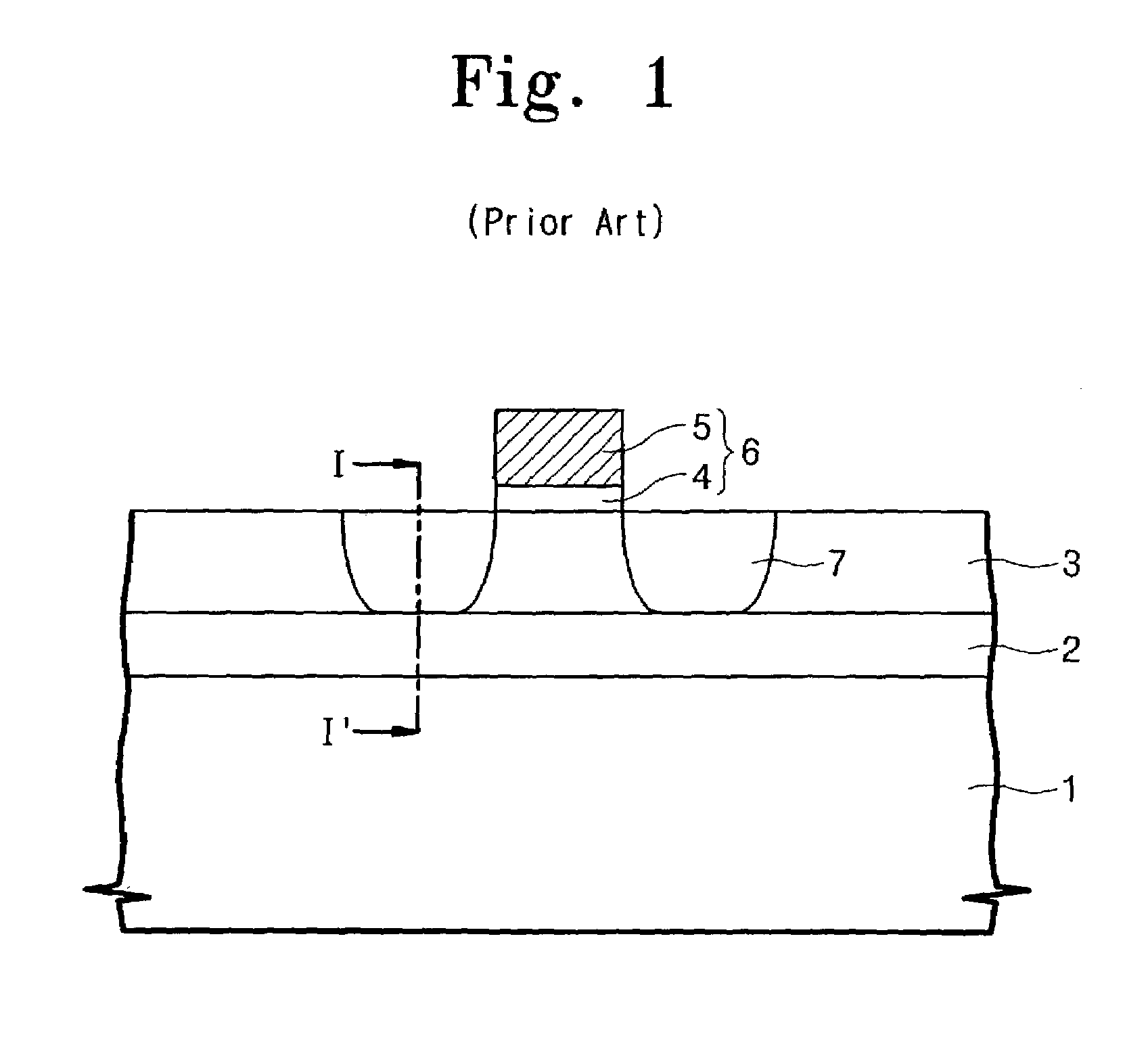

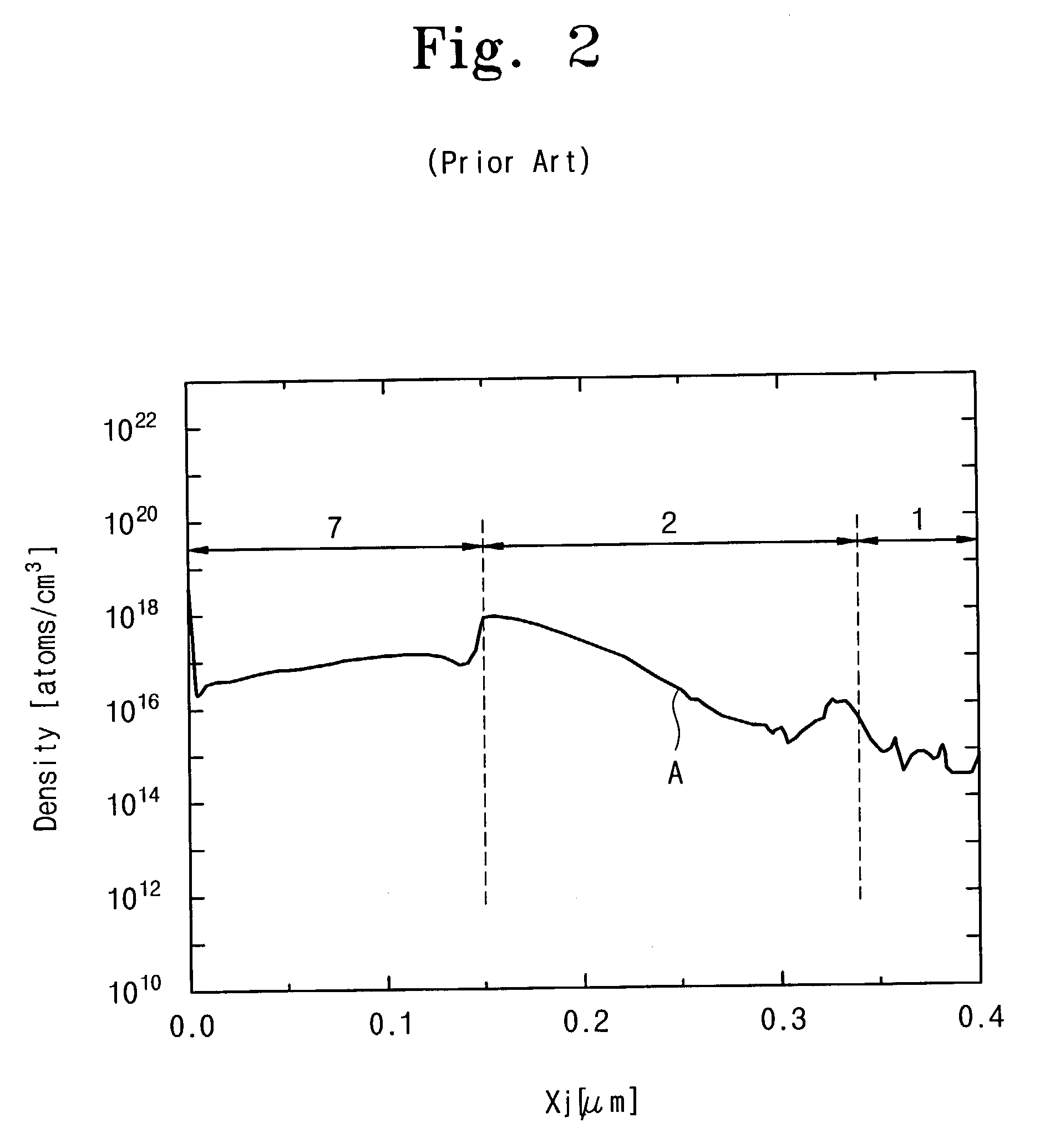

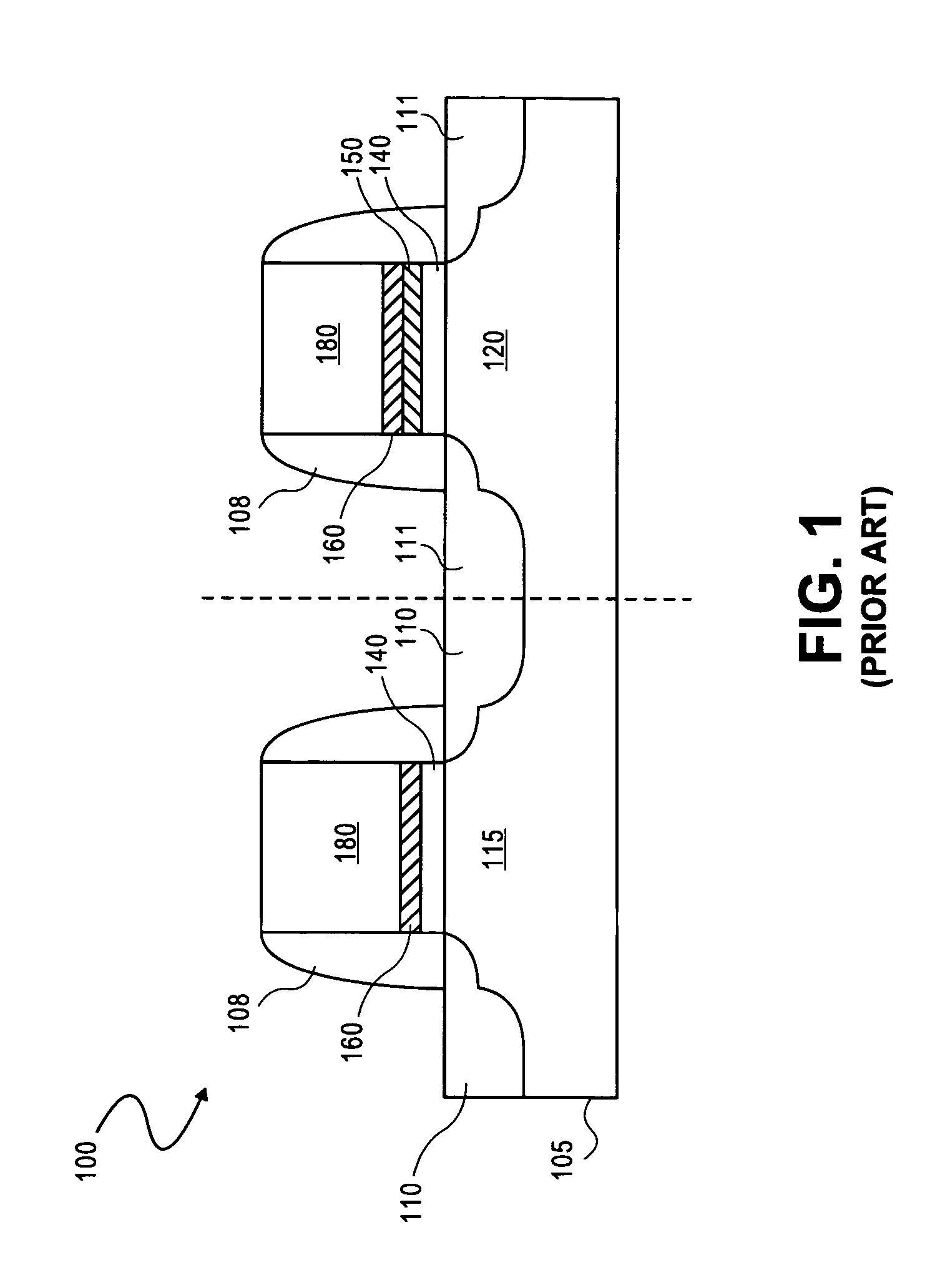

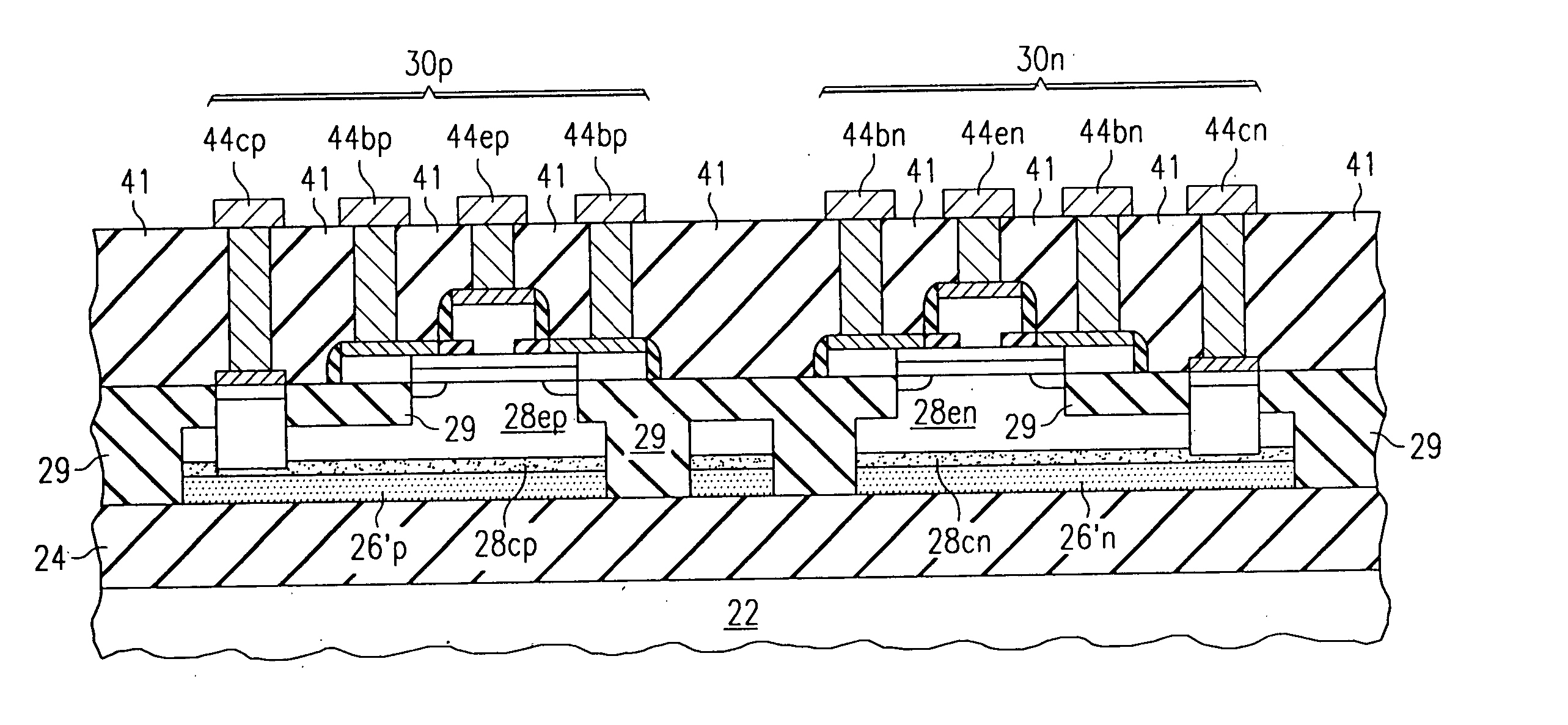

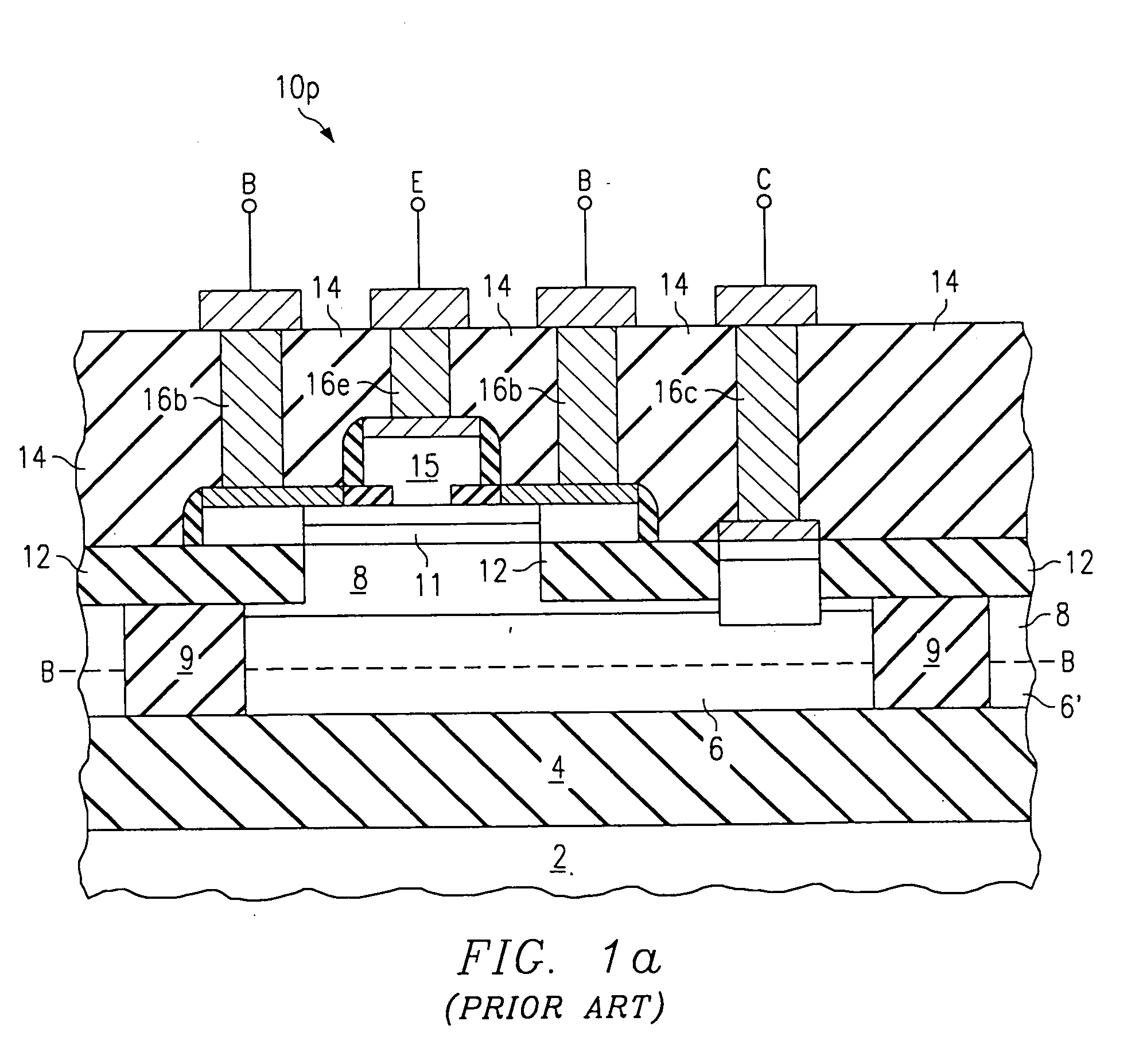

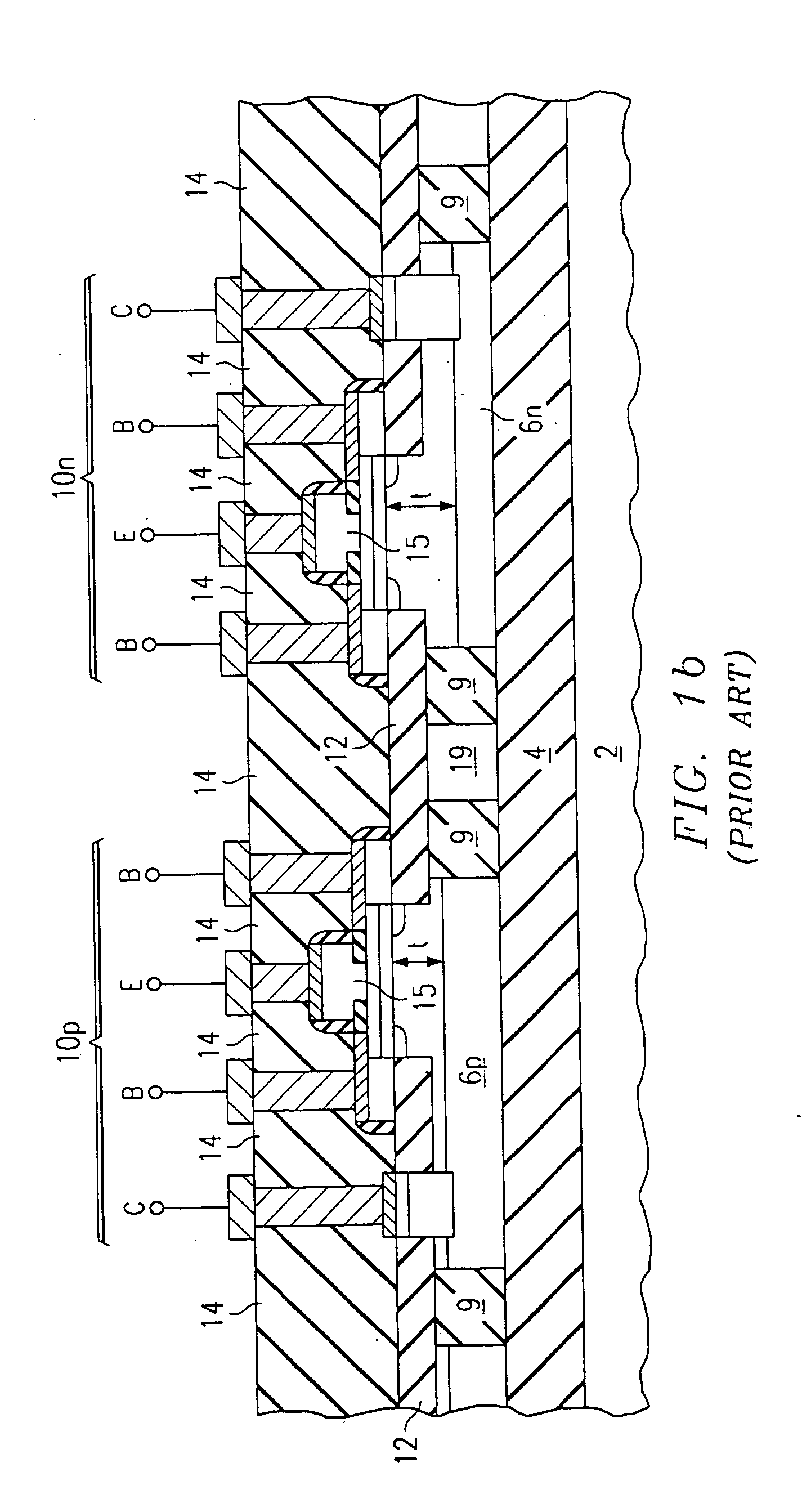

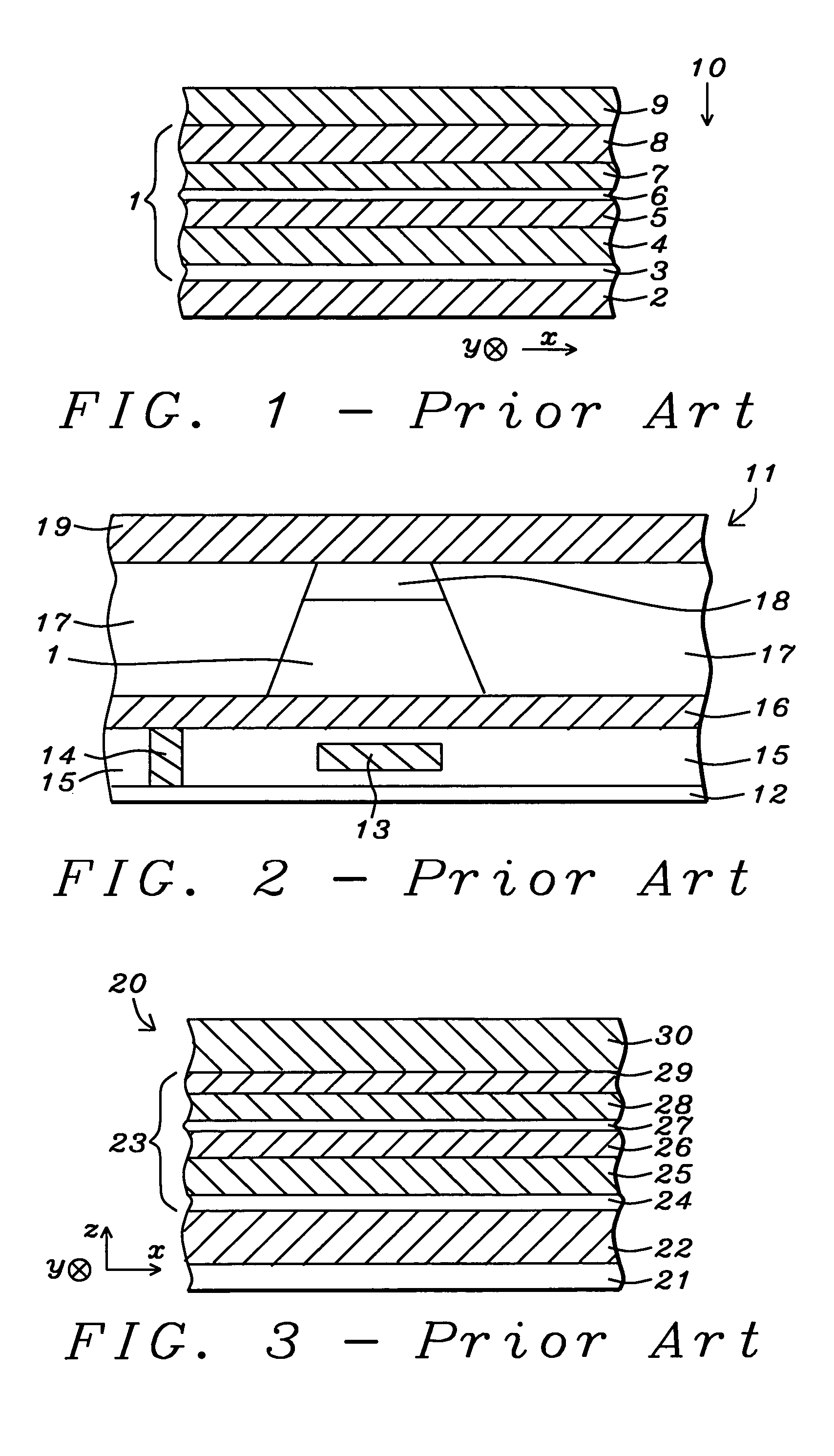

Control of dopant diffusion from buried layers in bipolar integrated circuits

InactiveUS20050250289A1Mitigating dopant diffusionReduce diffuseTransistorSemiconductor/solid-state device manufacturingDopantDiffusion

An integrated circuit and method of fabricating the integrated circuit is disclosed. The integrated circuit includes vertical bipolar transistors (30, 50, 60), each having a buried collector region (26′). A carbon-bearing diffusion barrier (28c) is disposed over the buried collector region (26′), to inhibit the diffusion of dopant from the buried collector region (26′) into the overlying epitaxial layer (28). The diffusion barrier (28c) may be formed by incorporating a carbon source into the epitaxial formation of the overlying layer (28), or by ion implantation. In the case of ion implantation of carbon or SiGeC, masks (52, 62) may be used to define the locations of the buried collector regions (26′) that are to receive the carbon; for example, portions underlying eventual collector contacts (33, 44c) may be masked from the carbon implant so that dopant from the buried collector region (26′) can diffuse upward to meet the contact (33). MOS transistors (70, 80) including the diffusion barrier (28) are also disclosed.

Owner:BABCOCK JEFFREY A +5

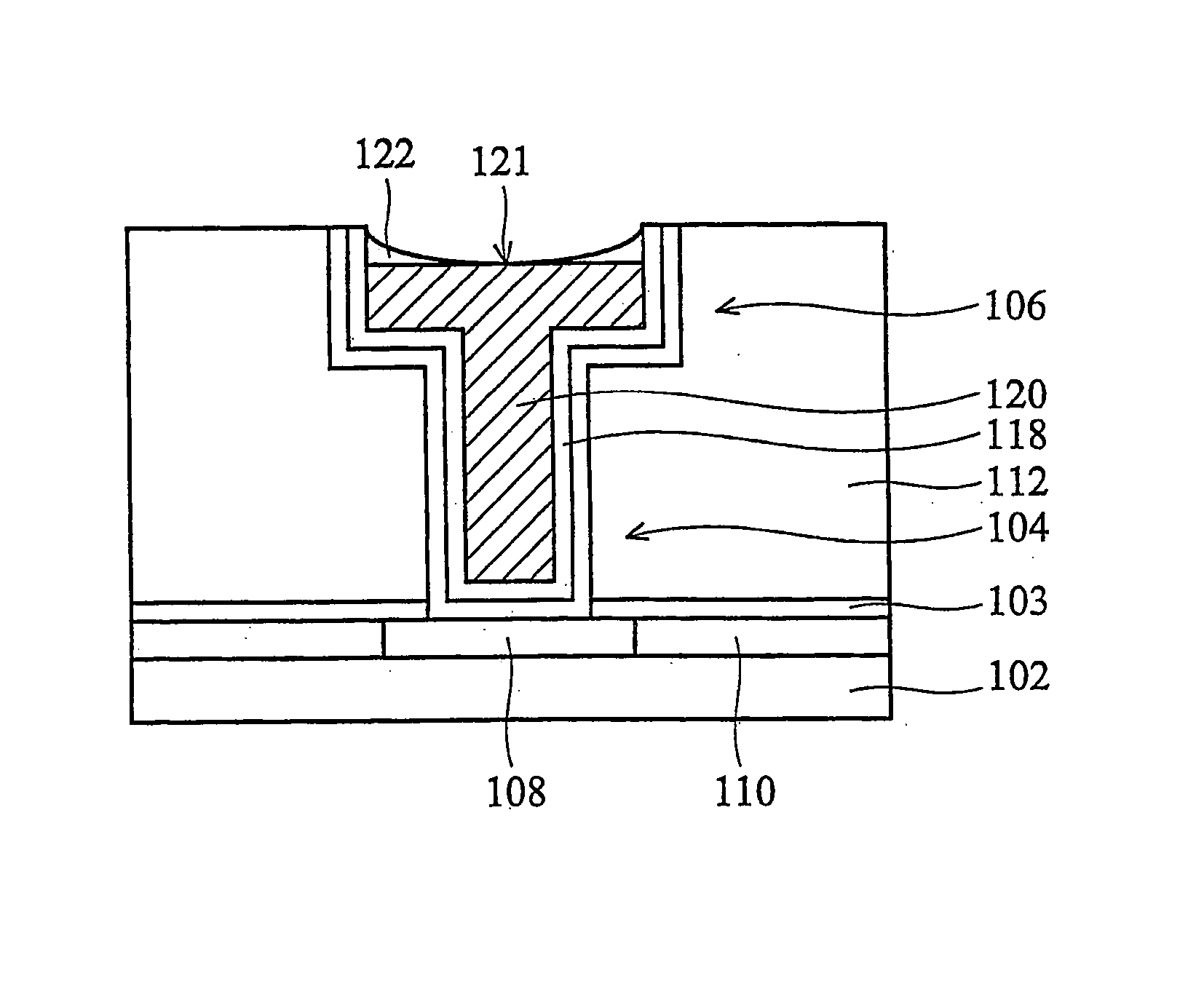

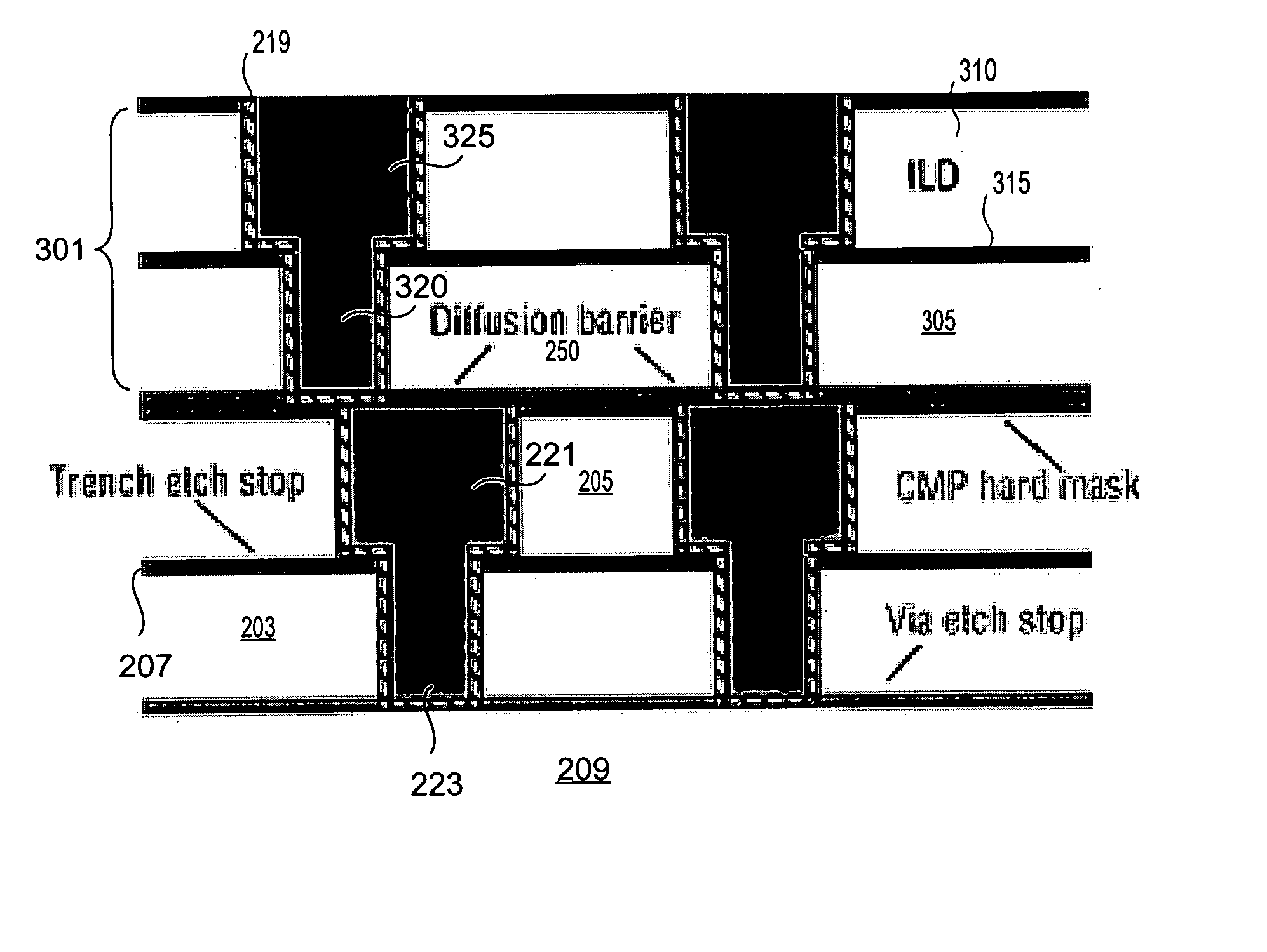

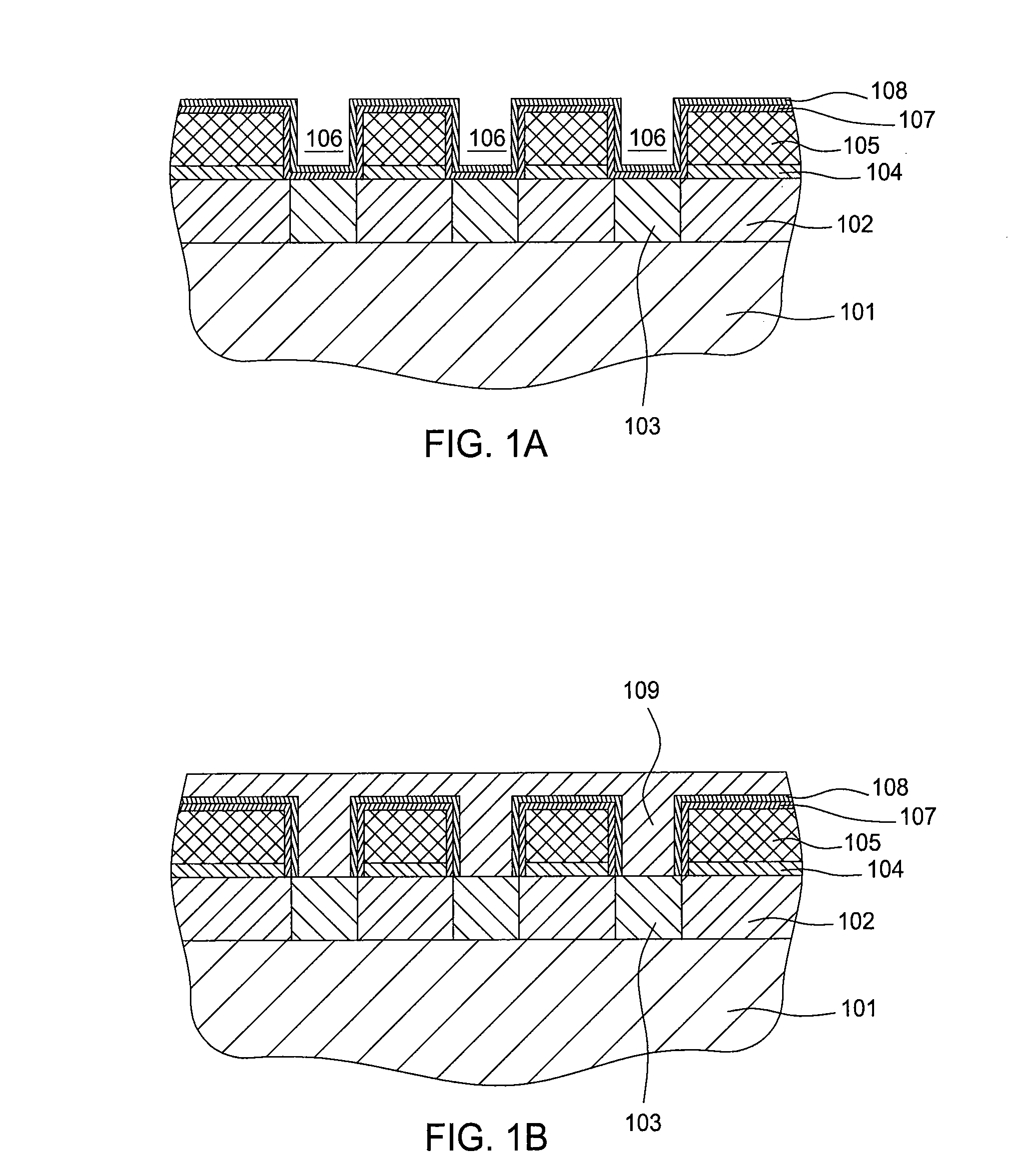

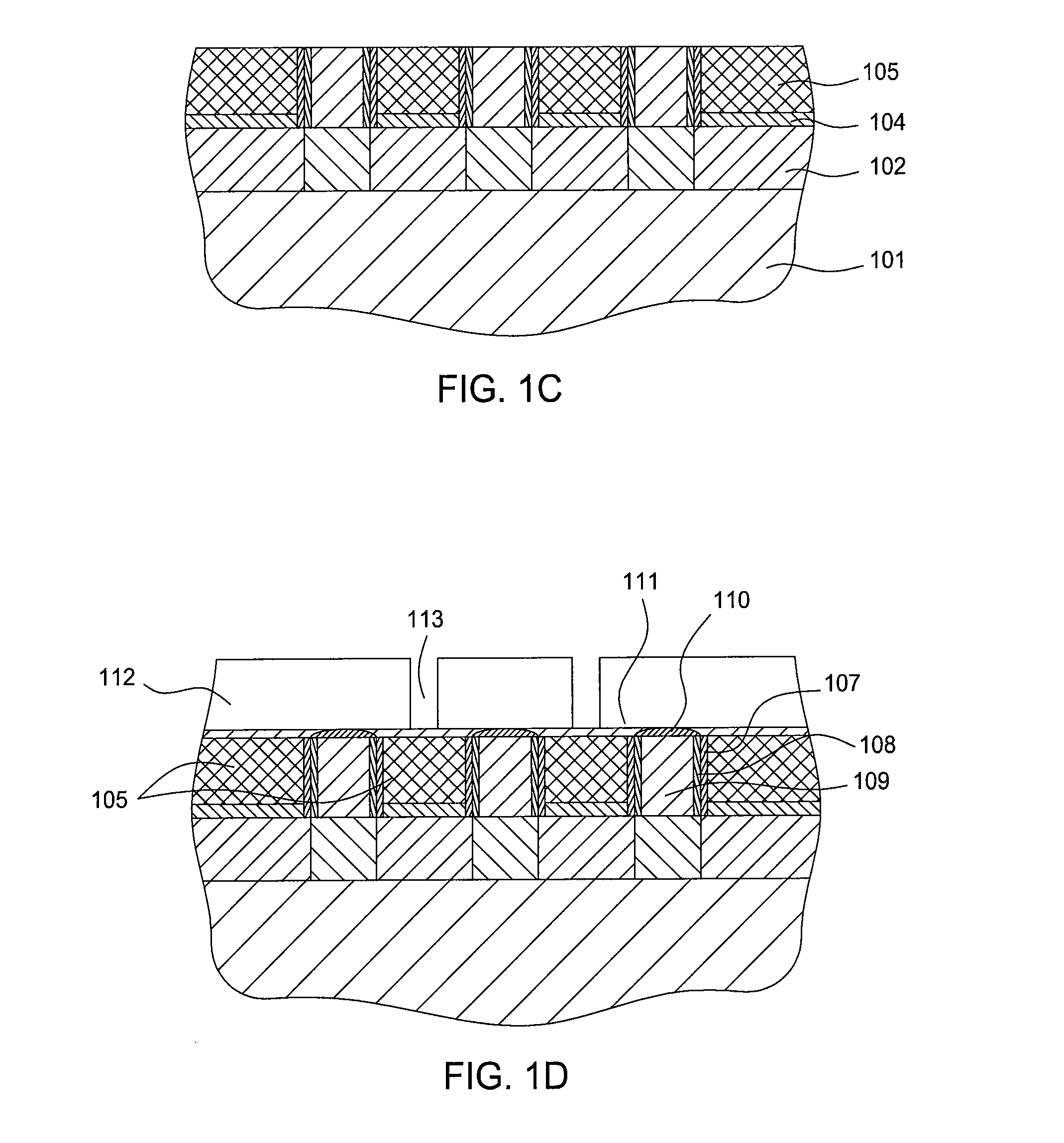

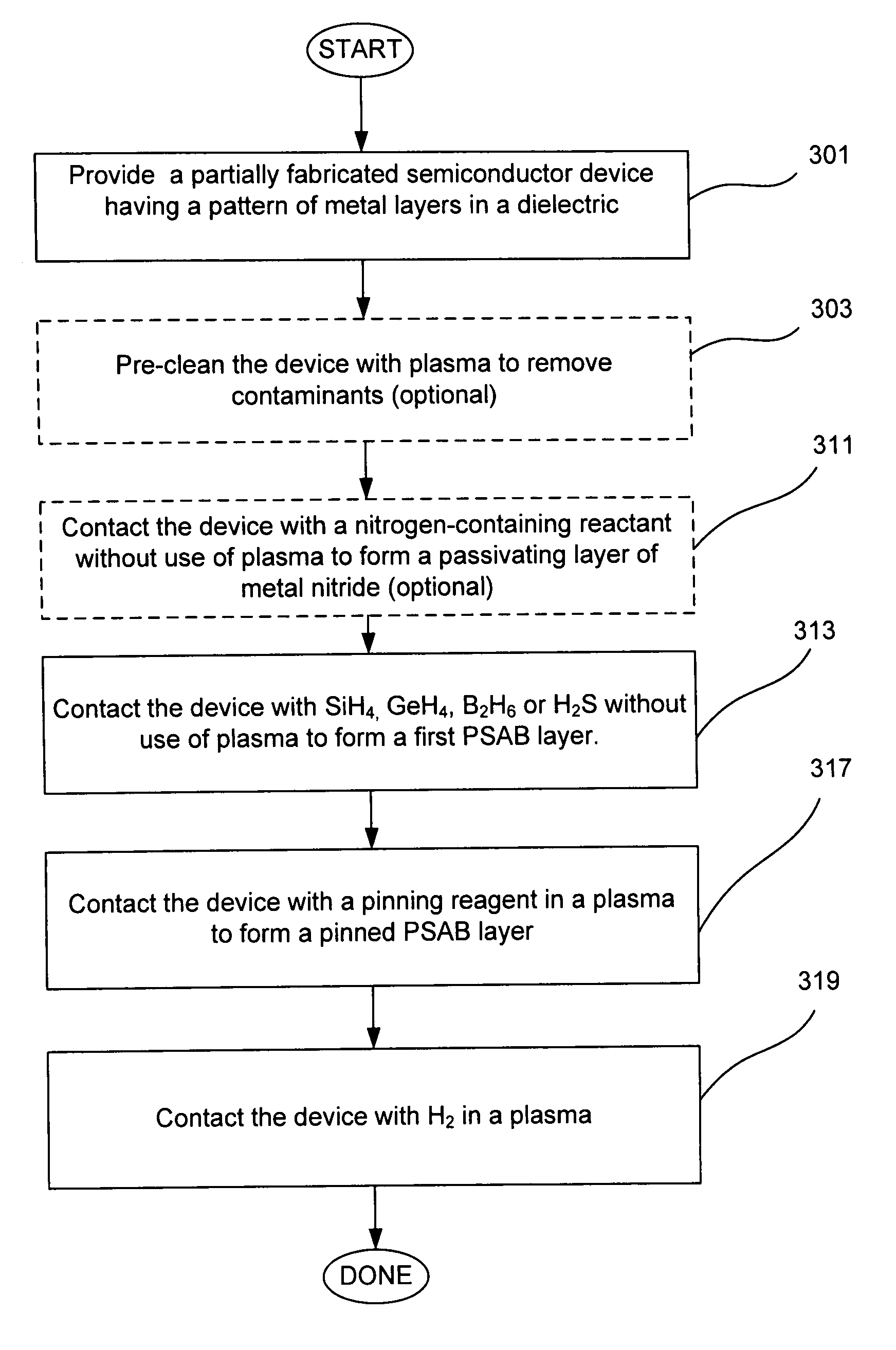

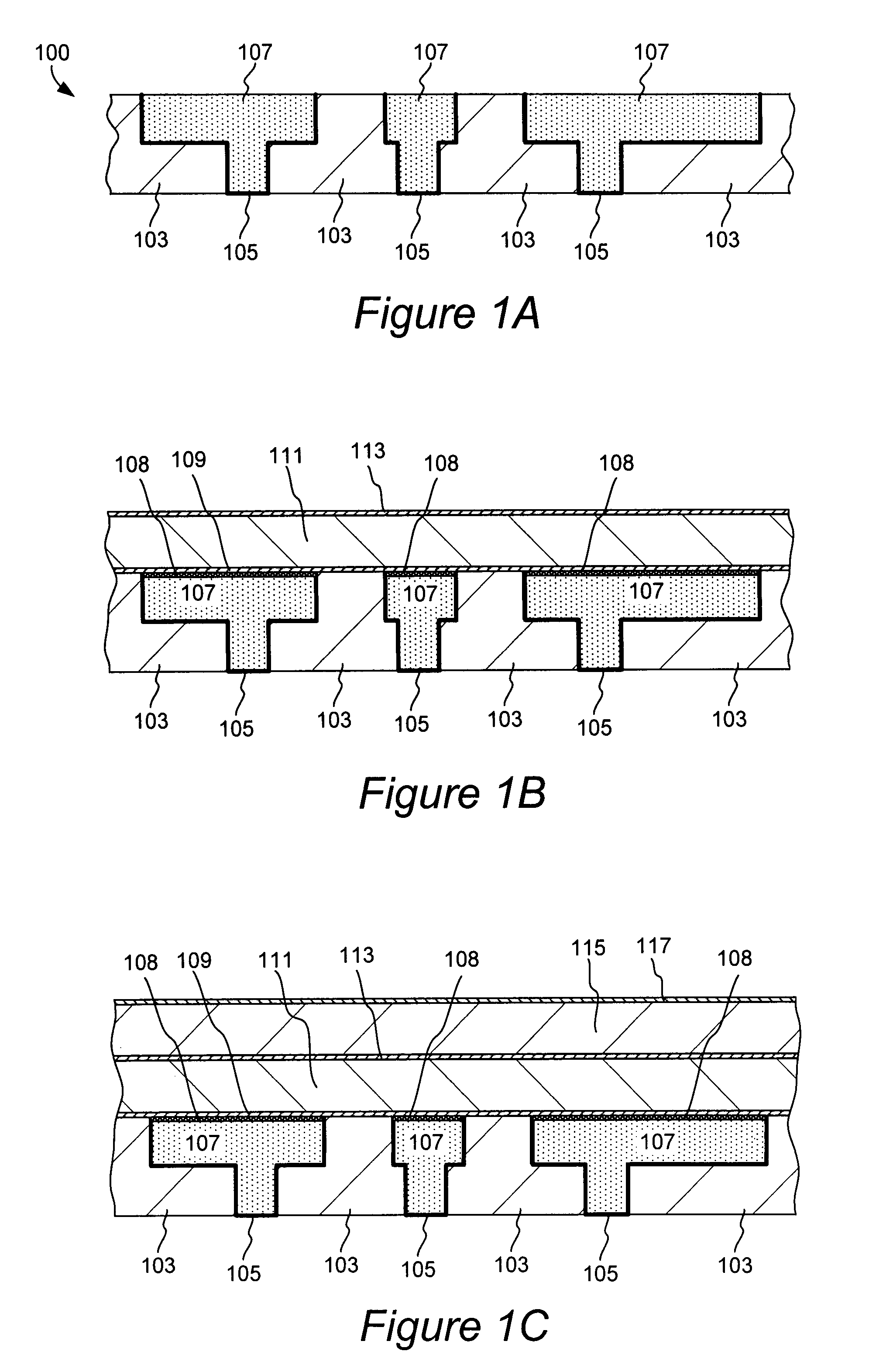

Protective self-aligned buffer layers for damascene interconnects

ActiveUS7727880B1Improving several propertyDecrease in metal electromigrationSemiconductor/solid-state device detailsSolid-state devicesSalicideMetal silicide

Protective self aligned buffer (PSAB) layers are layers of material that are selectively formed at the surface of metal layers in a partially fabricated semiconductor device. In a Damascene interconnect, PSAB layer typically resides at an interface between the metal layer and a dielectric diffusion barrier layer. PSAB layers promote improved adhesion between a metal layer and an adjacent dielectric diffusion barrier layer. Further, PSAB layers can protect metal surfaces from inadvertent oxidation during fabrication process. A PSAB layer may be formed entirely within the top portion of a metal layer, by, for example, chemically converting metal surface to a thin layer of metal silicide. Thickness of PSAB layers, and, consequently resistance of interconnects can be controlled by partially passivating metal surface prior to formation of PSAB layer. Such passivation can be accomplished by controllably treating metal surface with a nitrogen-containing compound to convert metal to metal nitride.

Owner:NOVELLUS SYSTEMS

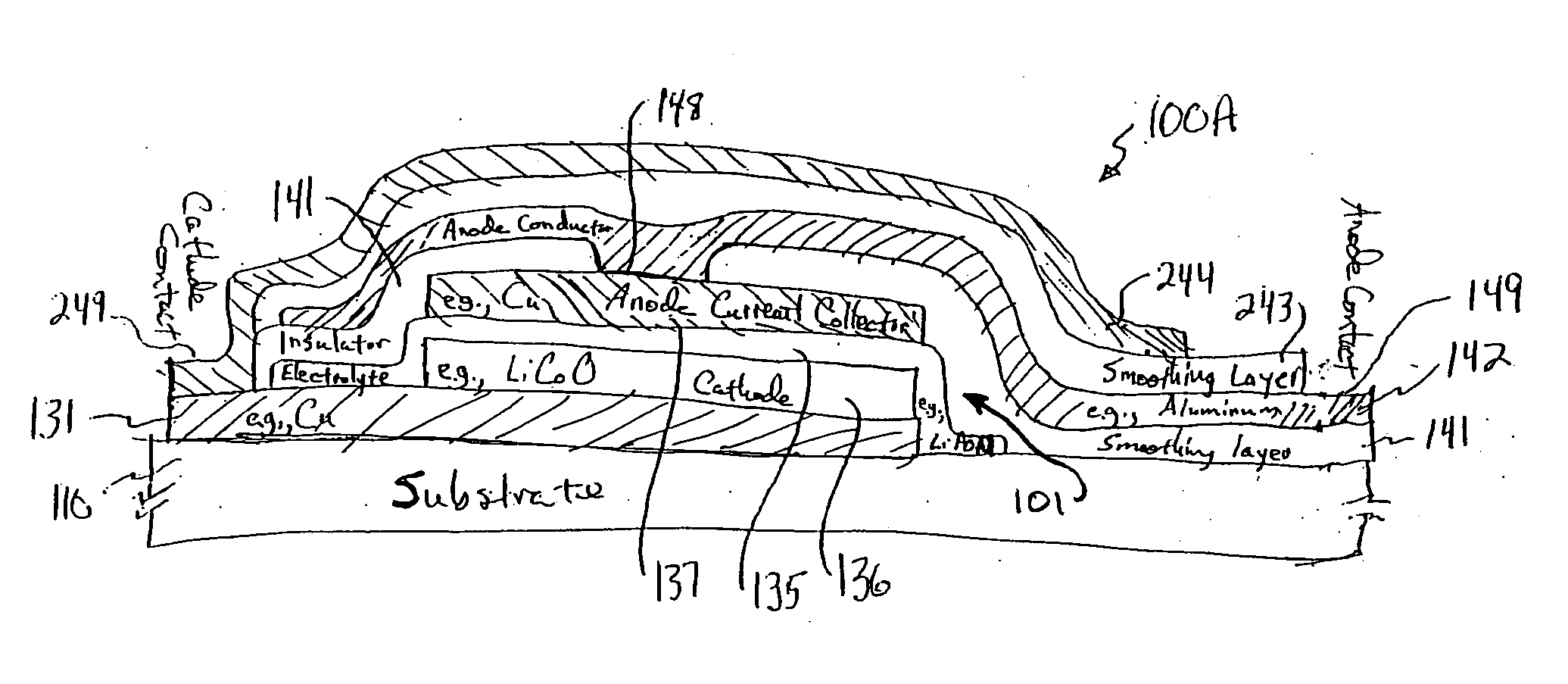

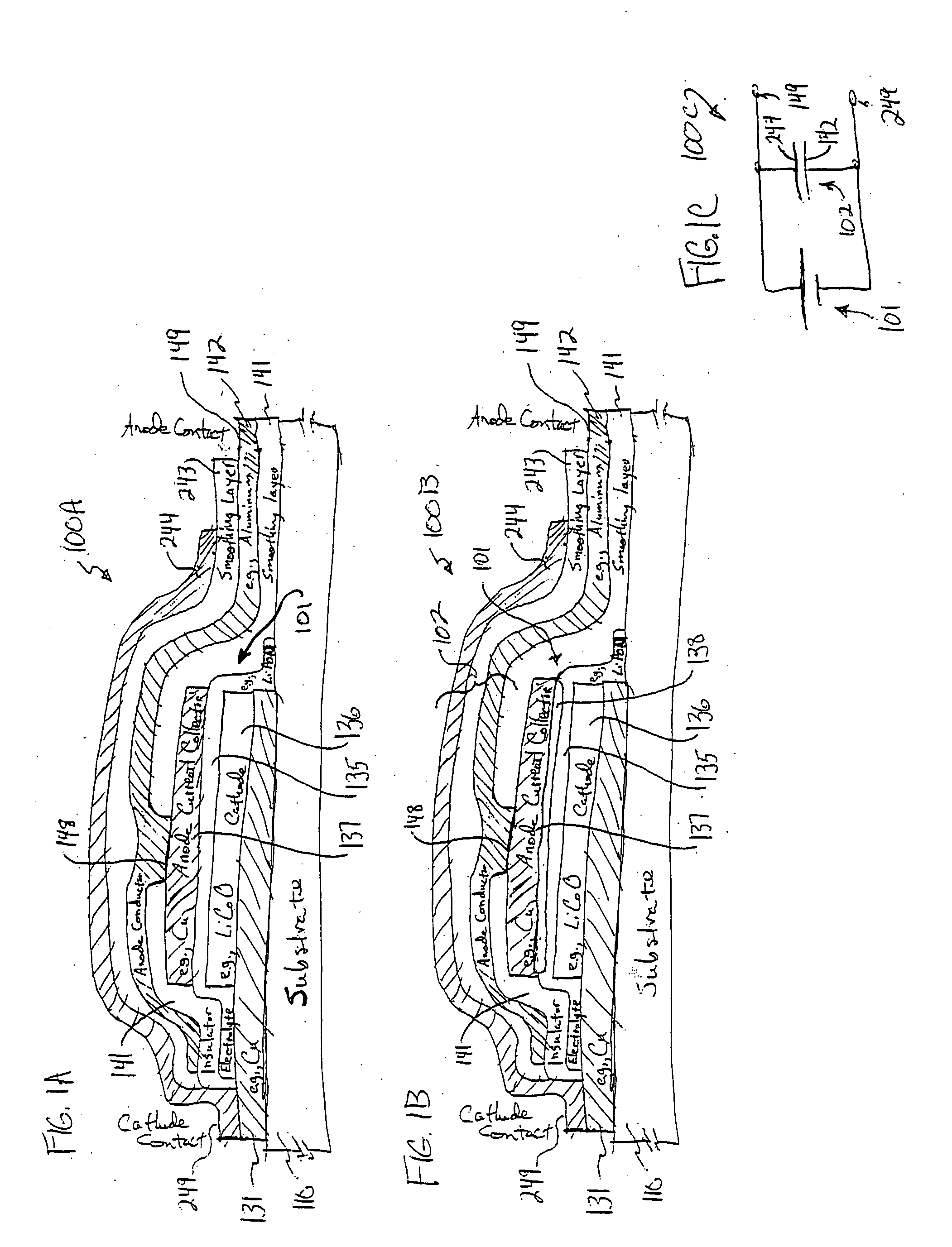

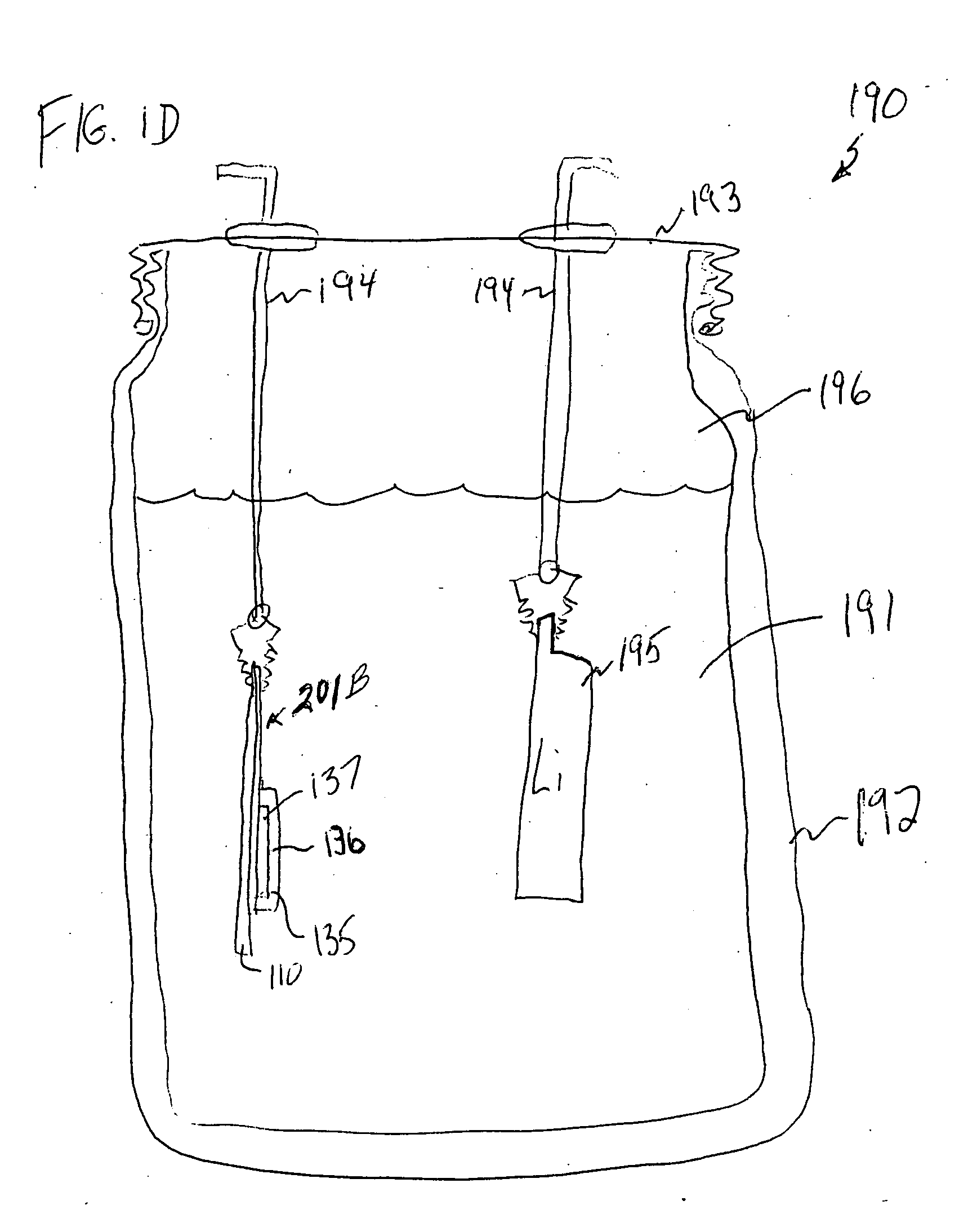

Layered barrier structure having one or more definable layers and method

InactiveUS20050147877A1Reduce transmissionLow rateFuel and primary cellsElectrode manufacturing processesDielectricLithium compound

A system provides an environmental barrier also useful for providing a circuit, for example, one having a thin-film battery such as one that includes lithium or lithium compounds connected to an electronic circuit. An environmental barrier is deposited as alternating layers, at least one of the layers providing a smoothing, planarizing, and / or leveling physical-configuration function, and at least one other layer providing a diffusion-barrier function. The layer providing the physical-configuration function may include a photoresist, a photodefinable, an energy-definable, and / or a maskable layer. The physical-configuration layer may also be a dielectric. A layered structure, including a plurality of pairs of layers, each pair including a physical configuration layer and a barrier layer with low gas-transmission rates, may be used in reducing gas transmission rate to beyond currently detectable levels.

Owner:CYMBET CORP

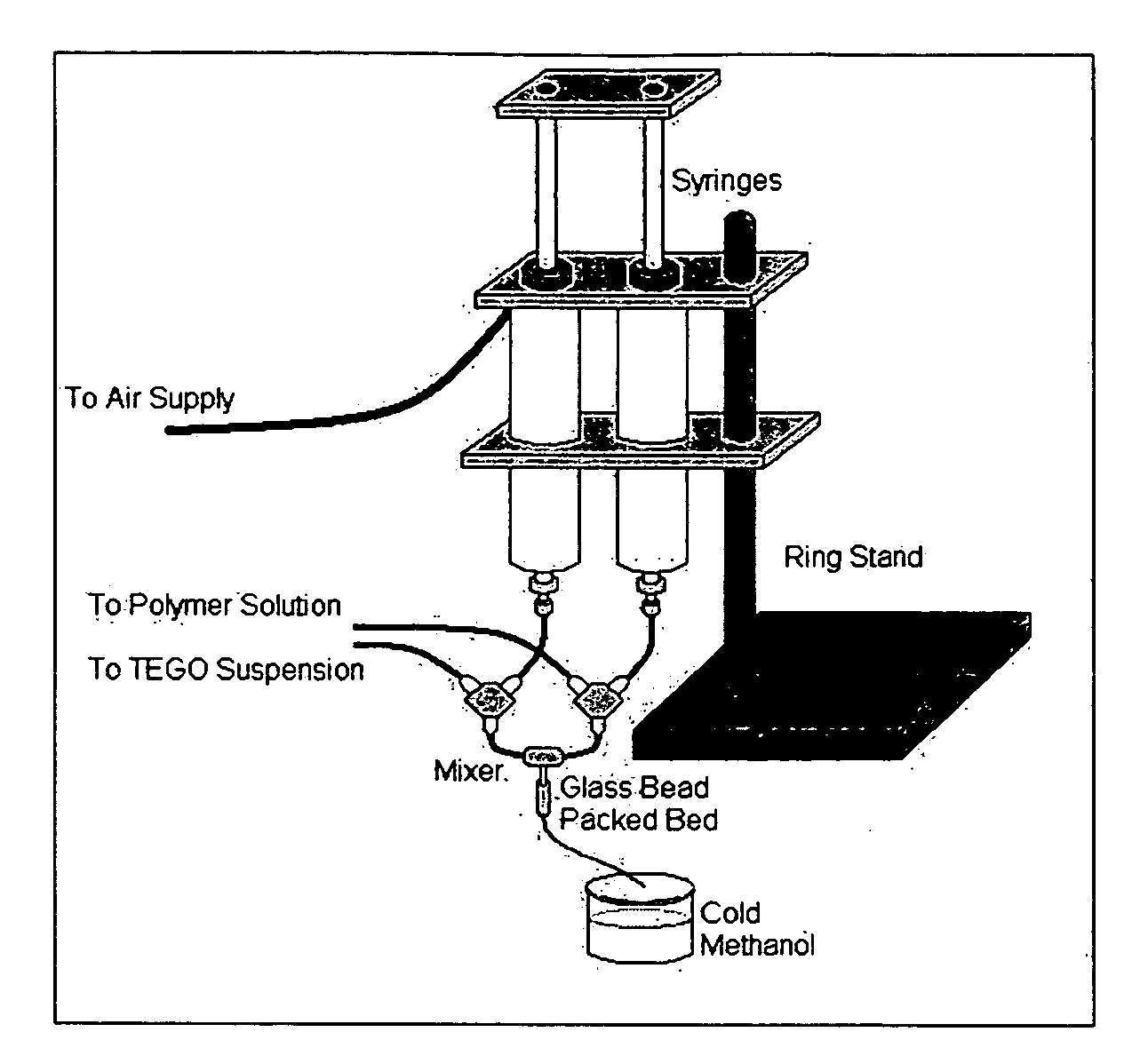

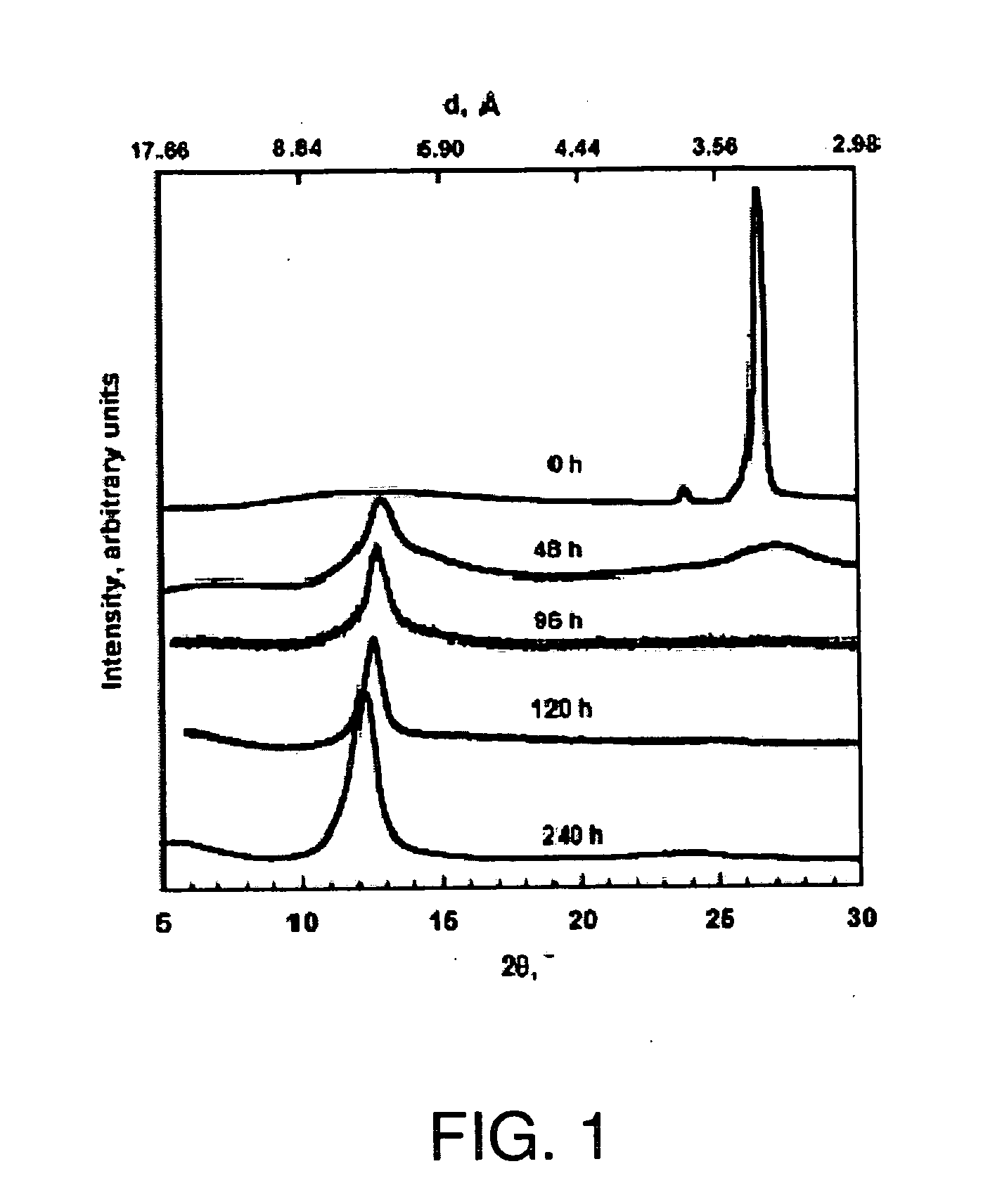

Functional graphene-polymer nanocomposites for gas barrier applications

InactiveUS20100096595A1Excellent gas barrier performanceImprove suppression propertiesMaterial nanotechnologyNanostructure manufactureNano compositesX-ray

Owner:THE TRUSTEES FOR PRINCETON UNIV

Method for forming metal replacement gate of high performance

InactiveUS6921711B2Semiconductor/solid-state device manufacturingSemiconductor devicesTitanium nitrideDiffusion barrier

A structure and method for a metal replacement gate of a high performance device is provided. A sacrificial gate structure is first formed on an etch stop layer provided on a semiconductor substrate. A pair of spacers is provided on sidewalls of the sacrificial gate structure. The sacrificial gate structure is then removed, forming an opening. Subsequently, a metal gate including an first layer of metal such as tungsten, a diffusion barrier such as titanium nitride, and a second layer of metal such as tungsten is formed in the opening between the spacers.

Owner:GLOBALFOUNDRIES U S INC

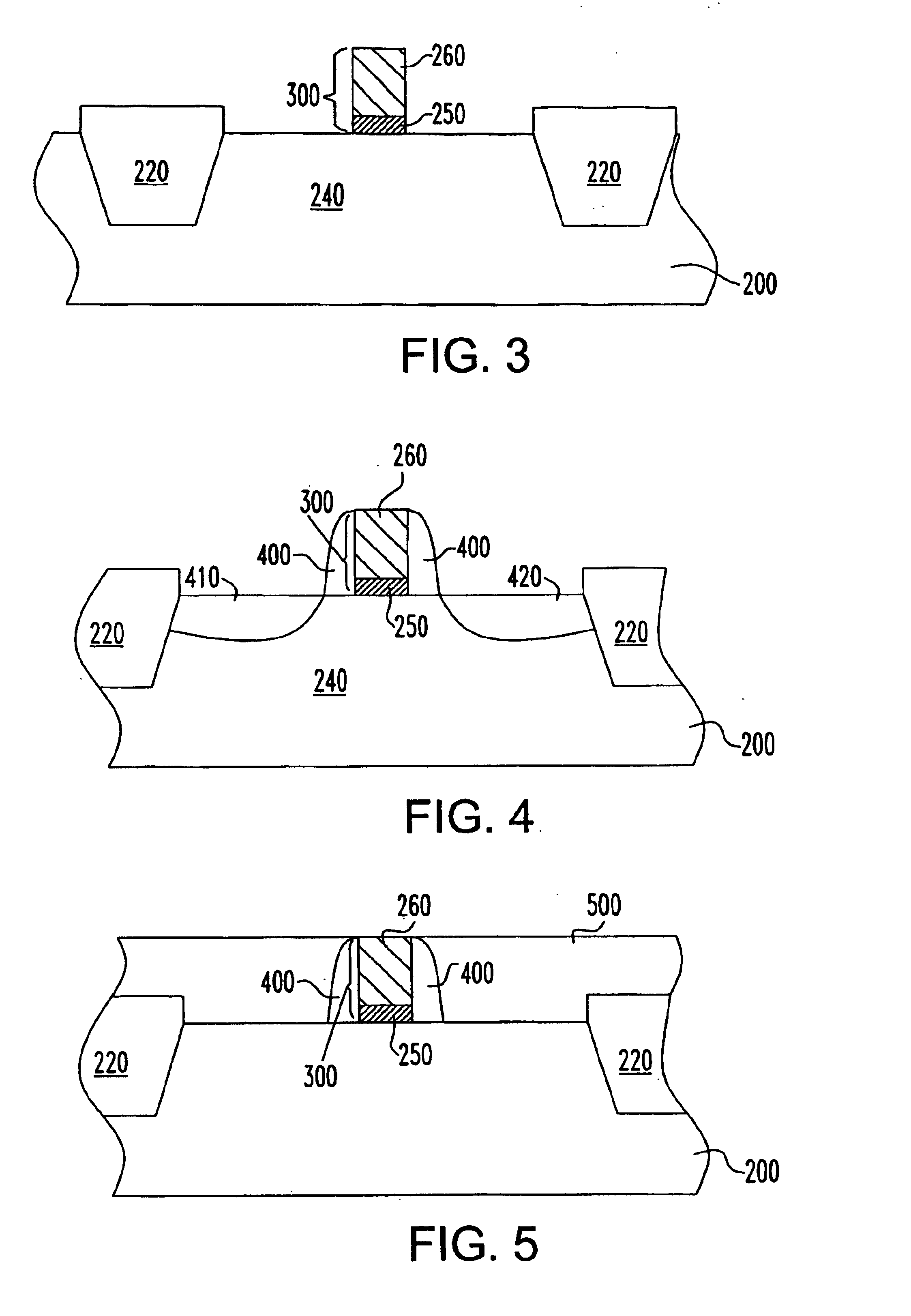

Capping structure for enhancing dR/R of the MTJ device

An MTJ in an MRAM array or in a TMR read head is comprised of a capping layer with a lower inter-diffusion barrier layer, an intermediate oxygen gettering layer, and an upper metal layer that contacts a top conductor. The composite capping layer is especially useful with a moderate spin polarization free layer such as a NiFe layer with a Fe content of about 17.5 to 20 atomic %. The capping layer preferably has a Ru / Ta / Ru configuration in which the lower Ru layer is about 10 to 30 Angstroms thick and the Ta layer is about 30 Angstroms thick. As a result, a high dR / R of about 40% is achieved with low magnetostriction less than about 1.0 E−6 in an MTJ in an MRAM array. Best results are obtained with an AlOx tunnel barrier layer formed by an in-situ ROX process on an 8 to 10 Angstrom thick Al layer.

Owner:HEADWAY TECH INC +1

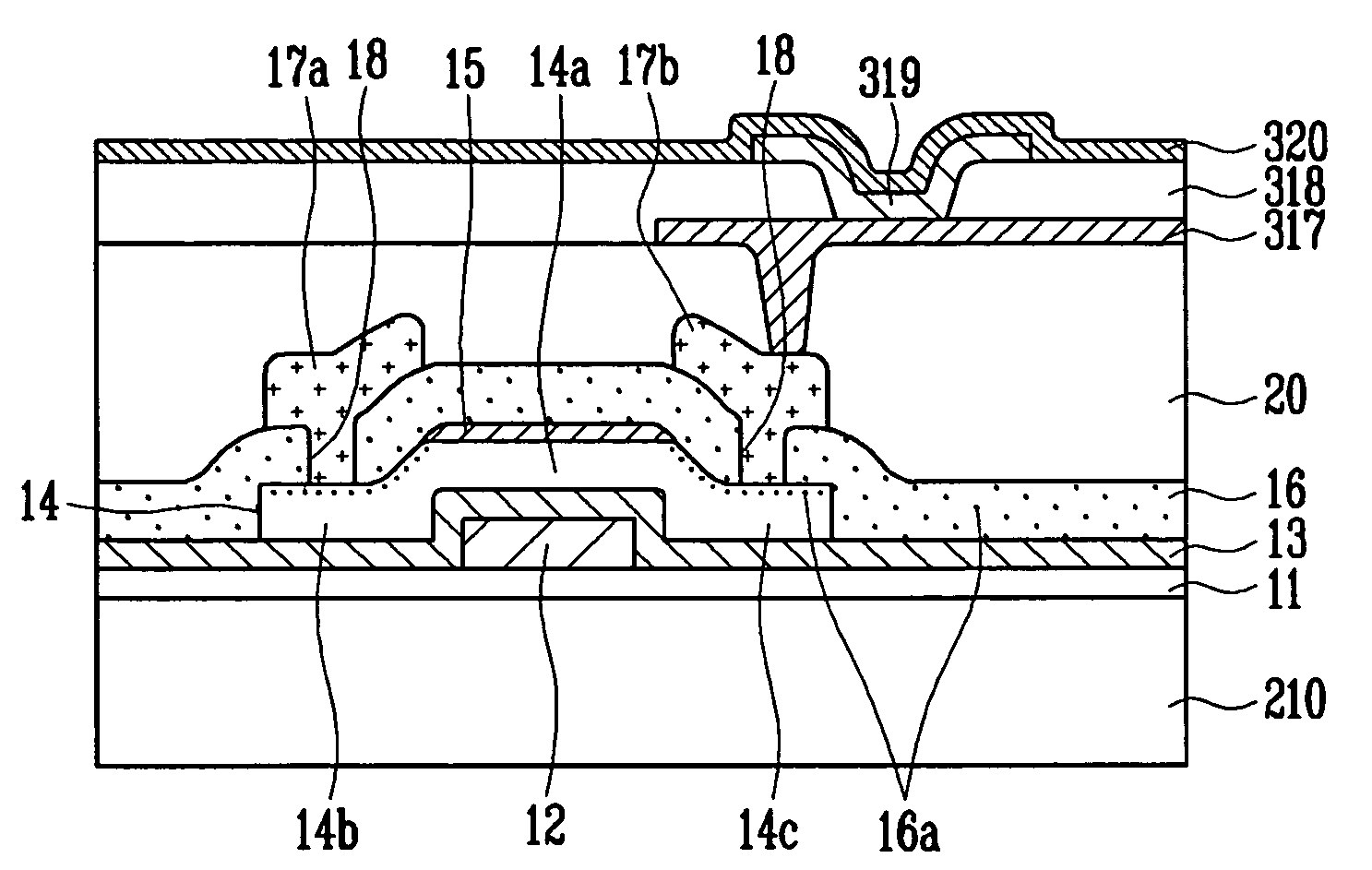

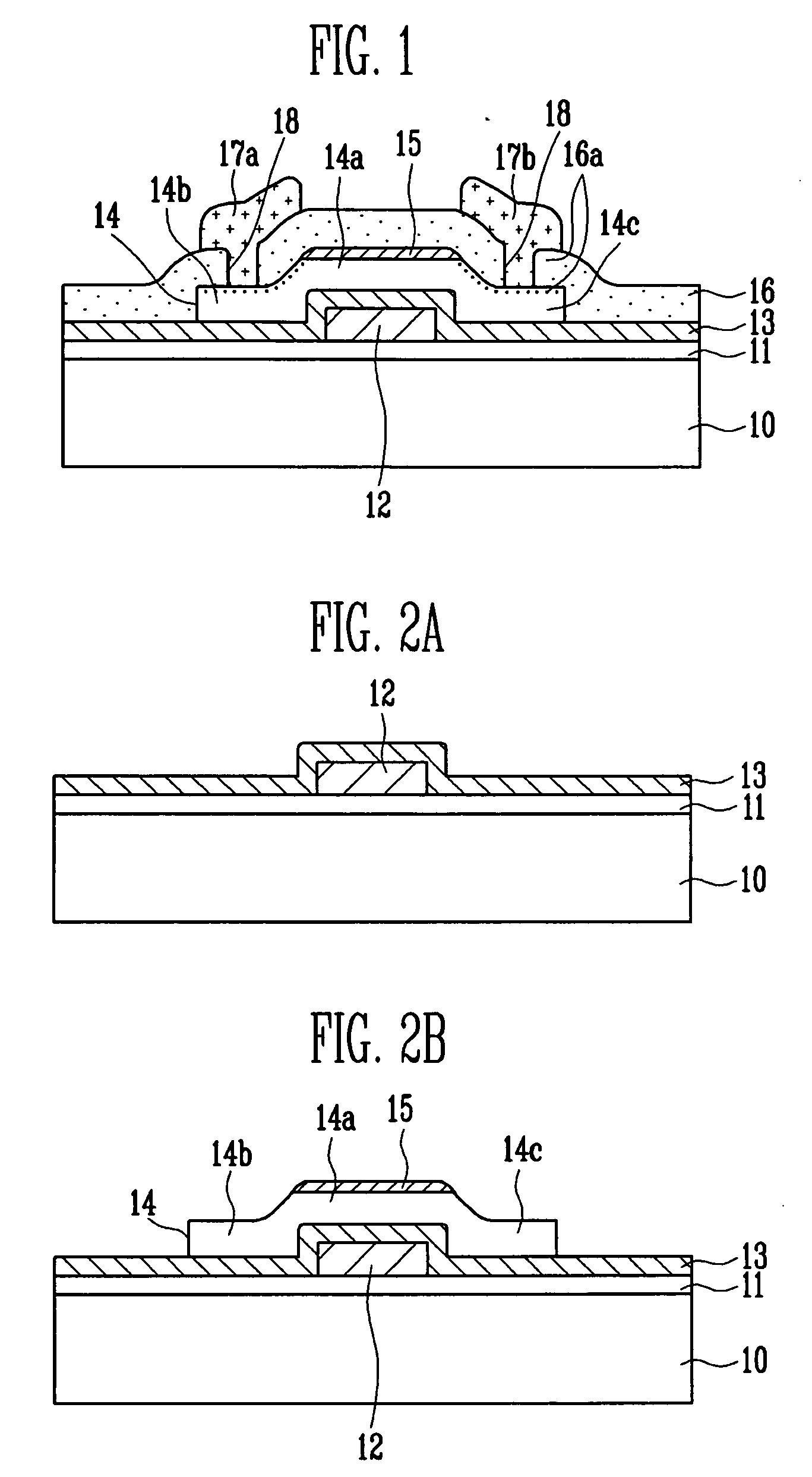

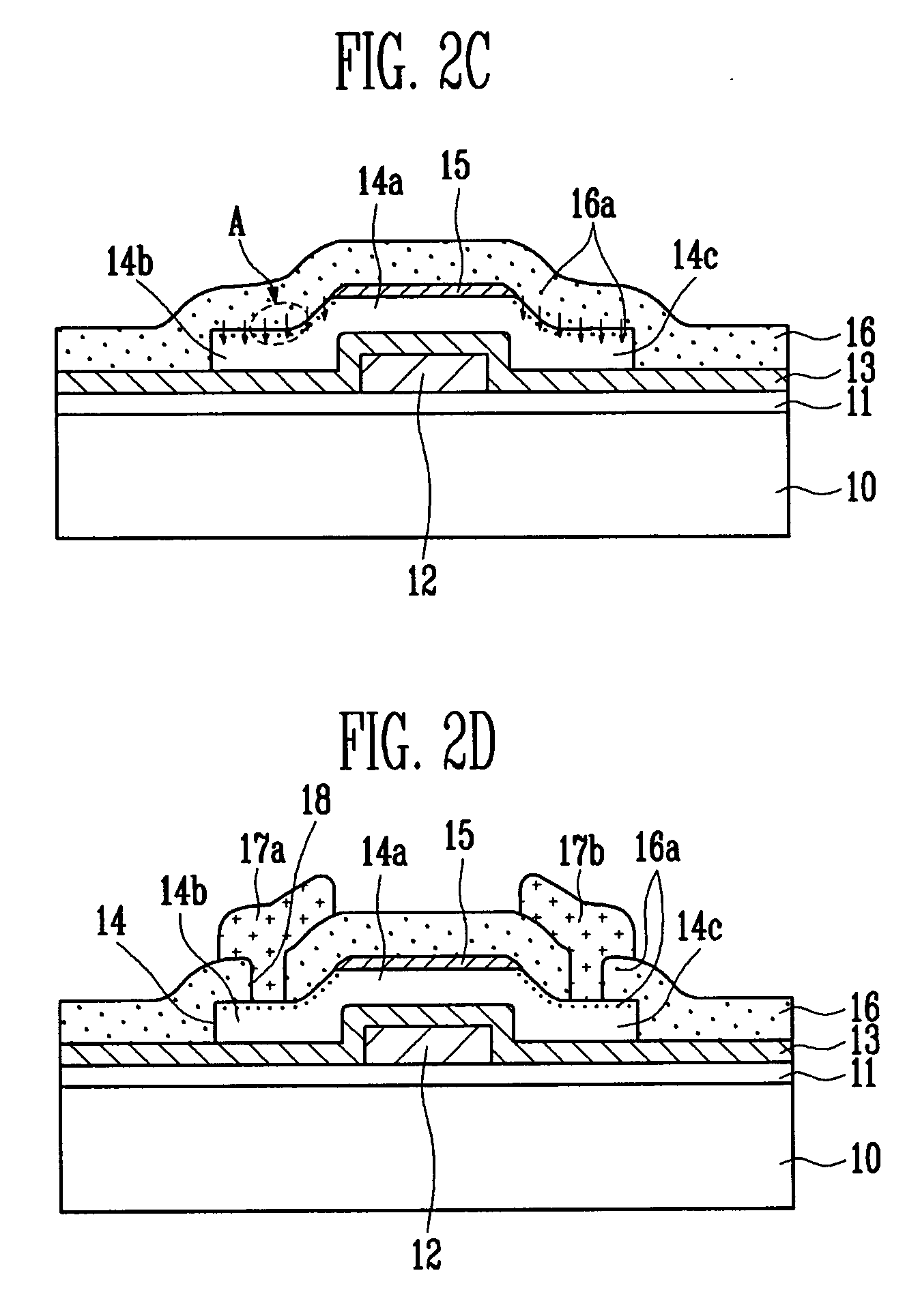

Thin film transistor, flat panel display device having the same, and associated methods

ActiveUS20080303020A1Minimizing diffusion of hydrogenSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerHydrogen

A thin film transistor includes a gate electrode, a first insulating layer on the gate electrode, a semiconductor layer on the gate electrode and separated from the gate electrode by the first insulating layer, the semiconductor layer including a channel region corresponding to the gate electrode, a source region, and a drain region, a hydrogen diffusion barrier layer on the semiconductor layer, the hydrogen diffusion barrier layer covering the channel region and exposing the source and drain regions, and a second insulation layer on the source and drain regions and on the hydrogen diffusion barrier layer, such that the hydrogen diffusion barrier layer is between the second insulation layer and the channel region.

Owner:SAMSUNG DISPLAY CO LTD

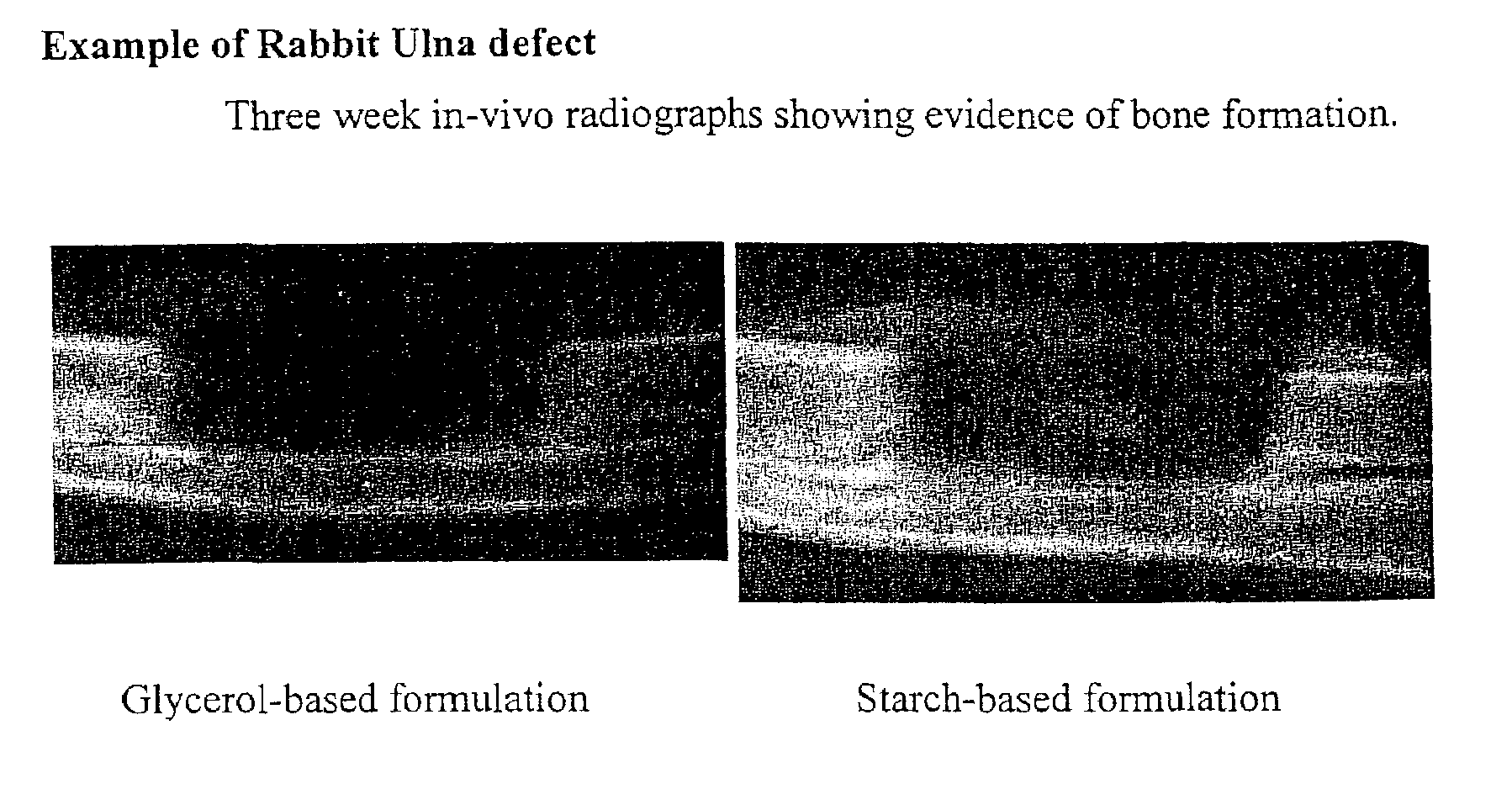

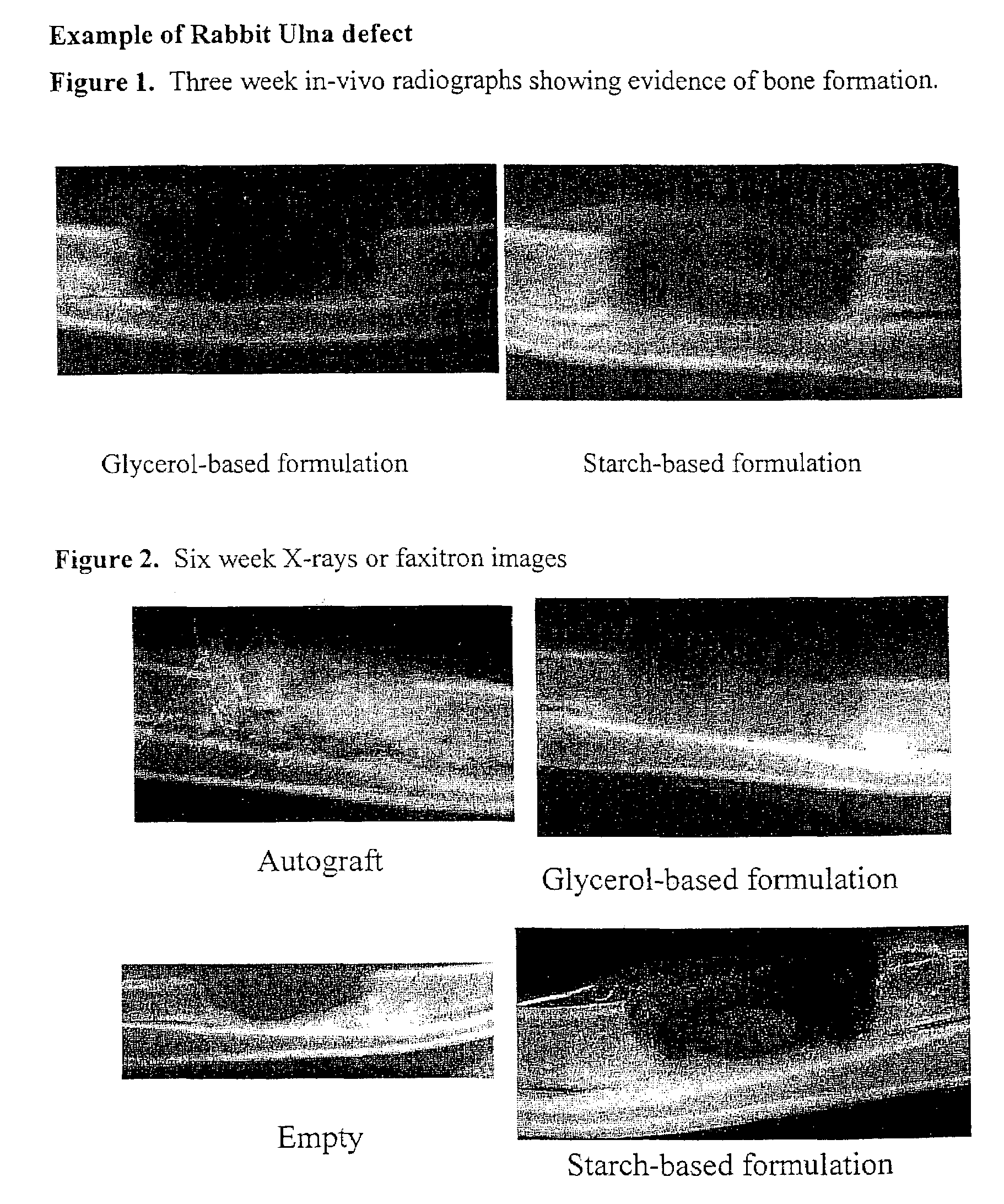

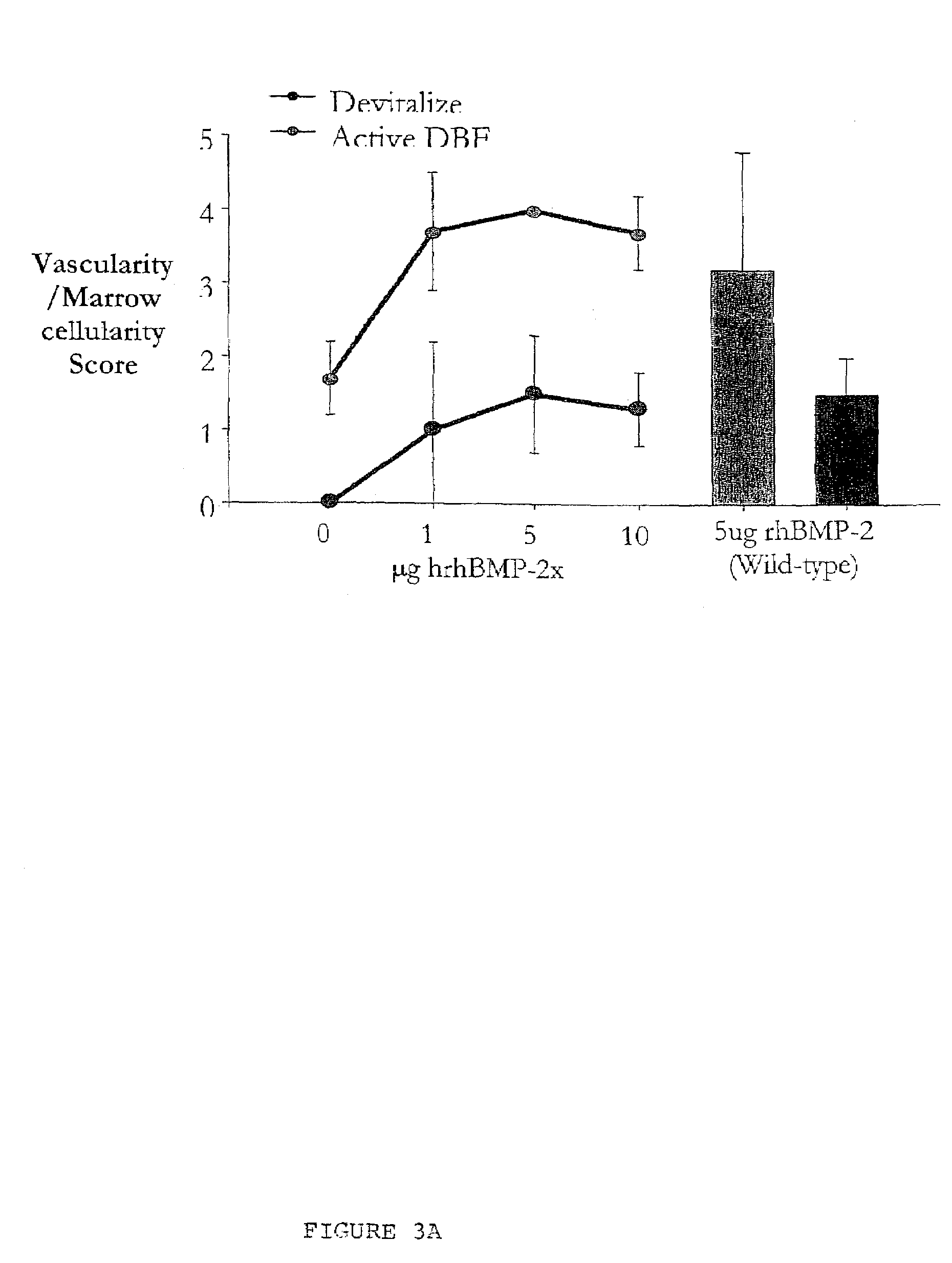

Bone graft

ActiveUS7163691B2Fast reduction in osteoinductiveGood curative effectOrganic active ingredientsImpression capsOSTEOINDUCTIVE FACTORIn vivo

An improved demineralized bone matrix (DBM) or other matrix composition is provided that has been mixed with a stabilizing agent that acts as (1) a diffusion barrier, (2) a enzyme inhibitor, (3) a competitive substrate, or (4) a masking moiety. A diffusion barrier acts as a barrier so as to protect the osteoinductive factors found in DBM from being degraded by proteolytic and glycolytic enzymes at the implantation site. Stabilizing agents may be any biodegradable material such as starches, modified starches, cellulose, dextran, polymers, proteins, and collagen. As the stabilizing agents degrades or dissolves in vivo, the osteoinductive factors such as TGF-β, BMP, and IGF are activated or exposed, and the activated factors work to recruit cells from the preivascular space to the site of injury and to cause differentiation into bone-forming cells. The invention also provides methods of preparing, testing, and using the inventive improved osteodinductive matrix compositions.

Owner:WARSAW ORTHOPEDIC INC

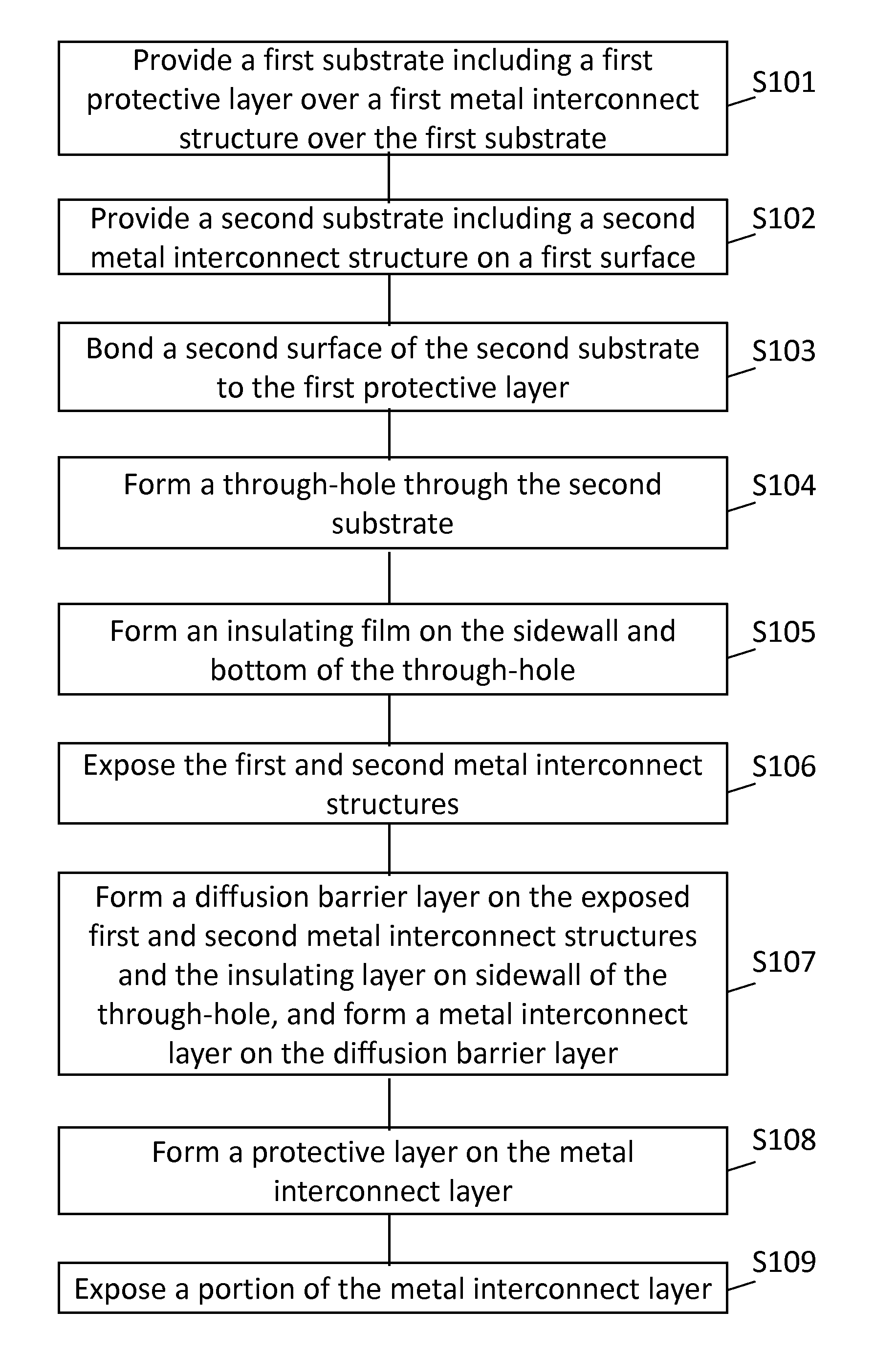

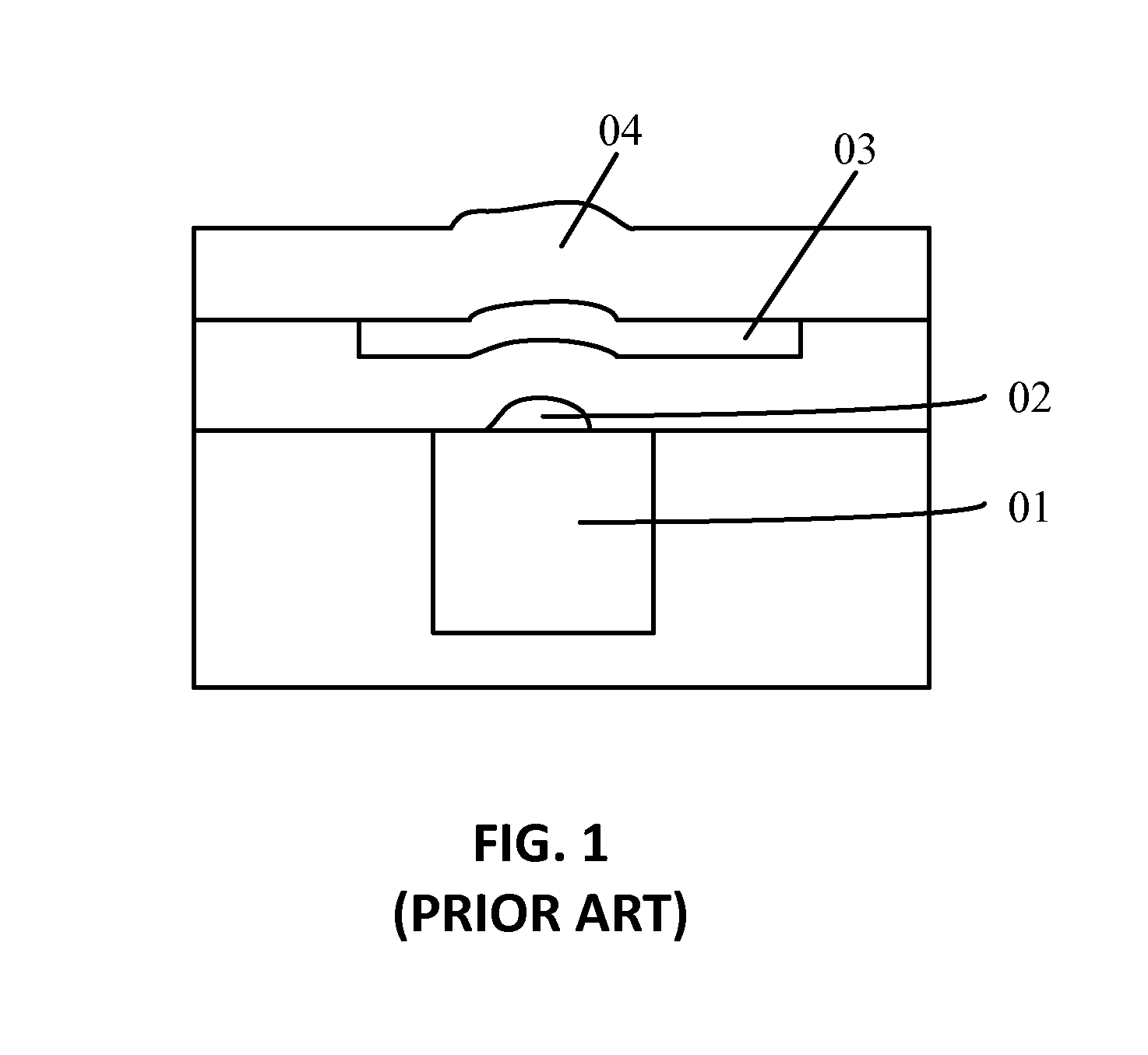

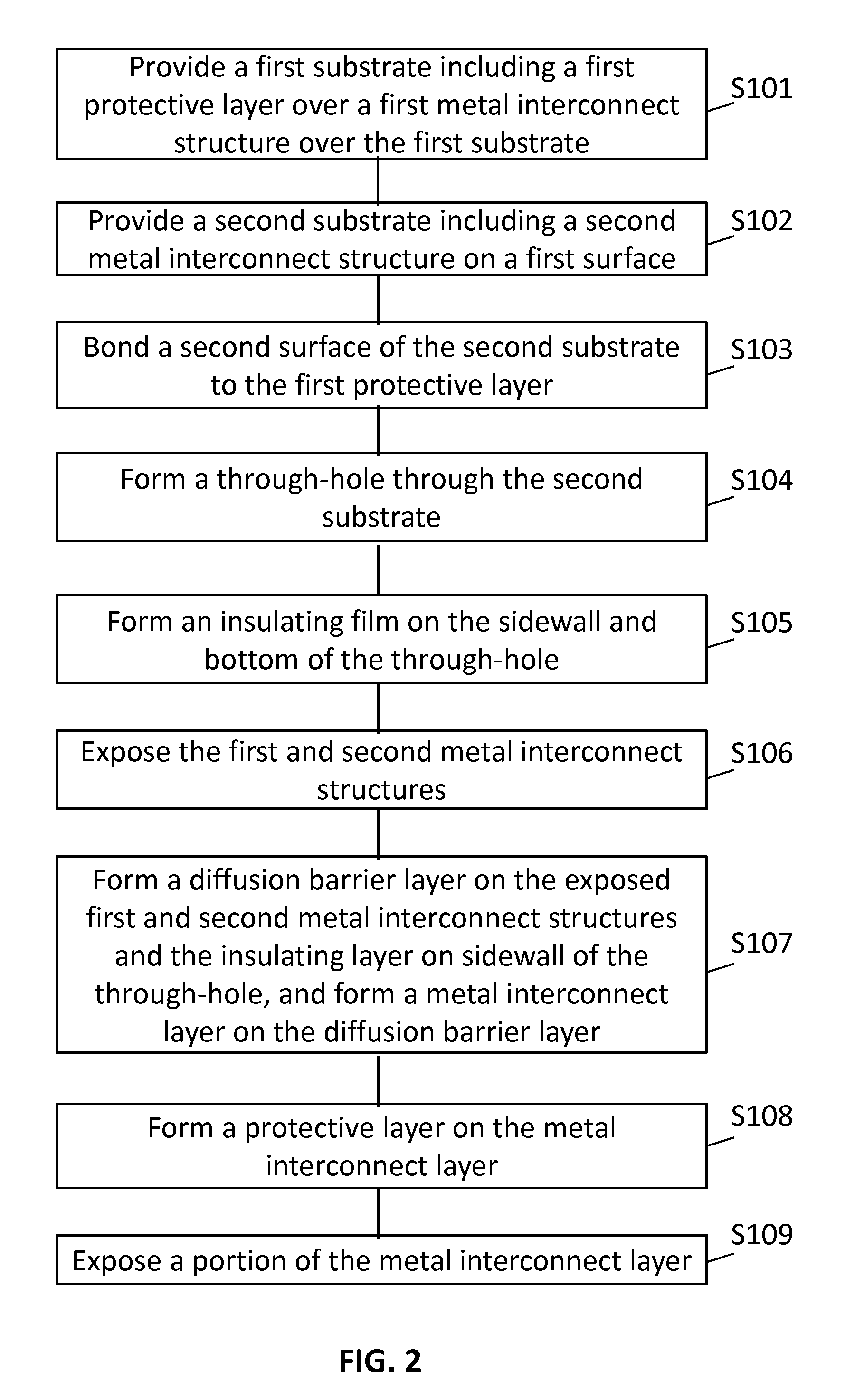

IC device including package structure and method of forming the same

ActiveUS20140015136A1Semiconductor/solid-state device detailsSolid-state devicesMetal interconnectEngineering

Various embodiments provide semiconductor devices including a package structure and methods of forming the semiconductor devices. In one embodiment, the package structure can include a through-hole at least partially filled by one or more layers of material(s) to form a through-hole interconnect between semiconductor devices in the package structure. The through-hole can be filled by an insulating layer, a diffusion barrier layer, a metal interconnect layer, and / or a protective layer having a total thickness from the sidewall of the through-hole of less than or equal to the radius of the through-hole.

Owner:SEMICON MFG INT (SHANGHAI) CORP