Control of dopant diffusion from buried layers in bipolar integrated circuits

a bipolar integrated circuit and dopant diffusion technology, applied in the field of semiconductor integrated circuits, can solve the problems of significant dopant concentration gradient, reduced effective collector resistance, and relatively resistive light-doped subcollectors, and achieve the effect of reducing the diffusion of dopan

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

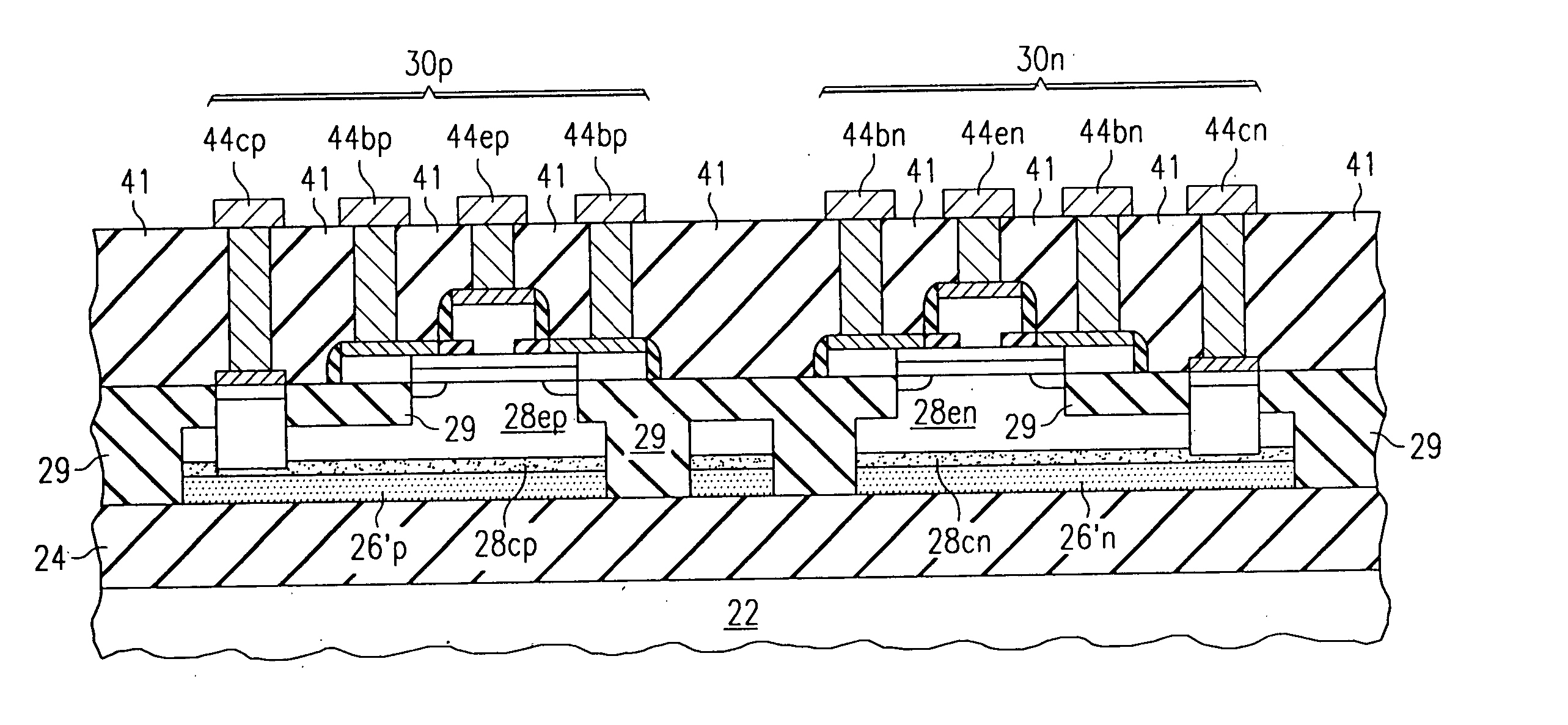

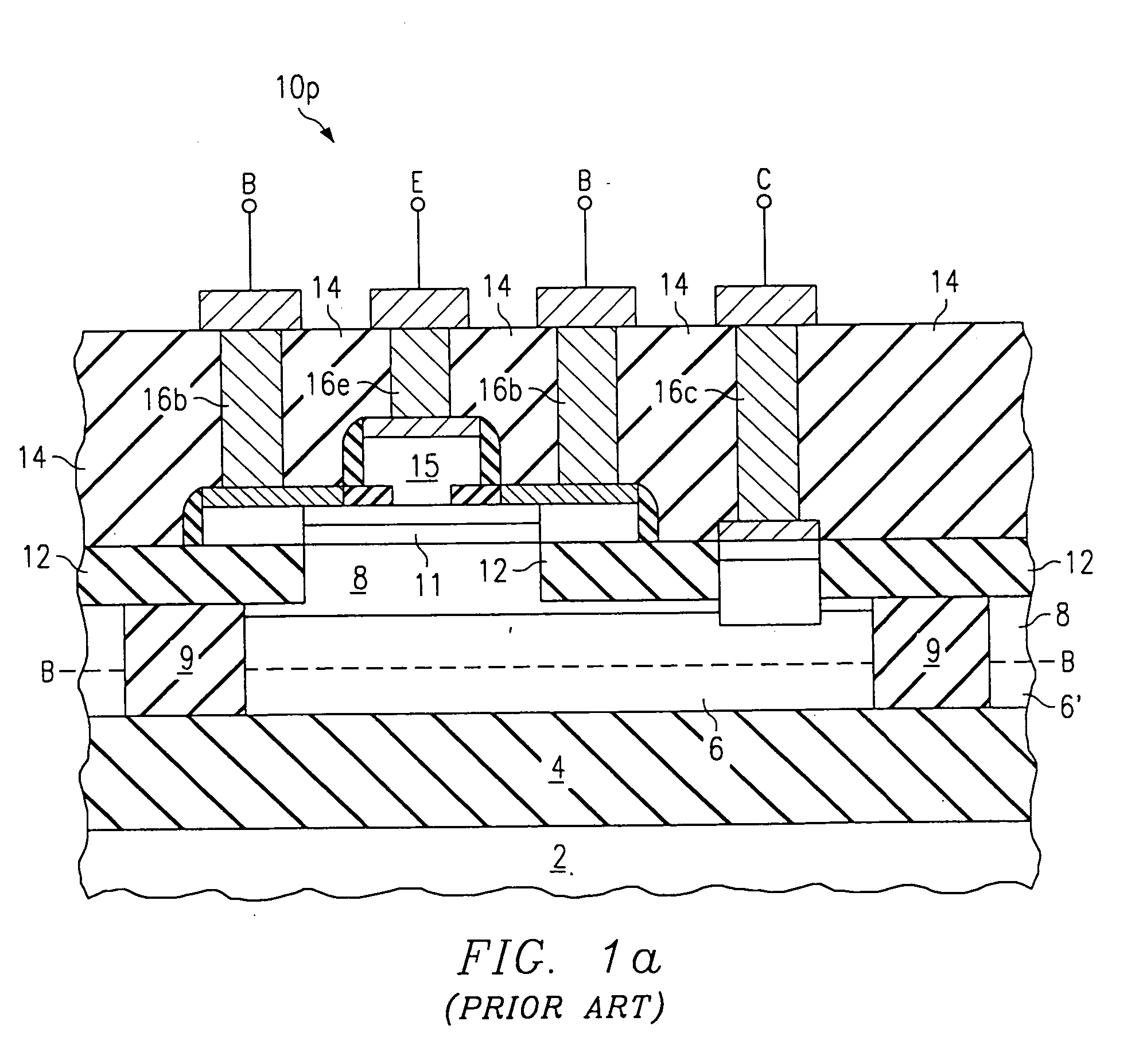

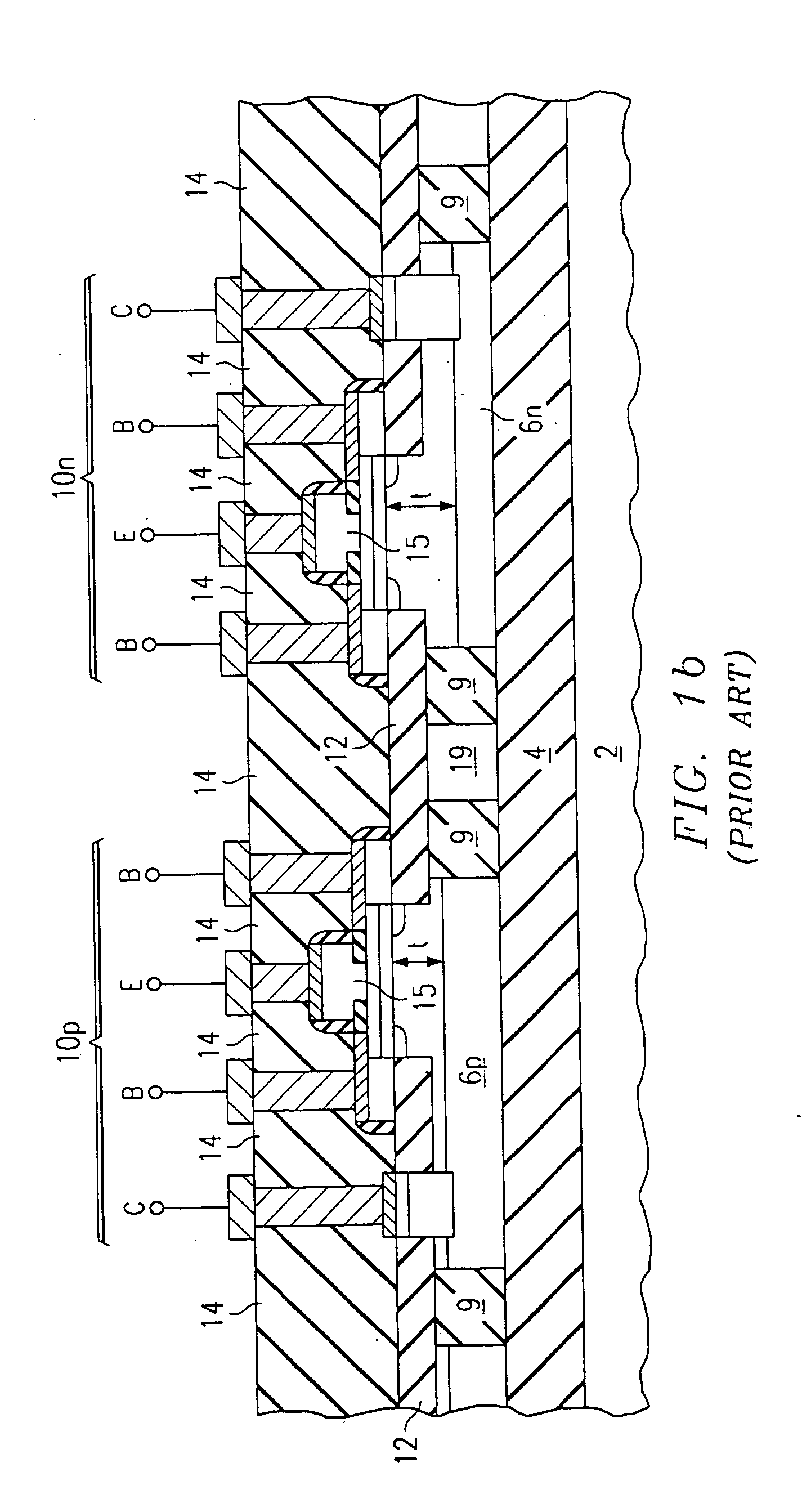

[0028] The present invention will now be described in connection with its preferred embodiments. These exemplary embodiments are directed to the fabrication of bipolar junction transistors in a silicon-on-insulator (SOI) structure. It will be appreciated by those skilled in the art having reference to this specification that the present invention may be used to form either p-n-p or n-p-n transistors, or both as may be used in a complementary bipolar or BiCMOS technology, as well as used in other alternative structures and methods of fabricating such structures. In addition, while this invention is particularly beneficial as applied to SOI structures, it is also contemplated that this invention may be utilized in bulk integrated circuit devices as well, where no buried insulator layer is present. Furthermore, while these embodiments are silicon or SiGe NPN and PNP bipolar transistors, it is contemplated that the present invention will be equally applicable to emerging bipolar technol...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More