Patents

Literature

46 results about "Error cancellation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Cancellation Errors. When one adds two numbers with opposite sign but with similar absolute values, the result may be quite inexact and the situation is referred to as loss, or cancellation, of significant digits.

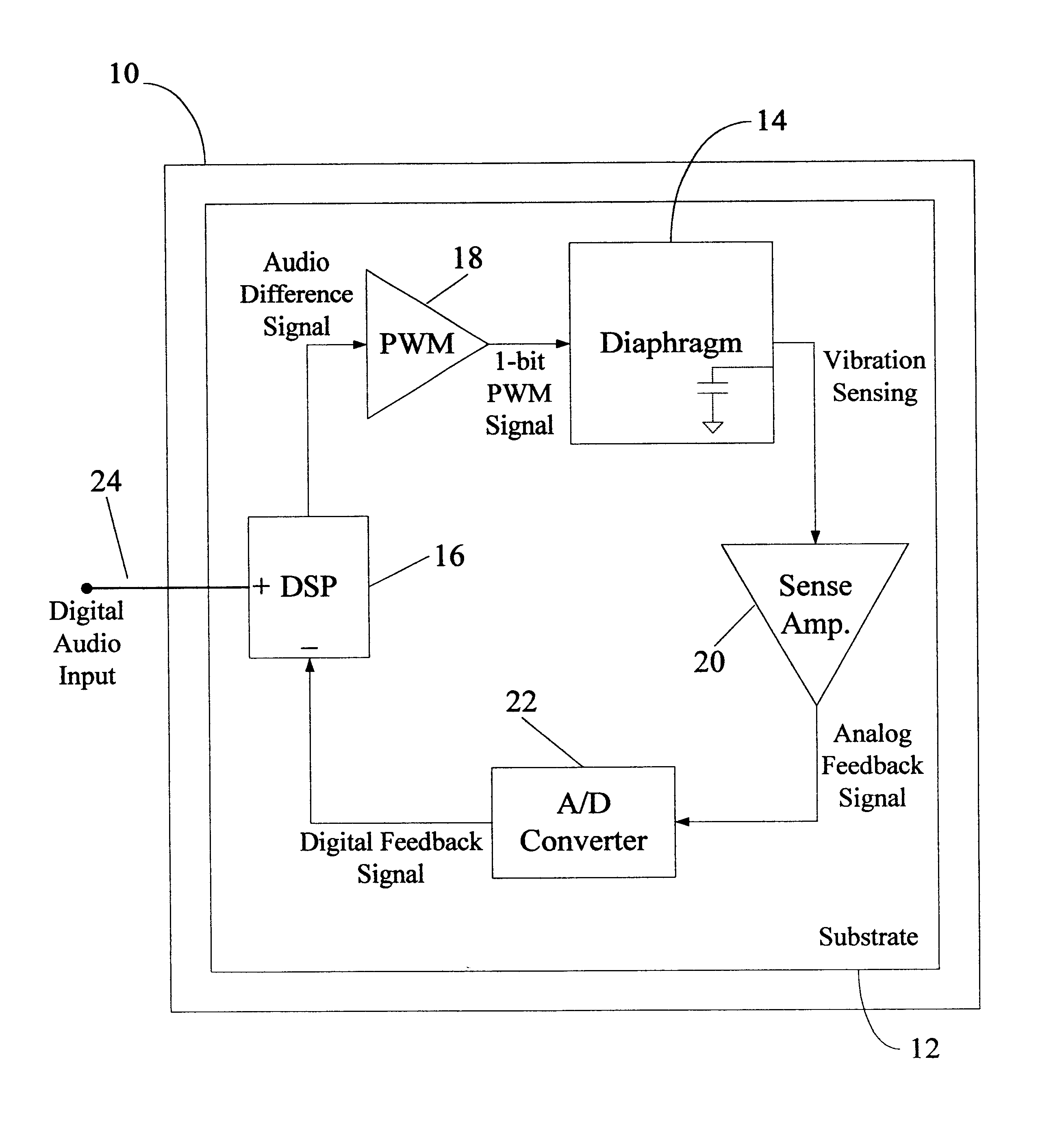

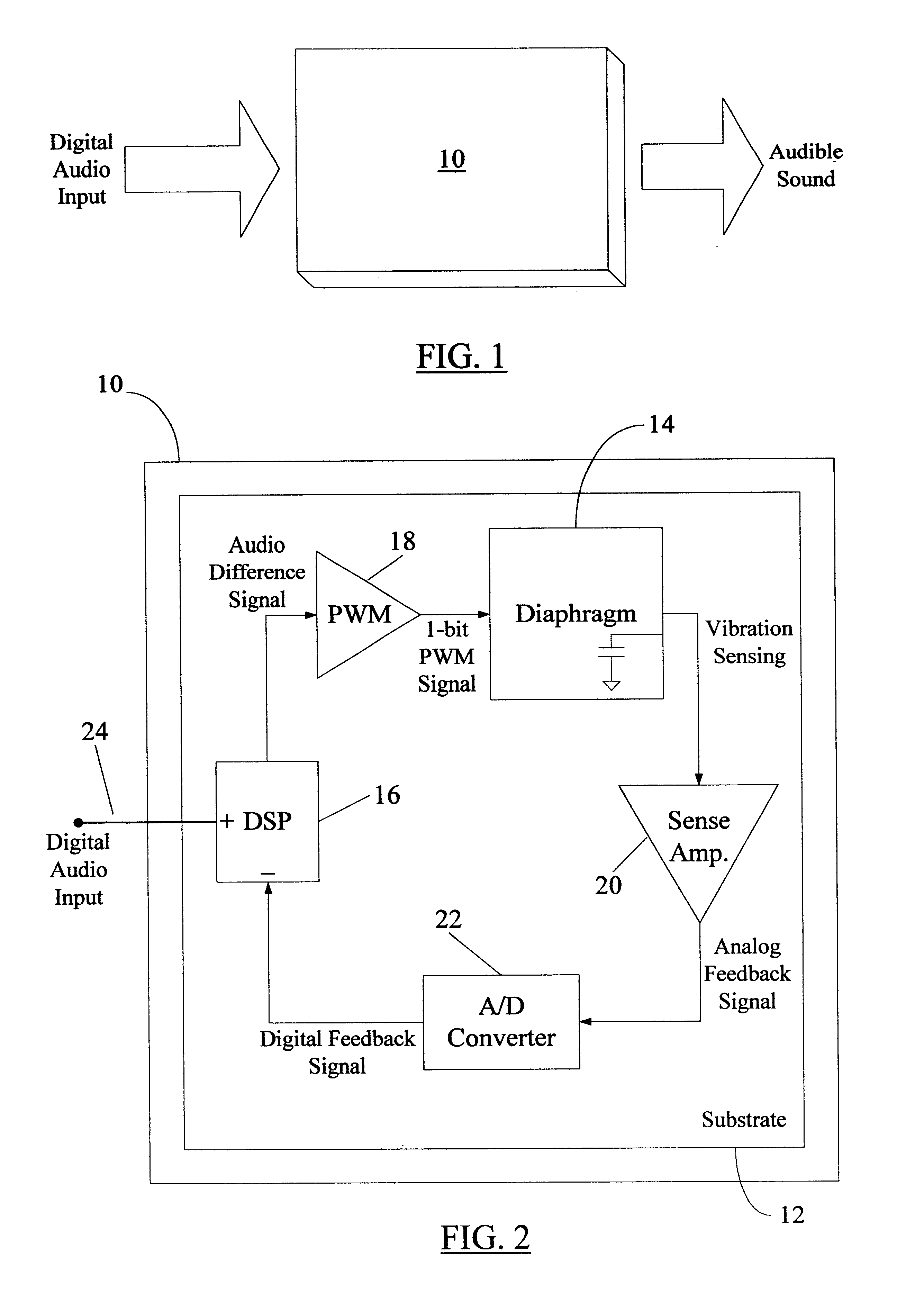

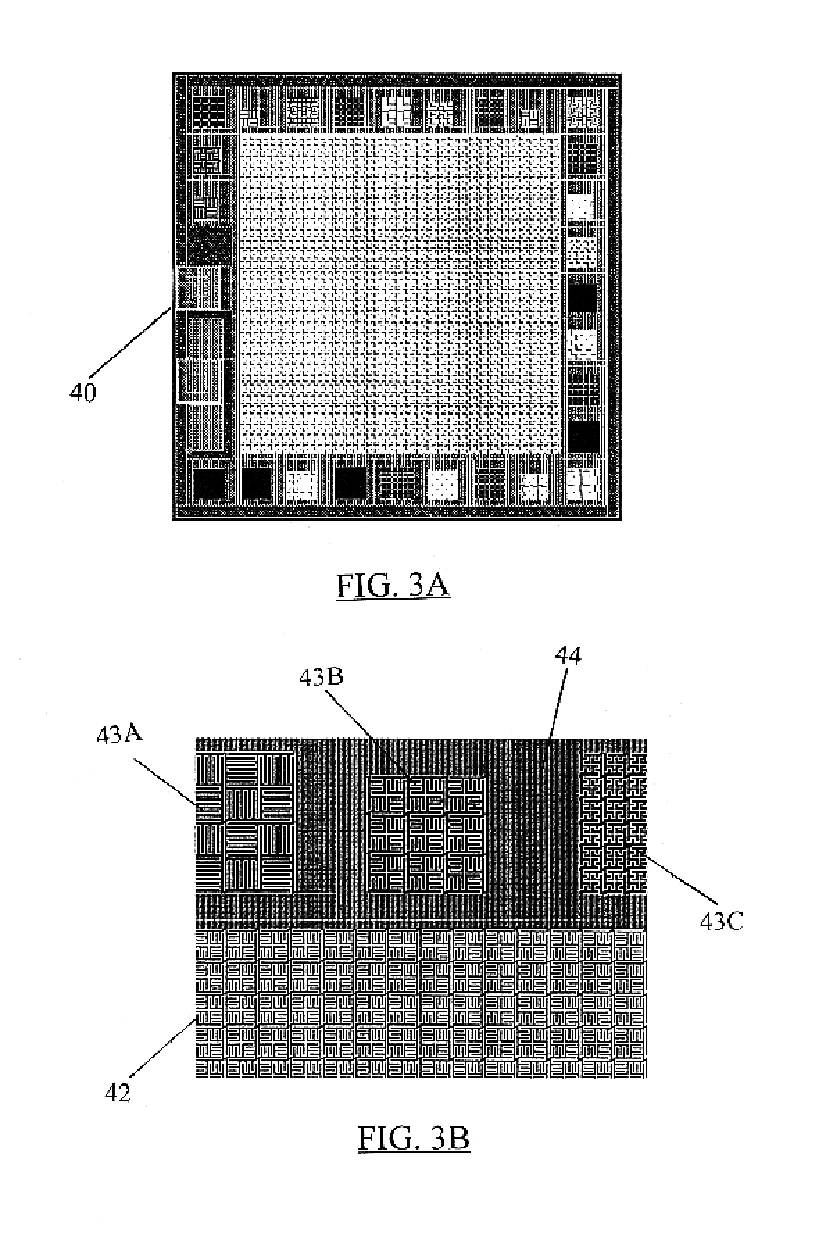

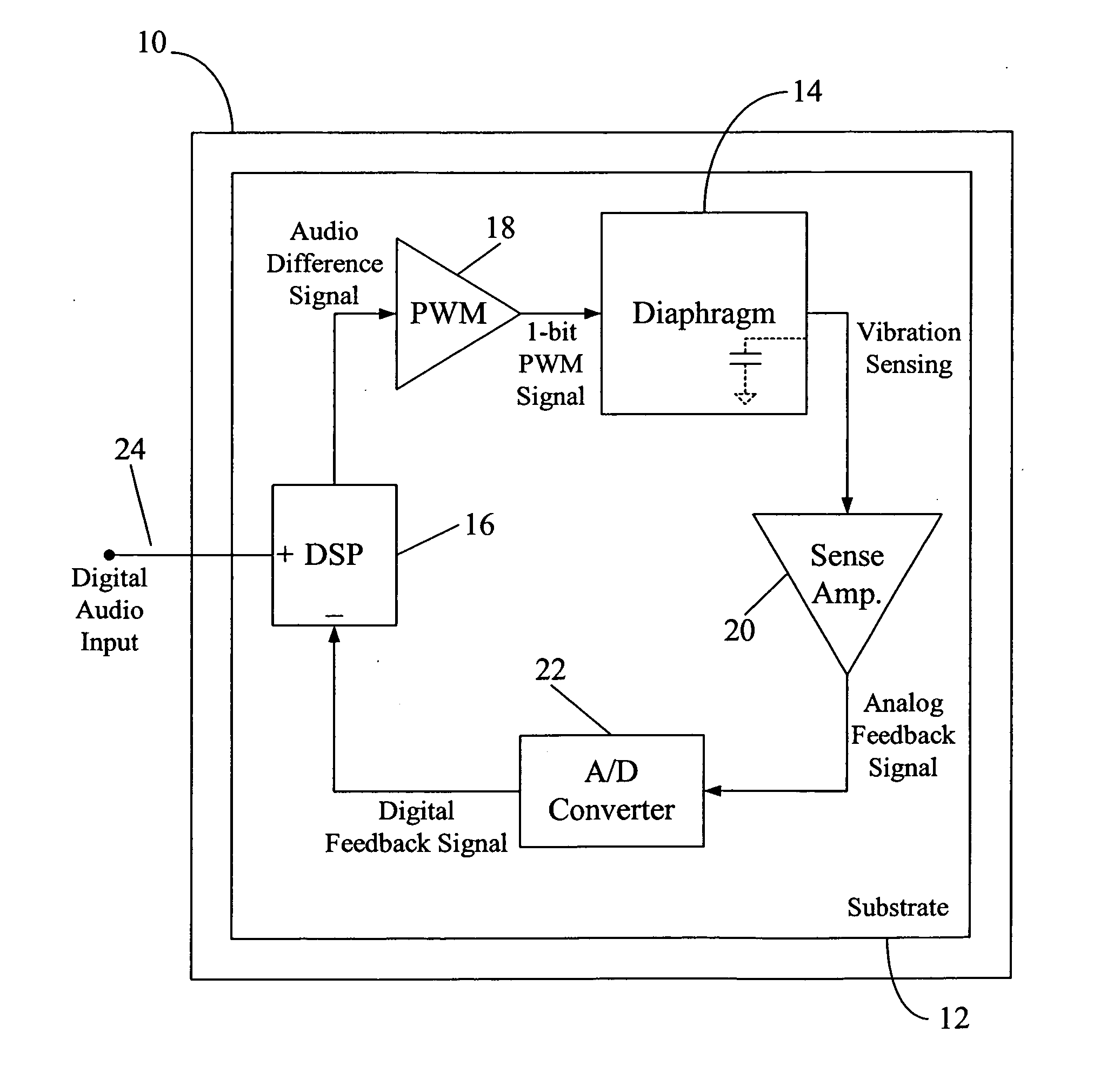

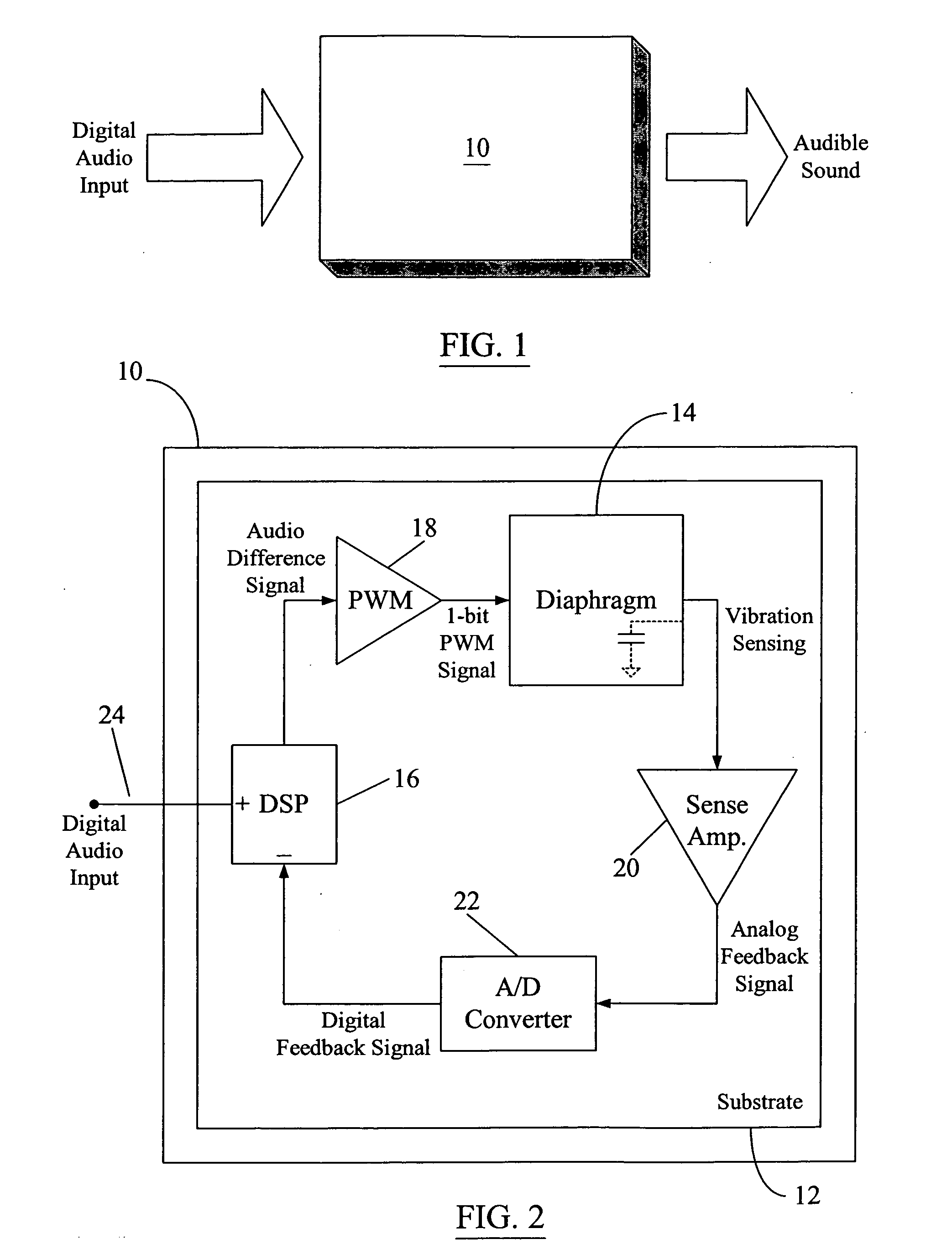

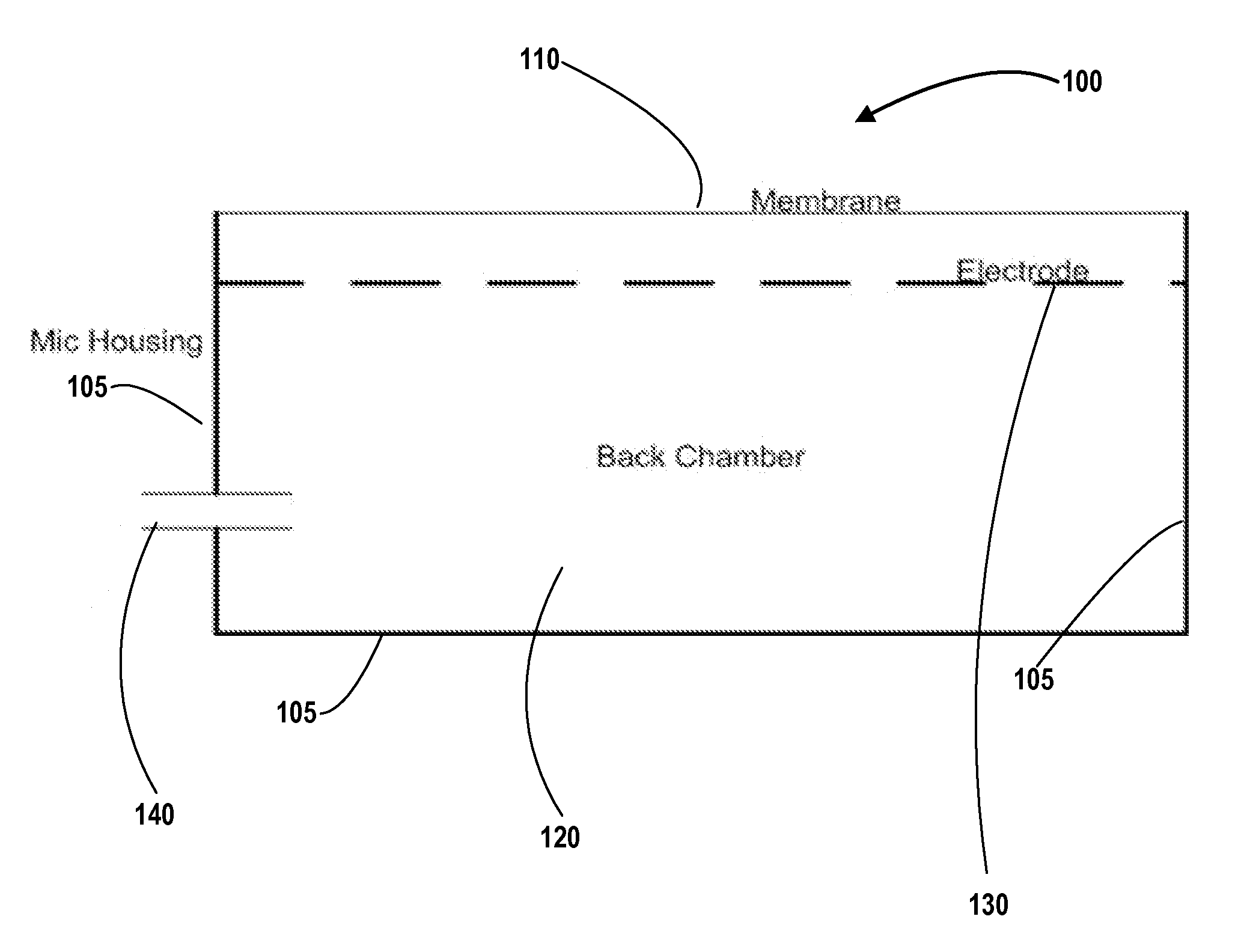

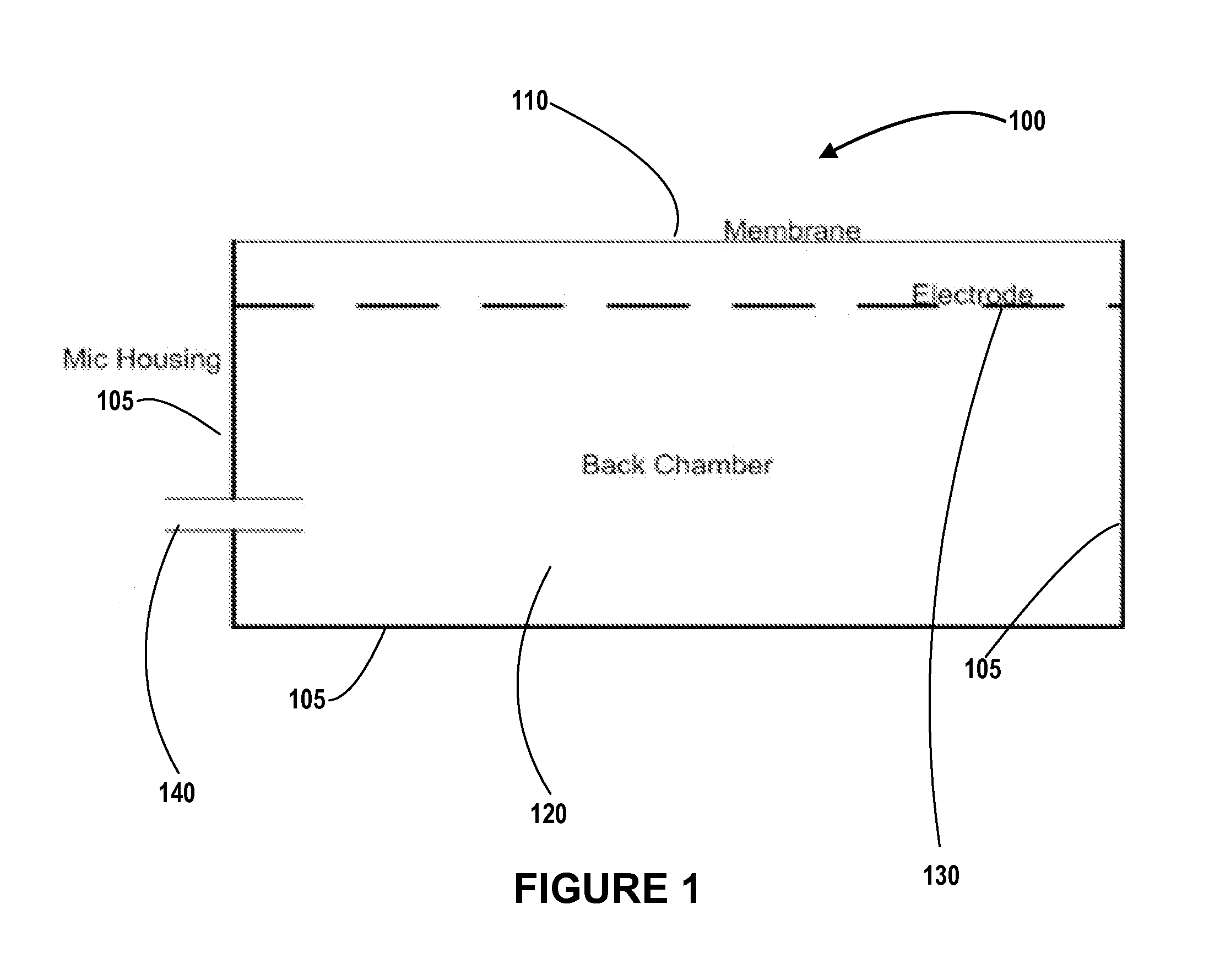

MEMS digital-to-acoustic transducer with error cancellation

InactiveUS6829131B1Low production costHigh quality audio reproductionCircuit-breaking switches for excess currentsTelevision system detailsTransducerEngineering

An acoustic transducer comprising a substrate; and a diaphragm formed by depositing a micromachined membrane onto the substrate. The diaphragm is formed as a single silicon chip using a CMOS MEMS (microelectromechanical systems) semiconductor fabrication process. The curling of the diaphragm during fabrication is reduced by depositing the micromachined membrane for the diaphragm in a serpentine-spring configuration with alternating longer and shorter arms. As a microspeaker, the acoustic transducer of the present invention converts a digital audio input signal directly into a sound wave, resulting in a very high quality sound reproduction at a lower cost of production in comparison to conventional acoustic transducers. The micromachined diaphragm may also be used in microphone applications.

Owner:CARNEGIE MELLON UNIV

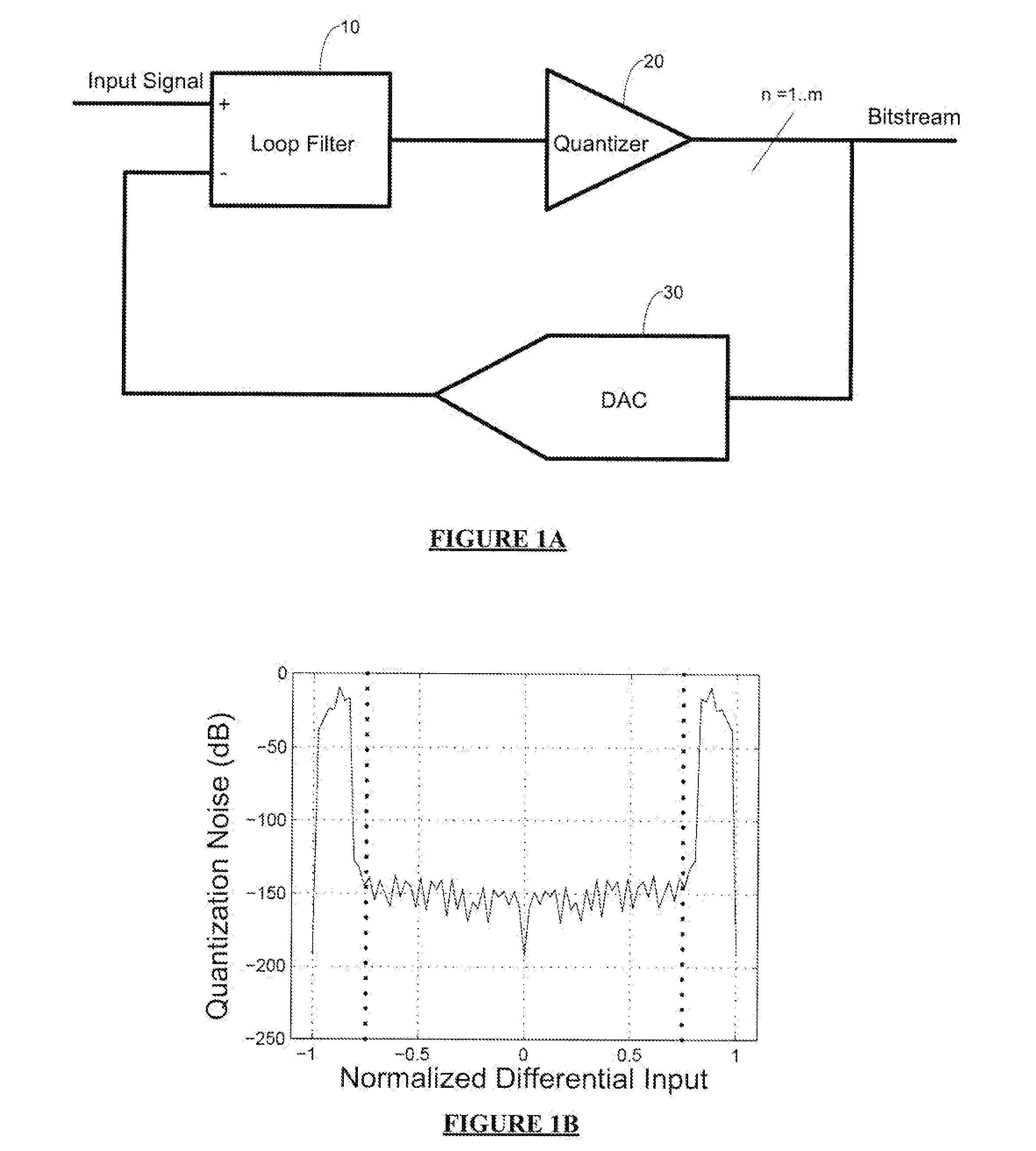

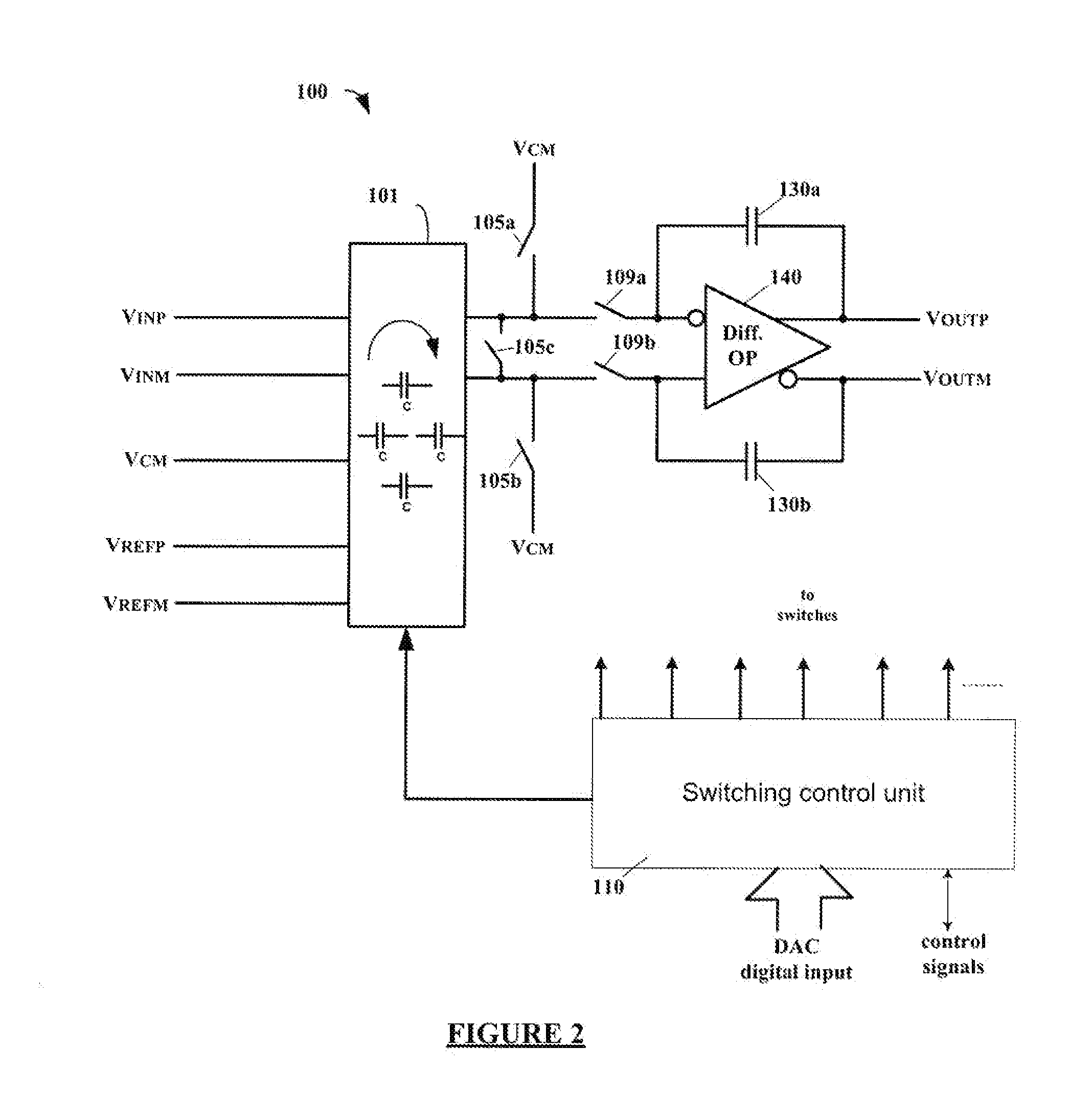

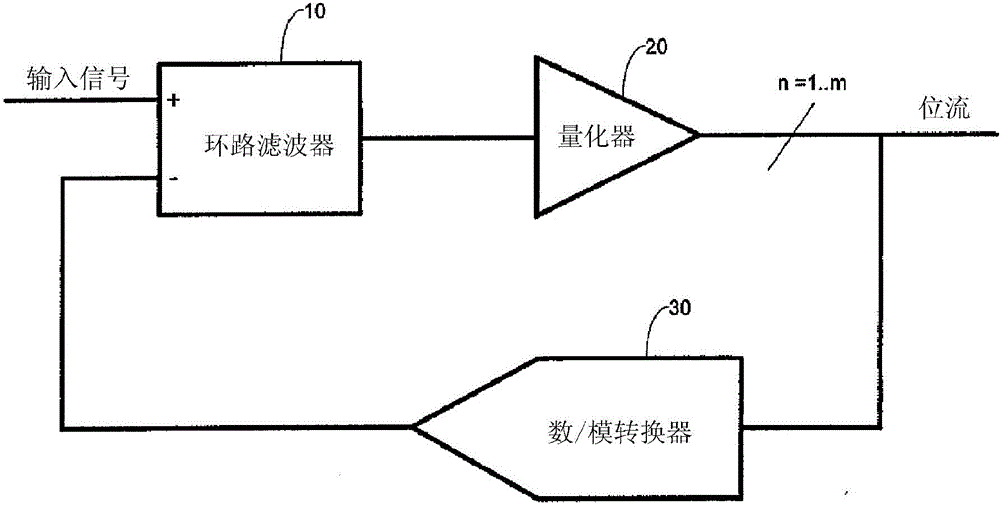

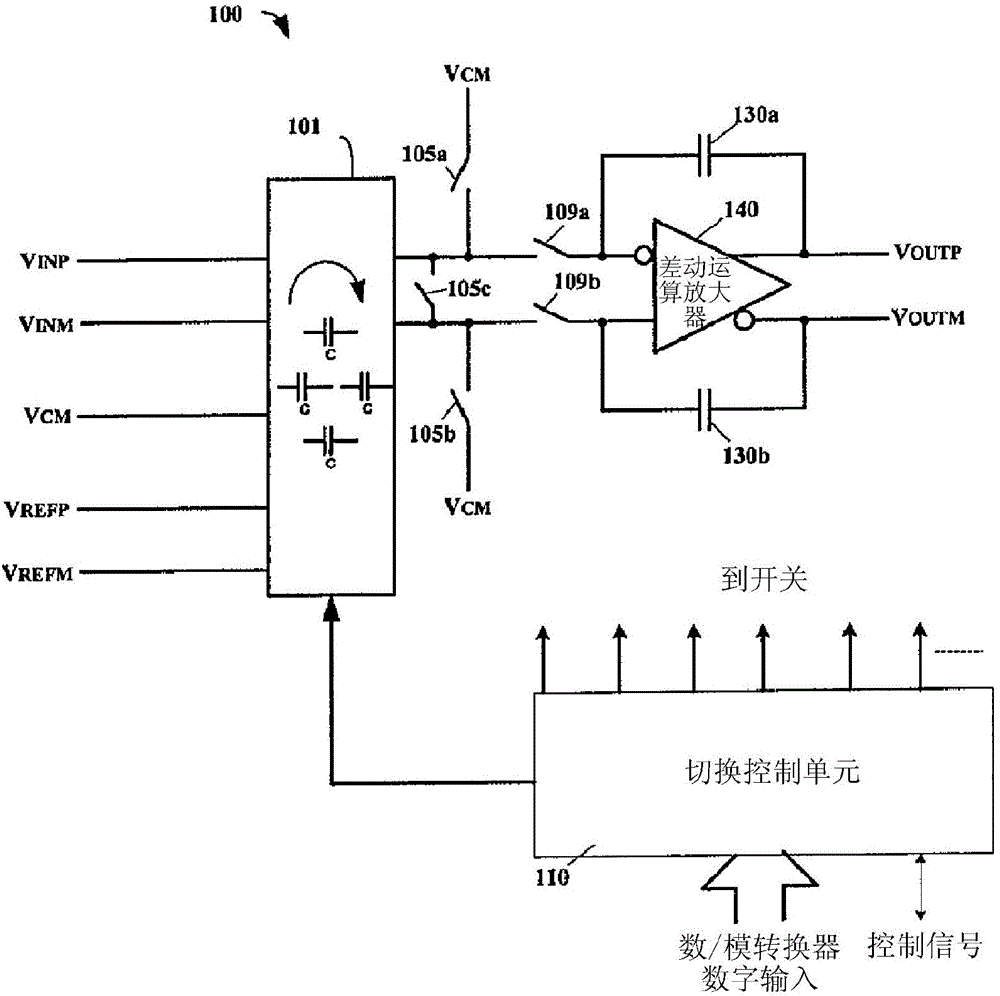

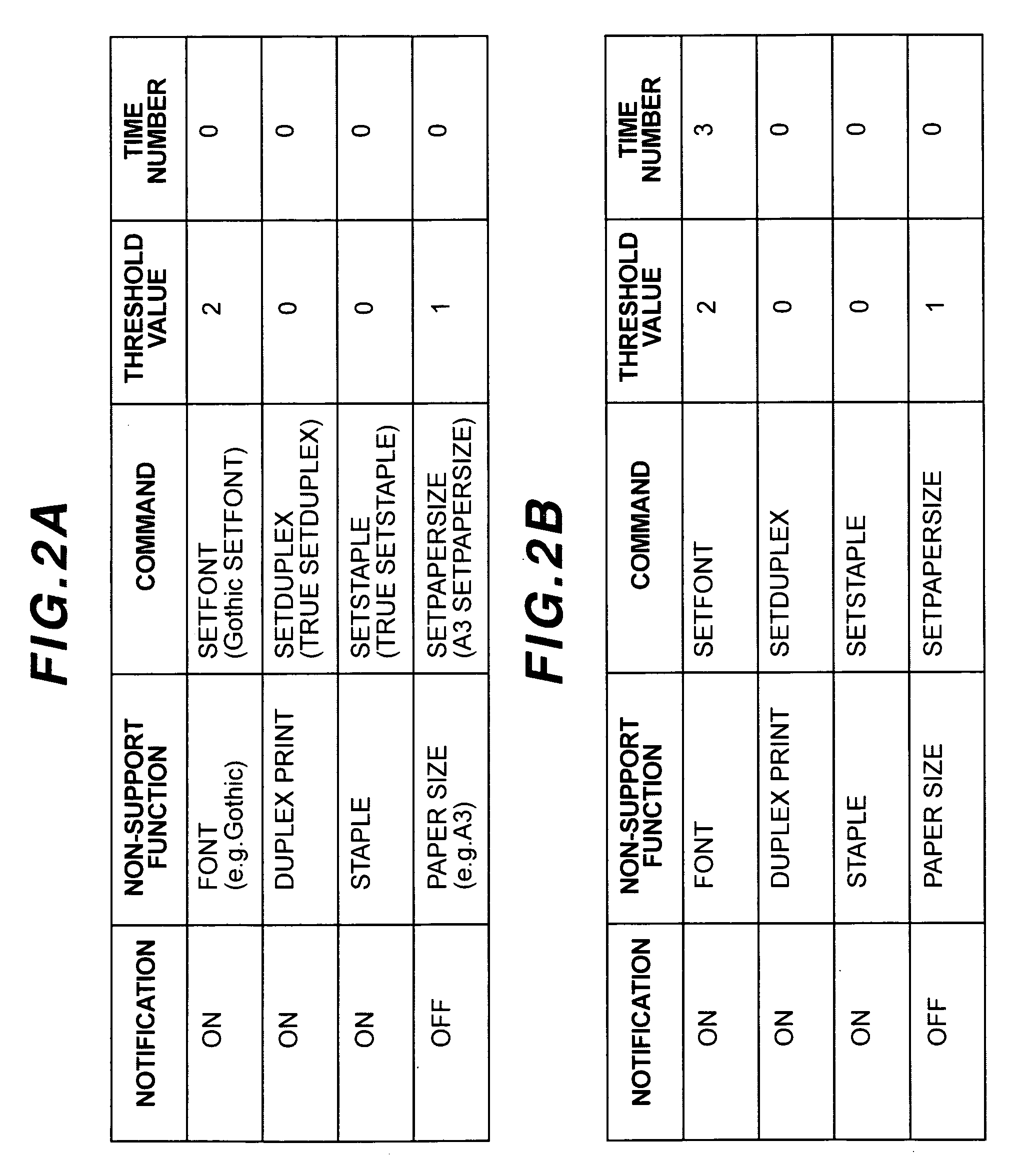

2-phase gain calibration and scaling scheme for switched capacitor sigma-delta modulator using a chopper voltage reference

ActiveUS20110163901A1Electric signal transmission systemsDelta modulationVoltage referenceEngineering

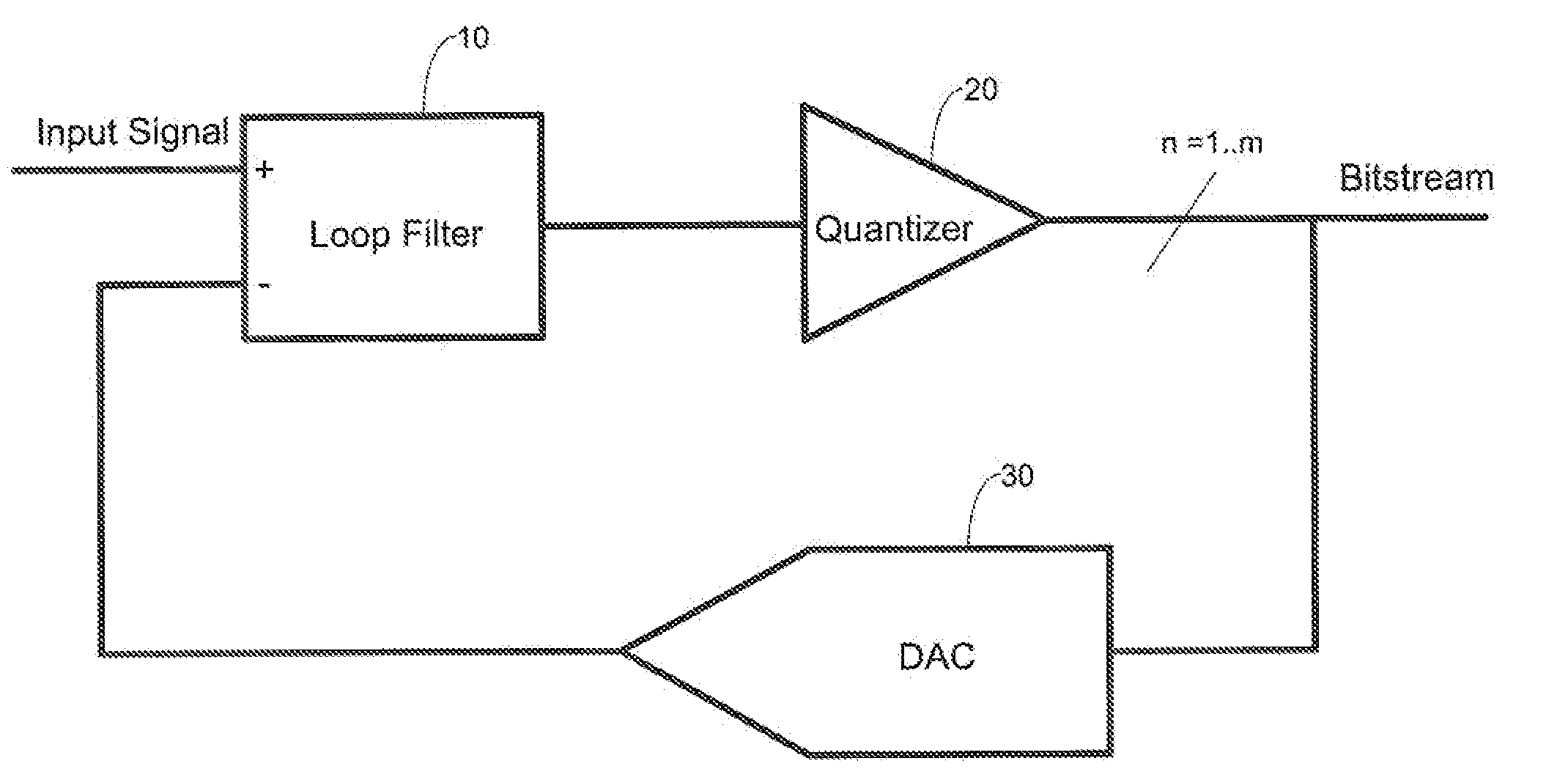

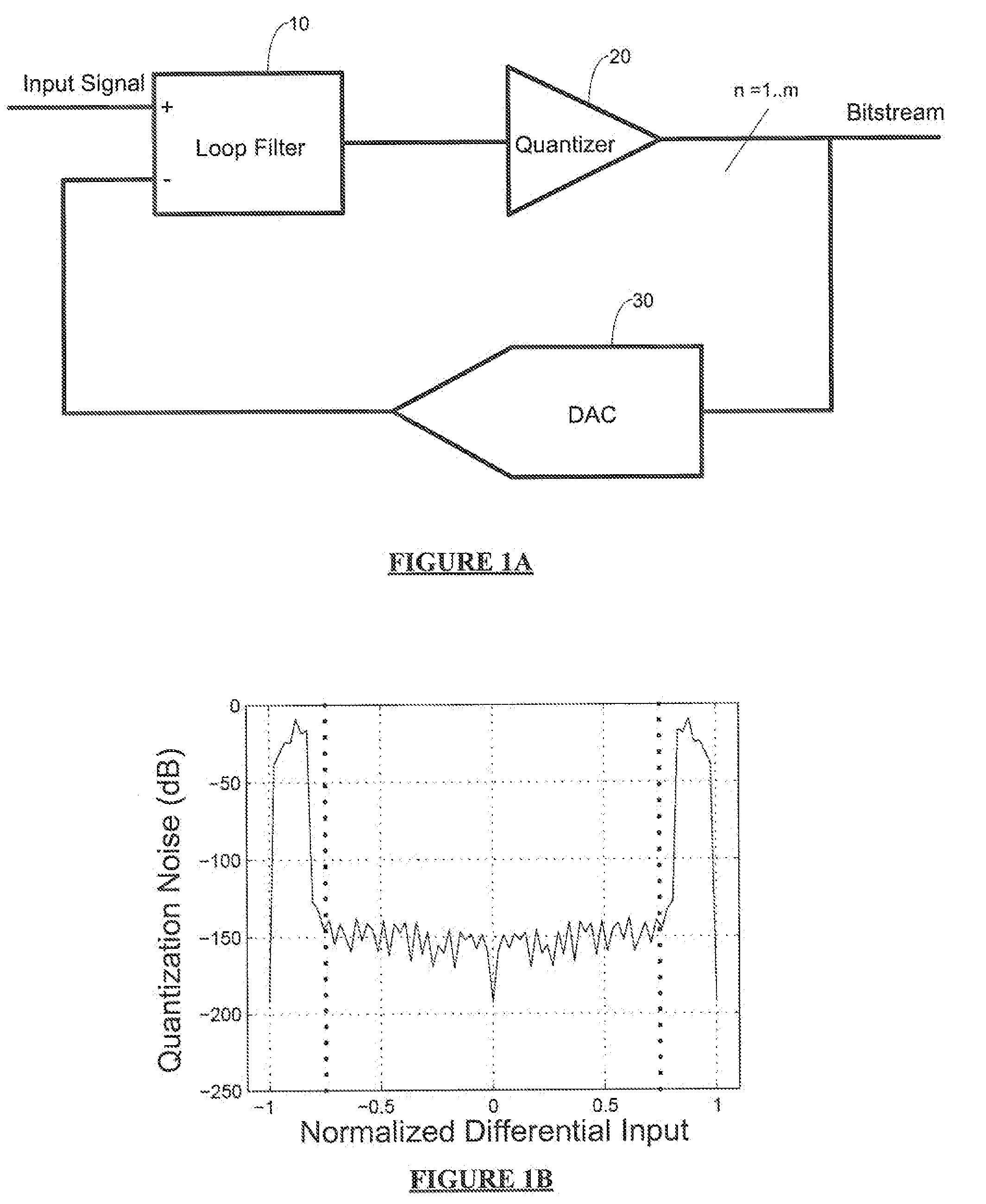

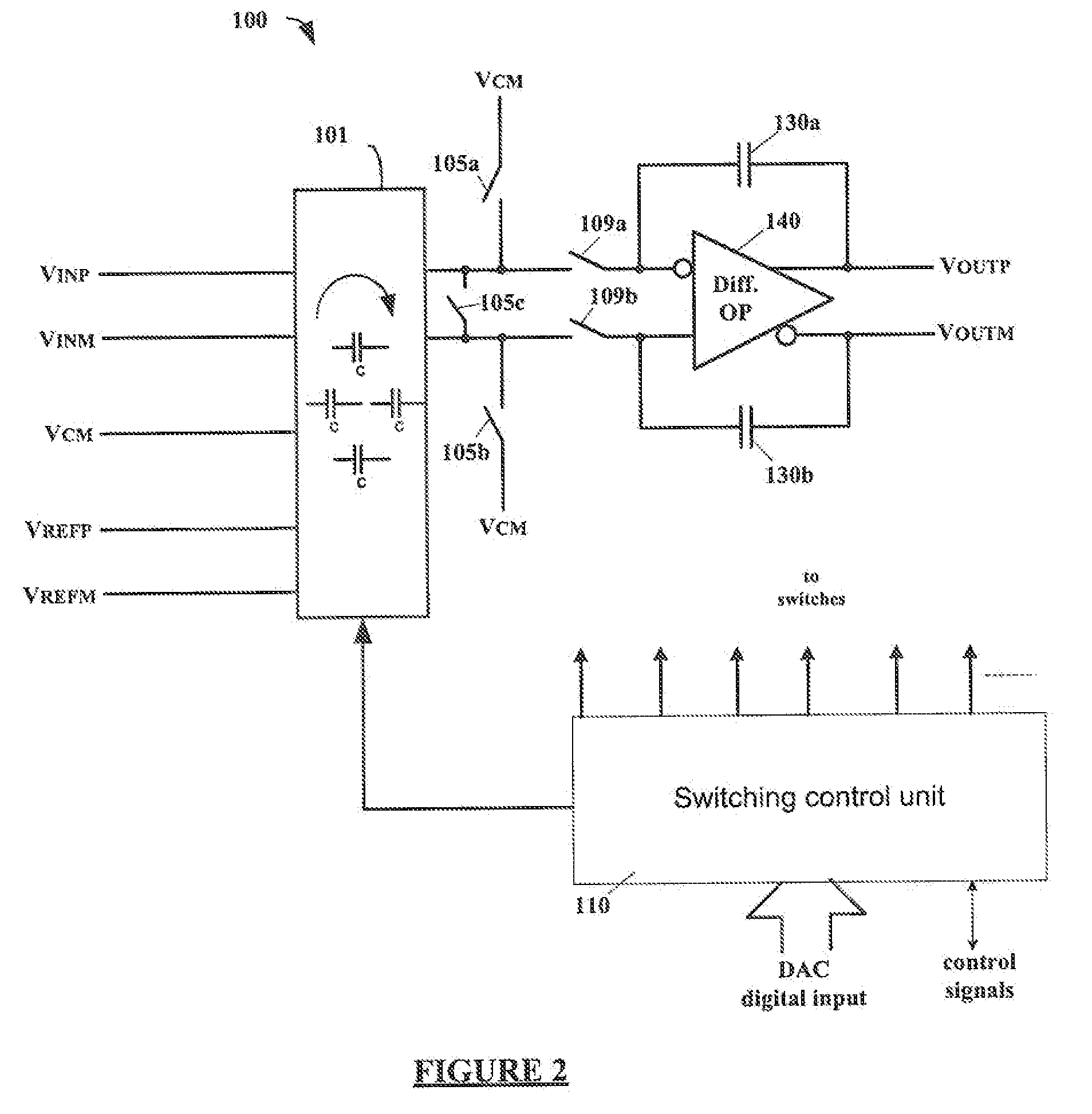

A sigma-delta modulator has a chopper voltage reference providing a reference signal having a clock dependent offset voltage, a single-bit or a multi-bit digital-to-analog converter (DAC); a plurality of capacitor pairs; a plurality of switches to couple any capacitor pair to an input or reference signal; and a control unit controlling sampling through said switches to perform a charge transfer in two phases wherein any capacitor pair can be selected to be assigned to the input or reference signal, wherein after a plurality of charge transfers a gain error cancellation is performed by rotating the capacitor pairs cyclically, and wherein a DAC output value and a reference offset state define switching sequences wherein each switching sequence independently rotates said capacitor pairs and wherein at least one switching sequence is selected depending on a current DAC output value and a current reference offset state.

Owner:MICROCHIP TECH INC

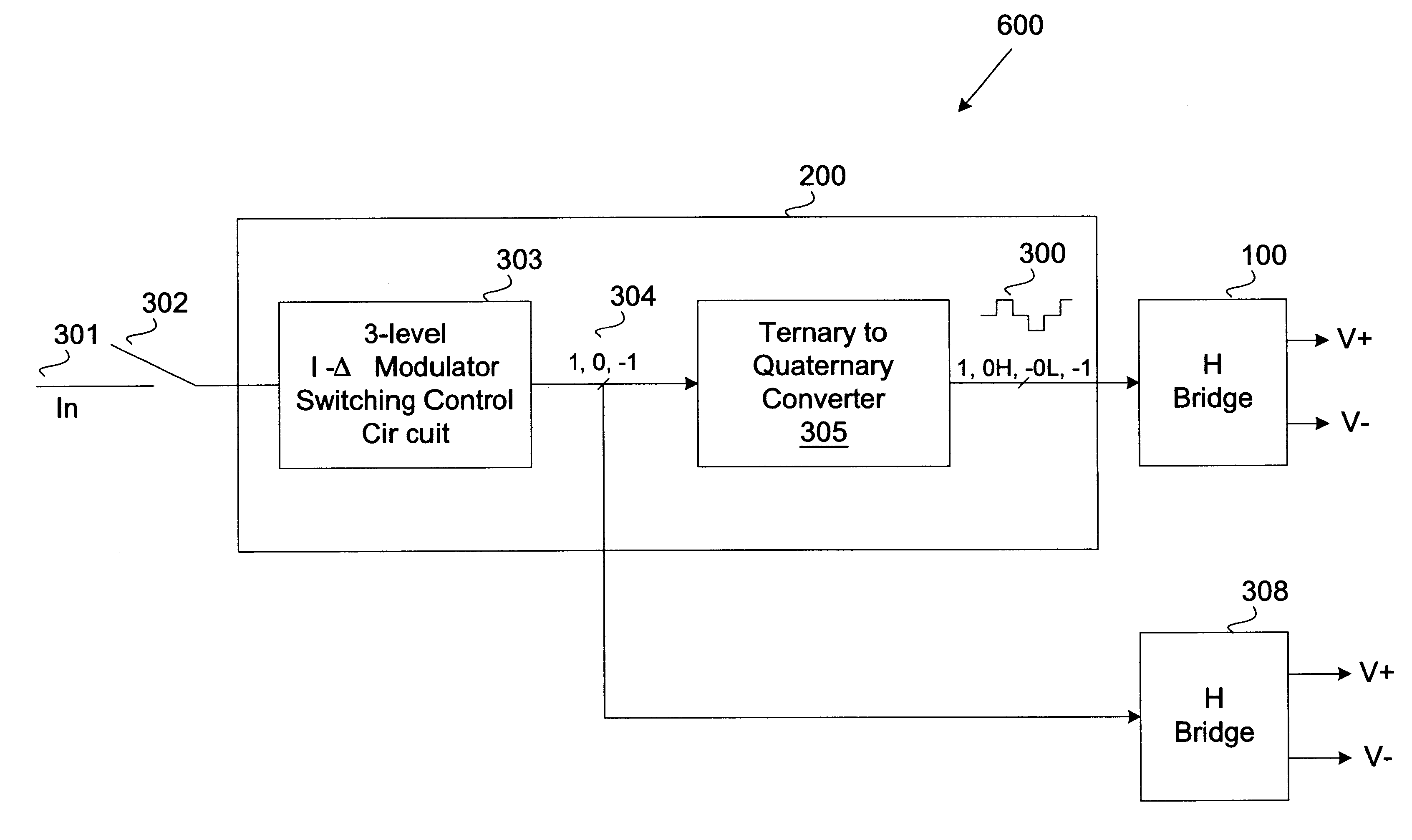

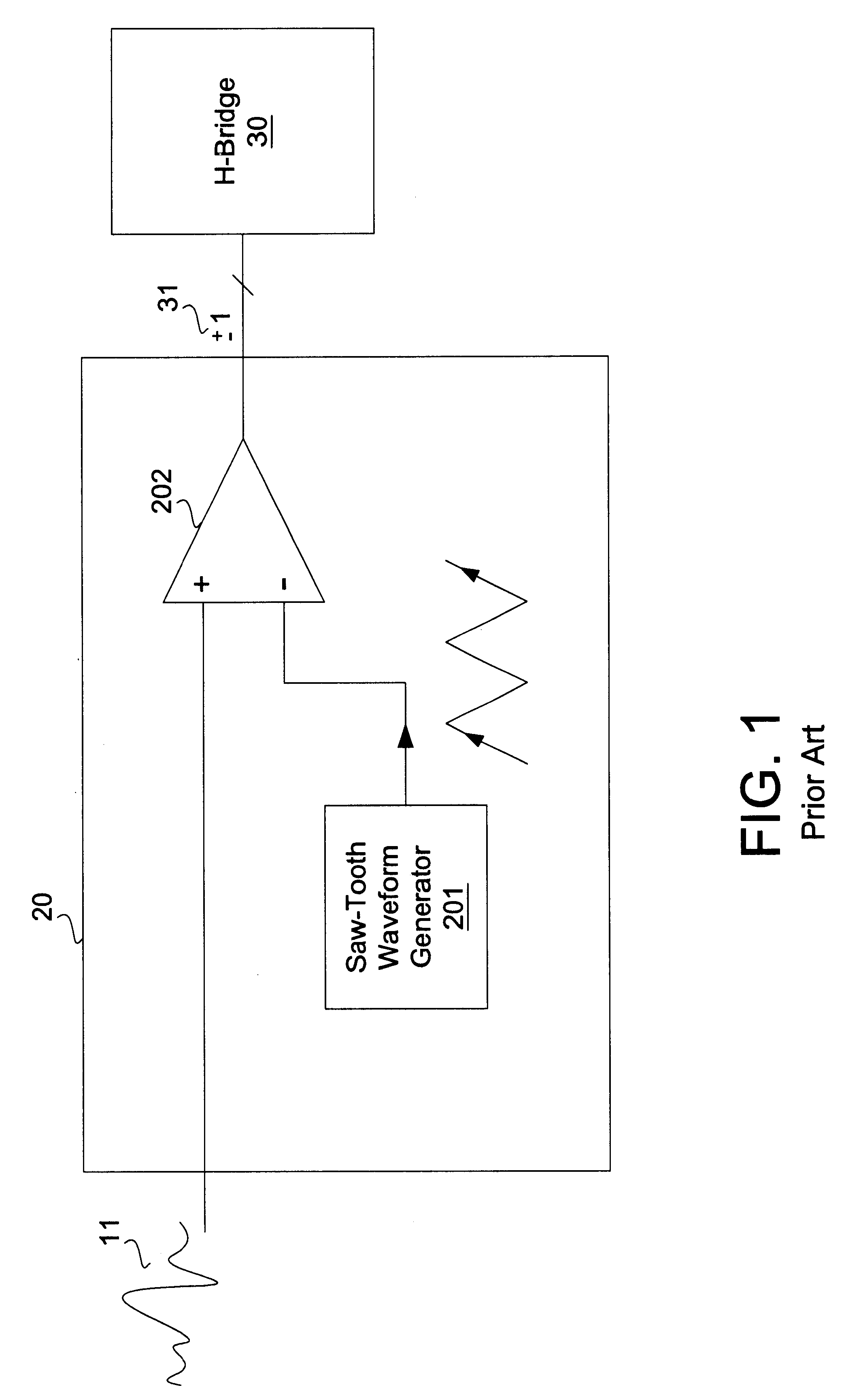

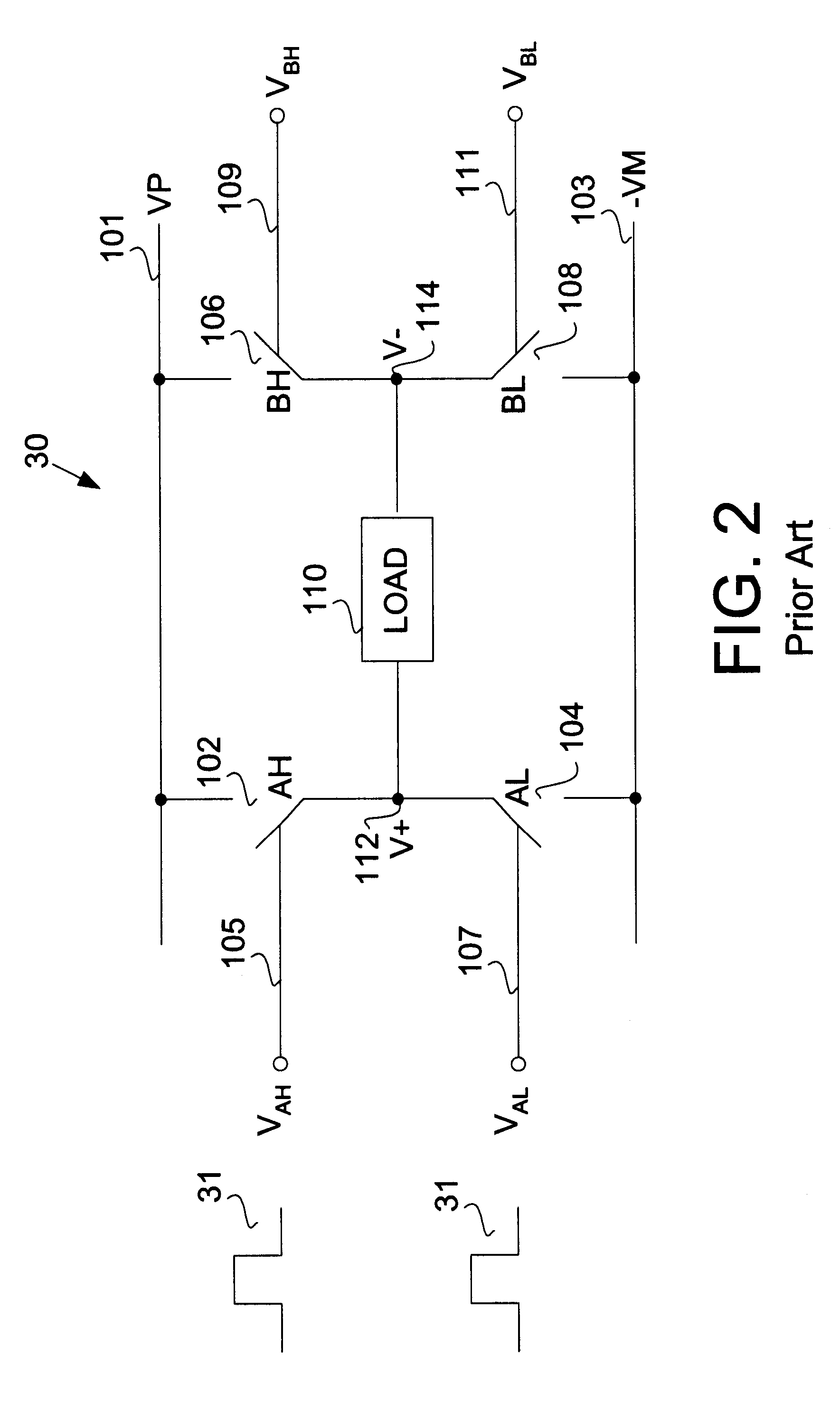

Switching amplifier incorporating return-to-zero quaternary power switch

Invention resides in a switching amplifier having a quaternary input control signal that provides quaternary levels (1, 0H, -1, and 0L) which is coupled to an H-bridge amplifier to provide error cancellation in switching amplifier output signal. The quaternary control signal alternates from a zero state at a high level ("0H") to a zero state at a low level ("0L") between each non-zero state (+1 or -1). In a preferred embodiment, a three-level sigma-delta modulator is provided for greater operational efficiency for ease of detecting zero states and minimizing power. The three-level sigma-delta modulator receives and converts an amplifier input signal into a ternary output signal that is then coupled to a ternary-to-quaternary converter to generate the quaternary control signal to provide as input to the H-bridge.

Owner:RALPH CHANG JONG

MEMS digital-to-acoustic transducer with error cancellation

InactiveUS20050013455A1Low production costSmall sizeTelevision system detailsPiezoelectric/electrostriction/magnetostriction machinesTransducerEngineering

An acoustic transducer comprising a substrate; and a diaphragm formed by depositing a micromachined membrane onto the substrate. The diaphragm is formed as a single silicon chip using a CMOS MEMS (microelectromechanical systems) semiconductor fabrication process. The curling of the diaphragm during fabrication is reduced by depositing the micromachined membrane for the diaphragm in a serpentine-spring configuration with alternating longer and shorter arms. As a microspeaker, the acoustic transducer of the present invention converts a digital audio input signal directly into a sound wave, resulting in a very high quality sound reproduction at a lower cost of production in comparison to conventional acoustic transducers. The micromachined diaphragm may also be used in microphone applications.

Owner:CARNEGIE MELLON UNIV

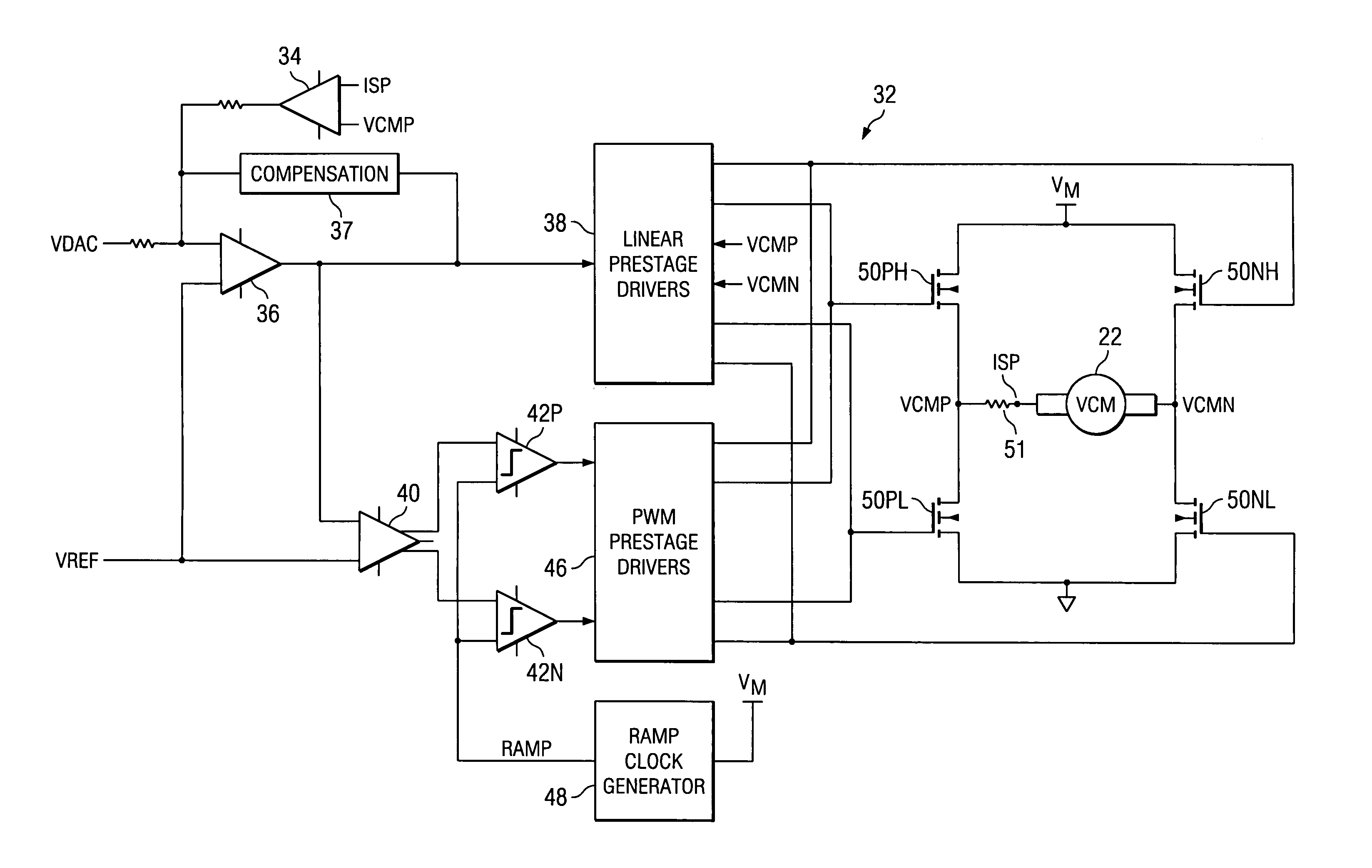

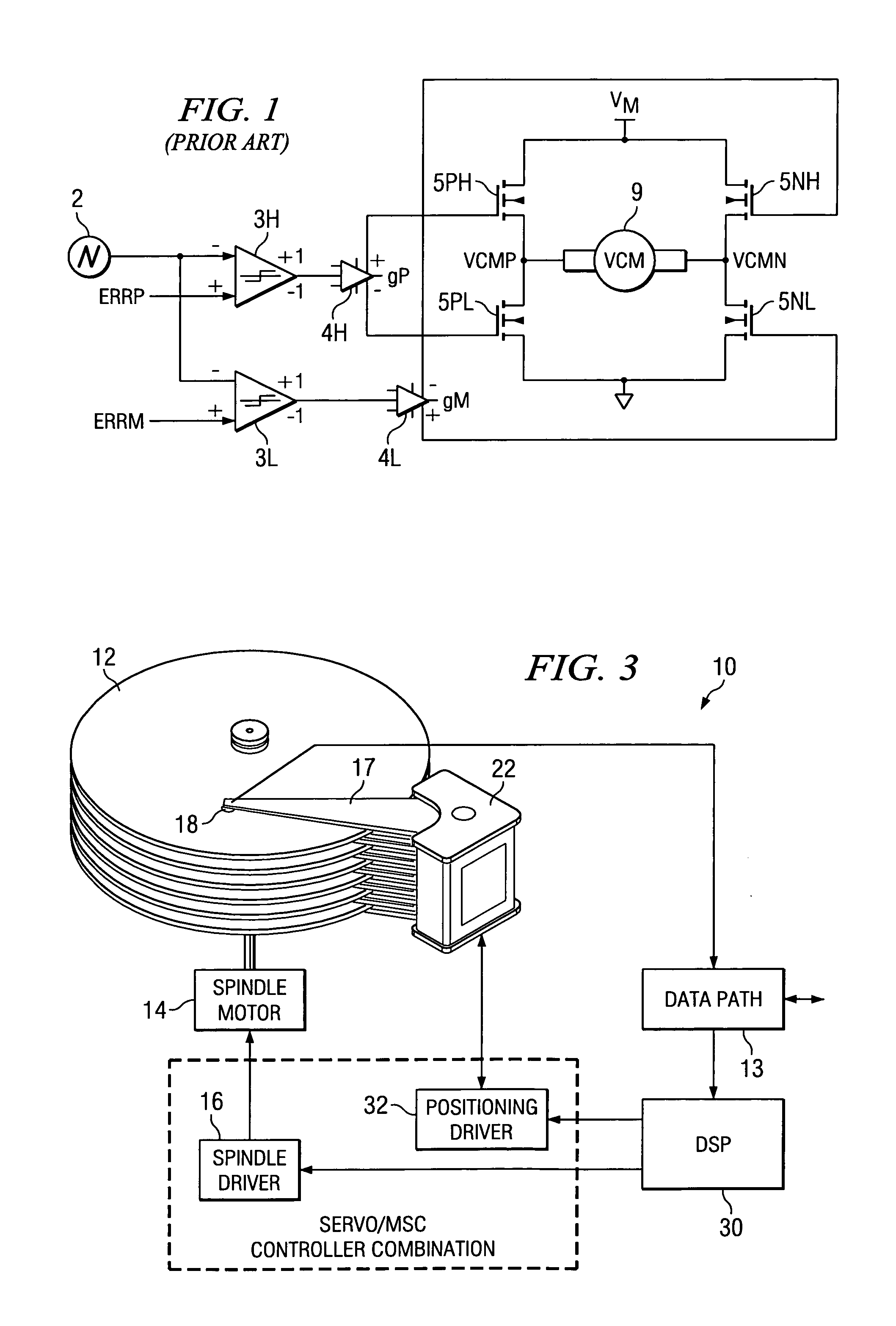

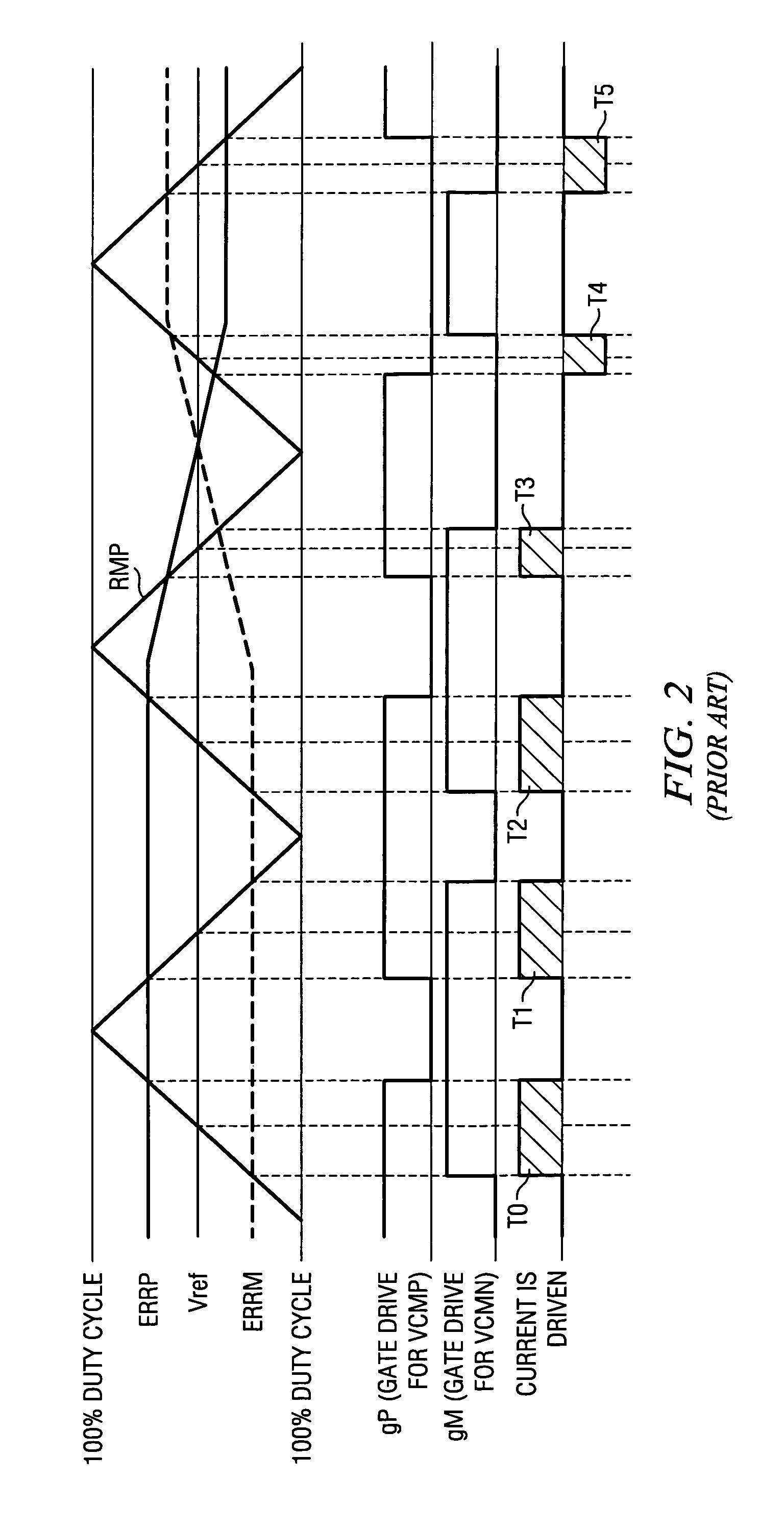

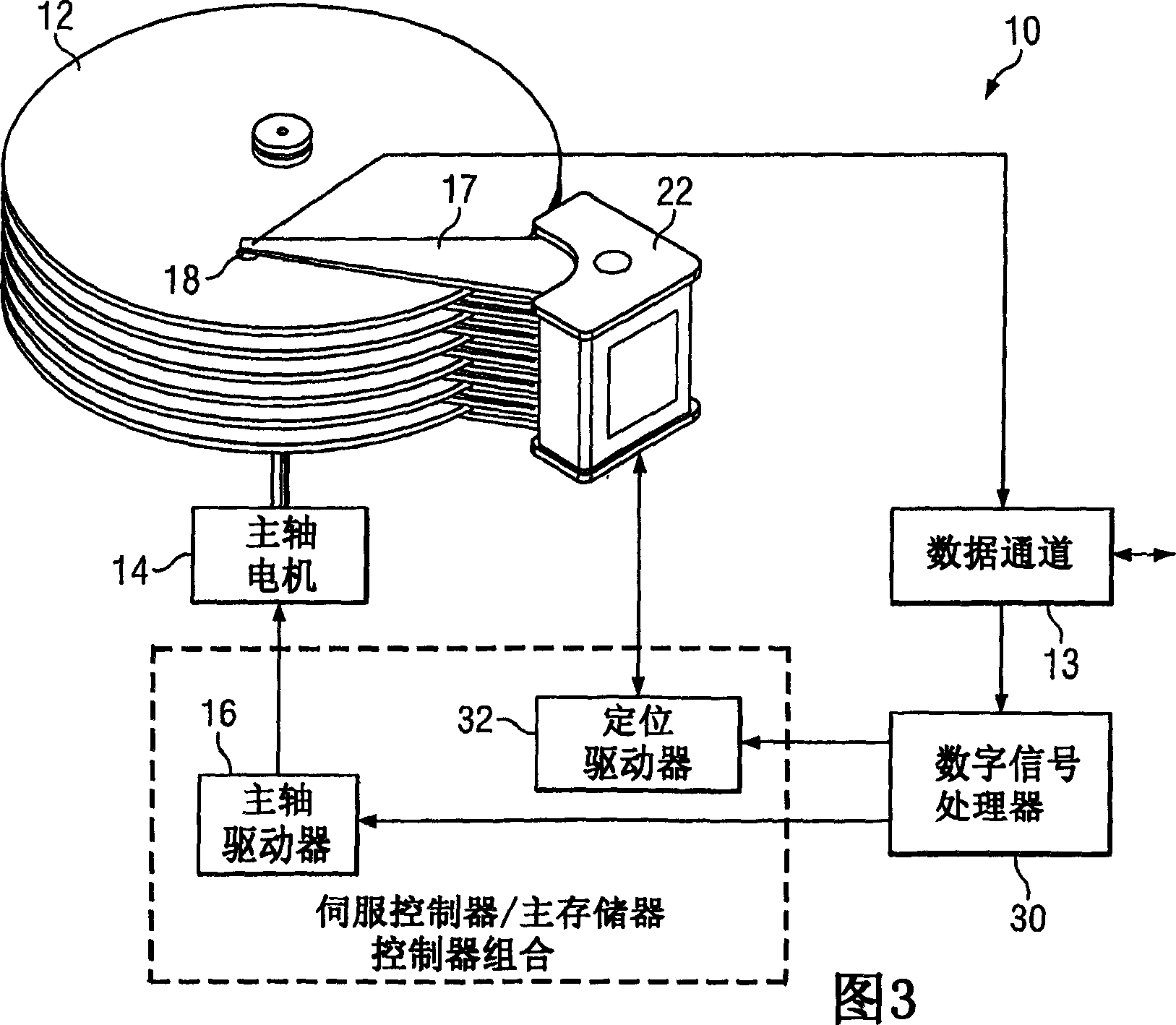

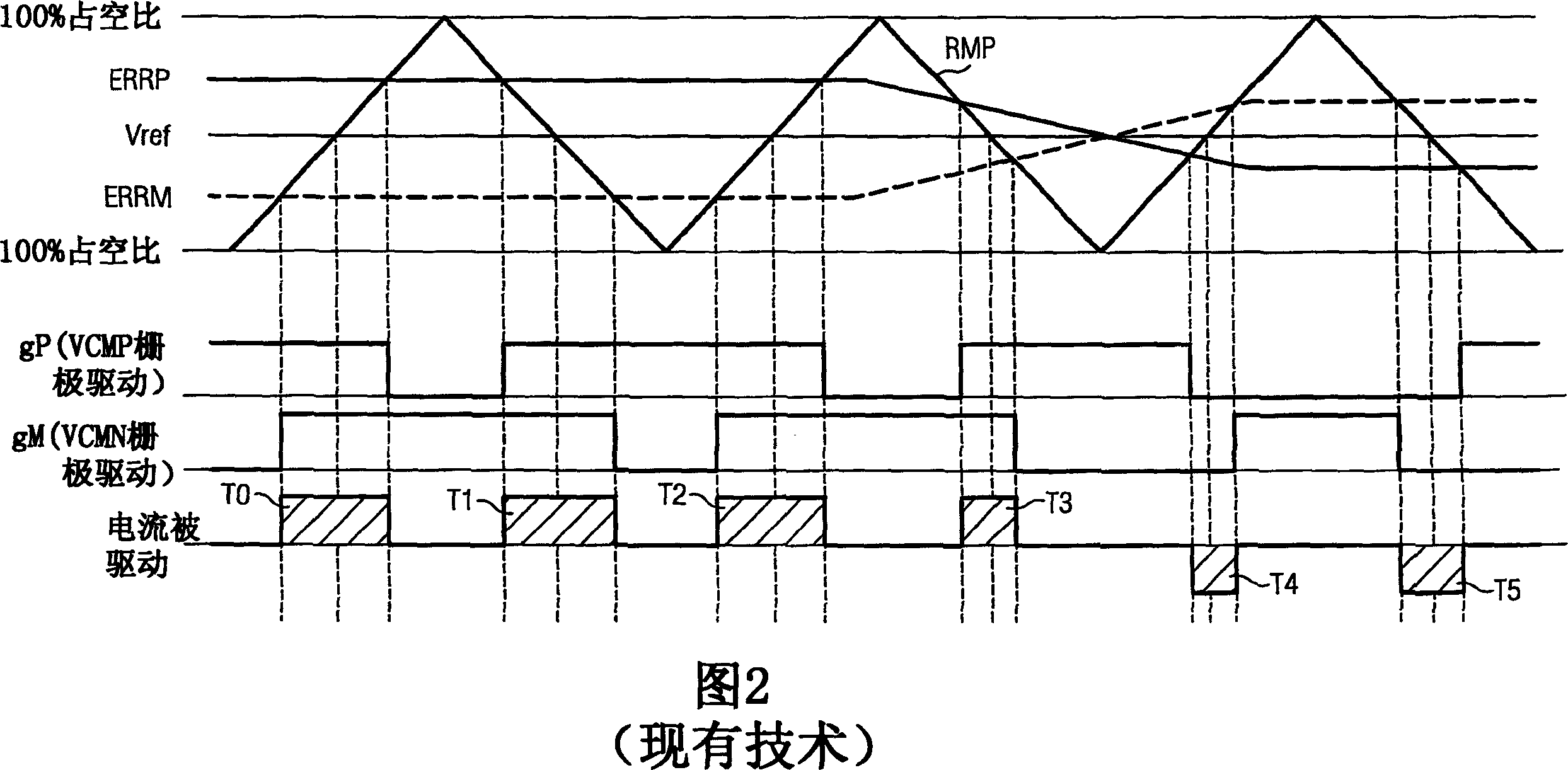

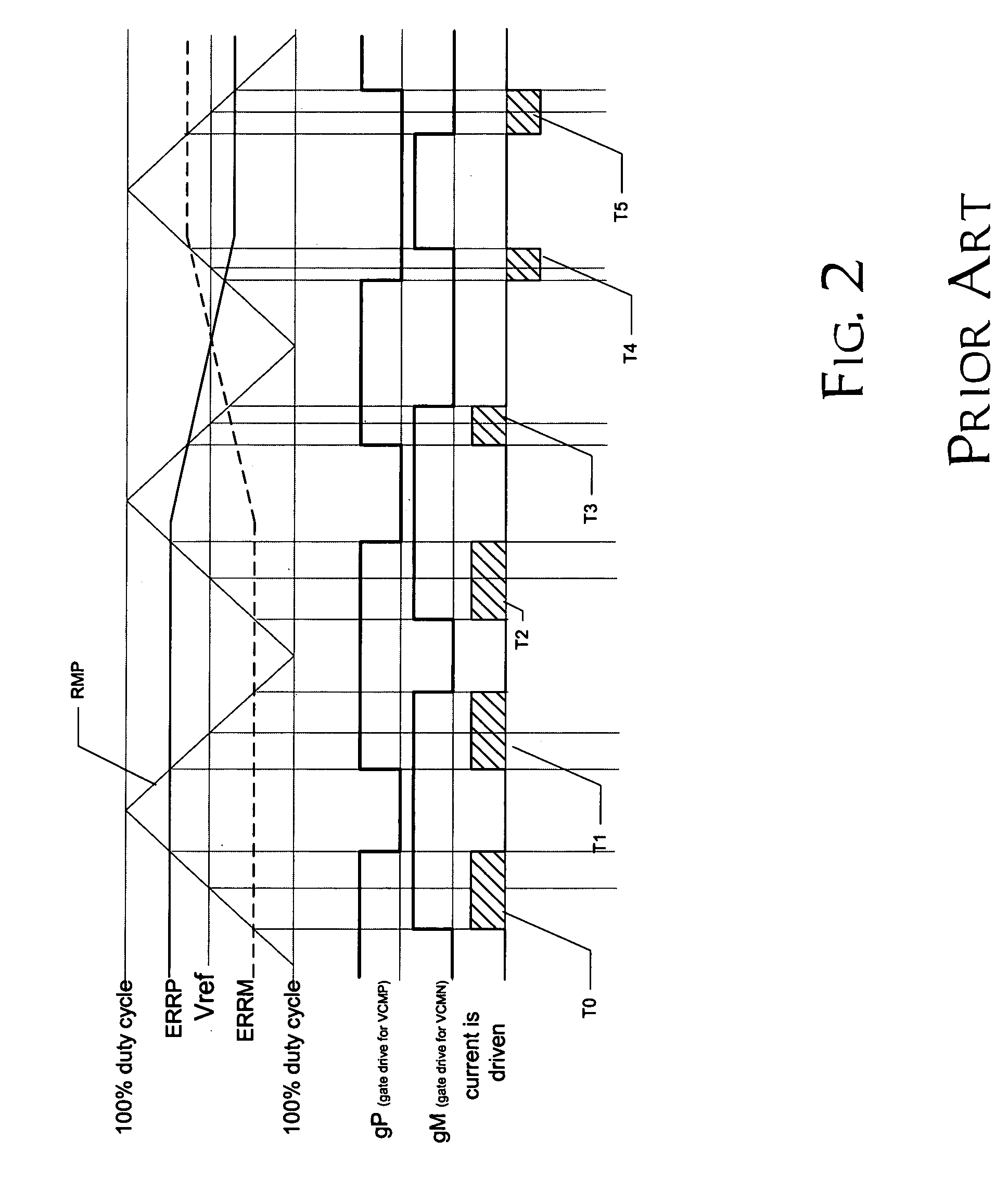

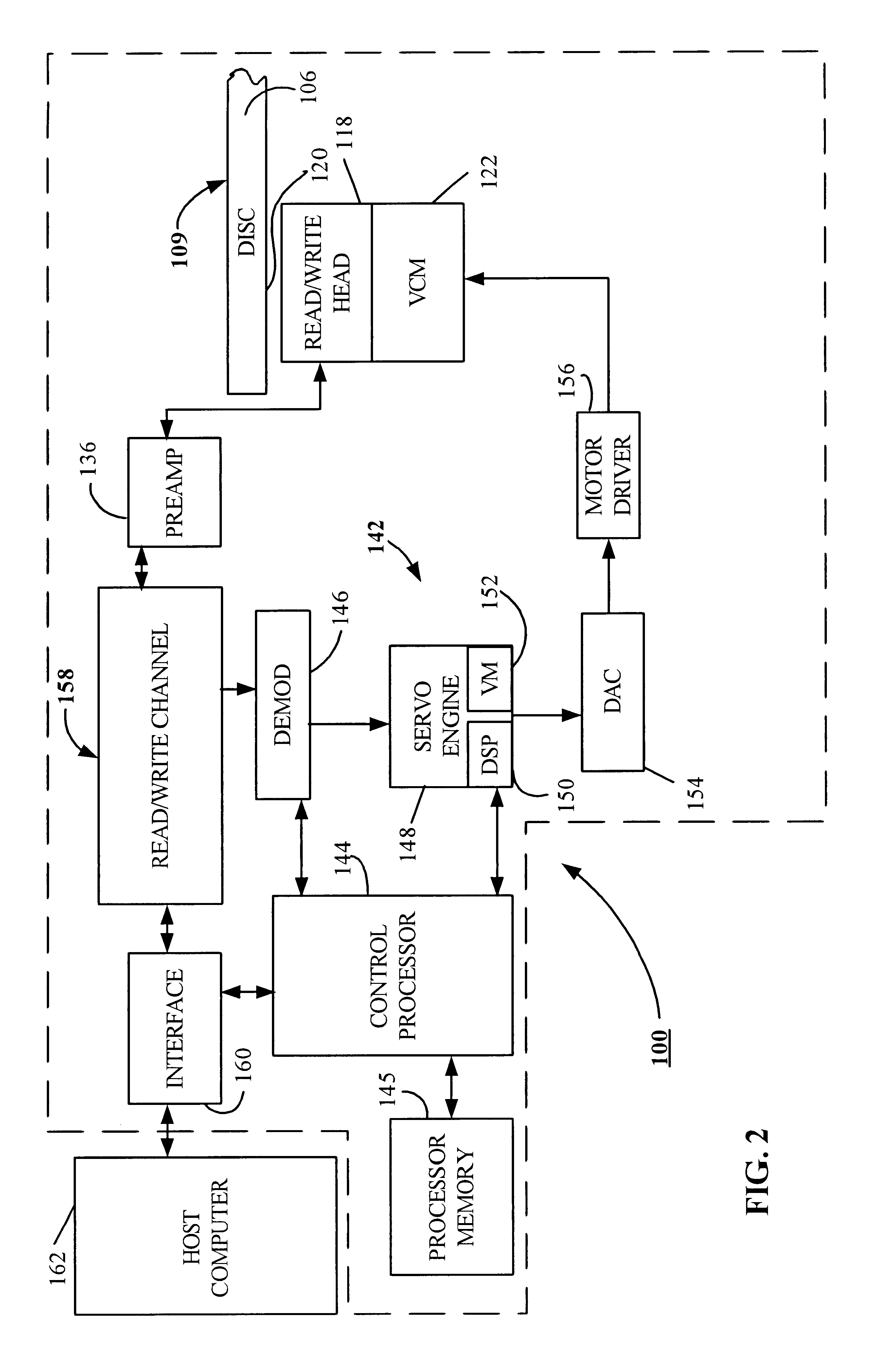

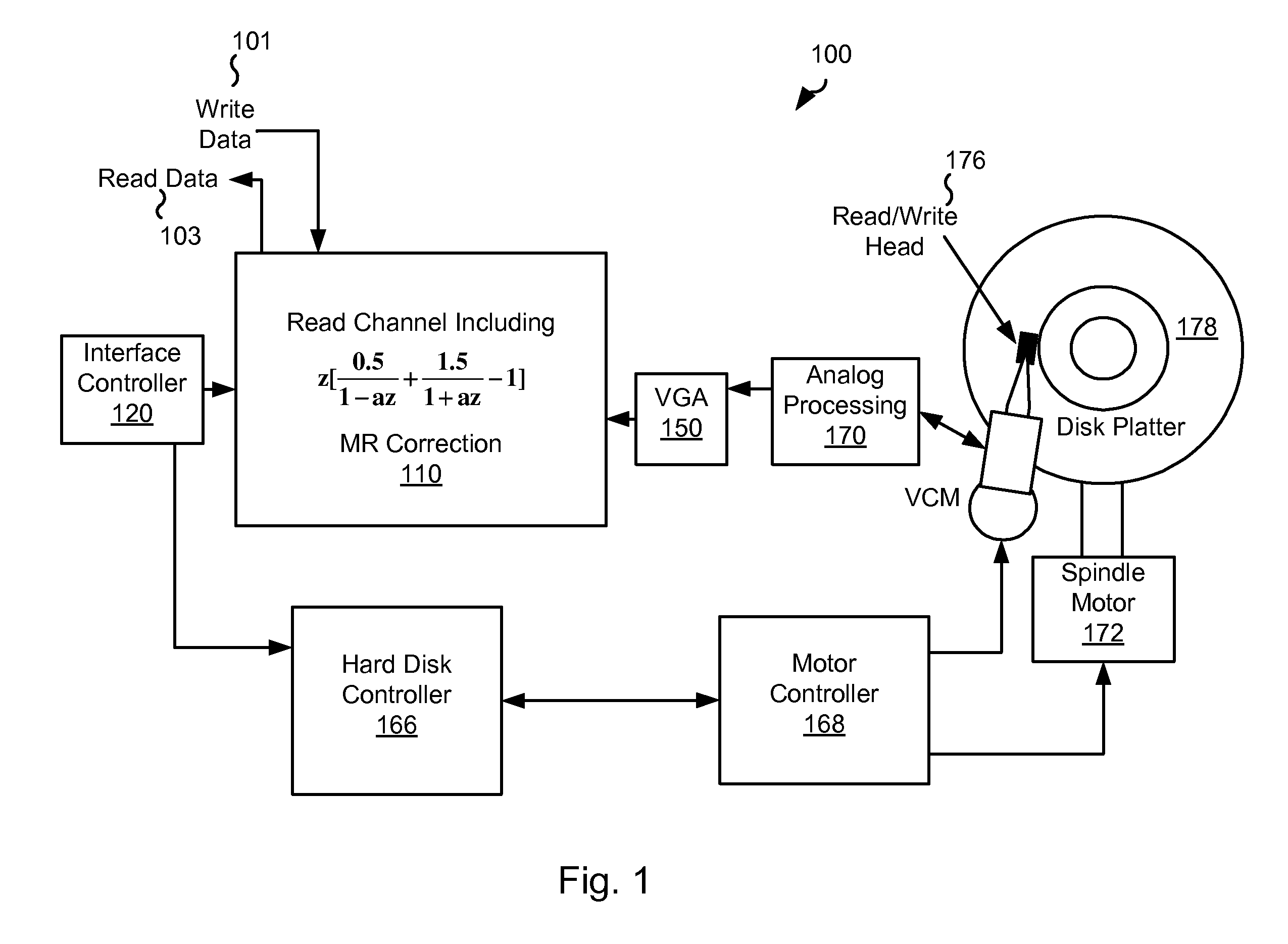

Rejection of power supply variations for gain error cancellation in pulse-width-modulated motor controllers

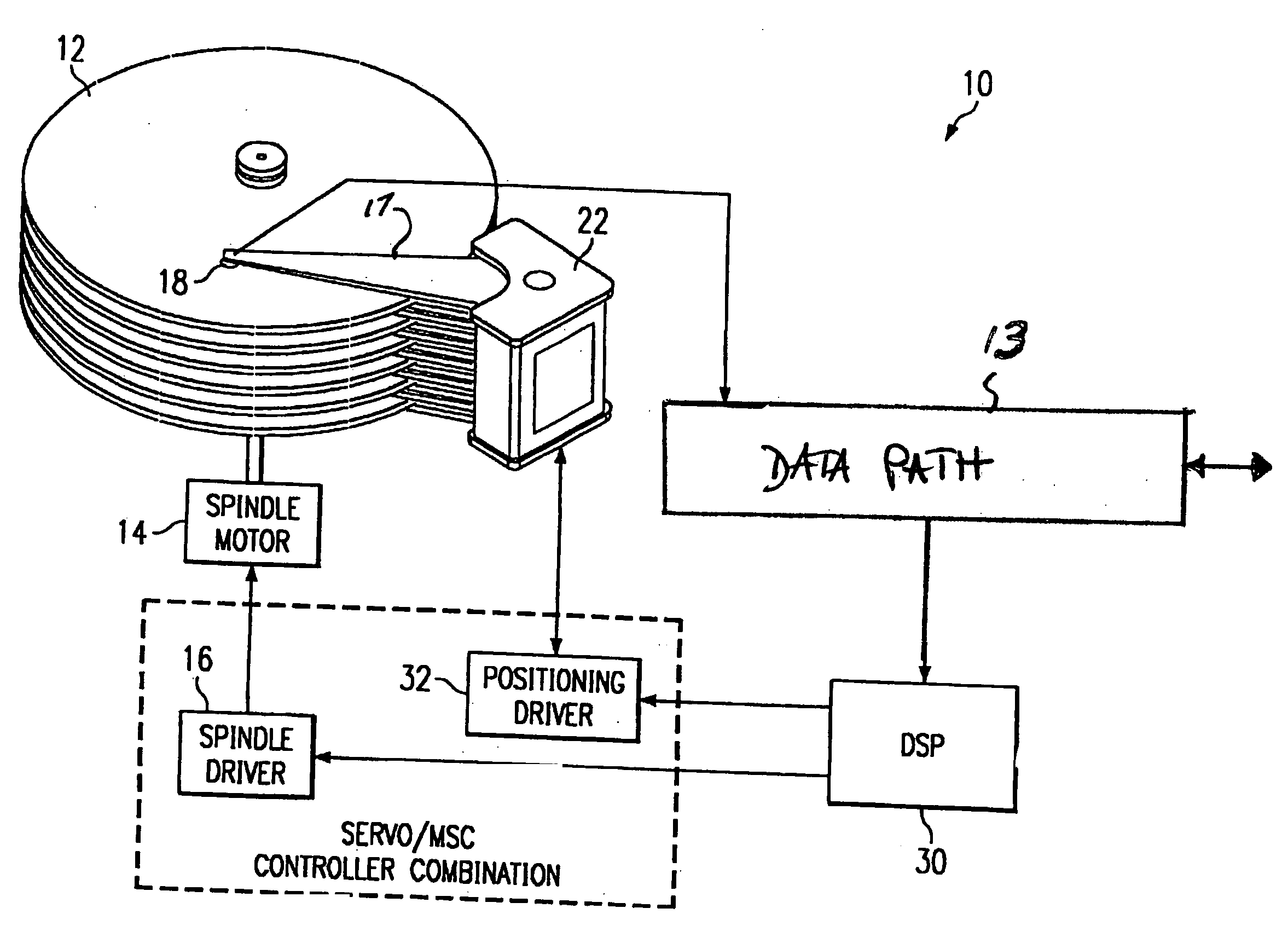

A positioning driver (32) for a voice coil motor (22) in a disk drive system (10) is disclosed. Pulse-width-modulated prestage drivers (46) are coupled to power transistors (50) arranged in an “H” bridge for driving the voice coil motor (22), biased with a power supply voltage (VM). The pulse-width-modulated prestage drivers (46) drive the power transistors (50) according to a comparison between an error signal from an error amplifier (36) and a ramp clock signal (RMP) generated by a ramp clock generator (46). The ramp clock generator (46) includes a control circuit (68) that modulates the high and low limits of the ramp clock signal (RMP) in response to variations in the power supply voltage (VM). This modulation of the high and low limits compensates for variations in the gain of the power transistors (50) resulting from variations in the power supply voltage (VM). The control circuit (68) may also modulate the slope of the ramp clock signal (RMP) according to variations in the power supply voltage (VM), for example to maintain a constant frequency.

Owner:TEXAS INSTR INC

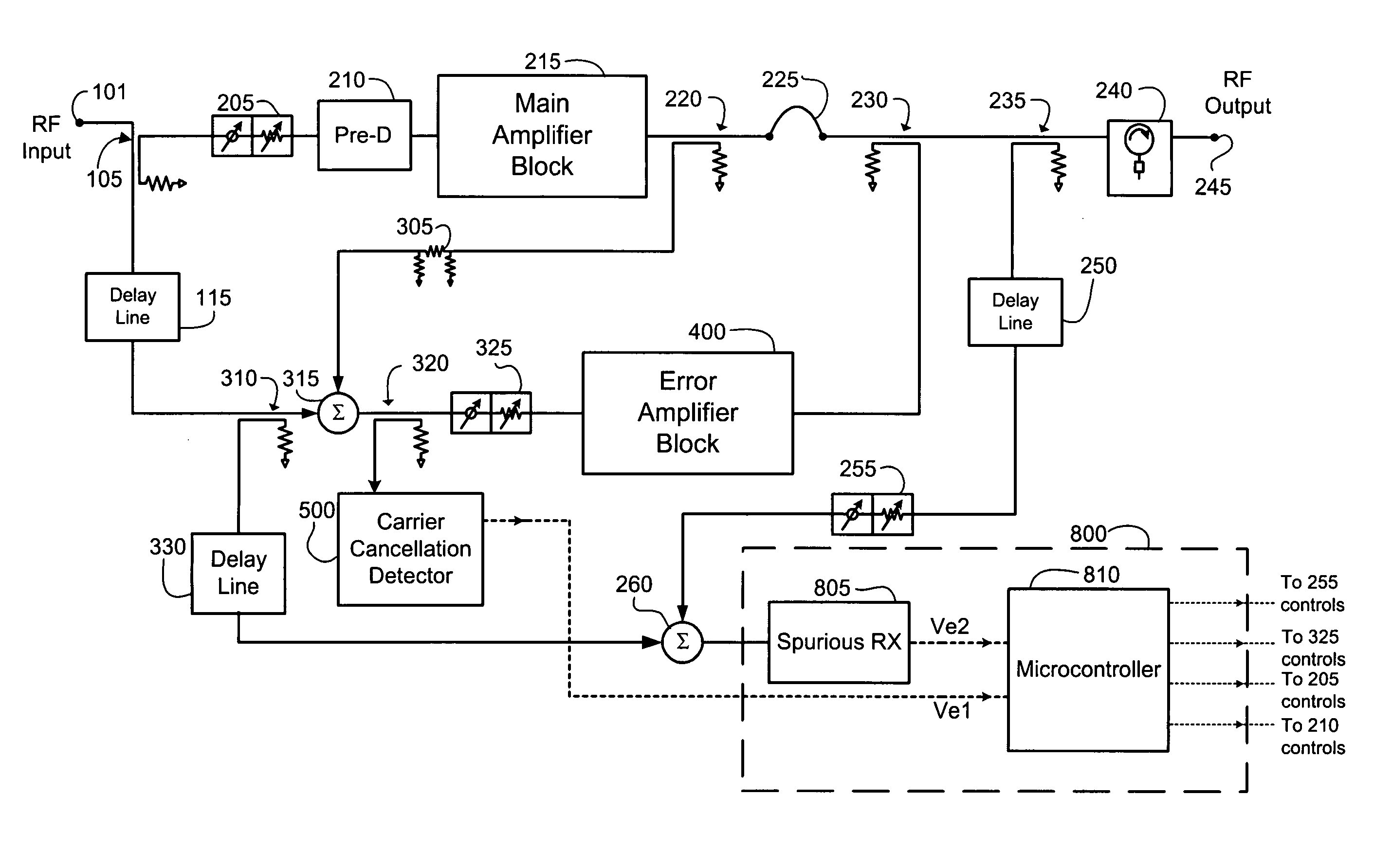

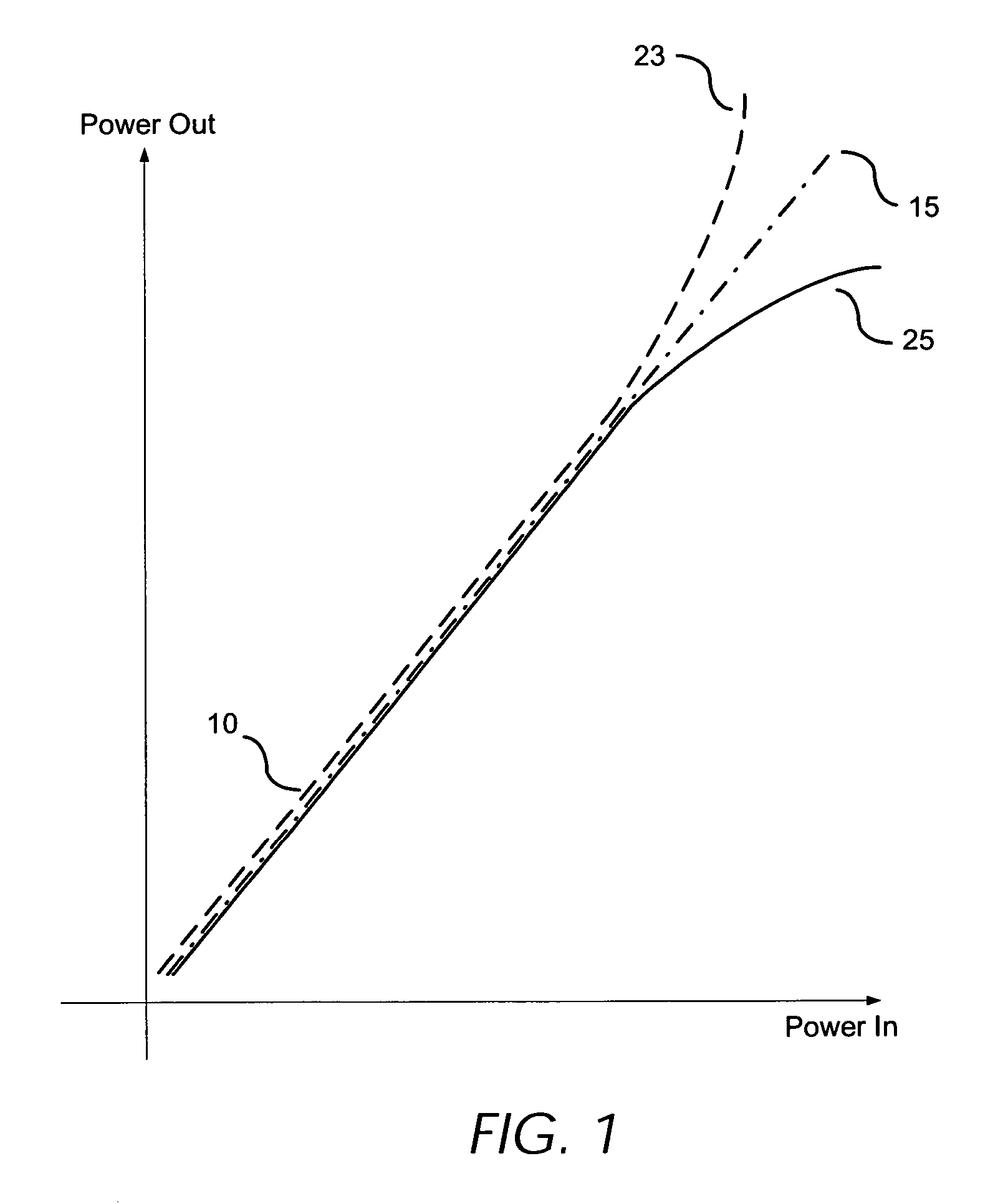

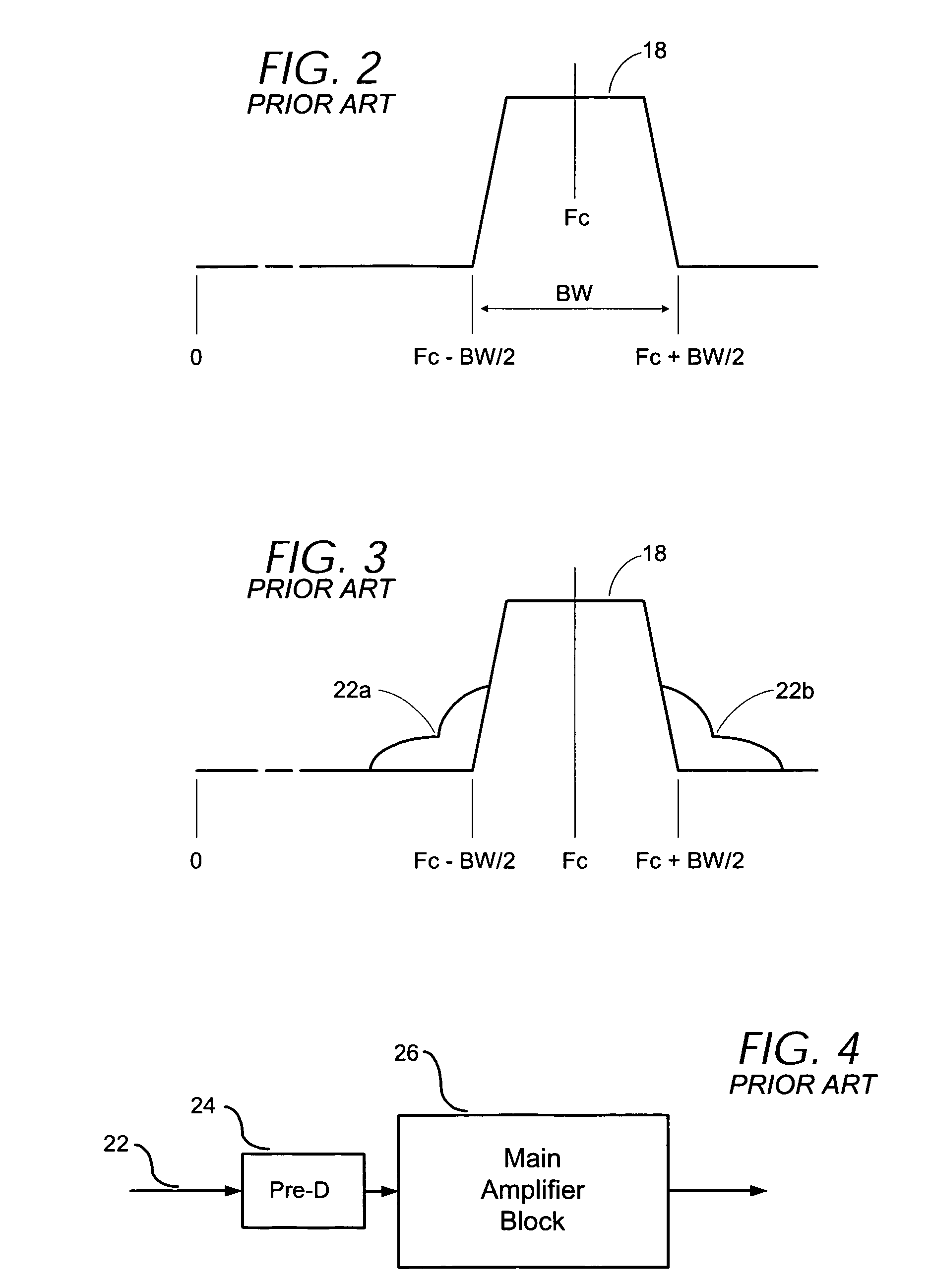

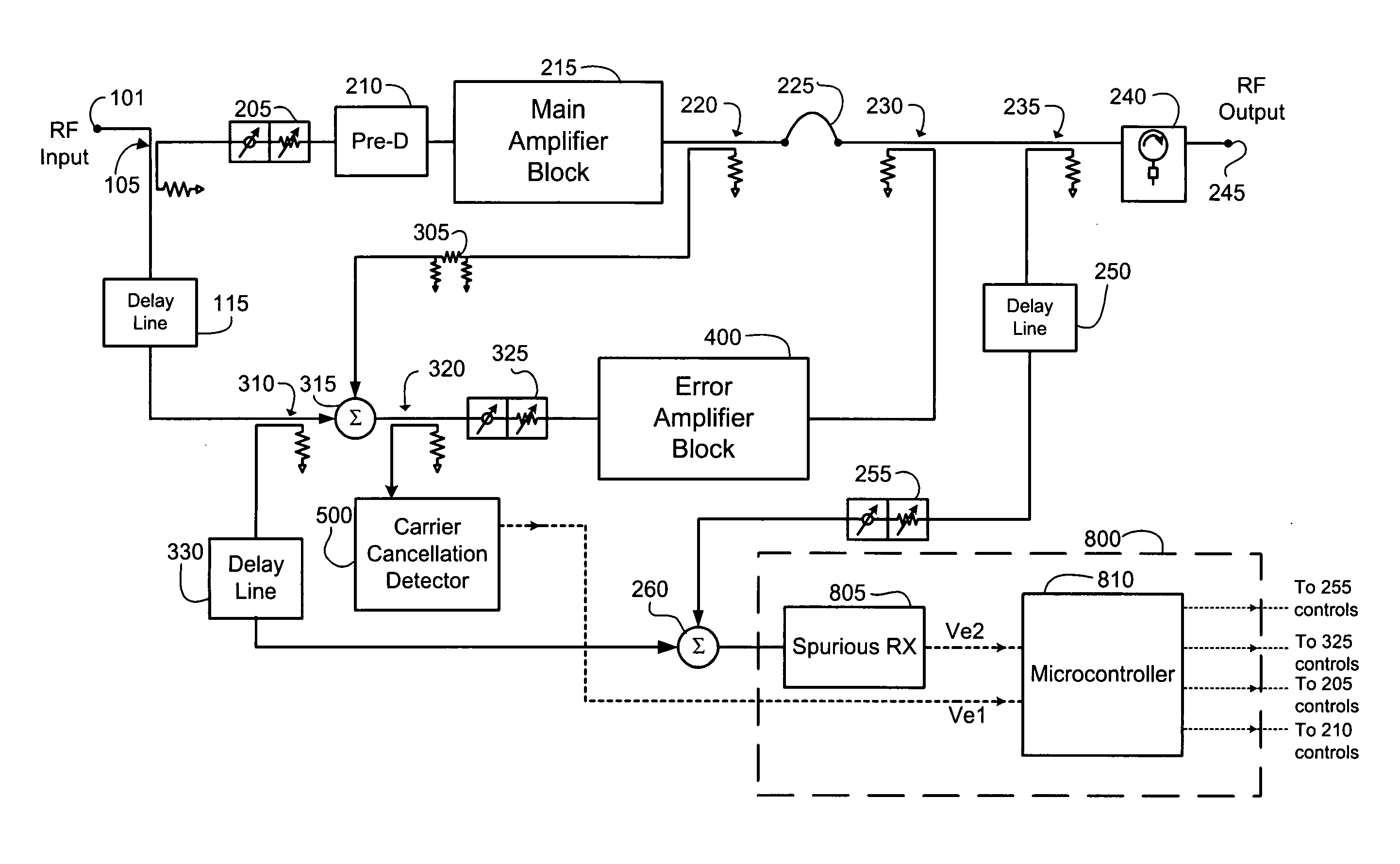

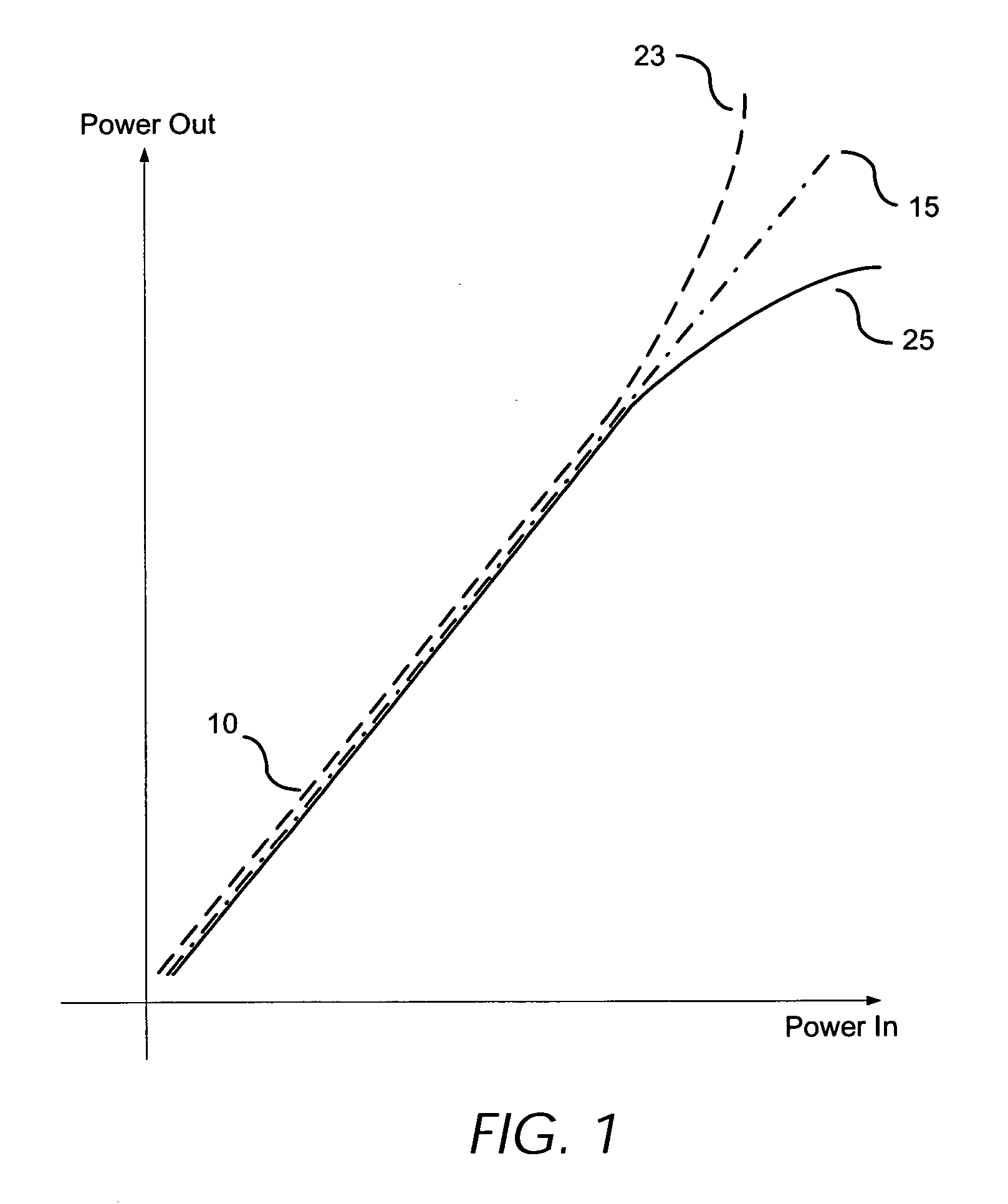

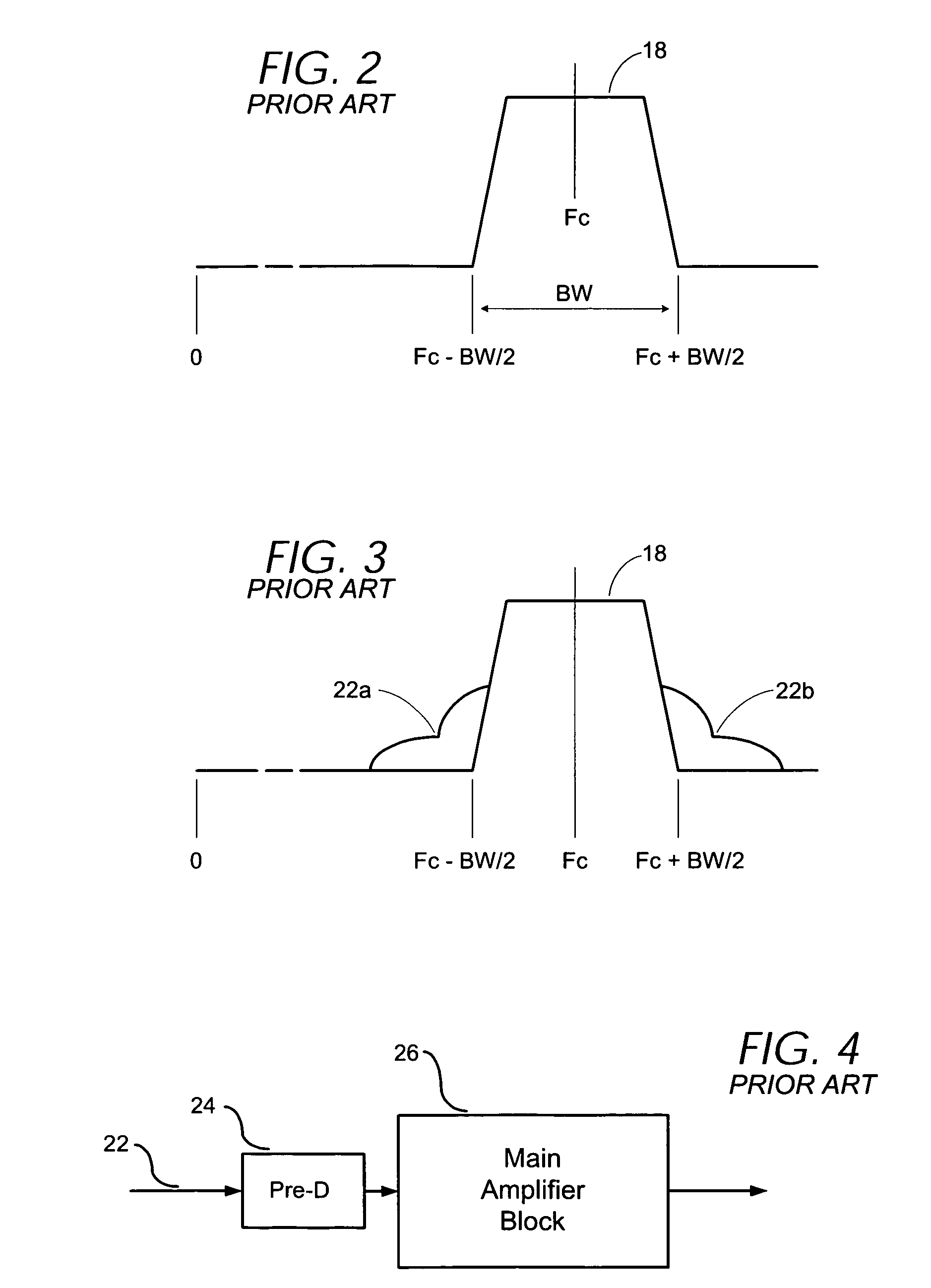

Enhanced efficiency feed forward power amplifier with delay mismatched error cancellation loop

ActiveUS7301397B2Avoid excessive delayAmplifier modifications to reduce non-linear distortionAmplifier with control circuitsLow distortionShort loop

Owner:INTEL CORP

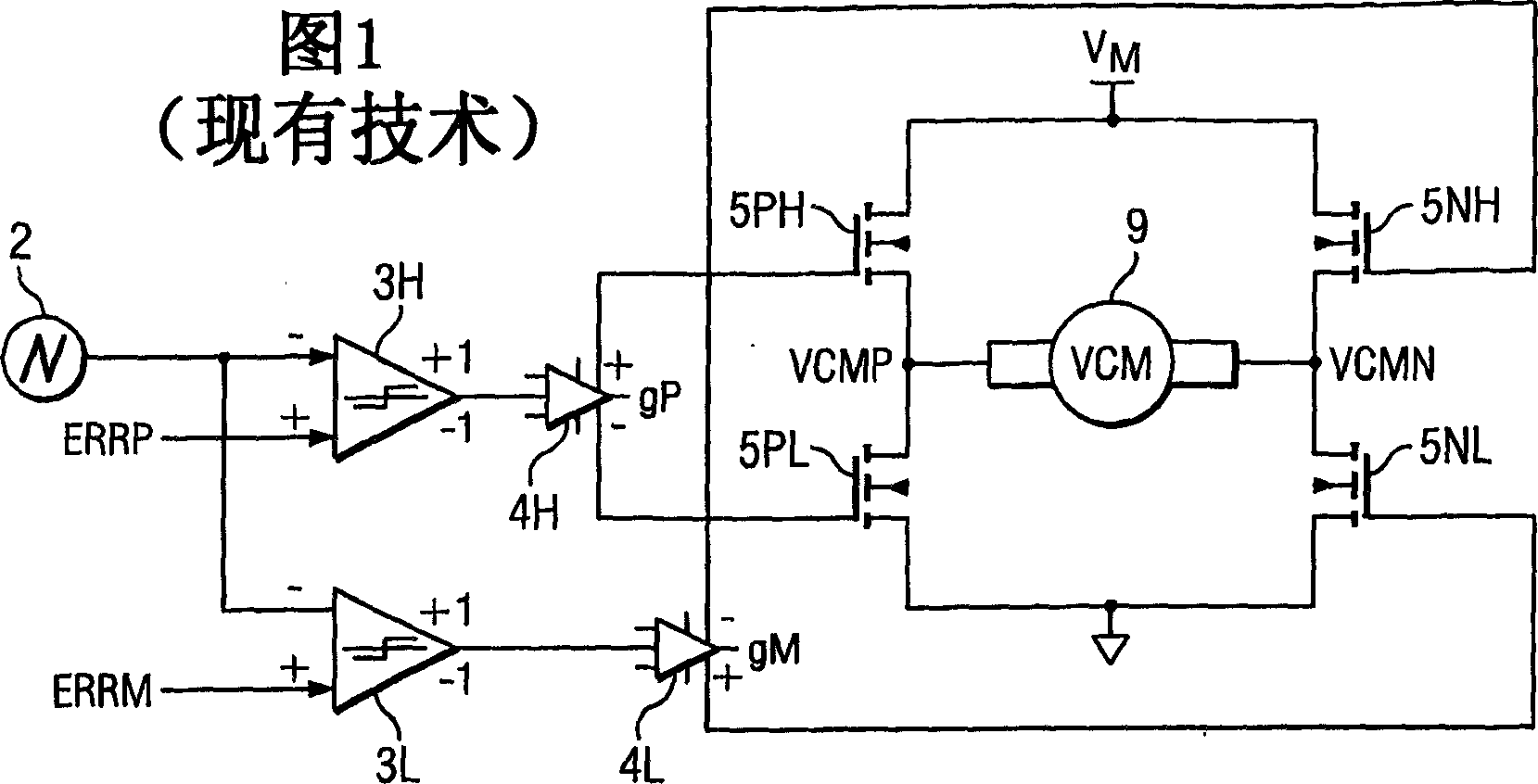

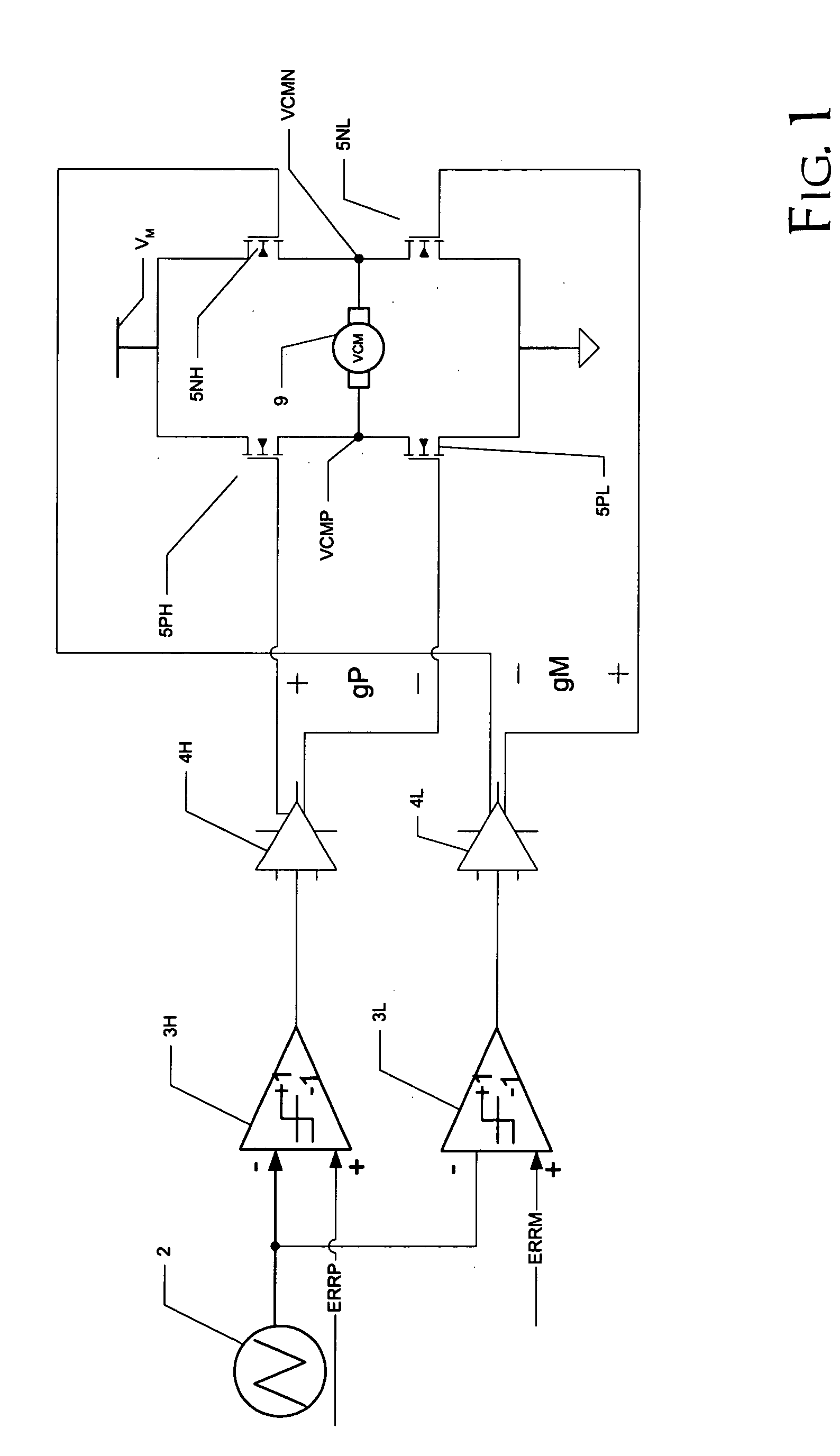

Inhibition of power supply variations for gain error cancellation in pulse-width-modulated motor controllers

A positioning driver (32) for a voice coil motor (22) in a disk drive system is disclosed. Pulse-width-modulated prestage drivers (46) are coupled to power transistors (50PH, 50NH, 50PL, 50NL) arranged in an 'H' bridge for driving the voice coil motor (22), biased with a power supply voltage (VM). The pulse-width-modulated prestage drivers (46) drive the power transistors (50PH, 50NH, 50PL, 50NL) according to a comparison between an error signal from an error amplifier (36) and a ramp clock signal (RMP) generated by a ramp clock generator (48). The ramp clock generator (48) includes a control circuit that modulates the high and low limits of the ramp clock signal (RMP) in response to variations in the power supply voltage (VM). This modulation of the high and low limits compensates for variations in the gain of the power transistors (50) resulting from variations in the power supply voltage (VM). The control circuit may also modulate the slope of the ramp clock signal (RMP) according to variations in the power supply voltage (VM), for example to maintain a constant frequency.

Owner:TEXAS INSTR INC

Enhanced efficiency feed forward power amplifier with delay mismatched error cancellation loop

ActiveUS20070018723A1Avoid excessive delayAmplifier modifications to reduce non-linear distortionAmplifier with control circuitsLow distortionAudio power amplifier

A delay mismatched feed forward power amplifier is disclosed. Loop 1 includes a main amplifier and is used to derive a carrier cancelled sample of the main amplifier output. Loop 2 includes an error amplifier used to amplify the carrier cancelled signal derived from Loop 1 operation in order to cancel distortion products generated due to the nonlinear nature of the main amplifier. Loop 2 also utilizes a very short Loop 2 delay line. A significant efficiency gain is provided due to reduced output power losses associated with the Loop 2 delay line. Lower output losses also results in lower distortion levels produced by the main amplifier. This, in turn, reduces the size and performance requirements placed on the error amplifier. A smaller and more efficient error amplifier is employed resulting in further amplifier system efficiency improvement. The delay mismatch is compensated by a third control loop, a special adaptive control algorithm or a combination thereof.

Owner:INTEL CORP

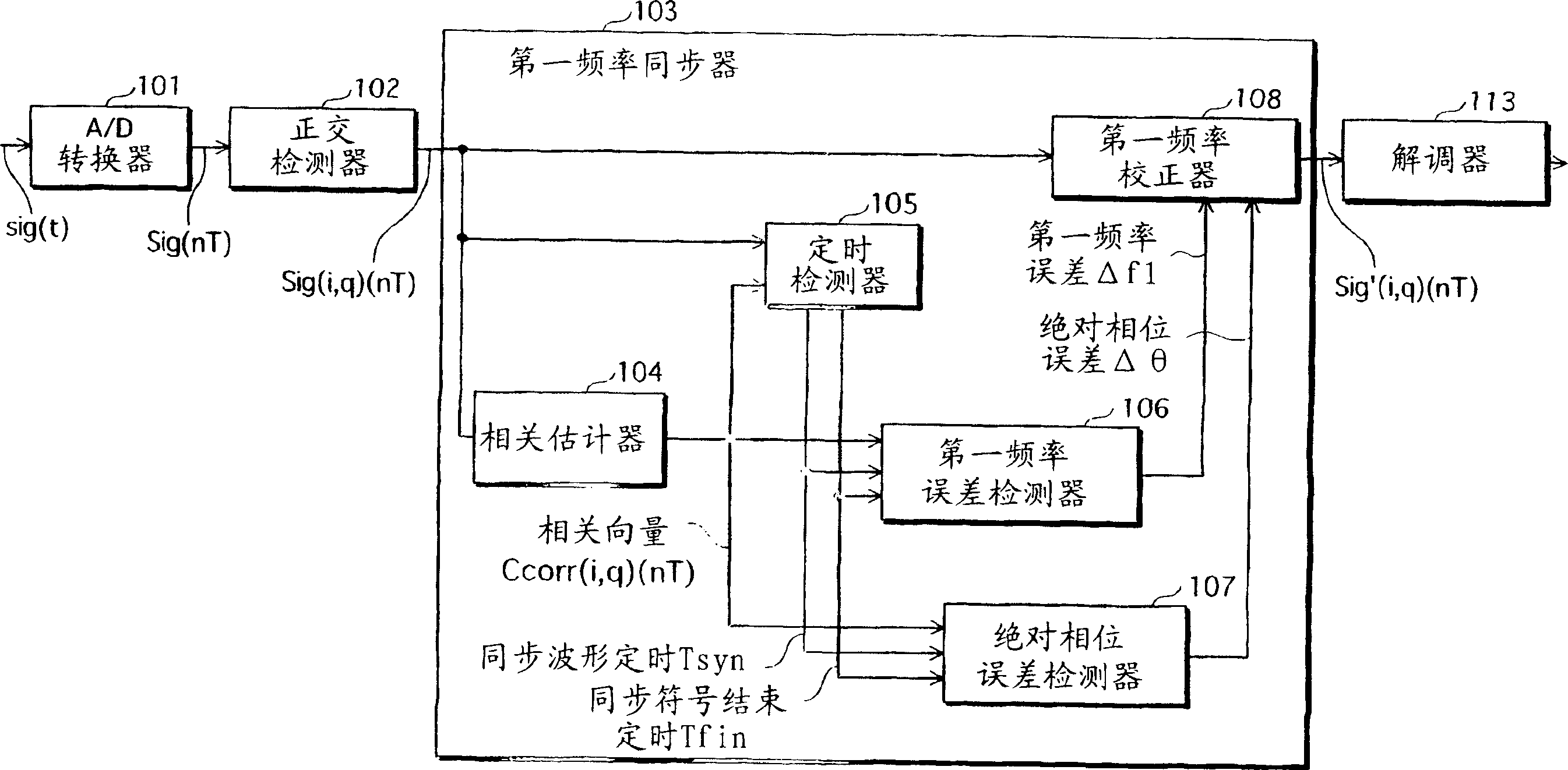

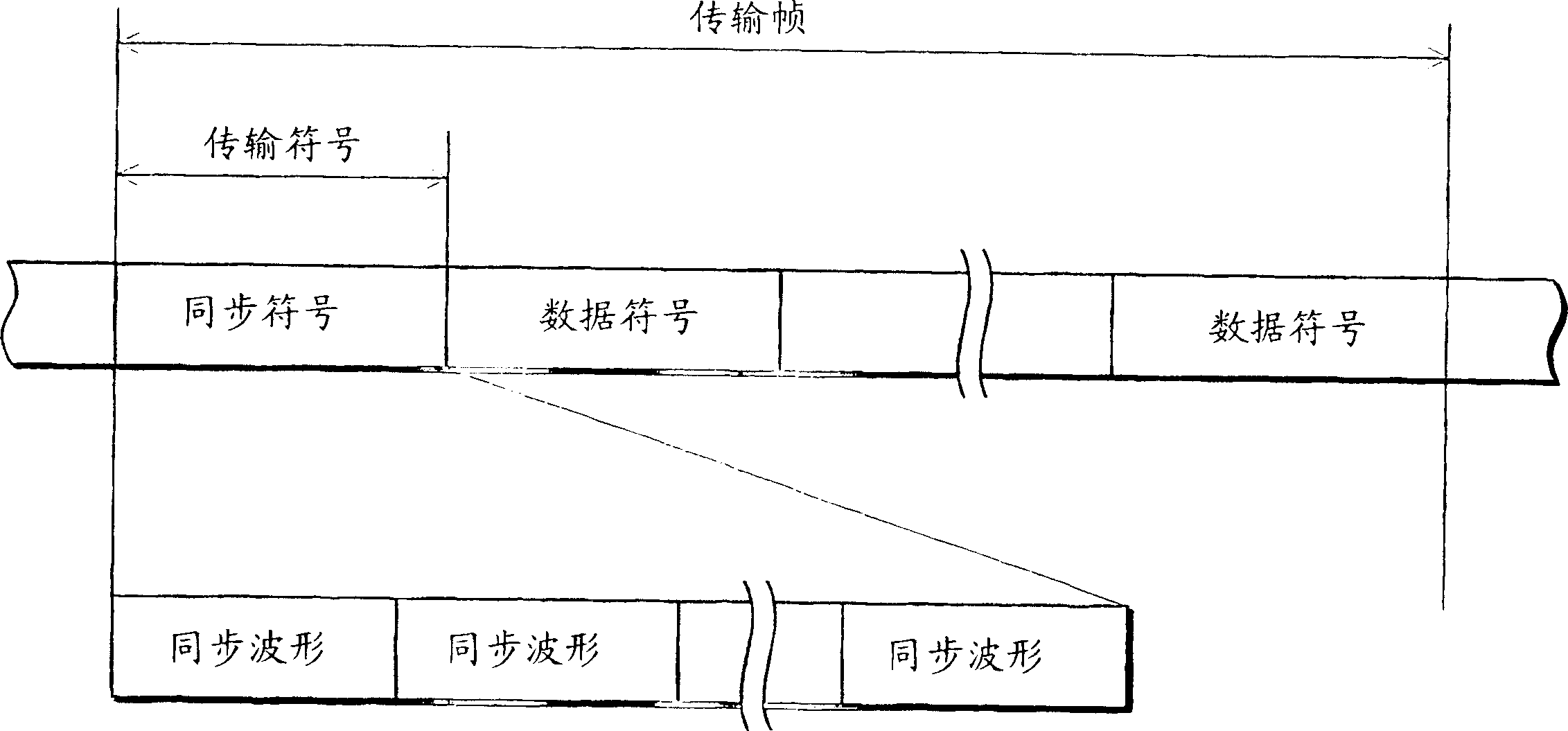

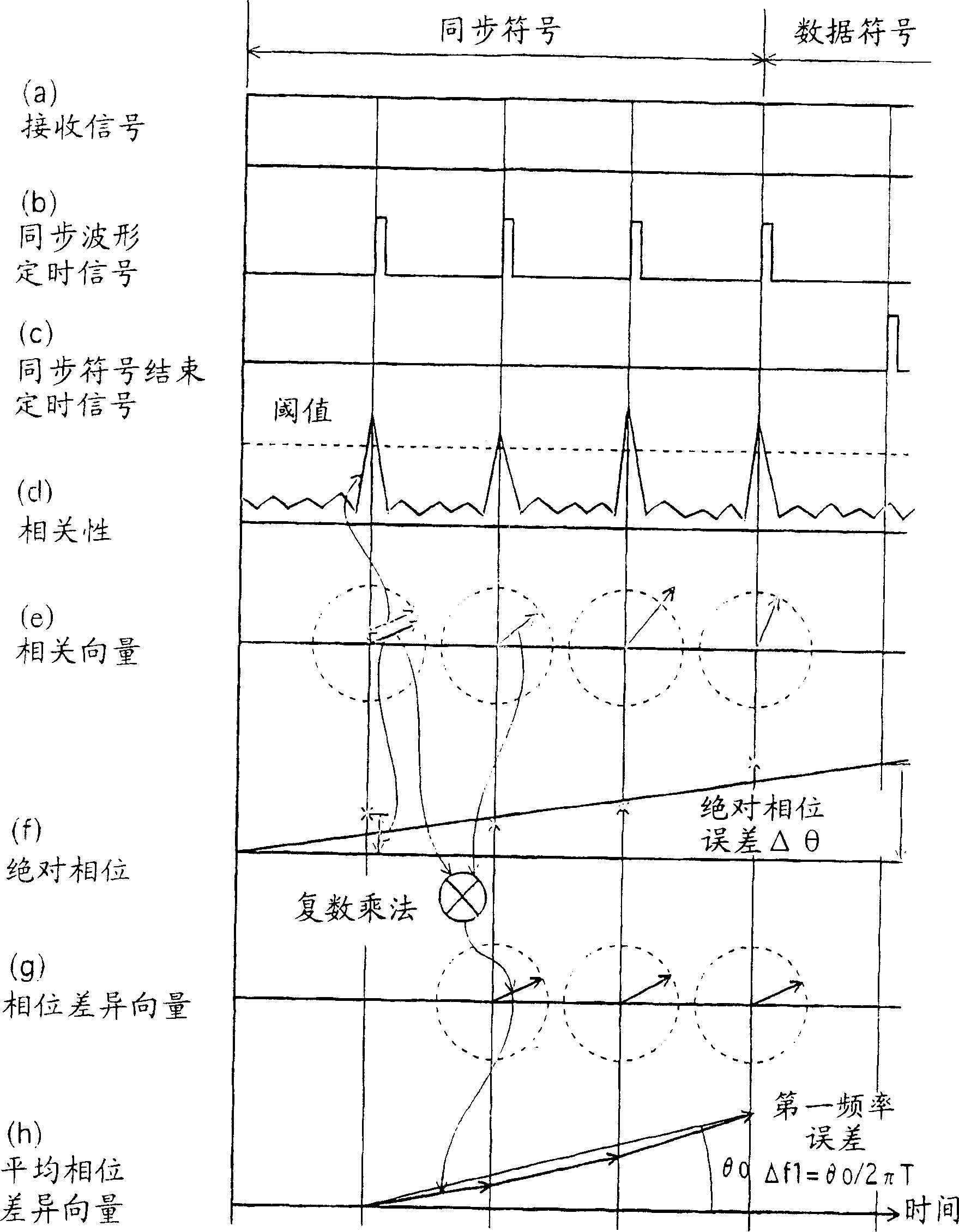

Frequency synchronization apparatus and frequency synchronization method

InactiveCN1768501ACarrier regulationSynchronisation signal speed/phase controlPhase differenceSignal correlation

The first frequency synchronization means (103) corresponds to the frequency synchronization device of the present invention. A higher device, eg a wireless receiver, provides a received signal to the first frequency synchronization means (103) via an A / D converter (101) and a quadrature detector (102). A sync symbol including a predetermined waveform at least twice is incorporated into the received signal. A correlation estimator (104) generates a reference signal representing the same waveform as the synchronization symbol, and sequentially finds a correlation vector between the received signal and the reference signal. The first signal error detector (106) finds the frequency error from the average phase difference of the predetermined correlation vectors, and finds the absolute phase error from the transition of the absolute phase of the predetermined correlation vectors. A first frequency corrector (108) simultaneously imparts a frequency shift and a phase rotation for canceling errors to the received signal.

Owner:PANASONIC CORP

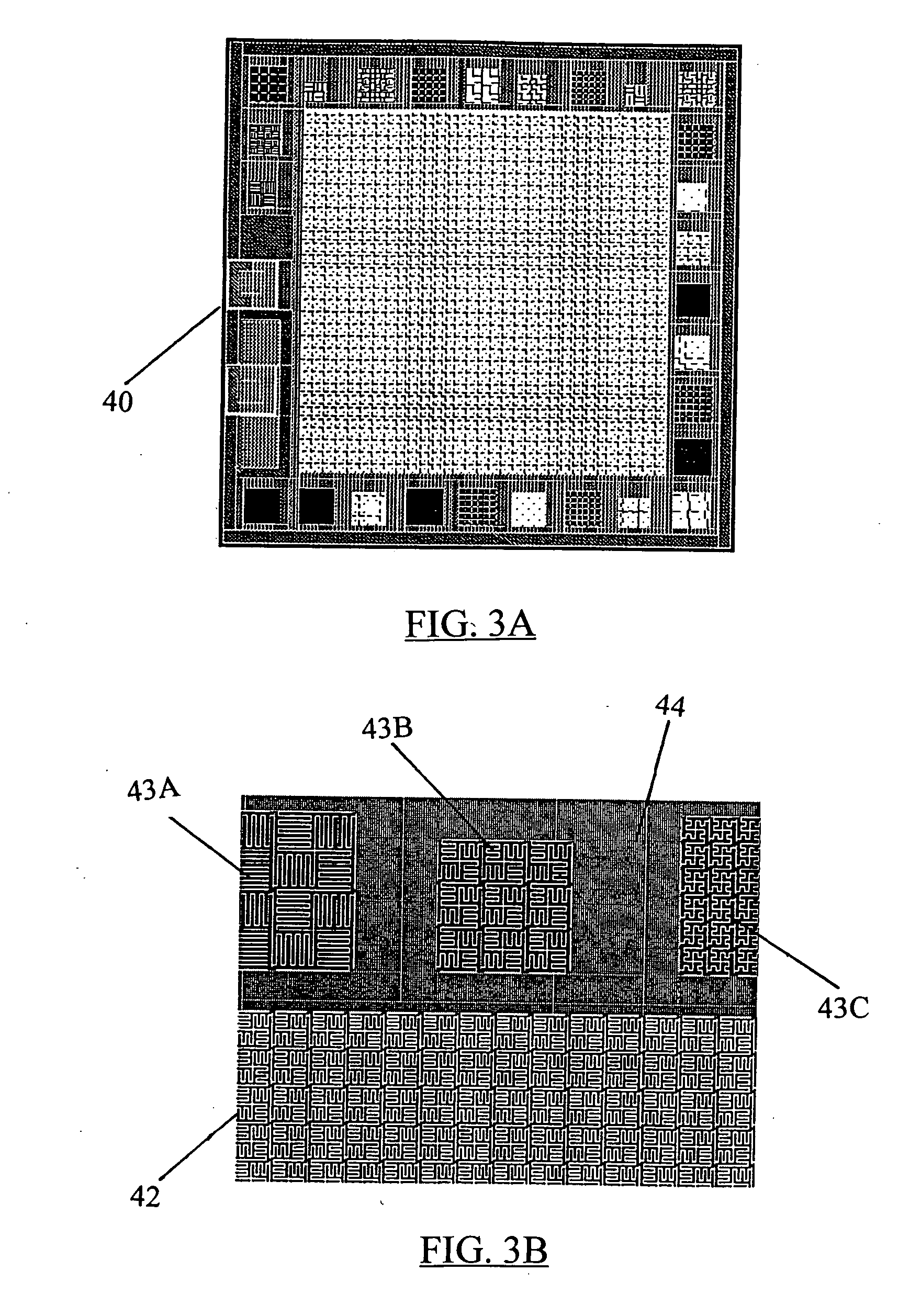

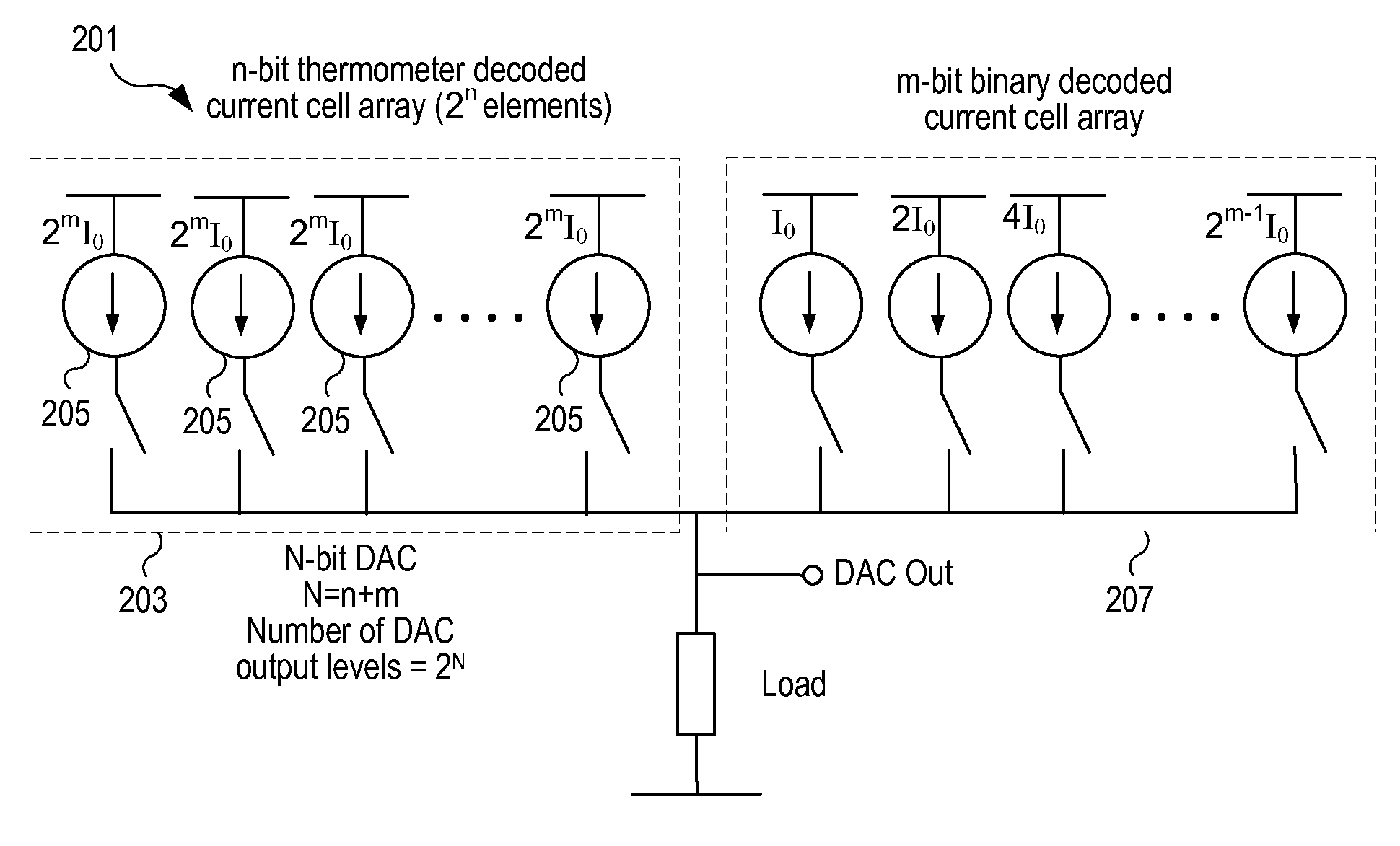

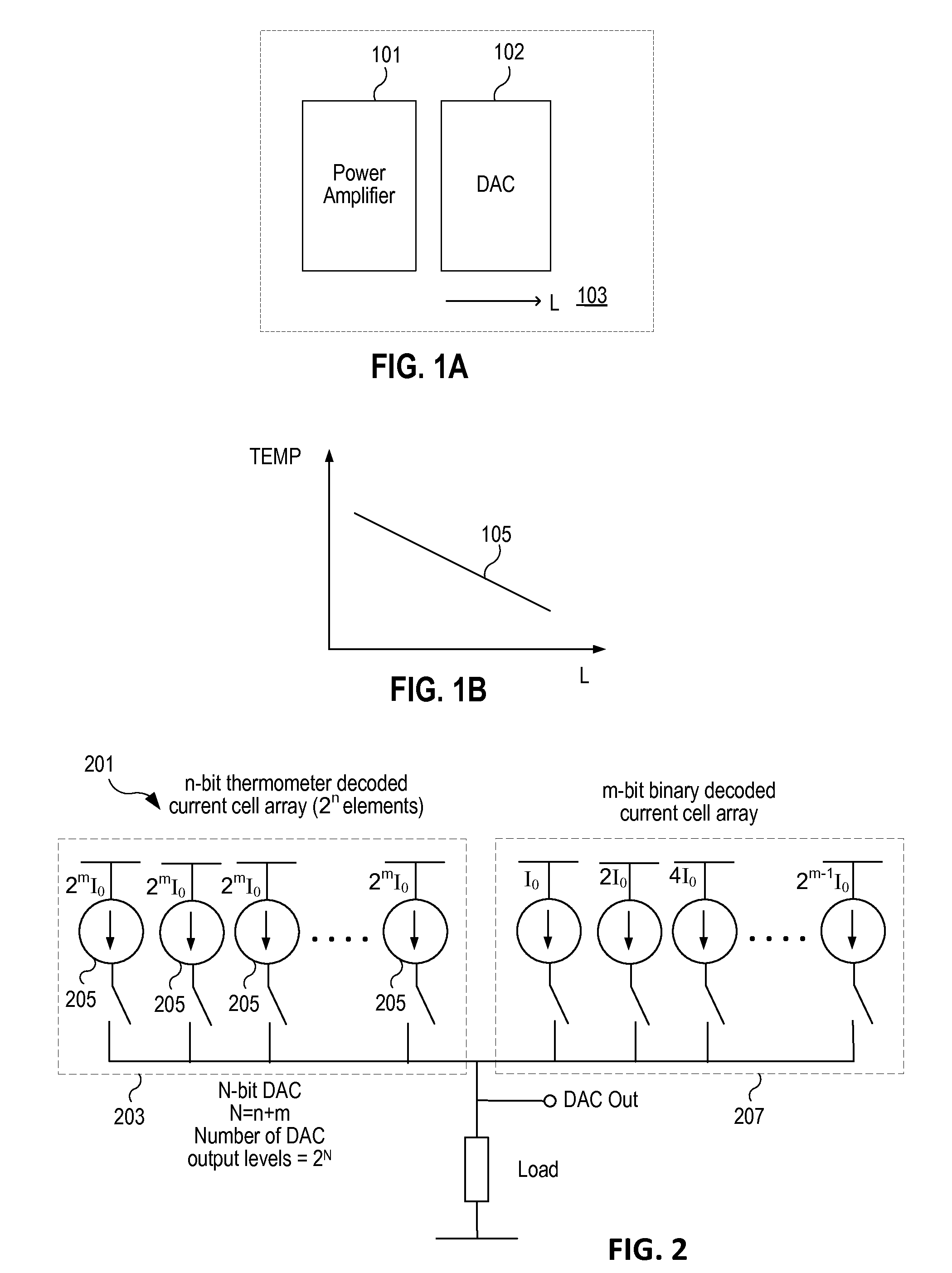

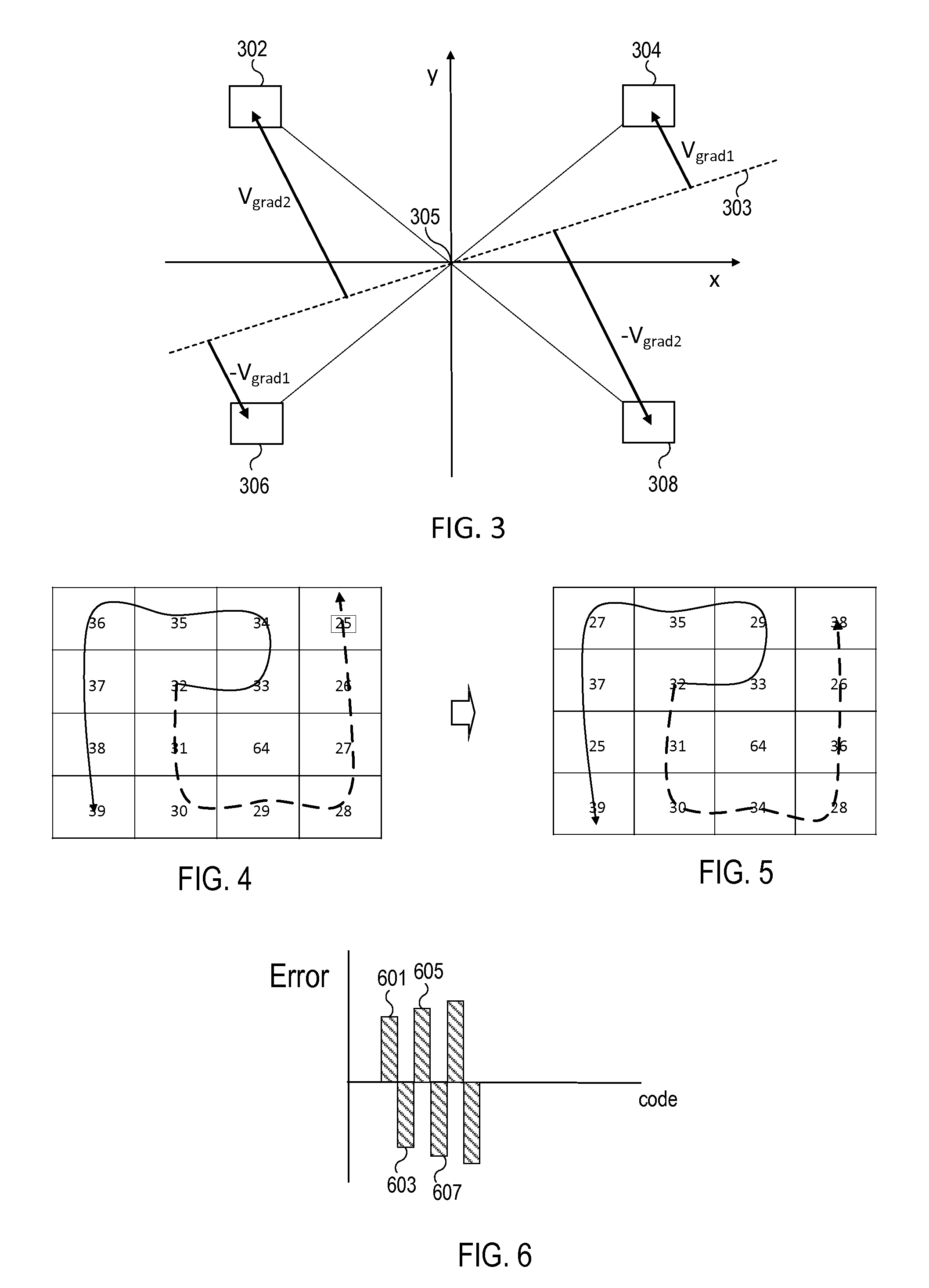

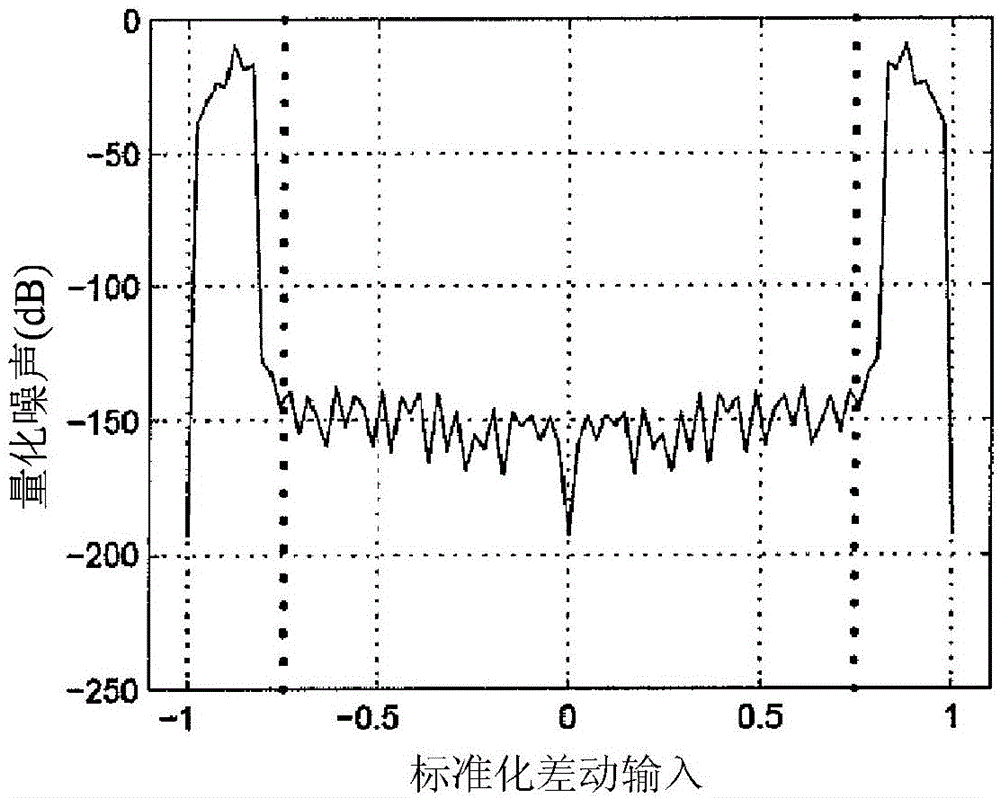

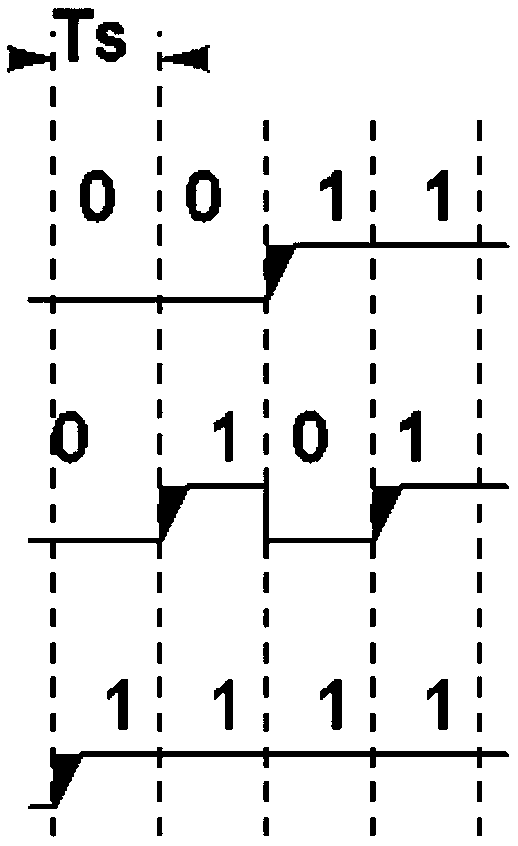

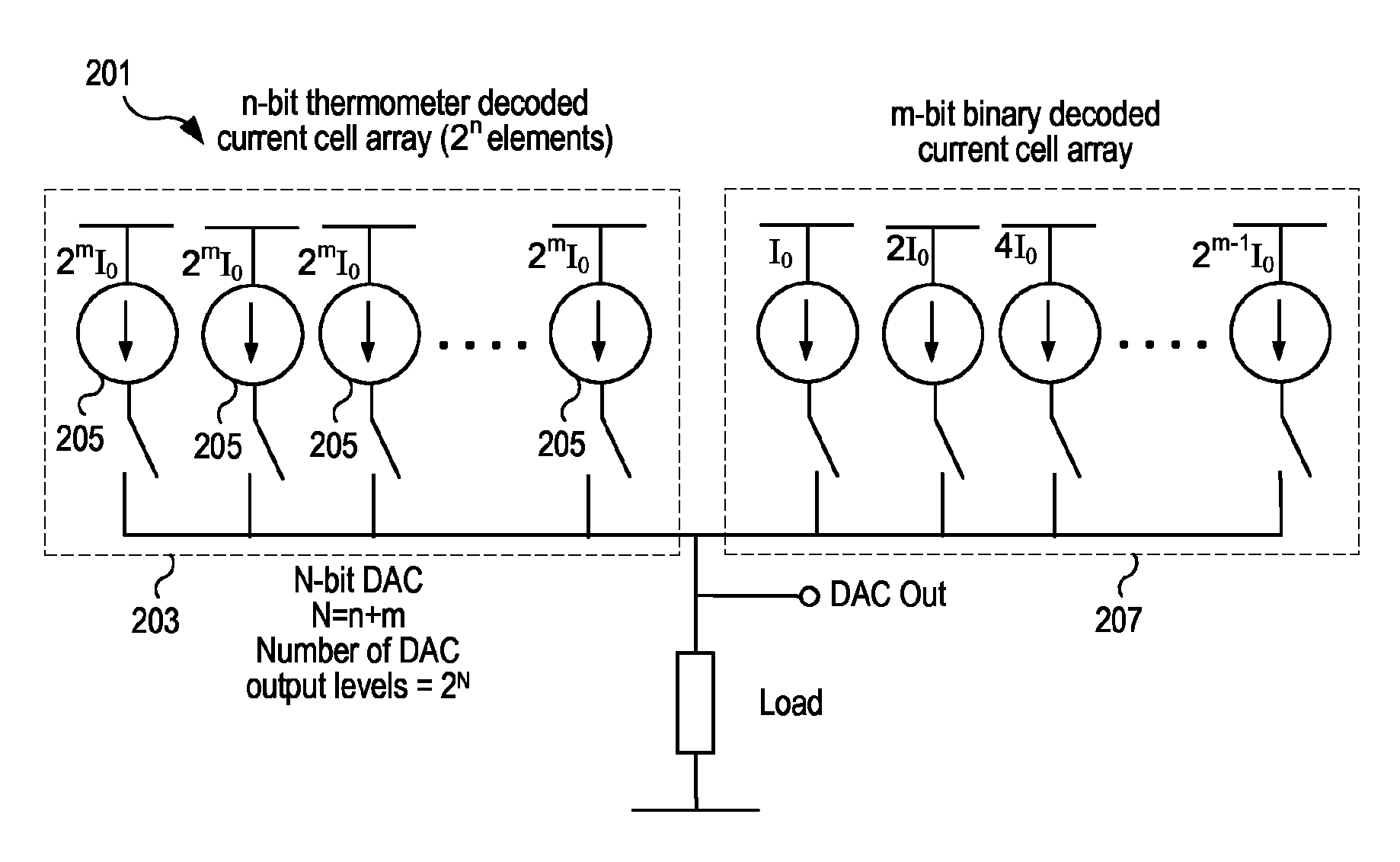

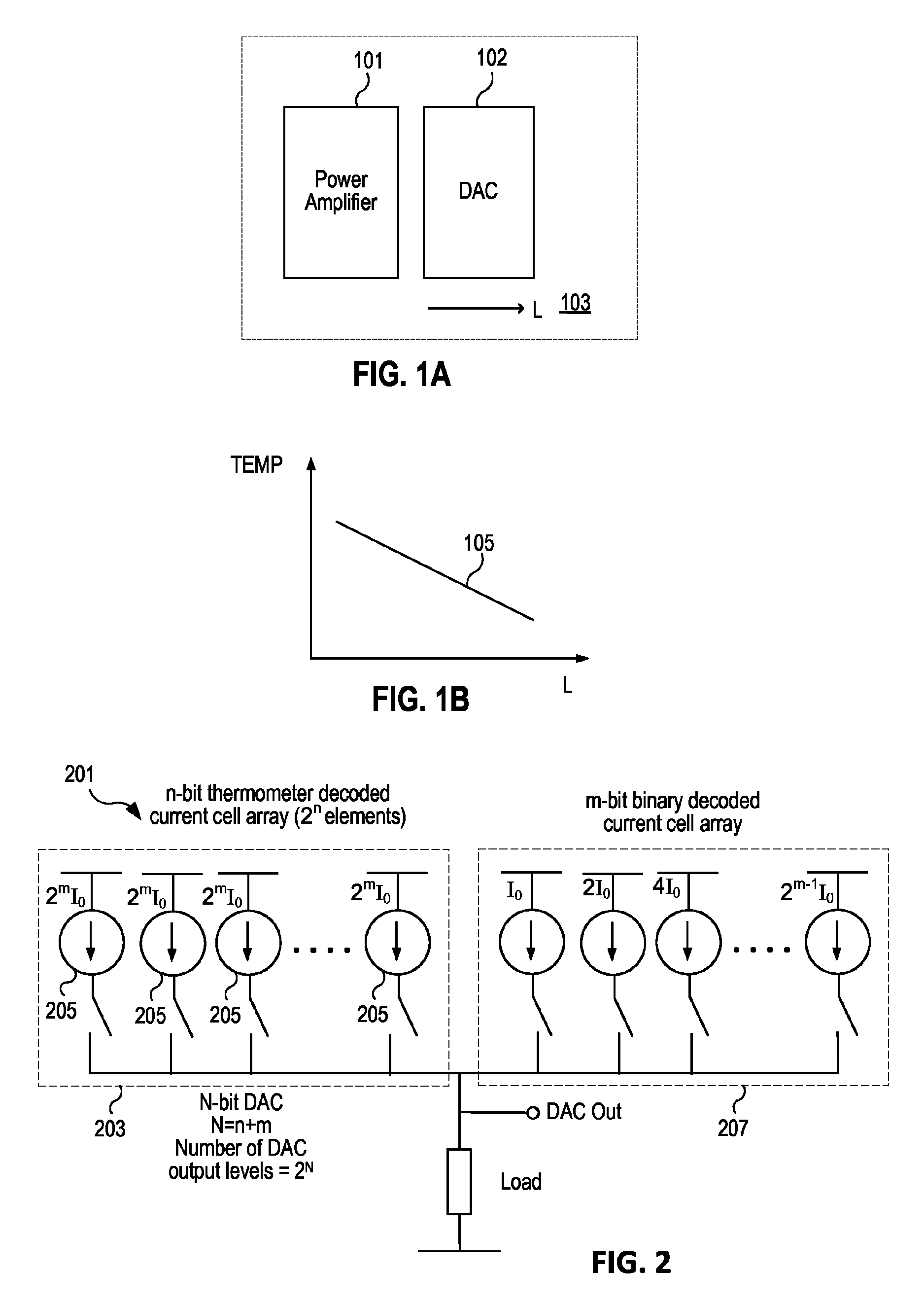

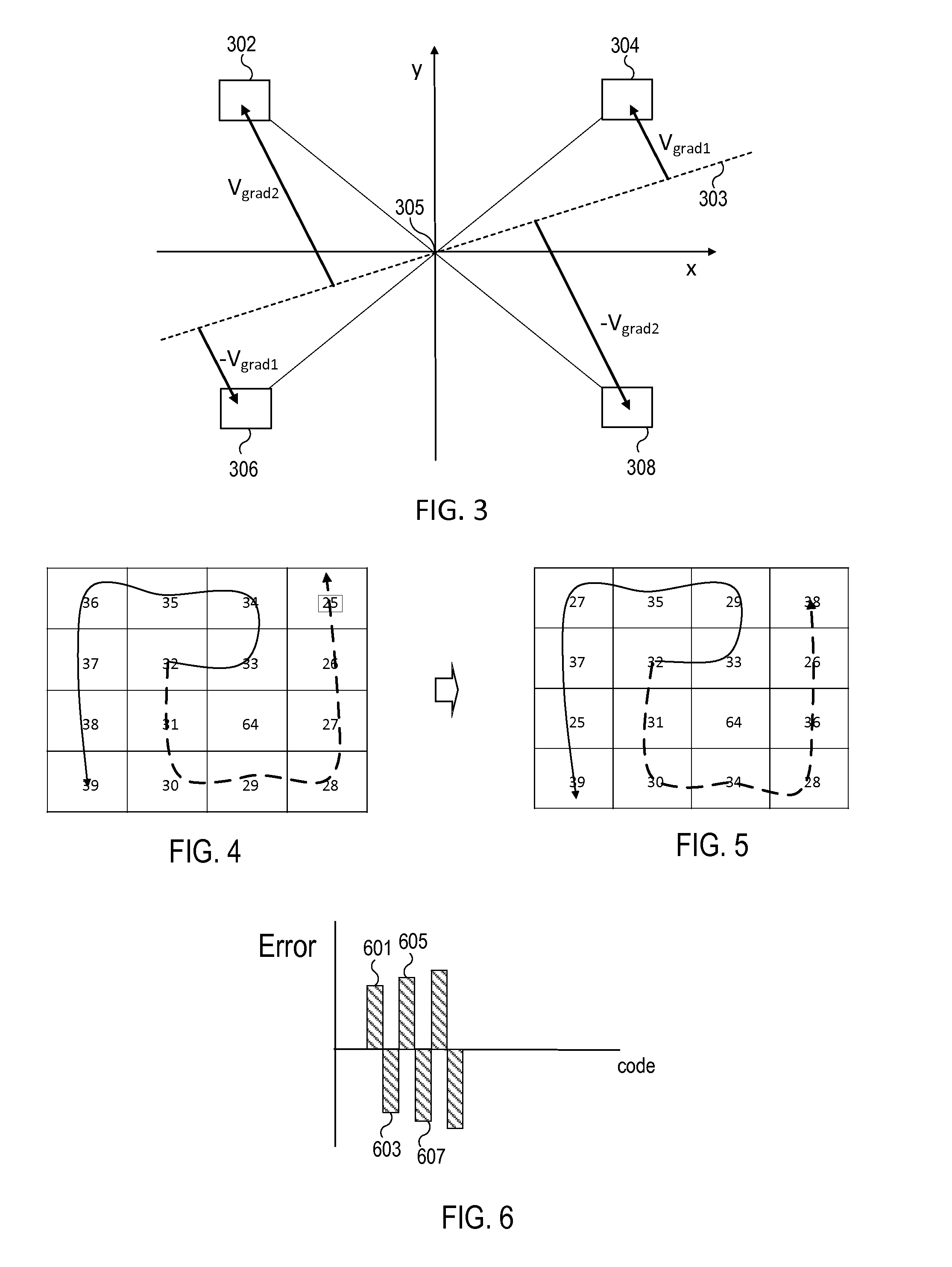

Dac current source matrix patterns with gradient error cancellation

ActiveUS20150042498A1Reducing first order gradient effectEliminate the effects ofElectric signal transmission systemsDigital-analogue convertorsNegative errorCurrent cell

First order gradient errors are canceled with no current source splitting by placing consecutive current sources symmetrically around the center of the array. Consecutive elements that correspond to small input amplitudes (mid-scale codes) make a smaller spatial jump than those correspond to larger signal amplitudes. Both linear and second order gradients are reduced by splitting each current cell into two and placing sub-elements symmetrically with respect to the center of the array to address the linear gradient effect. To address second order gradients, current element placement follows a pattern such that consecutive element pairs are chosen with one of the pair being placed with respect to the zero error contour of the second order gradient so as to have a positive error and the second of the pair being placed so as to have a negative error resulting in reduced second order error accumulation.

Owner:SKYWORKS SOLUTIONS INC

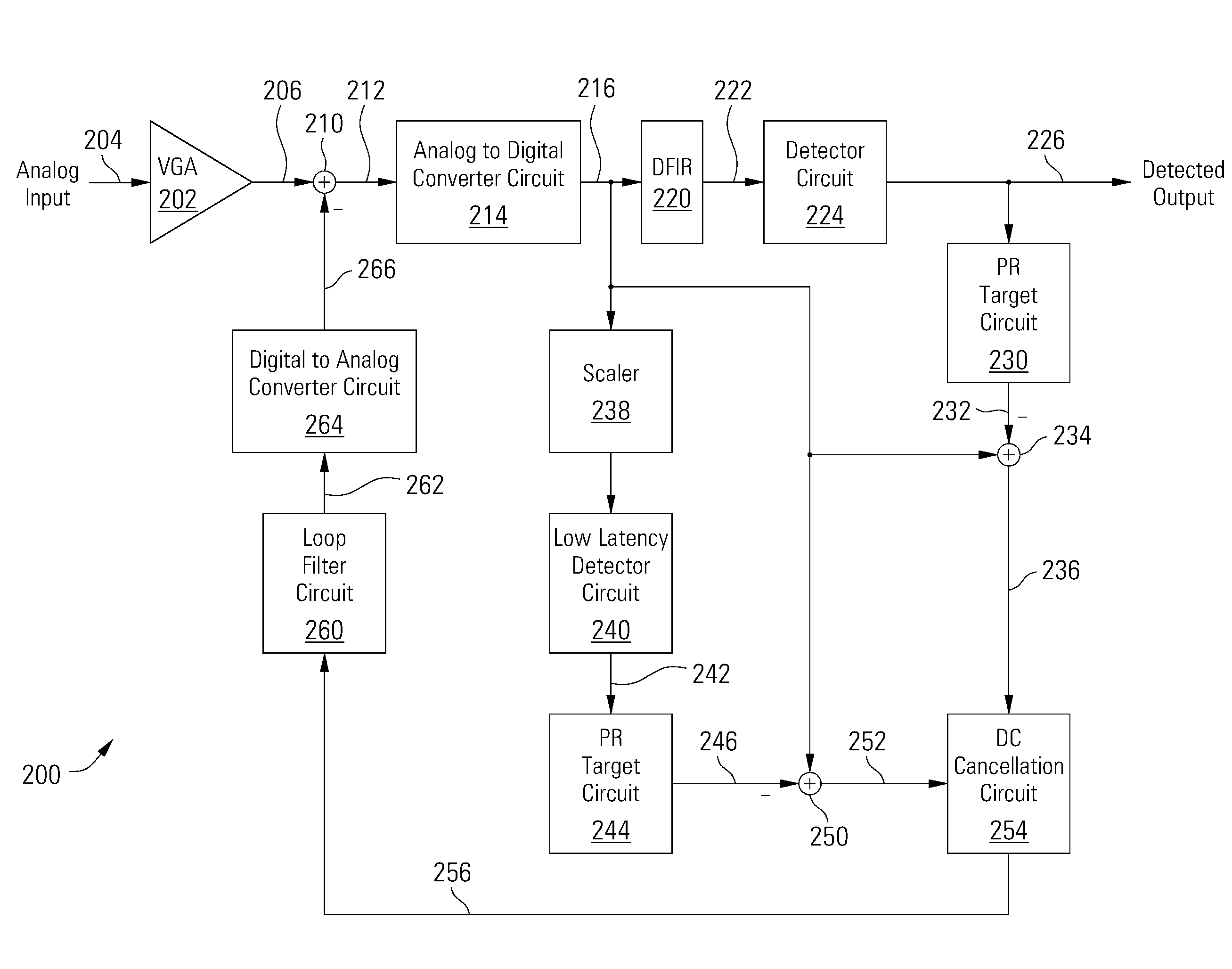

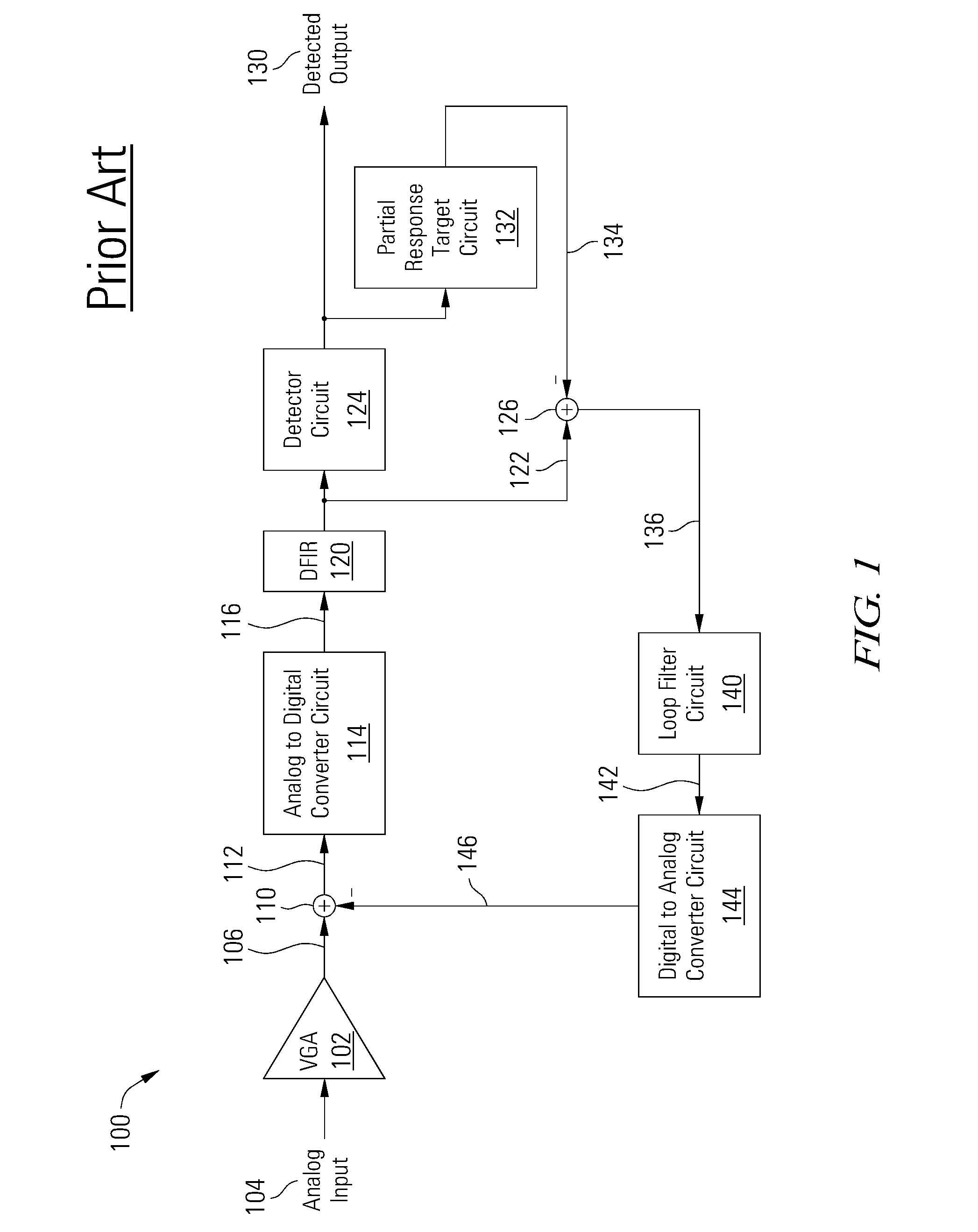

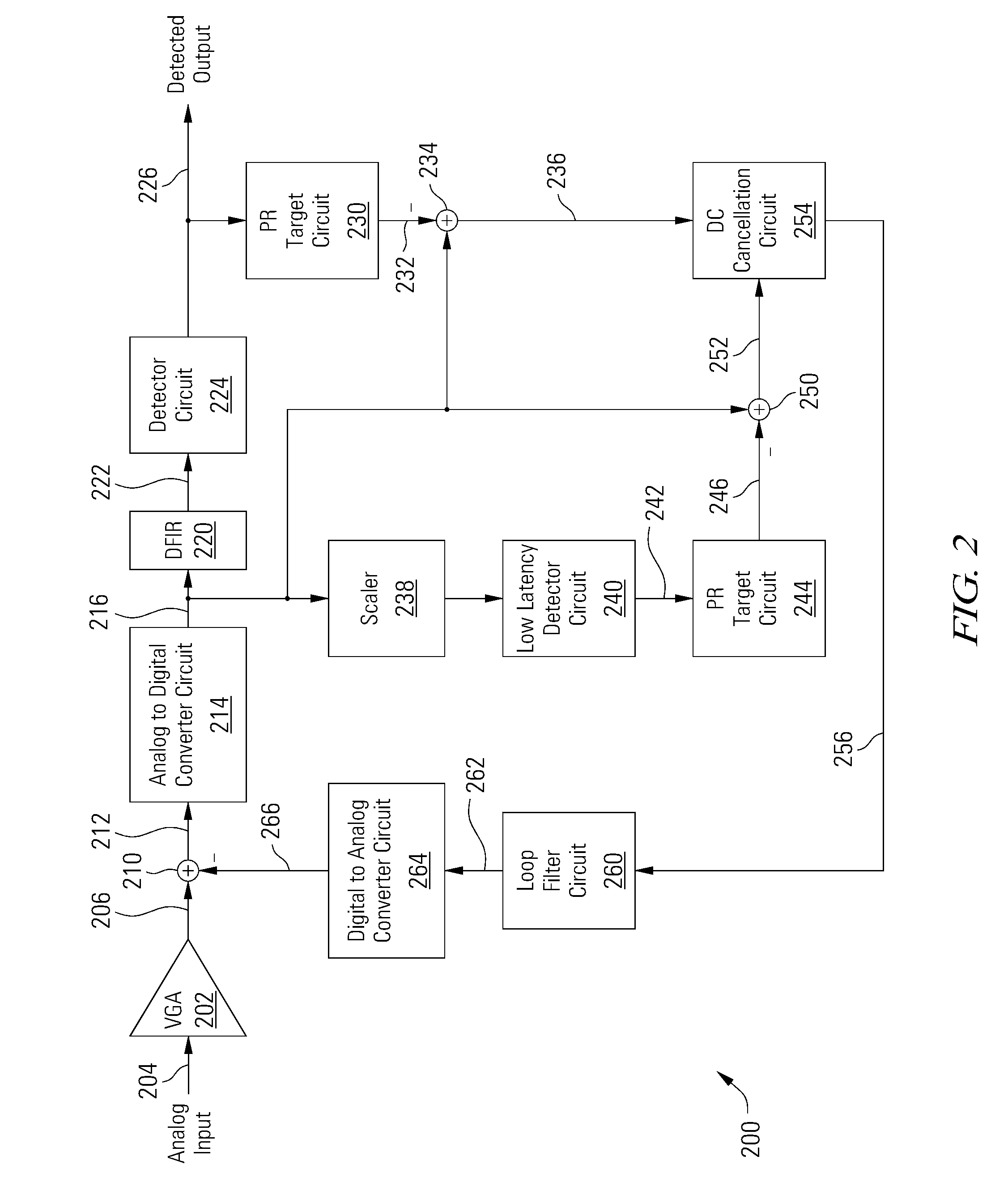

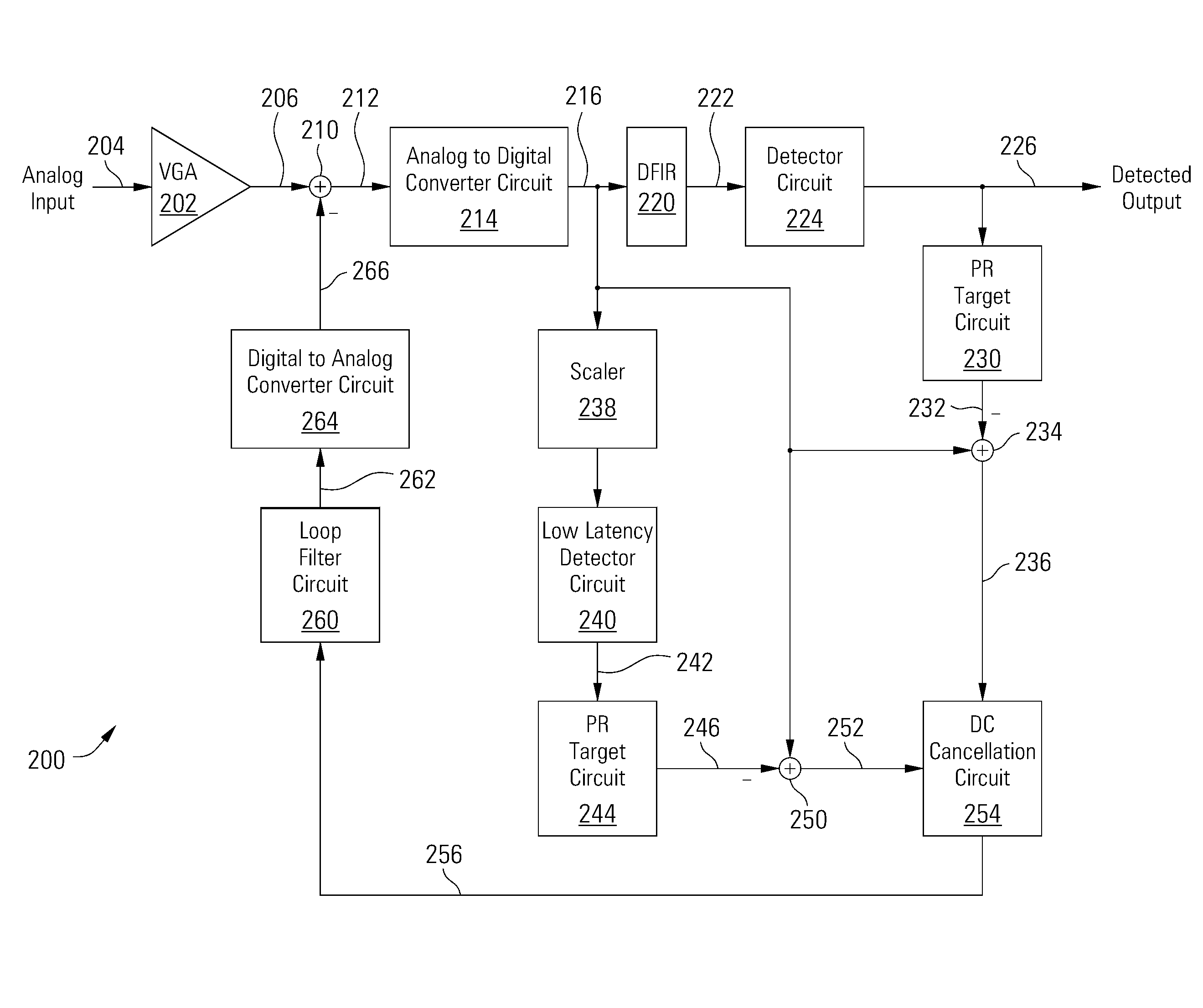

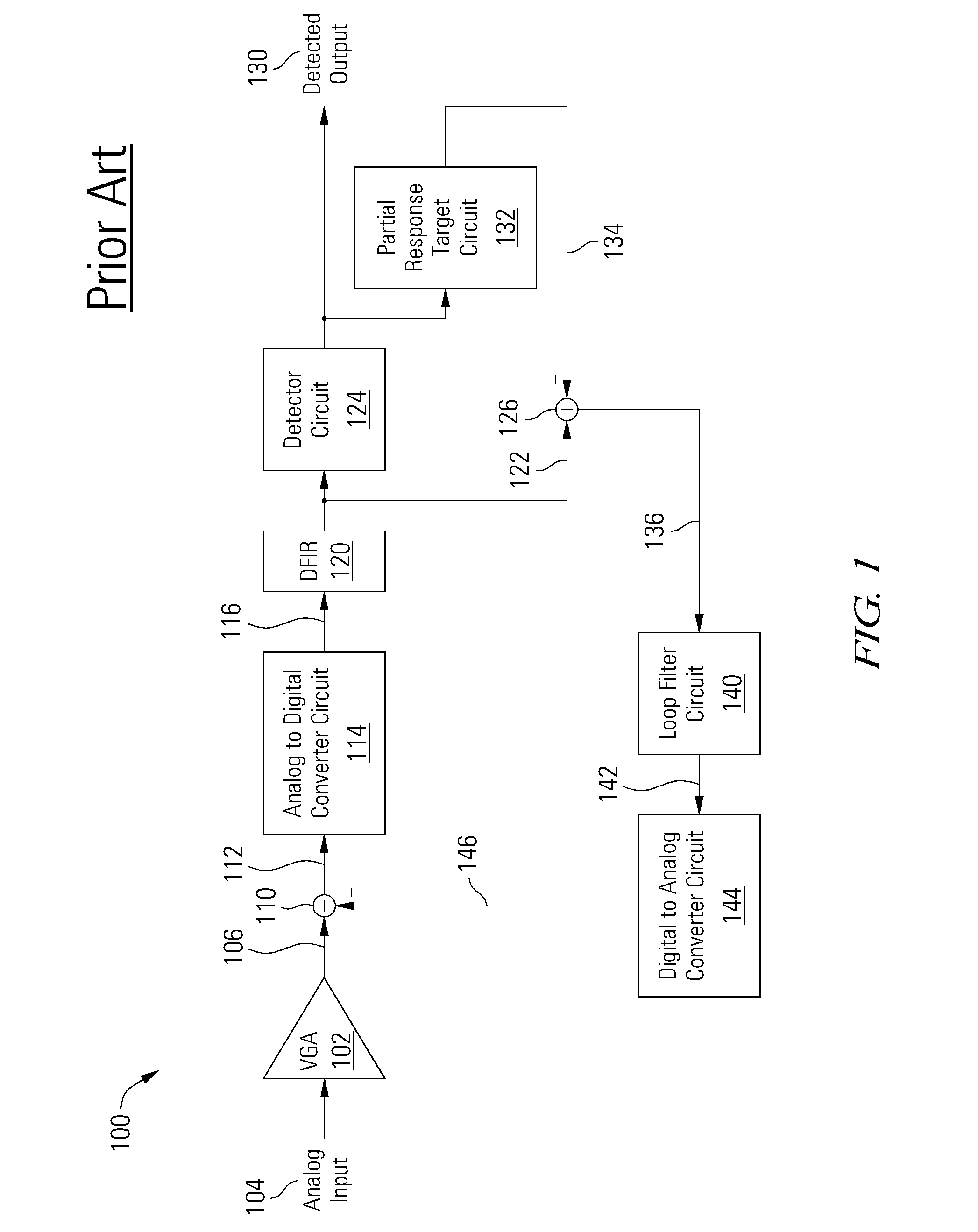

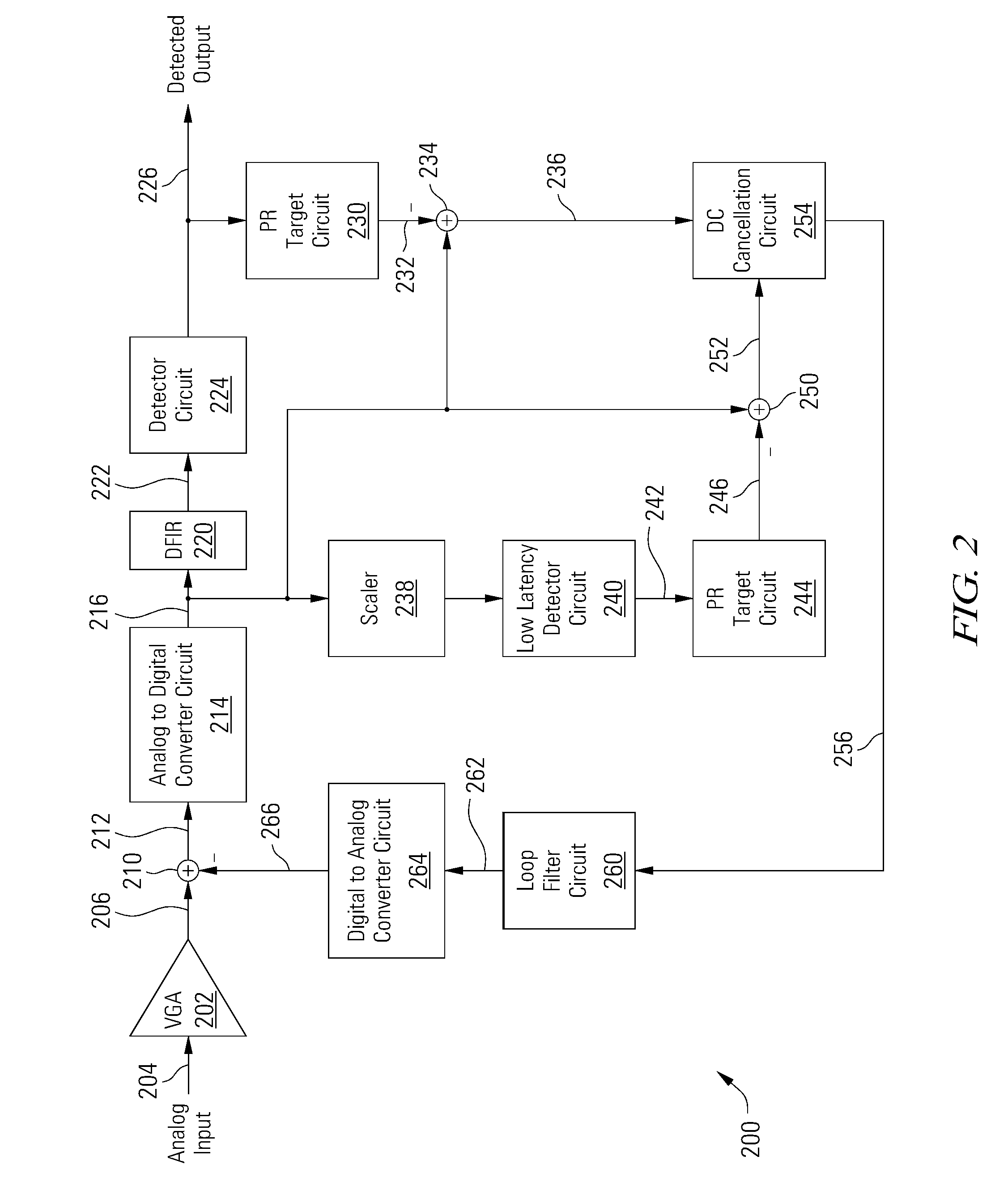

Low Latency Multi-Detector Noise Cancellation

ActiveUS20130007570A1Reduce distractionsData representation error detection/correctionCode conversionDetector circuitsLatency (engineering)

Various embodiments of the present invention provide systems and methods for data processing. For example, a data processing circuit is disclosed that includes first and second data detectors and an error cancellation circuit. The first data detector is operable to perform a data detection process on a first signal derived from a data input to yield a detected output. The second data detector circuit is operable to perform a data detection process on a second signal derived from the data input to yield a second detected output. The error cancellation circuit is operable to combine a first error signal derived from the detected output with a second error signal derived from the second detected output to yield a feedback signal. The feedback signal is operable to modify the data input during a subsequent period.

Owner:AVAGO TECH INT SALES PTE LTD

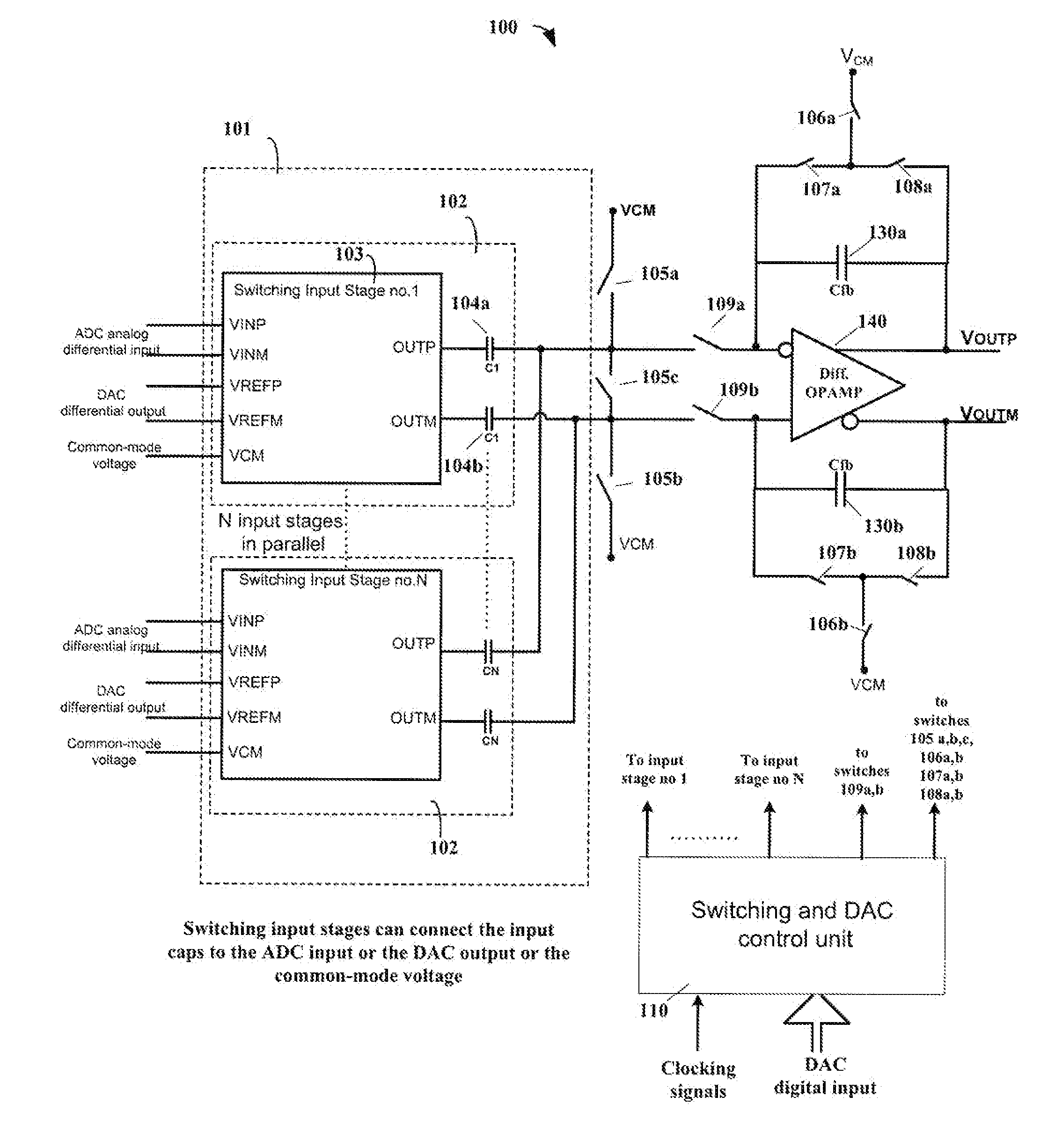

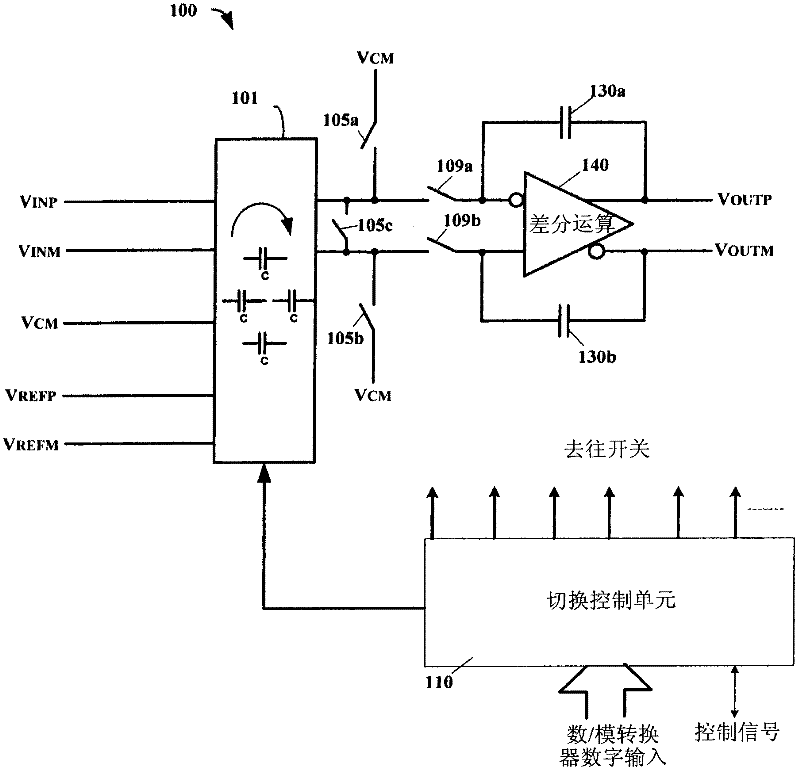

2-phase gain calibration and scaling scheme for switched capacitor sigma-delta modulator using a chopper voltage reference

ActiveCN103069719AAnalogue conversionPhysical parameters compensation/preventionVoltage referenceEngineering

A sigma-delta modulator has a chopper voltage reference providing a reference signal having a clock dependent offset voltage, a single-bit or a multi-bit digital-to-analog converter (DAC); a plurality of capacitor pairs; a plurality of switches to couple any capacitor pair to an input or reference signal; and a control unit controlling sampling through said switches to perform a charge transfer in two phases wherein any capacitor pair can be selected to be assigned to the input or reference signal, wherein after a plurality of charge transfers a gain error cancellation is performed by rotating the capacitor pairs cyclically, and wherein a DAC output value and a reference offset state define switching sequences wherein each switching sequence independently rotates said capacitor pairs and wherein at least one switching sequence is selected depending on a current DAC output value and a current reference offset state.

Owner:MICROCHIP TECH INC

2-Phase Gain Calibration And Scaling Scheme For Switched Capacitor Sigma-Delta Modulator

ActiveUS20110012767A1Electric signal transmission systemsAnalogue conversionCapacitanceError cancellation

A sigma-delta modulator may have a plurality of capacitor pairs, a plurality of switches to couple any pair of capacitors from the plurality of capacitor pairs selectively to an input signal or a reference signal, and a control unit operable to control sampling through the switches to perform a charge transfer in two phases wherein any pair of capacitors can be selected to be assigned to the input signal or the reference signal, and wherein after a plurality of charge transfers a gain error cancellation is performed by rotating the capacitor pairs cyclically such that after a rotation cycle, each capacitor pair has been assigned a first predetermined number of times to the input signal, and has also been assigned a second predetermined number of times to the reference signal.

Owner:MICROCHIP TECH INC

Rejection of power supply variations for gain error cancellation in pulse-width-modulated motor controllers

A positioning driver (32) for a voice coil motor (22) in a disk drive system (10) is disclosed. Pulse-width-modulated prestage drivers (46) are coupled to power transistors (50) arranged in an “H” bridge for driving the voice coil motor (22), biased with a power supply voltage (VM). The pulse-width-modulated prestage drivers (46) drive the power transistors (50) according to a comparison between an error signal from an error amplifier (36) and a ramp clock signal (RMP) generated by a ramp clock generator (46). The ramp clock generator (46) includes a control circuit (68) that modulates the high and low limits of the ramp clock signal (RMP) in response to variations in the power supply voltage (VM). This modulation of the high and low limits compensates for variations in the gain of the power transistors (50) resulting from variations in the power supply voltage (VM). The control circuit (68) may also modulate the slope of the ramp clock signal (RMP) according to variations in the power supply voltage (VM), for example to maintain a constant frequency.

Owner:TEXAS INSTR INC

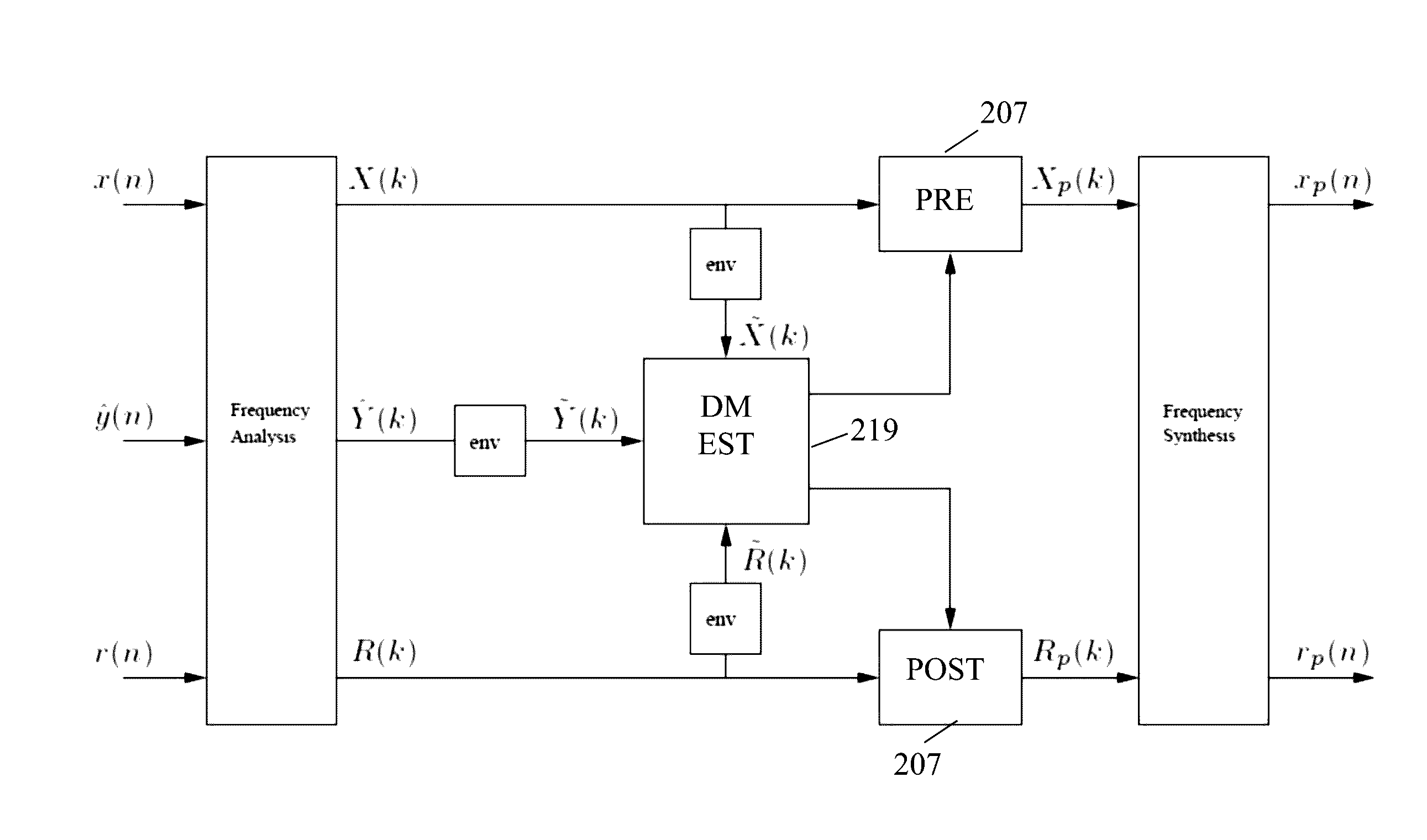

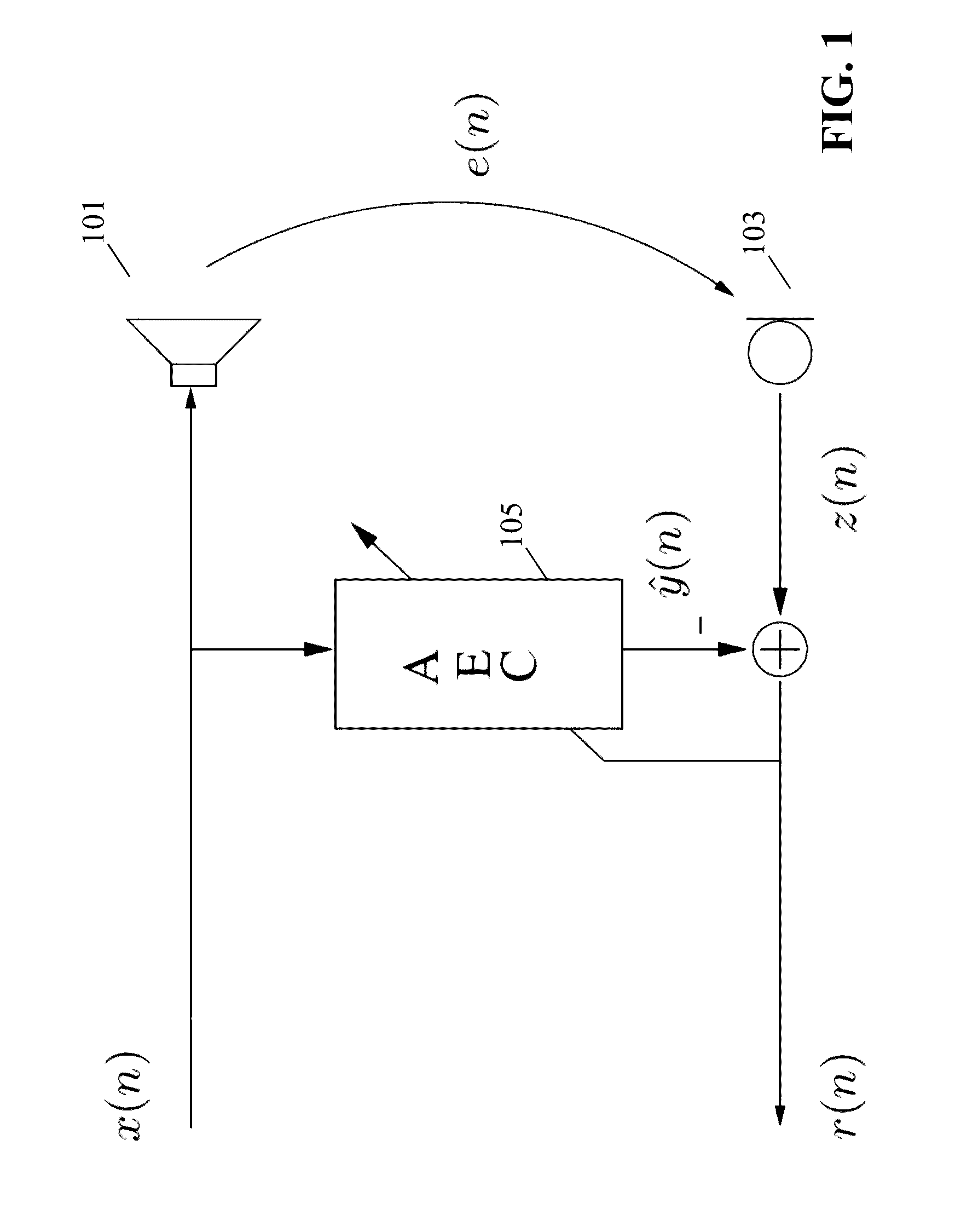

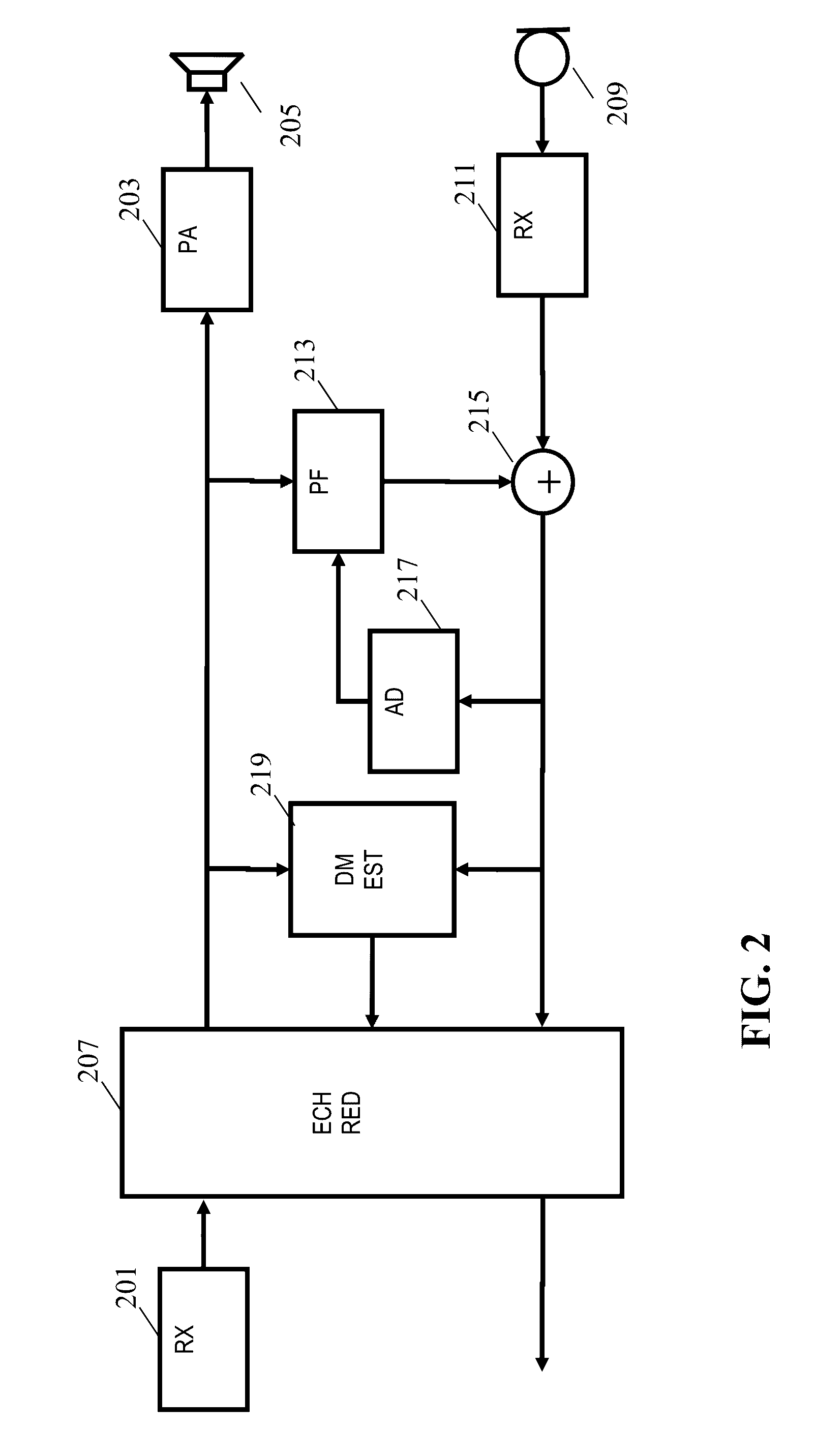

Echo cancellation

ActiveUS20160309042A1Easy to solveReducing and preventing non-linear effect of renderingTwo-way loud-speaking telephone systemsSound producing devicesSuppressorReducer

An audio echo suppressor comprises a first receiver (201) which receives a first audio signal for rendering by a loud-speaker (205) and a second receiver (211) which receives a microphone signal. A linear echo-cancellation filter (213) generates a first compensation signal from the first audio signal and a compensator (215) generates a residual signal by compensating the microphone signal for the first compensation signal. A first adapter (217) determines filter parameters for the linear echo-cancellation filter (213). An estimator (219) generates distortion measures where each distortion measure is indicative of the contribution to the residual signal in a frequency interval outside a first frequency interval. The residual signal results from rendering of signal components of the first audio signal that are within the first frequency interval. An echo reducer (207) then performs echo suppression based on the distortion measures. The approach may provide improved echo suppression, especially of non-linear echoes caused by non-linear effects.

Owner:SHENZHEN TCL CREATIVE CLOUD TECH CO LTD

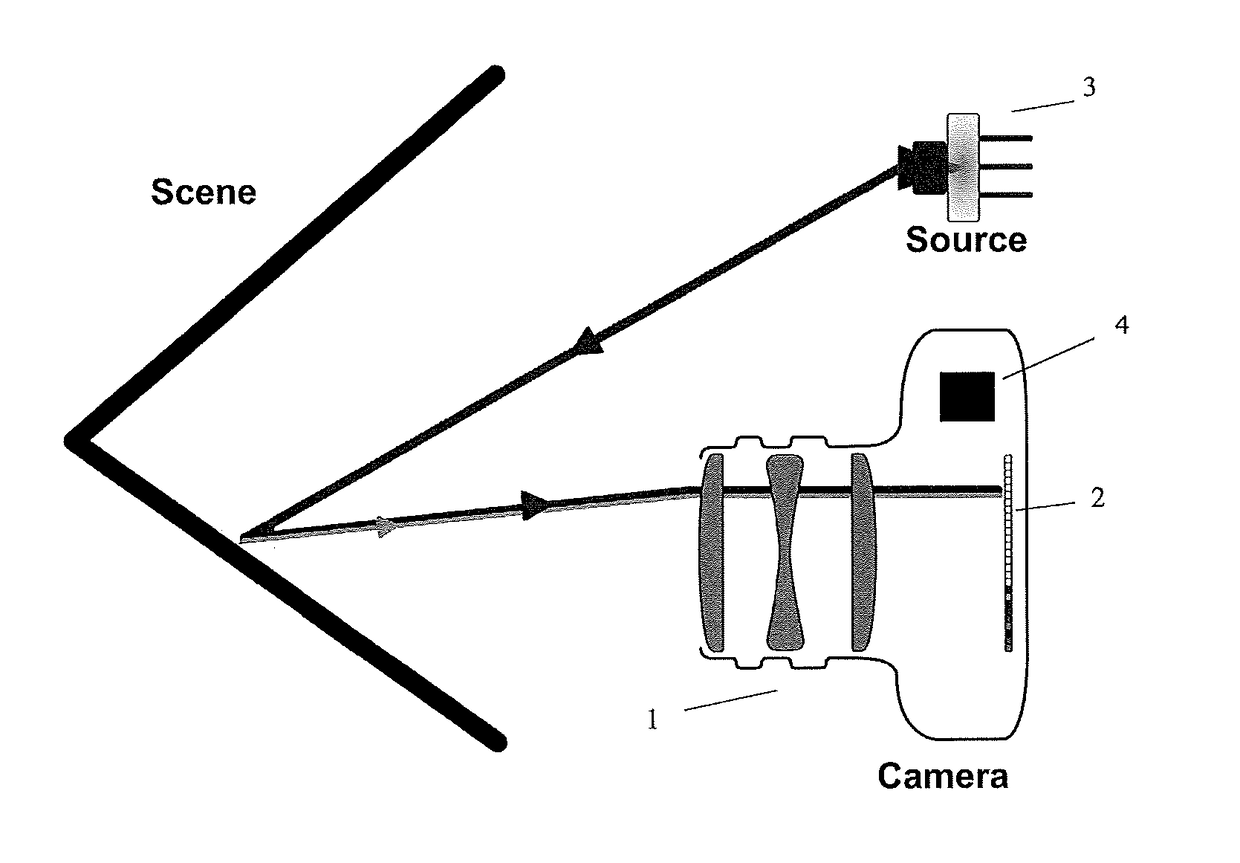

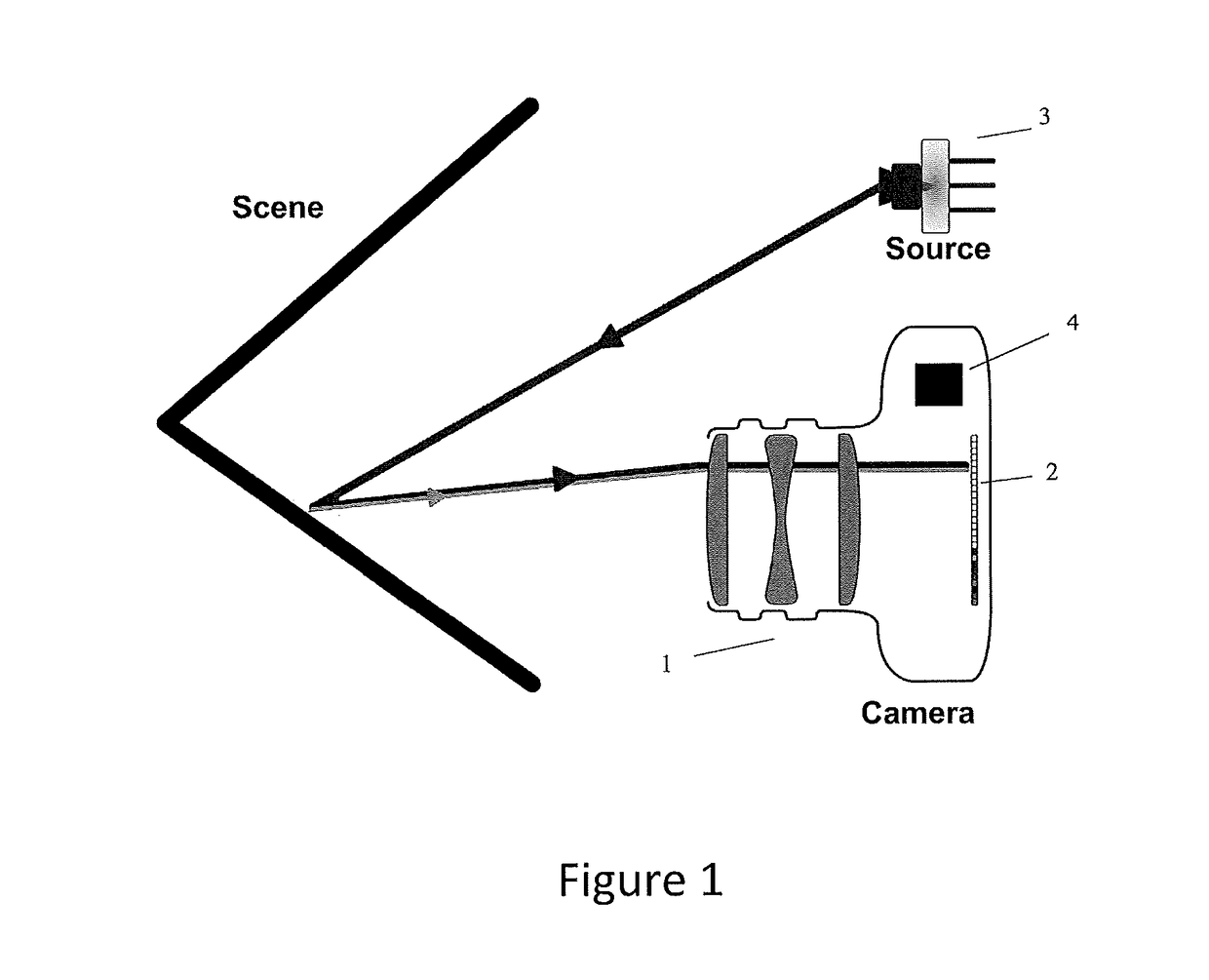

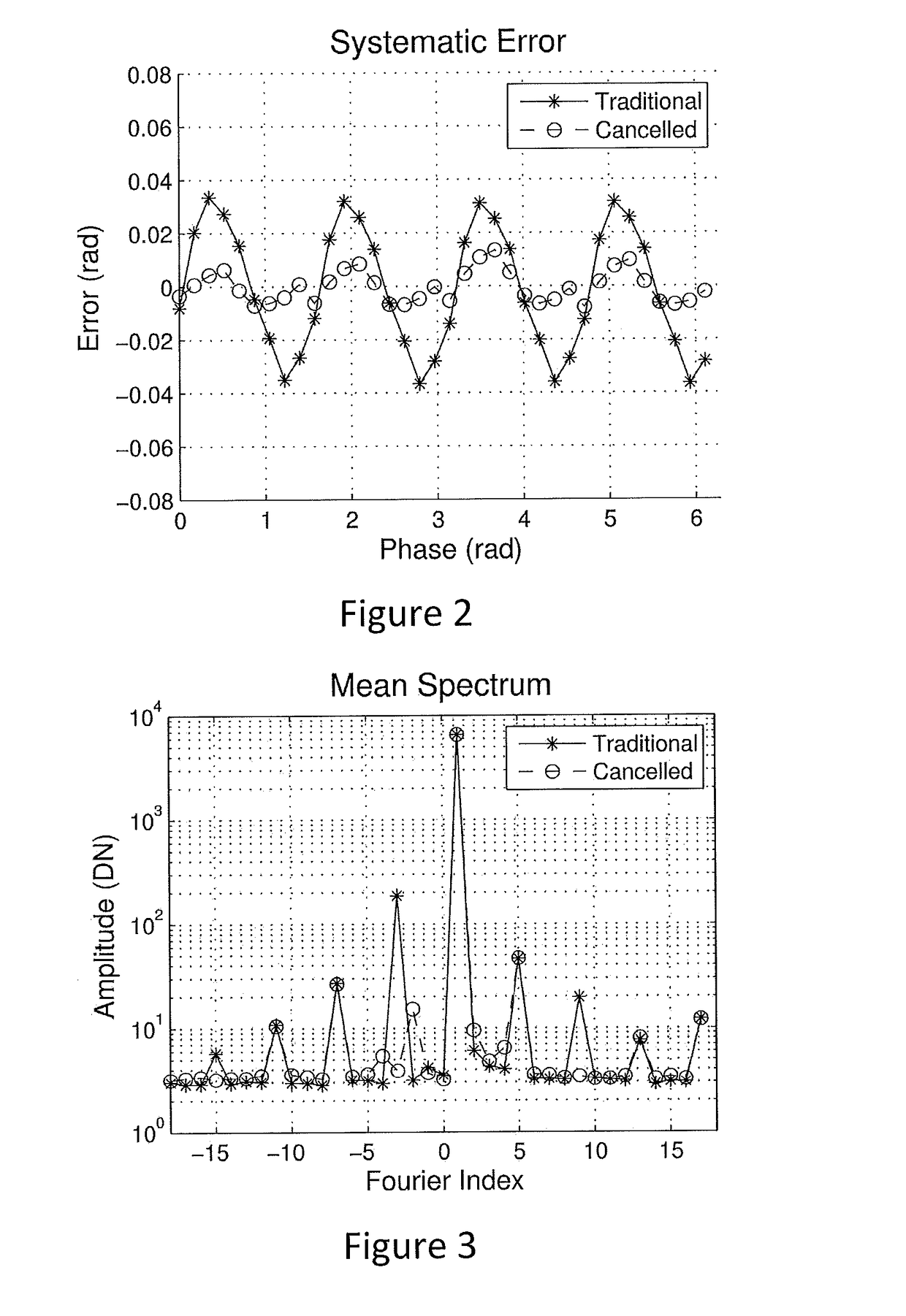

Signal harmonic error cancellation method and apparatus

In one aspect the invention provides a time of flight camera system which includes a time of flight transmitter arranged to transmit modulated radiation at a target, and a phase adjustment element configured to adjust the phase of a source modulation signal used to modulate the radiation transmitted at the target. This phase adjustment element provides a set of phase separated output signals, each output signal provided having one of a set phase offsets values applied, where at least one of these phase offset values is the cancellation phase value of another member of the set of phase offset values. The camera system also includes an image sensor modulated with the source modulation signal and configured to measure radiation reflected from a target, and a processor arranged to receive the image sensor measurements and being programmed to resolve range information from the measurements received by the image sensor.

Owner:CHRONOPTICS LTD

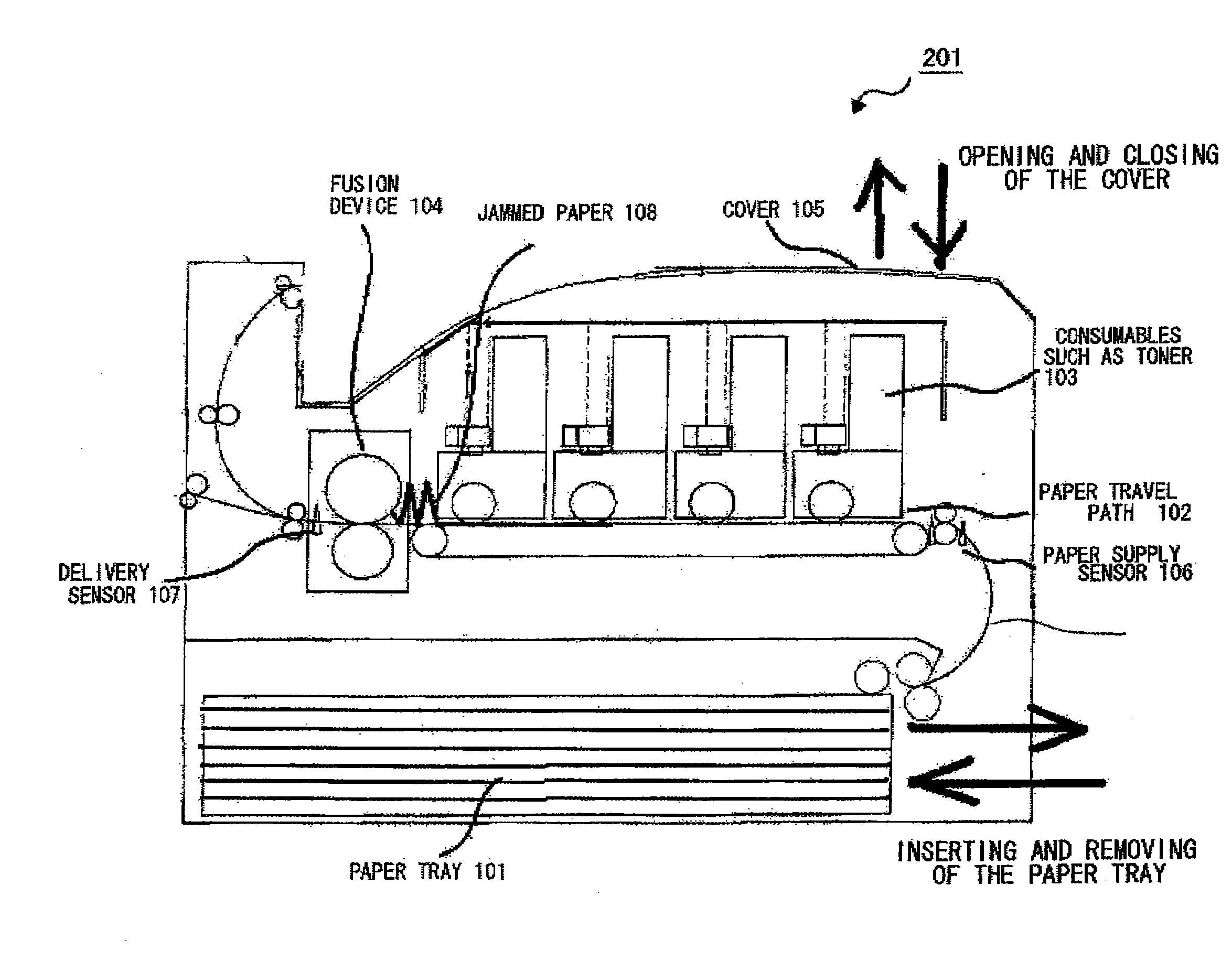

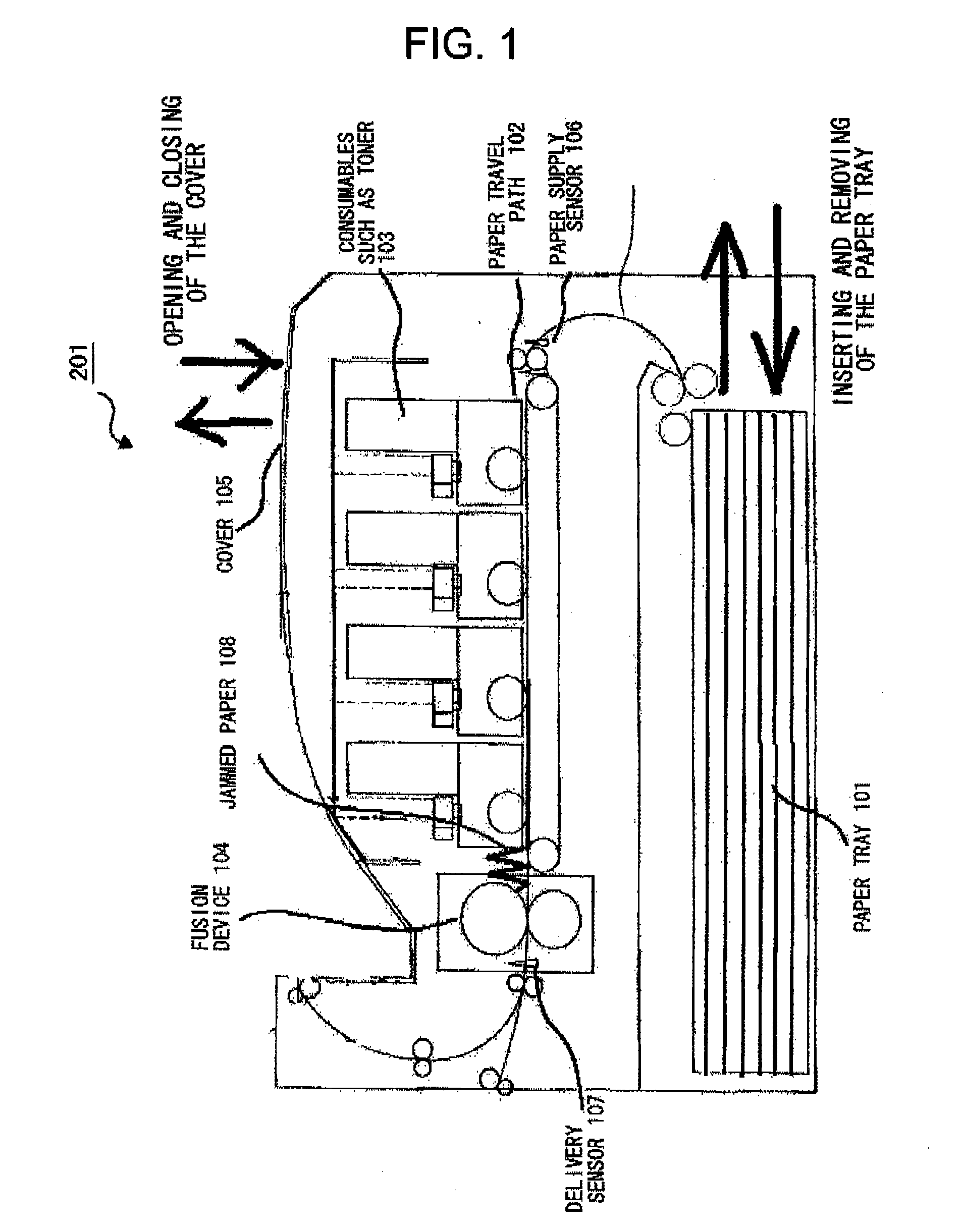

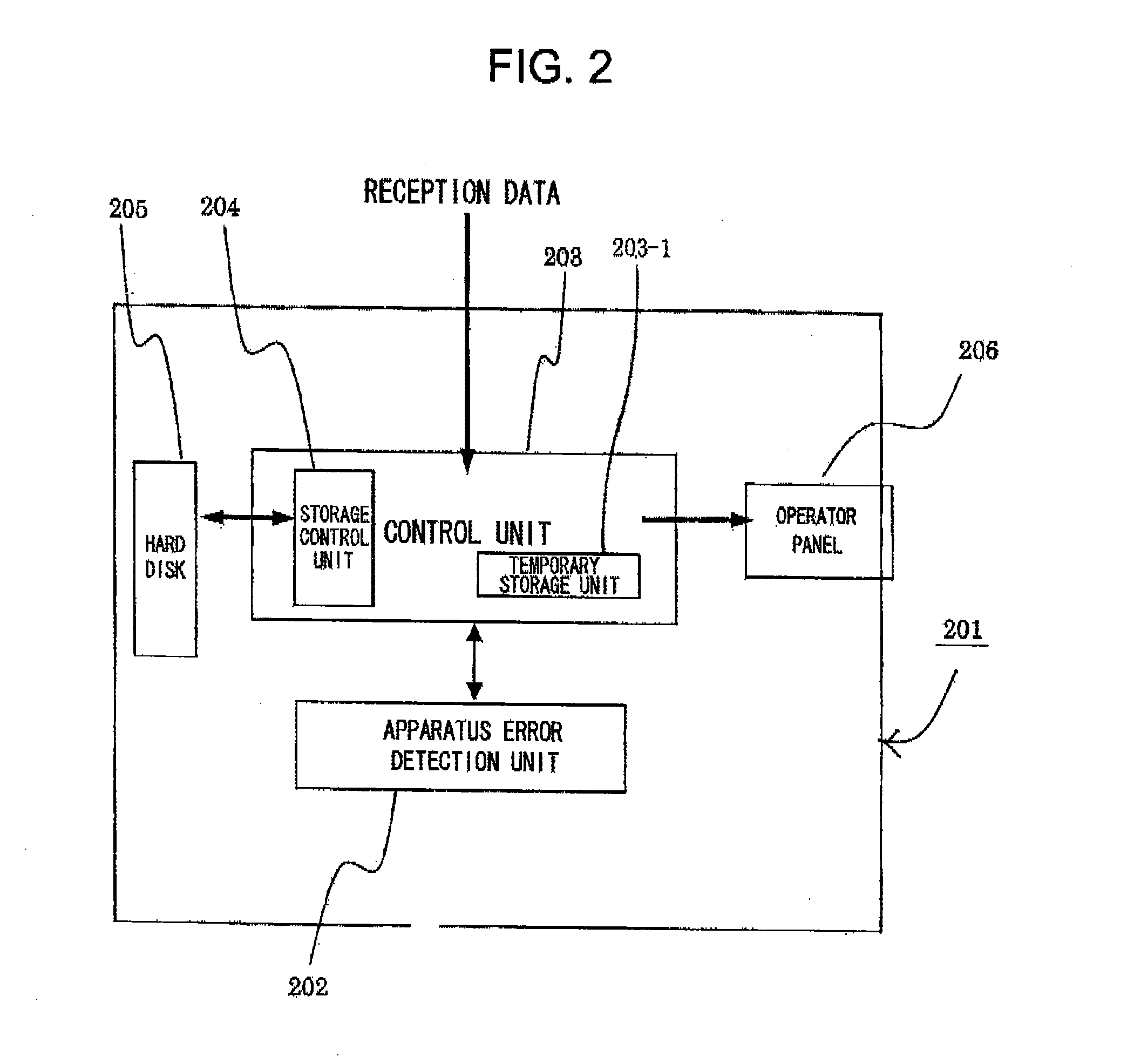

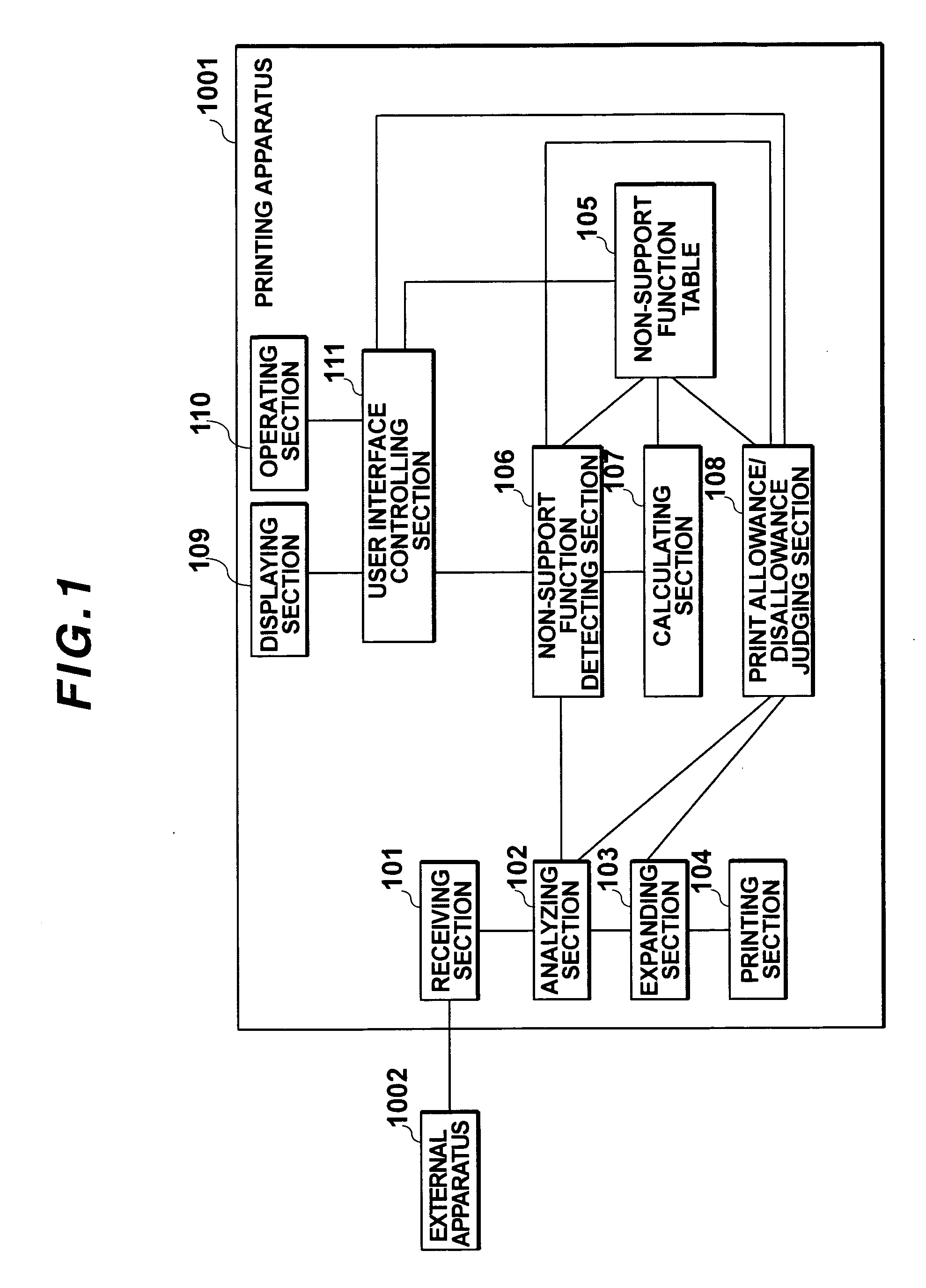

Image Forming Apparatus

InactiveUS20070067683A1Eliminate the effects ofRemove effect accessDigitally marking record carriersDigital computer detailsHard disc driveImage formation

To remove effects on the access of the hard disk drive apparatus (HDD), caused by the shock at a time where the user pulls out the paper tray, the image forming apparatus of the present invention includes an apparatus error detection unit for detecting the removal and occurrence of errors requiring the intervention of the user, an information storage unit for bringing the pickup unit near the rotating recording medium to record and reproduce information, and a memory control unit for stopping access to the information storage unit from a time where the error is detected by the apparatus error detection unit until a time where removal of the error is detected.

Owner:OKI DATA CORP

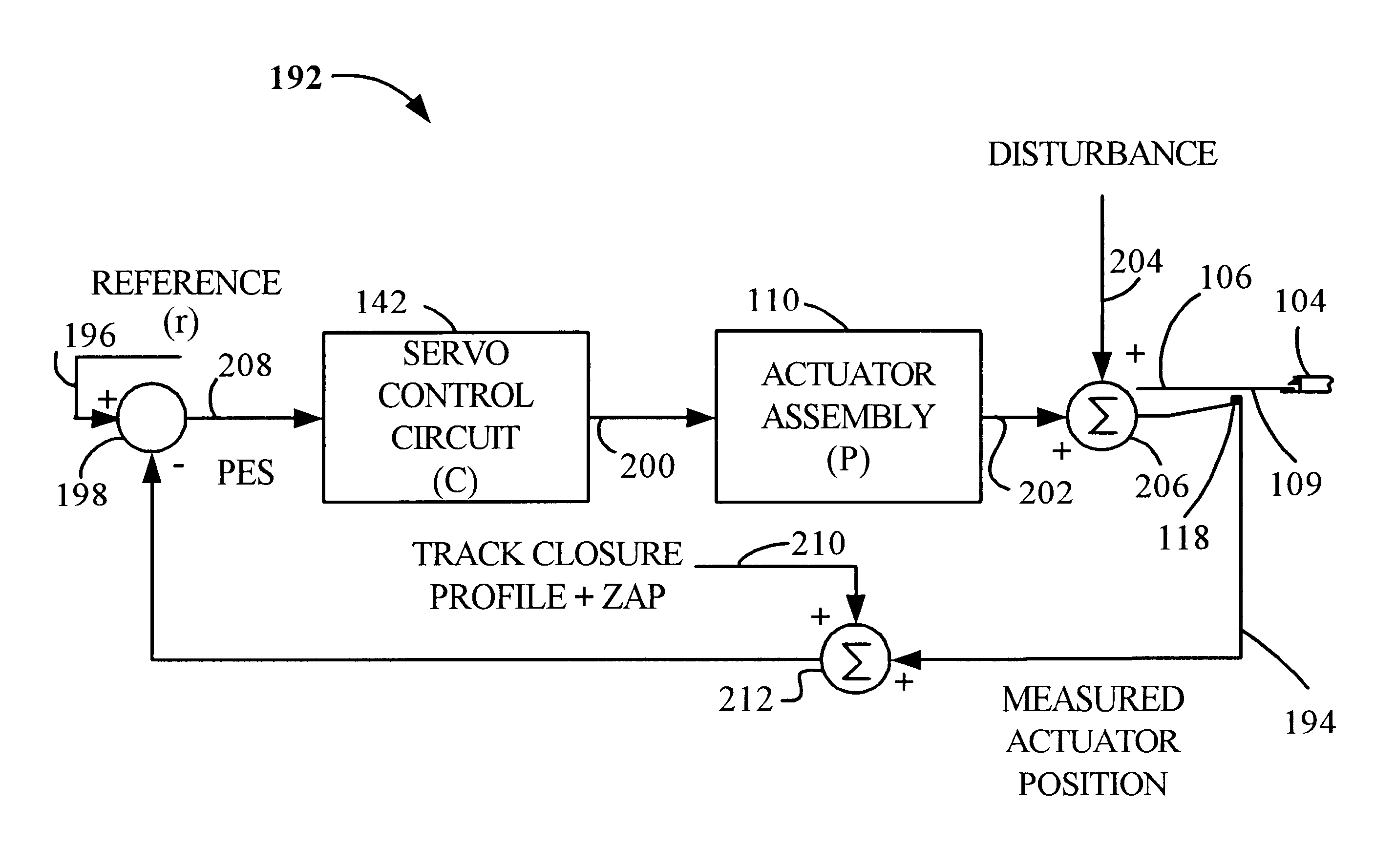

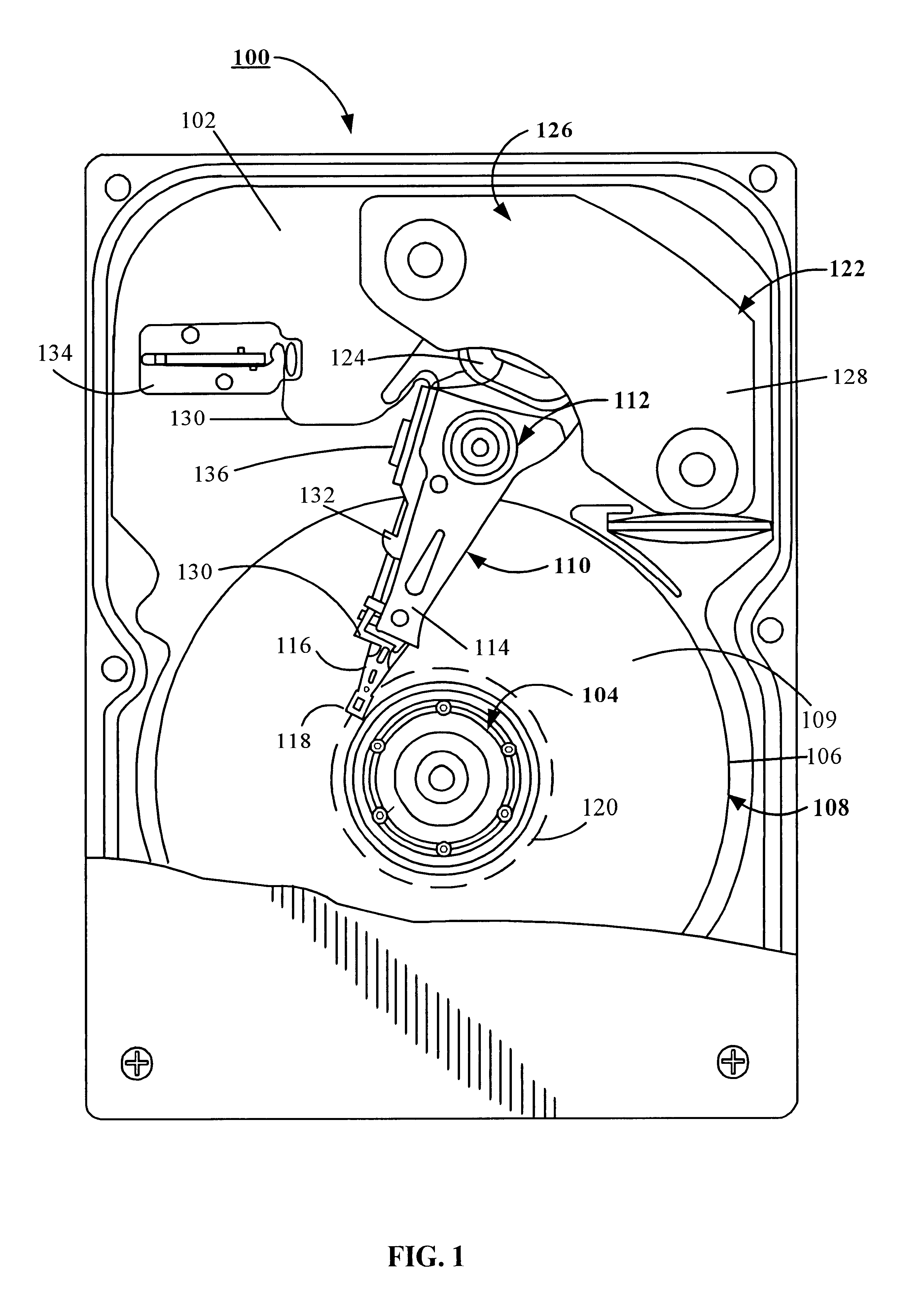

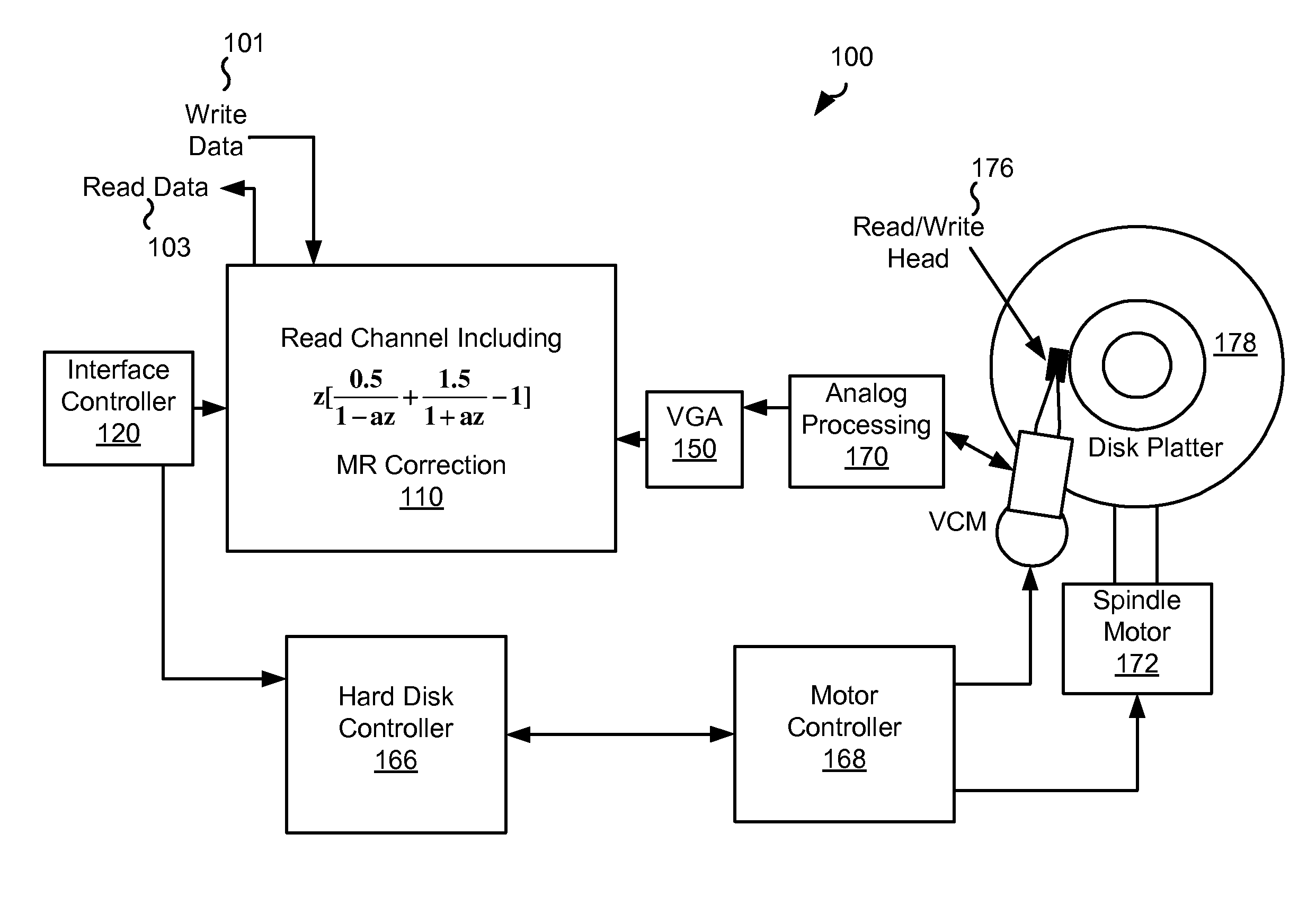

Track closure error cancellation for a disc drive

InactiveUS6882497B2Inaccurate trackingRecord information storageAlignment for track following on disksEngineeringControl circuit

Track closure errors written into servo sectors of an information track of a disc of a disc drive are resolved from a position control signal generated by a servo control circuit of a data storage device by steps comprising: determining a value for the track closure error from a position error signal, establishing a track closure profile based on the value of the track closure error, and injecting the track profile into the servo control circuit as a feed forward compensation input for the position error signal to resolve the track closure error from the position control signal.

Owner:SEAGATE TECH LLC

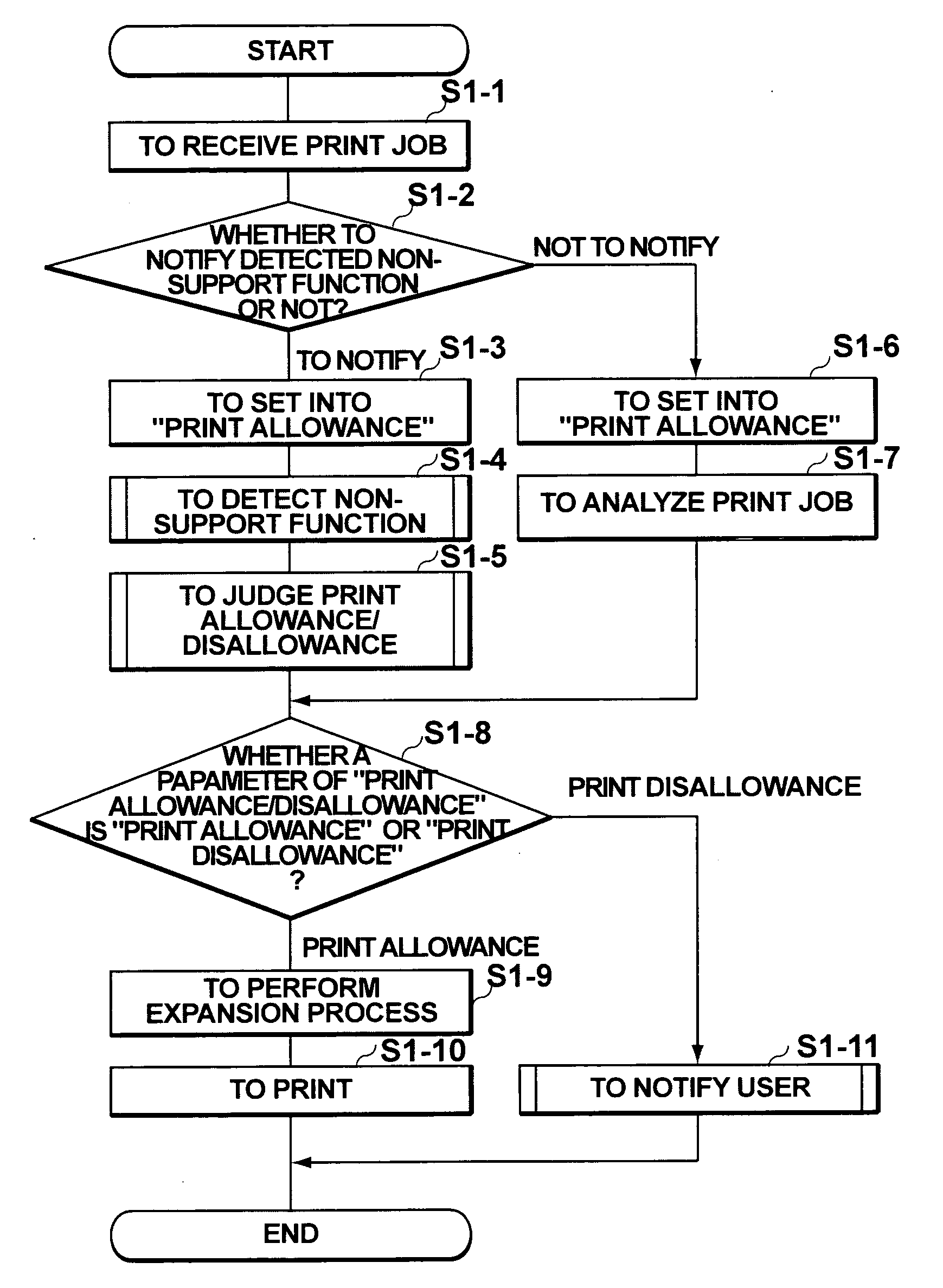

Printing apparatus

InactiveUS20080297826A1Visual presentationElectrographic process apparatusError cancellationComputer engineering

Owner:OKI DATA CORP

2-phase gain calibration and scaling scheme for switched capacitor sigma-delta modulator

ActiveCN102414989AAnalogue conversionPhysical parameters compensation/preventionError cancellationRotation cycle

A sigma-delta modulator may have a plurality of capacitor pairs, a plurality of switches to couple any pair of capacitors from the plurality of capacitor pairs selectively to an input signal or a reference signal, and a control unit operable to control sampling through the switches to perform a charge transfer in two phases wherein any pair of capacitors can be selected to be assigned to the input signal or the reference signal, and wherein after a plurality of charge transfers a gain error cancellation is performed by rotating the capacitor pairs cyclically such that after a rotation cycle, each capacitor pair has been assigned a first predetermined number of times to the input signal, and has also been assigned a second predetermined number of times to the reference signal.

Owner:MICROCHIP TECH INC

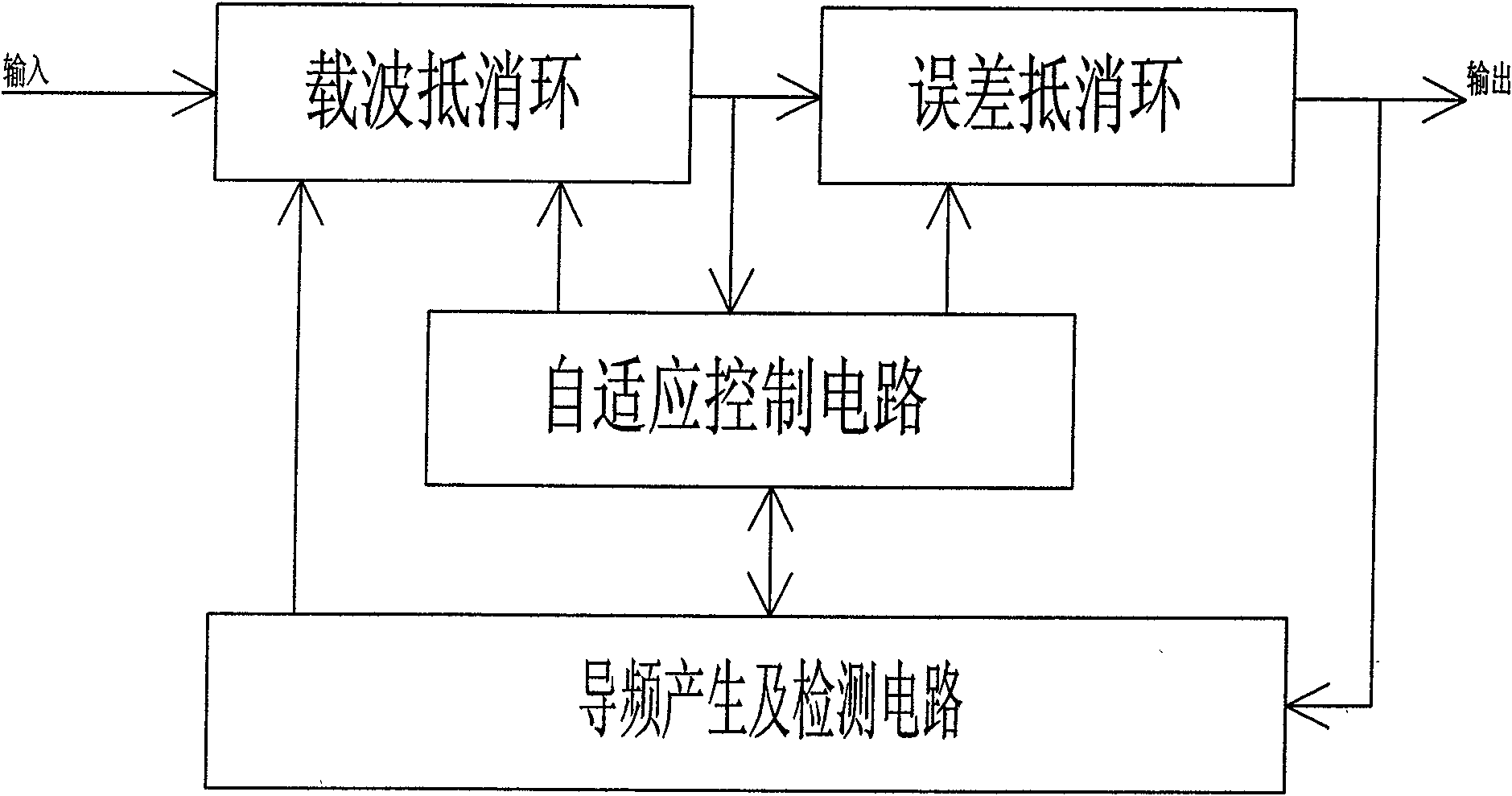

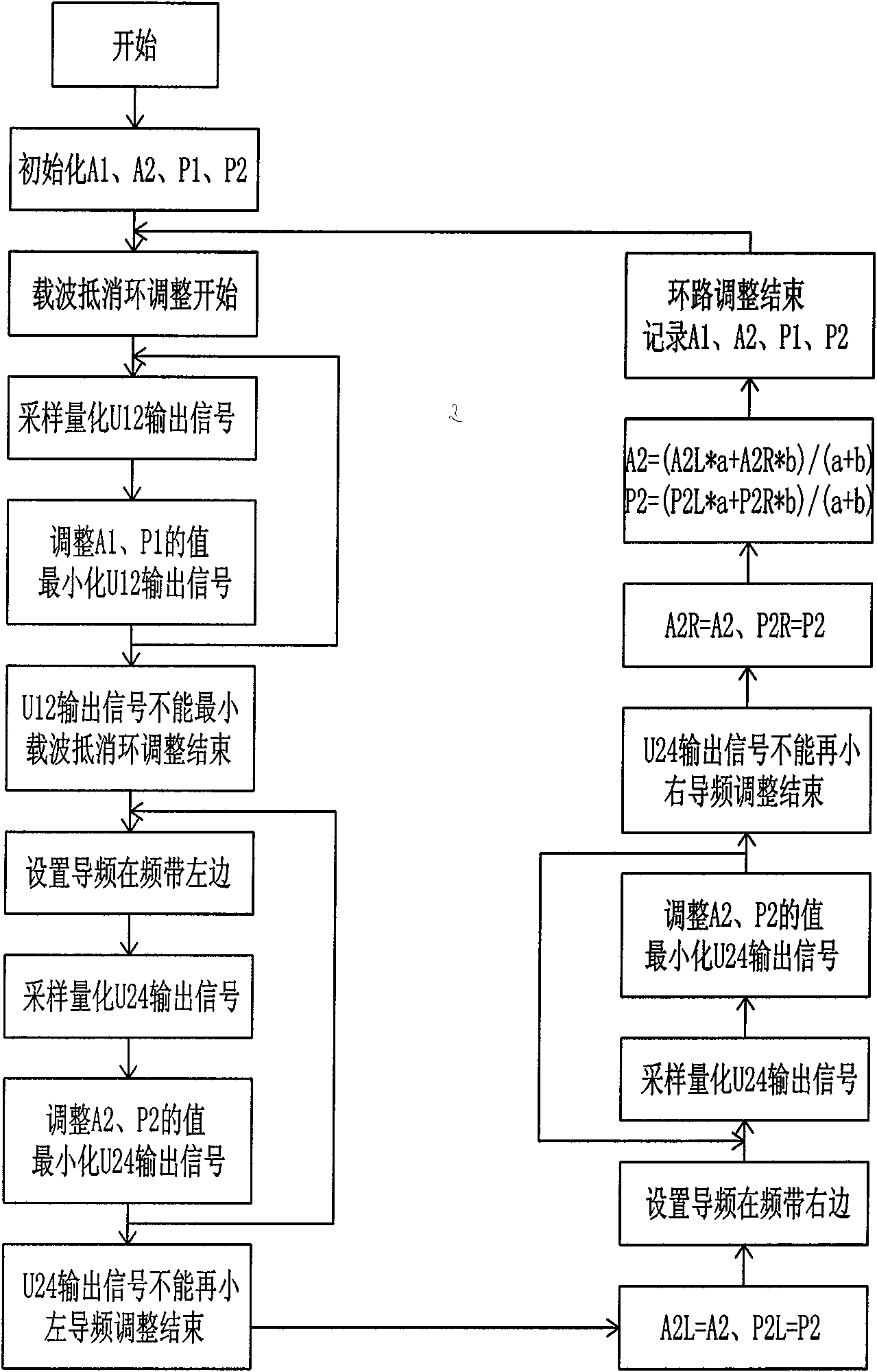

Self-adaptive feedforward linear power amplifier device based on pilot frequency and control method

InactiveCN101572528AImprove linearityImprove efficiencyAmplifier modifications to reduce non-linear distortionHigh frequency amplifiersLinear power amplifierCarrier signal

The invention relates to a self-adaptive feedforward linear power amplifier device based on pilot frequency and a control method. The device comprises a carrier cancellation ring, an error cancellation ring, a pilot frequency generation and detection circuit and a self-adaptive control circuit; the carrier cancellation ring is used for extracting error signals generated by active power amplification; the pilot frequency generation and detection circuit and the self-adaptive control circuit are used for monitoring amplitude phase matching in two loop circuits and adjusting the amplitude and the phase by the control method in a self-adaptive mode so as to lead the cancellation effect of the loop circuit to be the best. The invention has the beneficial effects that the self-adaptive feedforward linear power amplifier device based on pilot frequency and the control method have compact structure, simple method, simple and effective control method, and greatly improves the linearity and efficiency of a radio-frequency power amplifier. By injecting cancellation degree of error signals to the output end of a pilot frequency signal monitoring device, the invention adjusts the amplitude phase matching of the carrier cancellation ring and the error cancellation ring in a self-adaptive mode and improves the stability and reliability of the radio-frequency power amplifier.

Owner:SUNWAVE COMM

Receiver circuits with feedforward signal path

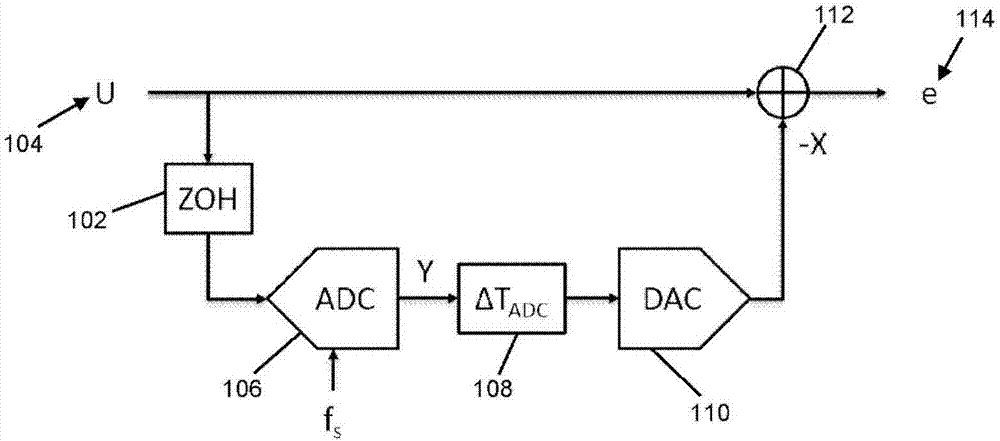

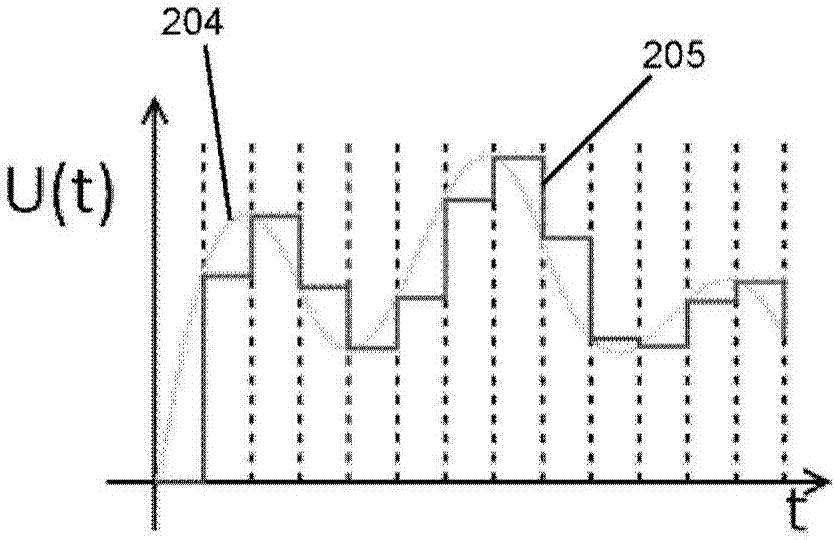

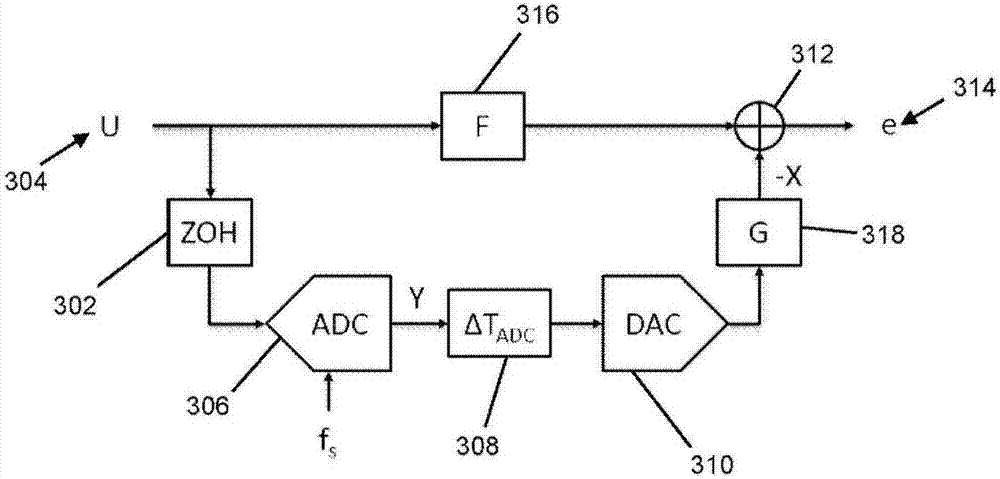

ActiveCN107342781AAnalogue/digital/analogue conversionLine-faulsts/interference reductionAnalog signalError cancellation

A receiver circuit comprising: an input terminal configured to receive an input-signal; a feedforward-ADC configured to provide a feedforward-digital-signal based on the input-signal; a feedforward-DAC configured to provide a feedforward-analogue-signal based on the feedforward-digital-signal; a feedforward-subtractor configured to provide an error-signal based on the difference between the feedforward-analogue-signal and the input-signal; an error-LNA configured to provide an amplified-error-signal based on the error-signal; an error-ADC configured to provide a digital-amplified-error-signal based on the amplified-error-signal; a mixer configured to down-convert a signal in a signal path between the input terminal and the error-ADC; and an error-cancellation-block configured to provide an error-cancelled-signal based on a difference between the digital-amplified-error-signal and the feedforward-digital-signal.

Owner:NXP BV

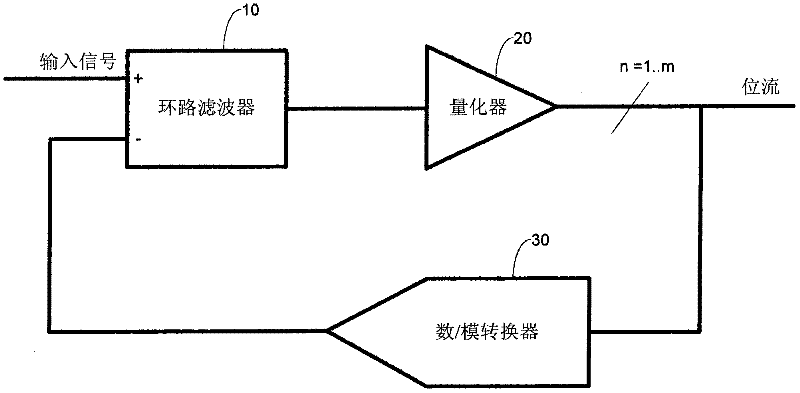

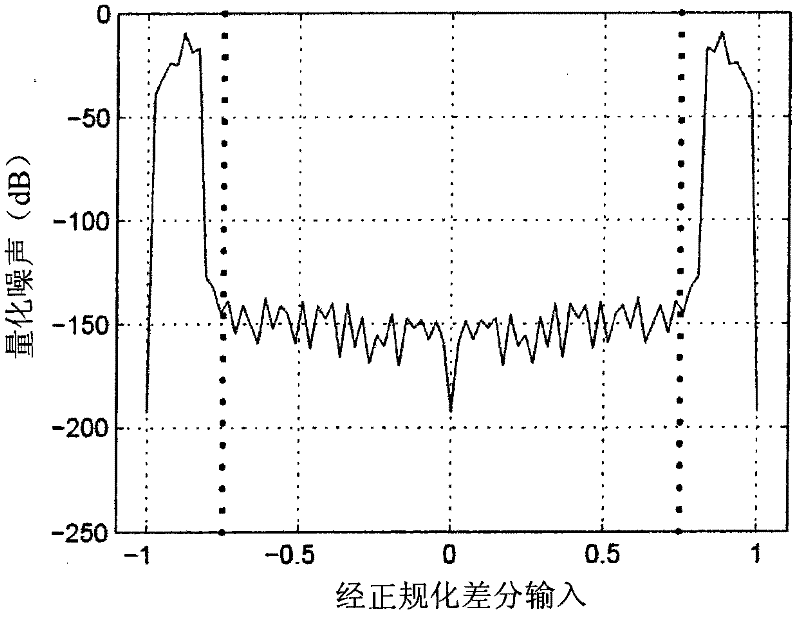

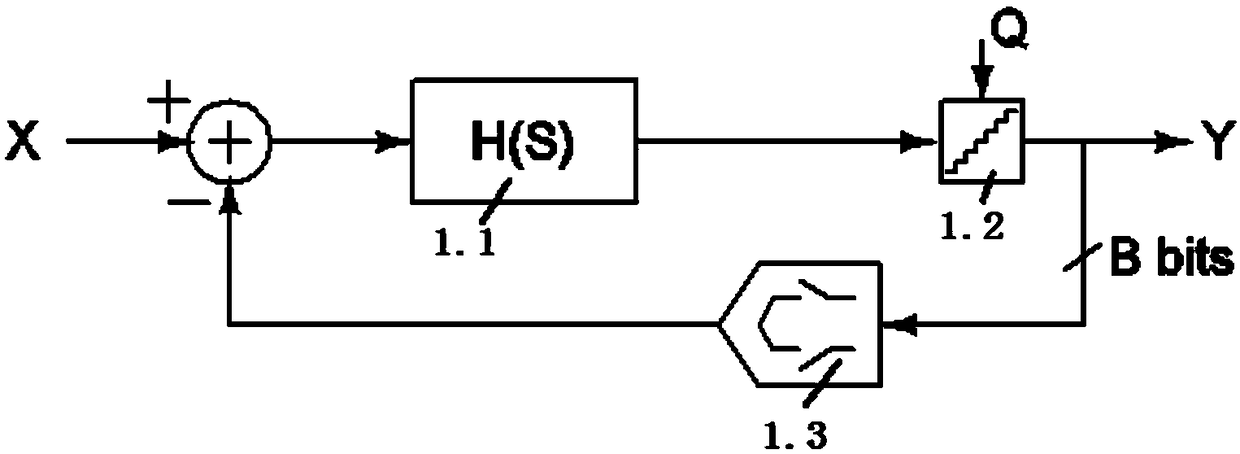

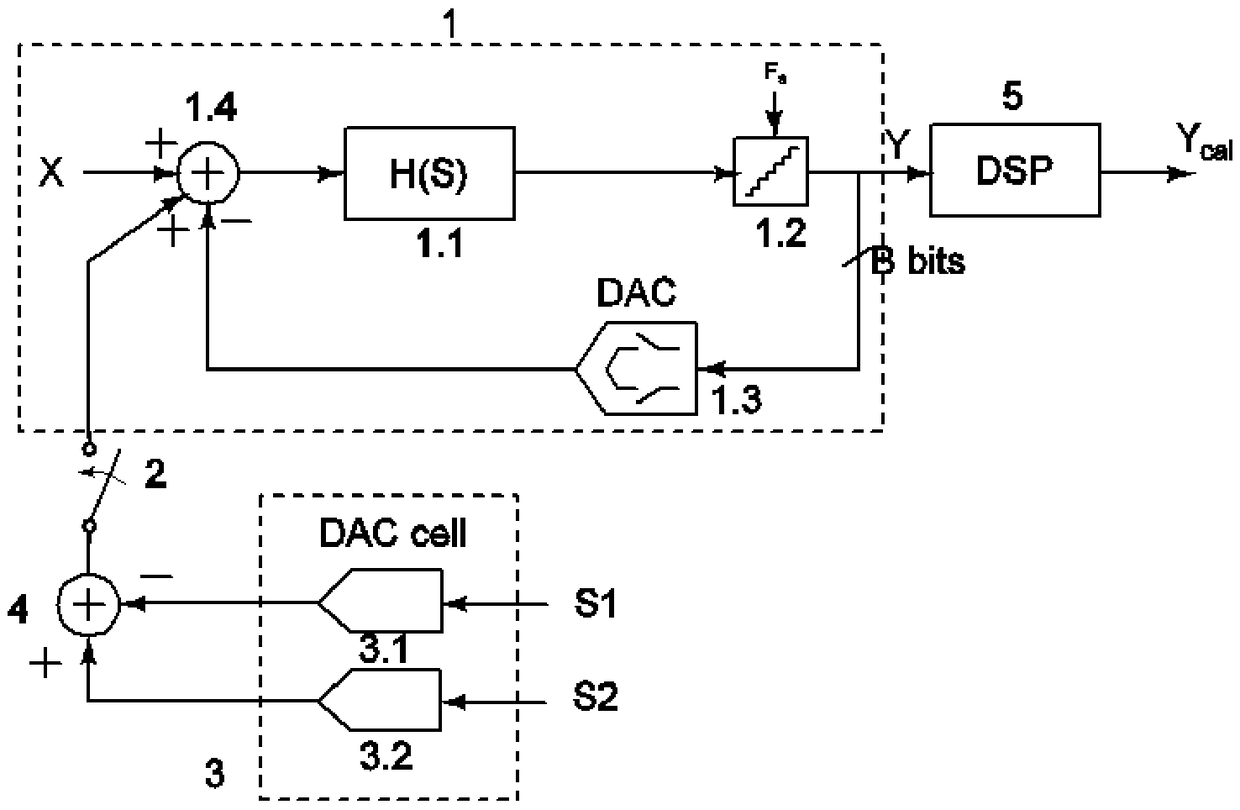

Oversampling analog-to-digital converter and dynamic error calibration method for feedback digital-to-analog converter thereof

ActiveCN108900195AEliminate dynamic errorsImprove performanceAnalogue/digital conversion calibration/testingDigital analog converterDigital down converter

The invention provides a continuous oversampling analog-to-digital converter and a digital calibration method for dynamic errors in a feedback analog-to-digital converter. The calibration method belongs to front desk calibration and includes the steps: firstly, setting the analog input of the analog-to-digital converter to zero in a dynamic error detection mode, connecting an additional calibration DAC unit group, adding a fixed digital signal to measure the dynamic errors of the feedback digital-to-analog converter in the analog-to-digital converter at the same time, and outputting and savingthe dynamic errors in a digital form; then disconnecting an additional calibration DAC unit group in a dynamic error cancellation mode, normally connecting the analog-to-digital converter to analog input, and subtracting the saved dynamic errors under a dynamic error detection mode from the converted digital output, to obtain the calibrated digital output without dynamic errors. The dynamic errors of the oversampling analog-to-digital converter can be effectively eliminated, by adding simple hardware cost and operation, to greatly improve the performance thereof, and the digital calibration method for dynamic errors is suitable for the continuous oversampling analog-to-digital converters with various performance indexes.

Owner:SHENZHEN GRADUATE SCHOOL TSINGHUA UNIV

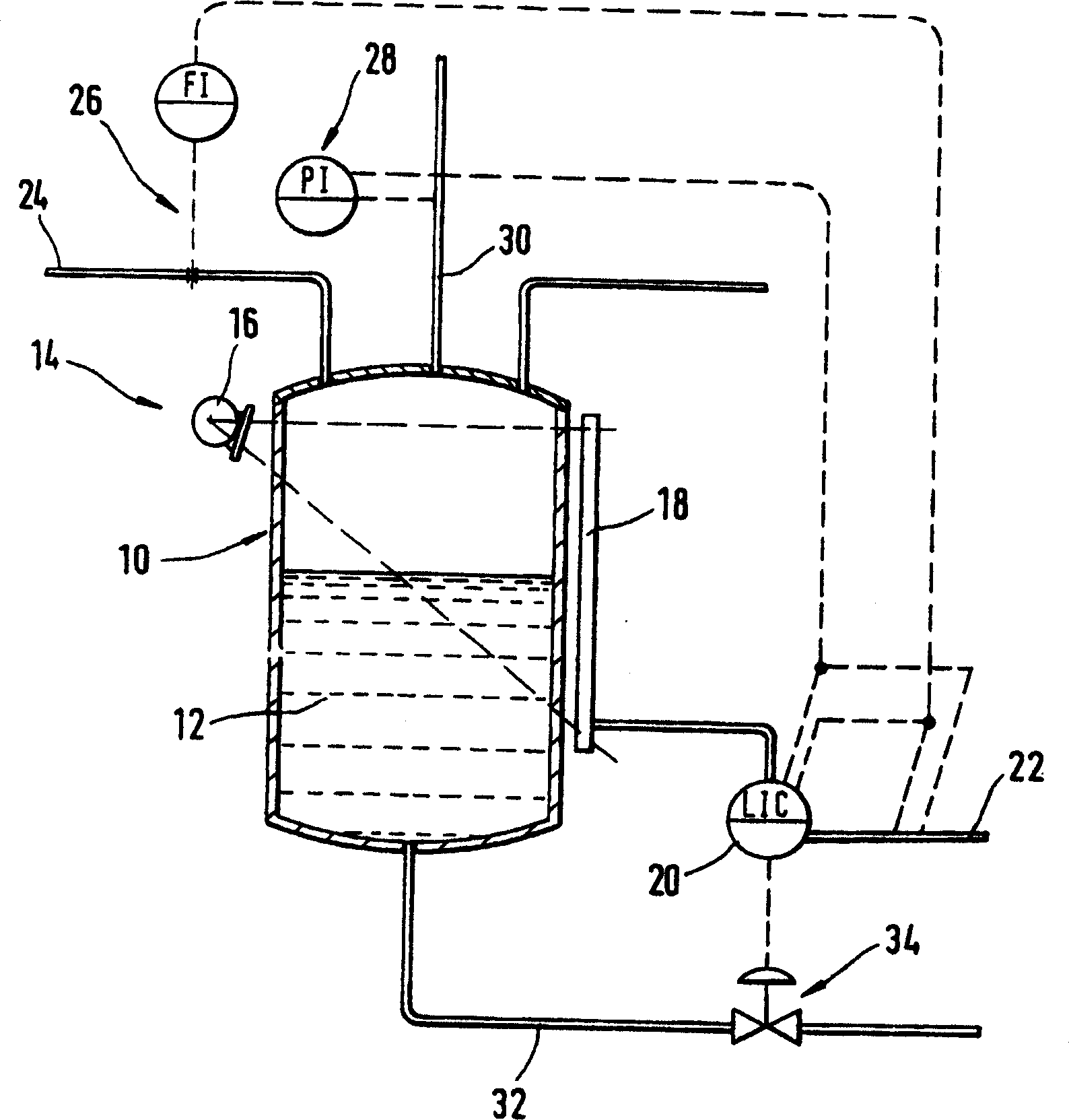

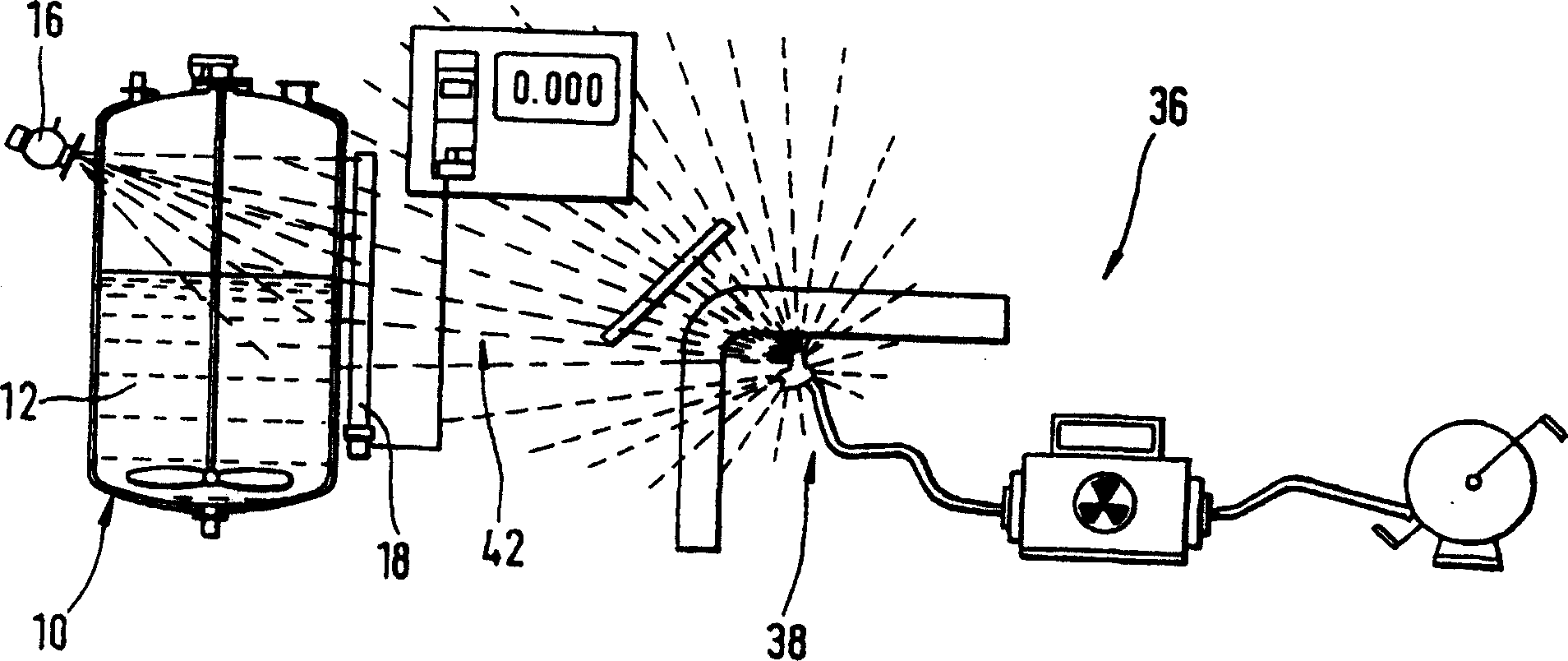

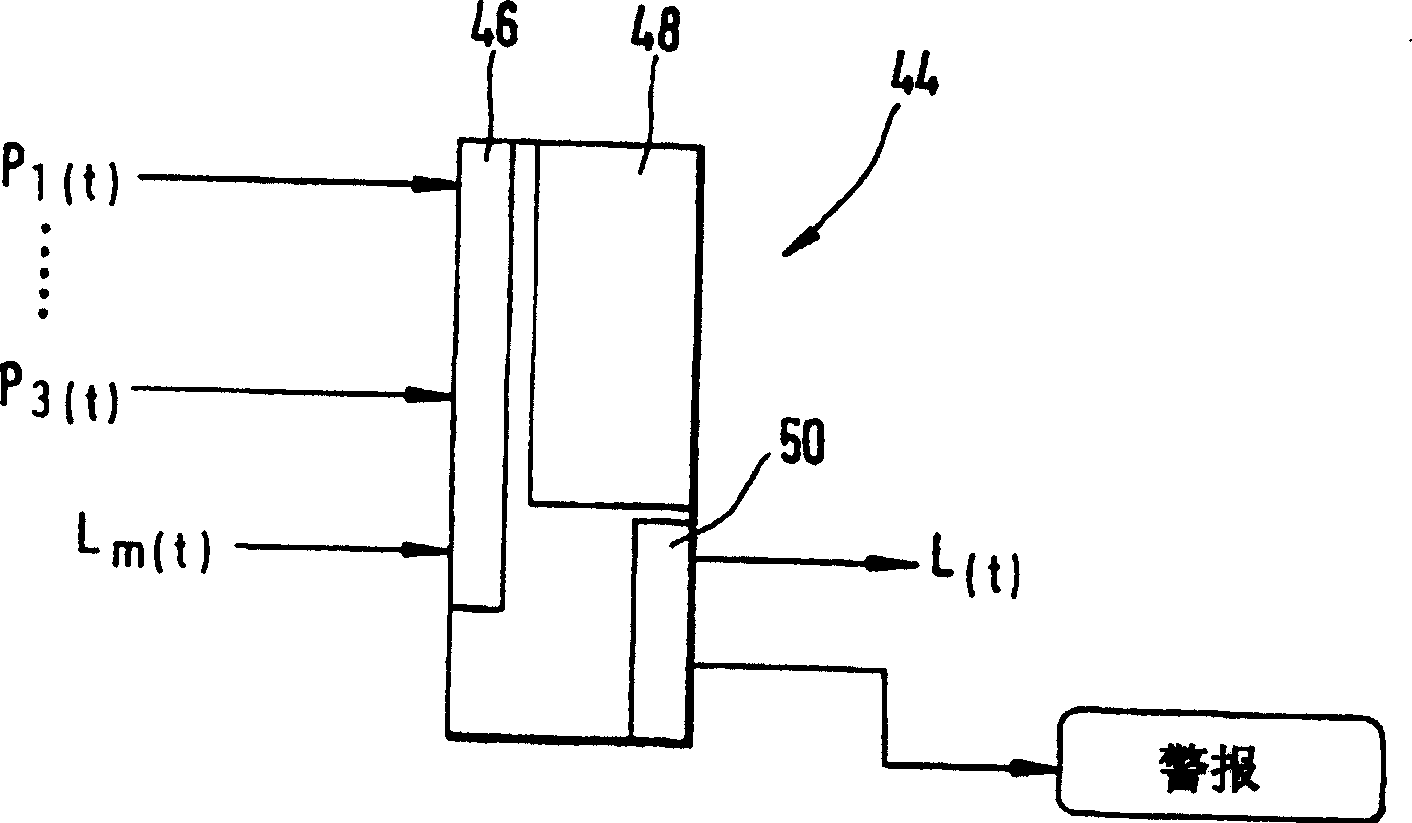

Methods and devices for erasing errors and compensating interference signals caused by gammagraphy in radiometric measuring systems

Owner:EHNDRESS KHAUZER GMBKH KO KG

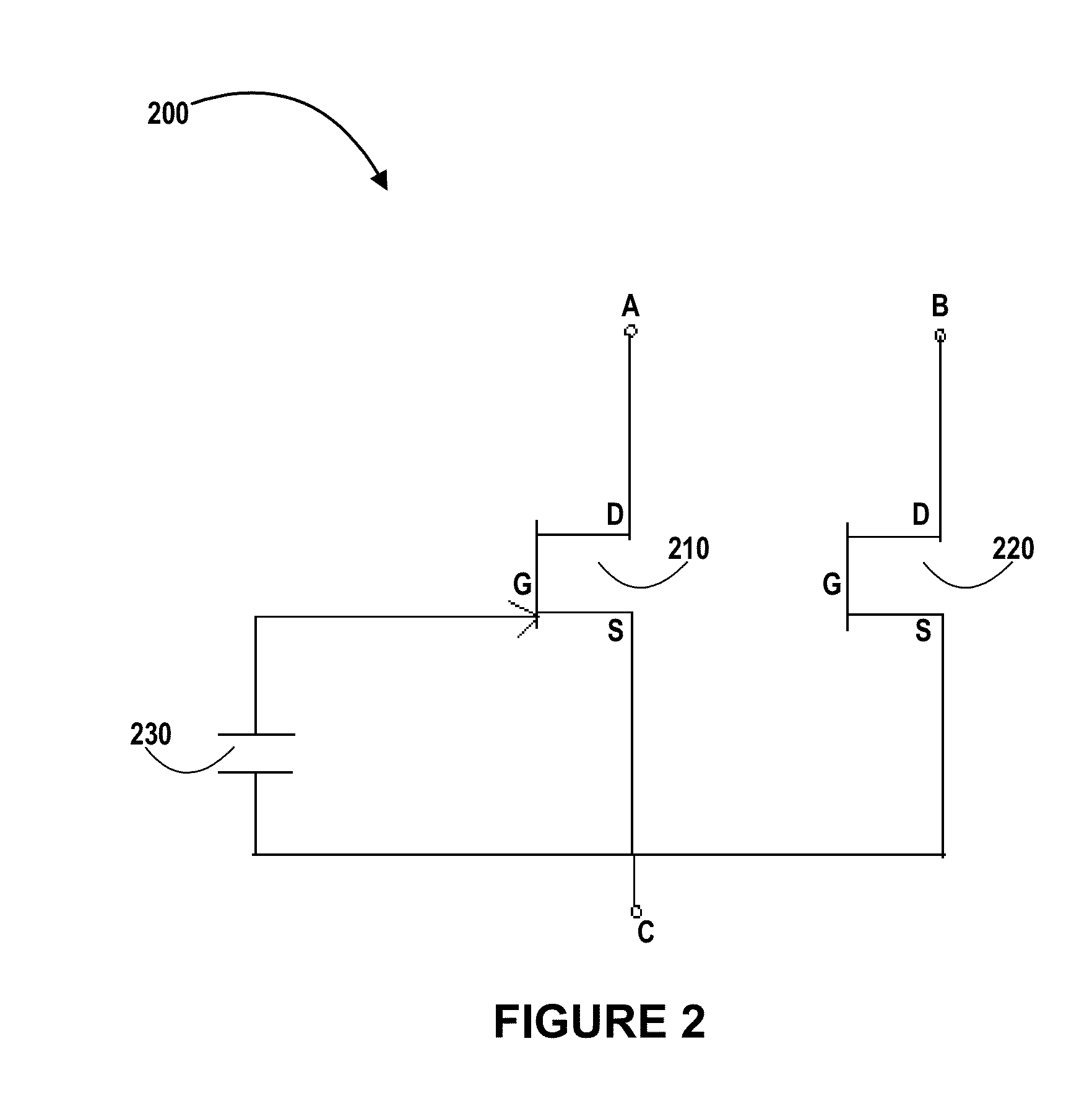

Echo cancellation

InactiveUS20130230183A1Weakening rangeIncreases magnitudeLow frequency amplifiersAudio amplifierCapacitanceReverse bias

The invention is directed to echo cancellation for a microphone system. An exemplary microphone system comprises a first transistor, wherein a gate terminal of the first transistor is connected to a ground terminal via a microphone electret element, the microphone electret element being associated with a capacitance and a voltage, the microphone electret element reverse biasing the first transistor; and a second transistor in parallel with the first transistor, wherein a gate terminal of the second transistor is connected to the ground terminal via a capacitor, the capacitance of the capacitor being selected to suppress at least a portion of a common mode signal, and wherein the gate terminal of the second transistor is not connected to the microphone electret element. The common mode signal comprises the echo, which may be the output of a speaker system that is received as input to the microphone system.

Owner:SONY MOBILE COMM INC

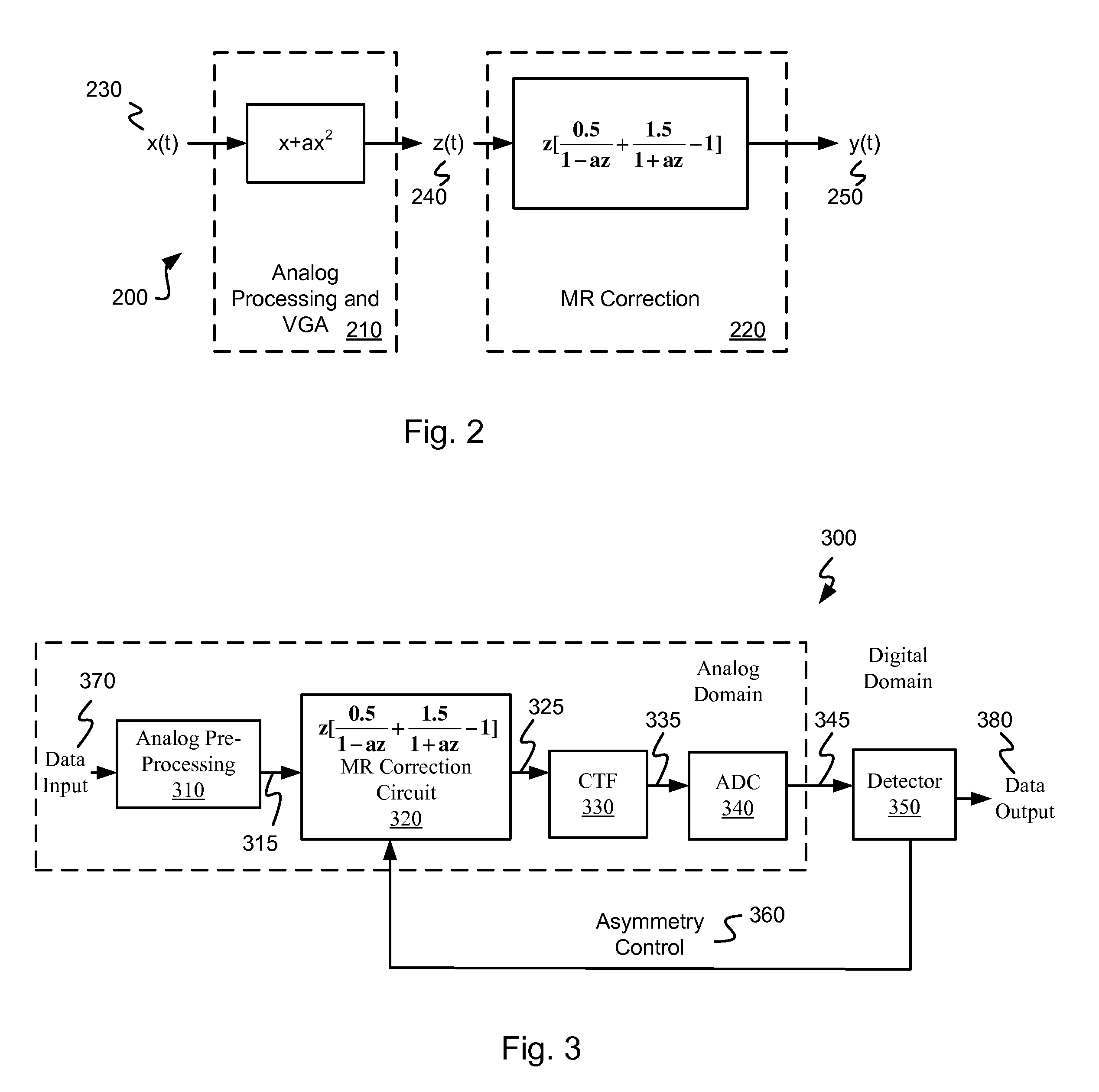

Systems and methods for high order asymmetry correction

Various embodiments of the present invention provide systems and methods for signal offset cancellation. For example, a method for error cancellation is disclosed. The method includes: receiving an input signal that includes a second order error component; applying a transfer function to the processed input to reduce the second order error component; and providing an output signal that is the result of applying the transfer function to the input signal.

Owner:AVAGO TECH INT SALES PTE LTD

Low latency multi-detector noise cancellation

ActiveUS8862972B2Reduce distractionsData representation error detection/correctionCode conversionDetector circuitsLatency (engineering)

Various embodiments of the present invention provide systems and methods for data processing. For example, a data processing circuit is disclosed that includes first and second data detectors and an error cancellation circuit. The first data detector is operable to perform a data detection process on a first signal derived from a data input to yield a detected output. The second data detector circuit is operable to perform a data detection process on a second signal derived from the data input to yield a second detected output. The error cancellation circuit is operable to combine a first error signal derived from the detected output with a second error signal derived from the second detected output to yield a feedback signal. The feedback signal is operable to modify the data input during a subsequent period.

Owner:AVAGO TECH INT SALES PTE LTD

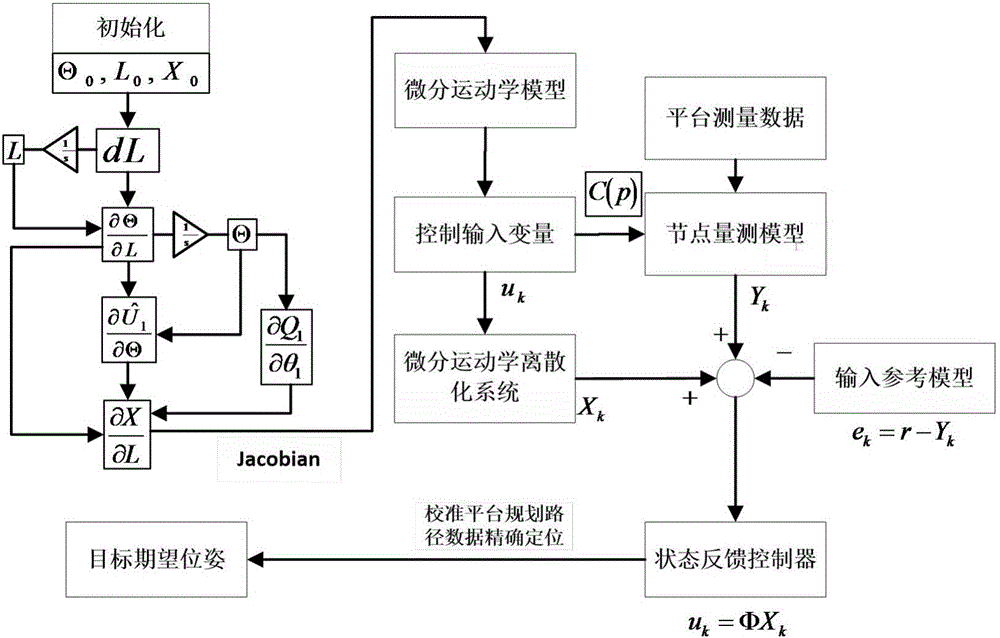

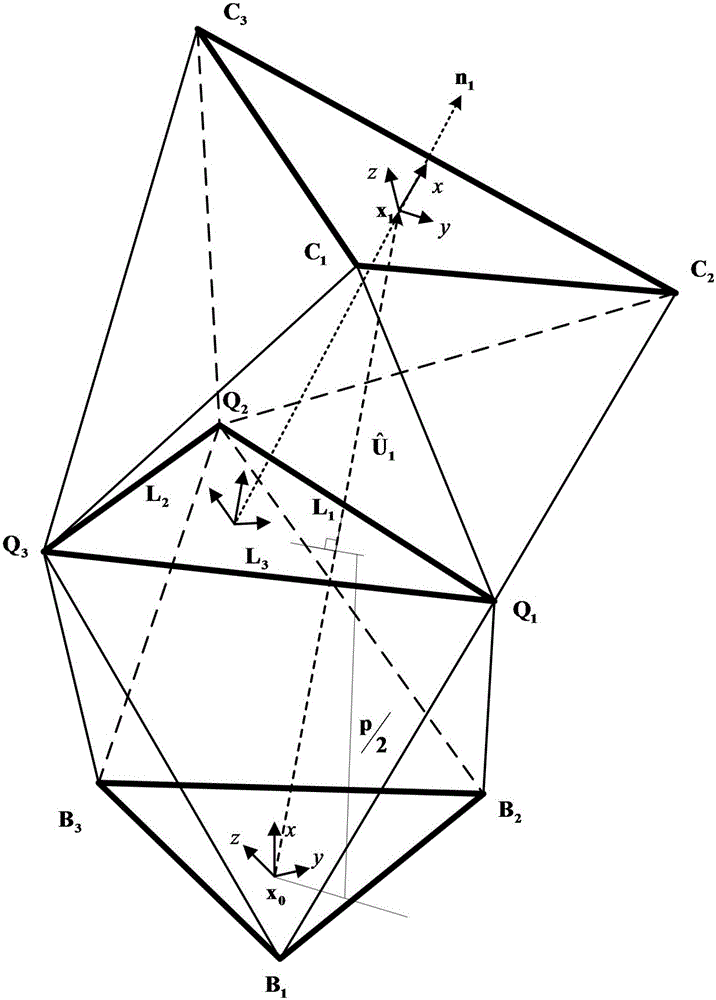

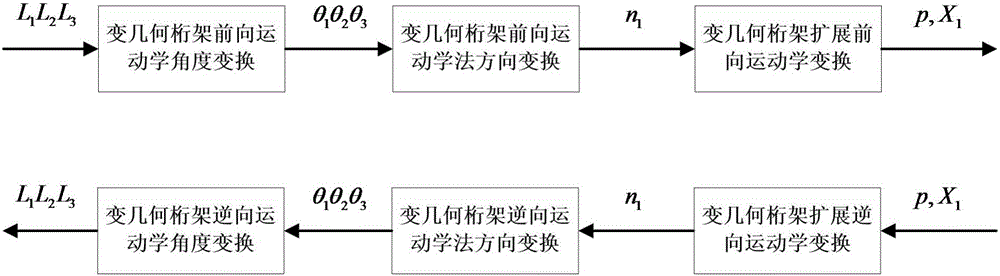

Variable geometry truss modeling positioning method

ActiveCN106055818AAchieve precise positioningRealize identificationGeometric CADSpecial data processing applicationsKinematicsMeasurement device

The invention discloses a model positioning method based on variable geometry truss differential kinematics. The method comprises the following steps: 1, initializing parameters, namely, theta0, L0 and X0 in a range of an operating space; 2, designing a length differential variable dL of a driving lever; 3, acquiring a differential mapping expression (as shown in the description) according to a constraint equation of a variable geometry truss structure; 4, calculating a differential affine (as shown in the description) depending on an angle, and obtaining an affine (as shown in the description) related to a node Q in a similar way; 5, determining a differential mapping (as shown in the description) in the center of a tail end of a structure according to a differential chain rule; 6, extracting a Jacobian matrix of a closing speed, establishing a differential kinematics equation of the variable geometry truss structure, and performing discretization on a differential kinematics system of the structure; 7, performing node measuring process tracking with reference to data provided by a measuring device of a mechanical arm platform, and obtaining a measurement module of the variable geometry truss structure; and 8, setting a clearance error function and integrating a differential module and the measurement module of the structure to achieve precise positioning of target expected pose error cancellation.

Owner:SHANGHAI JIAO TONG UNIV

DAC current source matrix patterns with gradient error cancellation

First order gradient errors are canceled with no current source splitting by placing consecutive current sources symmetrically around the center of the array. Consecutive elements that correspond to small input amplitudes (mid-scale codes) make a smaller spatial jump than those correspond to larger signal amplitudes. Both linear and second order gradients are reduced by splitting each current cell into two and placing sub-elements symmetrically with respect to the center of the array to address the linear gradient effect. To address second order gradients, current element placement follows a pattern such that consecutive element pairs are chosen with one of the pair being placed with respect to the zero error contour of the second order gradient so as to have a positive error and the second of the pair being placed so as to have a negative error resulting in reduced second order error accumulation.

Owner:SKYWORKS SOLUTIONS INC

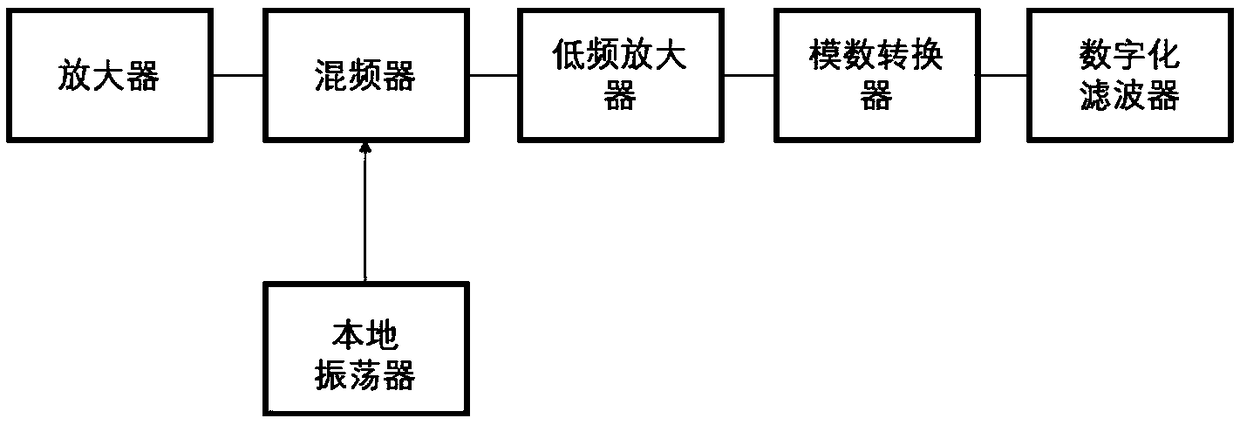

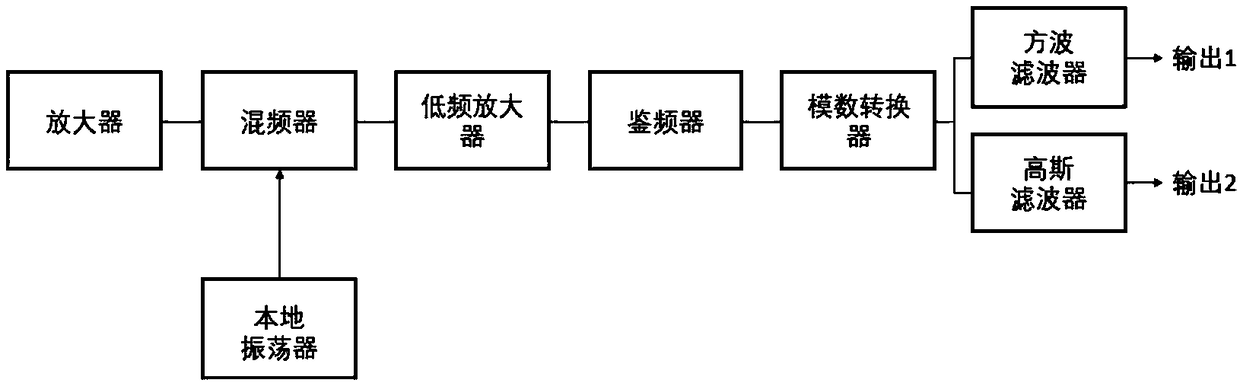

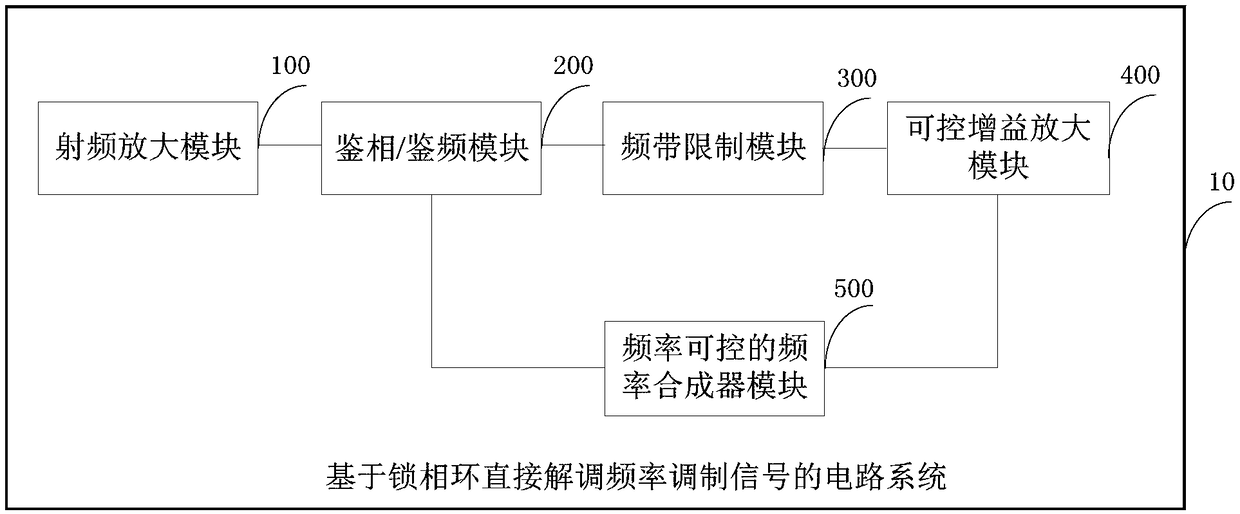

Circuit system and control method for directly demodulating frequency modulated signal based on phase-locked loop

PendingCN109004930AEliminate errorsSimple structurePulse automatic controlHigh frequency amplifiersPhase differenceCarrier signal

The invention provides a circuit system and a control method for directly demodulating a frequency modulated signal based on a phase-locked loop, wherein the system comprises an amplification module for amplifying an input radio frequency signal; a phase discrimination / frequency discrimination module for acquiring a frequency difference and a phase difference between the local oscillator and the amplified radio frequency signal; a band limiting module connected with the phase detection / frequency discrimination module to limit the bandwidth according to the frequency difference and the phase difference and amplify the bandwidth; a controllable gain amplification module that adjusts the amplitude of the output signal of the band limiting module in a controllable manner; and a frequency-controllable frequency synthesizer module which is connected with the controllable gain amplification module and the phase discrimination / frequency discrimination module, and generates corresponding frequency change according to the frequency difference and phase difference signal after gain adjustment, so as to carry out frequency adjustment and tracking. The system has the advantages of simple structure, low power consumption and strong performance, which can also be used for carrier frequency tracking and carrier error cancellation on the basis of demodulation of conventional frequency shift keying.

Owner:TSINGHUA UNIV