Patents

Literature

143results about "Analogue/digital/analogue conversion" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Methods and apparatus for wireless network connectivity

ActiveUS7450543B2Keep in touchTransmission path divisionRadio/inductive link selection arrangementsControl signalAsynchronous network

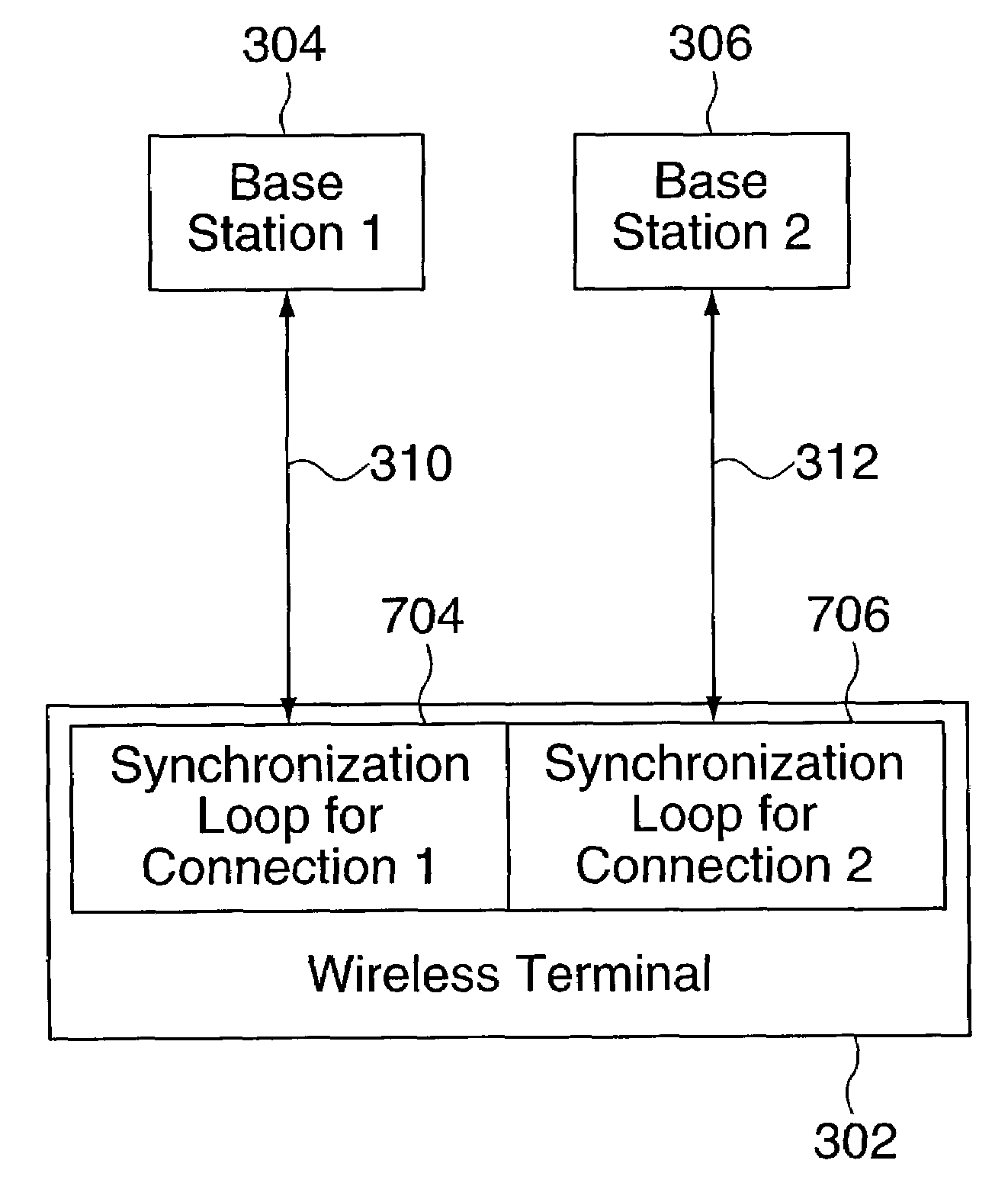

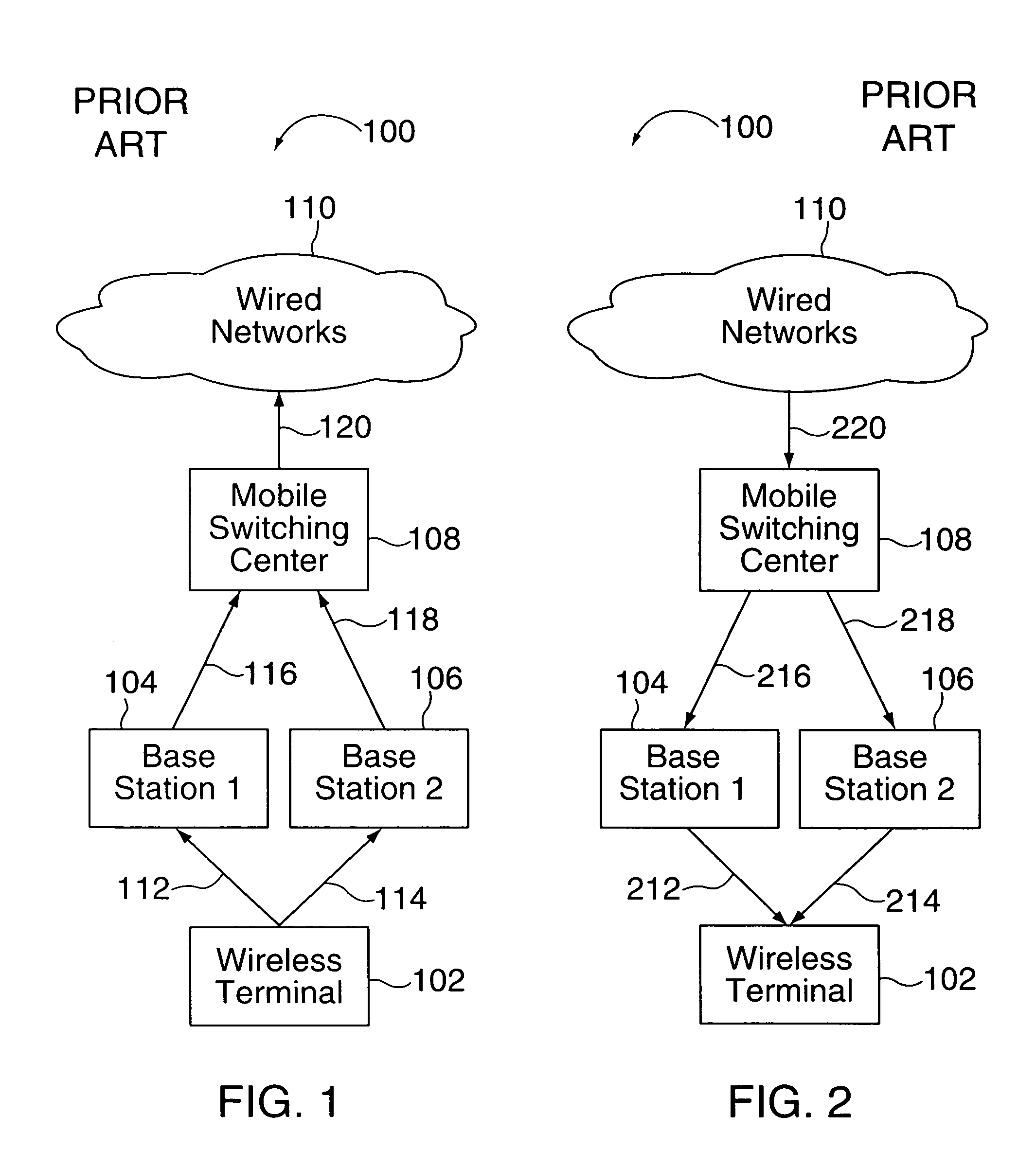

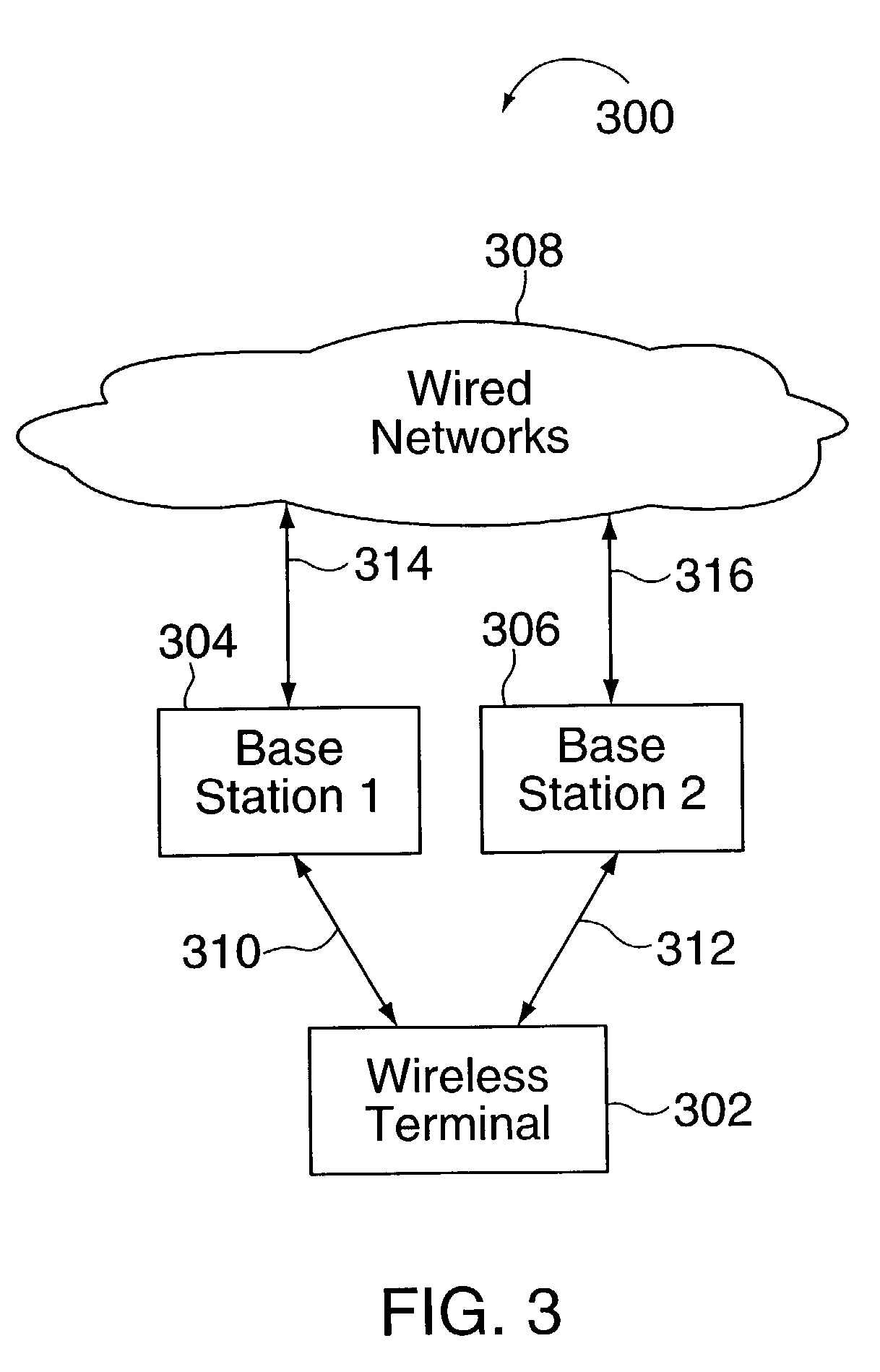

Methods and apparatus which allow a wireless terminal (302) to simultaneously maintain connections with multiple base stations (304, 306) are described. Each wireless terminal (302) is capable of supporting multiple separate timing and / or other control loops one, for each base station connection thereby allowing the connections to operate independently and in parallel. Different control signals and / or data are transmitted on each connection that is established with a base station (302, 306). In this manner base stations (302, 306) receive different data allowing for asynchronous data transmission. The data received by the base stations (302, 306) can be supplied to a wired asynchronous network (308) without the need to combine the received data prior to supplying it to the wired network (308). The communications techniques of the invention can be used to implement soft handoffs without the need to duplicate data transmissions to multiple base stations.

Owner:QUALCOMM INC

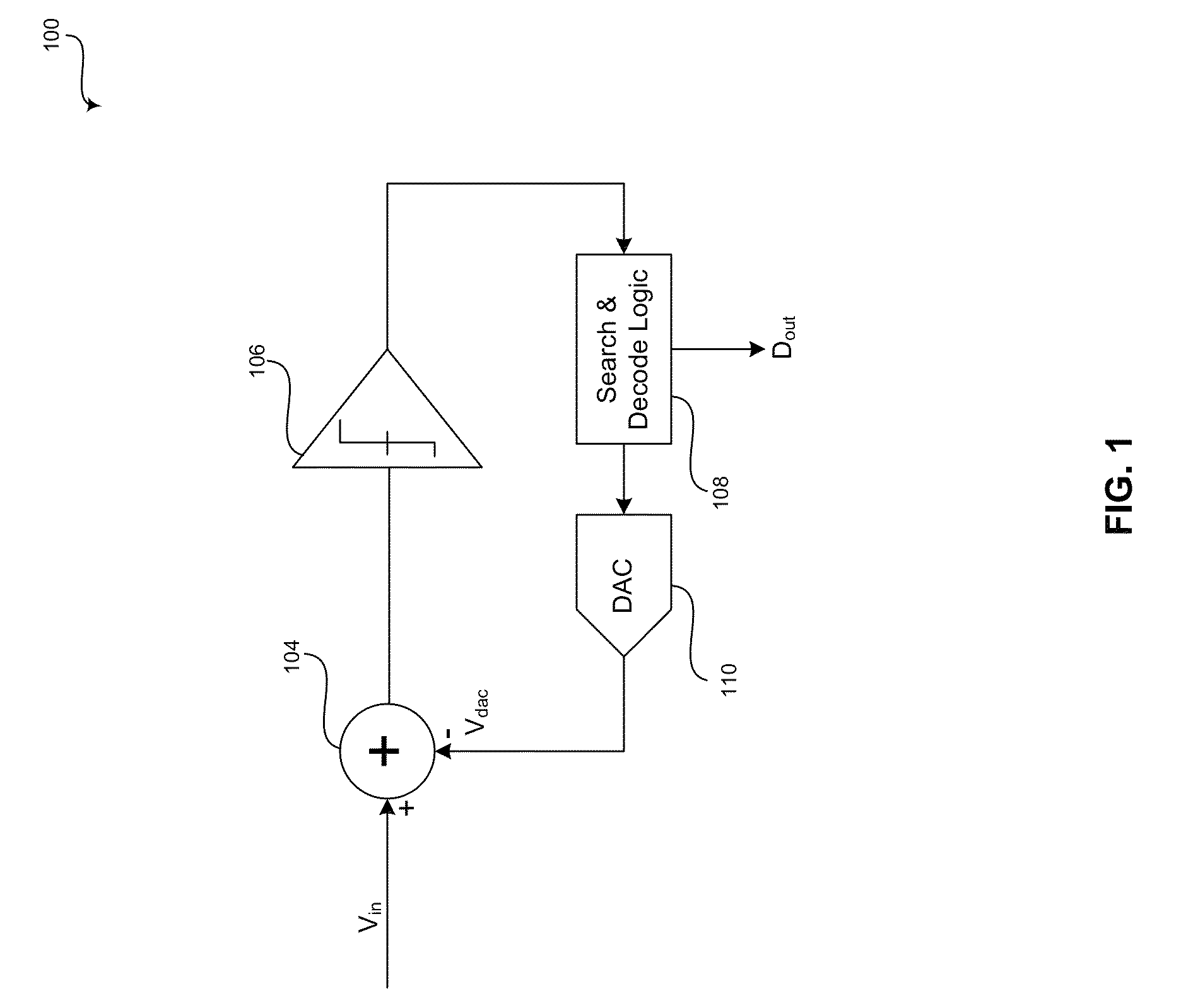

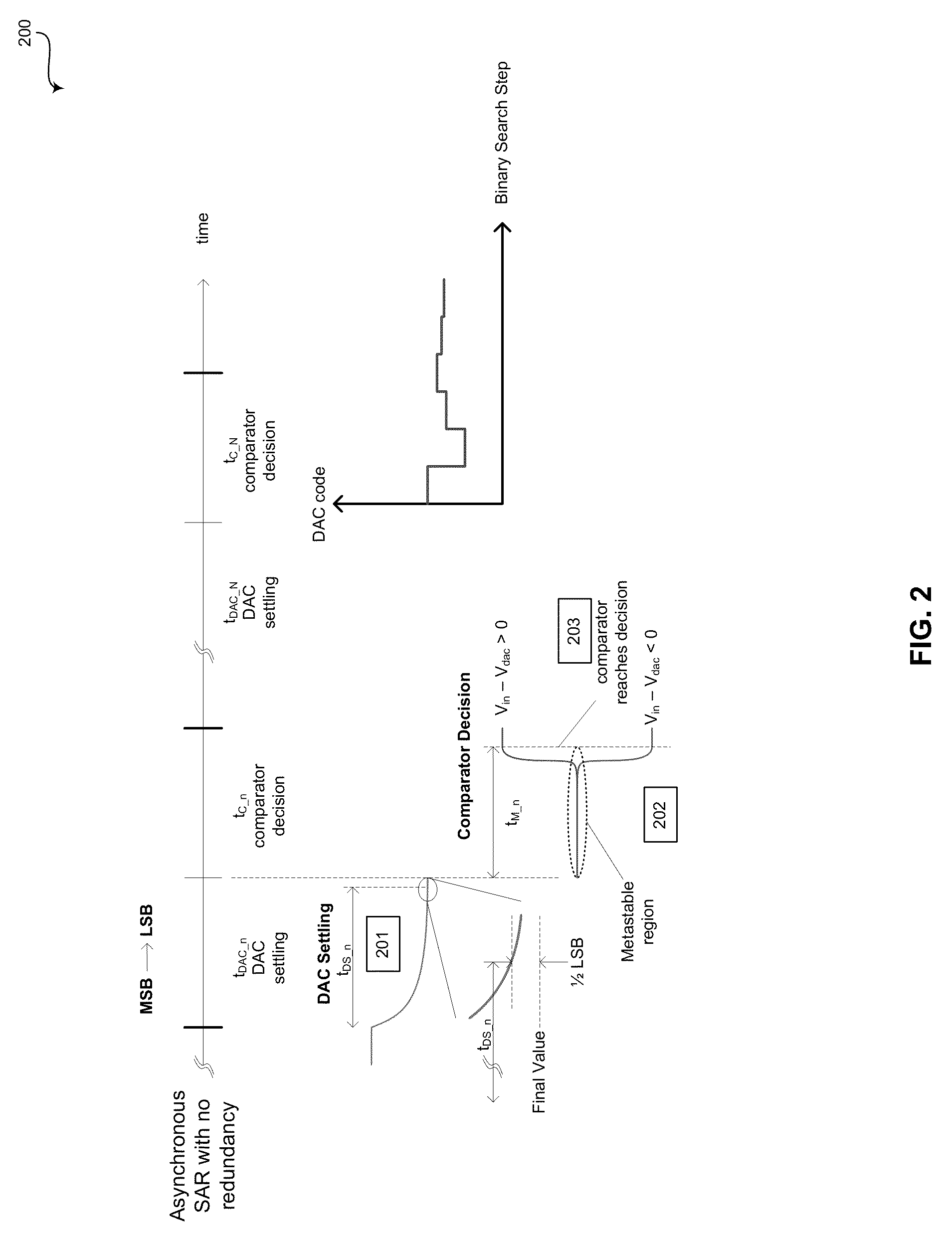

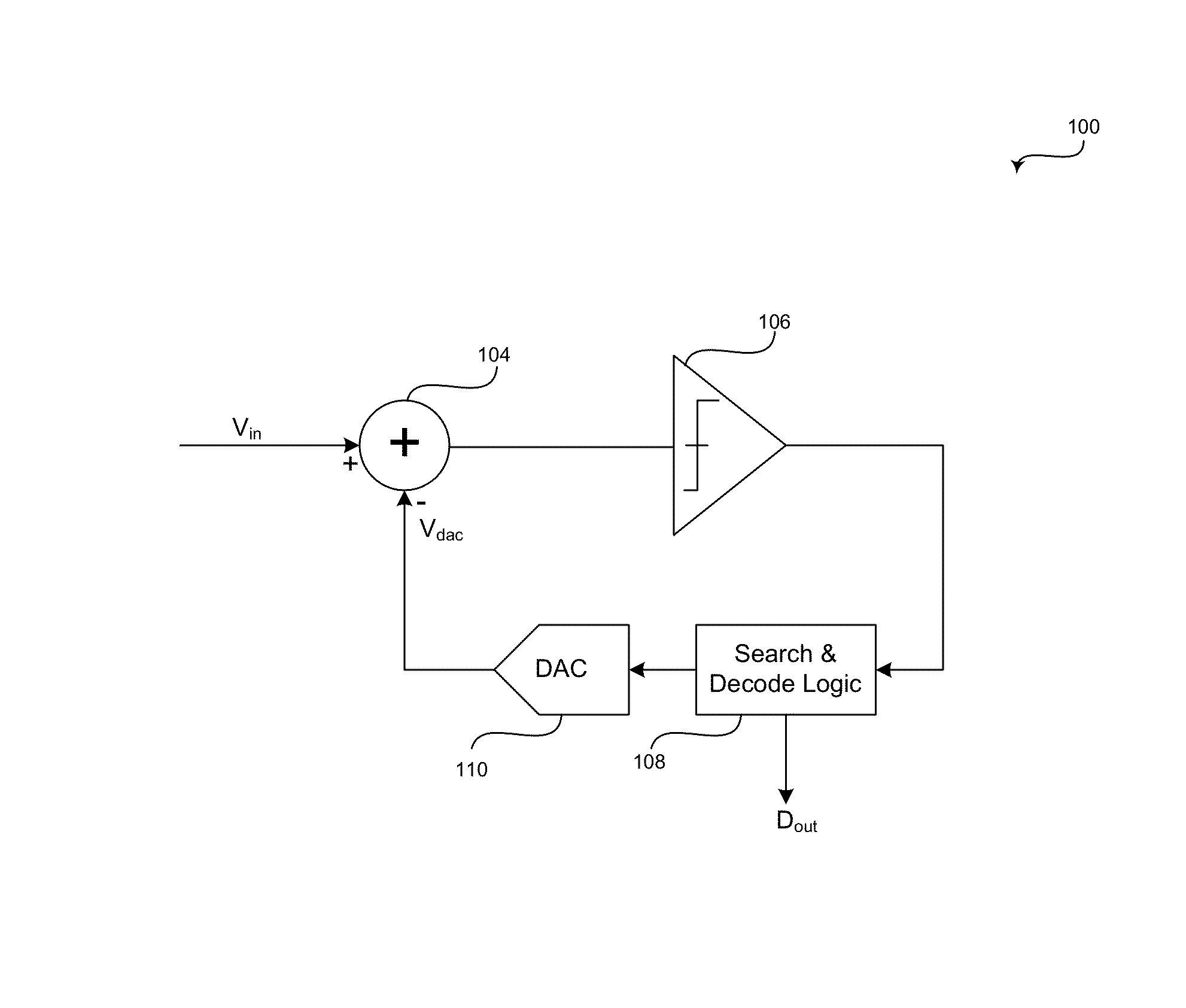

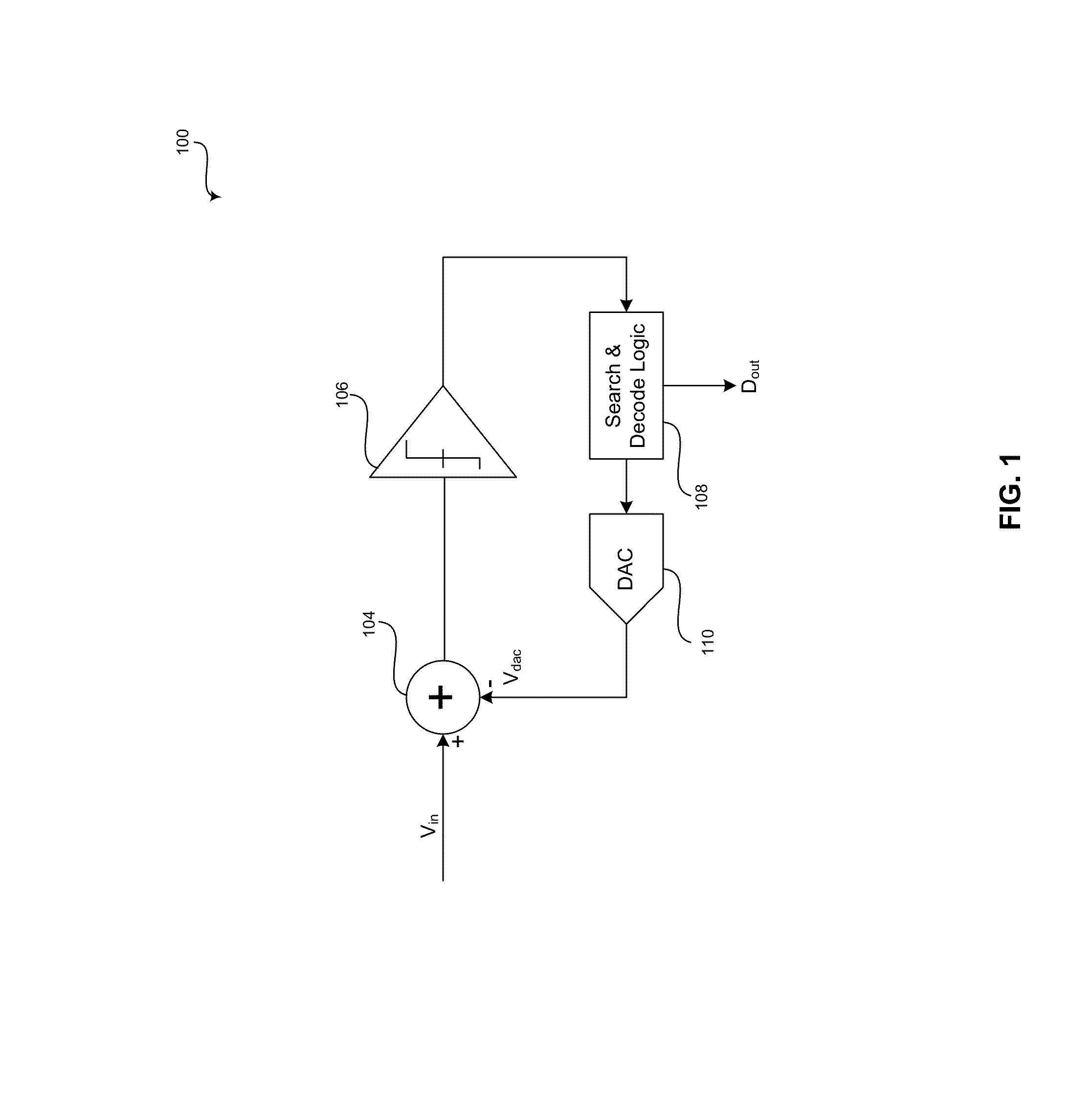

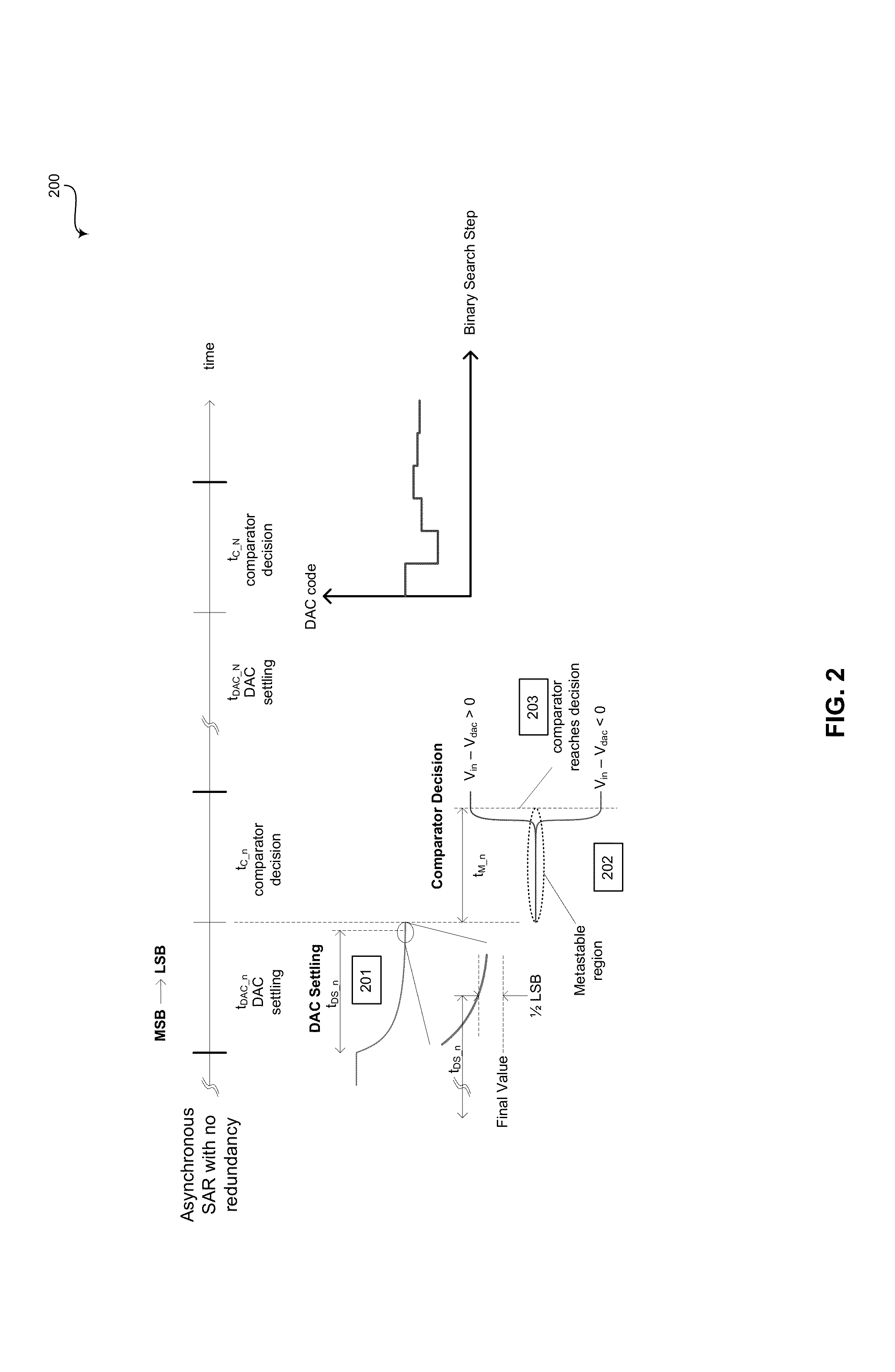

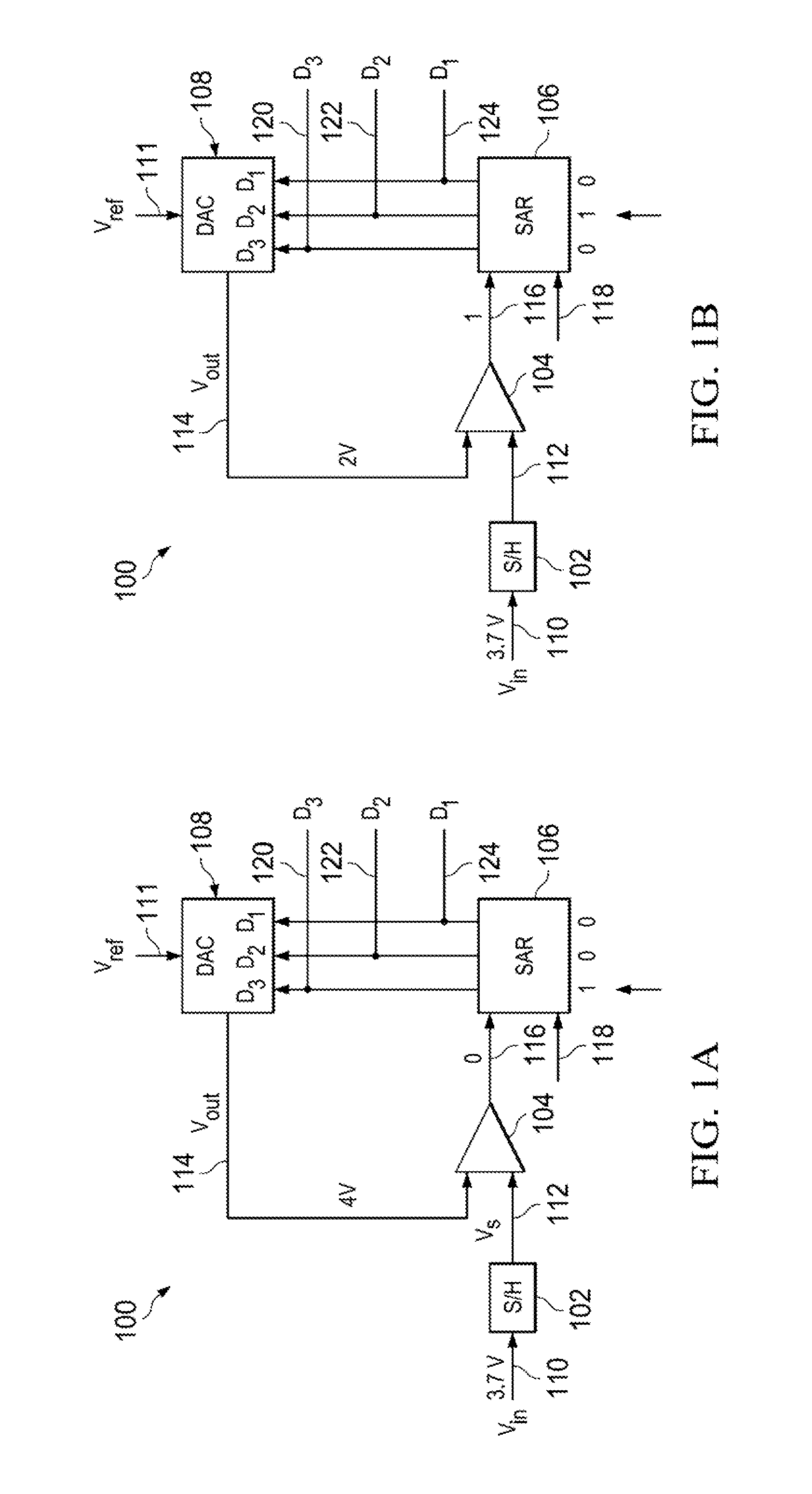

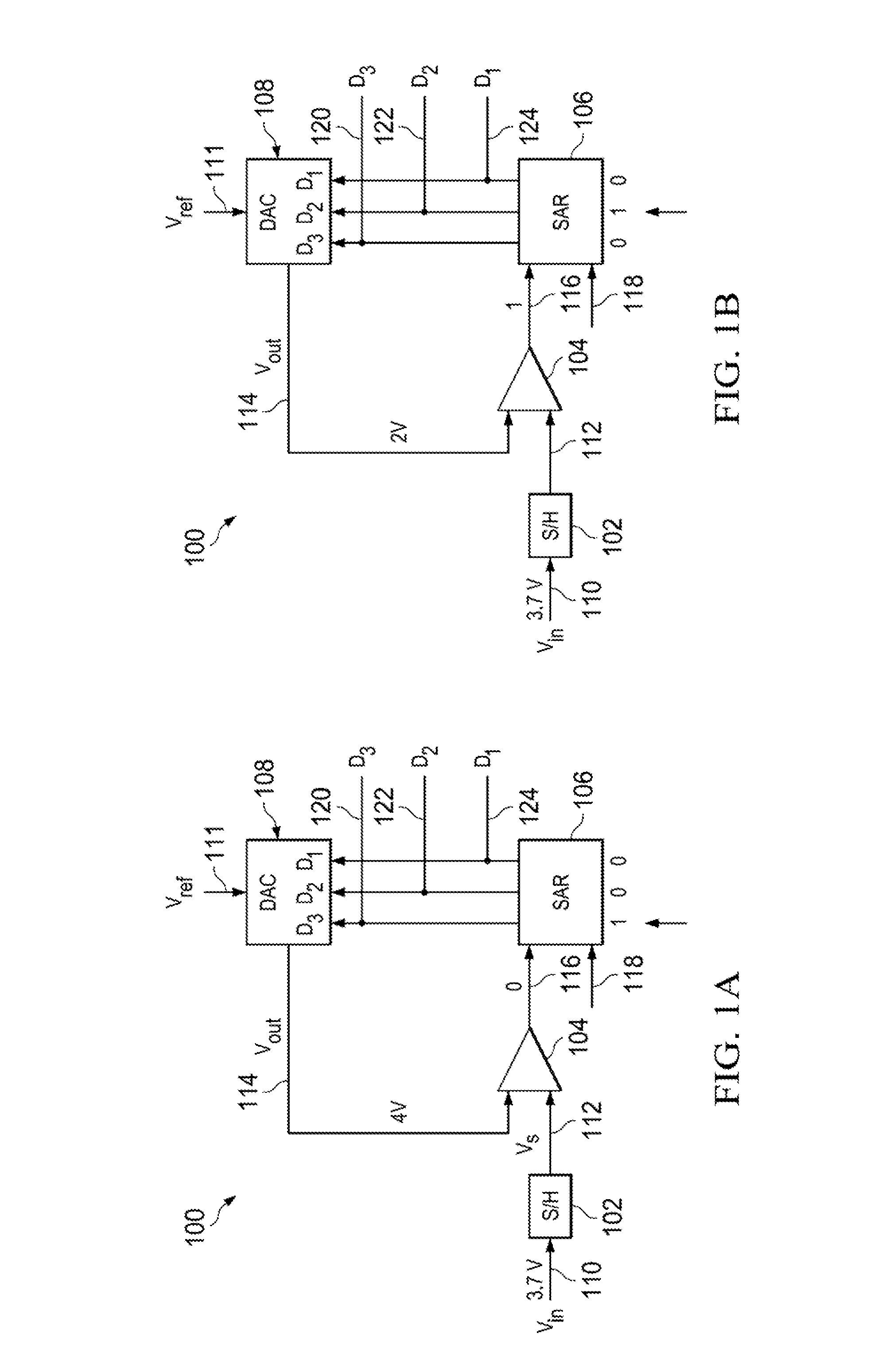

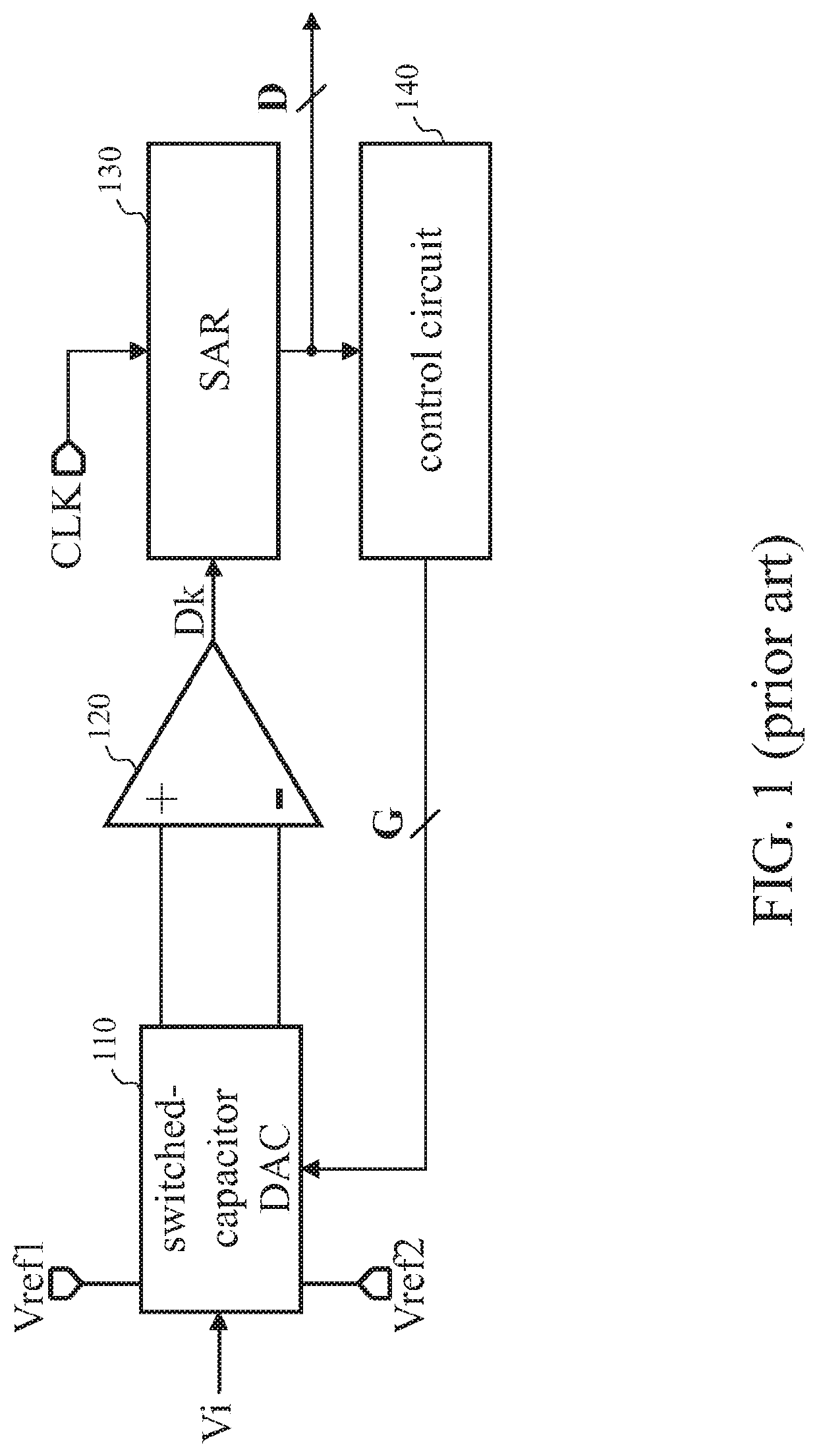

Method and system for asynchronous successive approximation register (SAR) analog-to-digital converters (ADCs)

ActiveUS8922415B2Electric signal transmission systemsAnalogue/digital/analogue conversionDigital down converterAnalog-to-digital converter

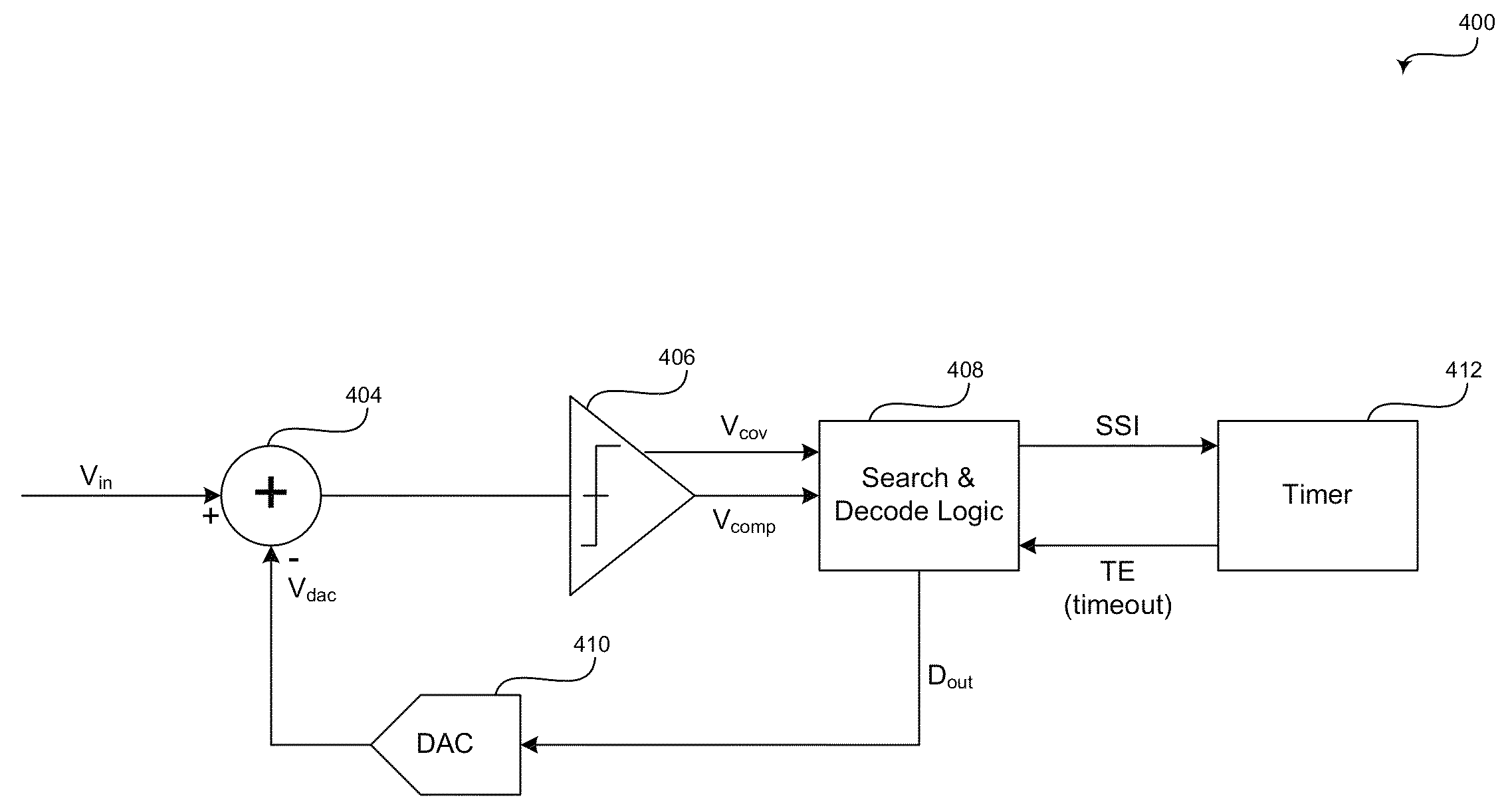

An asynchronous successive approximation register analog-to-digital converter (SAR ADC), which utilizes one or more overlapping redundant bits in each digital-to-analog converter (DAC) code word, is operable to generate an indication signal that indicates completion of each comparison step and indicates that an output decision for each comparison step is valid. A timer may be initiated based on the generated indication signal. A timeout signal may be generated that preempts the indication signal and forces a preemptive decision, where the preemptive decision sets one or more remaining bits up to, but not including, the one or more overlapping redundant bits in a corresponding digital-to-analog converter code word for a current comparison step to a particular value. For example, the one or more remaining bits may be set to a value that is derived from a value of a bit that was determined in an immediately preceding decision.

Owner:MAXLINEAR INC

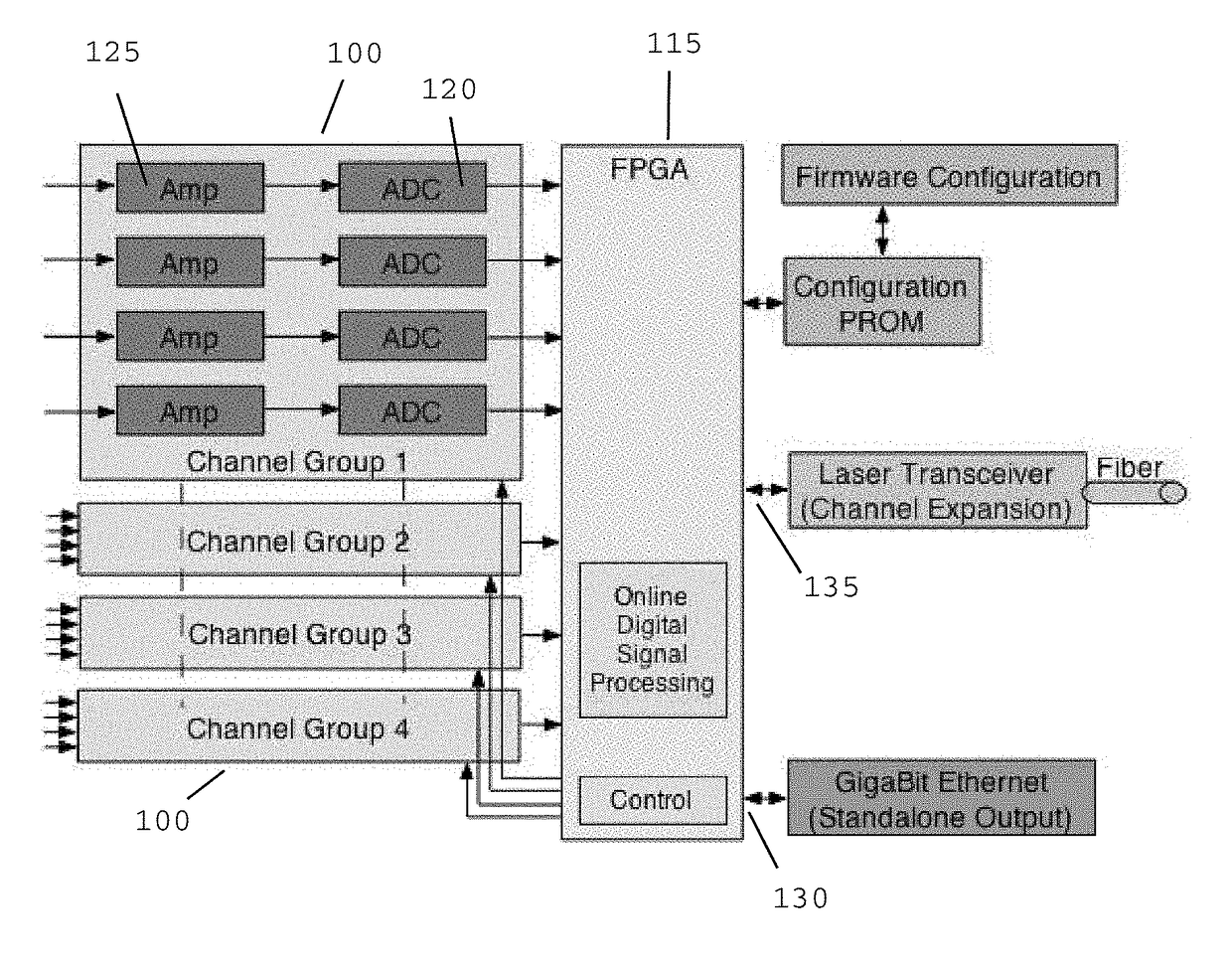

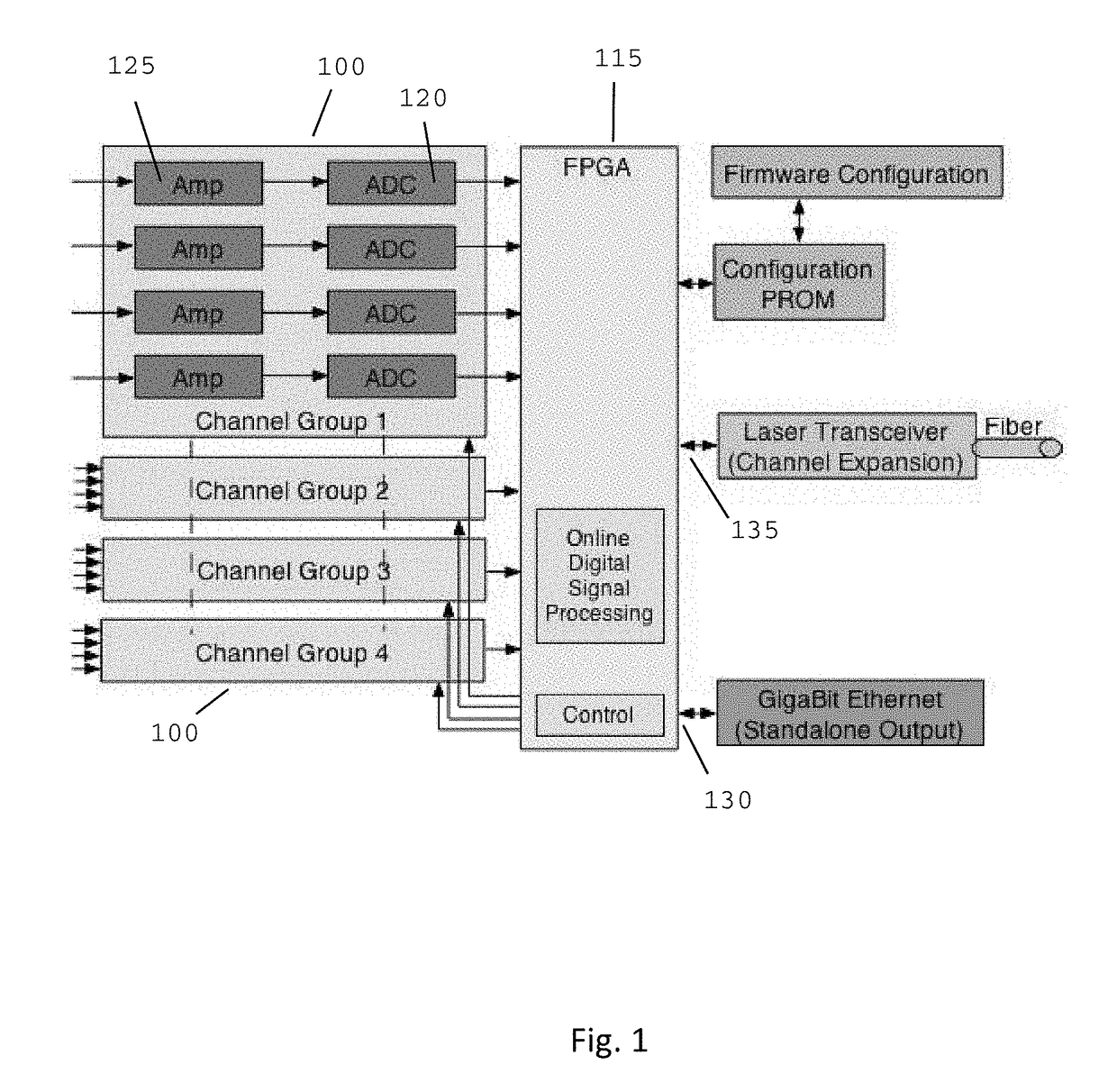

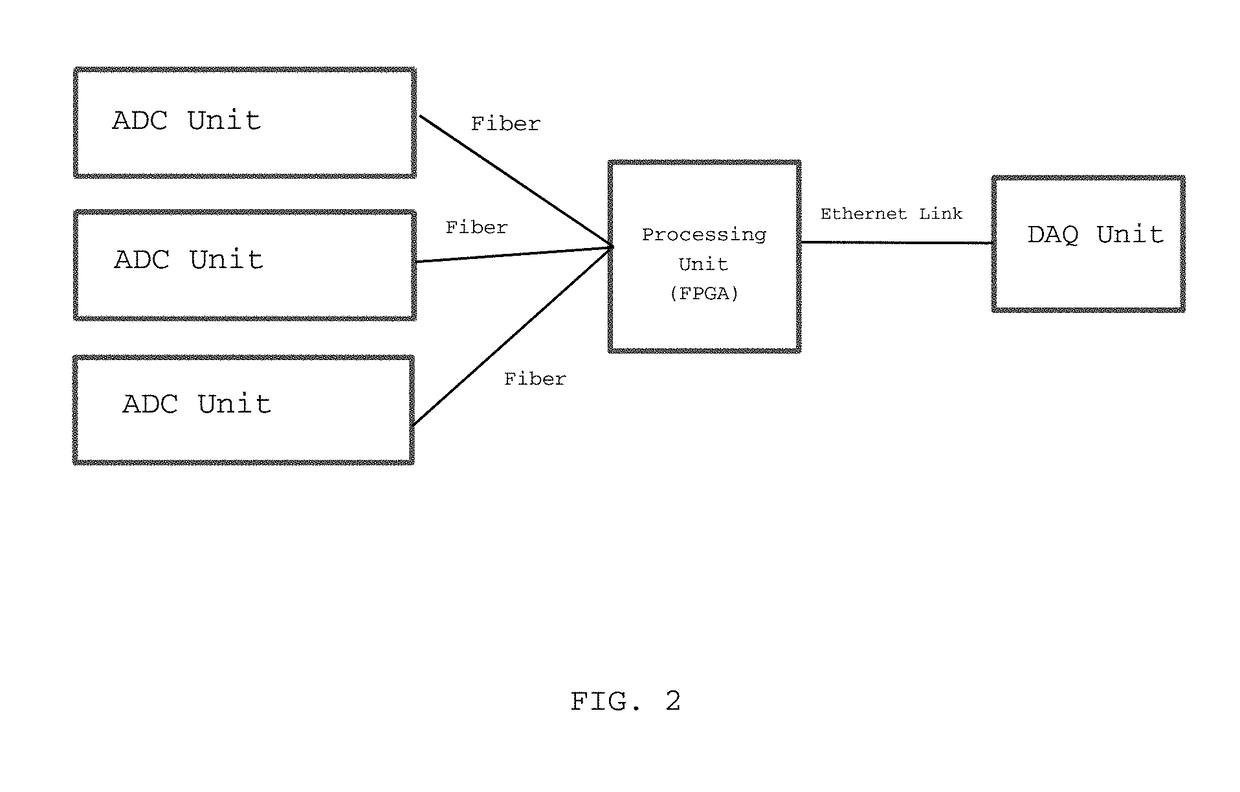

Method and apparatus to digitize pulse shapes from radiation detectors

ActiveUS10027340B1Improve scalabilityReduce data volumeElectric signal transmission systemsAnalogue/digital/analogue conversionData acquisitionDetector array

A field programmable gate array based multi-channel flash ADC unit combined with a high speed multi-lane data communications channel / Ethernet-like modular intercommunication providing a complete but easily expandable high-speed data acquisition system. This apparatus and method permits high-speed pulse-shape digitalization allowing position resolution imaging of particles having a range of energies and is scalable to achieve the efficient capture of coincident data from large electromagnetic detector arrays.

Owner:JEFFERSON SCI ASSOCS LLC

Method and system for asynchronous successive approximation register (SAR) analog-to-digital converters (ADCS)

ActiveUS20140043175A1Electric signal transmission systemsAnalogue/digital/analogue conversionA d converterAnalog-to-digital converter

An asynchronous successive approximation register analog-to-digital converter (SAR ADC), which utilizes one or more overlapping redundant bits in each digital-to-analog converter (DAC) code word, is operable to generate an indication signal that indicates completion of each comparison step and indicates that an output decision for each comparison step is valid. A timer may be initiated based on the generated indication signal. A timeout signal may be generated that preempts the indication signal and forces a preemptive decision, where the preemptive decision sets one or more remaining bits up to, but not including, the one or more overlapping redundant bits in a corresponding digital-to-analog converter code word for a current comparison step to a particular value. For example, the one or more remaining bits may be set to a value that is derived from a value of a bit that was determined in an immediately preceding decision.

Owner:MAXLINEAR INC

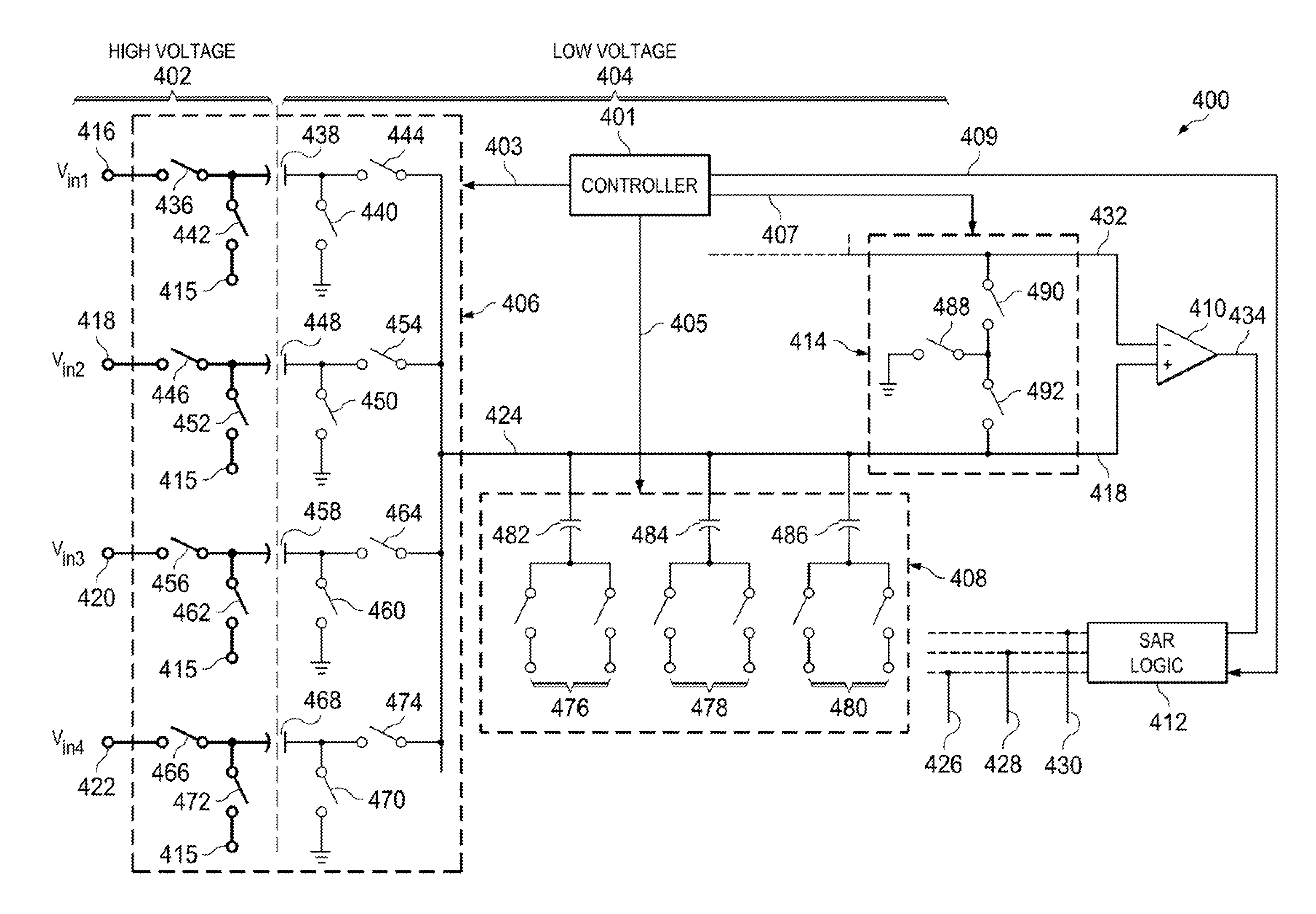

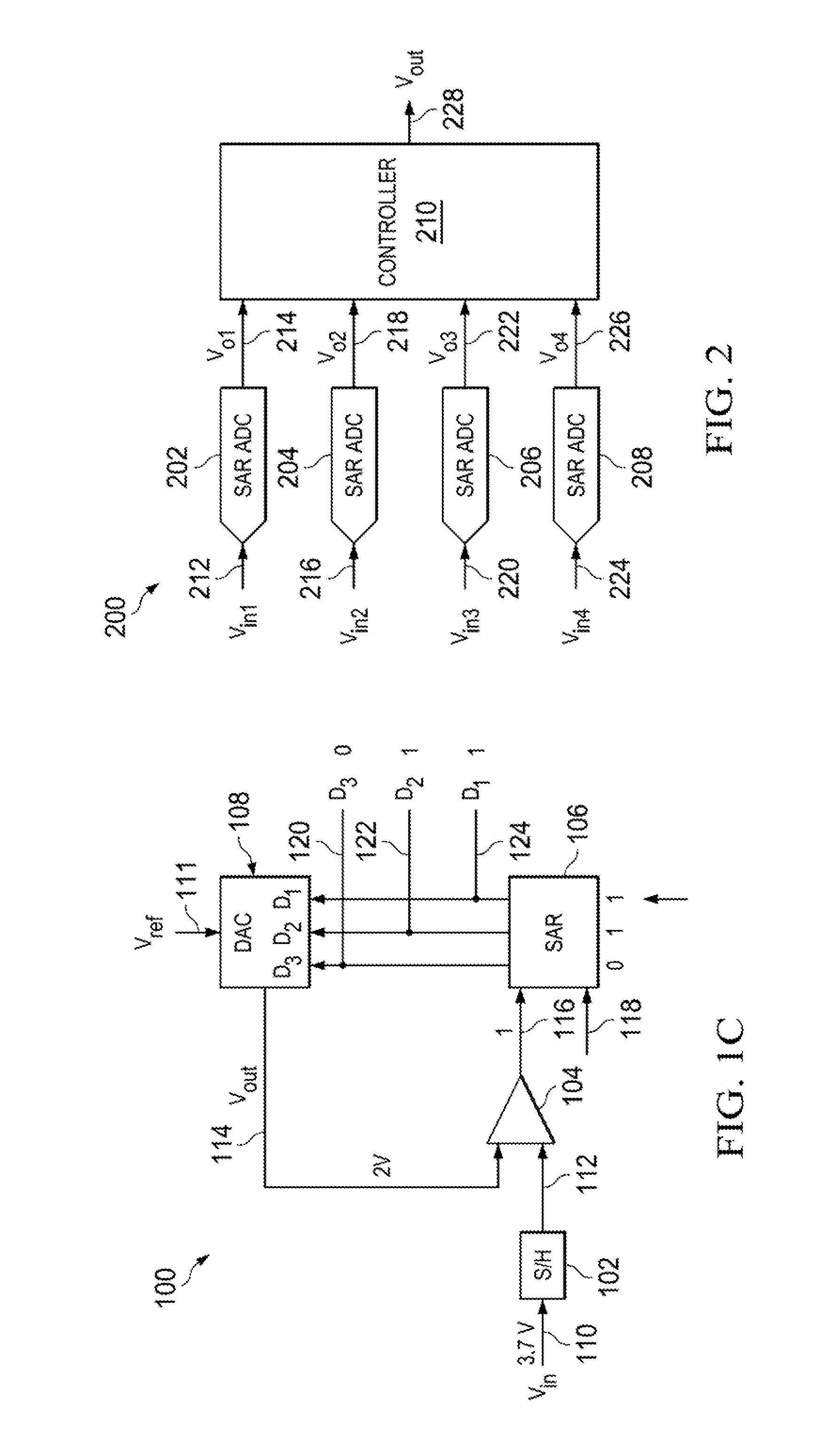

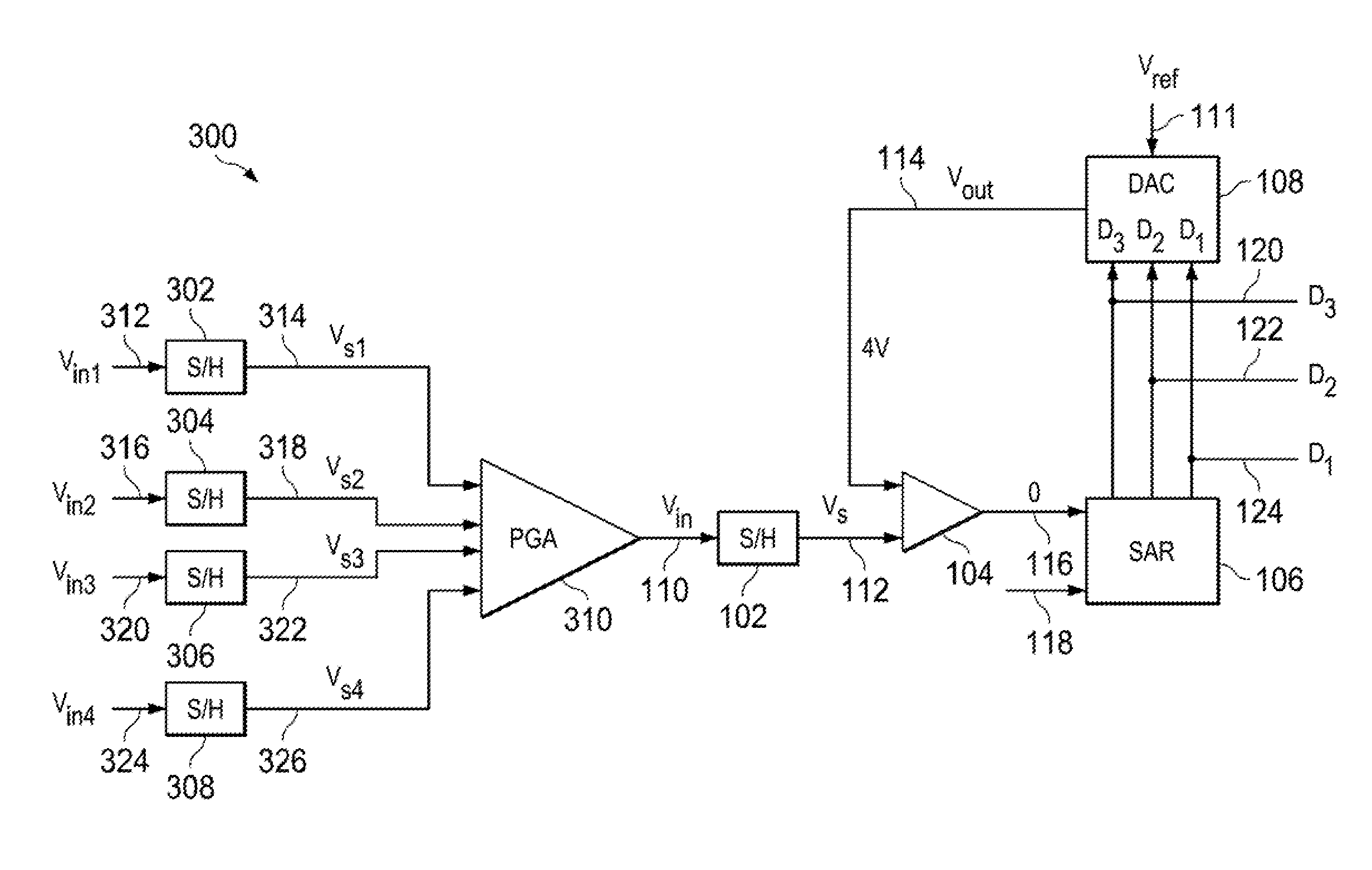

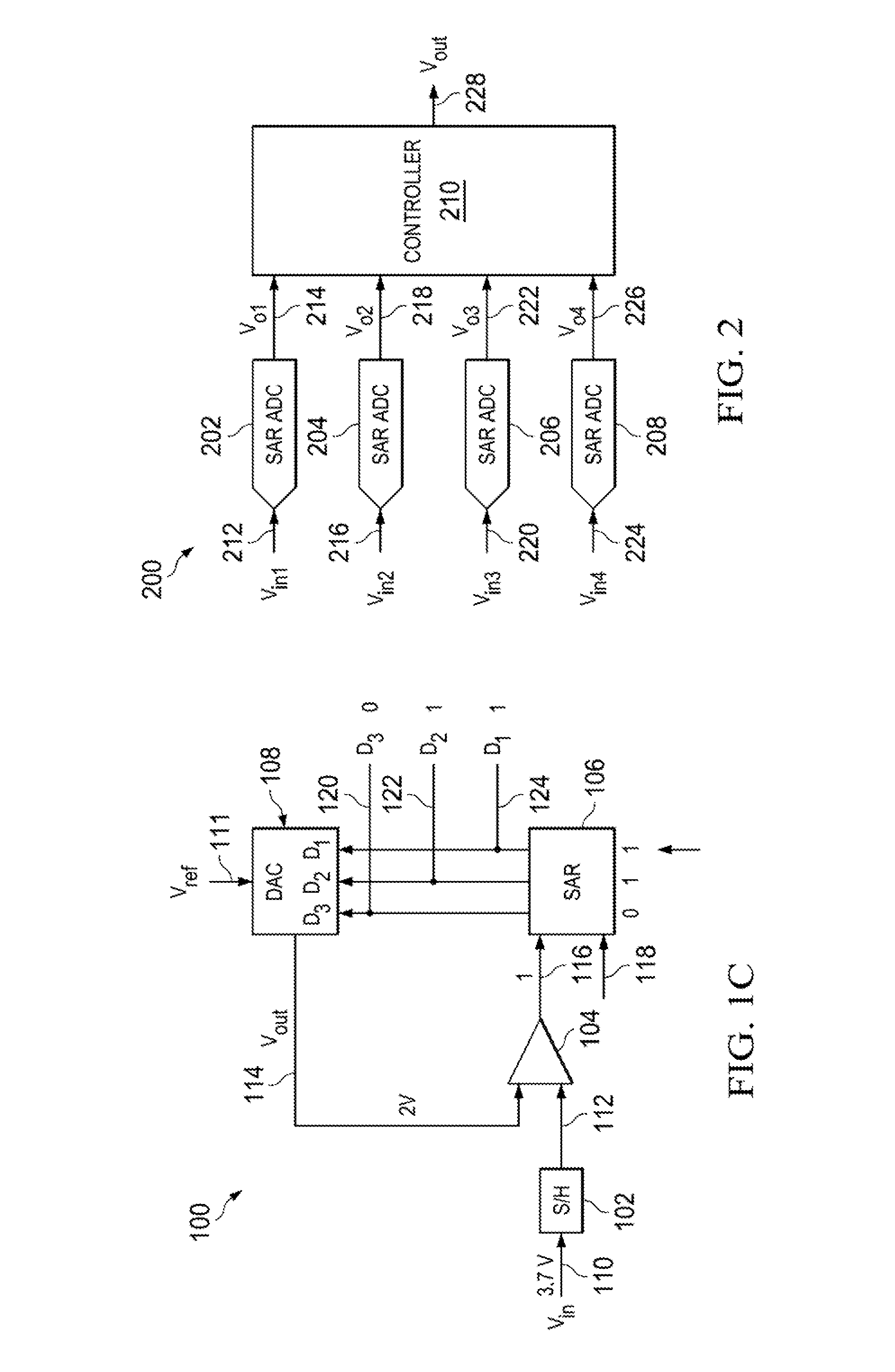

System and method for multi channel sampling SAR ADC

ActiveUS20150372691A1High error rateElectric signal transmission systemsAnalogue/digital/analogue conversionComparatorSample and hold

A device includes a SAR, a comparator, a DAC and a multichannel passive S / H component. The multichannel passive S / H component is able to sample and hold a plurality of analog voltages in parallel. The multichannel passive S / H component is further able to serially feed the plurality of sampled and held analog voltages to the SAR, comparator and DAC, such that each analog voltage is serially converted to a digital representation.

Owner:TEXAS INSTR INC

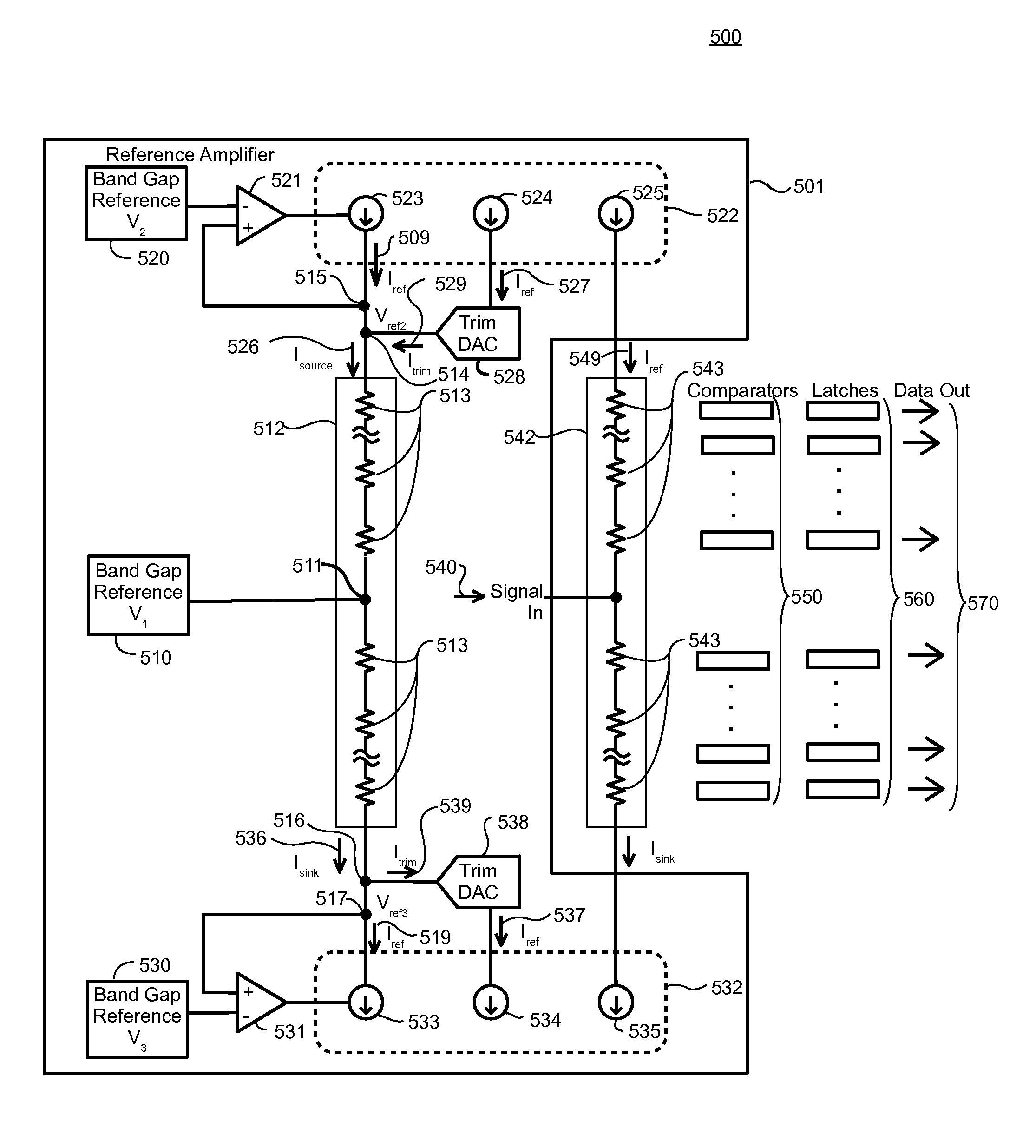

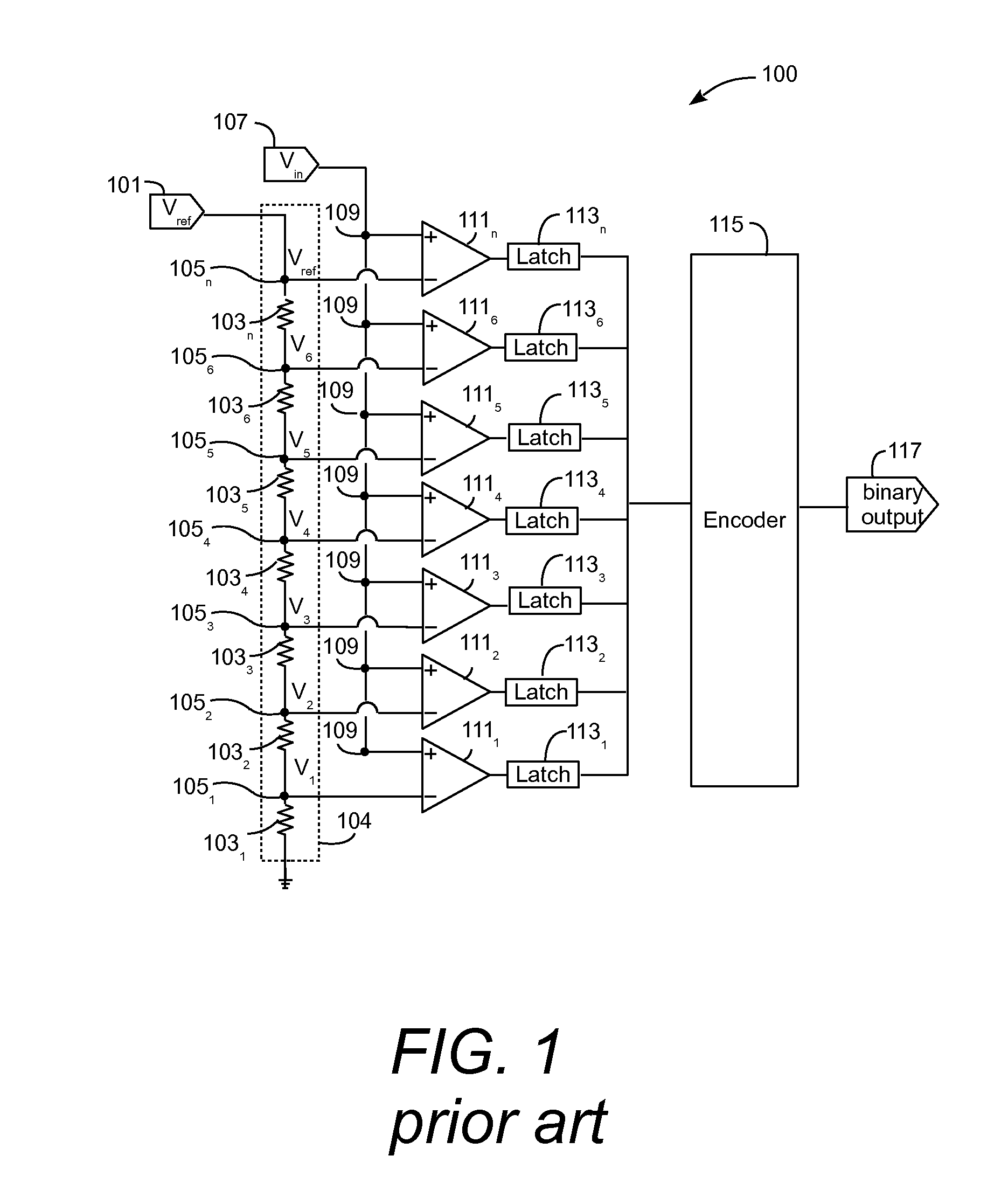

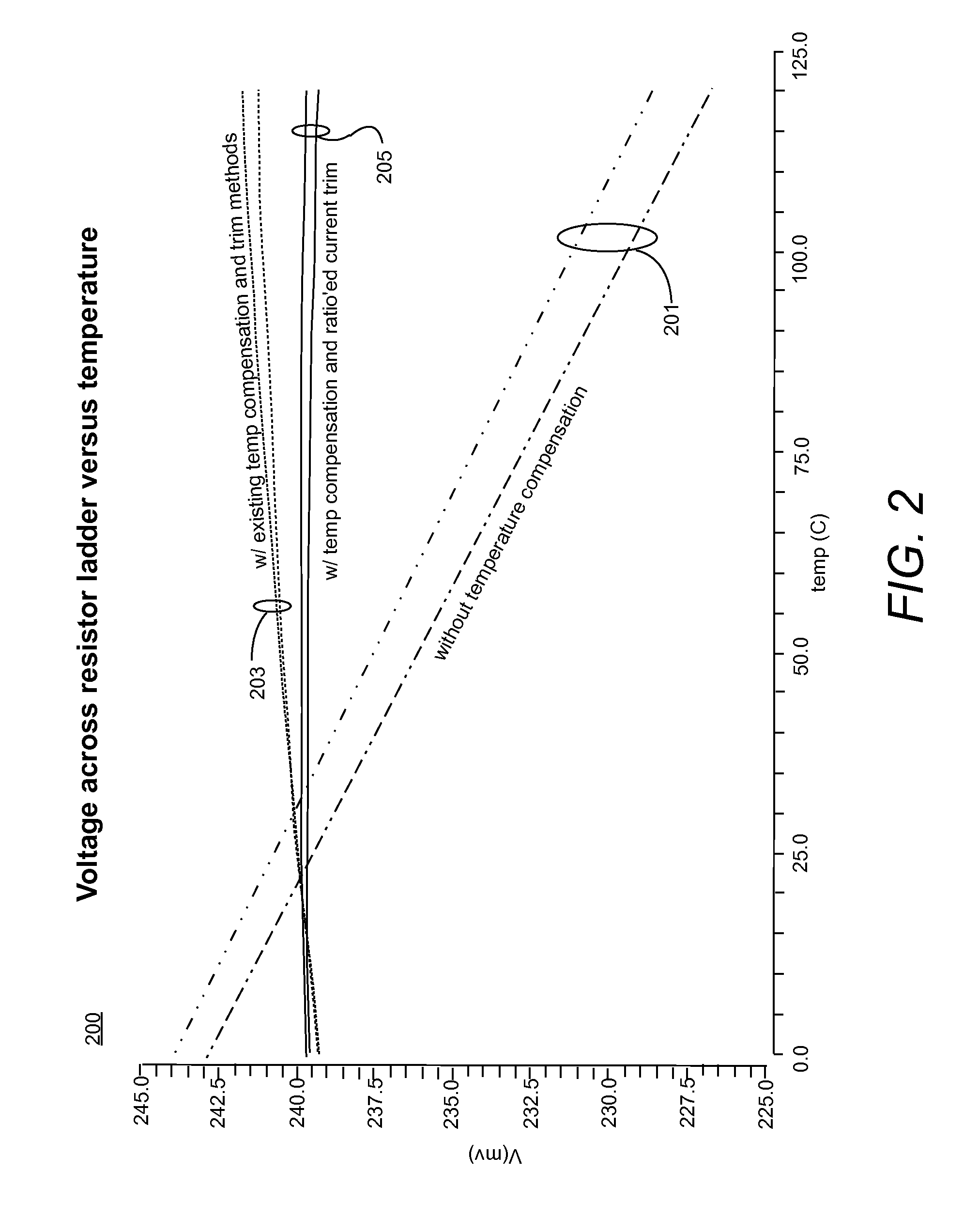

Apparatus and method for temperature compensated gain and mismatch trim in subranging quantizers and analog to digital converters

ActiveUS9214950B1Electric signal transmission systemsAnalogue/digital/analogue conversionPower flowReference current

A flash analog to digital converter (ADC) provides a temperature compensated trim current by applying a first temperature compensated reference current across a replica resistor ladder. The reference current is mirrored to a trim digital to analog converter, which outputs a fractional portion of the temperature compensated reference current. The proportional trim current is then fed back to the reference current to provide a trimmed temperature compensated reference current. The trimmed reference current is mirrored across the output resistor ladder providing a trimmed current in which the trim varies along with temperature changes due to the trim current being a proportion of the temperature compensated reference current. A proportional trim current which varies with temperature changes is applied to the gain current trim and mismatch current trim in a DAC of a quantizing stage of a sub-ranging ADC.

Owner:LOCKHEED MARTIN CORP

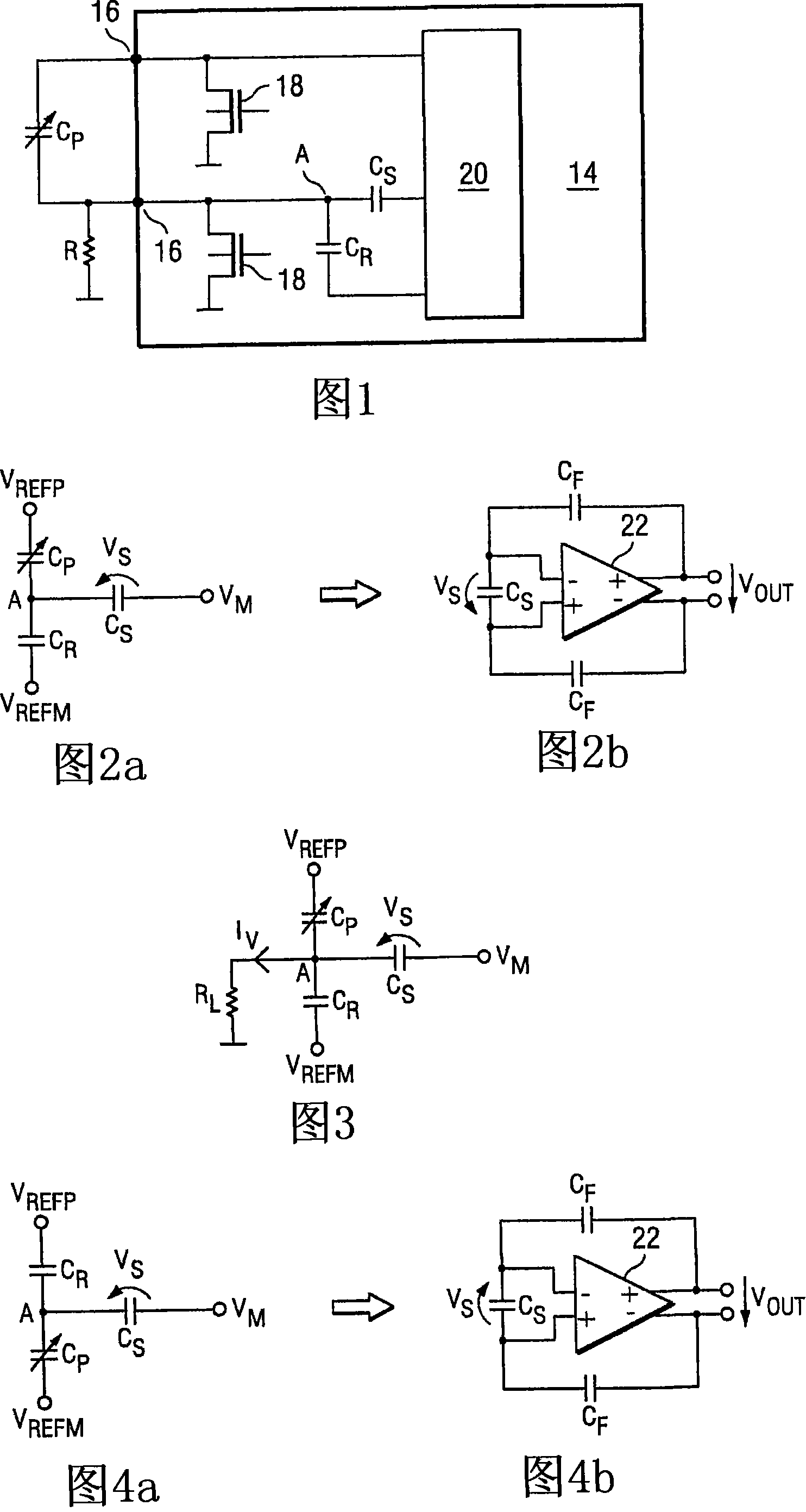

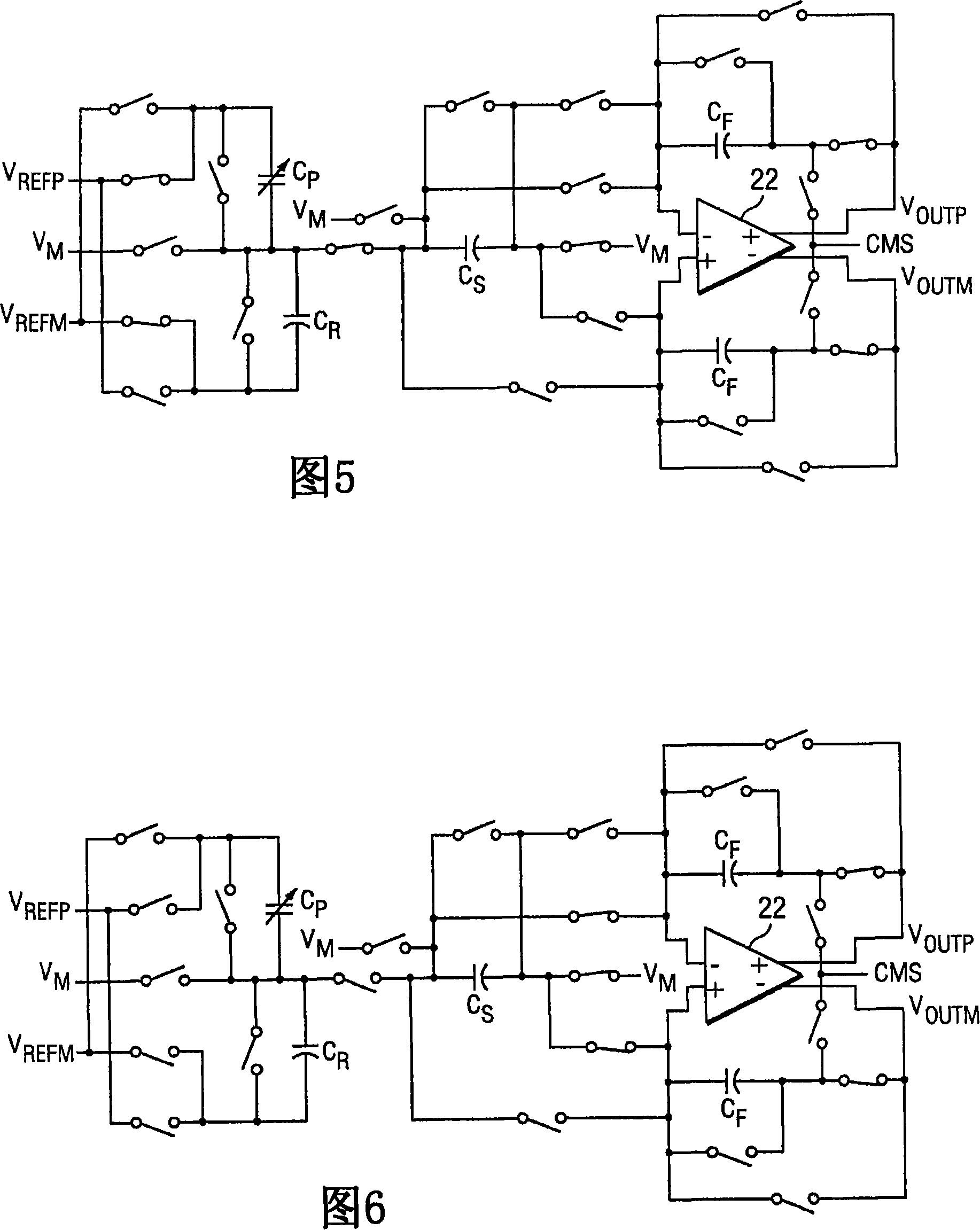

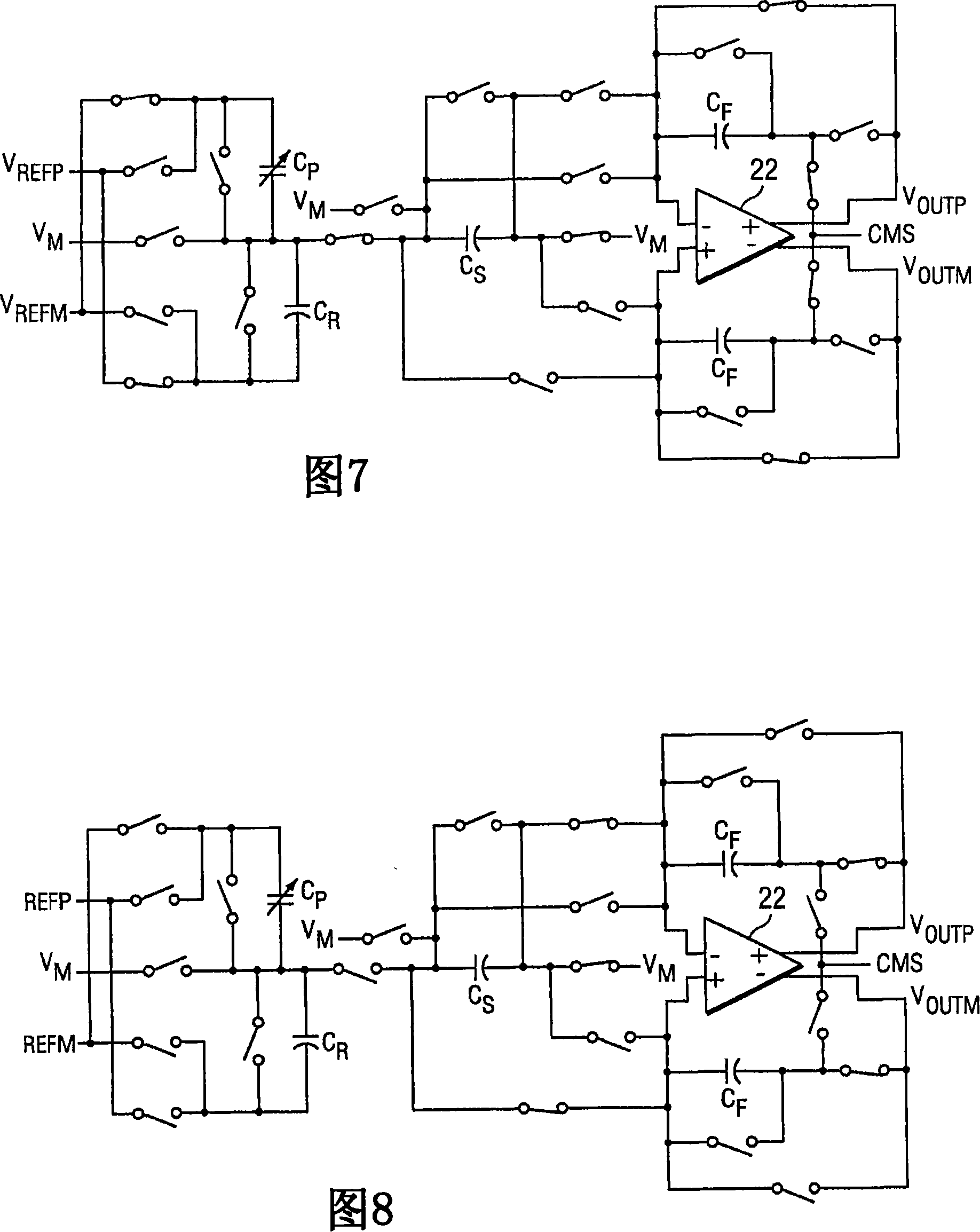

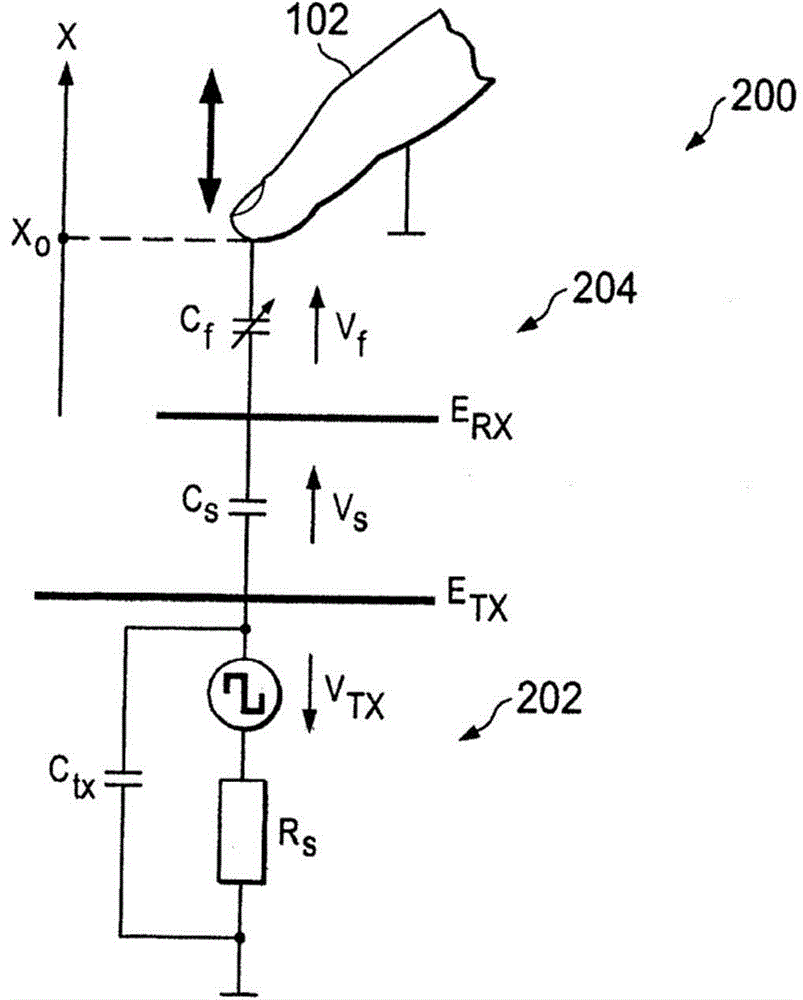

Capacitance-to-voltage conversion method and apparatus

ActiveCN101198876ACapacitance measurementsAnalogue/digital/analogue conversionCapacitanceVoltage converter

A method of capacitance-to-voltage conversion using an external sensing capacitor (CP) and a capacitance-to-voltage converter (14) implemented on an integrated readout circuit comprising a reference capacitor (CR), a sampling capacitor ( Cs) and a sampling amplifier (22), with its input (16) connected to the sensing capacitor (CP). The method comprises the following steps: a) Applying a reference voltage (Vref) to a sensing capacitor (CP) and a reference capacitor (CR) connected in series, and charging a sampling capacitor (Cs) to the sensing capacitor (CP) and reference capacitor (CR ) between the potential at the interconnection node (A); b) connecting the sampling capacitor (Cs) to the input of the sampling amplifier. The method further comprises the following steps: c) applying a reference voltage (Vref) with a polarity opposite to that in step a) to the sensing capacitor (CP) and reference capacitor (Cs) connected in series, and charging the sampling capacitor (Cs) to the potential at the interconnection node (A) between the sensing capacitor (CP) and the reference capacitor (CR), and d) connecting the sampling capacitor (Cs) to the sampling amplifier in the opposite polarity to that in step b) of these inputs.

Owner:TEXAS INSTR INC

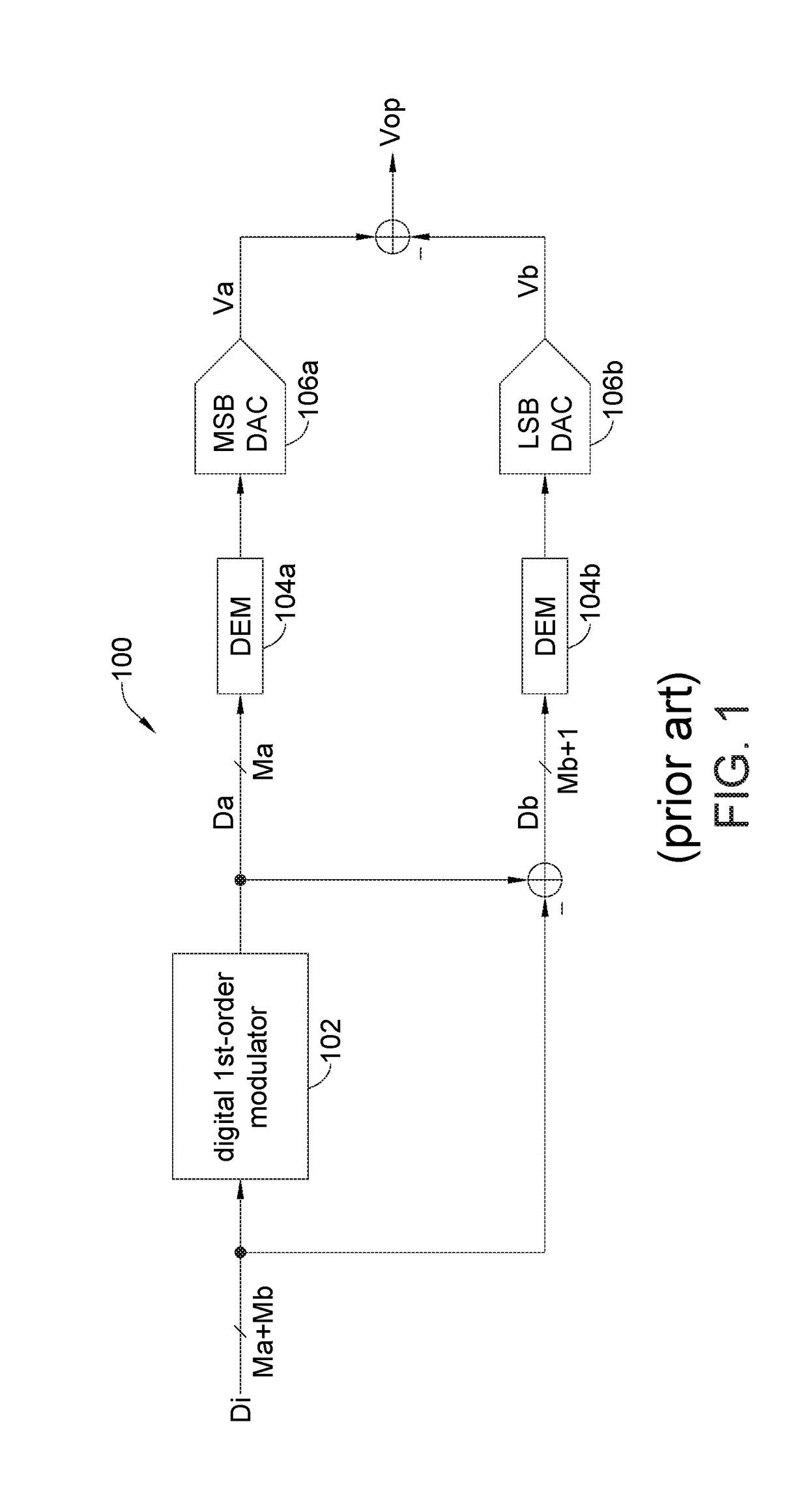

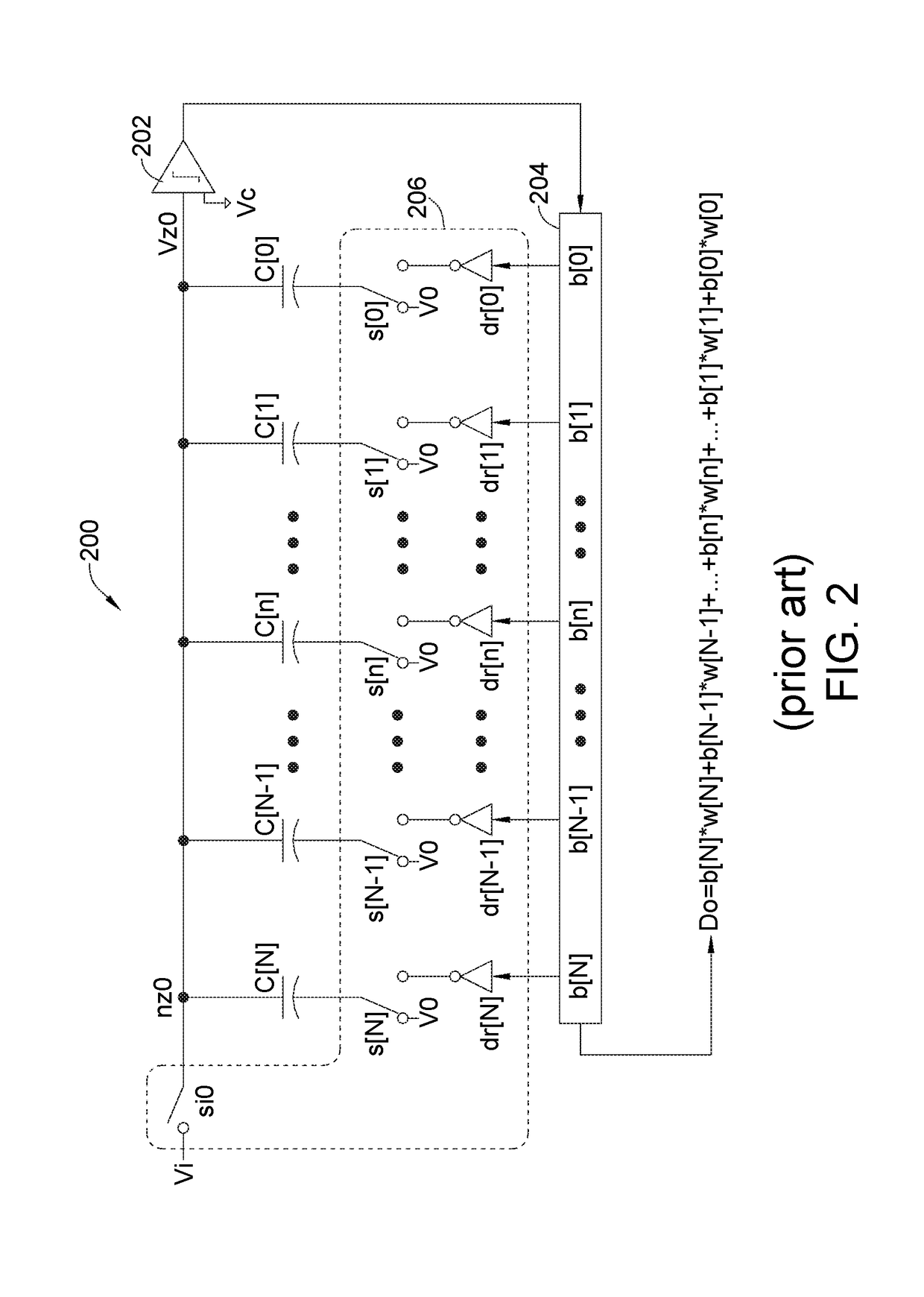

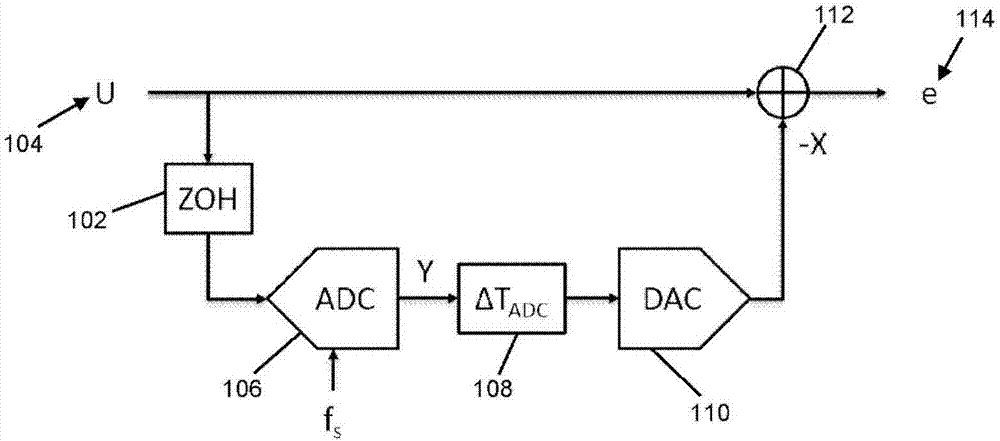

System for conversion between analog domain and digital domain with mismatch error shaping

ActiveUS20170077937A1Analogue/digital/analogue conversionAnalogue conversionElectrical and Electronics engineeringEngineering

The invention provides a system for conversion between analog domain and digital domain with mismatch error shaping, including a DAC, a first injection circuit couple to the DAC, and a second injection circuit coupled to the DAC. The DAC generates a first analog value in response to a first digital value, and generates a second analog value in response to a second digital value. The first injection circuit enables an analog injection value to be injected to the second analog value when the DAC generates the second analog value, wherein the analog injection value is converted from a digital injection value formed by a subset of bits of the first digital value. The second injection circuit combines the digital injection value and one of the following: the second digital value and a related value obtained according to the second analog value.

Owner:MEDIATEK INC

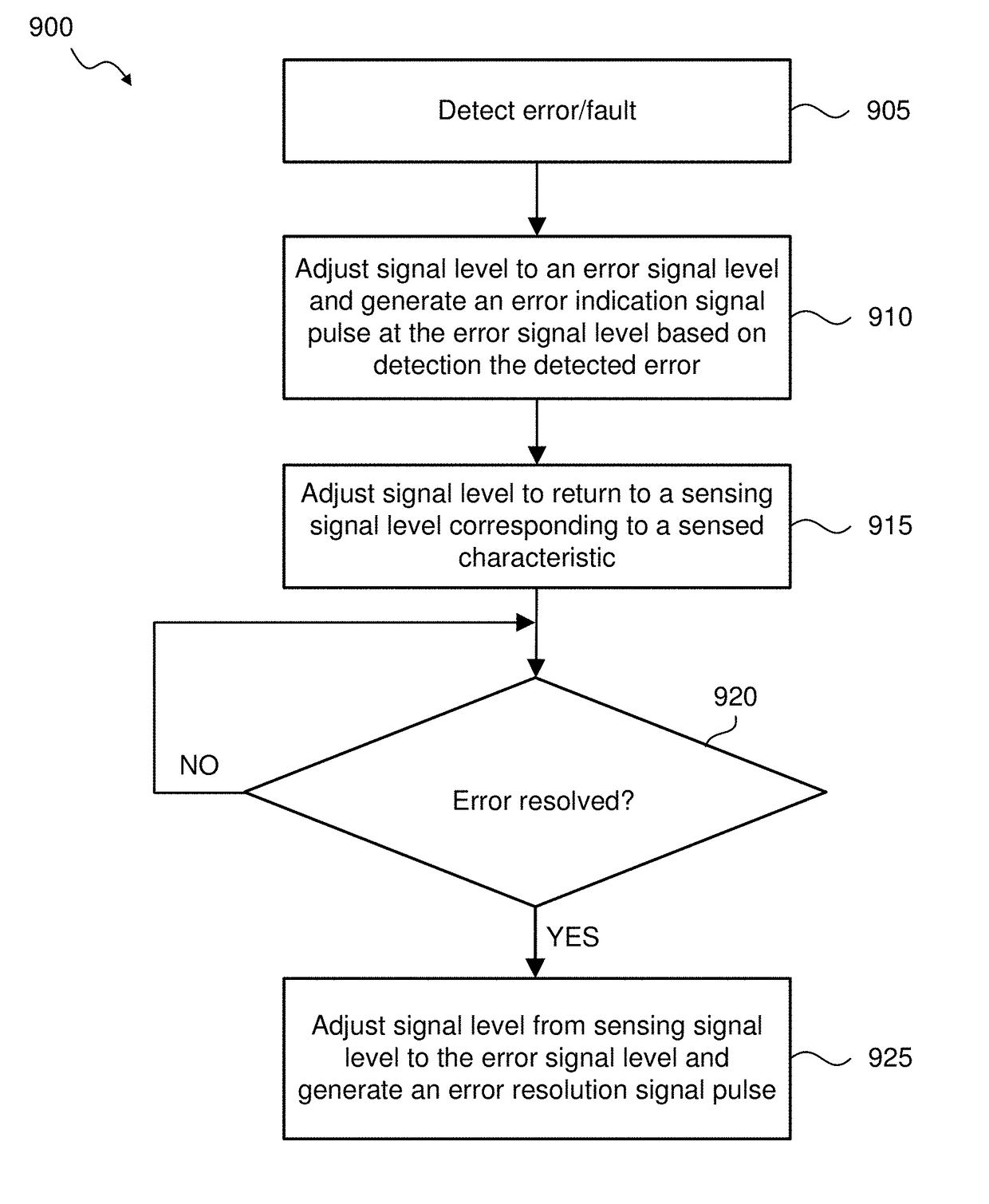

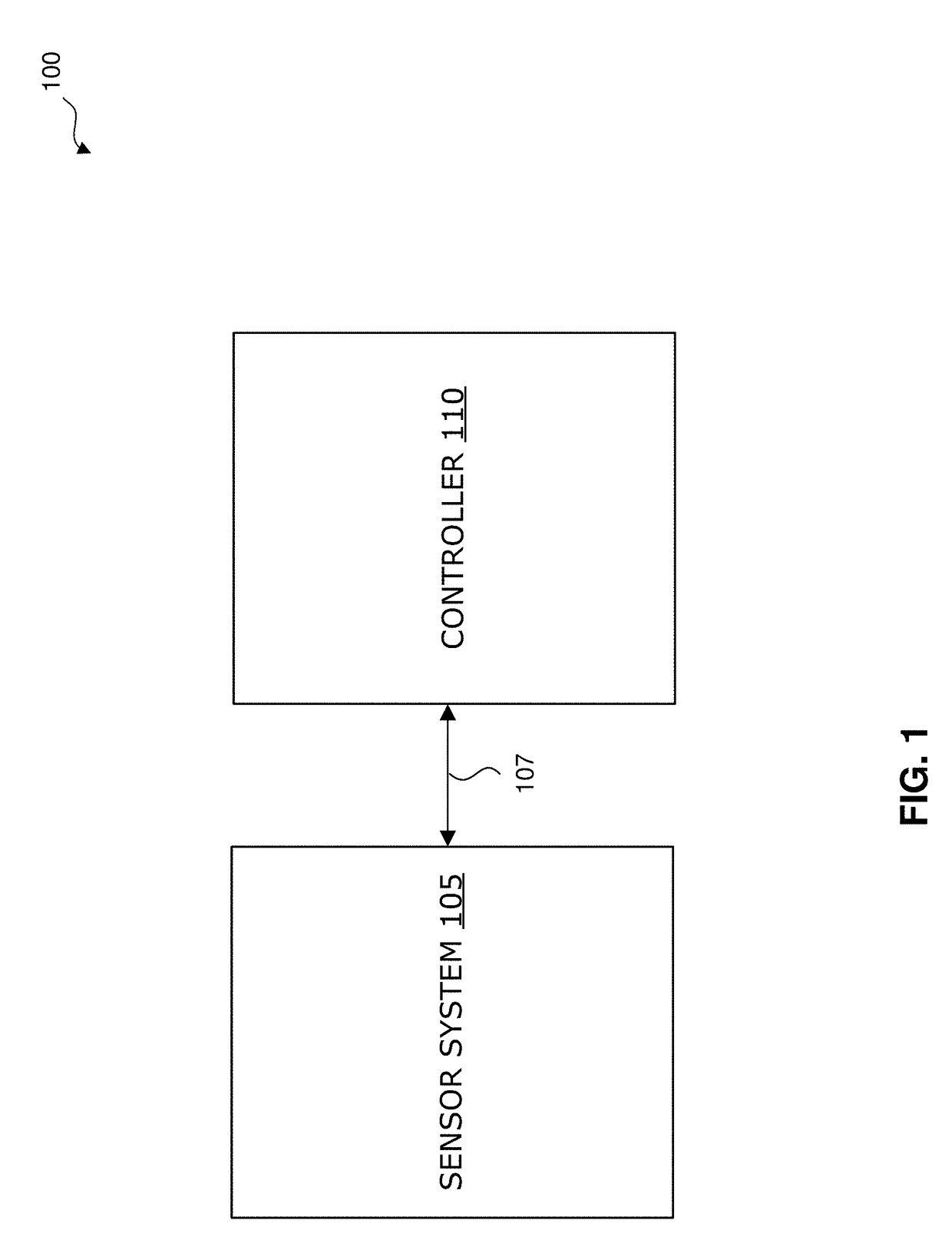

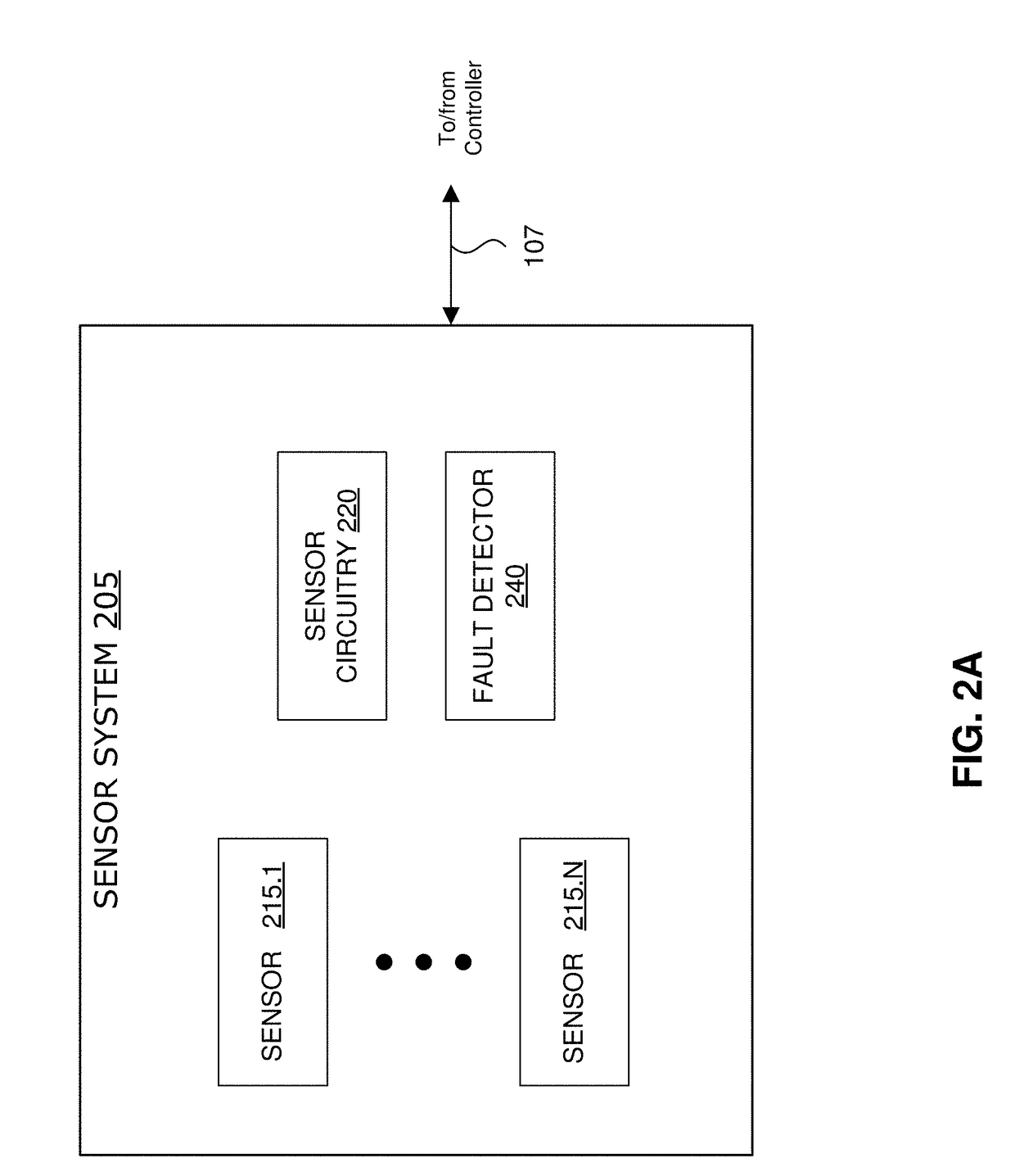

Signal protocol fault detection system and method

ActiveUS20180129196A1Programme controlElectric signal transmission systemsSignaling protocolSensor system

In systems, such as sensor systems, an output signal of the system (e.g. output of the sensor corresponding to a sensed characteristic) can be generated and provided. In response to a detected error, the output signal can be adjusted to generate an error indication signal pulse to indicate that an error has been detected. The output signal can then be adjusted to return to a signal level corresponding to the sensed characteristic. In response to the error being resolved, an error resolution signal pulse can be generated.

Owner:INFINEON TECH AG

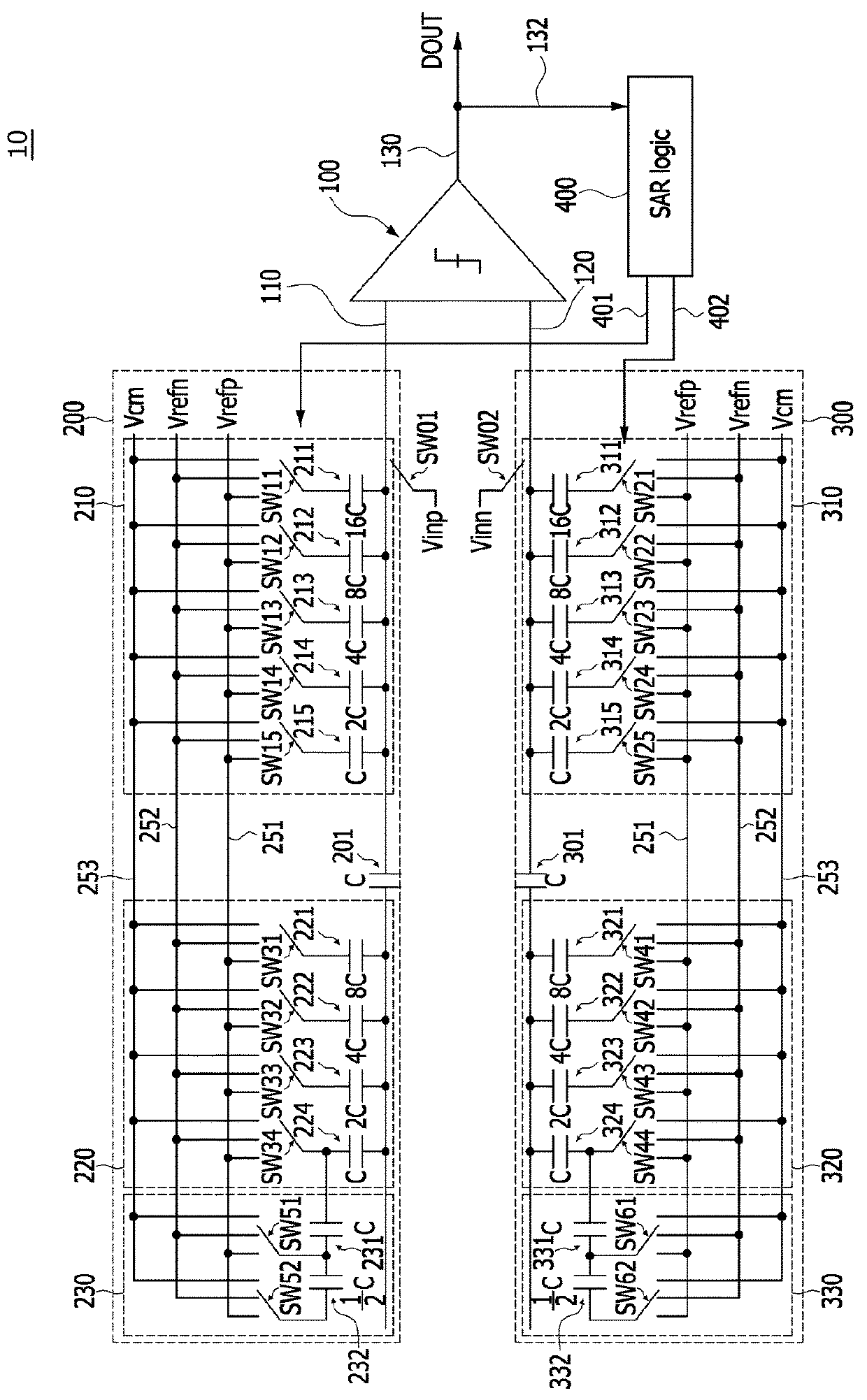

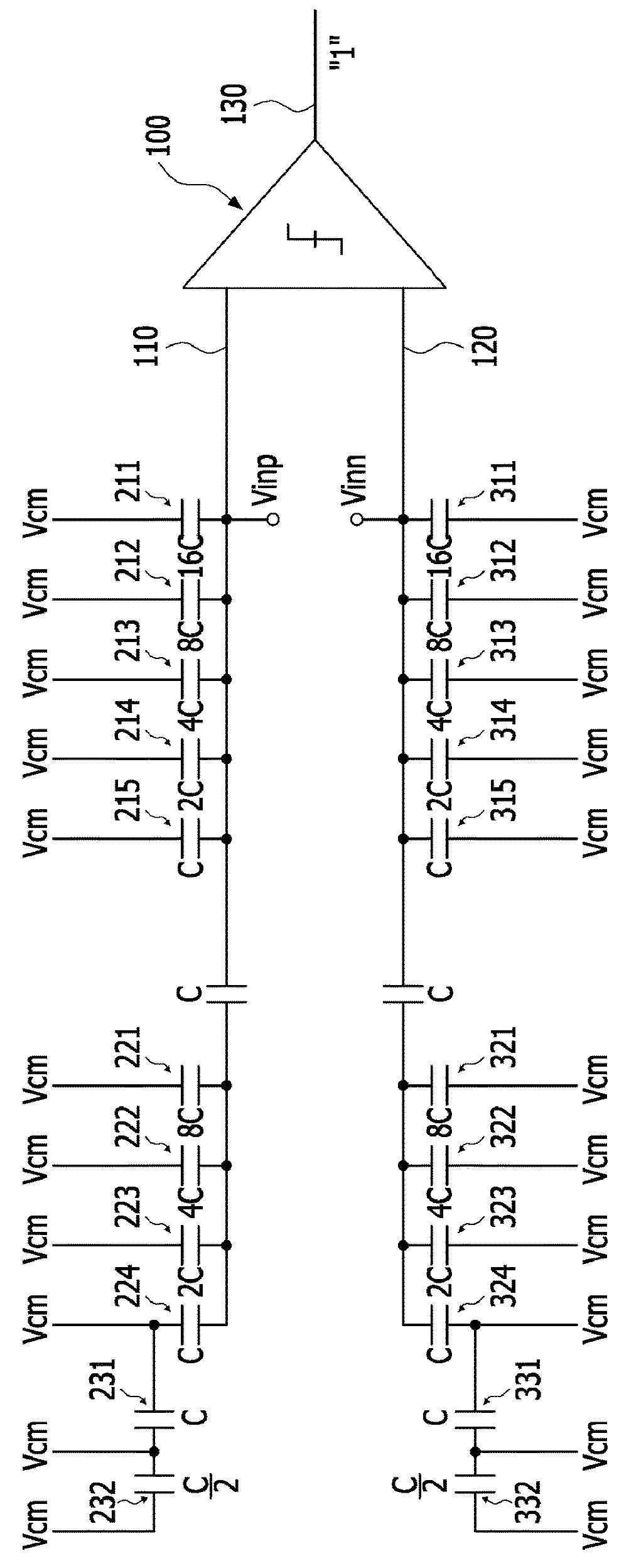

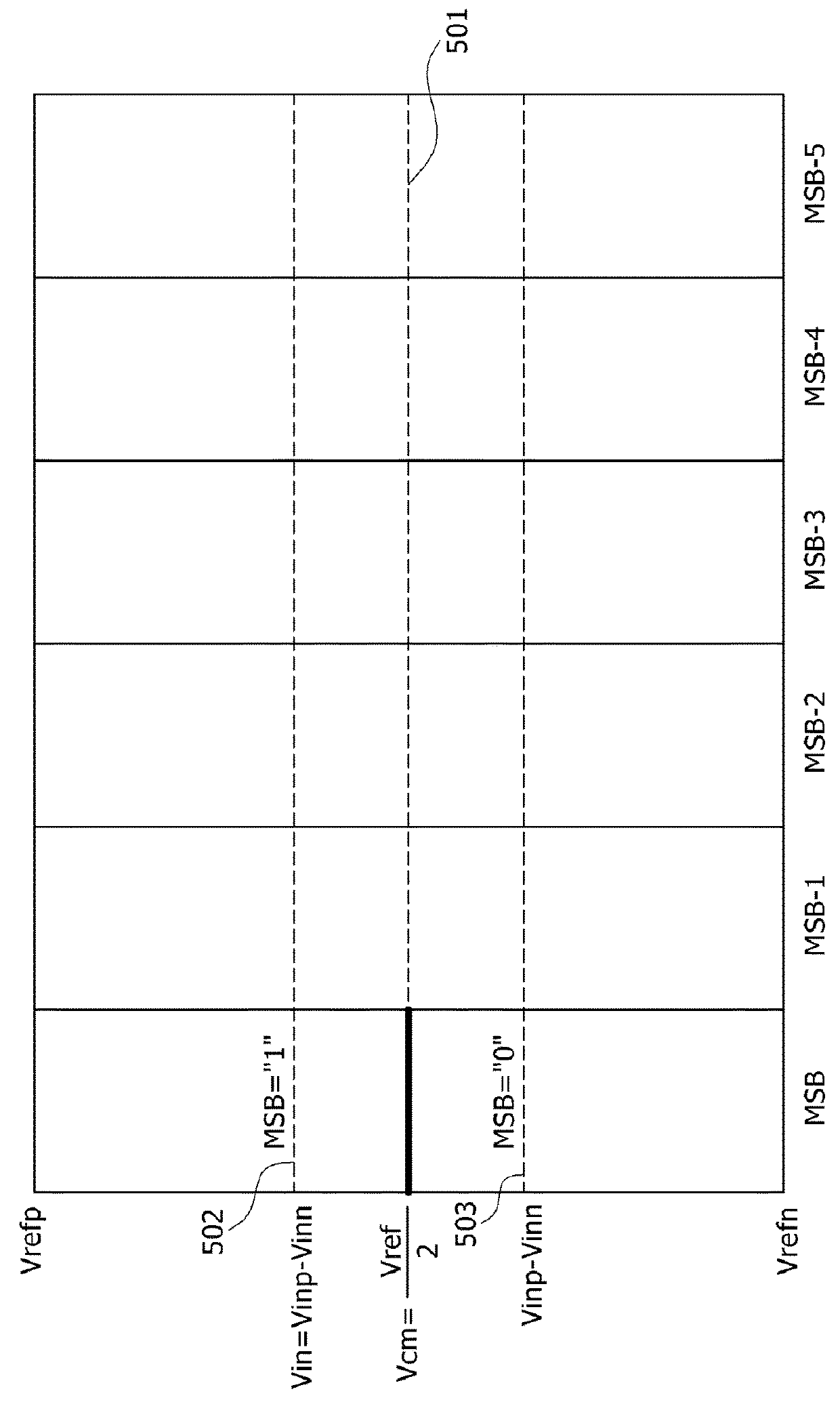

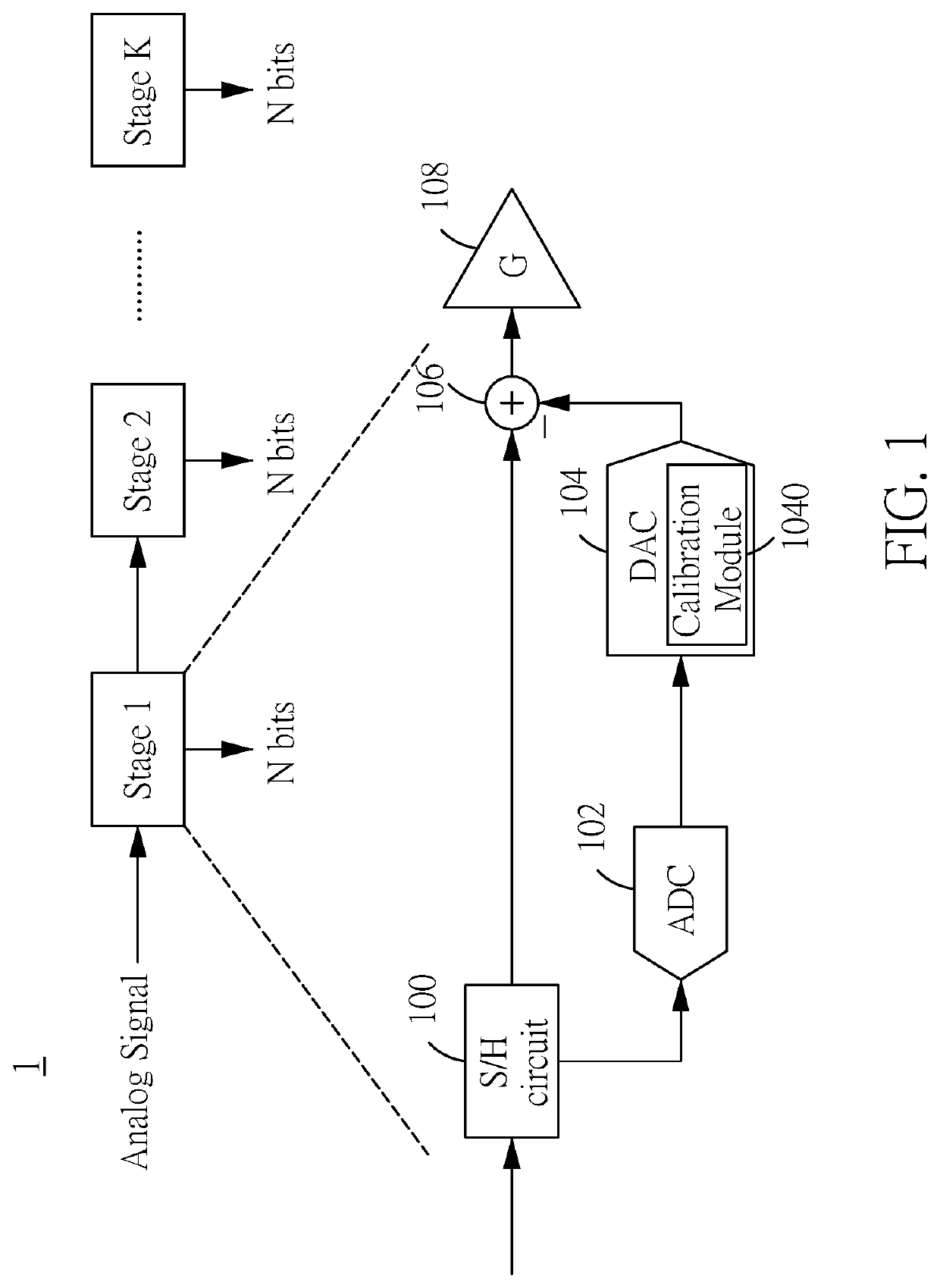

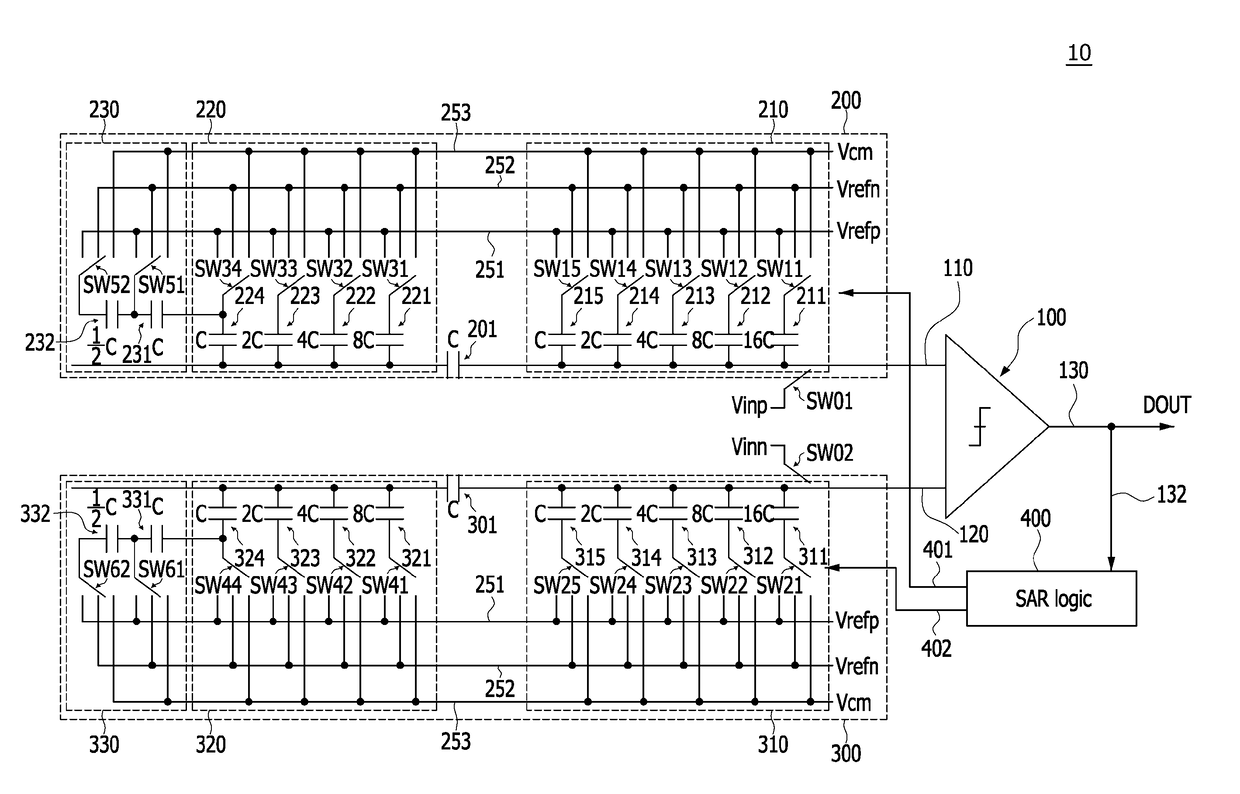

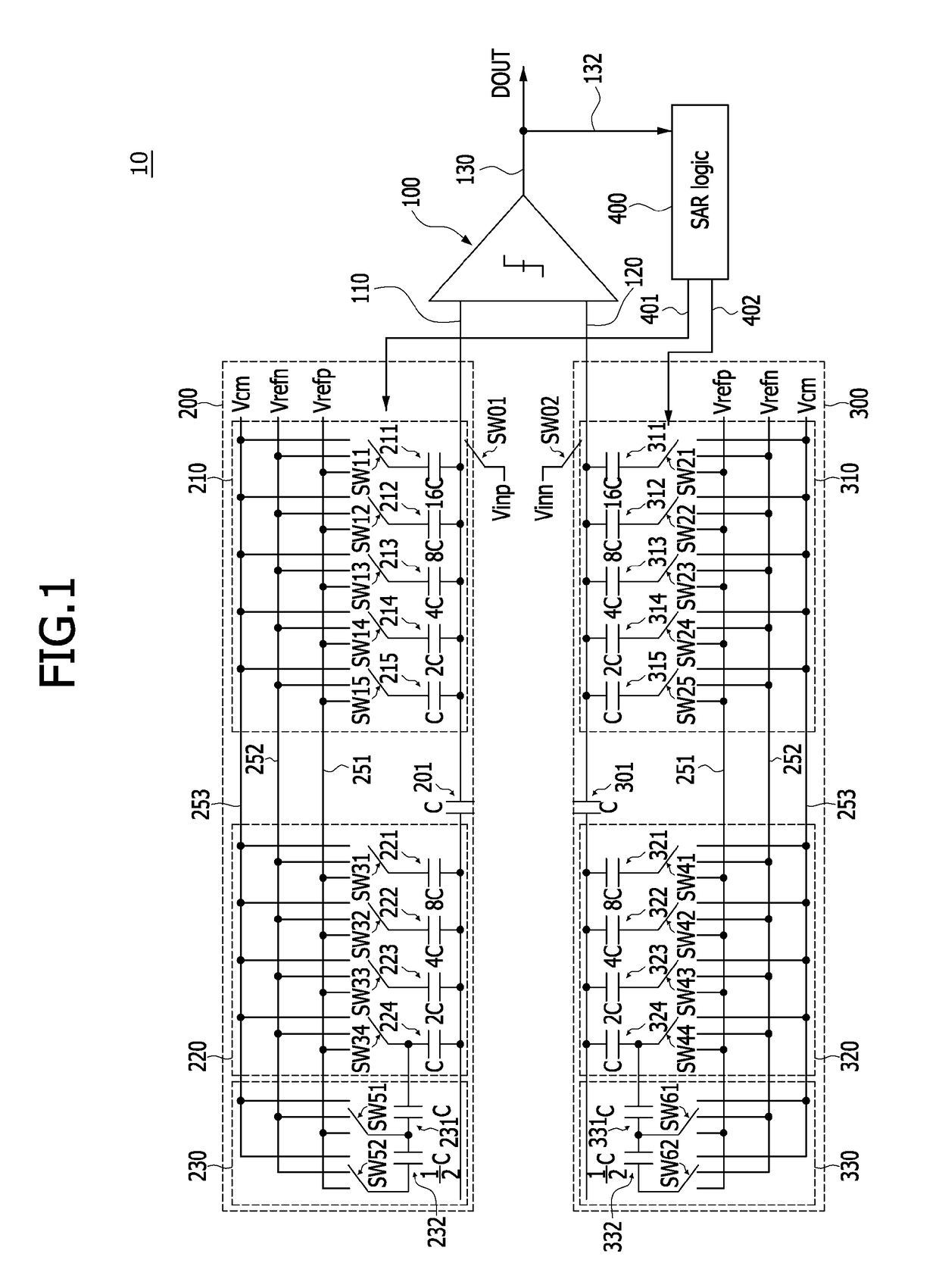

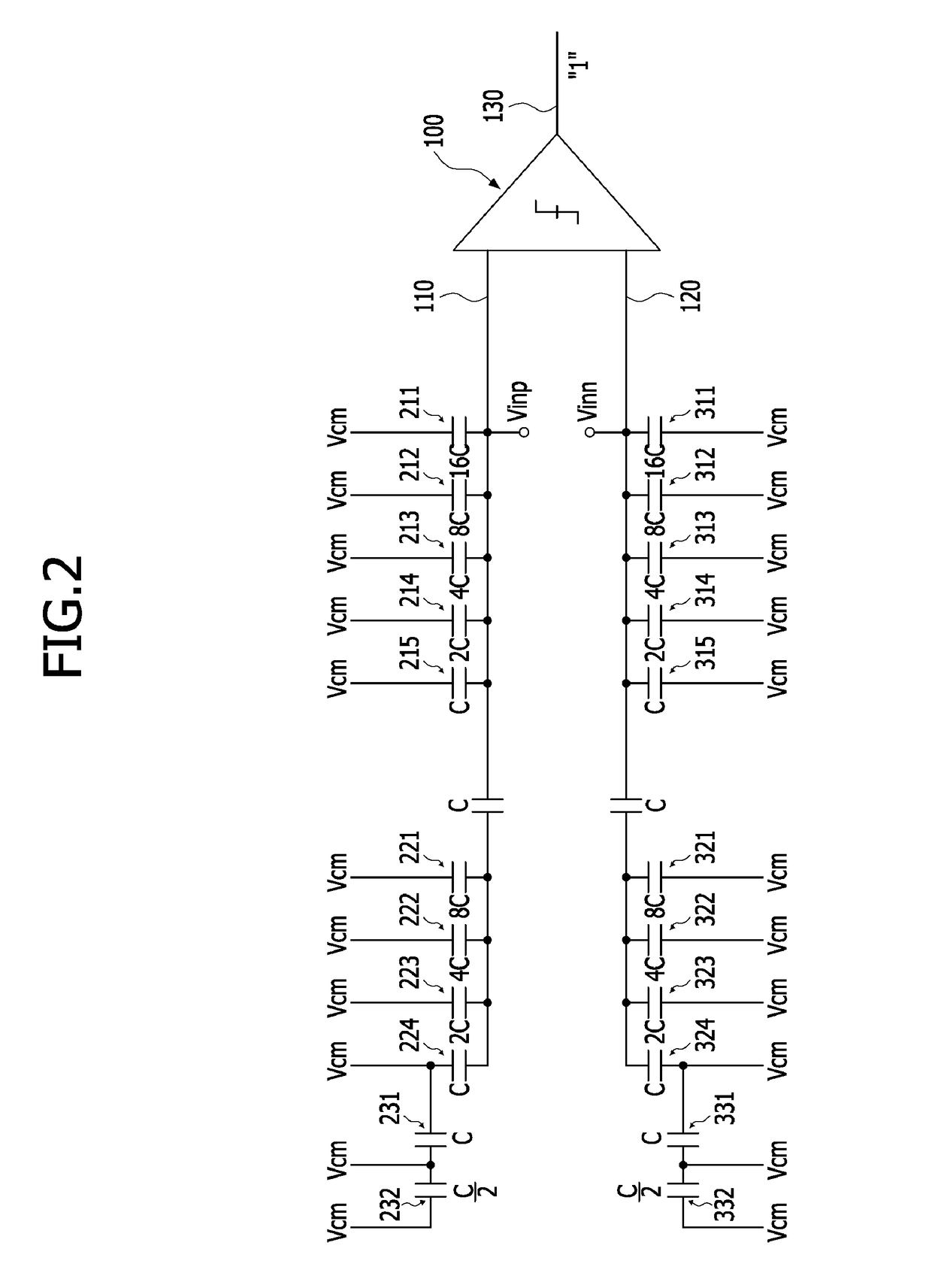

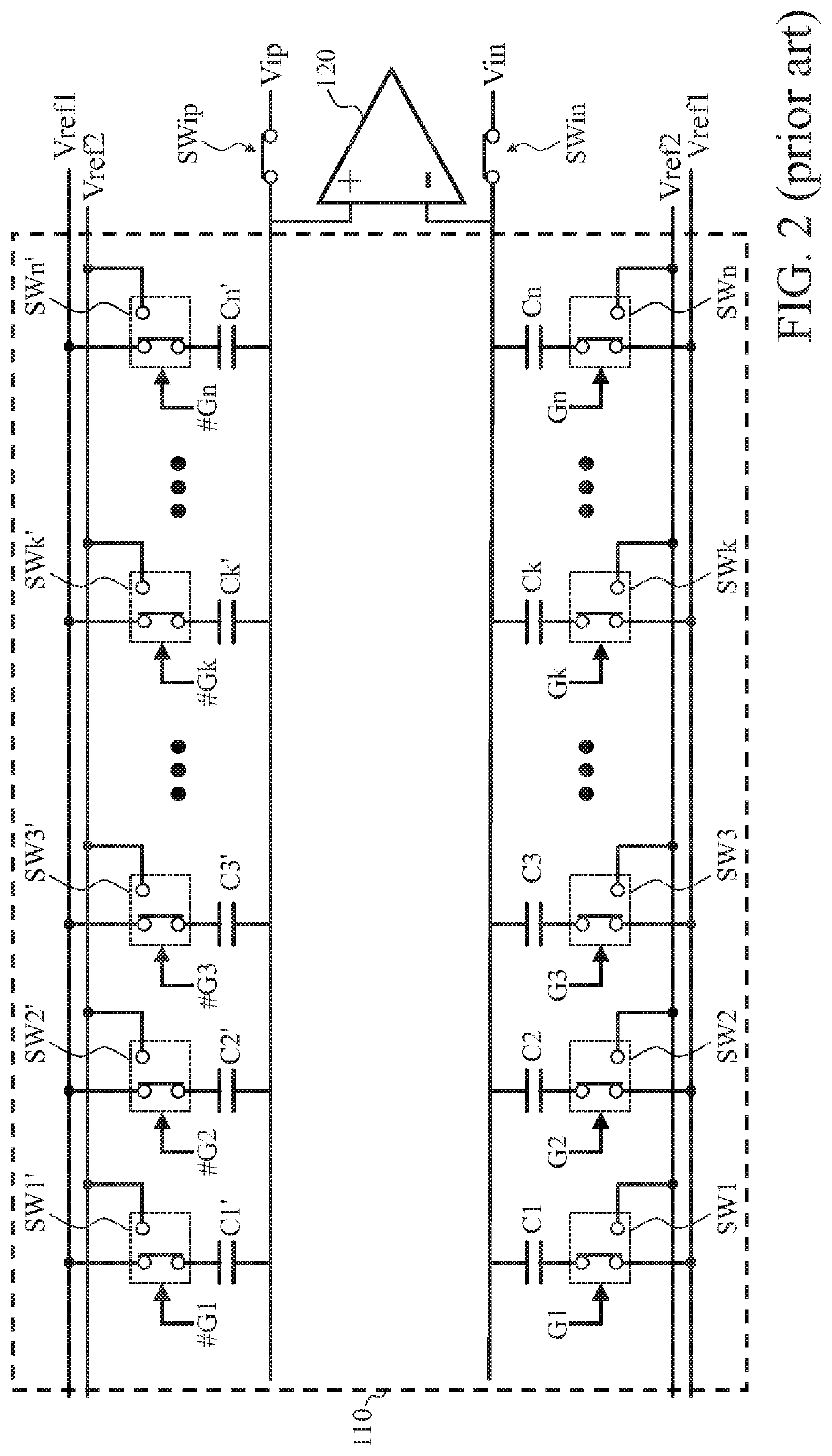

Successive approximation register analog-digital converter having a split-capacitor based digital-analog converter

ActiveUS20180269893A1Electric signal transmission systemsAnalogue/digital/analogue conversionDigital analog converterProcessor register

A successive approximation register analog-digital converter including a split-capacitor based digital-analog converter includes a comparator, a split-capacitor based digital-analog converter including a positive capacitor array and a negative capacitor array, and a successive approximation register logic. The positive capacitor array and the negative capacitor array each includes a positive capacitor array of a first stage and a negative capacitor array of a first stage that generate input signals of the comparator corresponding to upper bits including an MSB, respectively, a positive capacitor array of a second stage and a negative capacitor array of a second stage that generate input signals corresponding to intermediate bits, and a positive capacitor array of a third stage and a negative capacitor array of a third stage that generate input signals corresponding to lower bits of an LSB and a next to bit of the LSB.

Owner:SK HYNIX INC

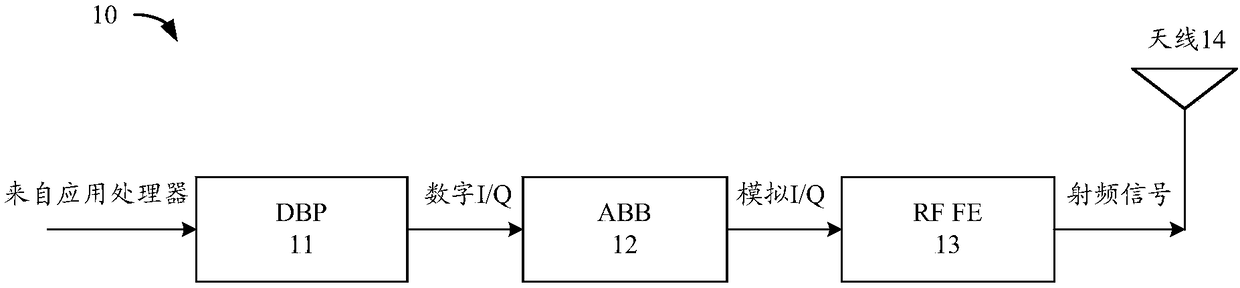

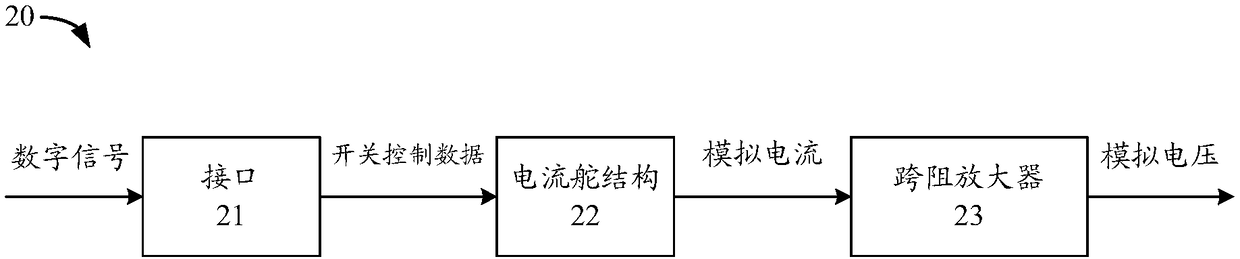

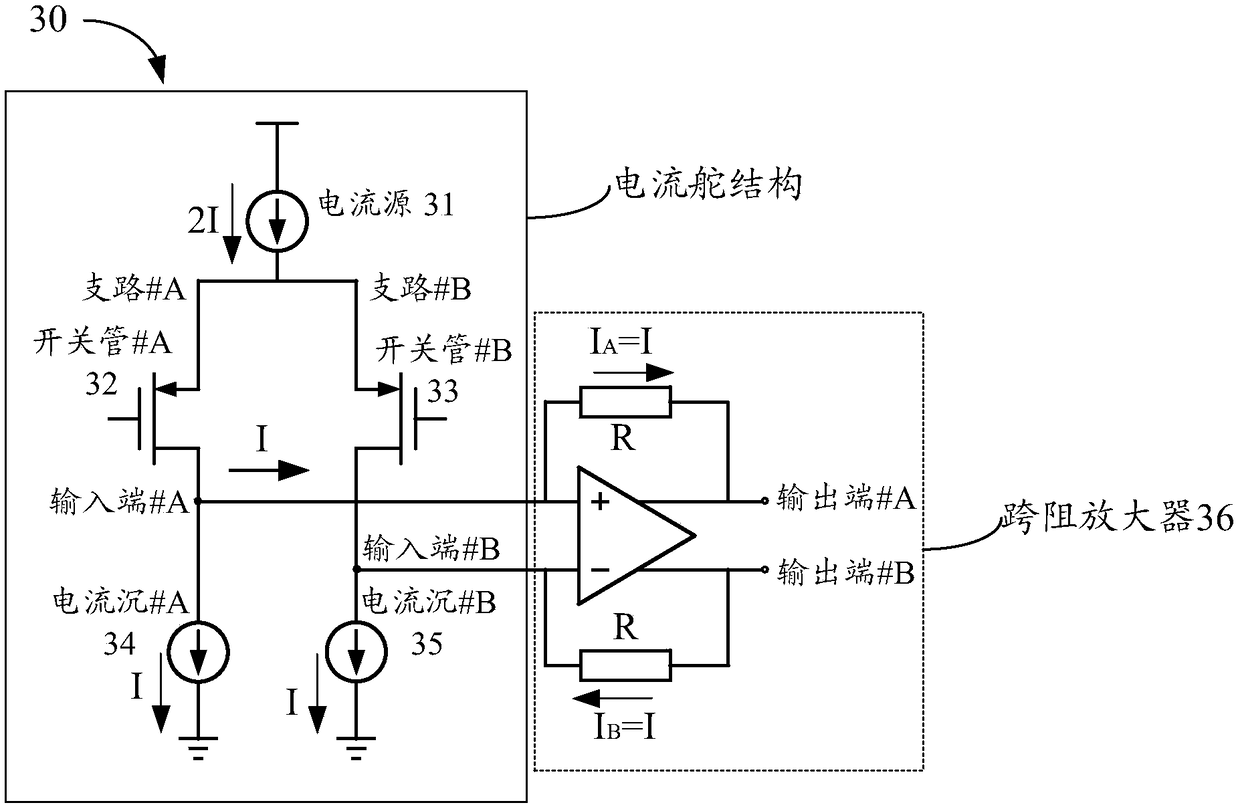

Digital-to-analog converter

ActiveCN108696278AReduce noiseReduce power consumptionElectric signal transmission systemsAnalogue/digital/analogue conversionAudio power amplifierTransimpedance amplifier

The present application provides a digital-to-analog converter capable of reducing quiescent current overhead and reducing static noise. The digital-to-analog converter comprises a first current source module, a first switch control module, and a transimpedance amplifier, wherein the first current source module is used for providing a current I1 for the digital-to-analog converter; the first switch control module is used for controlling turn-on or turn-off between each branch and a transimpedance amplifier in the digital-to-analog converter according to a to-be-converted digital signal; the current I1 provided by the first current source module flows into the transimpedance amplifier via a turned-on branch; and the transimpedance amplifier is used for converting the current I1 provided bythe first current source module into an analog voltage and outputting the analog voltage.

Owner:HUAWEI TECH CO LTD

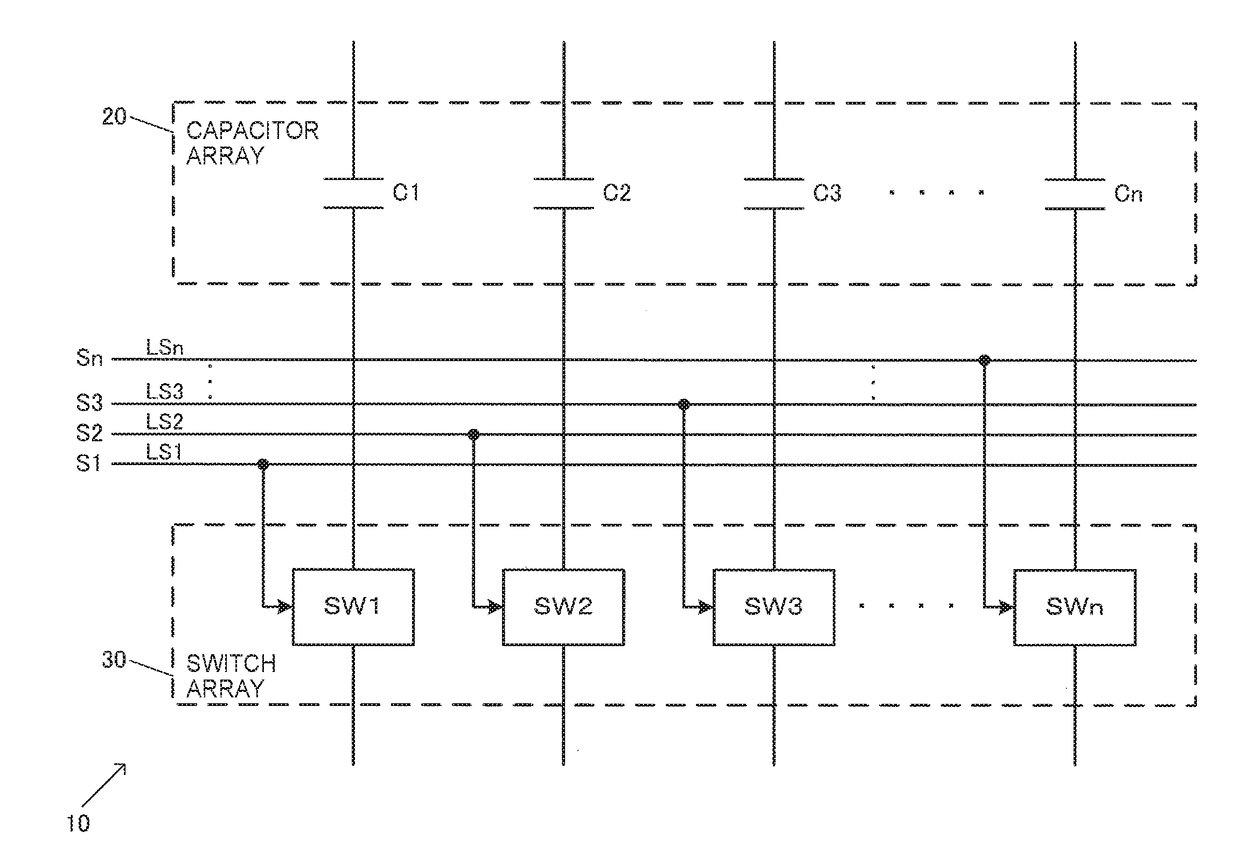

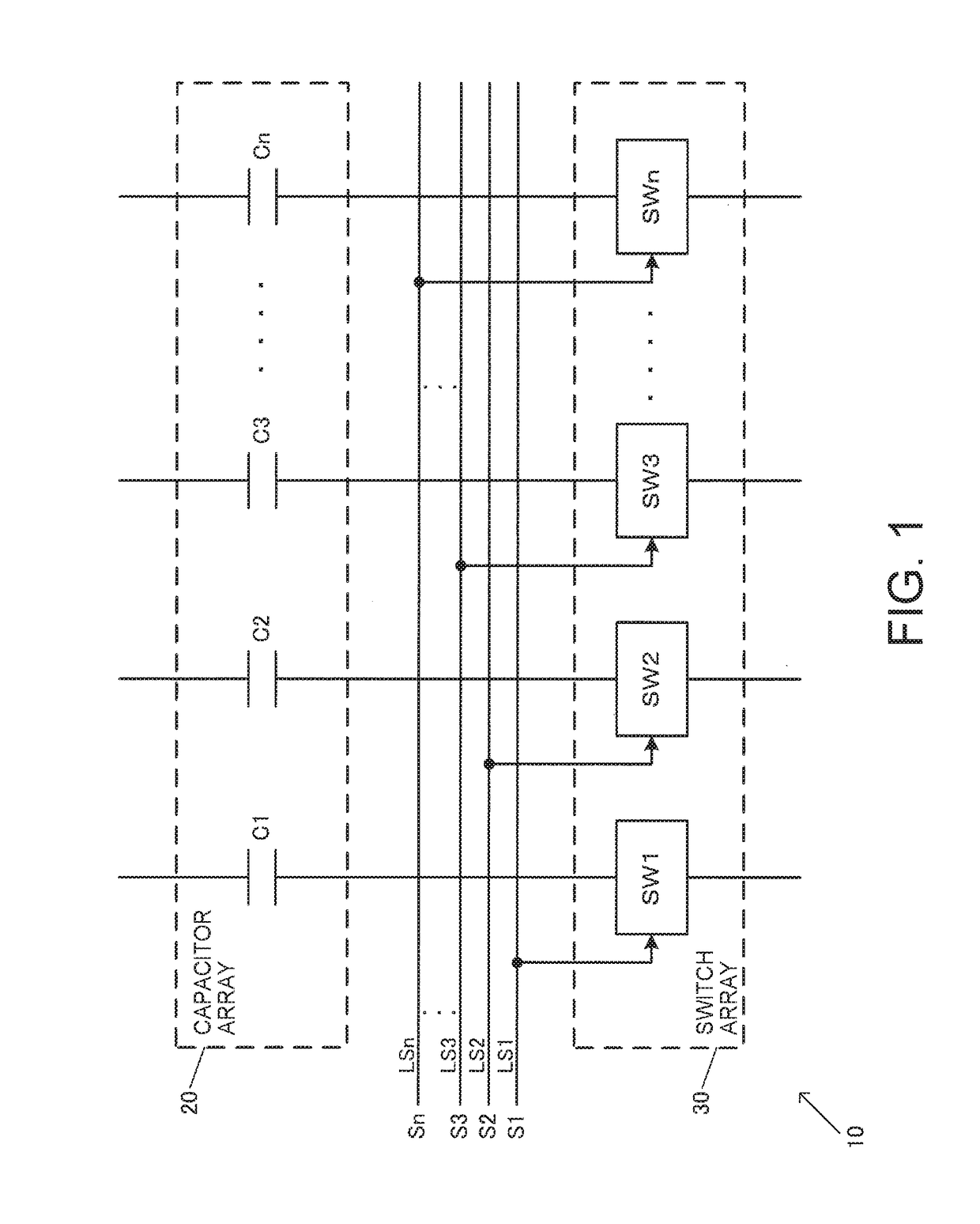

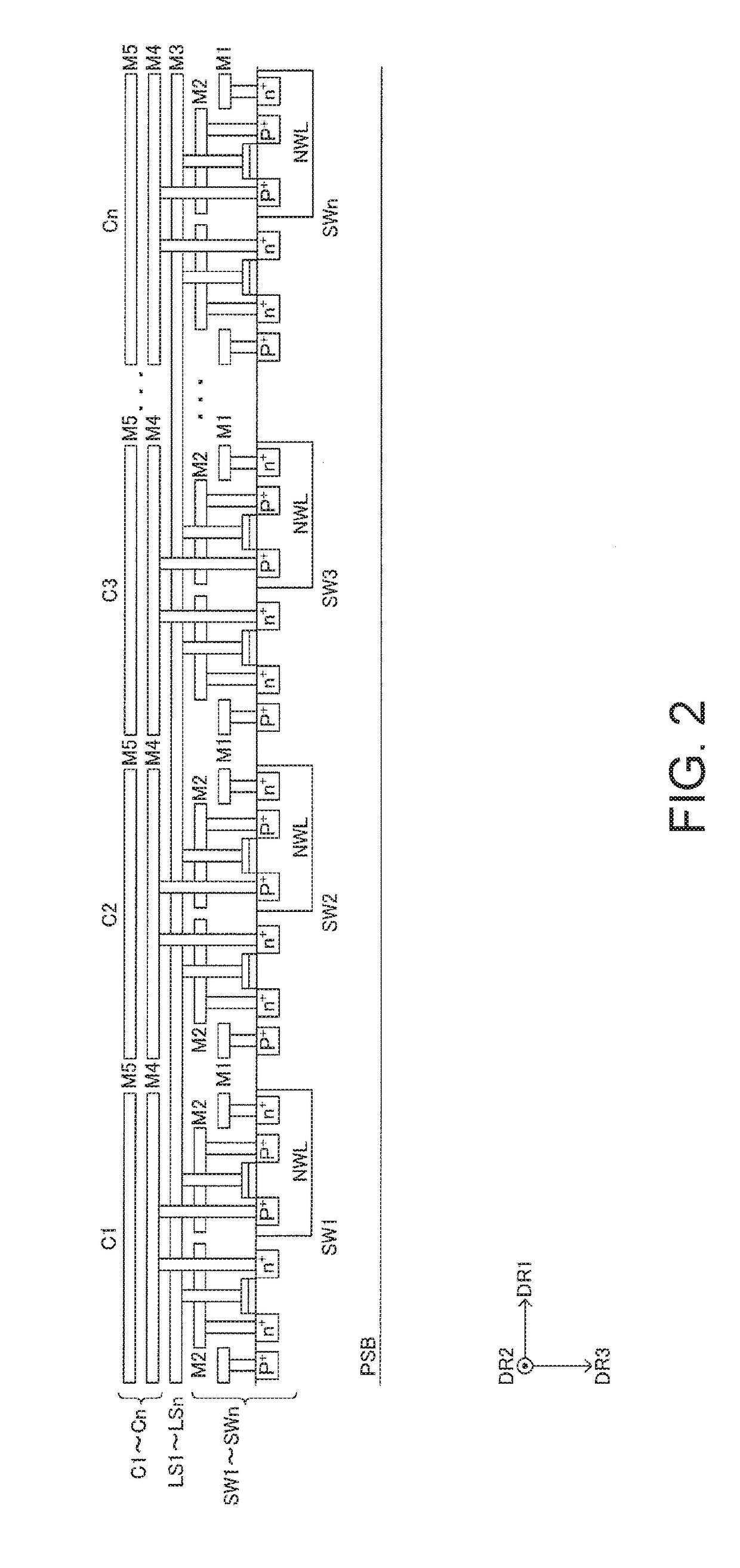

Capacitor circuit, circuit device, physical quantity detecting device, electronic apparatus, and moving object

ActiveUS20170365414A1Improve circuit performanceSmall area highElectric signal transmission systemsAnalogue/digital/analogue conversionControl signalEngineering

A capacitor circuit includes: a capacitor array including a plurality of capacitors; a switch array including a plurality of switch circuits, the switch circuits being respectively connected to the capacitors of the capacitor array; a plurality of switch control signal lines supplied with a plurality of switch control signals; and a substrate having a major surface on which the switch circuits are formed. At least part of the capacitors of the capacitor array is formed of a first conductive layer. The switch control signal lines are formed of a second conductive layer provided between the major surface and the first conductive layer. The capacitor array and the switch array are disposed so as to overlap each other at least in part in a plan view when viewed in a normal direction of the major surface.

Owner:SEIKO EPSON CORP

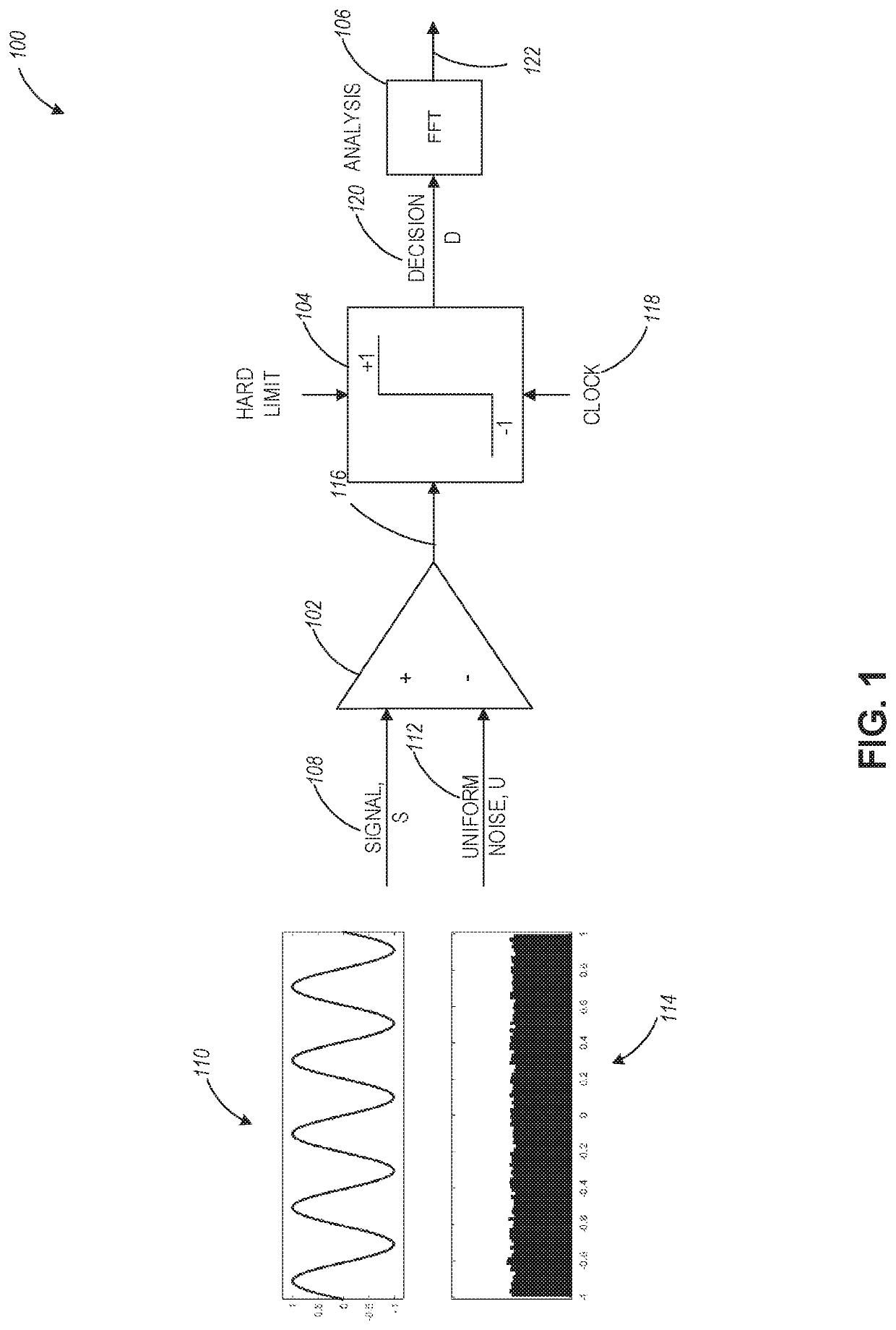

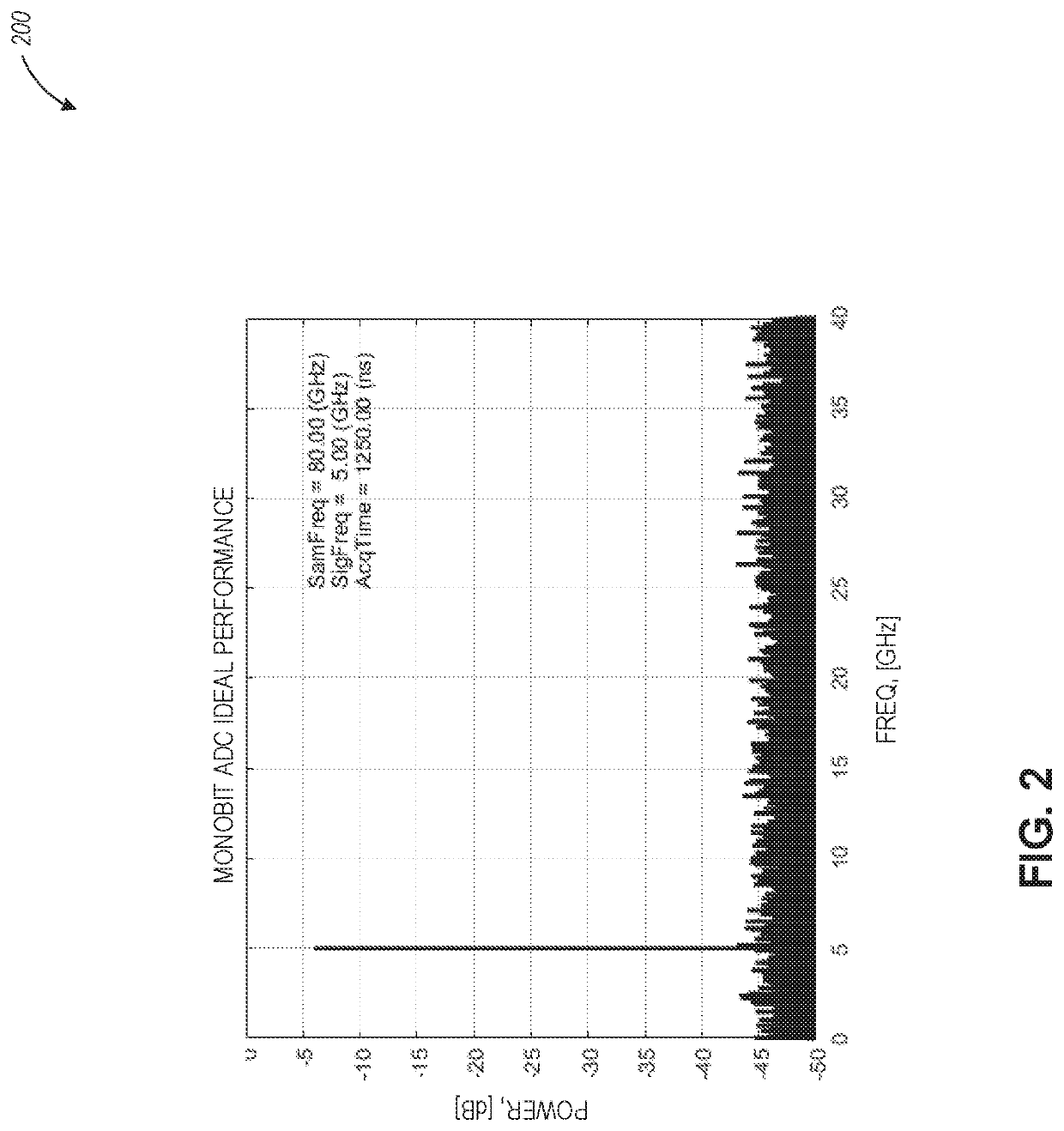

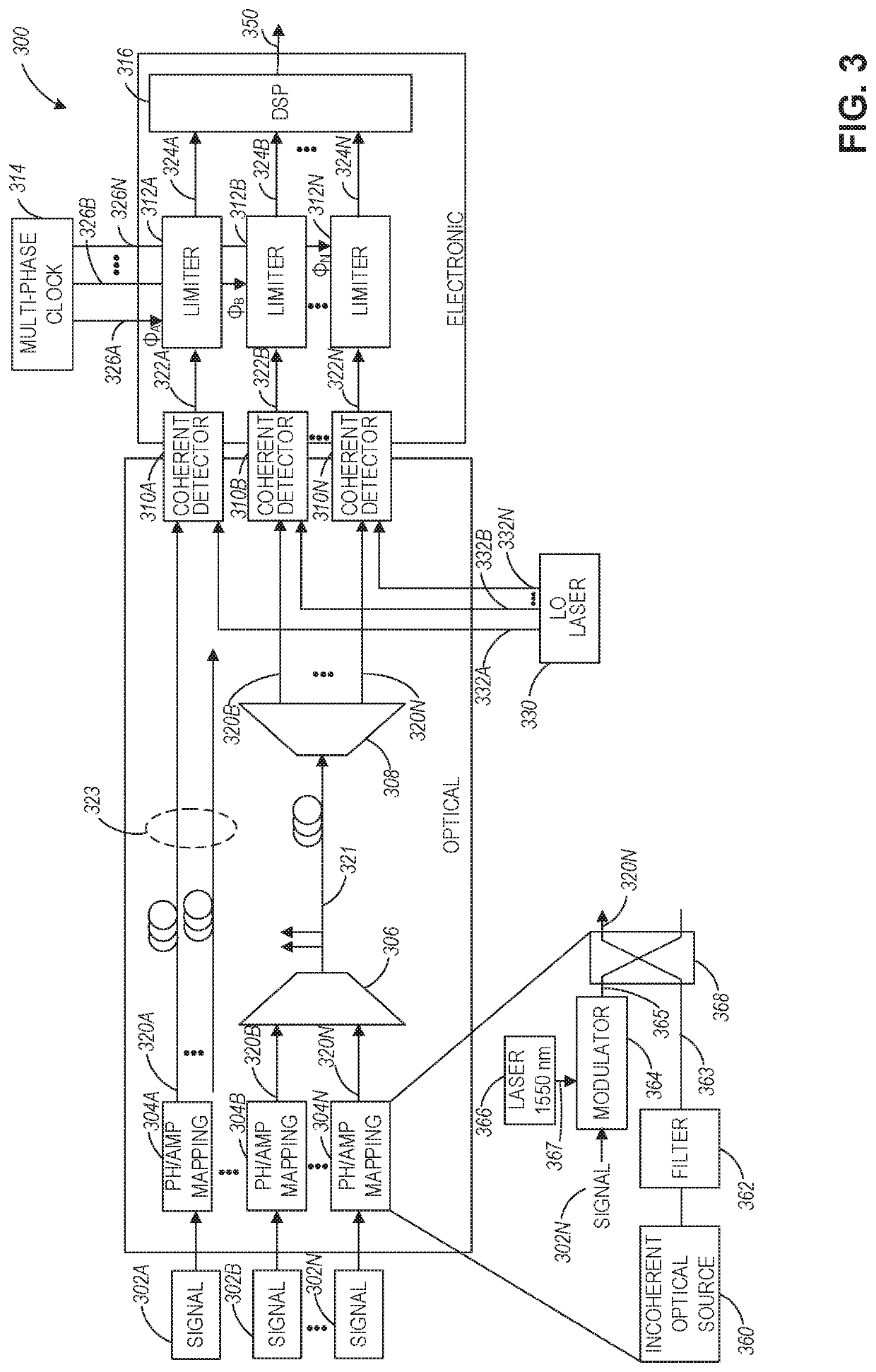

Distributive photonic monobit analog-to-digital converter

ActiveUS10700700B1Electric signal transmission systemsAnalogue/digital/analogue conversionPhotodetectorPhase difference

A distributive photonic monobit analog-to-digital converter includes a plurality of signal processing chains configured to receive a corresponding plurality of analog input electrical signals. Each processing chain includes an incoherent optical source configured to generate an optical noise signal, an optical modulator configured to modulate an analog input electrical signal of the plurality of analog input electrical signals onto an input optical signal to generate an optical modulated signal, a coupler configured to couple the optical modulated signal with the optical noise signal to generate a coupled signal, a photodetector configured to generate a phase difference between the optical modulated signal and the optical noise signal using the coupled signal, and a limiter configured to output a decision signal based on the phase difference and using a clock signal. A multi-phase clock generator is configured to generate the clock signal for each of the plurality of signal processing chains.

Owner:RAYTHEON CO

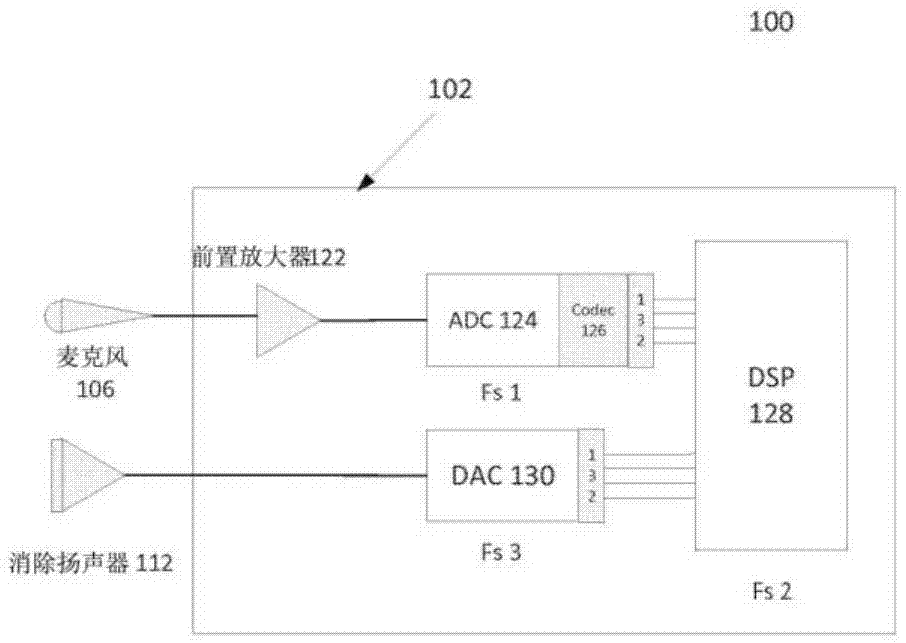

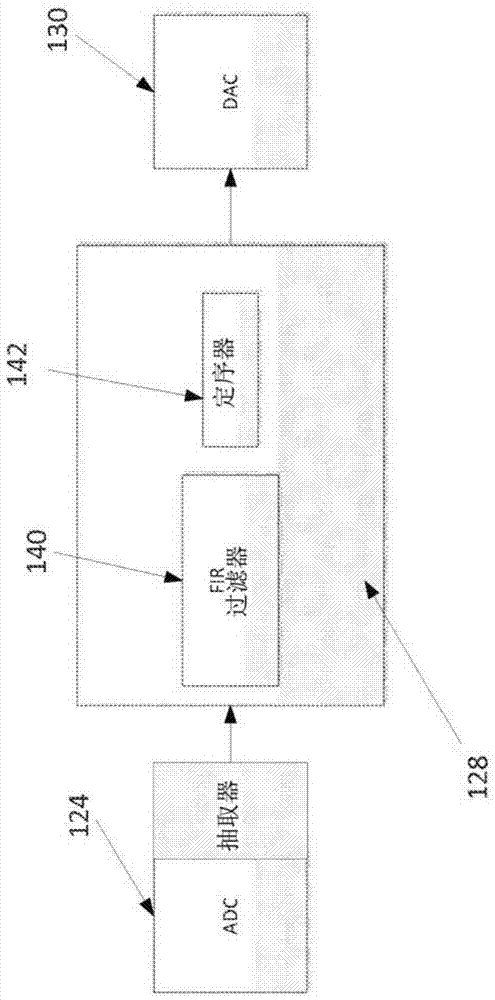

Systems and methods for noise canceling

ActiveCN105453169AAnalogue/digital/analogue conversionSound producing devicesTransport layerData transmission

Active Noise Cancellation (ANC) systems and methods that reduce latency to improve performance. In certain embodiments the systems sample a noise signal using a sample period to create a stream of digital signal data that is representative of the noise signal. A data transport layer carries the digital signal data to a signal processor. The transport layer temporally organizes the digital signal data to place the digital signal data within an initial phase of a sample period. The remaining phase of the sample period is set to a duration that allows the signal processor to process the digital signal data carried in the initial phase and to output the processed data during the same sample period. In this way, the processing of data occurs within one sample period and the latency is reduced and predictable.

Owner:ANALOG DEVICES INC

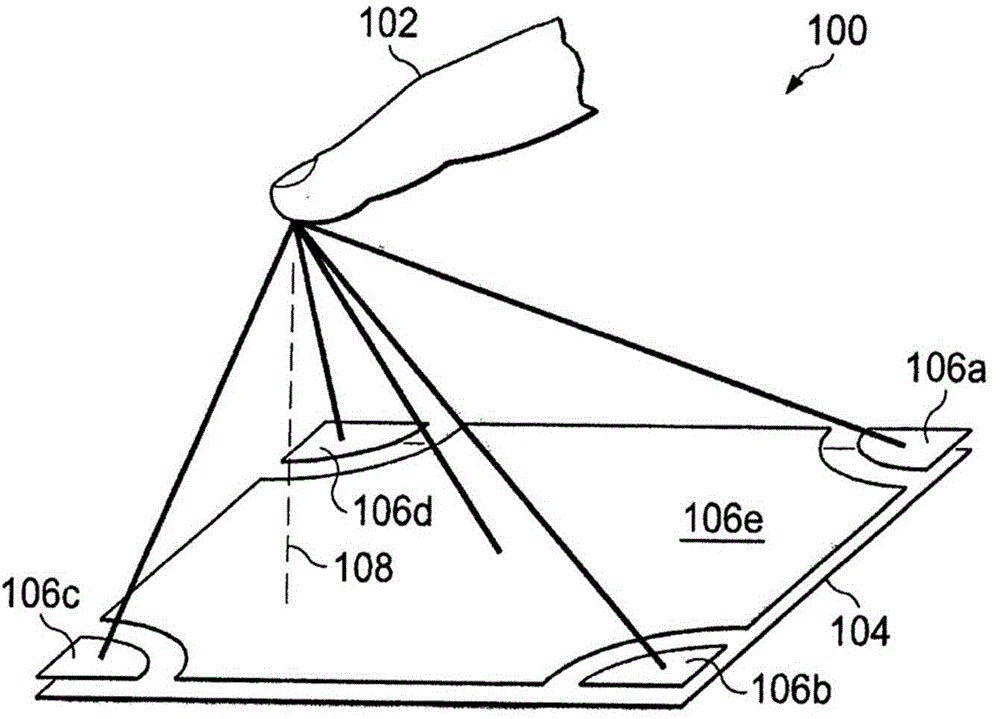

Signal processing for a capacitive sensor system with robustness to noise

ActiveCN104662393ACapacitance measurementsAnalogue/digital/analogue conversionCapacitive sensingSelf adaptive

A capacitive sensor includes a transmit electrode configured to provide an alternating electric field to a sensor; one or more receive electrodes for detecting variations in the alternating electric field; and an adaptive frequency adjustment unit configured to adjust an operating frequency of the alternating electric field responsive to detection of a noise measure, such as noise power.

Owner:MICROCHIP TECH GERMANY II

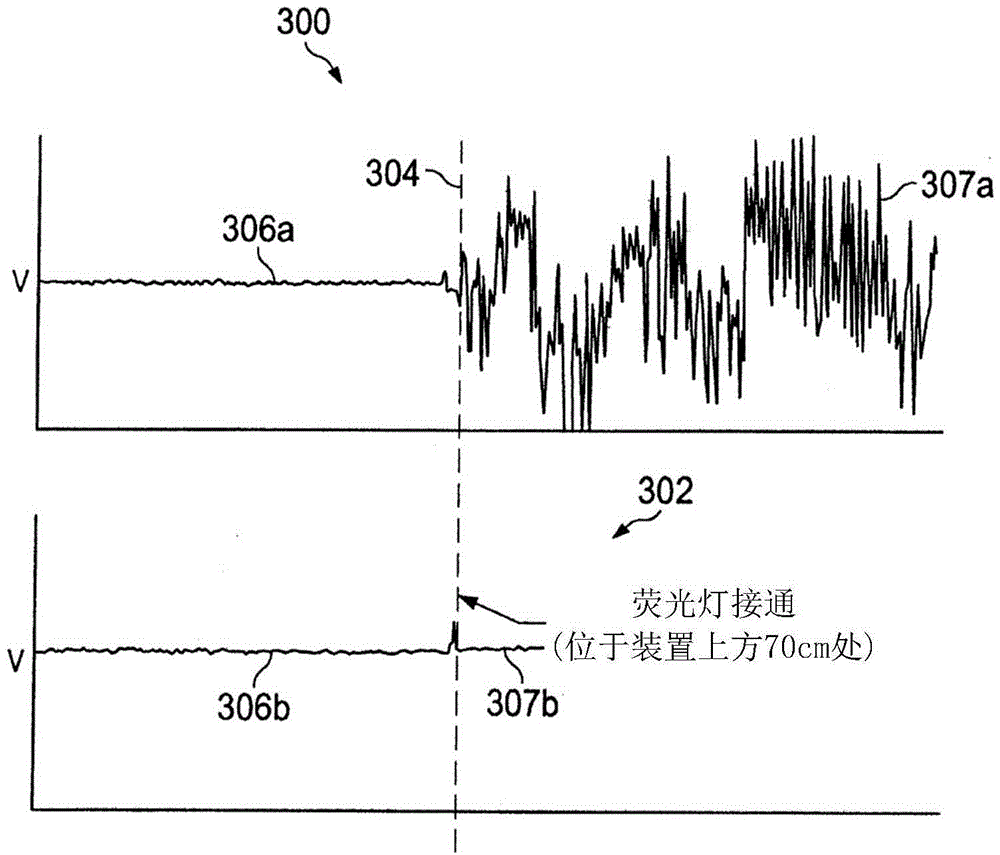

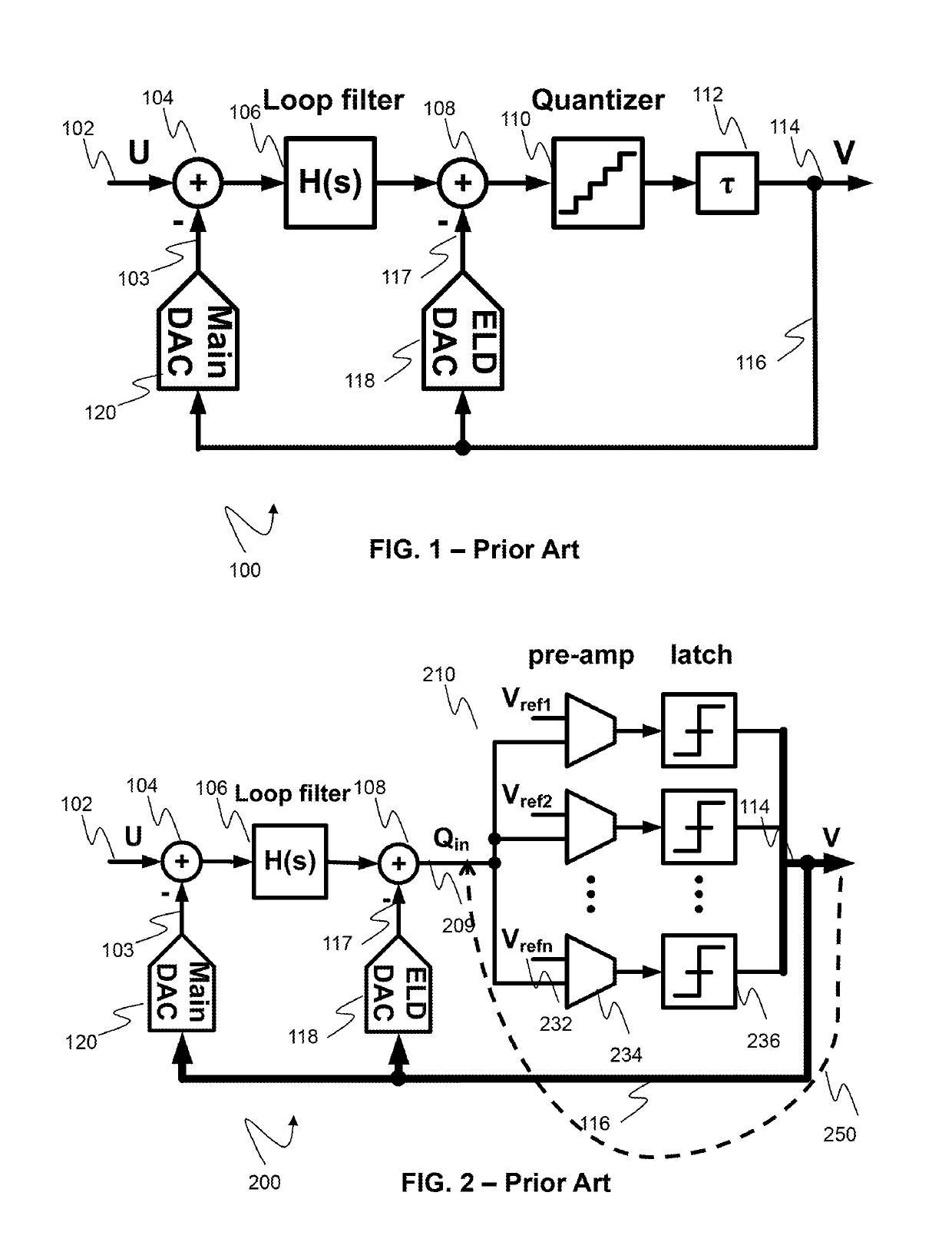

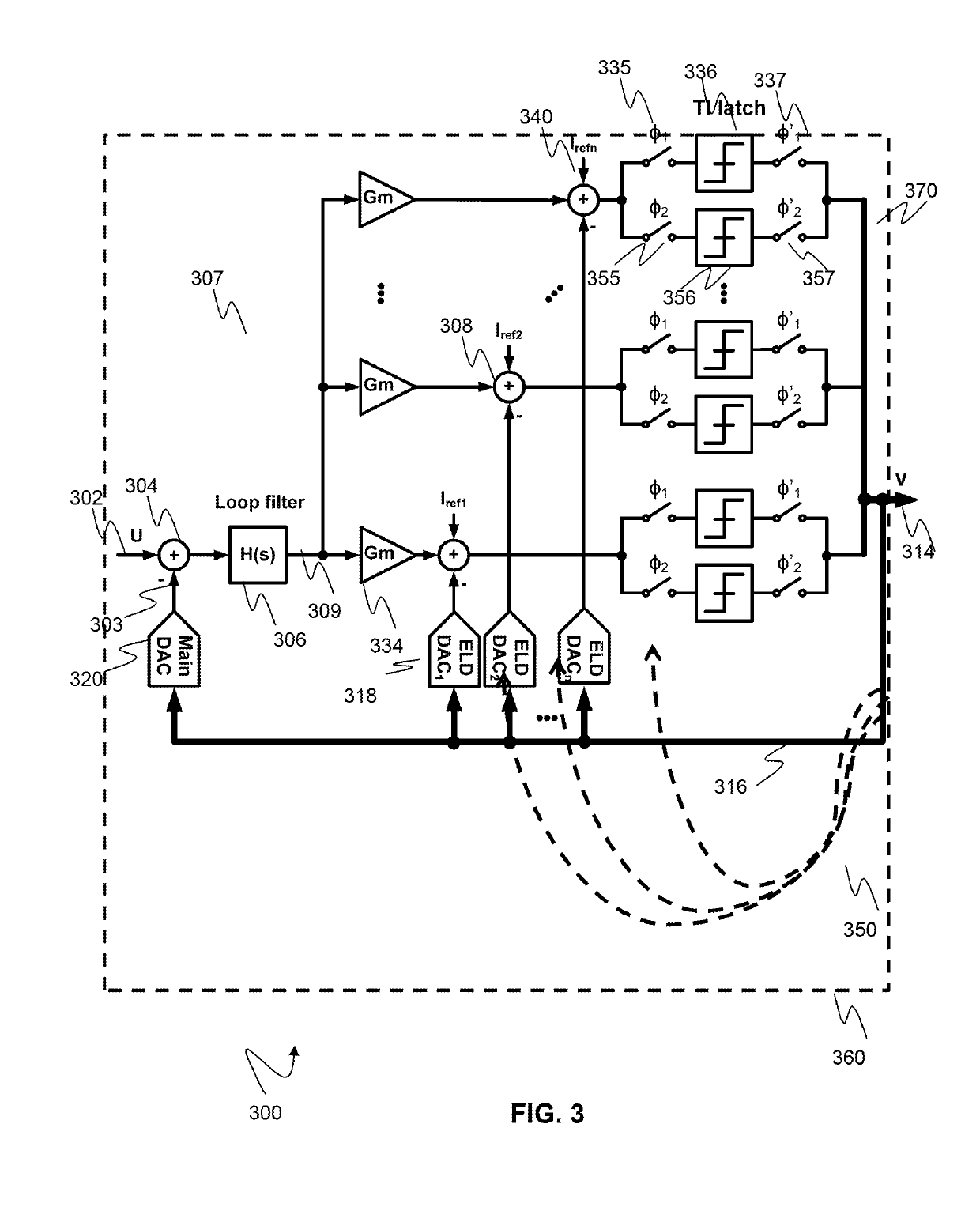

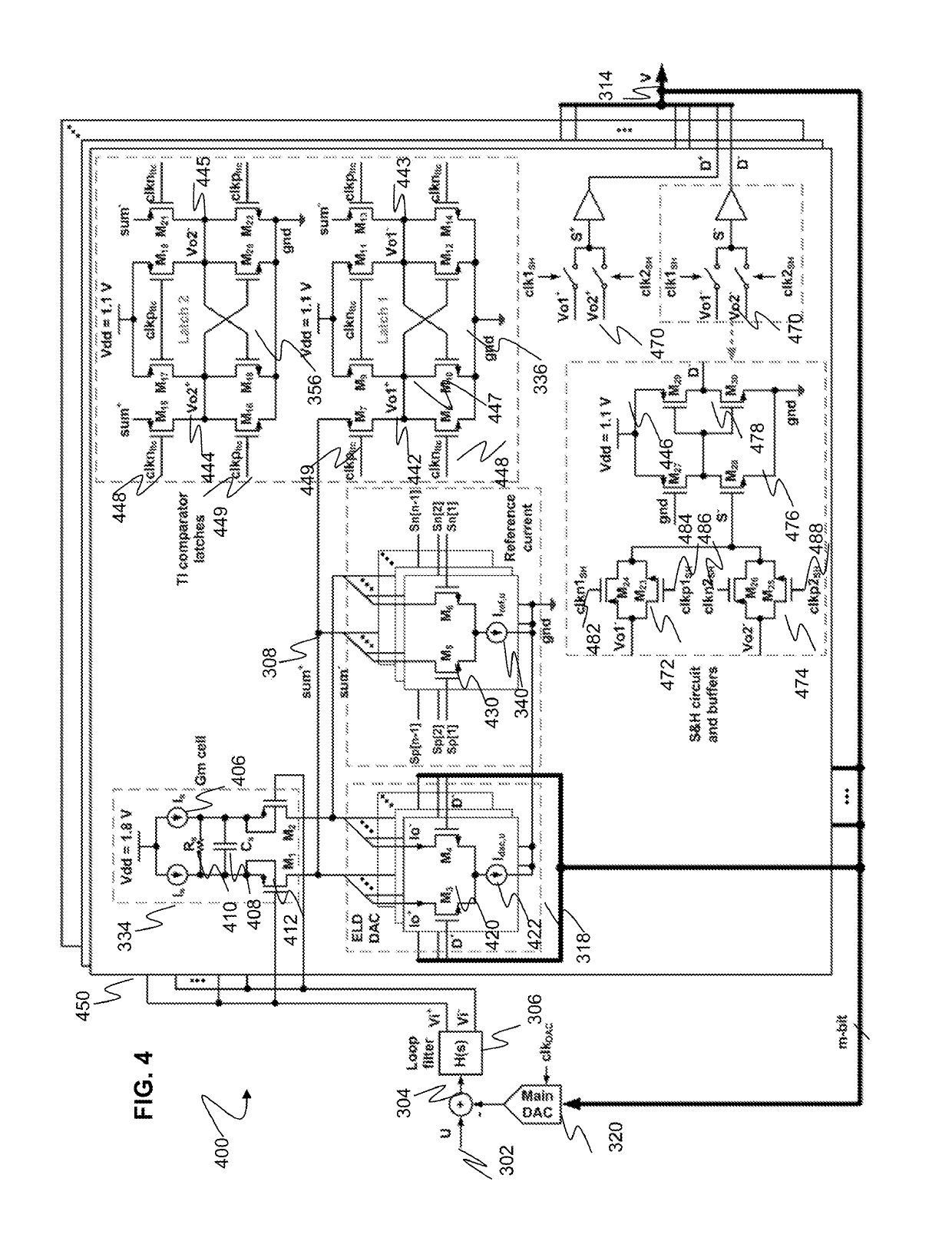

Sigma delta modulator, integrated circuit and method therefor

ActiveUS10439634B2Electric signal transmission systemsAnalogue conversionLoop filterDigital analog converter

A multi-bit continuous-time sigma-delta modulator, SDM, includes an input configured to receive an input analog signal; a first summing junction configured to subtract a feedback analog signal from the input analog signal; a loop filter configured to filter an output signal from the first summing junction (304): an analog-to-digital converter, ADC, configured to convert the filtered analog output signal to a digital output signal; and a feedback path for routing the digital output signal to the first summing junction. The feedback path includes a plurality of digital-to-analog converters, DACs, configured to convert the digital output signal to an analog form. The ADC comprises a plurality of N-bit comparator latches that are each locally time-interleaved with at least a pair of latches and configured to function in a complementary manner and provide a combined complementary output.

Owner:NXP BV

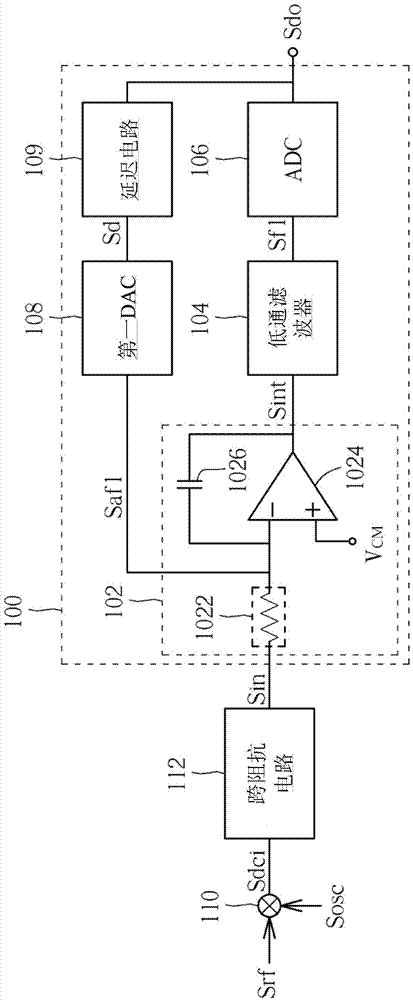

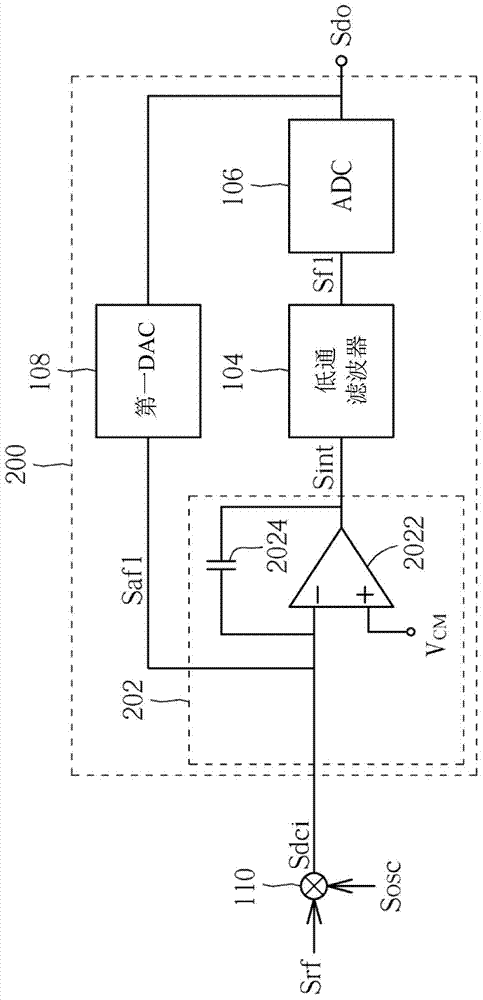

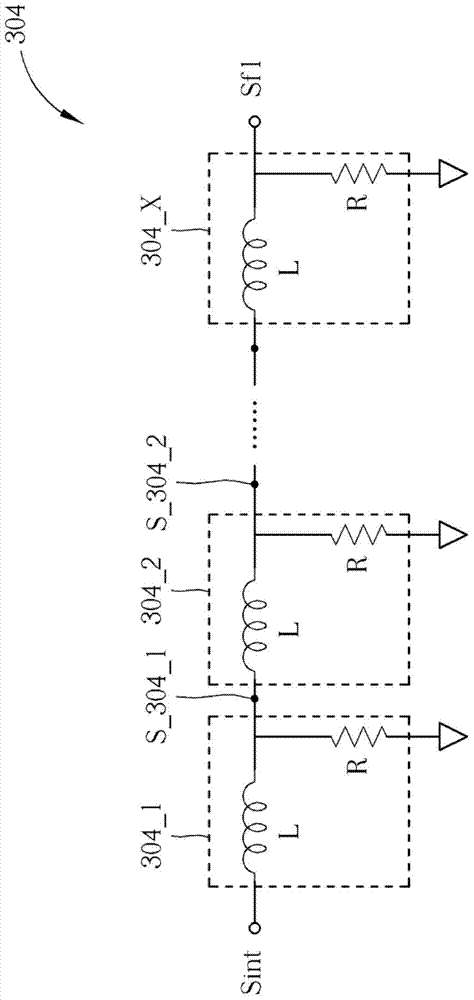

Analog-to-digital converting device and analog-to-digital converting method

ActiveCN104716959ALow costOptimized areaAnalogue/digital/analogue conversionAnalogue conversionIntegratorAnalog feedback

An analog-to-digital converting device (100, 200) includes: an integrator (102, 202) arranged to generate an integrating signal according to an analog input signal and a first analog feedback signal; a low-pass filter (104, 304, 404, 504, 604, 704) arranged to generate a first filtered signal according to the integrating signal; an analog-to-digital converter (106) arranged to generate a digital output signal according to the first filtered signal; and a first digital-to-analog converter (108) arranged to generate the first analog feedback signal according to the digital output signal.

Owner:MEDIATEK INC

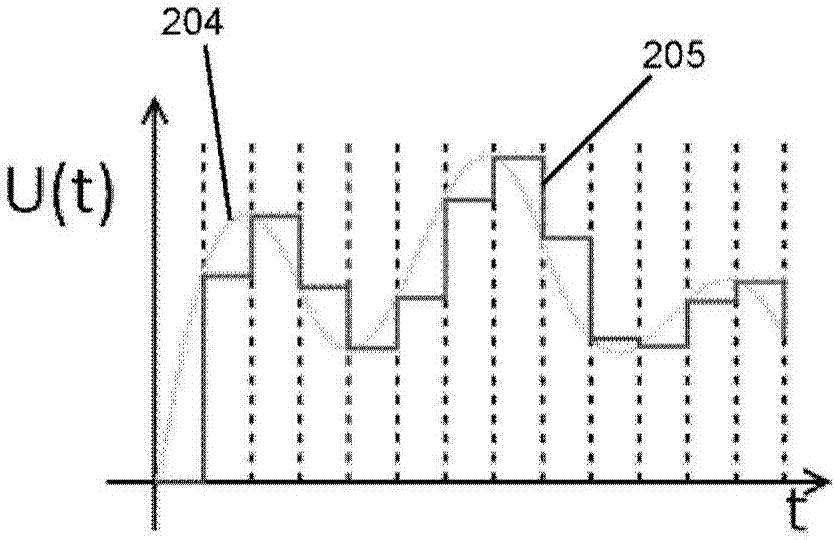

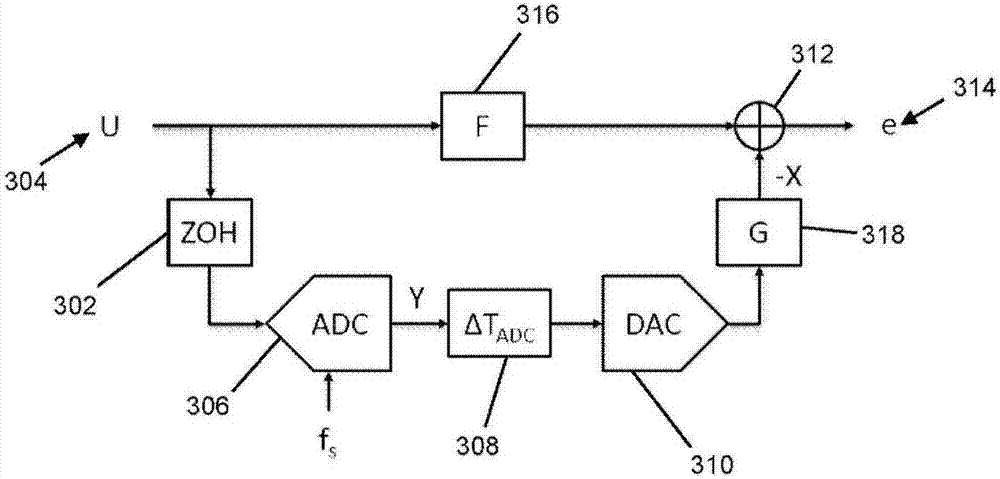

Receiver circuits with feedforward signal path

ActiveCN107342781AAnalogue/digital/analogue conversionLine-faulsts/interference reductionAnalog signalError cancellation

A receiver circuit comprising: an input terminal configured to receive an input-signal; a feedforward-ADC configured to provide a feedforward-digital-signal based on the input-signal; a feedforward-DAC configured to provide a feedforward-analogue-signal based on the feedforward-digital-signal; a feedforward-subtractor configured to provide an error-signal based on the difference between the feedforward-analogue-signal and the input-signal; an error-LNA configured to provide an amplified-error-signal based on the error-signal; an error-ADC configured to provide a digital-amplified-error-signal based on the amplified-error-signal; a mixer configured to down-convert a signal in a signal path between the input terminal and the error-ADC; and an error-cancellation-block configured to provide an error-cancelled-signal based on a difference between the digital-amplified-error-signal and the feedforward-digital-signal.

Owner:NXP BV

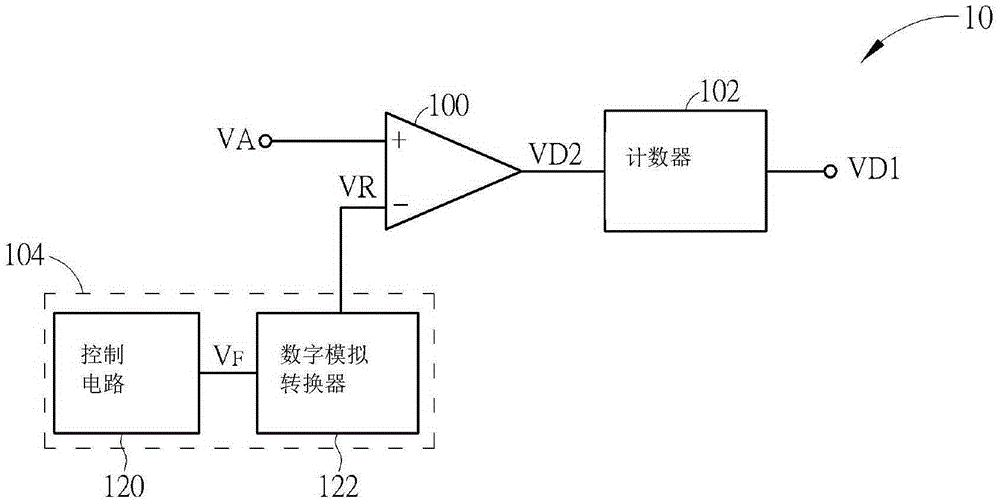

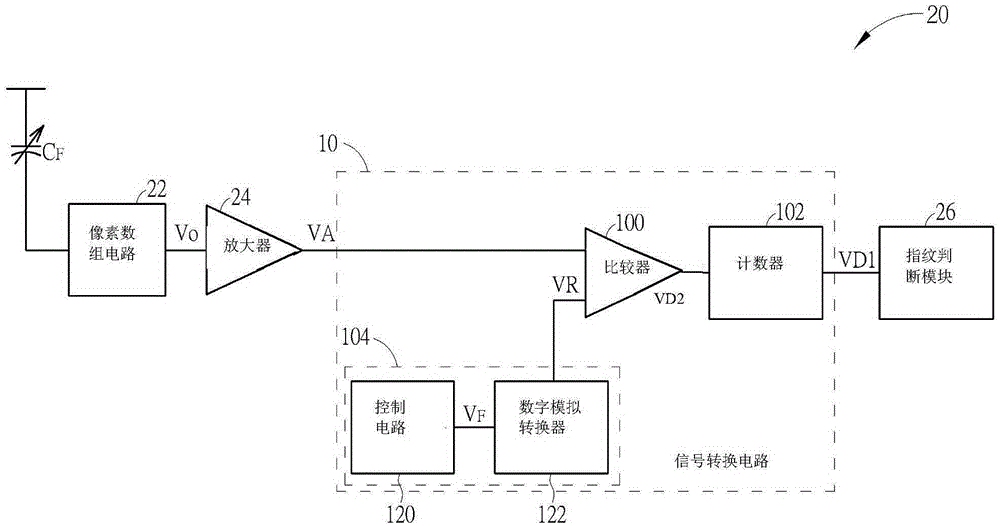

Signal conversion circuit and fingerprint identification system

InactiveCN105281769ASimple structureReduce areaPower saving provisionsAnalogue/digital/analogue conversionVoltage generatorEngineering

The invention provides a signal conversion circuit and a fingerprint identification system. The signal conversion circuit is used for generating a first digital signal according to a first analog signal. The signal conversion circuit comprises a comparator and a counter, wherein the comparator comprises a first input end for receiving the first analog signal, a second input end which is connected to a reference voltage generator and used for receiving a reference voltage, and an output end for outputting a second digital signal; and the counter is connected to the output end, and used for generating the first digital signal. The signal conversion circuit provided by the invention has the advantages of simple circuit structure, small circuit area, low cost and low power consumption.

Owner:SHENZHEN GOODIX TECH CO LTD

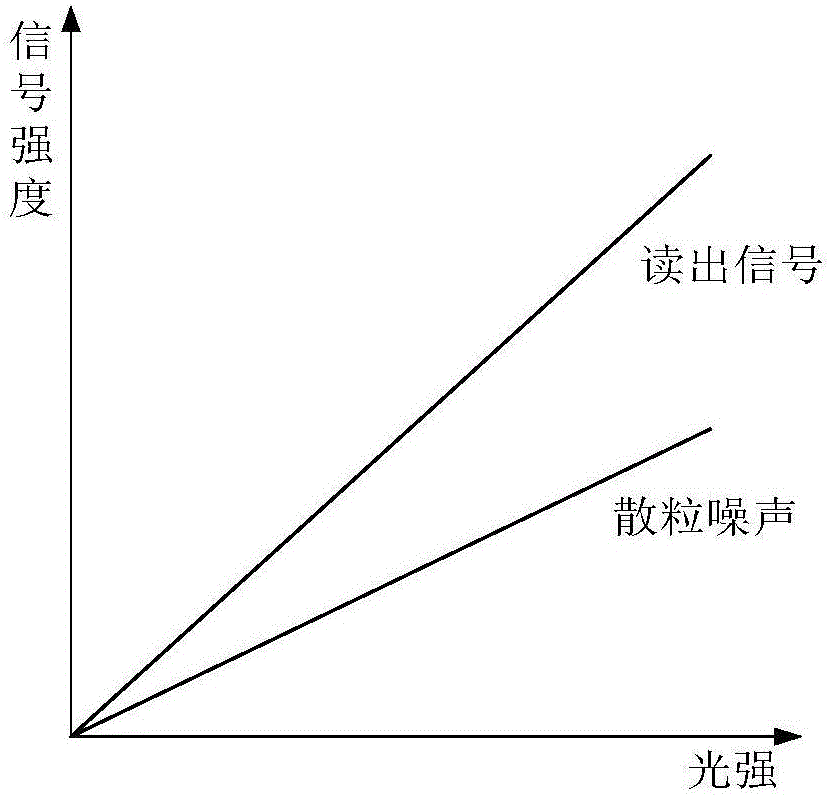

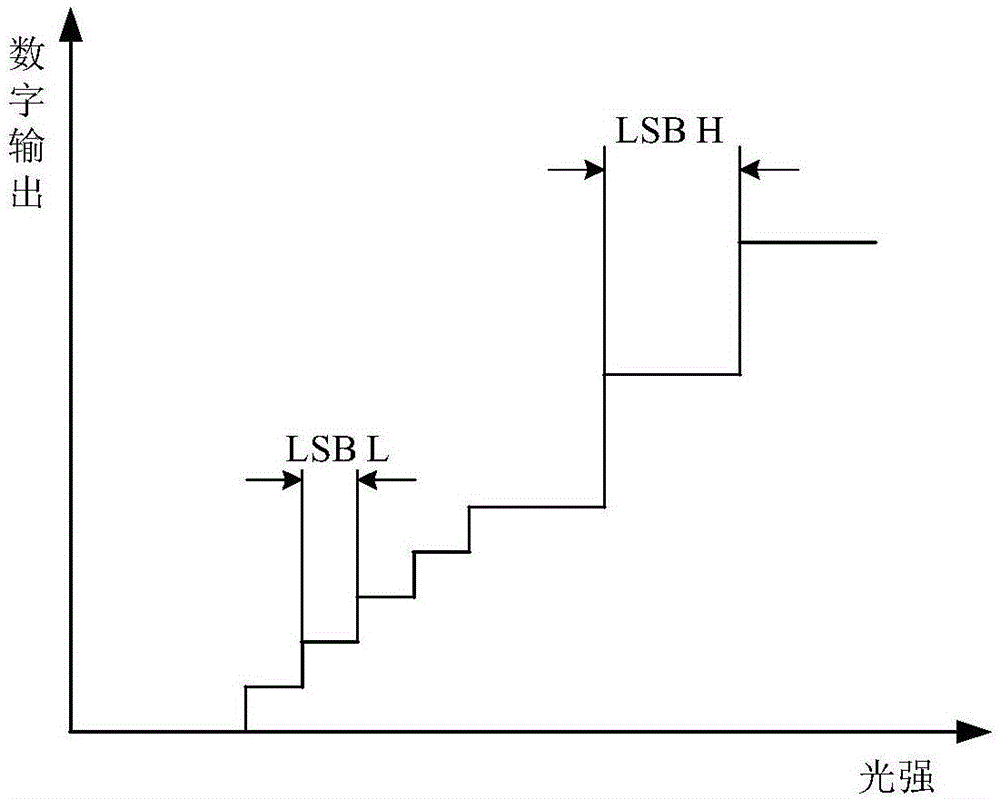

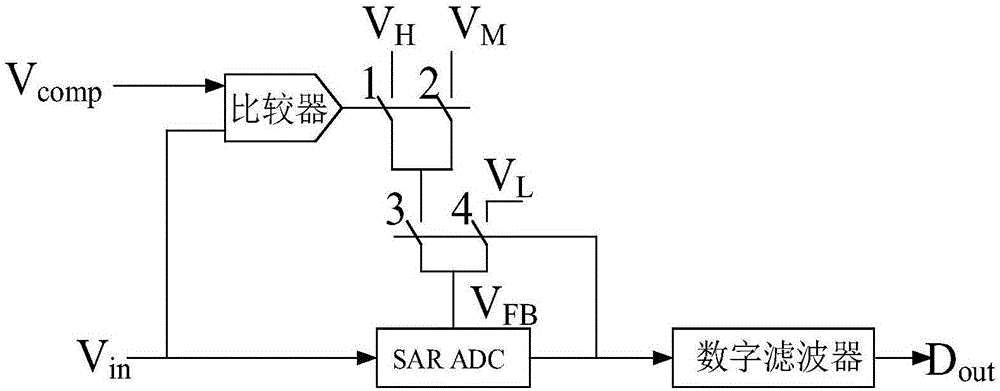

Successive approximation type ADC adjusting reference voltage adaptively

InactiveCN106656191ANo need to increase the quantization periodHigh precisionPower saving provisionsElectric signal transmission systemsVoltage referenceEngineering

The invention relates to a successive approximation type ADC adjusting a reference voltage adaptively, belongs to the technical field of design of analog integrated circuit, and aims at using a high reference voltage under high illumination, using a low reference under low illumination and further realizing high-precision quantification under the lower illumination needless of increase of extra power consumption and conversion periods. The successive approximation type ADC is composed of a front-end comparator module, an SAR ADC main body module, four reference voltage control switches of the SAR ADC main body module and a digital filter module; an input signal Vin is connected with the positive input end of the front-end comparator, and the negative input end of the front-end comparator is connected with a reference level Vcomp; output of the front-end comparator is connected with the reference voltage control switches 1 and 2; and the input signal is also connected with the input end of the SAR ADC main body module. The successive approximation type ADC adjusting a reference voltage adaptively is mainly applied to design and manufacture occasions of the analog integrated circuit.

Owner:TIANJIN UNIV

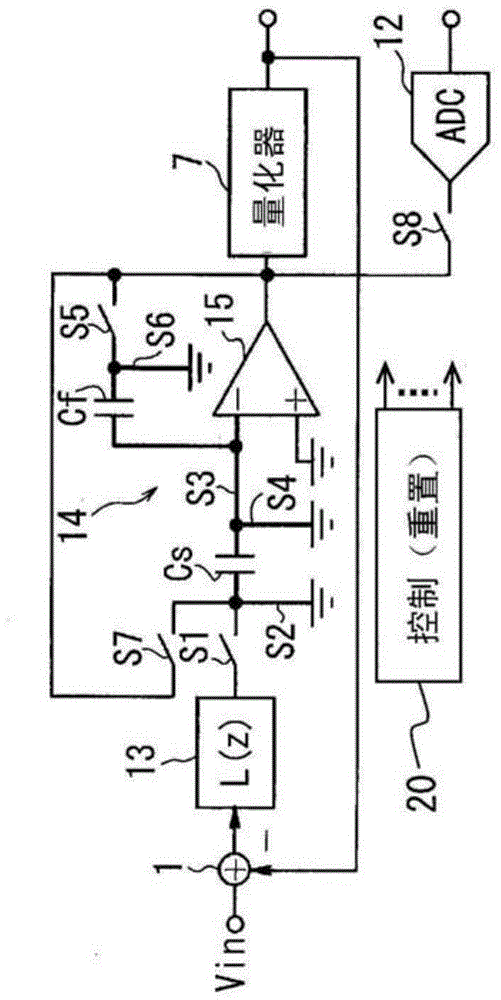

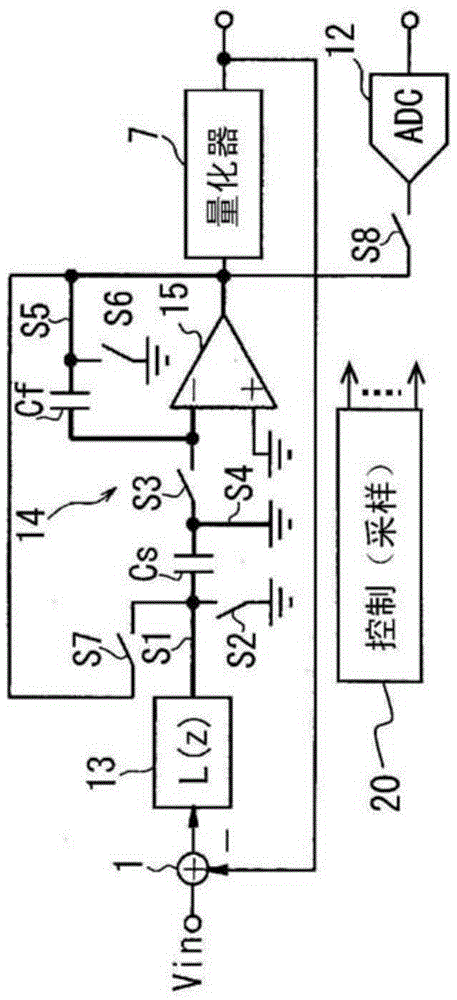

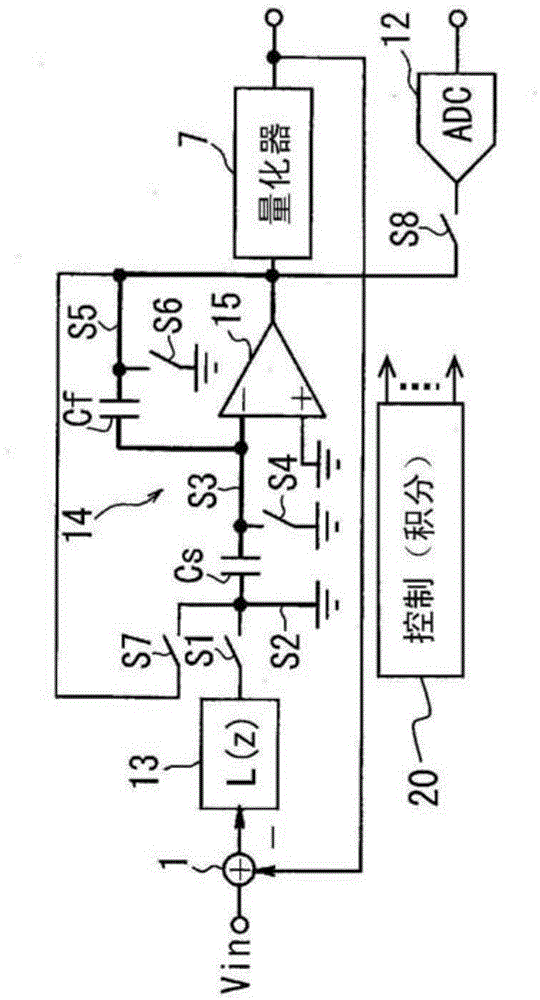

A/D conversion system

ActiveCN104467841AAnalogue/digital/analogue conversionAnalogue conversionLoop filterAudio power amplifier

An input signal (Vin) is quantized by a quantizer (7) after being passed through plural loop filters (13,14). A last-stage loop filter is formed of an operational amplifier (15) for generating an output signal (Vin), a sampling capacitor (Cs) for sampling the input signal, an integrating capacitor for integrating the signal sampled by the capacitor and plural switches (S1 to S7) for switching over signal paths. A control circuit controls on / off states of the switches to discharge the sampling capacitor and the integrating capacitor and causes the loop filter to repeat a sampling operation and an integrating operation plural times. The control circuit (20) lastly connects the sampling capacitor and the integrating capacitor to a state, which is opposite to the state of the integrating operation time and turns on a converting switch (S8) so that the A / D converter A / D-converts the output signal of the loop filter.

Owner:DENSO CORP

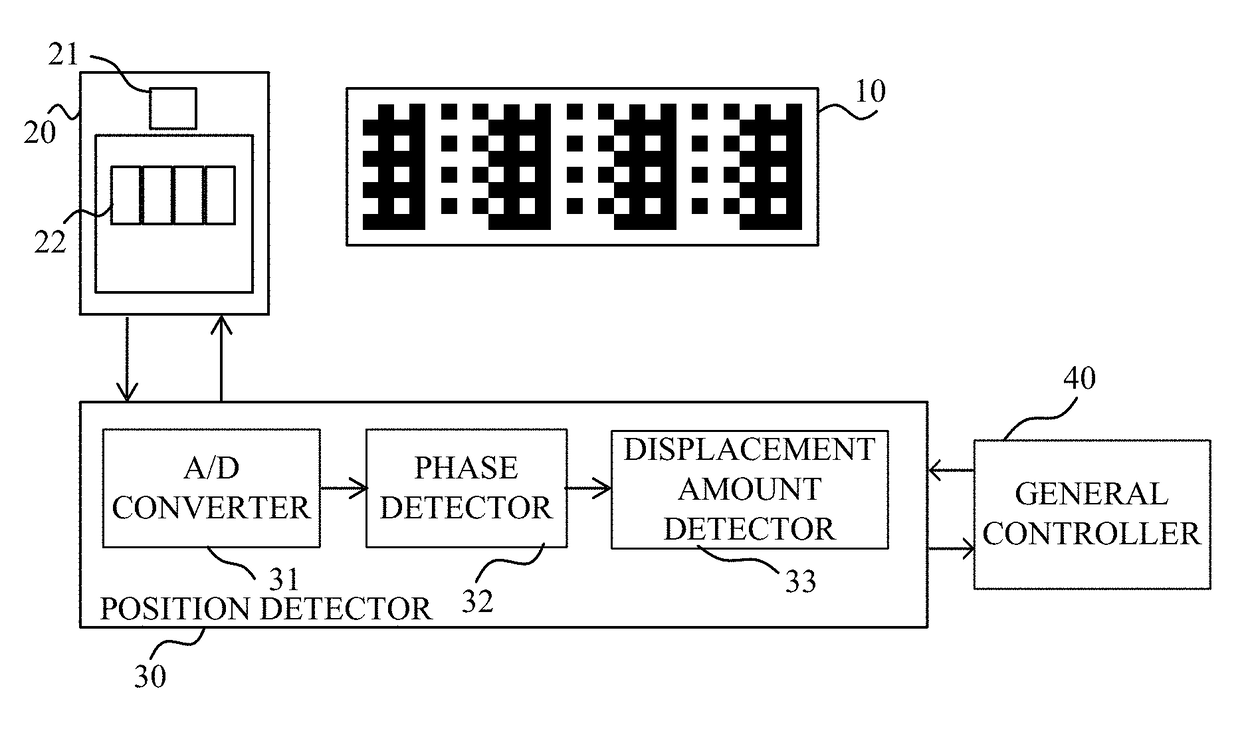

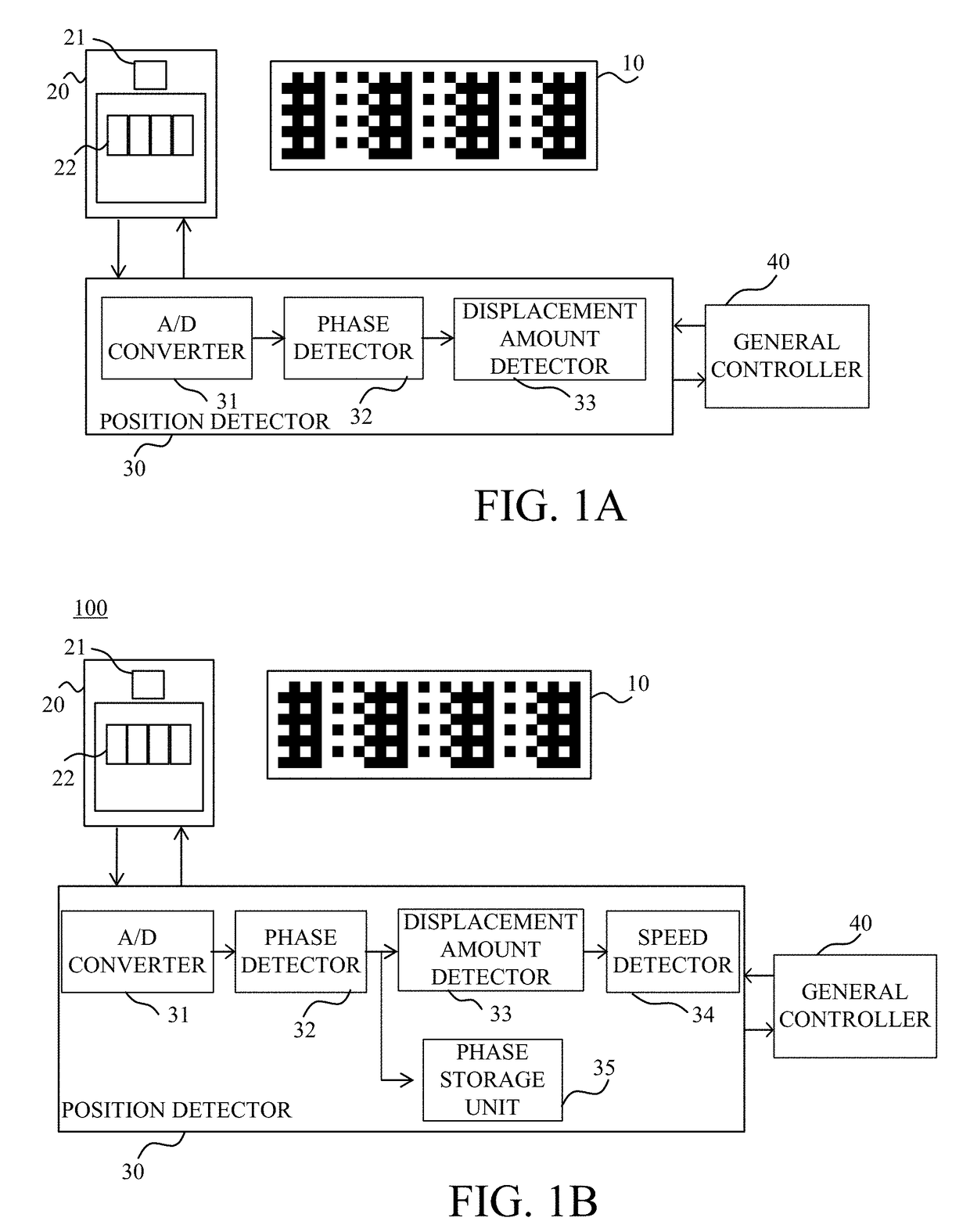

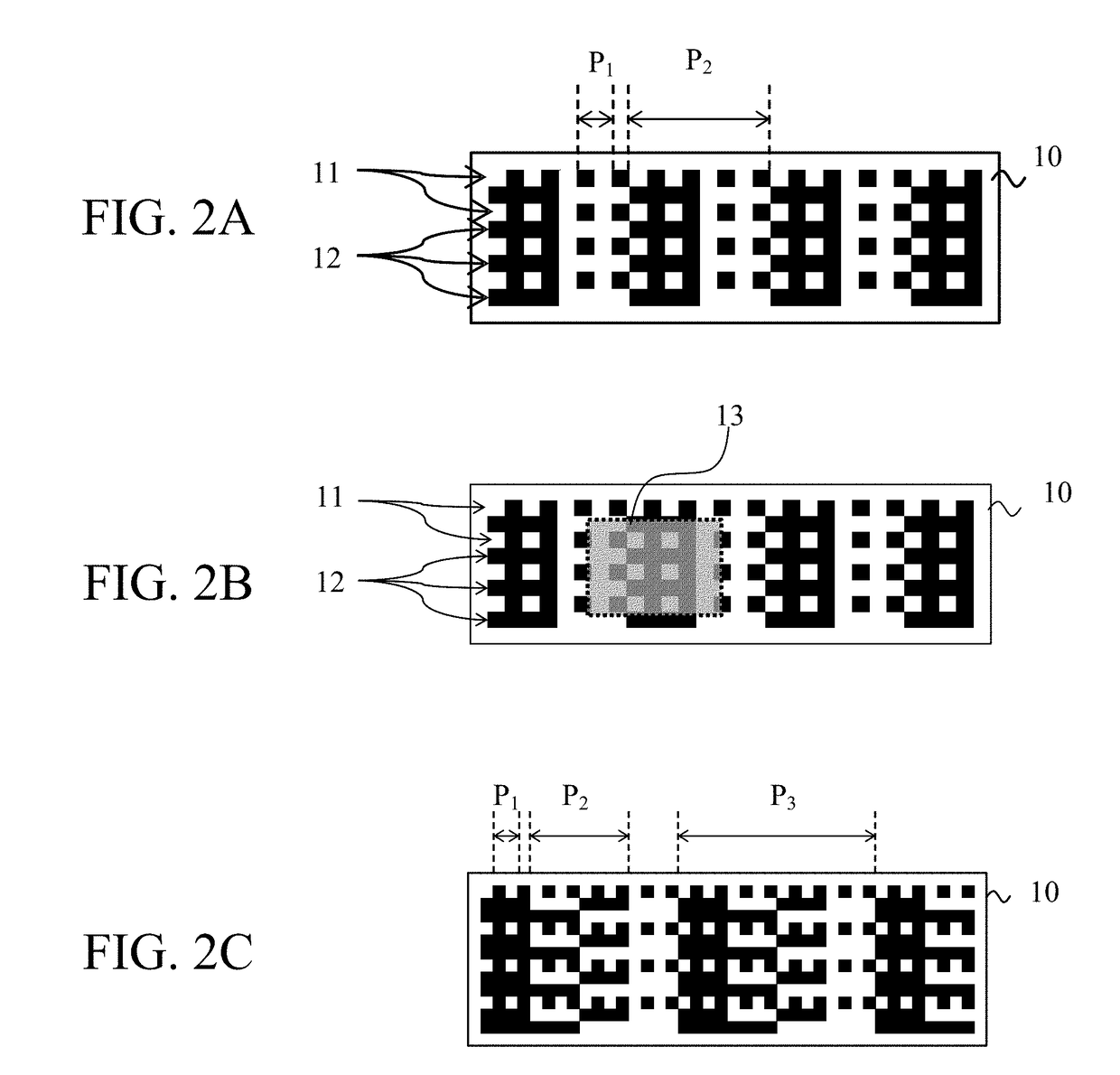

Encoder and apparatus having the same

ActiveUS20180058885A1Accurate calculationAnalogue/digital/analogue conversionConverting sensor outputRelative displacementComputer hardware

An encoder includes a scale, a detector, and a processor. The processor executes a second process while executing a first process, calculates a first relative position of one of the scale and the detector to the other of the scale and the detector when a calculation of a relative position between them starts, and then calculates a second relative position of the one to the other based on a relative displacement amount between them and the first relative position.

Owner:CANON PRECISION

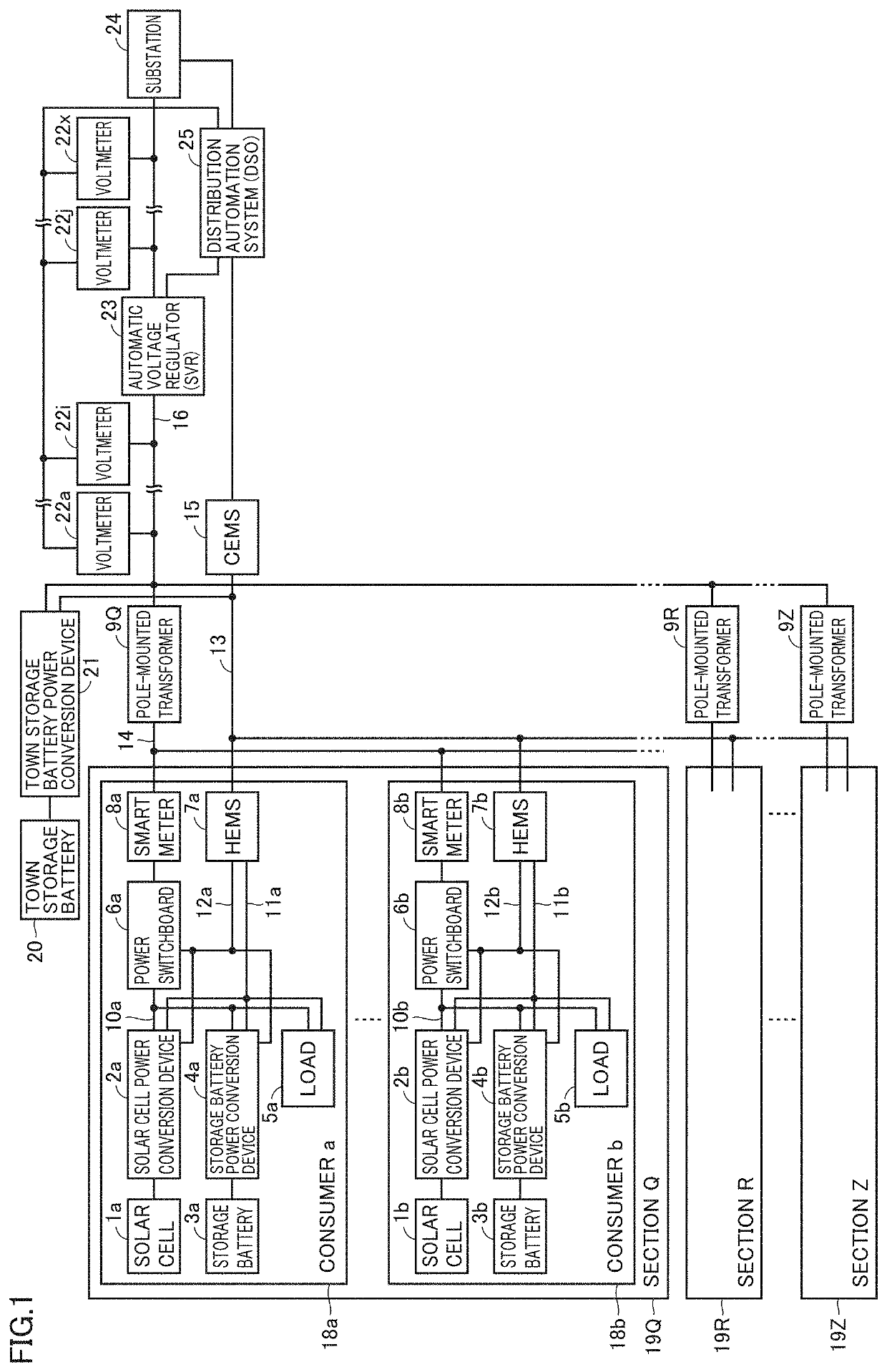

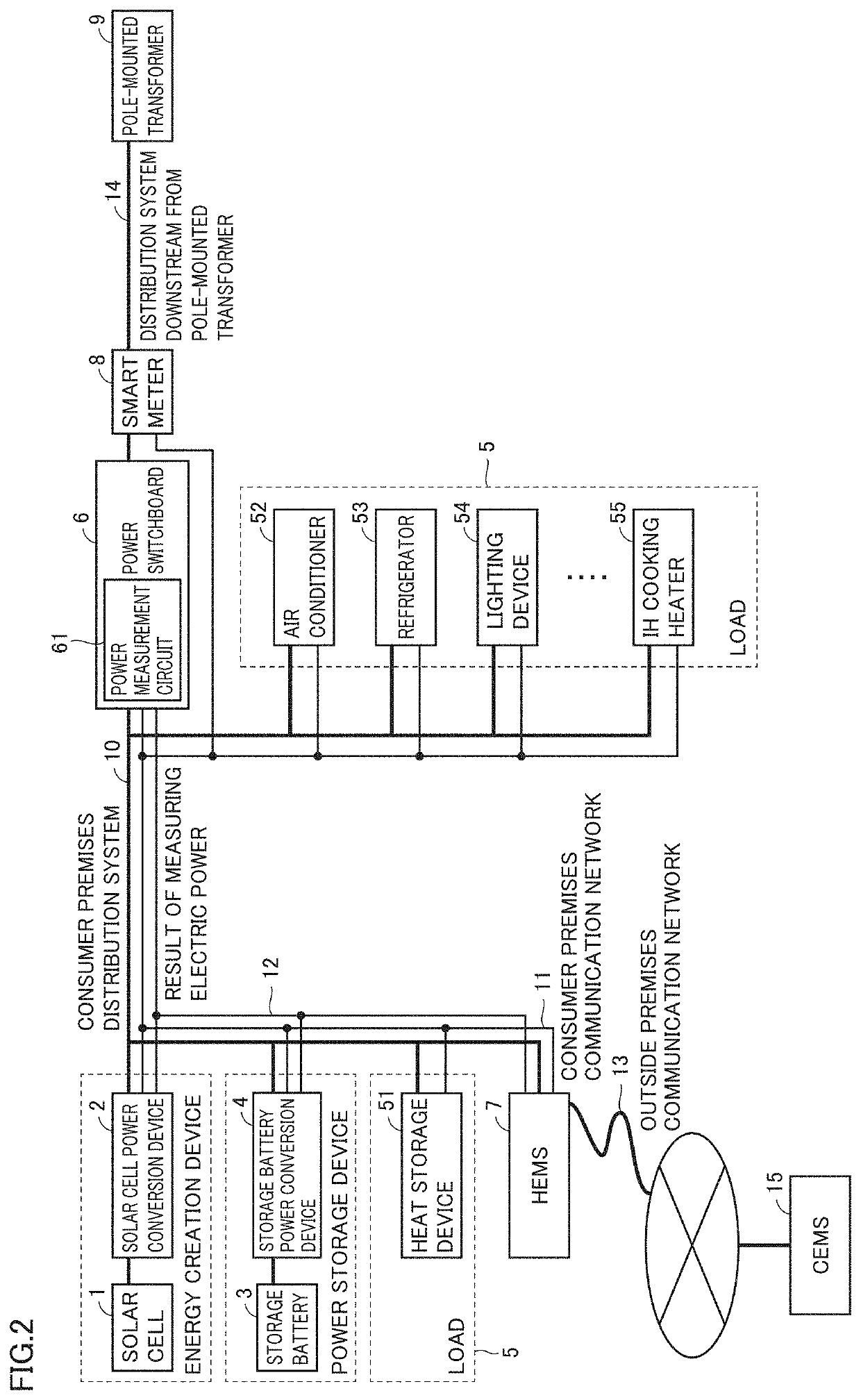

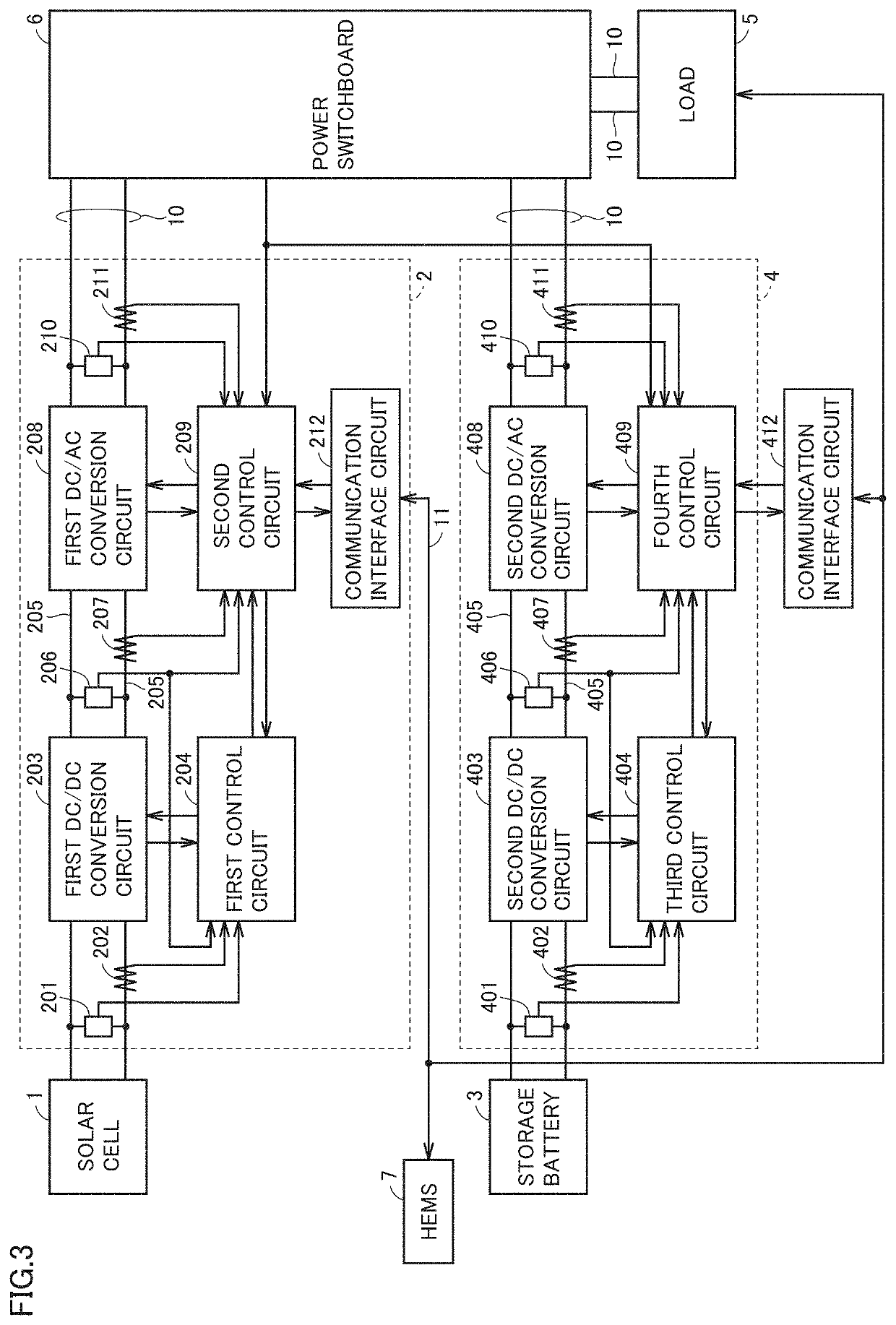

Power conversion device

ActiveUS20210028625A1Suppresses voltage fluctuationsElectric signal transmission systemsAnalogue/digital/analogue conversionSolar batteryVoltage range

A solar cell power conversion device is disposed between a solar cell and a consumer premises distribution system. A storage battery power conversion device is disposed between a storage battery and the consumer premises distribution system. When an AC effective voltage in the consumer premises distribution system deviates from a voltage range defined in accordance with dead zone information transmitted from HEMS, system voltage stabilization control for returning the AC effective voltage to fall within the voltage range is performed by control of active power and reactive power that are output from a first DC / AC conversion circuit and a second DC / AC conversion circuit.

Owner:MITSUBISHI ELECTRIC CORP

System and method for multi channel sampling SAR ADC

ActiveUS9270293B2Electric signal transmission systemsAnalogue/digital/analogue conversionComparatorSample and hold

A device includes a SAR, a comparator, a DAC and a multichannel passive S / H component. The multichannel passive S / H component is able to sample and hold a plurality of analog voltages in parallel. The multichannel passive S / H component is further able to serially feed the plurality of sampled and held analog voltages to the SAR, comparator and DAC, such that each analog voltage is serially converted to a digital representation.

Owner:TEXAS INSTR INC

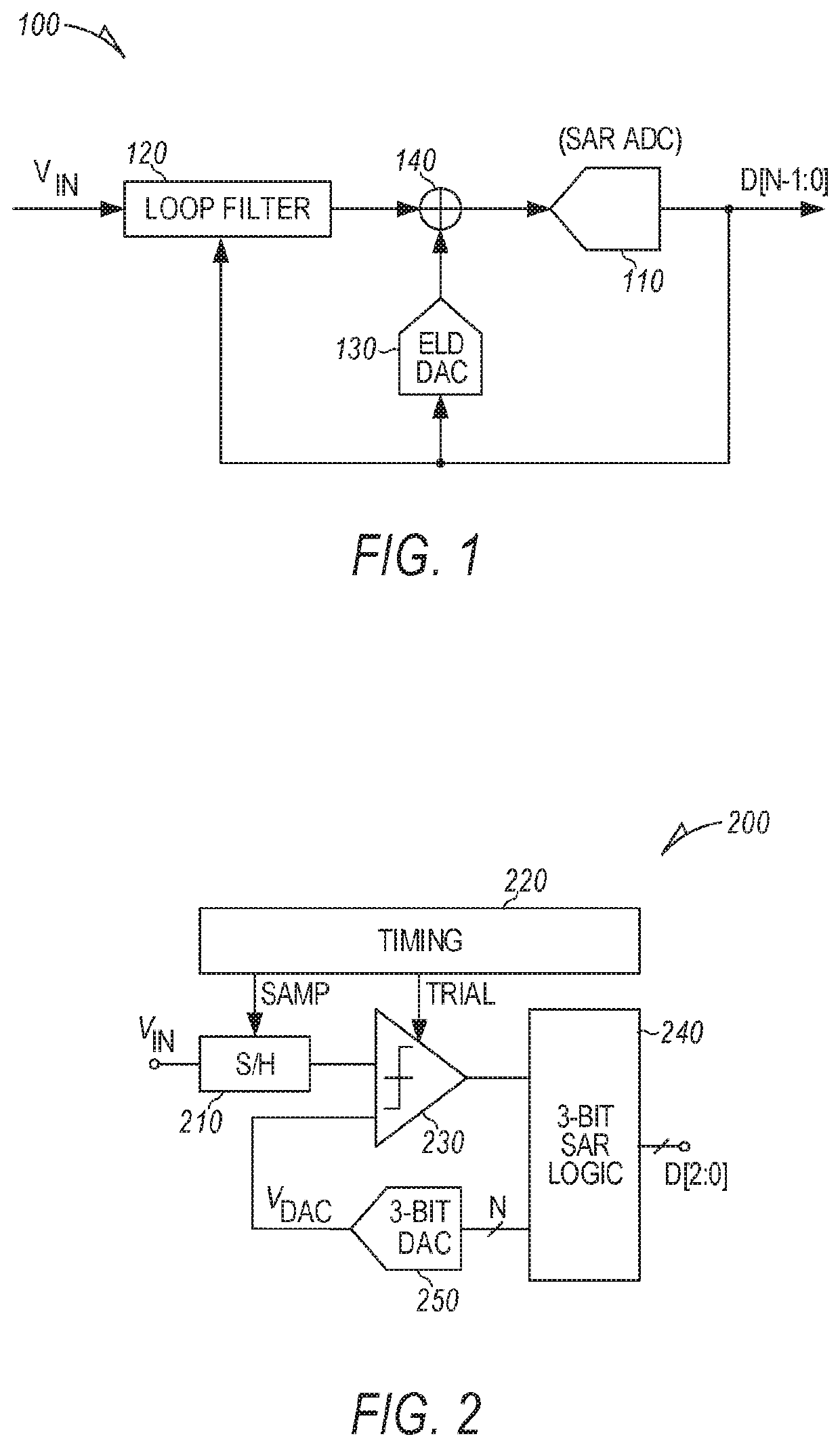

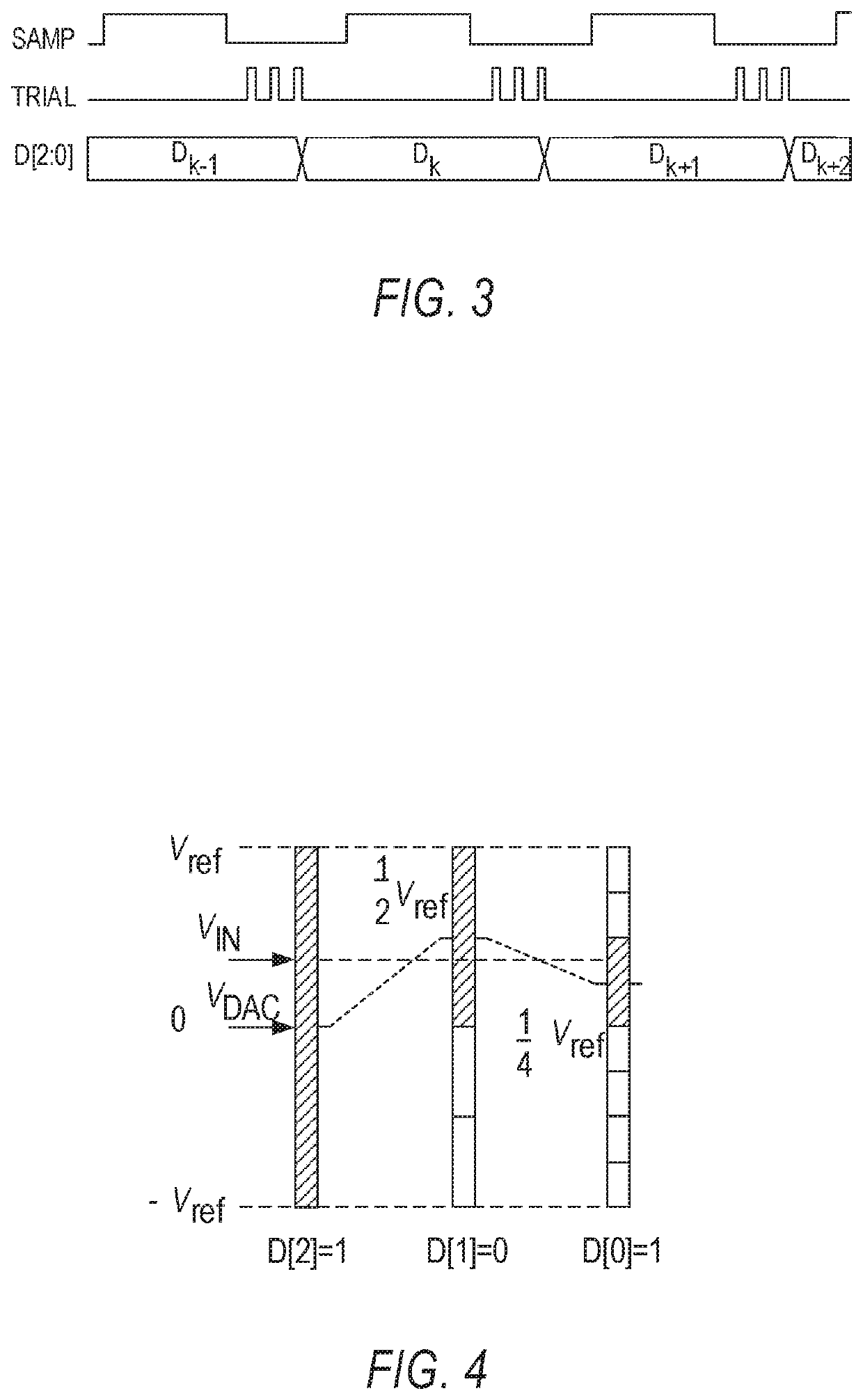

Method to embed ELD DAC in SAR quantizer

ActiveUS10886937B1Use minimizedMaintains its operational flexibilityElectric signal transmission systemsAnalogue conversionCapacitanceA d converter

Methods and devices are described for controlling excess loop delay (ELD) gain compensation in a digital-to-analog converter (DAC) of a successive approximation register (SAR) analog-to-digital converter (ADC) by using DAC unit elements in the ELD DAC and DACs for the SAR ADC efficiently. The ELD DAC and DAC partially share DAC units (e.g. capacitors or current sources) to minimize total DAC units used to limit area and power usage while maintaining operational flexibility. Different configurations provide ELD gains of less than or greater than one. A dedicated sampling capacitor is also provided to allow flexible gain control by capacitance ratio.

Owner:ANALOG DEVICES INT UNLTD

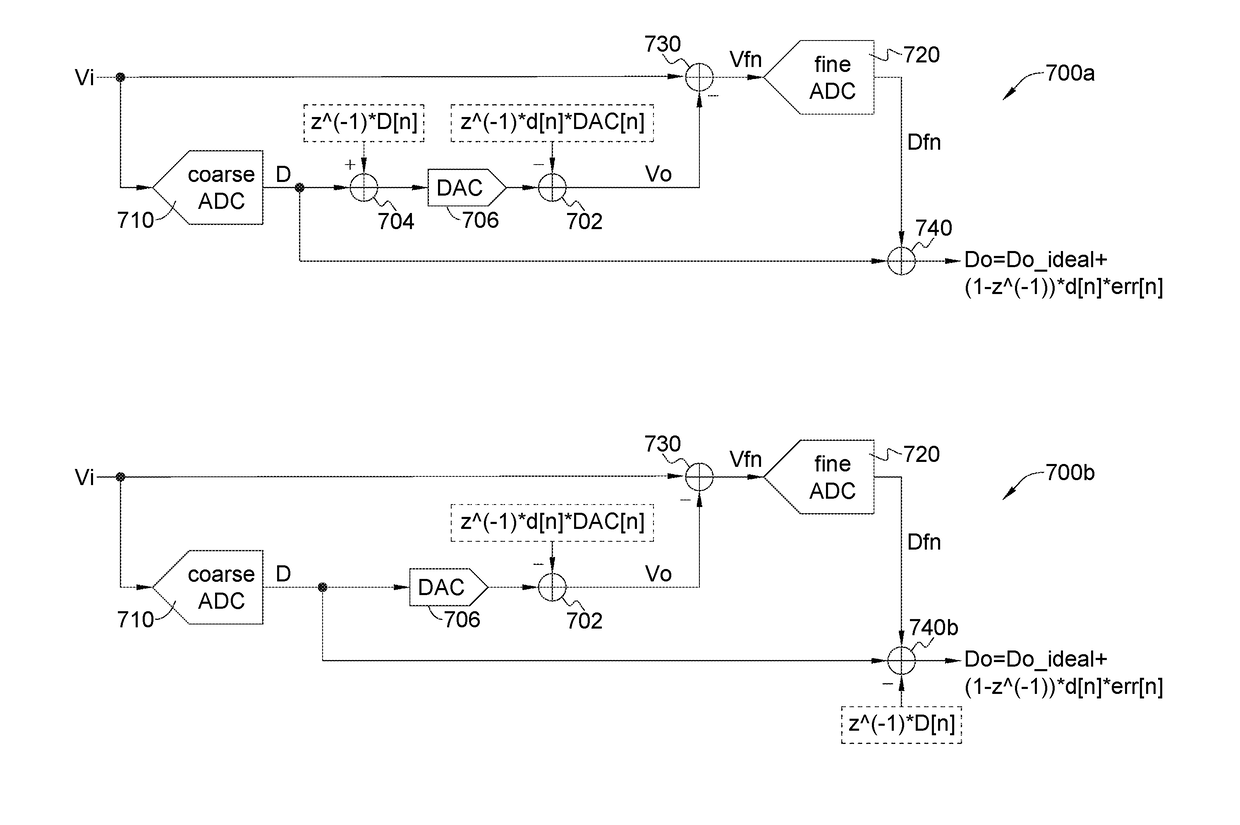

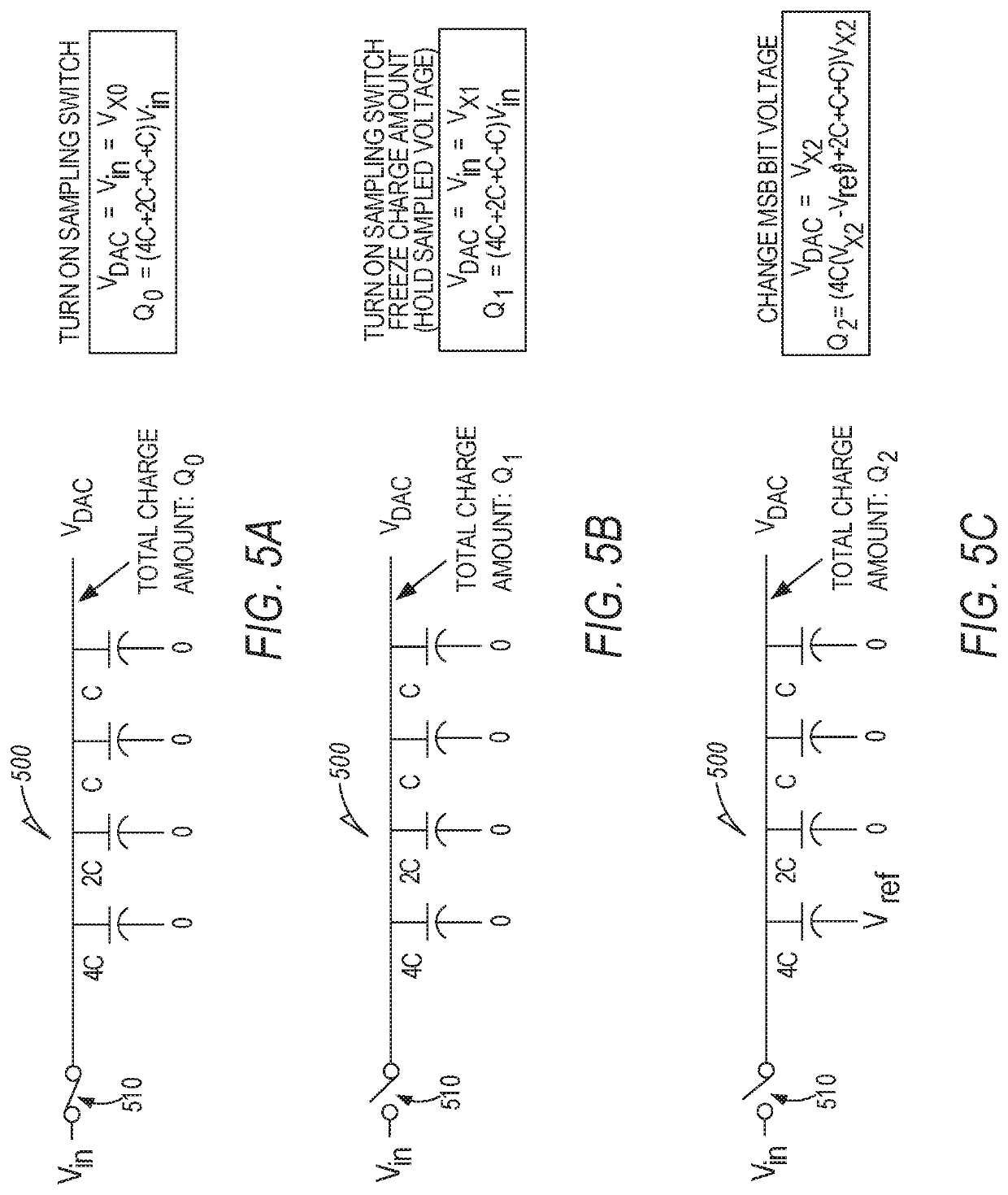

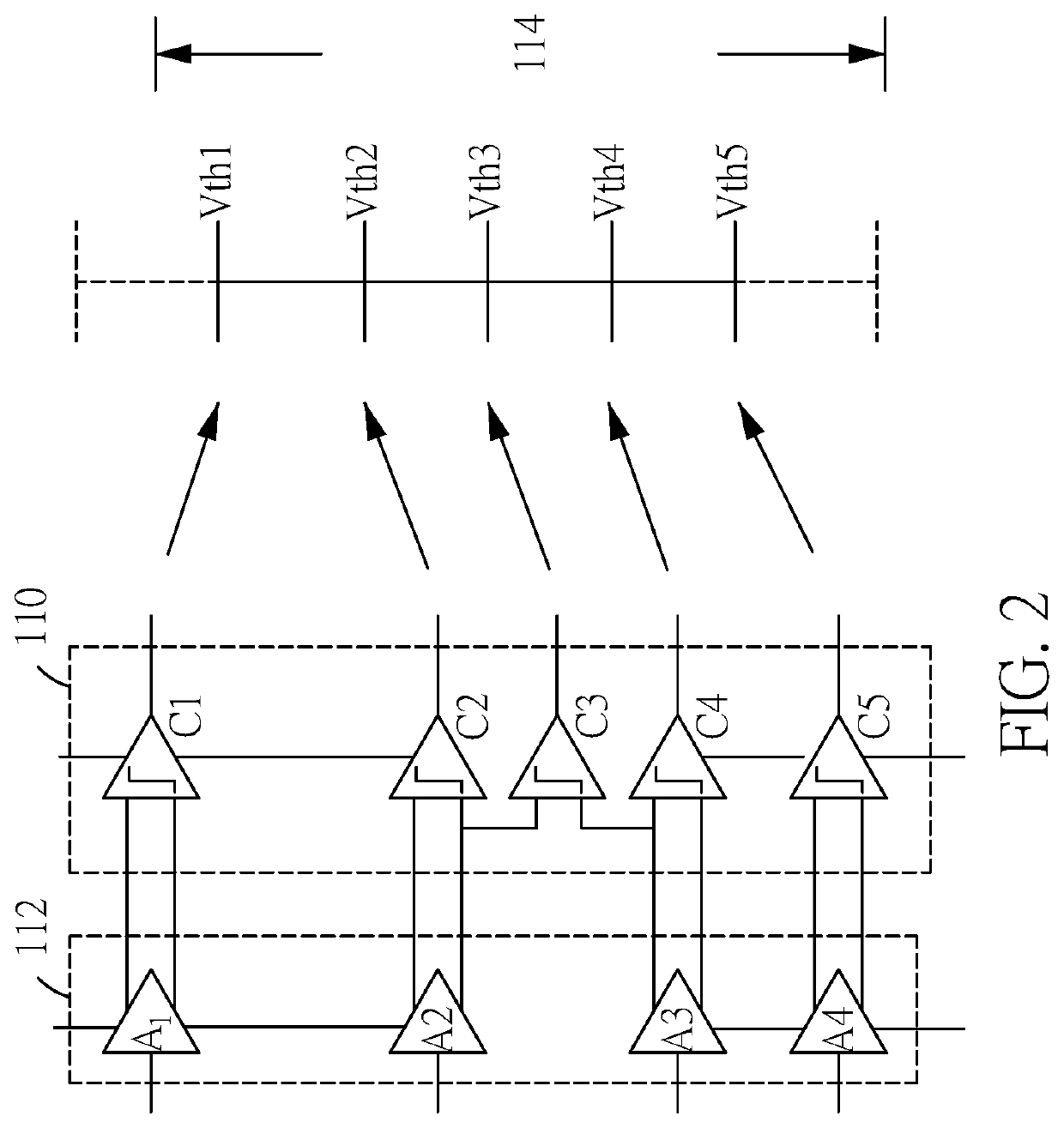

Gain calibration device and method for residue amplifier of pipeline analog to digital converter

ActiveUS10826516B2Improve linearityUneven distributionElectric signal transmission systemsGain controlConvertersSoftware engineering

A gain calibration device for an ADC residue amplifier includes a DAC and a flash ADC. The DAC is configured to convert the digital signal to an analog signal, and the DAC includes a calibration module used in the gain calibration of the ADC residual amplifier. The flash ADC is configured to generate a digital signal, the flash ADC includes a plurality of comparators, the total number of the plurality of comparators is equal to the number of output bits of the flash ADC, and the comparators are configured to be unevenly distributed in an input range.

Owner:REALTEK SEMICON CORP

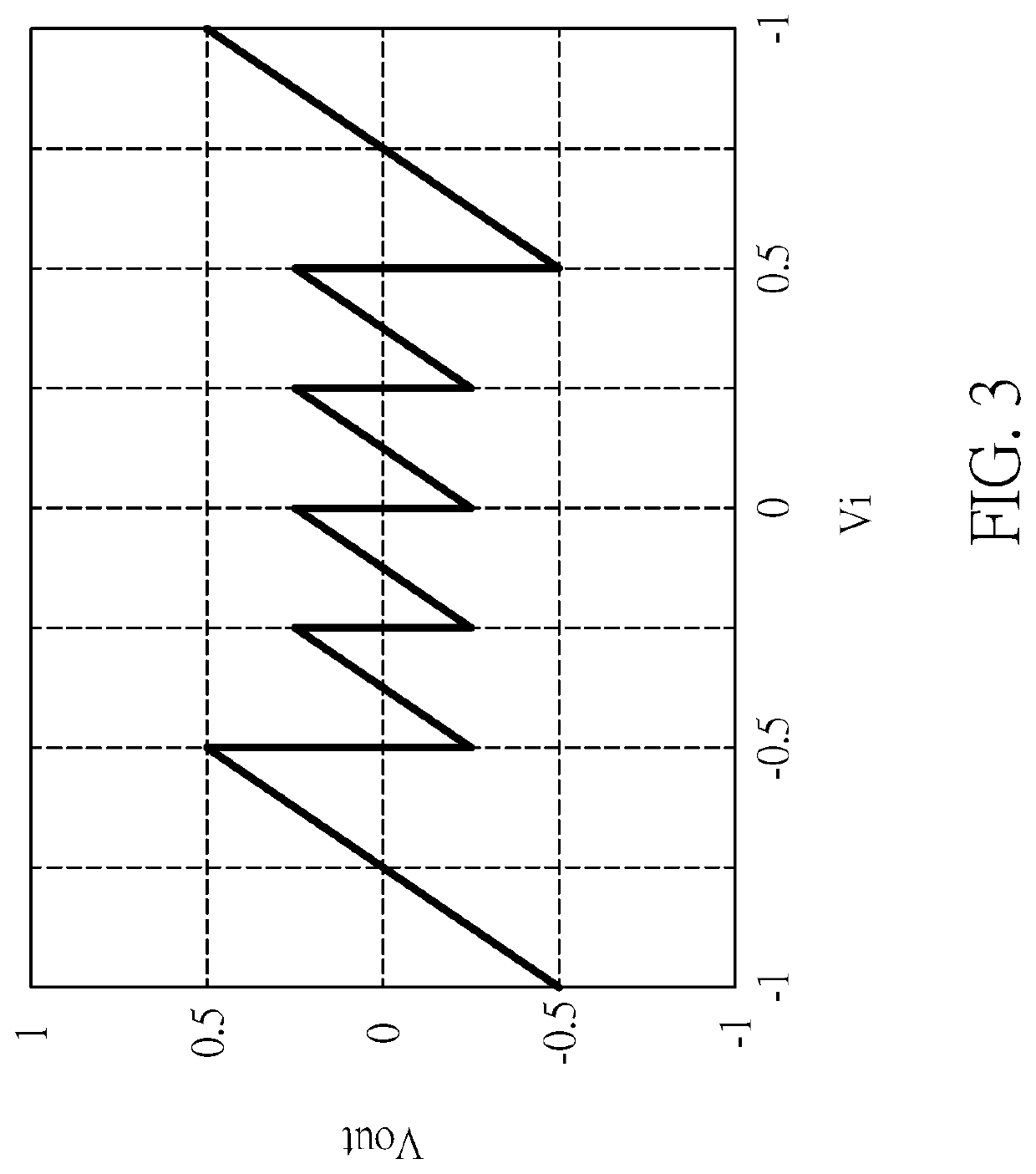

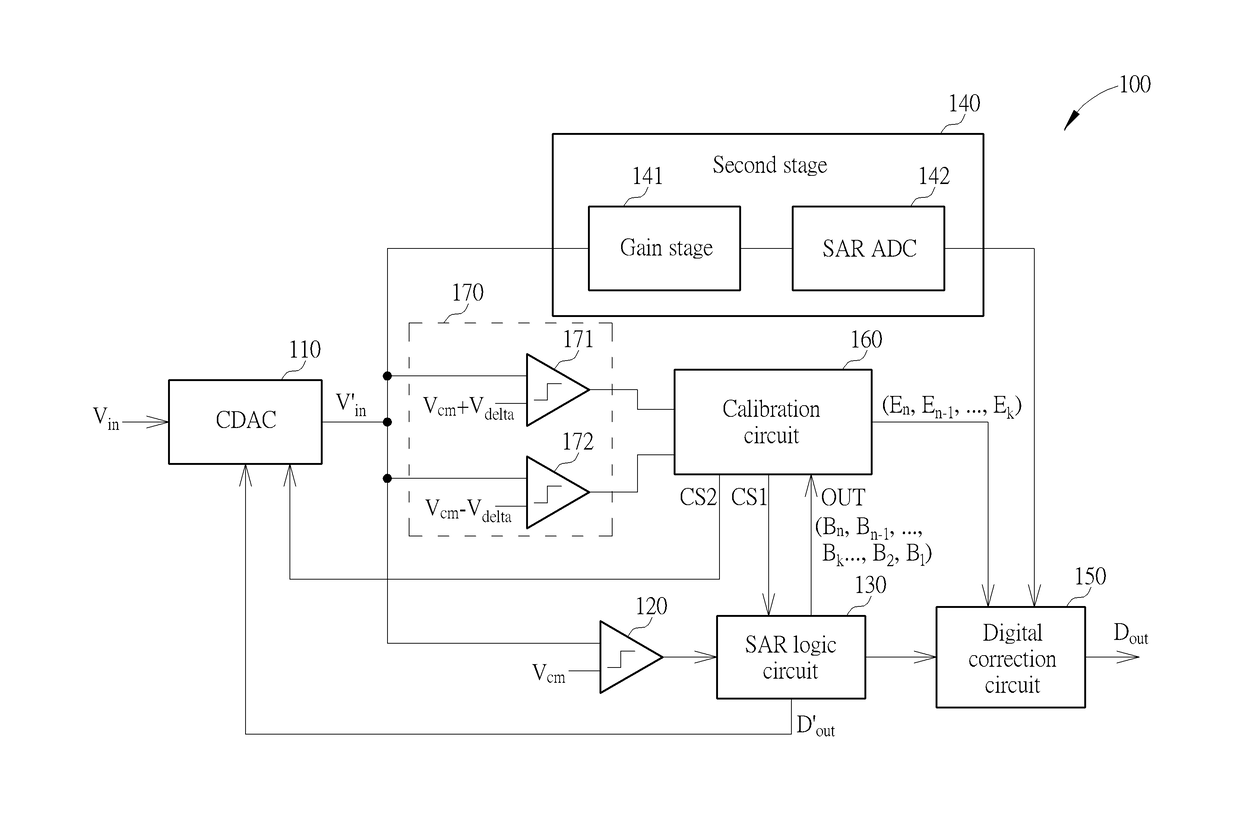

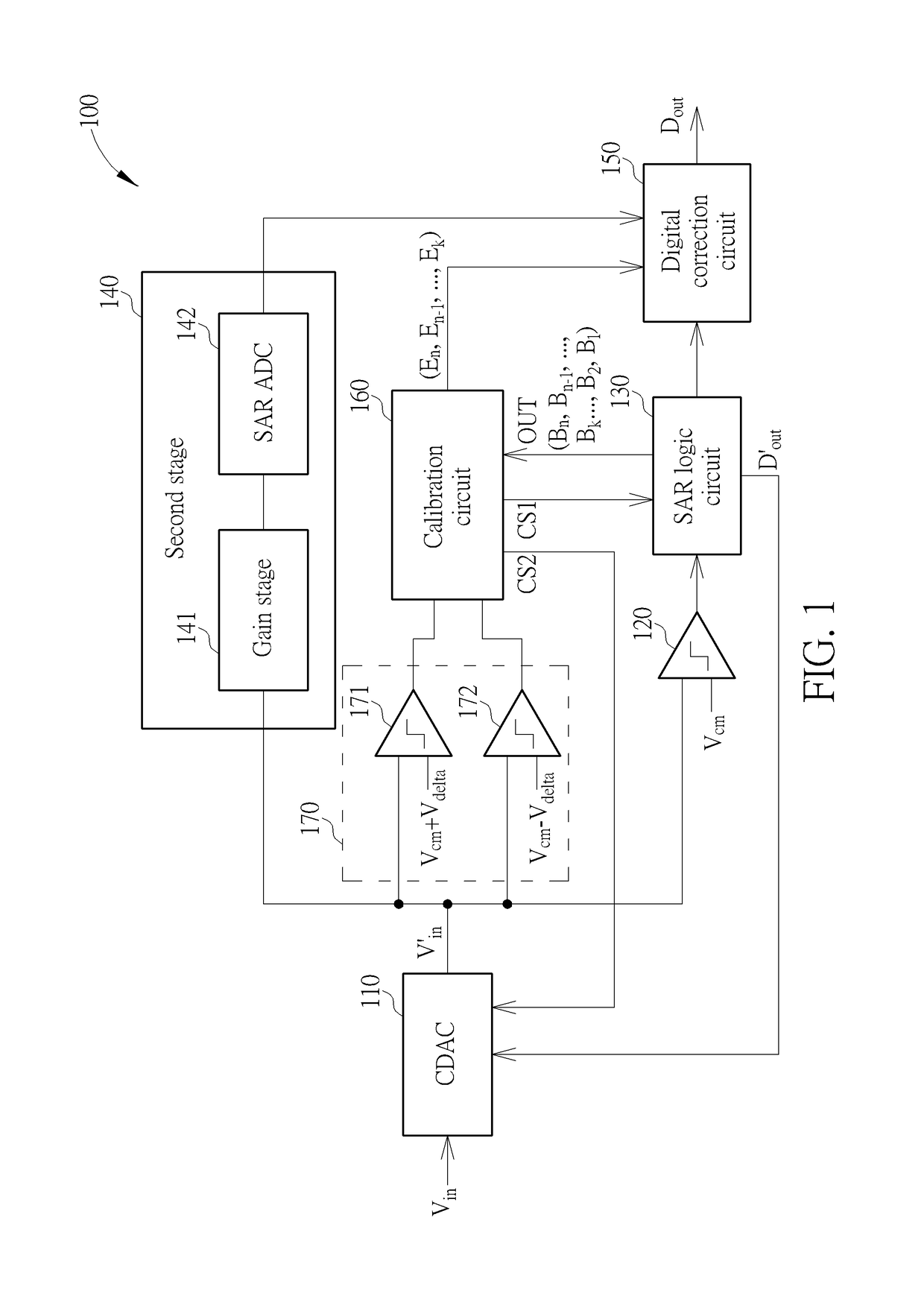

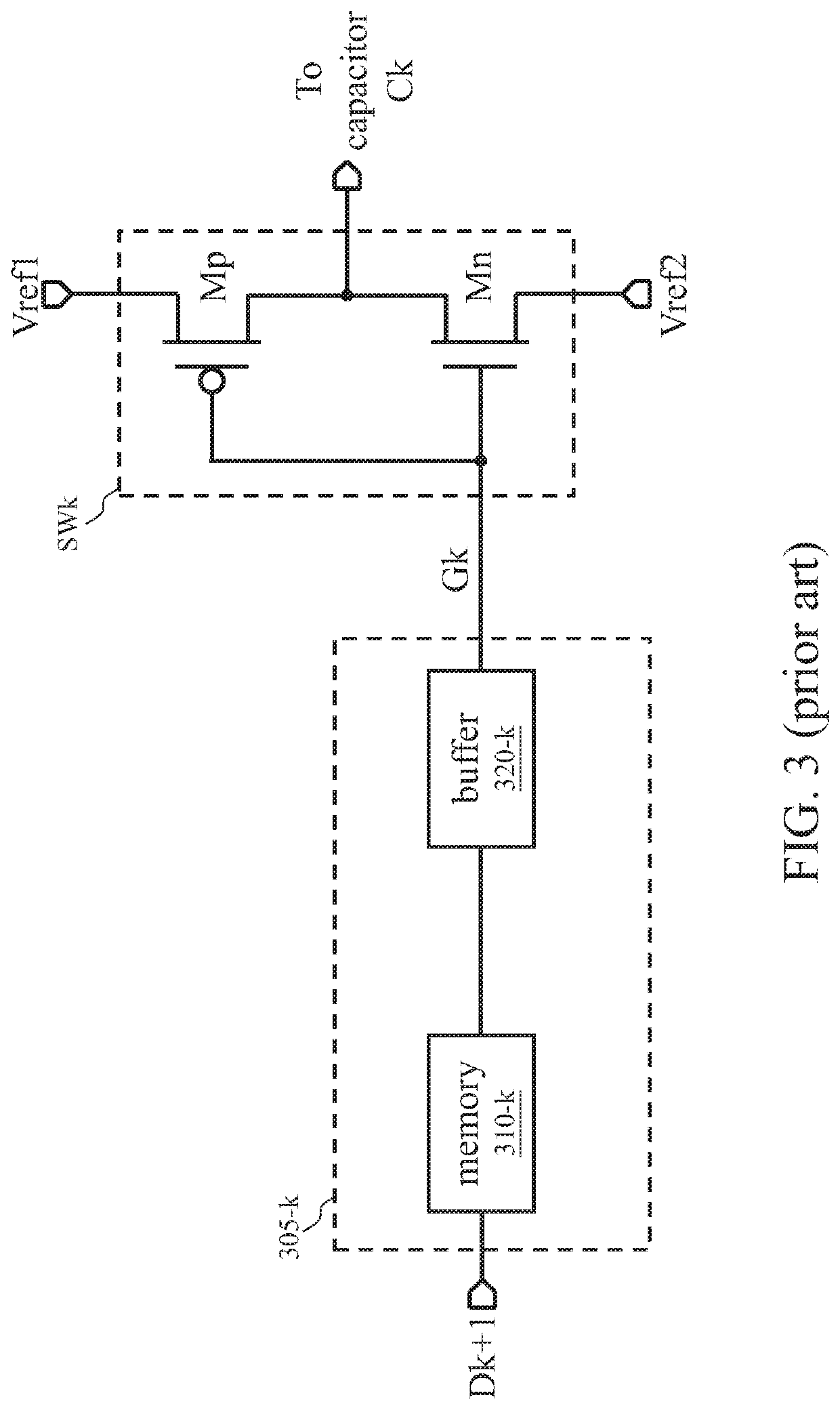

Successive approximation register analog-to-digital converter applying calibration circuit, associated calibrating method, and associated electronic device

ActiveUS10128862B2Electric signal transmission systemsAnalogue/digital/analogue conversionDigital down converterComputer module

A Successive Approximation Register (SAR) Analog-to-Digital Converter (ADC) including: a comparing module and a calibration circuit. The comparing module is arranged to generate a first comparison result by comparing an input voltage value of the SAR ADC with a first voltage value and a second result by comparing the input voltage value with a second voltage value; the calibration circuit coupled to the comparing module is for generating a determination result determining whether the input voltage value is in a range according to the first comparison result and the second comparison result, and enters a calibration mode according to the determination result.

Owner:MEDIATEK INC

Successive approximation register analog-digital converter having a split-capacitor based digital-analog converter

ActiveUS10135457B2Electric signal transmission systemsAnalogue/digital/analogue conversionDigital analog converterProcessor register

A successive approximation register analog-digital converter including a split-capacitor based digital-analog converter includes a comparator, a split-capacitor based digital-analog converter including a positive capacitor array and a negative capacitor array, and a successive approximation register logic. The positive capacitor array and the negative capacitor array each includes a positive capacitor array of a first stage and a negative capacitor array of a first stage that generate input signals of the comparator corresponding to upper bits including an MSB, respectively, a positive capacitor array of a second stage and a negative capacitor array of a second stage that generate input signals corresponding to intermediate bits, and a positive capacitor array of a third stage and a negative capacitor array of a third stage that generate input signals corresponding to lower bits of an LSB and a next to bit of the LSB.

Owner:SK HYNIX INC

Control circuit and control method of successive approximation register analog-to-digital converter

ActiveUS10715167B2Improve speed and performanceEasy to control speedElectric signal transmission systemsAnalogue/digital/analogue conversionCapacitanceConverters

Owner:REALTEK SEMICON CORP

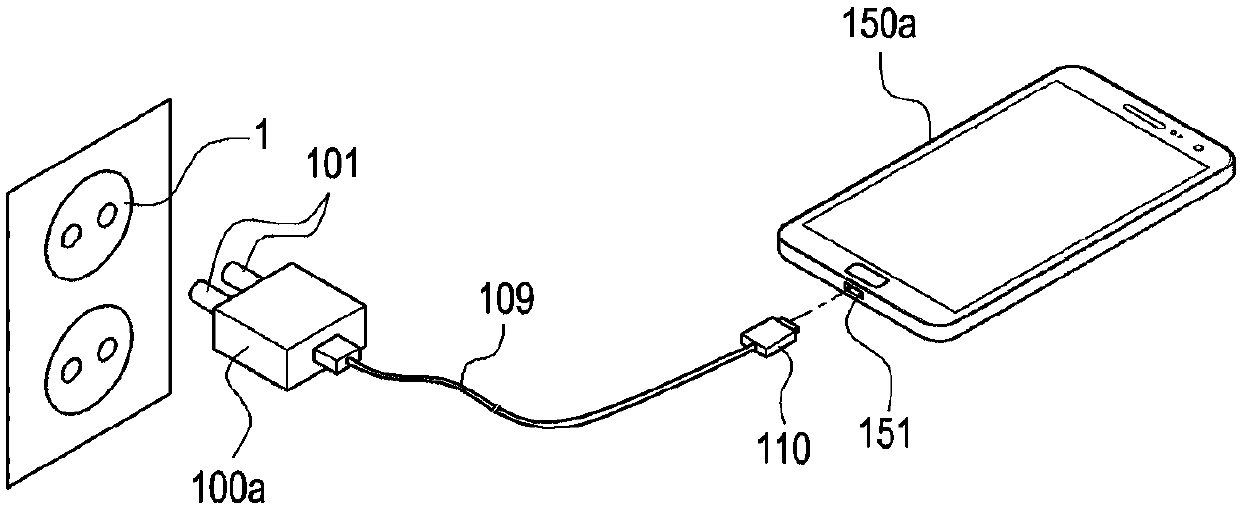

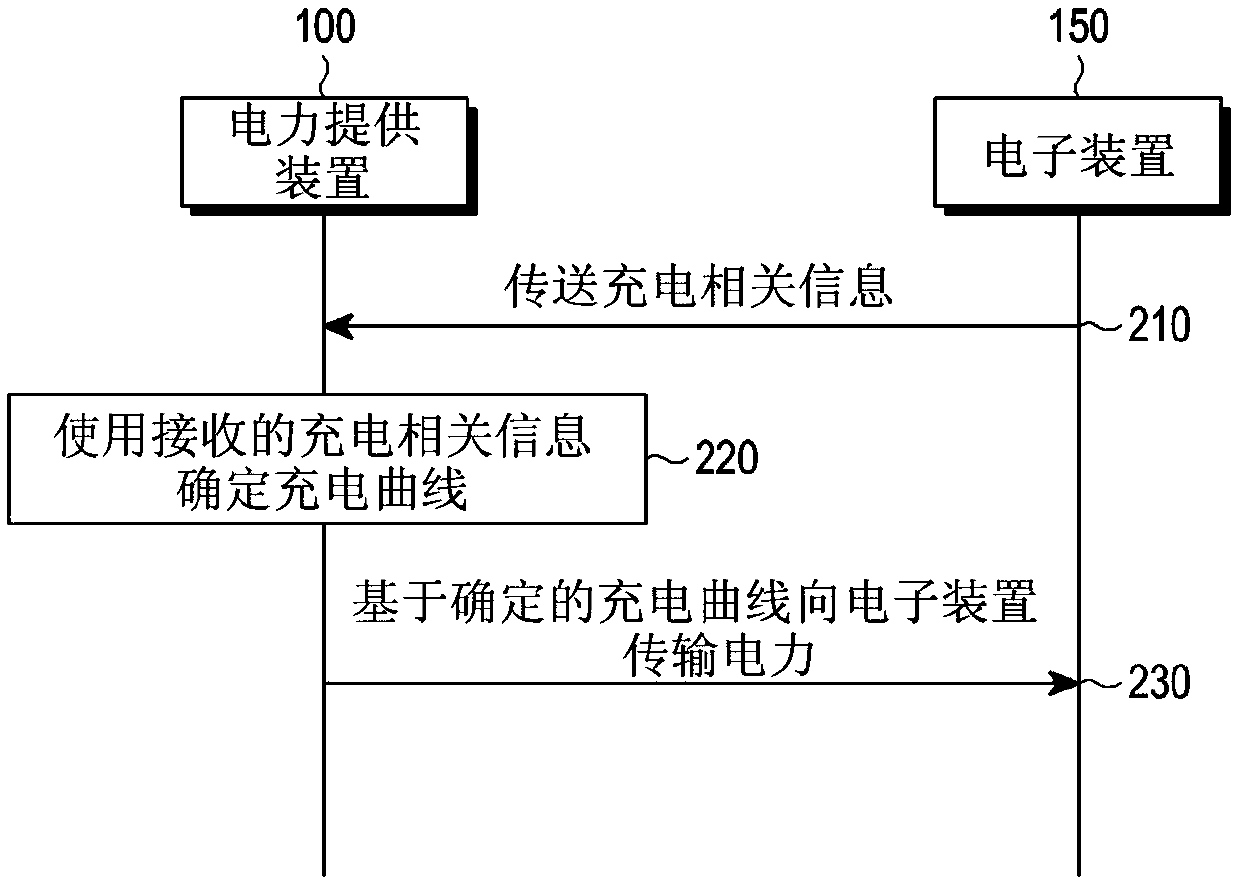

Power supply apparatus, electronic device receiving power, and control method therefor

ActiveCN109643902ANear-field transmissionAc-dc conversion without reversalSoftware engineeringBattery cell

A power supply apparatus according to various embodiments of the present disclosure comprises: a charger that regulates at least one of voltage and current of power supplied from a power supply sourceand supplies the power to an electronic device; and a processor, wherein the processor can receive, from the electronic device, at least one of identification information of the electronic device andinformation related to a battery of the electronic device, and control the charger to regulate at least one of the voltage and the current of the power by using at least one of the identification information of the electronic device and the information related to the battery of the electronic device.

Owner:SAMSUNG ELECTRONICS CO LTD