Patents

Literature

46 results about "Residue amplifier" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

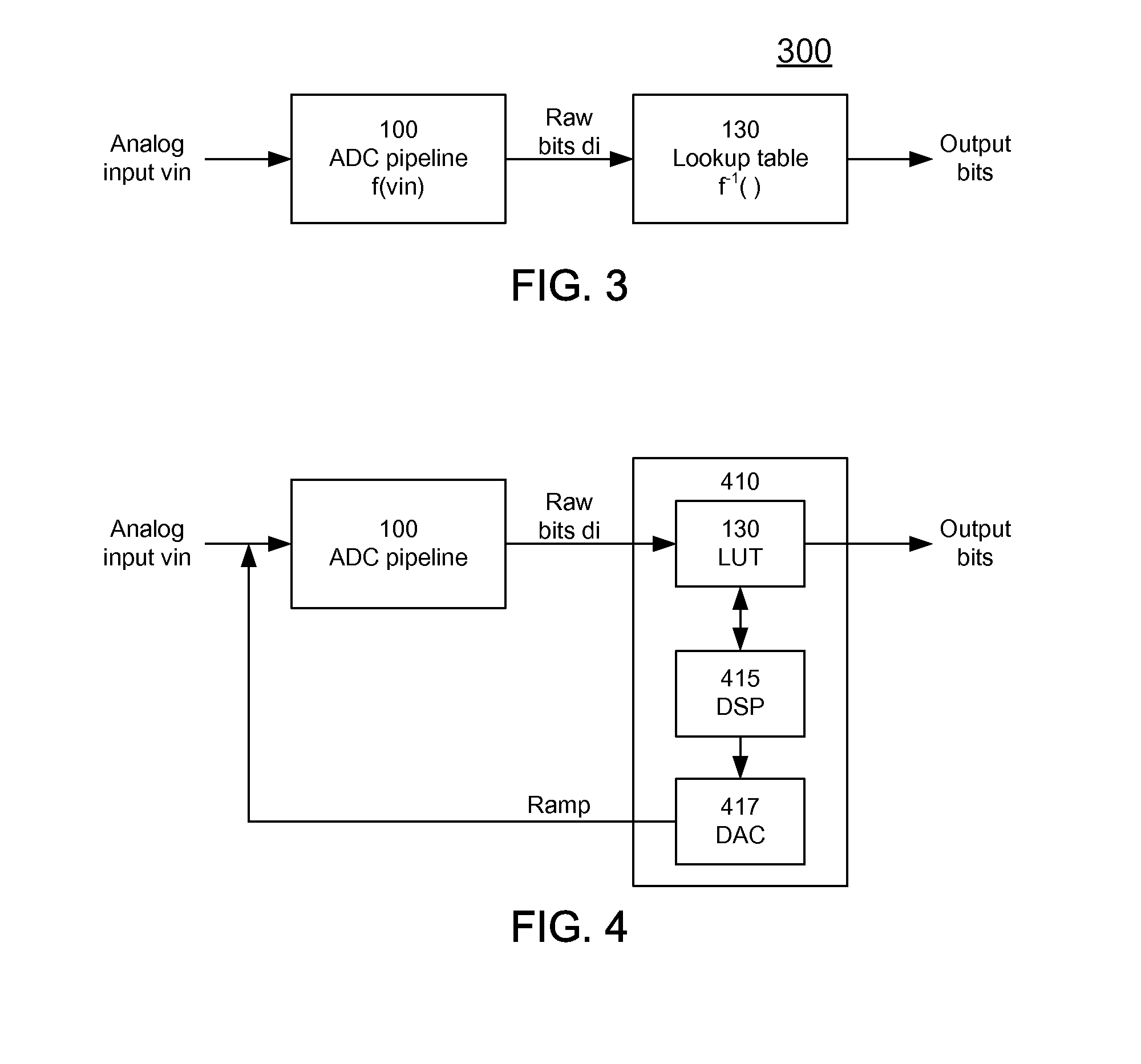

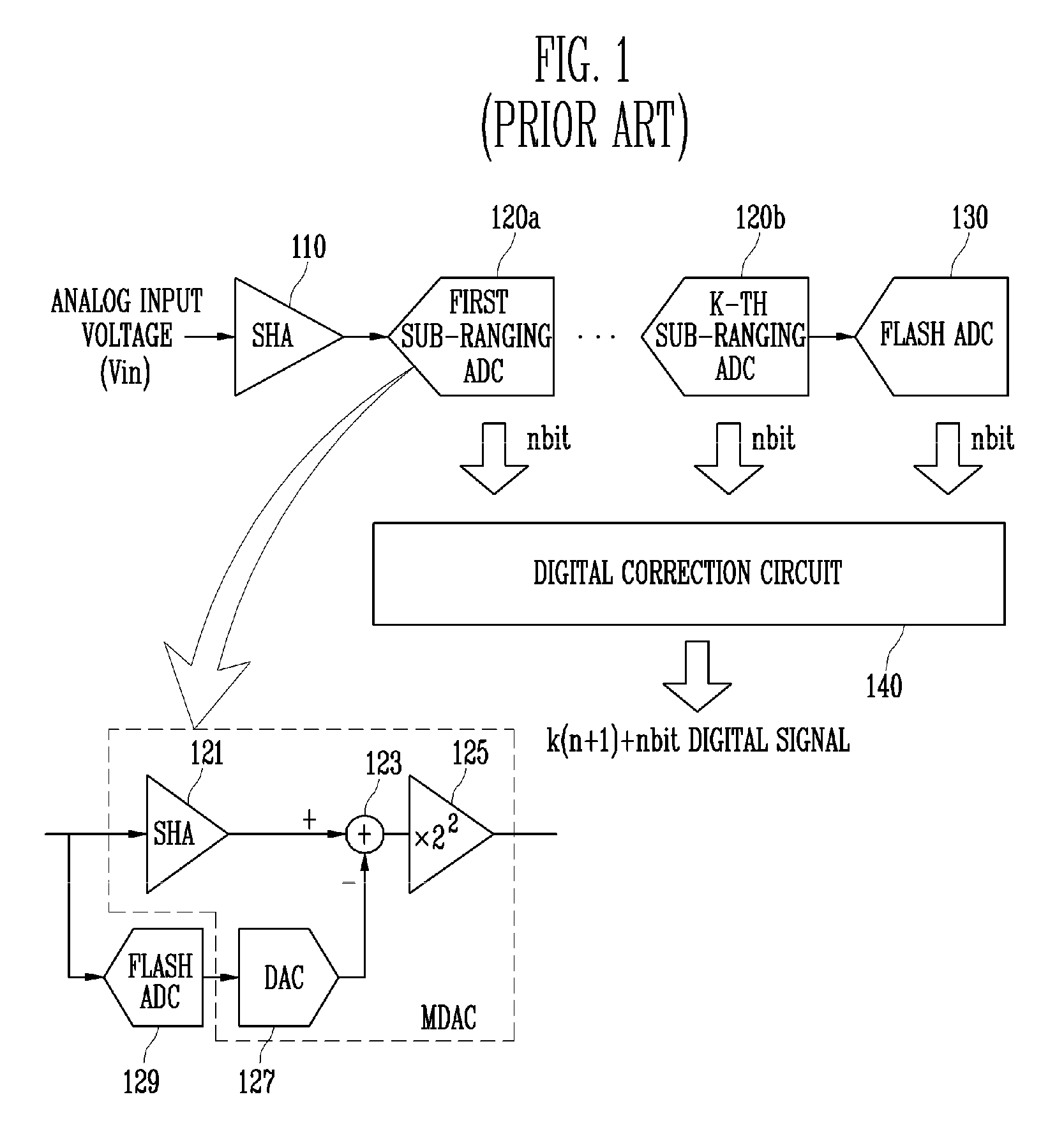

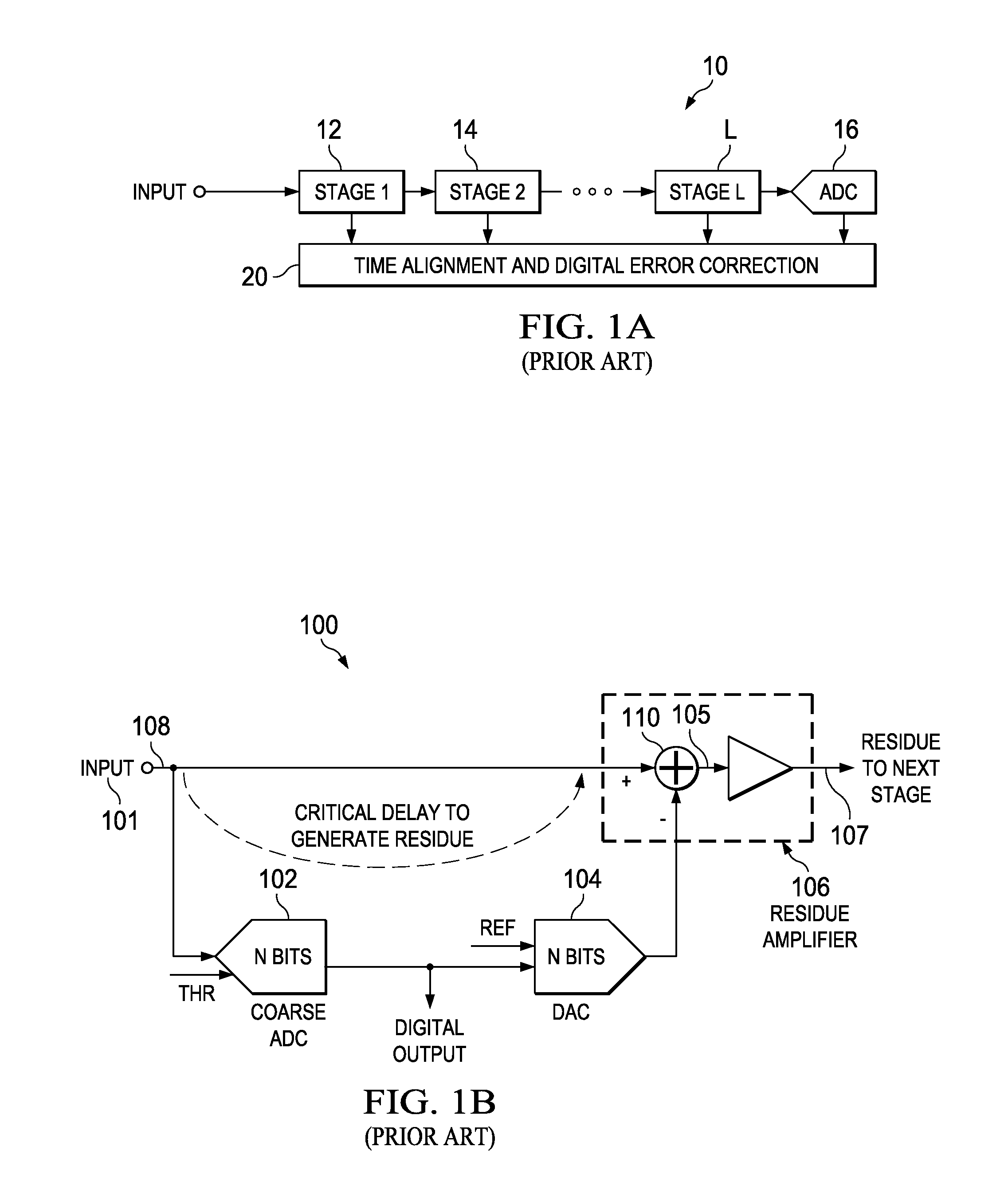

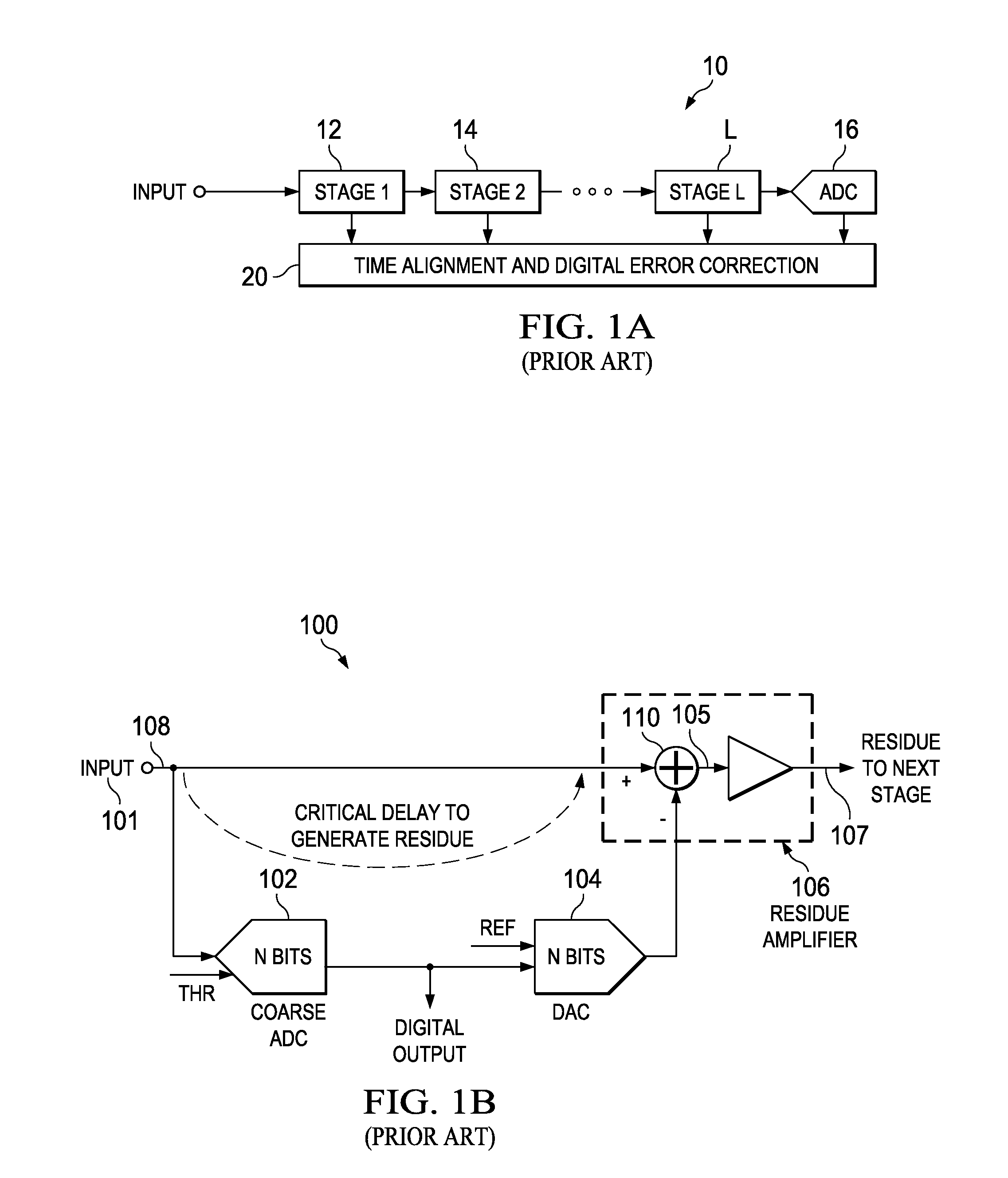

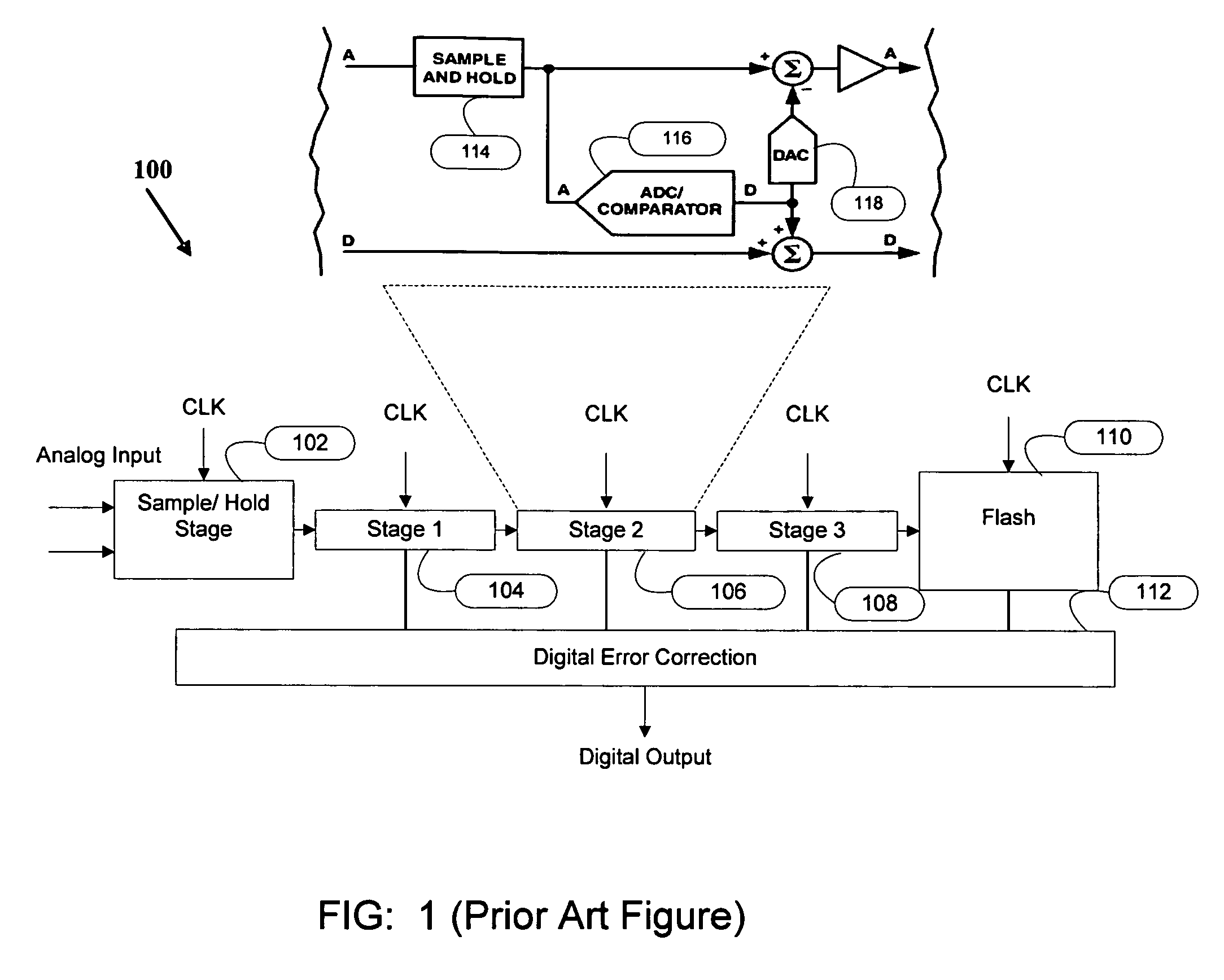

Digital background correction of nonlinear error ADC's

ActiveUS7602323B2Electric signal transmission systemsPhysical parameters compensation/preventionNonlinear circuit elementsDigital down converter

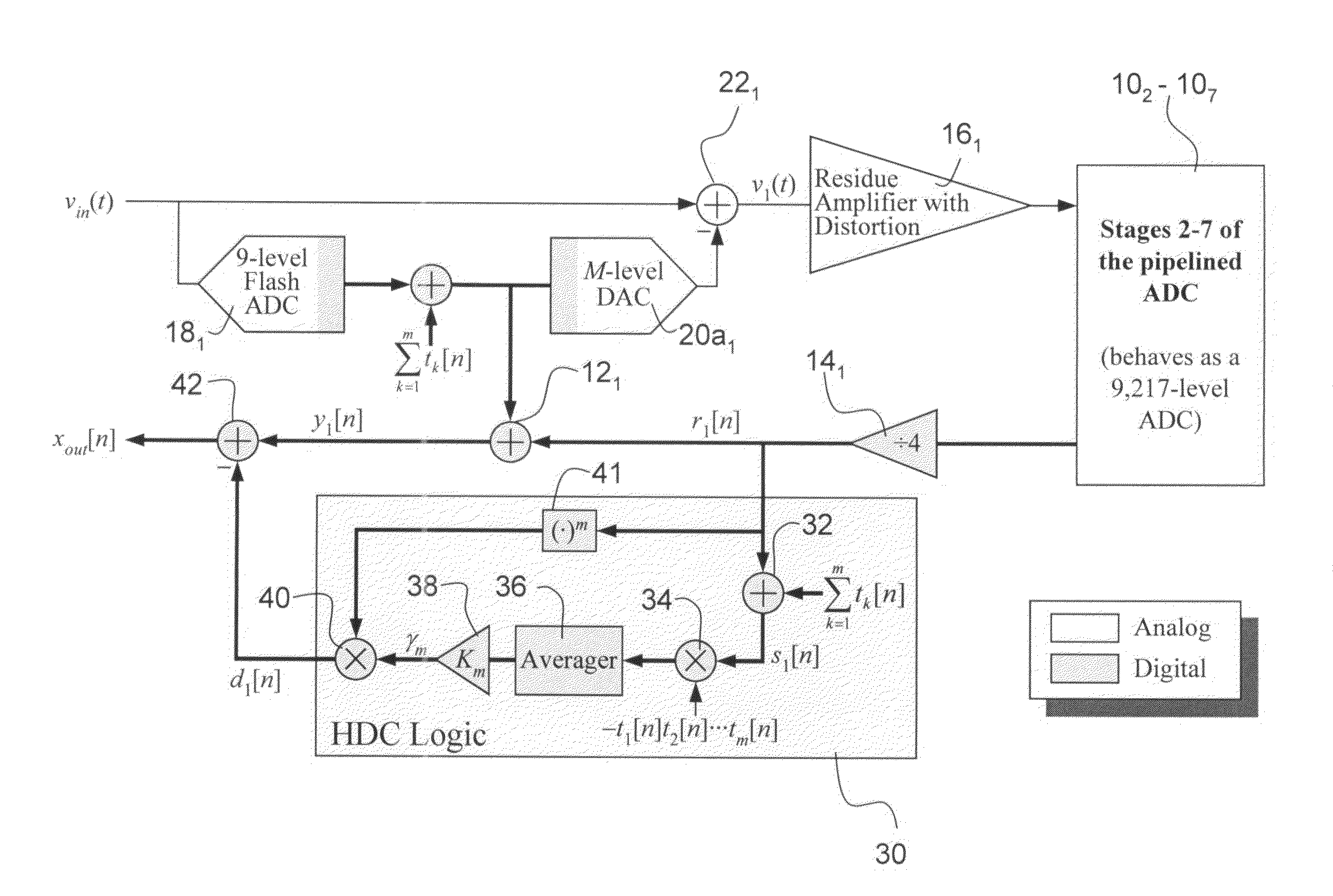

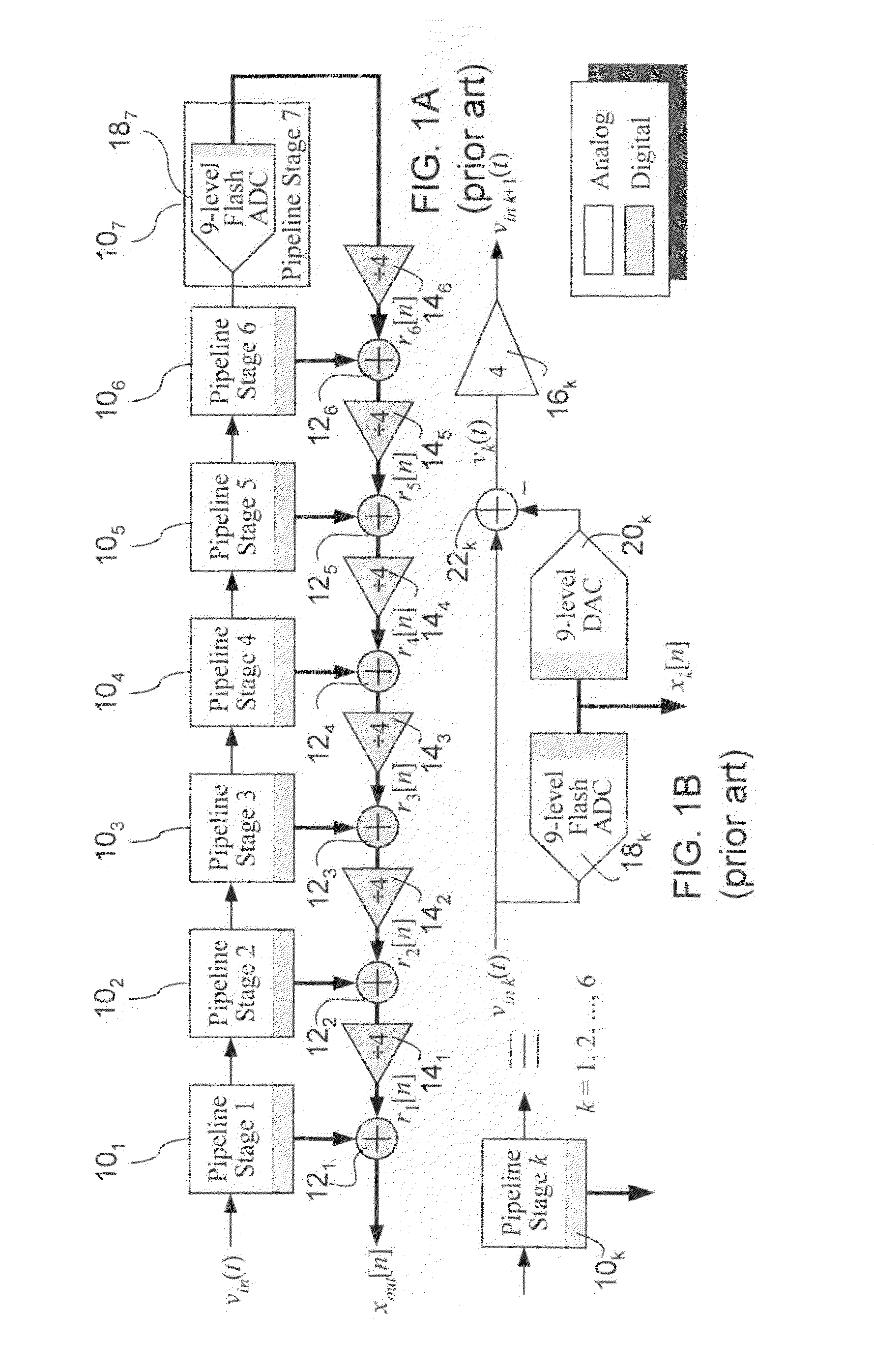

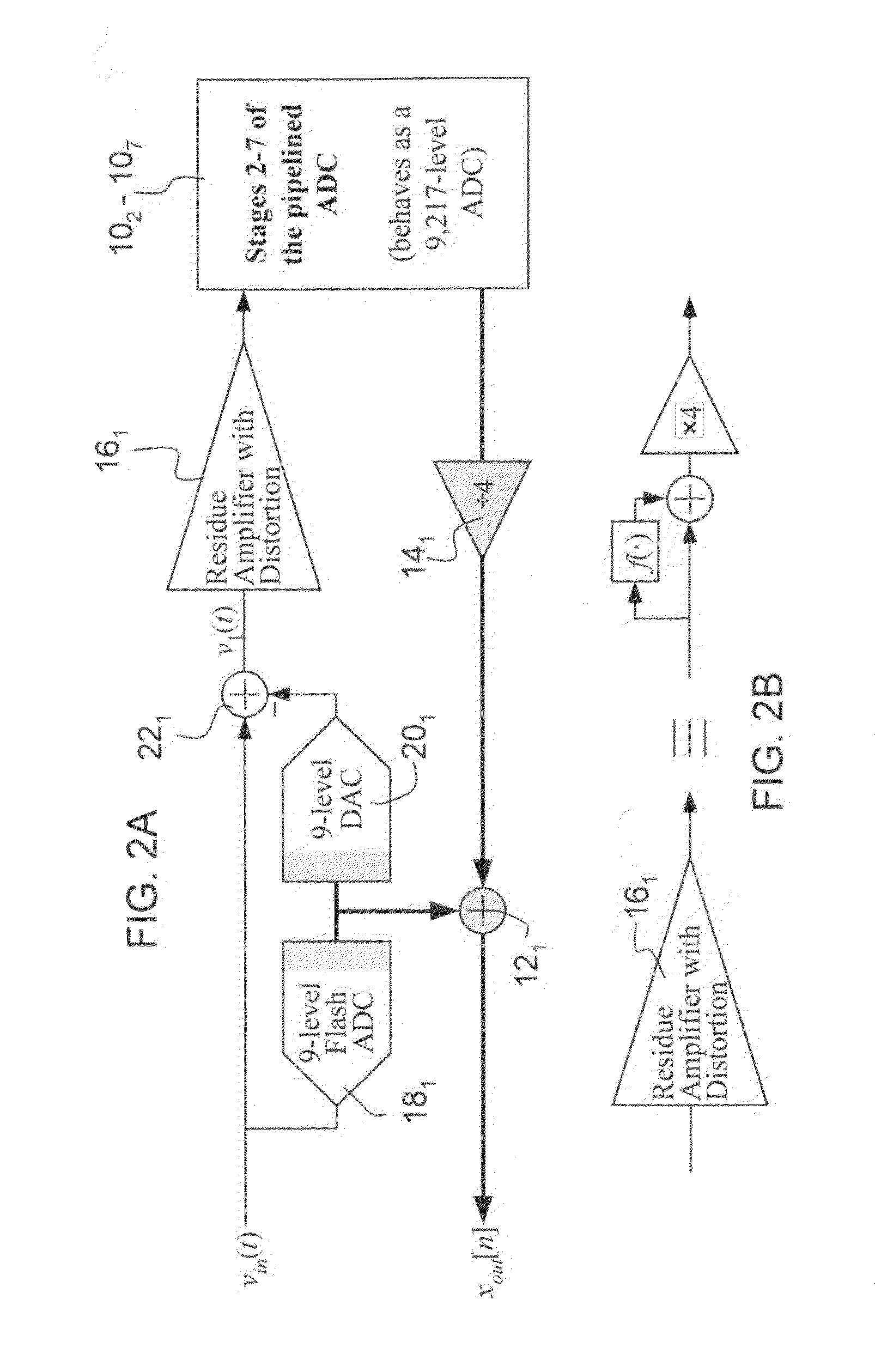

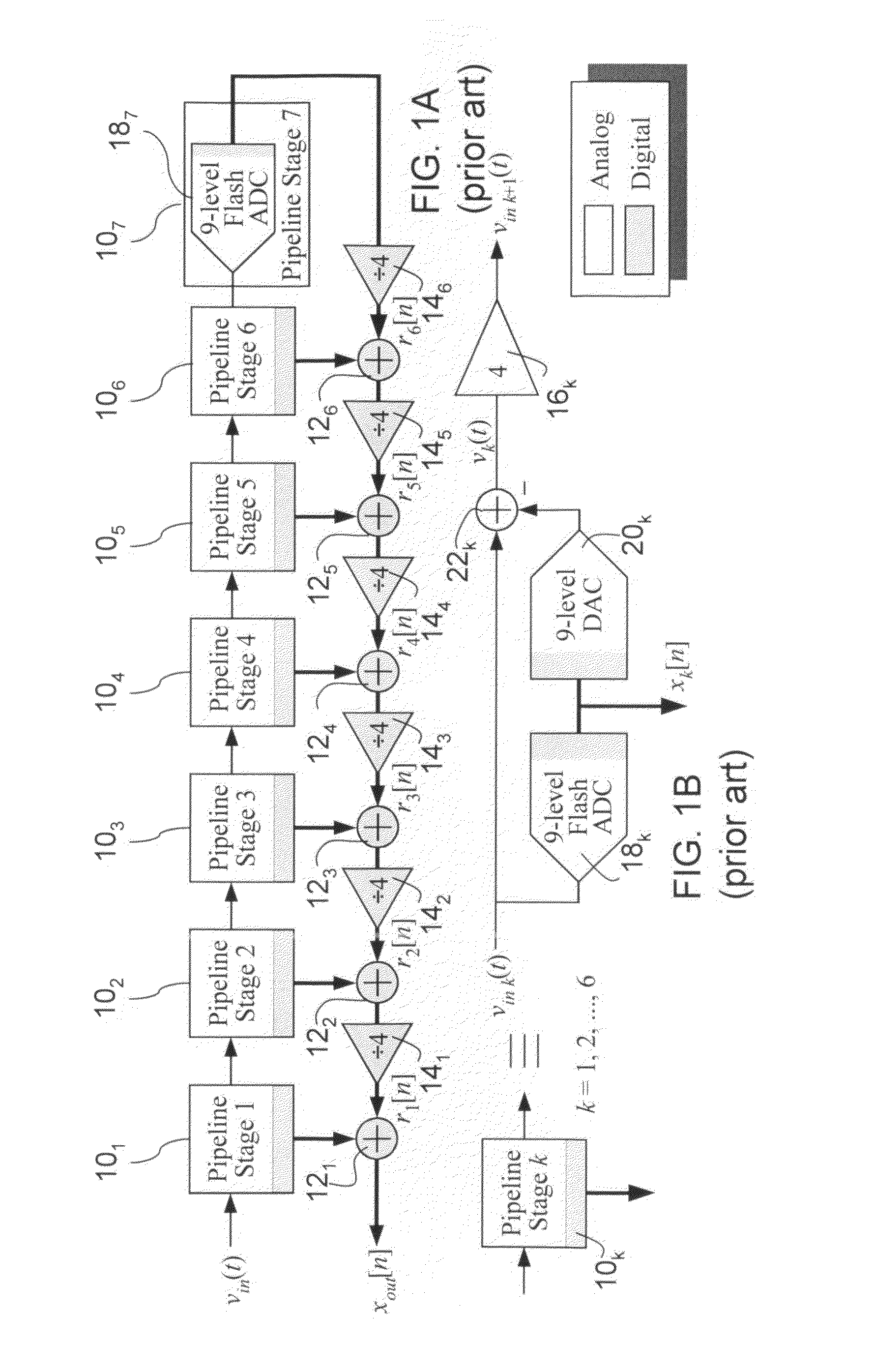

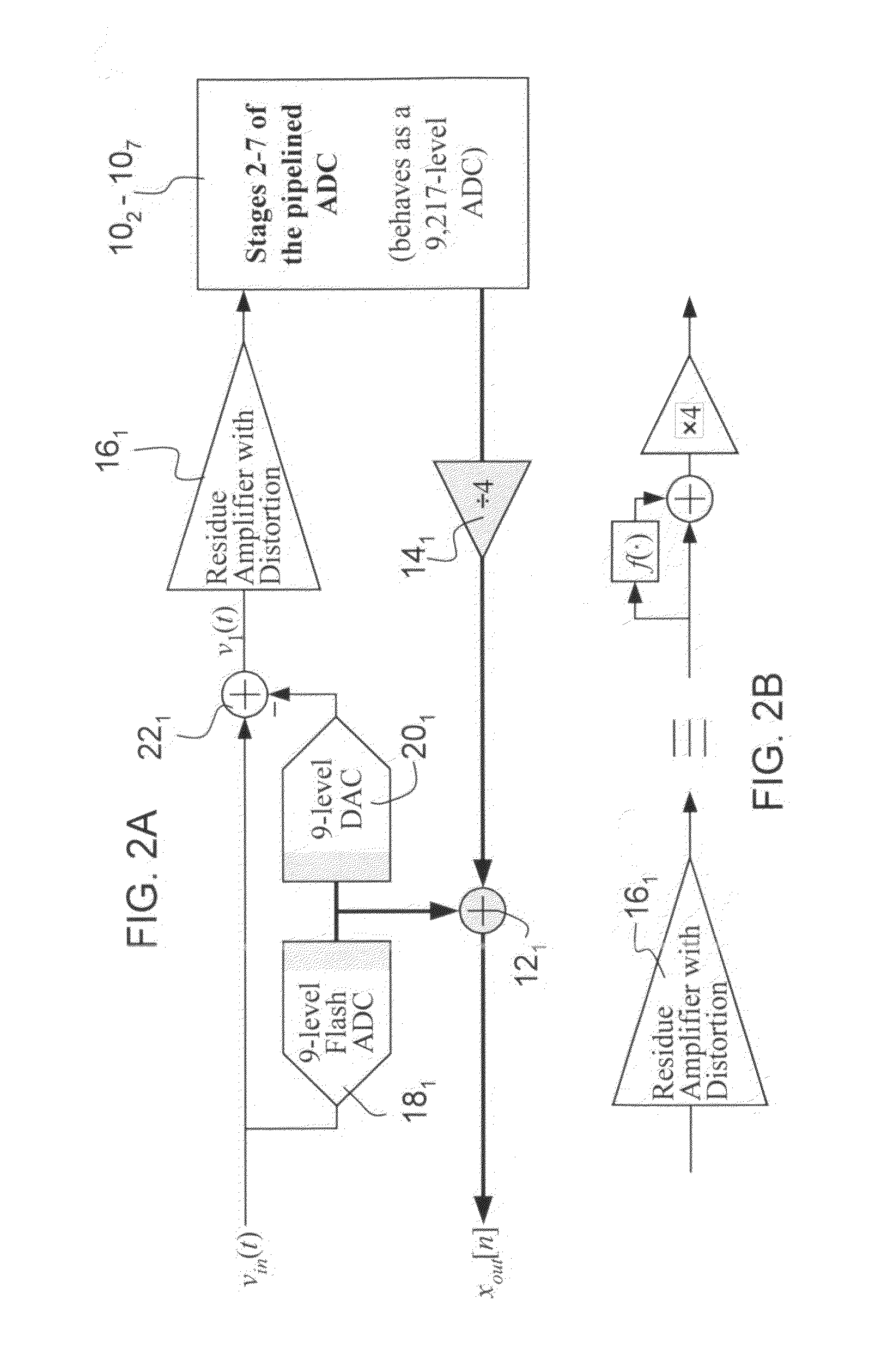

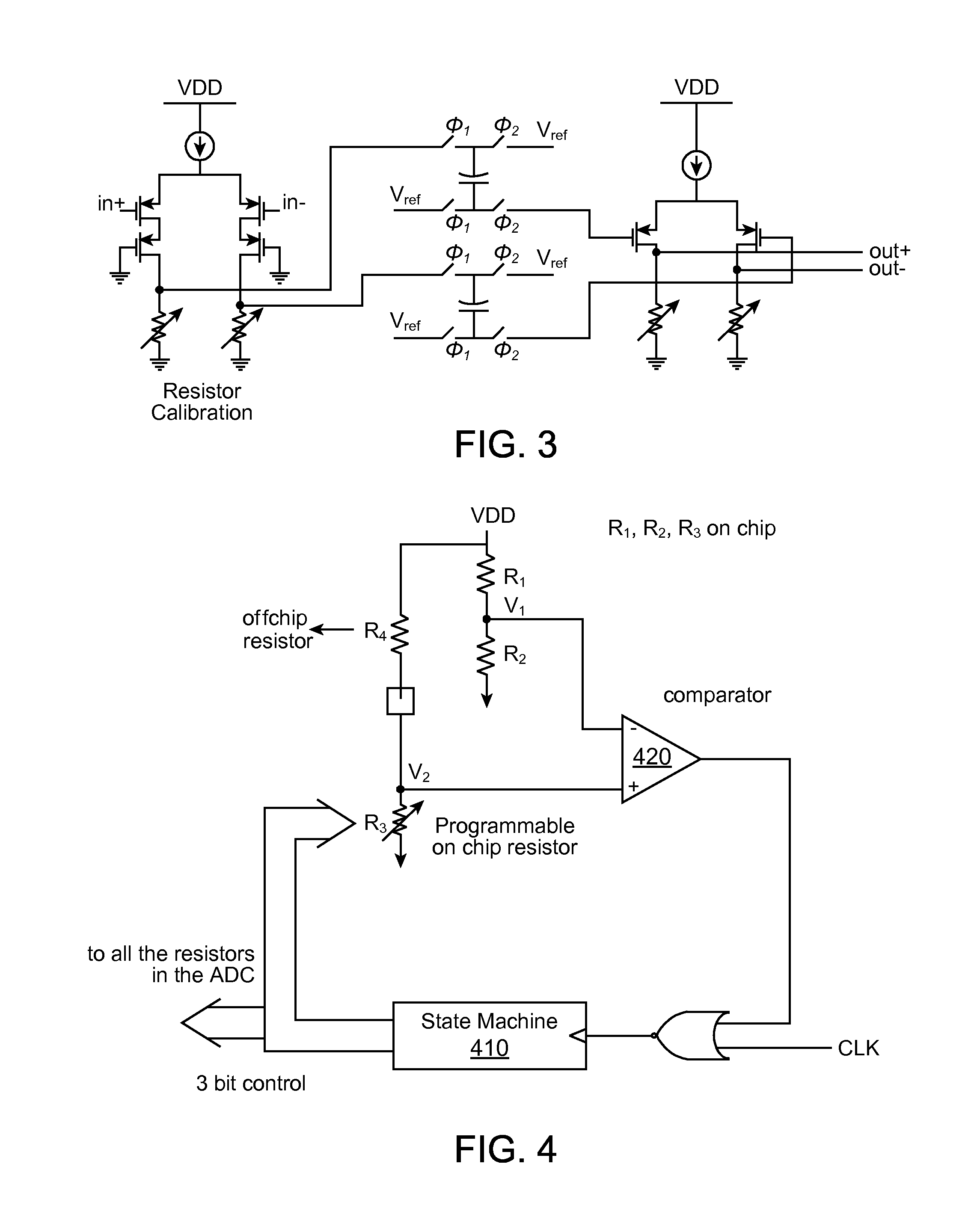

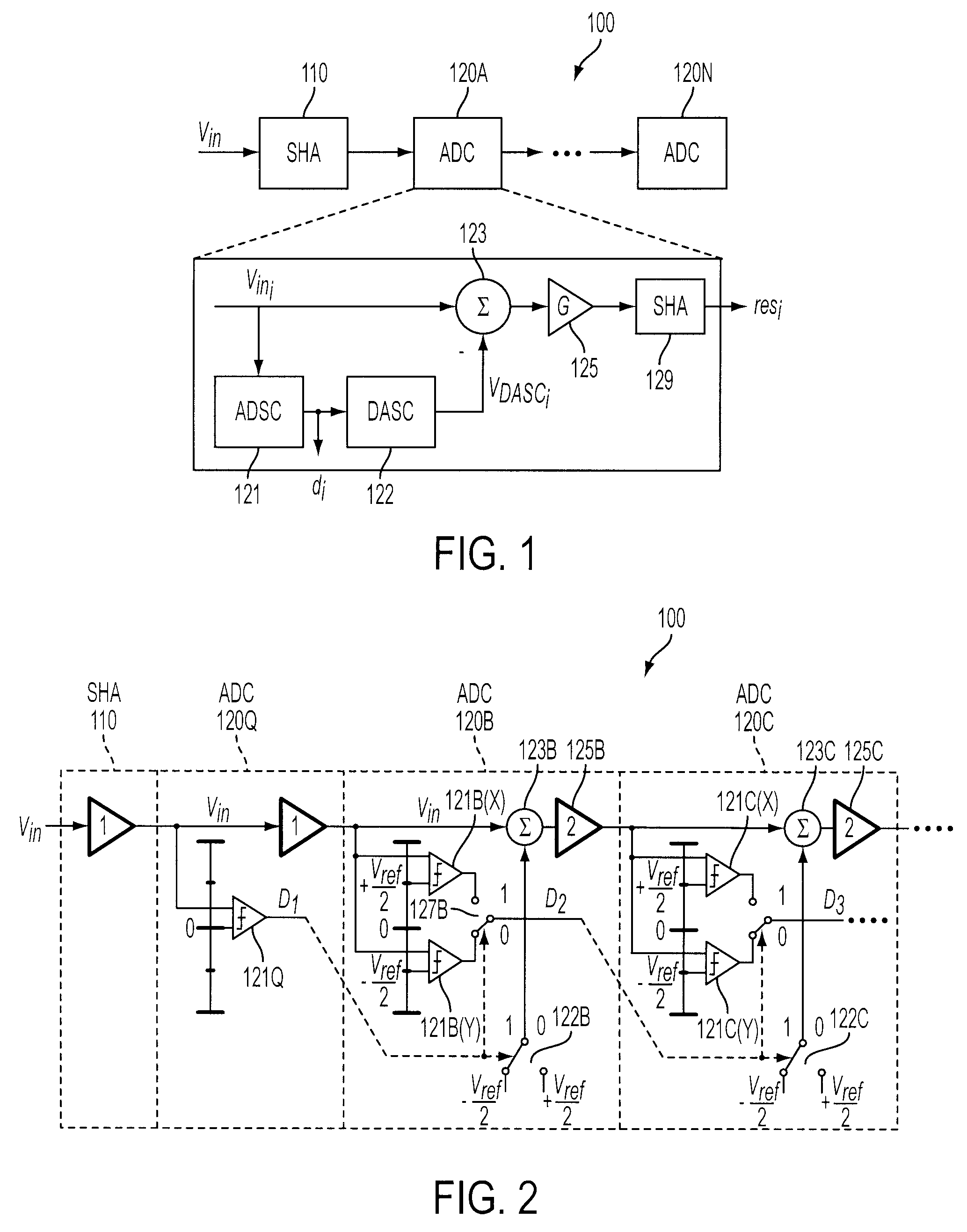

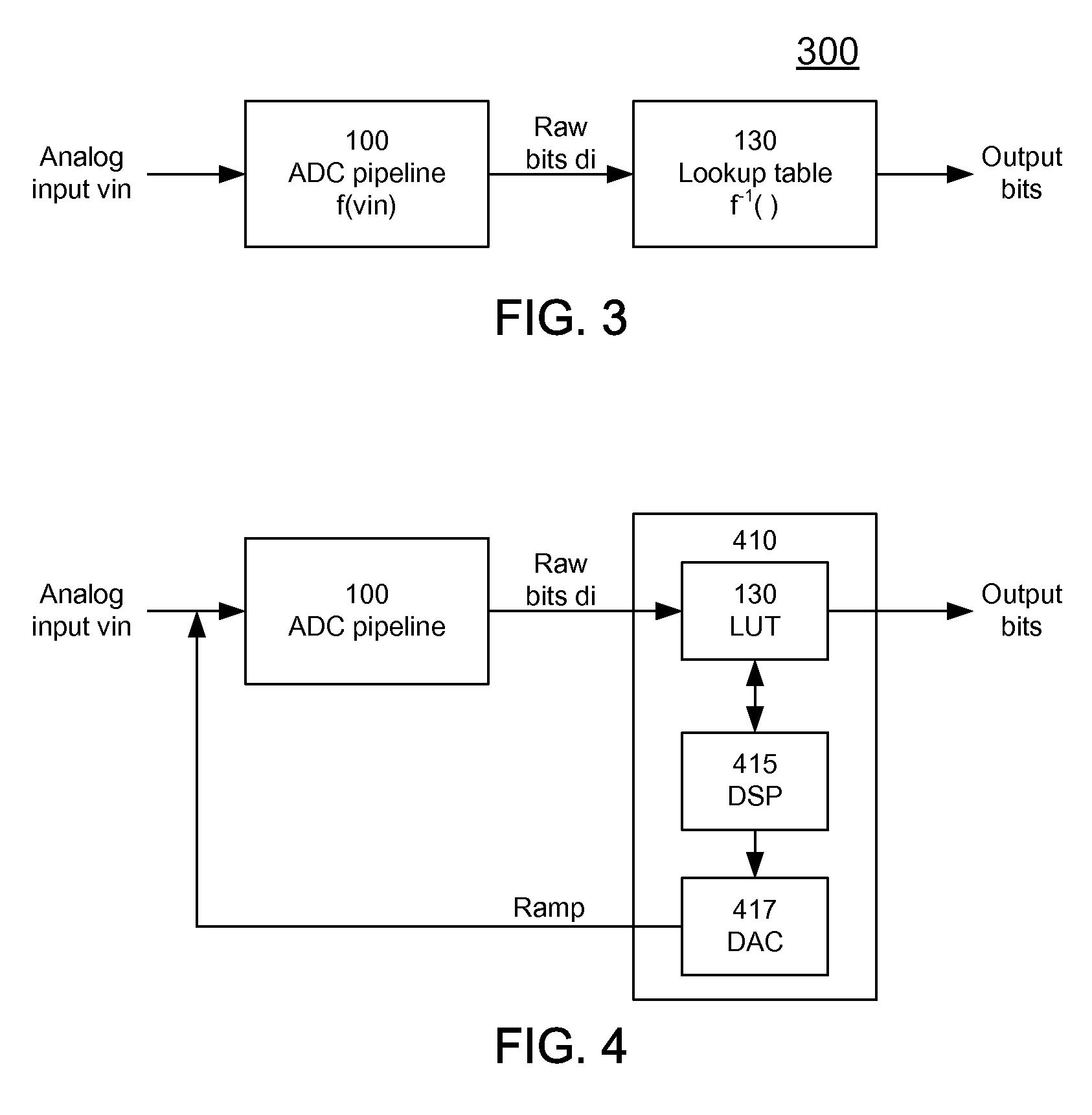

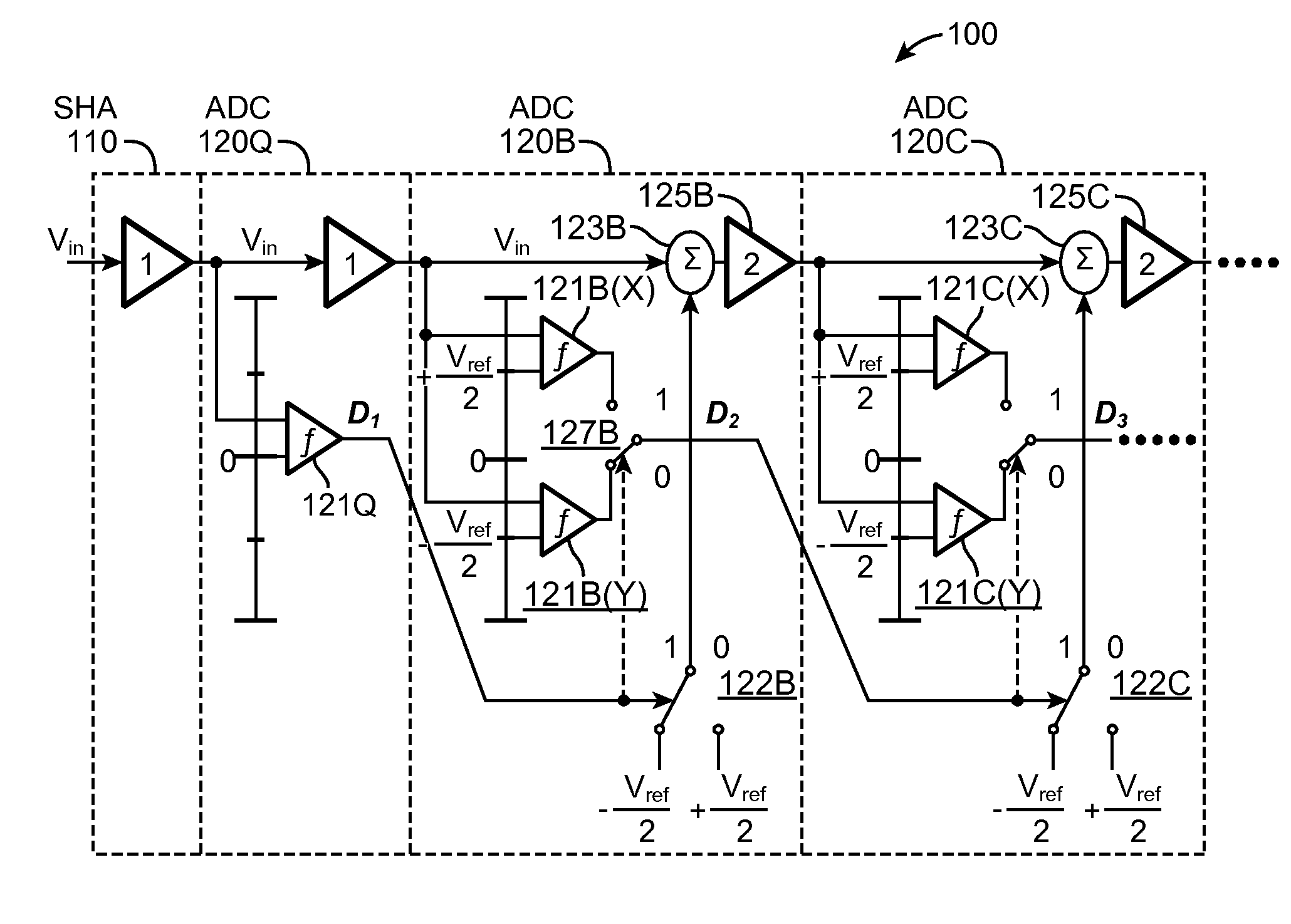

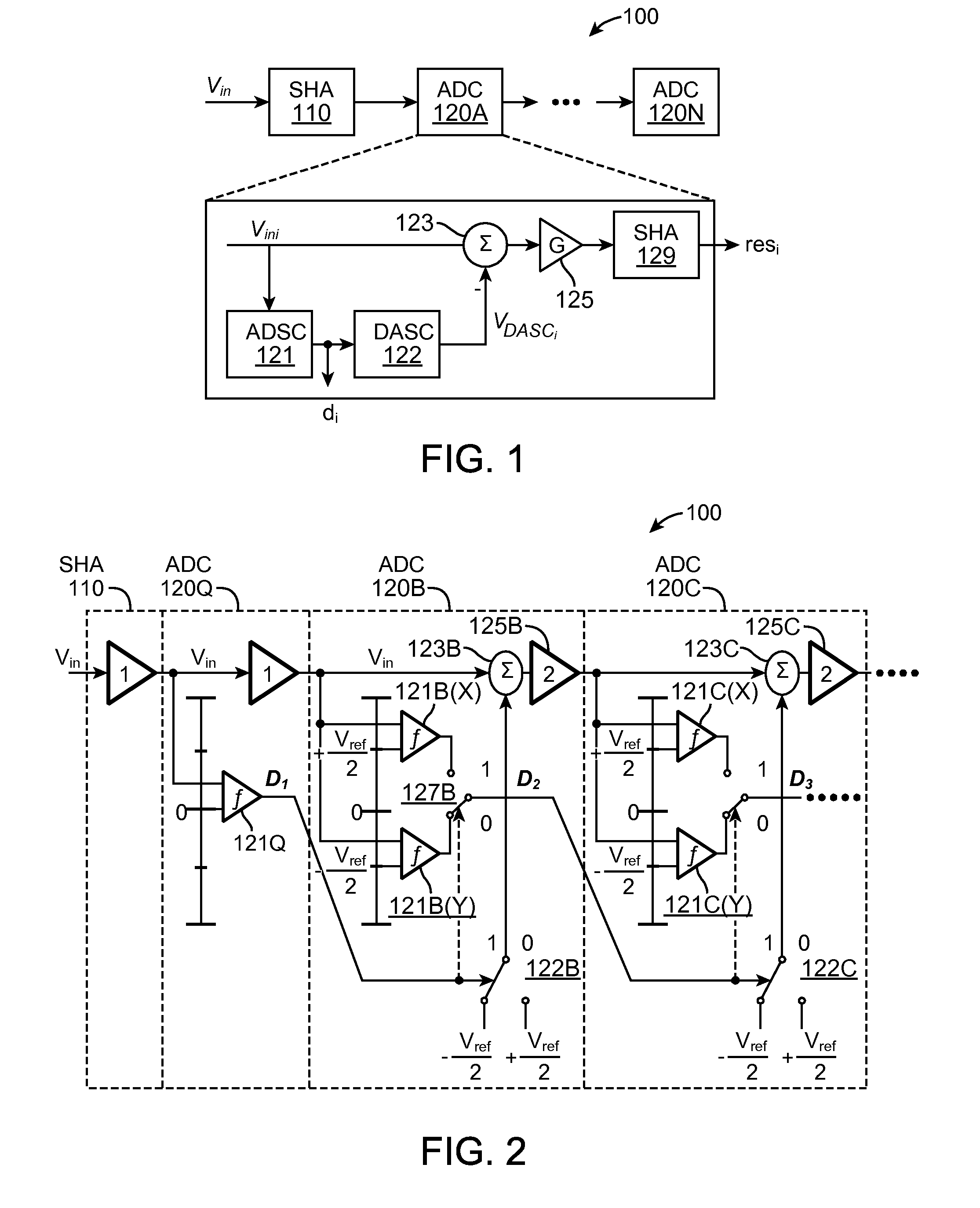

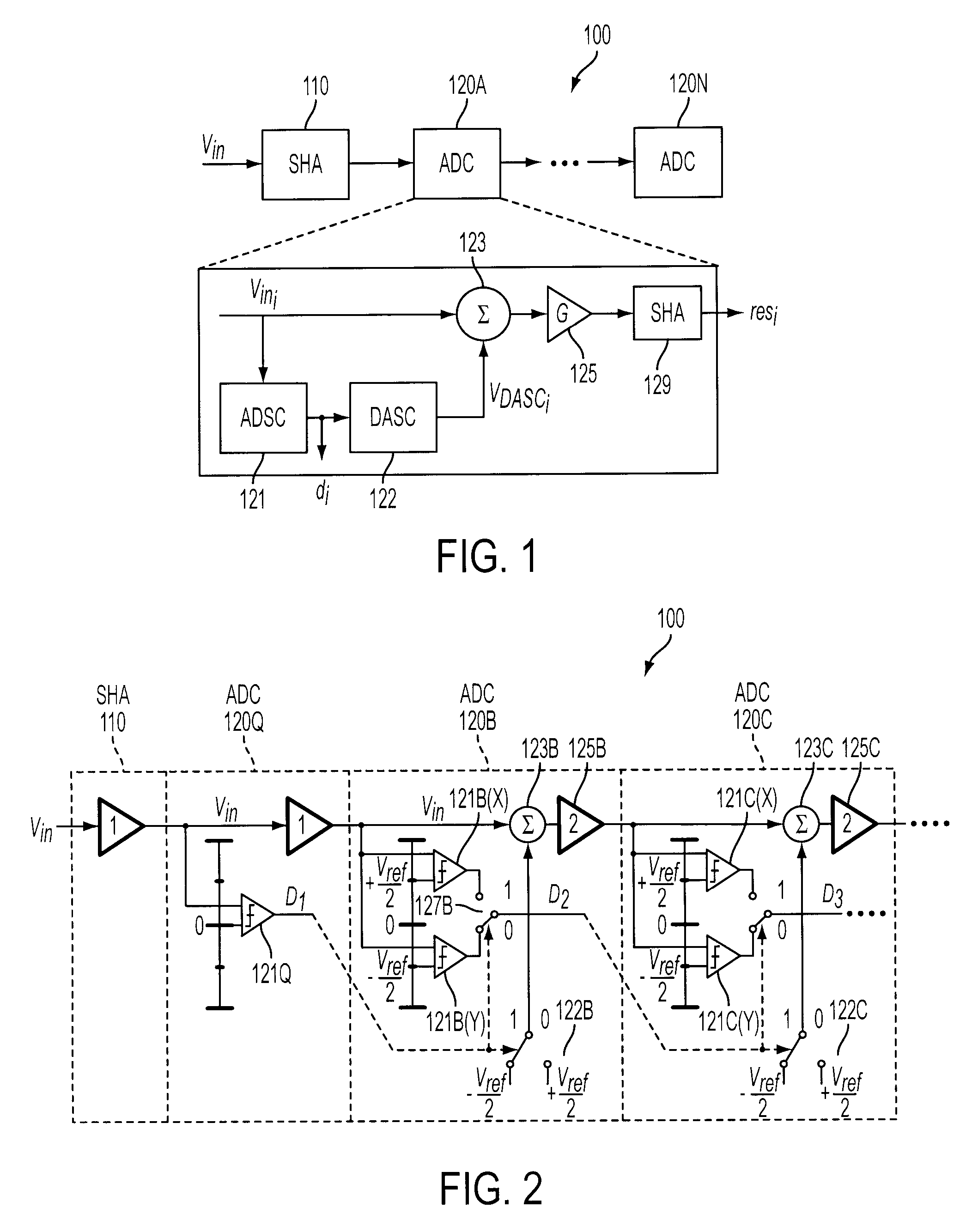

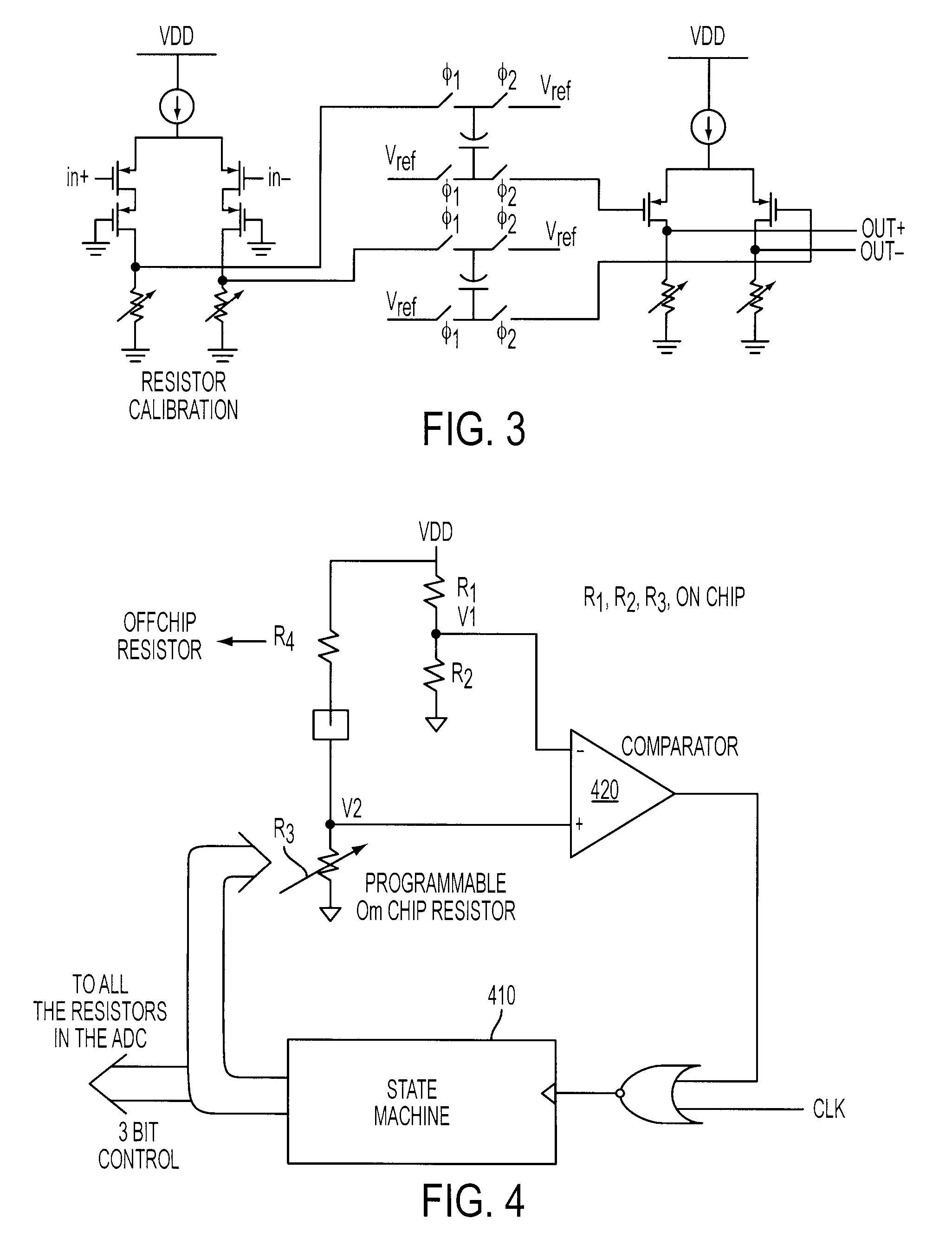

The invention provides circuits and methods for estimating and correcting nonlinear error in analog to digital converters that is introduced by nonlinear circuit elements, for example one or more residue amplifiers in a pipelined analog to digital converter integrated circuit. In a preferred method of the invention, pseudo random calibration sequences are introduced into the digital signal to be converted by a flash digital to analog converter in one or more initial stages of the pipelined analog to digital converter circuit. A digital residue signal of the output of the one or more initial pipelined analog to digital converter stages is sampled. Intermodulation products of the pseudo random calibration sequences that are present in the digital residue signal are determined to estimate nonlinear error introduced by the residue amplifier in the one or more stages. A digital correction signal is provided to the output of the one or more stages to cancel estimated nonlinear error.

Owner:RGT UNIV OF CALIFORNIA

Digital background correction of nonlinear error ADC's

ActiveUS20080258949A1Electric signal transmission systemsPhysical parameters compensation/preventionNonlinear circuit elementsDigital down converter

The invention provides circuits and methods for estimating and correcting nonlinear error in analog to digital converters that is introduced by nonlinear circuit elements, for example one or more residue amplifiers in a pipelined analog to digital converter integrated circuit. In a preferred method of the invention, pseudo random calibration sequences are introduced into the digital signal to be converted by a flash digital to analog converter in one or more initial stages of the pipelined analog to digital converter circuit. A digital residue signal of the output of the one or more initial pipelined analog to digital converter stages is sampled. Intermodulation products of the pseudo random calibration sequences that are present in the digital residue signal are determined to estimate nonlinear error introduced by the residue amplifier in the one or more stages. A digital correction signal is provided to the output of the one or more stages to cancel estimated nonlinear error.

Owner:RGT UNIV OF CALIFORNIA

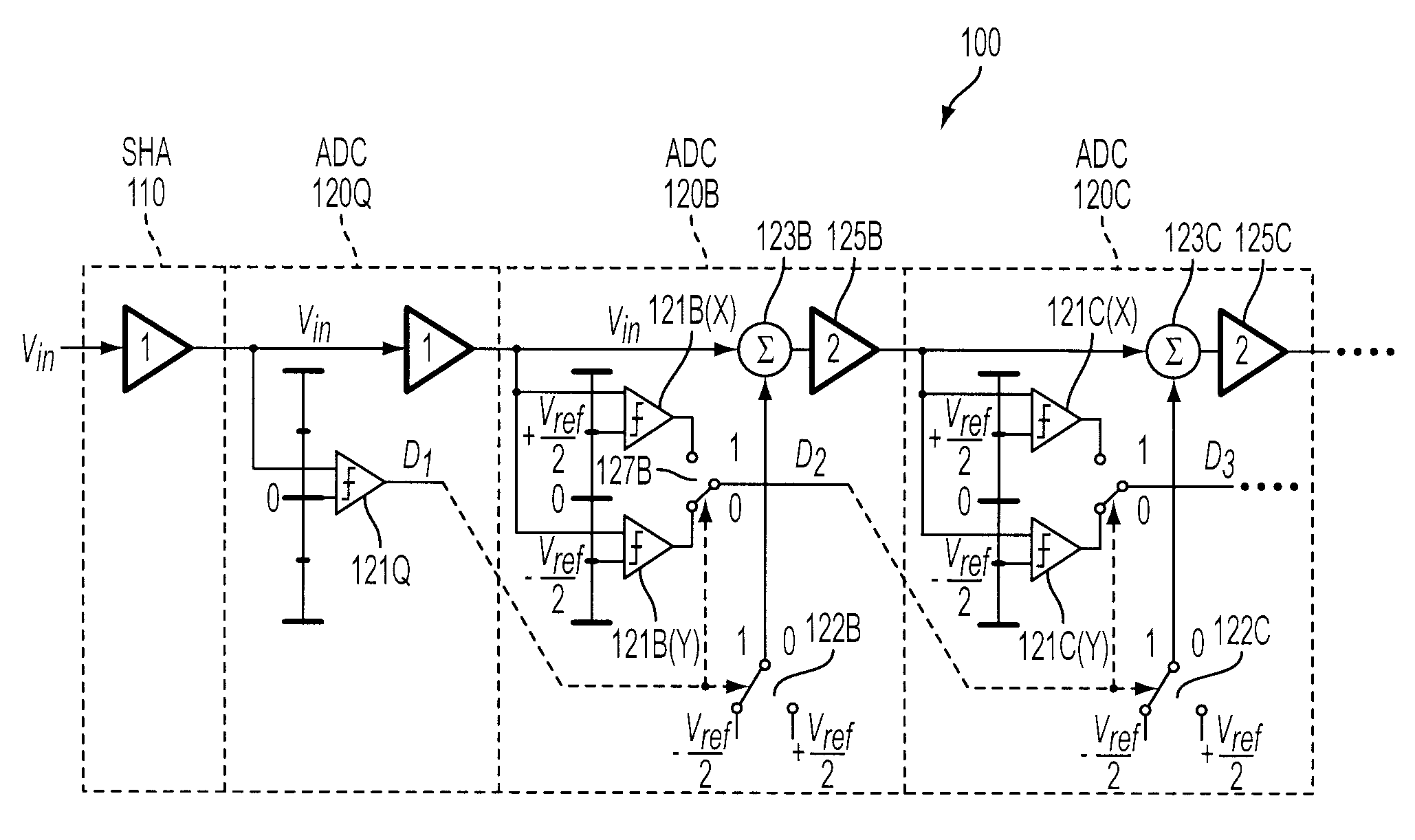

Analog-to-digital Converter Using Lookahead Pipelined Architecture and Open-loop Residue Amplifiers

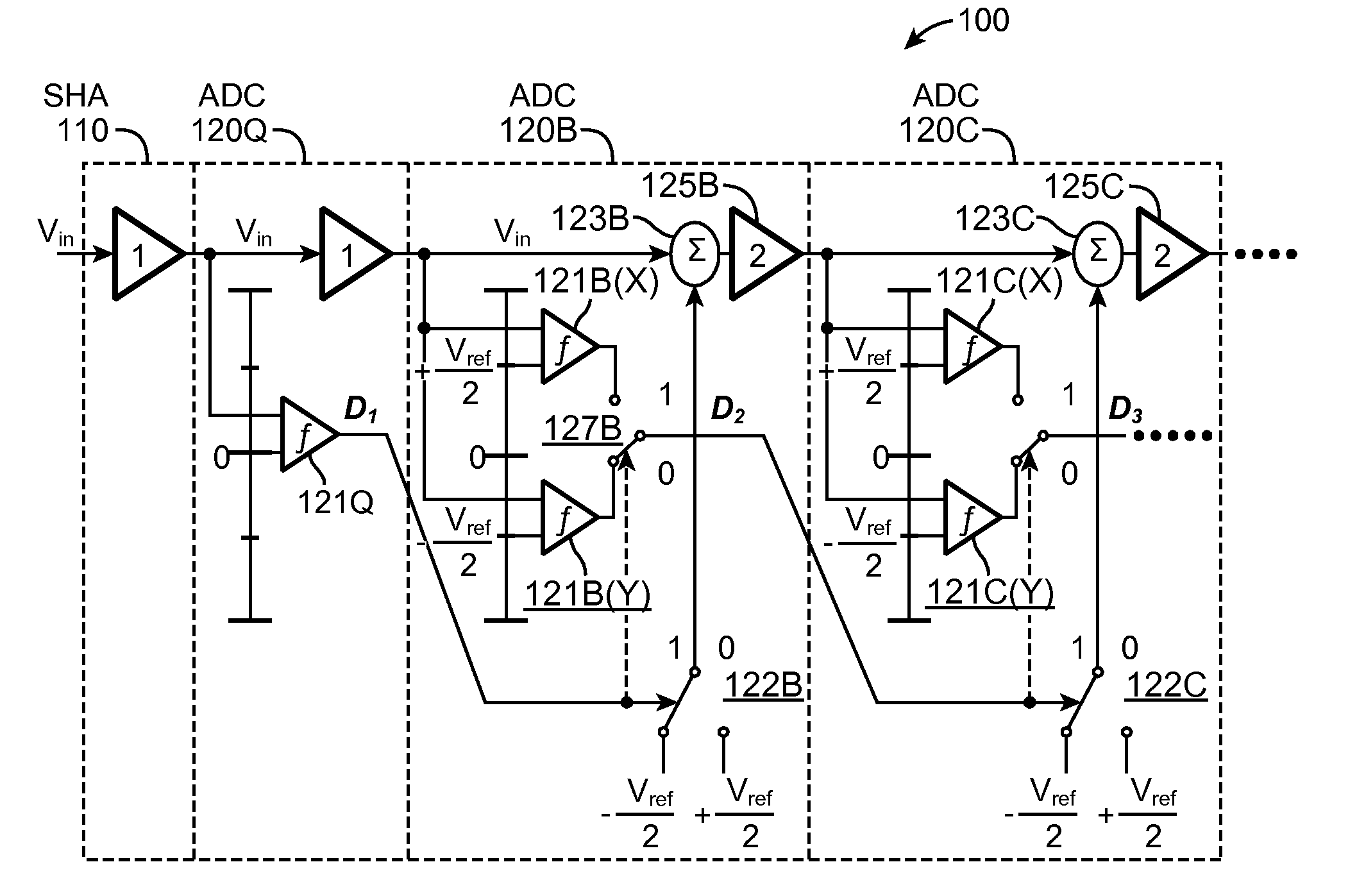

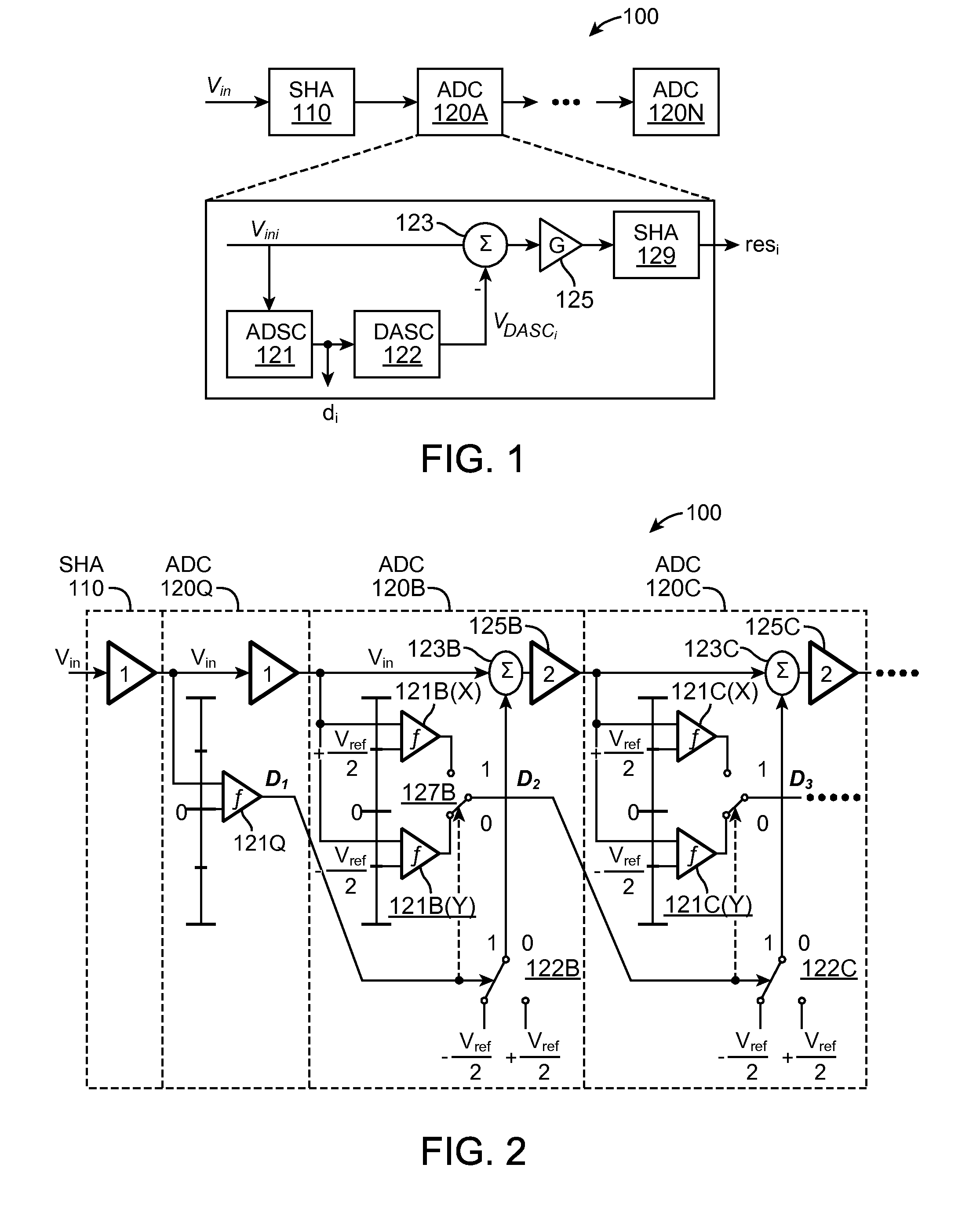

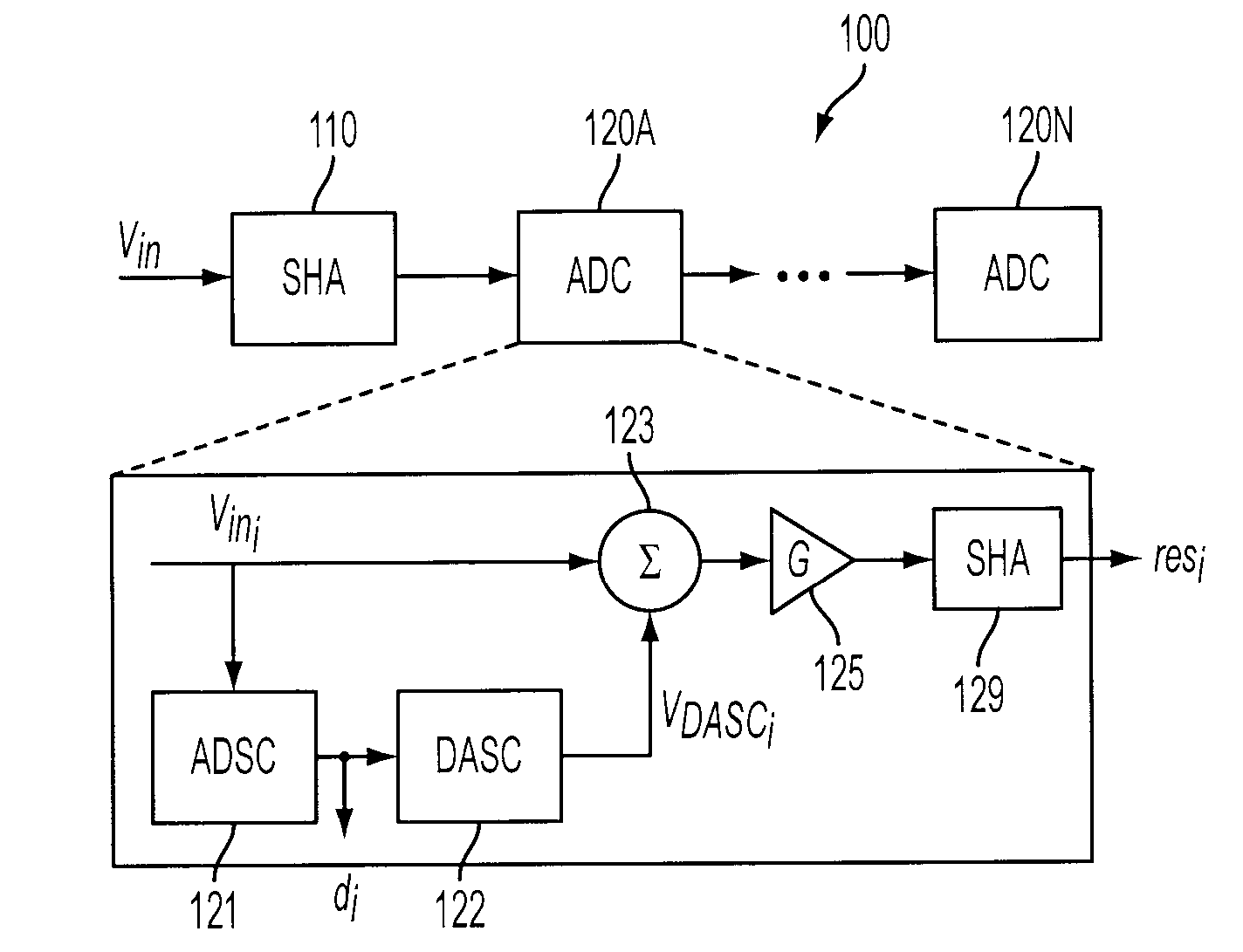

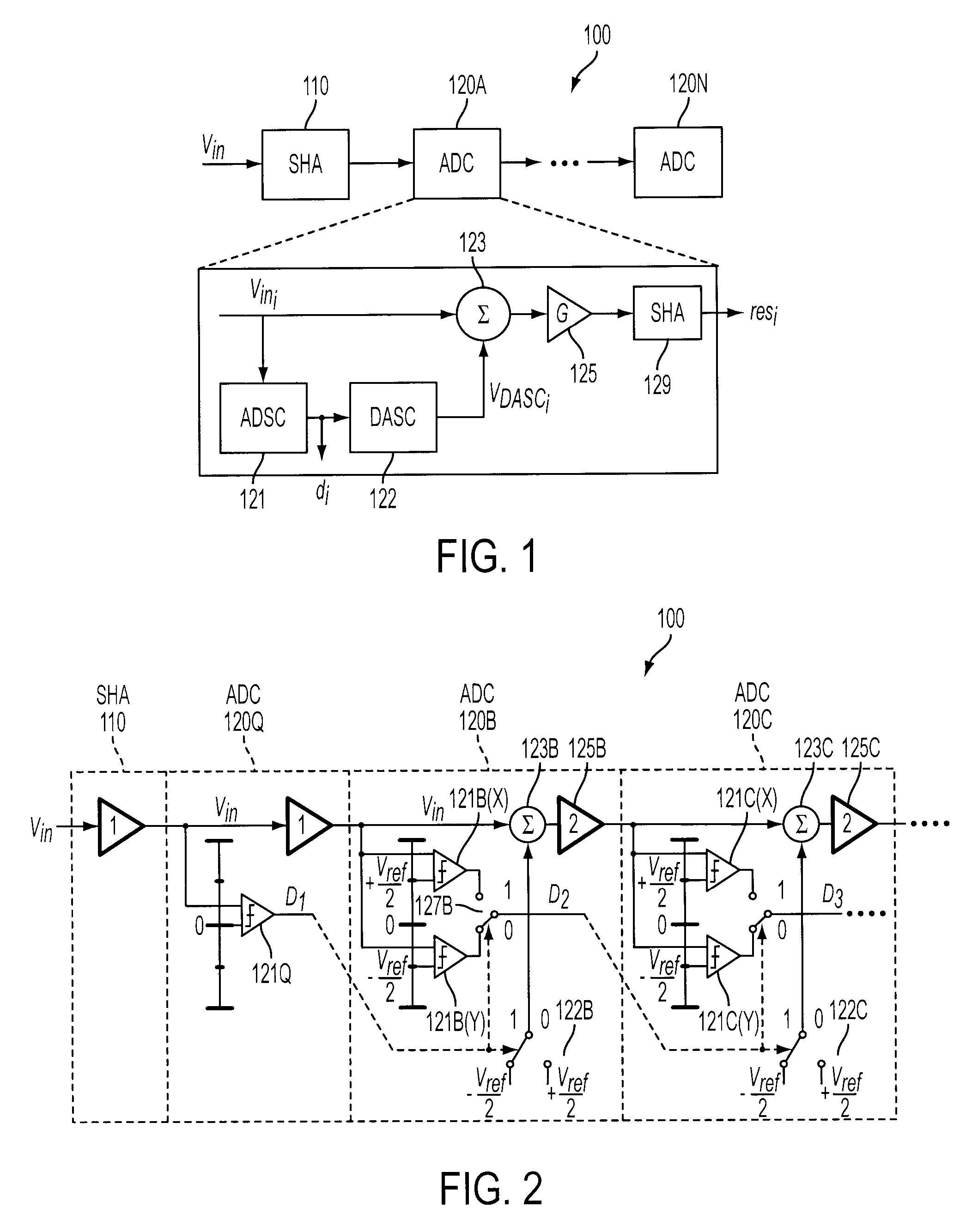

ActiveUS20070176814A1Reduce power consumptionOvercome limitationsElectric signal transmission systemsAnalogue-digital convertersEngineeringResidue amplifier

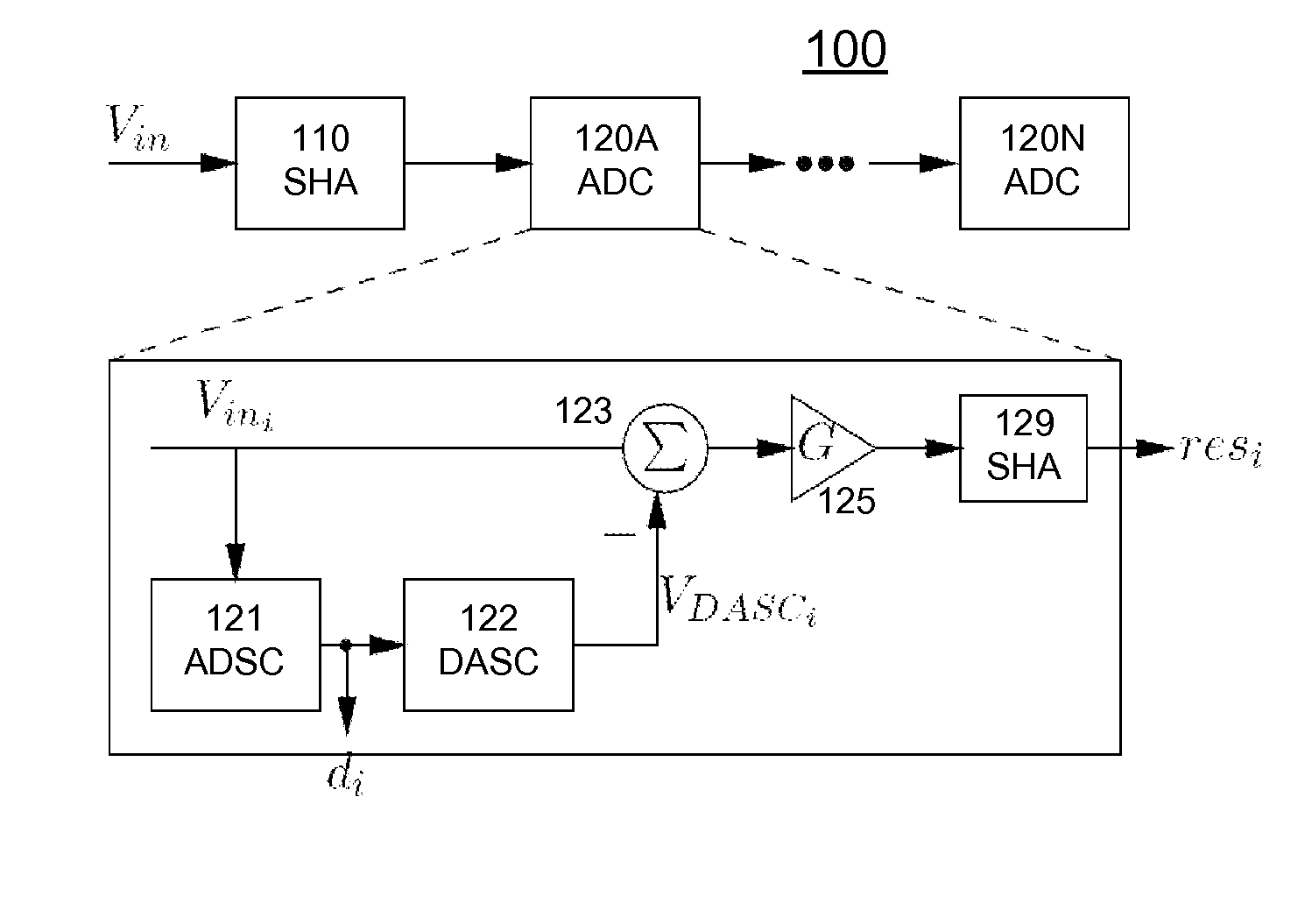

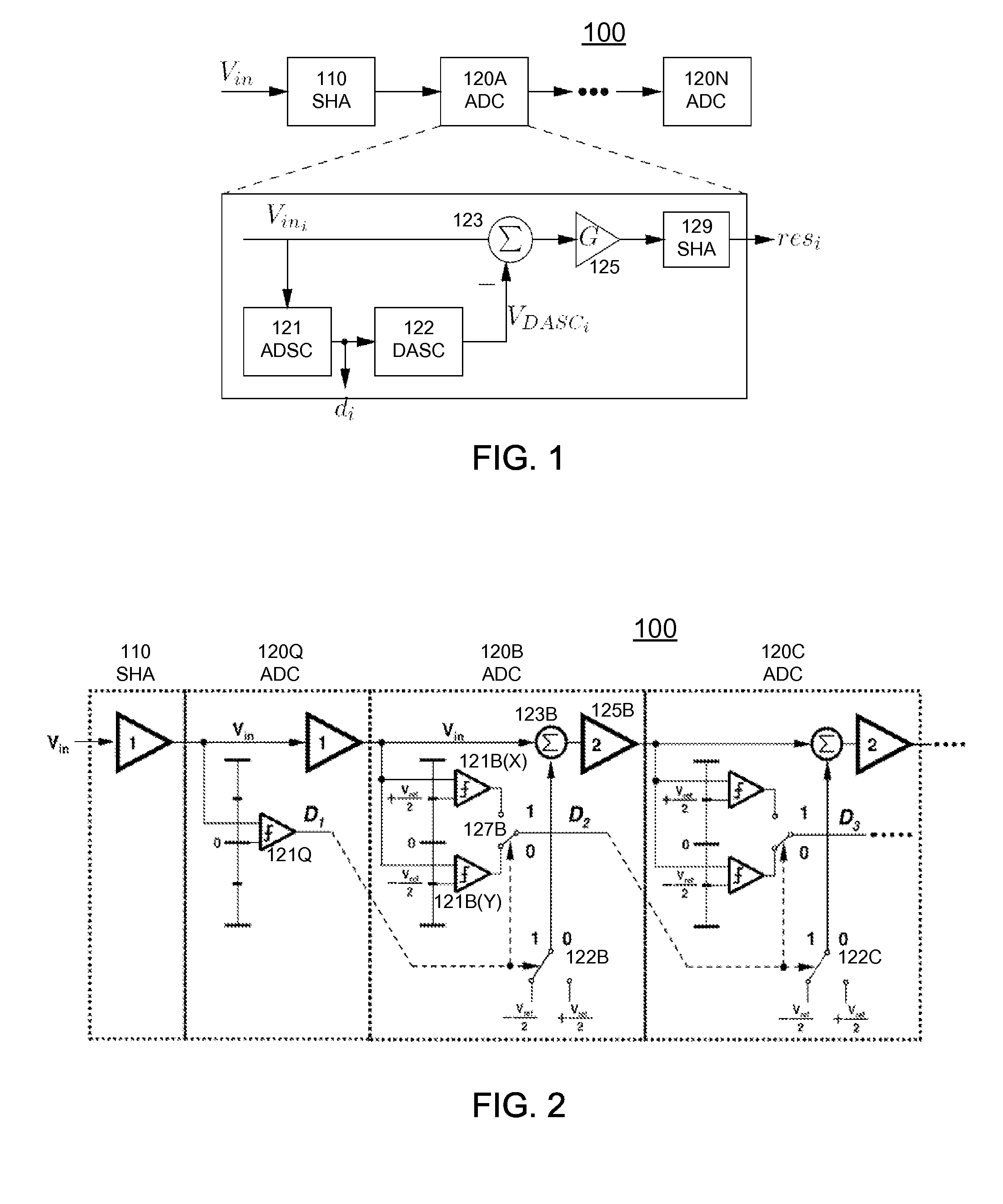

A lookahead pipelined ADC architecture uses open-loop residue amplifiers with calibration. This approach is able to achieve a high-speed, high-accuracy ADC with reduced power consumption. In one aspect, an ADC pipeline unit includes a plurality of lookahead pipeline stages (i.e., an ADC lookahead pipeline) coupled to a calibration unit. The ADC lookahead pipeline uses open-loop residue amplifiers. The calibration unit compensates for non-linearity in the open-loop amplifiers.

Owner:MARVELL ASIA PTE LTD

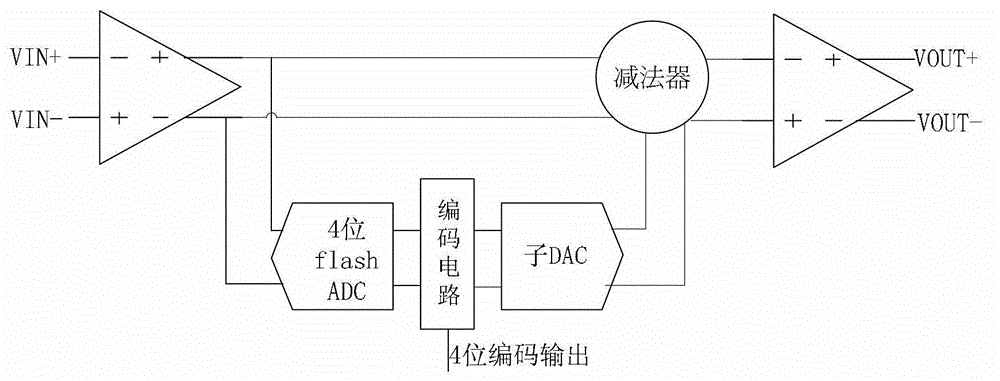

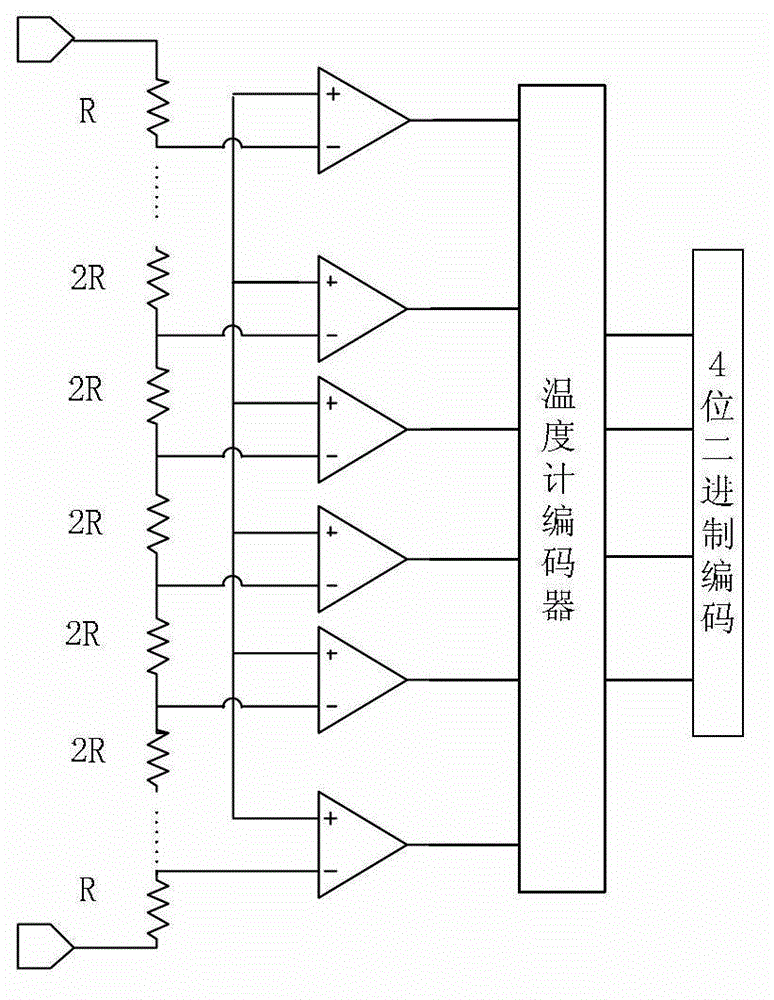

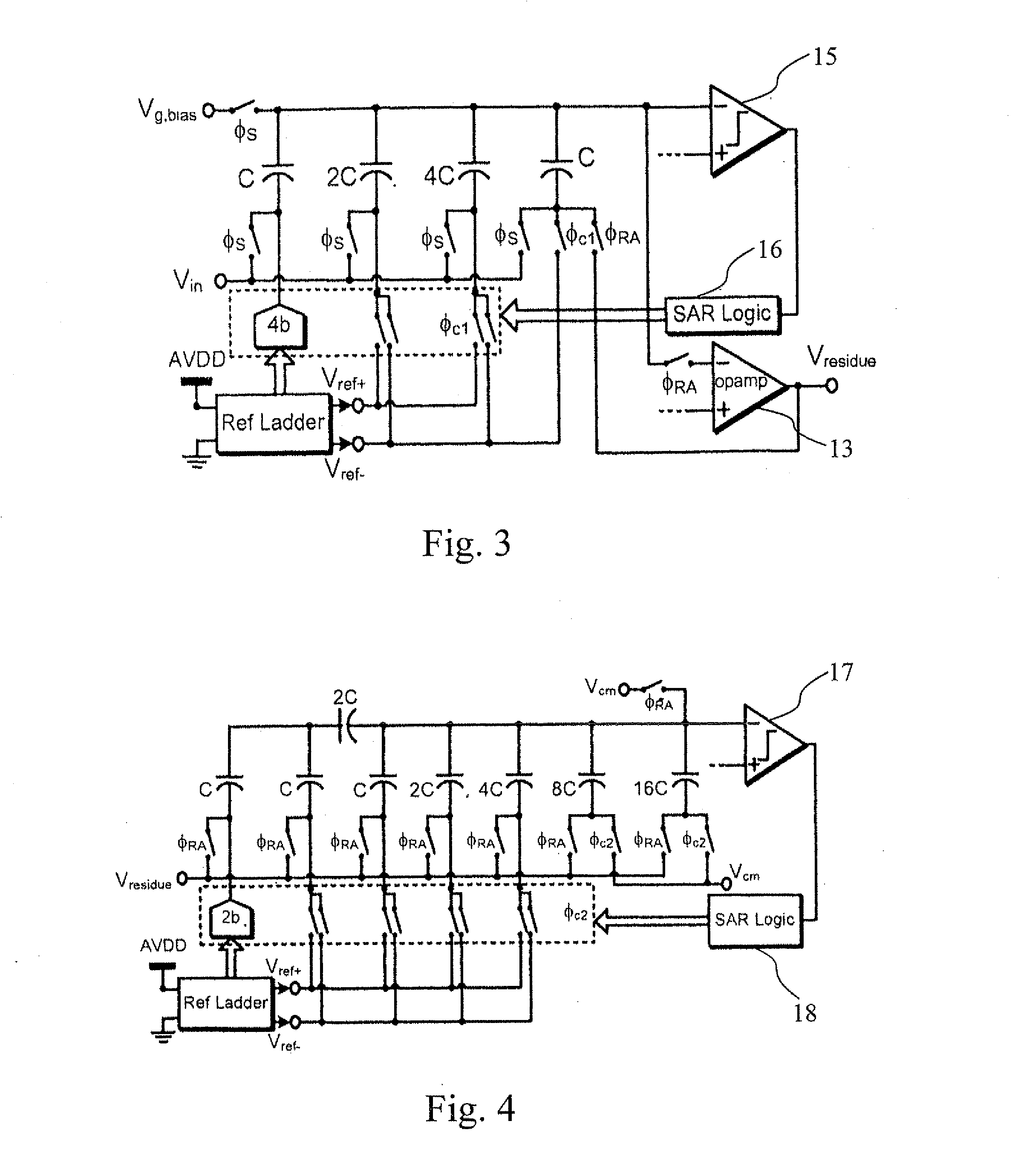

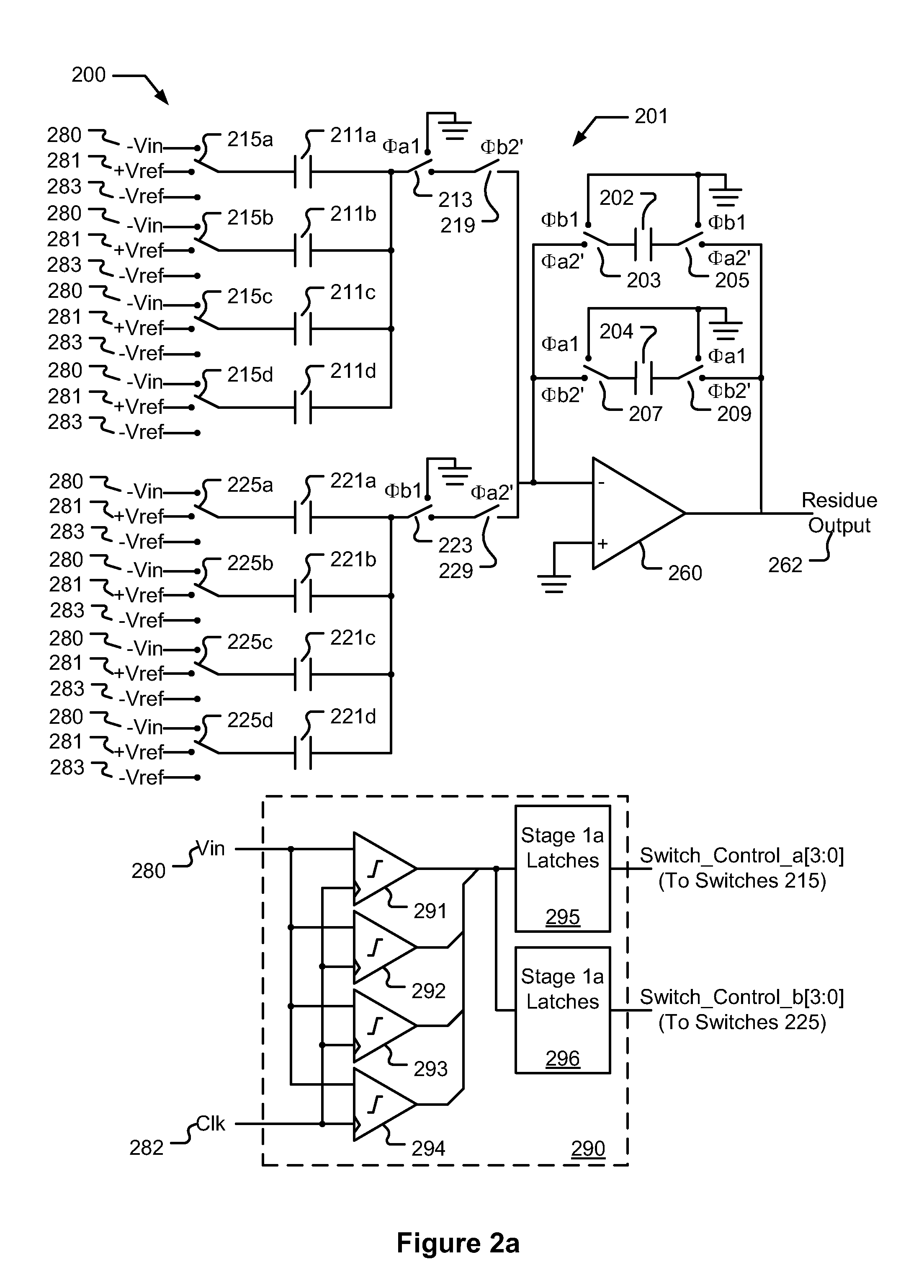

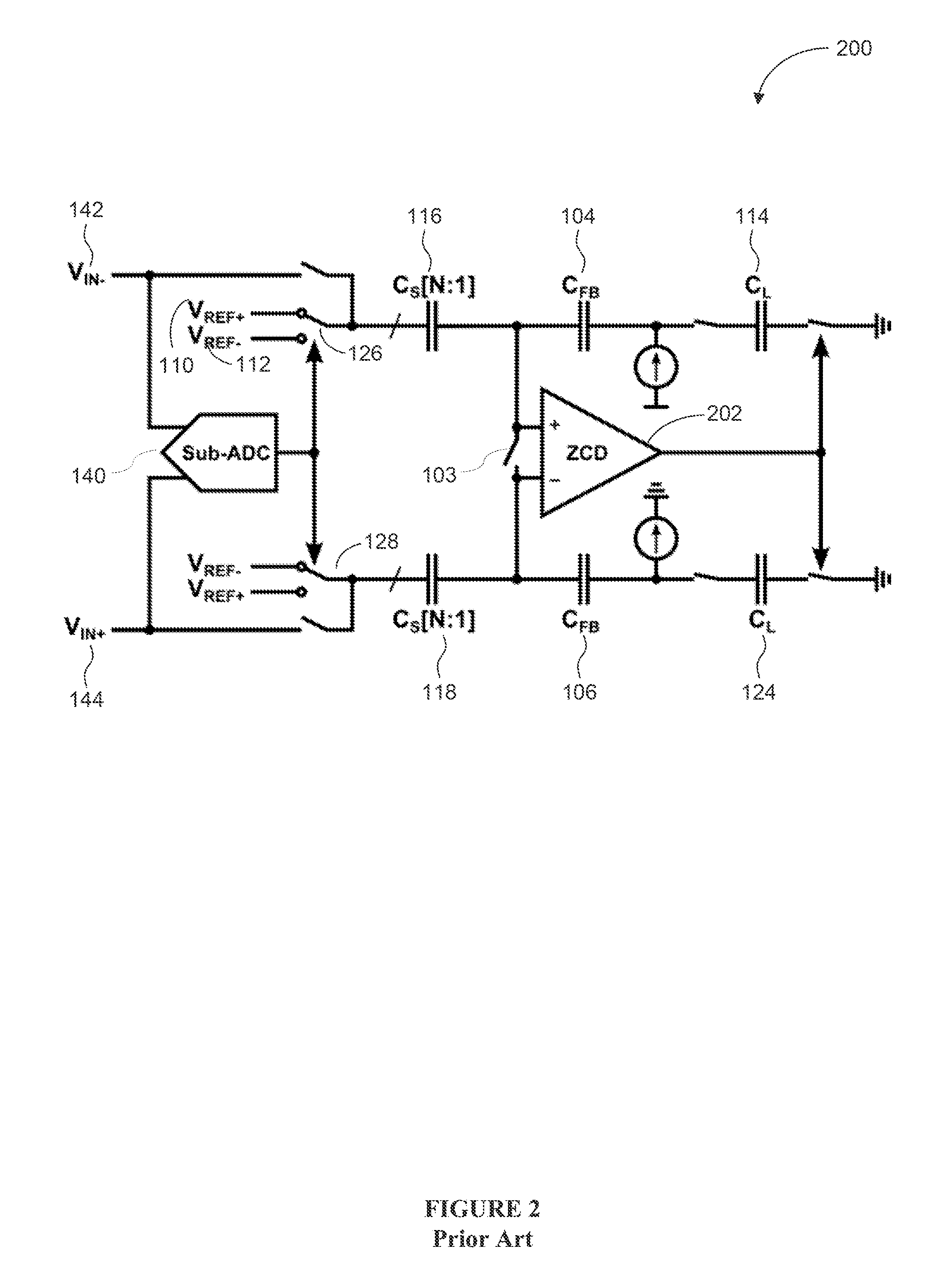

First-stage circuit structure of pipelined analog-to-digital converter

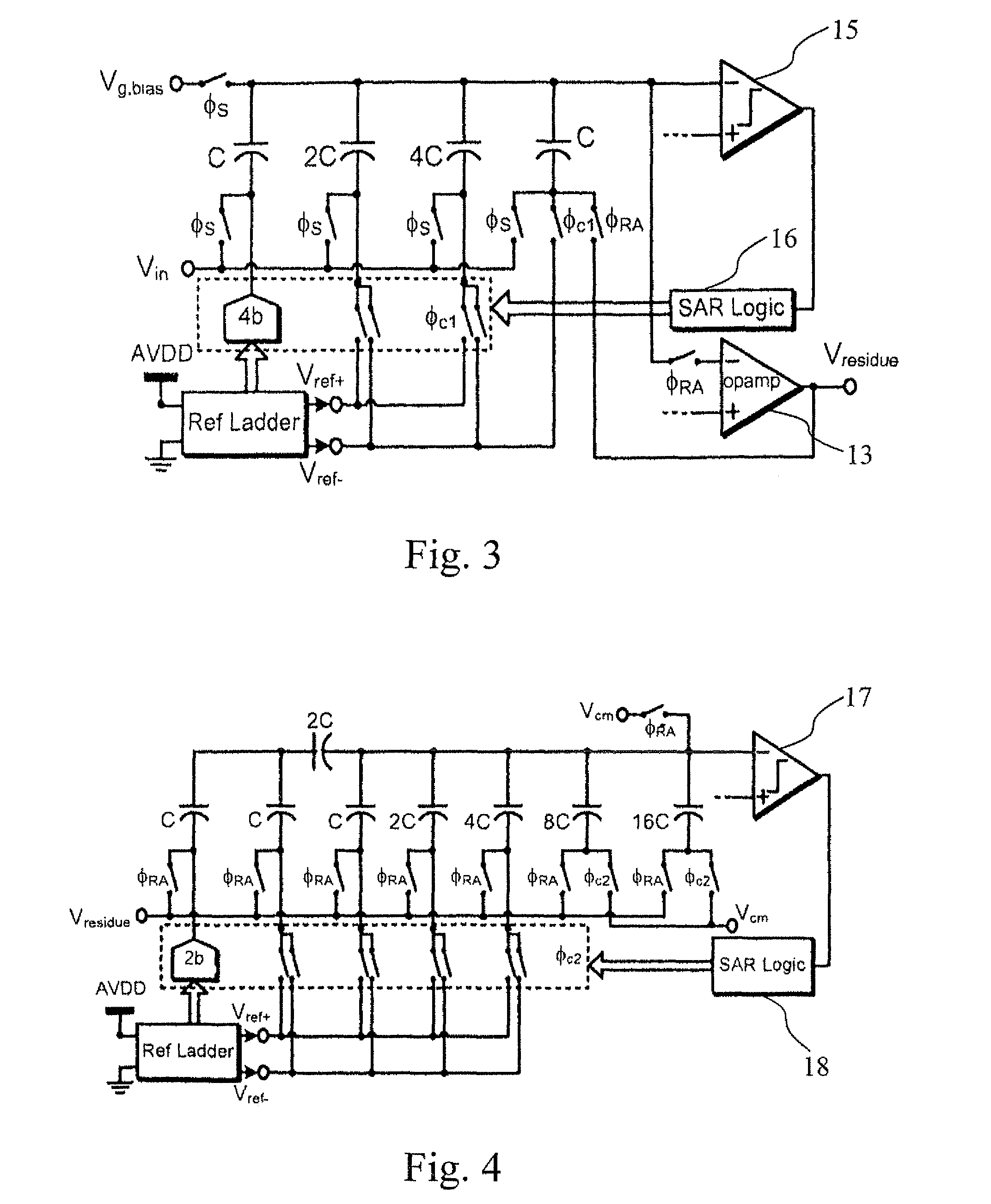

InactiveCN102983863AGuaranteed accuracyReduce design pressureAnalogue-digital convertersCapacitanceDigital down converter

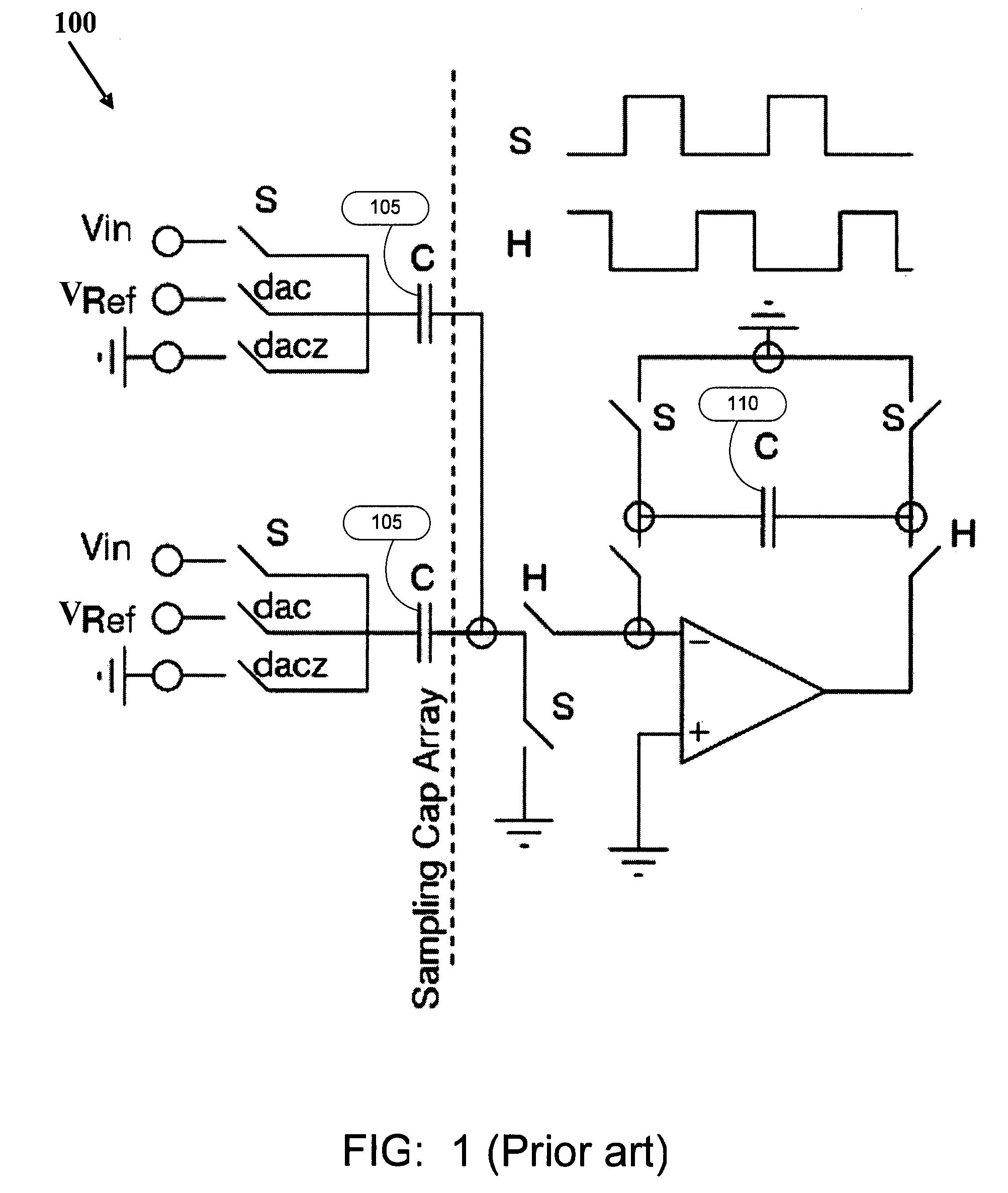

The invention discloses a first-stage circuit structure of a pipelined analog-to-digital converter, which comprises a 4-digit fully parallel analog-to-digital converter, a code circuit and a residue gain analog-to-digital converter. A two-phase non-overlapping clock is adopted, a sampling phase samples input voltage, and a maintaining phase amplifies residual voltage. The residue gain analog-to-digital converter consists of a sub analog-to-digital converter, a subtracter and a residue amplifier. During sampling, the 4-digit fully parallel analog-to-digital converter conducts comparison and quantification on the input voltage and generates a 16-digit thermometer code which is converted to a 4-digit binary output code by the encoder. A lower pole plate of a sampling capacitor array is connected with the input voltage, and an upper pole plate thereof is connected with a common mode level for sampling an input. During maintaining, the sub analog-to-digital converter outputs different voltages to the sampling capacitor array according to a control of the thermometer code; subtraction from the input voltage is accomplished according to twice charge conservation; and a feedback capacitor is in bridge connection with the two ends of the residue amplifier to amplify the residual voltage by 8 times for use by a backward-stage circuit.

Owner:TIANJIN UNIV

Analog-to-digital converter

ActiveUS20090243907A1Reduce power consumptionOvercome limitationsElectric signal transmission systemsAnalogue-digital convertersAudio power amplifierA d converter

A lookahead pipelined ADC architecture uses open-loop residue amplifiers with calibration. This approach is able to achieve a high-speed, high-accuracy ADC with reduced power consumption. In one aspect, an ADC pipeline unit includes a plurality of lookahead pipeline stages (i.e., an ADC lookahead pipeline) coupled to a calibration unit. The ADC lookahead pipeline uses open-loop residue amplifiers. The calibration unit compensates for non-linearity in the open-loop amplifiers.

Owner:MARVELL ASIA PTE LTD

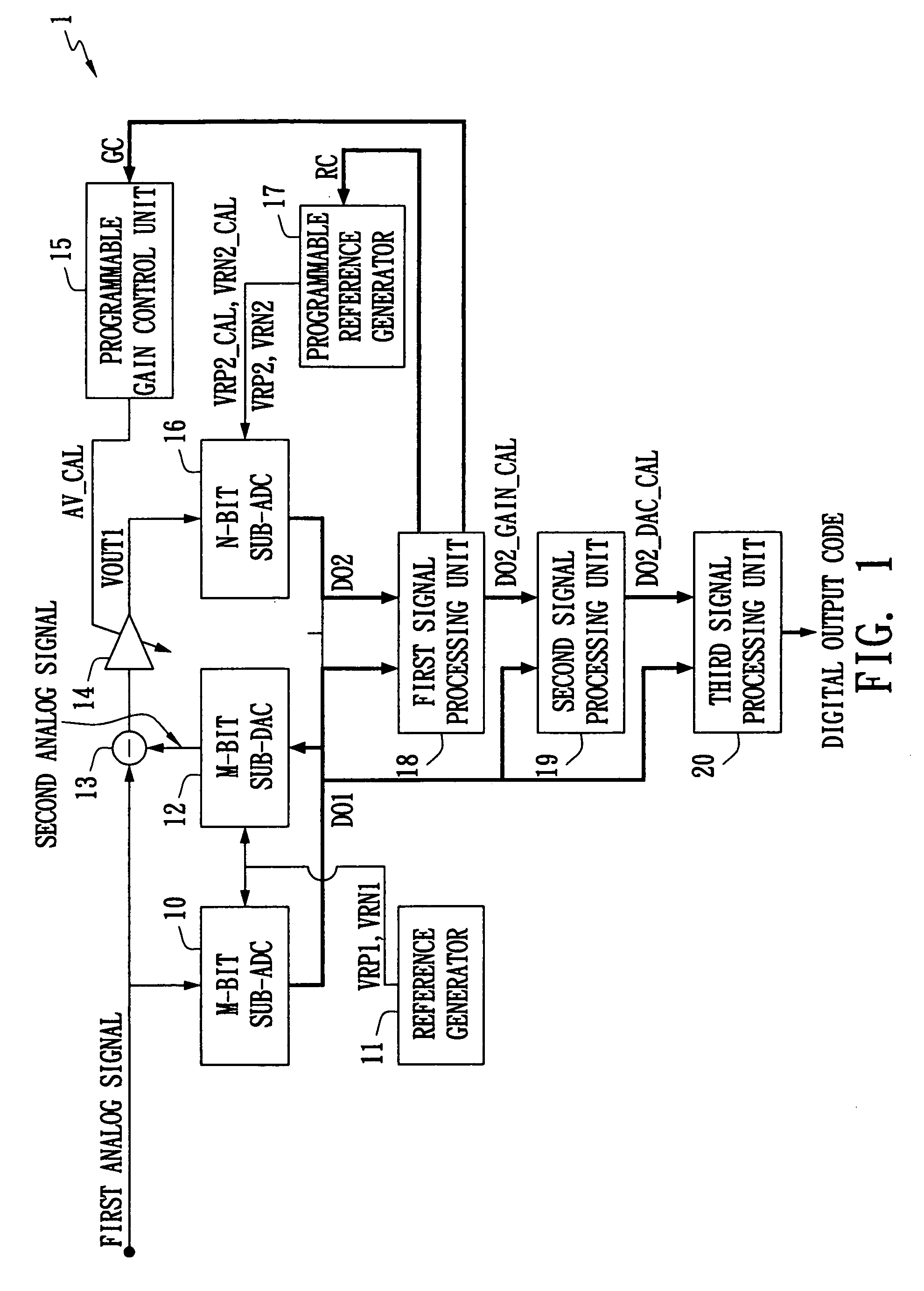

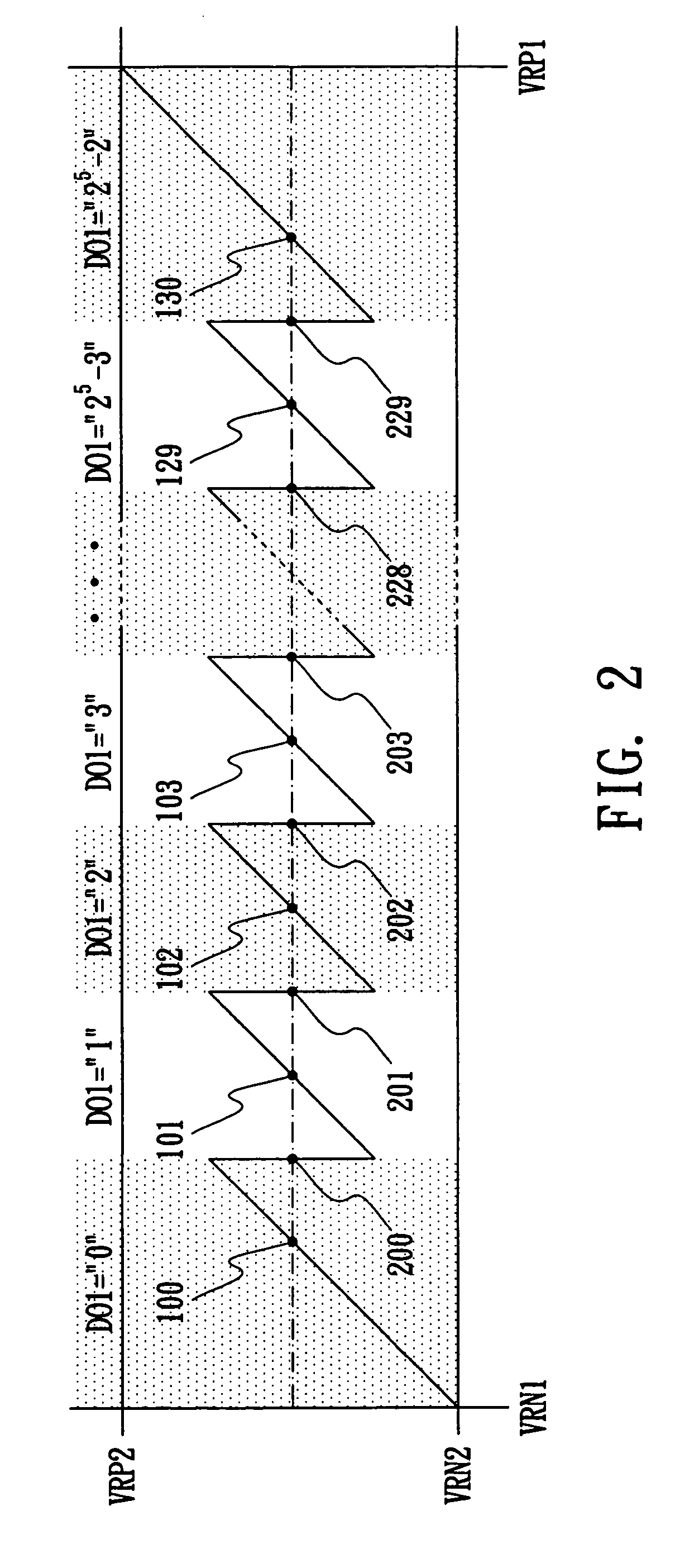

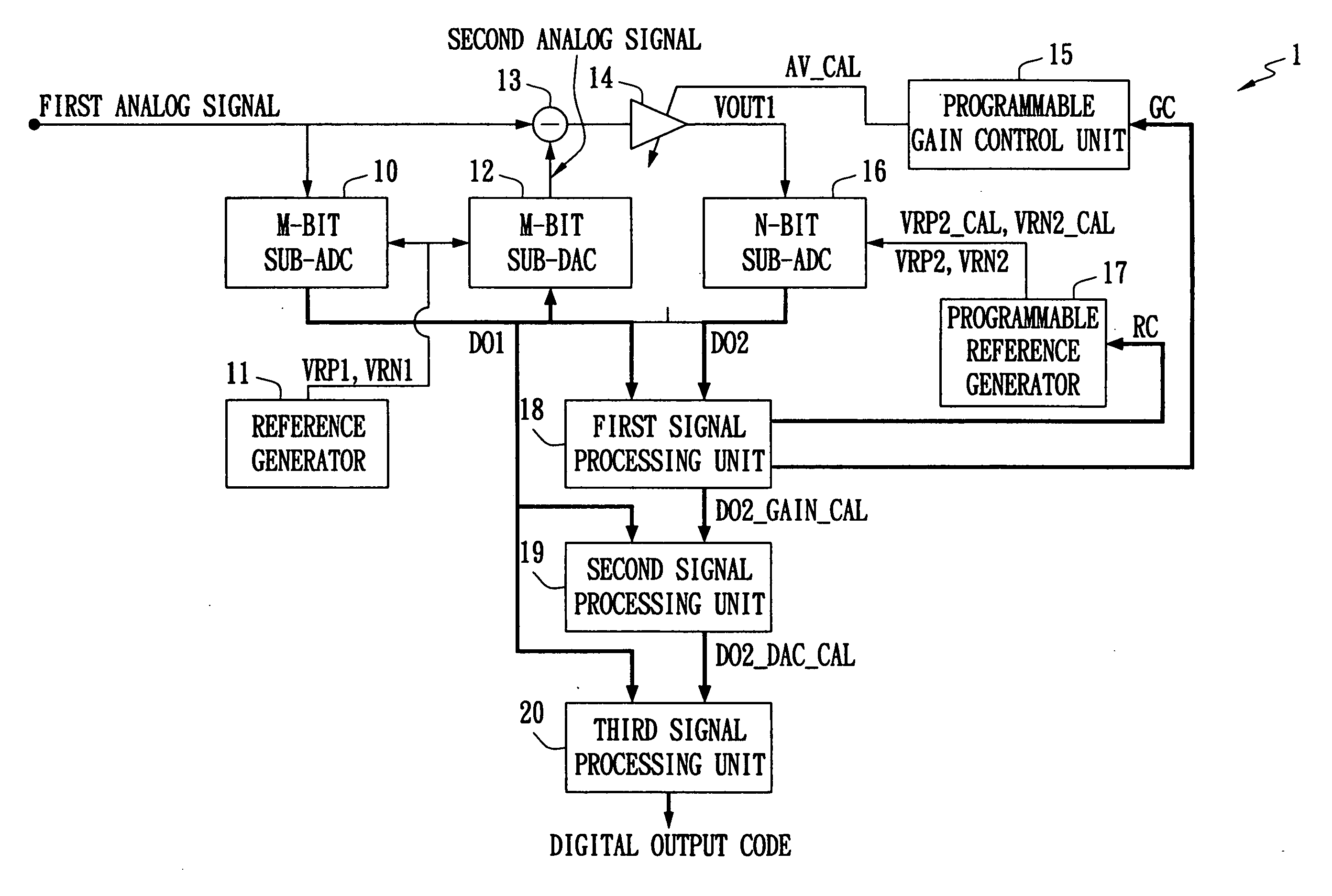

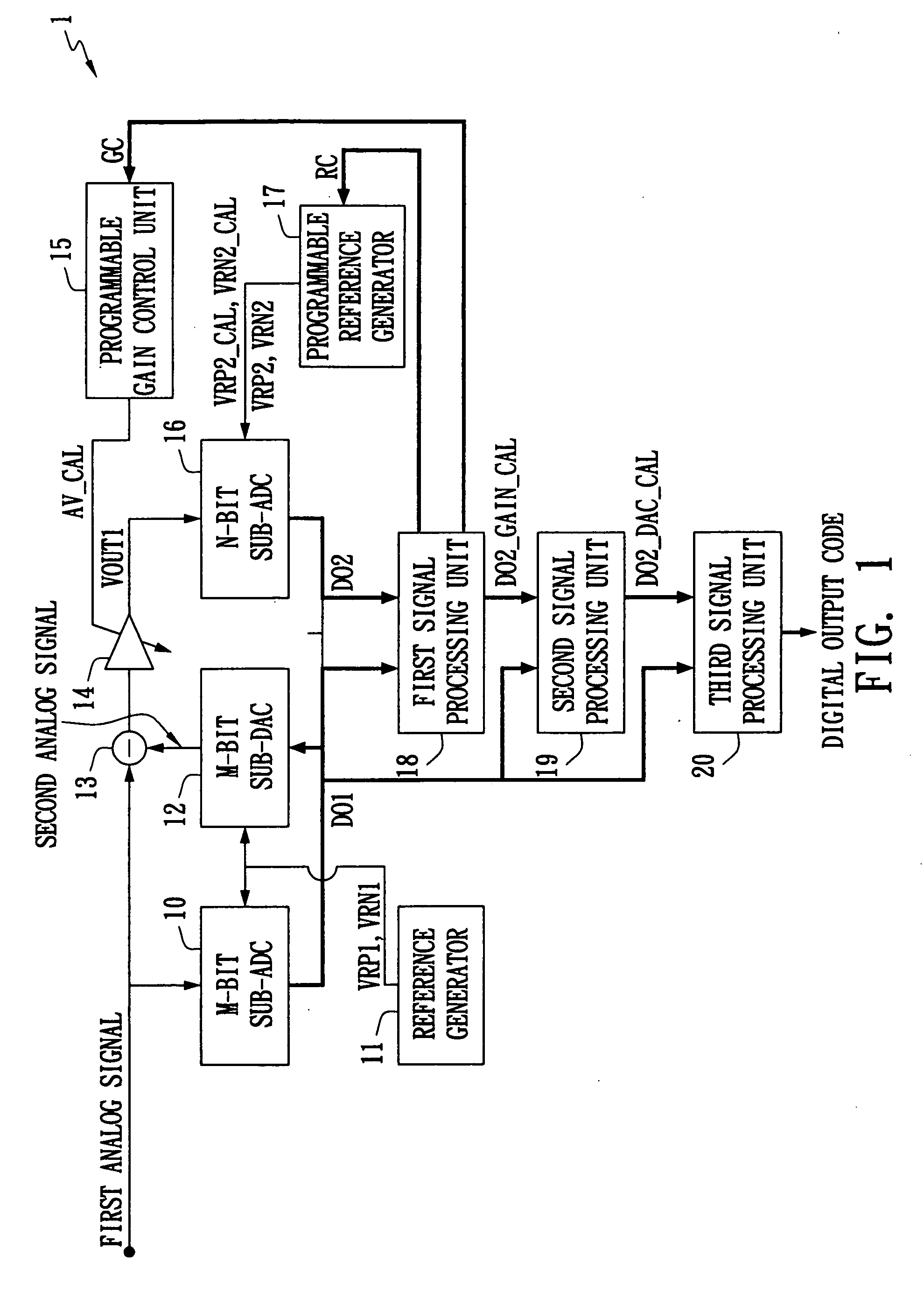

Multi-step analog/digital converter and on-line calibration method thereof

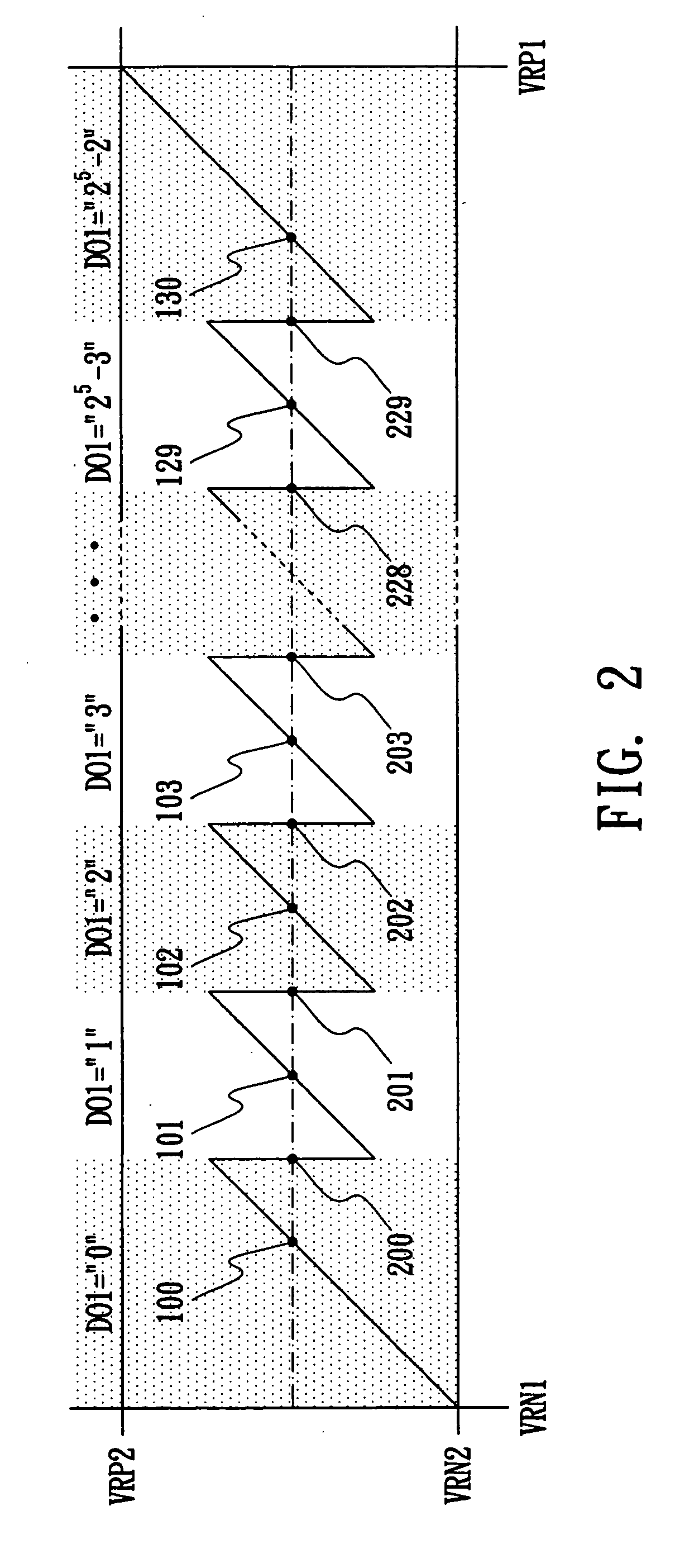

InactiveUS7142138B2Decrease phenomenonPrecision requirement of the residue amplifier are reducedElectric signal transmission systemsAnalogue/digital conversion calibration/testingDigital down converterVoltage reference

Owner:NATIONAL TSING HUA UNIVERSITY

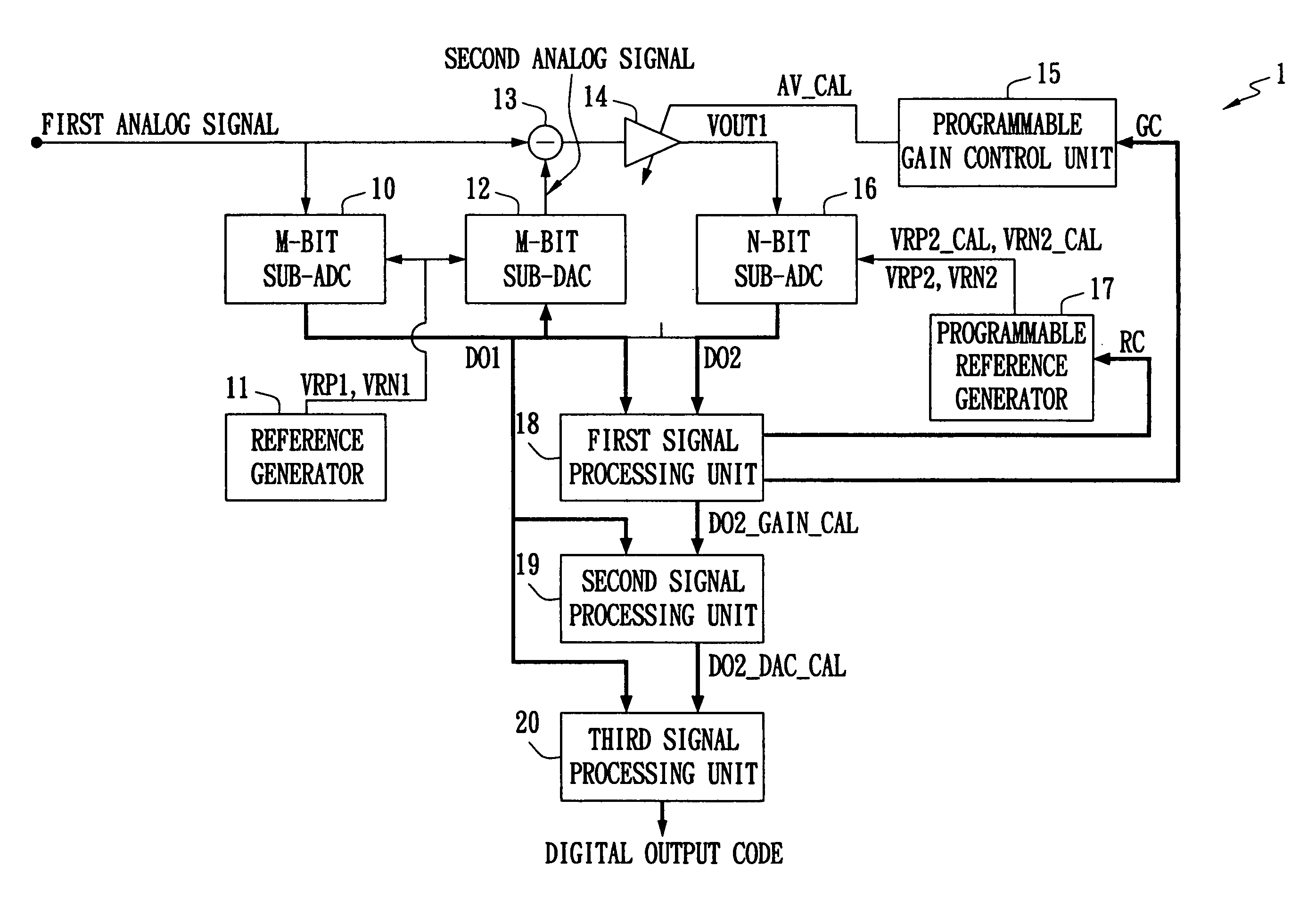

Multi-step analog/digital converter and on-line calibration method thereof

InactiveUS20060208933A1Decrease phenomenonPrecision requirement of the residue amplifier are reducedElectric signal transmission systemsAnalogue/digital conversion calibration/testingEngineeringAnalog signal processing

The present invention discloses an on-line calibration method, which utilizes two calibration algorithms running in the background without interrupting the normal operation of the analog signal process. The method includes performing a residue amplifier gain error calibration and performing a DAC non-linearity calibration. The residue amplifier gain error calibration can reduce the gain error of the residue amplifier for a missing code or a missing decision level phenomenon. The DAC non-linearity calibration can relax the matching requirement of passive components in current semiconductor processes. The present invention discloses a two-step ADC (Analog-to-Digital Converter), which includes a first signal processing unit, a second signal processing unit, a programmable gain control unit and a programmable reference voltage generator, performing the on-line calibration method.

Owner:NATIONAL TSING HUA UNIVERSITY

Analog-to-digital converter

ActiveUS20090096647A1Reduce power consumptionOvercome limitationsElectric signal transmission systemsAnalogue-digital convertersEngineeringResidue amplifier

A lookahead pipelined ADC architecture uses open-loop residue amplifiers with calibration. This approach is able to achieve a high-speed, high-accuracy ADC with reduced power consumption. In one aspect, an ADC pipeline unit includes a plurality of lookahead pipeline stages (i.e., an ADC lookahead pipeline) coupled to a calibration unit. The ADC lookahead pipeline uses open-loop residue amplifiers. The calibration unit compensates for non-linearity in the open-loop amplifiers.

Owner:MARVELL ASIA PTE LTD

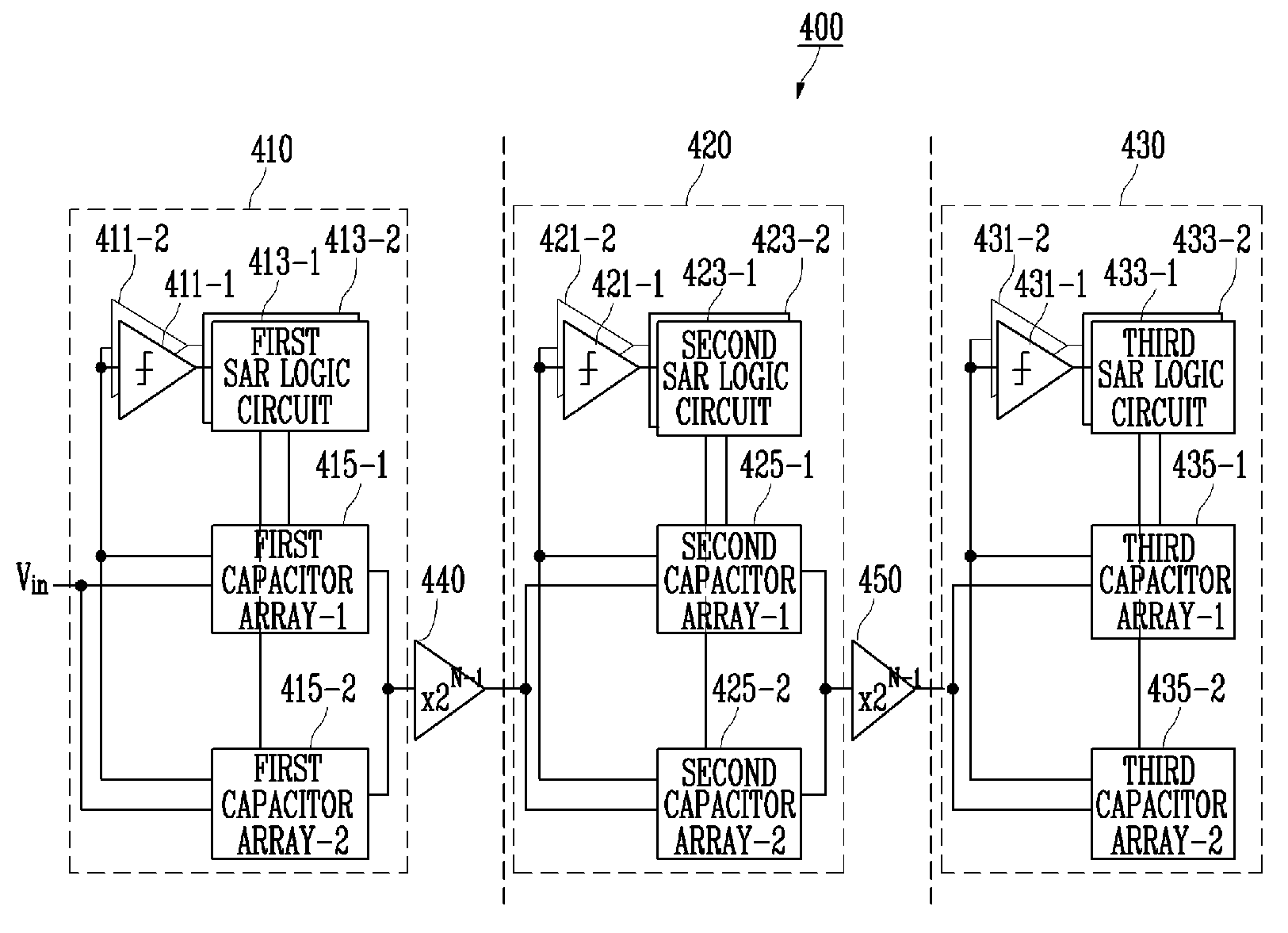

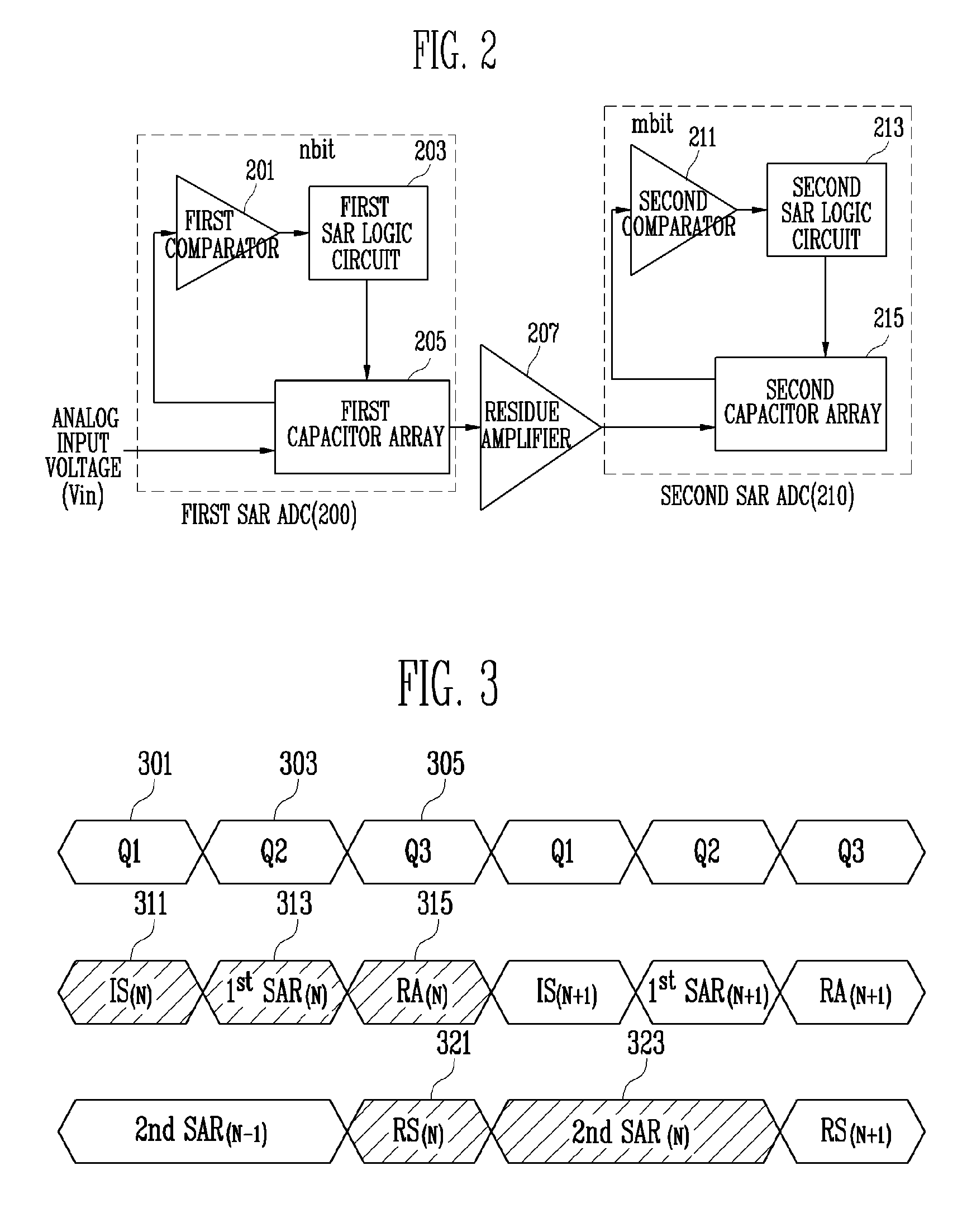

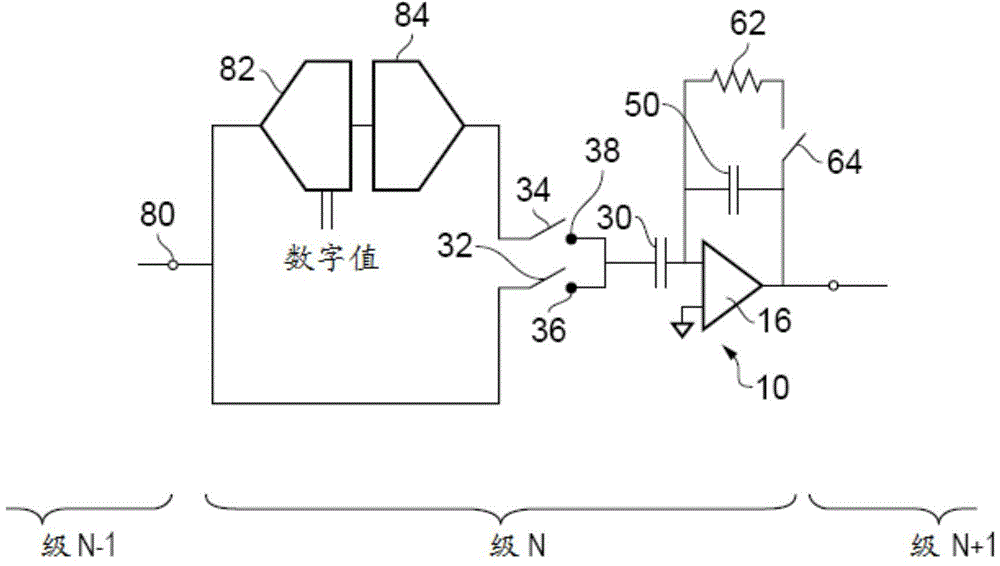

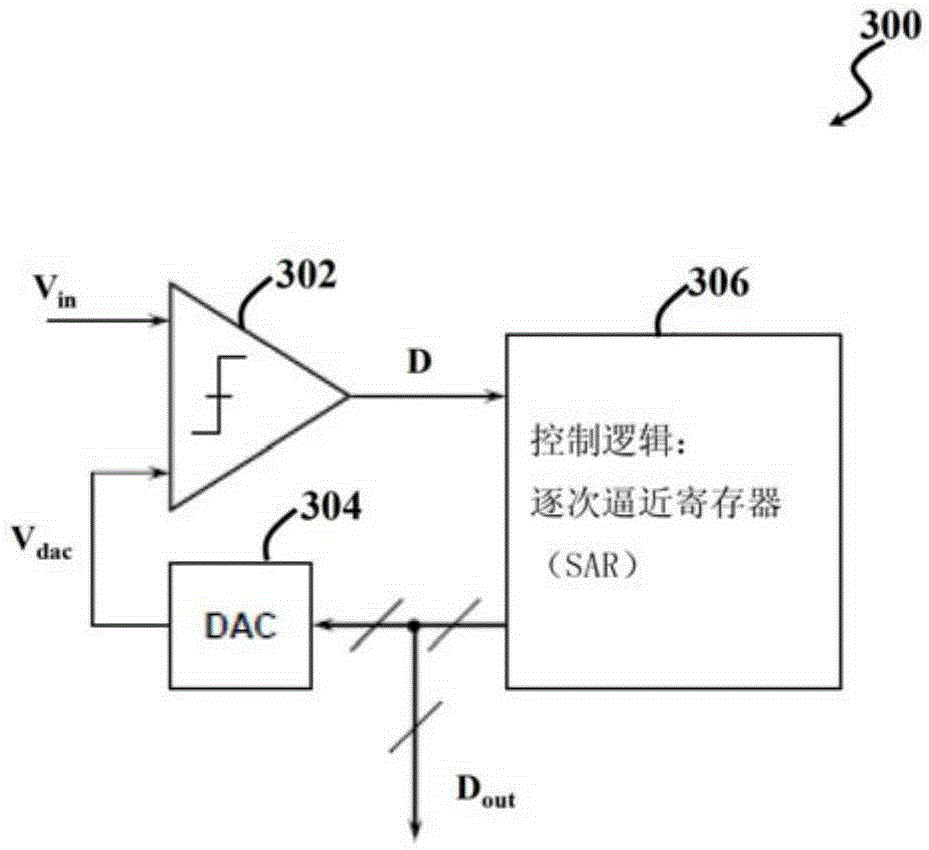

Multi-stage dual successive approximation register analog-to-digital convertor and method of performing analog-to-digital conversion using the same

InactiveUS7978117B2Reduce areaReduce power consumptionElectric signal transmission systemsAnalogue-digital convertersAudio power amplifierEngineering

A multi-stage dual successive approximation register analog-to-digital converter (SAR ADC) and a method of performing analog-to-digital conversion using the same are provided. The multi-stage dual SAR ADC includes: a plurality of SAR ADC stages for converting an analog input voltage into a predetermined bit digital signal, each SAR ADC stage being serially connected to one another and including two SAR ADCs; and at least one residue amplifier respectively connected between every two successive SAR ADC stages, amplifying residue voltage output from a previous SAR ADC stage to output the amplified residue voltage to a next SAR ADC stage. The two SAR ADCs of the previous SAR ADC stage share the residue amplifier.

Owner:ELECTRONICS & TELECOMM RES INST

Analog-to-digital converter using lookahead pipelined architecture and open-loop residue amplifiers

ActiveUS7576676B2Reduce power consumptionOvercome limitationsElectric signal transmission systemsAnalogue-digital convertersResidue amplifierAnalog-to-digital converter

A lookahead pipelined ADC architecture uses open-loop residue amplifiers with calibration. This approach is able to achieve a high-speed, high-accuracy ADC with reduced power consumption. In one aspect, an ADC pipeline unit includes a plurality of lookahead pipeline stages (i.e., an ADC lookahead pipeline) coupled to a calibration unit. The ADC lookahead pipeline uses open-loop residue amplifiers. The calibration unit compensates for non-linearity in the open-loop amplifiers.

Owner:MARVELL ASIA PTE LTD

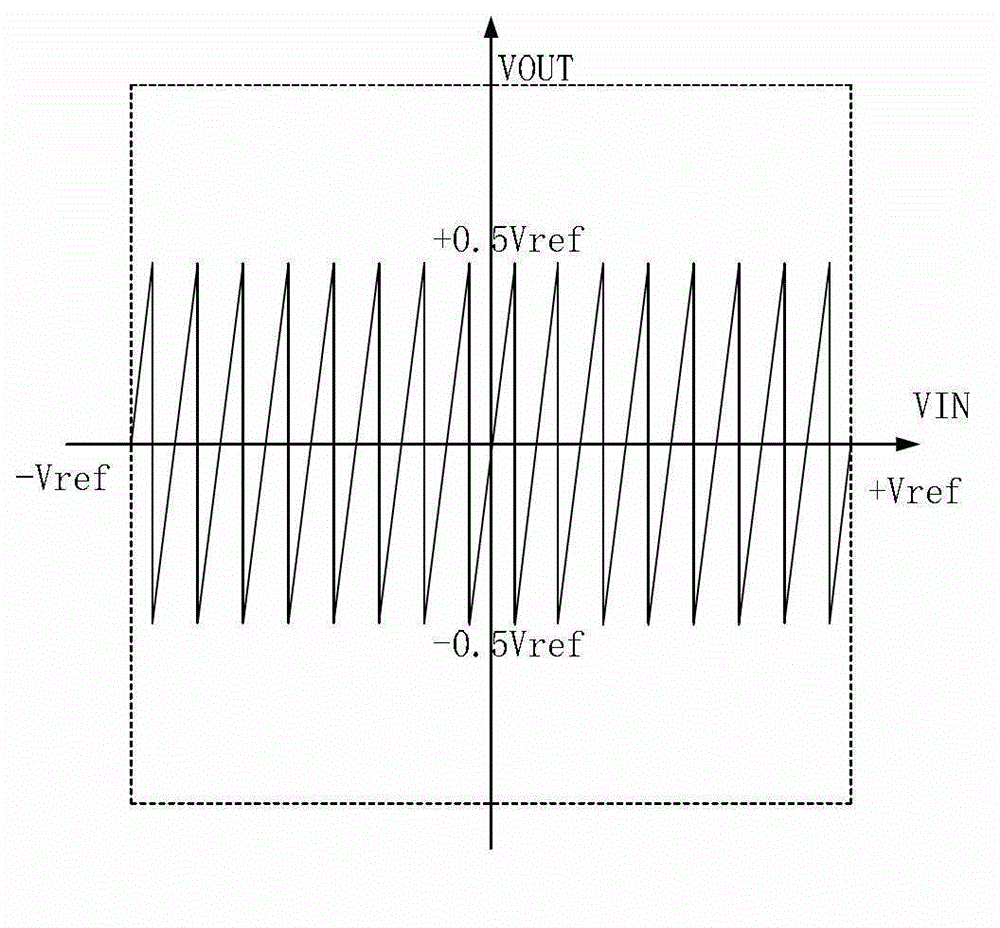

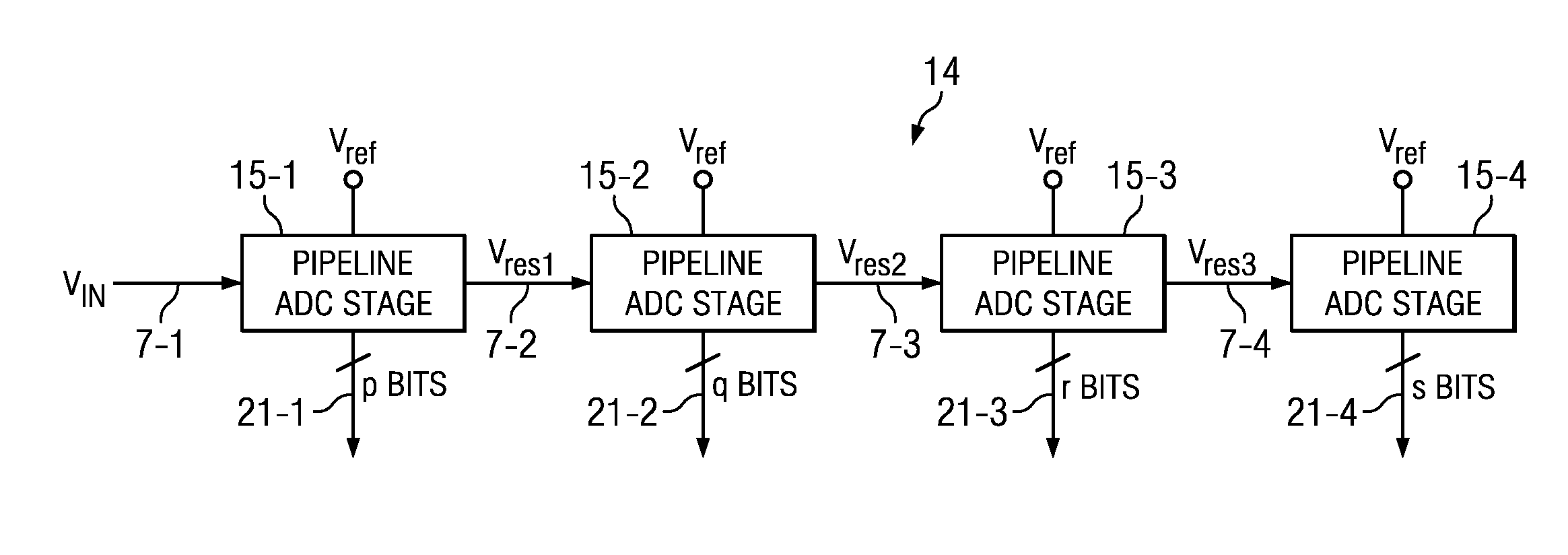

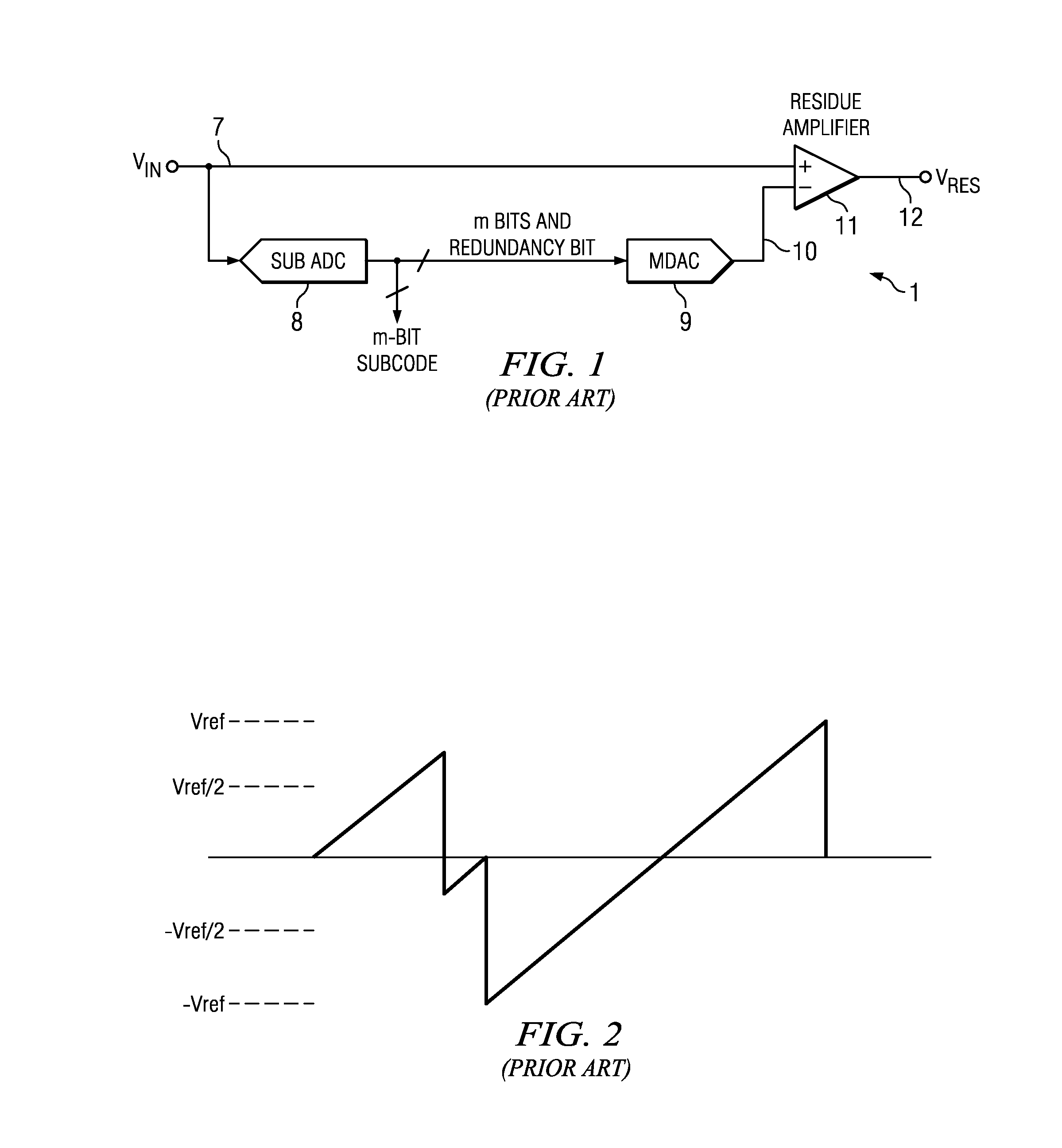

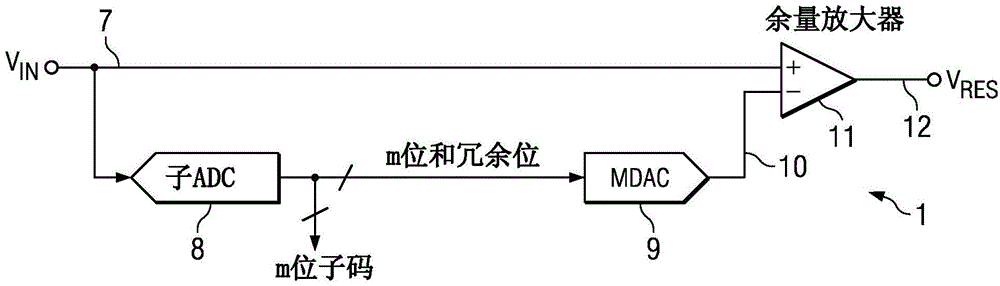

Circuitry and method for reducing area and power of a pipeline ADC

ActiveUS20140062736A1Avoid problemsLessElectric signal transmission systemsAnalogue-digital convertersLevel shiftingAudio power amplifier

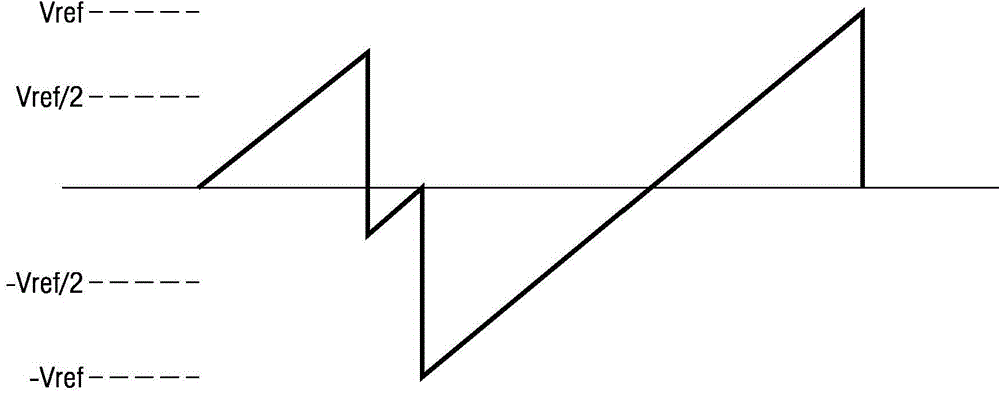

A pipeline ADC (analog-to-digital converter) (14) includes a residue amplifier (7) for applying a first residue signal (Vres1) to a first input of a residue amplifier (11A) and to an input of a sub-ADC (8) for resolving a predetermined number (m) of bits and producing a redundancy bit in response to the first residue signal. A level-shifting MDAC (9A) converts the predetermined number of bits and the redundancy bit to an analog signal (10) on the a second input of the residue amplifier, which amplifies the difference between the first residue signal and the analog signal to generate a second residue signal (Vres2). The MDAC causes the residue amplifier to shift the second residue signal back within a predetermined voltage range (±Vref / 2) by the end of the amplifying if the second residue signal is outside of the predetermined voltage range.

Owner:TEXAS INSTR INC

Analog-to-digital converter

ActiveUS8094056B2Reduce power consumptionOvercome limitationsElectric signal transmission systemsAnalogue-digital convertersResidue amplifierAnalog-to-digital converter

A lookahead pipelined ADC architecture uses open-loop residue amplifiers with calibration. This approach is able to achieve a high-speed, high-accuracy ADC with reduced power consumption. In one aspect, an ADC pipeline unit includes a plurality of lookahead pipeline stages (i.e., an ADC lookahead pipeline) coupled to a calibration unit. The ADC lookahead pipeline uses open-loop residue amplifiers. The calibration unit compensates for non-linearity in the open-loop amplifiers.

Owner:MARVELL ASIA PTE LTD

Analog to digital converter circuit

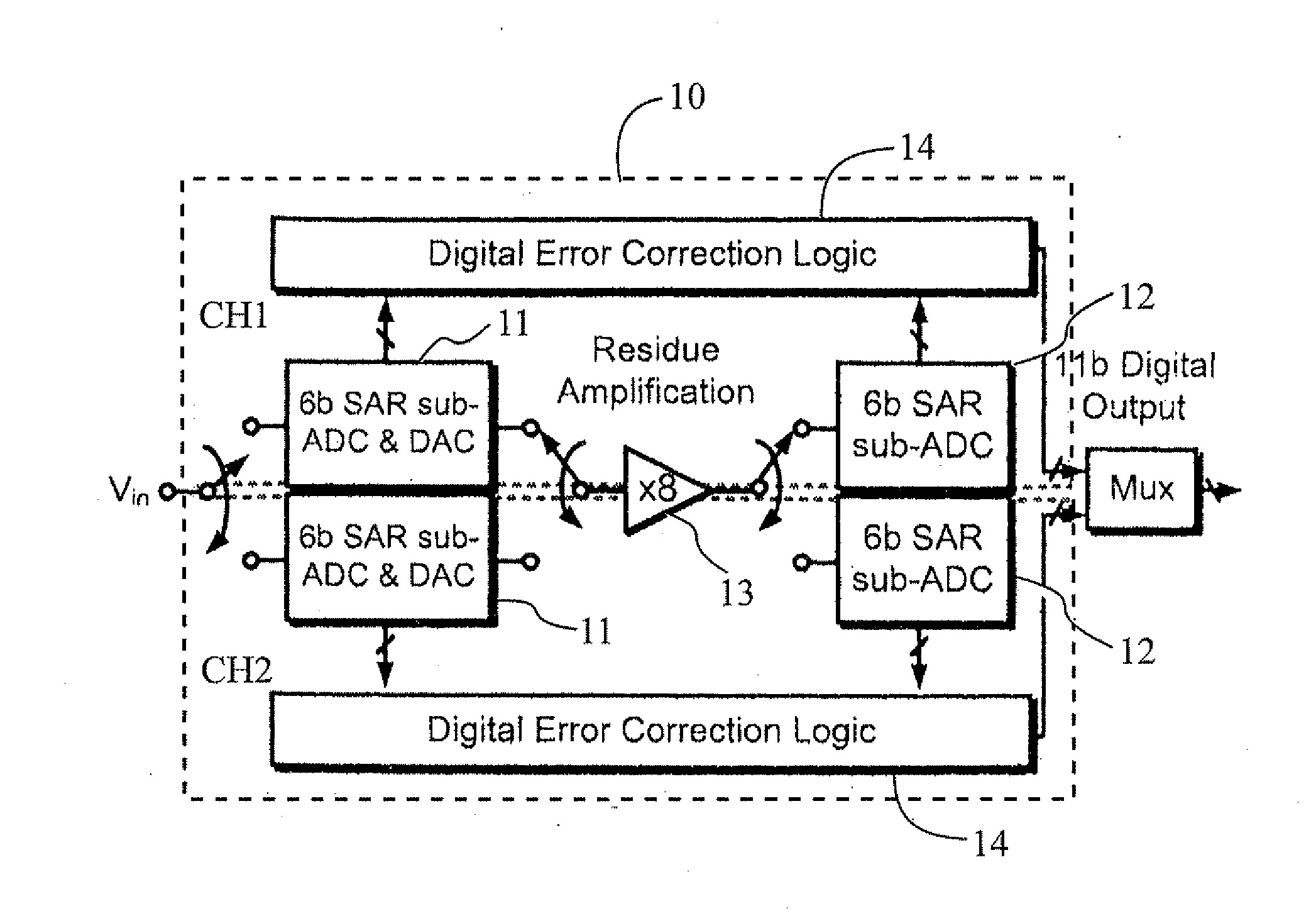

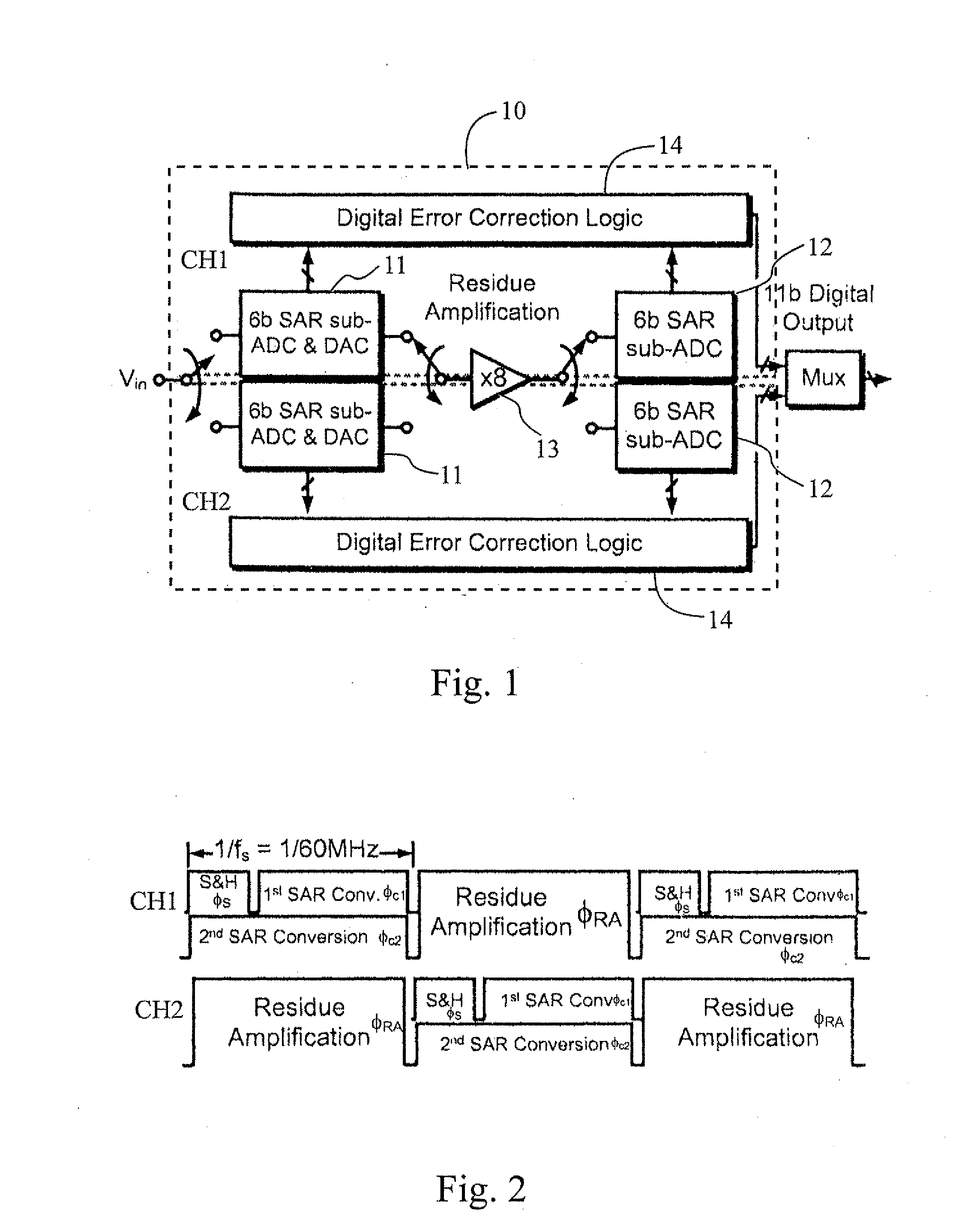

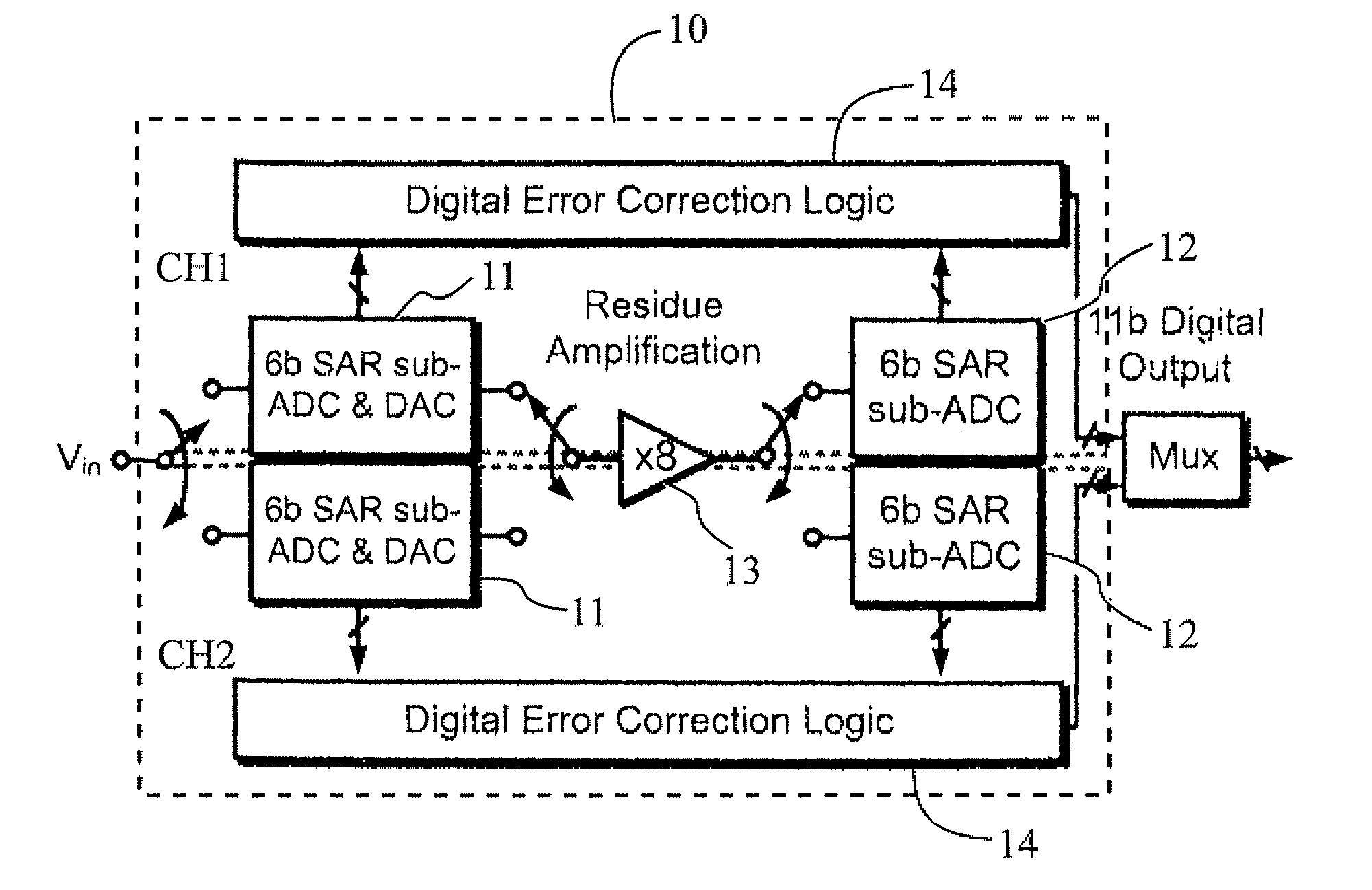

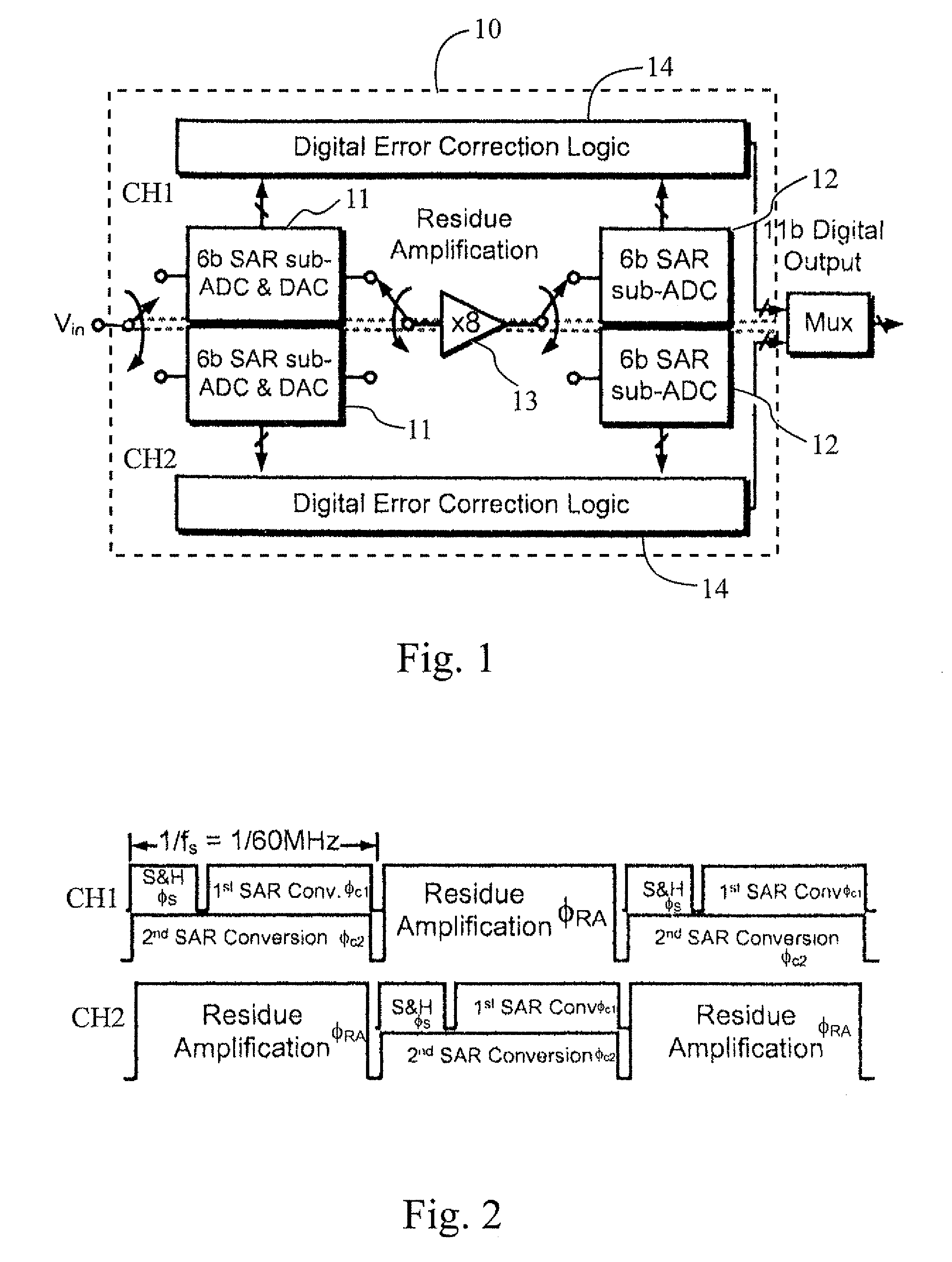

ActiveUS20120229313A1Reduce power consumptionAccuracyElectric signal transmission systemsResistance/reactance/impedenceSub thresholdA d converter

The present invention provides an analog-to-digital converter (ADC) circuit comprising two time-interleaved successive approximation register (SAR) ADCs. Each of the two time-interleaved SAR ADCs comprises a first stage SAR sub-ADC, a residue amplifier, a second stage SAR sub-ADC and a digital error correction logic. The residue amplifier is shared between the time-interleaved paths, has a reduced gain and operates in sub-threshold to achieve power effective design

Owner:UNIVERSITY OF MACAU

Analog-to-digital converter

ActiveUS7808417B2Reduce power consumptionOvercome limitationsElectric signal transmission systemsAnalogue-digital convertersA d converterEngineering

Owner:MARVELL ASIA PTE LTD

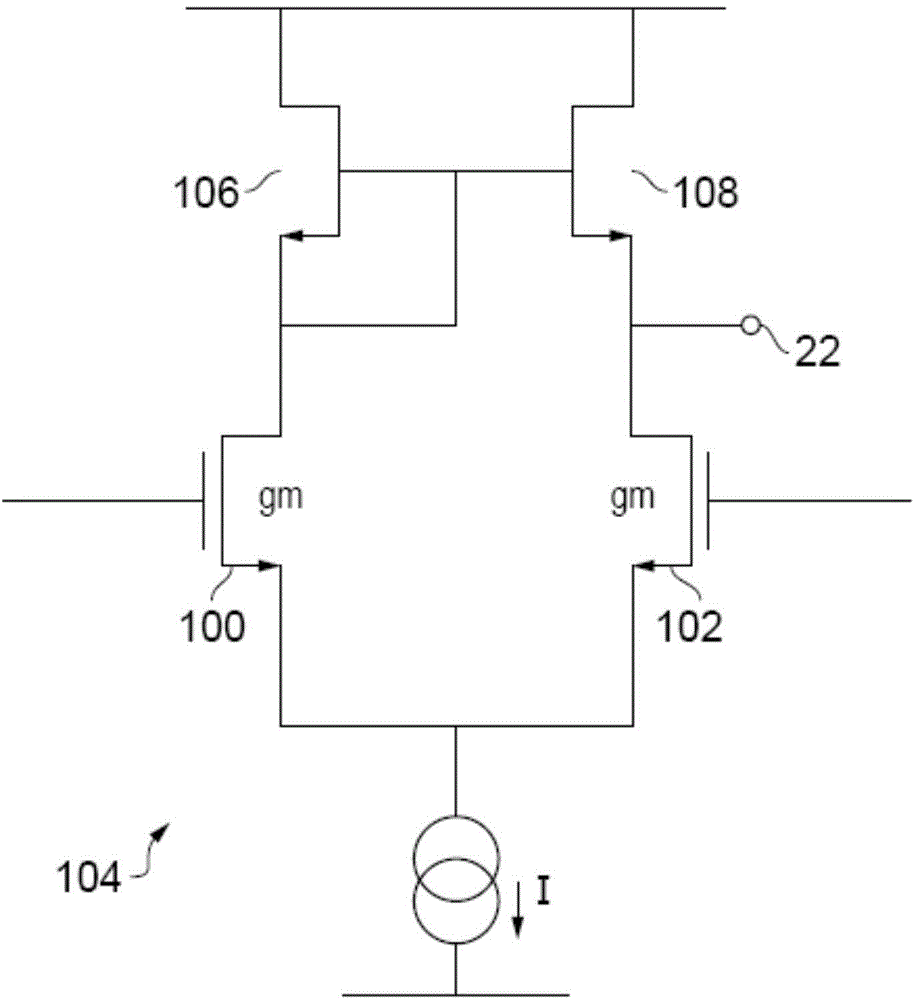

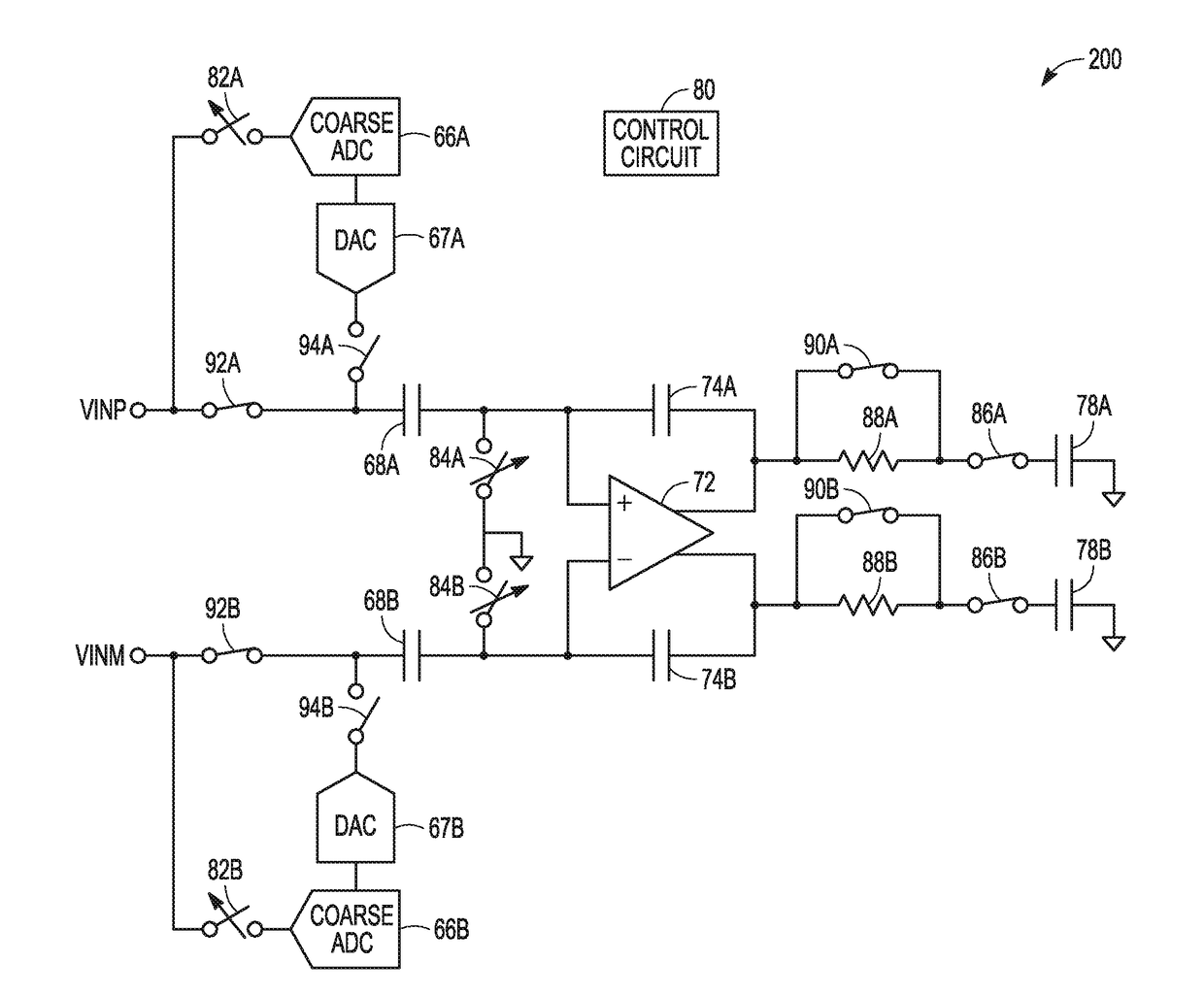

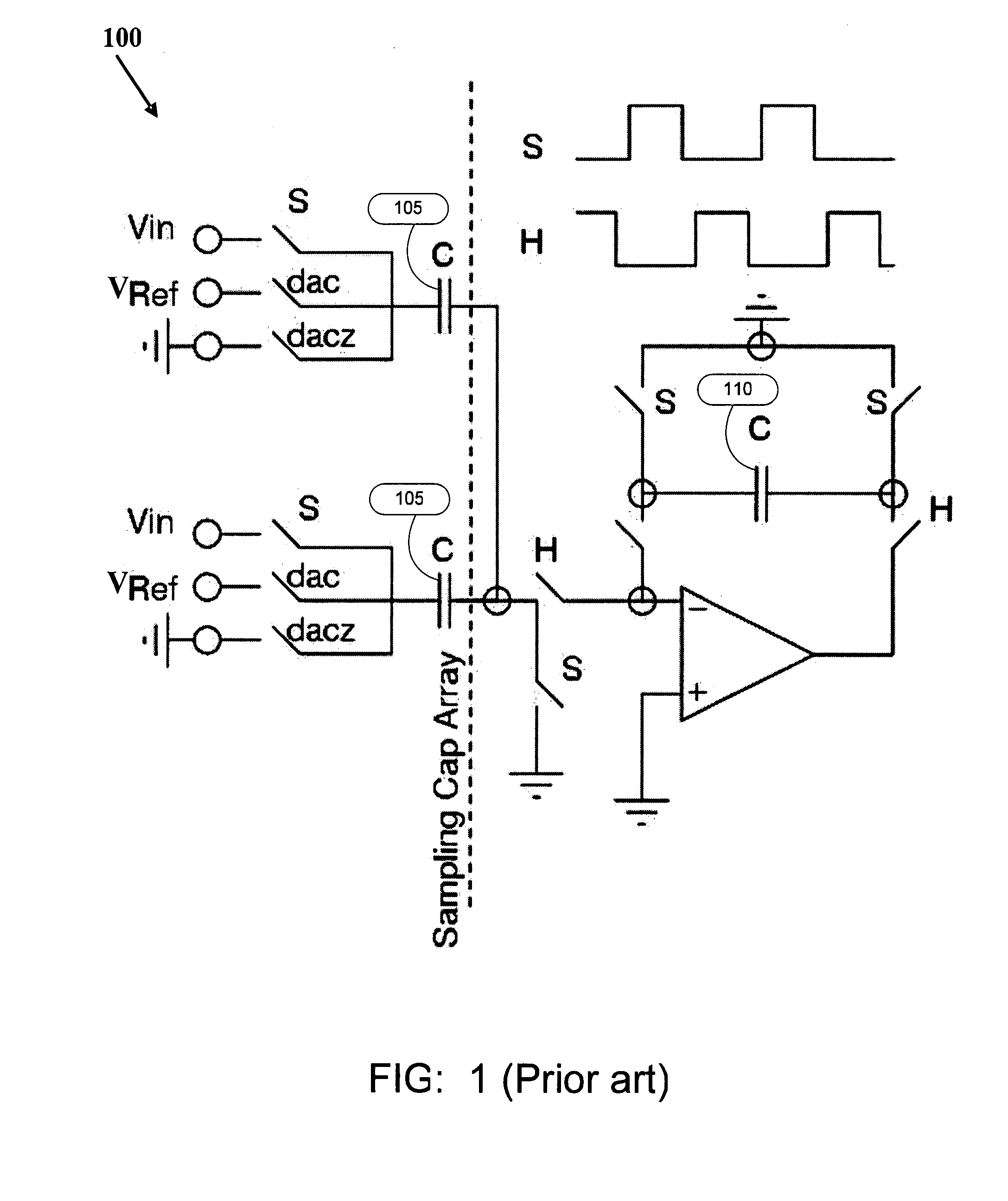

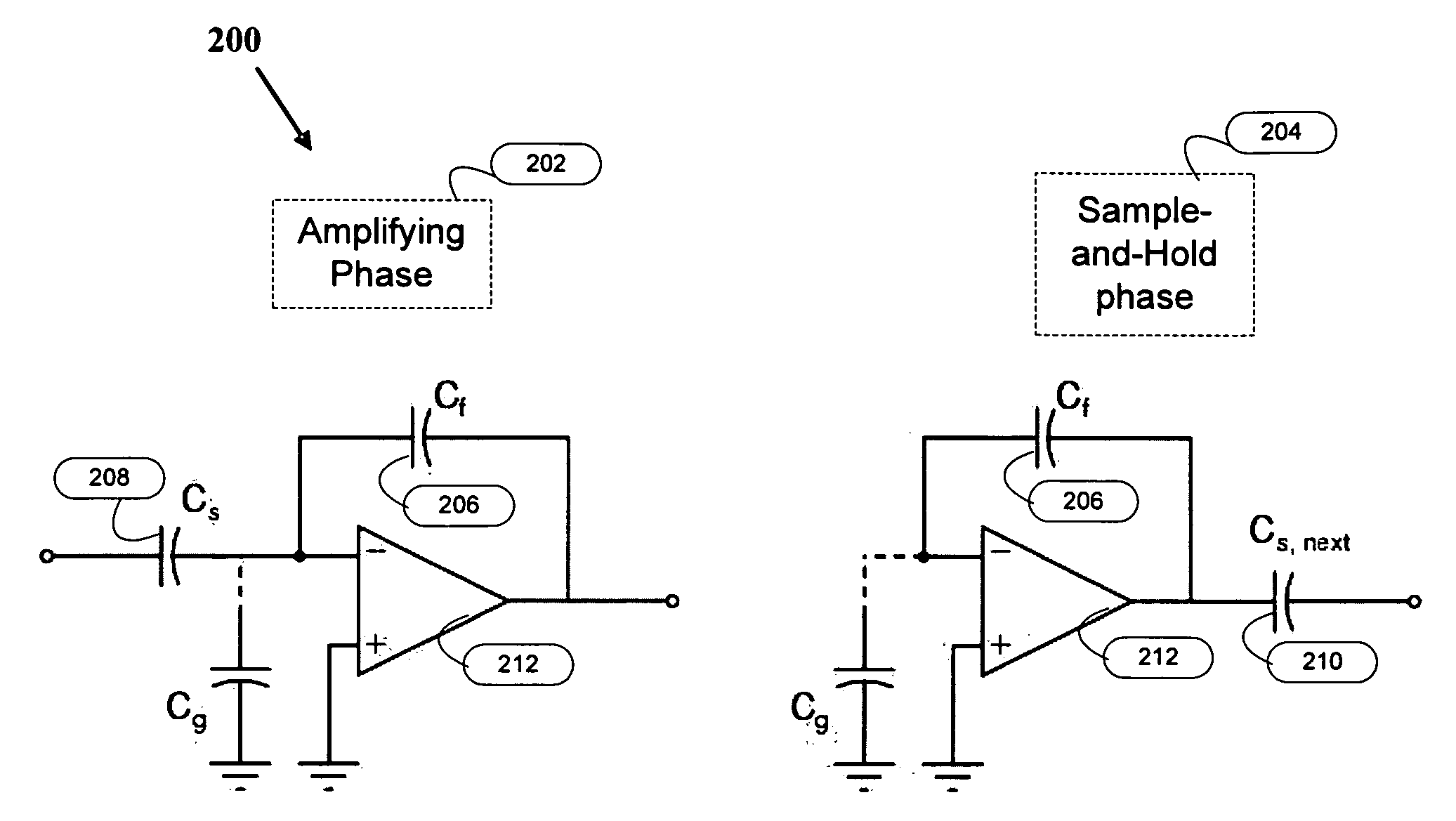

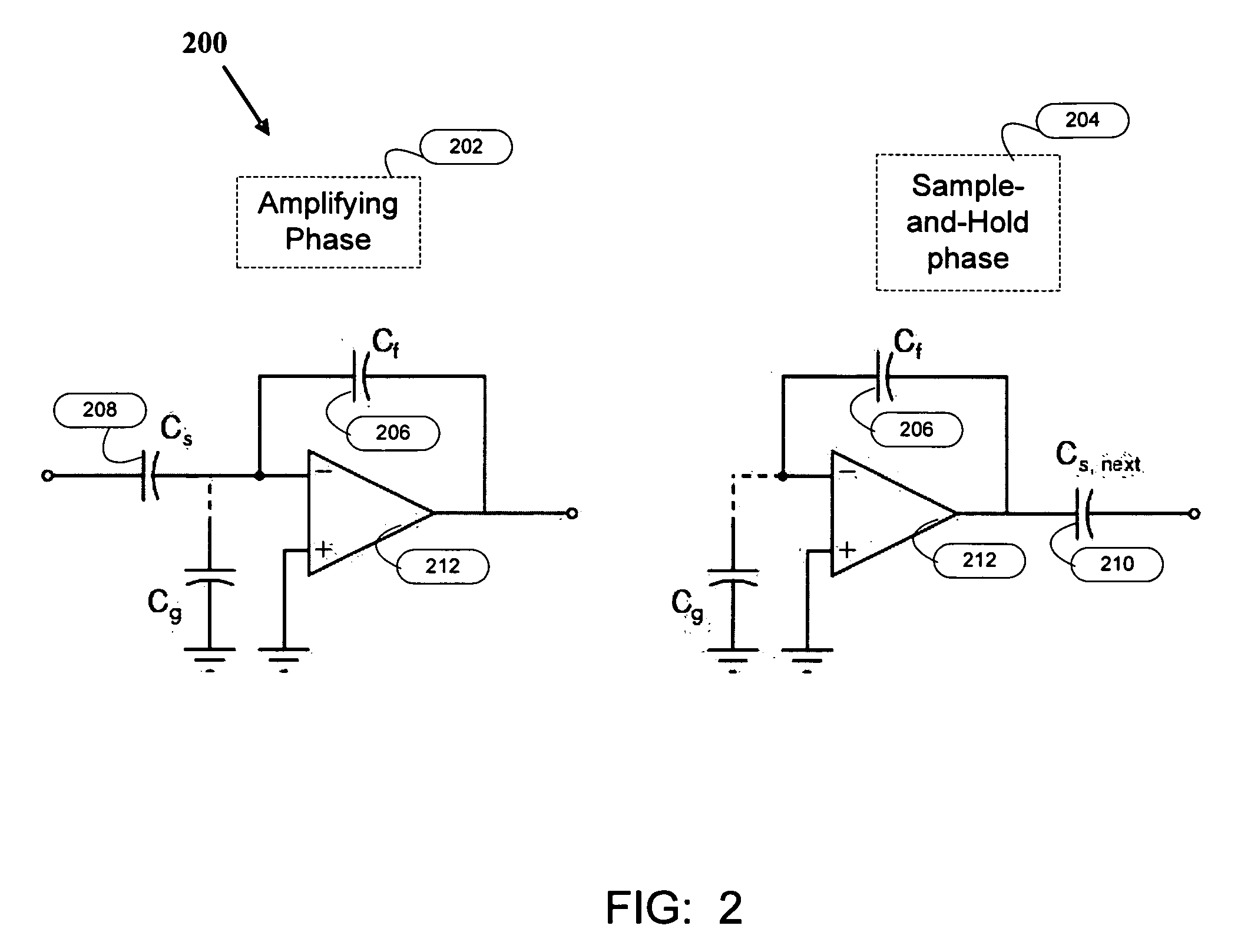

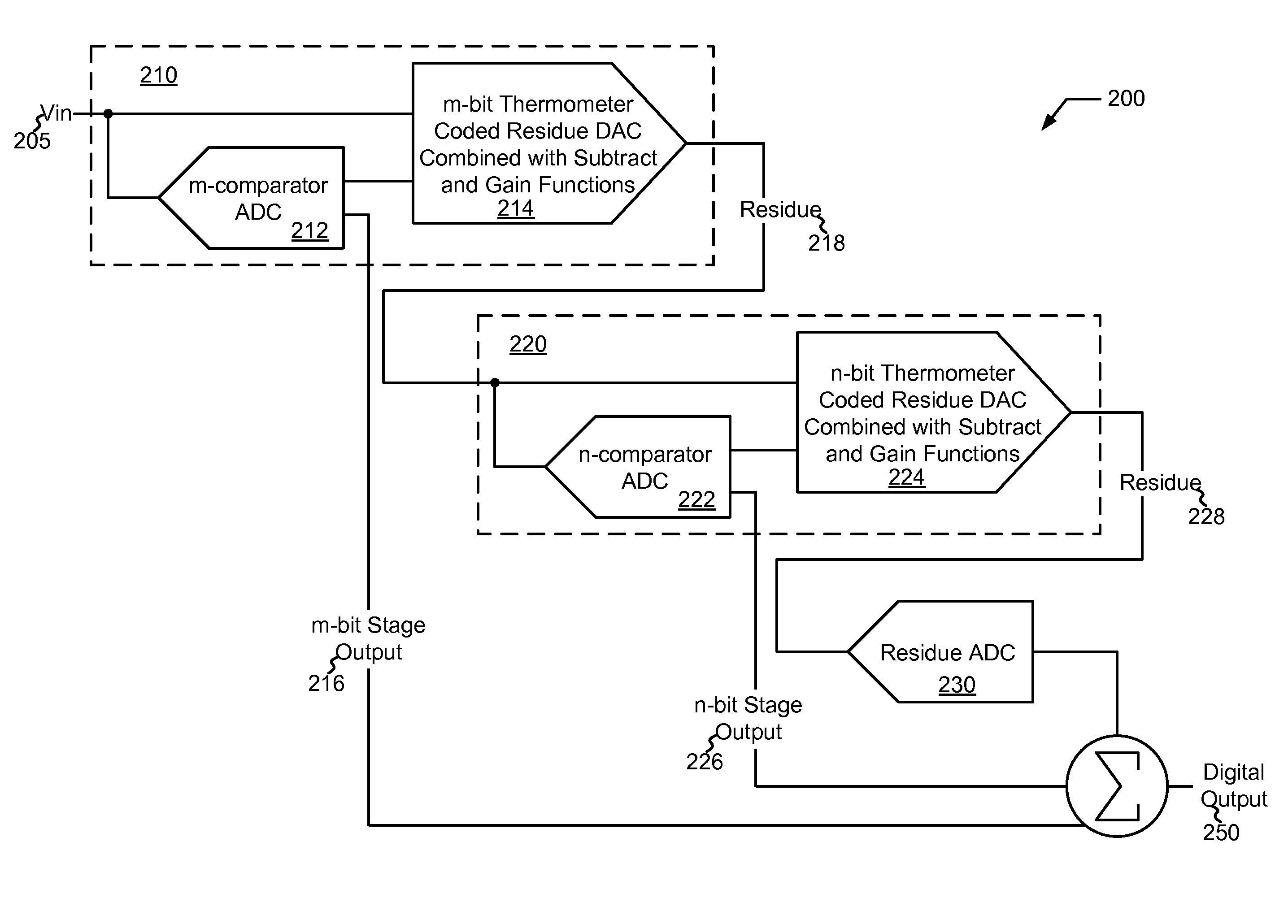

Systems and methods for pipelined analog to digital conversion

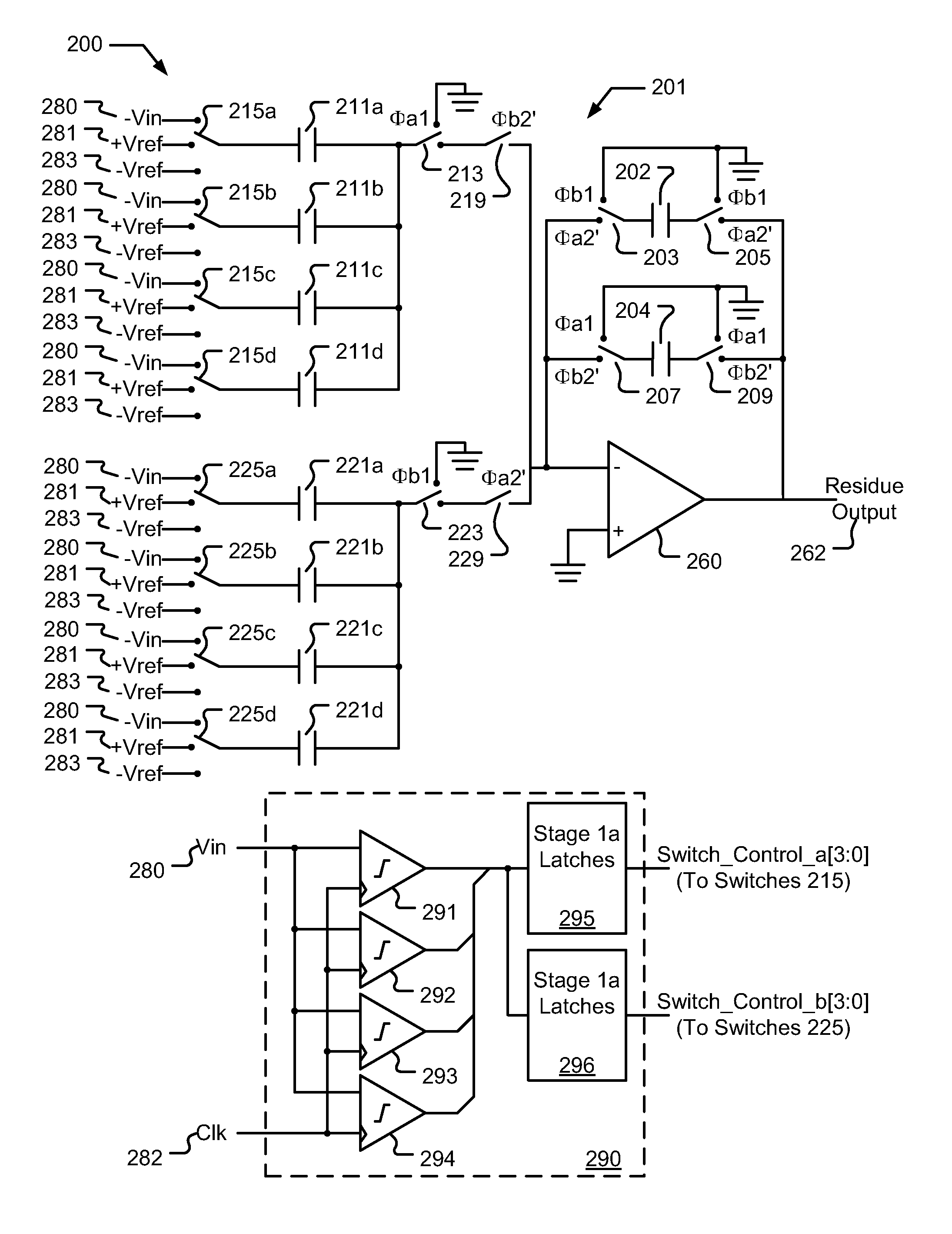

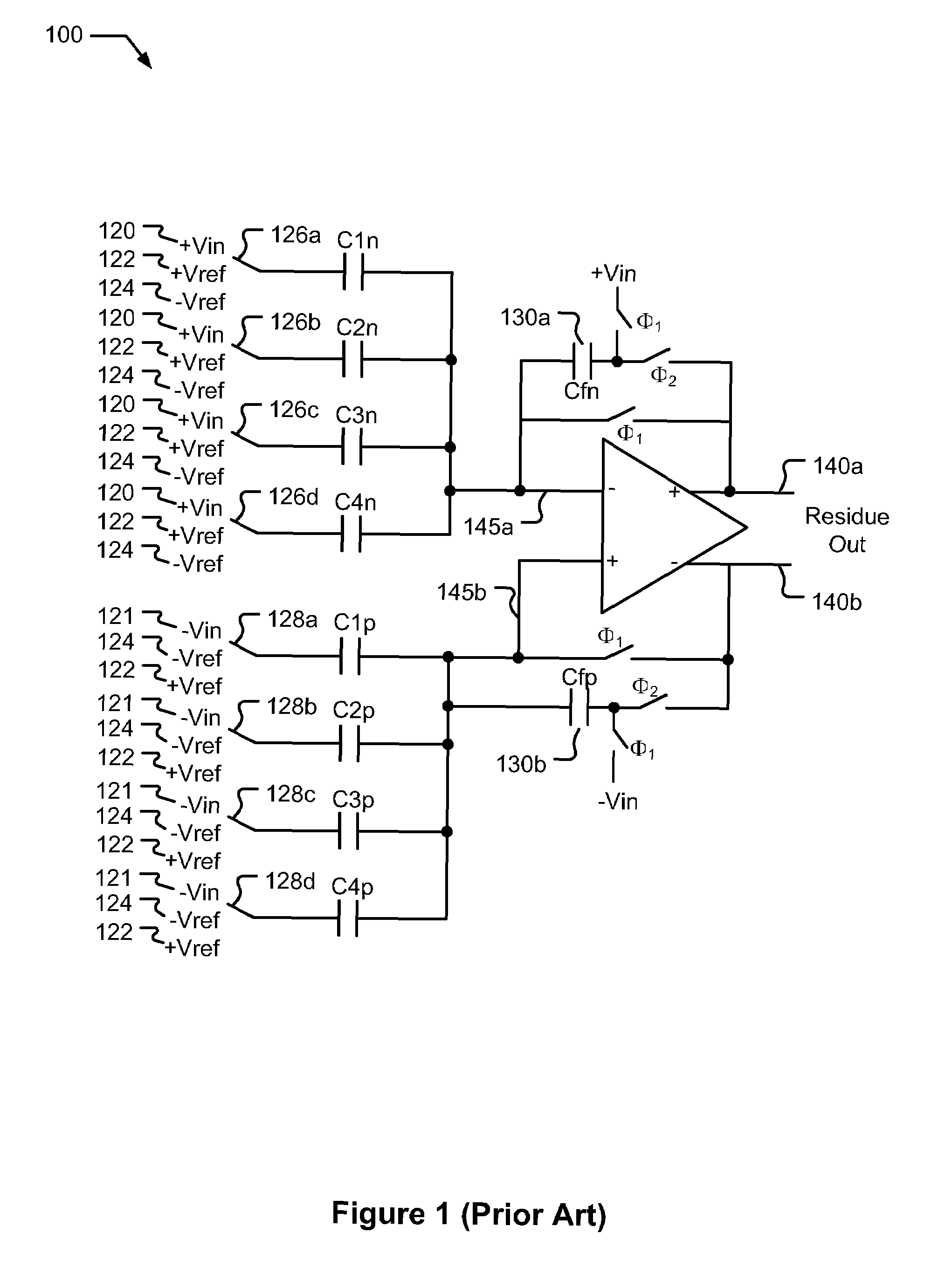

ActiveUS7551115B2Electric signal transmission systemsAnalogue-digital convertersCapacitanceAudio power amplifier

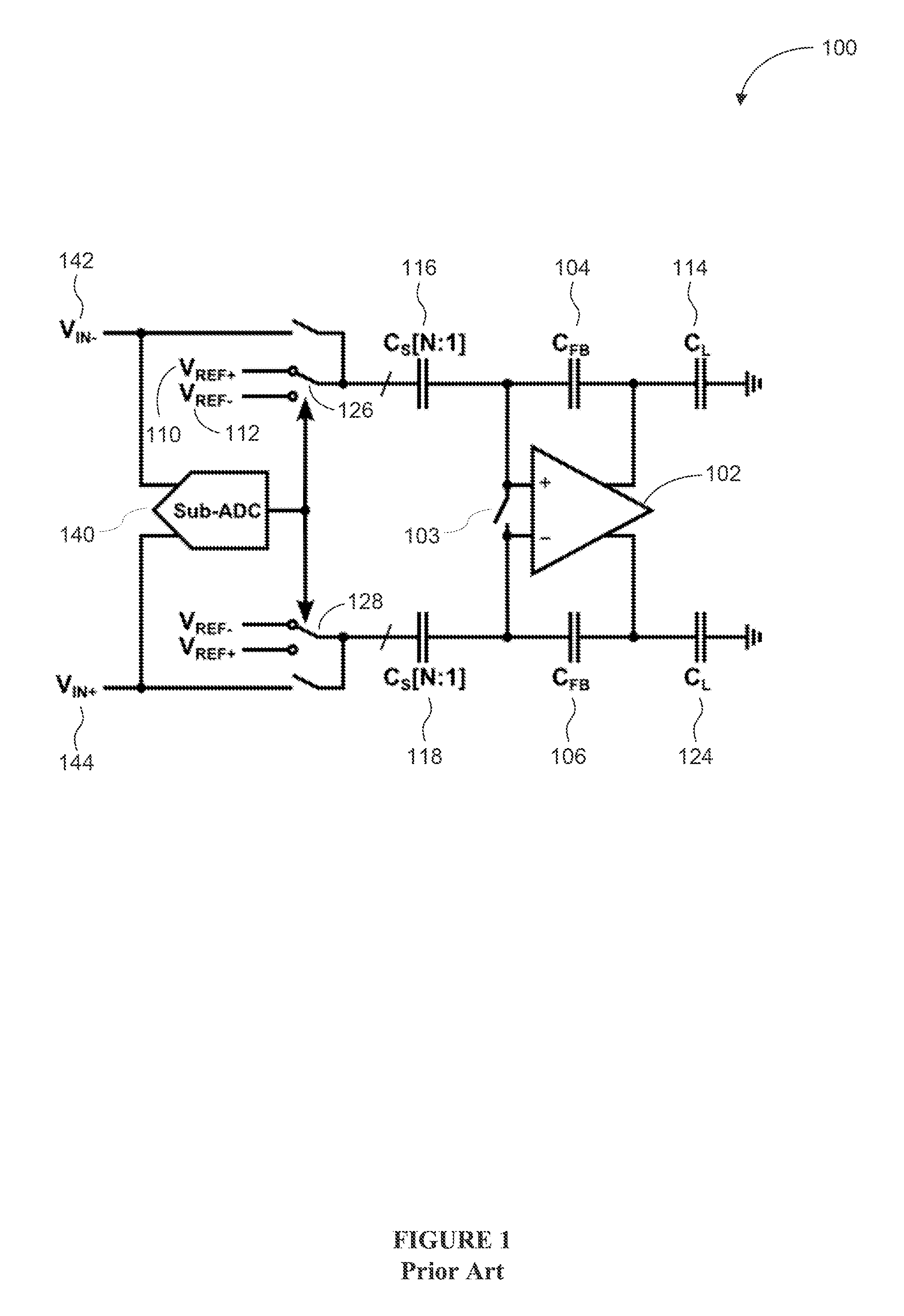

Various embodiments of the present invention provide systems and circuits that provide for conversion of analog signals to digital signals. For example, various embodiments of the present invention provide methods for performing analog to digital conversions that include providing an analog to digital converter with a residue amplifier that is associated with a first capacitance set that includes a first feedback capacitor and first set of input capacitors, and a second capacitance set that includes a second feedback capacitor and second set of input capacitors. The methods further include performing a first sample of an analog input voltage by charging the first set of input capacitors from the analog voltage input during a first period; amplifying the first sample during a second period; performing a second sample of the analog input voltage by charging the second set of input capacitors from the analog voltage input during a third period; and amplifying the second sample during a fourth period.

Owner:AVAGO TECH INT SALES PTE LTD

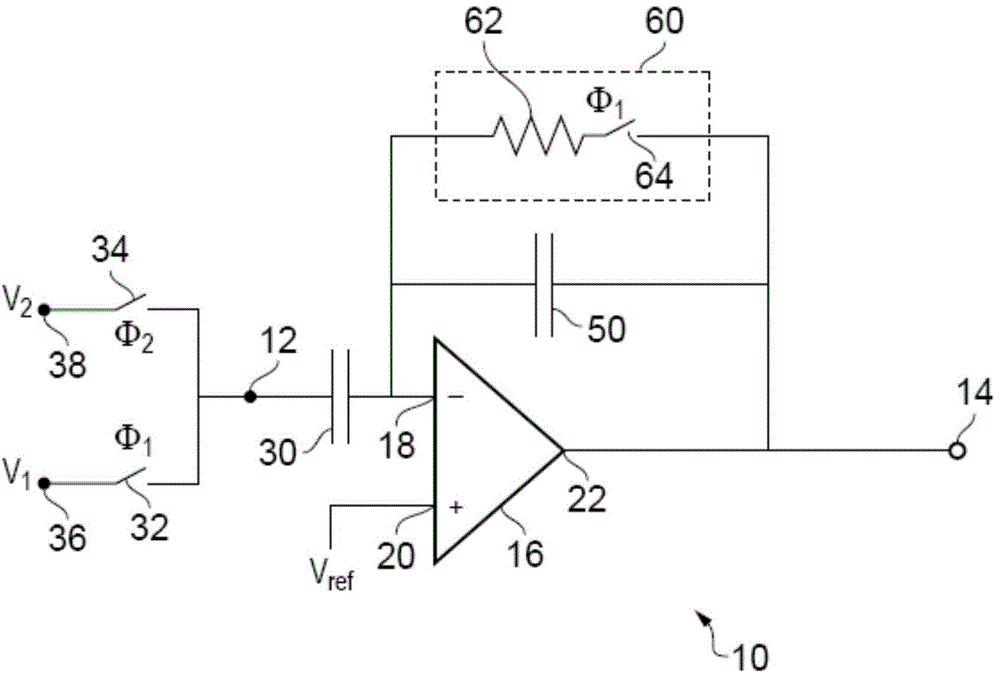

Amplifier, a residue amplifier, and an ADC including a residue amplifier

An amplifier, comprising: an input node; an output node; a gain stage having a gain stage inverting input, a gain stage non-inverting input and a gain stage output; a feedback capacitor connected in a signal path between the gain stage output and the gain stage inverting input; a sampling capacitor connected between the input node and the gain stage non-inverting input, and a controllable impedance in parallel with the feedback capacitor, wherein the controllable impedance is operable to switch between a first impedance state in which it does not affect current flow through the feedback capacitor, and a second impedance state in which it cooperates with the feedback capacitor form a bandwidth limiting circuit.

Owner:ANALOG DEVICES INT UNLTD

Time-interleaved pipelined-SAR analog to digital converter with low power consumption

ActiveUS8427355B2Reduce power consumptionAccuracyElectric signal transmission systemsResistance/reactance/impedenceSub thresholdTime interleaved

Owner:UNIVERSITY OF MACAU

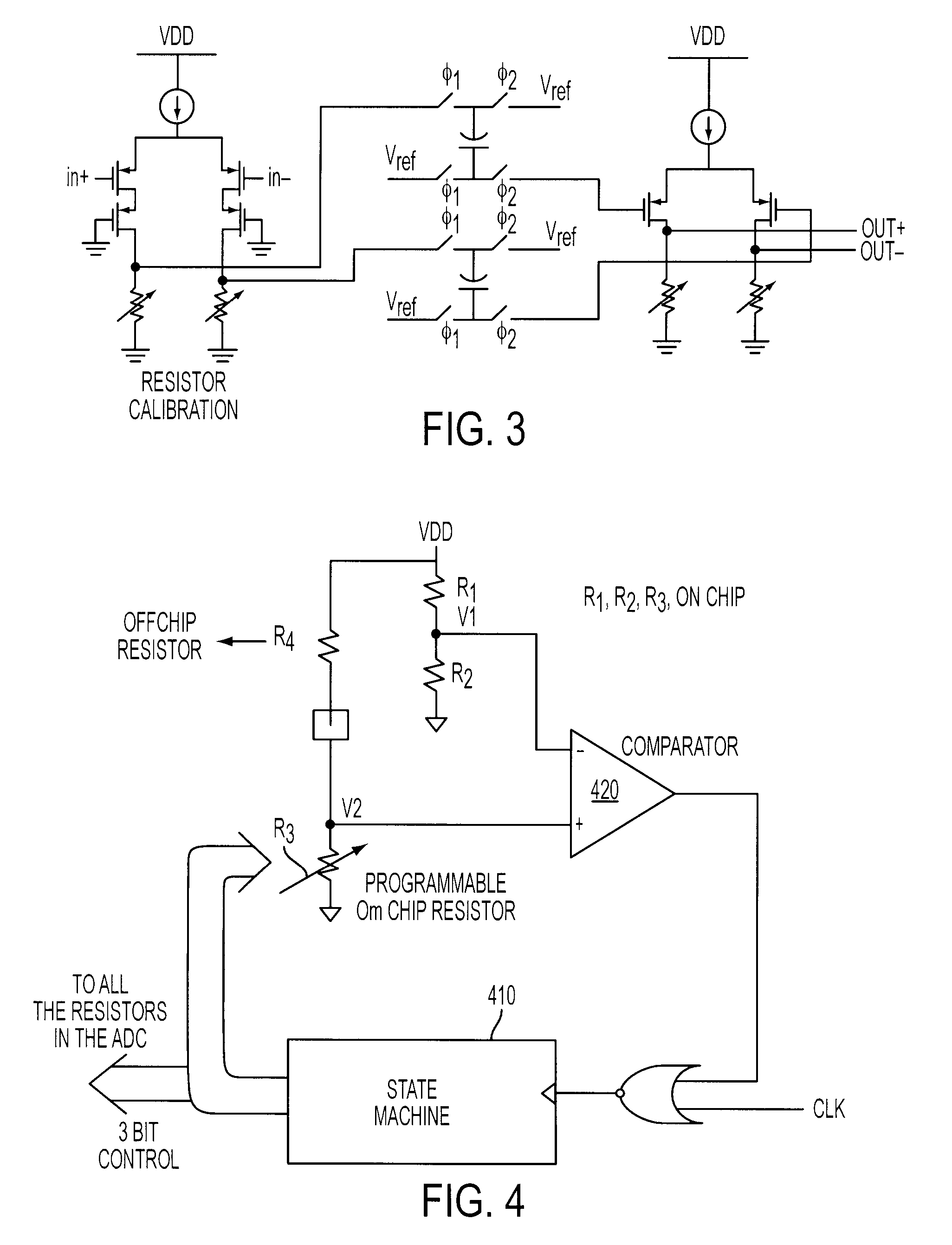

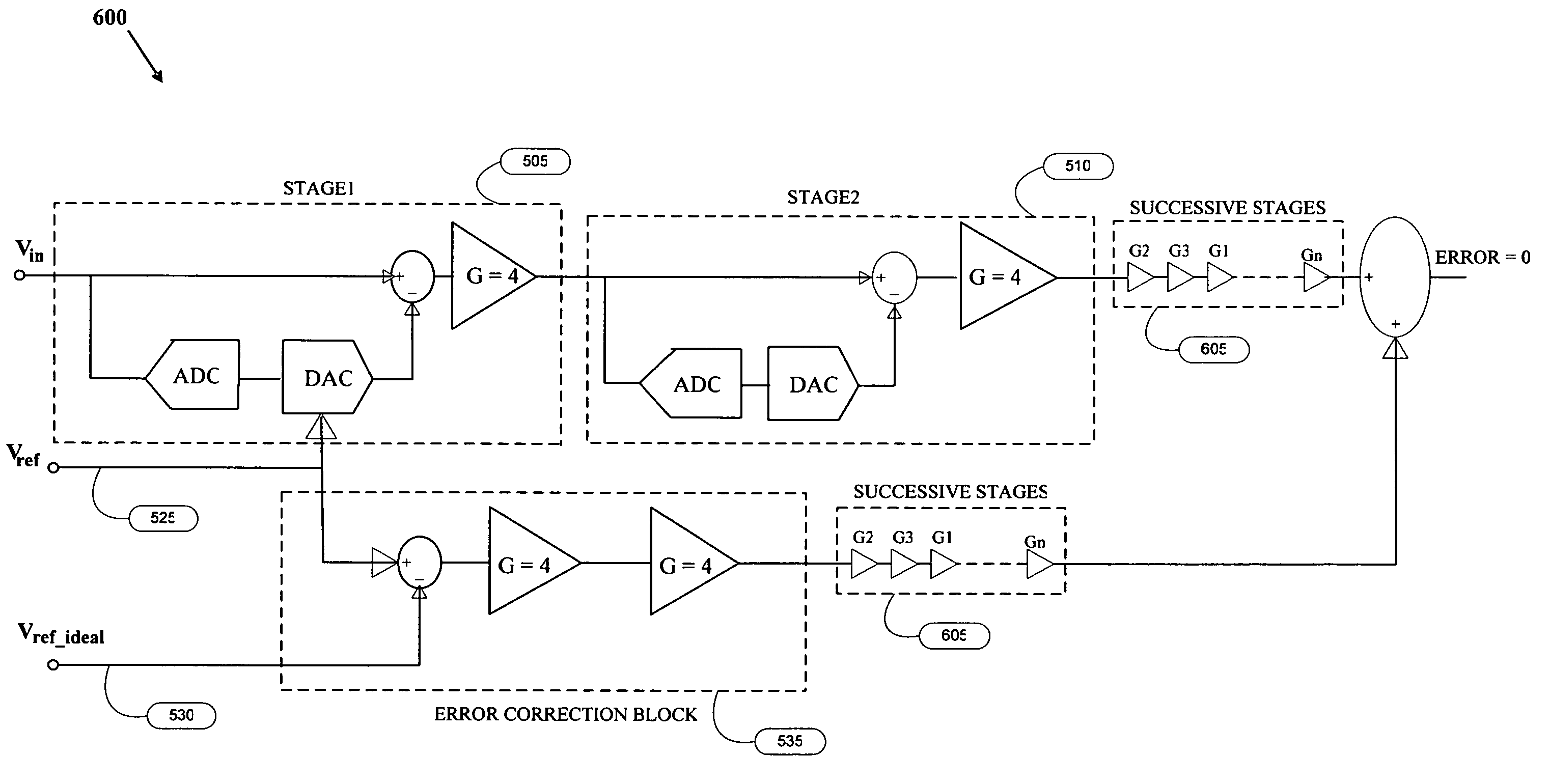

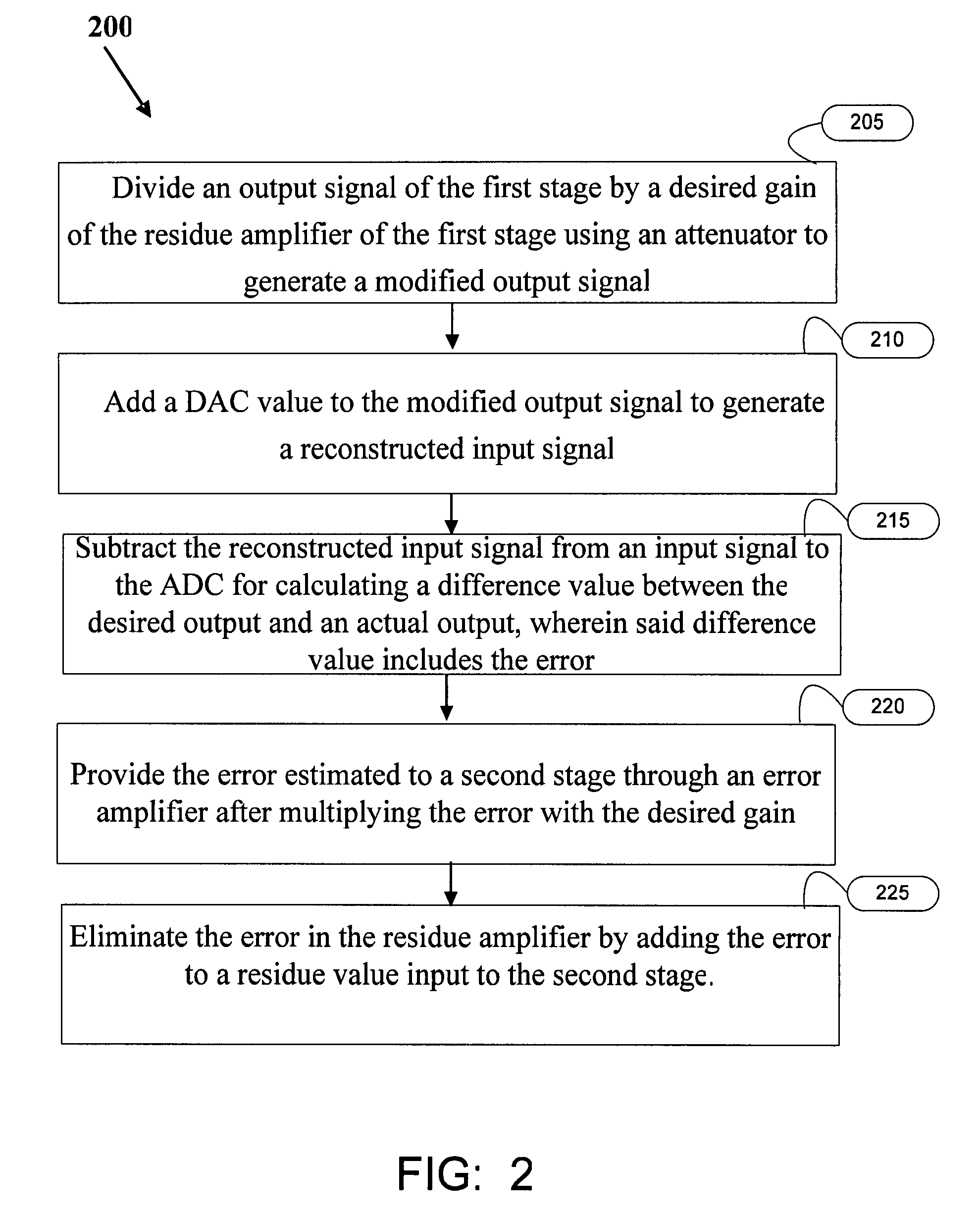

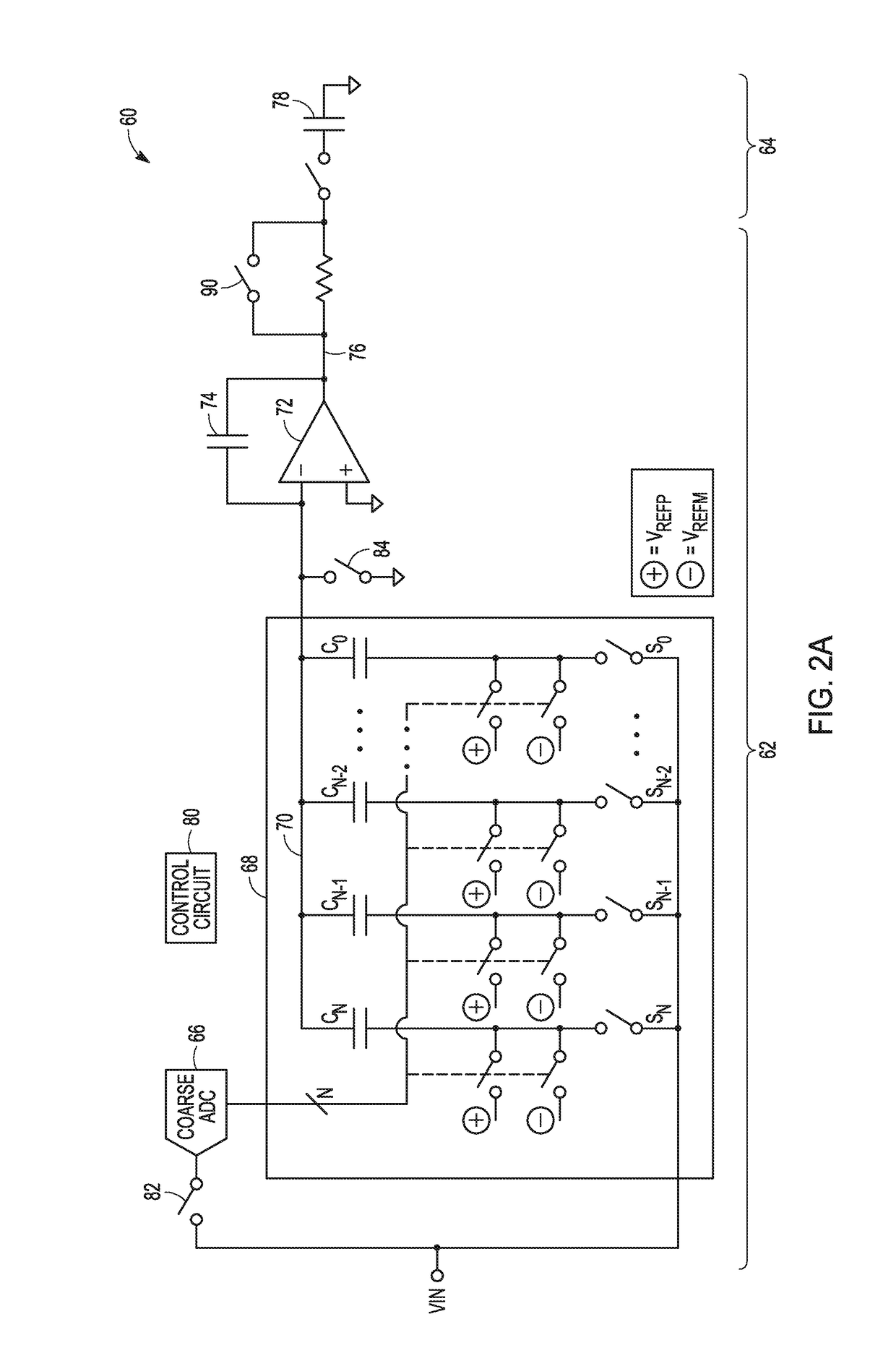

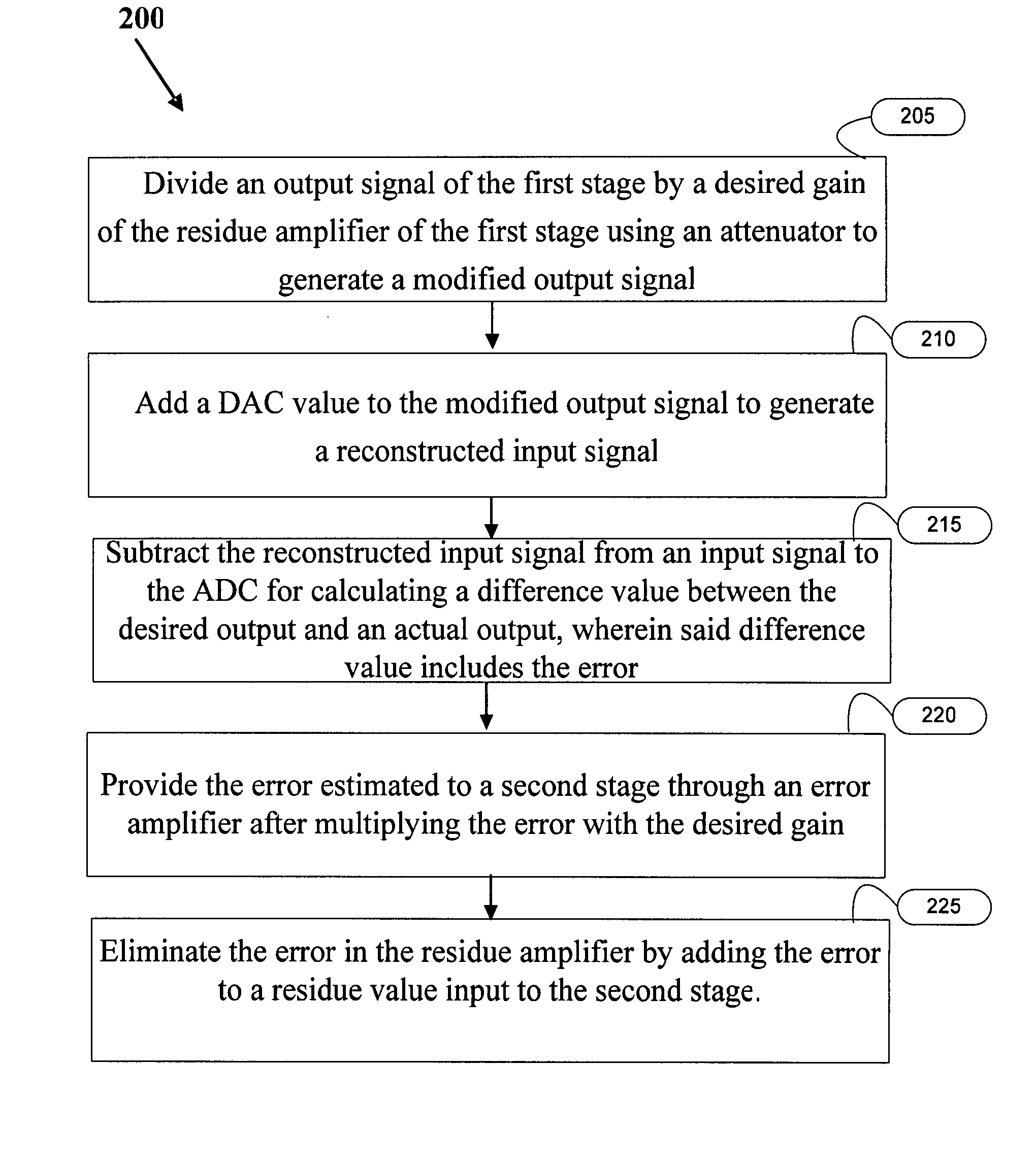

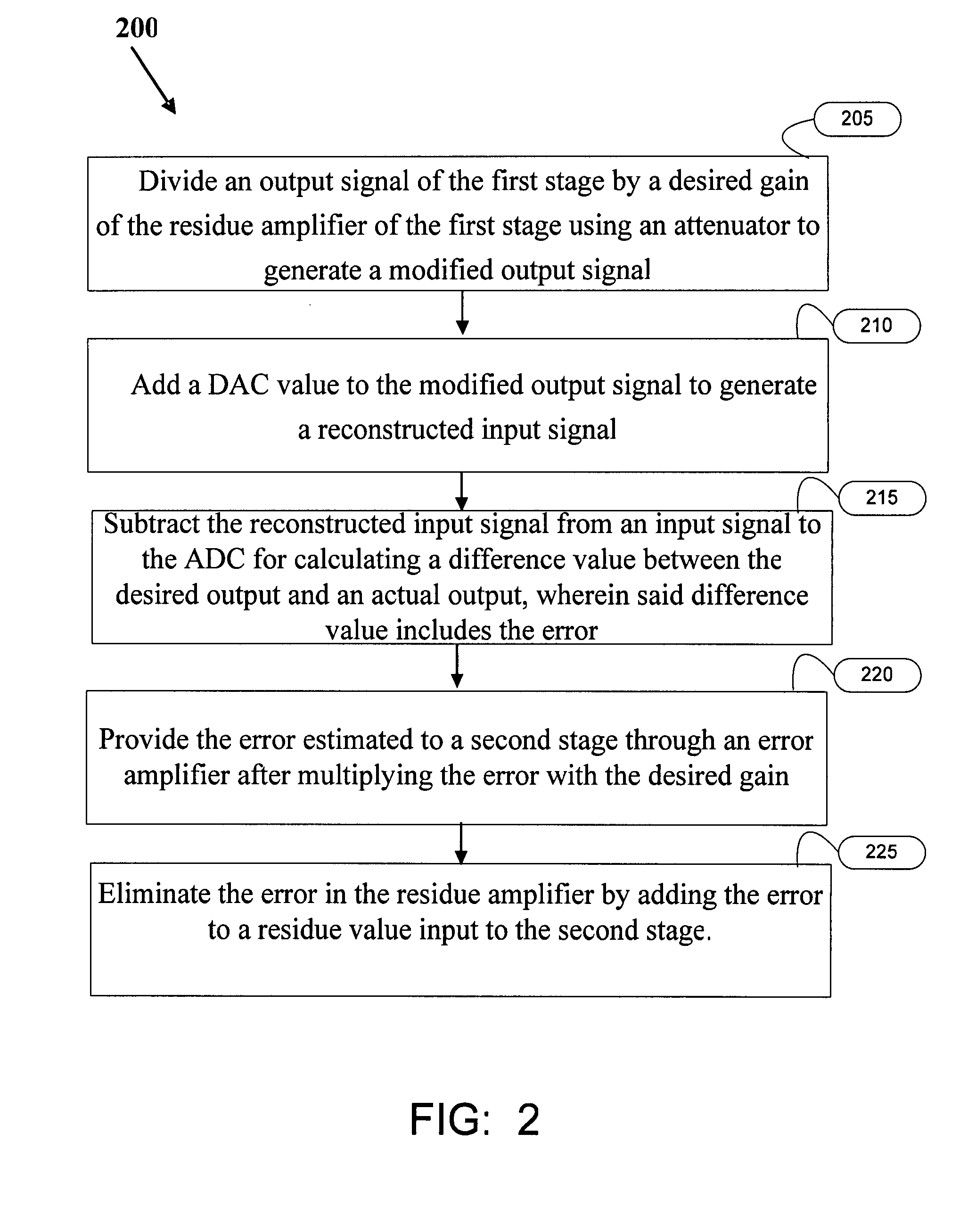

Methods and systems for designing high resolution analog to digital converters

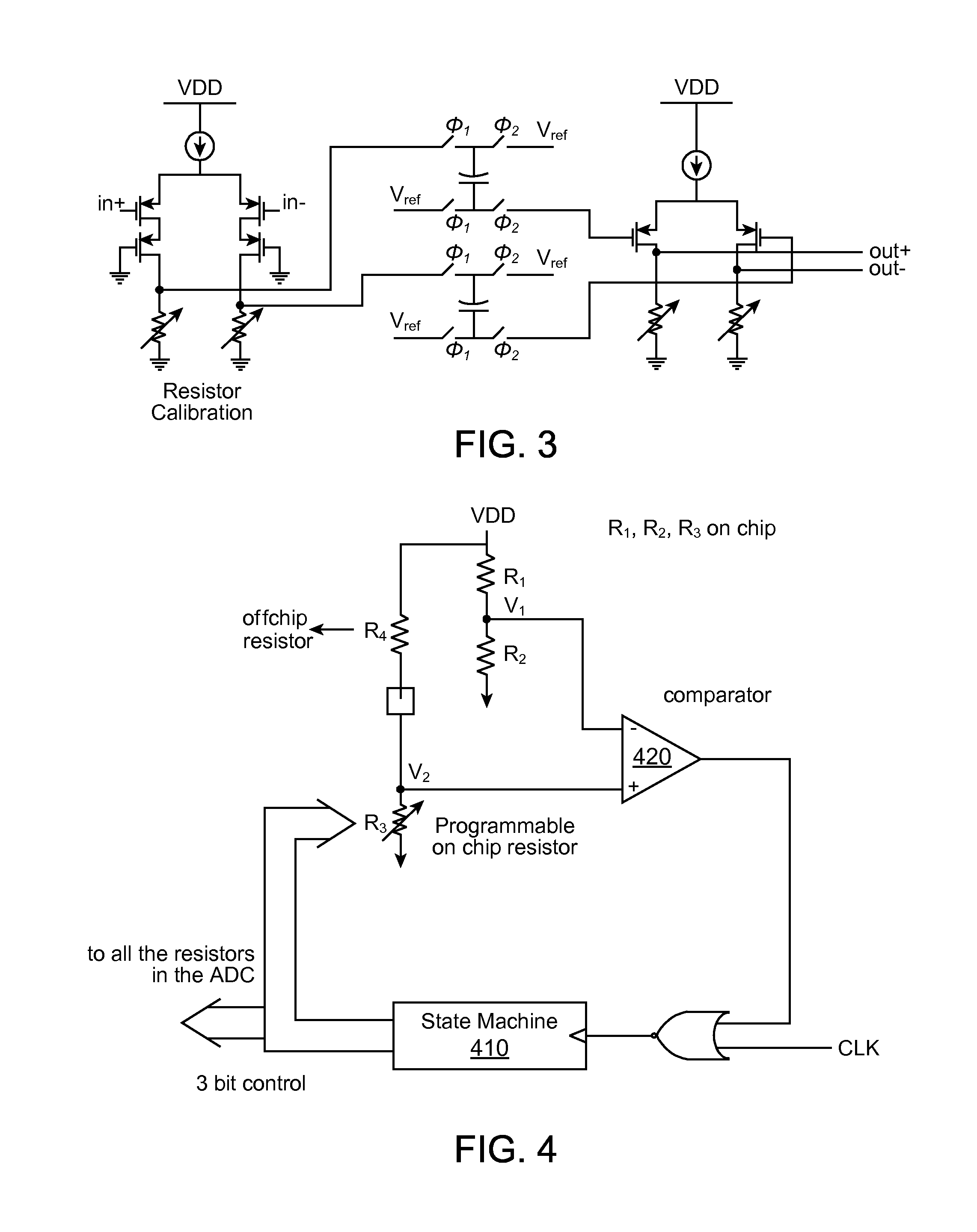

InactiveUS7570191B2Eliminate errorsImprove errorElectric signal transmission systemsAnalogue-digital convertersDigital down converterAudio power amplifier

Methods and systems for designing a high resolution analog to digital converter (ADC) by eliminating the errors in the ADC stages. An error correction architecture and method eliminate the gain error and settling error of the residue amplifier in a pipelined ADC stage. A reference voltage error correction architecture and method eliminate the reference voltage error due to the sampling action in the ADC. The gain error correction method calculates the gain error using an error amplifier and eliminates the gain error at a later stage of the ADC. The reference voltage error correction method calculates the reference voltage error using an ideal reference voltage and corrects the error at a later stage of the ADC. Therefore, the constraints of gain and settling of the residue amplifier is significantly reduced.

Owner:COSMIC CIRCUITS PRIVATE LIMITED

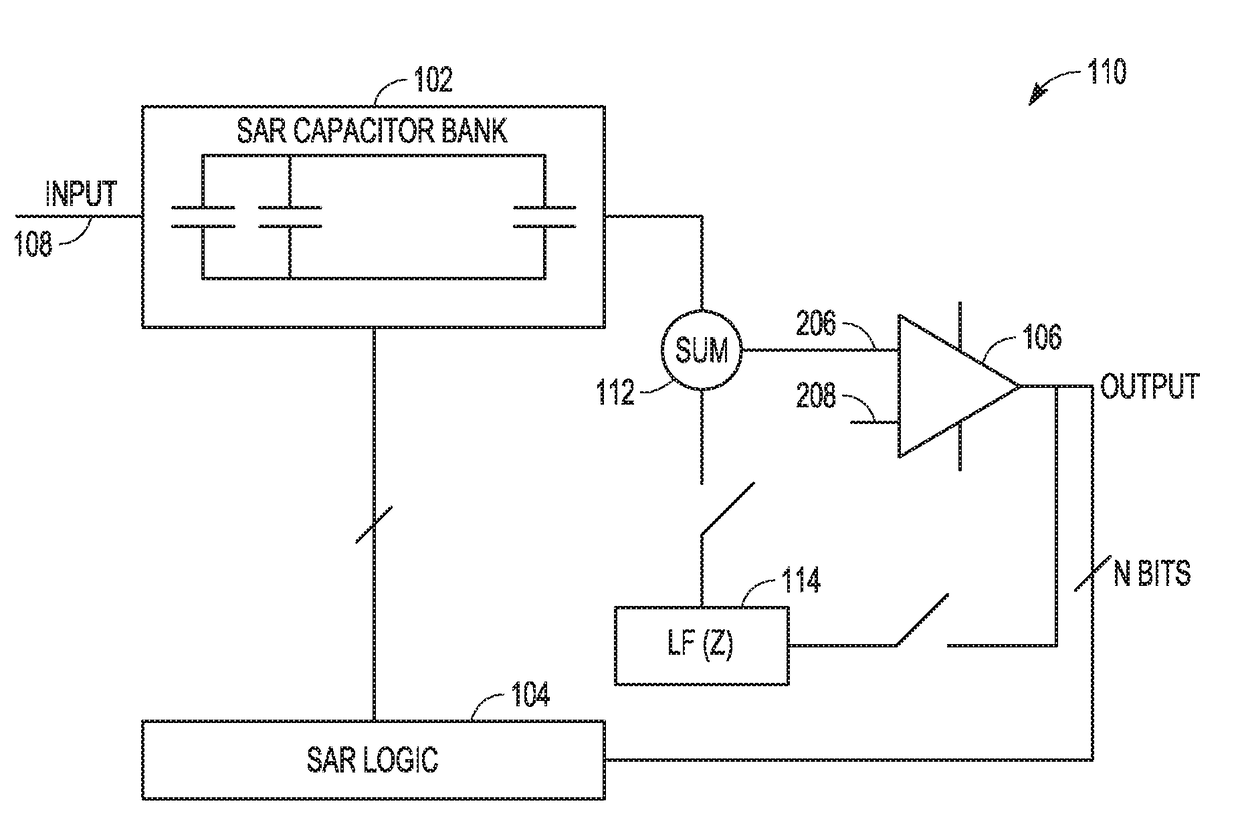

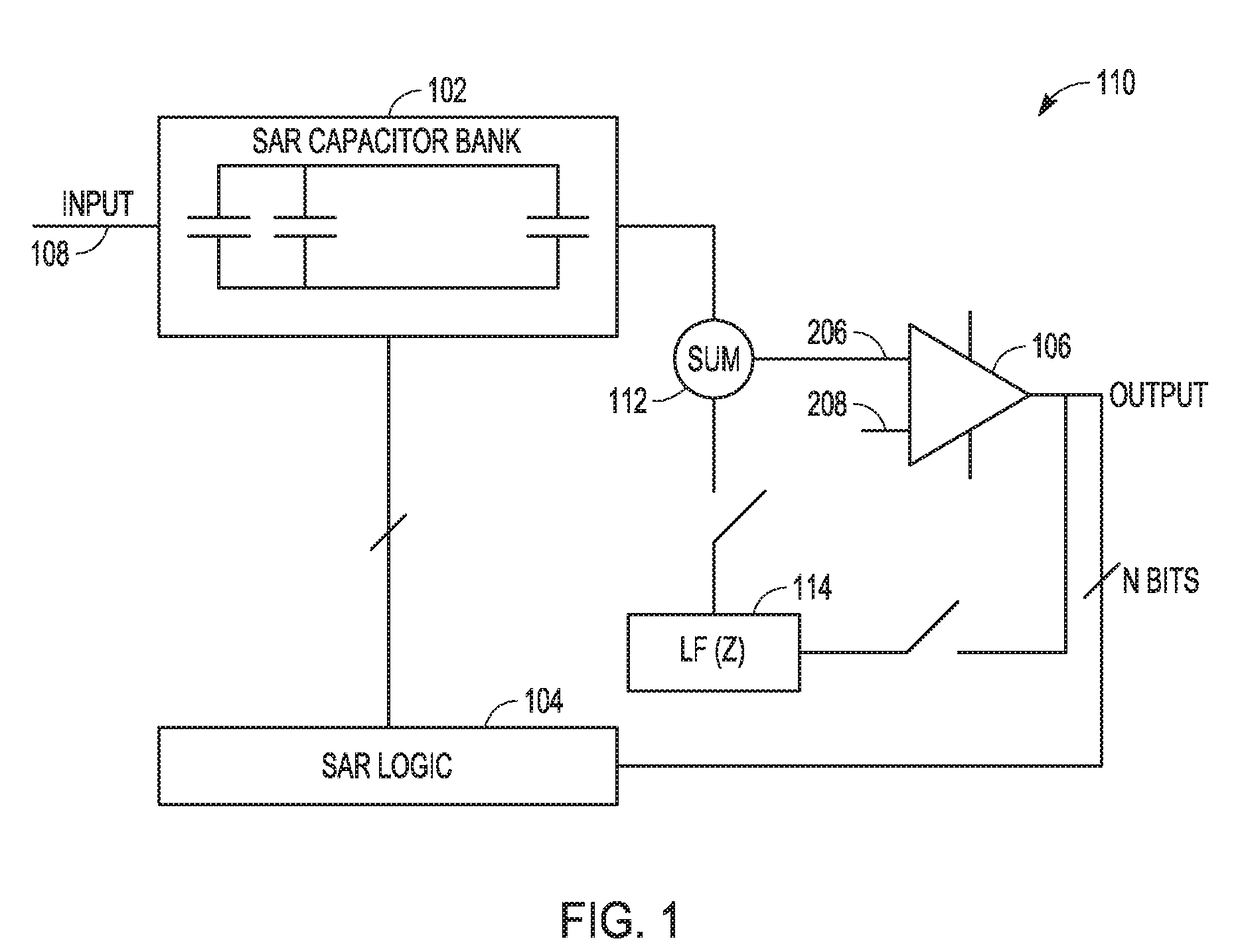

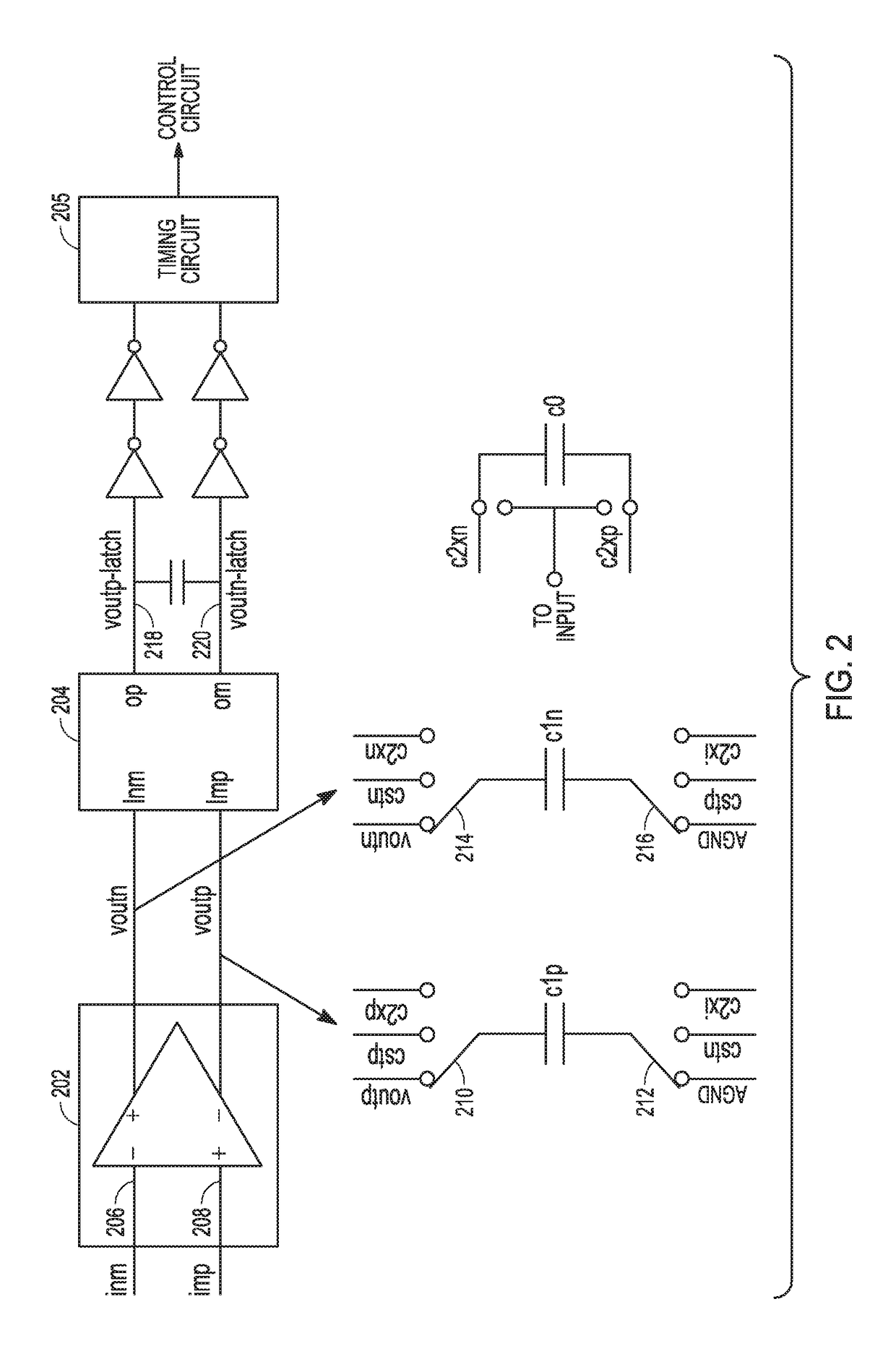

Analog-to-digital converter reusing comparator for residue amplifier for noise shaping

ActiveUS20180309458A1Efficient reuseEfficient noise-shapingAnalogue conversionPhysical parameters compensation/preventionAudio power amplifierComparators circuits

Some or all of a comparator circuit of an analog-to-digital converter (ADC) circuit can be efficiently repurposed or reused for residue amplification for efficient noise-shaping, e.g., in a noise-shaping feedback configuration. A preamplifier portion of a comparator circuit in an oversampling ADC can be re-purposed to provide an amplifier to amplify or otherwise modify a residue left after the bit trials of a conversion cycle. The amplified or modified residue can then be used elsewhere, for example, for noise-shaping by applying a noise transfer function (NTF), a result of which can then be fed back (e.g., summed with the next sampled input at an input of the comparator circuit for use in the N bit trials of the next ADC cycle).

Owner:ANALOG DEVICES INC

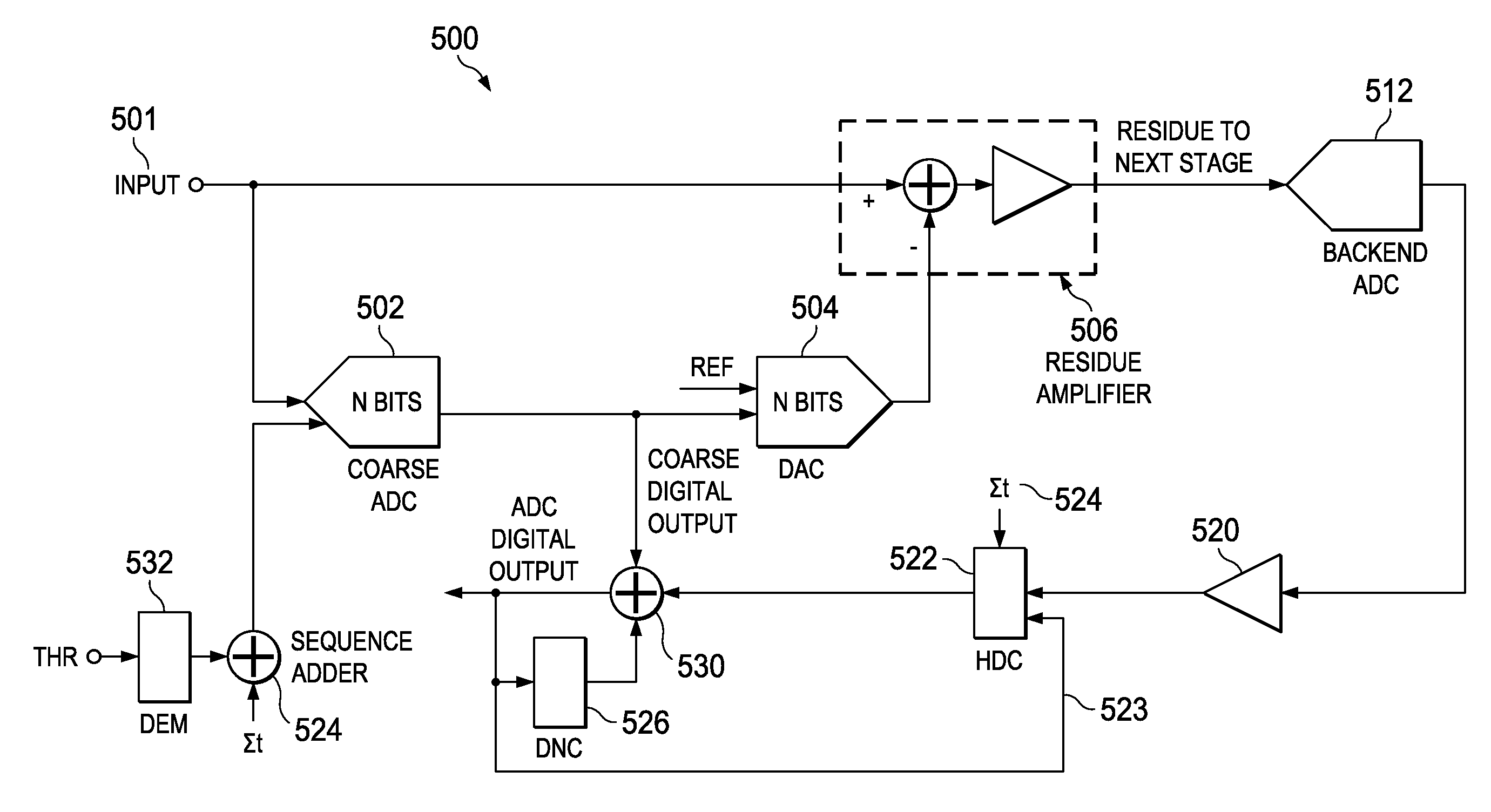

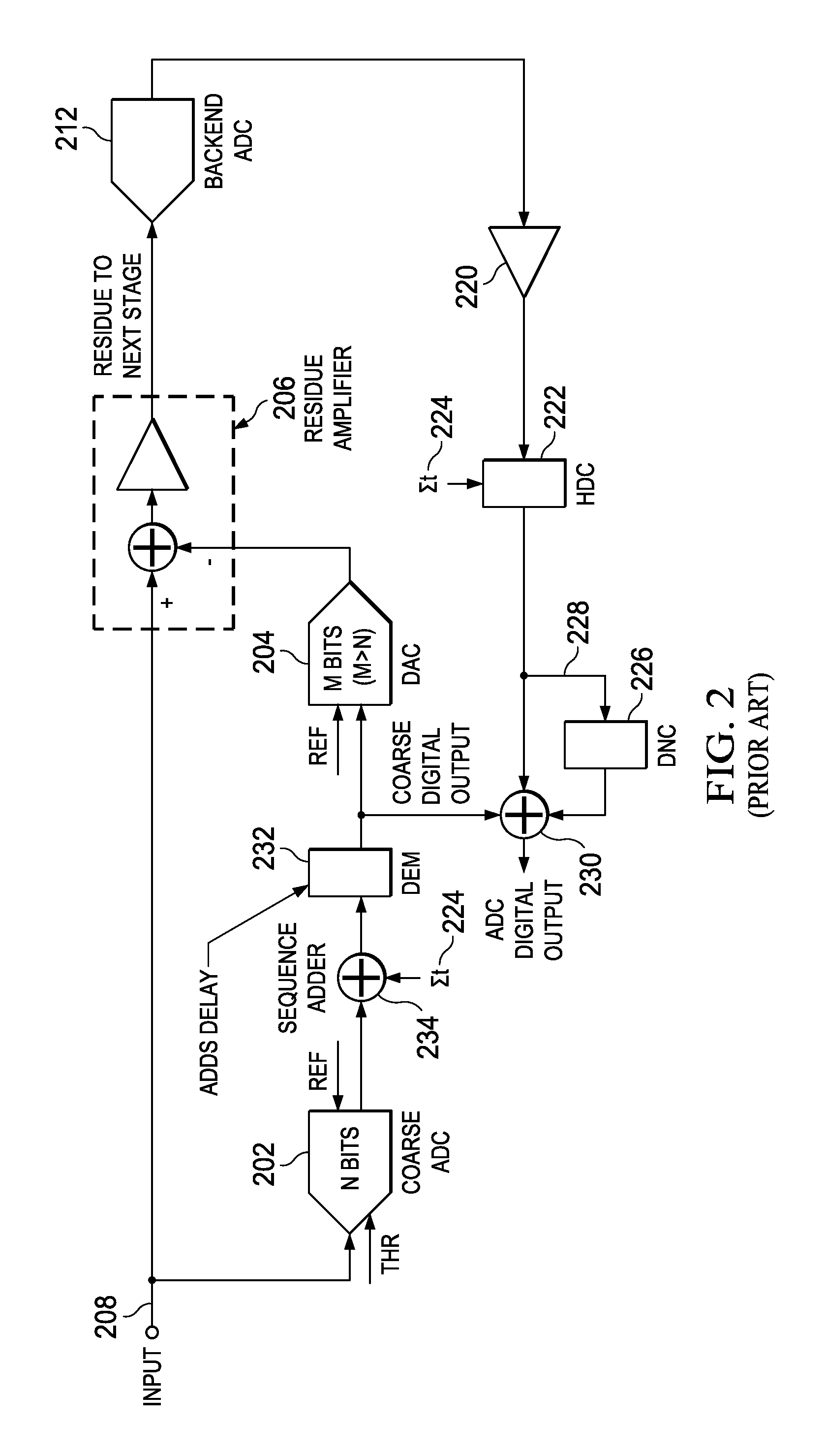

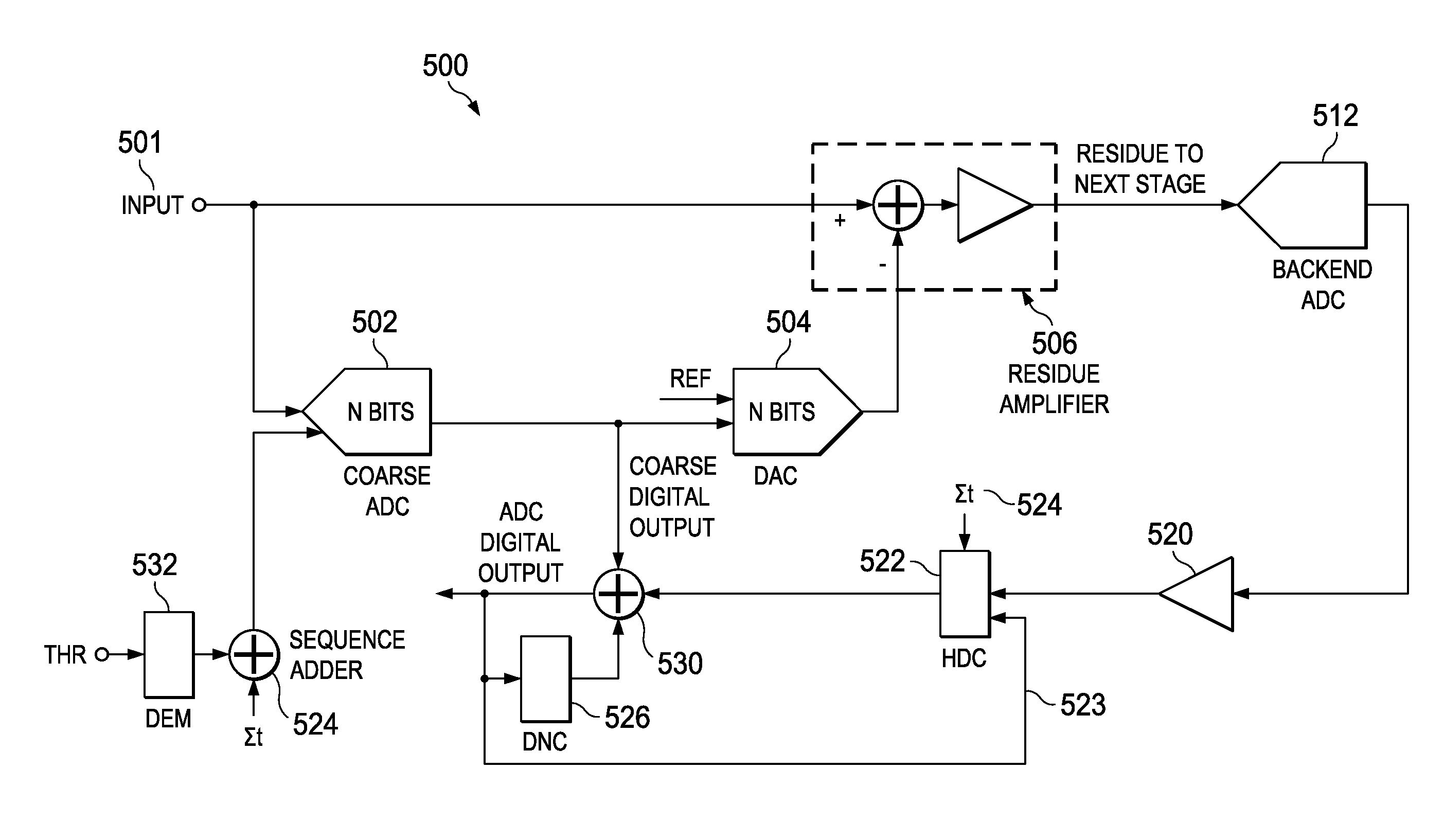

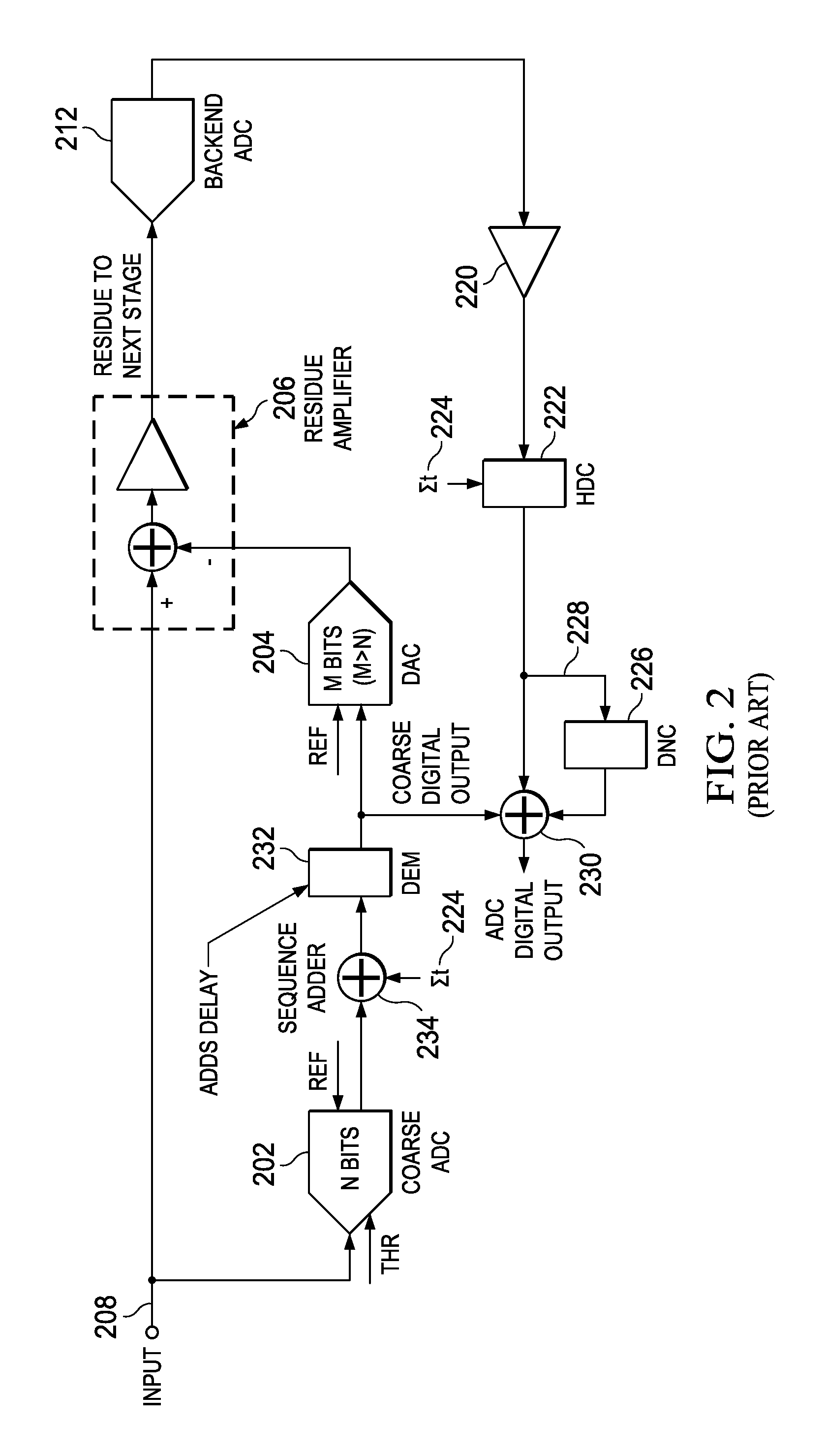

Modified dynamic element matching for reduced latency in a pipeline analog to digital converter

ActiveUS8791844B2Accurate estimateElectric signal transmission systemsAnalogue-digital convertersDigital down converterAudio power amplifier

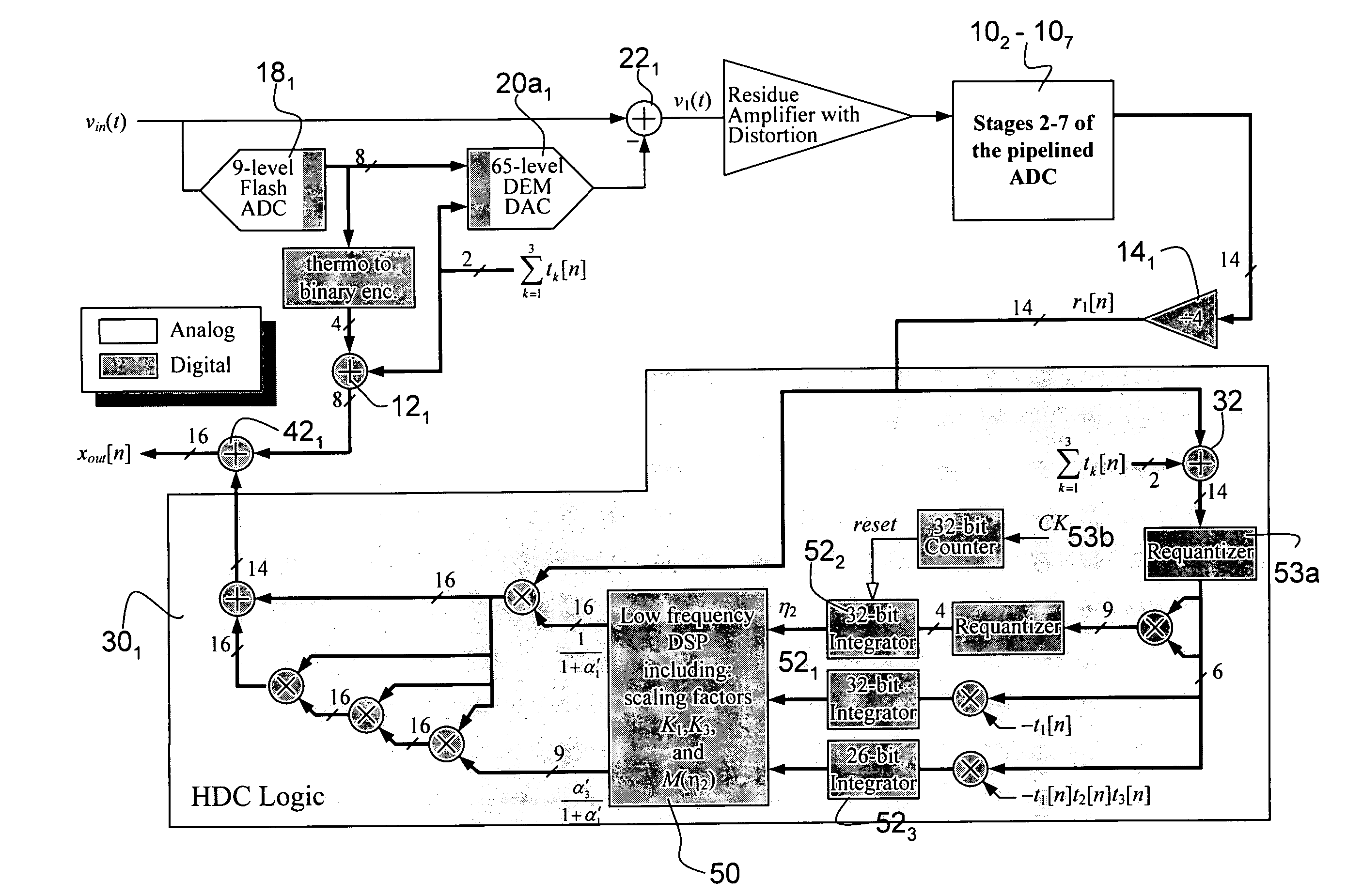

A circuit in an analog-to-digital converter (ADC) includes an amplifier configured to receive an output of a backend DAC; a harmonic distortion correction circuit (HDC) coupled to the amplifier and configured to correct distortion components due to the residue amplifier present in a digital signal from the backend ADC, the HDC circuit providing an output to an adder, the adder receiving a coarse digital output from a coarse ADC; and a DAC noise cancellation circuit (DNC) configured to provide an output to the adder, wherein the DNC circuit is configured to correct distortion components due to the DAC present in the digital signal from the backend ADC; wherein the output of the adder is an ADC digital output and wherein the ADC digital output forms an input to the HDC and the DNC.

Owner:MICROCHIP TECH INC

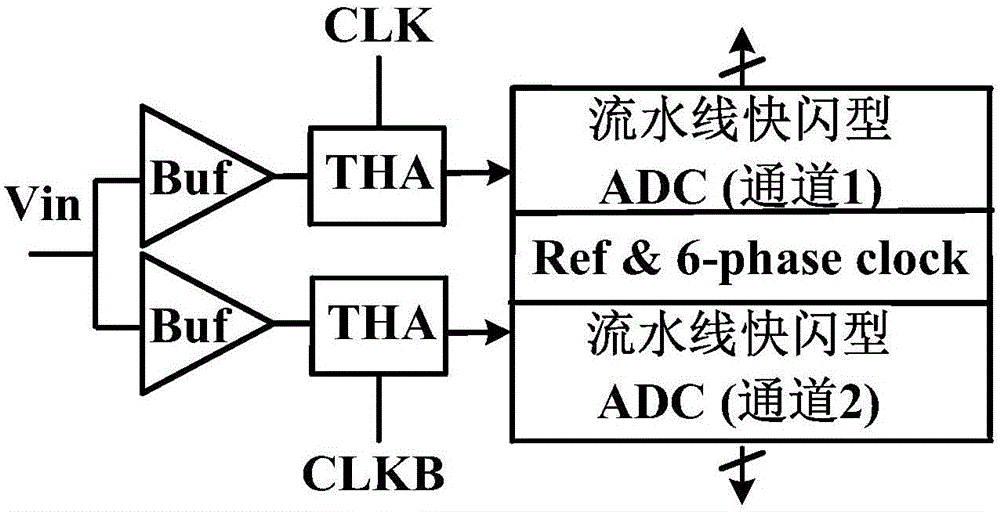

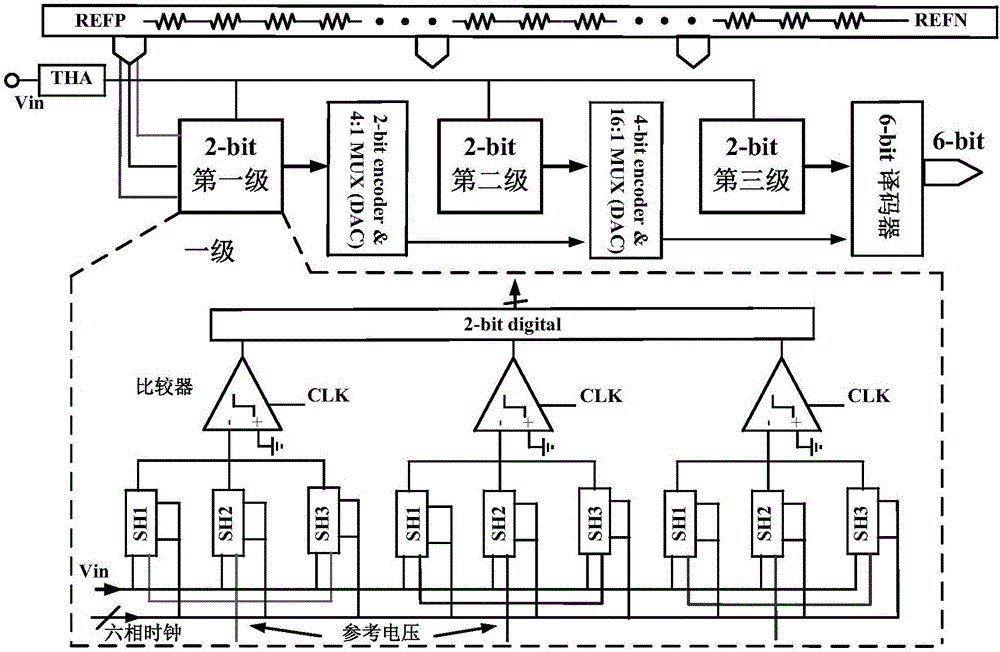

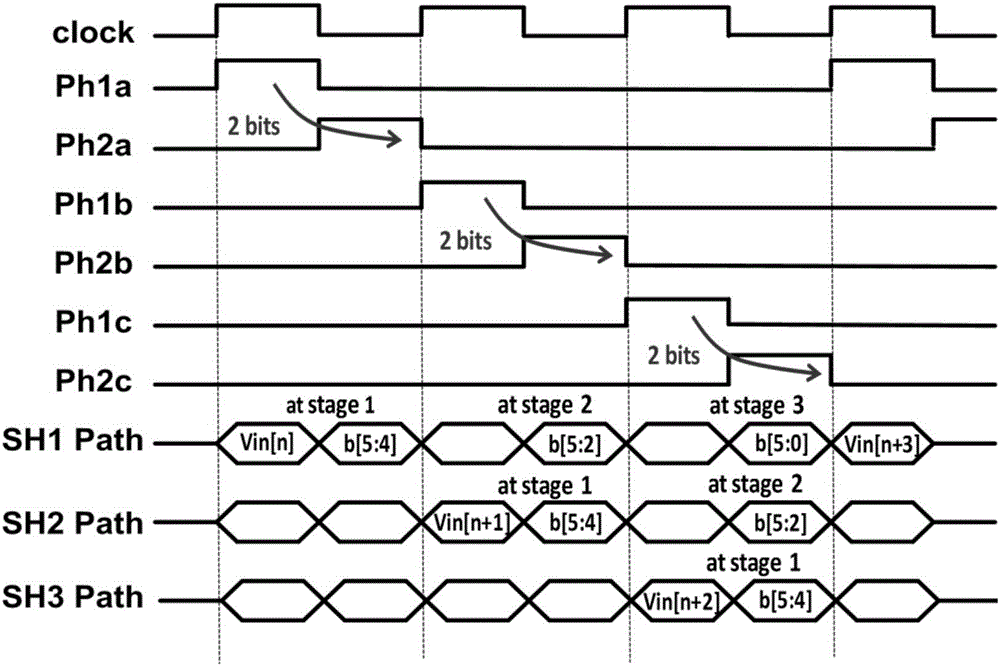

Dual-channel time interleaved asynchronous assembly line flash analog-to-digital converter

InactiveCN106341133AReduce power consumptionPower saving provisionsElectric signal transmission systemsDigital down converterImage resolution

The invention provides a dual-channel time interleaved asynchronous assembly line flash analog-to-digital converter comprising a first buffer, a second buffer, a first tracking and holding circuit, a second tracking and holding circuit, a first single-channel 6-bit asynchronous assembly line flash ADC and a second single-channel 6-bit asynchronous assembly line flash ADC. According to the ADC, the dual-channel time interleaved asynchronous assembly line flash structure is adopted, and multiple asynchronous sampling channels and low-power-consumption multiphase clock generators are adopted in the asynchronous assembly line flash structure of each channel so that a residue amplifier which is high in power consumption and limited in bandwidth can be eliminated, and the analog-to-digital converter is suitable for high-speed, low-power-consumption and medium resolution application.

Owner:SOUTHEAST UNIV WUXI INST OF TECH INTEGRATED CIRCUITS

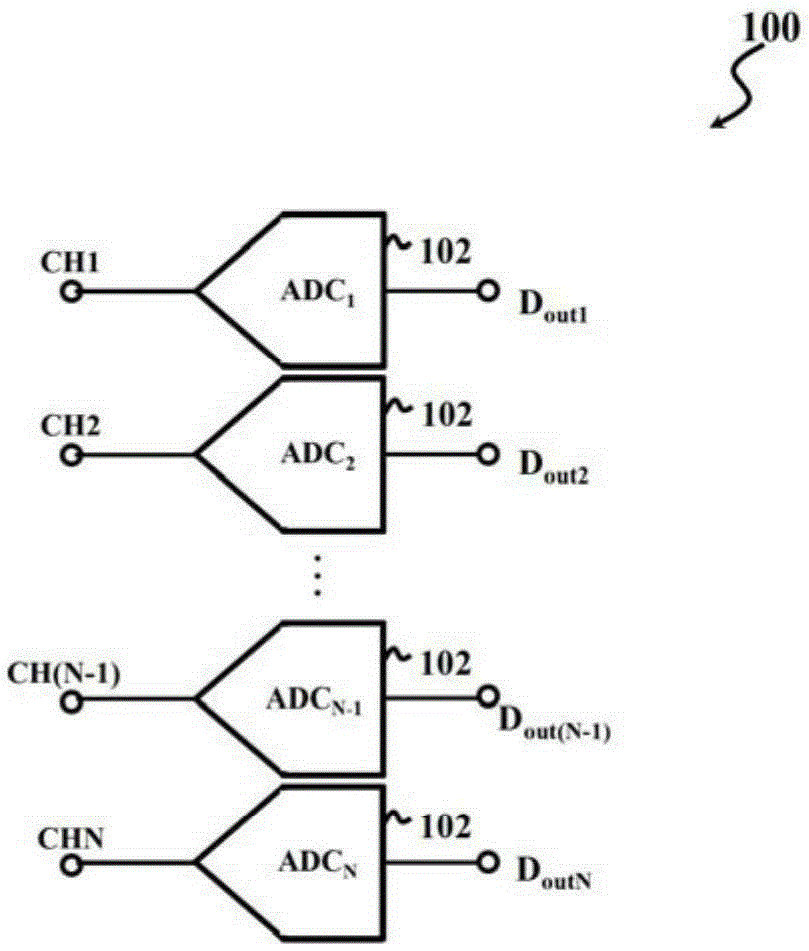

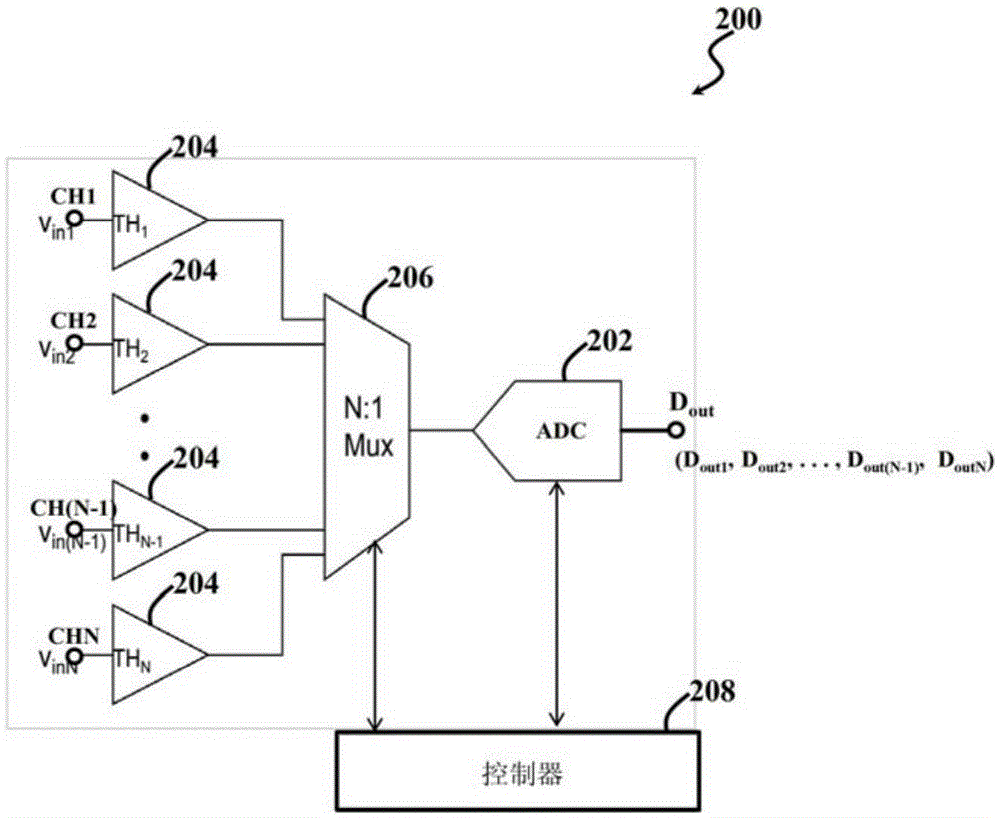

Multichannel analog-to-digital converter

InactiveCN105790766APower saving provisionsElectric signal transmission systemsAudio power amplifierMultiplexer

Multichannel successive approximation register (SAR) analog-to-digital converters (ADC), along with methods and systems for multichannel SAR analog-to-digital conversion, are disclosed herein. An exemplary multichannel SAR ADC can include a first SAR ADC for each of a plurality of input channels, and a second SAR ADC, a multiplexer, and a residue amplifier shared among the plurality of input channels. The multiplexer can select an analog residue signal from one of the first SAR ADCs for conversion by the second SAR ADC. The residue amplifier can amplify the selected analog residue signal. The second SAR ADC, multiplexer, and / or residue amplifier may be shared among all of the plurality of input channels. Where the multichannel SAR ADC includes N input channels, the second SAR ADC, multiplexer, and / or residue amplifier may be shared among b channels of the N input channels.

Owner:ANALOG DEVICES GLOBAL

Correlated double sampling analog-to-digital converter

ActiveUS10128859B1Small sample sizeReduce die areaPower saving provisionsElectric signal transmission systemsAudio power amplifierEngineering

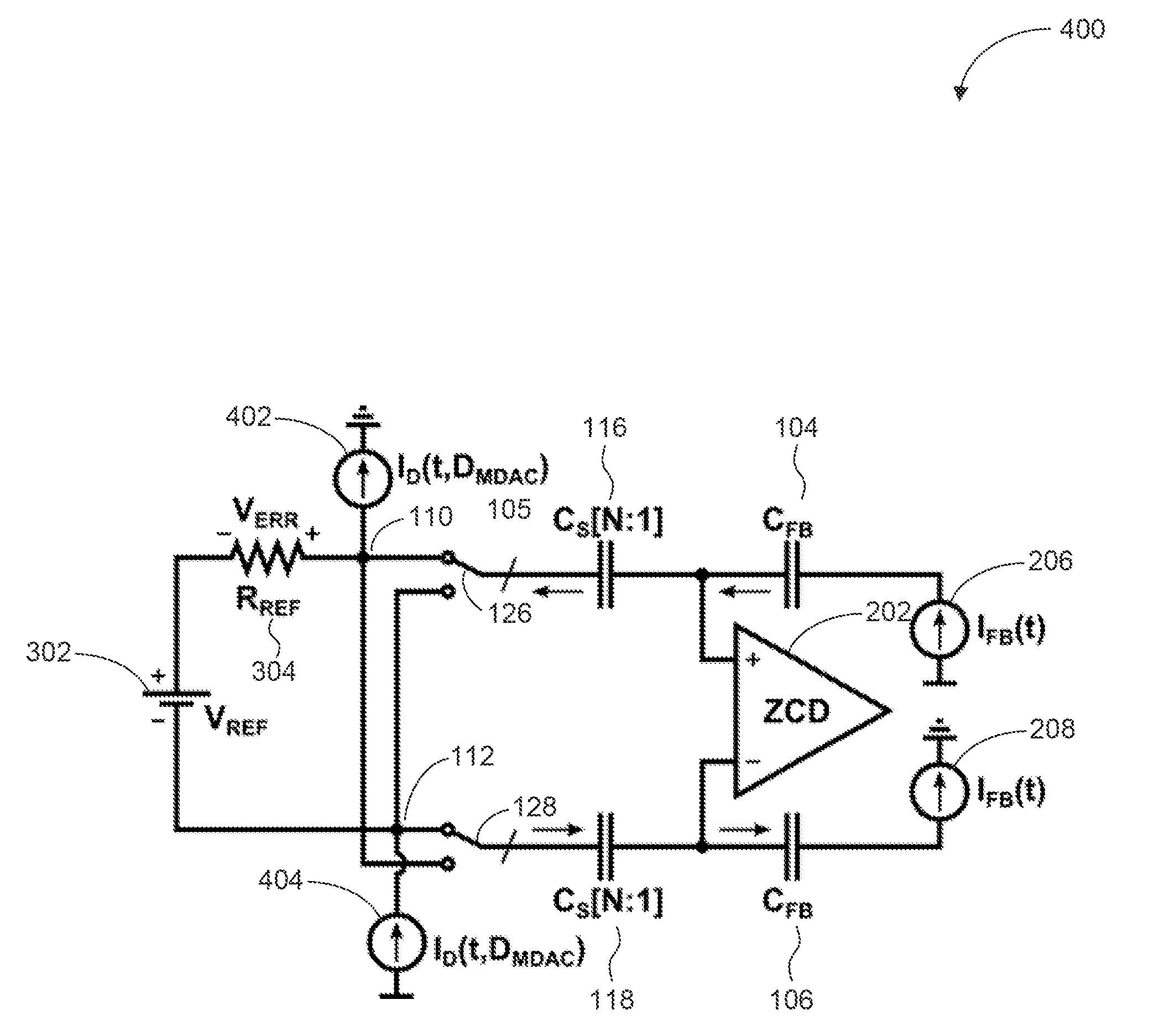

Techniques are described to cancel kT / C sampling noise and residue amplifier sampling noise while also reducing power consumption in a pipelined analog-to-digital converter circuit.

Owner:ANALOG DEVICES GLOBAL UNLTD

Methods and systems for designing high resolution analog to digital converters

InactiveUS20070285298A1High resolutionEliminate errorsElectric signal transmission systemsAnalogue-digital convertersAudio power amplifierEngineering

Methods and systems for designing a high resolution ADC by eliminating the errors in the ADC stages. An error correction architecture and method of the embodiments of the invention eliminate the gain error and settling error of the residue amplifier in a pipelined ADC stage. A reference voltage error correction architecture and method of the embodiments of the invention eliminate the reference voltage error due to the sampling action in the ADC. The gain error correction method calculates the gain error using an error amplifier and eliminates the gain error at a later stage of the ADC. The reference voltage error correction method calculates the reference voltage error using an ideal reference voltage and corrects the error at a later stage of the ADC. The constraints of gain and settling of the residue amplifier is significantly reduced using the embodiments of the invention.

Owner:COSMIC CIRCUITS PRIVATE LIMITED

Modified Dynamic Element Matching For Reduced Latency In A Pipeline Analog To Digital Converter

ActiveUS20130027231A1Accurate estimateOvercome problemsElectric signal transmission systemsAnalogue-digital convertersAudio power amplifierResidue amplifier

A circuit in an analog-to-digital converter (ADC) includes an amplifier configured to receive an output of a backend DAC; a harmonic distortion correction circuit (HDC) coupled to the amplifier and configured to correct distortion components due to the residue amplifier present in a digital signal from the backend ADC, the HDC circuit providing an output to an adder, the adder receiving a coarse digital output from a coarse ADC; and a DAC noise cancellation circuit (DNC) configured to provide an output to the adder, wherein the DNC circuit is configured to correct distortion components due to the DAC present in the digital signal from the backend ADC; wherein the output of the adder is an ADC digital output and wherein the ADC digital output forms an input to the HDC and the DNC.

Owner:MICROCHIP TECH INC

Circuitry and method for reducing area and power of a pipeline ADC

ActiveCN104685790AAnalogue-digital convertersAnalogue/digital conversion calibration/testingLevel shiftingAudio power amplifier

A pipeline ADC (analog-to-digital converter) (14) includes a residue amplifier (7) for applying a first residue signal (Vres1) to a first input of a residue amplifier (11A) and to an input of a sub-ADC (8) for resolving a predetermined number (m) of bits and producing a redundancy bit in response to the first residue signal. A level-shifting MDAC (9A) converts the predetermined number of bits and the redundancy bit to an analog signal (10) on the a second input of the residue amplifier, which amplifies the difference between the first residue signal and the analog signal to generate a second residue signal (Vres2). The MDAC causes the residue amplifier to shift the second residue signal back within a predetermined voltage range (±Vref / 2) by the end of the amplifying if the second residue signal is outside of the predetermined voltage range.

Owner:TEXAS INSTR INC

MDAC with differential current cancellation

ActiveUS20140375487A1Inhibit currentReduced settling timeElectric signal transmission systemsDigital-analogue convertorsAudio power amplifierVoltage reference

Various embodiments of the invention provide for cancellation of a residue amplifier output charging current at the reference voltage source of the reference buffer thereby preventing the charging current from altering the effective reference voltage of a reference buffer. In certain embodiments, current cancellation is accomplished by subtracting a current of the same magnitude.

Owner:MAXIM INTEGRATED PROD INC

System and method for reducing power dissipation in an analog to digital converter

InactiveUS20090295609A1Reduce power consumptionReduce in quantityElectric signal transmission systemsAnalogue-digital convertersDigital down converterAudio power amplifier

Owner:COSMIC CIRCUITS PRIVATE LIMITED

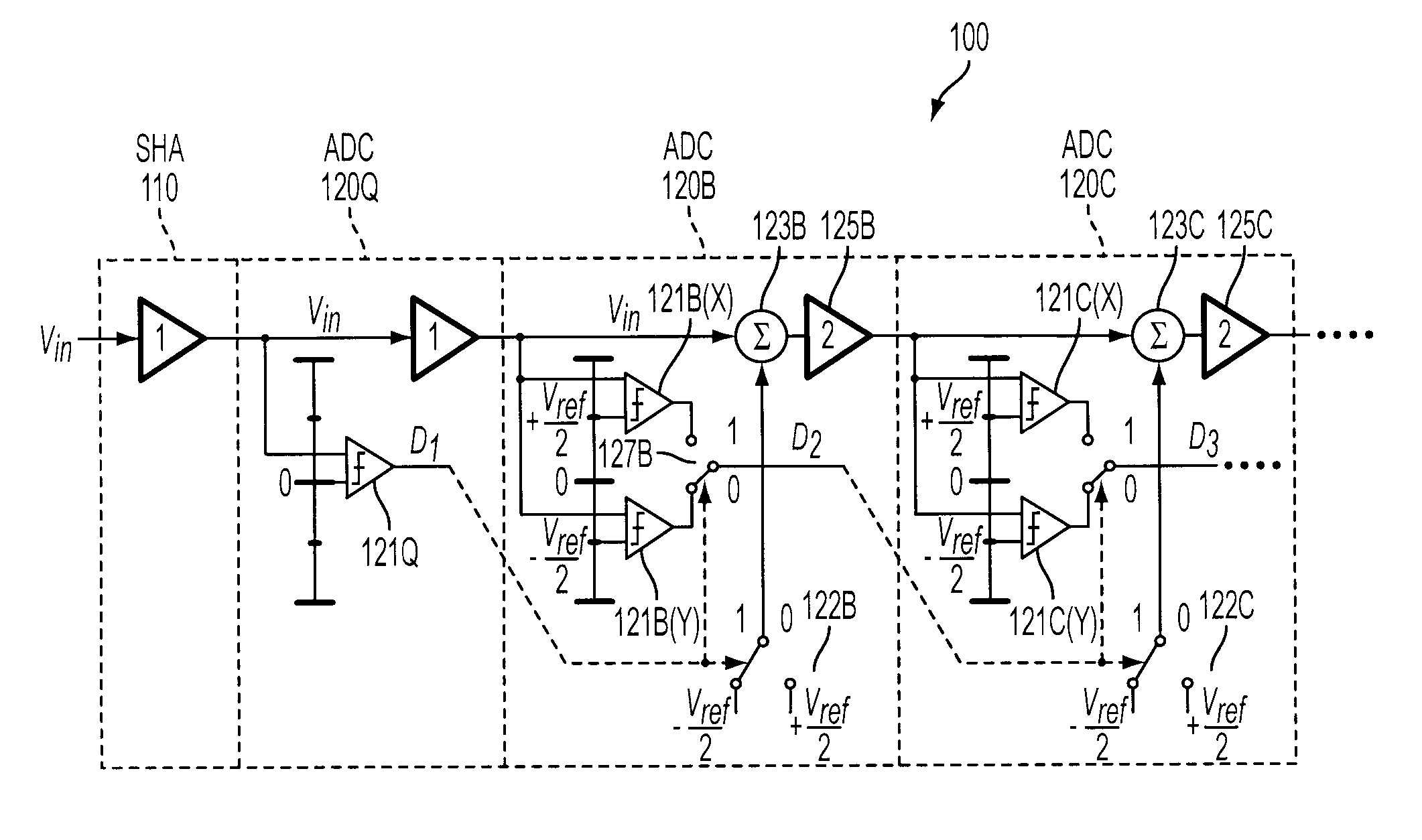

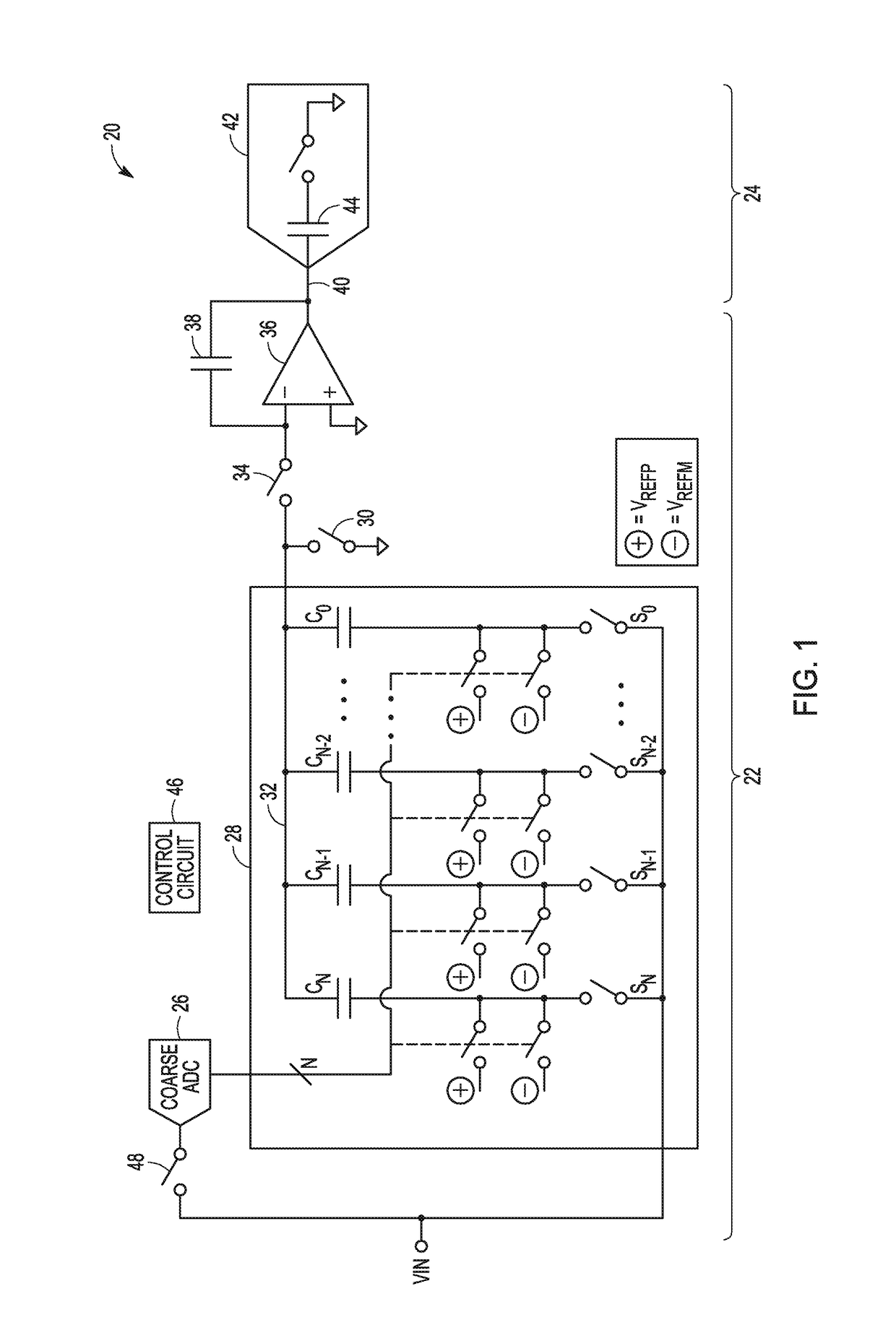

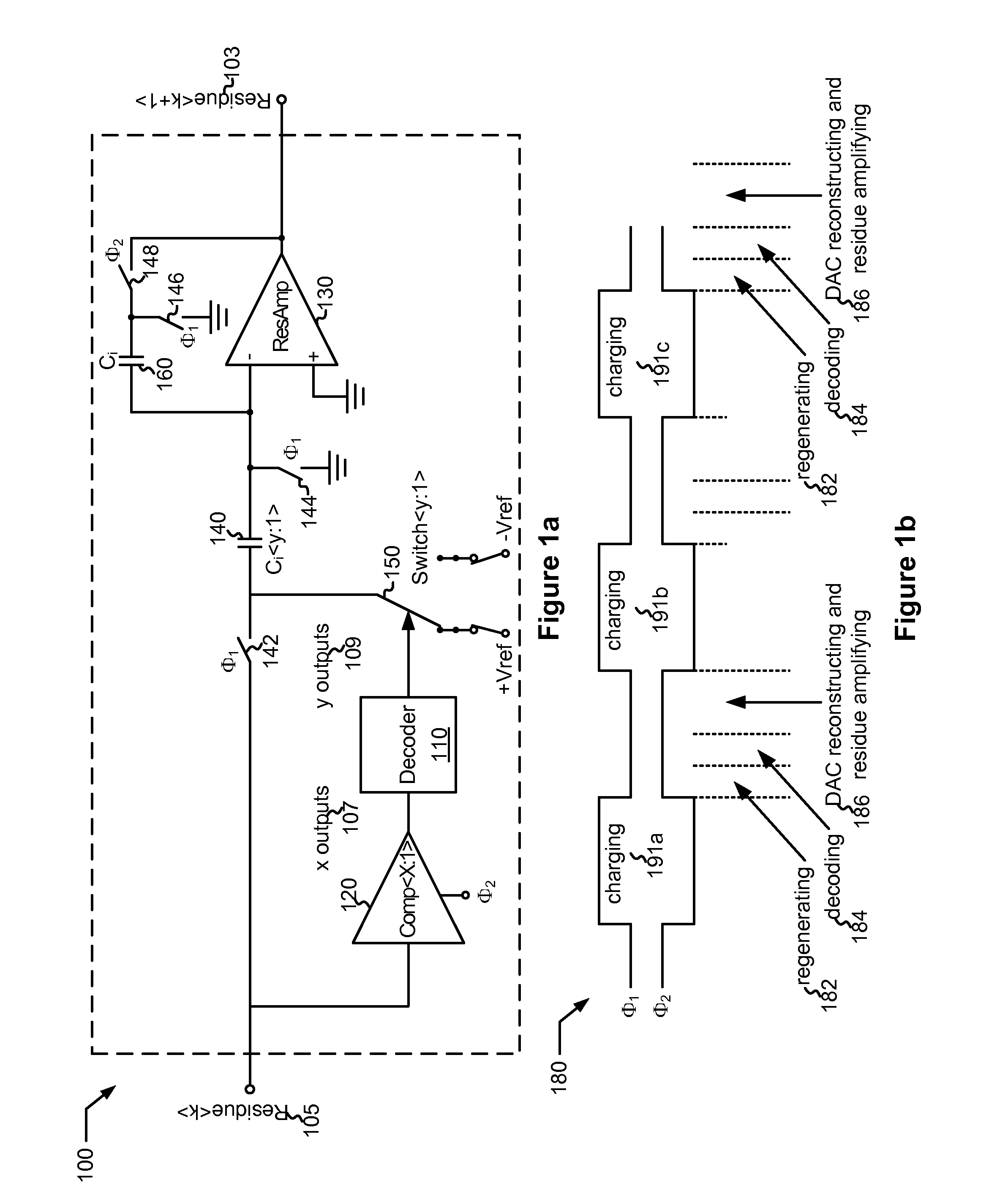

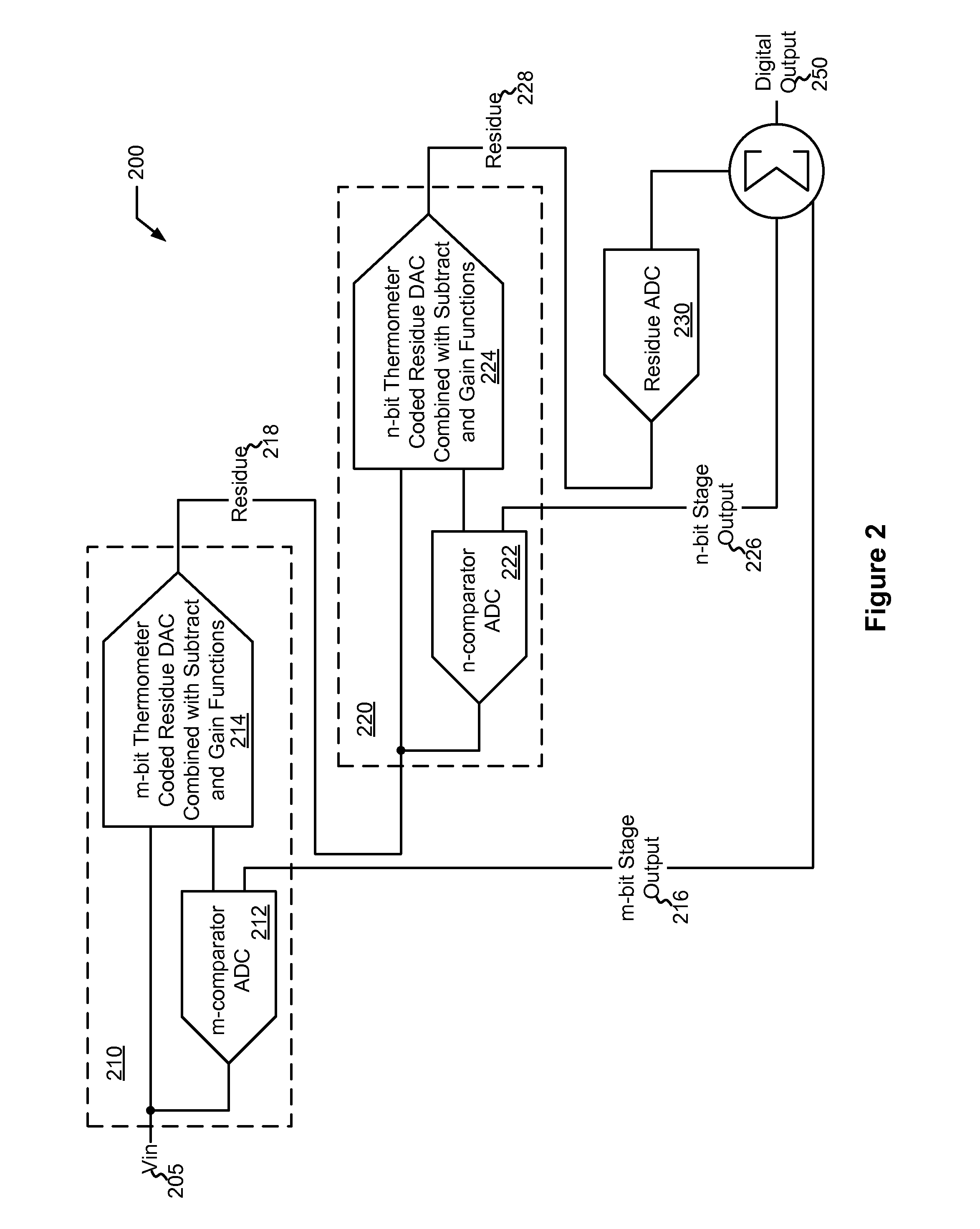

Multi-bit per stage pipelined analog to digital converters

InactiveUS7573417B2Electric signal transmission systemsAnalogue-digital convertersAudio power amplifierAnalog signal

Various embodiments of the present invention provide systems and circuits that provide for conversion of analog signals to digital signals. For example, various embodiments of the present invention provide pipelined analog to digital converters. Such converters include a sub-converter and a residue amplifier. The sub-converter receives an analog input, and provides a digital representation of the analog input including a number of bits. A gain of the residue amplifier is controlled by selectably setting a group of switches. Each of the number of bits output from the sub-converter electrically controls a respective one of the switches.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

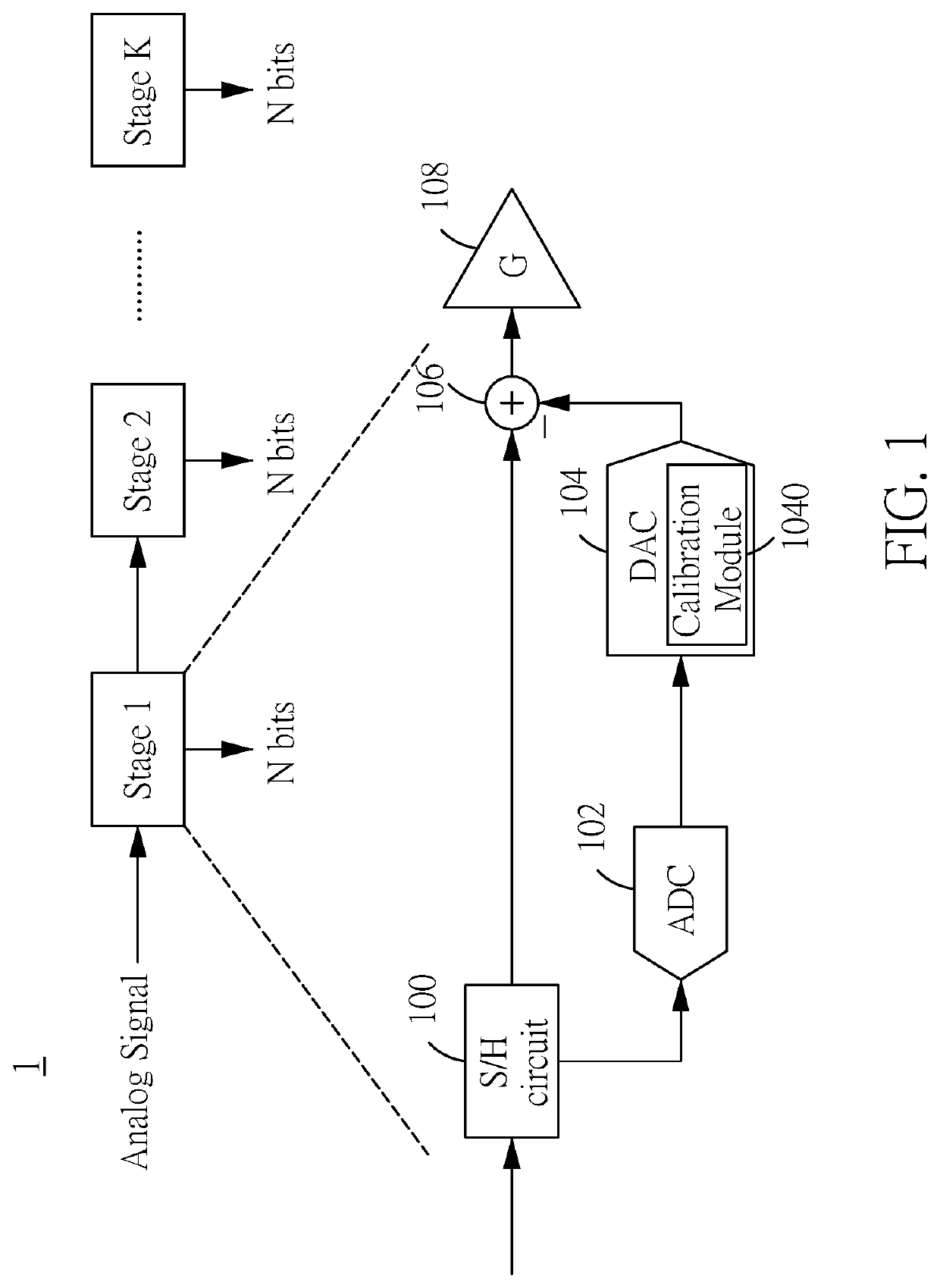

Gain calibration device and method for residue amplifier of pipeline analog to digital converter

ActiveUS10826516B2Improve linearityUneven distributionElectric signal transmission systemsGain controlConvertersSoftware engineering

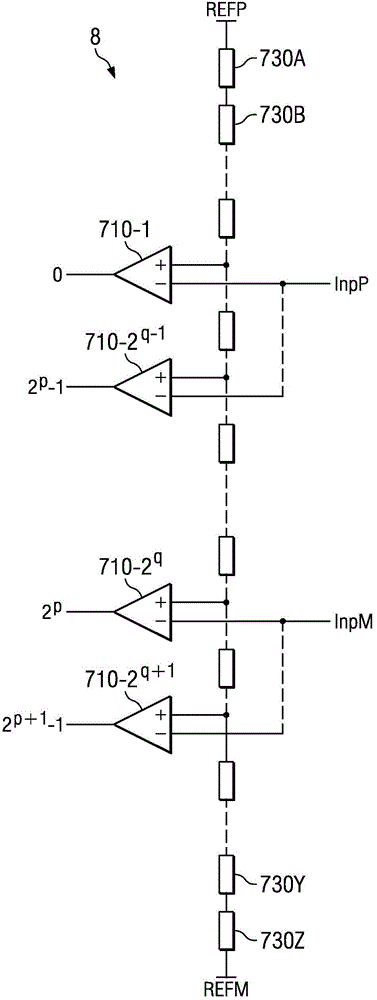

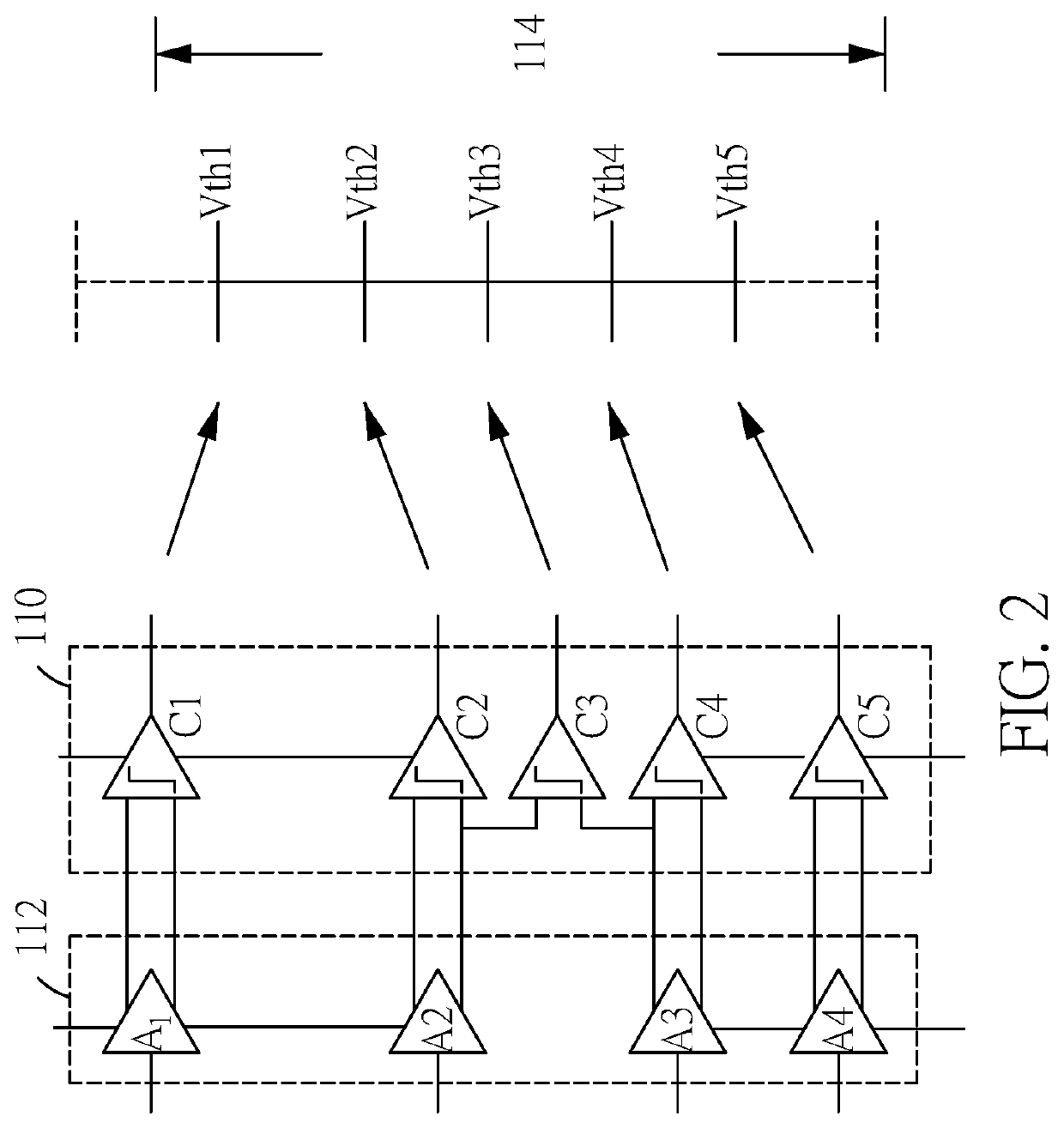

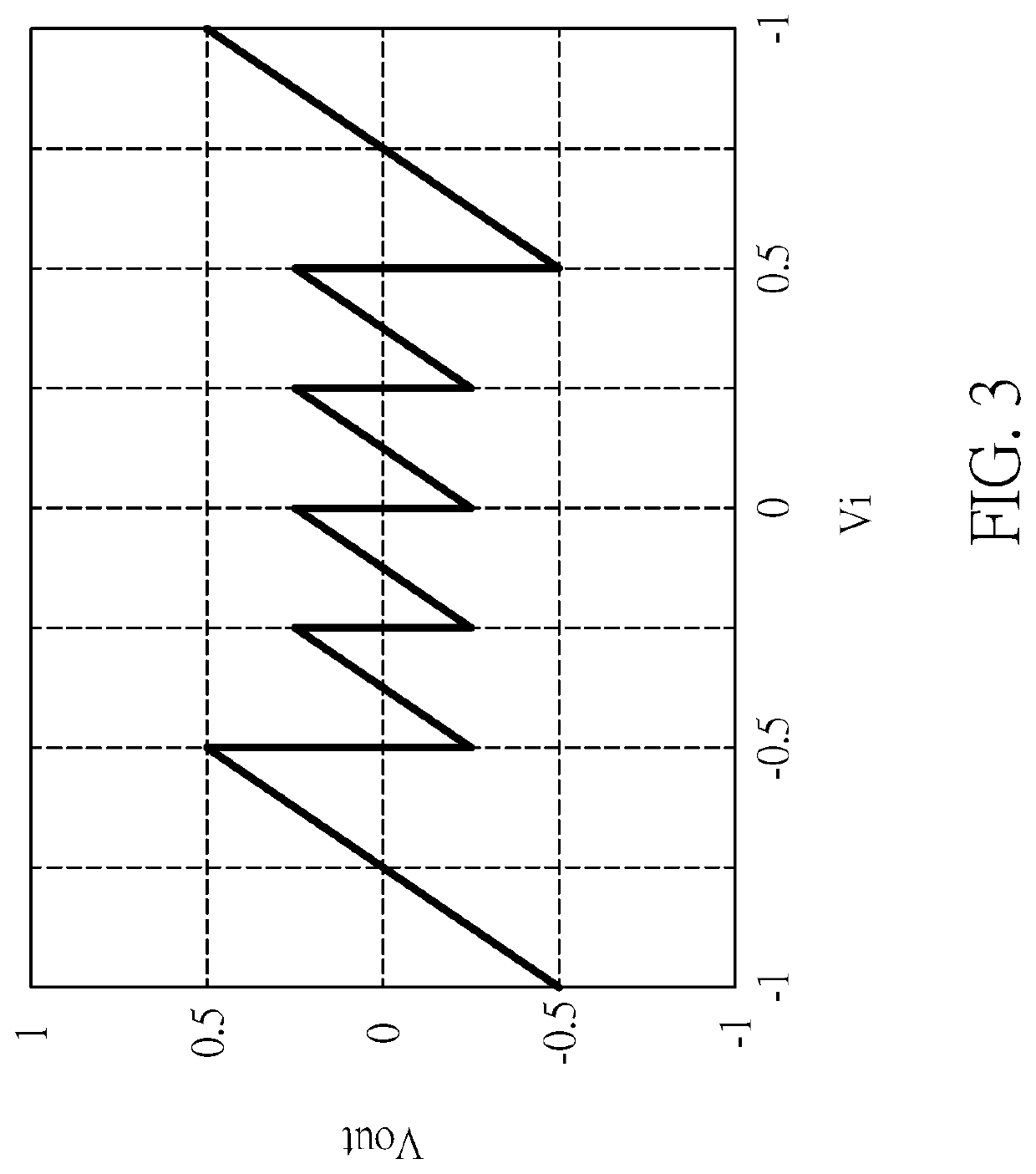

A gain calibration device for an ADC residue amplifier includes a DAC and a flash ADC. The DAC is configured to convert the digital signal to an analog signal, and the DAC includes a calibration module used in the gain calibration of the ADC residual amplifier. The flash ADC is configured to generate a digital signal, the flash ADC includes a plurality of comparators, the total number of the plurality of comparators is equal to the number of output bits of the flash ADC, and the comparators are configured to be unevenly distributed in an input range.

Owner:REALTEK SEMICON CORP