Patents

Literature

31 results about "Digital error correction" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

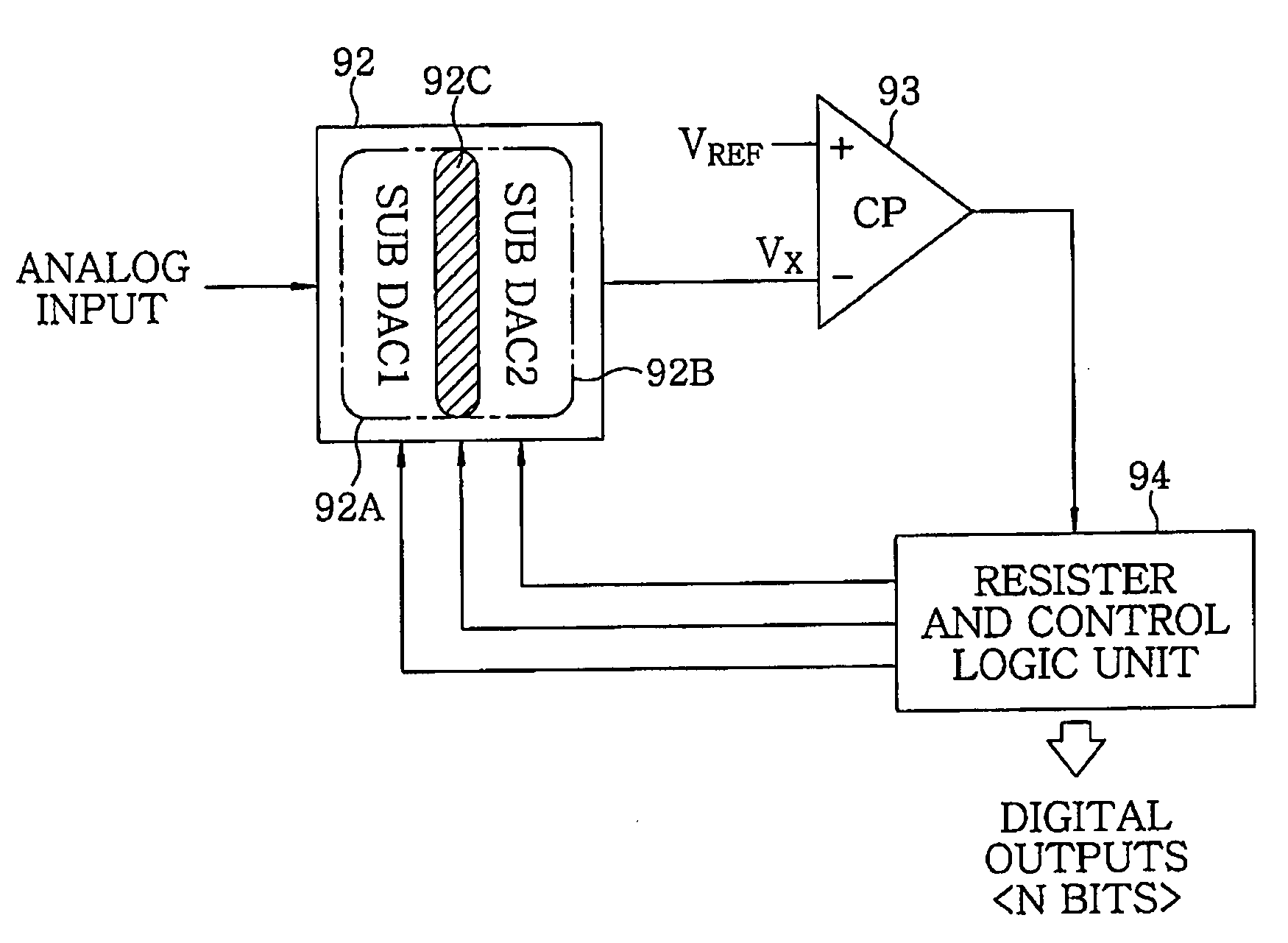

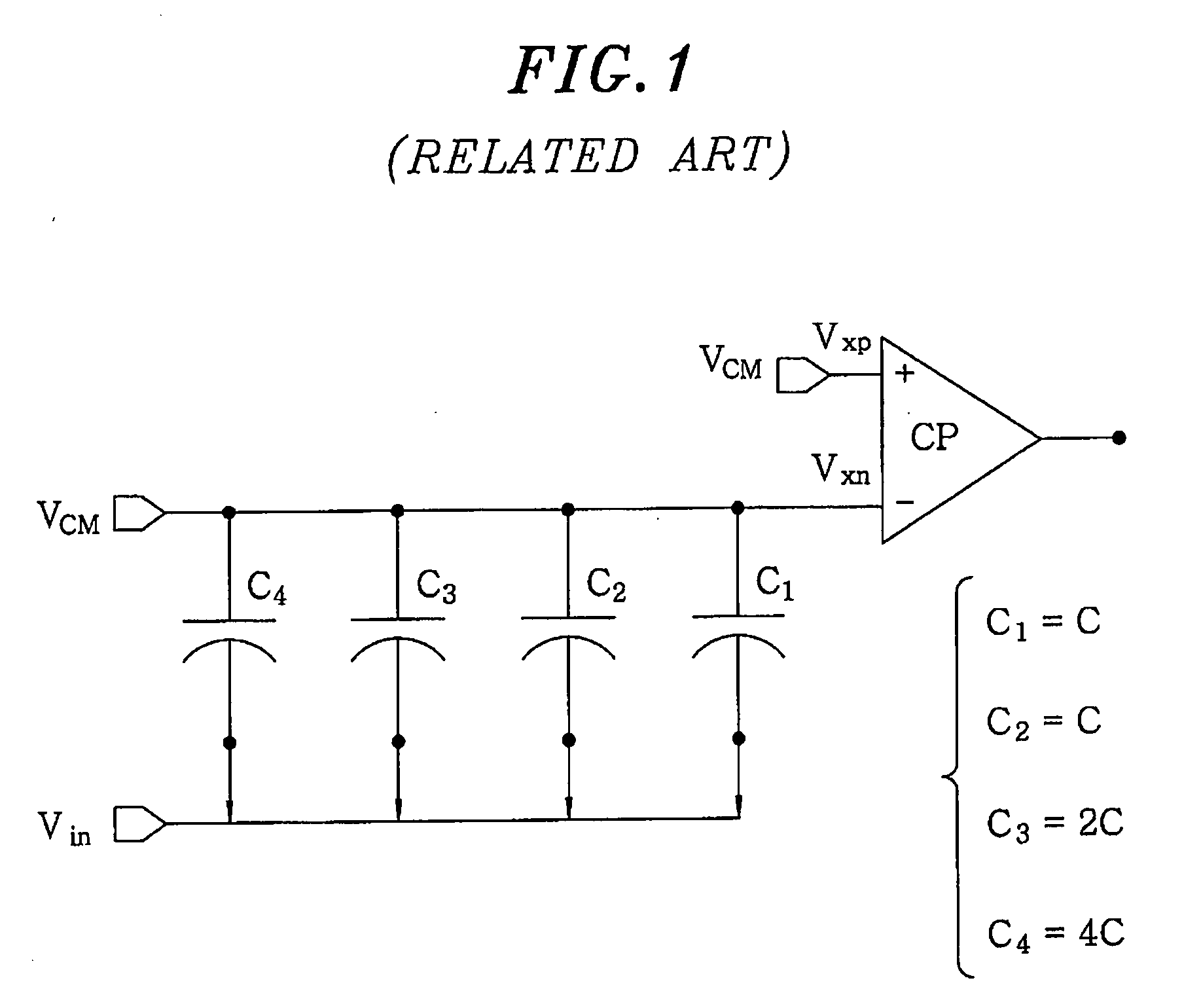

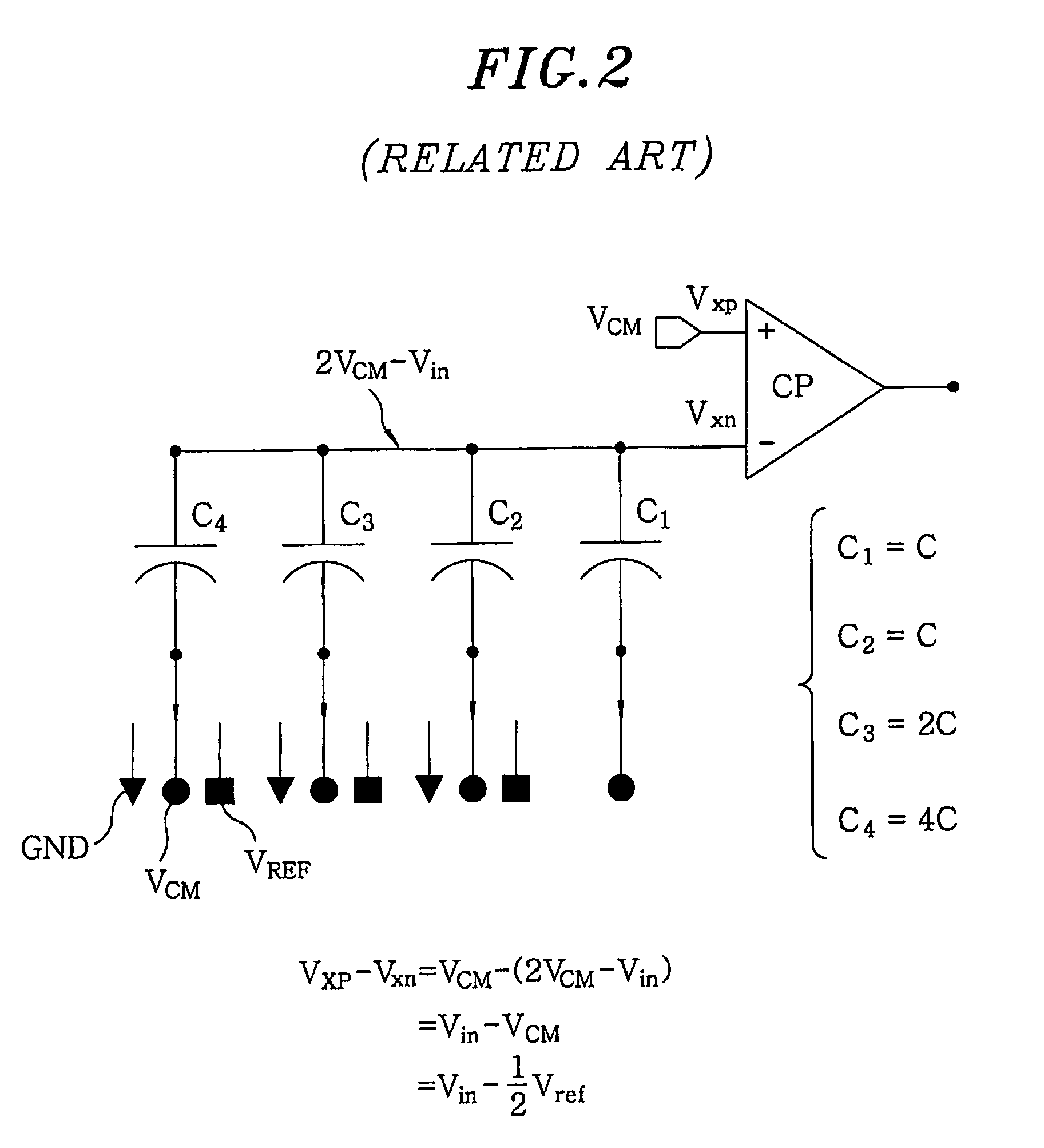

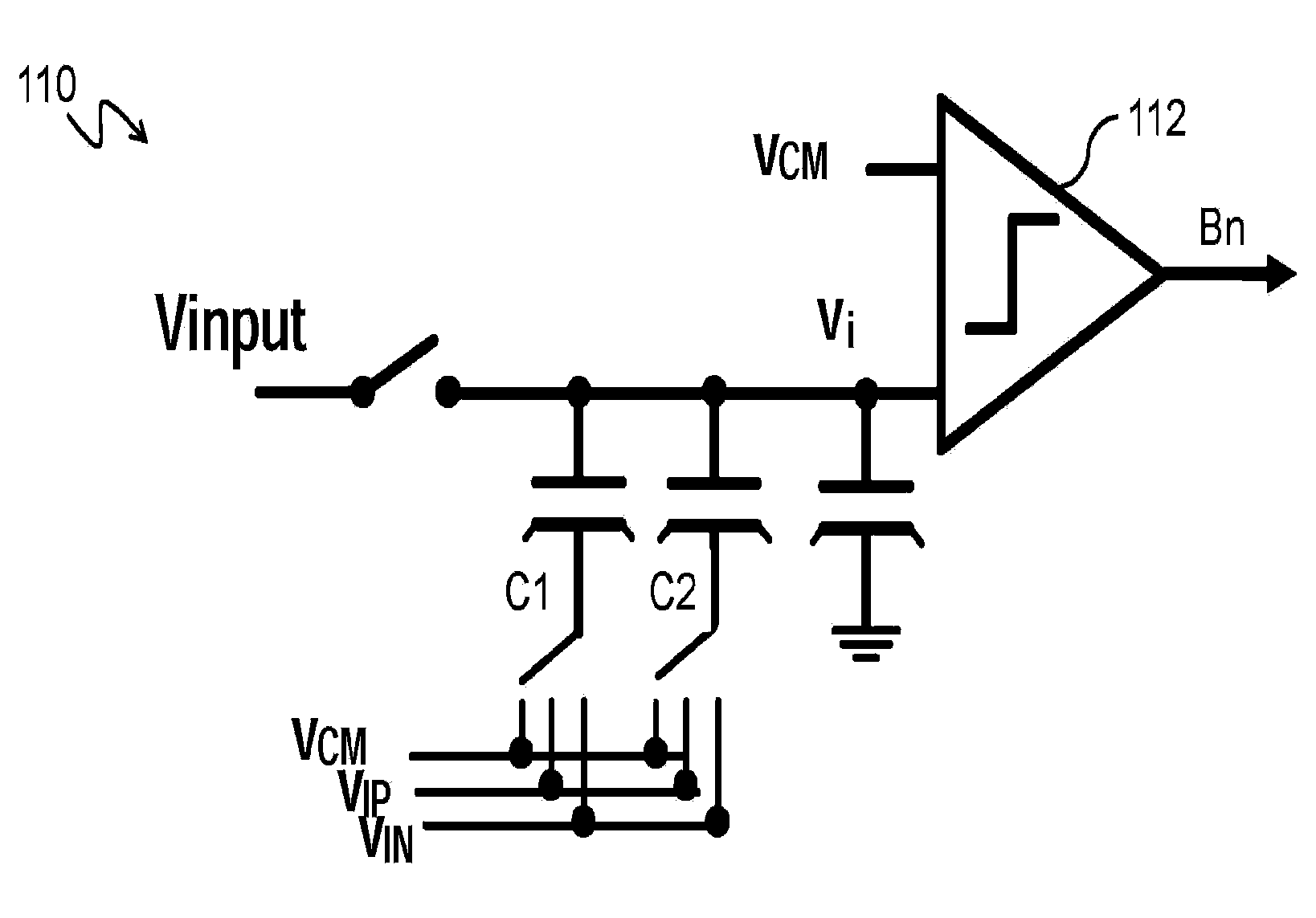

Method and apparatus for digital error correction for binary successive approximation ADC

ActiveUS20100109924A1Electric signal transmission systemsAnalogue-digital convertersDigital analog converterProcessor register

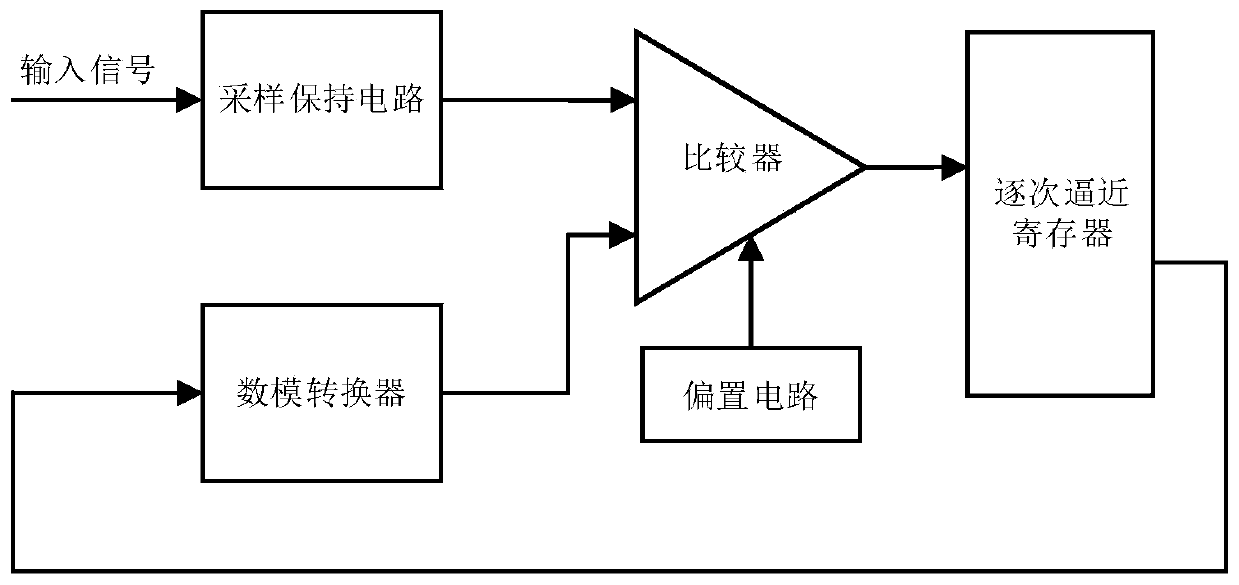

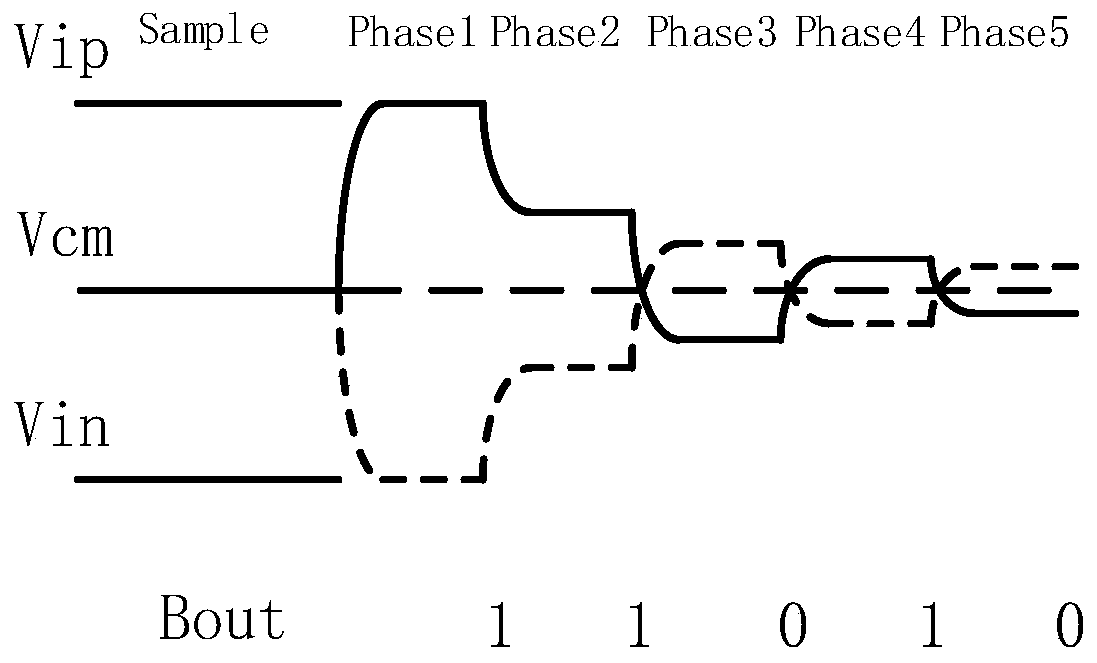

An apparatus for digital error correction in a successive approximation (SAR) analog to digital converter (ADC) includes a binary weighted digital to analog converter (DAC) which can be virtually divided into multiple sub-DACs for redundancy insertion; and a comparator configured to compare the analog input with a DAC level corresponding to digital. The apparatus further includes a register and control logic unit configured to control a switching operation for DAC and to add output codes obtained from sub-DACs to output the added code as a final A / D converted code.

Owner:KOREA ADVANCED INST OF SCI & TECH

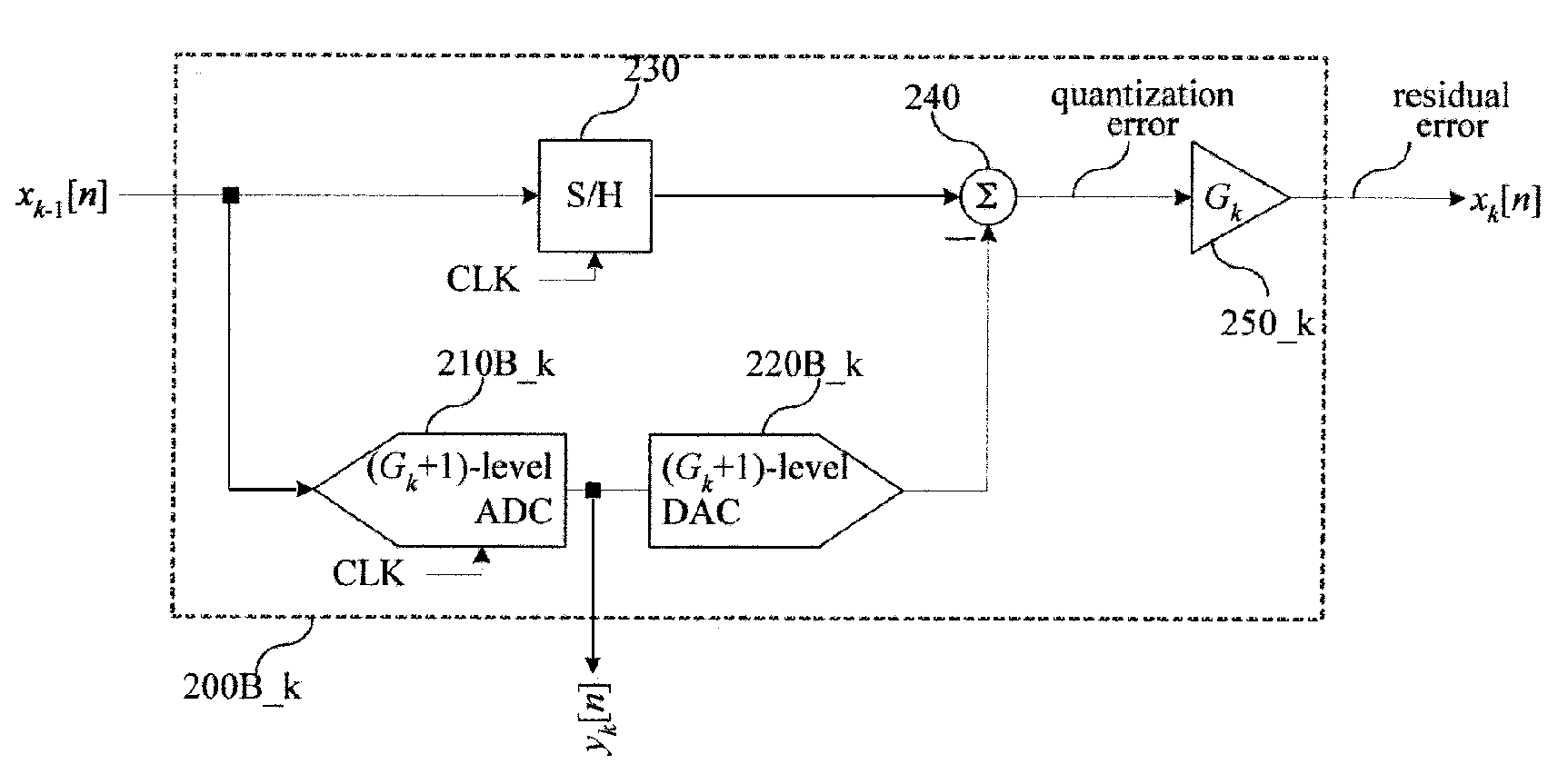

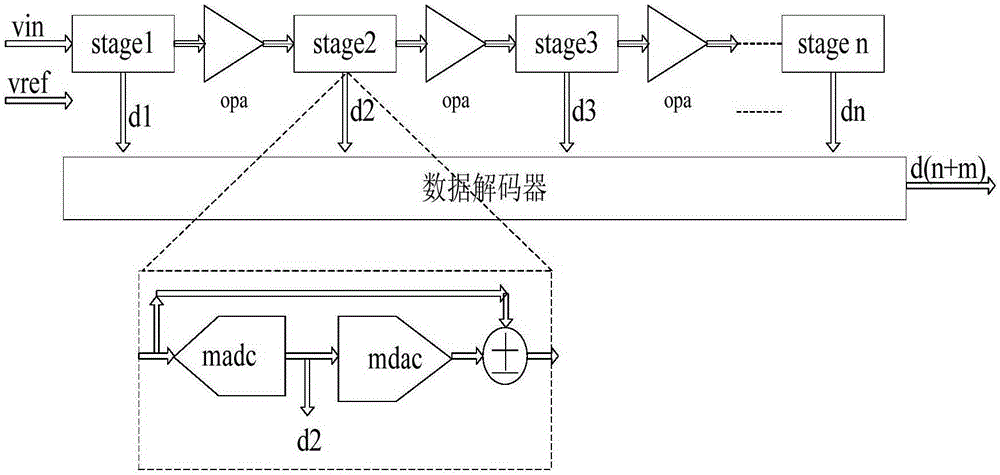

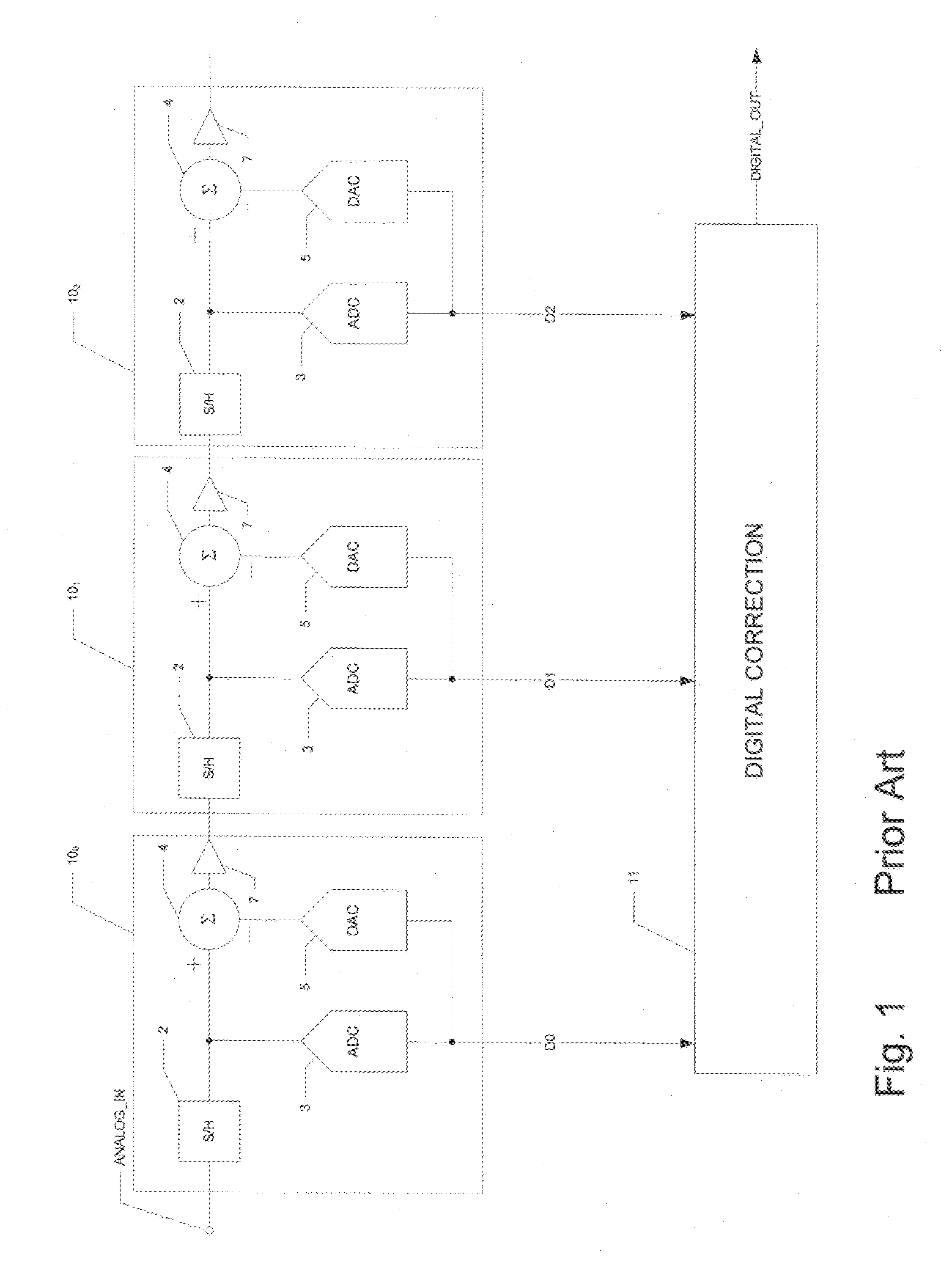

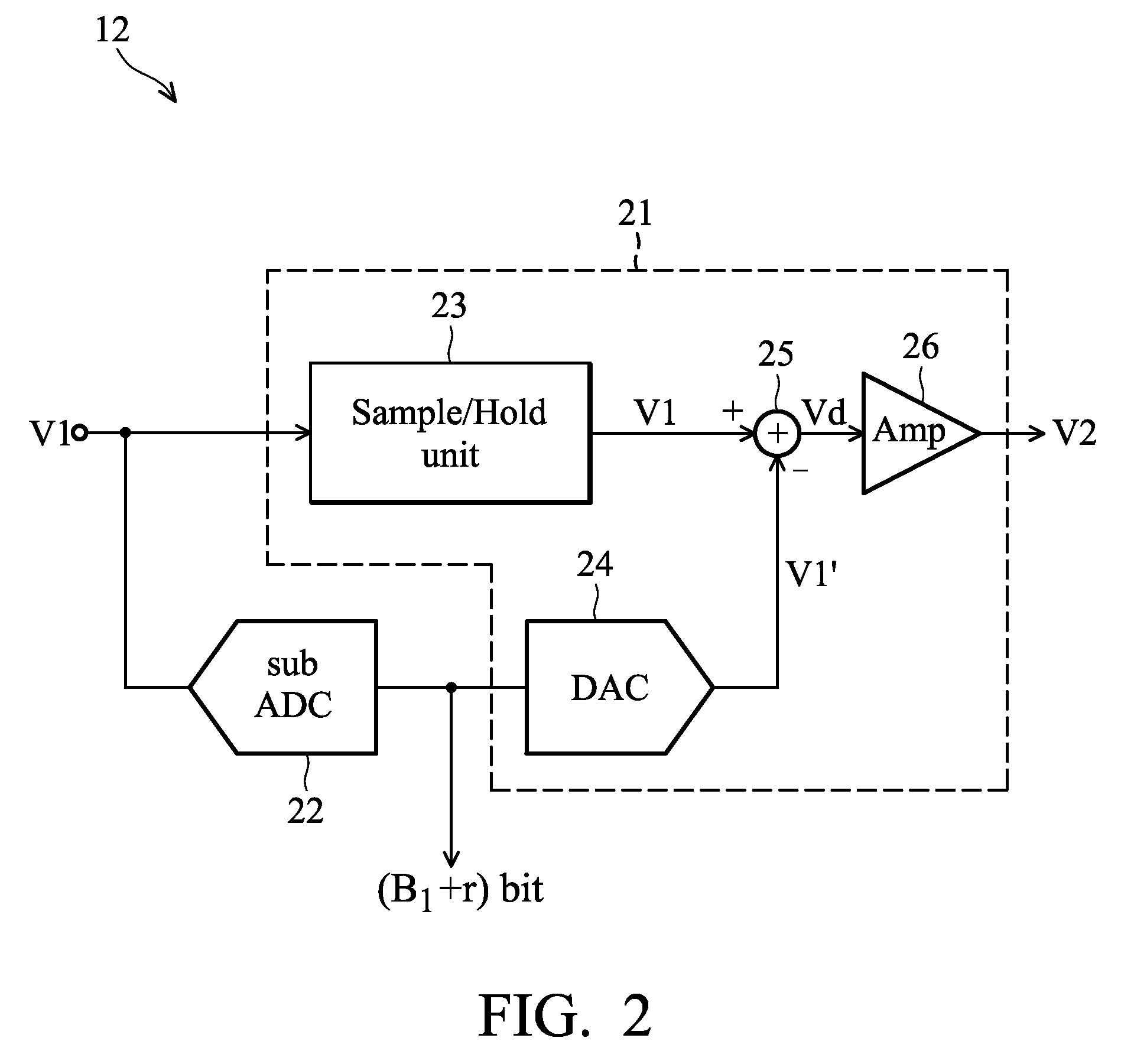

Pipeline ADC with minimum overhead digital error correction

ActiveUS7280064B2Electric signal transmission systemsAnalogue-digital convertersComputer scienceDigital error correction

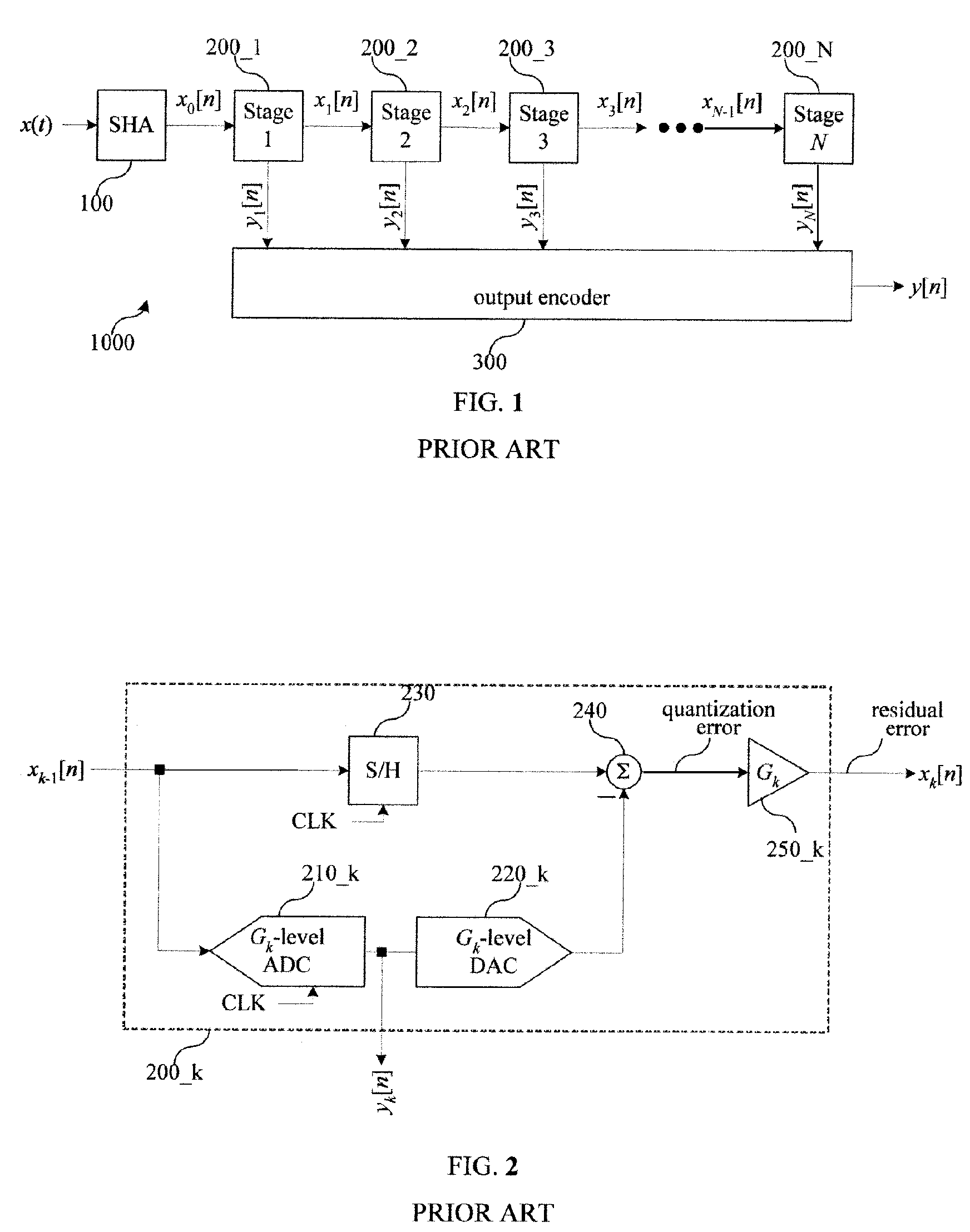

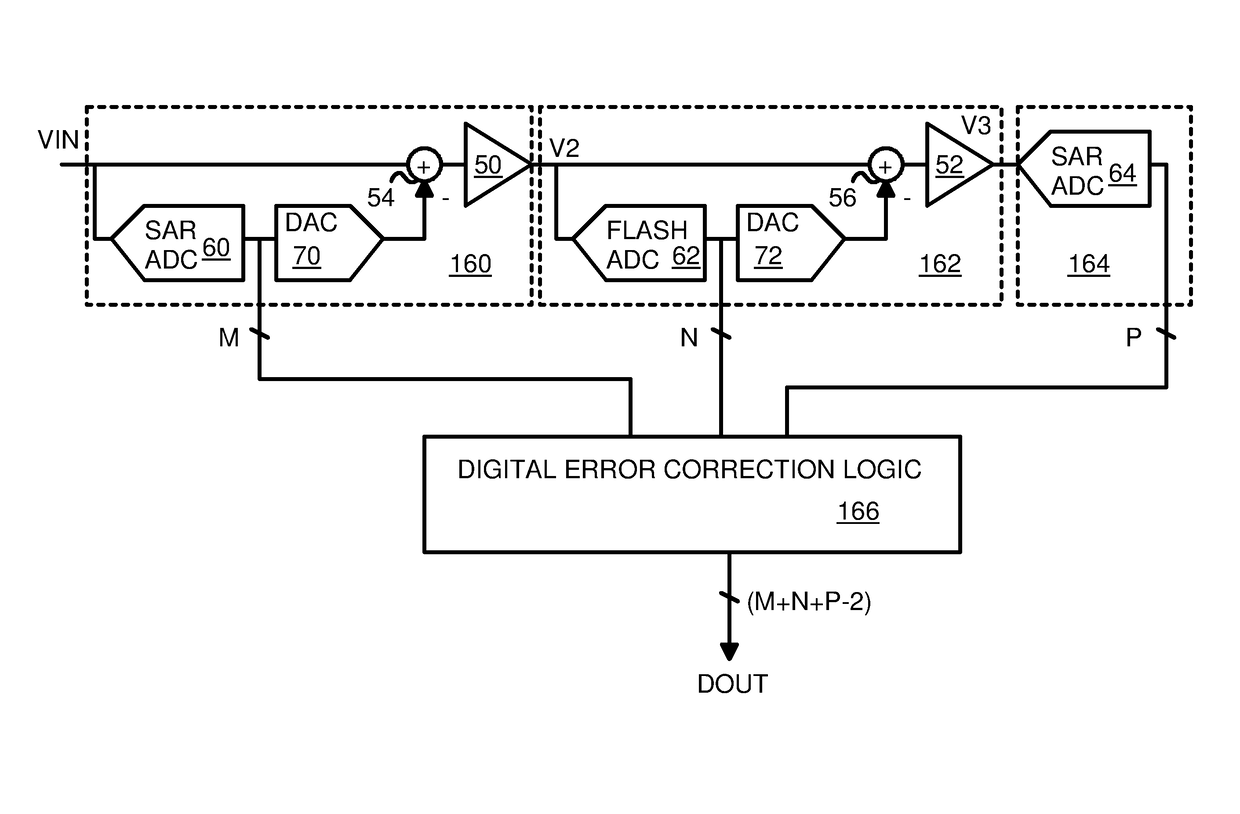

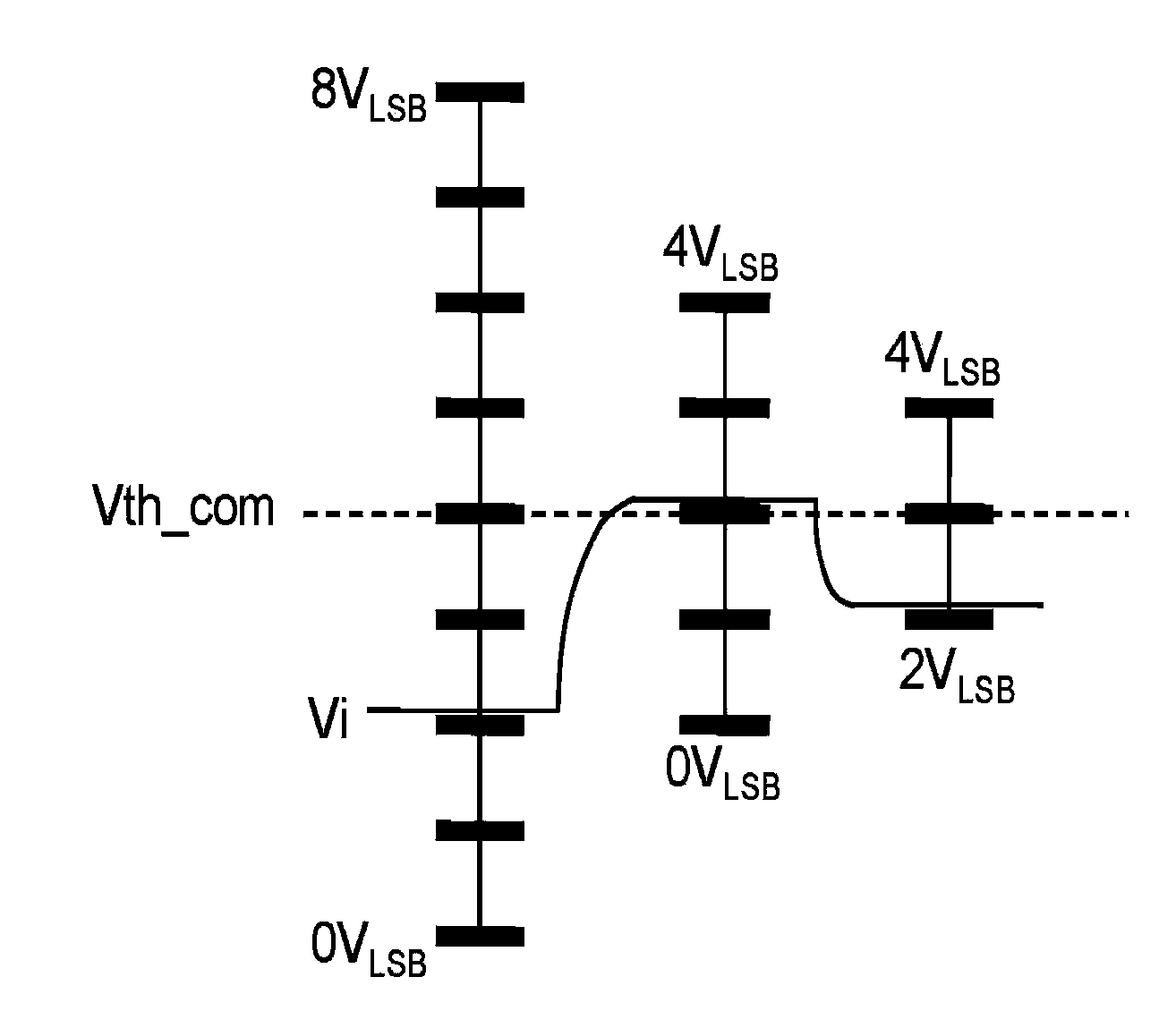

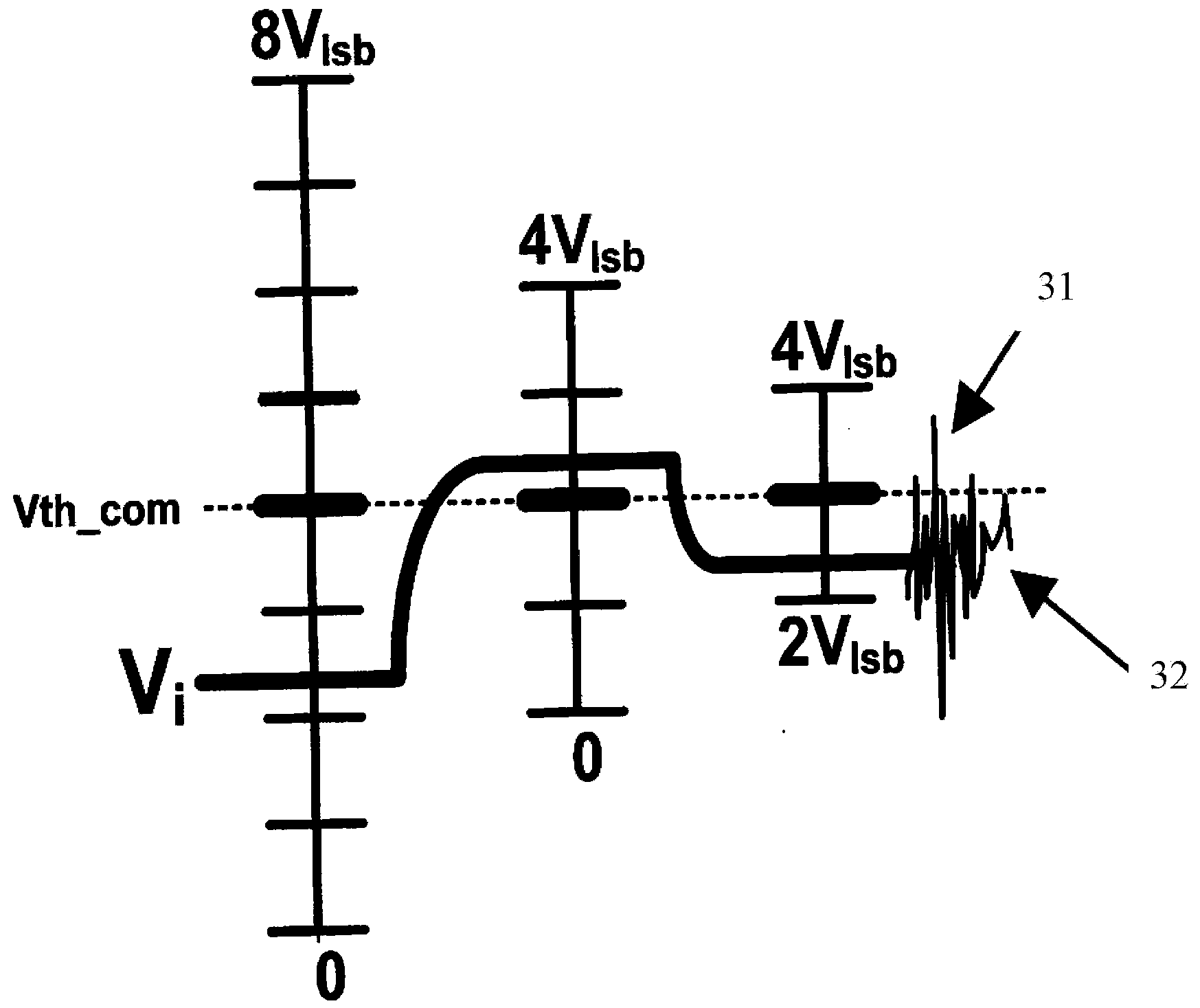

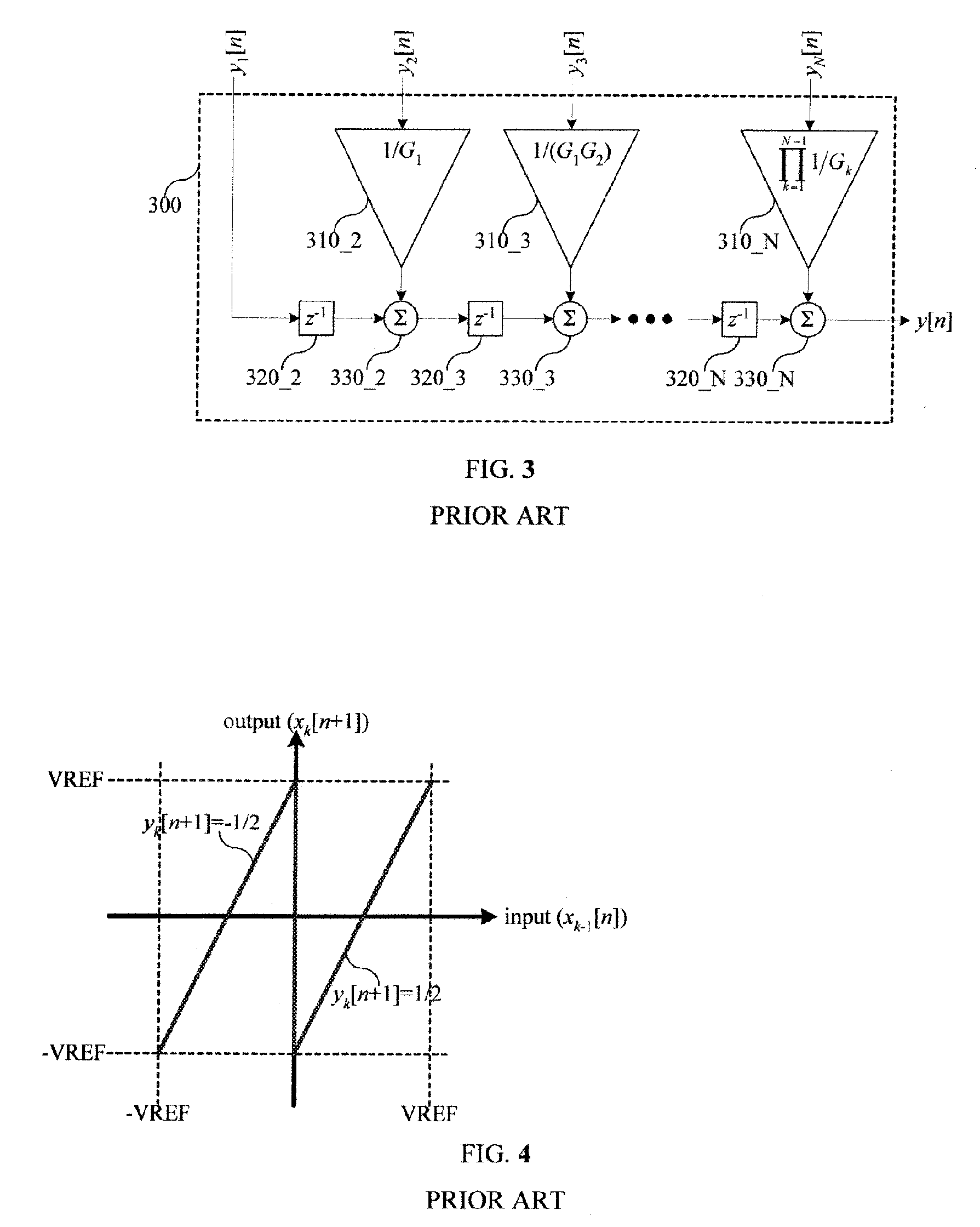

The most hardware efficient way to implement an N-stage pipeline ADC is to use (G+1)-level ADC-DAC for its first (N−1) stages and use (2·G−1)-level ADC for the last stage, where G is the inter-stage gain. For the fist (N−1) stages using (G+1)-level ADC-DAC, the (G+1) levels are uniformly distributed between −(G−1) / G and (G−1) / G; inclusively. The spacing between two adjacent levels is 2(G−1) / G2. For the last stage using (2·G−1)-level ADC, the (2·G−1)-levels are uniformly distributed between −(G−1) / G and (G−1) / G, inclusively. The spacing between two adjacent levels is 1 / G.

Owner:REALTEK SEMICON CORP

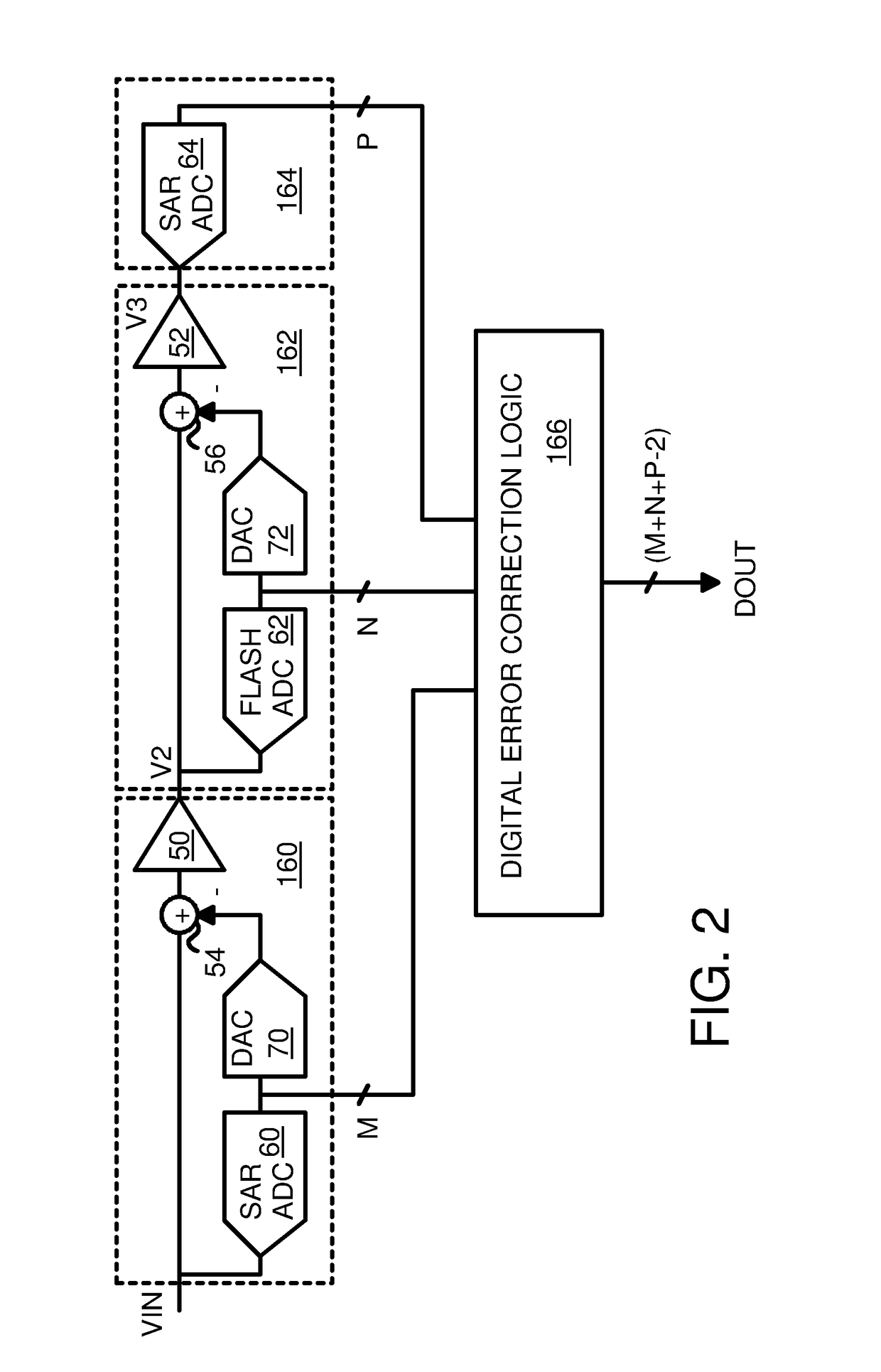

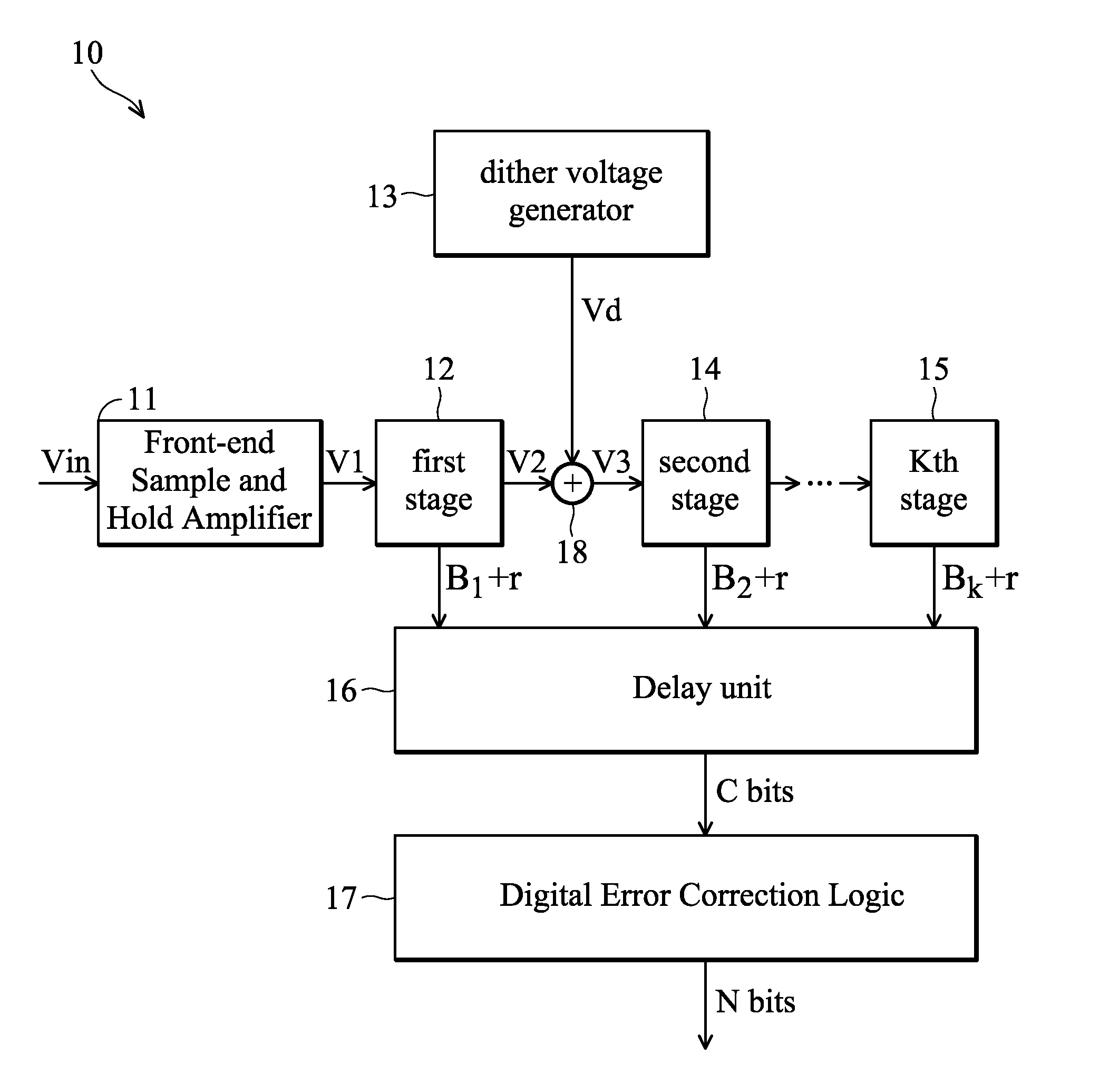

Multi-stage hybrid analog-to-digital converter

ActiveUS10103742B1Electric signal transmission systemsAnalogue-digital convertersAudio power amplifierLeast significant bit

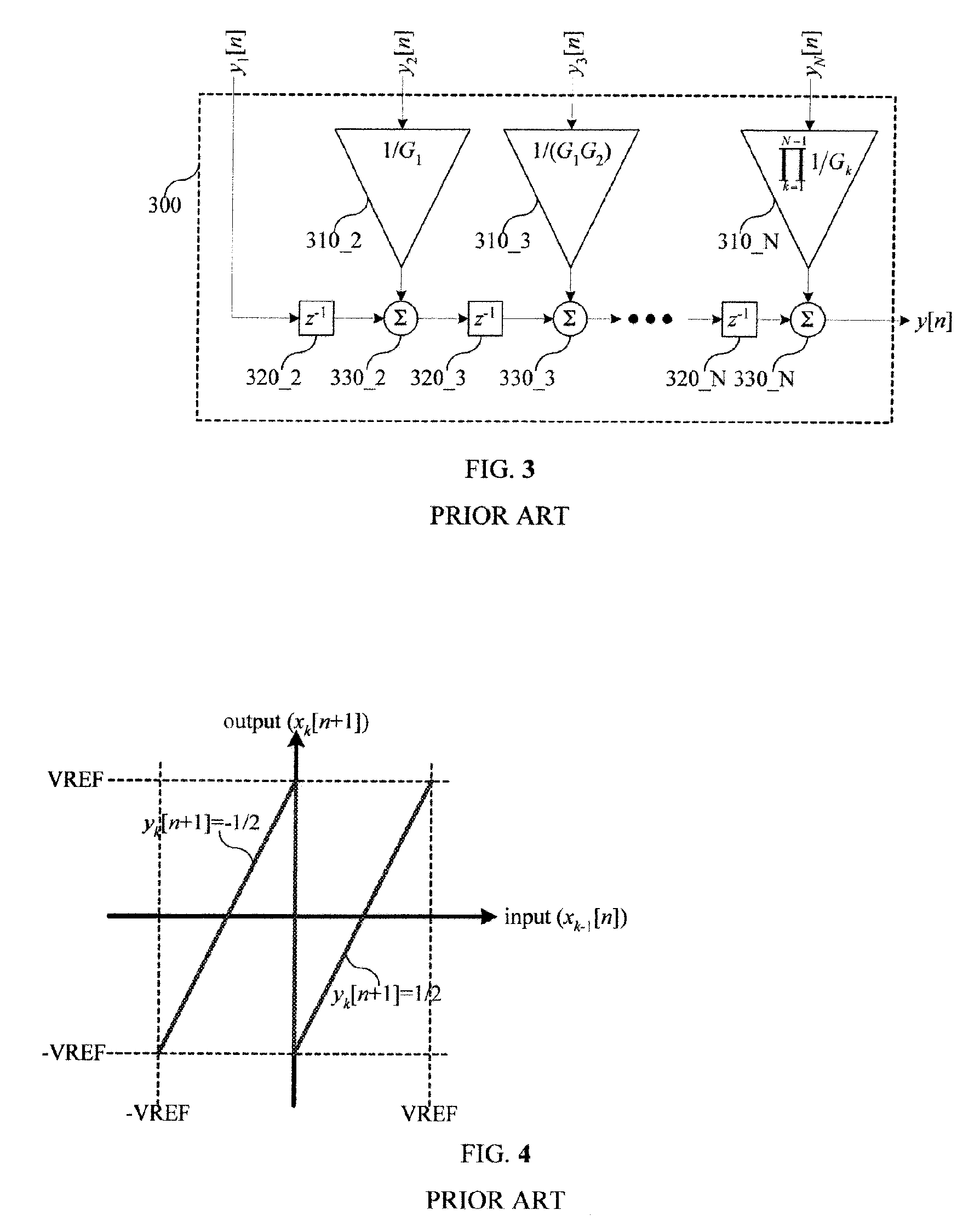

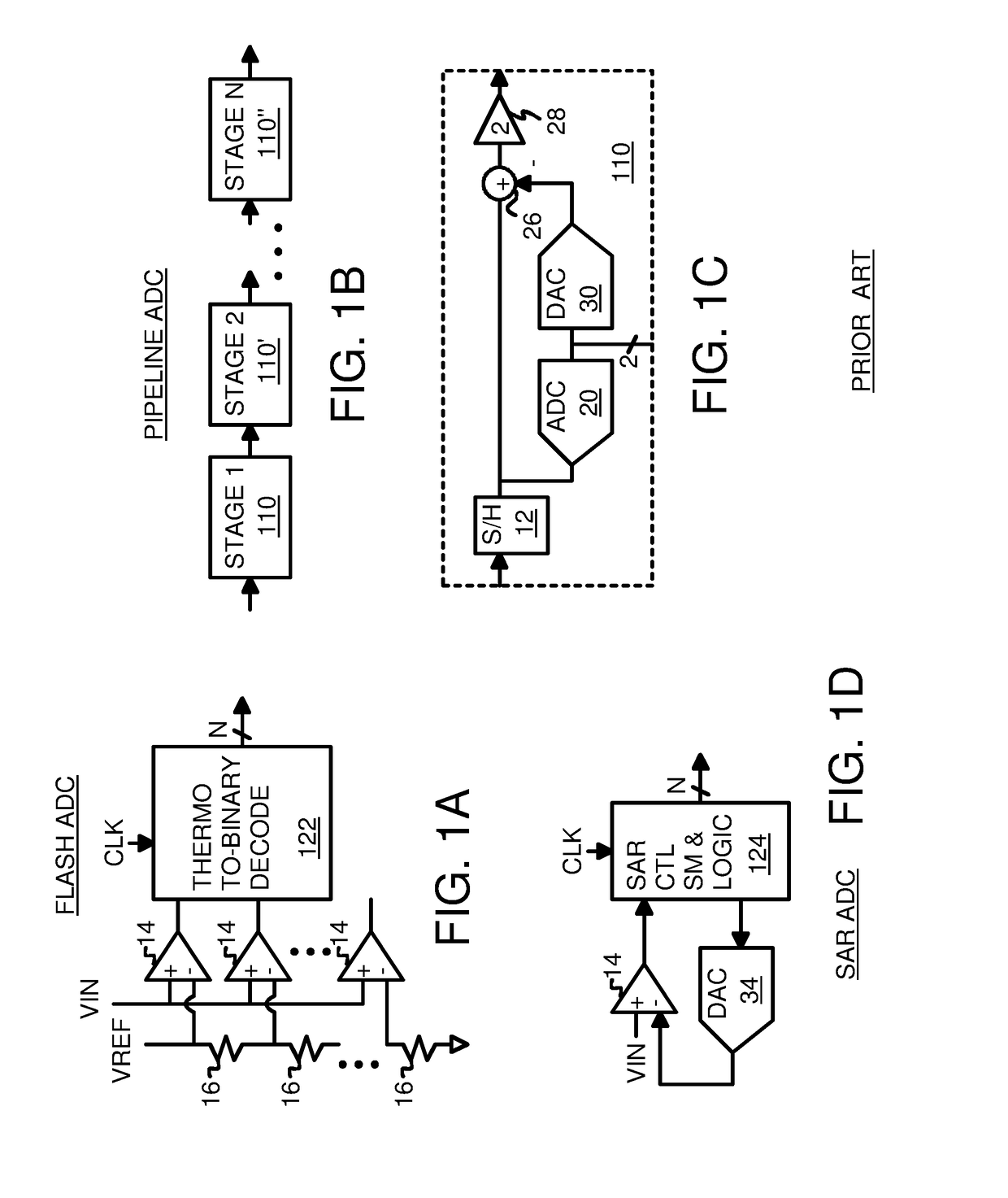

A hybrid Analog-to-Digital Converter (ADC) has multiple stages. A first stage and a final stage each use a Successive-Approximation Register (SAR) ADC to generate the Most-Significant-Bits (MSBs) and the Least-Significant-Bits (LSBs) over successive internal cycles. Middle stage(s) use a faster flash ADC with multiple comparators in parallel to generate the middle binary bits, which are then re-converted by a Digital-to-Analog Converter (DAC) and subtracted from the stage's input analog voltage to generate a difference that is amplified by a residual amplifier that outputs an amplified voltage to the next stage. The first stage also has this multiplying DAC structure to convert the MSBs to an amplified voltage to the first of the middle stages. Finally, digital error correction logic removes redundant binary bits between stages. Initial and final SAR stages of 4 and 8 bits with a 4-bit middle stage provide a hybrid ADC of 14-bit precision.

Owner:HONG KONG APPLIED SCI & TECH RES INST

Anti-noise successive approximation analog to digital conversion method

InactiveUS8749412B1Successful methodElectric signal transmission systemsPhysical parameters compensation/preventionAnalog feedbackEngineering

An anti-noise successive approximation analog to digital conversion method is provided with the steps of instructing a comparison control circuit to perform a predetermined number of extra comparison cycles in a plurality of valid bit cycles and outputting a plurality of digital signals wherein no digital to analog feedback is perform; instructing a digital error correction circuit to correct any digital signals having erroneous bits due to noise interference in the outputted digital signals and output a bit or byte as a result of the correction, the bit or byte being defined as a noise free digital output bit or byte; and performing a successive approximation analog to digital conversion based on the digital output bit or byte if there are any subsequent bit cycles.

Owner:TSAI JIN SHY

ADC with digital error correction

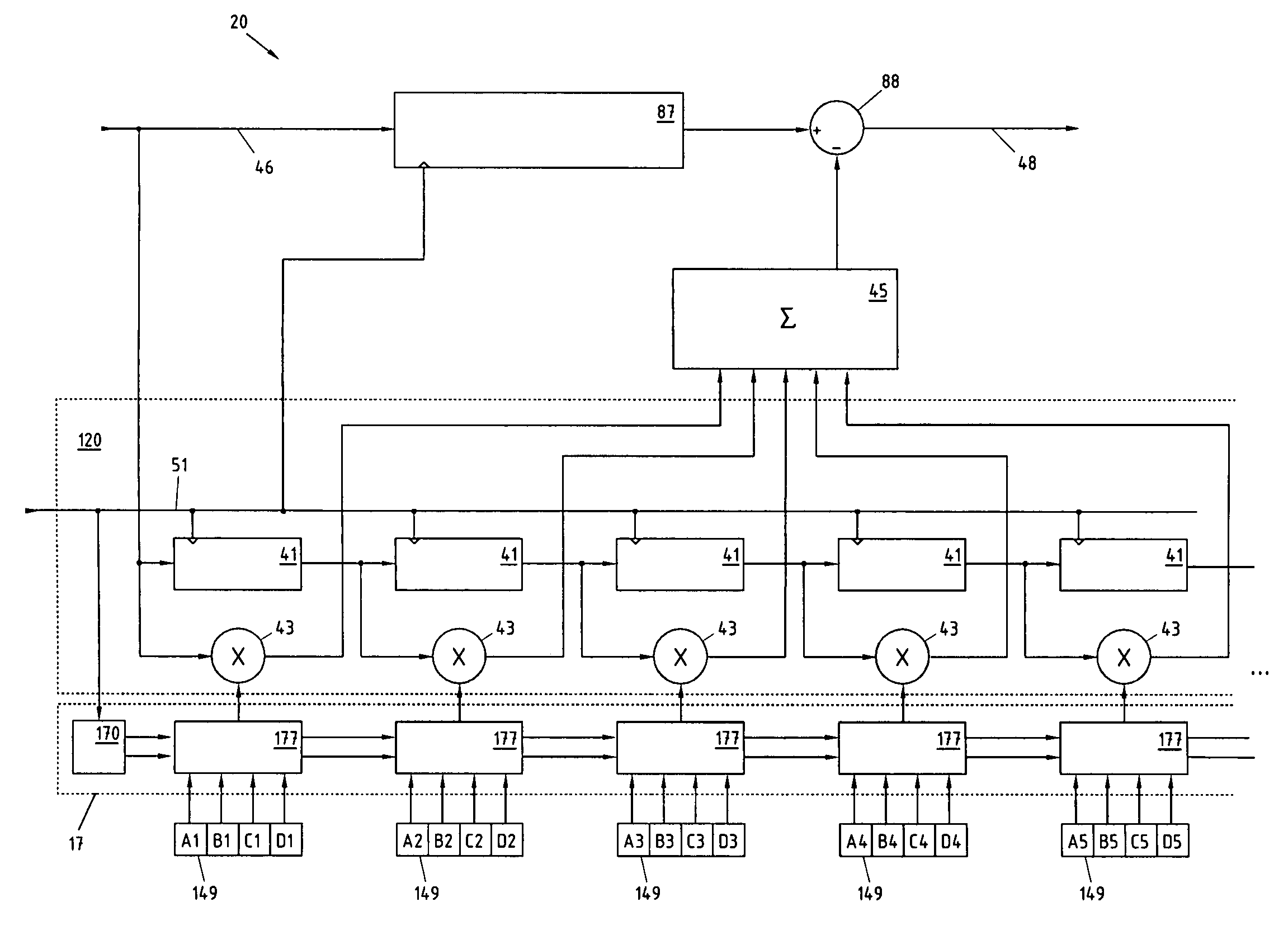

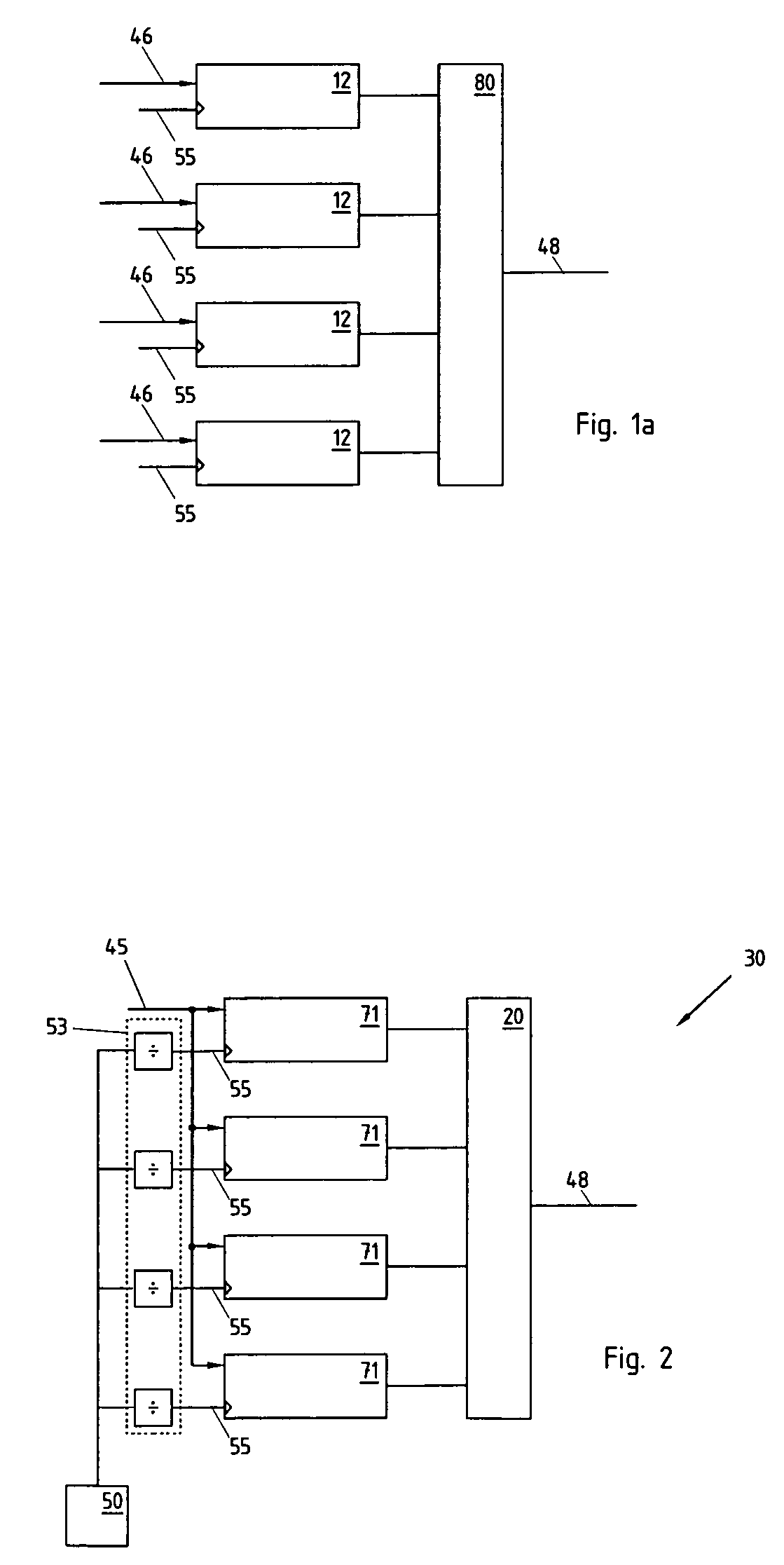

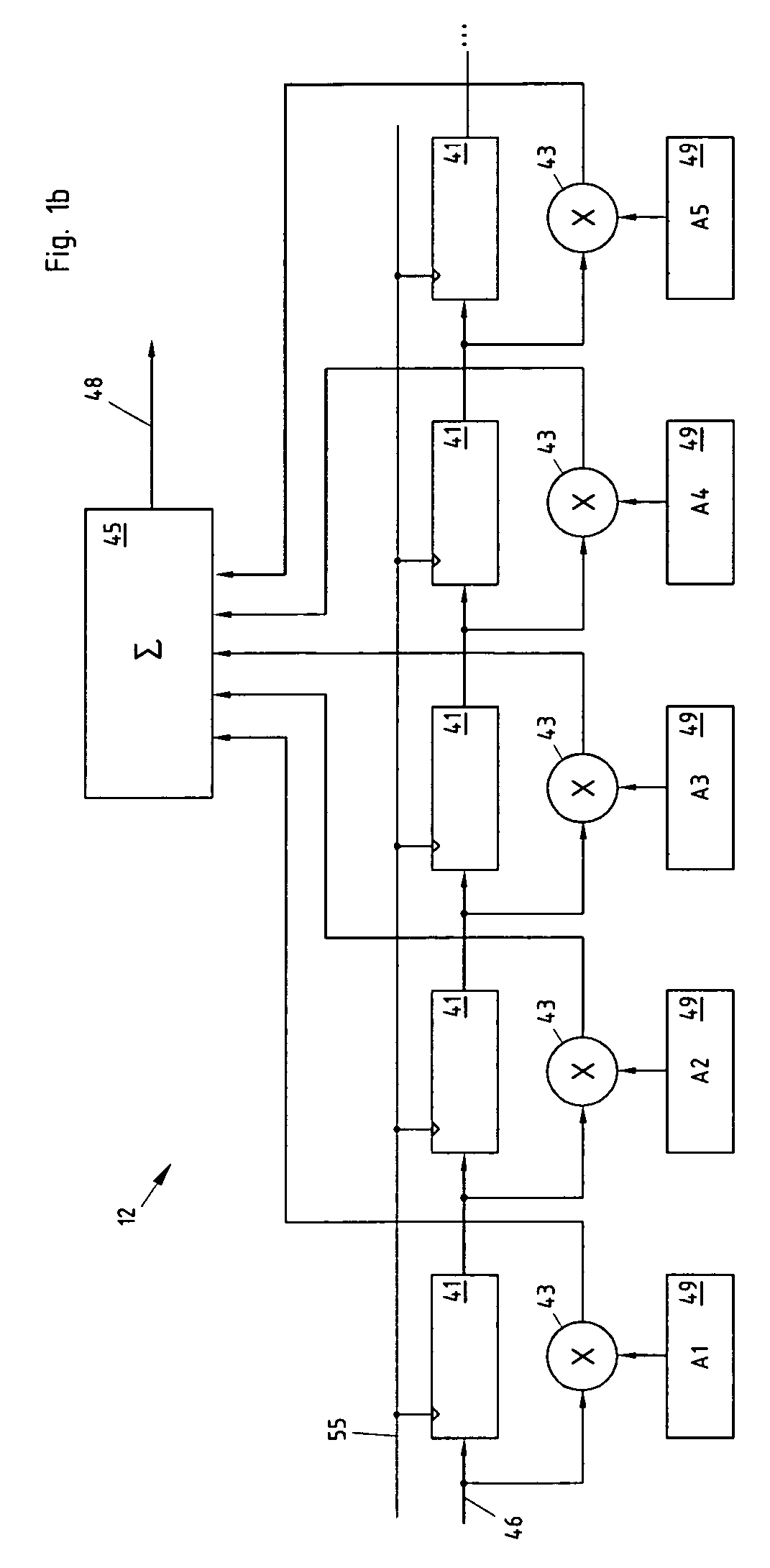

ActiveUS20050151679A1Electric signal transmission systemsDigital technique networkBinary multiplierA d converter

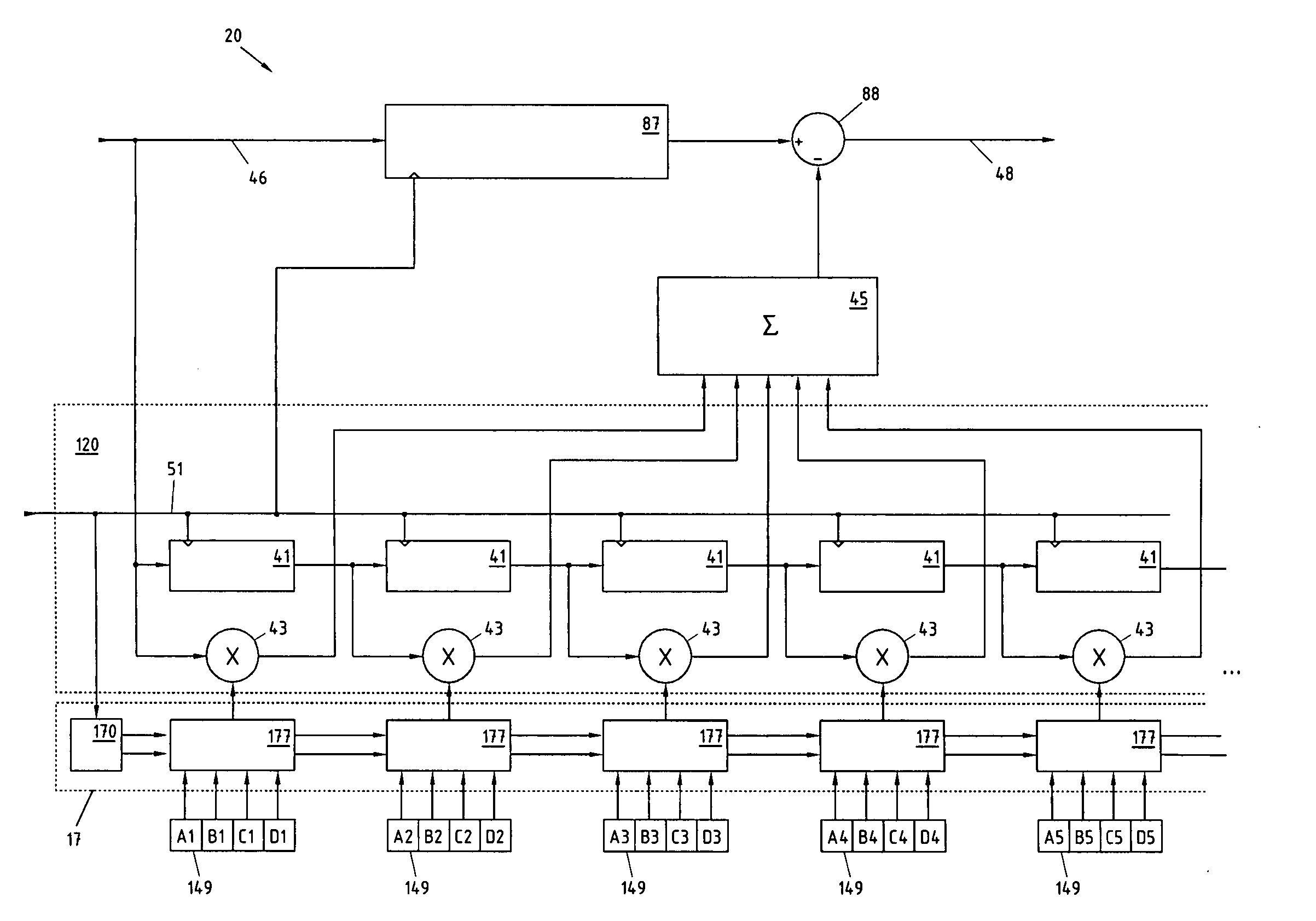

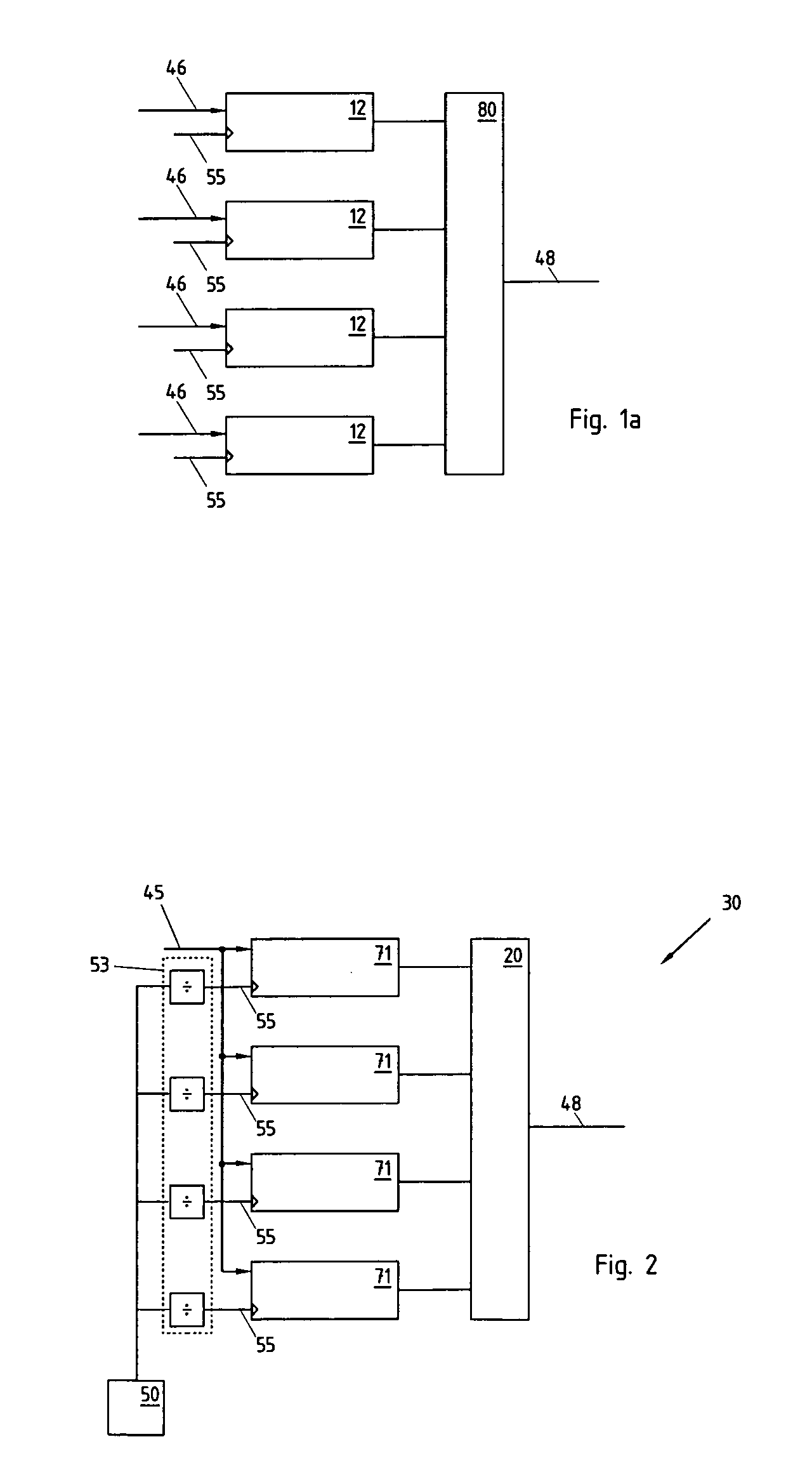

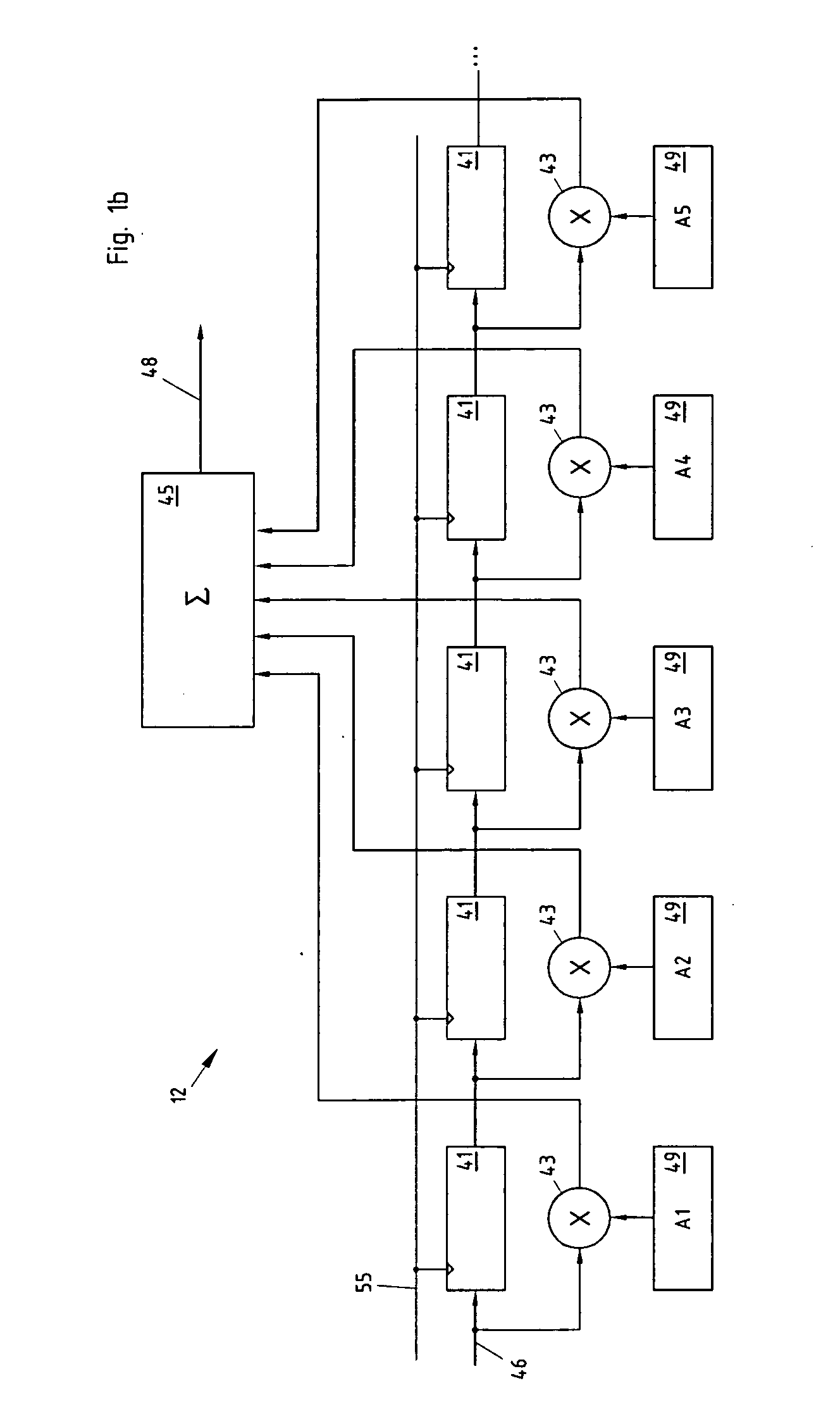

Interleaved Analogue to Digital converter, comprising a plurality of individual ADCs (71). A digital filter stage (20) is used for equalizing the responses of the individual ADCs, and comprises a FIR filter in which the coefficient table is cyclically reloaded between ADCs' samples, in order to reduce the number of multipliers required.

Owner:KEYSIGHT TECH

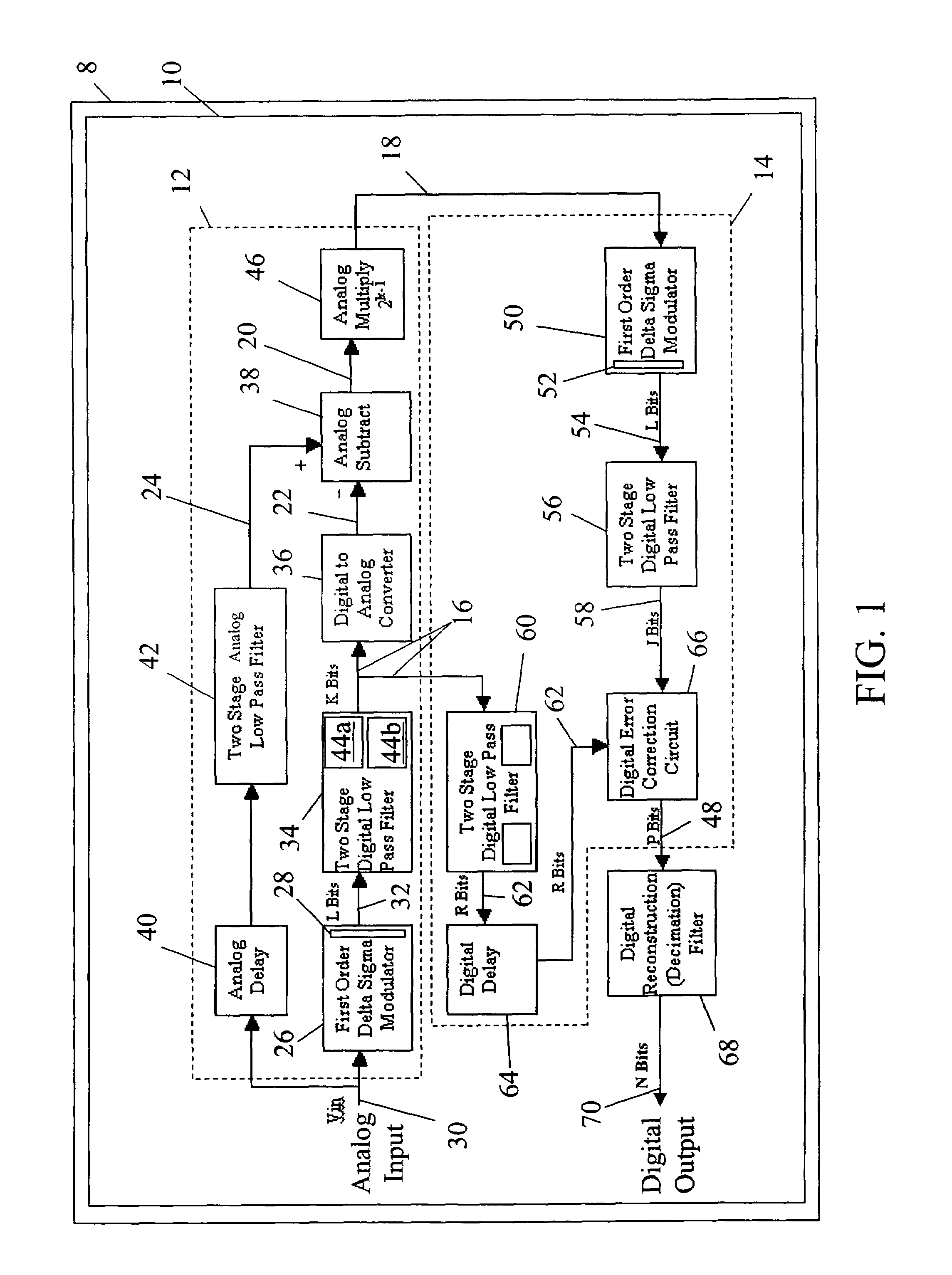

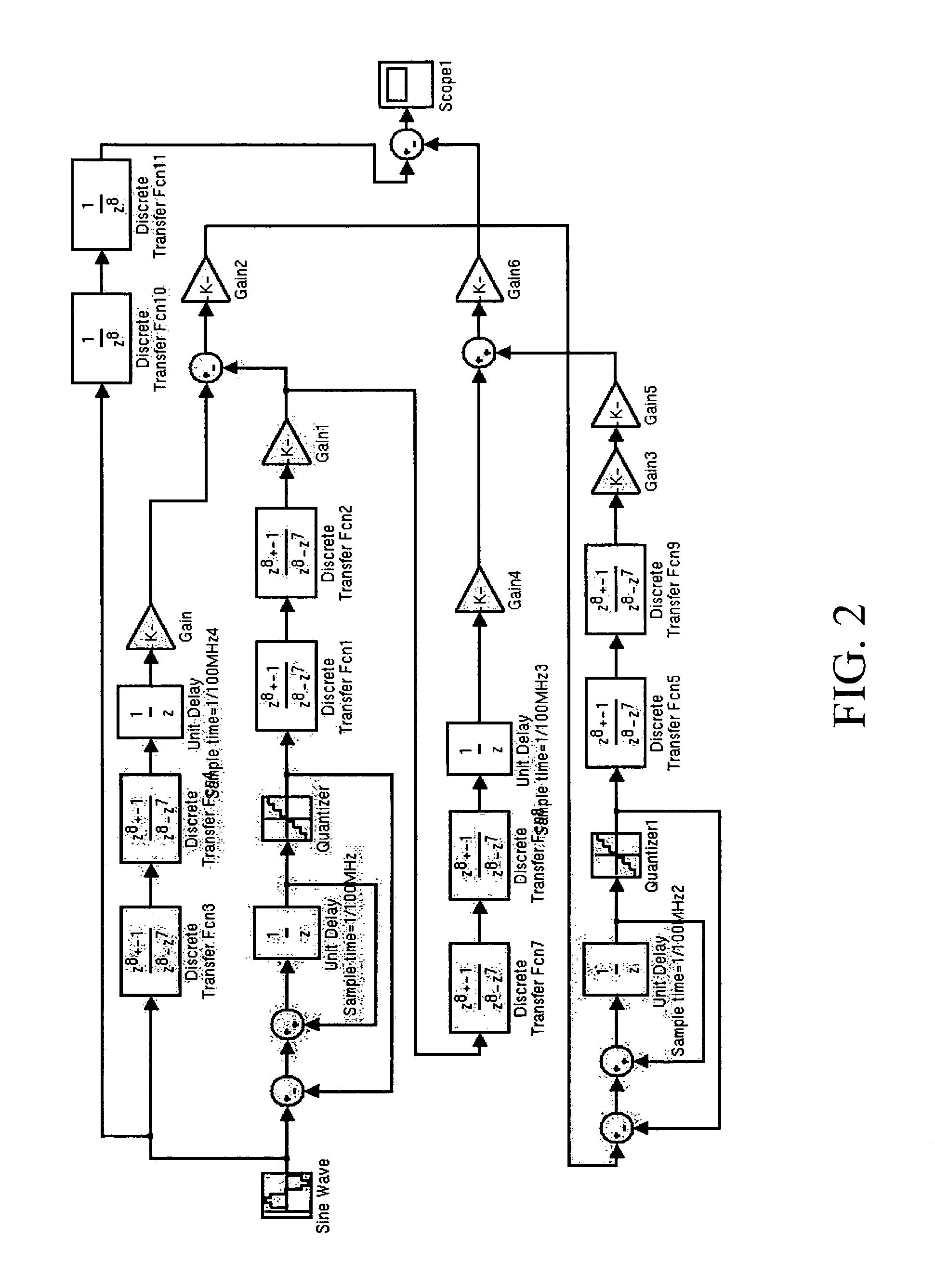

Pipelined delta sigma modulator analog to digital converter

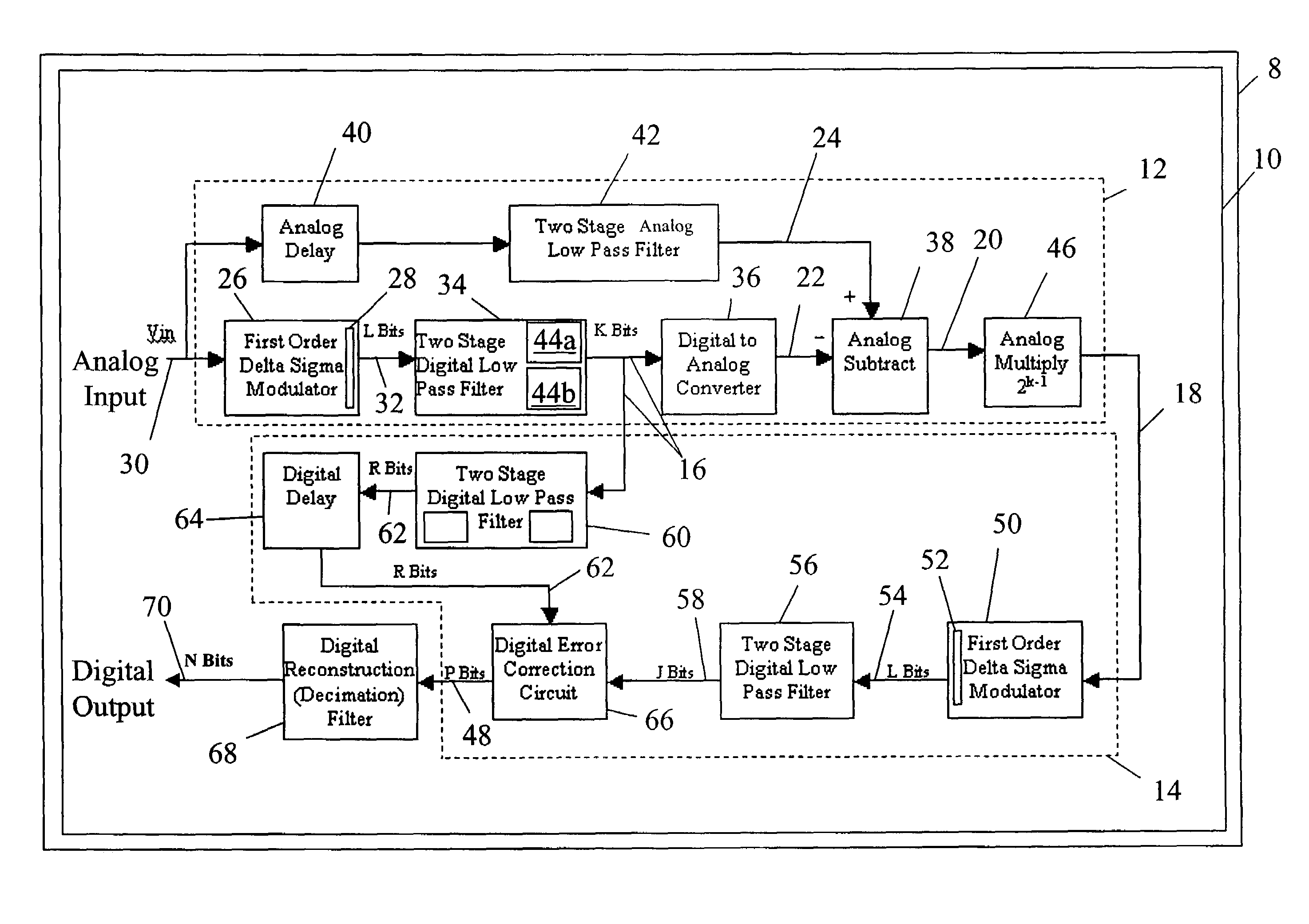

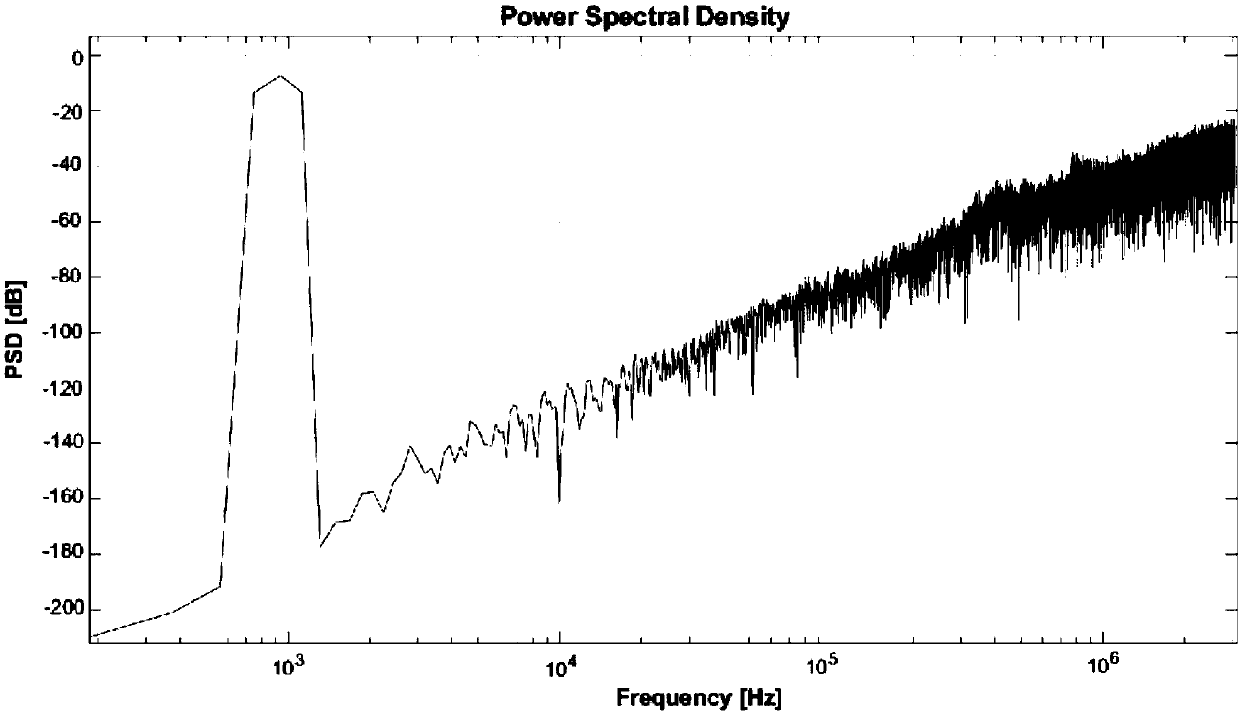

InactiveUS7034730B2Suitable performanceHigh resolution performanceElectric signal transmission systemsDelta modulationDigital down converterEngineering

A pipelined delta-sigma modulator (PDSM) analog to digital converter (ADC) architecture is disclosed where each stage of the pipelined ADC includes a delta sigma modulator with a digital low pass filter and a corresponding analog low pass filter that precisely matches the digital low pass filter. An error signal is generated at each stage based on the difference of the low pass filtered analog input and the low pass filtered digital output of the delta sigma modulator (after converting to an analog signal). The digital outputs of each stage are passed through the appropriate low pass filter stages so all digital signals have been subjected to the same filtering prior to combining in a digital error correction circuit. The present invention also uses a compensation filter to correct any errors in the pass band caused by the low pass filtering and to help reject unwanted noise outside the pass band.

Owner:WRIGHT STATE UNIVERSITY

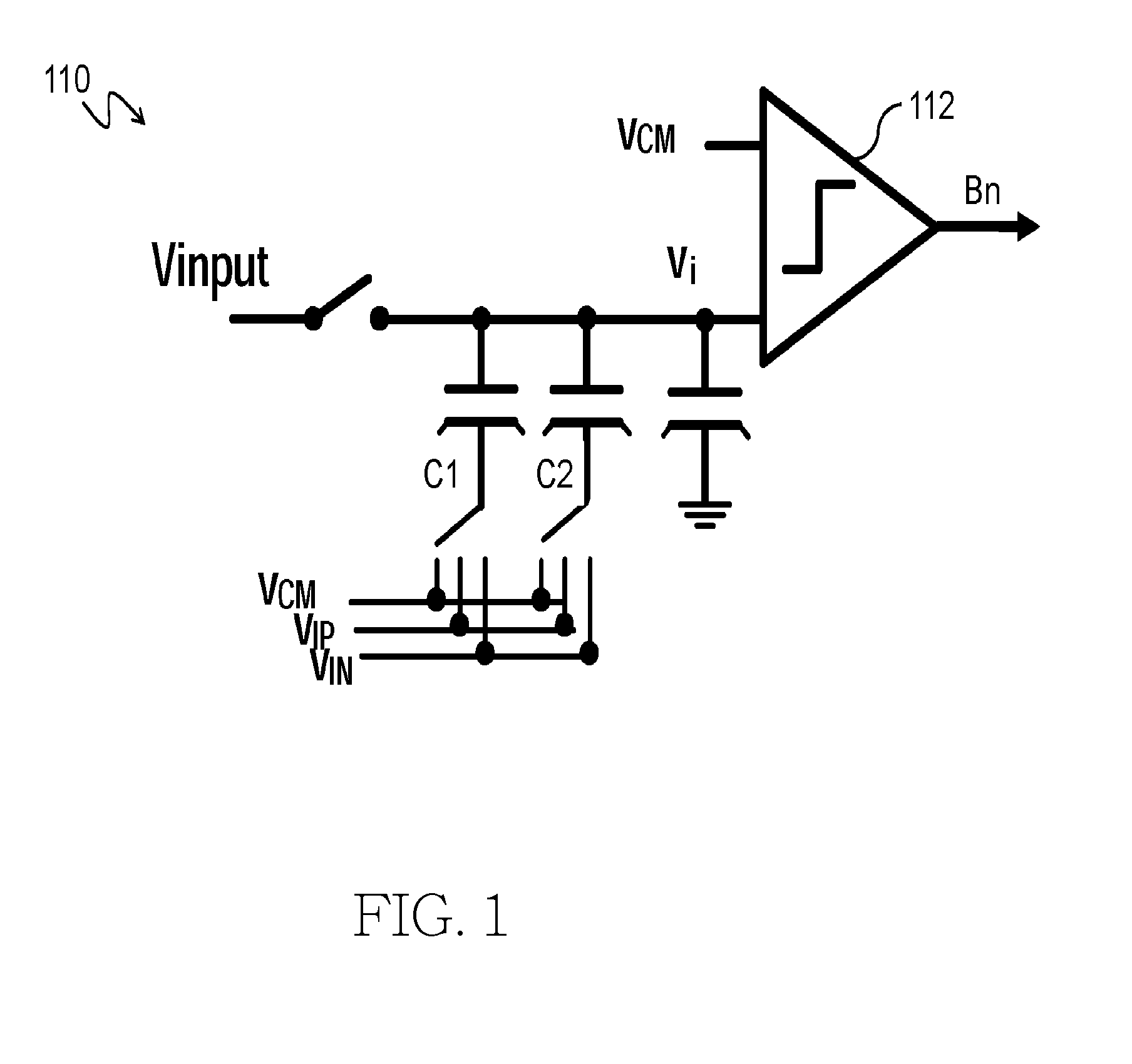

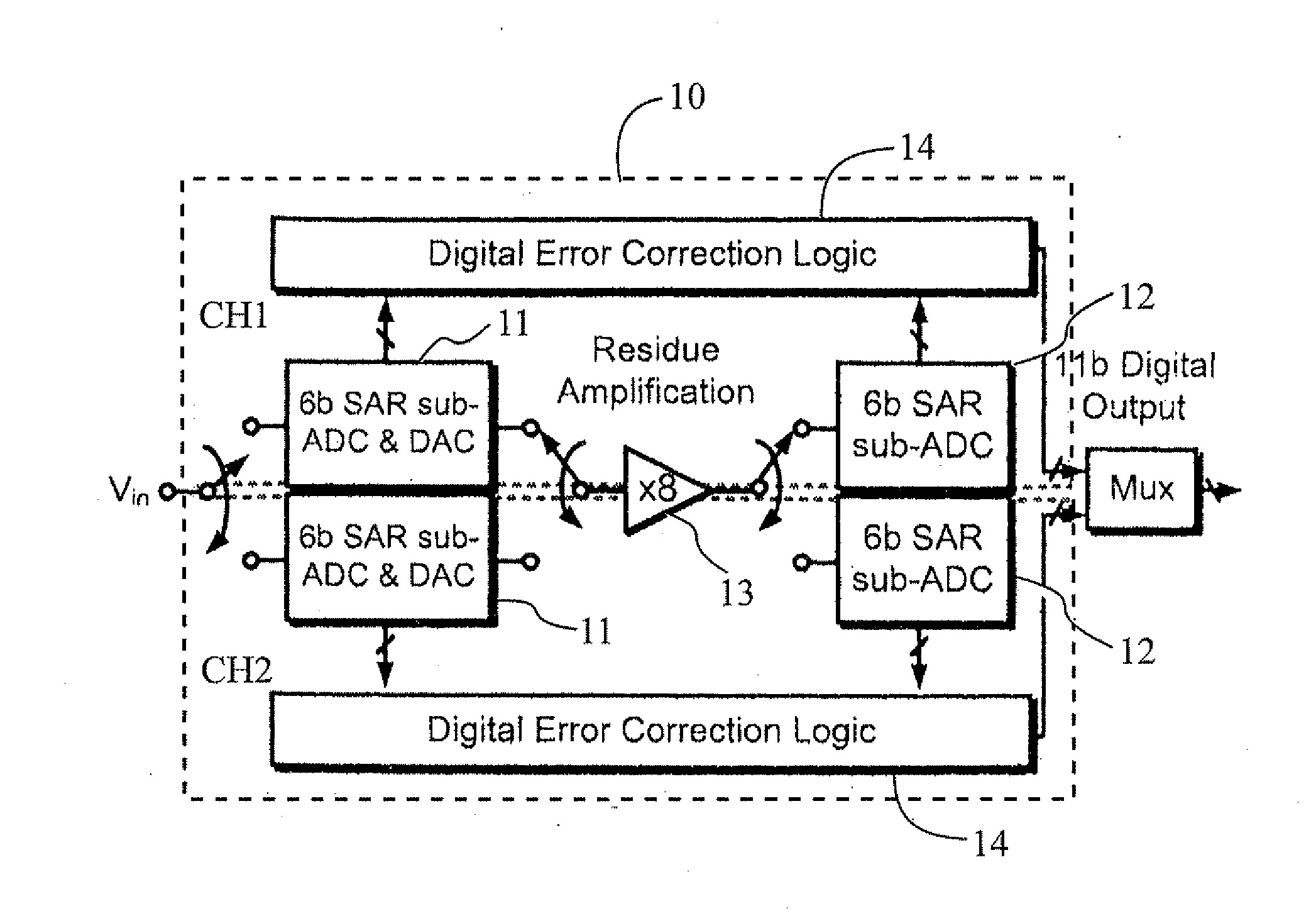

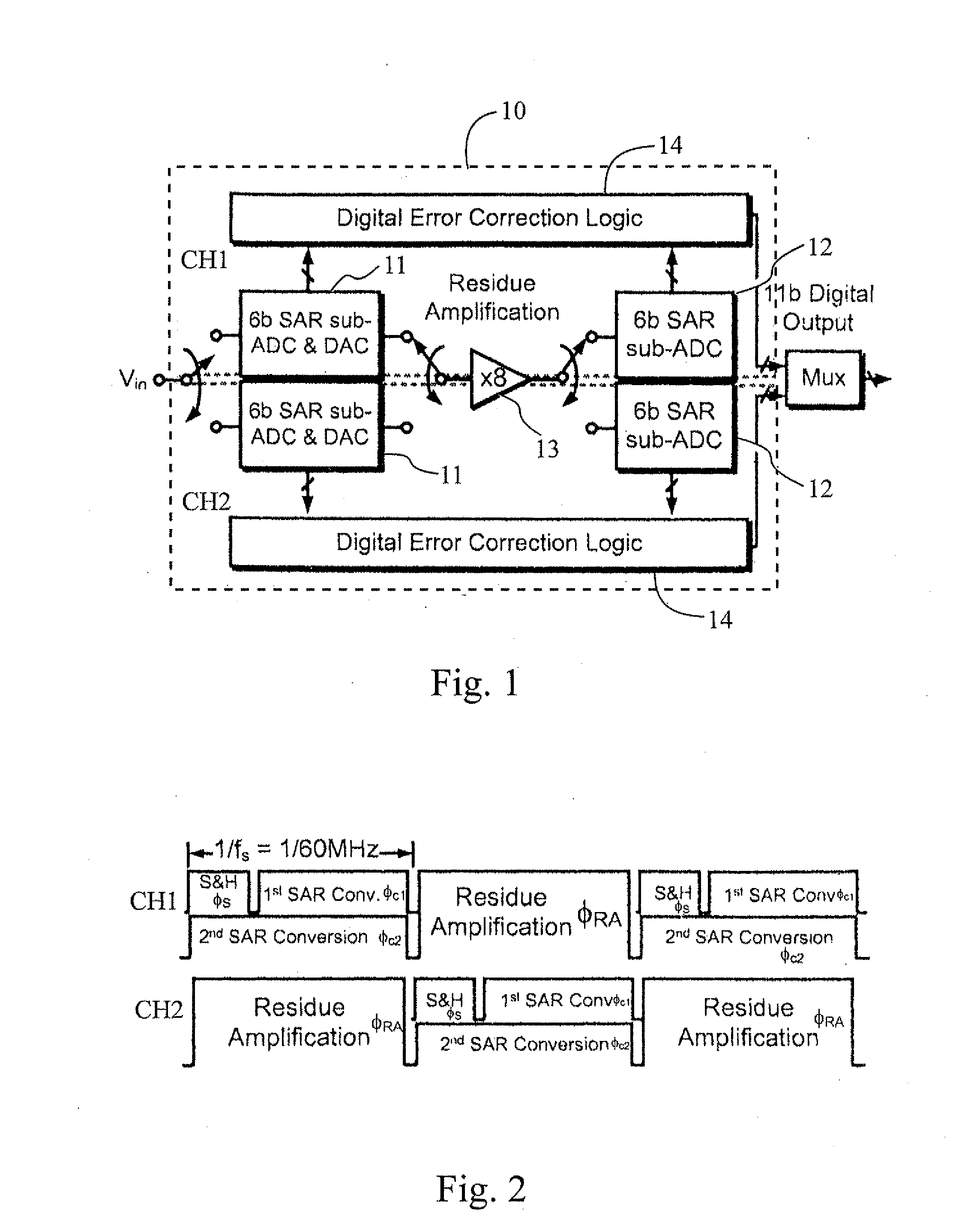

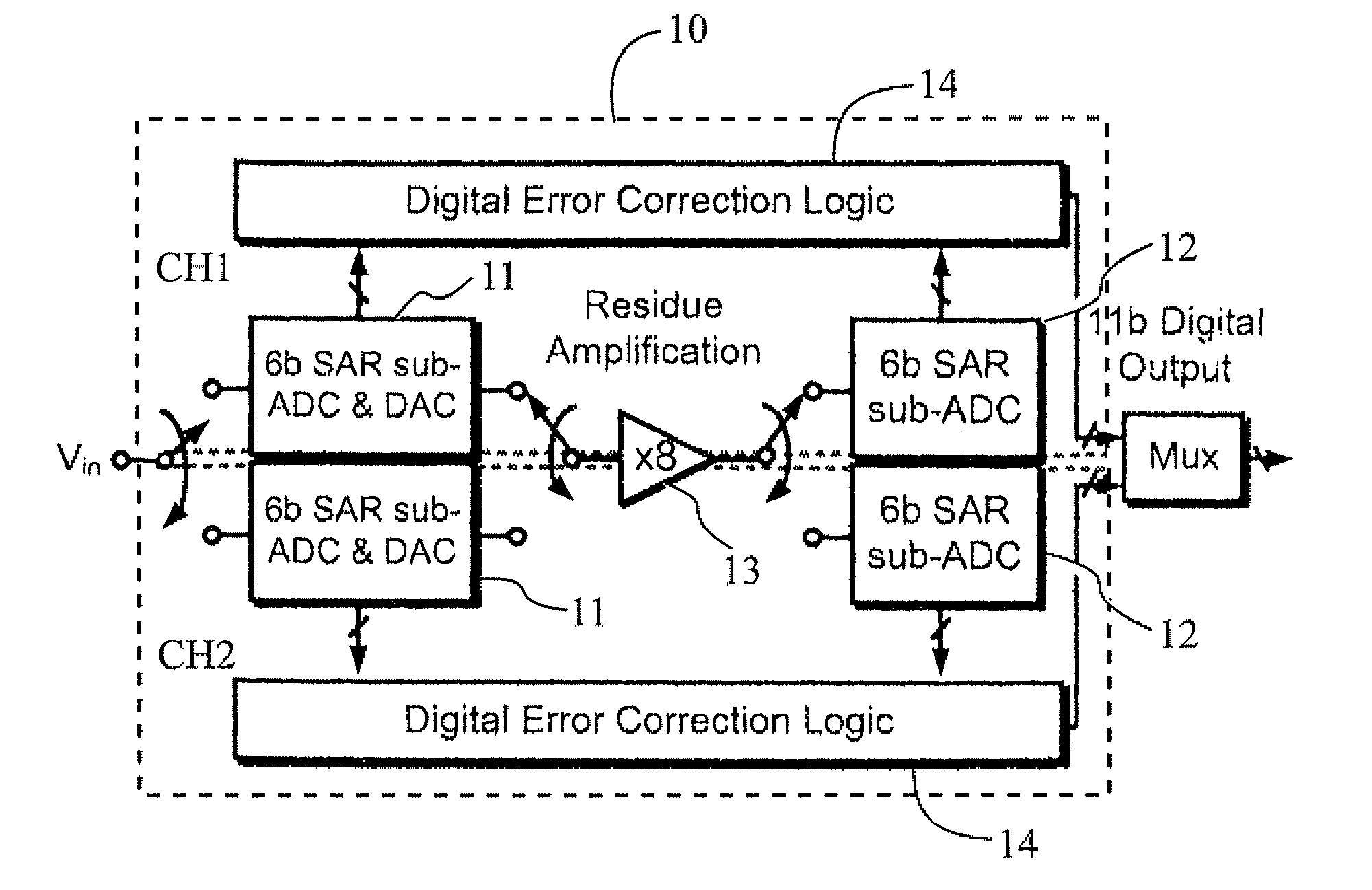

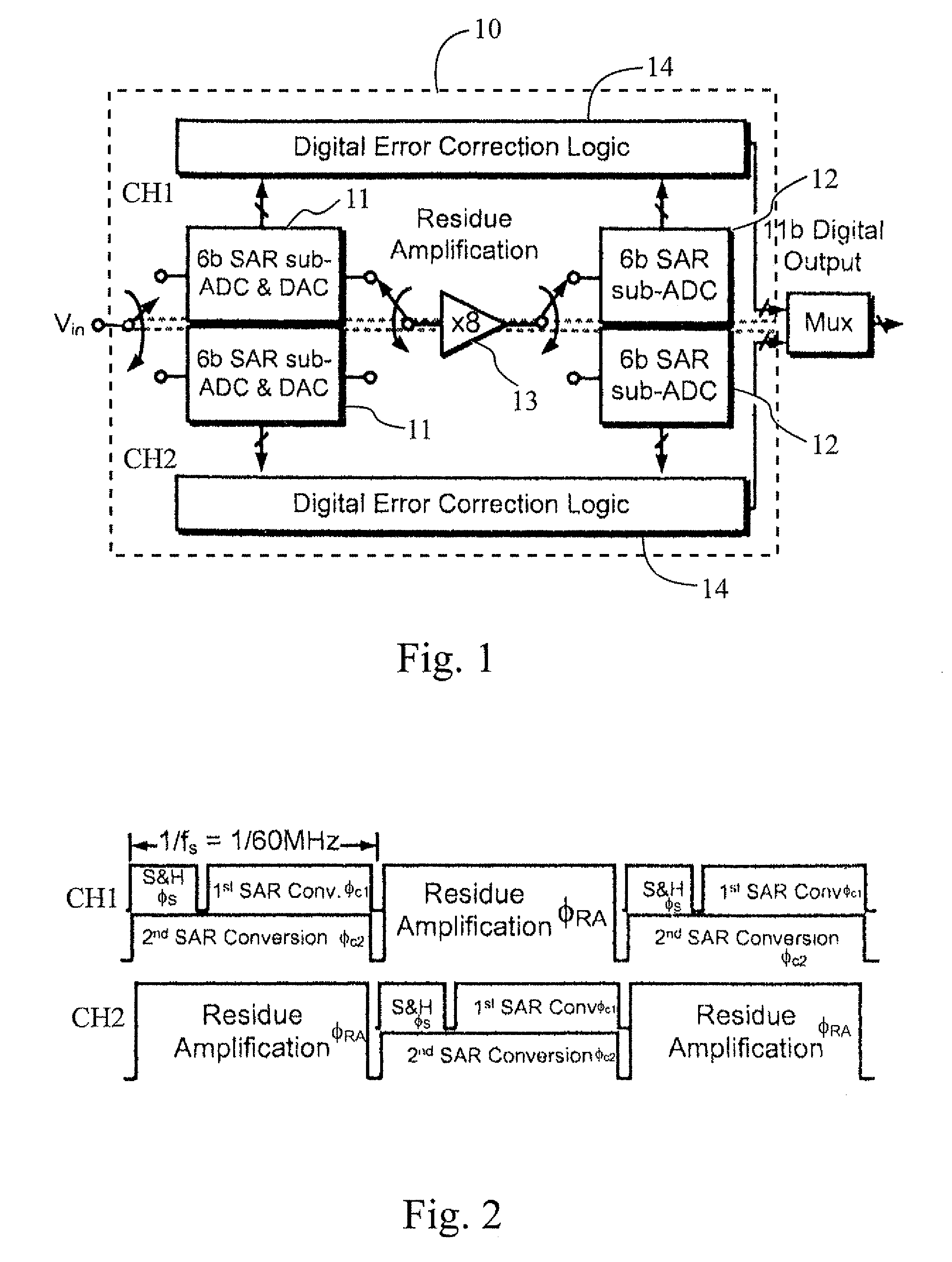

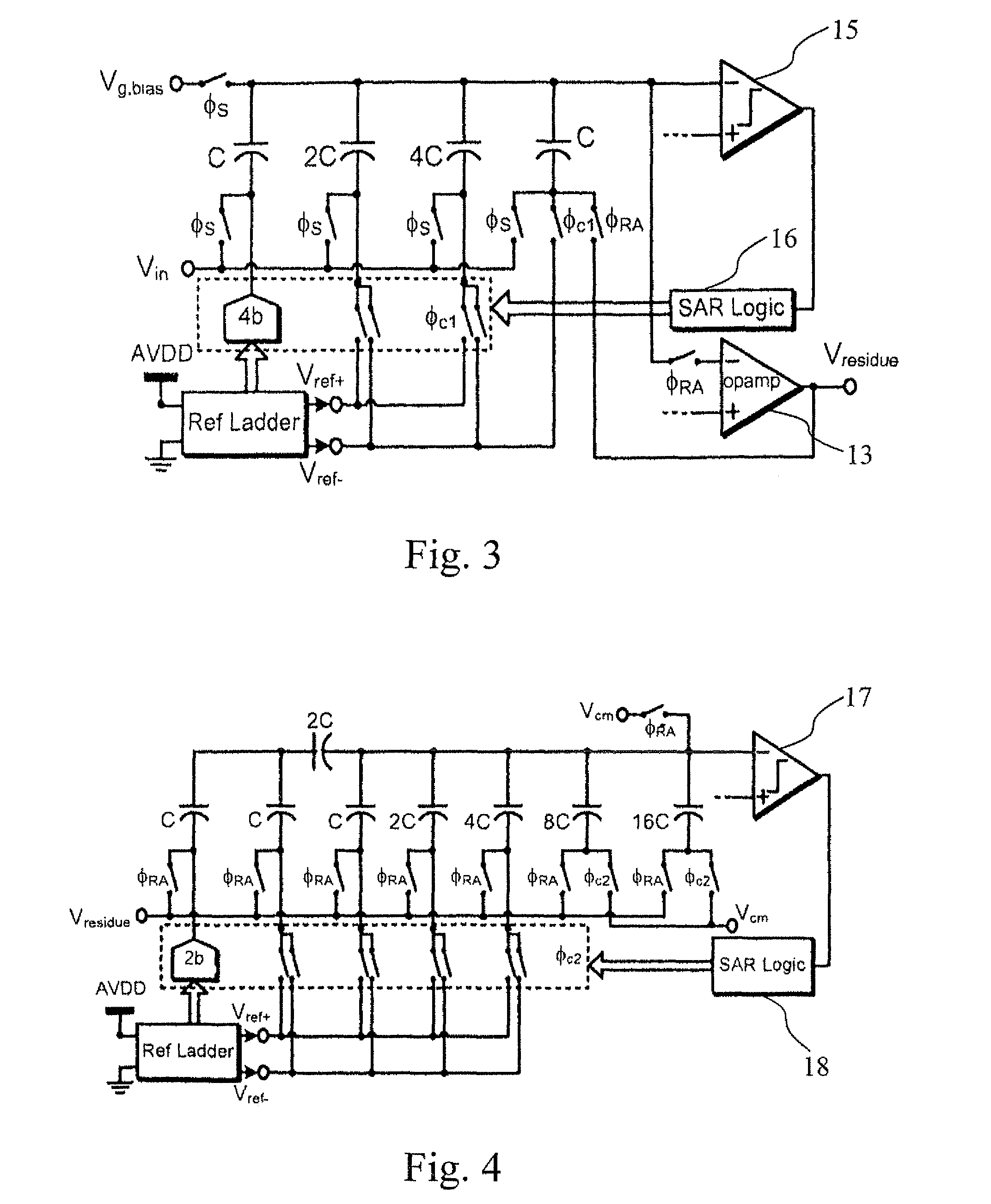

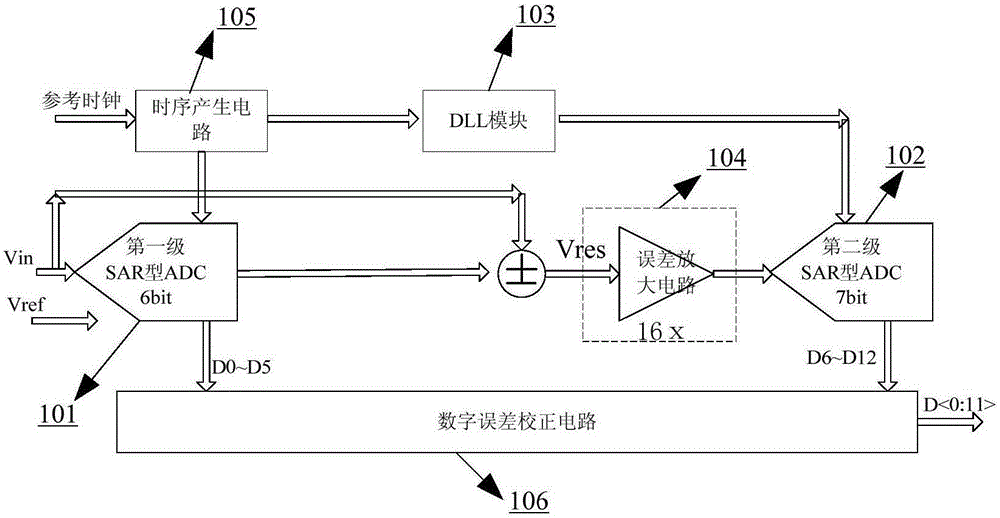

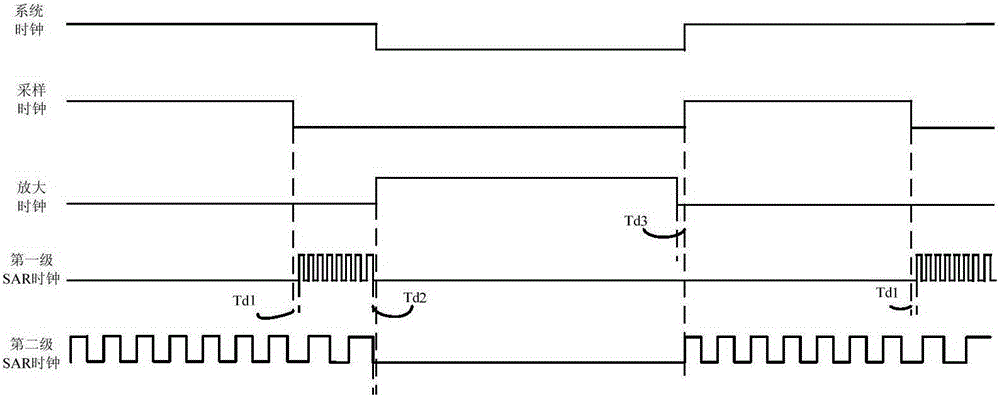

Analog to digital converter circuit

ActiveUS20120229313A1Reduce power consumptionAccuracyElectric signal transmission systemsResistance/reactance/impedenceSub thresholdA d converter

The present invention provides an analog-to-digital converter (ADC) circuit comprising two time-interleaved successive approximation register (SAR) ADCs. Each of the two time-interleaved SAR ADCs comprises a first stage SAR sub-ADC, a residue amplifier, a second stage SAR sub-ADC and a digital error correction logic. The residue amplifier is shared between the time-interleaved paths, has a reduced gain and operates in sub-threshold to achieve power effective design

Owner:UNIVERSITY OF MACAU

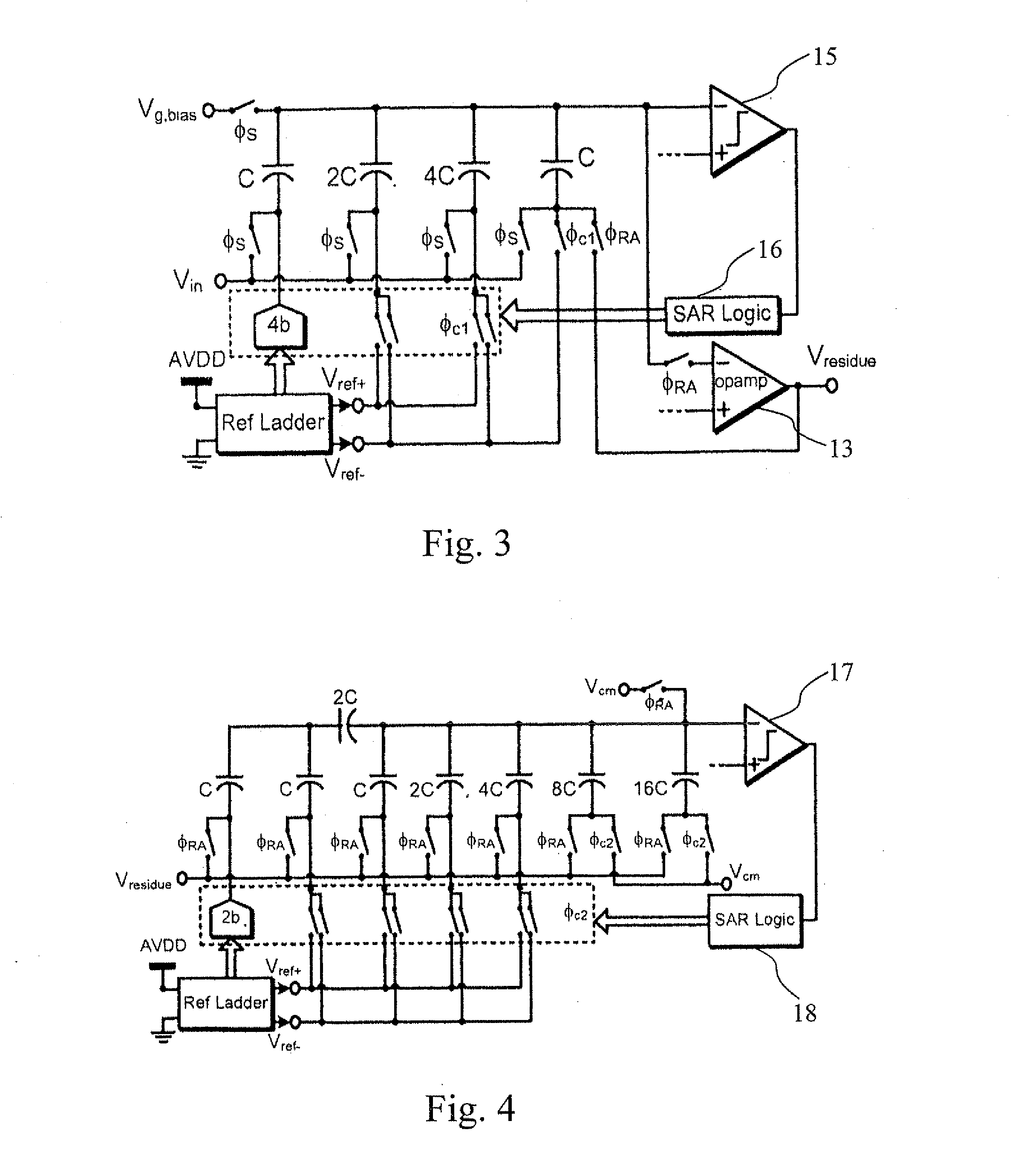

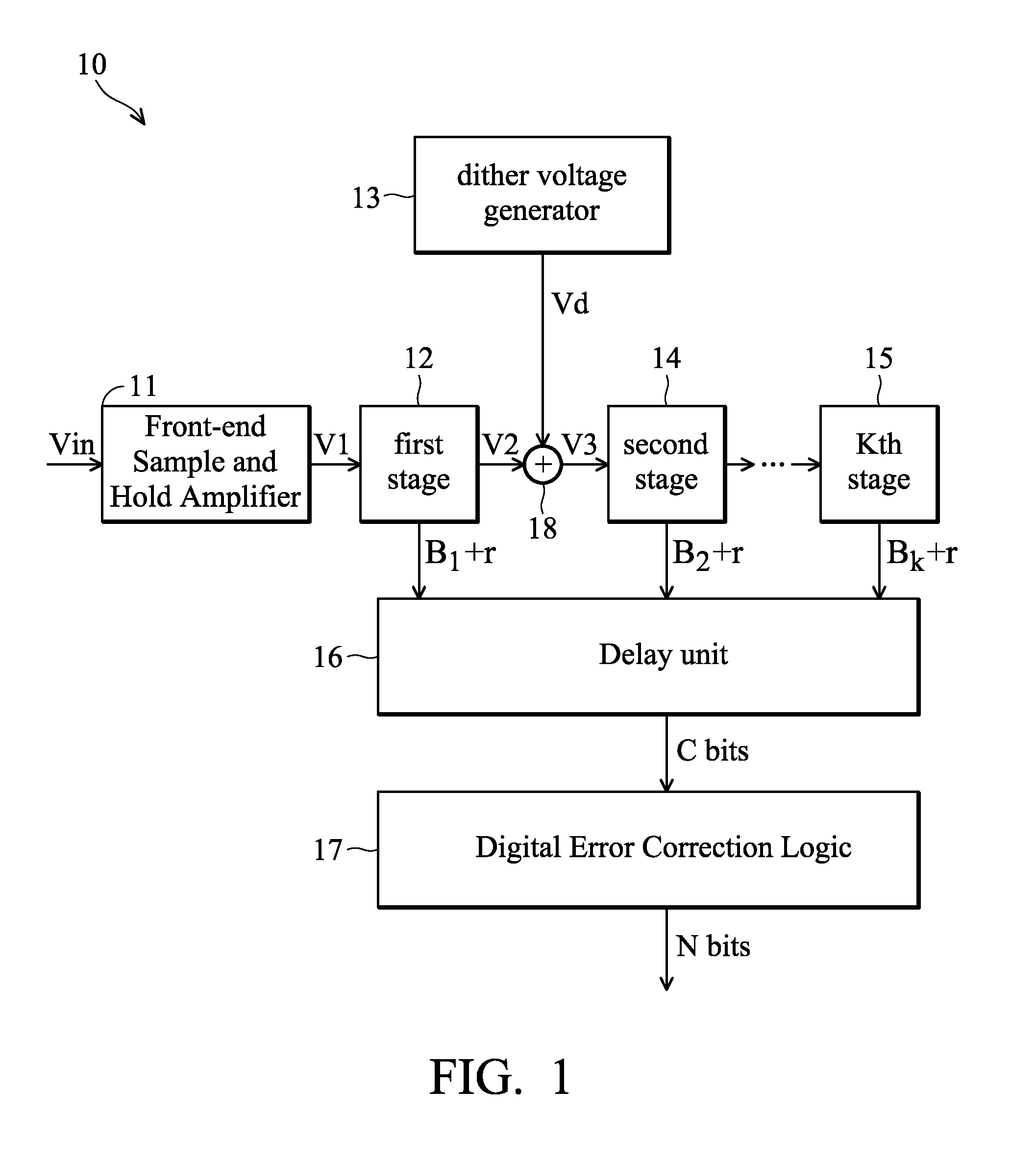

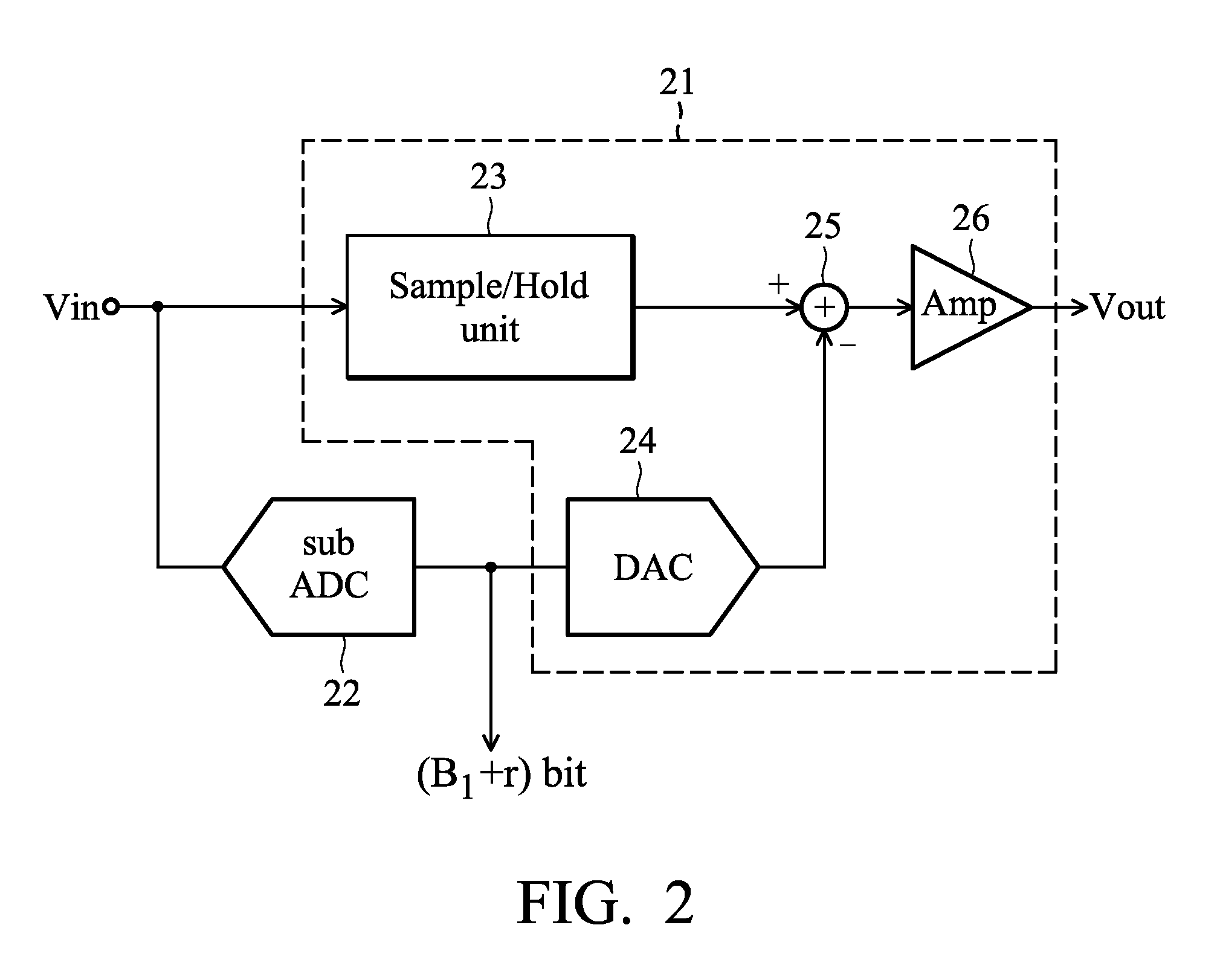

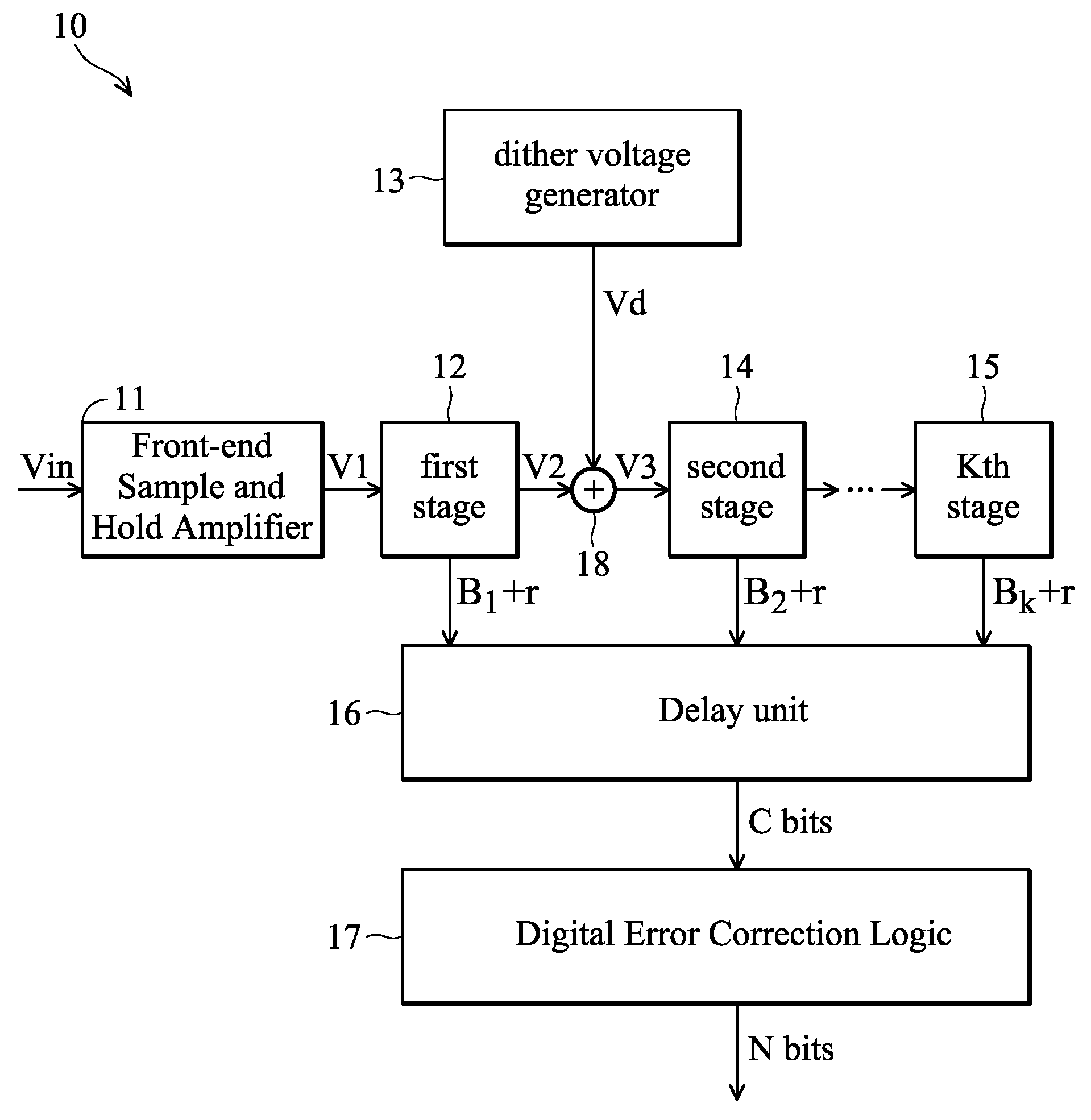

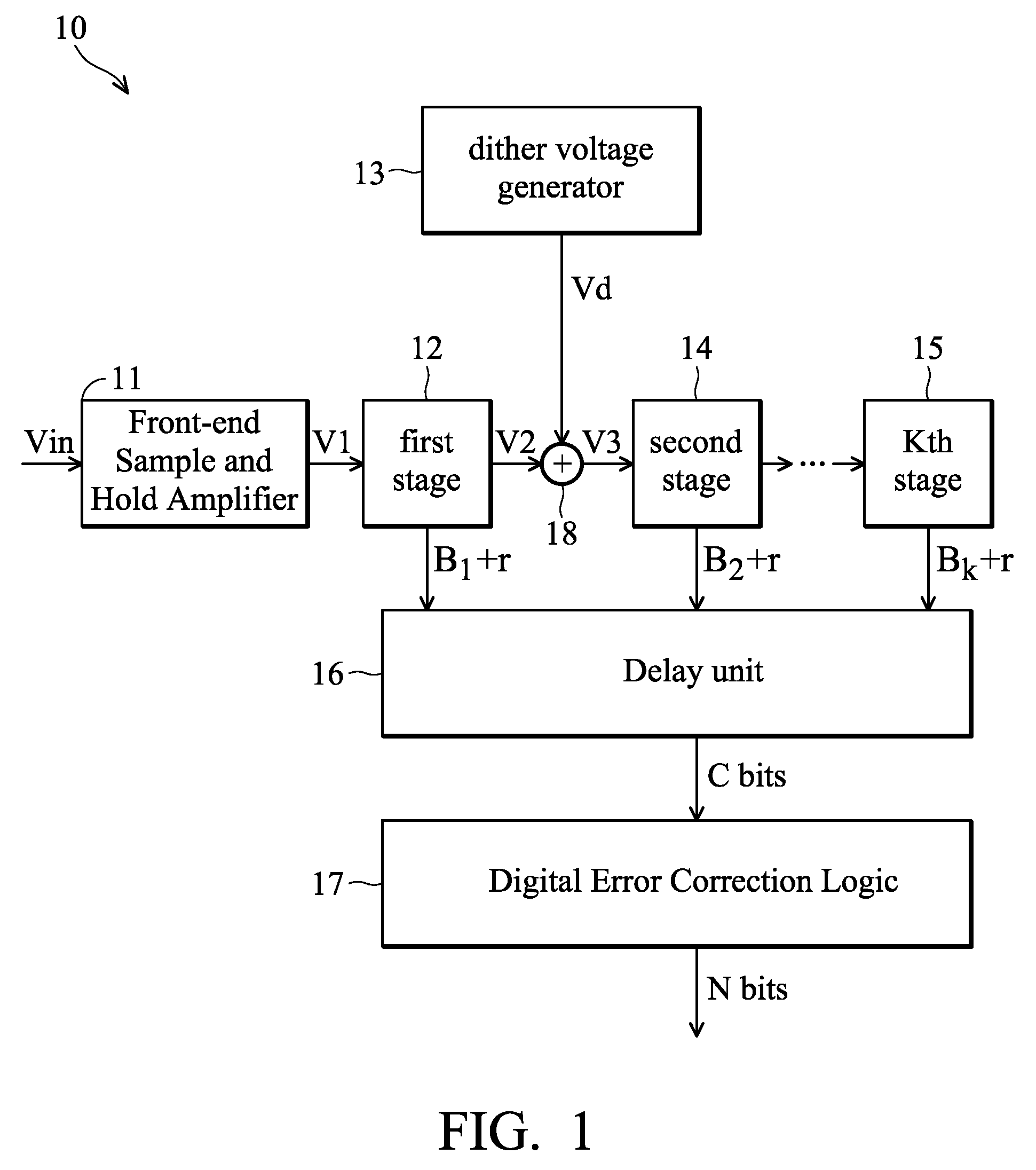

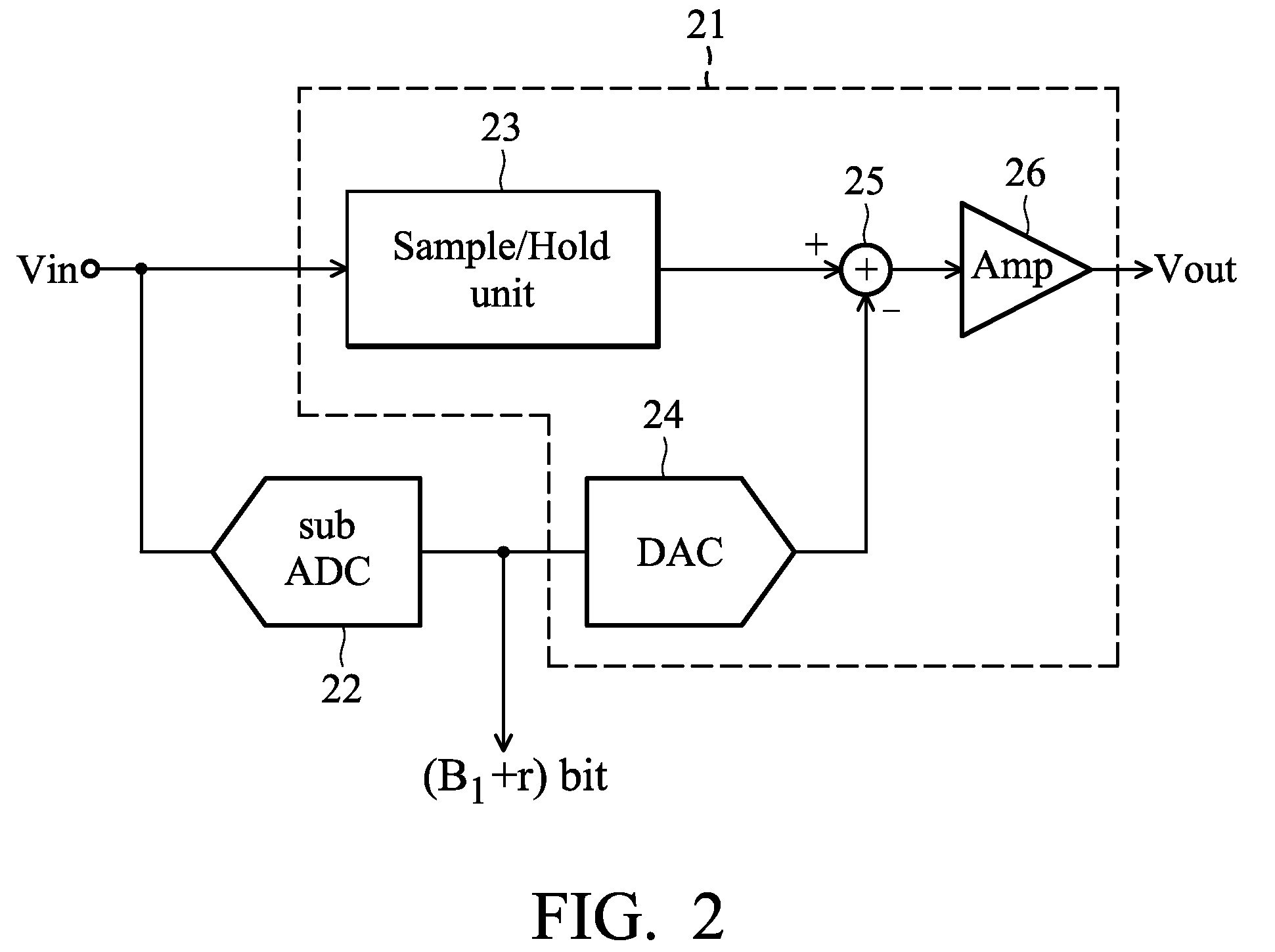

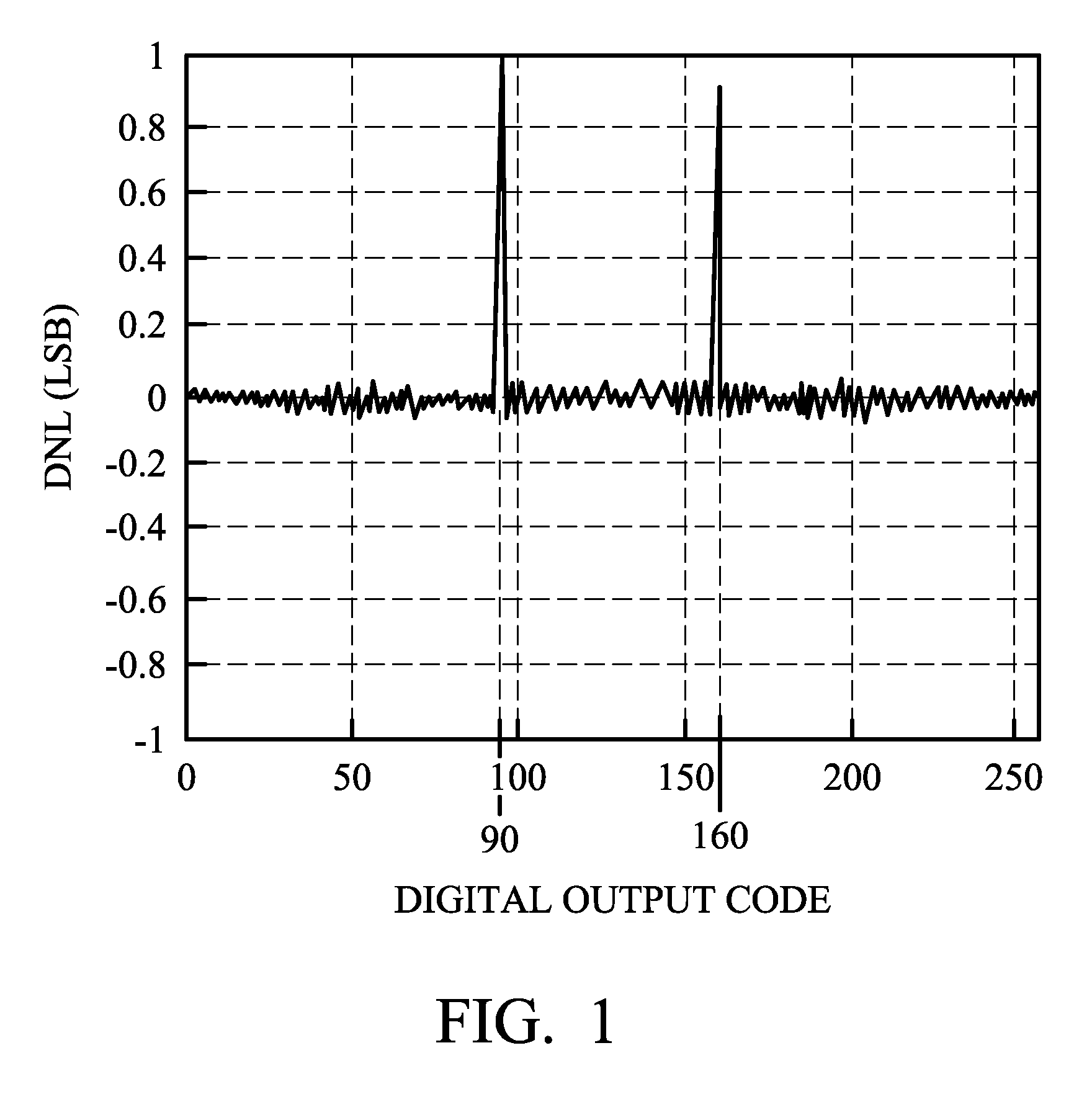

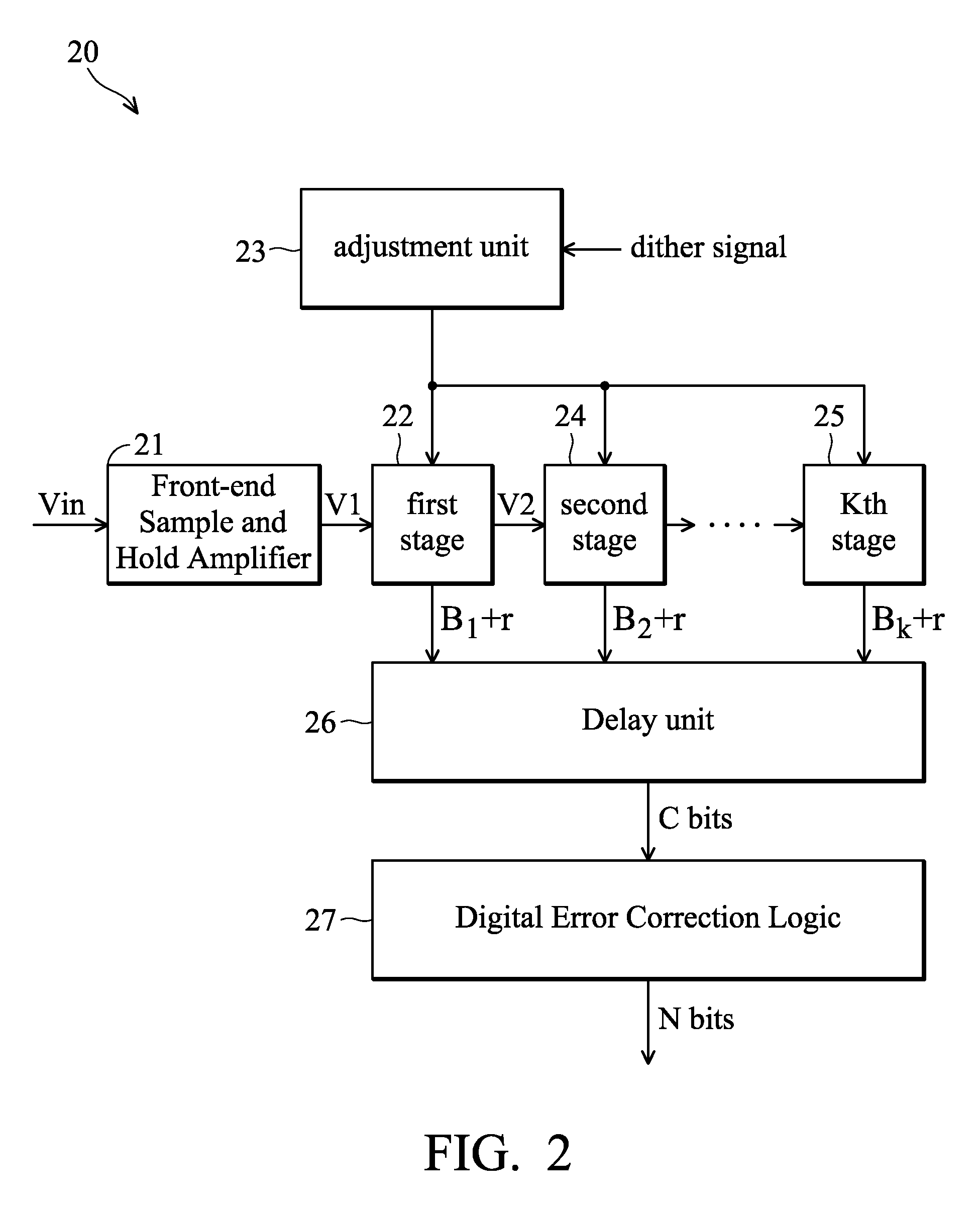

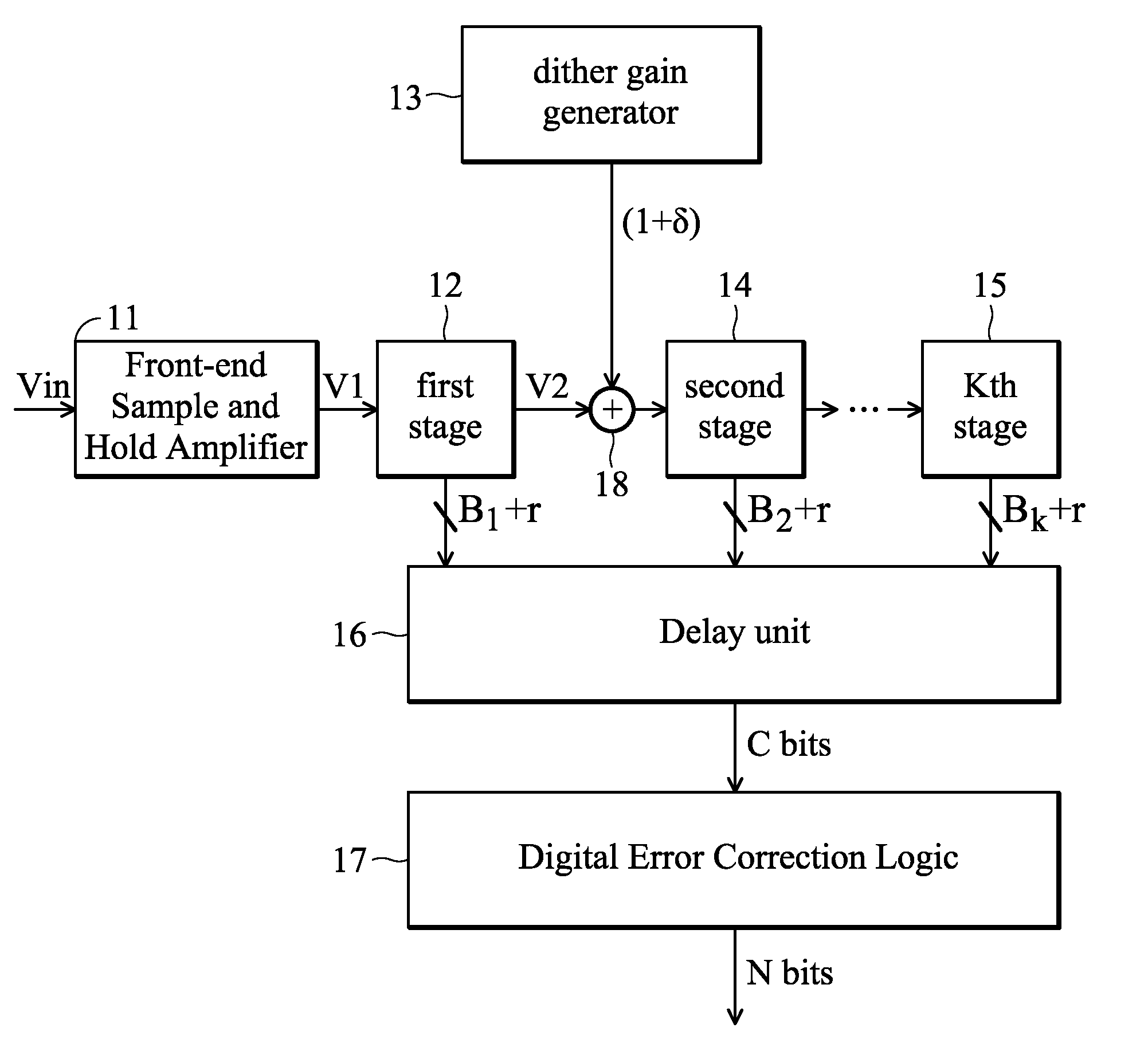

Analog to digital converter having digital correction logic that utilizes a dither signal to correct a digital code

InactiveUS7830287B1Electric signal transmission systemsAnalogue-digital convertersAnalog-to-digital converterAnalog to information converter

An analog to digital converter is provided. The converter comprises a dither gain generator, a first stage, an adder, a second stage, and a digital error correction logic. The dither gain generator generates a dither gain. The first stage receives a first voltage to generate a first digital code and a second voltage. The adder is coupled to the first stage and adds the dither voltage to the second voltage to generate a third voltage. The second stage receives the third voltage to generate a second digital code. The digital error correction logic receives and corrects the first digital code and the second digital code to generate a digital code corresponding to the first voltage.

Owner:HIMAX MEDIA SOLUTIONS

Time-interleaved pipelined-SAR analog to digital converter with low power consumption

ActiveUS8427355B2Reduce power consumptionAccuracyElectric signal transmission systemsResistance/reactance/impedenceSub thresholdTime interleaved

Owner:UNIVERSITY OF MACAU

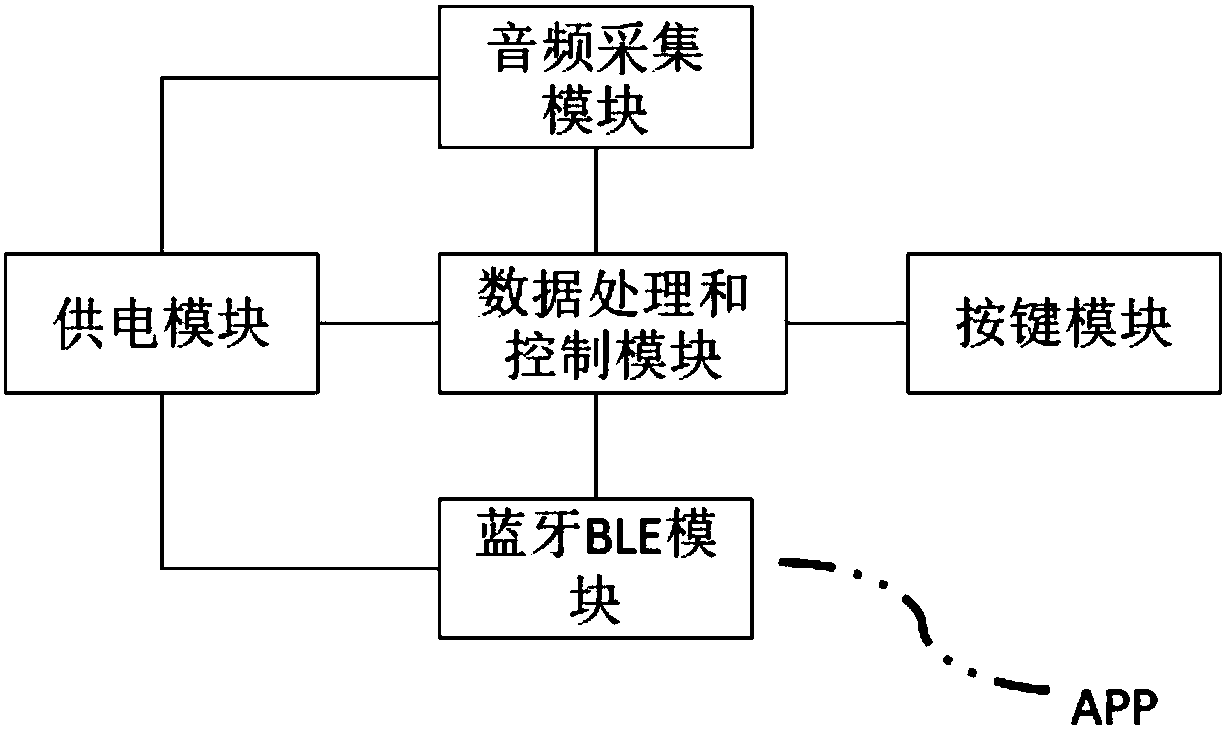

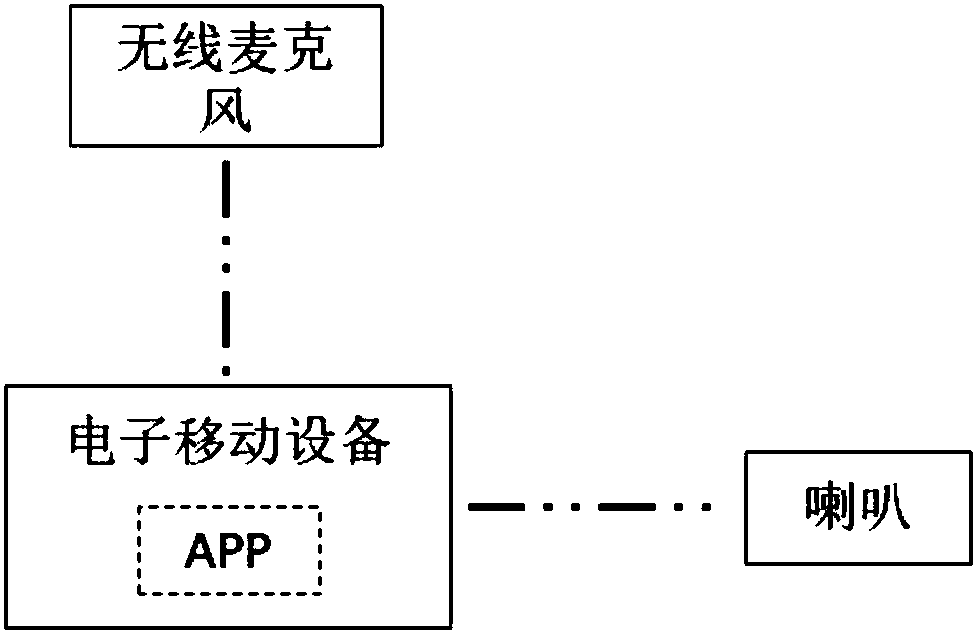

Wireless microphone based on Bluetooth BLE transmission

PendingCN108513224AReduce power consumptionLow costSignal processingLoudspeaker signals distributionWireless microphoneSound quality

The invention relates to the technical field of audio processing devices, and particularly relates to a wireless microphone based on Bluetooth BLE transmission. A data processing and control module encodes and compresses an audio signal, and a Bluetooth BLE module transmits the audio signal encoded and compressed by the data processing and control module to electronic mobile equipment through a Bluetooth BLE mode, instead of traditional Bluetooth audio transmission modes such as BR / EDR. The wireless microphone can be applied to, for example, mobile phones, Bluetooth speakers, loudspeakers andthe like, can further achieve the transmission and playback of audios, and can meet a wide range of application requirements, such as karaoke entertainment, square dancing and the like; moreover, theBluetooth BLE has low power consumption, low cost and higher applicability, and cannot be restricted by the traditional Bluetooth applications such as BR / EDR; and an original audio signal is subjectedto digital AD sampling, the data processing and control module uses processor compression, digital error correction and compensation algorithms, and also combines with a traffic control algorithm forpackaging, thereby, the sound quality can be guaranteed, good scalability and compatibility can be achieved, and strong practical values and market promotion values can be realized.

Owner:BEIJING NEWSMY FENGHUANG SCI & TECH

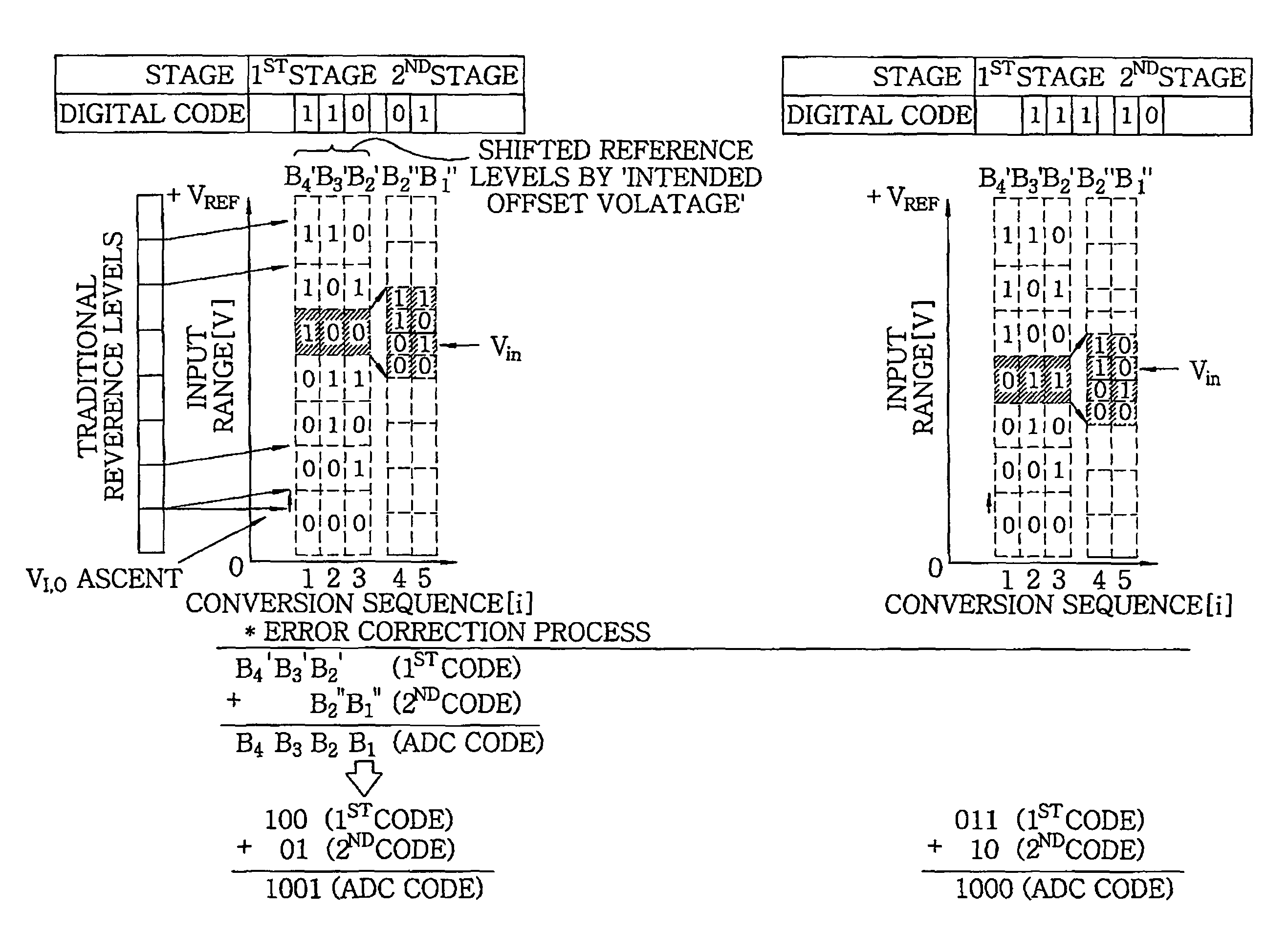

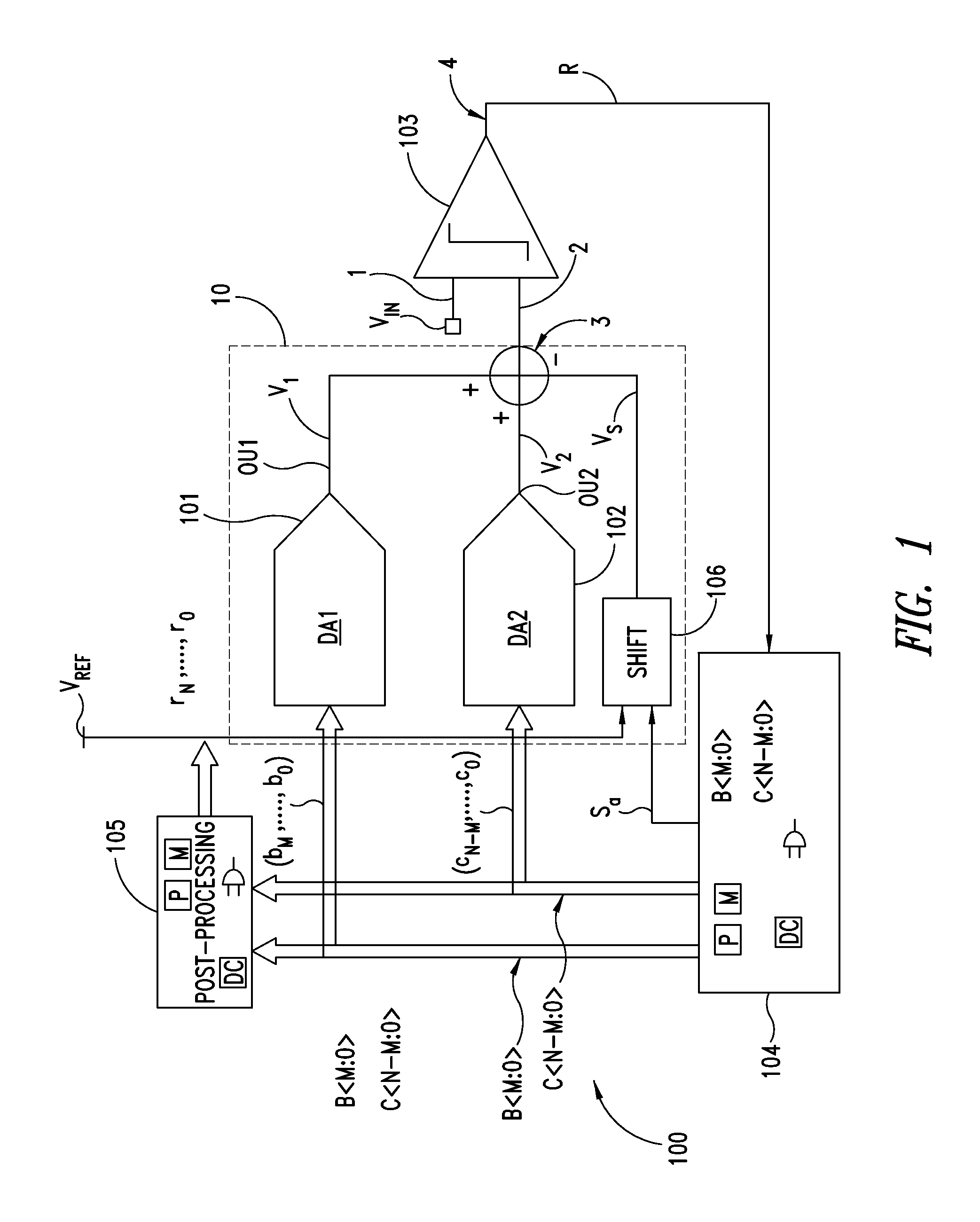

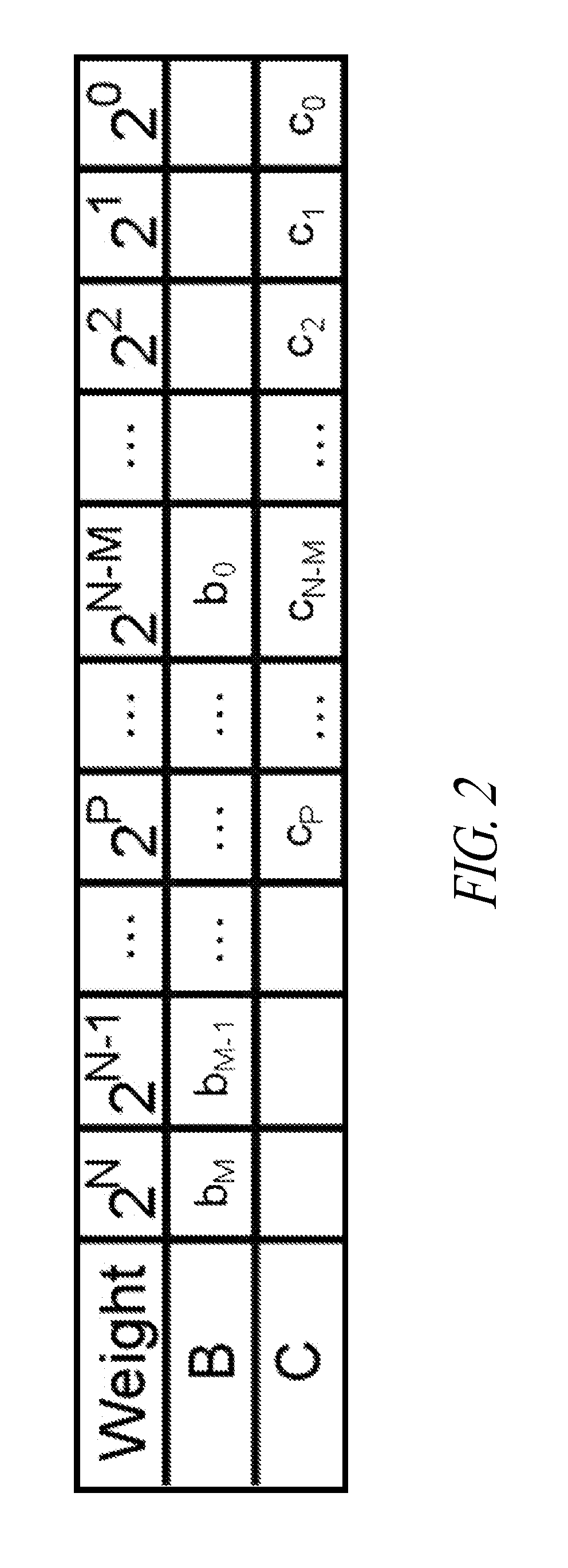

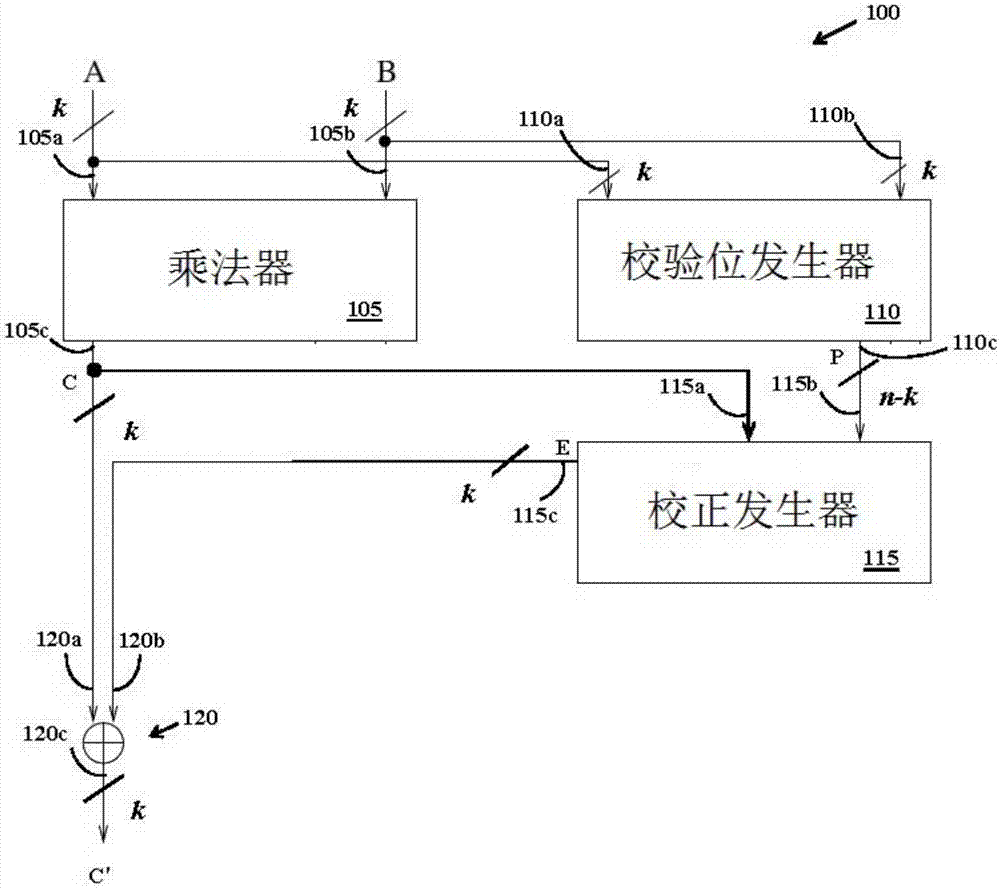

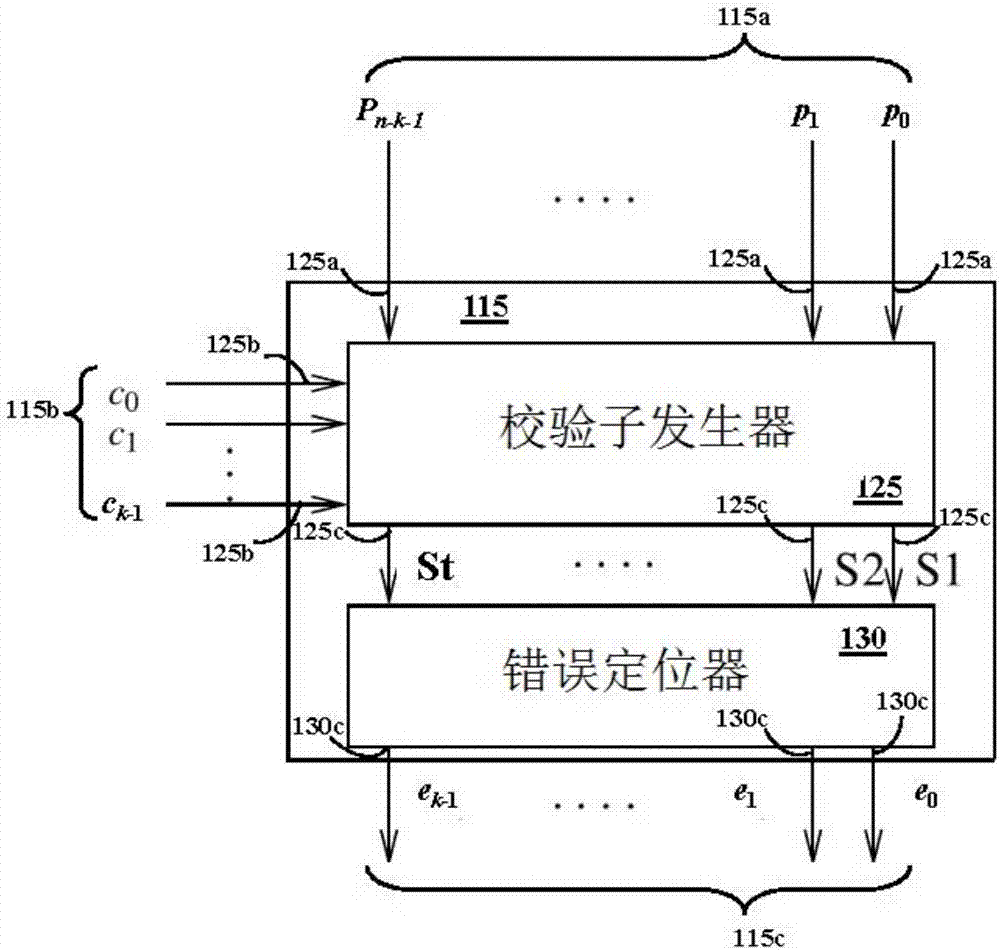

Method and apparatus for digital error correction for binary successive approximation ADC

ActiveUS7986253B2Electric signal transmission systemsAnalogue-digital convertersDigital analog converterProcessor register

An apparatus for digital error correction in a successive approximation (SAR) analog to digital converter (ADC) includes a binary weighted digital to analog converter (DAC) which can be virtually divided into multiple sub-DACs for redundancy insertion; and a comparator configured to compare the analog input with a DAC level corresponding to digital. The apparatus further includes a register and control logic unit configured to control a switching operation for DAC and to add output codes obtained from sub-DACs to output the added code as a final A / D converted code.

Owner:KOREA ADVANCED INST OF SCI & TECH

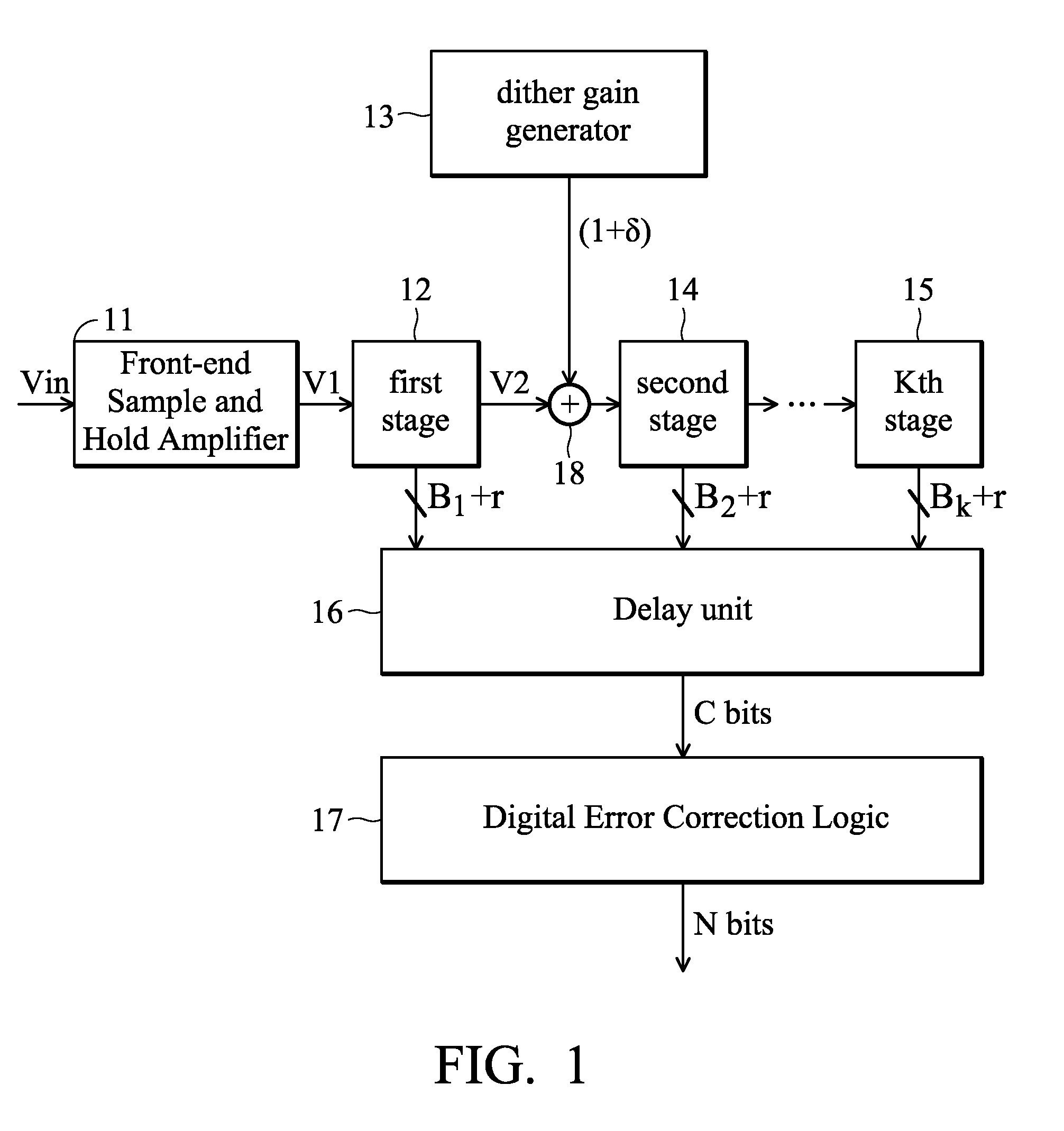

Analog to digital converter

InactiveUS20100283641A1Electric signal transmission systemsAnalogue-digital convertersAnalog-to-digital converterAnalog to information converter

An analog to digital converter is provided. The converter comprises a dither gain generator, a first stage, an adder, a second stage, and a digital error correction logic. The dither gain generator generates a dither gain. The first stage receives a first voltage to generate a first digital code and a second voltage. The adder is coupled to the first stage and adds the dither voltage to the second voltage to generate a third voltage. The second stage receives the third voltage to generate a second digital code. The digital error correction logic receives and corrects the first digital code and the second digital code to generate a digital code corresponding to the first voltage.

Owner:HIMAX MEDIA SOLUTIONS

Digital to analog converter

ActiveCN105187066AReduce in quantityIncreased complexityAnalogue/digital conversionElectric signal transmission systemsVoltage reference12-bit

Owner:GUANGZHOU RUNXIN INFORMATION TECH +1

Anti-noise gradual approximation type analog digital conversion device and method thereof

InactiveCN104052483AImprove the immunityImprove stabilityAnalogue/digital conversionElectric signal transmission systemsValue setDigital analog converter

The invention discloses an anti-noise gradual approximation type analog digital conversion device and a method thereof. The device mainly comprises a gradual approximation type analog digital converter, a digital error correction circuit and a redundancy comparison control circuit, wherein the gradual approximation type analog digital converter comprises a first comparator, a digital analog converter and a gradual approximation type control circuit. The method comprises steps that: a redundancy comparison period is carried out in a random valid bit period, before accomplishment of the redundancy comparison period, comparison motion is carried out only by a comparator, extra digital analog feedback is not carried out, after all outputs of the comparator within the redundancy comparison period are filtered through a digital low pass filter or is checked through a reference table, a digital value set is outputted, and a digital value is designated as the digital value in the valid bit period.

Owner:蔡金狮

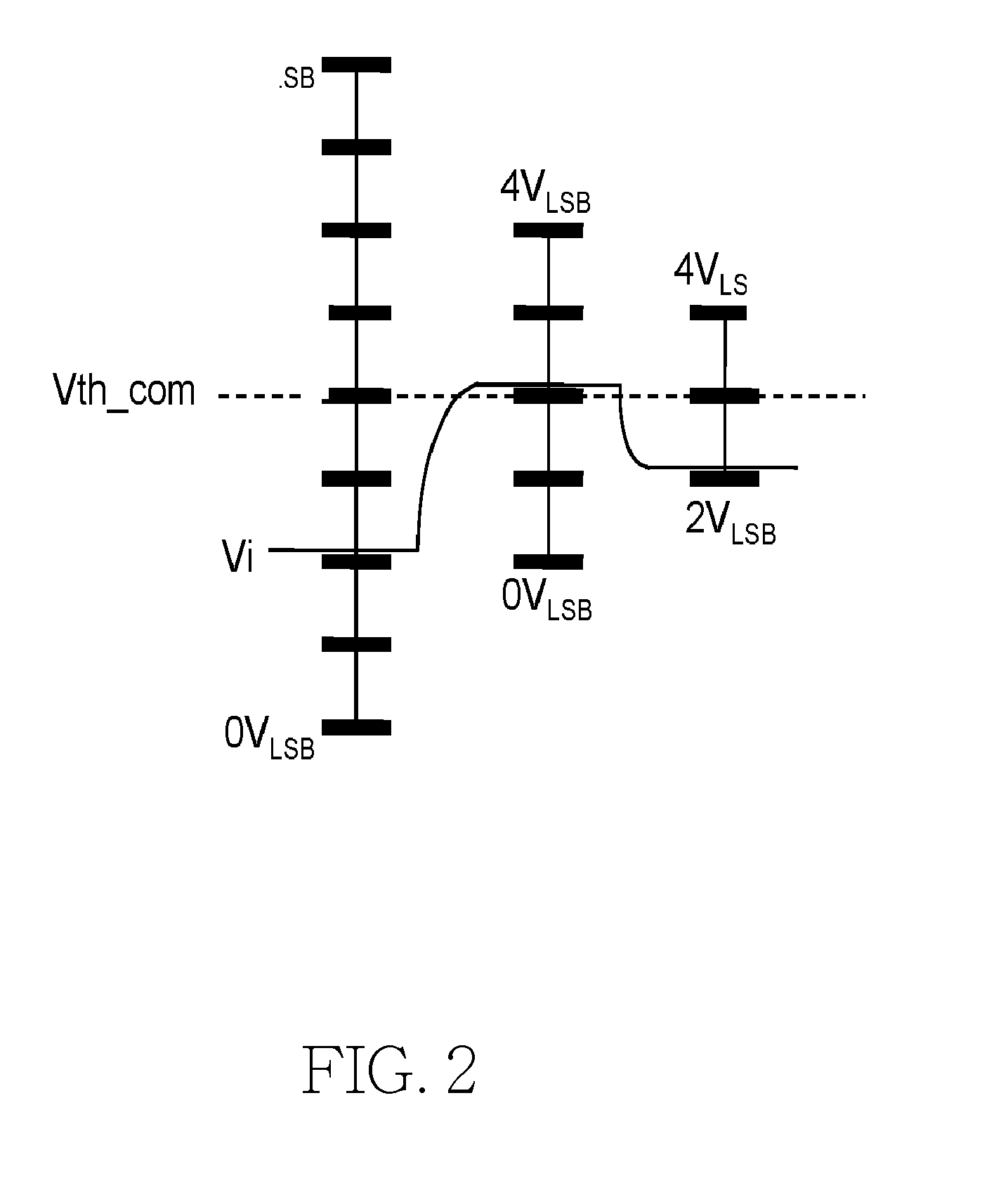

Pipeline ADC with Minimum Overhead Digital Error Correction

ActiveUS20070052573A1Electric signal transmission systemsAnalogue-digital convertersComputer scienceAdjacent level

The most hardware efficient way to implement an N-stage pipeline ADC is to use (G+1)-level ADC-DAC for its first (N-1) stages and use (2·G−1)-level ADC for the last stage, where G is the inter-stage gain. For the fist (N-1) stages using (G+1)-level ADC-DAC, the (G+1) levels are uniformly distributed between −(G−1) / G and (G−1) / G; inclusively. The spacing between two adjacent levels is 2(G−1) / G2. For the last stage using (2·G−1)-level ADC, the (2·G−1)-levels are uniformly distributed between −(G−1) / G and (G−1) / G; inclusively. The spacing between two adjacent levels is 1 / G

Owner:REALTEK SEMICON CORP

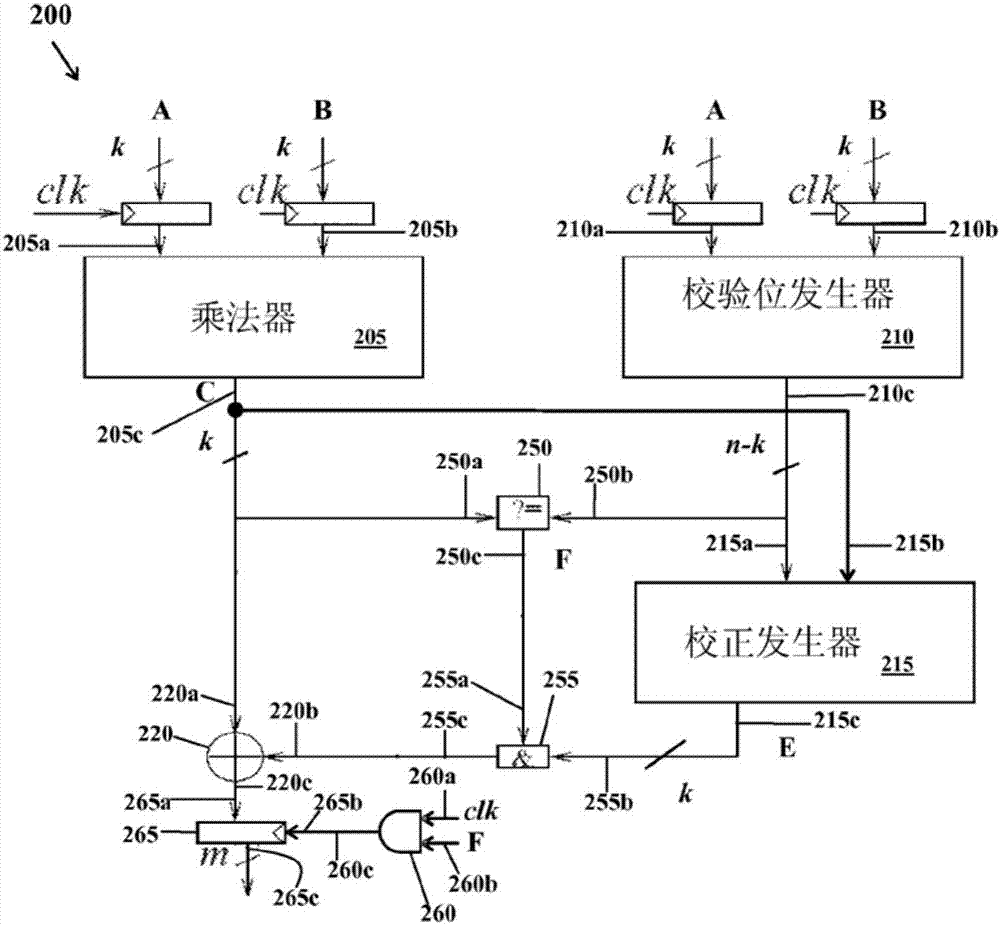

Digital error correction

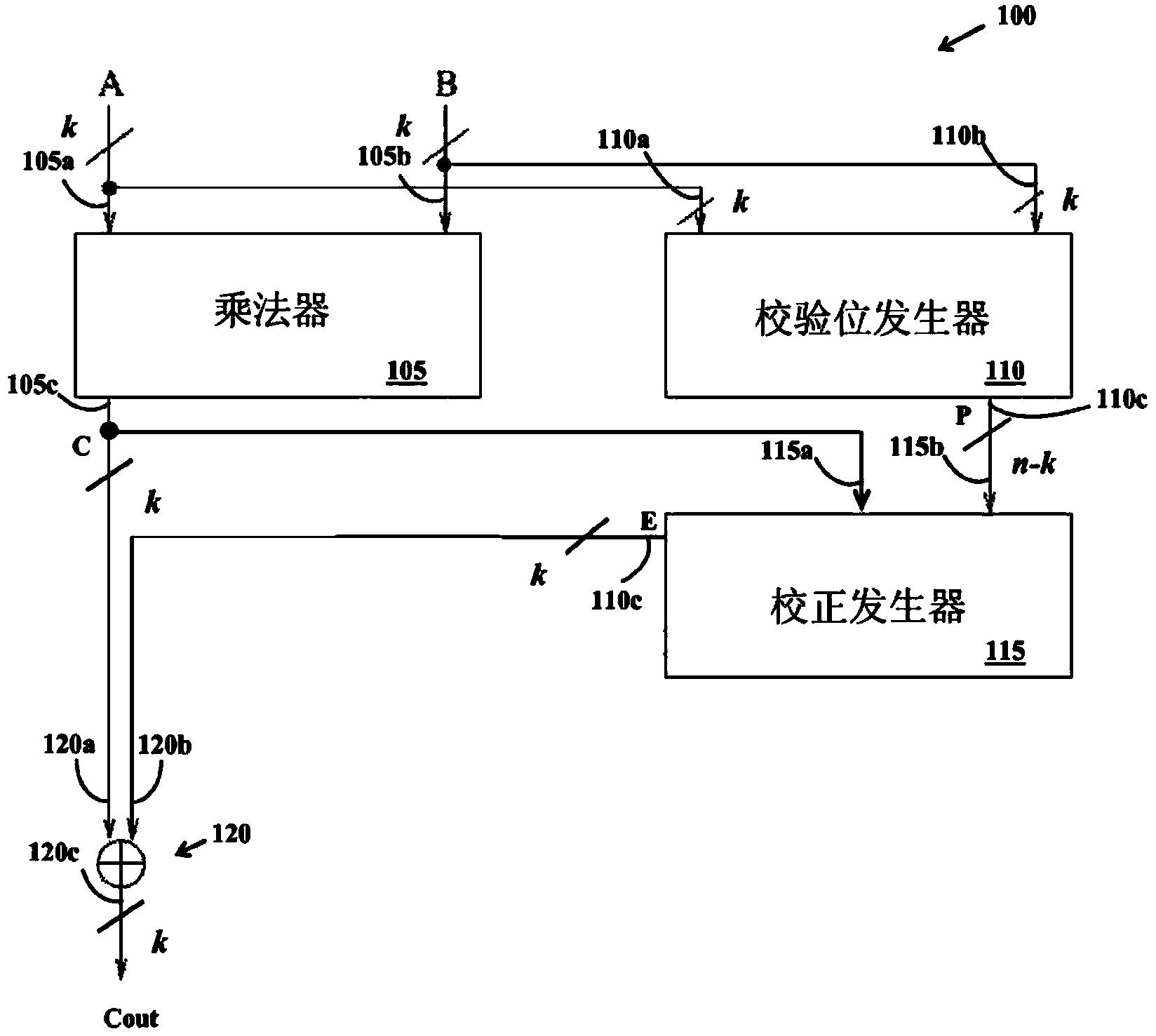

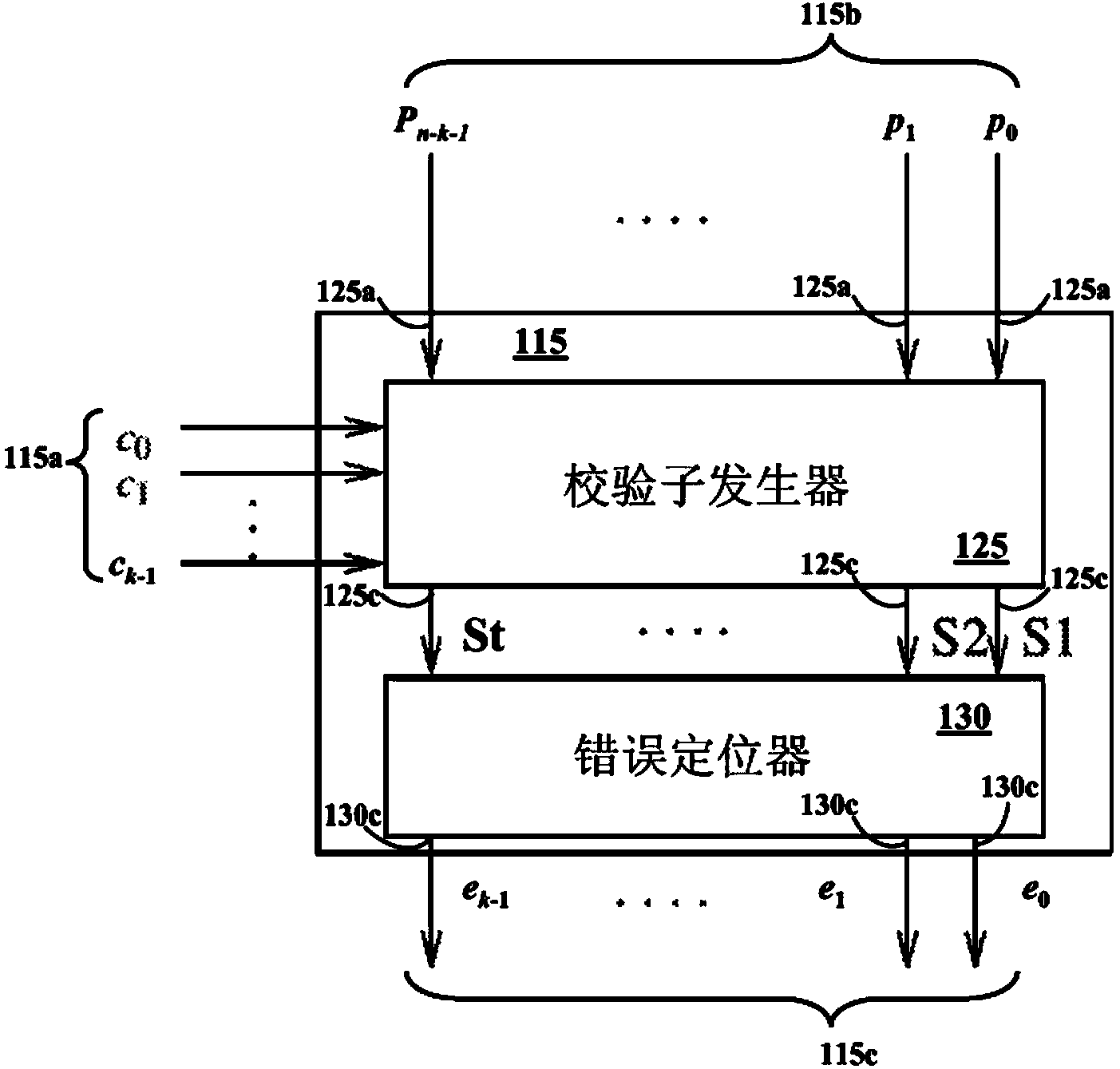

ActiveCN103890732ADetection errorCorrection errorError preventionCyclic codesError correctingDigital error correction

An error-correcting circuit comprises: a component arranged to generate a first output from a first input and a second input; an error detector arranged to generate an error flag indicative of whether or not it has detected an error in the first output, based on the first output,the first input and the second input; a correction generator suitable for generating a correcting output after a first time period beginning with a timing event, based on the first output, the first input and the second input; and an output generator arranged to generate an output of the error-correcting circuit after a second time period beginning with the timing event. If the error flag indicates that an error has been detected in the first output then the second time period may be longer than the first time period, otherwise the second time period may be not longer than the first time period.; If the error flag indicates that an error has been detected in the first output then the output of the error-correcting circuit may comprise a combination of the first output and the correcting output whereby the error detected in the first output is corrected, otherwise the output of the error-correcting circuit may correspond directly to the first output.

Owner:OXFORD BROOKES UNIVERSITY

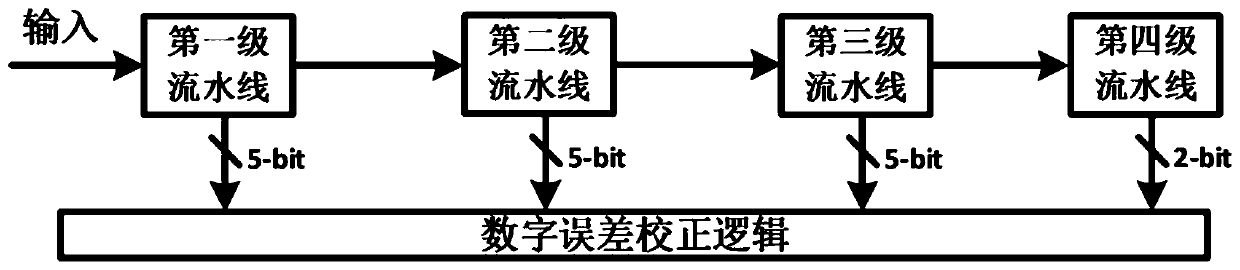

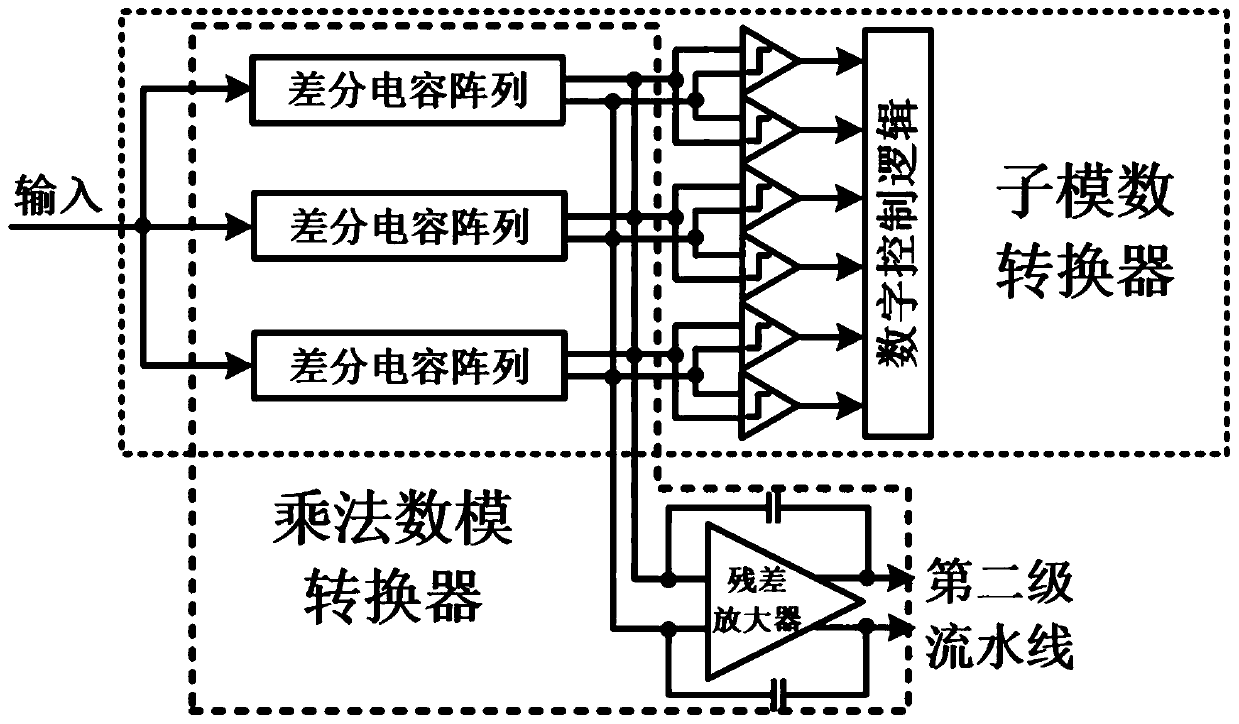

Novel fourteen-bit assembly line-successive approximation type analog-to-digital converter

ActiveCN111446964AIncrease conversion rateReduce power consumptionAnalogue/digital conversionElectric signal transmission systemsA d converterAssembly line

The invention relates to a novel fourteen-bit assembly line-successive approximation type analog-to-digital converter, which comprises a first-stage assembly line, a second-stage assembly line, a third-stage assembly line, a fourth-stage assembly line and digital error correction logic, wherein the first-stage assembly line, the second-stage assembly line and the third-stage assembly line are of afive-bit successive approximation type analog-to-digital converter structure, and one of the five bits is a redundant bit; the fourth-stage assembly line is a two-bit successive approximation type analog-to-digital converter; and an input signal passes through the first-stage assembly line, the second-stage assembly line, the third-stage assembly line and the fourth-stage assembly line to obtaina converted digital code, and the converted digital code is input into the digital error correction logic for processing to obtain a fourteen-bit digital code. The converter has the advantages of highconversion rate and low power consumption.

Owner:SHANGHAI JIAO TONG UNIV

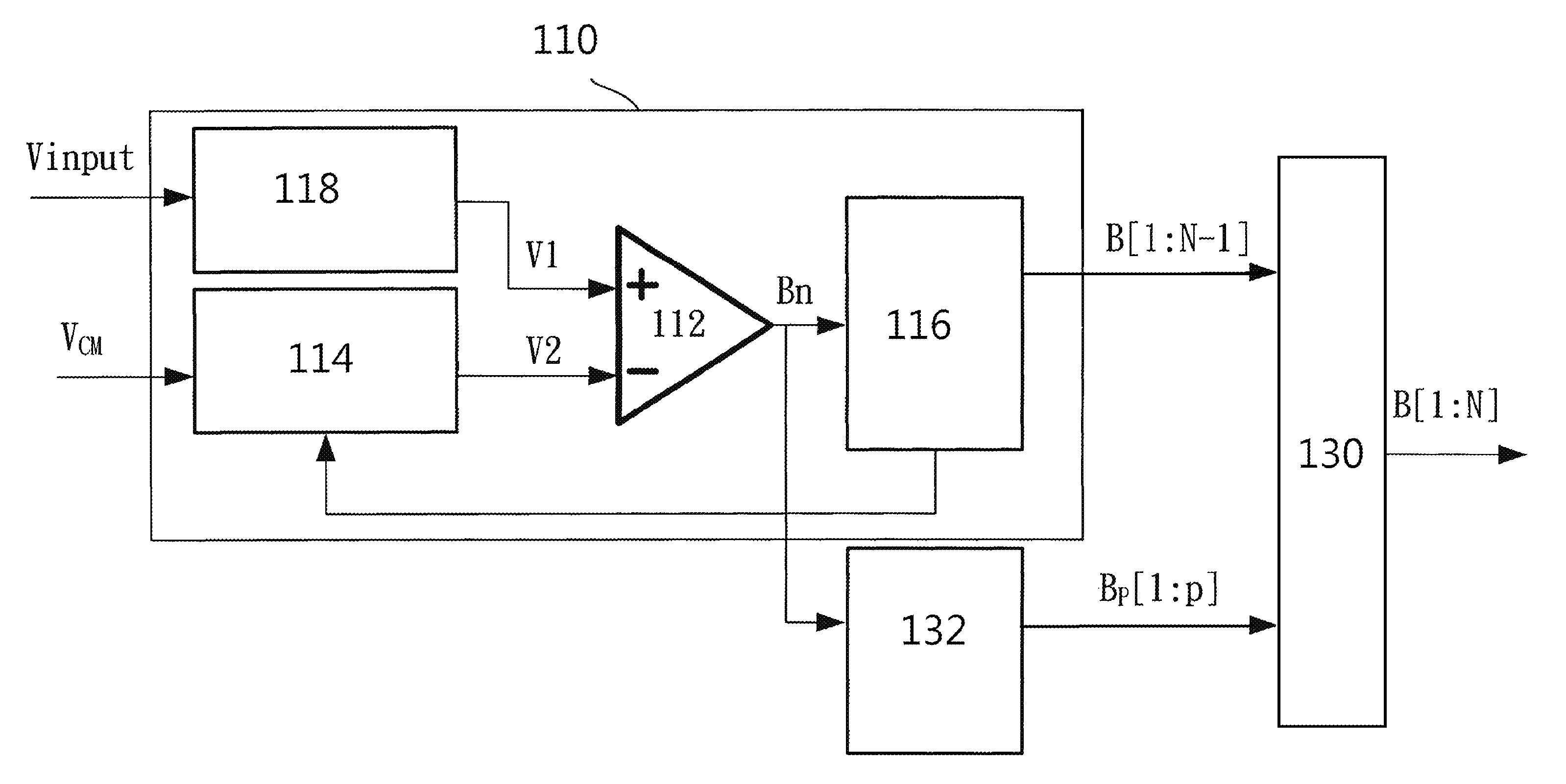

Method for digital error correction for binary successive approximation analog-to-digital converter (ADC)

ActiveUS9473162B2Electric signal transmission systemsAnalogue/digital/analogue conversionA d converterVoltage shift

An analog input voltage is converted to a digital code by, generating a first set of confirmed bits based on a first series of comparisons of an output of a digital-to-analog converter with the analog input voltage and generating a second set of confirmed bits based on a second series of comparisons of the output of the digital-to-analog converter with the analog input voltage. The first set of confirmed bits is independent of the second series of comparisons. The bits of the digital output code corresponding to the analog input voltage are generated based on the first set of confirmed bits, the second set of confirmed bits and a constant value representative of a voltage shift introduced in the digital-to-analog converter between the first series of comparisons and the second series of comparisons.

Owner:STMICROELECTRONICS INT NV

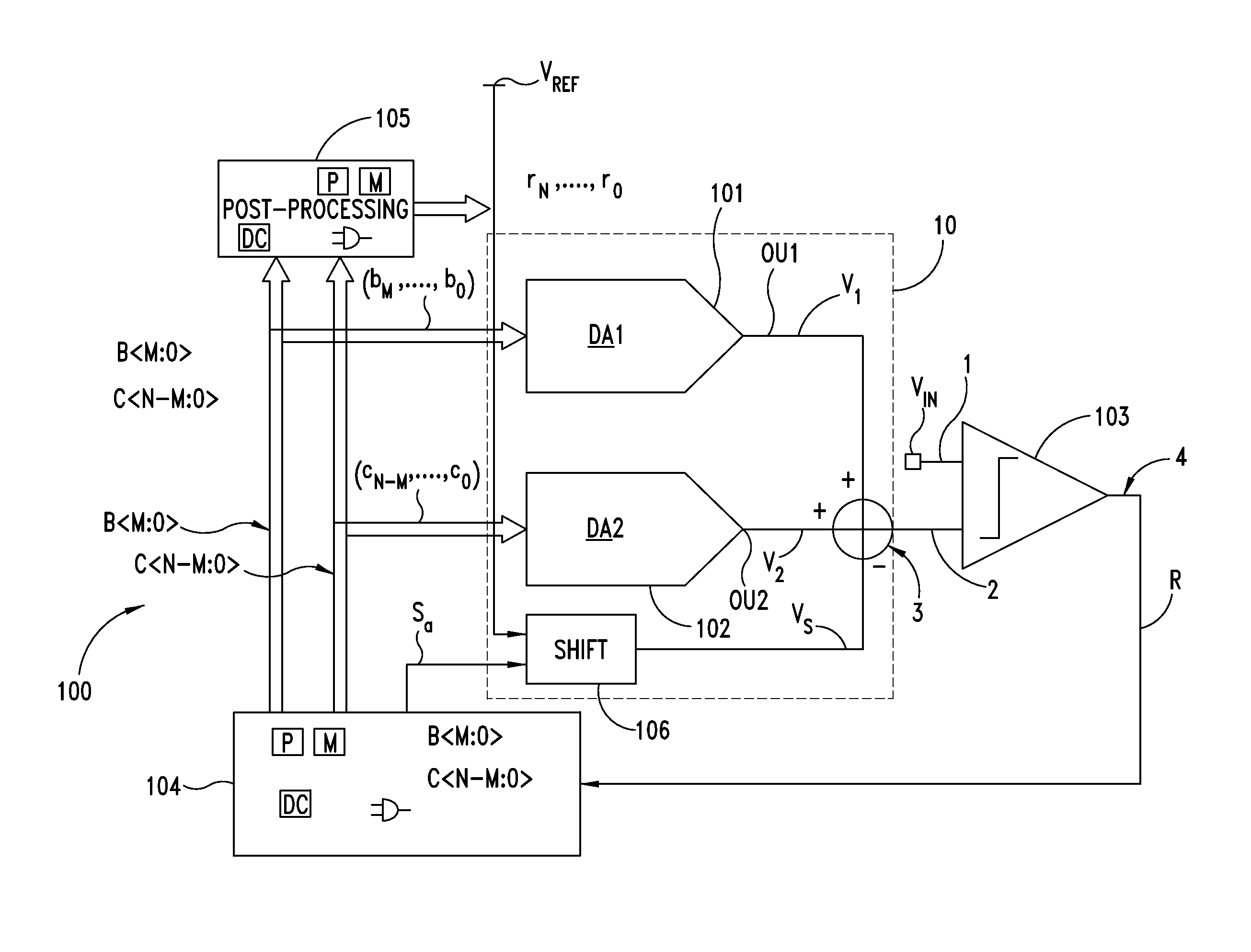

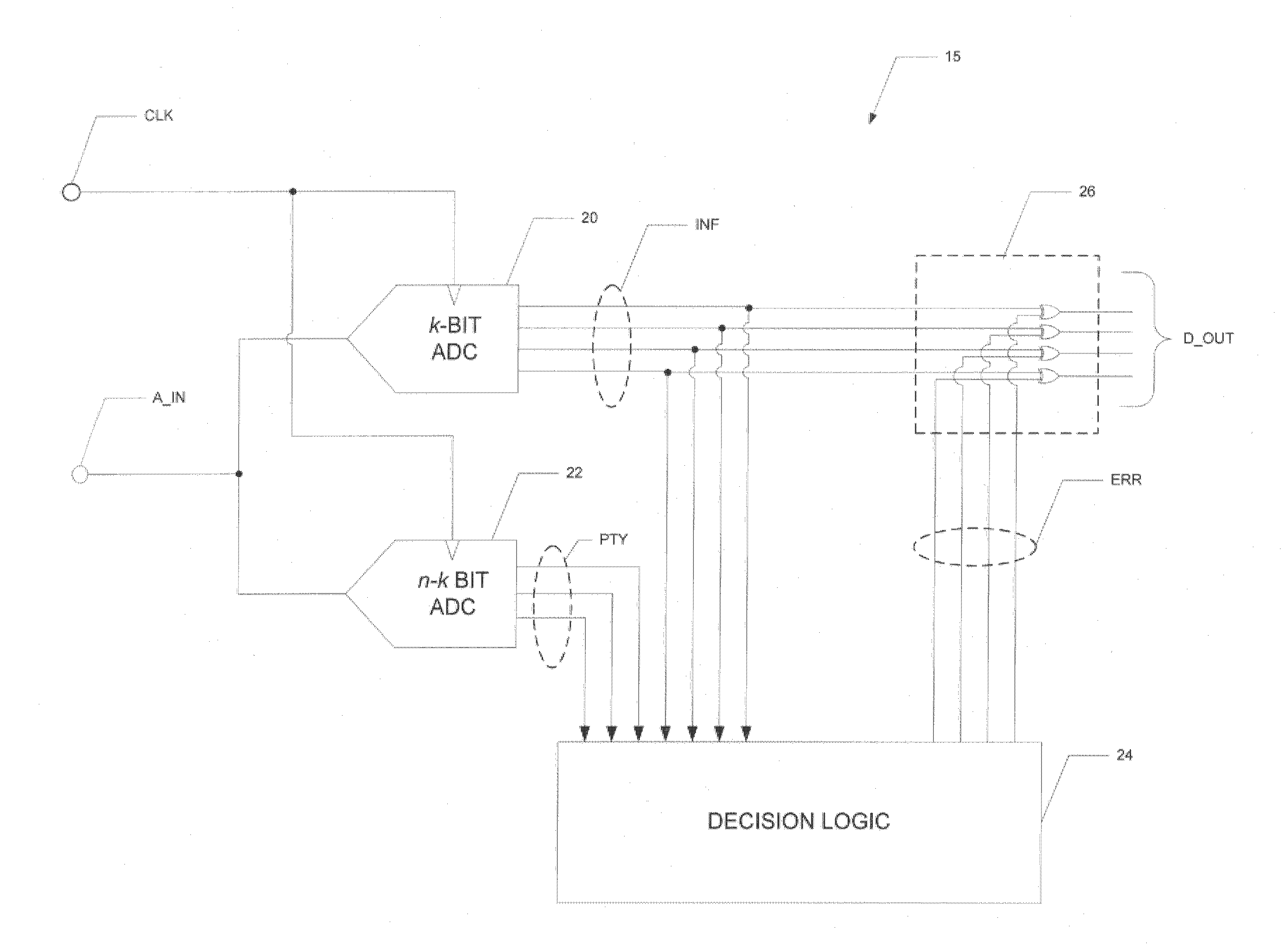

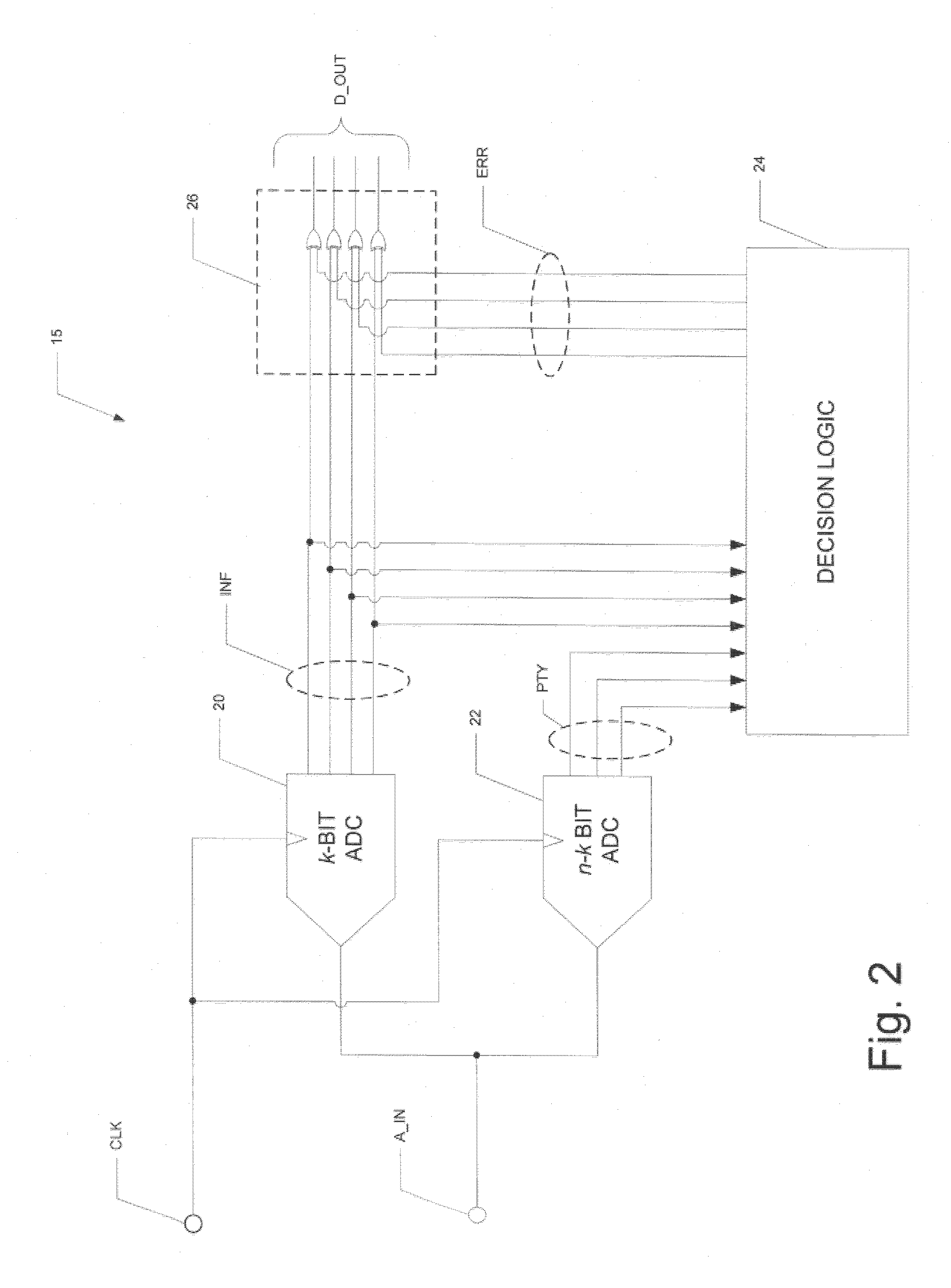

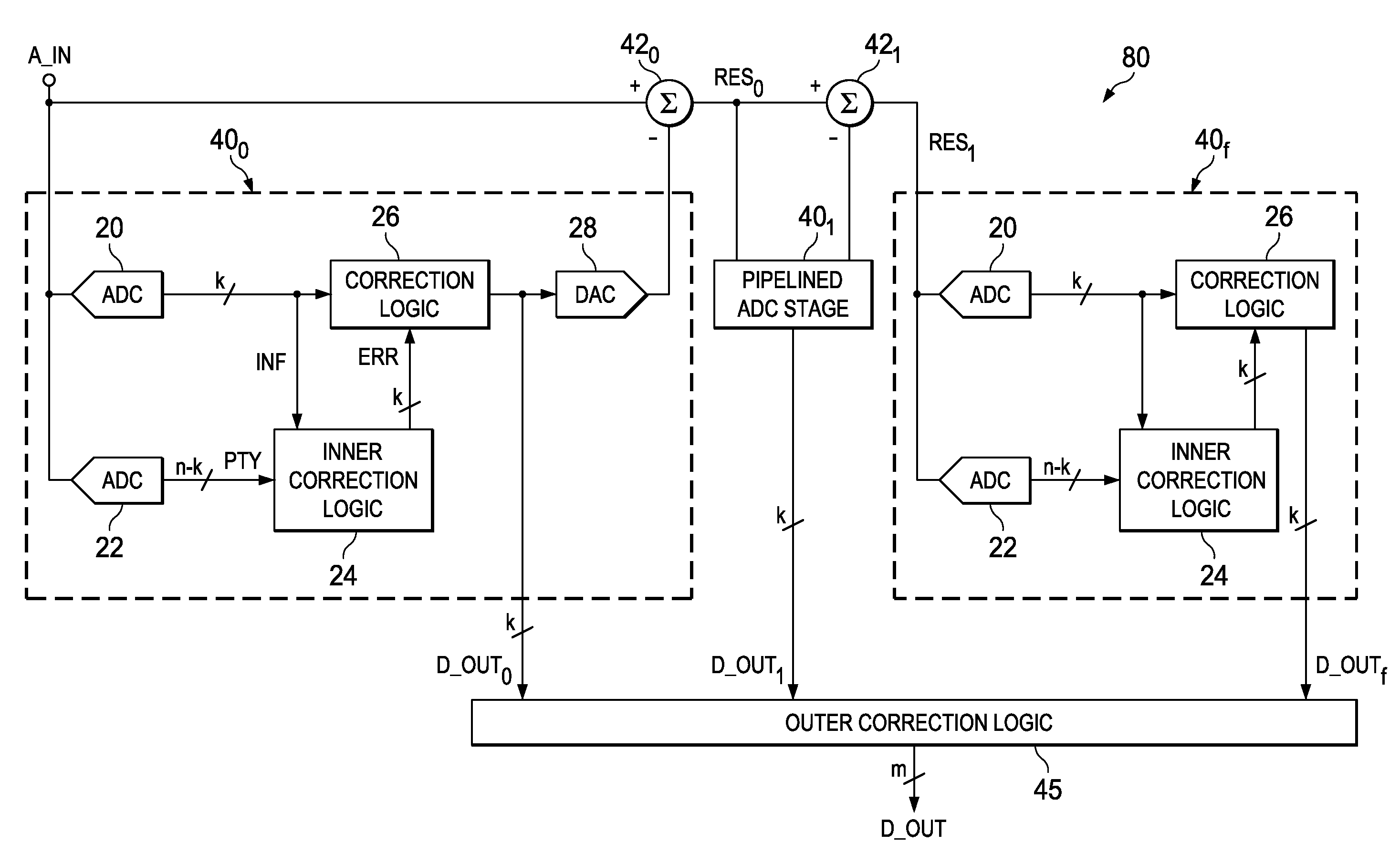

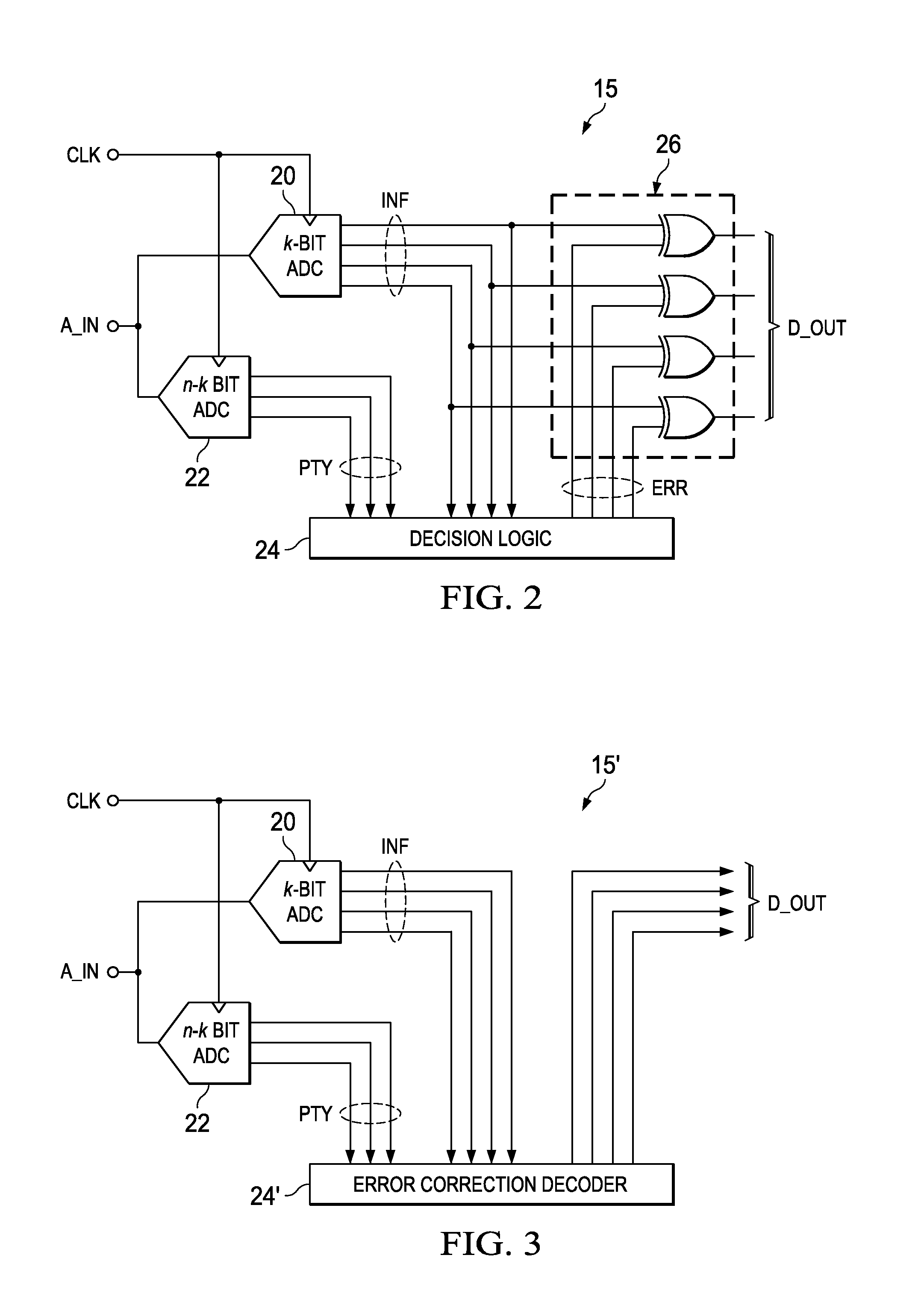

Digital Error Correction in an Analog-to-Digital Converter

ActiveUS20130106628A1High accuracy conversionModest circuit complexityElectric signal transmission systemsError preventionAnalog-to-digital converterConcatenation

An analog-to-digital converter (ADC) function in which digital error correction is provided. Parallel ADC stages are synchronously clocked to convert an analog input signal into digital words; at least one of the digital outputs is encoded according to an error correction code. Decision logic circuitry decodes a code word comprised of the concatenation of the digital outputs from the parallel stages, to derive a digital output from which the digital output word corresponding to the analog input signal can be derived. The decision logic circuitry can provide an error signal used to correct the state of one or more bits of the digital output from one of the ADC stages, for the case of a systematic code; alternatively, the decision logic circuitry can directly decode the code word to provide the digital output. The architecture may be applied to stages in a pipelined ADC.

Owner:TEXAS INSTR INC

ADC with digital error correction

ActiveUS7079059B2Electric signal transmission systemsDigital technique networkBinary multiplierA d converter

Interleaved Analogue to Digital converter, comprising a plurality of individual ADCs (71). A digital filter stage (20) is used for equalizing the responses of the individual ADCs, and comprises a FIR filter in which the coefficient table is cyclically reloaded between ADCs' samples, in order to reduce the number of multipliers required.

Owner:KEYSIGHT TECH

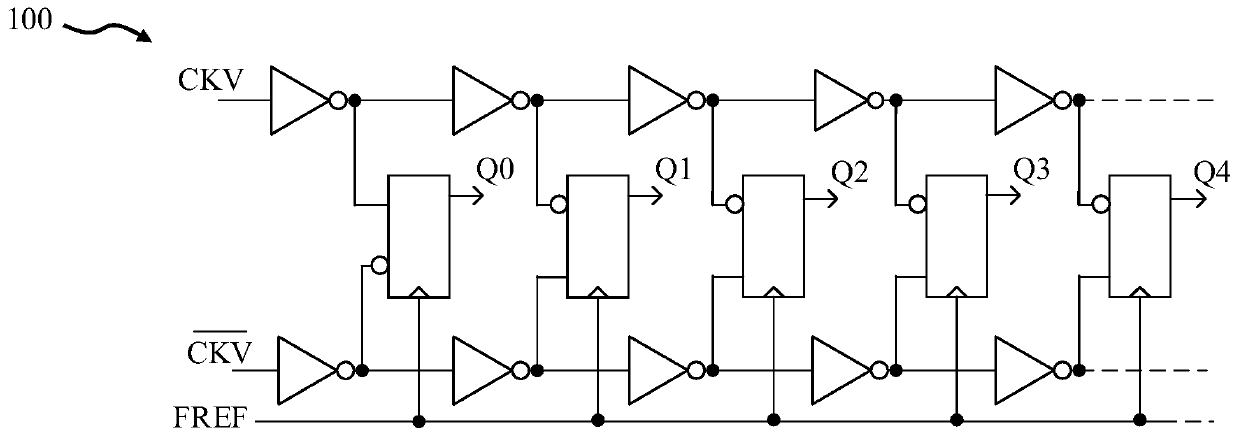

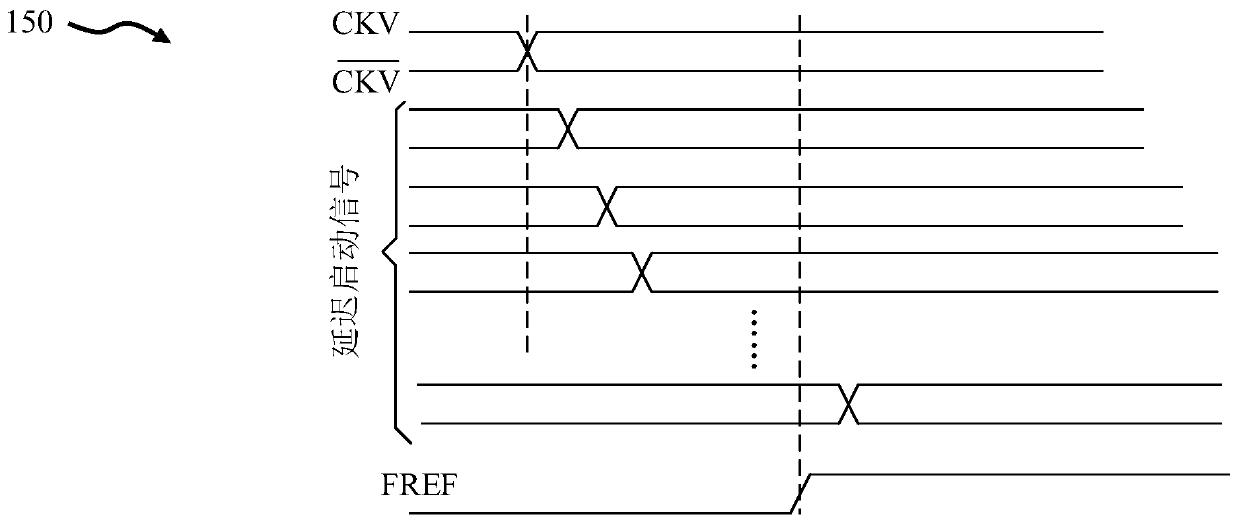

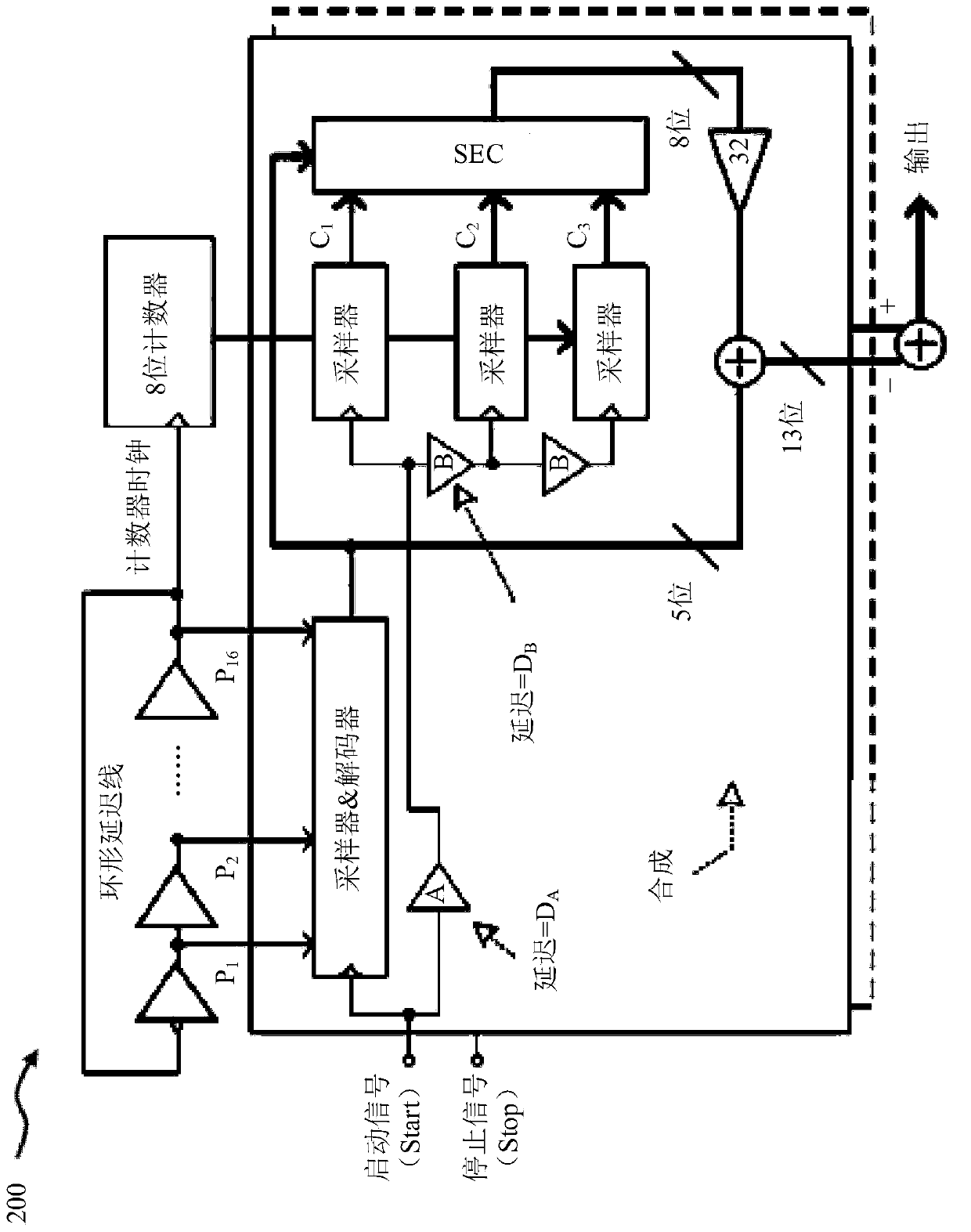

Time-to-digital converter

A time-to-digital converter (TDC) (300) is disclosed, which comprises a ring oscillator module (302) and a digital error correction module (304). The ring oscillator module is configured to receive asampling signal, an addressing signal, and a preset signal, and includes: a ring oscillator (3022) arranged with a plurality of inverters (3024); a phase sampler (3028) configured to sample phase signals generated by the inverters of the ring oscillator for generating a first output signal, on receipt of the sampling signal; a counter clock generator (3028) configured to generate first and secondclock signals, based on receipt of the sampling signal and respective phase signals generated by the first and last inverters of the ring oscillator; first and second counters (3030, 3032) configuredto respectively generate first and second counter output signals, based on receipt of the first and second clock signals respectively: and a data sampler (3034) configured to sample the first and second counter output signals to respectively generate second and third output signals. The digital error correction module is arranged to process the first, second and third output signals for generatinga digital signal representative of a time difference between receipt of a start signal and receipt of a stop signal by the TDC.

Owner:HUAWEI INT

Digital error correction in an analog-to-digital converter

ActiveUS8547257B2Improve accuracyModest circuit complexityElectric signal transmission systemsError preventionA d converterAnalog-to-digital converter

An analog-to-digital converter (ADC) function in which digital error correction is provided. Parallel ADC stages are synchronously clocked to convert an analog input signal into digital words; at least one of the digital outputs is encoded according to an error correction code. Decision logic circuitry decodes a code word comprised of the concatenation of the digital outputs from the parallel stages, to derive a digital output from which the digital output word corresponding to the analog input signal can be derived. The decision logic circuitry can provide an error signal used to correct the state of one or more bits of the digital output from one of the ADC stages, for the case of a systematic code; alternatively, the decision logic circuitry can directly decode the code word to provide the digital output. The architecture may be applied to stages in a pipelined ADC.

Owner:TEXAS INSTR INC

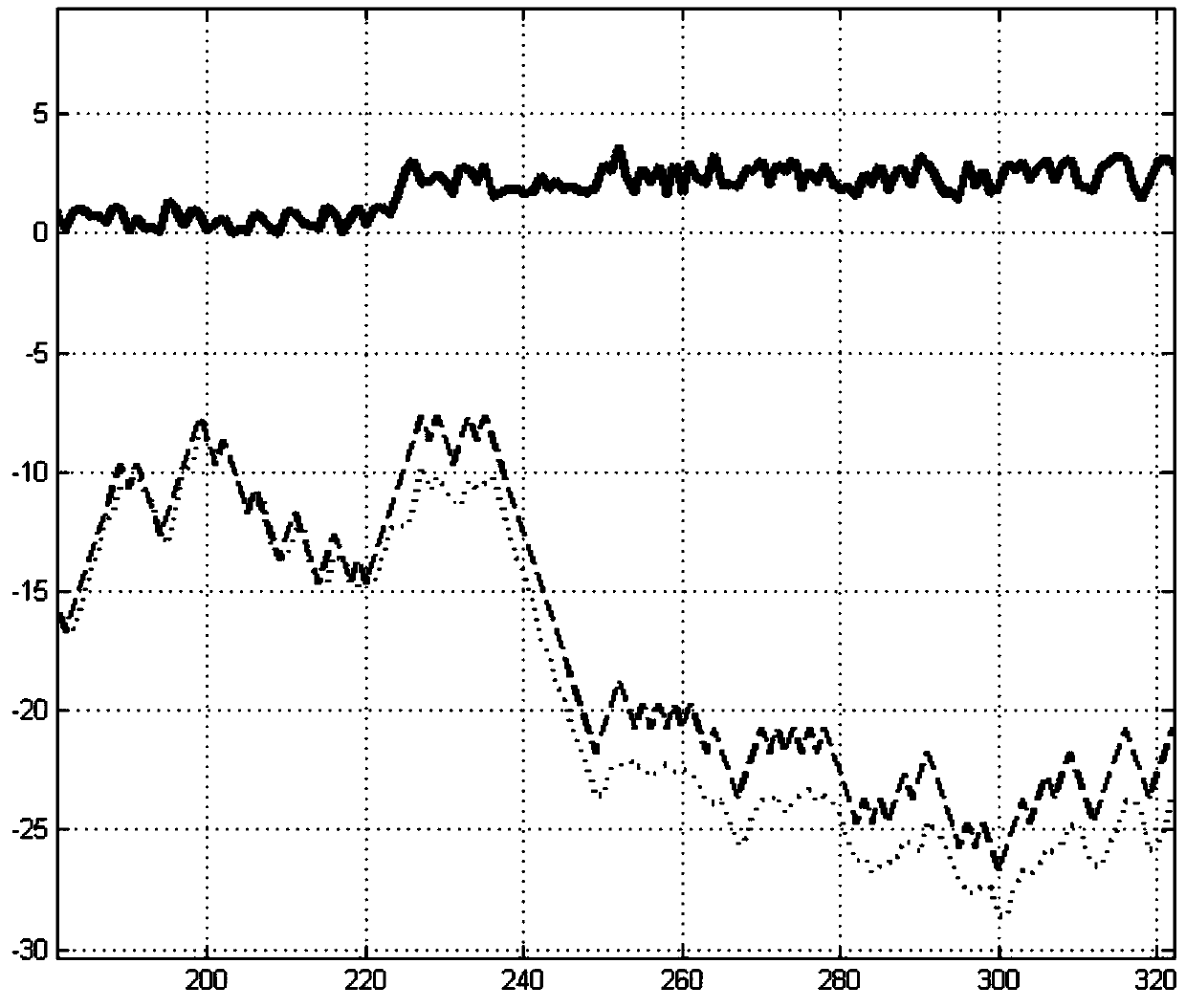

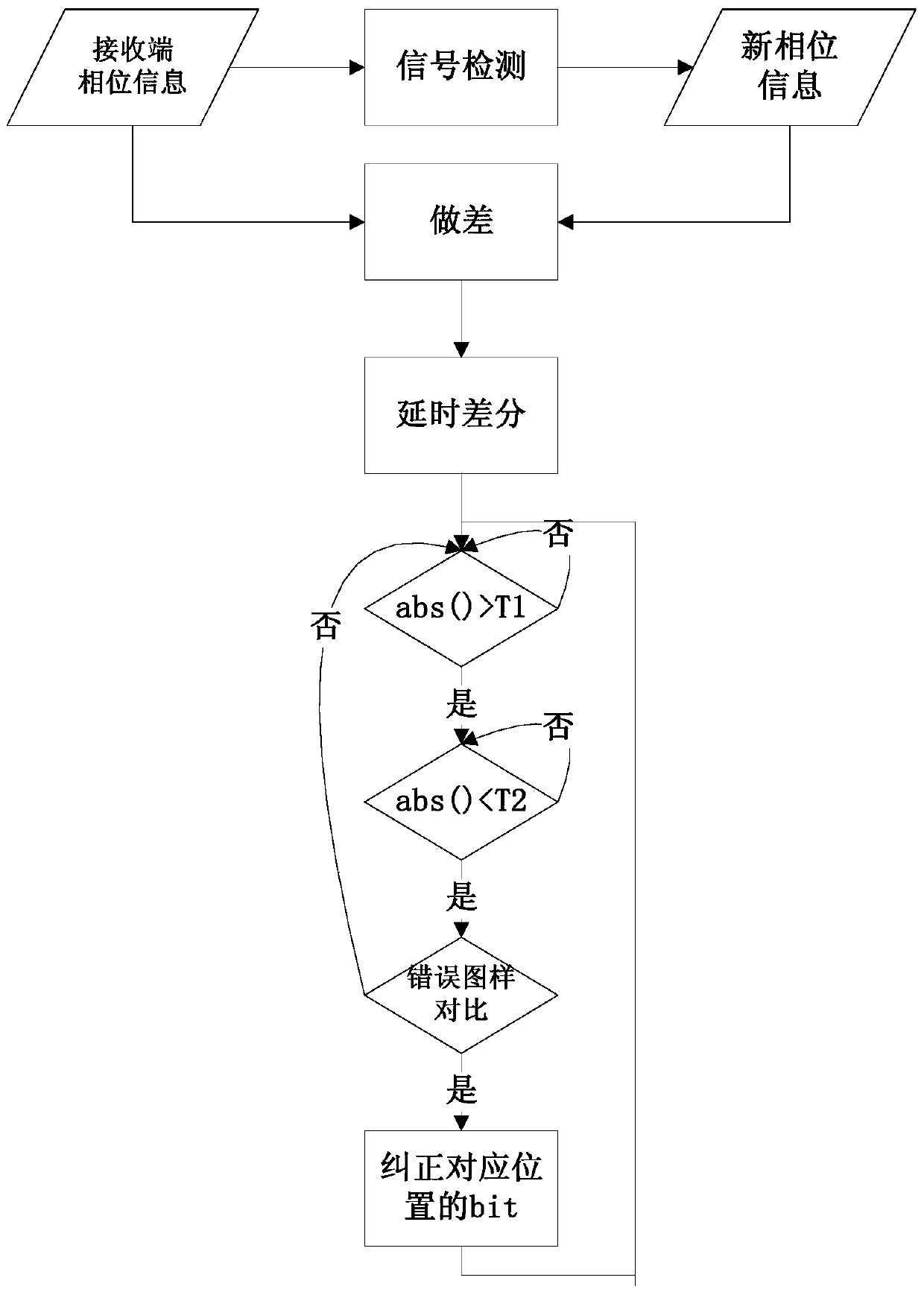

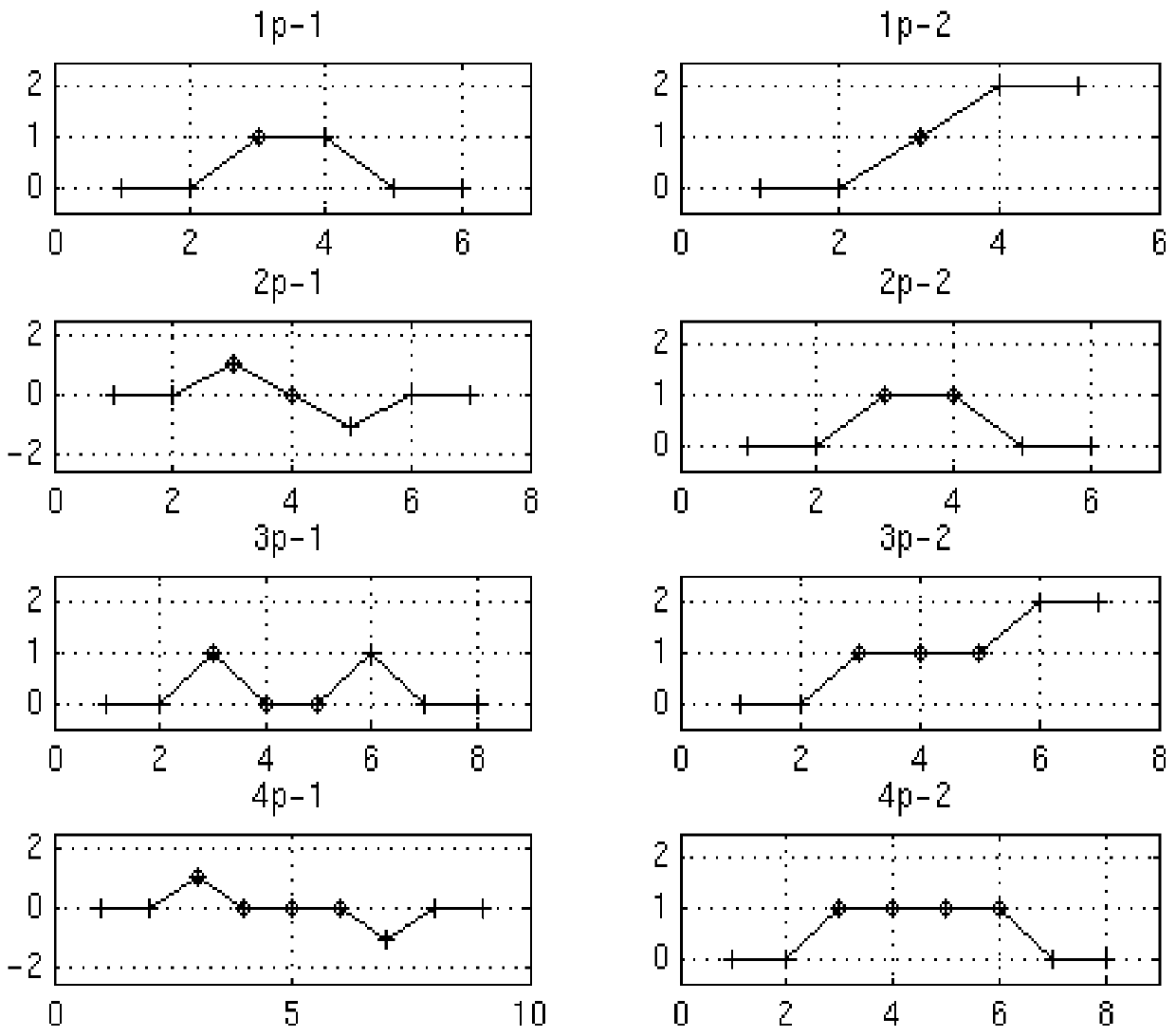

Digital detection and error correction algorithm for fsk modulation system

InactiveCN104702550BGood resistance to residual frequency deviationImprove error correction performanceError preventionFrequency-modulated carrier systemsCorrection algorithmDifferential phase

The invention relates to a digital detection and error correction algorithm for FSK modulation system, which includes the following steps: the first step: extracting the original phase information from the received data; the second step: performing signal detection to obtain the received signal; the second step Step 3: Calculate new phase information; Step 4: Compare and make difference to obtain differential phase information; Step 5: Delay difference to obtain the difference of differential phase information; Step 6: Determine whether the difference of differential phase information exceeds the first Threshold, if it is, enter the error correction state, otherwise continue to judge; the seventh step: in the error correction state, judge whether the influence of the error bit is over, if it is, obtain the receiving error pattern, if not, then continue to judge; the eighth step: set The received error pattern is compared with the known error pattern to determine the position of the error bit. The error correction method of the invention has better ability to resist residual frequency deviation, improves error correction performance, and ensures high precision of detection results.

Owner:中科威发半导体(苏州)有限公司

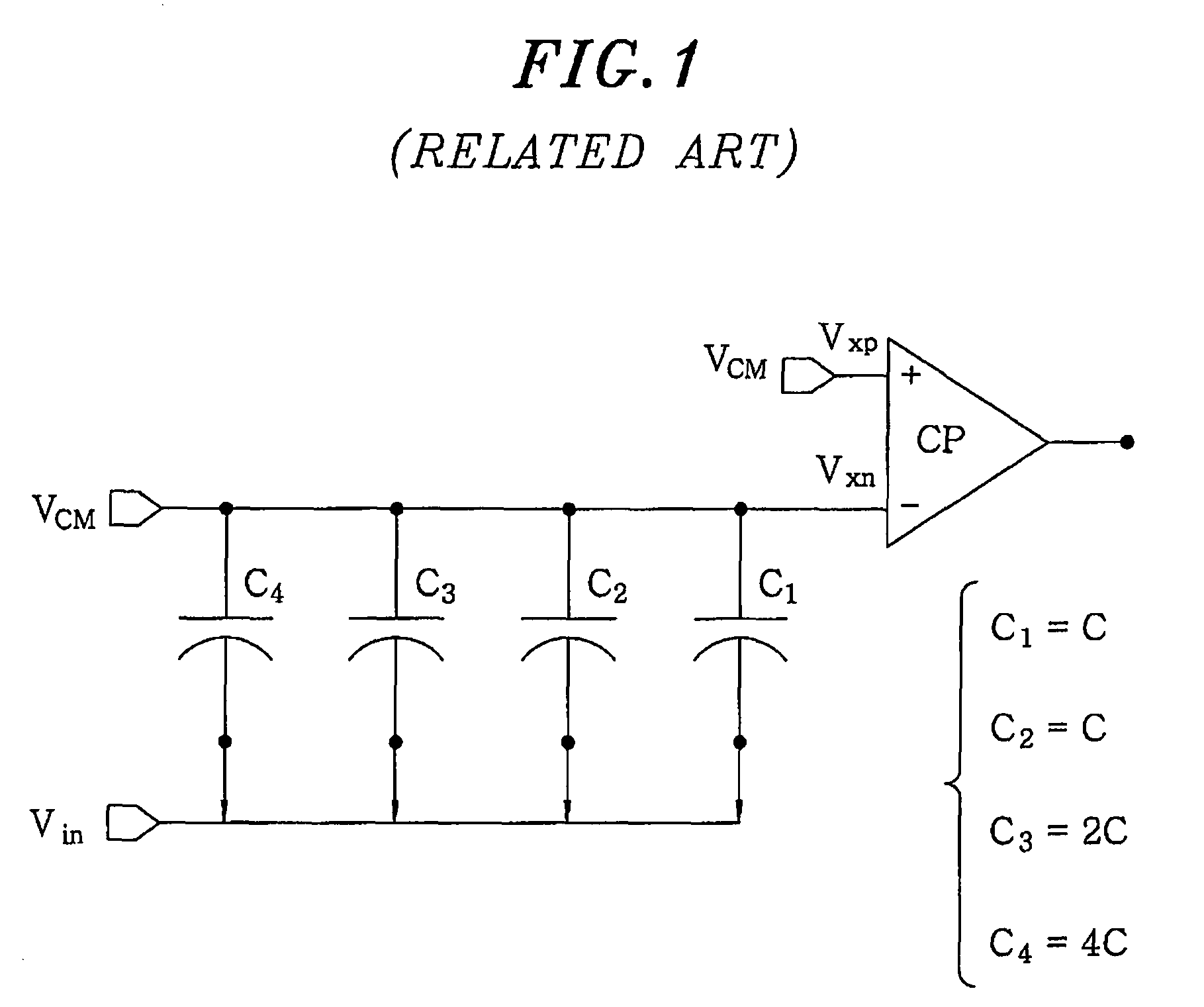

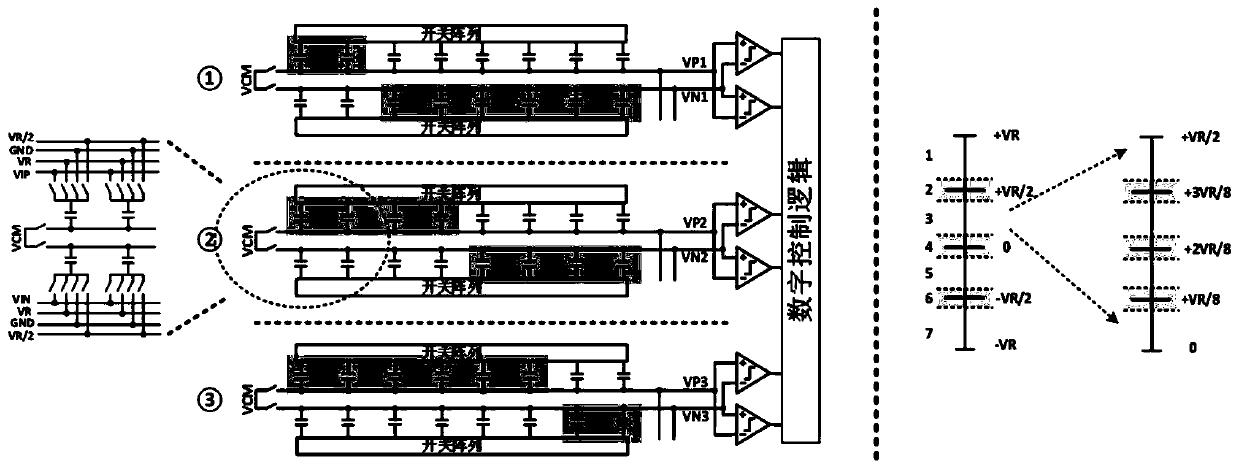

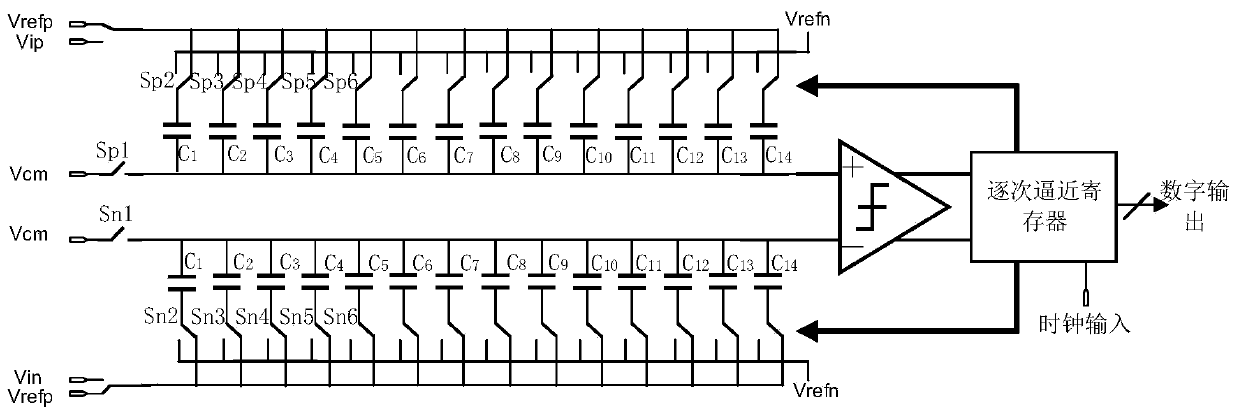

A high-precision array analog-to-digital converter for cmos image sensors

InactiveCN107172372BReduced dynamic performanceMinimize dynamic performance degradationTelevision system detailsColor television detailsAnalog circuit designCapacitance

The invention discloses a high-precision array analog-to-digital converter applied to a CMOS image sensor, which belongs to the technical field of analog circuit design and includes a sample-and-hold circuit, a comparator, a digital-to-analog converter, a successive approximation register, and a digital error correction circuit; The analog-to-digital converter described above adopts a fully differential structure. The input signal is output to the top board of the capacitor array through a sample-and-hold circuit and connected to the input terminal of the comparator. The output terminal of the comparator is connected to the successive approximation register. The successive approximation register controls the capacitor array according to the result of the comparator And store it, and output it to the digital error correction circuit to get the final binary output. In the present invention, the capacitor array is divided into three capacitor arrays, wherein each capacitor array adopts a non-binary redundant capacitor architecture design, and the incomplete establishment of the circuit, the jitter and noise of the reference voltage and the metastable state of the dynamic comparator are caused There is a degree of tolerance for comparison errors. A dynamic comparator is also used without quiescent current, which effectively reduces the power consumption of the overall circuit.

Owner:JILIN UNIV

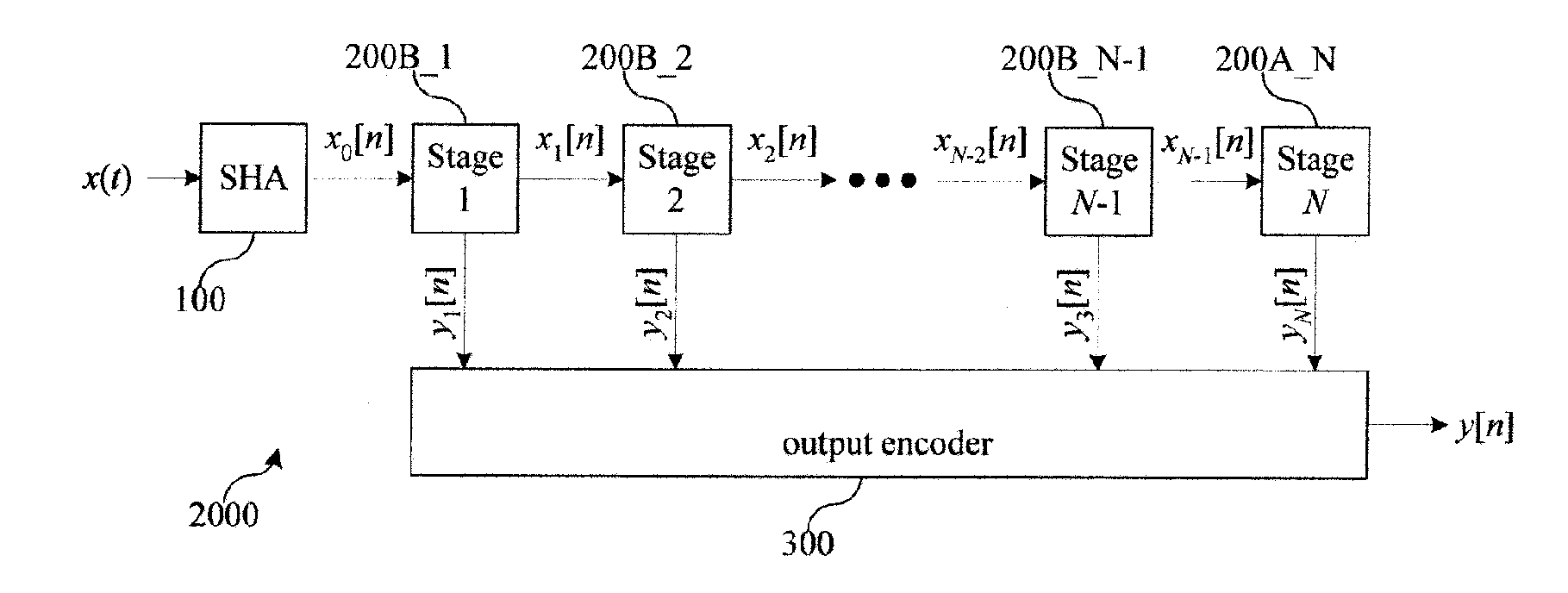

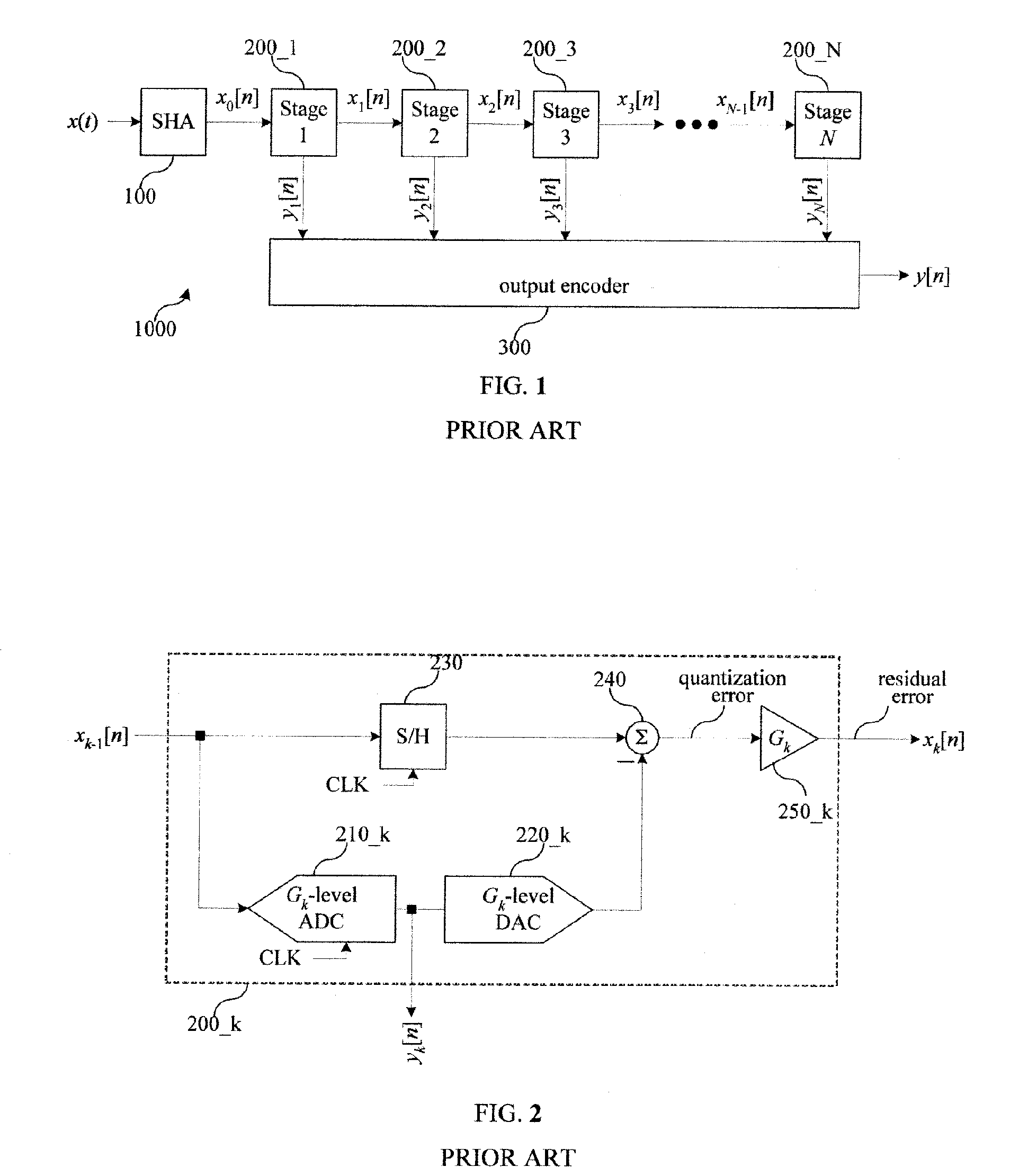

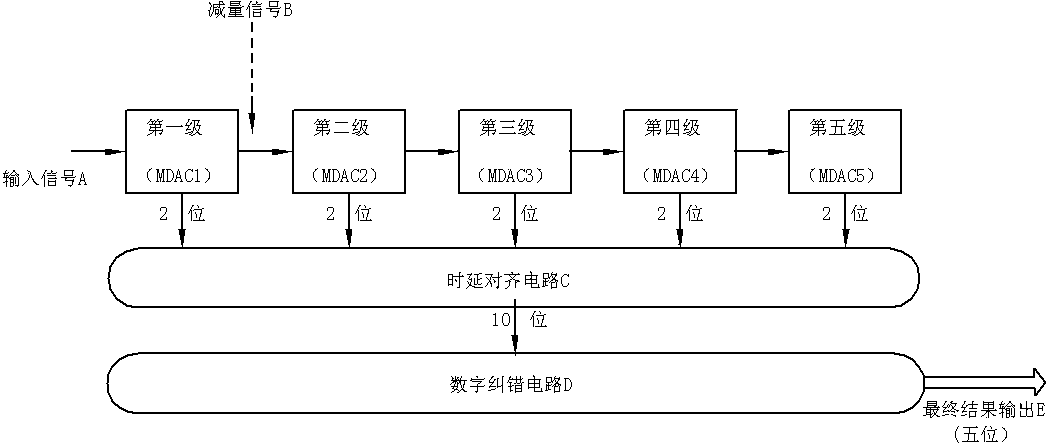

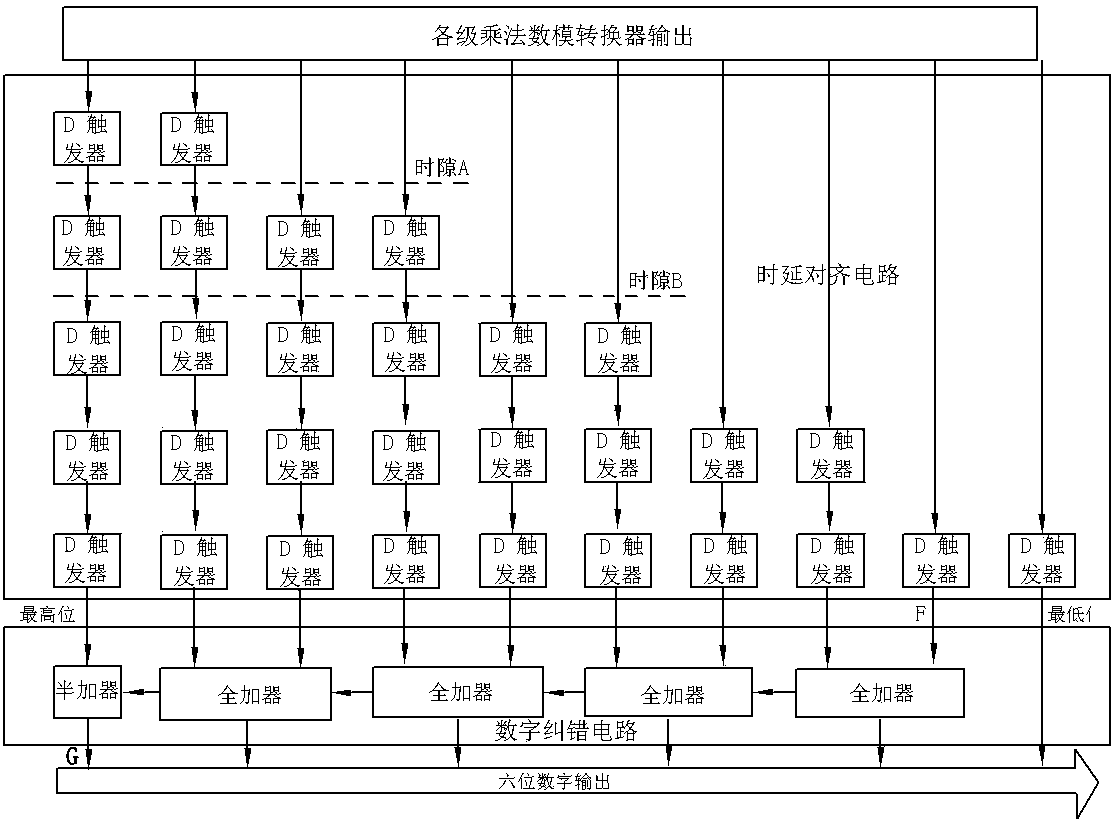

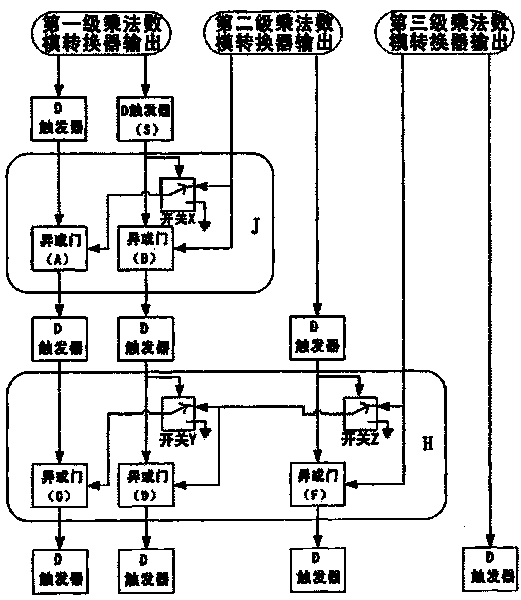

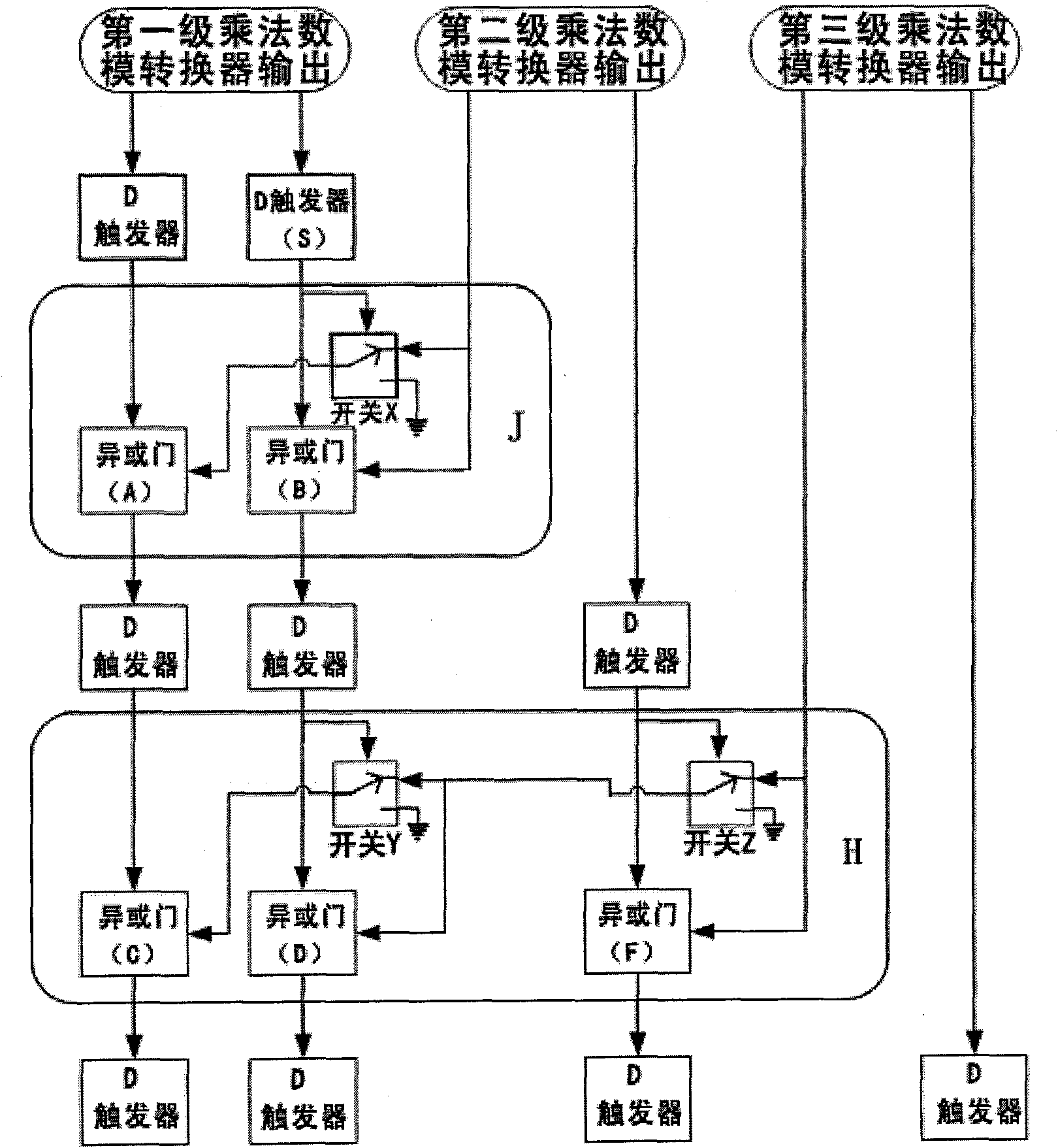

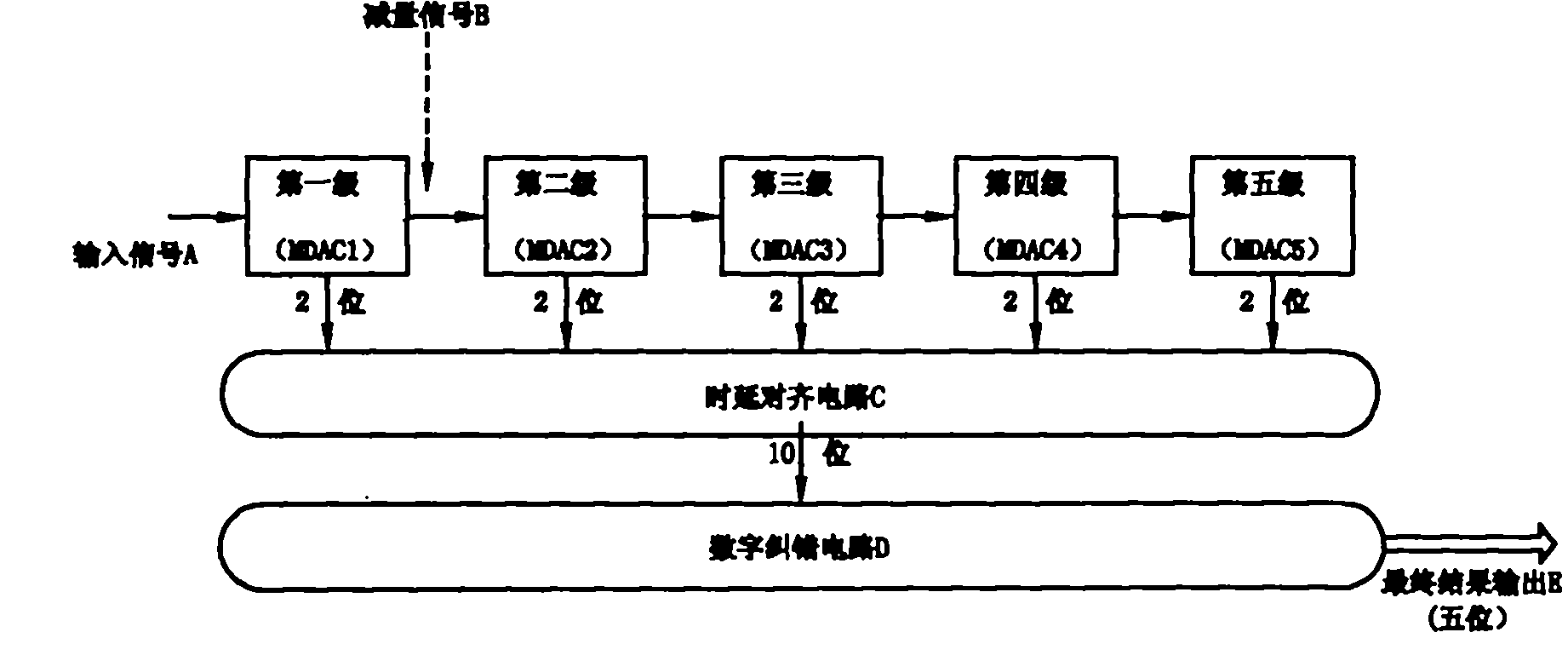

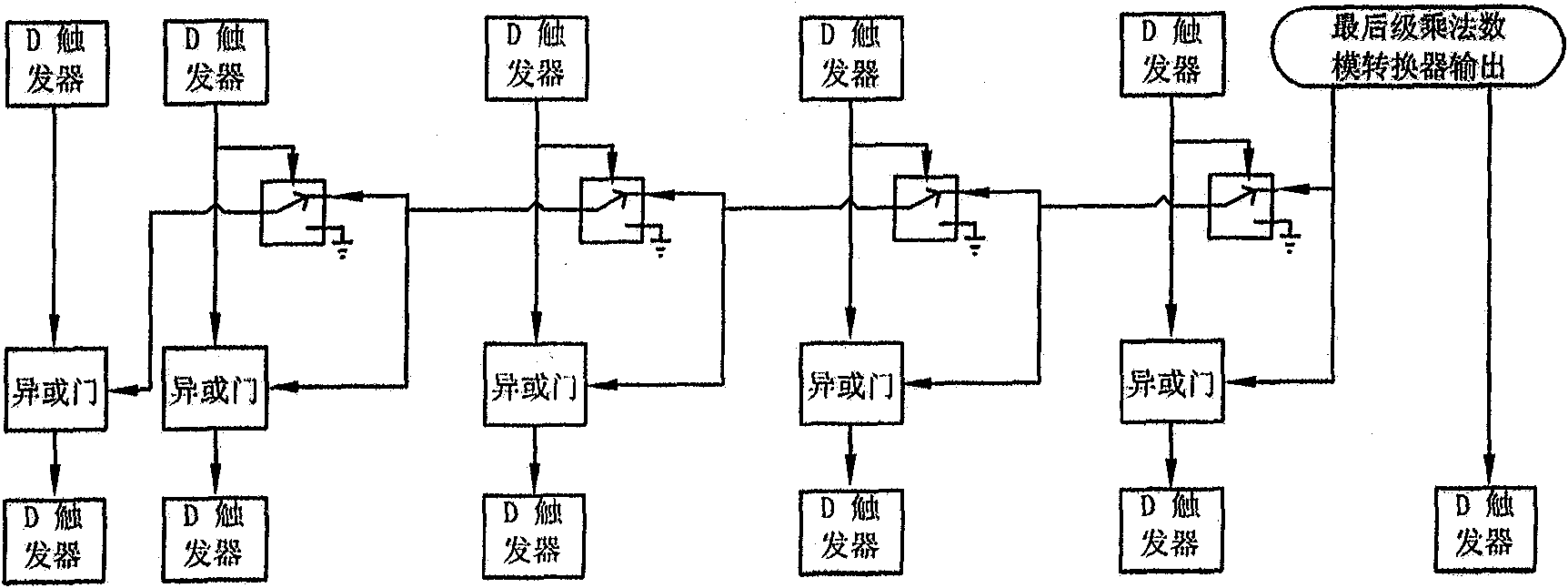

A time-sharing digital error correction circuit for a high-speed pipelined analog-to-digital converter

ActiveCN101807921BReduce Design ComplexityControl areaAnalogue-digital convertersAnalogue/digital conversion calibration/testingTime delaysAnalog signal

The invention provides a time-sharing digital error correction circuit device of a high-speed flow line type analog-digital converter, which meets the requirement of the extreme converting rate on transmission delay, can provide a simplified digital error correction circuit, effectively controls the chip area, reduces the complexity of the circuit design and improves the design efficiency. Analog signals are input to each level of multiplication digital-analog conversion circuit device, and the output signals of each level of multiplication digital-analog conversion circuit device comprise a high order and a low order. The invention is characterized in that by utilizing a delay link gap in time delay alignment, high orders output by the current level of multiplication digital-analog conversion circuit and all orders output by all preceding level of multiplication digital-analog conversion circuits are respectively processed by digital error correction in the respective level of digital error correction circuit, and then the high order output by the next level of multiplication digital-analog conversion circuit is processed by digital error correction by entering the next level of digital error correction circuit until complete output digital signals are finally output to finish complete digital-analog conversion.

Owner:杭州思泰微电子有限公司

digital error correction

An error correction circuit comprising: a component, an error detector, a correction generator and an output generator, wherein the component is arranged to generate a first output from a first input and a second input; the error detector is arranged to generate a first output based on said first output, said first input and said second input generate an error flag indicating whether an error has been detected in said first output; said correction generator being adapted to an output, said first input and said second input, to generate a corrected output after a first time period starting from a timing event; said output generator is arranged to follow a second time period starting from a timing event An output of an error correction circuit is produced. If the error flag indicates that an error has been detected in the first output, the second time period may be longer than the first time period, otherwise the second time period may not be longer than the first time period long. If the error flag indicates that an error has been detected in the first output, the output of the error correction circuit may comprise a combination of the first output and the corrected output such that an error detected in the first output The detected error is corrected, otherwise the output of the error correction circuit may correspond directly to the first output.

Owner:OXFORD BROOKES UNIVERSITY

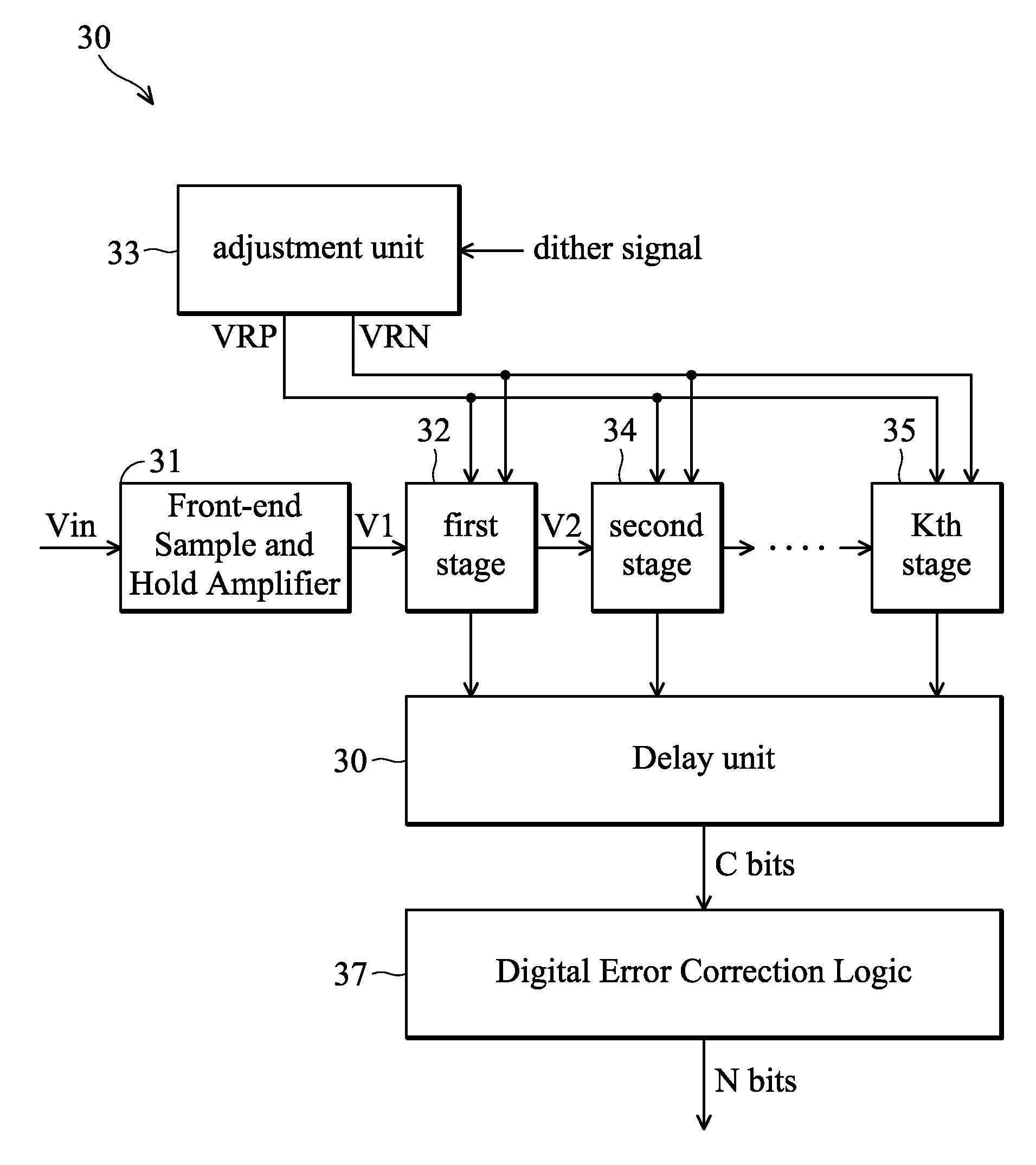

Analog to digital converter

InactiveUS20100309038A1Electric signal transmission systemsAnalogue-digital convertersDigital down converterAnalog-to-digital converter

An analog to digital converter is provided. The converter comprises a first stage, an adjustment unit and a digital error correction logic. The first stage has a first sensing range and receives a first voltage to generate a first digital code. The adjustment unit adjusts the first sensing range of the first stage. The digital error correction logic receives and corrects the first digital code to generate a digital code corresponding to the first voltage.

Owner:HIMAX MEDIA SOLUTIONS

Time-sharing digital error correction circuit device of high-speed flow line type analog-digital converter

ActiveCN101807921AReduce Design ComplexityControl areaAnalogue-digital convertersAnalogue/digital conversion calibration/testingDigital down converterTime delays

The invention provides a time-sharing digital error correction circuit device of a high-speed flow line type analog-digital converter, which meets the requirement of the extreme converting rate on transmission delay, can provide a simplified digital error correction circuit, effectively controls the chip area, reduces the complexity of the circuit design and improves the design efficiency. Analog signals are input to each level of multiplication digital-analog conversion circuit device, and the output signals of each level of multiplication digital-analog conversion circuit device comprise a high order and a low order. The invention is characterized in that by utilizing a delay link gap in time delay alignment, high orders output by the current level of multiplication digital-analog conversion circuit and all orders output by all preceding level of multiplication digital-analog conversion circuits are respectively processed by digital error correction in the respective level of digital error correction circuit, and then the high order output by the next level of multiplication digital-analog conversion circuit is processed by digital error correction by entering the next level of digital error correction circuit until complete output digital signals are finally output to finish complete digital-analog conversion.

Owner:杭州思泰微电子有限公司

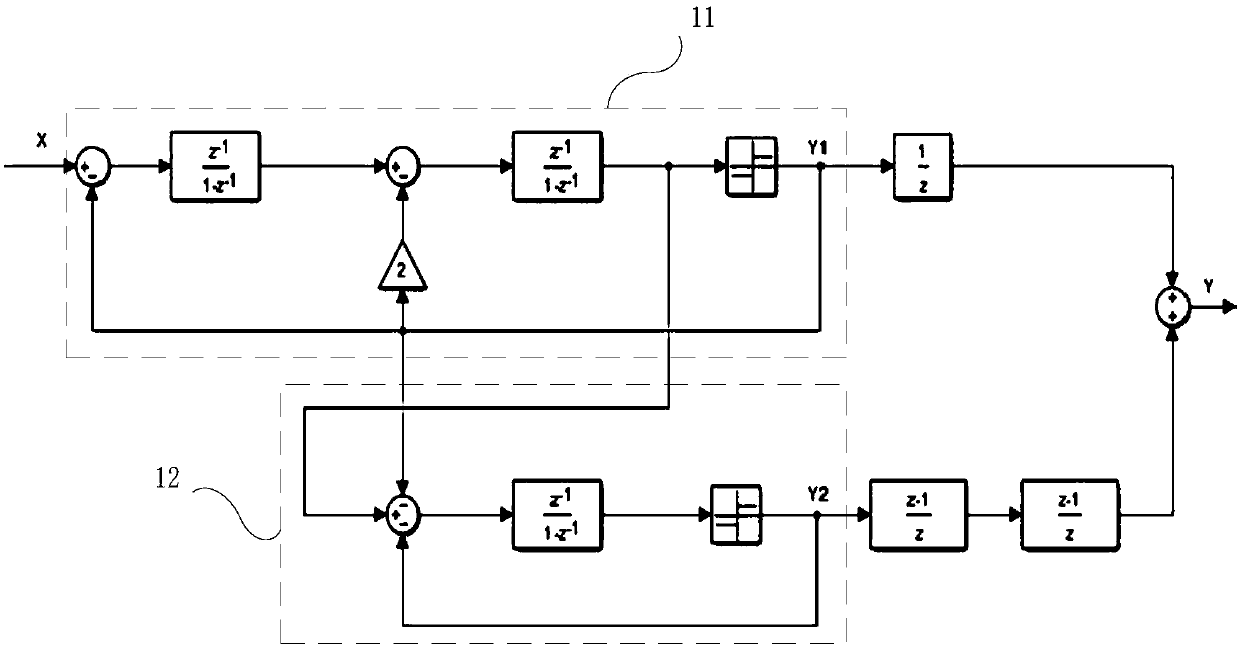

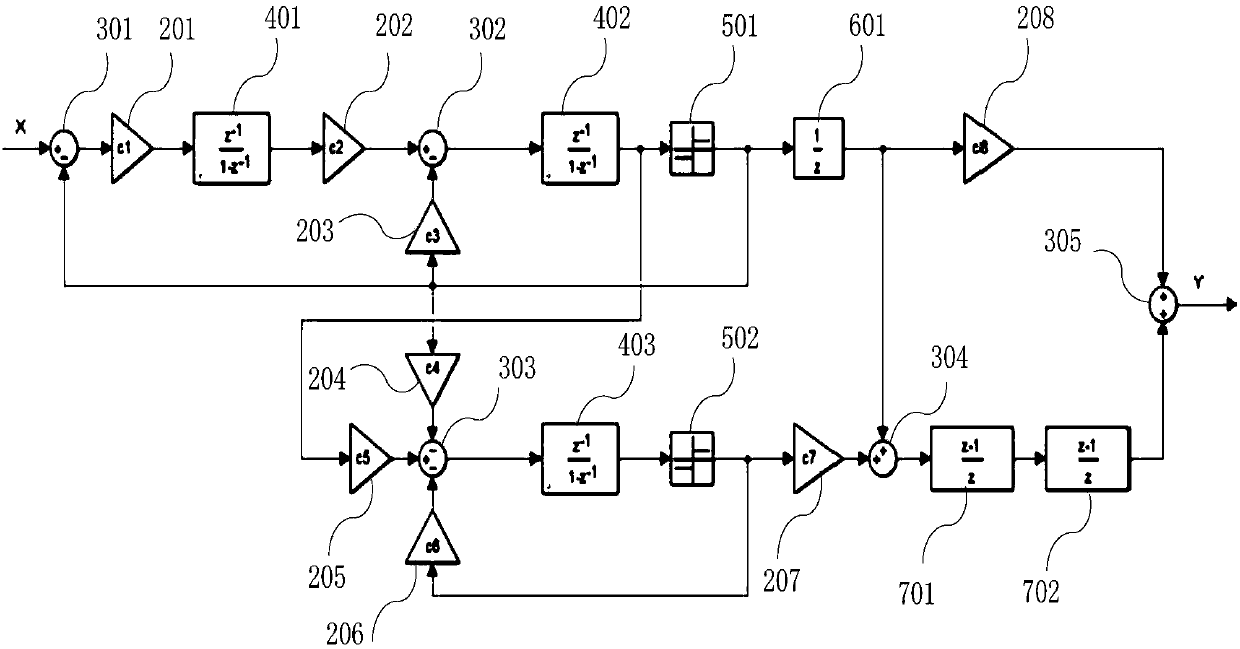

Modulator of 2-1 type MASH structure

InactiveCN109672448AImproved noise suppressionImprove pole-zero positionAnalogue conversionSignal-to-noise ratio (imaging)Engineering

The invention relates to the field of analog-to-digital circuits. For the problem that the signal-to-noise ratio of the modulator of the existing 2-1 type MASH structure is low, a modulator of 2-1 type MASH structure is proposed, which sets appropriate gain parameters in the modulator of the existing 2-1 type MASH structure to adjust the noise transfer function (NTF) of the modulator to improve the position of the zero pole, so that the quantization noise of the first stage is canceled out through the digital error correction logic due to the output of a first-stage modulator and the output ofa second-stage modulator, and the noise suppression effect within the signal bandwidth is enhanced. The structure is applicable to modulators in analog-to-digital conversion of audios.

Owner:SICHUAN CHANGHONG ELECTRIC CO LTD

Analog to digital converter

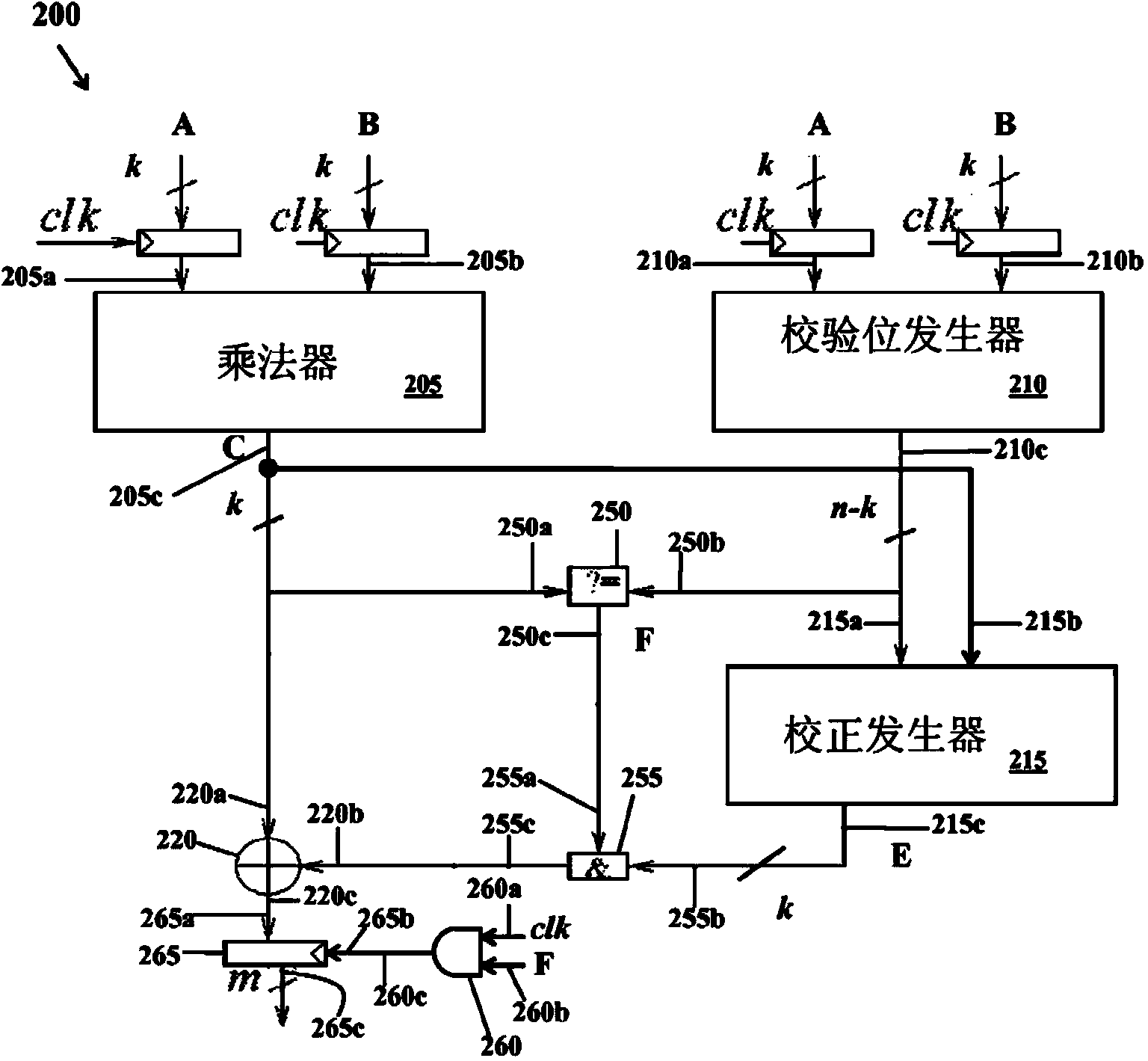

InactiveUS20100283646A1Electric signal transmission systemsAnalogue-digital convertersAnalog to information converterDigital error correction

An analog to digital converter is provided. The converter comprises a dither gain generator, a first stage, a multiplier, a second stage and a digital error correction logic. The dither gain generator generates a dither gain. The first stage receives a first voltage to generate a first digital code and a second voltage. The multiplier is coupled to the first stage and multiplies the second voltage with the dither gain to generate a third voltage. The second stage receives the third voltage to generate a second digital code. The digital error correction logic receives and corrects the first digital code and the second digital code to generate a digital code corresponding to the first voltage.

Owner:HIMAX MEDIA SOLUTIONS