Patents

Literature

404 results about "4-bit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computer architecture, 4-bit integers, memory addresses, or other data units are those that are 4 bits wide. Also, 4-bit CPU and ALU architectures are those that are based on registers, address buses, or data buses of that size. A group of four bits is also called a nibble and has 2⁴ = 16 possible values.

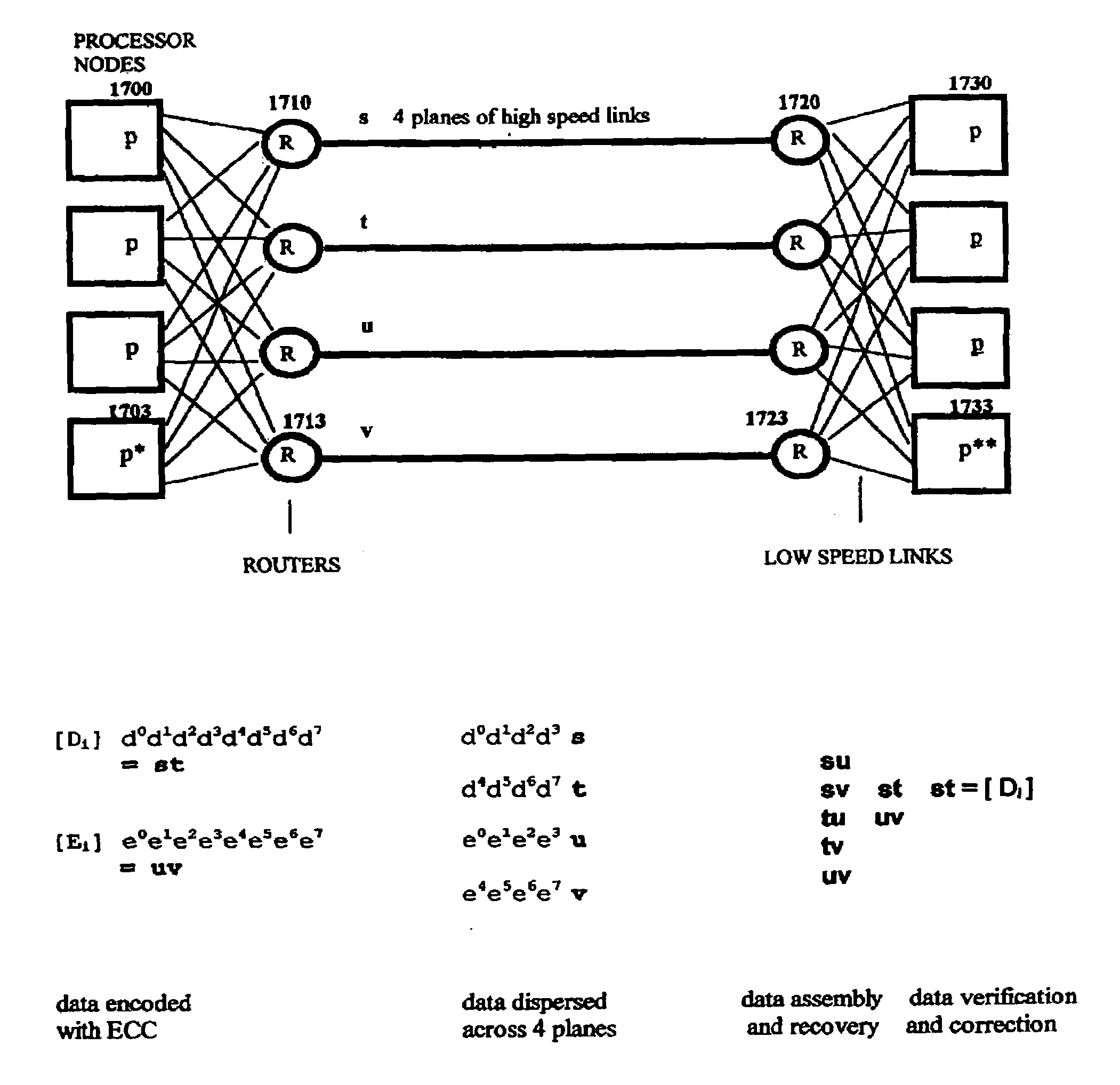

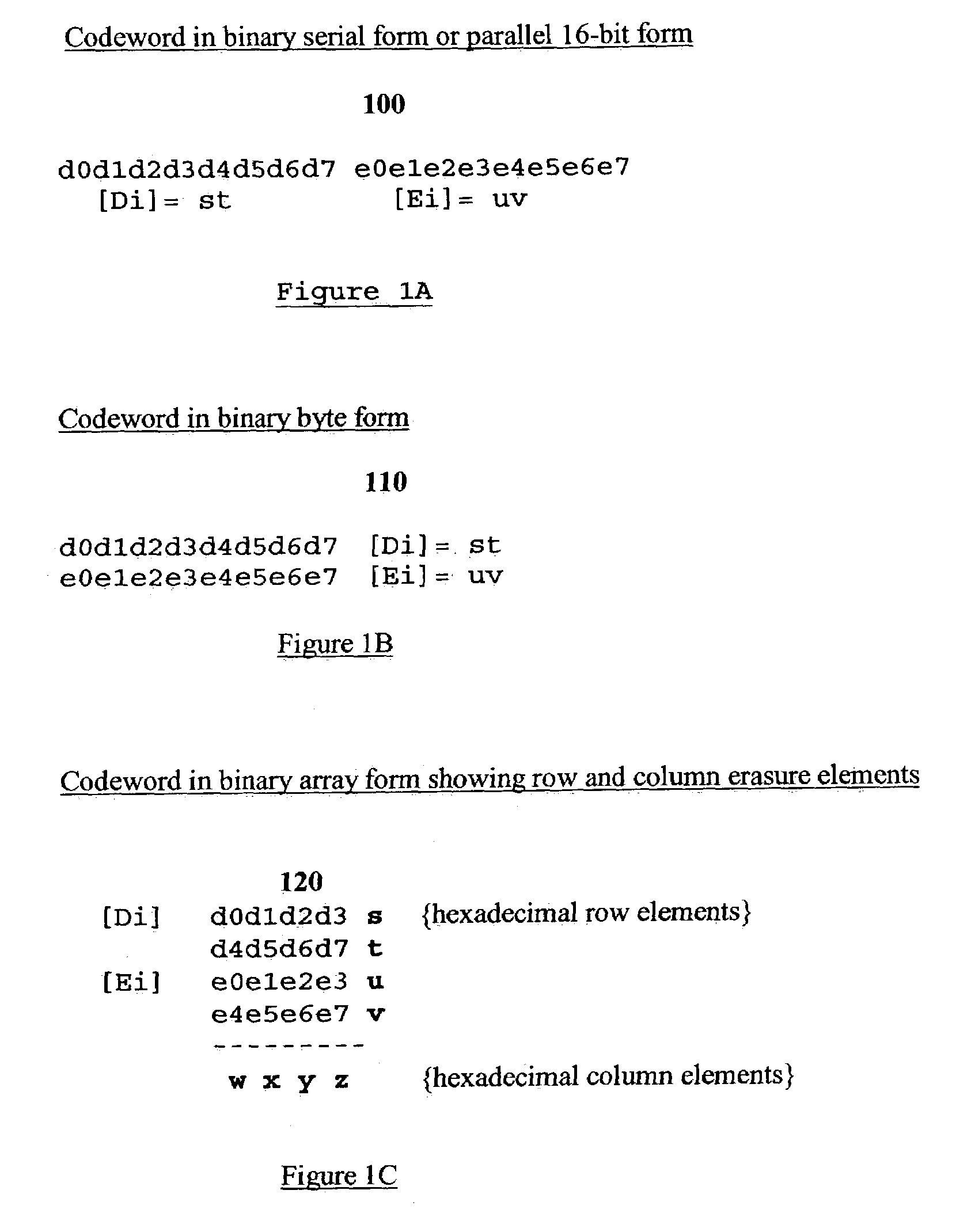

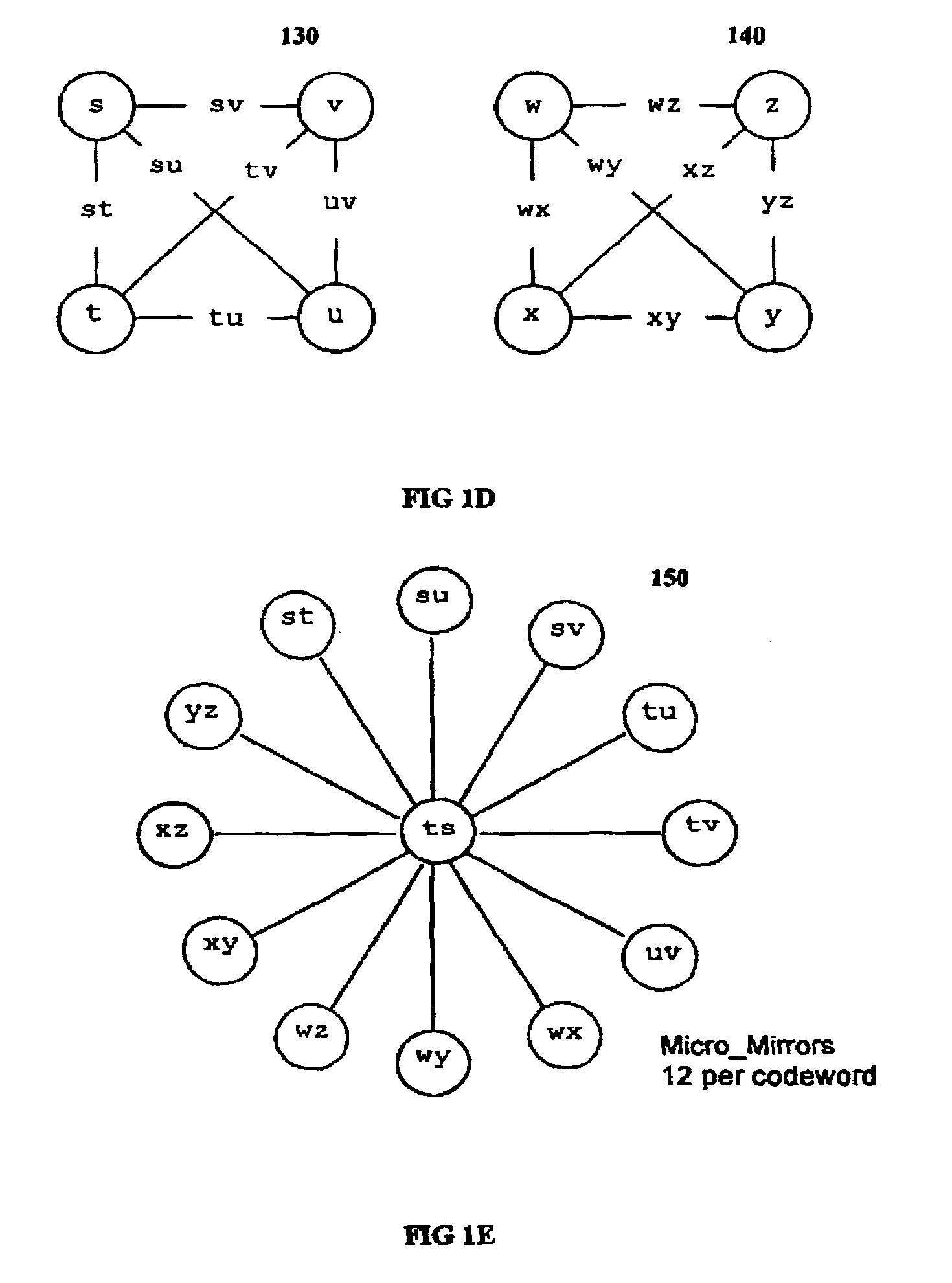

Multi-dimensional data protection and mirroring method for micro level data

ActiveUS7103824B2Detection errorLow common data sizeCode conversionCyclic codesData validationData integrity

The invention discloses a data validation, mirroring and error / erasure correction method for the dispersal and protection of one and two-dimensional data at the micro level for computer, communication and storage systems. Each of 256 possible 8-bit data bytes are mirrored with a unique 8-bit ECC byte. The ECC enables 8-bit burst and 4-bit random error detection plus 2-bit random error correction for each encoded data byte. With the data byte and ECC byte configured into a 4 bit×4 bit codeword array and dispersed in either row, column or both dimensions the method can perform dual 4-bit row and column erasure recovery. It is shown that for each codeword there are 12 possible combinations of row and column elements called couplets capable of mirroring the data byte. These byte level micro-mirrors outperform conventional mirroring in that each byte and its ECC mirror can self-detect and self-correct random errors and can recover all dual erasure combinations over four elements. Encoding at the byte quanta level maximizes application flexibility. Also disclosed are fast encode, decode and reconstruction methods via boolean logic, processor instructions and software table look-up with the intent to run at line and application speeds. The new error control method can augment ARQ algorithms and bring resiliency to system fabrics including routers and links previously limited to the recovery of transient errors. Image storage and storage over arrays of static devices can benefit from the two-dimensional capabilities. Applications with critical data integrity requirements can utilize the method for end-to-end protection and validation. An extra ECC byte per codeword extends both the resiliency and dimensionality.

Owner:HALFORD ROBERT

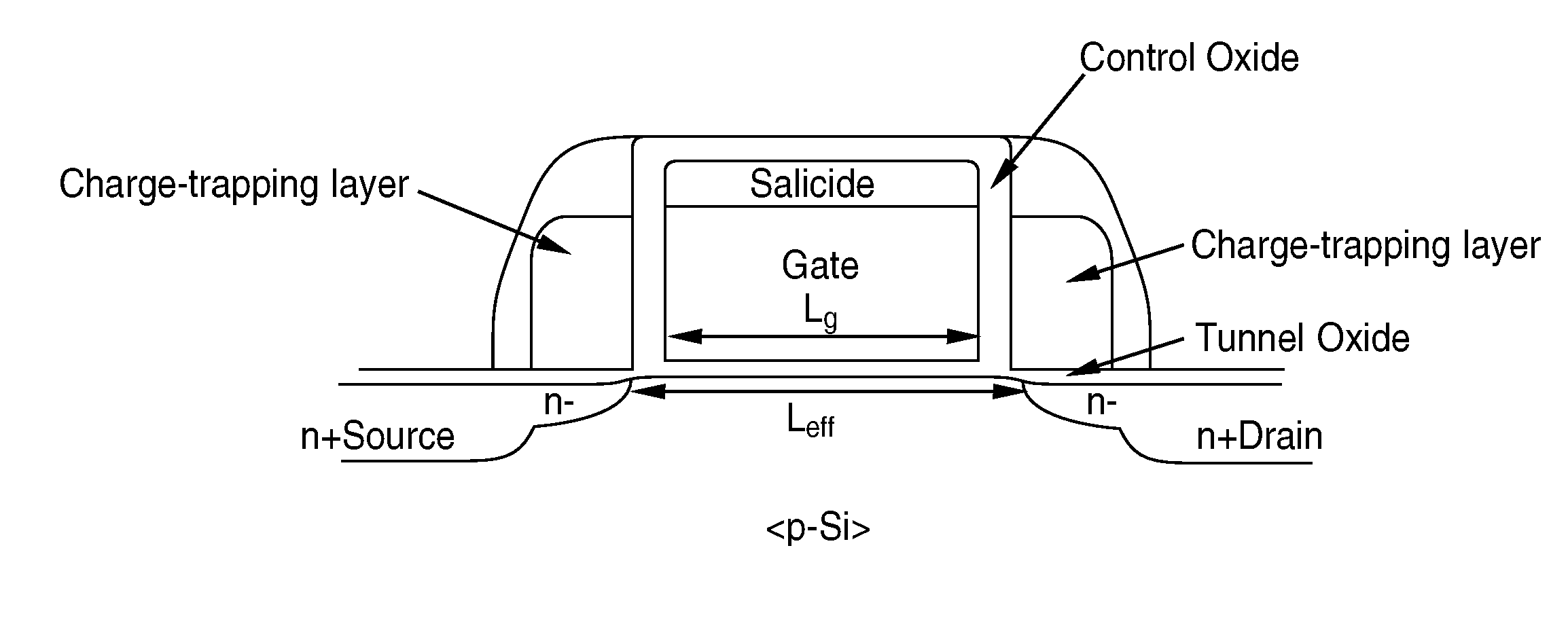

Multi-bit-per-cell nvm structures and architecture

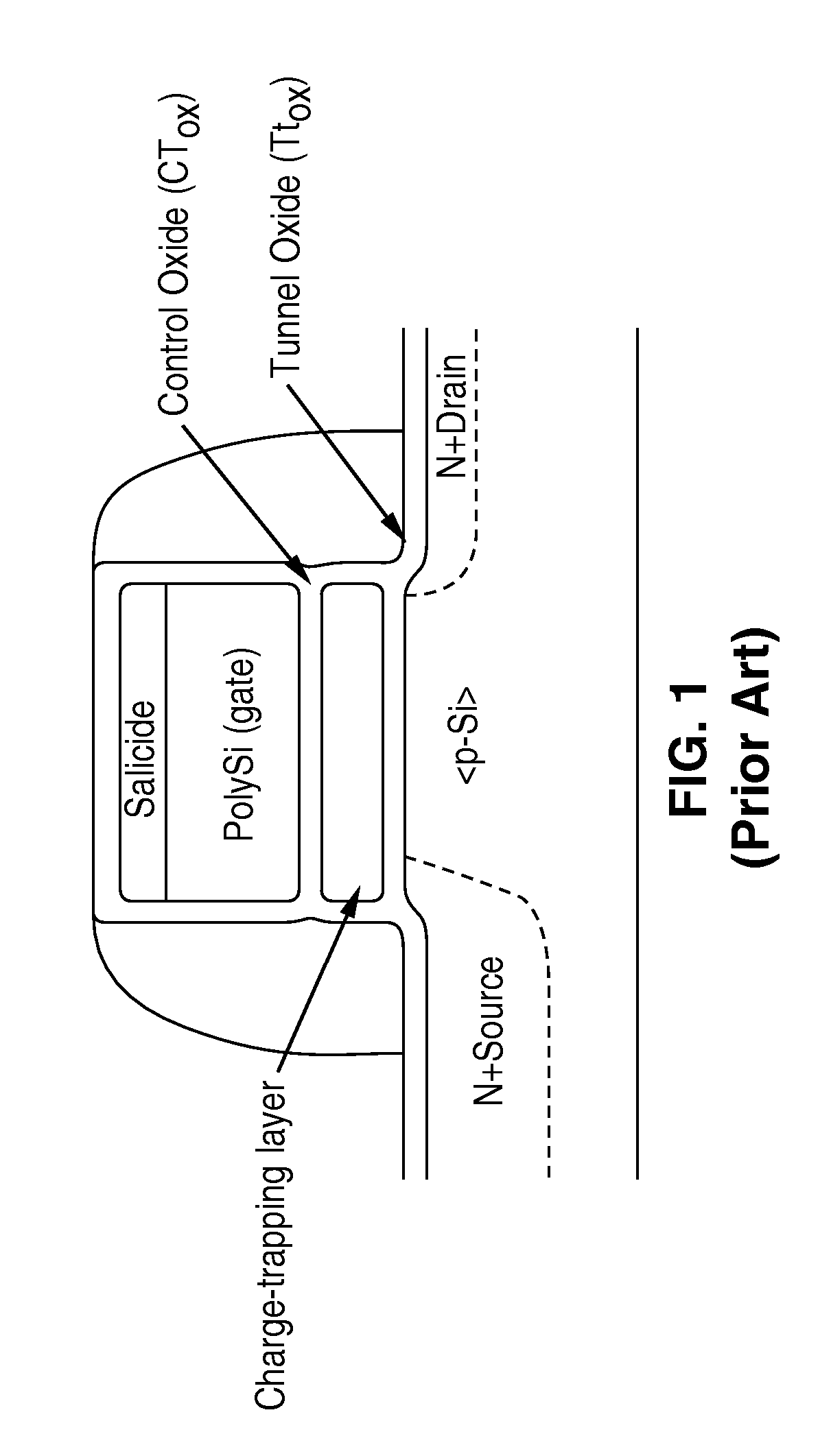

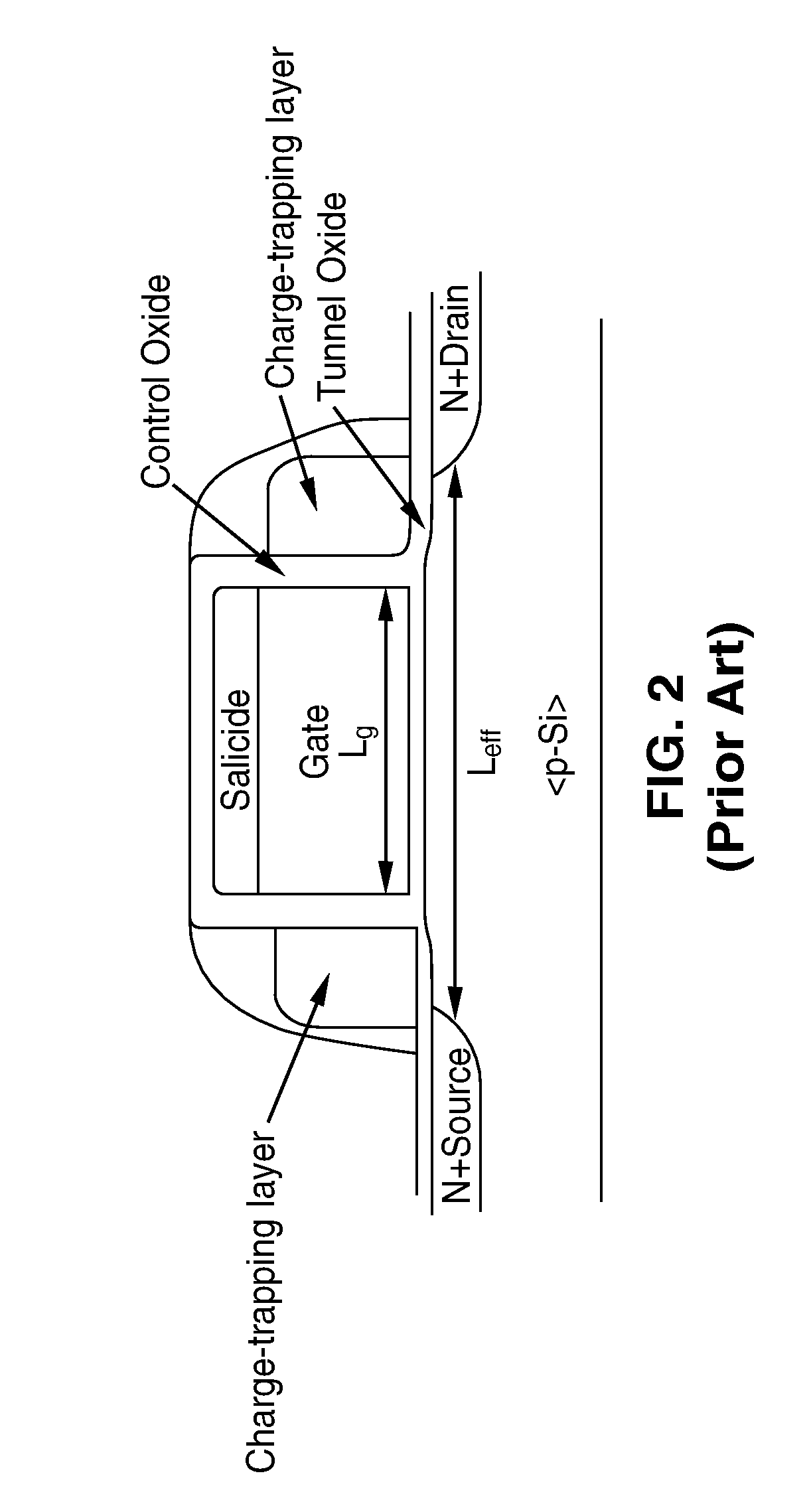

InactiveUS20070164352A1High sensitivityReduce sensitivitySolid-state devicesRead-only memoriesGate dielectricEngineering

A transistor structure, such as a Double-gated FET (DG FET), that has been modified to include a charge-trapping region used to store either 2- or 4-bits of information. The charge-trapping region can, for example, be embedded in the gate dielectric stack underneath each gate electrode, or placed on the sidewalls of each gate electrode.

Owner:RGT UNIV OF CALIFORNIA

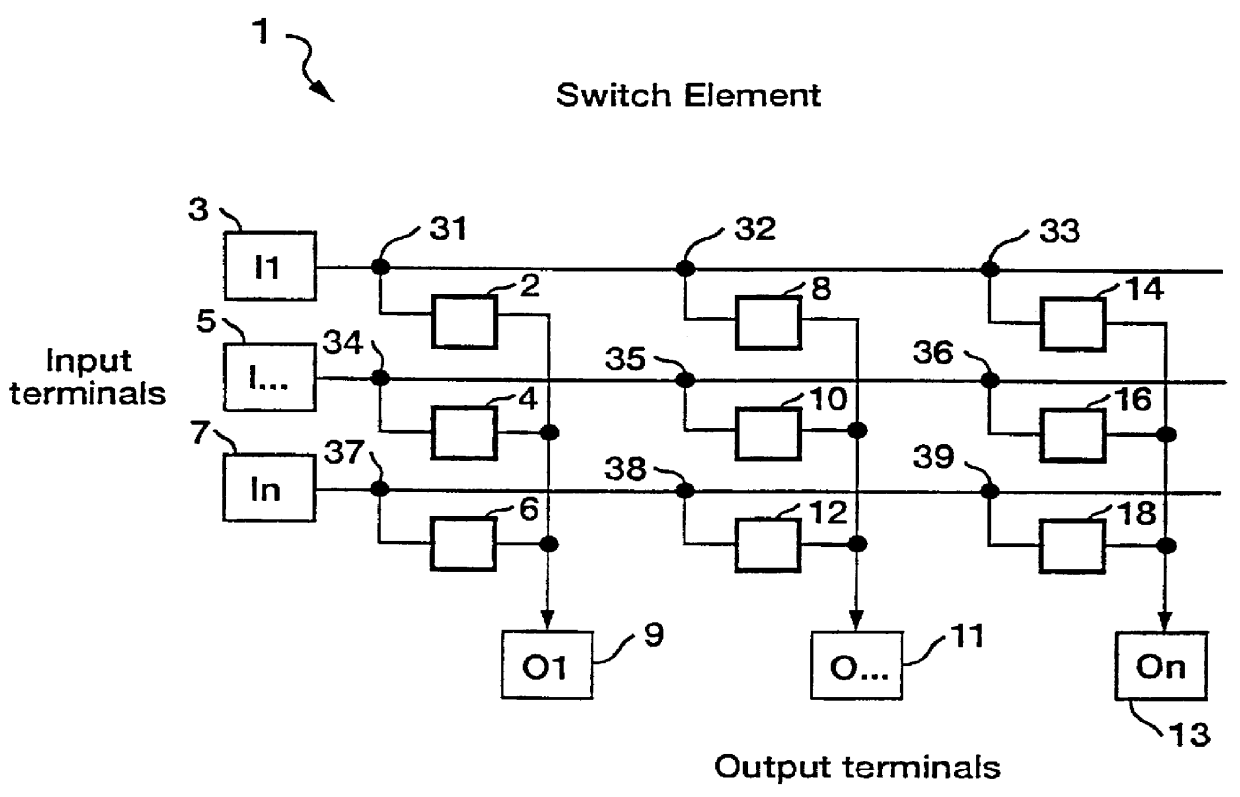

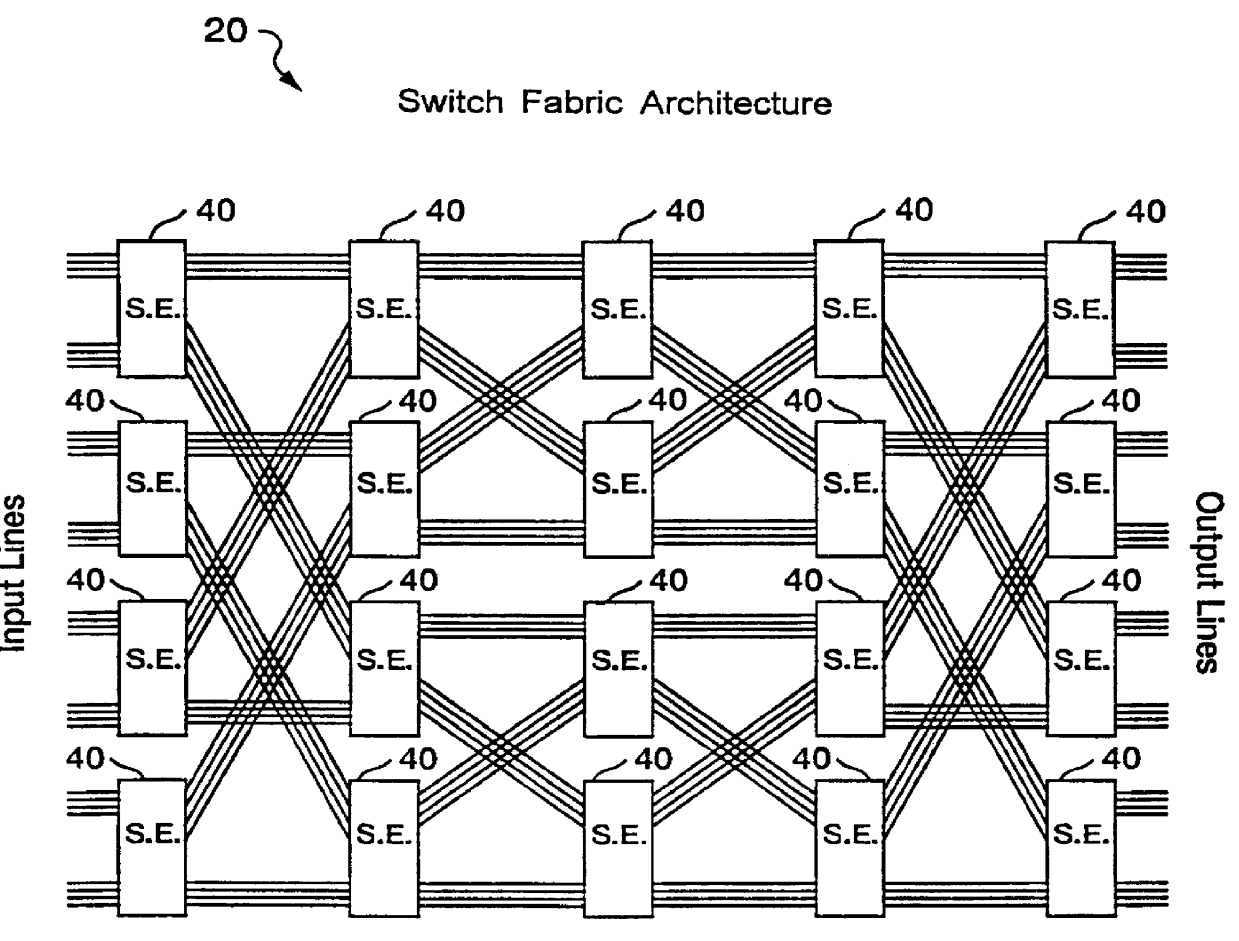

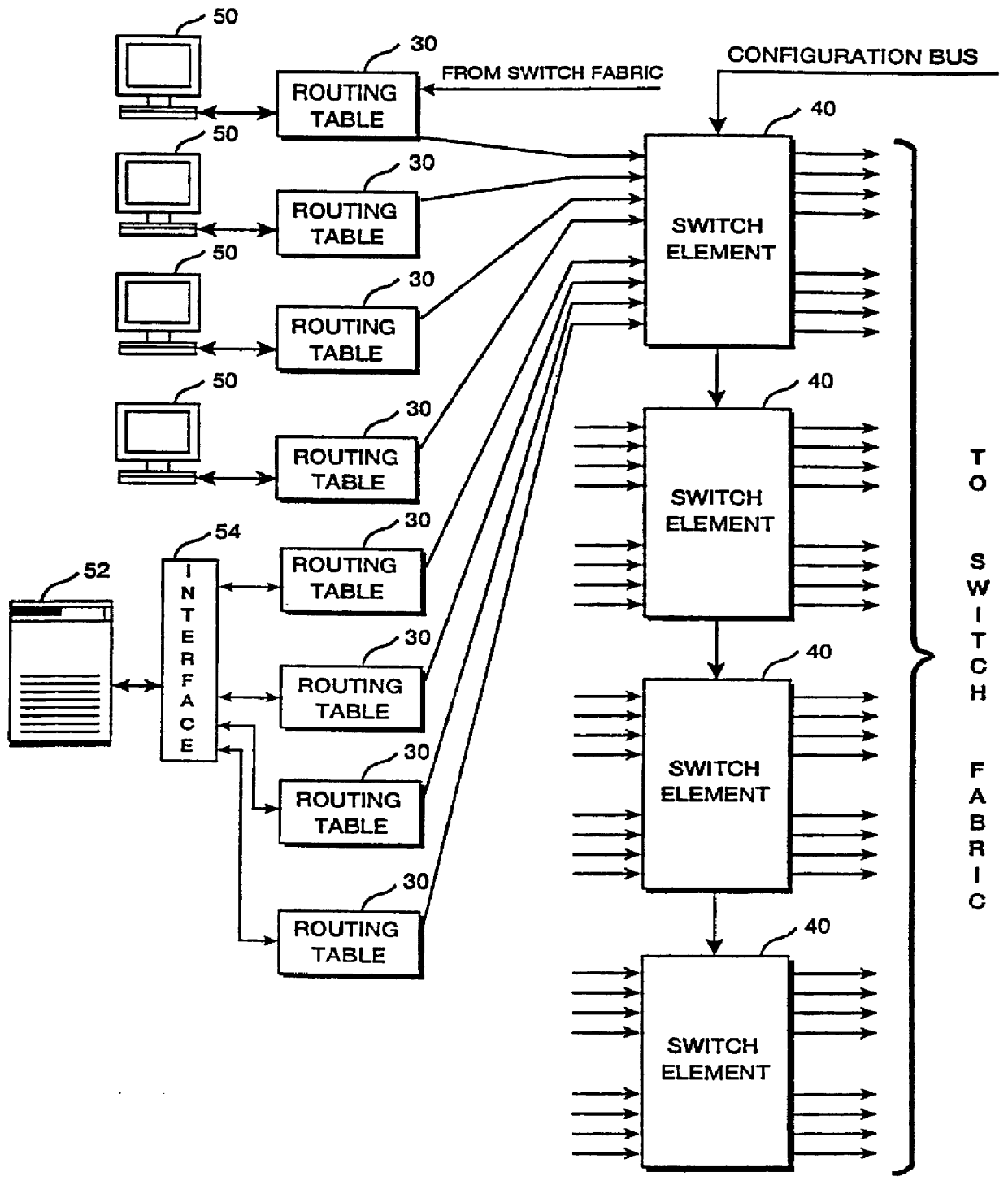

ATM architecture and switching element

An ATM switching system architecture of a switch fabric-type is built of, a plurality of ATM switch element circuits and routing table circuits for each physical connection to / from the switch fabric. A shared pool of memory is employed to eliminate the need to provide memory at every crosspoint. Each routing table maintains a marked interrupt linked list for storing information about which ones of its virtual channels are experiencing congestion. This linked list is available to a processor in the external workstation to alert the processor when a congestion condition exists in one of the virtual channels. The switch element circuit typically has up to eight 4-bit-wide nibble inputs and eight 4-bit-wide nibble outputs and is capable of connecting cells received at any of its inputs to any of its outputs, based on the information in a routing tag uniquely associated with each cell.

Owner:PMC SEIRRA

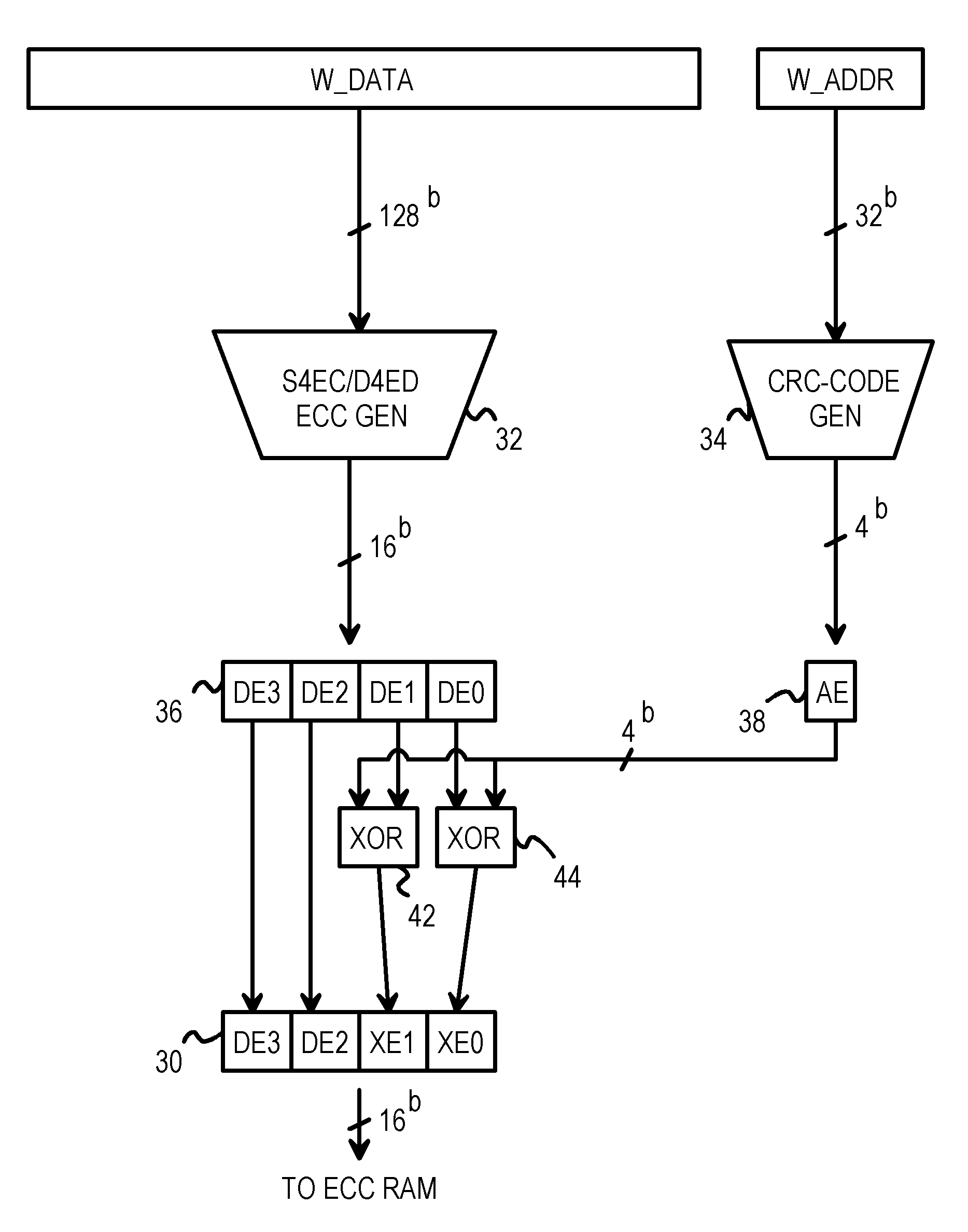

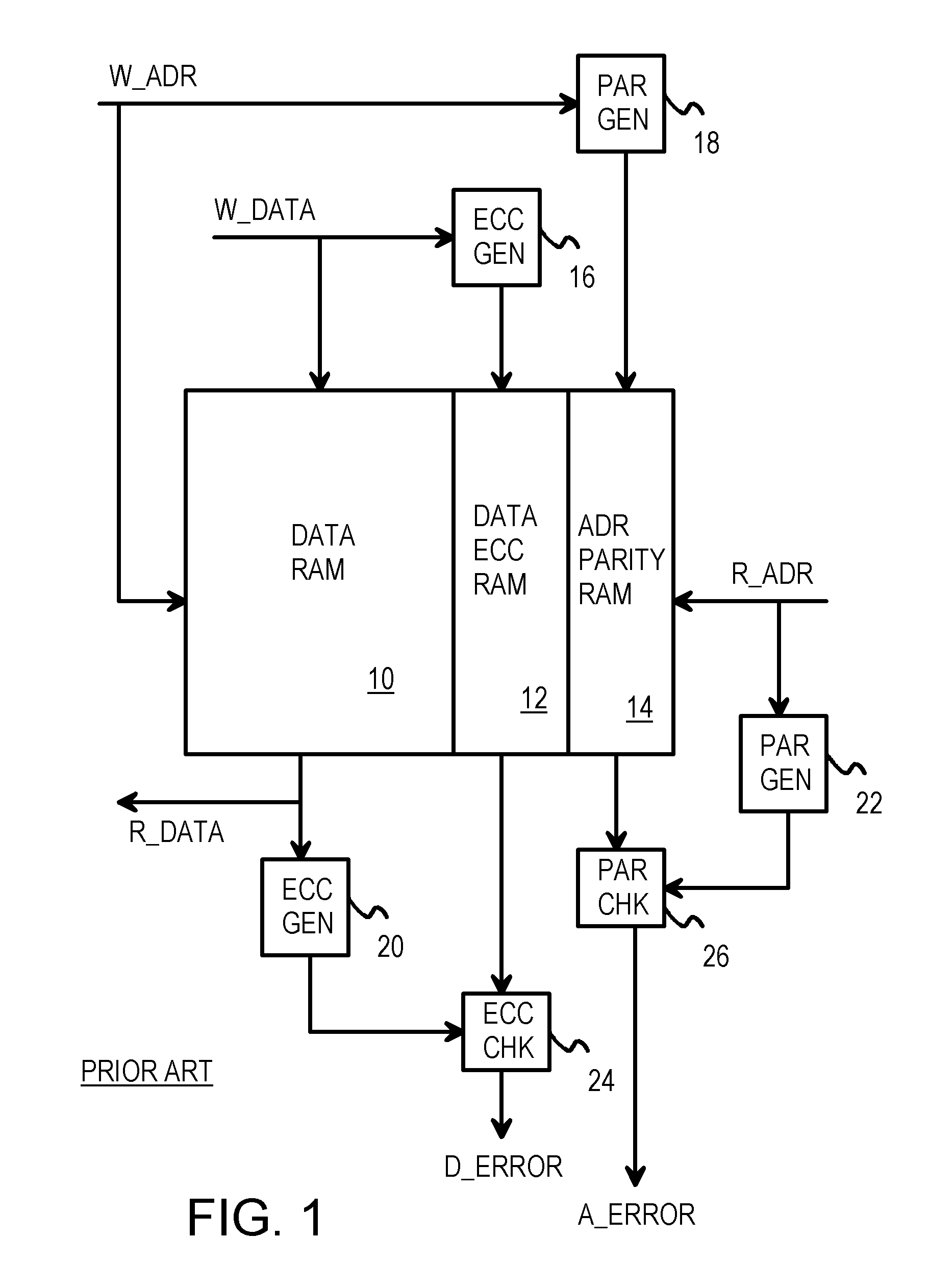

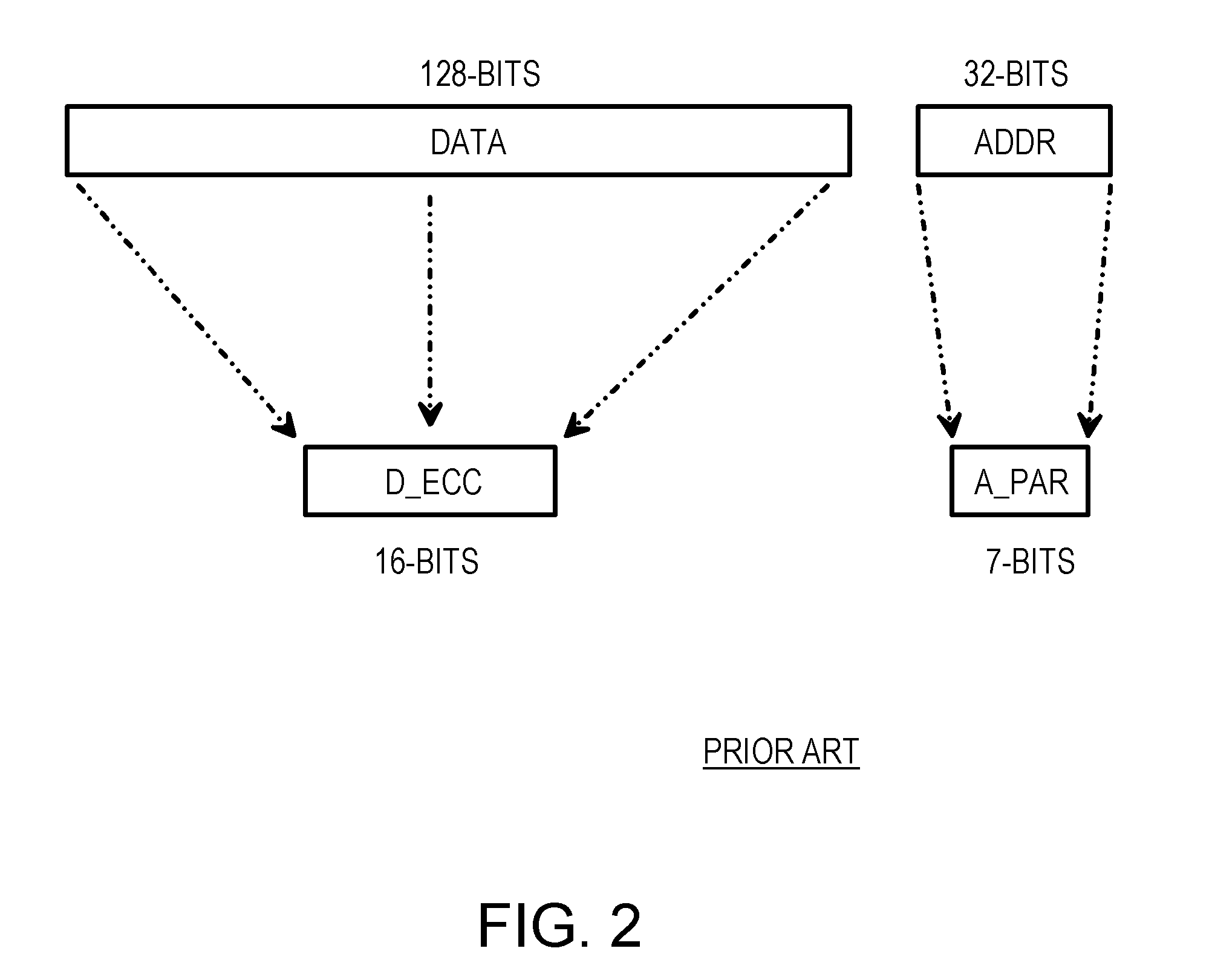

Address error detection by merging a polynomial-based CRC code of address bits with two nibbles of data or data ECC bits

A memory system provides data error detection and correction and address error detection. A Single-byte Error-Correcting / Double-byte Error-Detecting (SbEC / DbED) code with the byte being a 4-bit nibble is used to detect up to 8-bit errors and correct data errors of 4 bits or less. Rather than generating address parity, which is poor at detecting even numbers of errors, a cyclical-redundancy-check (CRC) code generates address check bits. A 32-bit address is compressed to just 4 address check bits using the CRC code. The 4 address check bits are merged (XOR'ed) with two 4-bit nibbles of the data SbEC / DbED code to generate a merged ECC codeword that is stored in memory. An address error causes a 2-nibble mis-match due to the redundant merging of the 4 address check bits with 2 nibbles of data correction code. The CRC code is ideal for detecting even numbers of errors common with multiplexed-address DRAMs.

Owner:AZUL SYSTEMS

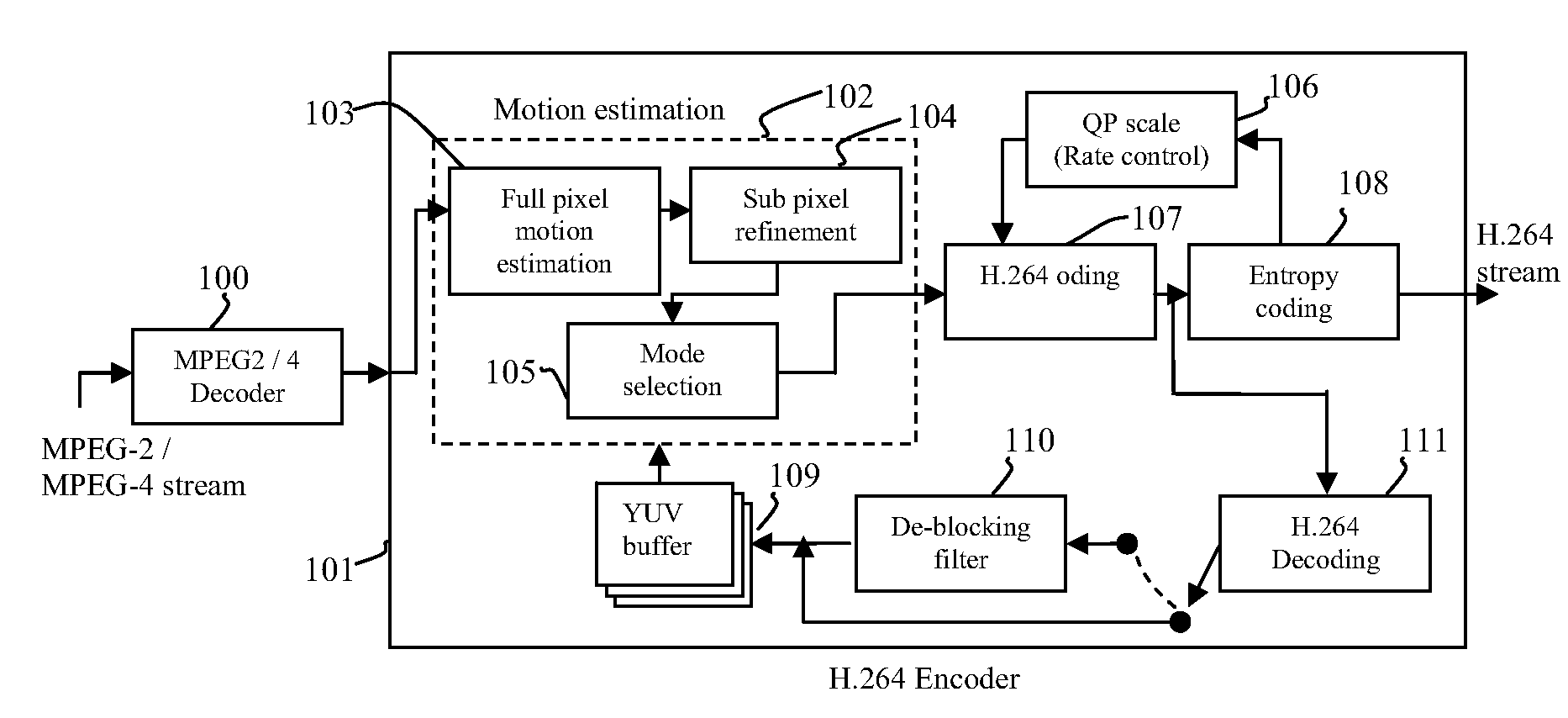

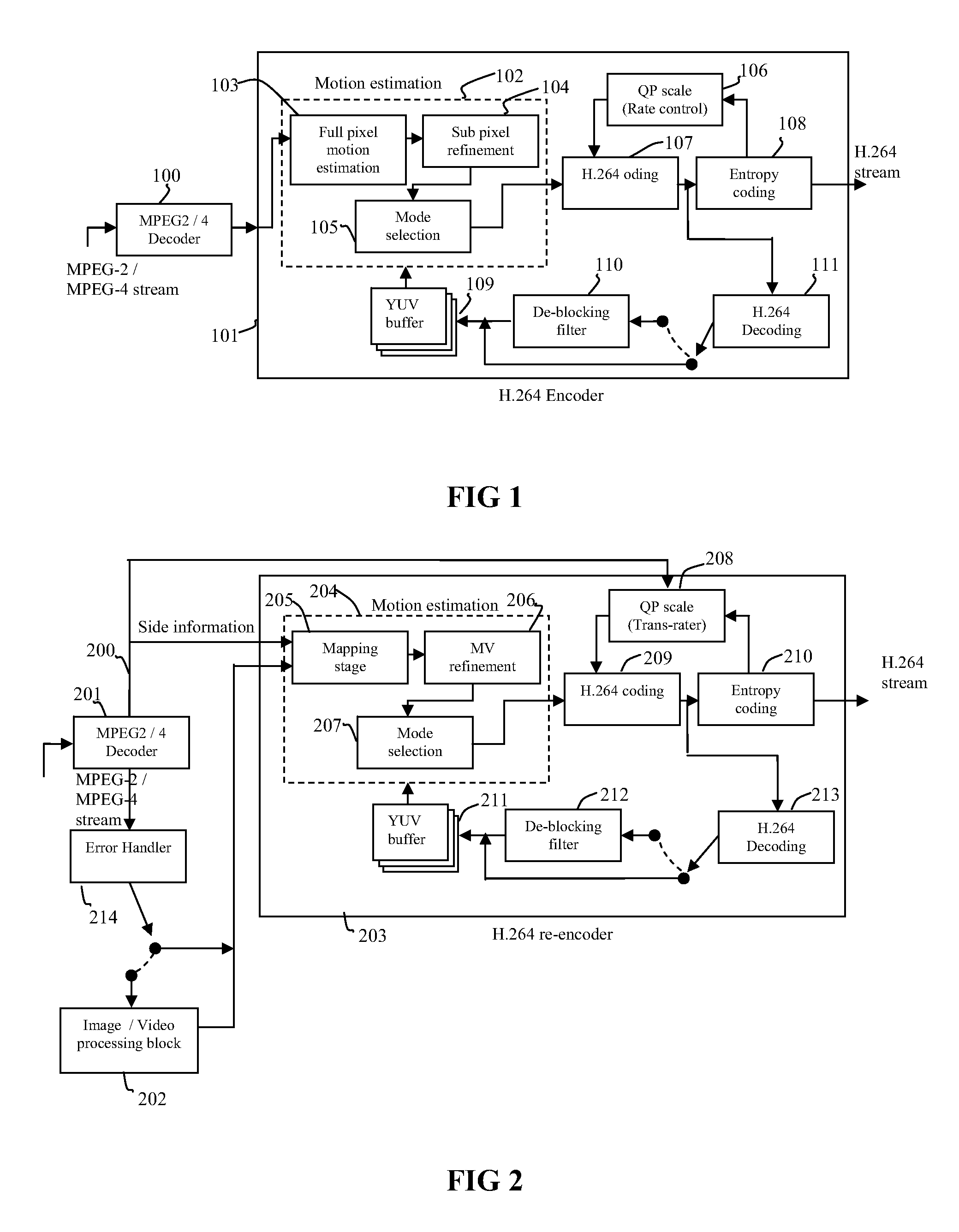

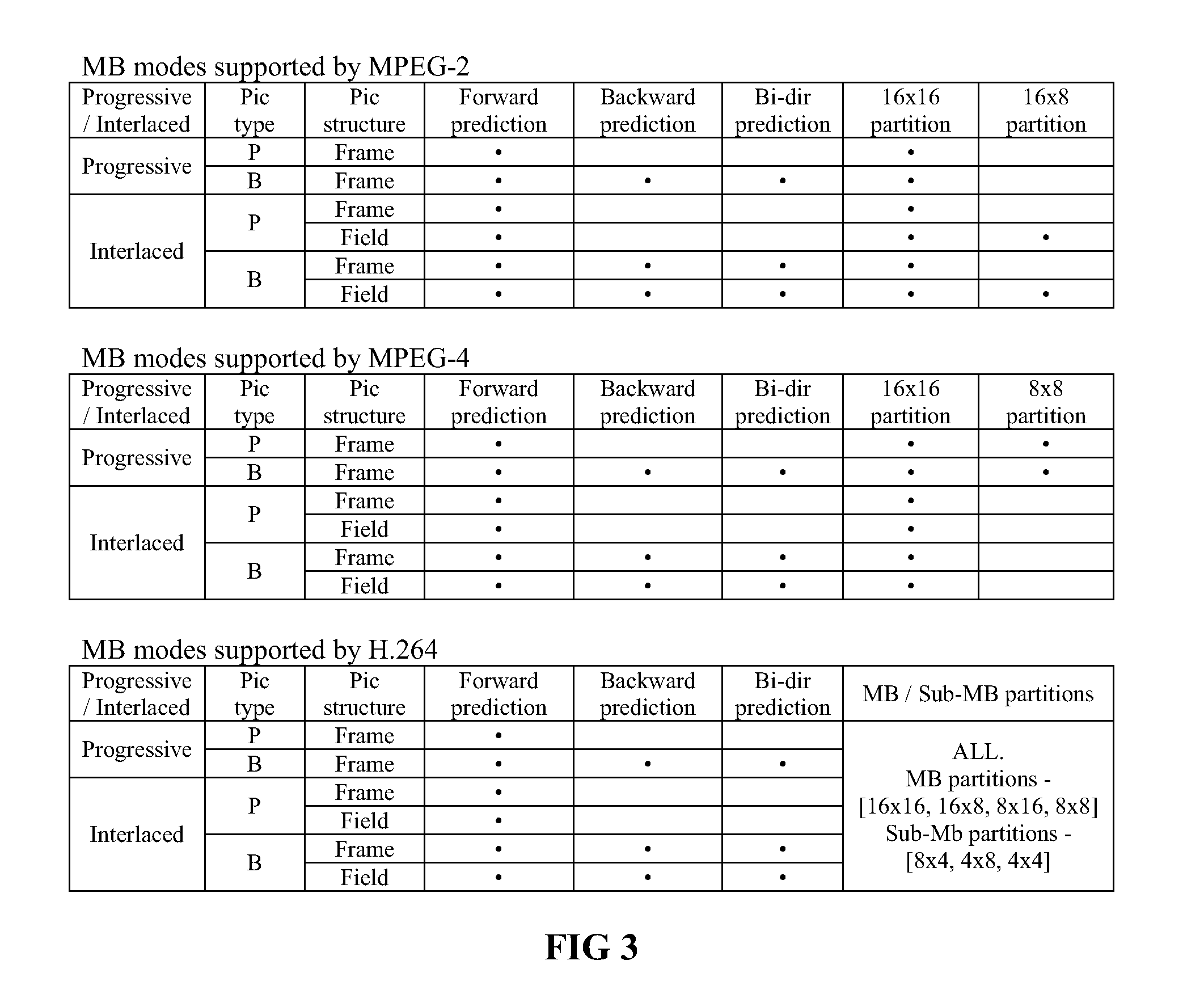

A technique for transcoding mpeg-2 / mpeg-4 bitstream to h.264 bitstream

ActiveUS20080043831A1Color television with pulse code modulationColor television with bandwidth reductionCoding blockTranscoding

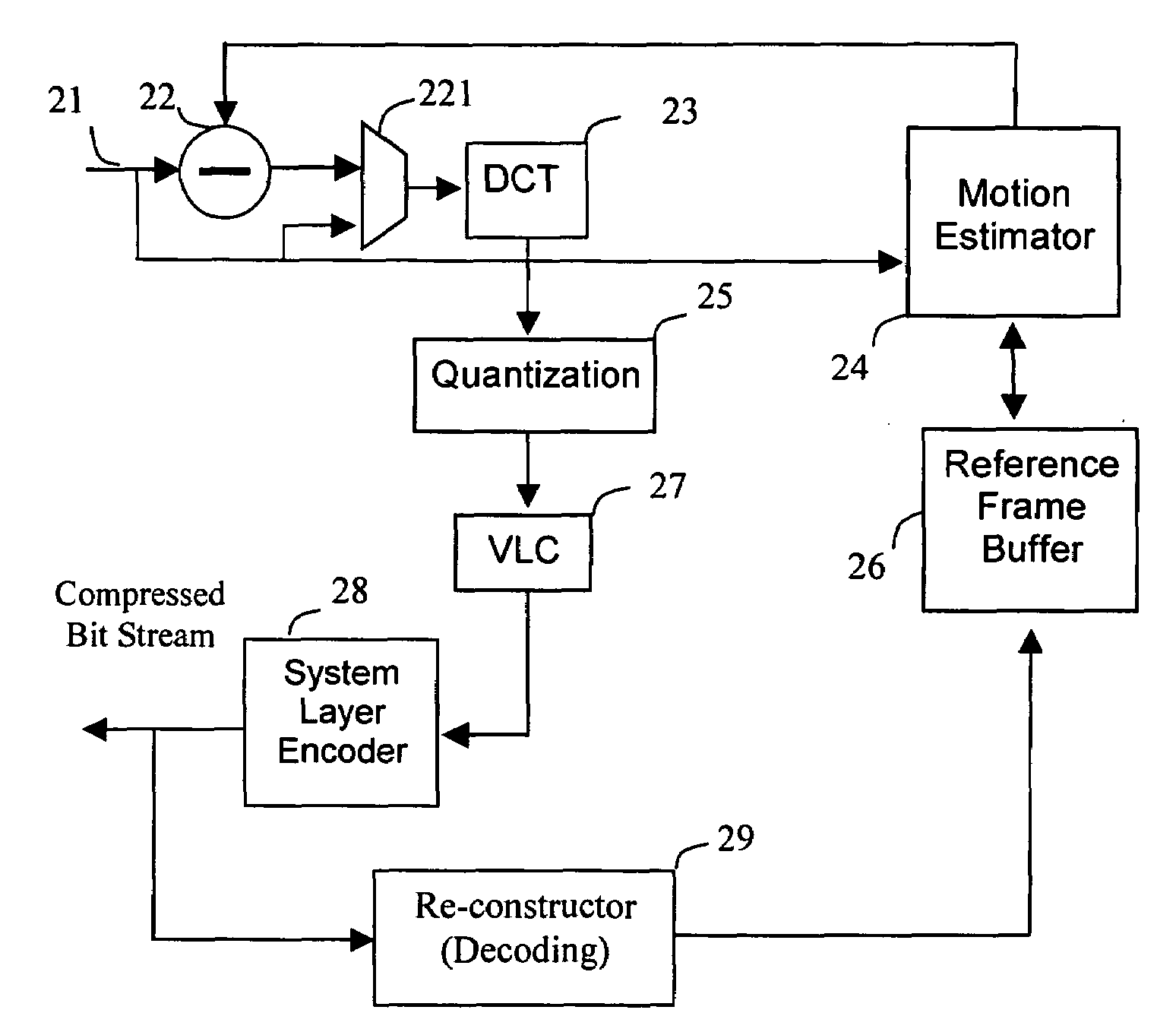

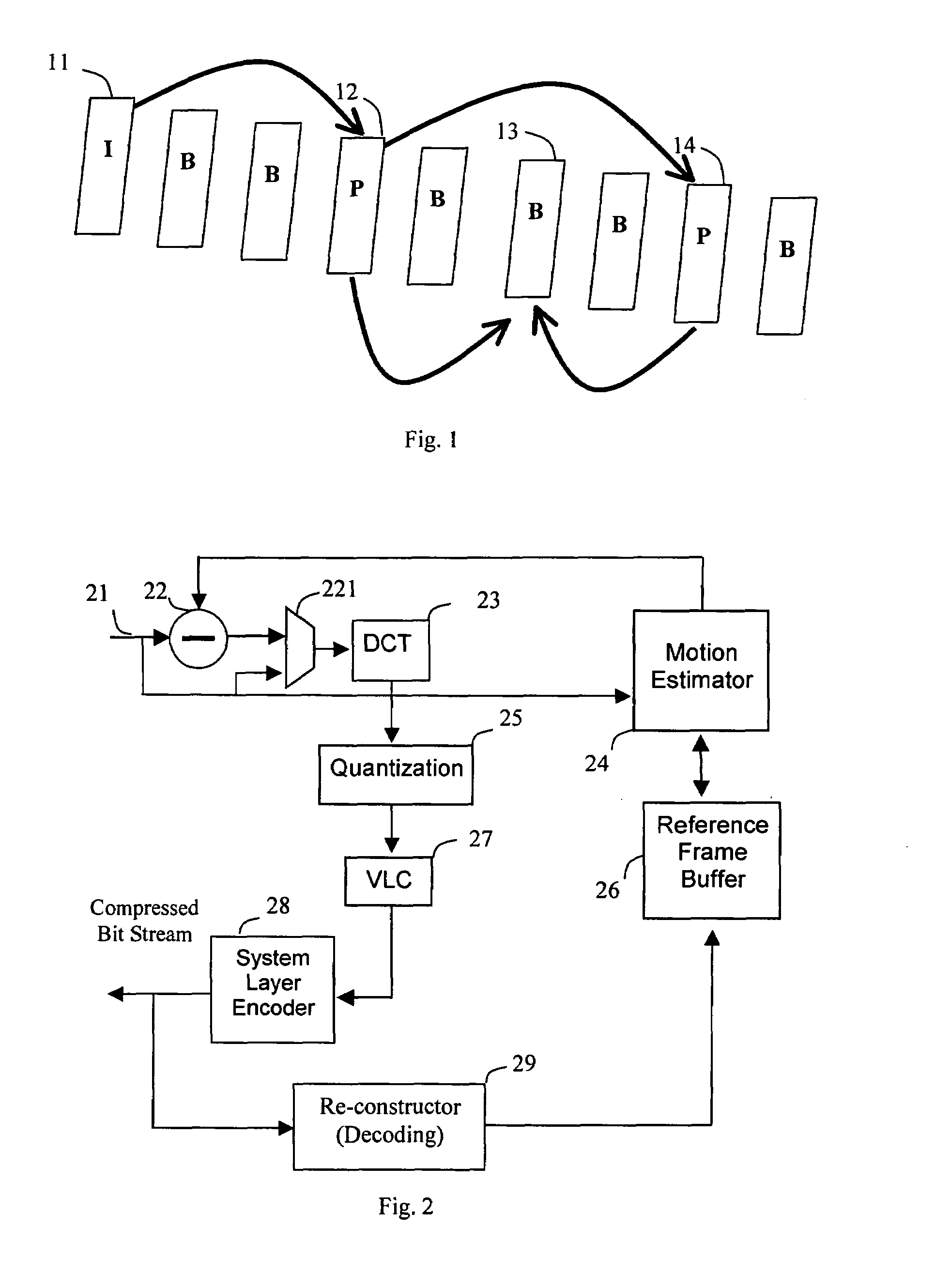

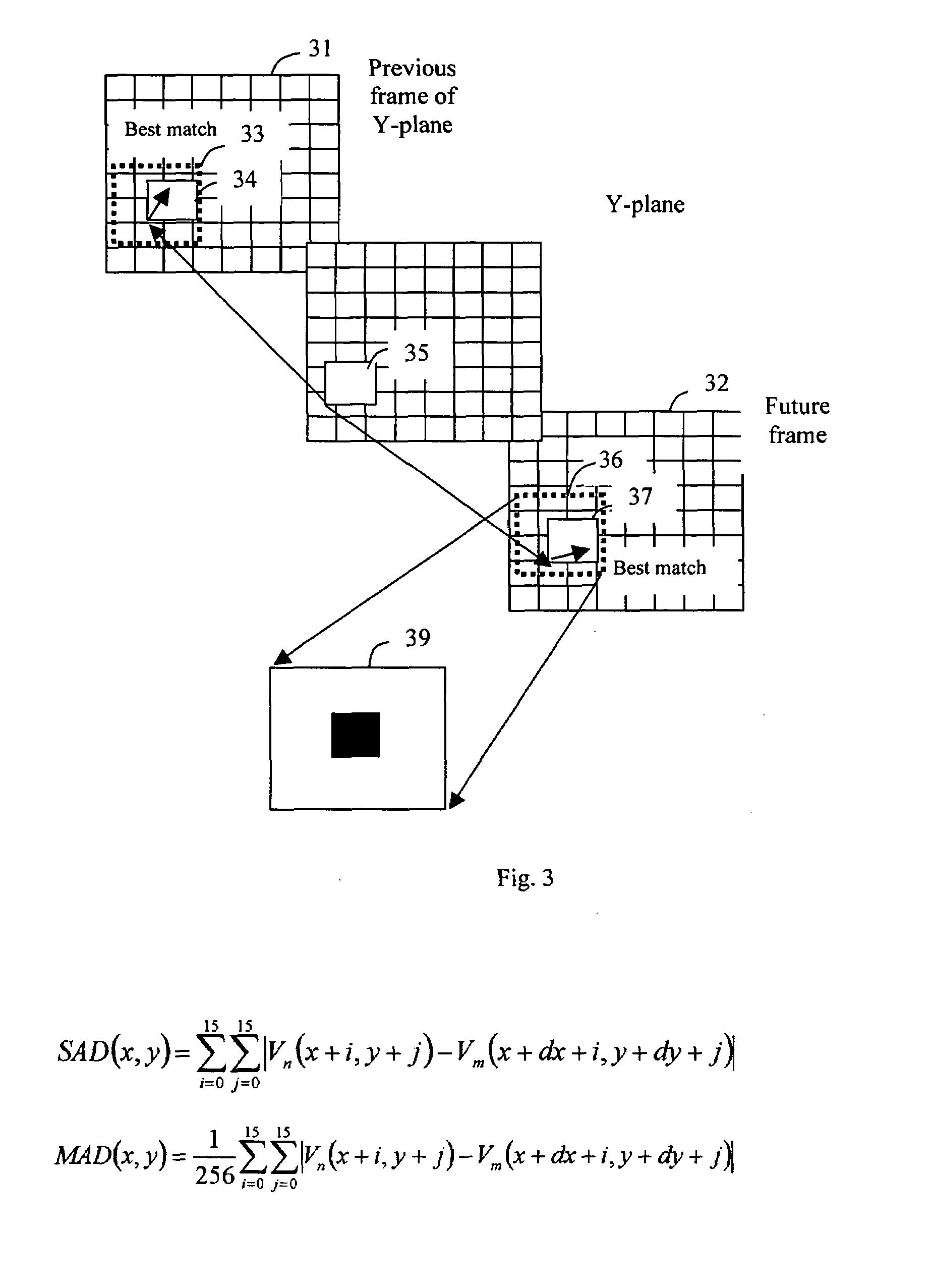

A method / system of transcoding an MPEG 2 / 4 bit stream into an H.264 format, handles an input MPEG 2 / 4 bit stream in a decoder, and identifies certain data in the input bit stream for reuse in the H.264 format; and, reuses the identified data in a re-encoder with assistance from a mapping module in transcoding by converting the input bit stream into an output H.264 format. The identified data includes information at a macrolevel and information at a picture level. The information at the macrolevel might comprise additional stages incorporated in the re-encoder module including a Mapping Process stage, a Sub Pixel Refinement stage, a Mode Selection stage to choose from Intra, Inter or Skip modes, followed by the standard H.264 encoding loop and the Entropy Coding Block. The information at the picture level might include; a) average quantizer of frame, and, b) total bits per frame.

Owner:ITTIAM SYST P

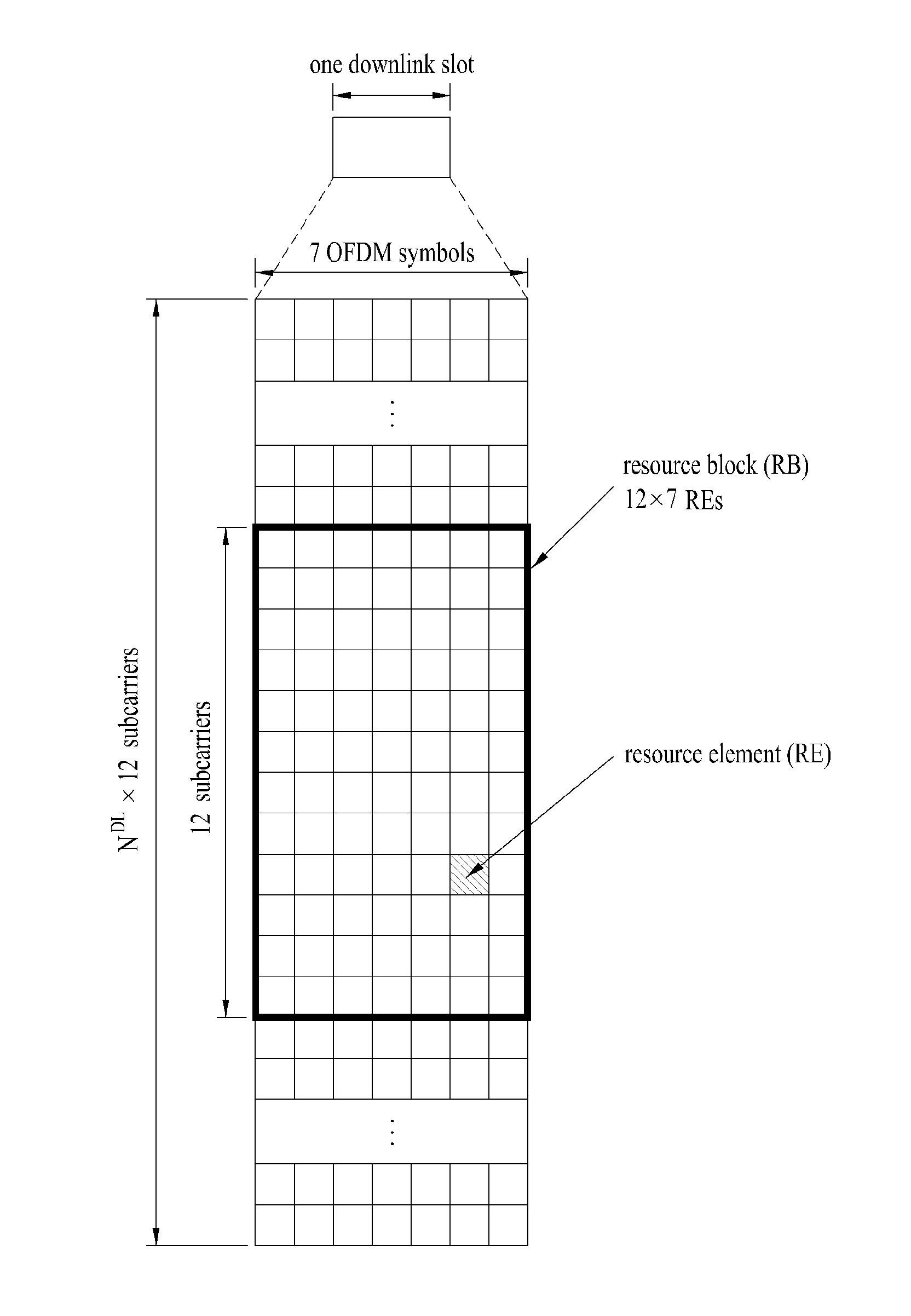

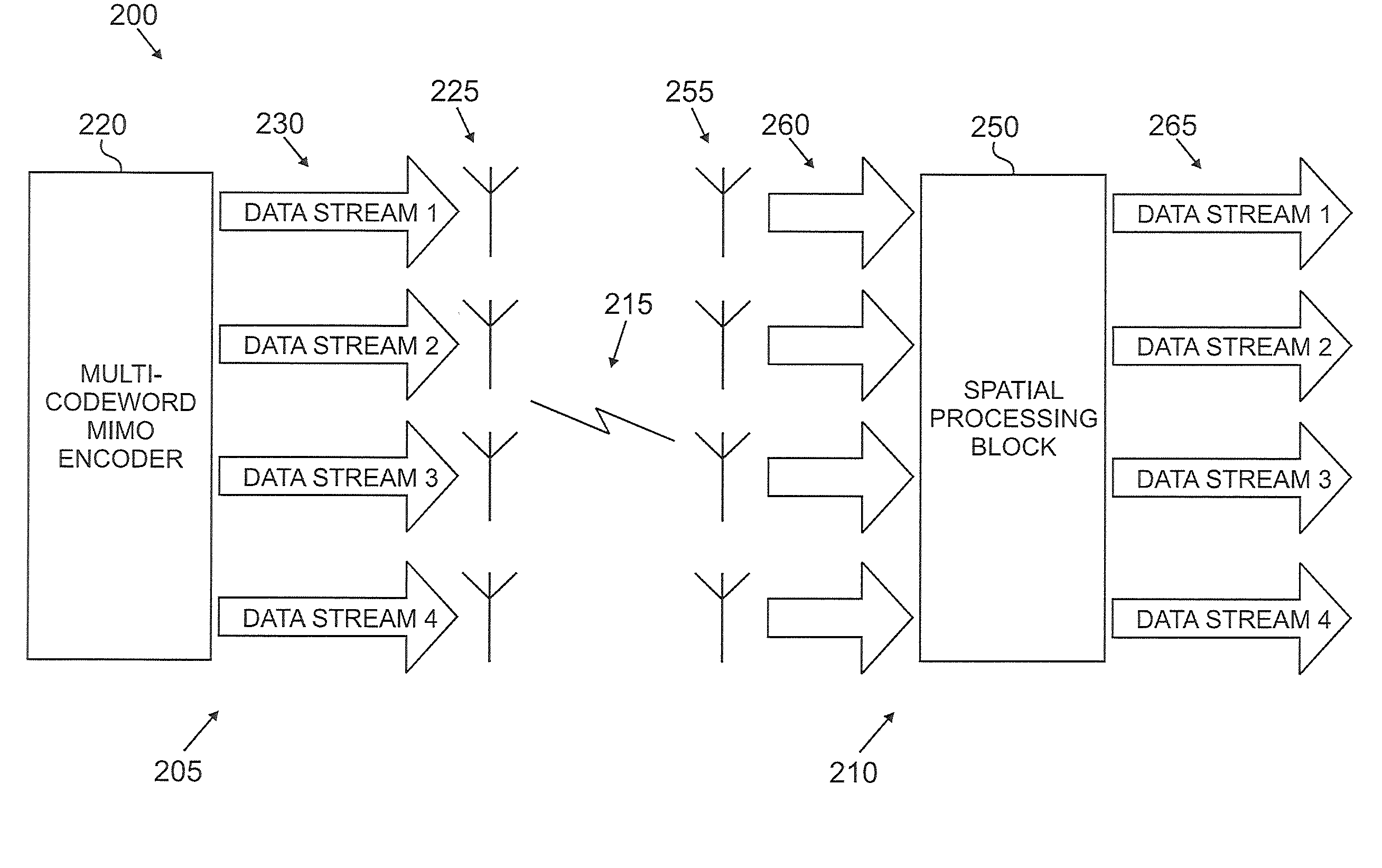

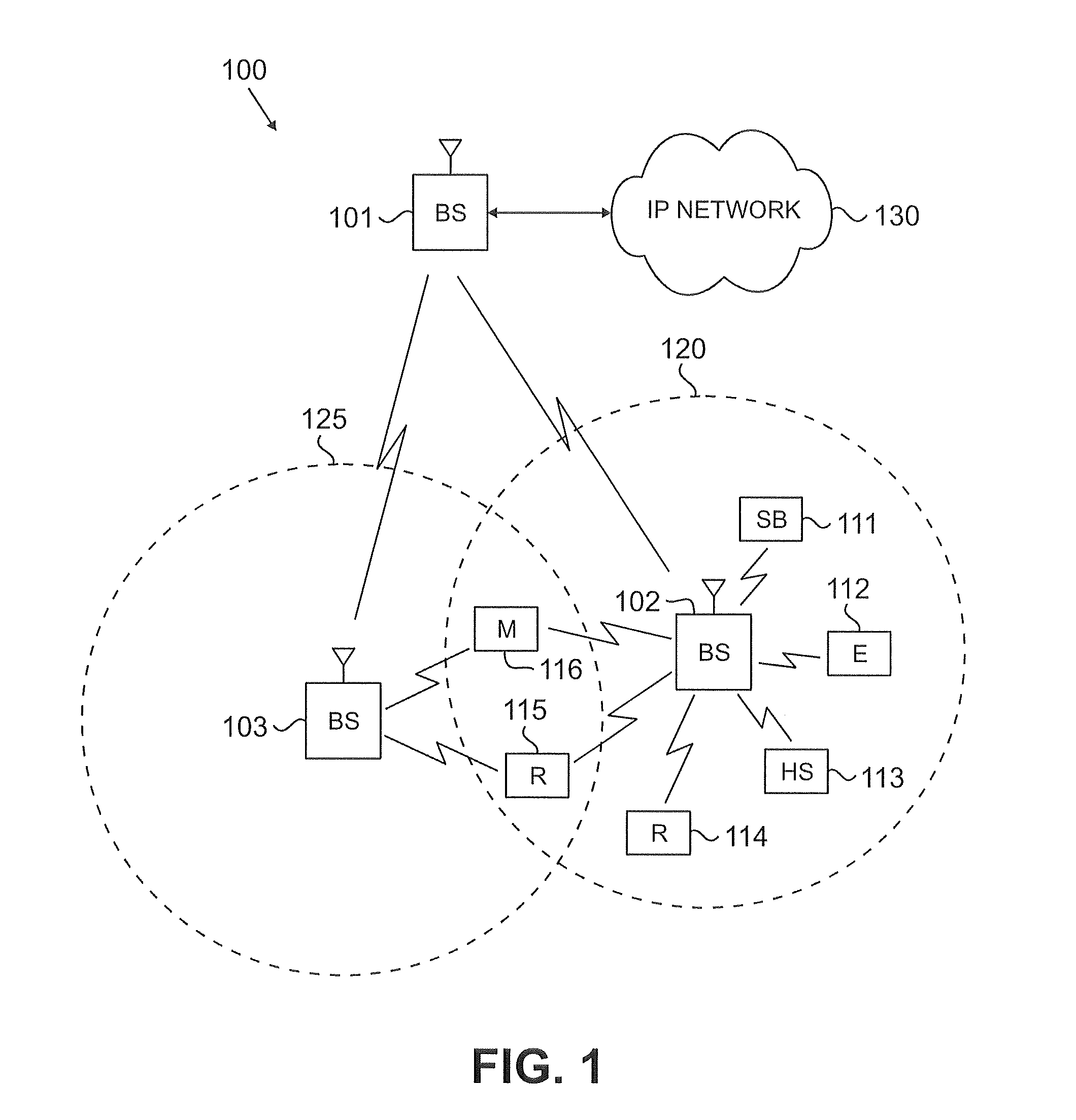

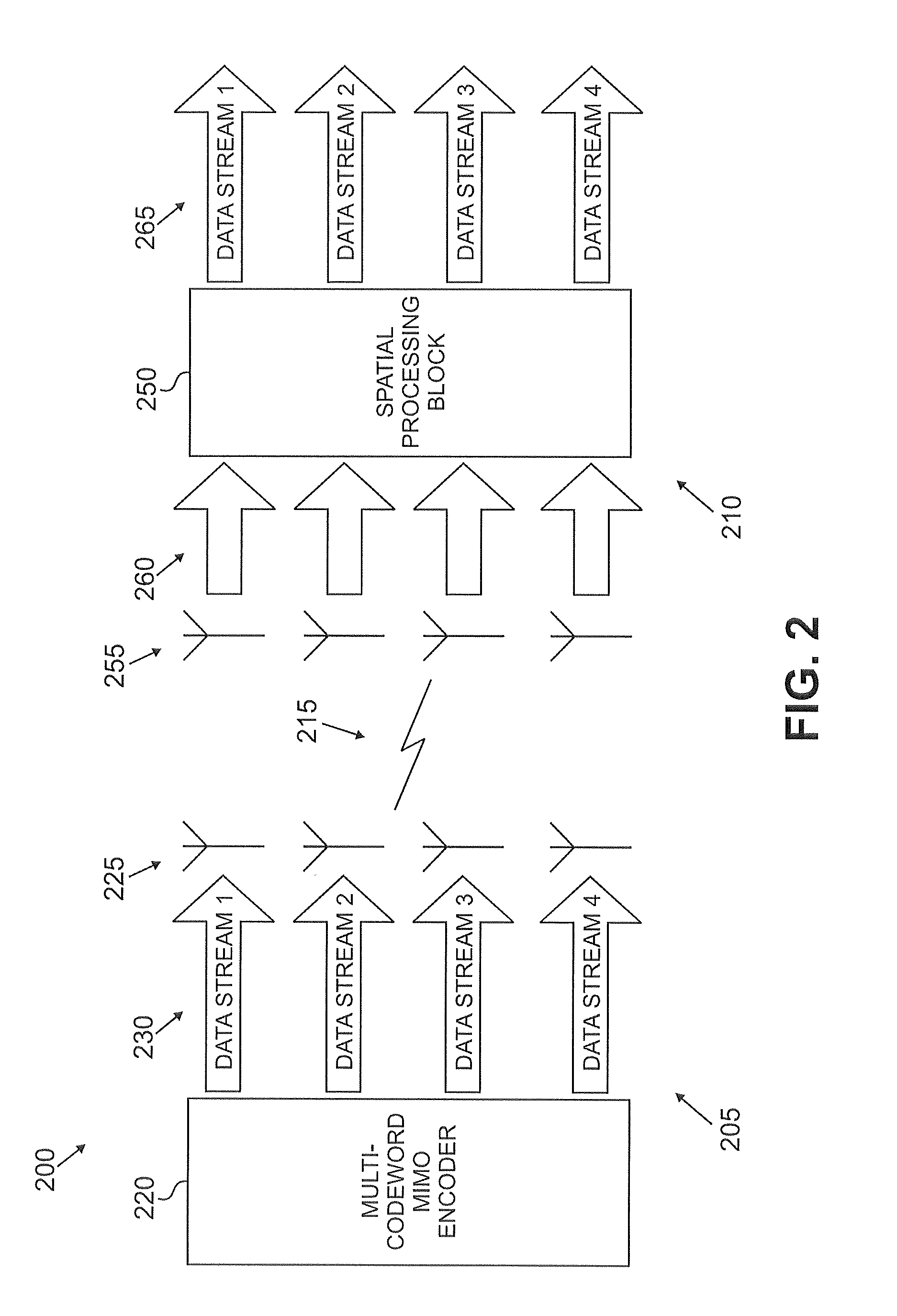

Method and apparatus for efficient feedback in a wireless communication system supporting multiple antenna

ActiveUS20120076236A1Easy to operatePolarisation/directional diversityTransmission path divisionChannel state informationCommunications system

A method and apparatus for transmitting effective channel status information (CSI) in a wireless communication system supporting multiple carriers are disclosed. A method for transmitting CSI of DL transmission via uplink in a wireless communication system includes transmitting a rank indicator (RI) at a first subframe, and transmitting a first precoding matrix indicator (PMI), a second PMI, and a wideband (WB) channel quality indicator (CQI) at a second subframe. UE preferred precoding matrix is indicated by a combination of the first PMI and the second PMI. A subsampled codebook for each precoding codebook of ranks from Rank-1 to Rank-4 is applied to the first PMI and the second PMI, and a sum of the first PMI and the second PMI for each of Rank-1 to Rank-4 is comprised of 4 bits.

Owner:LG ELECTRONICS INC

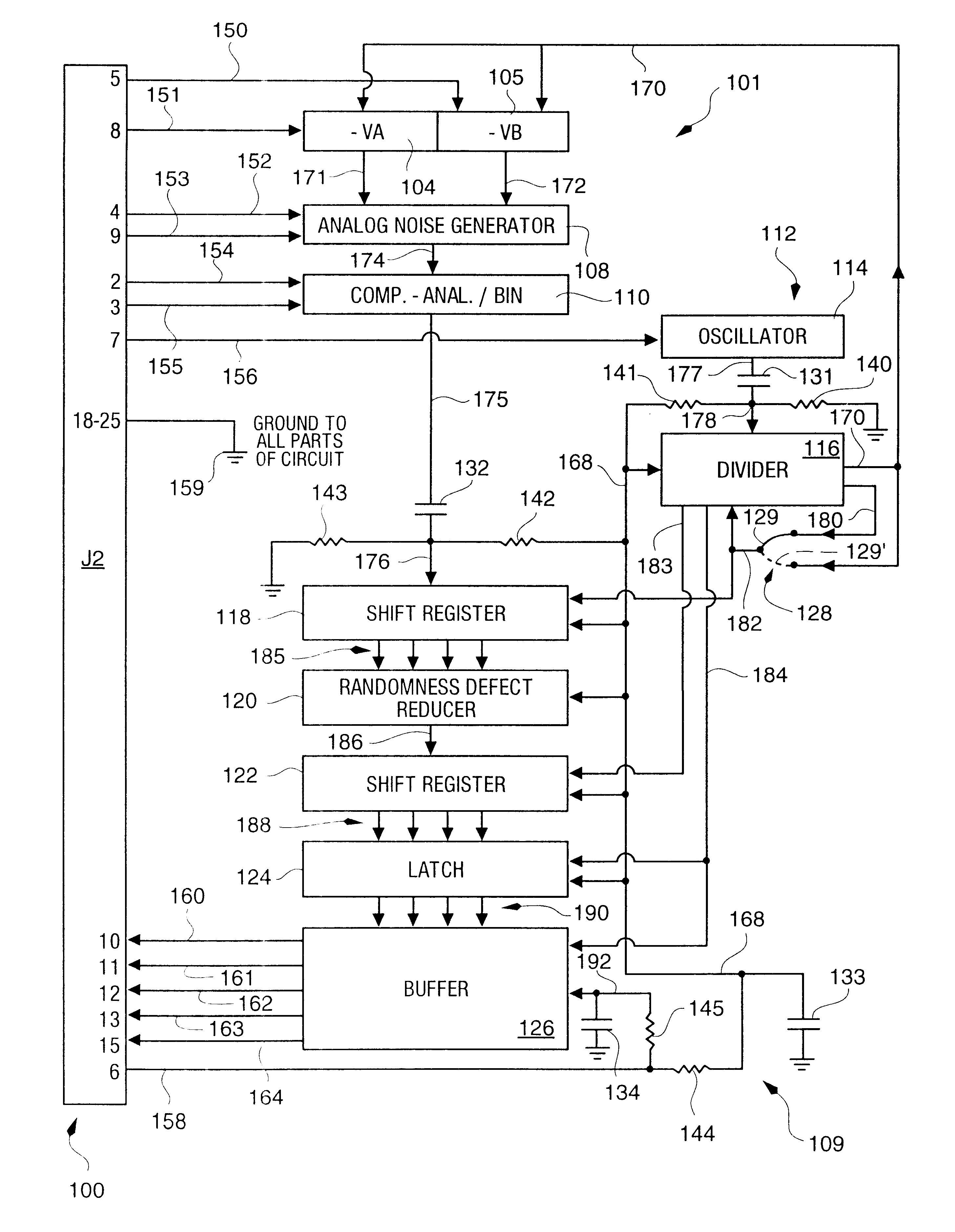

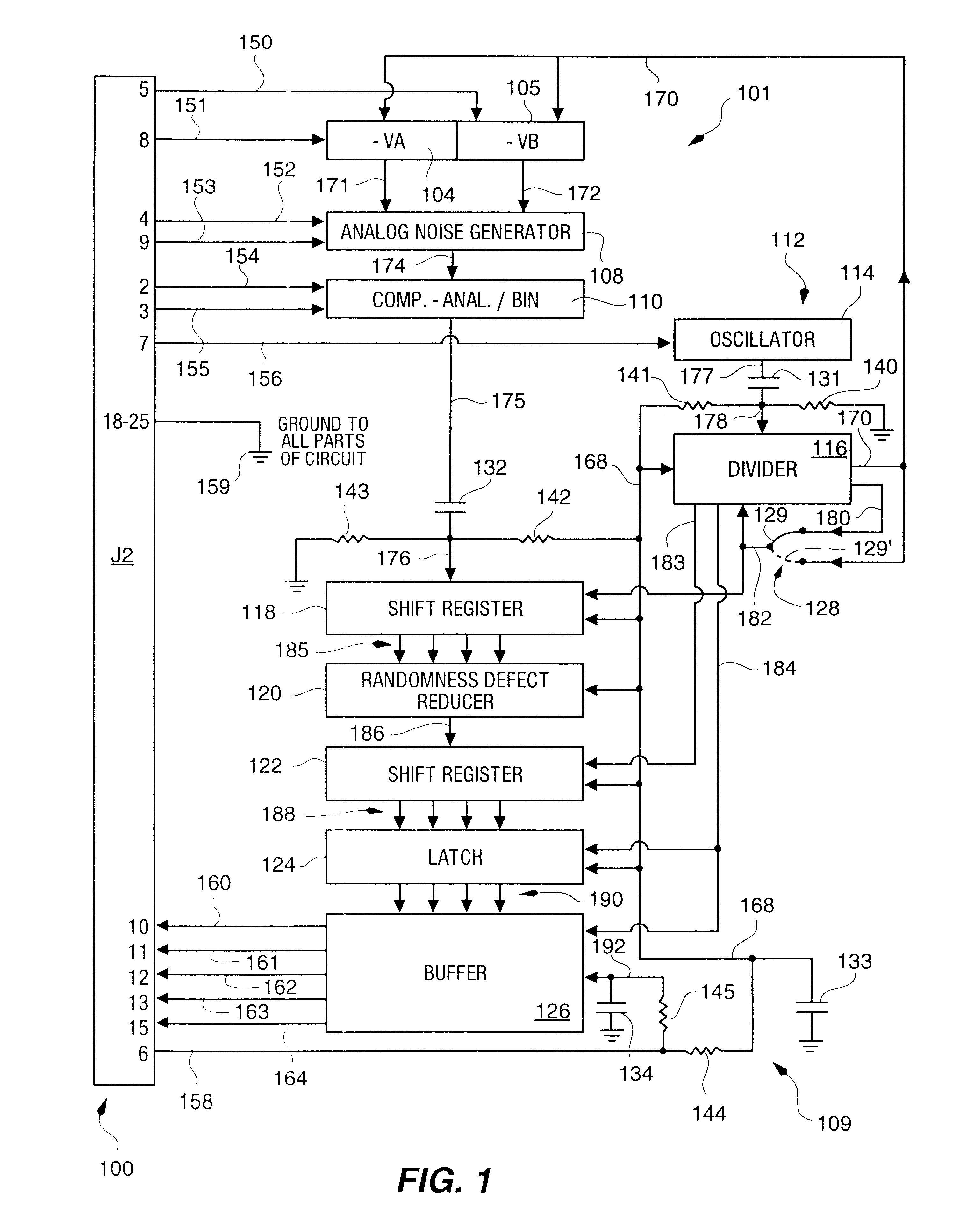

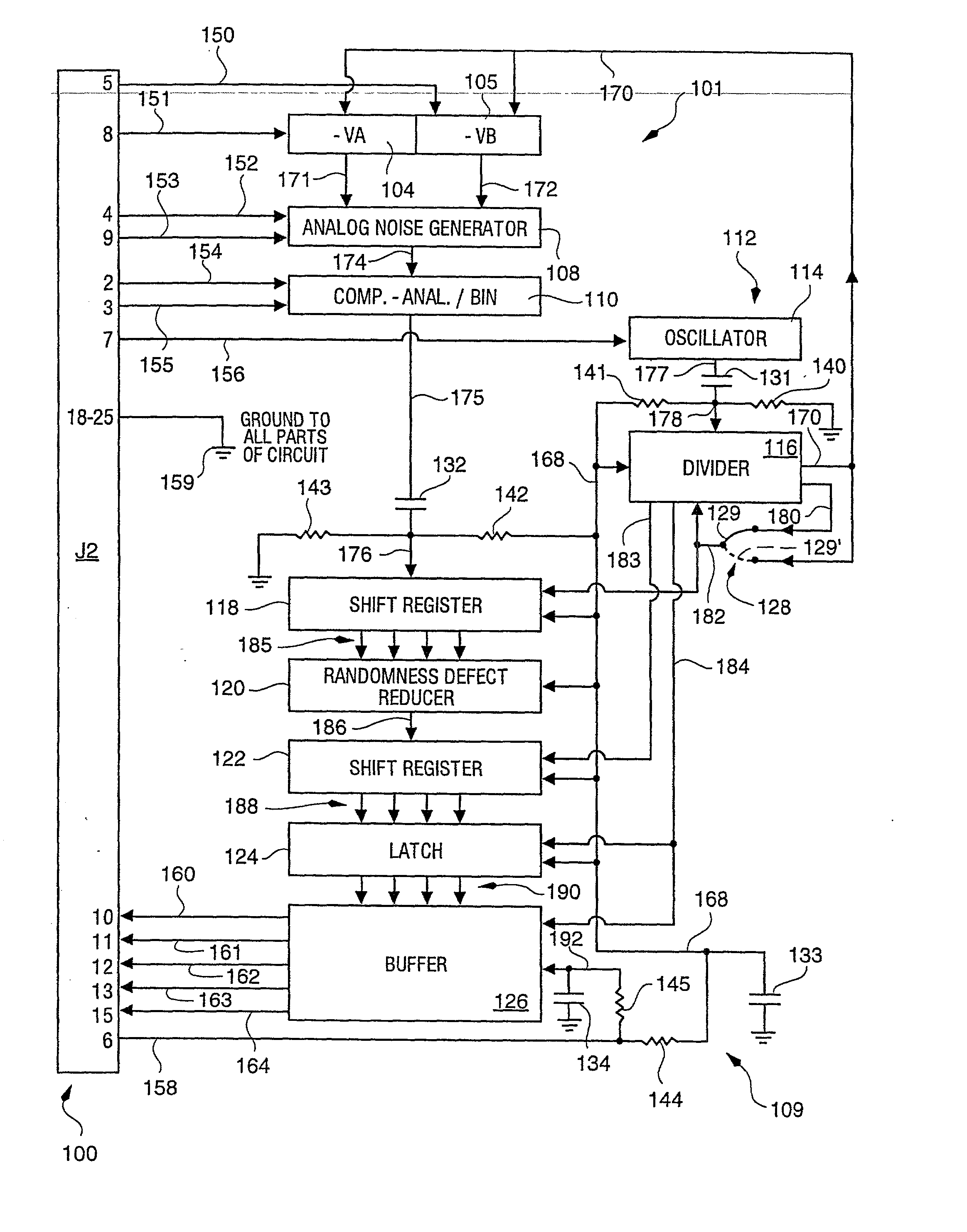

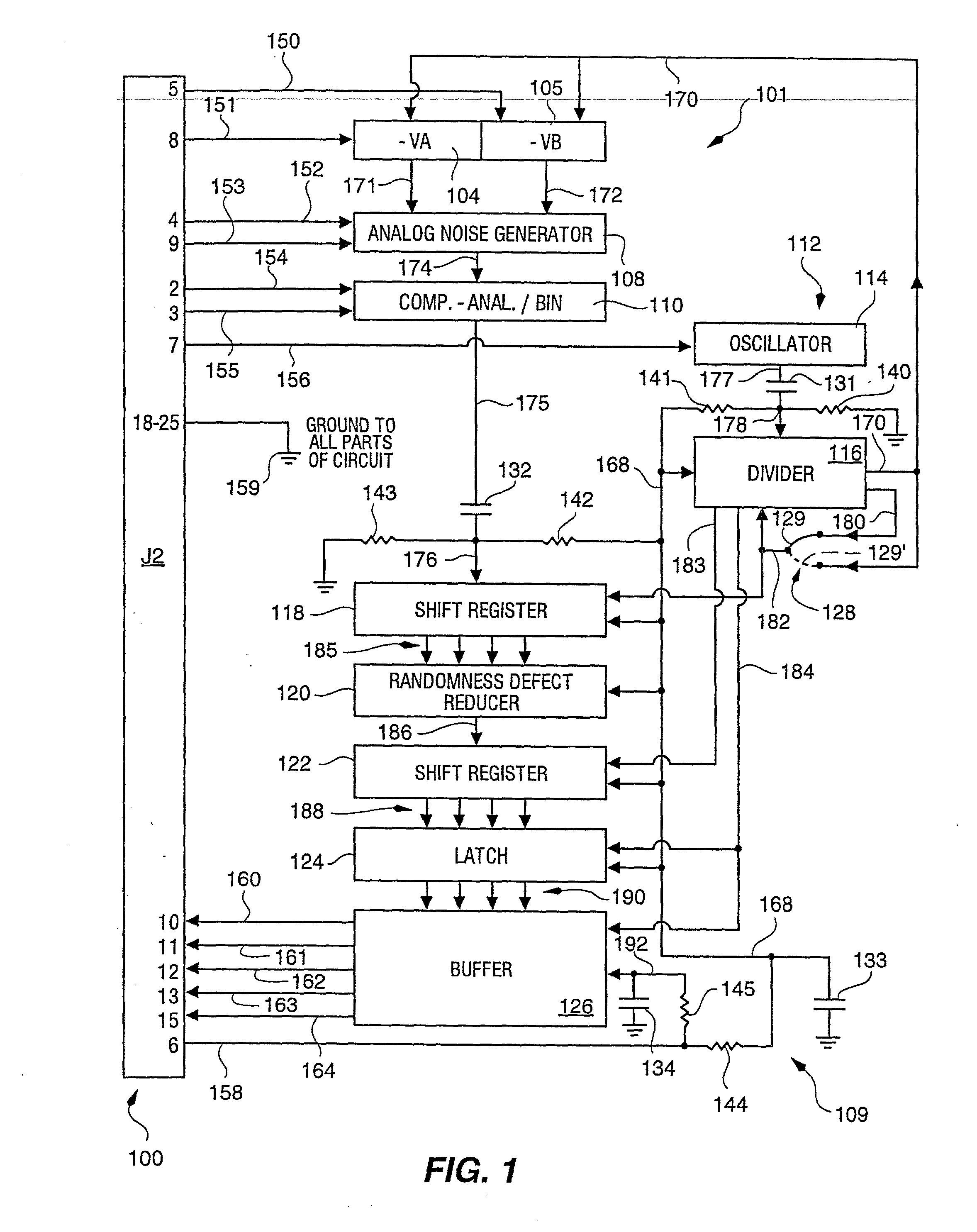

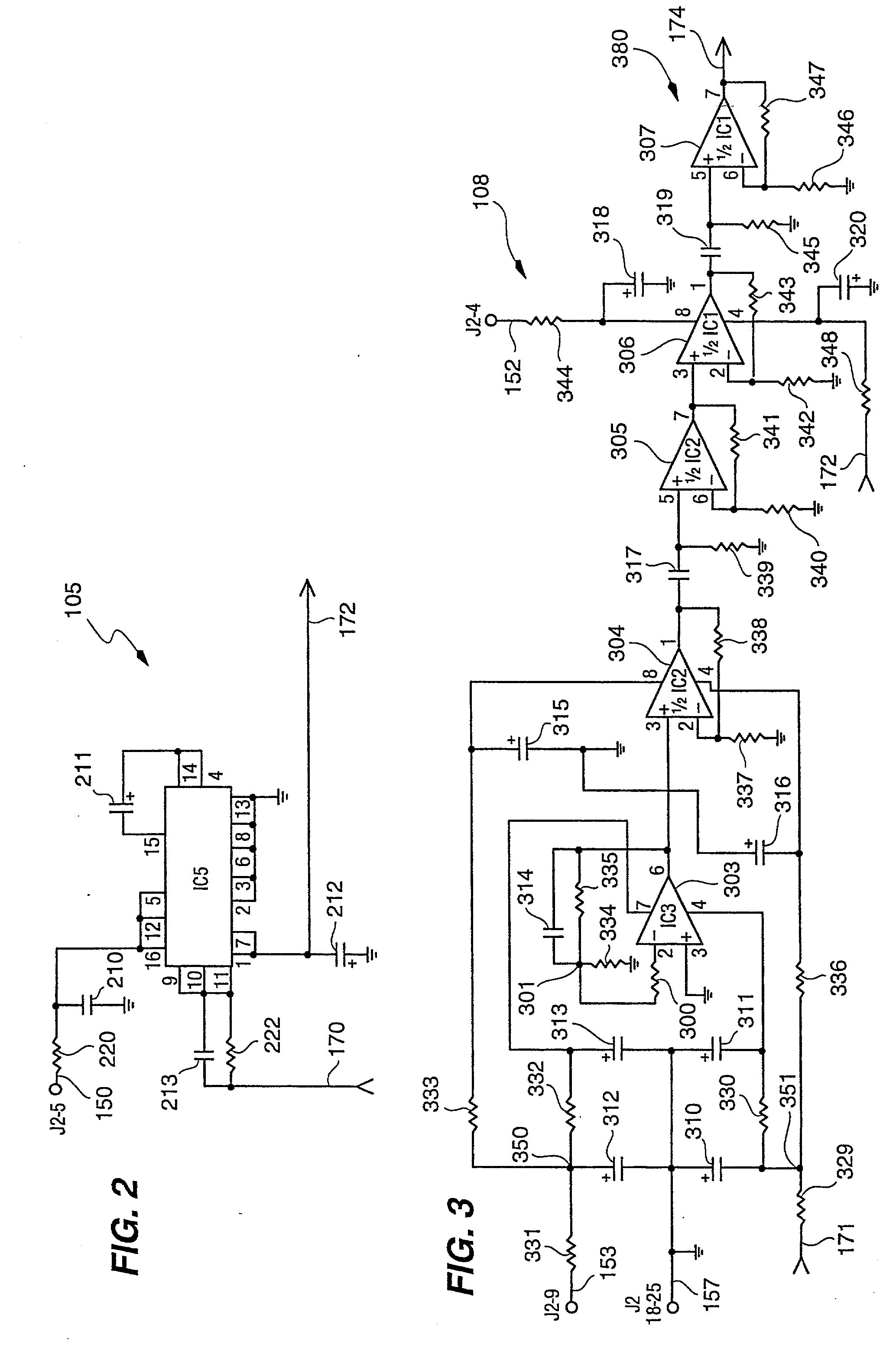

Random number generator and generation method

InactiveUS6324558B1Improve its ability to generateReduce defectsRandom number generatorsDigital function generatorsCmos comparatorShift register

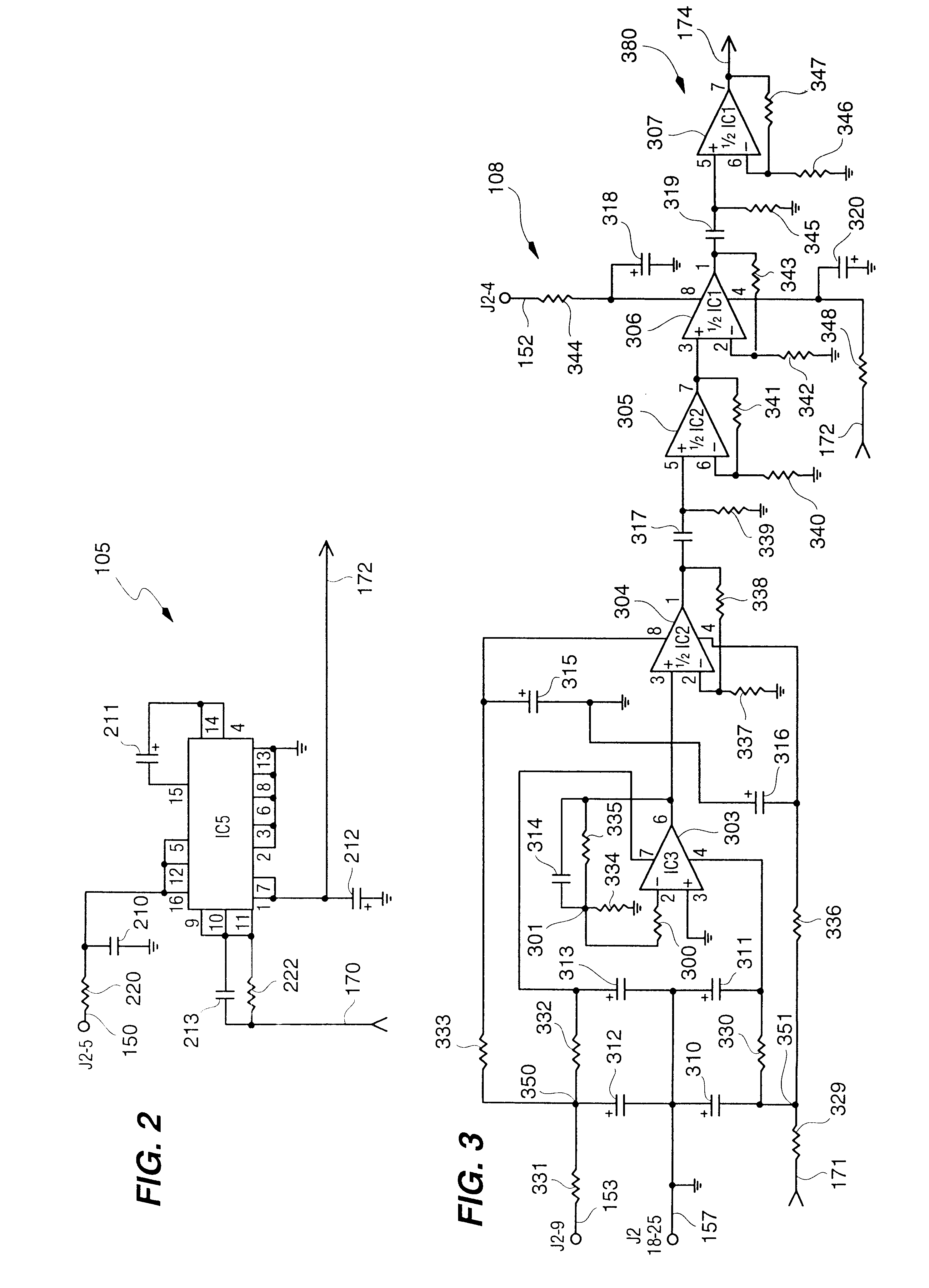

An RNG circuit is connected to the parallel port of a computer. The circuit includes a flat source of white noise and a CMOS amplifier circuit compensated in the high frequency range. A low-frequency cut-off is selected to maintain high band-width yet eliminate the 1 / f amplifier noise tail. A CMOS comparator with a 10 nanosecond rise time converts the analog signal to a binary one. A shift register converts the serial signal to a 4-bit parallel one at a sample rate selected at the knee of the serial dependence curve. Two levels of XOR defect correction produce a BRS at 20 kHZ, which is converted to a 4-bit parallel word, latched and buffered. The entire circuit is powered from the data pins of the parallel port. A device driver interface in the computer operates the RNG. The randomness defects with various levels of correction and sample rates are calculated and the RNG is optimized before manufacture.

Owner:QUANTUM WORLD

Method of digital video reference frame compression

ActiveUS20080170626A1High complexityAccelerated programColor television with pulse code modulationColor television with bandwidth reductionDigital videoLossless compression algorithm

The digital video referencing frame image is compressed block by block by applying lossless compression algorithm to pixel components with full length, or 1 bit, 2 bits, 3 bits or 4 bits LSB bits truncation. If a sub-block has high complexity which results in more than 3 bits error for most pixel components, a transfer algorithm with quantization and VLC coding is applied to compress this sub-block. Should the complexity is higher than a threshold or at least one sub-block having error of more than 3 bits for most pixel components, truncating 1 LSB bit of sub-block with simple pattern to save more bits to be allocate to code the sub-block with highest complex pattern.

Owner:TAIWAN IMAGINGTEK

Methods and apparatus to generate multiple antennas transmit precoding codebook

ActiveUS20100034308A1Modulated-carrier systemsDiversity/multi-antenna systemsClosed loopComputer science

A device and method for generating a codebook. The device includes a generator. The codebook generator is configured to generate a precoding codebook using an 8-PSK alphabet-based 4 bits 4 TX and 8 TX antennas for use in a closed-loop SU-MIMO scheme. According to aspects of the present disclosure, it is possible to generate a precoding codebook for use in 8 Transmission Antenna systems.

Owner:SAMSUNG ELECTRONICS CO LTD

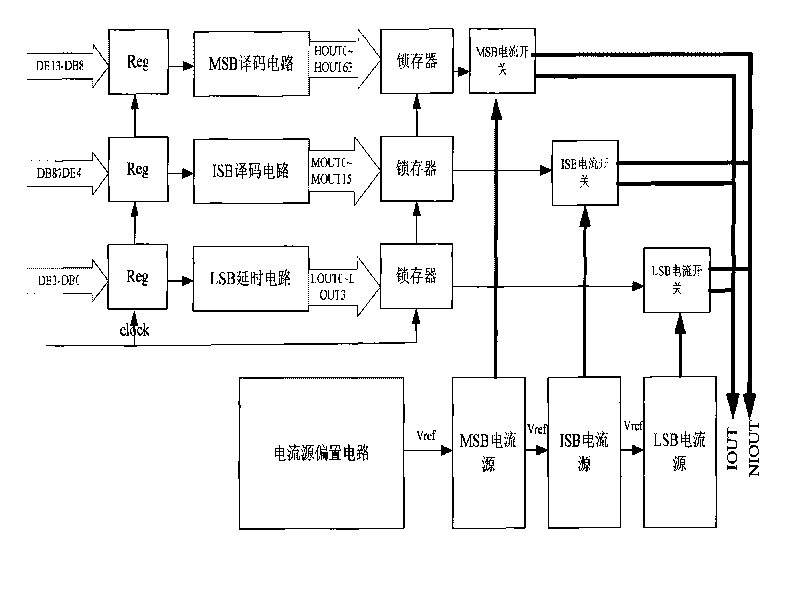

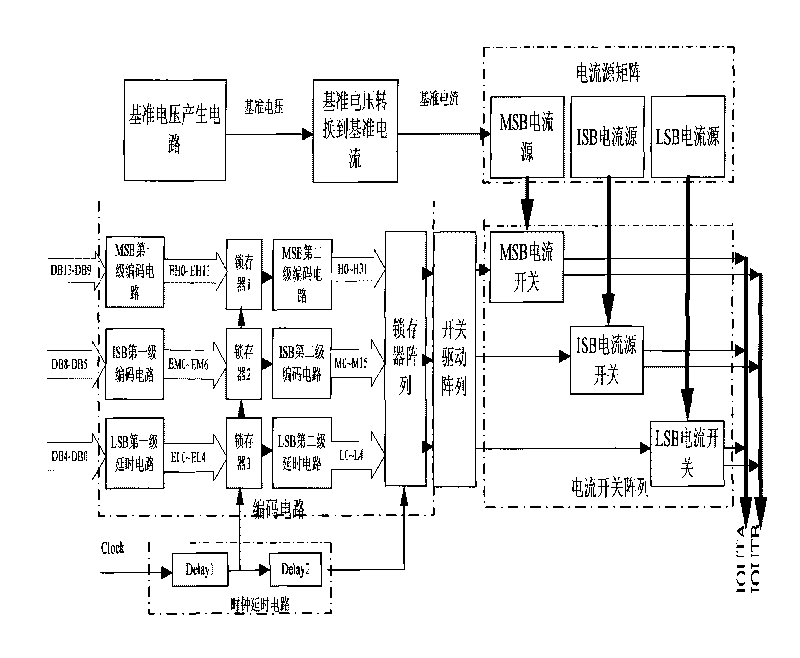

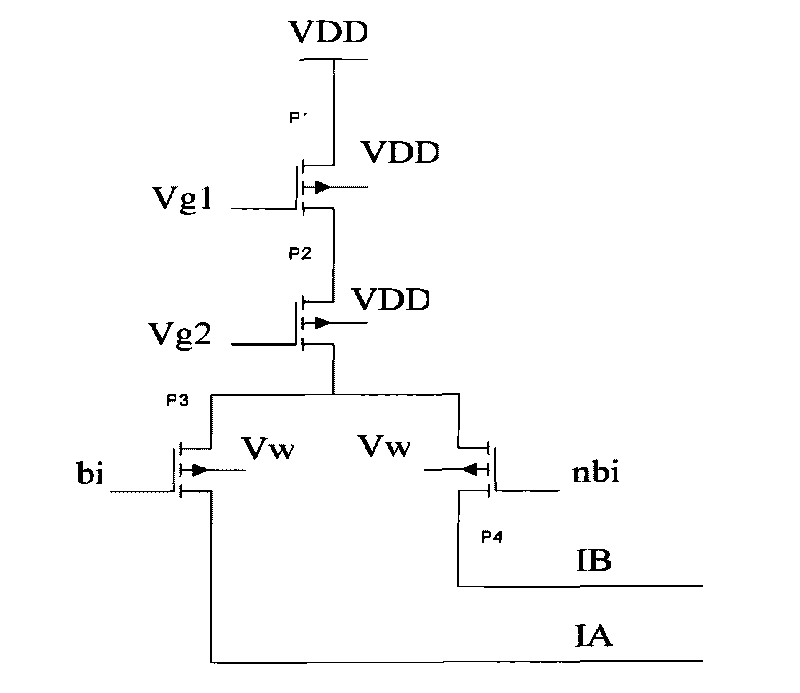

Segmented current-steering digital-to-analog converter

InactiveCN101741389AReduce areaReduce power consumptionDigital-analogue convertorsDriver circuitCommunications system

The invention discloses a high-speed high-accuracy digital-to-analog conversion circuit. The circuit comprises a reference voltage generation circuit, a reference voltage-to-reference current conversion circuit, a coding circuit, a current source matrix and a switch array, wherein the coding circuit has a two-stage water-flowing type coding structure, a switch driving circuit array is connected between the two-stage water-flowing type coding circuit and the switch array, and a two-stage clock delay circuit is connected between a clock input signal and the two-stage coding circuit and provides a clock signal to the two-stage water-flowing type coding circuit; and the current source matrix, a current switch and the coding circuit have a '5+4+5' segmental structure, namely high 5 bits and middle 4 bits have a thermometer code structure, and low 5 bits have a binary code structure. The high-speed high-accuracy digital-to-analog conversion circuit effectively reduces the area and the power consumption of chips, reduces the complexity of the coding circuit, increases conversion rate, reduces burrs, and improves the dynamic characteristics of a digital-to-analog converter. The high-speed high-accuracy digital-to-analog conversion circuit is used for digital processing systems, audio / video conversion systems and communication systems.

Owner:XIDIAN UNIV

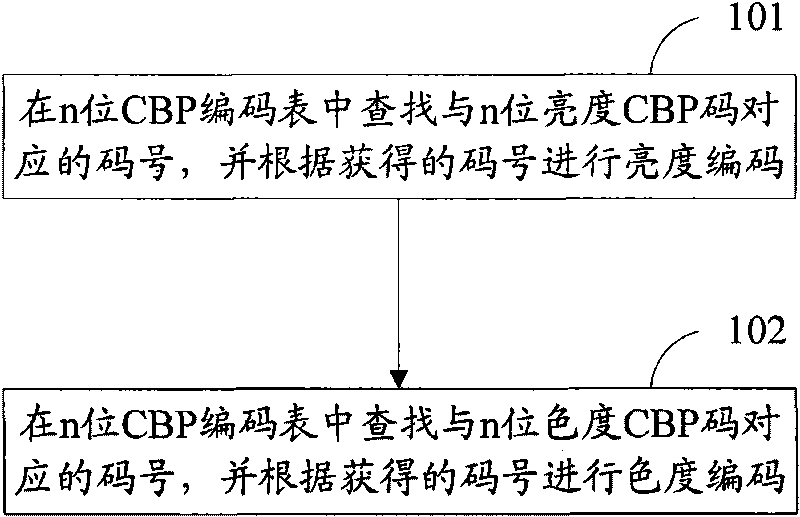

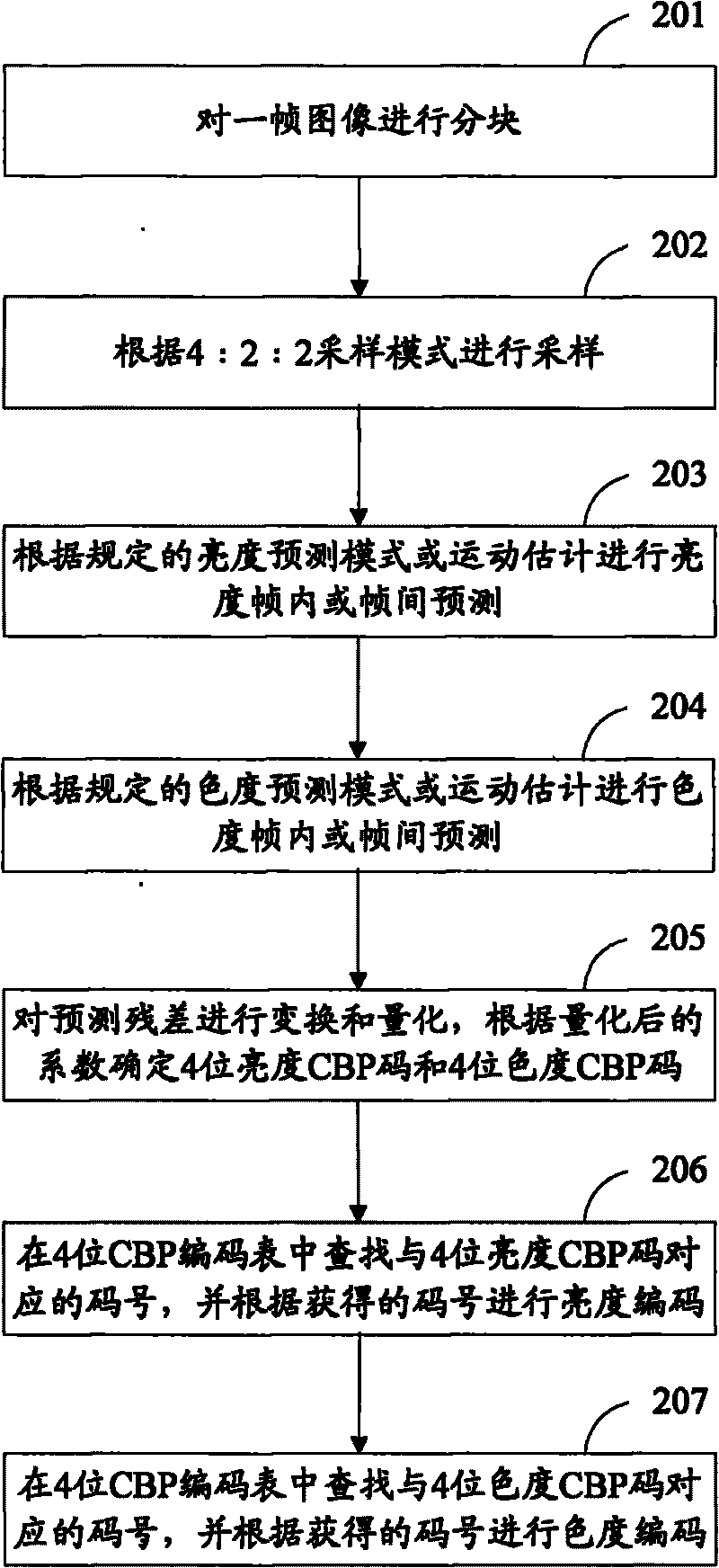

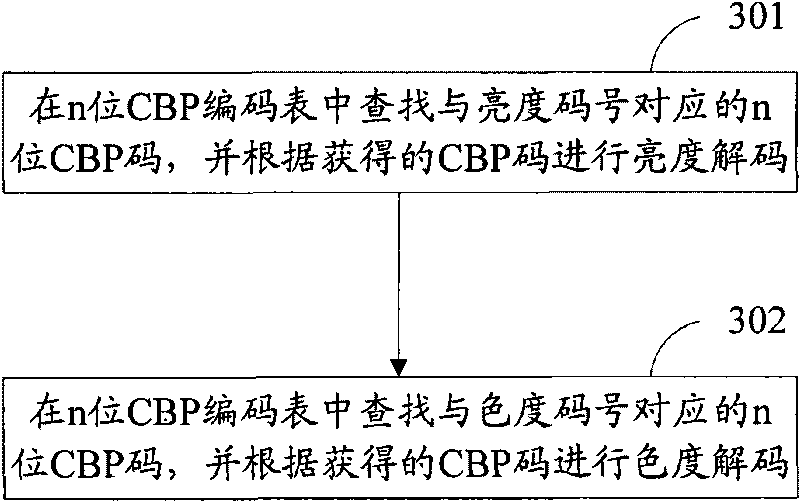

Image coding method and device

ActiveCN101742330ASave storage spaceImprove coding efficiencyTelevision systemsDigital video signal modificationProgramming languageCode table

The invention discloses an image coding method for improving coding efficiency. The method comprises the following steps: searching a 4-bit CBP code table for the code number corresponding to a 4-bit luminance CBP code and carrying out luminance coding according to the obtained code number; and searching the 4-bit CBP code table for the code number corresponding to a 4-bit chroma CBP code and carrying out chroma coding according to the obtained code number. The invention also discloses a device for realizing the method.

Owner:VIMICRO ELECTRONICS CORP +1

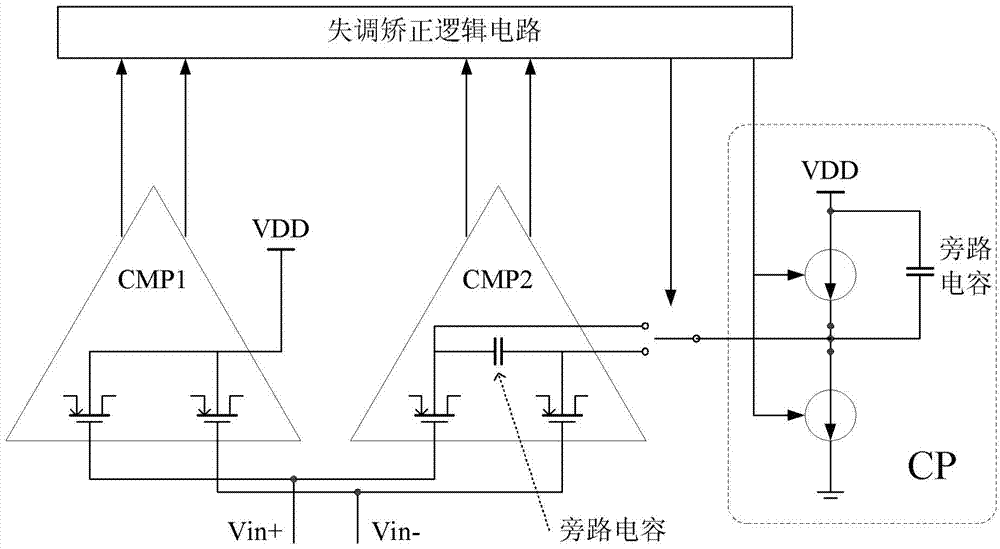

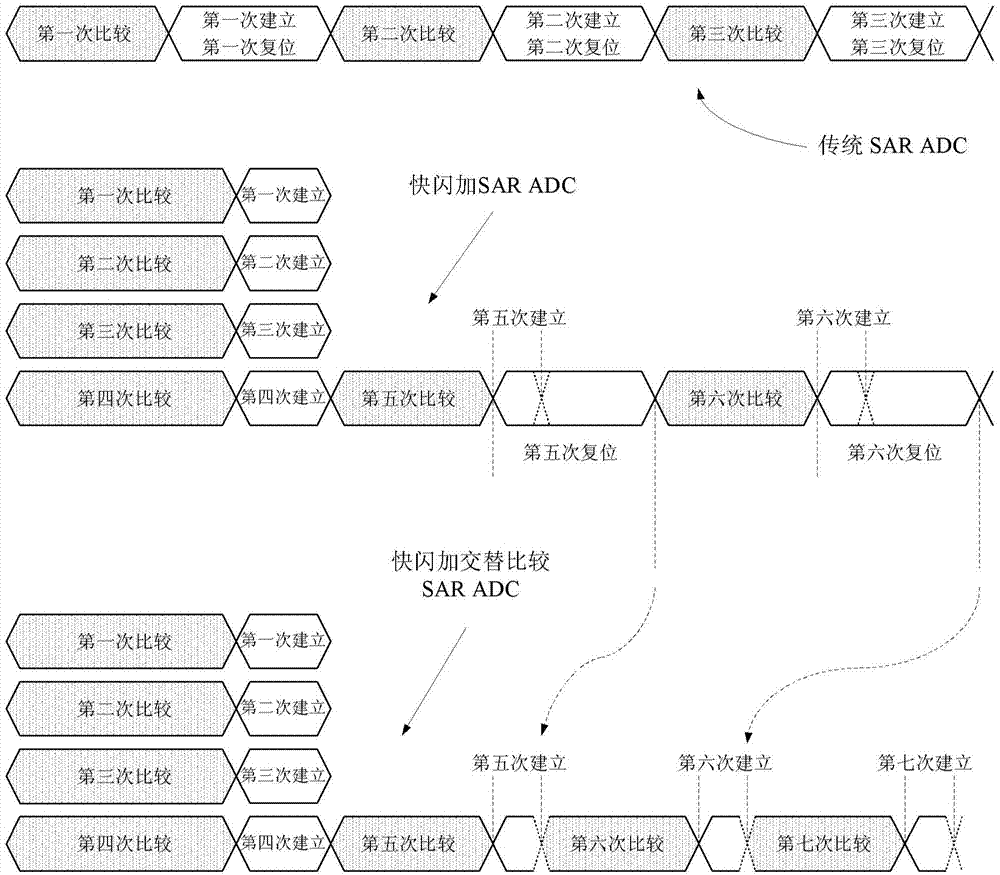

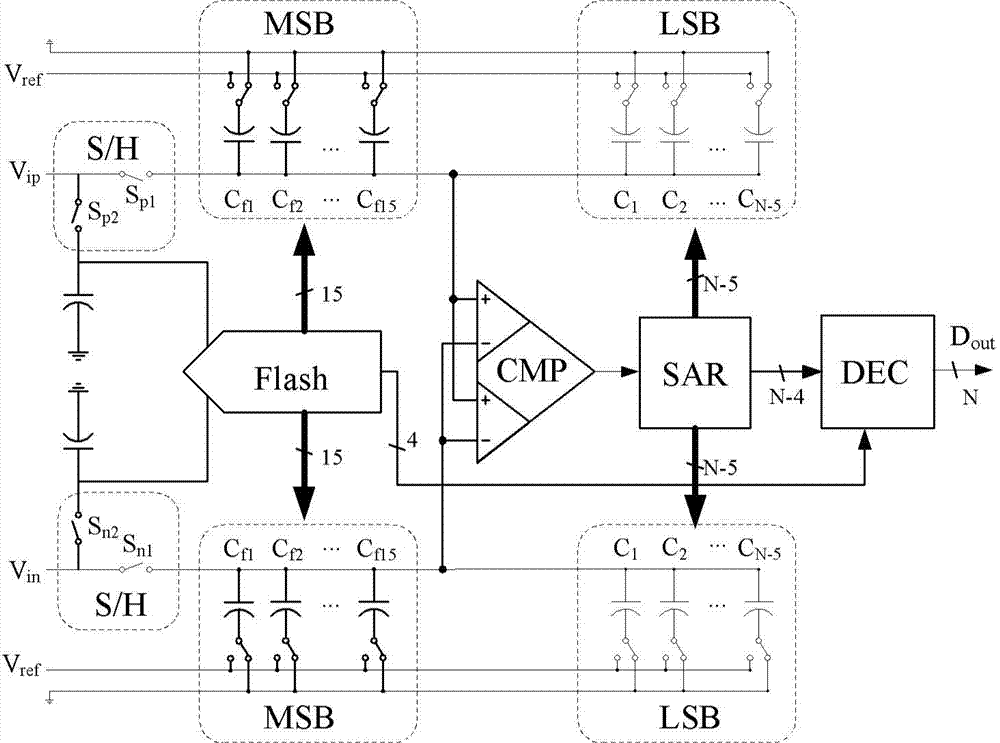

High speed quick flashing plus alternating comparison type successive approximation analog to digital converter

InactiveCN103905049AReduce the number of cyclesShorten analysis timeAnalogue/digital conversionElectric signal transmission systemsCapacitanceEngineering

The invention discloses a high speed quick flashing plus alternating comparison type successive approximation analog to digital converter which comprises a first sampling circuit, a second sampling circuit, a first capacitance array, a second capacitance array, a 4 bit quick flashing type sub-ADC, an alternate comparator, a logic control circuit and a digital weighted circuit, wherein both the first capacitance array and the second capacitance array comprise a thermometer code high effective bit capacitance array and a sub-binary low effective bit capacitance array. By the adoption of the high speed quick flashing plus alternating comparison type successive approximation analog to digital converter, through adding the quick flashing type sub-ADC before a cycle parsing process, cycle times can be effectively reduced and parsing time is shortened; through the introduction of the alternate comparator, the comparator reset time in a traditional structure is eliminated, the speed bottleneck is broken through and parsing speed is accelerated; the added quick flashing type sub-ADC bit number is low, and interpolation technology and a dynamic circuit structure are adopted, so that the increased power consumption is small, and the achieving cost is low cost is achieved; moreover, the introduced alternate comparator does not increase the total comparison times, so that power consumption does not increase.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

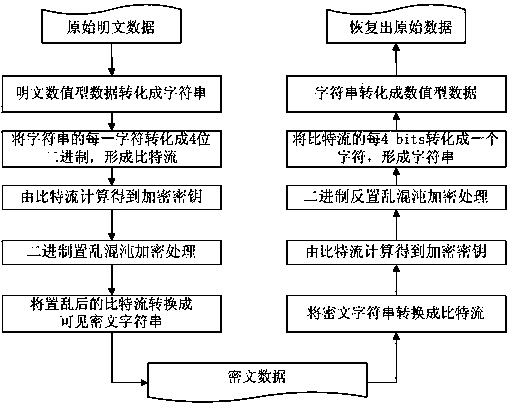

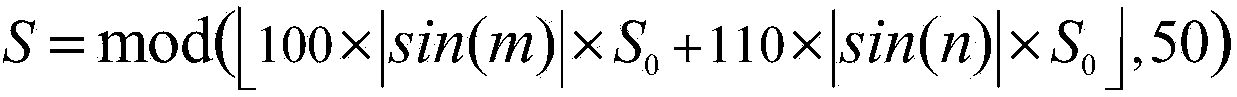

Encryption and decryption method for numeric type data

ActiveCN103532701AEnsure safetyGuaranteed feasibilityEncryption apparatus with shift registers/memoriesOriginal dataCiphertext

The invention discloses an encryption and decryption method for numeric type data. The method comprises the following steps that the numeric type data is converted into character strings; each character is sequentially converted into 4 bits according to the correspondence relationship between the numeric characters and the binary system, and a bit stream is formed; the number of 0 and 1 in the bit stream is counted, and an encryption secret key is obtained through calculation; the encryption secret key is utilized, a chaotic sequence with the pseudo-random property is generated by a chaotic system, in addition, chaotic signals are taken from the chaotic sequence and are sequenced in an ascending sequence, and the bit stream is scrambled according to the positions in accordance with the scrambling rule; the corresponding relationship between the four-digit binary coding mode and the visible ciphertext characters is utilized for converting the scrambled bit stream into the visible ciphertext character strings, and the ciphertext can be decrypted and recovered into the original data type data through adopting the similar method. According to the method provided by the invention, the corresponding table customization is adopted, the numeric type data is subjected to binary scrambling chaotic encryption processing, the safety and the feasibility of the data encryption are ensured, and in addition, the encryption efficiency is also greatly improved.

Owner:南通九盛软件有限公司

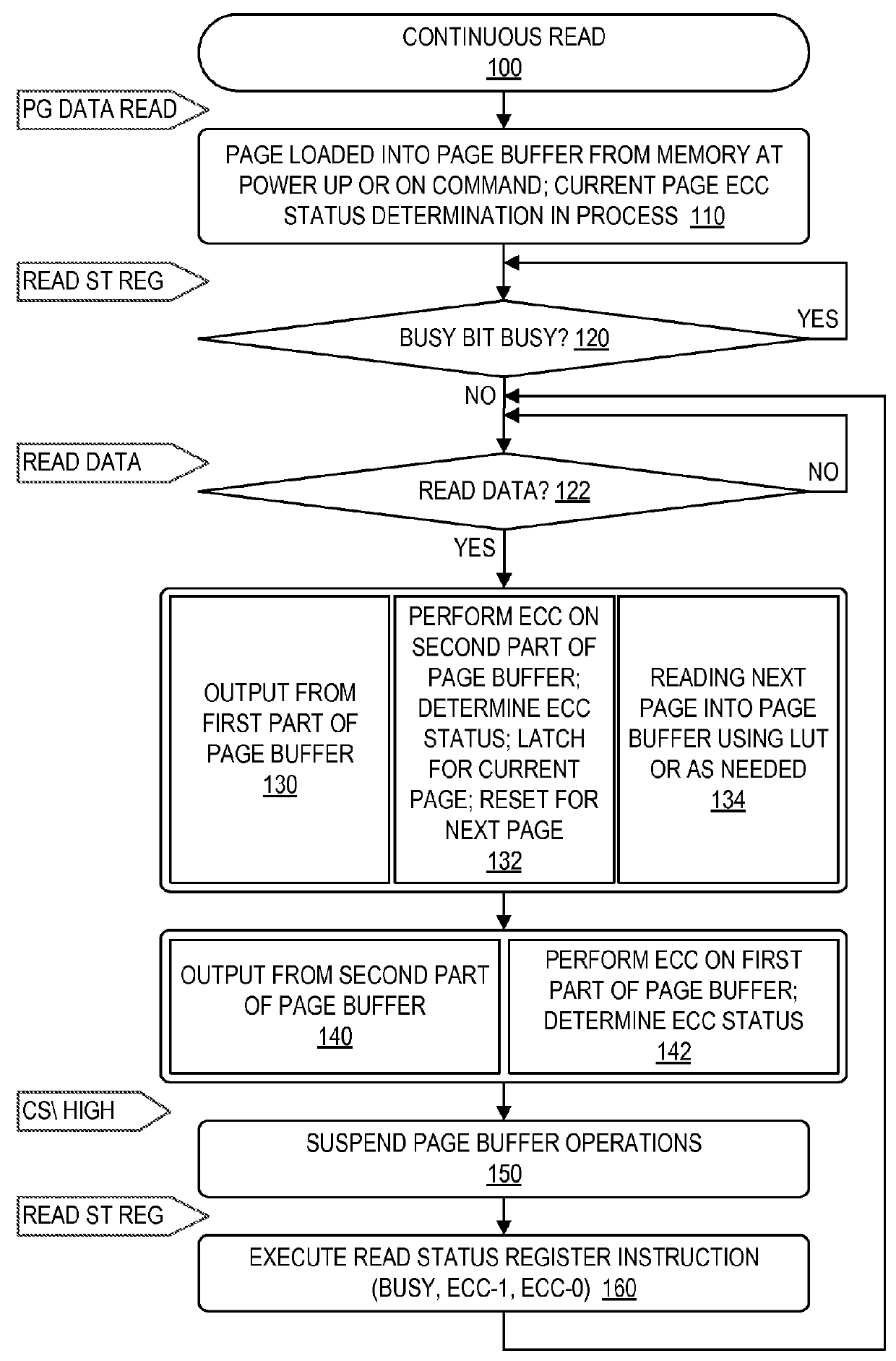

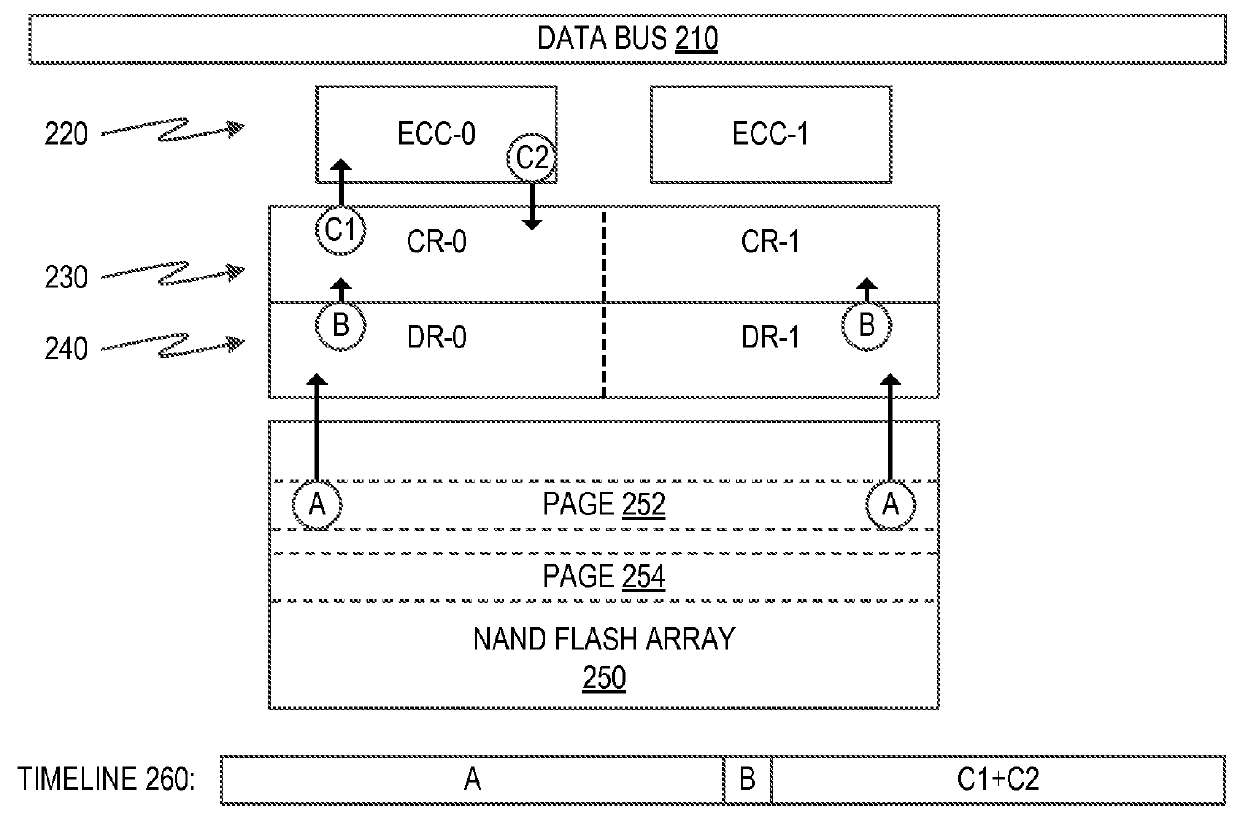

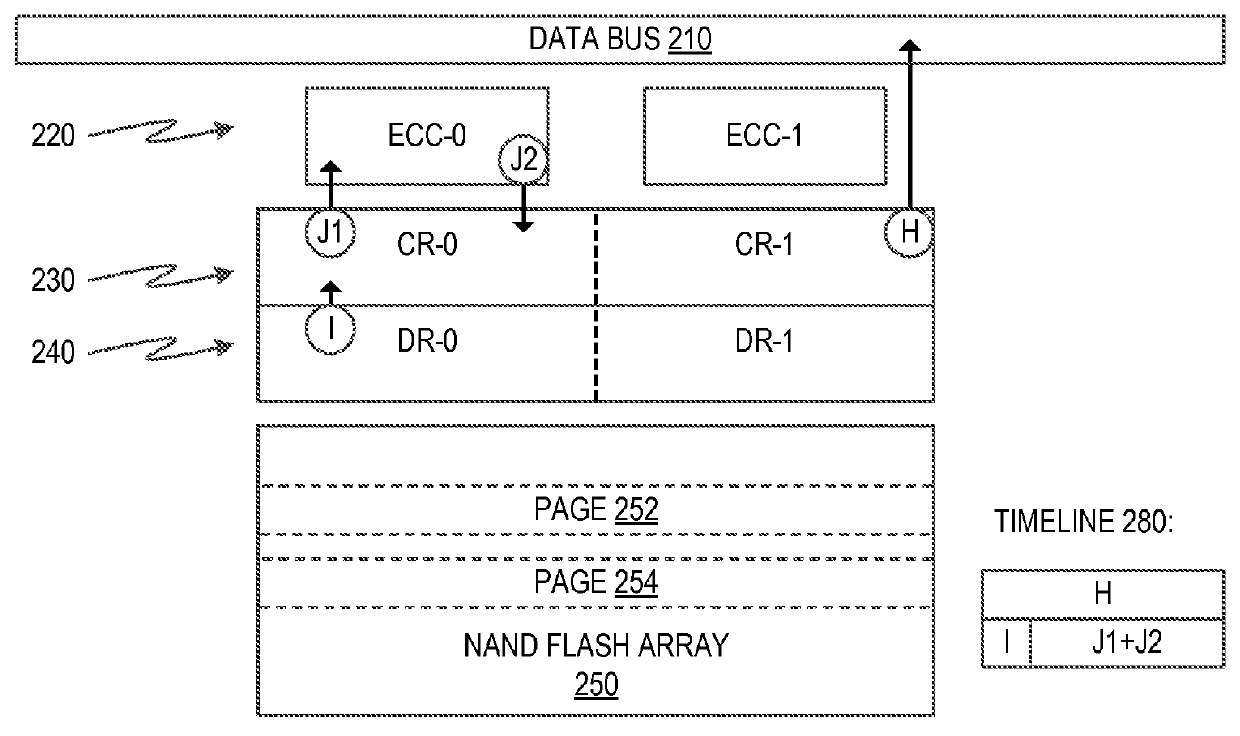

NAND Flash Memory Having Internal ECC Processing and Method of Operation Thereof

A continuous read operation may be achieved by using a data buffer having a partitioned data register and a partitioned cache register, user configurable internal ECC associated with the cache register, and fast bad block management. During a data read operation, the ECC status may be indicated by ECC status bits. The status (1:1), for example, may indicate for the Continuous Read Mode that the entire data output contains more than 4 bits errors / page in multiple pages. However, one may wish to know the ECC status of each page or of each page partition. For the former, the ECC status for the entire page may be determined and made in the status register at the end of the output of the page. For the latter, the ECC status of each page partition may be determined and output before output of the corresponding page partition.

Owner:WINBOND ELECTRONICS CORP

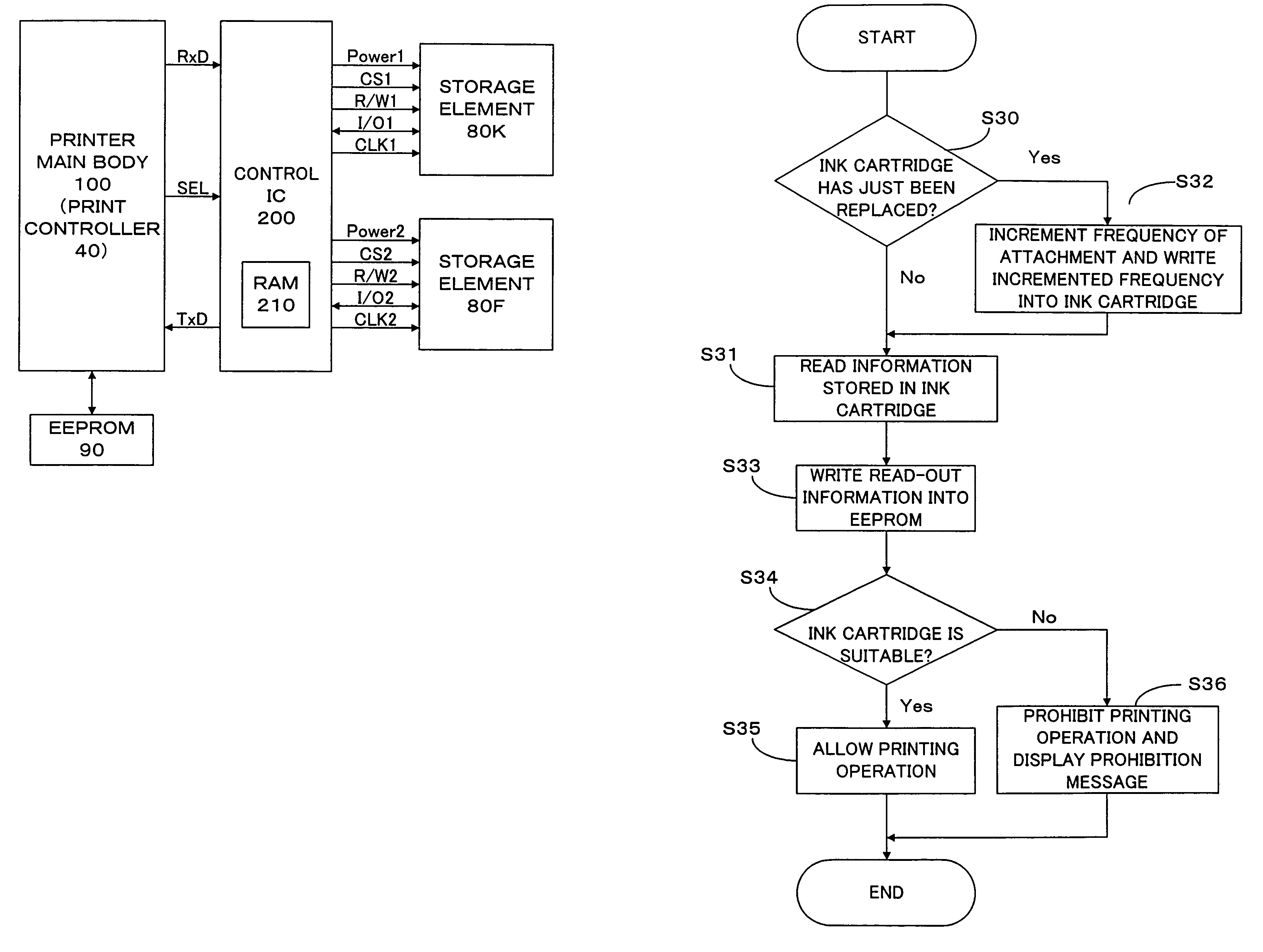

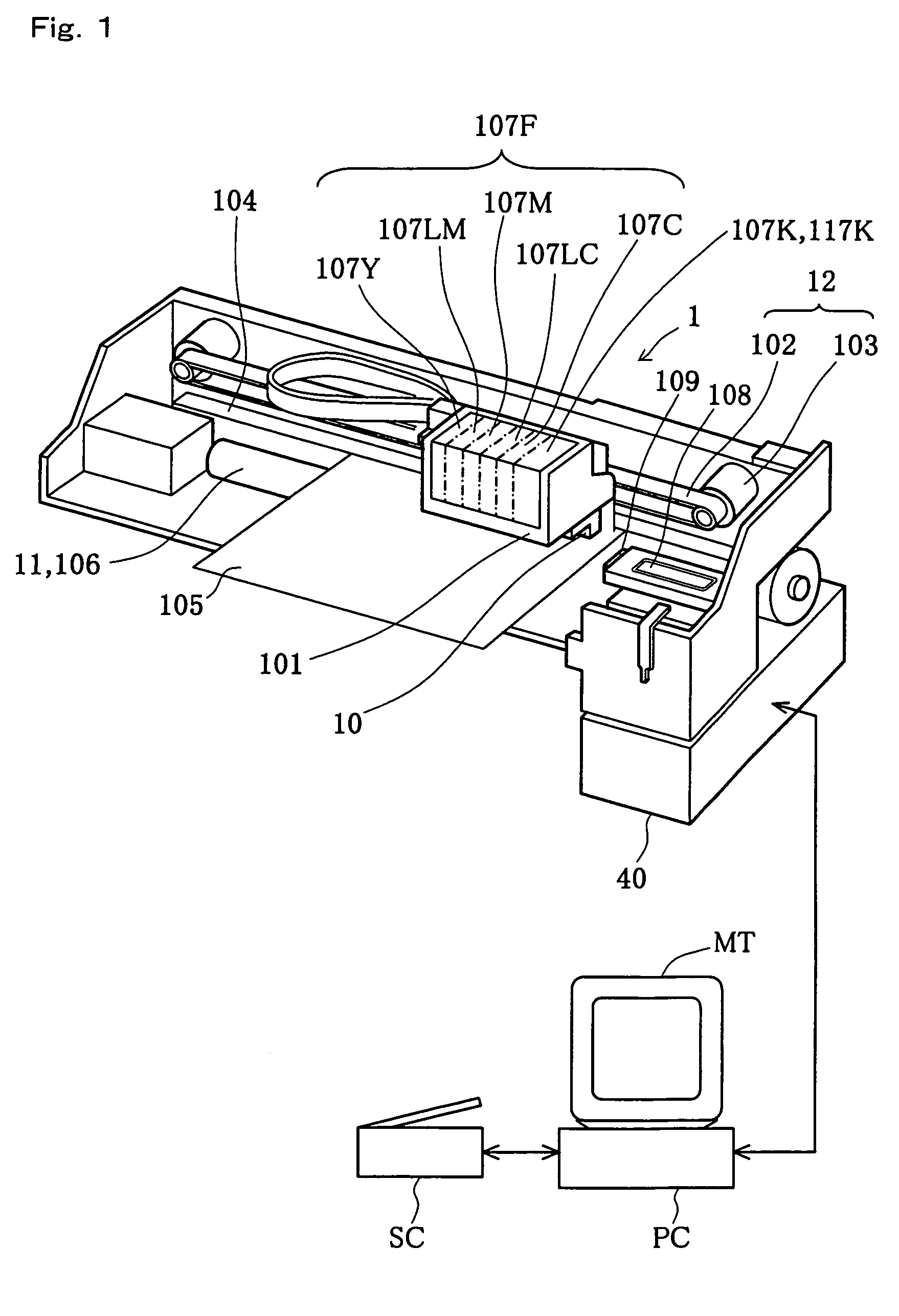

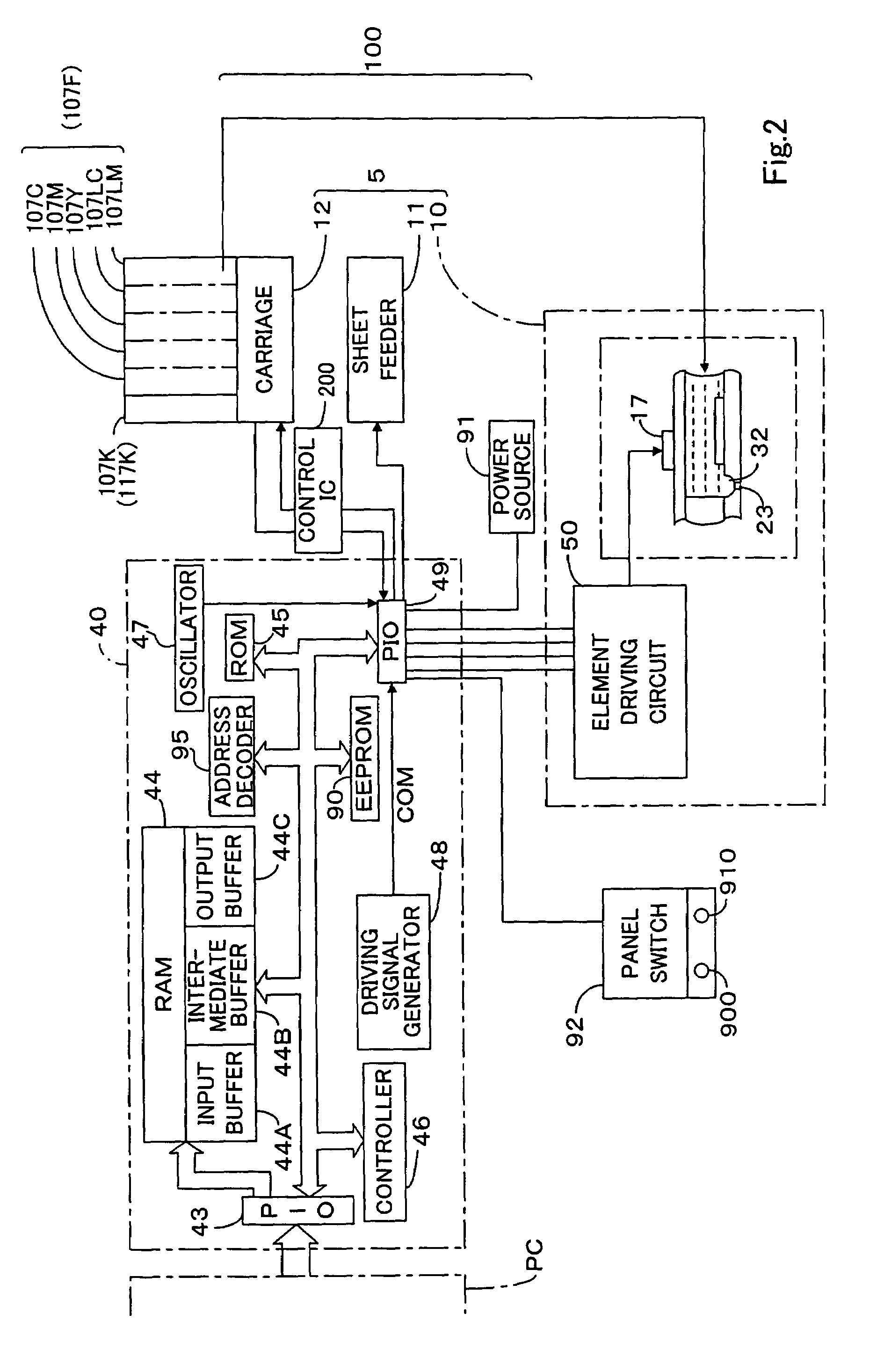

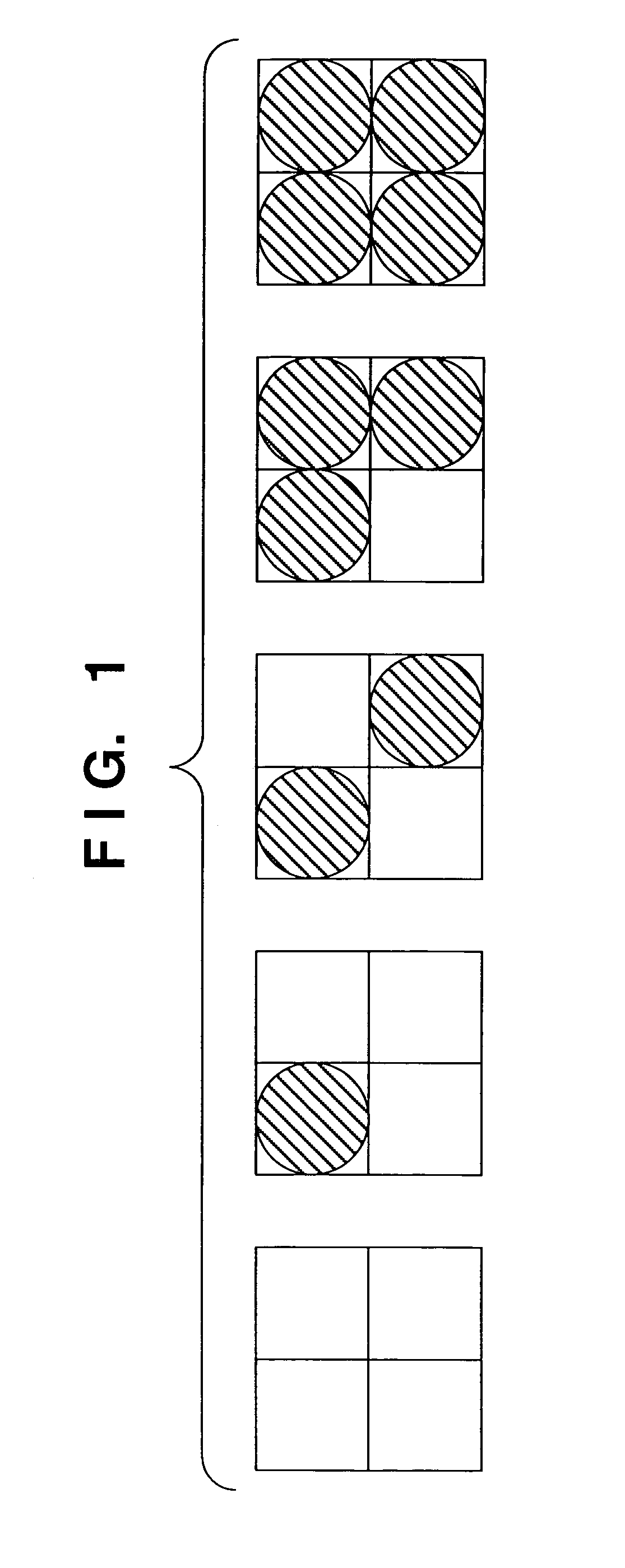

Method of normality decision with regard to ink cartridge and printer actualizing the method

InactiveUS6995861B1Digitally marking record carriersDigital computer detailsComputer scienceInformation storage

An ink cartridge of the present invention has a storage element, in which plural pieces of specific information relating to an ink cartridge are stored at specific addresses having predetermined data lengths. For example, a piece of information on the year of manufacture is registered in a data length of 7 bits, a piece of information on the month of manufacture is registered in a data length of 4 bits, and a piece of information on the date of manufacture is registered in a data length of 5 bits. A piece of information on the time (hour) of manufacture is registered in a data length of 5 bits, and a piece of information on the time (minute) of manufacture is registered in a data length of 6 bits. The technique of the present invention determines whether the storage element incorporated in the ink cartridge is normal or abnormal, based on the piece of information on the month of manufacture. This arrangement ensures the easy and adequate determination of whether or not the information stored in the storage element is destroyed.

Owner:SEIKO EPSON CORP

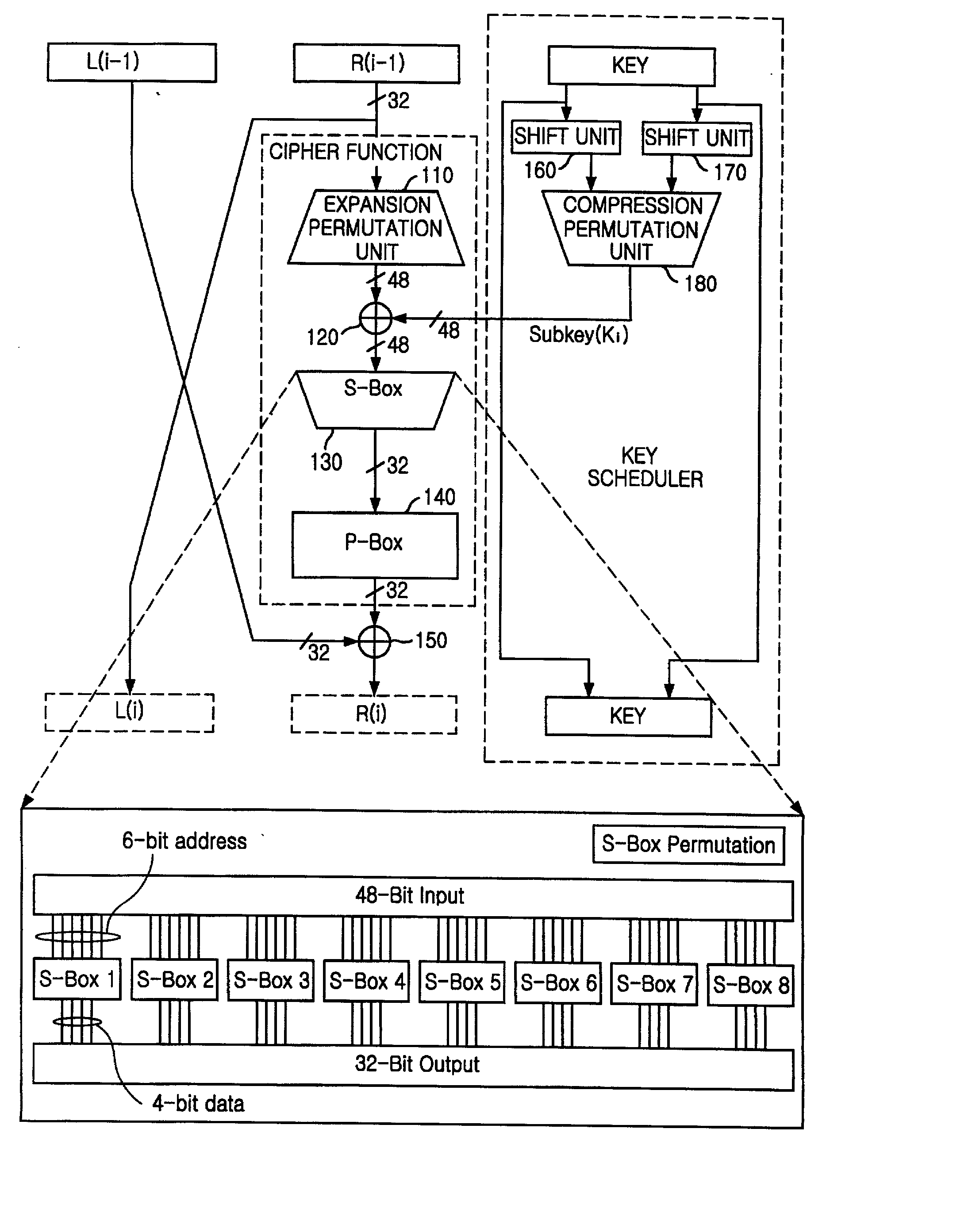

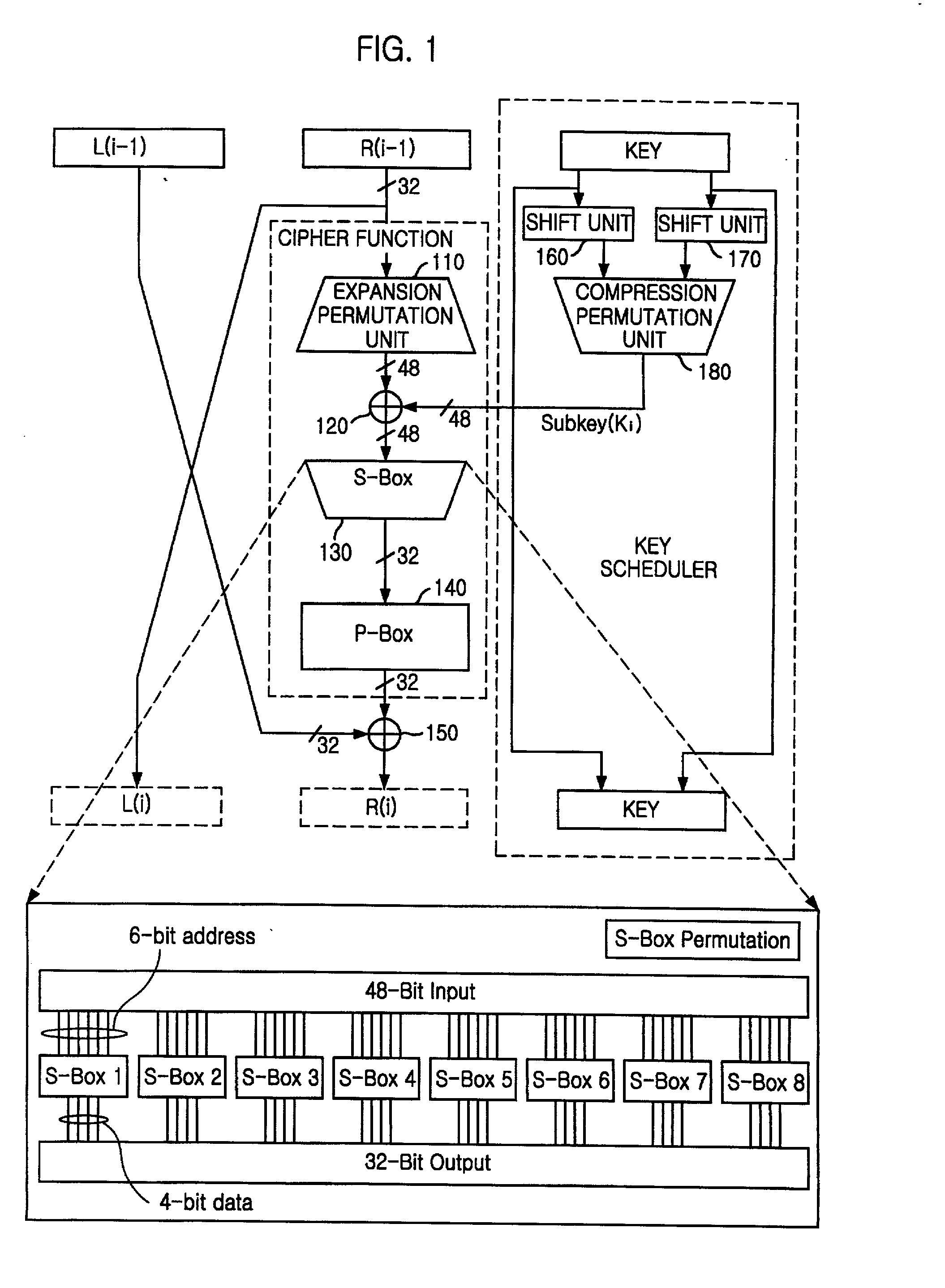

Encryption apparatus using data encryption standard algorithm

InactiveUS20020003876A1Improve process capabilityEncryption apparatus with shift registers/memoriesSecret communicationS-boxMultiplexer

An encryption device eliminates data contention and minimizes area by accessing twice data for a given time by using a memory device of two times faster access time. The encryption device for performing encryption of plain text blocks using data encryption standard algorithm, wherein the encryption device includes an initial permutation unit, a data encryption unit having n-stage (n is an even number) pipeline structure using a first clock, a second clock and a third clock, and an inverse initial permutation unit, the encryption device includes: a multiplexer for selecting one of n / 3 48-bit inputs; 8 S-Boxes, each for receiving 6-bit address among the selected 48-bit and outputting 4-bit data; a demultiplexer for distributing 32-bit data from the S-Boxes to n / 3 outputs; and a controller for control the multiplexer and the demultiplexer with a fourth clock and a fifth clock, wherein the fourth and the fifth clock are faster than the first, the second and the third clocks by n / 3 times.

Owner:ABOV SEMICON

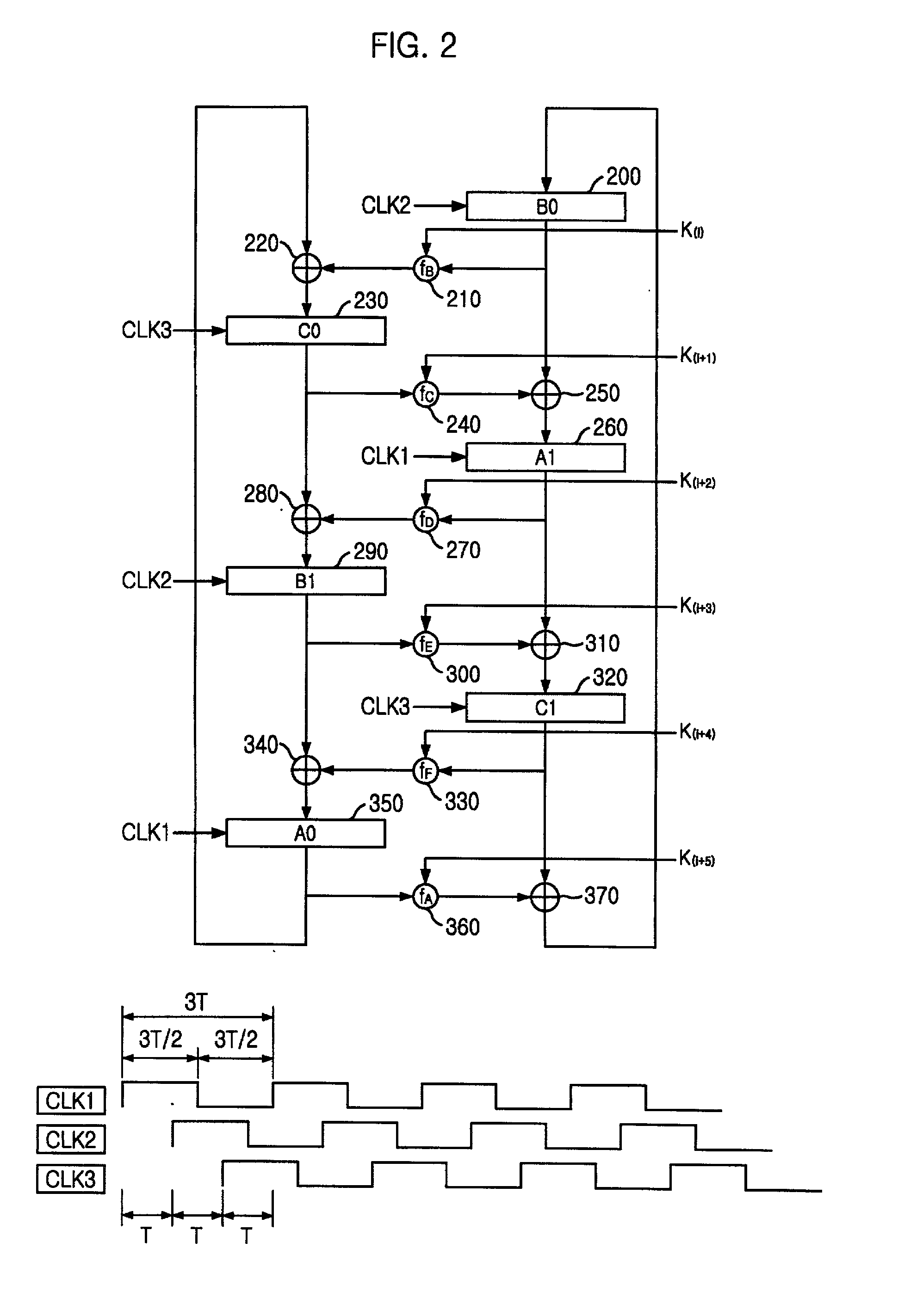

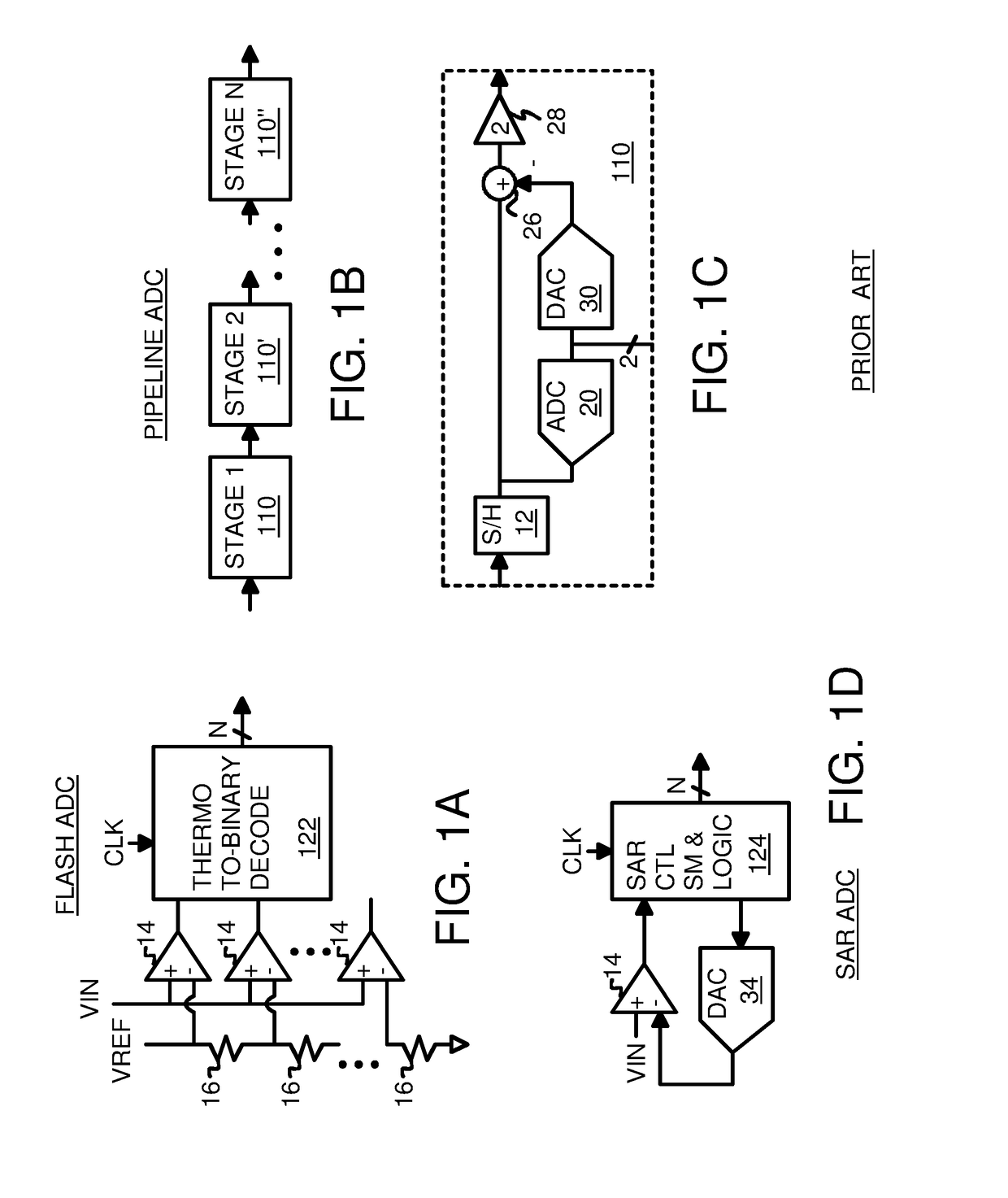

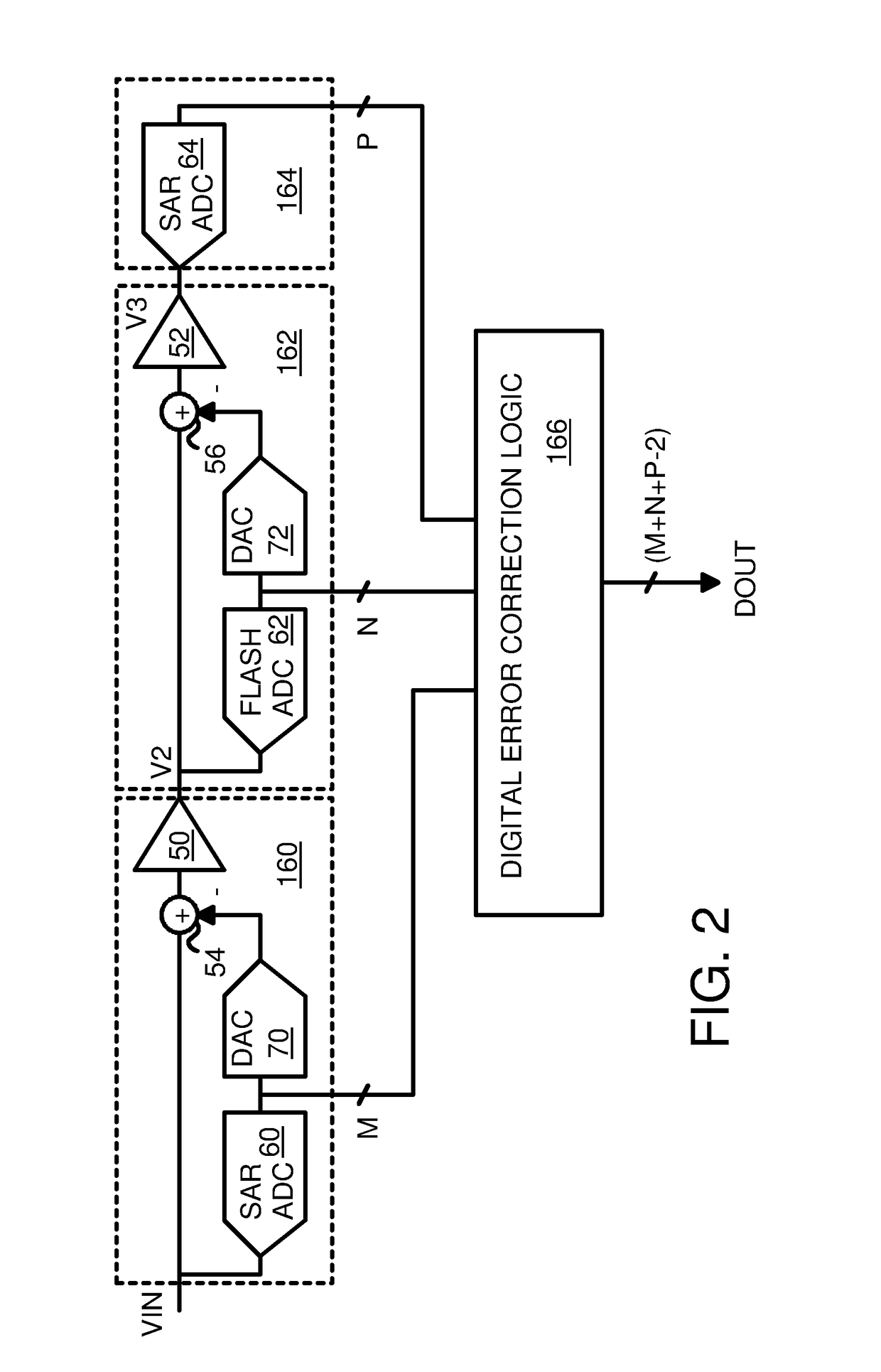

Multi-stage hybrid analog-to-digital converter

ActiveUS10103742B1Electric signal transmission systemsAnalogue-digital convertersAudio power amplifierLeast significant bit

A hybrid Analog-to-Digital Converter (ADC) has multiple stages. A first stage and a final stage each use a Successive-Approximation Register (SAR) ADC to generate the Most-Significant-Bits (MSBs) and the Least-Significant-Bits (LSBs) over successive internal cycles. Middle stage(s) use a faster flash ADC with multiple comparators in parallel to generate the middle binary bits, which are then re-converted by a Digital-to-Analog Converter (DAC) and subtracted from the stage's input analog voltage to generate a difference that is amplified by a residual amplifier that outputs an amplified voltage to the next stage. The first stage also has this multiplying DAC structure to convert the MSBs to an amplified voltage to the first of the middle stages. Finally, digital error correction logic removes redundant binary bits between stages. Initial and final SAR stages of 4 and 8 bits with a 4-bit middle stage provide a hybrid ADC of 14-bit precision.

Owner:HONG KONG APPLIED SCI & TECH RES INST

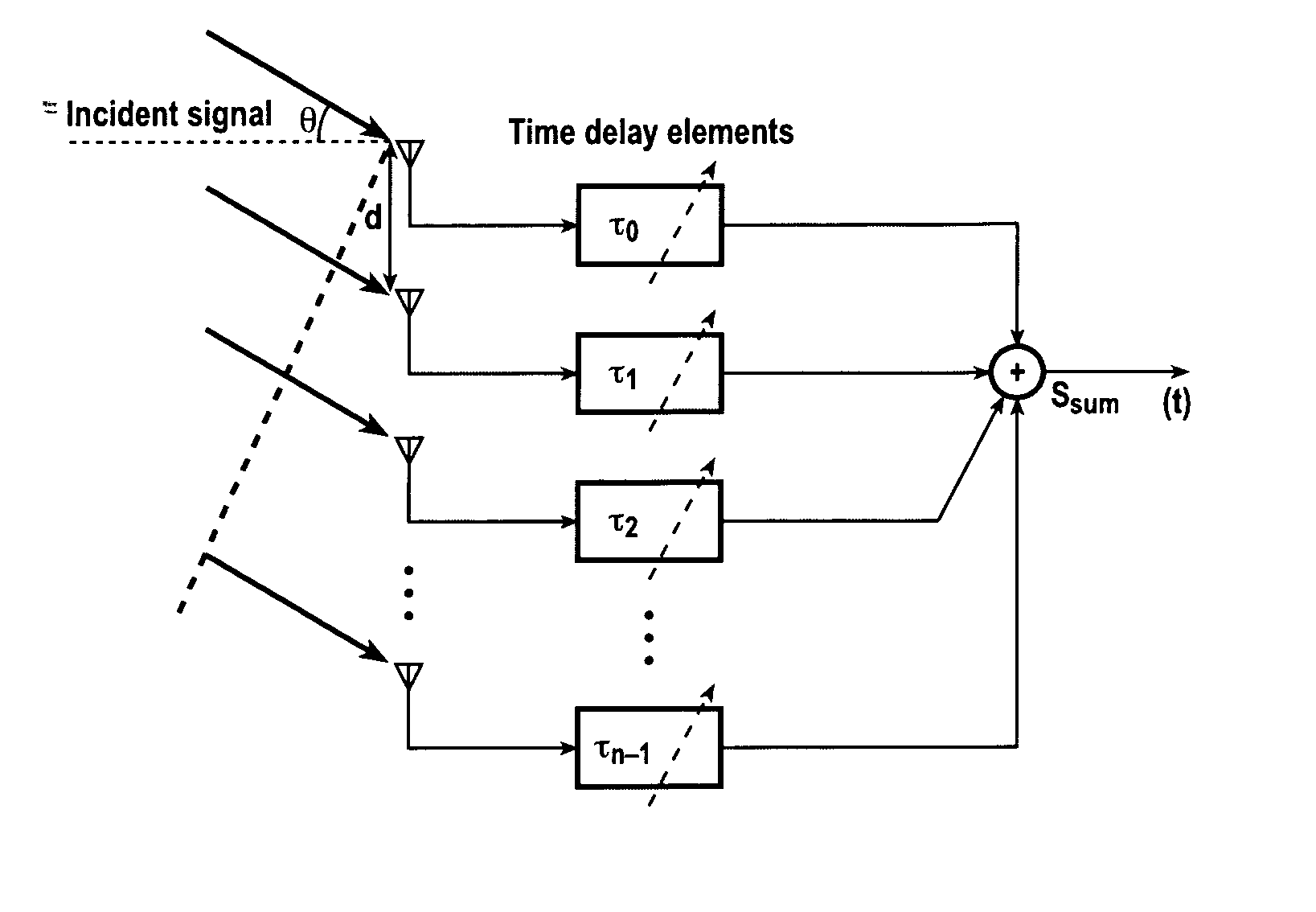

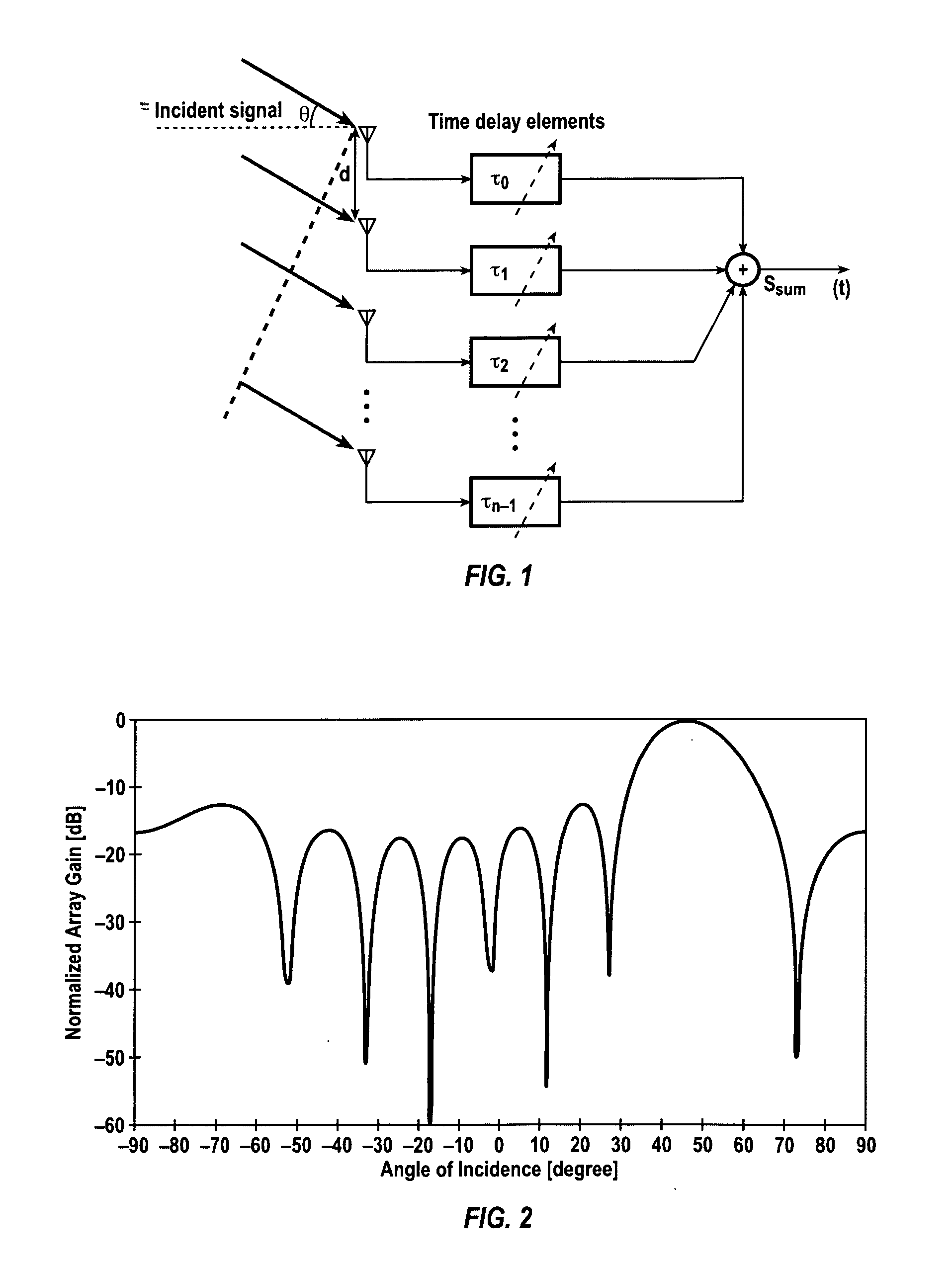

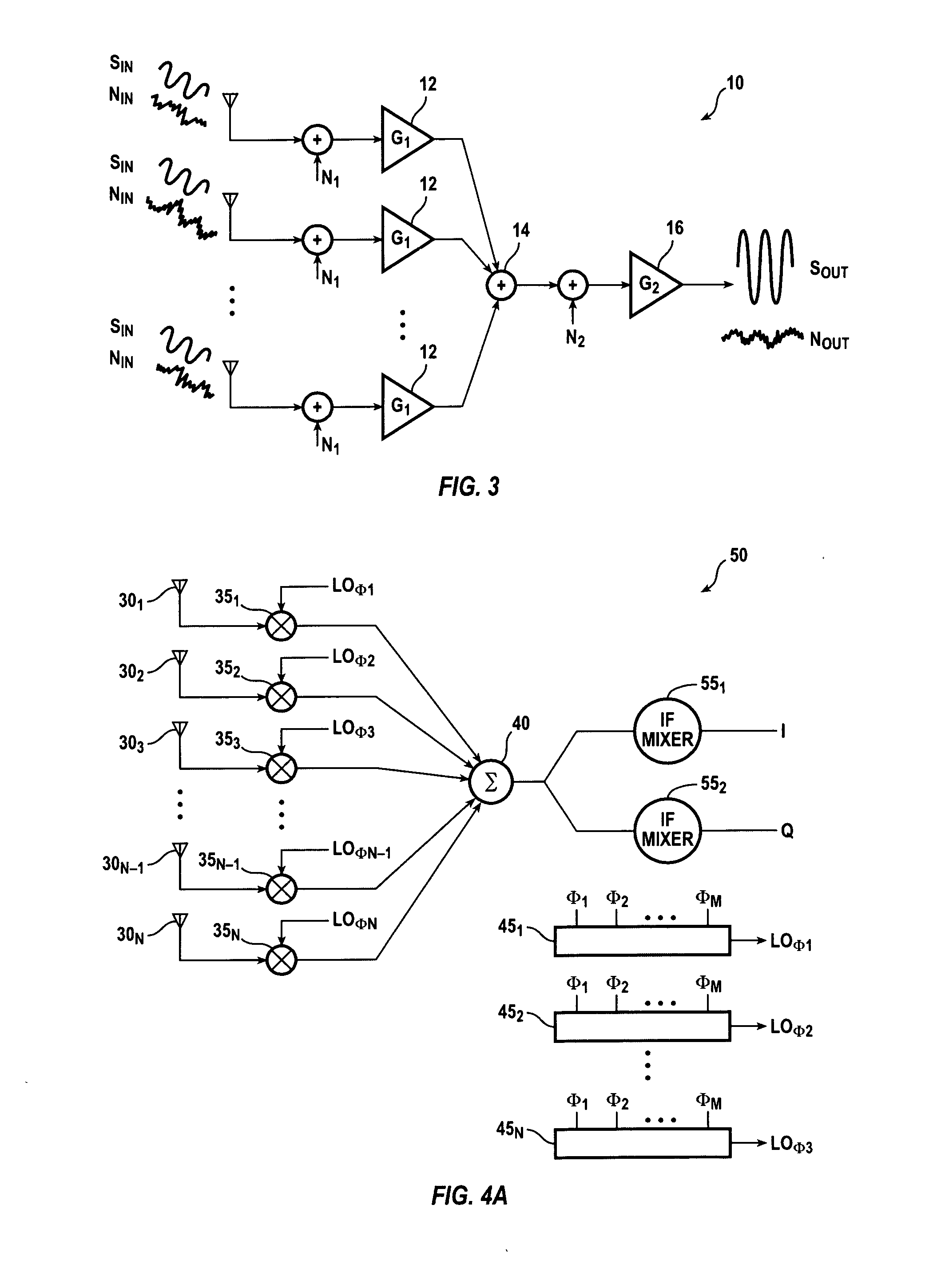

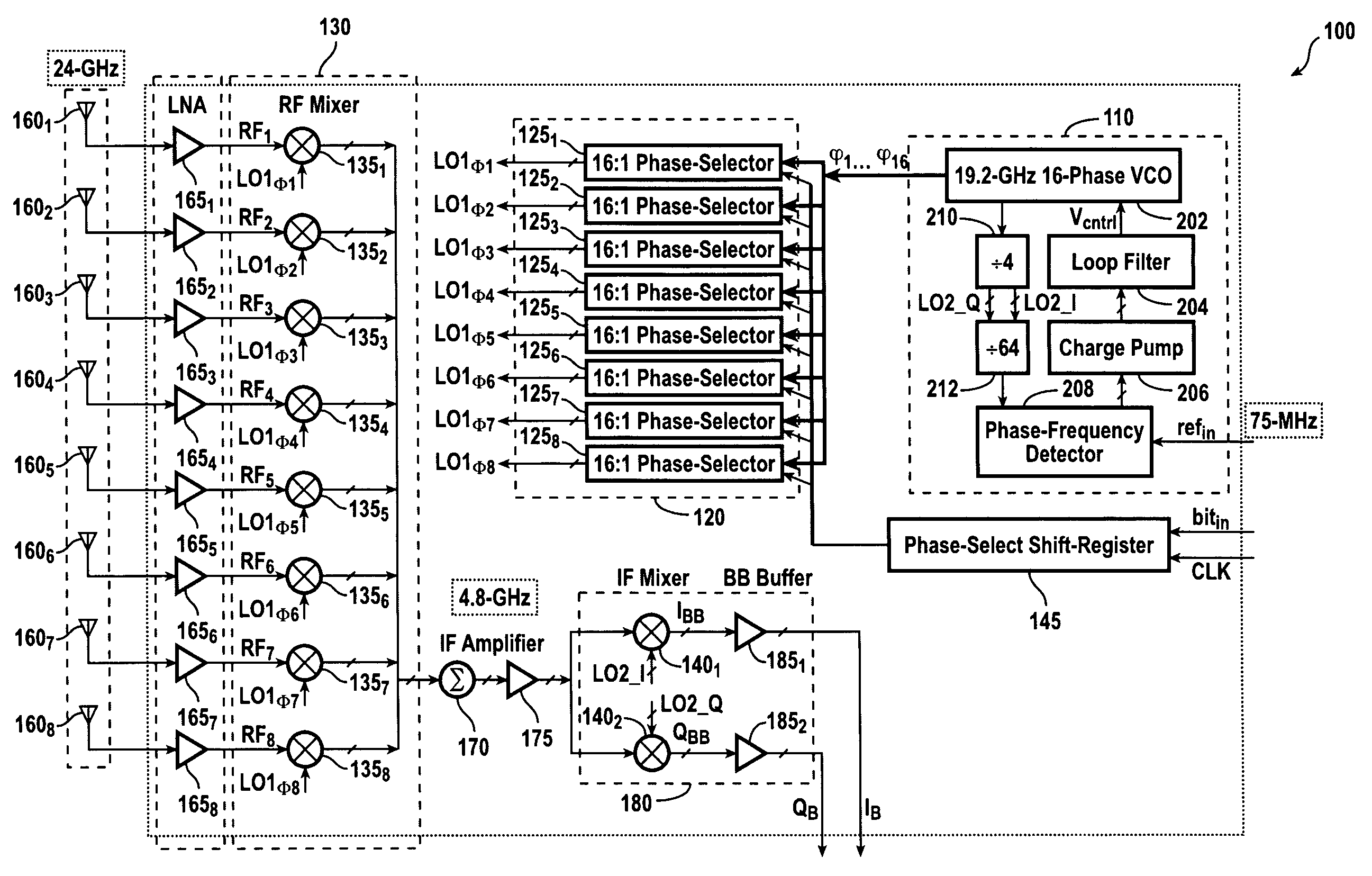

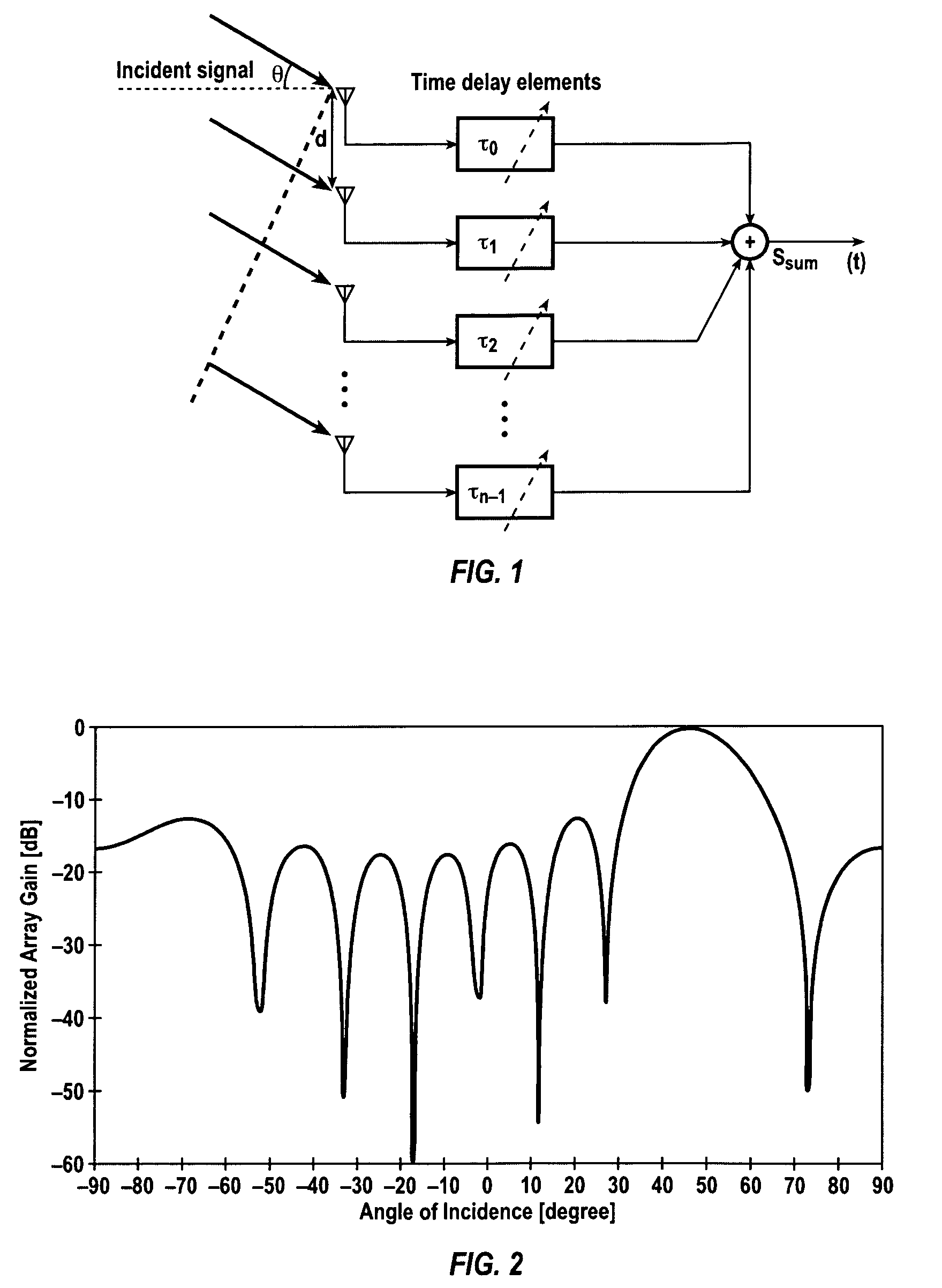

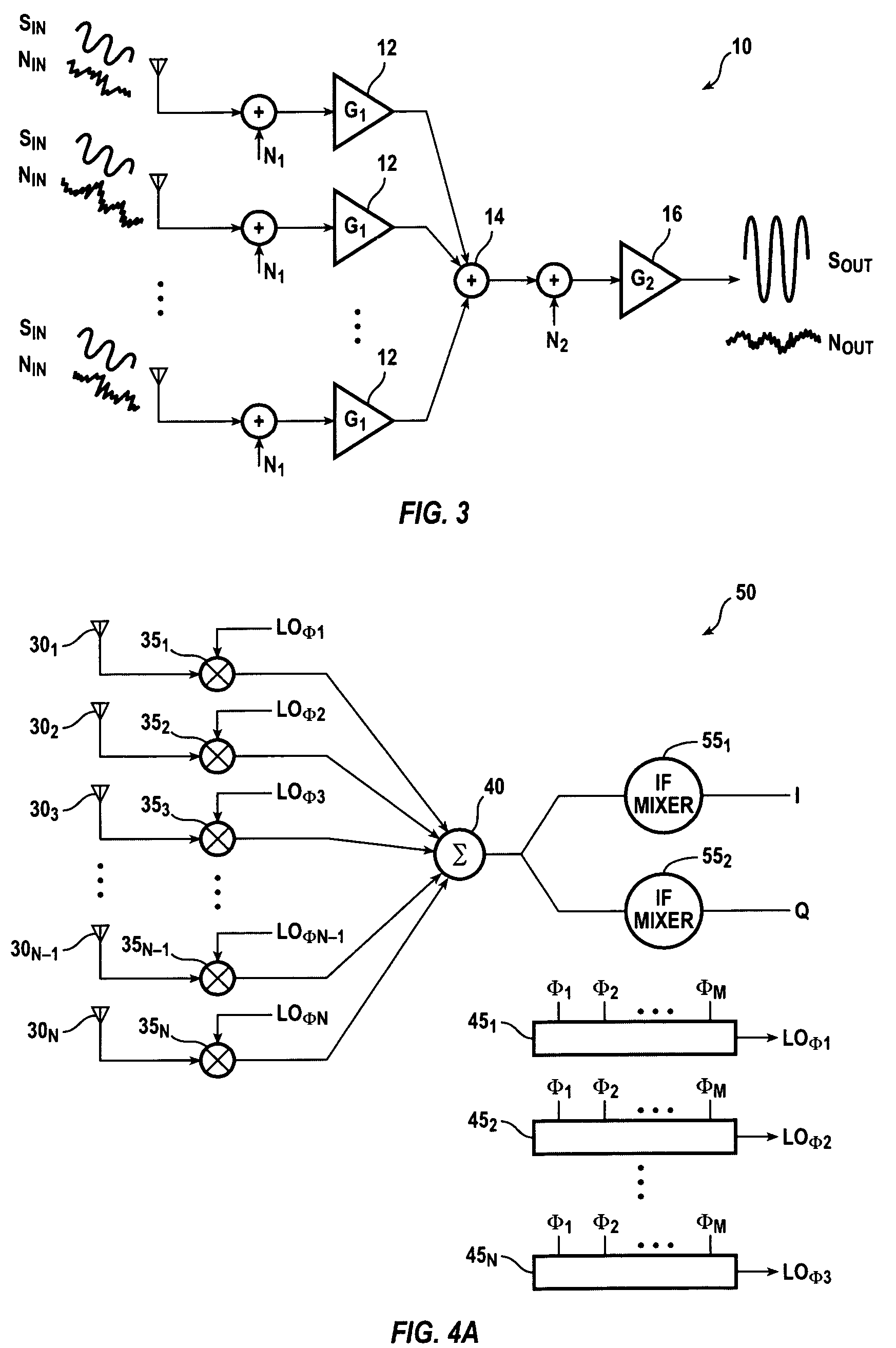

Monolithic silicon-based phased arrays for communications and radars

A phased-array receiver is adapted so as to be fully integrated and fabricated on a single silicon substrate. The phased-array receiver is operative to receive a 24 GHz signal and may be adapted to include 8-elements formed in a SiGe BiCMOS technology. The phased-array receiver utilizes a heterodyne topology, and the signal combining is performed at an IF of 4.8 GHz. The phase-shifting with 4 bits of resolution is realized at the LO port of the first down-conversion mixer. A ring LC VCO generates 16 different phases of the LO. An integrated 19.2 GHz frequency synthesizer locks the VCO frequency to a 75 MHz external reference. Each signal path achieves a gain of 43 dB, a noise figure of 7.4 dB, and an IIP3 of −11 dBm. The 8-path array achieves an array gain of 61 dB, a peak-to-null ratio of 20 dB, and improves the signal-to-noise ratio at the output by 9 dB.

Owner:CALIFORNIA INST OF TECH

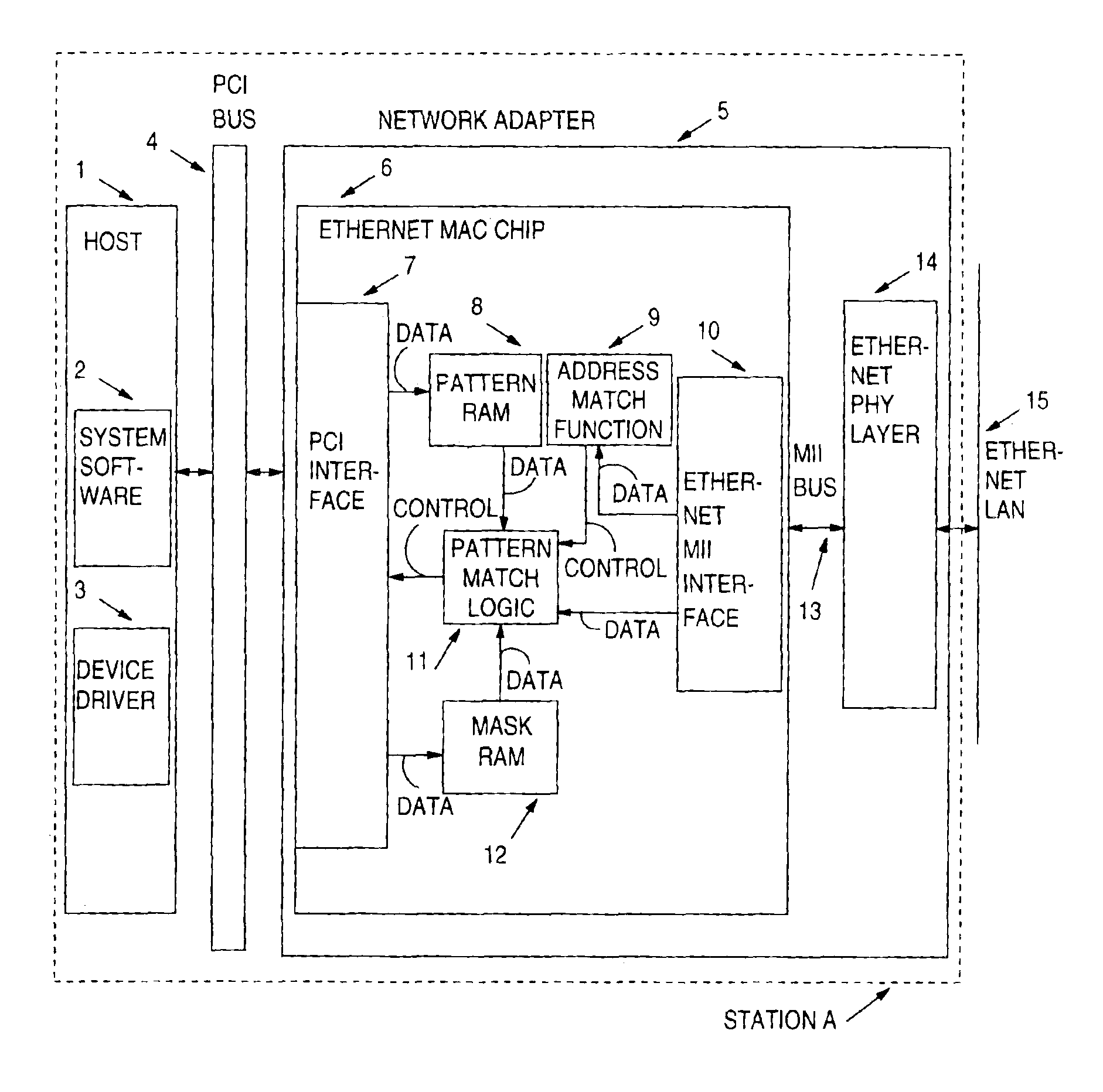

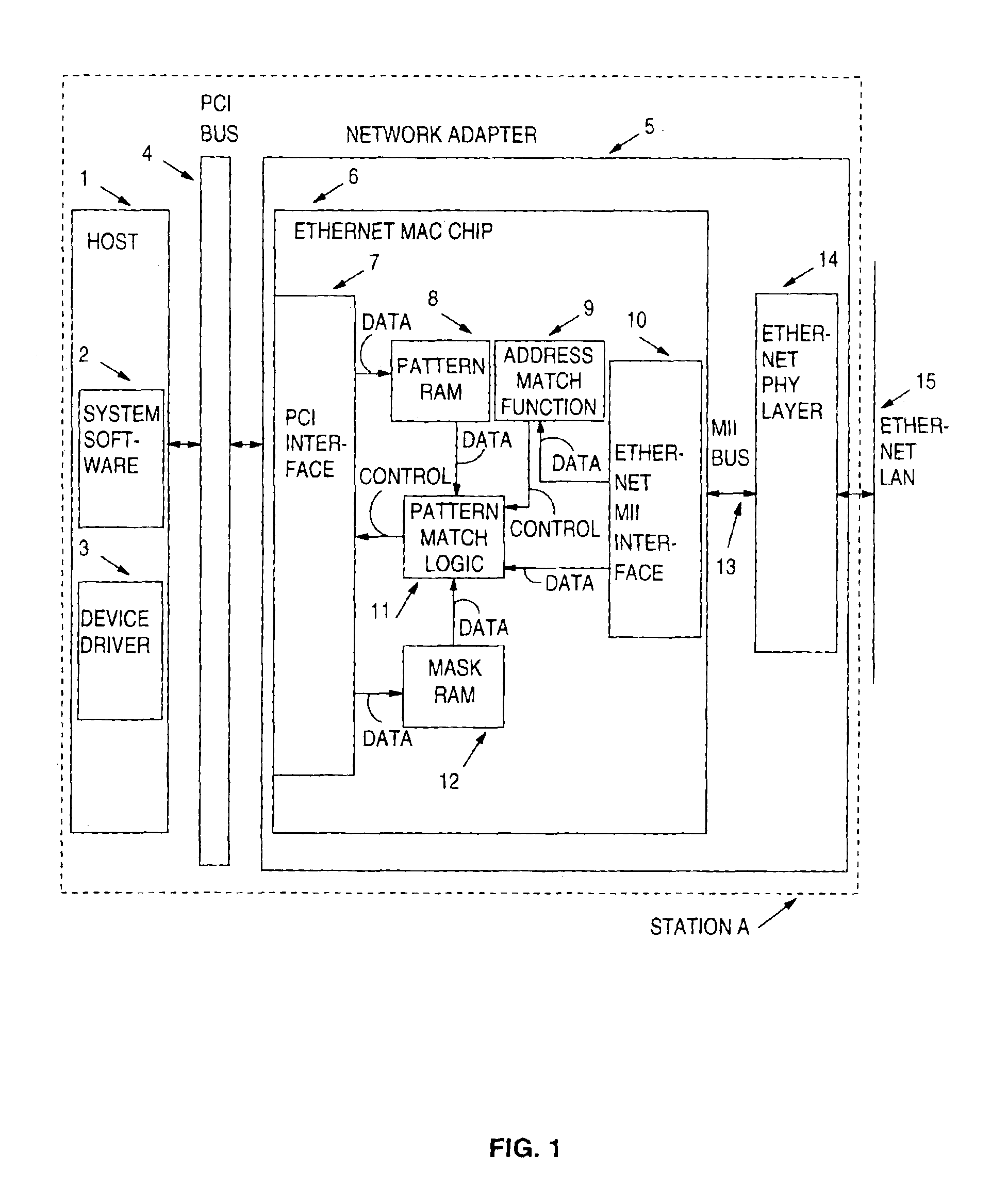

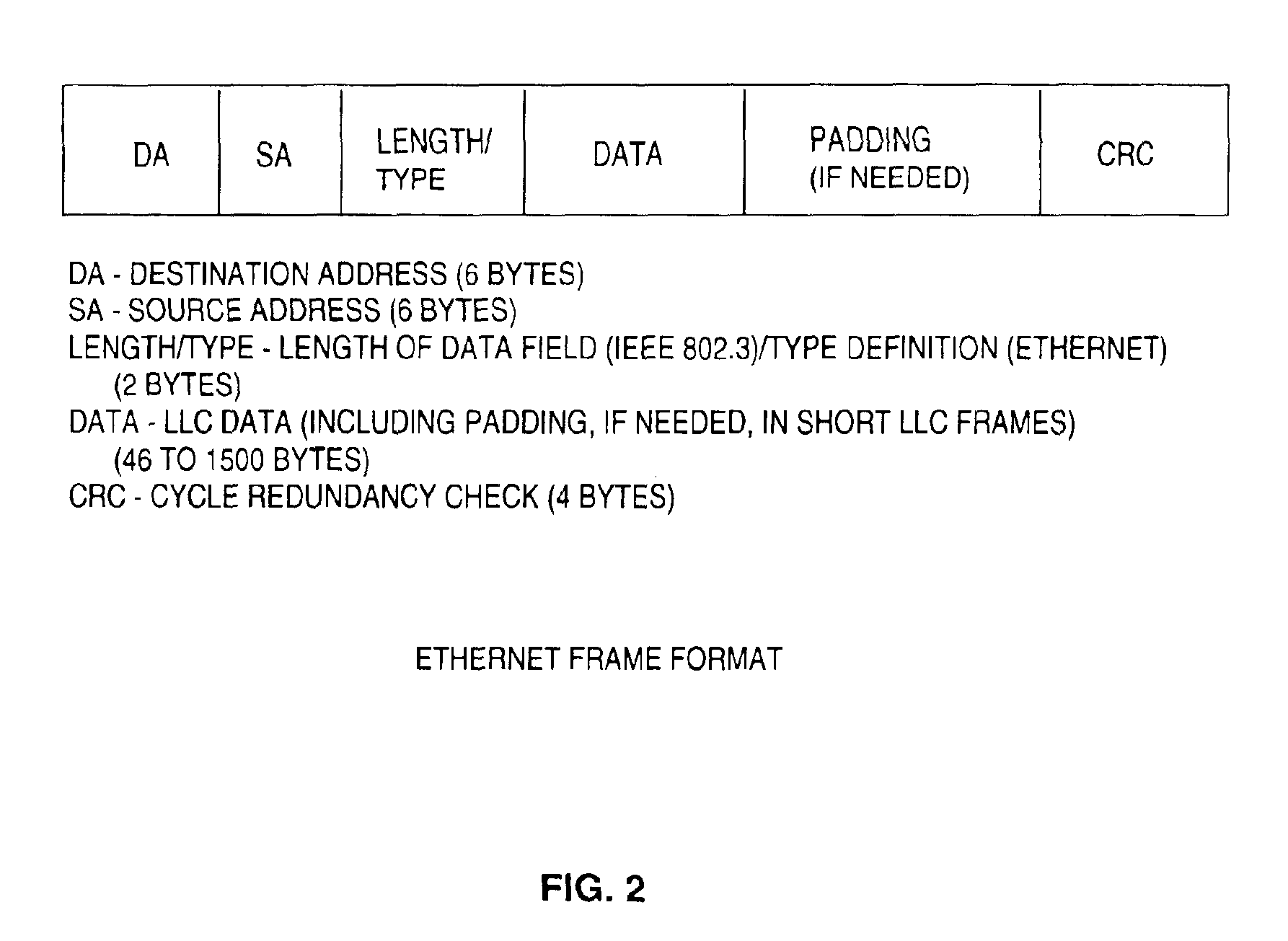

Pattern matching in communications network where first memory stores set of patterns, and second memory stores mask data identifying patterns in the first memory

InactiveUS6938040B2Energy efficient ICTDigital data processing detailsTelecommunicationsPattern matching

Stations in a communications network are awakened by matching a pattern received from the communications network with patterns in the stations. When a match occurs, the stations are awakened. The patterns are arranged contiguously on word boundaries. A nibble (4 bits) in a mask word identifies the part of the pattern word to be used in the comparison.

Owner:IBM CORP

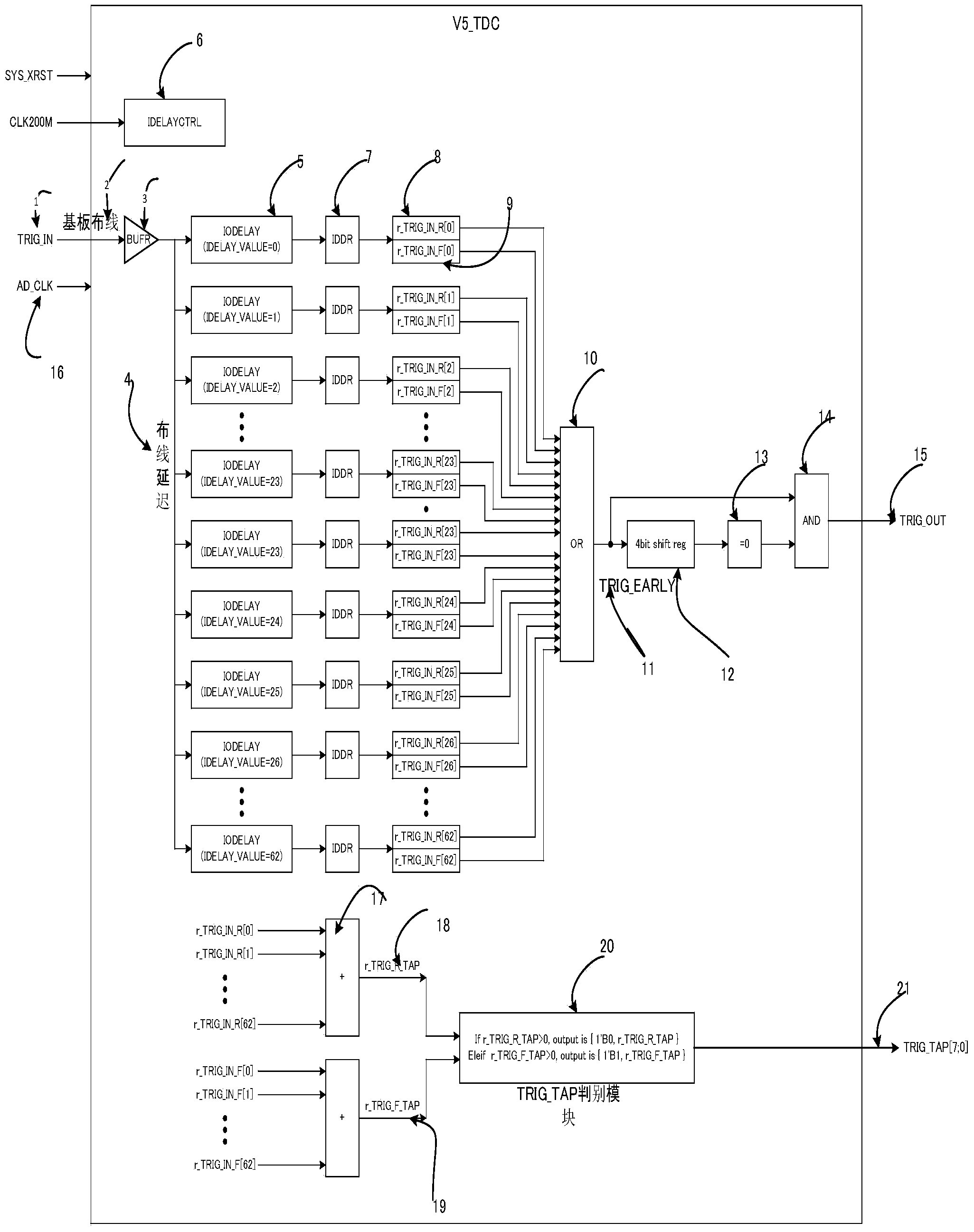

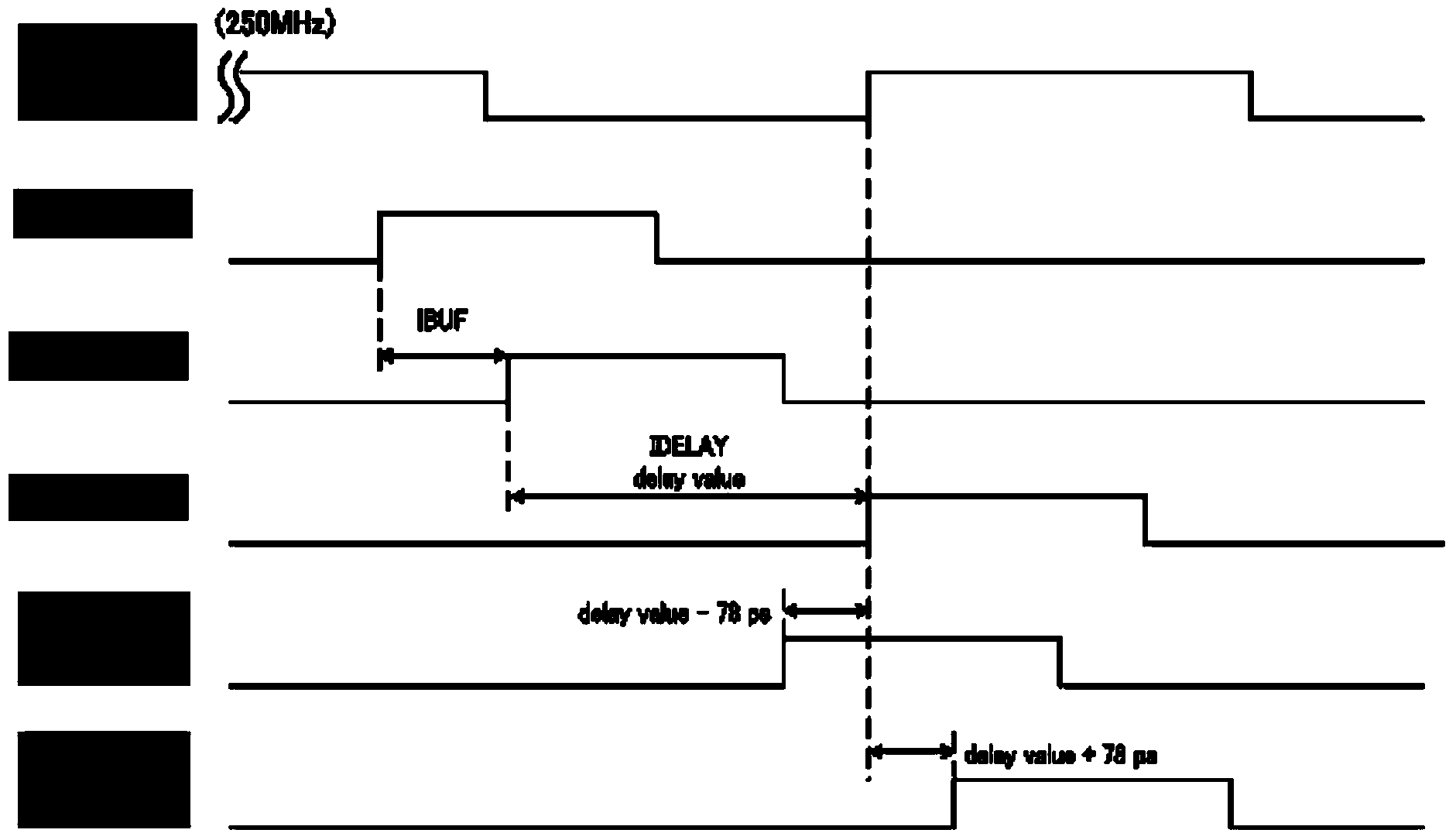

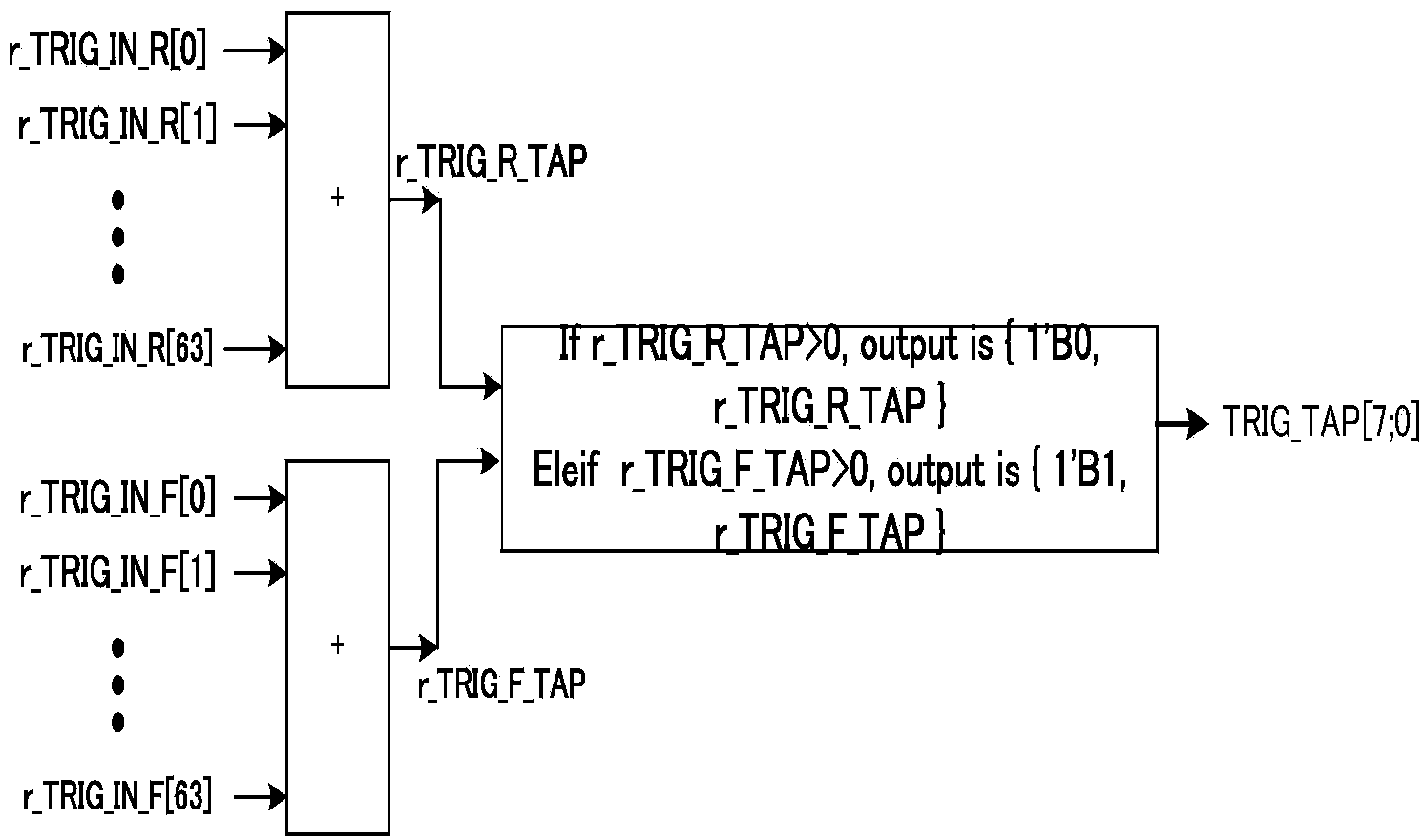

TDC (time/digital conversion) method and device based on FPGA (field programmable gate array) fine delay unit

ActiveCN104363021ASolve the technical problems of accurate delay measurementMeet the needs of measurement accuracyAnalogue/digital conversionElectric signal transmission systemsShift registerComputer module

A TDC (time / digital conversion) method based on an FPGA (field programmable gate array) fine delay unit is characterized in that a laser pulse trigger signal FRIG_IN (1) is processed by a substrate wiring delay (2) before reaching to a buffer BUFR (3) and is processed by a 64-line wiring delay (4) before reaching a 64-level fine delay unit IODEALY module (5); 1tap (78ps) is added to each level or each line of a fine delay unit IODELAY in order; delay precision of the 64-level fine delay unit IODEALY module (5) is controlled via a delay correcting unit IDELAYCTRL module (6); a signal subjected to bilateral sampling is processed by OR logic (10) into a primary judgment signal of a trigger signal; the primary judgment signal is processed by a 4-bit shift register 4bit shift reg (12), equal 0 logic (13) and AN gate logic (14) finally into a signal TRIG_OUT (15).

Owner:NANJING UNIV

Monolithic silicon-based phased arrays for communications and radars

A phased-array receiver is adapted so as to be fully integrated and fabricated on a single silicon substrate. The phased-array receiver is operative to receive a 24 GHz signal and may be adapted to include 8-elements formed in a SiGe BiCMOS technology. The phased-array receiver utilizes a heterodyne topology, and the signal combining is performed at an IF of 4.8 GHz. The phase-shifting with 4 bits of resolution is realized at the LO port of the first down-conversion mixer. A ring LC VCO generates 16 different phases of the LO. An integrated 19.2 GHz frequency synthesizer locks the VCO frequency to a 75 MHz external reference. Each signal path achieves a gain of 43 dB, a noise figure of 7.4 dB, and an IIP3 of −11 dBm. The 8-path array achieves an array gain of 61 dB, a peak-to-null ratio of 20 dB, and improves the signal-to-noise ratio at the output by 9 dB.

Owner:CALIFORNIA INST OF TECH

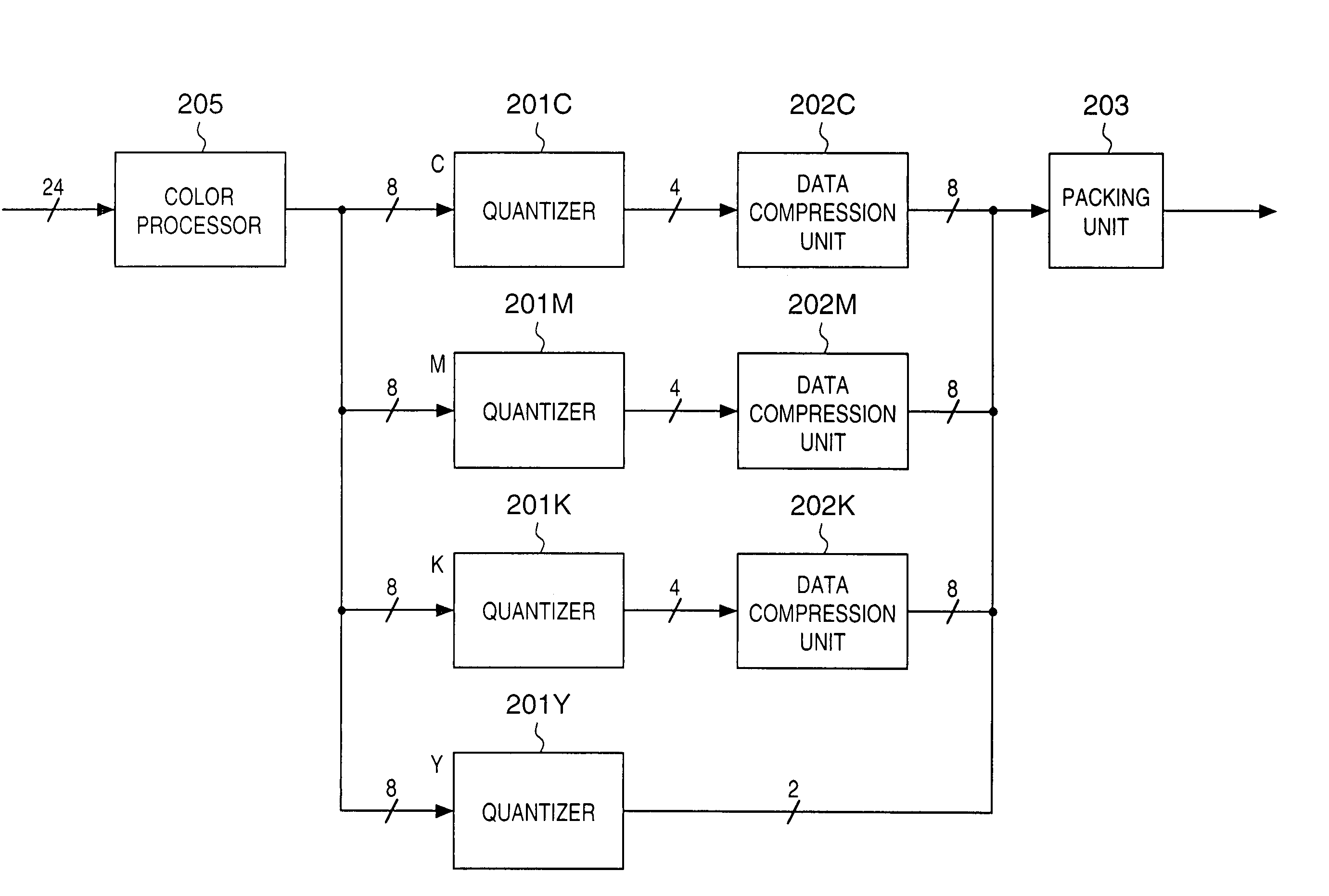

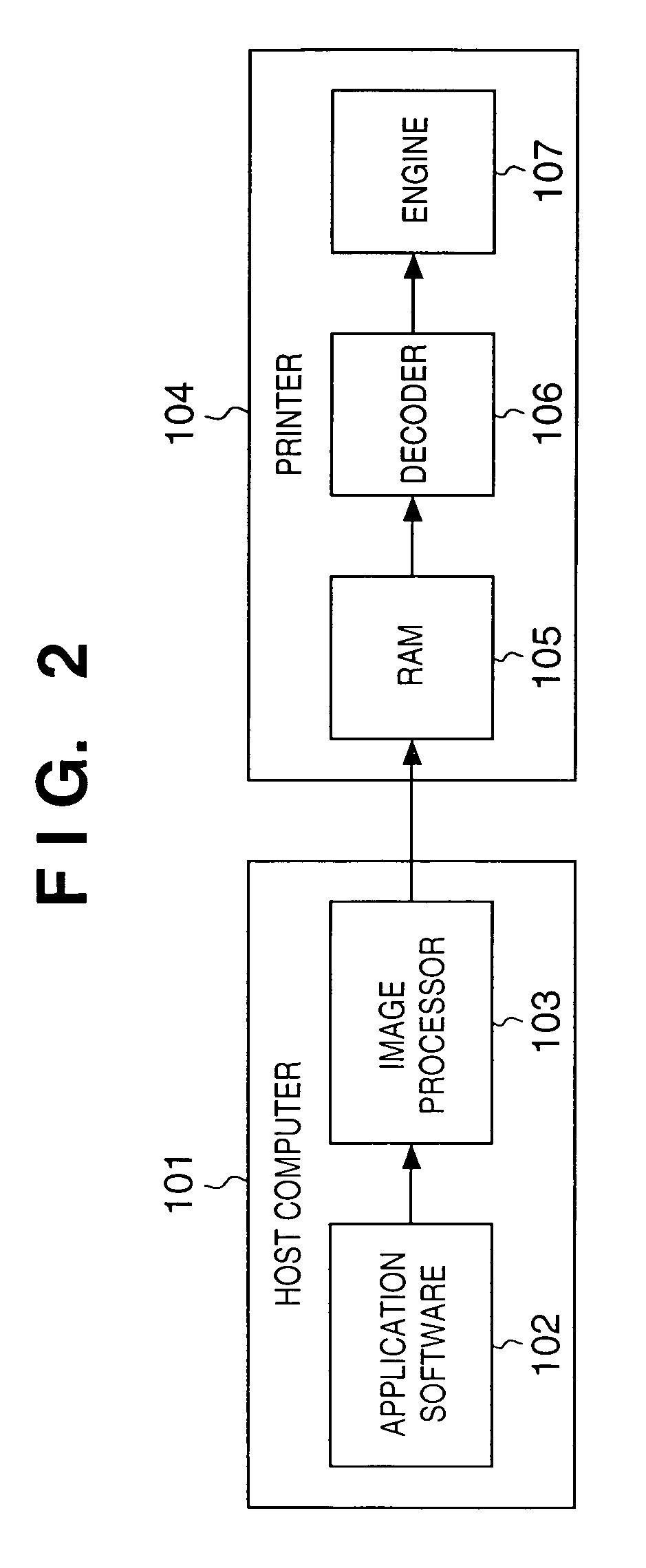

Image processing apparatus and method, and storage medium

InactiveUS6967745B1Reduce redundancyReduce image qualityImage enhancementDigitally marking record carriersImaging processing16-bit

Owner:CANON KK

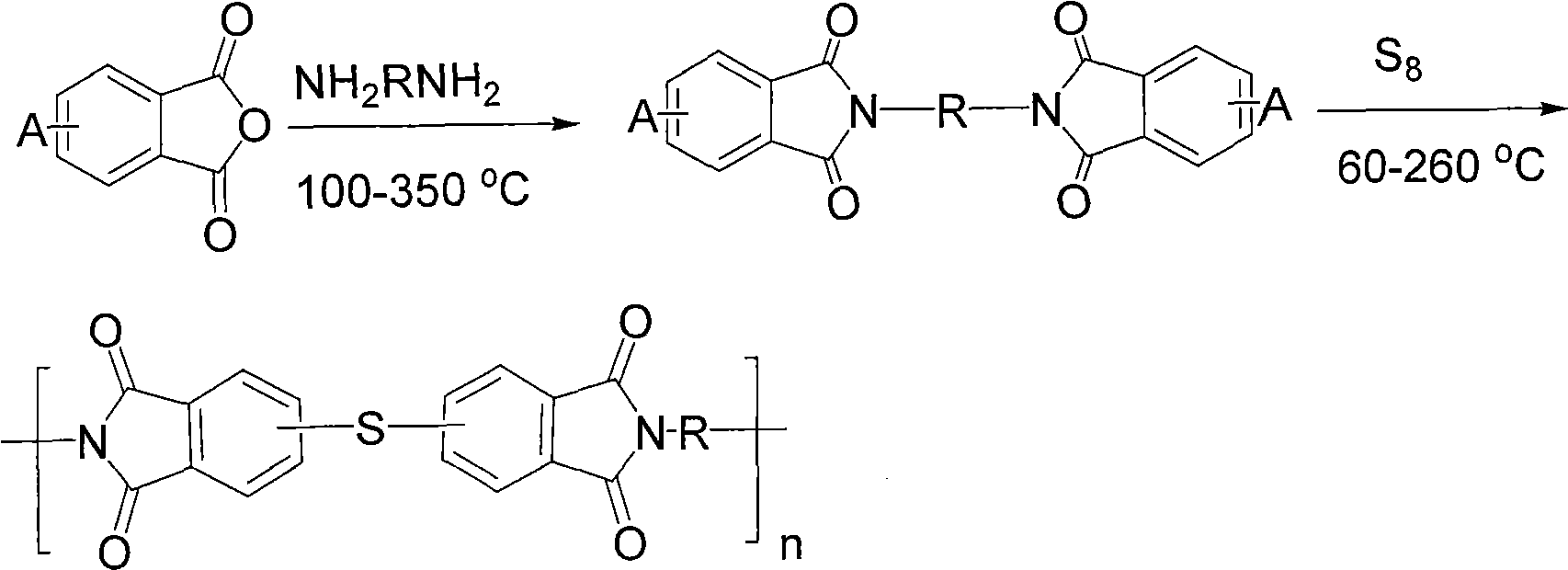

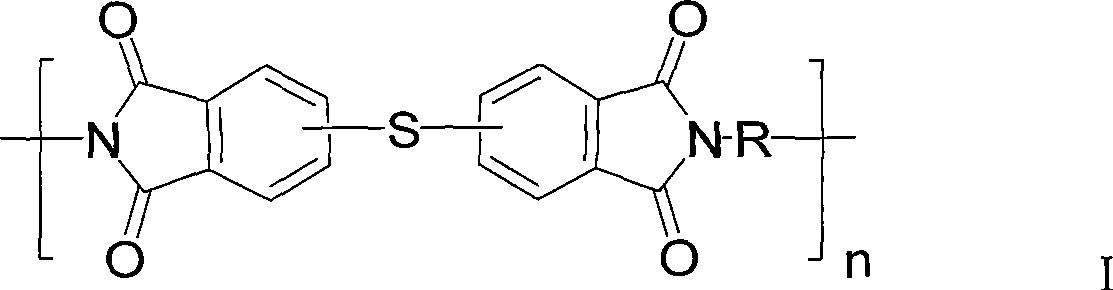

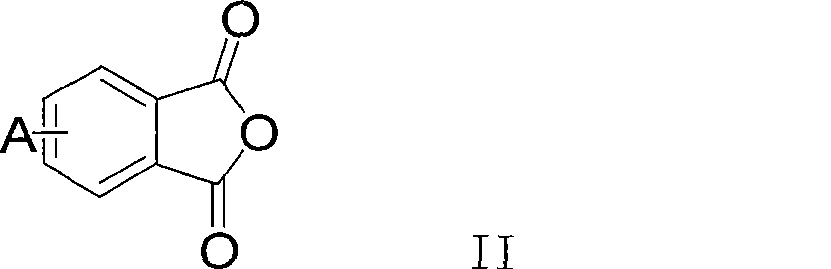

Polythioetherimide and preparation method thereof

The invention relates to polythioetherimide and a preparation method thereof. The method is characterized by comprising the following steps: mono-substituted phthalic anhydride isomer with structural formula II is adopted as a reaction material to react with organic diamine NH2RNH2 with half mol equivalent weight at the temperature of about 100 DEG C to about 350 DEG C to generate binary-substituted phthalimide; then binary-substituted phthalimide and sulfur with about equimolar equivalent weight are subjected to coupling polymerization reaction at the temperature of about 60 DEG C to about 260 DEG C under the existence of reducing agent, catalyst and reaction auxiliary agent to generate polythioetherimide resin with structural formula I; and the molecular weight of the resin can be adjusted by end capping agent. The preparation method can greatly reduce the preparation cost and reaction steps, the whole process is more reasonable and practical, and the obtained resin has superior comprehensive properties such as good heat resistance, mechanical properties, melting processing property and the like, can be widely applied in the related fields such as high-temperature resistant engineering plastics, films, adhesives, enameled wires, foamed plastics, fiber, advanced composite materials and the like; in the structural formula II, A substituent is chlorine atom or nitro at 3-bit or 4-bit; and in the structural formula I, R is substituted or unsubstituted organic group.

Owner:NINGBO INST OF MATERIALS TECH & ENG CHINESE ACADEMY OF SCI +1

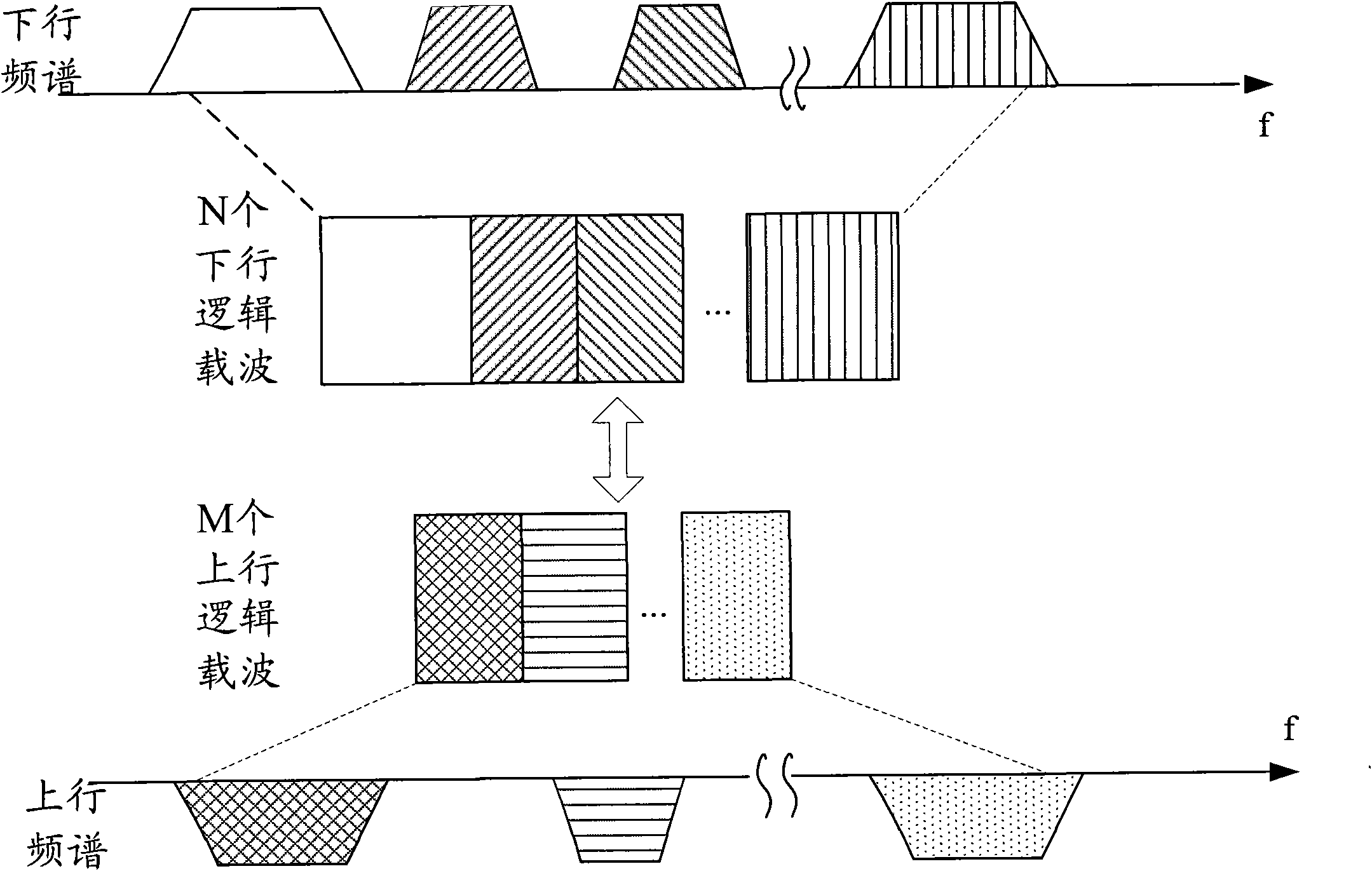

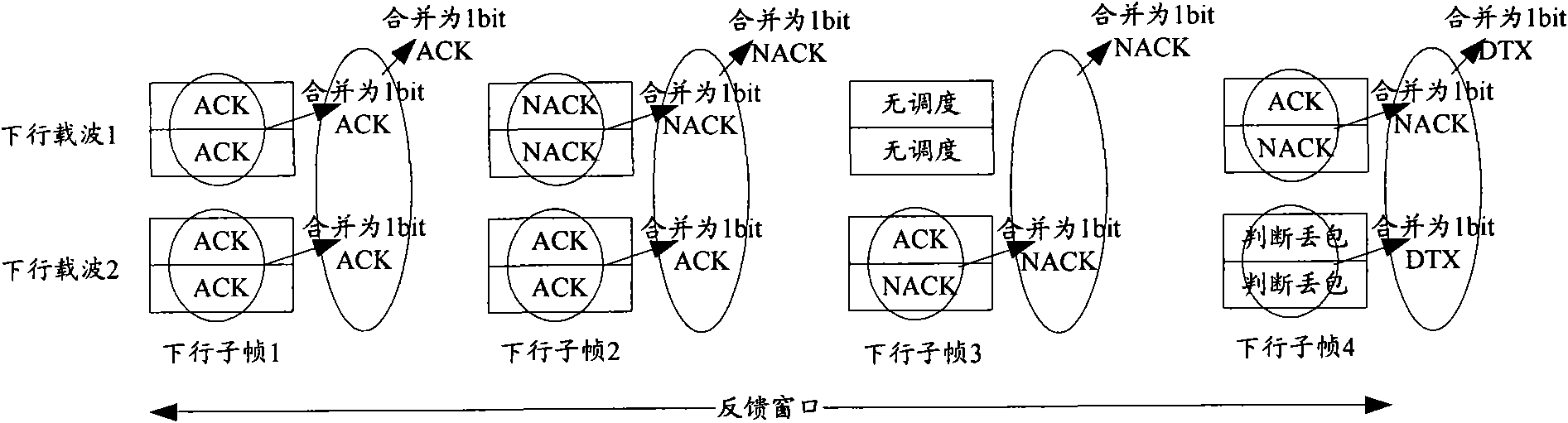

Channel resource determination method of ACK/NACK feedback information and equipment

ActiveCN102469599AAvoid situations where alternative channel resources cannot be determinedError prevention/detection by using return channelWireless communicationTerminal equipmentCarrier signal

An embodiment of the invention discloses a channel resource determination method of ACK / NACK feedback information and equipment. Through applying a technical scheme of the embodiment, alternative channel resource can be determined in an application scene employing a PUCCH format 1b with channel selection scheme. A determination problem of channel resource needed by channel selection is solved when a terminal device employs the PUCCH format 1b with channel selection scheme to transmit ACK / NACK feedback information which is subjected to configuration downlink intercarrier merging. A situation that the alternative channel resource can not be determined according to present implicit channel resource which is determined by a PDCCH which is transmitted only through a downlink main carrier is avoided. To a scene that the ACK / NACK feedback information is larger than 4 bits, transmission of the ACK / NACK feedback information through the PUCCH format 1b with channel selection scheme is realized. The method and the equipment are mainly suitable for a TDD system.

Owner:DATANG MOBILE COMM EQUIP CO LTD

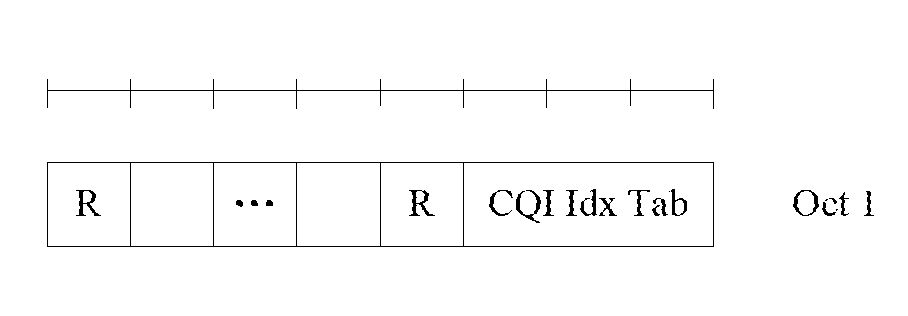

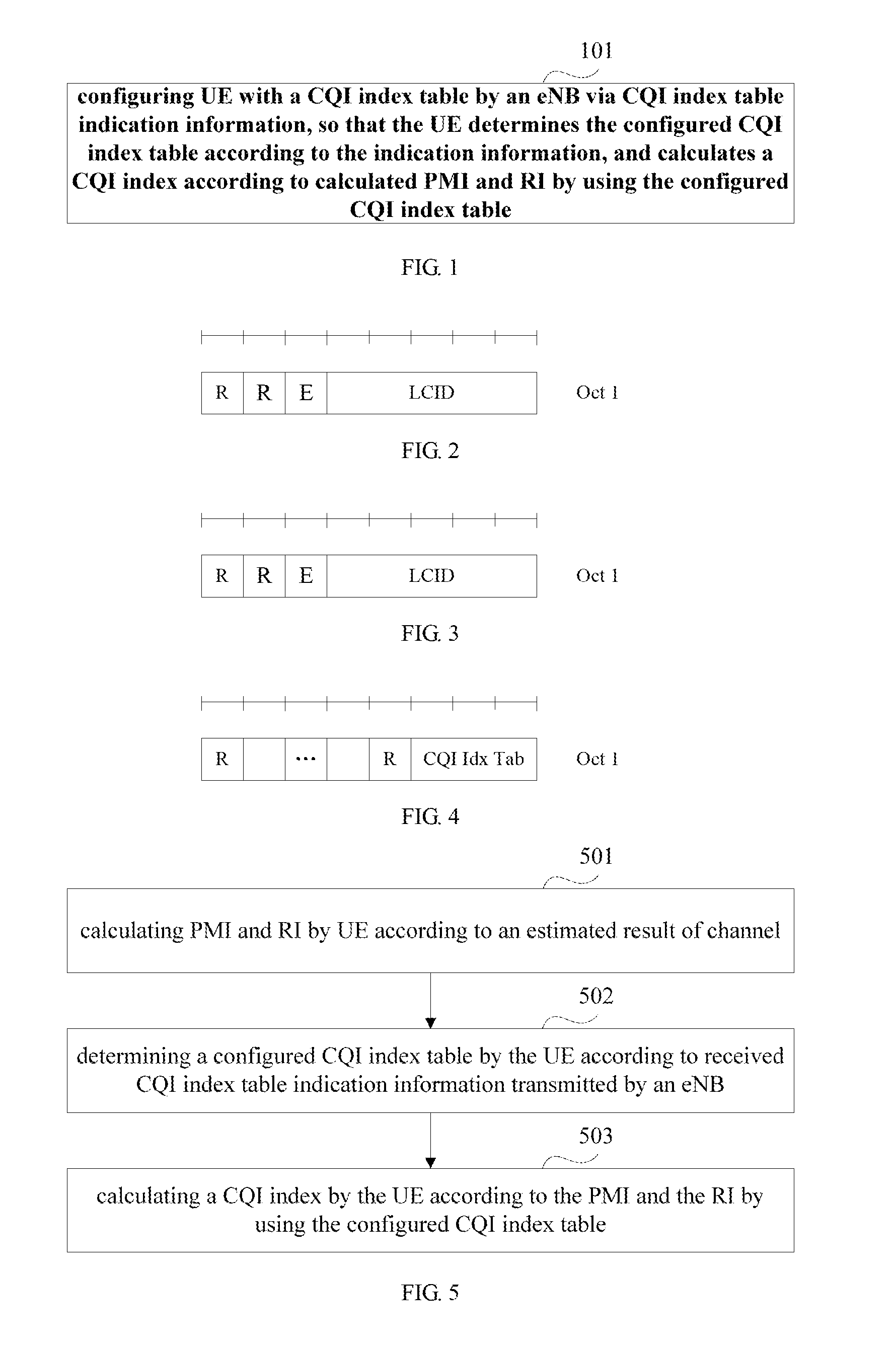

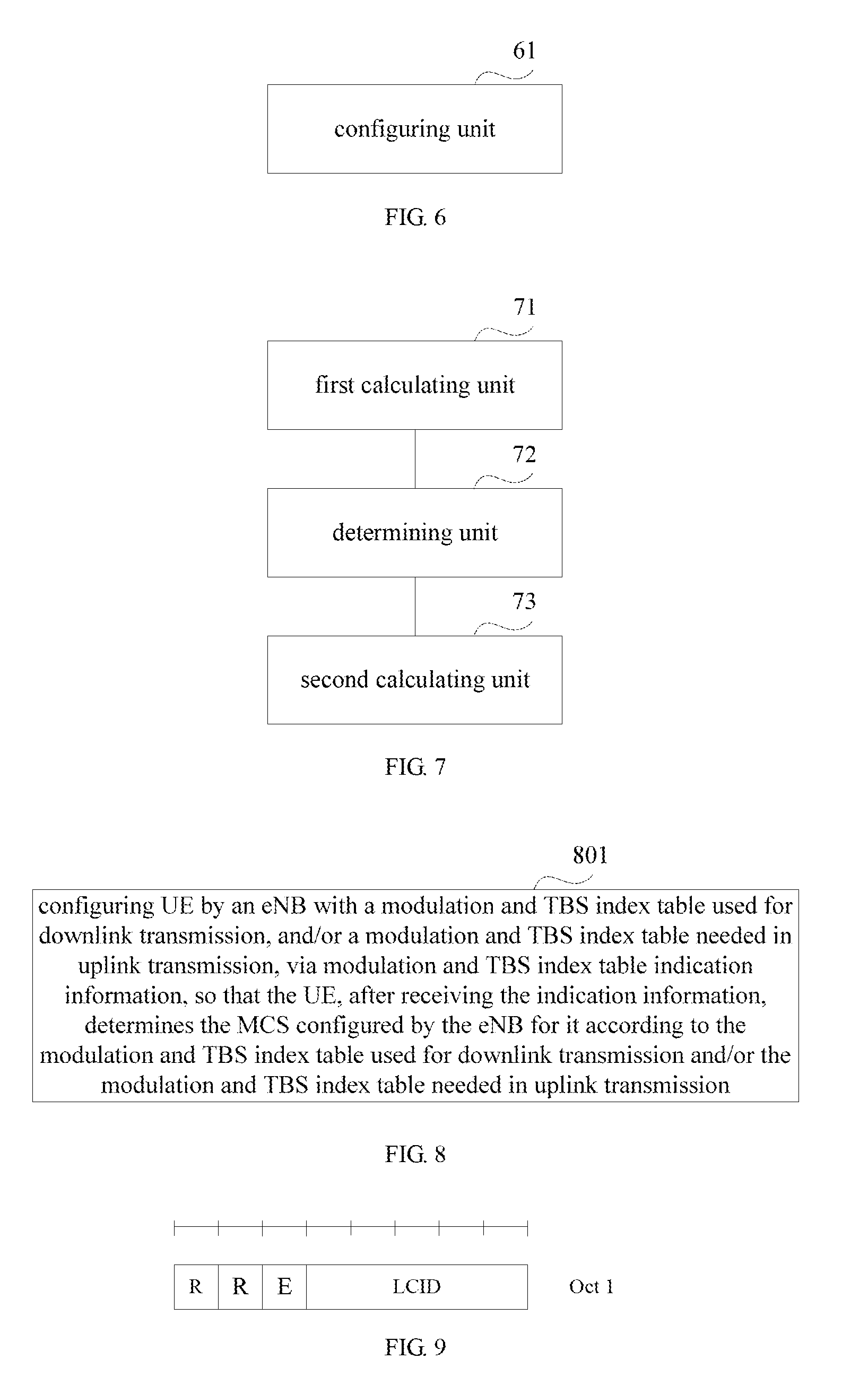

Method and apparatus for configuring channel quality indicator and method and apparatus for configuring modulation and coding scheme

ActiveUS20160013918A1Normal configurationSignal allocationSignalling characterisationBit numberingPrecoding matrix

Embodiments of the present disclosure provide a method and apparatus for configuring channel quality indicator (CQI) and a method and apparatus for configuring modulation and coding scheme. The method for configuring CQI includes: configuring UE with a CQI index table by an eNB via CQI index table indication information, so that the UE determines the configured CQI index table according to the indication information, and calculates a CQI index according to calculated precoding matrix indicator (PMI) and rank indication (RI) by using the configured CQI index table. With the embodiments of the present disclosure, the eNB may configure different UEs with different ‘4-bit CQI tables’ and / or ‘modulation and TBS index tables’ while keeping the CQI index and the IMCS bit number unchanged. Therefore, not only the CQI index and the IMCS bit number need not to be increased, but also normal configuration of the LTE system may be ensured.

Owner:FUJITSU CONNECTED TECH LTD

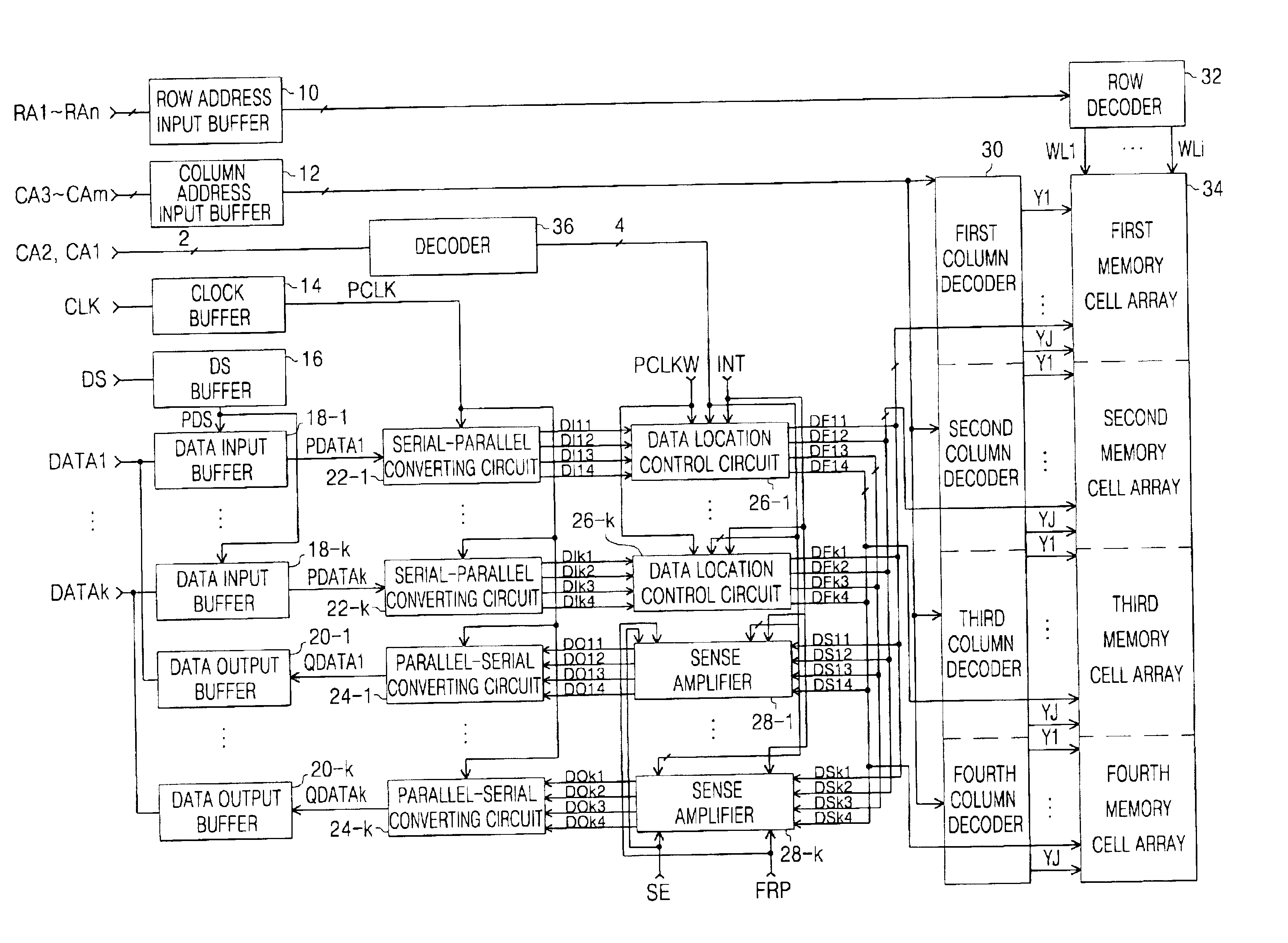

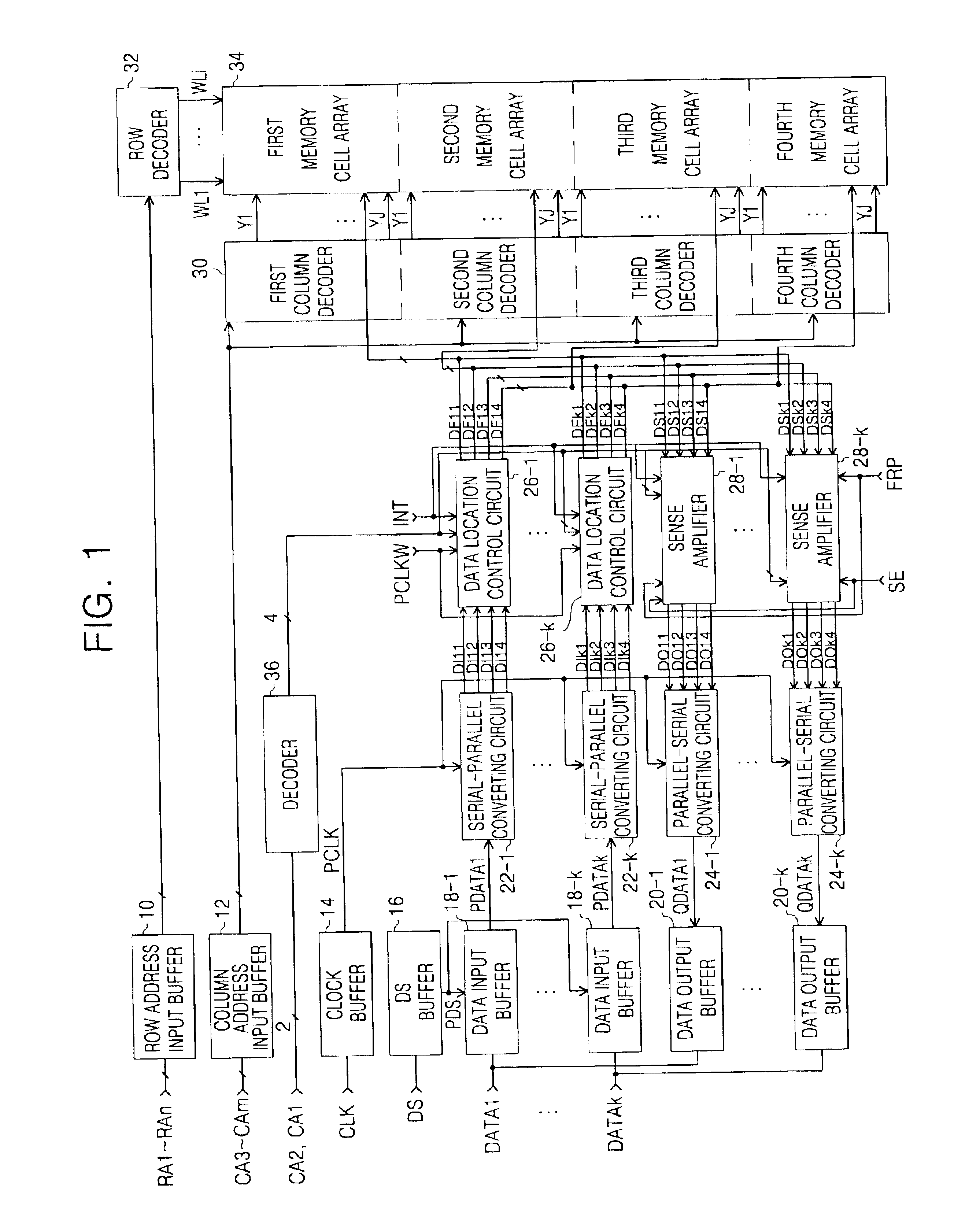

Synchronous semiconductor memory device and method of processing data thereof

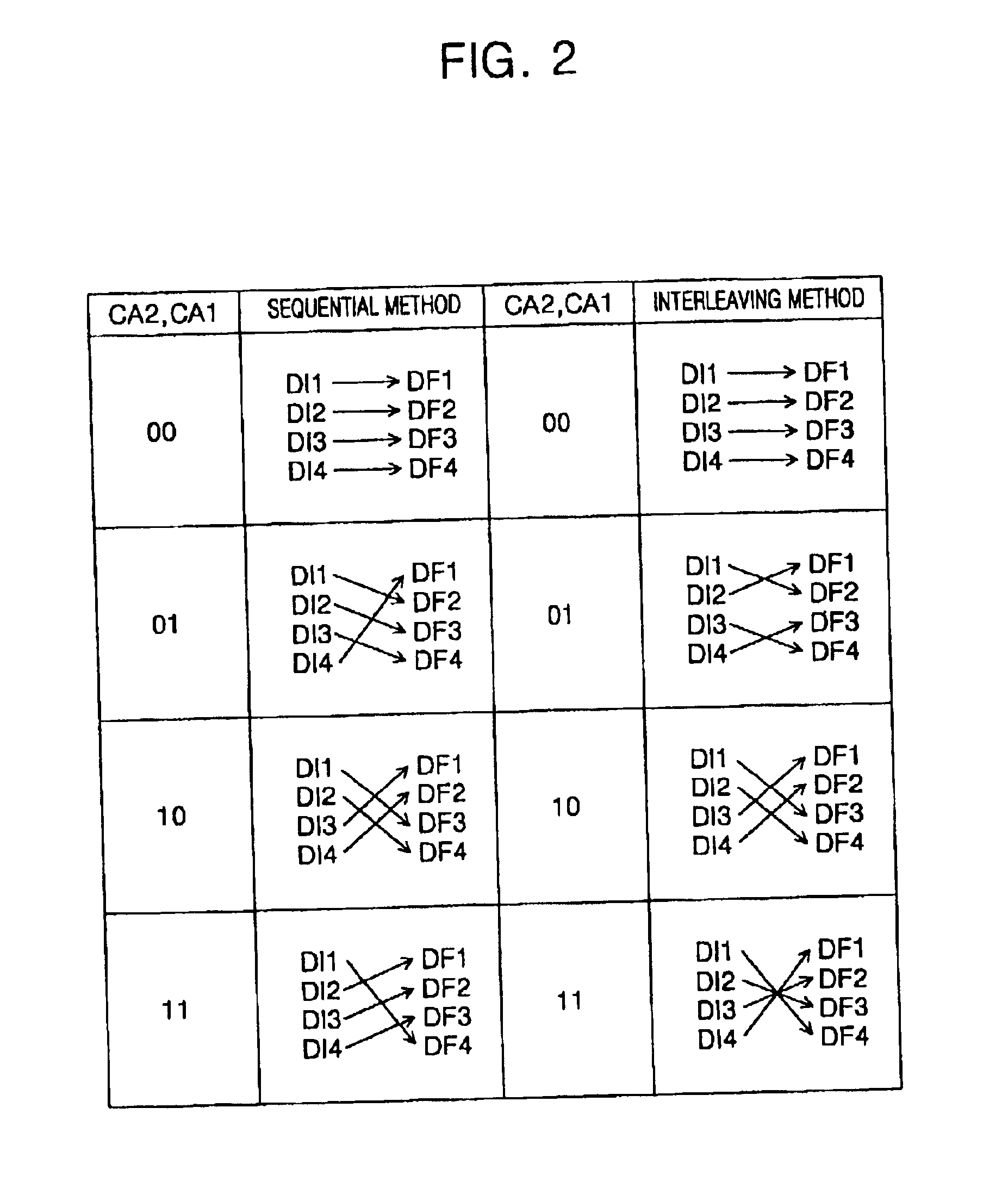

The present invention involves a synchronous semiconductor memory device having a 4-bit prefetch mode a method of processing a data thereof, comprising first to fourth memory cell arrays each having memory cells, a serial-parallel converting means converting a plurality of 4-bit data serially applied during a write operation into a plurality of 4-bit parallel data, a data loation control means location-controlling and outputting each of the plurality of the 4-bit parallel data output from the serial-parallel converting means in response first to fourth decoding signals generated by decoding the 2-bit column address to the first to fourth memory cell arrays, by a sequential method or by an interleaving method, during the write operation, a sense amplifier amplifying a plurality of 4-bit data output from each of the first to fourth memory cell arrays, and location-controlling and outputting them in response the first to fourth decoding signals, by a sequential method or by an interleaving method, during a read operation, and a parallel-serial converting means converting and outputting a plurality of 4-bit parallel data output from the sense amplifier during a read operation into a plurality of 4-bit serial data, whereby the circuit configuration is simple.

Owner:SAMSUNG ELECTRONICS CO LTD

Memory circuit

ActiveUS7237175B2Correction errorDigital storageRedundant data error correctionWrite bitHemt circuits

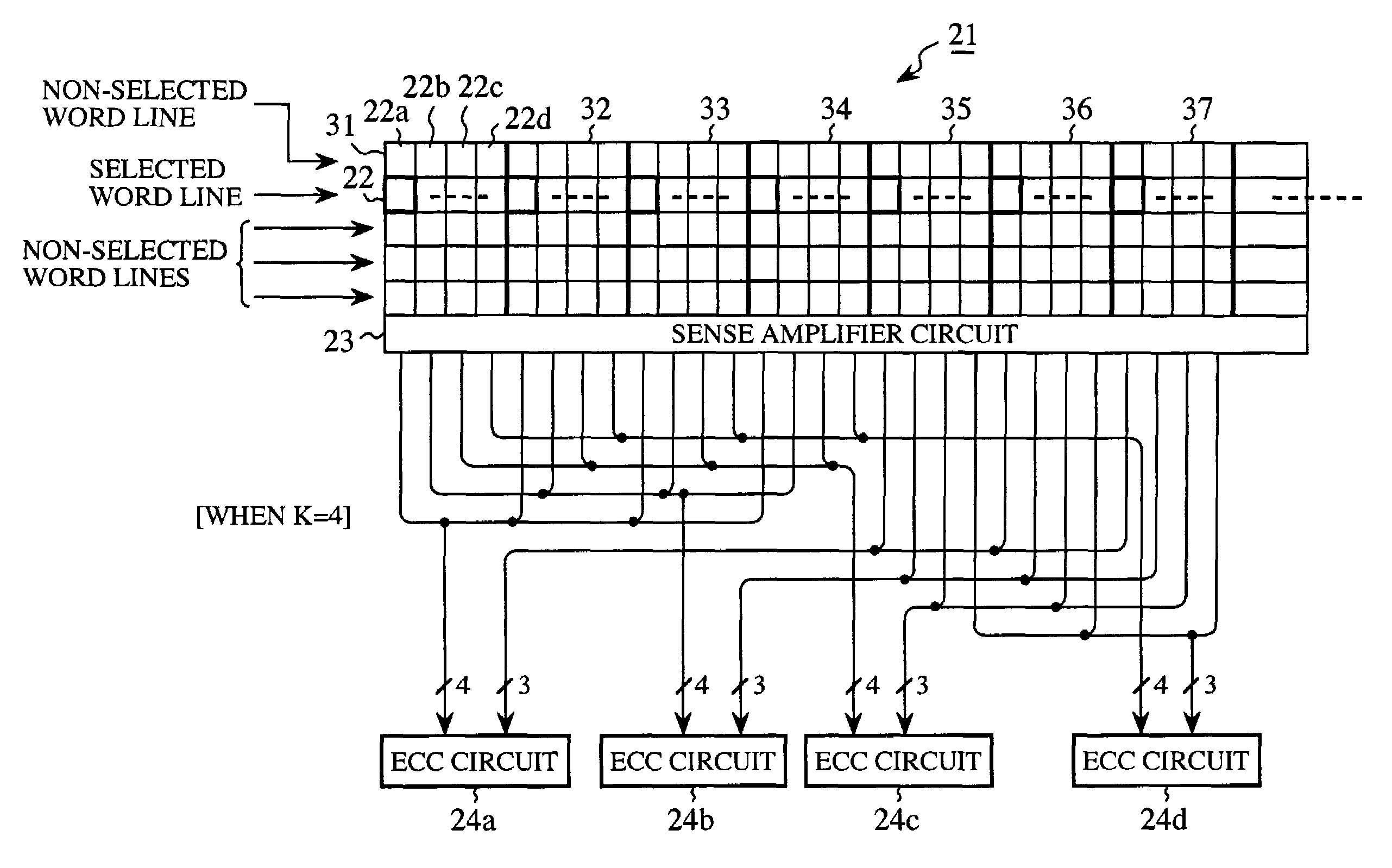

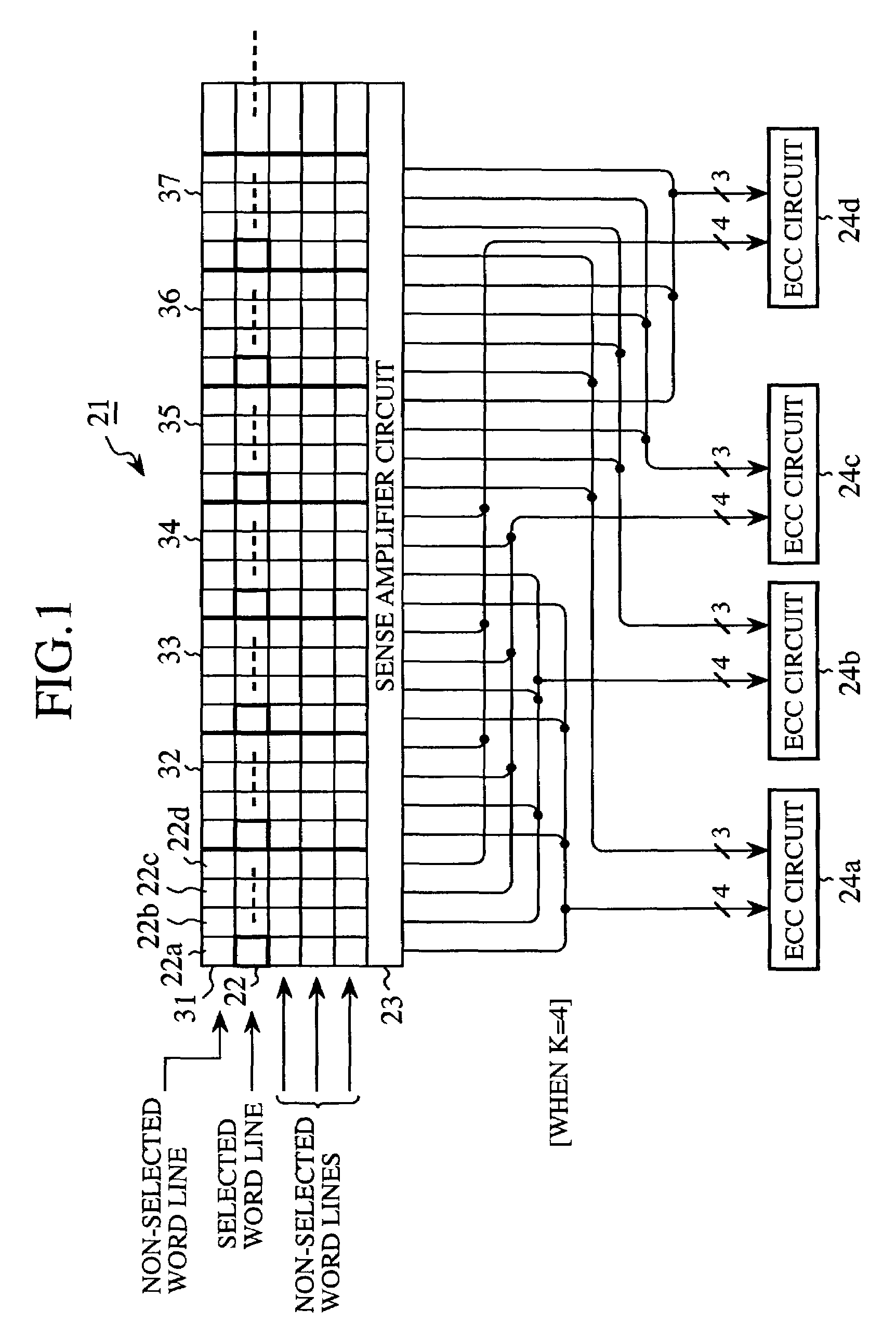

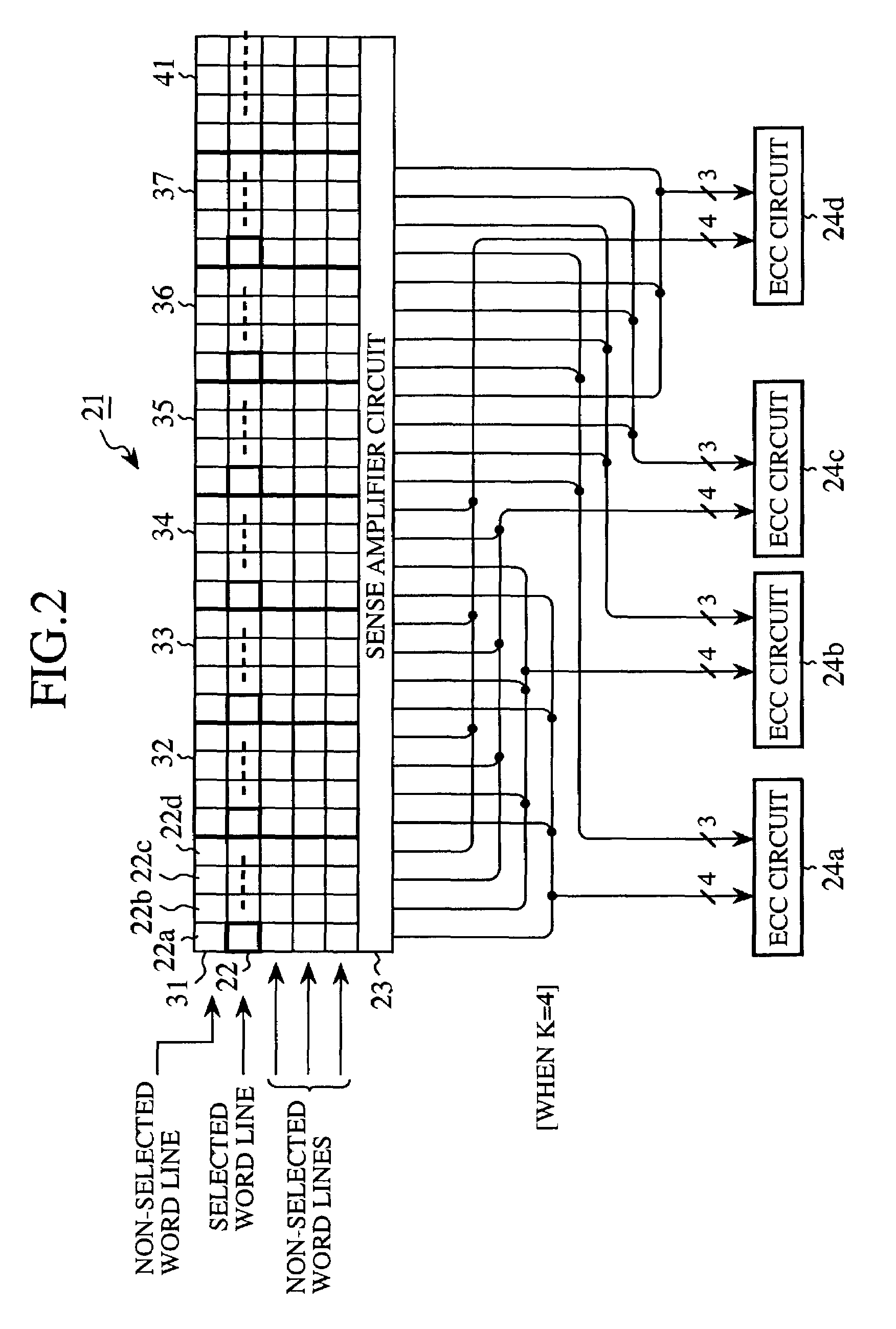

When to a memory cell array 21 a read / write operation is performed of the 7-bit data in which parity bits of 3 bits are added to data of 4 bits, an error correction is carried out in concern to each of the 7-bit data. The memory cell array is divided into memory units 31 to 37 each of which has four bits which are arranged along a direction of a word line. On writing the 7-bit data in the memory cell array, bits of the 7-bit data that are different from one another are written as written bit data along the direction of the word line in the memory units 31 to 37, respectively. In the 7-bit data, the written bit data has an interval of four bits. Error correcting circuits performs an error correction of the 7-bit data in each of the 7-bit data.

Owner:RENESAS ELECTRONICS CORP

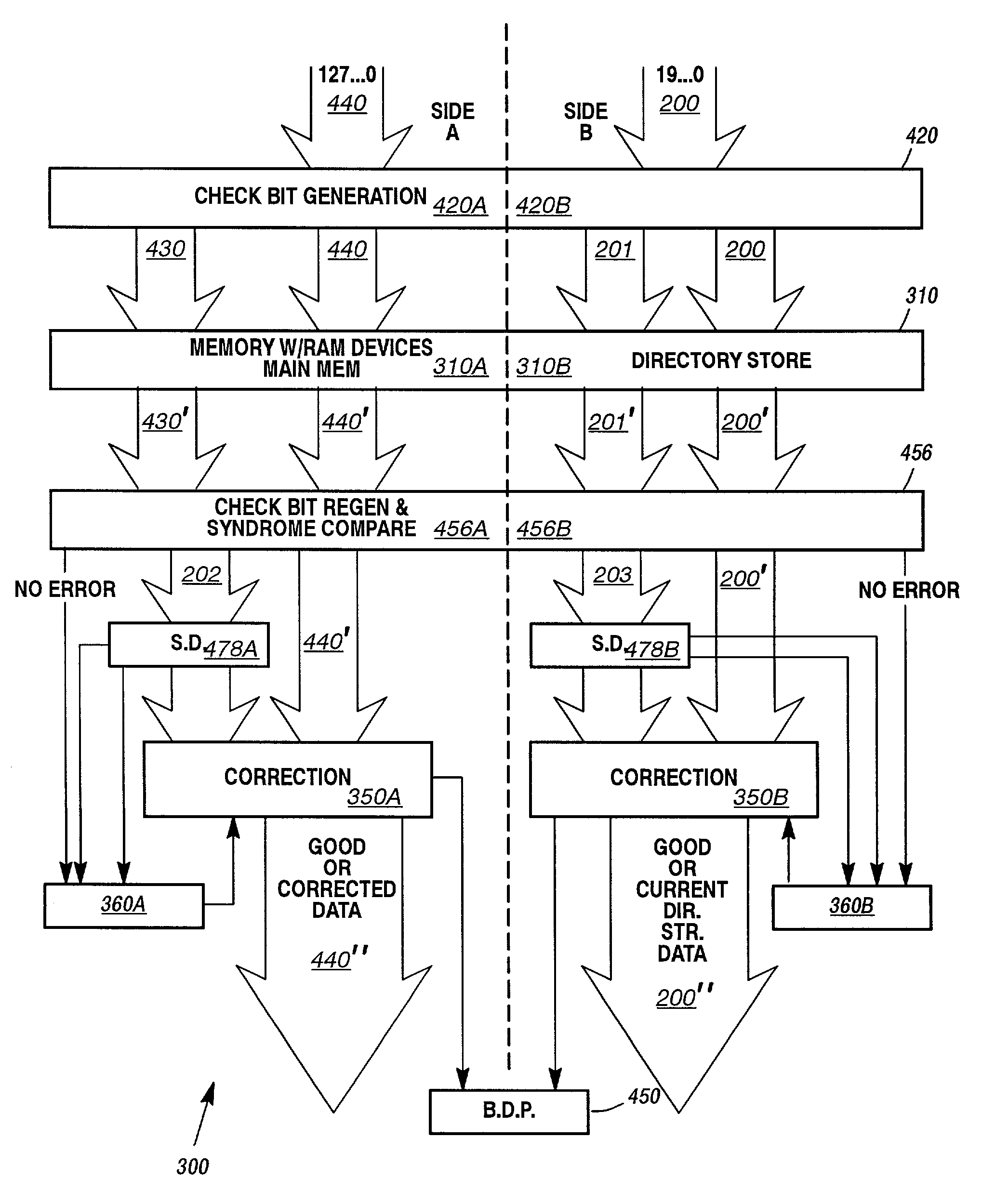

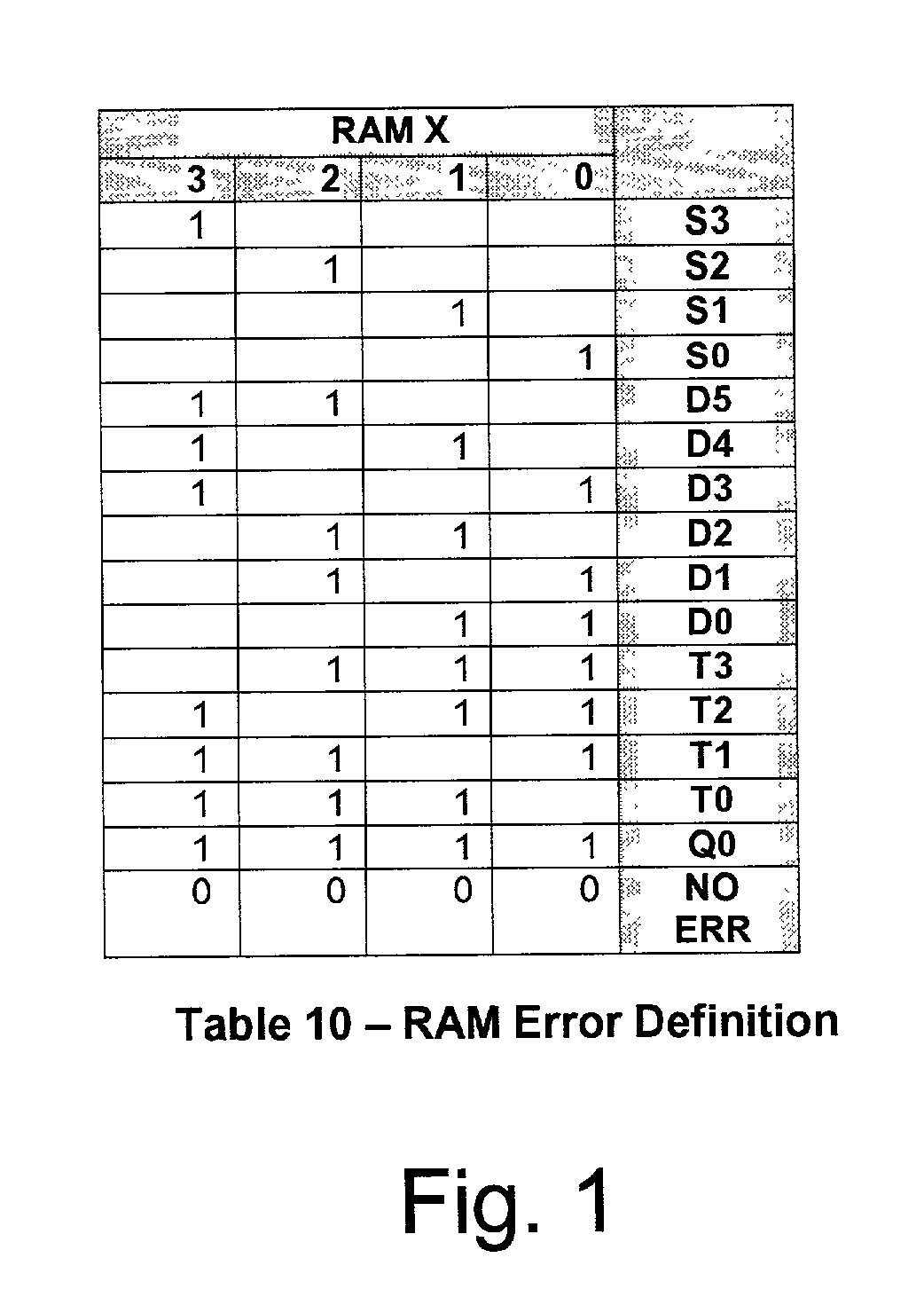

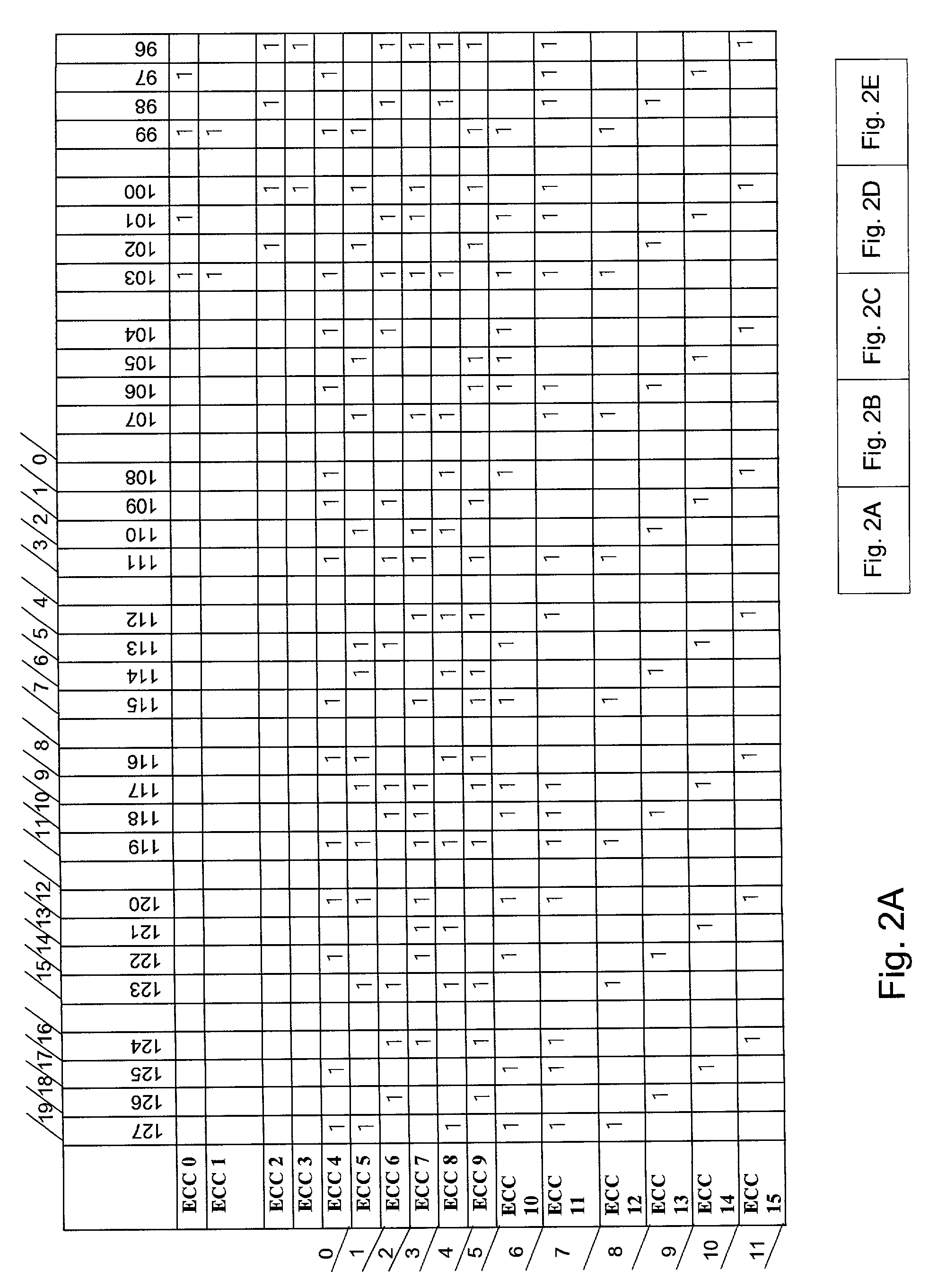

Familial correction with non-familial double bit error detection for directory storage

Error correction and error detection related to DRAM chip failures, particularly adapted server memory subsystems. The application of a code for 128 bit memories is applied to a 20 bit directory store to improve reliability of the directory store memory of the computer system. The code uses ×4 bit DRAM devices organized in a code word of 20 data bit words and 12 check bits. These 12 check bits provide a code capable of 4 bit adjacent error correction within a family (i.e., in a ×4 DRAM) and double bit non-adjacent error detection across the entire 20 bit word, with single bit correction across the word as well. Each device can be though of as a separate family of bits, errors occurring in more than one family are not correctable, but may be detected if only one bit in each of two families is in error. Syndrome generation and regeneration are used together with a specific large code word. Decoding the syndrome and checking it against the regenerated syndrome yield data sufficient for providing the features described.

Owner:UNISYS CORP

Random number generator and generation method

InactiveUS20020169810A1Improve its ability to generateReduce defectsRandom number generatorsDigital function generatorsCmos comparatorShift register

An RNG circuit is connected to the parallel port of a computer. The circuit includes a flat source of white noise and a CMOS amplifier circuit compensated in the high frequency range. A low-frequency cut-off is selected to maintain high band-width yet eliminate the 1 / f amplifier noise tail. A CMOS comparator with a 10 nanosecond rise time converts the analog signal to a binary one. A shift register converts the serial signal to a 4-bit parallel one at a sample rate selected at the knee of the serial dependence curve. Two levels of XOR defect correction produce a BRS at 20 kHZ, which is converted to a 4-bit parallel word, latched and buffered. The entire circuit is powered from the data pins of the parallel port. A device driver interface in the computer operates the RNG. The randomness defects with various levels of correction and sample rates are calculated and the RNG is optimized before manufacture.

Owner:QUANTUM WORLD

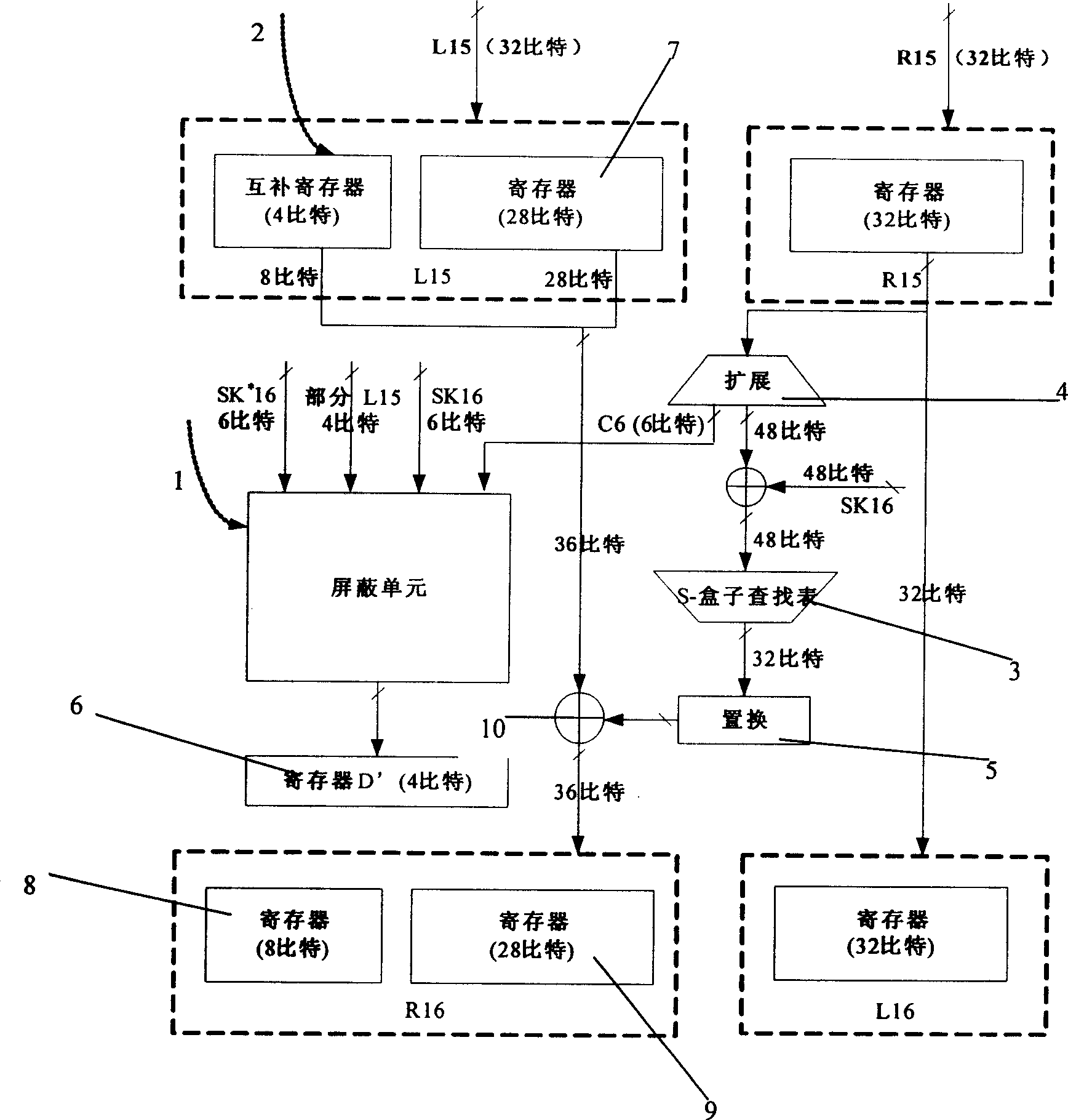

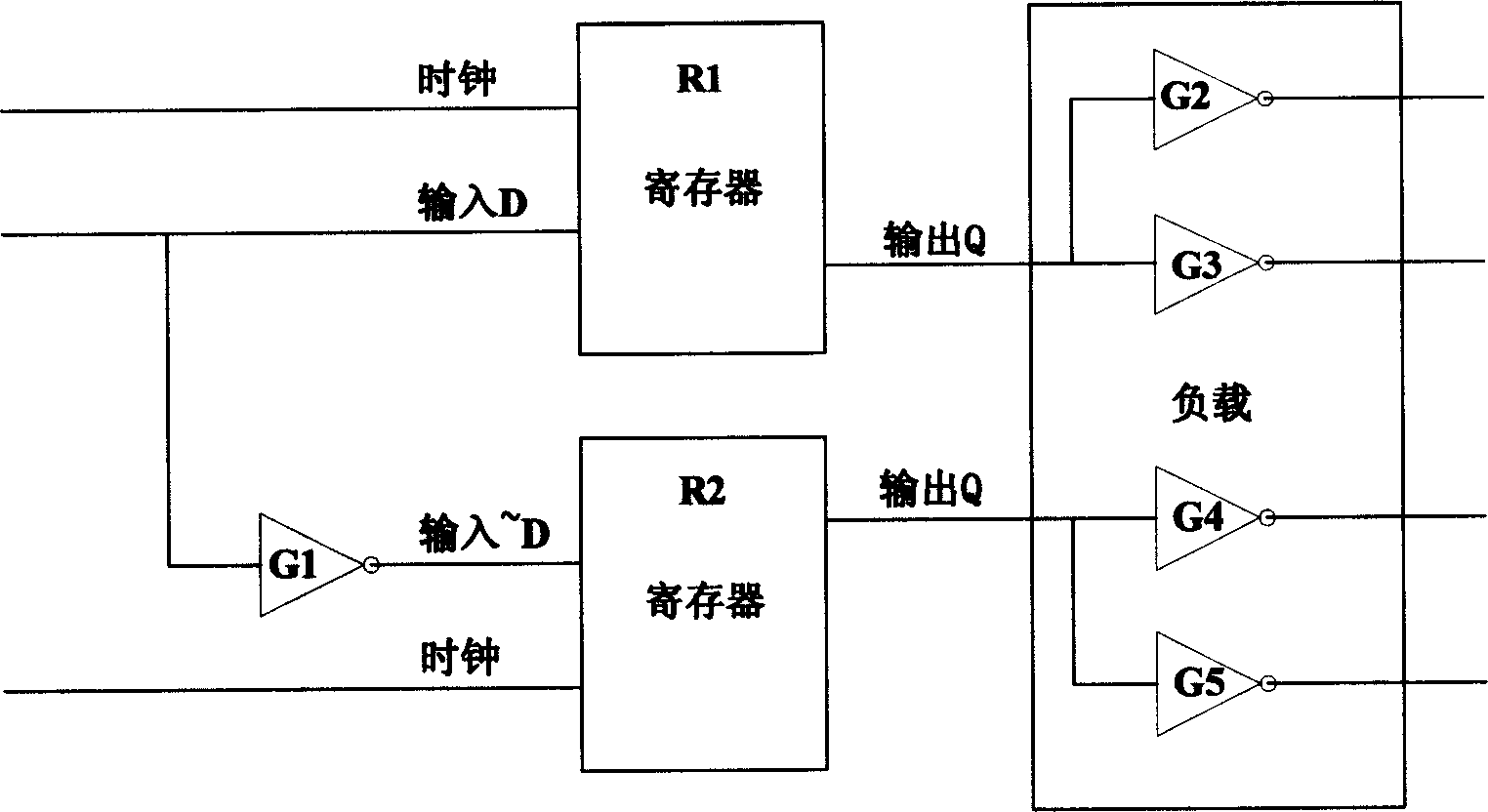

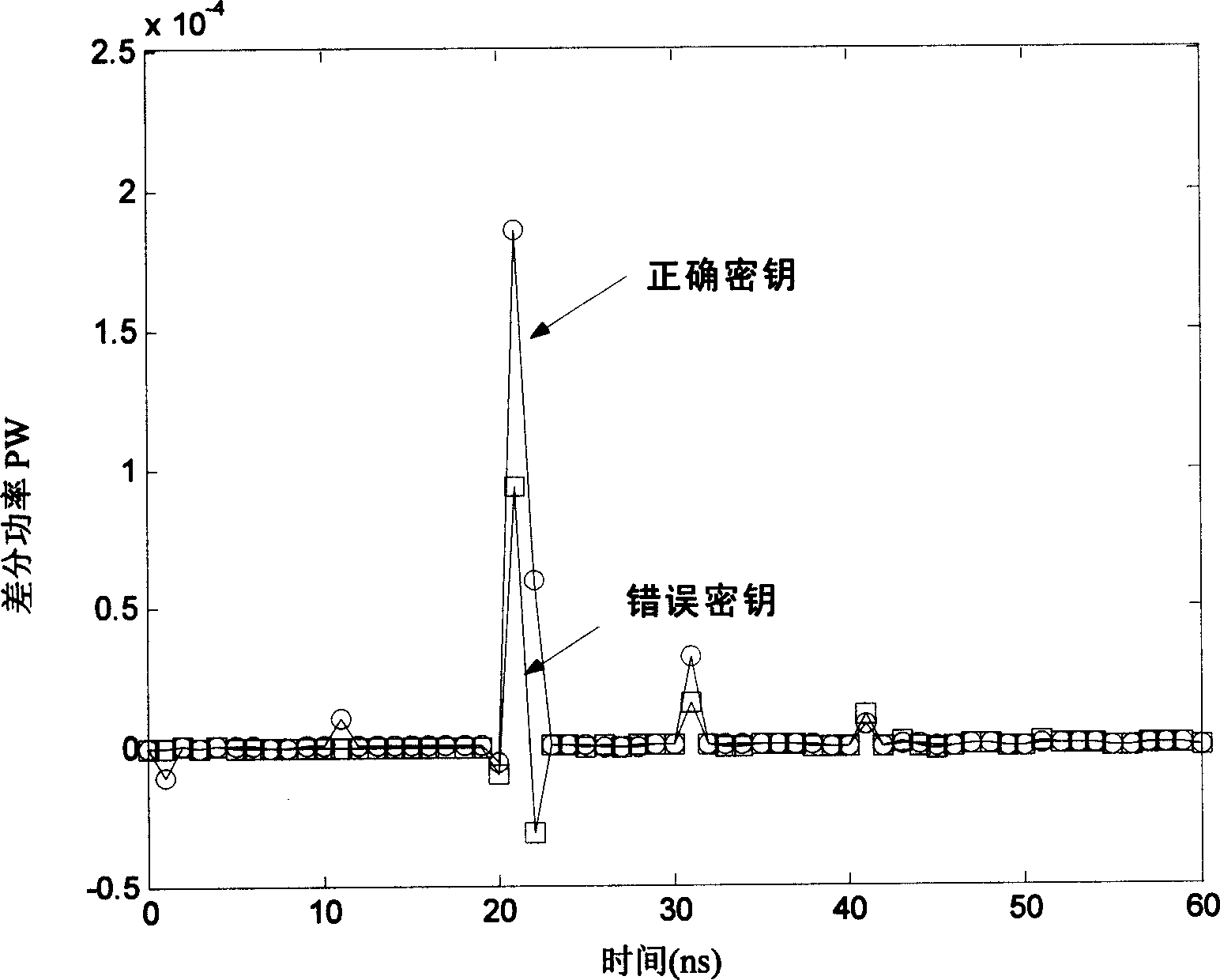

Differential power consumption analysis shield circuit for DES encrypted chip

InactiveCN1753357AEncryption apparatus with shift registers/memoriesProcessor registerInformation security

This invention relates to a differential power loss analysis screen circuit applied in the DES ciphered chips composed of a screen unit and a complementary register unit to be connected with each other combining the basic structure of the DES ciphered plan. This invention is mainly against the cryptographic key of the 16-turn operation of the DES ciphered flow, the operation results of the 15-turn are sent to registers L15 and R15, in which, L15 is composed of two parts: an ordinary one of 28 bit and complementary one of 4 bit, part results of the 15-turn operation, the sub- cryptographic key of the 16-turn and the preset false sub-cryptographic key are sent to the screen unit.

Owner:FUDAN UNIV +1