Patents

Literature

172 results about "Dynamic circuit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

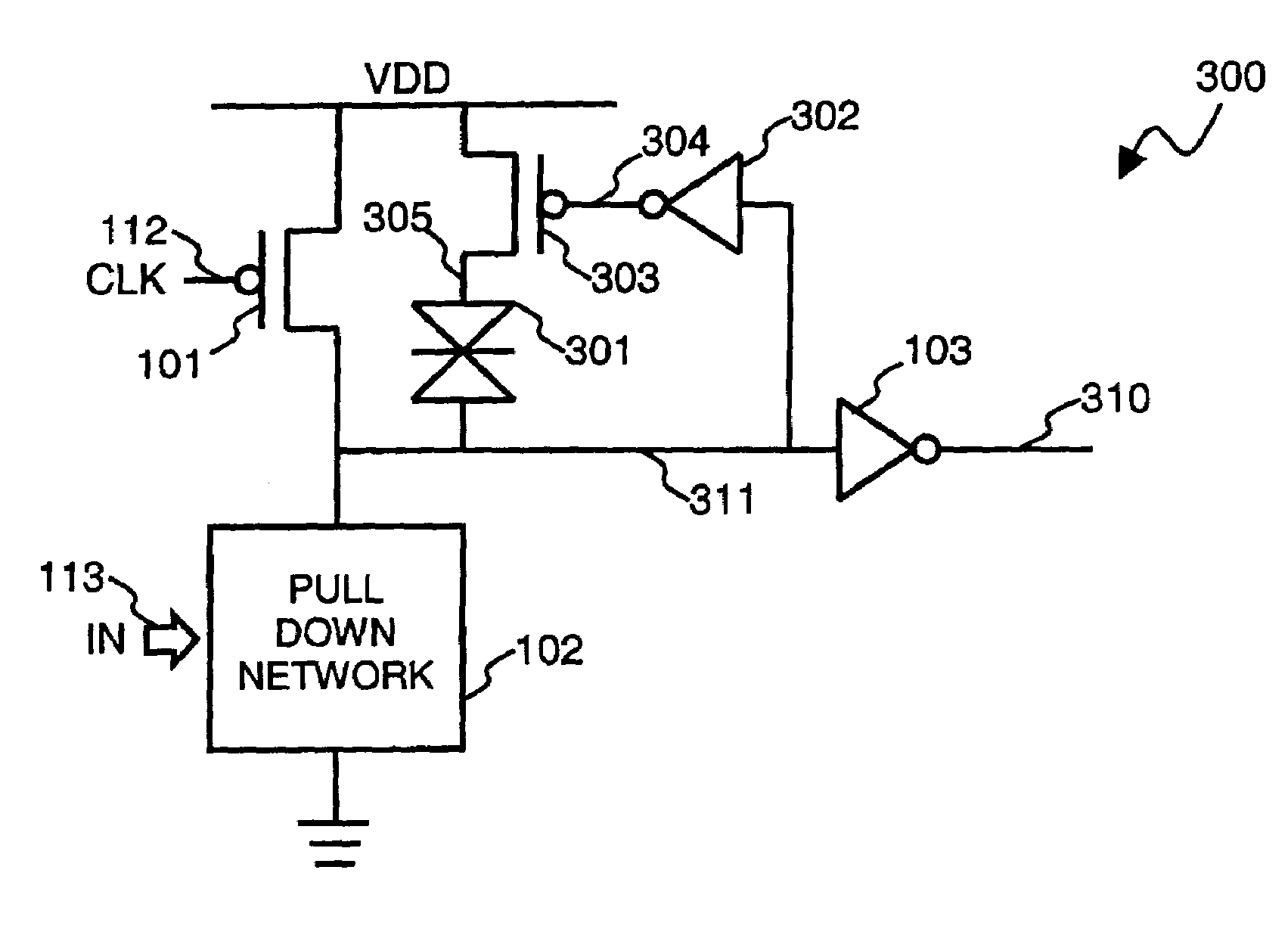

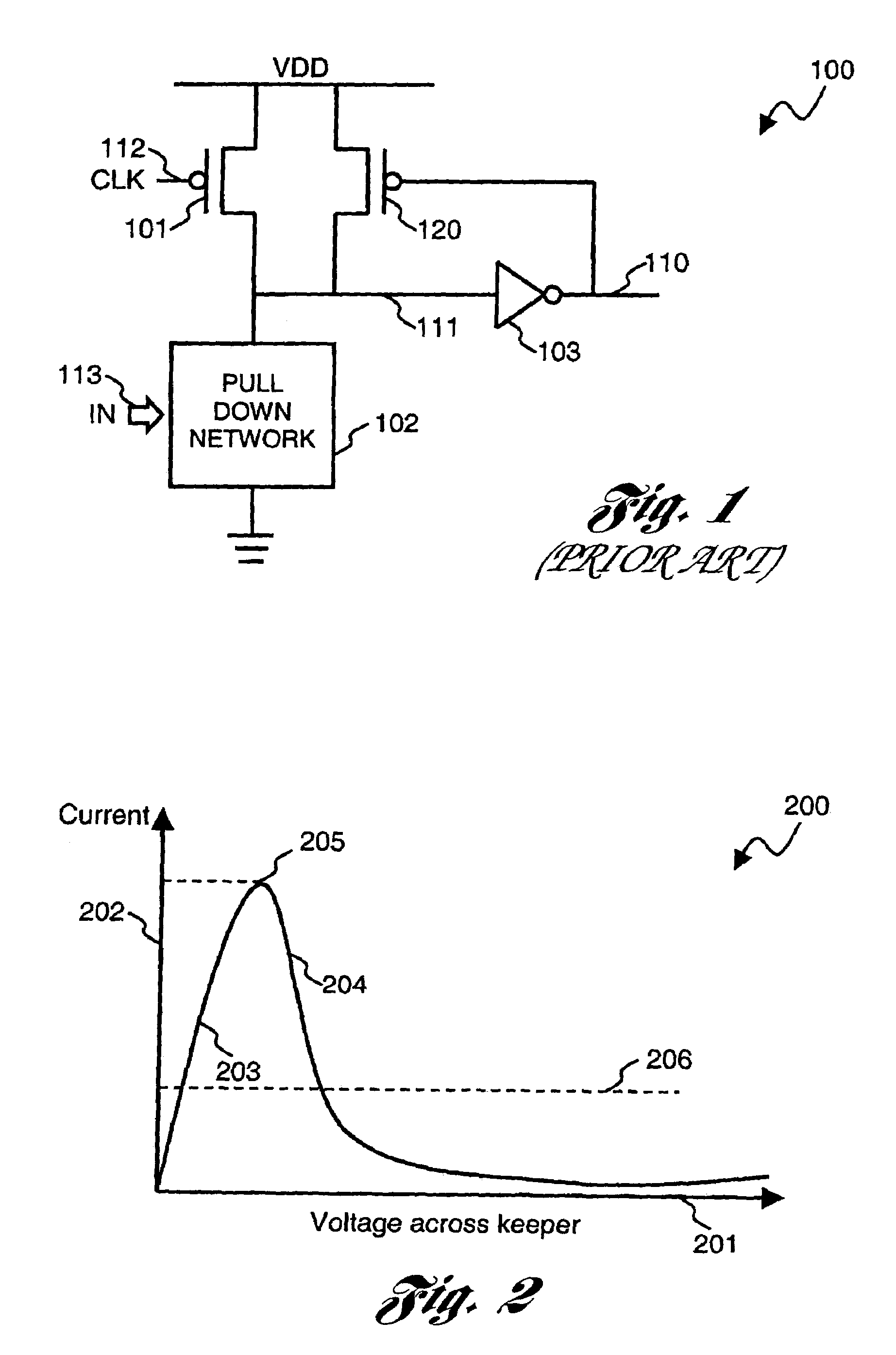

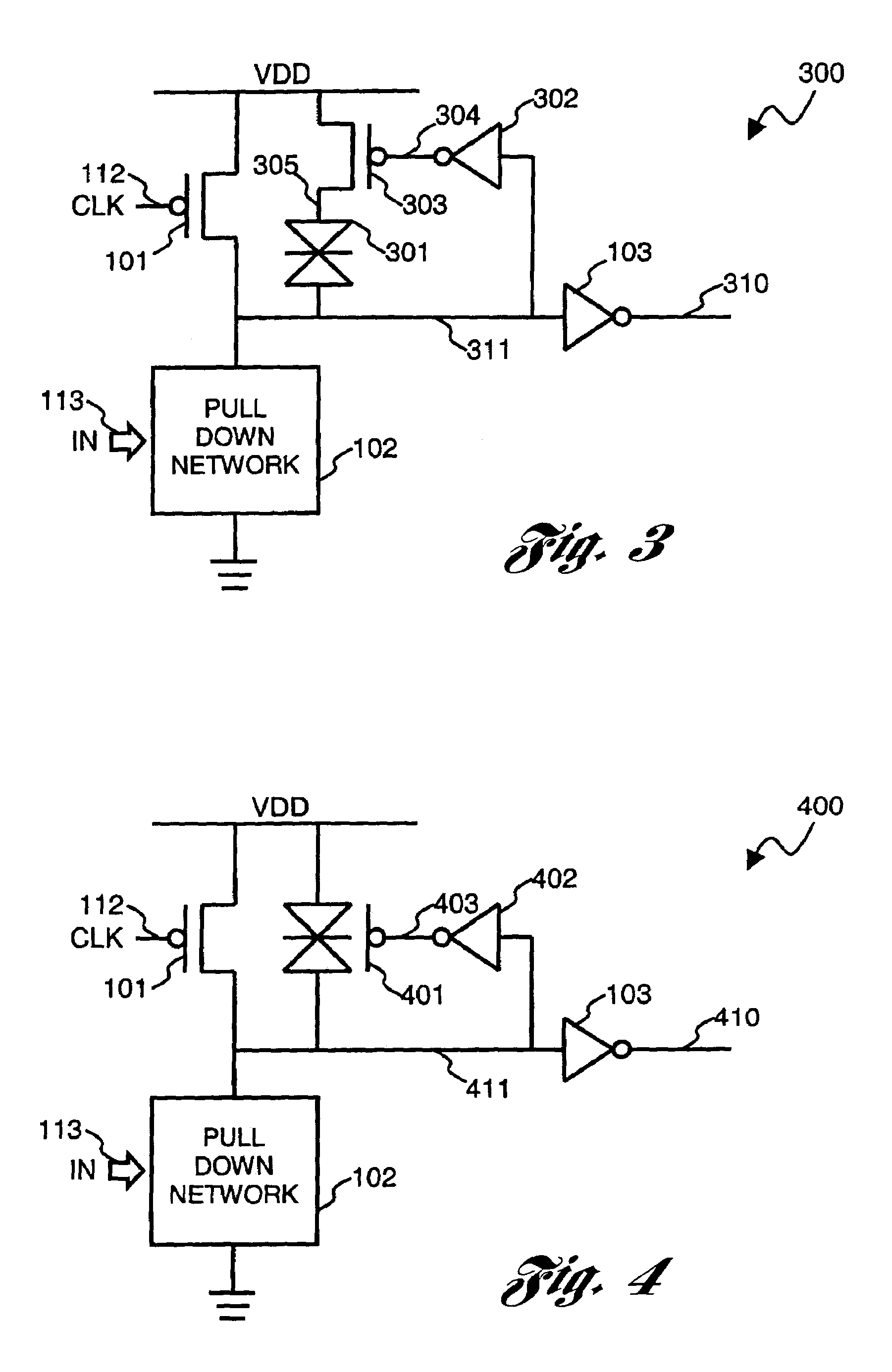

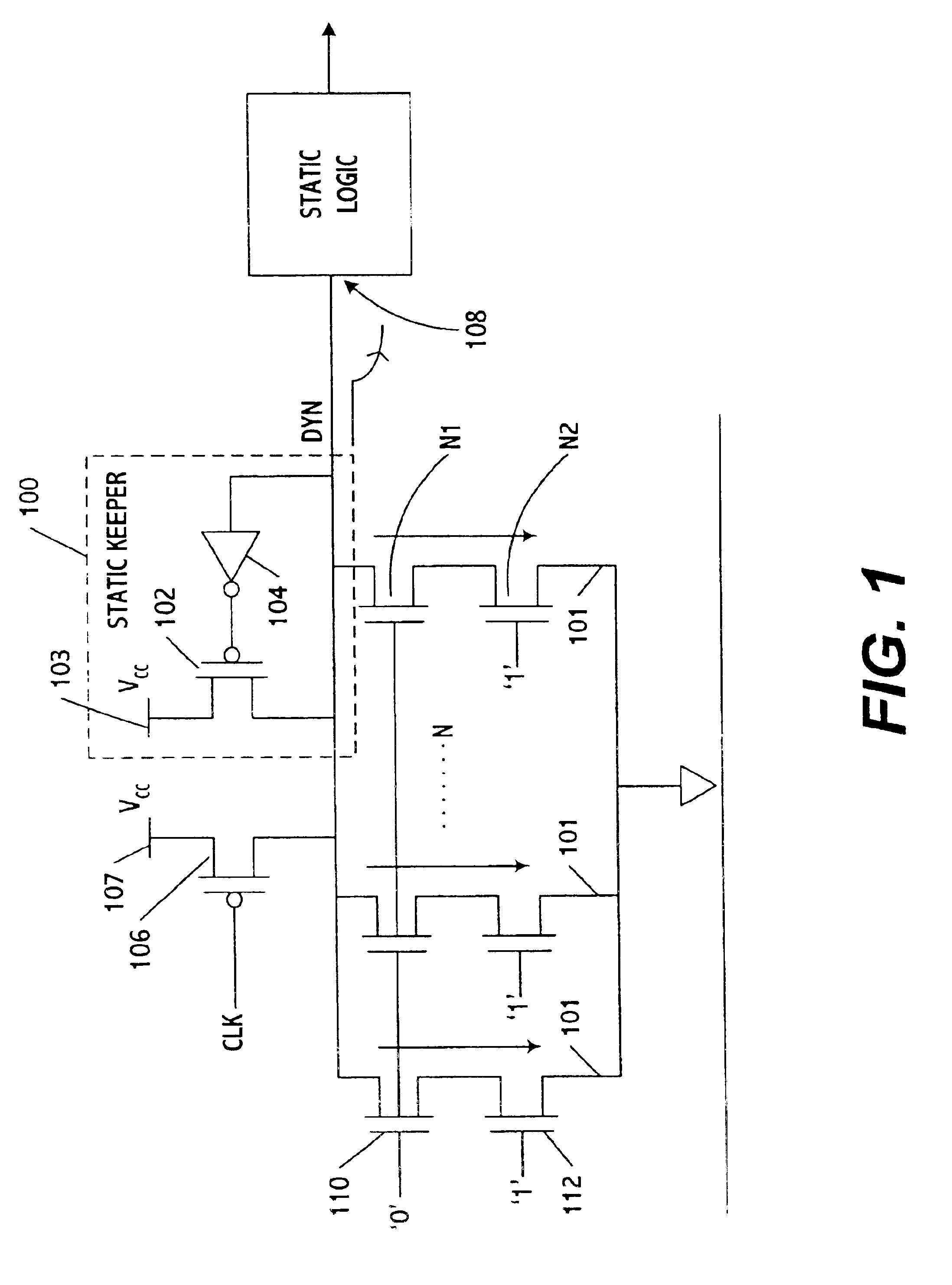

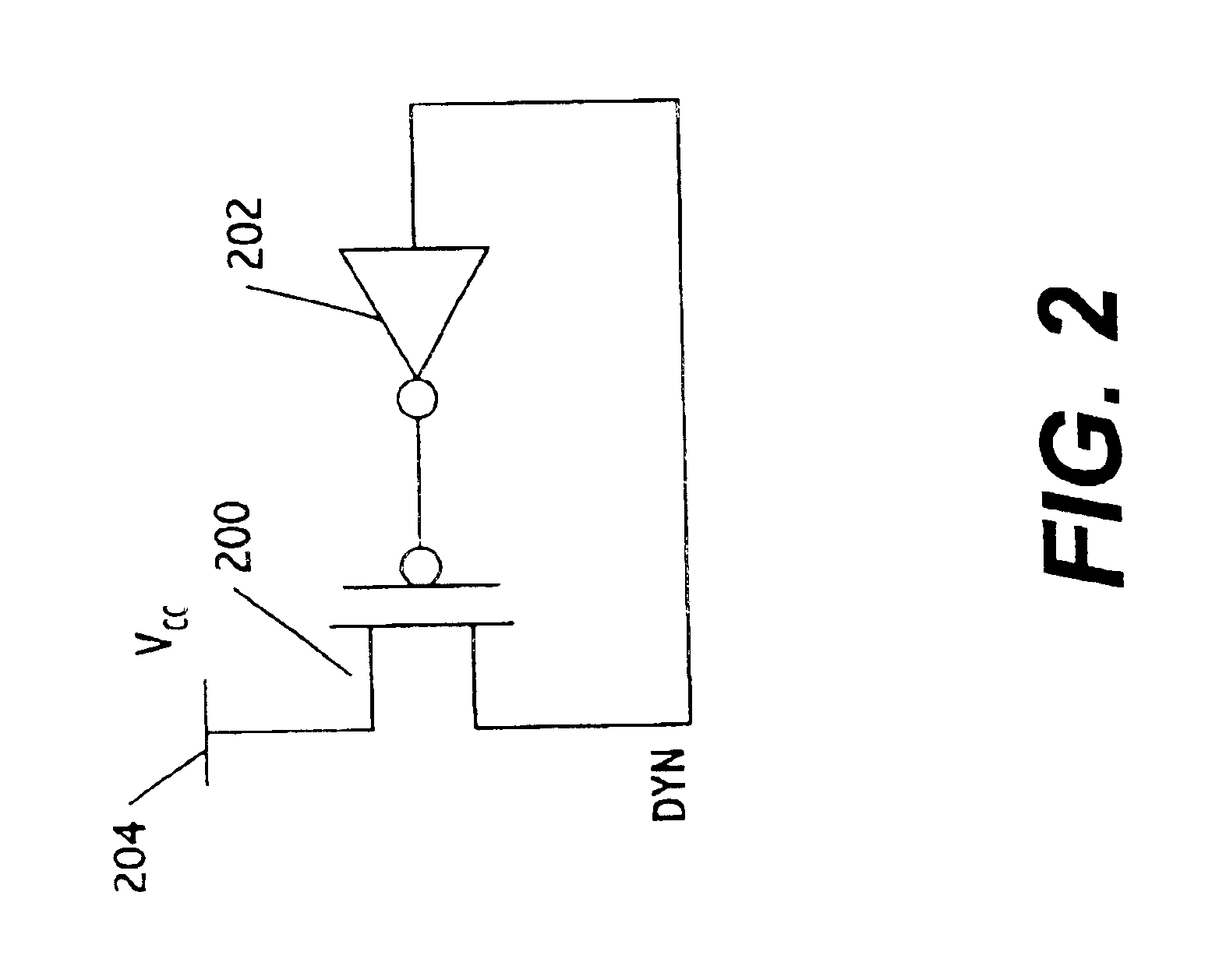

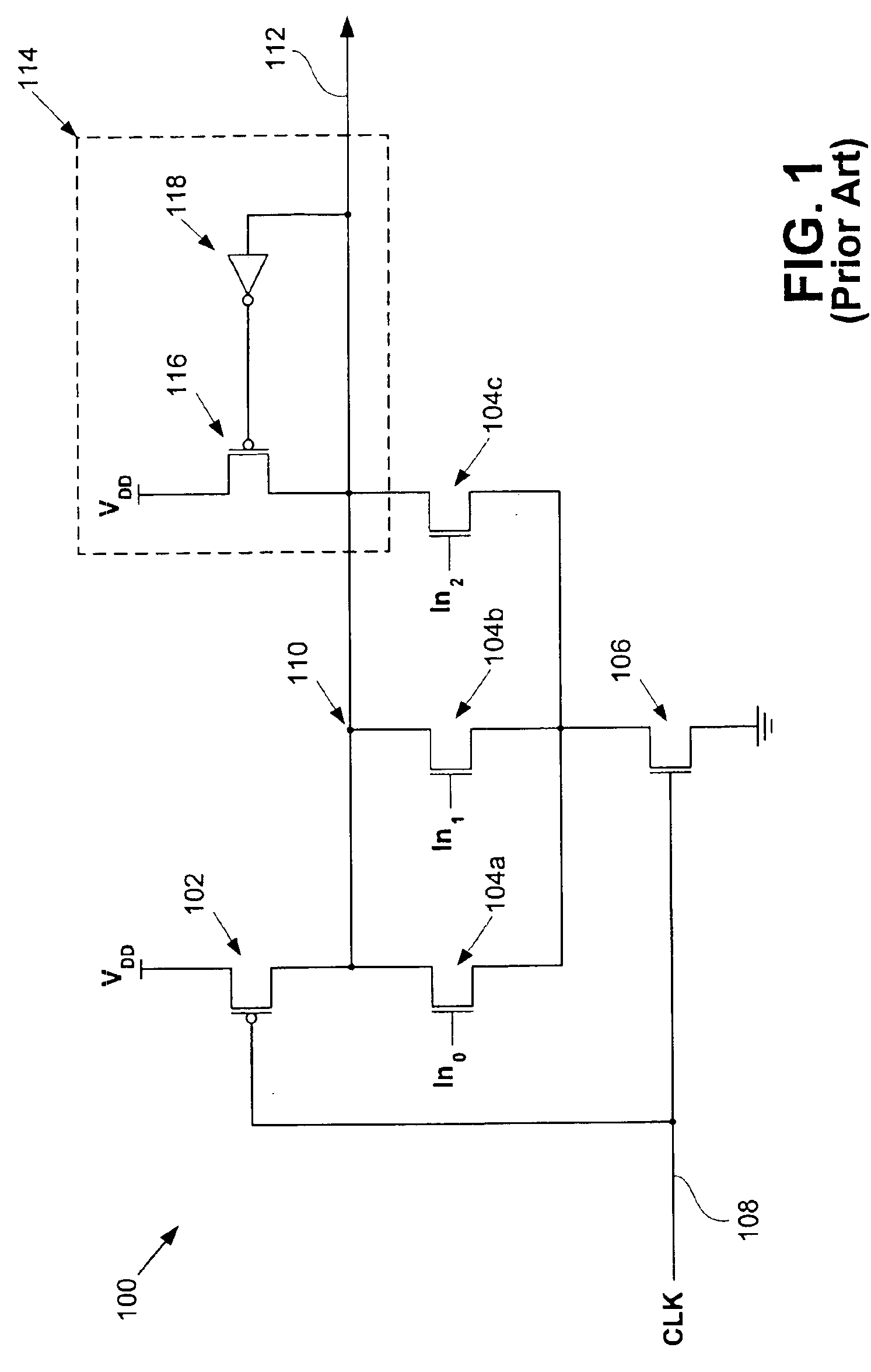

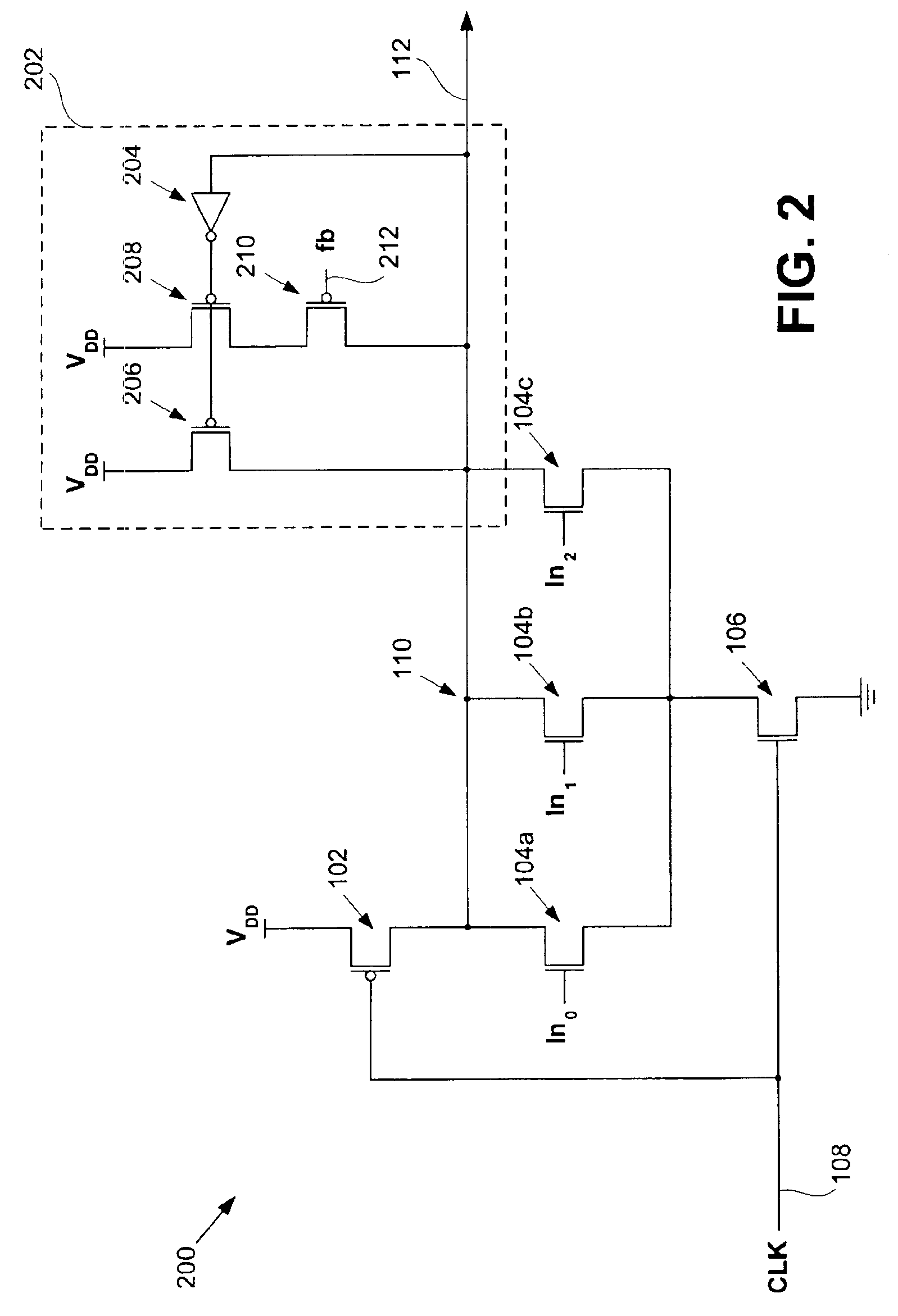

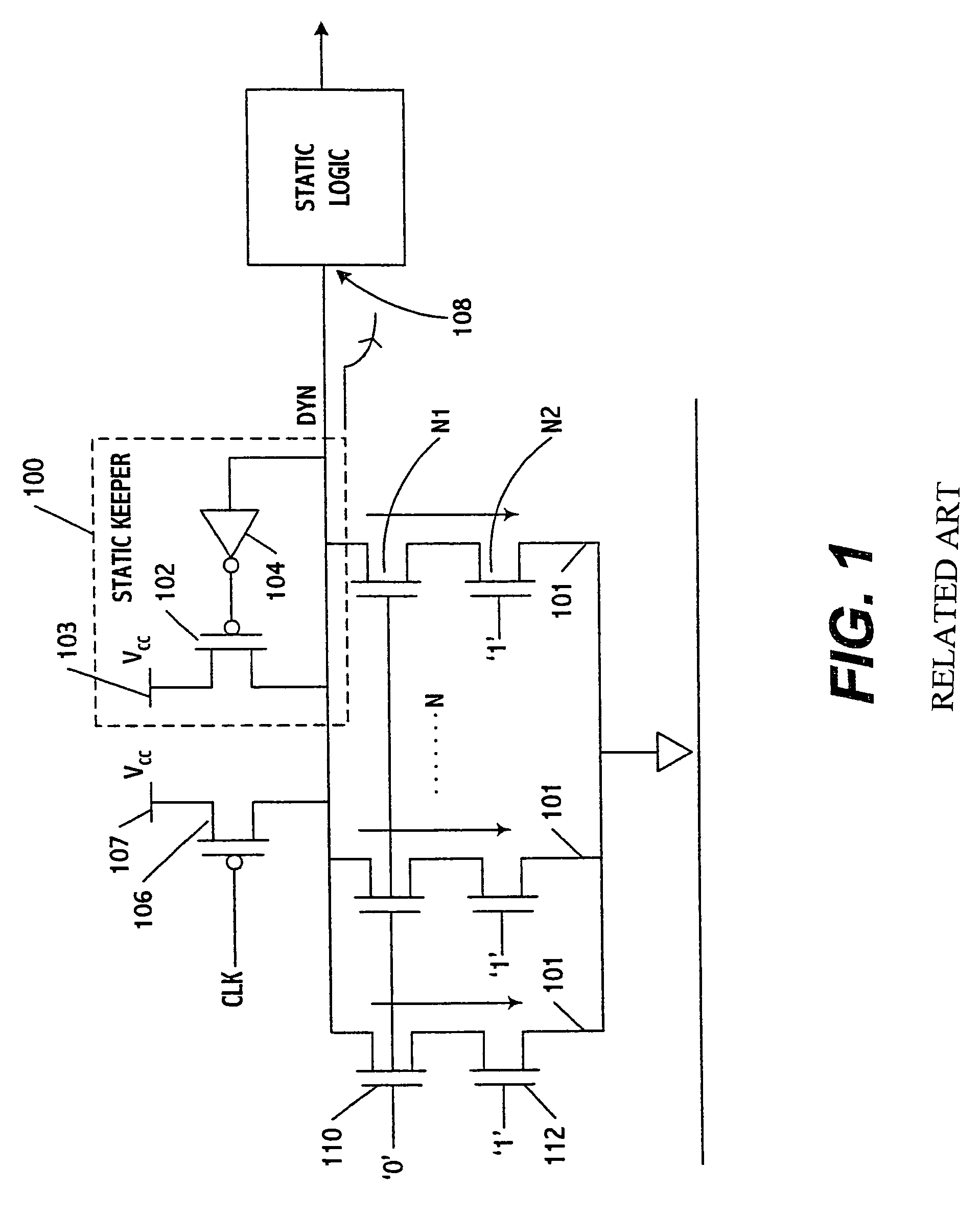

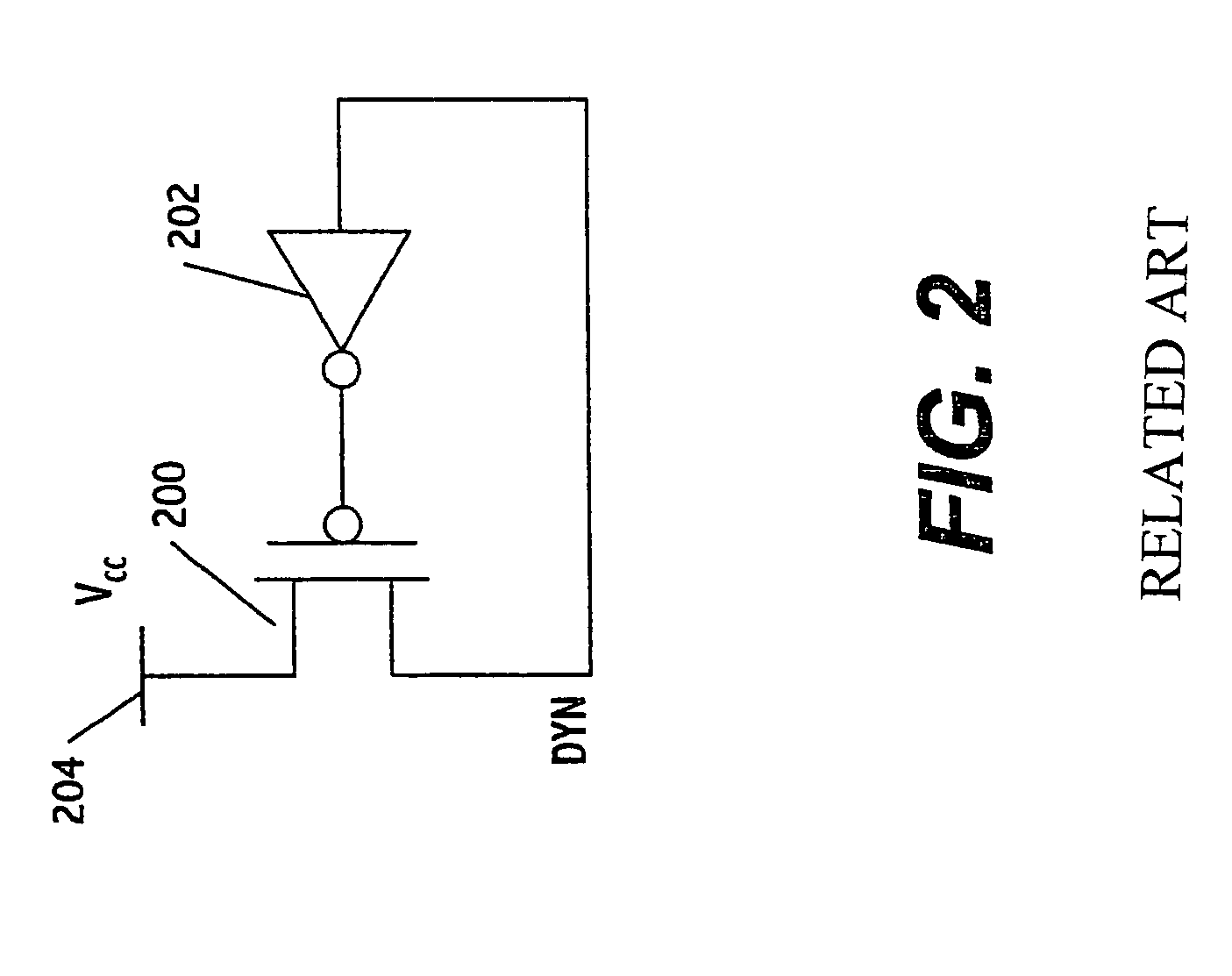

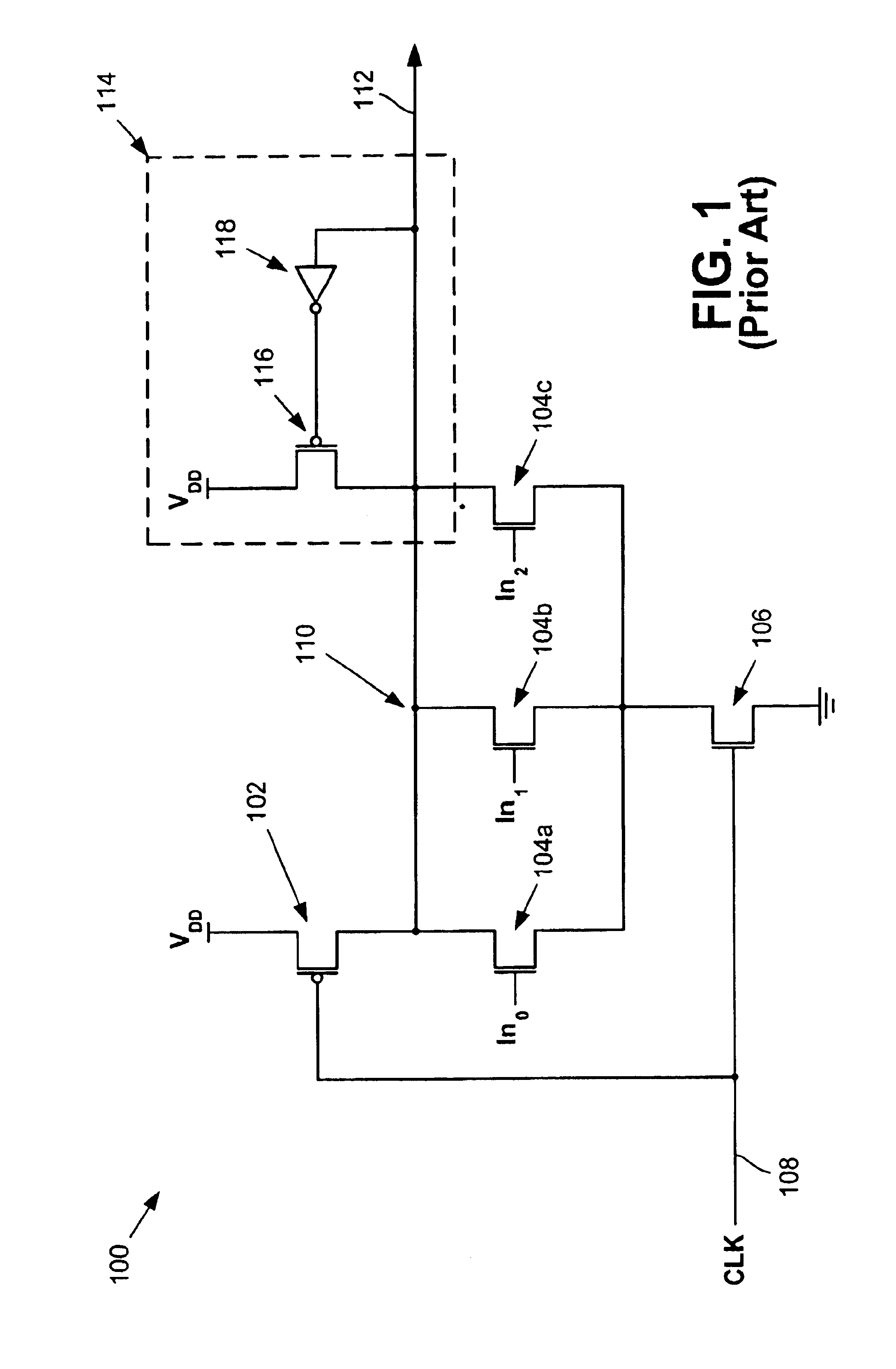

Dynamic circuits having improved noise tolerance and method for designing same

InactiveUS7088143B2Improved dynamic circuitsImprove methodLogic circuits characterised by logic functionElectrical resistance and conductanceEngineering

A number of different dynamic circuits having improved noise tolerance and a method for designing same are provided. The circuits include a power supply node and a precharge node. Keeper circuitry is connected to the nodes and has a current-voltage characteristic that exhibits a negative differential resistance property to improve noise tolerance of the circuits.

Owner:RGT UNIV OF MICHIGAN

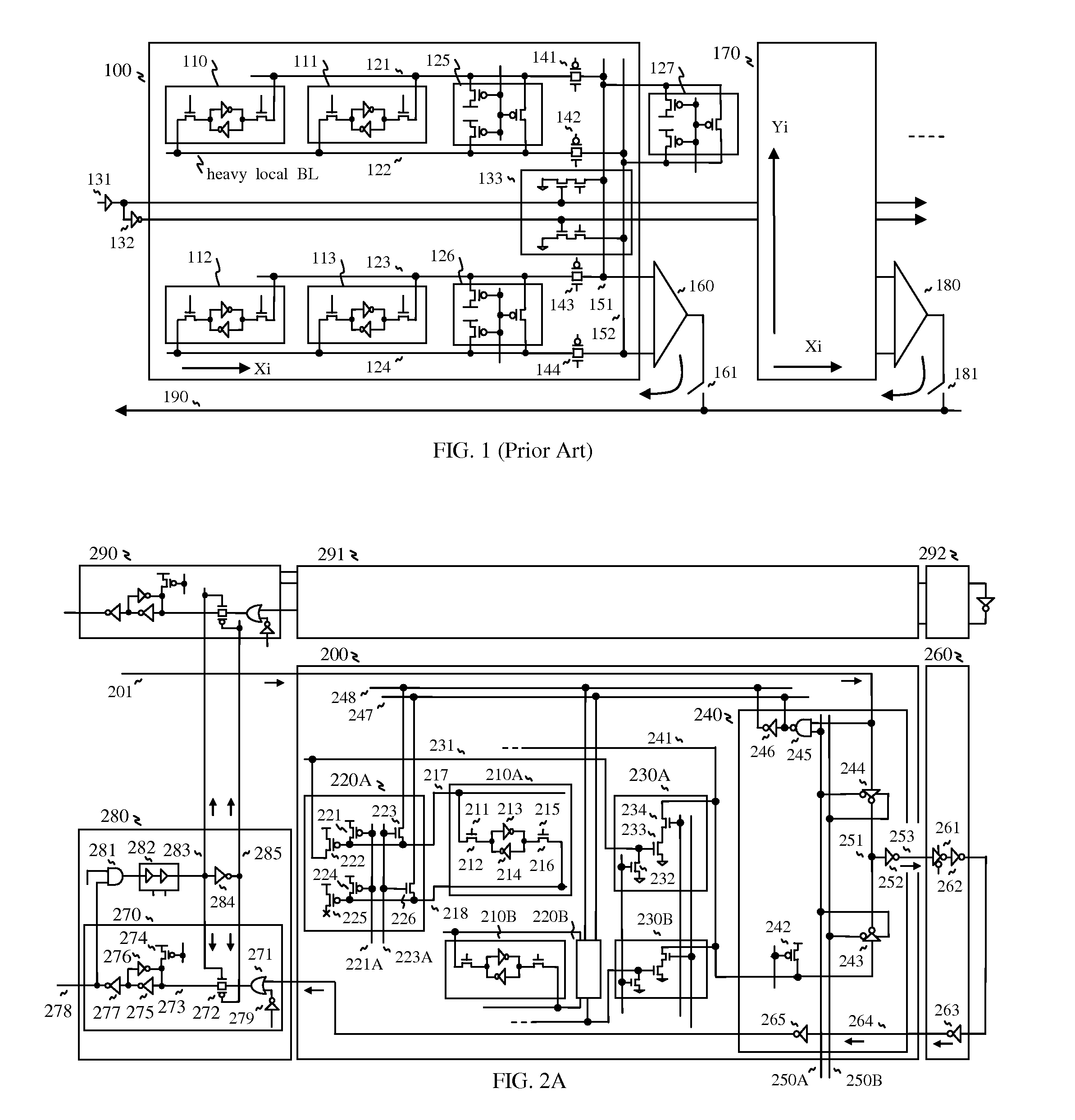

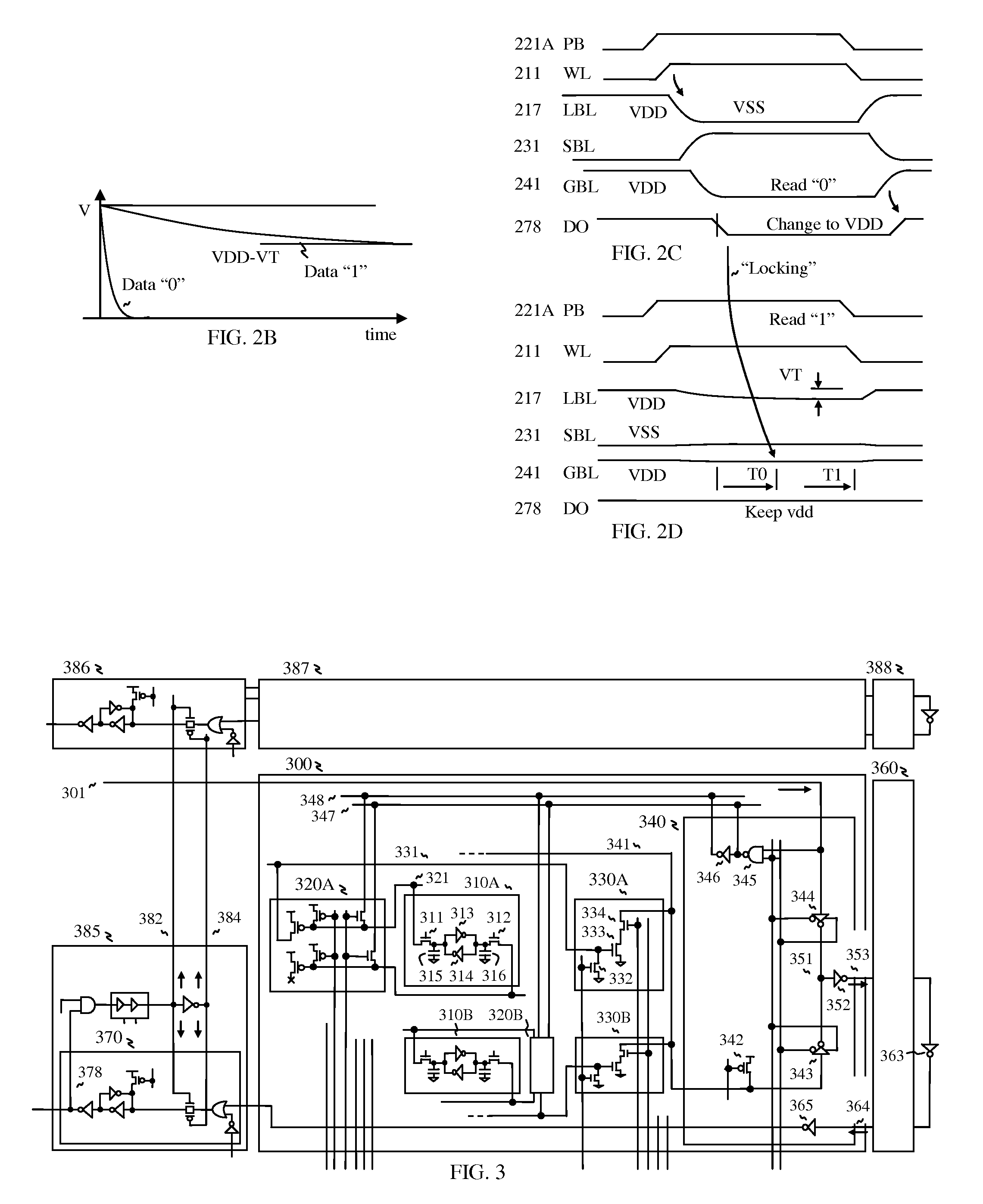

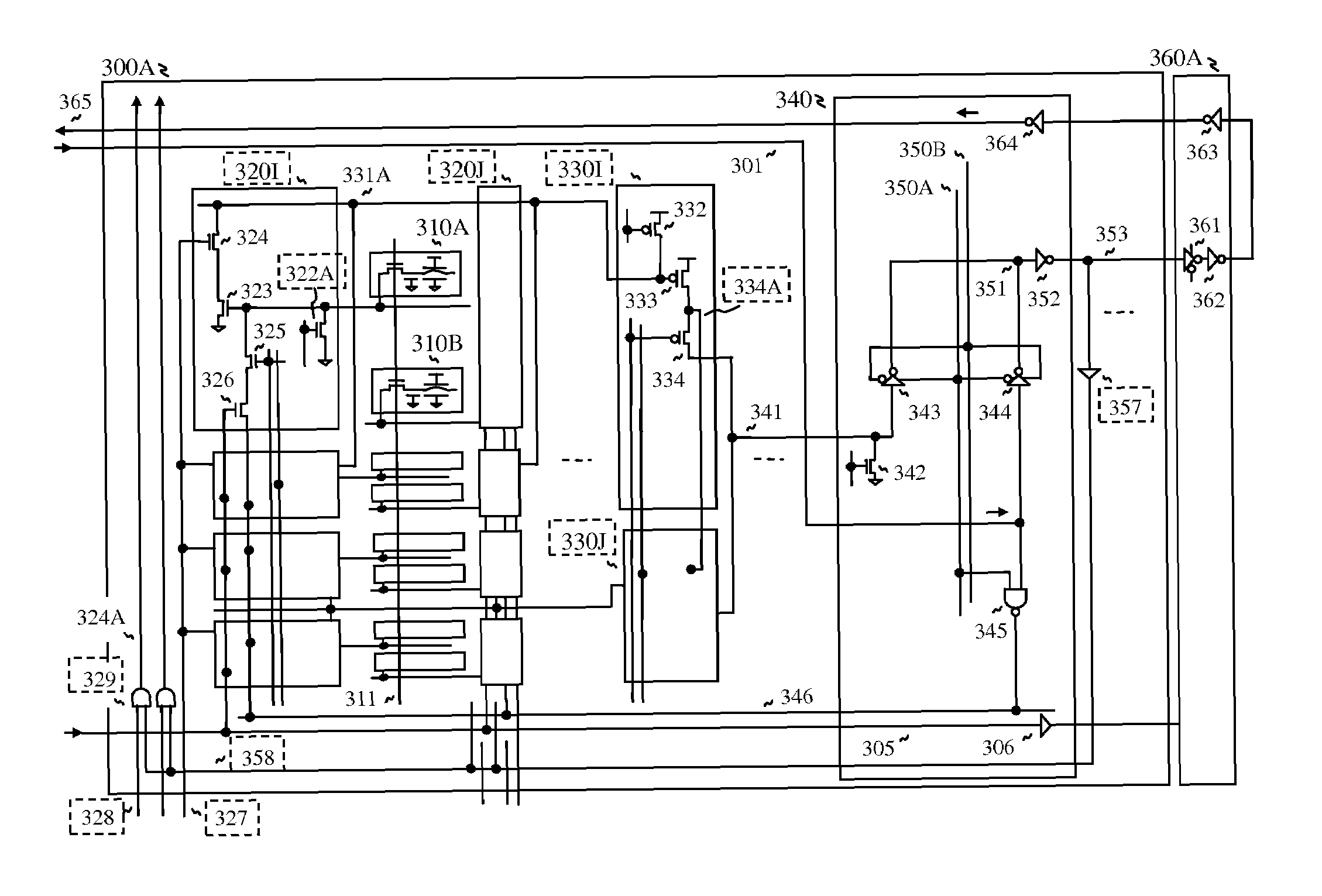

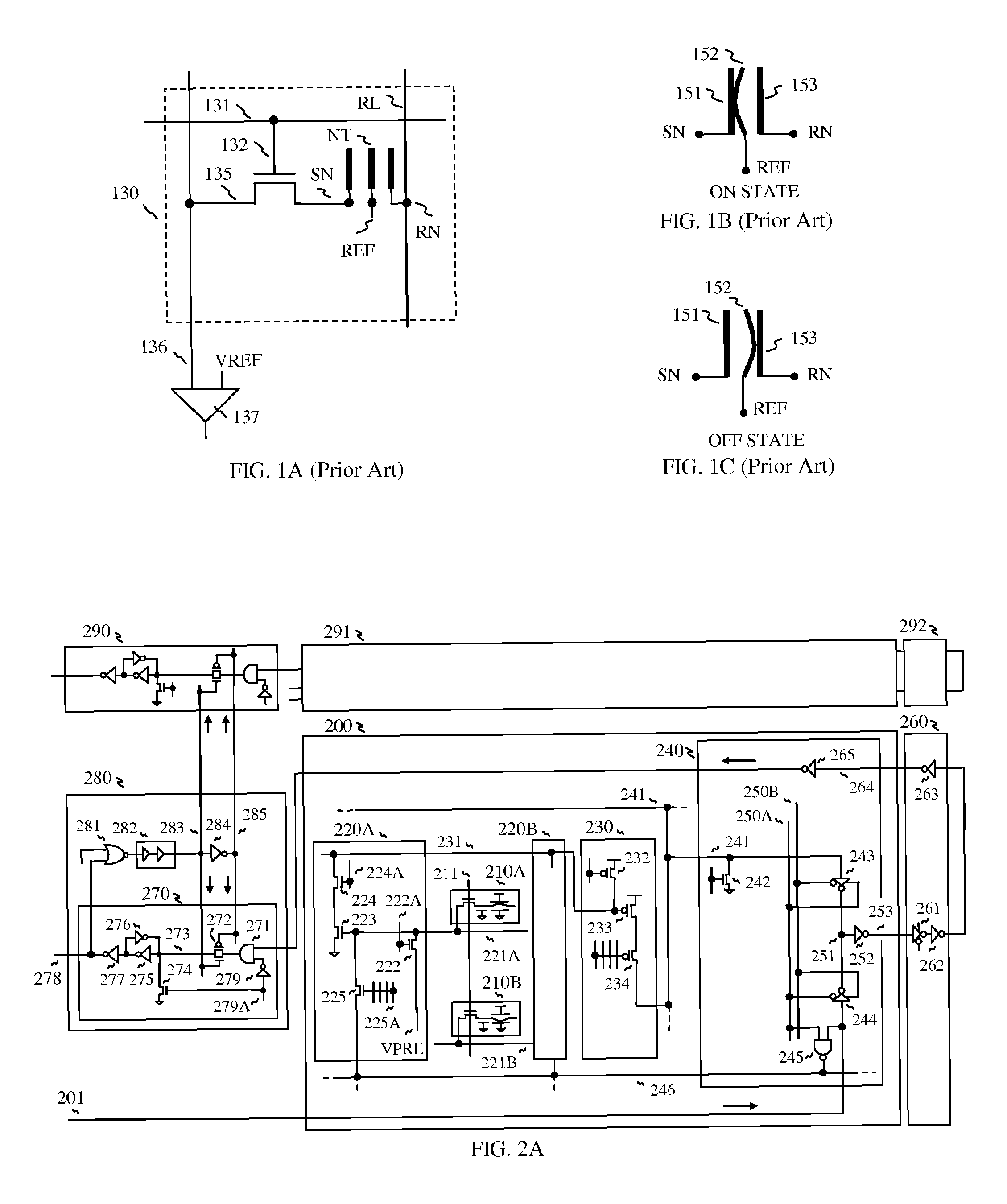

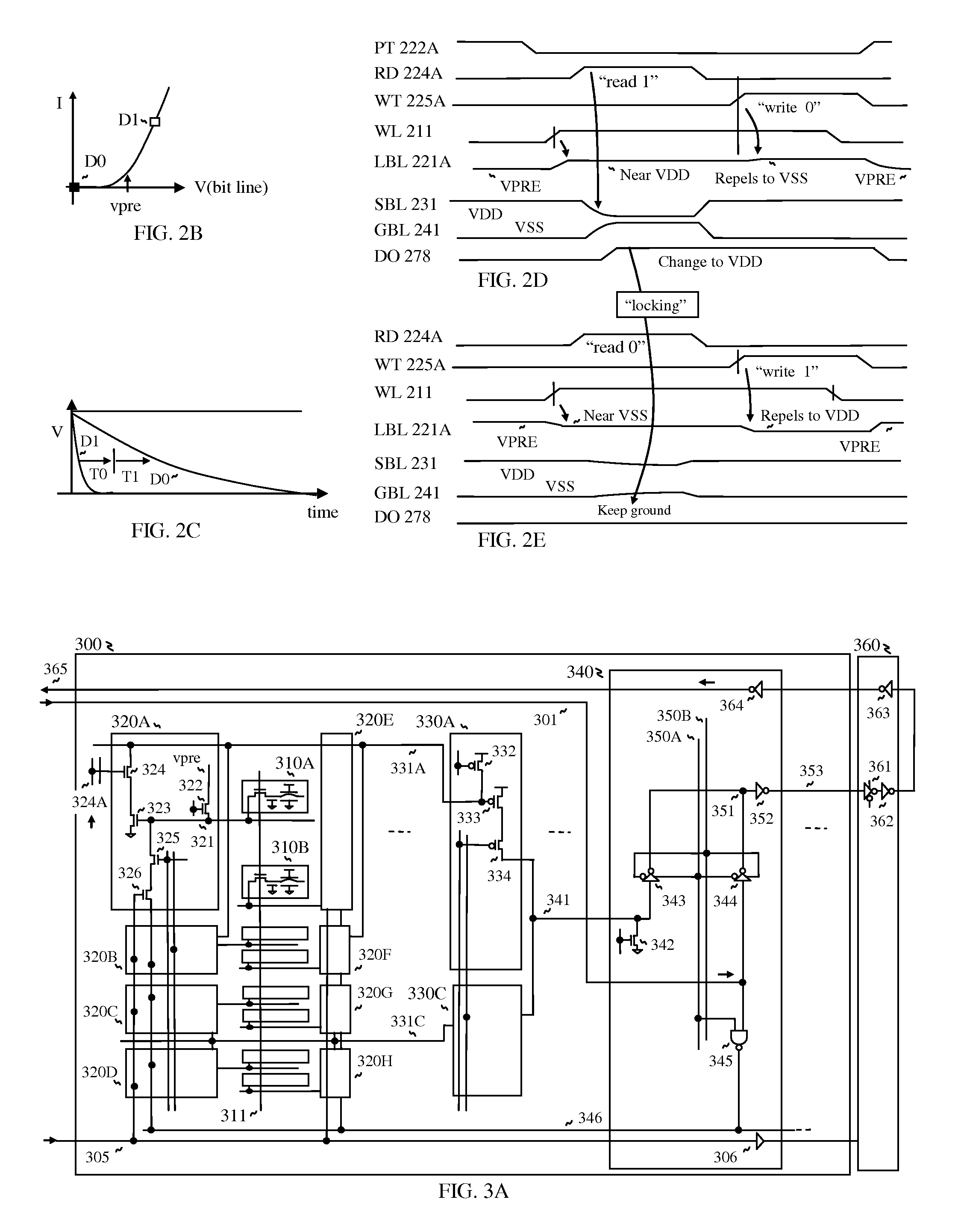

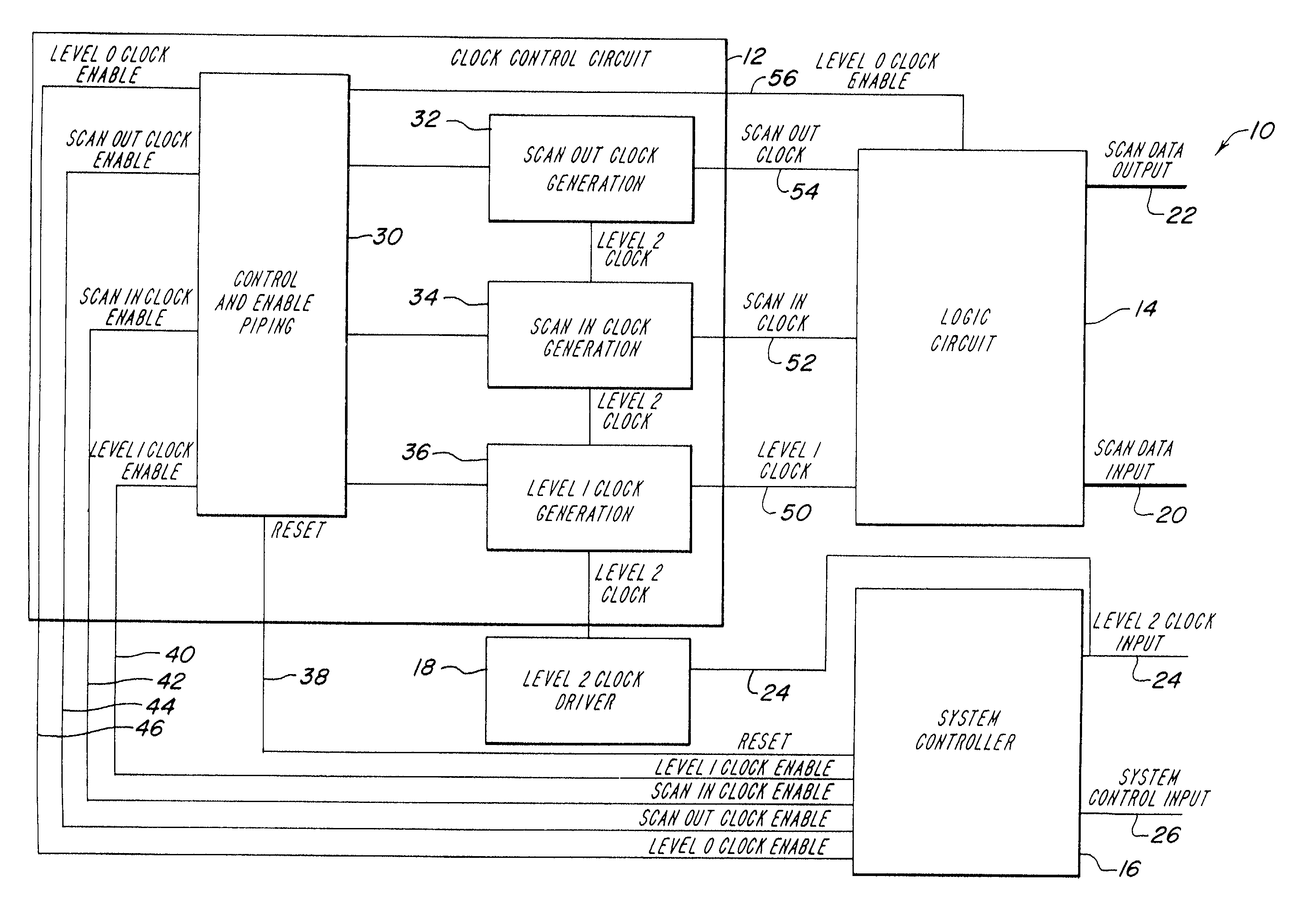

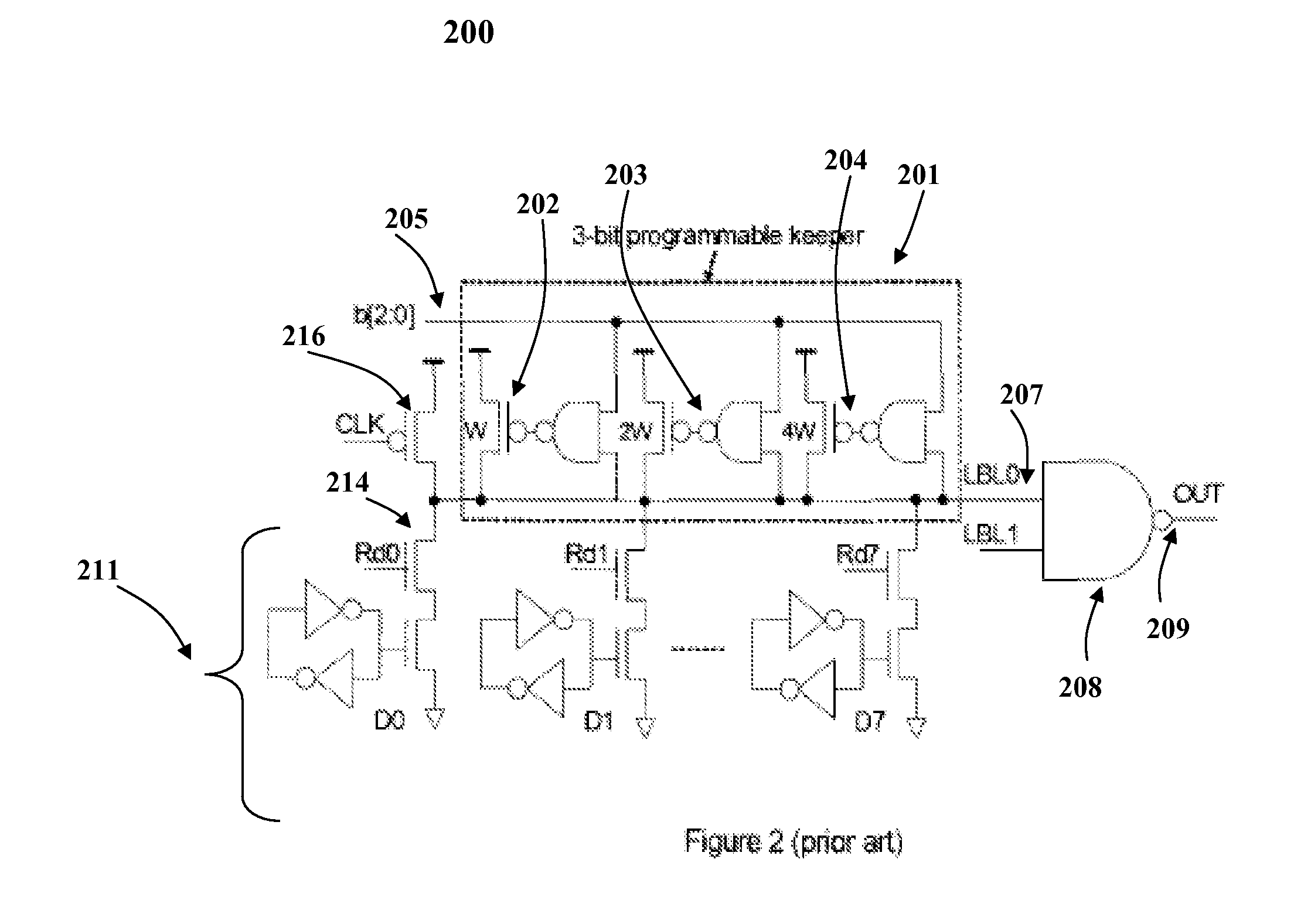

High speed SRAM

InactiveUS20100054011A1Reduce power consumptionEliminating penetration currentDigital storageBit lineAudio power amplifier

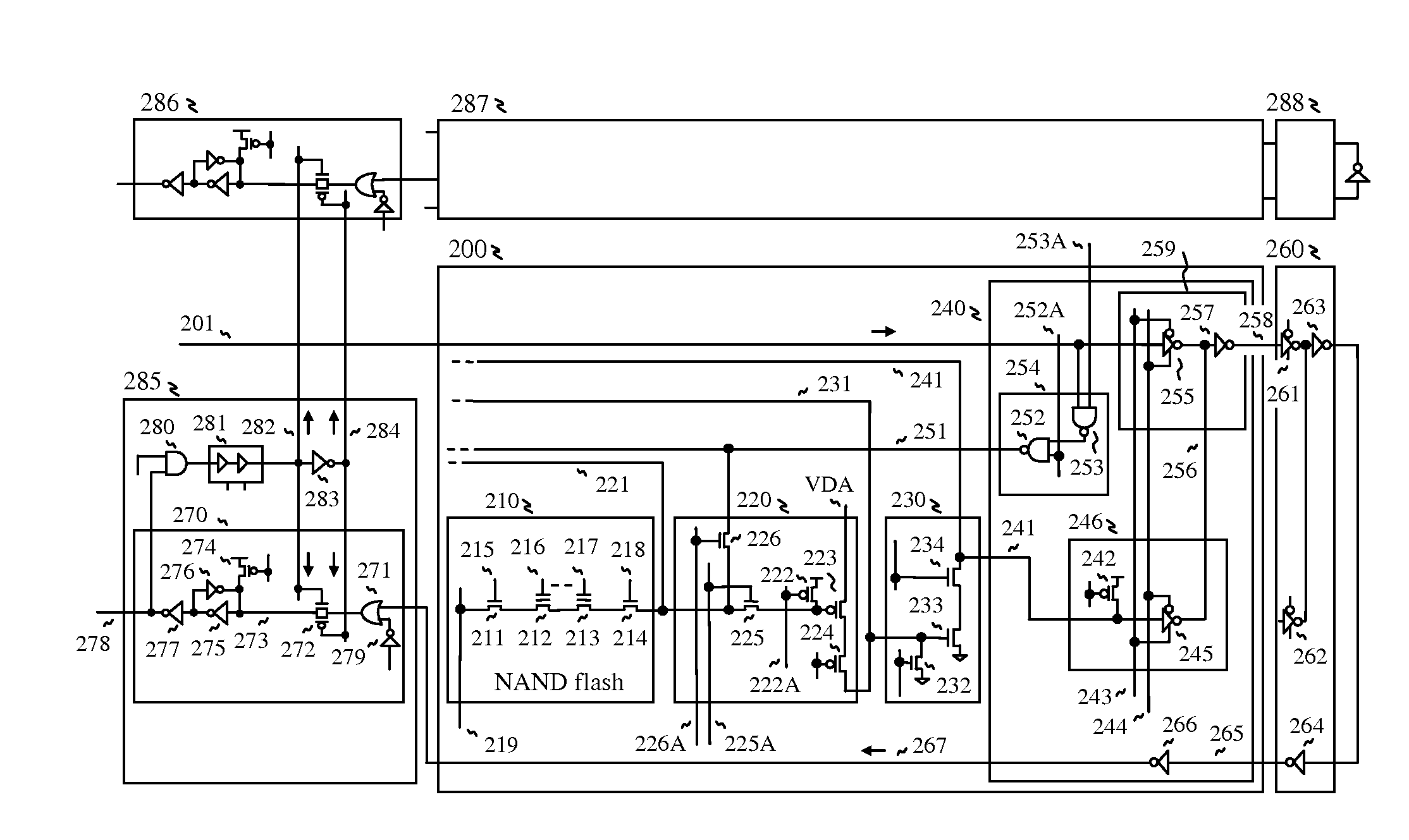

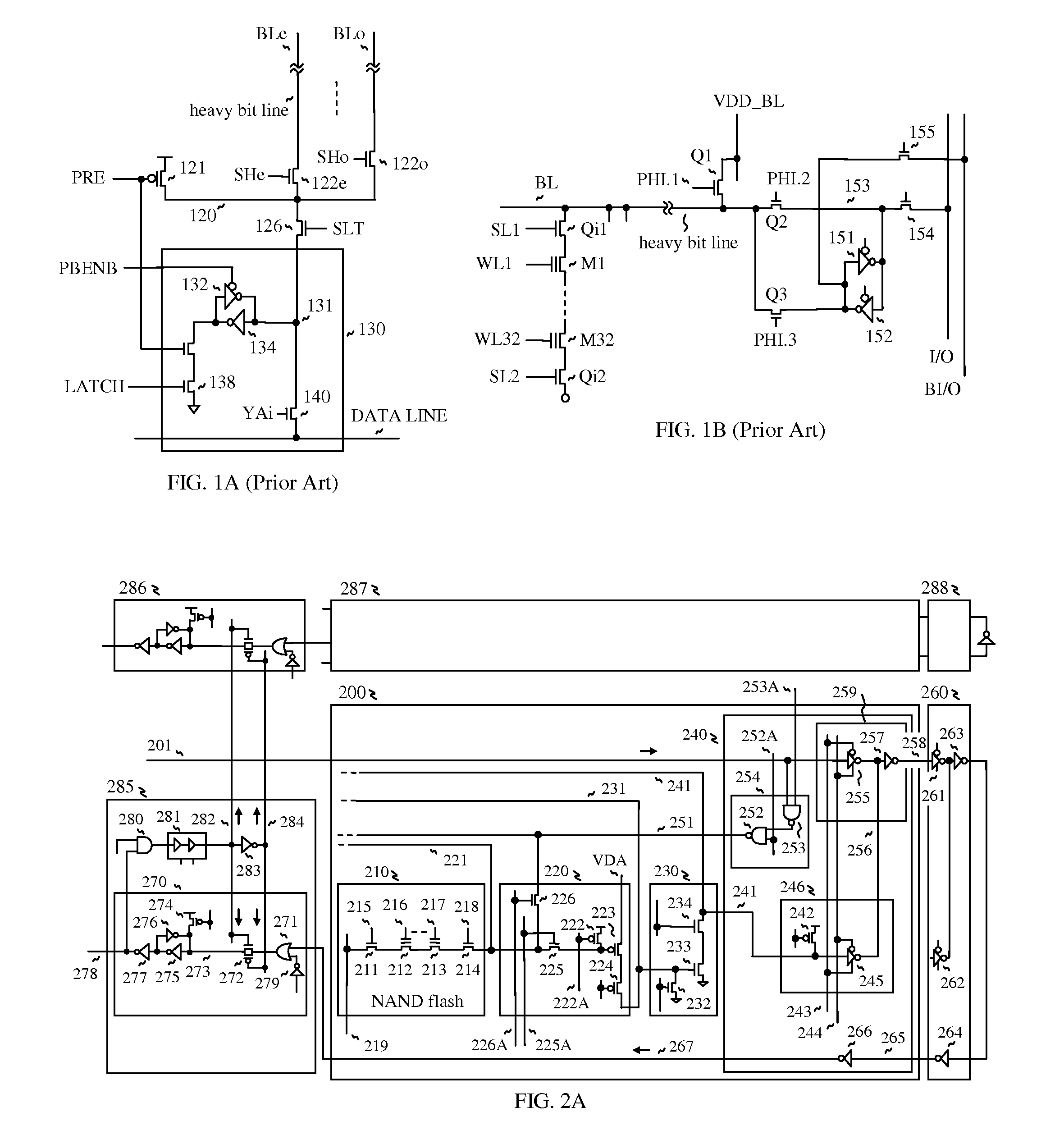

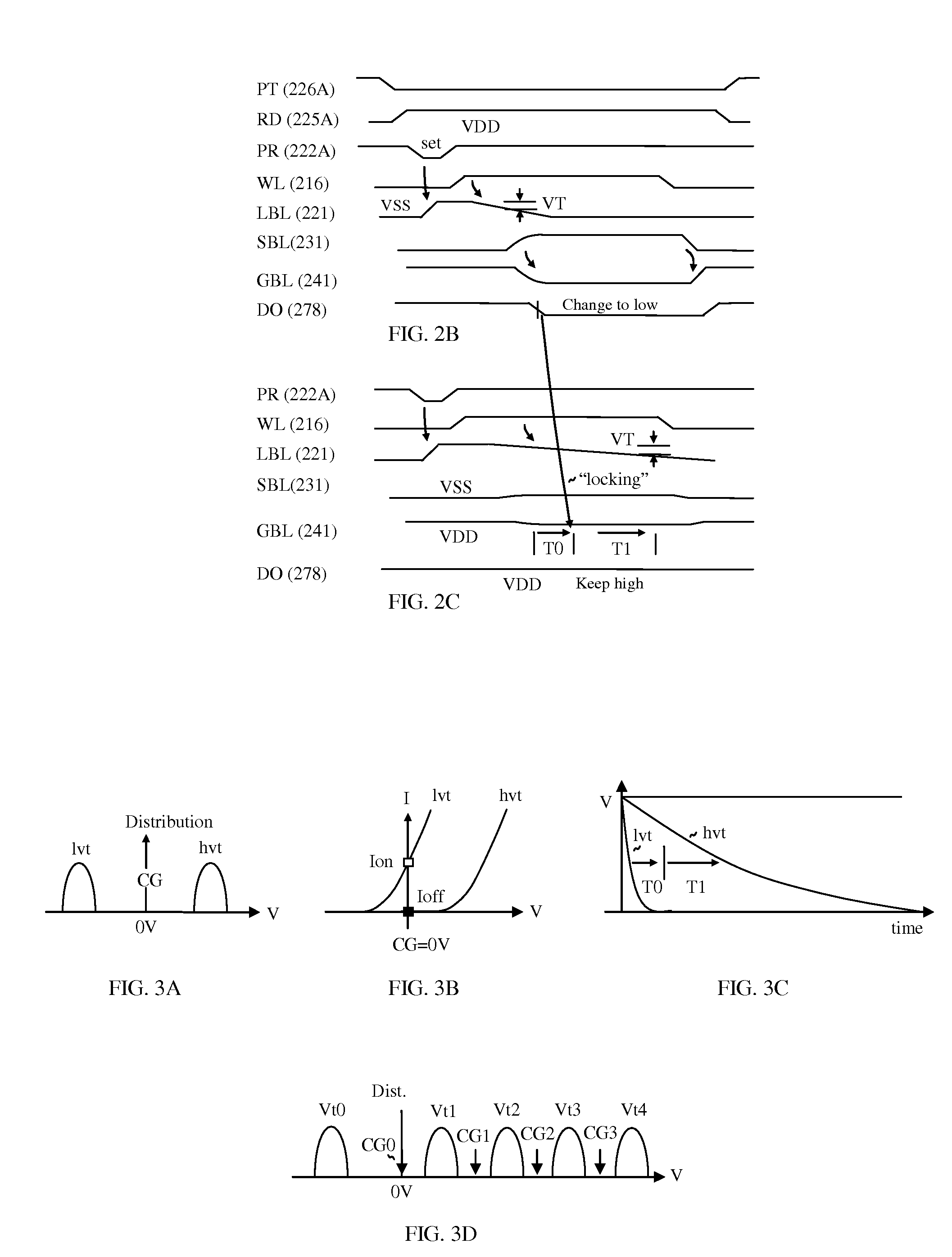

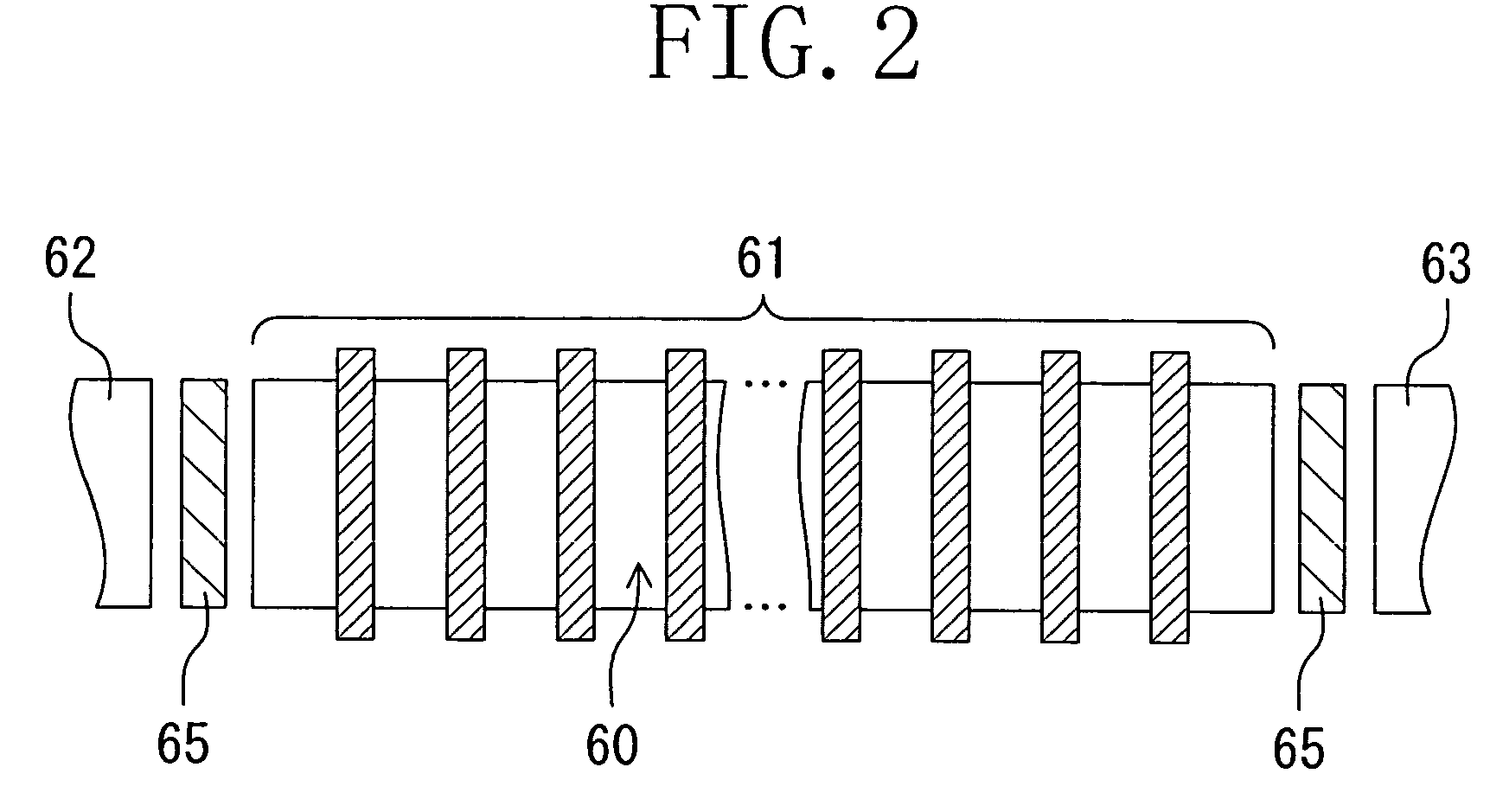

High speed SRAM is realized such that a first dynamic circuit serves as a local sense amp for reading a memory cell through a lightly loaded local bit line, a second dynamic circuit serves as a segment sense amp for reading the local sense amp, and a tri-state inverter serves as an inverting amplifier of a global sense amp for reading the segment sense amp. When reading, a voltage difference in the local bit line is converted to a time difference for differentiating low data and high data by the sense amps for realizing fast access with dynamic operation. Furthermore, a buffered data path is used for achieving fast access and amplify transistor of the sense amps is composed of relatively long channel transistor for reducing turn-off current. Additionally, alternative circuits and memory cell structures for implementing the SRAM are described.

Owner:FRONTEON

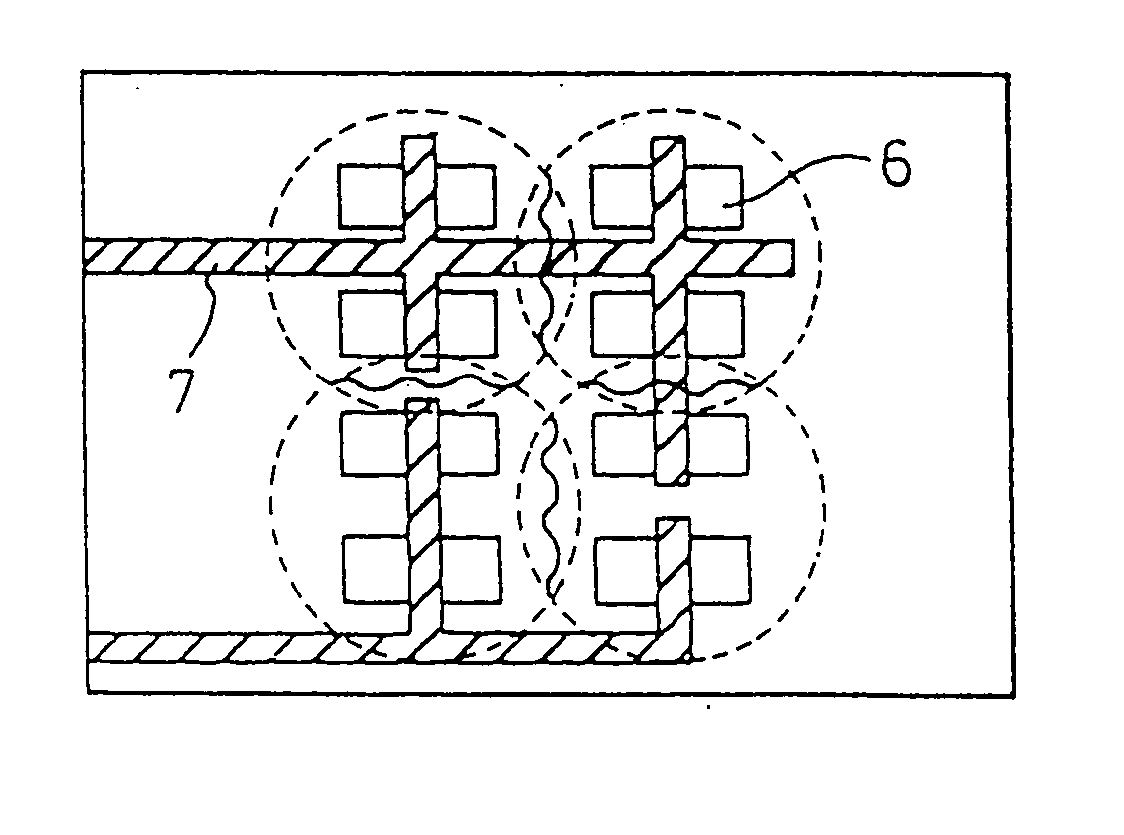

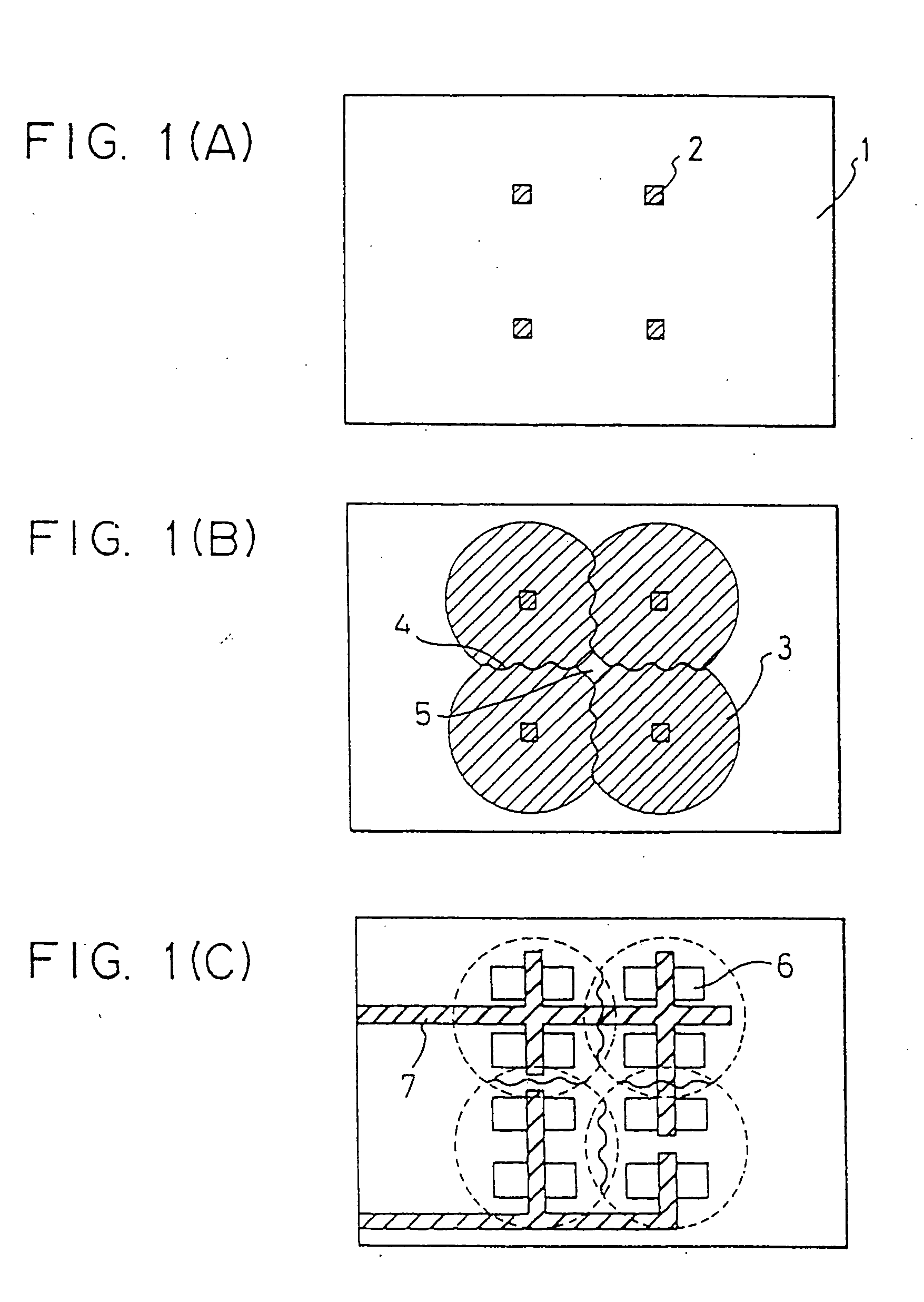

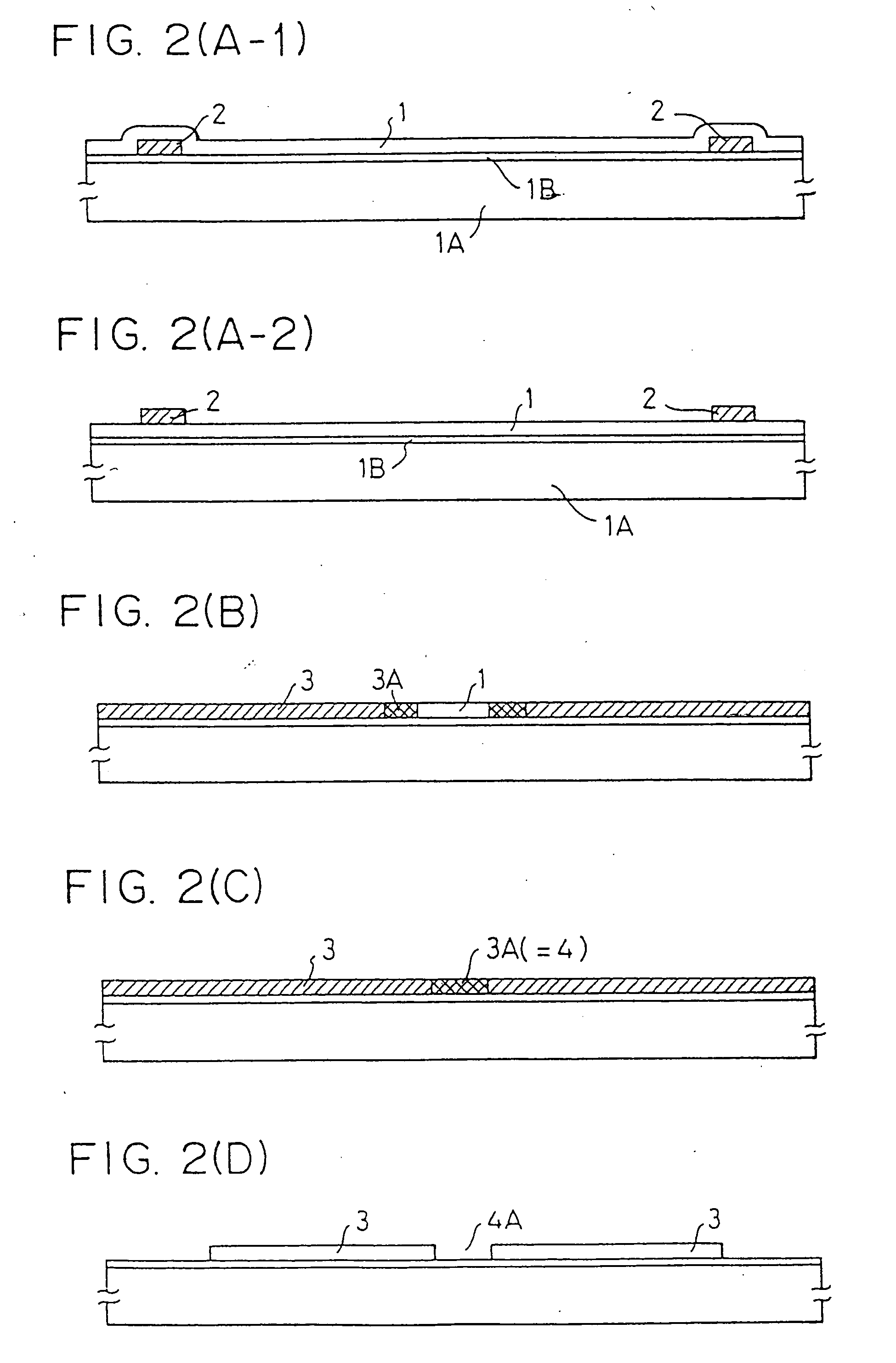

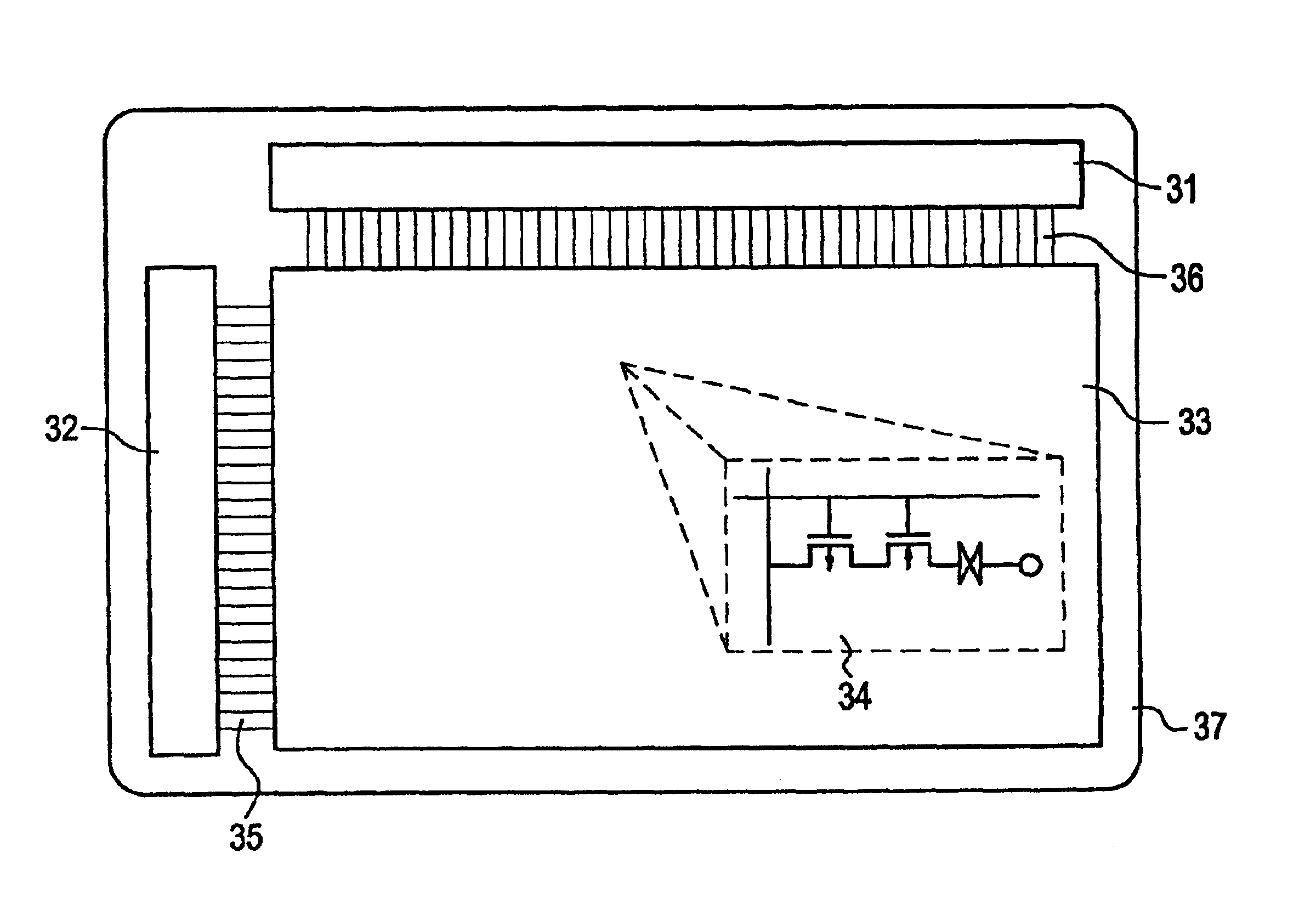

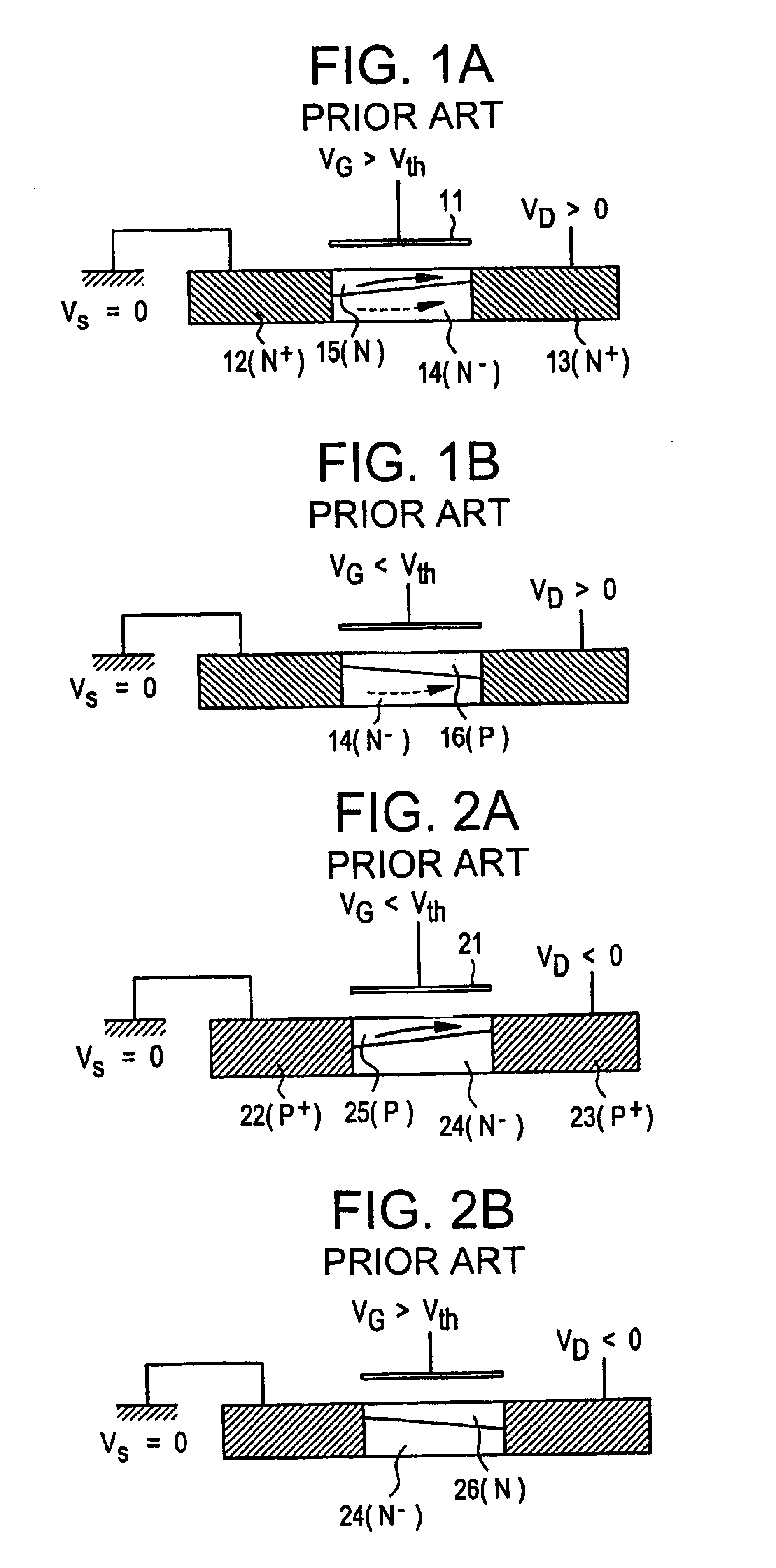

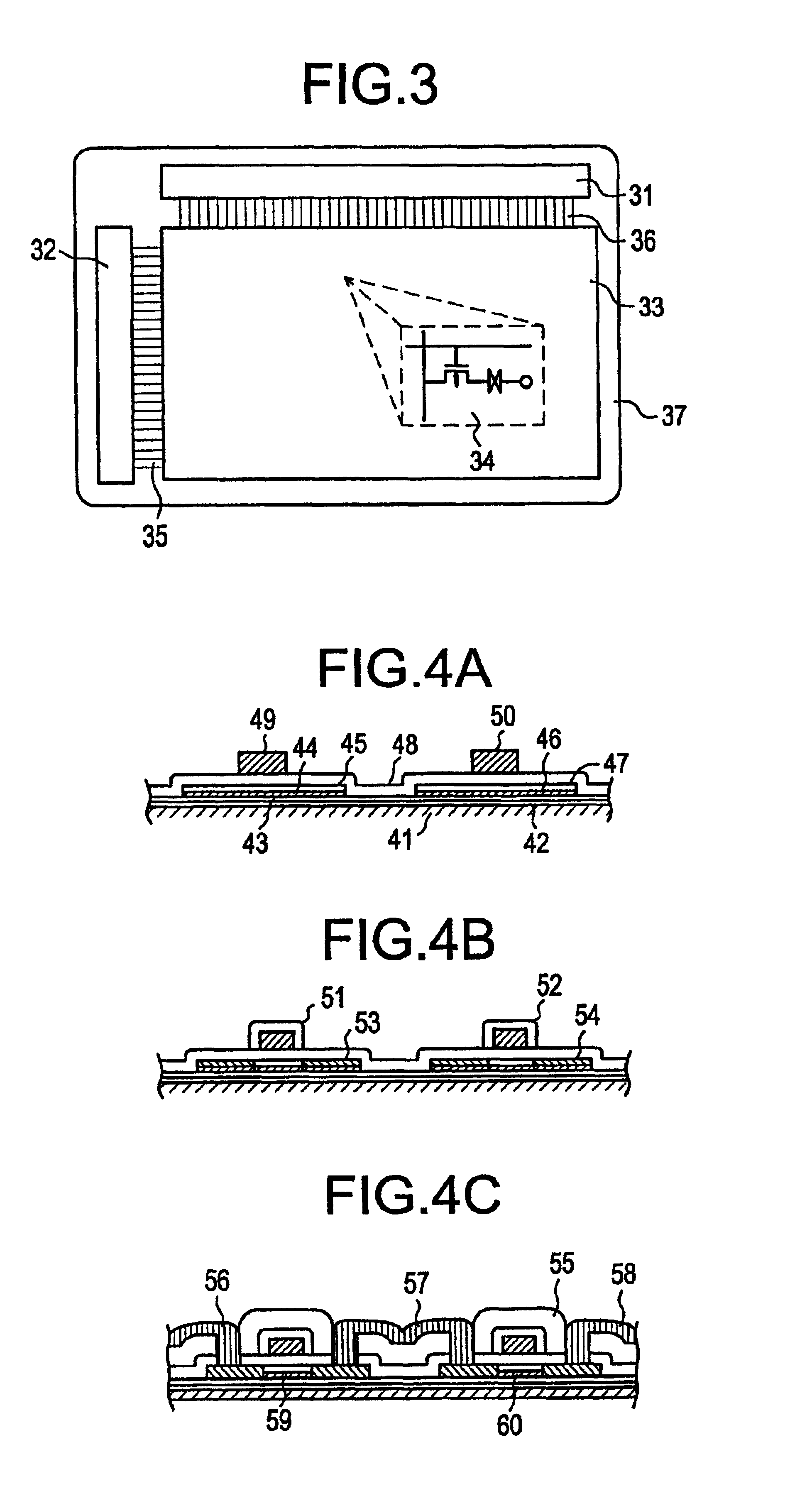

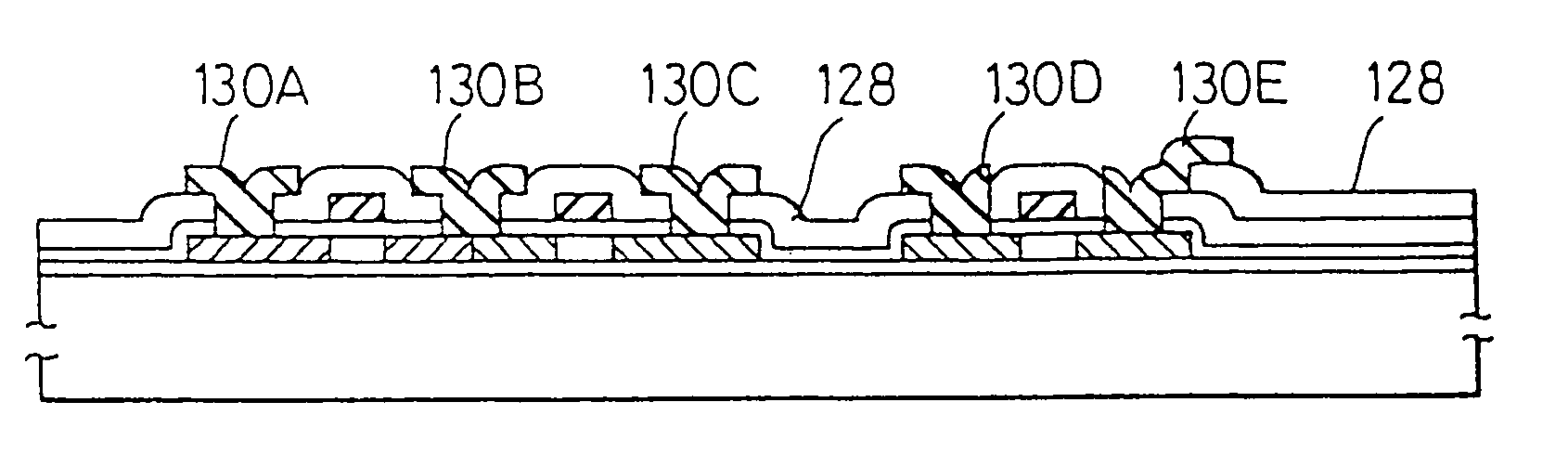

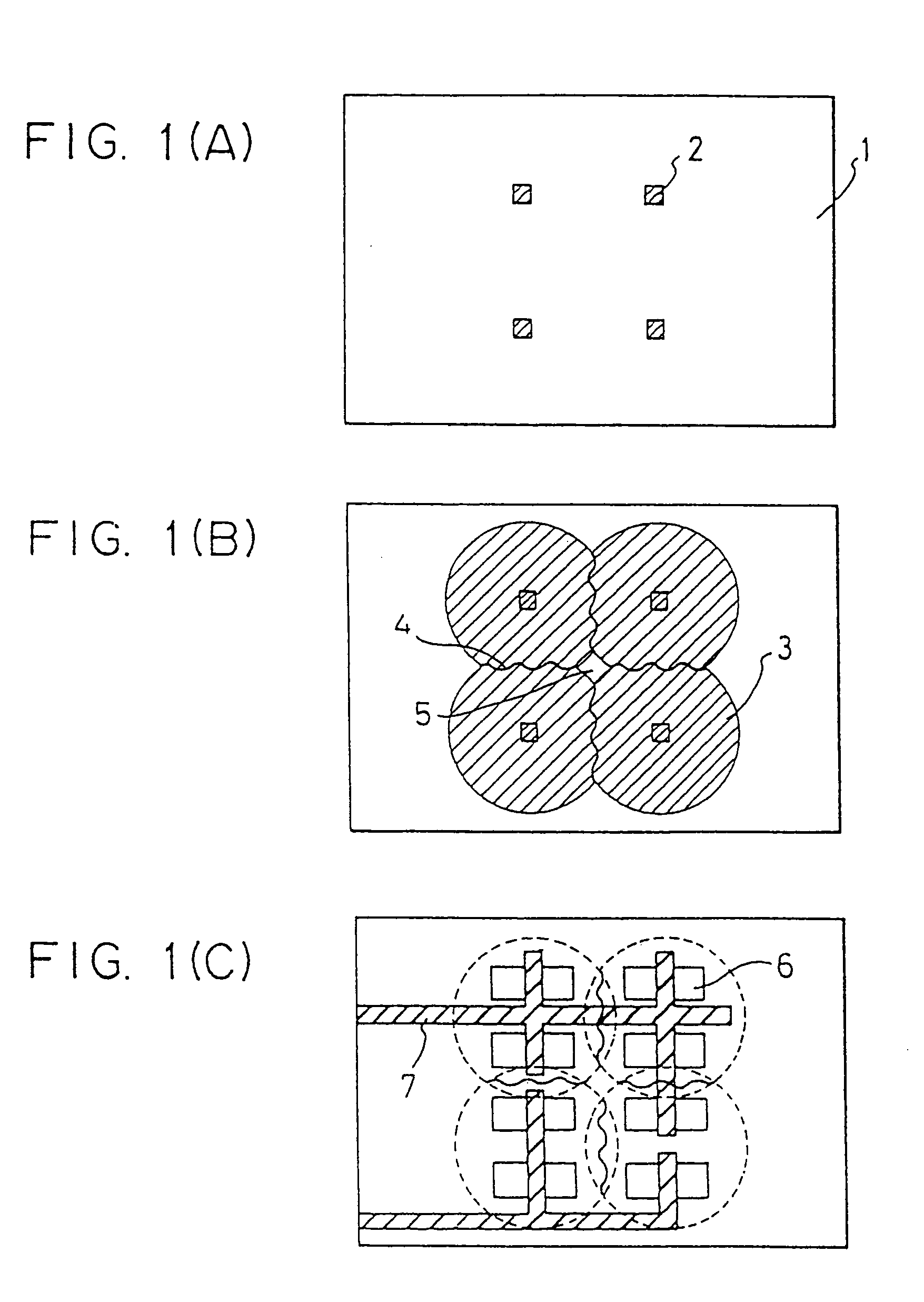

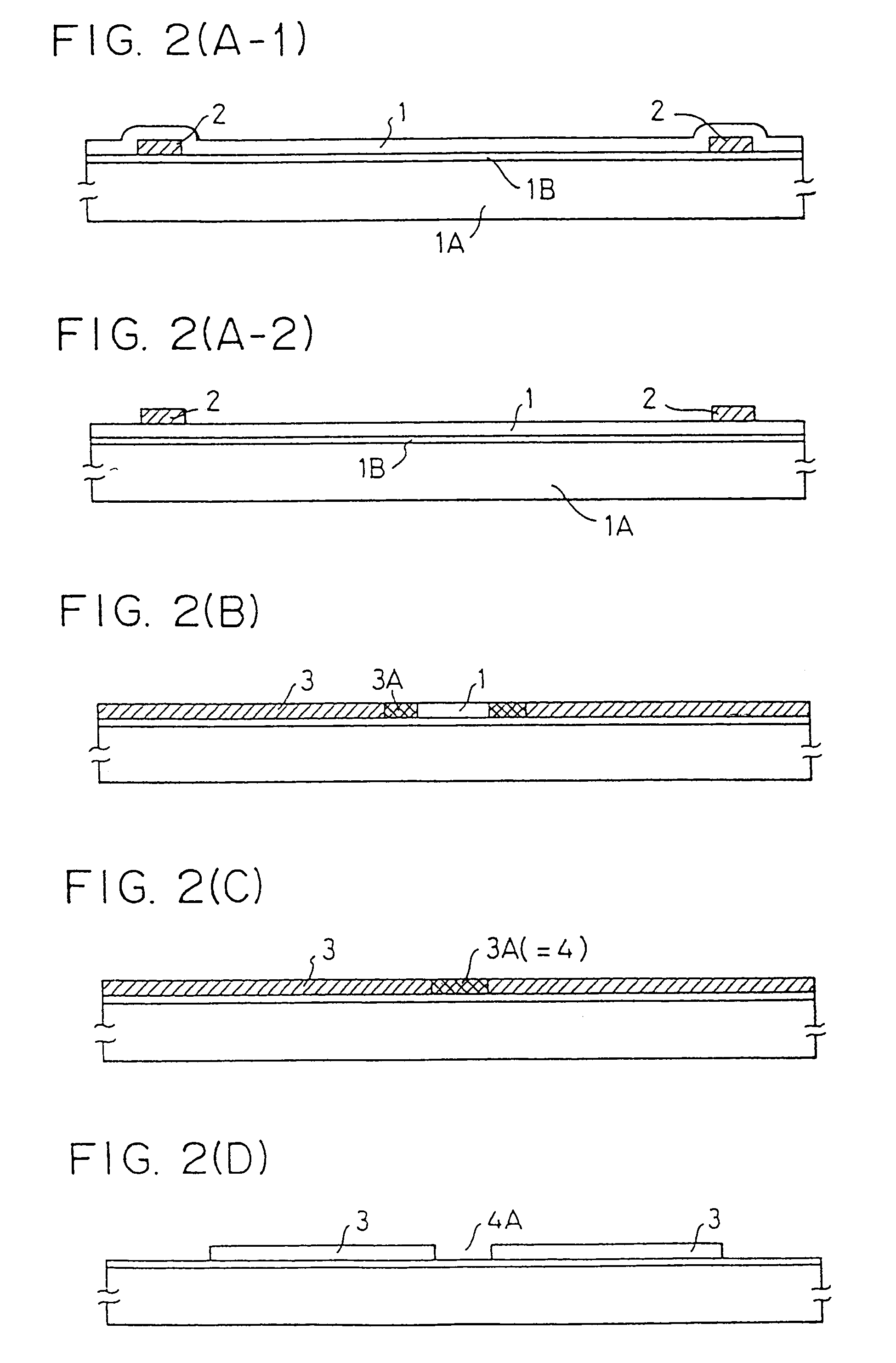

Semiconductor device and method for manufacturing the same

InactiveUS20050020006A1Small amount of resistanceImprove mobilityStatic indicating devicesSolid-state devicesIridiumManganese

A method for manufacturing a semiconductor device such as a thin film transistor using a crystal silicon film is provided. The crystal silicon film is obtained by selectively forming films, particles or clusters containing nickel, iron, cobalt, ruthenium, rhodium, paradium, osmium, iridium, platinum, scandium, titanium, vanadium, chrome, manganese, copper, zinc, gold, silver or silicide thereof in a form of island, line, stripe, dot or film on or under an amorphous silicon film and using them as a starting point, by advancing its crystallization by annealing at a temperature lower than a normal crystallization temperature of an amorphous silicon. A transistor whose leak current is low and a transistor in which a mobility is high are obtained in the same time in structuring a dynamic circuit having a thin film transistor by selectively forming a cover film on a semiconductor layer which is to become an active layer of the transistor and by thermally crystallizing it thereafter.

Owner:SEMICON ENERGY LAB CO LTD

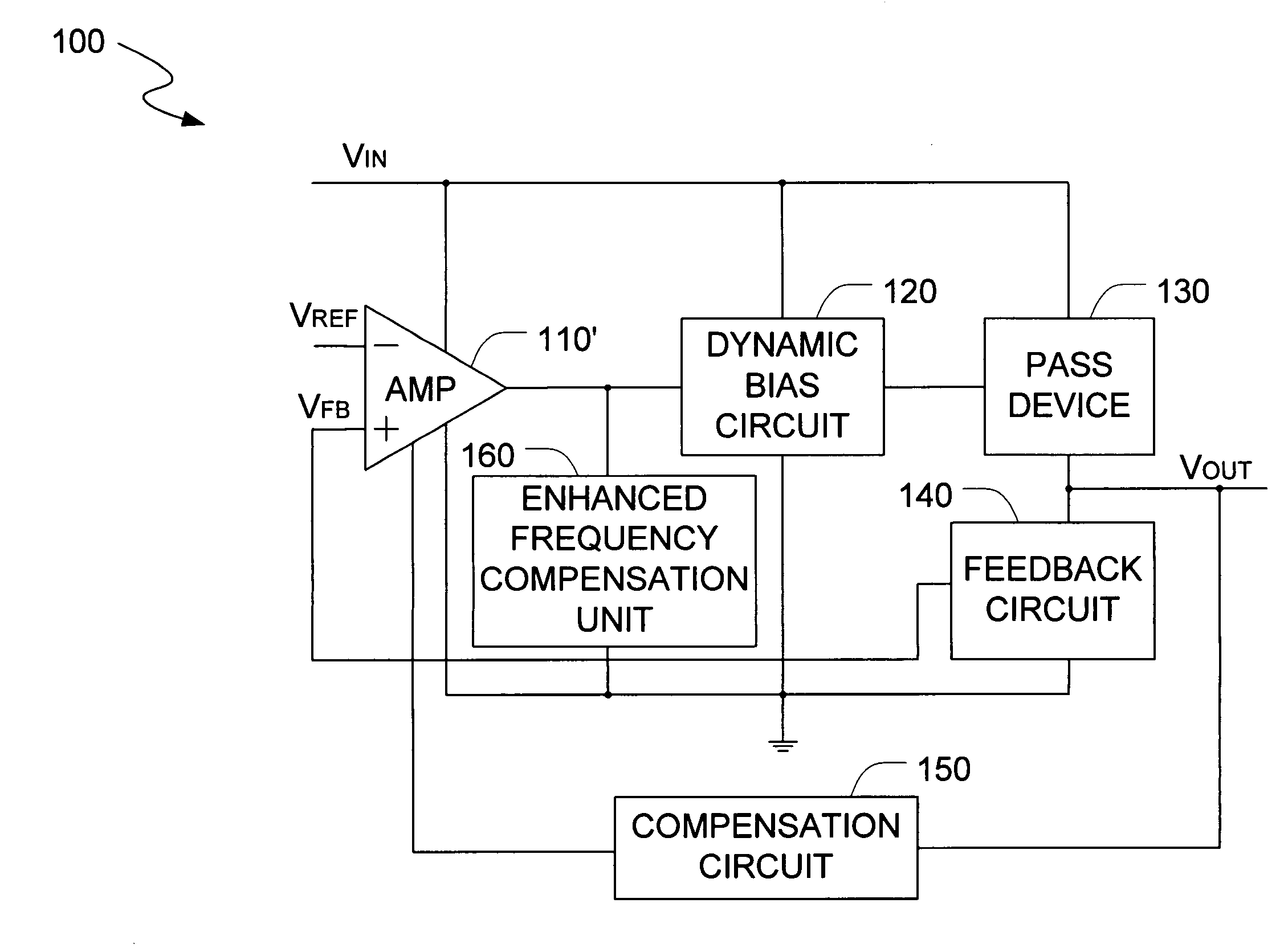

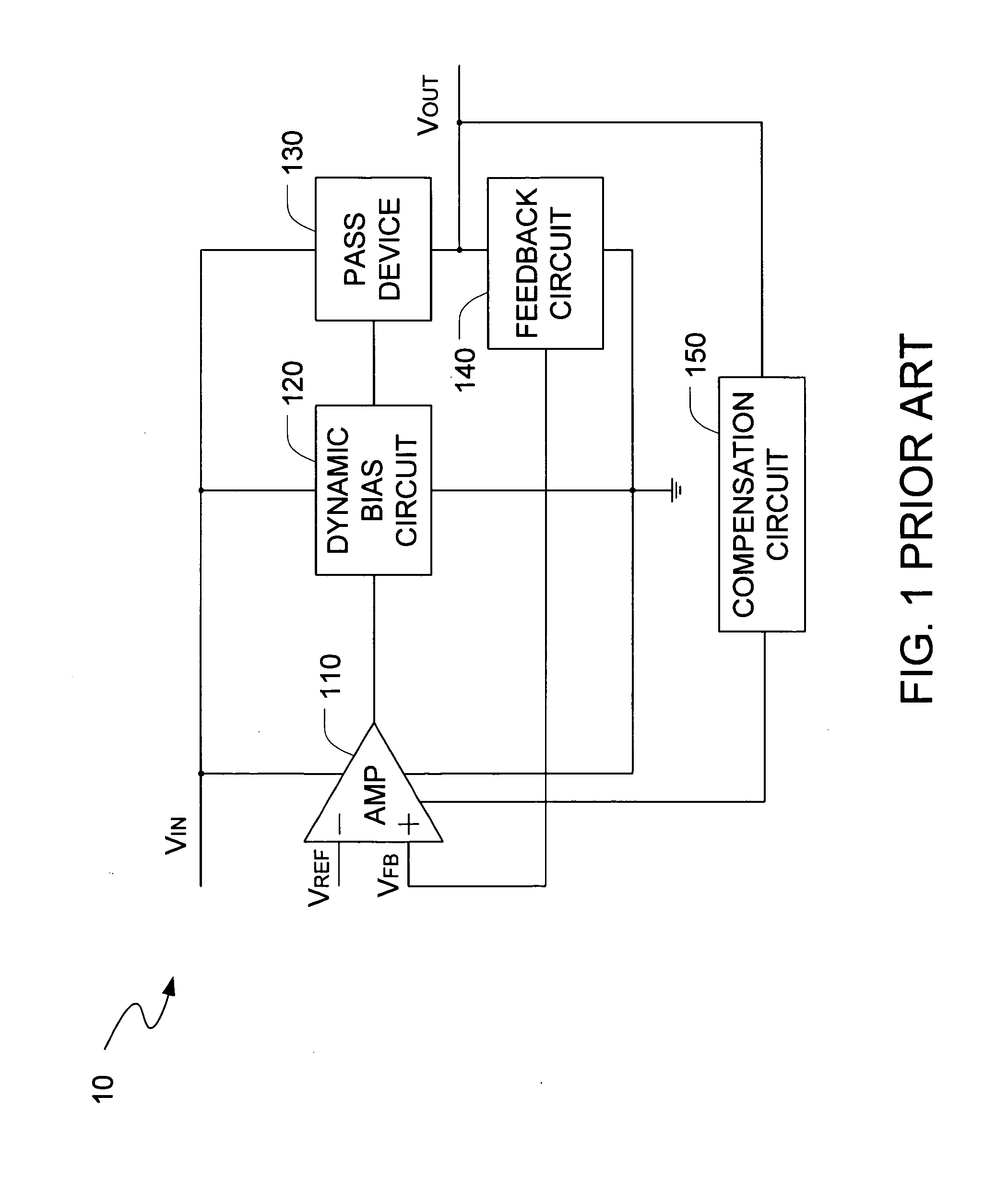

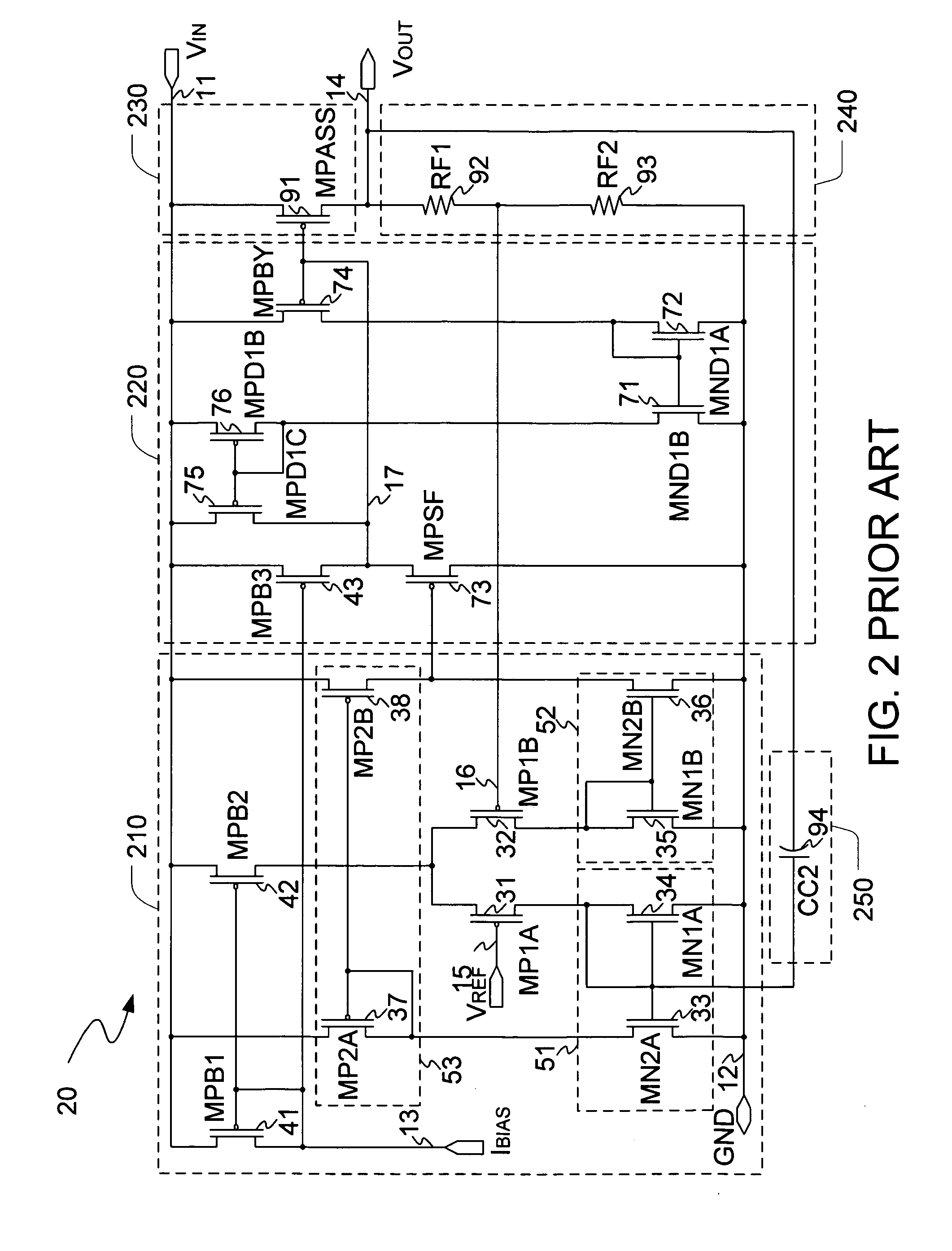

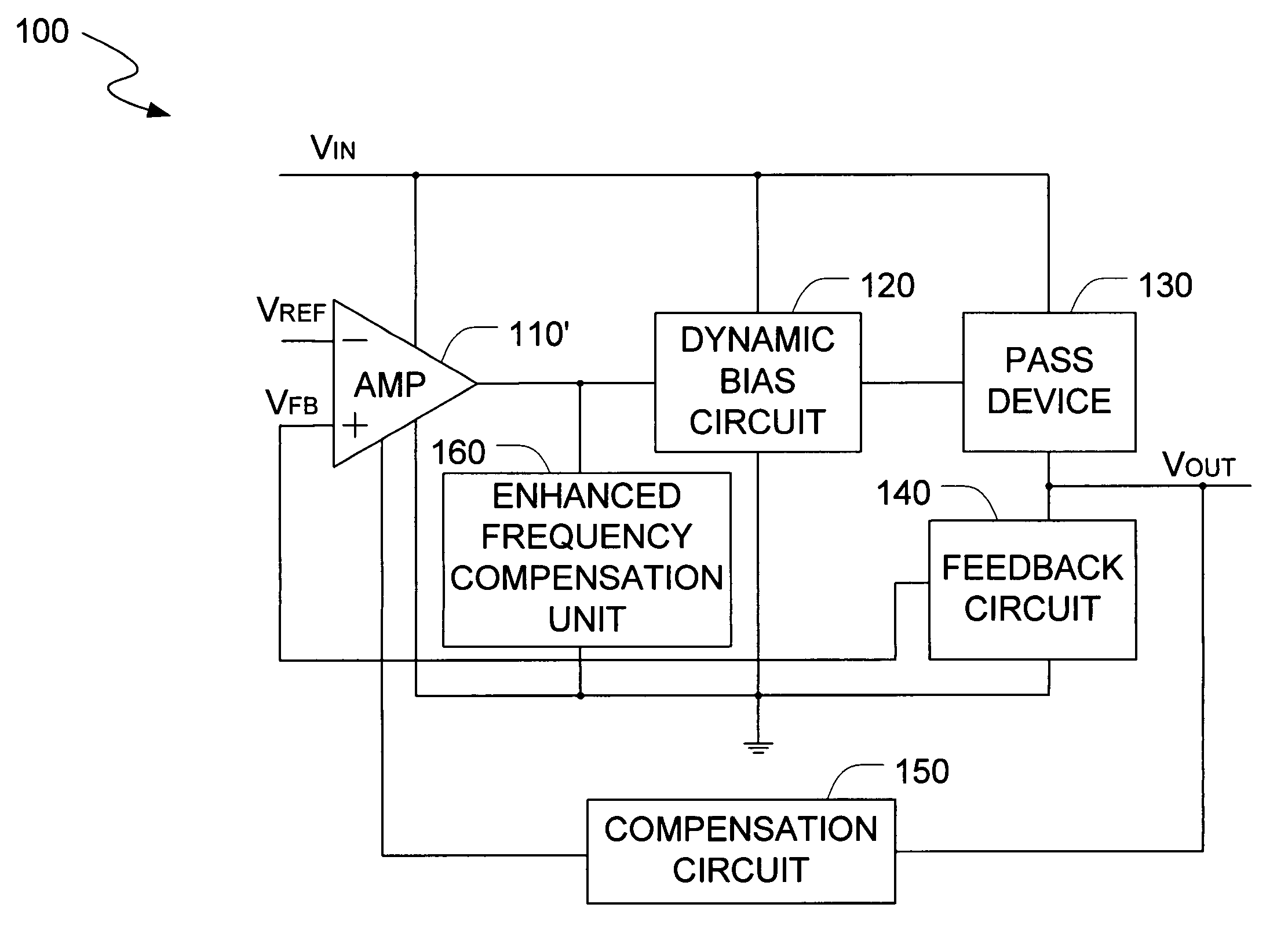

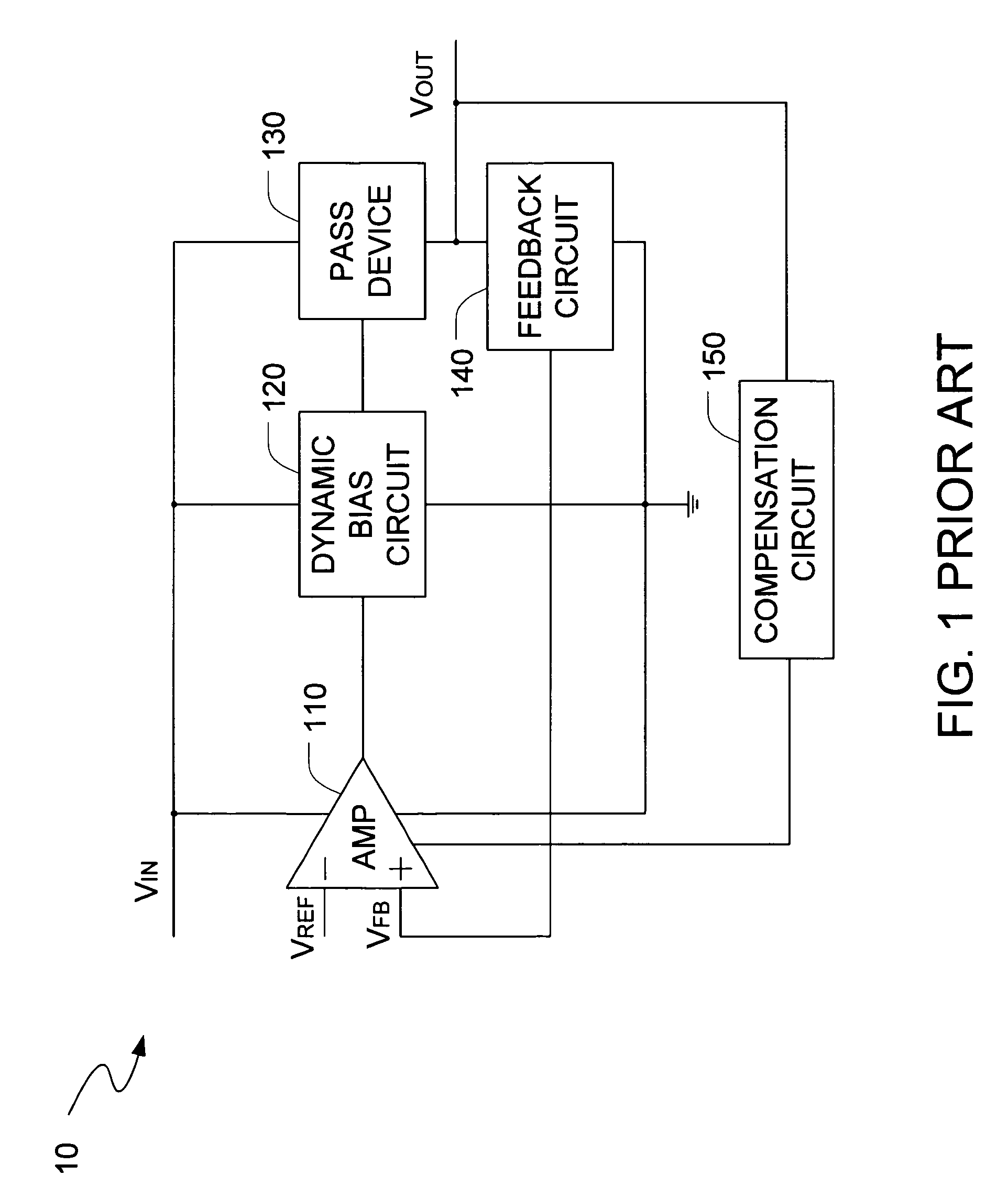

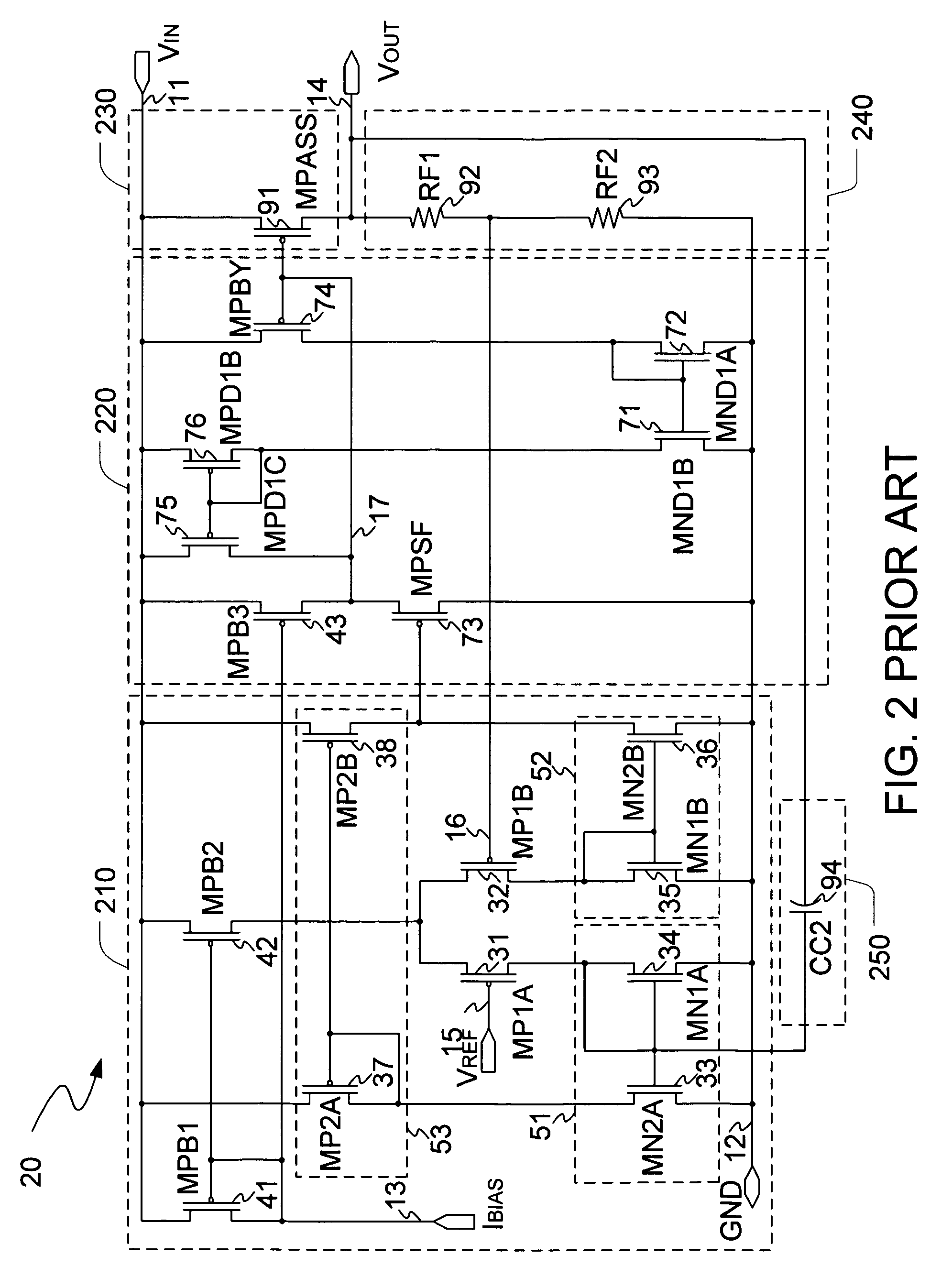

Low drop-out voltage regulator with enhanced frequency compensation

InactiveUS20060192538A1Enhanced frequency compensation capacityIncrease conversion rateElectric variable regulationFrequency compensationAudio power amplifier

The present invention is a voltage regulator circuit with enhanced frequency compensation. The voltage regulator includes an error amplifier, a dynamic bias circuit, an enhanced frequency compensation unit, a pass device and a compensation circuit. A signal from the pass device acts as an input signal of the error amplifier and is compared with another input signal, producing a differential signal. The differential signal is amplified and then provided to the dynamic circuit and the enhanced frequency compensation unit. The enhanced frequency compensation unit is provided such that a zero reference value in a left-hand plane can be generated to optimize the compensation for the voltage regulator circuit. The error amplifier includes a capacitor for compensating an output voltage of the voltage regulator circuit.

Owner:O2 MICRO INT LTD

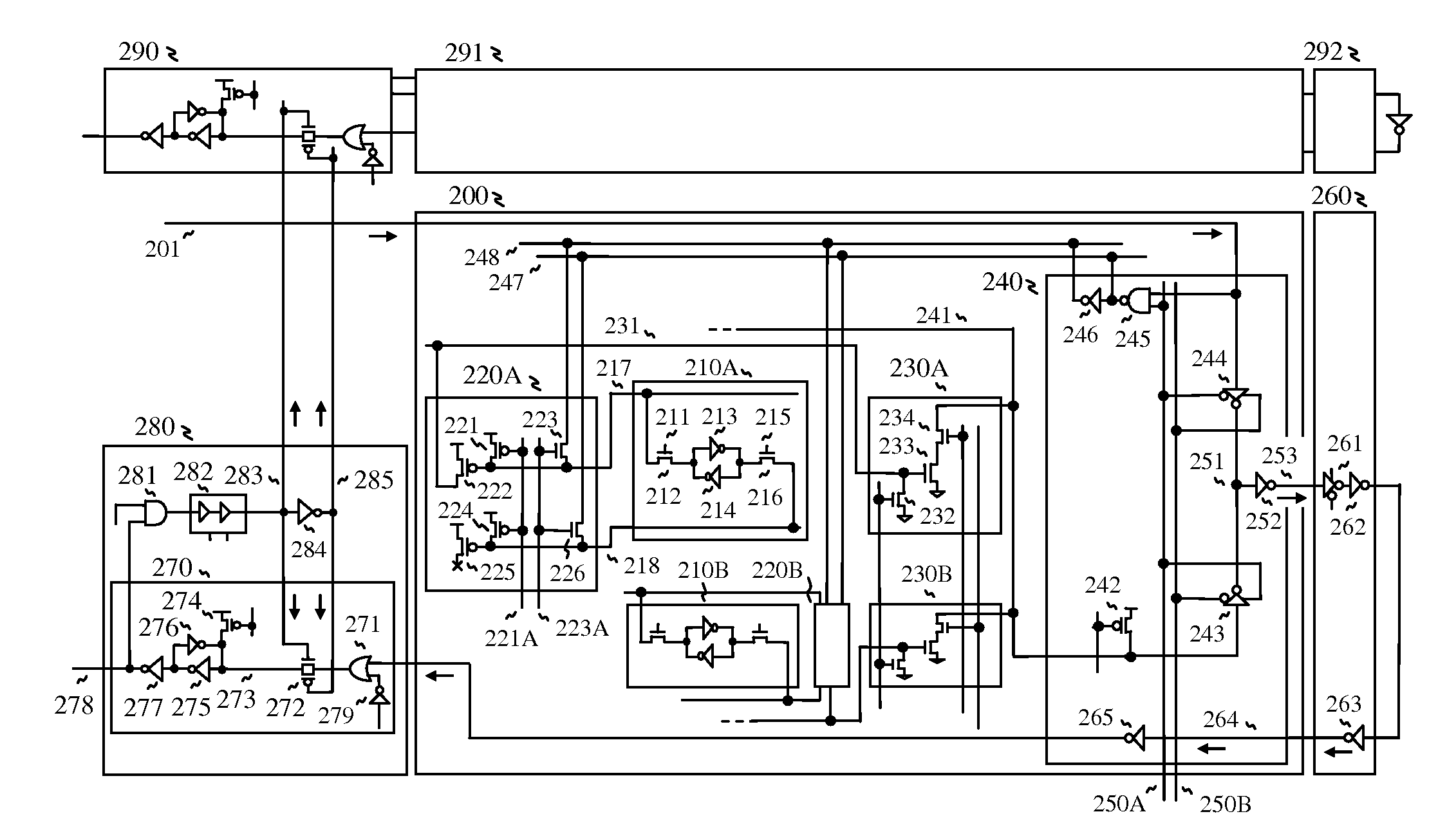

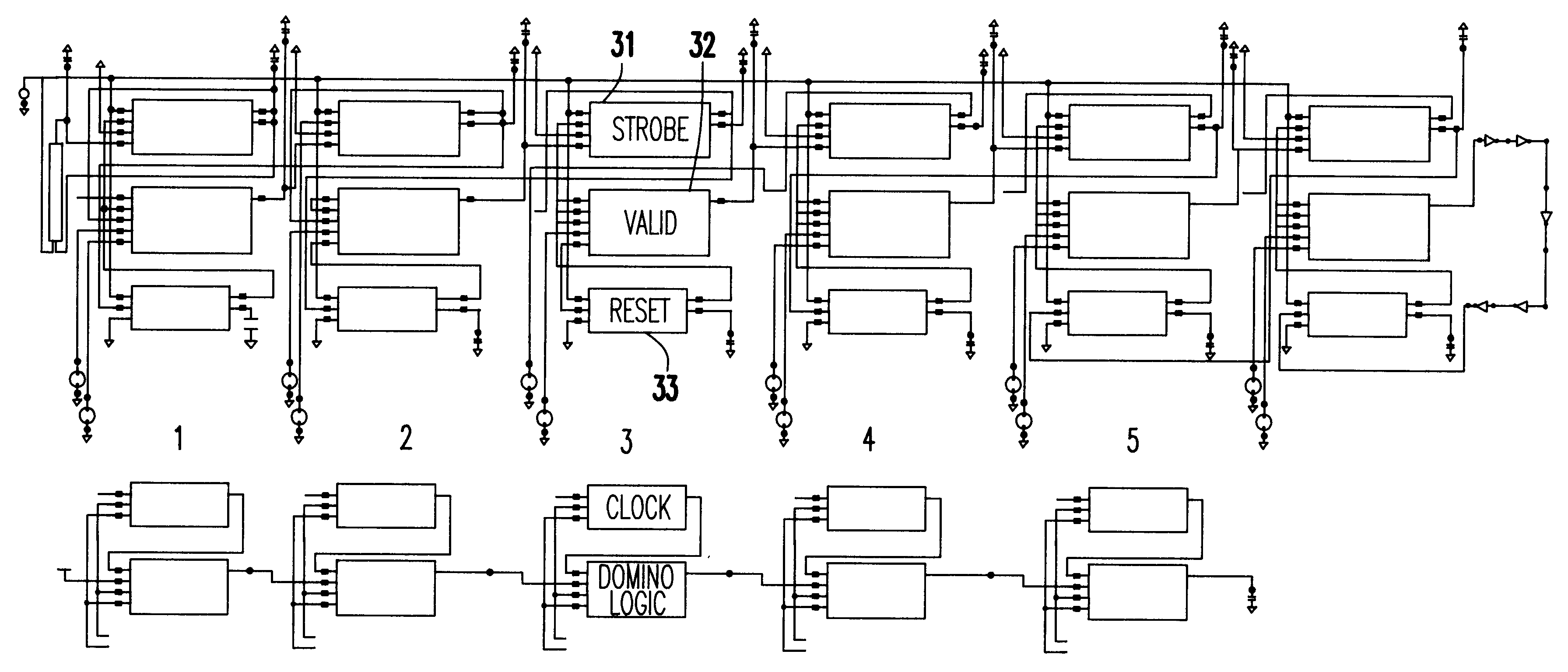

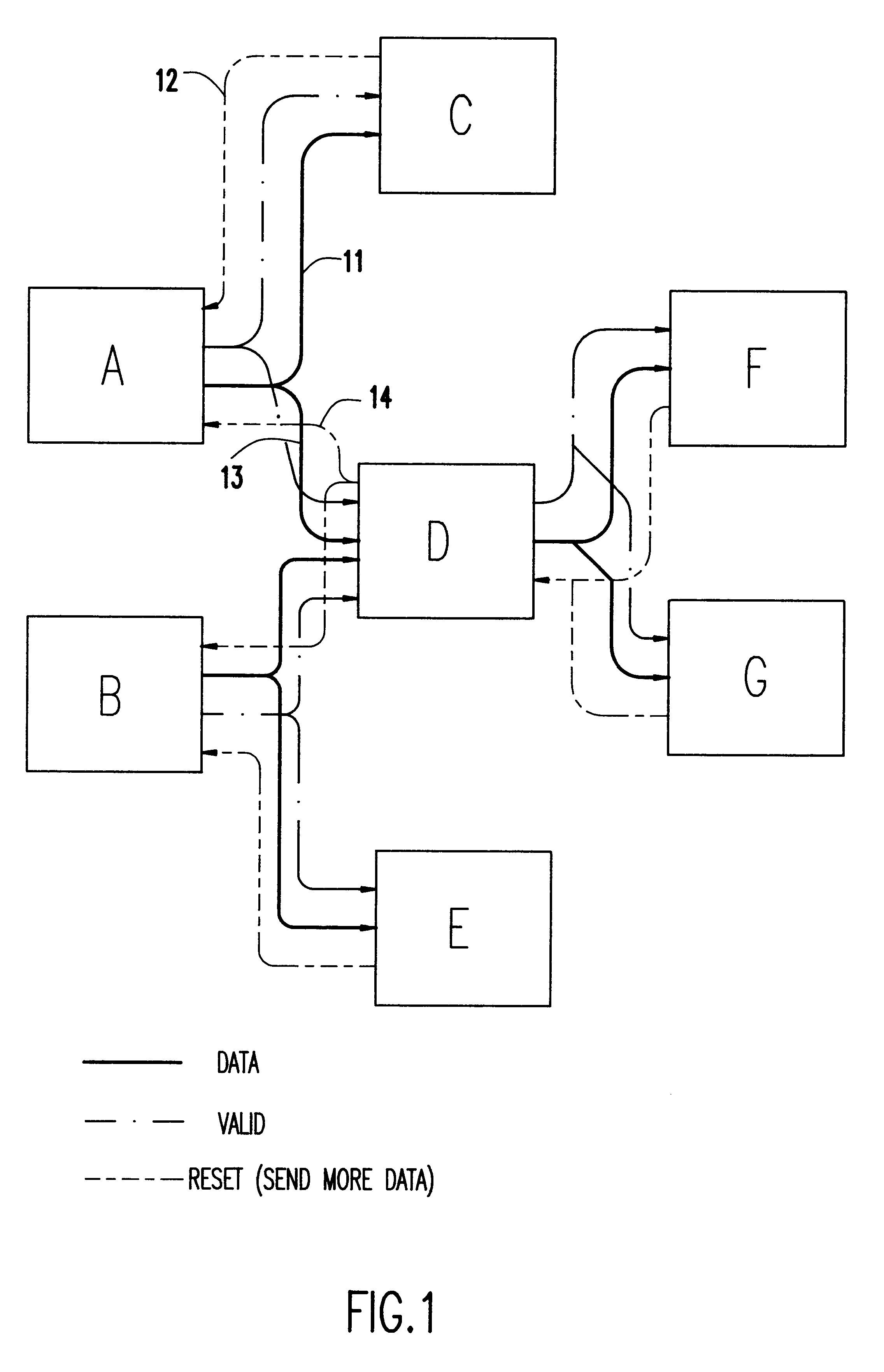

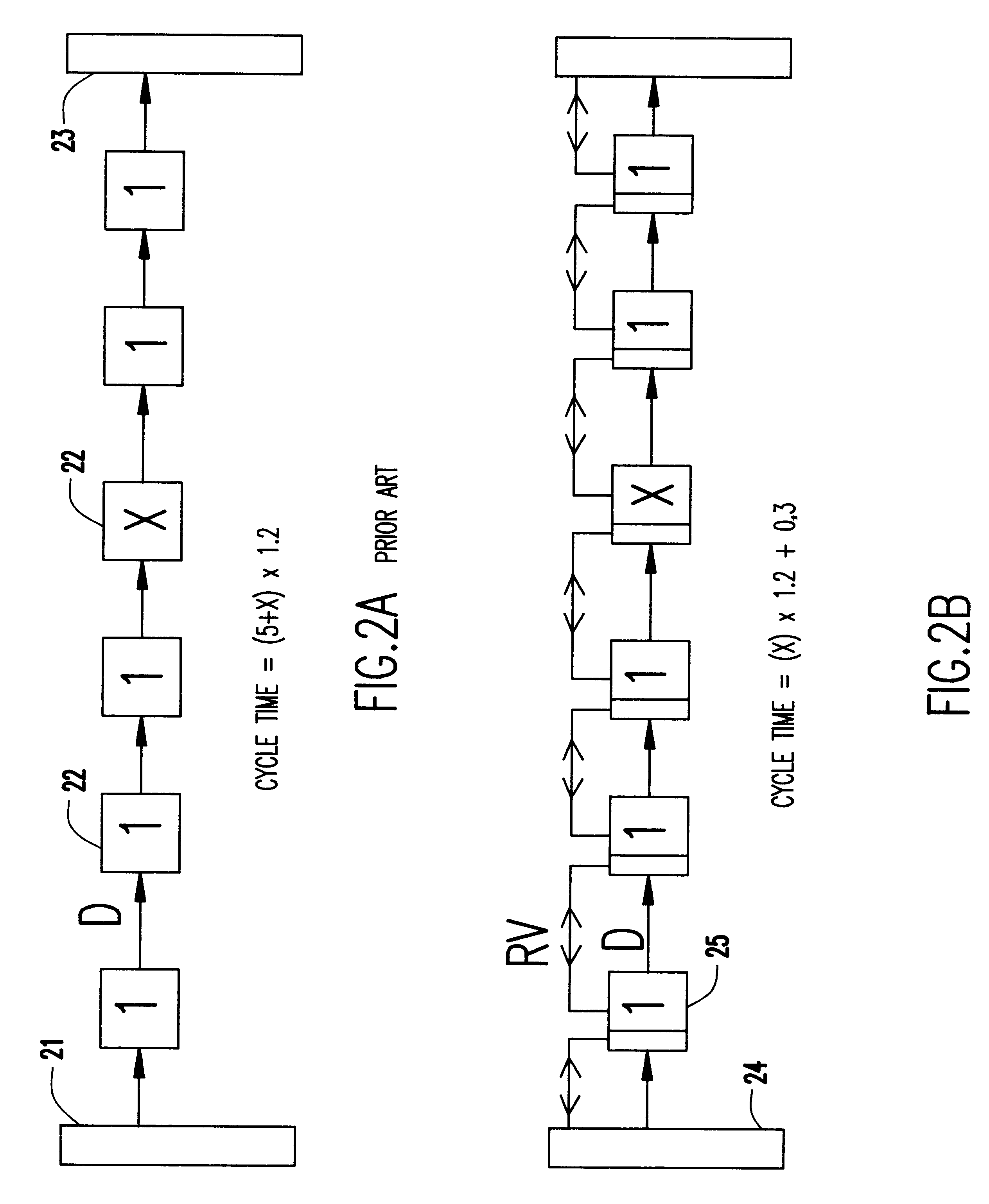

Interlocked pipelined CMOS

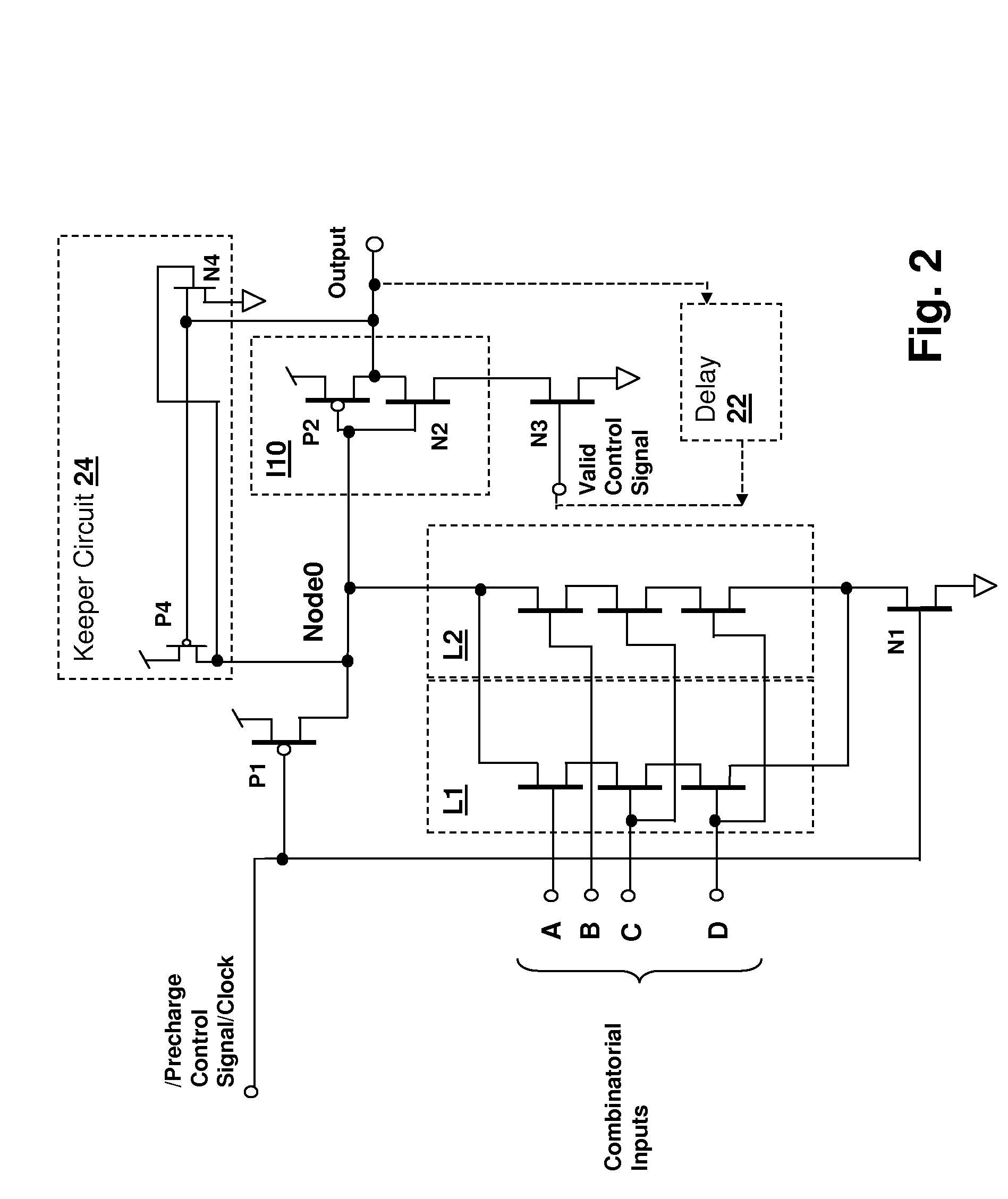

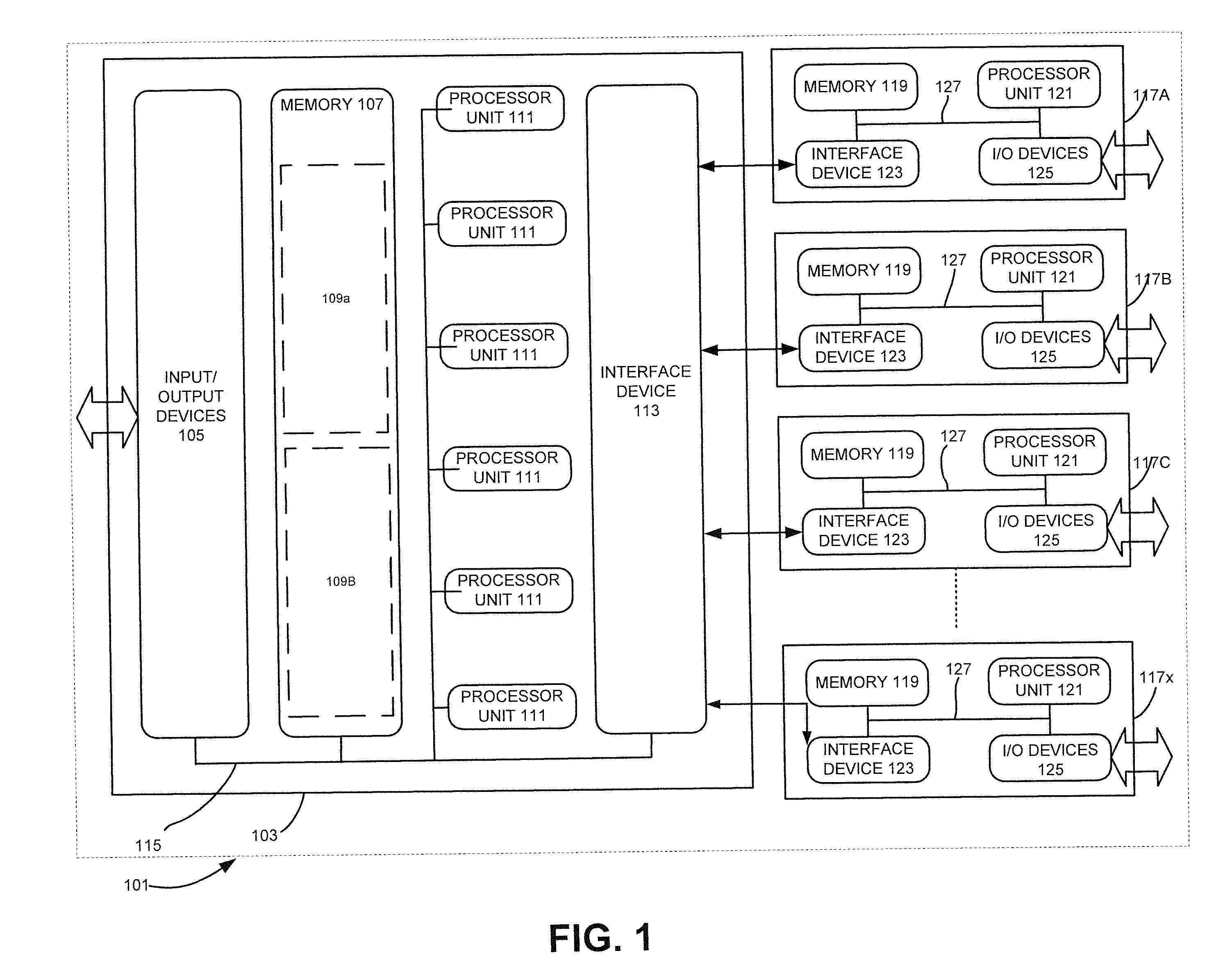

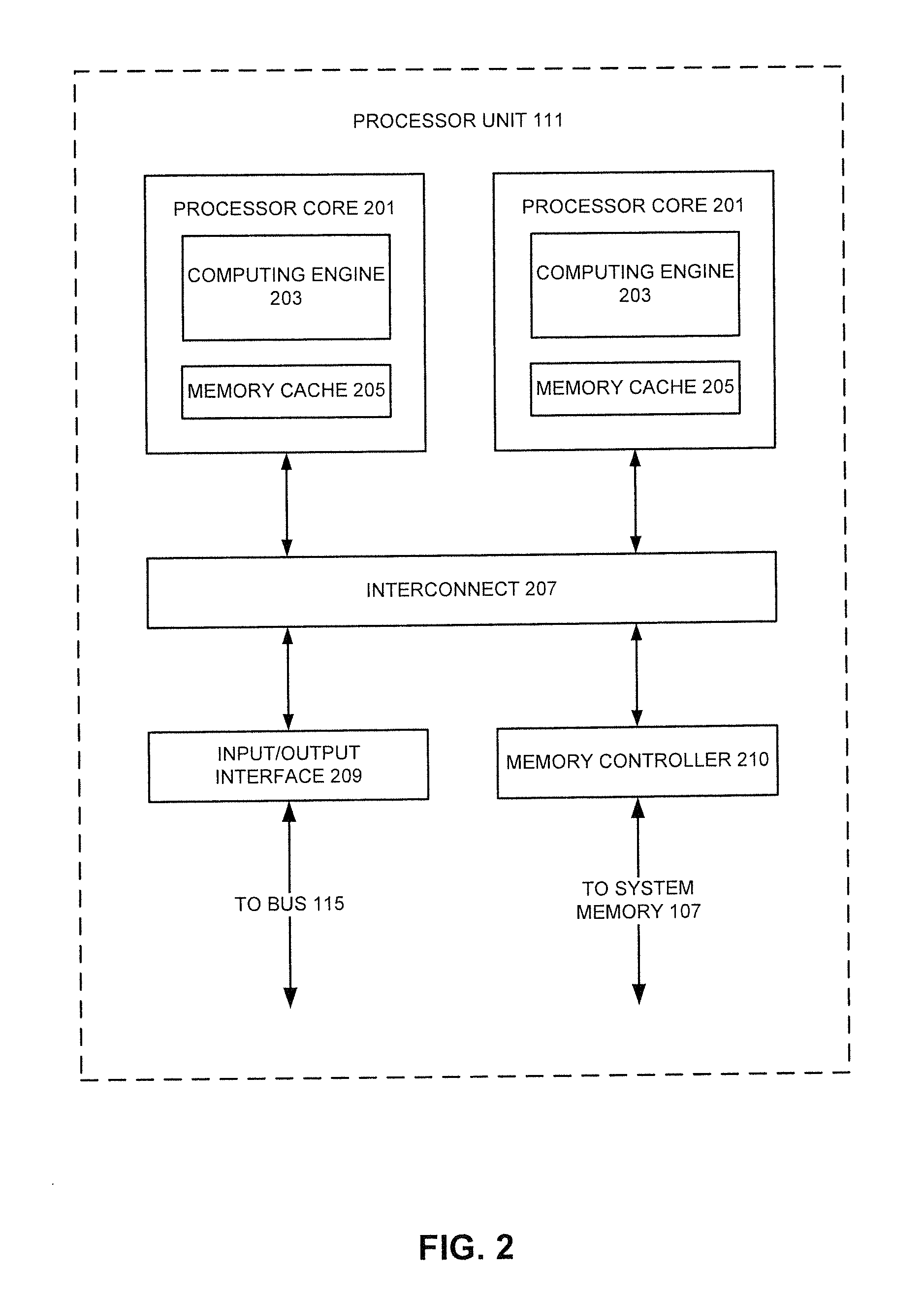

An interlocked pipelined CMOS (IPCMOS) family of logic circuits provides extremely high performance pipelined operation and guarantees error free operation where variations in timing are compensated for automatically by the circuits. The IPCMOS logic circuits also provide a standard interface that makes it possible to interface different macro types easily. The IPCMOS logic circuits feature interlocking in both the forward and reverse directions. This "handshaking" guarantees error free timing and makes it possible to eliminate the need for a global clock at the macro level. Timing signals are generated locally at the macro level from the handshaking signals between macros. This makes it possible for the local circuits to deal with global timing variations caused by power supply noise, ACLV, and parameter variations. The macros operate in a pipelined mode with data advancing automatically from macro to macro with the timing controlled by the local handshaking signals. This pipelined operation results in an extremely fast cycle time. Another feature of IPCMOS is that the data inputs to a macro are only sampled when the data is in a valid state. making the concept of a standard macro interface possible. With this standard interface, different logic types such as static and dynamic circuits can be easily interconnected and the concept of reusable macros becomes a reality.

Owner:IBM CORP

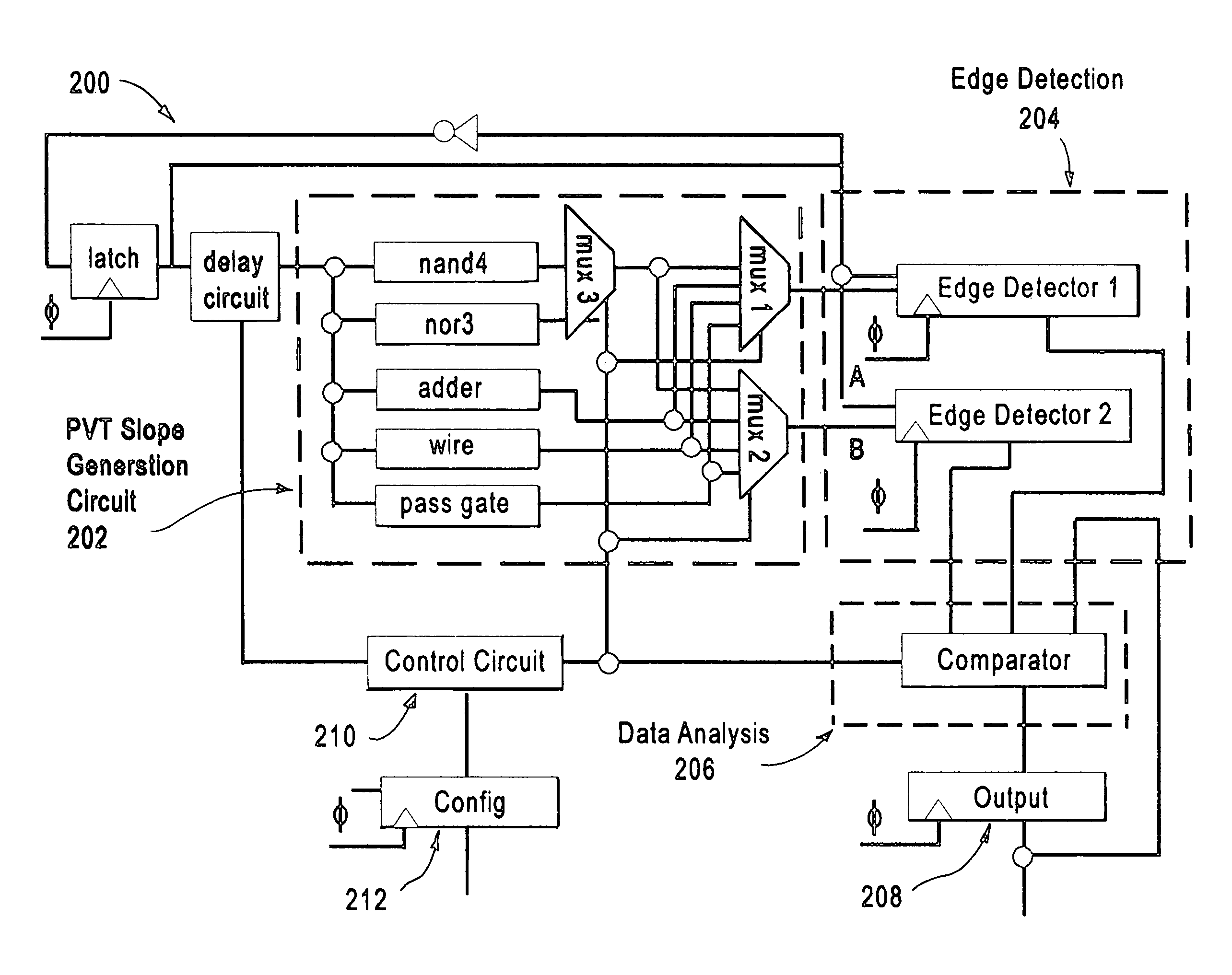

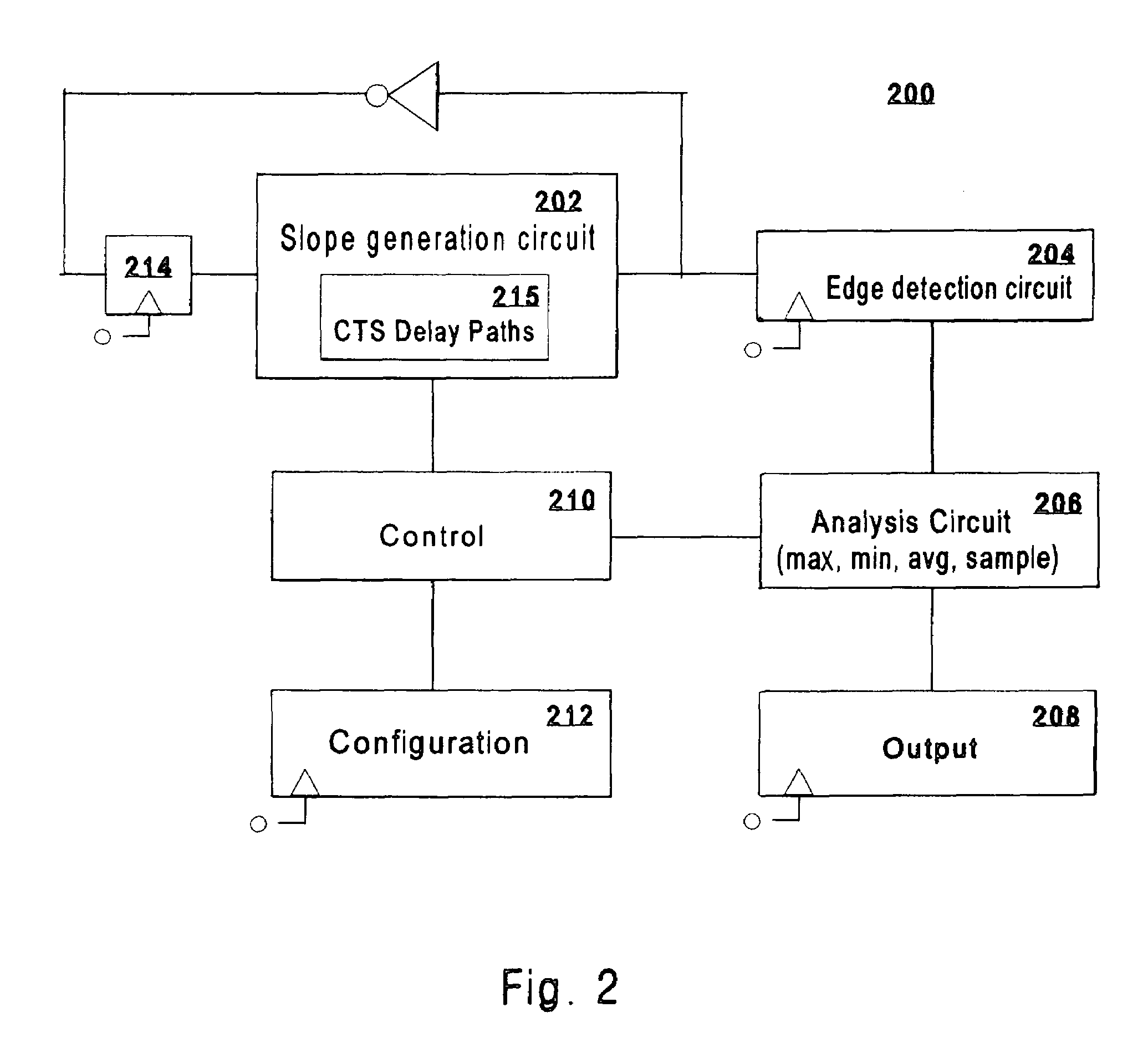

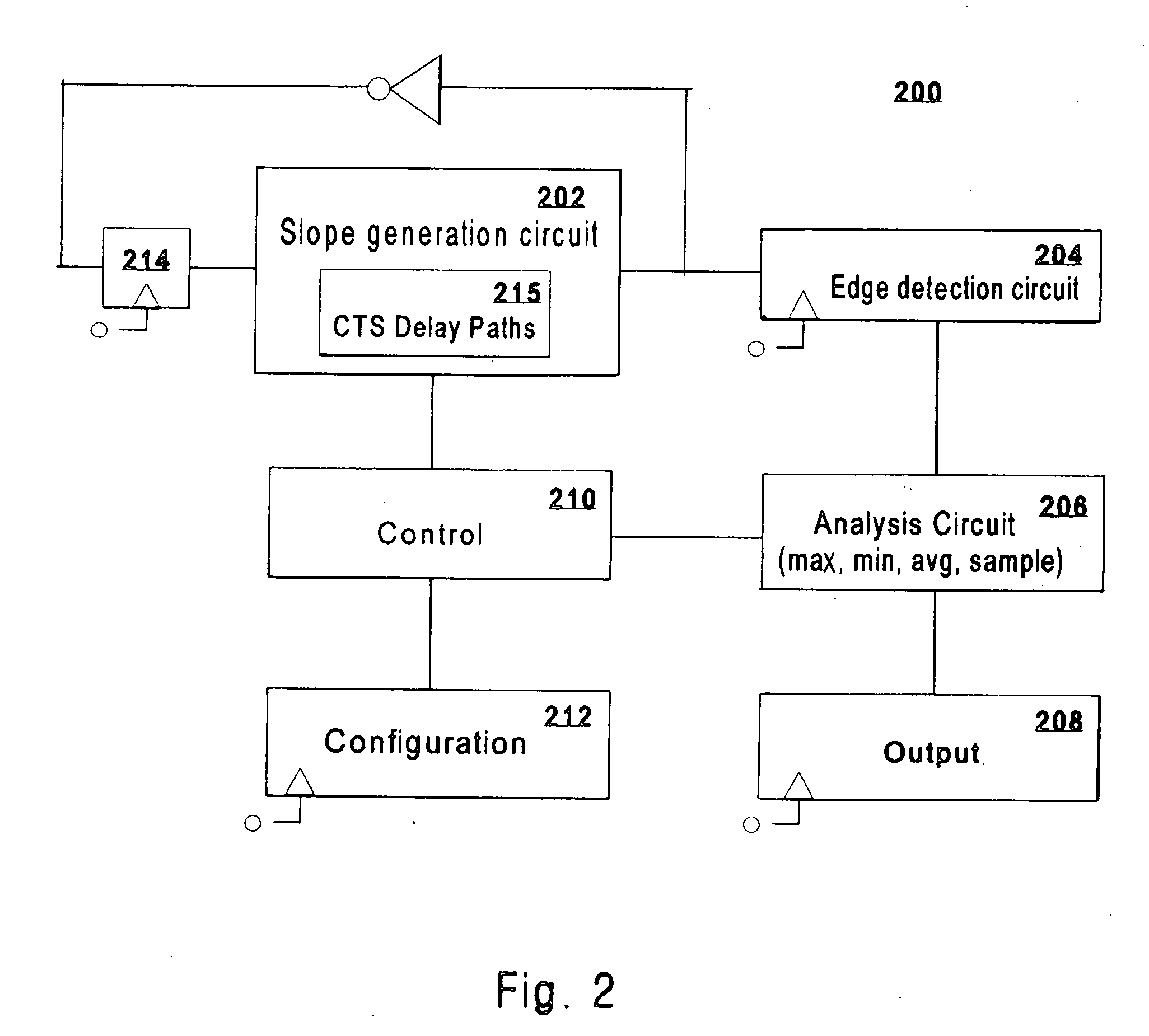

Circuit for dynamic circuit timing synthesis and monitoring of critical paths and environmental conditions of an integrated circuit

InactiveUS7576569B2Multiple input and output pulse circuitsPulse characteristics measurementsEngineeringCritical path method

A circuit for dynamically monitoring the operation of an integrated circuit under differing temperature, frequency, and voltage (including localized noise and droop), and for detecting early life wear-out mechanisms (e.g., NBTI, hot electrons).

Owner:INT BUSINESS MASCH CORP

Current mirror based multi-channel leakage current monitor circuit and method

A current mirror multi-channel leakage monitor circuit and method measures die leakage and generates digital keeper control bits to control a process compensated dynamic circuit. The leakage monitor enables high resolution on-chip leakage measurements in multiple locations on a die, thereby saving test time and enabling both die to die and within die process compensation.

Owner:INTEL CORP

Electric device, matrix device, electro-optical display device and semiconductor memory having thin-film transistors

InactiveUS6953713B2Increase currentGood reproducibilityTransistorStatic indicating devicesCMOSDevice material

Owner:SEMICON ENERGY LAB CO LTD

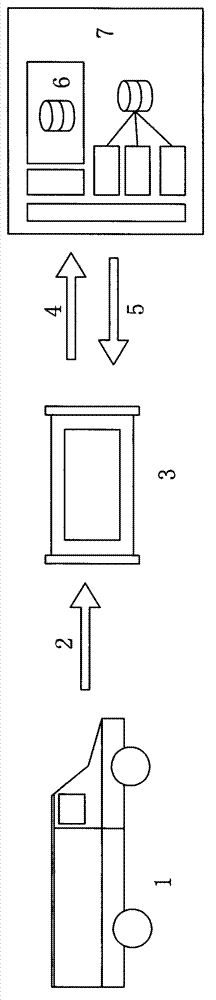

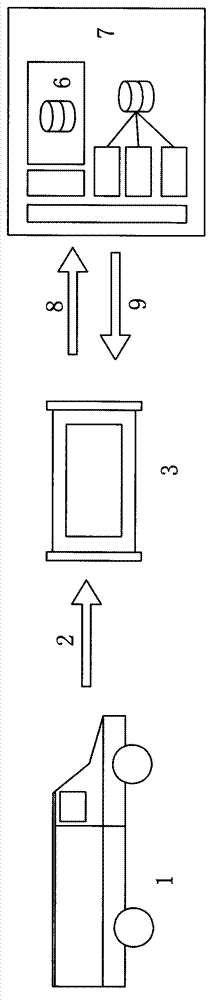

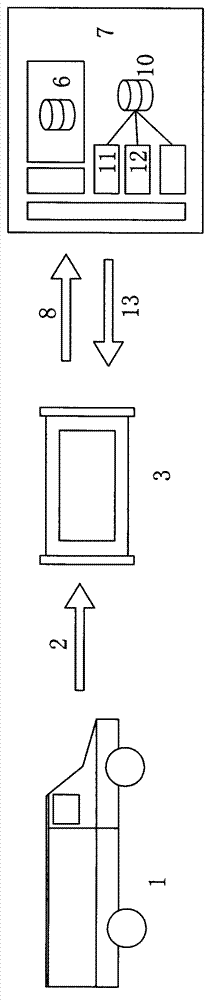

Maintenance information and expert system-based automobile failure diagnosis method

InactiveCN103048989AImprove work efficiencyImprove accuracyElectric testing/monitoringData synchronizationDynamic data

The invention discloses a maintenance information and expert system-based automobile failure diagnosis method, which comprises the following steps of: (1) establishing an internet-based automobile maintenance information database; (2) simultaneously establishing an expert system on a network server; (3) performing an initialization stage, i.e., performing a data synchronization stage of an automobile failure diagnostic apparatus and the maintenance information database; (4) performing a data fusion display stage; and (5) performing an intelligent failure judgment stage. The maintenance information and expert system-based automobile failure diagnosis method has the beneficial effects that maintenance information data is synchronously displayed when an automobile is tested by using the automobile failure diagnostic apparatus, so that query of the maintenance information data is facilitated, meanwhile, effects such as a dynamic data list and a dynamic circuit diagram can be realized through data fusion, and the user experience is enhanced; and in addition, judgment of experiment level can be provided during automobile failure diagnosis, so that the working efficiency and the precision of automobile diagnosis are improved.

Owner:王志欣

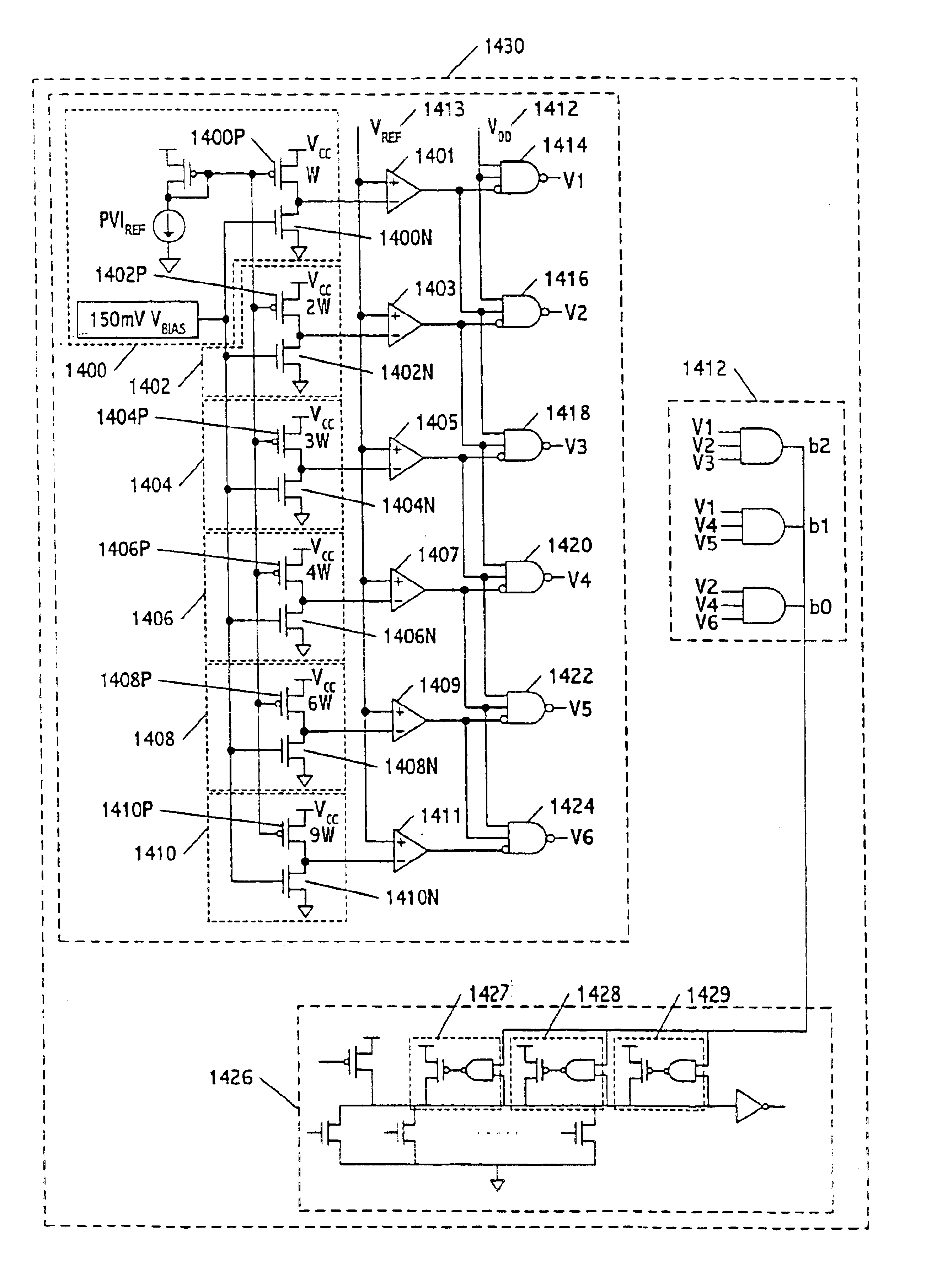

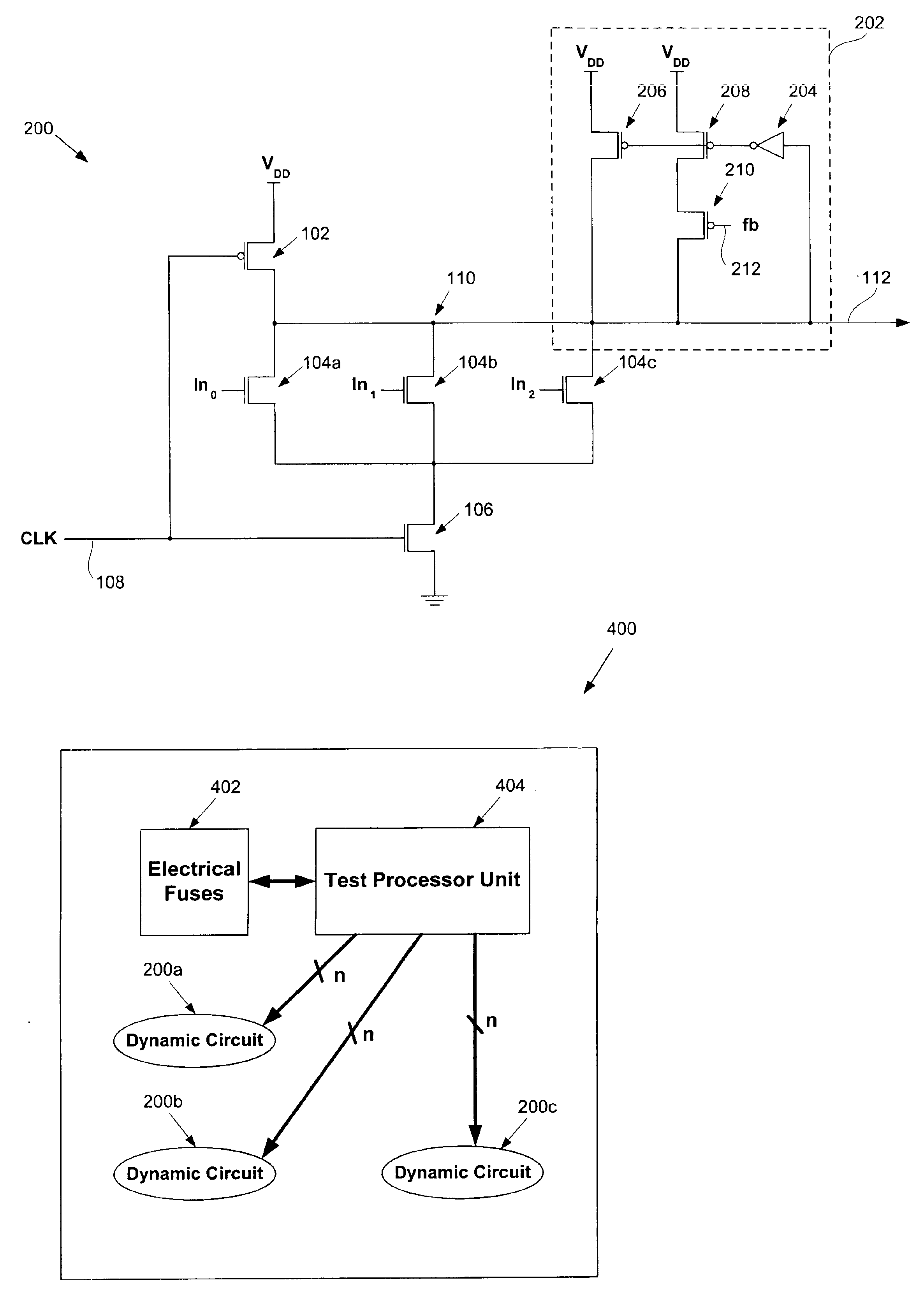

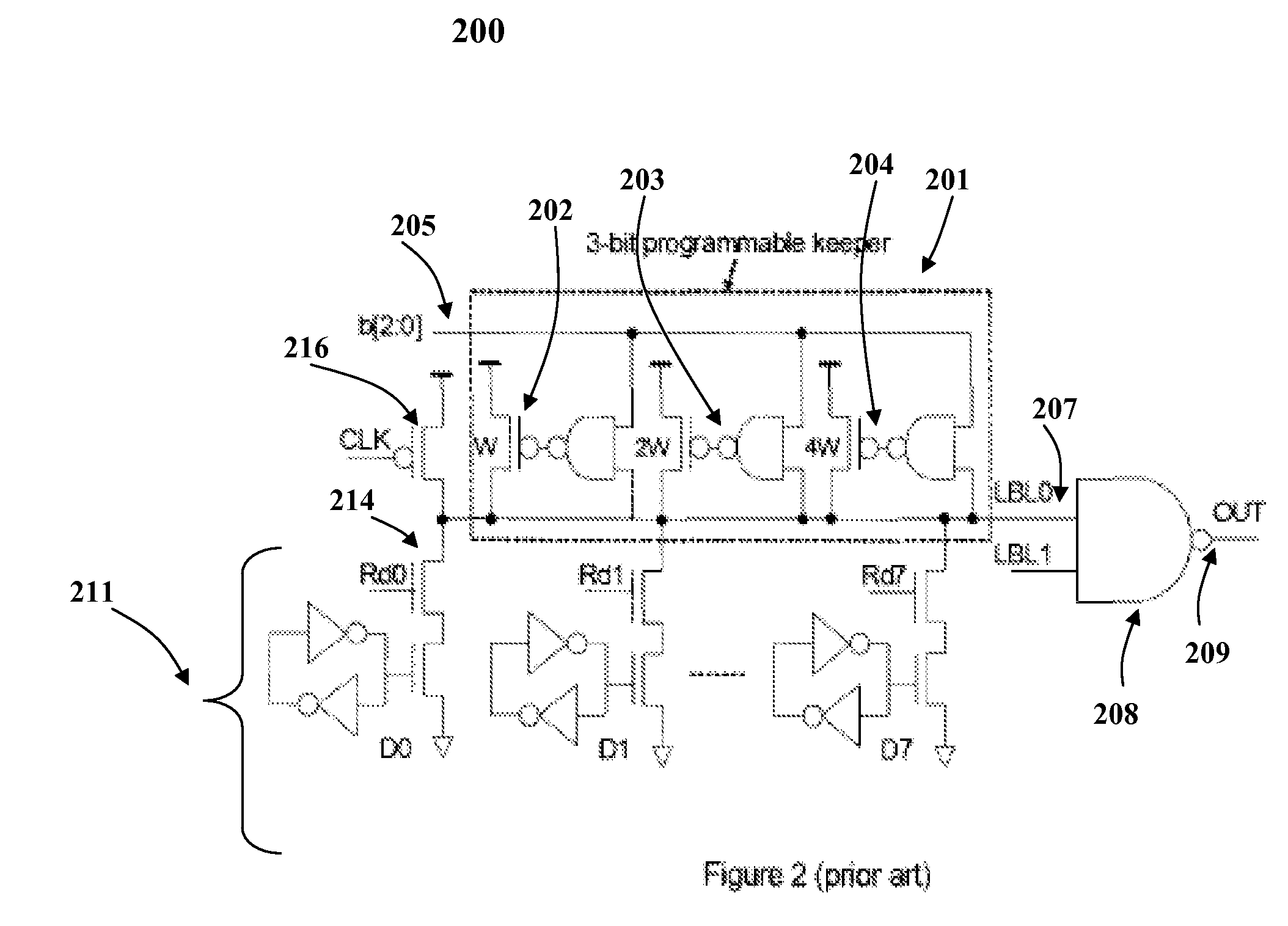

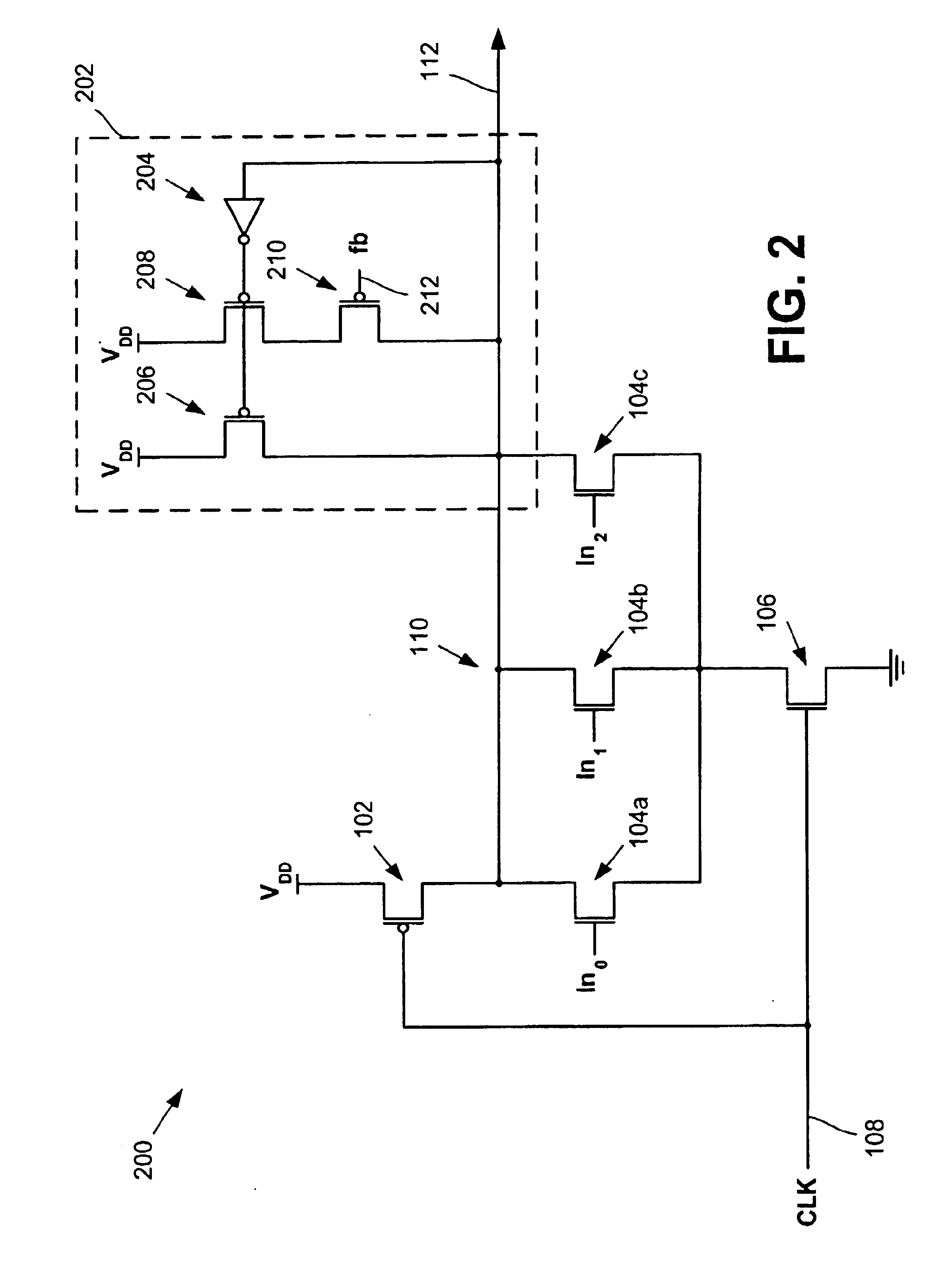

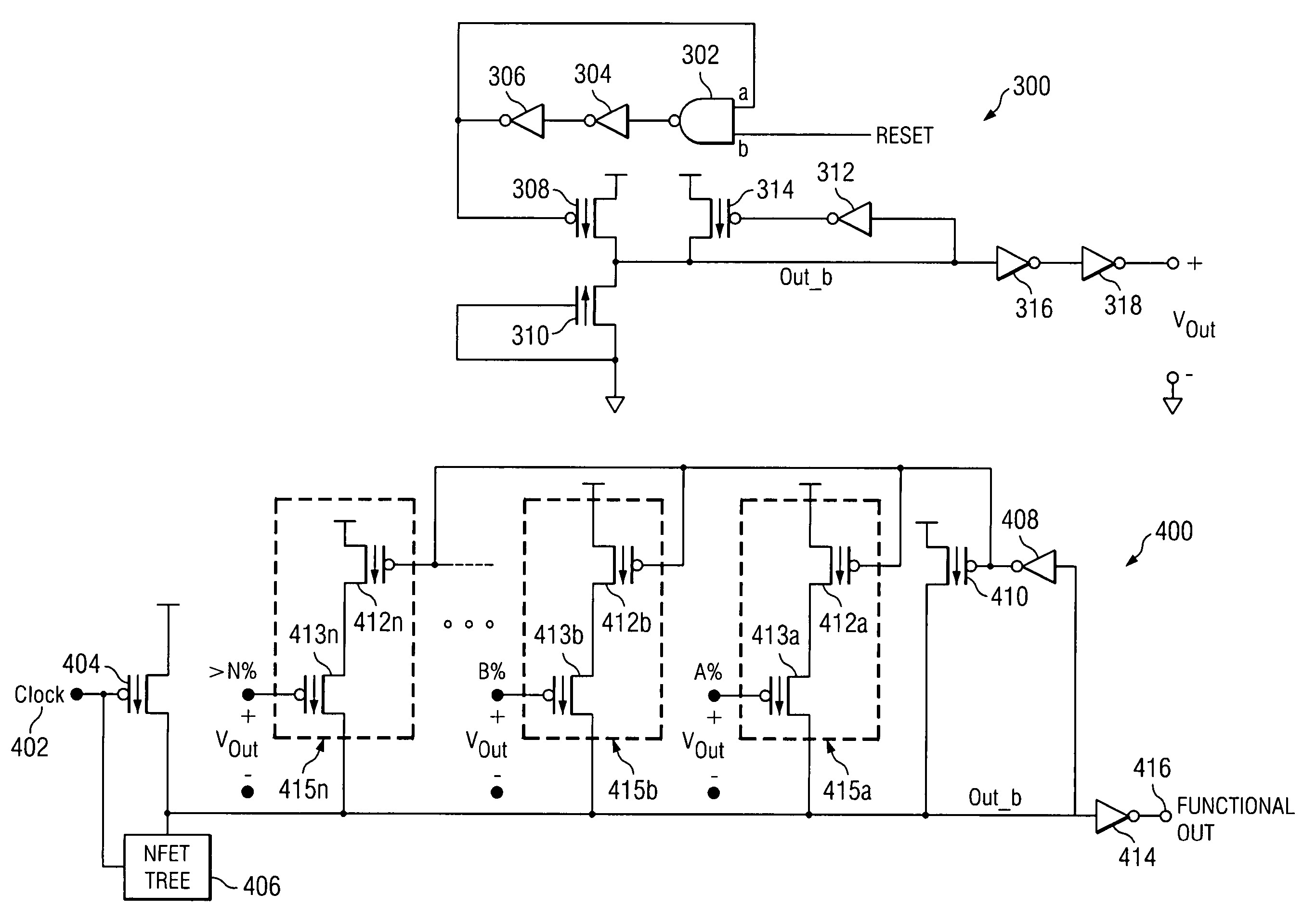

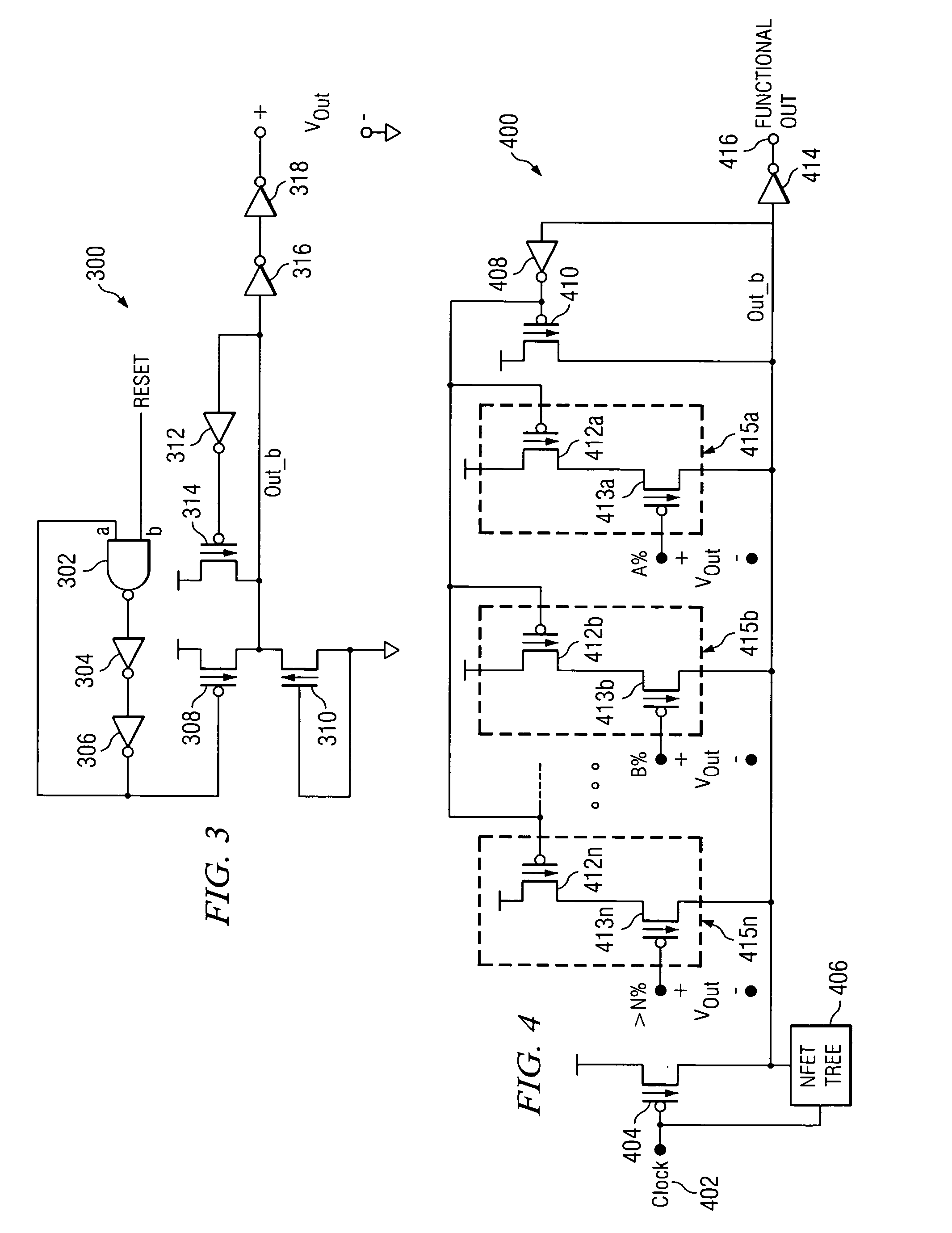

Adaptive keeper sizing for dynamic circuits based on fused process corner data

An invention is provided for an adaptive keeper circuit. The adaptive keeper circuit includes a first keeper transistor having a first terminal in electrical communication with a power supply and a second terminal in electrical communication with an internal dynamic node. In addition, a second keeper transistor is included that is configured in parallel to the first keeper transistor. The second keeper transistor also has a first terminal in electrical communication with the power supply. The second keeper transistor can be added to the first keeper transistor using a feedback bit line, which is configured to control current flow between the second keeper transistor and the internal dynamic node based on a state of the feedback bit line. The state of the feedback bit line is based on a process corner characteristic of the die. Additional keeper transistors and corresponding feedback bit lines can be added to the keeper circuit to increase flexibility.

Owner:ORACLE INT CORP

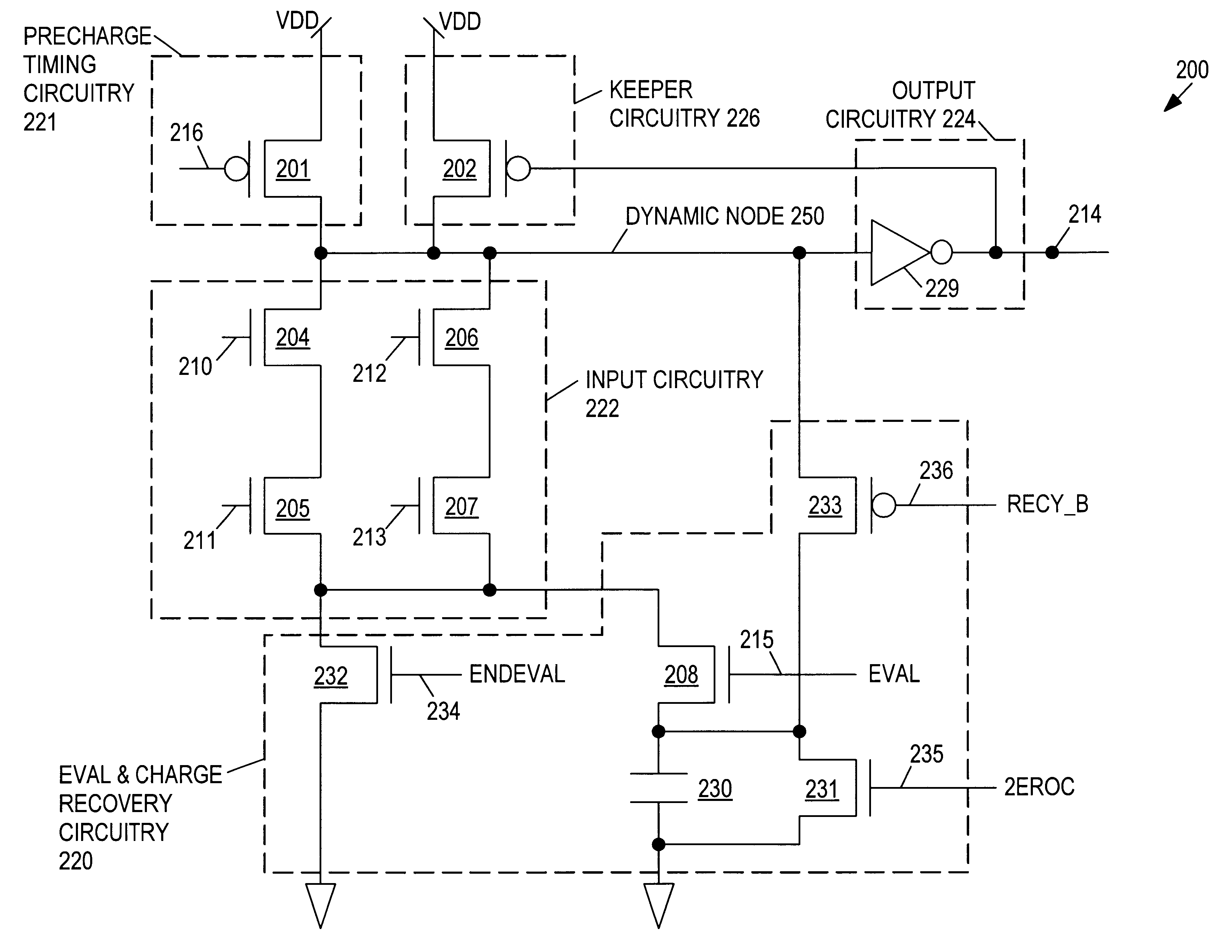

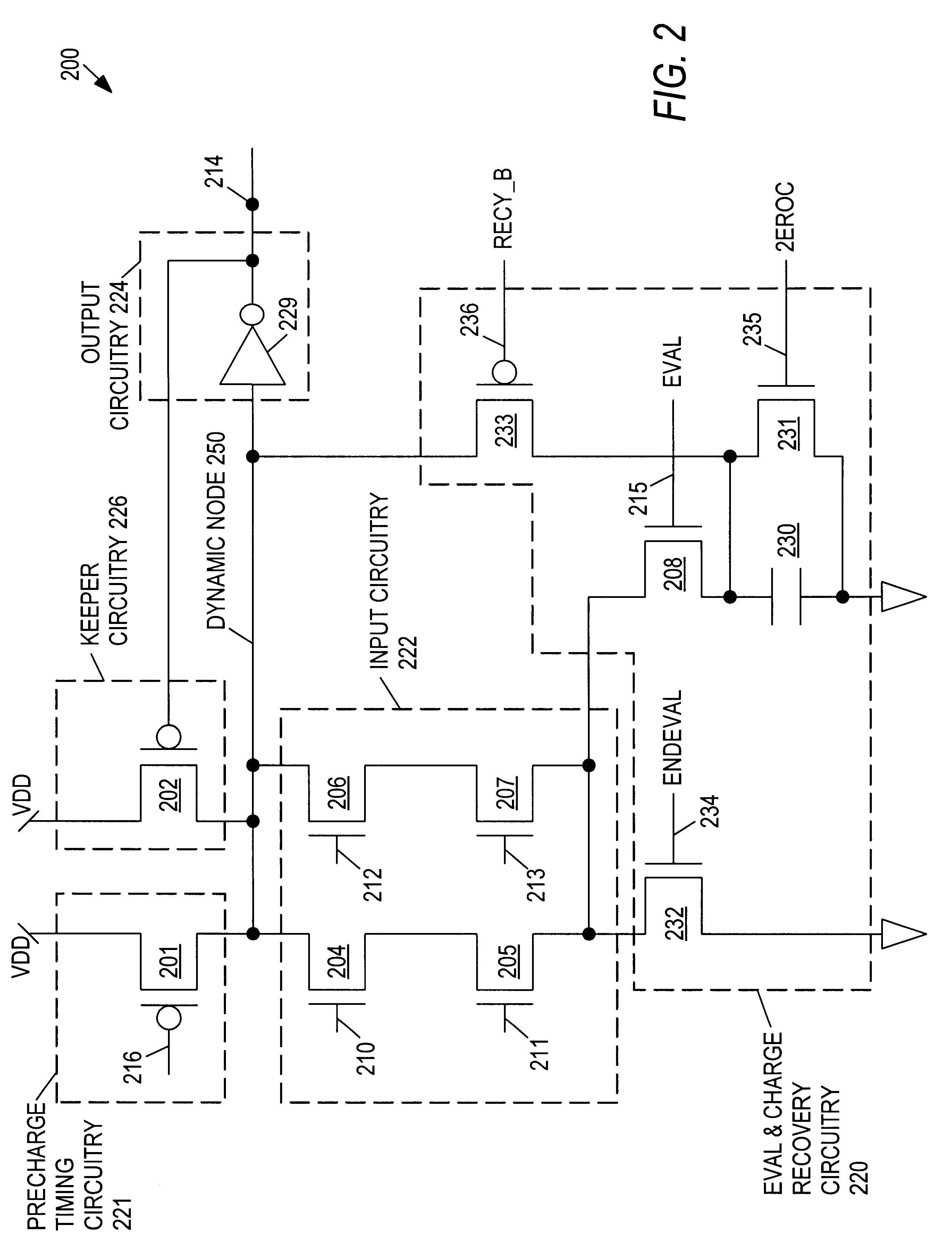

Charge recovery for dynamic circuits

InactiveUS6570408B2Power reduction by energy recoveryPower reduction by adiabatic operationEvaluation IntervalCharge recovery

In one aspect, a method for charge recovery in dynamic circuitry includes discharging a dynamic node during an evaluation interval by input circuitry coupled to the dynamic node responsive to one or more input signals. The discharging includes transferring the charge from the dynamic node to a capacitor during the evaluation time interval. The dynamic node is charged during a precharge interval by a voltage source and precharge timing circuitry coupled to the dynamic node responsive to a precharge signal. The charging includes transferring the charge from the capacitor back to the dynamic node.

Owner:GOOGLE LLC

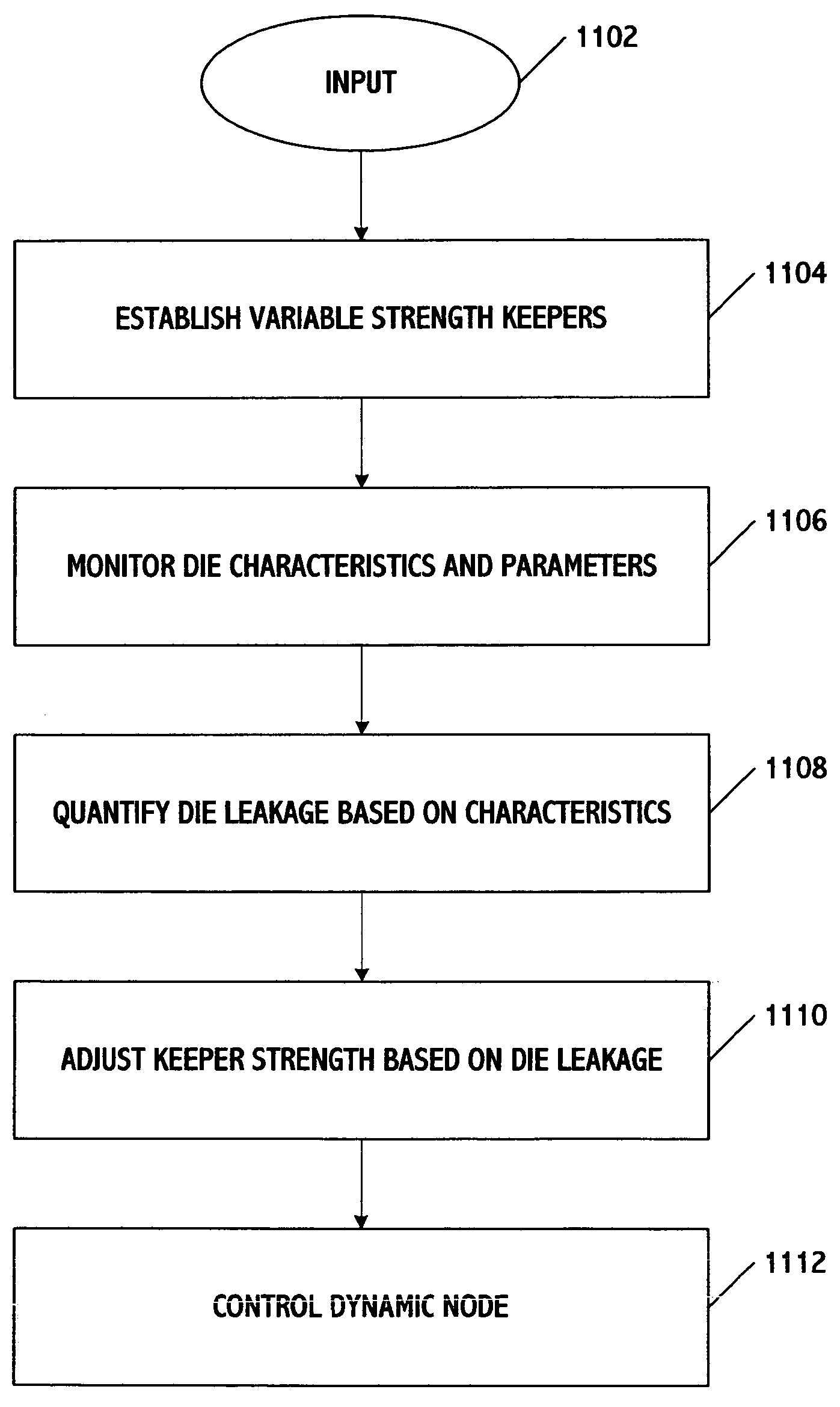

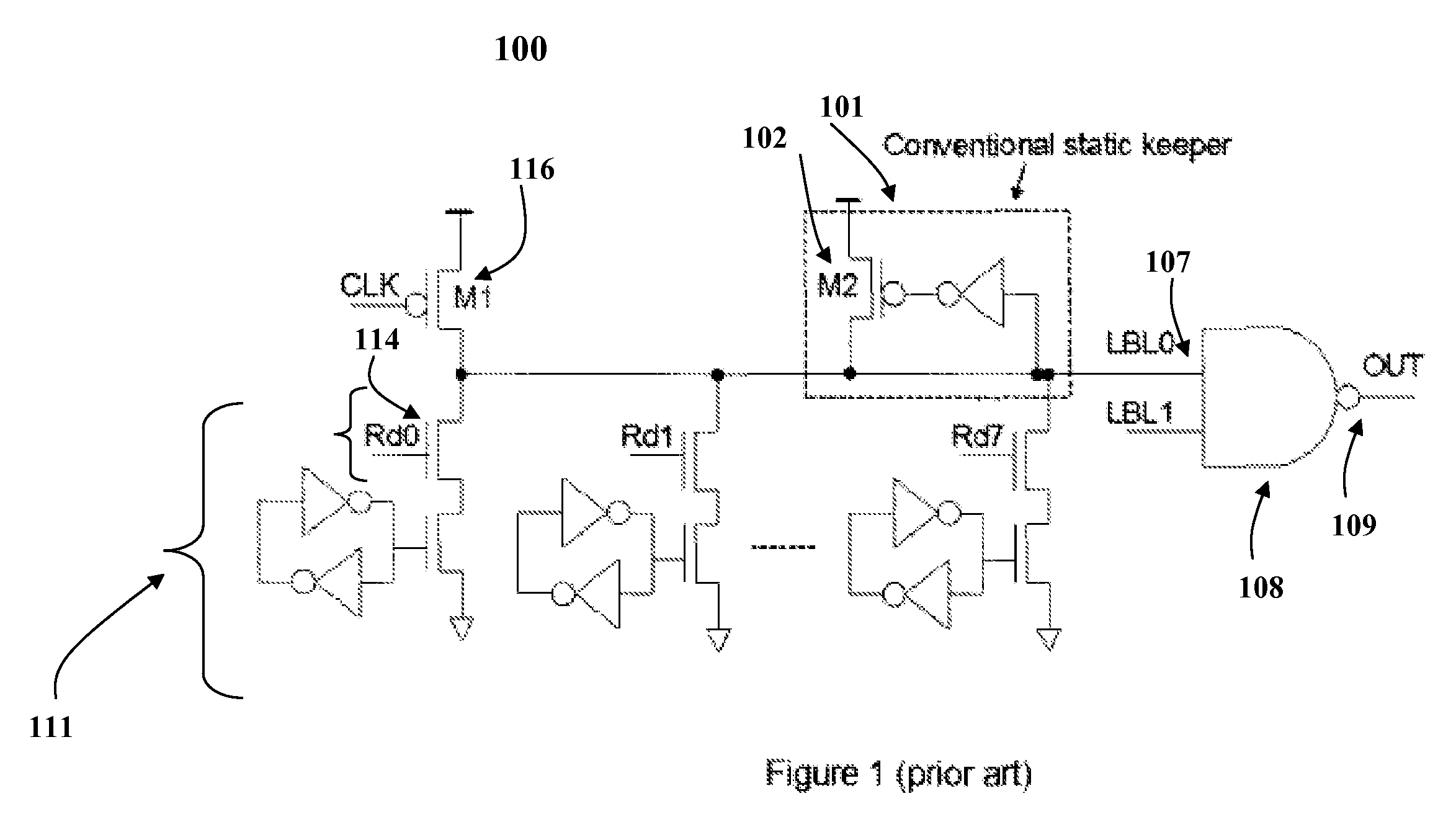

Robust variable keeper strength process-compensated dynamic circuit and method

InactiveUS7002375B2Reliability increasing modificationsLogic circuits characterised by logic functionRobustificationIntrinsics

A variable keeper strength based process-compensated dynamic circuit and method provides a robust digital way to overcome the intrinsic parameter variation present in manufactured die. Using a process-compensated dynamic circuit, the wide robustness and delay distribution becomes narrower which improves performance without sacrificing worst-case robustness. The strength of the keeper is programmed depending on the amount of die leakage. The keeper will have an optimal strength for the best and worst case leakage, allowing better performance with improved worst-case robustness.

Owner:TAHOE RES LTD

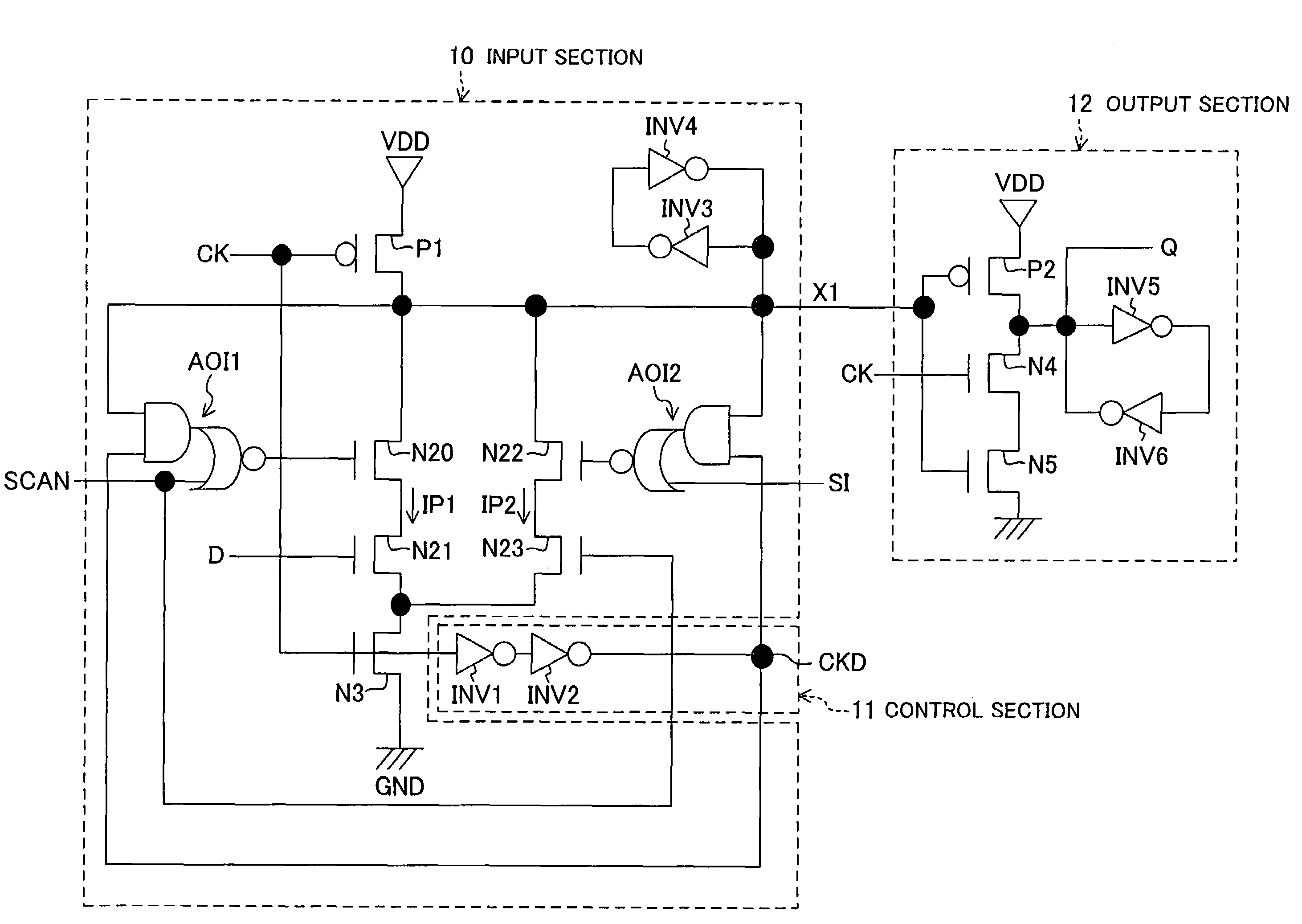

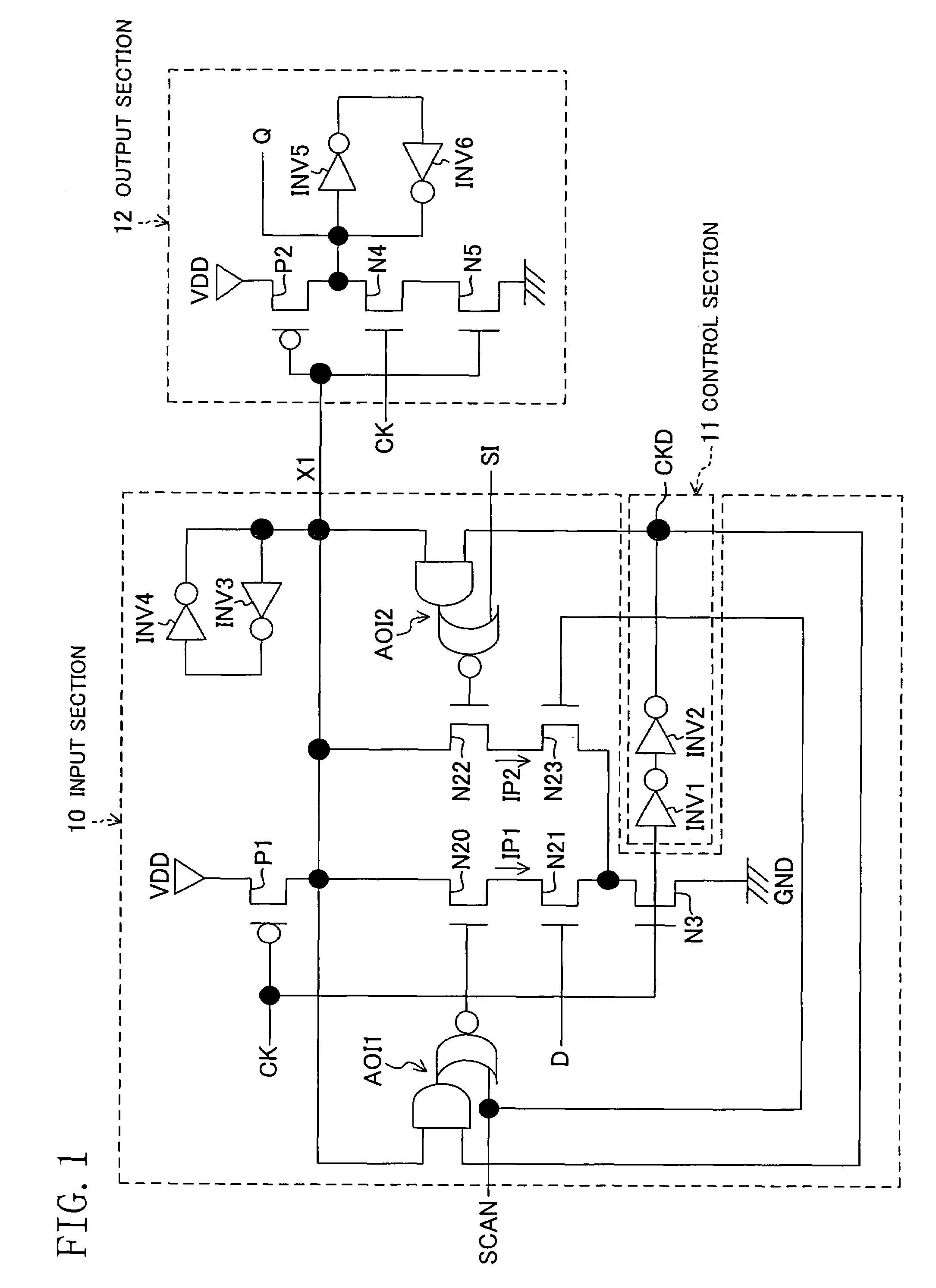

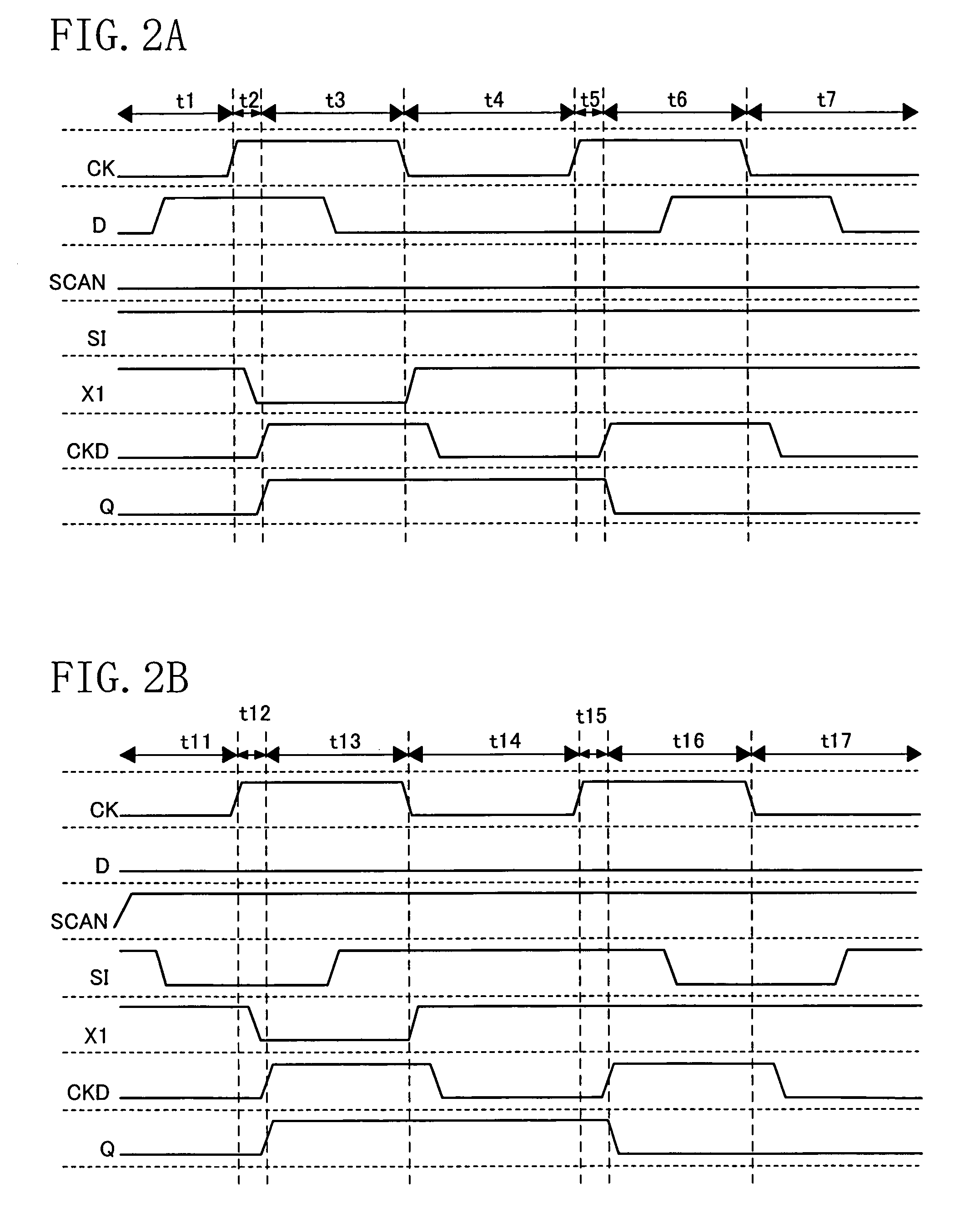

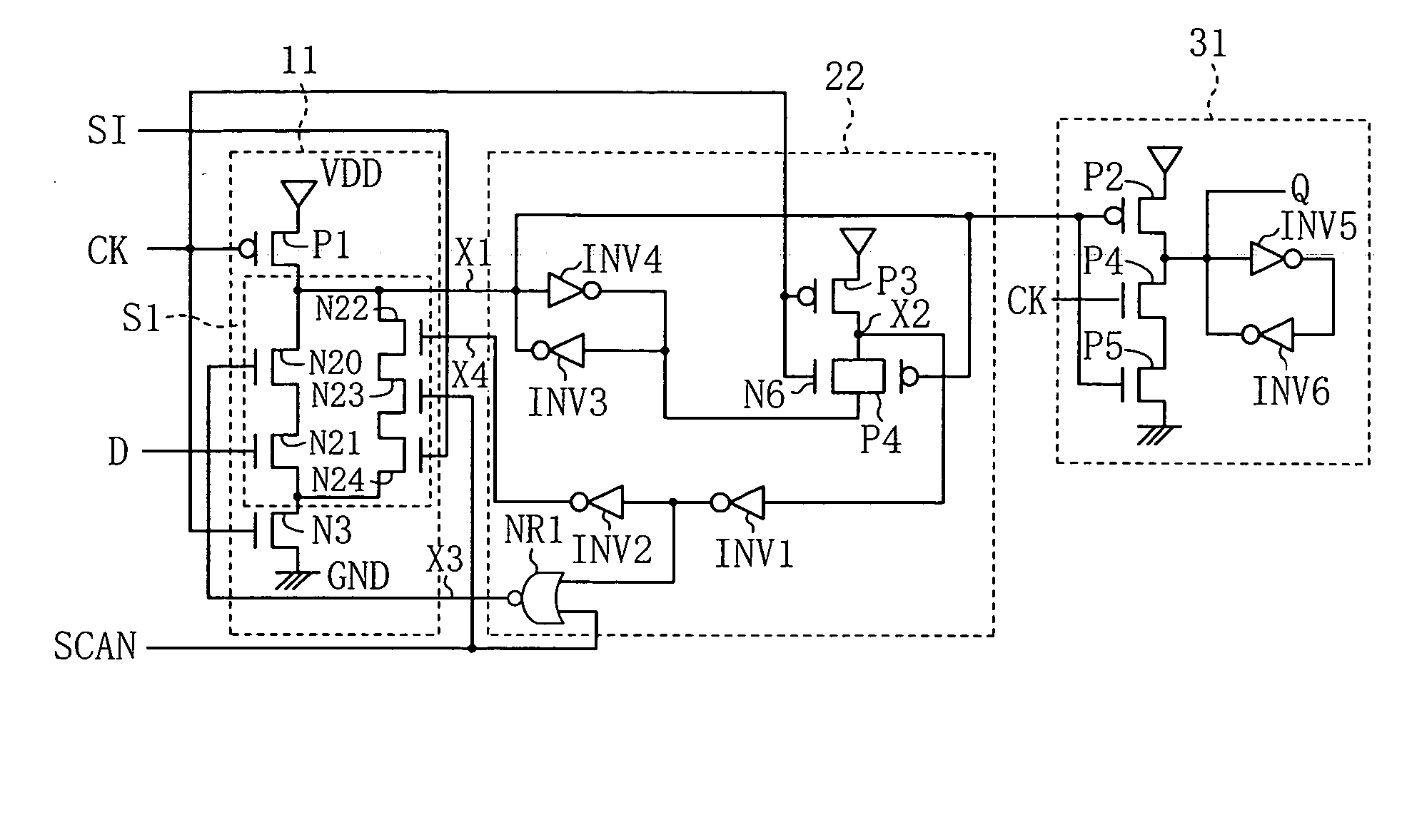

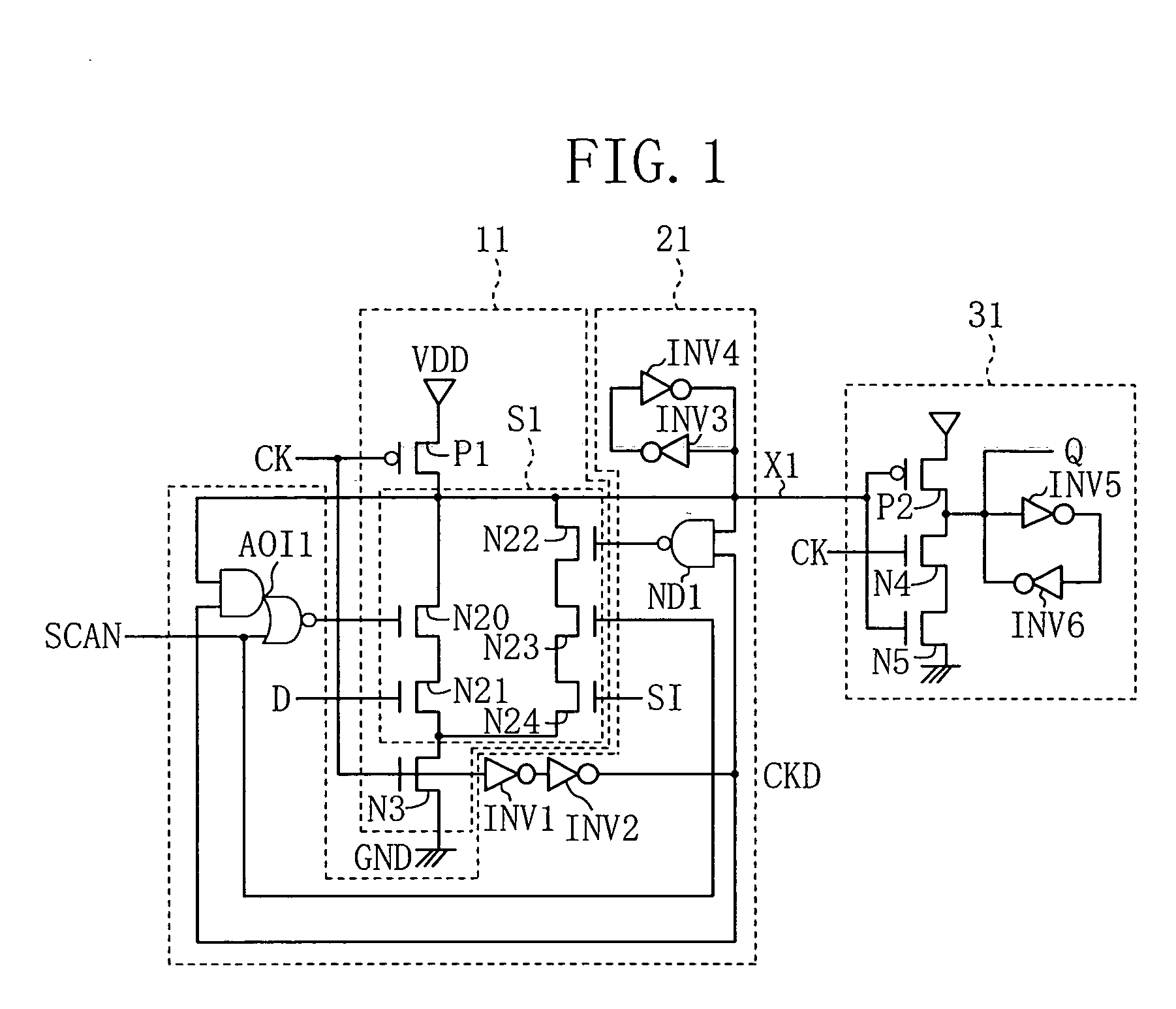

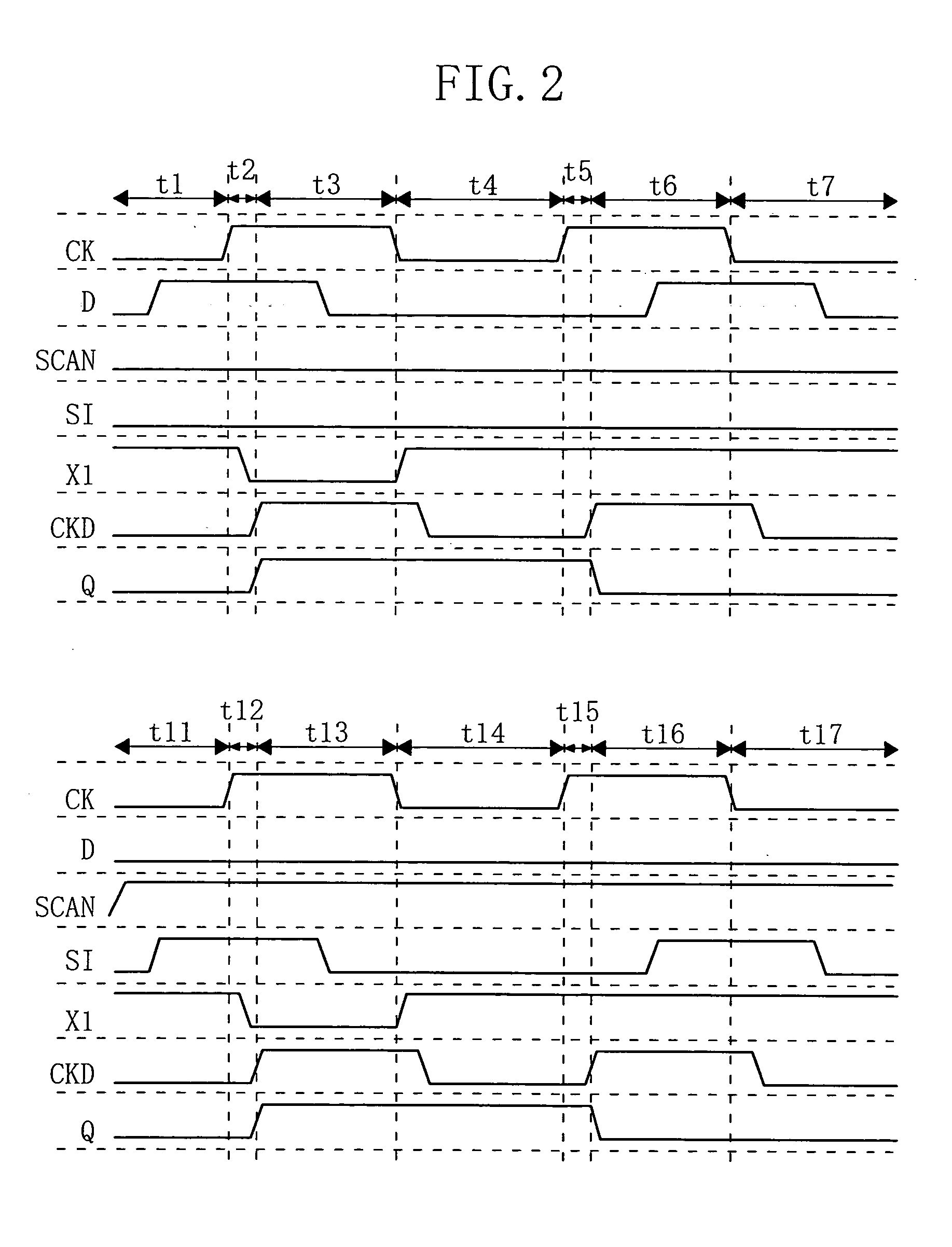

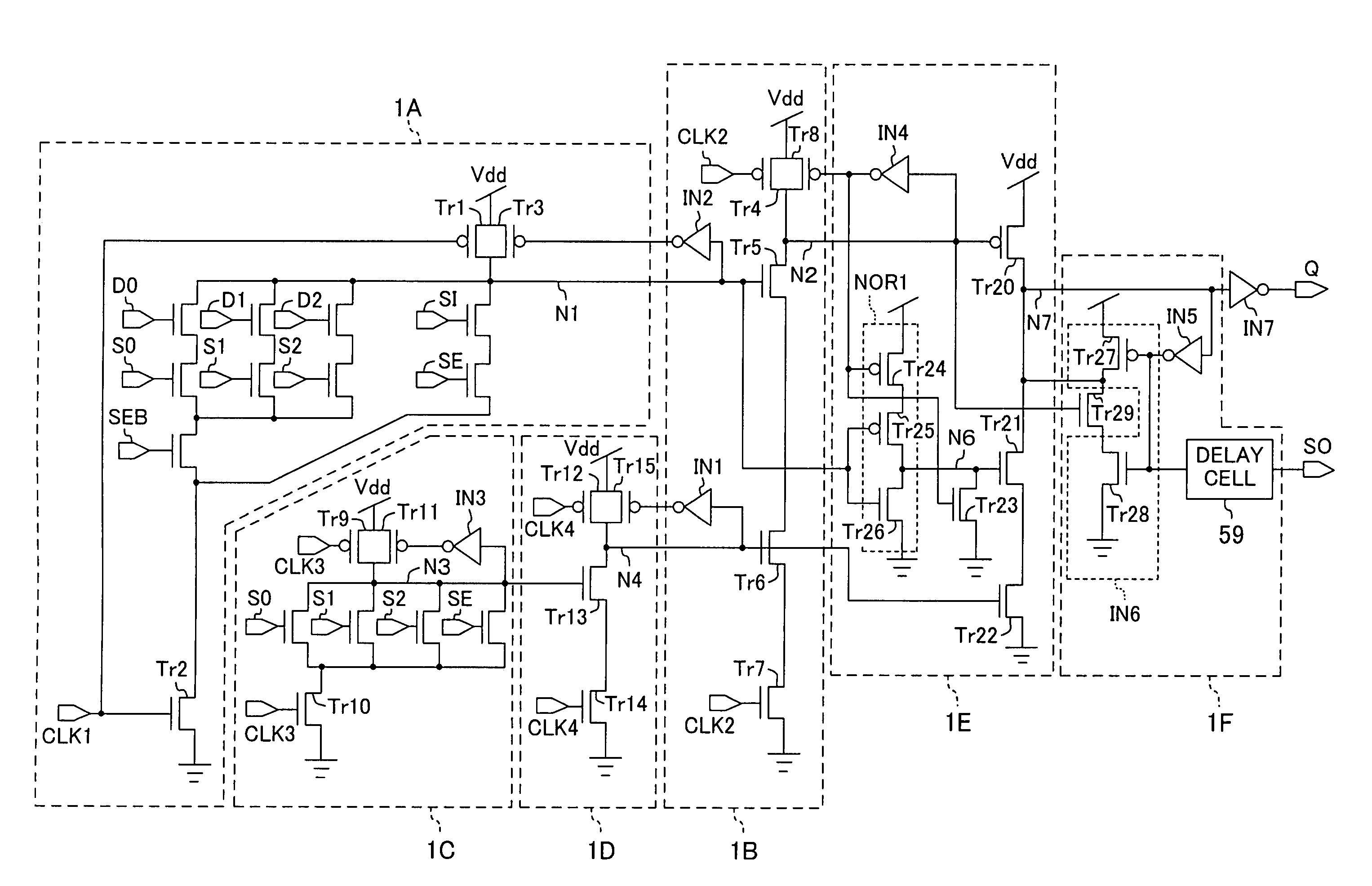

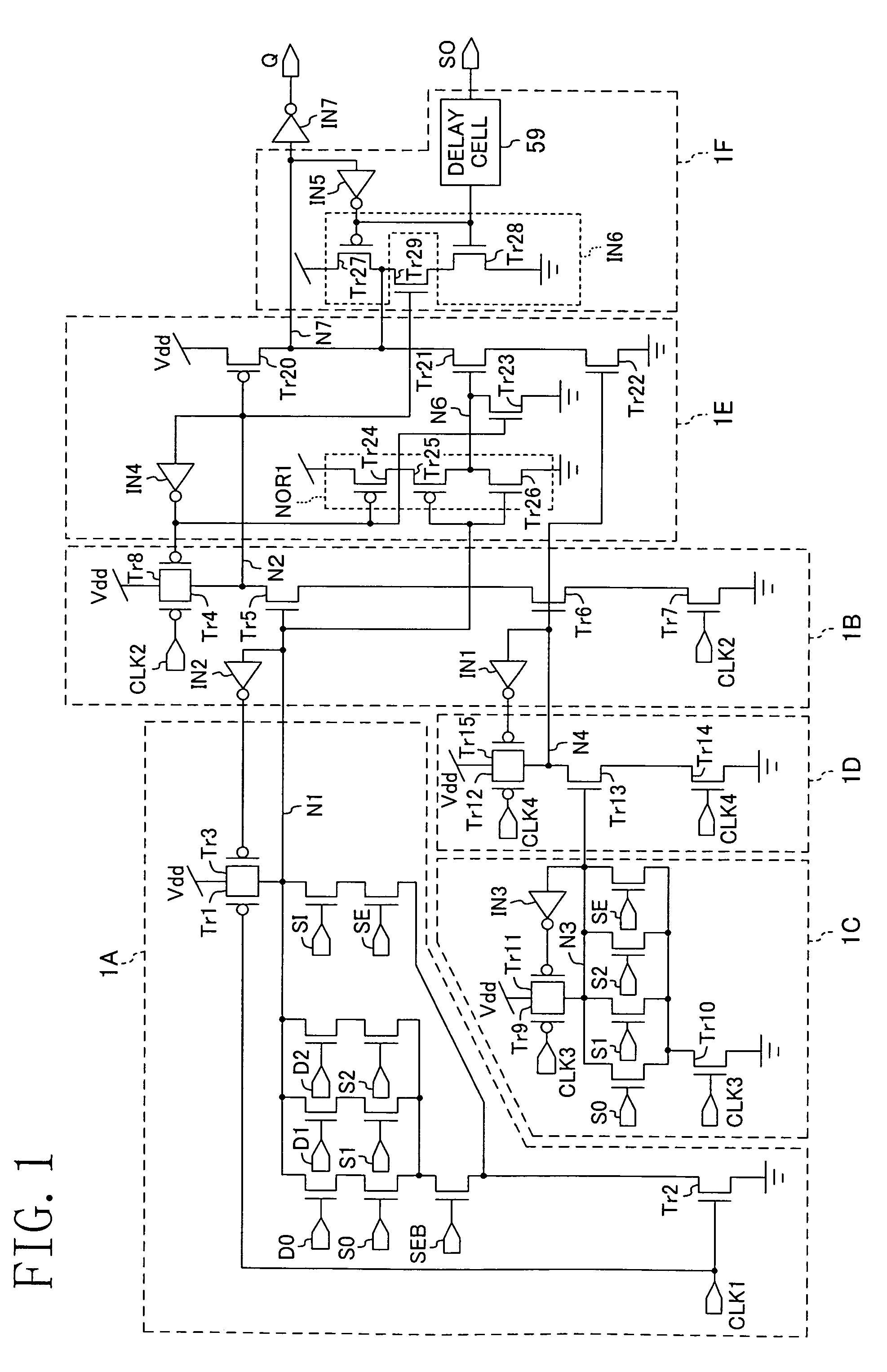

Flip-flop circuit

InactiveUS7345519B2High speedReduce in quantityElectrical testingElectric pulse generatorTest inputControl signal

A scan flip-flop circuit including an input section employing a dynamic circuit and an output section employing a static circuit, capable of latching in data within a period of a pulse width that is shorter than the clock cycle, wherein only three N-type transistors are connected in series in the input section employing a dynamic circuit. A data signal is input directly to one of the three N-type transistors. On the other hand, a test input signal is input to an AND / OR inverter circuit. The AND / OR inverter circuit receives, as a control signal, the potential of the node obtained as the clock signal passes through two inverter circuits. Therefore, there is required only a short hold time for the test input signal.

Owner:PANASONIC CORP

Low power carbon nanotube memory

InactiveUS7675768B1Reduce operating powerTotal current dropNanoinformaticsDigital storageBit lineAudio power amplifier

Low power carbon nanotube memory is realized such that a first dynamic circuit serves as a local sense amp for reading a memory cell through a lightly loaded local bit line, a second dynamic circuit serves as a segment sense amp for reading the local sense amp, a first tri-state inverter serves as an inverting amplifier of a global sense amp, and a second tri-state inverter serves as a bypass circuit for bypassing output from previous memory block. When reading, a voltage difference in the local bit line is converted to a time difference for differentiating high data and low data by the sense amps for realizing low power with dynamic operation. In particular, amplify transistor of the sense amps is composed of relatively long channel transistor for reducing turn-off current. And buffered data path is used for achieving fast data transfer. Additionally, alternative circuits and memory cell structures are described.

Owner:FRONTEON

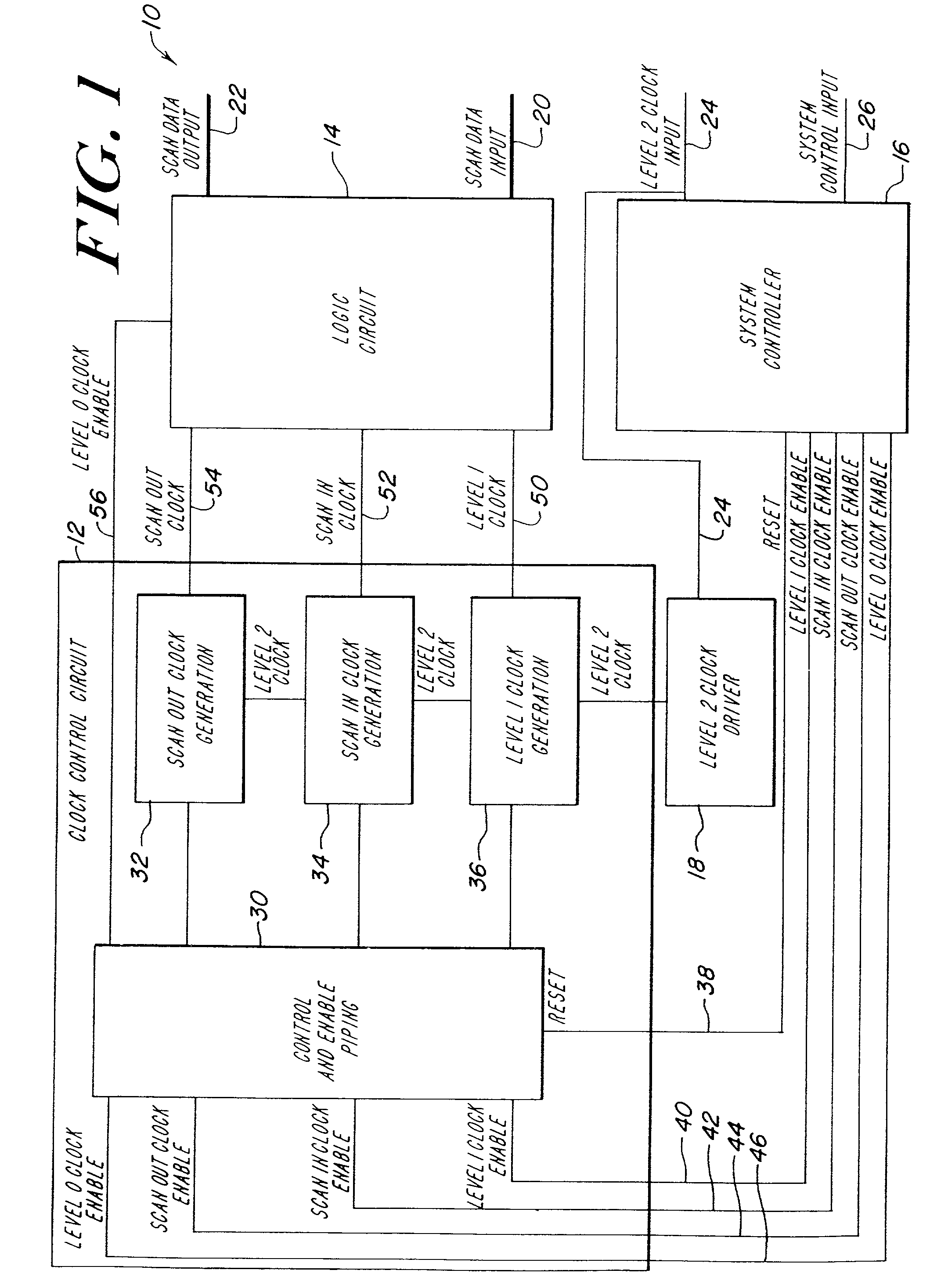

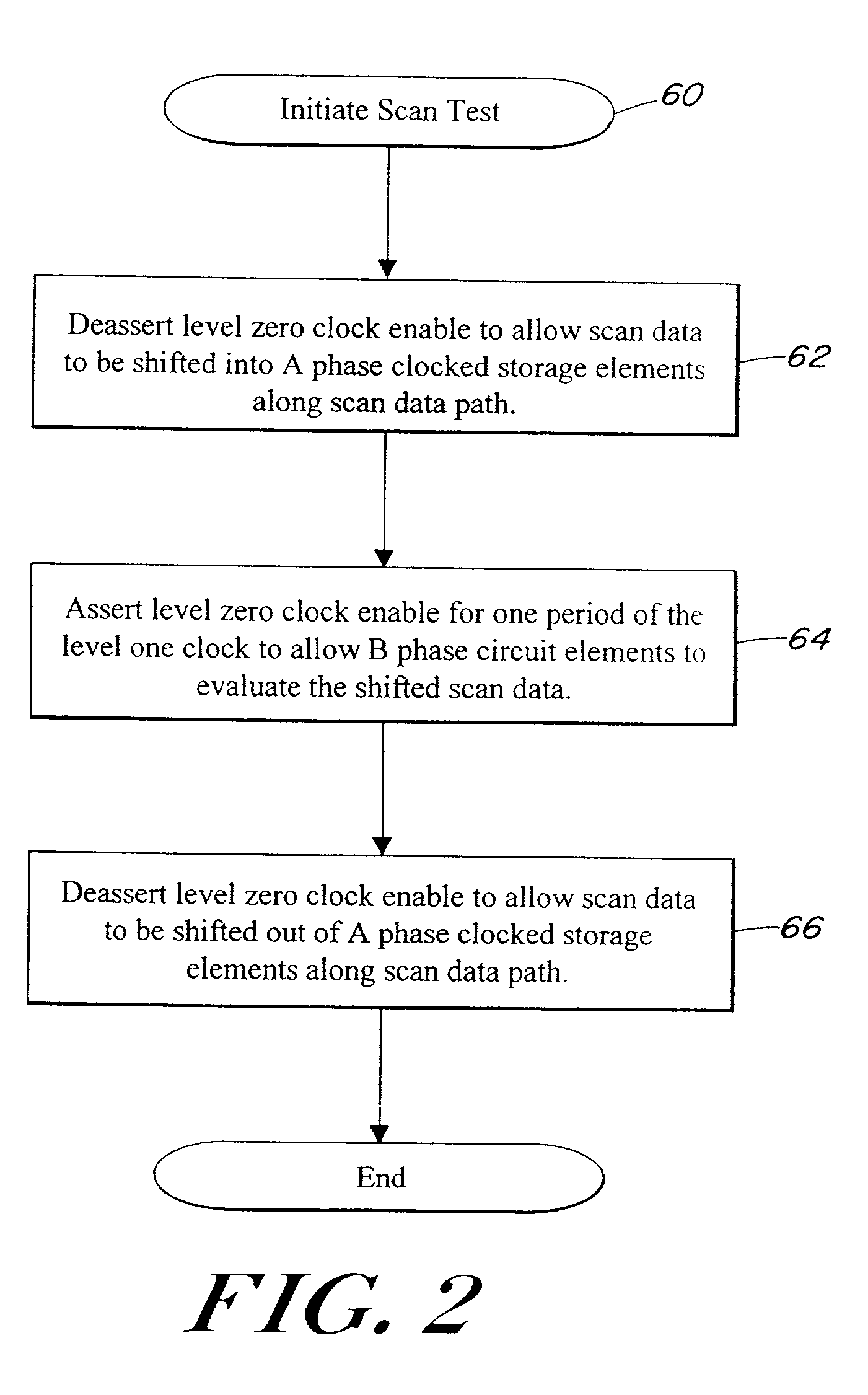

Method for scan testing and clocking dynamic domino circuits in VLSI systems using level sensitive latches and edge triggered flip flops

InactiveUS7000164B2Impacting speedImpacting efficiencyElectronic circuit testingGenerating/distributing signalsMultiplexerVlsi systems

A system and method is provided for scan control and observation of a logical circuit that does not halt the operation of the system clock. Thus, all dynamic circuits within the system continue to evaluate and precharge normally. Moreover, the traditional method of placing a multiplexer before the data input of a clocked storage element to perform scan control and observation is no longer required. Consequently, the system and method provide a more efficient manner in which to perform scan control and observation of a logical circuit.

Owner:ORACLE INT CORP

Scan flip flop, semiconductor device, and production method of semiconductor device

InactiveUS7157930B2Reduce in quantityHigh speedLogic circuits characterised by logic functionElectrical testingTest inputData signal

There is provided a flip flop circuit with a scan structure which is formed by an input section of a dynamic circuit and an output section of a static circuit wherein data is taken in within an interval of a short pulse width as compared with a clock cycle. In the dynamic circuit of the input section, the number of serially-connected MOS transistors to which a data signal is input is smaller than the number of serially-connected MOS transistors to which a test input signal is input. With this structure, the speed of operation is increased at the time of data storage for a data signal input, and the number of MOS transistors is reduced.

Owner:PANASONIC CORP

Method and ring oscillator circuit for measuring circuit delays over a wide operating range

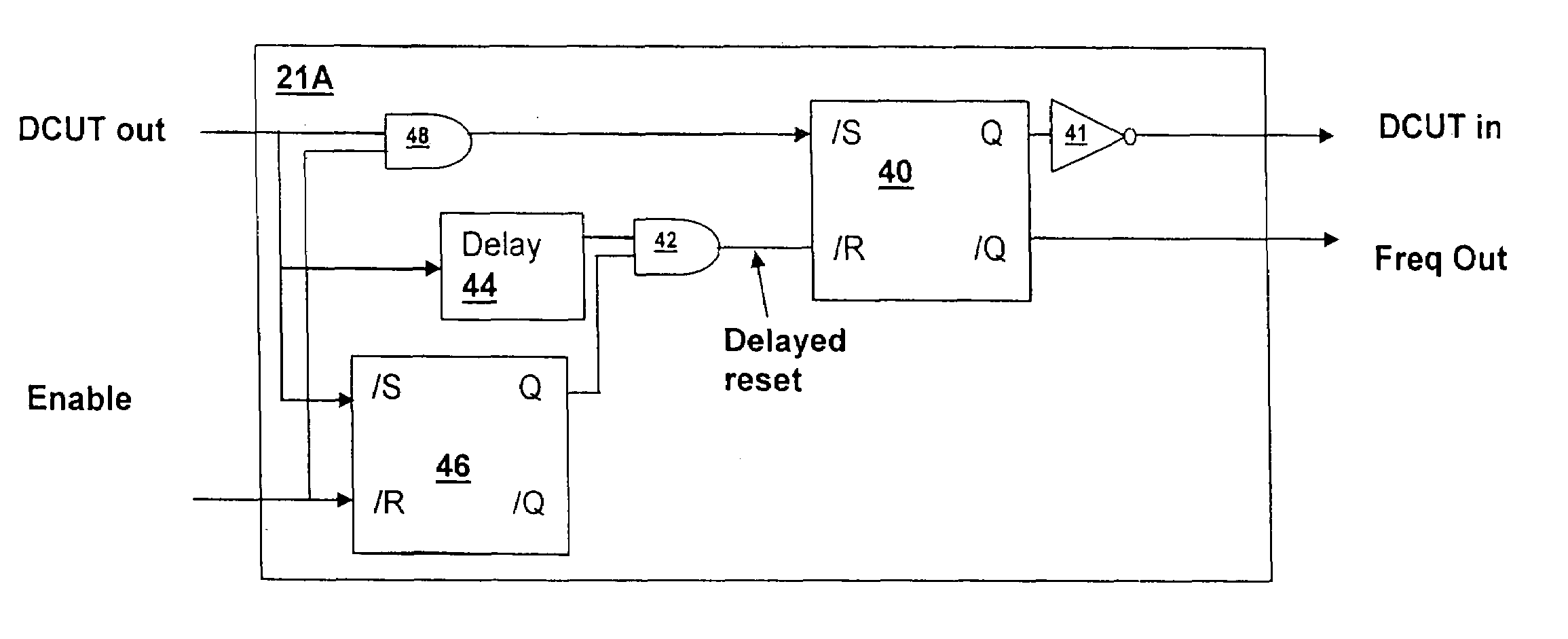

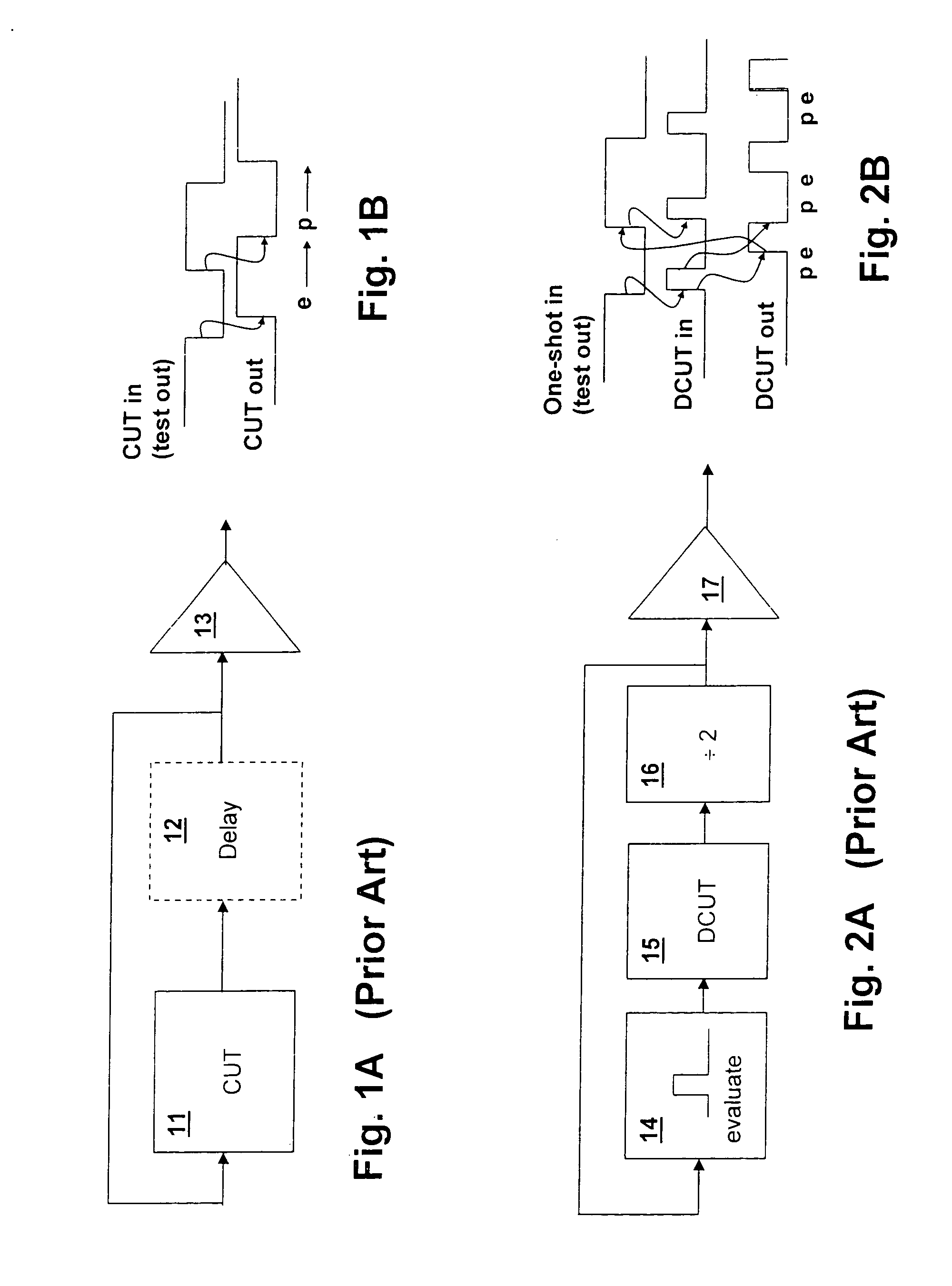

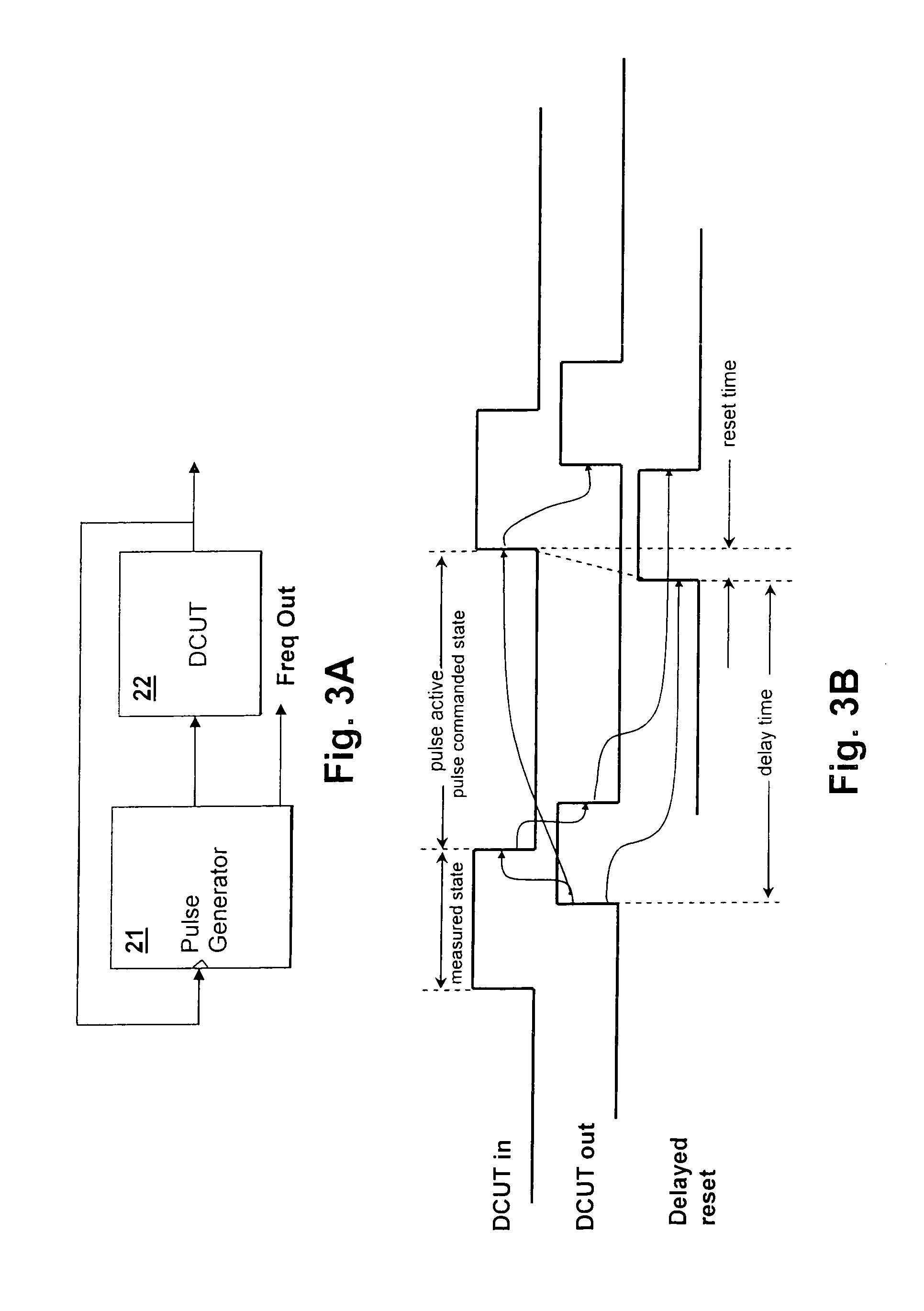

InactiveUS7046094B2Leakage can changeElectrical testingPulse generation by logic circuitsCapacitancePre-charge

A method and ring oscillator circuit for measuring circuit delays over a wide operating range permits improved analysis of dynamic circuits. A pulse generator circuit provides a pulse to an input of a dynamic circuit under test, which may be a pre-charge or evaluation pulse that is triggered by a transition of an output of the dynamic circuit that occurs during the state opposite that of the state commanded by the pulse. The action of the circuit provides for measuring any amount of delay to the next transition in the opposite state irrespective of the pulse width. By providing a wide-range of operation, characteristics such as leakage, charge sharing, data dependent node capacitance, previous value dependence as well as other dynamic circuit behaviors may be determined. The ring oscillator circuit includes an enable start circuit that causes a first pulse to be generated by the one-shot when the ring oscillator circuit is enabled.

Owner:INT BUSINESS MASCH CORP

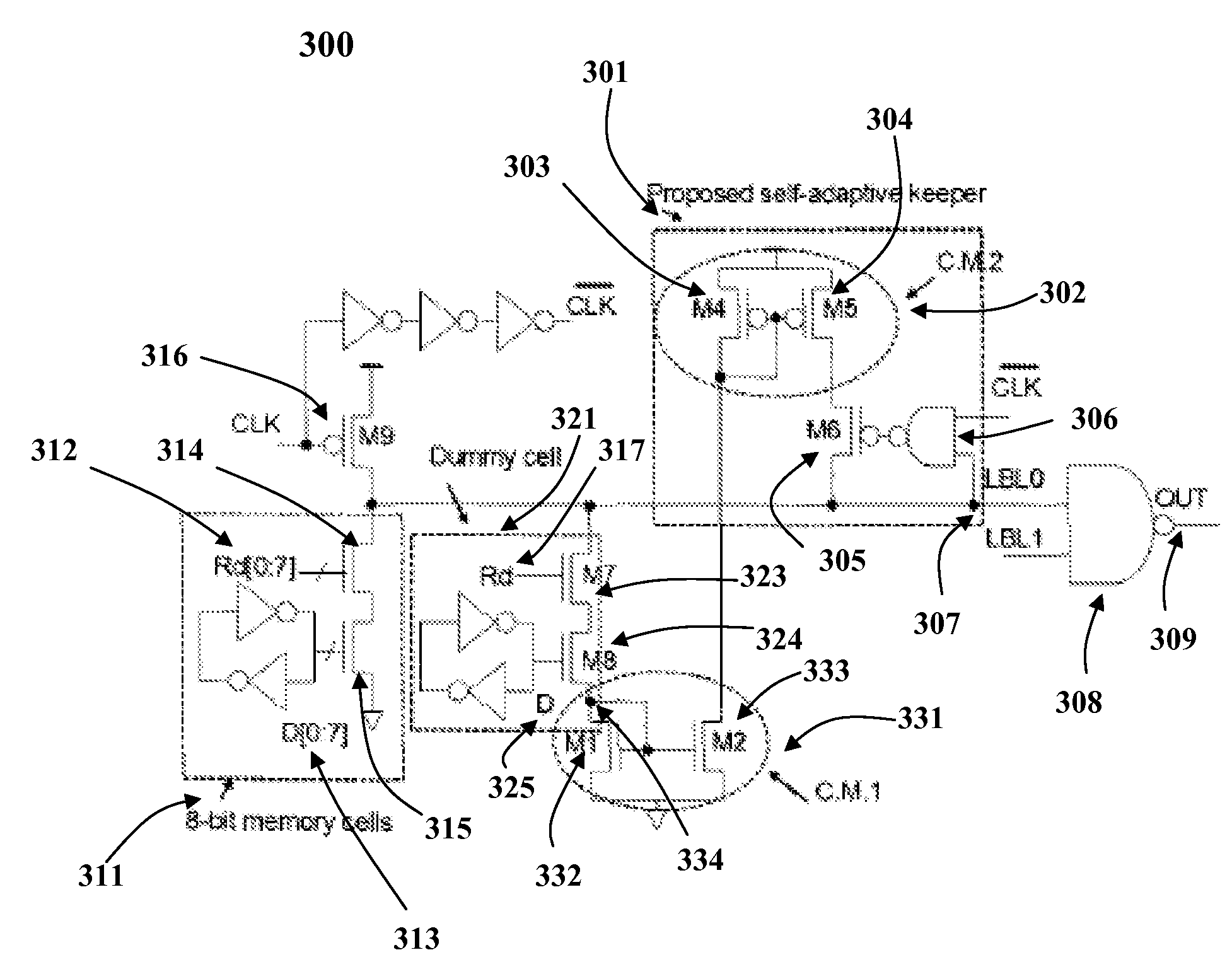

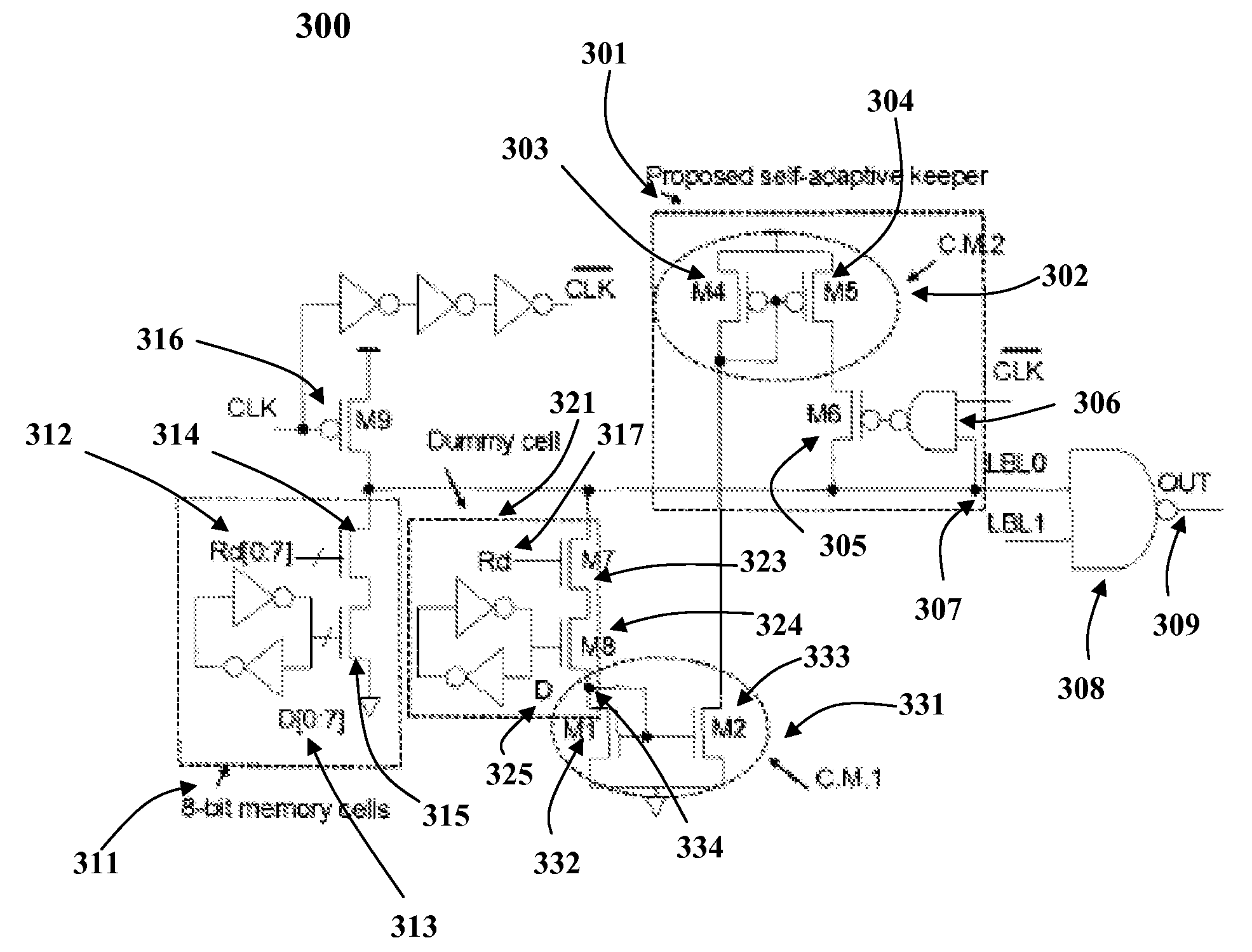

Compensation for leakage current from dynamic storage node variation by the utilization of an automatic self-adaptive keeper

InactiveUS7417469B2Optimal current strengthEliminate the effects ofLogic circuits characterised by logic functionDigital storageVirtual cellVoltage drop

A method and system for automatically detecting and optimally compensating a wide range of die leakage currents in dynamic circuits is presented. A self-adaptive keeper tracks the leakage and reduces the leakage effects by optimally controlled compensation current. The self-adaptive keeper utilizes a 2-stage embedded current mirror circuit, a dummy cell and a keeper transistor to compensate leakage current. The load impact of the self-adaptive keeper on the dynamic circuit components (for example, the impact on memory cells) is minimized by a dummy cell which detects and matches the instant leakage current. Amplification in the 2-stage embedded current mirror circuit provides an optimal current strength in the keeper transistor. The optimally amplified leakage current is utilized to compensate for a leakage induced voltage drop at the circuit's output. Thus, the self-adaptive keeper ensures the robustness of the circuit in real time and does not create any negative trade-off on read latency.

Owner:INT BUSINESS MASCH CORP

Circuit for Dynamic Circuit Timing Synthesis and Monitoring of Critical Paths and Environmental Conditions of an Integrated Circuit

InactiveUS20080104561A1Multiple input and output pulse circuitsPulse characteristics measurementsEngineeringCritical path method

A circuit for dynamically monitoring the operation of an integrated circuit under differing temperature, frequency, and voltage (including localized noise and droop), and for detecting early life wear-out mechanisms (e.g., NBTI, hot electrons).

Owner:IBM CORP

High speed flash memory

InactiveUS20100054039A1Total current dropReduce power consumptionSolid-state devicesRead-only memoriesBit lineAudio power amplifier

Owner:KIM JUHAN

Low drop-out voltage regulator with enhanced frequency compensation

InactiveUS7218083B2Improve the compensation effectIncrease conversion rateElectric variable regulationFrequency compensationDifferential signaling

Owner:O2 MICRO INT LTD

Compensation for leakage current variation by the utilization of an automatic self-adaptive keeper

InactiveUS20080111616A1Optimal current strengthEliminate the effects ofLogic circuits characterised by logic functionDigital storageVoltage dropEngineering

A method and system for automatically detecting and optimally compensating a wide range of die leakage currents in dynamic circuits is presented. A self-adaptive keeper tracks the leakage and reduces the leakage effects by optimally controlled compensation current. The self-adaptive keeper utilizes a 2-stage embedded current mirror circuit, a dummy cell and a keeper transistor to compensate leakage current. The load impact of the self-adaptive keeper on the dynamic circuit components (for example, the impact on memory cells) is minimized by a dummy cell which detects and matches the instant leakage current. Amplification in the 2-stage embedded current mirror circuit provides an optimal current strength in the keeper transistor. The optimally amplified leakage current is utilized to compensate for a leakage induced voltage drop at the circuit's output. Thus, the self-adaptive keeper ensures the robustness of the circuit in real time and does not create any negative trade-off on read latency.

Owner:IBM CORP

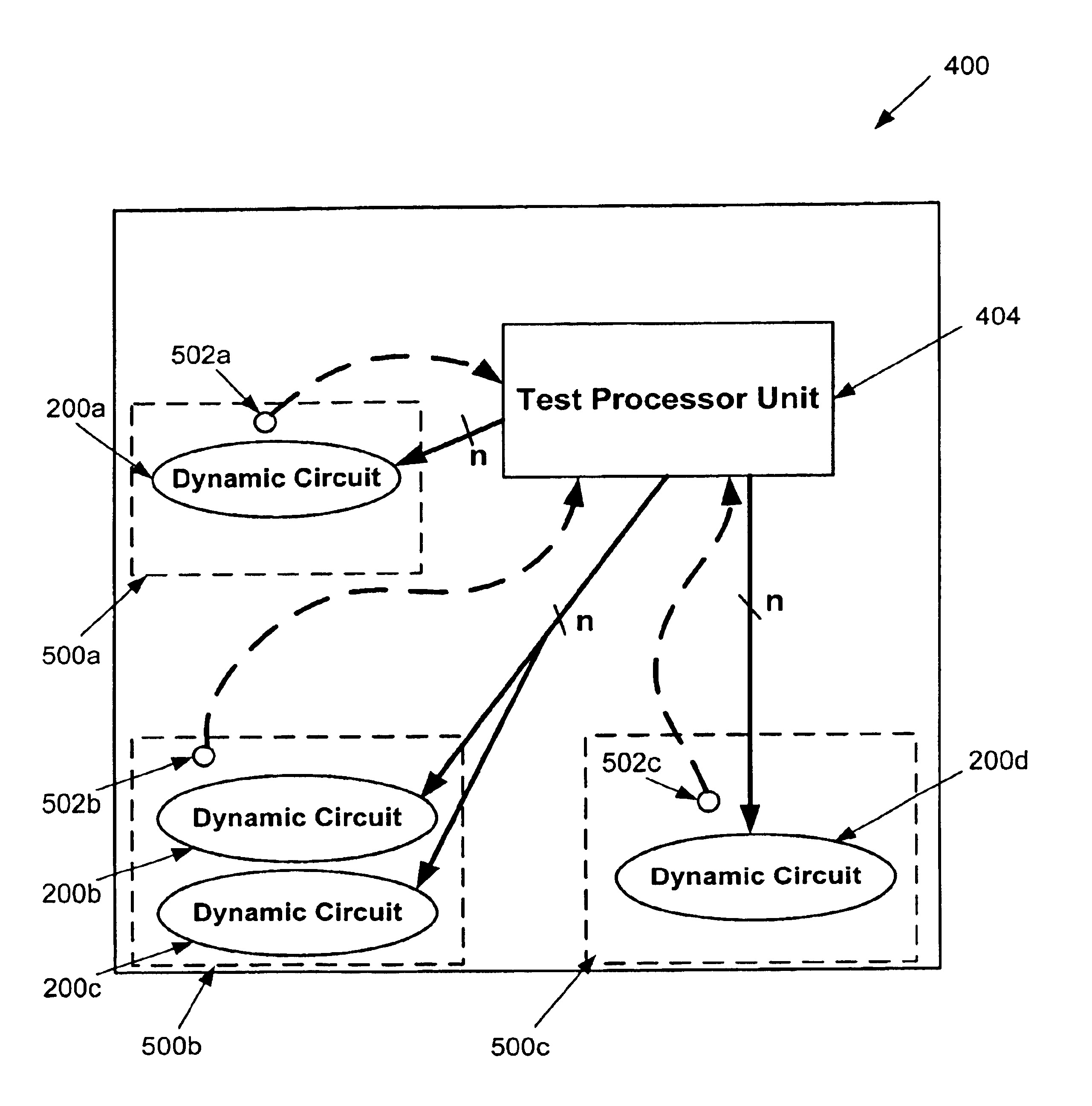

Process monitor based keeper scheme for dynamic circuits

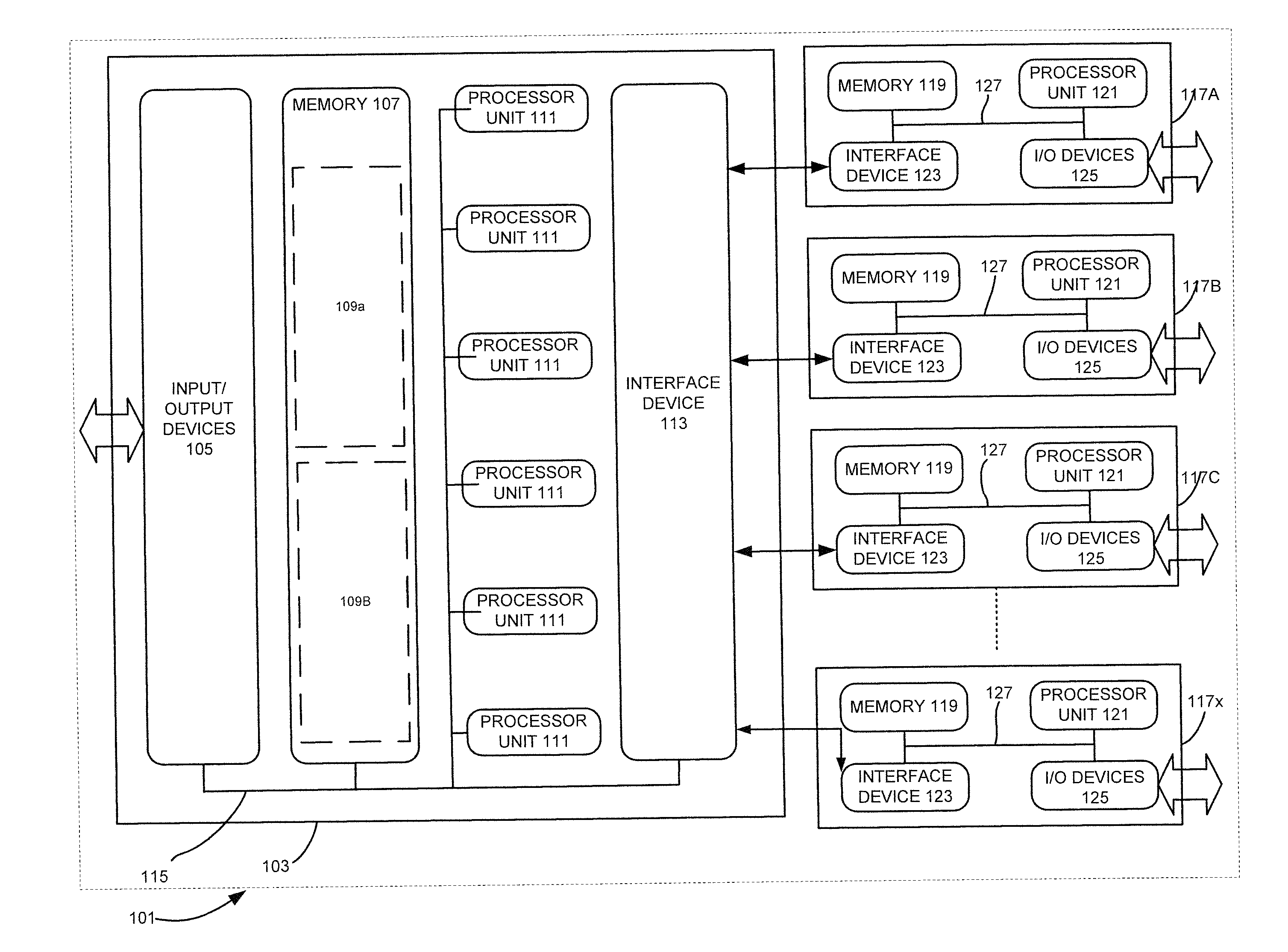

An invention is disclosed for a process monitor based keeper scheme for dynamic circuits. A semiconductor die having a process monitor based keeper scheme of the embodiments of the present invention generally includes a plurality of dynamic circuits, each having an adaptive keeper circuit capable of being adjusted based on a bit code. In addition, a plurality of process monitors is included. Each process monitor is disposed within a corresponding die block, which defines a local area of the die. The process monitors are capable of detecting process corner data for the corresponding die block. In communication with each process monitor and the plurality of dynamic circuits is a test processor unit. The test processor unit obtains process corner data for each die block from the process monitor disposed within the die block, and provides a bit code based on the process corner data to the dynamic circuits disposed within the die block.

Owner:ORACLE INT CORP

Leakage sensing and keeper circuit for proper operation of a dynamic circuit

InactiveUS7202704B2Logic circuits characterised by logic functionIndividual semiconductor device testingDetector circuitsEngineering

A method and apparatus for ensuring proper operation of a dynamic circuit is provided. A dynamic circuit instance has a plurality of outputs connected to a respective one of a plurality of leakage detector circuits. An output of each leakage detector circuit is connected with a respective one of a plurality of keeper circuits that reside at the dynamic circuit. Each of the plurality of keeper circuits has a unique size ratio with respect to a logic element size of the dynamic circuit.

Owner:IBM CORP

Method for manufacturing a thin film transistor device

InactiveUS7622335B2Lowering blocking energyEasy to useStatic indicating devicesSolid-state devicesIridiumManganese

A method for manufacturing a semiconductor device such as a thin film transistor using a crystal silicon film is provided. The crystal silicon film is obtained by selectively forming films, particles or clusters containing nickel, iron, cobalt, ruthenium, rhodium, paradium, osmium, iridium, platinum, scandium, titanium, vanadium, chrome, manganese, copper, zinc, gold, silver or silicide thereof in a form of island, line, stripe, dot or film on or under an amorphous silicon film and using them as a starting point, by advancing its crystallization by annealing at a temperature lower than a normal crystallization temperature of an amorphous silicon. A transistor whose leak current is low and a transistor in which a mobility is high are obtained in the same time in structuring a dynamic circuit having a thin film transistor by selectively forming a cover film on a semiconductor layer which is to become an active layer of the transistor and by thermally crystallizing it thereafter.

Owner:SEMICON ENERGY LAB CO LTD

Dynamic logic circuit apparatus and method for reducing leakage power consumption via separate clock and output stage control

InactiveUS7202705B2Reduce power consumptionFast timePower reduction by control/clock signalPower inverterSufficient time

A dynamic logic circuit apparatus and method for reducing leakage power consumption via separate clock and output stage control reduces power consumption of processors and other systems incorporating dynamic circuits. The power control signal may be a delayed version of the logic clock and turns on the output inverter foot device after the dynamic node has had sufficient time to evaluate, providing a fast evaluate time and reducing leakage through the inverter input when the foot device is off. Alternatively, a coarsely timed static power control signal may be used to control the inverter foot devices. The drains of the inverter foot devices can be commonly connected across multiple circuits, reducing the foot device total area.

Owner:INT BUSINESS MASCH CORP

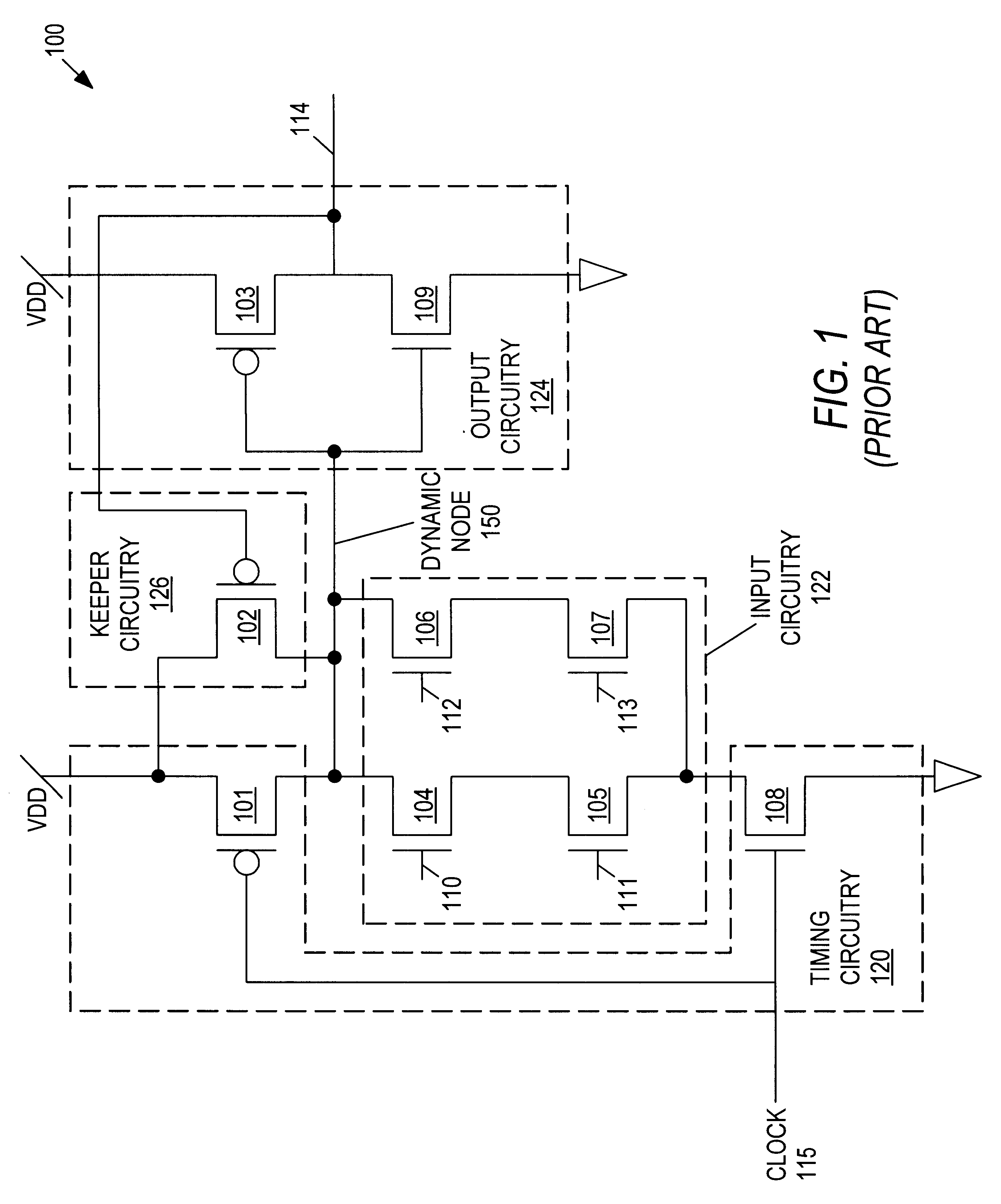

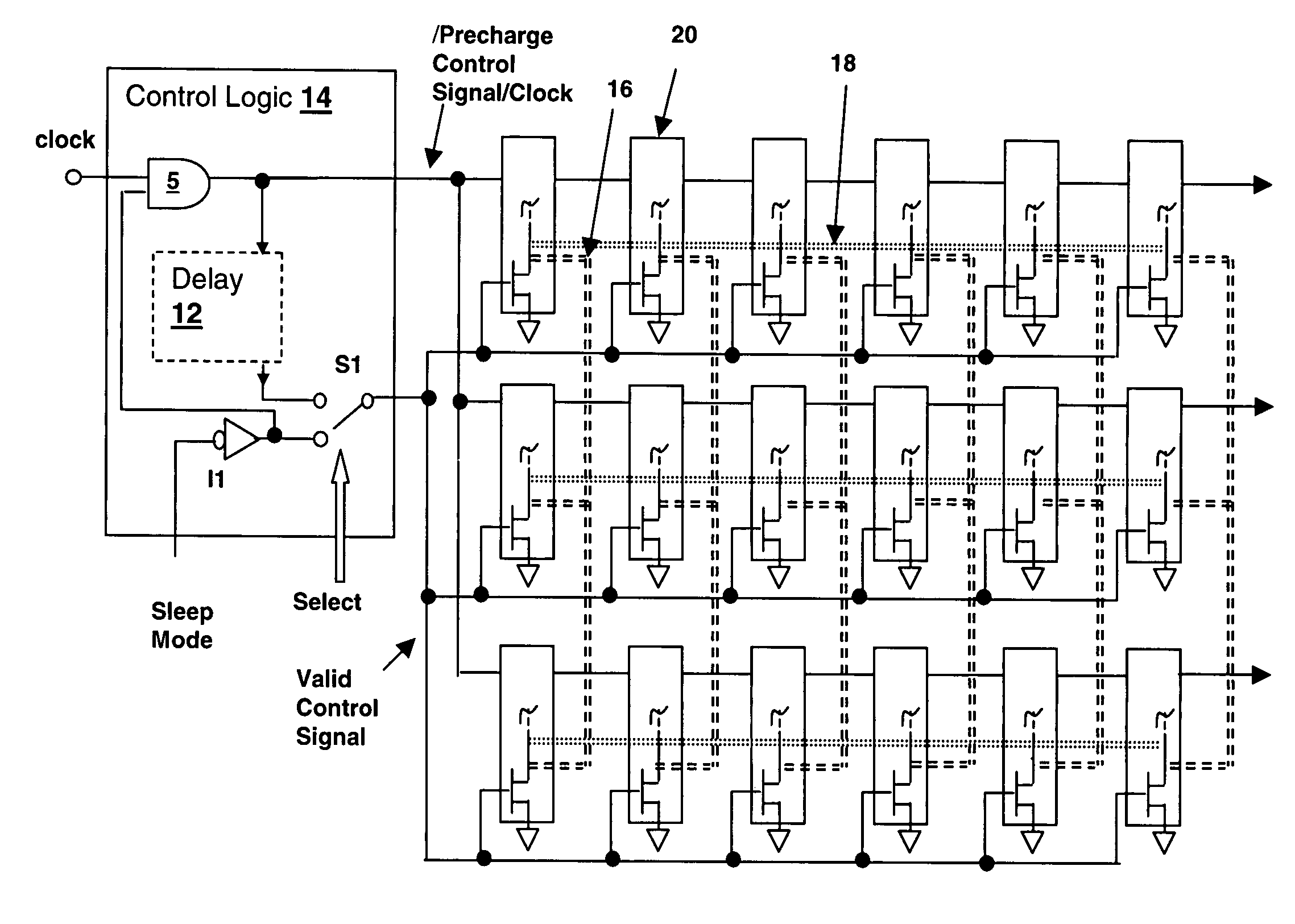

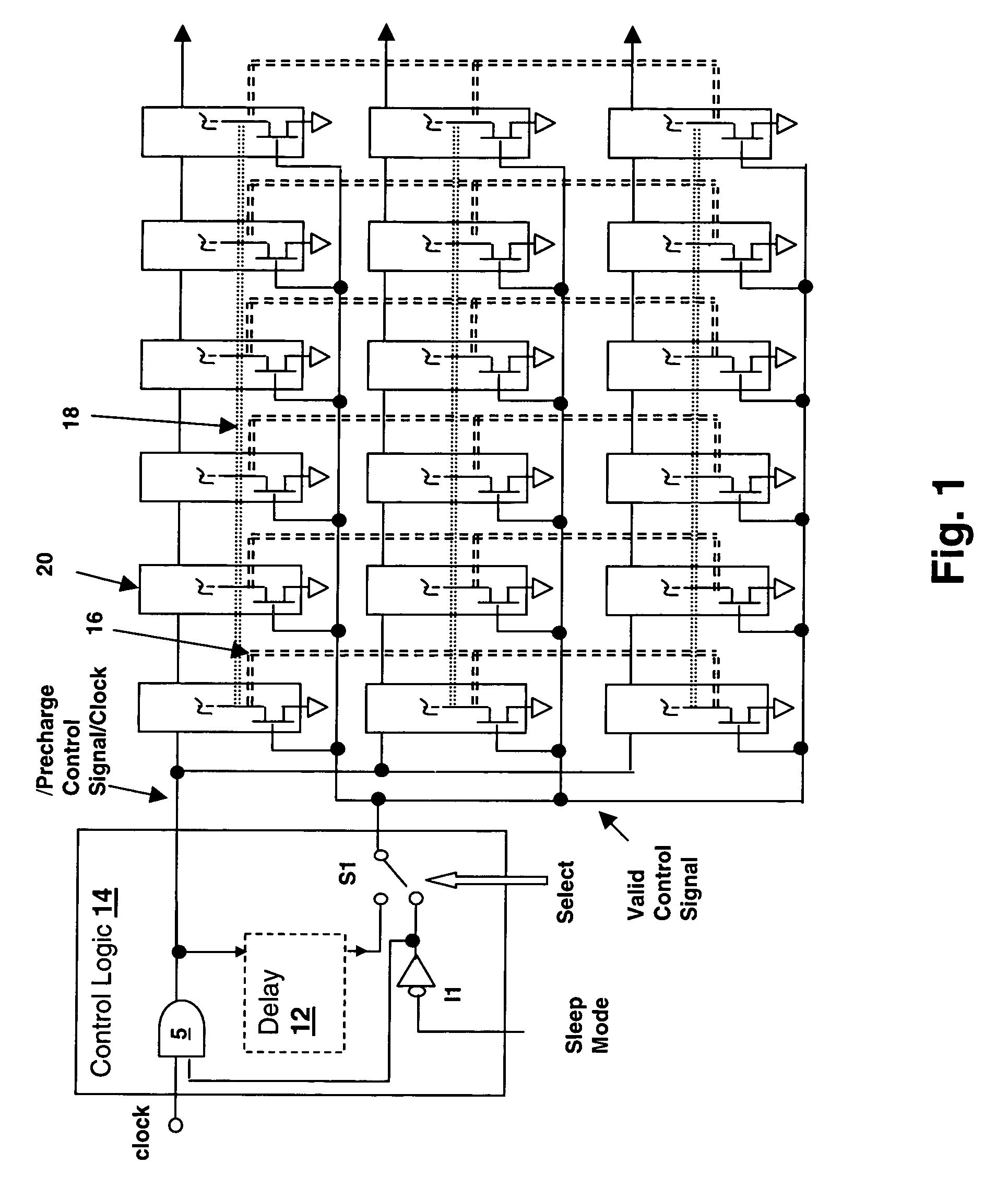

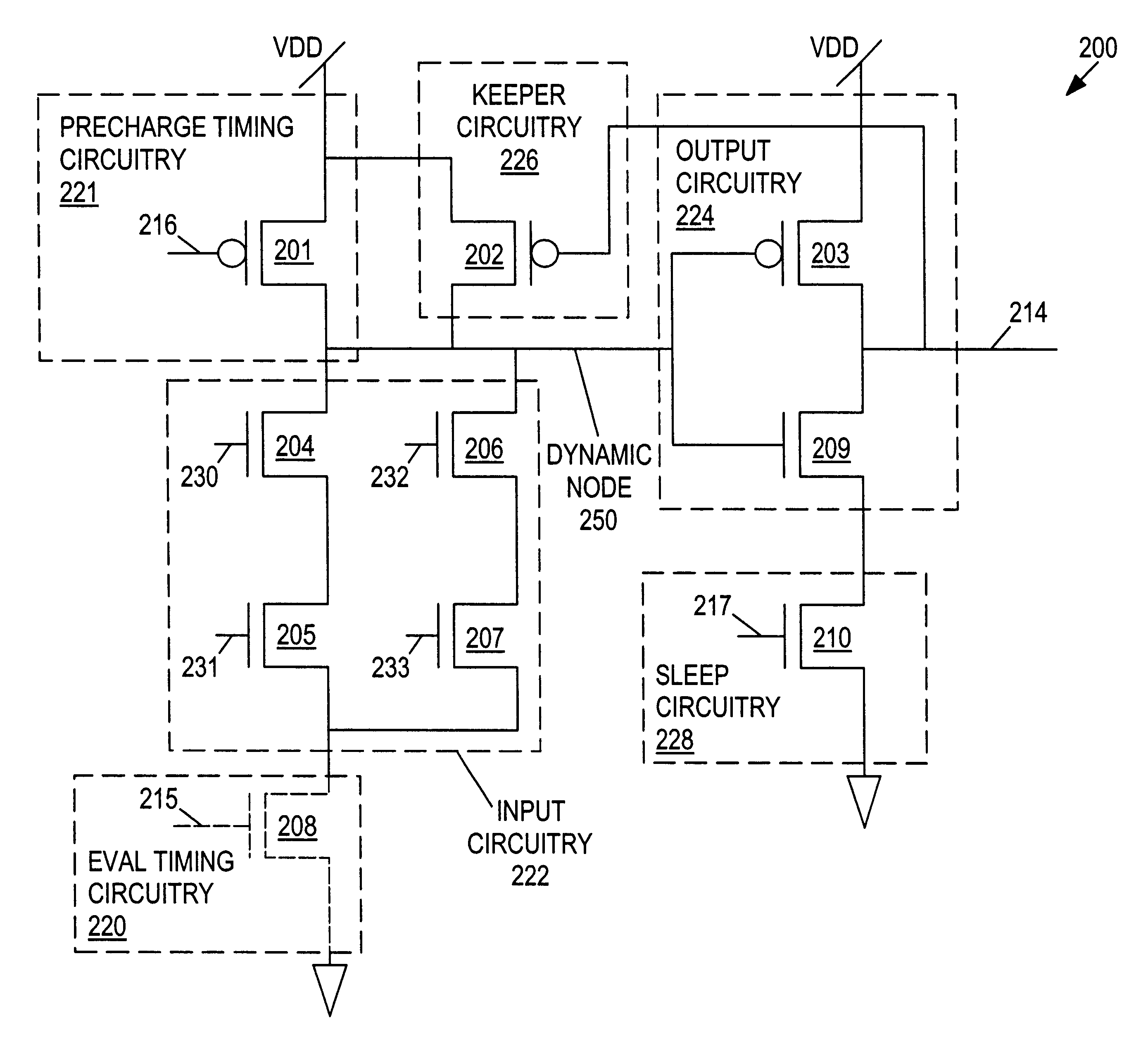

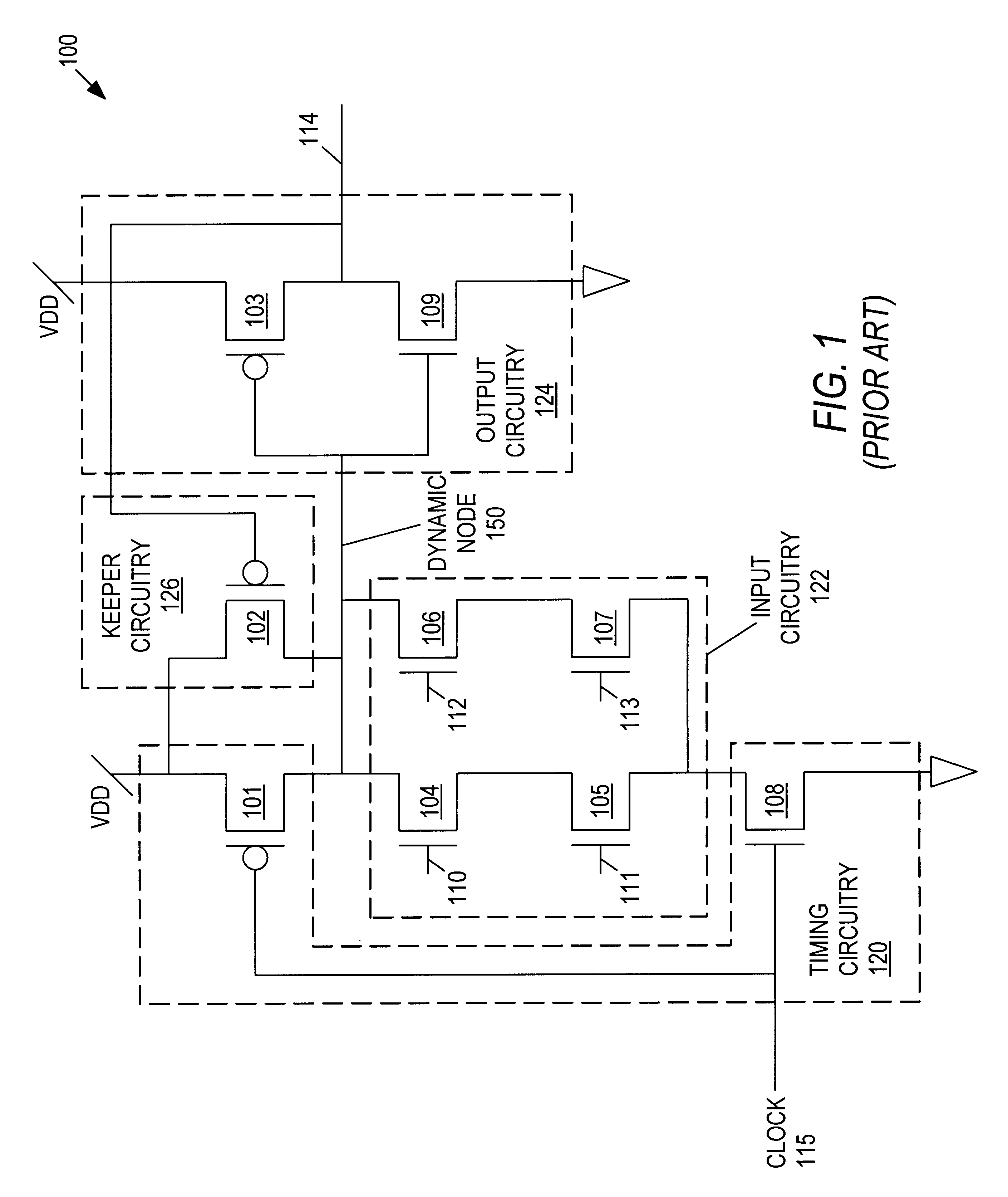

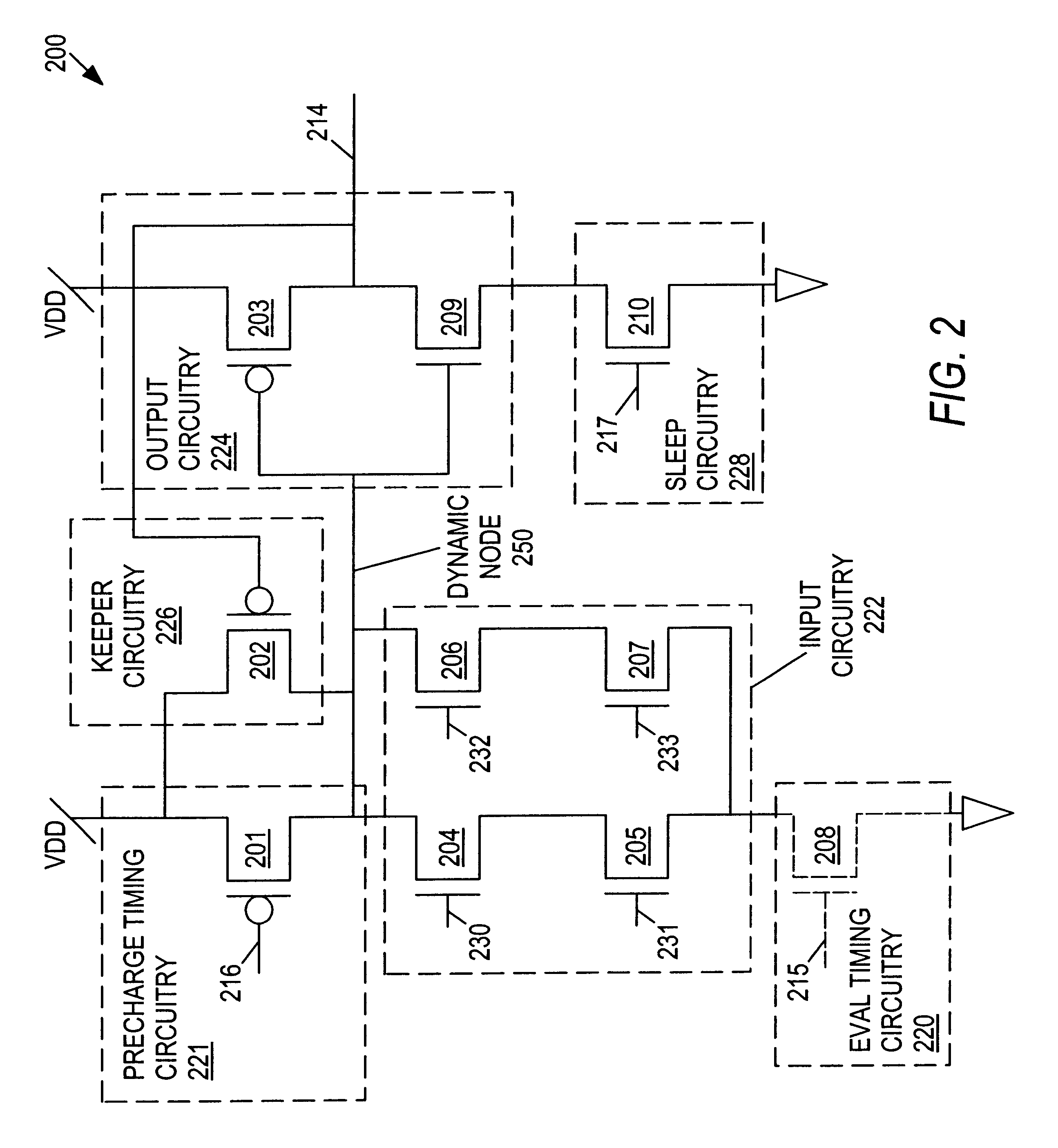

Low leakage sleep mode for dynamic circuits

InactiveUS6545512B2Power reduction by control/clock signalElectric pulse generatorEvaluation IntervalLow voltage

In one aspect, a method for a sleep mode in a dynamic circuit includes driving a dynamic node to an operating voltage state during a precharge interval by precharge timing circuitry coupled to the dynamic node and a voltage source responsive to a precharge signal. The dynamic node is selectively pulled to a low voltage state during an evaluation interval by input circuitry coupled to the dynamic node responsive to one or more input signals. The dynamic node voltage is inverted by output circuitry coupled to the dynamic node and to an output node. The output node is isolated from ground during a sleep interval responsive to a sleep signal by sleep circuitry coupled to the output circuitry.

Owner:INT BUSINESS MASCH CORP

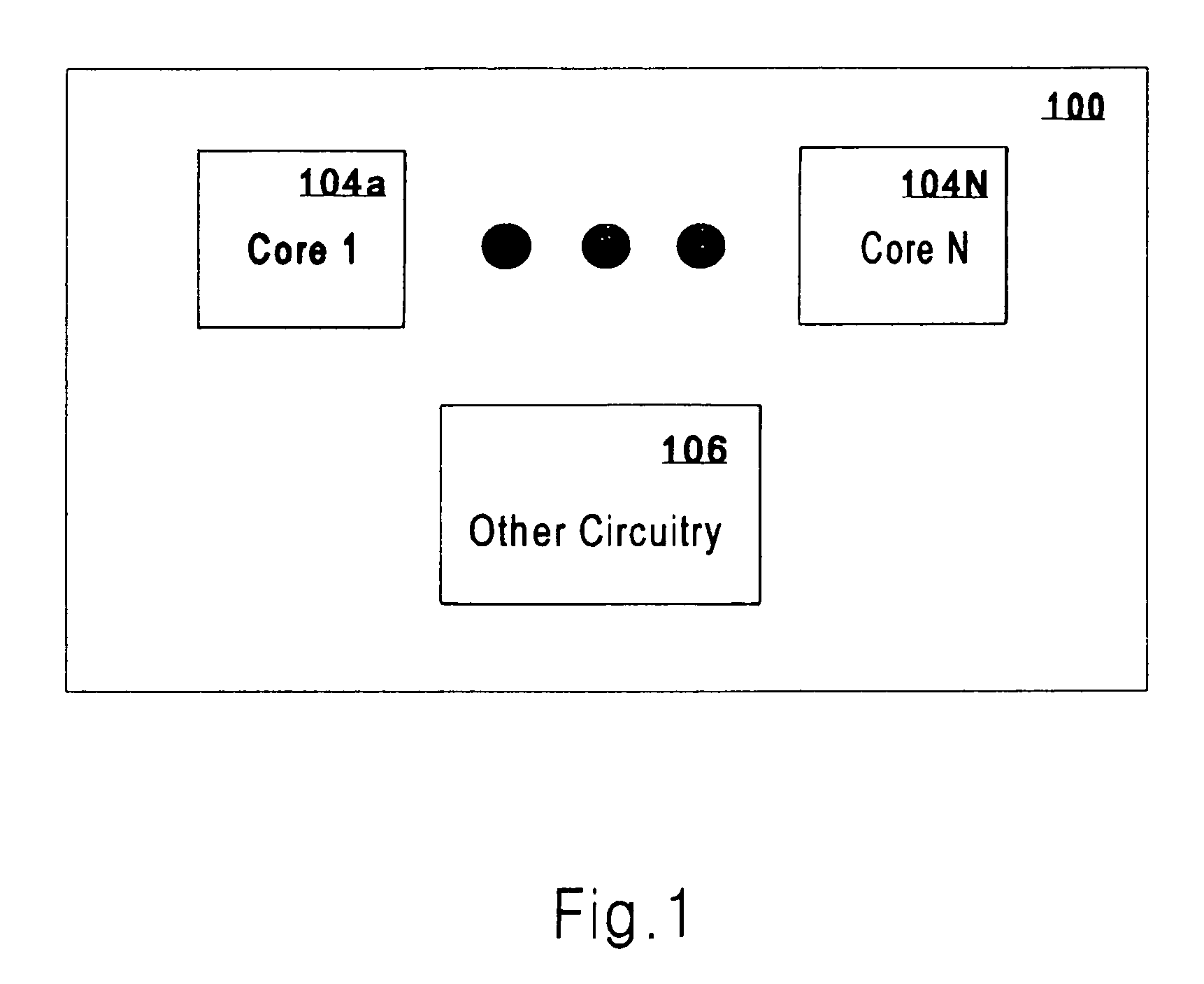

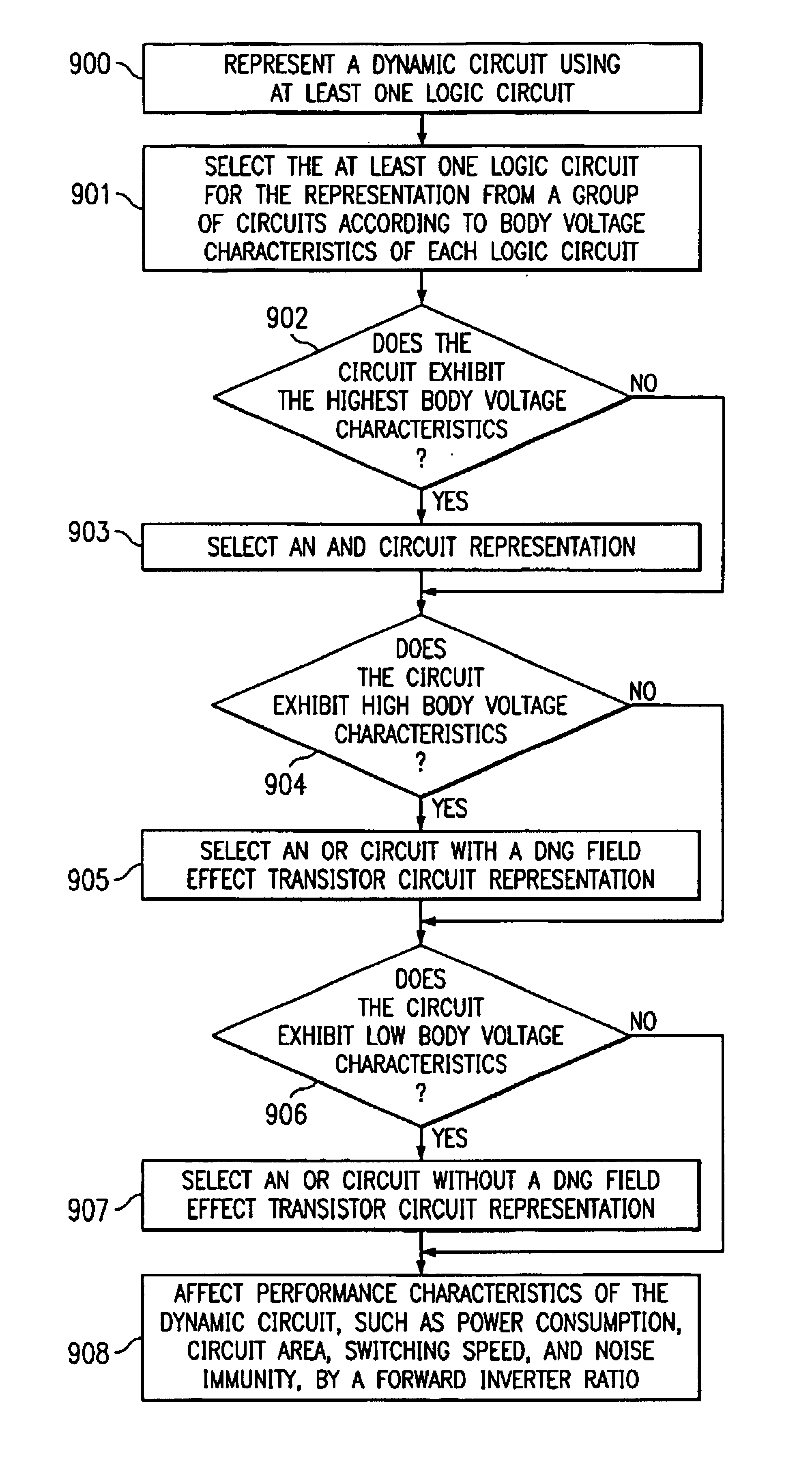

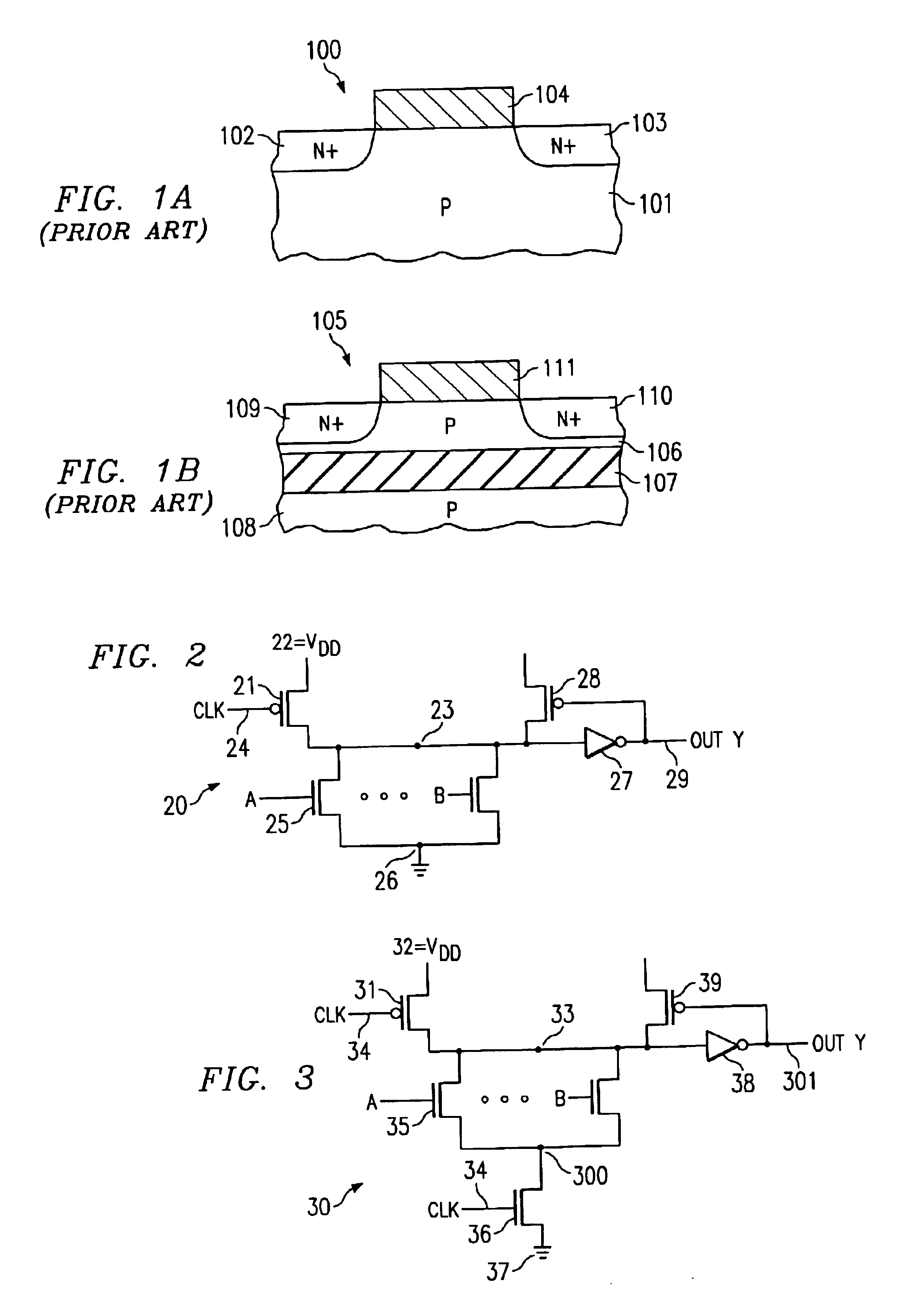

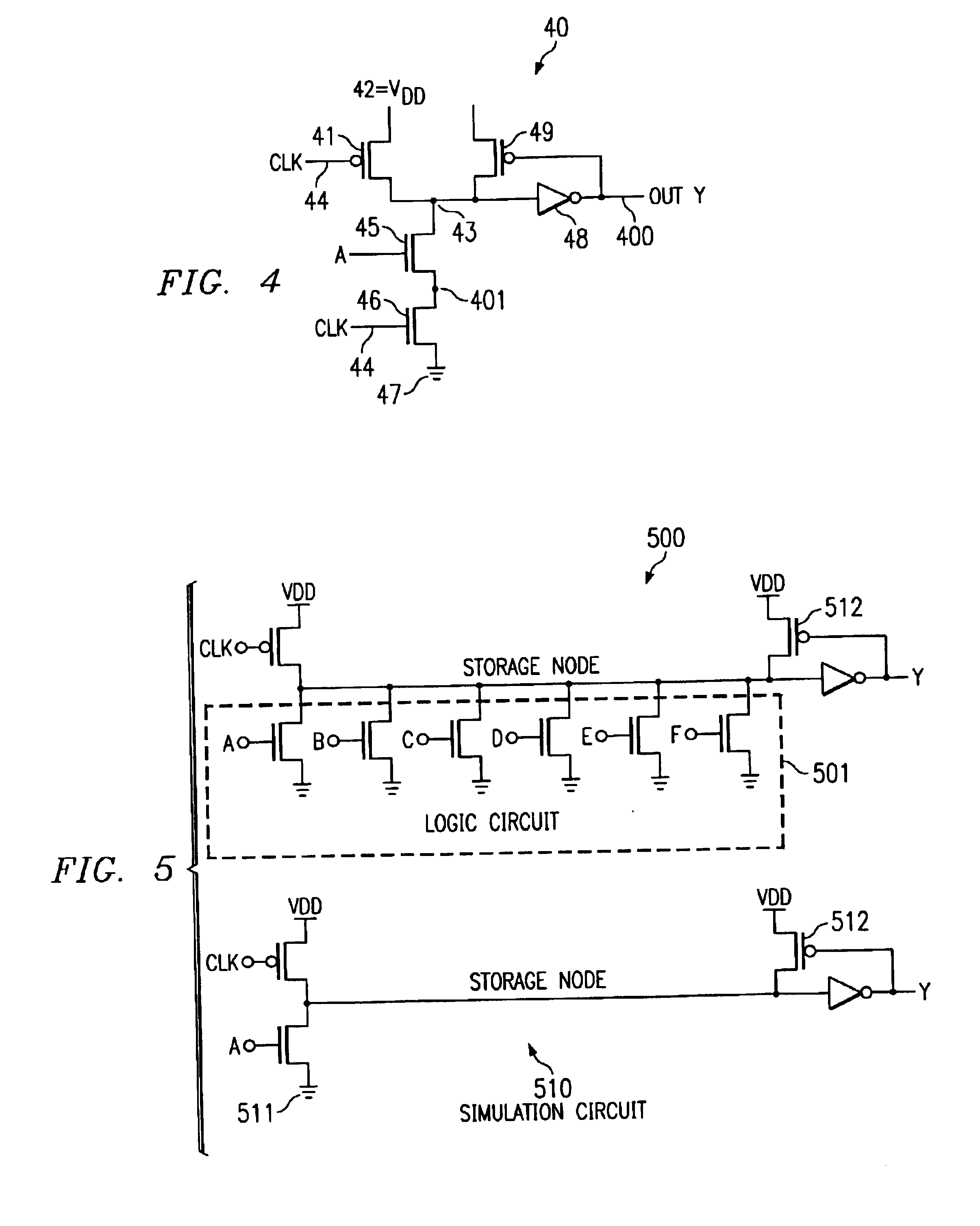

System and method for designing dynamic circuits in a SOI process

InactiveUS6931607B2Solid-state devicesSemiconductor/solid-state device manufacturingField-effect transistorLogic circuitry

A system and method is disclosed for designing a dynamic circuit in a silicon-on-insulator (SOI) process comprising the steps of representing the dynamic circuit using at least one logic circuit, wherein the at least one logic circuit is selected from a group consisting of: an OR circuit with a DNG field effect transistor (FET), an OR circuit, and an AND circuit, and wherein the at least one logic circuit is selected according to body voltage characteristics of each circuit in the group.

Owner:SAMSUNG ELECTRONICS CO LTD

Dynamic Design Partitioning For Diagnosis

Aspects of the invention relate to techniques for fault diagnosis based on dynamic circuit design partitioning. According to various implementations of the invention, a sub-circuit is extracted from a circuit design based on failure information of one or more integrated circuit devices. The extraction process may comprise combining fan-in cones of failing observation points included in the failure information. The extraction process may further comprise adding fan-in cones of one or more passing observation points to the combined fan-in cones of the failing observation points. Clock information of test patterns and / or layout information of the circuit design may be extracted and used in the sub-circuit extraction process. The extracted sub-circuit may then be used for diagnosing the one or more integrated circuit devices.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

Semiconductor integrated circuit

InactiveUS7282957B2Guaranteed uptimeAvoid changeLogic circuits characterised by logic functionElectric pulse generatorData selectionEngineering

Owner:PANASONIC CORP