Patents

Literature

171 results about "Circuit extraction" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The electric circuit extraction or simply circuit extraction, also netlist extraction, is the translation of an integrated circuit layout back into the electrical circuit (netlist) it is intended to represent. This extracted circuit is needed for various purposes including circuit simulation, static timing analysis, signal integrity, power analysis and optimization, and logic to layout comparison. Each of these functions require a slightly different representation of the circuit, resulting in the need for multiple layout extractions. In addition, there may be a postprocessing step of converting the device-level circuit into a purely digital circuit, but this is not considered part of the extraction process.

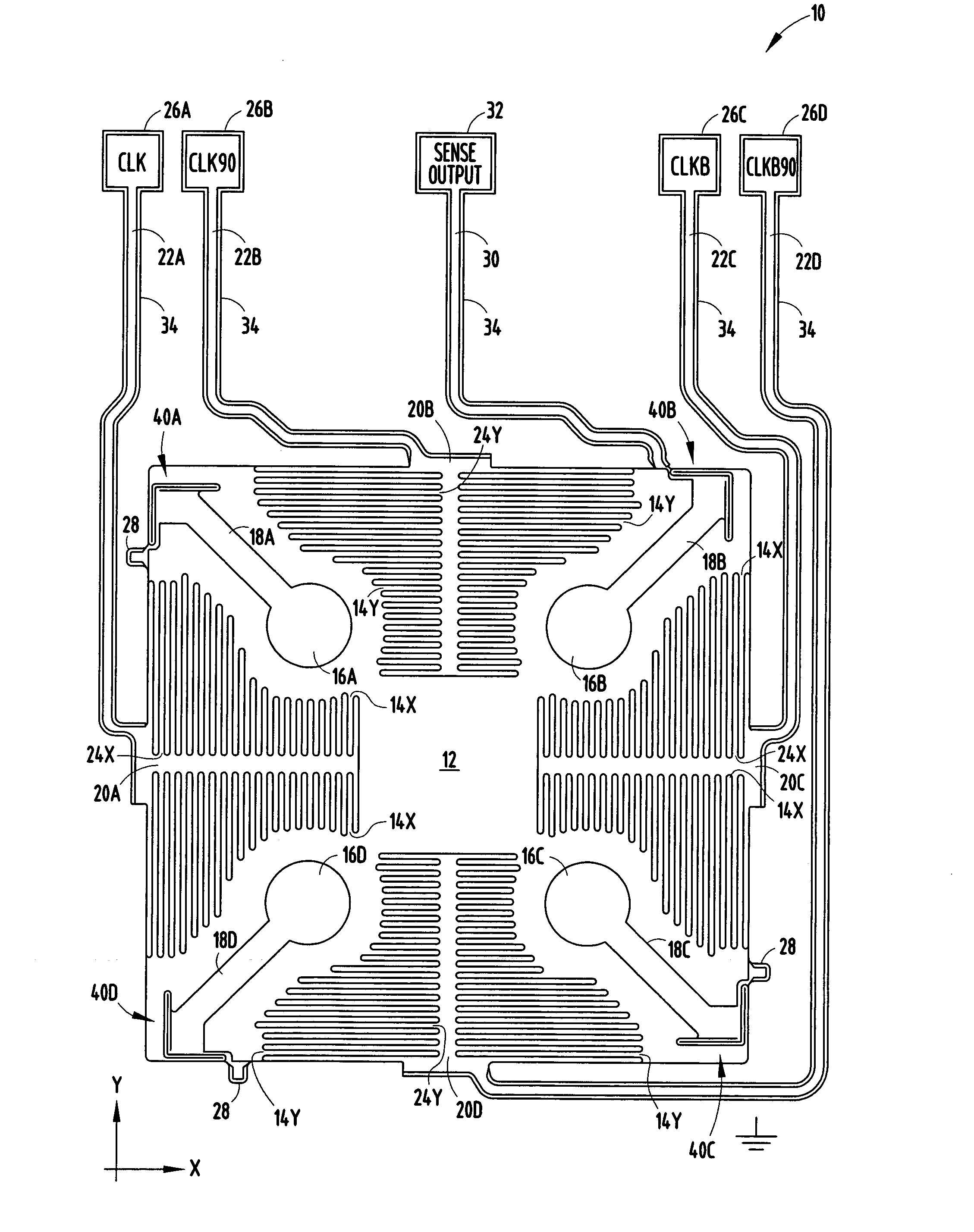

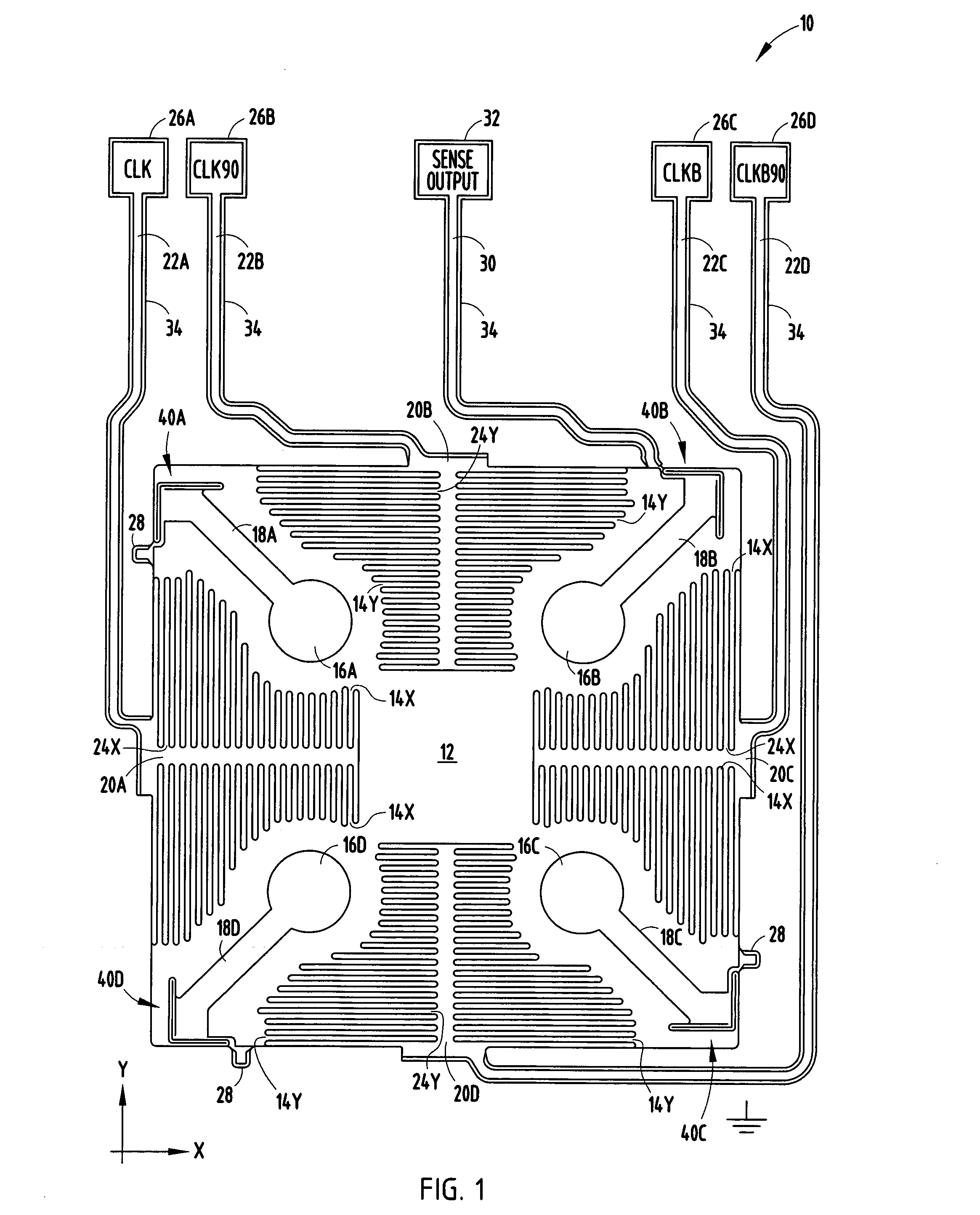

Clock generator for generating accurate and low-jitter clock

ActiveUS6900676B1Accurate and low jitterPulse automatic controlGenerating/distributing signalsControl signalPhase difference

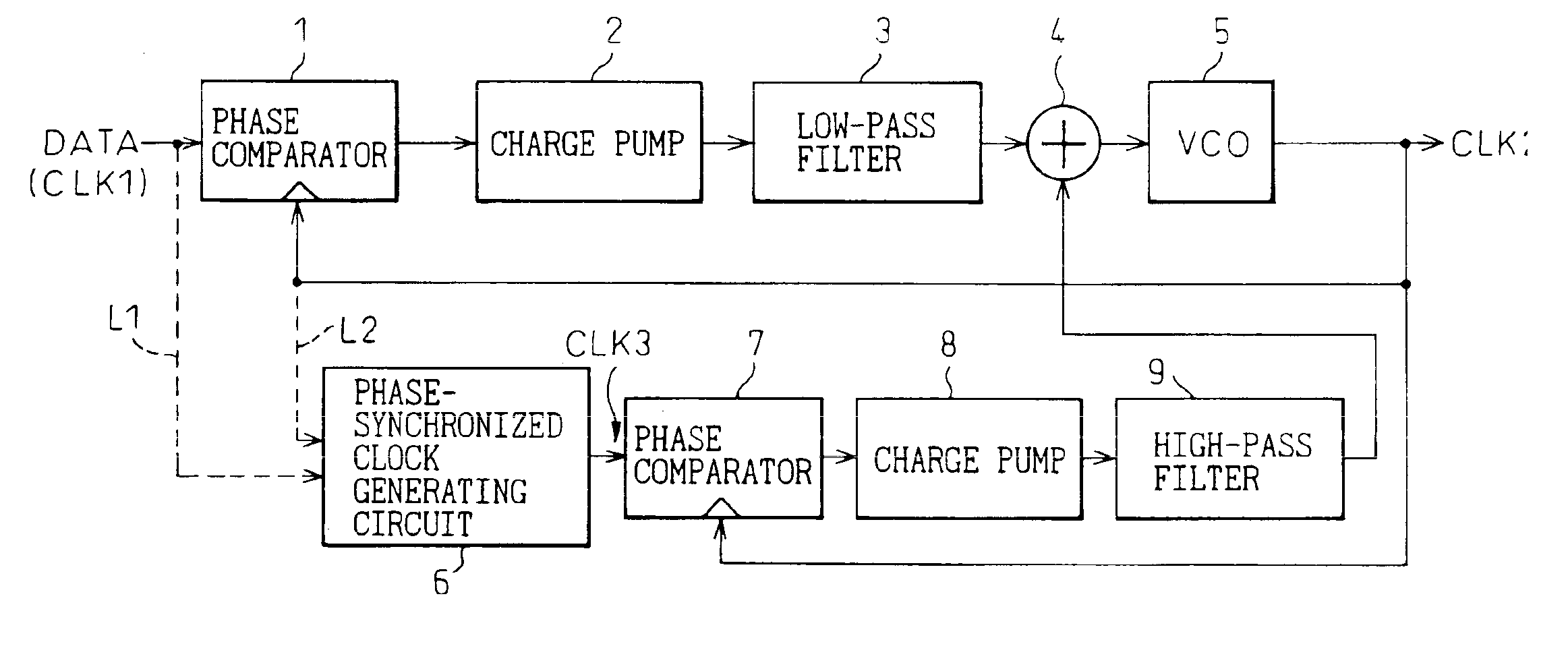

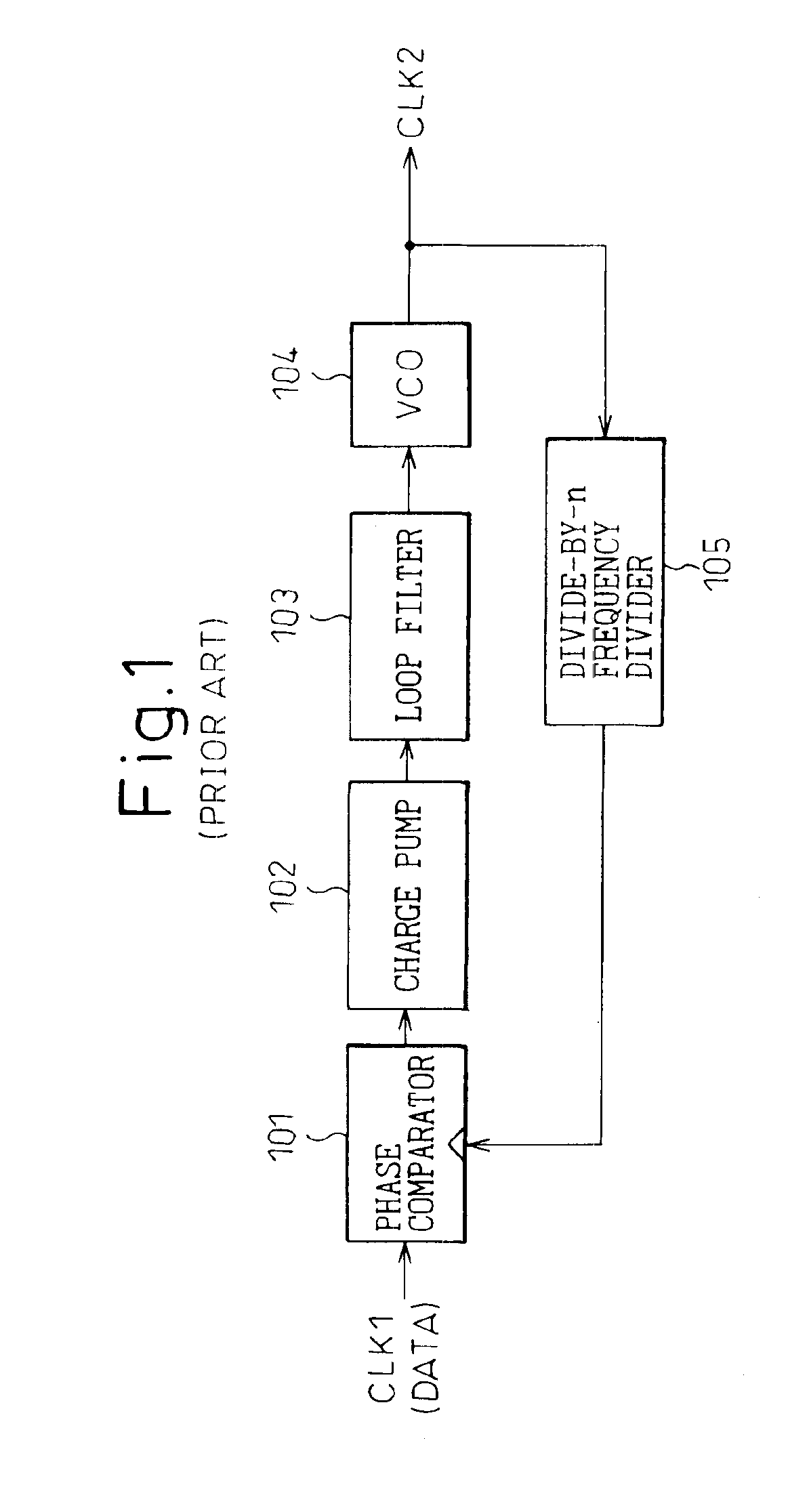

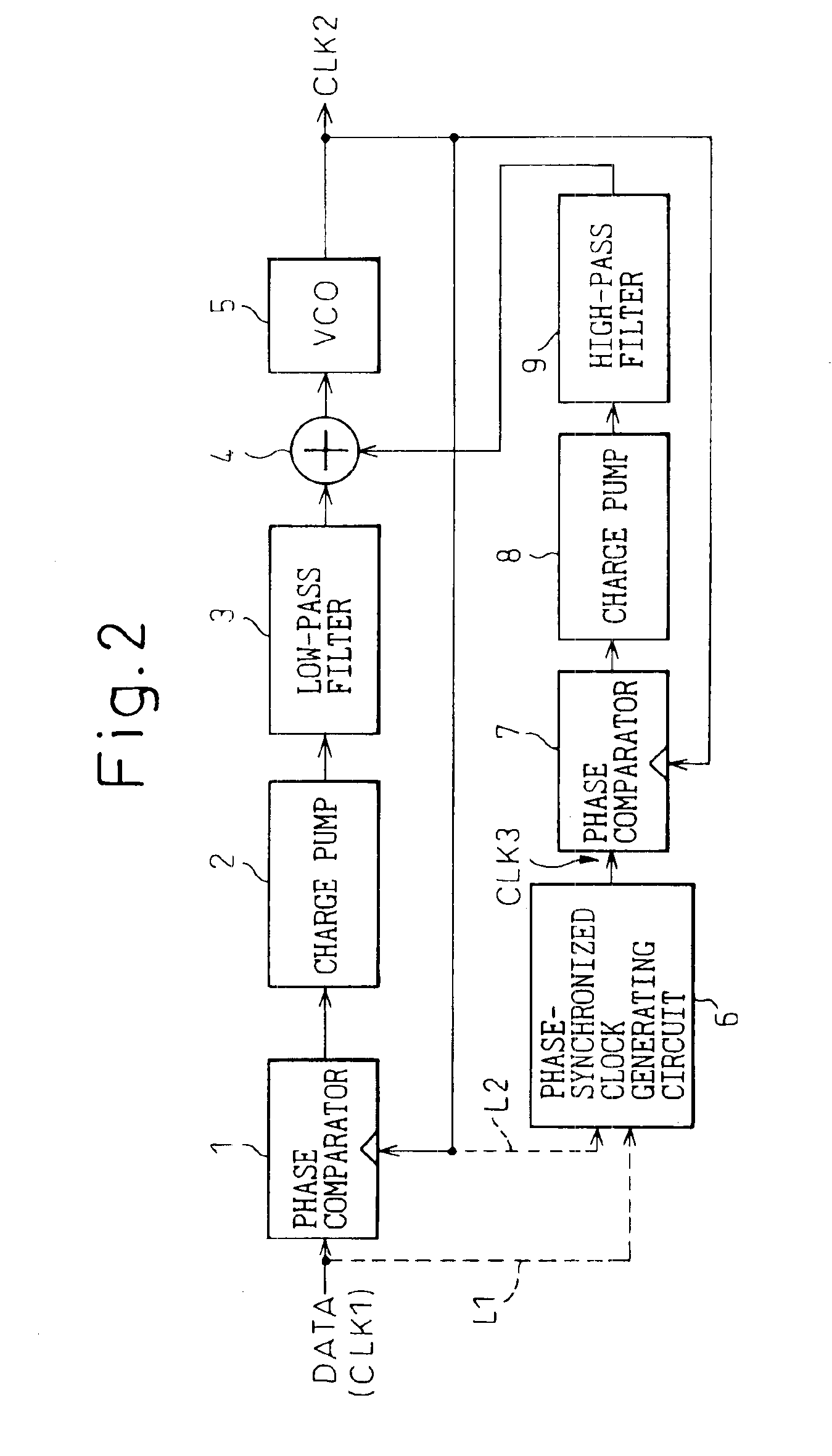

A clock generator has a clock generating circuit, a phase difference detection circuit, and a control signal generating circuit. The clock generating circuit has a function for varying a clock phase in accordance with a control signal, the phase difference detection circuit compars the clock phase output from the clock generating circuit with a phase of a reference waveform, and detecting a phase difference therebetween, and the control signal generating circuit generates a control signal for controlling the clock phase of the clock generating circuit, based on phase difference information obtained from the phase difference detection circuit. The phase difference detection circuit has a plurality of phase detection units, at least one of the plurality of phase detection units carries out a direct phase detection in which a phase of the clock is directly compared with the phase of the reference waveform, and at least the other one of the plurality of phase detection units carries out an indirect phase detection using a phase-synchronized waveform generating circuit generating a waveform synchronized in phase with the reference waveform or an output of the clock generating circuit and a phase information extracting circuit extracting phase information from the phase-synchronized waveform.

Owner:FUJITSU LTD

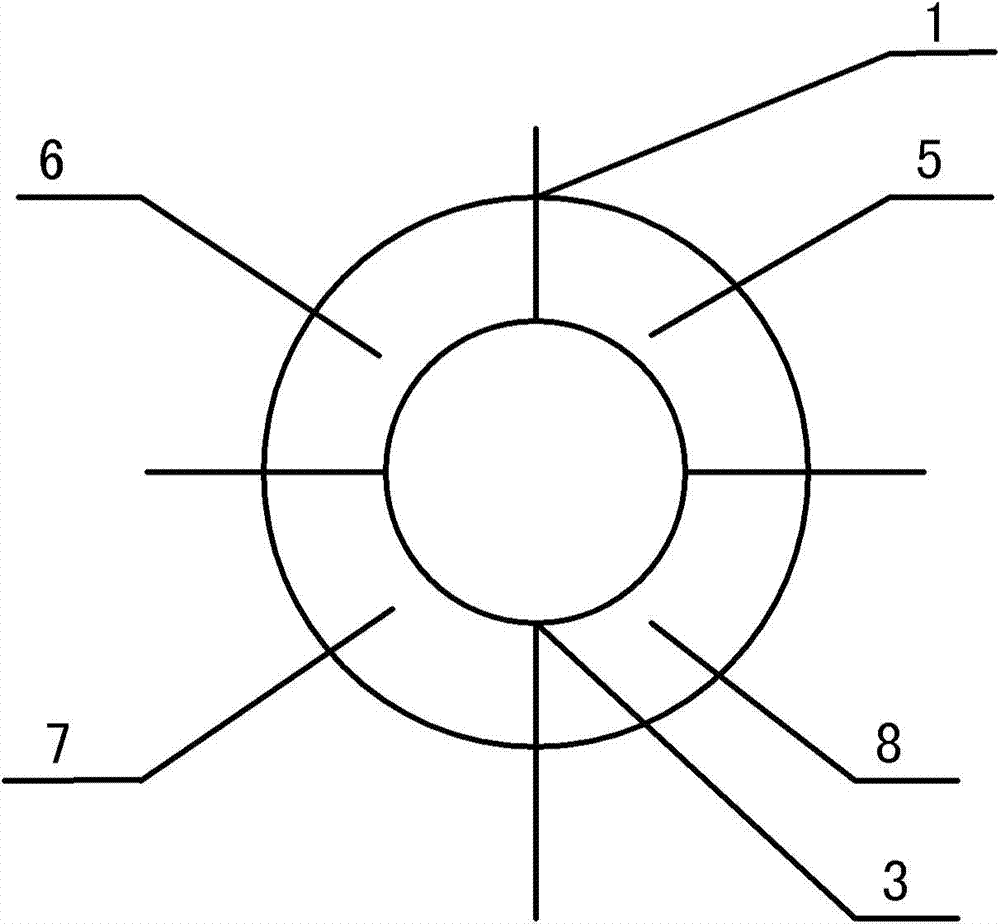

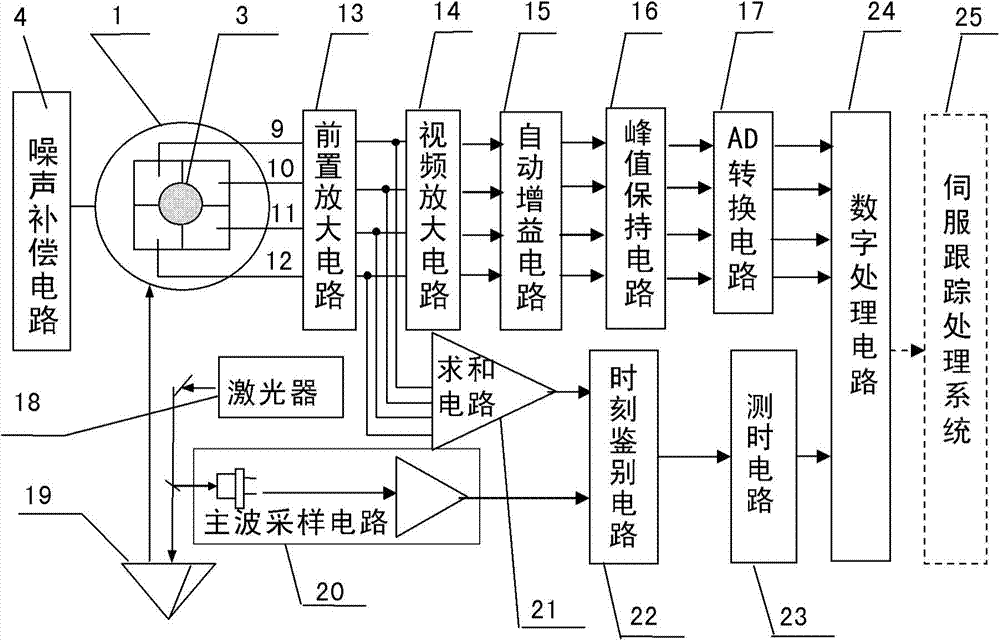

Measuring device and method for target line-of-sight angel offset and distance

ActiveCN103499819AHigh sensitivityEnsuring Gain StabilityElectromagnetic wave reradiationMeasurement devicePhotodetector

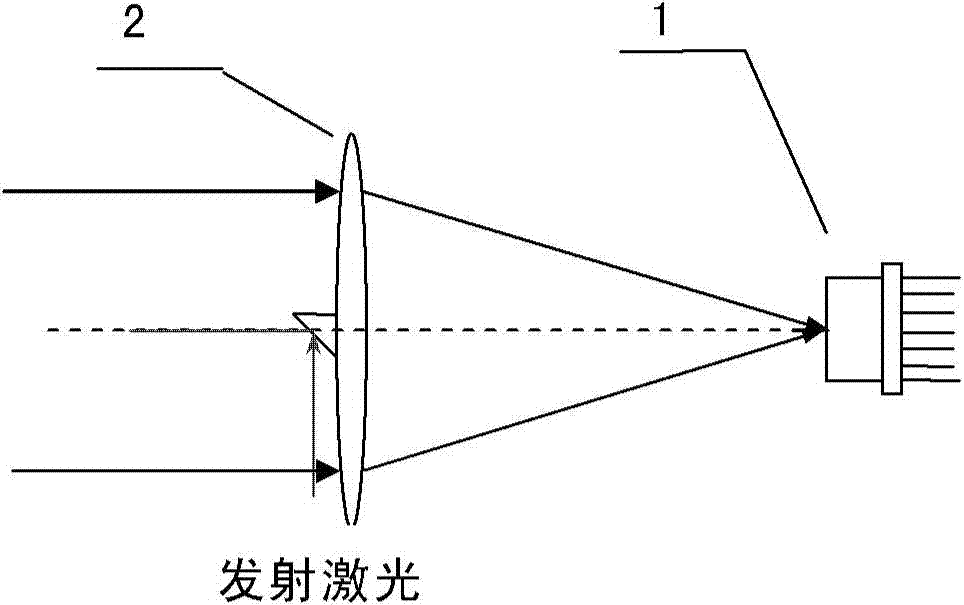

The invention provides a measuring device and method for the target line-of-sight angel offset and distance. The device is composed of a four-quadrant avalanche photodetector, a receiving and sending optical unit, a noise compensation circuit, a four-circuit front amplification circuit, a video amplification circuit, an automatic gain amplification circuit, a peak keeping circuit, an AD conversion circuit, a laser, a dominant wave sampling circuit, a summing circuit, a time identifying circuit, a time test circuit and a digital processing circuit, wherein the receiving and sending optical unit enables narrow pulse laser rays emitted by the laser to be converged on the photoelectric detector to form echo light spots after target reflection, photovoltaic conversion of the four-quadrant avalanche photodetector, front amplification, video amplification and automatic gain amplification are conducted, narrow-pulse peak keeping is conducted, transmission of the AD conversion circuit is conducted, and the digital processing circuit extracts the digital line-of-sight angel offset; summing is conducted on the four-circuit front amplification circuit, the dominant wave sampling circuit is combined, the time identifying circuit determines laser emitting and echo coming and returning time, the time is transmitted to the time identifying circuit to be measured, and the digital processing circuit decodes the corresponding distance.

Owner:INST OF OPTICS & ELECTRONICS - CHINESE ACAD OF SCI

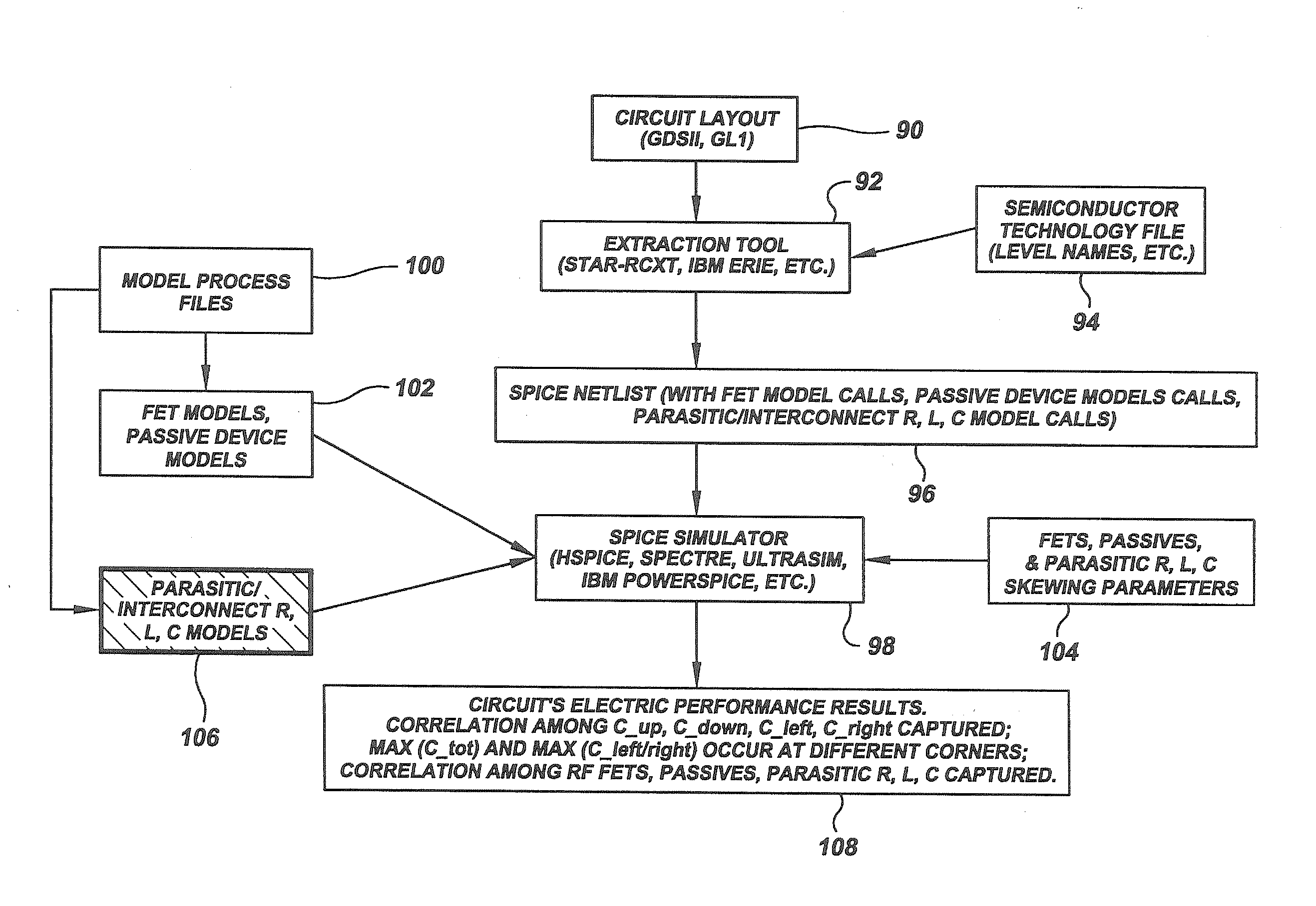

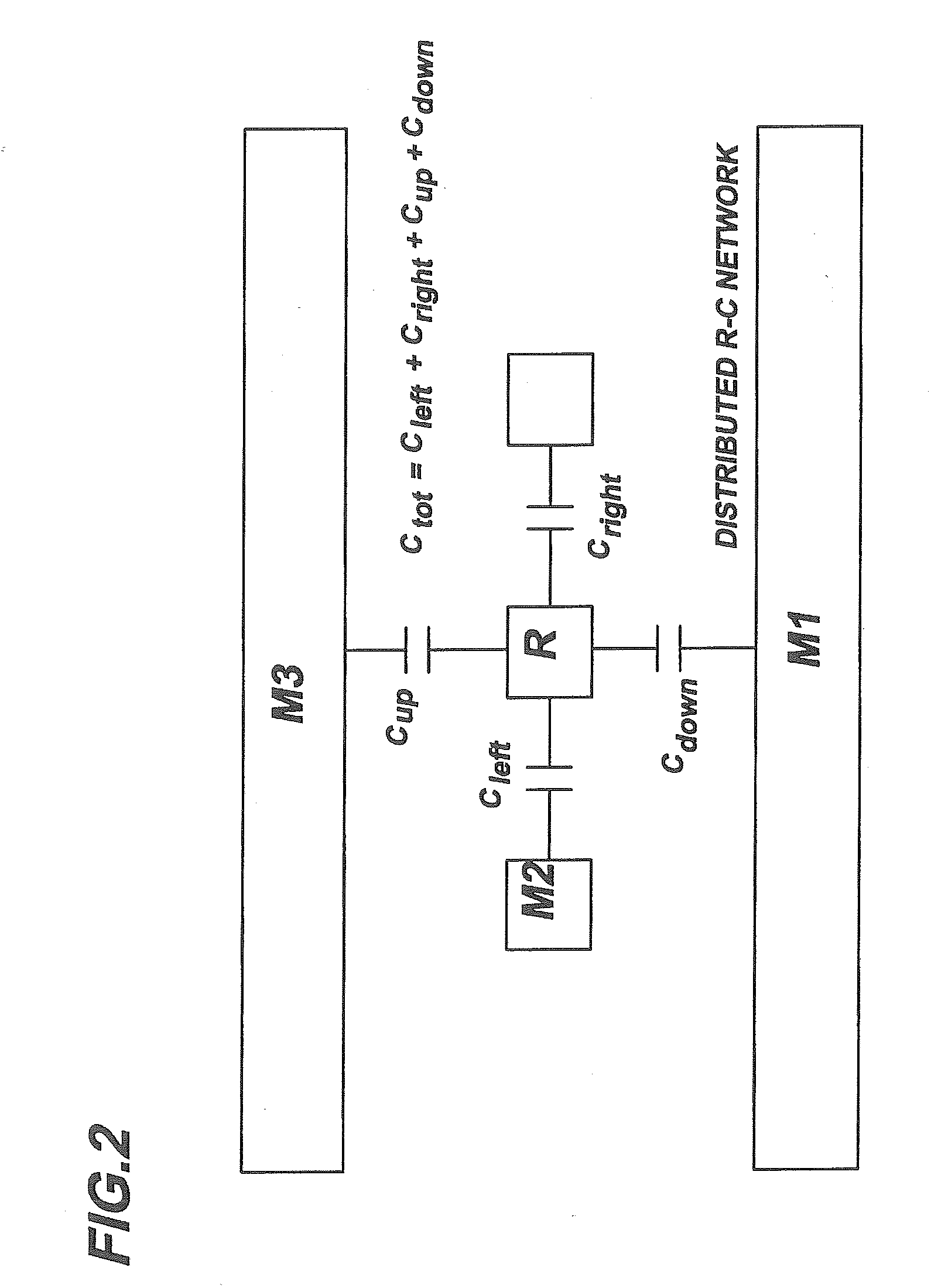

Method for treating parasitic resistance, capacitance, and inductance in the design flow of integrated circuit extraction, simulations, and analyses

InactiveUS20080028353A1Detecting faulty computer hardwareComputer aided designElectrical resistance and conductanceCapacitance

An extraction, simulation, and analysis combined method is employed to account for the parasitic couplings from interconnect wires. Variations of parasitic resistance, capacitance, and inductance are used in circuit analysis calculators, including considering the variations of the parasitics on worst case circuit performance, skewing, and statistical Monte Carlo analysis. Each parasitic element is modeled as a call-up function with associated process distributions. Circuit analysis, such as a SPICE analysis is performed on the selected models.

Owner:IBM CORP

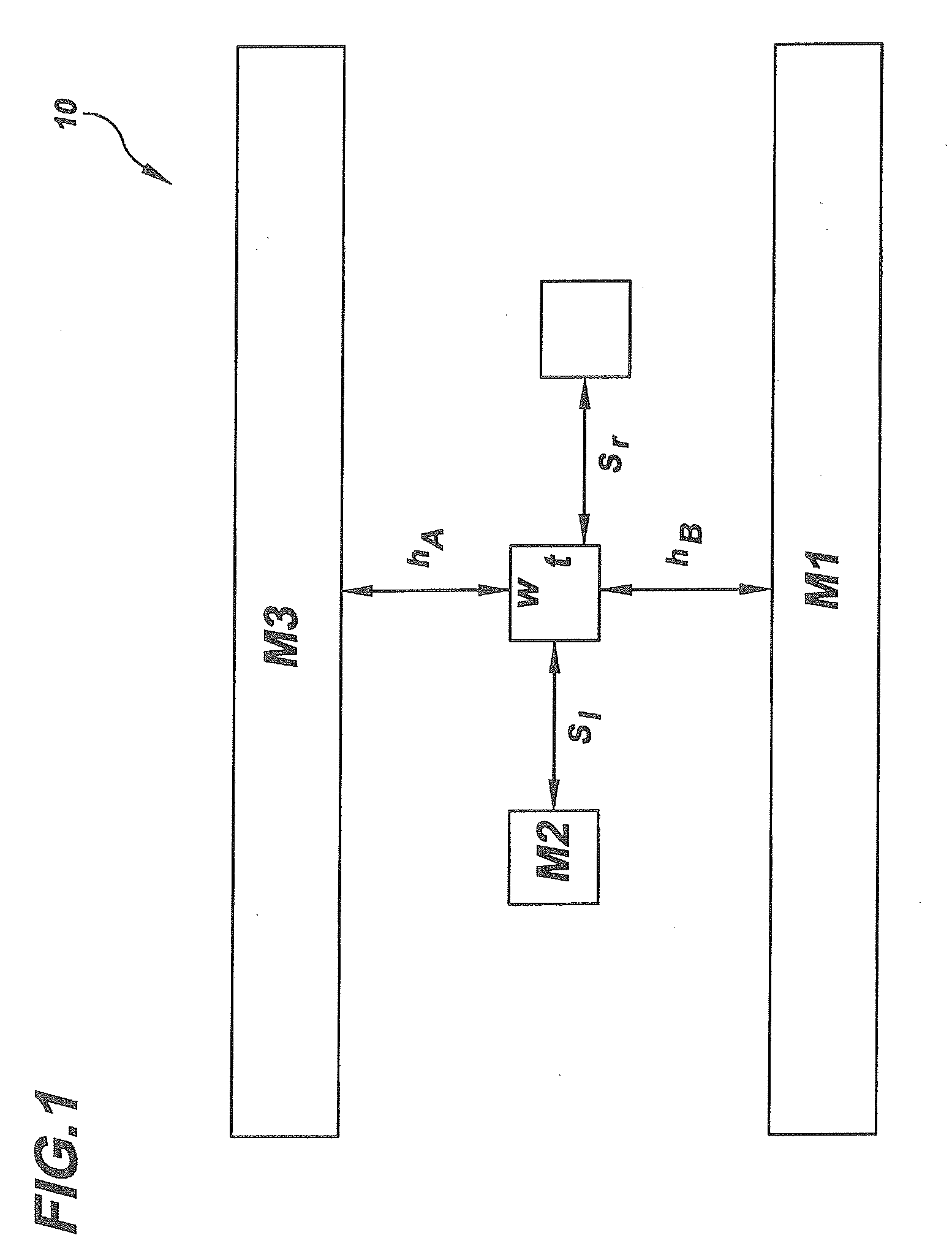

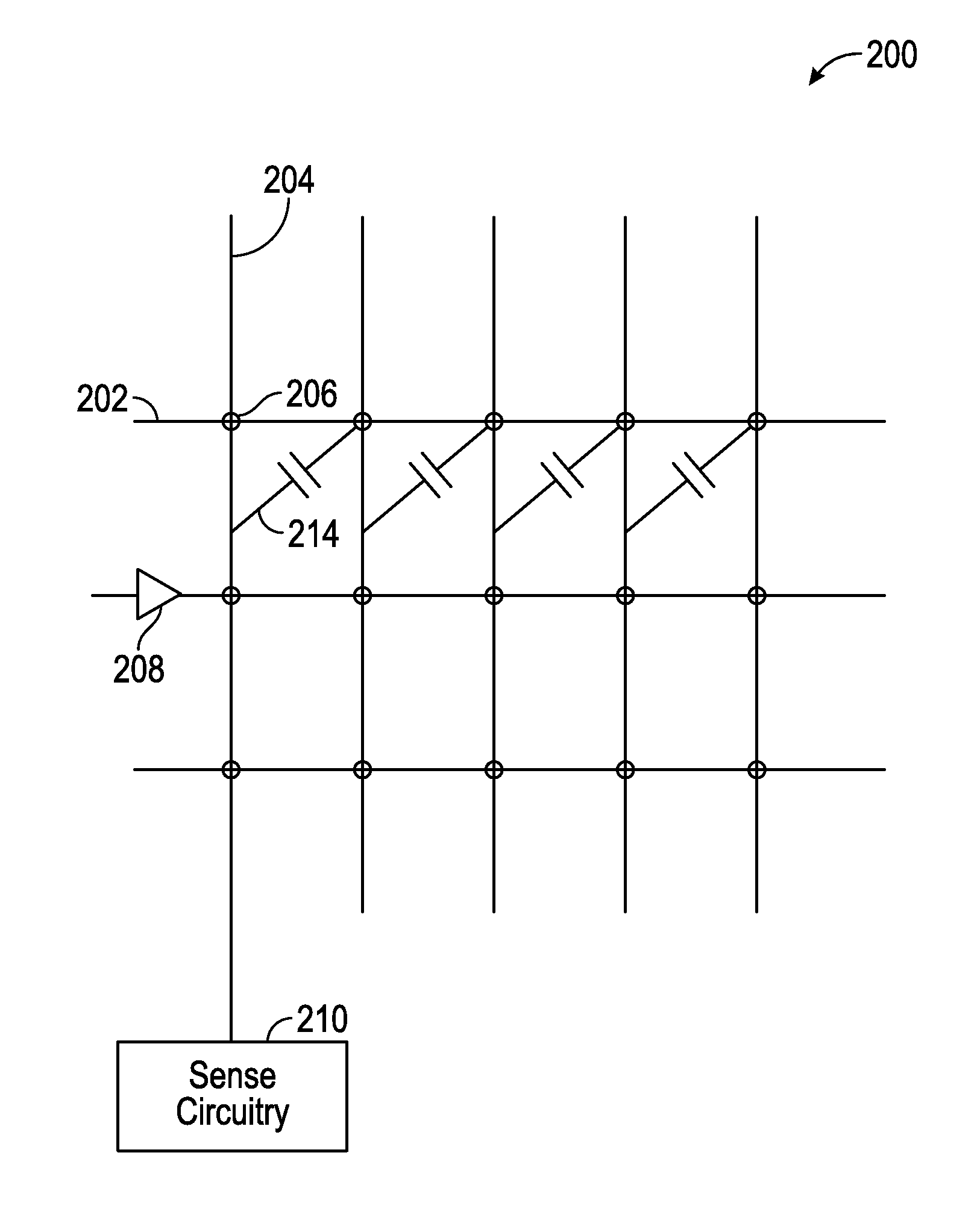

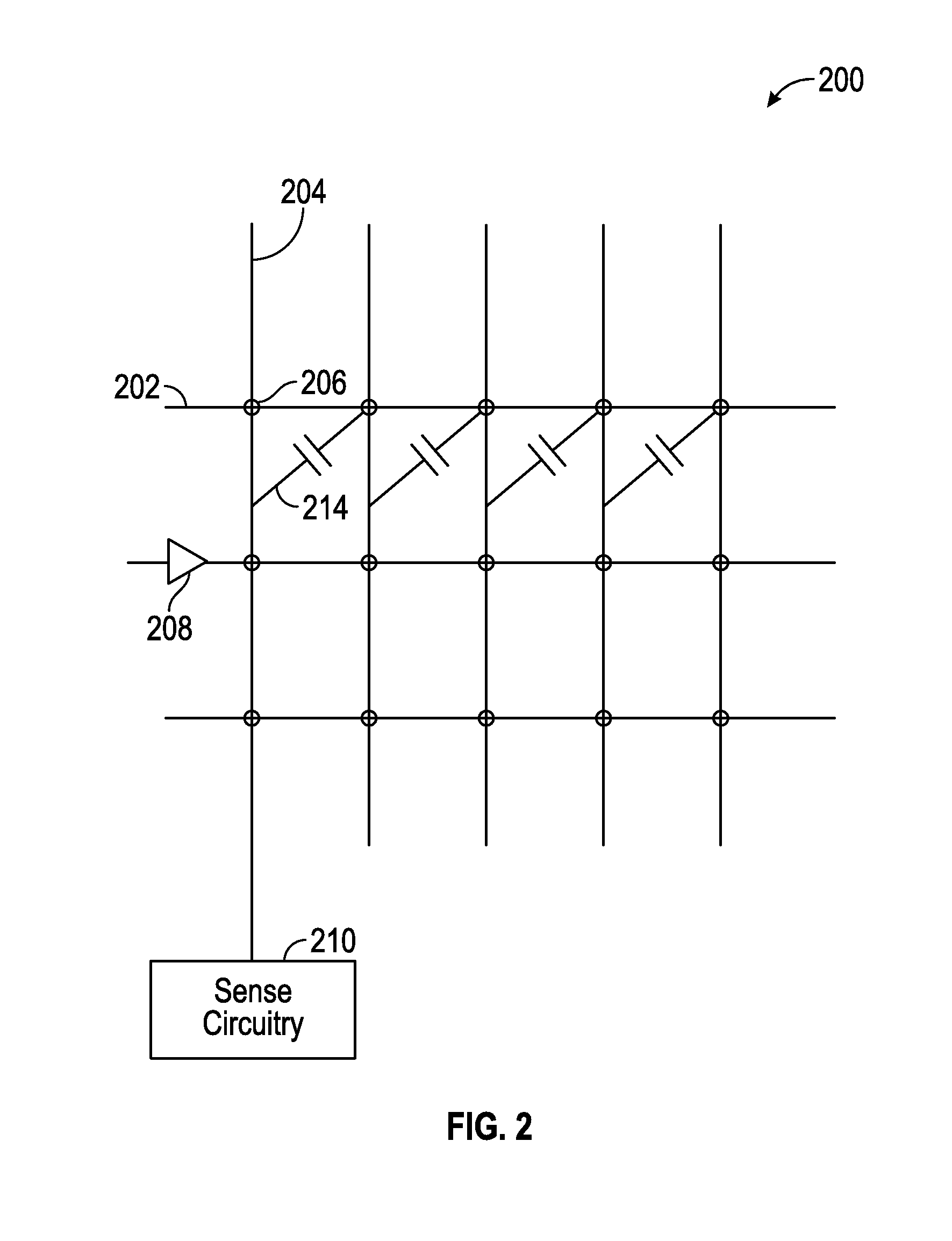

Simultaneous self- and mutual capacitance sensing

ActiveUS20150331535A1Reduced dynamic rangeEliminate offset effectsTelevision system detailsTelevision system scanning detailsCircuit extractionEngineering

A touch controller. The touch controller can include first sense circuitry configured to be coupled to a first electrode on a touch sensor panel, the first sense circuitry configured to sense a first self-capacitance associated with the first electrode, and a first mutual capacitance associated with the first electrode. In some examples, the first sense circuitry can be configured to sense the first self-capacitance and the first mutual capacitance simultaneously. In some examples, the touch controller can further include a first mixer and a second mixer coupled to the first sense circuitry, the first mixer configured to demodulate a first output from the first sense circuitry to extract information about the first self-capacitance from the first output, the second mixer configured to demodulate the first output from the first sense circuitry to extract information about the first mutual capacitance from the first output.

Owner:APPLE INC

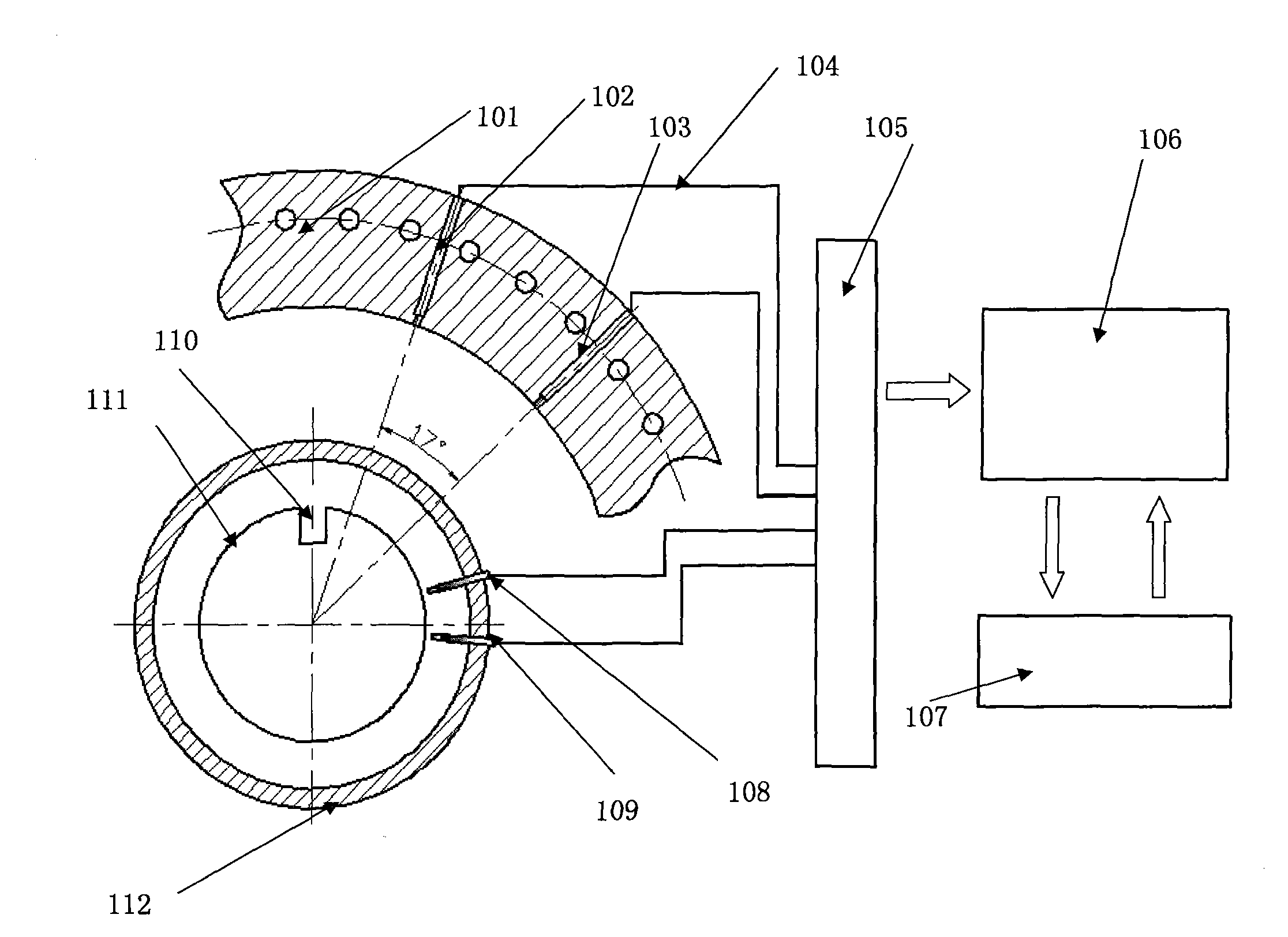

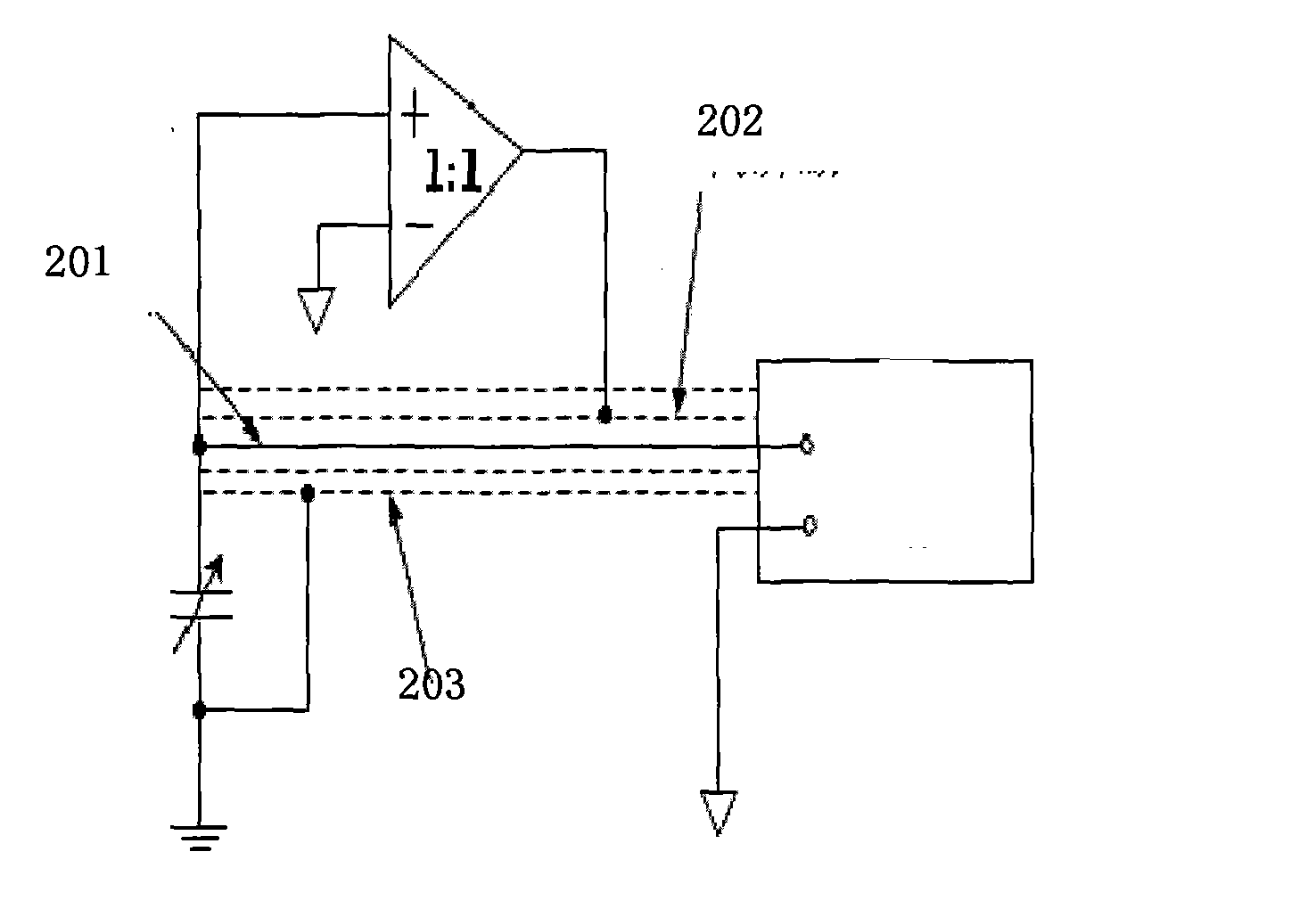

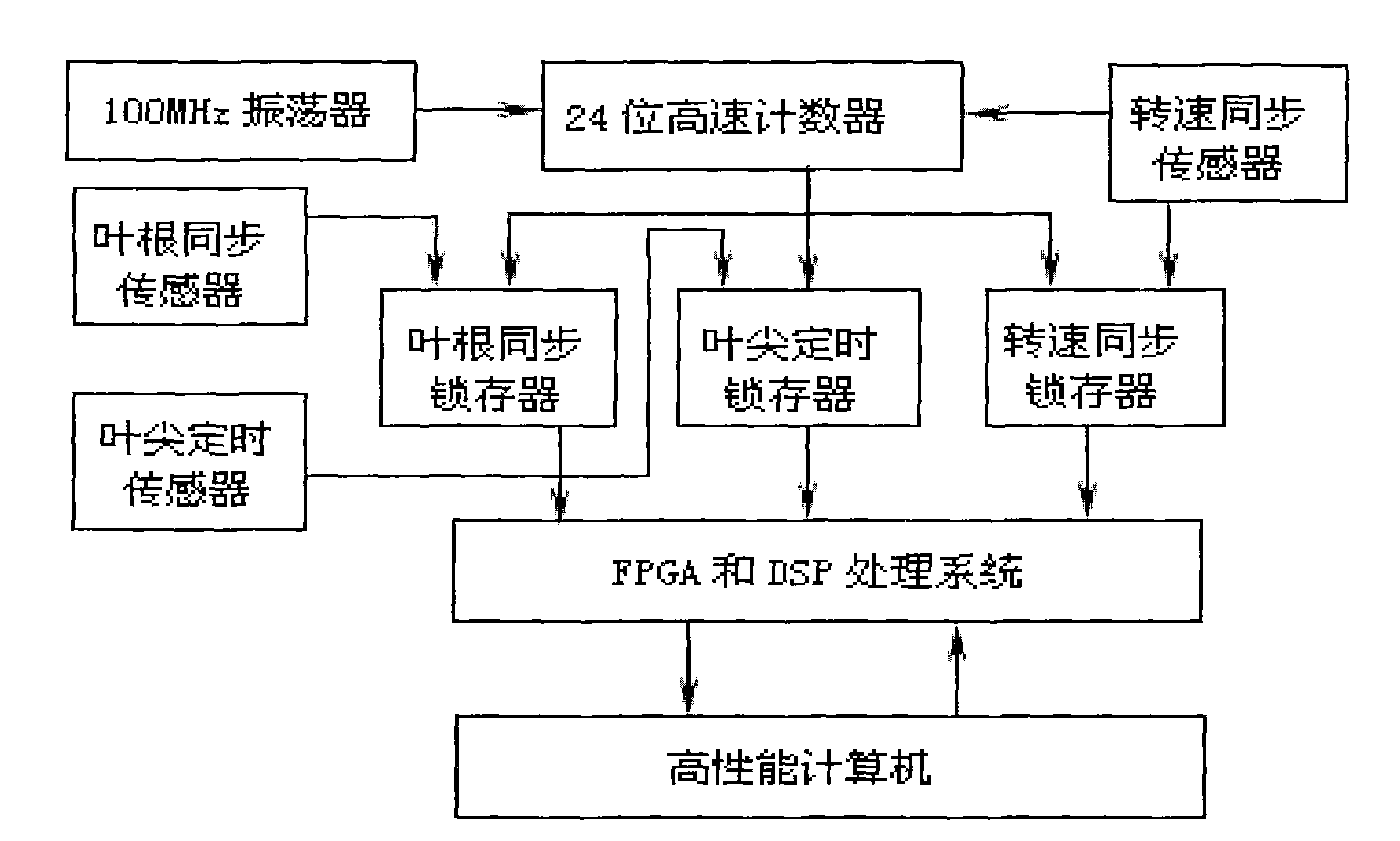

Real-time on-line monitoring apparatus of blade vibration of flue gas turbine

InactiveCN102735326AReal-time monitoring of vibrationHigh precisionSubsonic/sonic/ultrasonic wave measurementUsing electrical meansCapacitanceFlue gas

The invention relates to a real-time on-line monitoring apparatus of blade vibration of a flue gas turbine. The monitoring apparatus comprises blade tip timing sensors, an angle reference sensor, a rotating speed synchronization sensor, a preprocessing system, a data integrated processing card, and a computer. The blade tip timing sensors, the angle reference sensor, and the rotating speed synchronization sensor are connected with the preprocessing system that is connected with the data integrated processing card; and the data integrated processing card is connected with the computer. According to the invention, the sensors employ double-shielded capacitance impulsers; single-core double-shielded wires are utilized as transmission lines of output signals; and a driving cable technology is utilized to effectively reduce a random error introduced by an environmental interference; and a charge amplification circuit is used to extract a capacitance pulse signal, thereby eliminating the system error basically and improving the measurement accuracy of the system.

Owner:CHINA SPECIAL EQUIP INSPECTION & RES INST

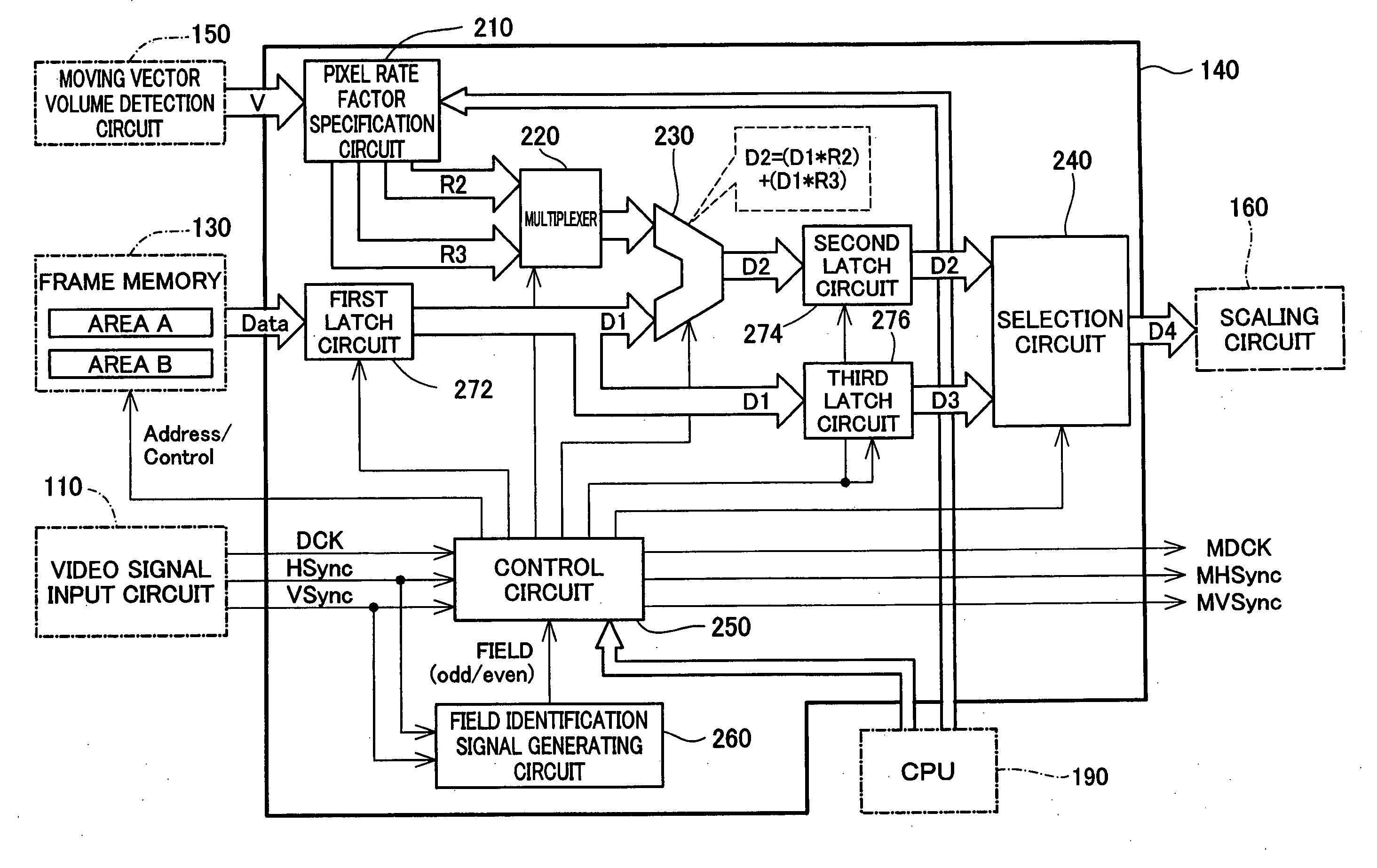

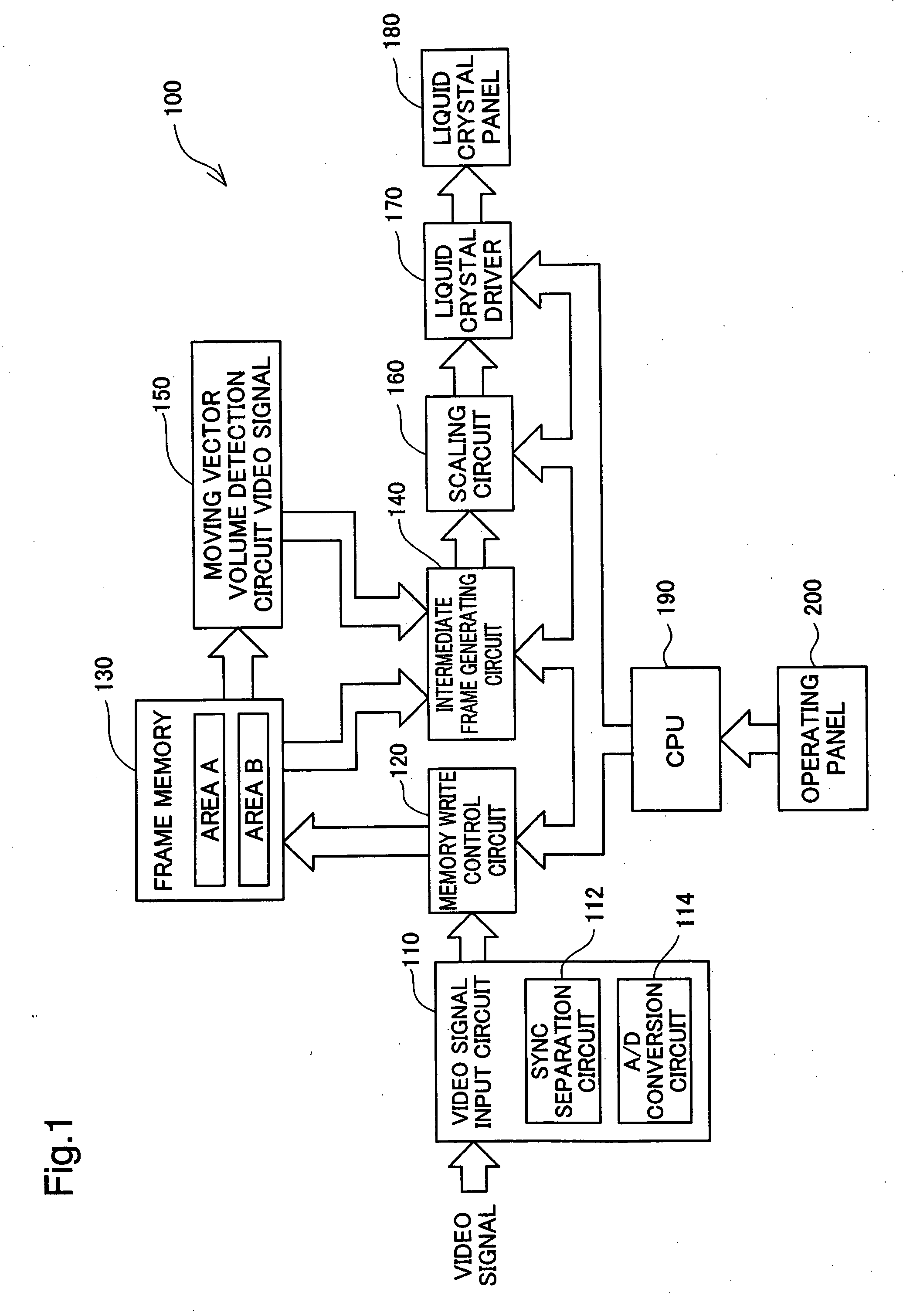

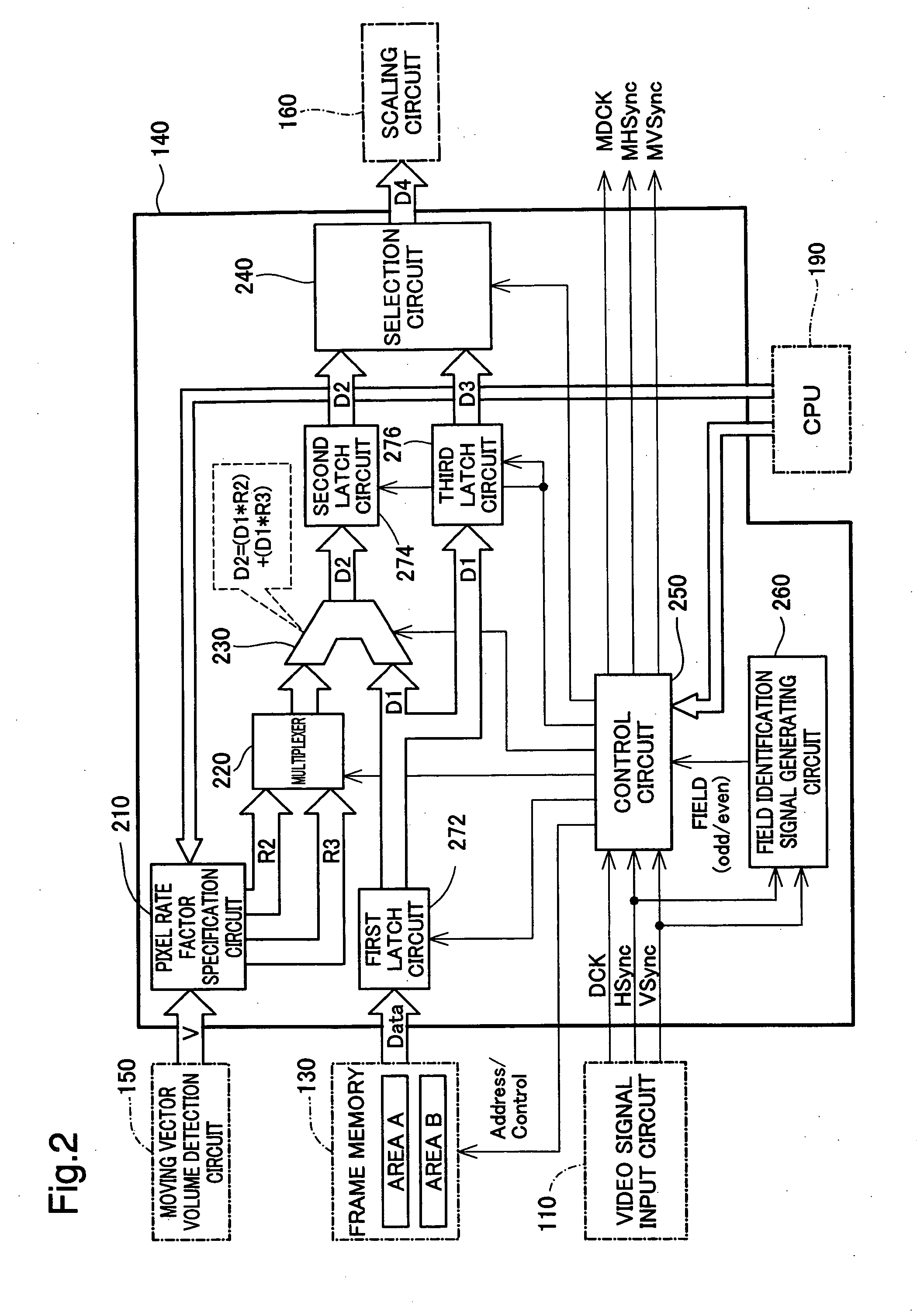

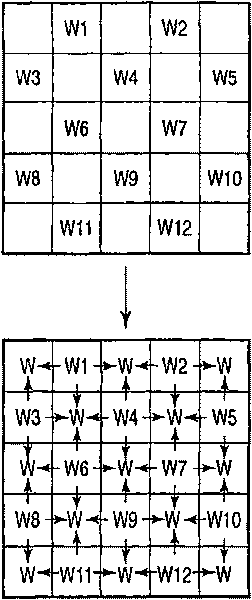

Moving image display device and method for moving image display

InactiveUS20070103585A1Avoid flickeringSmooth displayTelevision system detailsColor signal processing circuitsCircuit extractionComputer science

In the moving image display device of the invention, a synthesis circuit inputs signals representing specified values of pixel rate factors R2 and R3 from a pixel rate factor specification circuit, while inputting overscanned frame image data D1 in the units of pixels from a 1st latch circuit. The synthesis circuit extracts a preset number of pixels corresponding to the specified value of the pixel rate factor R2 from a prior frame image, while extracting a preset number of pixels corresponding to the specified value of the pixel rate factor R3 from a latter frame image. The positions of pixels to be extracted from the latter frame image are complementary to the positions of pixels to be extracted from the prior frame image. The synthesis circuit combines the extracted pixels of the prior frame image with the extracted pixels of the latter frame image by a logical OR operation to generate intermediate frame image data D2. This technique of the invention is significantly simpler than the prior art technique but still effectively prevents flicker in a moving image to ensure smooth display of the moving image.

Owner:SEIKO EPSON CORP

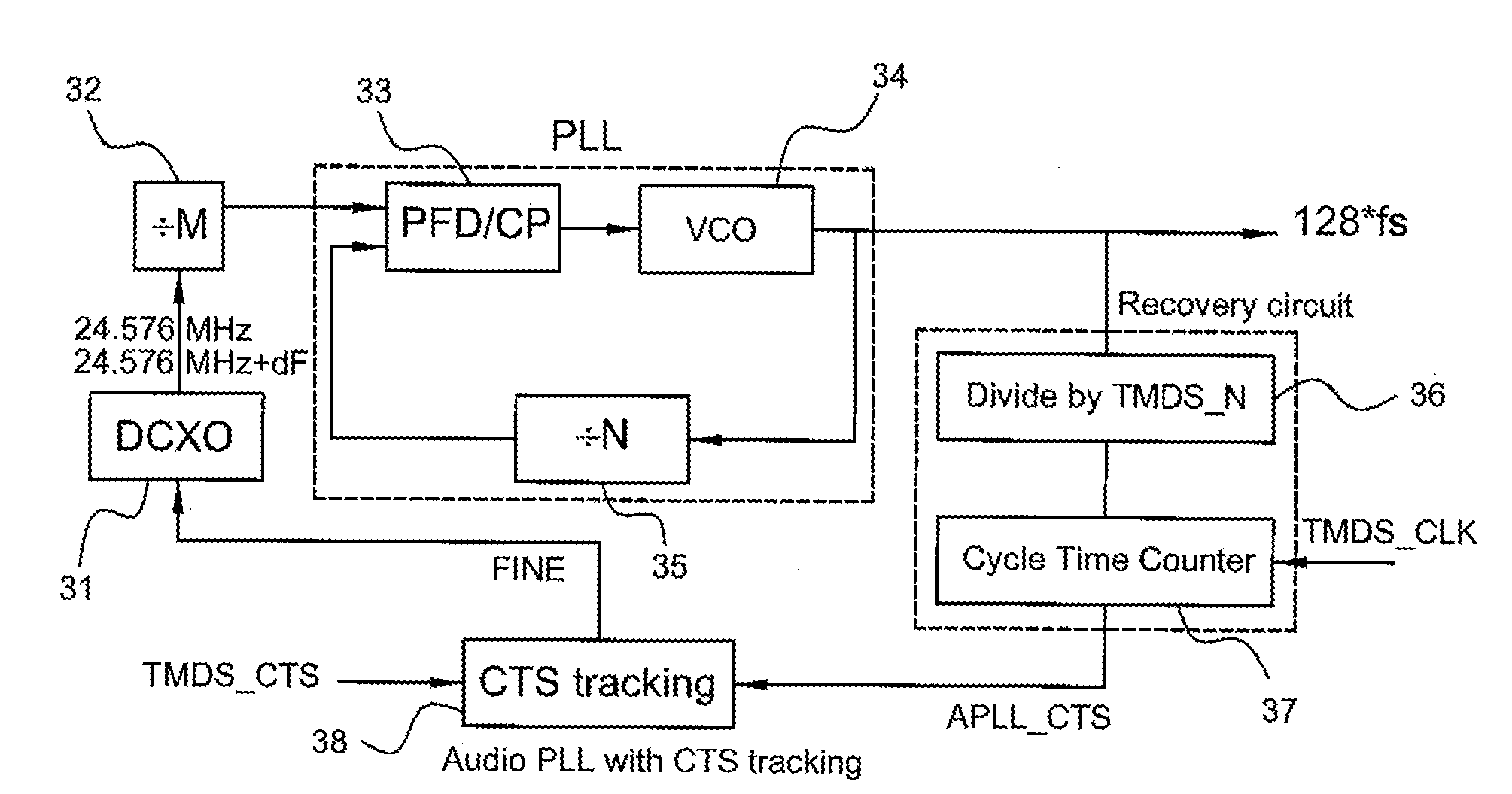

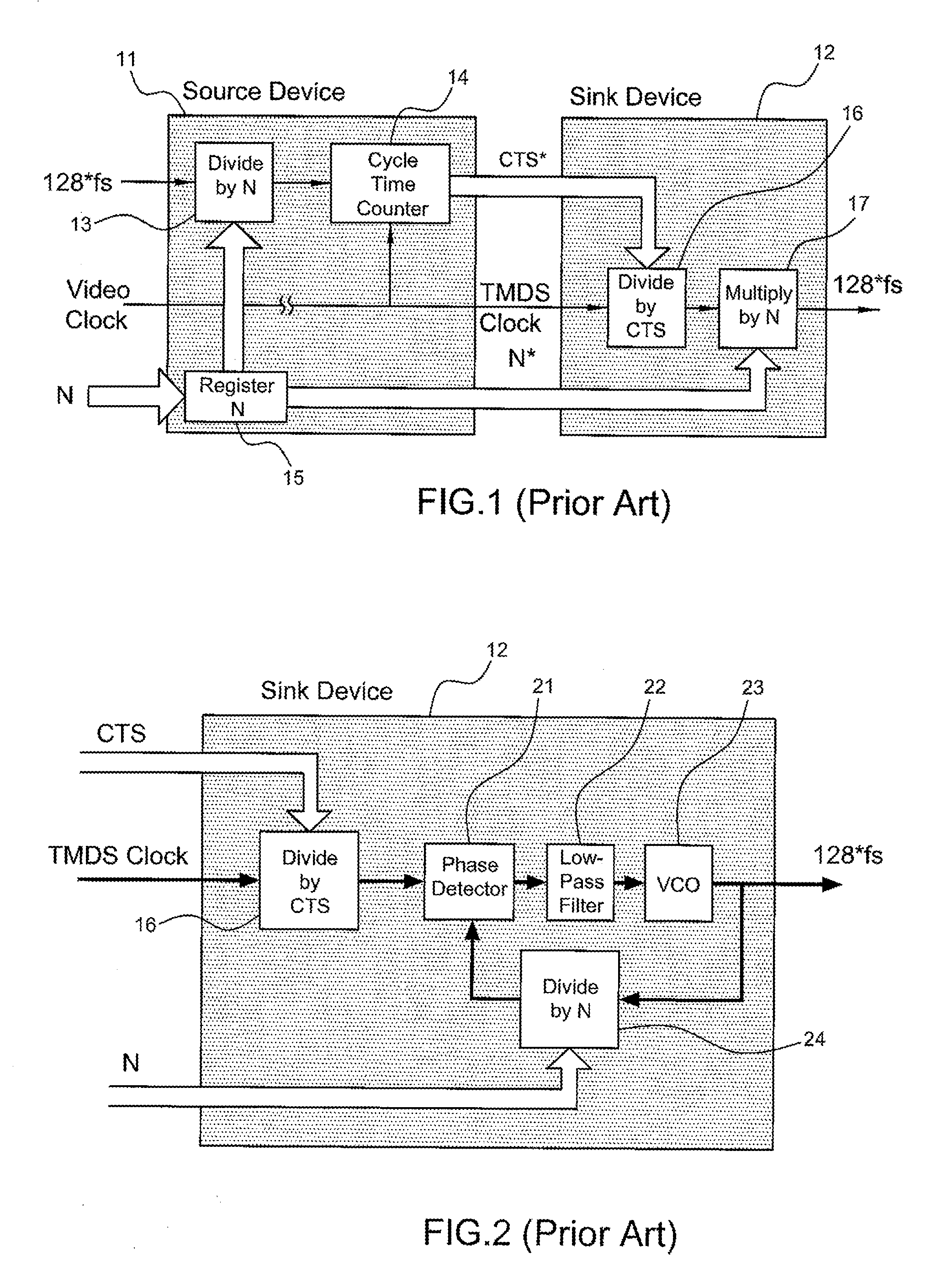

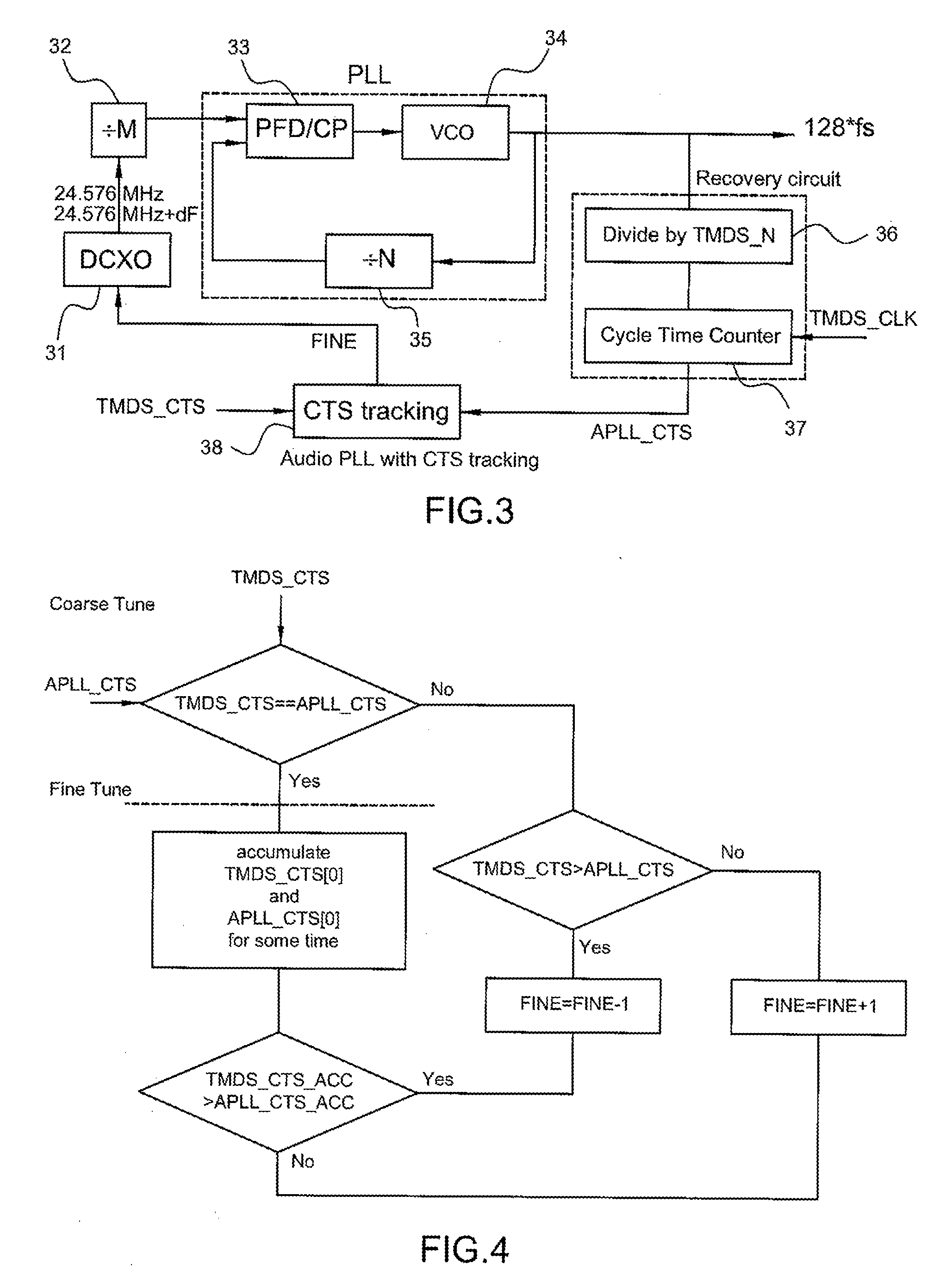

Audio clock regenerator with precisely tracking mechanism

ActiveUS20080298532A1Accurate frequencyPulse automatic controlPicture reproducers using cathode ray tubesHDMIPhase locked loop circuit

In an HDMI system, the clock regenerator proposed by the HDMI specification may suffer external noise because the input clock of a phase lock loop circuit in a sink device of the HDMI system is too slow. This slow input clock causes the phase lock loop circuit unable to adjust and reduce the jitter of an audio clock regenerated in the sink device. Therefore, one embodiment of the present invention provides a clock regenerator to extract the relationship between the regenerated audio clock and a video clock received by the sink device from other source devices. The clock regenerator may comprise a phase lock loop circuit, a recovery circuit, a crystal oscillator and a tracking circuit. The crystal oscillator generates a crystal clock. The phase lock loop circuit receives the crystal clock and regenerates an audio clock. The recovery circuit extracts the relationship between the audio clock and the received video clock. The tracking circuit tunes the frequency of the crystal clock based on the extracted relationship.

Owner:HIMAX TECH LTD

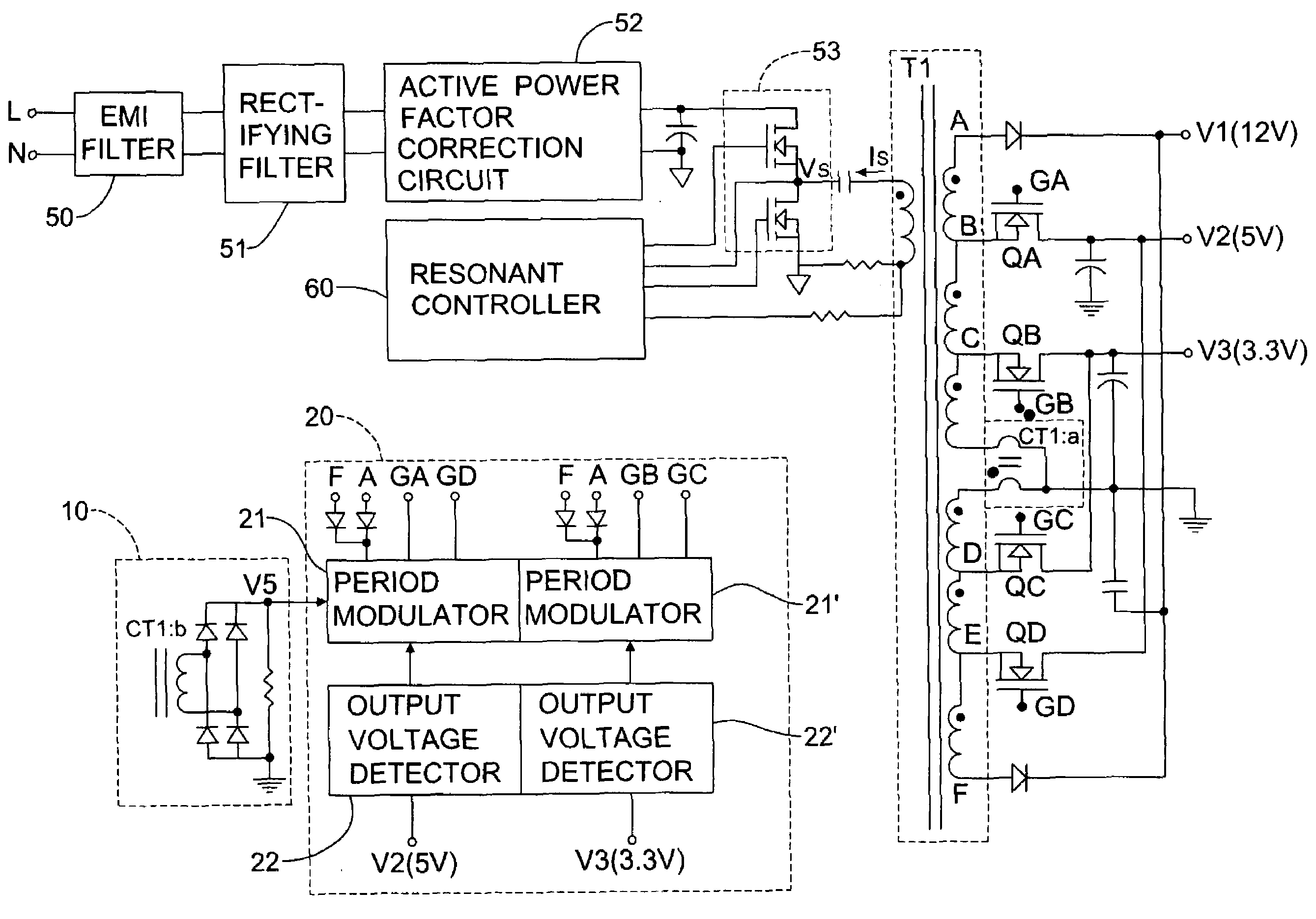

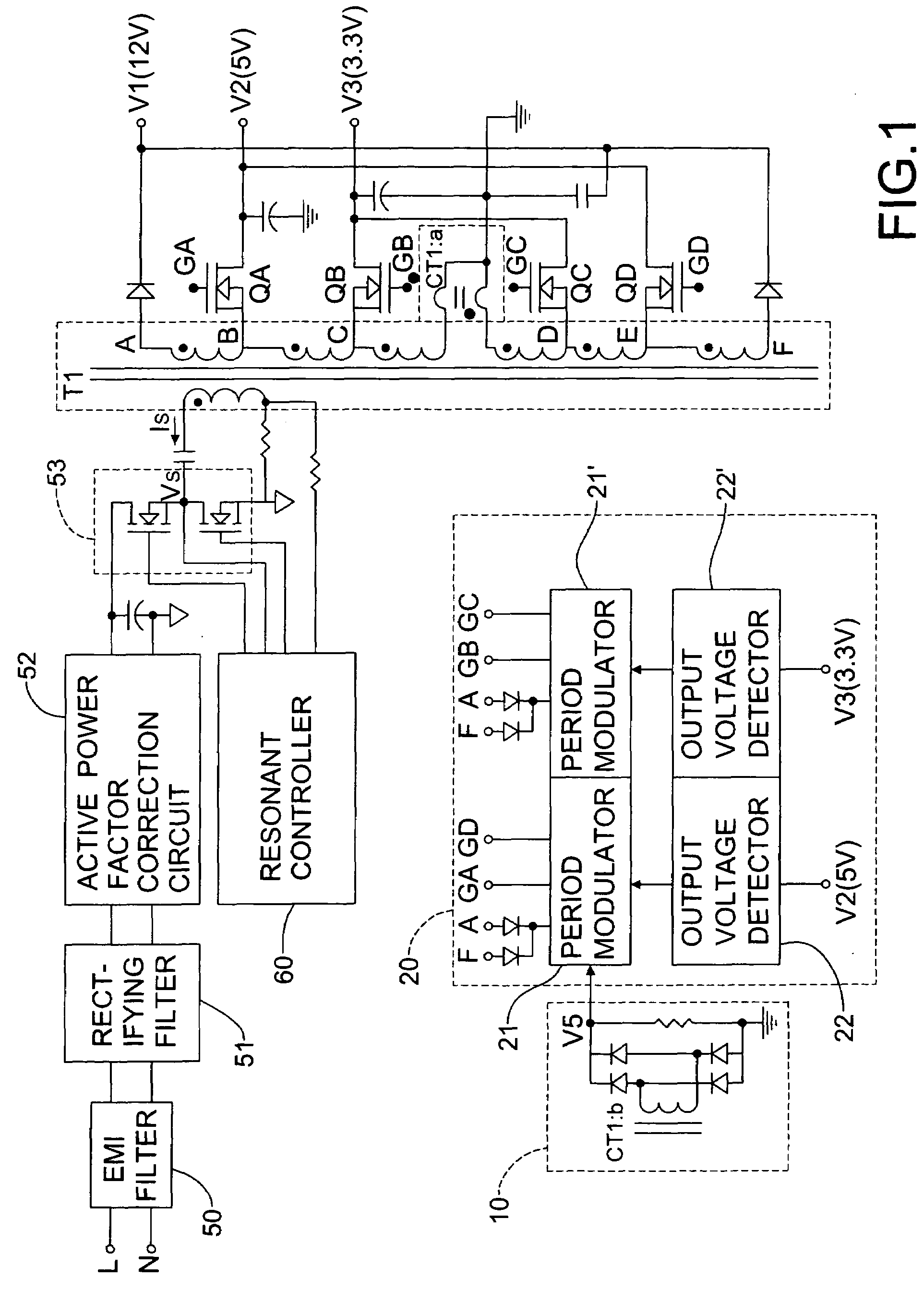

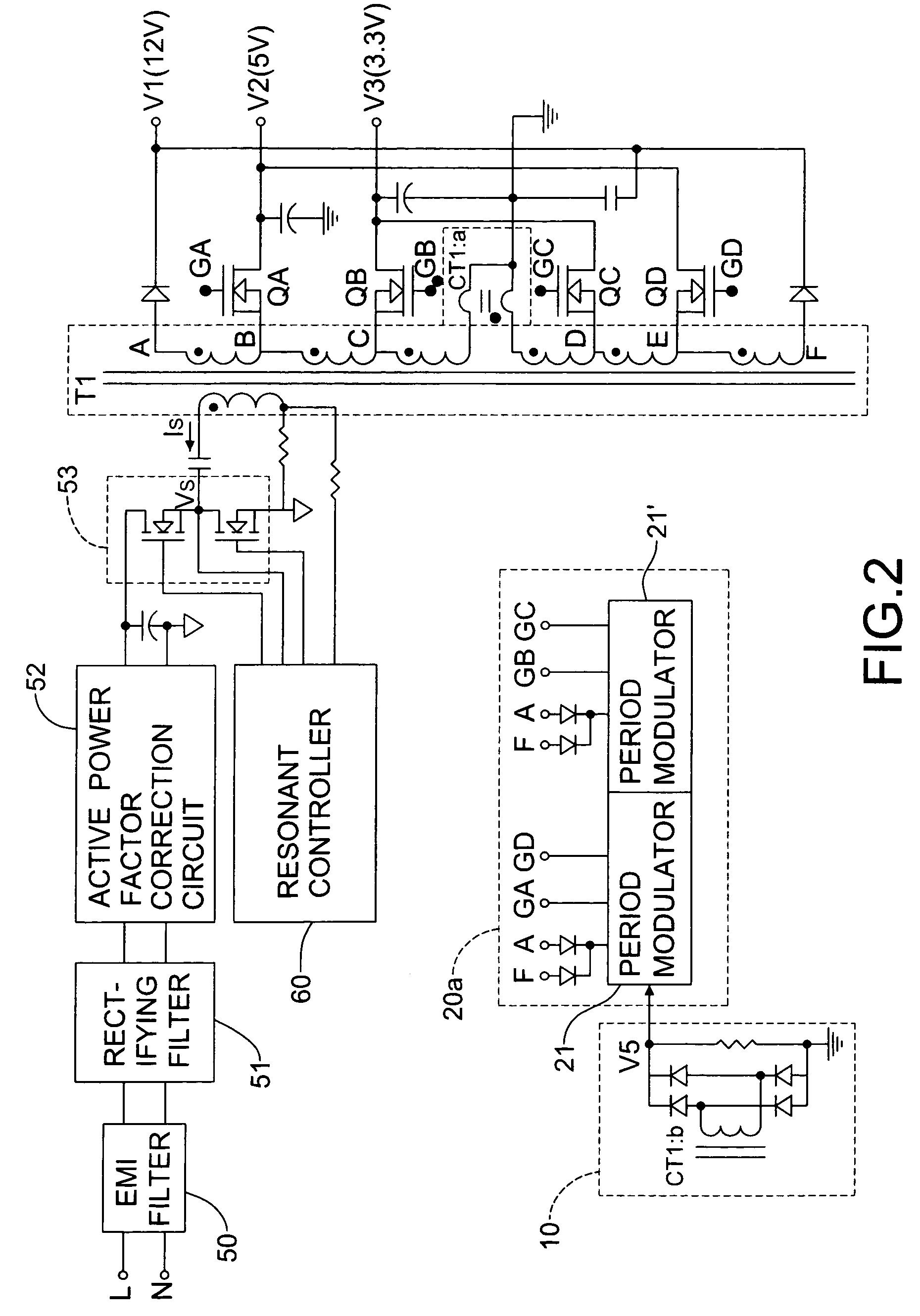

Synchronous voltage modulation circuit for resonant power converter

InactiveUS20070297198A1Stable power outputConduction period is increased and decreasedEfficient power electronics conversionDc-dc conversionResonant power convertersResonance

A synchronous voltage modulation circuit for resonance power converter has a resonance current extracting unit and at least one duty cycle modulation circuit. The resonance current extracting unit extracts the resonance current of the transformer for each duty cycle modulation circuit. The duty cycle modulation circuit controls the conduction period of the electronic switch on the secondary side of the transformer according to the power usage of the load connected to the power output and the resonance frequency of the resonance current on the transformer detected by the resonance current extracting unit. The conduction period increases or decreases symmetrically with respect to the central axis. The power converter output of the resonance power converter converter forms a closed loop control, thereby providing stable power to its load.

Owner:ACBEL POLYTECH INC

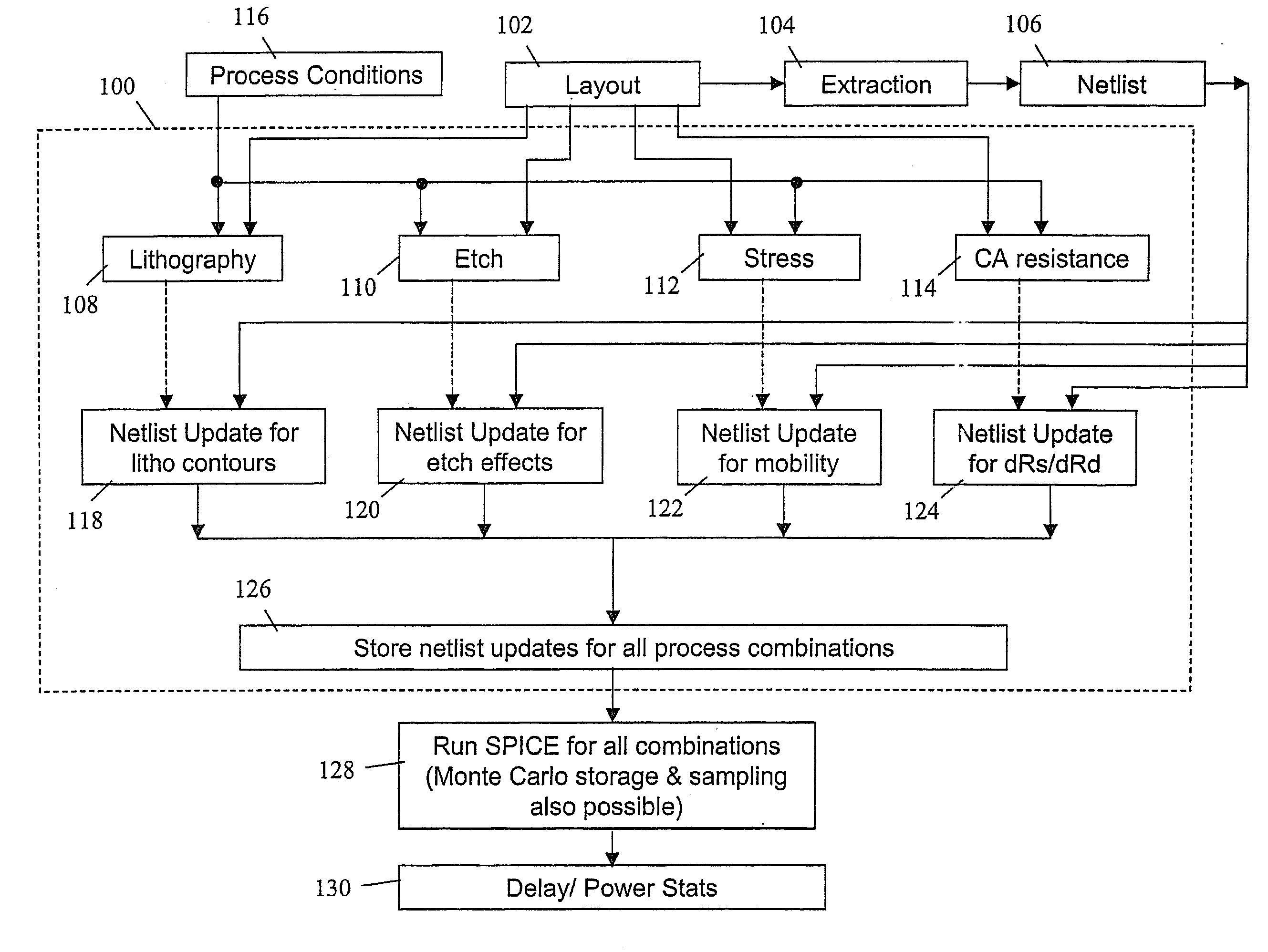

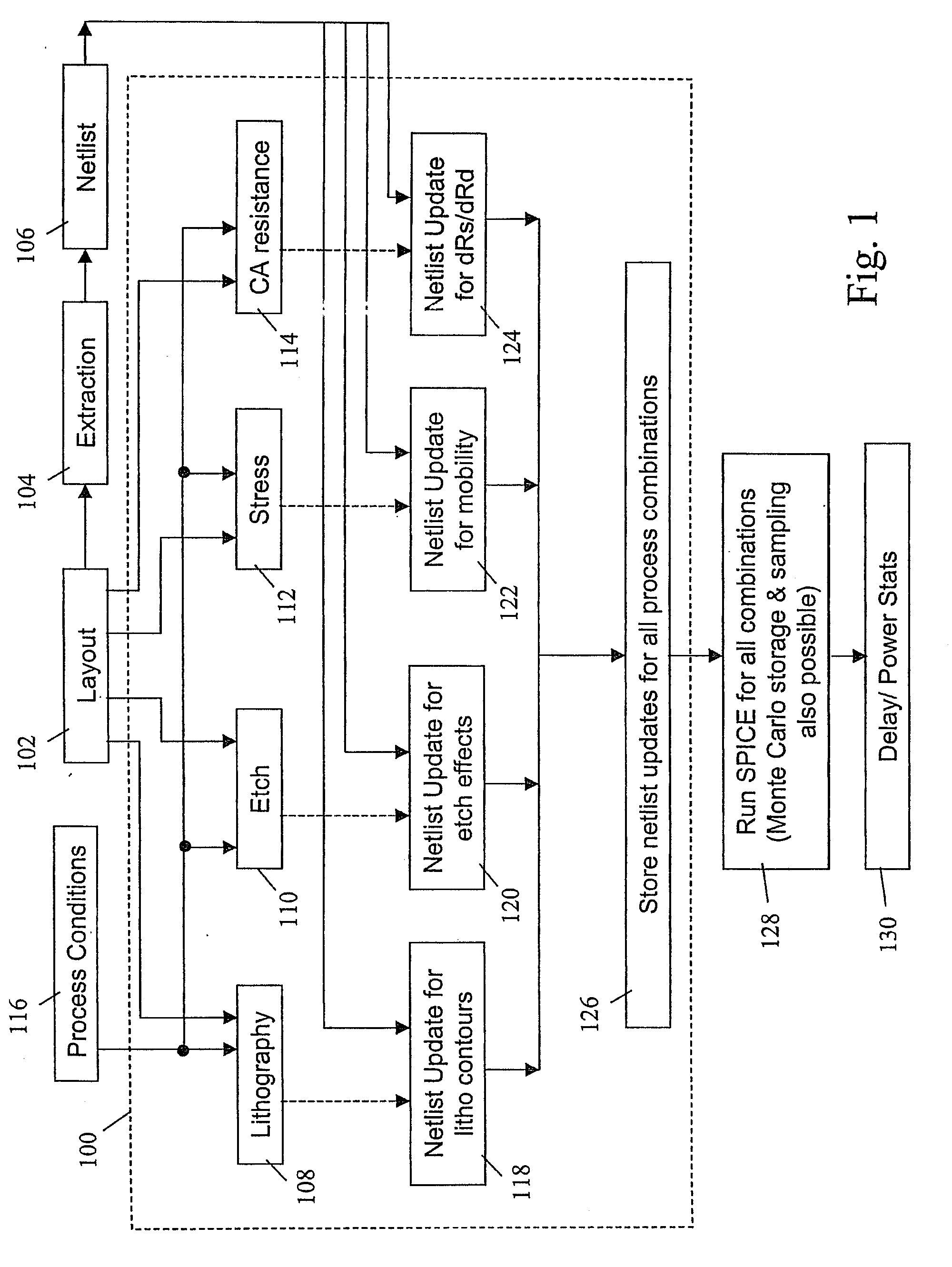

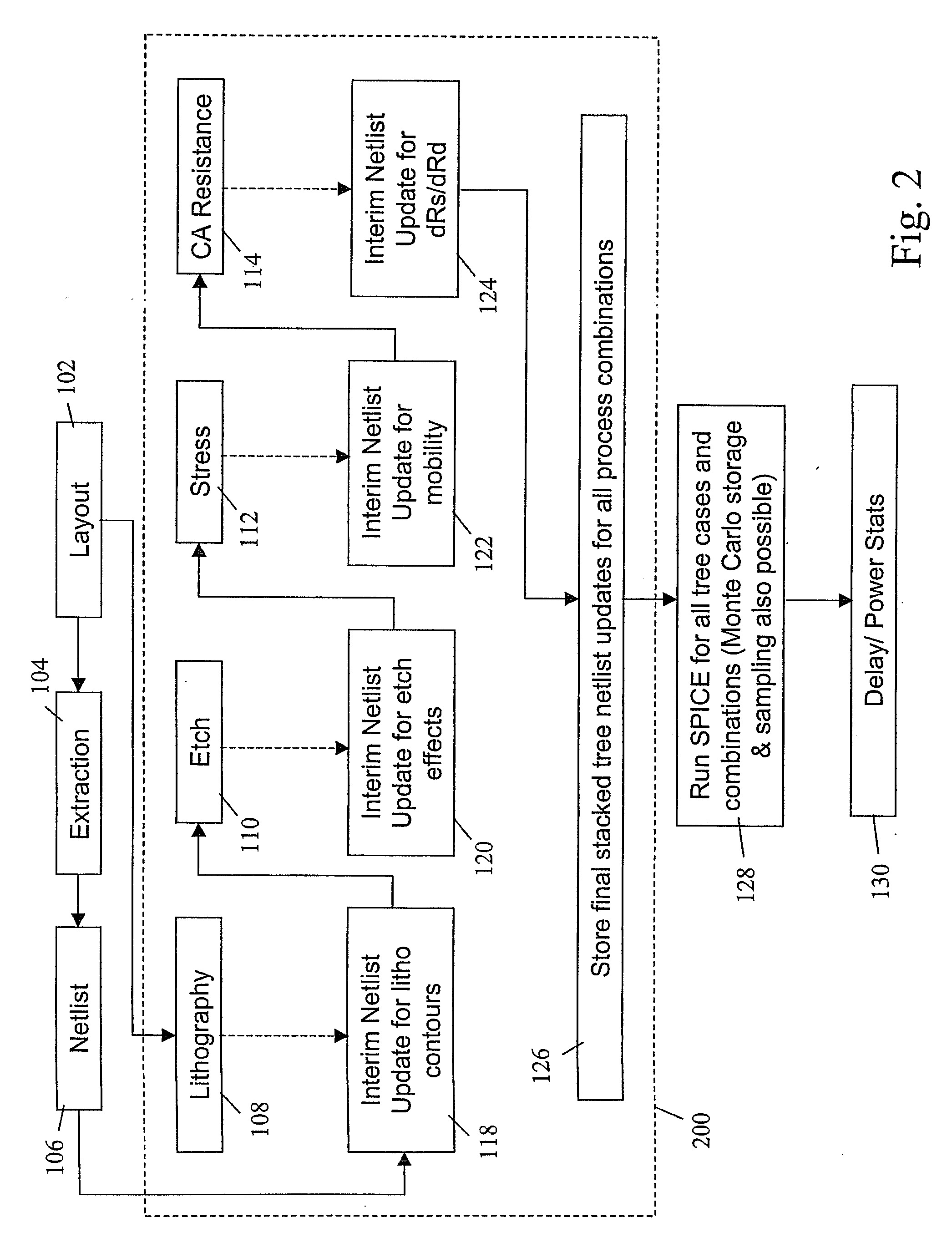

Analyzing Multiple Induced Systematic and Statistical Layout Dependent Effects On Circuit Performance

InactiveUS20100269079A1Design optimisation/simulationProbabilistic CADComputer architectureCircuit extraction

A method for implementing systematic, variation-aware integrated circuit extraction includes inputting a set of processing conditions to a plurality of variation models, each model corresponding to a separate systematic, parametric variation associated with semiconductor manufacturing of an integrated circuit layout; generating, for each variation model, a netlist update attributable to the associated variation, wherein the netlist update is an update with respect to an original netlist extracted from the integrated circuit layout; and storing the netlist updates generated for each of the processing conditions.

Owner:GLOBALFOUNDRIES INC

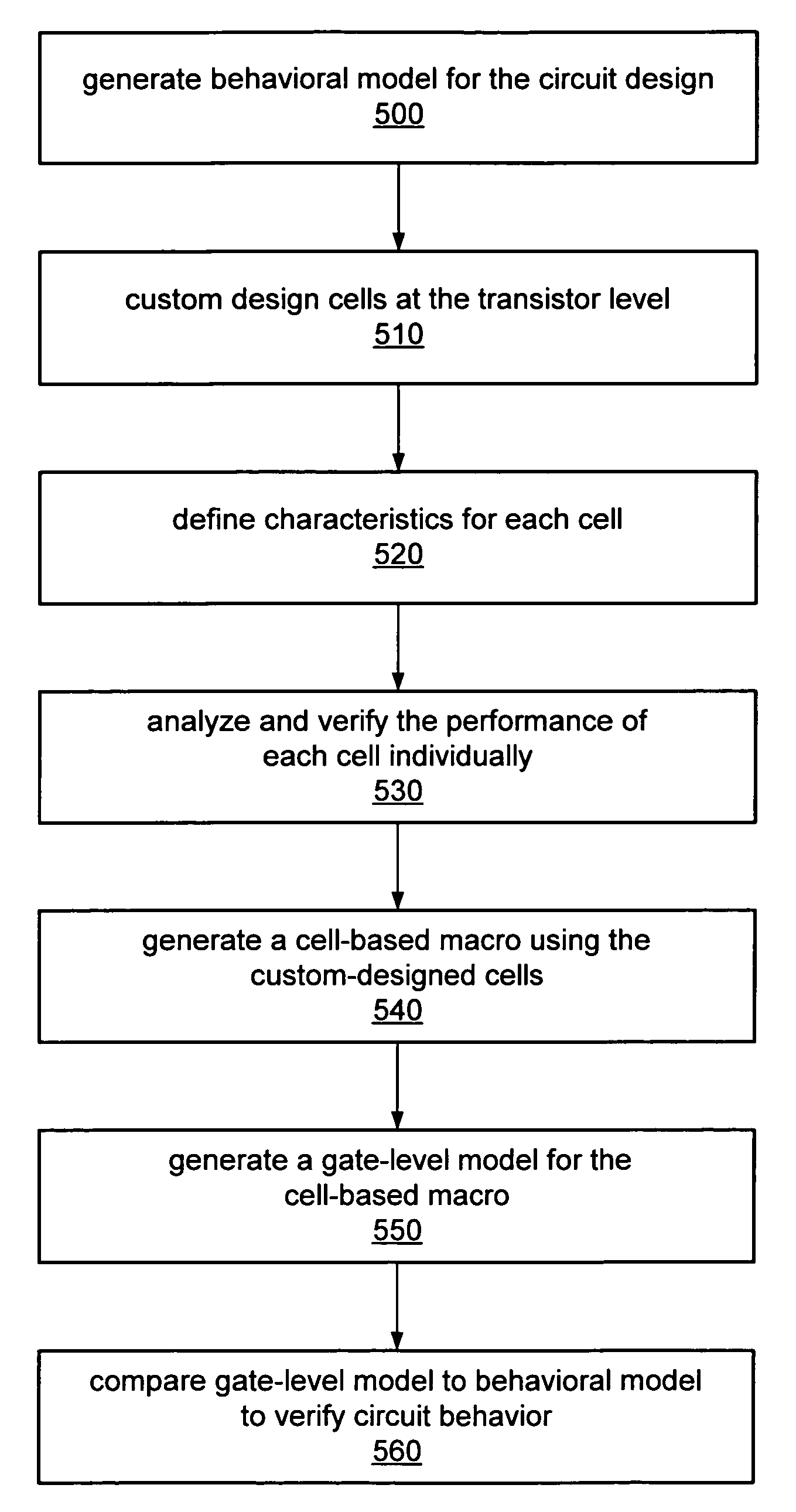

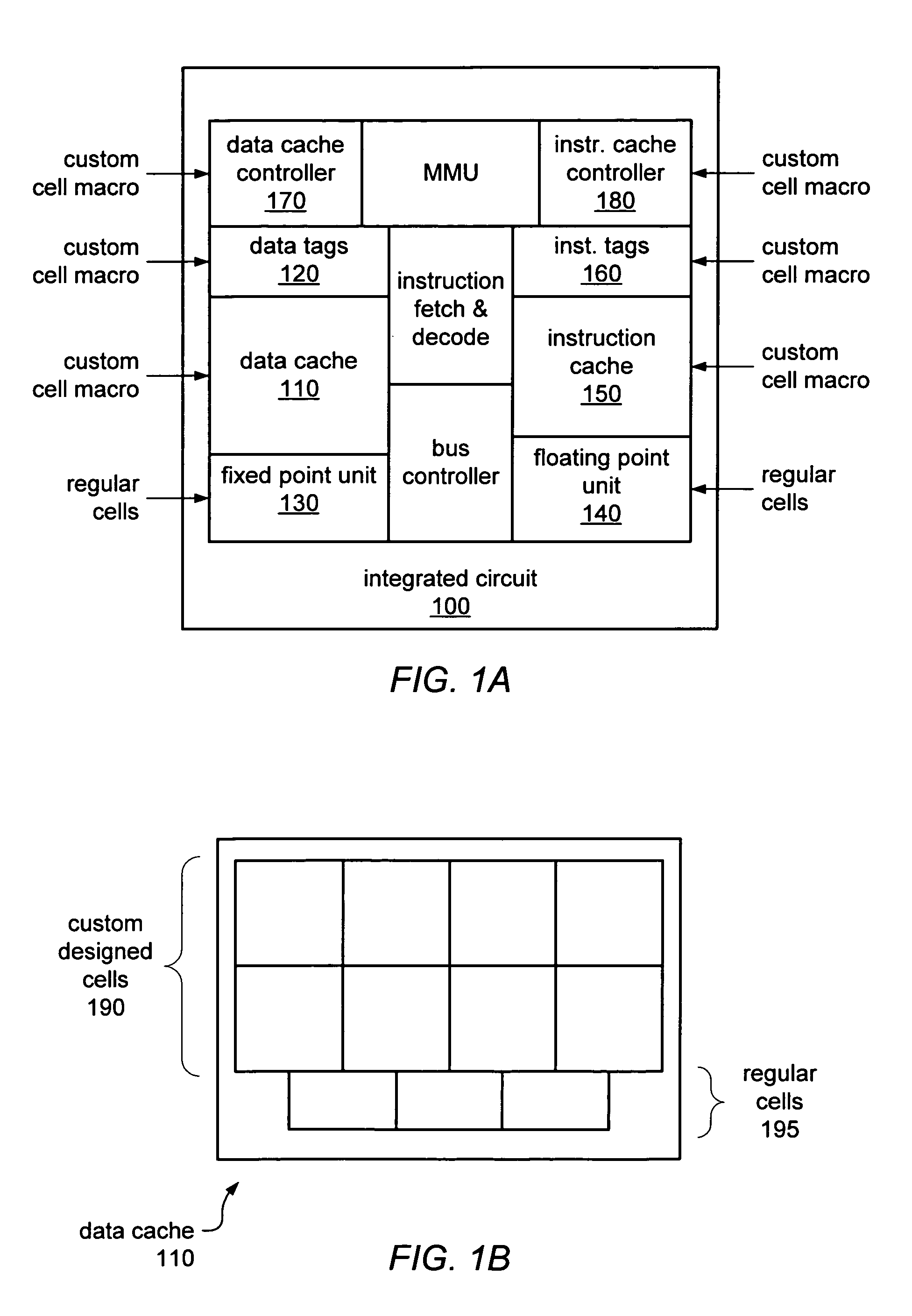

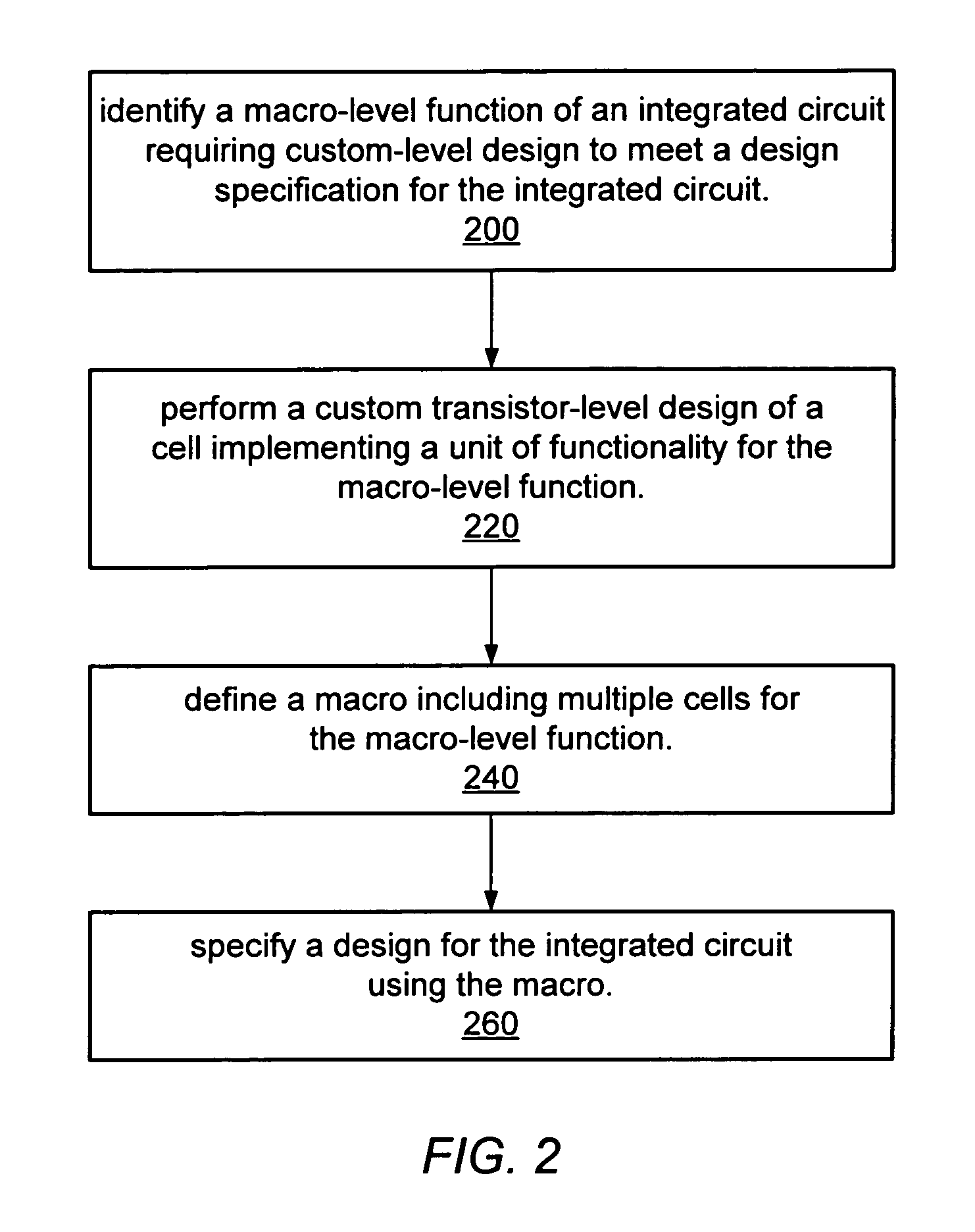

Integrated circuit design with cell-based macros

InactiveUS7401310B1CAD circuit designSoftware simulation/interpretation/emulationStatic timing analysisValidation methods

A method for designing integrated circuits may include custom designing, at the transistor level, individual cells to be incorporated into cell-based macros. A macro-level function of an integrated circuit's design specification requiring custom, transistor-level design may be identified and custom cells may be designed at the transistor-level to meet the design specification. Custom designed cells may be included in cell-based macros, thus allowing cell-based simulation and verification methodologies and tools to be used on the integrated circuit design. Static timing analysis, circuit extraction and other characteristics may be defined for each custom cell and the timing analysis and circuit extraction for cell-based macros may be defined based on the timing and extraction information for the custom cells included in the macro.

Owner:GLOBALFOUNDRIES INC

Dual-axis accelerometer

InactiveUS20050235751A1Acceleration measurement using interia forcesAcceleration measurement in multiple dimensionsCapacitanceAccelerometer

A dual-axis accelerometer and processing circuit are provided. The accelerometer has a plurality of fixed electrodes supported on a substrate and fixed capacitive plates arranged in first and second sensing axes. An inertial mass is suspended over a cavity and includes movable capacitive plates arranged to provide a capacitive couplings with the fixed capacitive plates. The inertial mass is movable relative to the plurality of fixed electrodes. The accelerometer has a plurality of support arms for supporting the inertial mass relative to the fixed electrodes and allowing movement of the inertial mass upon experiencing acceleration along the first and second sensing axes. The accelerometer further has inputs for receiving input signals and an output for providing an output signal which varies as a function of the capacitive coupling and is indicative of sensed acceleration. The processing circuit extracts the components of acceleration along the first and second sensing axes.

Owner:DELPHI TECH INC

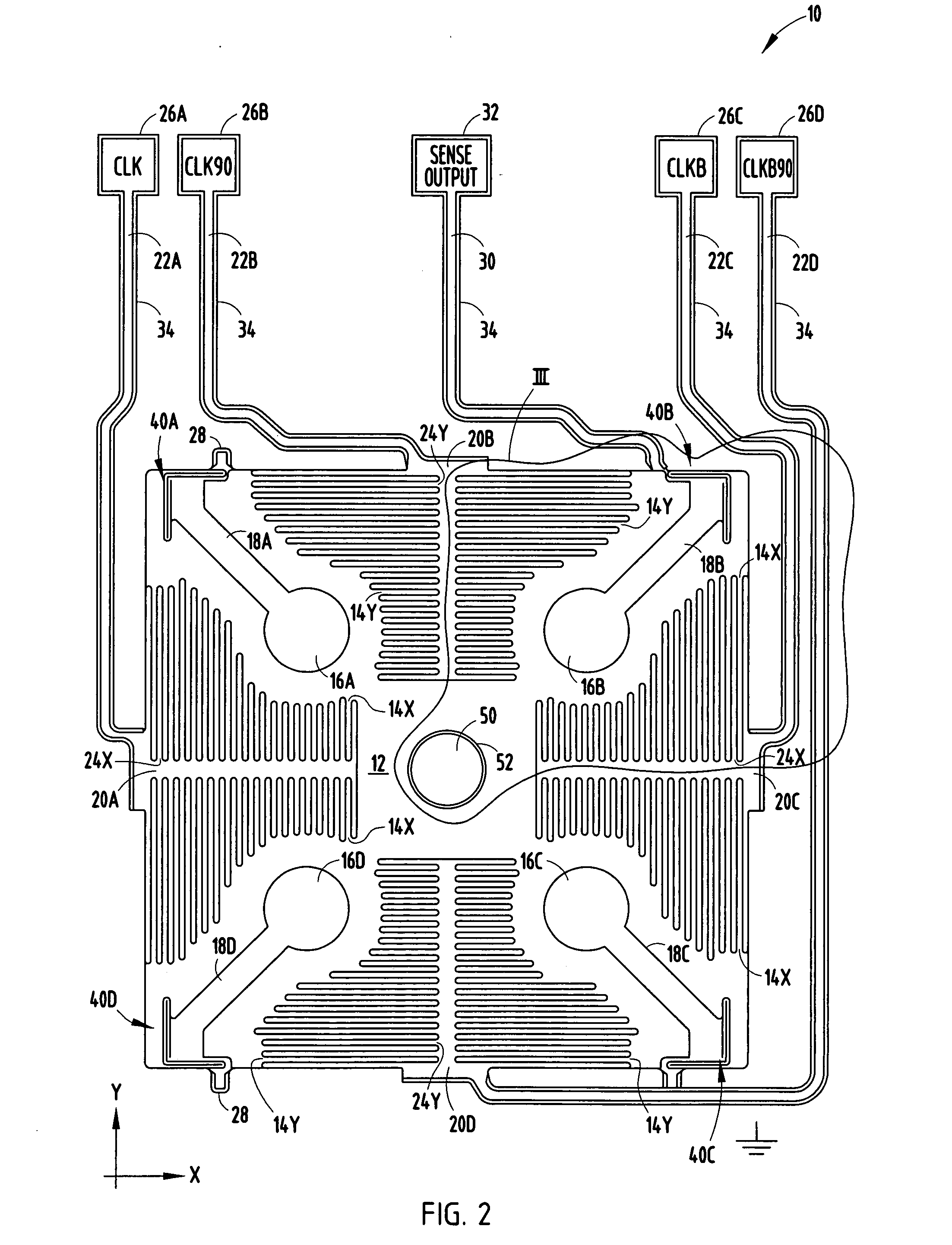

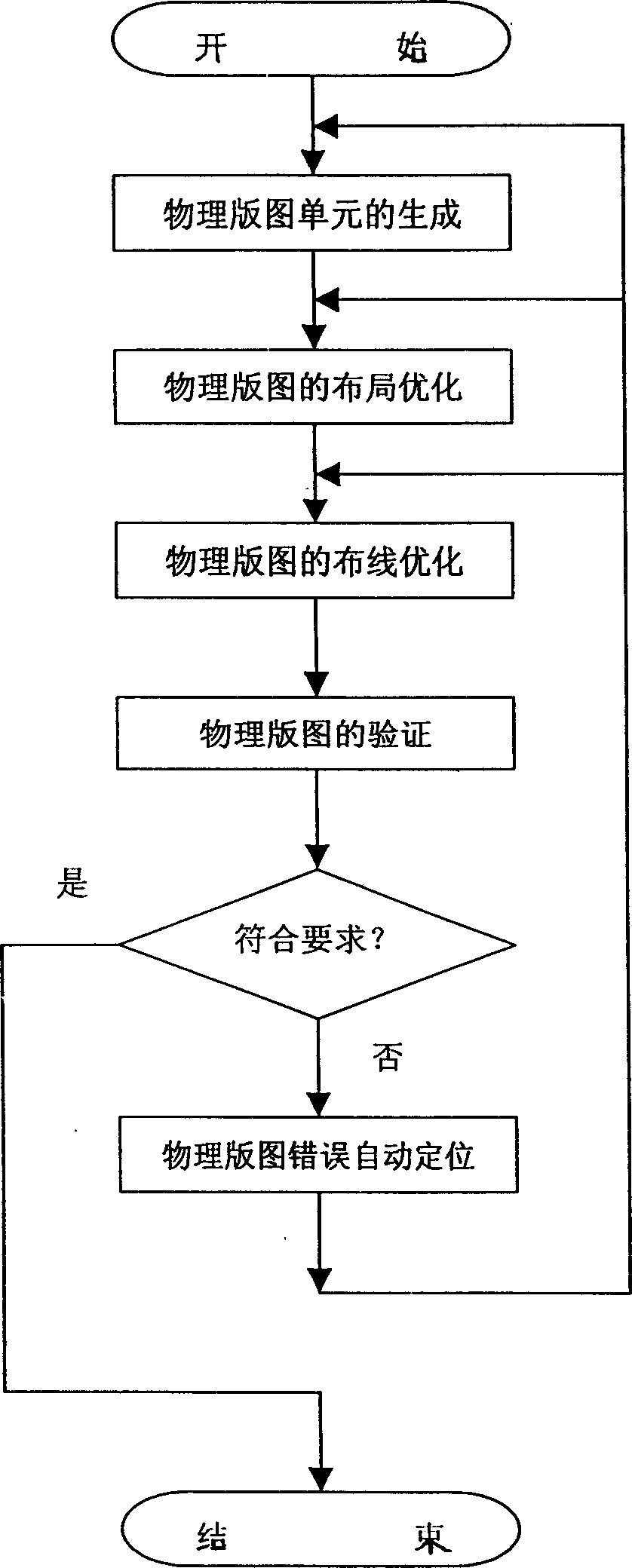

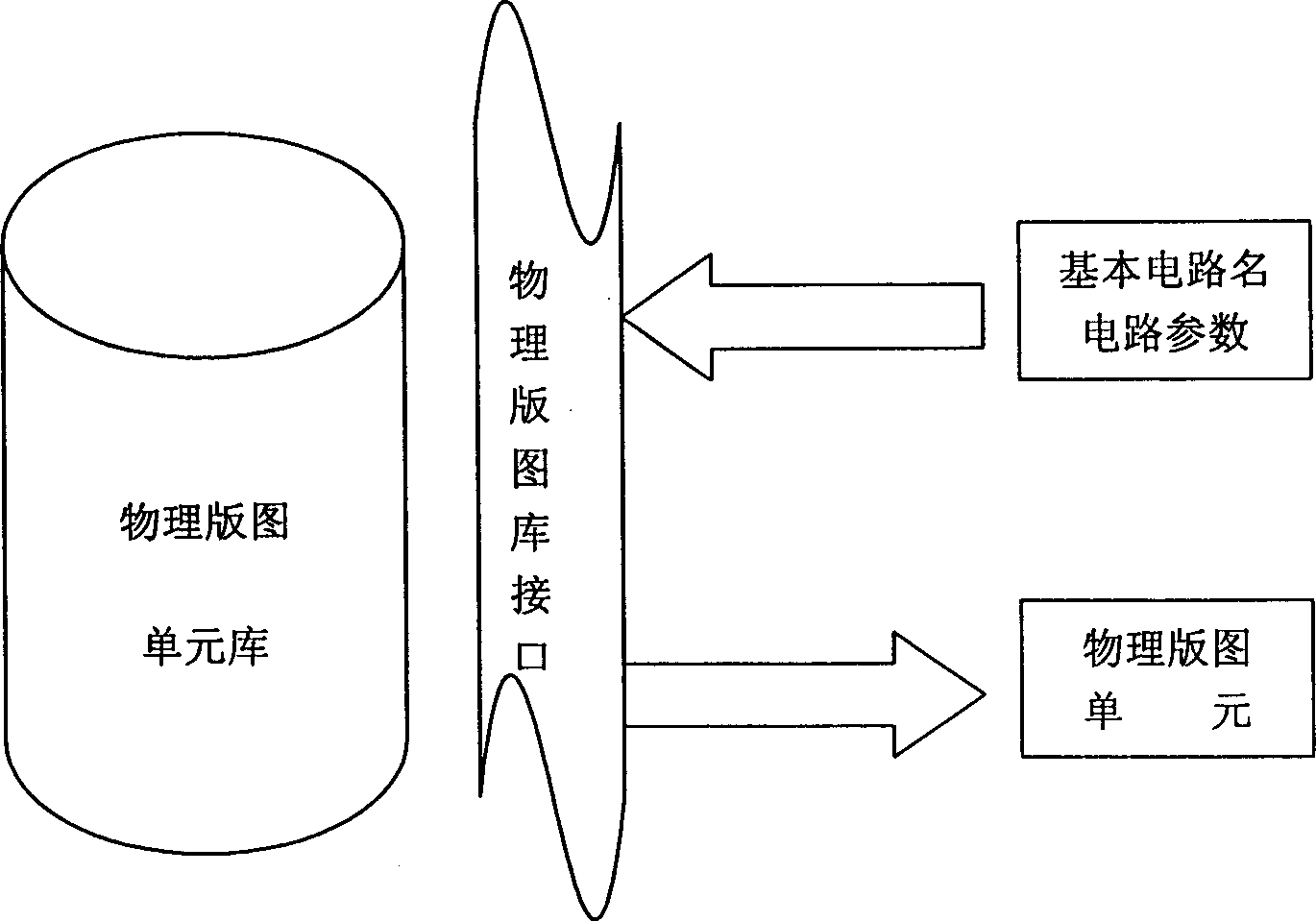

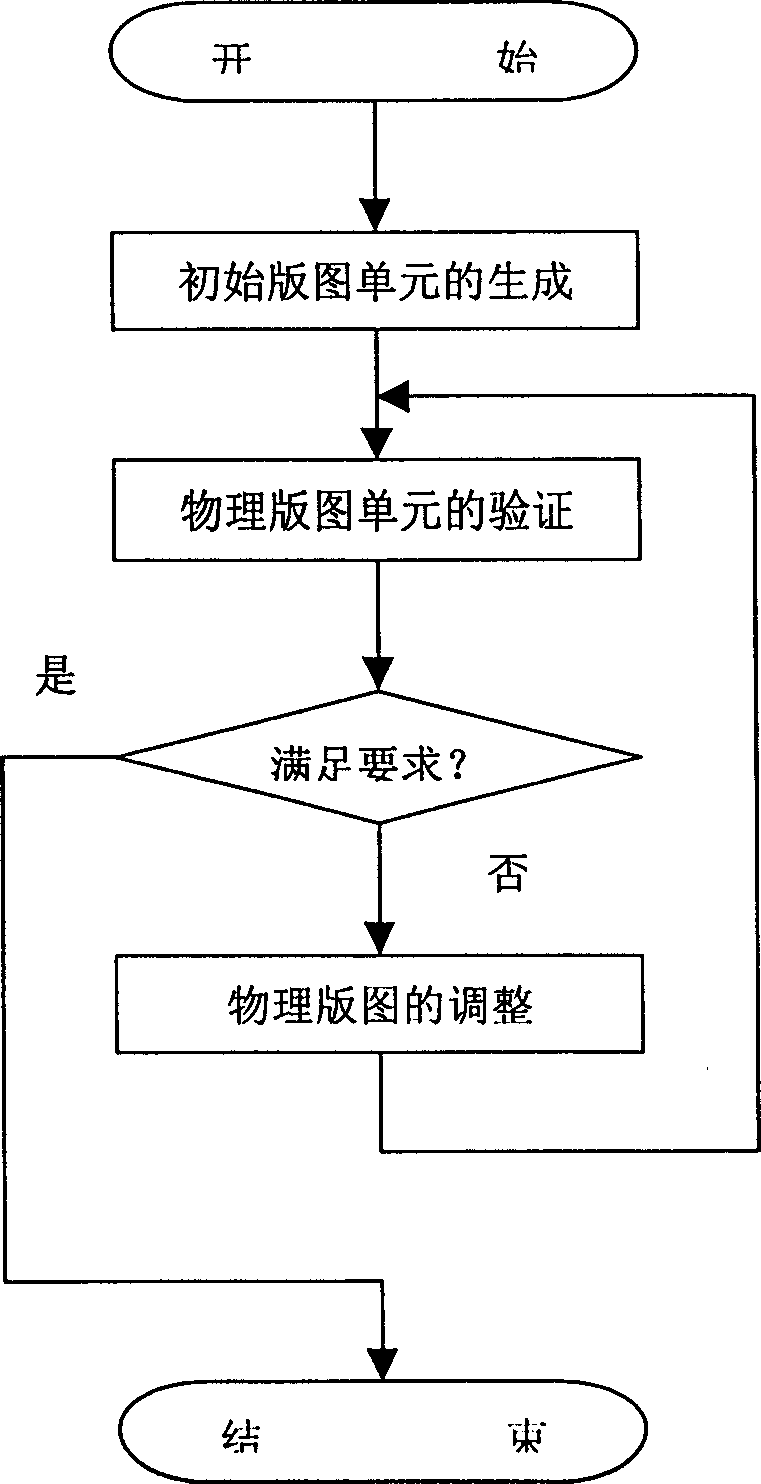

Physic design method for analog and radio frequency integrated circuit

InactiveCN1510737AAvoid loopsSolid-state devicesSemiconductor/solid-state device manufacturingDatabase interfaceUnit generator

The present invention is a method for generating automatically the physical patterns of the analog and RF integrated circuits, extracting the pattern circuits, verifying the pattern circuits and positioning the pattern errors of the same. The object of the invention is to design the physical patterns of the analog and RF integrated circuits as automatically as possible, avoid the constraint condition by manual analysis and avoid the circulation of distributing-extracting-verifying. The invention comprises the following steps: generating the physical pattern unit, distributing the physical pattern, wiring the physical pattern, verifying the physical pattern and positioning automatically the physical pattern error. The invention uses the integrated physical pattern unit generator and physical pattern database interface to provide the physical pattern unit; uses the distributing technology based on signal flow to optimize the area and the property of pattern; adjusts automatically the extracting accuracy of pattern parasitic parameters to increase the extracting speed; uses the macro-model to increase the emulating speed and the capacity of circuit and uses the emulation comparing technology to position the pattern error.

Owner:AIKESAILI MICROELECTRONICS TECH BEIJING

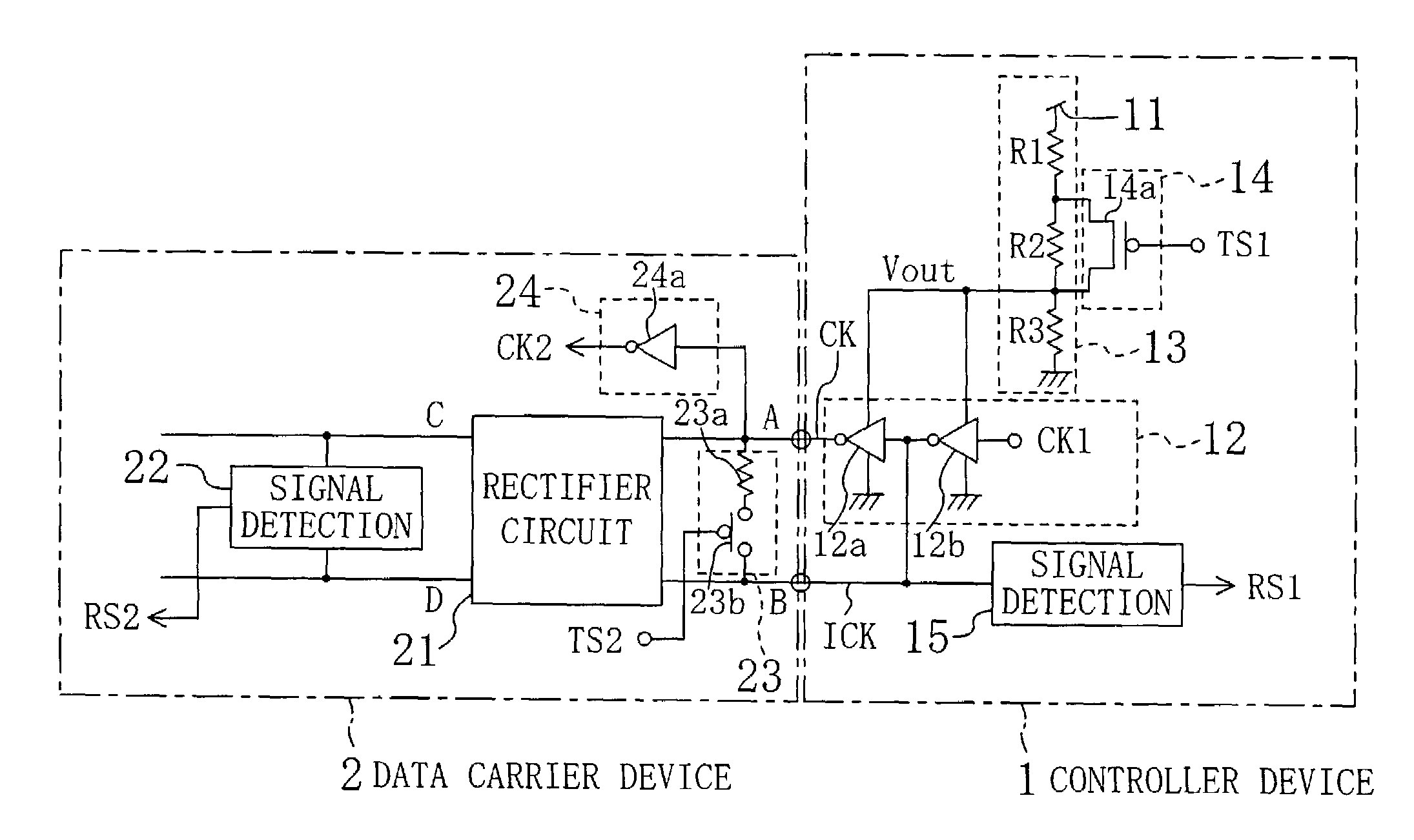

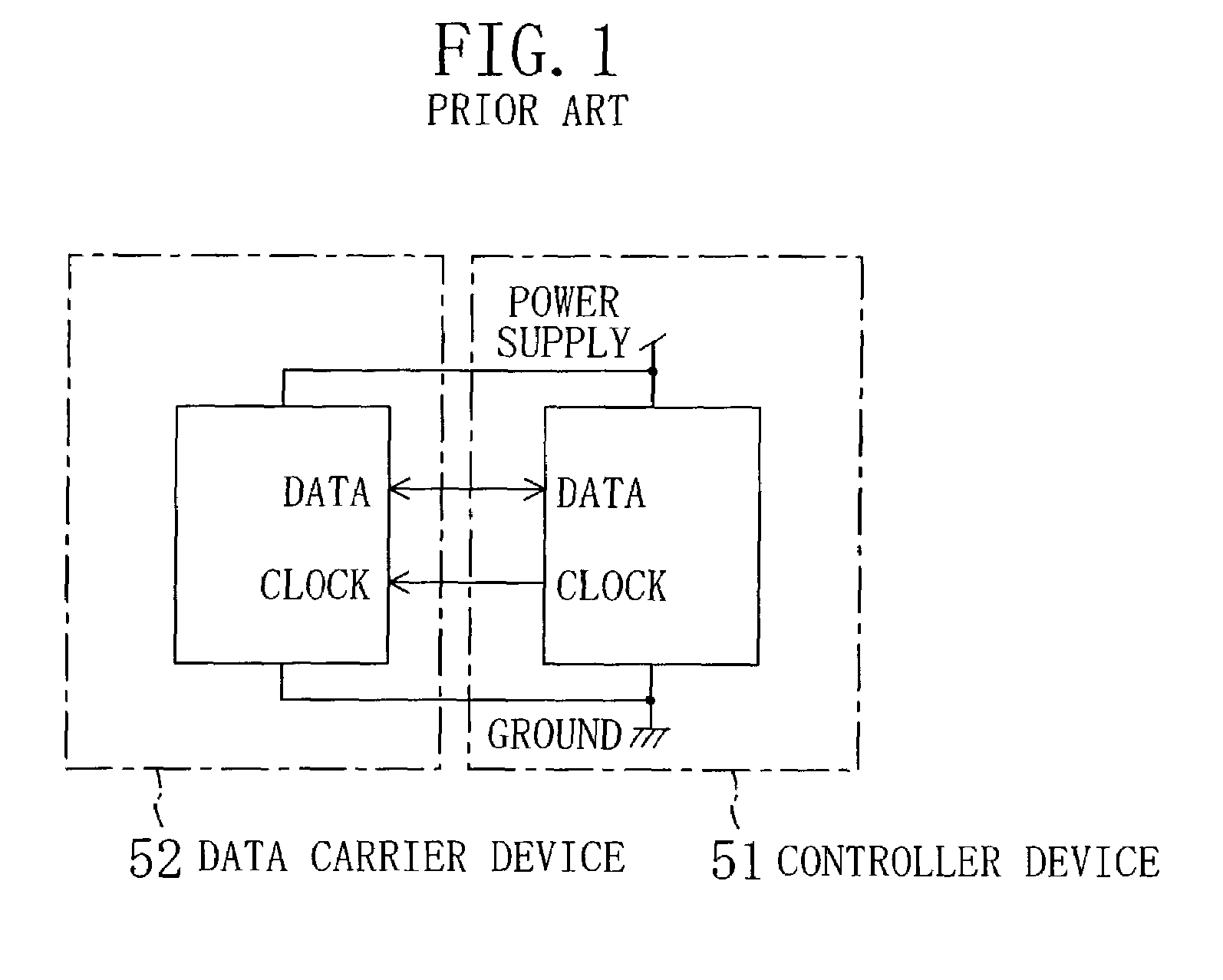

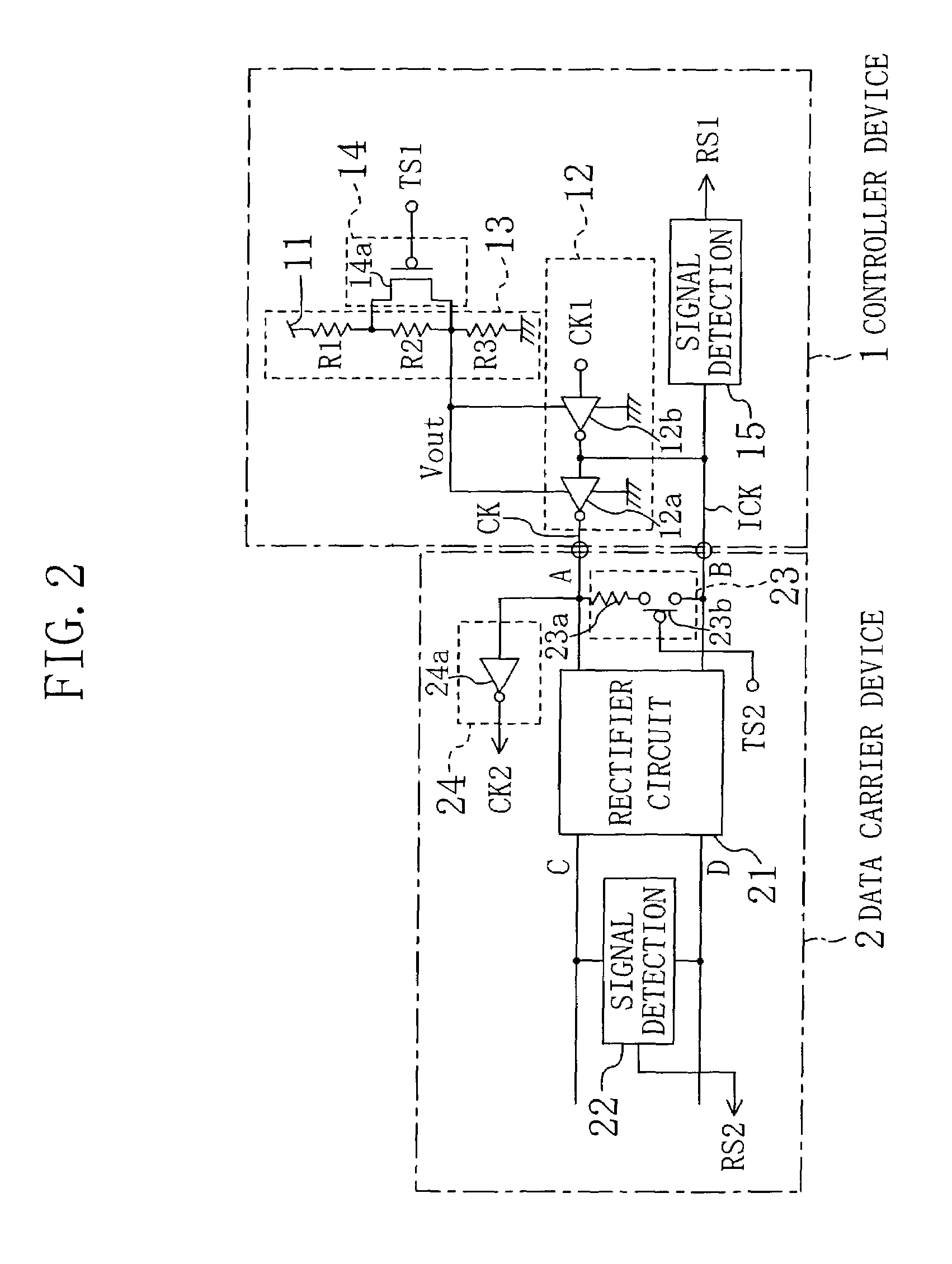

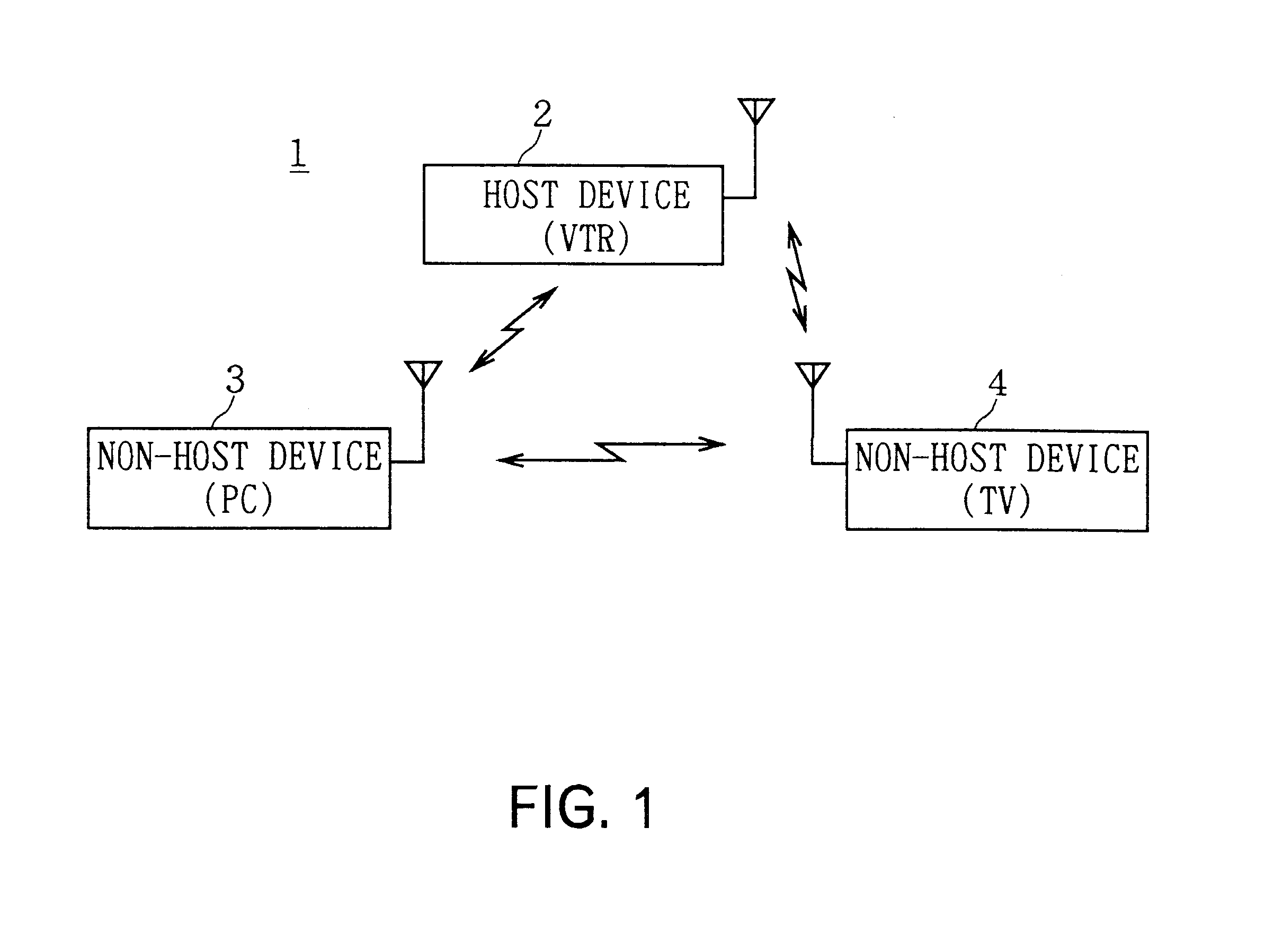

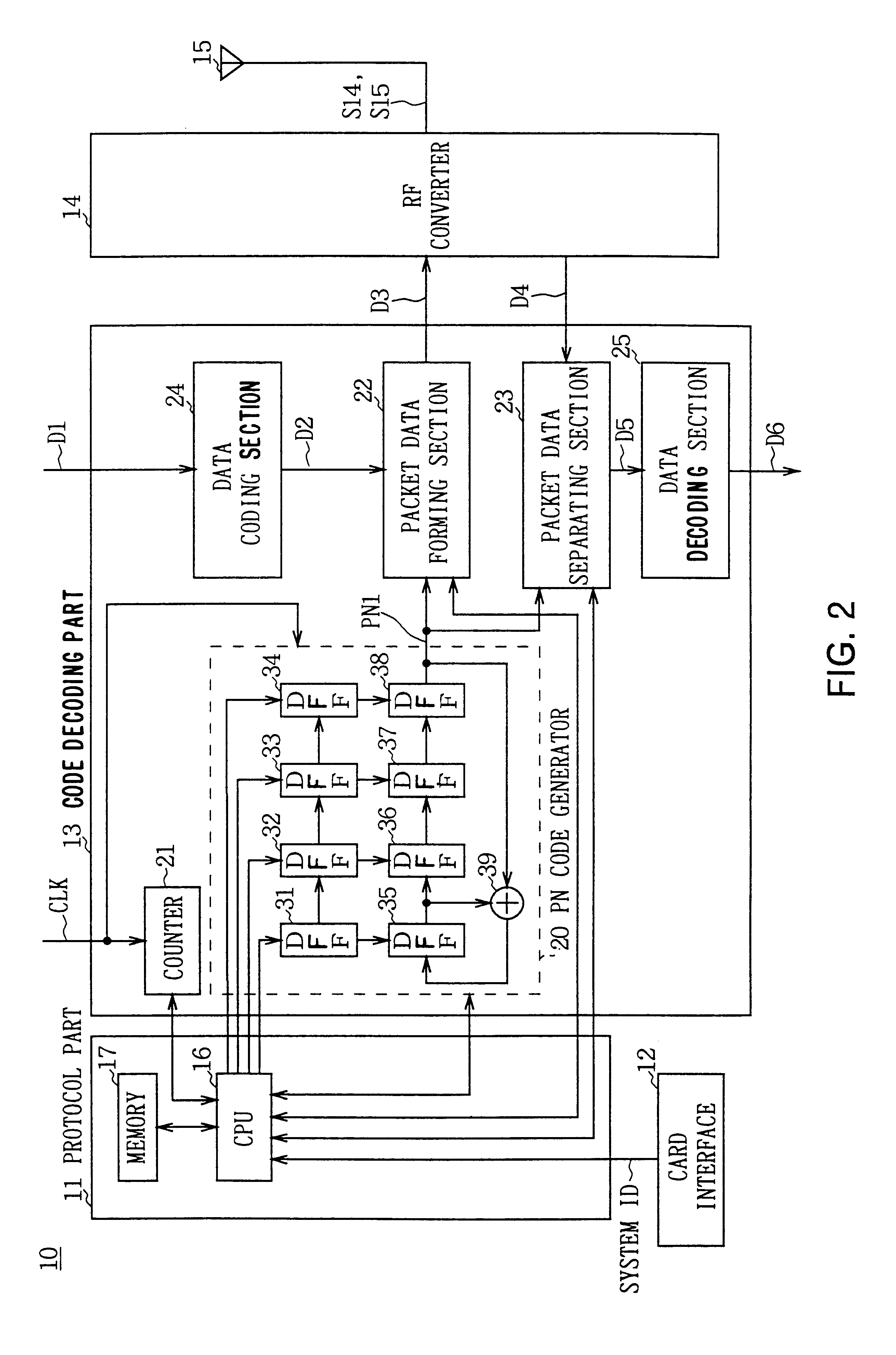

Data communication system, controller device and data communication method

InactiveUS7113547B2Increase powerReduce power consumptionModulated-carrier systemsData switching current supplyElectricityCommunications system

In a controller device, when a first transmitting signal is at a “L” level, a first operation voltage is high and the amplitude of signals CK and ICK is large, and on the contrary, the amplitude is small when the first transmitting signal is at a “H” level. In a data carrier device, the signals CK and ICK are subjected to full-wave rectification by a rectifier circuit so as to generate a second operation voltage, and a first receiving signal is extracted from the second operation voltage by a first signal detection circuit. On the other hand, in the data carrier device, when a second transmitting signal is at a “L” level, impedance between two contacts is small and the amplitude of the signals CK and ICK is small, and on the contrary, the amplitude is large when the second transmitting signal is at a “H” level. In the controller device, change of the amplitude of the signal ICK is extracted as a second receiving signal by a second signal detection circuit. Accordingly, supply of power and clock and two-way serial data communication can be simultaneously executed between the controller device and the data carrier device through merely two contacts.

Owner:COLLABO INNOVATIONS INC

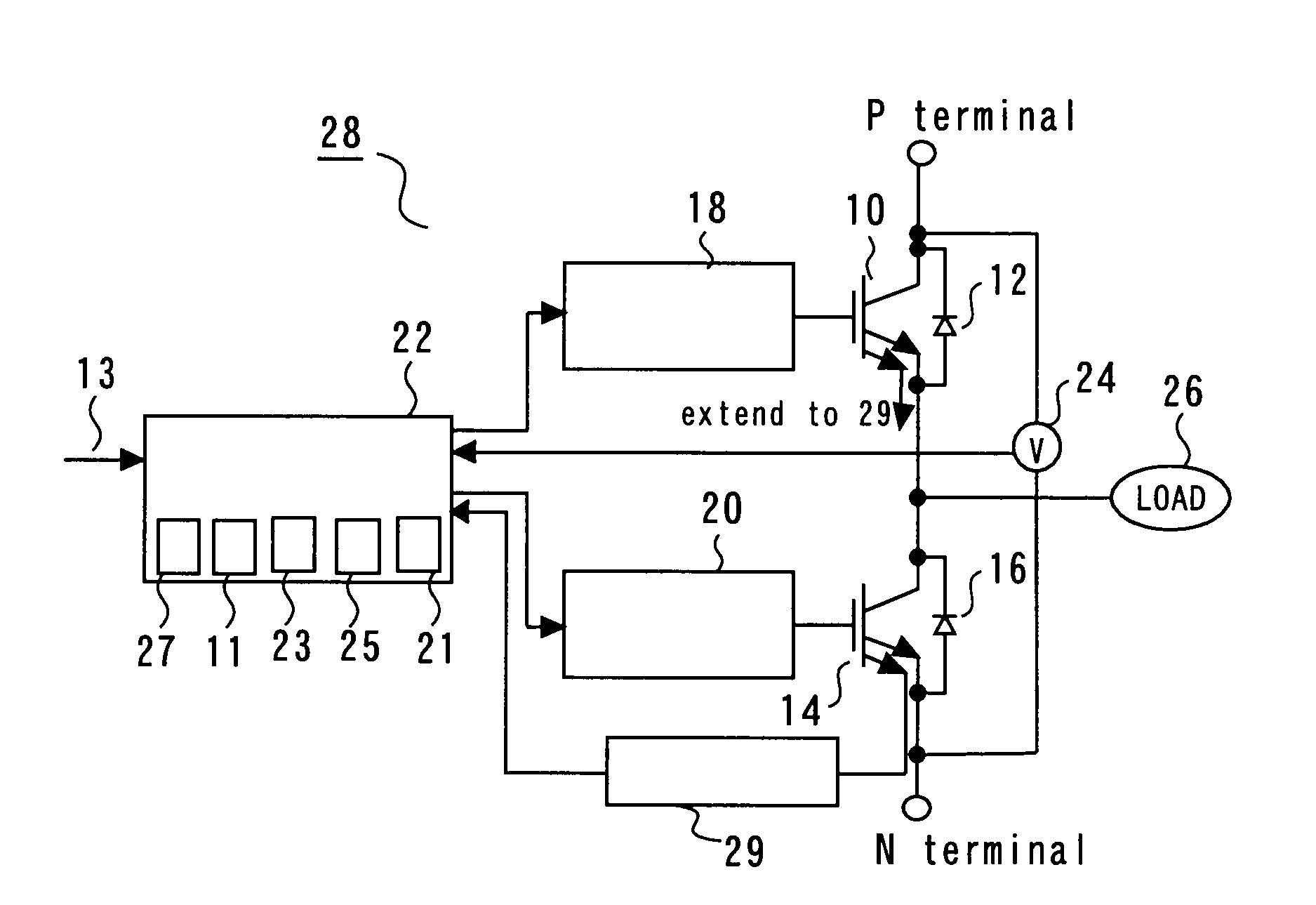

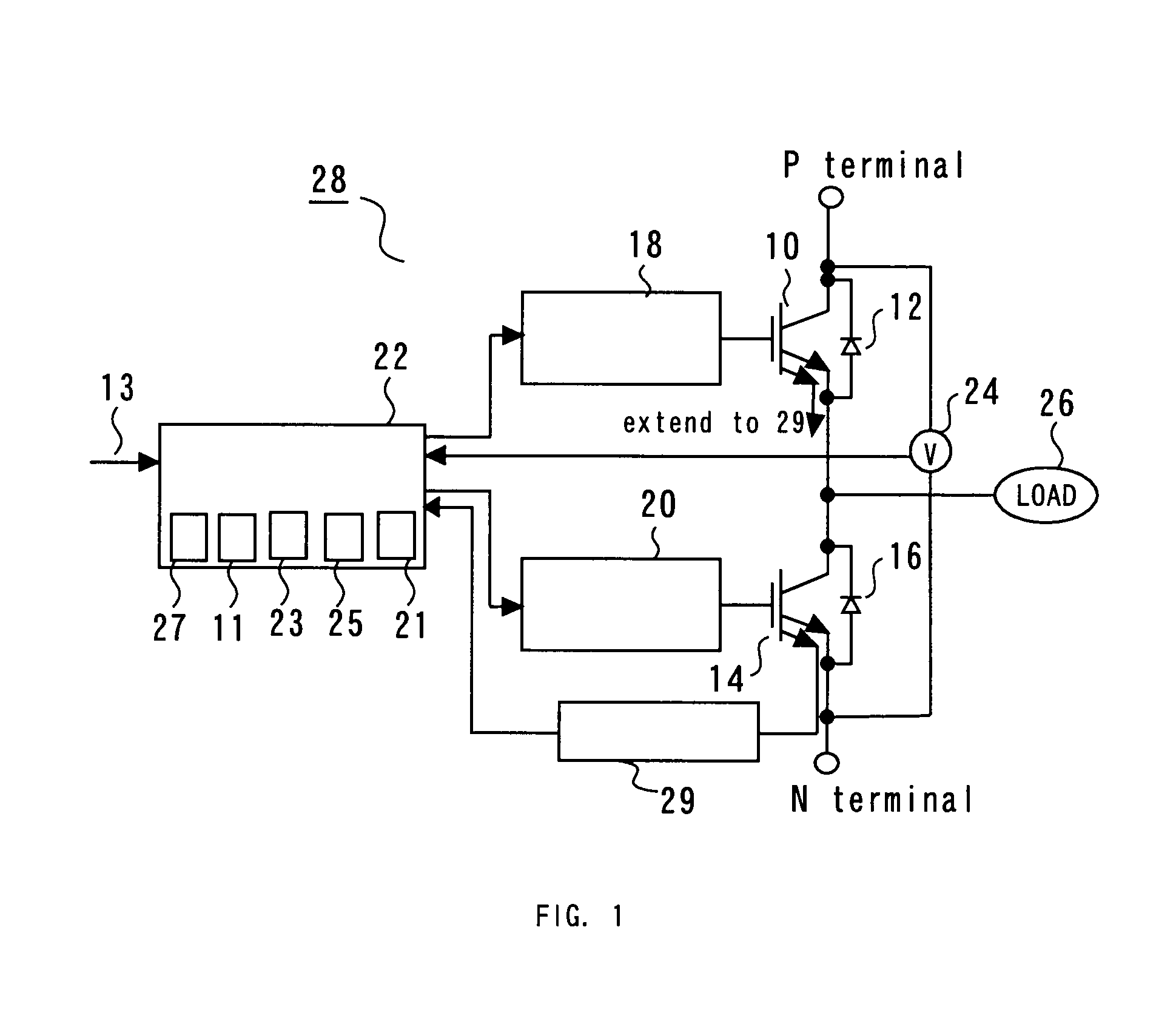

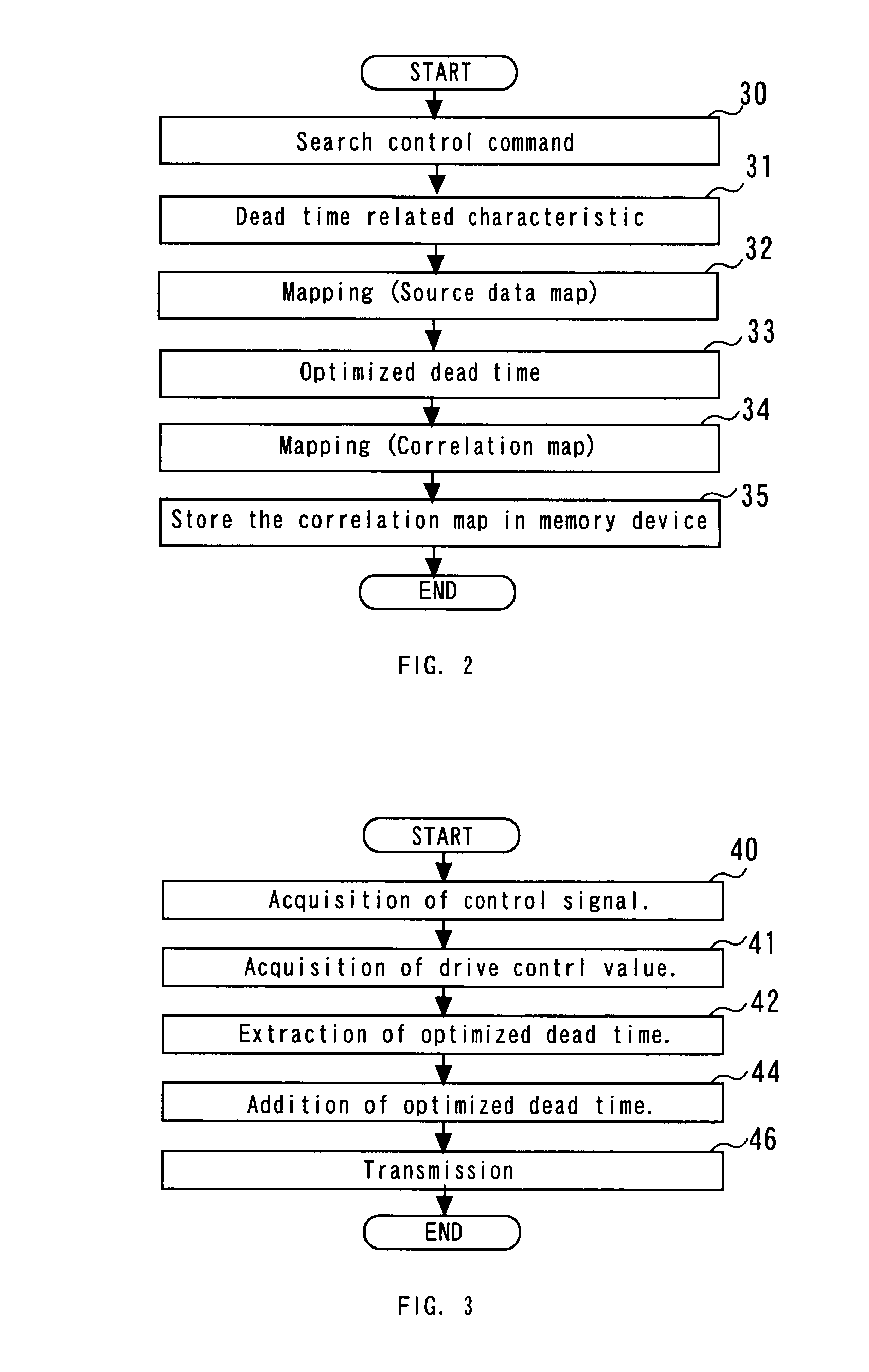

Semiconductor device

ActiveUS20090096502A1Optimum dead timeSimple processElectronic switchingElectric pulse generatorDead timeCircuit extraction

The present invention provides a semiconductor device includes arms formed by two semiconductor elements, a map memory device which stores therein a correlation map between a control value for each of the arms and an optimized dead time to be set for the control value or is capable of storing the same therein, drive control value acquiring means for acquiring a drive control value of each of the arms, and a dead time generating circuit for extracting the optimized dead time corresponding to the drive control value from the correlation map. The time taken until the other of the semiconductor elements is turned on after one thereof has received a command to turn off the same is the optimized dead time extracted by the dead time generating circuit.

Owner:MITSUBISHI ELECTRIC CORP

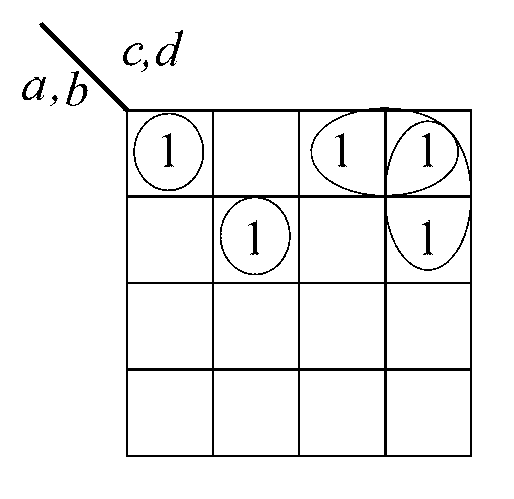

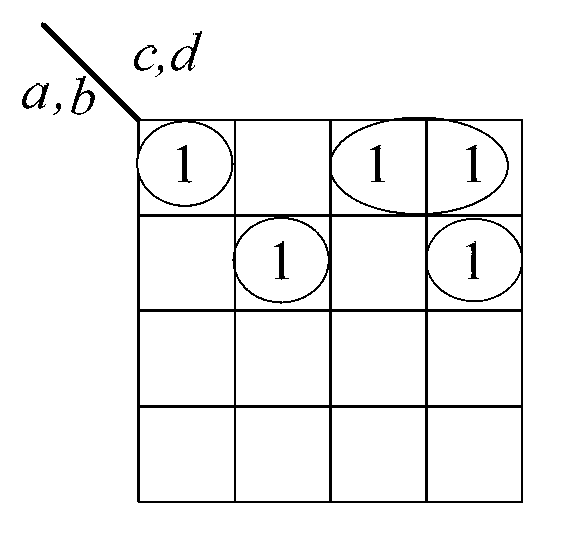

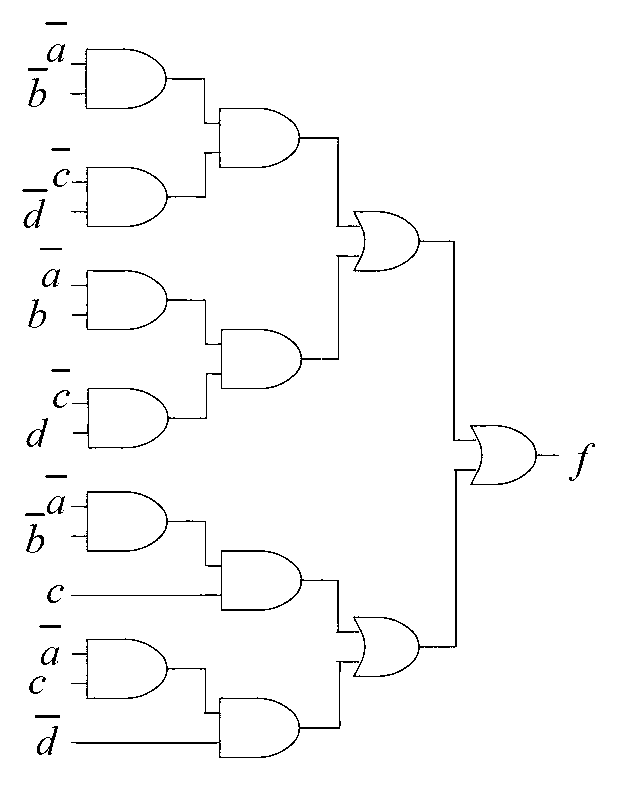

Sub-circuit extracting method of digital logic circuit

ActiveCN103236837AImprove general performanceRelaxed constraintsLogic circuits characterised by logic functionCircuit extractionComputer science

The invention discloses a sub-circuit extracting method of a digital logic circuit. By the aid of disjoint sharp-operations between logic function product terms, the product term set belonging to the logic functions corresponding to the sub circuits is eliminated from the product term set of the logic functions corresponding to original circuits, so that sub-circuit extraction from the original circuits is realized. A novel circuit construction method with sub circuits is further provided to be equivalent to logic functions of the original circuits.

Owner:NINGBO UNIV

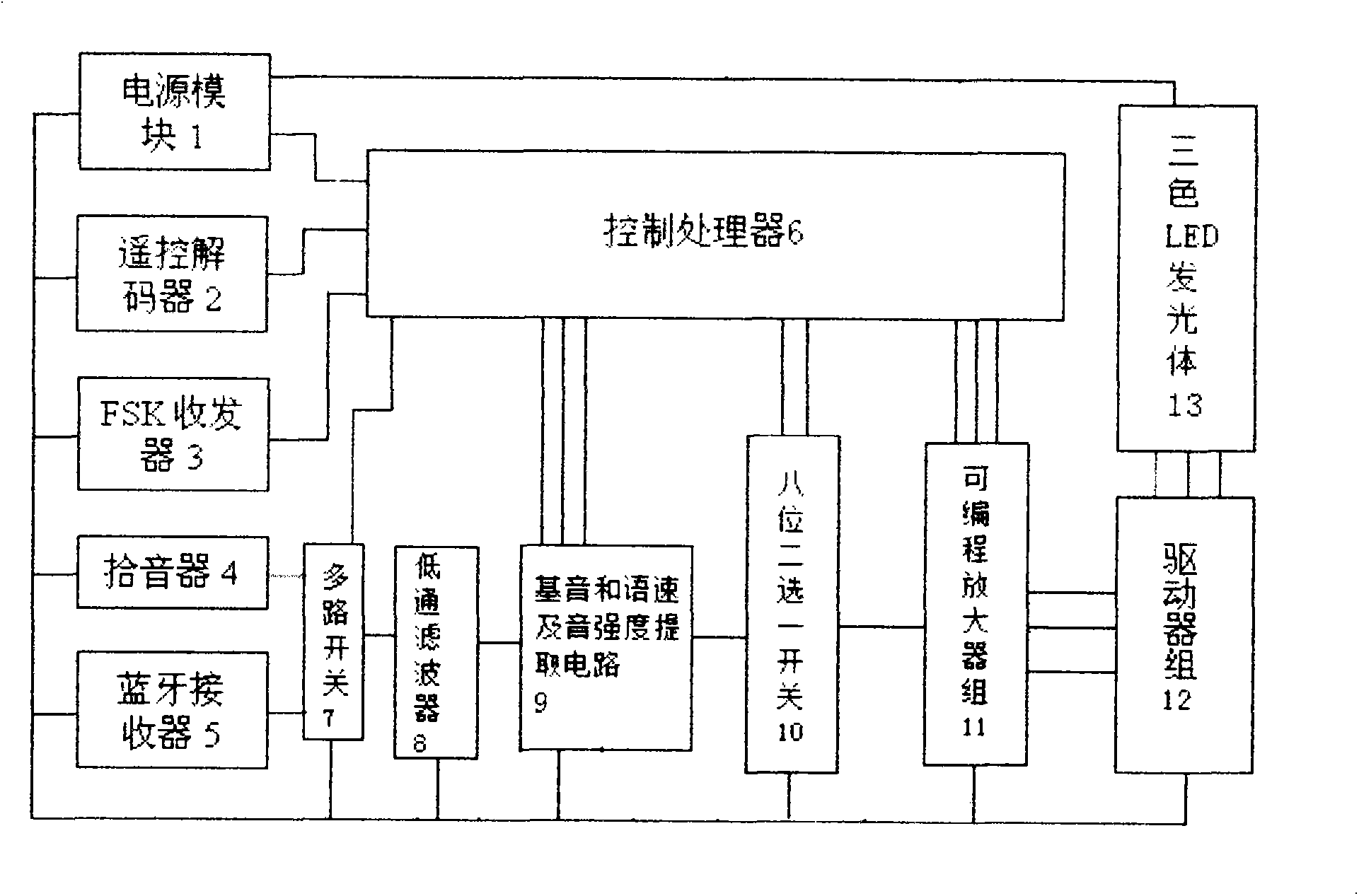

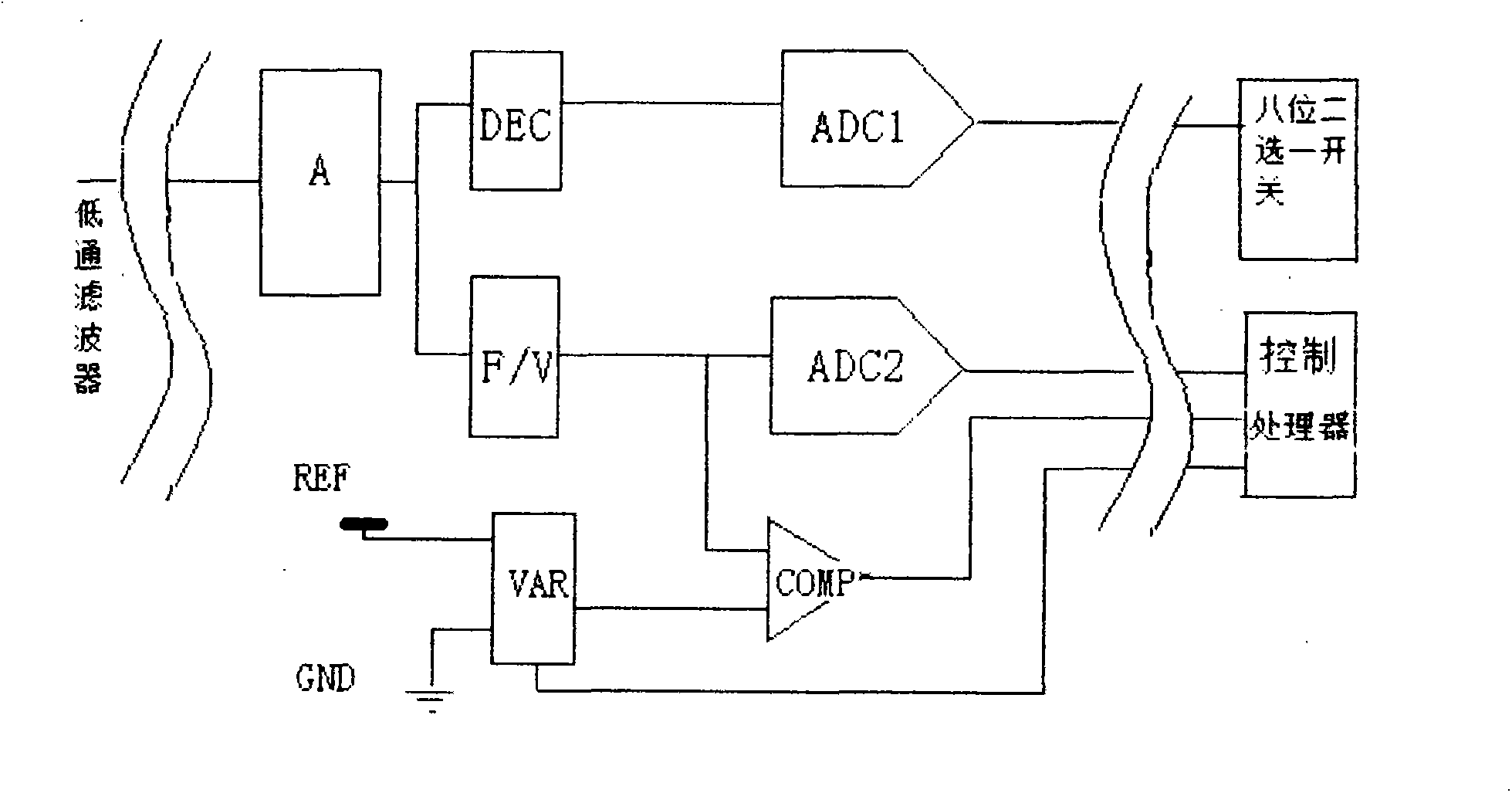

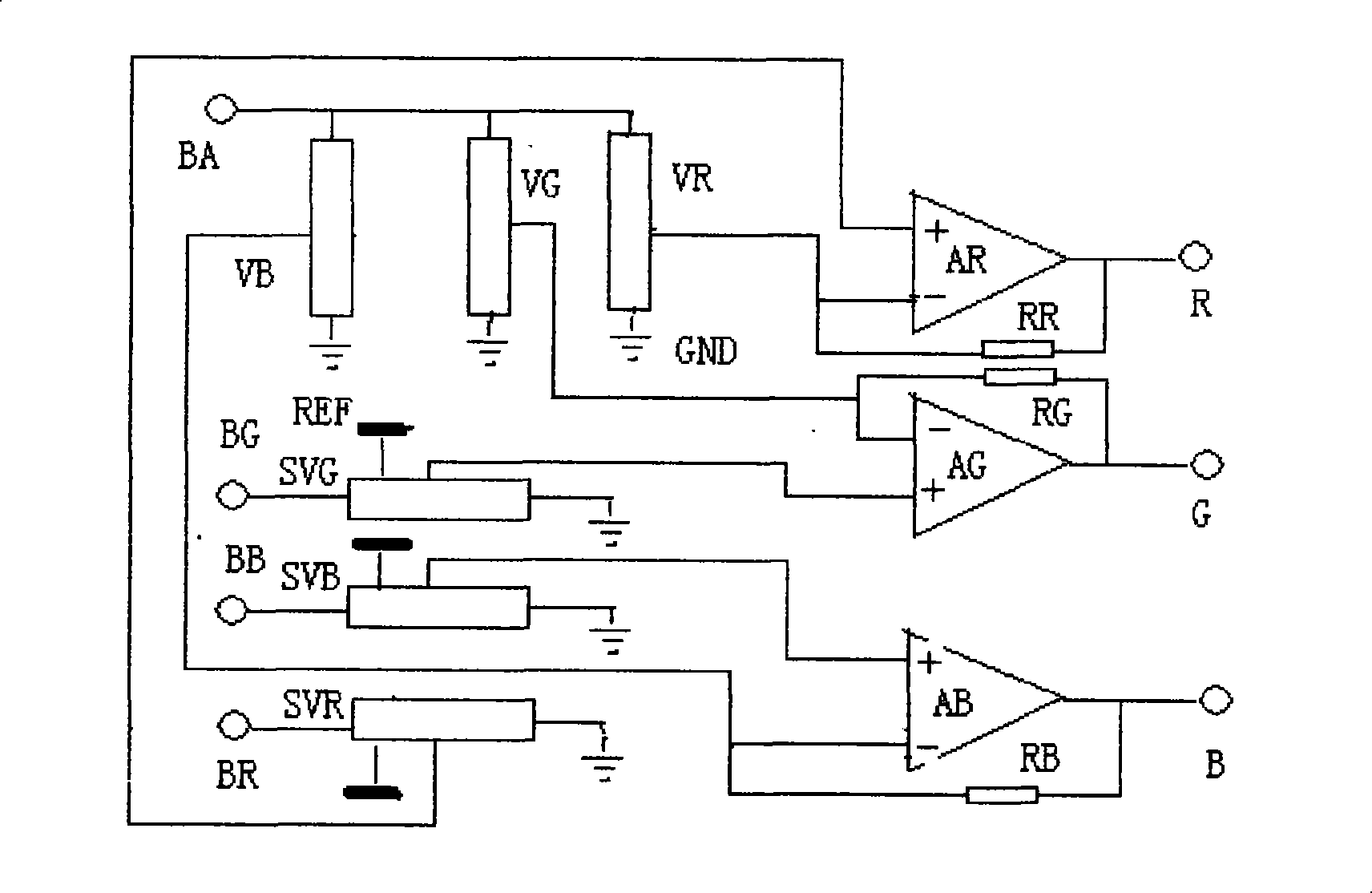

Driving device of emotional control of LED light color and brightness change

InactiveCN103889109ARealize the combinationAchieve real-time performanceElectric light circuit arrangementEnergy saving control techniquesCircuit extractionTransmission technology

The invention discloses a driving device of the emotional control of LED light color and brightness change. Based on the association of three basic acoustic characteristic quantities of fundamental tone in voice, speaking speed or voice pause time and voice intensity with four emotion of calmness, happiness, sadness, anger, the acoustic characteristic quantities are extracted through a circuit and a CIE color system and an industrial HSL primary color ring are employed to carry out a special algorithm operation to drive the LED light color and brightness to change, and a purpose of the real-time and automatic brightness adjustment is realized. At the same time, the wireless remote control, wireless bus and communication technology, a microprocessor special algorithm, Bluetooth audio transmission technology and new technology of LED luminescent material are integrated in the device, an LED lamp driving control device with moodiness, individuation, romance, energy saving and environmental protection and 'mood-video' conversion is realized, and the perfect combination of energy saving, lighting, emotional catharsis and comfort and lighting art is realized.

Owner:WUHAN ALADIN TECH CO LTD

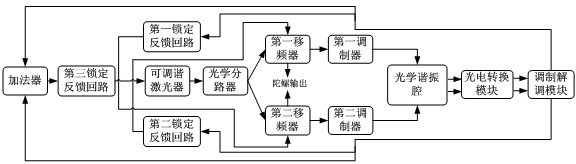

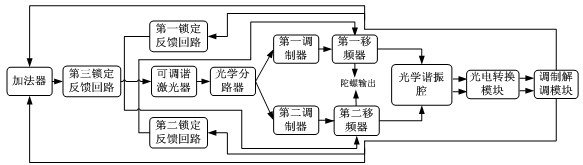

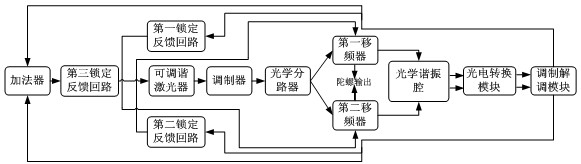

Two-path loop-locked resonant mode optical gyro

ActiveCN102331258AImprove reciprocityEliminate reciprocity noiseSagnac effect gyrometersCircuit extractionFrequency shift

The invention discloses a two-path loop-locked resonant mode optical gyro, which comprises an optical system comprising a tunable laser, an optical splitter, optical frequency shifters, optical modulators, an optical resonant cavity, a photoelectric conversion module and the like, and a processing circuit consisting of a demodulation module and feedback lock modules. In the optical gyro, two paths of signals with gyro rotation information are extracted by the processing circuit, and the frequency shift quantities of two paths of frequency shifters are respectively changed through two feedbacklock modules; simultaneously the two paths of signals are added together and then locked at the central point of clockwise and anticlockwise optical path resonant frequencies of the resonant cavity after the laser frequency is controlled by a third feedback lock module; and finally the frequency shift quantity outputs of the two paths of frequency shifters are subtracted each other to obtain a gyro signal. The two-path loop-locked resonant mode optical gyro disclosed by the invention is conductive to improving the reciprocity of the resonant mode optical gyro and better eliminating reciprocity noise, is conductive to improving the linear and the dynamic range of a gyro system, and is conductive to reducing the optical power difference of clockwise and anticlockwise light paths in the cavity and reducing optical Kerr noise.

Owner:ZHEJIANG UNIV

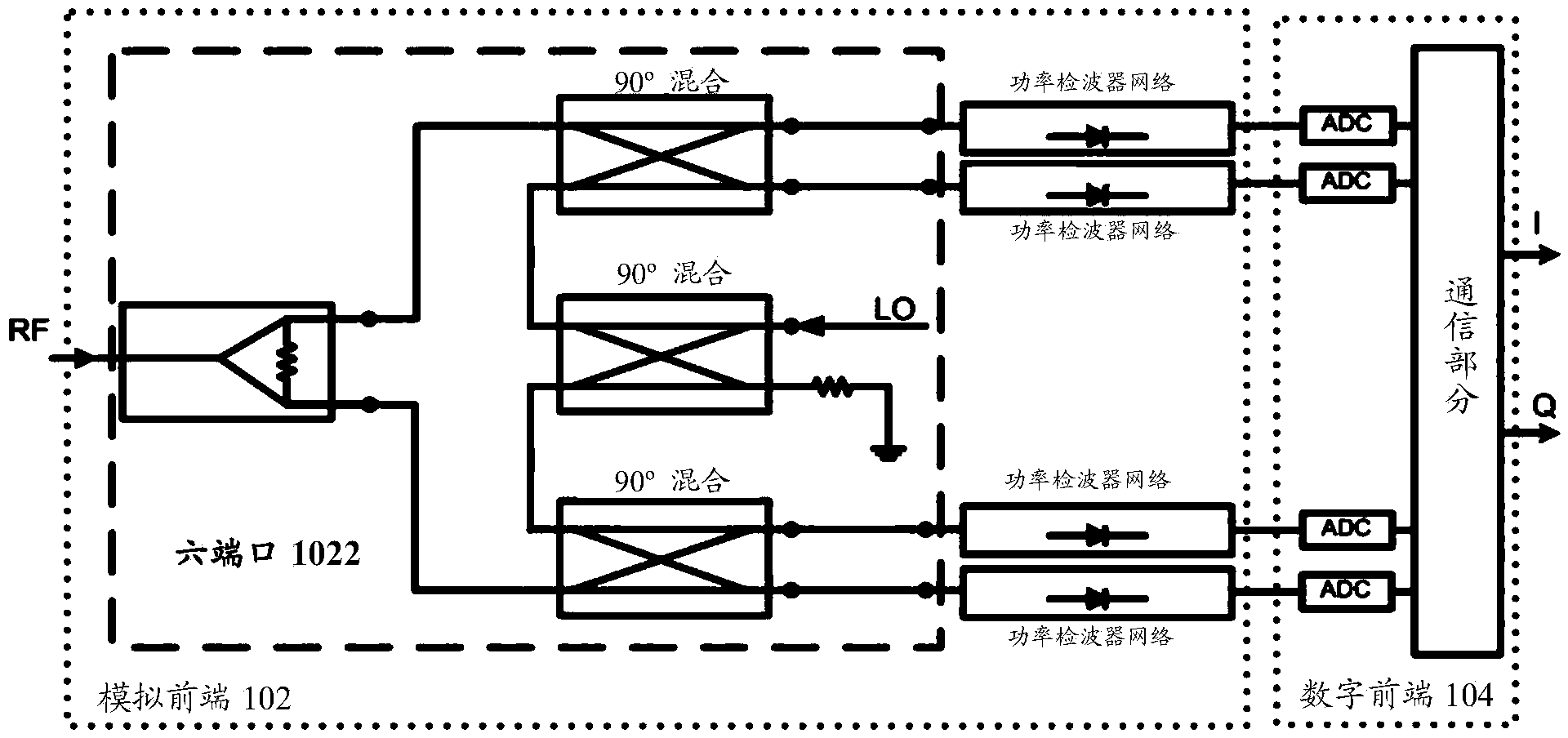

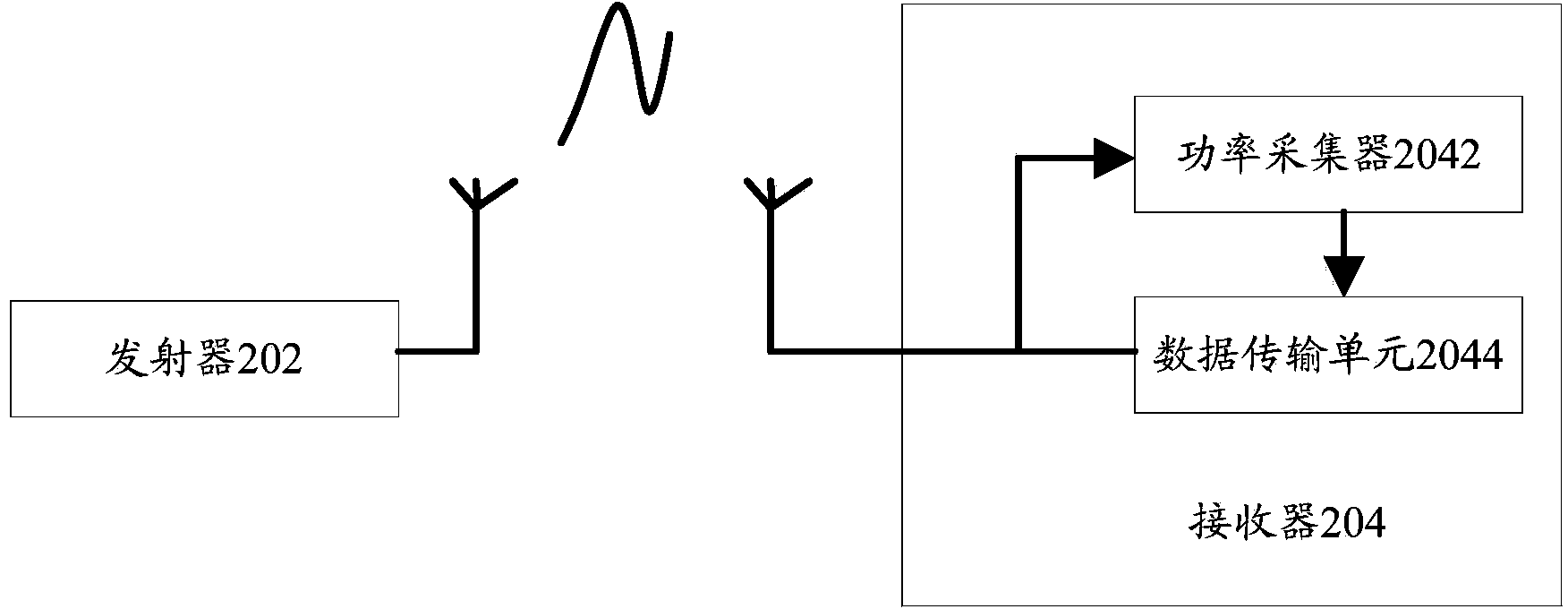

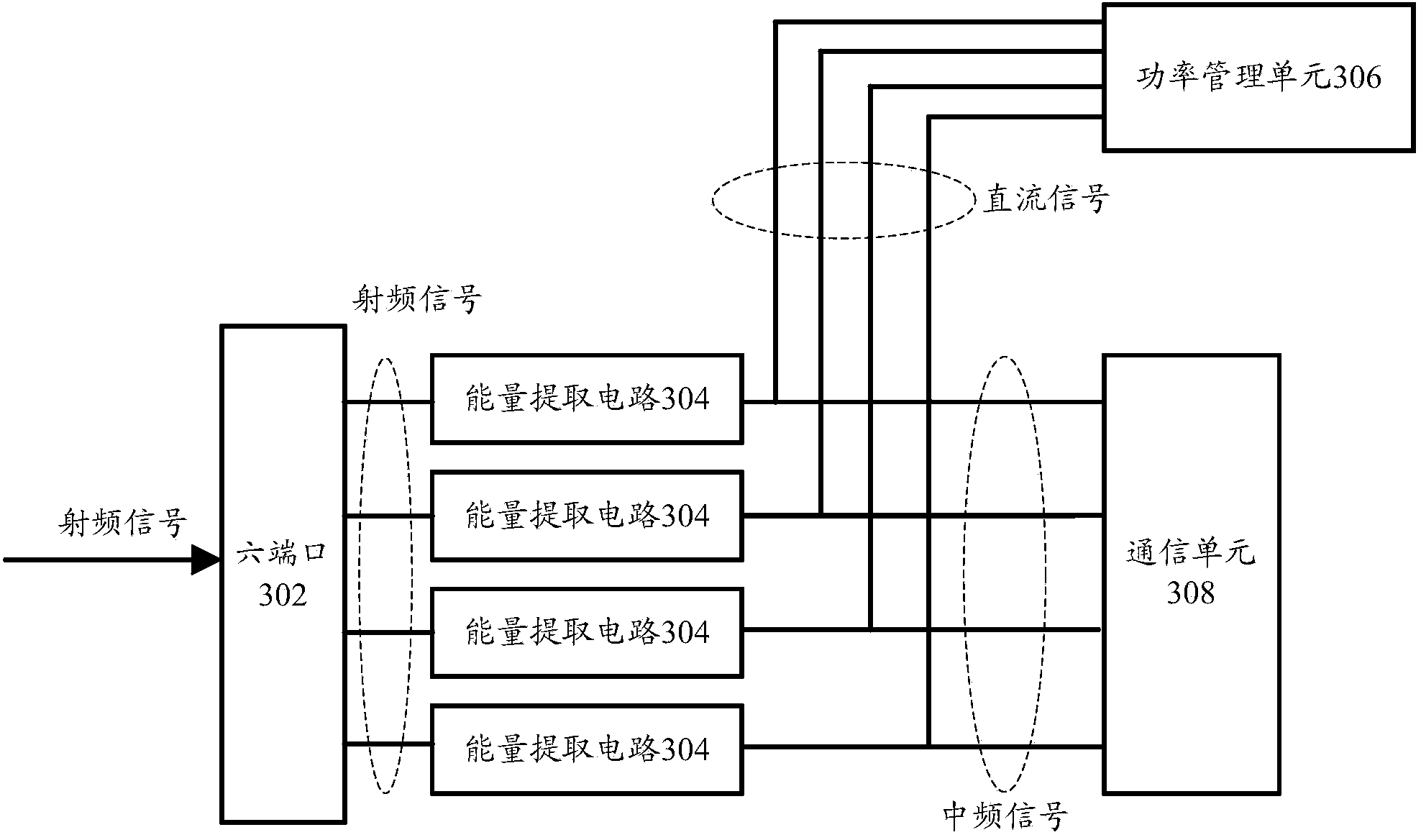

Receiving device and method for simultaneously performing radio frequency energy extraction and data communication

ActiveCN104113145ARealize the collectionElectromagnetic wave systemCircuit arrangementsRadio frequency energyCommunication unit

The invention provides a receiving device and a method for simultaneously performing radio frequency energy extraction and data communication. The receiving device comprises a receiving port, an energy extraction circuit and a power management unit, wherein the receiving port is used for receiving radio frequency signals coming from the outside; the energy extraction circuit is connected to the receiving port and used for extracting power signals and data signals out of the radio frequency signals, outputting the power signals to a power management unit and outputting the data signals to a communication unit; and the power management unit is connected with the energy extraction circuit and used for receiving the power signals and storing energy extracted by the energy extraction circuit. According to the technical scheme, wireless energy collection and data communication can be performed simultaneously, and accordingly a mobile device or a handheld device can provide electric energy for itself while performing data communication.

Owner:杭州浙海企业管理有限公司

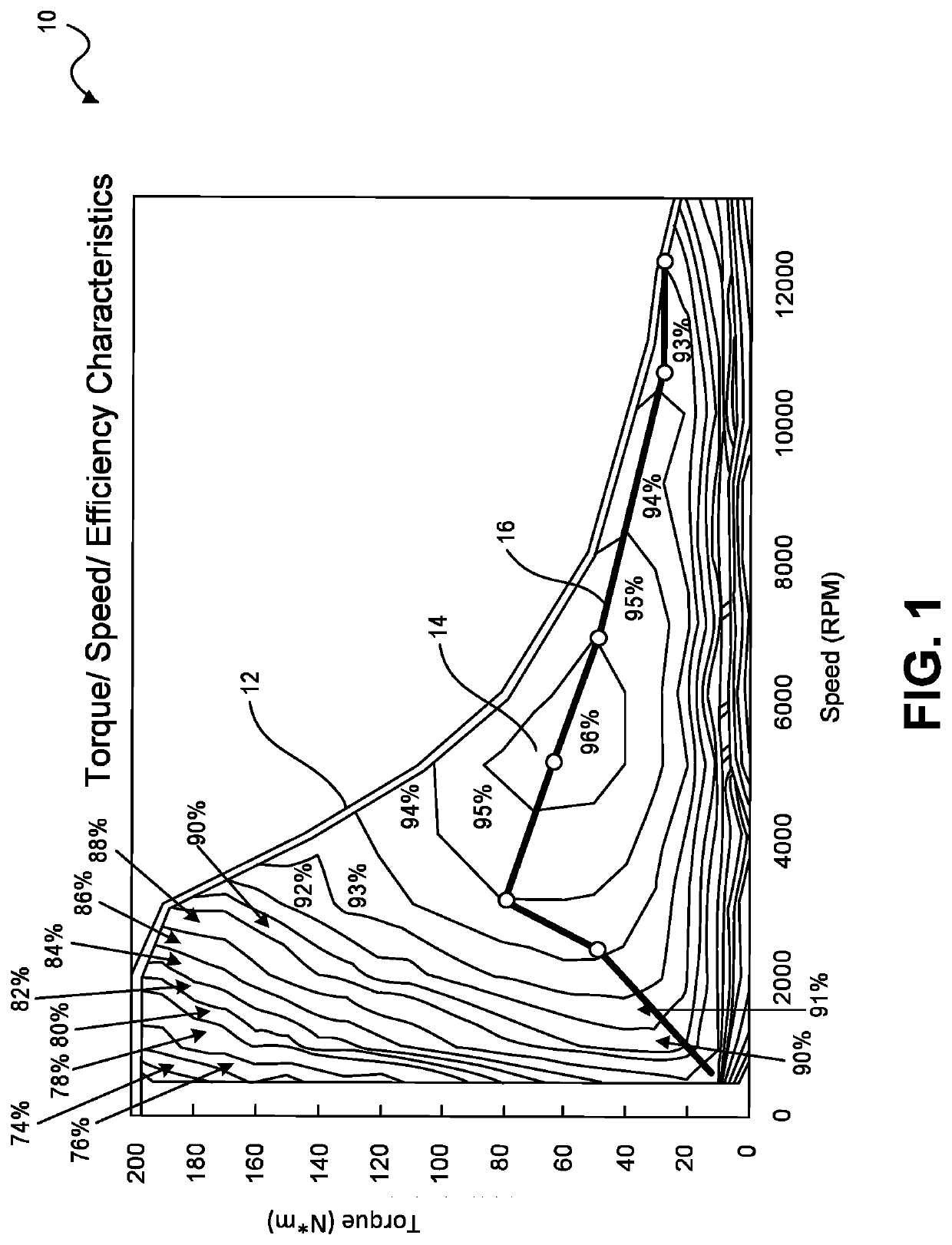

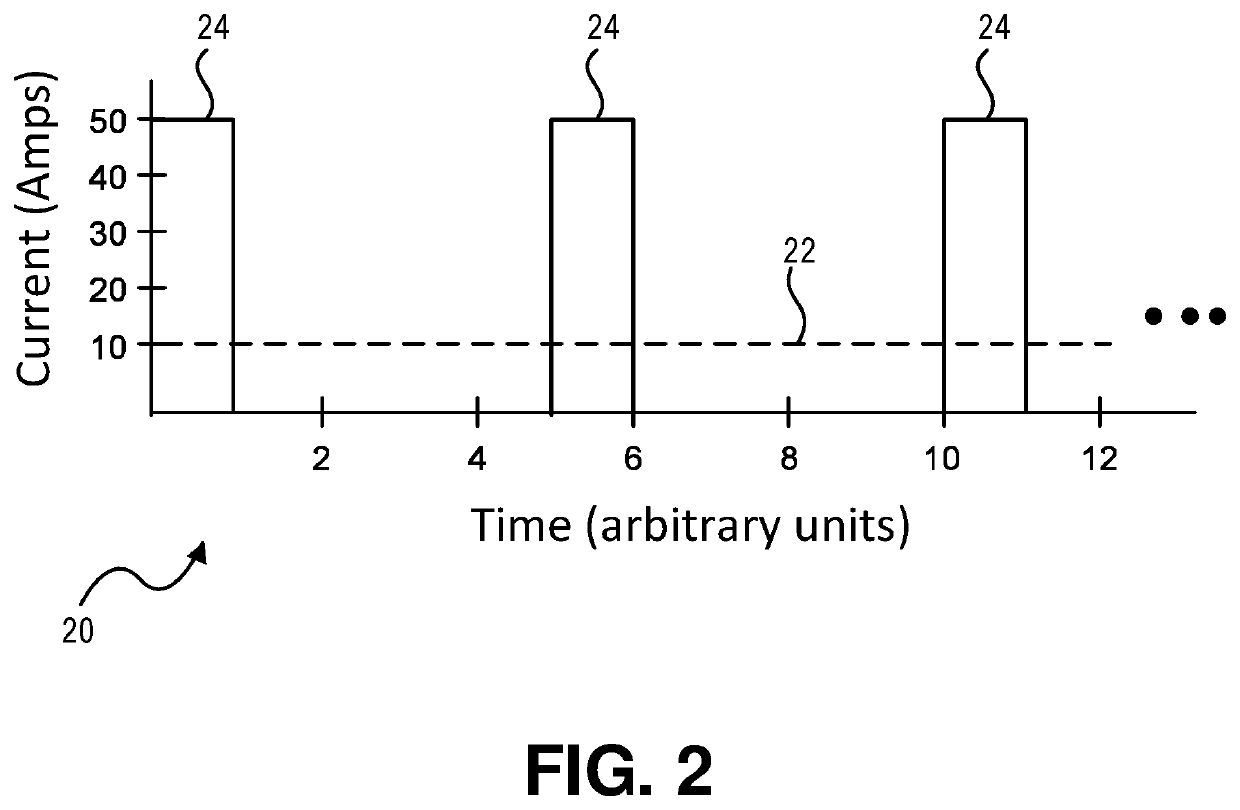

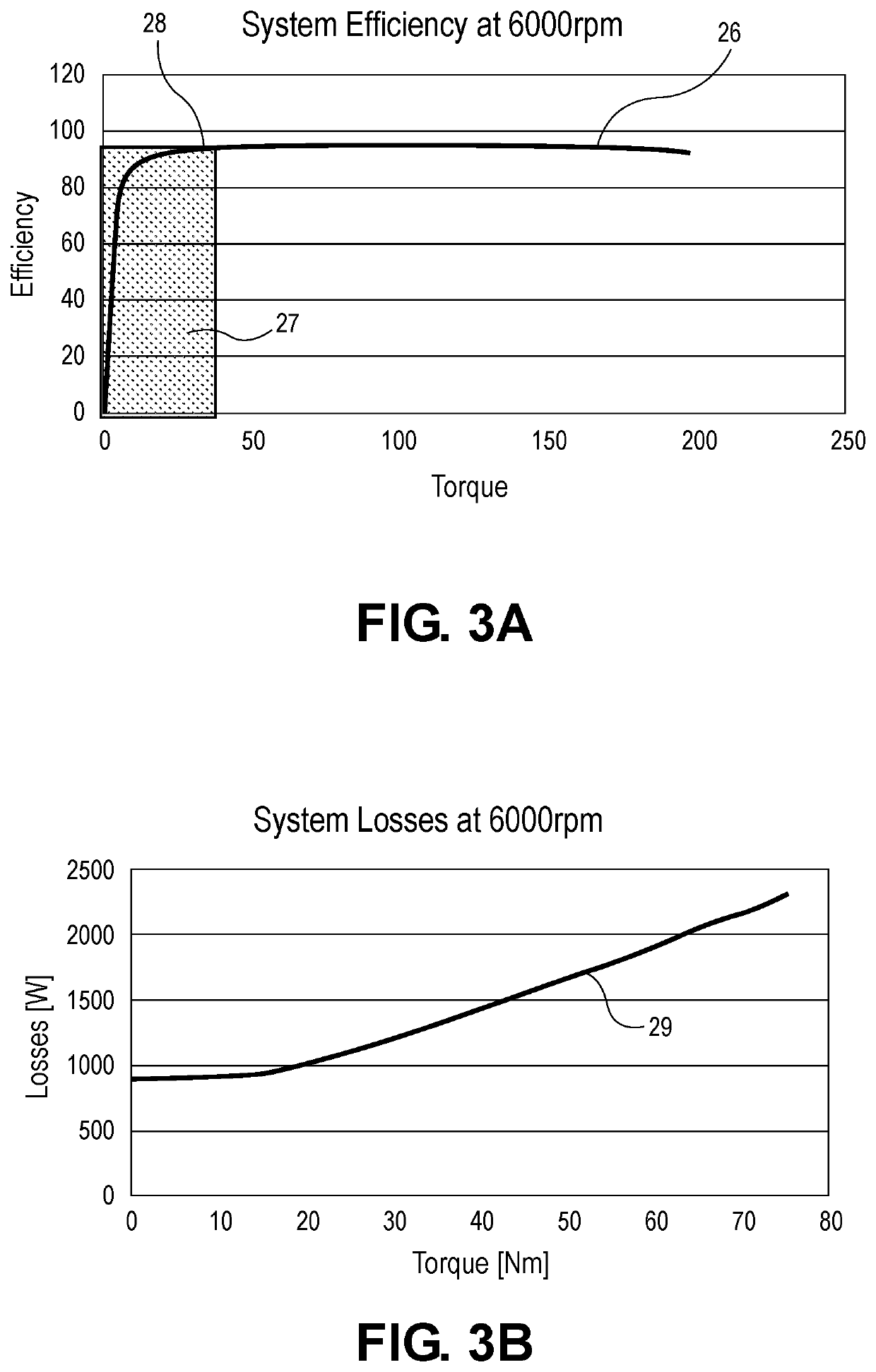

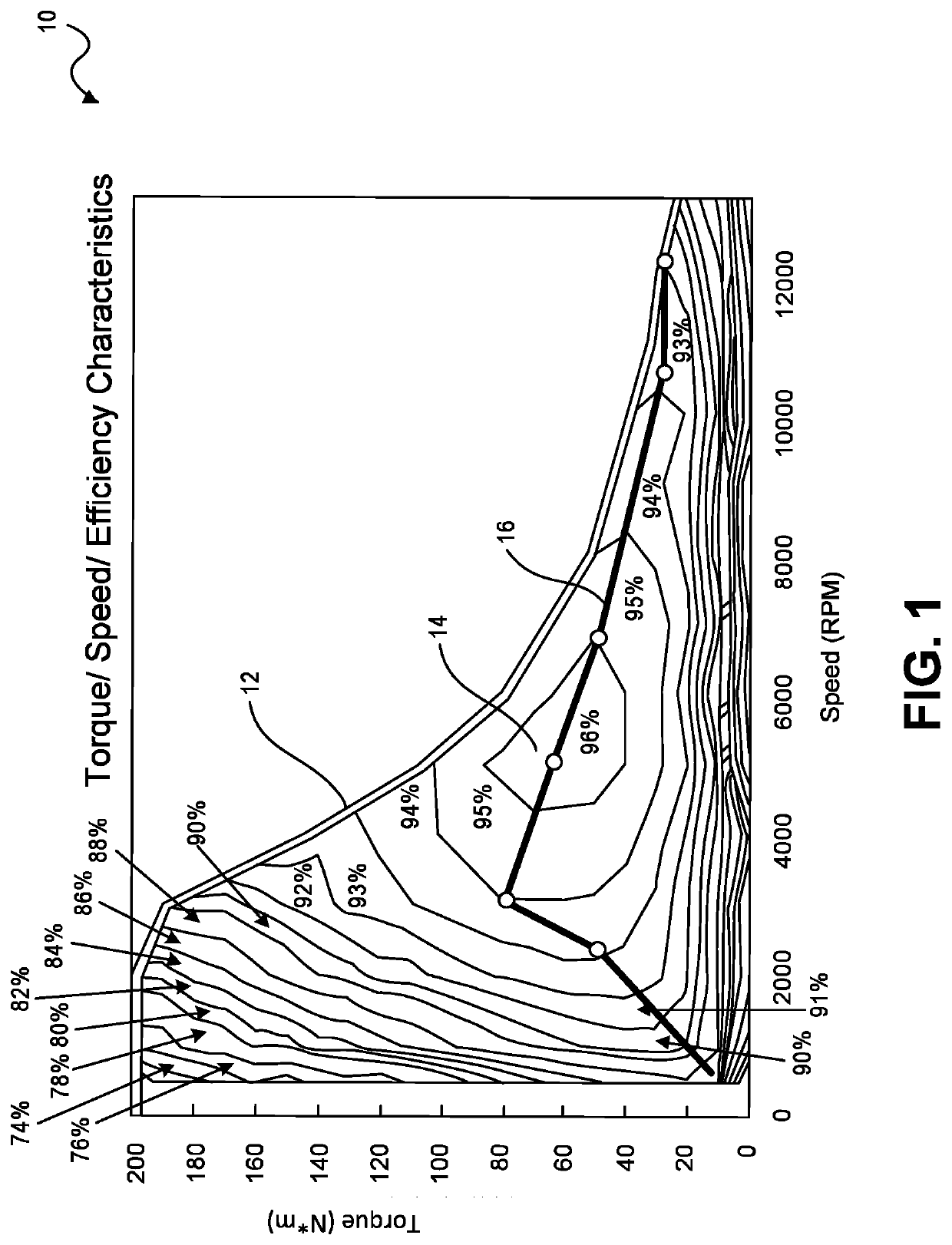

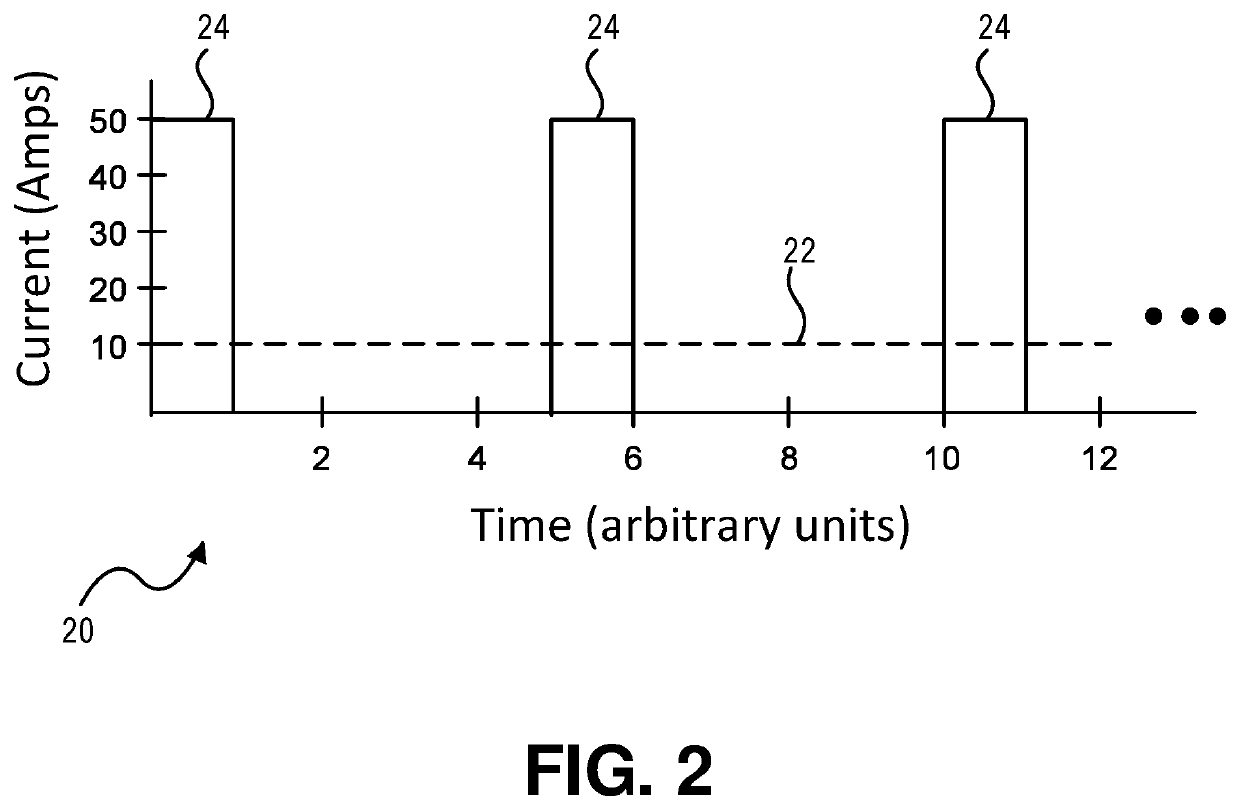

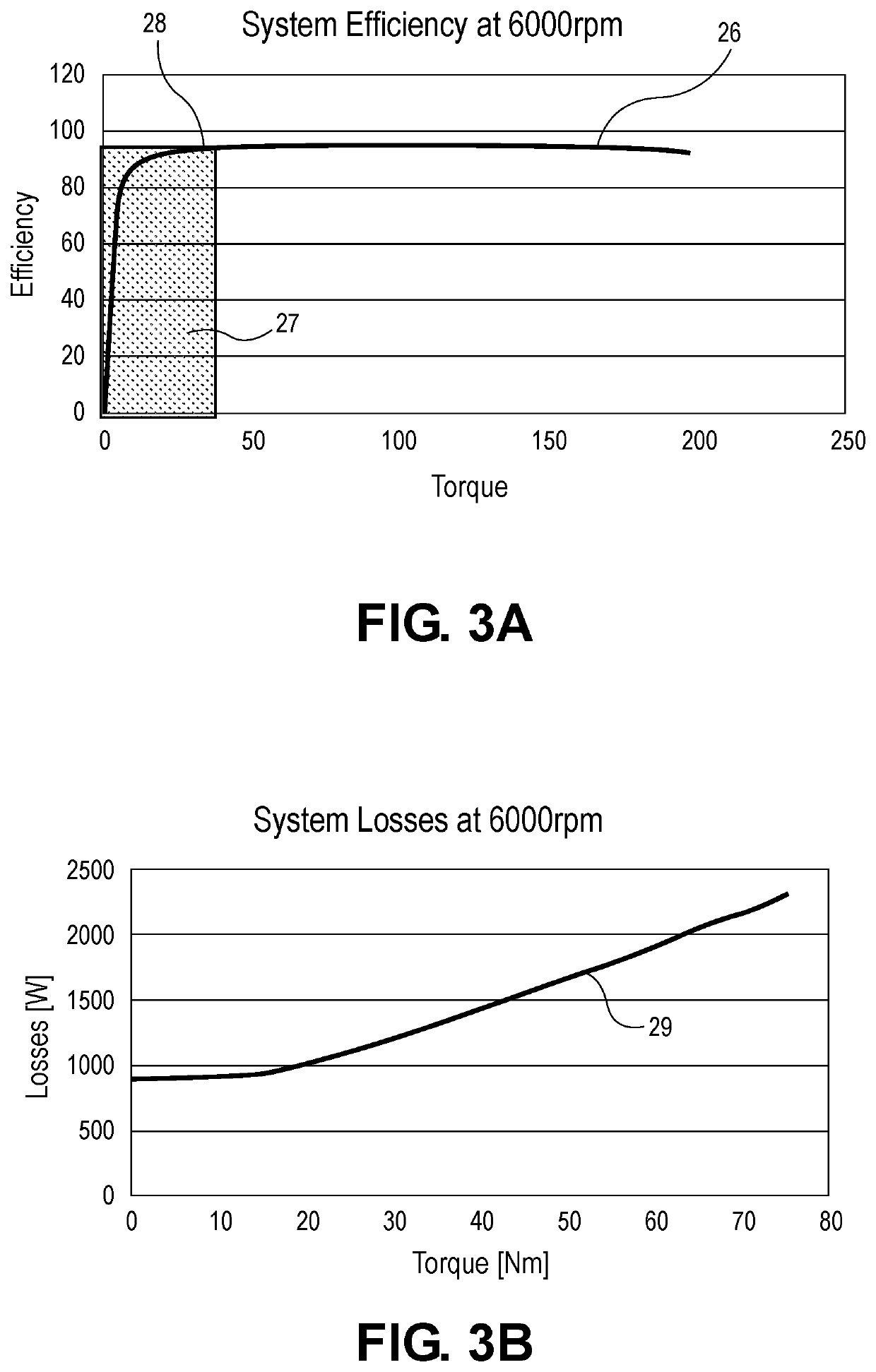

Boosted converter for pulsed electric machine control

ActiveUS10944352B2Reduce rise and fall timesEasy to operateSpeed controllerMotor control for low load efficiencyConvertersPulse control

A boost circuit is arranged to reduce rise and fall times of pulsed power used for pulsed control operation of electric machines. Magnetic energy present in the electric machine at the end of a pulse is extracted by the boost circuit to reduce the pulse fall time. The energy is stored by the boost circuit and then applied at the beginning of a subsequent pulse to reduce the rise time. By reducing rise and fall times compared to not using such a boost circuit, machine efficiency is improved.

Owner:TULA ETECH INC

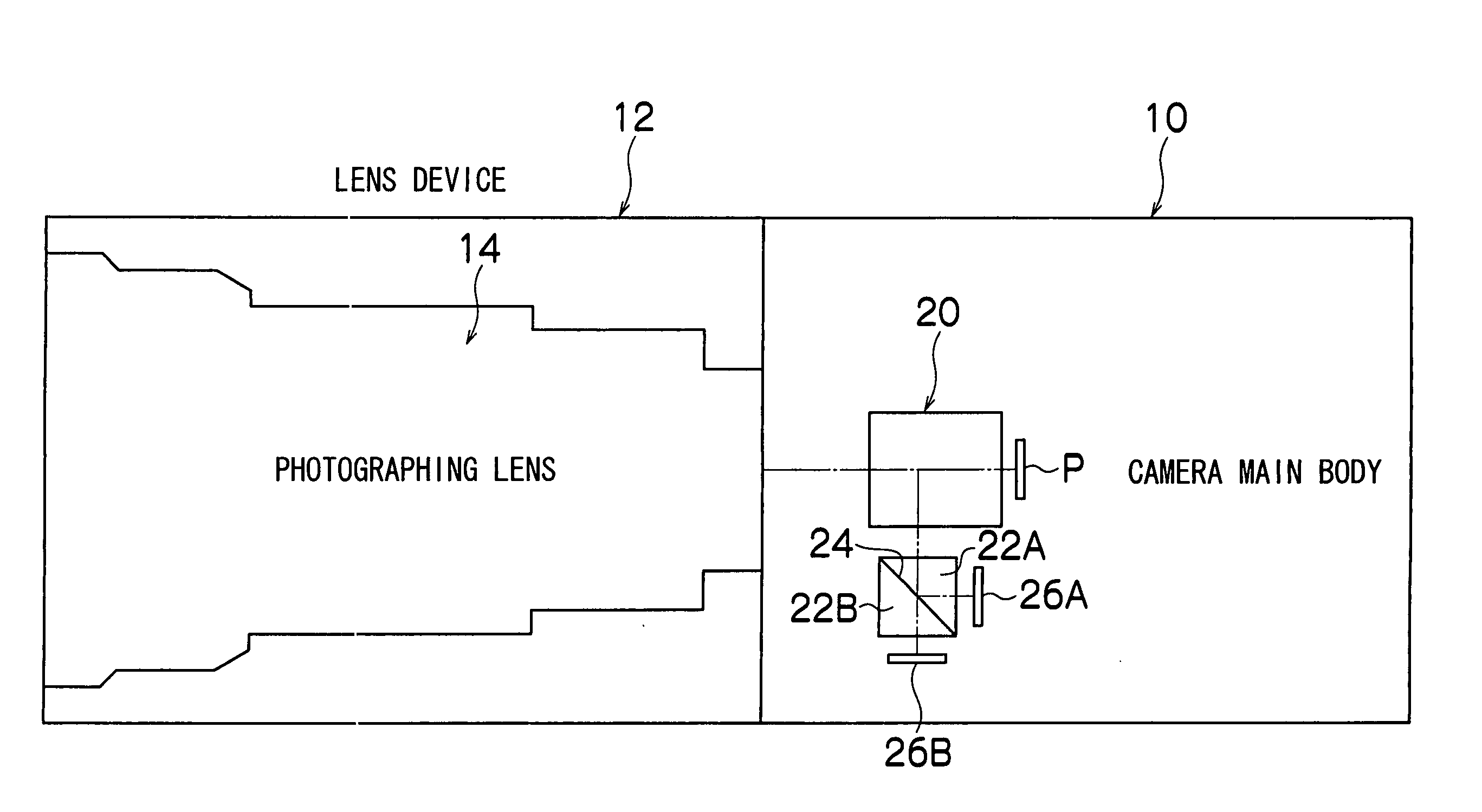

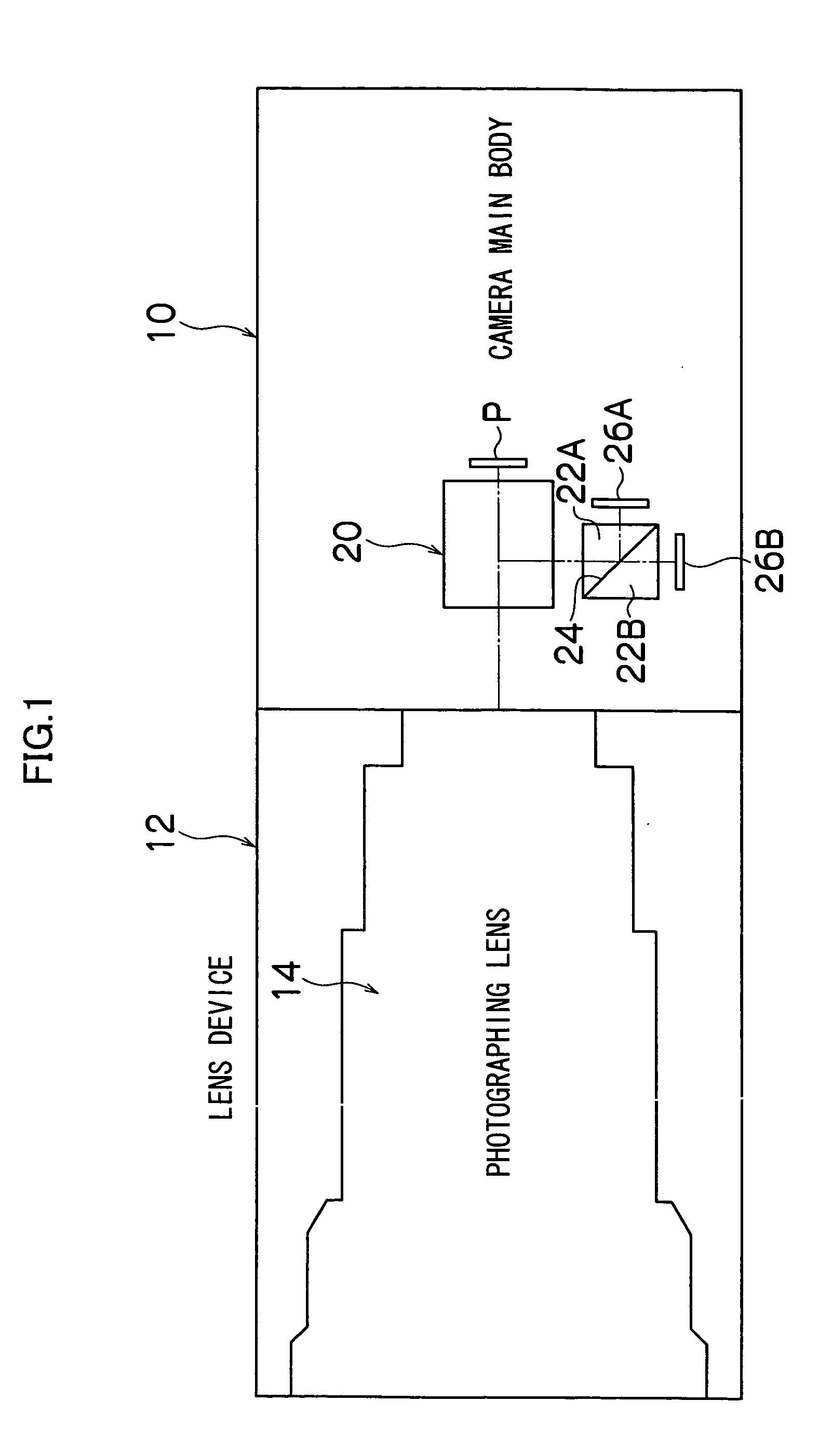

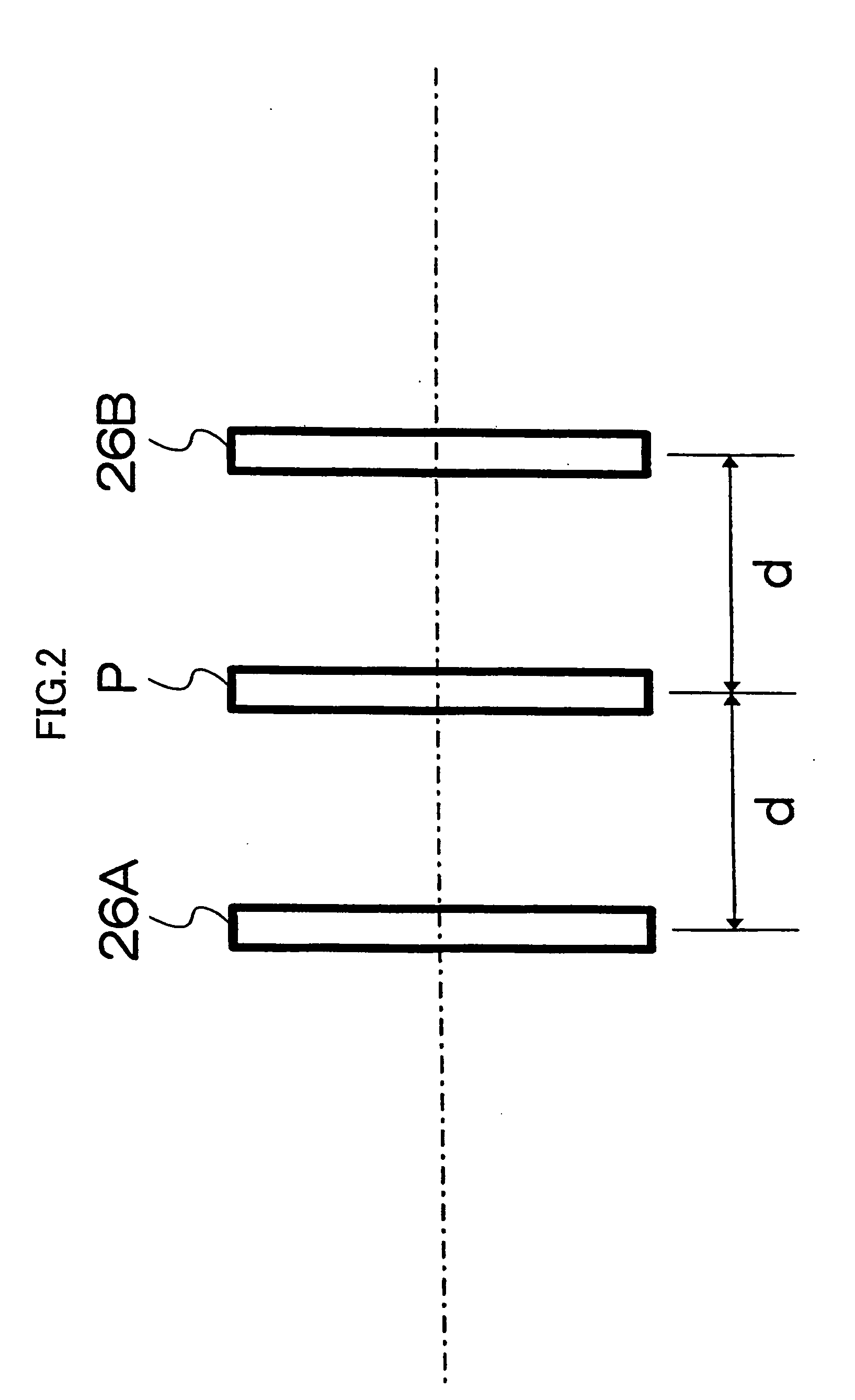

Autofocus system

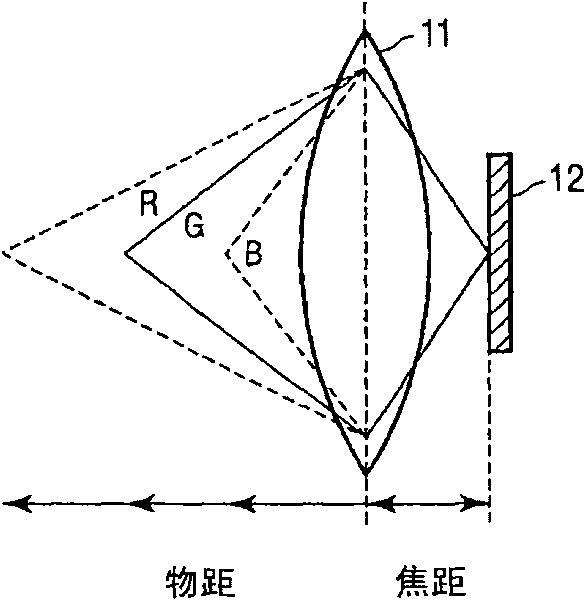

InactiveUS20050110890A1Enabling luminance levelPerformed surely and accuratelyTelevision system detailsColor television detailsElectronic shutterCircuit extraction

Two imaging elements for AF, each having a different optical path length, are mounted to a camera main body. The automatic focus adjustment is performed based on the video signal of the AF area extracted by the gate circuits from the video signal acquired by the imaging elements. The electronic shutter function of the imaging elements is controlled based on the video signal of the AF area extracted by the gate circuits, so as to enable the exposure adjustment for the AF area to be performed.

Owner:FUJI PHOTO OPTICAL CO LTD

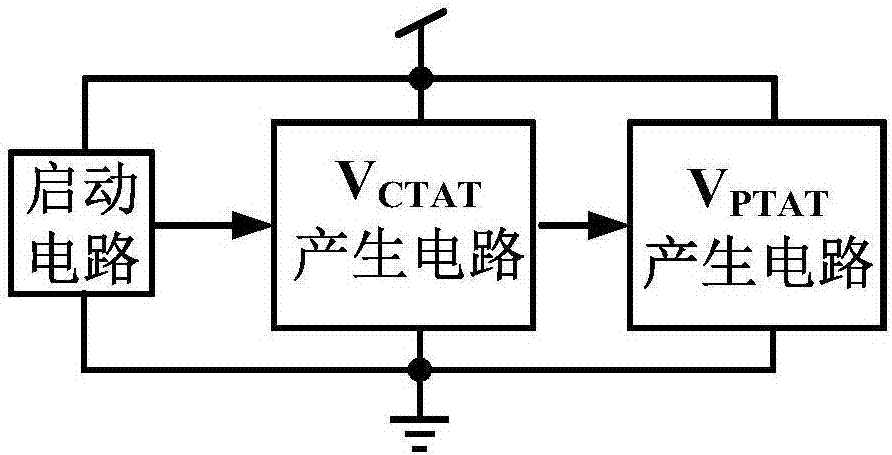

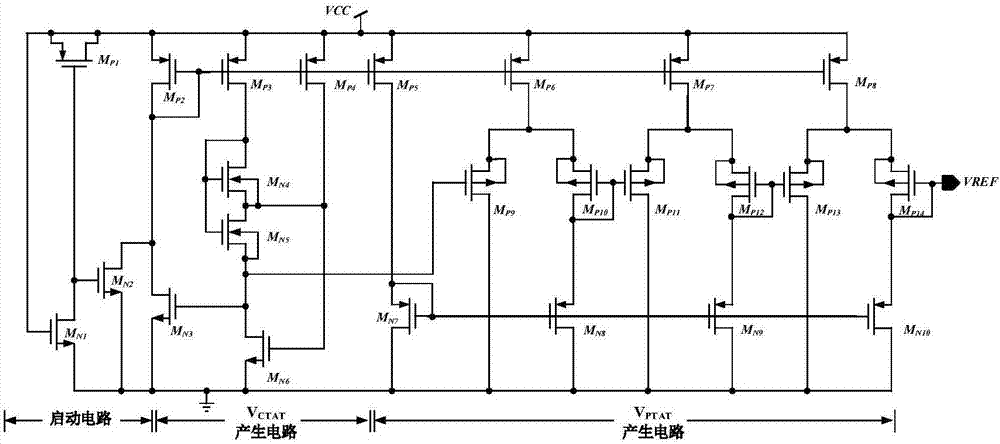

CMOS subthreshold reference circuit with low power consumption and low temperature drift

The invention discloses a CMOS subthreshold reference circuit with low power consumption and low temperature drift and belongs to the technical field of power management. The CMOS subthreshold reference circuit comprises a start-up circuit, a negative temperature coefficient voltage generator circuit and a positive temperature coefficient voltage generator circuit. The start-up circuit enables the grid end of a first NMOS transistor to be pulled up at the initial stage of the reference circuit so that the circuit is out of the zero state and begins to work normally, and after that, the start-up circuit quits. The negative temperature coefficient voltage generator circuit extracts the threshold voltage VTHN of the NMOS transistor and takes the threshold voltage VYHN as the negative temperature coefficient voltage. The positive temperature coefficient voltage generator circuit utilizes the MOS transistor having equal drain source and different width-to-length ratio and working at the subthreshold region to generate positive temperature coefficient voltage. The positive temperature coefficient voltage and the negative temperature coefficient voltage output from the negative temperature coefficient voltage generator circuit are superposed to output reference voltage VREF. The reference circuit has the characteristic of approximating zero temperature within a certain temperature range and can realize ultra-low power consumption at mu W order.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

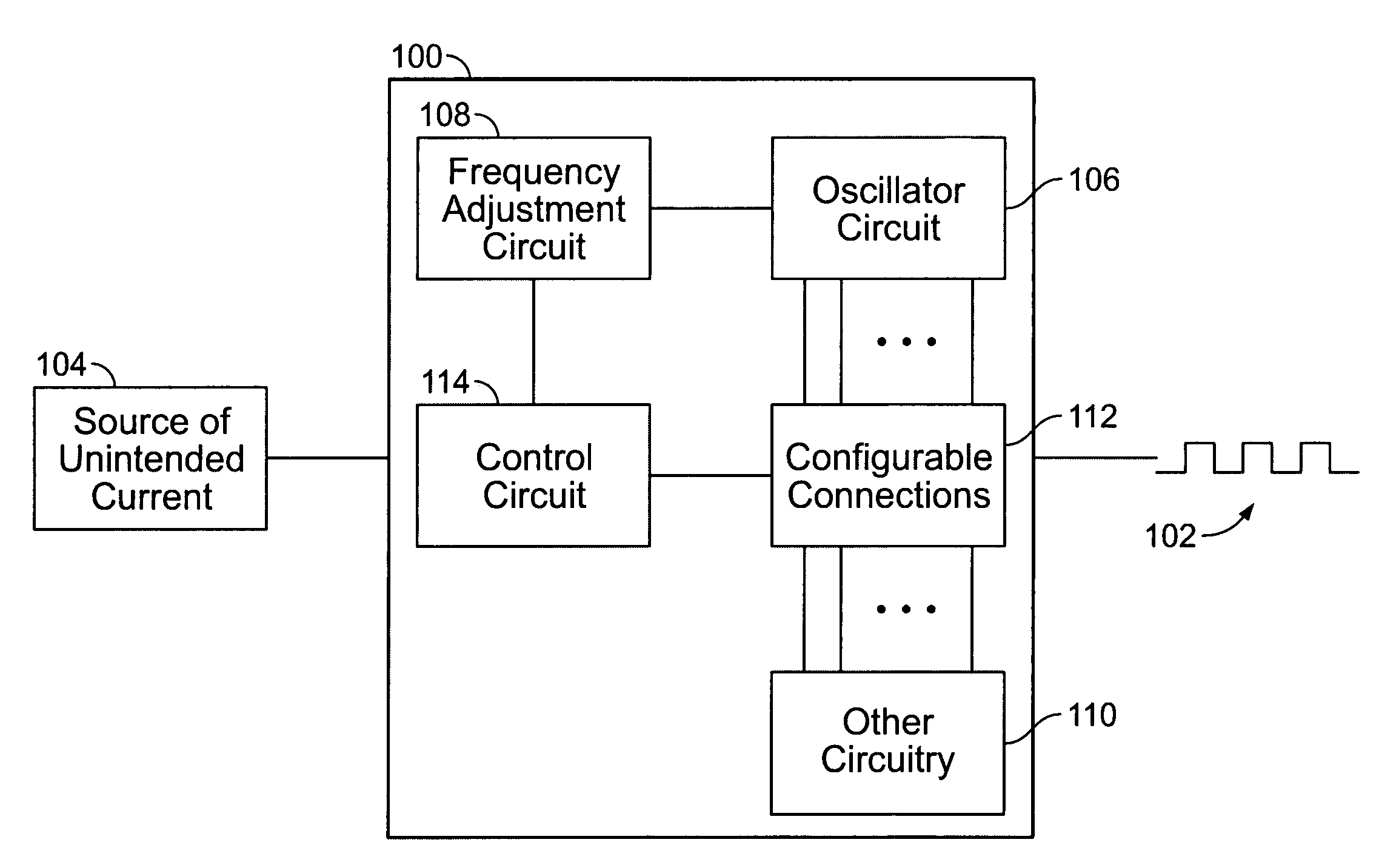

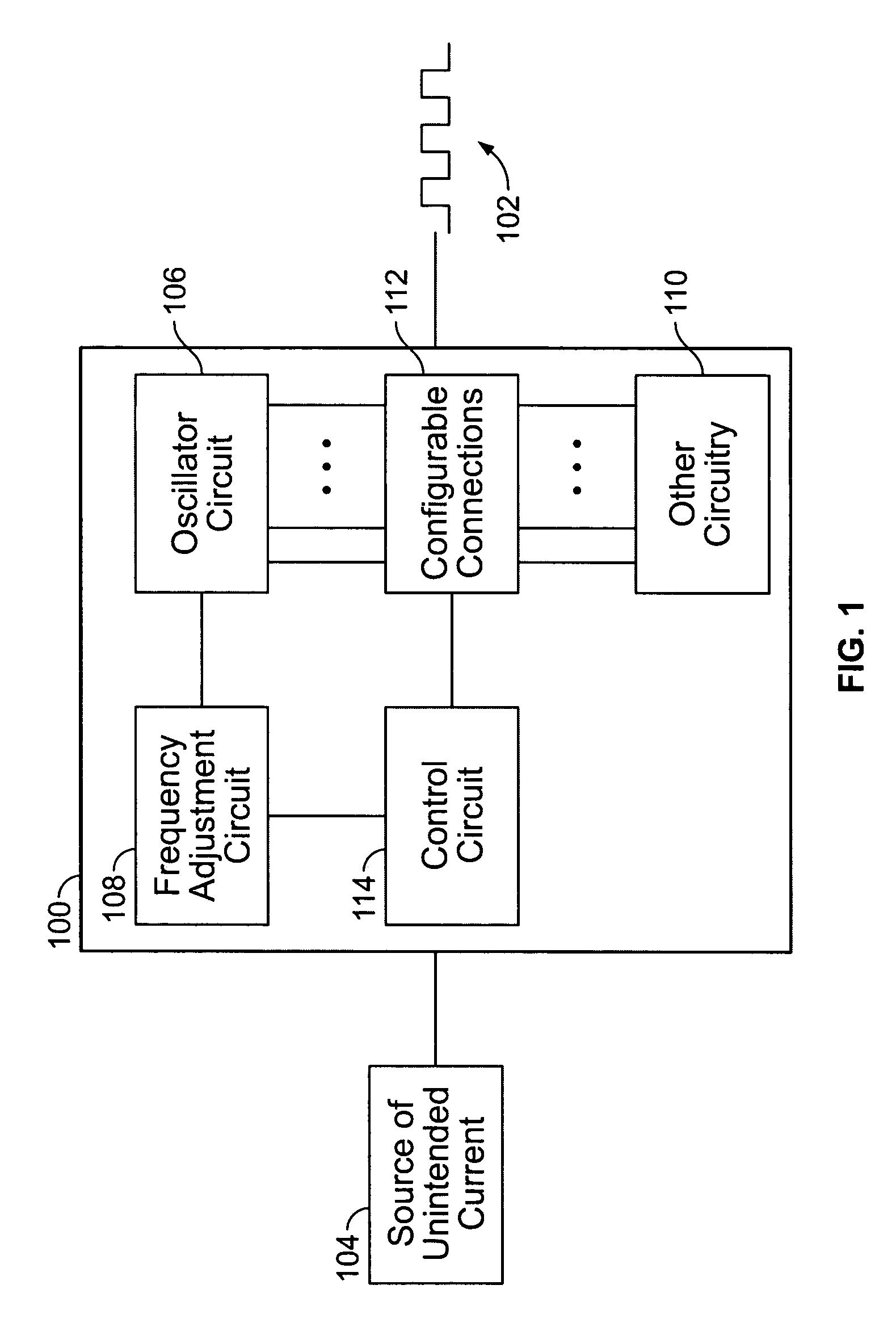

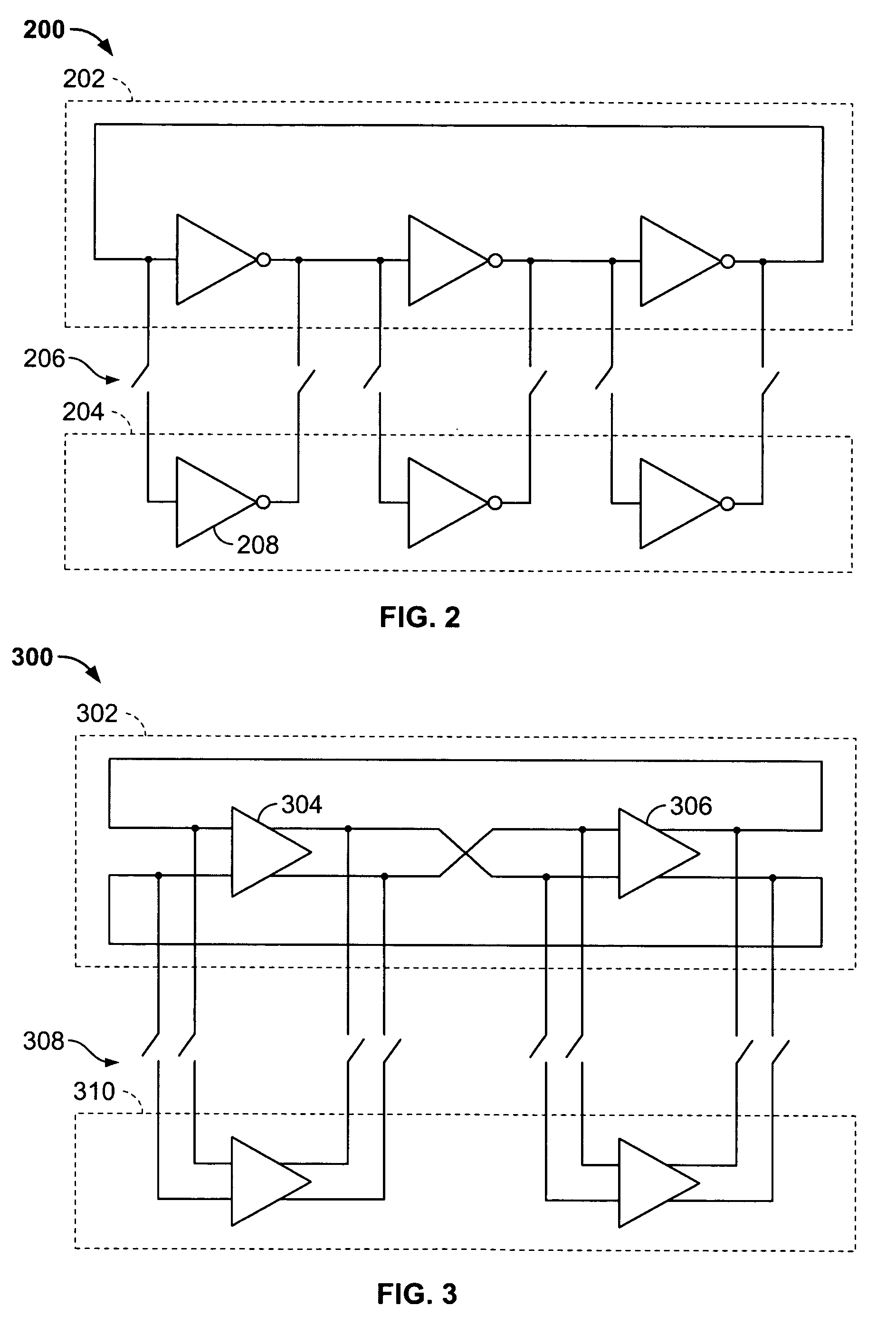

Systems and methods for mitigating phase jitter in a periodic signal

ActiveUS7411464B1Phase jitterIncrease volumePulse automatic controlGenerator stabilizationCircuit extractionEngineering

An oscillator circuit can generate a periodic signal, and a frequency adjustment circuit can adjust the frequency of the periodic signal. The periodic signal may include phase jitter. In one aspect of the invention, the phase jitter may be mitigated by connecting other circuitry to the oscillator circuit and allowing the other circuitry to draw current. In one embodiment, the other circuitry is connected in parallel with the oscillator circuit. In one embodiment, the other circuitry is configured to draw greater current to mitigate more phase jitter and to draw less current to mitigate less phase jitter. In one embodiment, a greater portion of the other circuitry is connected to the oscillator circuit for higher frequencies and a lesser portion of the other circuitry is connected to the oscillator circuit for lower frequencies.

Owner:ALTERA CORP

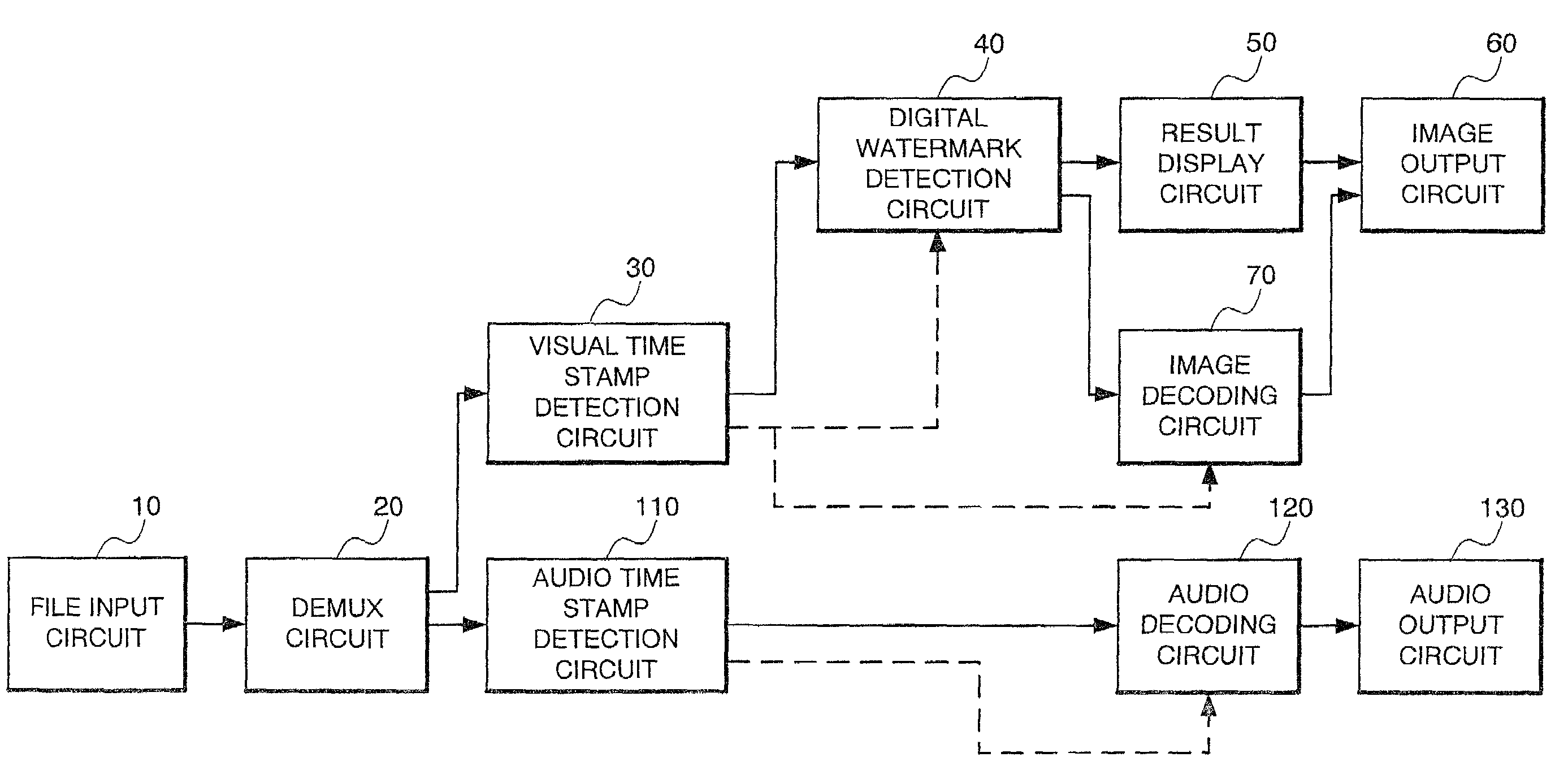

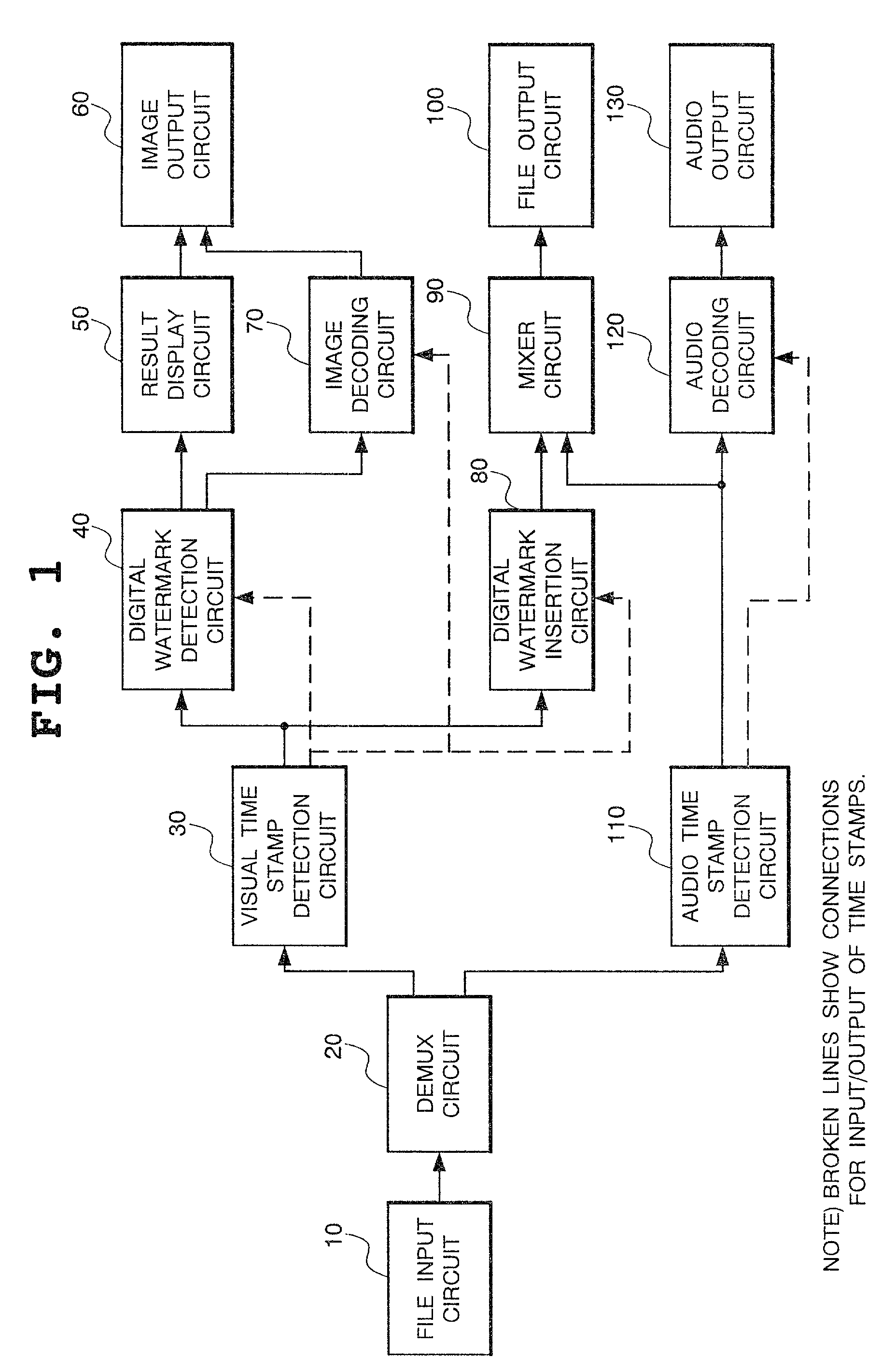

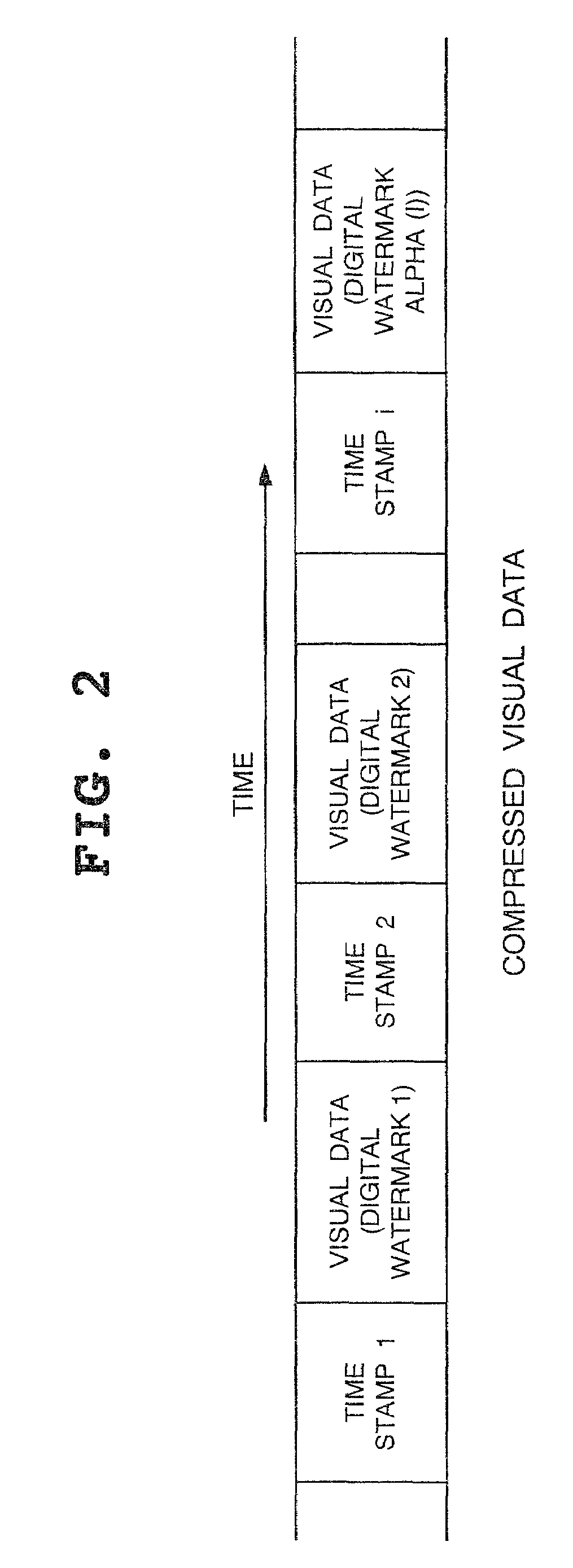

Digital watermarking device, digital watermark insertion method and digital watermark detection method

InactiveUS7224799B2Small scaleUser identity/authority verificationVisual presentationComputer hardwareData stream

When inserting several types of digital watermark information into the digital information, the visual time stamp detection circuit extracts the time stamps corresponding to the visual data in the visual data stream and the digital watermark insertion circuit specifies the types of the digital watermark information to be inserted corresponding to the extracted time stamps and inserts the digital watermark information of the applicable types into the visual data so that such information is synthesized with the audio data by the mixer circuit.

Owner:NEC PERSONAL COMPUTERS LTD

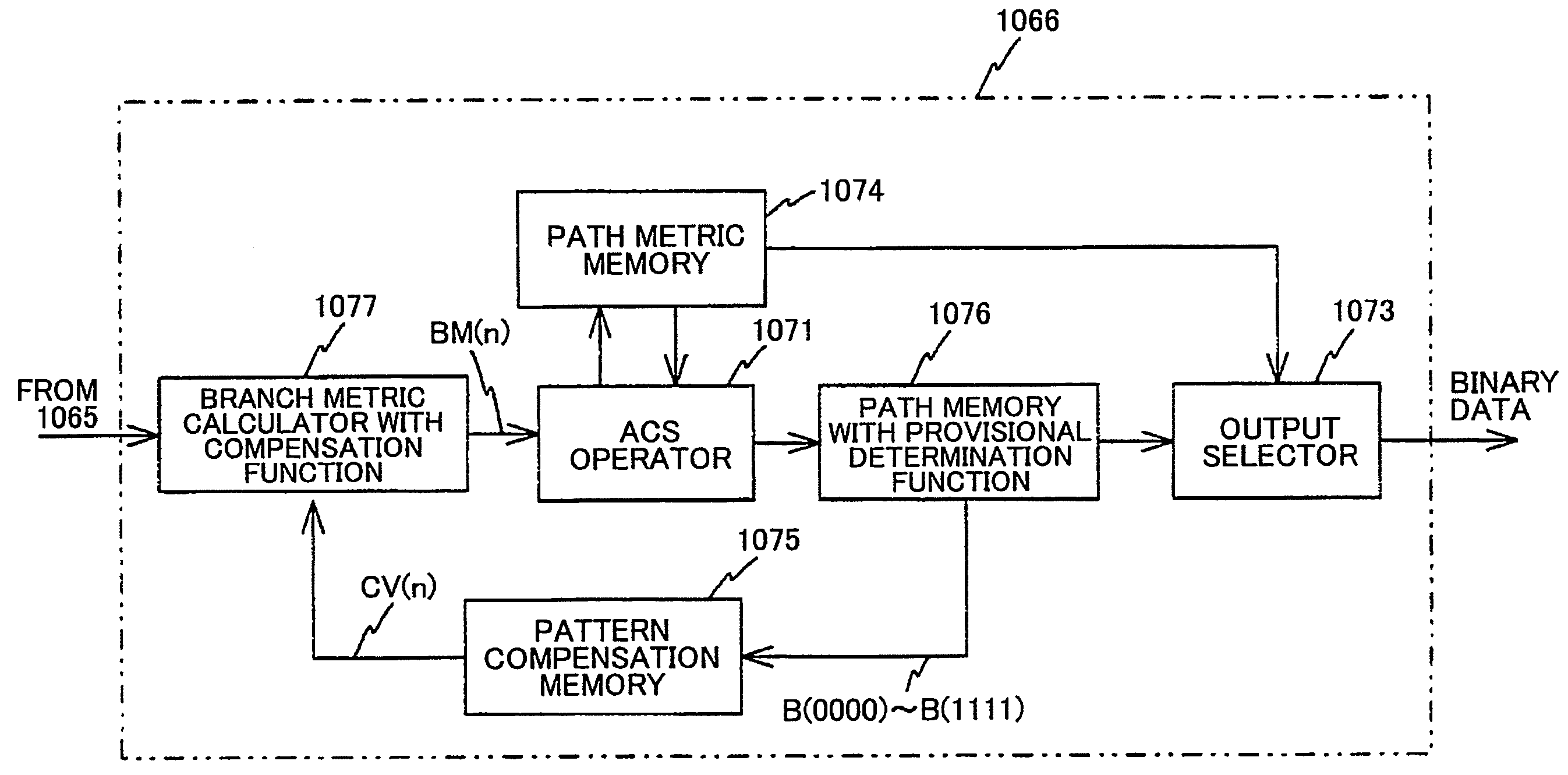

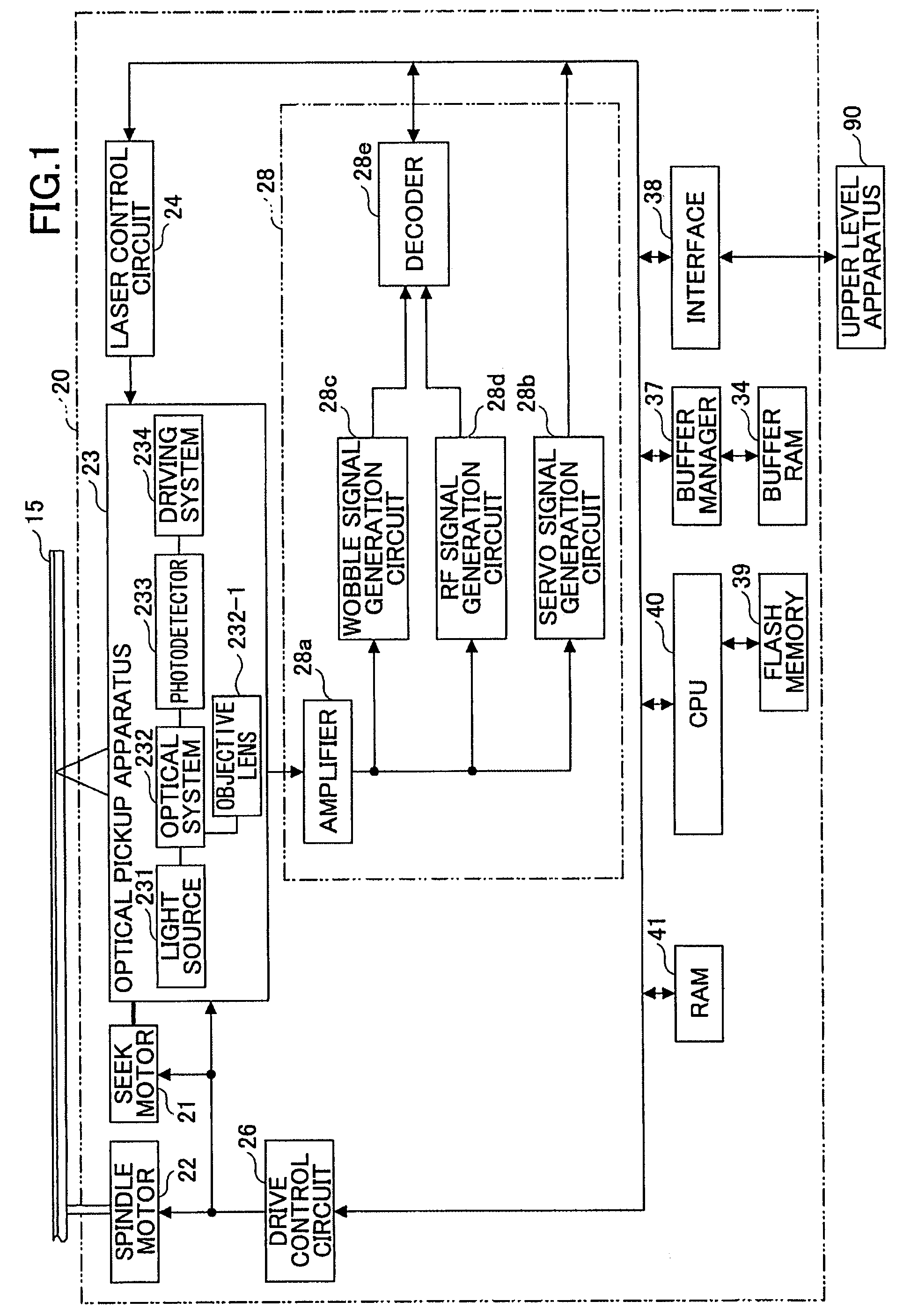

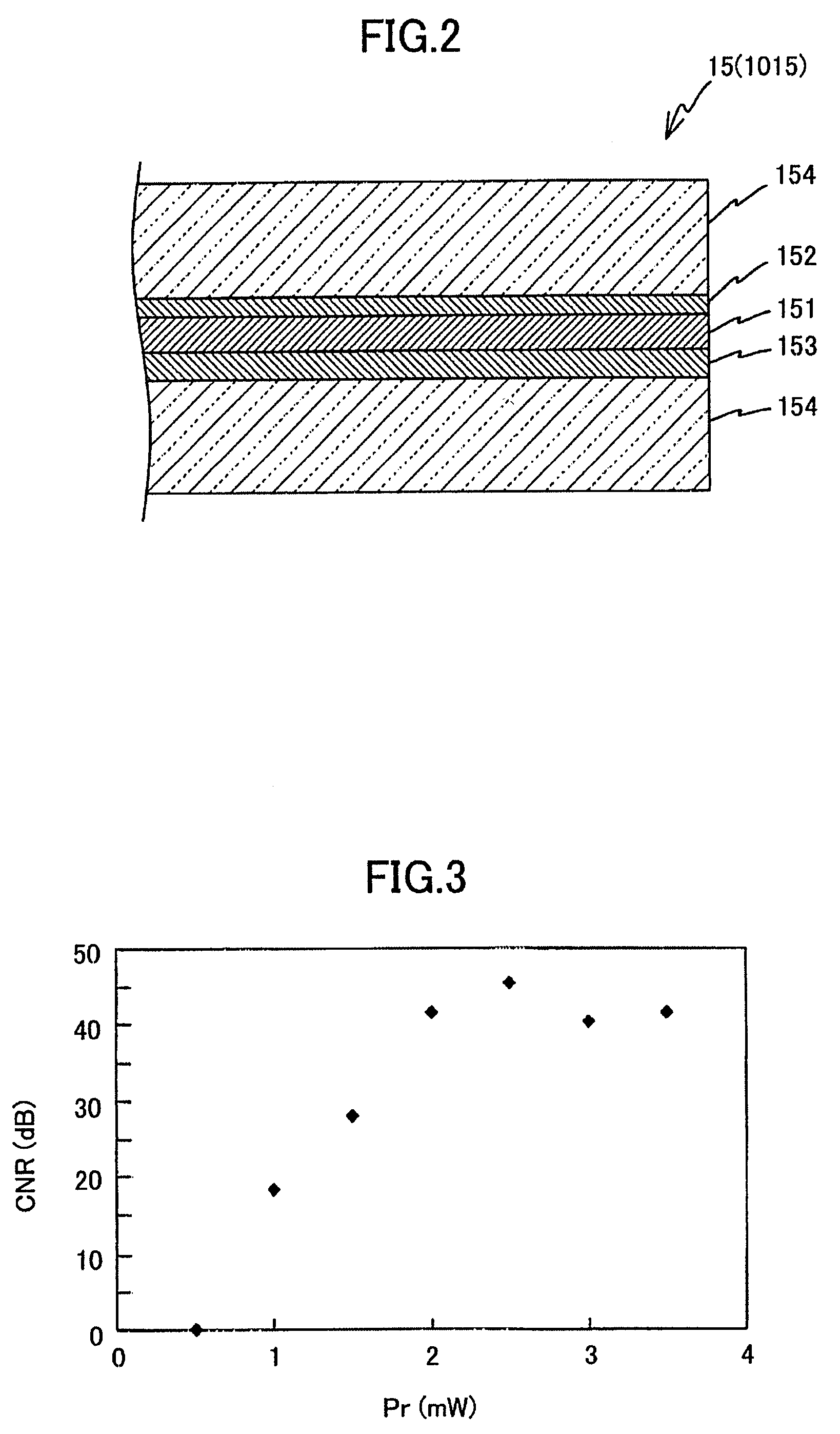

Data reproduction method and apparatus, disk, and recording/reproduction apparatus, using PRML method

InactiveUS7830766B2Television system detailsModification of read/write signalsPhase correctionPhase distortion

A data reproduction apparatus for reproducing recorded data from an optical disk by using a PRML detection method is disclosed that includes an optical head including a light source, an optical system having an objective lens for condensing light emitted from the light source to the optical disk, and a photodetector for receiving light reflected from the optical disk, a signal generation circuit for generating an RF signal from a signal output from the photodetector, a phase correction circuit for correcting phase distortion of the RF signal when the recorded data are recorded in recording marks arranged with a pitch less than a diffraction limit, a clock extraction circuit for extracting a clock from the corrected RF signal, and a decoding circuit for decoding the recorded data from the RF signal in synchronization with the clock extracted by the clock extraction circuit.

Owner:RICOH KK

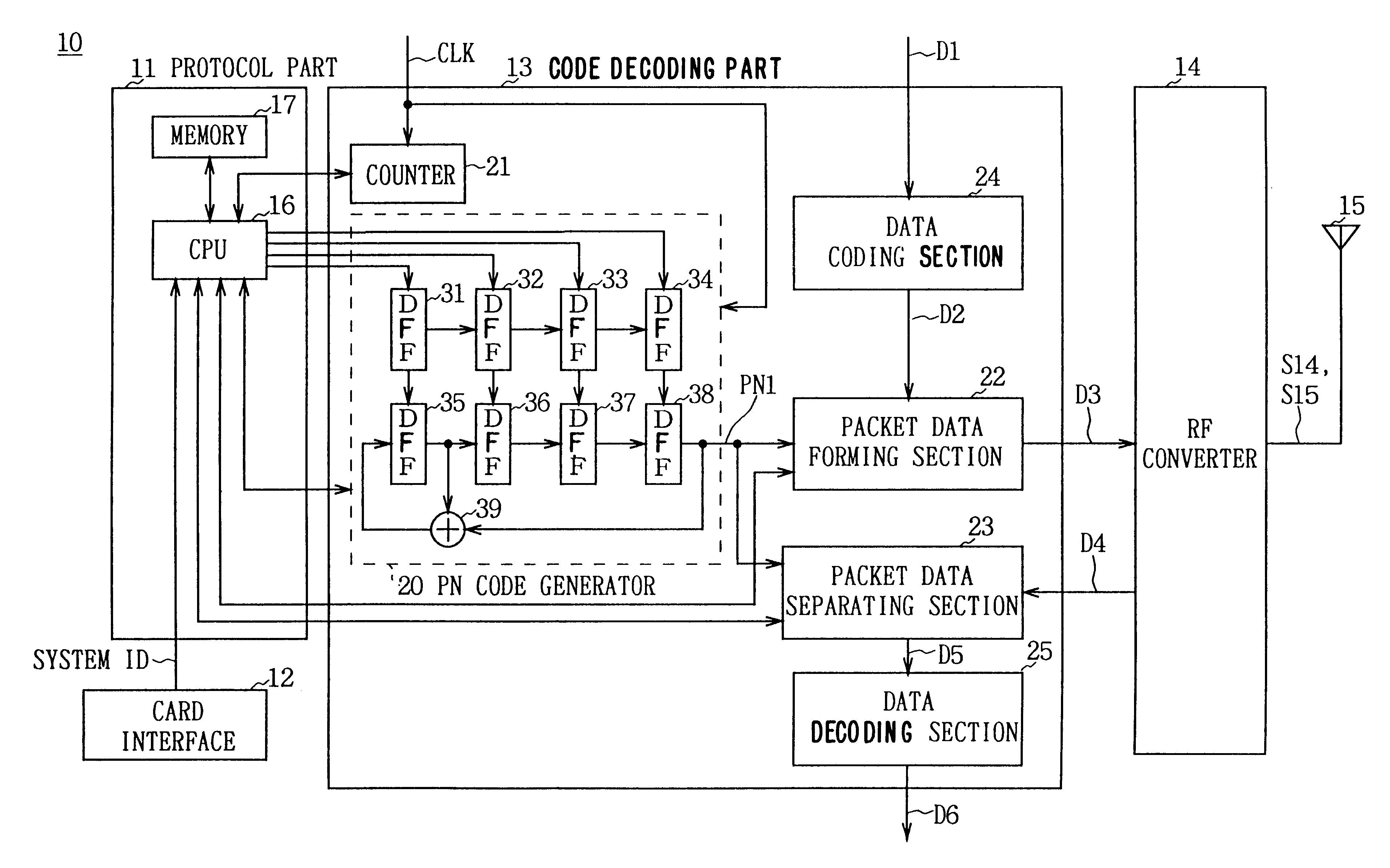

Signal receiving device and radio transmission device and radio transmission method

InactiveUS6487238B1Television system detailsMultiple keys/algorithms usageCircuit extractionInformation data

A signal receiving device, and a radio transmission device and radio transmission method utilized a code sequence extracting circuit for receiving transmission data that is information data to be transmitted having a code sequence of a fixed bit length, formed based on prescribed identification data, and for extracting the code sequence from said transmission data received, a comparison circuits for comparing the code sequence previously allocated to the receiving side with the code sequence of the transmission data extracted by the code sequence extracting circuit, and a control unit for conducting control based on the information data of the transmission data when the comparison result of said comparison circuit shows identity.

Owner:SONY CORP

Boosted converter for pulsed electric machine control

ActiveUS20200212834A1Operation efficiency can be improvedShortened fall timeSpeed controllerMotor control for low load efficiencyConvertersPulse control

A boost circuit is arranged to reduce rise and fall times of pulsed power used for pulsed control operation of electric machines. Magnetic energy present in the electric machine at the end of a pulse is extracted by the boost circuit to reduce the pulse fall time. The energy is stored by the boost circuit and then applied at the beginning of a subsequent pulse to reduce the rise time. By reducing rise and fall times compared to not using such a boost circuit, machine efficiency is improved.

Owner:TULA ETECH INC

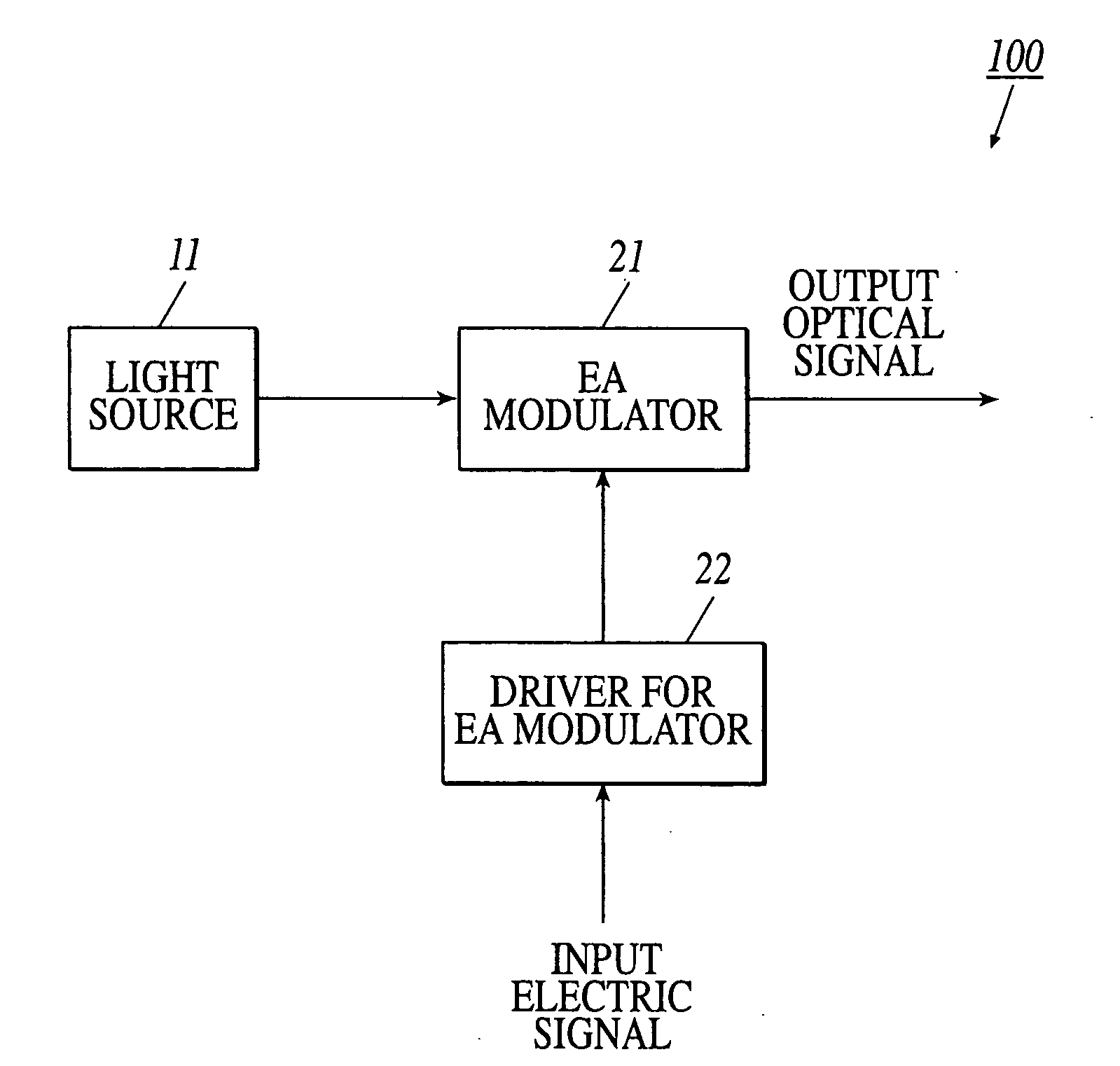

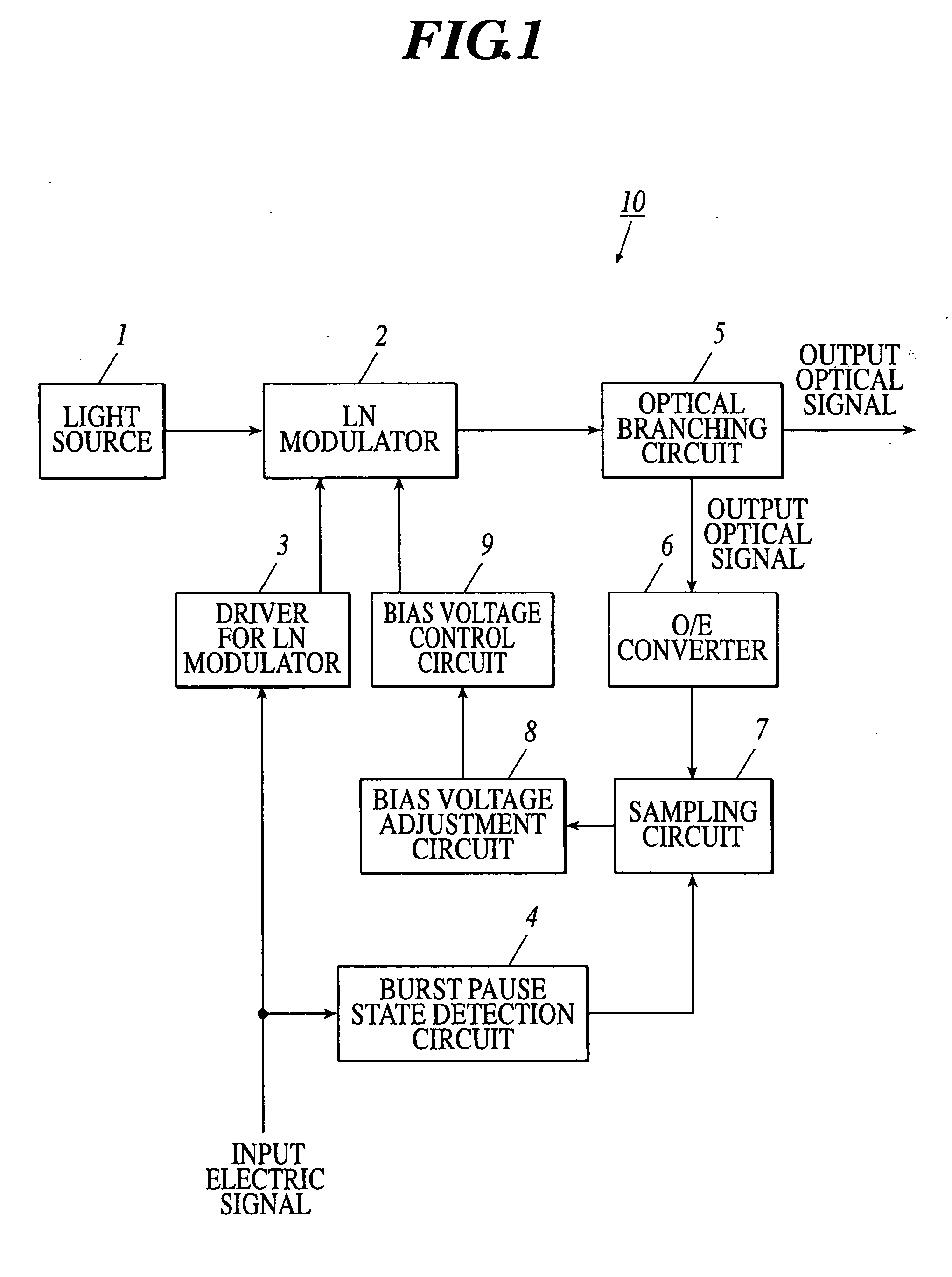

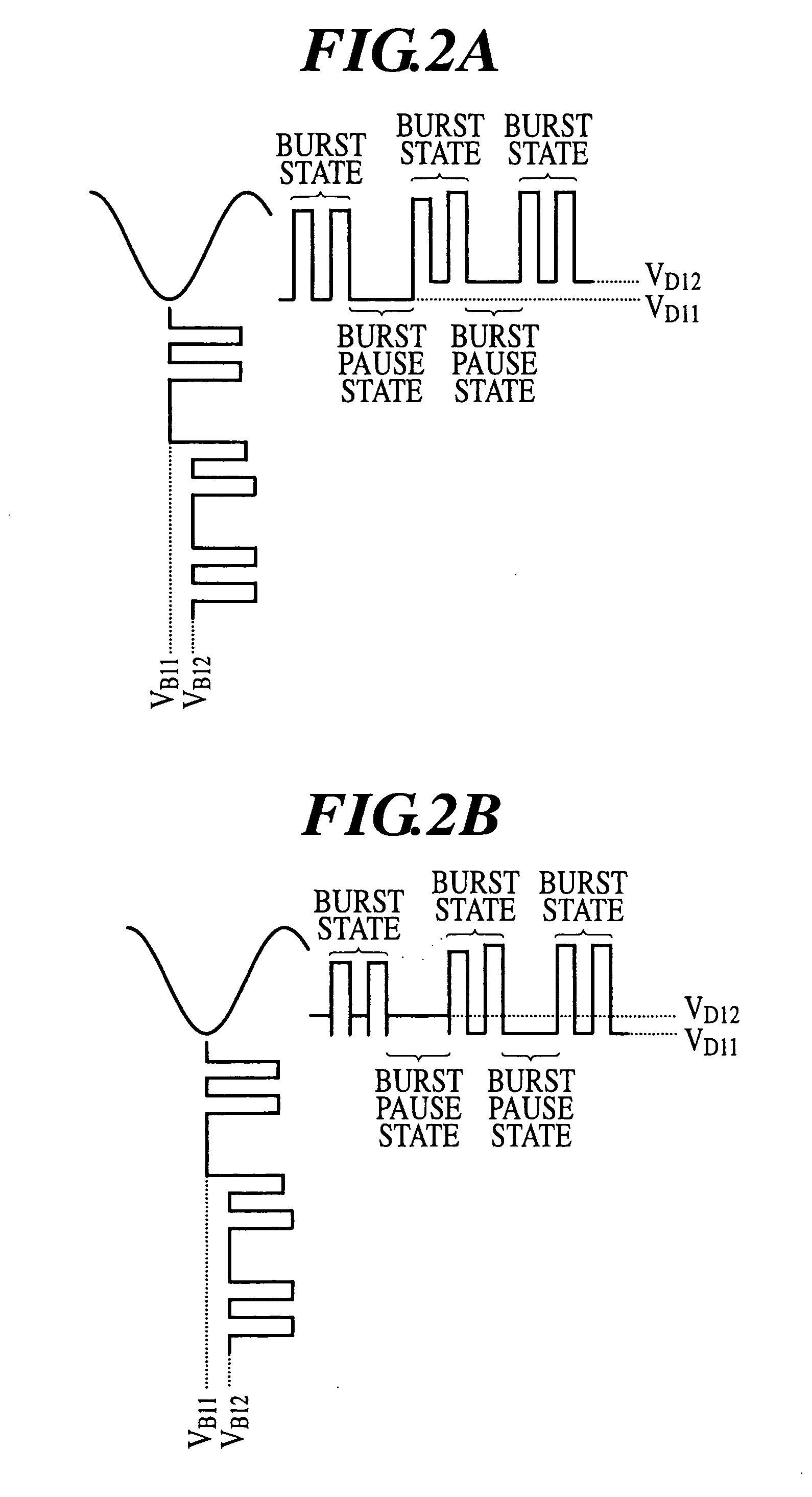

Light modulation apparatus and light modulator control method

A light modulation apparatus including a Mach-Zehnder type light modulator, a driver for modulator outputting a control signal according to an input electric signal, a light branching circuit branching the output light signal, and a bias control circuit applying a bias voltage to the light modulator based on the branched light signal, the apparatus further comprises: a burst pause state detection circuit detecting a pause state of a burst signal included in the input electric signal; a photoelectric transducer converting an output light signal branched by the light branching circuit into an electric signal; a sampling circuit extracting the electric signal converted while the pause state is detected by the burst pause state; and a bias voltage adjustment circuit adjusting a bias voltage value of the bias voltage based on a voltage level of the extracted electric signal.

Owner:YOKOGAWA ELECTRIC CORP

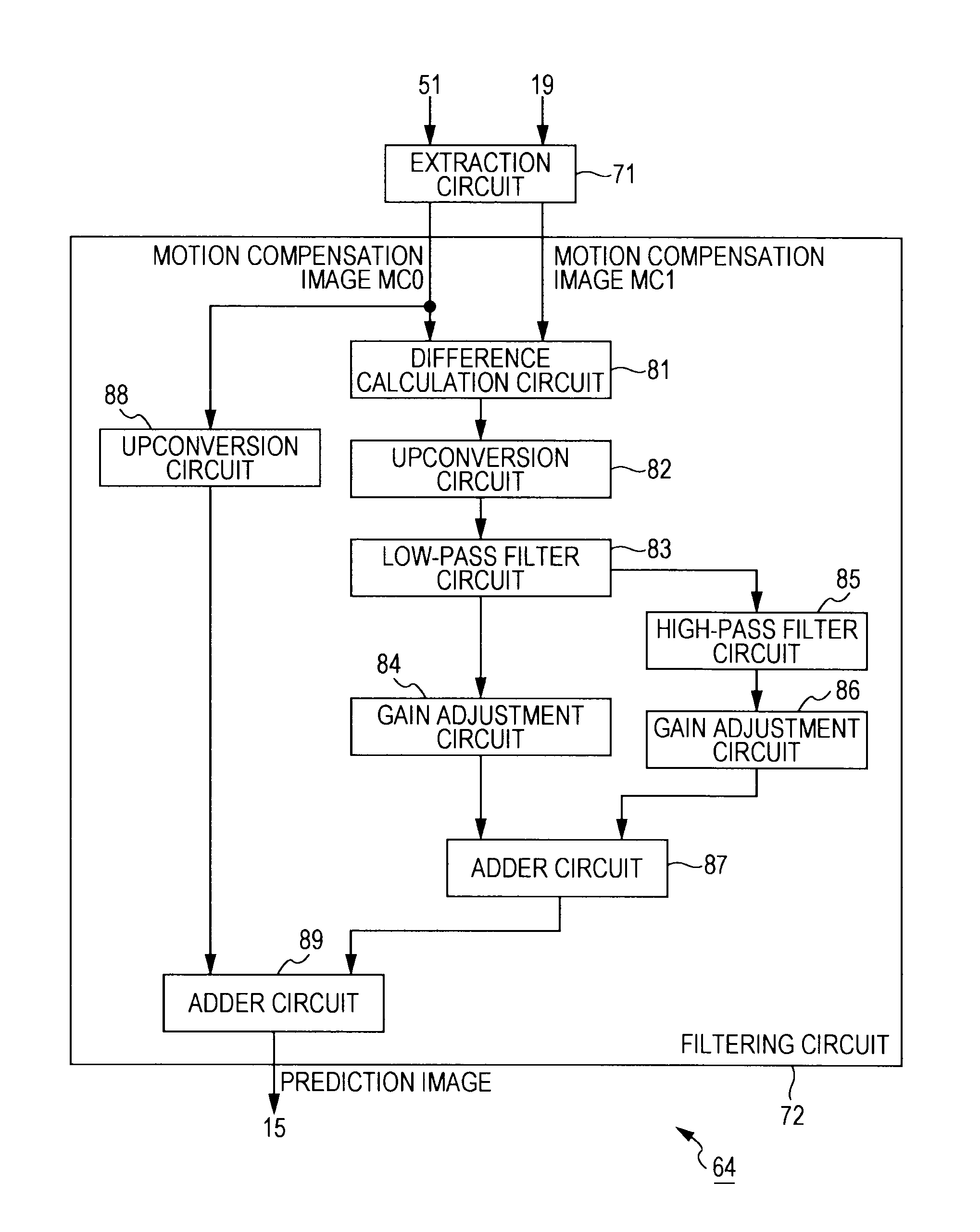

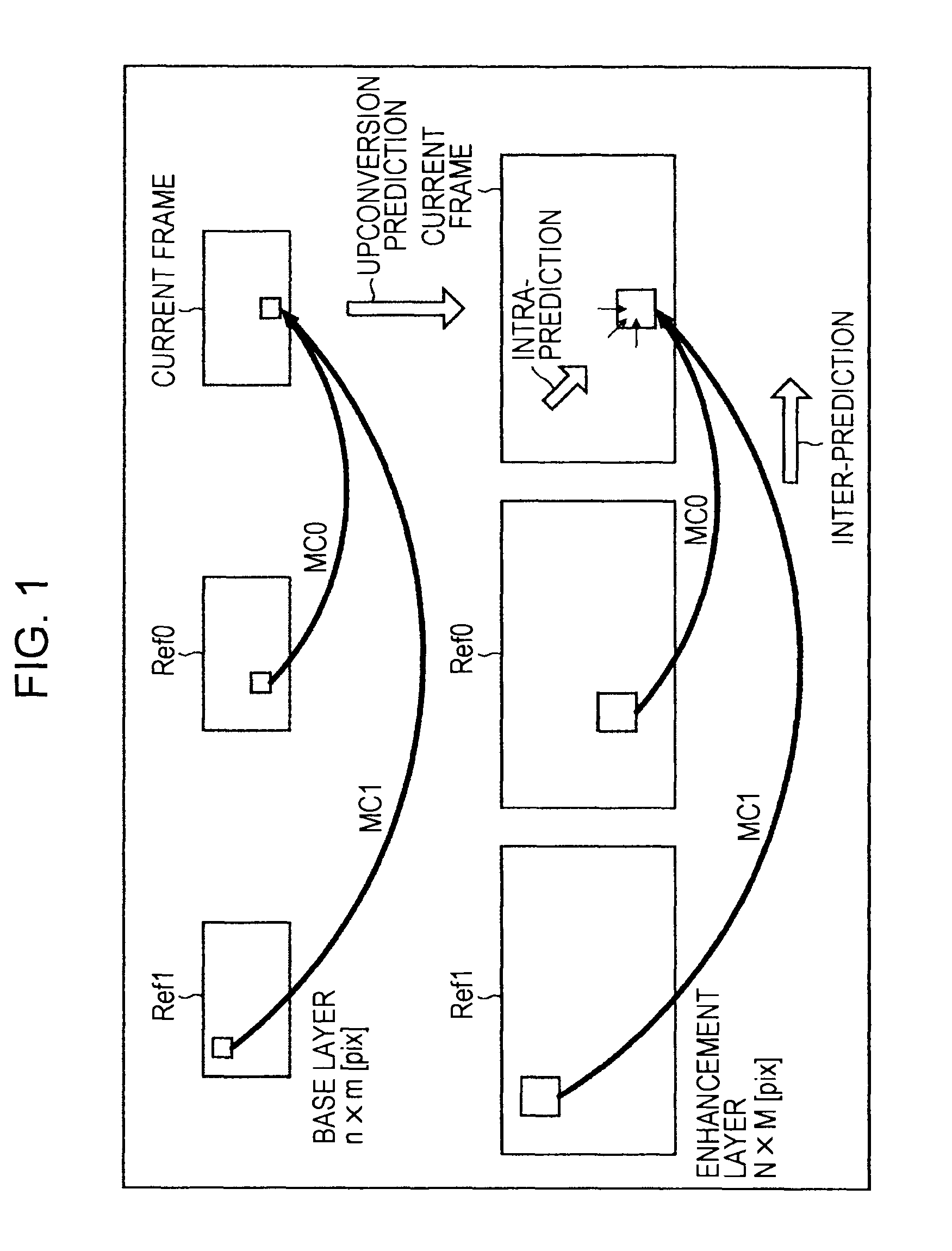

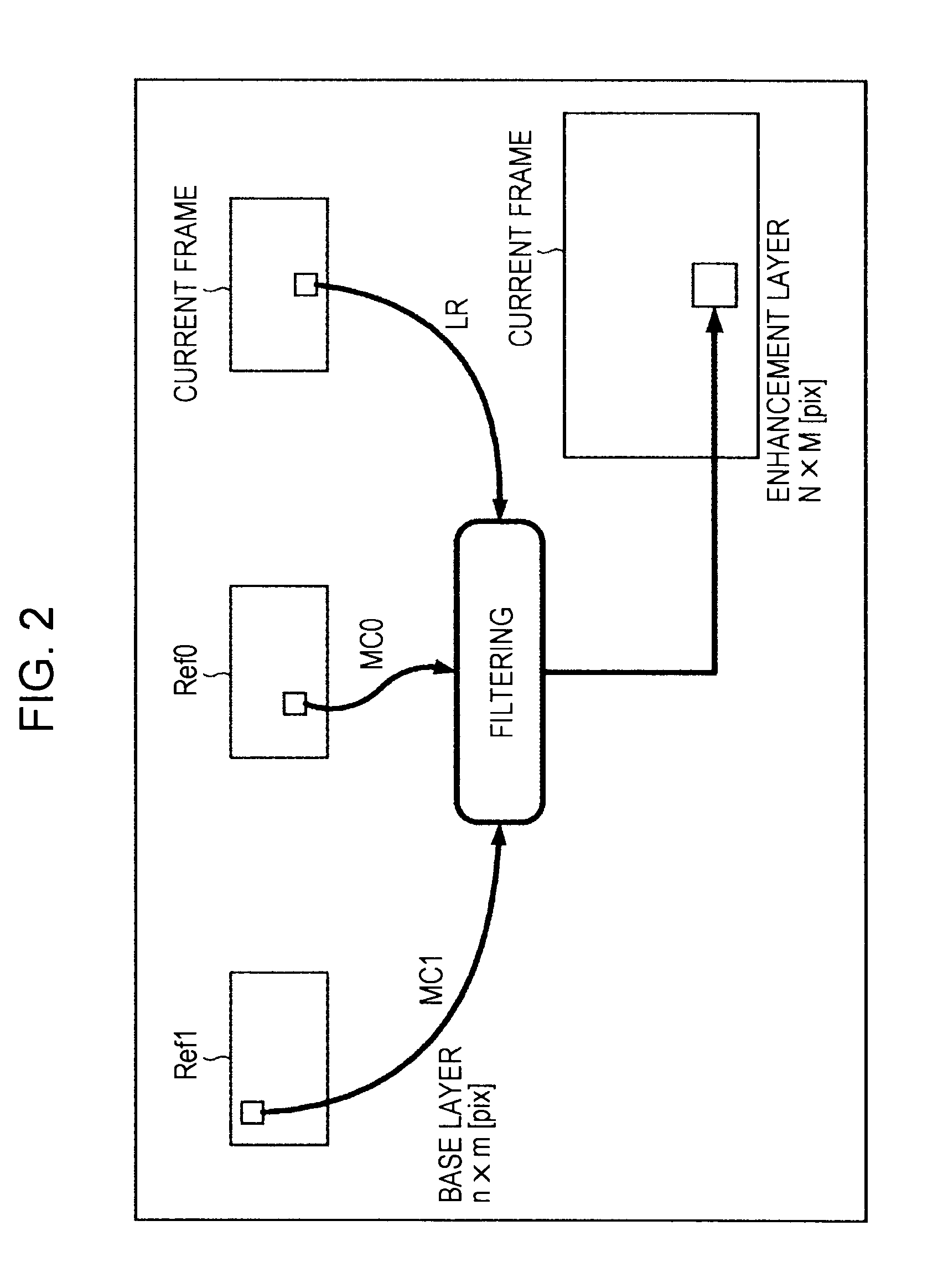

Image processing apparatus and method

InactiveUS8824542B2Easy loadingImprove efficiencyColor television with pulse code modulationColor television with bandwidth reductionImaging processingImage resolution

An image processing apparatus and method that can improve encoding efficiency while preventing an increase in load. An extraction circuit of a filtering prediction circuit extracts motion compensation images for generating a prediction image in a high-resolution enhancement layer from reference frames in a low-resolution base layer. A filtering circuit of the filtering prediction circuit performs filtering, which involves upconversion and which uses analysis in the time direction, on a plurality of motion compensation images in the base layer extracted by the extraction circuit to generate a prediction image in the enhancement layer. The image processing apparatus may be an encoding apparatus or a decoding apparatus.

Owner:SONY CORP

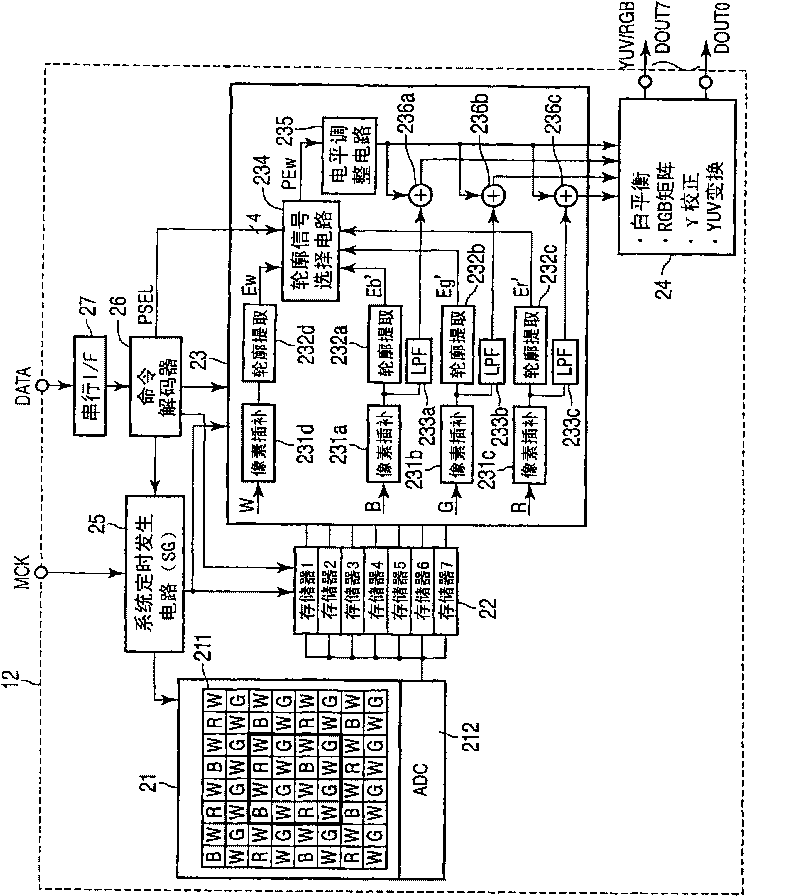

Solid-state image pickup device

InactiveCN101742103ATelevision system detailsColor signal processing circuitsSolid massControl signal

The solid-state image pickup device includes a sensor unit and a focus adjustment circuit, the focus adjustment circuit including a contour extraction circuit which extracts contour signals from wavelength signals W, B, G, and R, a contour signal selection circuit which receives a control signal and the plurality of contour signals extracted by the contour extraction circuit, and selects and outputs a contour signal having a desired wavelength band in accordance with the control signal, and a plurality of addition circuits which add the wavelength signals before the contour signals are extracted by the contour extraction circuit to a contour signal output from a contour signal output circuit.

Owner:KK TOSHIBA

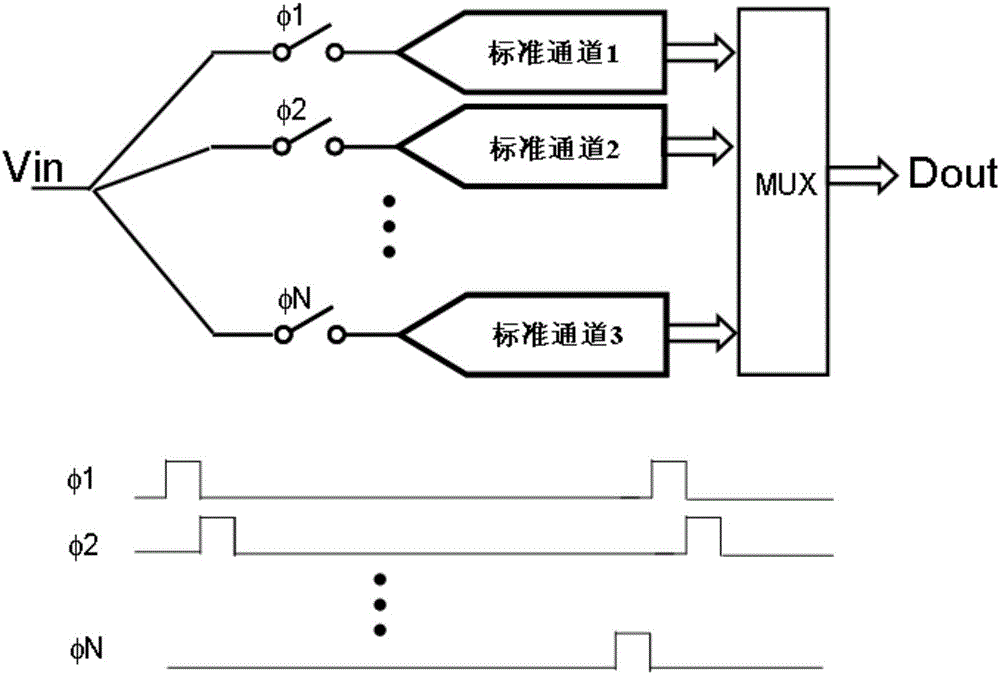

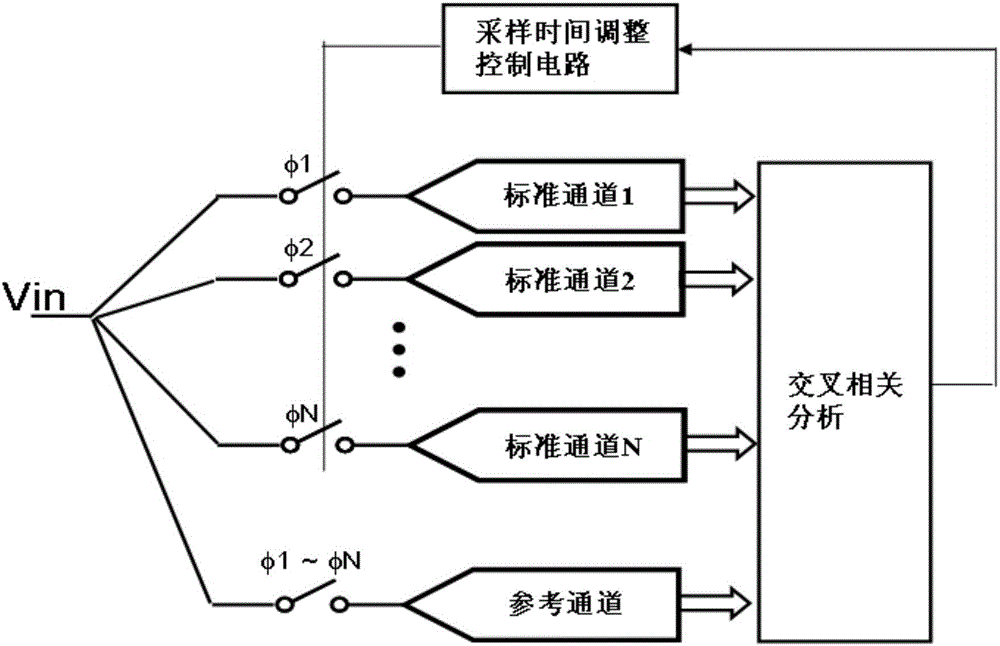

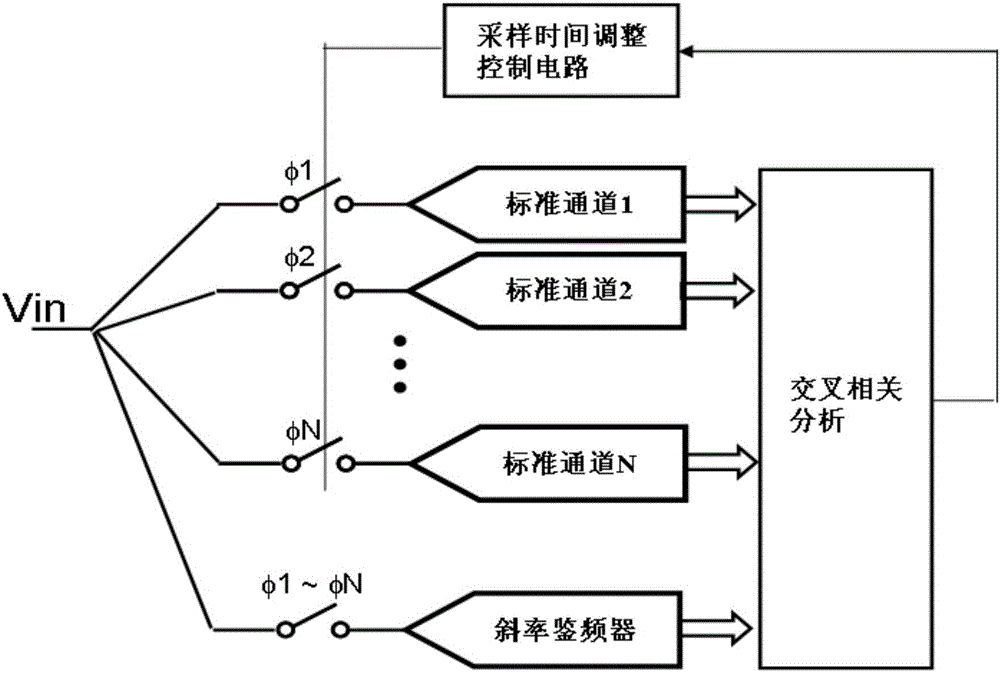

Time domain interleaving analog-digital converter sample time mismatch calibration method and system

ActiveCN105871377ASimple structureAvoid affecting sample timeAnalogue-digital convertersPhysical parameters compensation/preventionTime domainDifferentiator

The present invention discloses a time domain interleaving analog-digital converter sample time mismatch calibration method and system. The system includes N standard channels and a reference channel, a sample time mismatch coefficient extracting circuit, and a sample time adjustment control circuit. Adjustment circuit control coefficients of a to-be-calibrated standard channel and a to-be-calibrated reference channel are extracted by the sample time mismatch coefficient extracting circuit, the adjustment circuit control coefficients are transmitted to the sample time adjustment control circuit, and the sample time adjustment control circuit controls a sample clock of the to-be-calibrated standard channel. Through adoption of the time domain interleaving analog-digital converter sample time mismatch calibration method and system, sample time calibration is not affected by amplitude errors, the circuit structure is simple to implement, a differentiator is not needed, and the method is rapid in convergence, has high calibration accuracy, and is not affected by signal amplitude and gain mismatch.

Owner:NANJING TIANYI HEXIN ELECTRONICS