Patents

Literature

2748 results about "Clock generator" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A clock generator is an electronic oscillator (circuit) that produces a timing signal (known as a clock signal and behaves as such) for use in synchronizing a circuit's operation. The signal can range from a simple symmetrical square wave to more complex arrangements. The basic parts that all clock generators share are a resonant circuit and an amplifier.

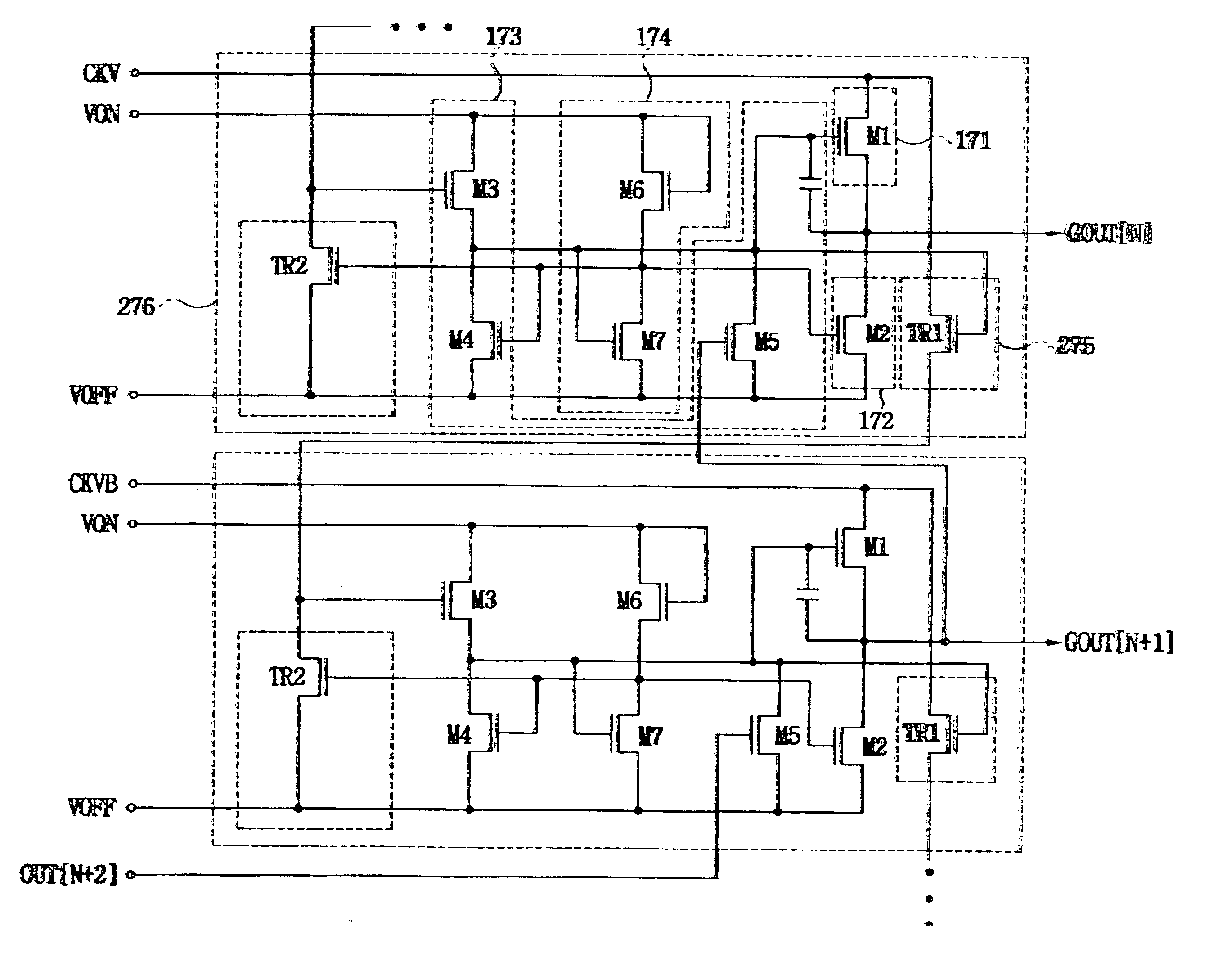

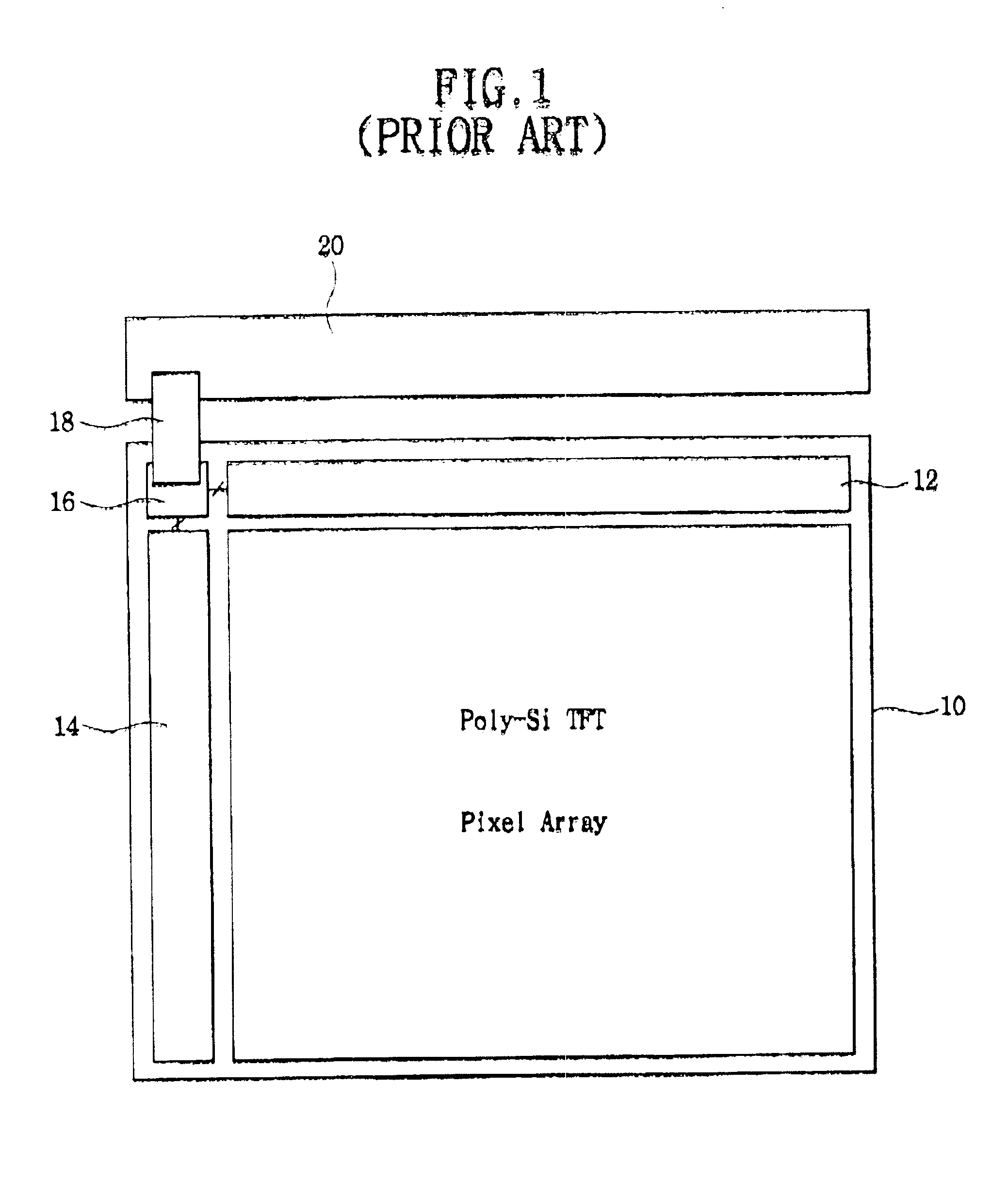

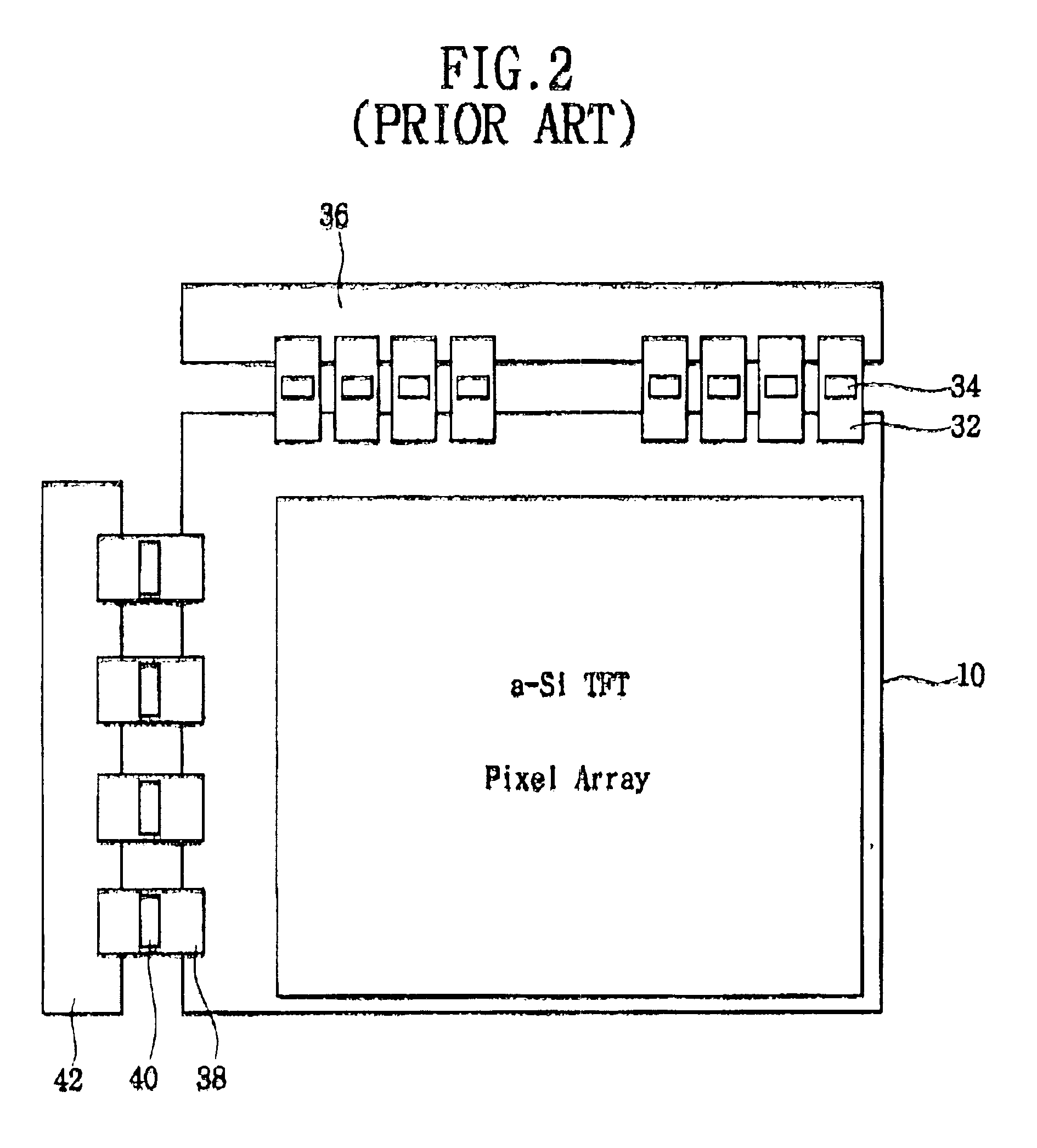

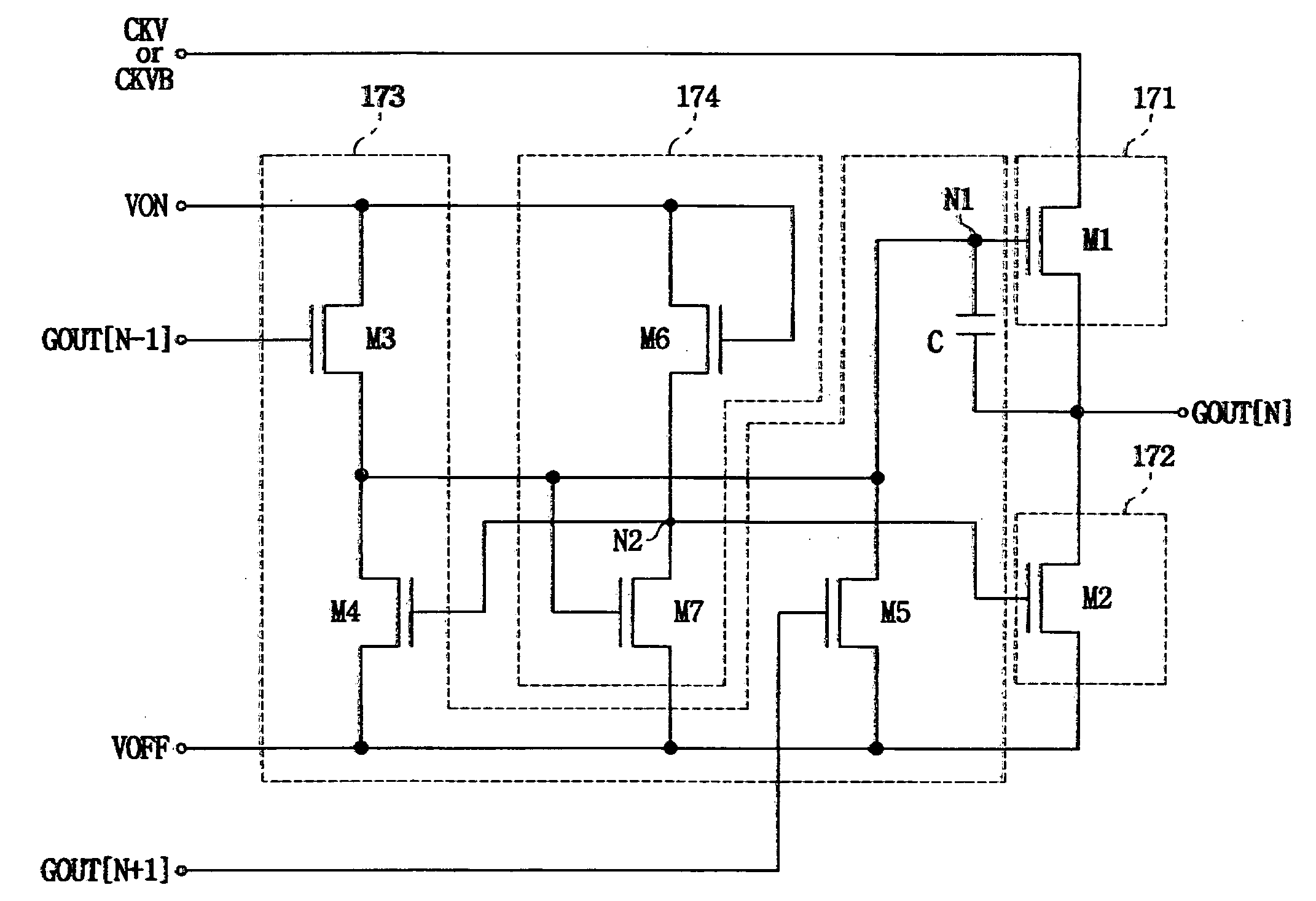

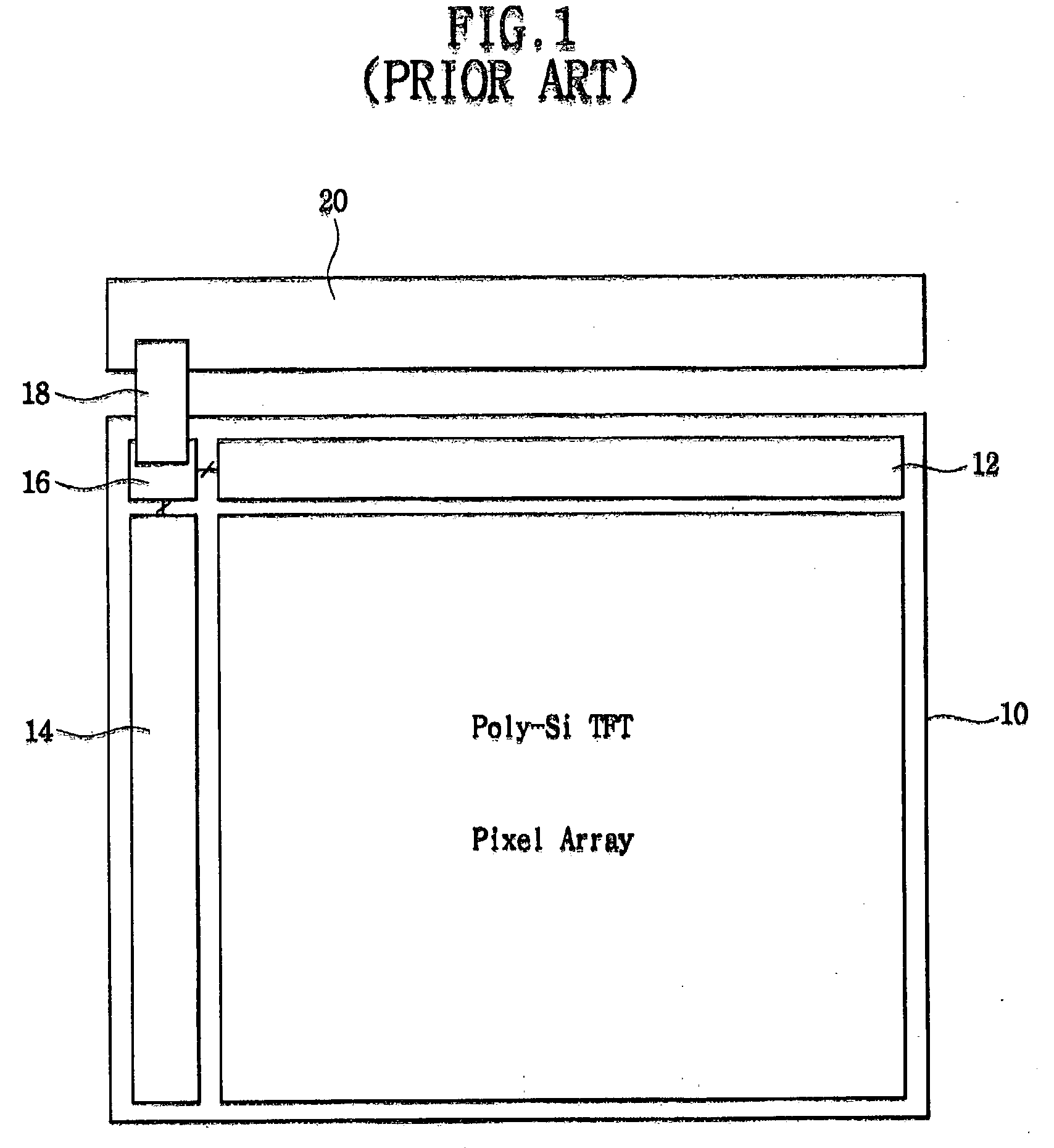

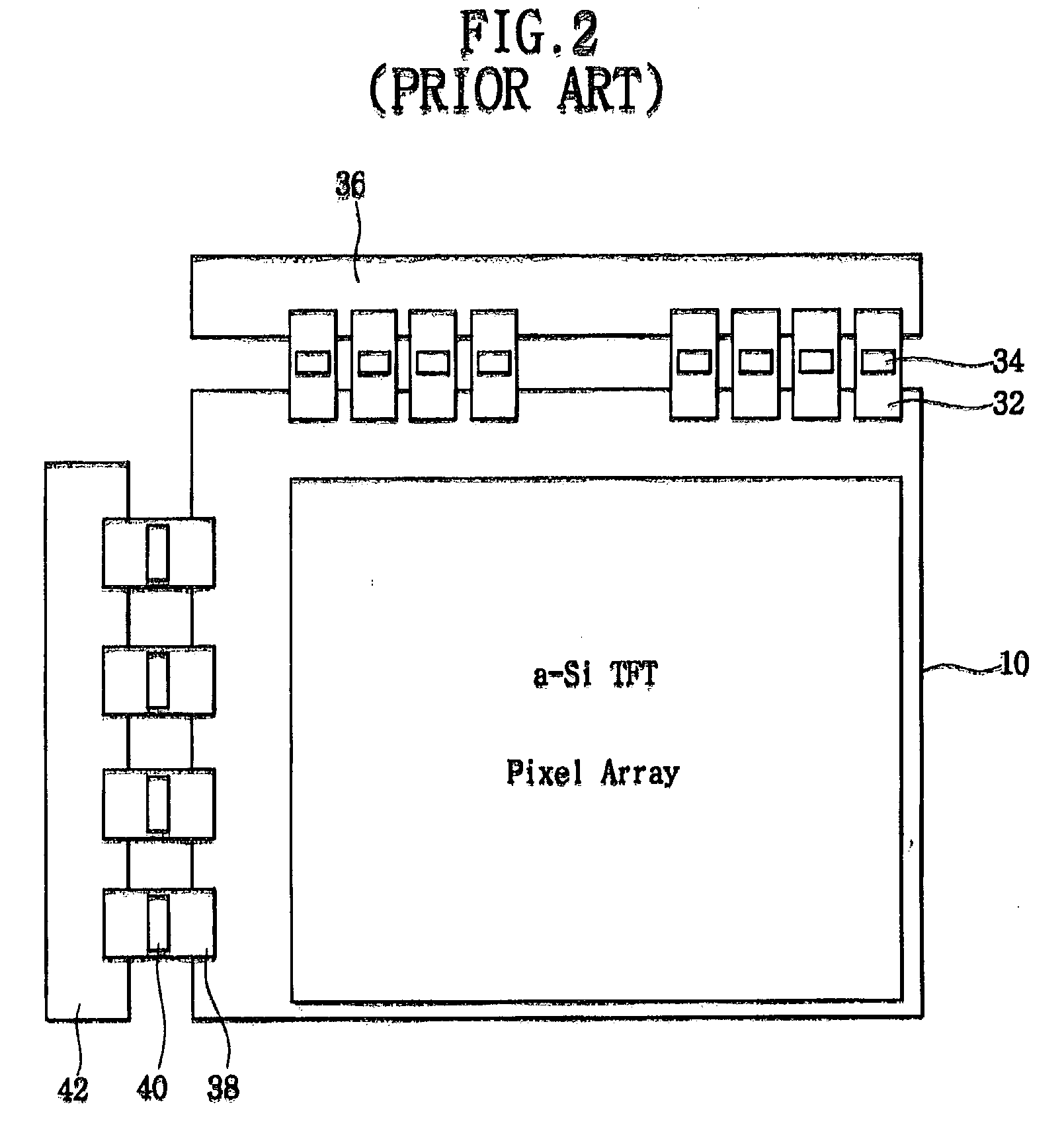

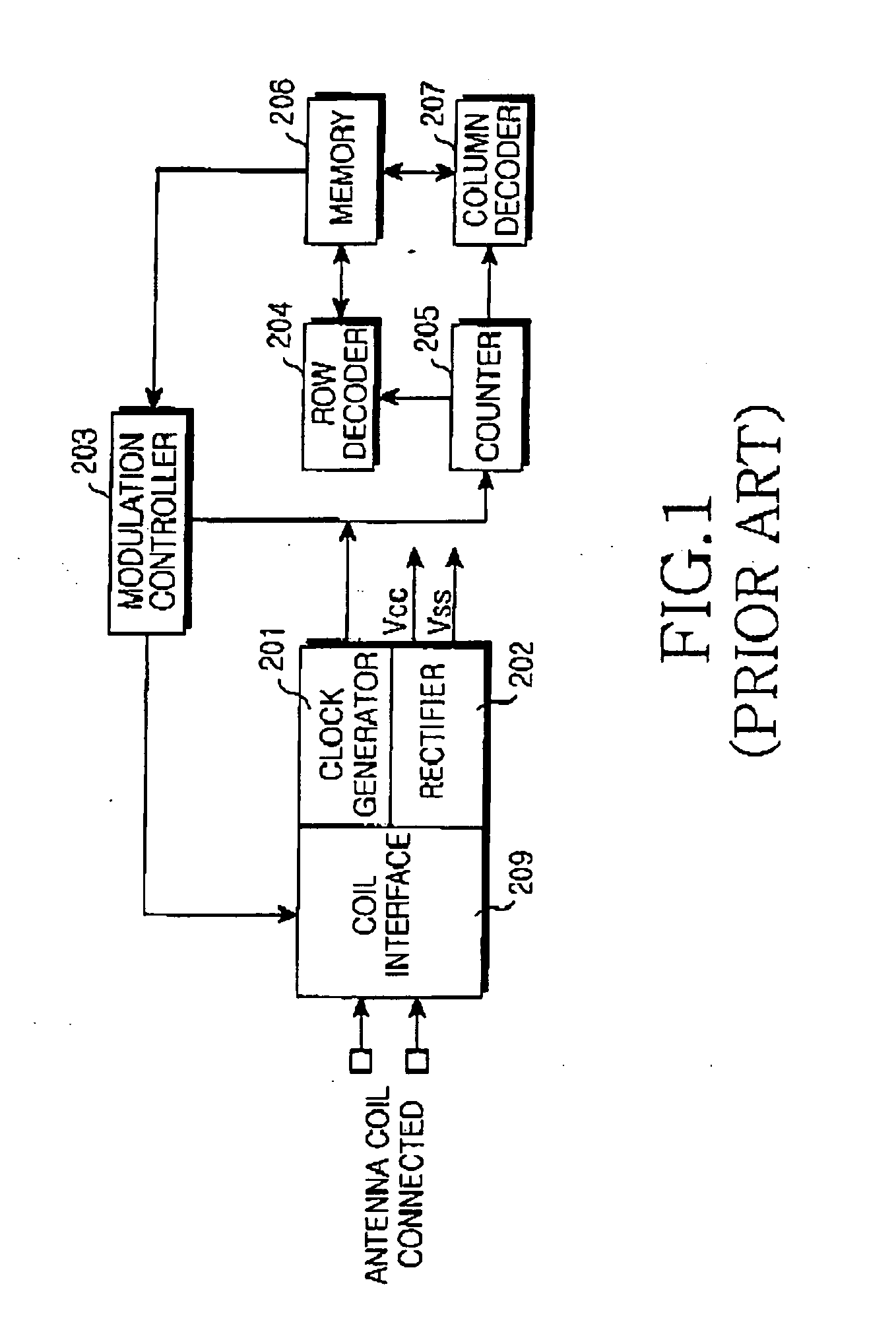

Method of driving a shift register, a shift register, a liquid crystal display device having the shift register

InactiveUS6845140B2InhibitionQuality improvementStatic indicating devicesDigital storageShift registerLiquid-crystal display

In a shift register and LCD device having the shift register that may be employed in the liquid crystal display device having a large screen size and a large resolution, the shift register includes stages cascade-connected with each other and each of the stages have a carry buffer for generating a carry signal. The pull-down transistor of each of the stages of the shift register is divided into a first pull-down transistor and a second pull-down transistor. A power voltage Vona larger than the power voltage Von applied to a clock generator is applied to the shift register. A signal delay due to the RC delay of the gate lines may be minimized, the shift register is independent of the variation of the threshold voltage of the TFTs, and image display quality may not be deteriorated.

Owner:SAMSUNG DISPLAY CO LTD

Method of driving a shift register, a shift register, a liquid crystal display device having the shift register

In a shift register and LCD device having the shift register that may be employed in the liquid crystal display device having a large screen size and a large resolution, the shift register includes stages cascade-connected with each other and each of the stages have a carry buffer for generating a carry signal. The pull-down transistor of each of the stages of the shift register is divided into a first pull-down transistor and a second pull-down transistor. A power voltage Vona larger than the power voltage Von applied to a clock generator is applied to the shift register. A signal delay due to the RC delay of the gate lines may be minimized, the shift register is independent of the variation of the threshold voltage of the TFTs, and image display quality may not be deteriorated.

Owner:SAMSUNG DISPLAY CO LTD

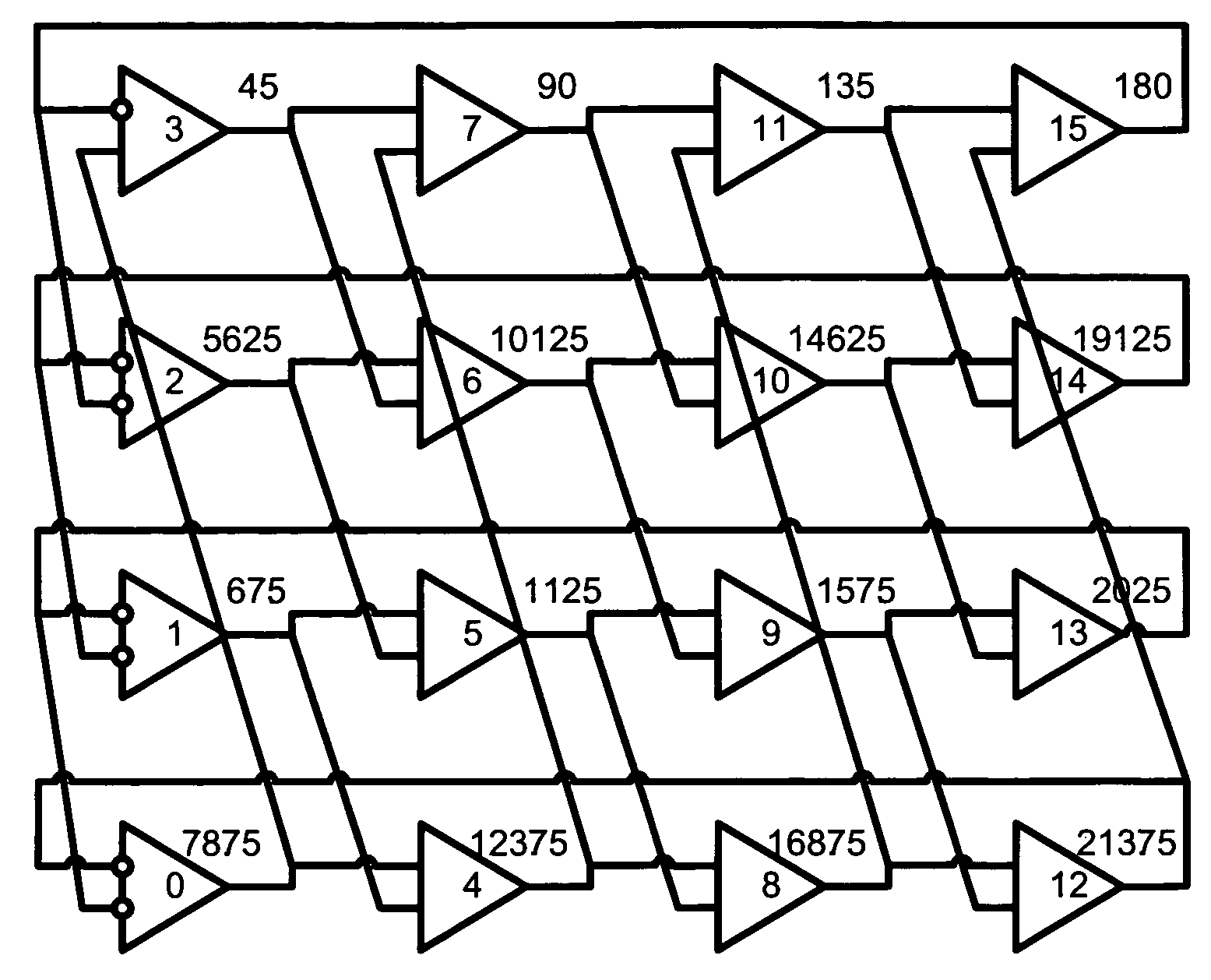

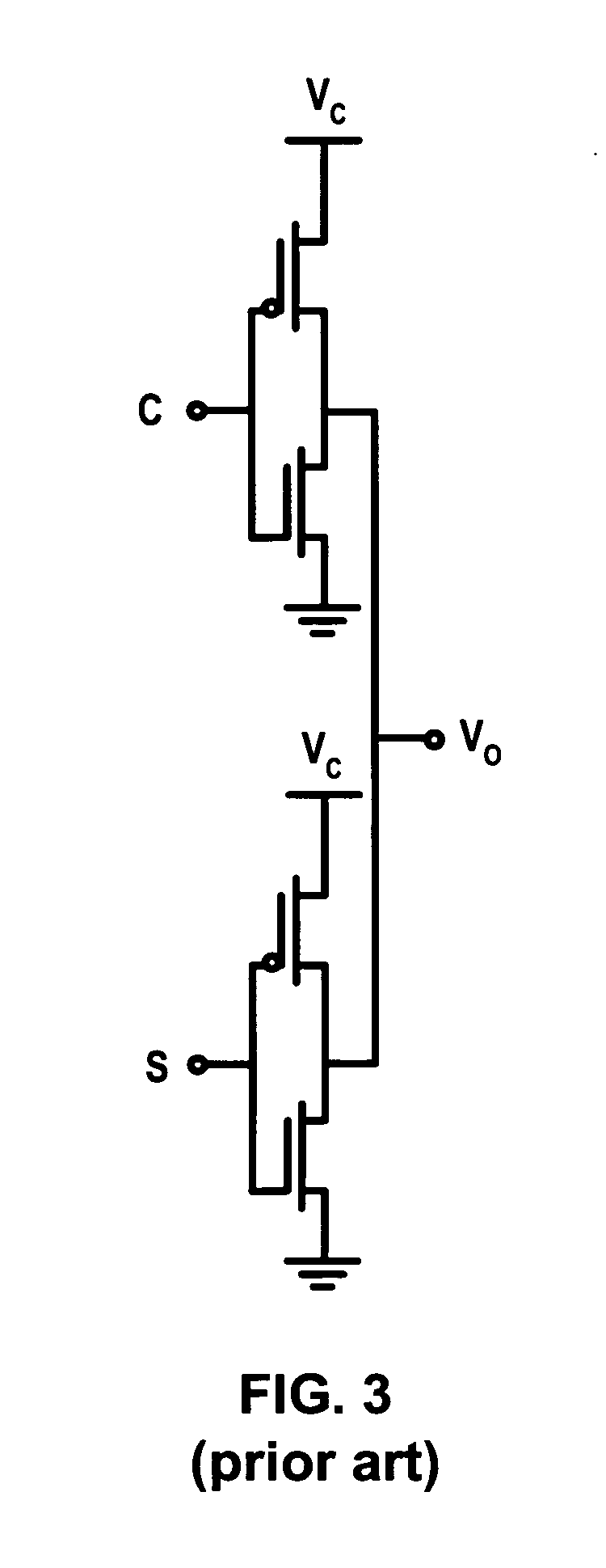

Array oscillator and polyphase clock generator

InactiveUS20060001496A1Increase speedReduce jitterPulse automatic controlPulse generation by logic circuitsMOSFETMultiplexing

The present invention relates generally to array oscillator circuits for use as phase delay generators. More particularly, the present invention relates to a novel array oscillator for providing a plurality of phases which have stable phase relationships. The present invention is particularly applicable to the generation of poly-phase clocks for receivers of very high speed interfaces which employ an over-sampling technique, or multiplexing, and for high speed logic. The array oscillator according to the invention comprises at least one ring oscillator having a plurality of at least two interconnected buffer stages including at least one, or any integer odd number of inverting stages and a series of non-inverting stages, wherein the buffer stages are formed of N-type MOSFET transistors.

Owner:ACUID +1

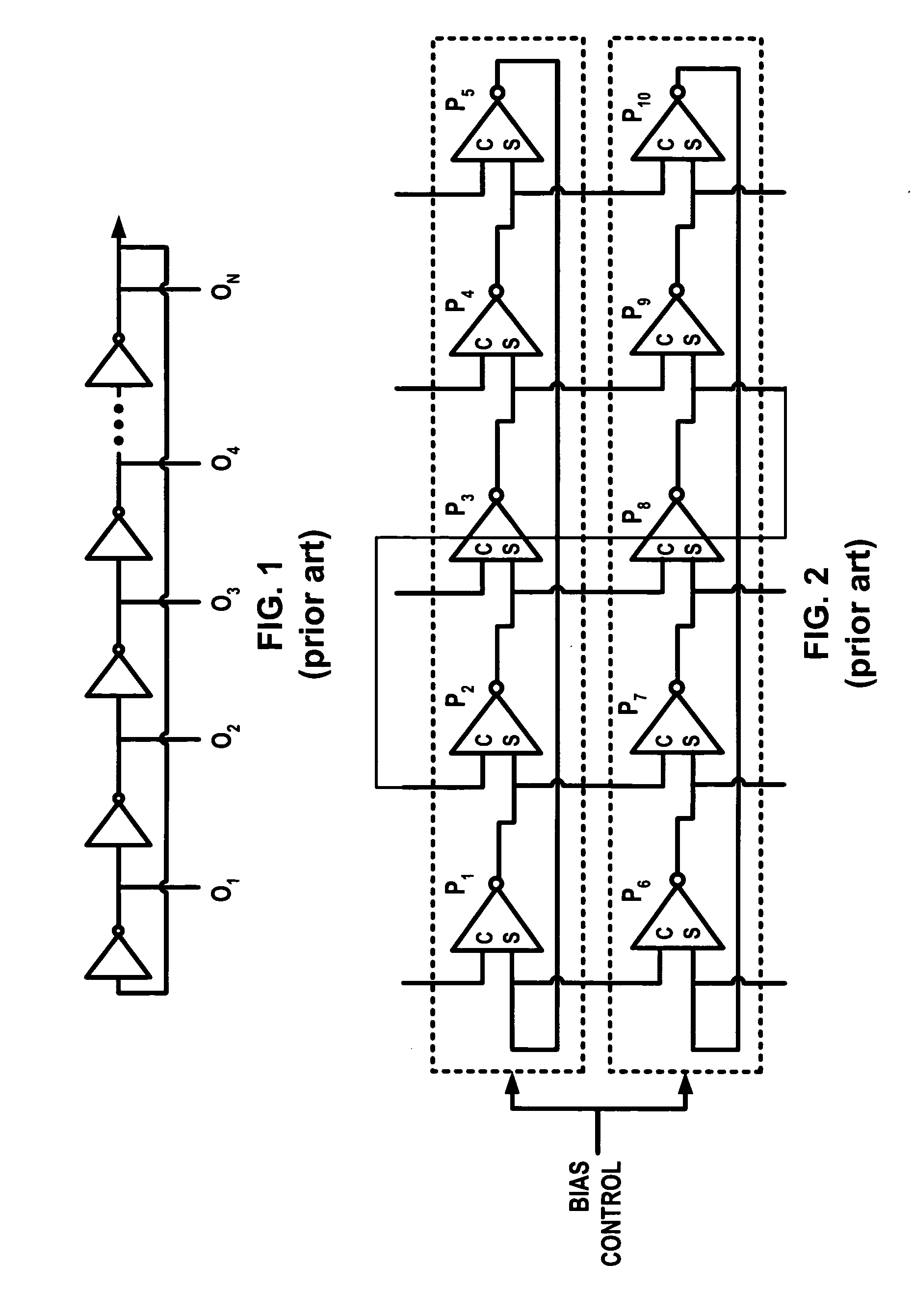

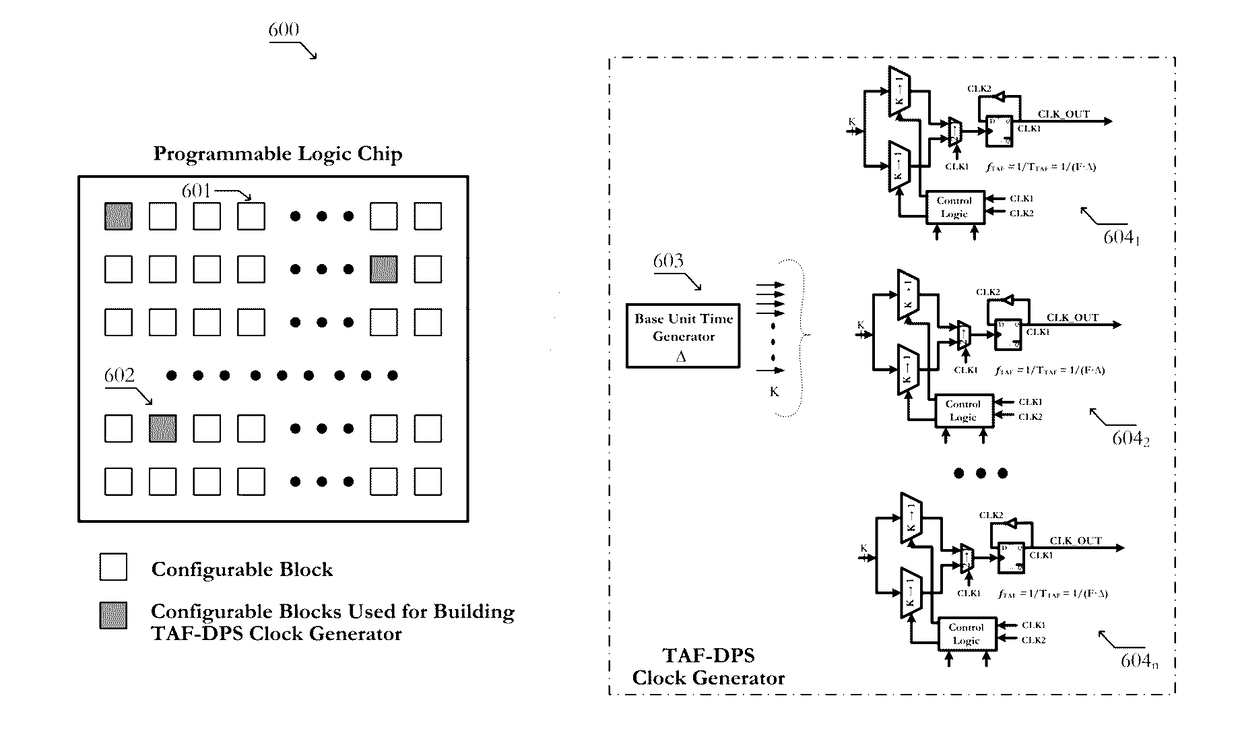

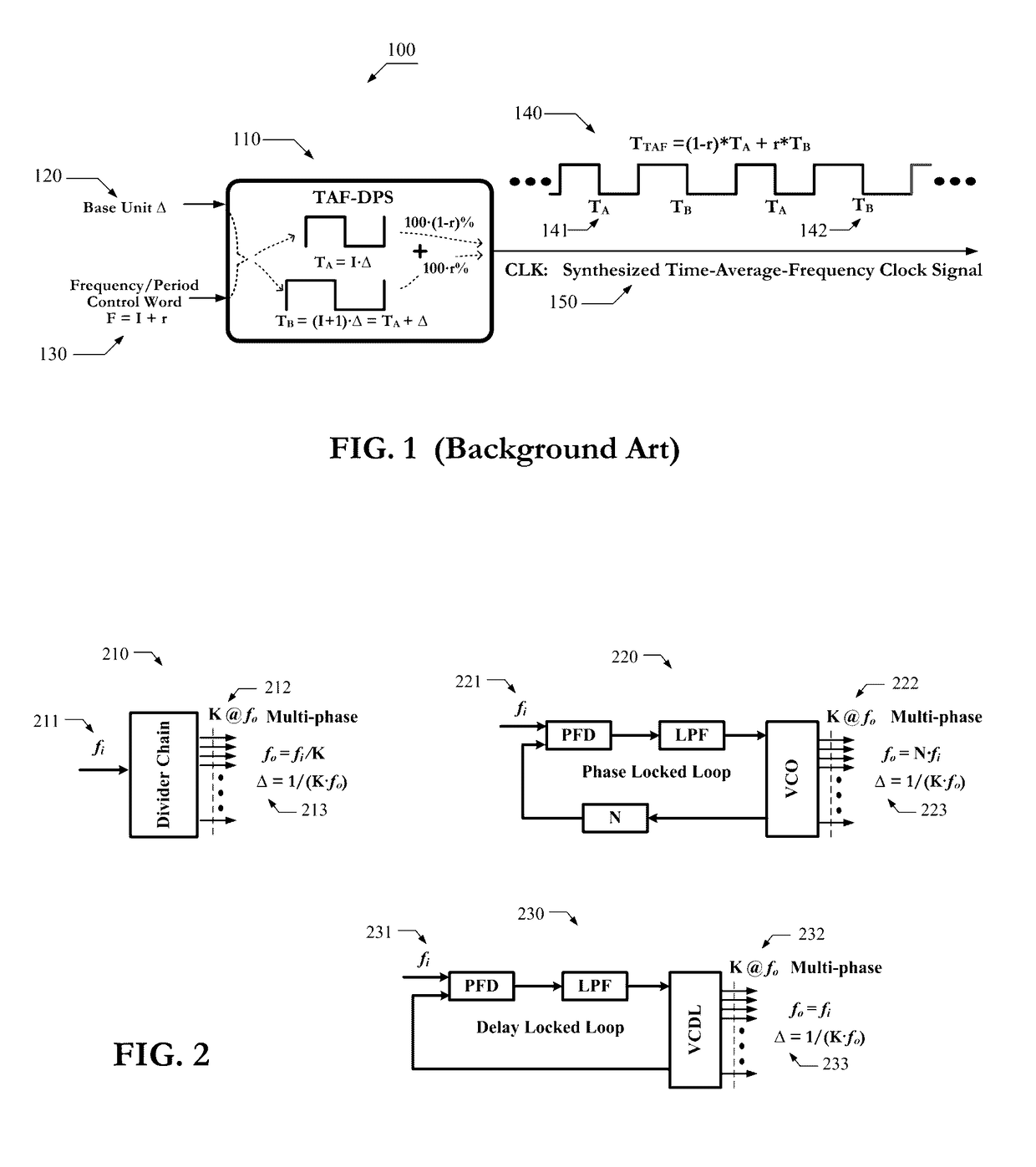

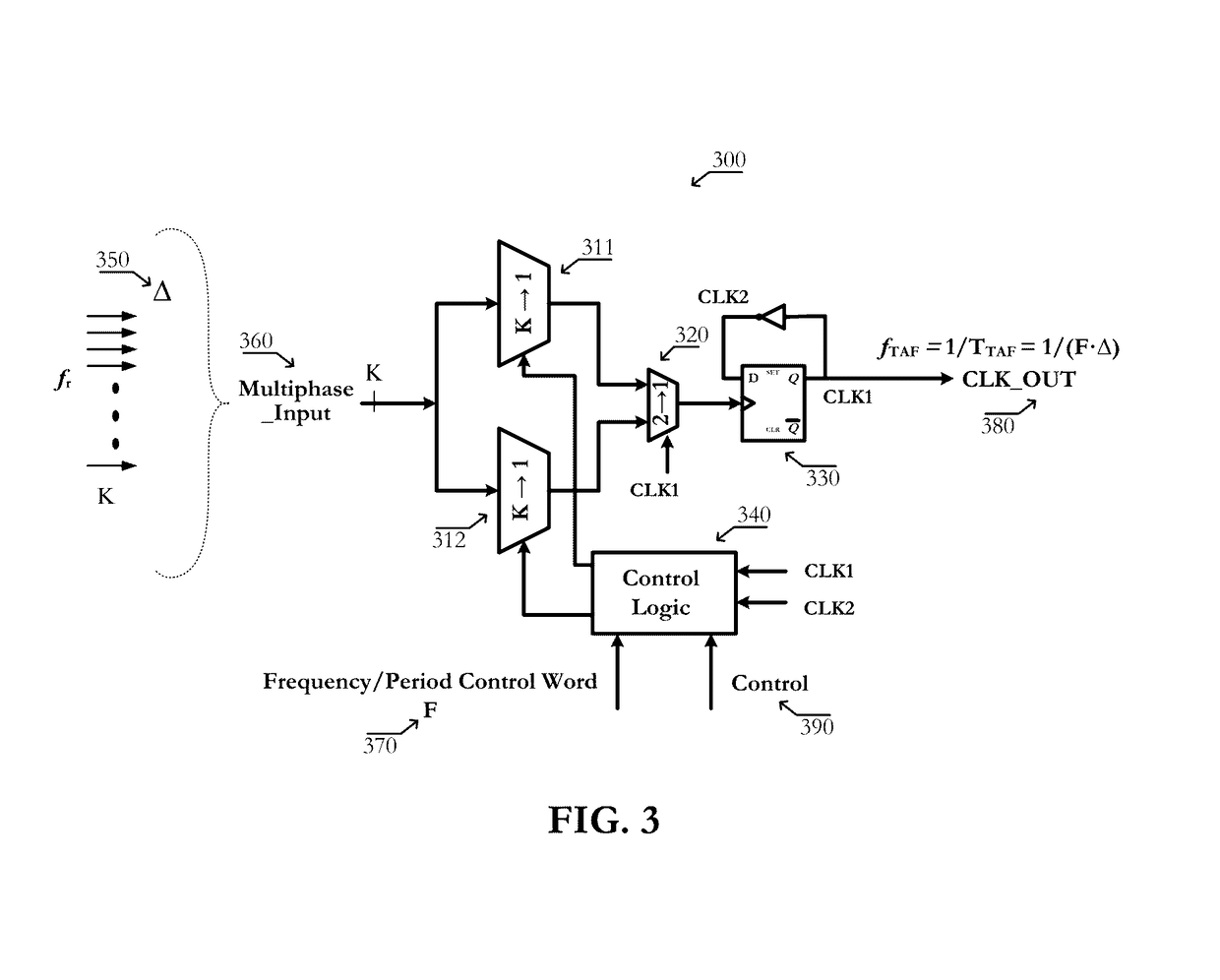

Circuits and methods of implementing time-average-frequency direct period synthesizer on programmable logic chip and driving applications using the same

ActiveUS9621173B1Innovative designPowerful frequency generation capabilityPulse automatic controlLogic circuits coupling/interface using field-effect transistorsUnit generatorProgrammable logic device

Circuits of a TAF-DPS clock generator implemented on programmable logic chip comprise: 1) a base time unit generator created from configurable blocks, or on-chip PLL, or on-chip DLL, said base time unit generator produces a plurality of phase-evenly-spaced-signals; 2) a TAF-DPS frequency synthesizer created by configuring configurable blocks of said programmable logic chip, said TAF-DPS frequency synthesizer takes said plurality of phase-evenly-spaced-signals as its input. Methods of creating flexible clock signal to drive application comprise: 1) selecting one or more strategic areas in said programmable logic chip; 2) creating one or more TAF-DPS clock generator for each said area by using the configurable resource in said area; 3) creating control function to control the frequency and duty-cycle of the TAF-DPS clock generator output, said control function can be circuit created from configuring configurable blocks, said control function can also be achieved by software; 4) driving the circuits in application by the flexible clock generated from said TAF-DPS clock generator.

Owner:XIU LIMING

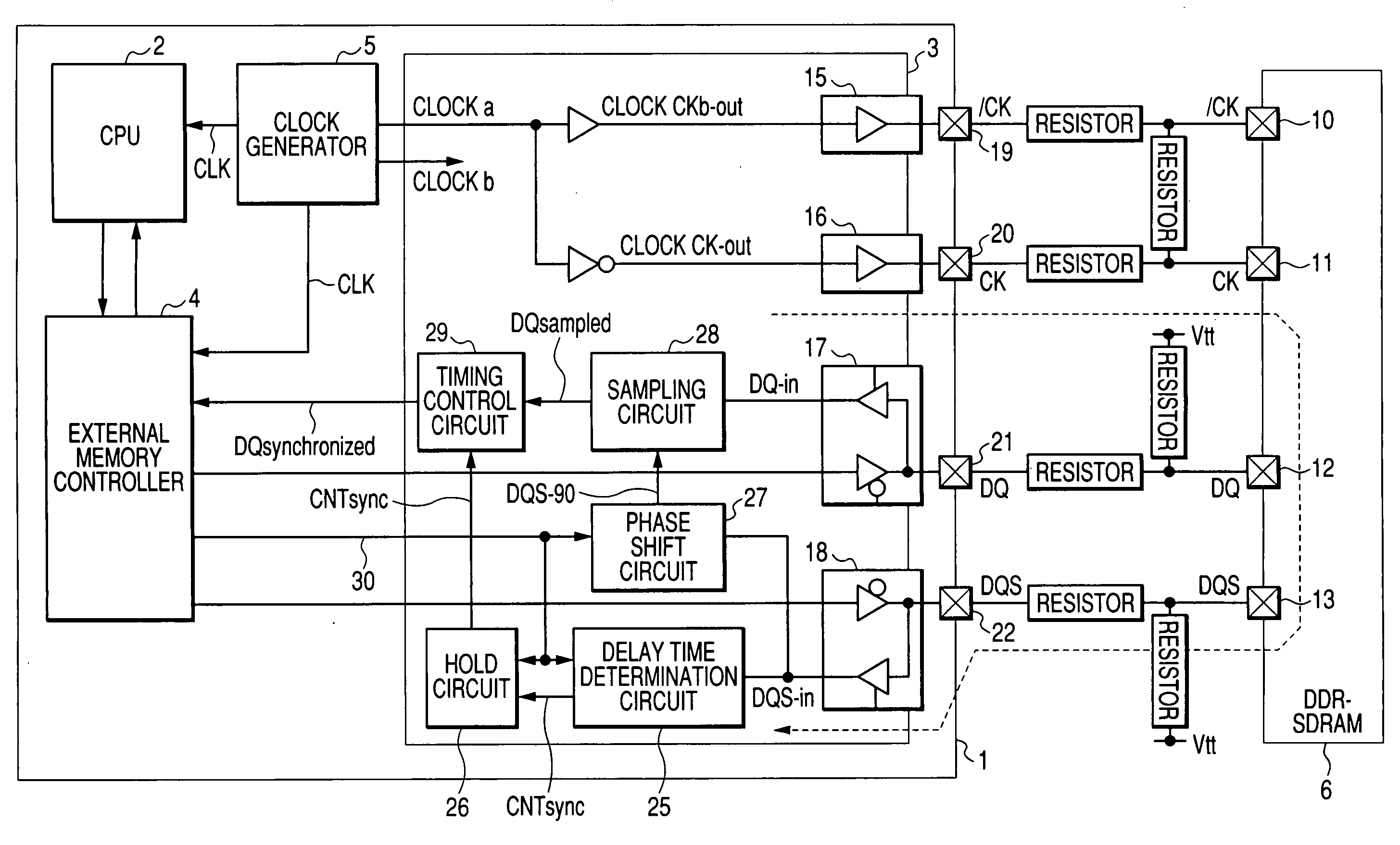

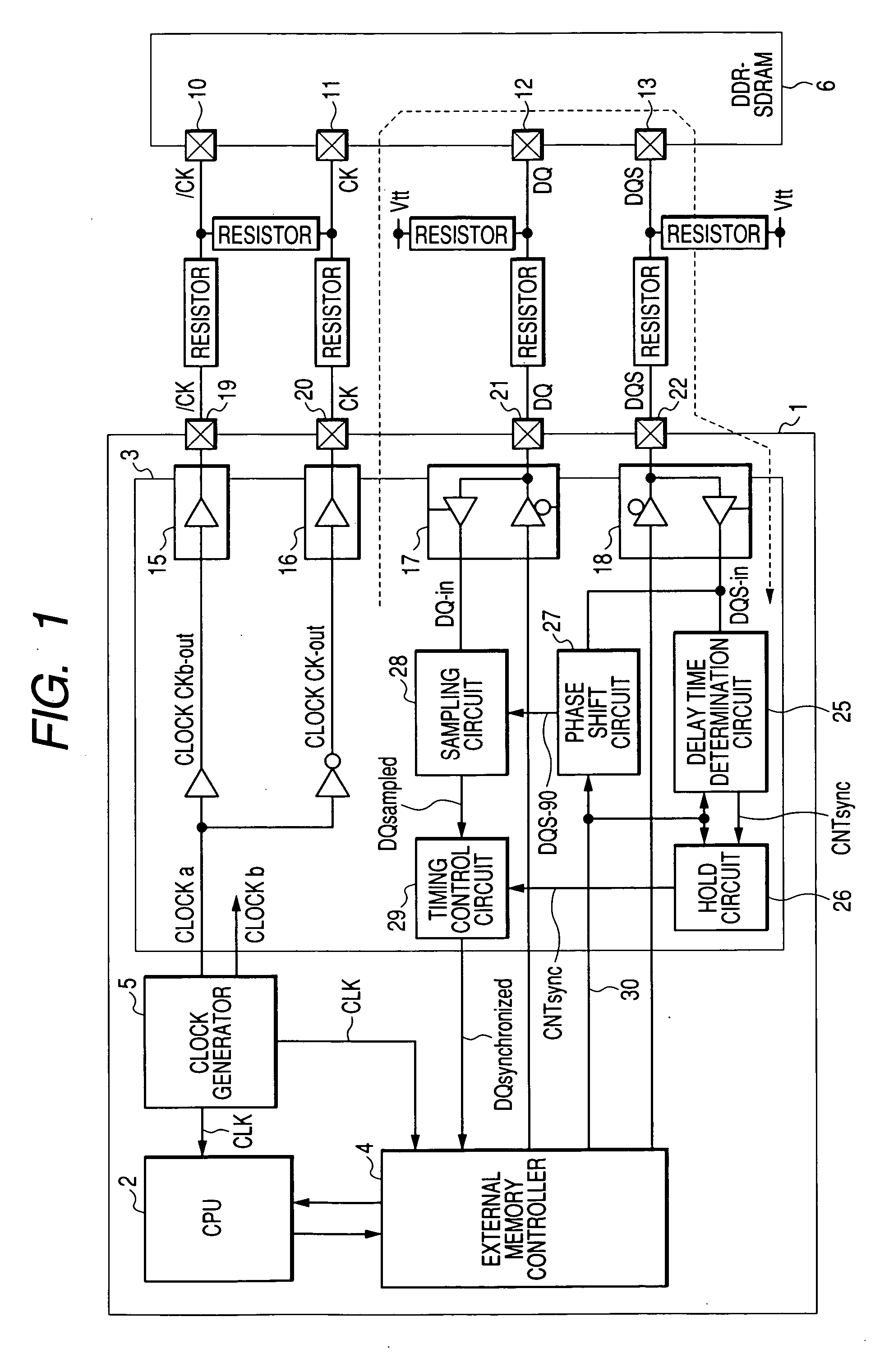

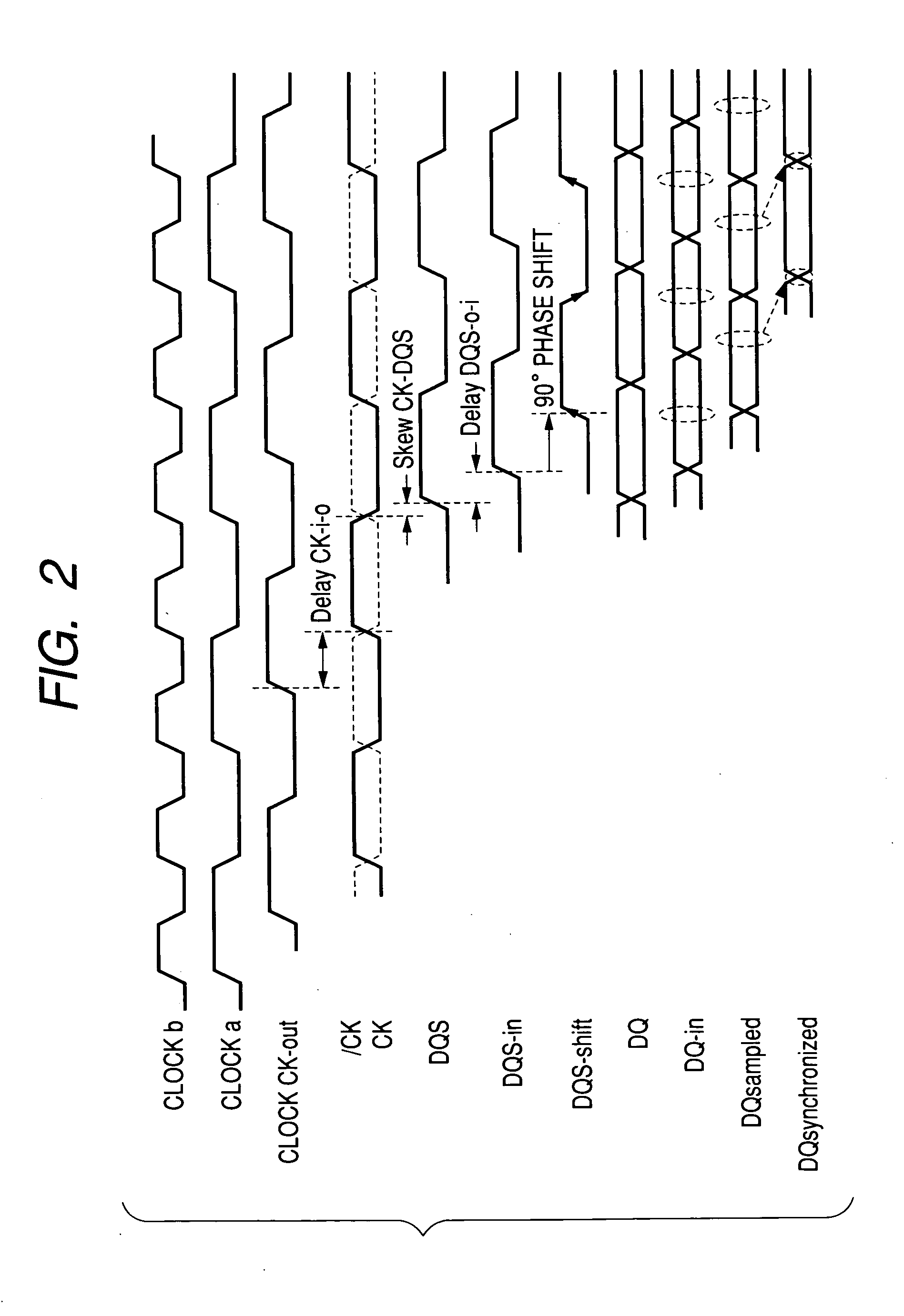

Semiconductor integrated circuit

ActiveUS20050047192A1Improve accuracyGuaranteed uptimeDigital storageGenerating/distributing signalsMemory interfaceComputer science

Owner:RENESAS ELECTRONICS CORP

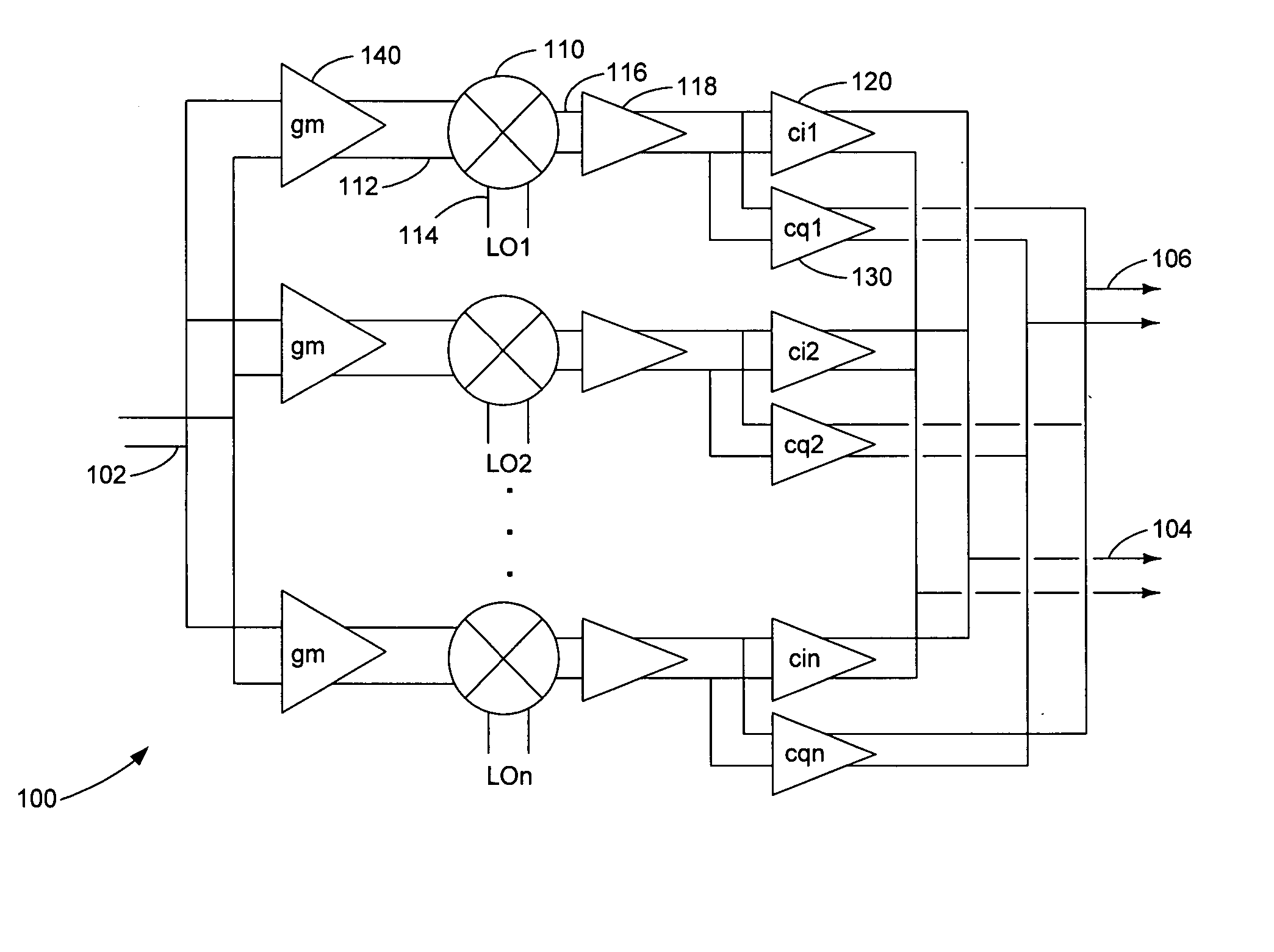

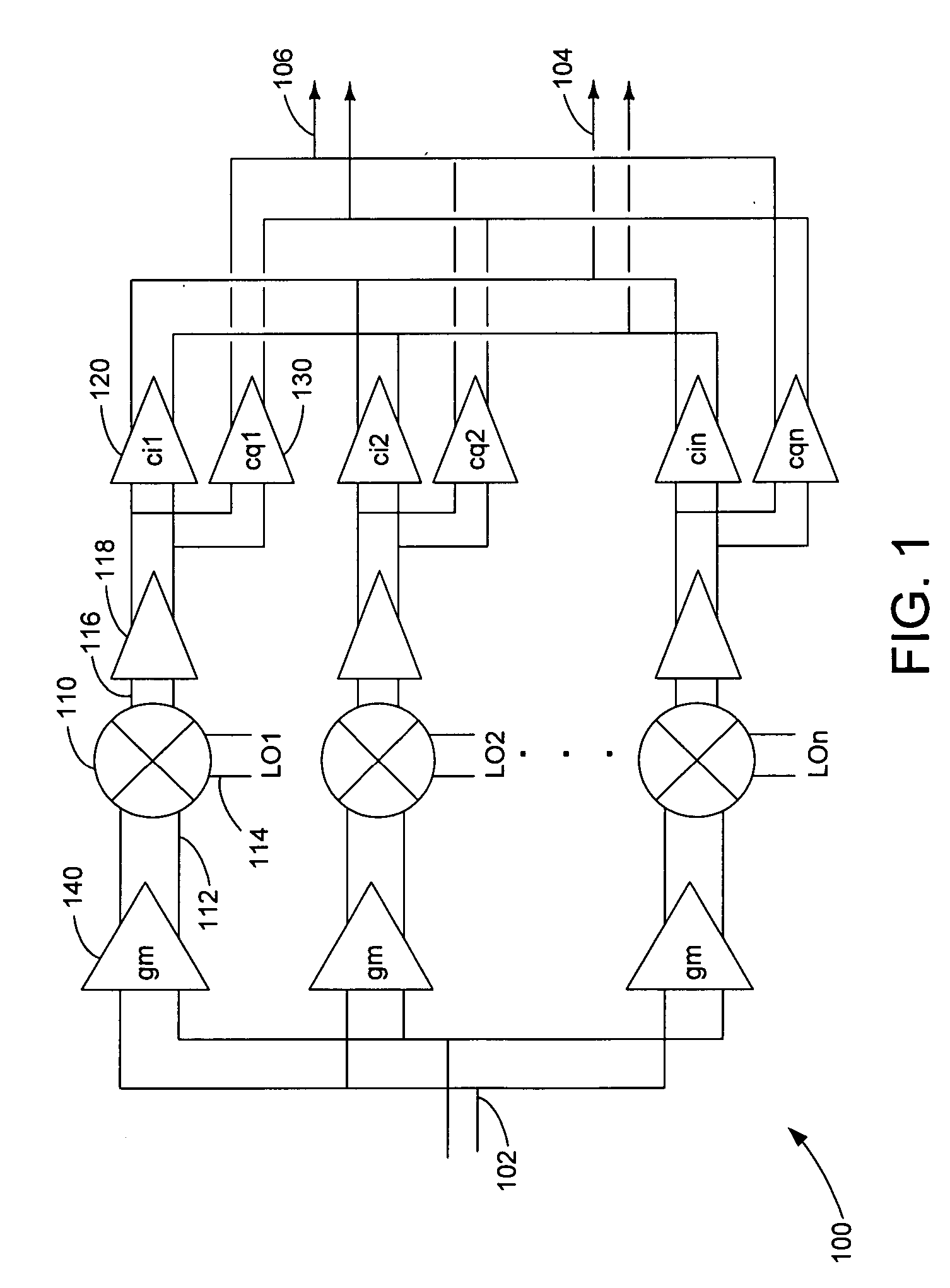

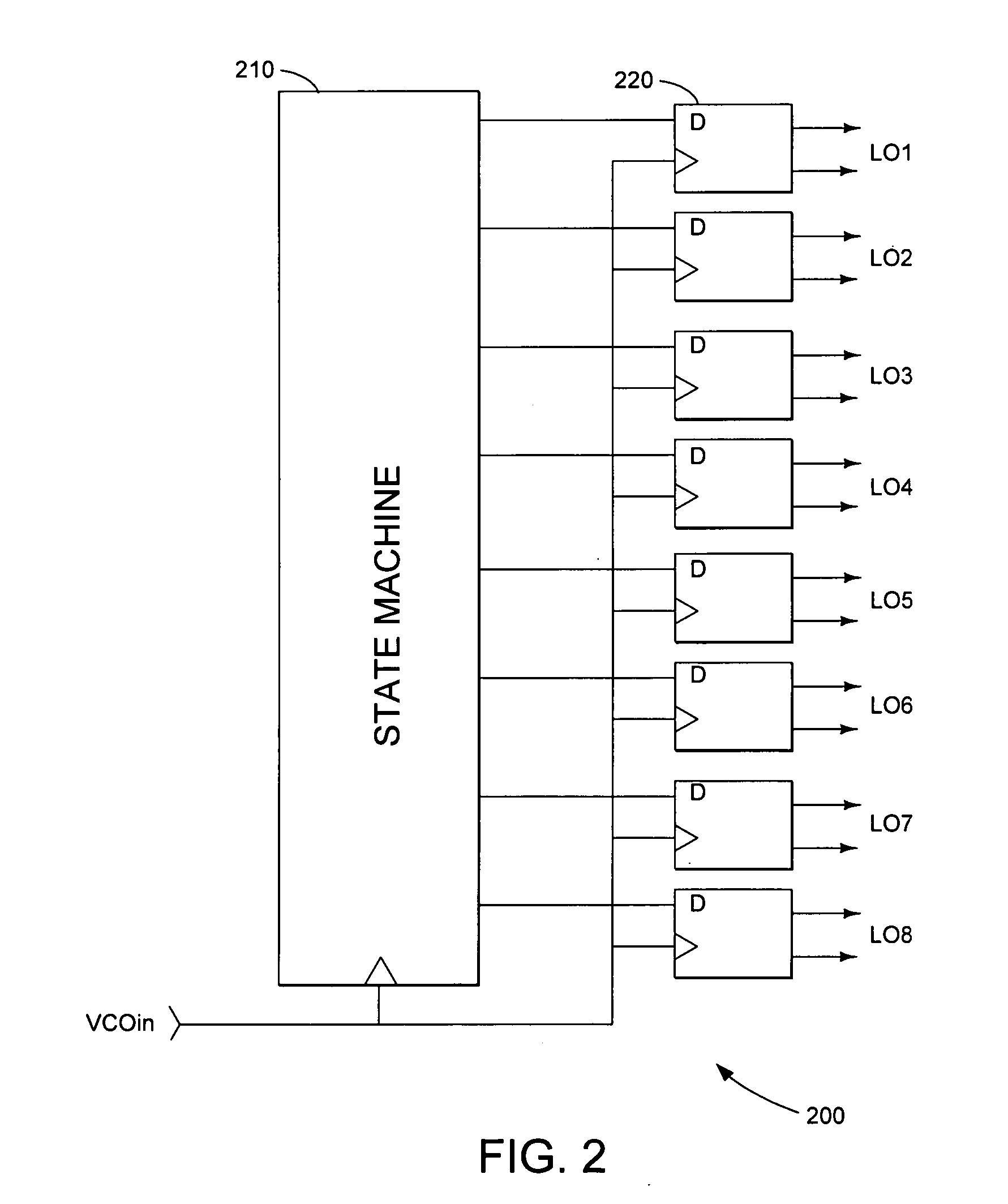

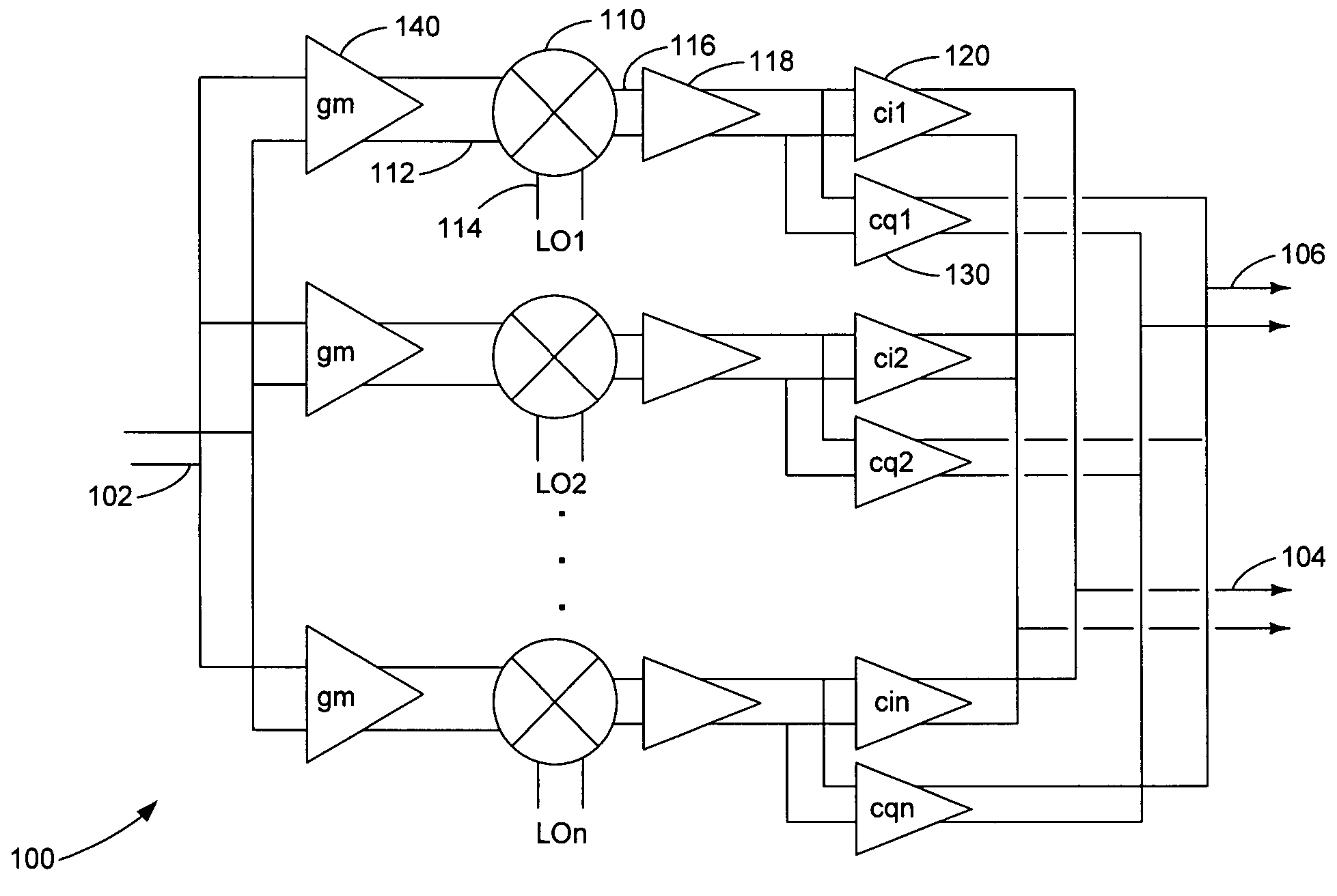

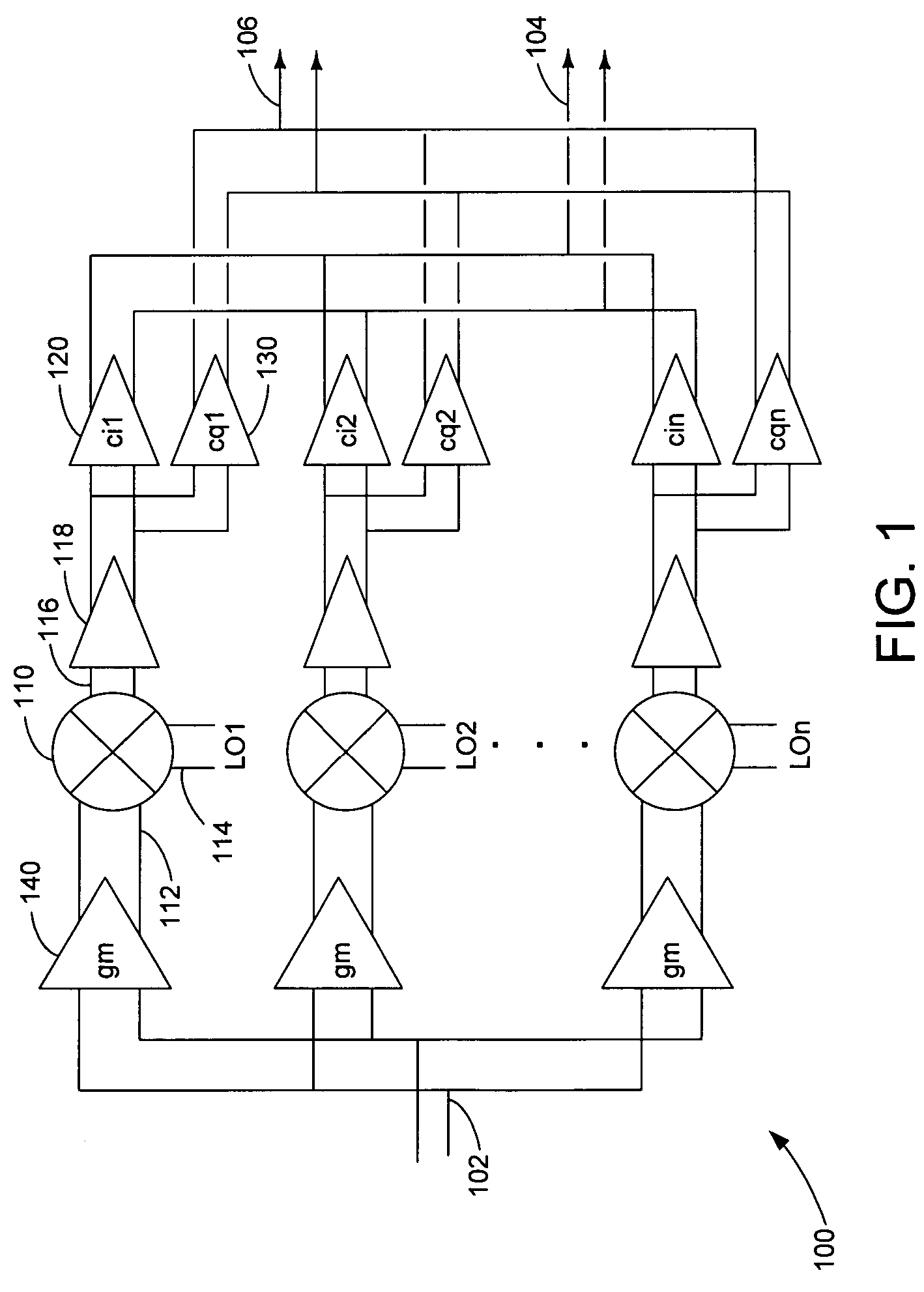

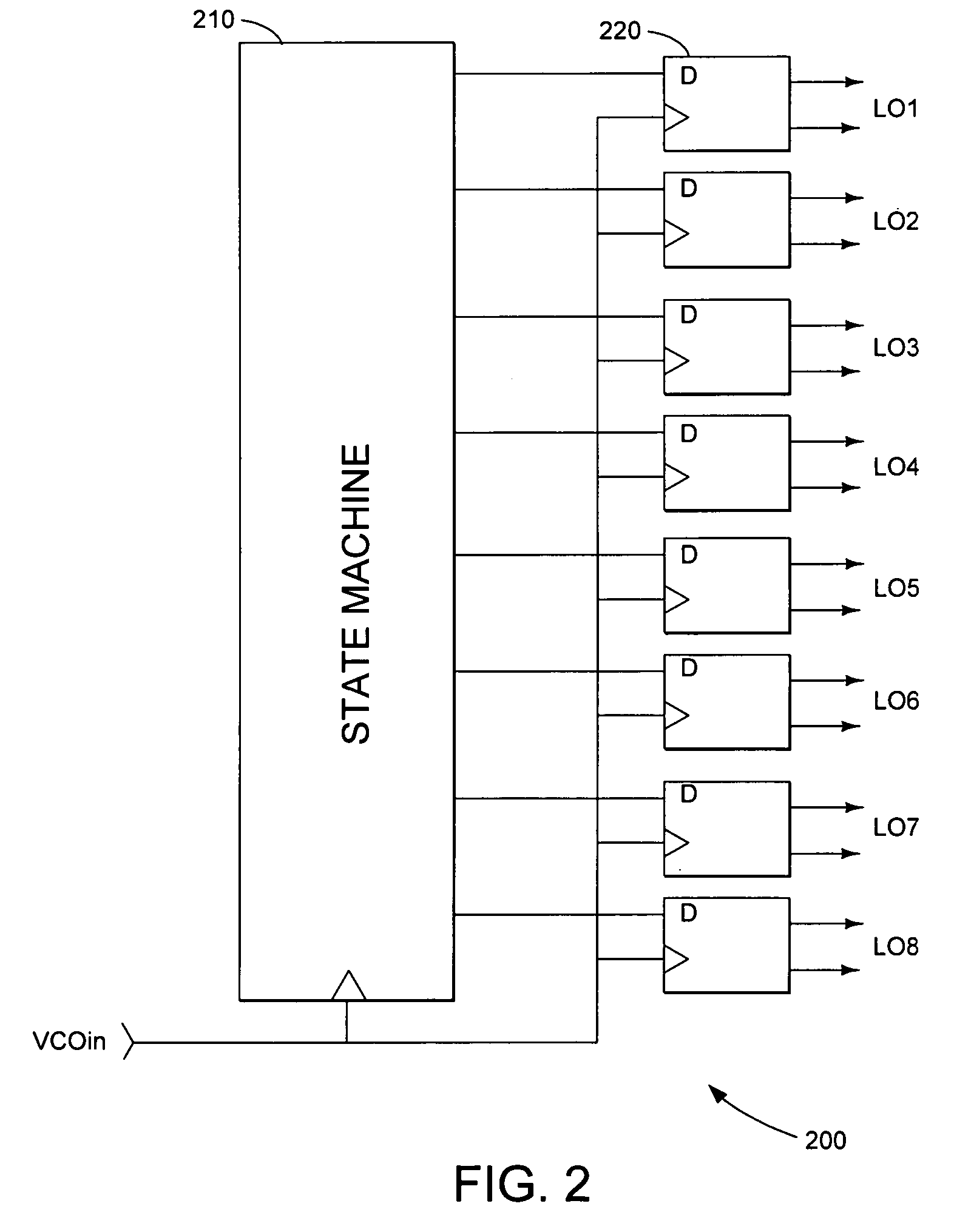

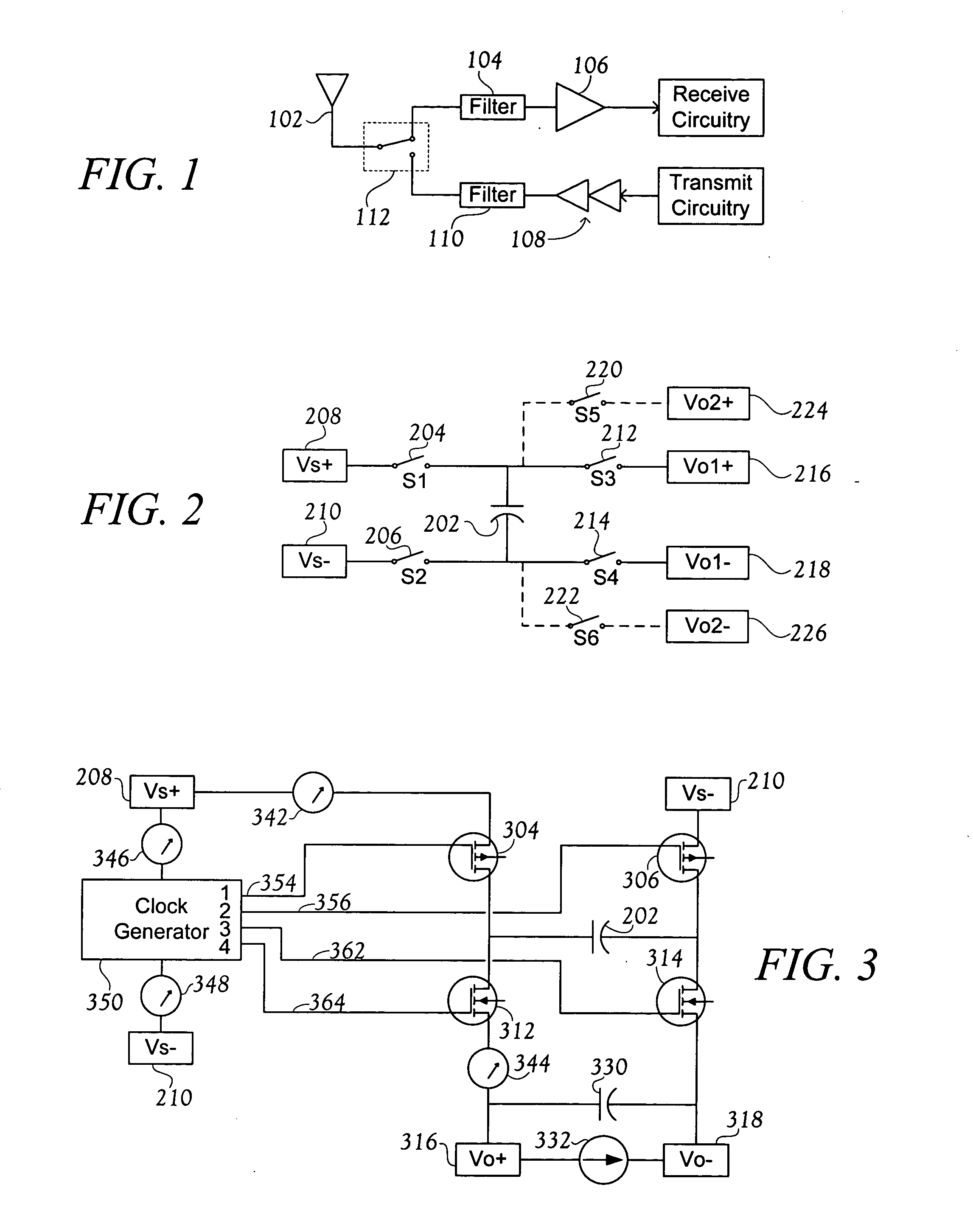

Harmonic suppression mixer and tuner

ActiveUS20050239430A1Enhanced inhibitory effectLess harmonic suppressionModulation transference balanced arrangementsTransmissionLow noiseHarmonic mitigation

A harmonic suppression mixer for down converting an RF signal to a complex I and Q baseband signal that uses a plurality of switching mixers each with a gain stage to produce a sinusoidal weighted sum of the mixer outputs. Odd harmonics output by each switching mixer is suppressed in the composite signal. A low skew local oscillator (LO) clock generator creates multiple LO phases and drives the mixers. The mixer can be used in low noise direct conversion RF tuners. The mixer is configurable by programming gain stage coefficient values to achieve a variable number of effective mixers used in combination. At low tuning frequencies, all available mixers are programmed with unique coefficients and driven by different LO clock phases to achieve maximum harmonic suppression. At high tuning frequencies, some mixers are paralleled and duplicate coefficients are programmed or mixers are disabled to reduce the number of effective mixers.

Owner:ENTROPIC COMM INC

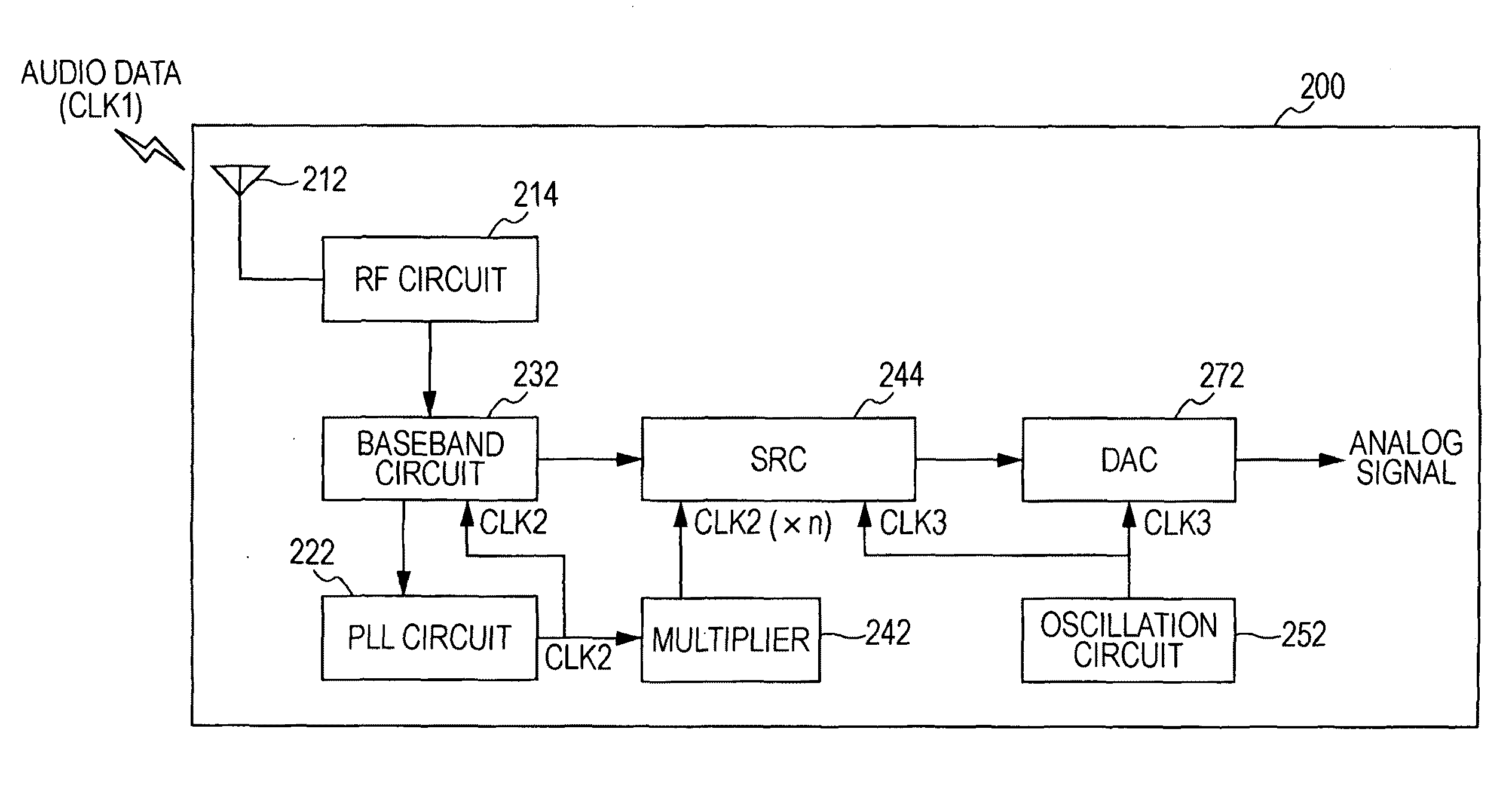

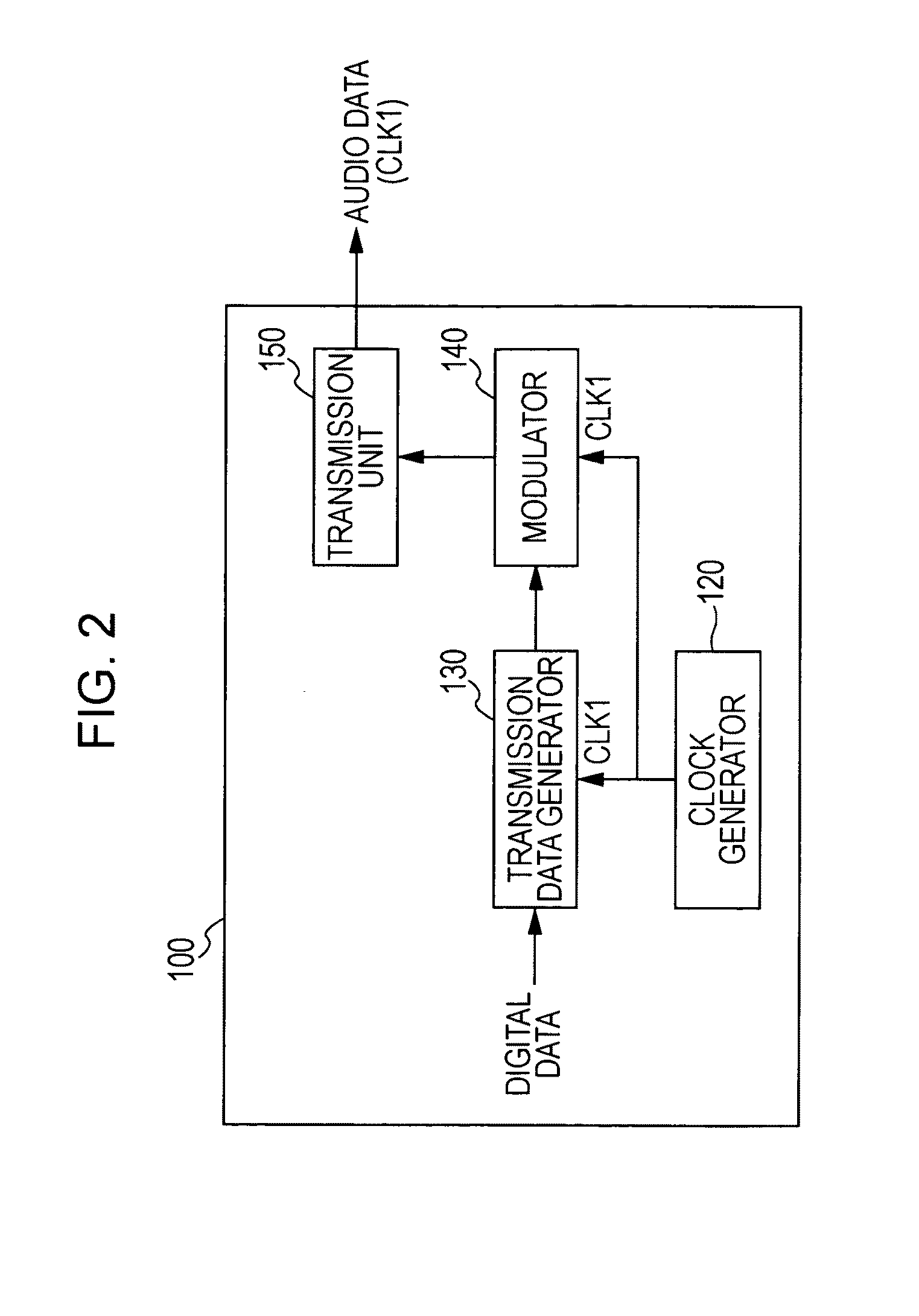

Audio data receiving apparatus, audio data receiving method, and audio data transmission and receiving system

InactiveUS8751026B2Quality improvementModification of read/write signalsRecord information storageData transmissionClock generator

An audio data receiving apparatus includes a receiving unit configured to receive audio data sampled in accordance with a first clock signal; a synchronization unit configured to generate a second clock signal that is synchronized with the first clock signal by extracting clock components contained in the audio data; a demodulator configured to demodulate the audio data in accordance with the second clock signal; an oversampling unit configured to oversample the audio data demodulated by the demodulator by using a frequency higher than a frequency of the second clock signal; a clock generator configured to generate a third clock signal having a frequency nearly equal to the first clock signal; and a data output unit configured to output the audio data oversampled by the oversampling unit in accordance with the third clock signal generated by the clock generator.

Owner:SONY CORP

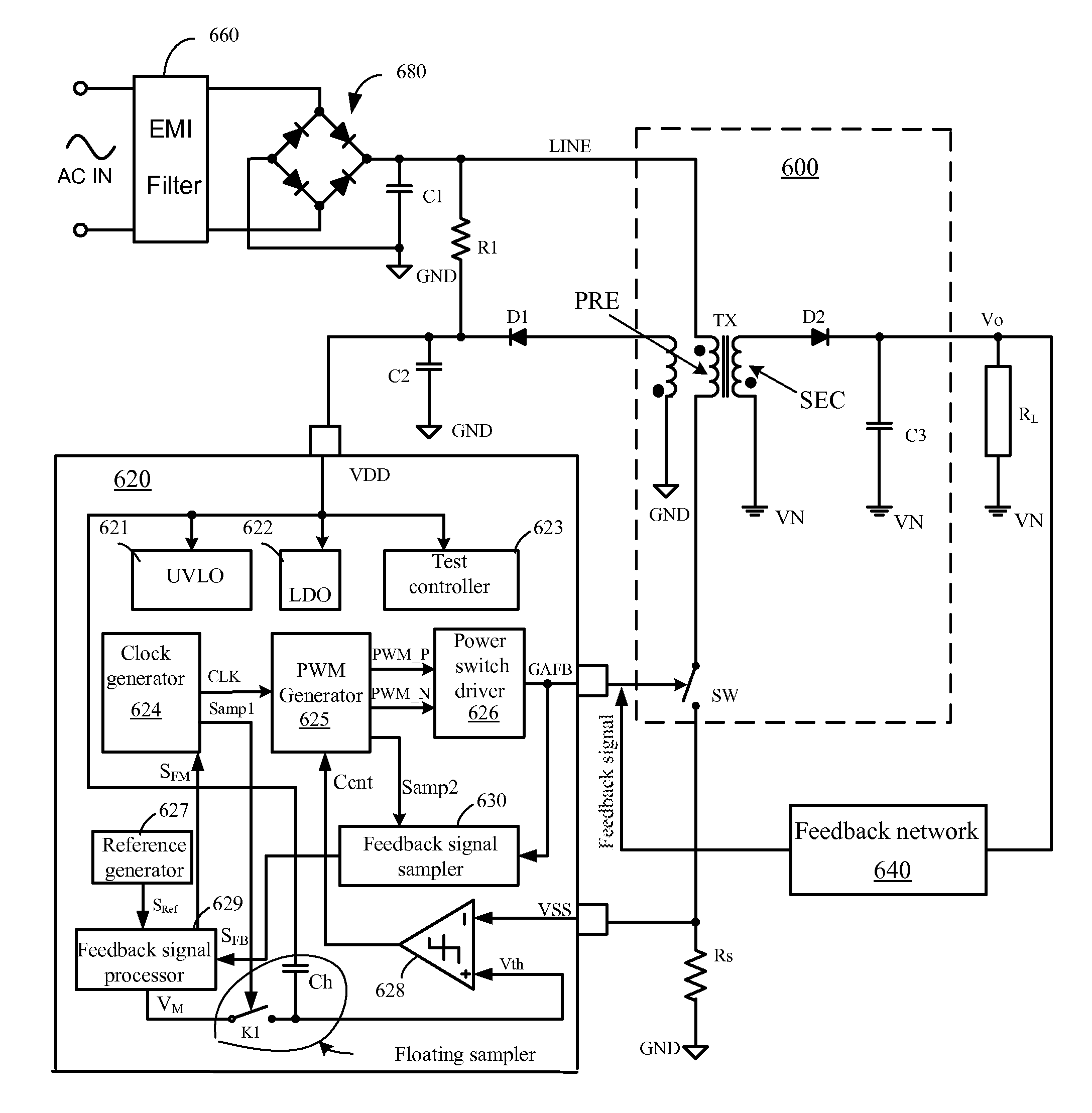

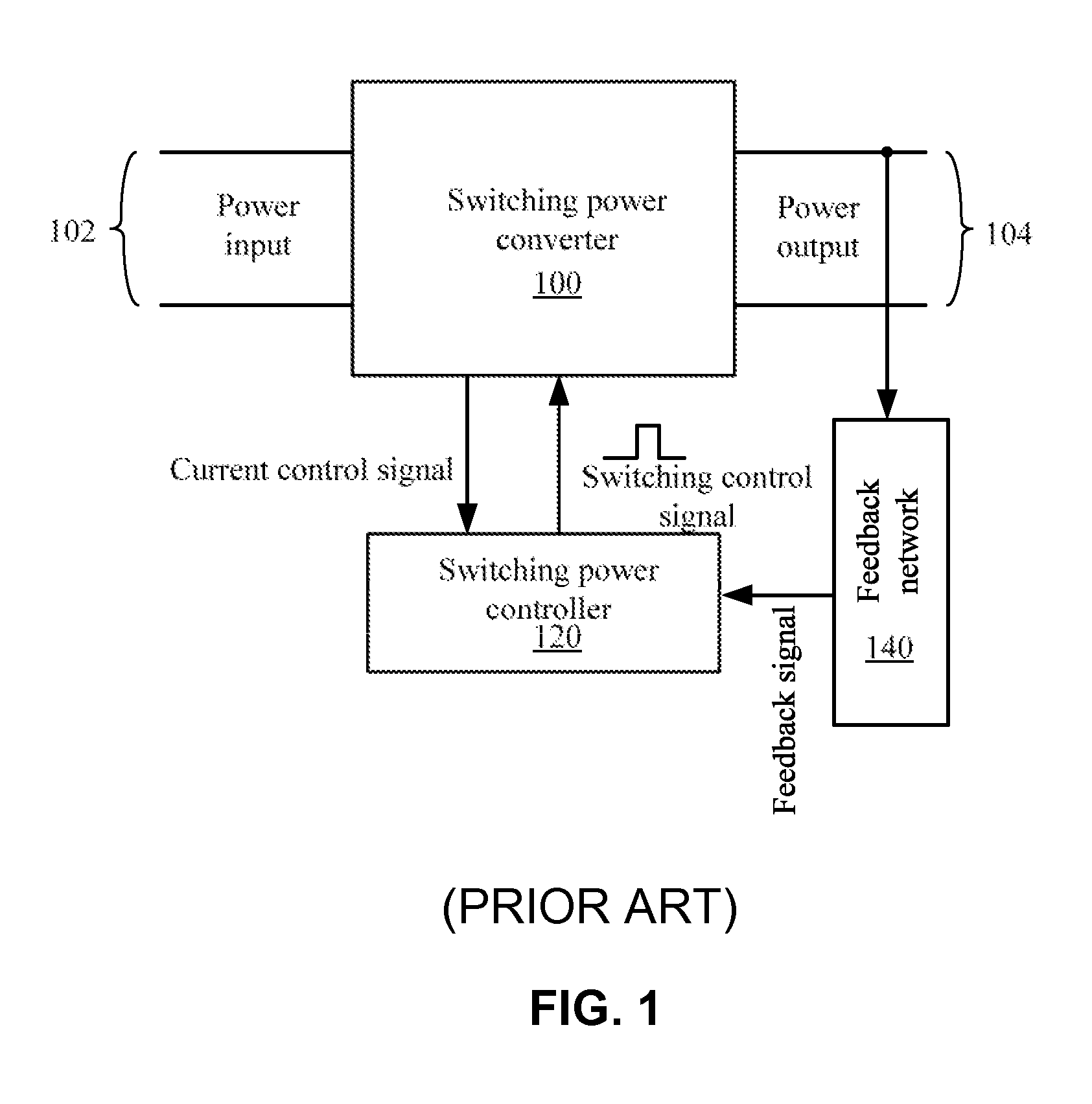

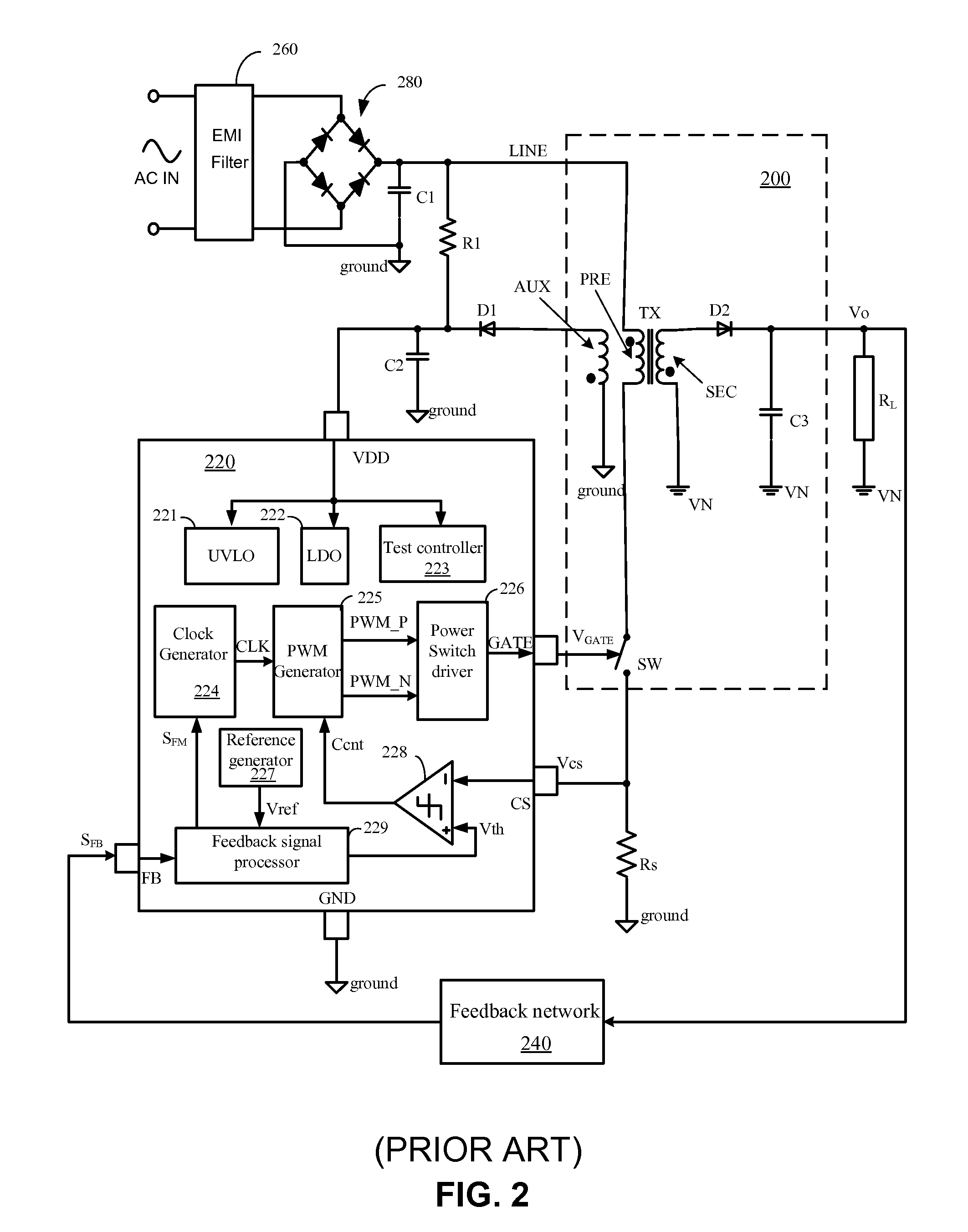

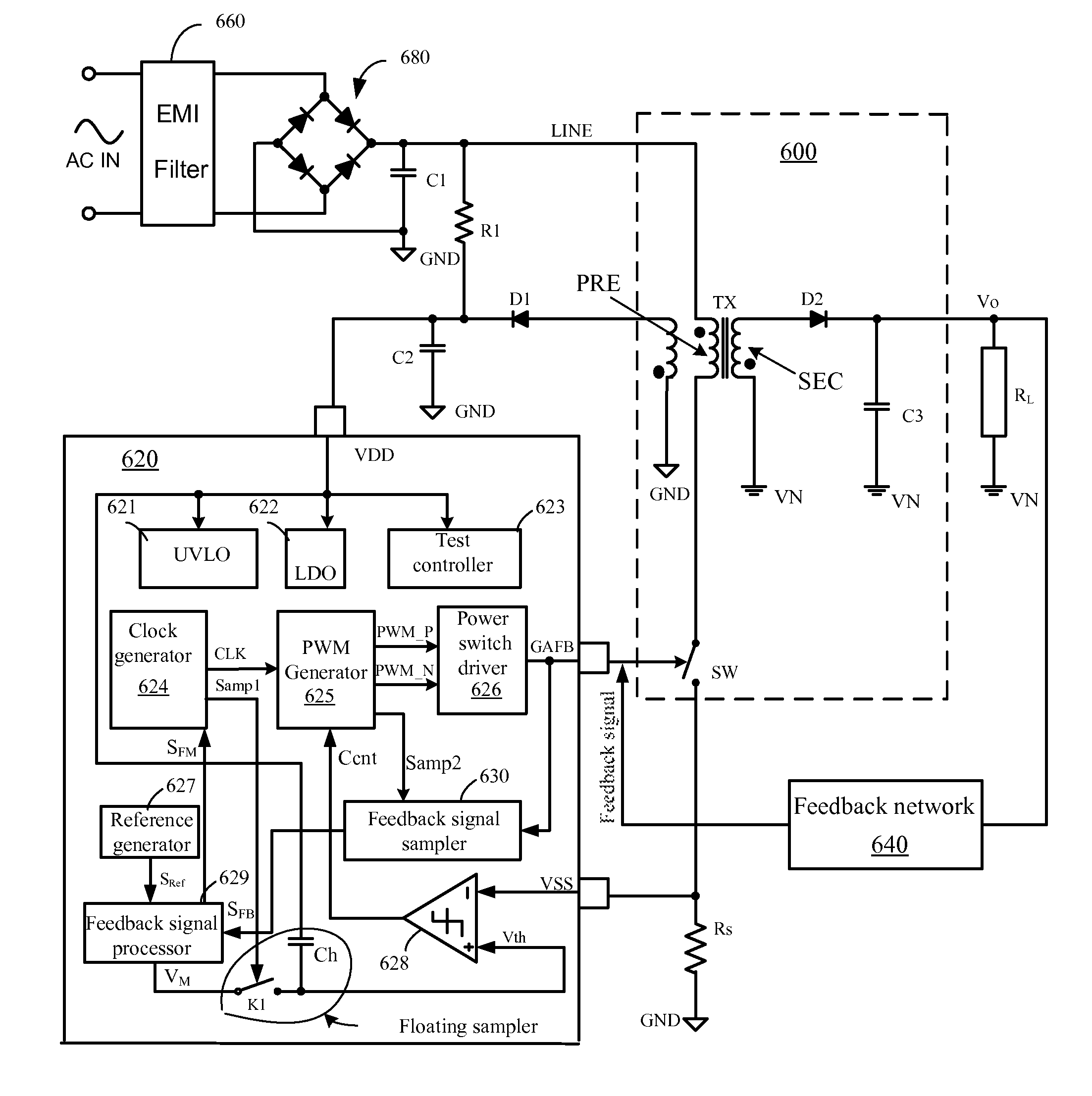

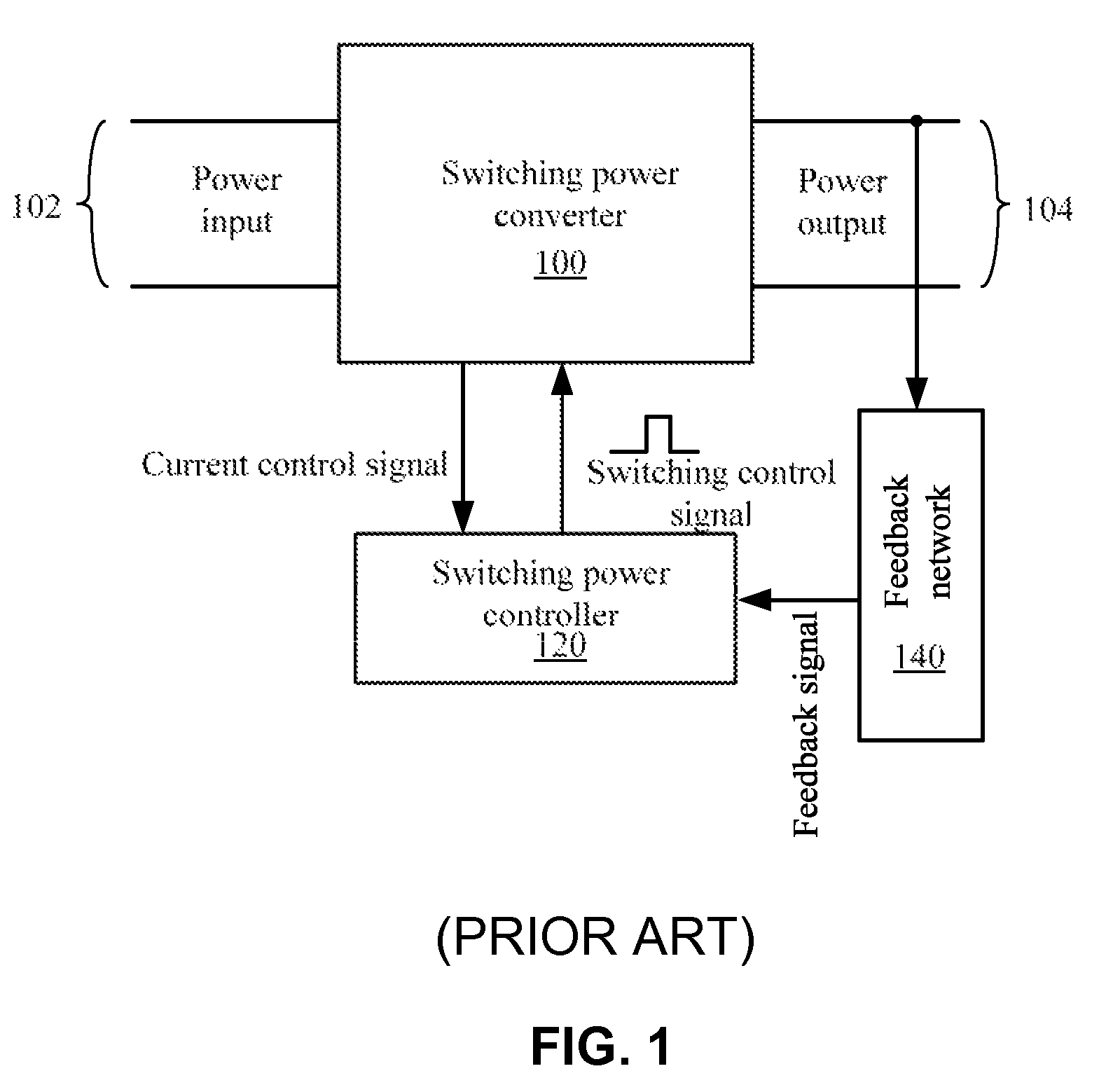

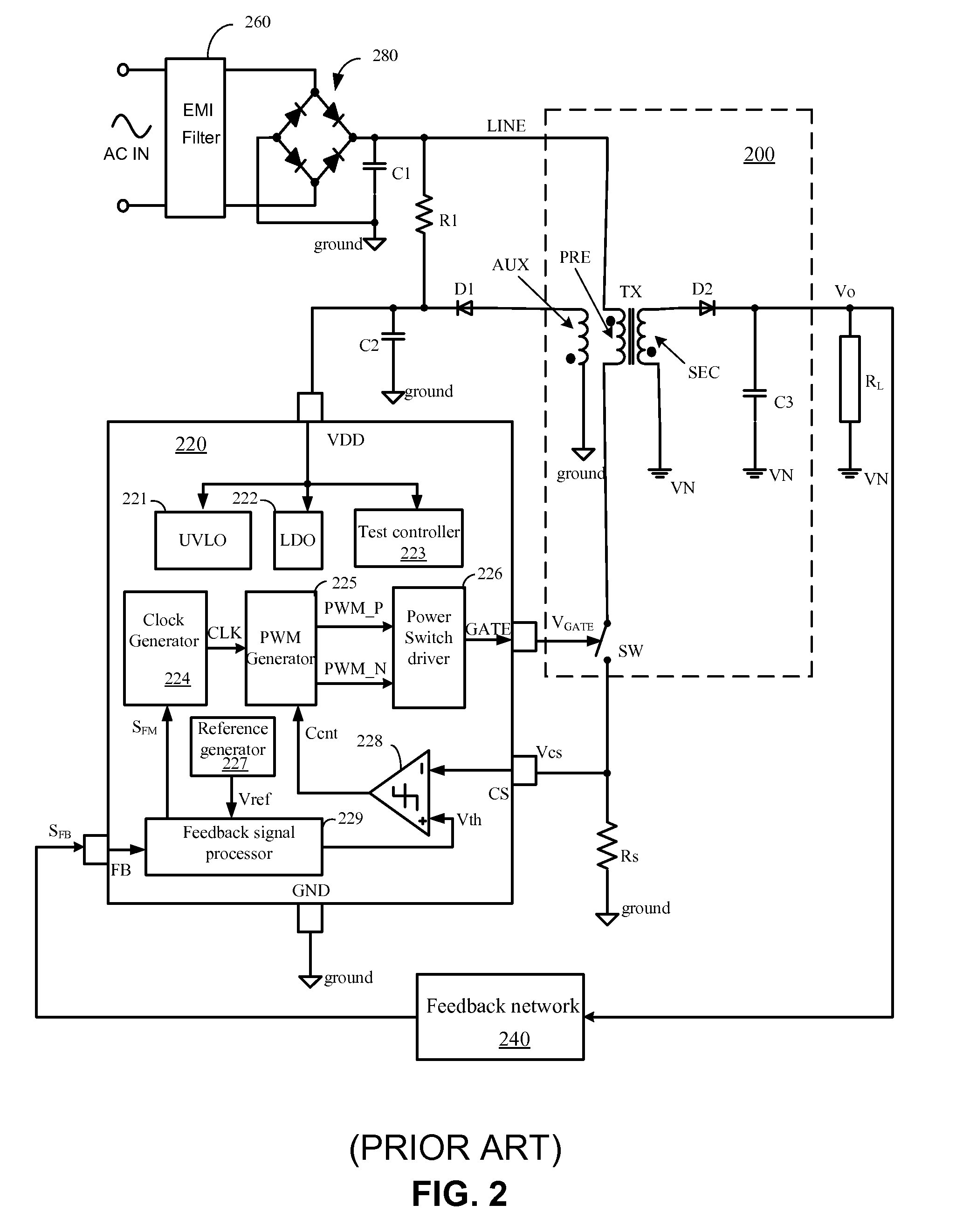

Switching Power Controller and System

ActiveUS20110096574A1Conversion with intermediate conversion to dcDc-dc conversionPower controllerClock generator

A switching power controller circuit comprises a first terminal pin for a high potential of a power supply for the controller circuit, a second terminal pin for providing output of switch drive signals and for receiving feedback signals, and a third terminal pin for receiving external current signals and for a low potential of the power supply. The switching power controller further comprises a clock generator, a pulse width modulation (PWM) generator, a reference generator, a power switch driver, a feedback signal sampler, a PWM comparator and a floating sampler.

Owner:GIANTEC SEMICON LTD

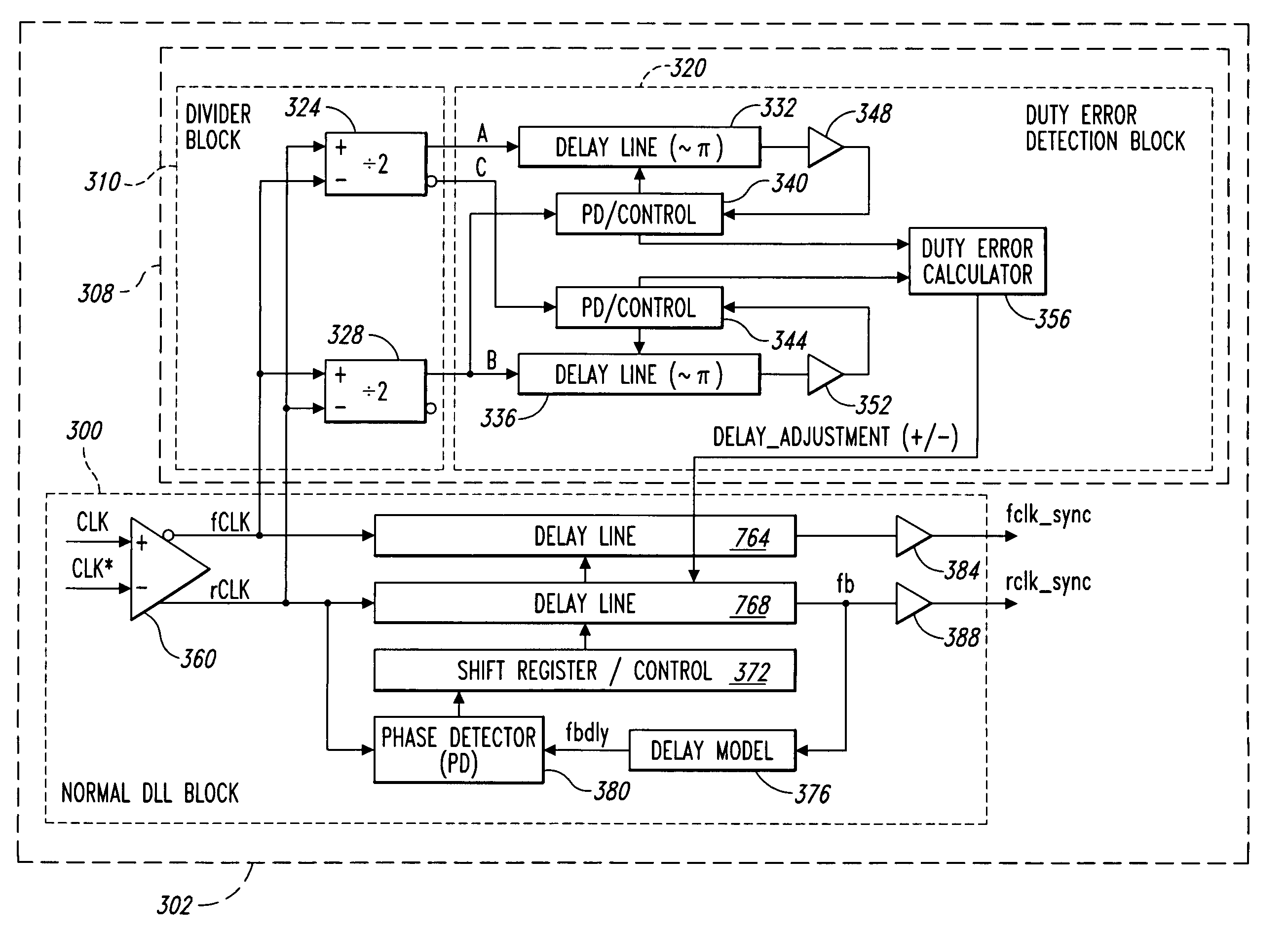

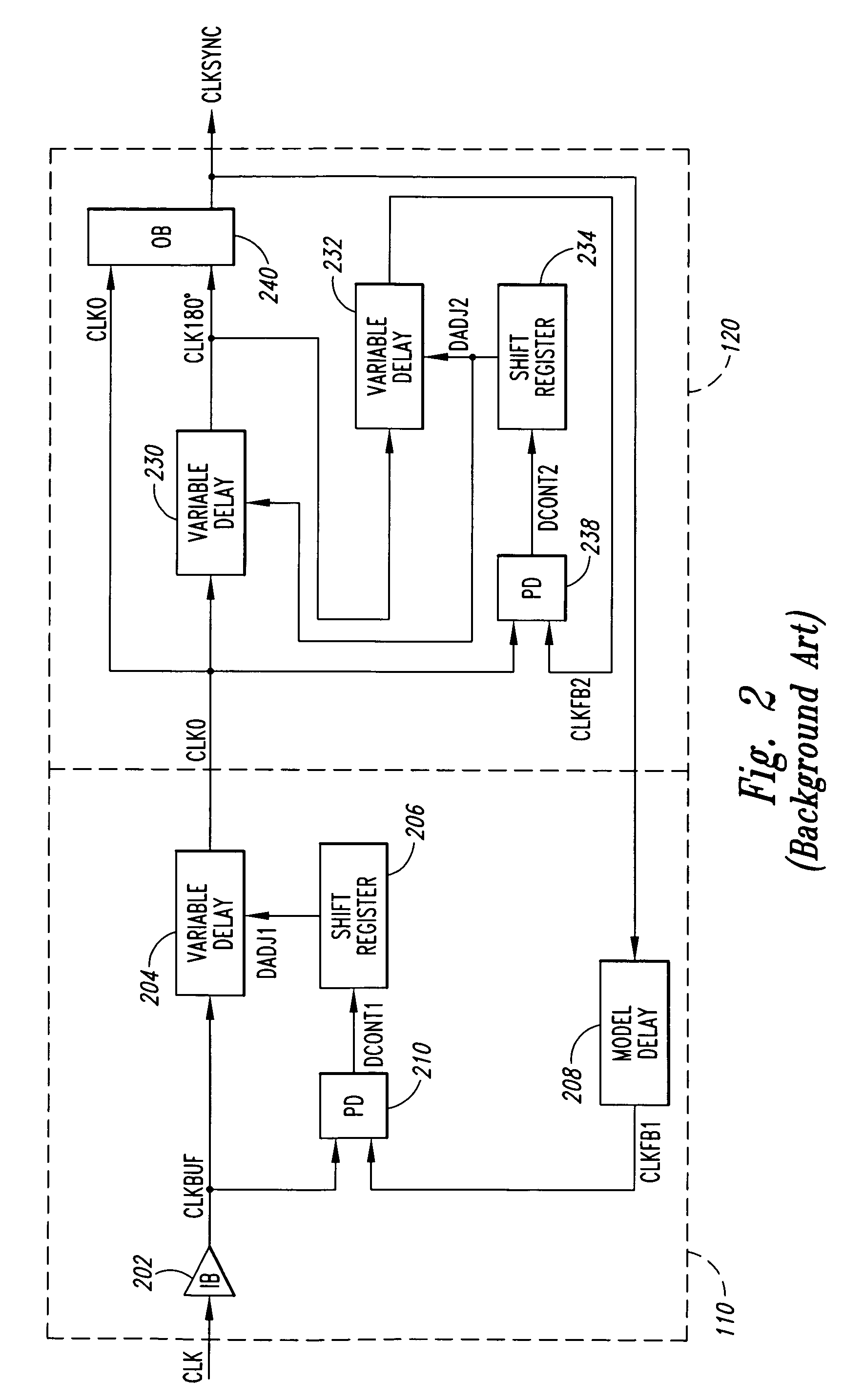

Clock generator having a delay locked loop and duty cycle correction circuit in a parallel configuration

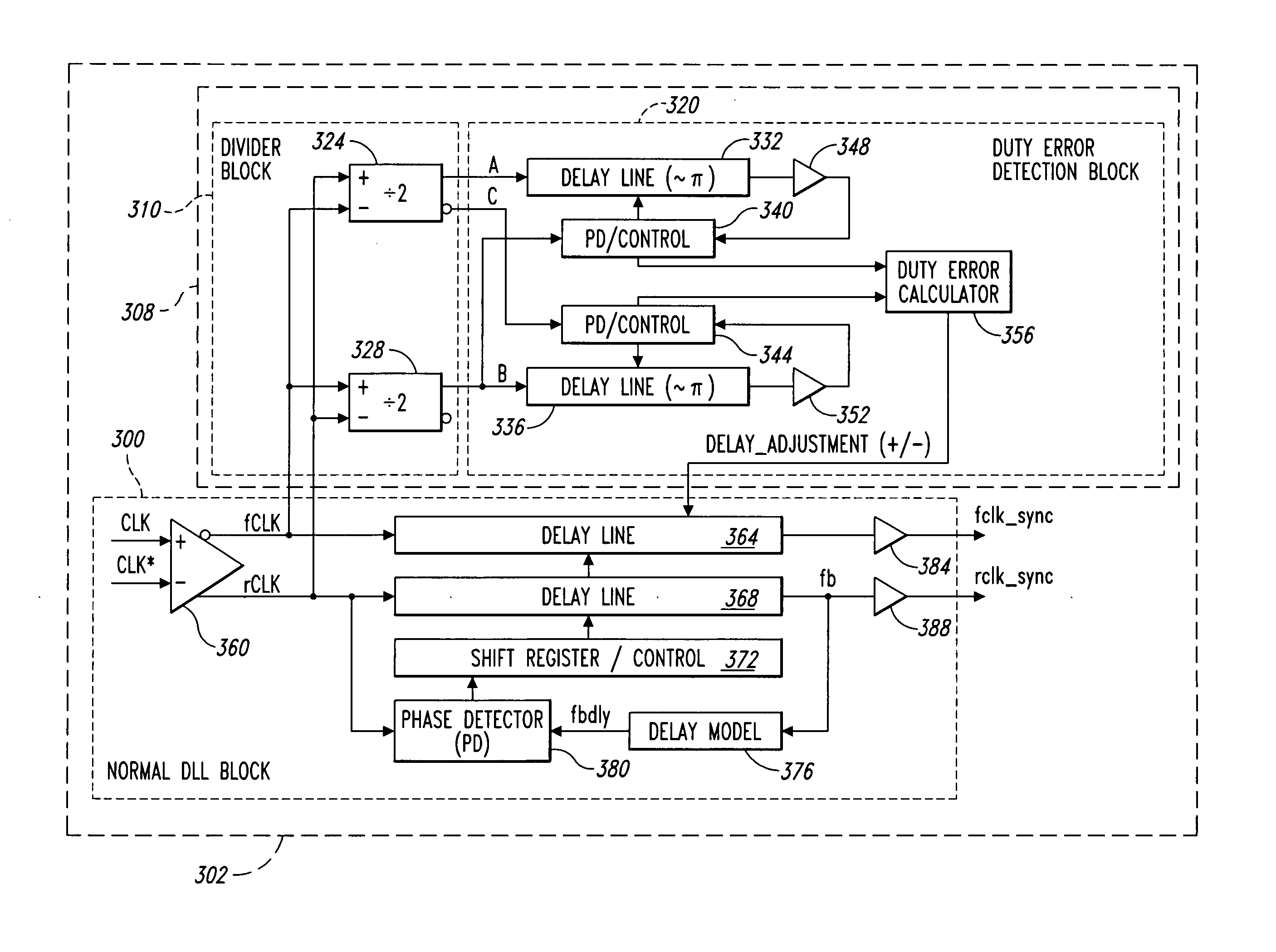

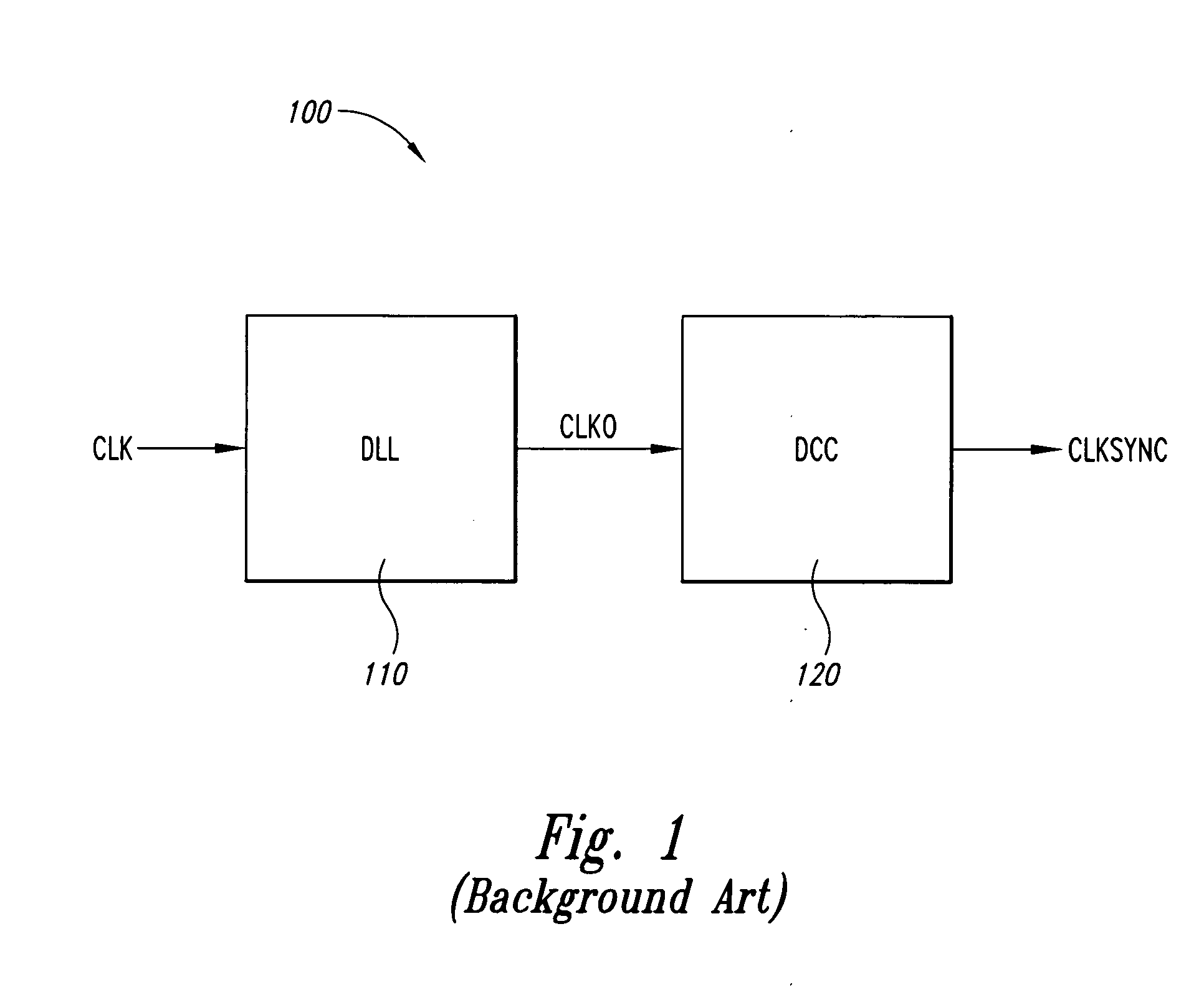

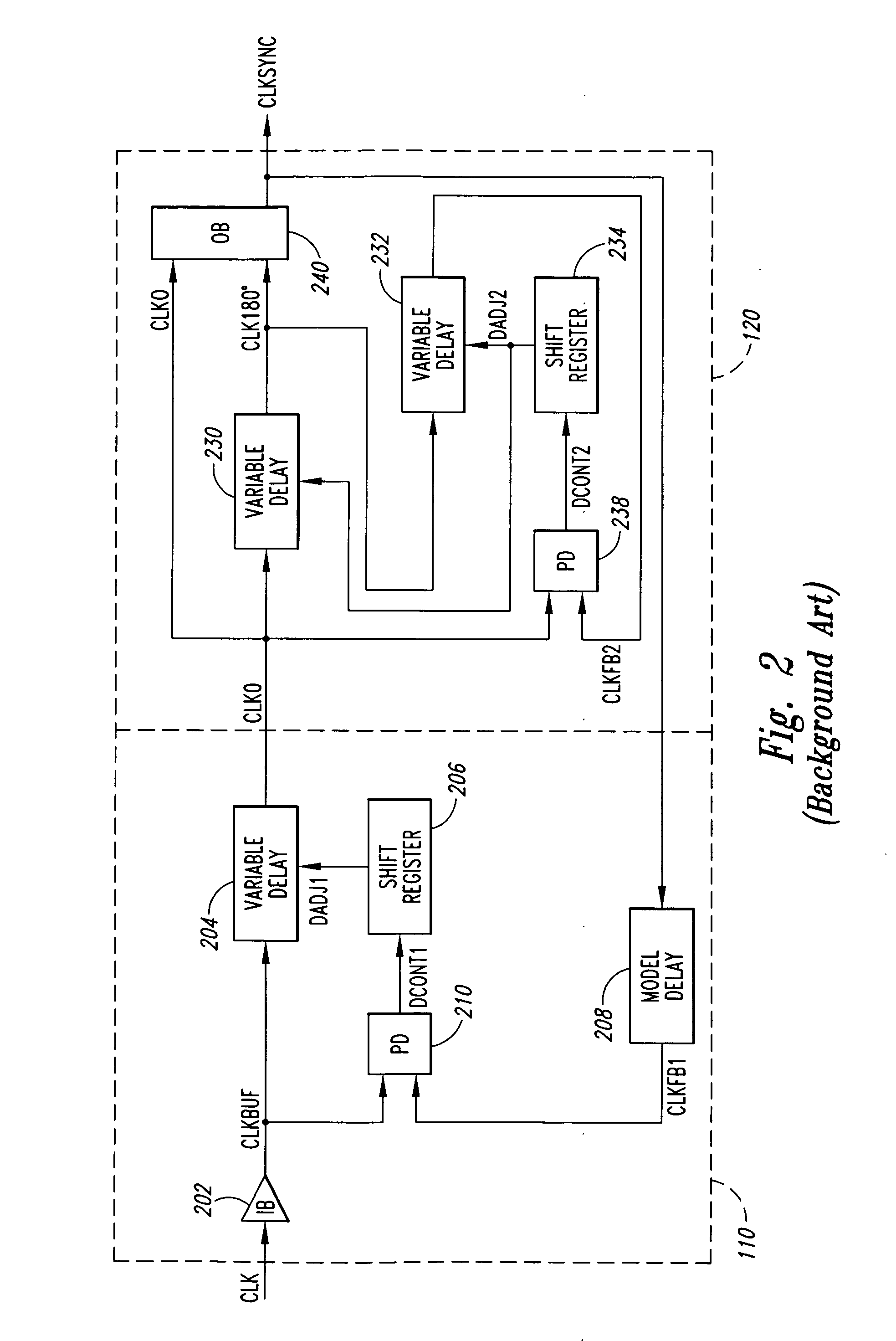

ActiveUS20070086267A1Pulse automatic controlManipulation where pulse delivered at different timesDelay-locked loopClock generator

A clock generator having a delay locked loop and a duty cycle correction circuit. The delay locked loop adjusts a first adjustable delay circuit to generate a first output clock signal that is synchronized with a first input clock signal and adjusts a second adjustable delay circuit to provide a delay that is equal to the first adjustable delay circuit. A duty cycle correction circuit is coupled to the first and second inputs of the delay locked loop and further coupled to the second adjustable delay circuit. The duty cycle correction circuit is configured to determine a duty cycle error of at least one of the first and second input clock signals and adjust the second adjustable delay circuit to provide a corrected delay compensating for the duty cycle error.

Owner:MICRON TECH INC

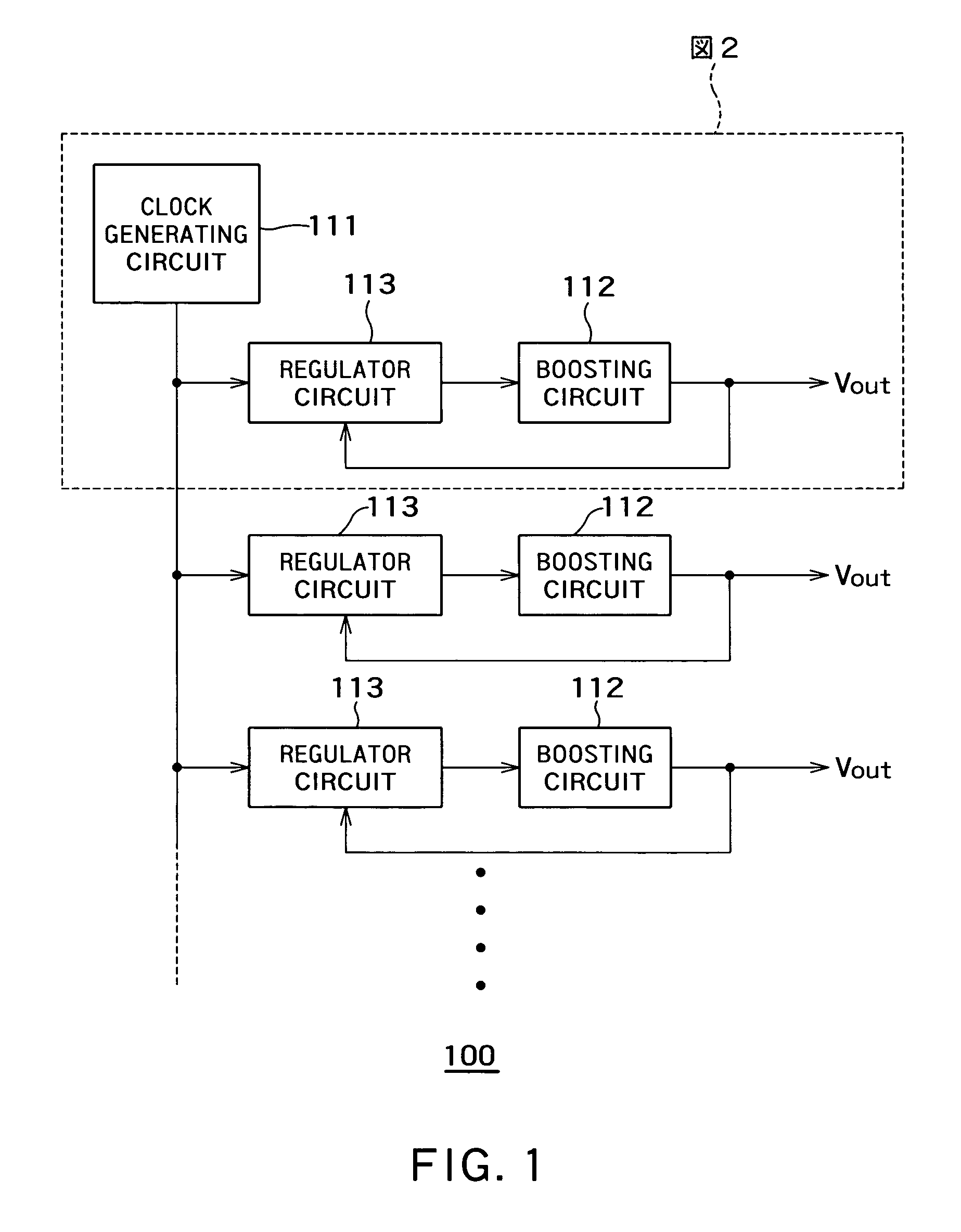

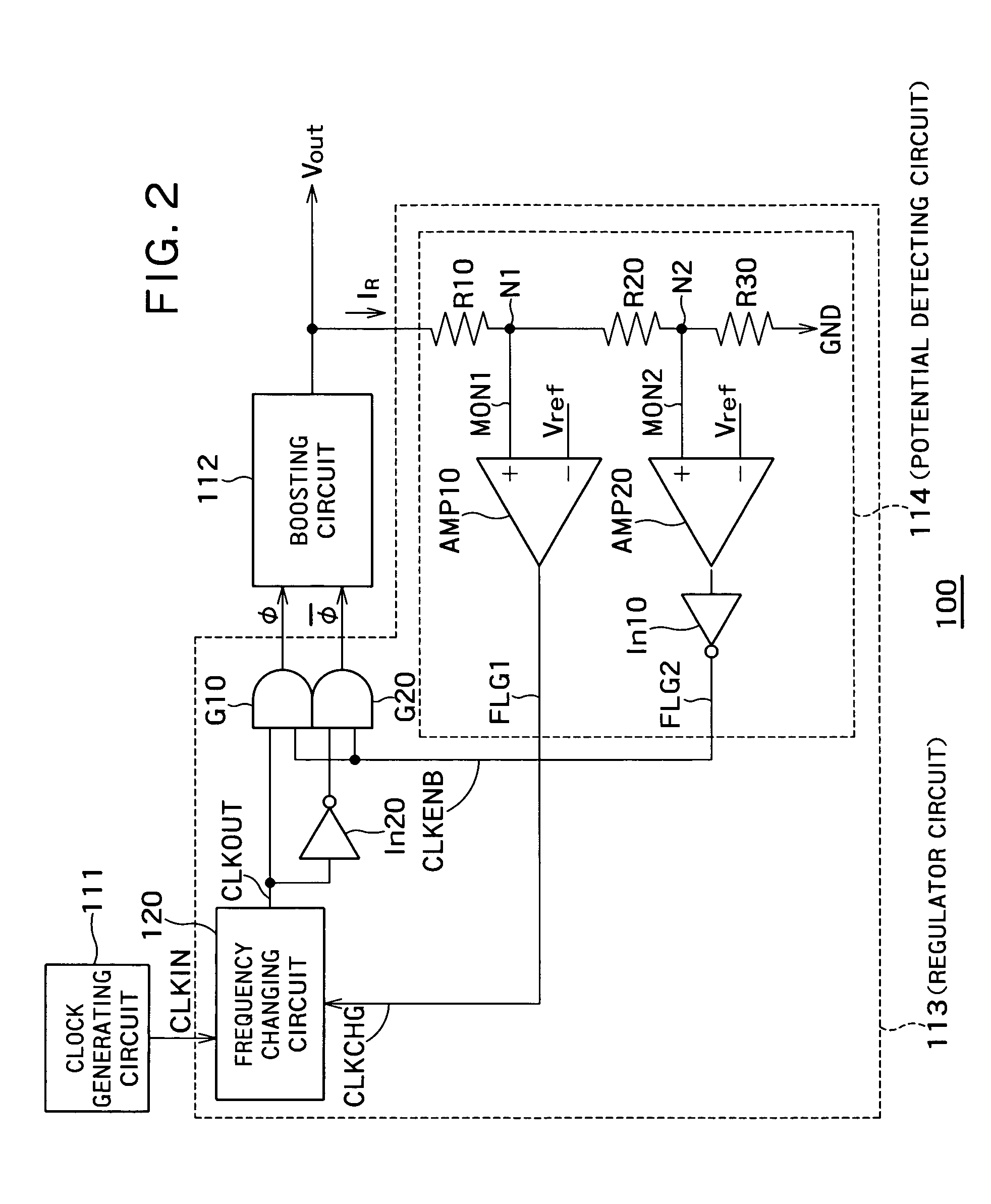

Semiconductor device and driving method of semiconductor device

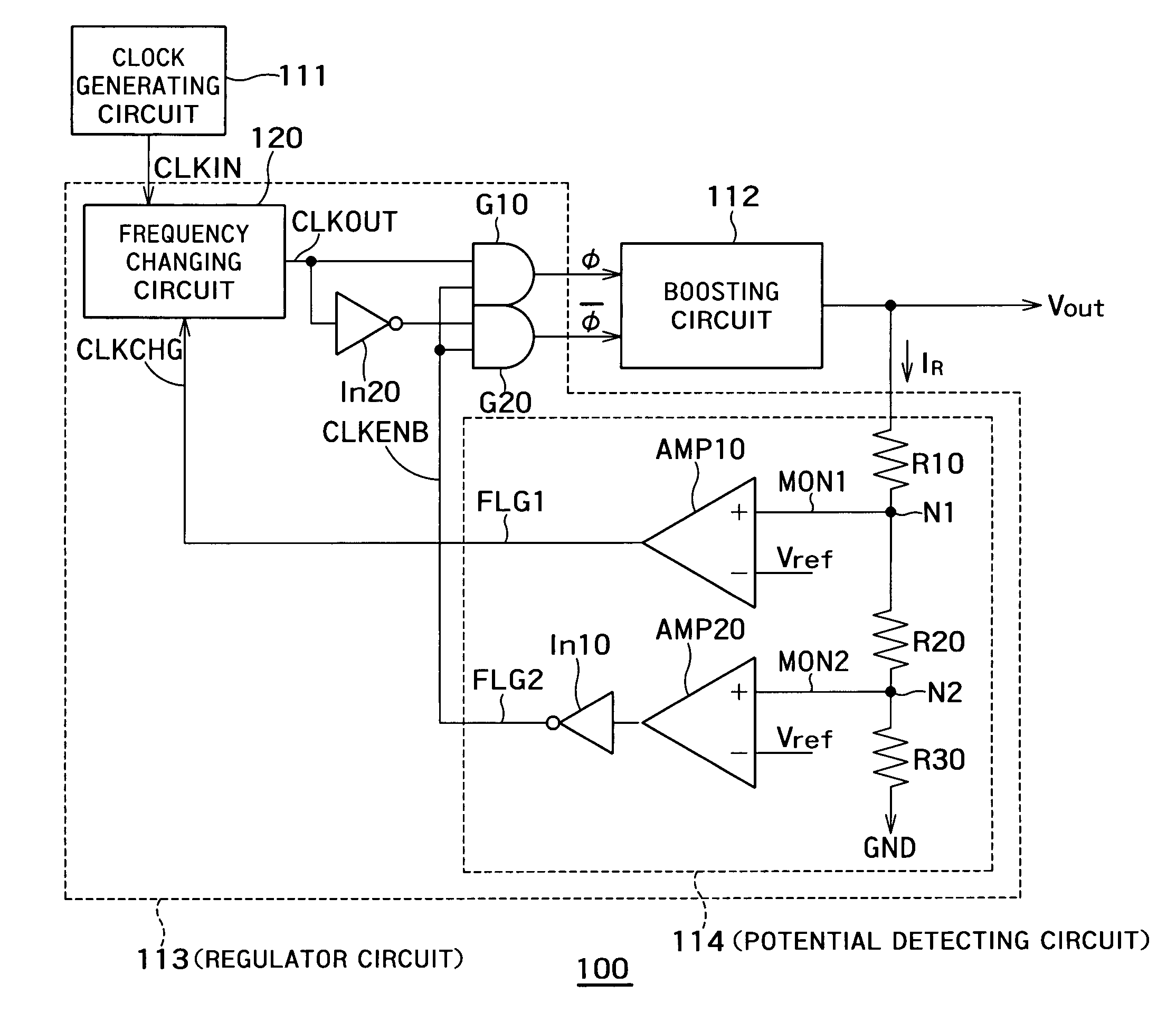

InactiveUS7253676B2Read-only memoriesApparatus without intermediate ac conversionFrequency changerEngineering

A semiconductor device that includes a clock generator which generates a clock signal; a booster which boosts a supply voltage by using the clock signal to output the boosted voltage; a potential detector which detects an output potential of the booster to output a frequency changing signal depending on the output potential; and a frequency changer which is interposed between the clock generator and the booster to change the frequency of the clock signal from the clock generator to the booster on the basis of the frequency changing signal.

Owner:KK TOSHIBA

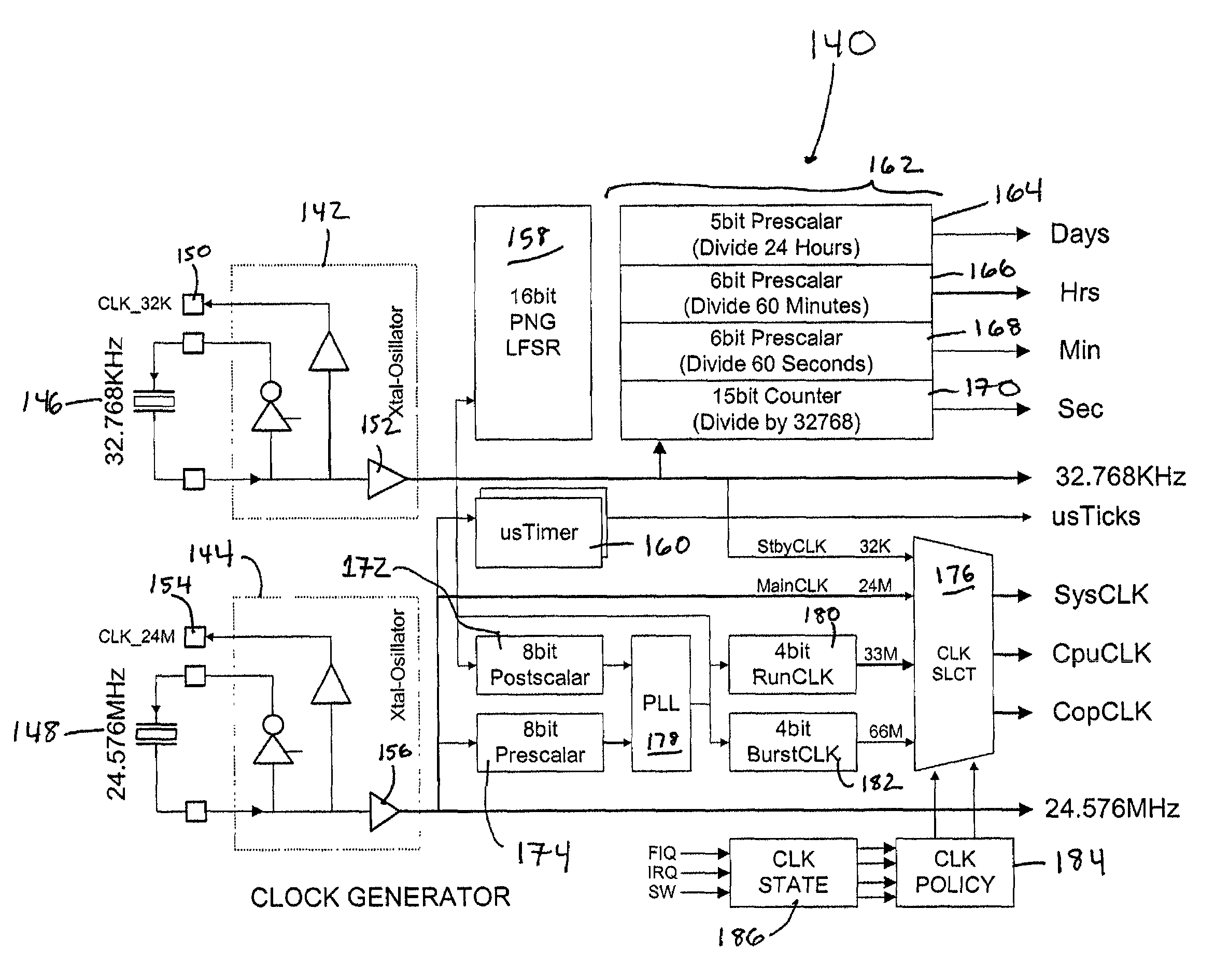

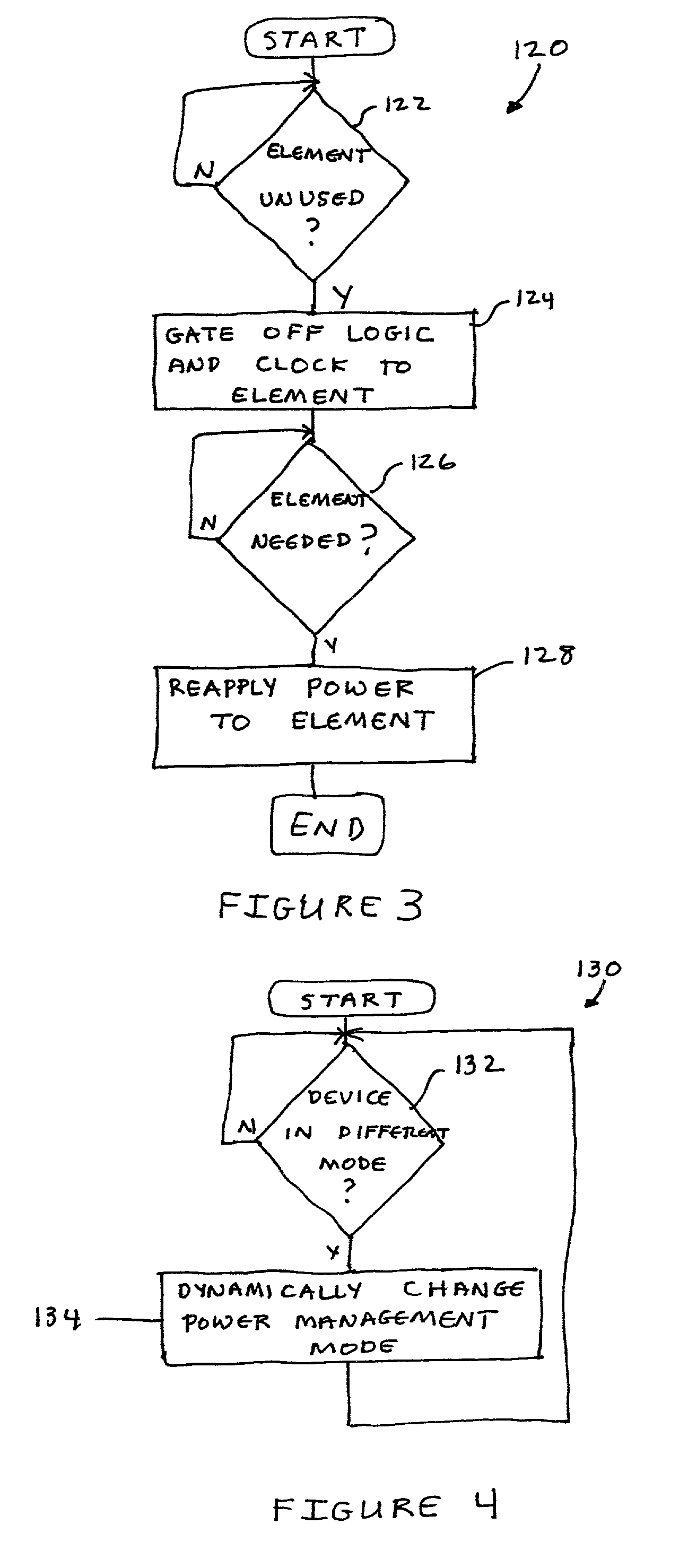

Dynamic power management of devices in computer system by selecting clock generator output based on a current state and programmable policies

InactiveUS6990594B2Maximize battery lifeMinimize powerEnergy efficient ICTCathode-ray tube indicatorsDynamic power managementElectrical battery

A power management system and method permit the total power consumption by a portable electronic device to be reduced so that the portable electronic device has a longer operating time on a limited power source, such as a battery. The system may also be used with devices that are powered by a more permanent source of power. The system may combine static power management techniques as well as dynamic power management techniques. The system may include a flexible clock generator.

Owner:NVIDIA CORP

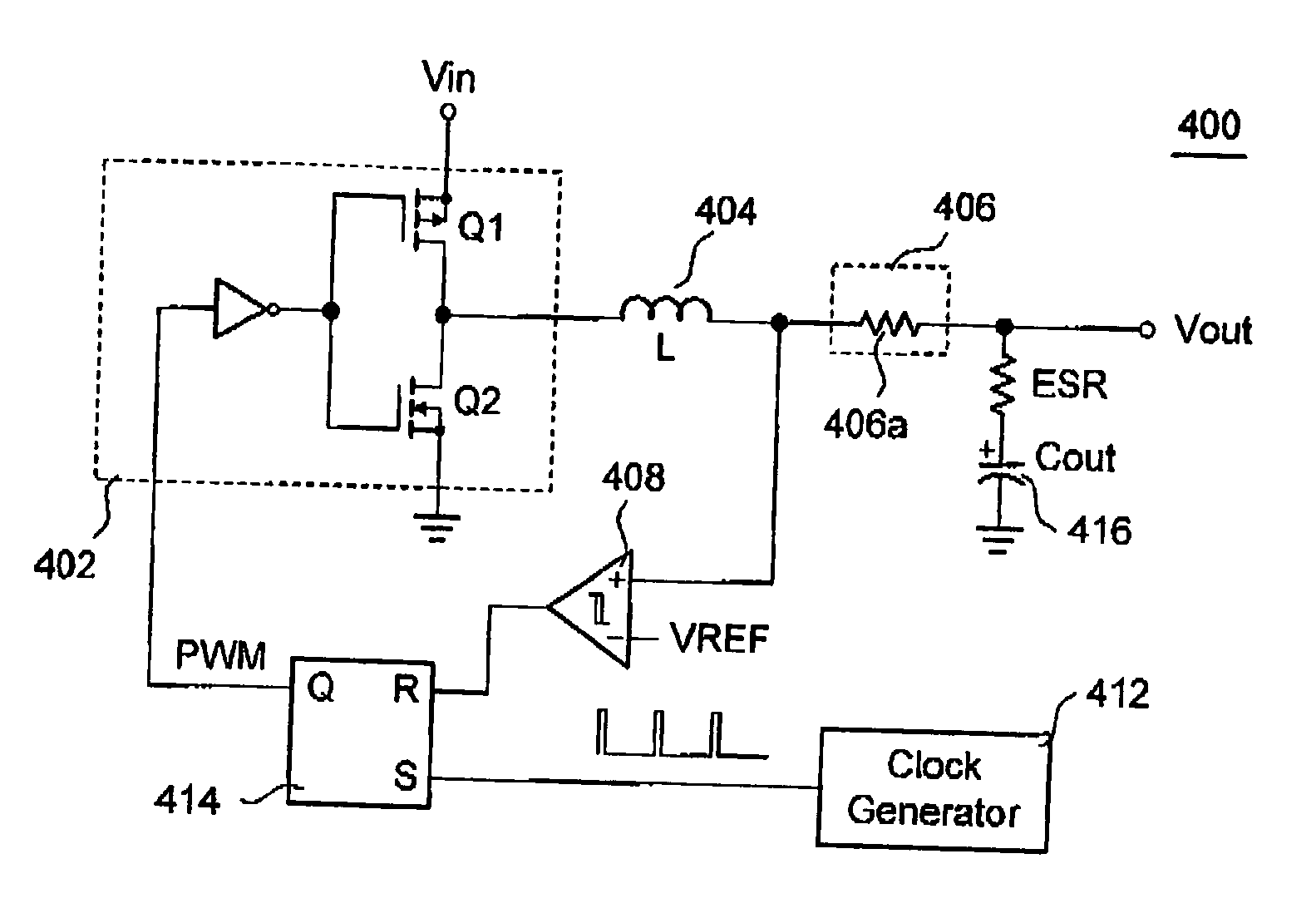

Direct mode pulse width modulation for DC to DC converters

InactiveUS20070063681A1Simple control circuitFast transient responseEfficient power electronics conversionDc-dc conversionCapacitanceEngineering

A DC to DC converter has an inverter, an inductor, a voltage sensor, a comparator, a clock generator, a driver and an output capacitor. The inverter converts an input voltage into a square-wave voltage. The inductor is electrically connected to an output of the inverter. The voltage sensor is electrically connected to the inductor and derives a sense voltage. The comparator compares the sense voltage and a reference voltage. The clock generator generates a reference clock pulse. The driver is triggered by the reference clock pulse and switches the inverter according to an output of the comparator. The output capacitor is electrically connected between the voltage sensor and the ground.

Owner:AMAZION ELECTRONICS

Switching power controller and system

ActiveUS8416596B2Conversion with intermediate conversion to dcDc-dc conversionPower controllerClock generator

Owner:GIANTEC SEMICON LTD

Harmonic suppression mixer and tuner

ActiveUS7519348B2Reduce leakageEnhanced inhibitory effectModulation transference balanced arrangementsTransmissionLow noiseHarmonic mitigation

A harmonic suppression mixer for down converting an RF signal to a complex I and Q baseband signal that uses a plurality of switching mixers each with a gain stage to produce a sinusoidal weighted sum of the mixer outputs. Odd harmonics output by each switching mixer is suppressed in the composite signal. A low skew local oscillator (LO) clock generator creates multiple LO phases and drives the mixers. The mixer can be used in low noise direct conversion RF tuners. The mixer is configurable by programming gain stage coefficient values to achieve a variable number of effective mixers used in combination. At low tuning frequencies, all available mixers are programmed with unique coefficients and driven by different LO clock phases to achieve maximum harmonic suppression. At high tuning frequencies, some mixers are paralleled and duplicate coefficients are programmed or mixers are disabled to reduce the number of effective mixers.

Owner:ENTROPIC COMM INC

Clock generator having a delay locked loop and duty cycle correction circuit in a parallel configuration

ActiveUS7227809B2Pulse automatic controlManipulation where pulse delivered at different timesDelay-locked loopClock generator

Owner:MICRON TECH INC

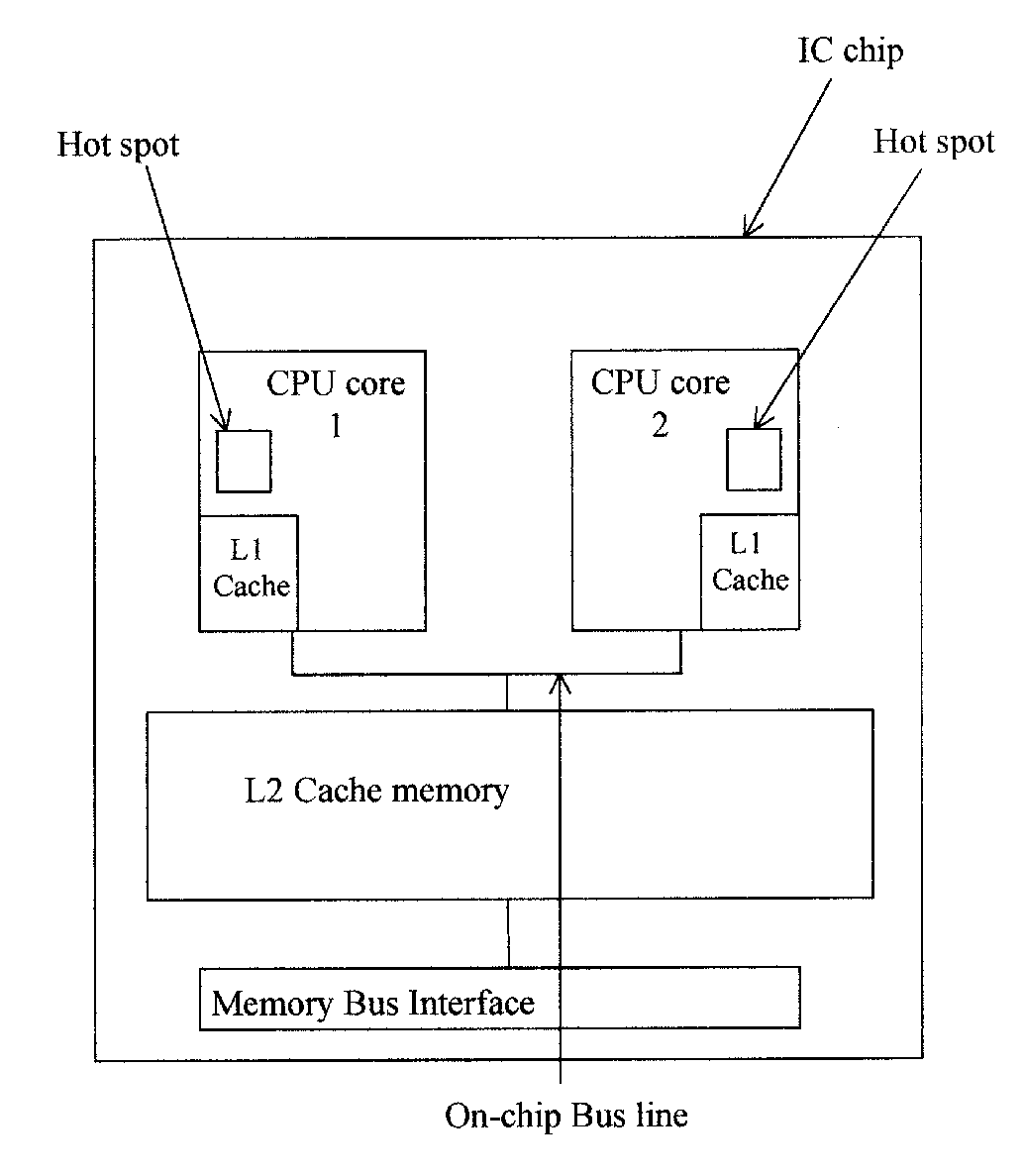

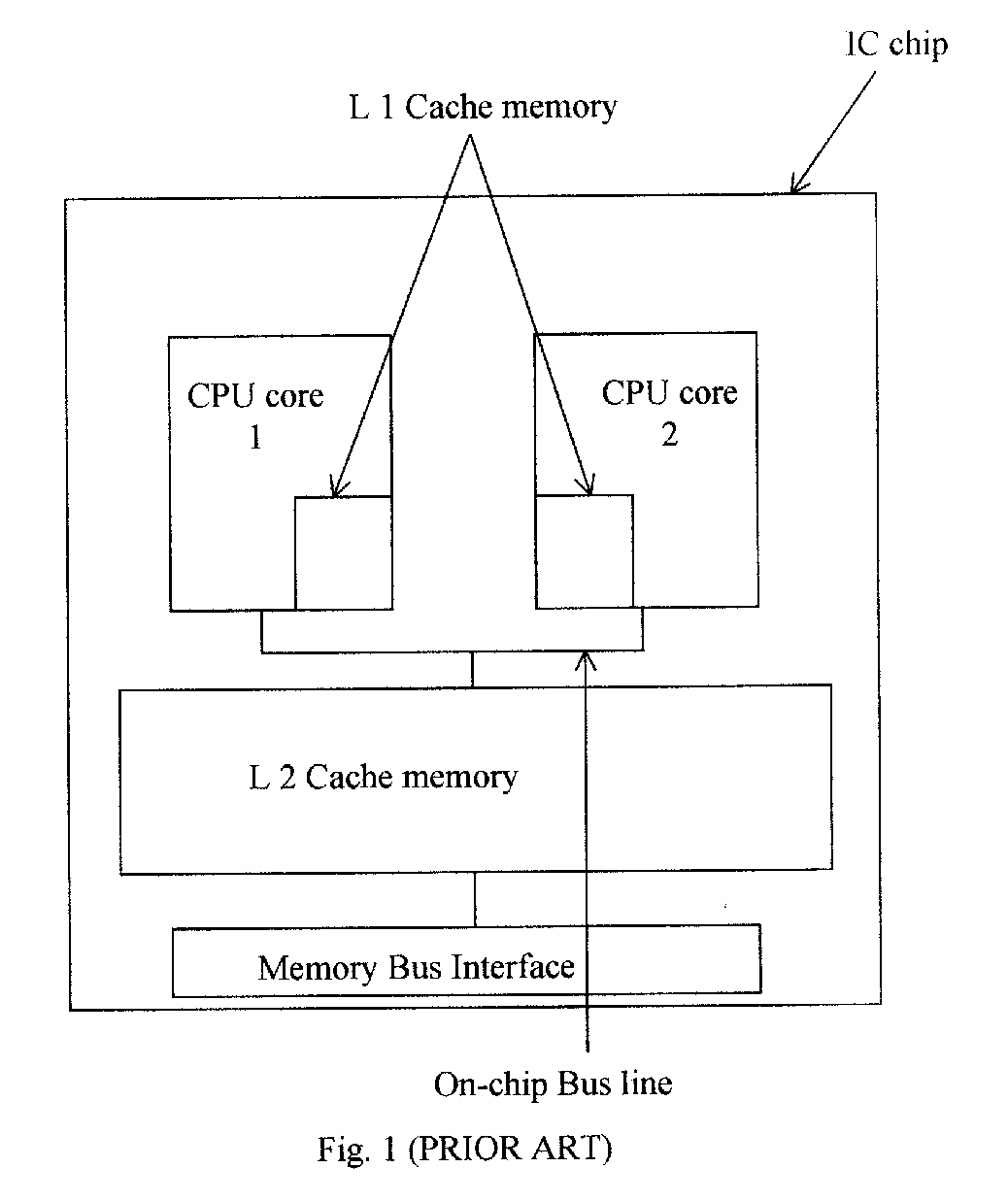

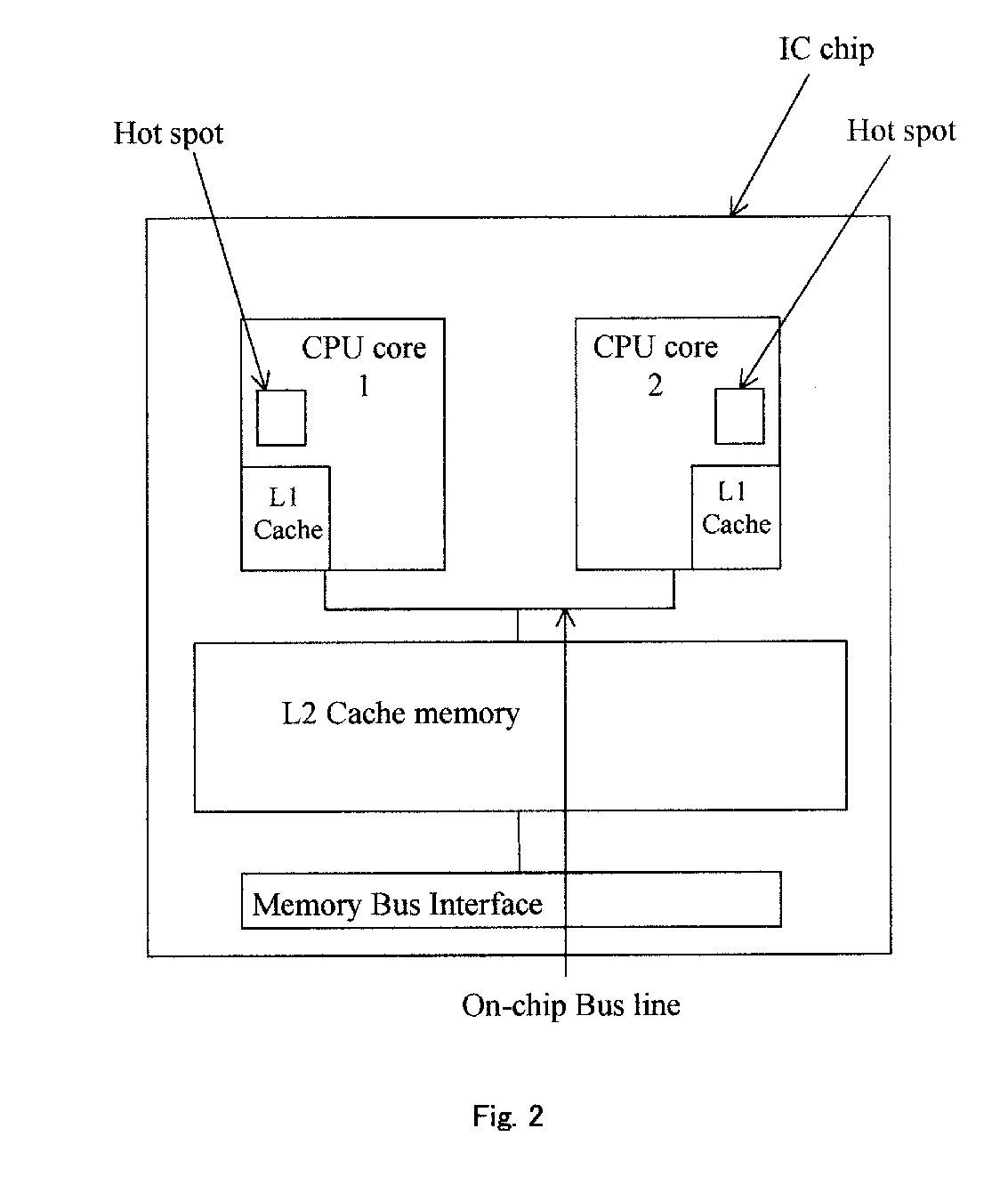

Chip layout for multiple CPU core microprocessor

InactiveUS20060171244A1Improve performanceEffective balanceEnergy efficient ICTDigital storageClock generatorEmbedded system

A microprocessor chip on a semiconducting substrate has at least two CPU cores that have hot spots on one side, a private cache memory for each CPU core that is located on the same side of said CPU core as the hot spot, a common cache memory that can be accessed by each CPU core, and an on-chip bus line connecting the CPU cores to the common cache memory. The CPU cores are located on each side of the on-chip bus line with their hot spots and their private cache memories positioned away from the on-chip bus line. Some of the CPU cores on the chip may be low power consumption CPU core and some of the CPU cores may be high speed CPU cores. The CPU cores may also be the same or different performance or purpose cores. A clock generator circuit may connect the CPU cores.

Owner:ANDO YOSHIYUKI

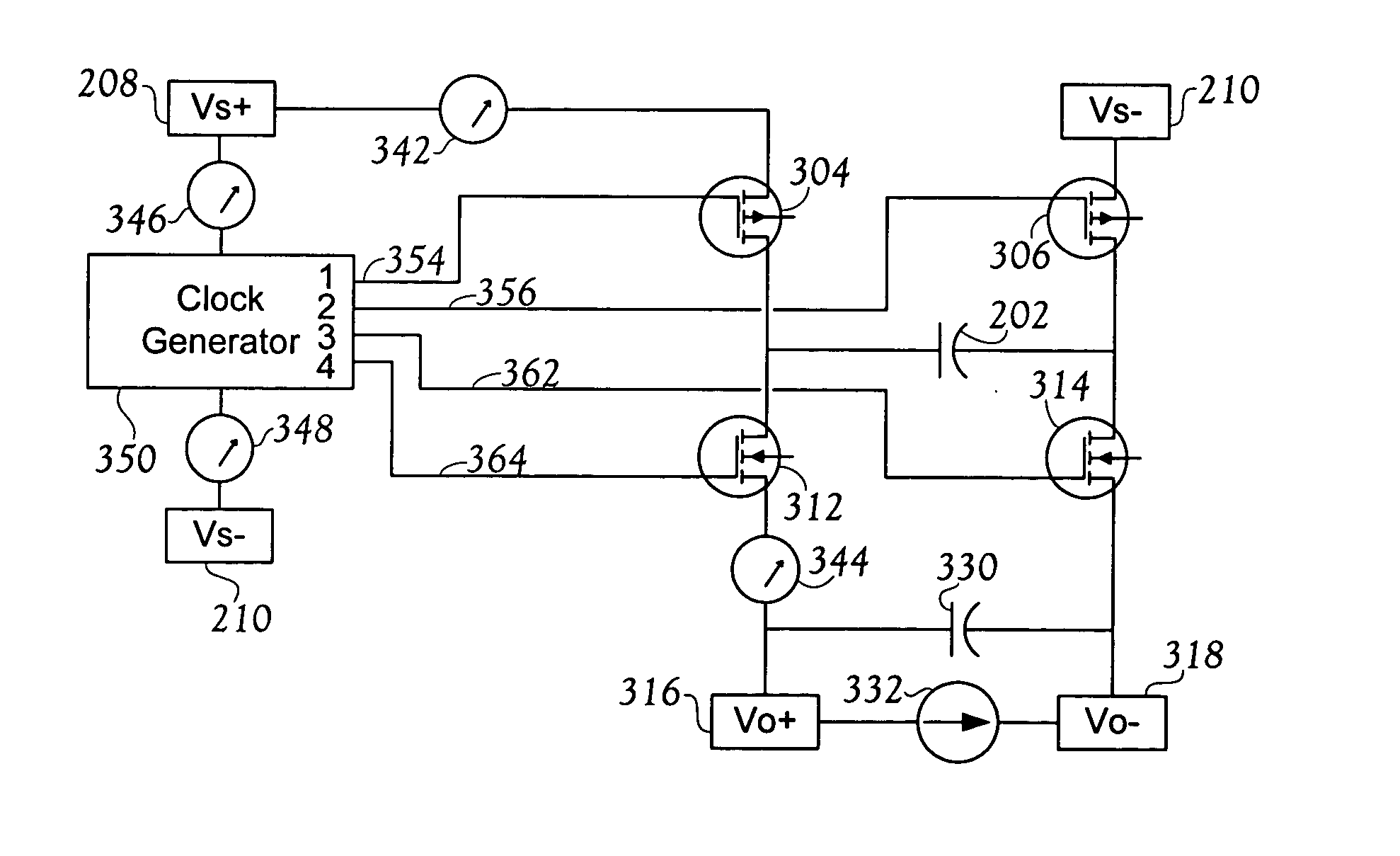

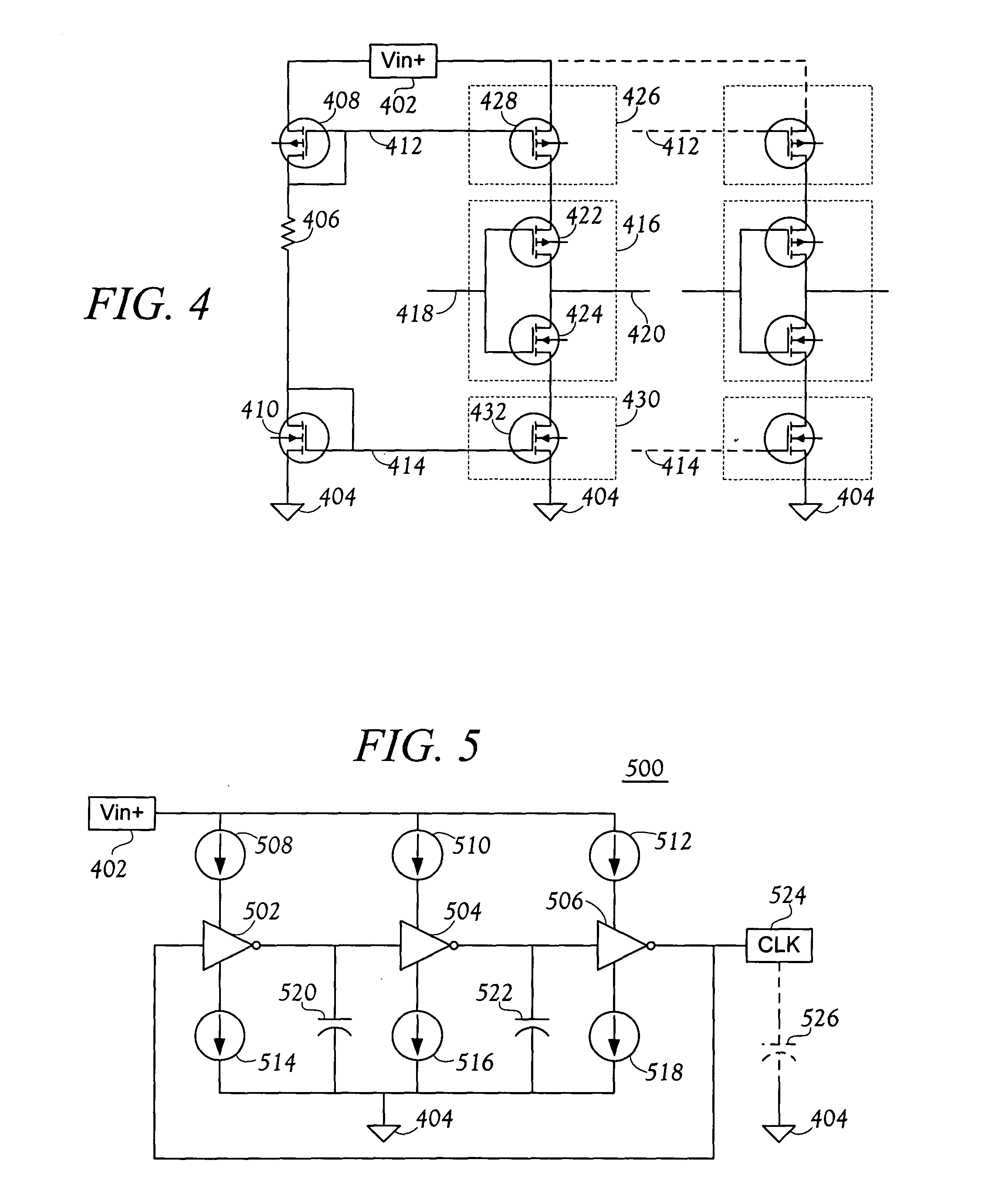

Low noise charge pump method and apparatus

ActiveUS20050052220A1Reduce noiseSimple designAc-dc conversionApparatus without intermediate ac conversionCapacitanceLow noise

A charge pump method and apparatus is described having various aspects. Noise injection from a charge pump to other circuits may be reduced by limiting both positive and negative clock transition rates, as well as by limiting drive currents within clock generator driver circuits, and also by increasing a control node AC impedance of certain transfer capacitor coupling switches. A single-phase clock may be used to control as many as all active switches within a charge pump, and capacitive coupling may simplify biasing and timing for clock signals controlling transfer capacitor coupling switches. Any combination of such aspects of the method or apparatus may be employed to quiet and / or simplify charge pump designs over a wide range of charge pump architectures.

Owner:PSEMI CORP

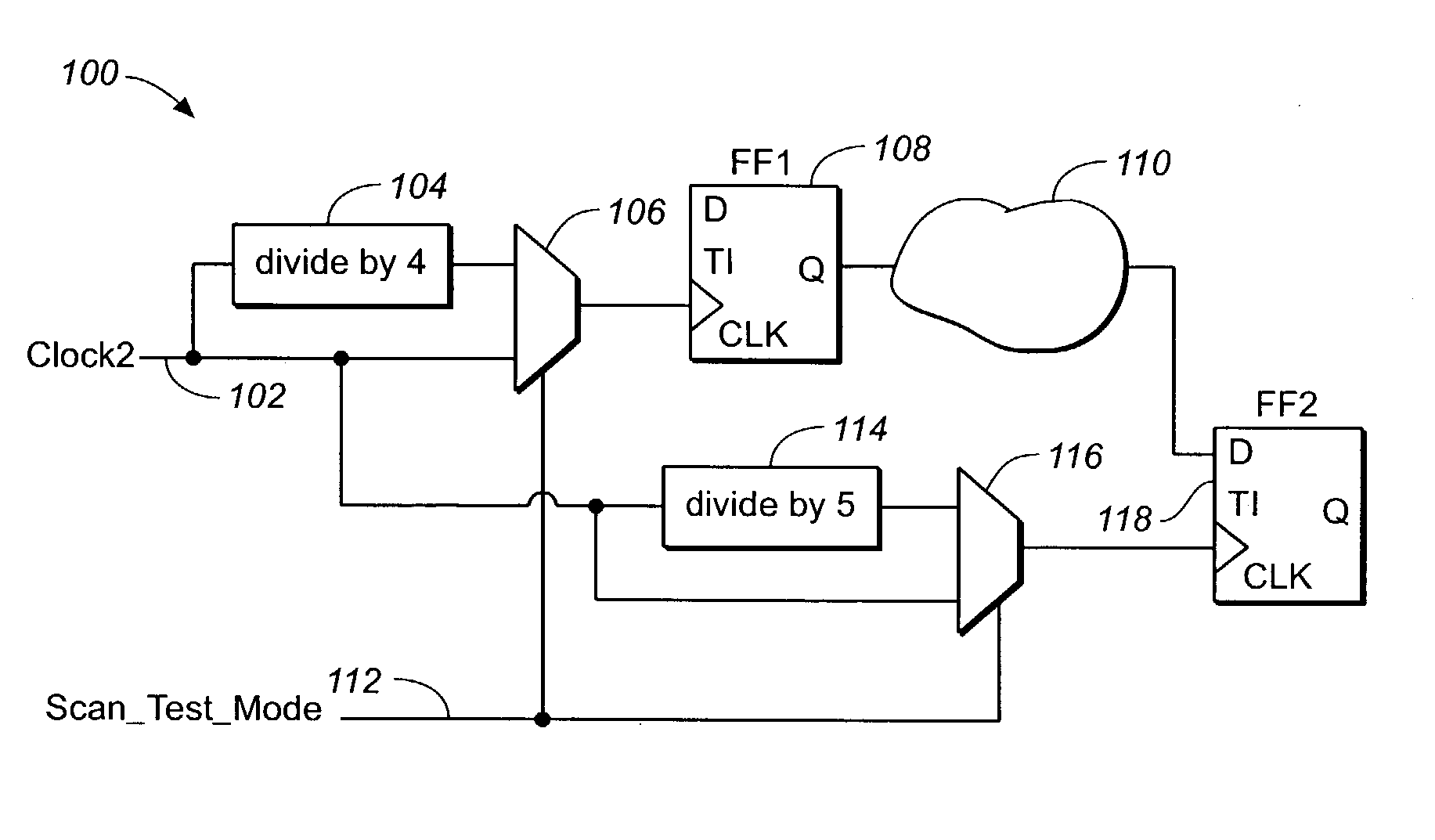

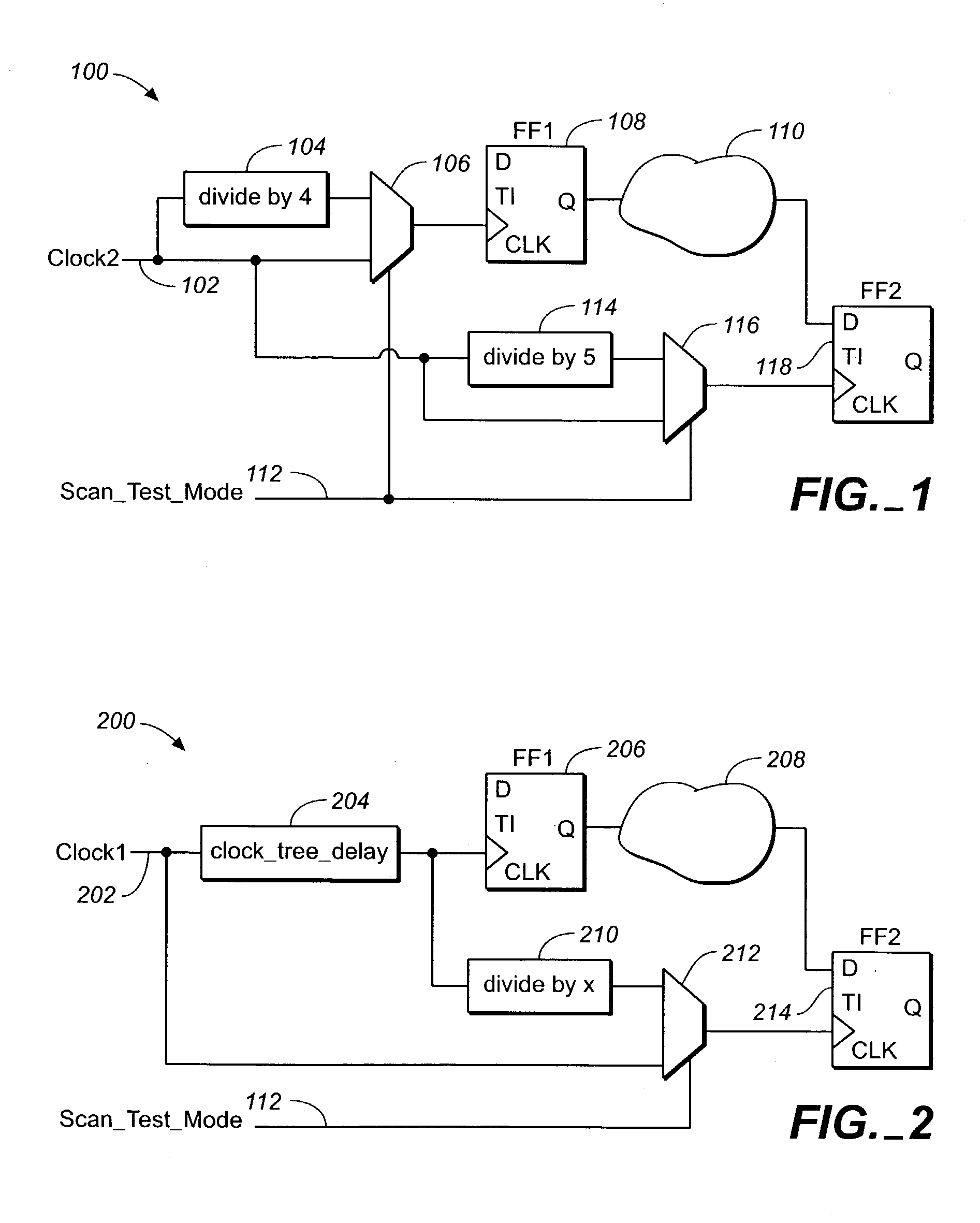

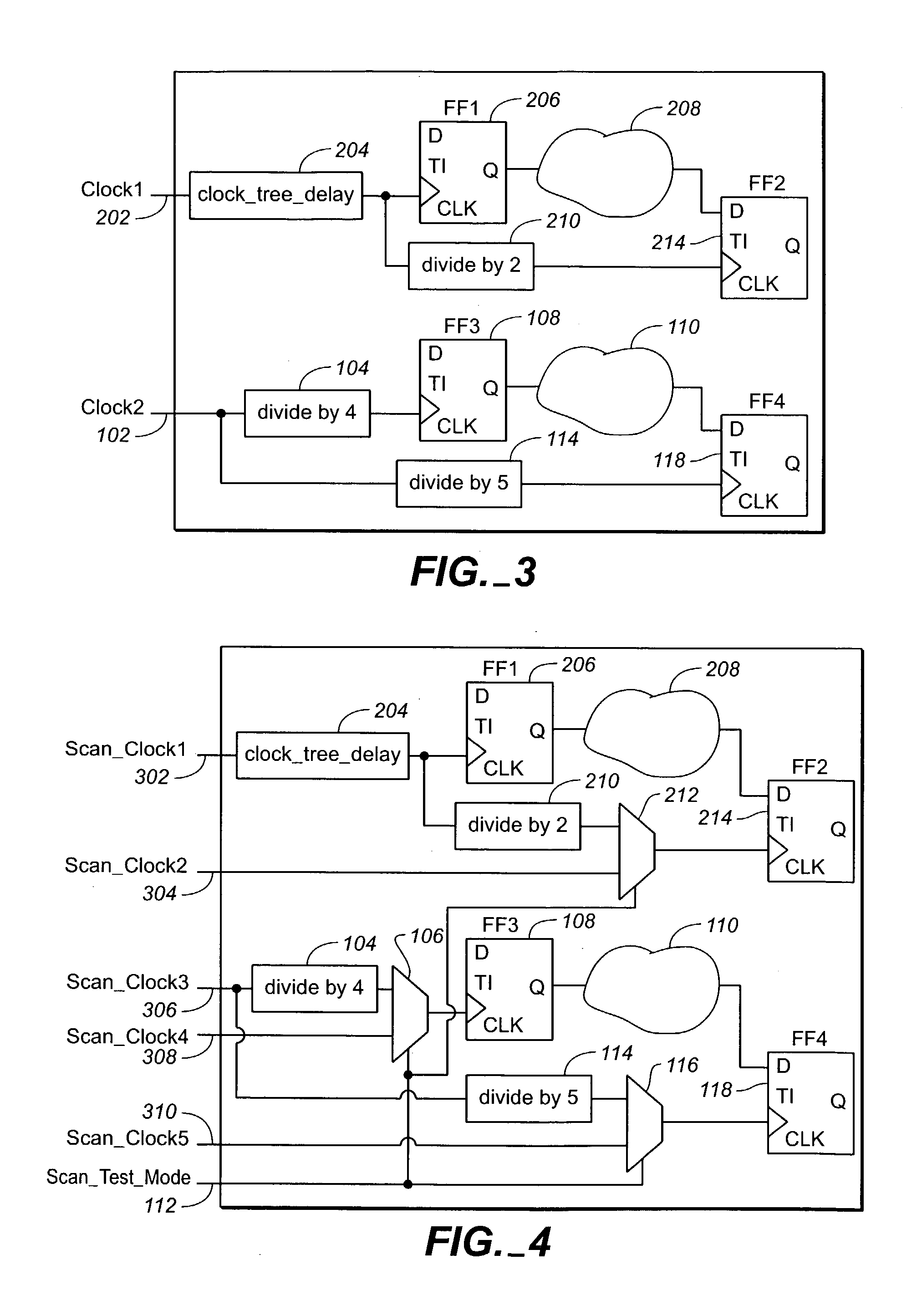

On-chip scan clock generator for asic testing

A a clock signal input for receiving a clock signal, a scan shift mode signal input for receiving a scan shift mode signal, and a sequence controller coupled to the clock signal input for gating a selected number of clock signal pulses at a time to generate a sequence of nonconcurrent scan clock signals at separate outputs respectively in response to a first state of the scan shift mode signal.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

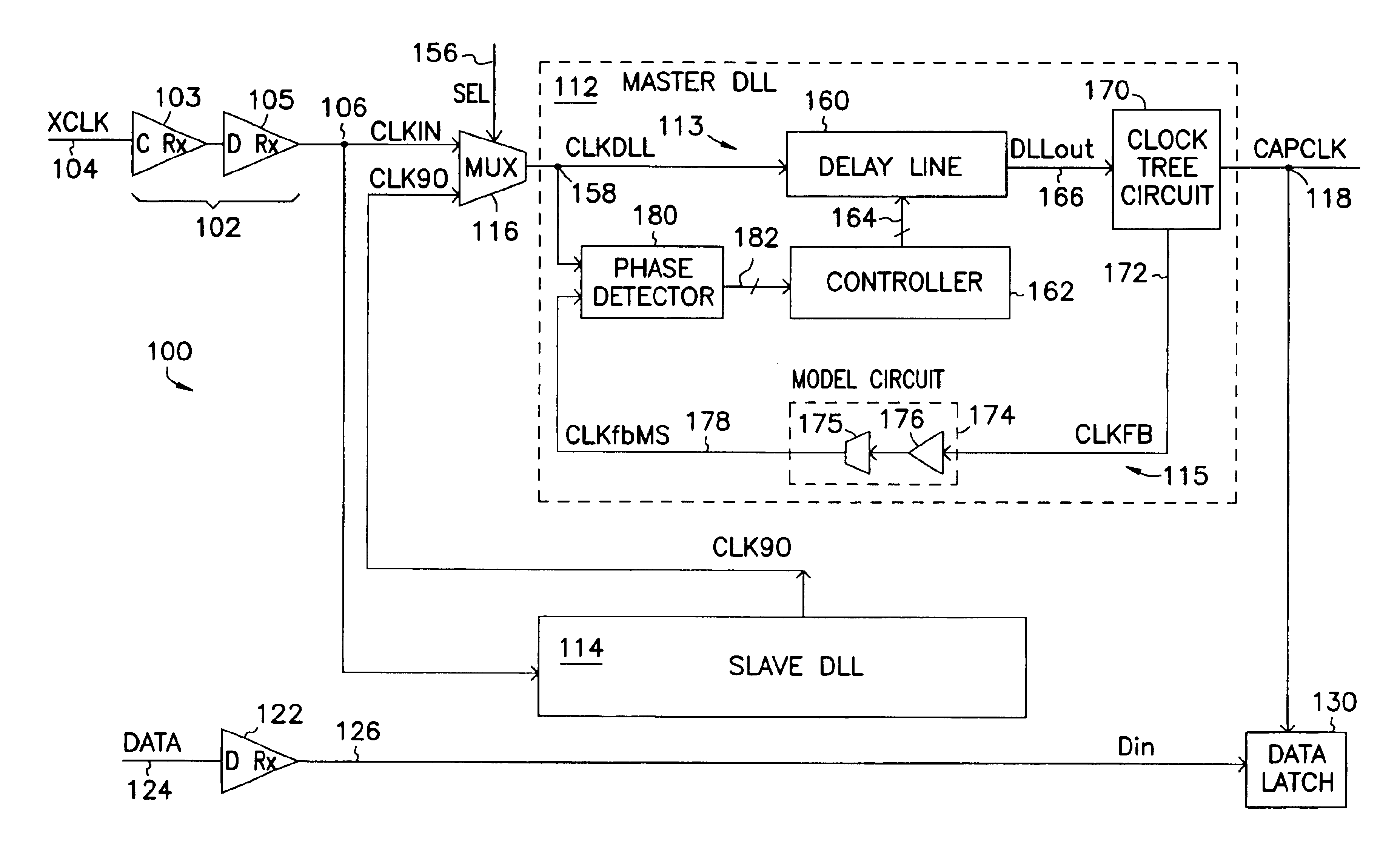

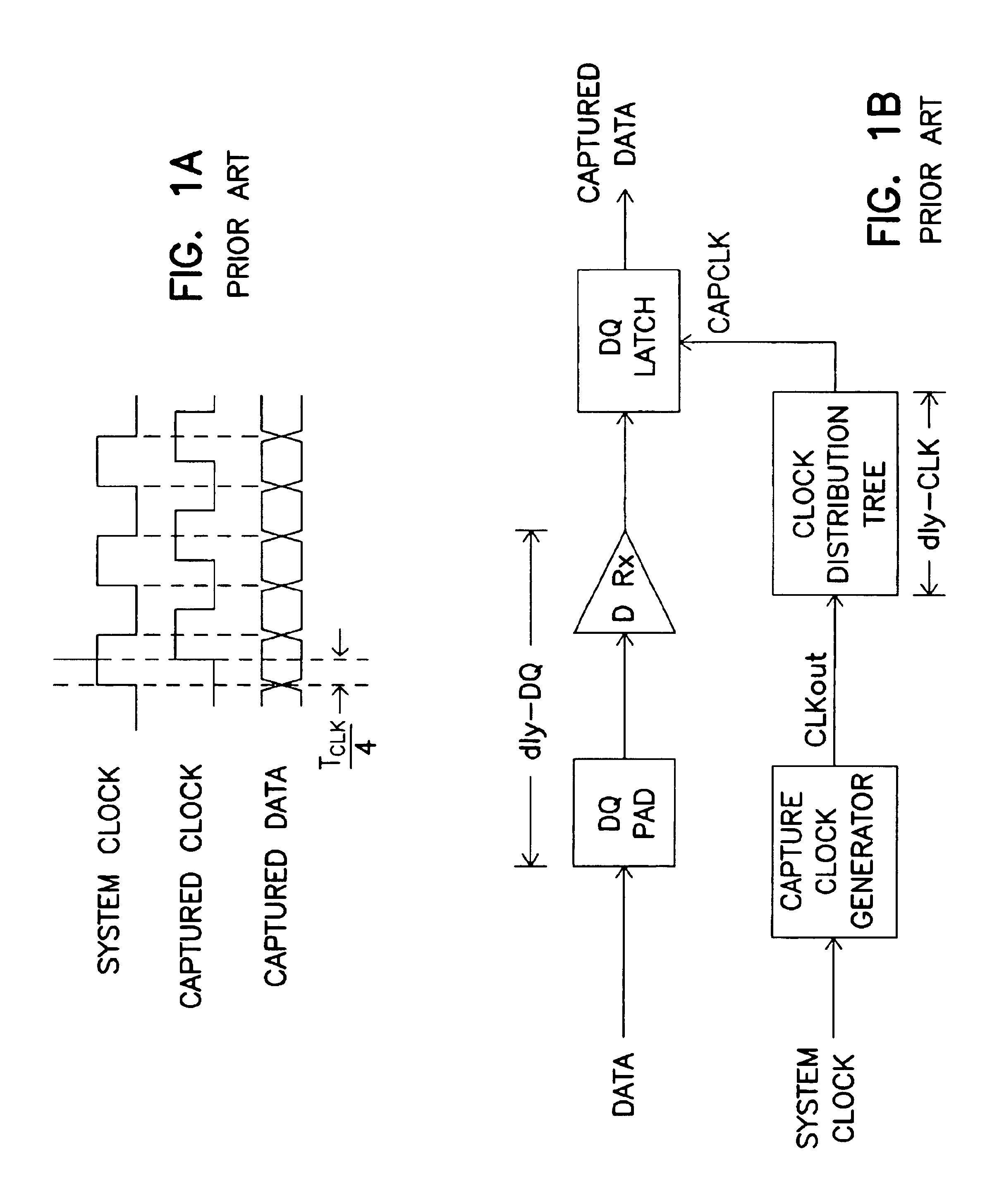

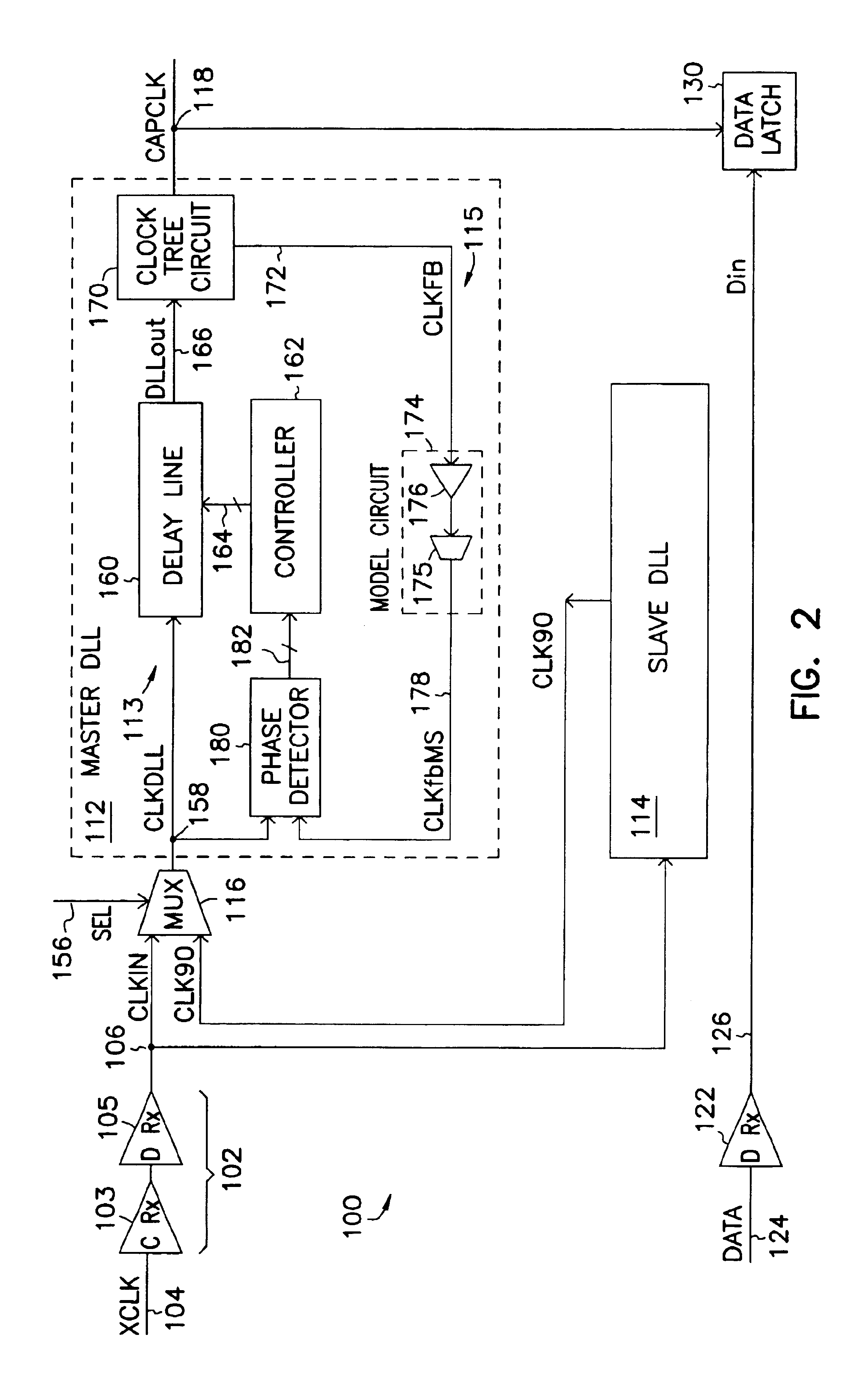

Capture clock generator using master and slave delay locked loops

A clock generator comprising a master delay locked loop (DLL) and a slave DLL to capture a data signal. The slave DLL generates a slave output signal based on a clock signal. The master DLL receives the slave output signal and compensates variations in delays of the data and clock signals to generate a capture clock signal. When the master and slave DLLs are locked, the capture clock signal is center aligned with the data signal.

Owner:ROUND ROCK RES LLC

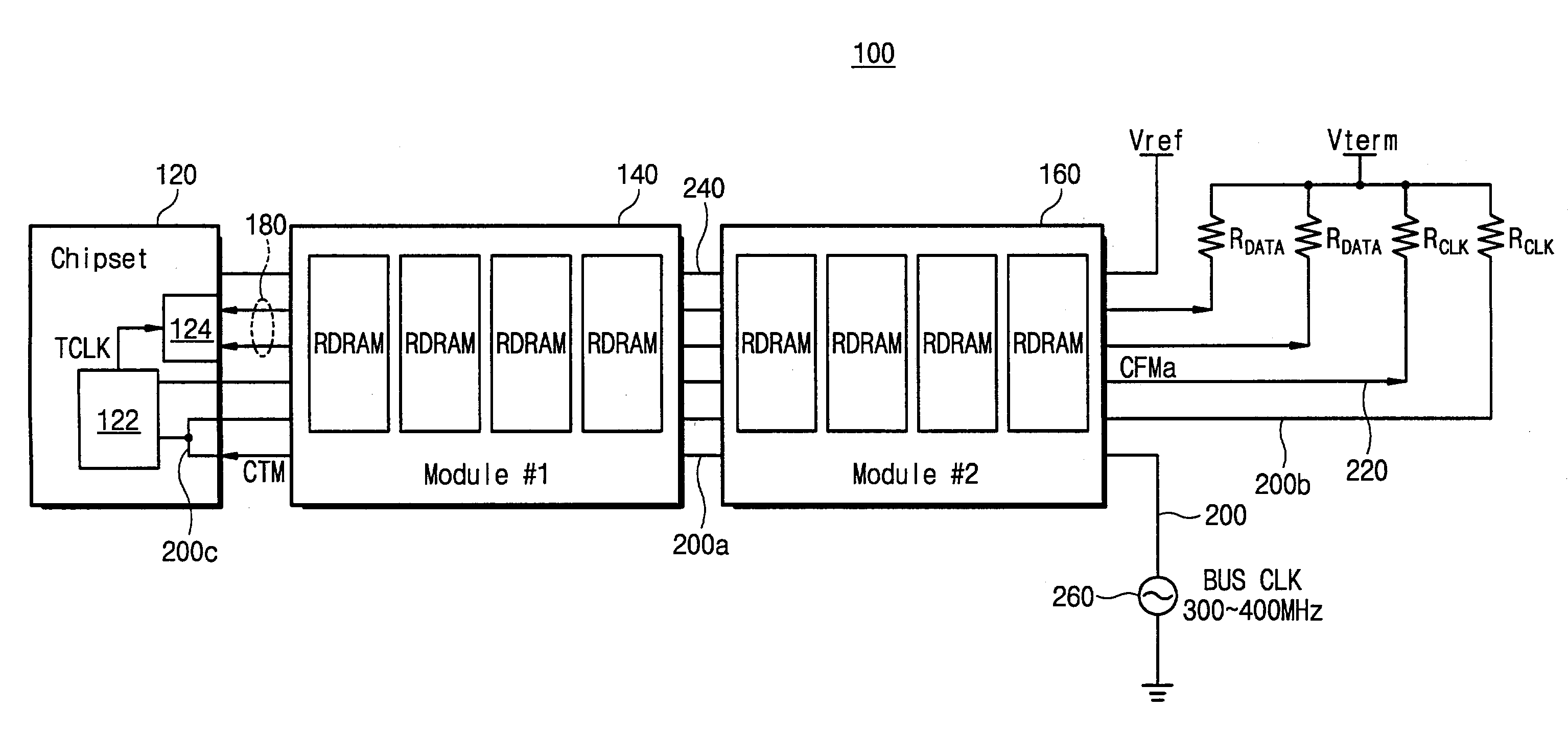

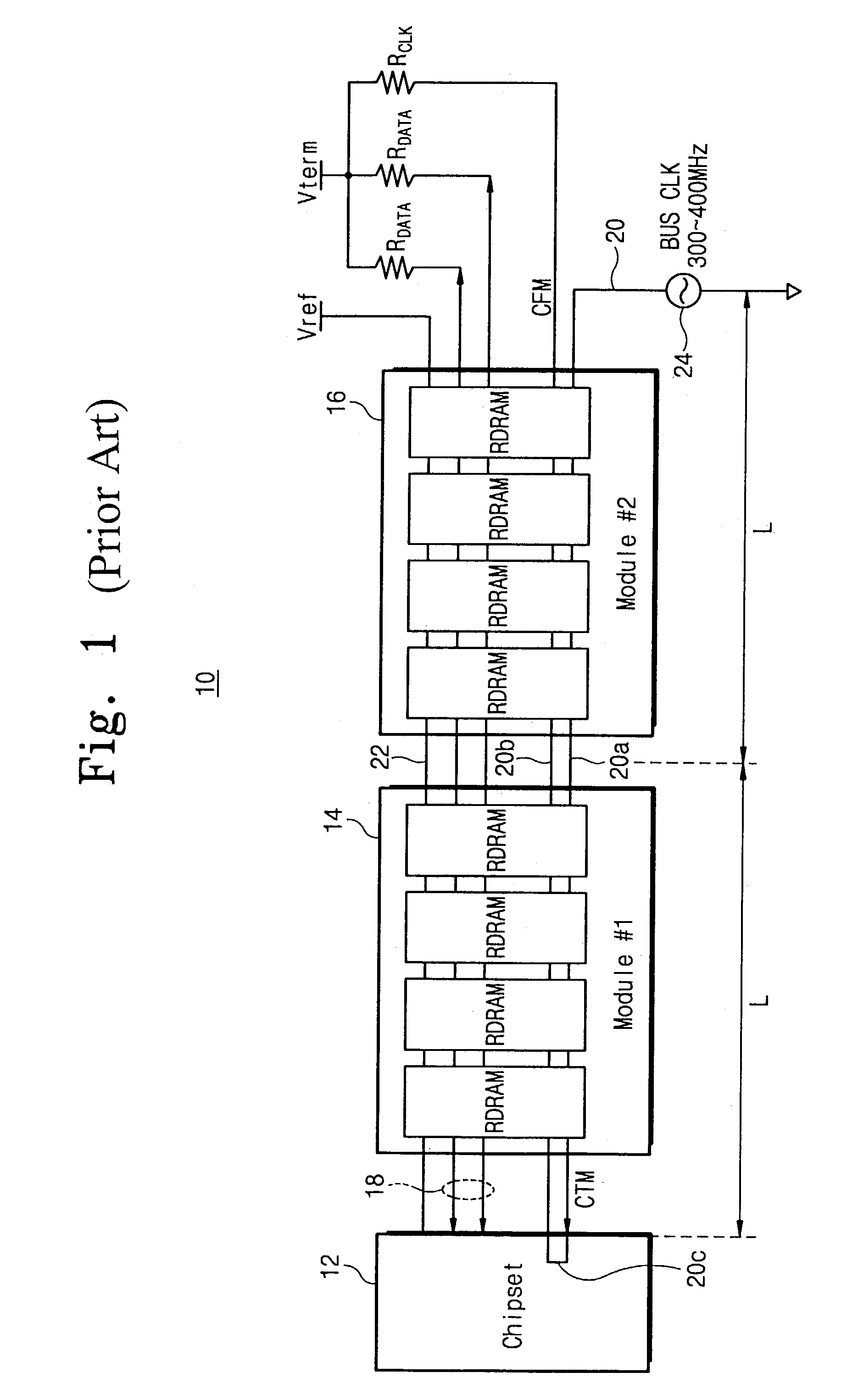

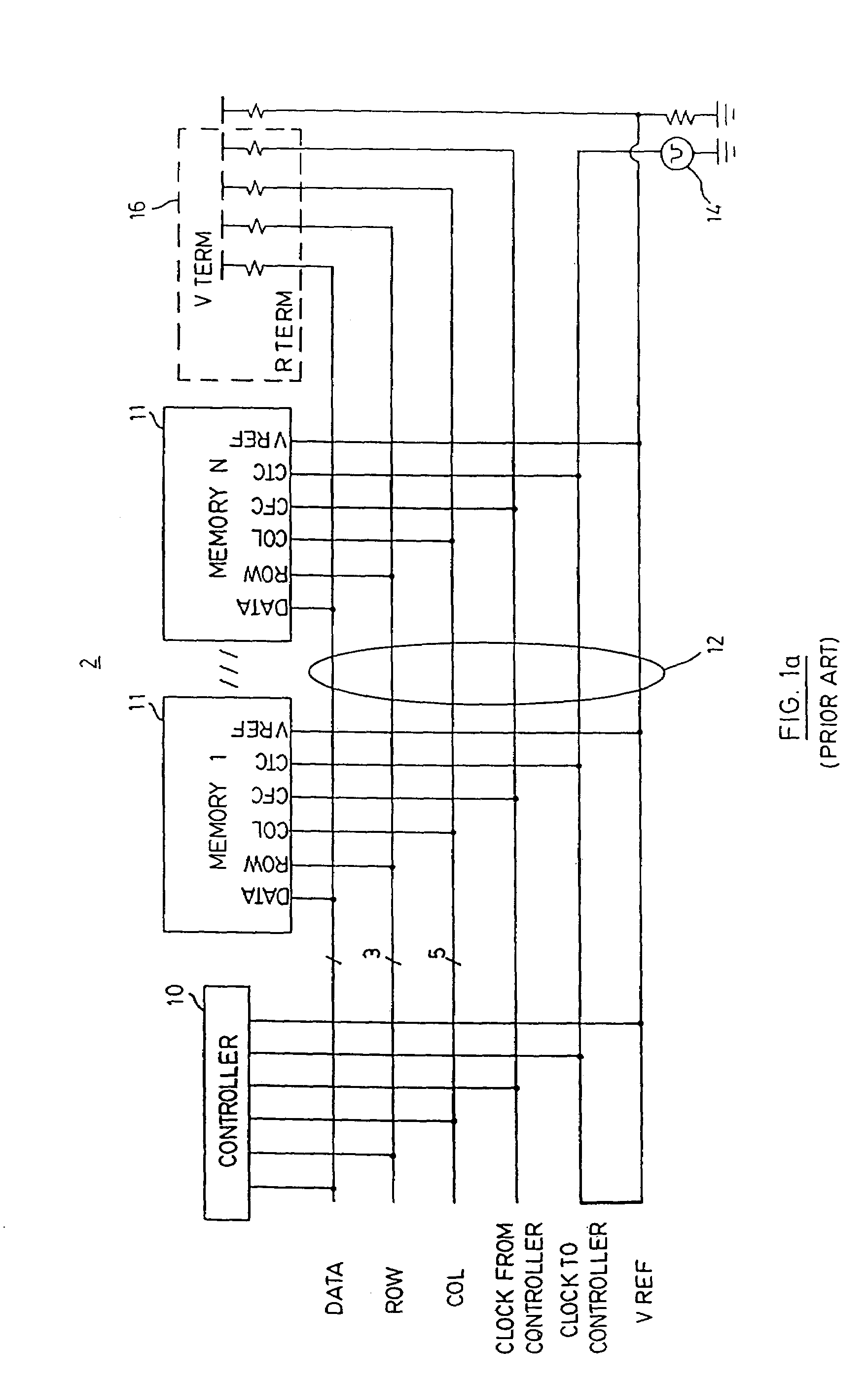

Information processing system has clock lines which are electrically isolated from another clock line electrically connected to clock buffer and termination voltage

ActiveUS7103792B2Prevents undesirable discrepancy of operational timingReduce deteriorationError detection/correctionData resettingInformation processingElectricity

A system includes modules, a clock generator that generates a first clock signal that is applied to the modules, and a chipset that controls the modules, the chipset having a clock buffer that generates a second clock signal. The system includes a first clock line that transfer the first clock signal to the clock buffer, the first clock line connected between the clock generator and a first termination circuit. The system includes a second clock line that transfer the second clock signal to the modules, the second clock line electrically isolated from the first clock line, the second clock line connected between the clock buffer and a second termination circuit.

Owner:SAMSUNG ELECTRONICS CO LTD

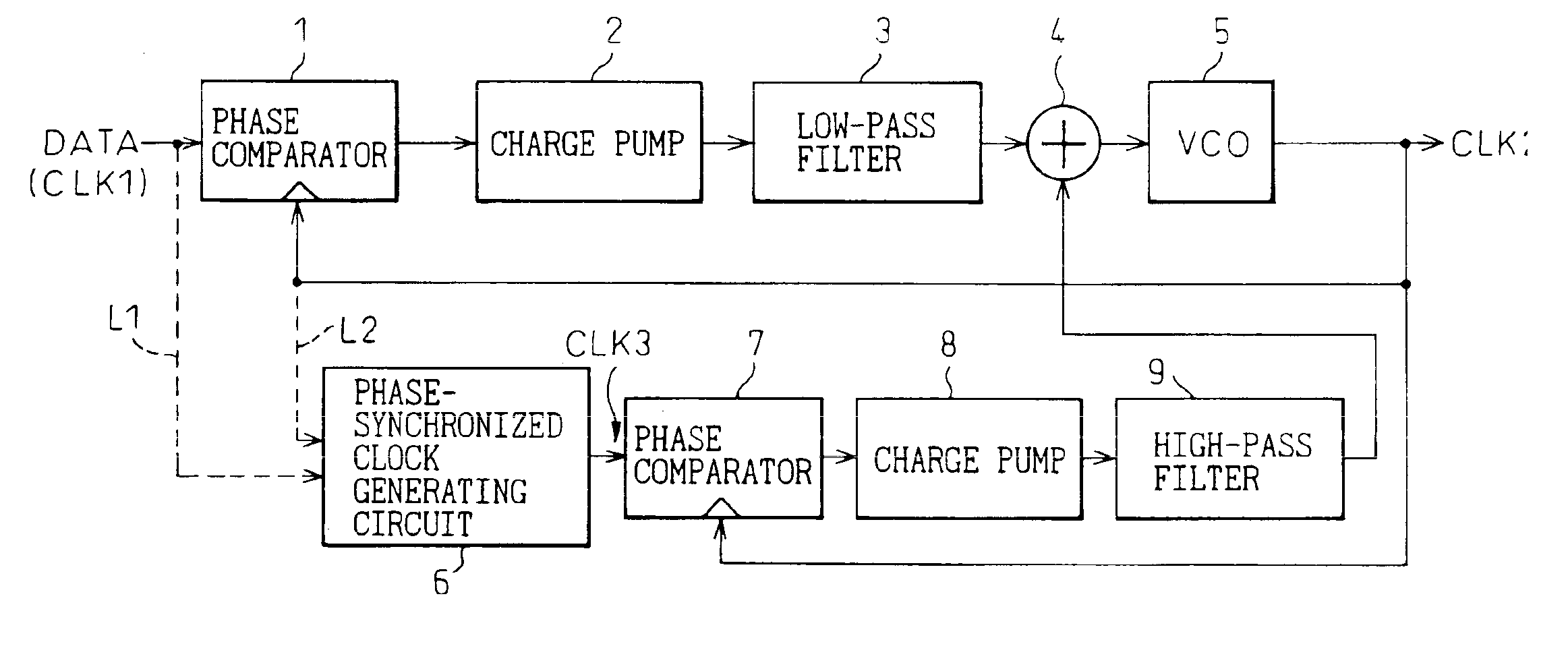

Clock generator for generating accurate and low-jitter clock

ActiveUS6900676B1Accurate and low jitterPulse automatic controlGenerating/distributing signalsControl signalPhase difference

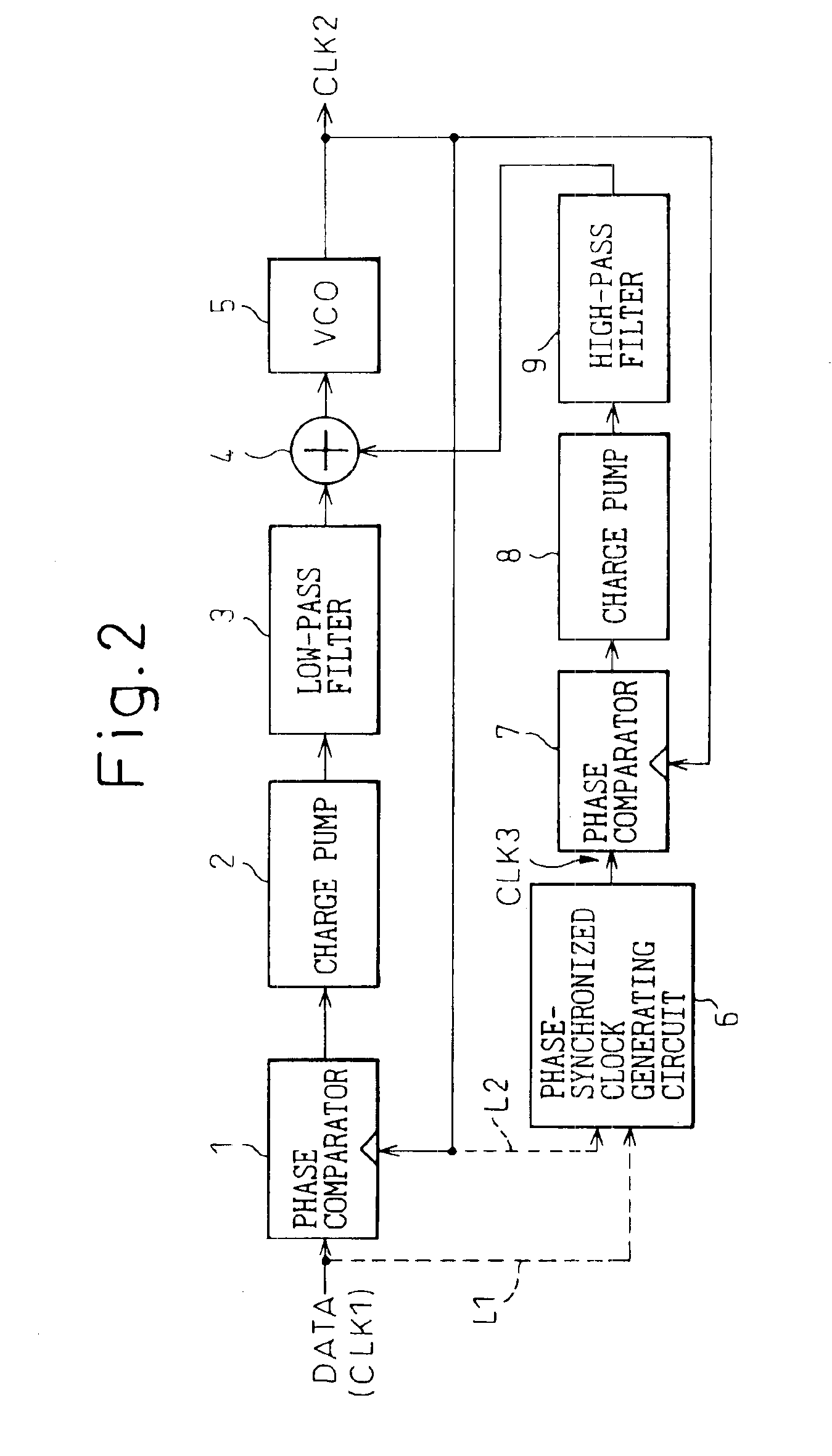

A clock generator has a clock generating circuit, a phase difference detection circuit, and a control signal generating circuit. The clock generating circuit has a function for varying a clock phase in accordance with a control signal, the phase difference detection circuit compars the clock phase output from the clock generating circuit with a phase of a reference waveform, and detecting a phase difference therebetween, and the control signal generating circuit generates a control signal for controlling the clock phase of the clock generating circuit, based on phase difference information obtained from the phase difference detection circuit. The phase difference detection circuit has a plurality of phase detection units, at least one of the plurality of phase detection units carries out a direct phase detection in which a phase of the clock is directly compared with the phase of the reference waveform, and at least the other one of the plurality of phase detection units carries out an indirect phase detection using a phase-synchronized waveform generating circuit generating a waveform synchronized in phase with the reference waveform or an output of the clock generating circuit and a phase information extracting circuit extracting phase information from the phase-synchronized waveform.

Owner:FUJITSU LTD

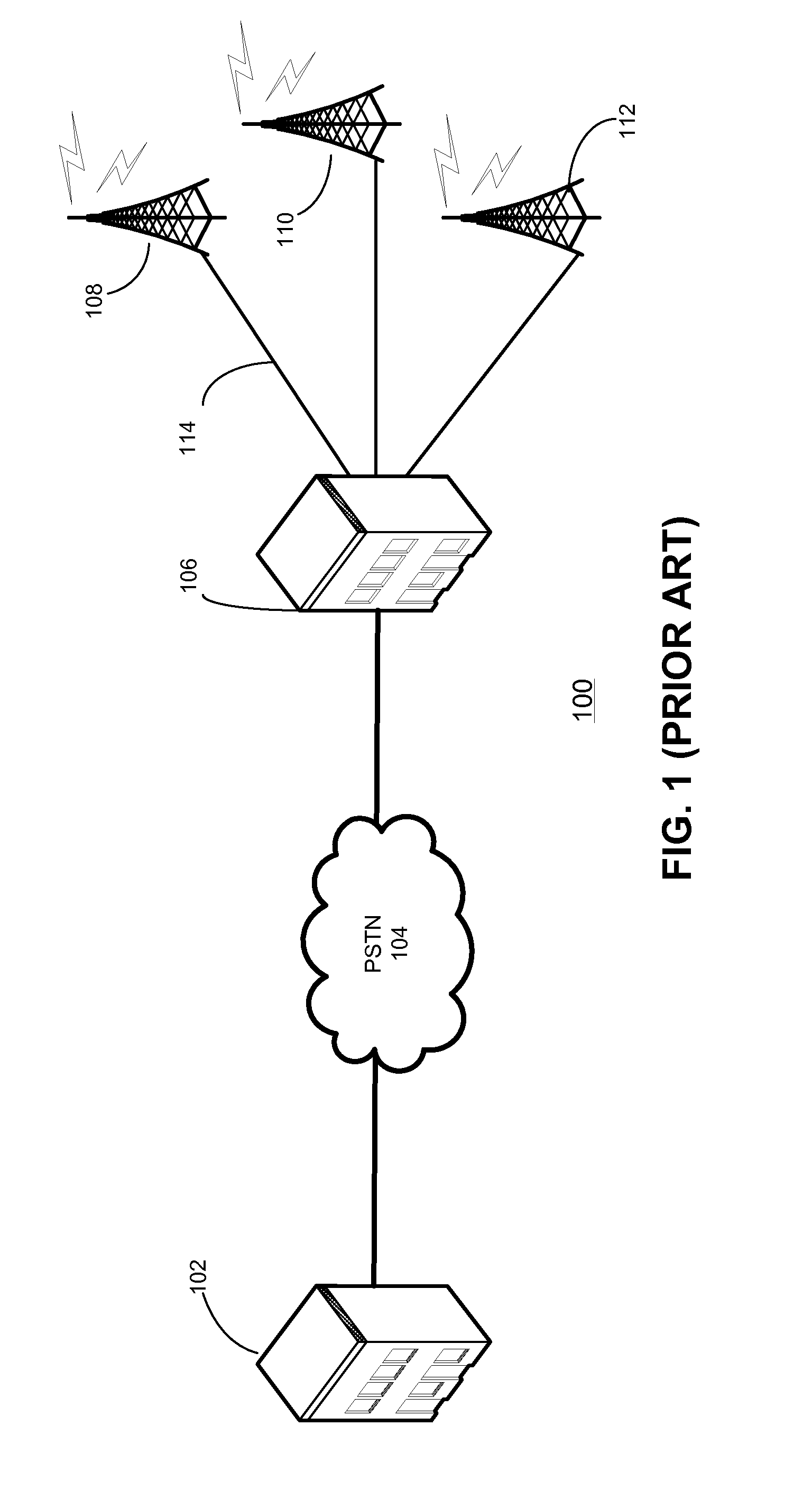

Network distributed remultiplexer for video program bearing transport streams

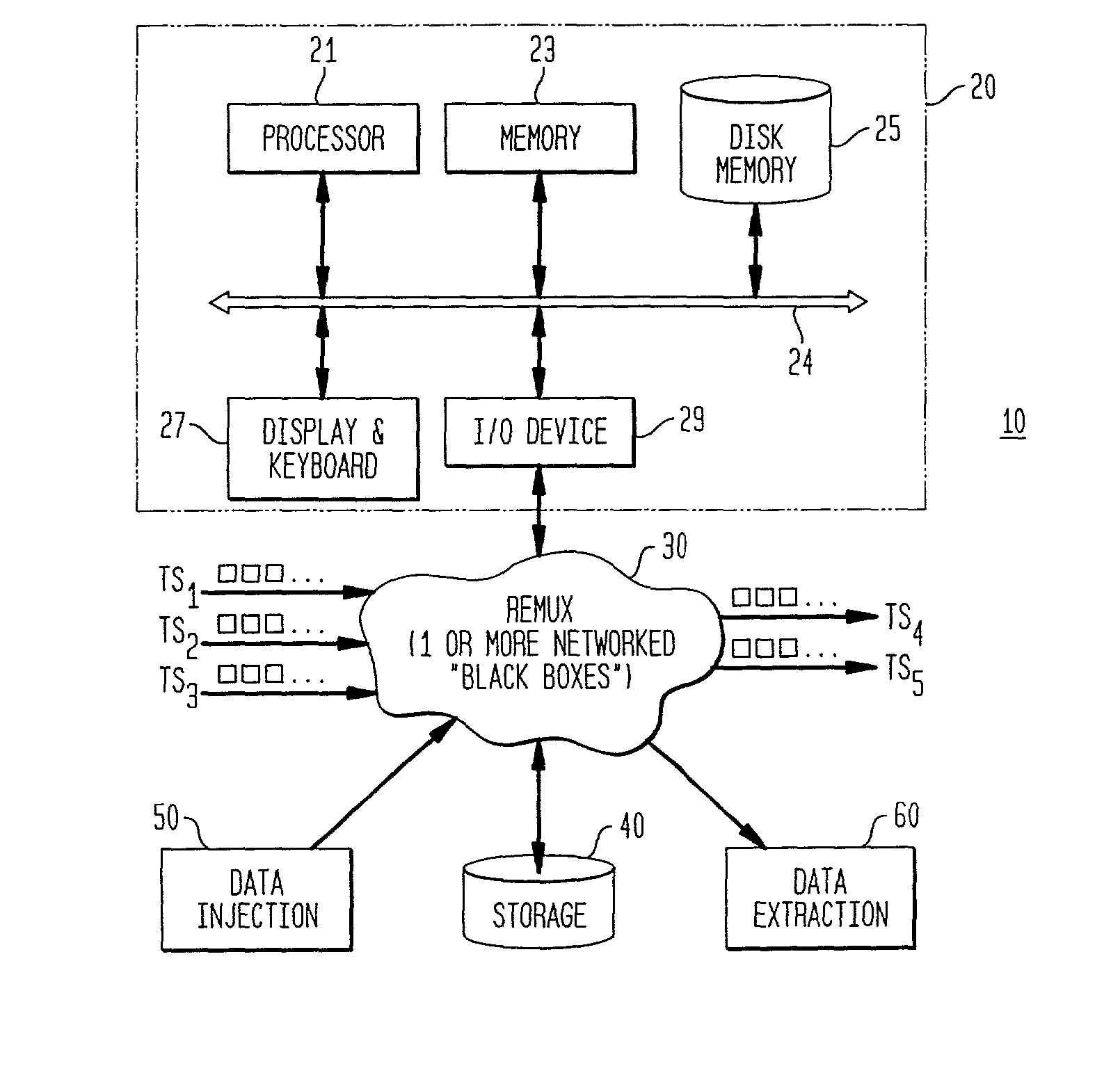

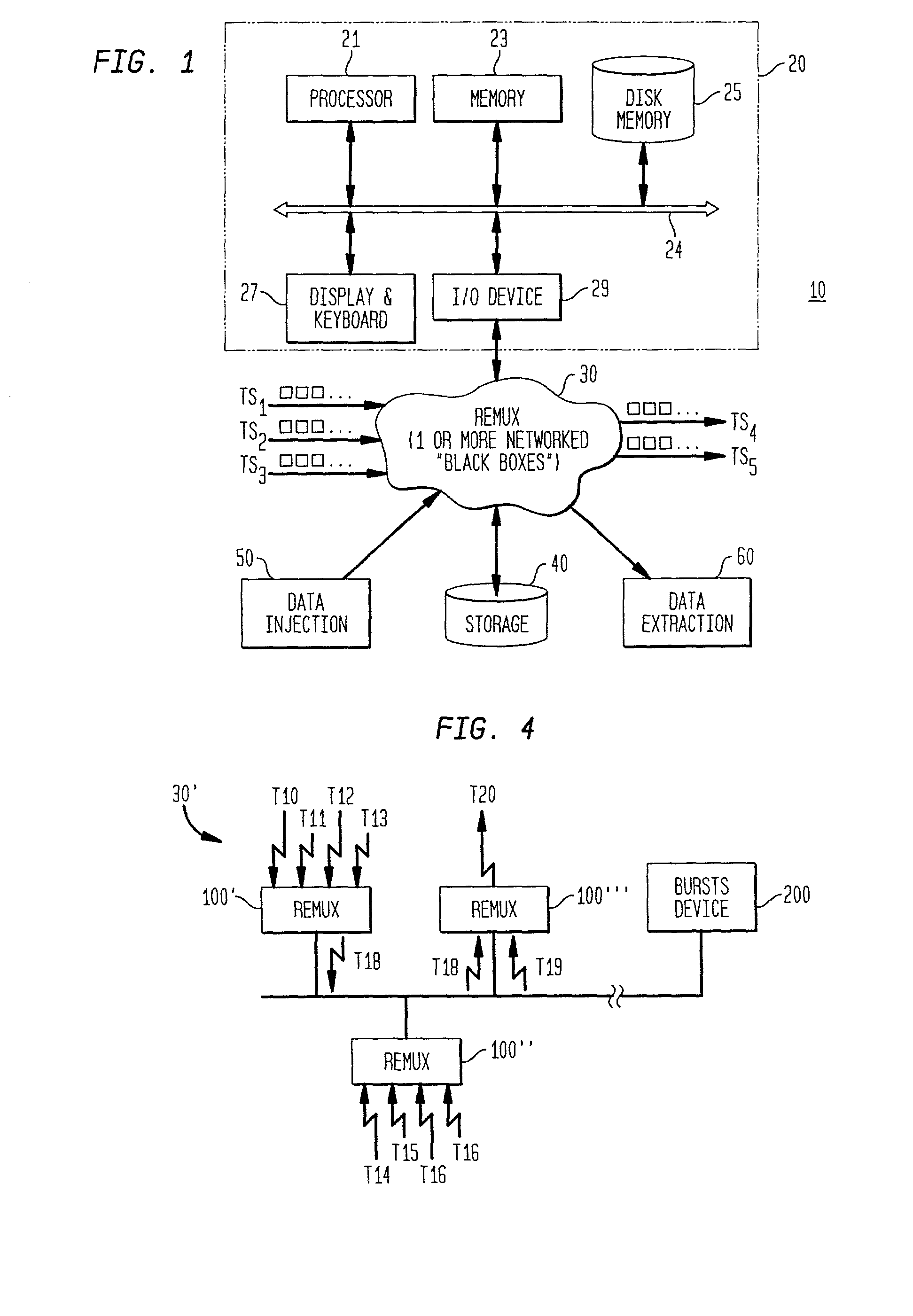

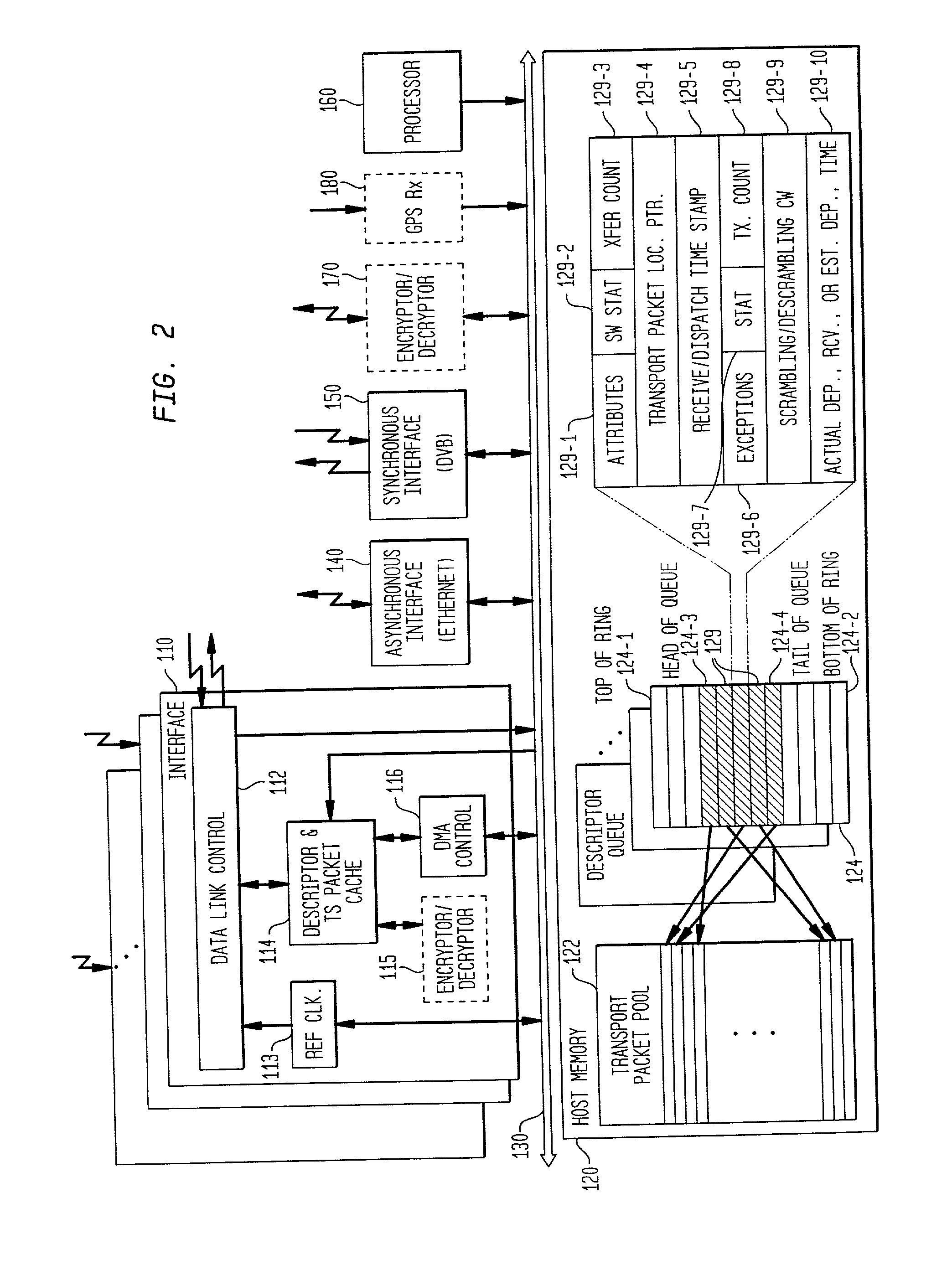

InactiveUS20020126711A1Flexible processIncrease flexibilityMultiplex system selection arrangementsTime-division multiplexProgram clock referenceMultiplexing

A method and system are provided for remultiplexing program bearing data. The remultiplexing method and system are applicable to MPEG-2 compliant transport streams carrying video programs. A descriptor based system is used for scheduling the timely output of transport packets wherein each descriptor records a dispatch time as well as a receipt time for each transport packet. The receipt time is used for estimating program clock reference adjustments, but final program clock reference adjustment is performed in hardware in relation to the precise output timing of each transport packets. A descriptor and transport packet caching technique is used for decoupling the synchronous receipt and transmission of transport packets from any asynchronous processing performed thereon. The descriptors can also be used for managing scrambling and descrambling control words (encryption and decryption keys). Remultiplexing functions may be distributed across a network. The remultiplexer can furthermore optimize the bandwidth of transport streams by replacing null transport packets with transport packet data to be inserted into the output transport stream. Program data transmitted via asynchronous communication links is re-timed and assistance is provided for outputting program data on such asynchronous communication links to reduce a variation in end-to-end delay incurred by the program data. Remultiplexing and program specific information can be searnlessly dynamically varied without stopping, or introducing a discontinuity in, the flow of outputted transport packets. A technique is also provided for locking multiple internal reference clock generators.

Owner:VENTURE LENDING & LEASING IV

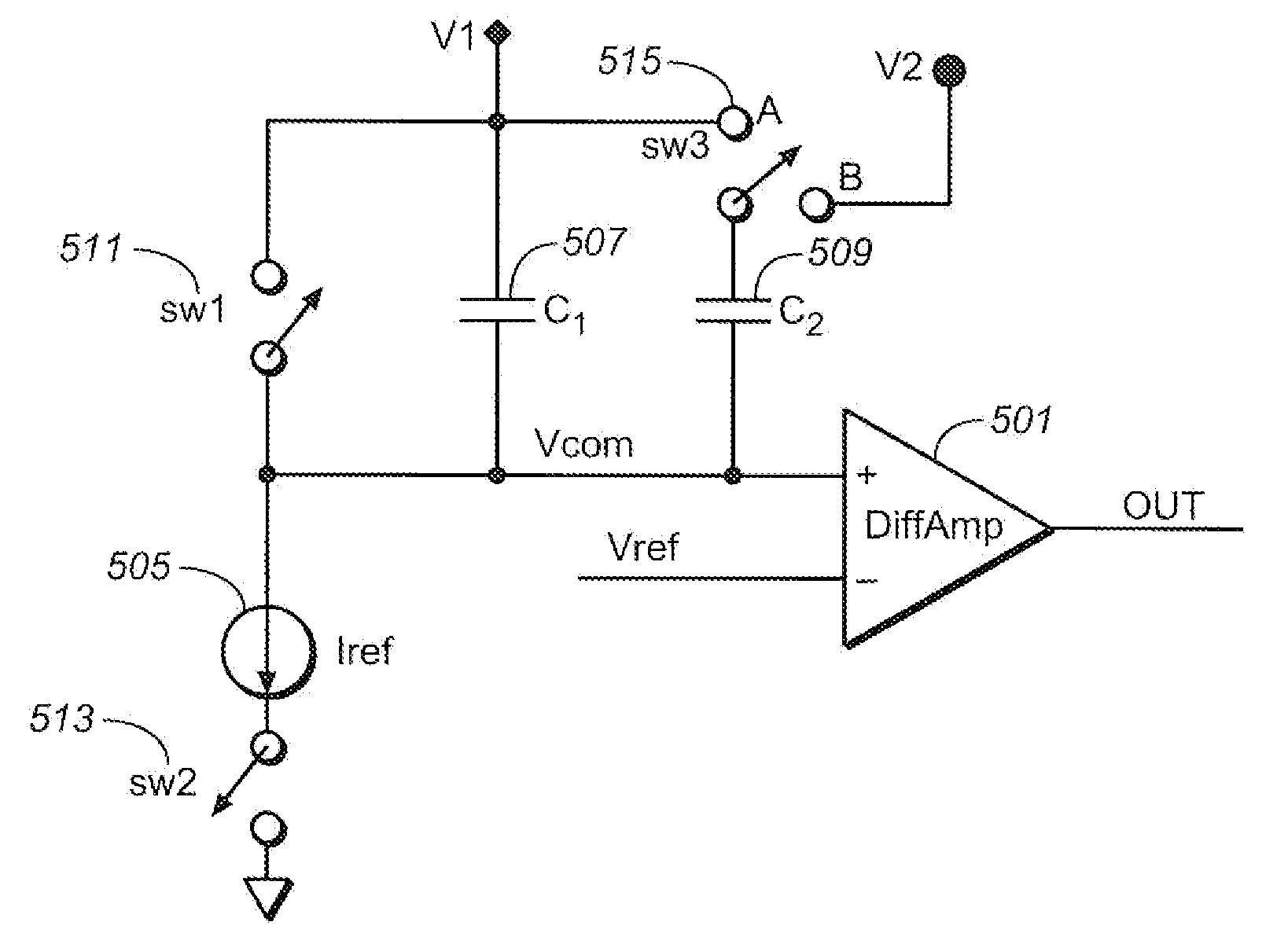

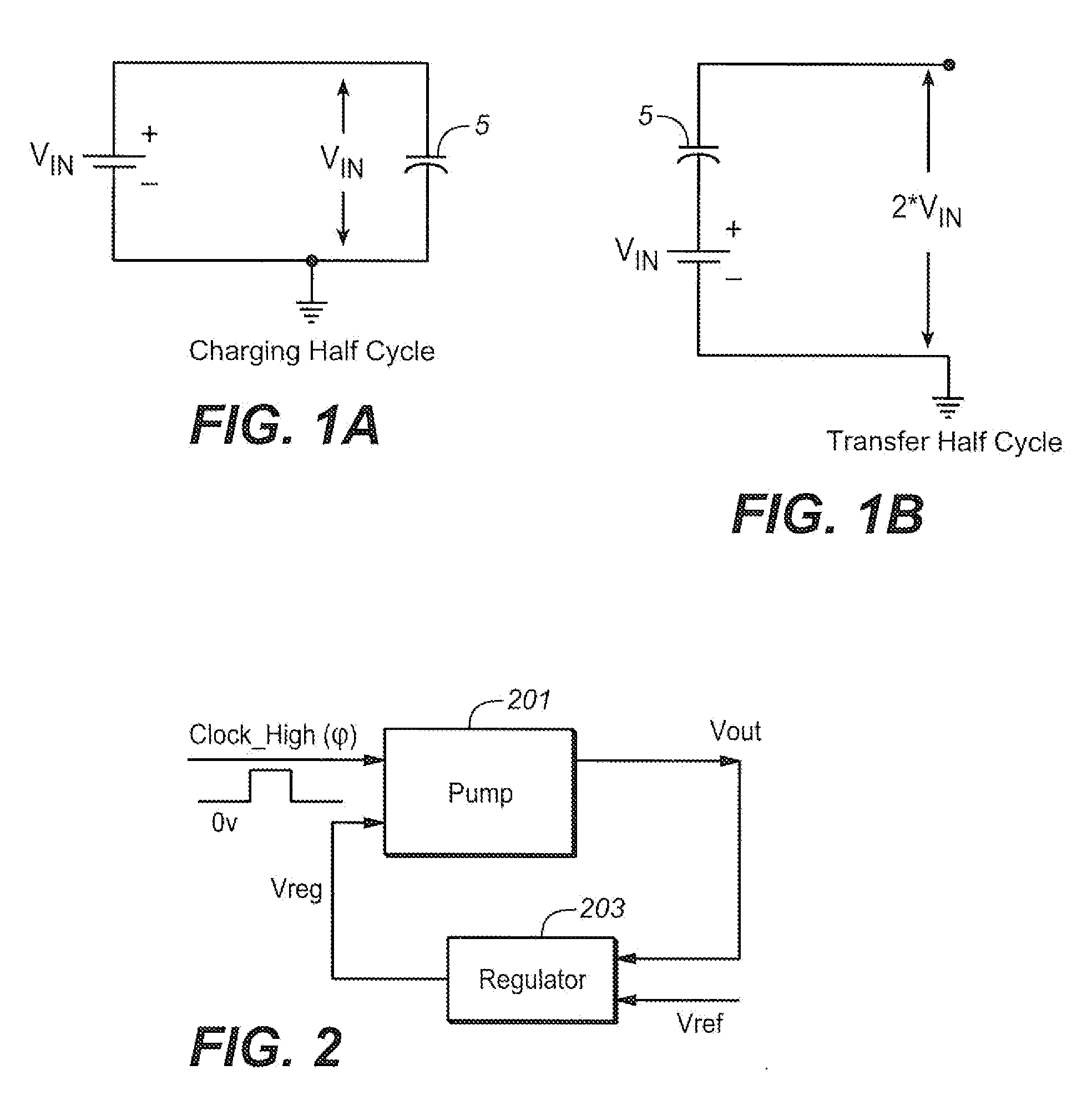

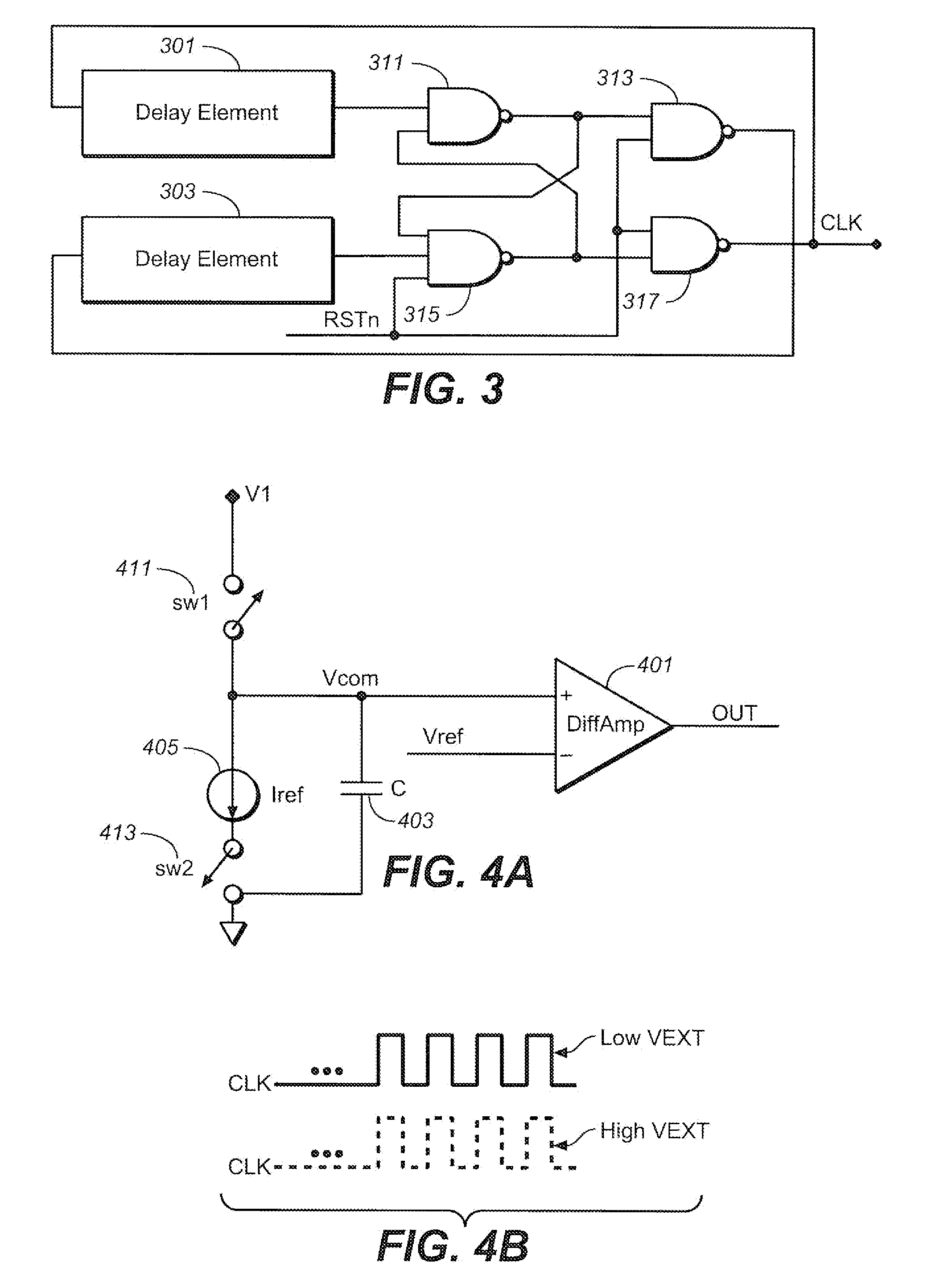

Clock Generator Circuit for a Charge Pump

ActiveUS20090315616A1Reduce power consumptionApparatus without intermediate ac conversionElectric variable regulationClock rateEngineering

Owner:SANDISK TECH LLC

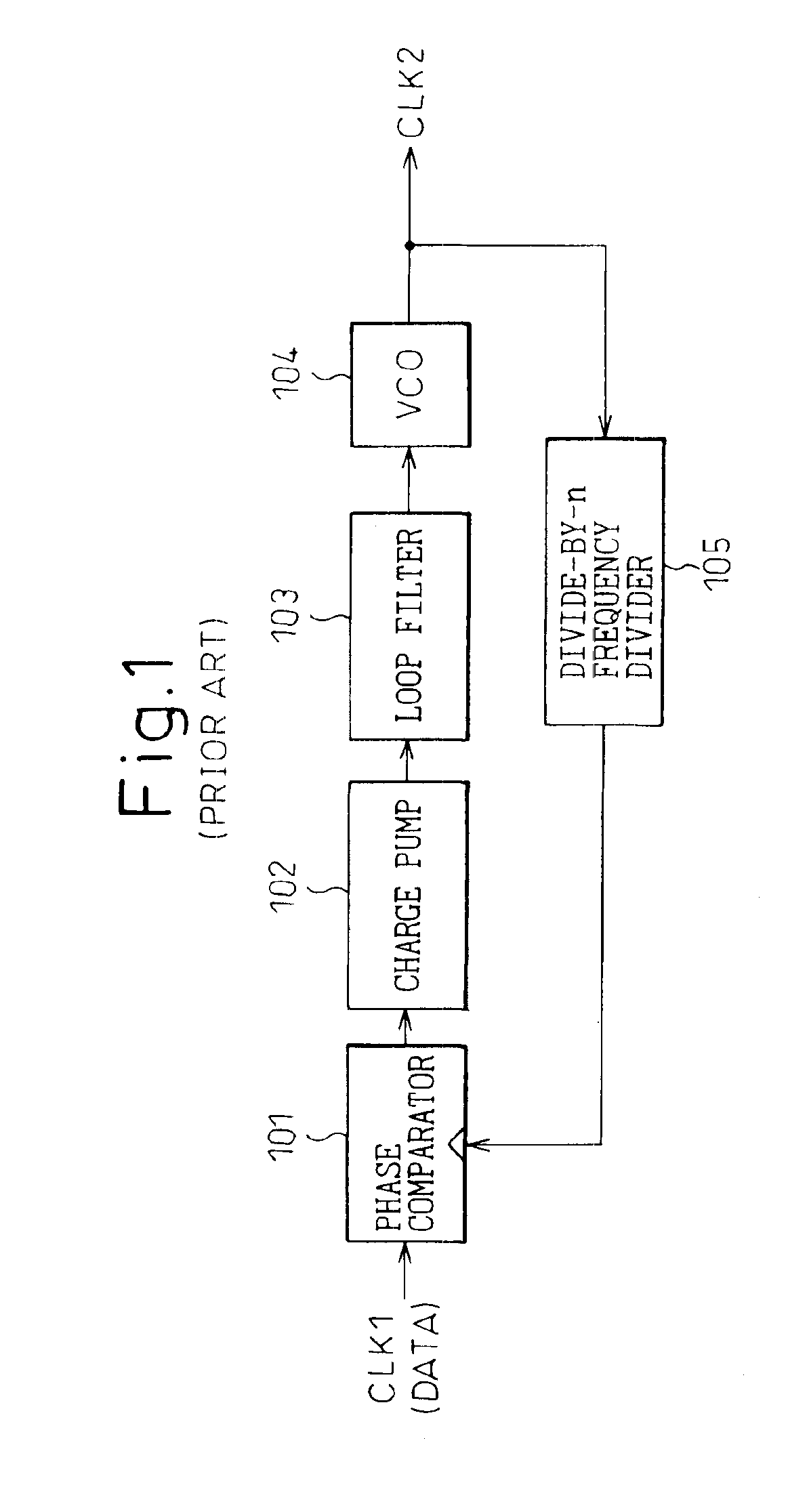

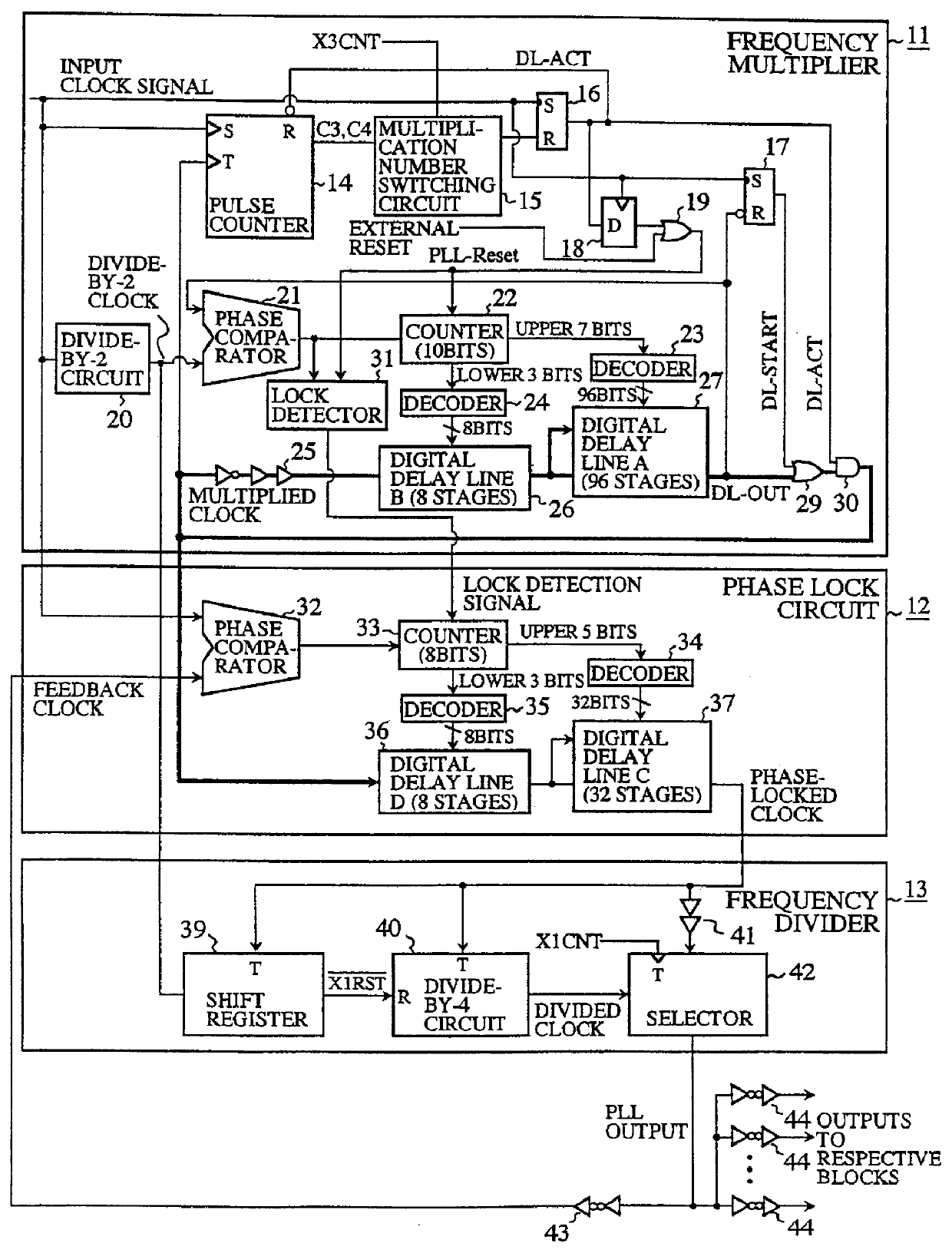

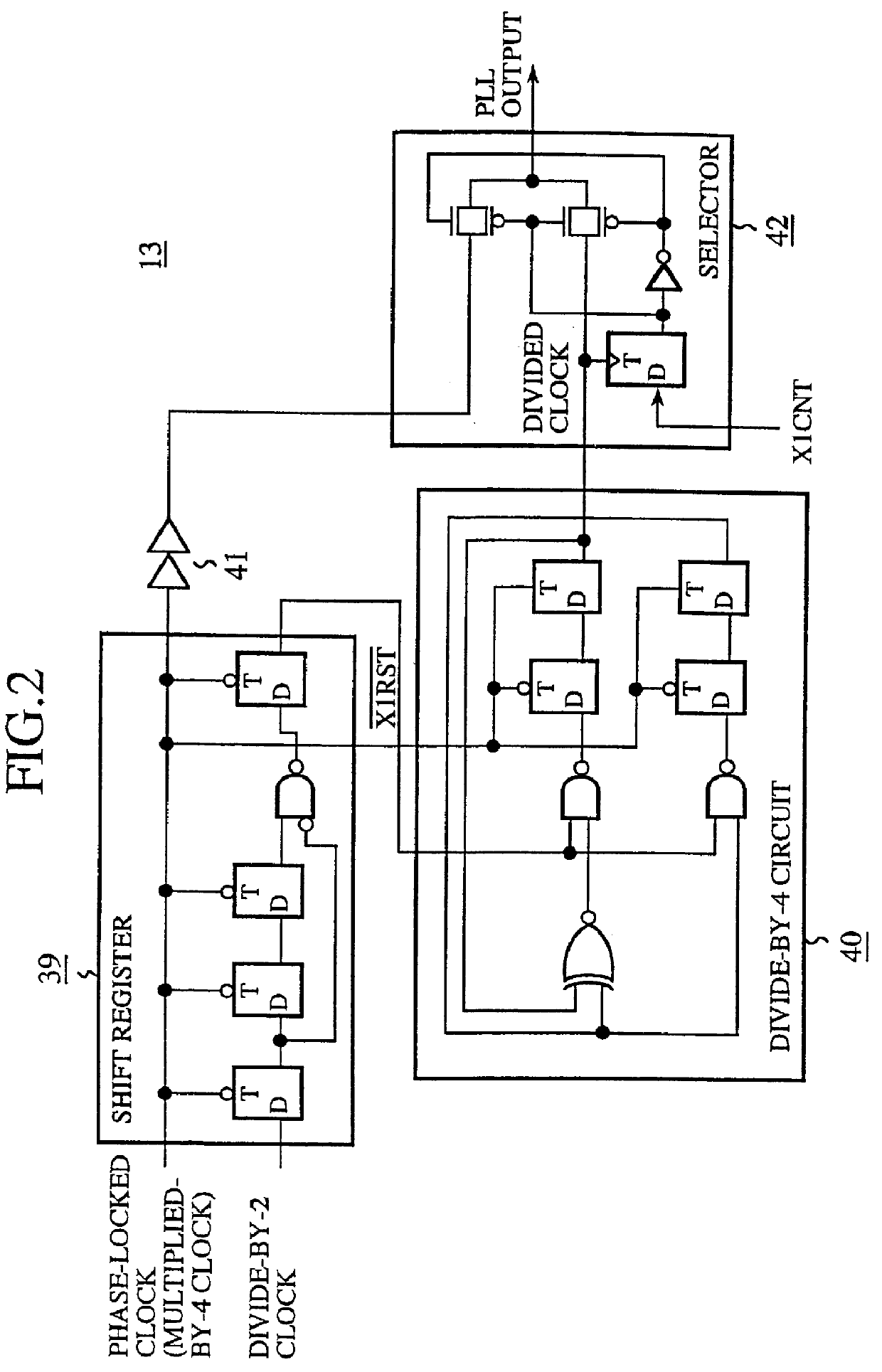

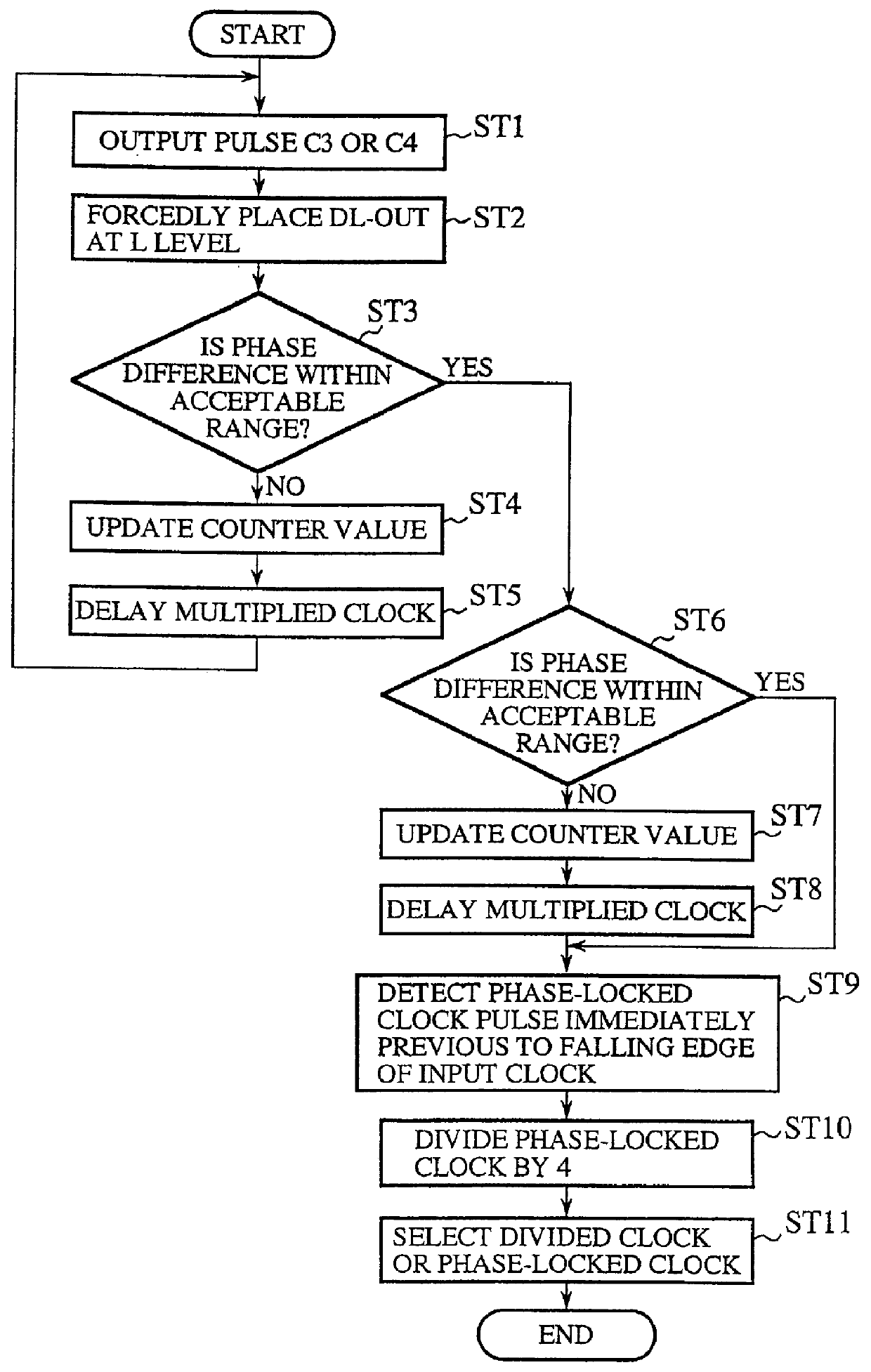

Clock generator and clock generating method capable of varying clock frequency without increasing the number of delay elements

InactiveUS6049238AReduce frequencyDelay lines pulse generationPulse automatic controlPhase differenceDelayed time

A clock generator including a frequency multiplier, a phase lock circuit and a frequency divider. The frequency multiplier generates a frequency multiplied clock by multiplying the frequency of an input clock. The phase lock circuit detects a phase difference between the input clock and a frequency divided clock, and generates, by delaying the frequency multiplied clock by an amount corresponding to the phase difference, a phase-locked clock with its phase locked with the input clock. The frequency divider detects in every fixed cycle a particular pulse of the phase-locked clock, and generates the frequency divided clock by dividing the phase-locked clock with reference to the particular pulse of the phase-locked clock. In particular, the frequency divider detects the particular pulse immediately previous to a falling edge of the input clock. This can reduce the phase difference between the input clock and the phase-locked clock, and hence to solve a problem of a conventional clock generator in that a delay time of a digital delay line in a phase lock circuit must be lengthened with a reduction in the multiplication number of the frequency multiplied clock, which requires a greater number of delay elements because of a large occupying area of the delay elements and a decoder, thereby increasing the circuit scale and cost of a chip to reduce the multiplication number of the frequency multiplied clock.

Owner:RENESAS ELECTRONICS CORP

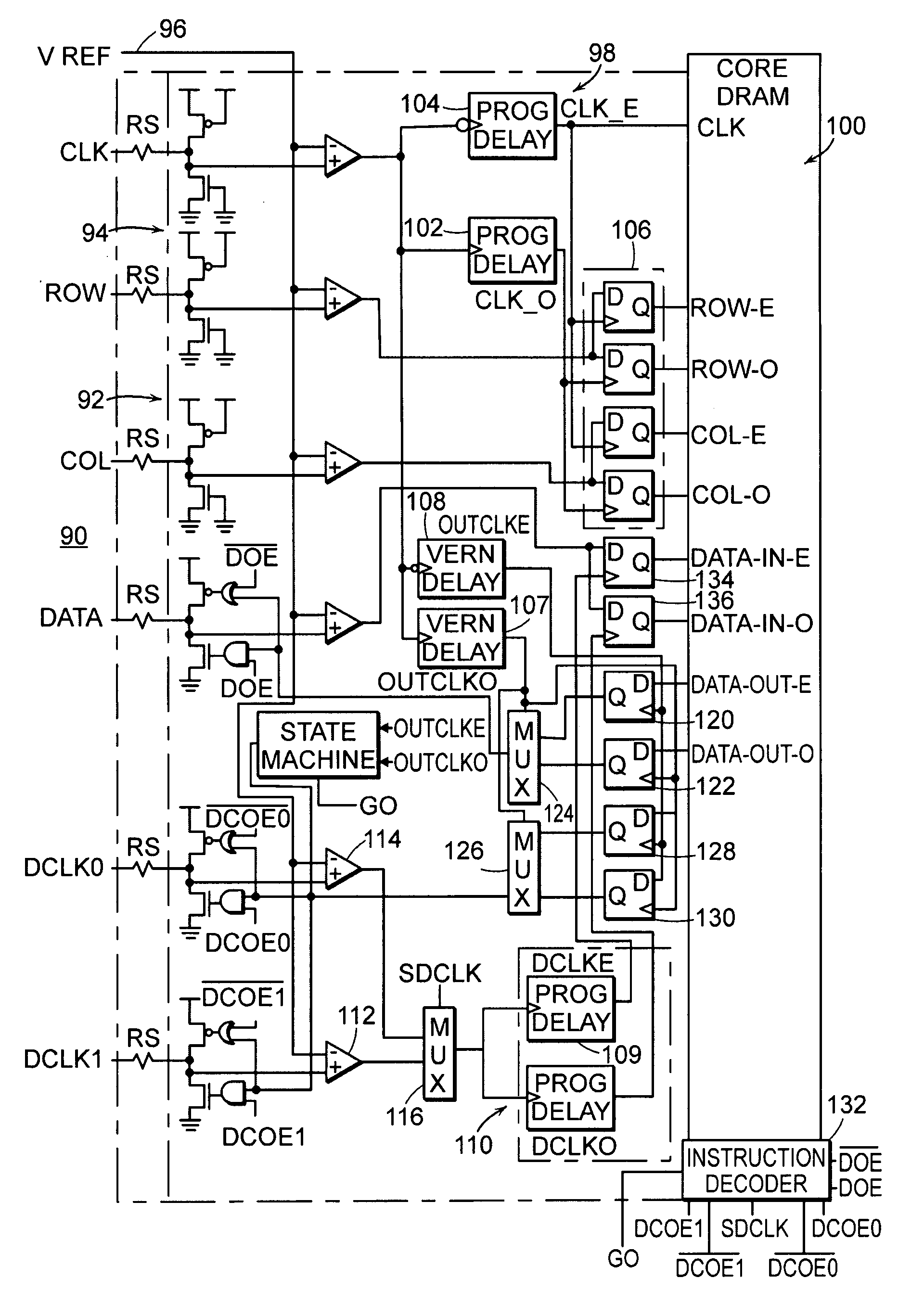

High bandwidth memory interface

InactiveUS7299330B2Improved high bandwidth chip-to-chip interfaceData transmission errorEnergy efficient ICTDigital storageComputer hardwareHigh bandwidth

Owner:CONVERSANT INTPROP MANAGEMENT INC

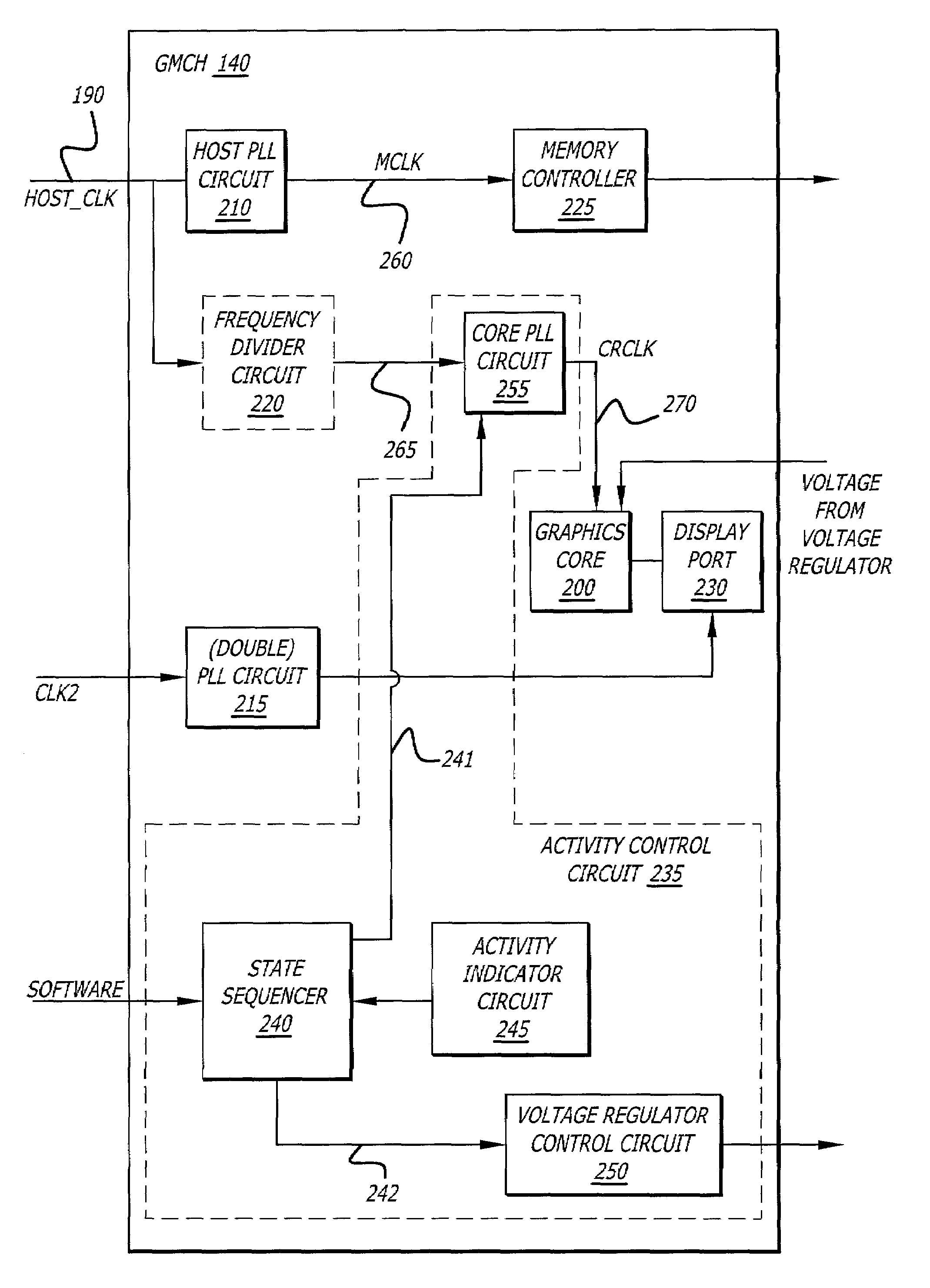

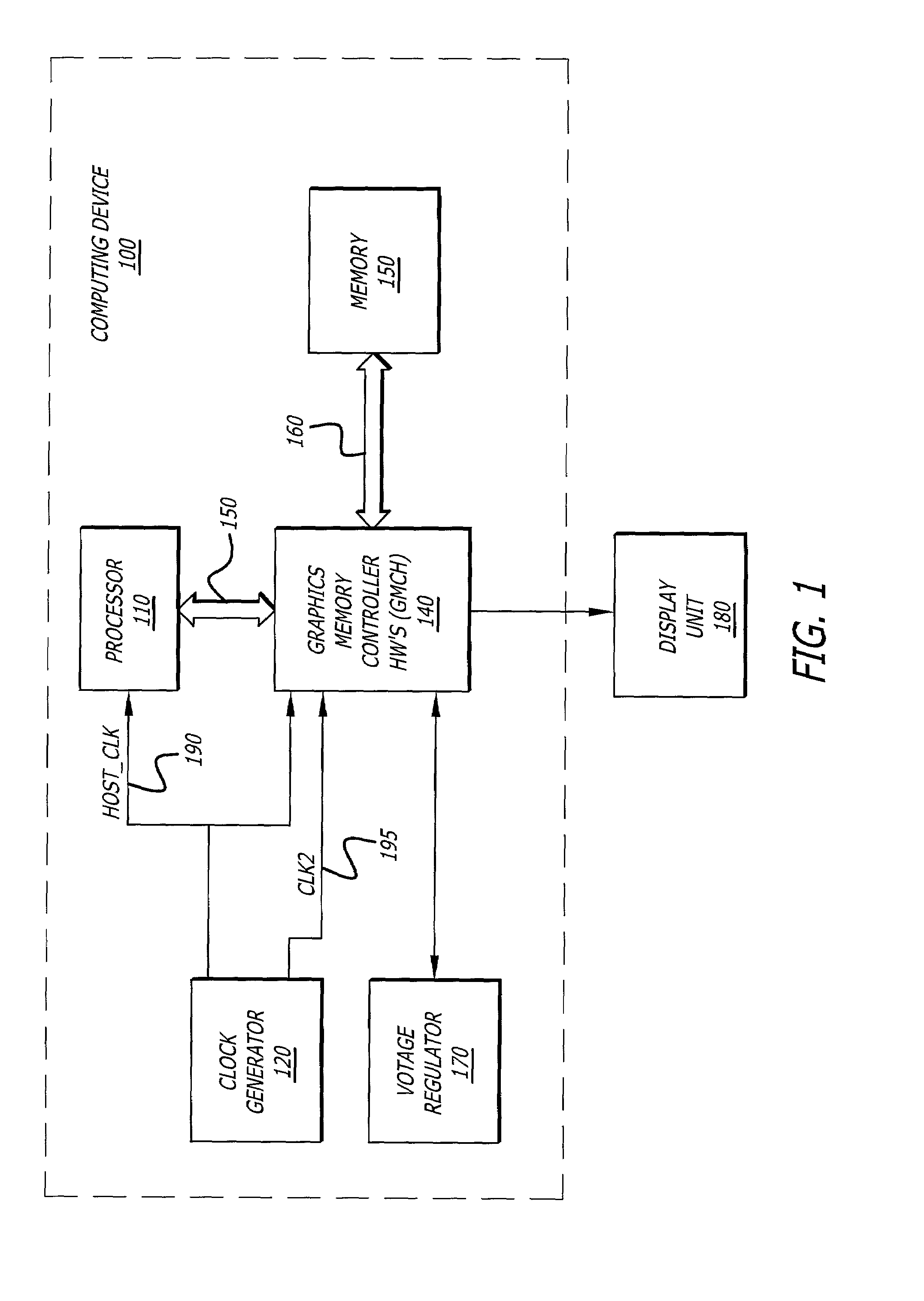

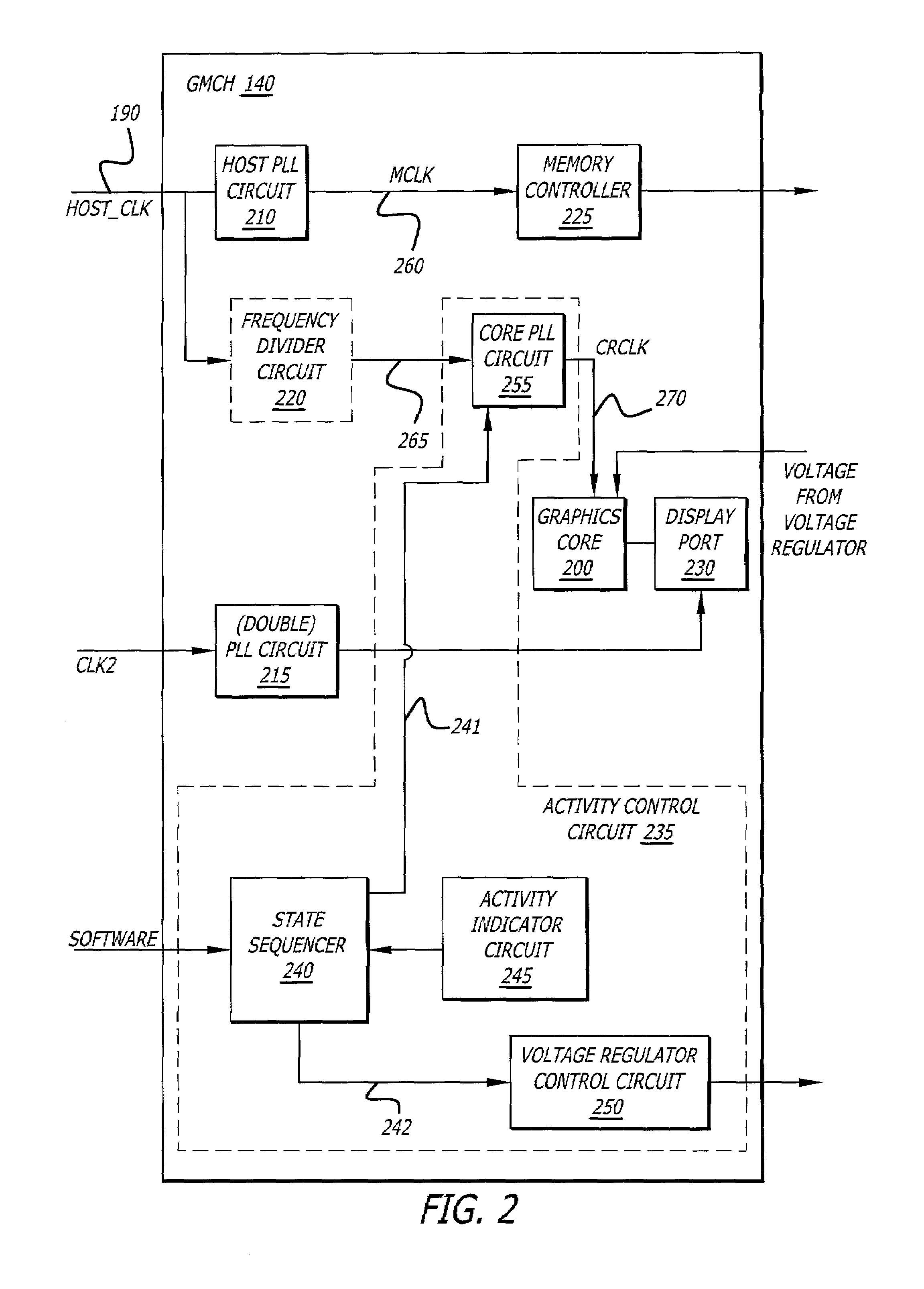

Power management for an integrated graphics device

In one embodiment of the invention, an integrated device is described that employs a mechanism to control power consumption of a graphics memory controller hub (GMCH) through both voltage and frequency adjustment of clock signal received from a clock generator. The GMCH comprises a graphics core and a circuit to alter operational behavior, such as the frequency of a render clock signal supplied to the graphics core. The circuit is adapted to monitor idleness of the graphics core and reduce a frequency level of the render clock signal if the idleness exceeds a determined percentage of time.

Owner:INTEL CORP

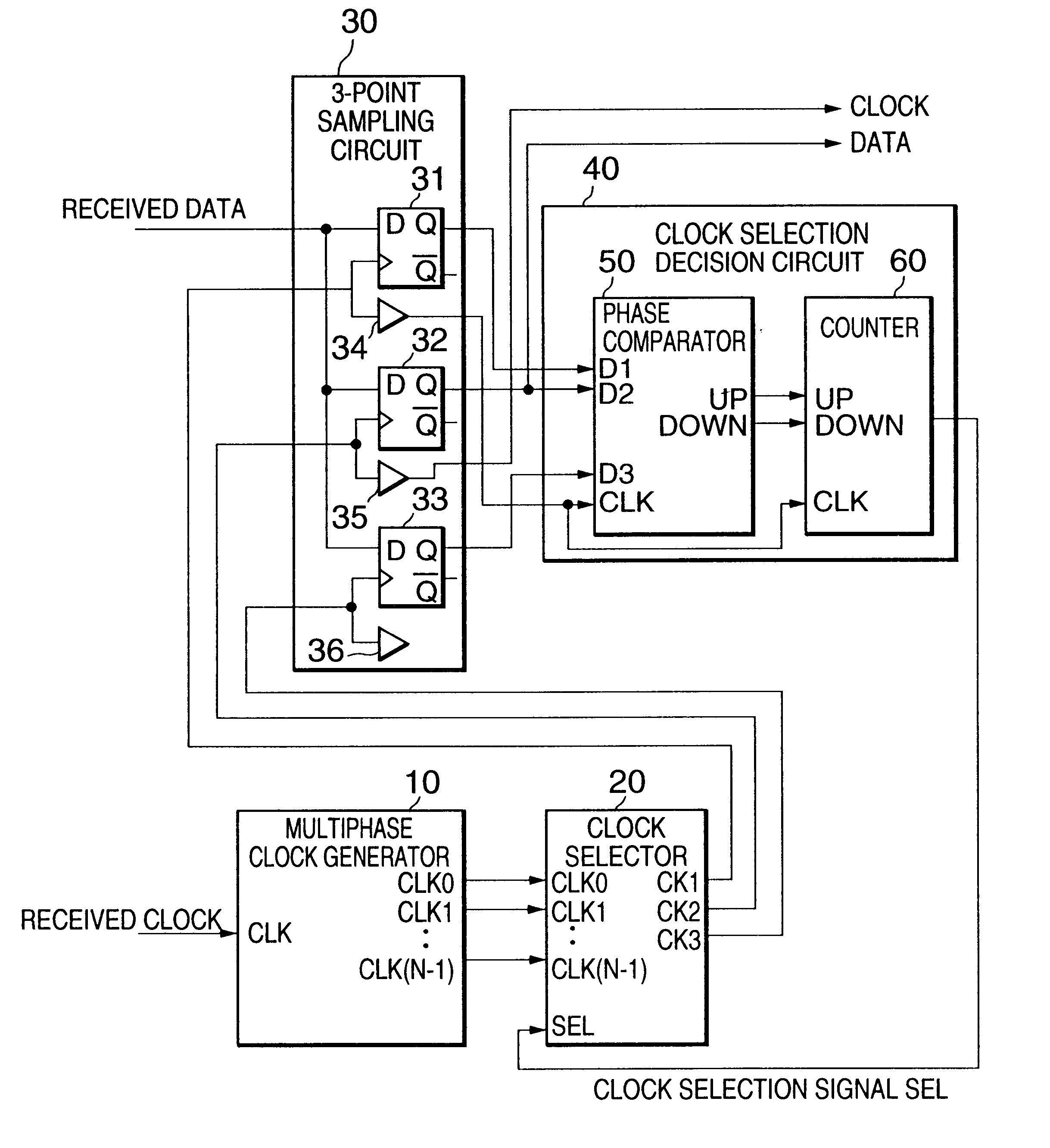

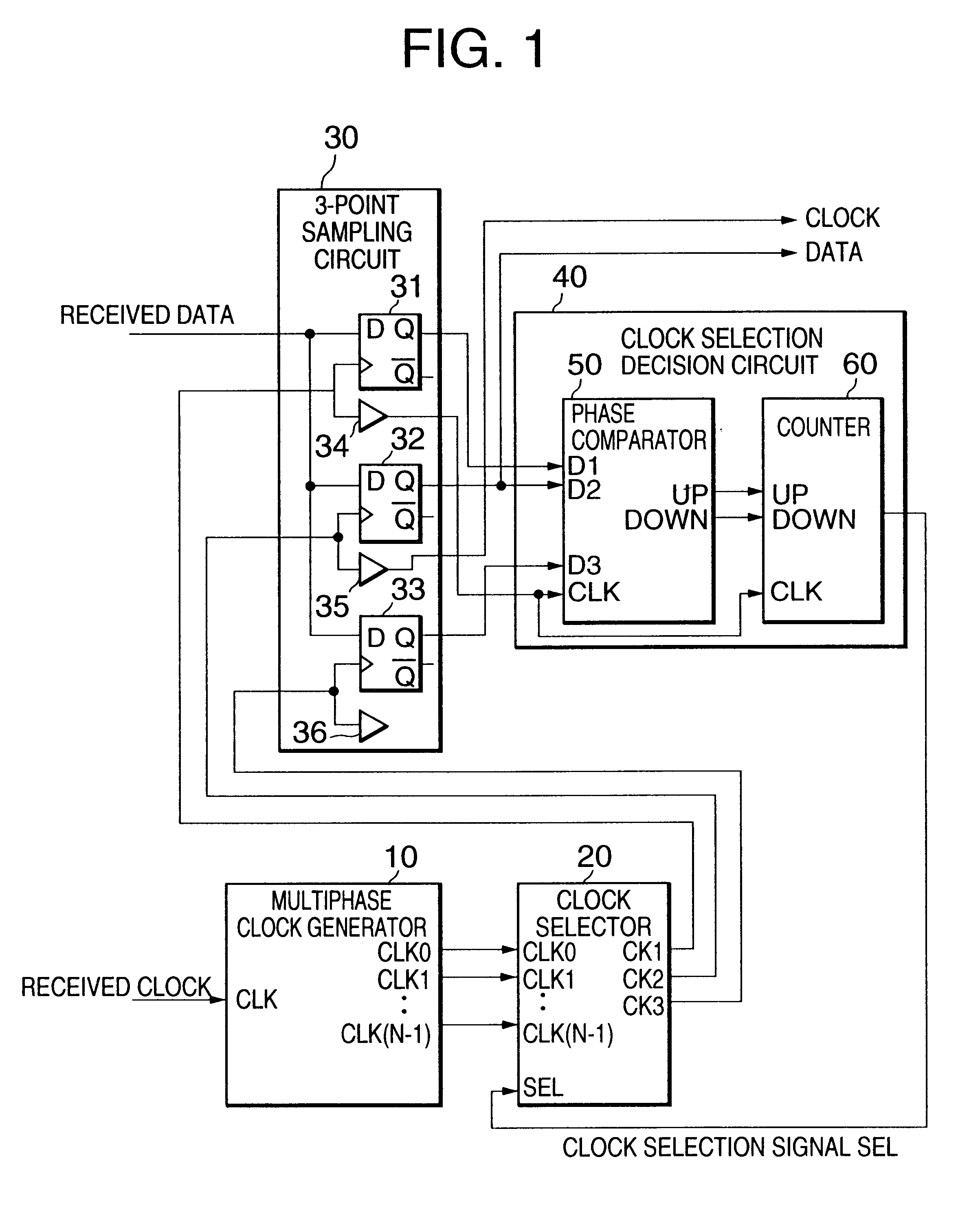

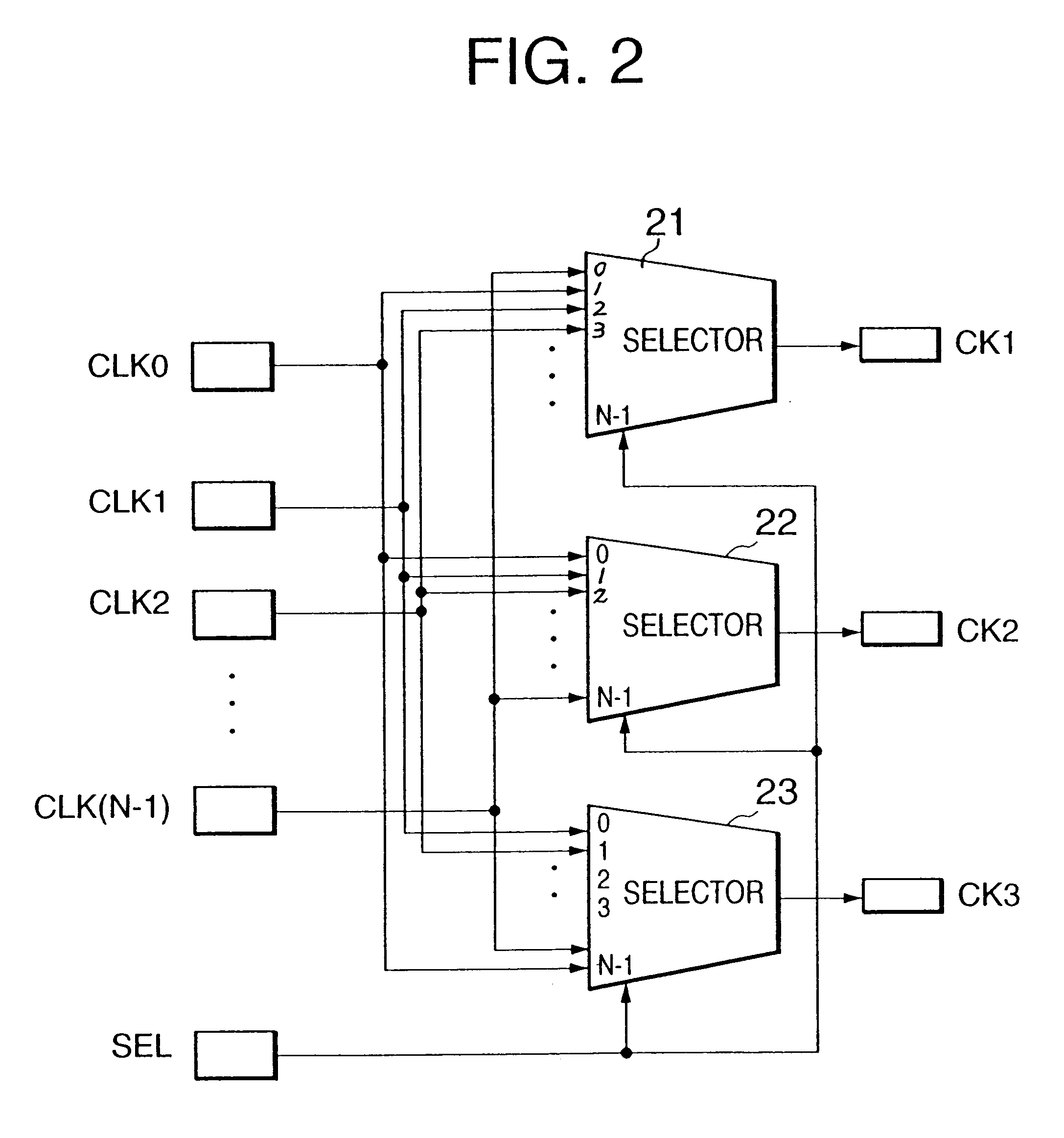

High-speed data receiving circuit and method

A high-speed data receiving circuit allowing correct and reliable data reception without the need for adjusting delays in circuits and interconnections is disclosed. A sampling circuit samples received data according to first, second, and third clock signals to produce first, second, and third streams of data. The first, second, and third clock signals sequentially have a predetermined phase difference between adjacent ones. A clock generator generates the first, second, and third clock signals having phases determined depending on a clock selection signal obtained by comparing the first, second, and third streams of data. The second clock signal is selected as an output clock signal and the second stream of data corresponding to said second clock signal is selected as an output data of the high-speed data receiving circuit.

Owner:NEC CORP

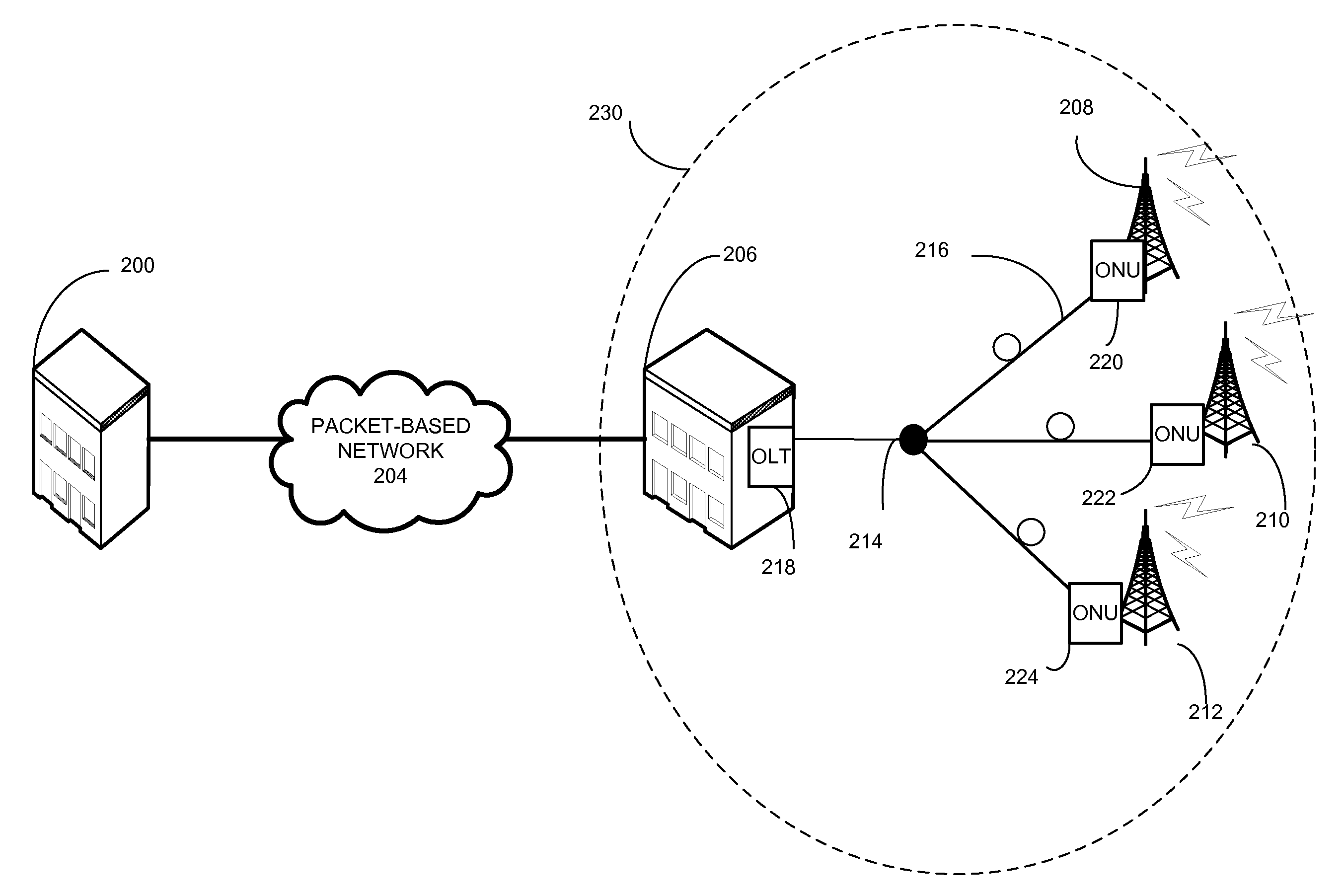

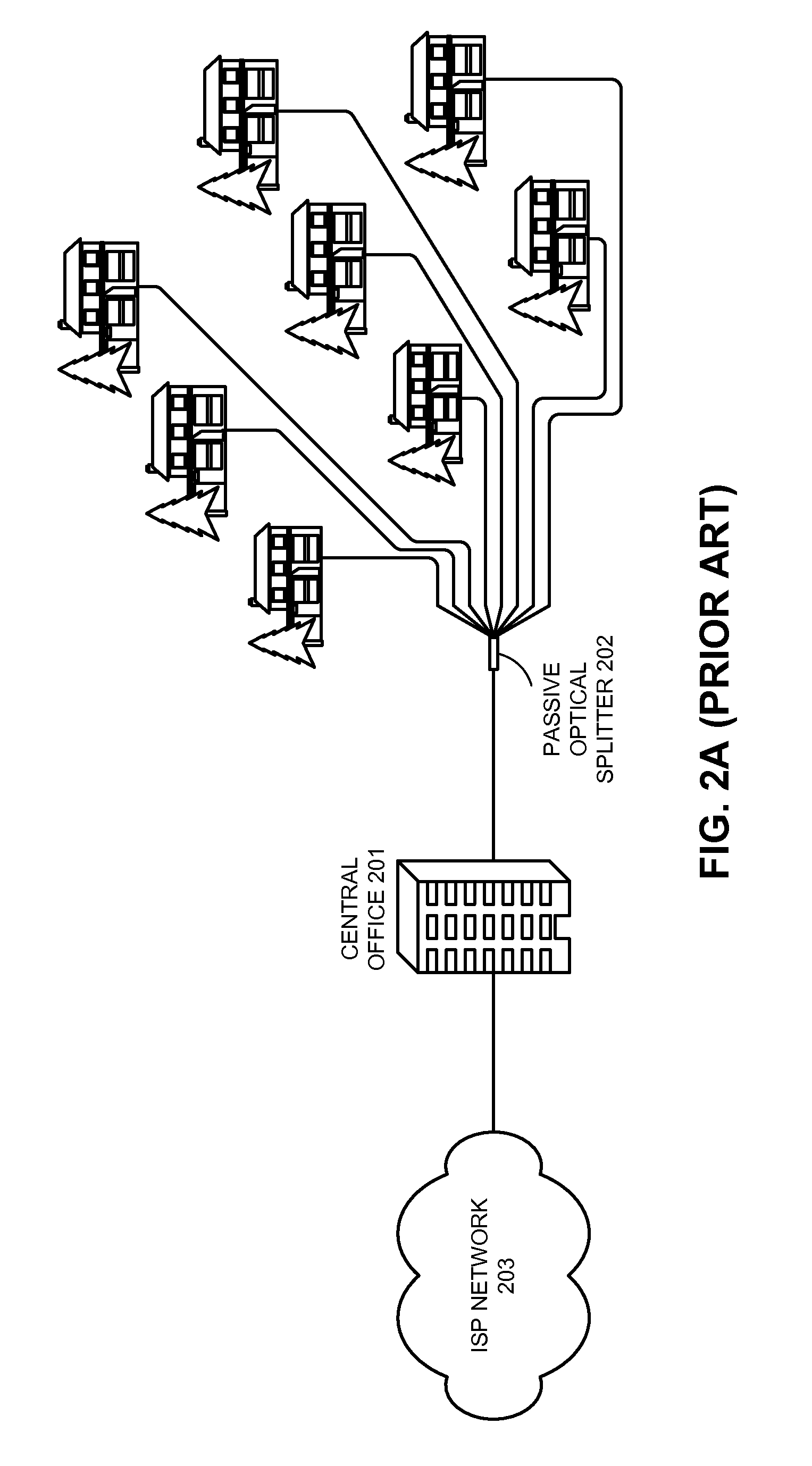

Synchronization transport over passive optical networks

ActiveUS20100098433A1Easy to transportMultiplex system selection arrangementsTime-division multiplexTransceiverClock recovery

One embodiment provides an Ethernet Passive Optical Network (EPON) system for clock transport. The system includes a reference clock configured to generate a frequency-reference signal, an optical line terminal (OLT) coupled to the reference clock, and an optical network unit (ONU). The OLT includes a clock generator configured to generate an OLT clock based on at least the frequency-reference signal. The ONU includes an optical transceiver, a clock recovery module, and a clock output mechanism. The optical transceiver is configured to transmit optical signals to and receive optical signals from the OLT. The clock-recovery module is configured to recover the frequency-reference signal from the received optical signals. The clock output mechanism is configured to output the recovered frequency-reference signal, thus facilitating transport of the frequency-reference signal over the EPON.

Owner:AVAGO TECH INT SALES PTE LTD

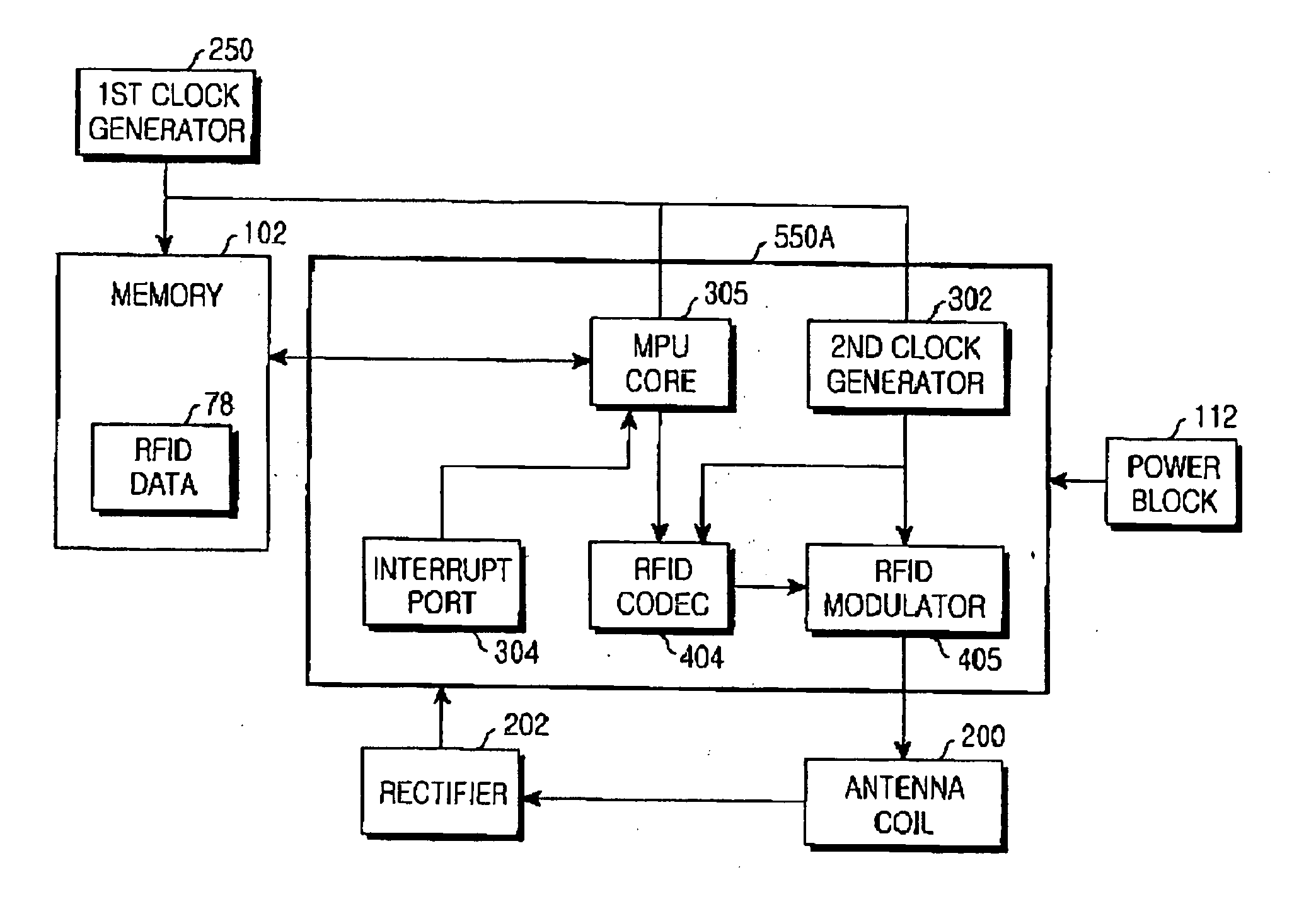

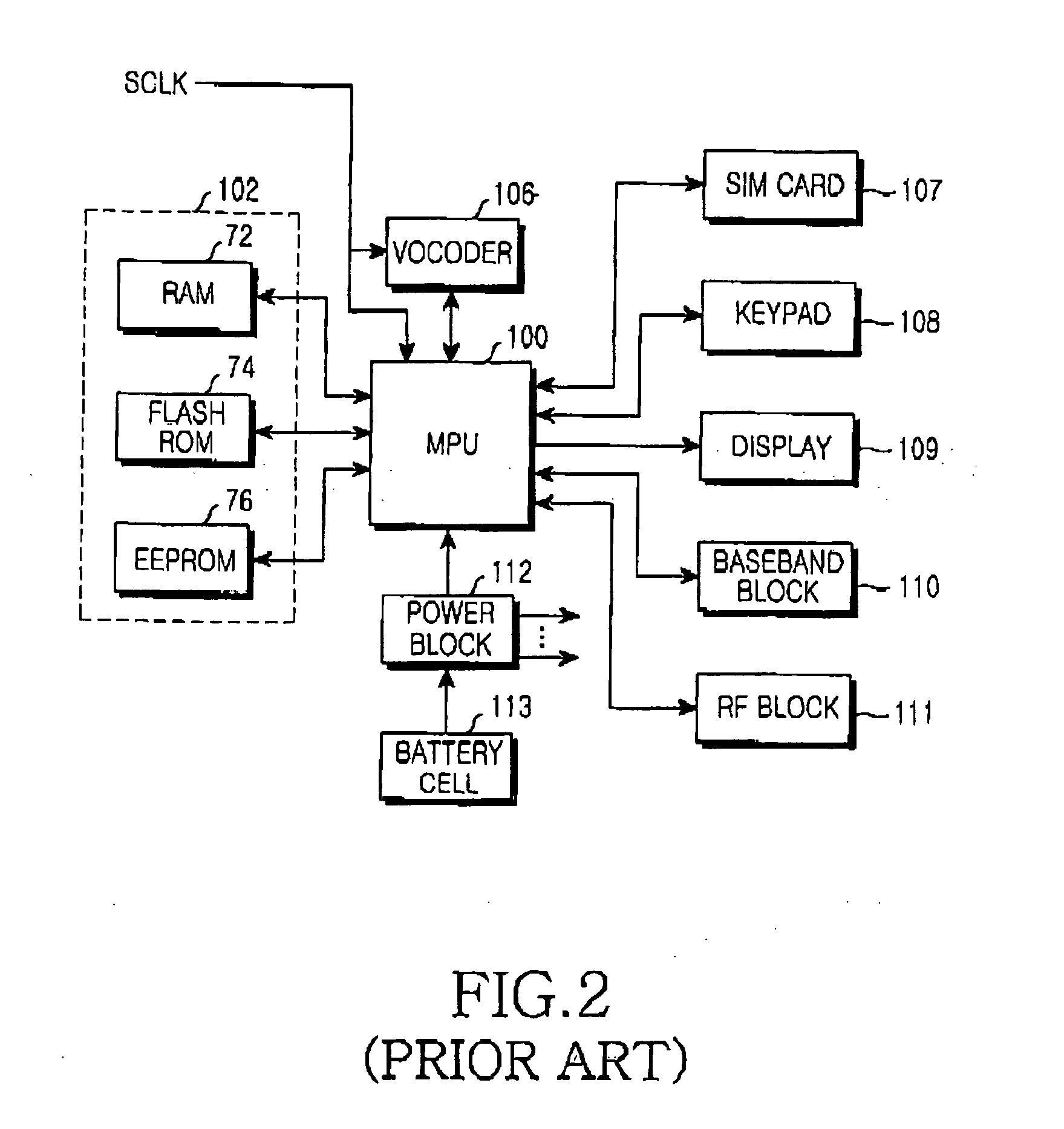

Mobile terminal circuit including an RFID tag and wireless identification method using the same

ActiveUS20050075079A1Electric signal transmission systemsMemory record carrier reading problemsRadio frequencyData storing

A mobile terminal circuit for transmitting radio frequency identification (RFID) data to an RFID reader. The mobile terminal circuit comprises an antenna for communication with the RFID reader; a memory portion for storing RFID data together with mobile terminal protocol data; a codec for encoding the RFID data into RFID codec data; a modulator connected to the codec, for modulating the RFID codec data into RFID modulation data; a processor connected to the memory portion, for extracting RFID data stored in the memory portion and delivering the extracted RFID data to the codec; a detector connected to the antenna and the processor, for informing the processor of approach of the RFID reader; a first clock generator connected to the processor and the memory portion, for providing operation timing to the processor and the memory portion; and a second clock generator connected to the first clock generator, the codec and the modulator, for providing operation timing to the codec and the modulator.

Owner:SAMSUNG ELECTRONICS CO LTD

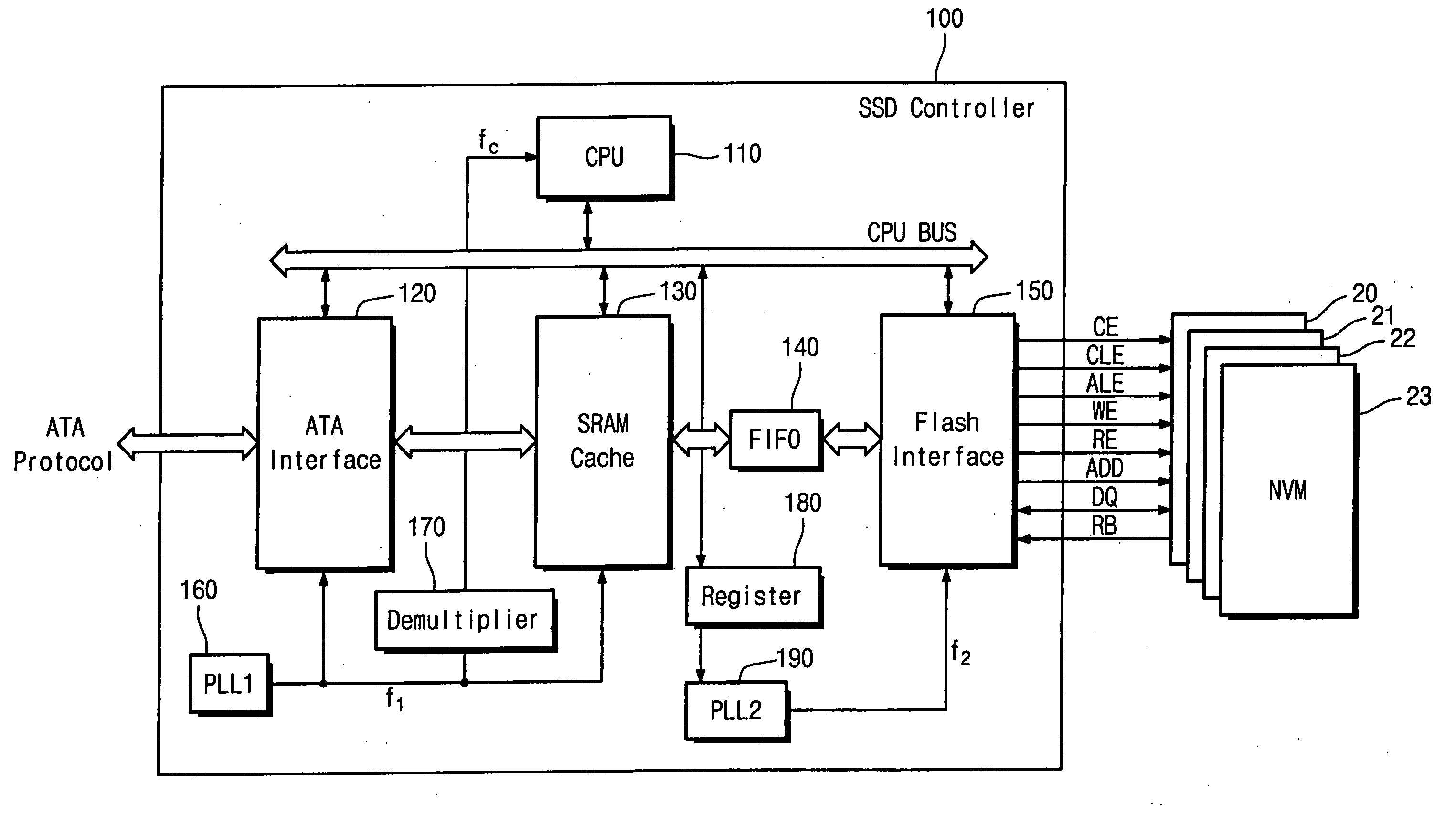

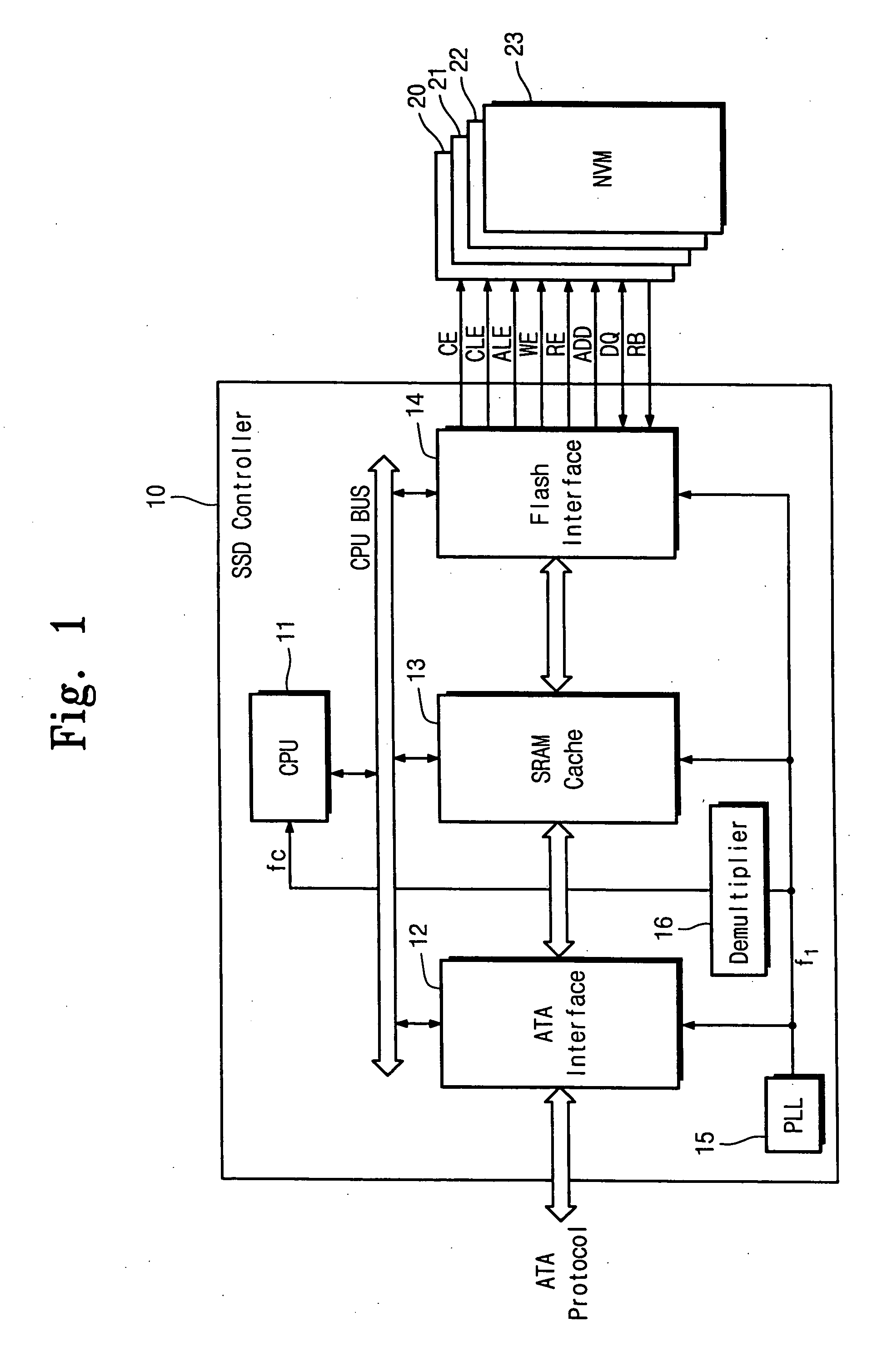

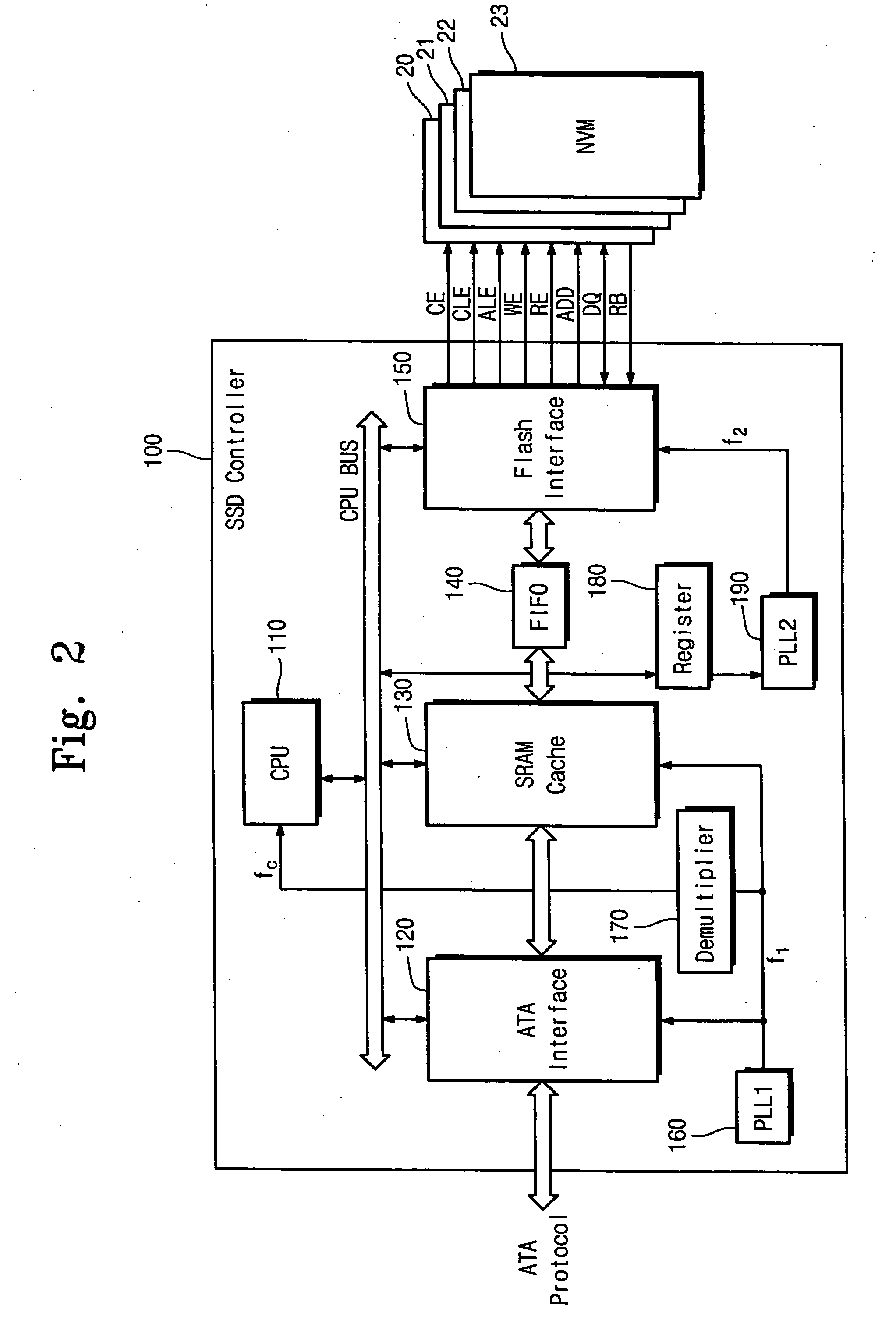

Semiconductor solid state disk controller

InactiveUS20070106836A1Memory architecture accessing/allocationGenerating/distributing signalsDisk controllerClock generator

A semiconductor solid state disk control device includes a flash interface configured to interface with the flash memory. The control device also includes a host interface configured to interface with the host. The control device also includes a first clock generator configured to generate a first driving clock to the host interface. The control device also includes a second clock generator configured to generate a second driving clock to the flash interface independent of the first clock generator.

Owner:SAMSUNG ELECTRONICS CO LTD