Patents

Literature

71results about "Delay lines pulse generation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Electronic circuitry

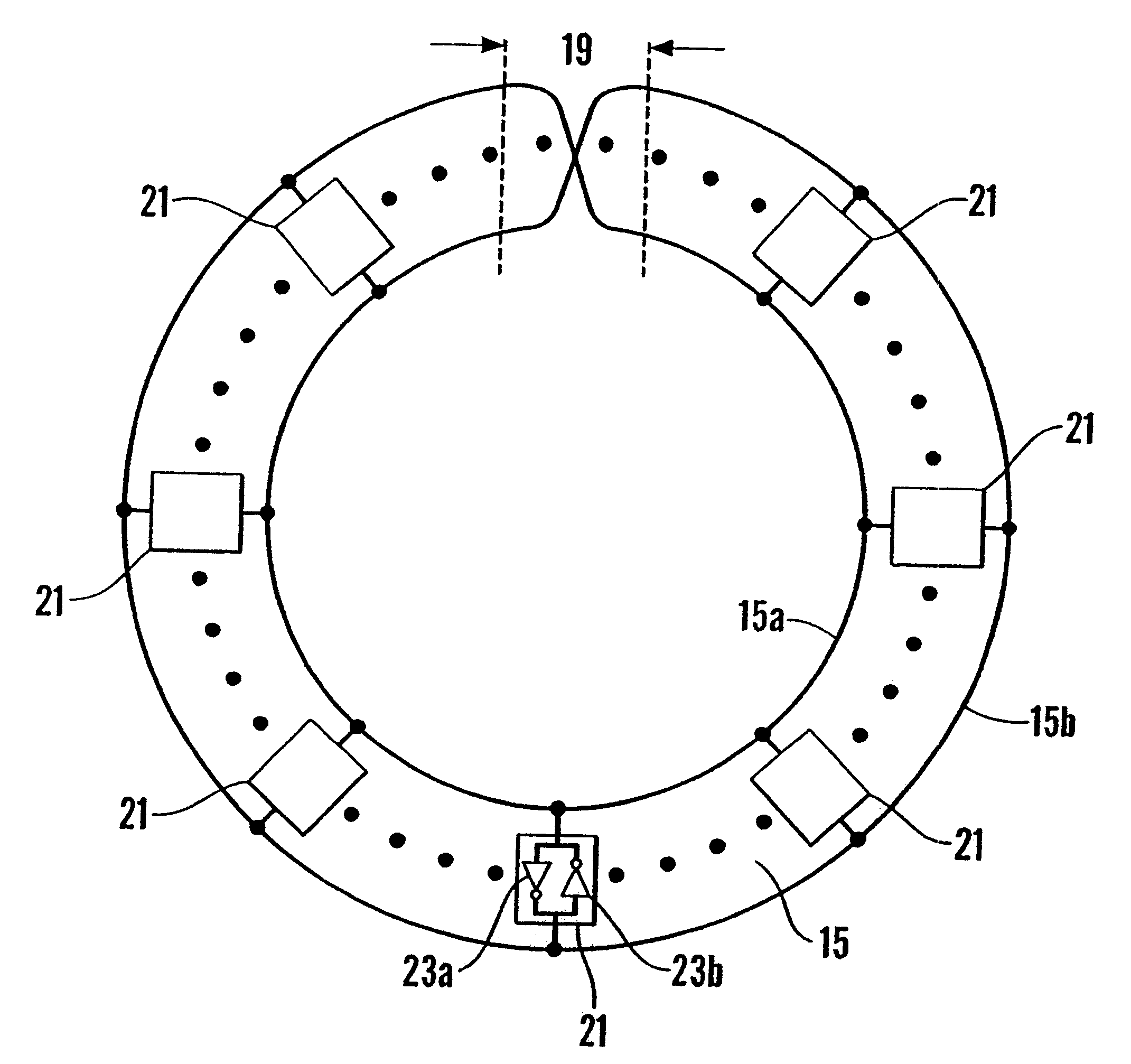

InactiveUS6556089B2Short fallShort riseDelay lines pulse generationPulse automatic controlCMOSBipolar signal

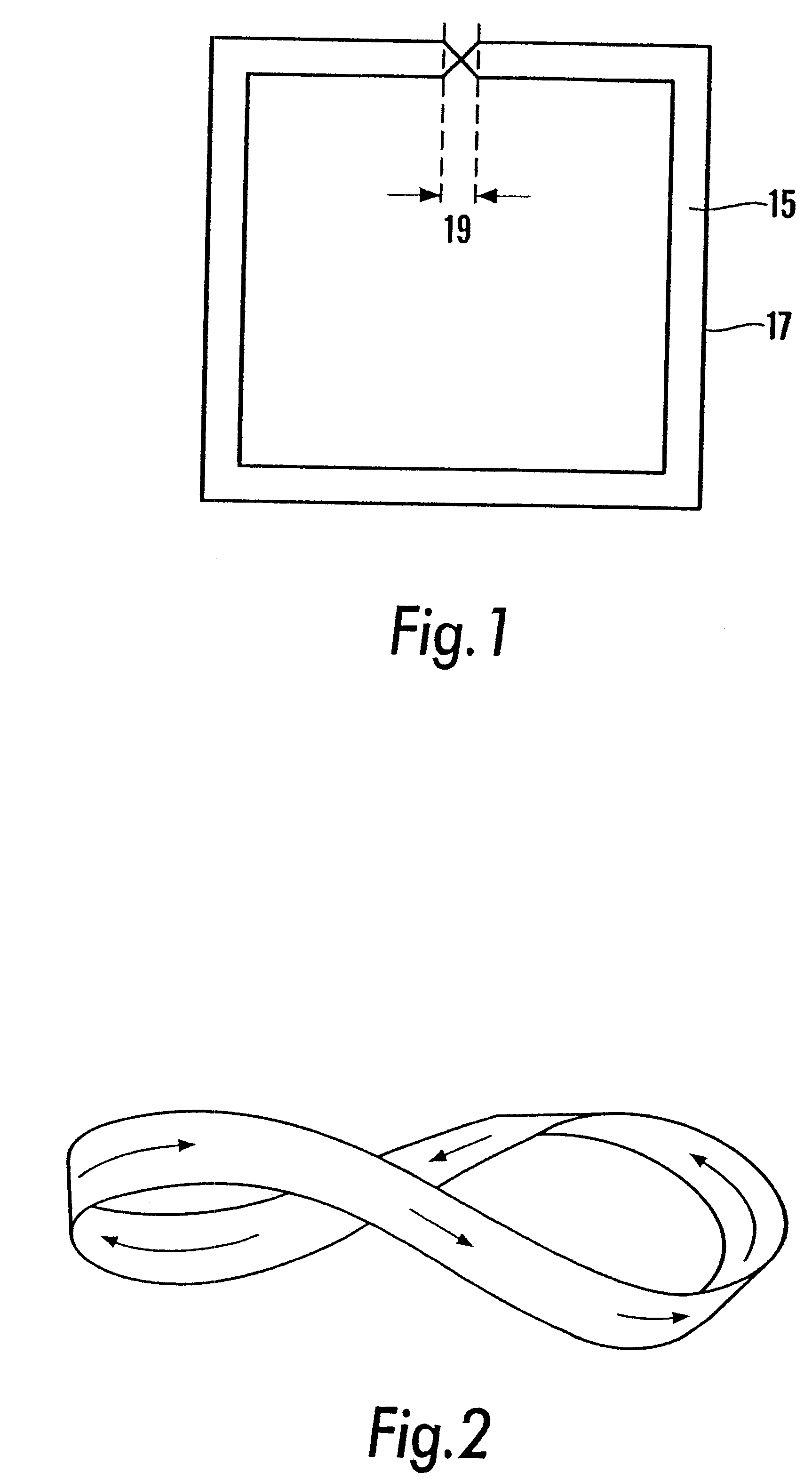

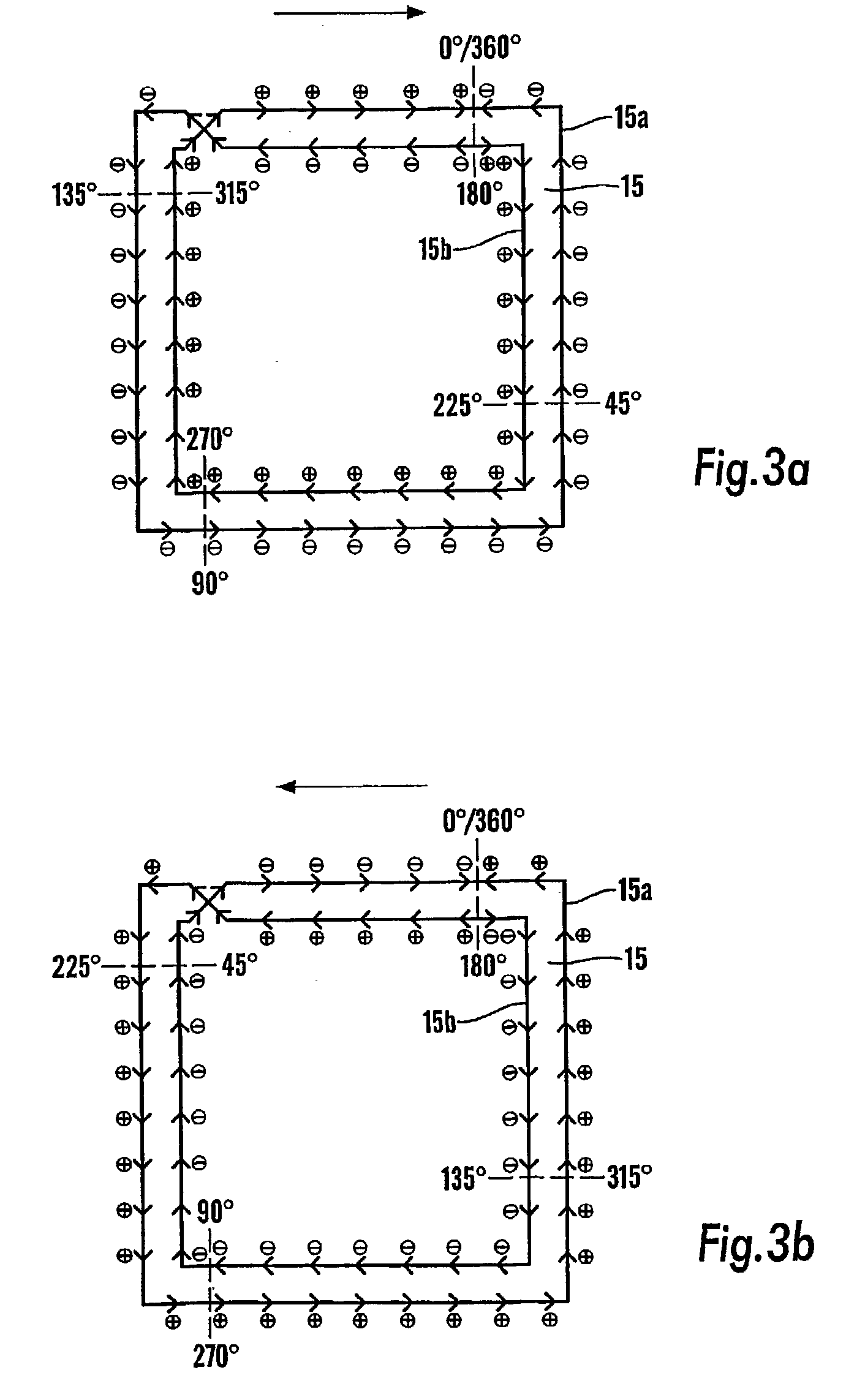

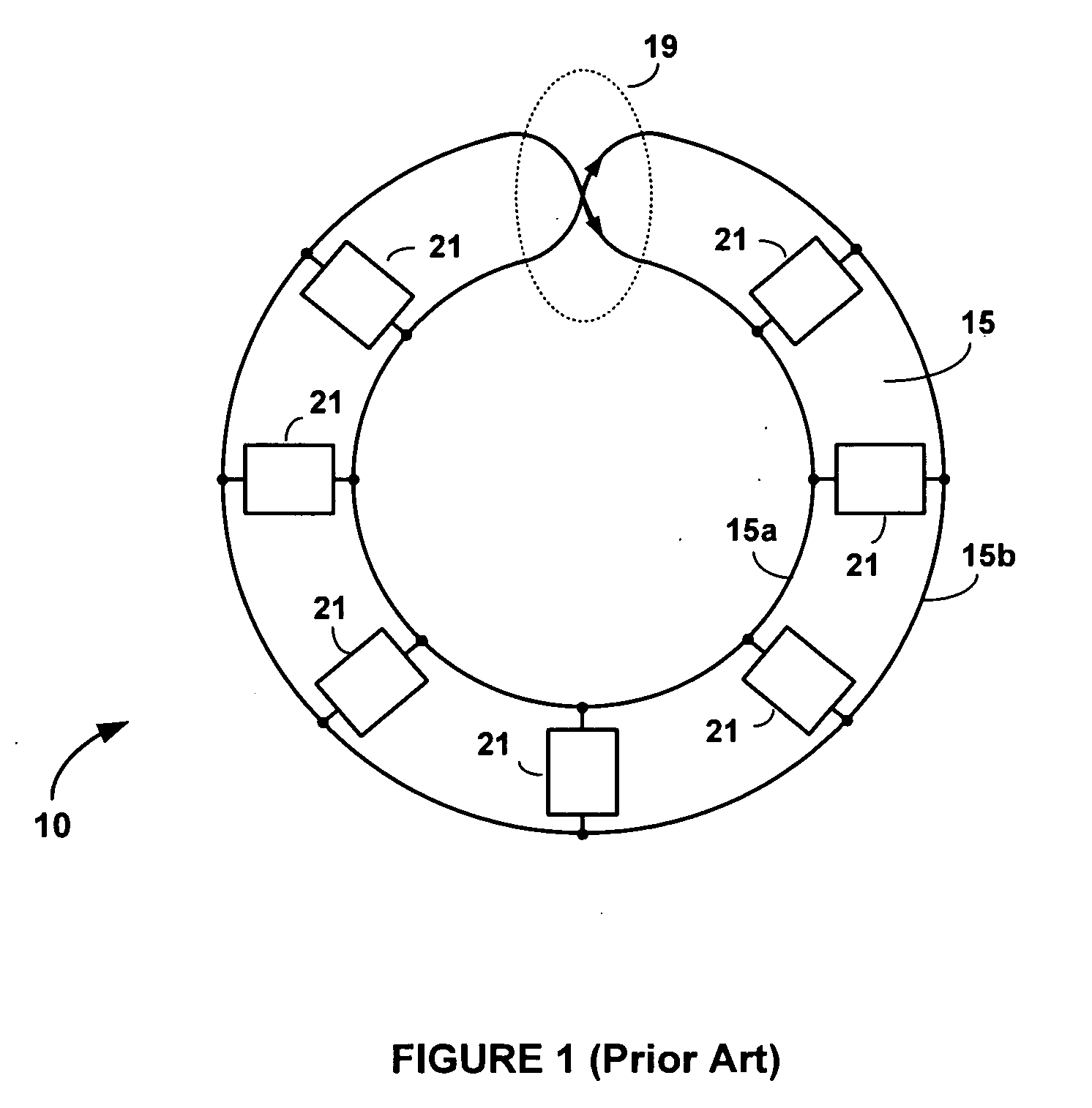

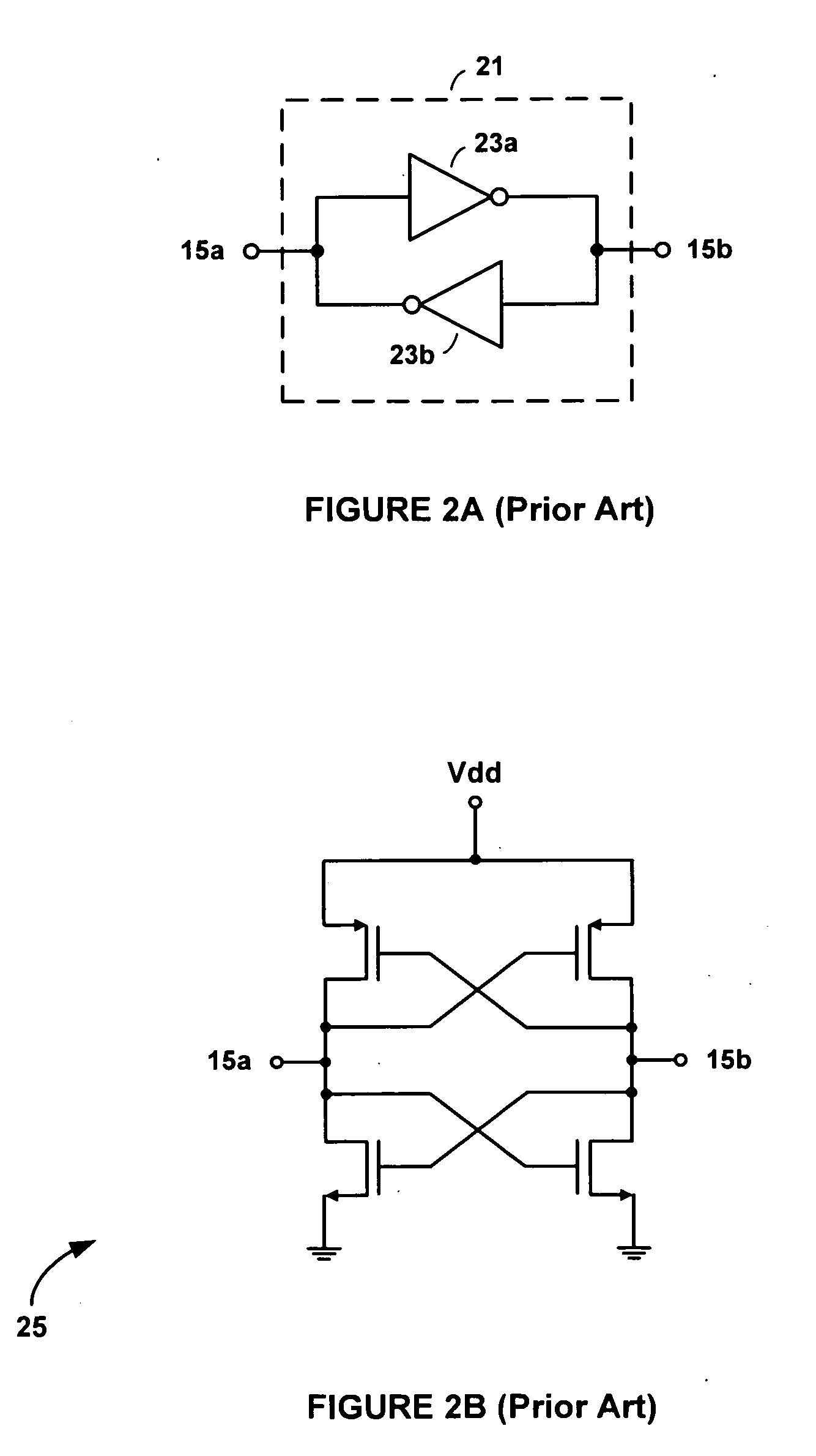

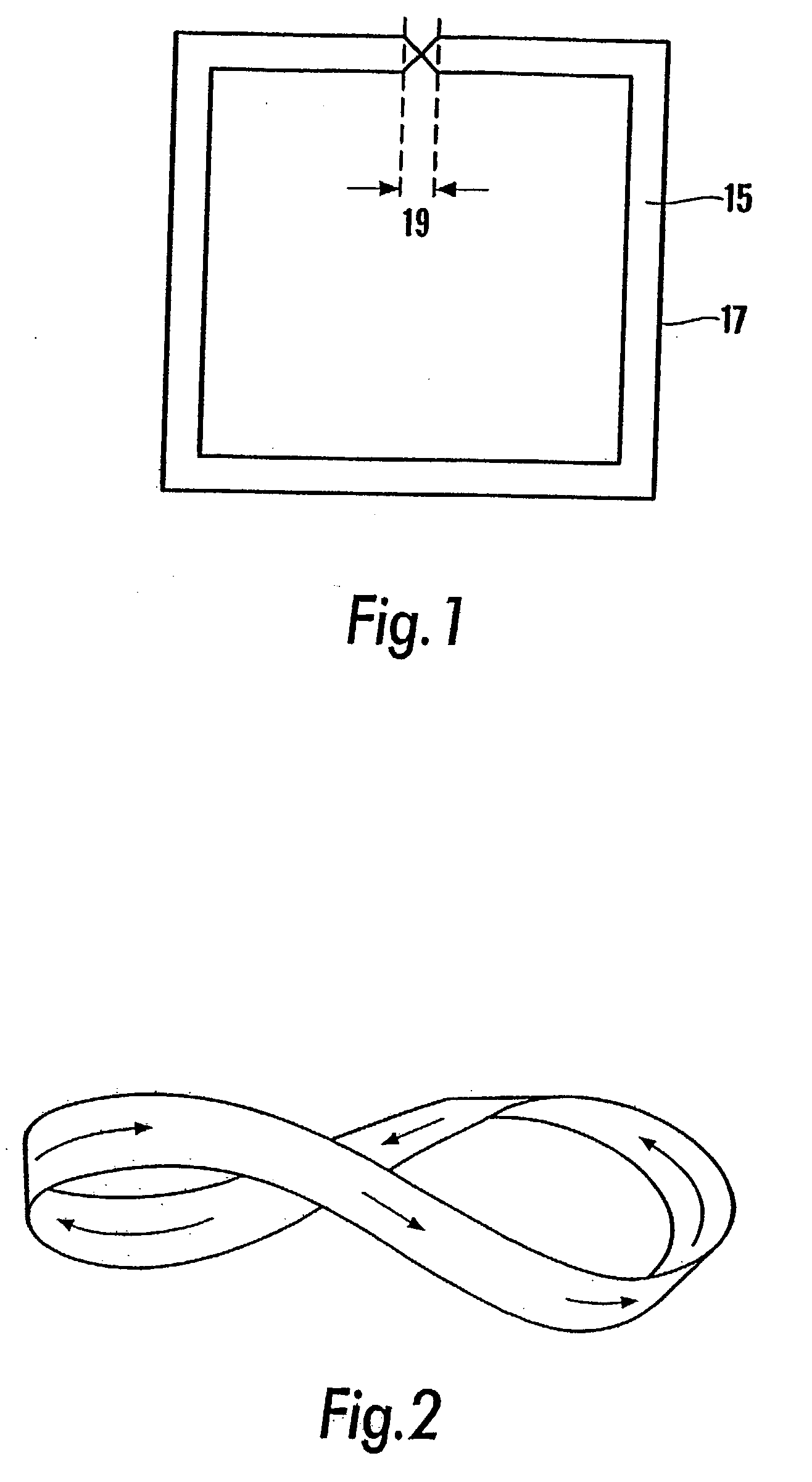

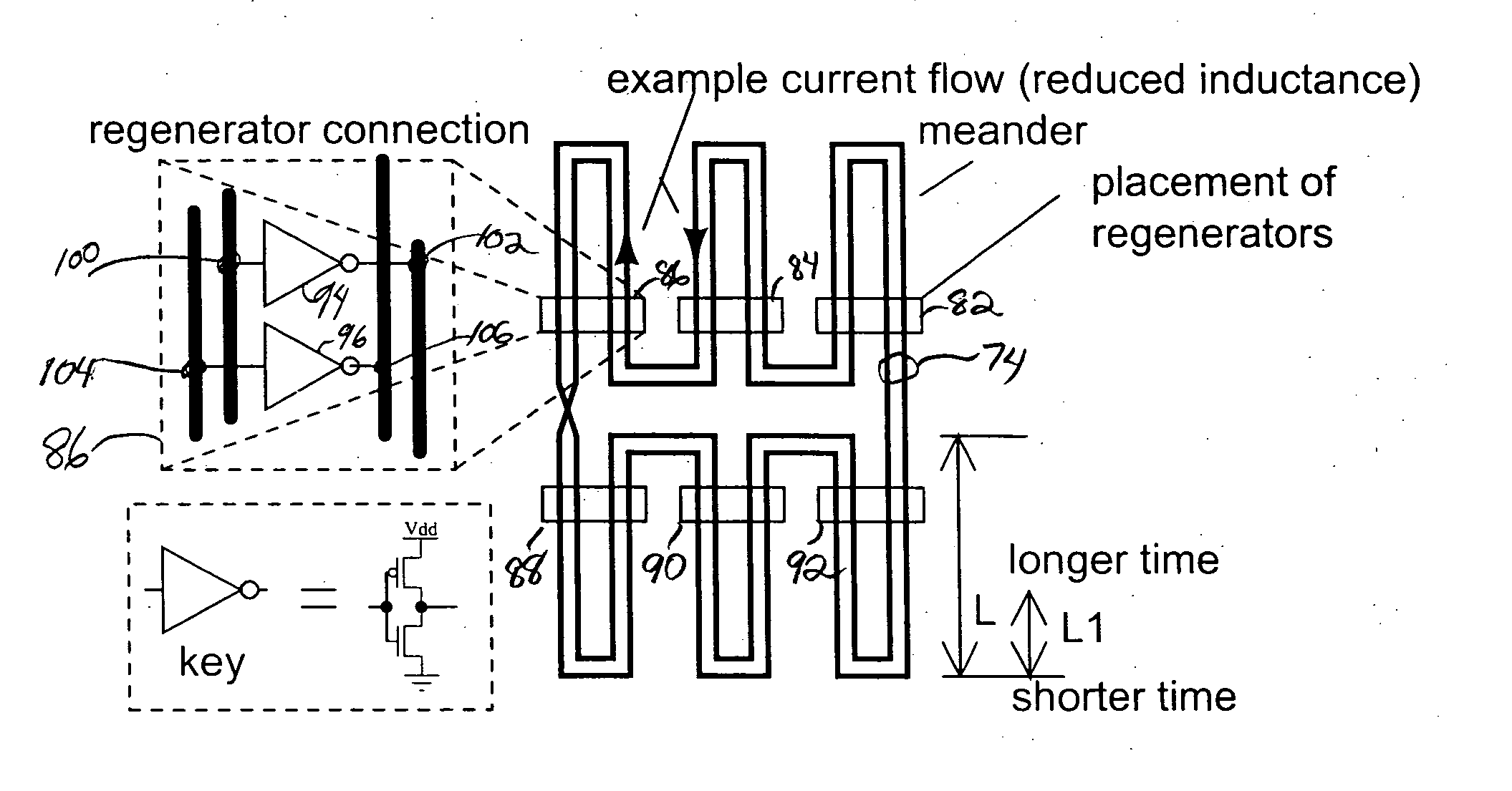

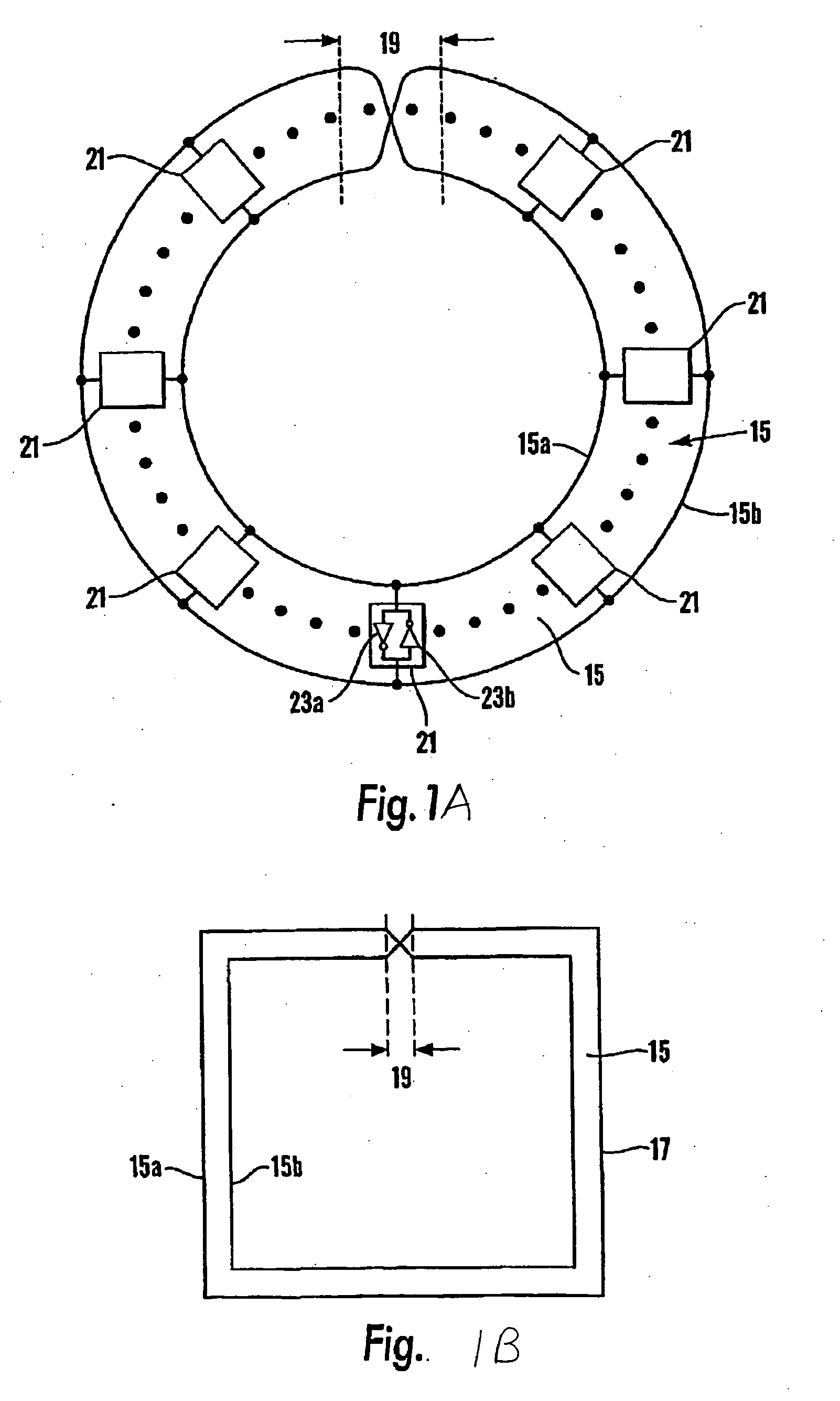

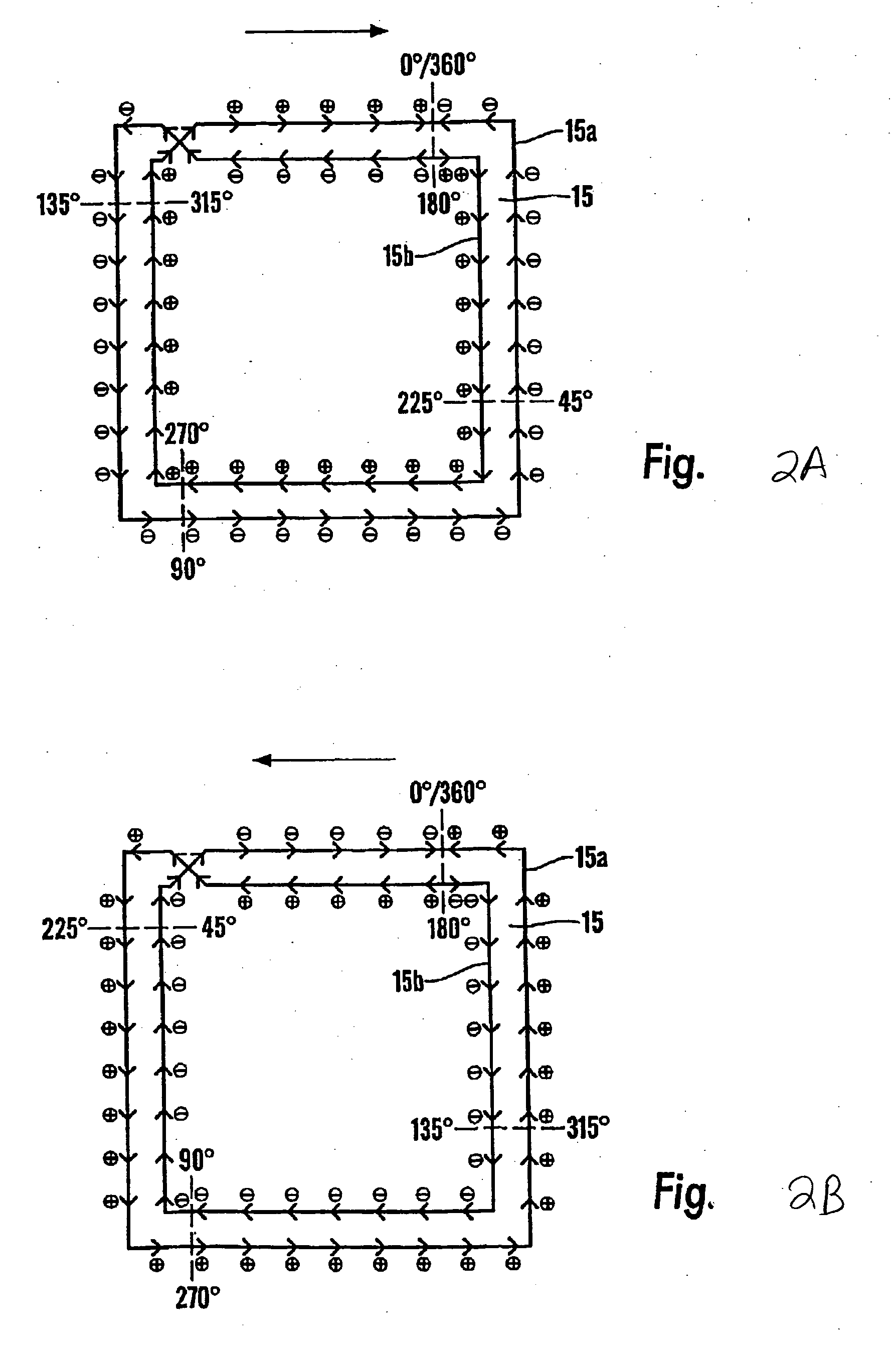

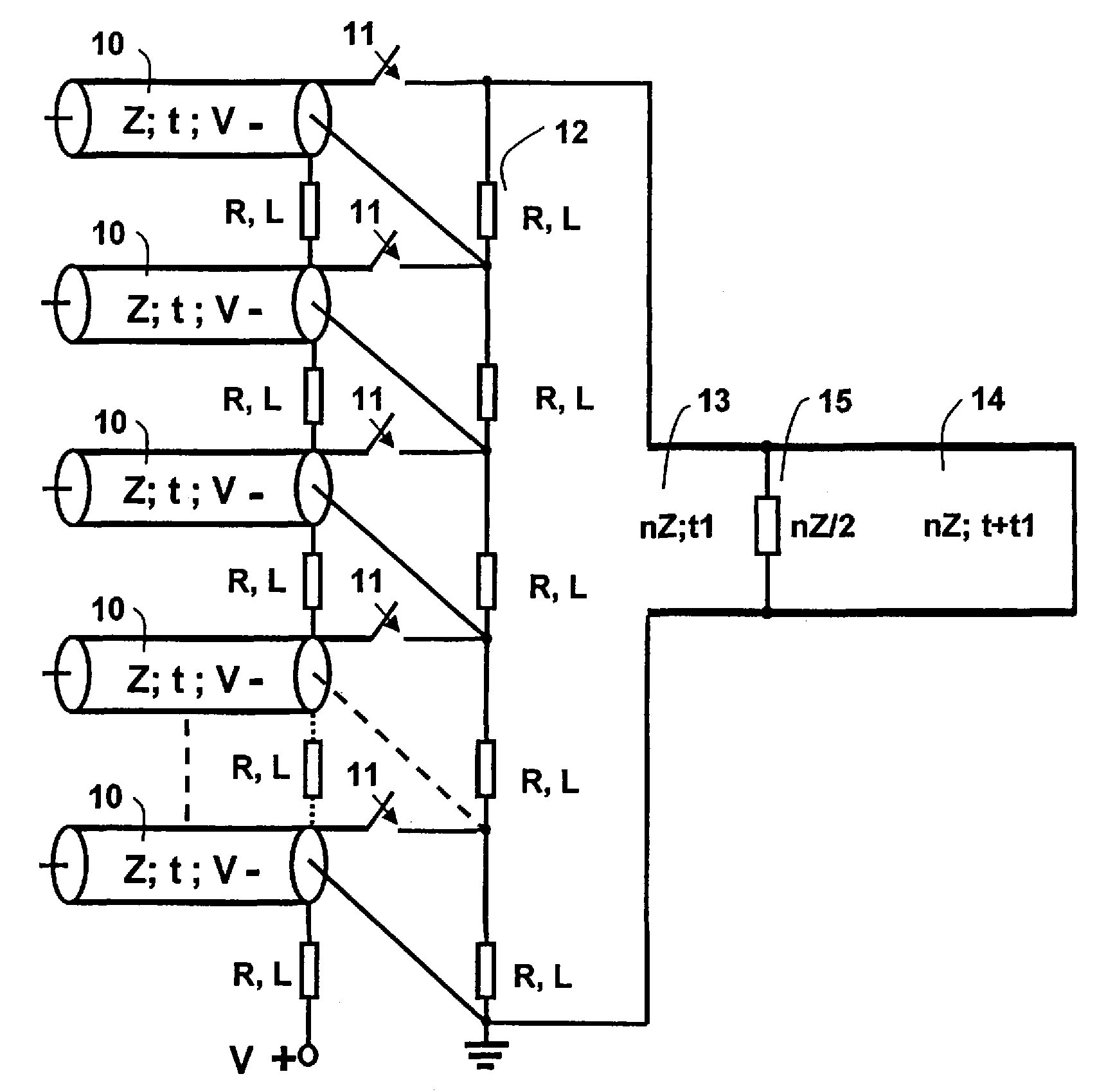

Timing signal generation and distribution are combined in operation of a signal path exhibiting endless electromagnetic continuity affording signal phase inversion and having associated regenerative active means. Two-or more-phases of substantially square-wave bipolar signals arise directly in travelling wave transmission-line embodiments compatible with semiconductor fabrication including CMOS. Coordination by attainable frequency synchronism with phase coherence for several such oscillating signal paths has intra-IC inter-IC and printed circuit board impact.

Owner:ANALOG DEVICES INC

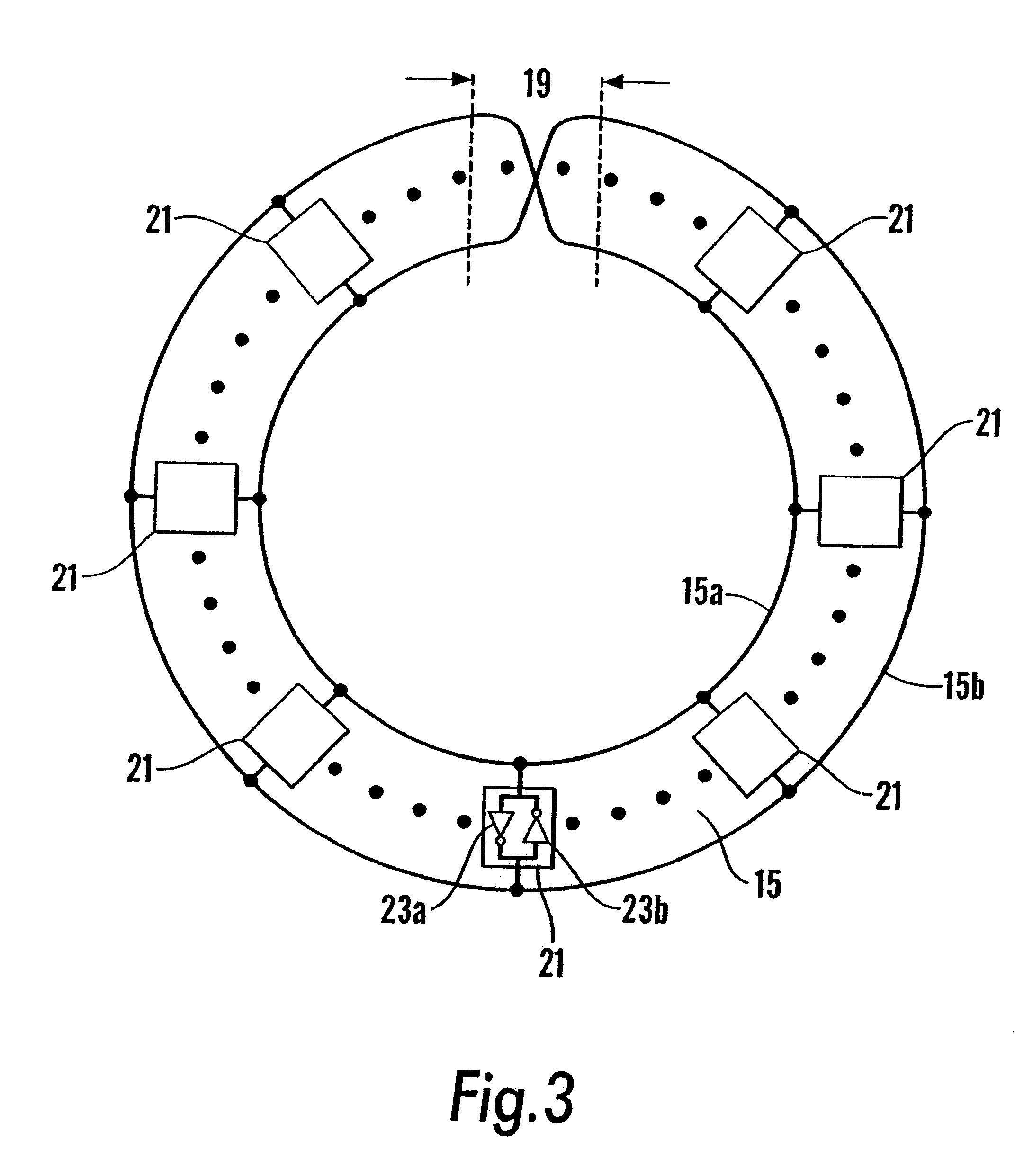

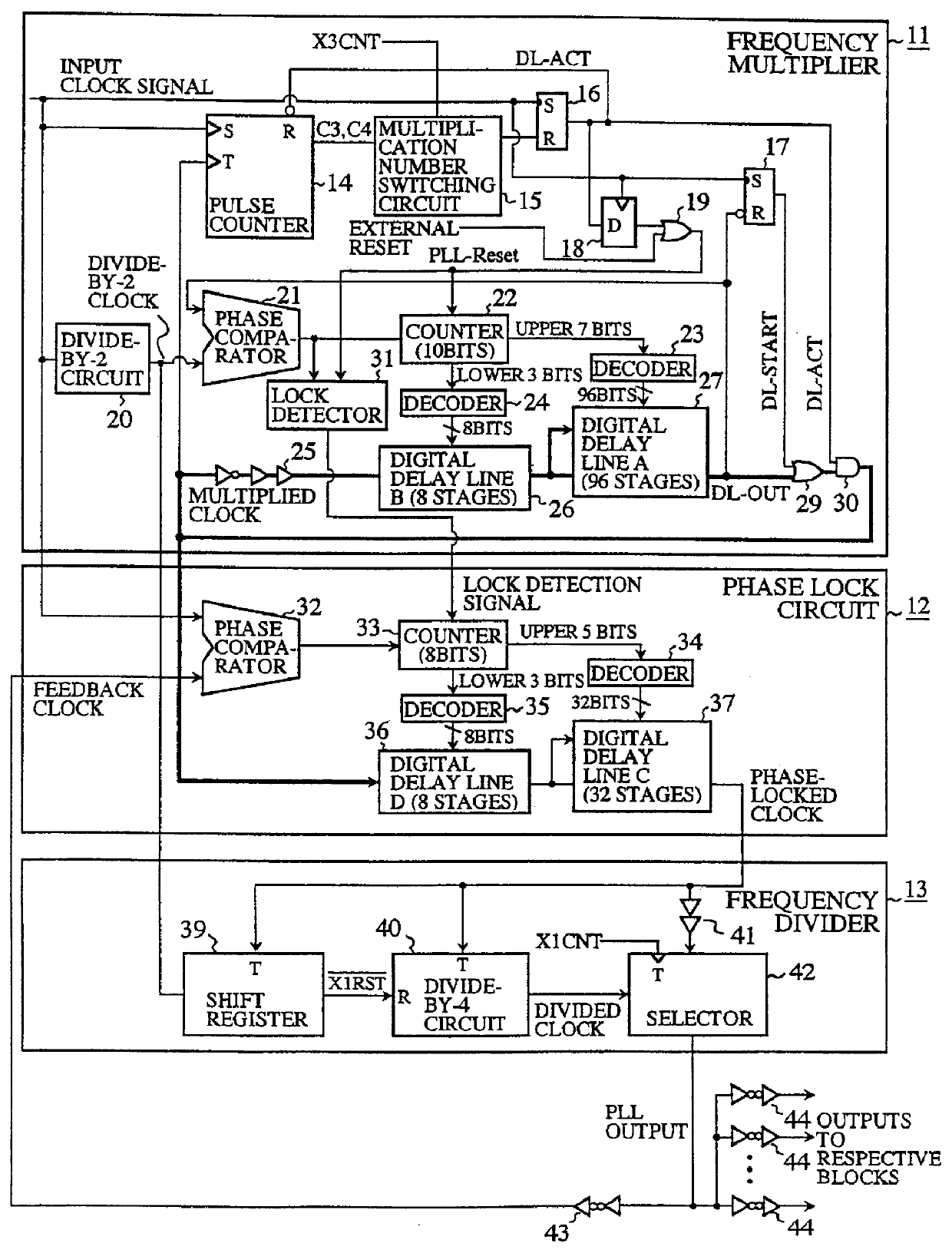

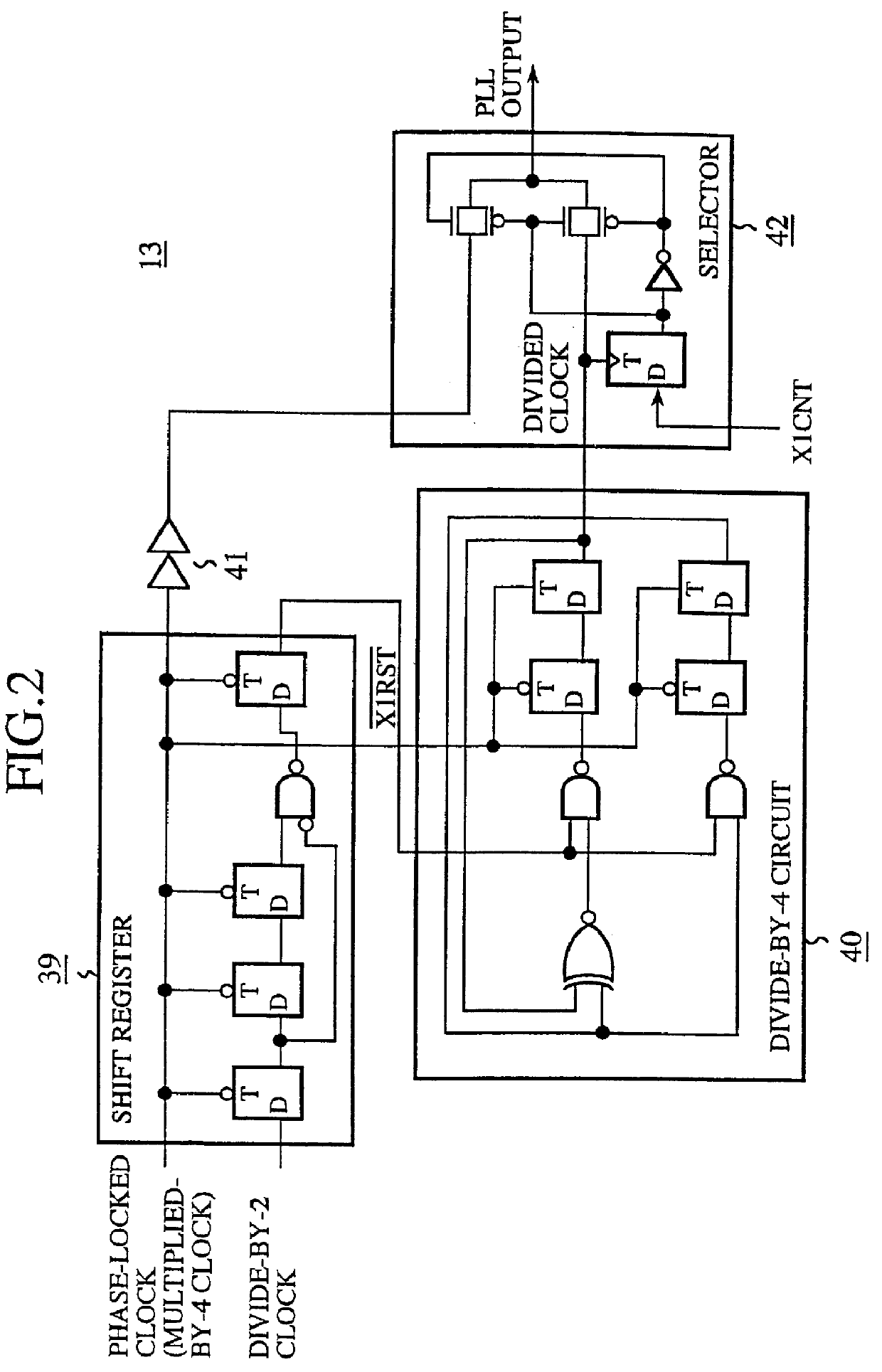

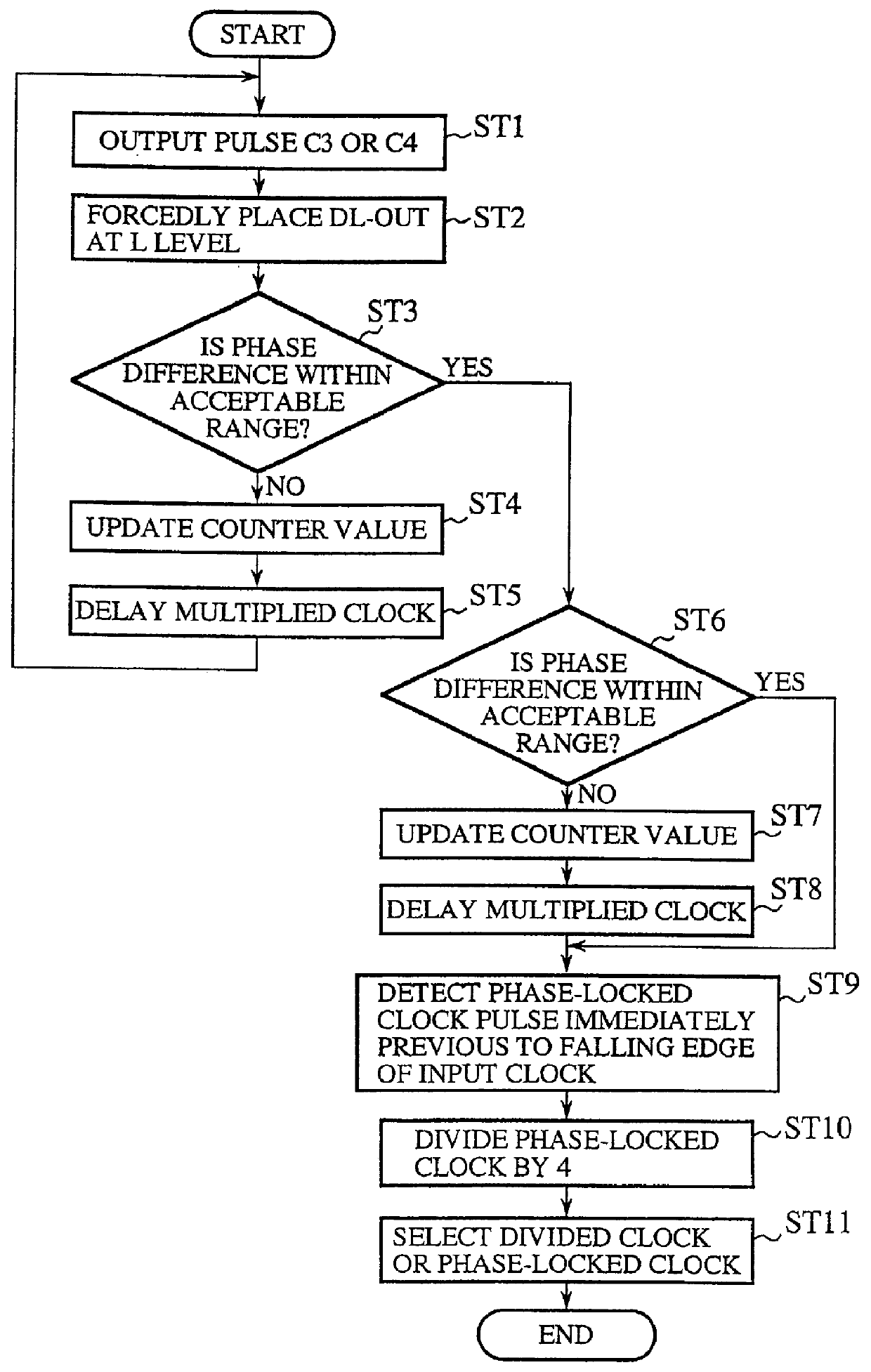

Clock generator and clock generating method capable of varying clock frequency without increasing the number of delay elements

InactiveUS6049238AReduce frequencyDelay lines pulse generationPulse automatic controlPhase differenceDelayed time

A clock generator including a frequency multiplier, a phase lock circuit and a frequency divider. The frequency multiplier generates a frequency multiplied clock by multiplying the frequency of an input clock. The phase lock circuit detects a phase difference between the input clock and a frequency divided clock, and generates, by delaying the frequency multiplied clock by an amount corresponding to the phase difference, a phase-locked clock with its phase locked with the input clock. The frequency divider detects in every fixed cycle a particular pulse of the phase-locked clock, and generates the frequency divided clock by dividing the phase-locked clock with reference to the particular pulse of the phase-locked clock. In particular, the frequency divider detects the particular pulse immediately previous to a falling edge of the input clock. This can reduce the phase difference between the input clock and the phase-locked clock, and hence to solve a problem of a conventional clock generator in that a delay time of a digital delay line in a phase lock circuit must be lengthened with a reduction in the multiplication number of the frequency multiplied clock, which requires a greater number of delay elements because of a large occupying area of the delay elements and a decoder, thereby increasing the circuit scale and cost of a chip to reduce the multiplication number of the frequency multiplied clock.

Owner:RENESAS ELECTRONICS CORP

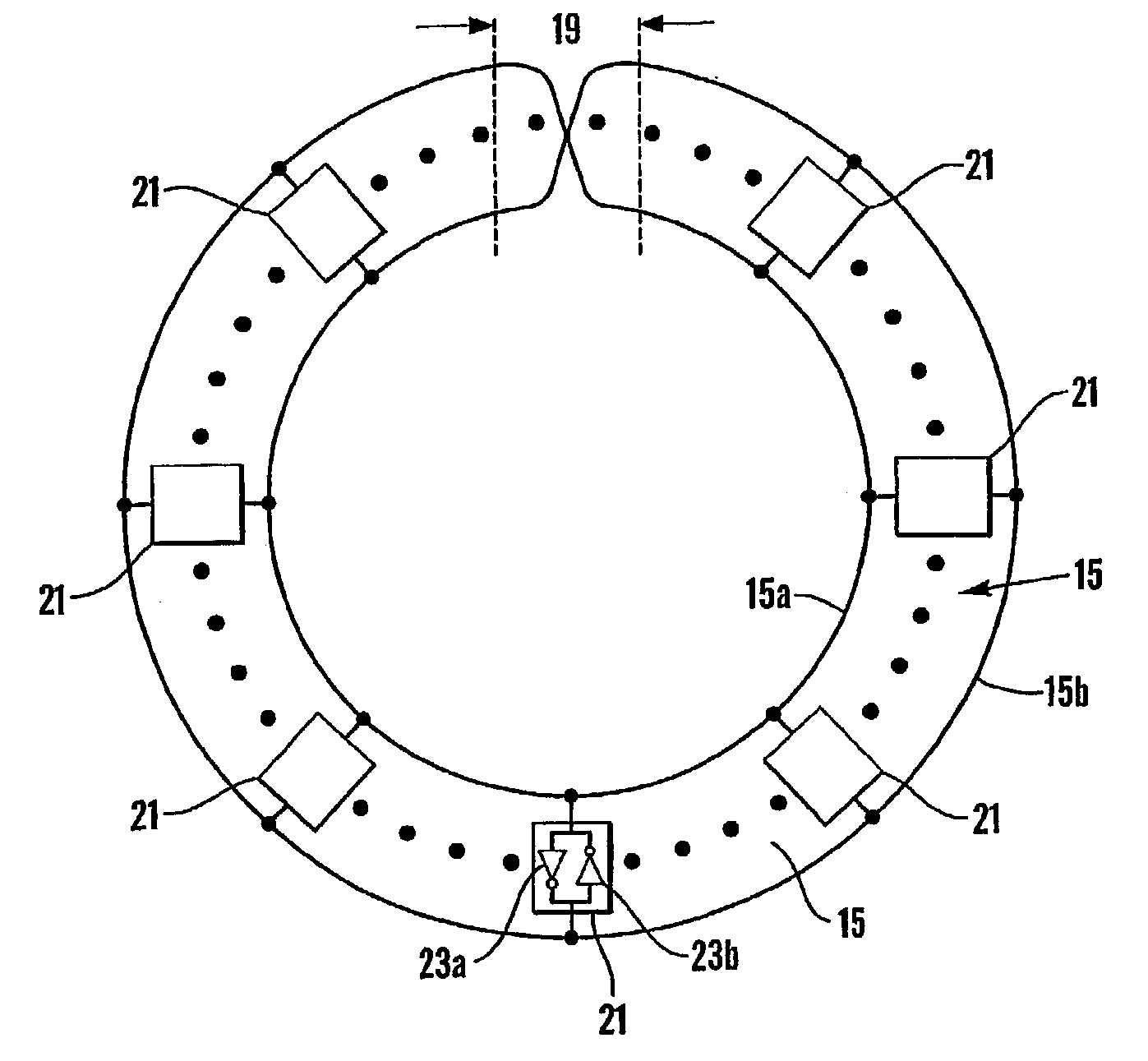

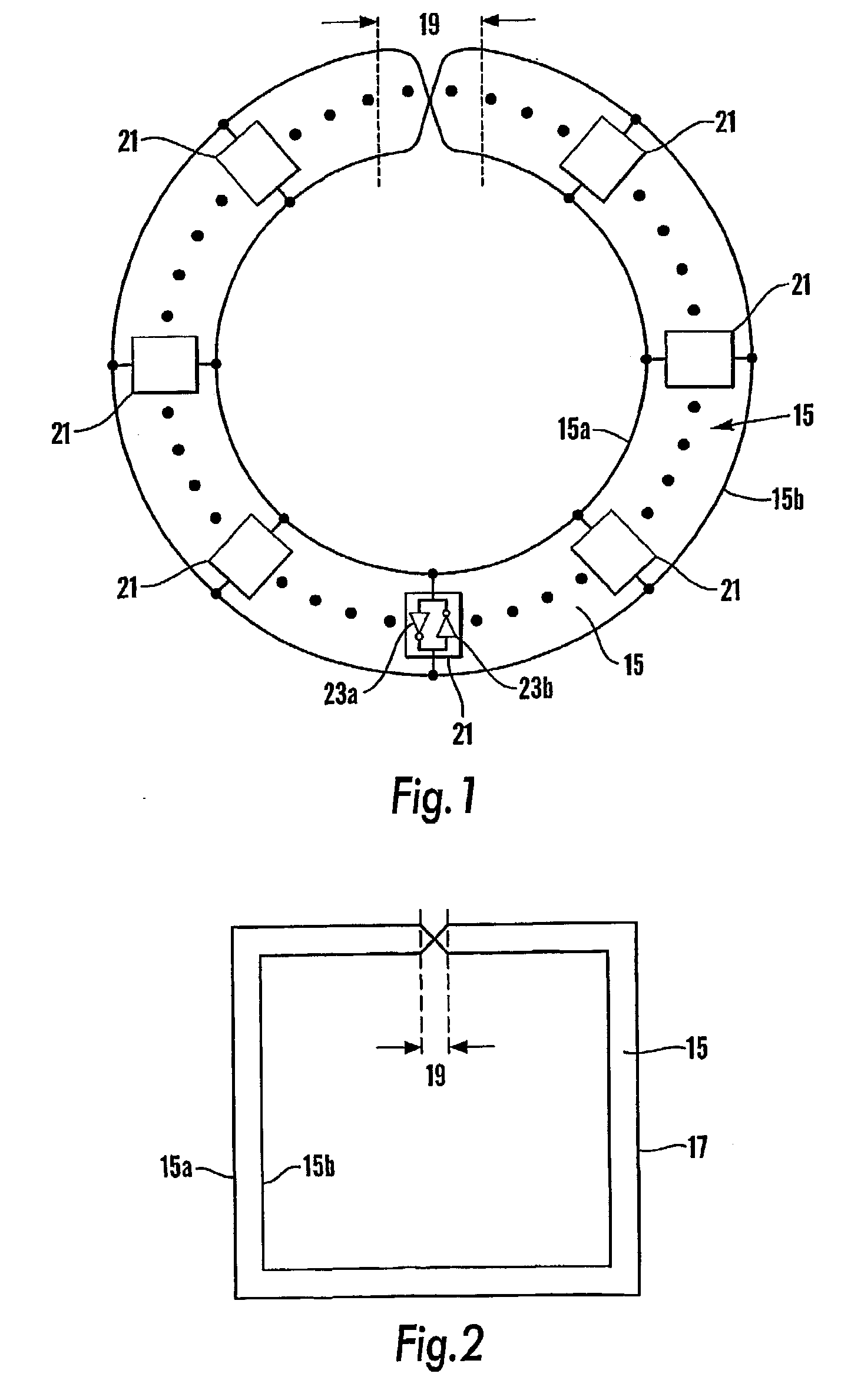

Electronic pulse generator and oscillator

InactiveUS20030151465A1Avoid problemsIncrease lossDelay lines pulse generationSemiconductor/solid-state device detailsFall timeFrequency regulation

Improvements in and relating to electronic pulse generation or oscillation circuitry based on a signal path exhibiting endless electromagnetic continuity and affording signal phase inversion in setting pulse duration or half-cycles of oscillation within time of signal traverse of said signal path, and having active switching means associated with said signal path to set rise and fall times of each said pulse or said half-cycle of oscillation, including for frequency adjustment by selective inductance and power saving without stopping pulse generation or oscillation.

Owner:ANALOG DEVICES INC

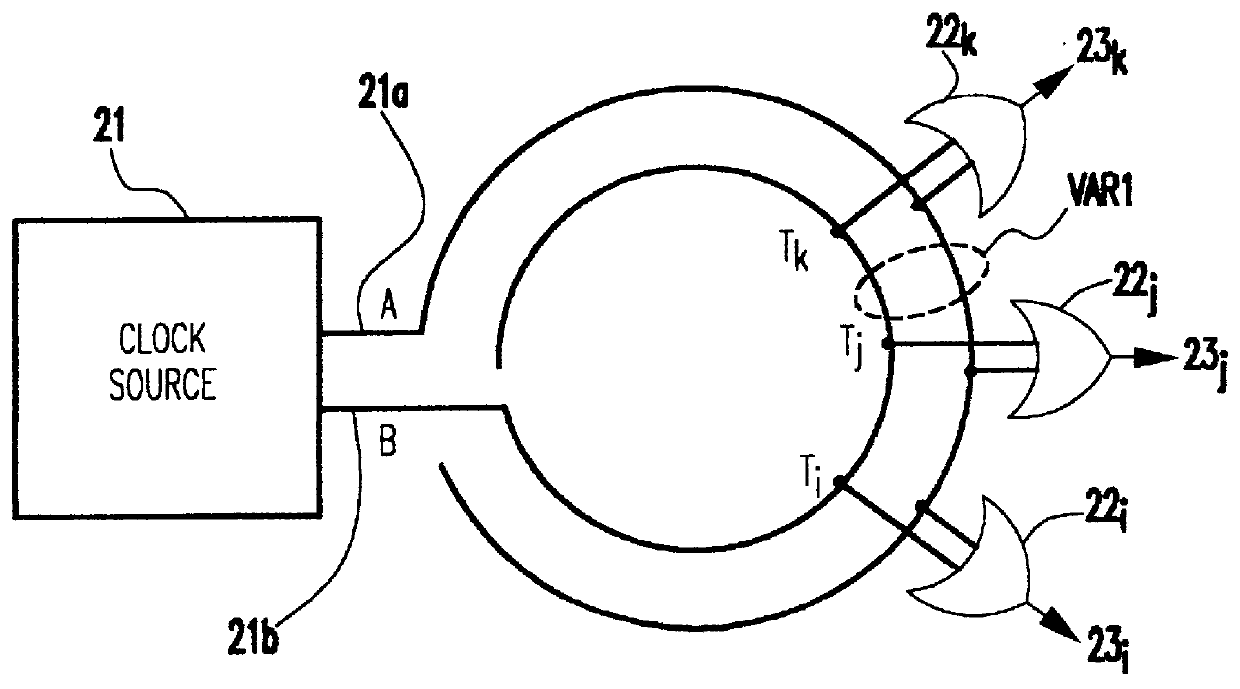

Phase error correction in rotary traveling wave oscillators

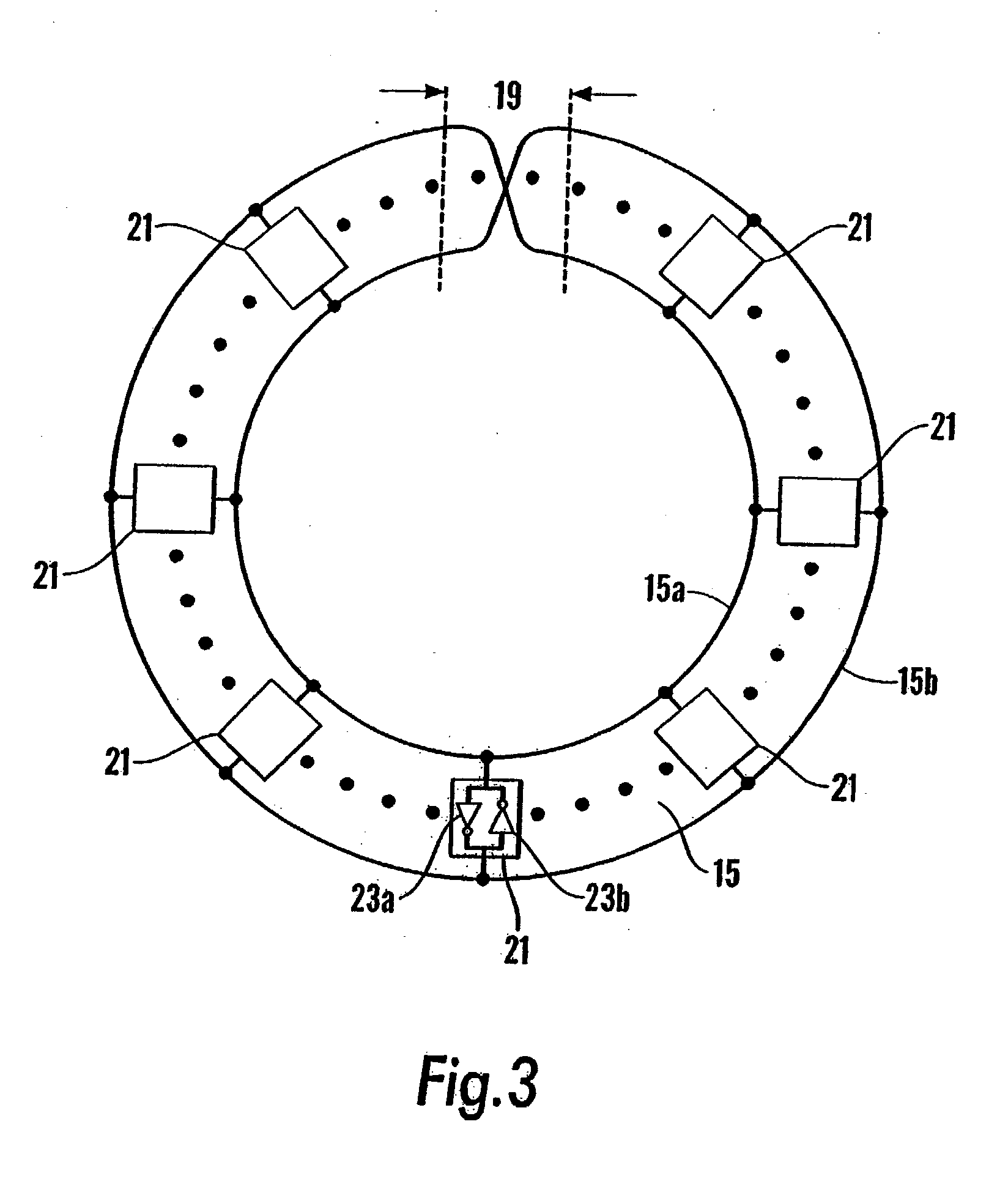

InactiveUS20100117744A1Reduce detected phase errorReduced phase velocityDelay lines pulse generationPulse generation by logic circuitsCapacitancePhase correction

An RTWO apparatus includes an N-phase RTWO (N is an integer greater than or equal to two) and a phase correction circuit. The N-phase RTWO includes a closed-loop transmission line formed as a Moebius strip. The closed-loop transmission line includes N transmission line segments, to which N voltage controlled capacitors are coupled. The N transmission line segments provide N output phases. The phase correction circuit operates to detect phase errors between output phases, and, depending on the detected phase errors, generates N control voltages for controlling the capacitances of the N voltage controlled capacitors. Controlling the capacitances of the N voltage controlled capacitors in this coordinated manner reduces the phase errors among the N output phases, thereby providing a phase accurate multi-phase RTWO output.

Owner:PANASONIC CORP

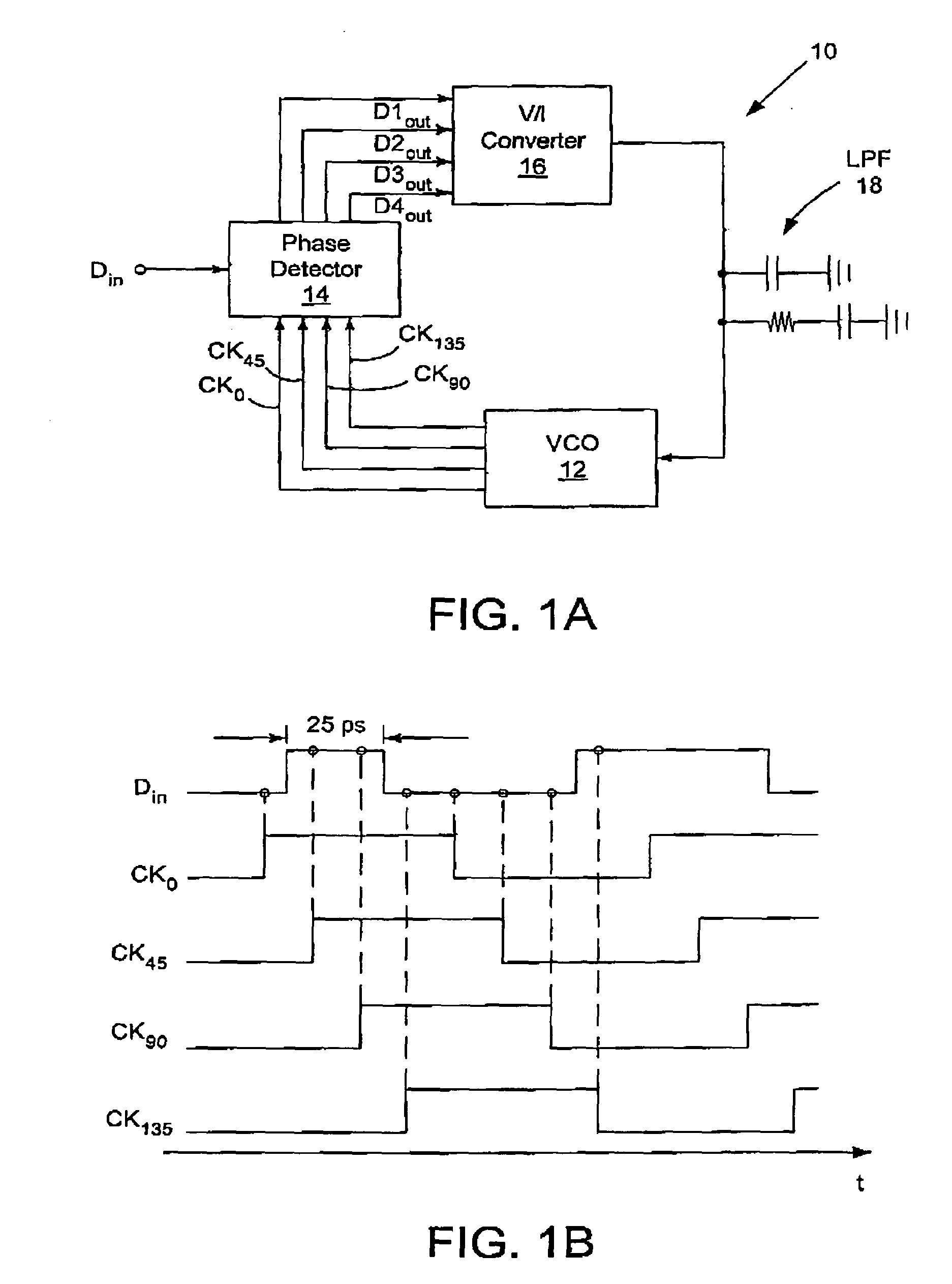

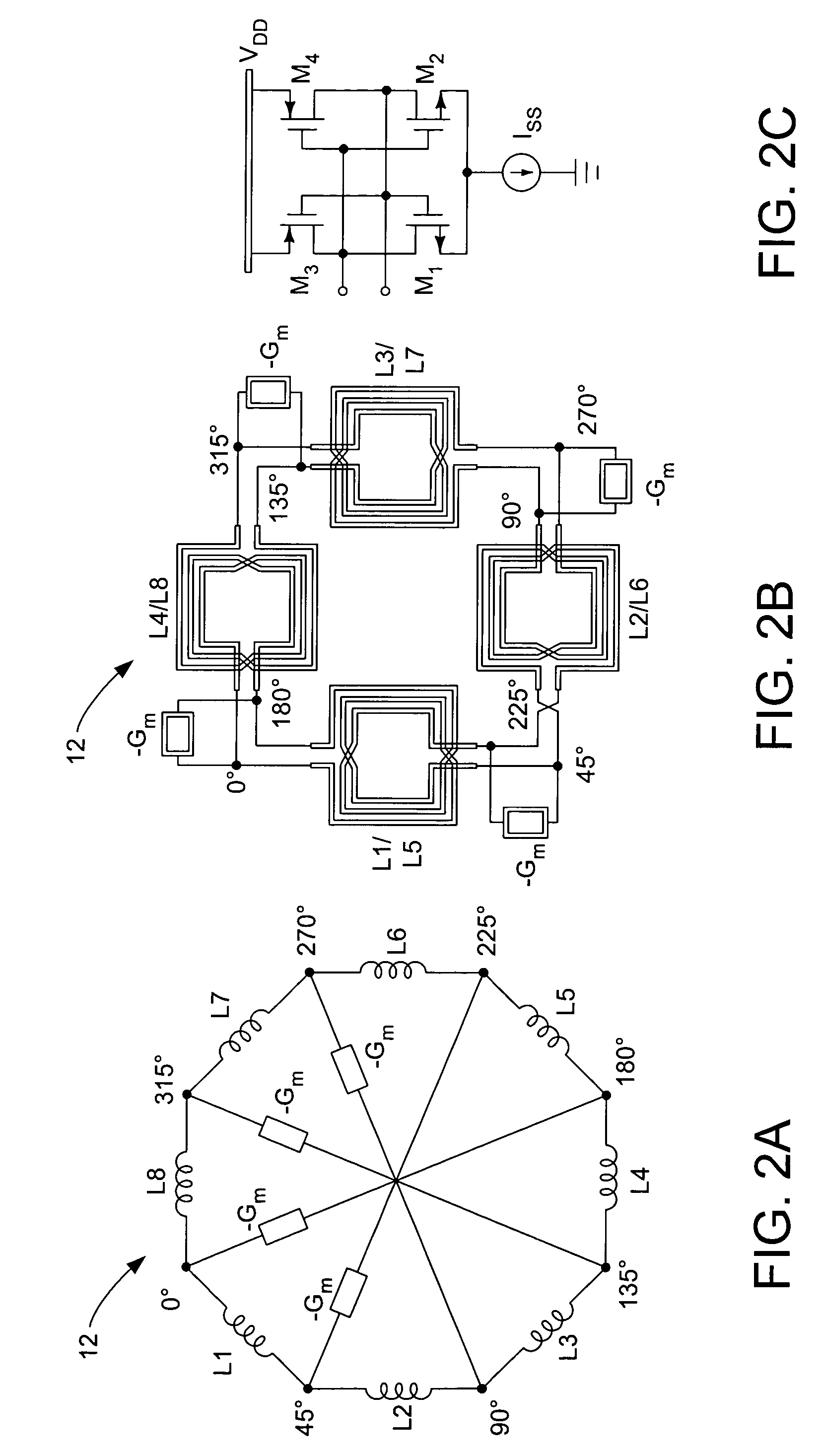

High-speed clock and data recovery circuit

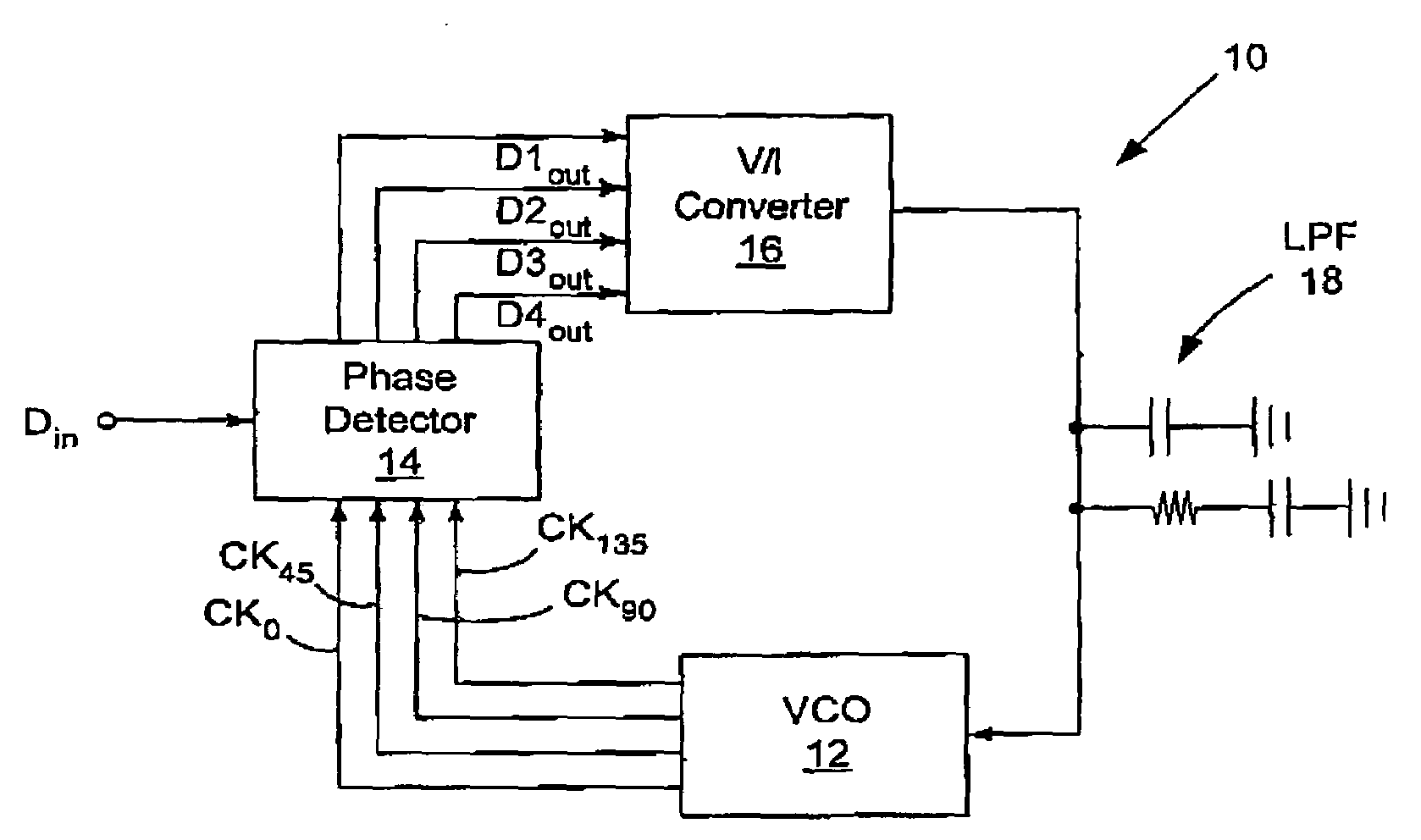

A 40-Gb / s clock and data recovery (CDR) circuit incorporates a quarter-rate phase detector and a multi-phase voltage controlled oscillator to re-time and de-multiplex a 40-Gb / s input data signal into four 10-Gb / s output data signals. The circuit is fabricated in 0.18 μm CMOS technology.

Owner:RGT UNIV OF CALIFORNIA

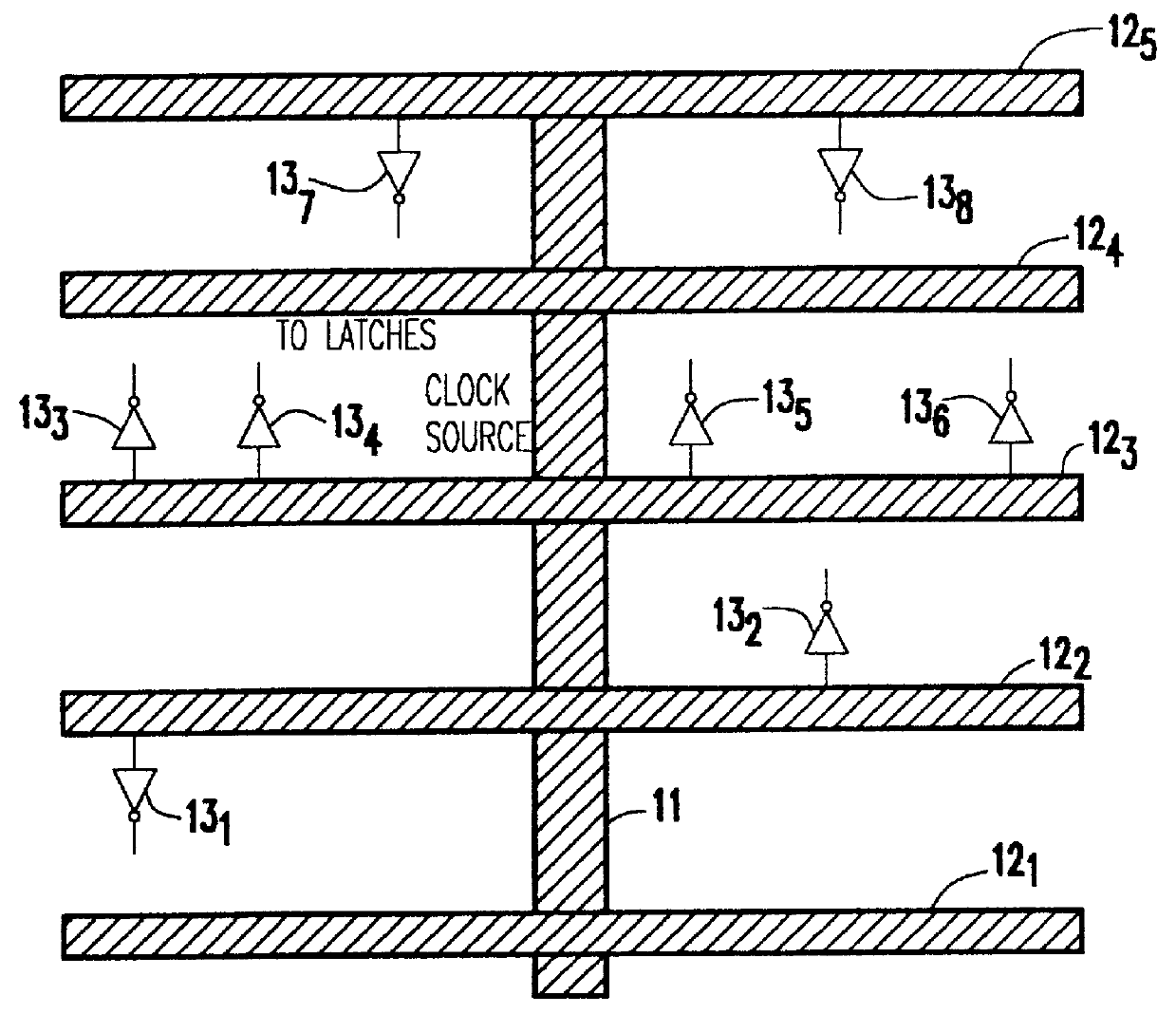

Clock distribution network with dual wire routing

InactiveUS6144224AMinimizing clock skewsModerate power consumptionDelay lines pulse generationSolid-state devicesNOR gateDistribution networks

A new clock distribution network design for VLSI circuits which effectively reduces skew without the area and power penalty associated with prior clock designs. Two wires emanating from the clock in opposite directions or, alternatively, two wires connected in series and running parallel, are used to route clock signals from the clock source to the next routing segment. The next routing segment routes clock signals to the tapping point near the circuit component by two emanated wires from the previous routing segment. Clock signals from the routing segments are fed through two-input NOR gates (alternatively, two-input NAND gates) to the clock pins. The clock signal arrival time is roughly equal to the simultaneous switching gate delay plus the average arrival times from the two paths, which turns out approximately the same across different tapping points, thus minimizing clock skews. Narrow wires may be used for routing, resulting in moderate power consumption.

Owner:IBM CORP

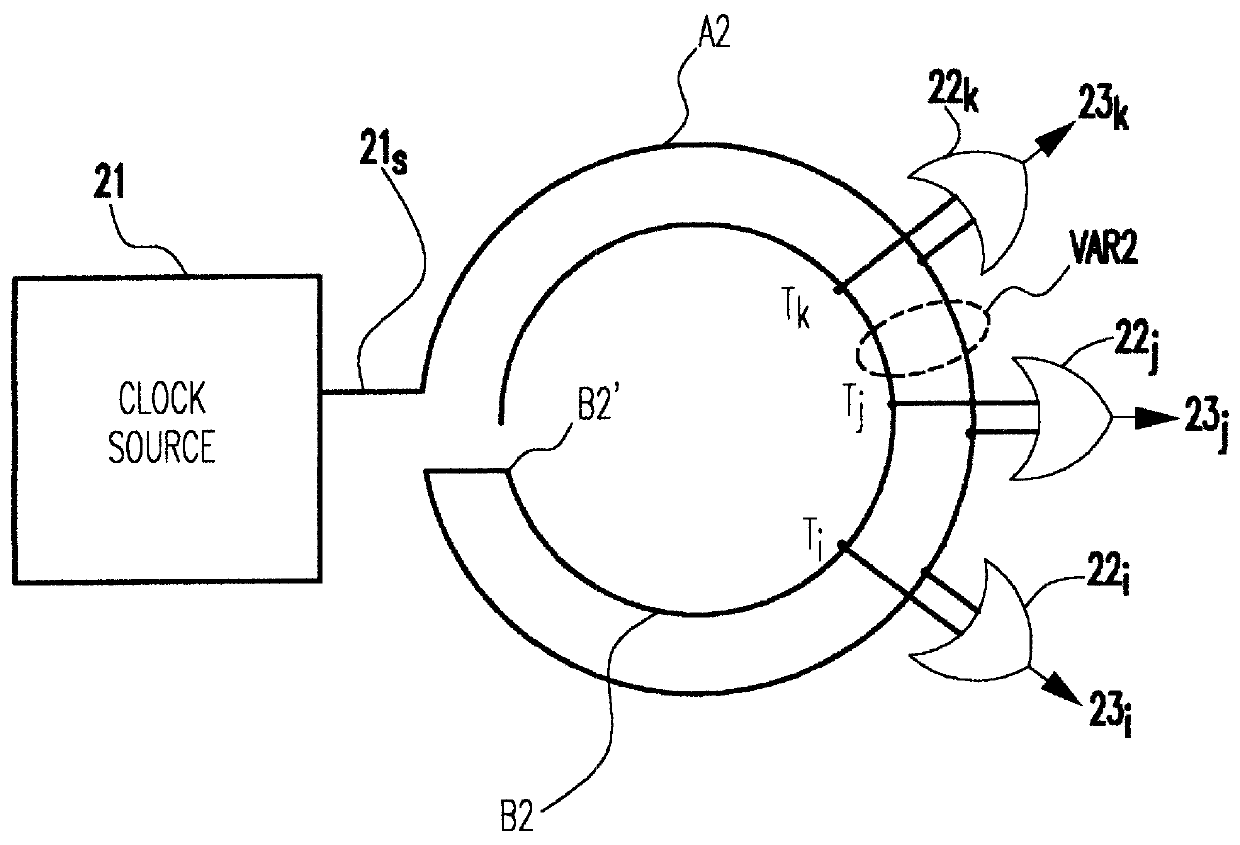

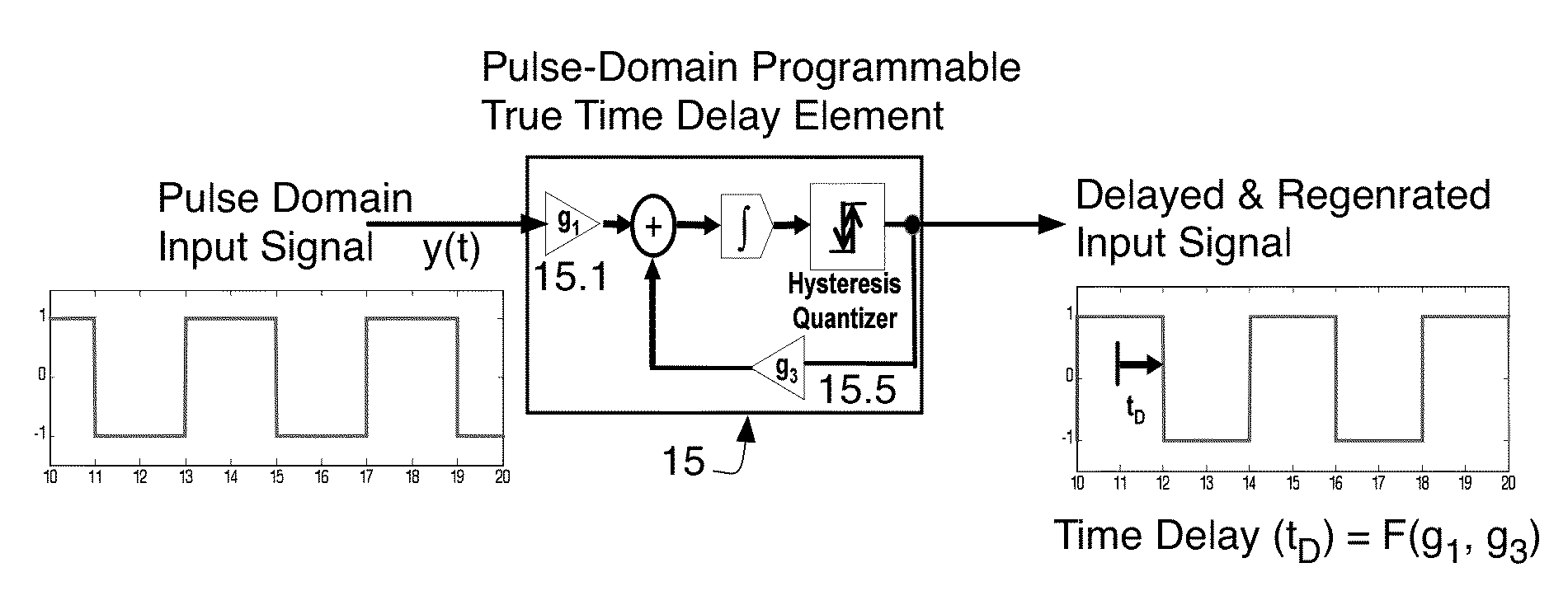

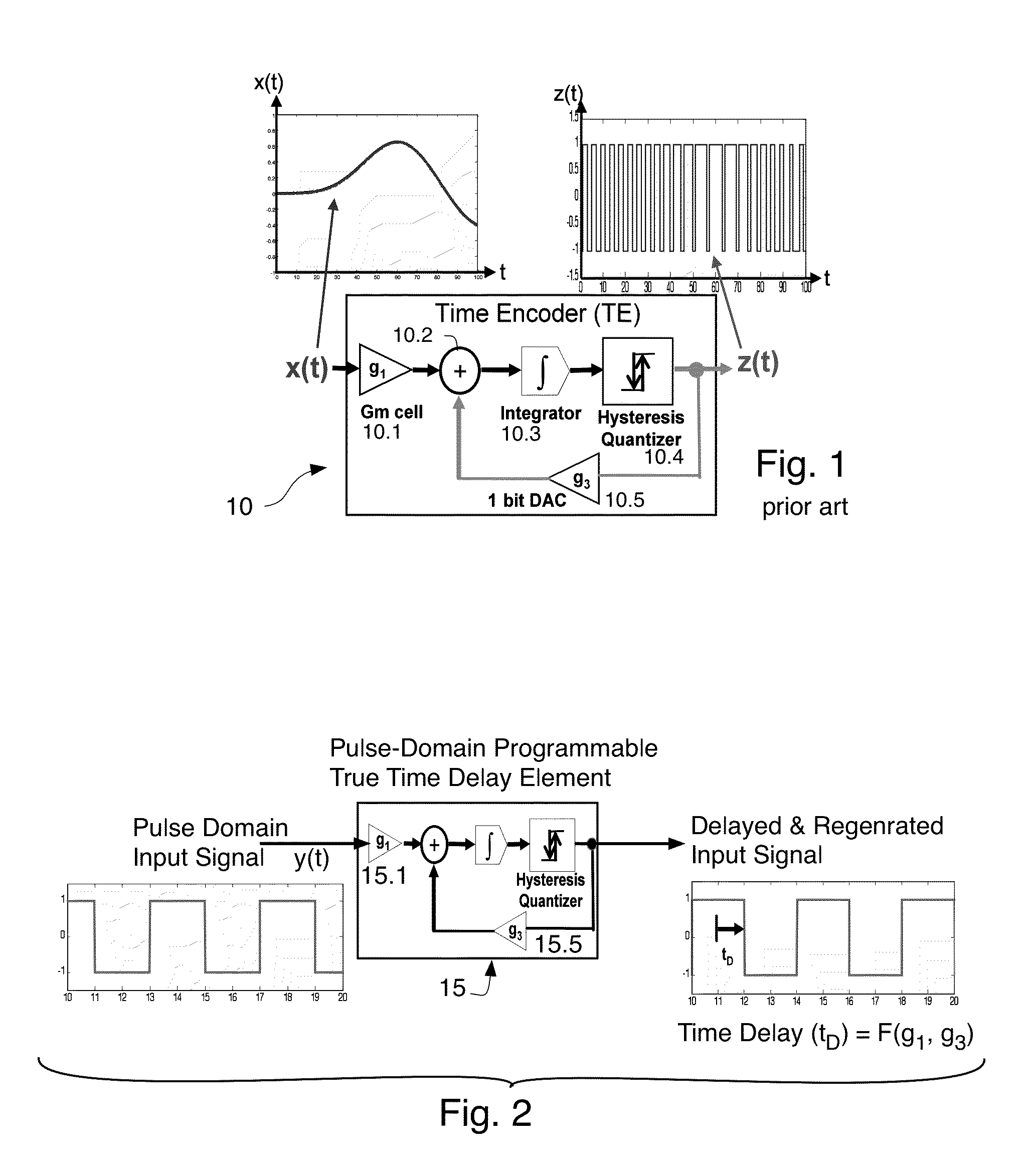

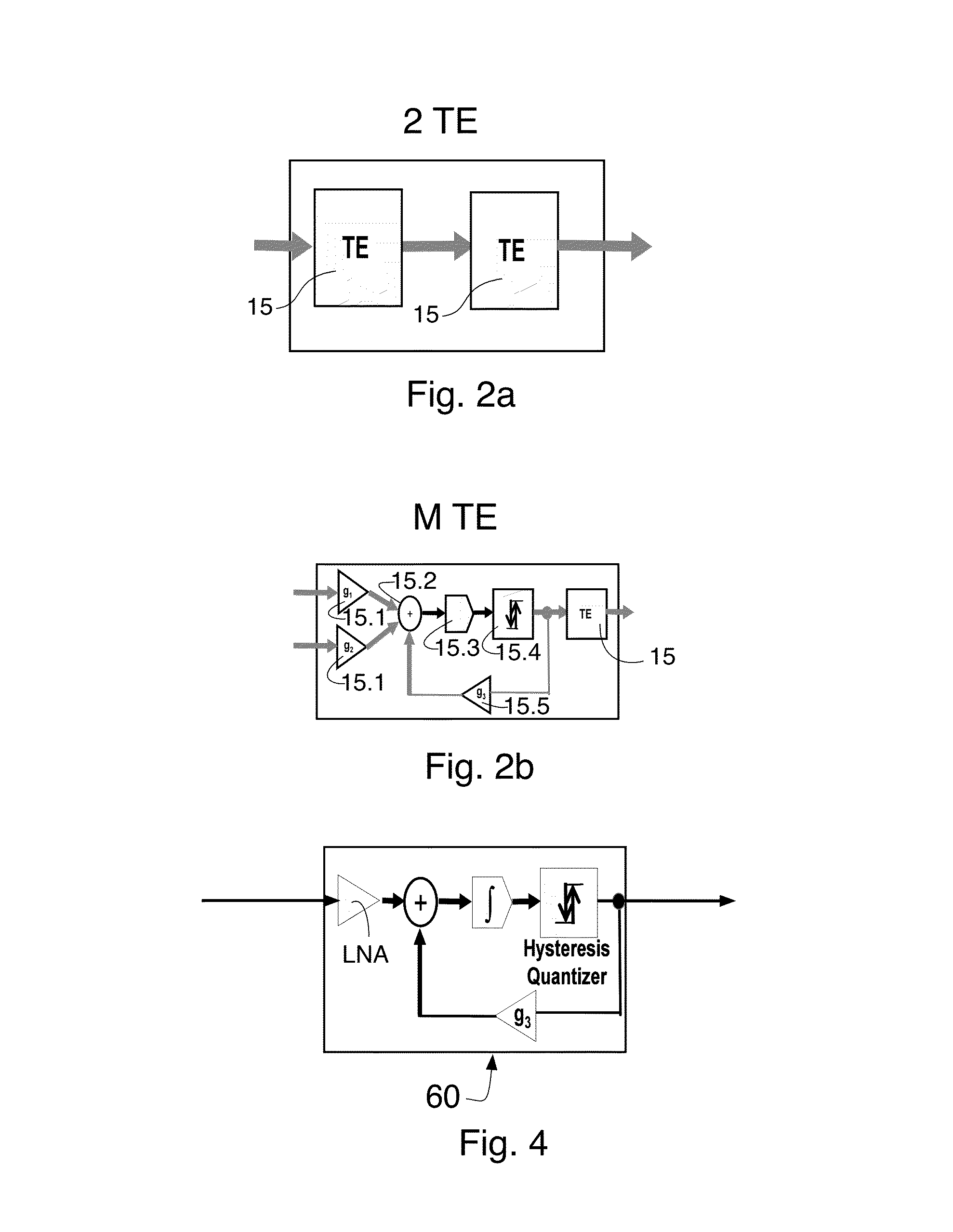

Time encoded circuits and methods and a time encoder based beamformer for use in receiving and transmitting applications

ActiveUS9154172B1Control delayDelay lines pulse generationPower reduction by control/clock signalComputer scienceEncoder

Owner:HRL LAB

Electronic circuitry

InactiveUS20030128075A1Rise and fall characteristicShort fallDelay lines pulse generationPulse automatic controlCMOSBipolar signal

Timing signal generation and distribution are combined in operation of a signal path exhibiting endless electromagnetic continuity affording signal phase inversion and having associated regenerative active means. Two-or more-phases of substantially square-wave bipolar signals arise directly in travelling wave transmission-line embodiments compatible with semiconductor fabrication including CMOS. Coordination by attainable frequency synchronism with phase coherence for several such oscillating signal paths has intra-IC inter-IC and printed circuit board impact.

Owner:ANALOG DEVICES INC

Low noise oscillator

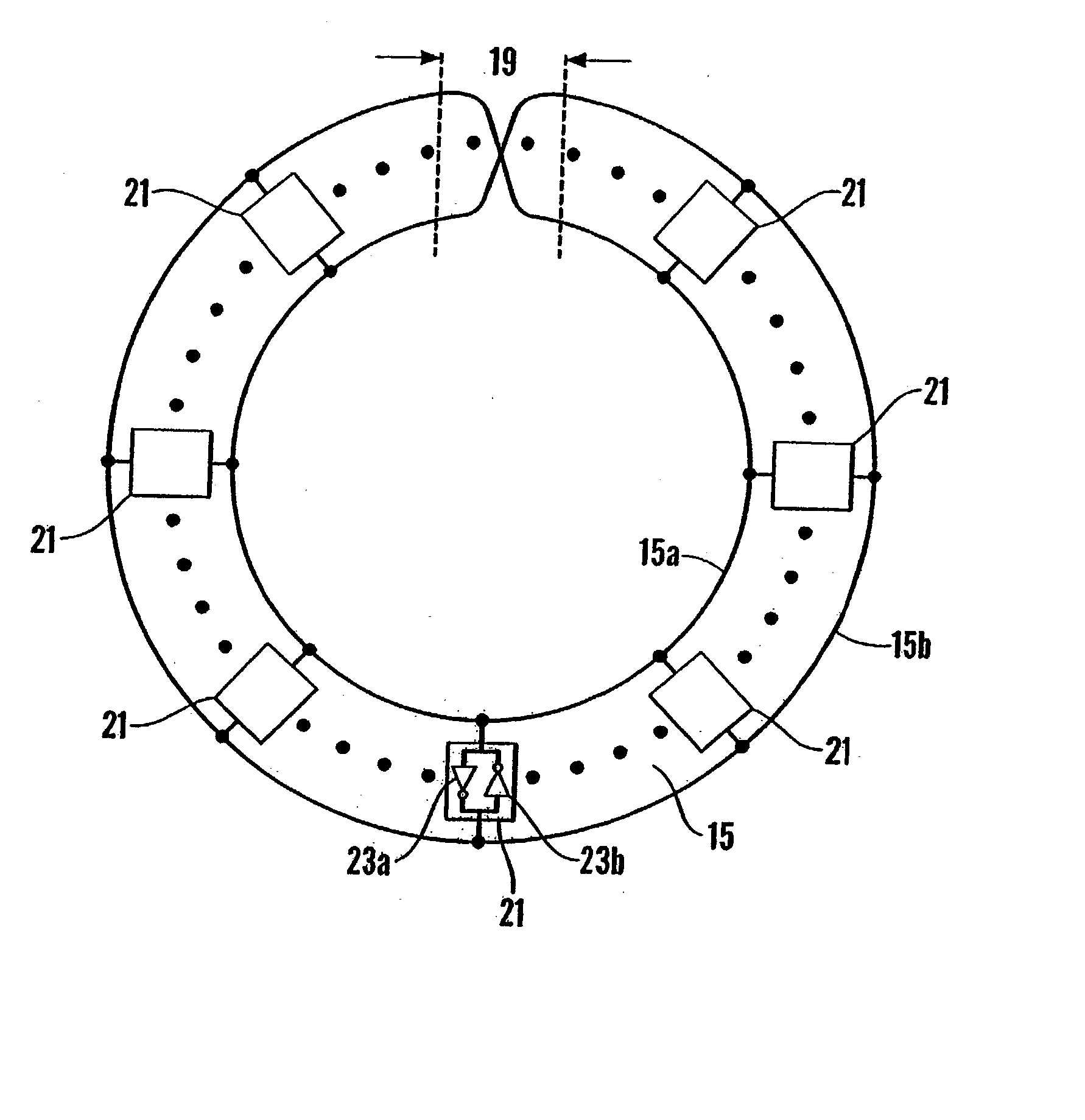

InactiveUS20050156680A1Reduce phase noiseSmall spacingDelay lines pulse generationSemiconductor/solid-state device detailsLow noiseElectrical conductor

A low noise oscillator constructed using a rotary traveling wave oscillator. The conductors of the rotary traveling wave oscillator provide at any tap position a pair of oppositely phased oscillations and these oscillations have slightly different phases at positions that are slightly different on the conductors. Regeneration devices establish and maintain oscillations on the conductors of the traveling wave oscillator. A regeneration device made from p-channel and n-channel transistors is connected to the conductors of the traveling wave oscillator in such a way that the gate connections of the transistors receive the traveling wavefront before the drains of the transistors receive the wavefront. By the time the regeneration device switches in response to the wavefront arriving at the gates of the transistors, the wavefront has arrived at the drains. This creates little or no disturbance to the wave on the conductors and results in low phase noise.

Owner:ANALOG DEVICES INC

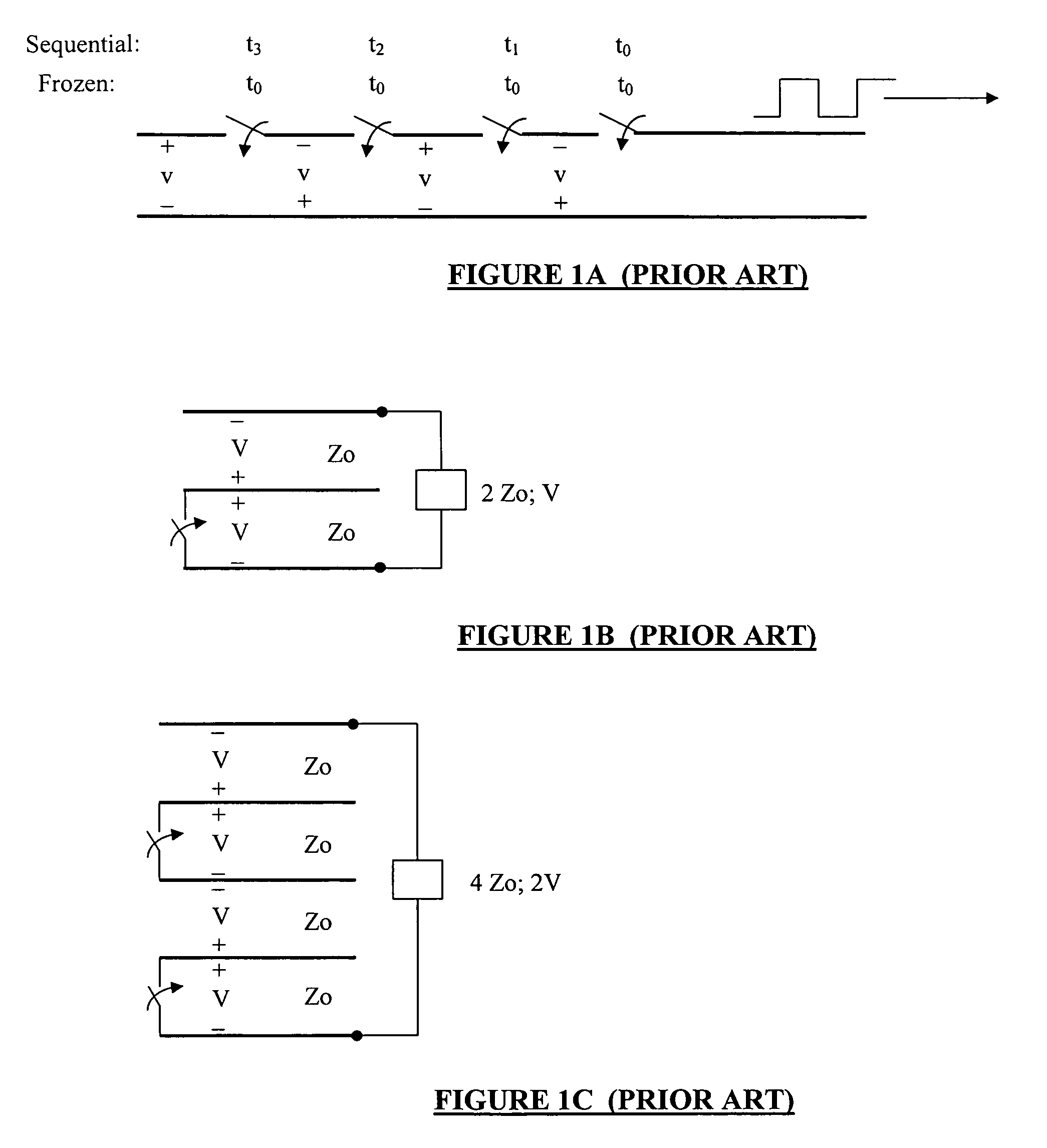

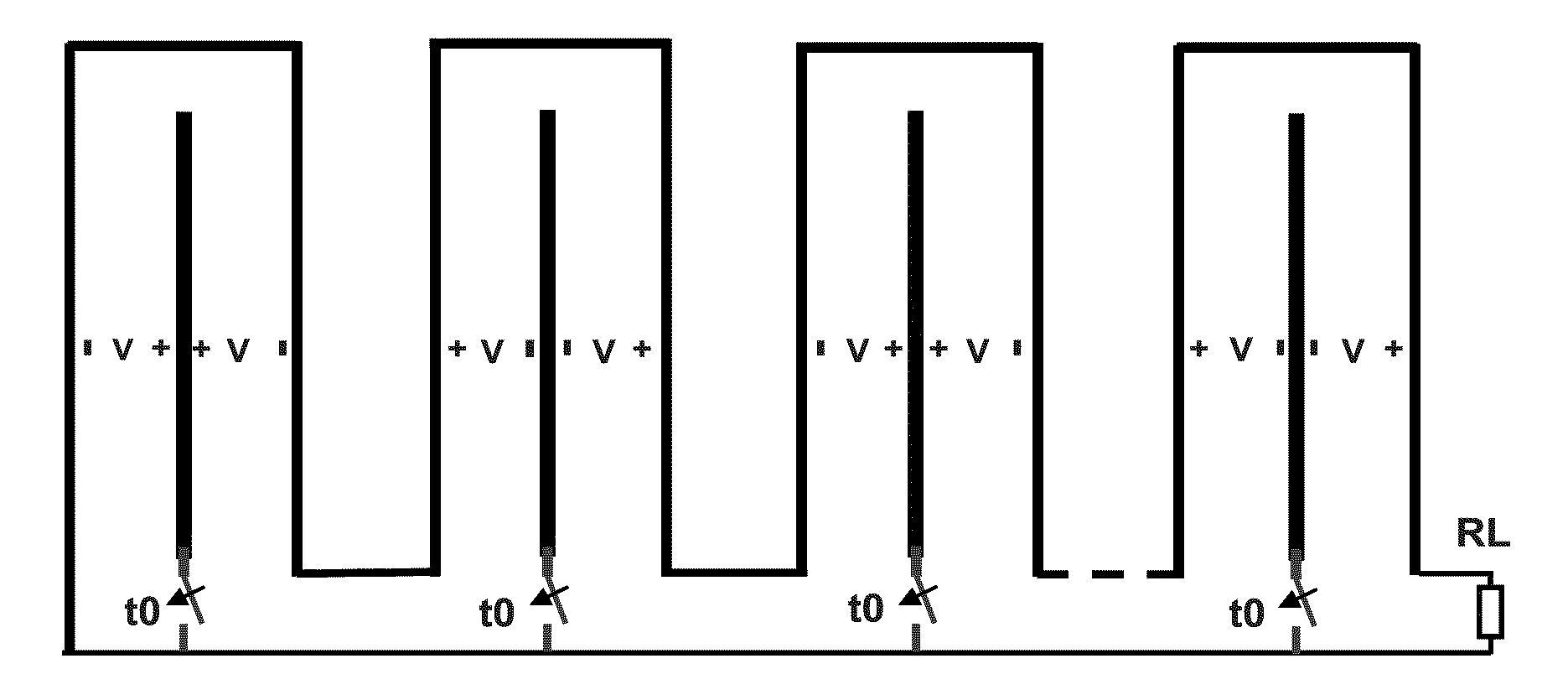

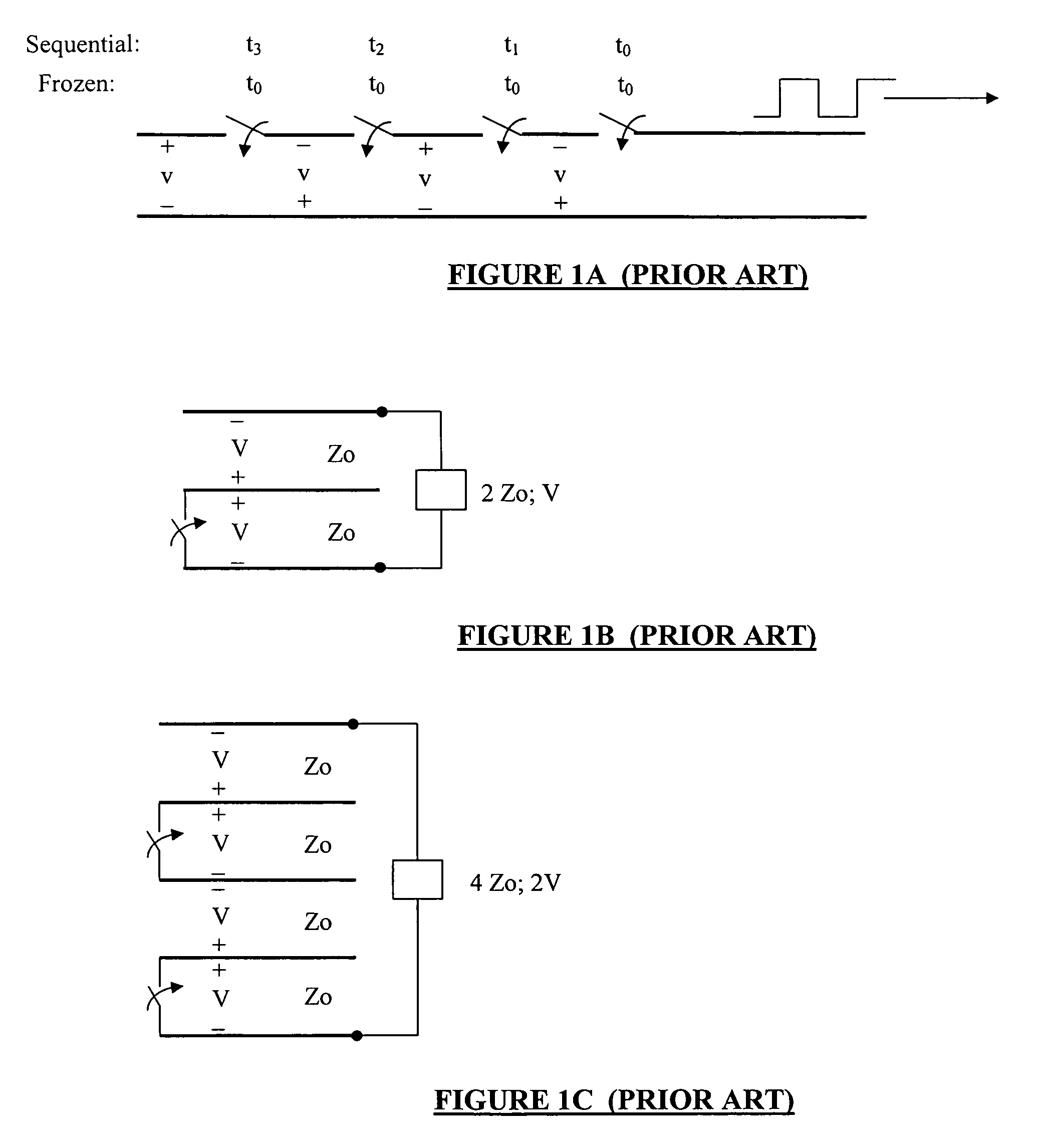

High power bipolar pulse generators

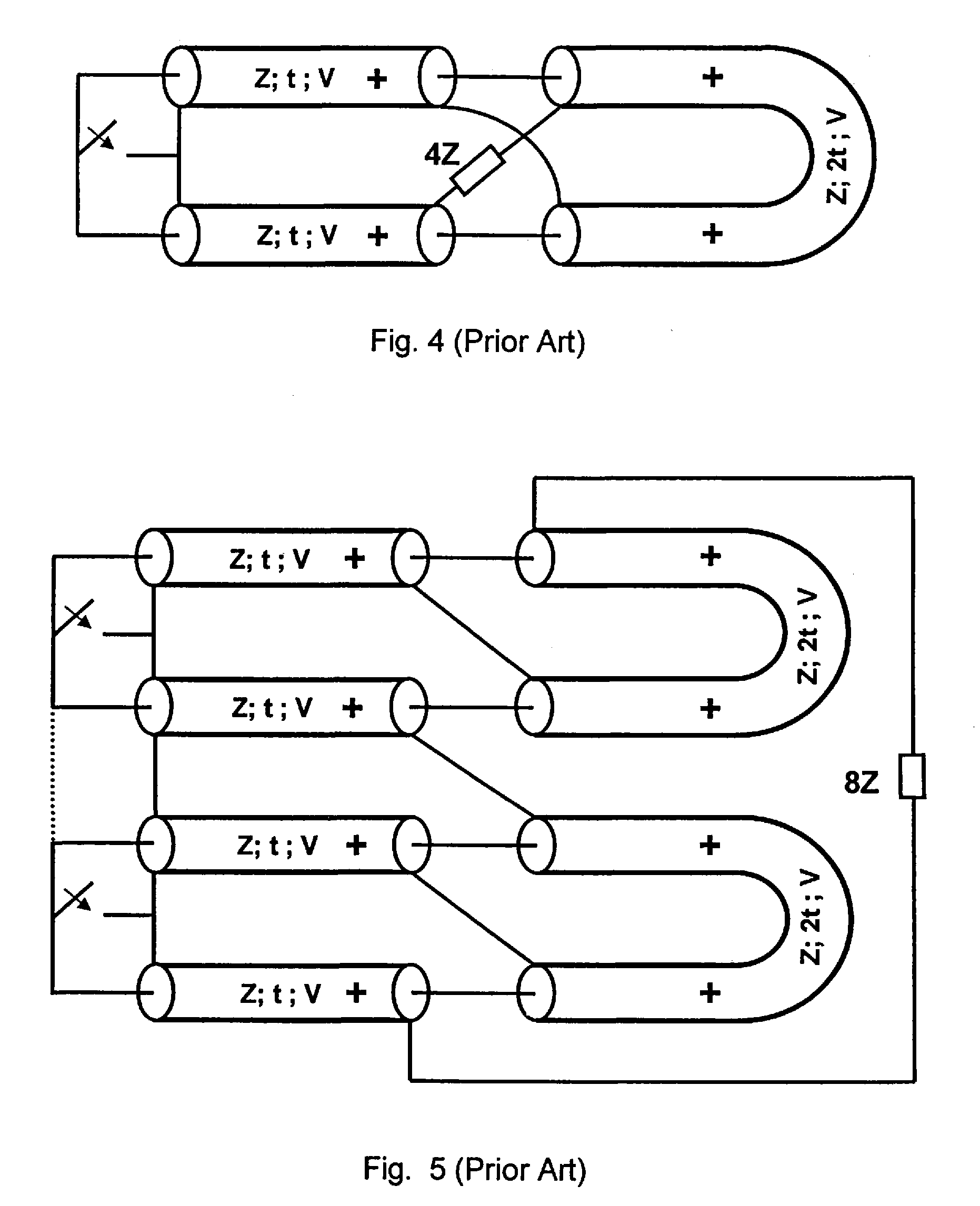

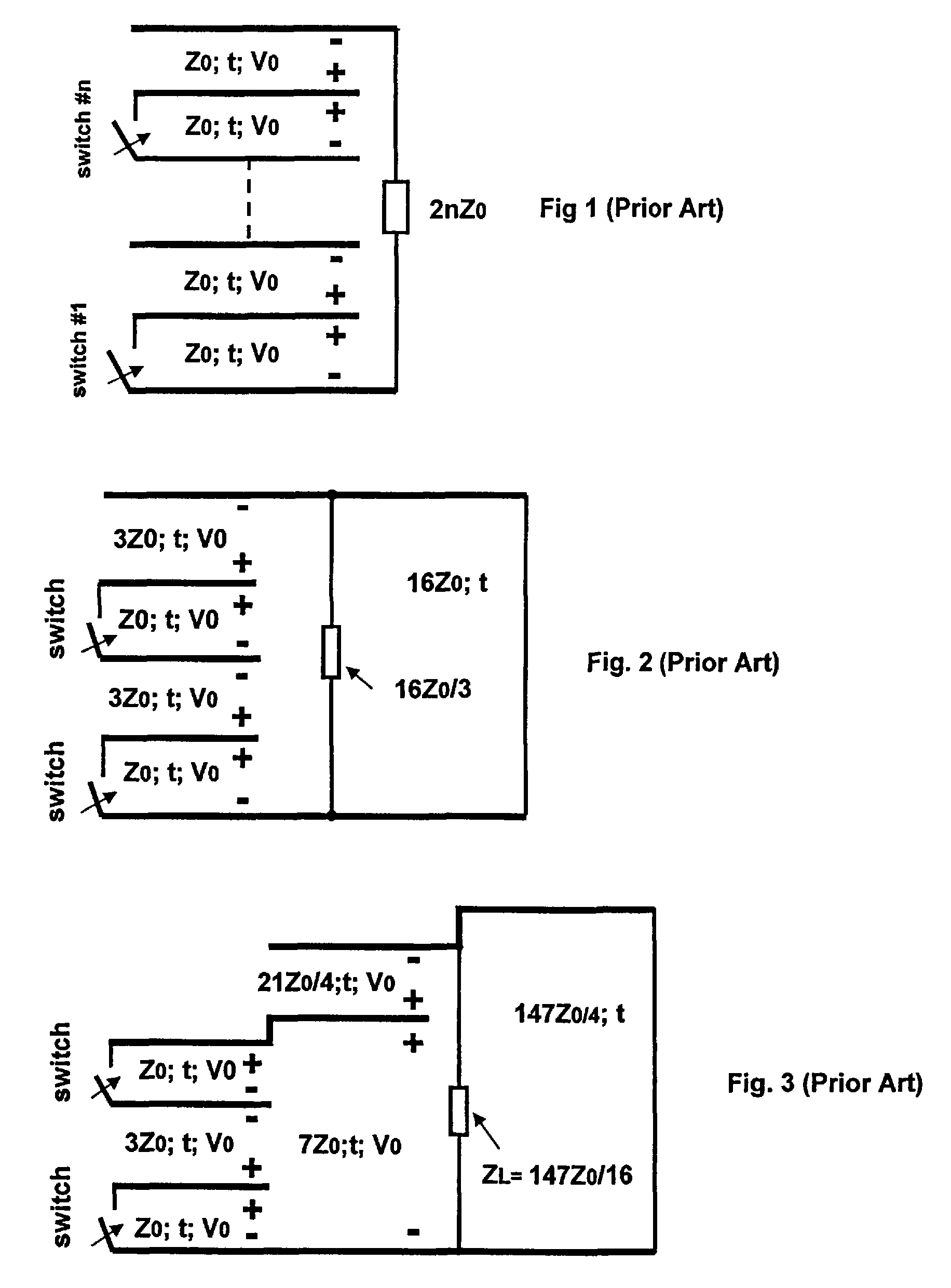

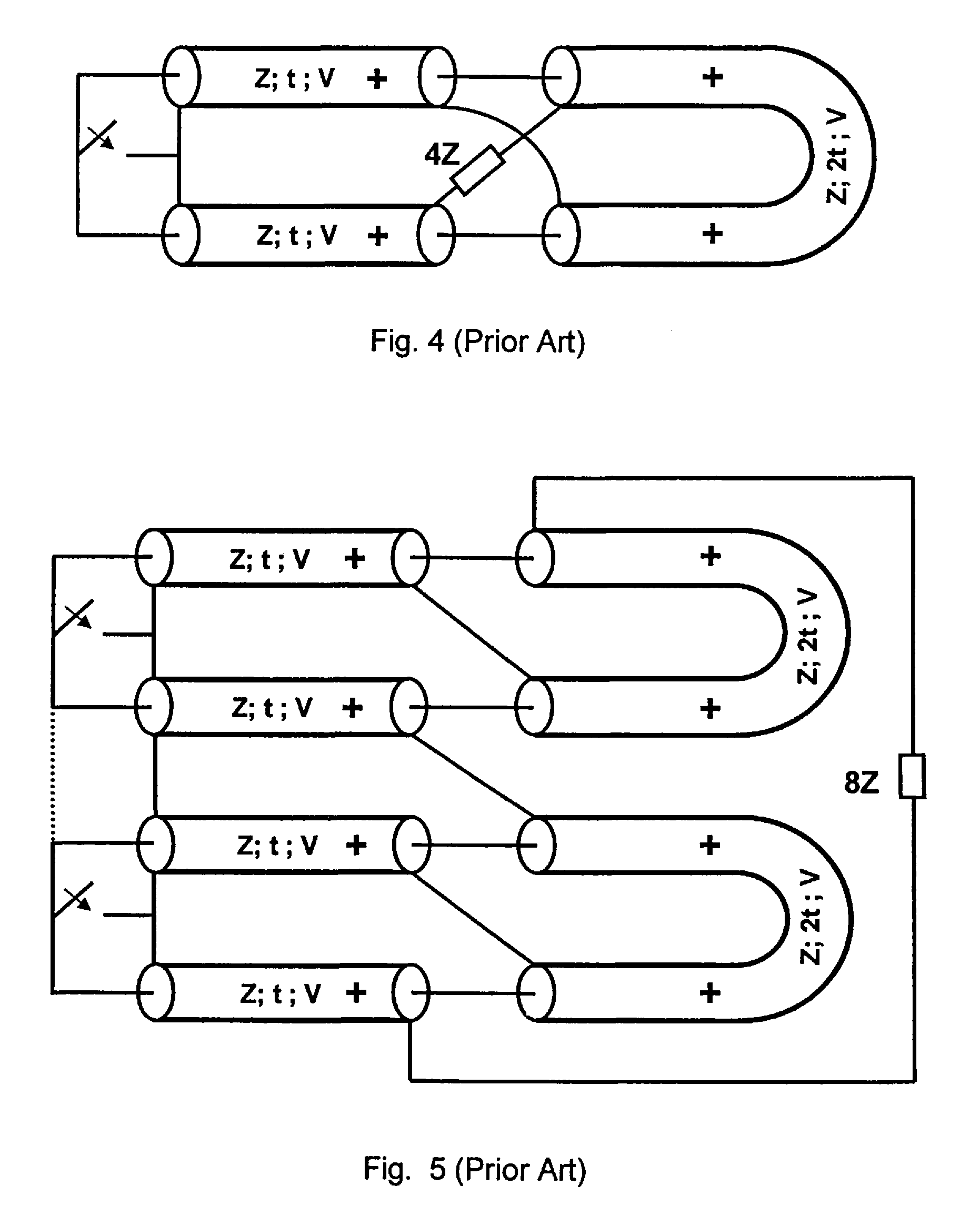

InactiveUS20100231278A1Simple structureImprove efficiencyDelay lines pulse generationPulse generation by energy-accumulating elementFiberEngineering

A bipolar pulse generator is implemented in a simple structure while providing a high efficiency design having a relatively low total size, while still allowing access by fibers used to control a photoconductive switch that activates the generator. The bipolar pulse generator includes a stacked Blumlein generator structure with an additional transmission line connected to a load at its near end and short-circuited at its distal end. An extra transmission line is positioned between the Blumlein generator's structure and the load provides specified limited gap between positive and negative sub-pulses. The bipolar pulse generator further includes a bended Blumlein generator structure, in which an existing intrinsic “stray” transmission line is used to provide the bipolar pulse. Still further, bipolar pulse generator includes stepped transmission lines, with additional switches positioned between steps, which are charged by different voltages.

Owner:BAE SYST INFORMATION & ELECTRONICS SYST INTERGRATION INC

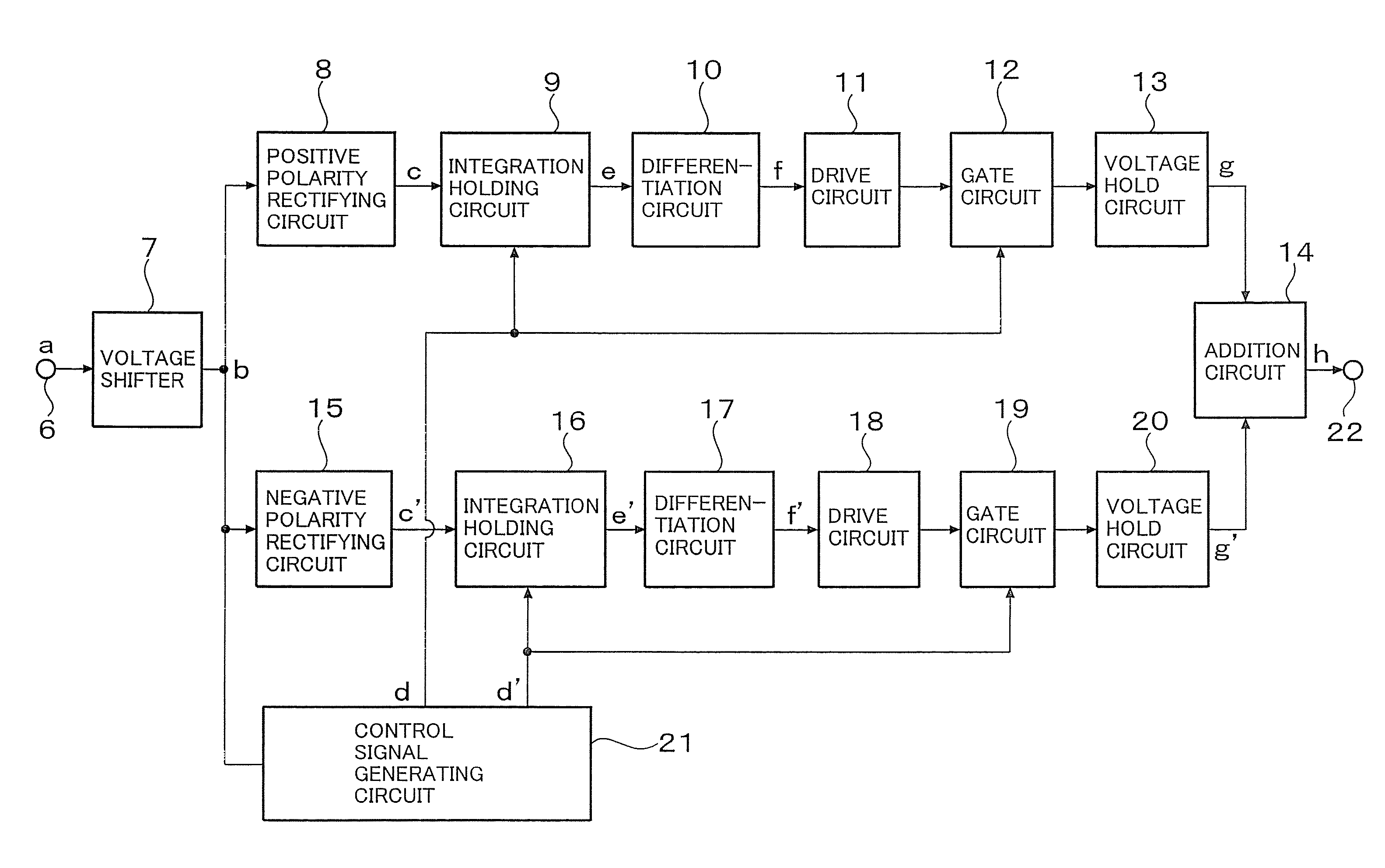

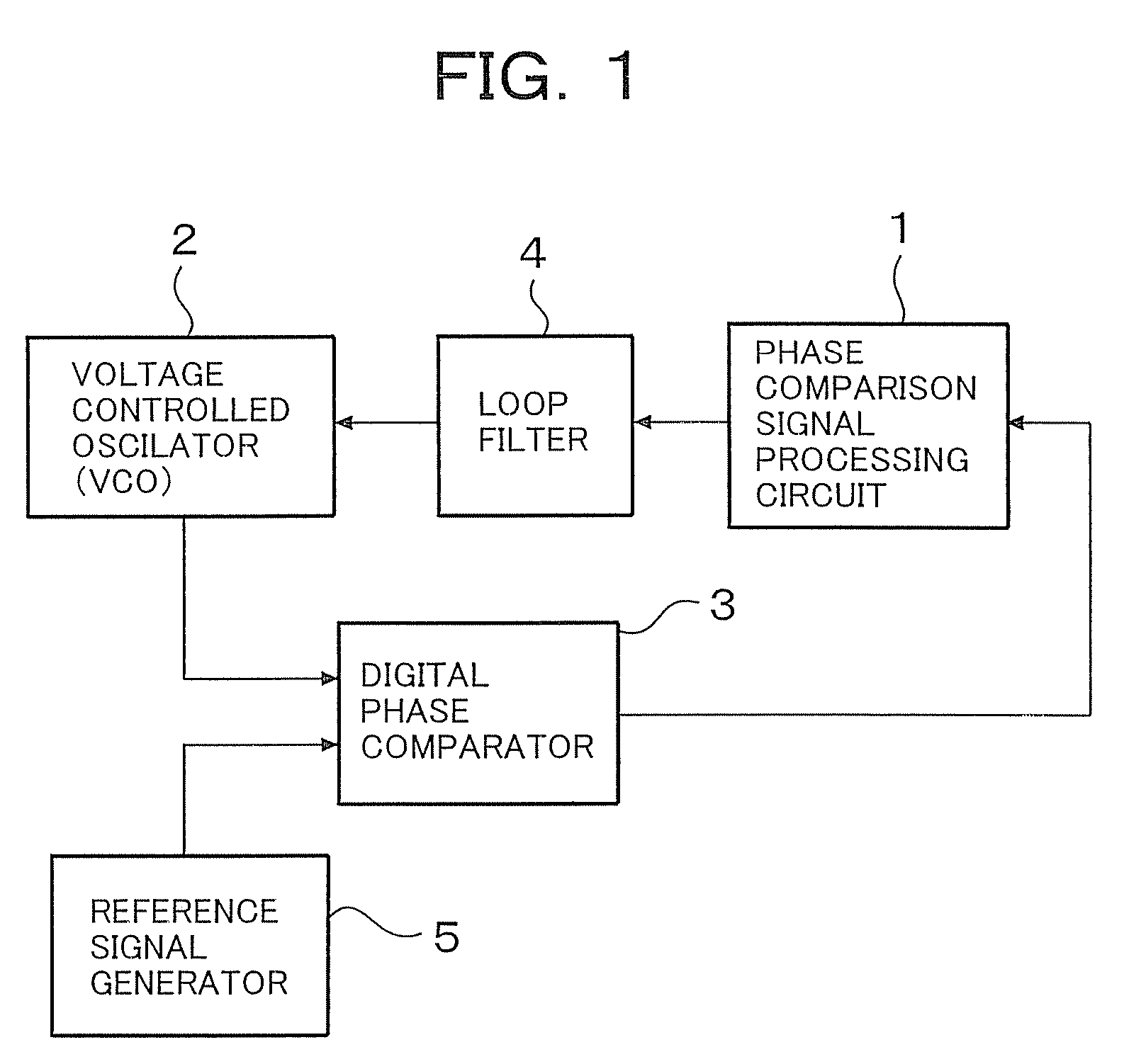

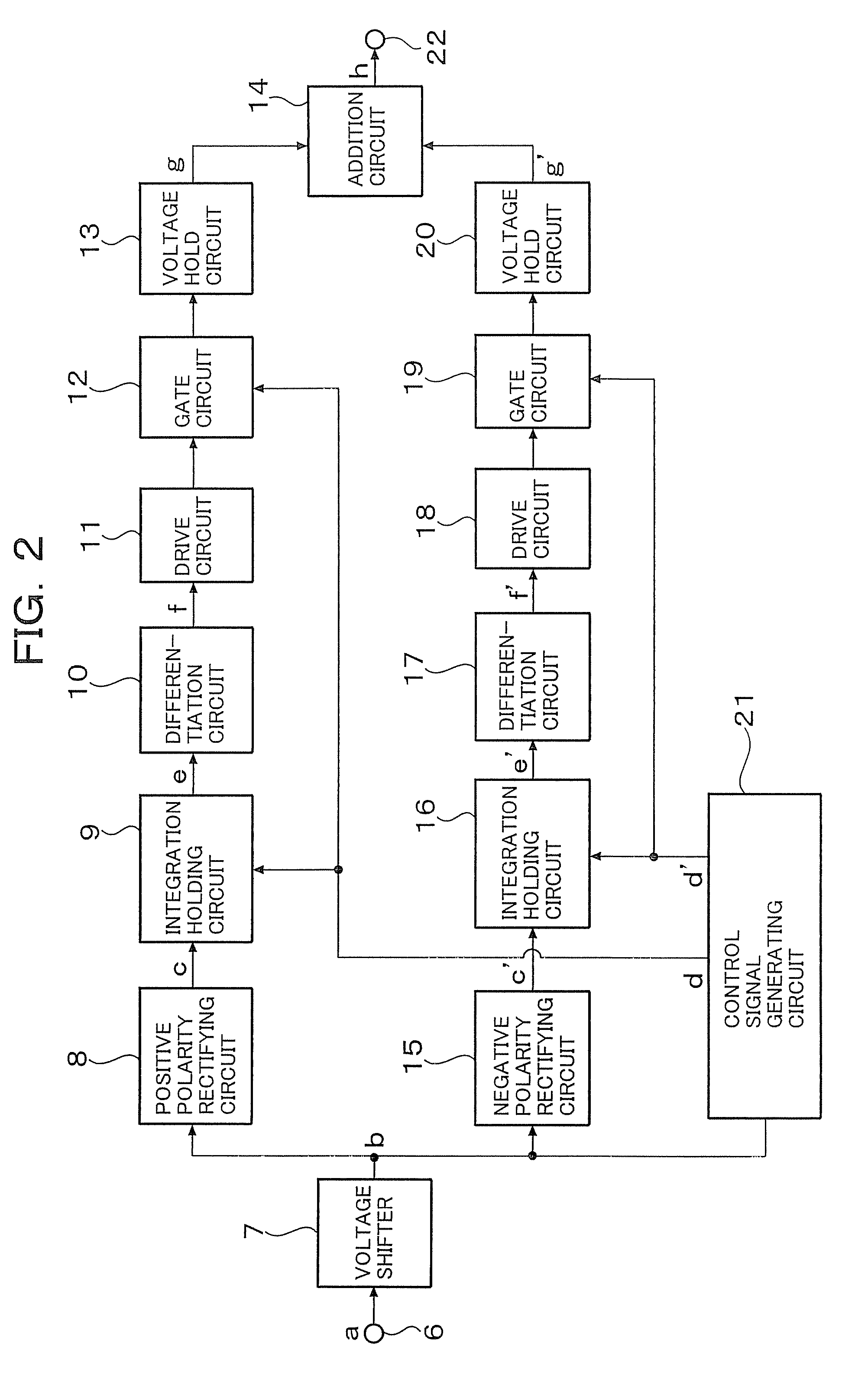

Phase comparison signal processing circuit

InactiveUS20080048742A1Improve response speedIncrease rangeDelay lines pulse generationPulse automatic controlBipolar signalSignal processing circuits

The present invention provides a phase comparison signal processing circuit which processes an output rectangular wave signal of a digital phase comparator of a PLL, expands a pullable-in frequency width of the PLL and shortens a synchronization time. The phase comparison signal processing circuit includes a first signal path which is parallel-connected between a voltage shifter for converting a rectangular wave signal to a bipolar signal and an output terminal and comprises a rectifying circuit, an integration holding circuit, a differentiation circuit, a gate circuit, a voltage hold circuit and a common addition circuit, a second signal path comprising a rectifying circuit, an integration holding circuit, a differentiation circuit, a gate circuit, a voltage hold circuit and the addition circuit, and a control signal generator for individually controlling the integration holding circuits and the gate circuits of the first and second signal paths. The rectification of the bipolar signal, integration and holding of rectified voltages, differentiation of integrated hold values, holding of differentiated outputs and addition of hold voltages are carried out at the first and second signal paths thereby to output a processed signal.

Owner:GEN RES OF ELECTRONICS INC

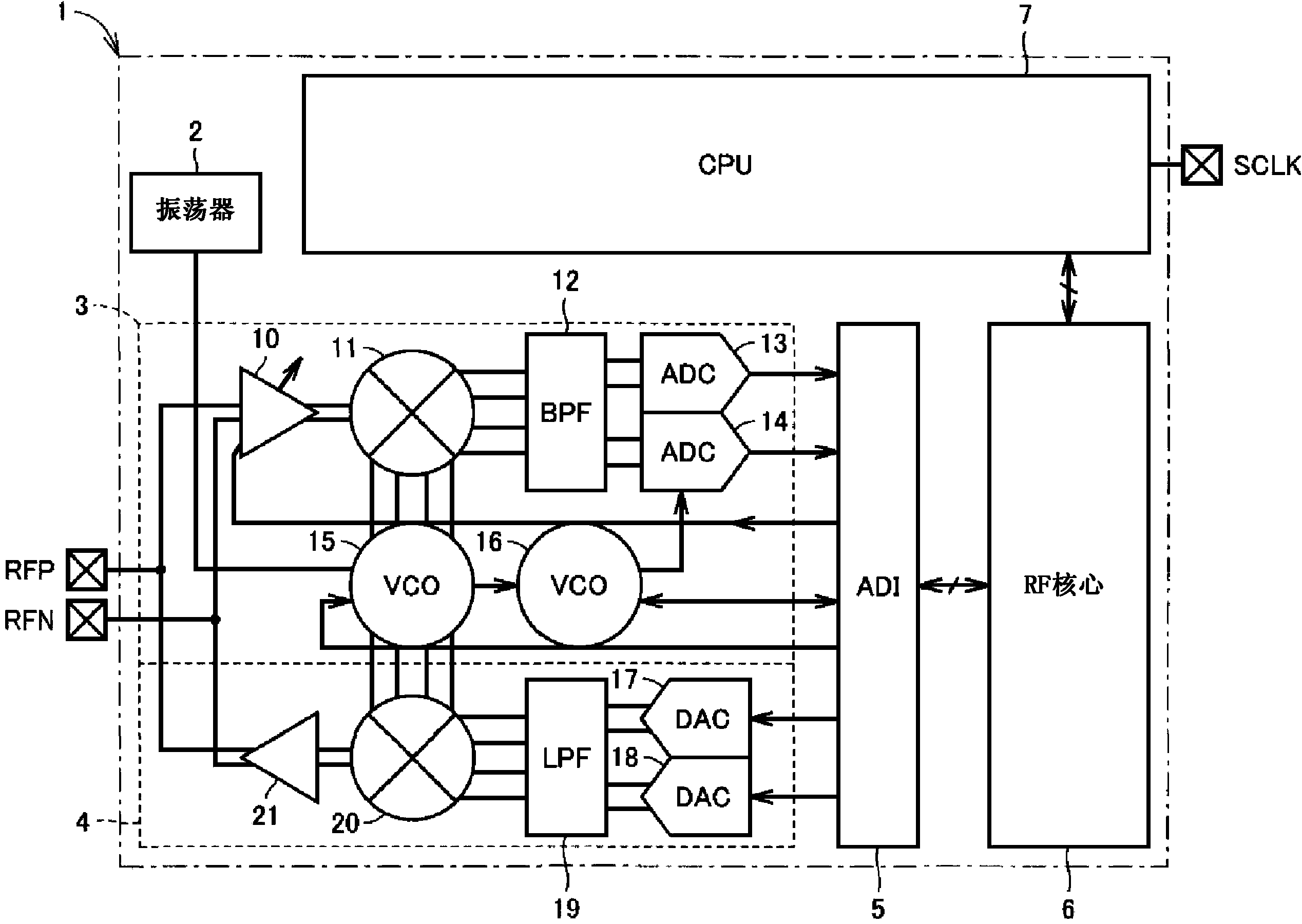

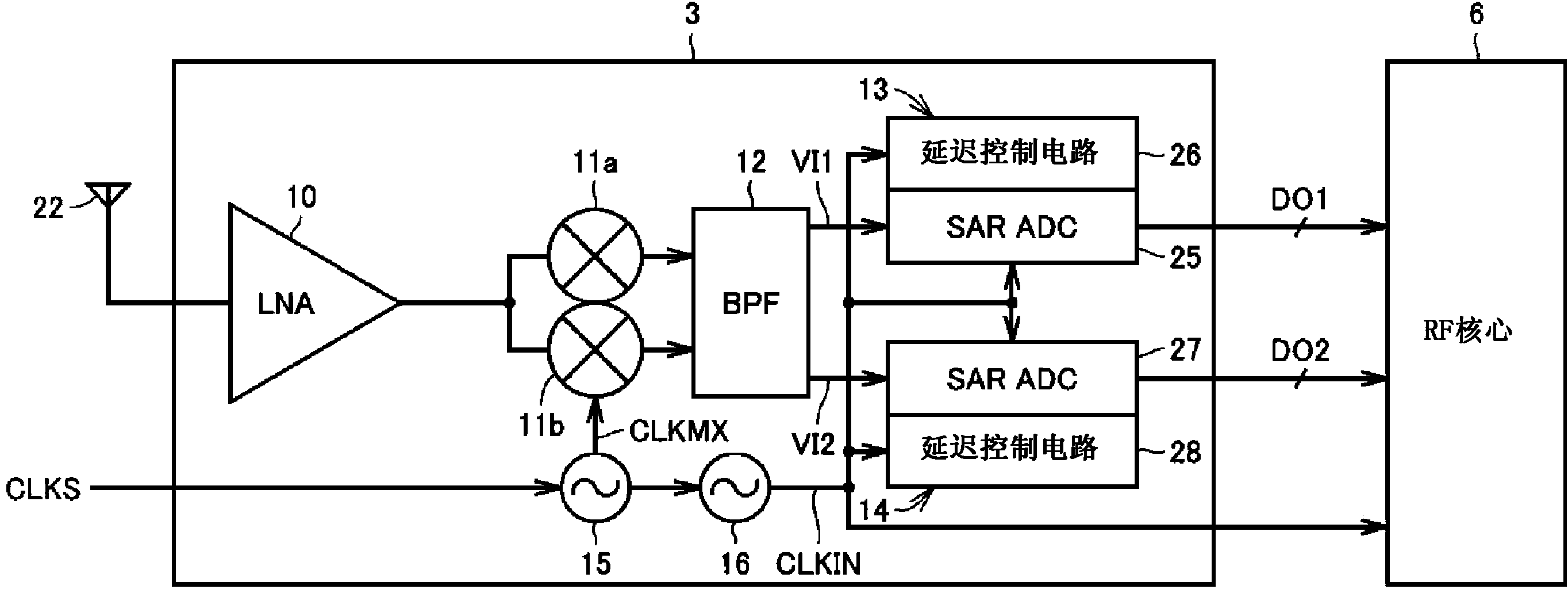

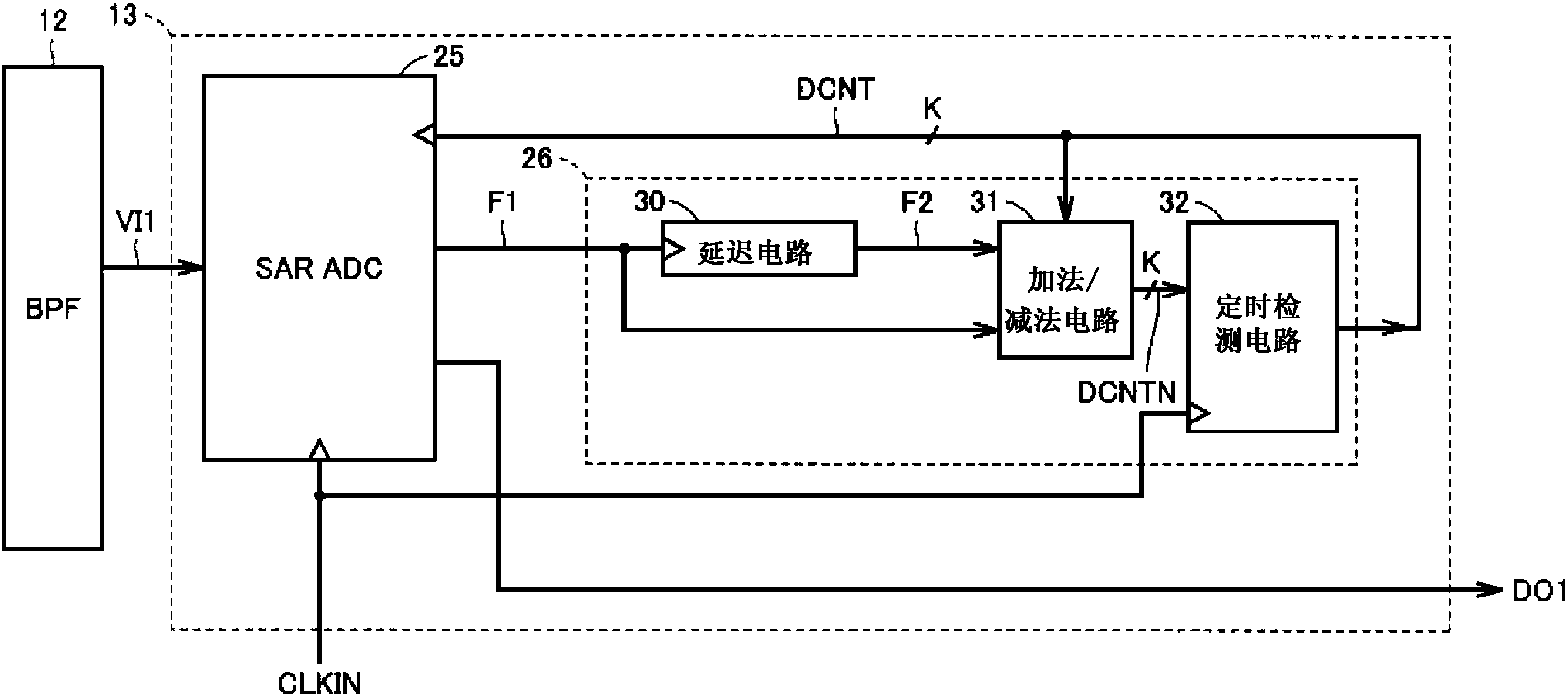

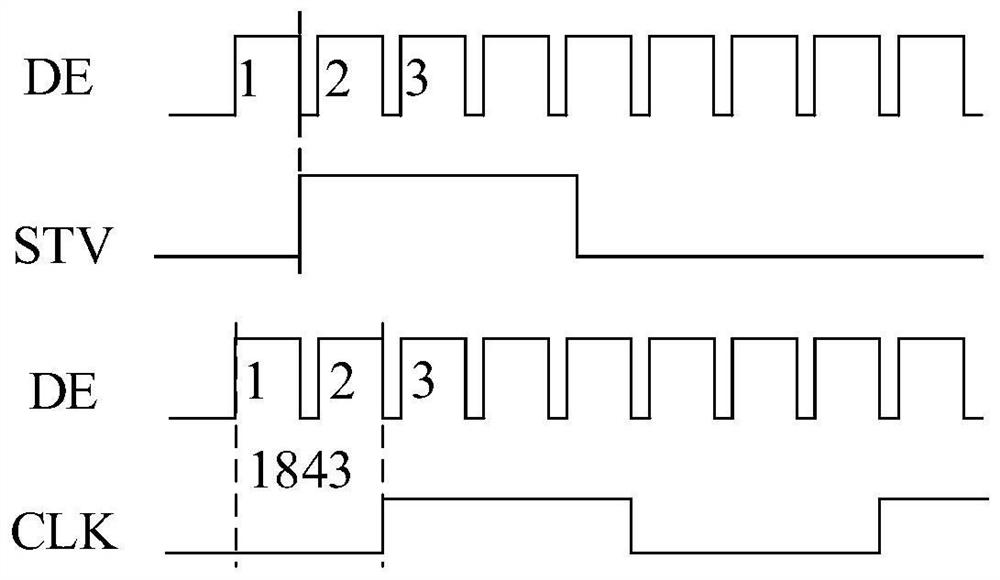

Semiconductor device

ActiveCN104348487AControl cycleDelay lines pulse generationElectric signal transmission systemsControl signalDelayed time

Owner:RENESAS ELECTRONICS CORP

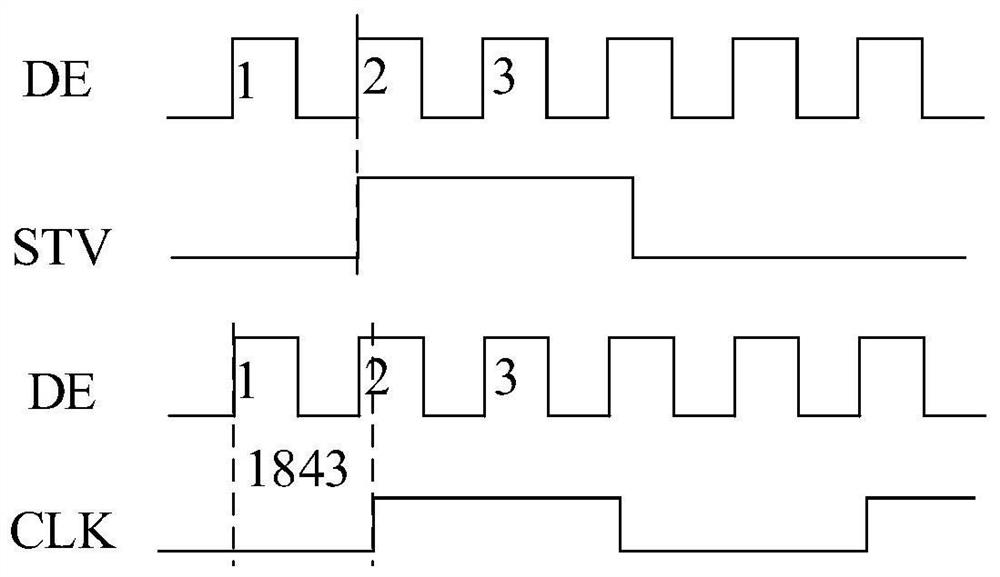

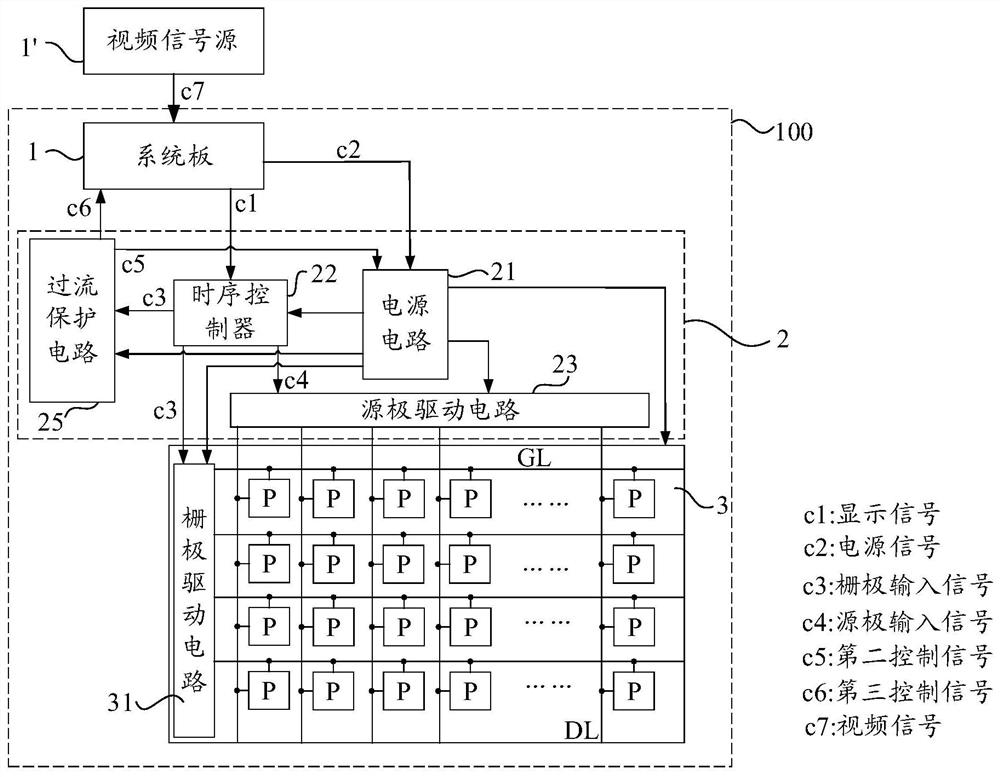

Over-current protection circuit, display device, drive circuit of display device and over-current protection method

ActiveCN111627376AReal-time detectionAvoid damageDelay lines pulse generationImpedence networksControl signalDisplay device

The invention provides an over-current protection circuit, a display device, a driving circuit of the display device and an over-current protection method, is applied to the technical field of display, and solves the problems of abnormal display and display panel damage caused by abnormal gate input signals due to abnormal display signals in the display device. The over-current protection circuitis configured to continuously detect a plurality of gate input signals input into a gate driving circuit, and comprises a sampling sub-circuit, a delay judgment sub-circuit and a counting control sub-circuit which are coupled in sequence. The over-current protection circuit outputs a second control signal for cutting off a signal input from the system board of the display device to the driving circuit of the display device when detecting that a gate input signal of which the voltage value is greater than a first preset voltage value exists in the plurality of gate input signals and a set condition is satisfied. The over-current protection circuit is used in a driving circuit of the display device.

Owner:HEFEI XINSHENG OPTOELECTRONICS TECH CO LTD +1

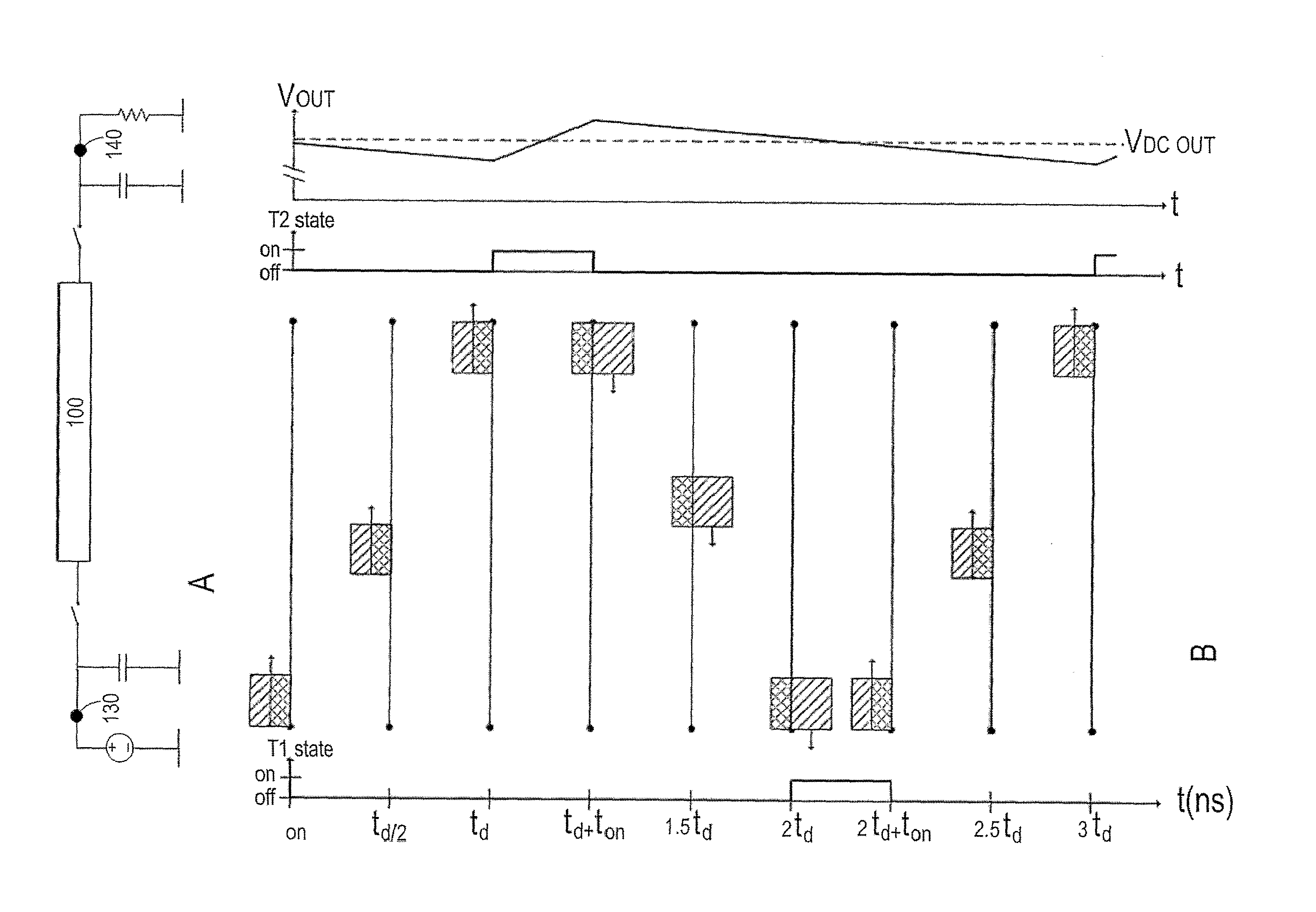

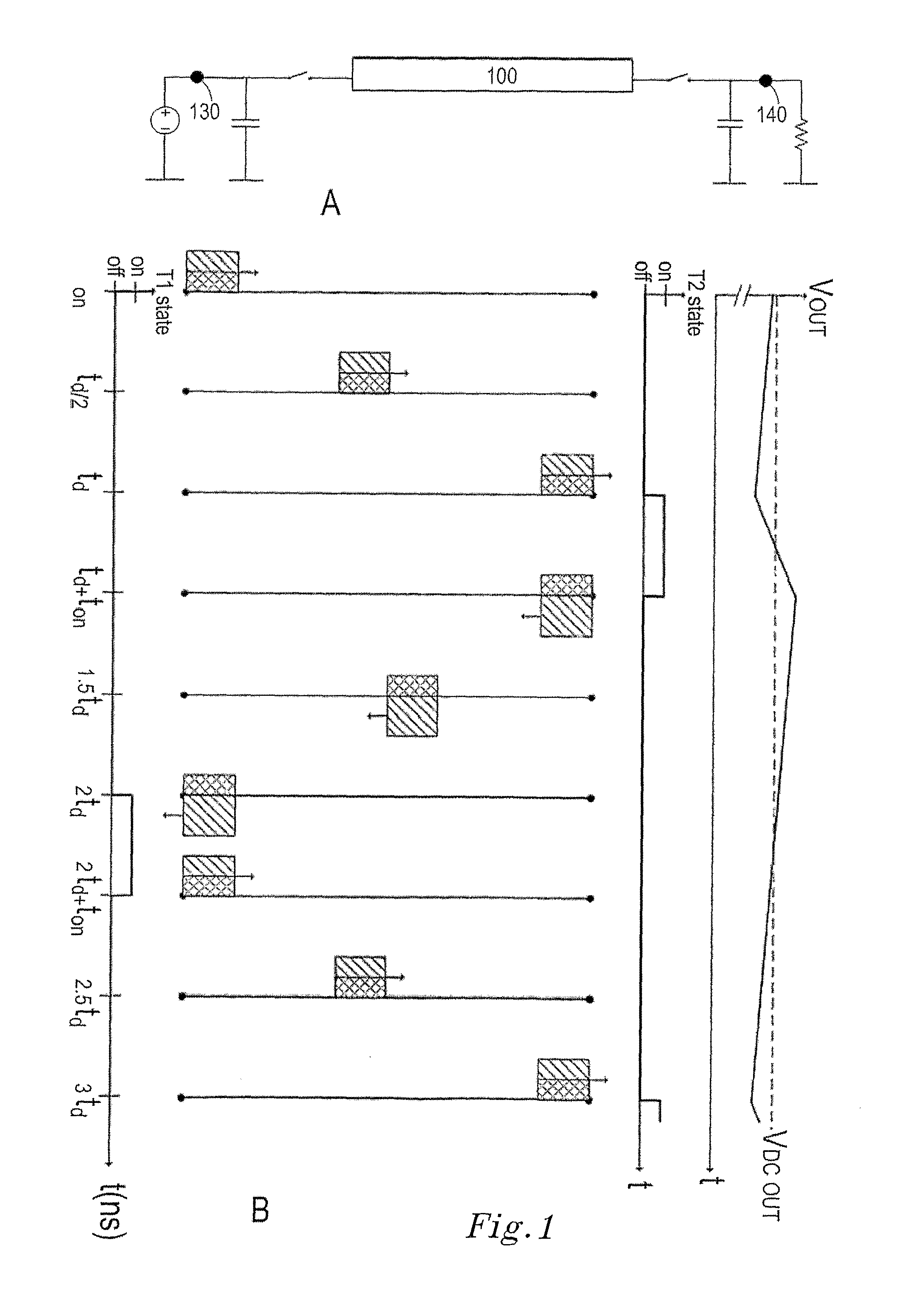

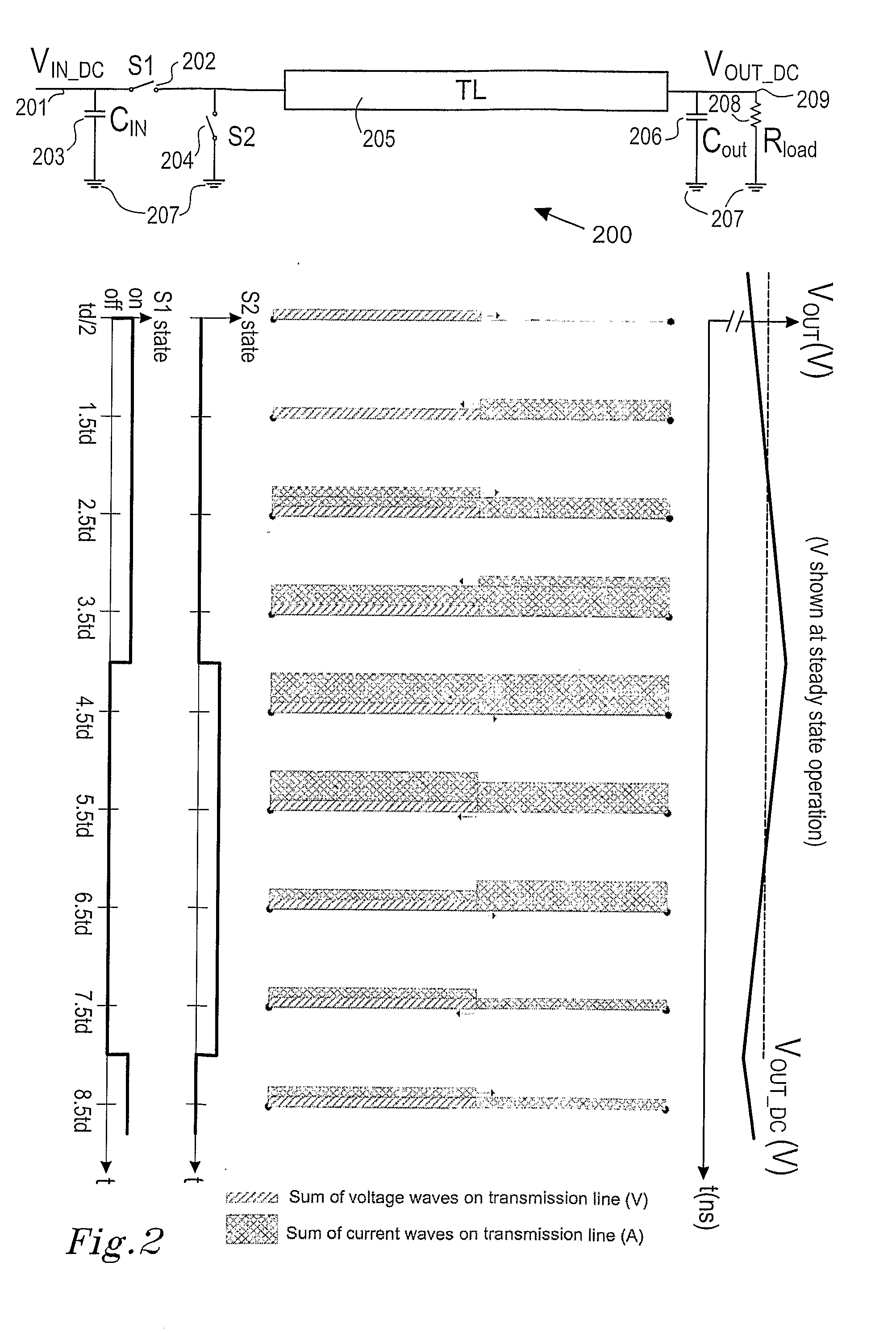

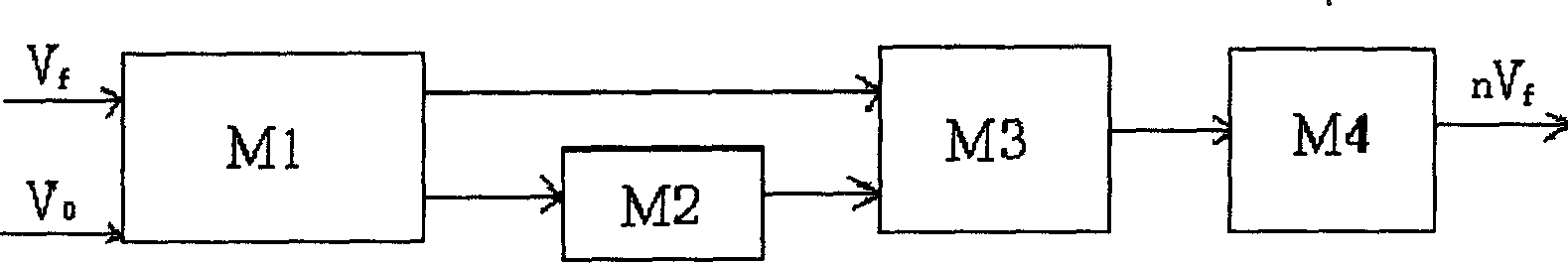

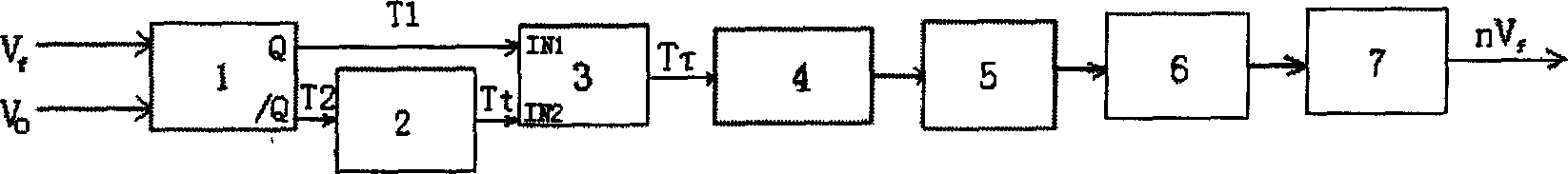

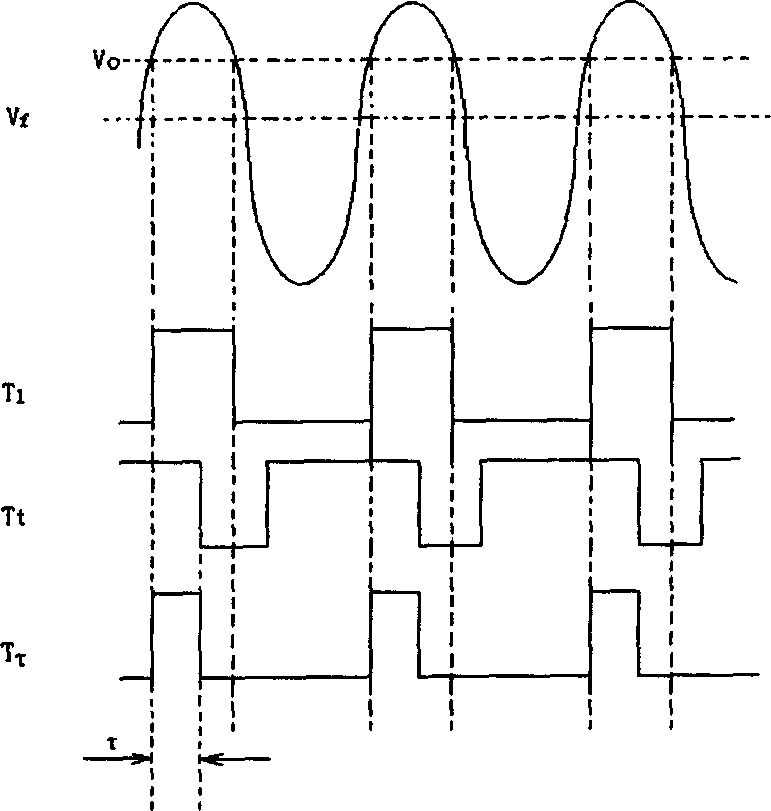

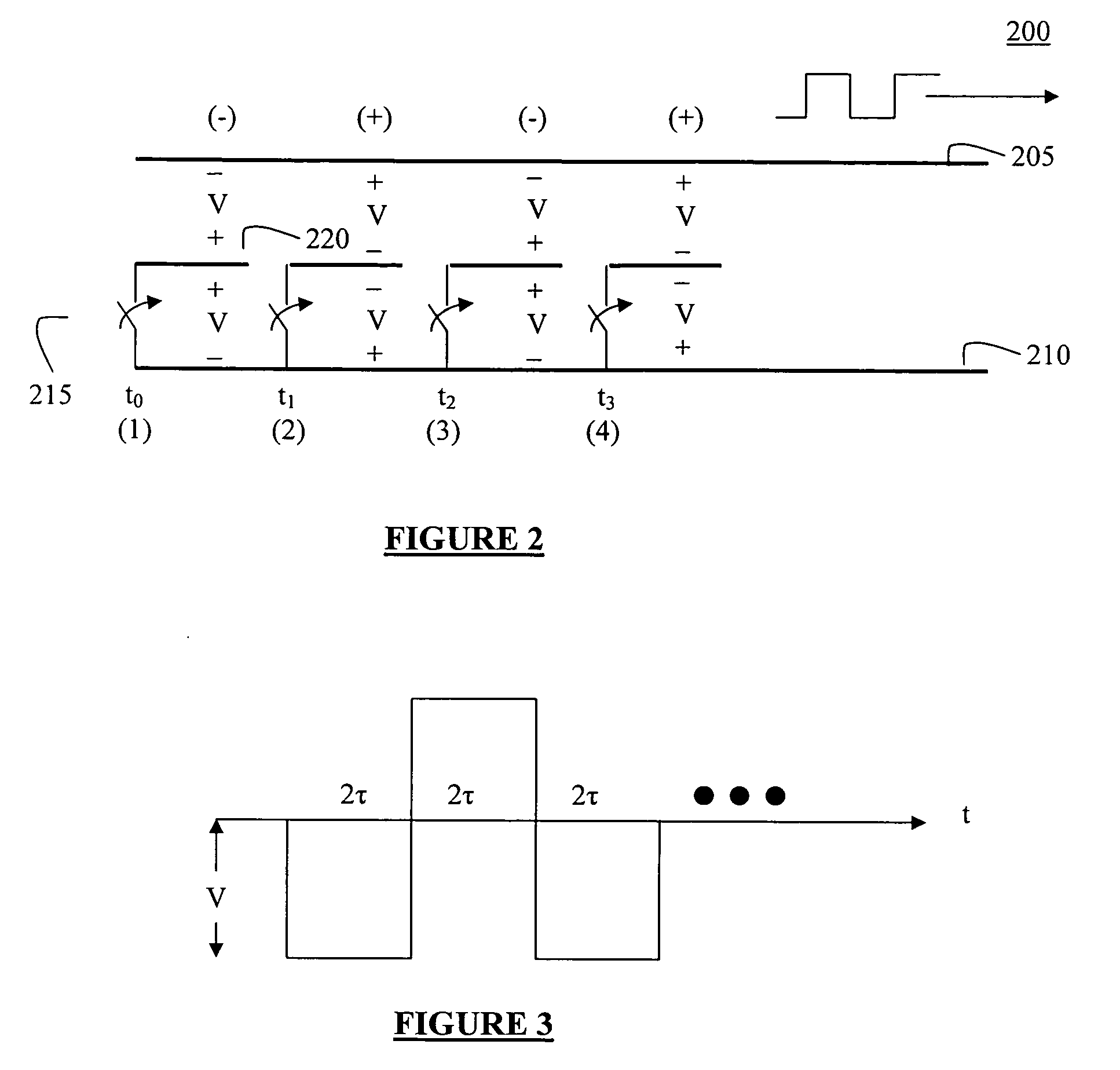

Sub sampling electrical power conversion

ActiveUS20110254594A1Low costRapid responseDelay lines pulse generationDc-dc conversionAmplifierTransmission delay

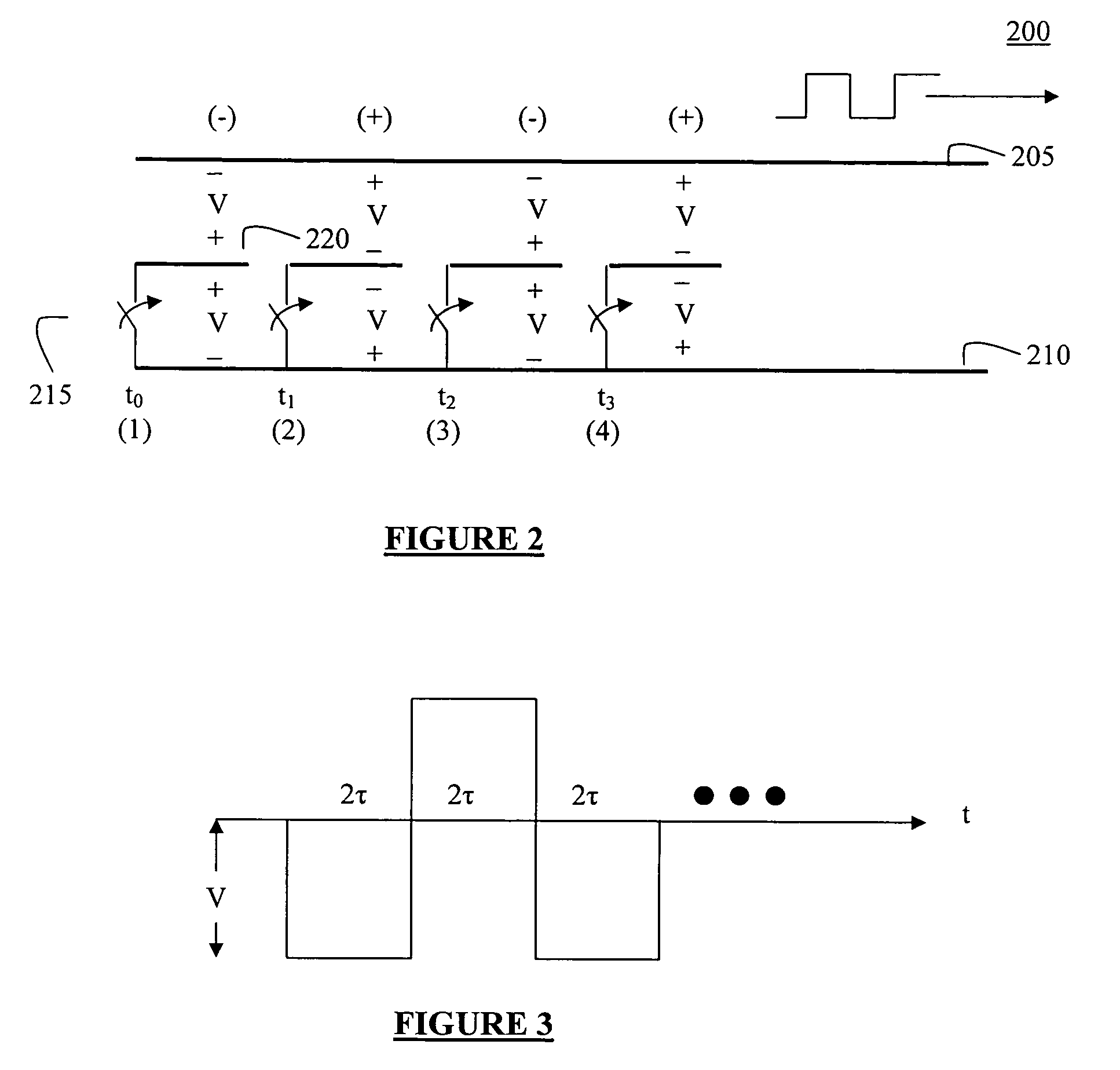

The present invention relates to a solution for electrical power conversion using a first gate (202, 302) for starting an electrical wave in a wave propagating medium (205, 306) acting as a transmission delay where an electrical wave propagates and due to reflections in the propagating medium a resulting wave builds up and is transferred to an output for delivering a power amplifier, DC / DC converter or similar function and the output is controlled using a second gate (204, 304).

Owner:TELEFON AB LM ERICSSON (PUBL)

Frequency multiplication method and frequency multiplier

InactiveCN1790903AReduce phase noiseRich in higher harmonicsDelay lines pulse generationPhase noiseAudio power amplifier

The invention discloses a frequency multiplication method and frequency multiplier. Wherein, first, accessing input signal into comparator to output square wave signal; second, outputting delayed square wave signal by AND gate delayer with delay time in nano-second level; third, inputting said two signals into two input end of logic AND gate correlator for calculation and output; fourthly, filtering and amplifying the narrow impulse from said correlator to complete the frequency multiplication. Wherein, it also comprises a linear amplifier and a power amplifier. This invention is simple and low cost, and had small phase noise in output signal.

Owner:WUHAN INST OF PHYSICS & MATHEMATICS CHINESE ACADEMY OF SCI

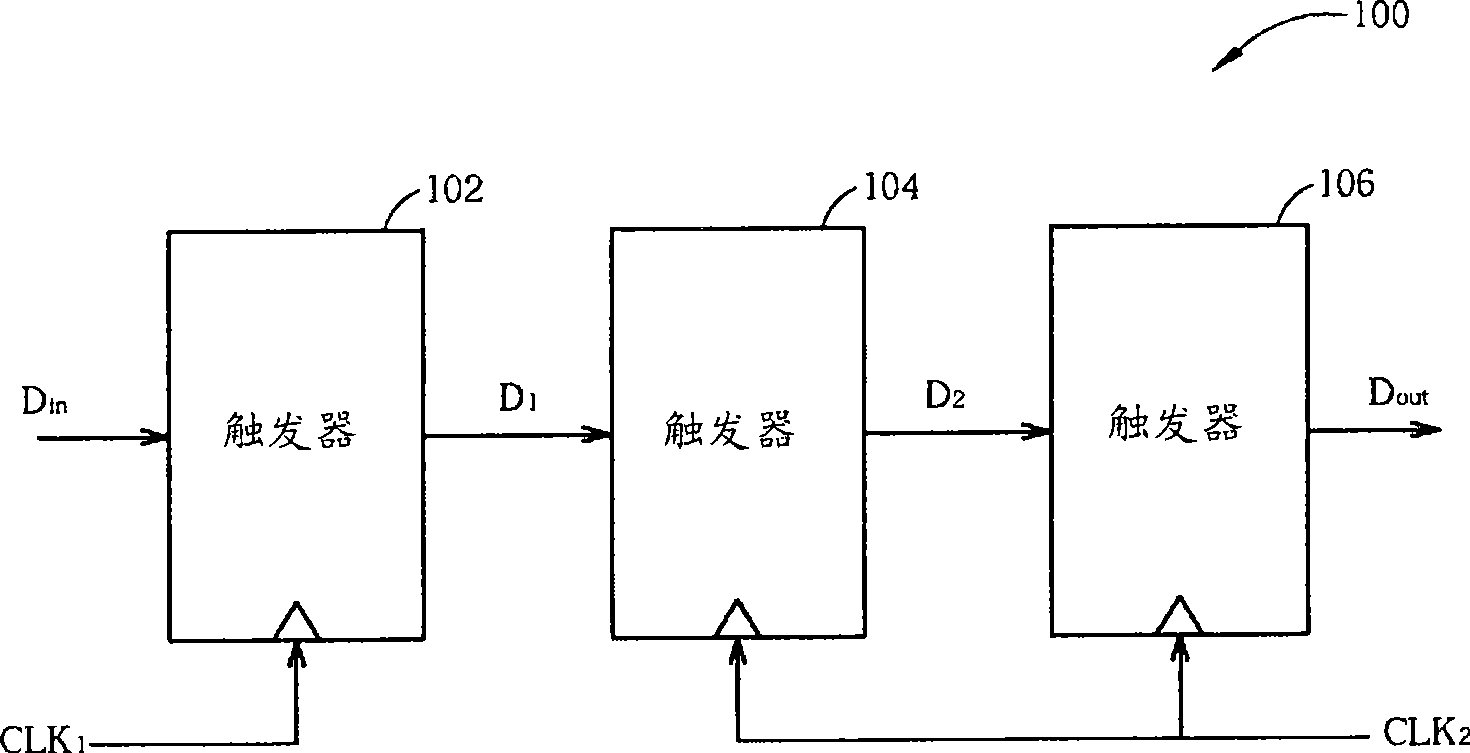

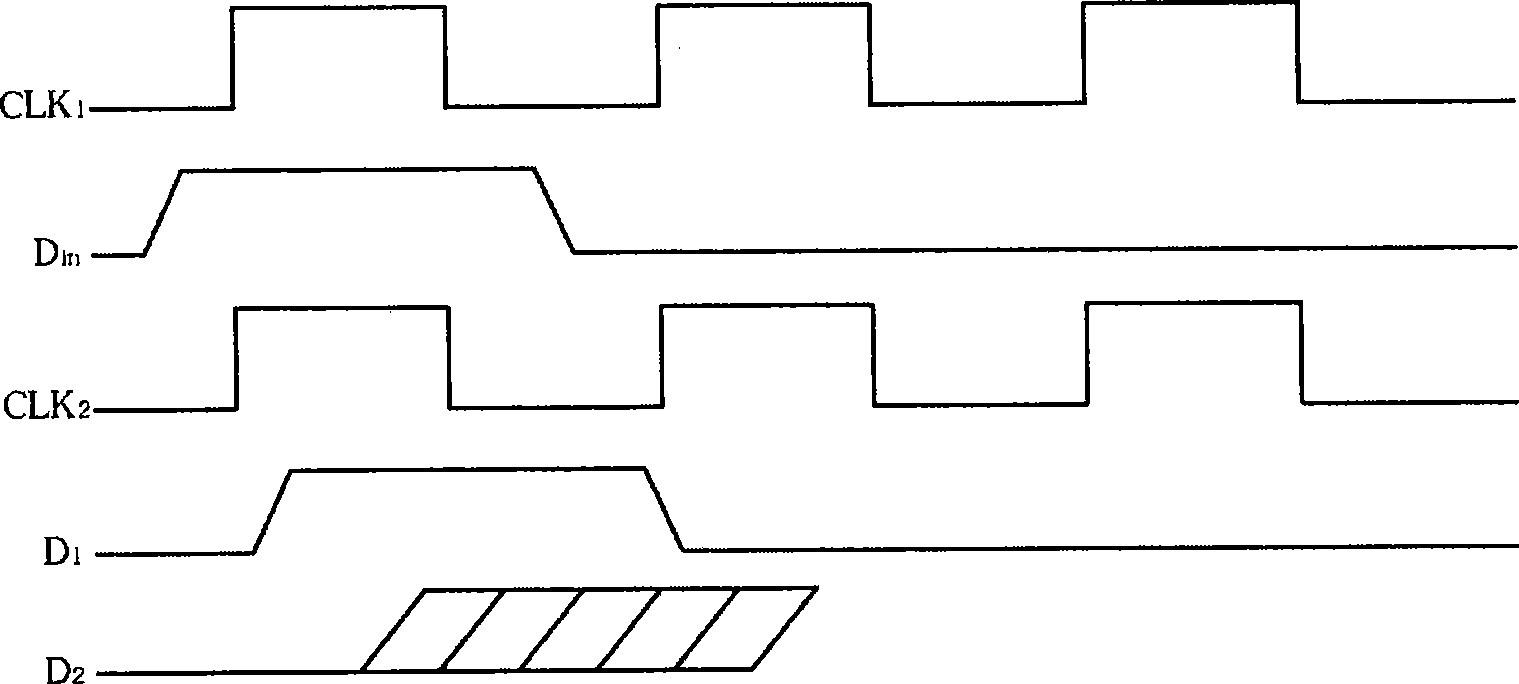

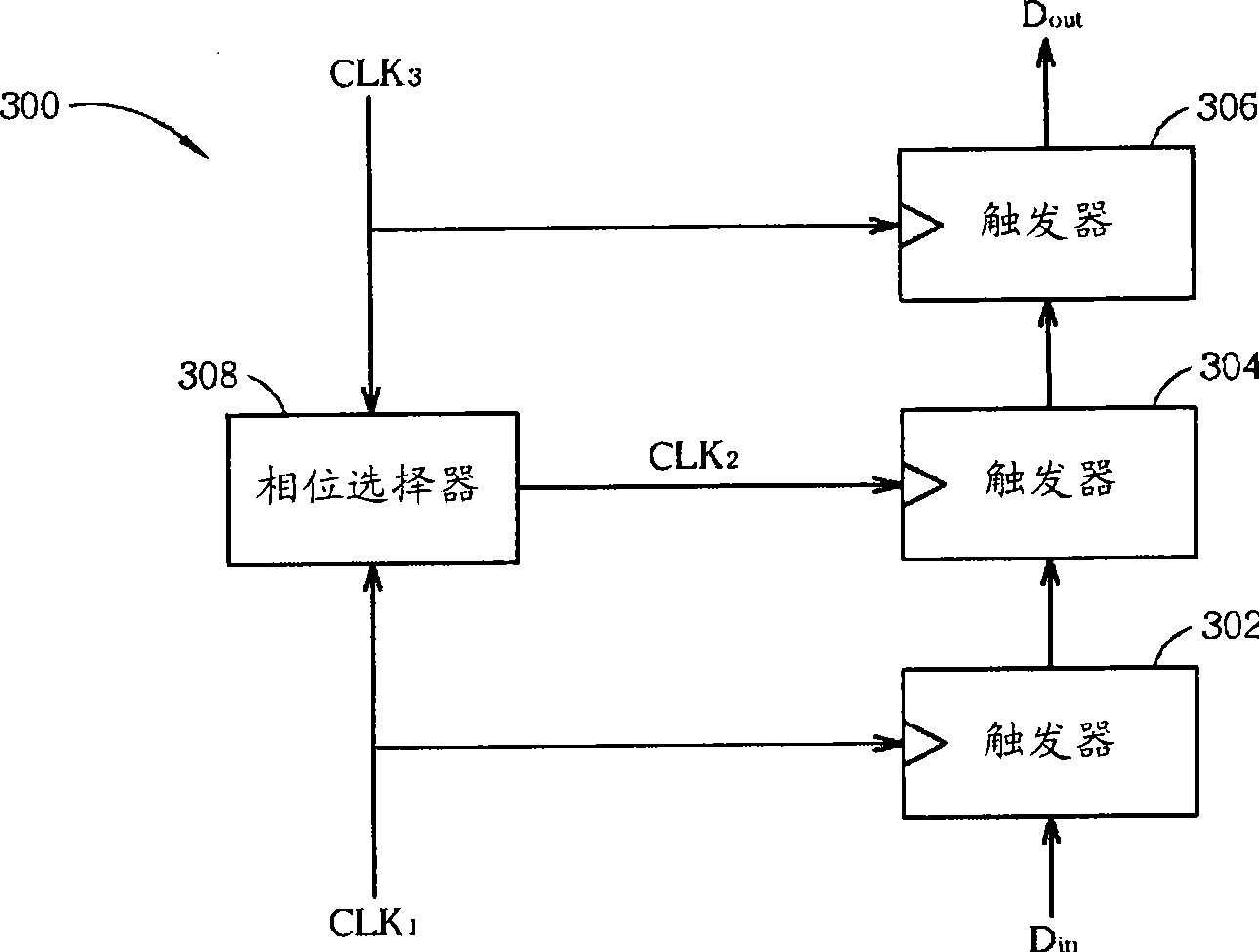

Data-latching circuit adopting phase selector

ActiveCN101521500ADelay lines pulse generationMultiple input and output pulse circuitsPhase relationClock signal

The invention provides a data-latching circuit. The data-latching circuit comprises a first data-latching unit, a second data-latching unit, a third data-latching unit and a phase selector, wherein the first data-latching unit is used for latching a first input data according to a first clock signal and outputting a first output data; the second data-latching unit is used for latching the first output data according to a second clock signal and outputting a second output data; the third data-latching unit is used for latching the second output data according to a third clock signal and outputting an output data; and the phase selector is coupled with the second data-latching unit and used for generating the second clock signal according to the phase relation between the first and the third clock signals and outputting the second clock signal to the second data-latching unit.

Owner:REALTEK SEMICON CORP

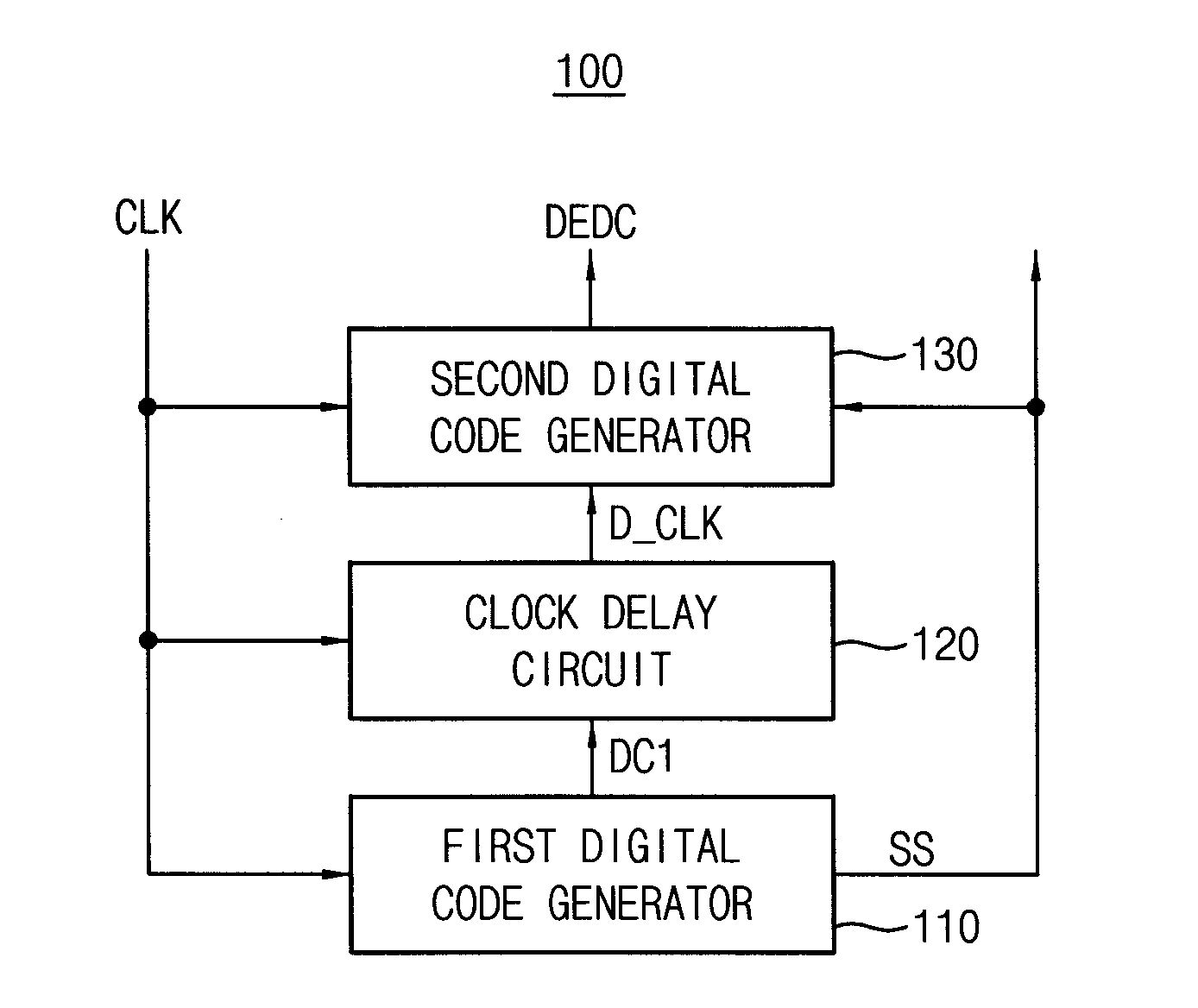

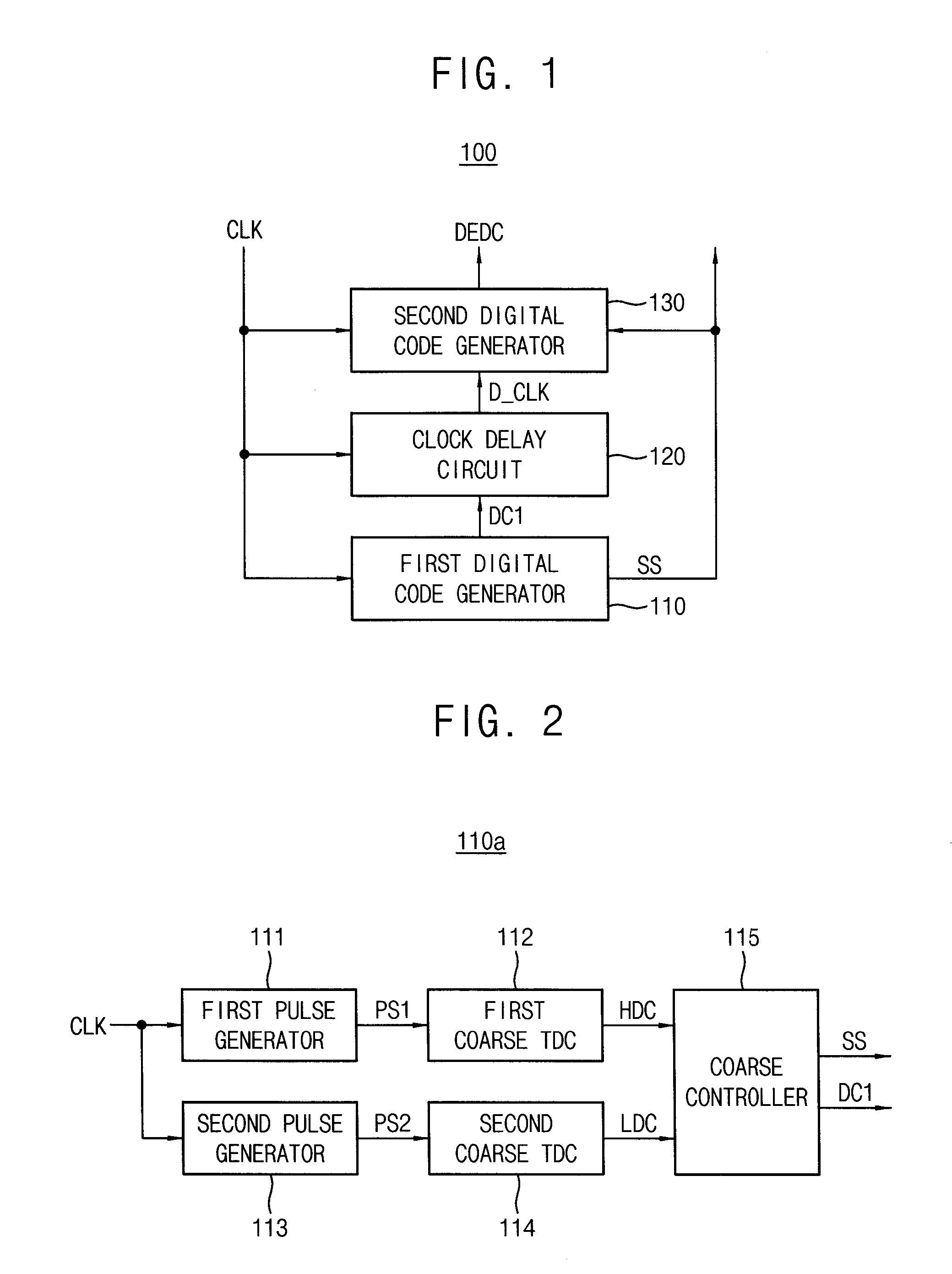

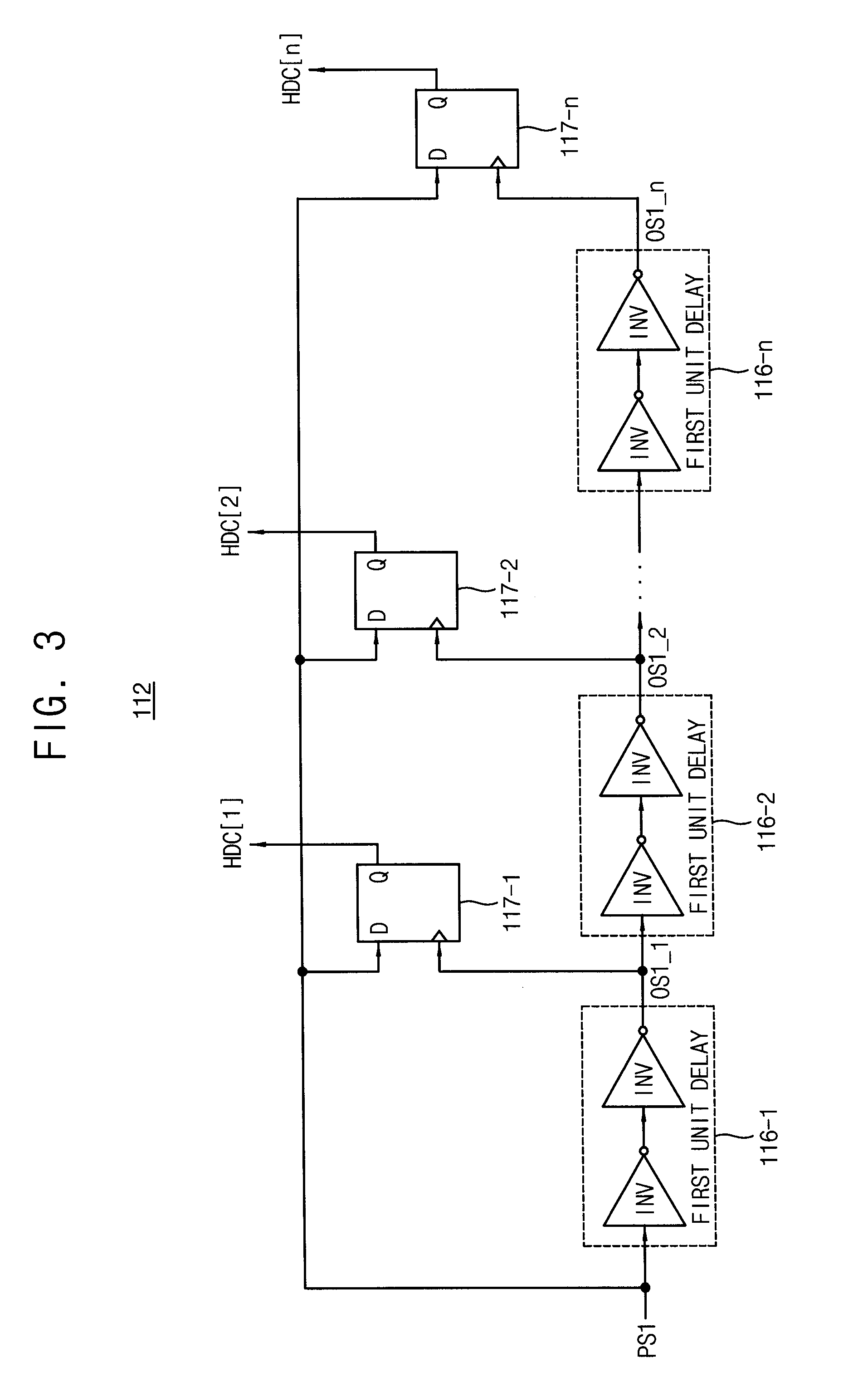

Duty cycle error detection device and duty cycle correction device having the same

In a duty cycle error detection device, a first digital code generator is configured to generate high and low codes corresponding to a lengths of high level low level periods, respectively, of a clock signal, generate a sign signal representing the longer period between the high level period and the low level period, and output one of the high and low digital codes corresponding to the shorter period as a first digital code. A clock delay circuit is configured to generate a delay clock signal by delaying the clock signal for a time corresponding to the first digital code, and a second digital code generator is configured to generate a duty error digital code corresponding to a length from a start of the longer period of the delay clock signal to an end of the longer period of the clock signal based on the sign signal.

Owner:SAMSUNG ELECTRONICS CO LTD

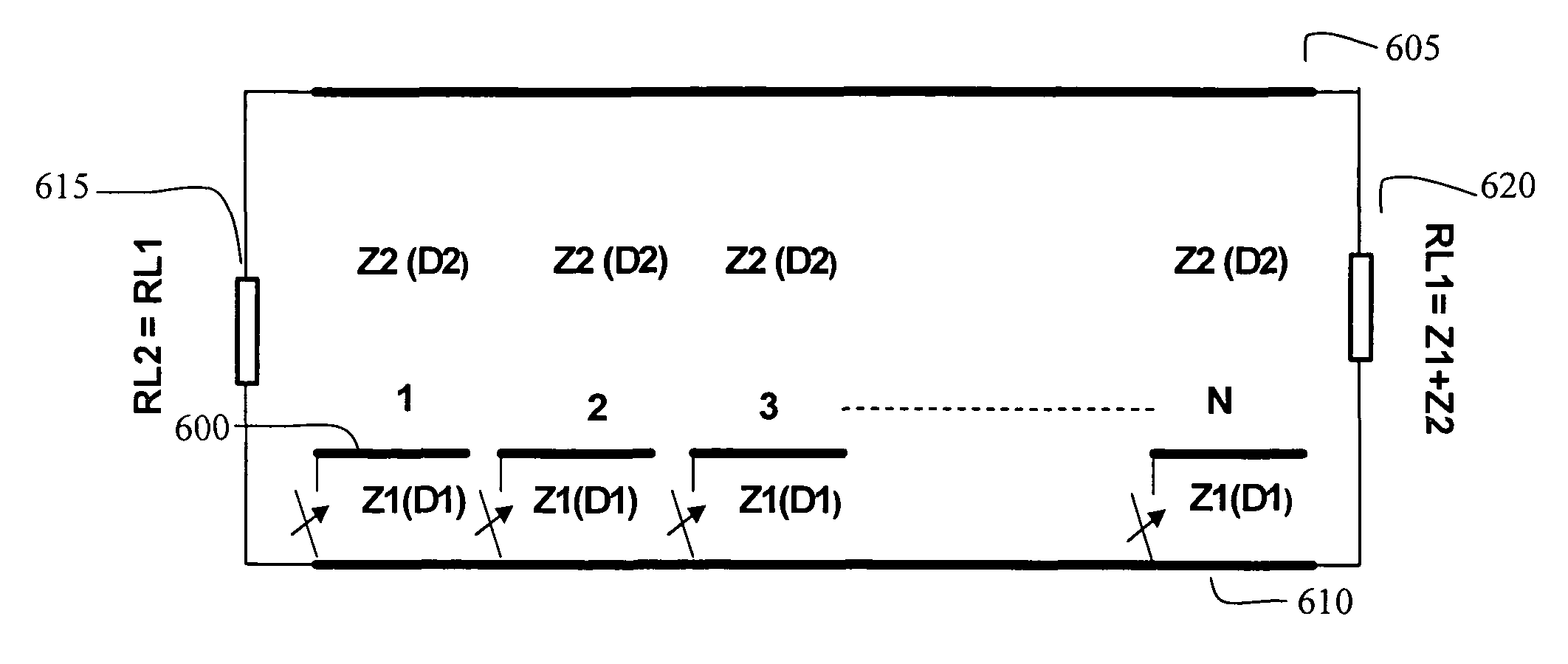

Method and apparatus for digital synthesis of long multi-cycle microwave pulses

ActiveUS20100001807A1Efficient processingLower impedanceDelay lines pulse generationTransmission control/equlisationMicrowaveElectrical conductor

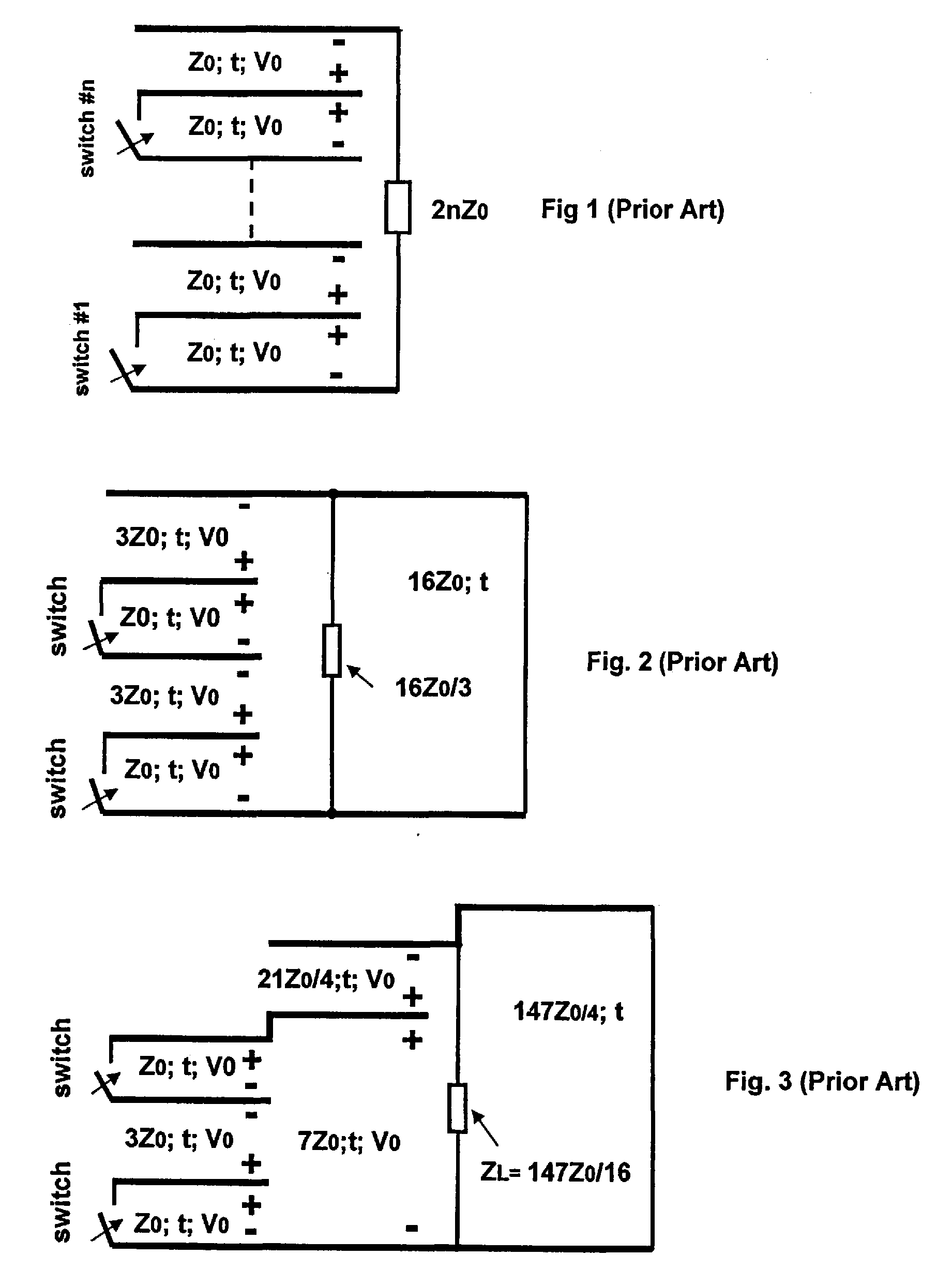

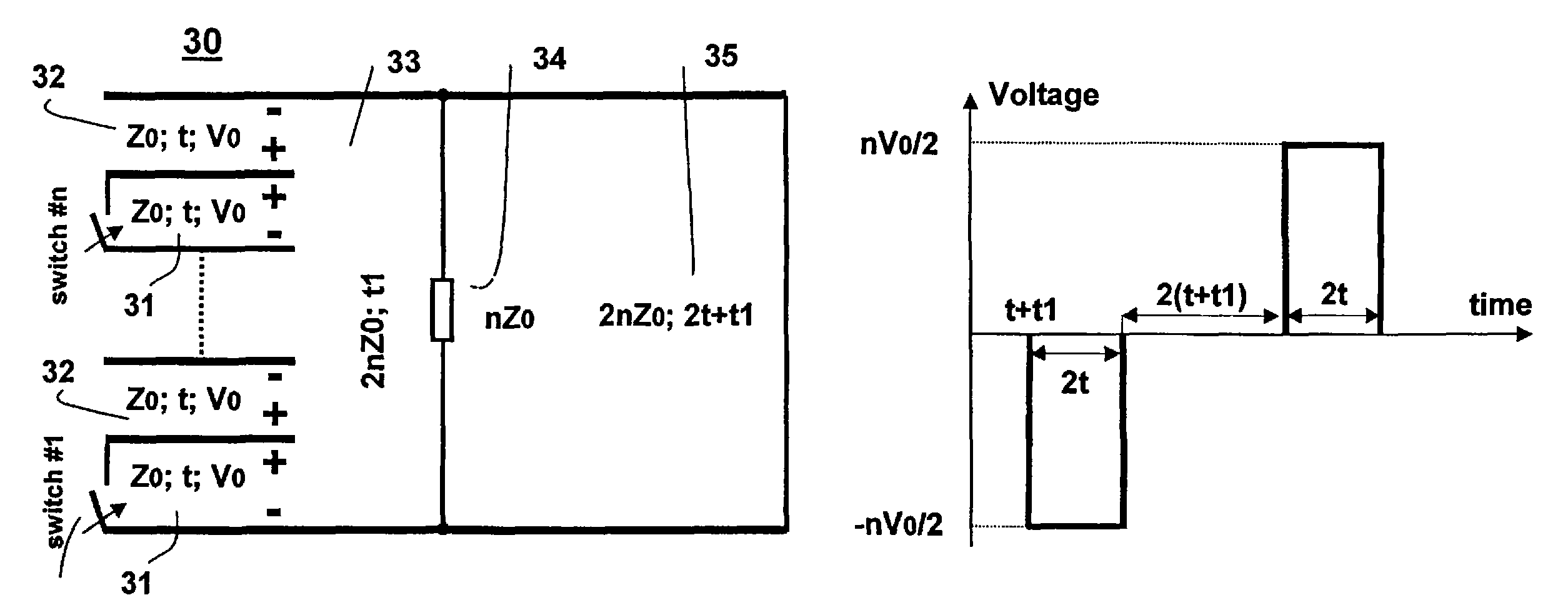

Conductive segments (transmission line conductors) are positioned within a transmission line structure in order to generate multi-cycle microwave pulses. The conductor segments are switchably coupled to one or the other conductor of the transmission lines, inside the transmission line structure. Microwave pulses may be induced in the transmission line by closing the switches in a controlled manner to discharge successive segments, or successive groups of segments, into the transmission lines. The induced pulses travel uninterrupted along the transmission lines in a desired direction to the load. Efficiency of systems and energy delivered to the load in multi-section transmission lines is increased and / or maximized by adjusting the ratio of characteristic impedances associated with the transmission line conductor segments according to an optimum ratio.

Owner:BAE SYST INFORMATION & ELECTRONICS SYST INTERGRATION INC

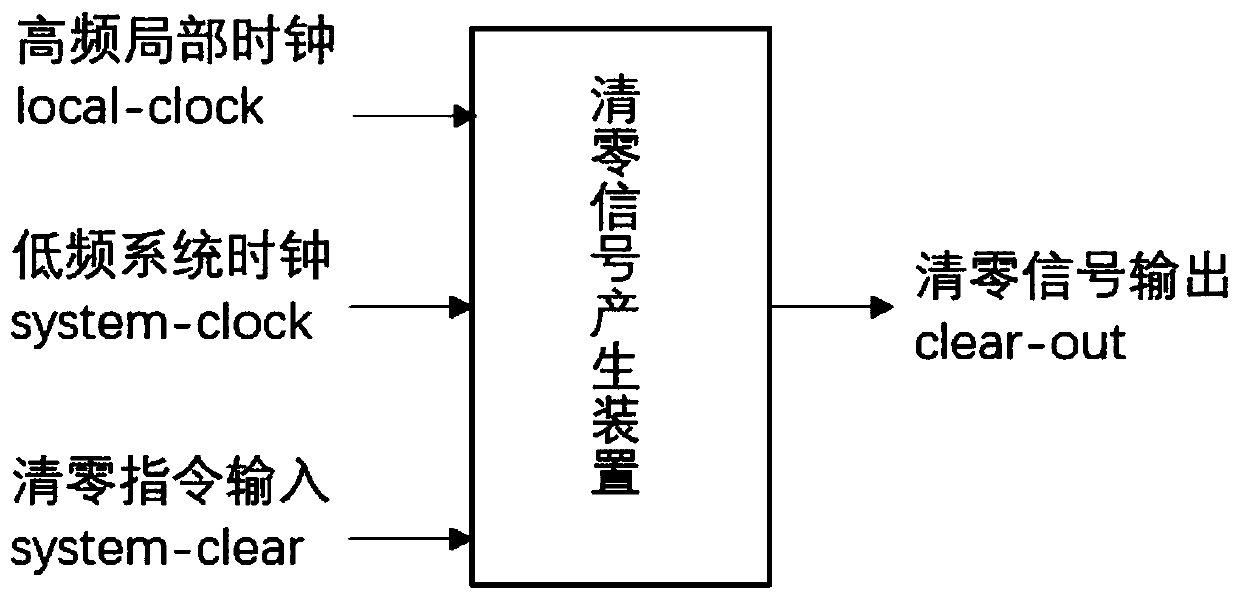

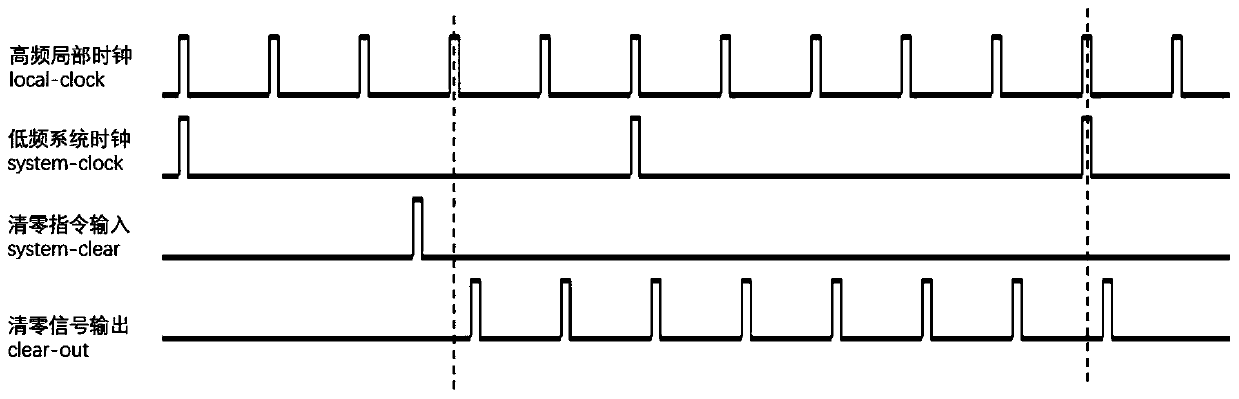

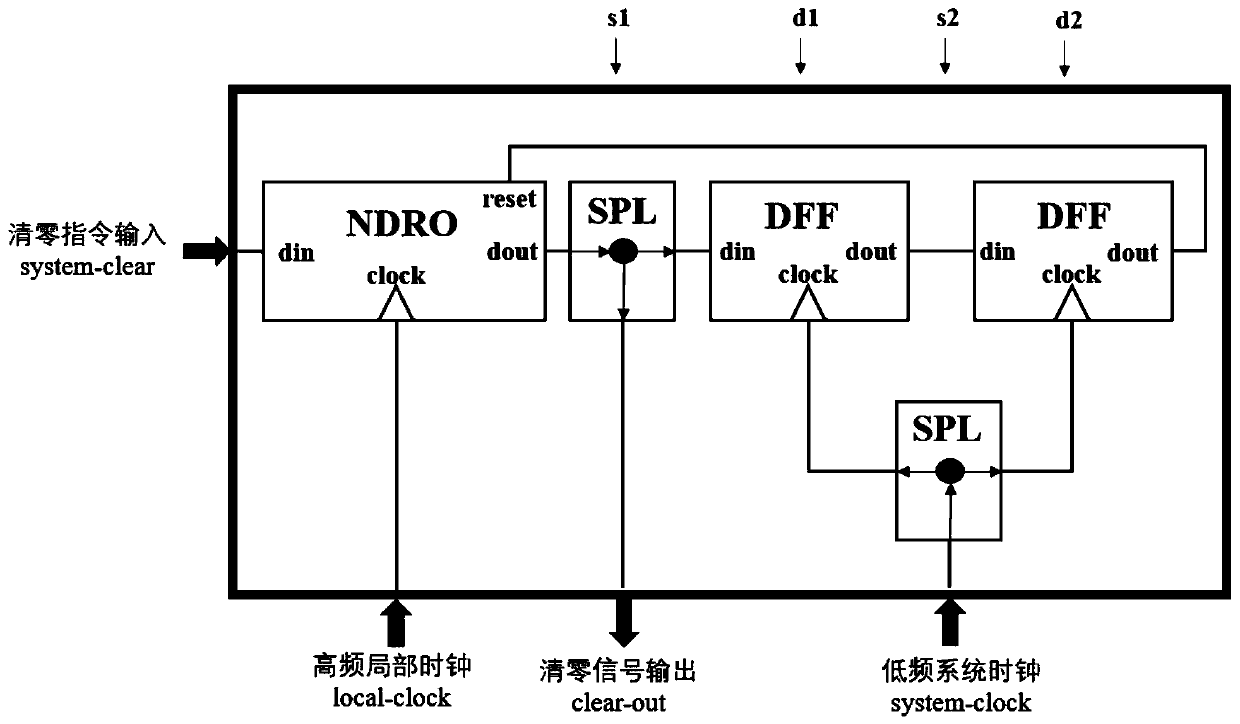

Zero clearing method and system for superconducting circuit

ActiveCN111147045ATimely and effectiveGuaranteed clearing effectDelay lines pulse generationSingle output arrangementsDelayed pulseSoftware engineering

The invention provides a zero clearing method and system for a superconducting circuit. The method comprises the following steps: sending a zero clearing instruction signal to an instruction input interface of a non-destructive read-out register, wherein the non-destructive reading register outputs data to a first magnetic flux quantum separation device according to the high-frequency local clocksignal, and the first magnetic flux quantum separation device separates the output data into a zero clearing signal and a trigger signal and inputs the zero clearing signal to a superconducting register between pipeline stages of the superconducting processor; inputting a low-frequency system clock signal to a second magnetic flux quantum separation device, wherein the second magnetic flux quantumseparation device splits the low-frequency system clock signal into a first low-frequency system clock pulse and a second low-frequency system clock pulse; the first D trigger outputs a signal pulseaccording to a trigger signal and a first low-frequency system clock pulse, the second magnetic flux quantum separation device outputs a delay pulse according to the signal pulse and a second low-frequency system clock pulse, and the non-destructive reading register resets according to the delay pulse so as to stop outputting a zero clearing signal.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

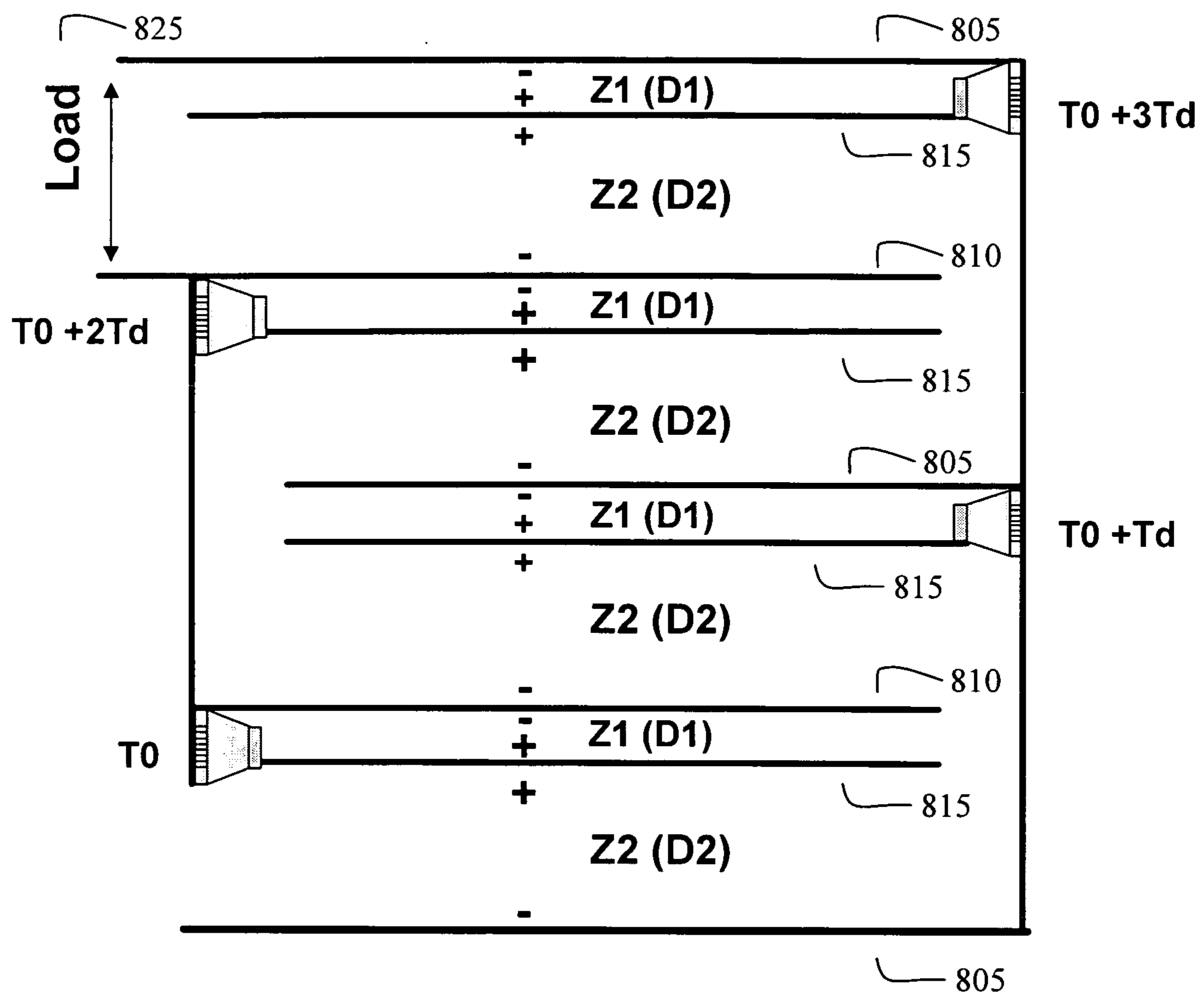

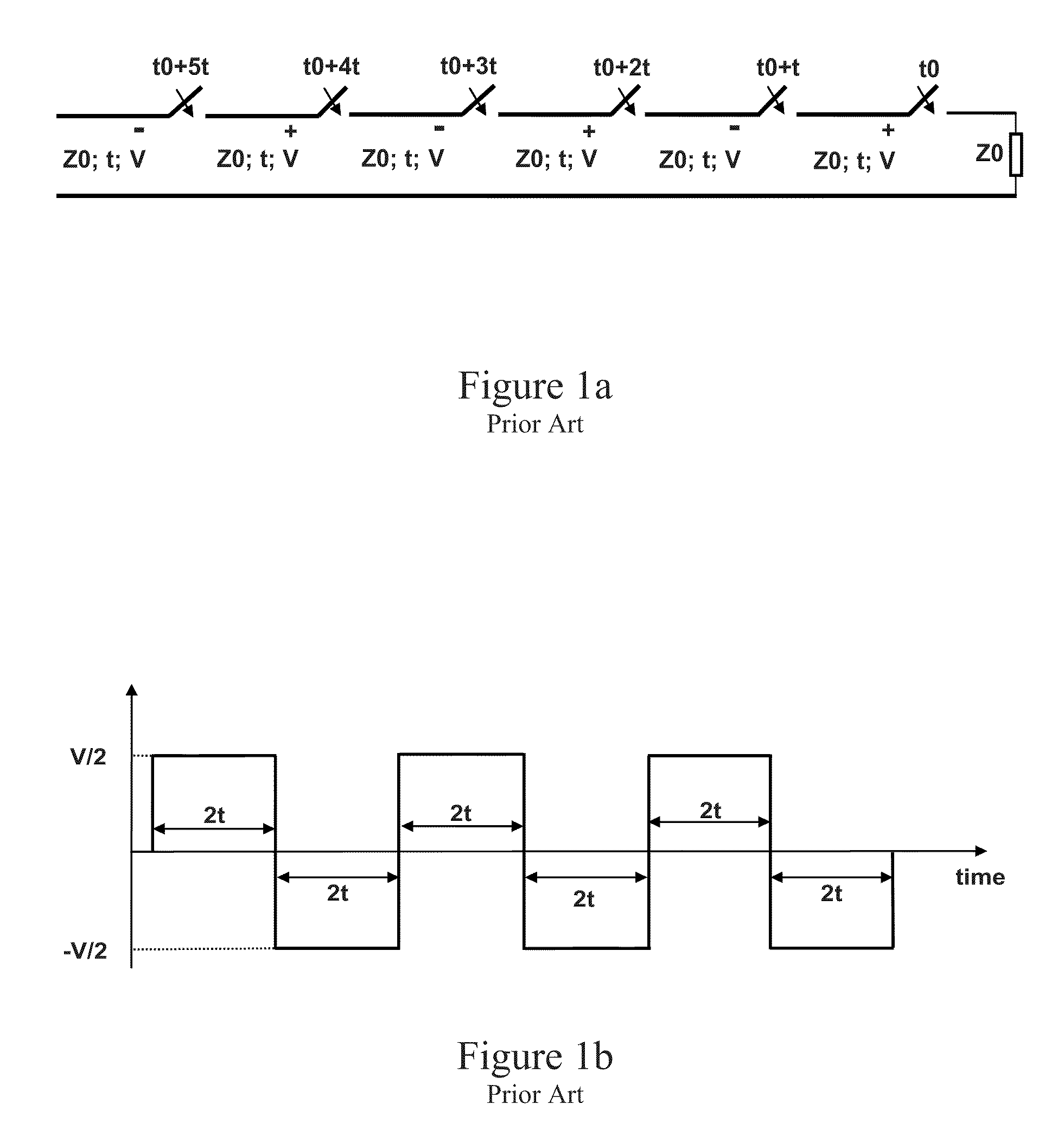

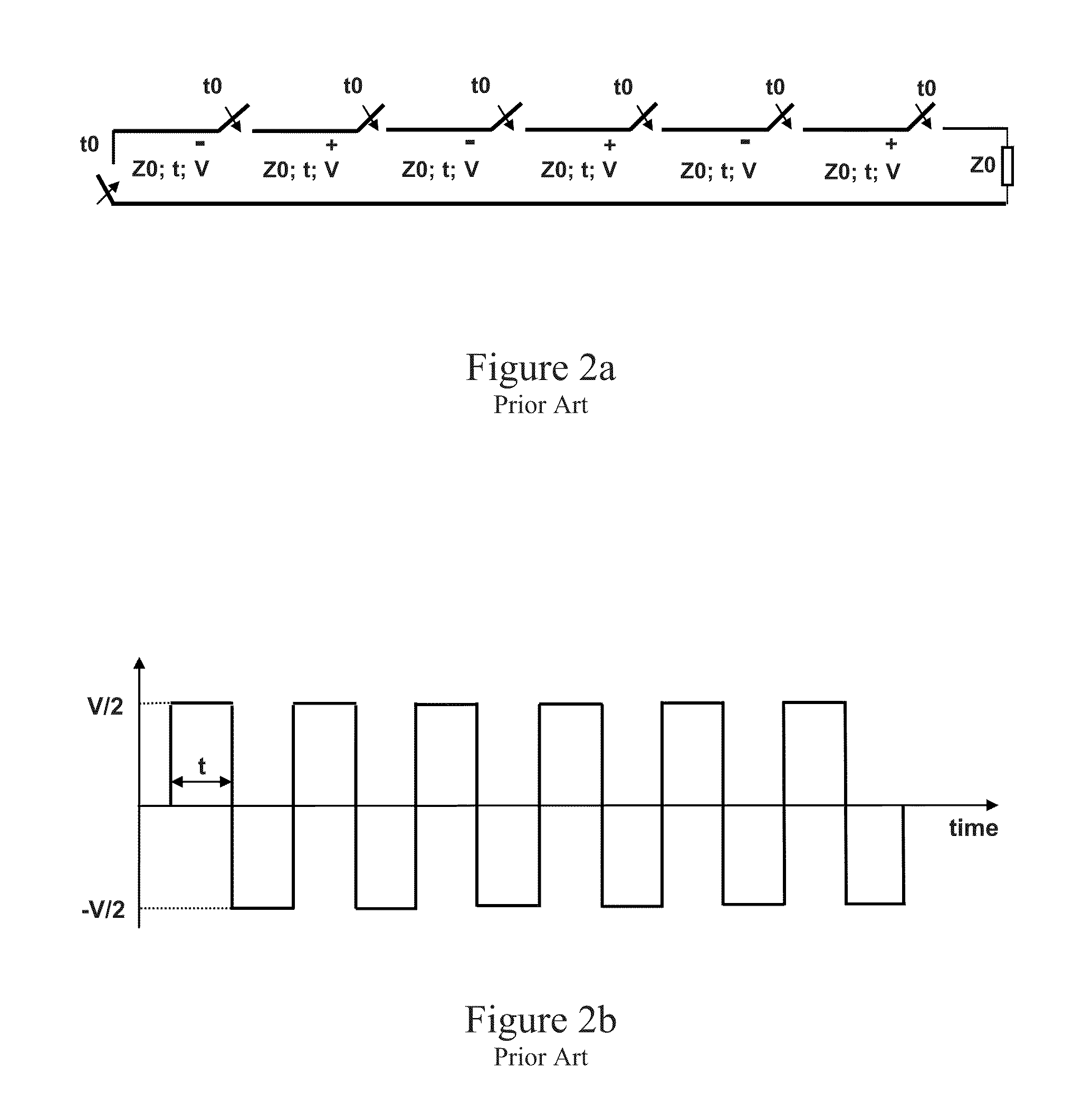

Compact multi-cycle high power microwave generator

InactiveUS20100194208A1Increasing frequency spectrumVariation in width of generatingDelay lines pulse generationTransmission control/equlisationElectrical conductorWave form

A compact multi-cycle high power microwave generator and a method of using the generator to generate microwave signals is disclosed and claimed. The apparatus includes one or more charged transmission line sections. Each transmission line section includes a first conductor that is section-specific and a second conductor that is common to all of the sections. A switch is associated with each section, each switch being operatively connected to a respective one of the first conductors. The apparatus includes third, common conductor that is not charged and that is operatively connected to each of the first conductors through its respective switch. The apparatus further includes a load, with the second conductor, the third conductor, and the load being operatively connected. Thus, the number of section-specific conductors, the number of charged transmission line sections, and the number of switches are all equal. Engagement of the switches generates a multi-cycle microwave pulse. Aspects, such as wavelength, frequency, and spacing, of the generated wave forms can be varied by including non-charged transmission lines intermediate the transmission line sections or varying the lengths of individual transmission line sections or varying the switching time.

Owner:BAE SYST INFORMATION & ELECTRONICS SYST INTERGRATION INC

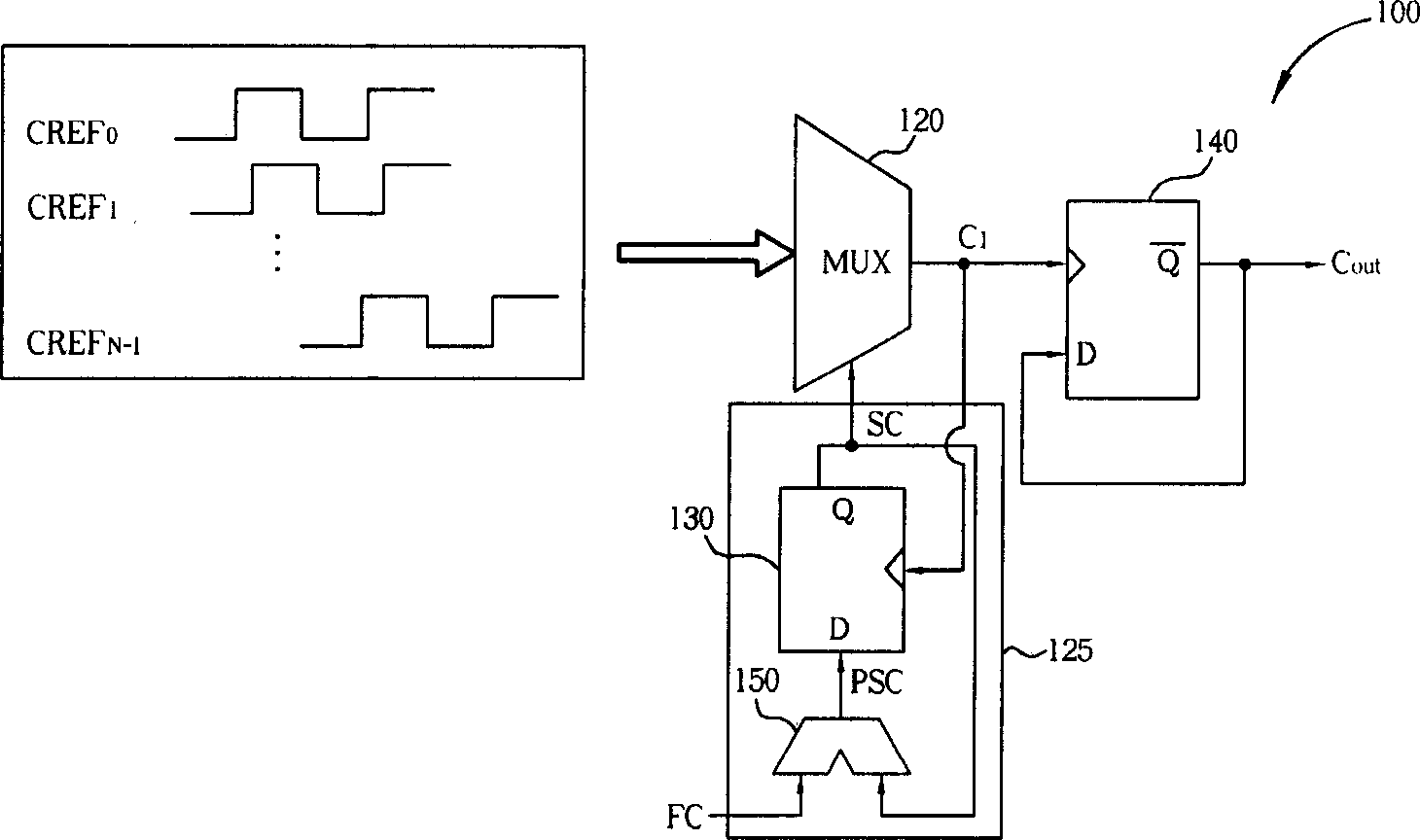

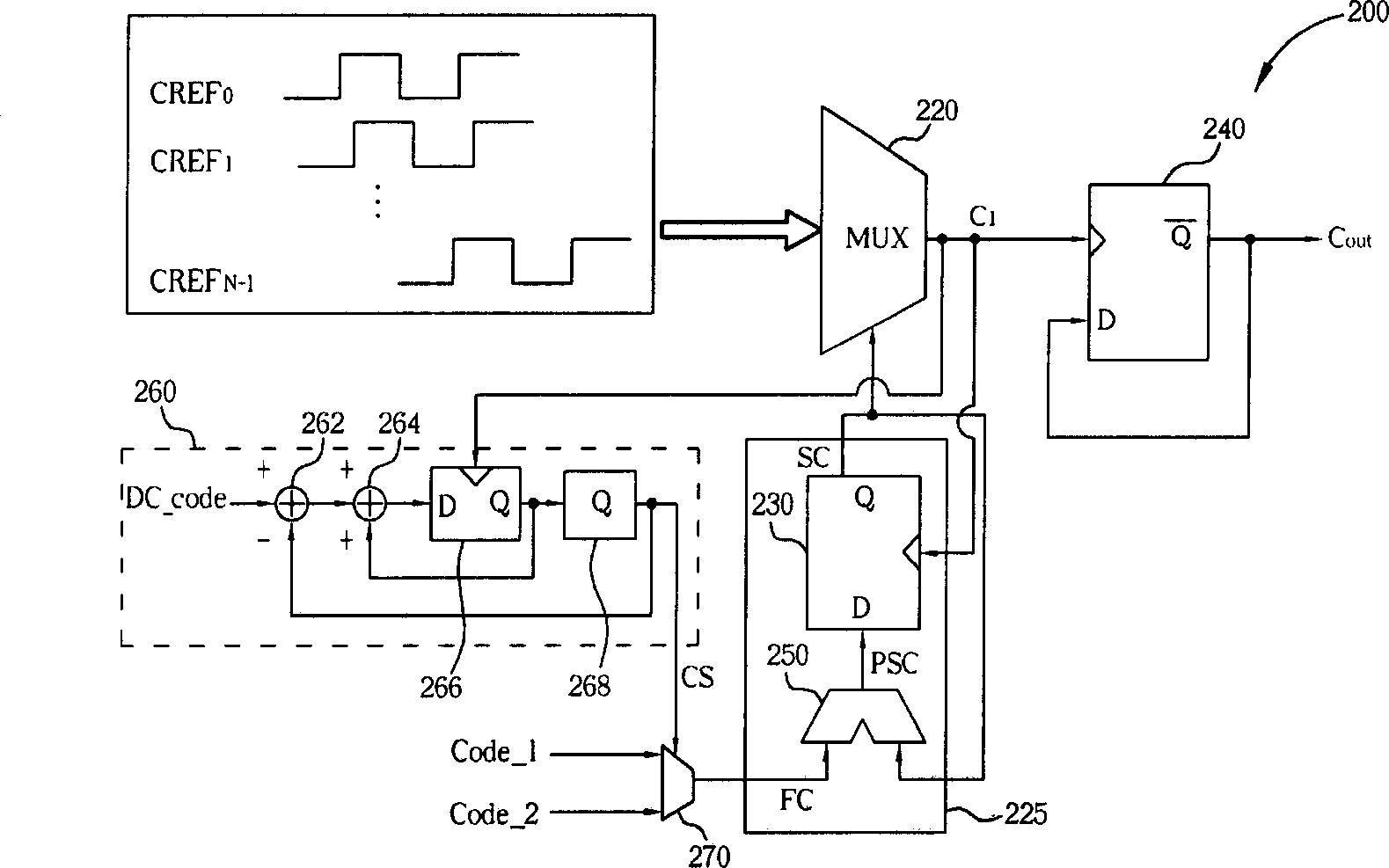

Clock generator circuit and related method for generating output clock signal

The present invention discloses a clock generator circuit for generating an output clock signal. The clock generator circuit includes: a random frequency code generator for generating a frequency code randomly, wherein the random frequency code generator is clocked by a first clock signal; an accumulator electrically connected to the random frequency code generator, for generating a selection code by accumulating the frequency code, wherein the accumulator is clocked by the first clock signal; a first multiplexer electrically connected to the accumulator, for selecting one of a plurality of reference clock signals as the first clock signal according to the selection code; and a toggle circuit electrically connected to the first multiplexer, being clocked by the first clock signal for generating the output clock signal. The invention can generate output clock signals selected with much more frequency.

Owner:MEDIATEK INC

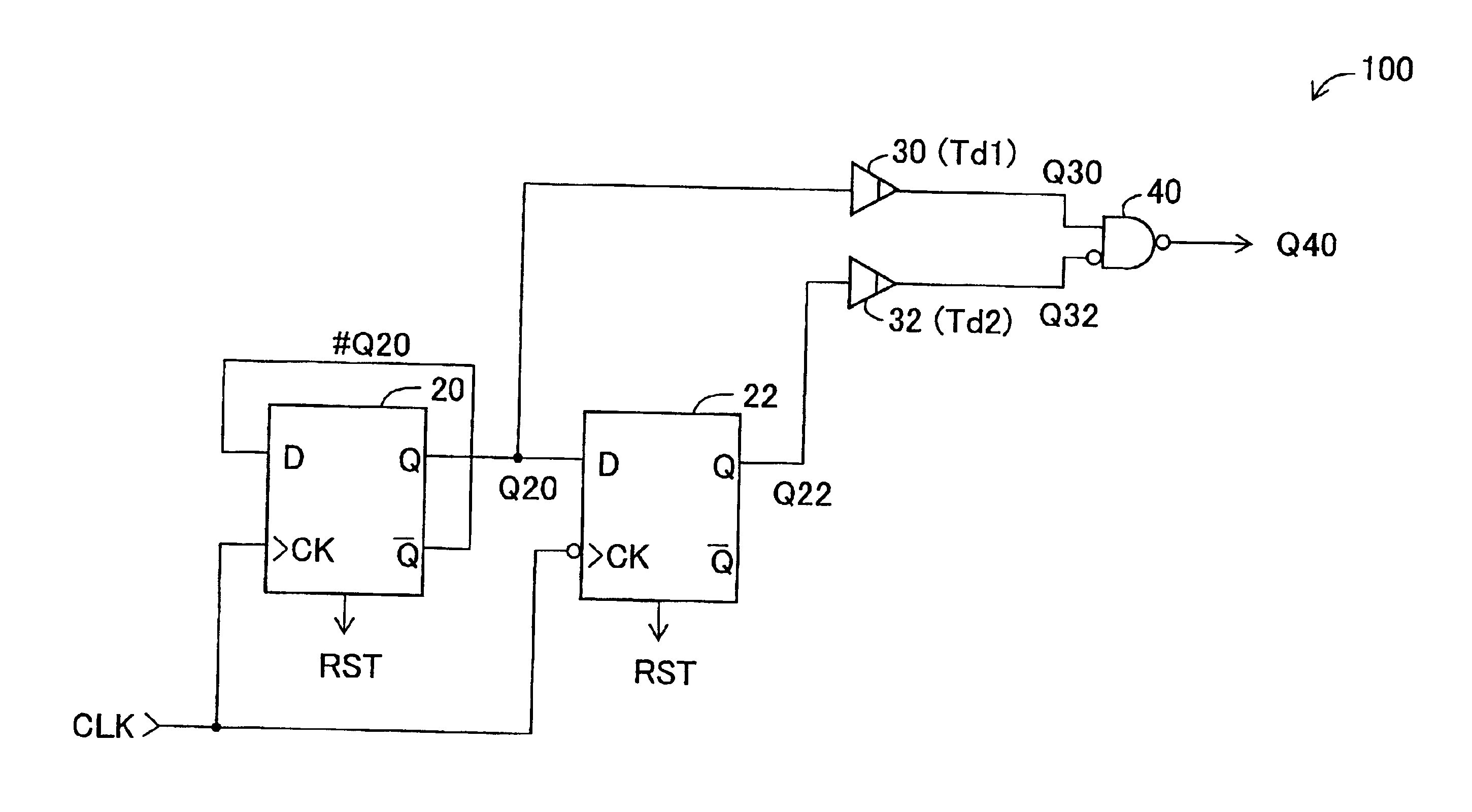

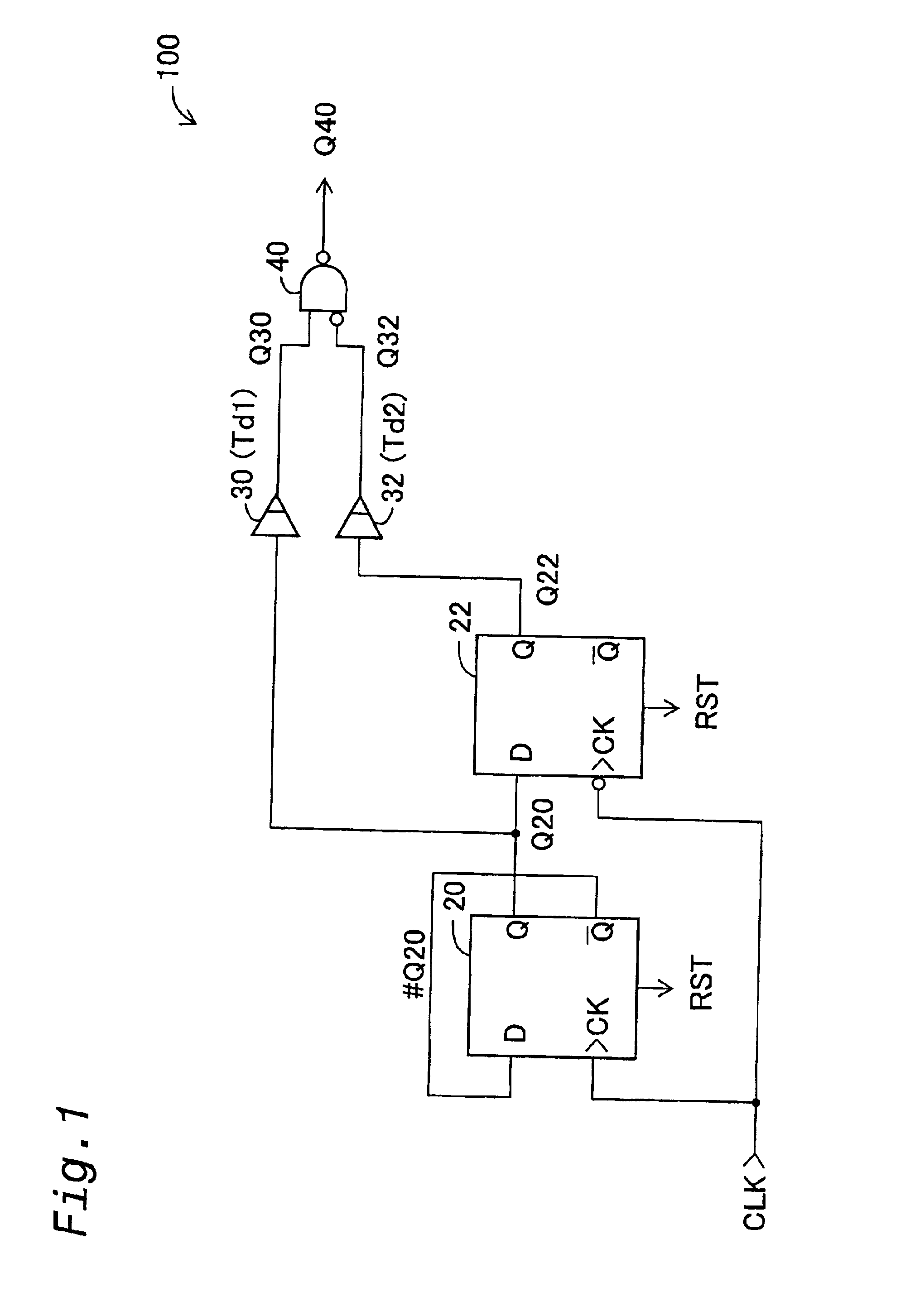

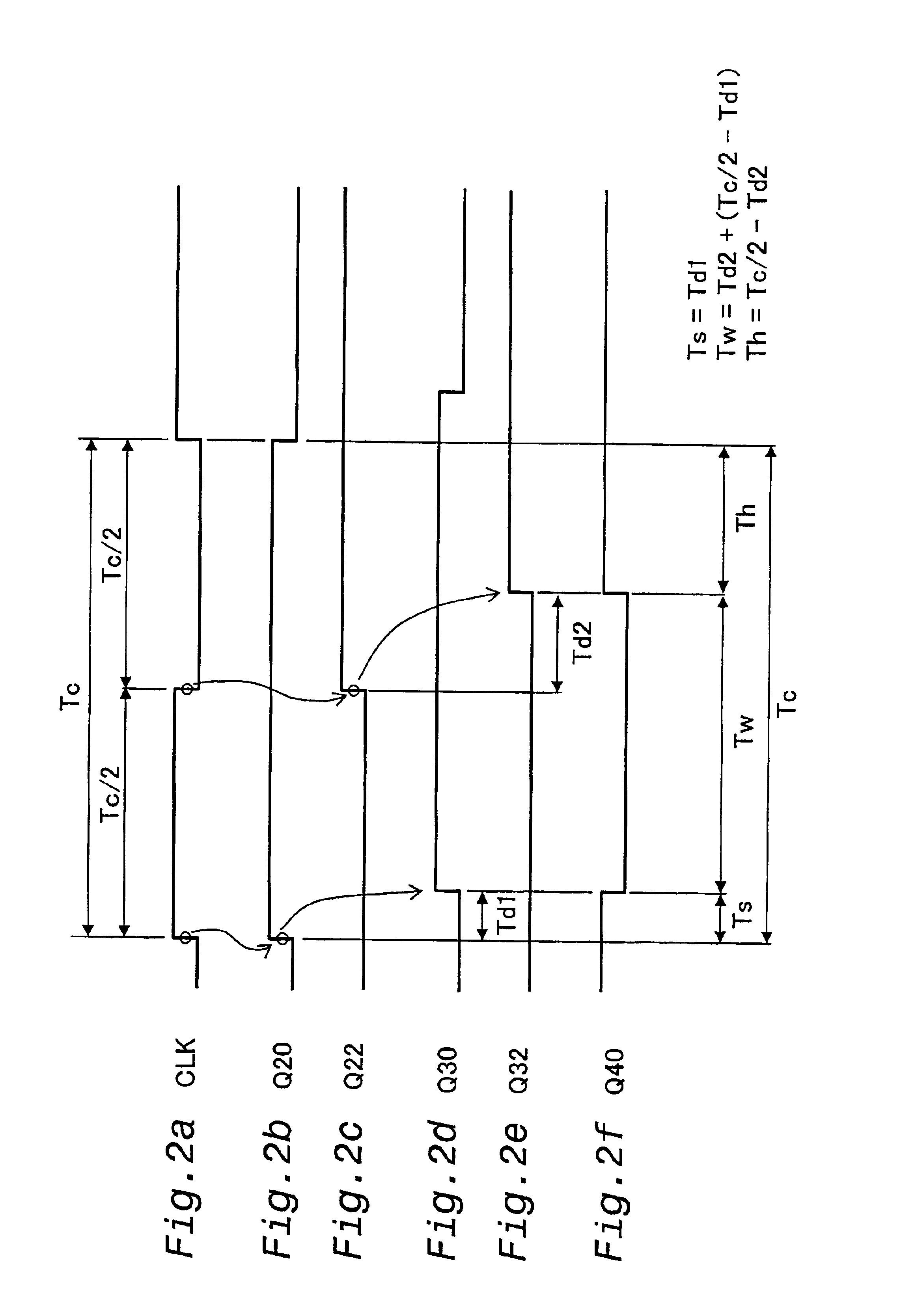

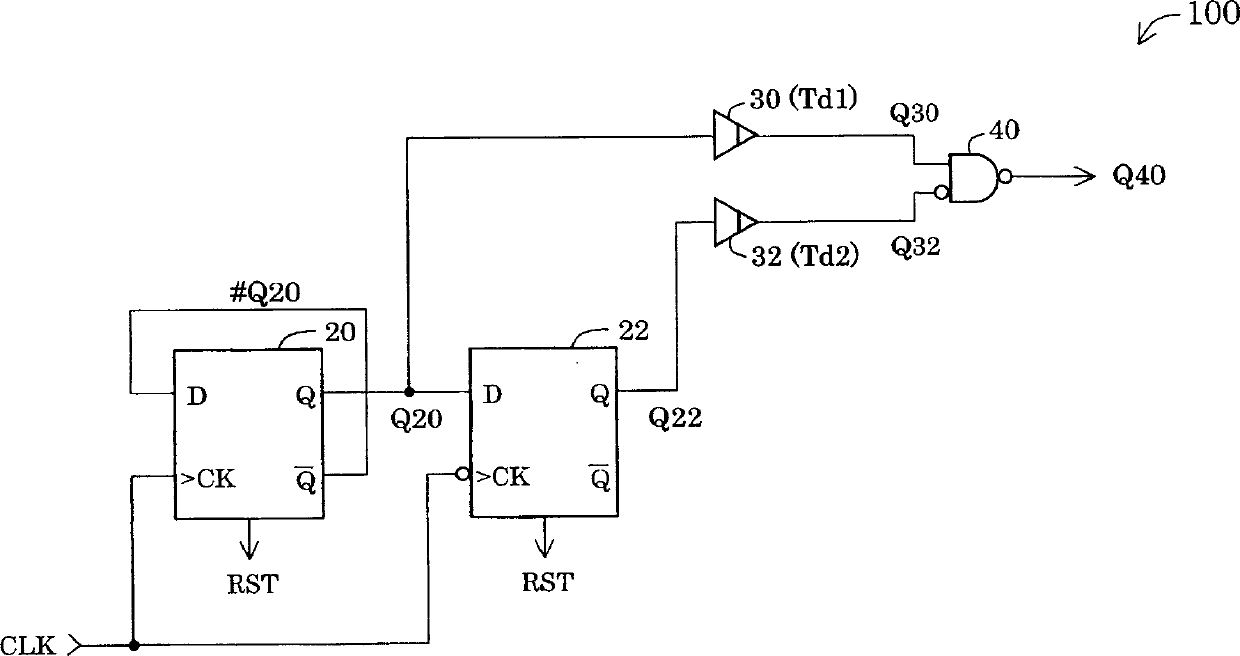

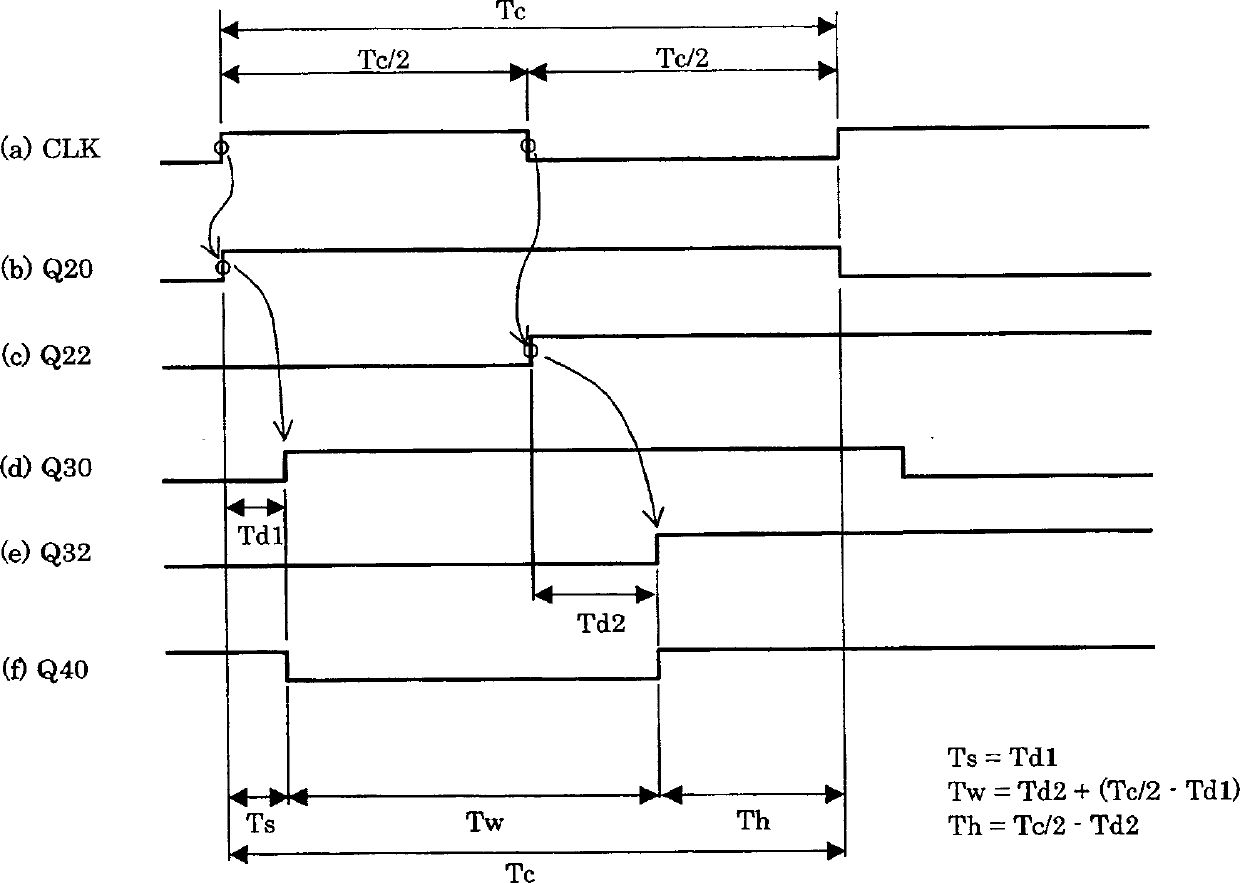

Generation of pulse signals from a clock signal

InactiveUS6895523B2Less effectMinimize impactTelevision system detailsRecord information storageTelecommunicationsSlave clock

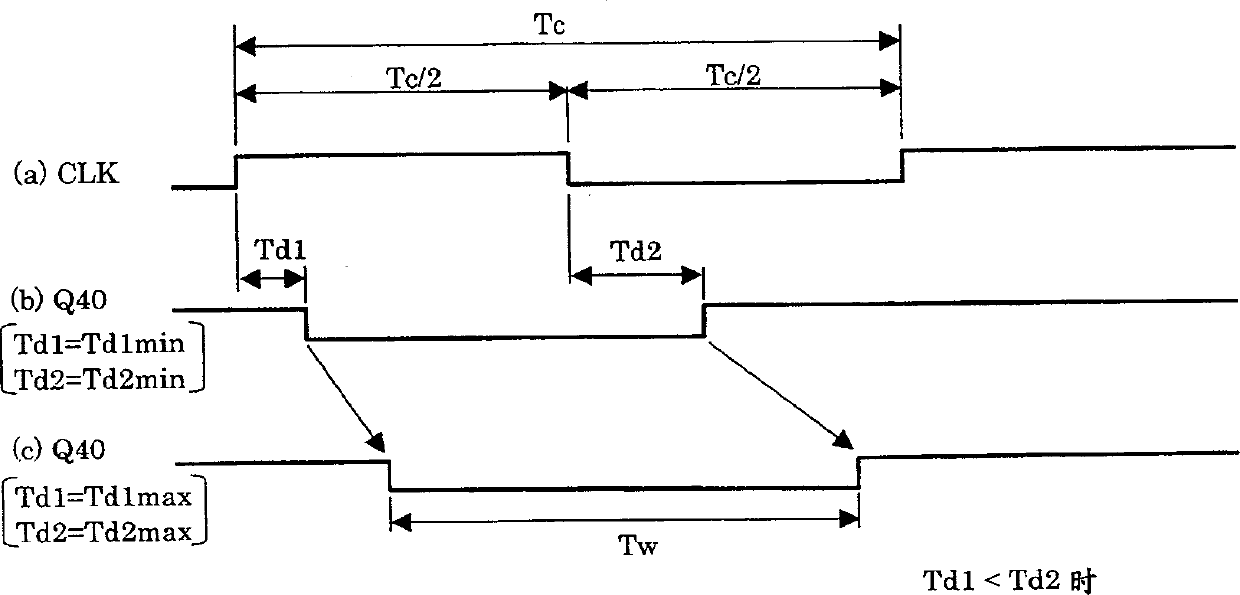

Two first delay signals Q30 and Q34 are generated such that edges thereof are delayed by a first delay time Td1 in relation to the rising edge of a clock signal CLK. Two second delay signals Q32 and Q36 are also generated such that edges thereof are delayed by a second delay time Td2 in relation to the trailing edge of the clock signal CLK. A pulse signal Sout is generated as a result of logic operations performed on the first delay signals Q30 and Q34 and the second delayed signals Q32 and Q36.

Owner:SEIKO EPSON CORP

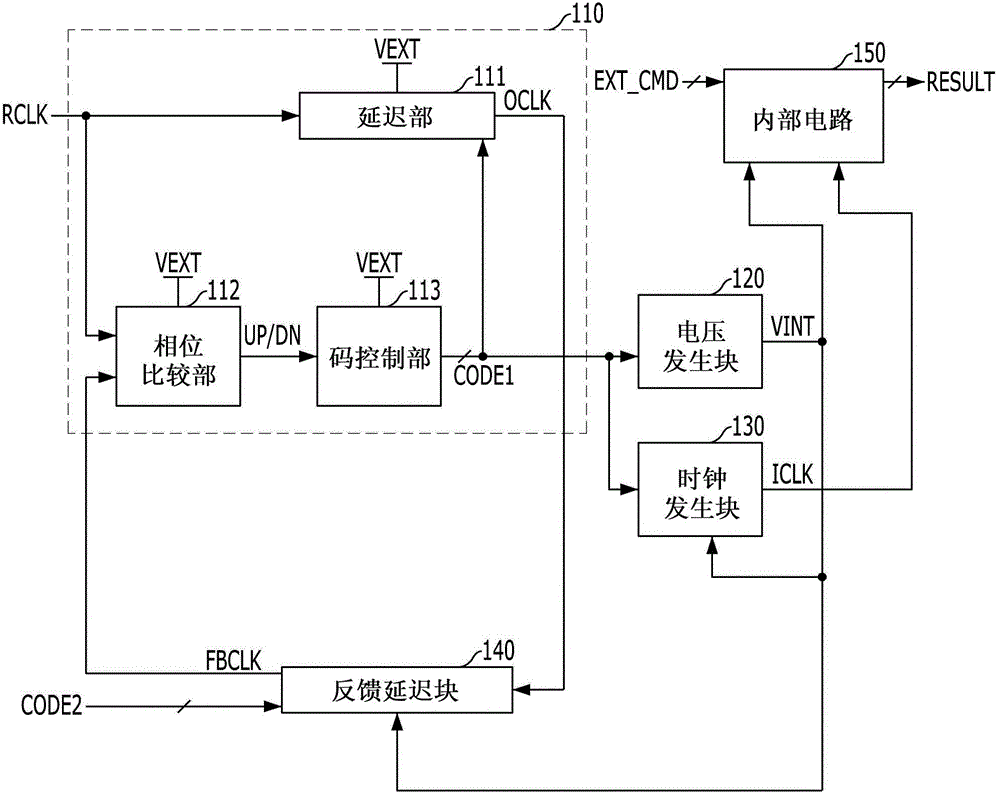

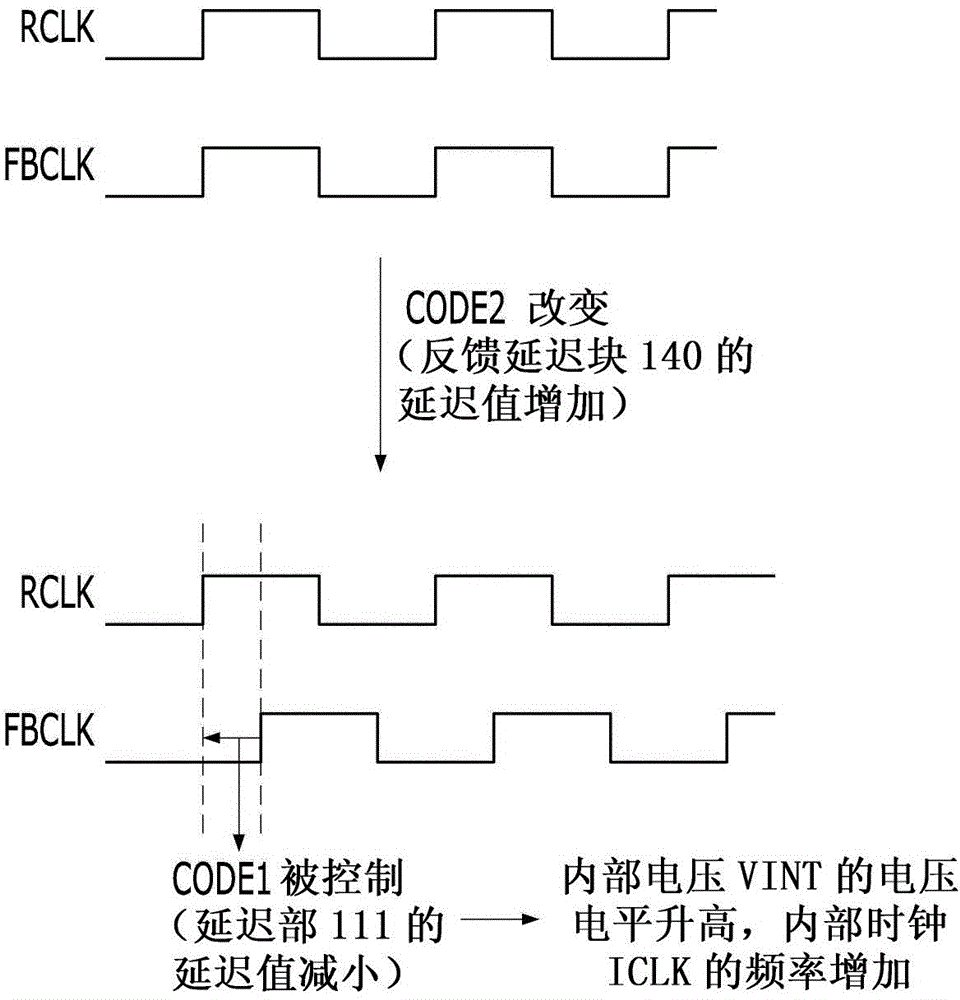

Semiconductor device, semiconductor system and method for operating semiconductor device

ActiveCN105096994AFast operationImprove operating speedDelay lines pulse generationPulse automatic controlPower semiconductor devicePhason

A semiconductor device includes a code generation block configured to generate an output clock by delaying a reference clock which is inputted from an exterior, control a delay value of the output clock based on a result of comparing phases of the reference clock and a feedback clock, and generate a first control code corresponding to the delay value of the output clock, a voltage generation block configured to generate an internal voltage with a voltage level corresponding to the first control code, a clock generation block configured to generate an internal clock with a frequency corresponding to the first control code, and a feedback delay block configured to generate the feedback clock by delaying the output clock by a delay value corresponding to a second control code.

Owner:SK HYNIX INC

Method and apparatus for digital synthesis of long multi-cycle microwave pulses

InactiveUS7986196B2Invention increased maximizedEfficient processingDelay lines pulse generationTransmission control/equlisationMicrowaveElectrical conductor

Conductive segments (transmission line conductors) are positioned within a transmission line structure in order to generate multi-cycle microwave pulses. The conductor segments are switchably coupled to one or the other conductor of the transmission lines, inside the transmission line structure. Microwave pulses may be induced in the transmission line by closing the switches in a controlled manner to discharge successive segments, or successive groups of segments, into the transmission lines. The induced pulses travel uninterrupted along the transmission lines in a desired direction to the load. Efficiency of systems and energy delivered to the load in multi-section transmission lines is increased and / or maximized by adjusting the ratio of characteristic impedances associated with the transmission line conductor segments according to an optimum ratio.

Owner:BAE SYST INFORMATION & ELECTRONICS SYST INTERGRATION INC

High power bipolar pulse generators

InactiveUS8004120B2Simple structureSmall sizeDelay lines pulse generationPulse generation by energy-accumulating elementFiberEngineering

A bipolar pulse generator is implemented in a simple structure while providing a high efficiency design having a relatively low total size, while still allowing access by fibers used to control a photoconductive switch that activates the generator. The bipolar pulse generator includes a stacked Blumlein generator structure with an additional transmission line connected to a load at its near end and short-circuited at its distal end. An extra transmission line is positioned between the Blumlein generator's structure and the load provides specified limited gap between positive and negative sub-pulses. The bipolar pulse generator further includes a bended Blumlein generator structure, in which an existing intrinsic “stray” transmission line is used to provide the bipolar pulse. Still further, bipolar pulse generator includes stepped transmission lines, with additional switches positioned between steps, which are charged by different voltages.

Owner:BAE SYST INFORMATION & ELECTRONICS SYST INTERGRATION INC

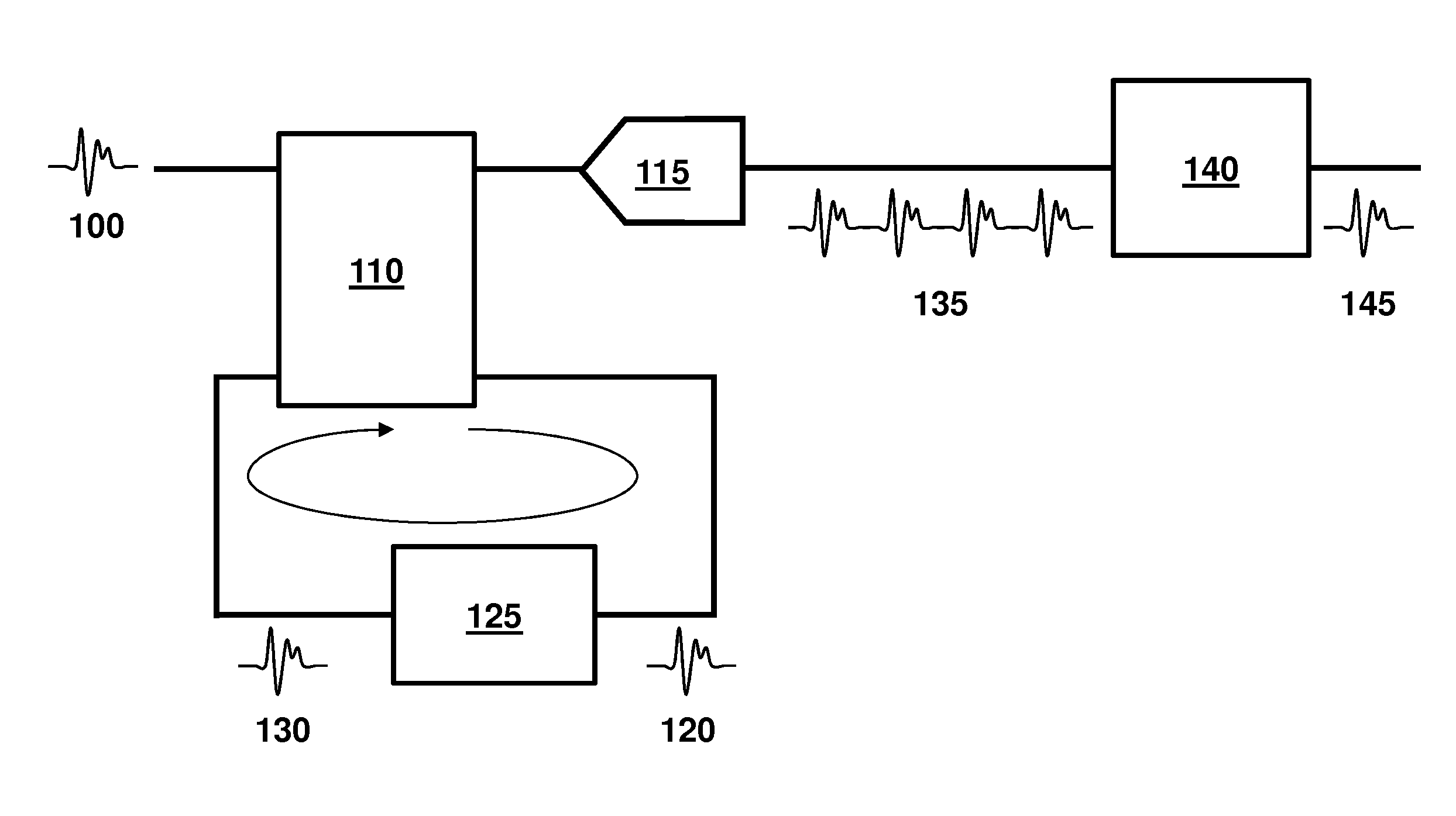

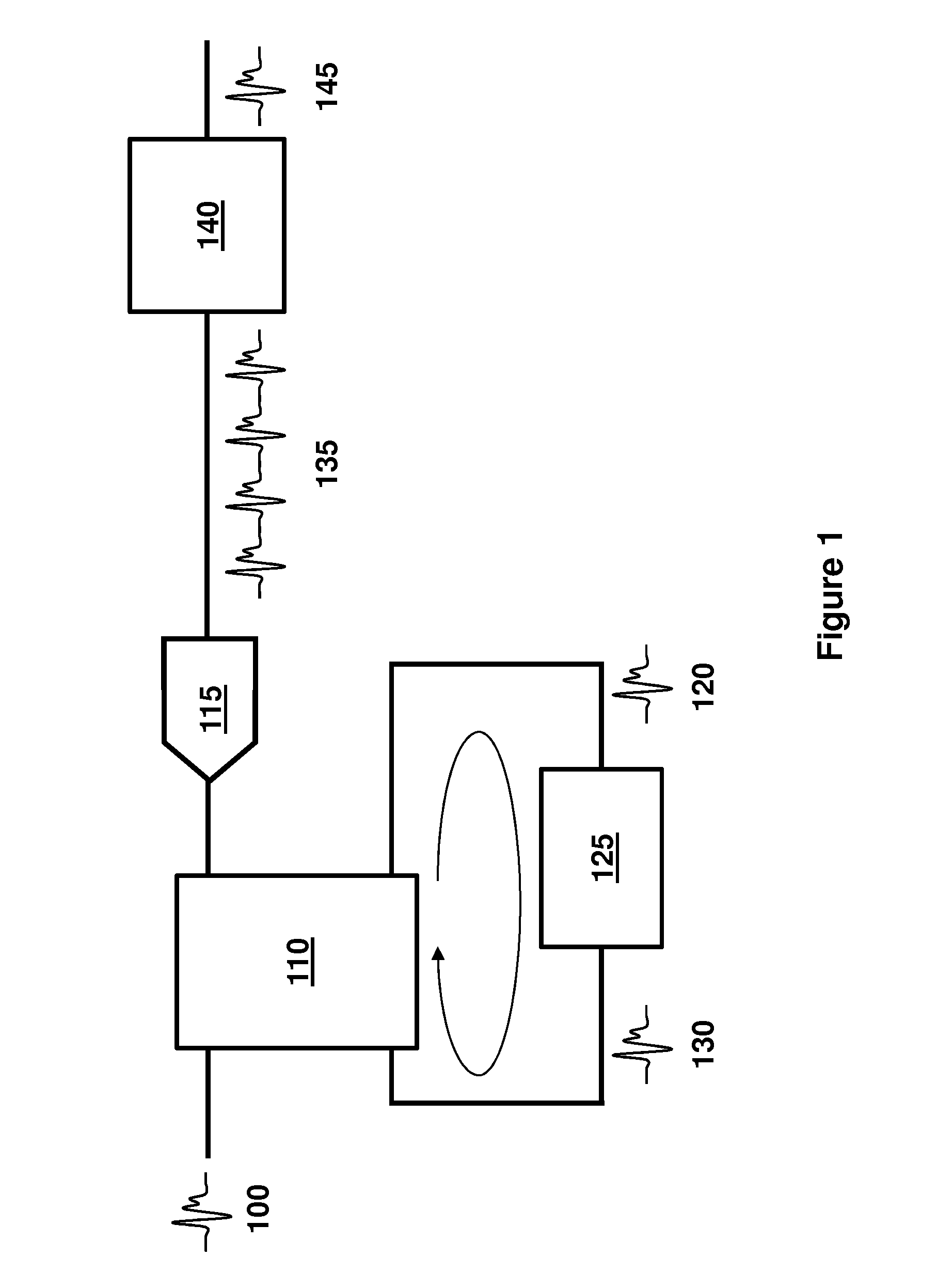

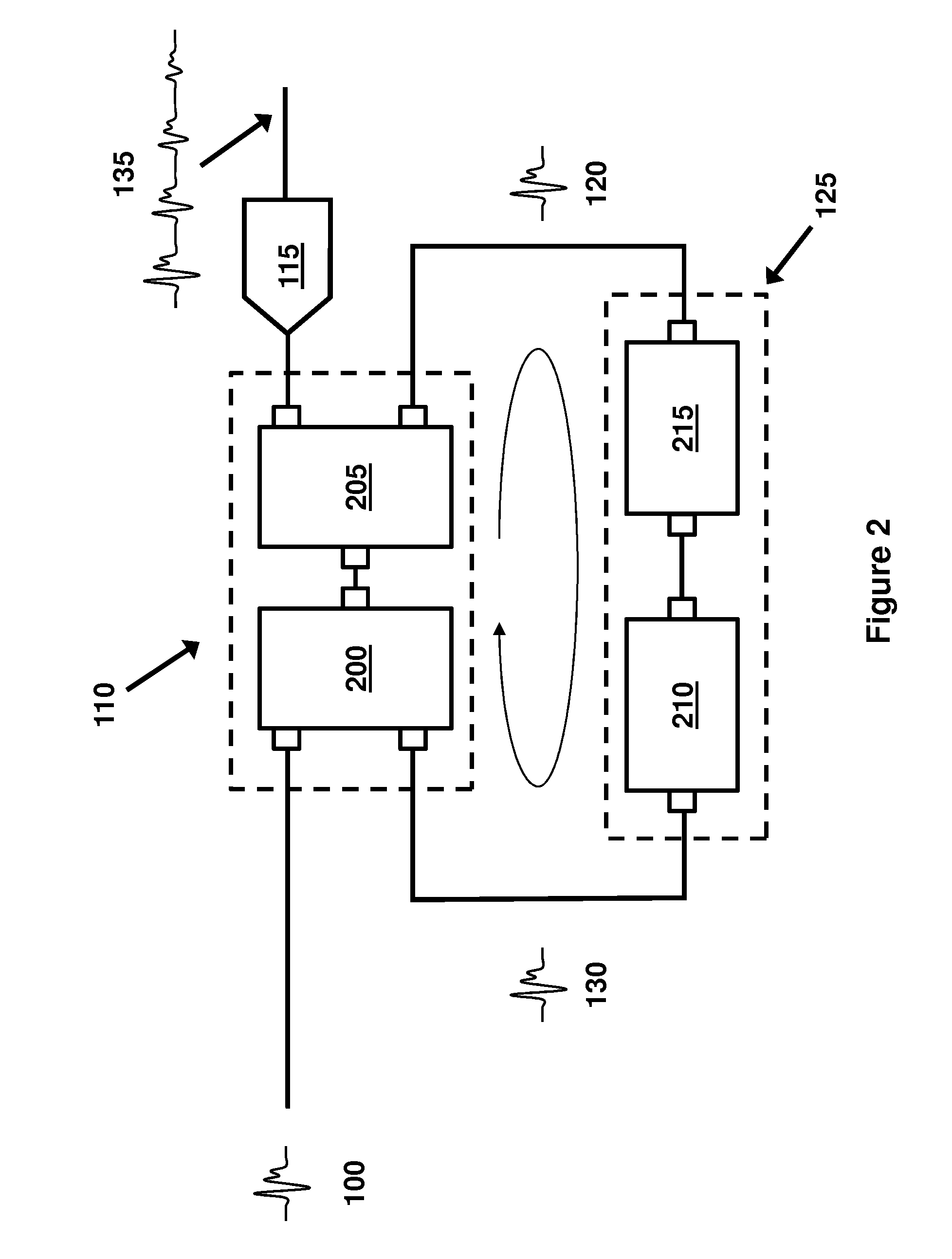

Circulating Resampling Digitizer

InactiveUS20160365868A1Reduce noiseHigh resolutionDelay lines pulse generationDigital variable displayElectricityInstrumentation

Embodiments of the present invention provide improved techniques for sampling events in electrical test equipment such as real-time oscilloscopes. A circulating resampling digitizer uses a delay loop to repeatedly acquire replicas of an input event. The replicas are used to create a series of events which may be output or stored in memory. Signal reconstruction techniques such as interleaving and / or averaging may be applied to the series in order to construct a digital representation of the original input event. The resulting representation may have a higher sample rate, lower noise, and higher vertical resolution than each event in the series. The disclosed techniques use low cost components and can be added to existing instruments with little or no modification.

Owner:TEKTRONIX INC

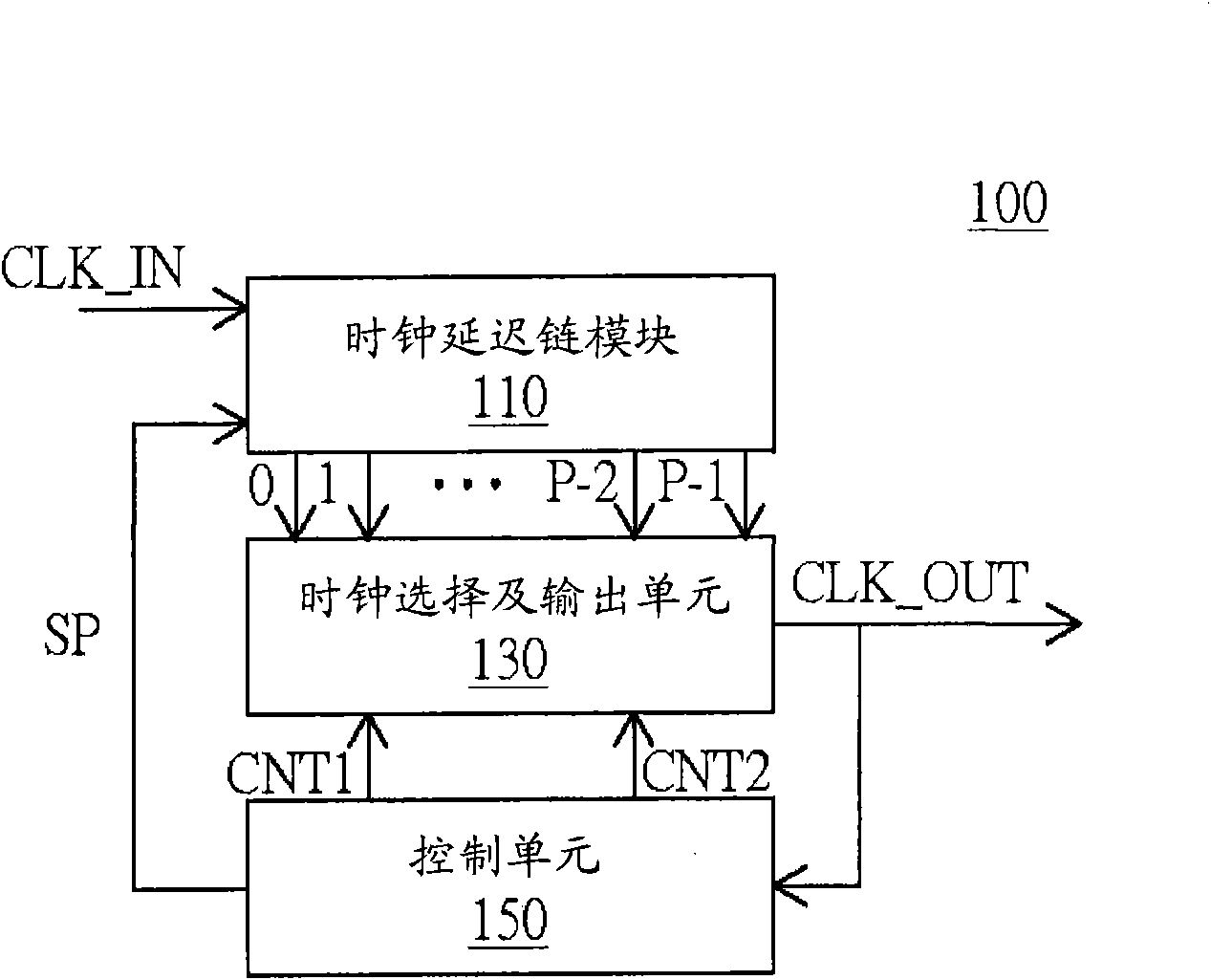

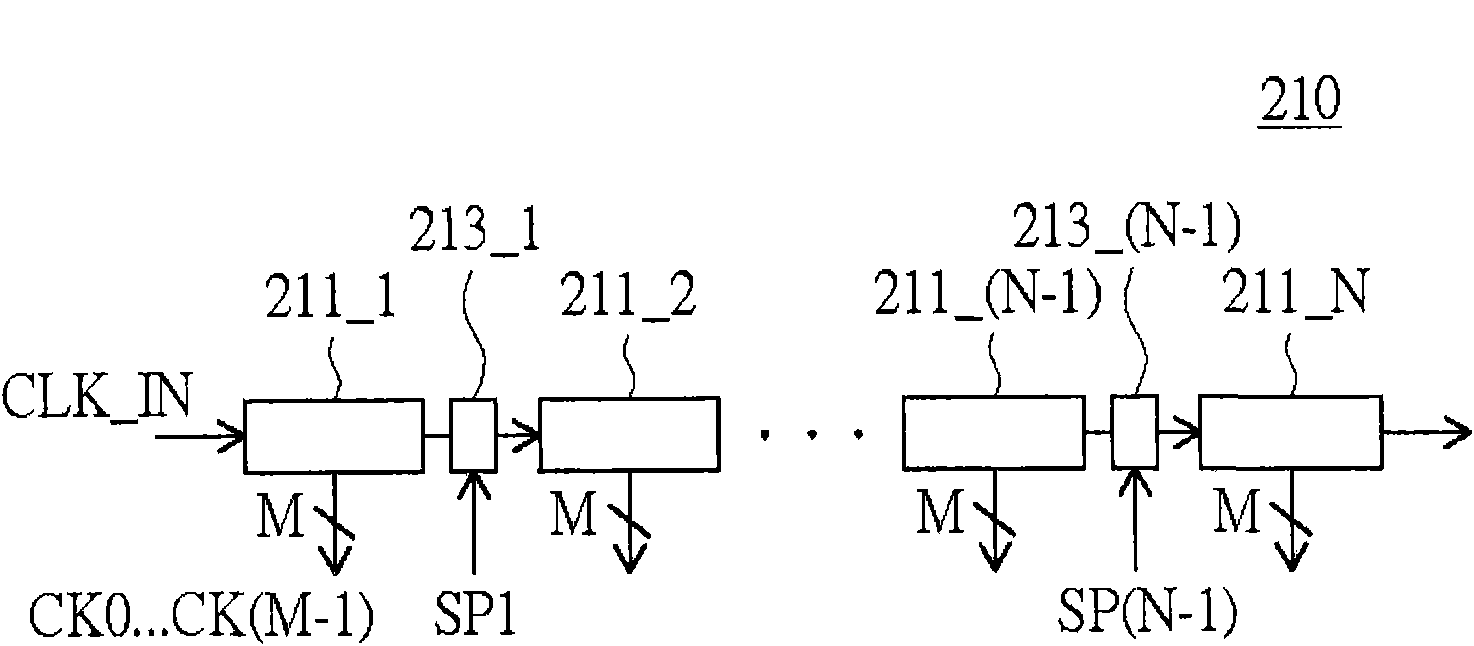

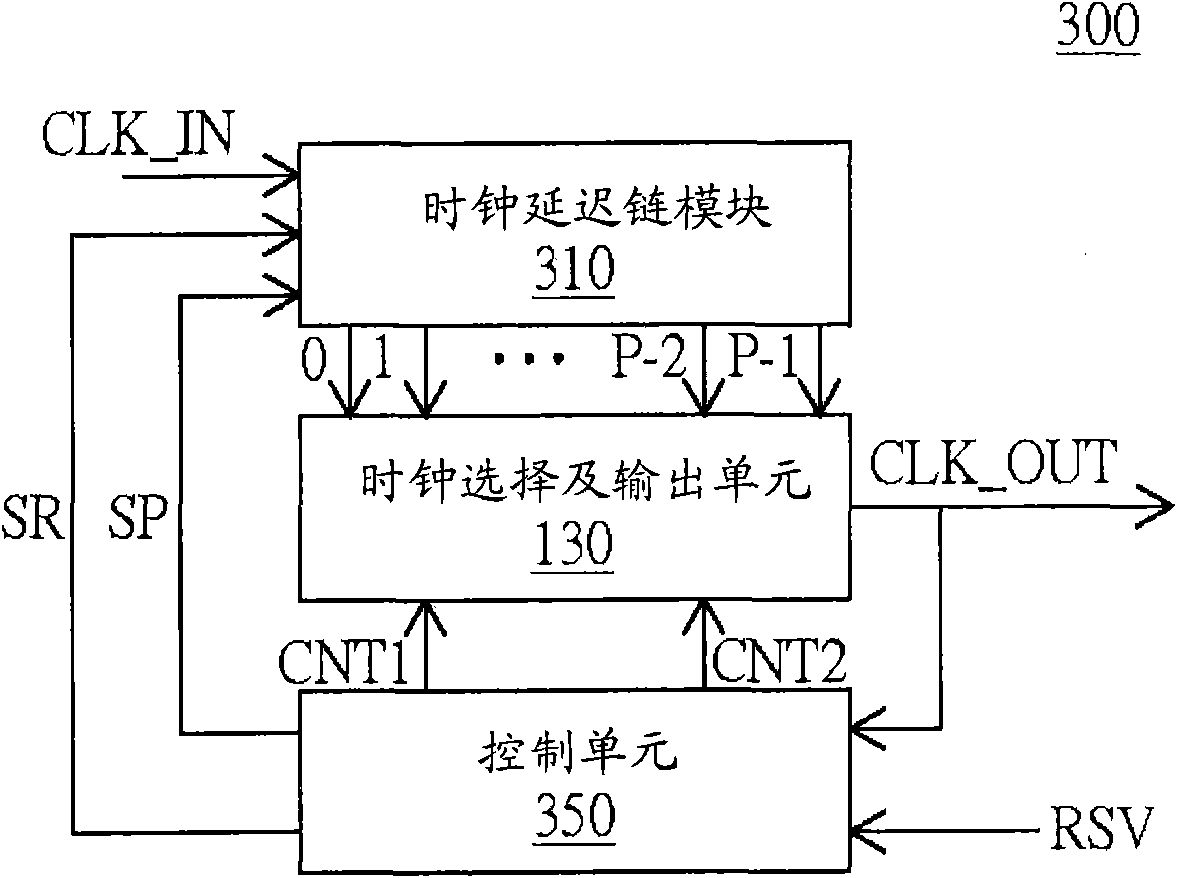

Spread spectrum clock generating circuit with power-saving control

InactiveCN101867356AIncrease elasticityThe spreading ratio can be changedDelay lines pulse generationSingle output arrangementsControl signalEngineering

The invention provides a clock spread spectrum generating circuit with power-saving control, which is used for carrying out spread spectrum on the input clock signals into output clock signals. The spread spectrum clock generating circuit comprises a clock delay chain module, a clock selection and output unit and a control unit, wherein the clock delay chain module comprises a plurality of clock delay chains and is used for generating a plurality of delay clock signals; the control unit can generate a plurality of counter signals according to the output clock signals and can generate a plurality of power-saving control signals according to the counter signals; the clock selection and output unit is used for selectively combining the delay clock signals to generate output clock signals according to the counter signals; and the clock delay chain module is used for selectively starting the clock delay chains according to the power-saving control signals, therefore, spread spectrum output clock signals can be effectively generated and the purpose of energy saving can be achieved.

Owner:RAYDIUM SEMICON

Formation of pulse signal from clock signal

Providing technology capable of satisfying a request value concerning the specified period of a pulse signal, without excessively lowering the cycle of a clock signal, even if considering fluctuation in delay time is taken into consideration, in a delay element. Two first delay signals Q30 and Q34 are generated such that edges thereof are delayed by a first delay time Td1 in relation to the rising edge of a clock signal CLK. Two second delay signals Q32 and Q36 are also generated such that edges thereof are delayed by a second delay time Td2 in relation to the trailing edge of the clock signal CLK. A pulse signal Sout is generated as a result of logic operations performed on the first delay signals Q30 and Q34 and the second delayed signals Q32 and Q36.

Owner:SEIKO EPSON CORP

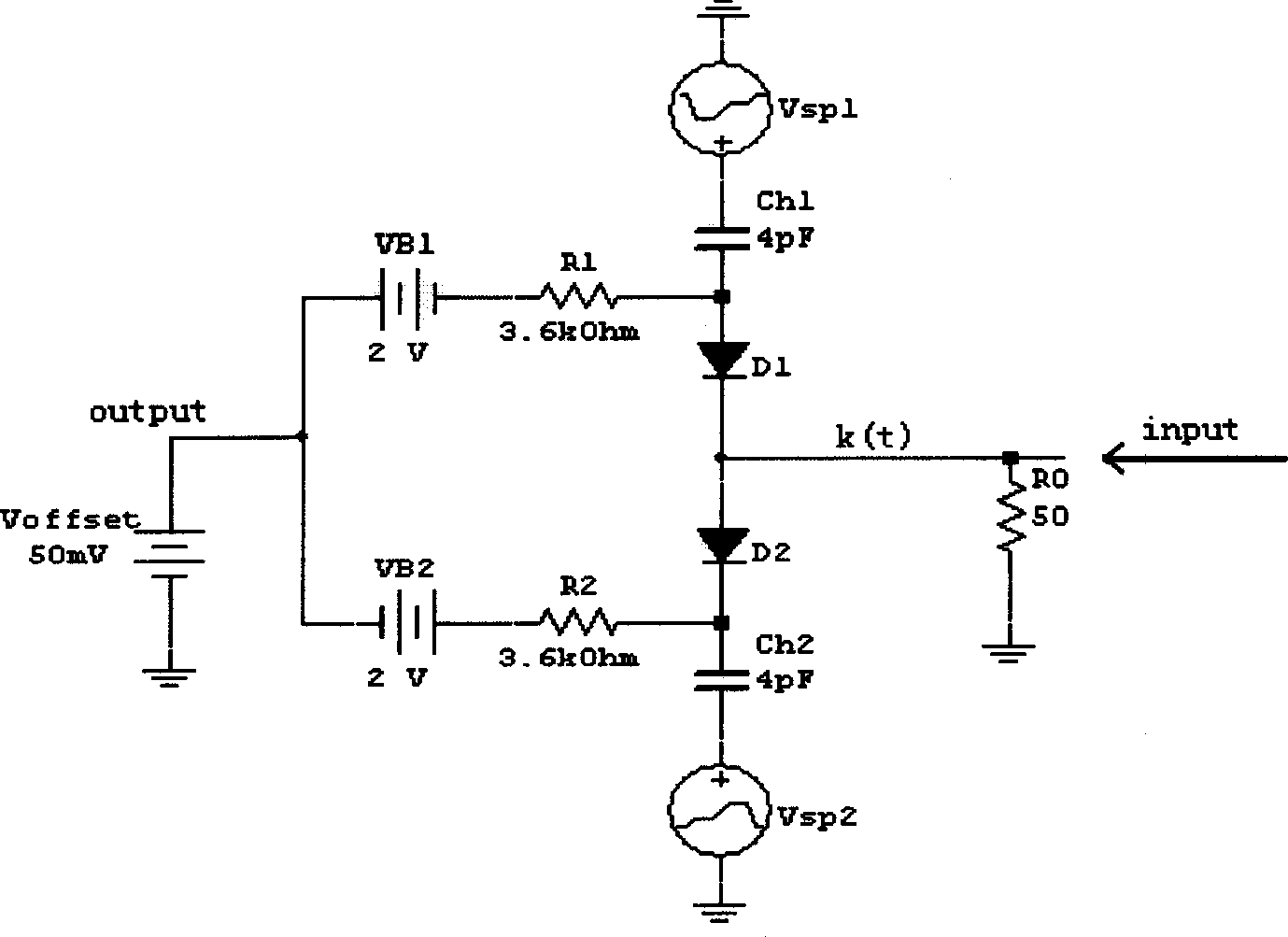

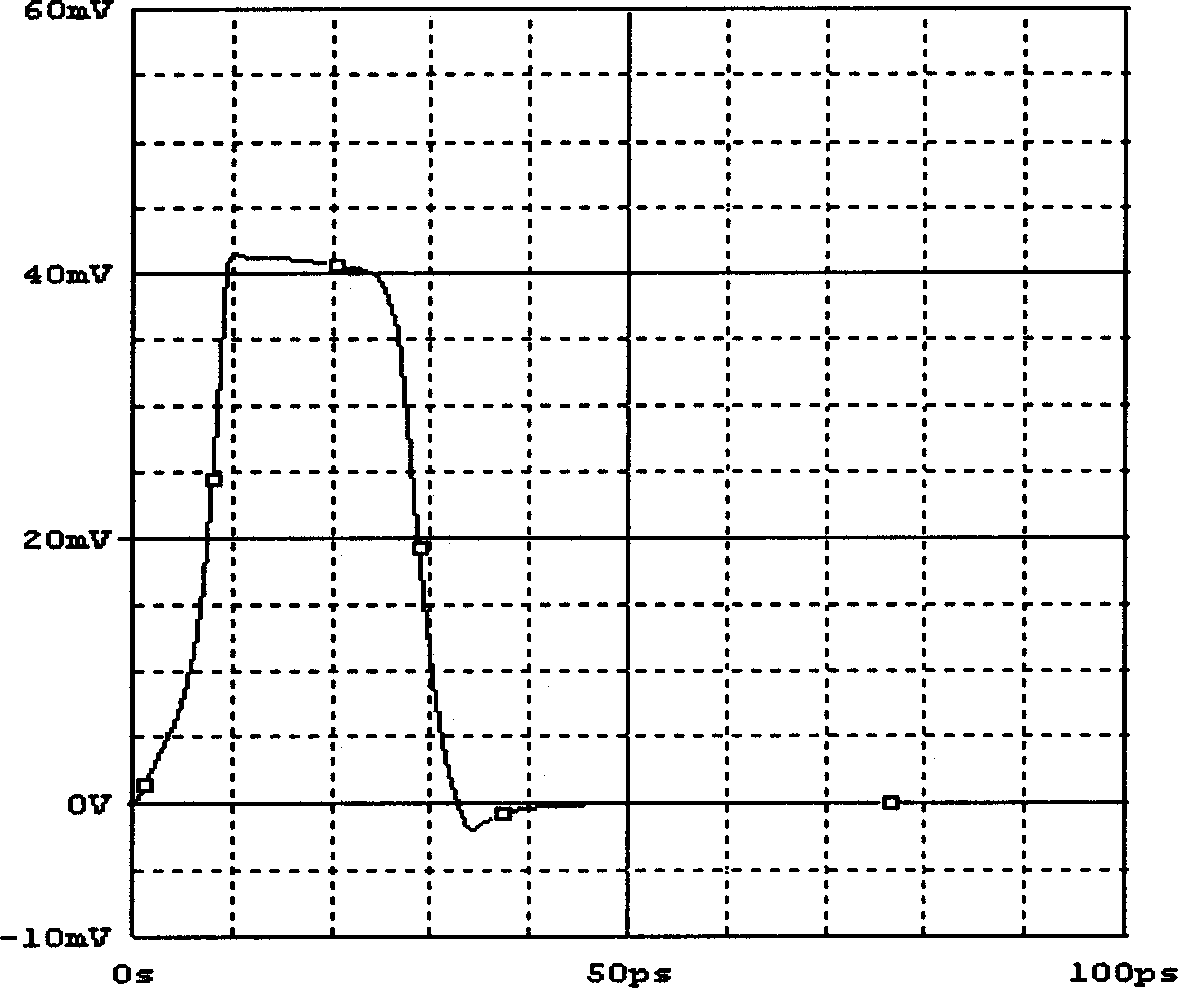

Method and apparatus for utilizing wide-band sampling oscillometer as signalling source

InactiveCN1819458AAchieve calibrationAccurate measurementDelay lines pulse generationTime-domain reflectometerTime domain

The method includes the following steps: Agilent86100A wideband samploscope with a double microwave diode balance sampling head circuit is selected as pulse signal generator; plug-in component is installed; the voltage is set in -300mV-50mV or +50mV-+300mV; Agilent86100B wideband samploscope for TDR signal is selected to match the delay of Agilent86100A wideband samploscope; a time domain reflectometer plug-in is installed; the trigger signal of Agilent86100A wideband samploscope is sent out; the signal triggering end of Agilent86100A wideband samploscope is connected to the TDR signal generating end of Agilent86100B wideband samploscope; its cable is connected to the input end of Agilent86100A wideband samploscope; adjusting vertical sensitivity and horizontal sensitivity of Agilent86100A wideband samploscope; setting the offset voltage of Agilent86100A wideband samploscope as zero; adjusting the delay time until Agilent86100A wideband samploscope generates high speed pulse signals. Its equivalent step impulse source has 8ps rise time.

Owner:BEIJING UNIV OF TECH

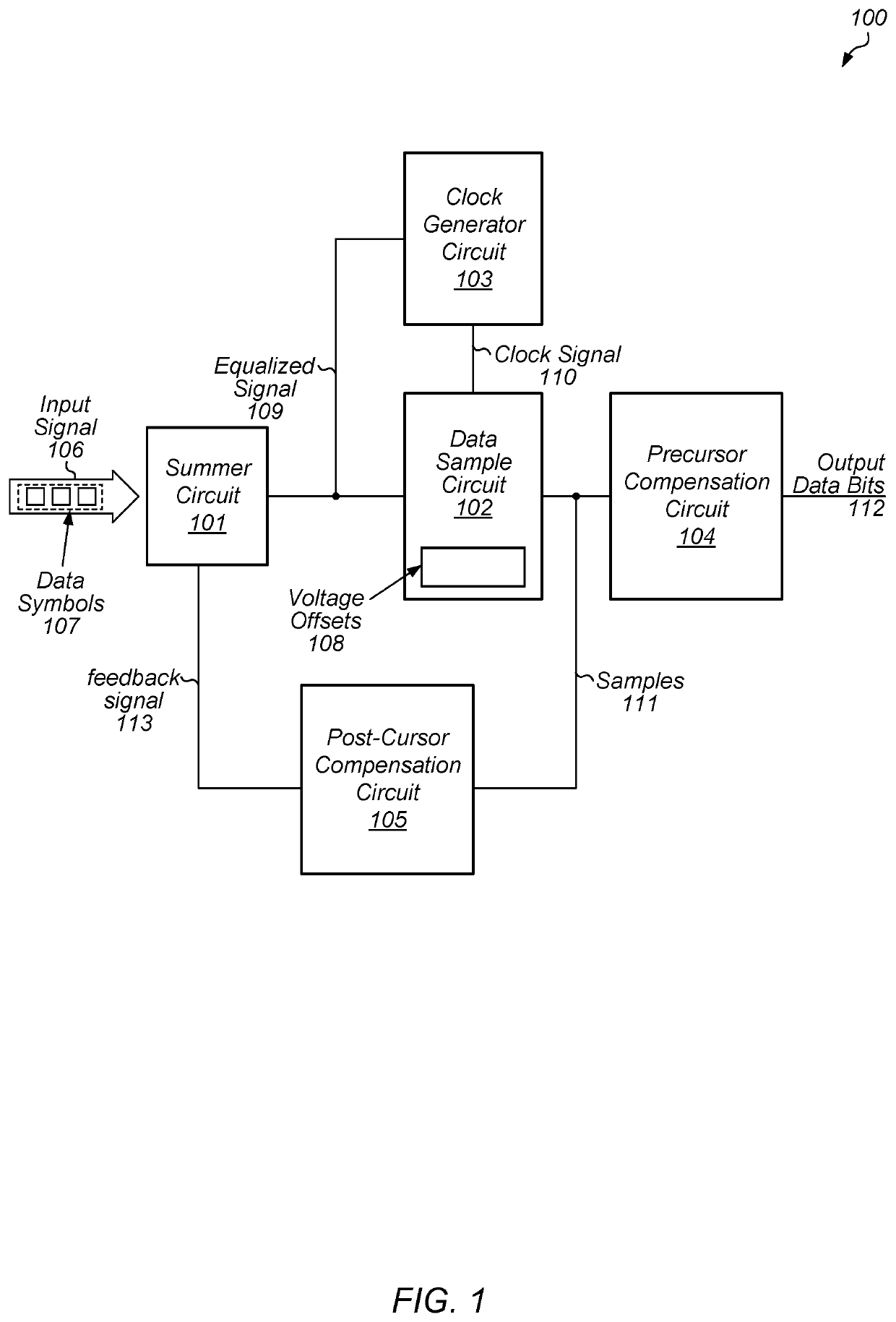

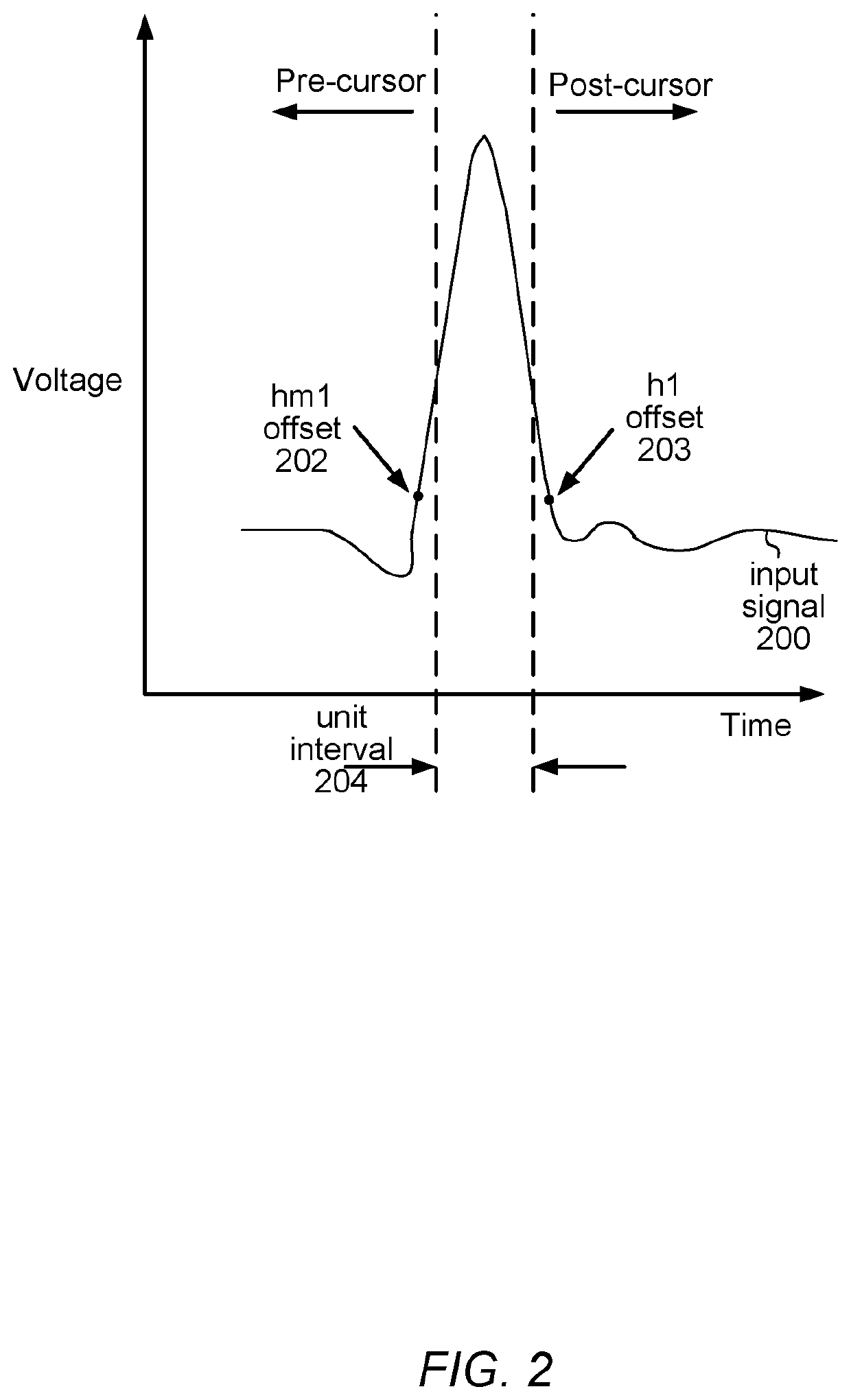

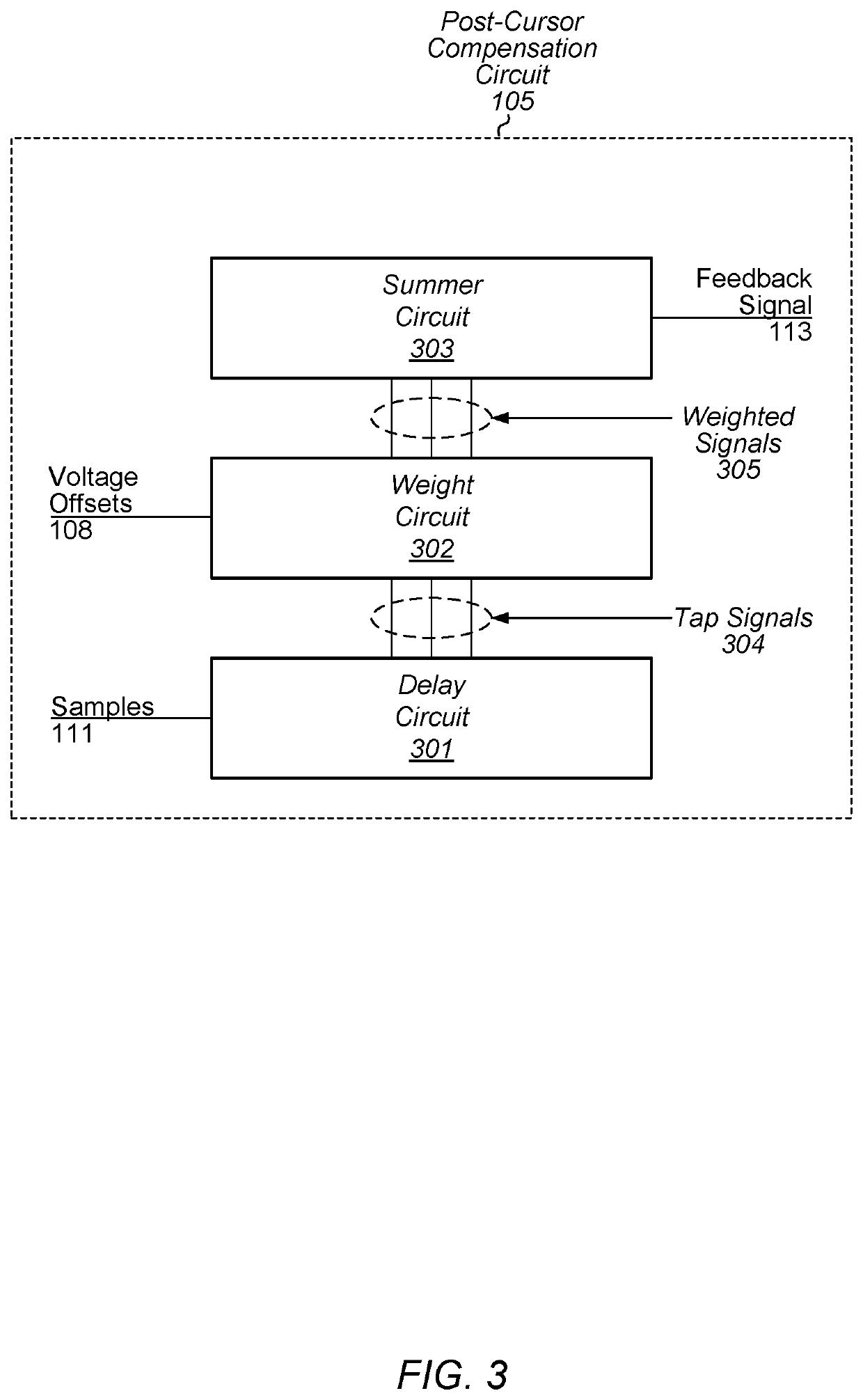

Adpative receiver with pre-cursor cancelation

ActiveUS20210135907A1Delay lines pulse generationSynchronisation error detectionEngineeringReal-time computing

A data receiver circuit includes a summer circuit configured to receive an input signal that encodes multiple data symbols, and combine the input signal with a feedback signal to generate an equalized input signal, which is used to generate a clock signal. The data receiver circuit also includes multiple data slicer circuits that sample, using the clock signal and multiple voltage offsets, to generate multiple samples for a particular data symbol. A precursor compensation circuit included in the data receiver circuit may generate an output value for the particular data symbol using the multiple samples. The data receiver circuit also includes a post cursor compensation circuit that generates the feedback signal using at least one of the multiple samples and a value of a previously received sample.

Owner:ORACLE INT CORP