Patents

Literature

97 results about "Bipolar signal" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In telecommunication, a bipolar signal is a signal that may assume either of two polarities, neither of which is zero. A bipolar signal may have a two-state non-return-to-zero (NRZ) or a three-state return-to-zero (RZ) binary coding scheme.

Electronic circuitry

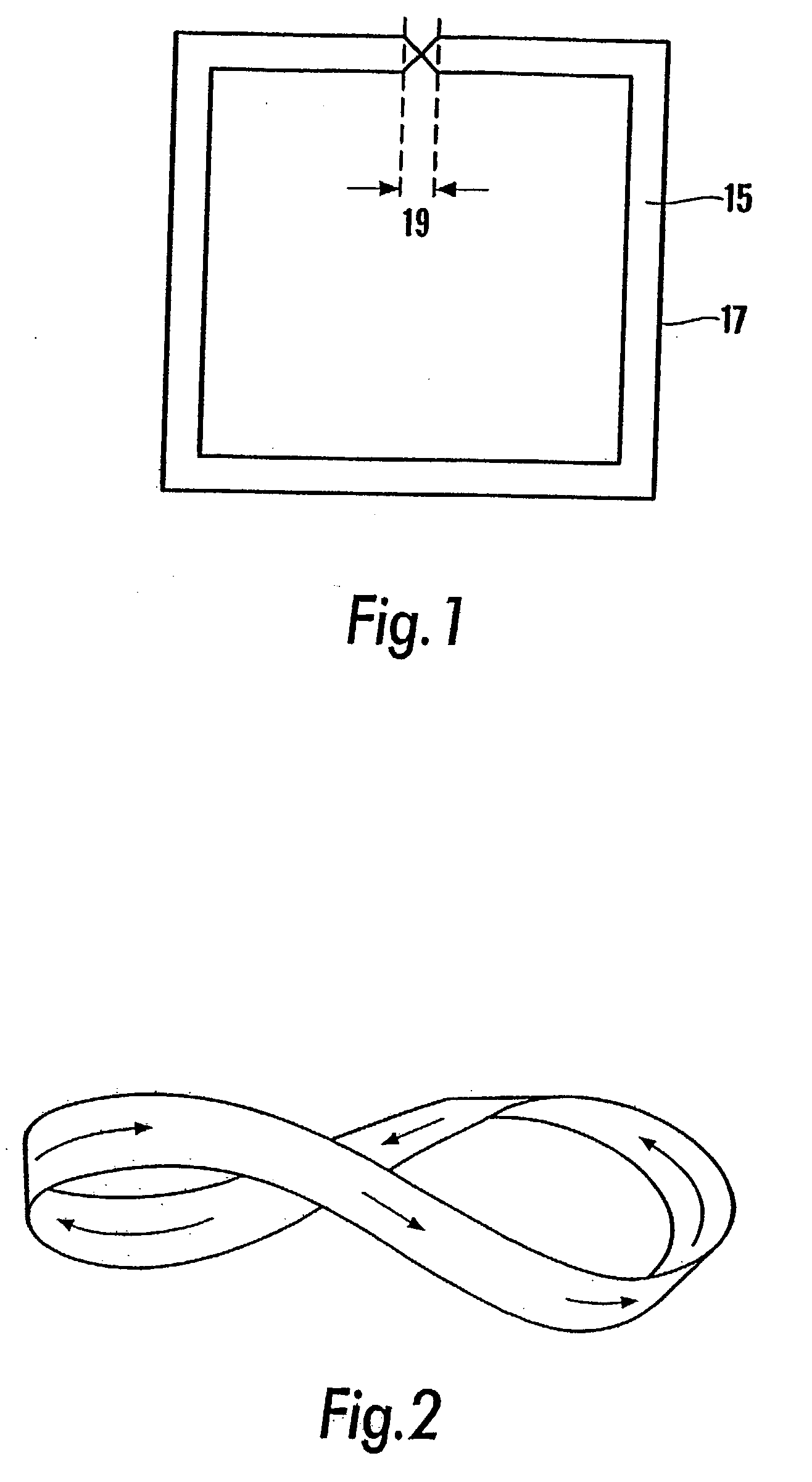

InactiveUS6556089B2Short fallShort riseDelay lines pulse generationPulse automatic controlCMOSBipolar signal

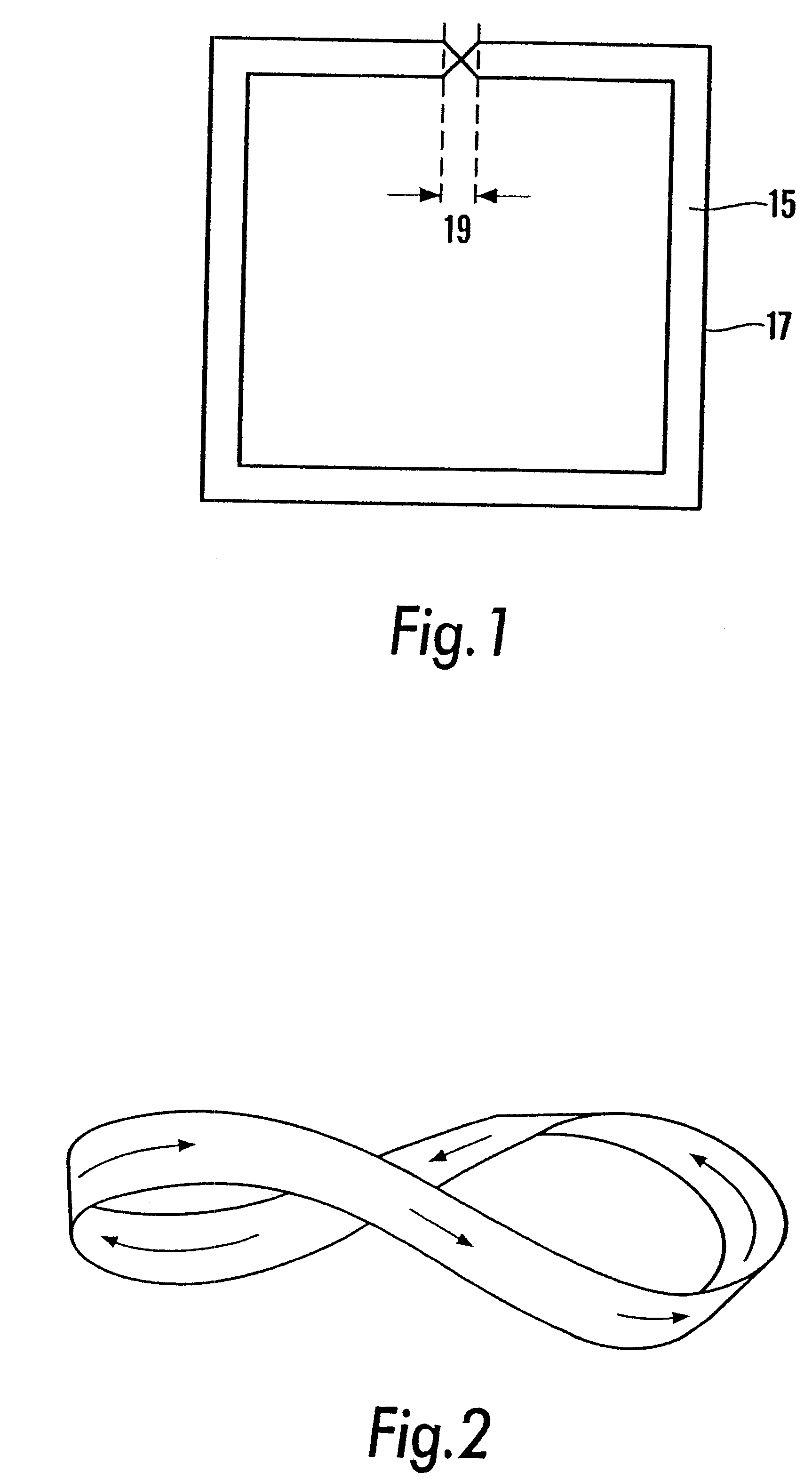

Timing signal generation and distribution are combined in operation of a signal path exhibiting endless electromagnetic continuity affording signal phase inversion and having associated regenerative active means. Two-or more-phases of substantially square-wave bipolar signals arise directly in travelling wave transmission-line embodiments compatible with semiconductor fabrication including CMOS. Coordination by attainable frequency synchronism with phase coherence for several such oscillating signal paths has intra-IC inter-IC and printed circuit board impact.

Owner:ANALOG DEVICES INC

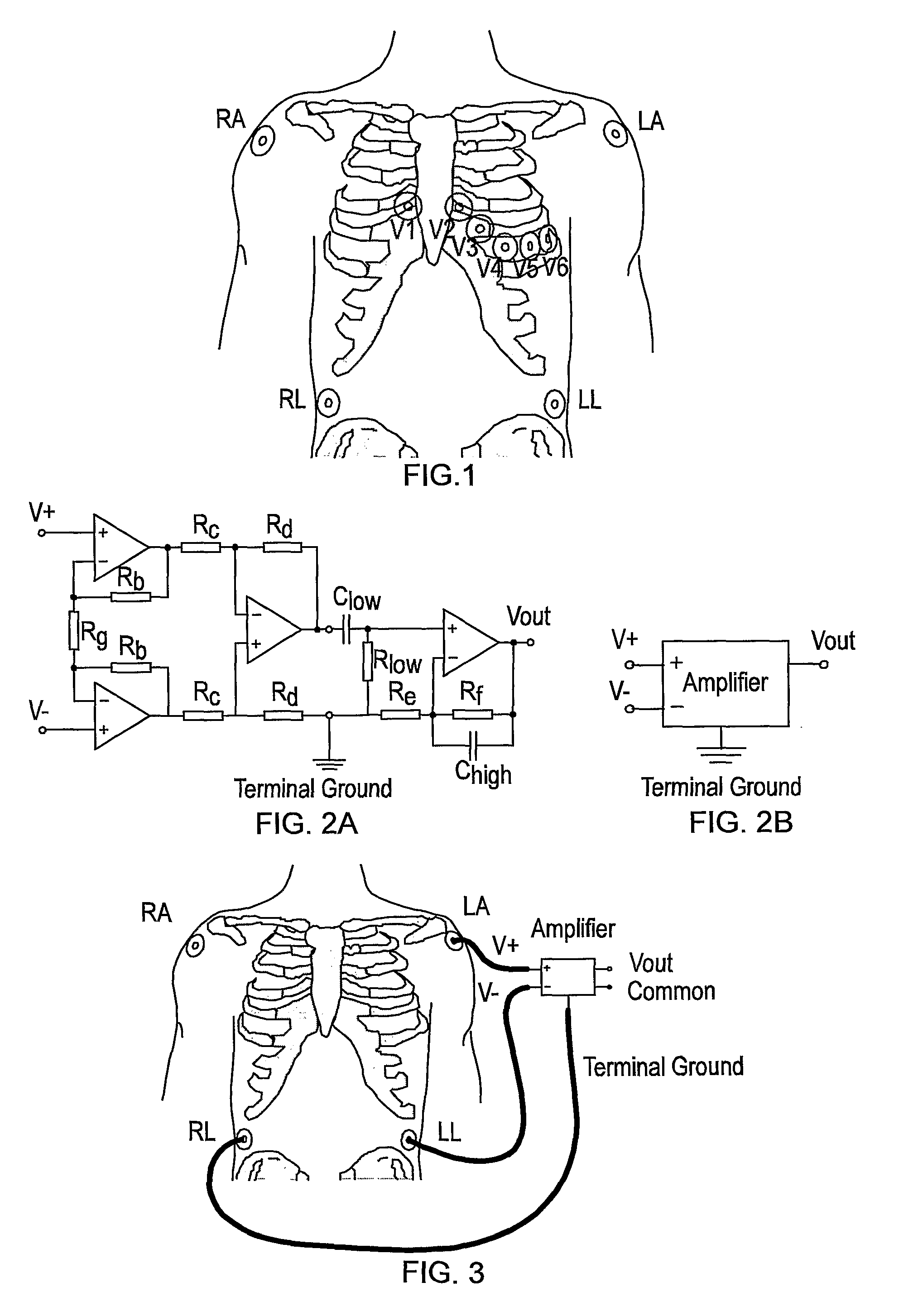

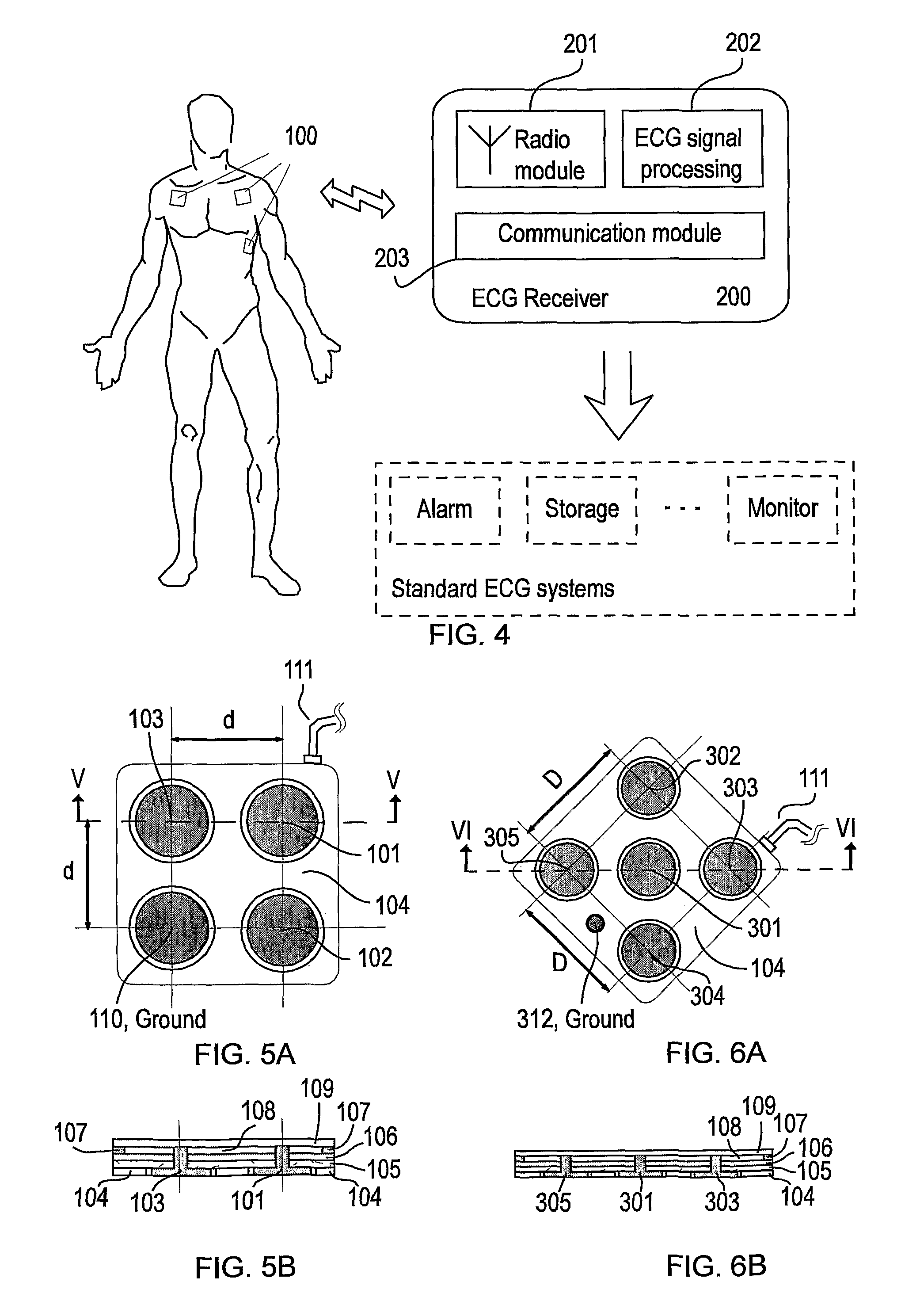

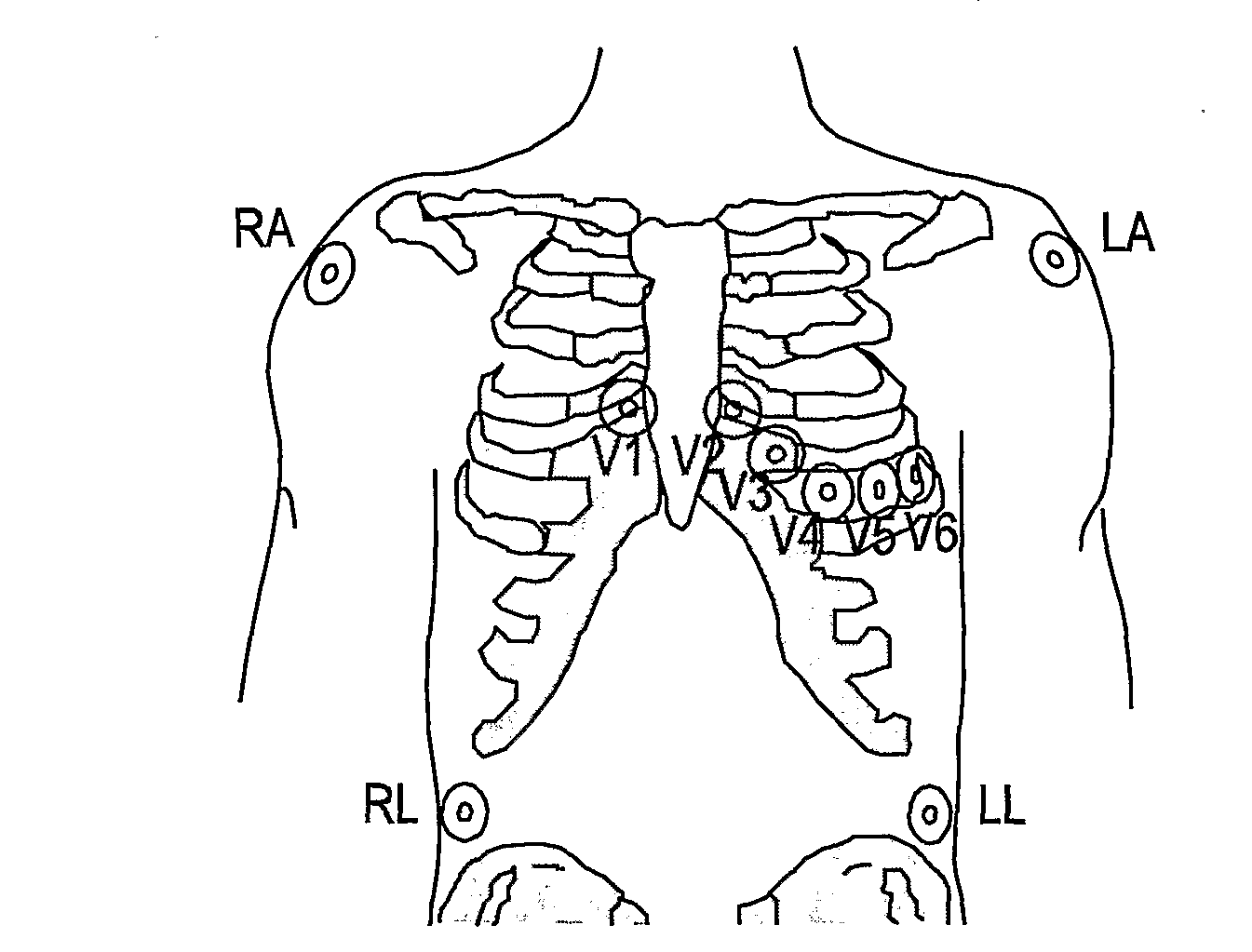

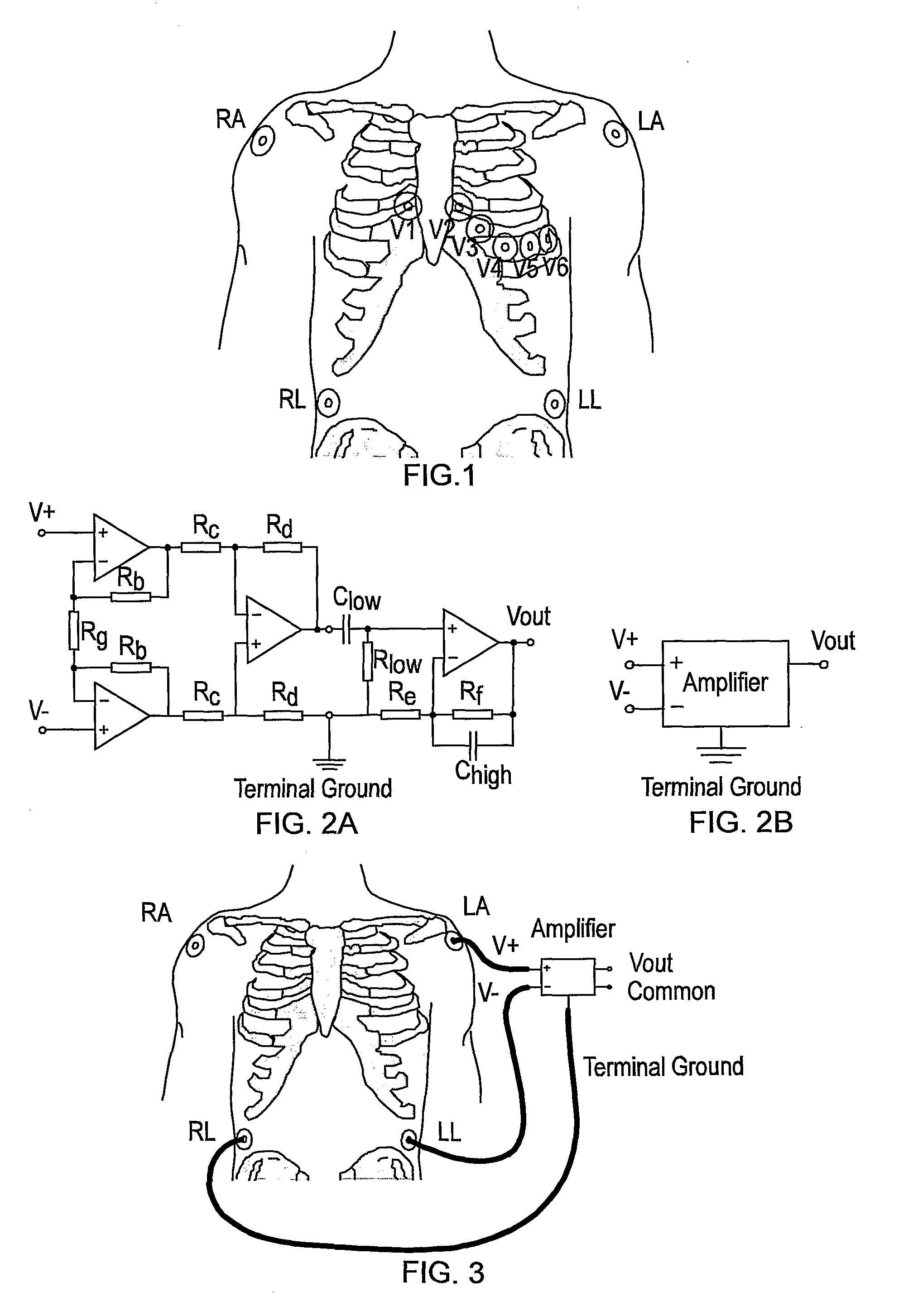

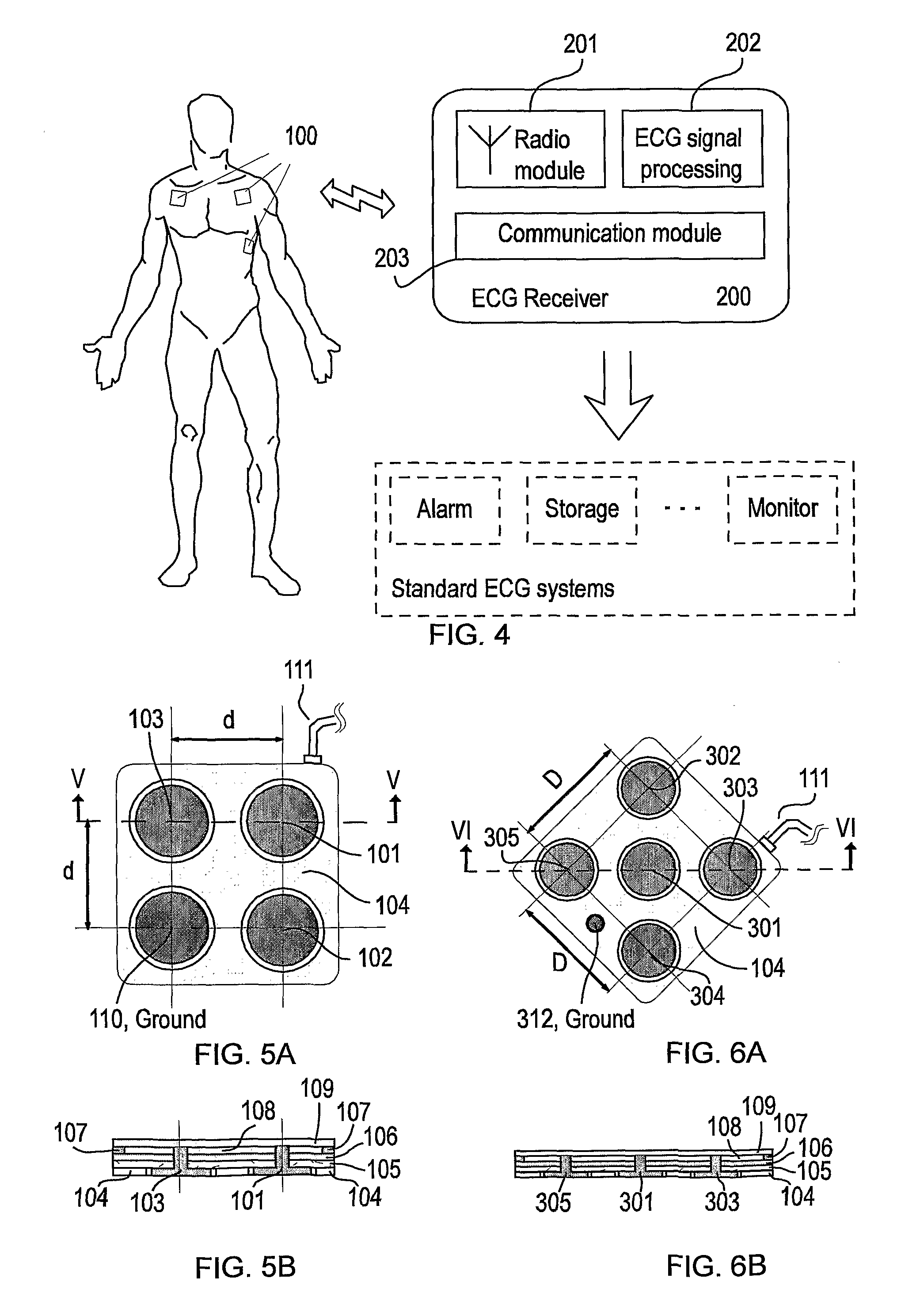

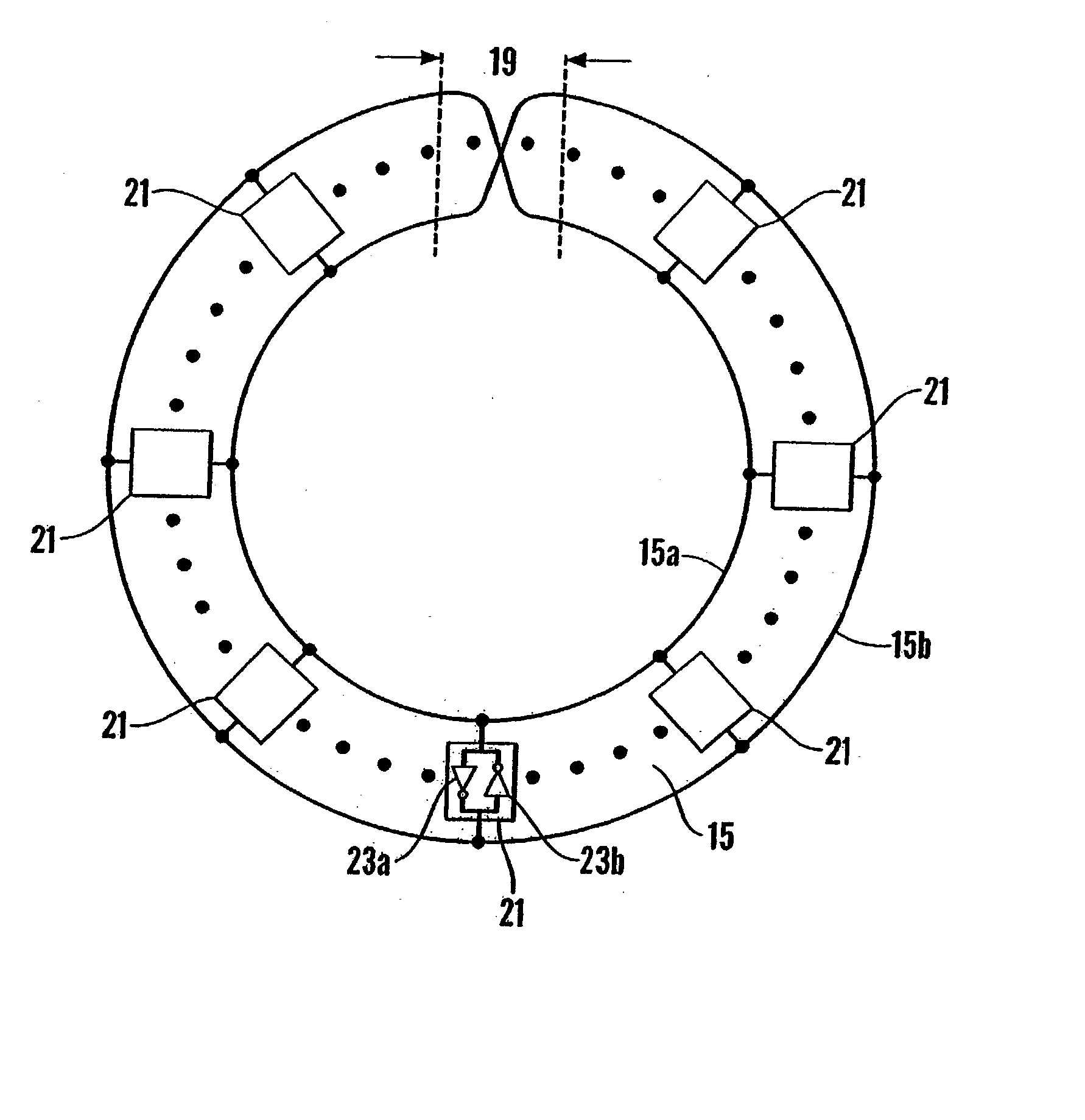

System and method for wireless generation of standard ECG leads and an ECG sensing unit therefor

ActiveUS8315695B2Eliminate the problemFreedom of movementElectrocardiographySensorsBipolar signalEcg lead

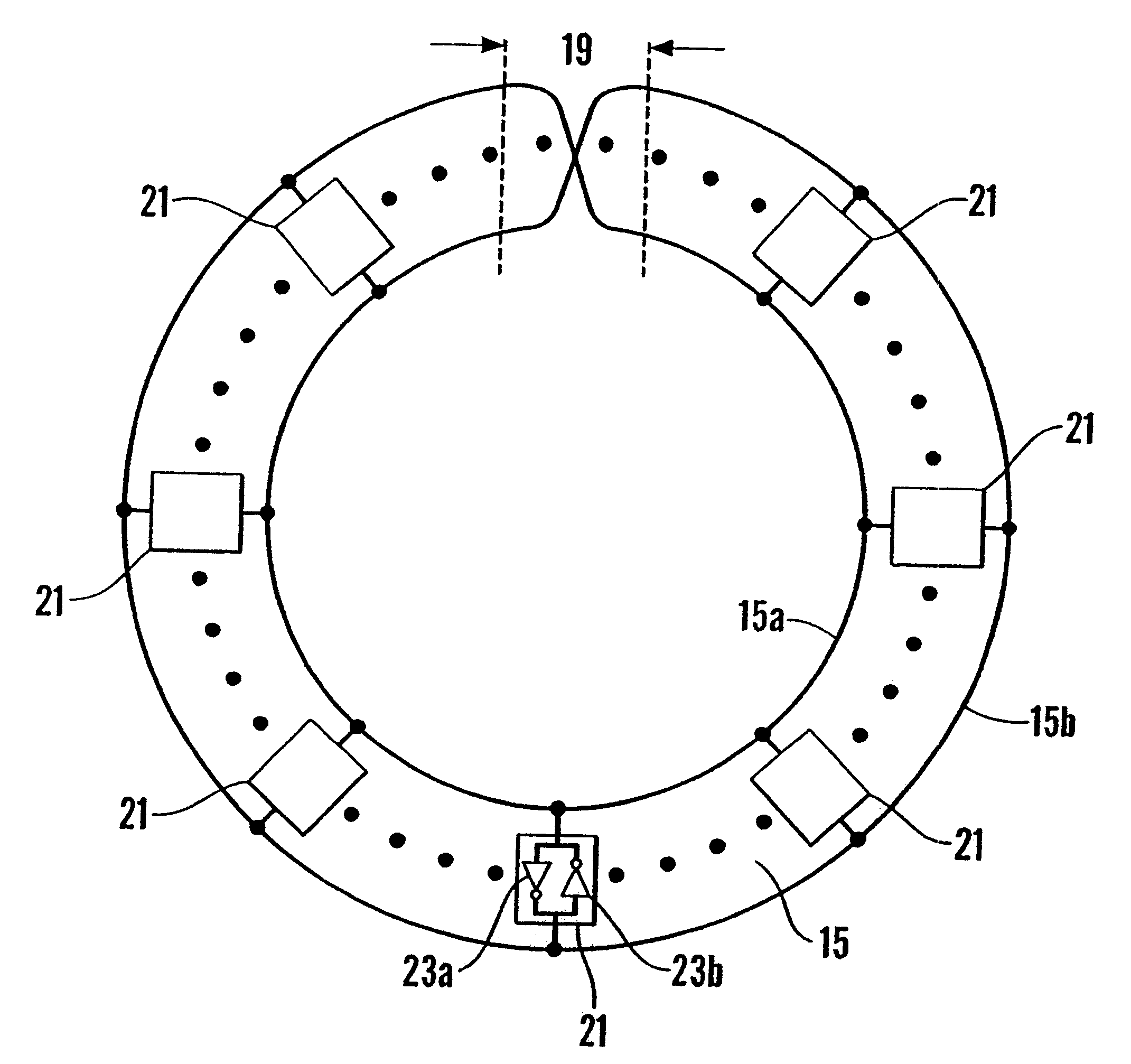

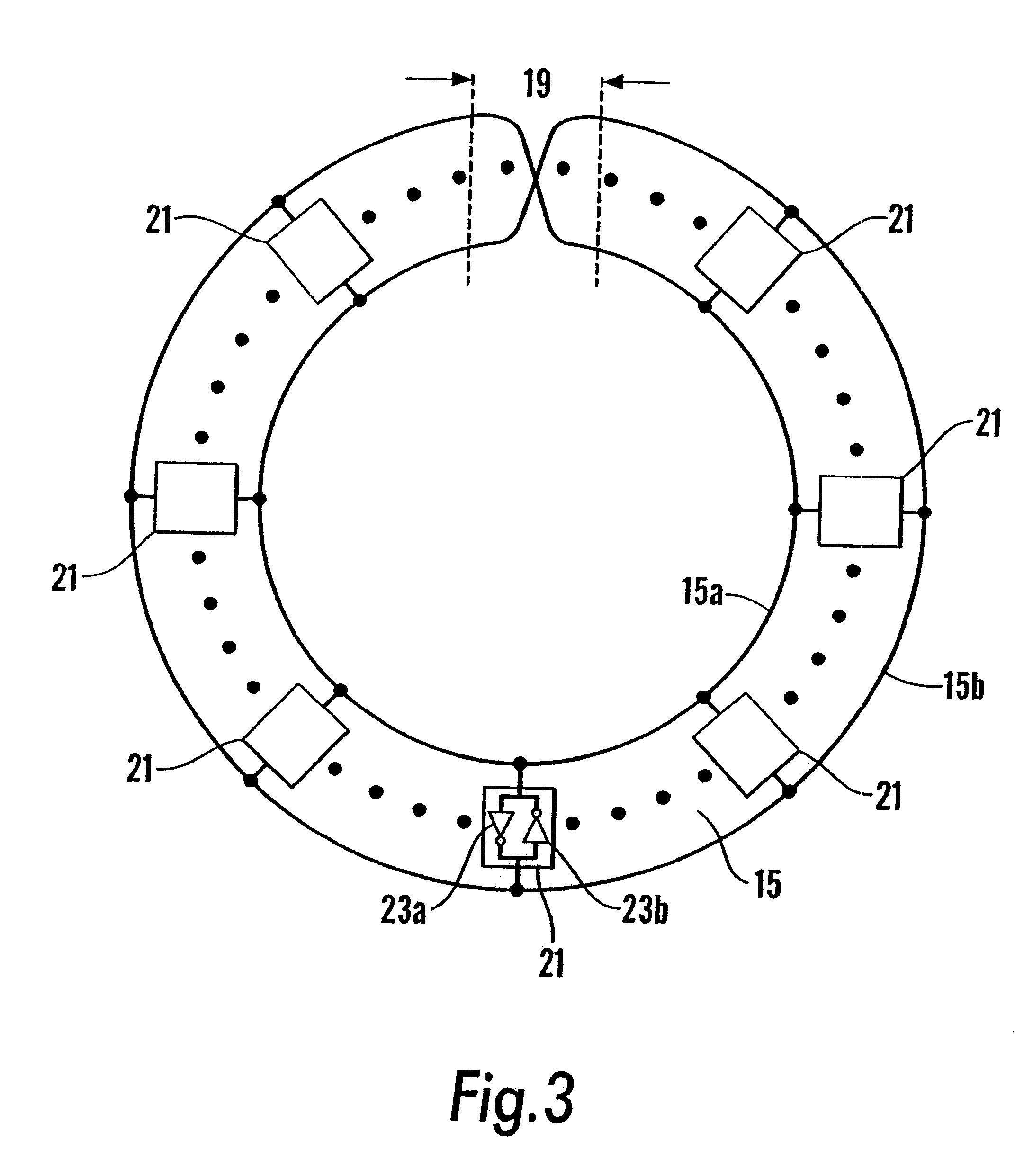

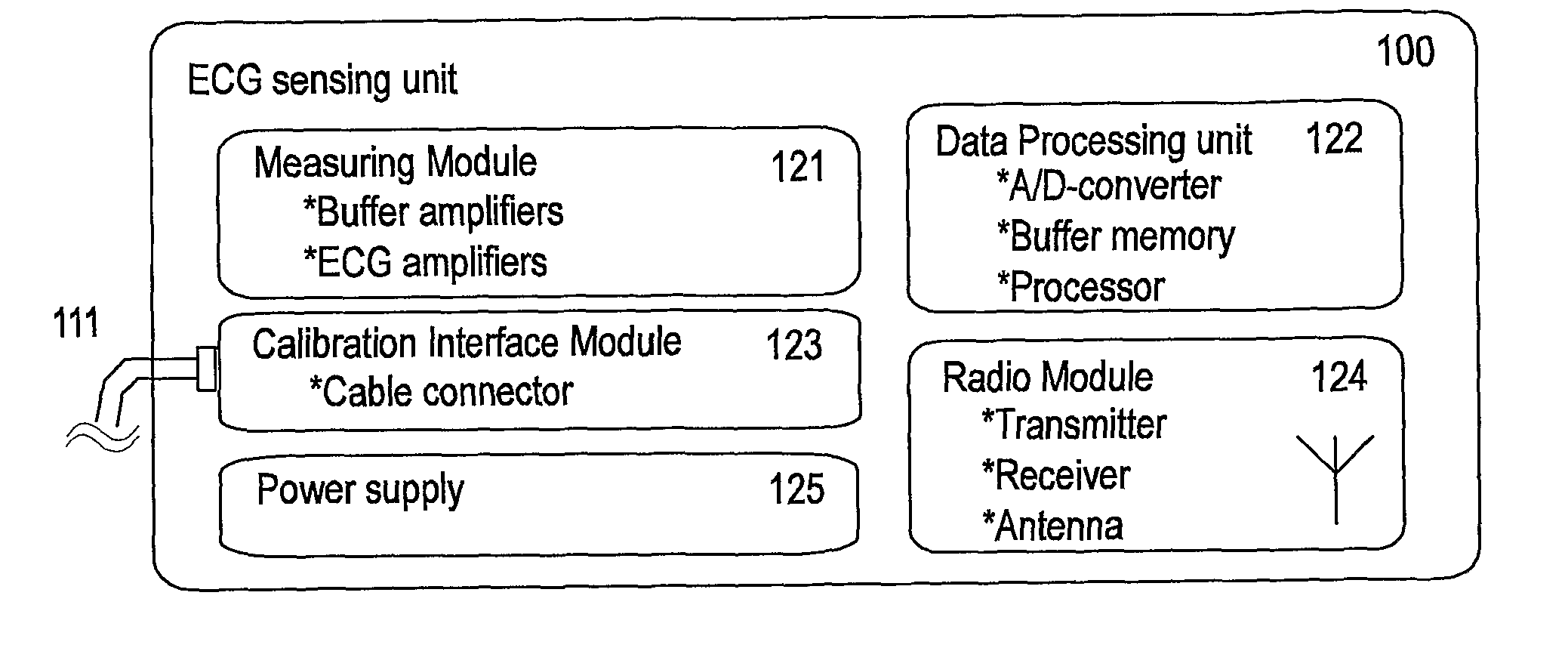

A system for wireless generation of at least one standard ECG lead comprises a plurality of electrodes for application to a subject at separate points thereof and a remote receiver station for generating at least one standard ECG lead from signals detected by a first group of said plurality of electrodes. The system further comprises a wireless sensing unit for generating at least two non-standard ECG signals from bipolar signals detected by a second group of the plurality of electrodes, a processor in the remote receiver station for calculation of a transform synthesizing each generated standard ECG lead from at least two of the non-standard ECG signals, a disconnection unit for disconnection of the first group of electrodes from the subject following the calculation, and a transfer unit for wireless transferring of the non-standard ECG signals to the remote receiver station following the disconnection of the first group of electrodes.

Owner:NOVOSENSE

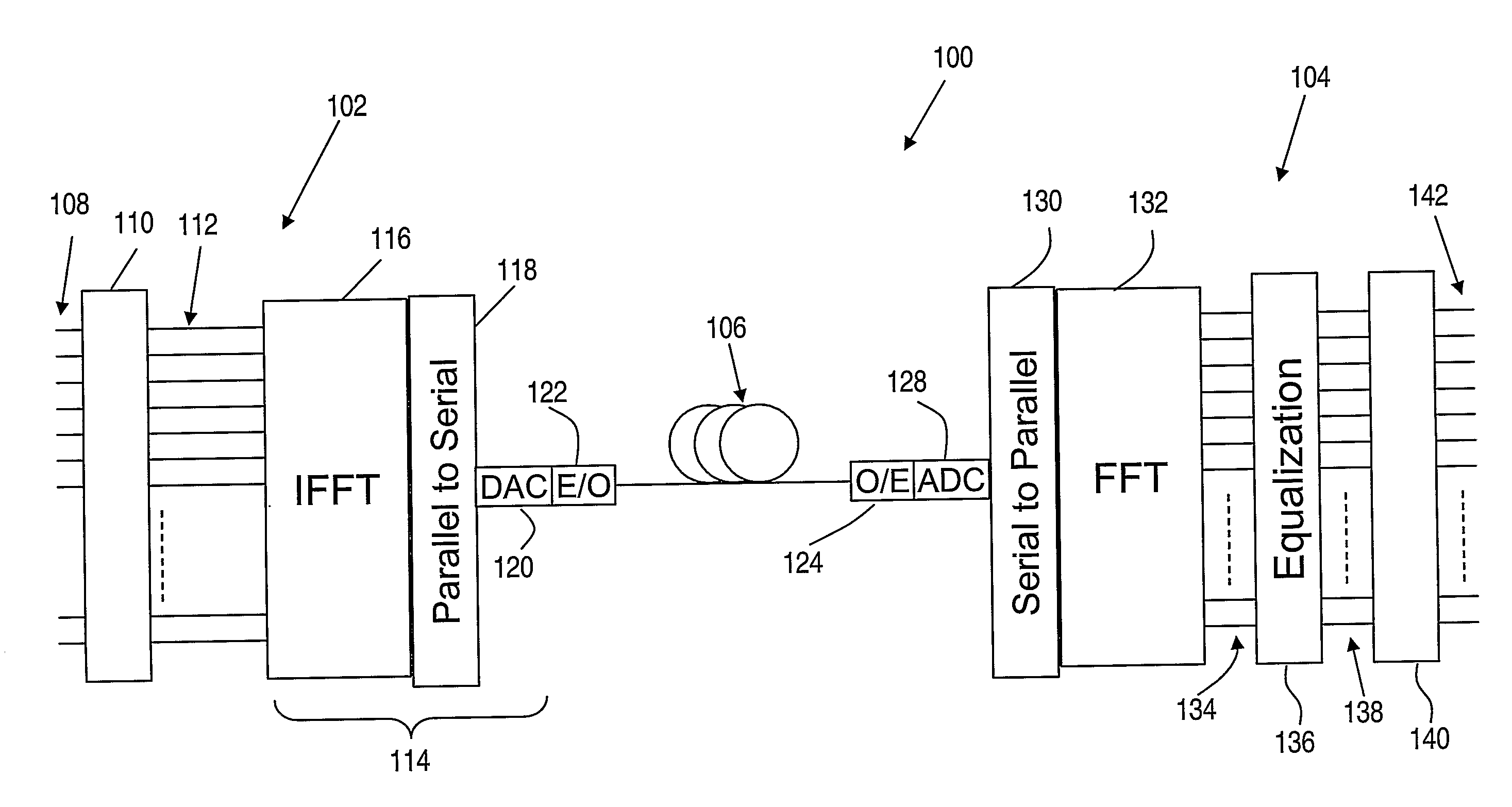

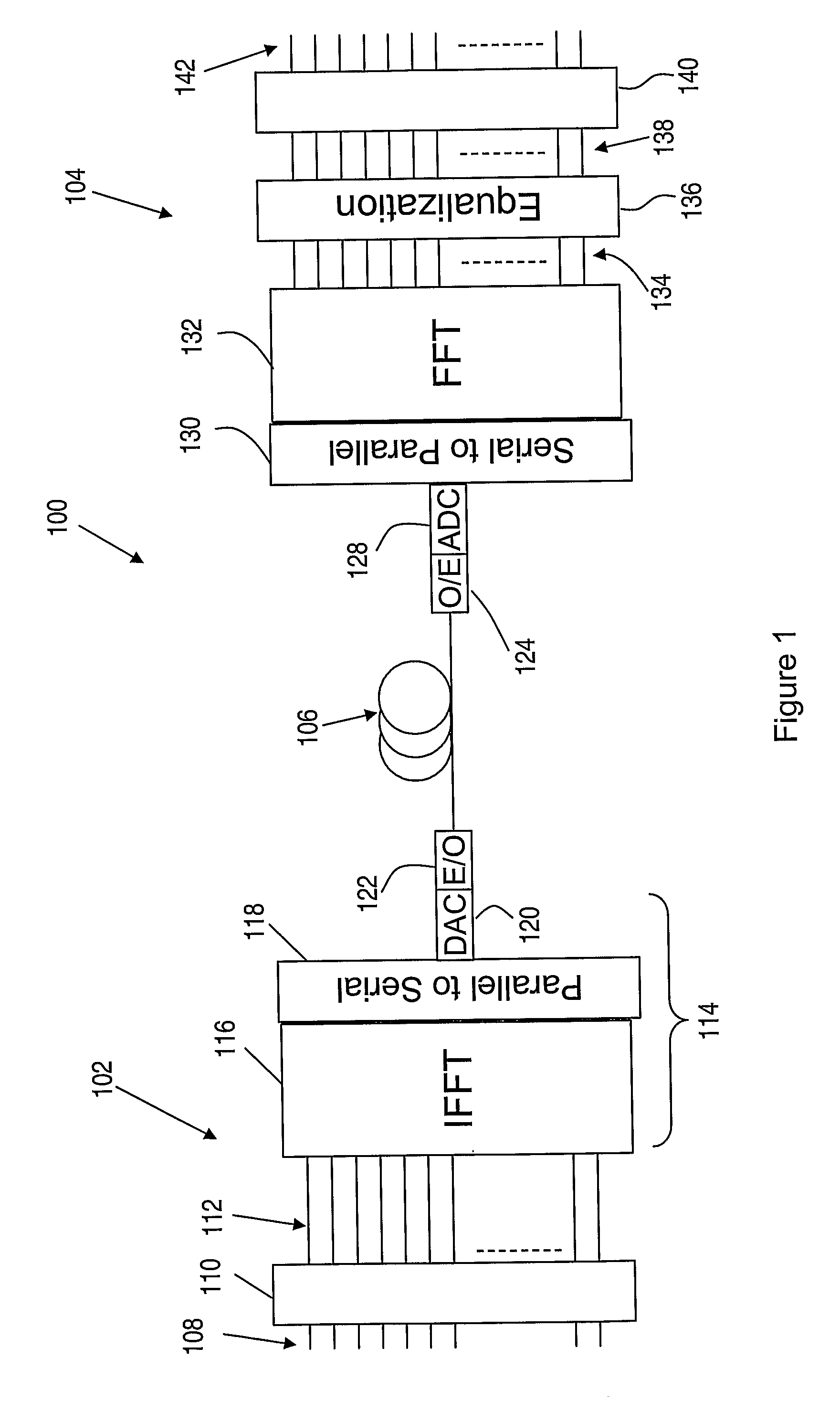

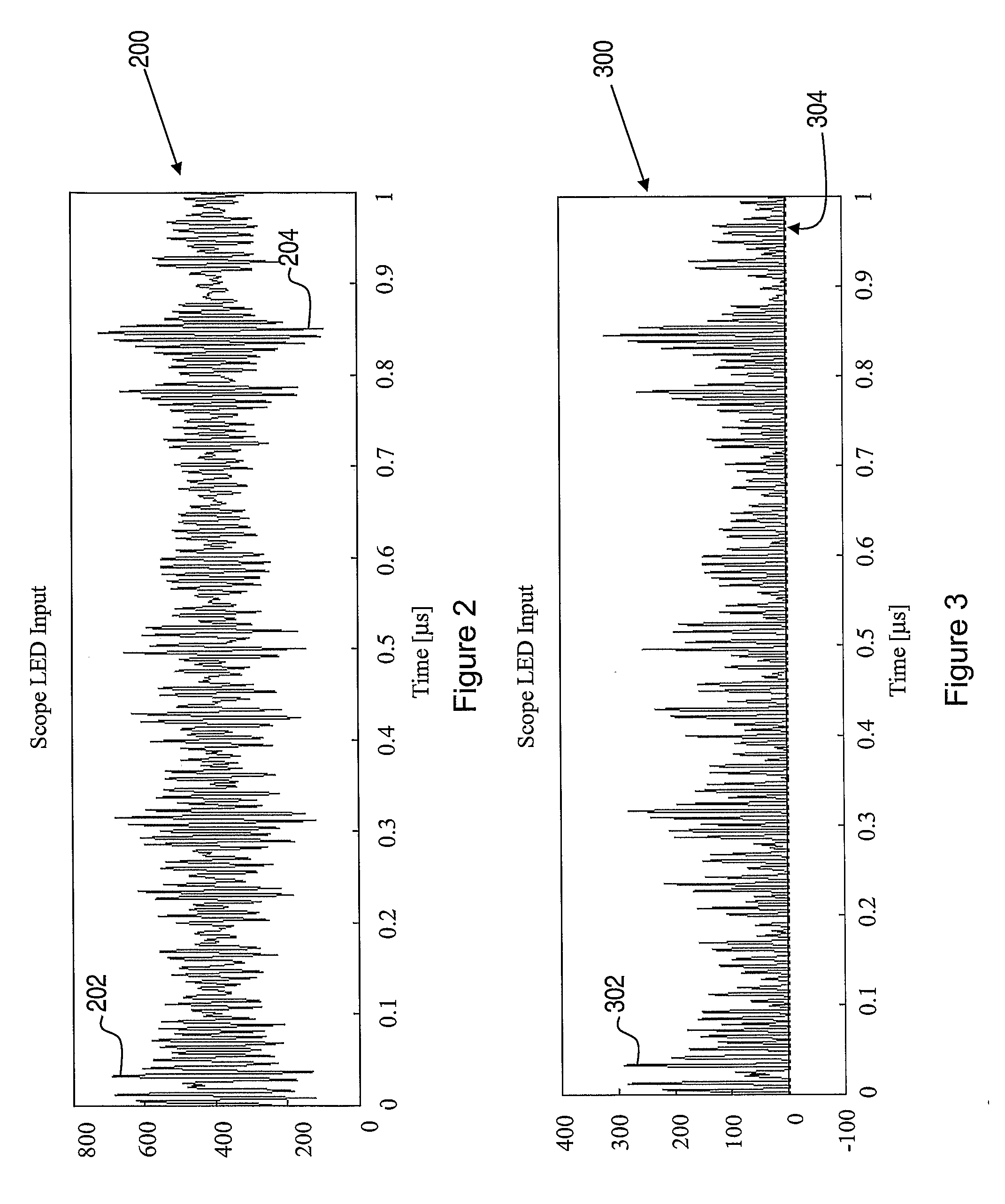

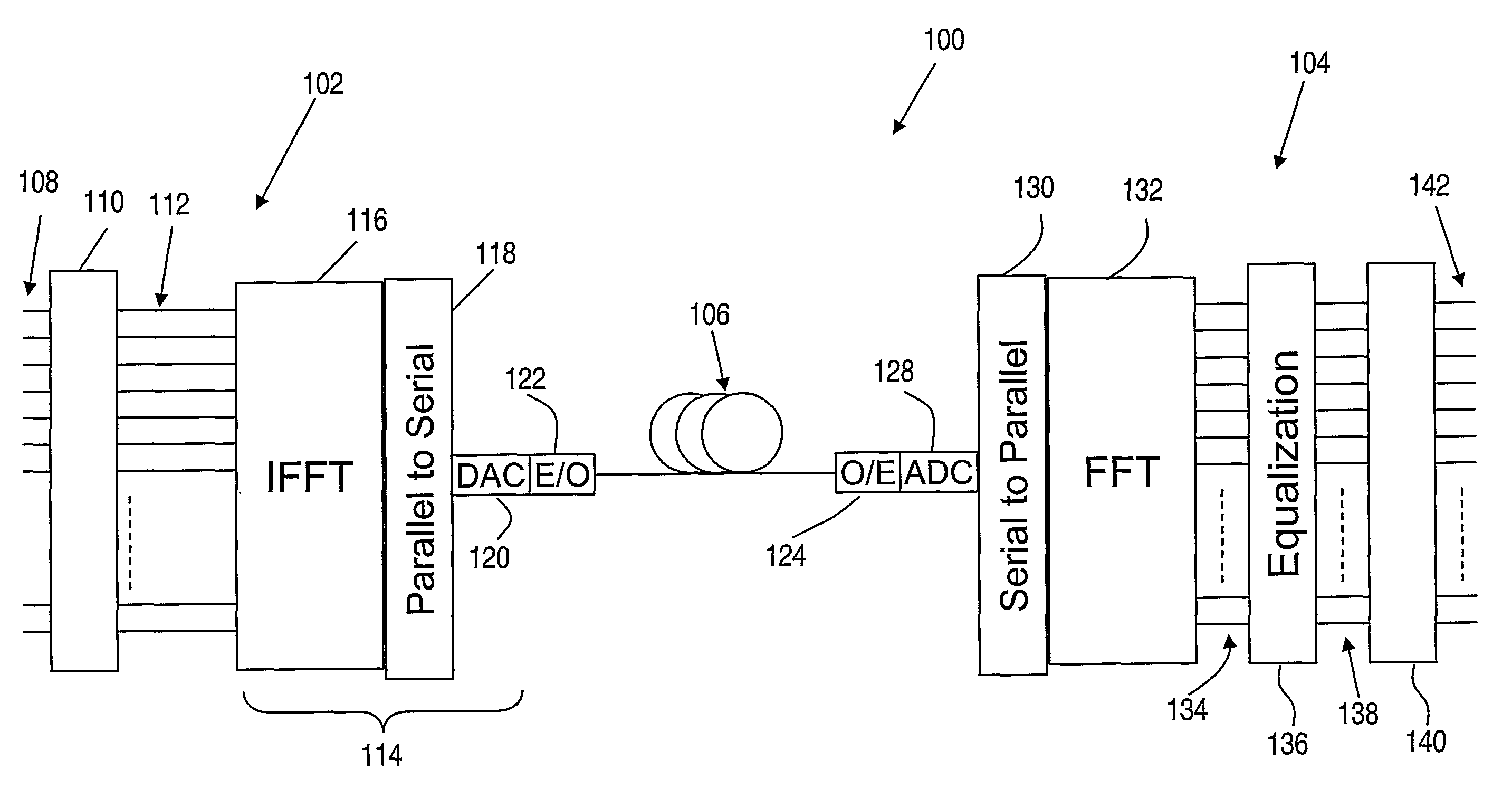

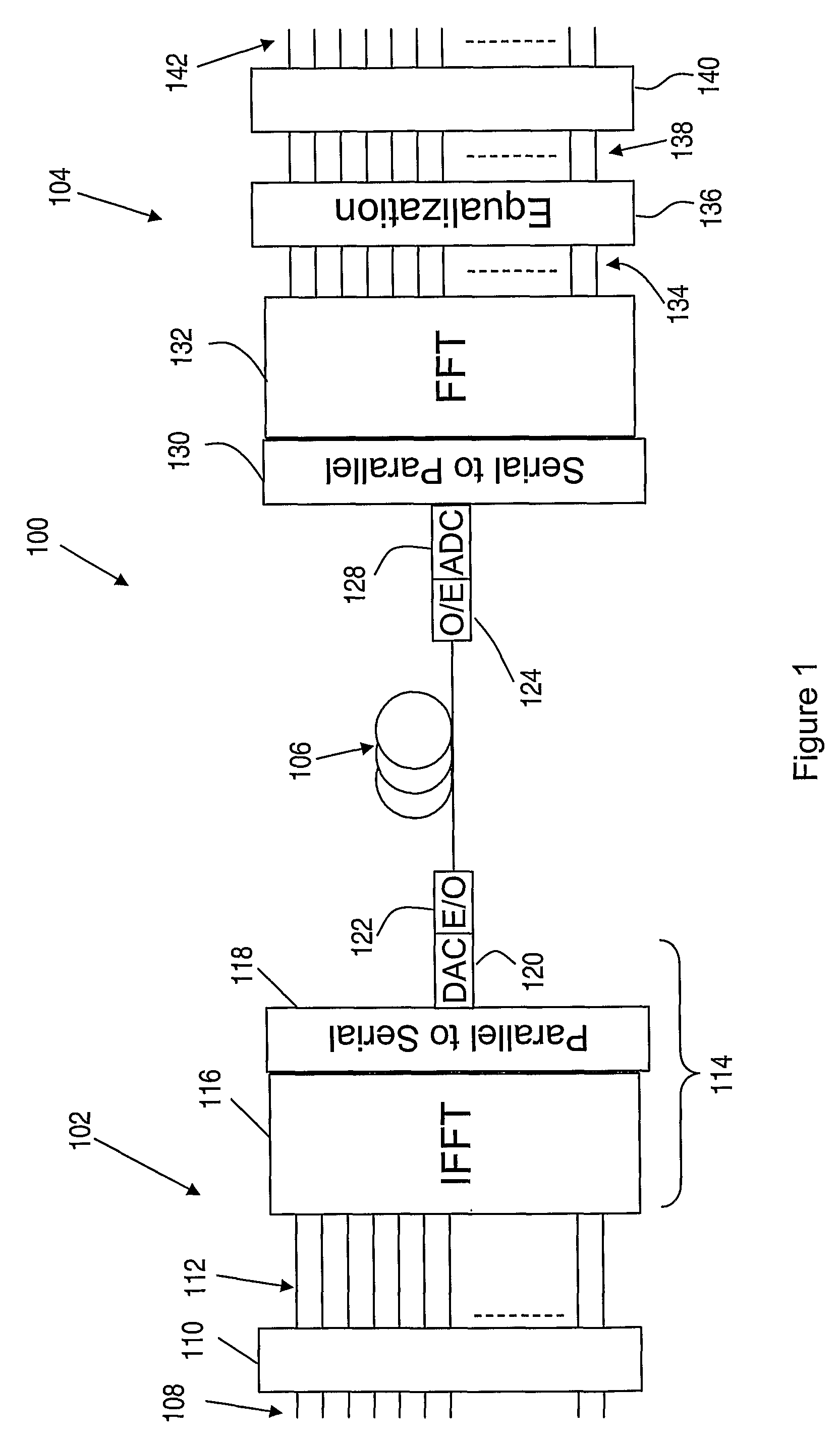

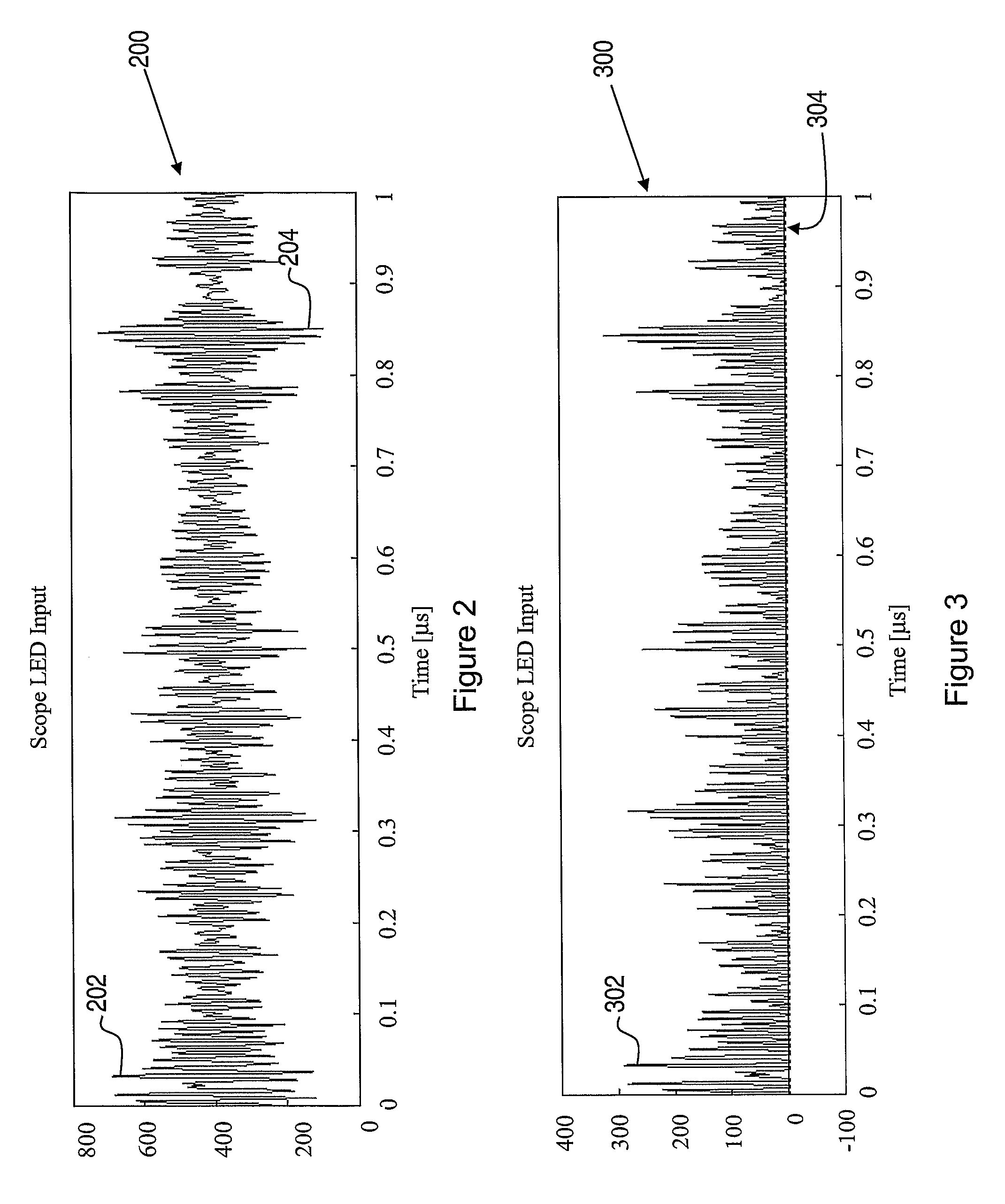

Methods and apparatus for optical transmission of digital signals

ActiveUS20090220239A1High levelImprove power efficiencyWavelength-division multiplex systemsFibre transmissionBipolar signalOptical data transmission

A method of communicating digital information over a dispersive optical channel includes encoding the digital information into a plurality of data blocks, each of which includes a number of bits of the information. A time-varying electrical signal is generated which corresponds with each of said data blocks. The time-varying electrical signal is applied to an optical transmitter (122) to generate an optical signal which includes an asymmetrically amplitude limited transmitted signal modulated onto an optical carrier. The optical signal is then transmitted over the dispersive optical channel (106). At a receiving apparatus (104) the optical signal is detected to produce an electrical signal which corresponds with the asymmetrically amplitude limited transmitted signal. A frequency domain equalisation of the electrical signal mitigates the effect of dispersion of the optical channel (106) on the transmitted optical signal, and the equalised signal is decoded to recover the encoded data blocks and the corresponding transmitted digital information. The method enables bipolar signals to be transmitted over a dispersive unipolar optical channel, and reduces or eliminates the need to apply a high optical bias level at the transmitter, thereby improving optical power efficiency and enabling output power levels to be maintained below applicable safe levels, while simultaneously enabling the effects of channel dispersion to be substantially mitigated.

Owner:MONASH UNIV

System and method for wireless generation of standard ECG leads and an ECG sensing unit therefor

ActiveUS20100234746A1Eliminate the problemFreedom of movementElectrocardiographySensorsBipolar signalEcg lead

A system for wireless generation of at least one standard ECG lead comprises a plurality of electrodes for application to a subject at separate points thereof and a remote receiver station for generating at least one standard ECG lead from signals detected by a first group of said plurality of electrodes. The system further comprises a wireless sensing unit for generating at least two non-standard ECG signals from bipolar signals detected by a second group of the plurality of electrodes, a processor in the remote receiver station for calculation of a transform synthesizing each generated standard ECG lead from at least two of the non-standard ECG signals, a disconnection unit for disconnection of the first group of electrodes from the subject following the calculation, and a transfer unit for wireless transferring of the non-standard ECG signals to the remote receiver station following the disconnection of the first group of electrodes.

Owner:NOVOSENSE

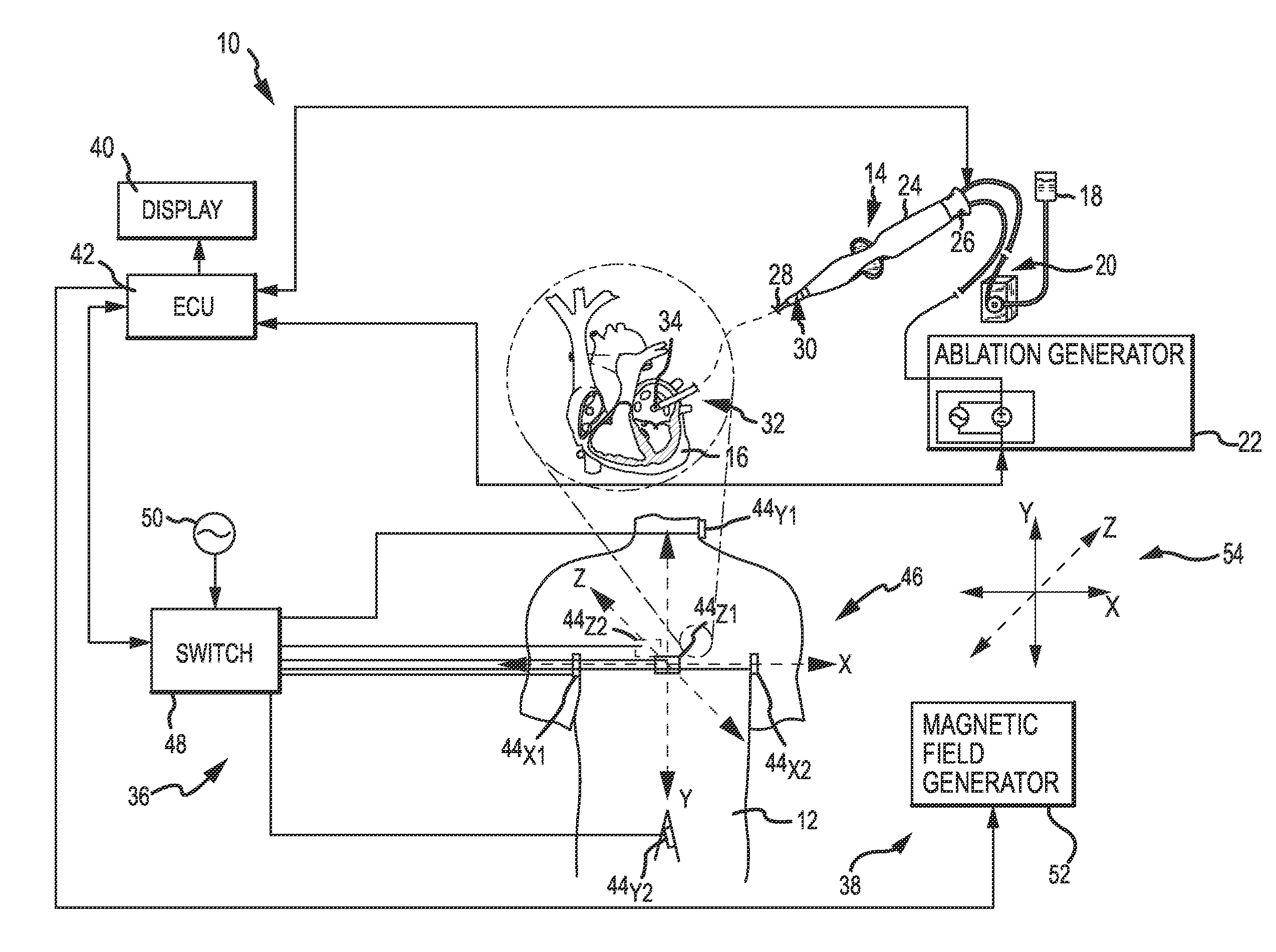

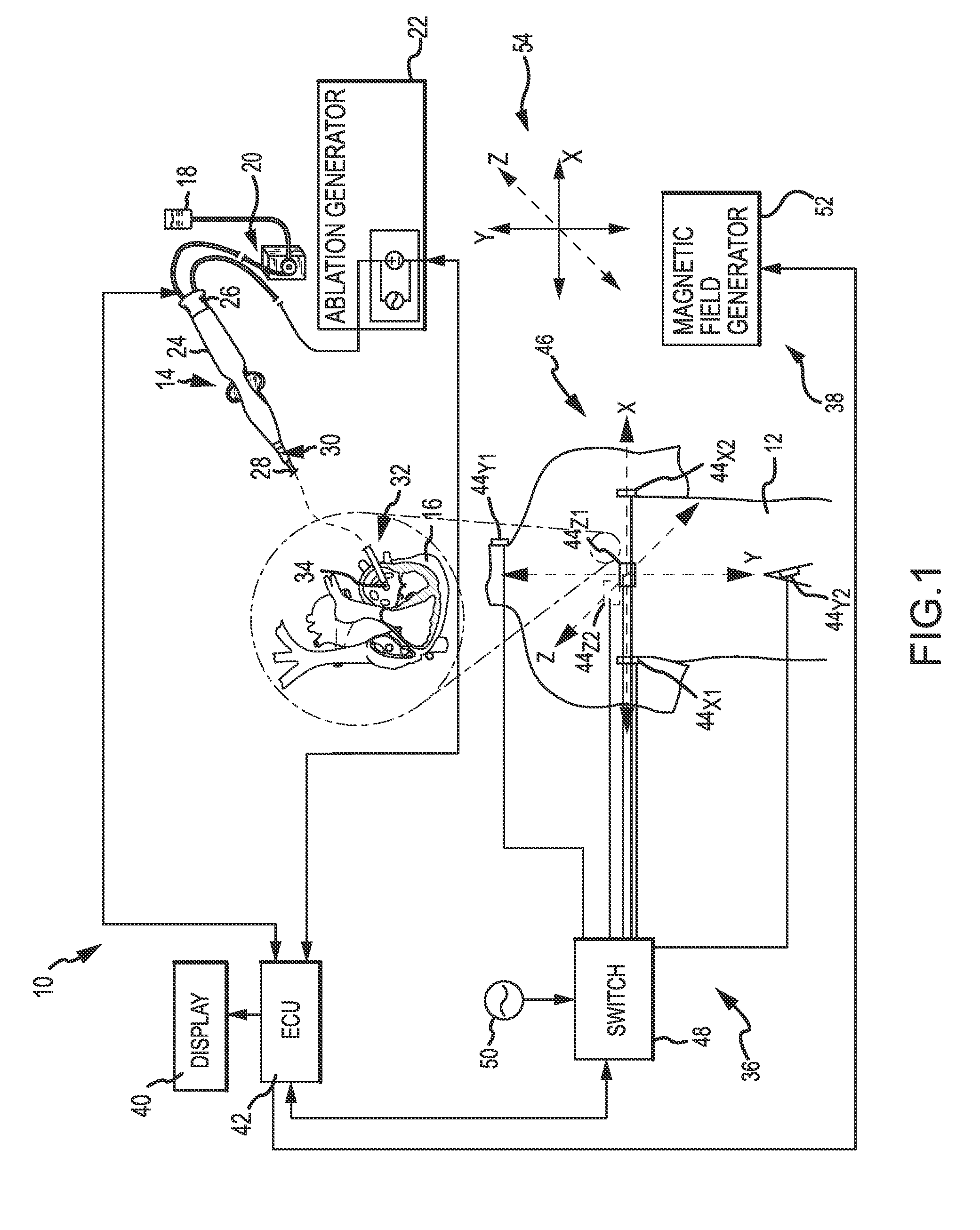

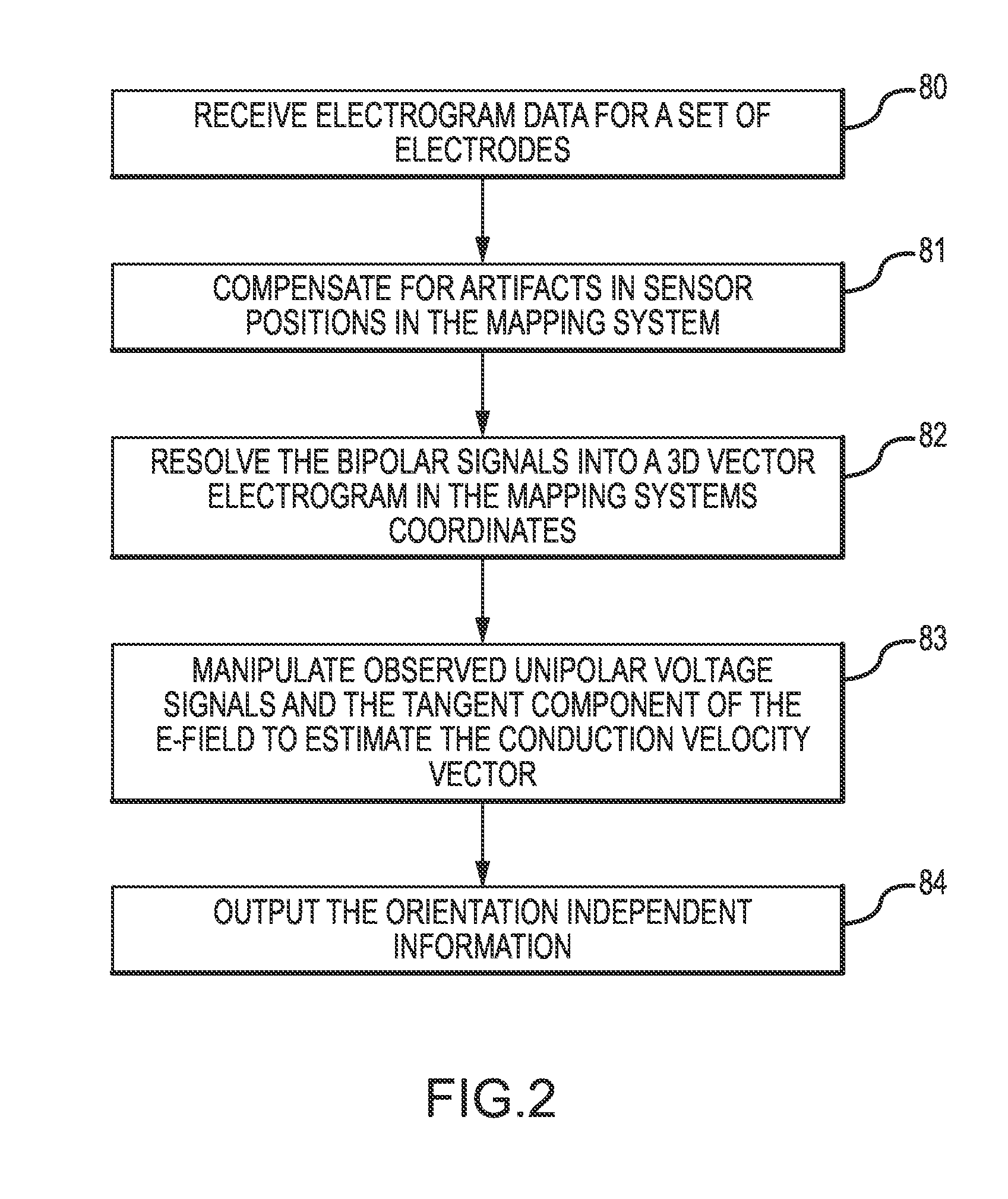

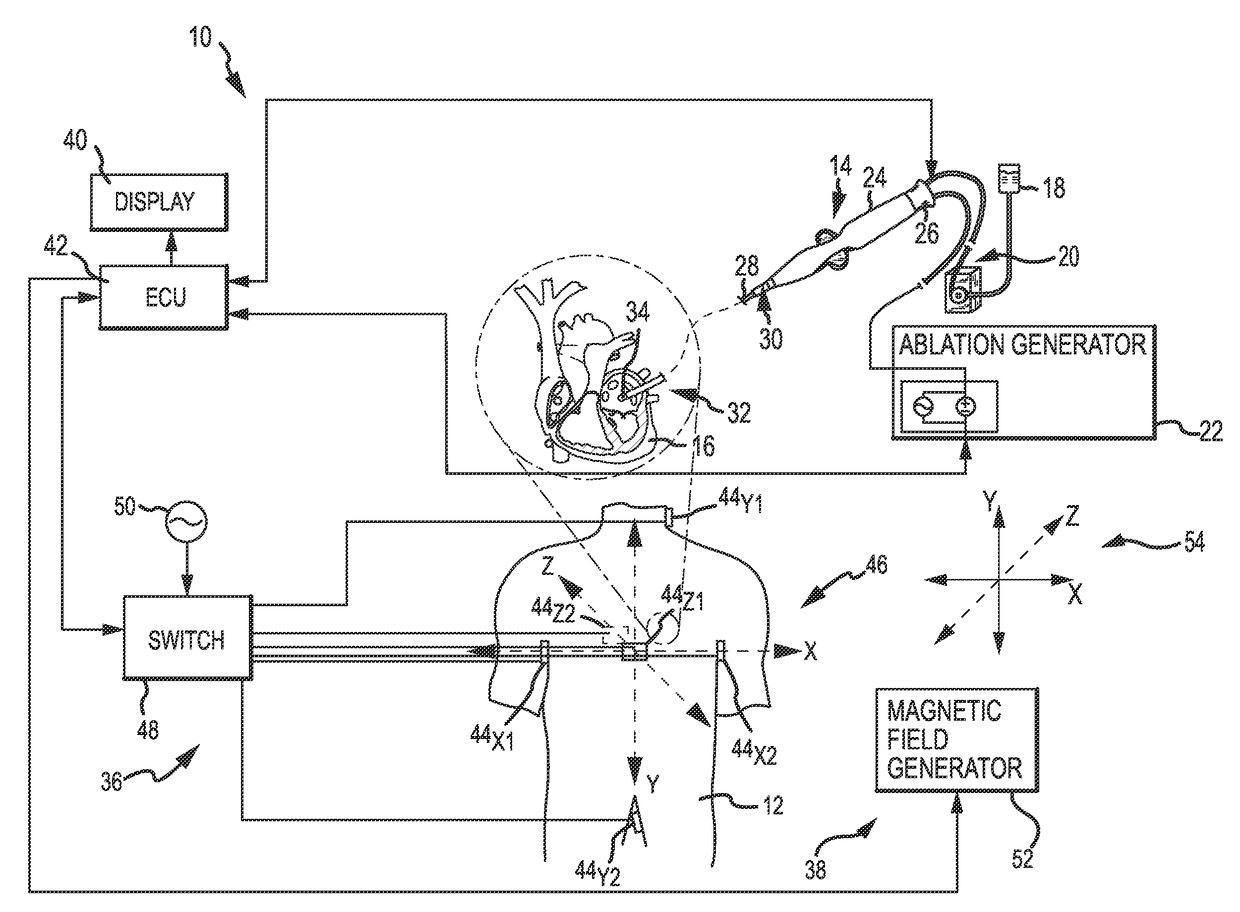

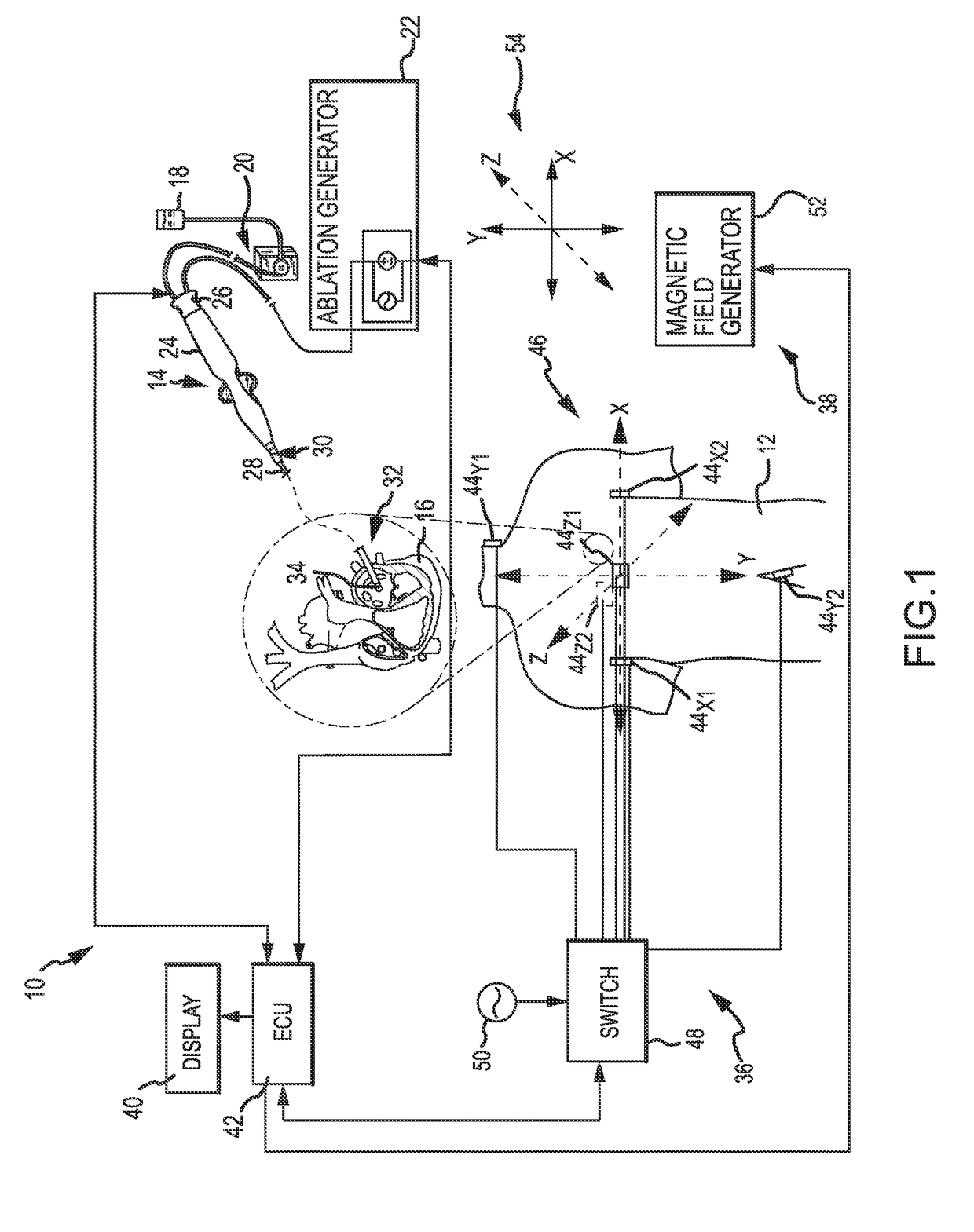

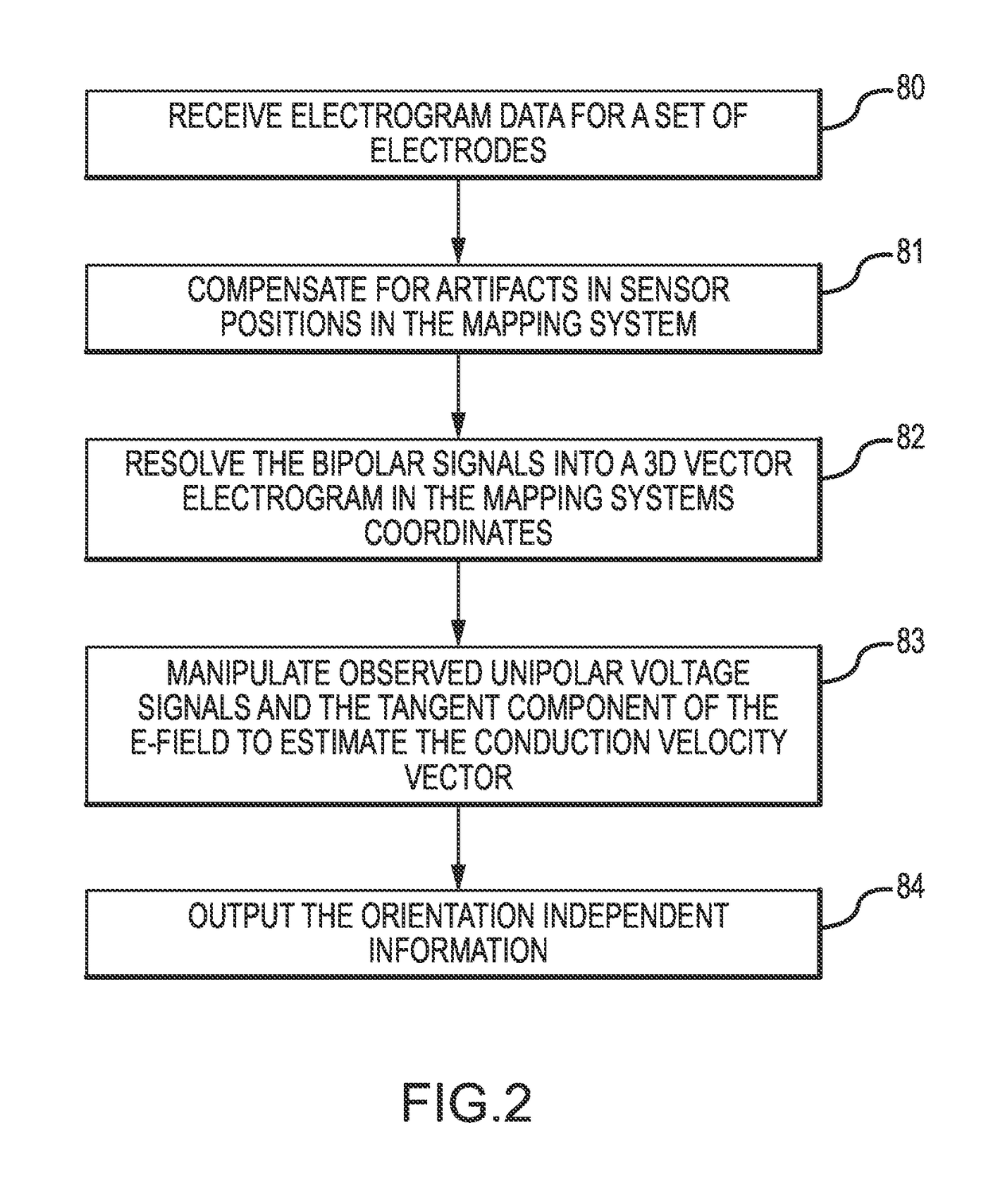

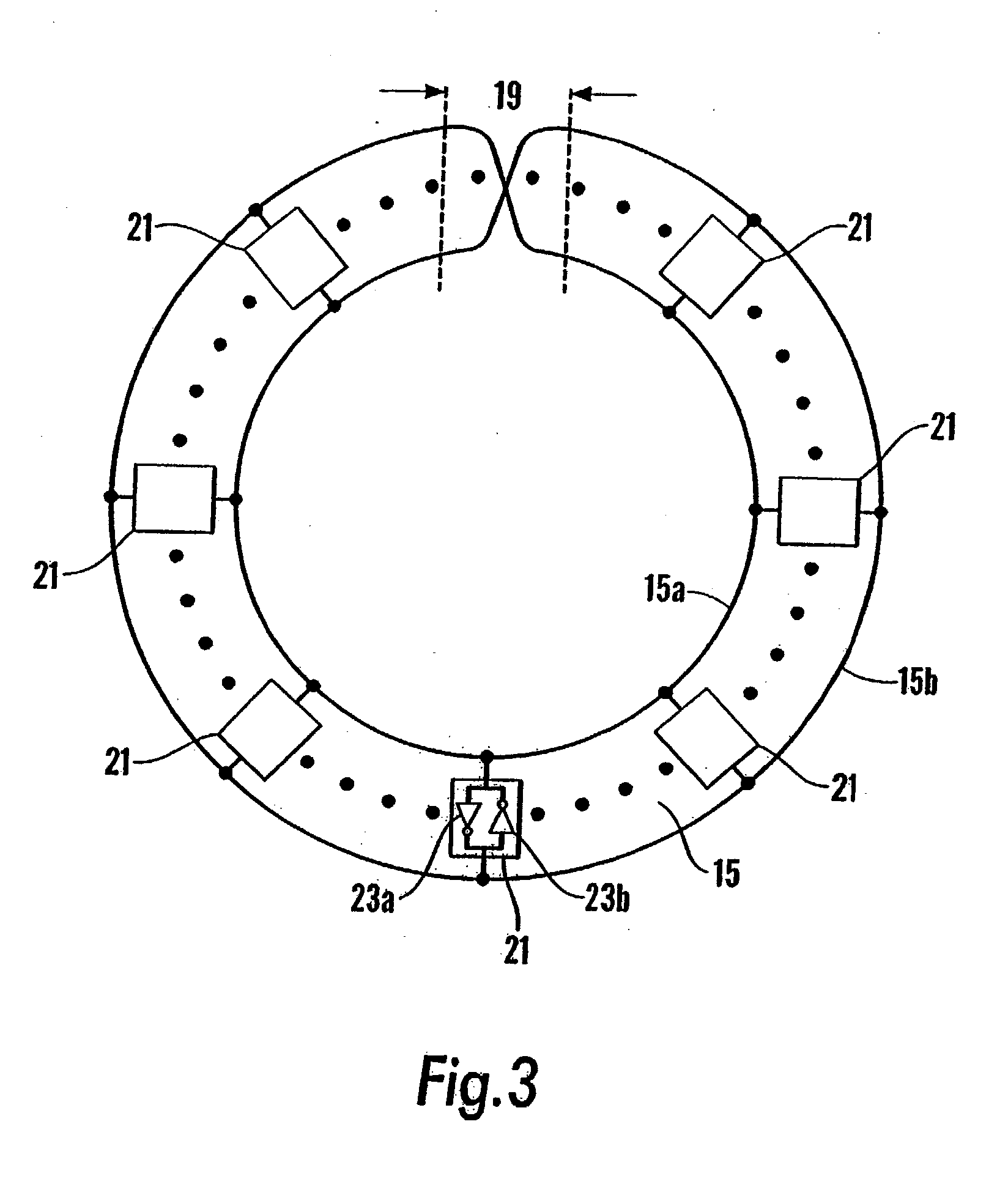

Utilization of electrode spatial arrangements for characterizing cardiac conduction conditions

A system and method are provided for determining electrophysiological data. The system comprises an electronic control unit that is configured to receive electrical signals from a set of electrodes, receive position and orientation data for the set of electrodes from a mapping system, compensate for position and orientation artifacts of the set of electrodes, compose cliques of a subset of neighboring electrodes in the set of electrodes, determine catheter orientation independent information of a target tissue, and output the orientation independent information to a display. The method comprising receiving electrogram data for a set of electrodes (80), compensating for artifacts in sensor positions in the mapping system (81), resolving the bipolar signals into a 3D vector electrogram in the mapping system coordinates (82), manipulating observed unipolar voltage signals and the tangent component of the e-field to estimate the conduction velocity vector (83), and outputting the catheter orientation independent information (84).

Owner:ST JUDE MEDICAL ATRIAL FIBRILLATION DIV

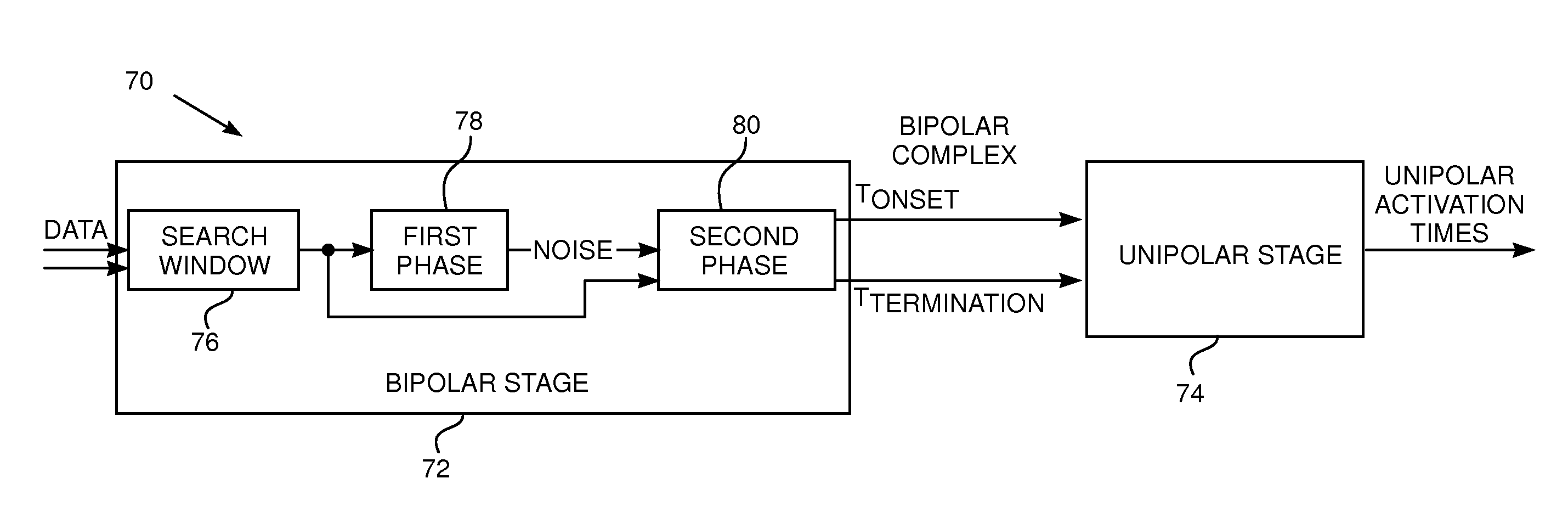

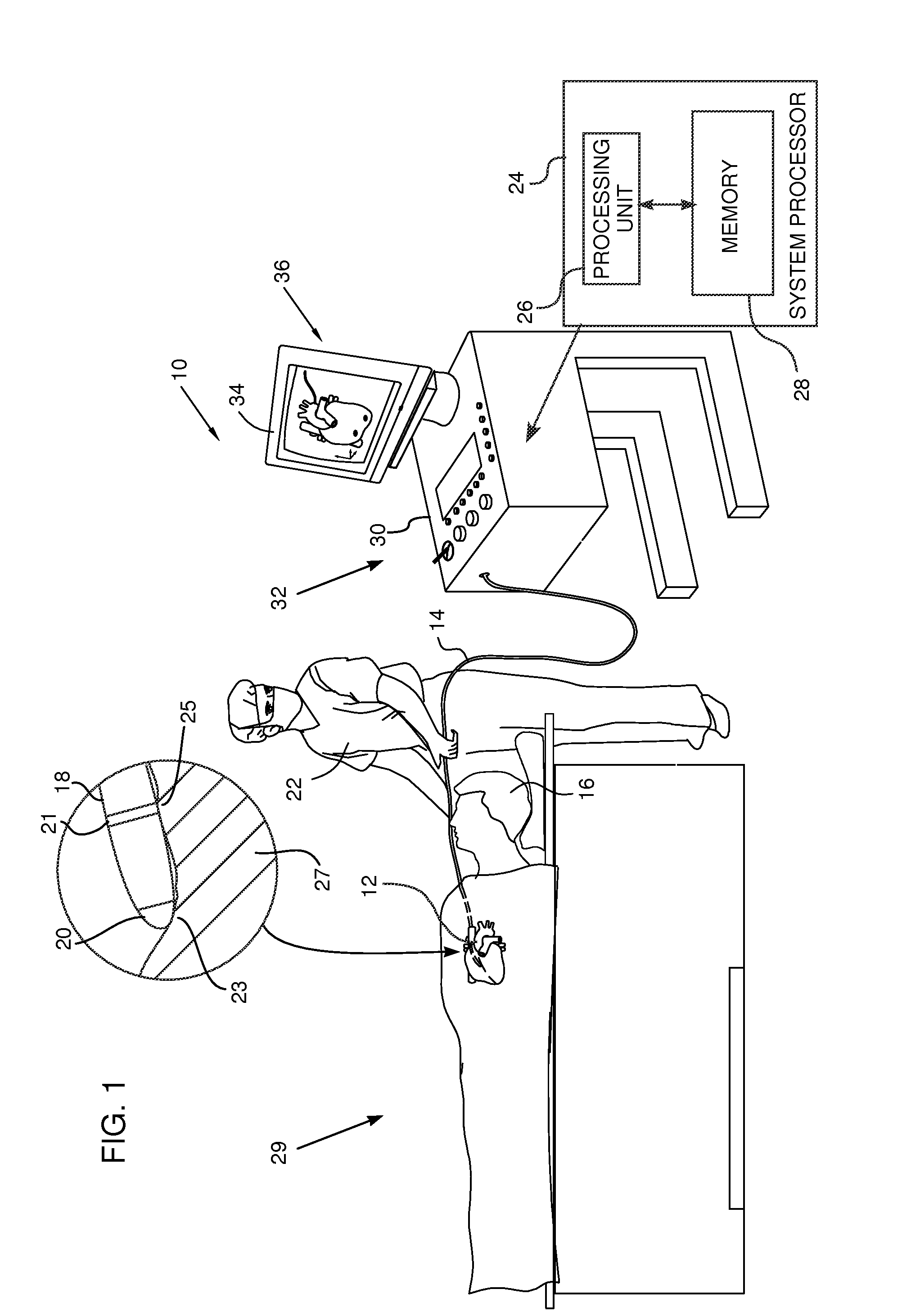

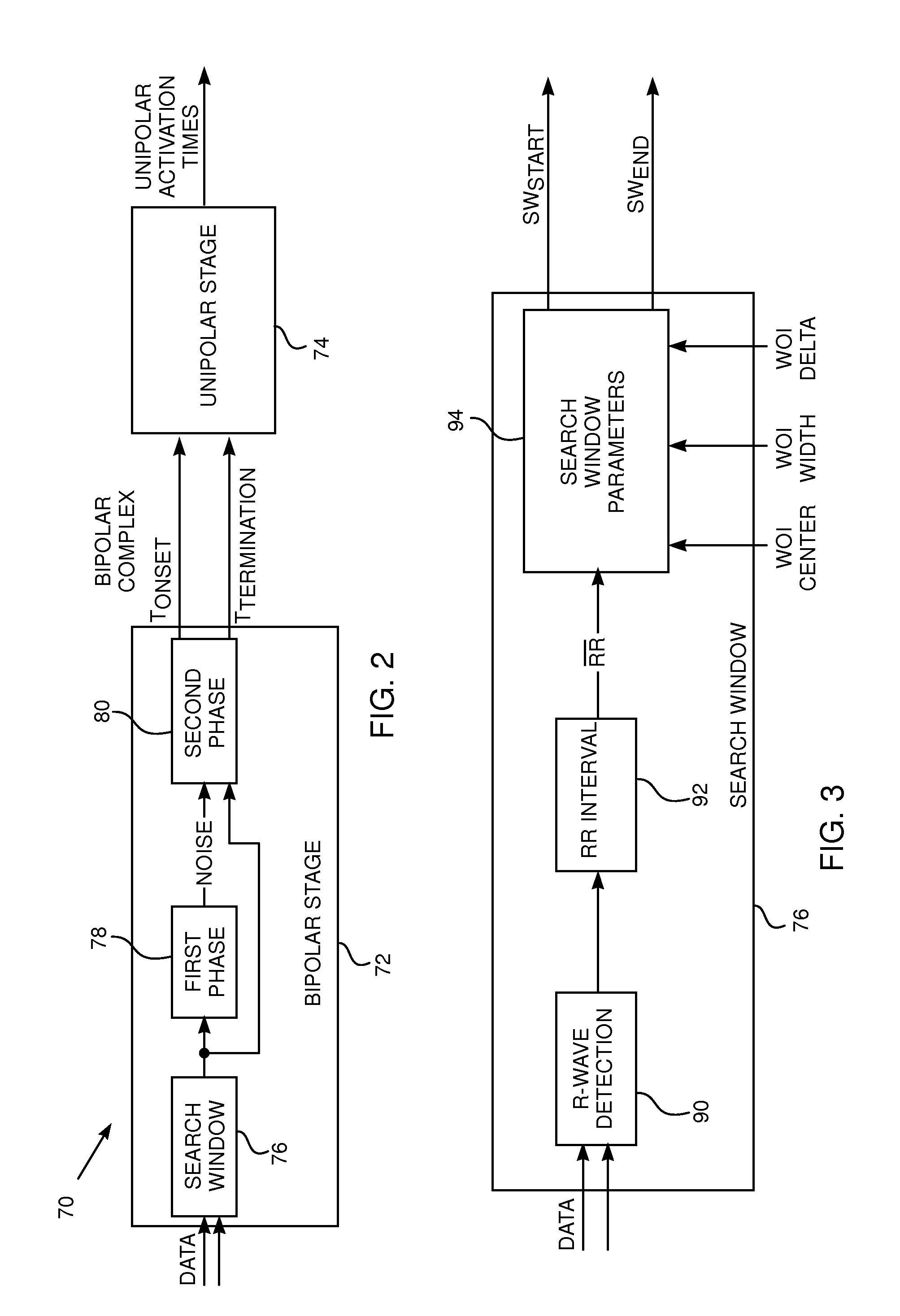

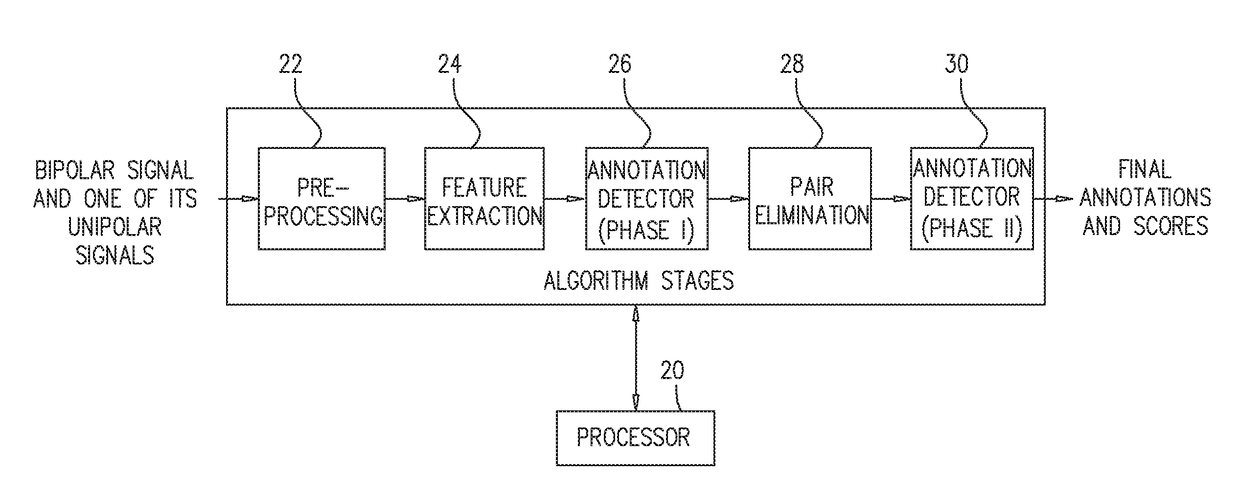

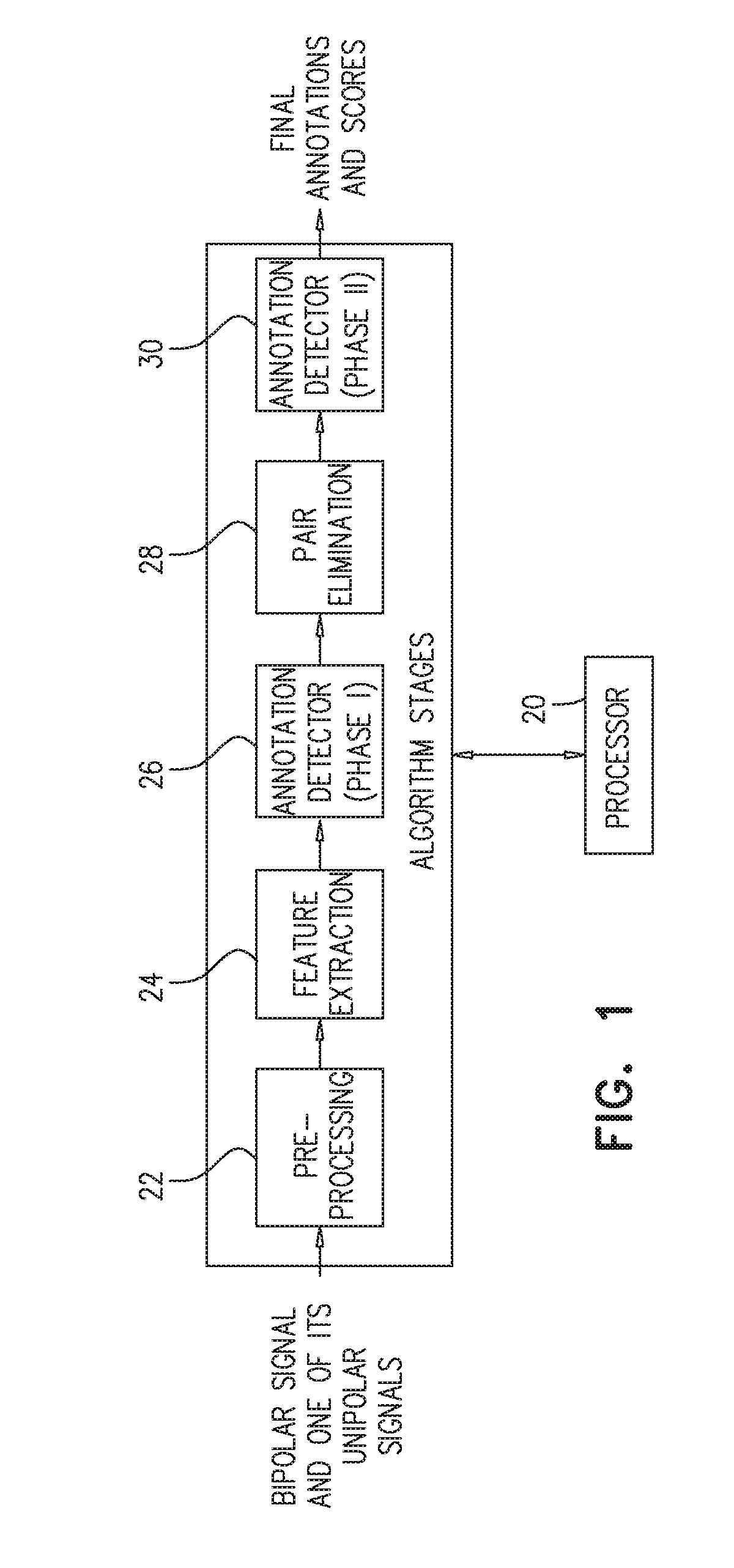

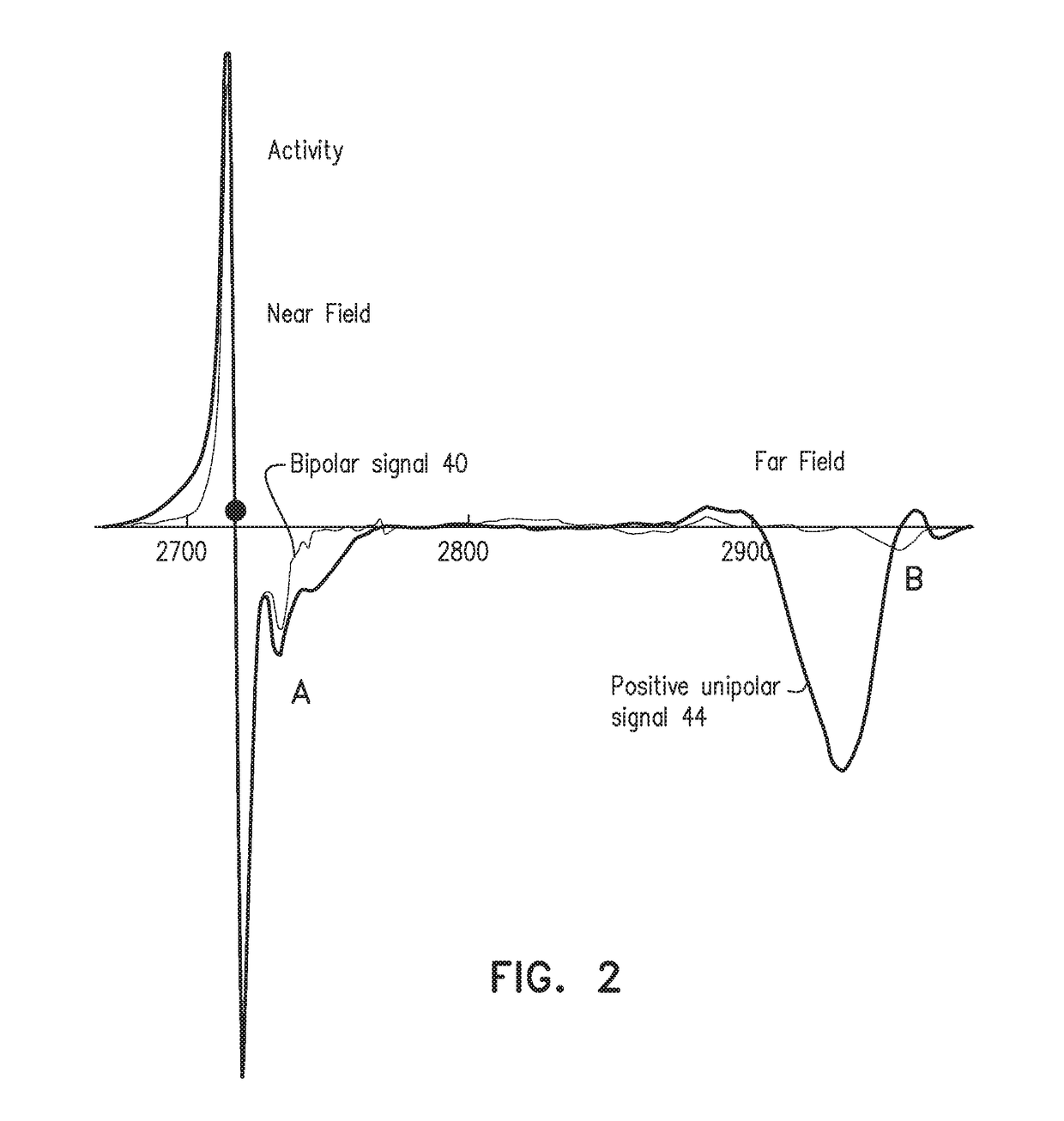

Cardiac activation time detection

A method for characterizing an electrocardiogram, including receiving a first unipolar signal from a first location of a heart and a second unipolar signal from a second location of the heart. The method further includes generating a bipolar signal from the first and second unipolar signals, and analyzing the bipolar signal to delineate a time period during which the first and second locations generate a bipolar complex. The method also includes analyzing the first unipolar signal within the time period to determine an activation time of the first location.

Owner:BIOSENSE WEBSTER (ISRAEL) LTD

Utilization of electrode spatial arrangements for characterizing cardiac conduction conditions

Owner:ST JUDE MEDICAL ATRIAL FIBRILLATION DIV

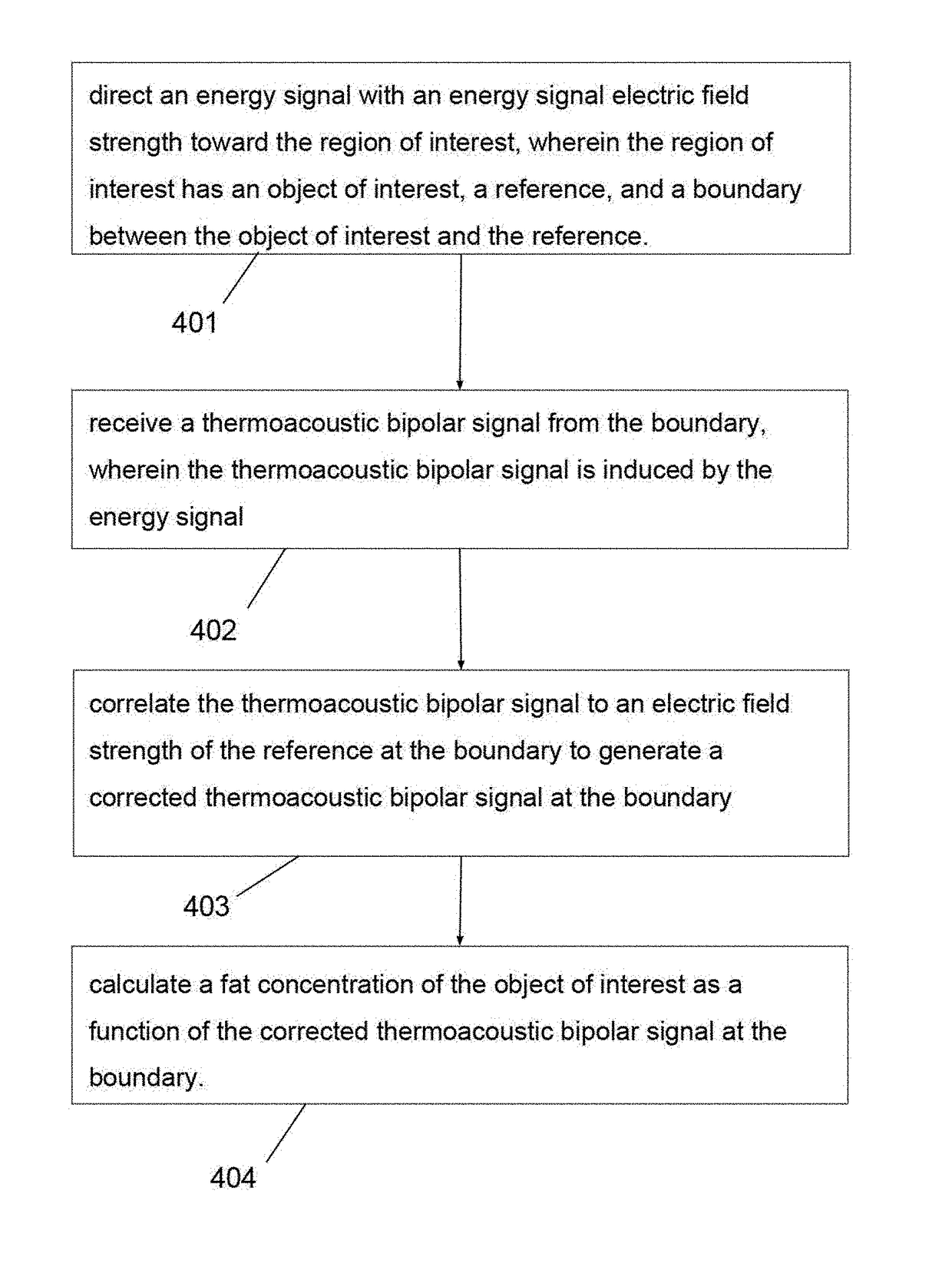

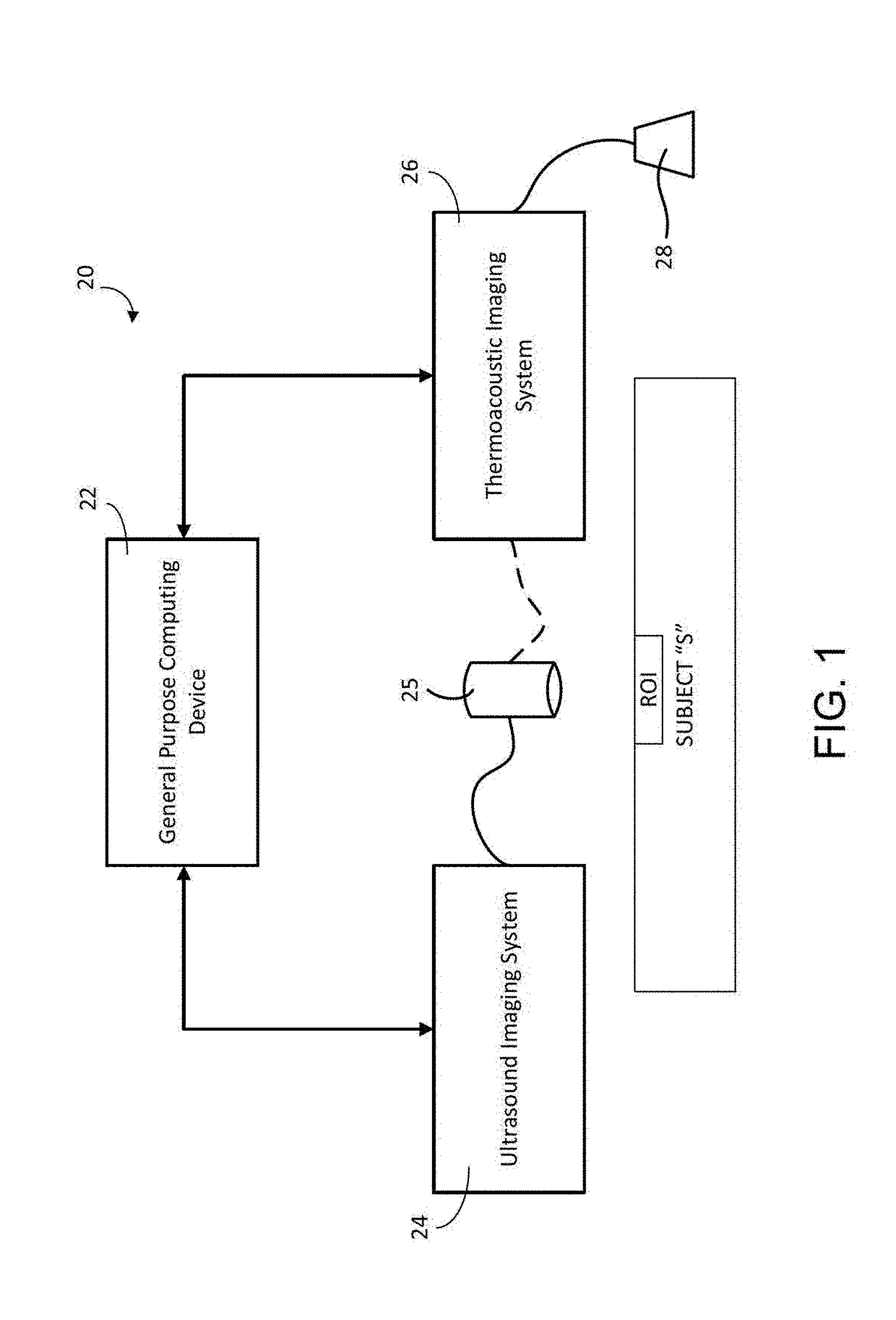

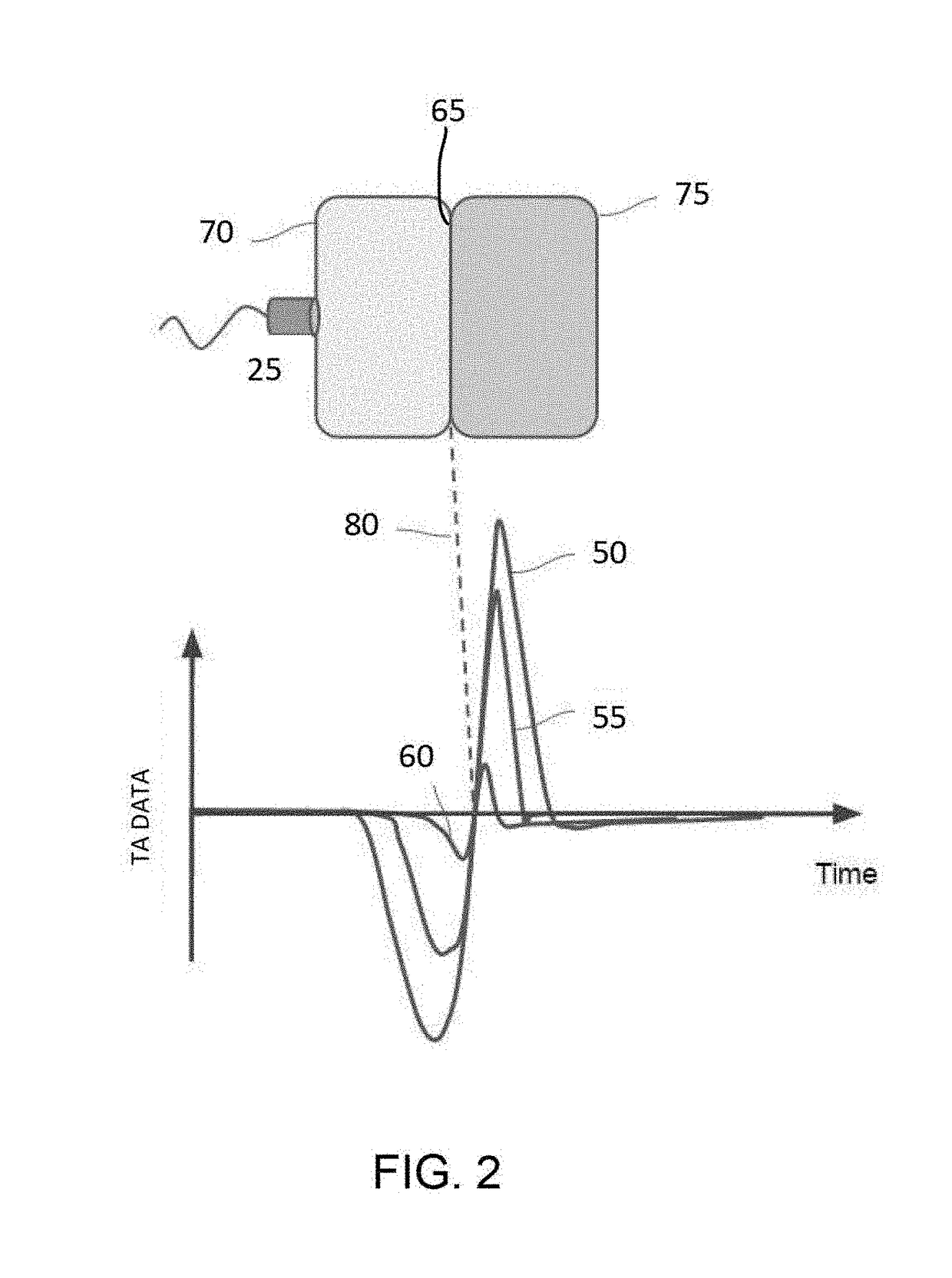

Method and system for estimating fractional fat content of an object

ActiveUS9888879B1Organ movement/changes detectionDiagnostic recording/measuringUltrasonic sensorBipolar signal

A method and system for estimating fractional fat content of an object of interest. An energy emitter is used to direct an energy signal with an energy signal electric field strength toward the region of interest, wherein the region of interest has an object of interest, a reference, and a boundary between the object of interest and the reference. Next, a thermoacoustic or ultrasonic transducer is used to receive a thermoacoustic bipolar signal from the boundary, wherein the thermoacoustic bipolar signal is induced by the energy signal. Finally, a machine is used to accept data from the energy emitter and thermoacoustic or ultrasonic transducer, correlate the thermoacoustic bipolar signal to an electric field strength of the reference at the boundary to generate a corrected thermoacoustic bipolar signal at the boundary, and calculate a fat concentration of the object of interest as a function of the corrected thermoacoustic bipolar signal at the boundary.

Owner:ENDRA LIFE SCI INC

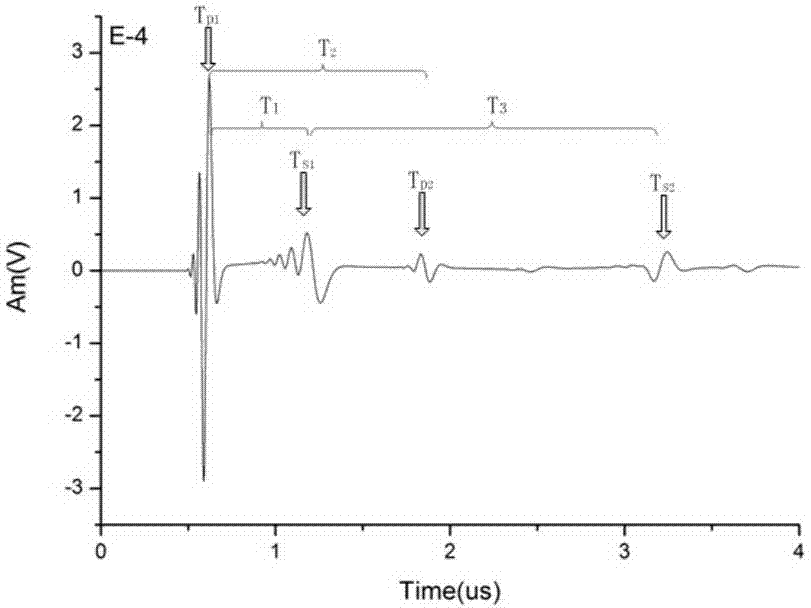

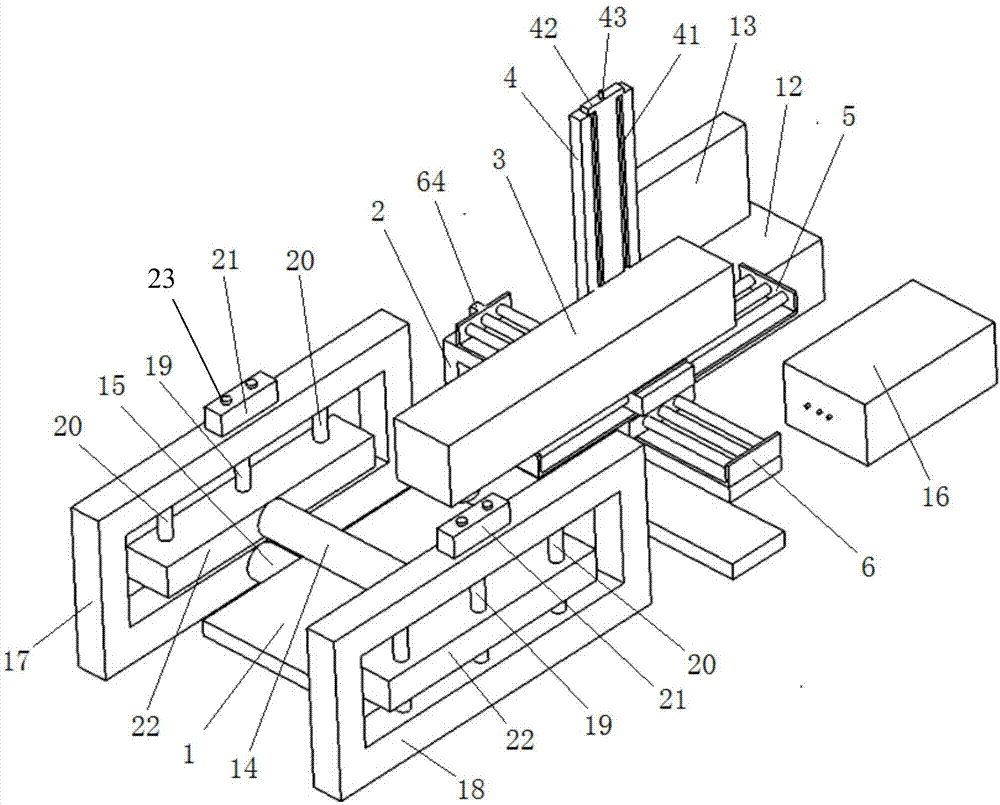

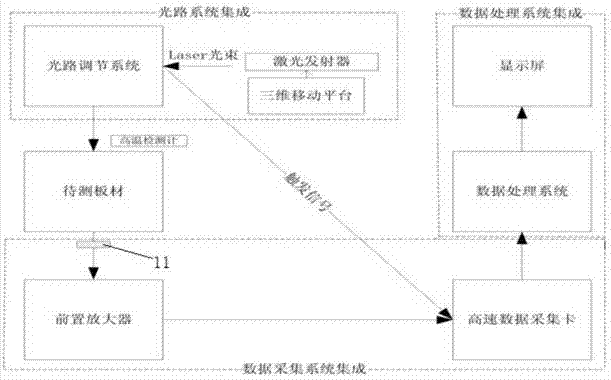

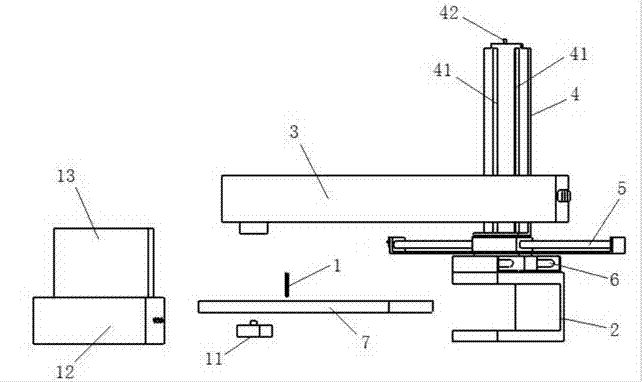

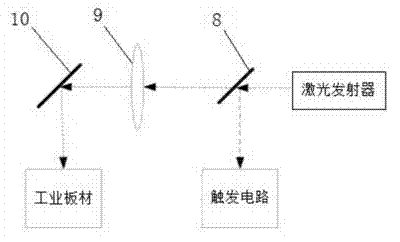

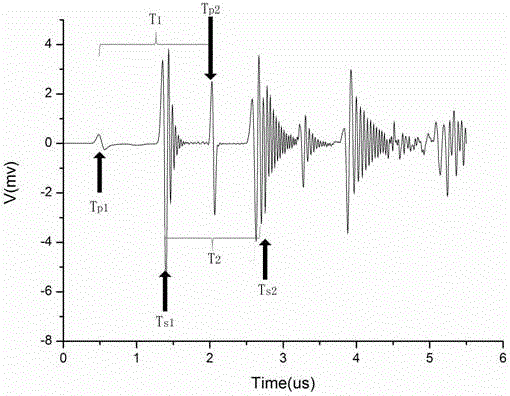

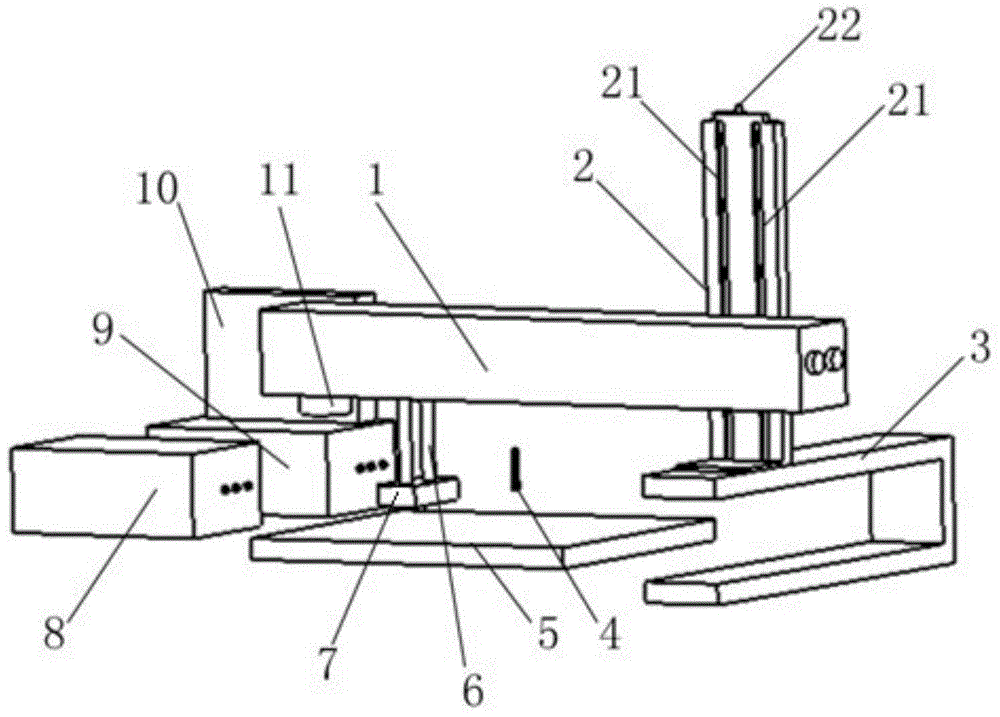

Sheet material thickness online detection and adjustment system based on laser ultrasonic

ActiveCN104707871ARealize non-contact measurementMeasuring Thickness UniformityRoll mill control devicesMeasuring devicesProcess systemsBipolar signal

A sheet material thickness online detection and adjustment system based on laser ultrasonic comprises a sheet material rolling mechanism and a sheet material thickness online detection mechanism. The sheet material rolling mechanism comprises an upper roller, a lower roller, an upper-lower roller interval adjust mechanism and a PLC control system, the sheet material thickness online detection mechanism comprises an optics system assembly, a high temperature testing meter, a data collection system assembly and a data process system assembly, the data process system assembly transforms bipolar signals which are aliased in peak values and complex in background noise into unipolar signals which are clear in peak values and low in background noise, so that the time that longitudinal wave and transverse wave reach the center of the bottom surface of the sheet material for the first two times is obtained, and thereby the sheet material thickness value is calculated, the measured sheet material thickness value is compared with a preset sheet material thickness value in the PLC control system, the PLC control system transmits forward rotating / backward rotation movement commands to a servo motor, so that the interval between the upper roller and the lower roller is adjusted, and the sheet material thickness value is made to be consistent with the preset sheet material thickness value.

Owner:ZHEJIANG UNIV

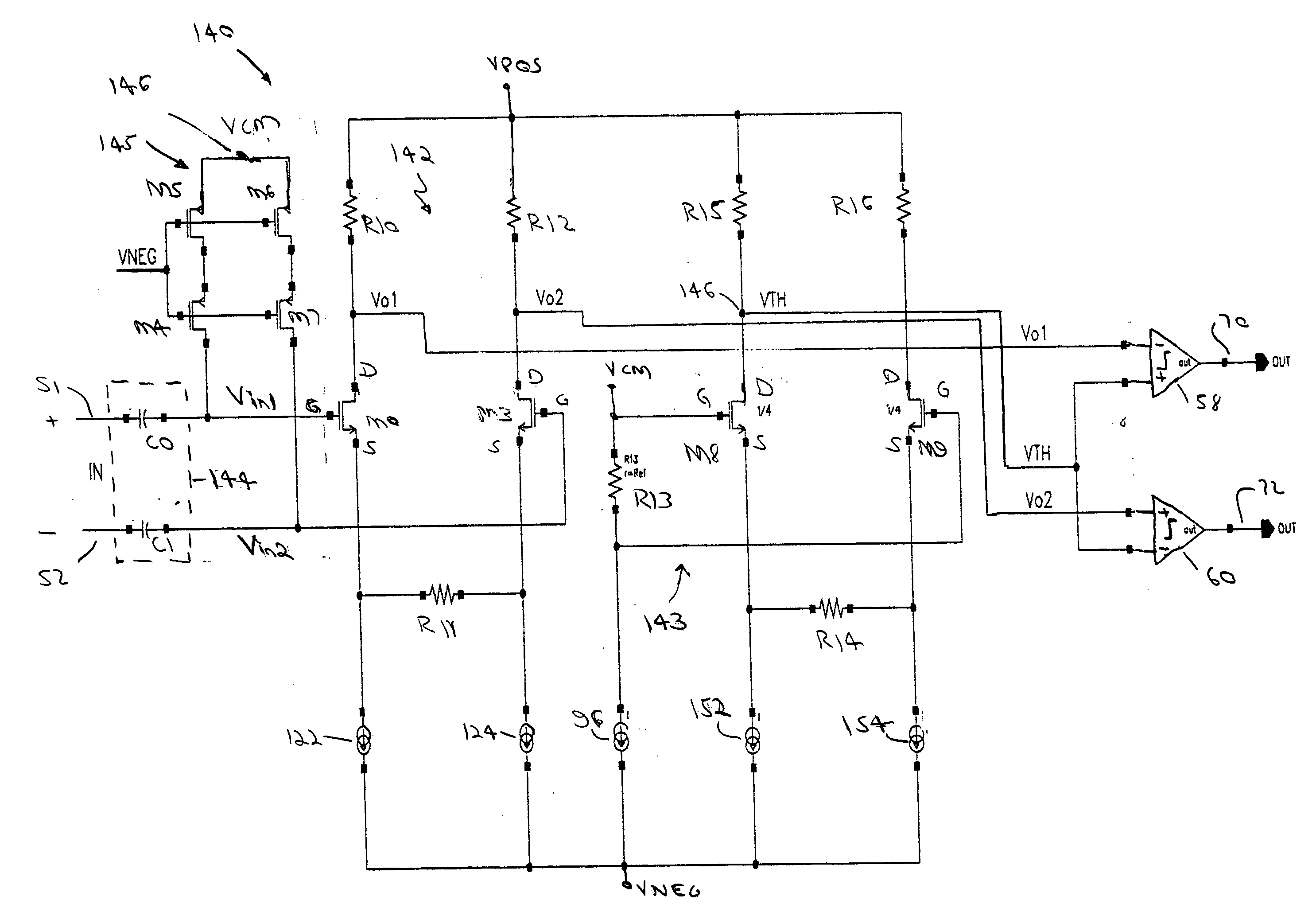

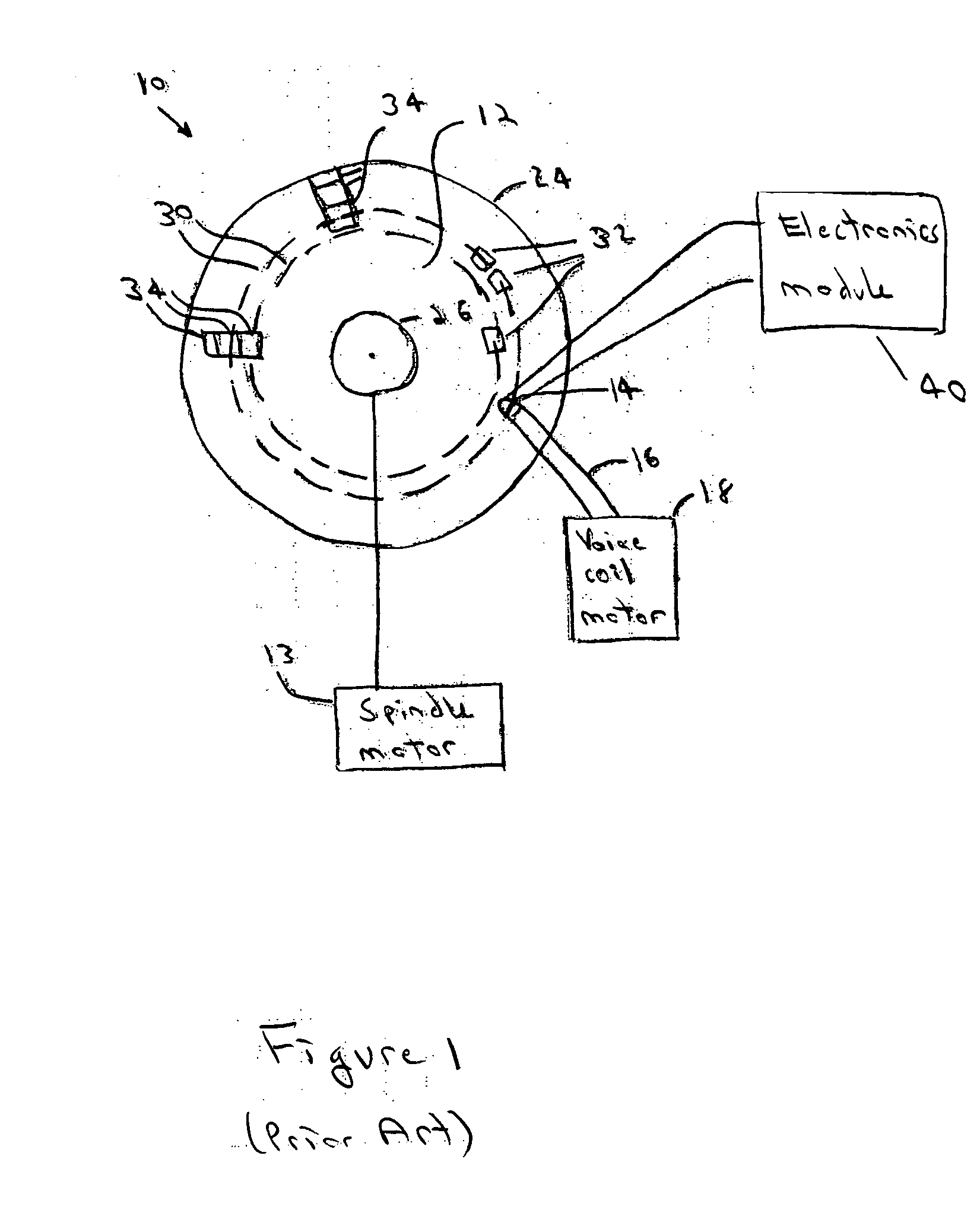

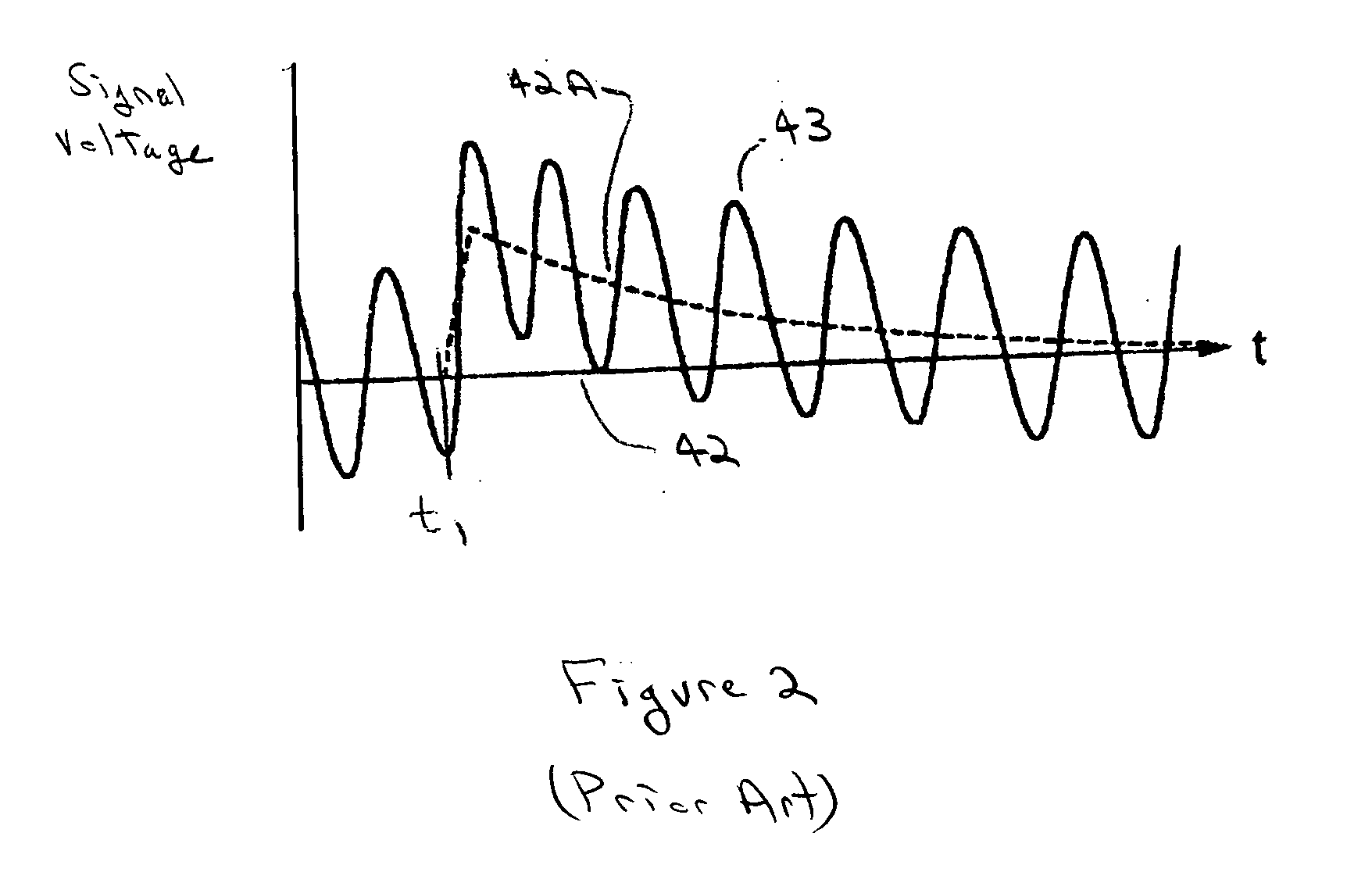

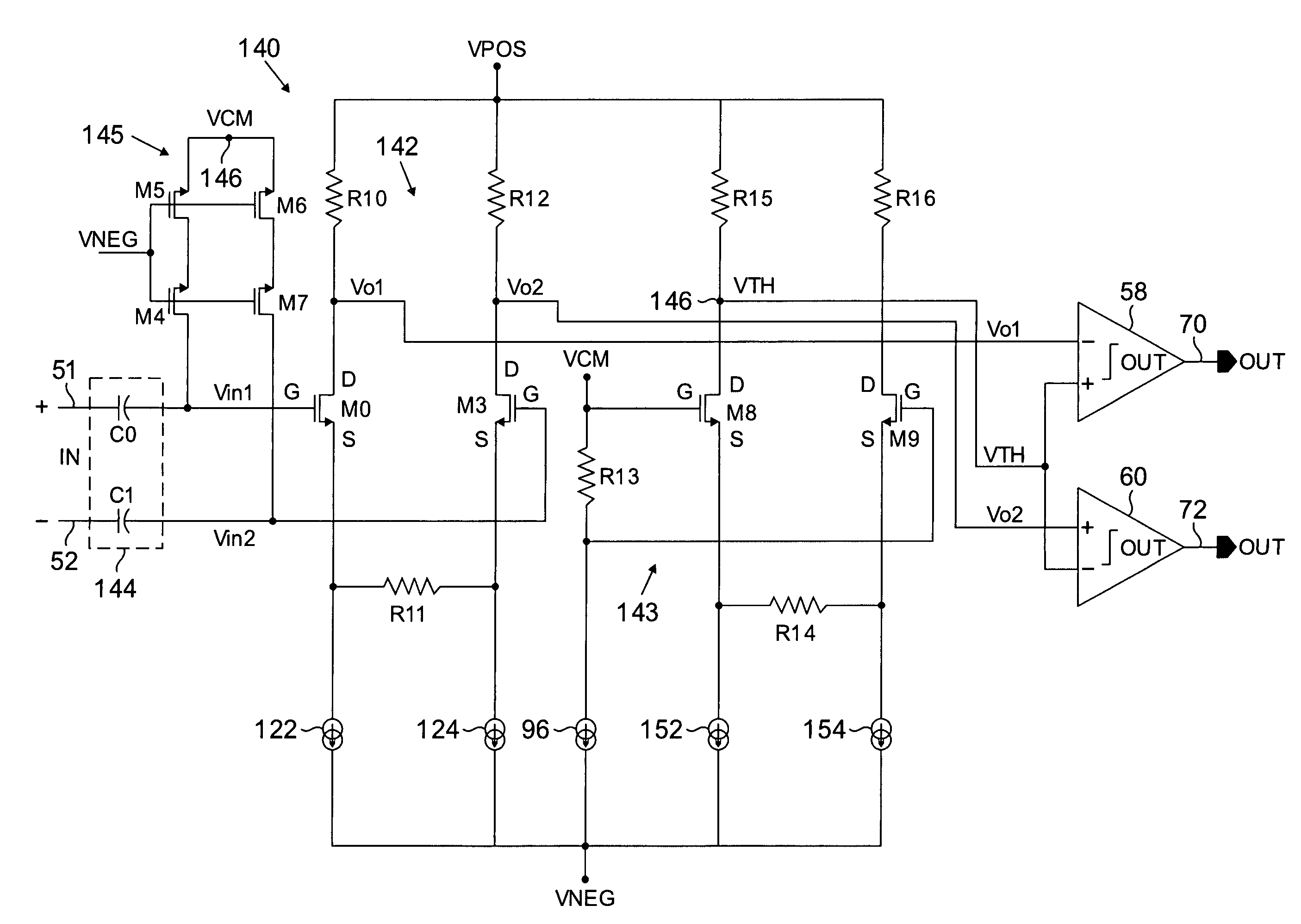

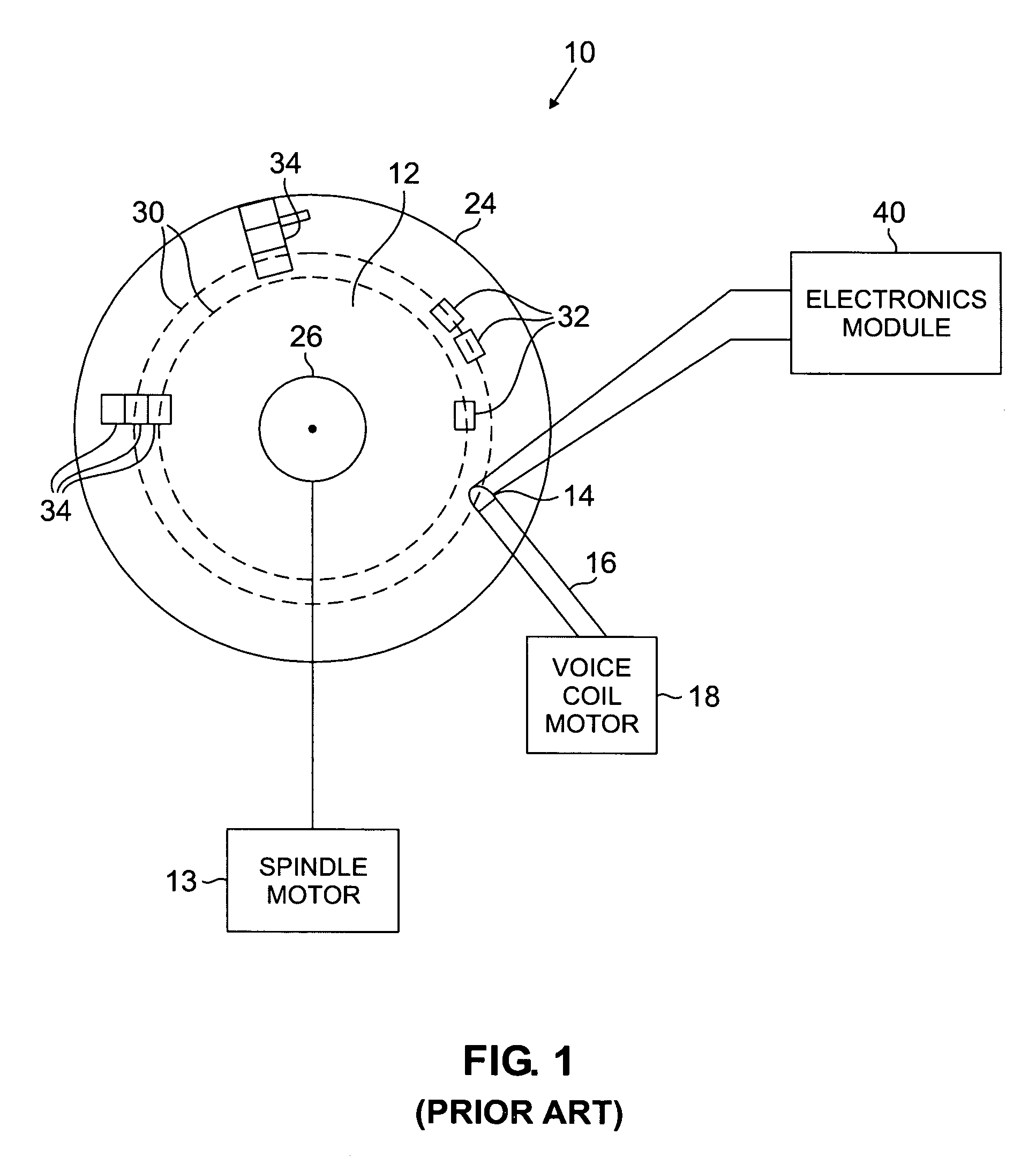

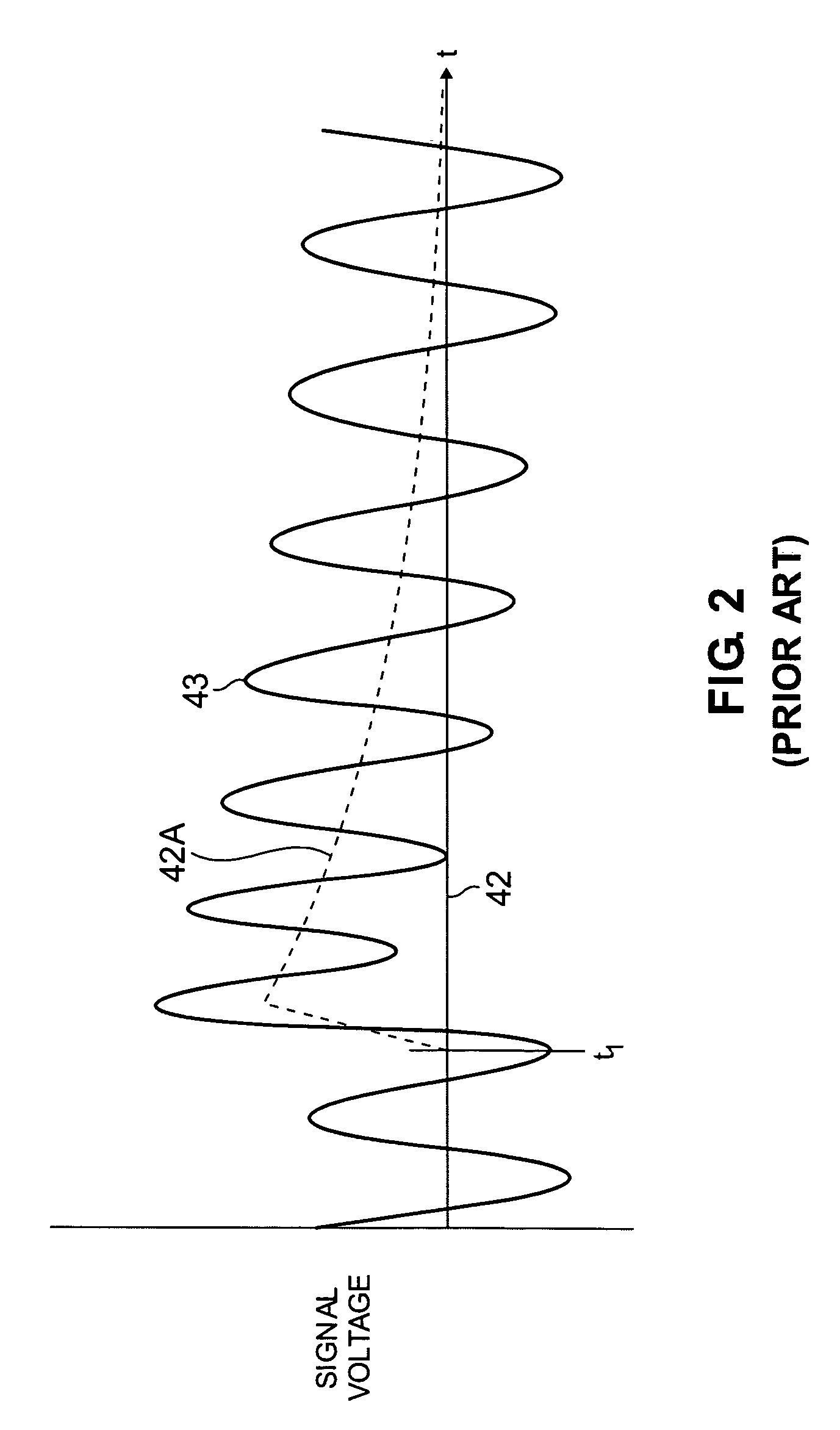

Variable threshold bipolar signal peak detector

InactiveUS20070070534A1Amplifier with semiconductor-devices/discharge-tubesRecord information storageBipolar signalEngineering

A method and apparatus for detecting signal peaks caused by a thermal asperity event in a magnetic recording media to reduce data reading errors introduced by the thermal asperity event. A common mode voltage is determined for differential signals representing data bits read from the magnetic recording media and a threshold voltage produced responsive to the common mode voltage. A comparator determines if either of the differential signals exceeds the threshold voltage, thereby indicating the occurrence of a thermal asperity event.

Owner:AVAGO TECH INT SALES PTE LTD

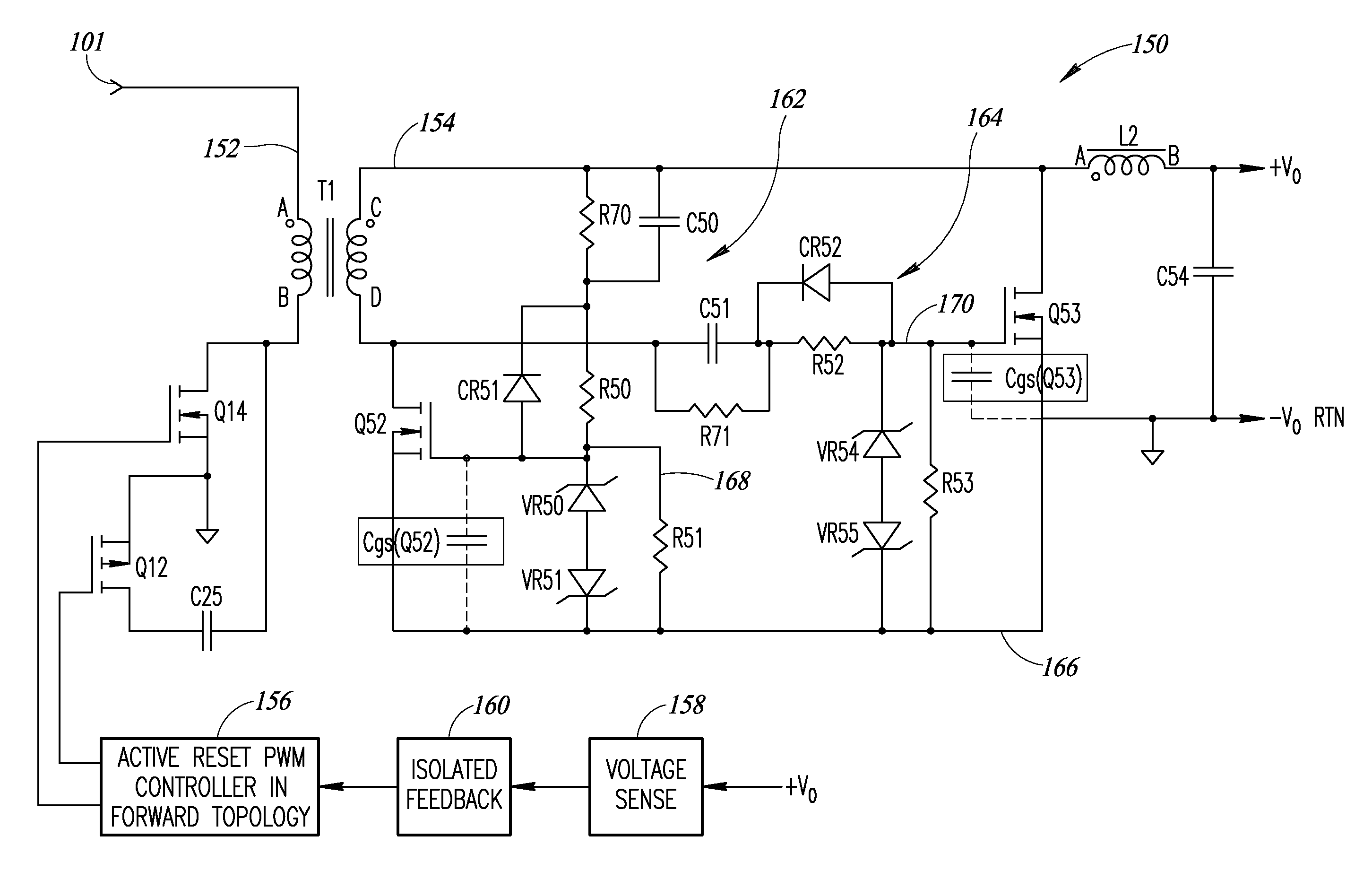

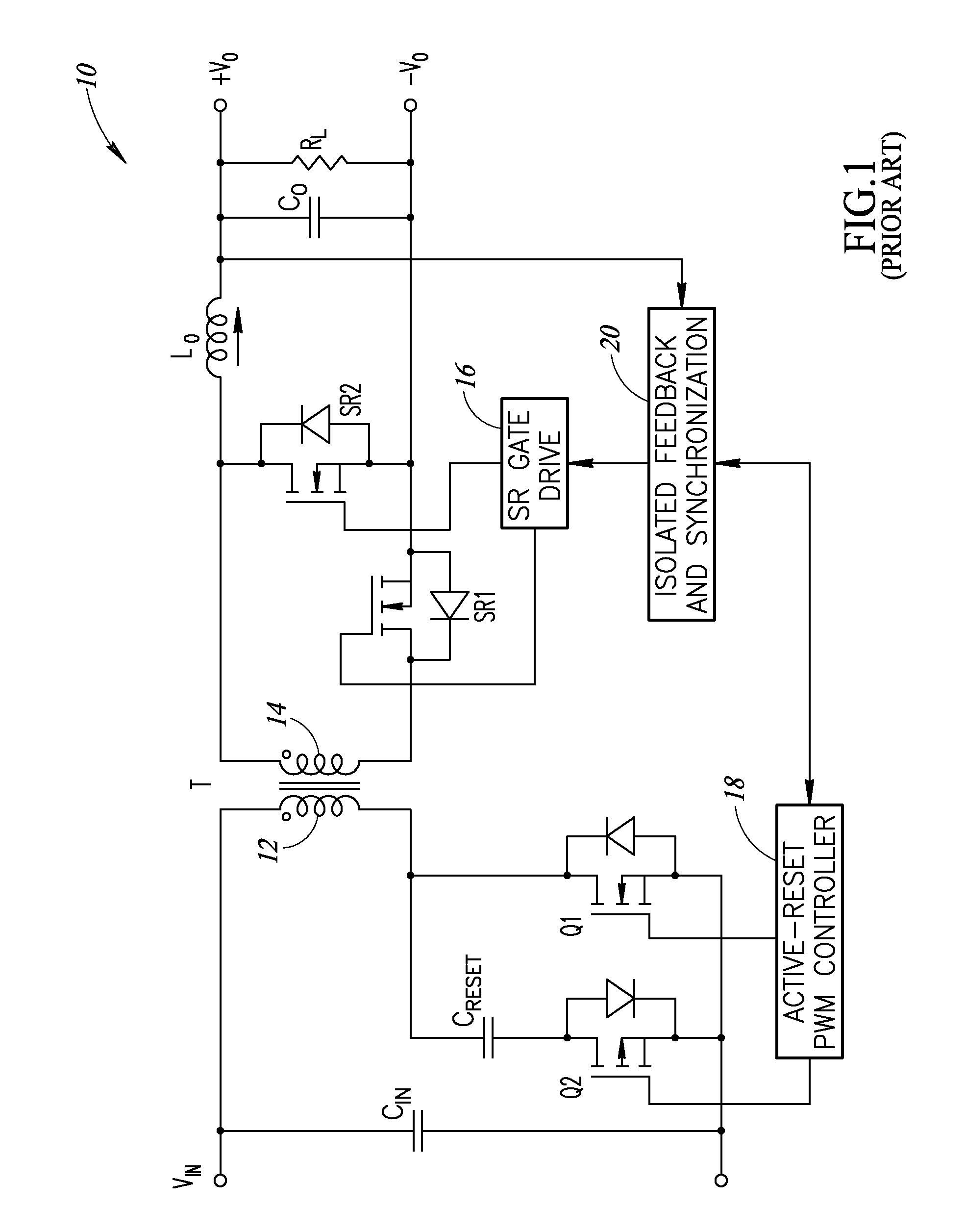

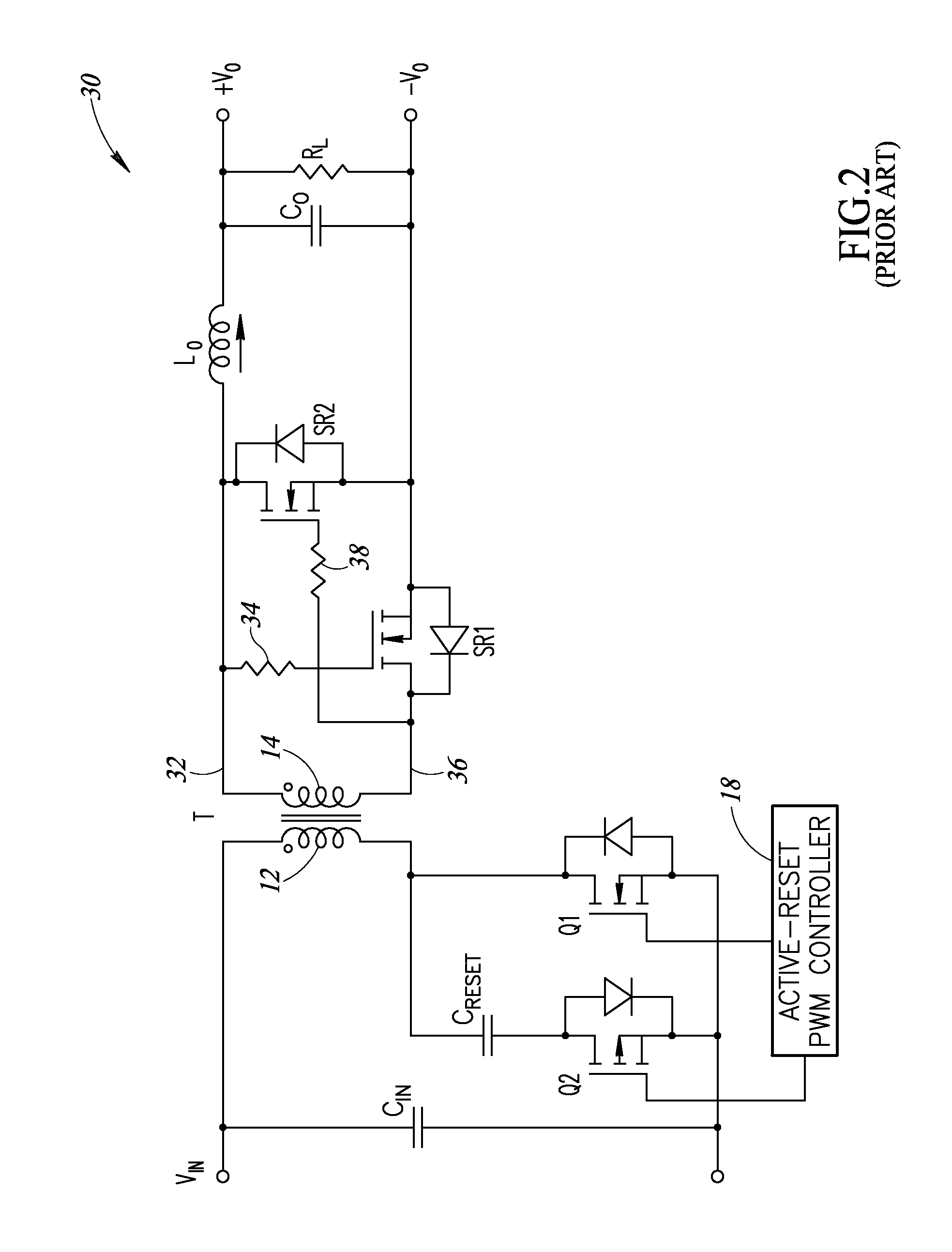

Automatic enhanced self-driven synchronous rectification for power converters

Systems and methods for providing a self-driven synchronous rectification circuit for an active-clamp forward converter which includes automatically enhancing synchronous MOSFETs and maximizing input voltage range. The gate signals for the synchronous MOSFETs are derived from a unipolar magnetic coupling signal instead of a bipolarized magnetic coupling signal. The unipolar signal is retained for fully enhanced driving of the MOSFETs at low line voltage and the unipolar signal is automatically converted to a bipolar signal at high line amplitude due to line variance to maximize input voltage range by utilizing non-polarized characteristics of the MOSFET gate-to-source voltage (Vgs). The circuit permits efficient scaling for higher output voltages such as 12 volts DC or 15 volts DC, without requiring extra windings on the transformer of the forward converter.

Owner:CRANE ELECTRONICS INC

Variable threshold bipolar signal peak detector

InactiveUS7626777B2Amplifier with semiconductor-devices/discharge-tubesRecord information storageBipolar signalComputational physics

A method and apparatus for detecting signal peaks caused by a thermal asperity event in a magnetic recording media to reduce data reading errors introduced by the thermal asperity event. A common mode voltage is determined for differential signals representing data bits read from the magnetic recording media and a threshold voltage produced responsive to the common mode voltage. A comparator determines if either of the differential signals exceeds the threshold voltage, thereby indicating the occurrence of a thermal asperity event.

Owner:AVAGO TECH INT SALES PTE LTD

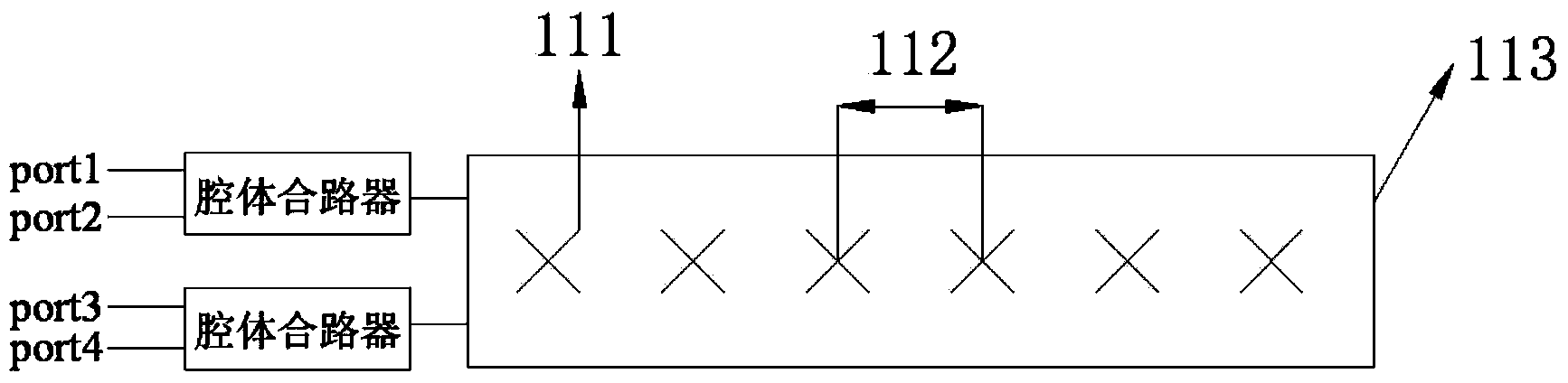

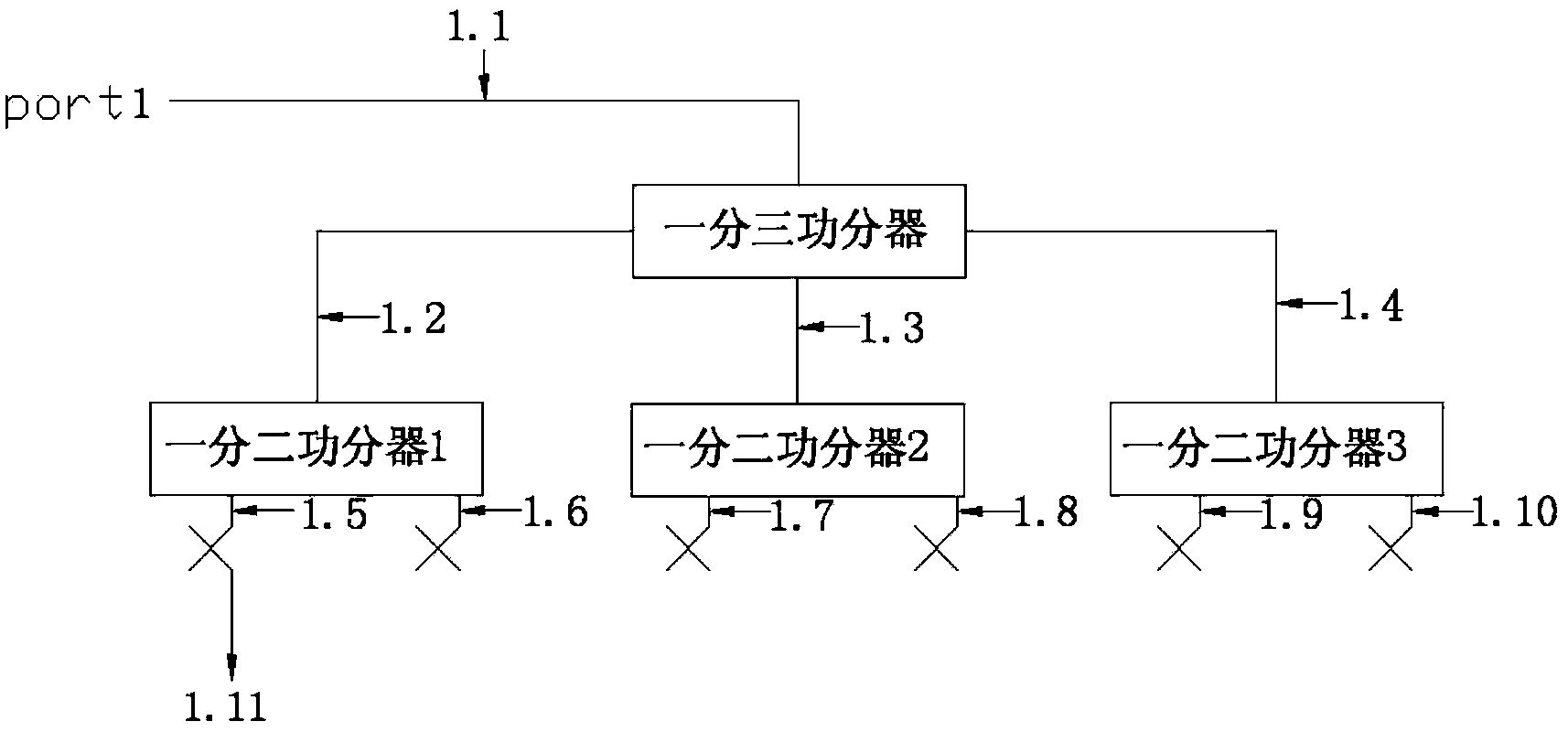

Multi-system-supported multi-antenna array

ActiveCN103715522AReduce the chance of installation errorsReduce cross-frequency interferenceIndividually energised antenna arraysPolarised antenna unit combinationsElectricityBipolar signal

The invention provides a multi-system-supported multi-antenna array. The multi-antenna array comprises more than two radiating units of the same form, a reflecting plate, a feed network and a group of antenna input-output ports, wherein the radiating units and the feed network are positioned on two different surfaces of the reflecting plate respectively; the radiating units are electrically connected with each other by virtue of the feed network; the antenna input-output ports are connected with the feed network; radio frequency signals are received or transmitted by virtue of the group of antenna input-output ports. Input-output ports of high-frequency and low-frequency signals can be independently controlled, bipolar signal coverage of + / -45 degrees is performed, and the multi-antenna array is simple in structure and low in cost.

Owner:WUHAN HONGXIN TELECOMM TECH CO LTD

Annotation of a wavefront

A method, including receiving a bipolar signal from a pair of electrodes in proximity to a myocardium of a human subject and receiving a unipolar signal from a selected one of the pair of electrodes. The method further includes computing a local unipolar minimum derivative of the unipolar signal, and a time of occurrence of the unipolar minimum derivative. The method also includes computing a bipolar derivative of the bipolar signal, evaluating a ratio of the bipolar derivative to the local unipolar minimum derivative, and when the ratio is greater than a preset threshold ratio value, identifying the time of occurrence as a time of activation of the myocardium.

Owner:BIOSENSE WEBSTER (ISRAEL) LTD

Electronic circuitry

InactiveUS20030128075A1Rise and fall characteristicShort fallDelay lines pulse generationPulse automatic controlCMOSBipolar signal

Timing signal generation and distribution are combined in operation of a signal path exhibiting endless electromagnetic continuity affording signal phase inversion and having associated regenerative active means. Two-or more-phases of substantially square-wave bipolar signals arise directly in travelling wave transmission-line embodiments compatible with semiconductor fabrication including CMOS. Coordination by attainable frequency synchronism with phase coherence for several such oscillating signal paths has intra-IC inter-IC and printed circuit board impact.

Owner:ANALOG DEVICES INC

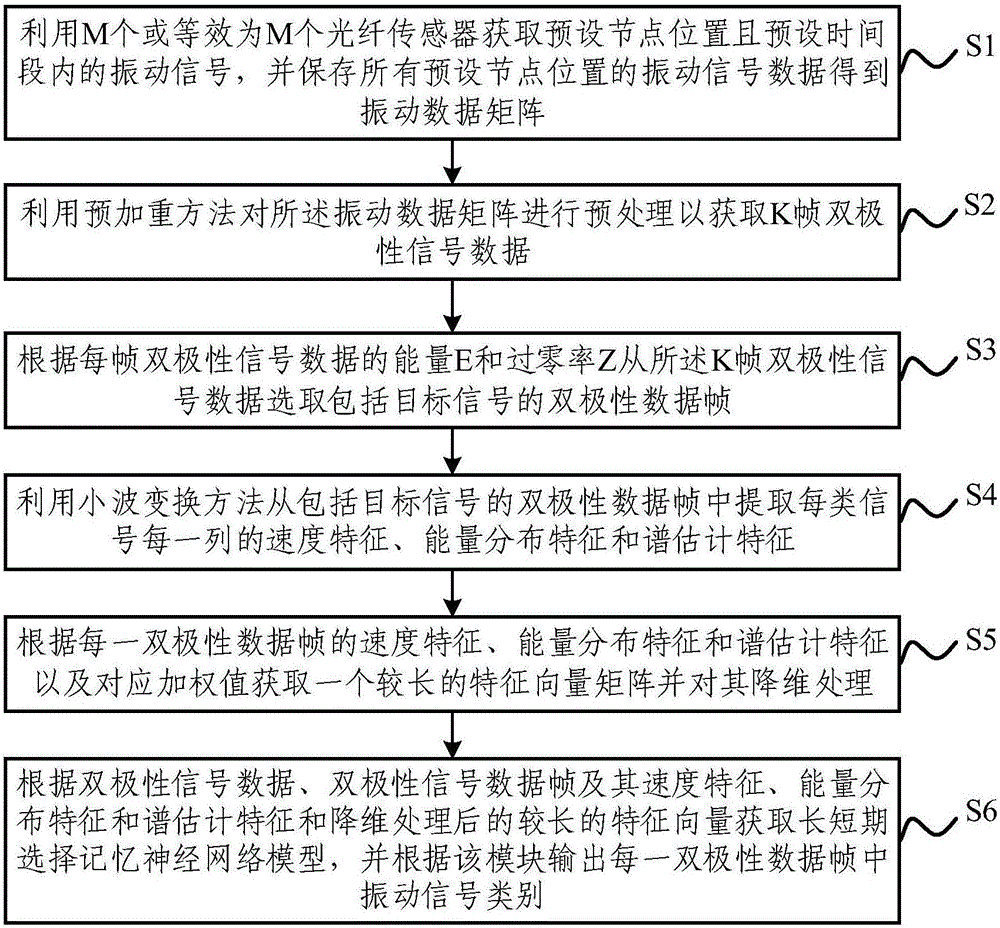

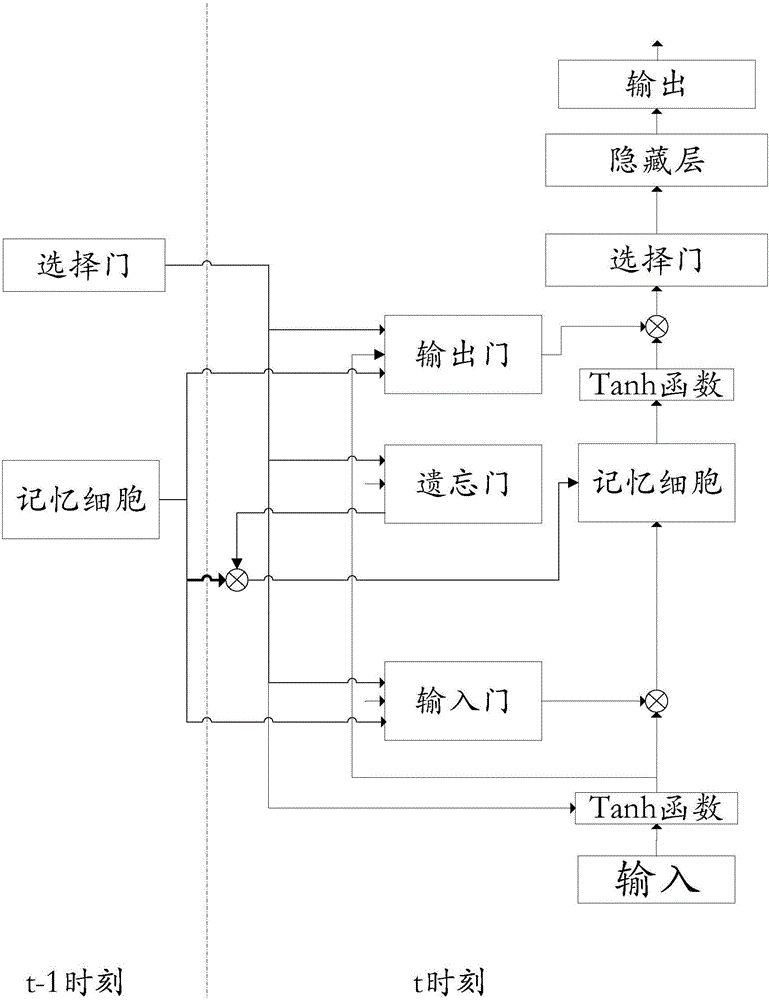

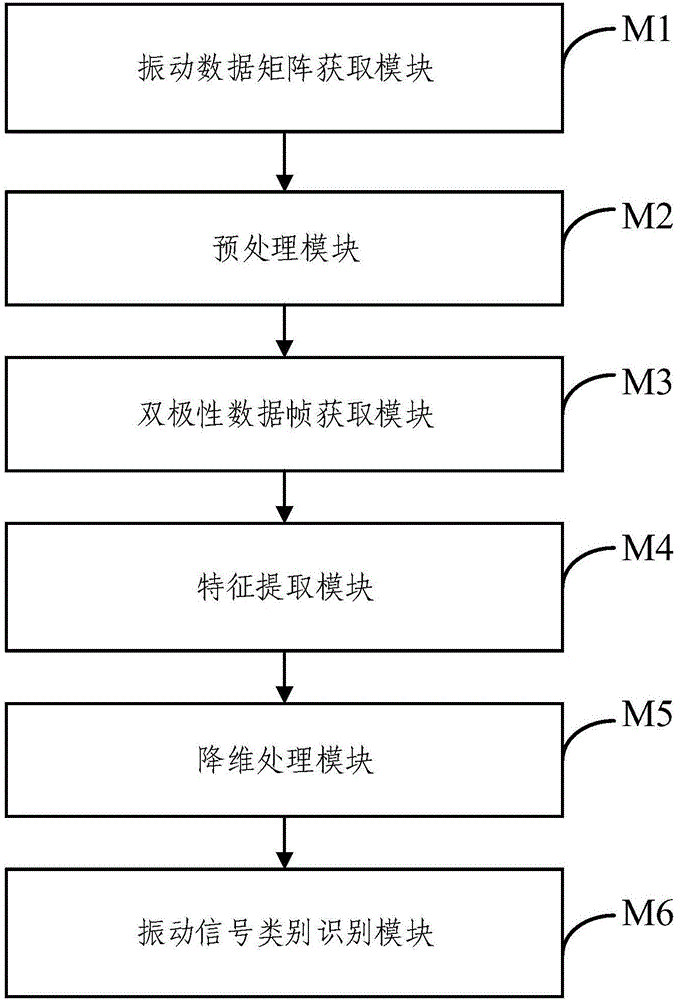

Target detecting and identifying method and target detecting and identifying system based on sound vibration signal

ActiveCN106646587AImprove recognition accuracyEasy to handleAcoustic presence detectionFeature vectorBipolar signal

The invention discloses a target detecting and identifying method and a target detecting and identifying system based on a sound vibration signal. The method comprises the steps of acquiring a vibration signal at a preset node position in a preset time period and storing the vibration signal into a vibration data matrix by means of M fiber sensors or equivalent M fiber sensors; performing preprocessing on the vibration data matrix by means of a pre-emphasis method, and selecting a bipolar data frame which comprises a target signal; extracting a speed characteristic, an energy distribution characteristic and a spectrum estimation characteristic of each row of each kind of signal from the bipolar data frame, acquiring a relatively long characteristic vector matrix according to each characteristic and a corresponding weighted value and performing dimension reduction on the relatively long characteristic vector matrix; and identifying the vibration signal kind of the bipolar signal data, the bipolar signal data frame and the relatively long characteristic vector after dimension reduction by means of a long-and-short-period selection memory neural network model. According to the target detecting and identifying method and the target detecting and identifying system, sound vibration signal identification is determined according to combined action of information in different steps, thereby improving target identification accuracy.

Owner:北京知觉科技有限公司

Methods and apparatus for optical transmission of digital signals

ActiveUS8107826B2High levelImprove power efficiencyWavelength-division multiplex systemsFibre transmissionBipolar signalOptical data transmission

A method of communicating digital information over a dispersive optical channel includes encoding the digital information into a plurality of data blocks, each of which includes a number of bits of the information. A time-varying electrical signal is generated which corresponds with each of said data blocks. The time-varying electrical signal is applied to an optical transmitter (122) to generate an optical signal which includes an asymmetrically amplitude limited transmitted signal modulated onto an optical carrier. The optical signal is then transmitted over the dispersive optical channel (106). At a receiving apparatus (104) the optical signal is detected to produce an electrical signal which corresponds with the asymmetrically amplitude limited transmitted signal. A frequency domain equalization of the electrical signal mitigates the effect of dispersion of the optical channel (106) on the transmitted optical signal, and the equalized signal is decoded to recover the encoded data blocks and the corresponding transmitted digital information. The method enables bipolar signals to be transmitted over a dispersive unipolar optical channel, and reduces or eliminates the need to apply a high optical bias level at the transmitter, thereby improving optical power efficiency and enabling output power levels to be maintained below applicable safe levels, while simultaneously enabling the effects of channel dispersion to be substantially mitigated.

Owner:MONASH UNIV

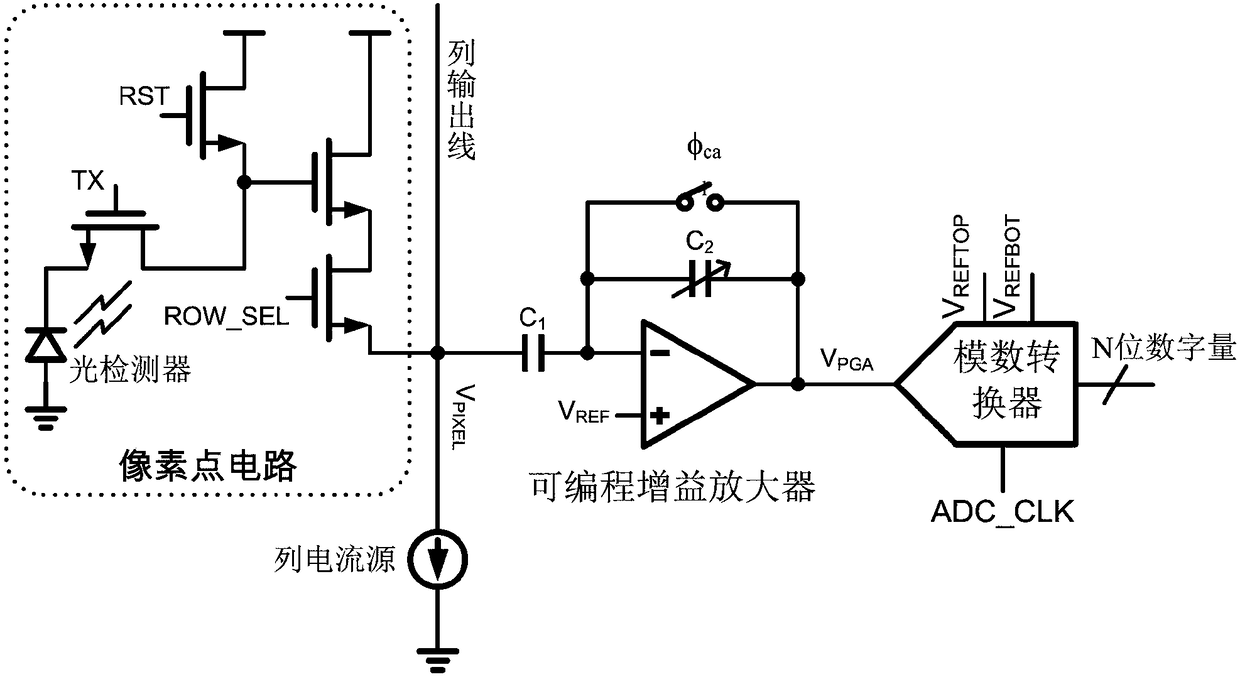

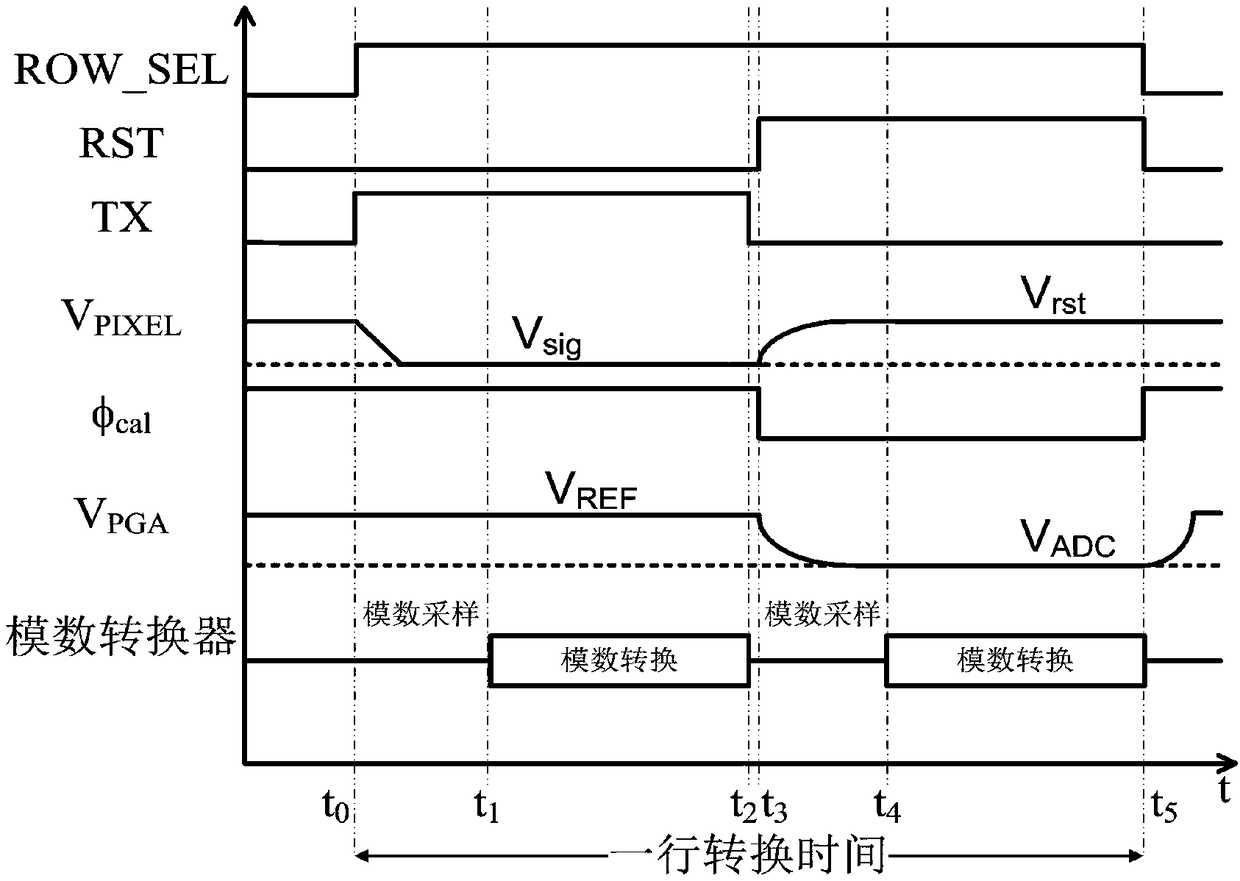

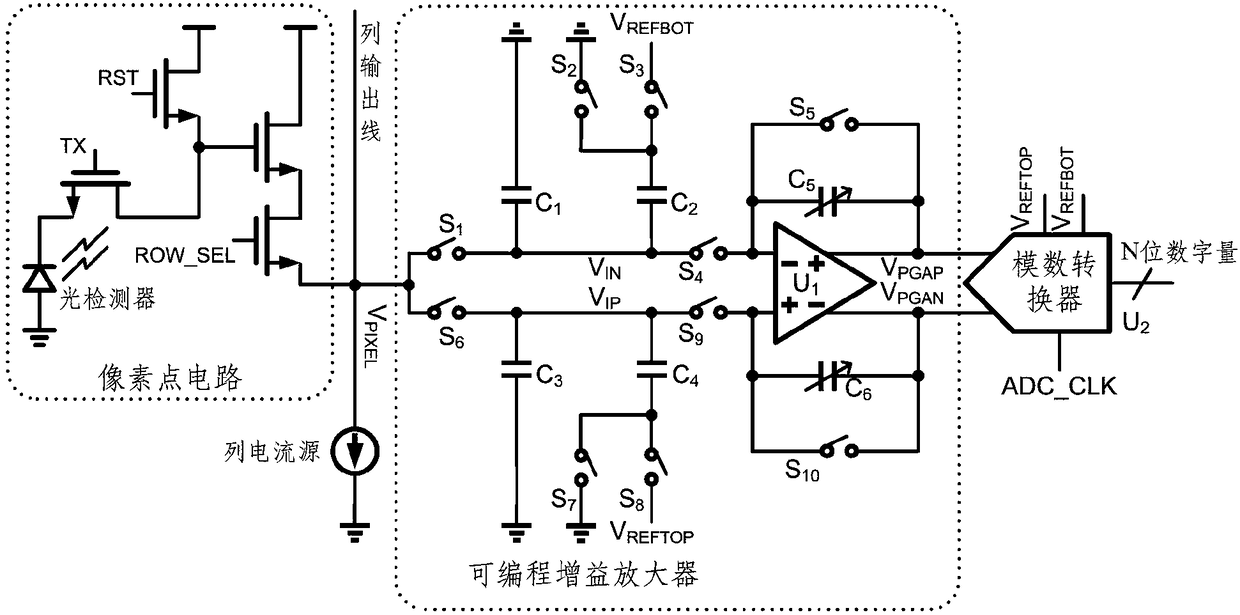

Column readout circuit for CMOS image sensor

ActiveCN108200364AIncreased maximum output voltage rangeImprove dynamic rangeTelevision system detailsColor television detailsCapacitanceBipolar signal

The invention discloses a column readout circuit for a CMOS image sensor. The circuit comprises a programmable gain amplifier for converting a single-end unipolar signal into a double-end bipolar signal, and a differential input two-step successive approximation analog-to-digital converter (SAR ADC), wherein a pixel point output voltage can be converted into the double-end bipolar signal through the programmable gain amplifier adopting the time-division and block-division sampling technology and the switch capacitor level transition technology, so that a dynamic signal range can be enlarged; and the double-end bipolar analog signal output by the programmable gain amplifier can be converted into a digital signal through the small-area differential input two-step SAR ADC, and the digital signal can be supplied to an imaging device. Therefore, the column readout circuit for the CMOS image sensor has the characteristics that a large dynamic range and a high frame frequency can be achieved.

Owner:ZHEJIANG UNIV

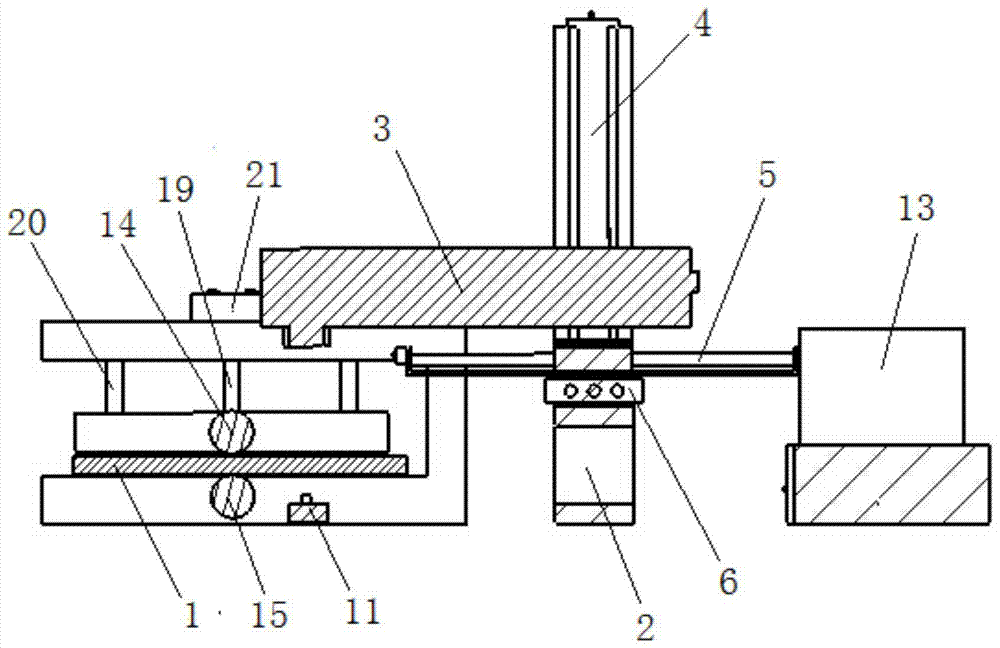

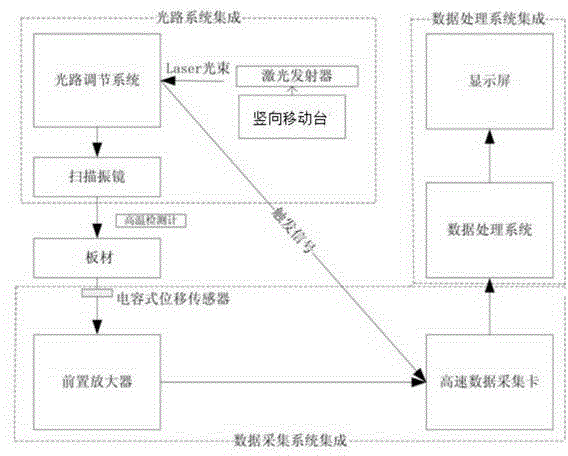

Sheet thickness online measurement system based on laser ultrasound

ActiveCN104729435AHigh movement accuracyRealize real-time online non-destructive testingUsing subsonic/sonic/ultrasonic vibration meansUsing optical meansLaser transmitterSonification

A sheet thickness online measurement system based on laser ultrasound comprises a light path system integration, a high-temperature detection meter, a data acquisition system integration and a data processing system integration, wherein the light path system integration comprises a U-shaped grounding frame, a three-dimensional mobile platform and a control cabinet integrating with a laser transmitter and a light path regulating system; the data acquisition system integration comprises a capacitive displacement sensor, a pre-amplifier and a high-speed data acquisition card, the capacitive displacement sensor is arranged at the first distance position below the alignment position of the bottom surface of a sheet, the data processing system integration converts bipolar signals having aliasing peak values and complex background noise into unipolar signals having clear peak values and low background noise, and therefore the time when longitudinal waves and transverse waves reach the alignment position of the bottom surface of the sheet first two times is accurately obtained, and the thickness of the sheet is calculated. The sheet thickness online measurement system has the advantages that the sheet thickness online measurement system is suitable for online measuring the thickness of the sheet under extreme environments such as high temperature, strong corrosion and high radiation, thickness measurement is accurate, and errors are small.

Owner:ZHEJIANG UNIV

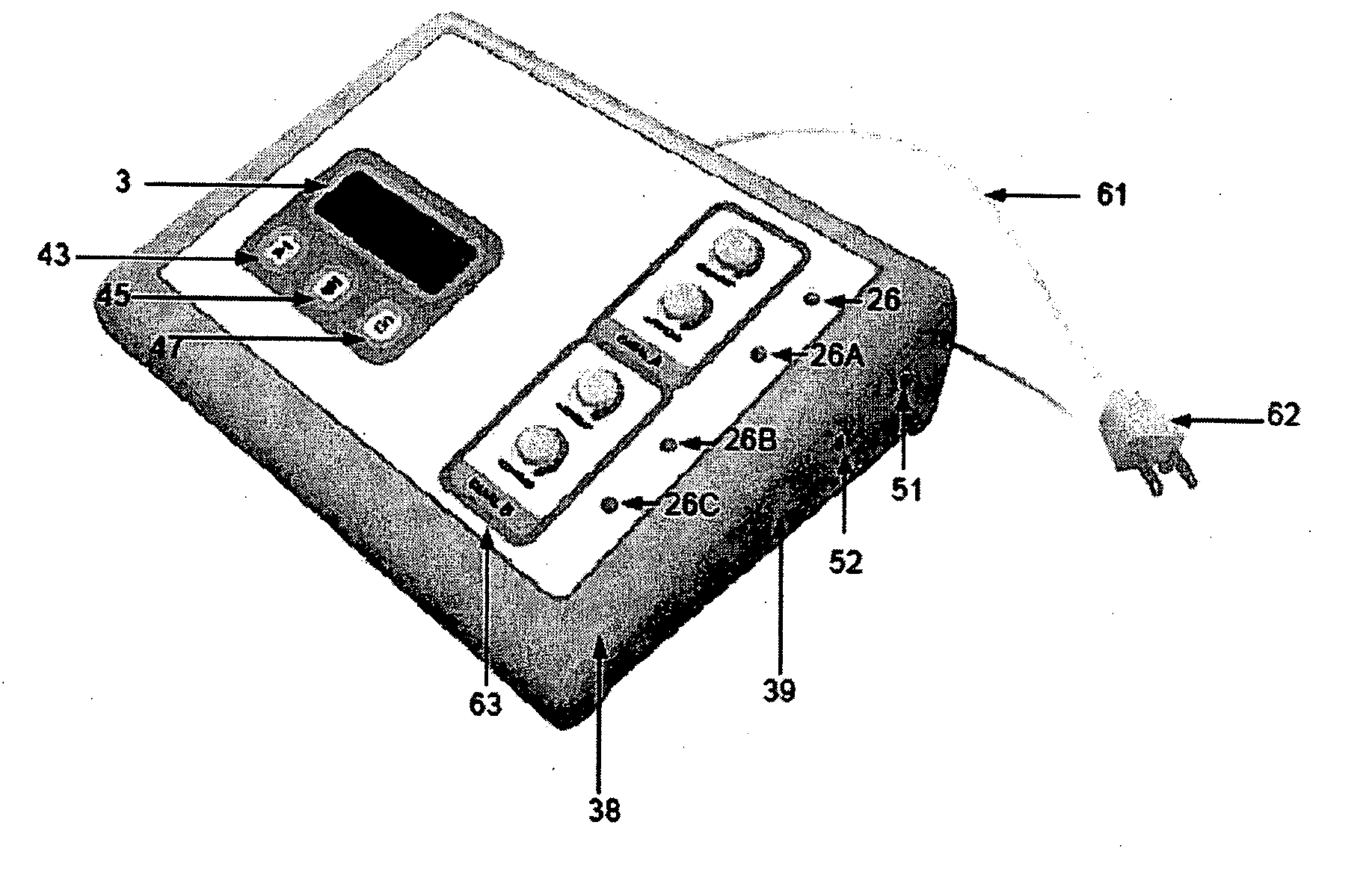

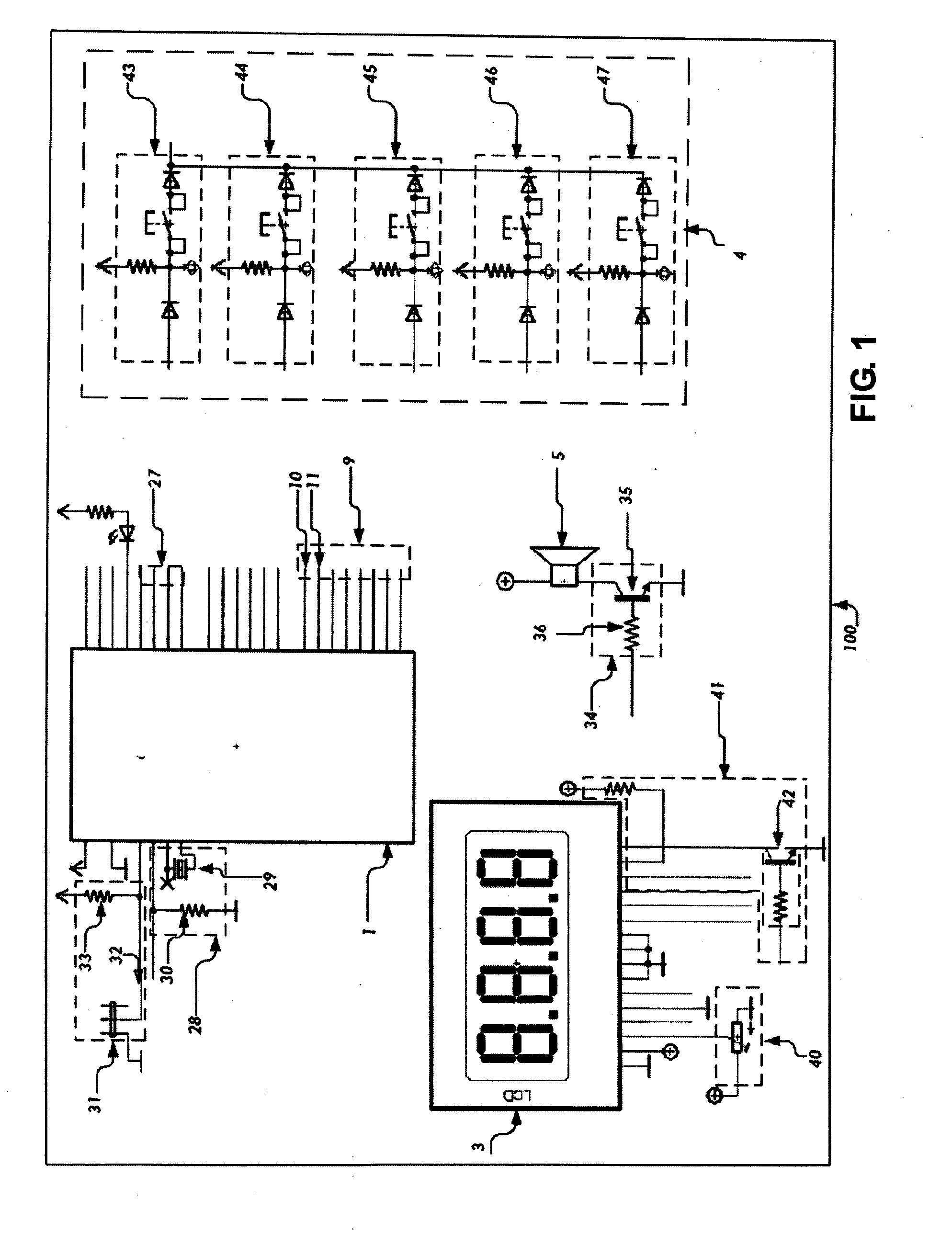

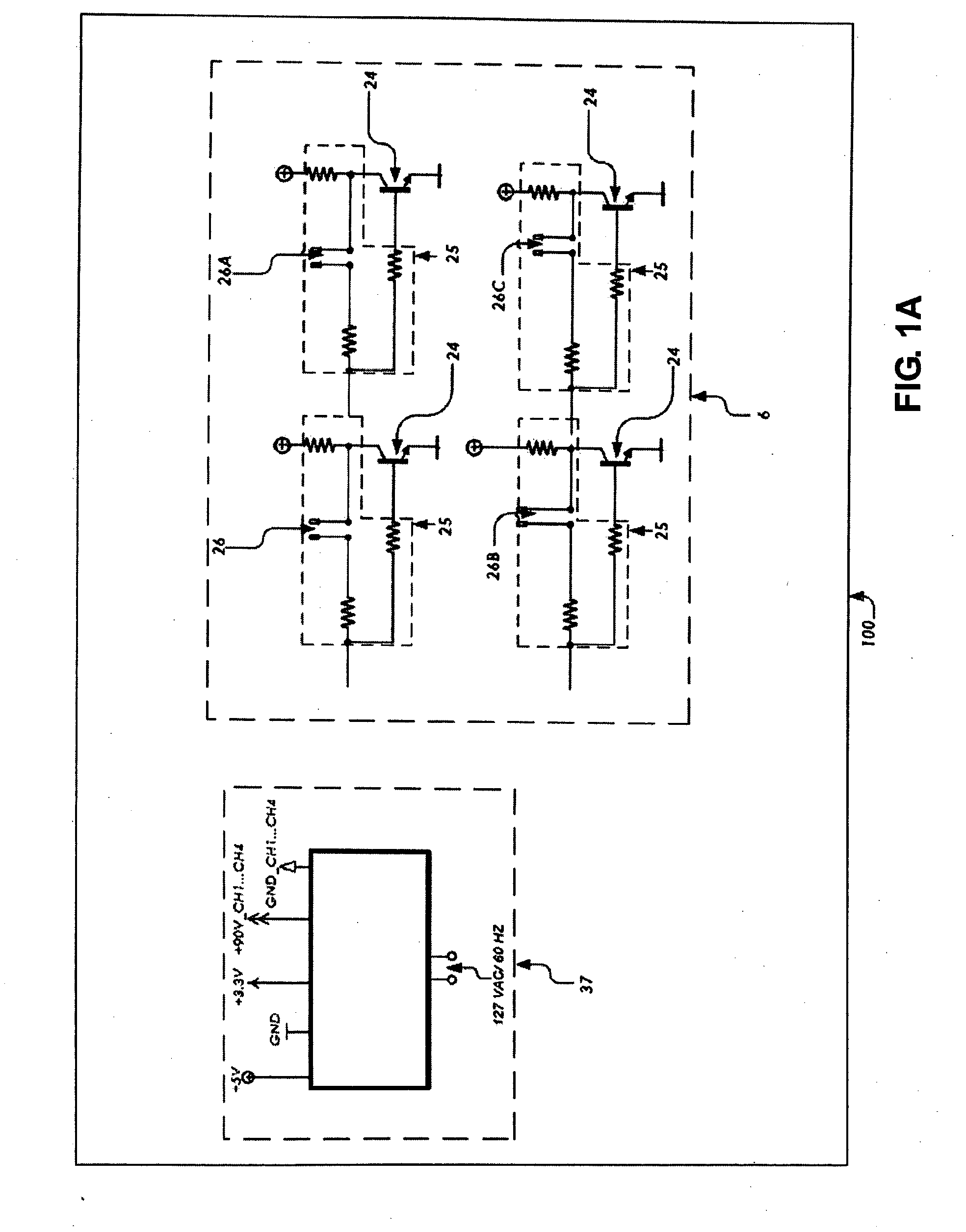

Low frequency electrical stimulator device for the prevention and treatment of chronic wounds

A low frequency electrical stimulation device for the prevention and healing of chronic wounds resulting from diabetes, or other type of pathology. This device applies electrical stimulation through a square bipolar signal, and a paused squared bipolar signal in at least one of the output channels, and at different therapy times and frequencies that will depend upon the specific needs of the patient.

Owner:PLASENCIA MOELLER CARLOS ARTURO +2

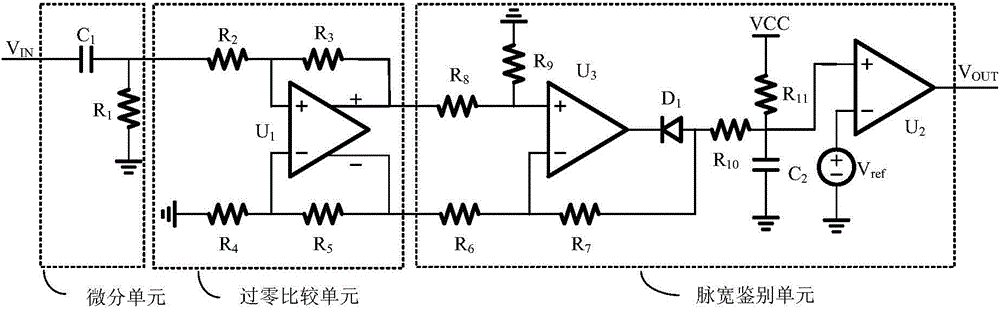

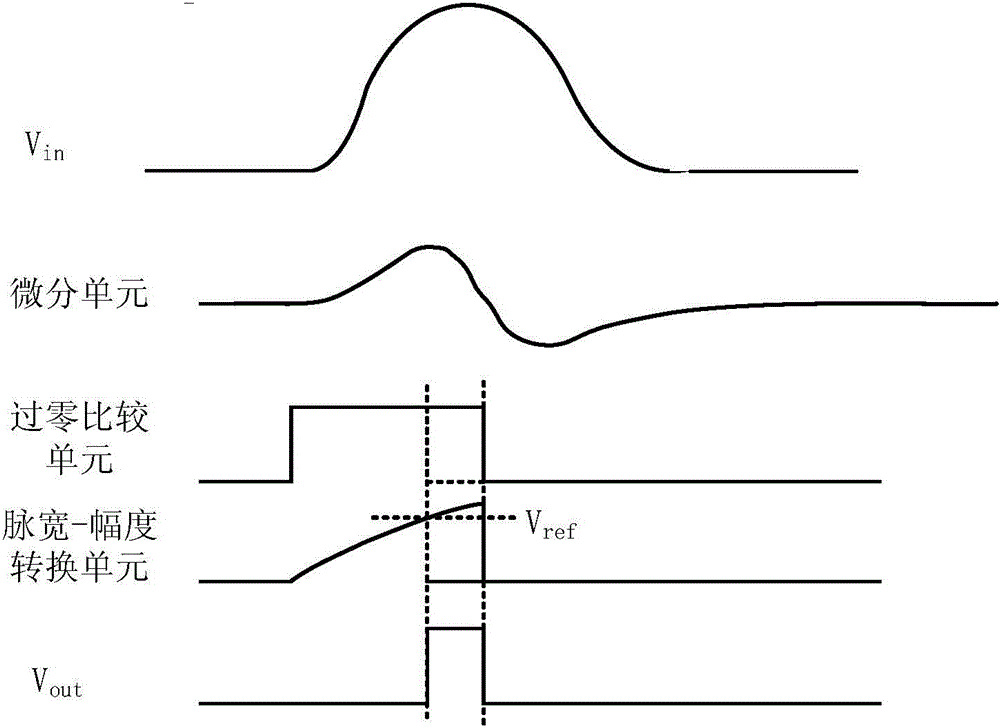

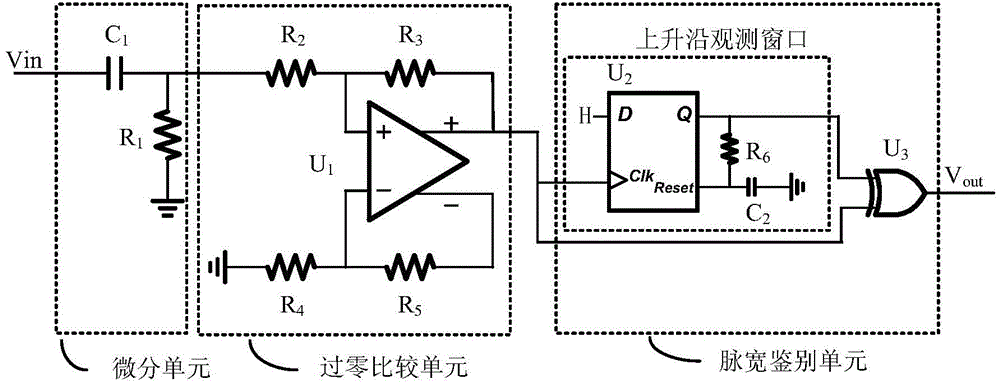

Slow rising edge pulse signal identification circuit

ActiveCN104836553ADoes not affect the zero-crossing time differenceSimple wayPulse descriminationBipolar signalSimple circuit

The invention relates to a slow rising edge pulse signal identification circuit. The slow rising edge pulse signal identification circuit includes a differential unit, a zero crossing comparison unit and a pulse width identification unit; the differential unit performs differential processing on unipolar photon pulse signals inputted from the outside, so that bipolar signals with two zero crossing points can be formed and transmitted to the zero crossing comparison unit; the zero crossing comparison unit converts the bipolar signals into digital pulse signals with a certain pulse width according to a set comparison threshold value, and transmits the digital pulse signals to the pulse width identification unit; and the pulse width identification unit judges whether the width of the digital pulse signals exceeds a set identification threshold value, and judges that the photon pulse signals inputted from the outside are slow rising edge signals and outputs a high-electric level pulse if the width of the digital pulse signals exceeds the set identification threshold value, otherwise, outputs a low-electric level pulse. The slow rising edge pulse signal identification circuit of the invention has the advantages of simple circuit form and high sensitivity.

Owner:BEIJING INST OF CONTROL ENG

Online plate thickness measuring system based on laser ultrasonics

ActiveCN104792285ARealize non-contact measurementAccurate calculationUsing subsonic/sonic/ultrasonic vibration meansUsing optical meansLaser transmitterSonification

An online plate thickness measuring system based on laser ultrasonics comprises a light path system integration module, a high-temperature detector, a data collection system integration module and a data processing system integration module. The light path system integration module comprises a U-shaped grounding frame, a vertical moving platform and a control cabinet, a laser transmitter, a light path adjusting system and a scanning galvanometer are integrated in the control cabinet, the data collection system integration module comprises a capacitive displacement sensor, a preposed amplifier and a high-speed data collection card, the capacitive displacement sensor is arranged at a first distance position above the upper surface of a plate, and the data processing system integration module converts bipolar signals with aliasing peak value and complex background noise into unipolar signals with clear peak value and low background noise so as to accurately acquire time when longitudinal wave and transverse wave reach an O point on the upper surface of the plate in two previous times to calculate thickness of the plate. The online plate thickness measuring system has the advantages that the system utilizes a laser ultrasonics principle to measure thickness and is suitable for online measuring of thickness of the plate in extreme environment with high temperature, high corrosion and high radiation, accurate in thickness measuring and few in thickness measuring error.

Owner:ZHEJIANG UNIV

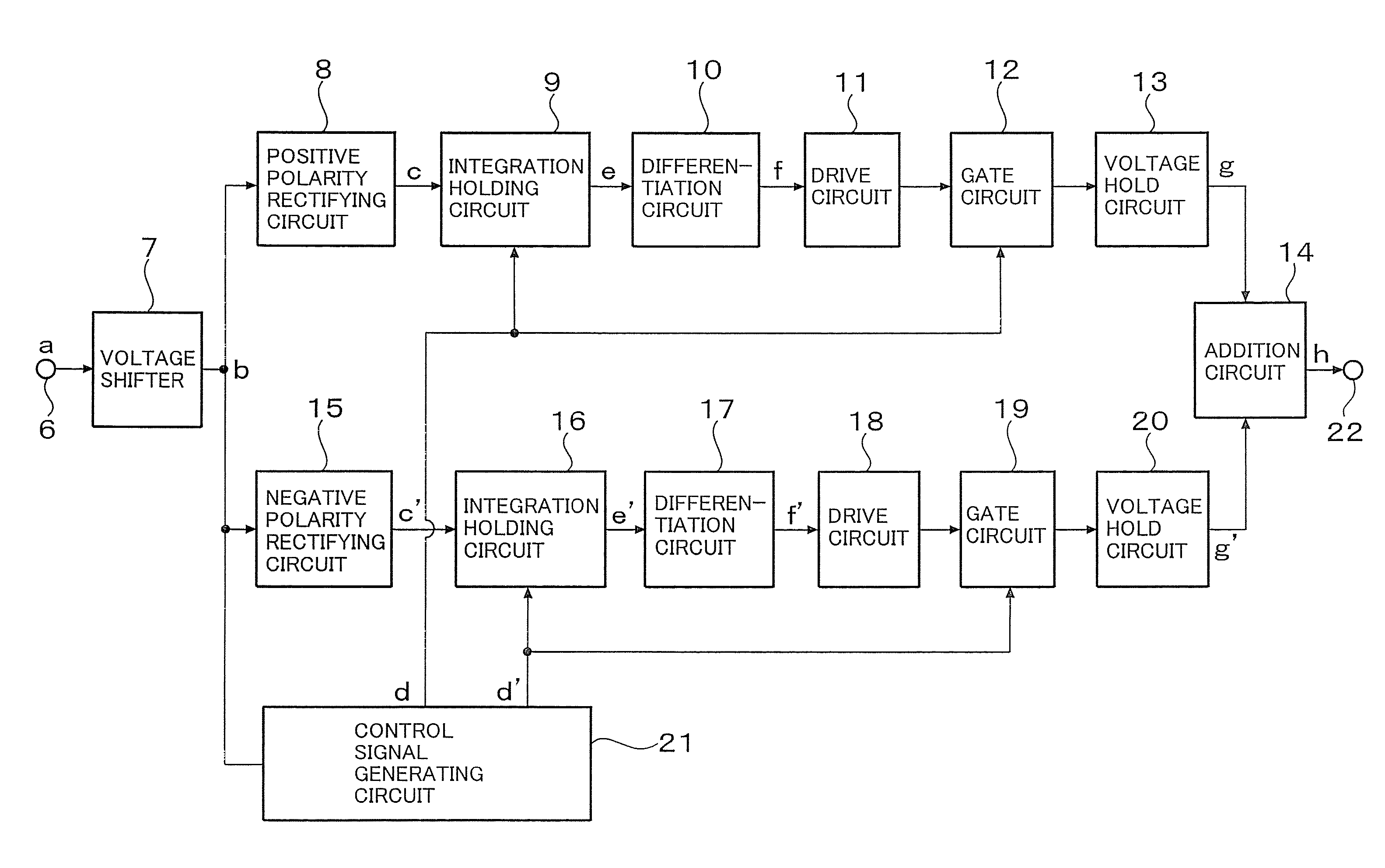

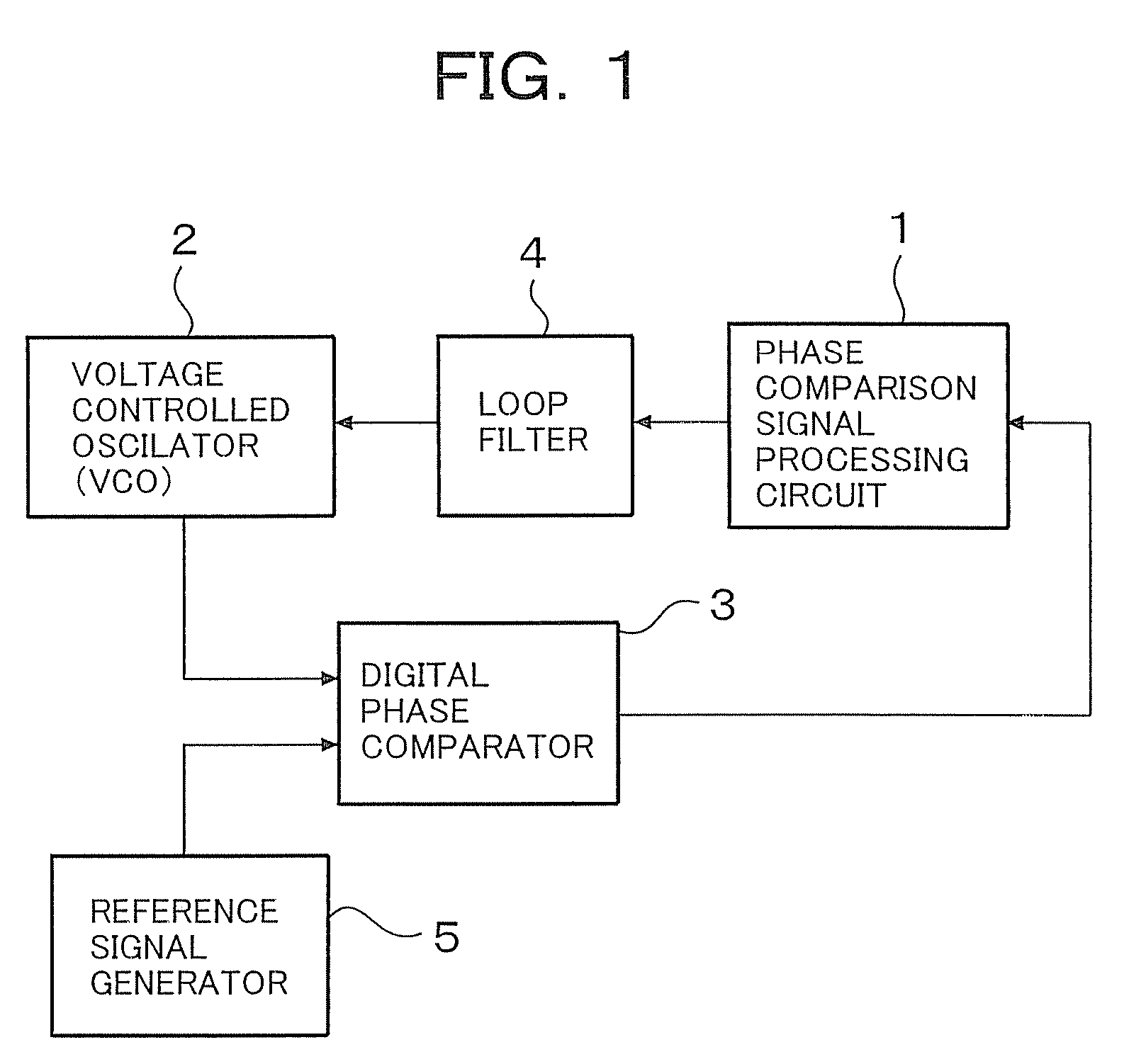

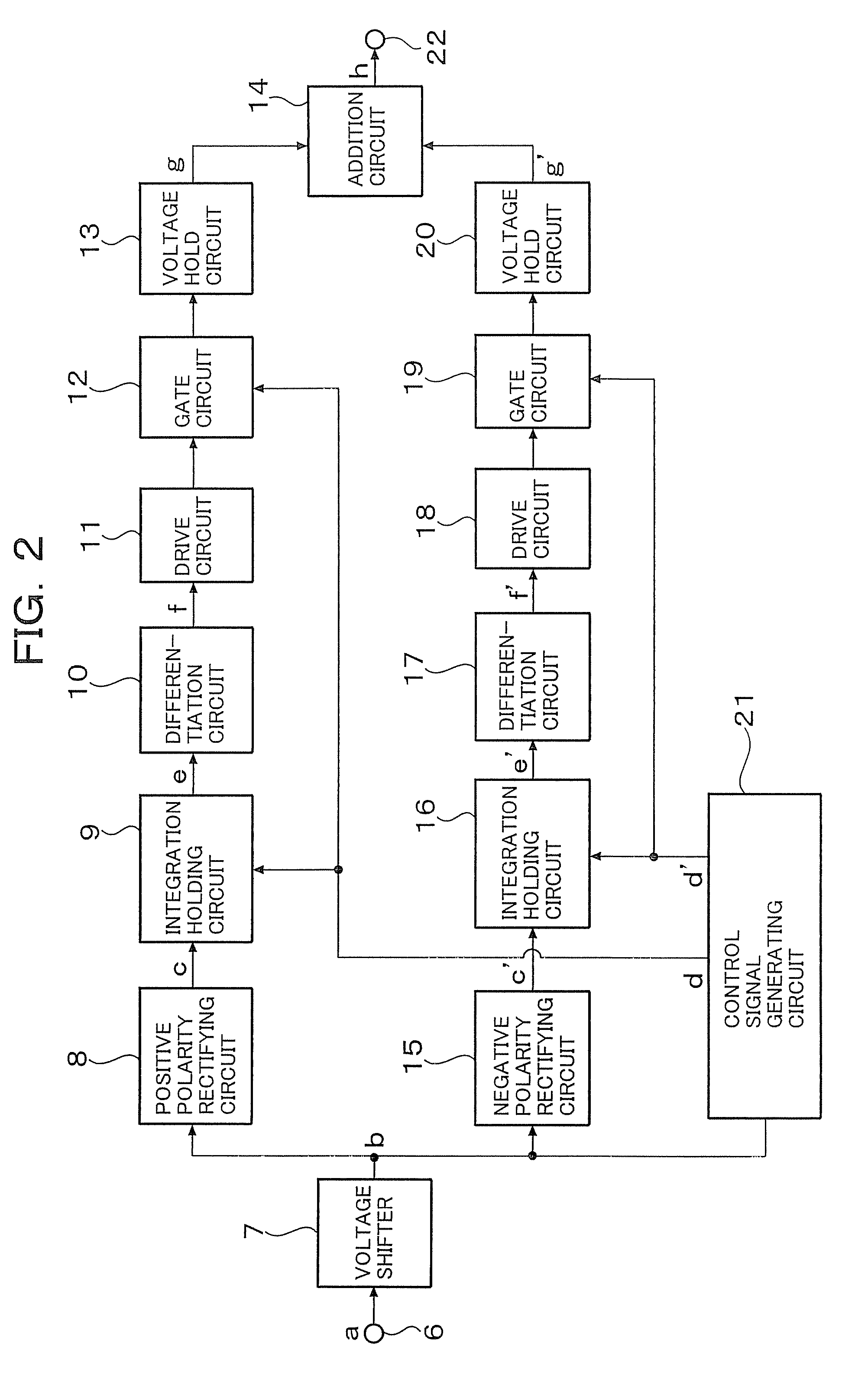

Phase comparison signal processing circuit

InactiveUS20080048742A1Improve response speedIncrease rangeDelay lines pulse generationPulse automatic controlBipolar signalSignal processing circuits

The present invention provides a phase comparison signal processing circuit which processes an output rectangular wave signal of a digital phase comparator of a PLL, expands a pullable-in frequency width of the PLL and shortens a synchronization time. The phase comparison signal processing circuit includes a first signal path which is parallel-connected between a voltage shifter for converting a rectangular wave signal to a bipolar signal and an output terminal and comprises a rectifying circuit, an integration holding circuit, a differentiation circuit, a gate circuit, a voltage hold circuit and a common addition circuit, a second signal path comprising a rectifying circuit, an integration holding circuit, a differentiation circuit, a gate circuit, a voltage hold circuit and the addition circuit, and a control signal generator for individually controlling the integration holding circuits and the gate circuits of the first and second signal paths. The rectification of the bipolar signal, integration and holding of rectified voltages, differentiation of integrated hold values, holding of differentiated outputs and addition of hold voltages are carried out at the first and second signal paths thereby to output a processed signal.

Owner:GEN RES OF ELECTRONICS INC

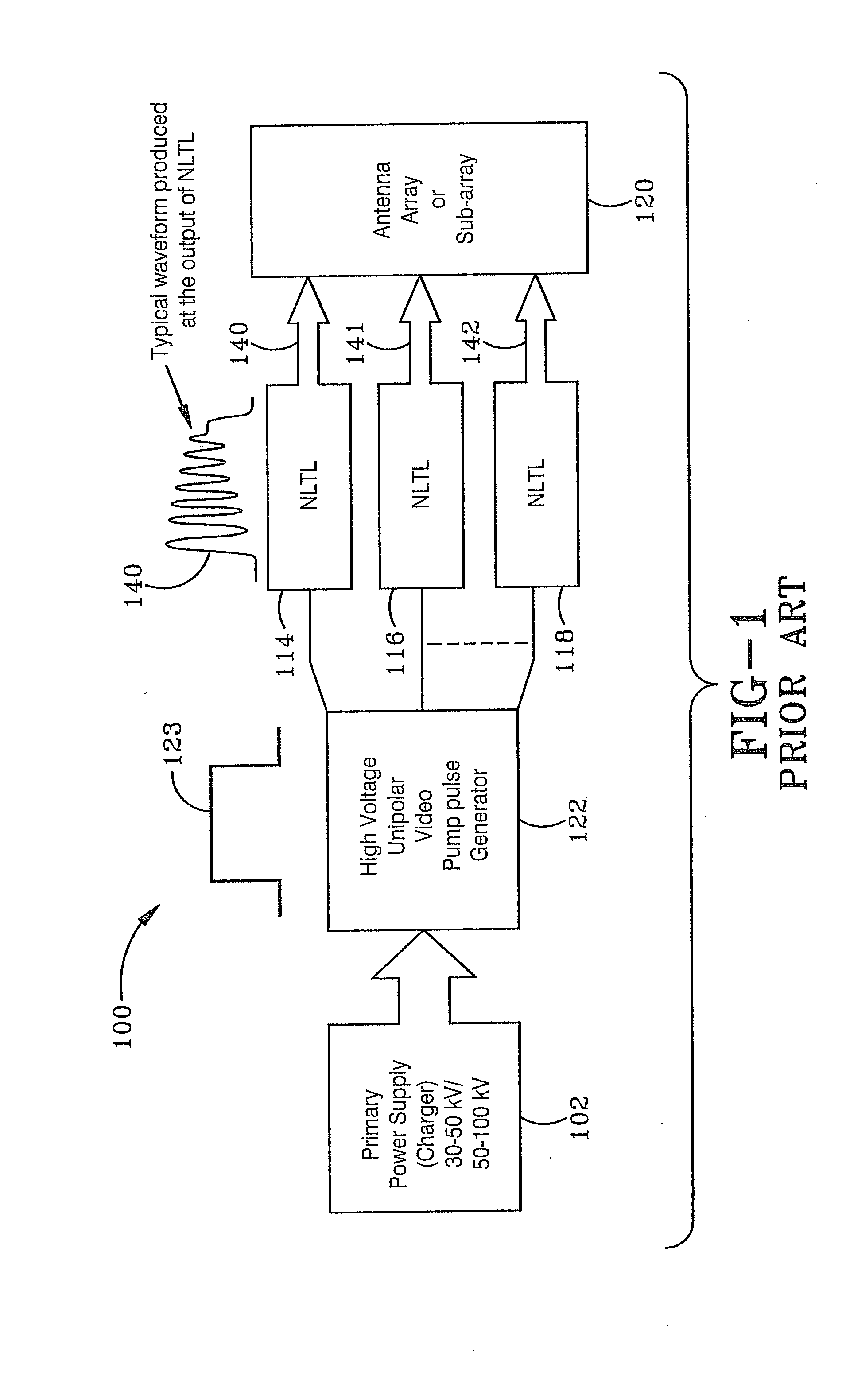

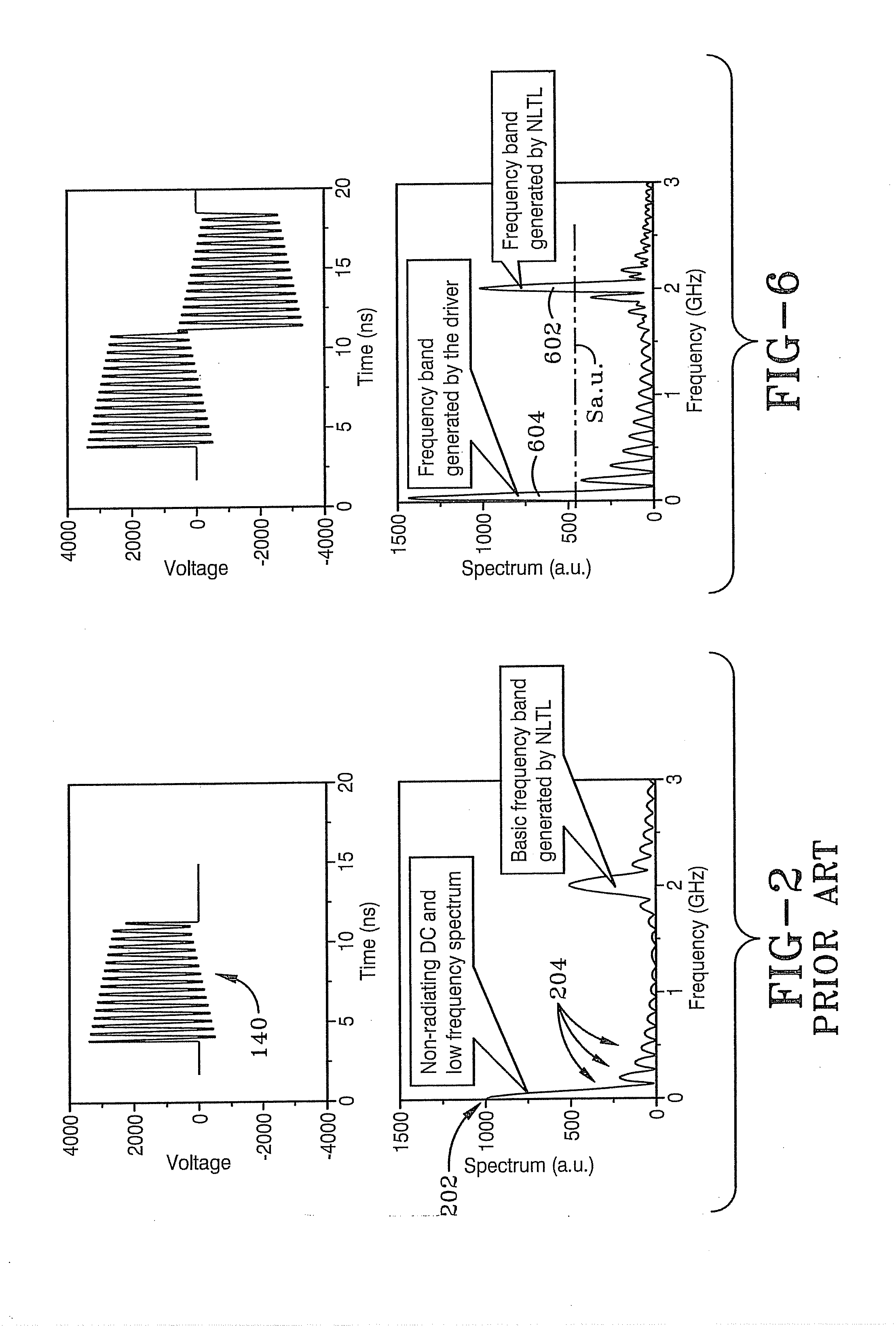

High power pulse generator

InactiveUS20110235742A1Improve system efficiencyIncreasing the output energy in short period of timeModulated-carrier systemsCommunication jammingFrequency spectrumBipolar signal

A systems, pulse generators, apparatus and methods for generating a high power signal are presented. A pulse generator includes a generator and a modulator unit. The generator generates a bipolar signal. The modulator unit modulates the bipolar signal with oscillating signals to generate a modulated bipolar signal with oscillating portions. The frequency spectrum of the modulated bipolar signal contains very little to no direct current (DC) component.

Owner:BAE SYST INFORMATION & ELECTRONICS SYST INTERGRATION INC

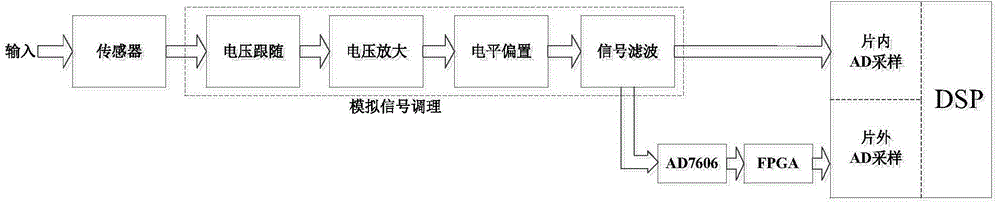

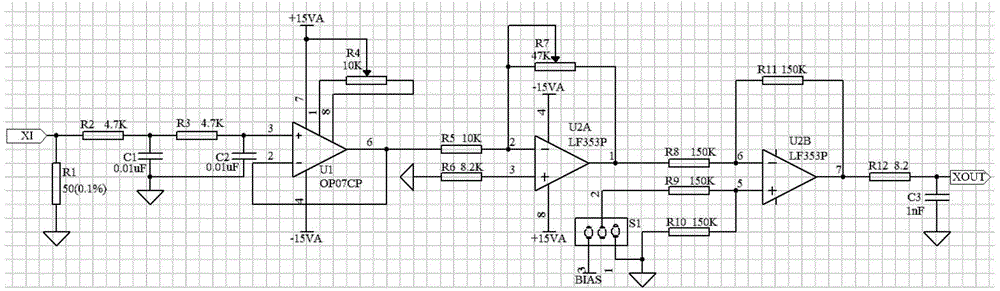

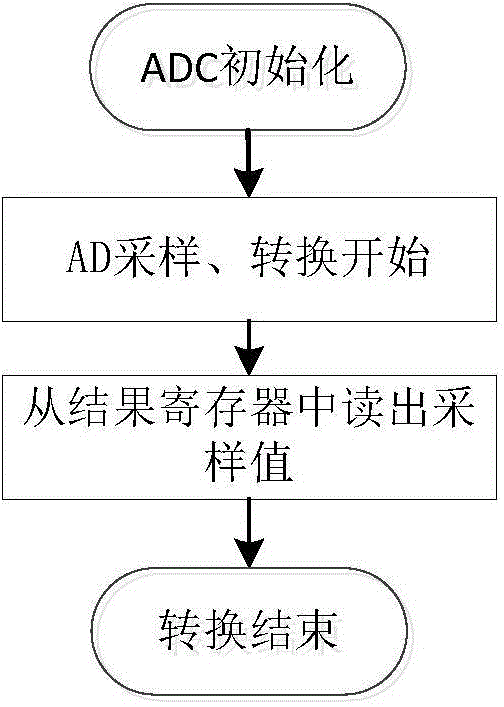

Sampling circuit compatible with unipolar and bipolar analog signals

InactiveCN104460462AIncrease off-chip samplingEasy to controlProgramme controlComputer controlBipolar signalElectric power system

The invention belongs to the technical field of signal collection and conditioning in power conversion and control systems of power systems, and relates to a sampling circuit compatible with unipolar and bipolar analog signals. The circuit comprises a signal collection circuit, an analog signal conditioning circuit, an external expansion AD unit, an external expansion FPGA unit and a DSP master control unit. A sensor transmits a collected signal to the analog signal conditioning circuit, the signal processed by the analog signal conditioning circuit is transmitted to an off-chip AD or an on-chip AD of a DSP, the off-chip AD is connected with a sampling pin distributed to the external expansion FPGA unit, and the external expansion FPGA unit is connected with the DSP master control unit in a bus mode, so that off-chip sampling data are read. The sampling circuit has the advantages that the circuit supports multi-channel input and is simple in structure and high in functionality; the sampling unit has the function of being compatible with unipolar and bipolar signal conditioning, and has the good compatibility, flexibility, selectivity, adaptability and high precision.

Owner:NORTH CHINA ELECTRIC POWER UNIV (BAODING)

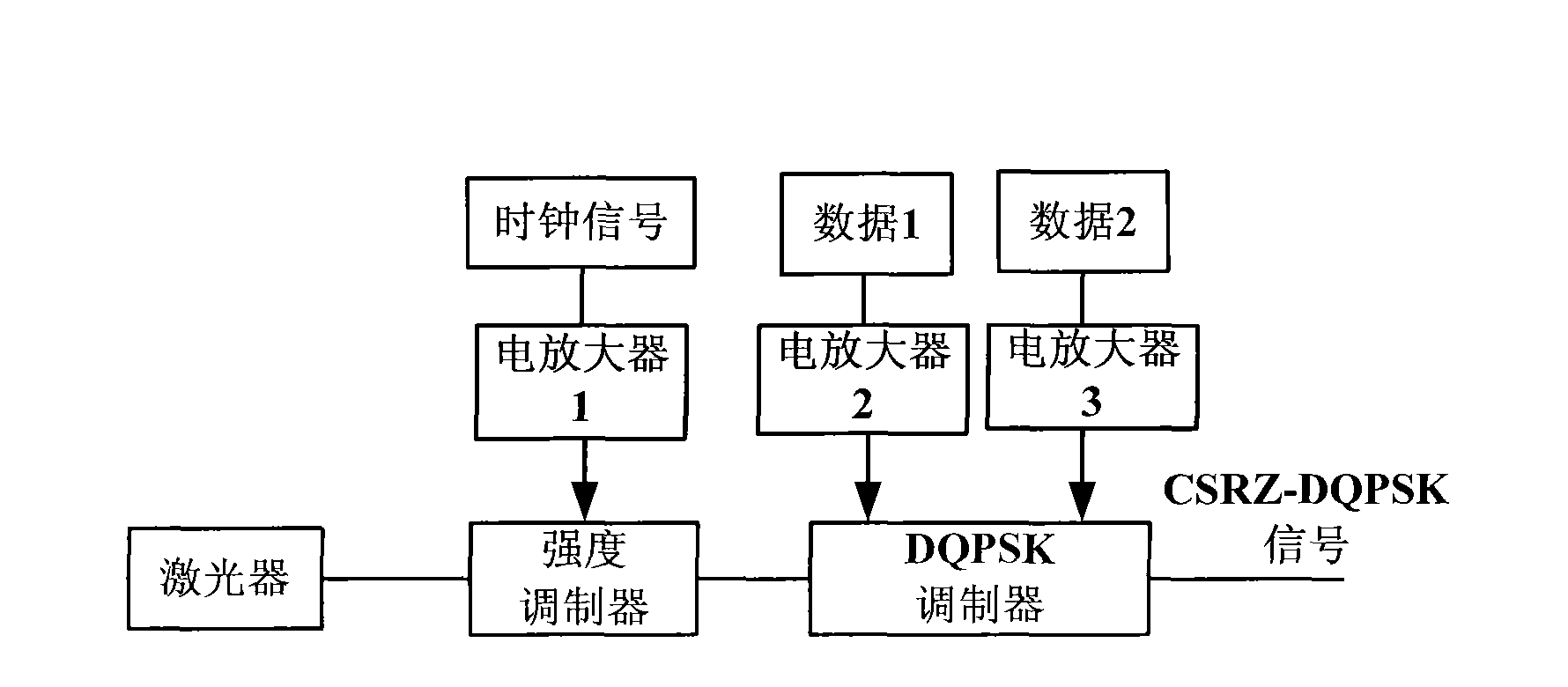

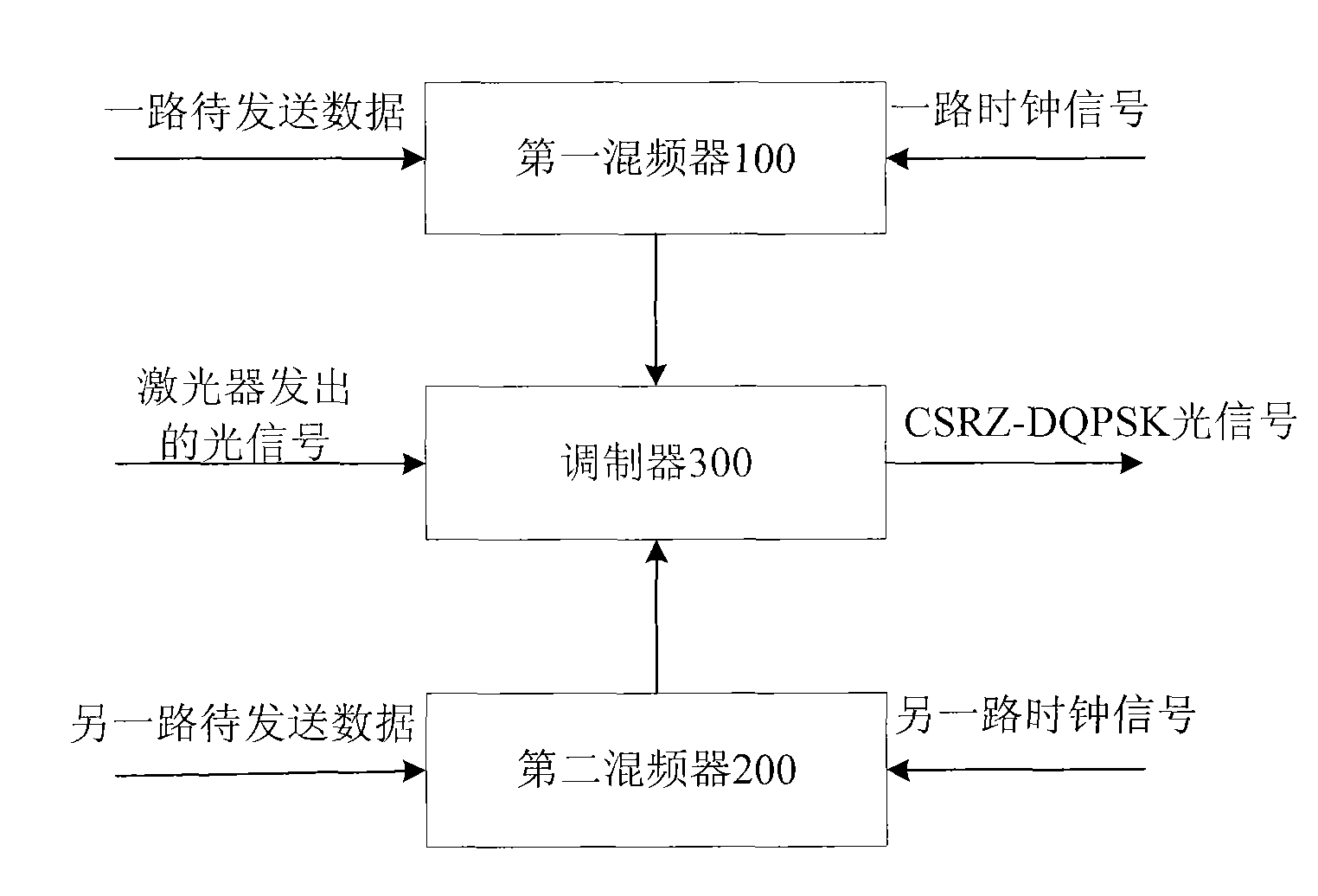

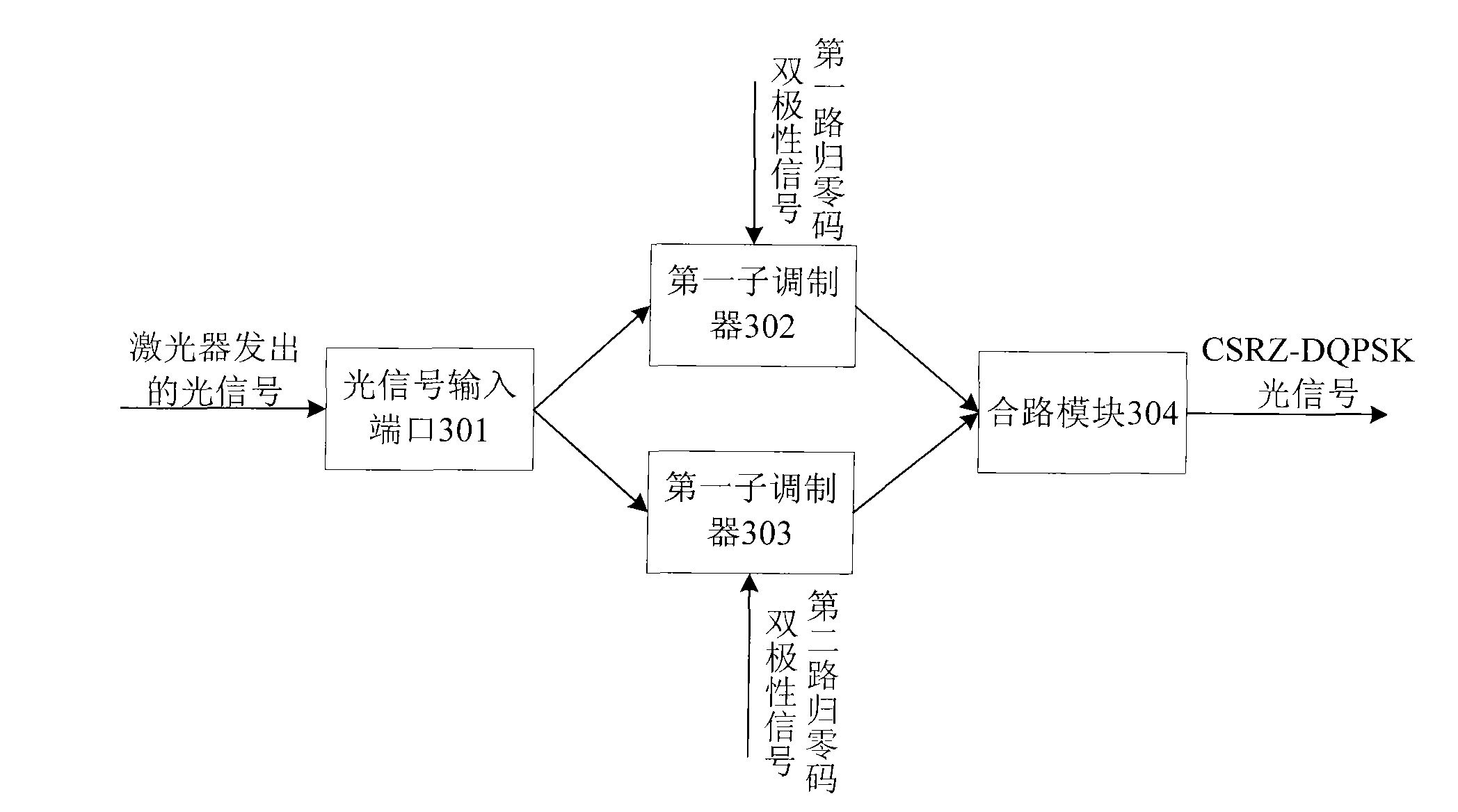

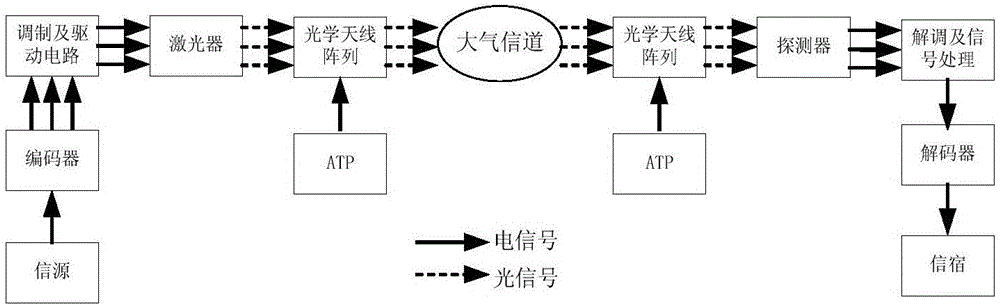

Optical transmitter and optical signal generating method

The invention discloses an optical transmitter and an optical signal generating method, which belong to the field of optical communication. The optical transmitter comprises a first frequency mixer, a second frequency mixer and a modulator; or the optical transmitter comprises a frequency mixer and the modulator. The method comprises the following steps: dividing the data to be transmitted into two paths which are mixed with two paths of clock signals respectively to generate two paths of return-to-zero bipolar signals; and respectively modulating the bipolar signals to generate a CSRZ-DQPSK optical signal. Or the method comprises the following steps: receiving the data to be transmitted and a sine clock signal, adjusting the phase of the sine clock signal to synchronize the phase of the sine clock signal and the data to be transmitted, and carrying out the frequency mixing to generate a Manchester code; and modulating the Manchester code to the optical signal to generate a Manchester optical signal. The method carries out the frequency mixing of the data to be transmitted and the clock signal and drives the modulator through the signal after frequency mixing to generate the CSRZ-DQPSK optical signal or the Manchester optical signal, thereby reducing the cost of the optical transmitter.

Owner:HUAWEI TECH CO LTD +1

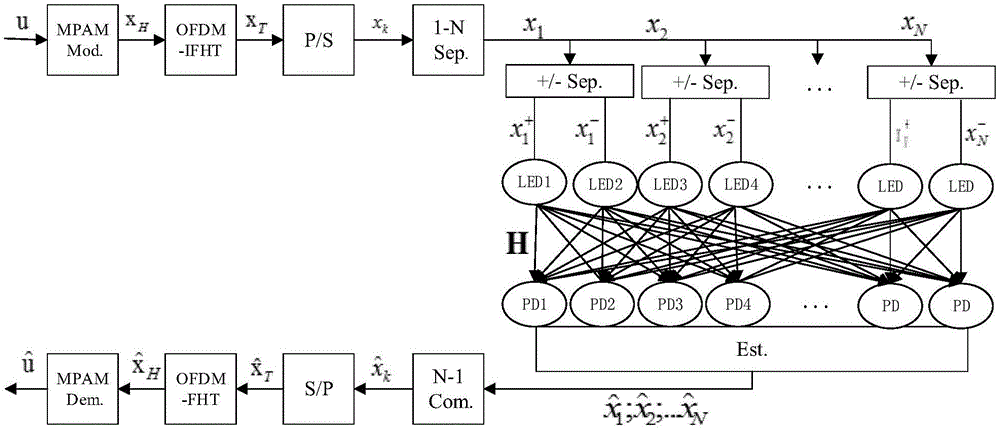

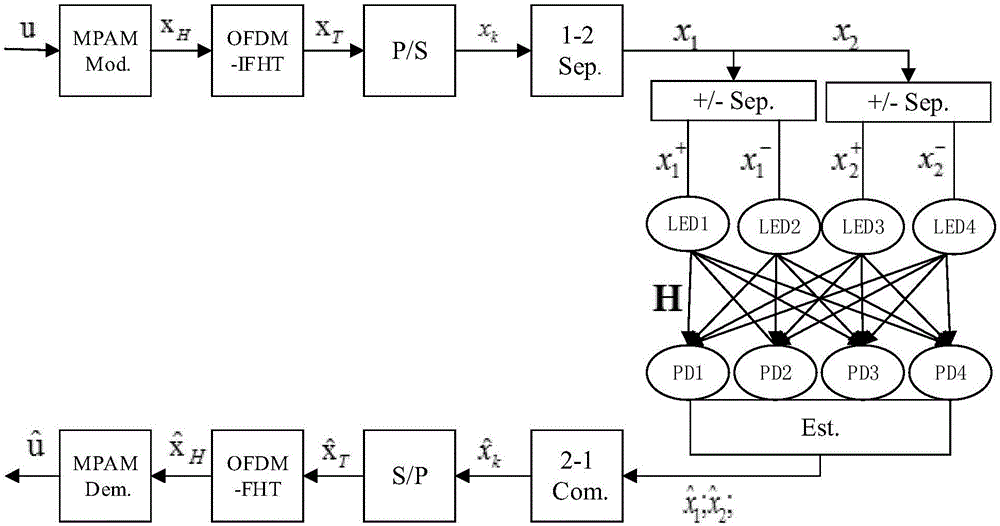

Hartley transform-based visible light communication space modulation method and implementation system therefor

ActiveCN106375004ASolve the problem that it cannot be directly used for visible light signal transmissionIncreased frequency efficiencyClose-range type systemsMulti-frequency code systemsBipolar signalDiscrete Hartley transform

The invention relates to a Hartley transform-based visible light communication space modulation method and an implementation system therefor. In the Hartley transform-based visible light communication space modulation method and the implementation system therefor, discrete Hartley transform is adopted for replacing discrete Fourier transform in OFDM; a real number output signal is obtained while that an IDHT input signal is real number is ensured; an output signal is still bipolar at this time, space modulation is introduced, a positive value real number signal is added on one lamp while an inverse value of a negative value real number signal is added on another lamp; while no Hermitian matrix is used and no direct current bias needs to be added, a problem that complex number bipolar signals cannot be directly applied to visible light signal transmission can be solved.

Owner:SHANDONG UNIV

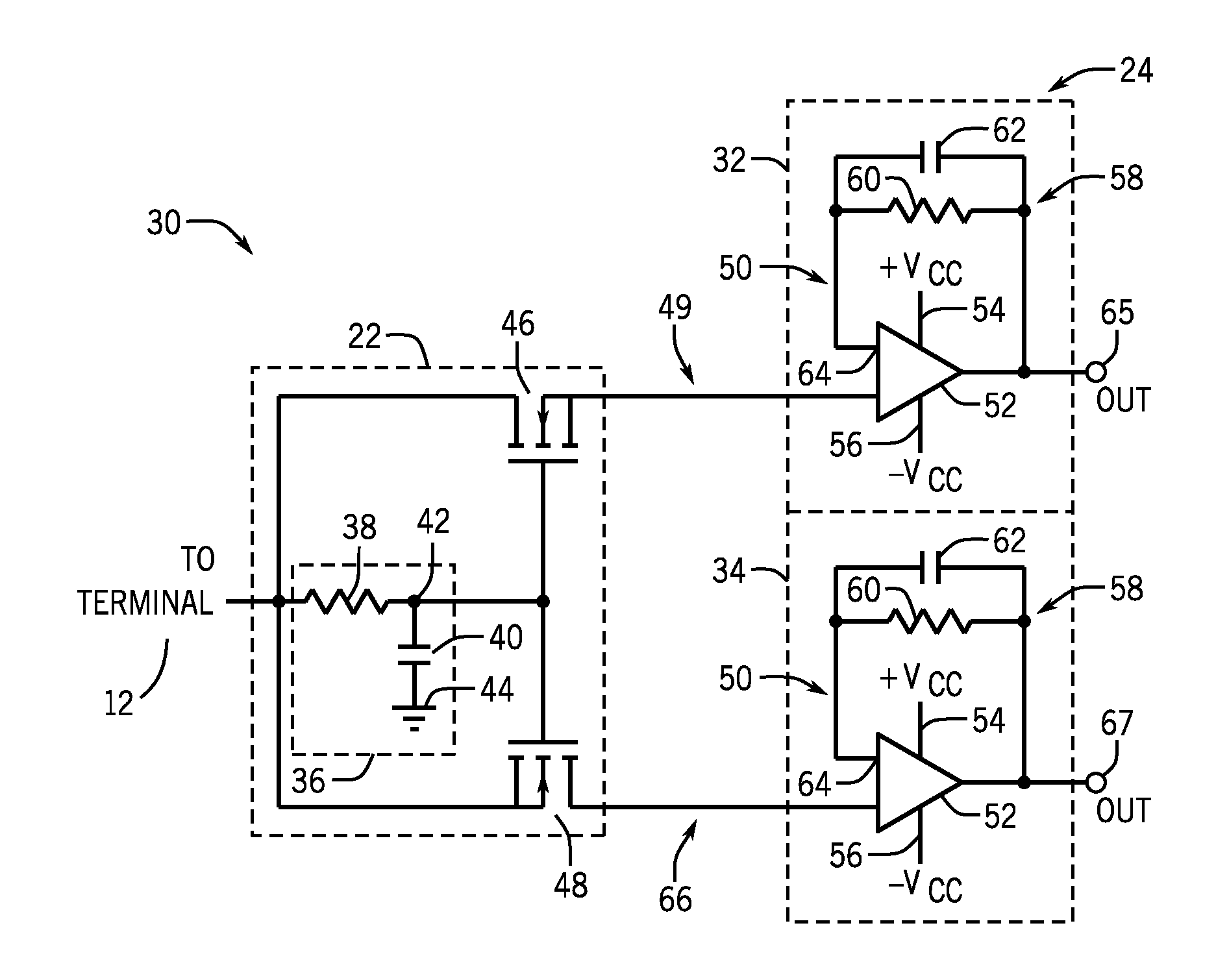

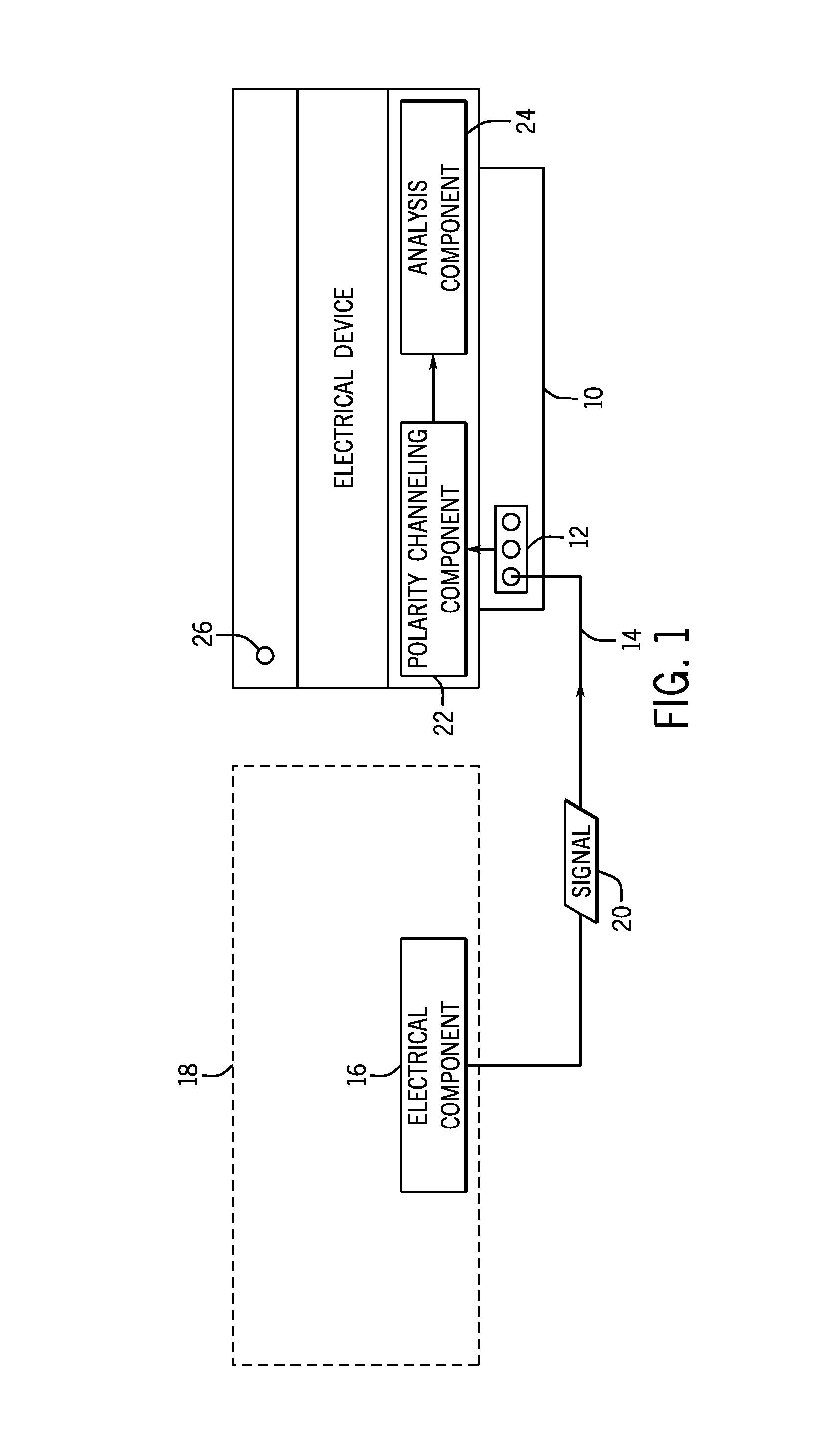

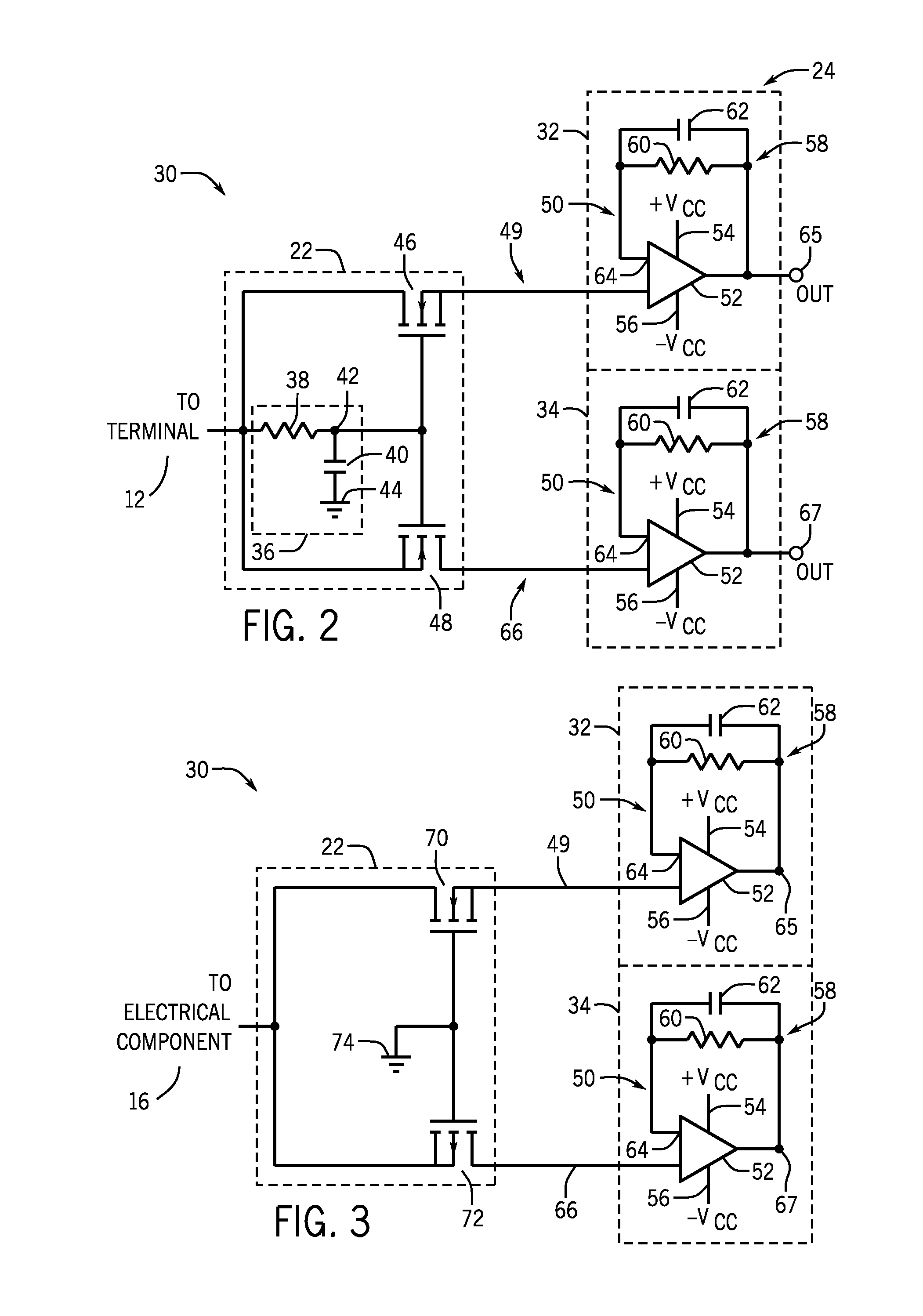

Automatic bipolar signal switching

ActiveUS8963615B1Electronic switchingAltering/correcting law of variationSignal routingBipolar signal

A system is provided that includes an input node configured to receive a signal indicative of sensor data. The system also includes a first transistor configured to route the signal to a positive channel when a polarity of the signal is positive. Moreover, the system includes a second transistor configured to route the signal to a negative channel when a polarity of the signal is negative. Additionally, the system includes the positive channel coupled to the first transistor configured to route the signal to an analysis component. Furthermore, the system includes the negative channel coupled to the second transistor and configured to route the signal to the analysis component.

Owner:BAKER HUGHES INC

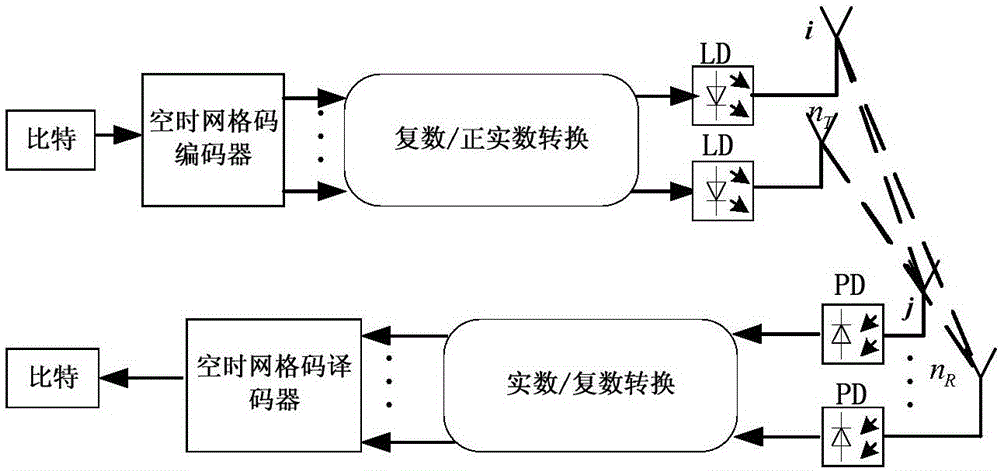

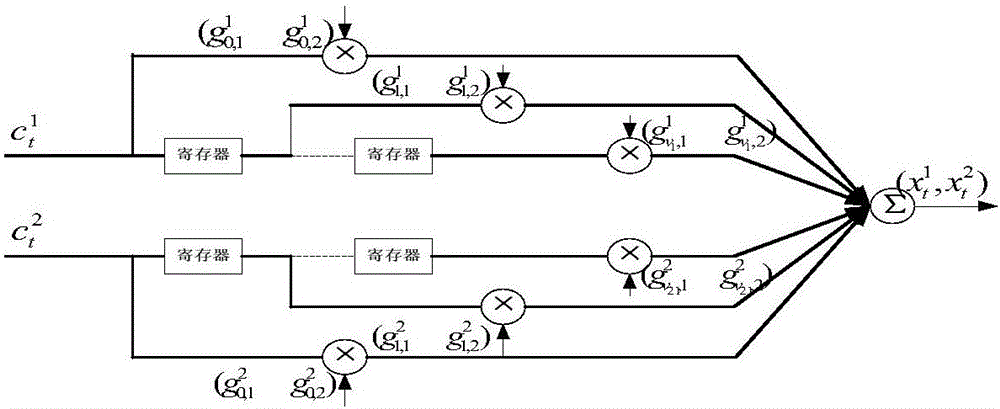

Light-space-time trellis code encoding method suitable for intensity modulation/direction detection

InactiveCN106357343AIncrease transfer rateAgainst turbulence effectsElectromagnetic transmittersFast Fourier transformPhotovoltaic detectors

The invention discloses alight-space-time trellis code encoding method suitable for intensity modulation / direction detection. The method comprises the following steps: I, encoding a binary bit stream to generate a QAM / PSK signal; II, implementing serial-to-parallel conversion on the output encoded signal; III, performing vector mapping on a signal output by a serial-to-parallel convertor, so that the mapped signal meets Hermitian symmetry; IV, performing fast Fourier transform of 2N points on the mapped signal, and adding a direct-current component; V, eliminating a negative signal; VI, converting a received optical signal into an electric signal by a photoelectric detector at a receiving end, and removing the direct-current component; VII, performing analog / digital conversion and 2N-point series-to-parallel conversion to obtain a parallel bipolar signal, and converting the parallel bipolar signal into a plural / negative signal through the fast Fourier transform; VIII, feeding an inversely-mapped signal into a space-time trellis code decoder through inverse mapping and parallel-to-series conversion to finish decoding.

Owner:LANZHOU UNIVERSITY OF TECHNOLOGY

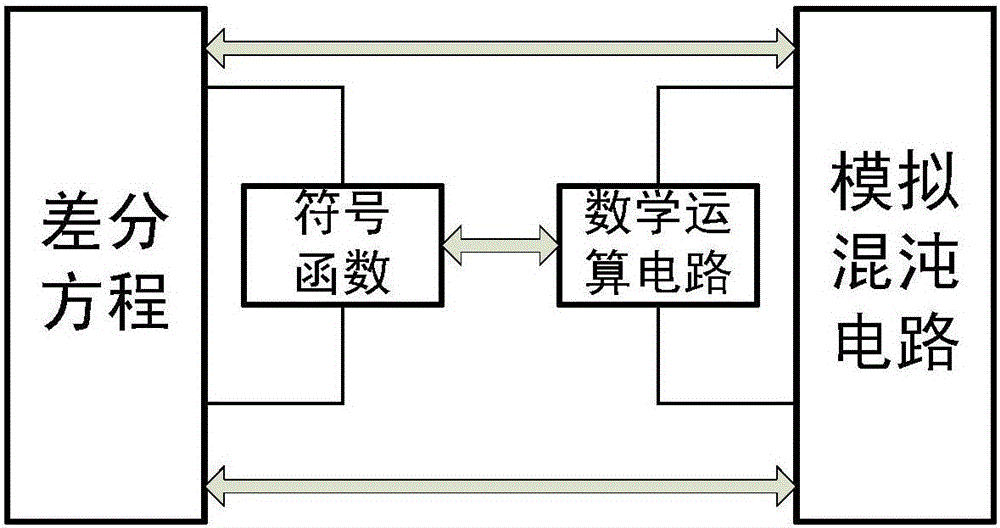

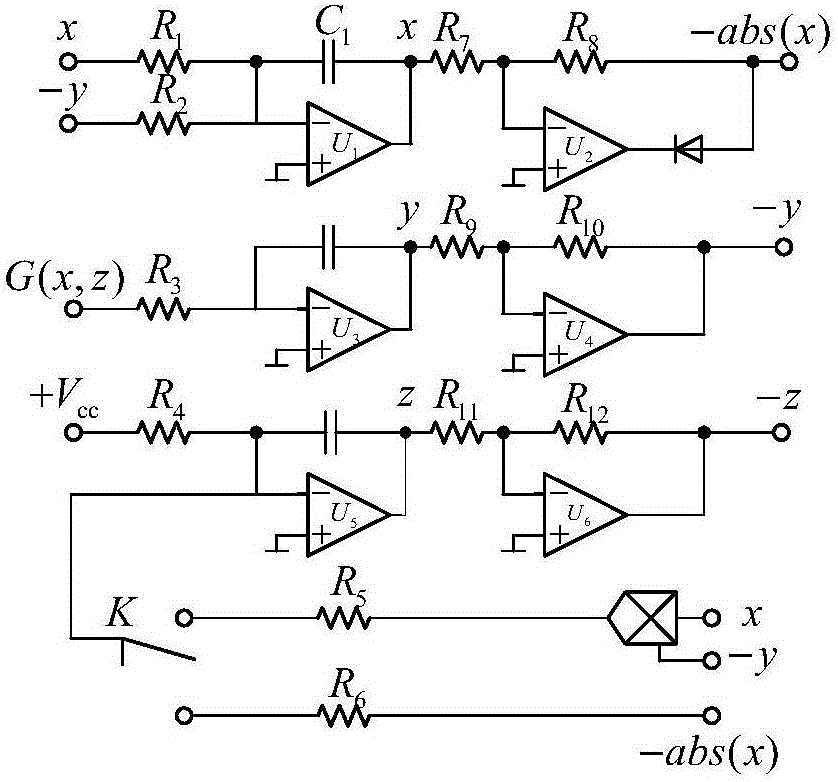

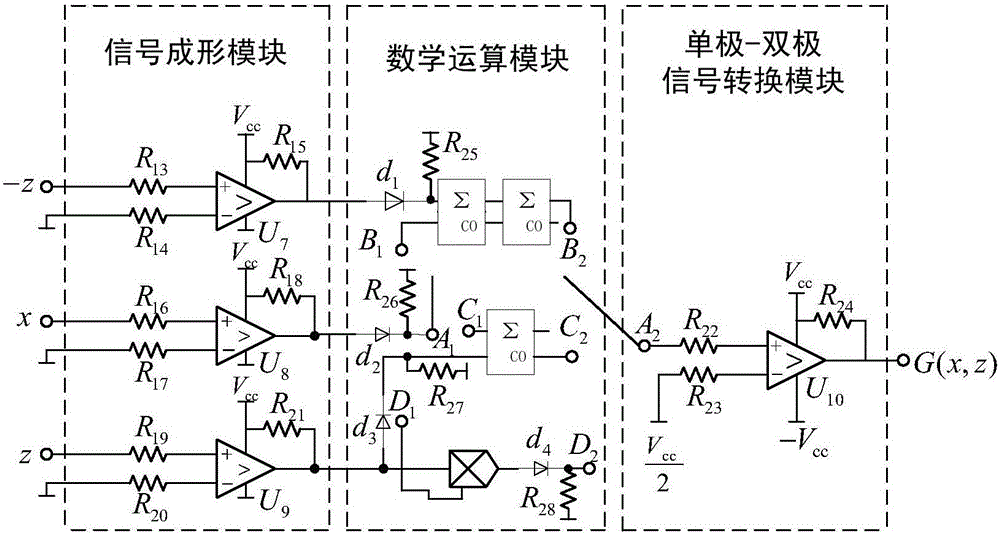

Digital-analog hybrid chaotic circuit containing mathematical operation circuit and operation method thereof

InactiveCN105790922AImprove utilization efficiencyLow costSecuring communication by chaotic signalsComplex mathematical operationsBipolar signalEngineering

The invention discloses a digital-analog hybrid chaotic circuit containing a mathematical operation circuit and an operation method thereof. According to the digital-analog hybrid chaotic circuit disclosed by the invention, the chaotic circuit composed of a difference equation and a symbolic function is realized in such a manner that the difference equation is realized by an analog circuit and the symbolic function is realized by the mathematical operation circuit. The analog circuit is composed of a resistor, a capacitor, an operational amplifier and other conventional analog devices. A digital circuit is composed of a signal forming module, a mathematical operation module and a unipolar-bipolar signal conversion module, wherein the mathematical operation module is composed of an adder, a multiplier and other conventional digital circuits. According to the digital-analog hybrid chaotic circuit disclosed by the invention, the digital devices are embedded in the traditional analog chaotic circuit to complete symbolic computation, and different chaotic systems can be realized by switching different mathematical operation modules in the same circuit, so the precision is very high, and the universality and the adaptability are relatively strong.

Owner:NANJING UNIV OF SCI & TECH