Patents

Literature

247results about "Pulse descrimination" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

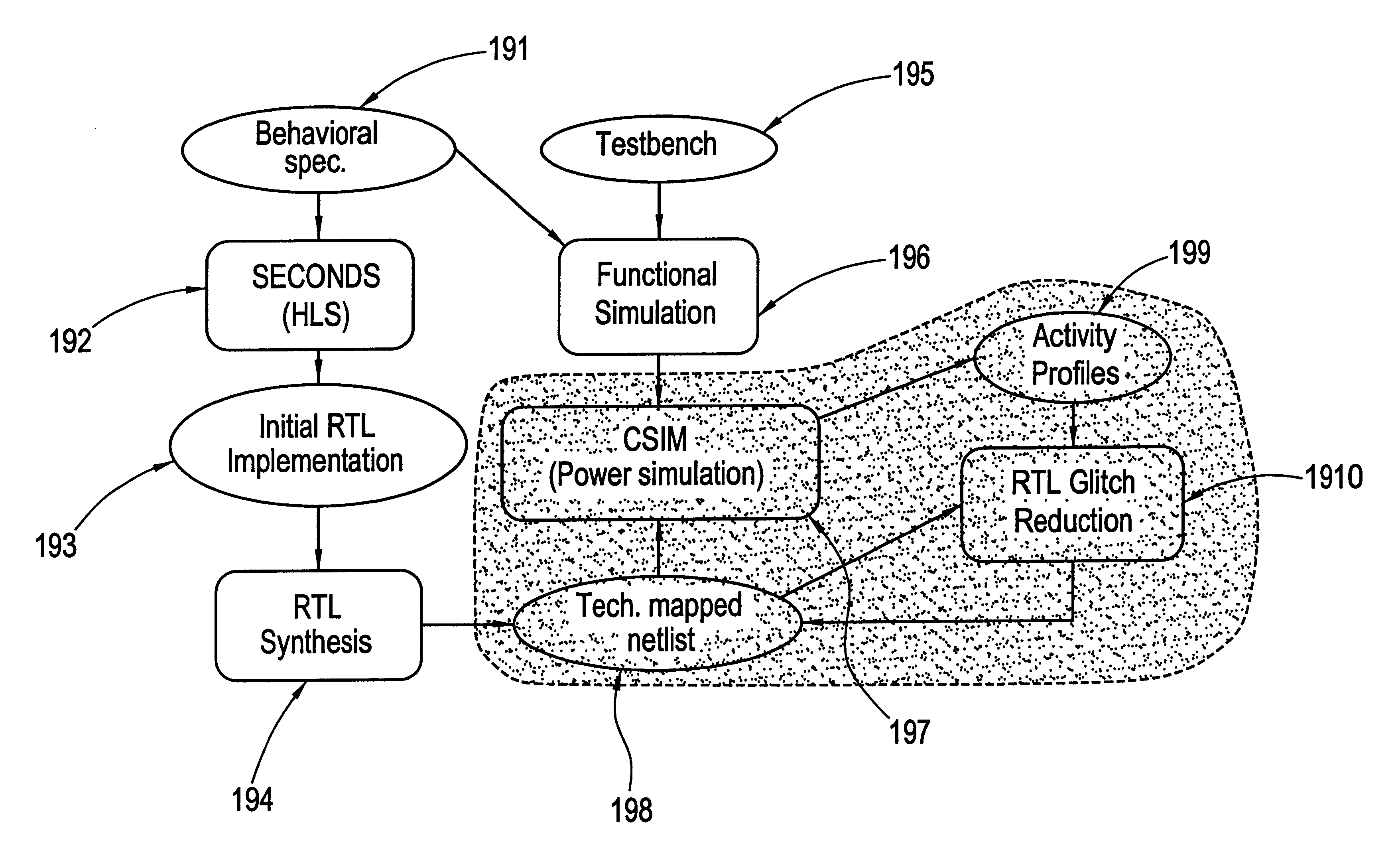

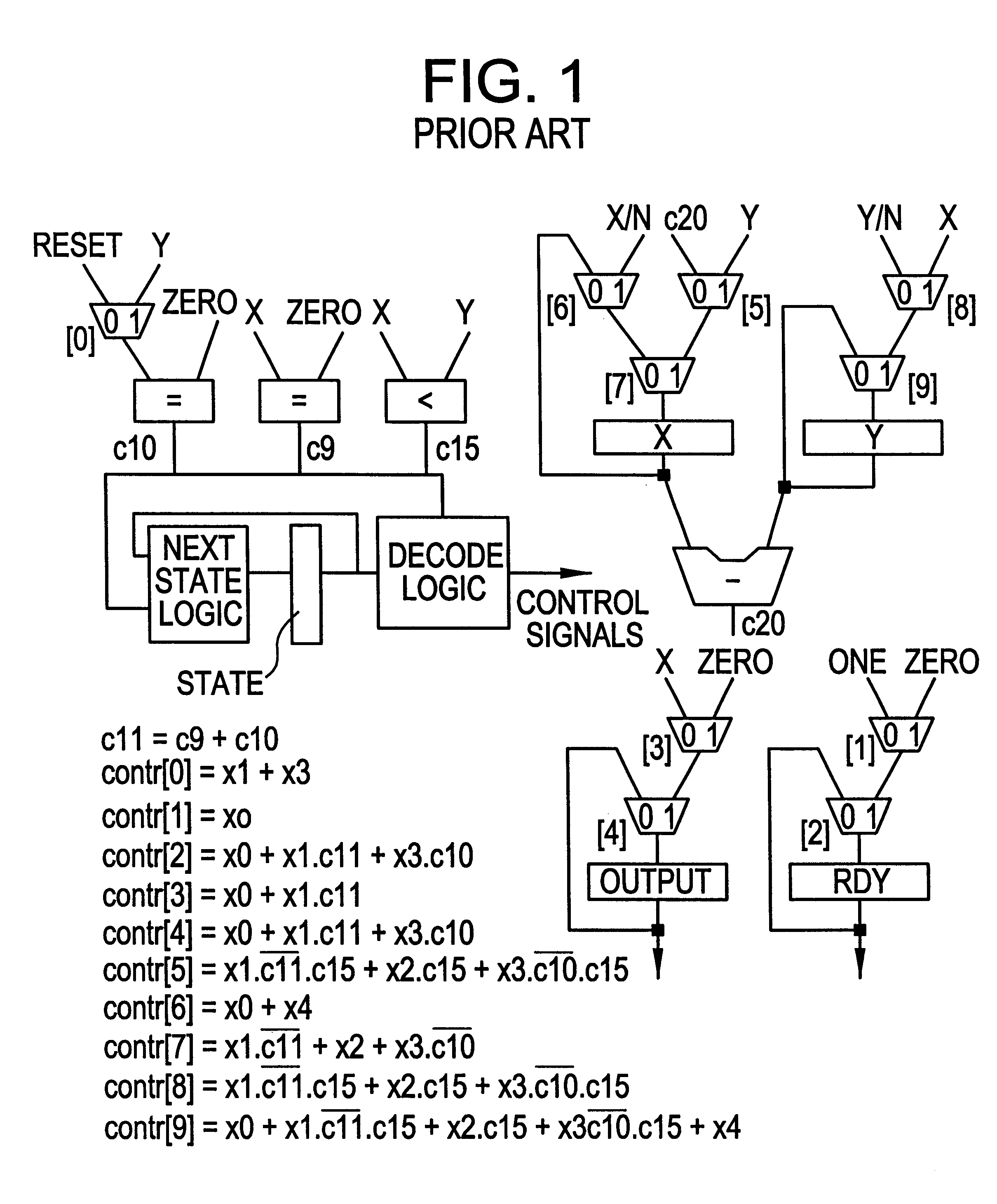

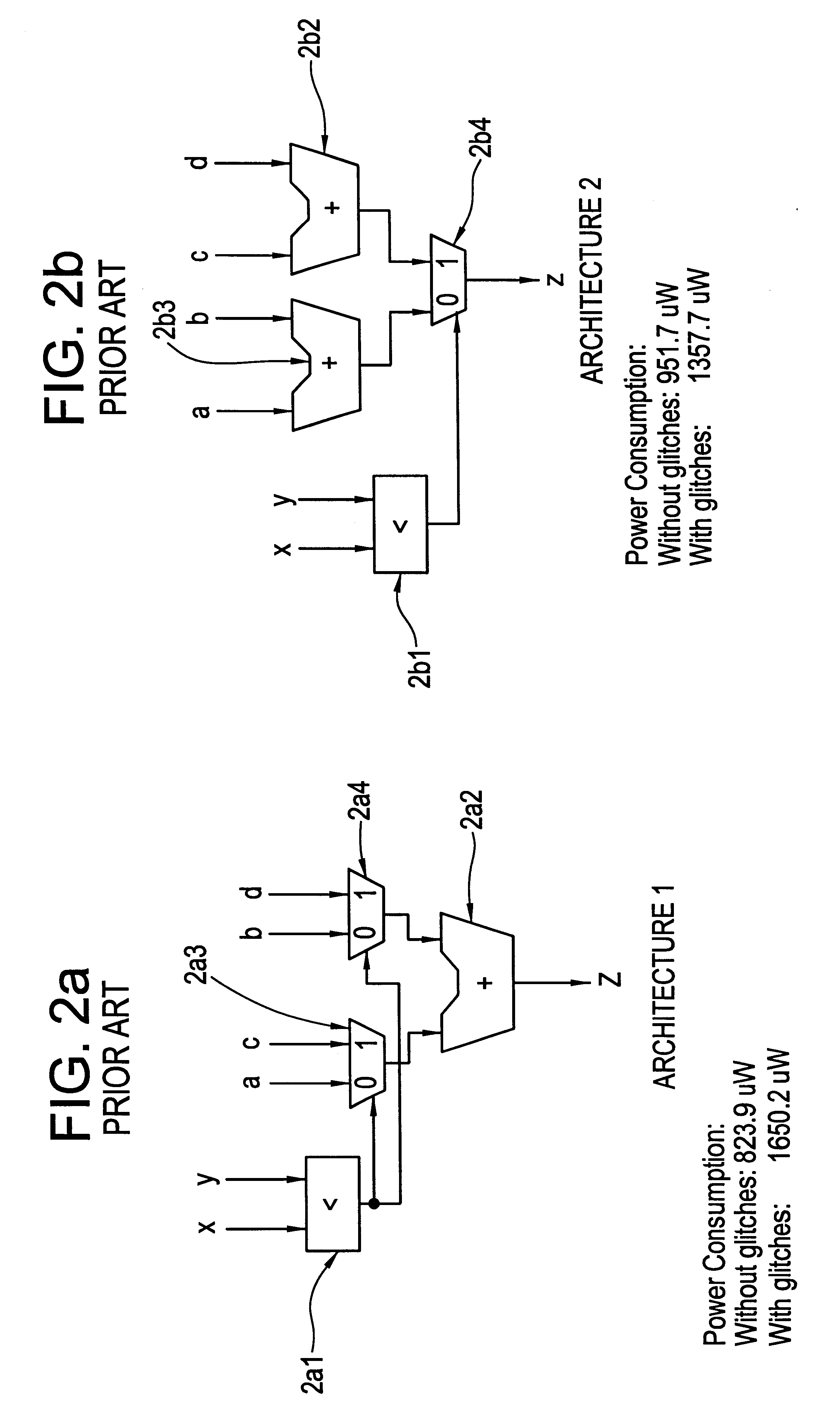

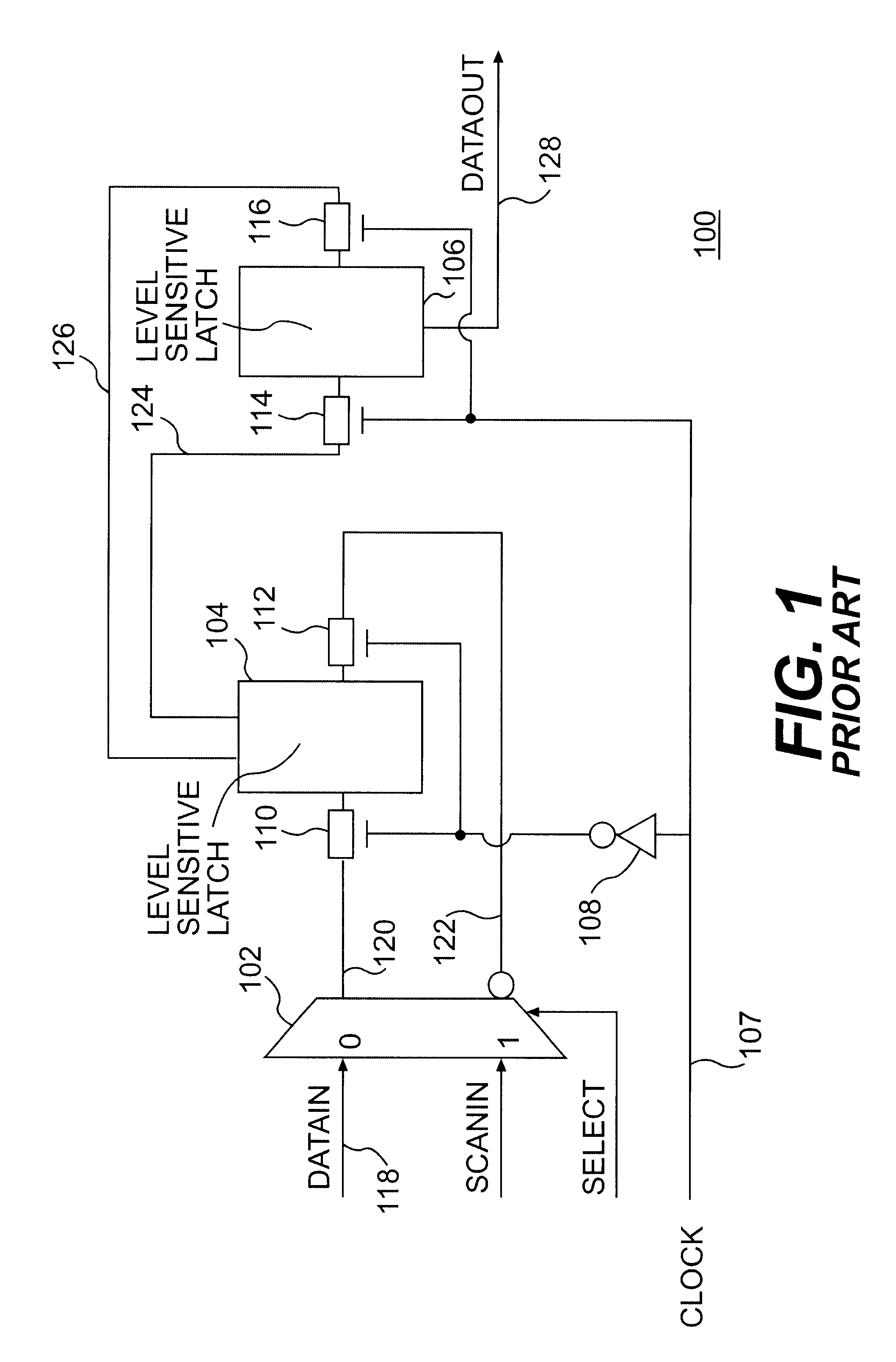

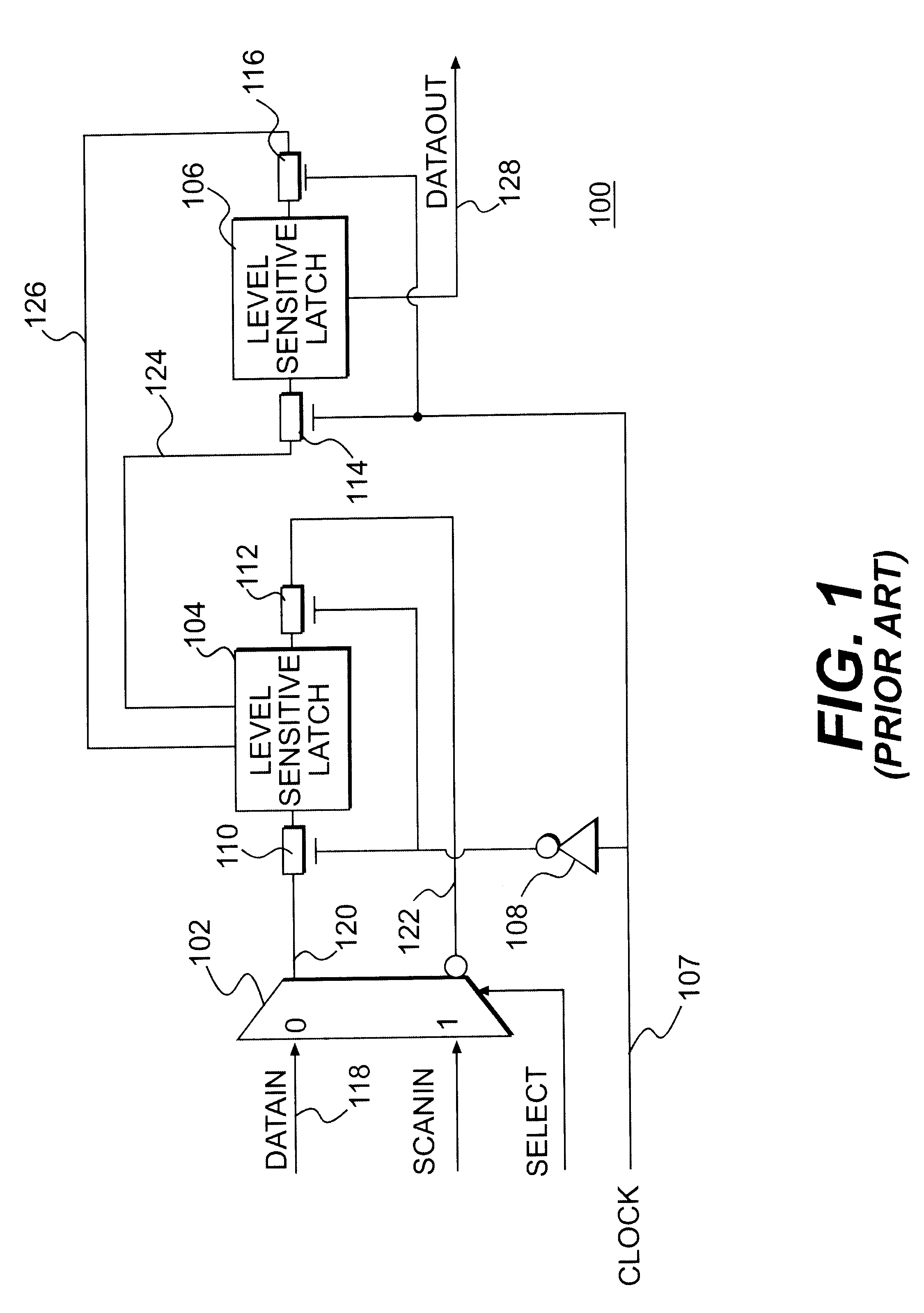

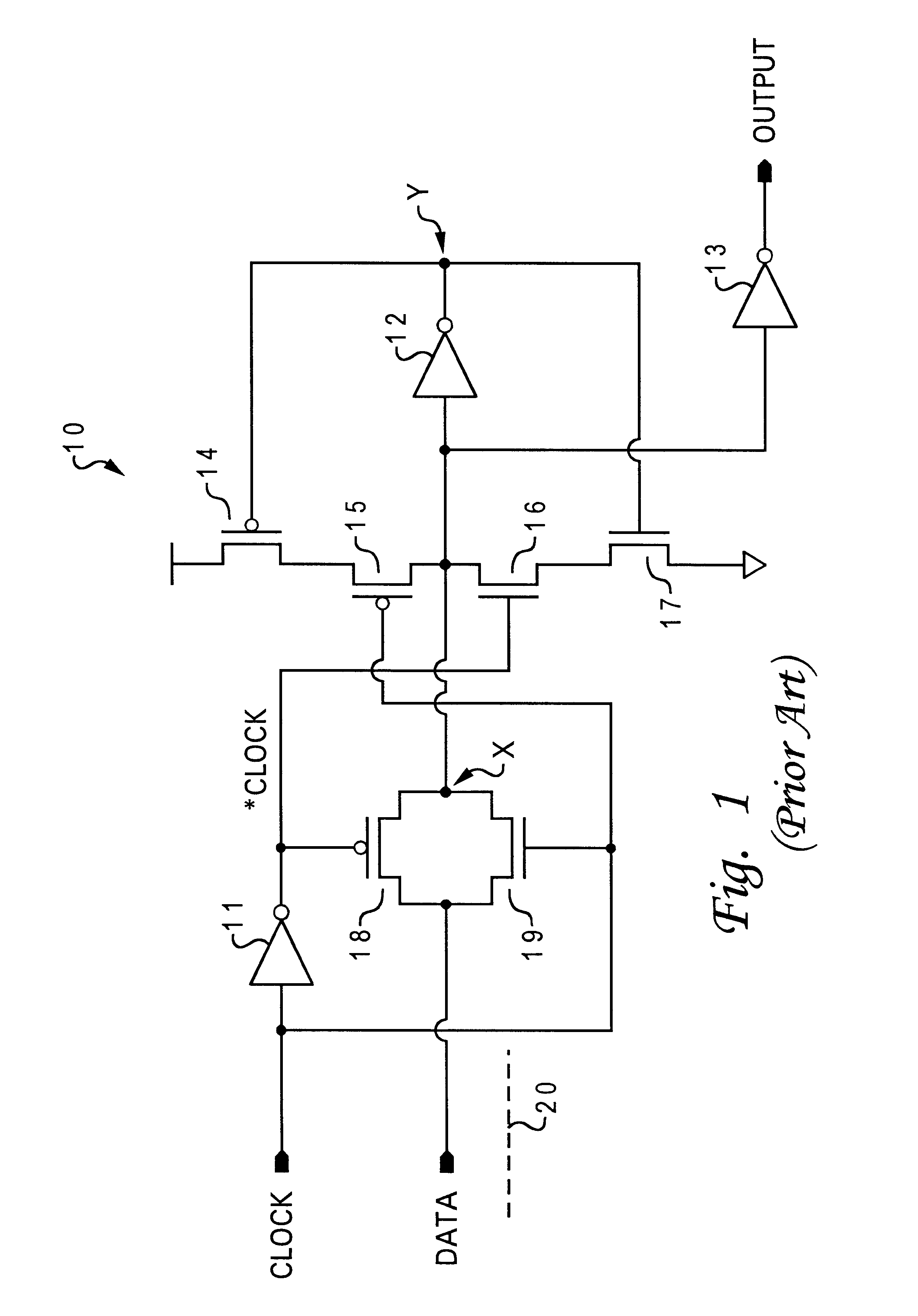

Register transfer level power optimization with emphasis on glitch analysis and reduction

InactiveUS6324679B1Reduce power consumptionLogic circuits characterised by logic functionDigital data processing detailsDatapath circuitsPathPing

A method and apparatus for design-for-low-power of register transfer level (RTL) controller / data path circuits that implement control-flow intensive specifications. The method of the invention focuses on multiplexer networks and registers which dominate the total circuit power consumption and reduces generation and propagation of glitches in both the control and data path parts of the circuit. Further the method reduces glitching power consumption by minimizing propagation of glitches in the RTL circuit through restructuring multiplexer networks (to enhance data correlations and eliminate glitchy control signals), clocking control signals, and inserting selective rising / falling delays, in order to kill the propagation of glitches from control as well as data signals. To reduce power consumption in registers, the clock inputs to registers are gated with conditions derived by an analysis of the RTL circuit, ensuring that glitches are not introduced on the clock signals.

Owner:NEC CORP

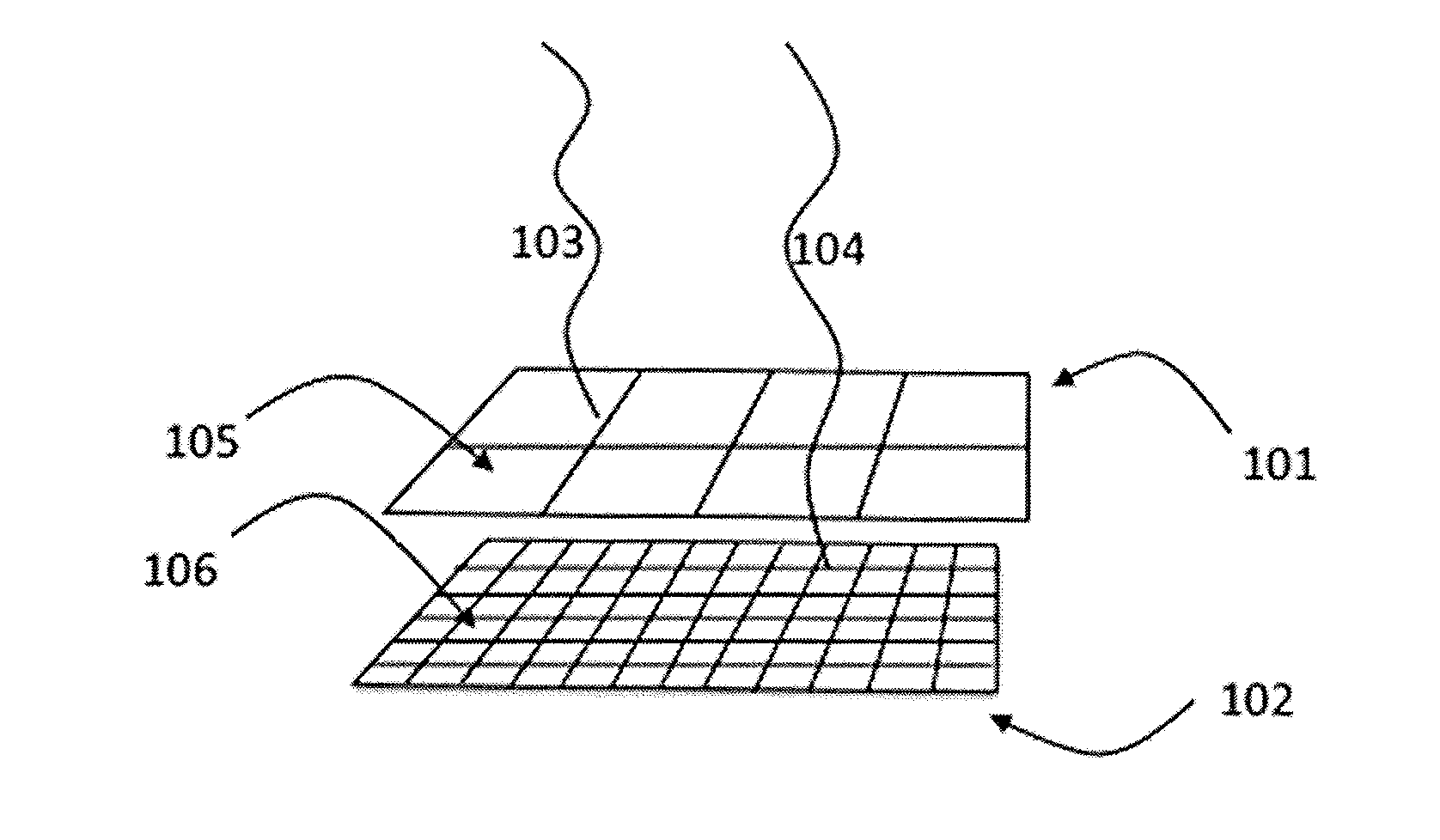

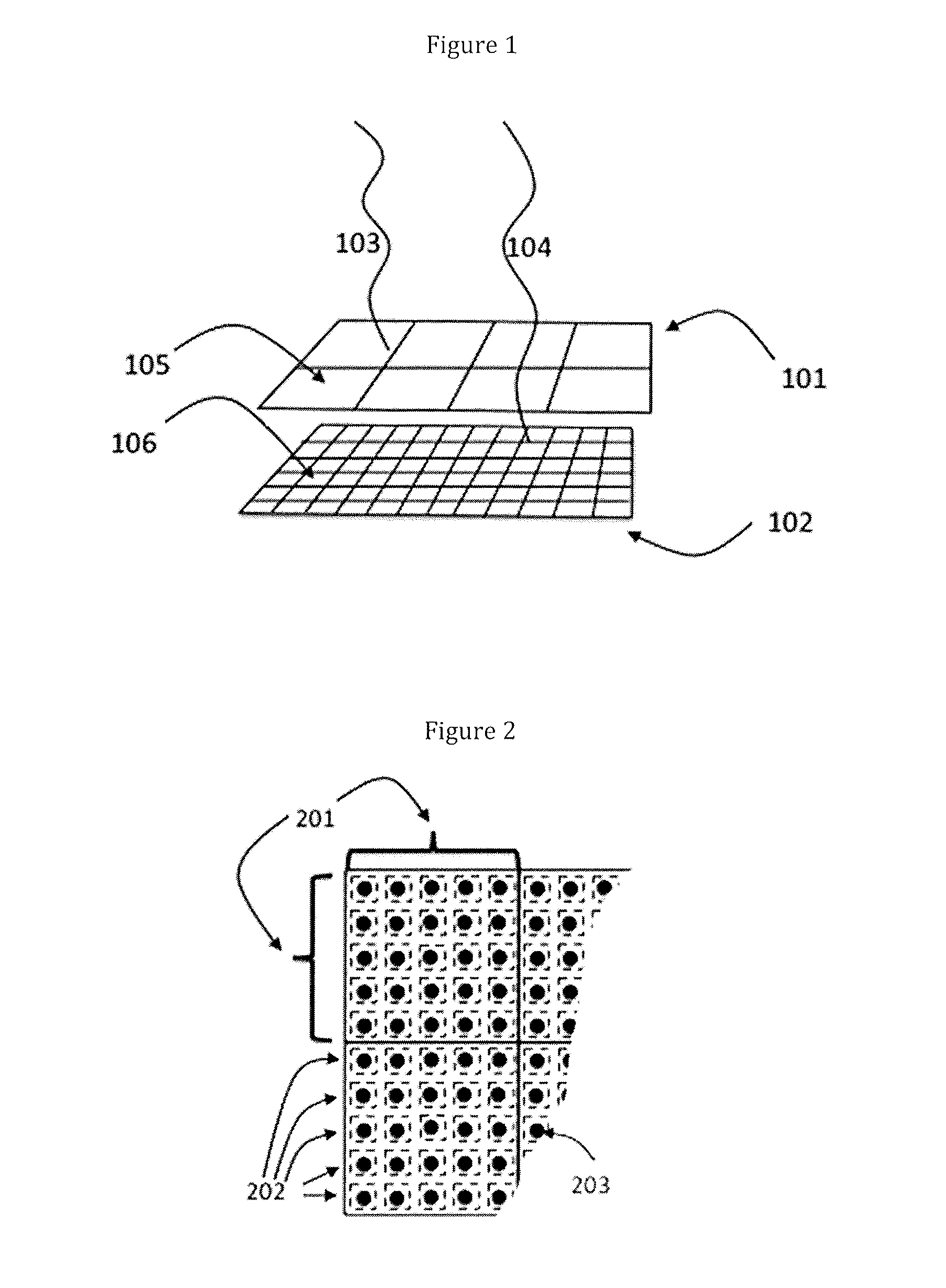

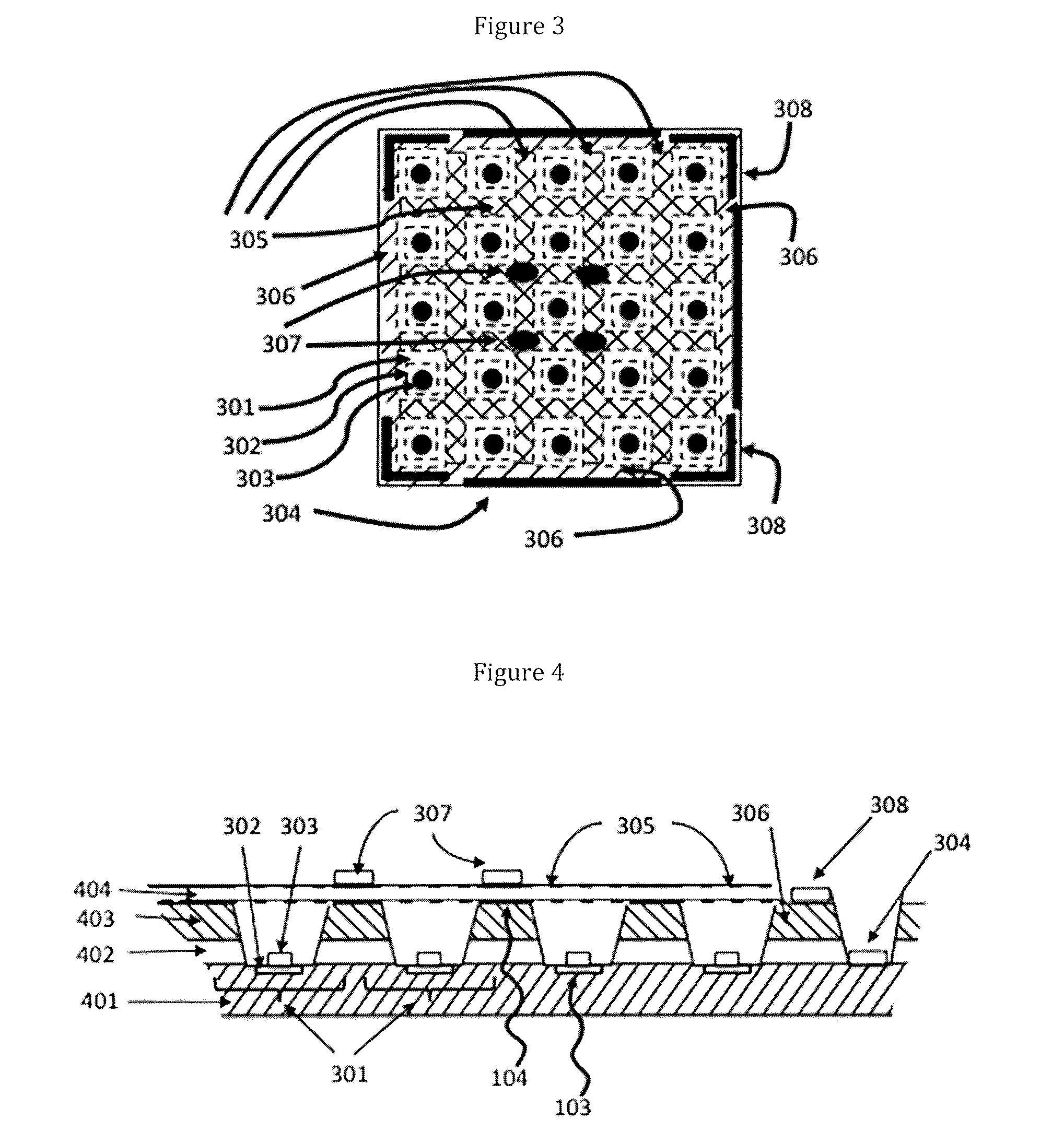

Dual Pixel Pitch Imaging Array with Extended Dynamic Range

InactiveUS20130076910A1Improve dynamic rangeImproved clutter suppression performanceTelevision system detailsColor television detailsImaging processingField of view

An integrated focal plane provides two co-aligned, overlapping pixel arrays in two formats, one with large pixels and low pixel count, the other with small pixels and high pixel count. Typically, the large pixels are 10 to 100 times larger in area than the small pixels. The dual arrays are disposed in a single detector substrate flip-chip bonded to a single readout circuit. They are sensitive to two infrared colors, one shorter and one longer wavelength band. The dual array focal plane concurrently provides two distinct pixel instantaneous fields of view within the same overall field of view as well as simultaneous fast and slow frame rates. The dual frame rates allow for combined fast sensing with sensitive imaging. Differing spatial and temporal data enables enhanced image processing for improved clutter rejection and detection performance. Differing gains combined with the dual frame rates provide an extended dynamic range.

Owner:SCOTT BASIL HENRY +2

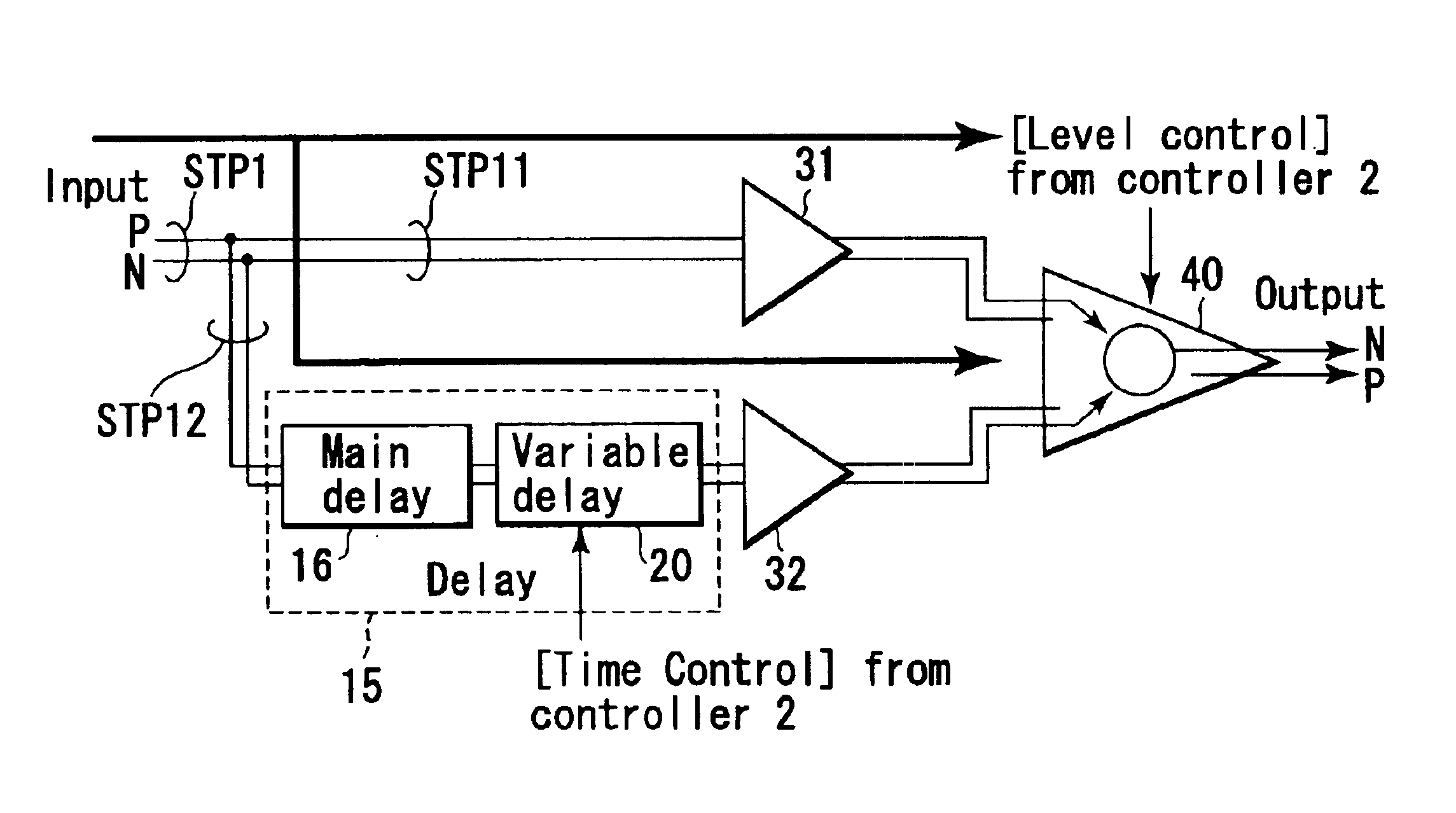

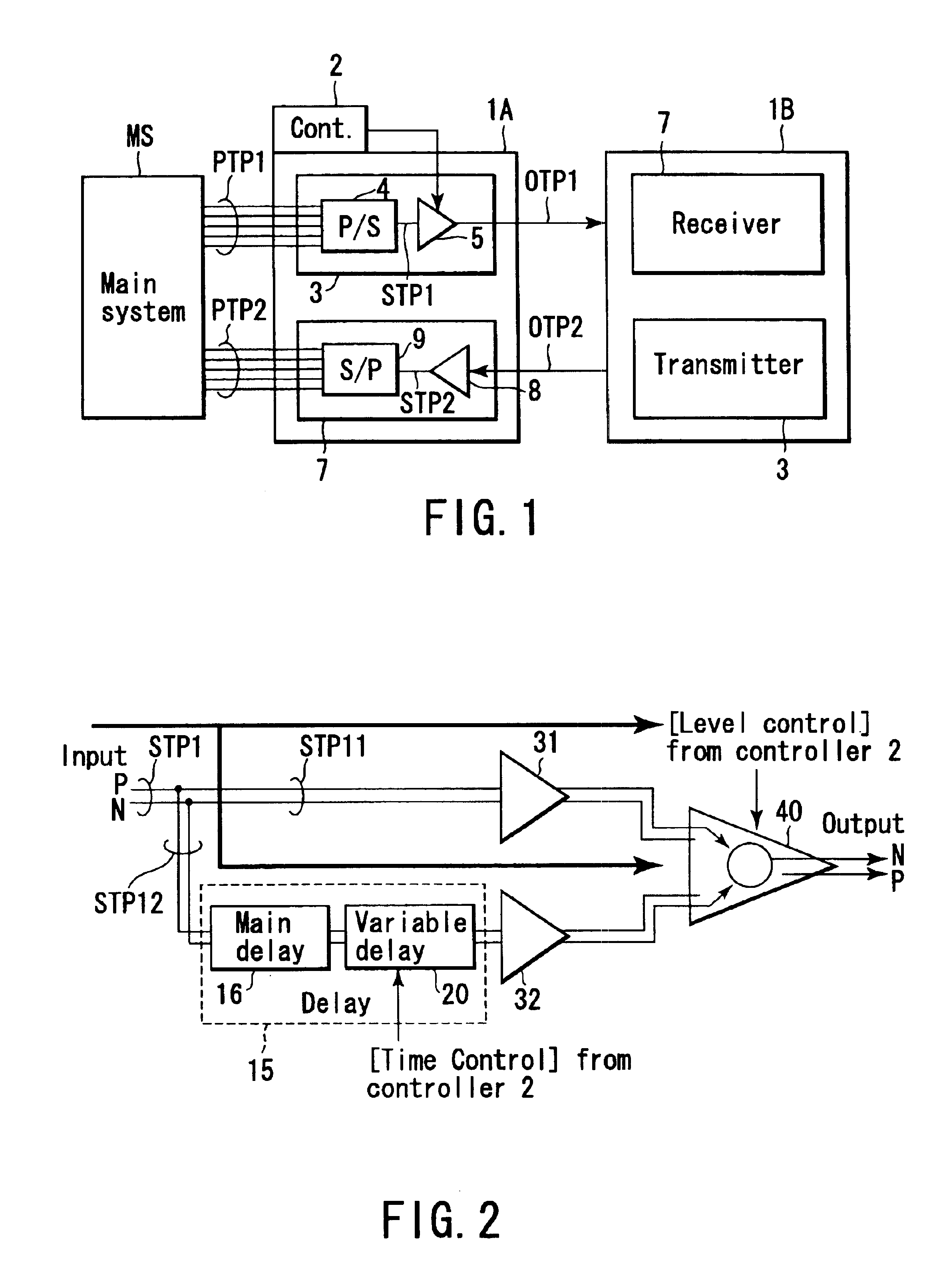

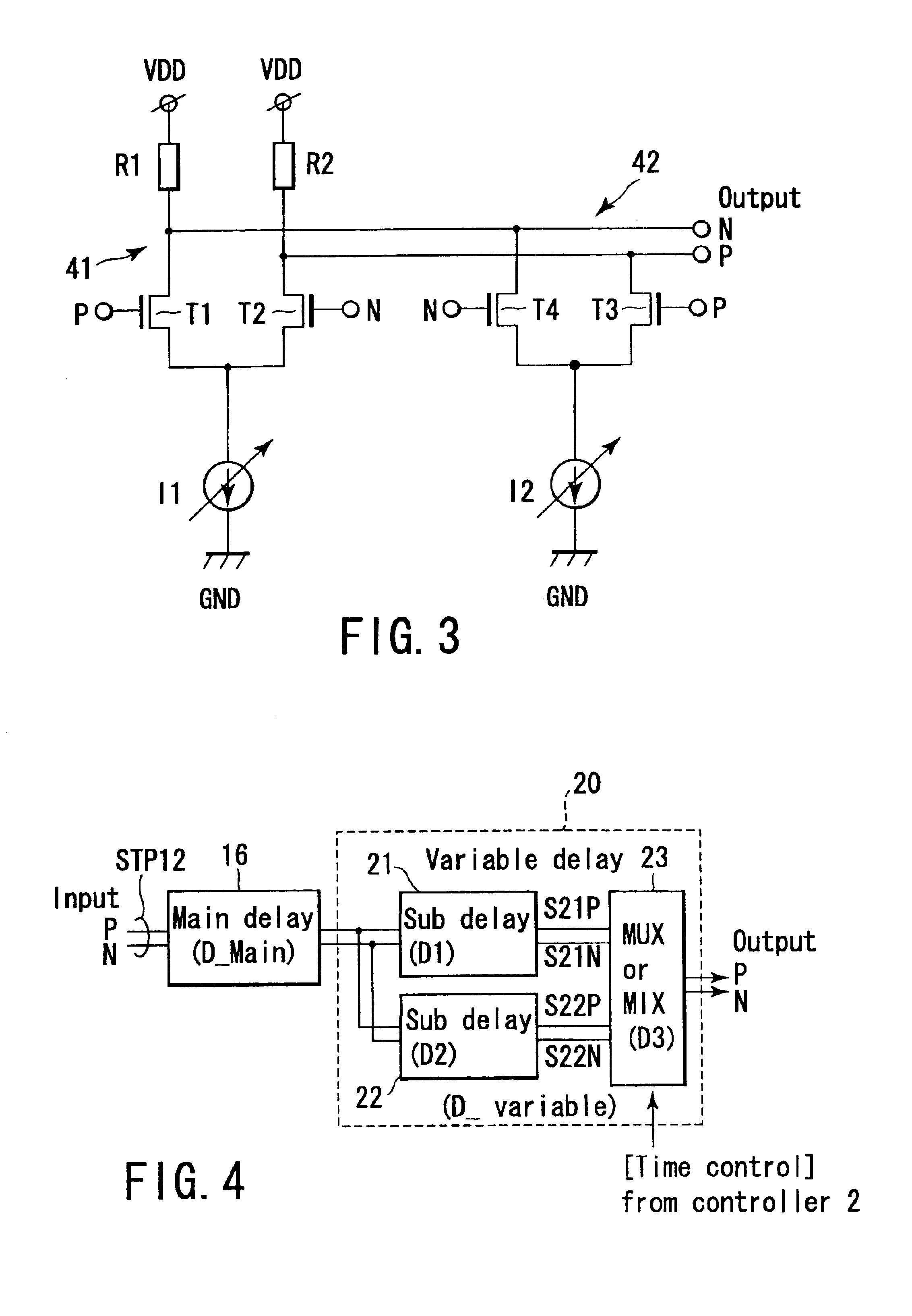

Differential data transmitter

A differential data transmitter includes a first pre-driver configured to receive a differential data signal, a delay circuit configured to receive the differential data signal in parallel with the first pre-driver, and output the differential data signal with a delay time, and a second pre-driver configured to receive an output signal from the delay circuit. The delay circuit is capable of changing the delay time in accordance with a control signal. An output driver is configured to receive first and second output signals from the first and second pre-drivers, and output a pre-emphasis waveform signal that corresponds to a subtraction signal between the first and second output signals.

Owner:KK TOSHIBA

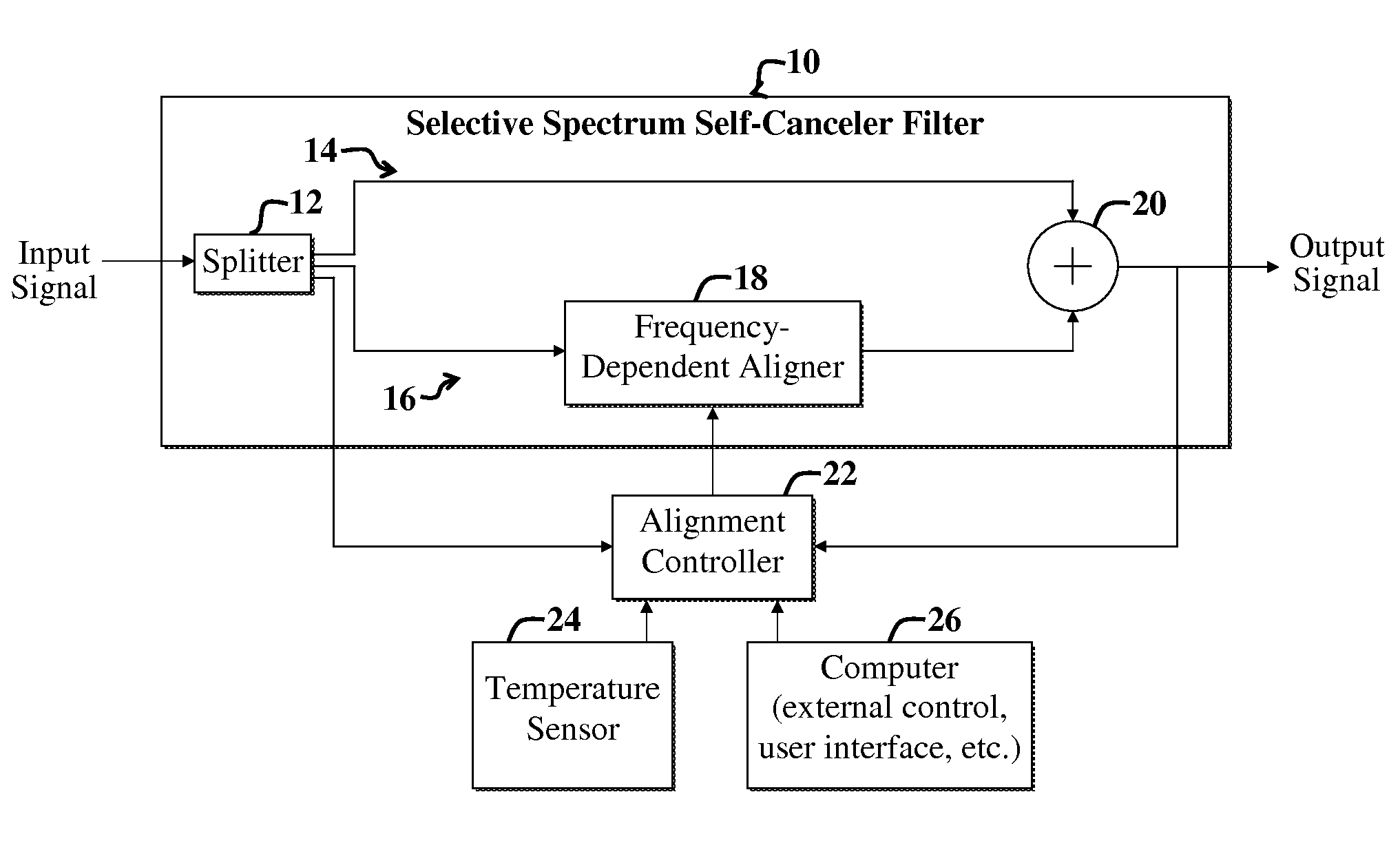

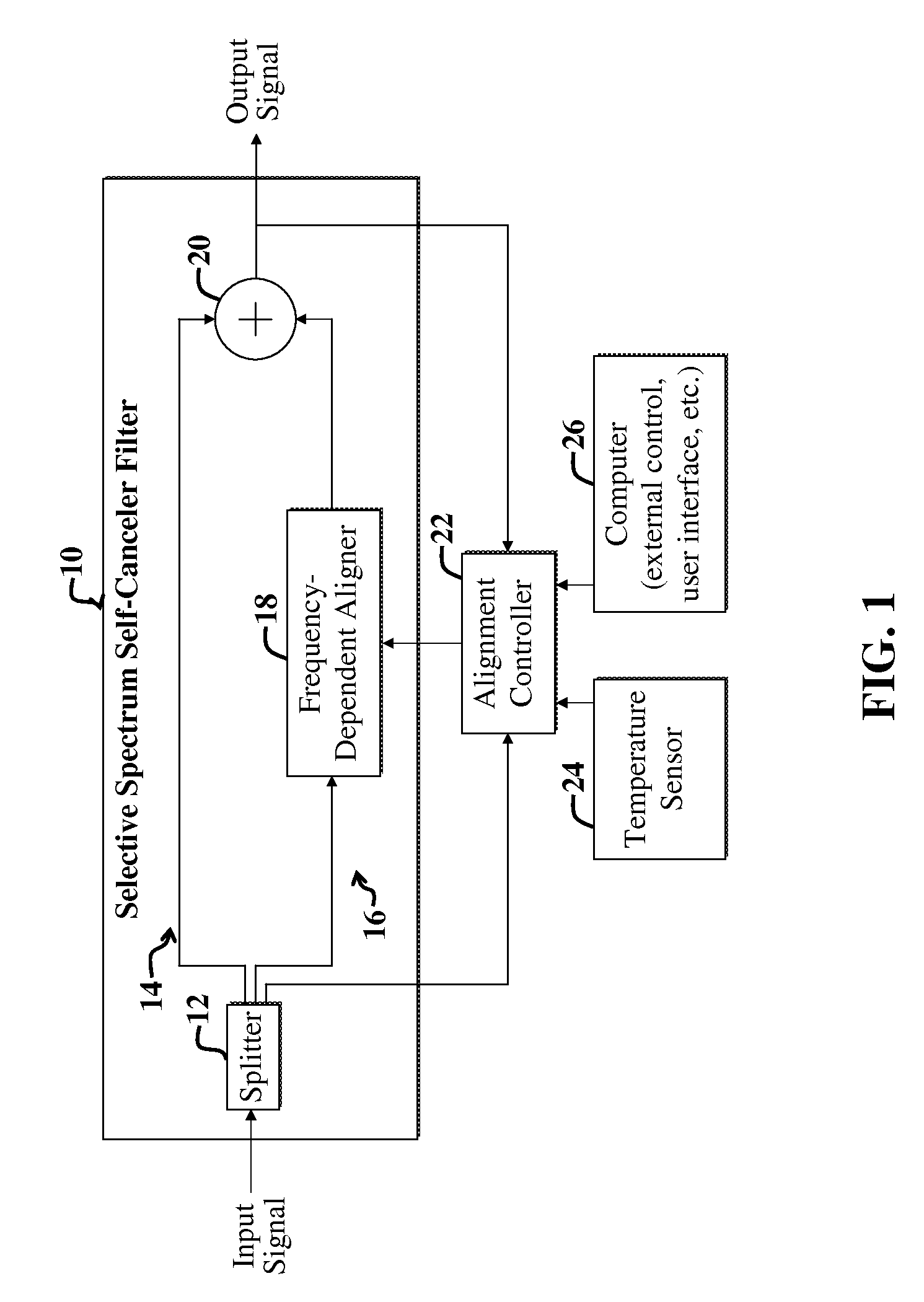

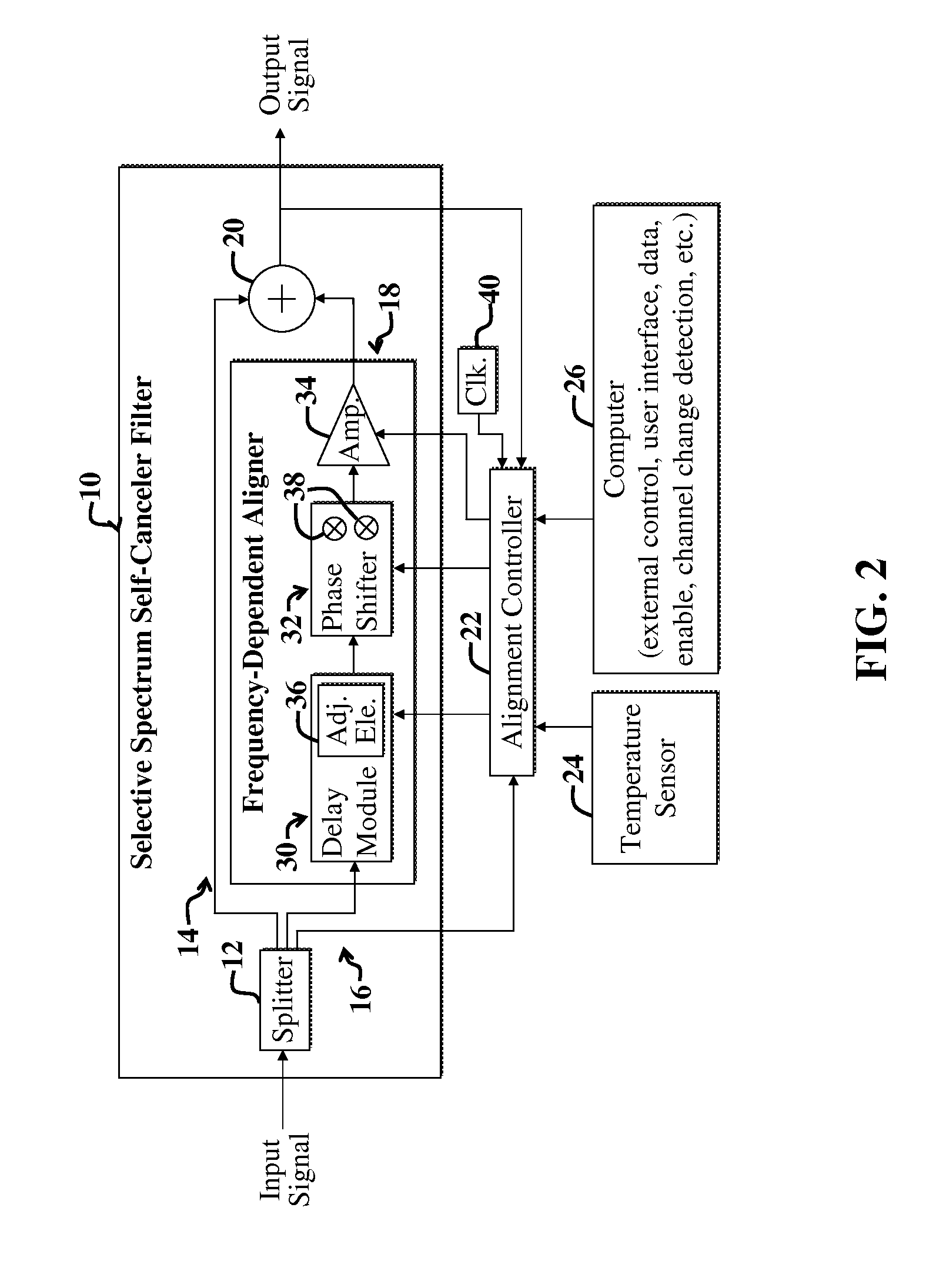

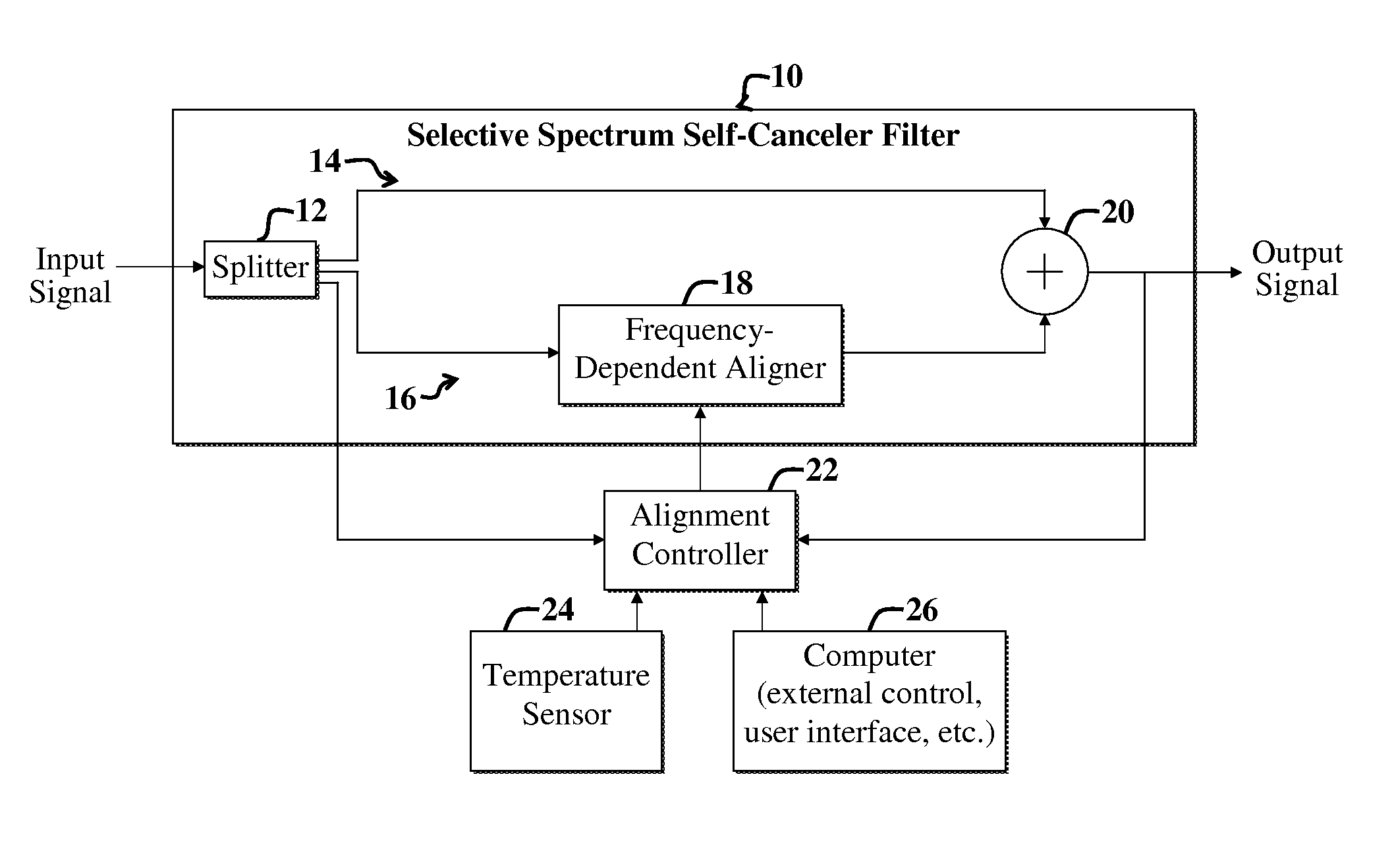

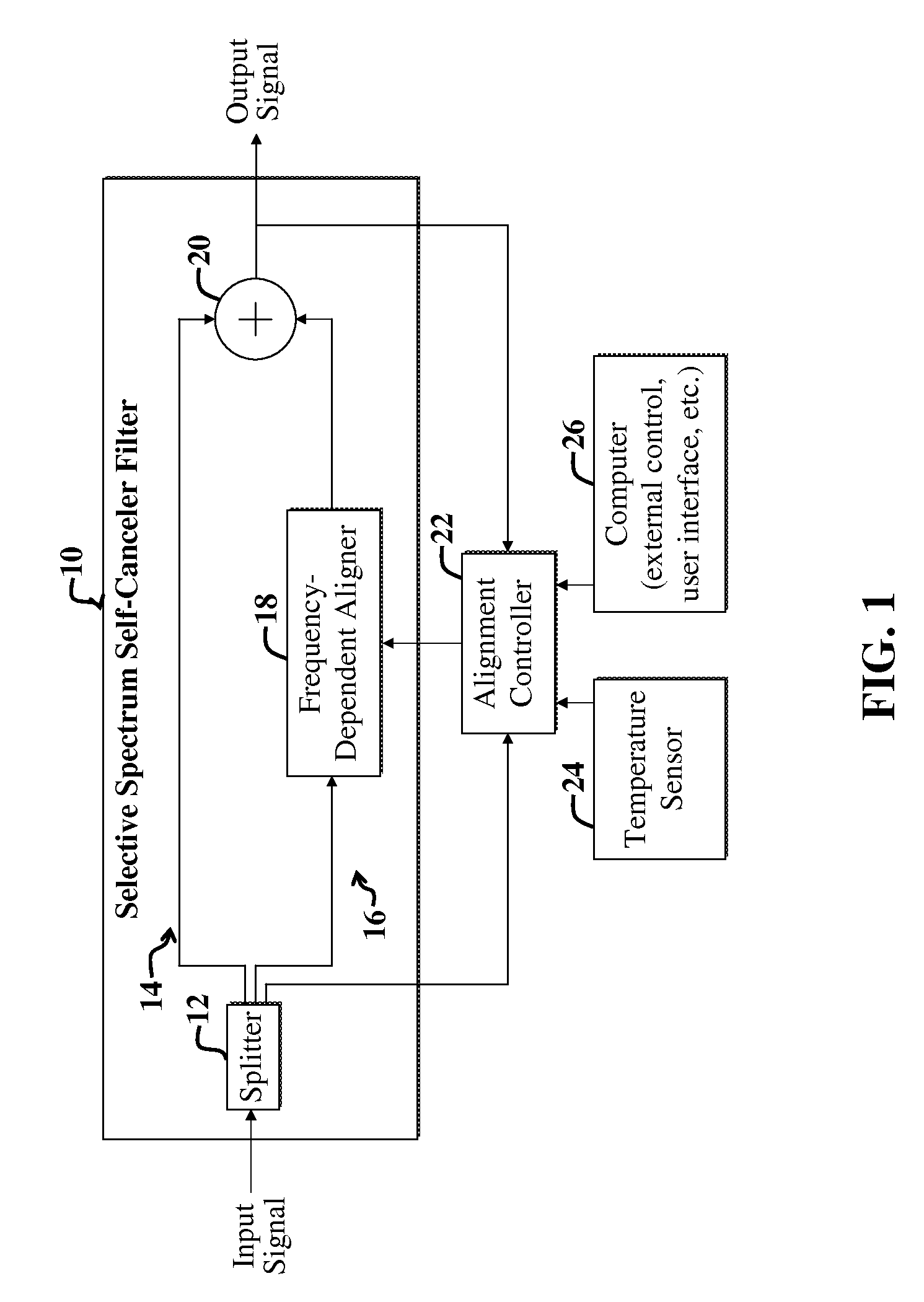

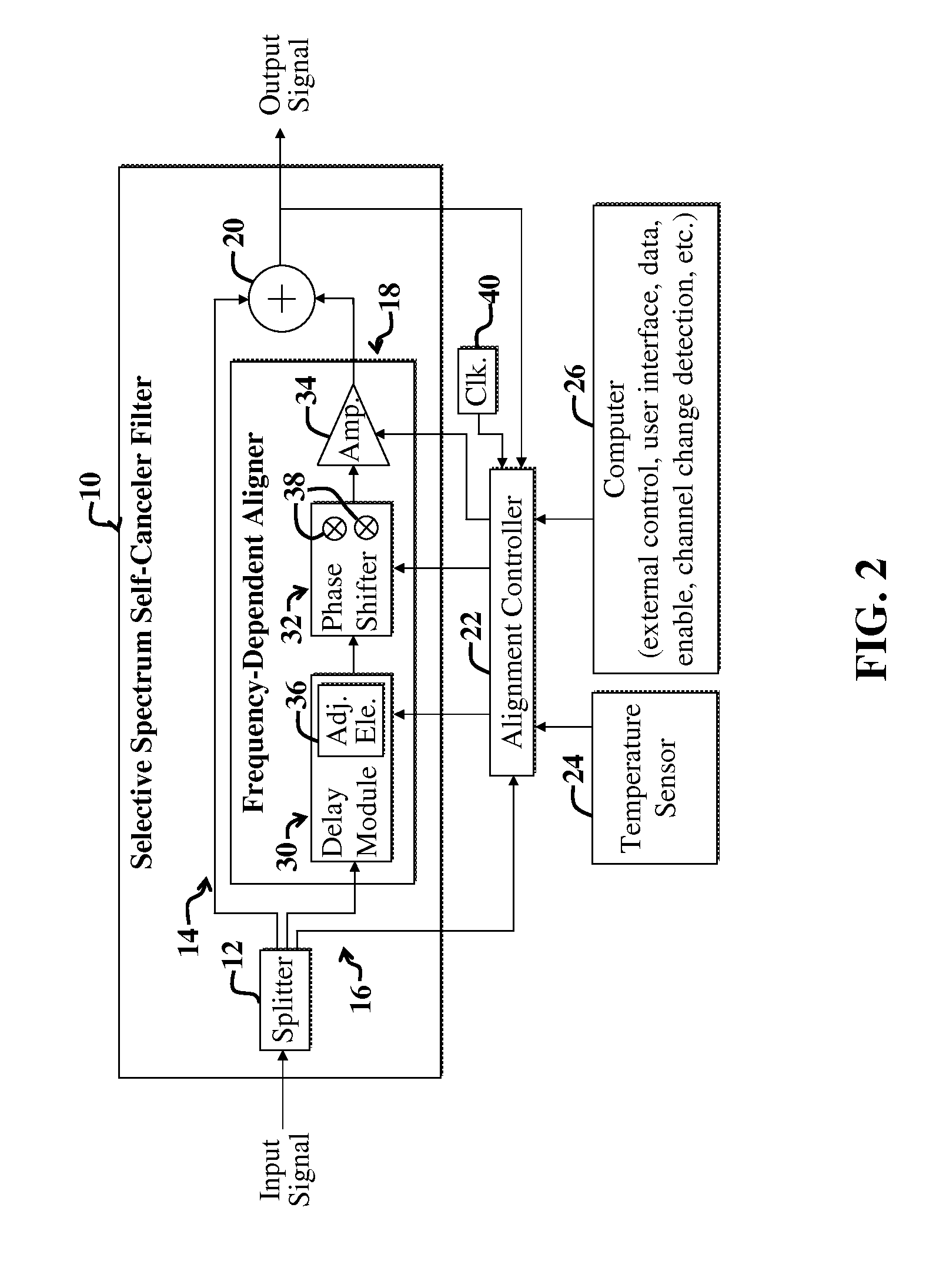

Filter shaping using a signal cancellation function

InactiveUS20100244943A1Active element networkPulse descriminationAudio power amplifierSignal cancellation

A signal filter and accompanying methods. In one embodiment, the filter includes a first mechanism for receiving a first signal. A second mechanism employs one or more modified representations of the first signal to cancel one or more frequency components of the first signal, yielding an output signal in response thereto. In a more specific embodiment, the first mechanism includes a splitter for receiving the first signal and splitting the first signal onto a first path and a second path. The second mechanism further includes one or more delay modules and one or more phase shifters in the first path and / or the second path. One or more controllable amplifiers are optionally included in the first path and / or the second path. The one or more delay modules, phase shifters, or amplifiers are responsive to one or more control signals from a controller. The controller is adapted to modify behavior of the second mechanism so that the filter is characterized by a desired frequency response.

Owner:INTERSIL INC

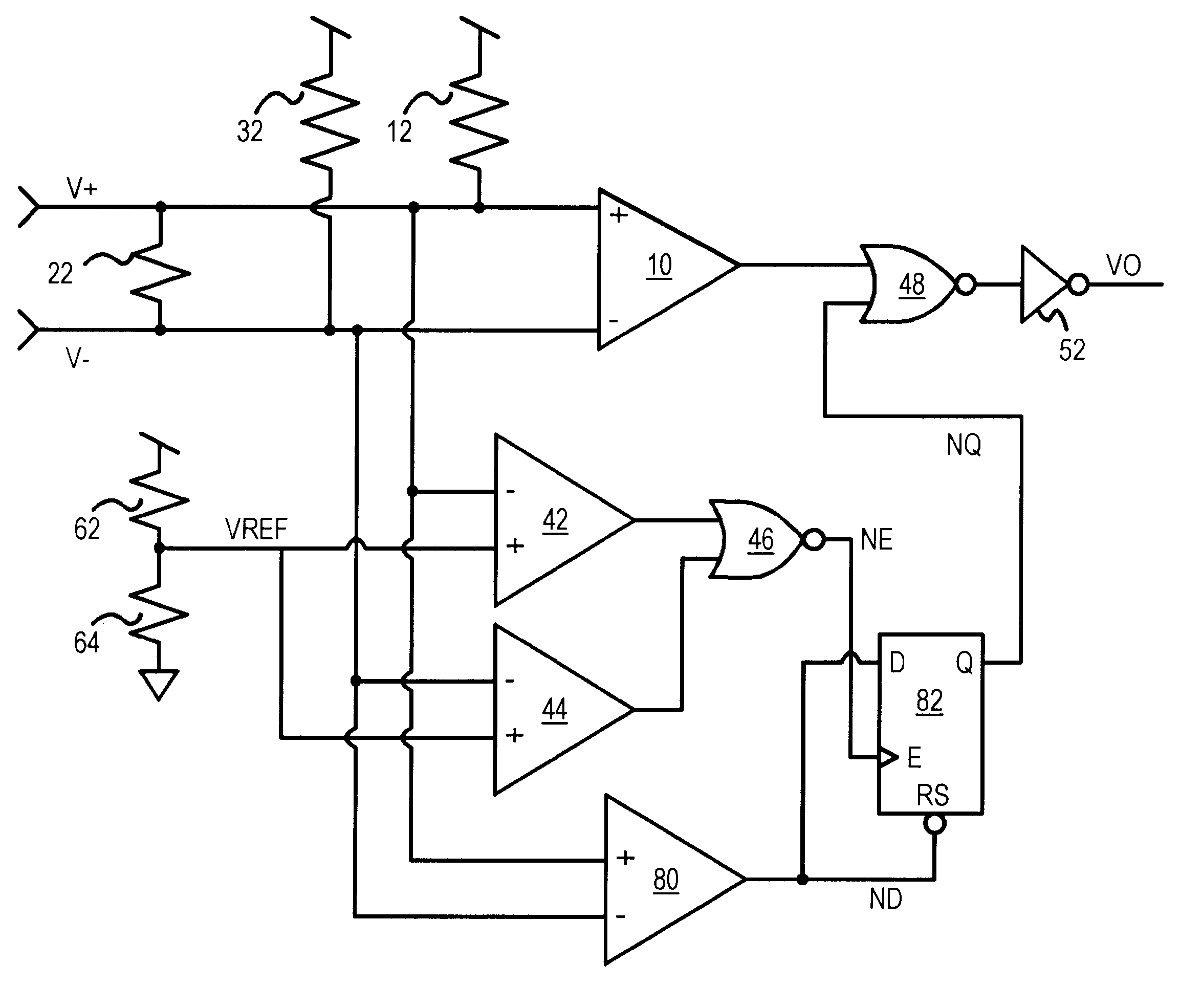

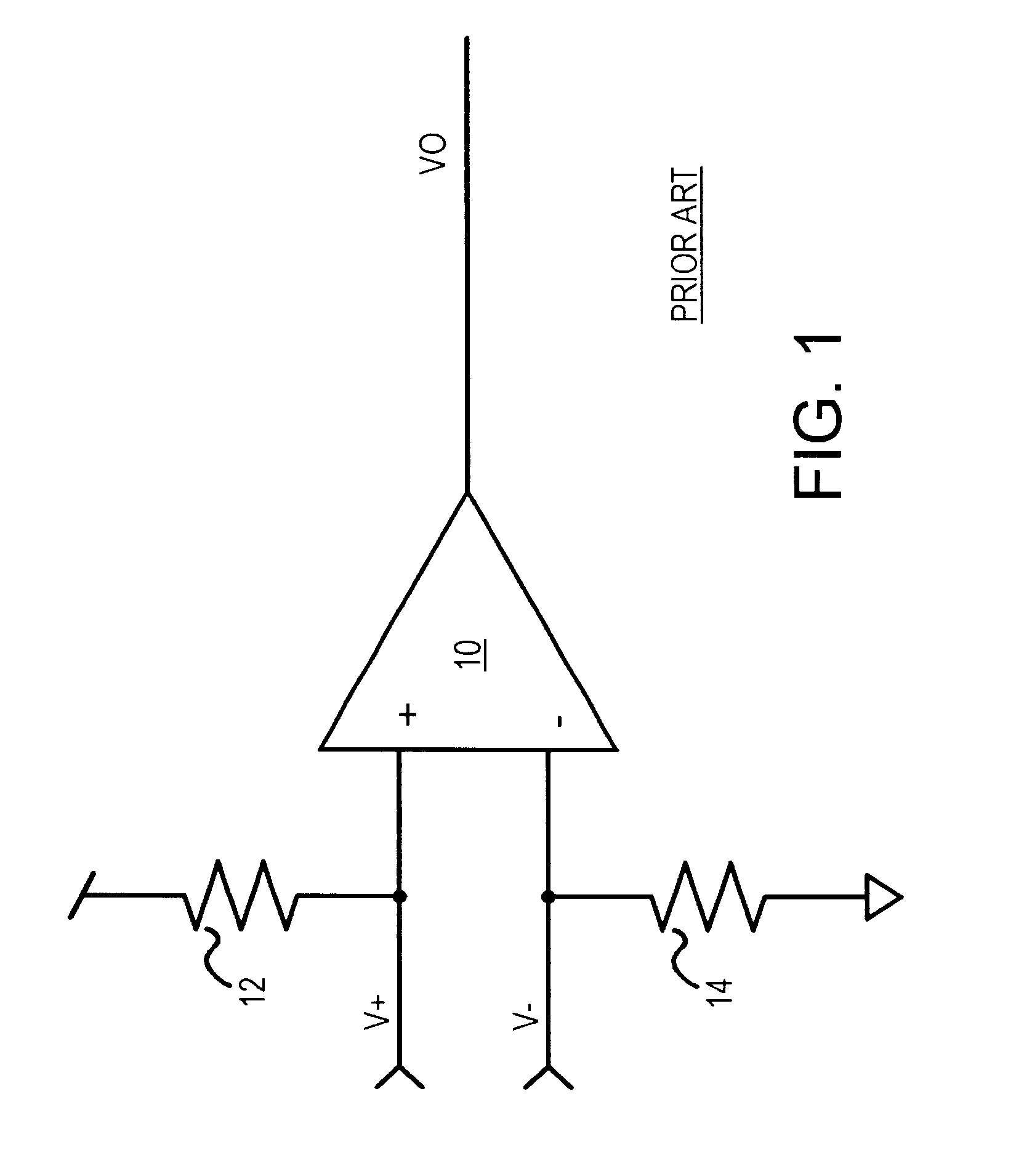

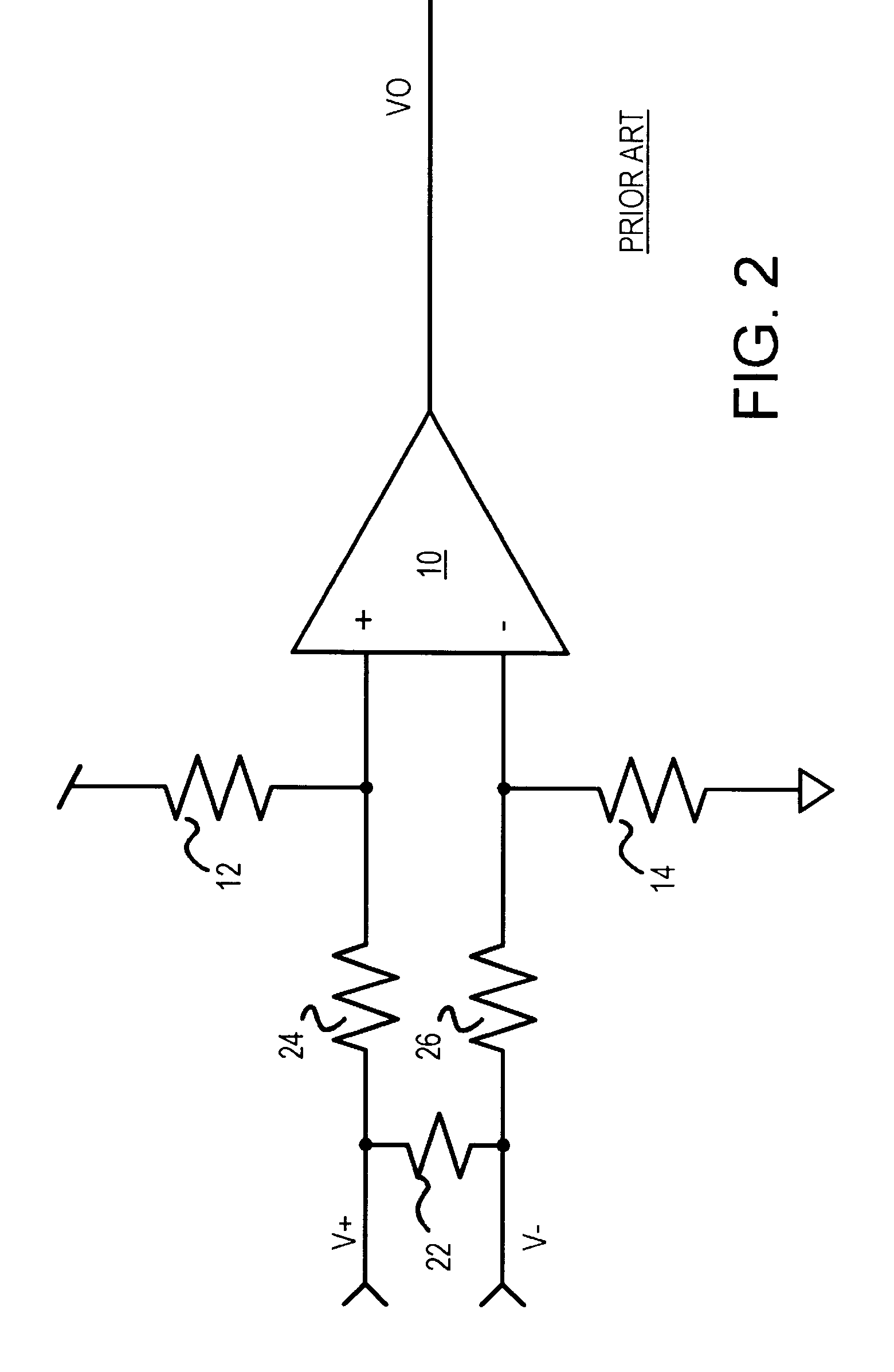

Latched active fail-safe circuit for protecting a differential receiver

InactiveUS6650149B1Multiple input and output pulse circuitsFail-safe circuitsAudio power amplifierEngineering

A fail-safe circuit for a differential receiver can tolerate noise. A latch is enabled when both differential inputs V+, V- rise above a reference voltage that is close to Vcc. The latch, once enabled, is set by an offset amplifier, signaling the fail-safe condition. The offset amplifier sets the latch when V+ is above or equal to V-. The differential amplifier has a small offset voltage to allow the latch to remain set when V+ and V- are equal in voltage. An output from a differential amplifier receiving V+ and V- can be blocked by a gate when the fail-safe condition is latched. Pullup resistors pull V+, V- to Vcc when an open failure occurs. The latch remains set when common-mode noise occurs on V+, V-, preventing noise from prematurely disabling the fail-safe condition. Such noise coupled into a broken cable is usually common-mode.

Owner:DIODES INC

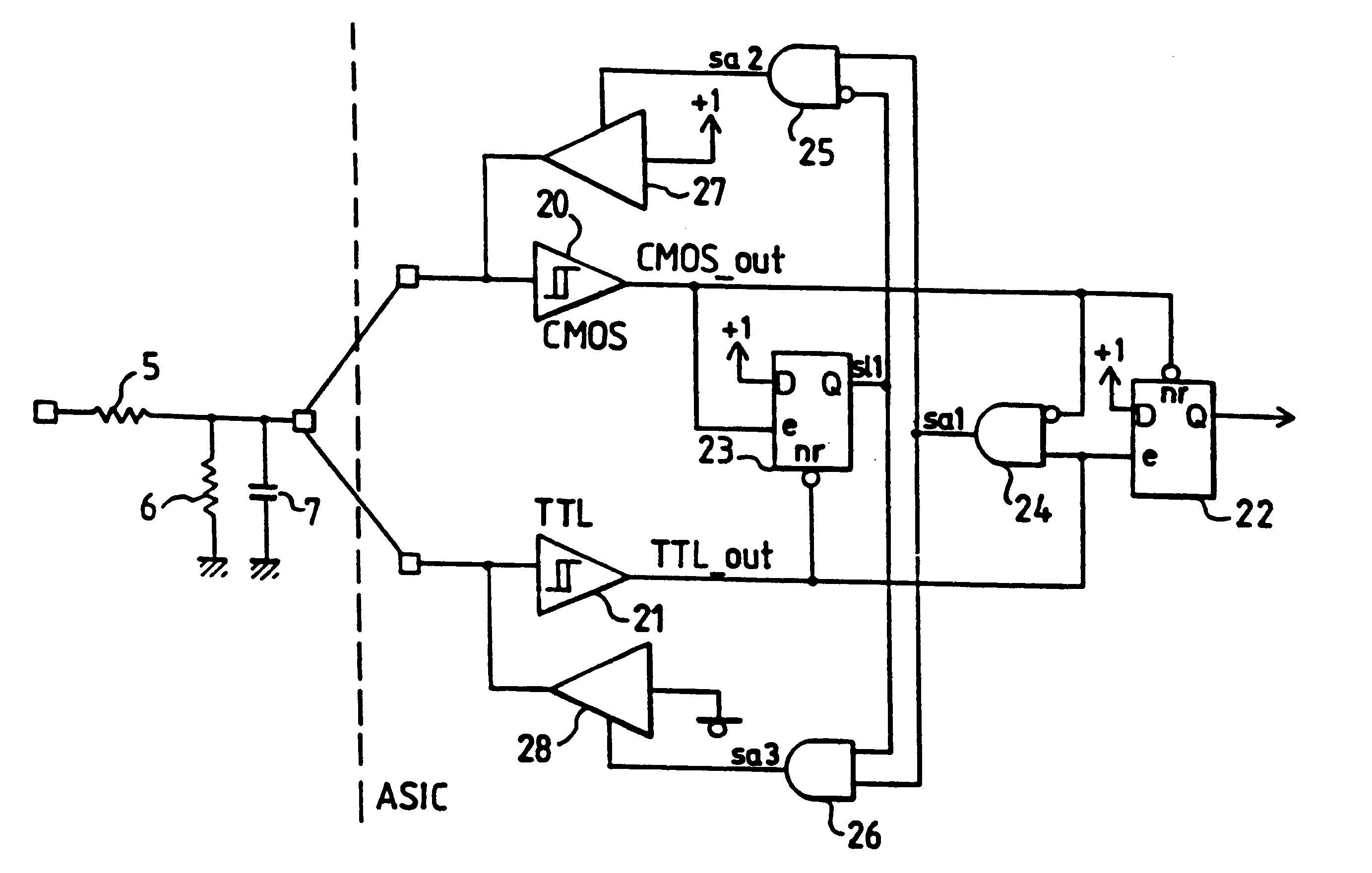

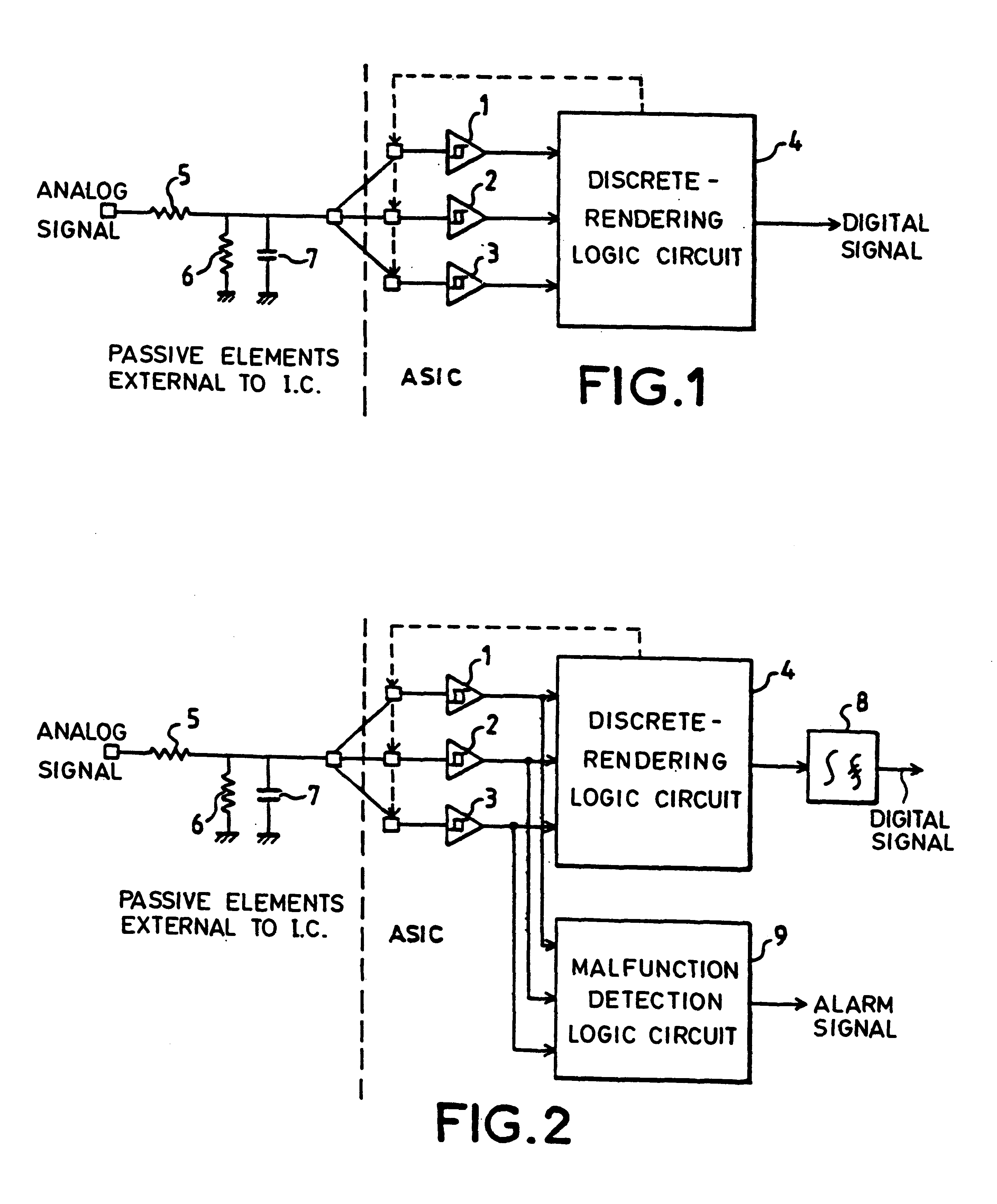

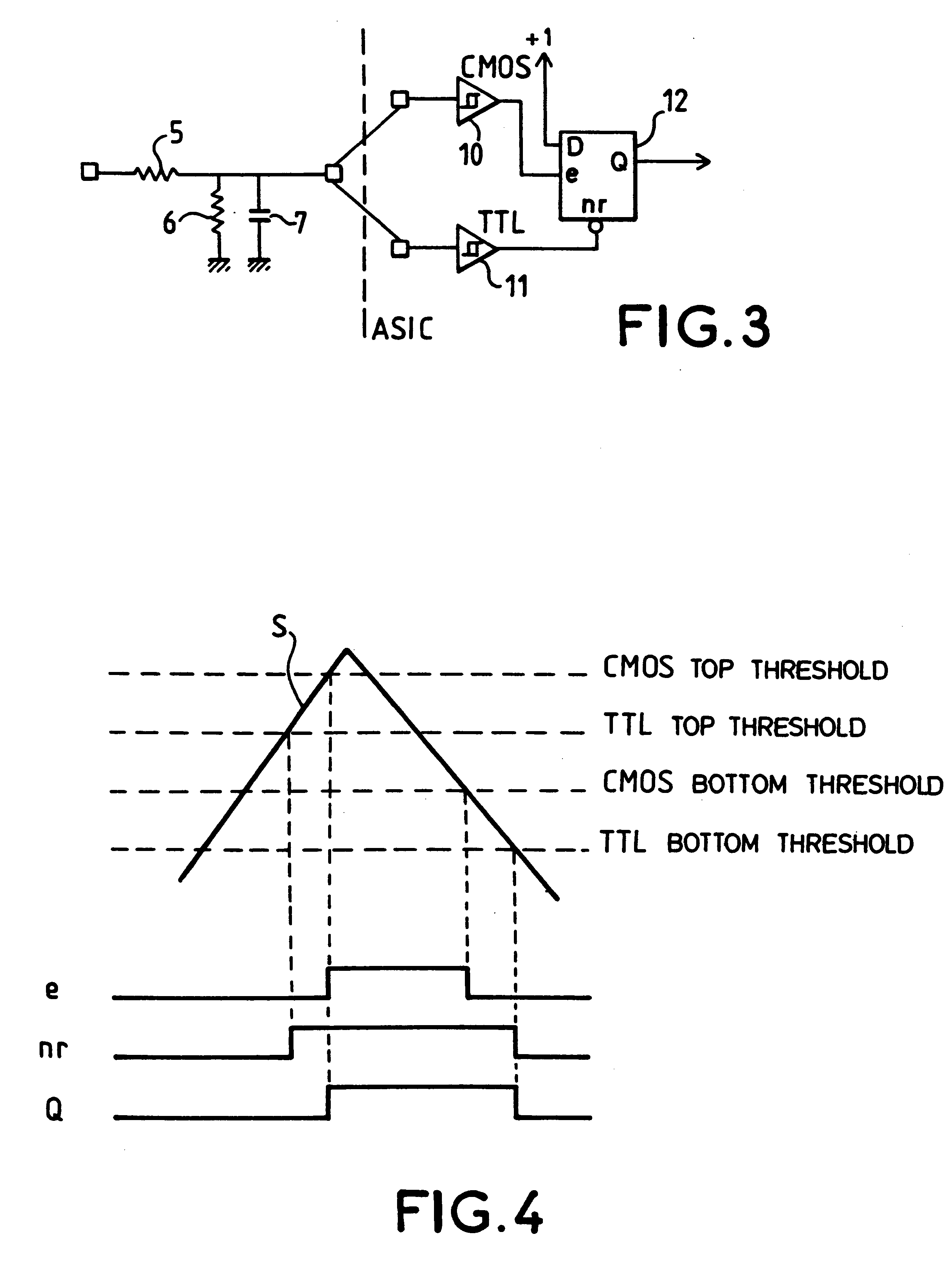

Circuit for the acquisition of binary analog signals

InactiveUS6204786B1Increase the number ofAnalogue/digital conversionElectric signal transmission systemsSchmitt triggerAnalog signal

The disclosure relates to the acquisition of a binary analog signal at input of a digital integrated circuit after its range of voltage variation has been matched with that acceptable by the digital integrated circuit by means of a resistive divider bridge. It is usual to define the architecture of an ASIC digital integrated circuit on the basis of libraries of pre-characterized cells. The disclosed device is designed to increase the possibilities of choice open to the integrated circuit designer, in enabling him to one pre-characterized cell of a Schmitt trigger for its top switching threshold and another for its bottom switching threshold. It consists of a circuit comprising, at input, a bank of Schmitt triggers of different types, followed by a discrete-rendering logic circuit deducing the logic state of the binary input analog signal of the combination of the output states of the input Schmitt triggers.

Owner:SEXTANT AVIONIQUE

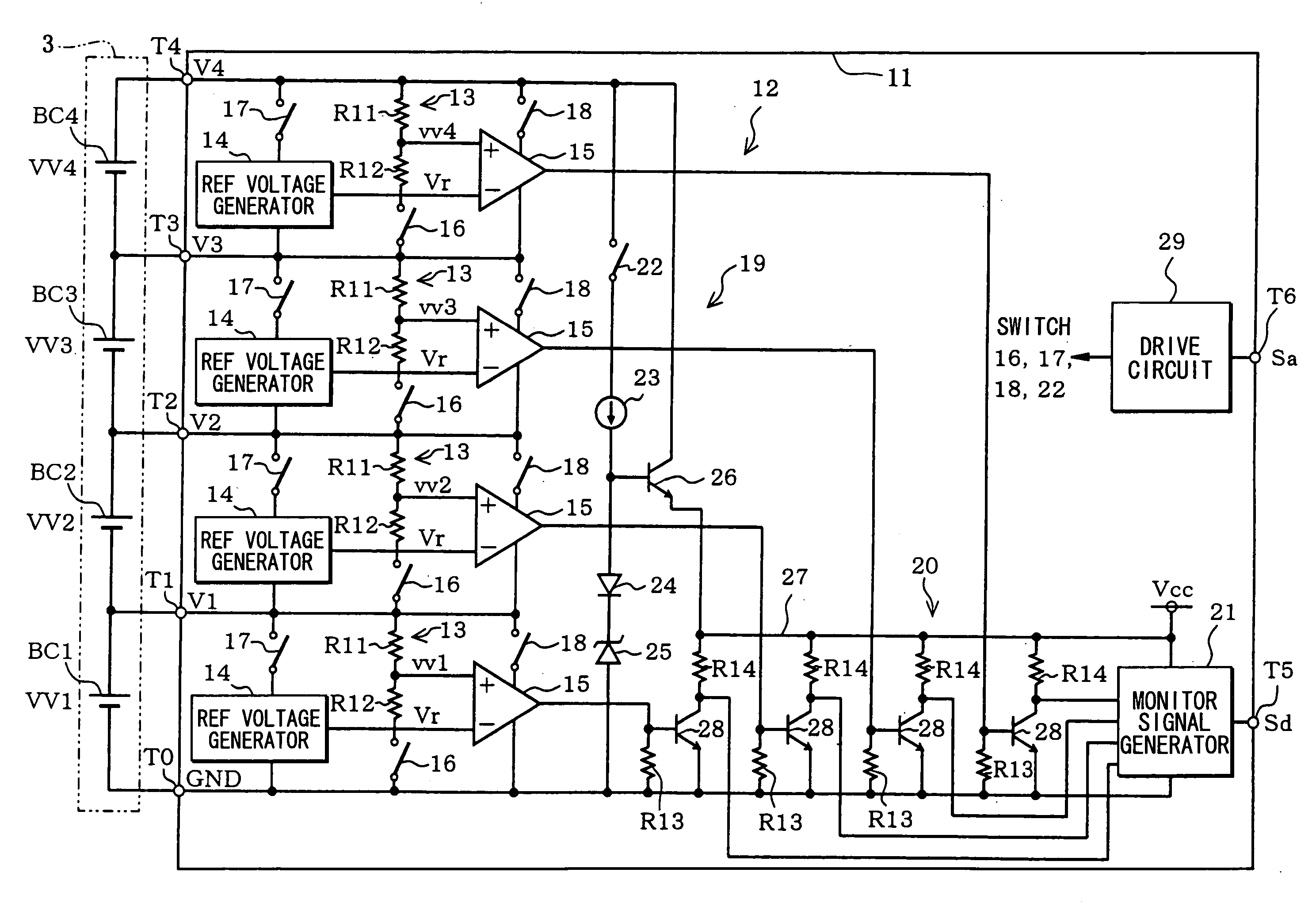

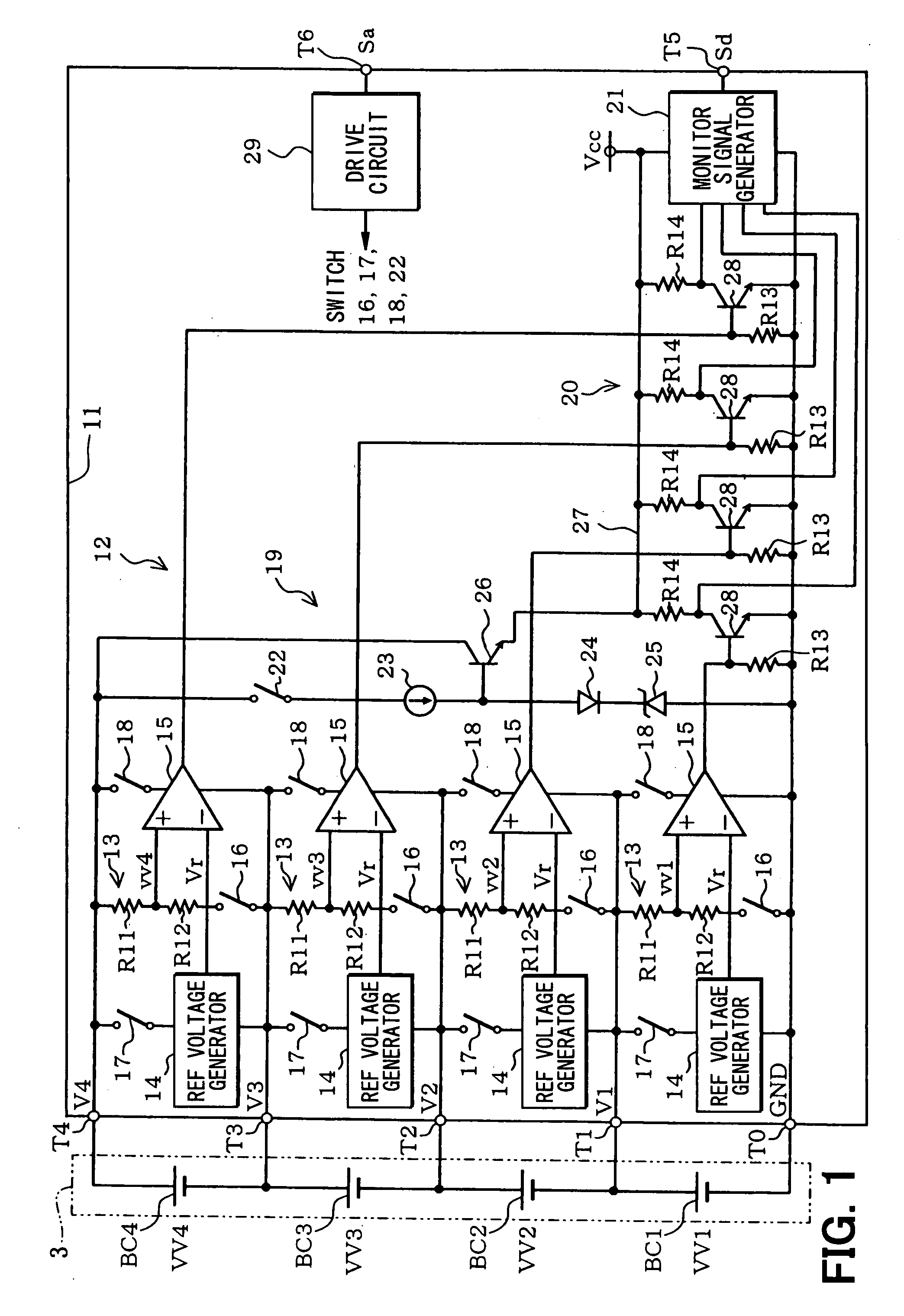

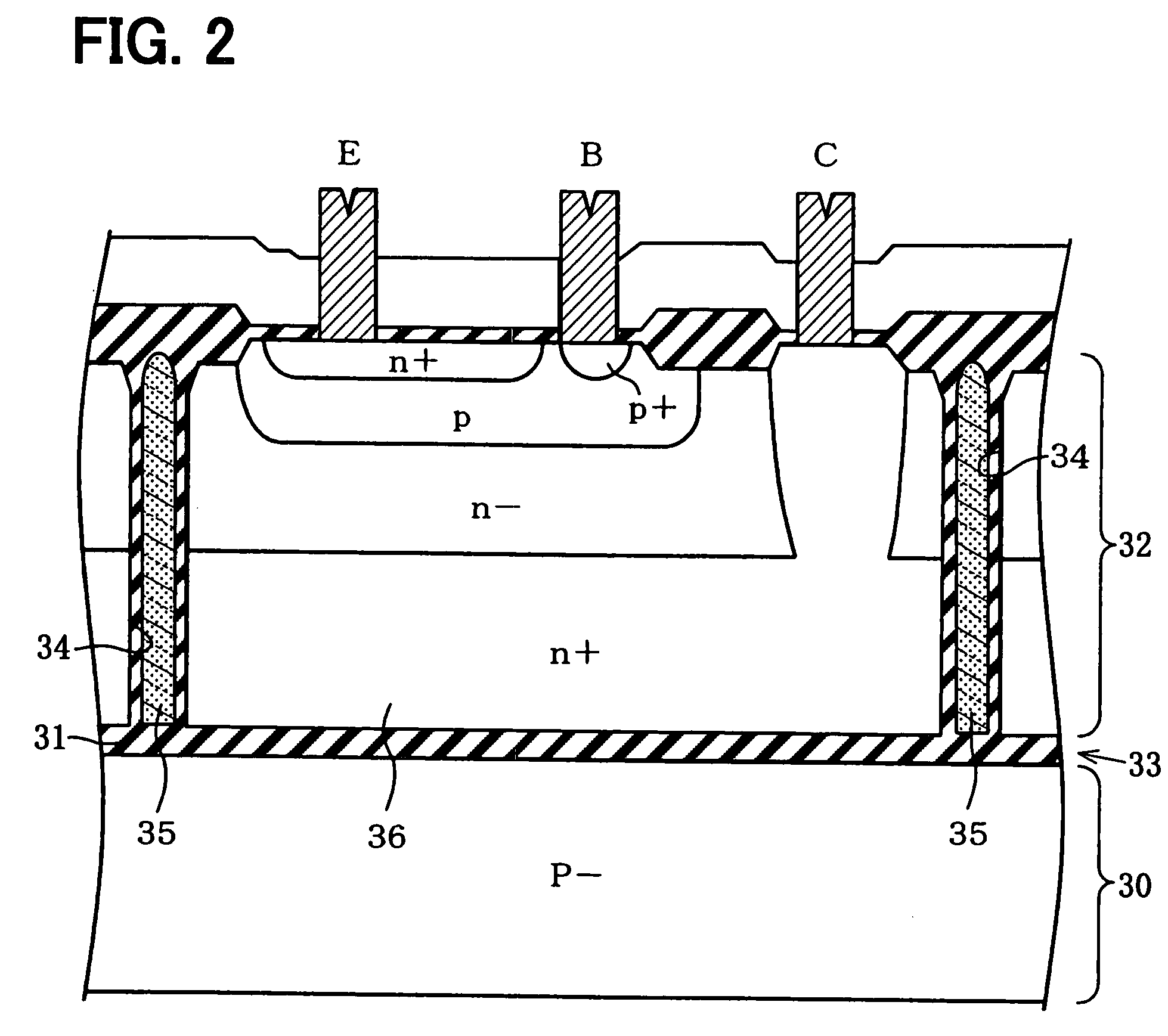

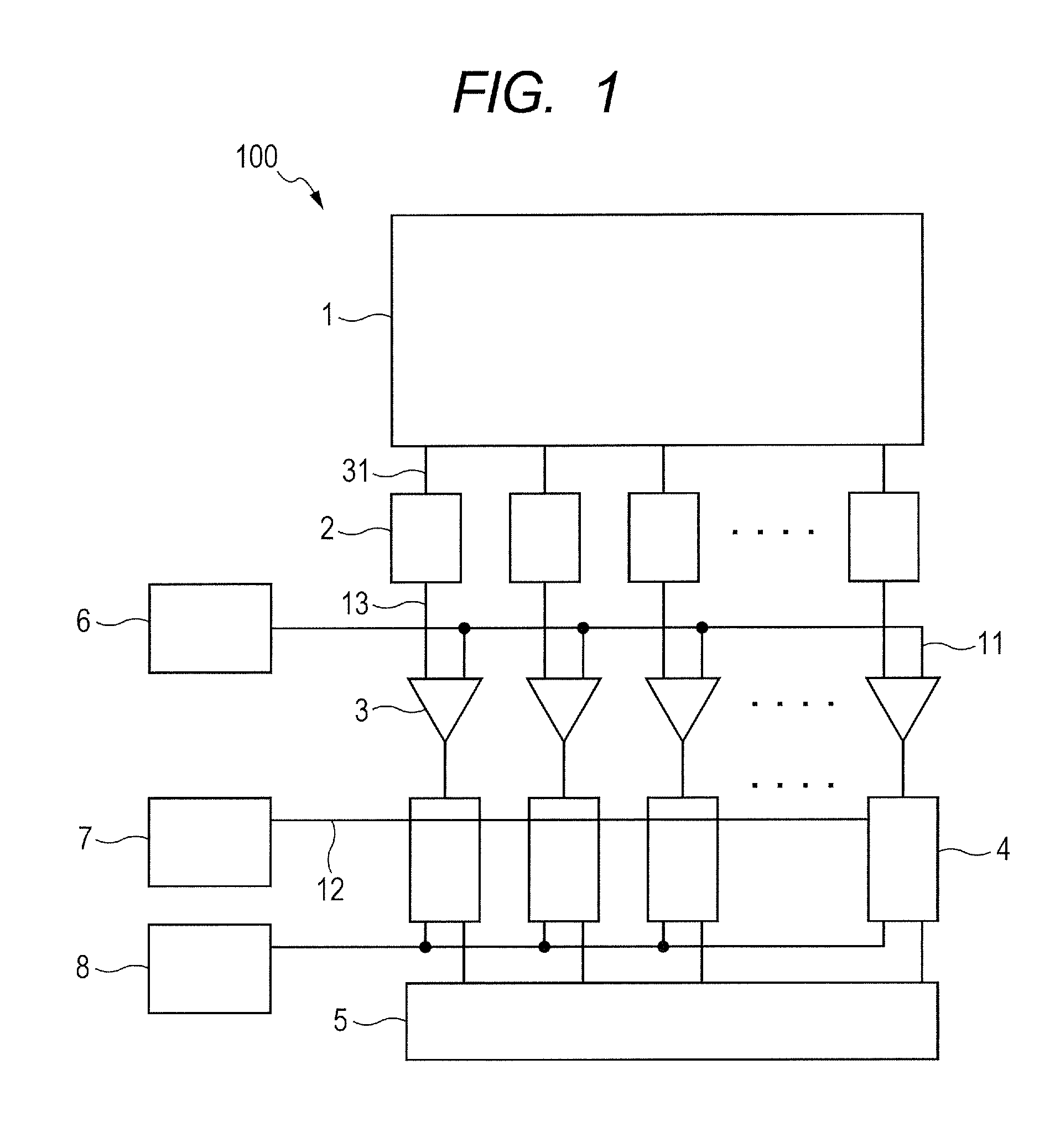

Semiconductor integrated circuit device

InactiveUS20080100266A1Reduce chip sizeTotal current dropCircuit monitoring/indicationIndicating/monitoring circuitsElectricityDevice form

A semiconductor integrated circuit device formed by a trench dielectric isolation technique has input terminals connected to positive and negative terminals of secondary cells of an assembled battery and includes monitor circuits for respectively monitoring cell voltages of the cells. Each monitor circuit includes a cell voltage detection circuit, a reference voltage generation circuit, and a comparison circuit. The cell voltage detection circuit divides a voltage between the input terminals connected to the positive and negative terminals of a corresponding cell and detects the cell voltage based on the divided voltage. The reference voltage generation circuit generates a reference voltage from the cell voltage. The comparison circuit is powered by the cell voltage of the corresponding cell and compares the divided voltage with the reference voltage.

Owner:DENSO CORP

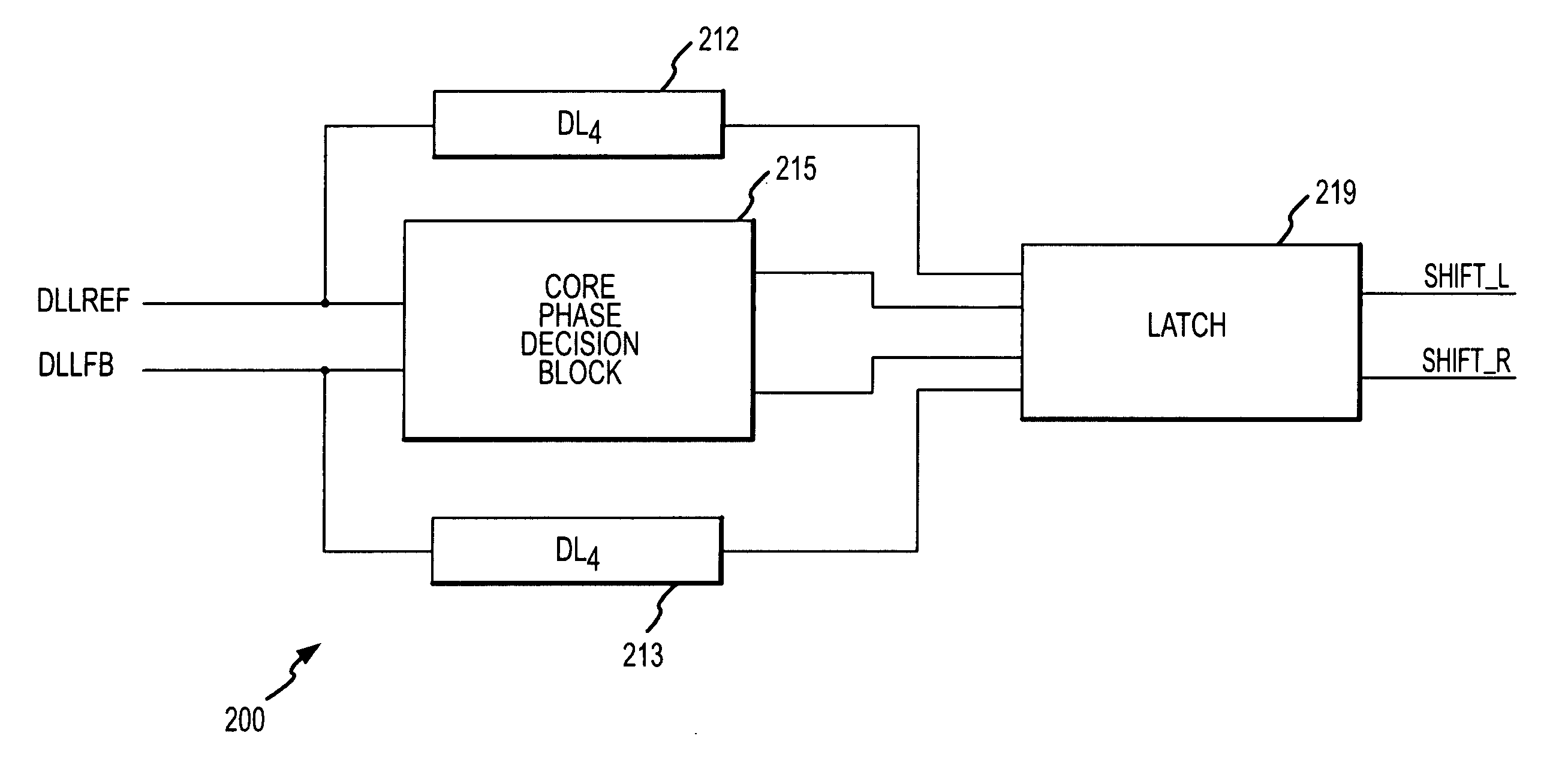

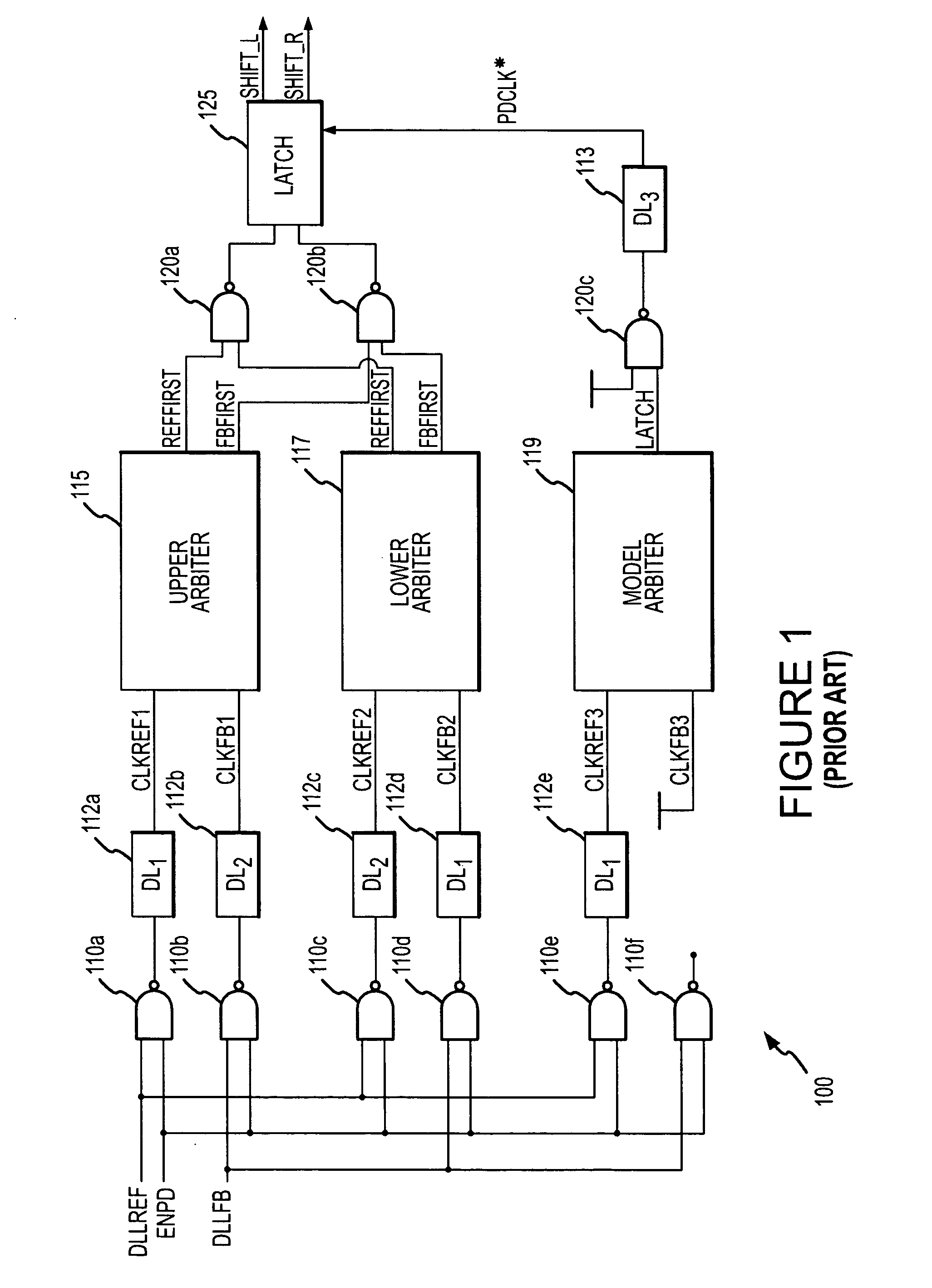

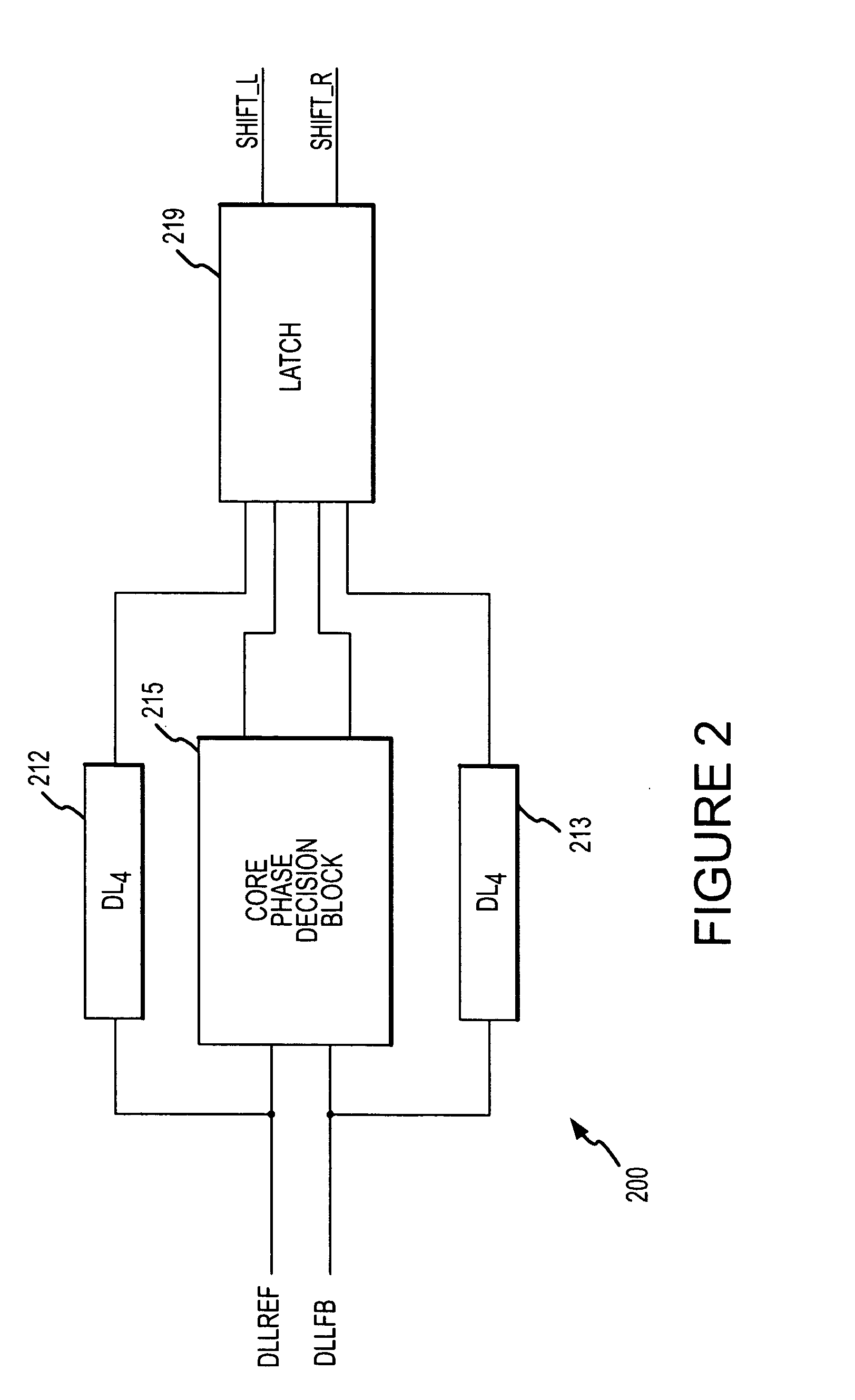

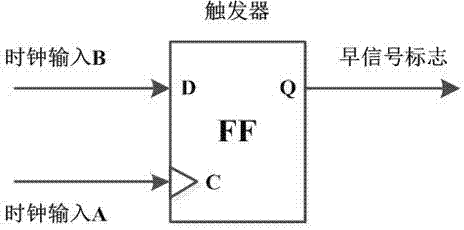

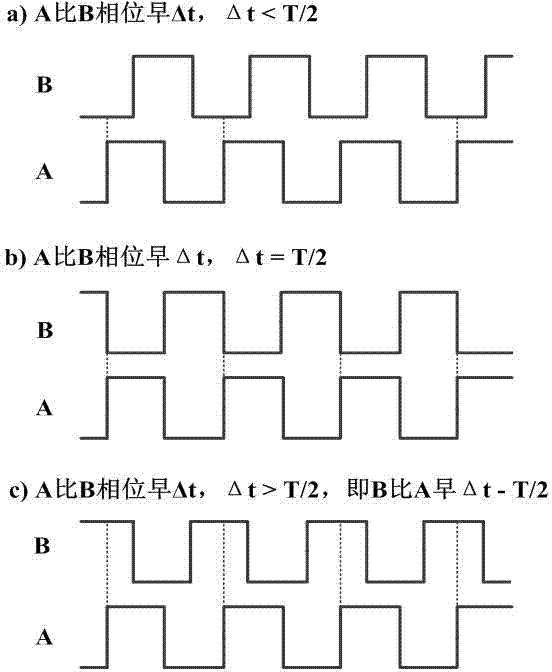

Fast response time, low power phase detector circuits, devices and systems incorporating the same, and associated methods

ActiveUS20080130396A1Reduce power consumptionRaise the possibilityMultiple input and output pulse circuitsPulse automatic controlDecision circuitPhase detector

A circuit for quickly accomplishing highly accurate phase detection using low power is described. The circuit includes a phase decision circuit that receives two clock signals and detects the phase relationship between the two signals by determining which signal was received first. In response, the phase decision circuit generates respective logic signals to reflect the phase relationship determination. The circuit also includes a latch circuit that receives the logic signals from the phase decision circuit and holds the phase relationship determination of the circuit a predetermined time after a predetermined transition of both clock signals have occurred. Methods and systems are also disclosed.

Owner:MICRON TECH INC

Method and device for eliminating signal noise

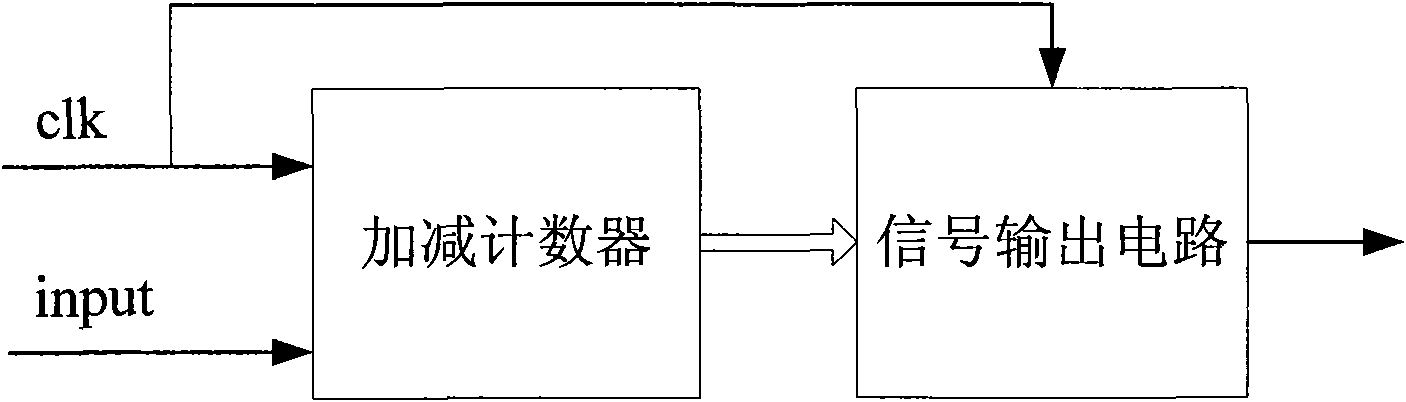

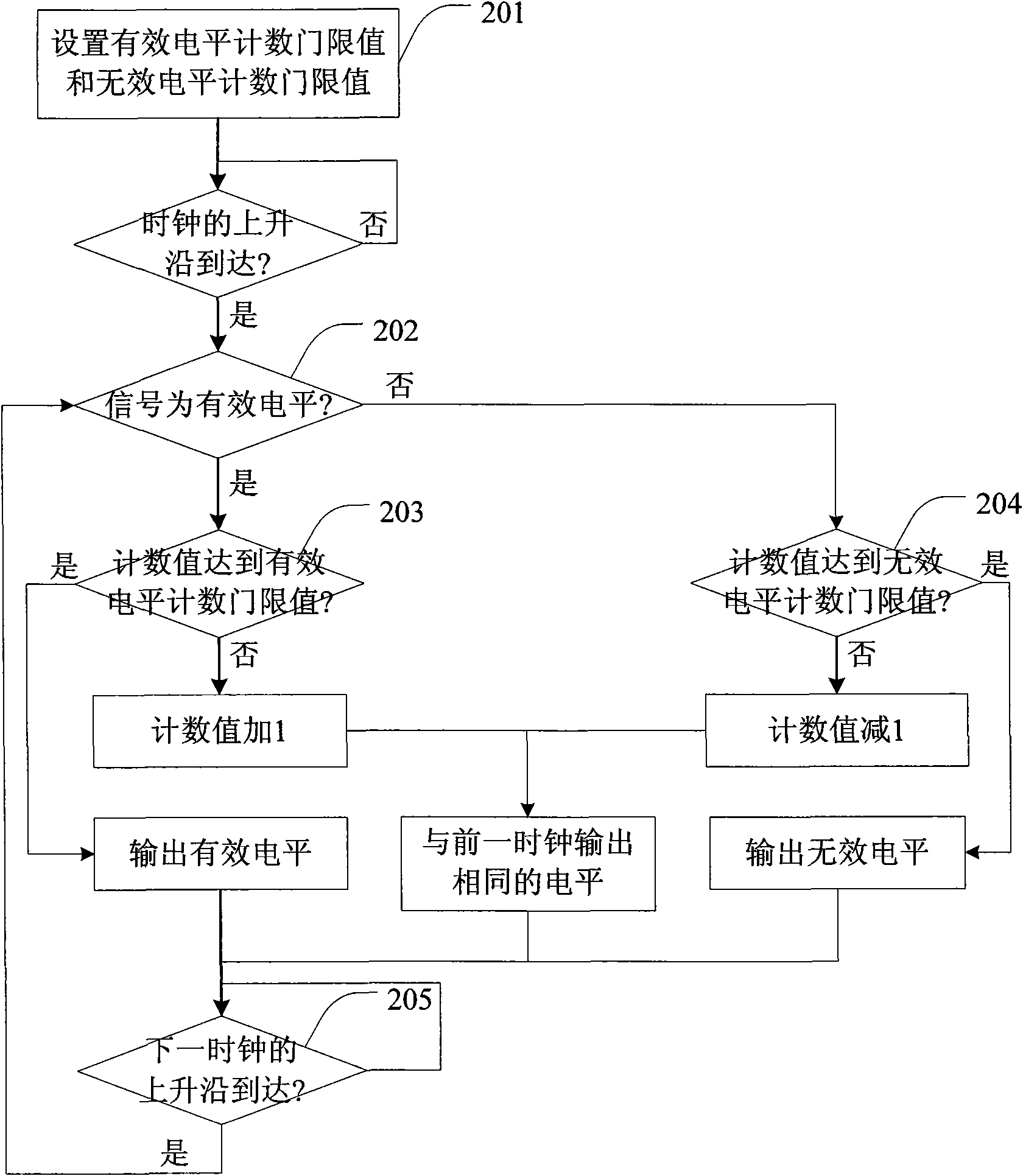

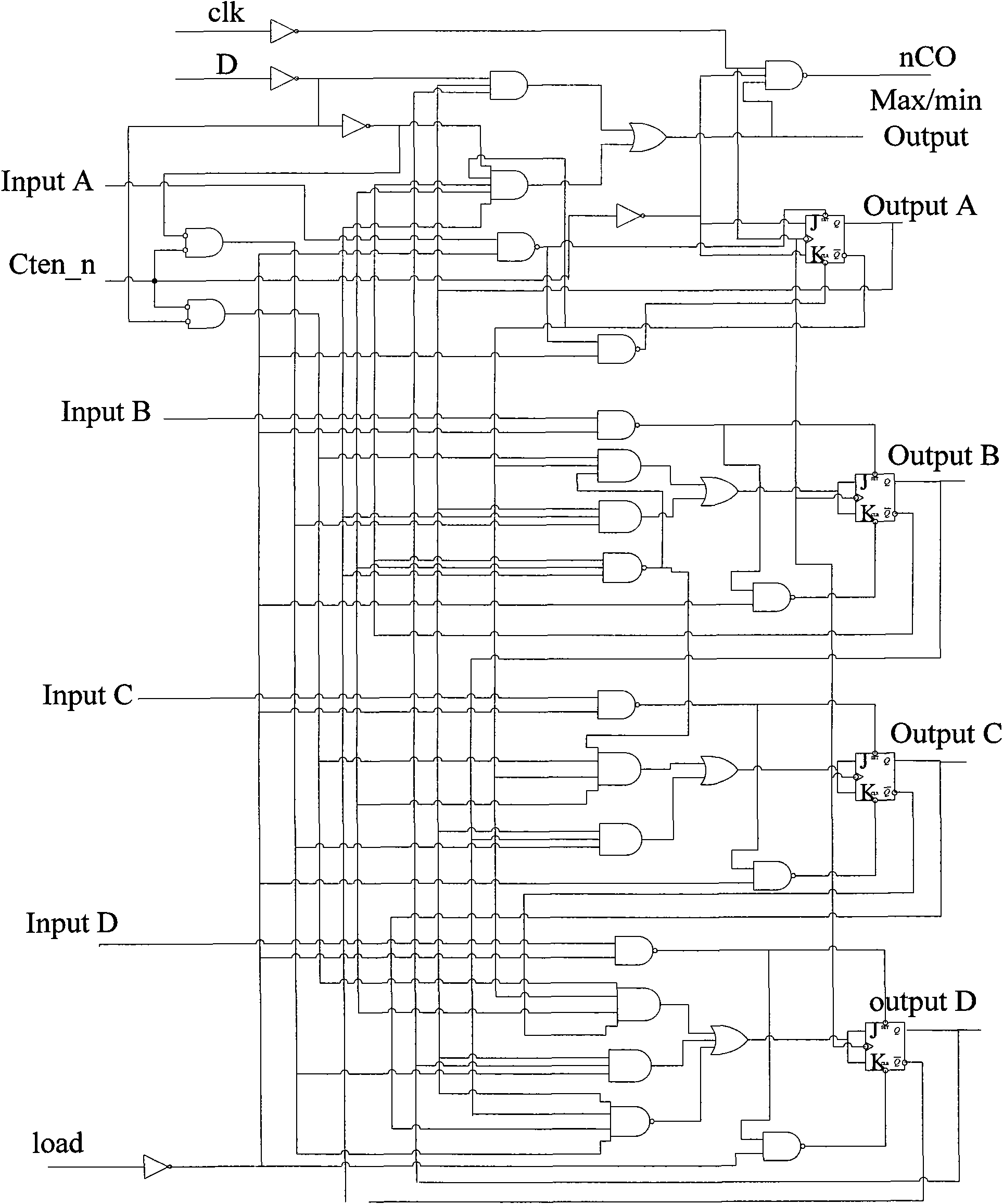

ActiveCN101568237ARemove completelyReduce difficultyPulse descriminationLogic circuit coupling/interface arrangementsComputer scienceGlitch removal

The invention discloses a method and device for eliminating signal noise, the device includes a backward-forward counter and a signal output circuit; the method for eliminating signal noise has the following steps: 1) setting valid and invalid level counting thresholds; 2) receiving the signal with signal noise needed to be eliminated by the backward-forward counter and beginning to count; when the rising edge of each clock arrives, if the signal is an valid electrical level, adding one on the current counting value, otherwise subtracting one; and the counting value does not increase / decrease until it reaches to a valid / invalid level counting threshold; meanwhile, the signal output circuit outputs signal without noise according to the counting value: when the rising edge of each clock arrives, if the counting value is a valid / invalid level counting threshold, then outputting valid / invalid level; if the counting value is between the valid and invalid level counting threshold, keeping the output equal to the output of the previous clock. The device provided by the invention can thoroughly eliminate wide noise, stably output signal without noise, and which is simple to be realized, thereby improving reliability of the system.

Owner:ZTE CORP

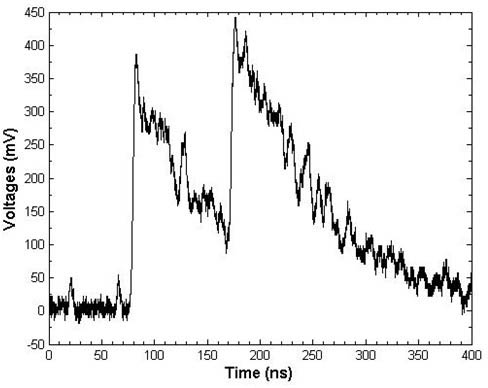

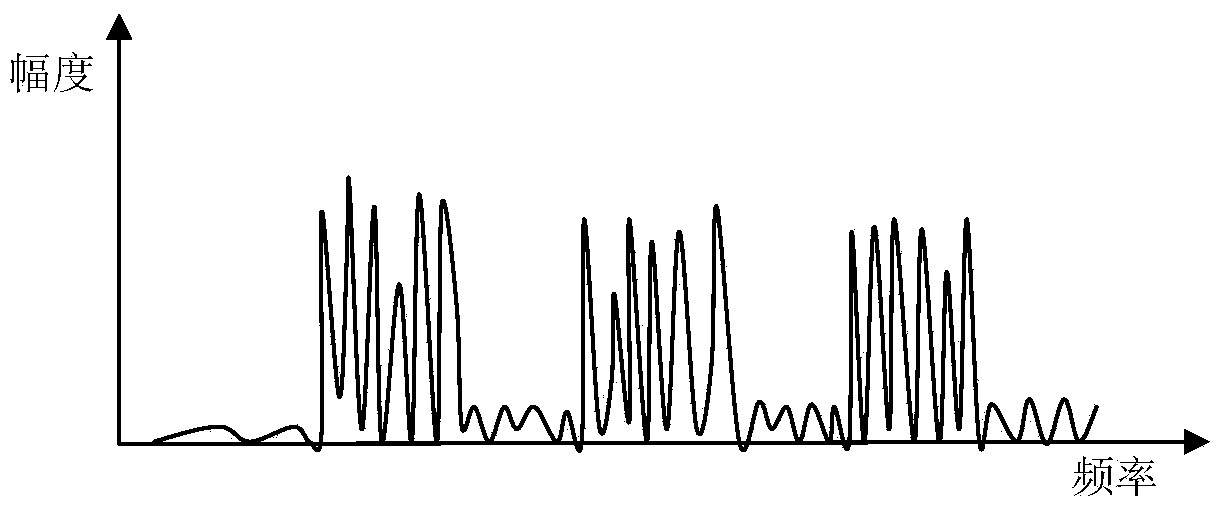

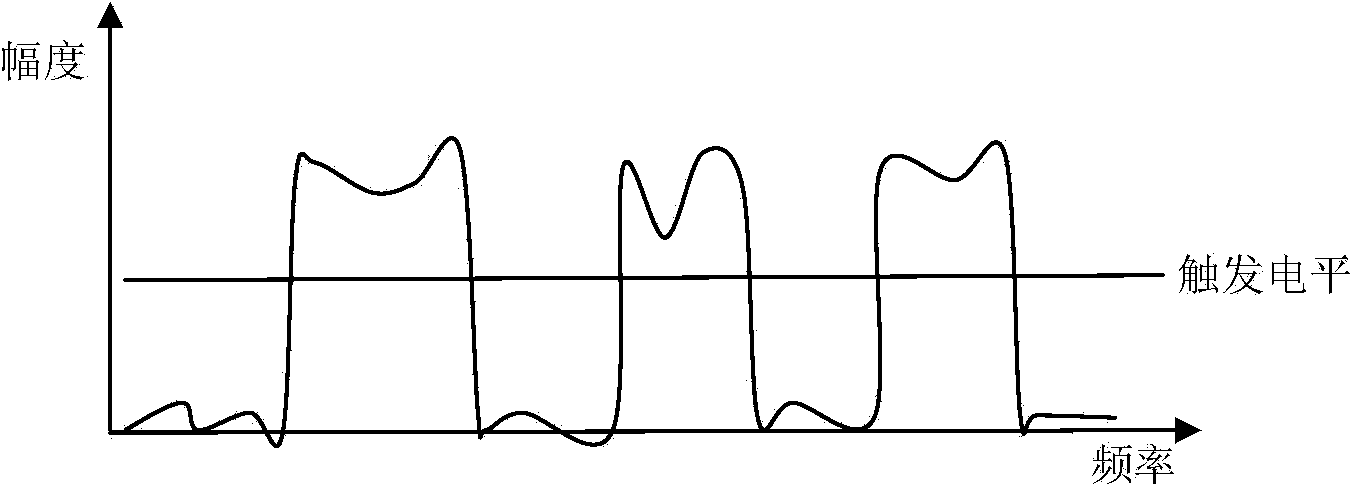

Digital pileup waveform processing method and system

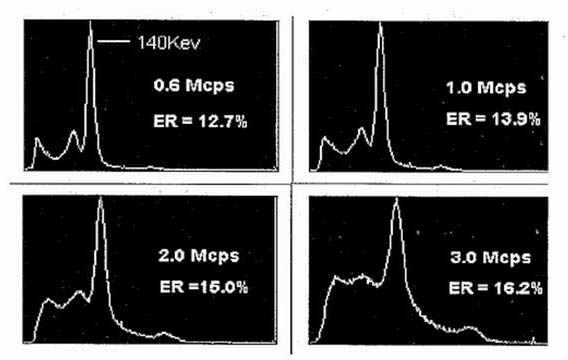

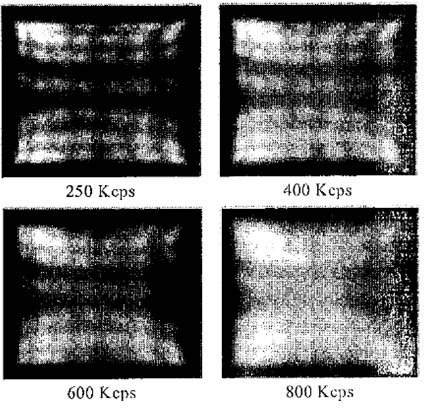

ActiveCN102073059AImprove signal-to-noise ratioReduce lossPulse descriminationX/gamma/cosmic radiation measurmentCounting rateSignal-to-noise ratio (imaging)

The invention discloses a digital pileup waveform processing method and a digital pileup waveform processing system. The method comprises the following steps of: determining a pulse rising edge area, and judging whether a pulse has a pileup waveform or not according to a time interval between adjacent pulse rising edges; and dividing a digital waveform determined as pileup according to the risingedge and the falling edge of the pulse, reconstructing single event pulse waveforms in turn by using the divided waveform, and extracting single pulse information from the reconstructed waveforms. The invention also discloses the pileup waveform processing system, which comprises a pileup waveform discrimination module, a pulse waveform division module and a pulse waveform reconstruction module. By the method and the system, the pileup pulse waveform can be effectively discriminated, each single event pulse waveform in the pileup is accurately reconstructed, information such as energy, time, amplitude, decay time constant, position and the like of the single event pulse is accurately recovered, and the counting rate of a system under high activity, and the signal-to-noise ratio of a measuring result are improved.

Owner:HUAZHONG UNIV OF SCI & TECH +1

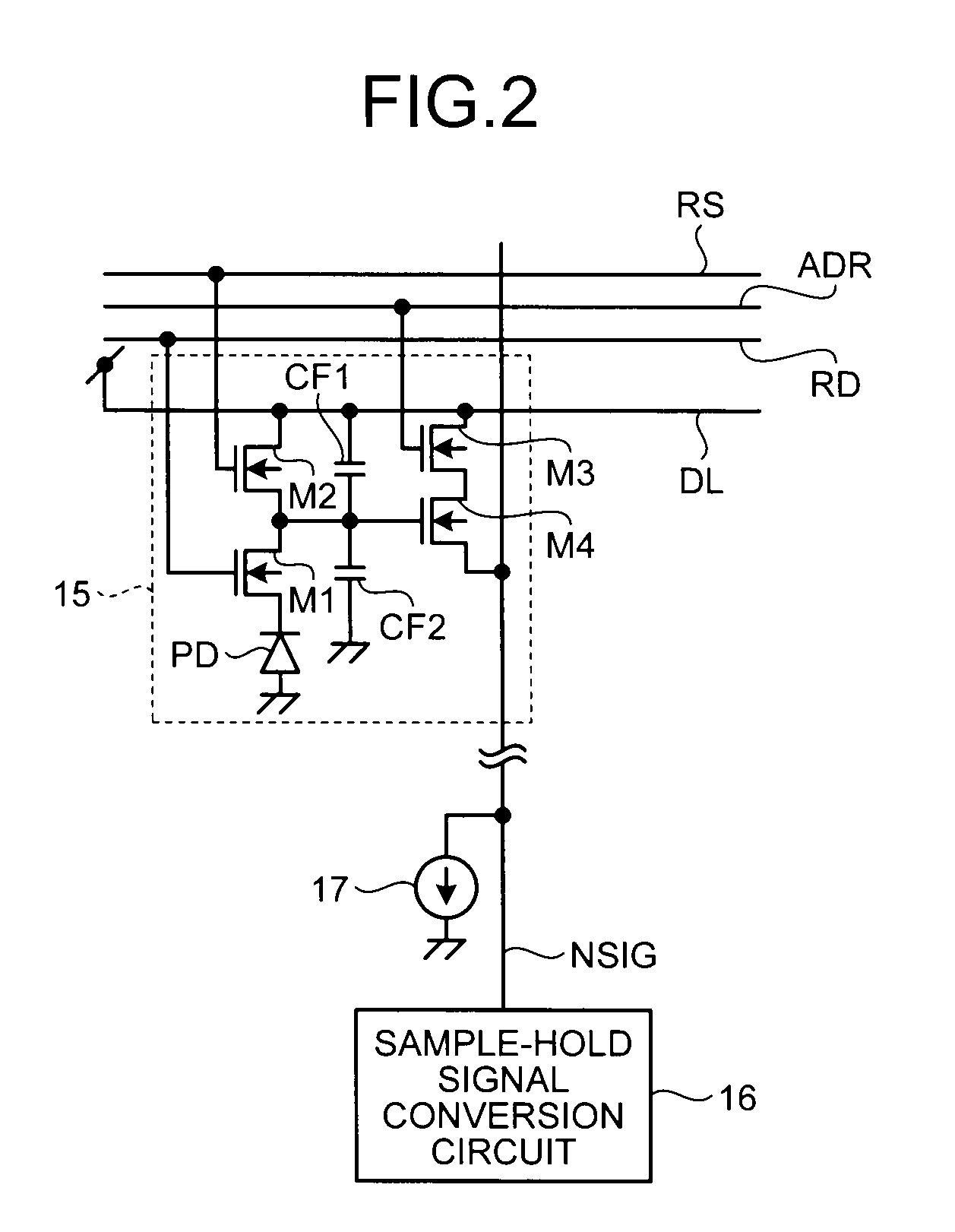

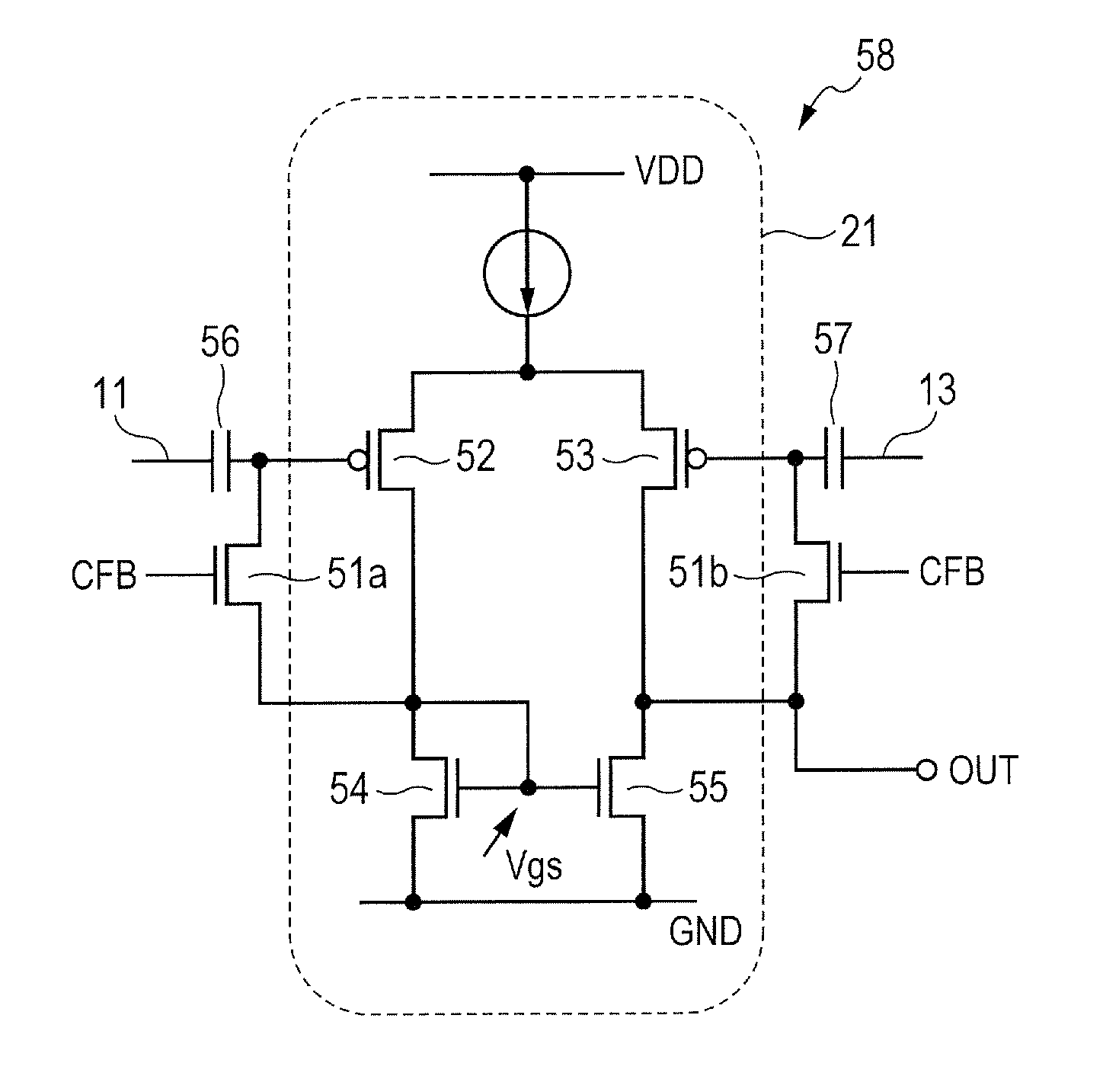

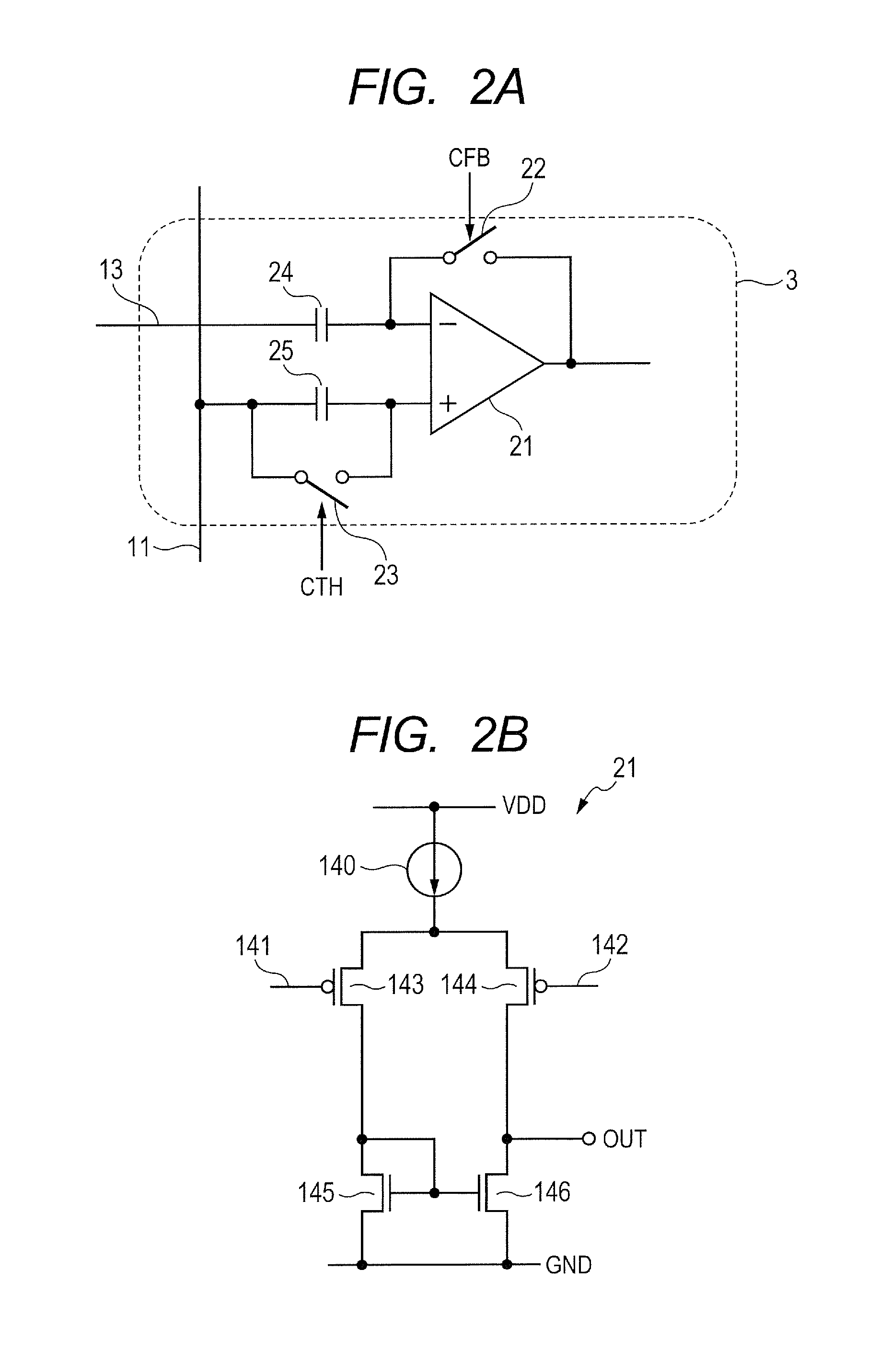

Power-supply-noise cancelling circuit and solid-state imaging device

A reference voltage generation circuit generates a reference voltage and outputs it to an amplifier reference voltage line. A power-supply-noise adding circuit adds power supply noise superimposed on a power supply to the reference voltage generated by the reference voltage generation circuit. A differential amplifier amplifies a difference between a voltage of a vertical signal line and a voltage of an amplifier reference voltage line and outputs the amplified voltage.

Owner:KK TOSHIBA

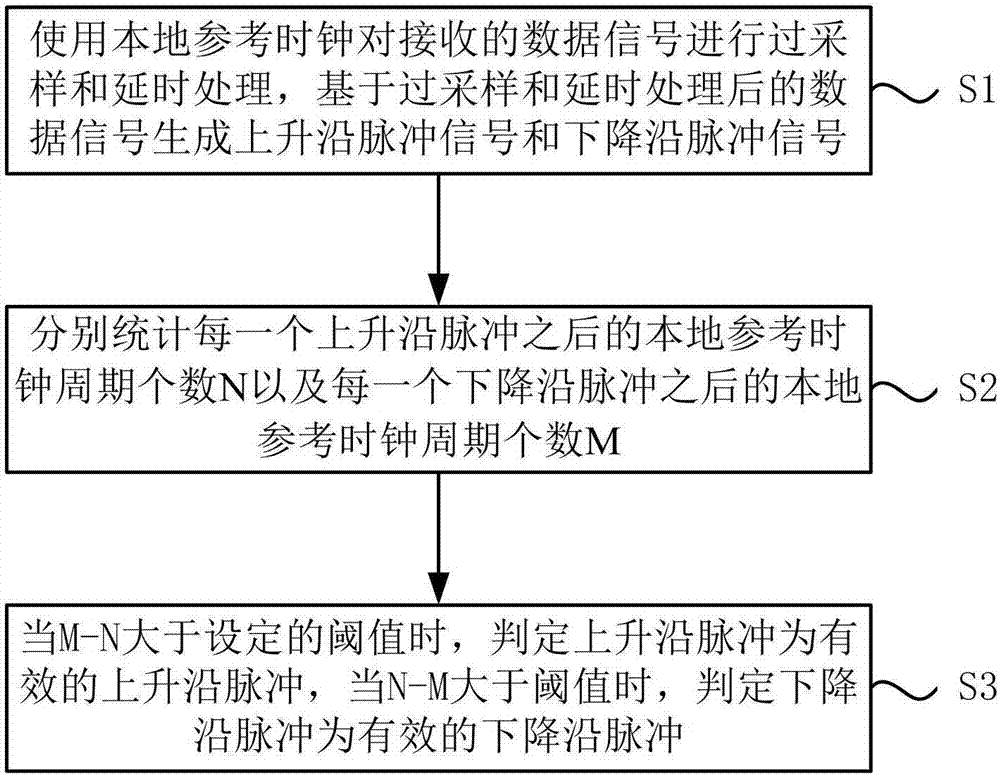

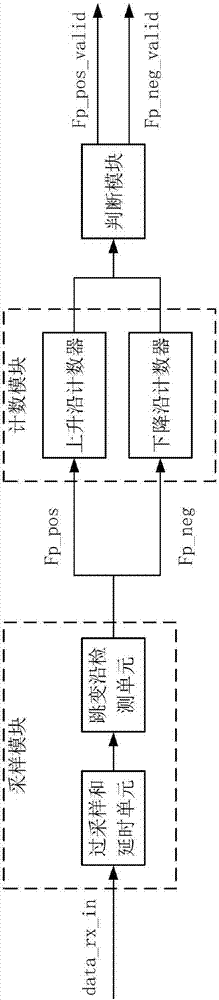

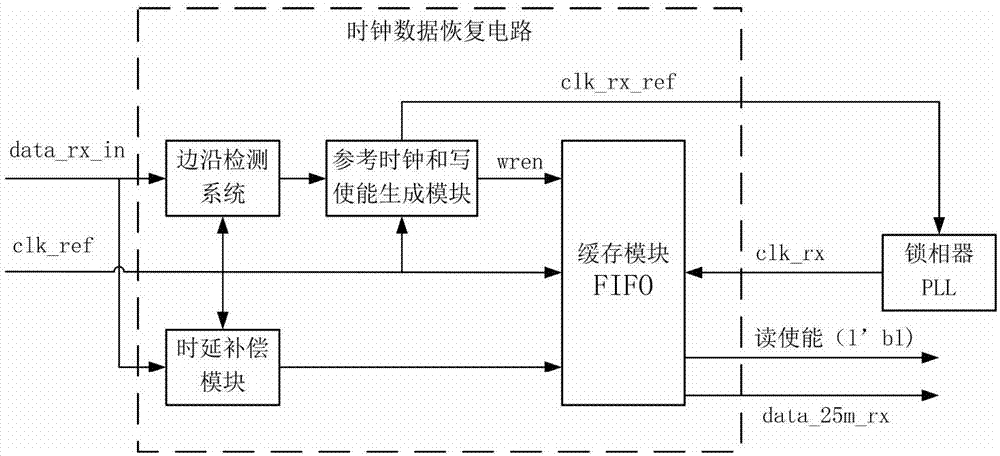

Edge detection method and system and clock and data recovery circuit based on FPGA (Field Programmable Gate Array)

ActiveCN107147379AImprove accuracyImprove reliabilityPulse automatic controlPulse descriminationData signalField-programmable gate array

The invention discloses an edge detection method and system and a clock and data recovery circuit based on an FPGA (Field Programmable Gate Array), and relates to the technical field of communication. The method comprises the following steps: performing over-sampling and delay processing on a received data signal by a local reference clock, and generating a rising edge pulse signal and a falling edge pulse signal based on the data signal being subjected to the over-sampling and delay processing, wherein the rising edge pulse signal comprises a plurality of rising edge pulses, and the falling edge pulse signal comprises a plurality of falling edge pulses; performing statistics to obtain the quantity N of local reference clock periods after the rising edge pulses and the quantity M of the local reference clock periods after the falling edge pulses respectively; and judging that the rising edge pulses are valid rising edge pulses when (M-N) is greater than a set threshold, and judging that the falling edge pulses are valid falling edge pulses when (N-M) is greater than the threshold. Through adoption of the edge detection method and system and the clock and data recovery circuit, the valid rising edge pulses and the valid falling edge pulses can be detected, and the accuracy and reliability of data signal sampling are improved.

Owner:FENGHUO COMM SCI & TECH CO LTD

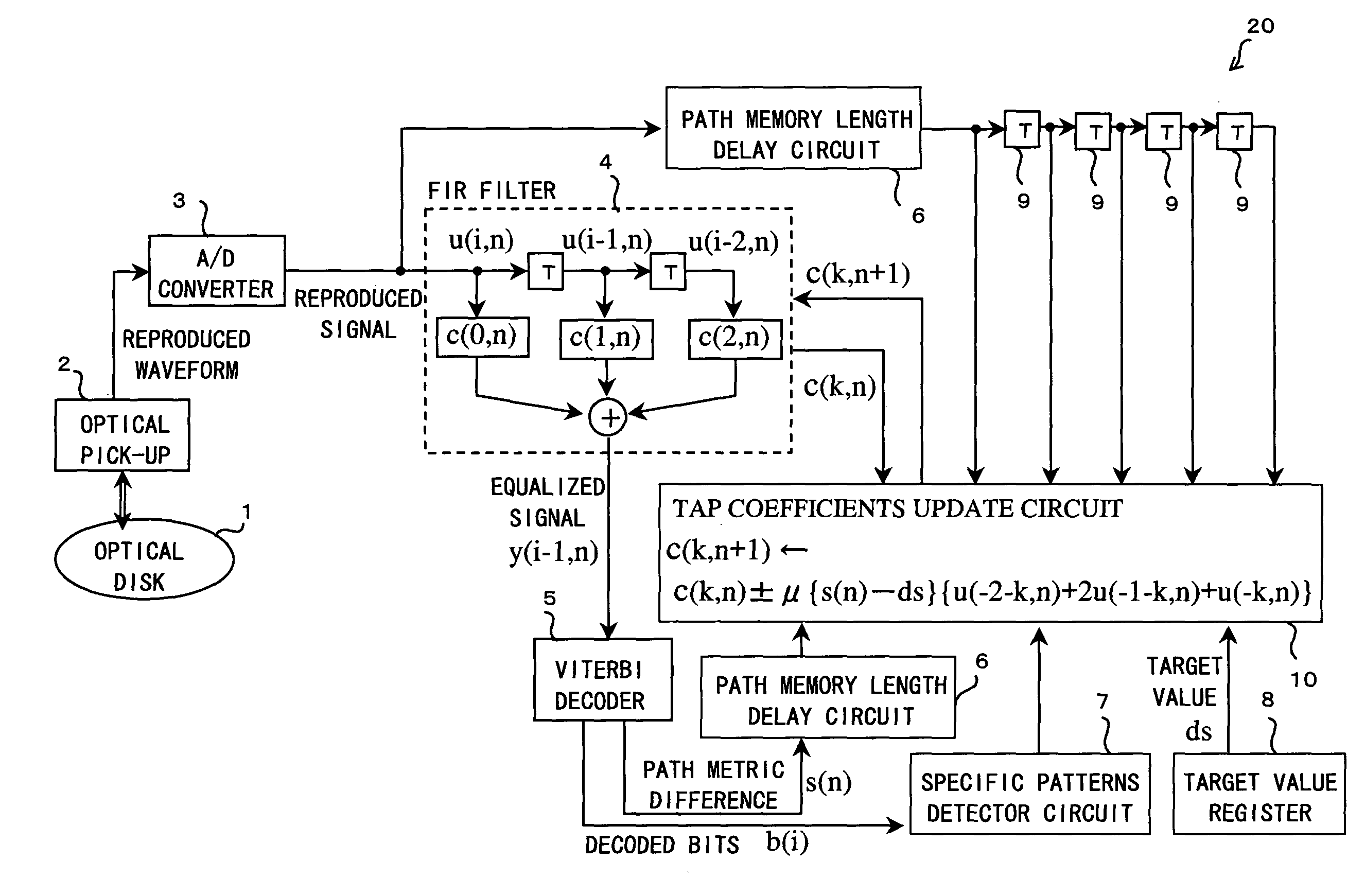

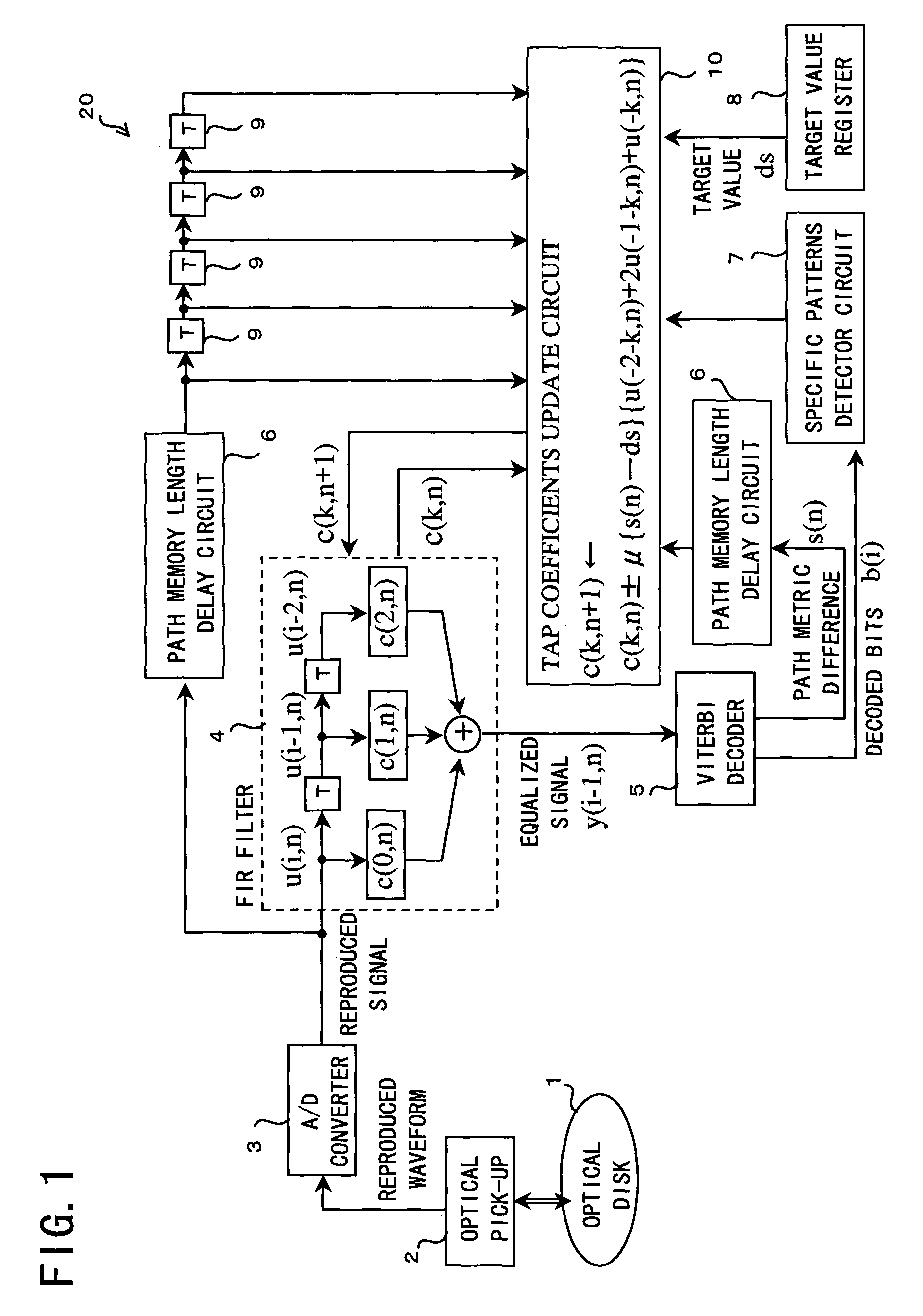

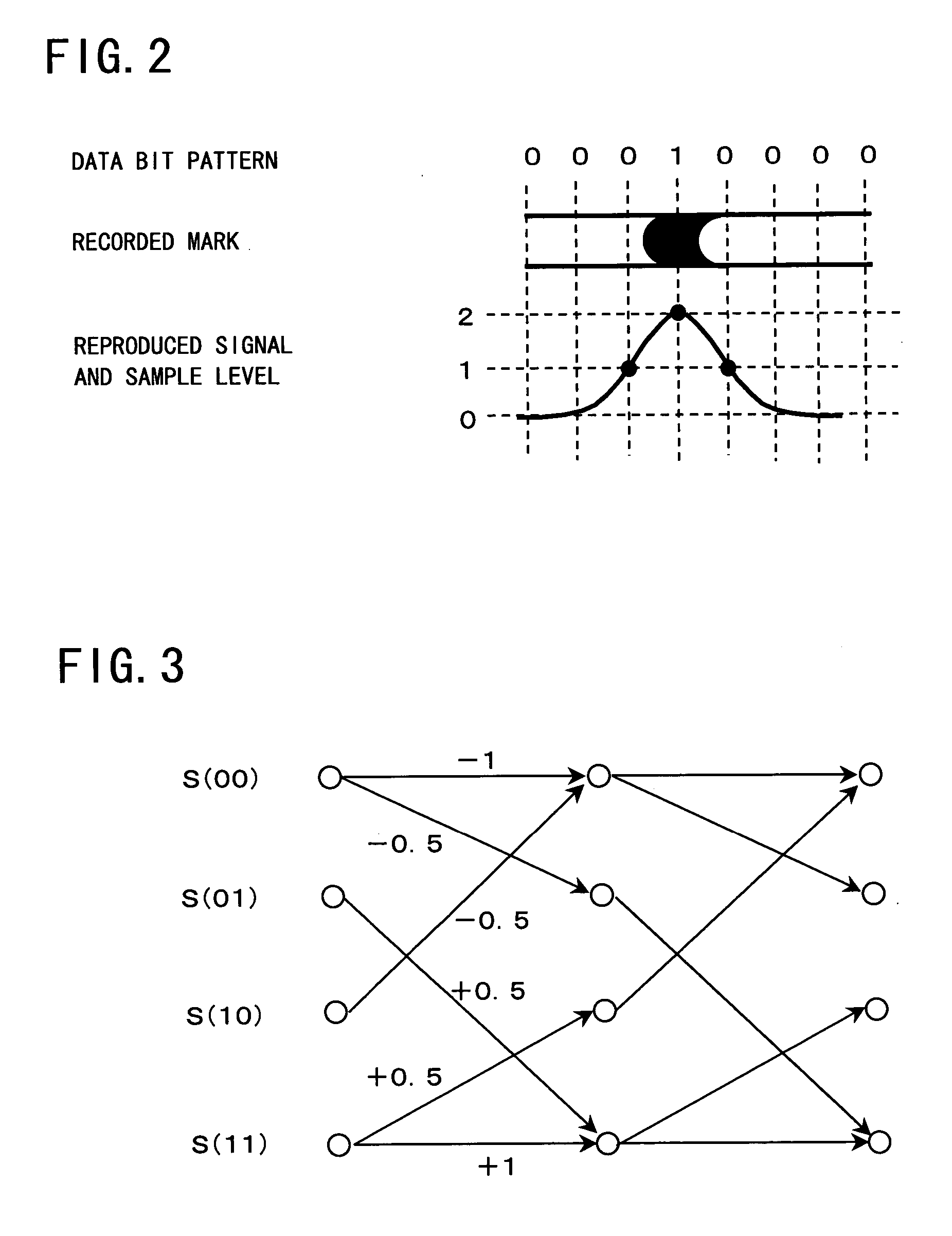

Adaptive waveform equalization for viterbi-decodable signal and signal quality evaluation of viterbi-decodable signal

InactiveUS7194674B2Convenient ArrangementEvaluate qualityMultiple-port networksData representation error detection/correctionSignal qualityMean square

Owner:SHARP KK

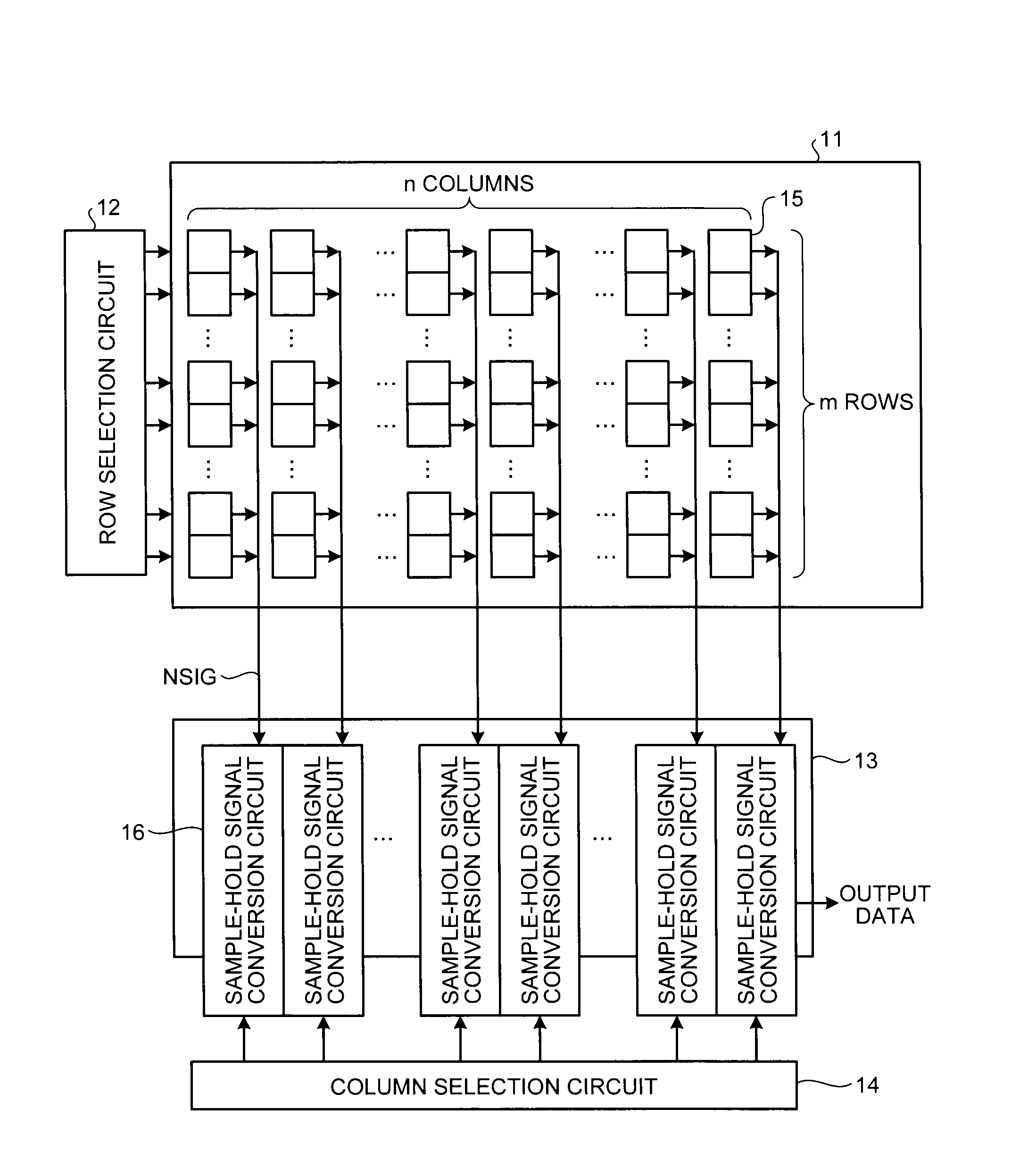

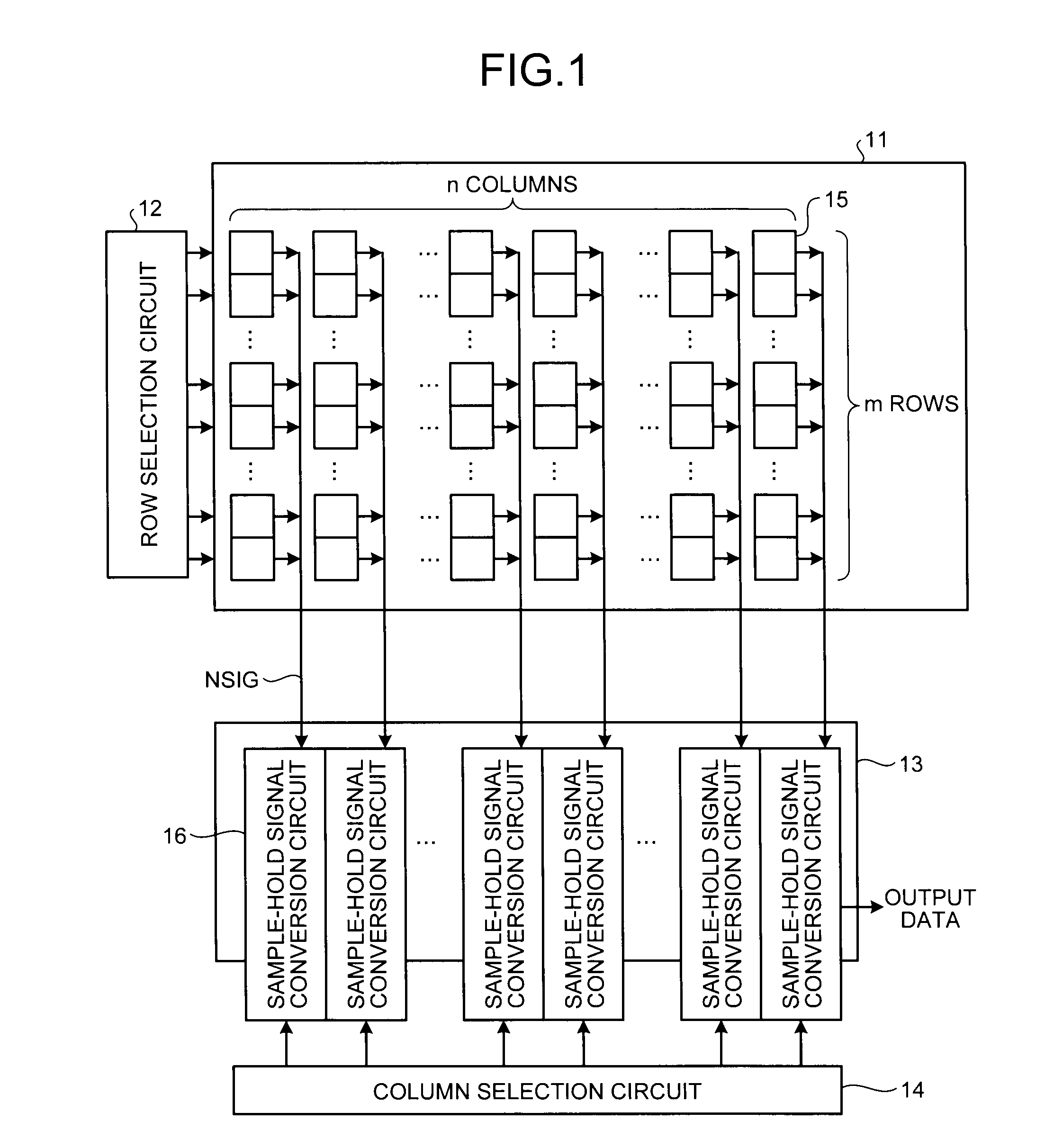

Comparator circuit, imaging apparatus using the same, and method of controlling comparator circuit

ActiveUS20150138411A1Analogue/digital conversionTelevision system detailsCapacitanceOffset cancellation

An object of the present invention is to provide a comparator which has an input voltage range larger than the case where a conventional offset cancel technique is used, while reducing an offset voltage. A comparator circuit includes: a comparator having an inverting input terminal, a non-inverting input terminal and an output terminal; a first switch having one terminal connected to the inverting input terminal and having the other terminal connected to the output terminal; a first capacitor which has one end connected with the inverting input terminal; a first signal input terminal which is another end of the first capacitor; and a second signal input terminal which selectively inputs either one of a fixed voltage and a comparing signal into the non-inverting input terminal.

Owner:CANON KK

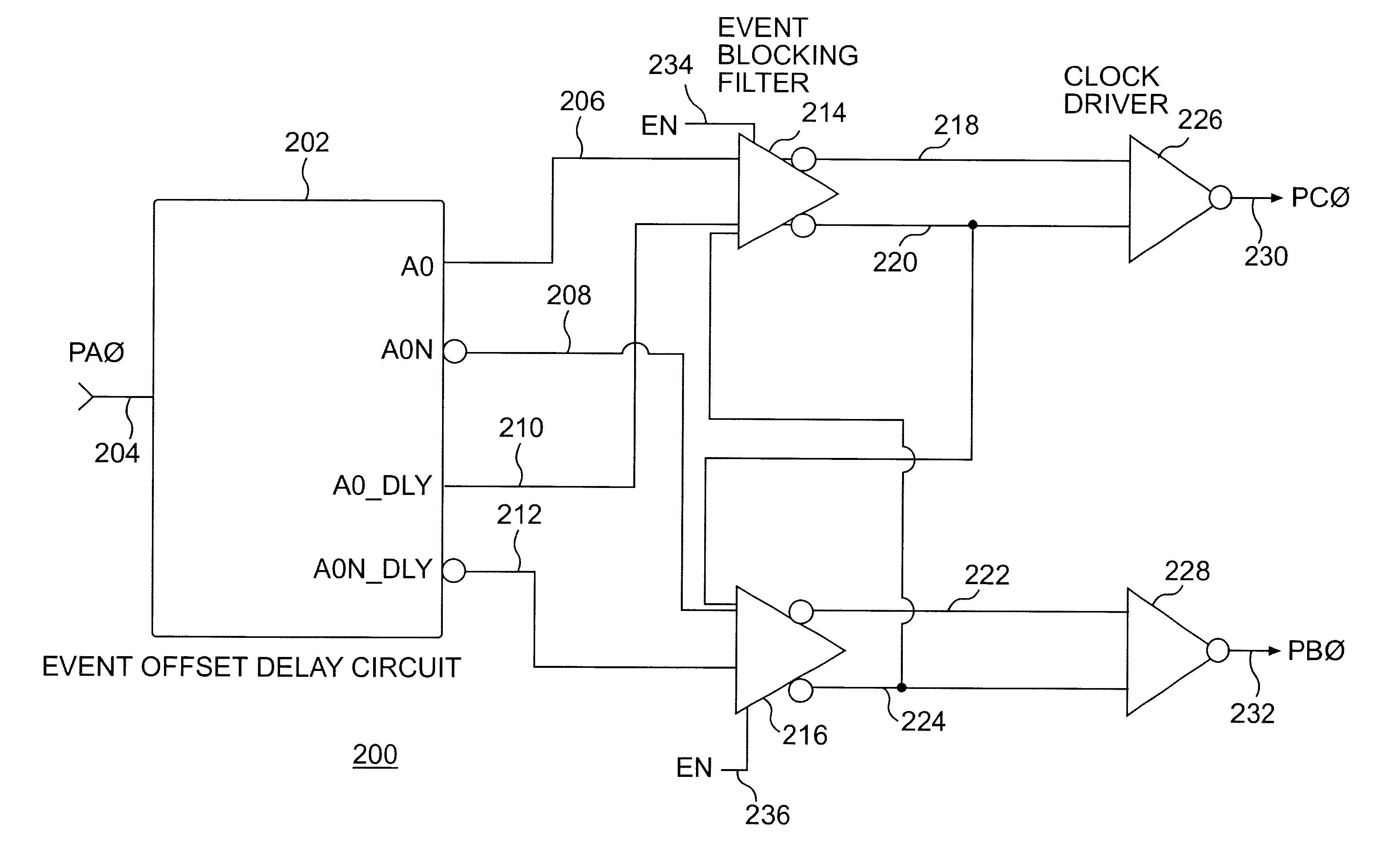

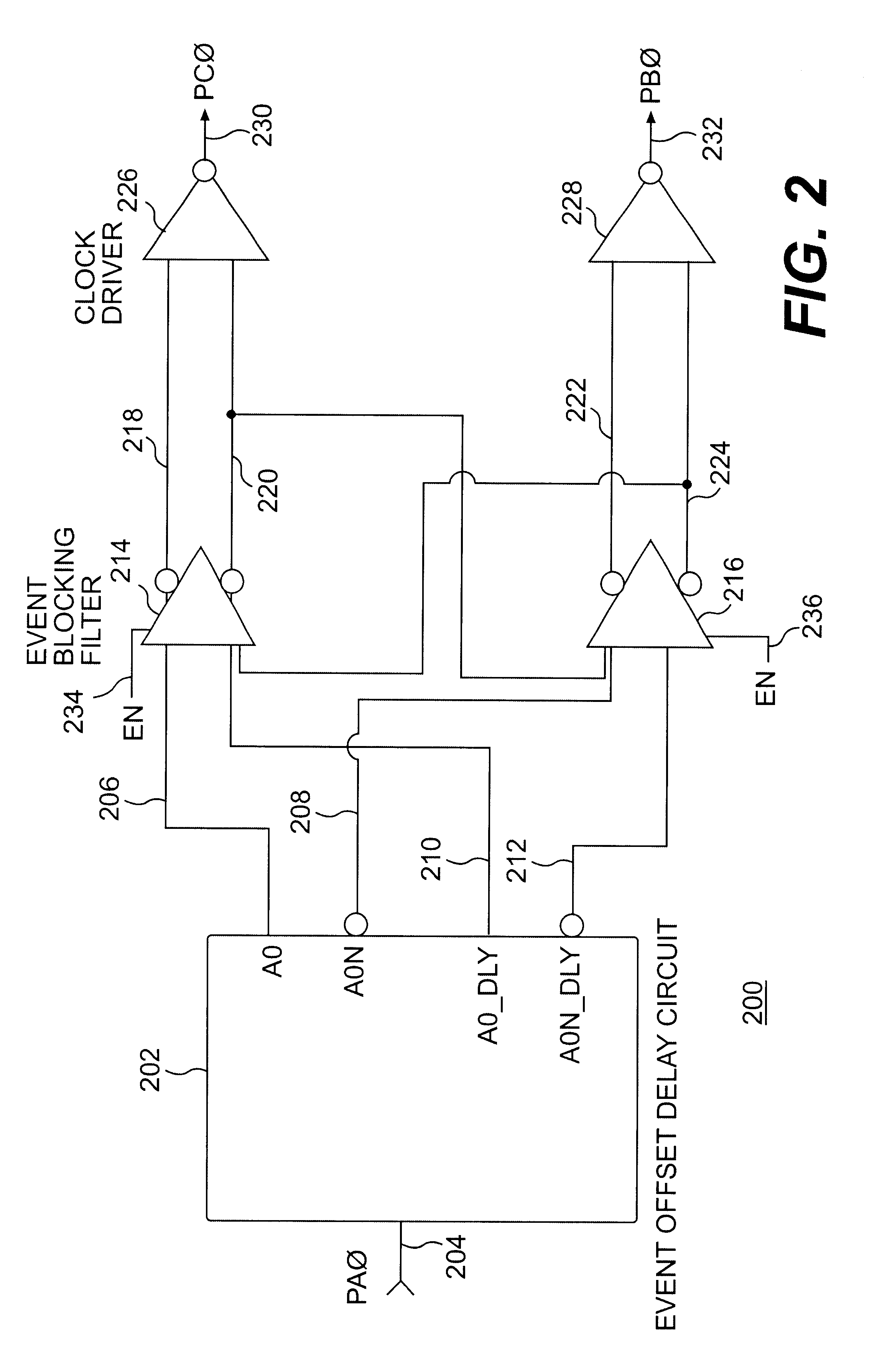

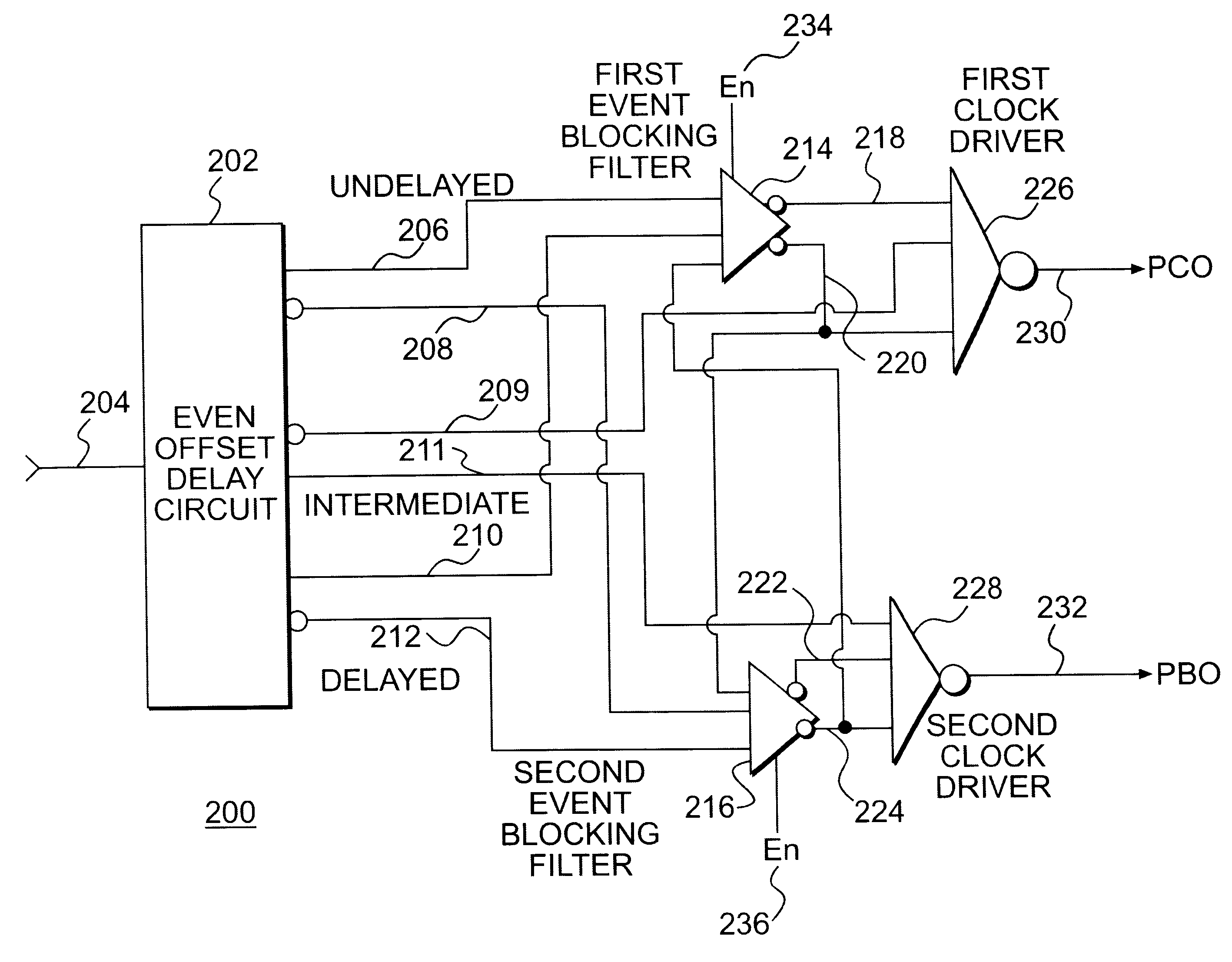

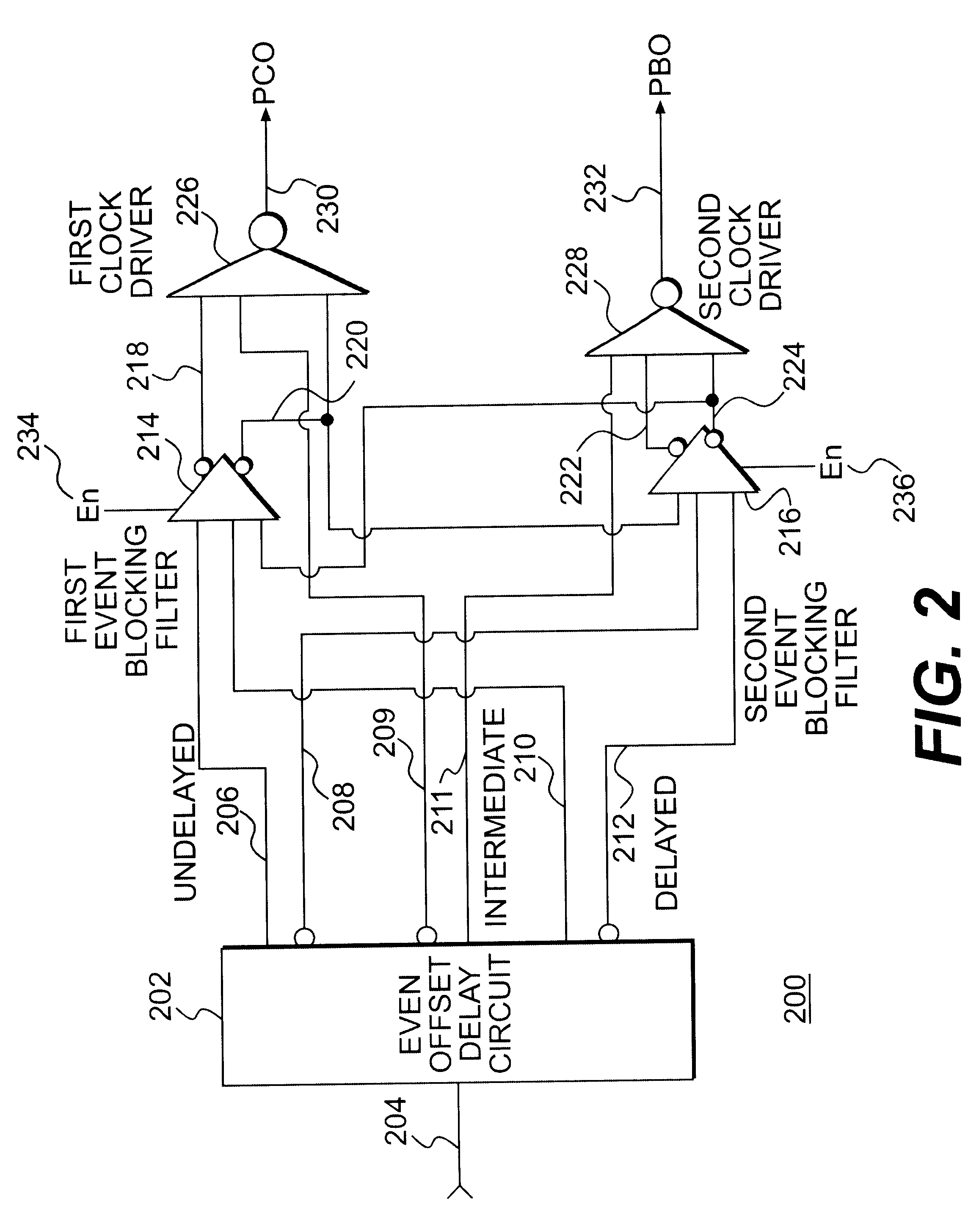

Method and apparatus for a single event upset (SEU) tolerant clock splitter

InactiveUS6362676B1Duration/width modulated pulse demodulationElectric pulse generatorSingle event upsetDuration time

A clock splitter circuit for providing a Single Event Upset (SEU) tolerant clock signals to latches in a space-based environment. The splitter circuit includes an event offset delay. The event offset delay receives an undelayed clock signal and generates an undelayed inverted clock, a delayed clock signal and an inverted delayed clock signal. The delayed clock signal and the inverted delayed clock signal are delayed by the known duration of Single Event Effects (SEE) on logic. The delayed and undelayed clock signals are passed to a pair of event blocking filters which block any disturbance in the undelayed and / or undelayed clock signals. The event blocking filters each generate a pair of in-phase inverted output signals. The event blocking filters are designed such that both pairs of outputs may not be low simultaneously. The in-phase output signals from each event blocking filter drive an inverting clock driver to provide a pair of SEU tolerant non-overlapping clock driver phase output signals to one or more latches.

Owner:FRANTORF INVESTMENTS

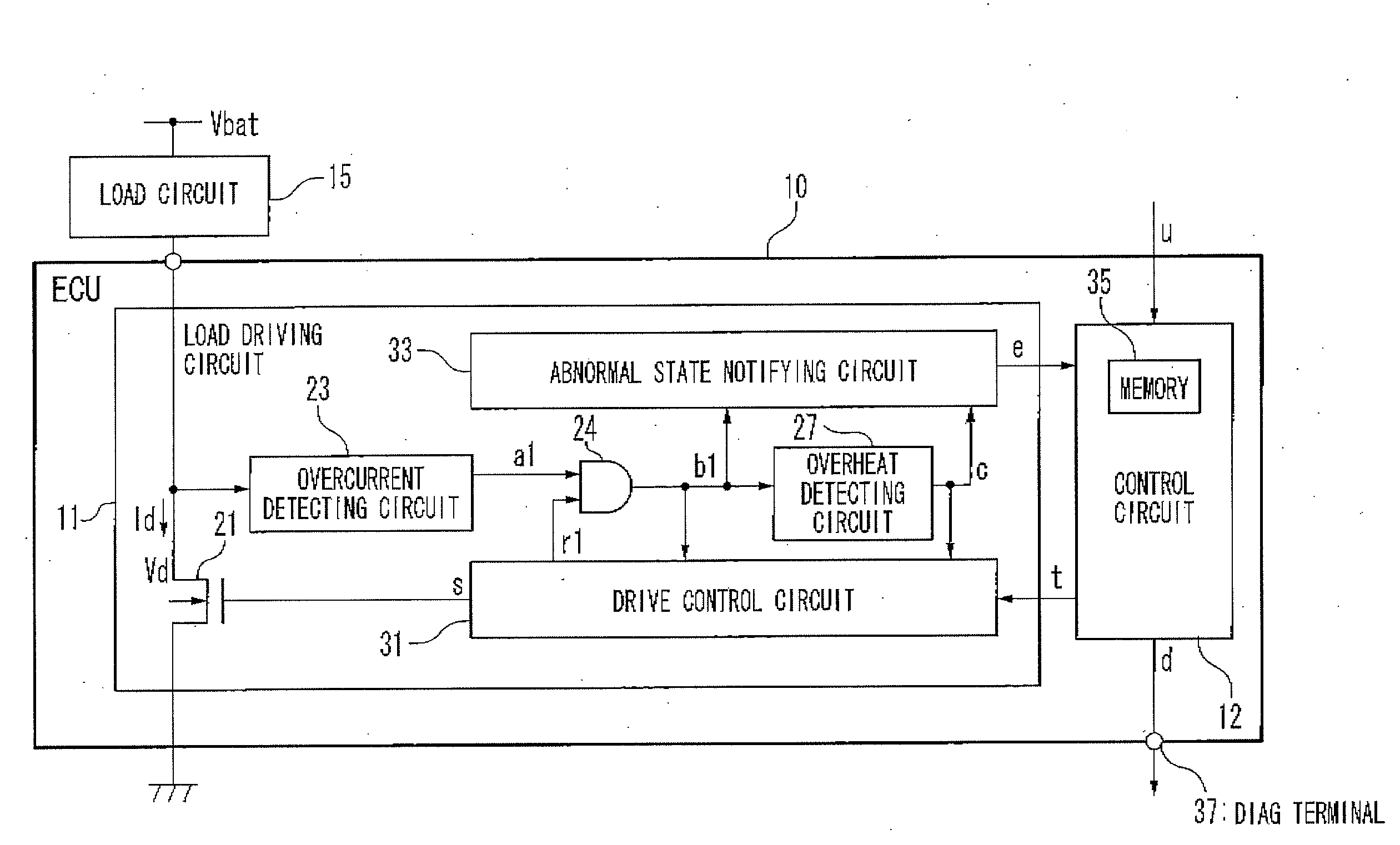

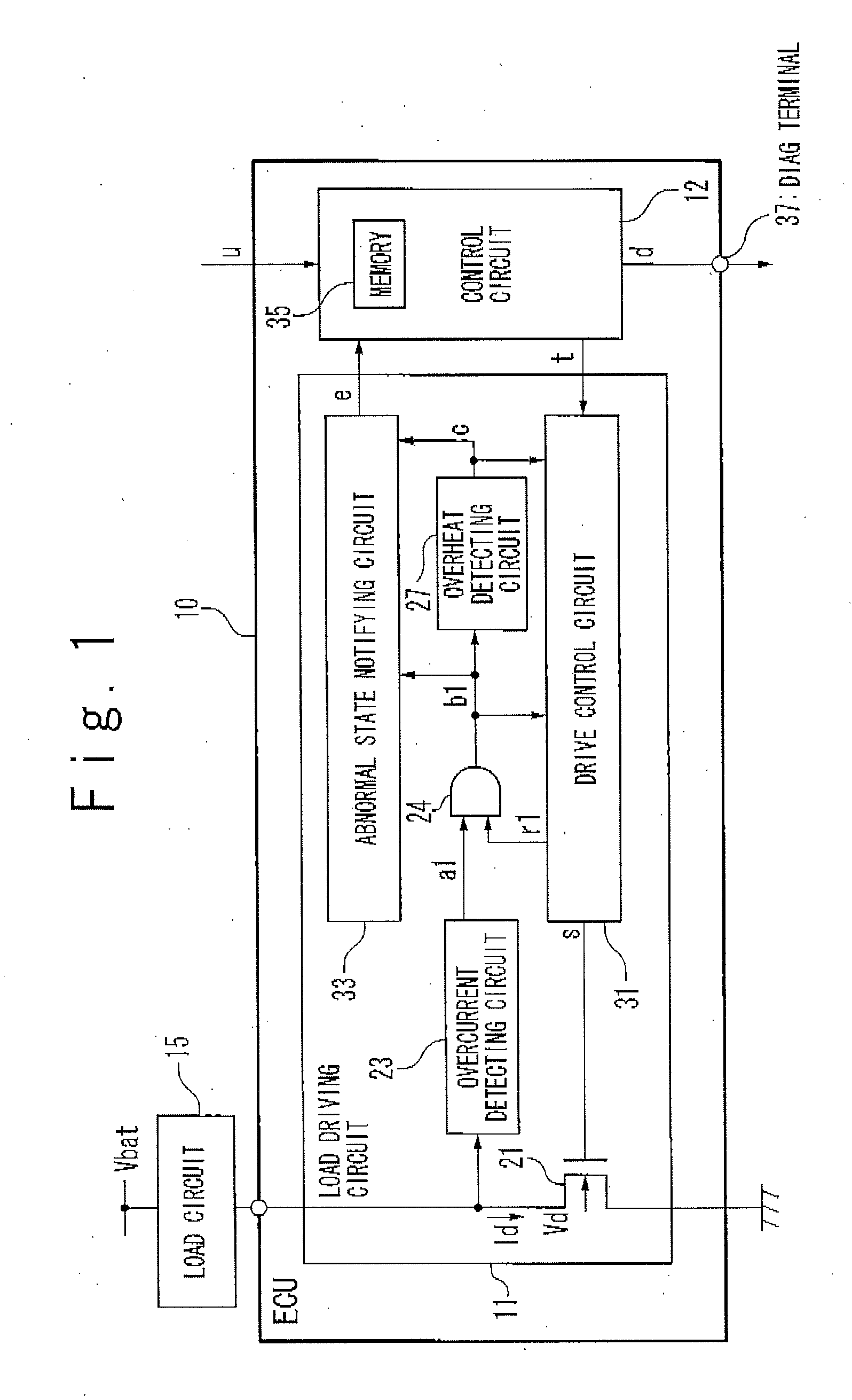

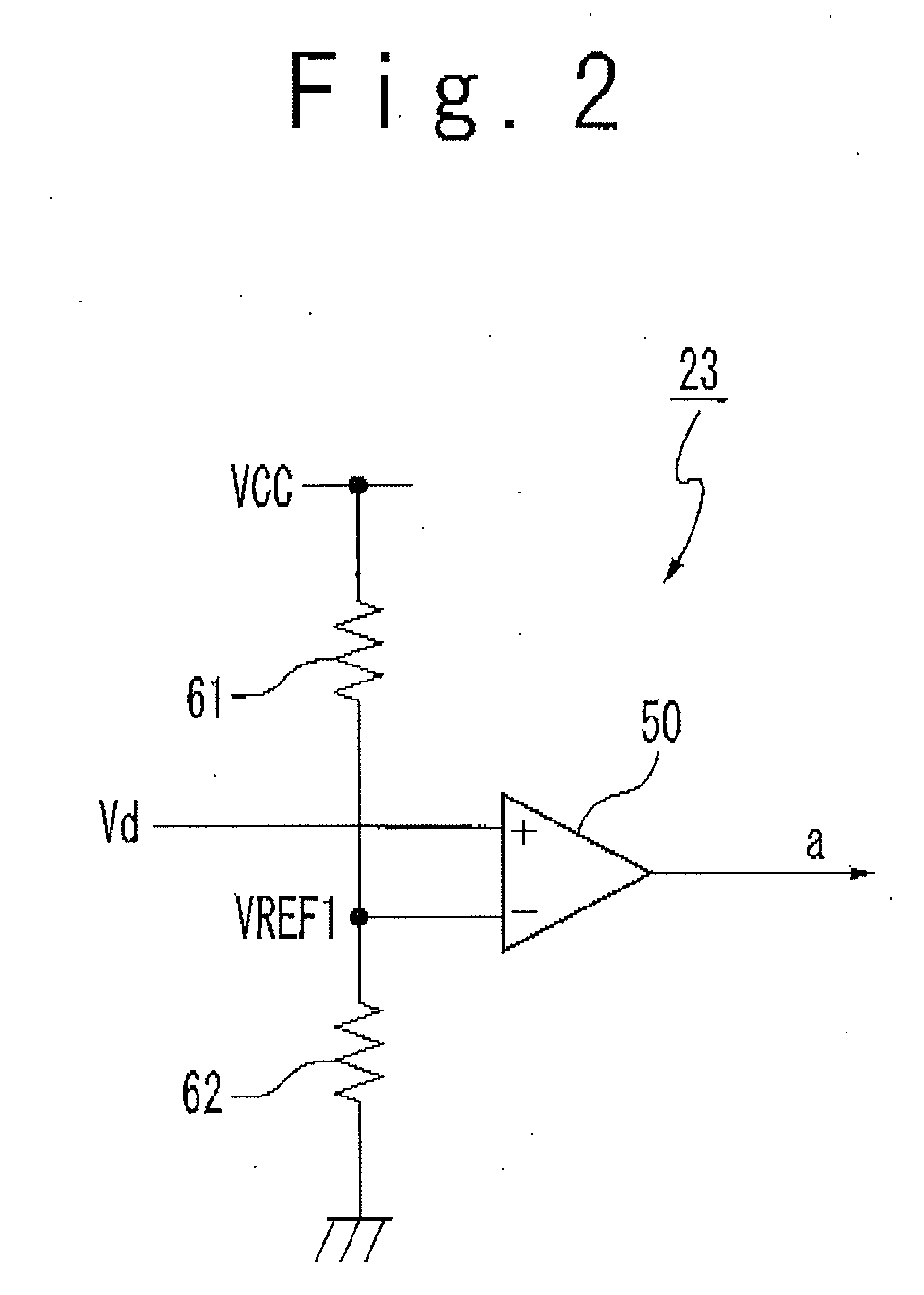

Semiconductor device and circuit protection method

InactiveUS20110058297A1Long-term reliabilityInhibition continuesTransistorMultiple input and output pulse circuitsPower semiconductor deviceLoad circuit

A semiconductor device includes a current supply section configured to control a current flowing through a load circuit; an overcurrent detecting section configured to detect based on the current, that an overcurrent flows through the load circuit, to output an overcurrent signal; and an overheat detecting circuit configured to detect that a peripheral temperature exceeds a detected temperature; in response to the overcurrent signal, and output an overheat detection signal. The overheat detecting circuit has a hysteresis to the detection temperature, and the detection temperature contains an overheat detection temperature used to detect an overheat state and a recovery temperature used to detect to have escaped from the overheat state. The semiconductor device further includes a drive control circuit configured to output the current control signal which indicates the quantity of the current flowing through the load circuit based on the overcurrent signal and the overheat detection signal in the electric current supply section.

Owner:RENESAS ELECTRONICS CORP

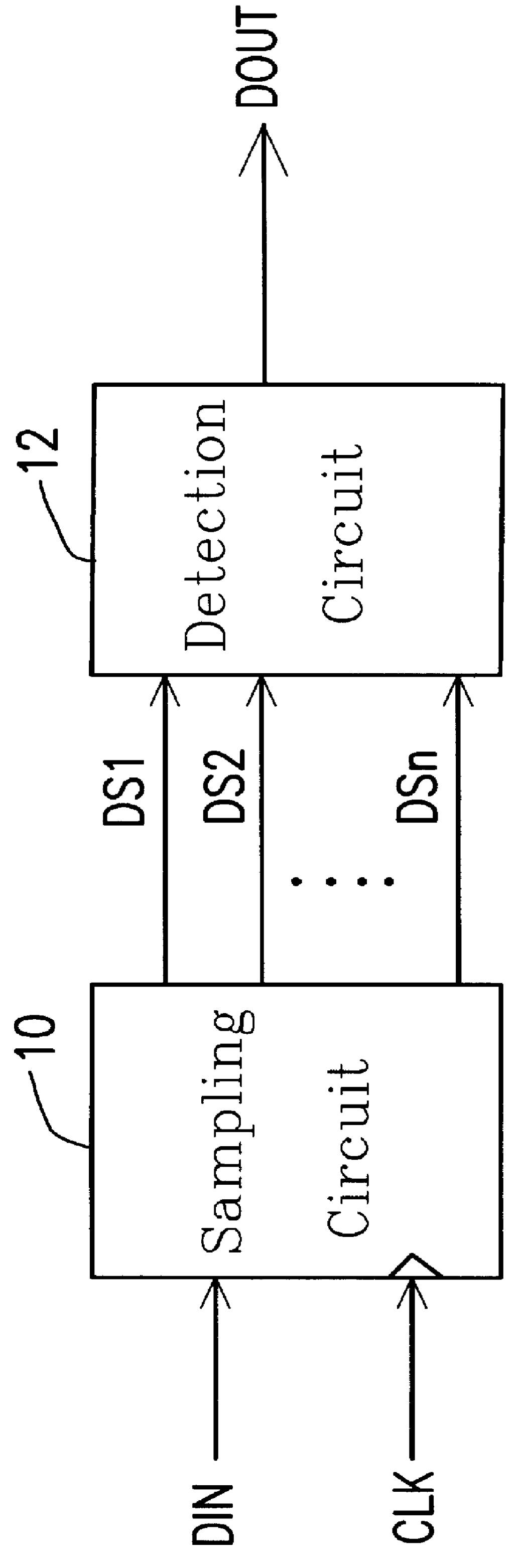

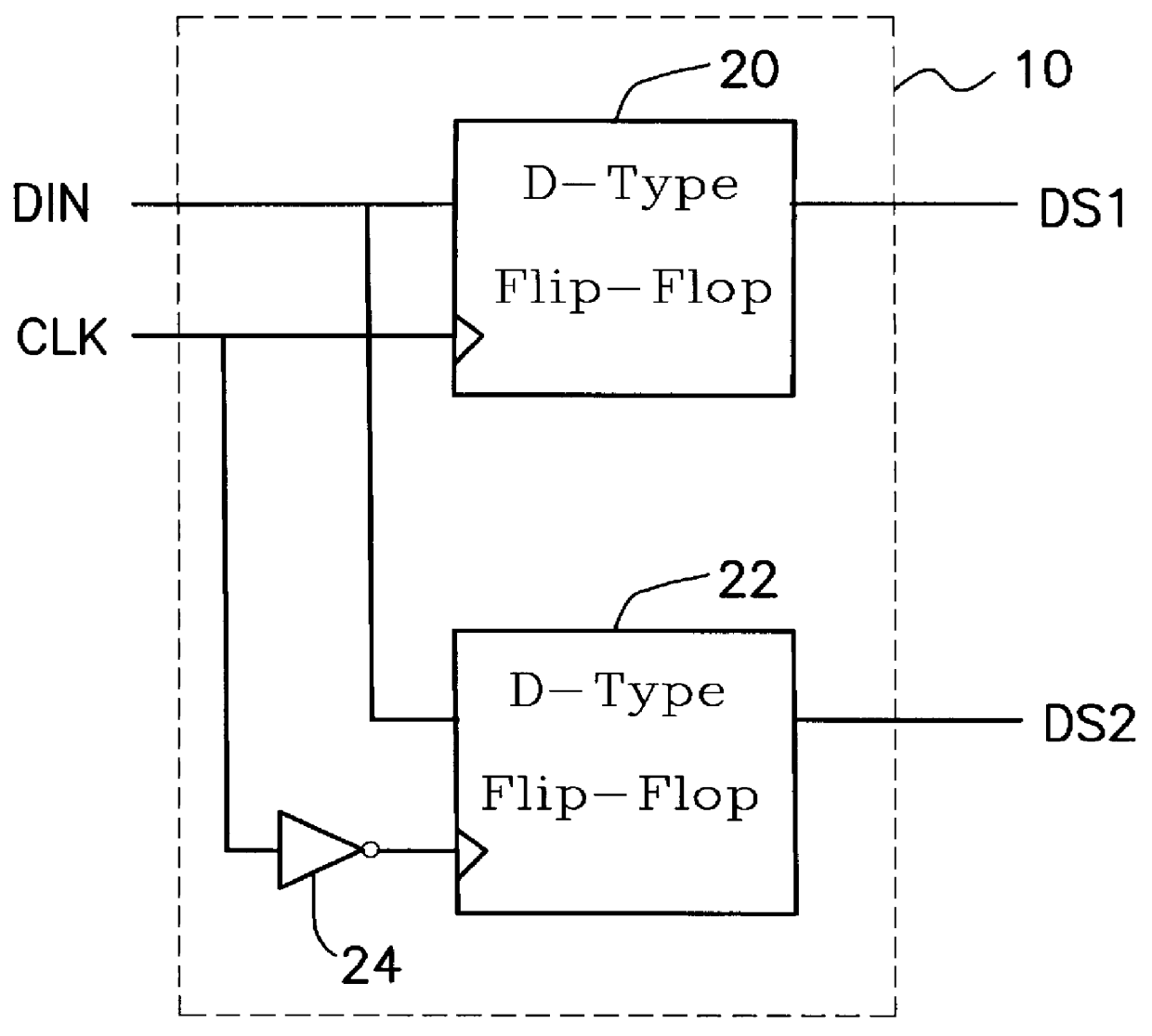

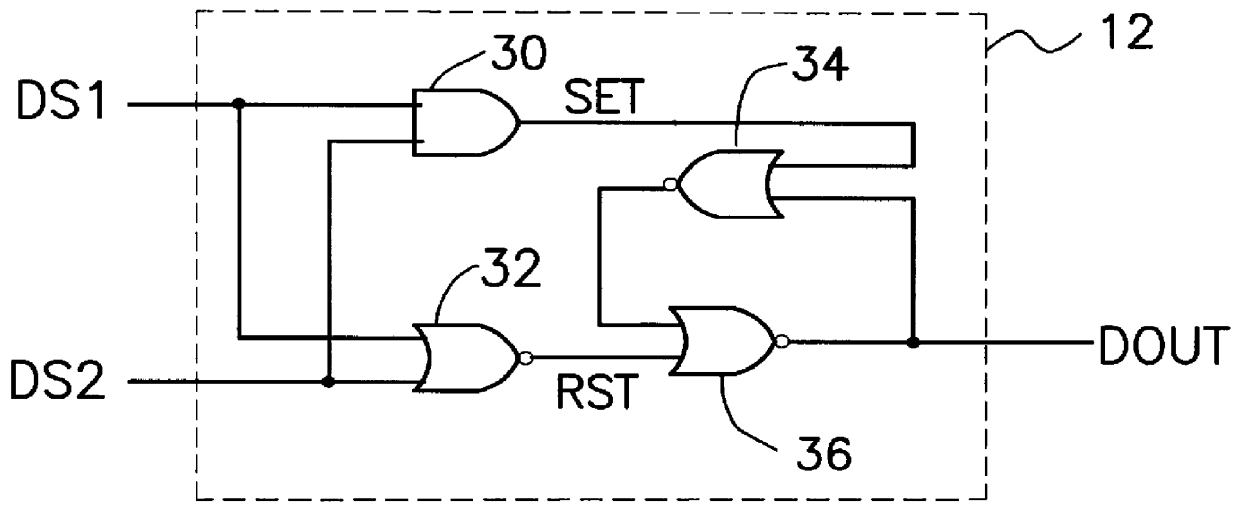

Digital pulse filtering circuit

InactiveUS6064704AReduce manufacturing costEasy to adjustError preventionLine-faulsts/interference reductionIntegrated circuitLow frequency

A digital pulse filtering circuit for filtering out pulses of specific pulse widths in a composite signal is provided. The digital pulse filtering circuit includes a sampling circuit for sampling the input composite signal based on a periodic clock signal to thereby generate a plurality of sampled signals of the input composite signal. In response to these sampled signals, a detection circuit outputs a low-frequency composite signal which is a filtered version of the input composite signal. The digital pulse filtering circuit is completely based on digital circuitry which can be built in integrated circuits. The cutoff frequency of the digital pulse filtering circuit is dependent on the frequency of the clock signal, which is very easy and accurate to adjust.

Owner:UNITED MICROELECTRONICS CORP

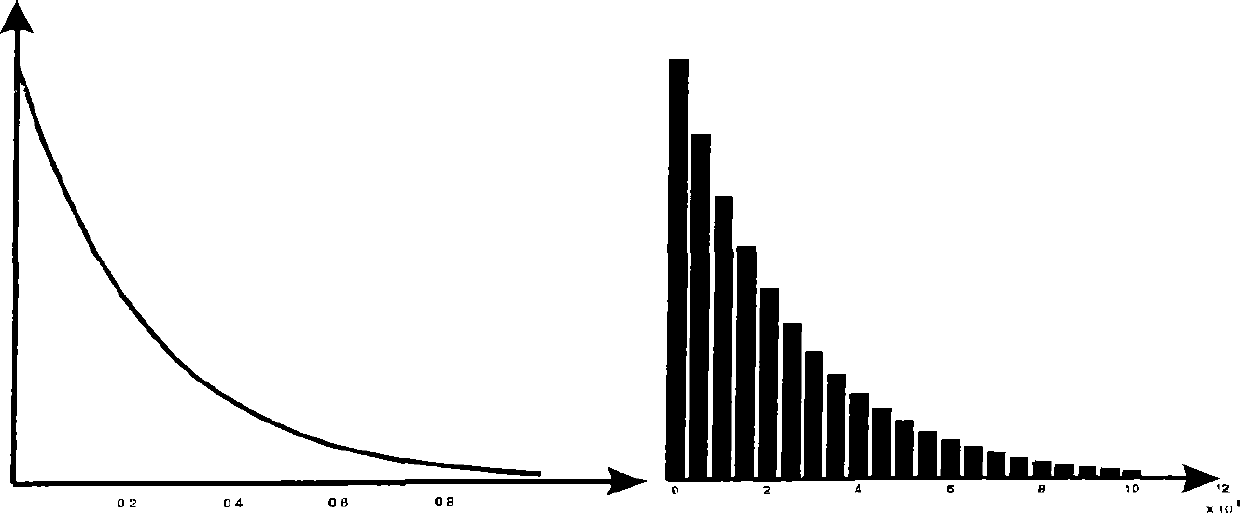

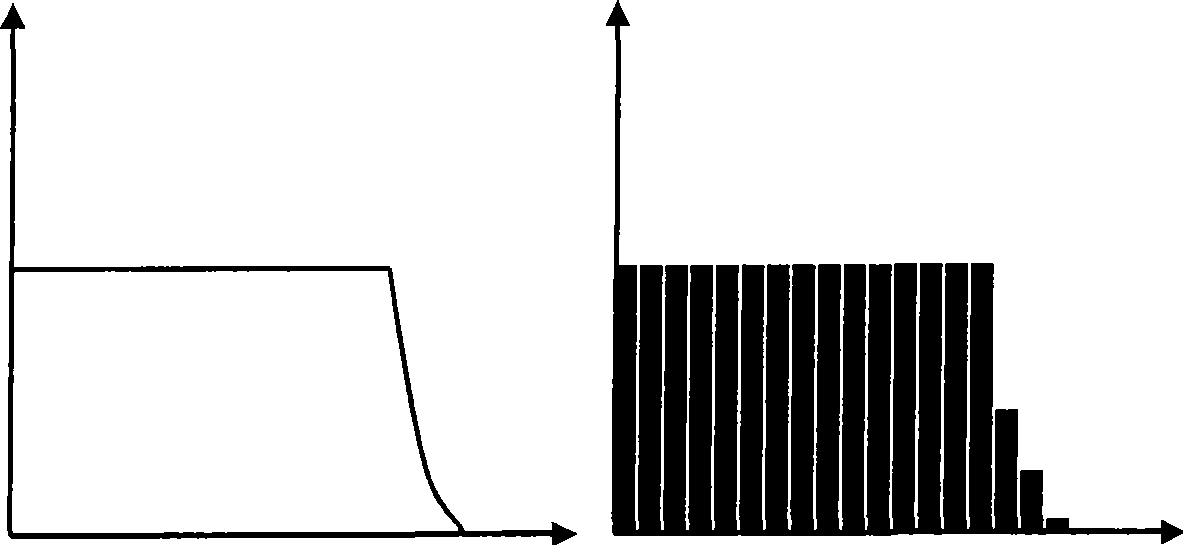

Mobile phone noise signal distinguishing method in electric appliance extra-high-frequency local discharging detection

ActiveCN101499862AEliminate distractionsTesting dielectric strengthTransmission monitoringPower equipmentElectric power

The invention discloses a discriminating method of cellphone noise signals in ultrahigh frequency partial discharge detection of electrical equipments, which comprises the following steps: a partial discharge pulse signal waveform is simulated according to pulse time width and pulse waveform decay time constant of a typical partial discharge pulse signal; a waveform coefficient K1 of the typical partial discharge pulse signal is computed, the ultrahigh frequency partial discharge detection of electrical equipments is implemented, and a certain number of discharge signal sampling point sequences of each possible partial discharge signal are obtained; an average value V and a largest pulse amplitude value Vmax of the sampling point sequences are respectively computed, and a waveform coefficient K that equals to V divided by Vmax is computed and judged, if the waveform coefficient K lies between 0 and K1, the pulse signal belongs to partial discharge pulse signals, and if the waveform coefficient K is larger than K1, the pulse signal belongs to cellphone pulse signals. The discriminating method of cellphone noise signals can simply and effectively discriminate the cellphone noise signal in the ultrahigh frequency partial discharge detection of electrical equipments, thus achieving the goal of eliminating the interference of cellphone noise signals.

Owner:RED PHASE INC

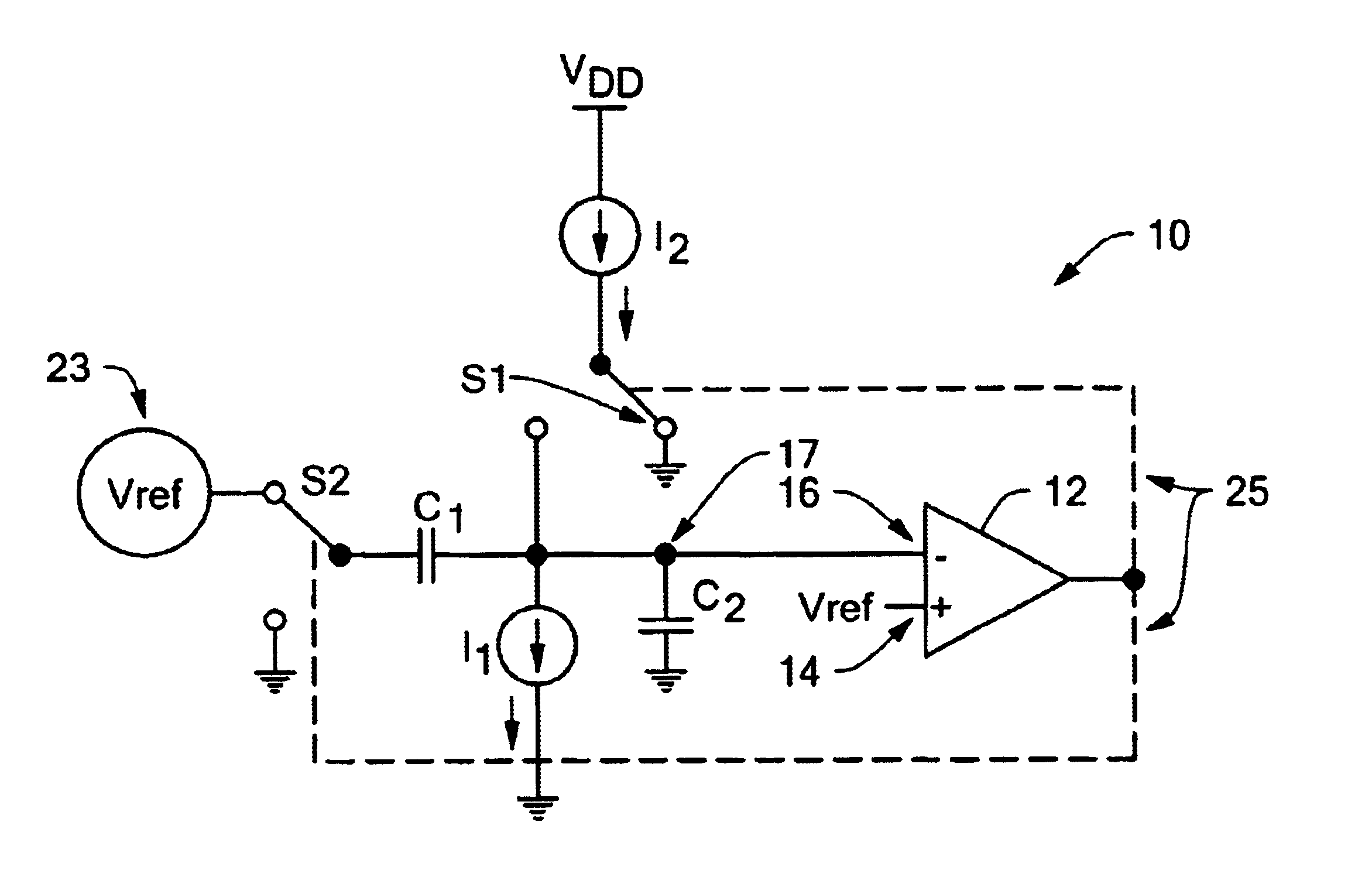

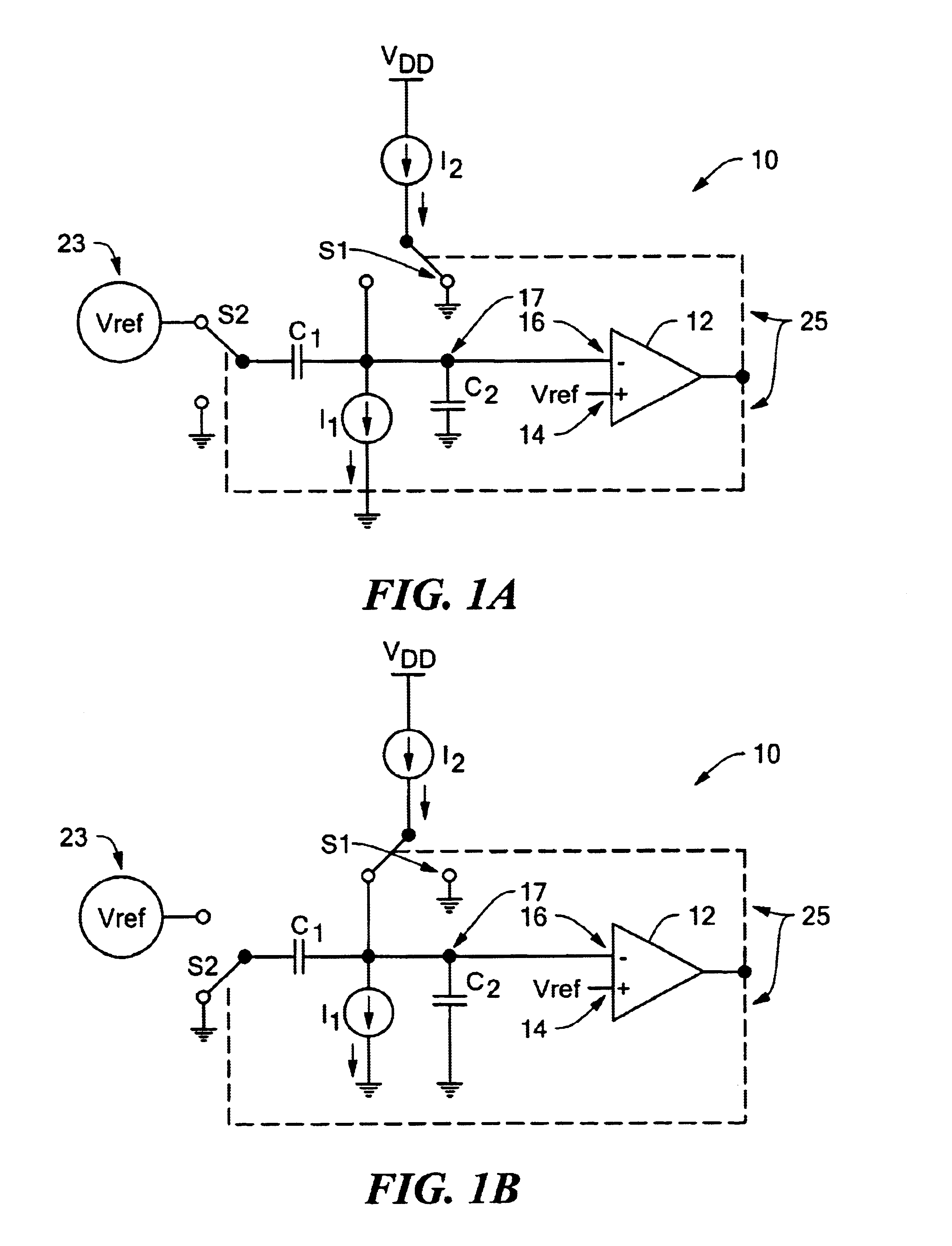

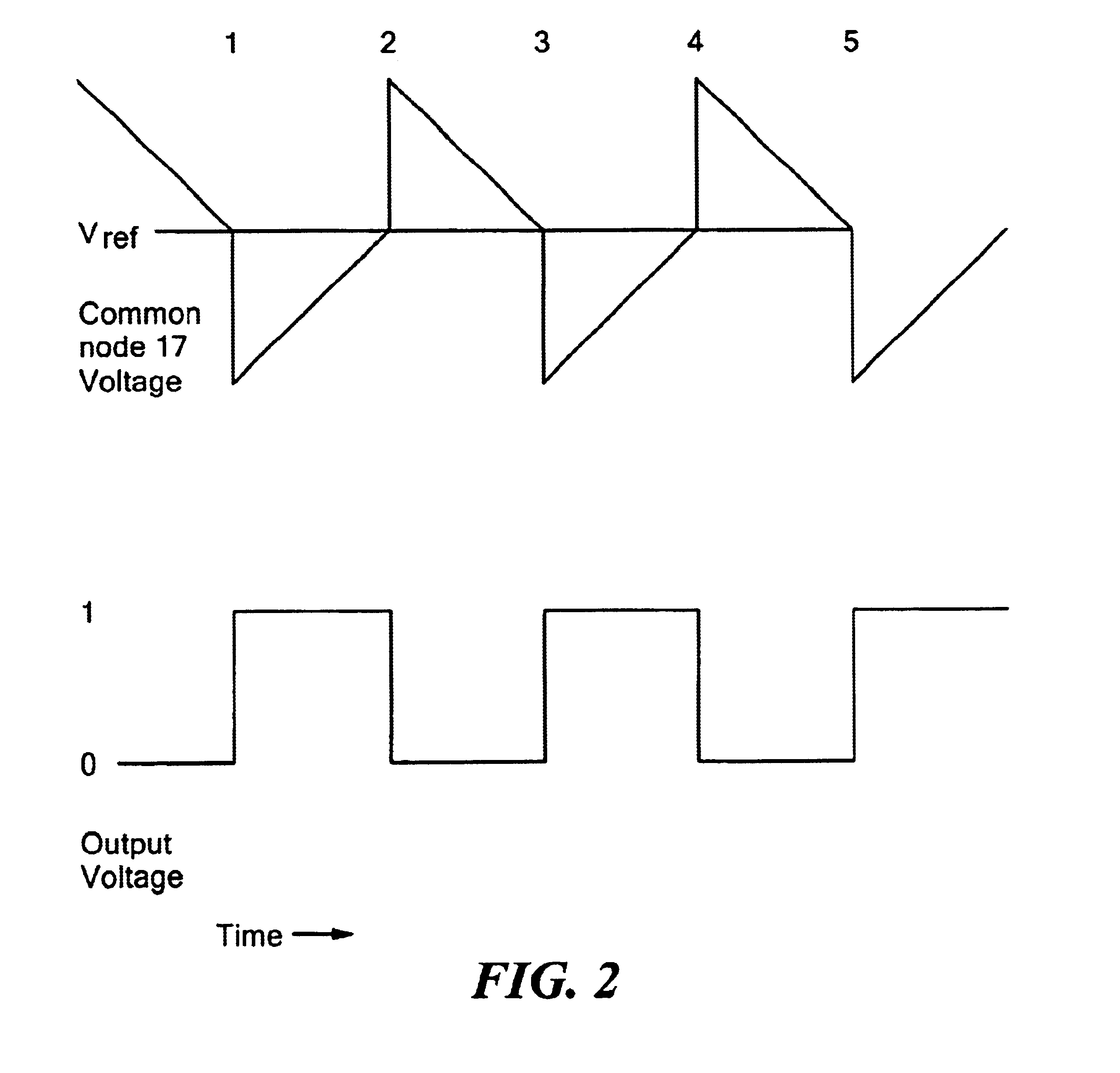

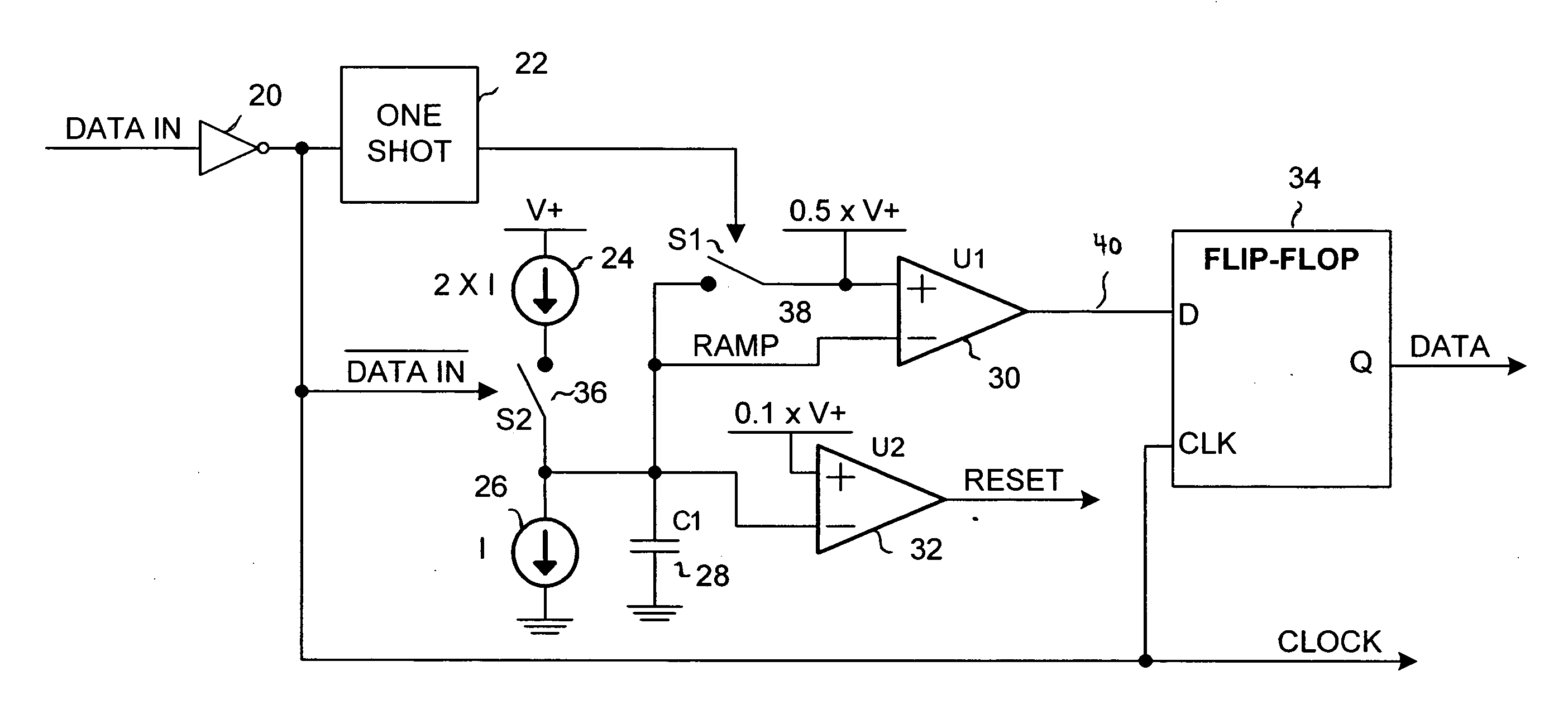

Stable oscillator

InactiveUS6853258B2Pulse generation by bipolar transistorsPulse automatic controlSwitched currentVoltage reference

An oscillator includes a comparator and a variable voltage element. The comparator has a first input set to a reference voltage, a second input, and an output configured to produce an output voltage as a function of the voltages at the first and second inputs. The variable voltage element delivers to the second input a second voltage that is a function of a switched current. The switched current is a function of the reference voltage.

Owner:ANALOG DEVICES INC

Filter shaping using a signal cancellation function

InactiveUS8380771B2Active element networkPulse descriminationAudio power amplifierSignal cancellation

A signal filter and accompanying methods. In one embodiment, the filter includes a first mechanism for receiving a first signal. A second mechanism employs one or more modified representations of the first signal to cancel one or more frequency components of the first signal, yielding an output signal in response thereto. In a more specific embodiment, the first mechanism includes a splitter for receiving the first signal and splitting the first signal onto a first path and a second path. The second mechanism further includes one or more delay modules and one or more phase shifters in the first path and / or the second path. One or more controllable amplifiers are optionally included in the first path and / or the second path. The one or more delay modules, phase shifters, or amplifiers are responsive to one or more control signals from a controller. The controller is adapted to modify behavior of the second mechanism so that the filter is characterized by a desired frequency response.

Owner:INTERSIL INC

Method and apparatus for a single upset (SEU) tolerant clock splitter

A clock splitter circuit for providing a single event upset (SEU) tolerant clock signal to latches in a space-based environment. The clock splitter circuit can include one or more event offset circuit delay circuits. The event offset delay receives a clock signal and generates a delayed clock signal. The event offset delay circuit can generate an inverted clock signal, a delayed inverted clock signal and a pair of intermediate clock signals. The delayed clock signal and inverted delayed clock signal can be delayed by the known duration of single event effects (SEE). The delayed and undelayed clock signals can be passed to an event blocking filter which can block any disturbance in the delayed and / or undelayed clock signals. A synchronizer can synchronize outputs of the event blocking filter prior to or coincident with being passed to corresponding inverting clock drivers. The synchronizers can also insure that the synchronized blocking filter outputs can not be low simultaneously. Intermediate clocks can also be provided corresponding to the inverting clock drivers. Outputs of the inverting clock driver can be a pair of SEU tolerant non-overlapping clock phase signals for driving one or more latches.

Owner:OL SECURITY LIABILITY CO

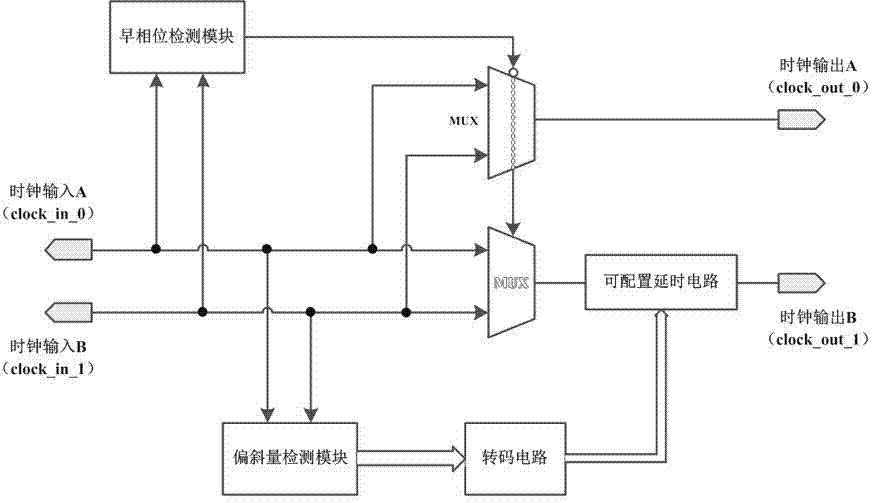

Skew detection and skew elimination regulation circuit for on-chip clock system of VLSI (very large scale integrated circuit)

InactiveCN103248341AReduced flexibilityIncrease flexibilityPulse shapingPulse descriminationVery large scale integrated circuitsMultiplexer

The invention belongs to the technical field of on-chip clocks of very large scale integrated circuits, and particularly relates to a skew detection and skew elimination regulation circuit for an on-chip clock system of a VLSI (very large scale integrated circuit). The circuit is composed of an early phase detection module, an offset detection module, a transcoding circuit, a configurable delay circuit and two alternative data selectors, wherein the early phase detection module is used for detecting the sequence of the phases of two clocks; output signals are sent to the two data selectors; the actual offset is detected by the two clocks through the offset detection module; the configurable delay circuit is controlled via the transcoding of the transcoding circuit; and the clock with the earlier phase is relayed by phases equivalent to the offset so as to ensure that an edge-aligned and phase removing two-phase clock is outputted. The circuit realizes a semi-custom design circuit based on a standard cell library, has the advantages of simple logic, controllable precision, excellent flexibility and the like, and is compatible with the current universal digital integrated circuit design flow inputted on basis of the hardware description language (HDL).

Owner:FUDAN UNIV

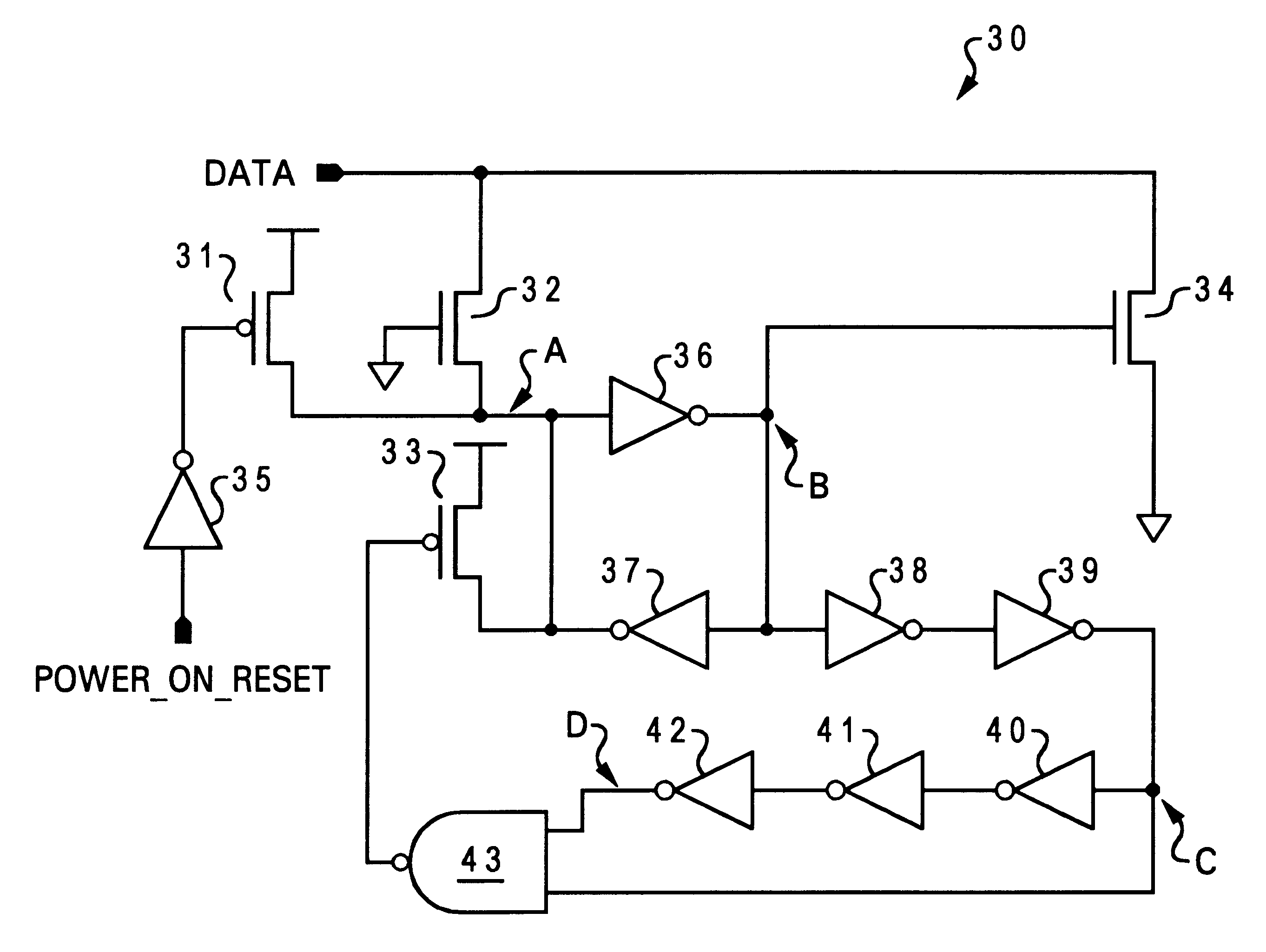

Noise suppression circuits for suppressing noises above and below reference voltages

A noise suppression circuit for suppressing noises above and below reference voltages is disclosed. The noise suppression circuit for suppressing noises includes a means for generating a power-on-reset signal, a clamping transistor, and a feedback circuit. The means for generating a power-on-reset signal presets an internal latch of the noise suppression circuit to a predetermined state, such as a logical high state. The clamping transistor restores the state of a data input of a circuit to which the noise suppression circuit is providing protection, after the occurrence of a noise coupling event. The feedback circuit then turns off the clamping transistor after a predetermined amount of time.

Owner:IBM CORP

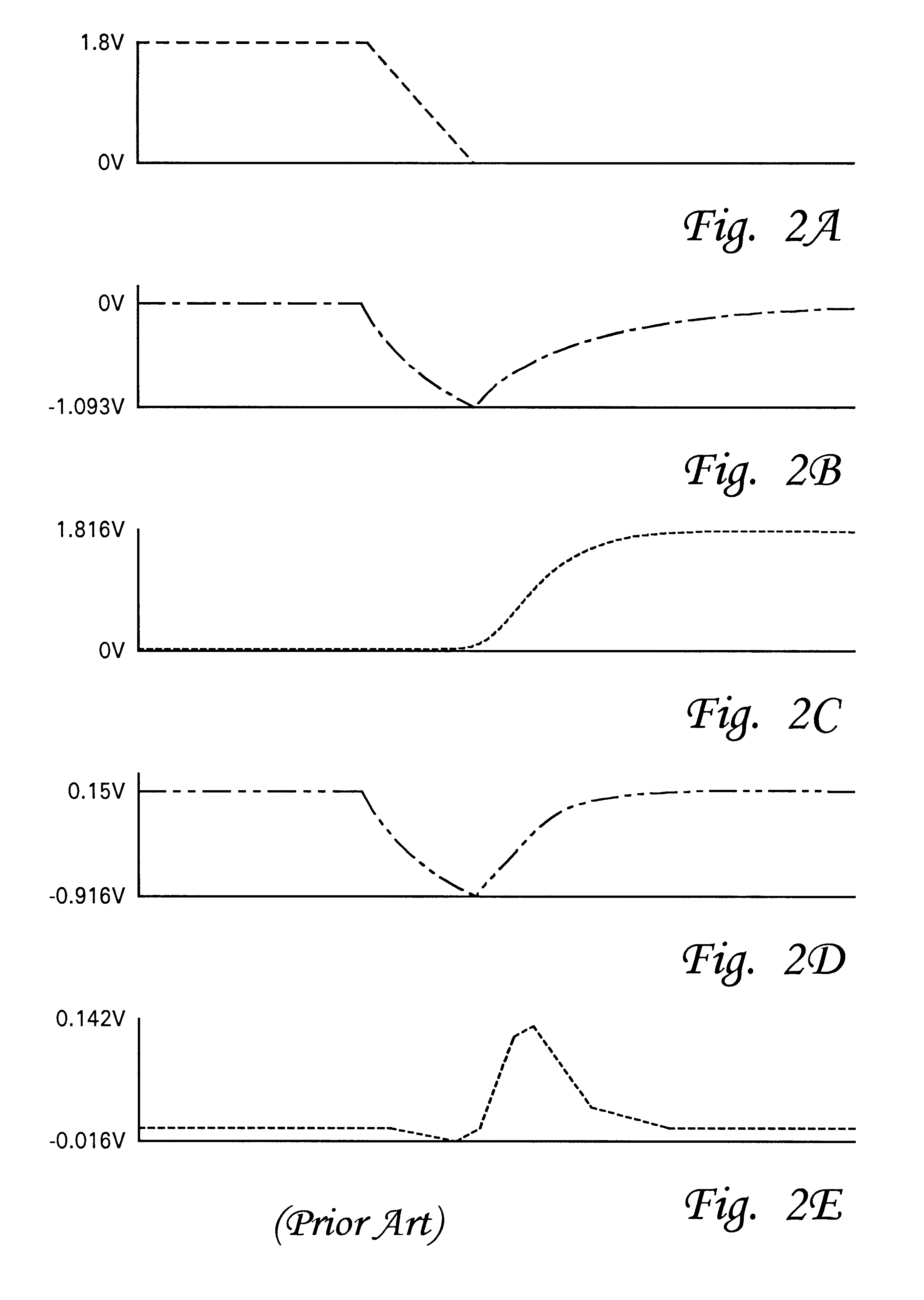

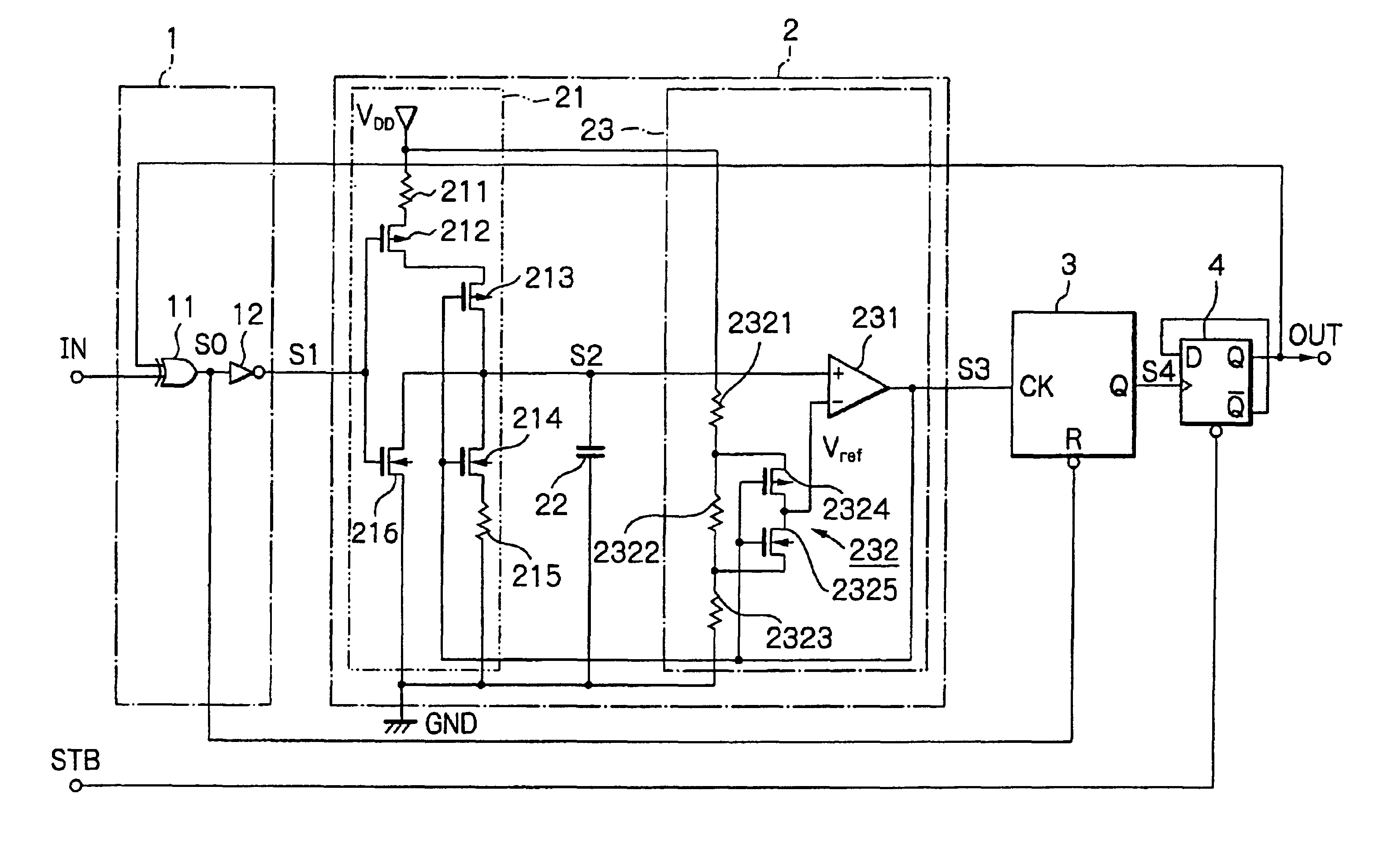

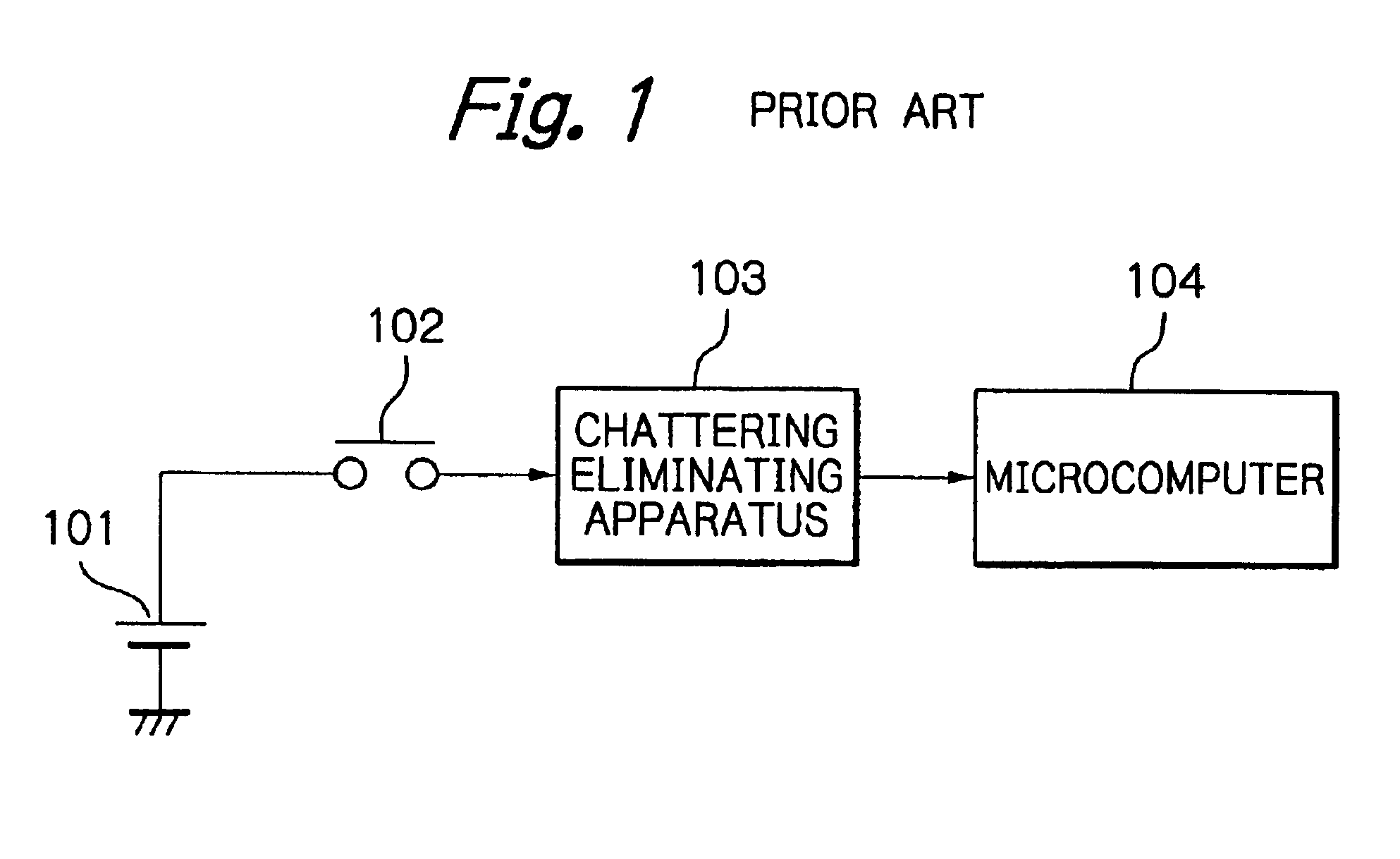

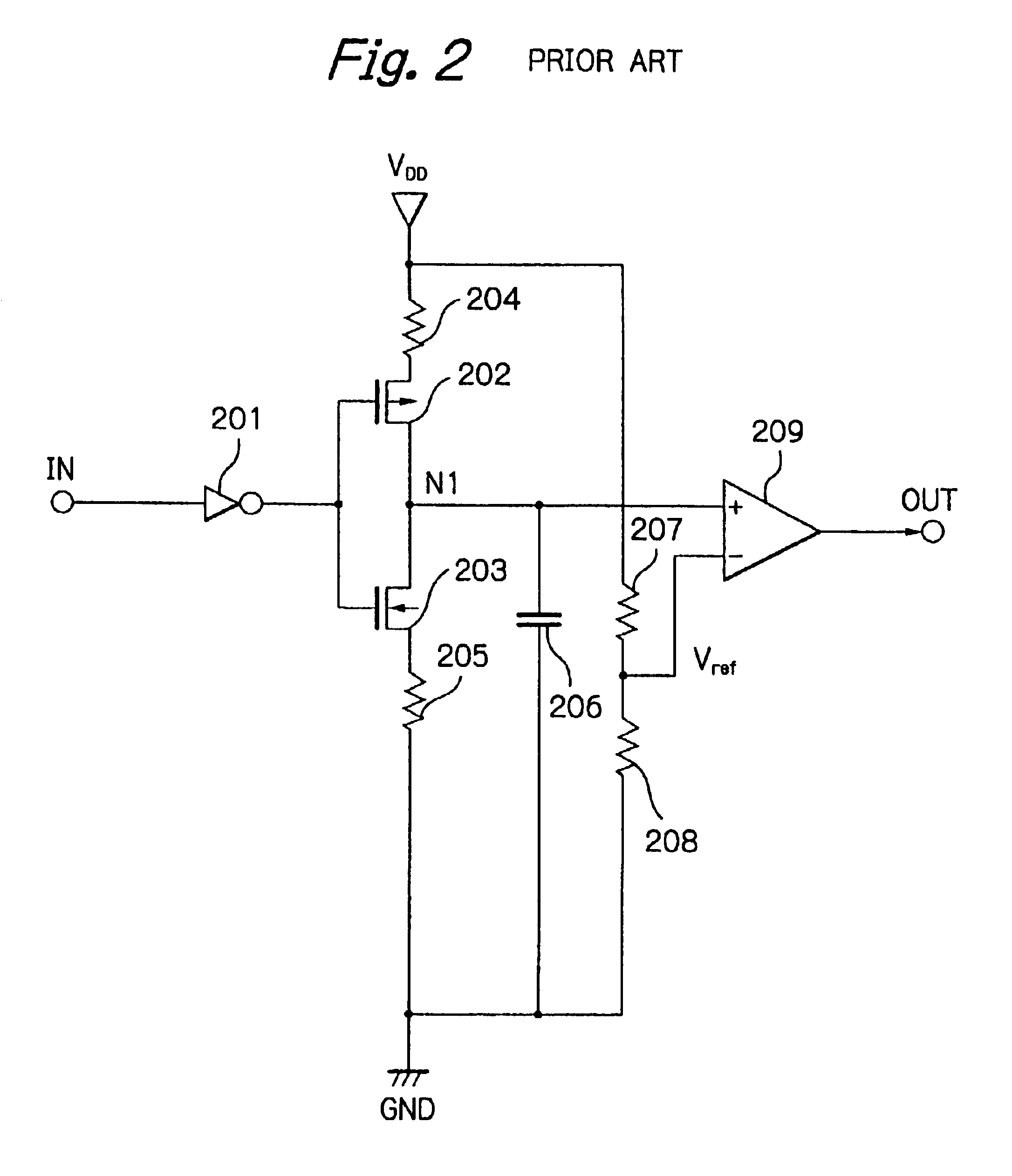

Chattering eliminating apparatus including oscillation circuit using charging and discharging operations

InactiveUS6873216B2Small sizeElectronic switchingElectric pulse generator circuitsCharge and dischargeElectrical and Electronics engineering

In a chattering eliminating apparatus, a coincidence circuit receives an input signal of the apparatus and an output signal of the apparatus to determine whether or not a level of the input signal of the apparatus is the same as a level of the output signal of the apparatus. An oscillation circuit carries out an oscillation operation only when the level of the input signal of the apparatus is not the same as the level of the output signal of the apparatus. A counter counts an output signal of the oscillation circuit, and is reset when the level of the input signal of the apparatus is the same as the level of the output signal of the apparatus. An output signal generating circuit inverts the level of the output signal of the apparatus when a counter value of the counter reaches a predetermined value.

Owner:NEC ELECTRONICS CORP

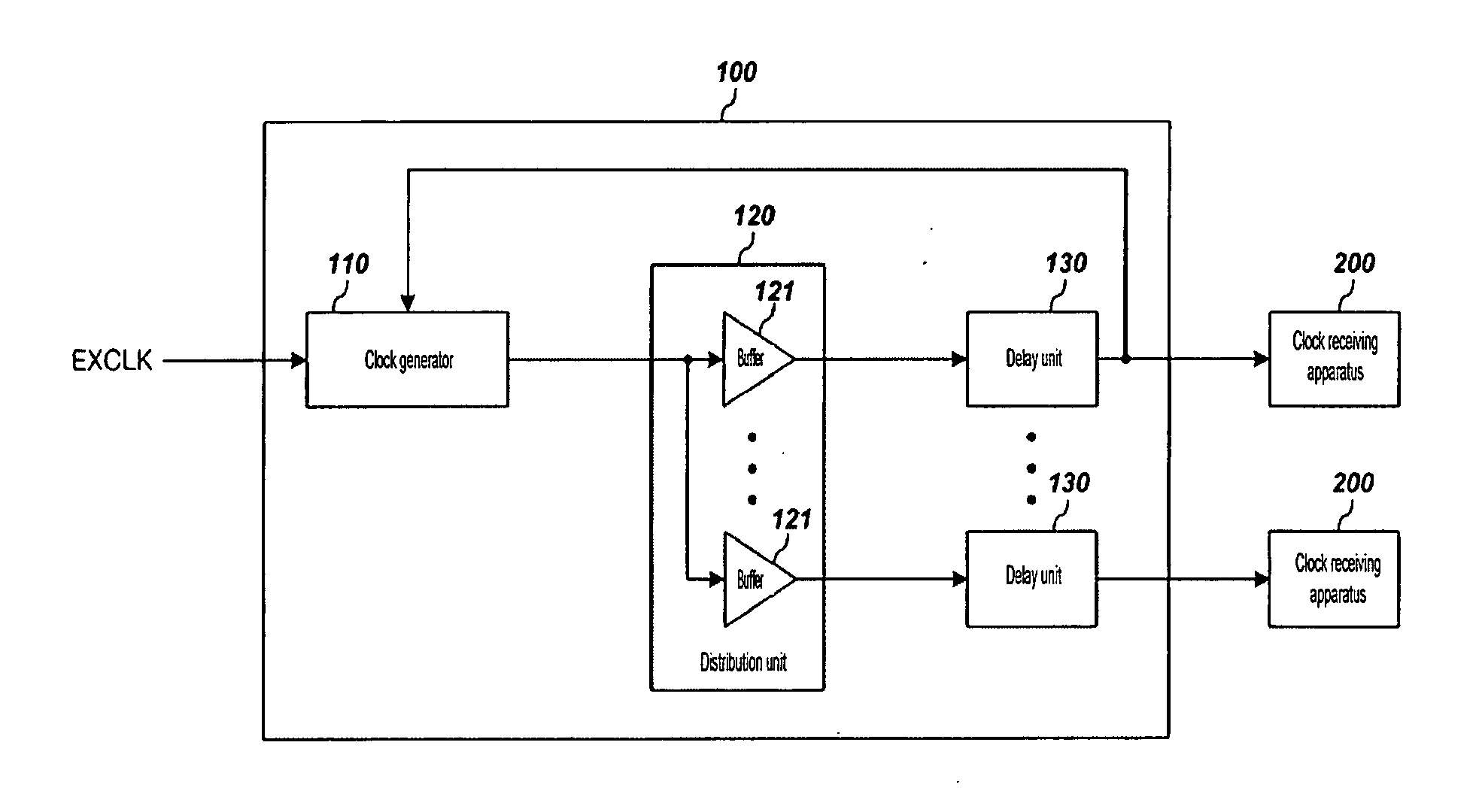

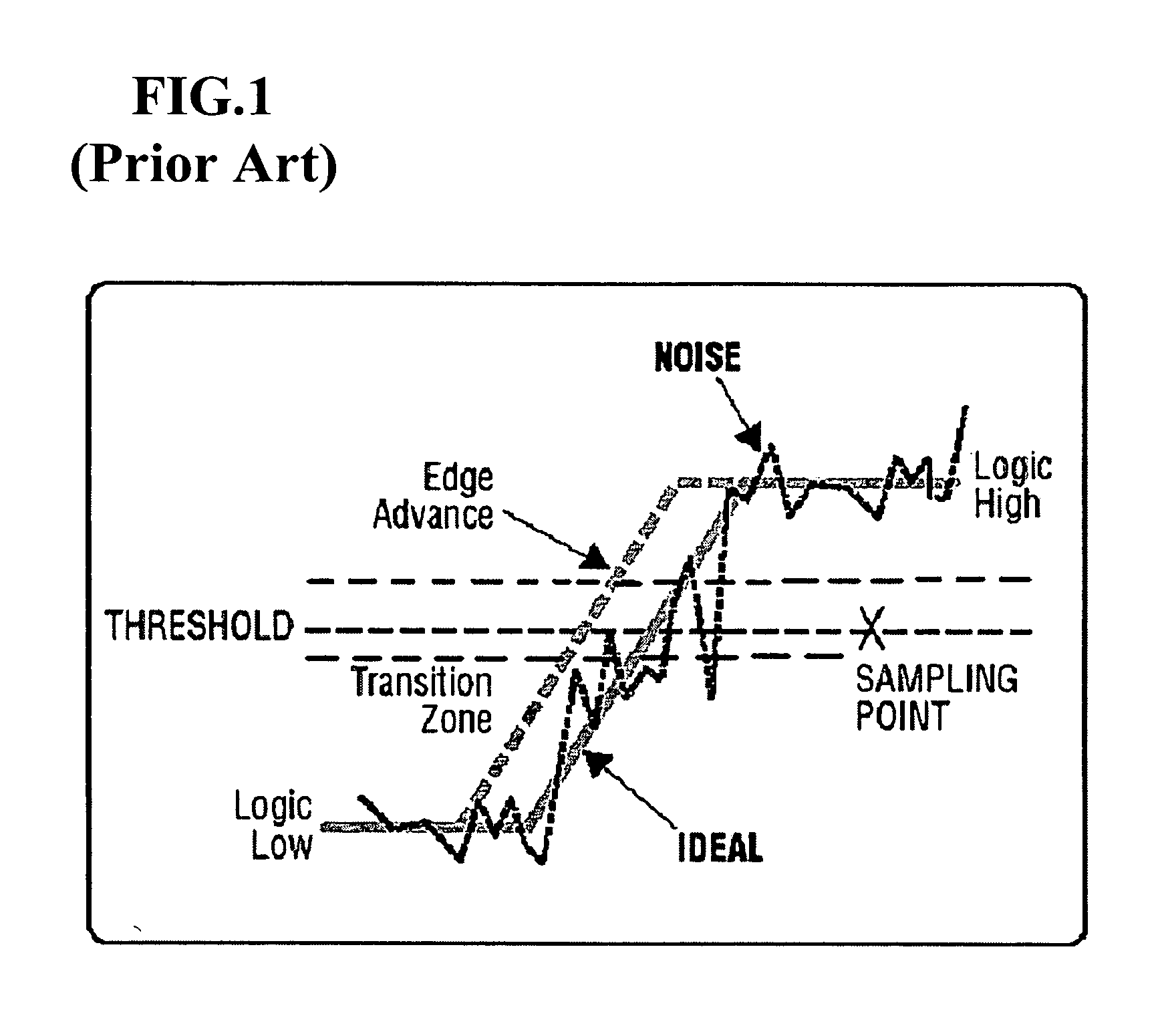

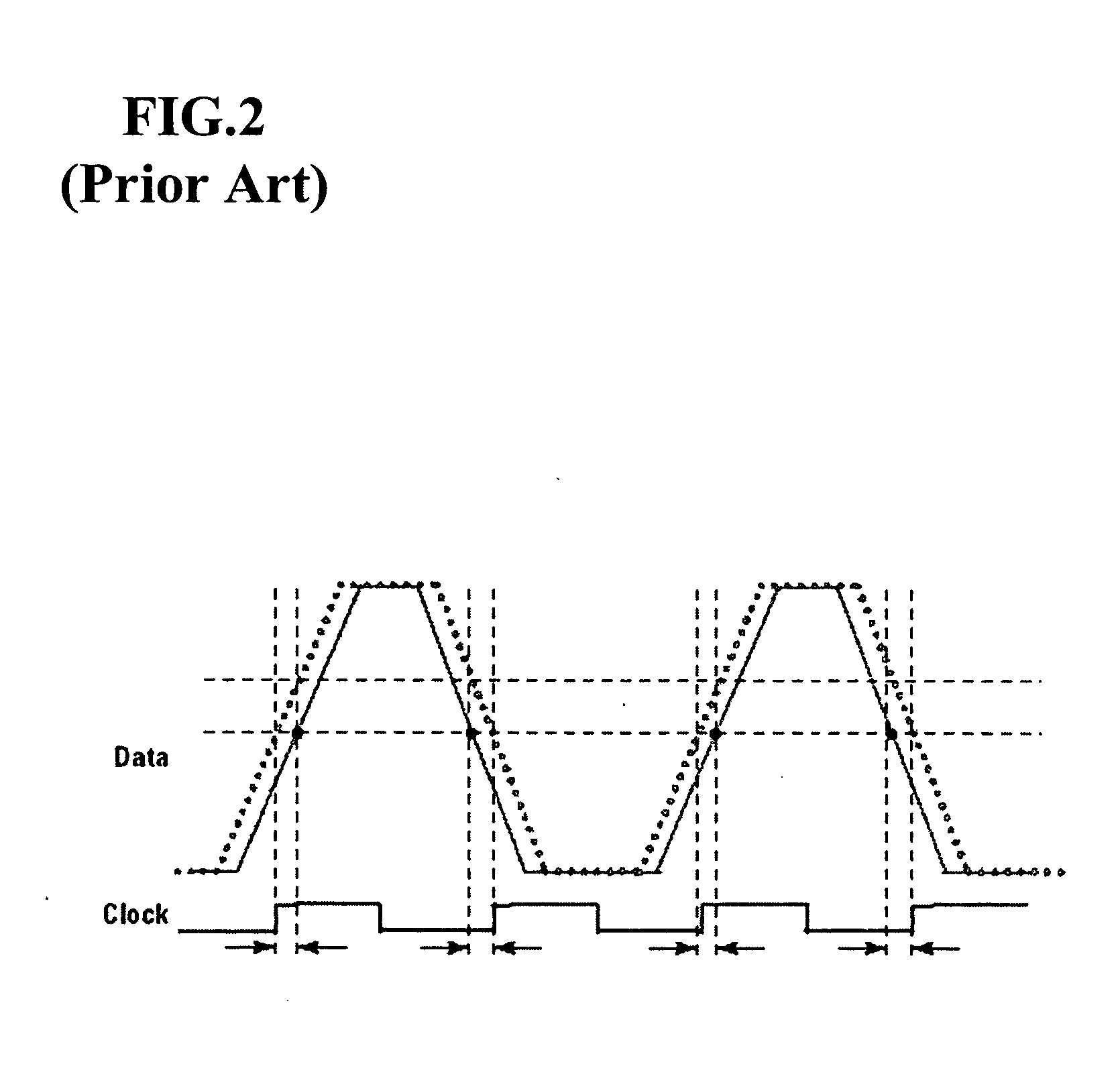

Clock signal generating apparatus and clock signal receiving apparatus

InactiveUS20070152727A1Cancel noiseEliminate deviationElectric pulse generatorPulse descriminationEngineeringPhase control

A clock signal generating apparatus including a clock generator, a distributor, a plurality of delay units, and generates a clock signal for synchronized driving of a system having a plurality of clock receiving apparatuses. The clock signal generator generates a clock signal for driving the system by using an external clock signal and a feedback clock signal. The distributor distributes the clock signal output to generate a plurality of distributed clock signals and outputs the plurality of distributed clock signals to the plurality of clock receiving apparatuses through a plurality of signal transmission paths. The plurality of delay units are respectively located on the plurality of signal transmission paths, control phases of the plurality of distributed clock signals to generate a plurality of phase-controlled clock signals, and transmit the plurality of phase-controlled clock signals to the plurality of clock receiving apparatuses.

Owner:SAMSUNG ELECTRONICS CO LTD +4

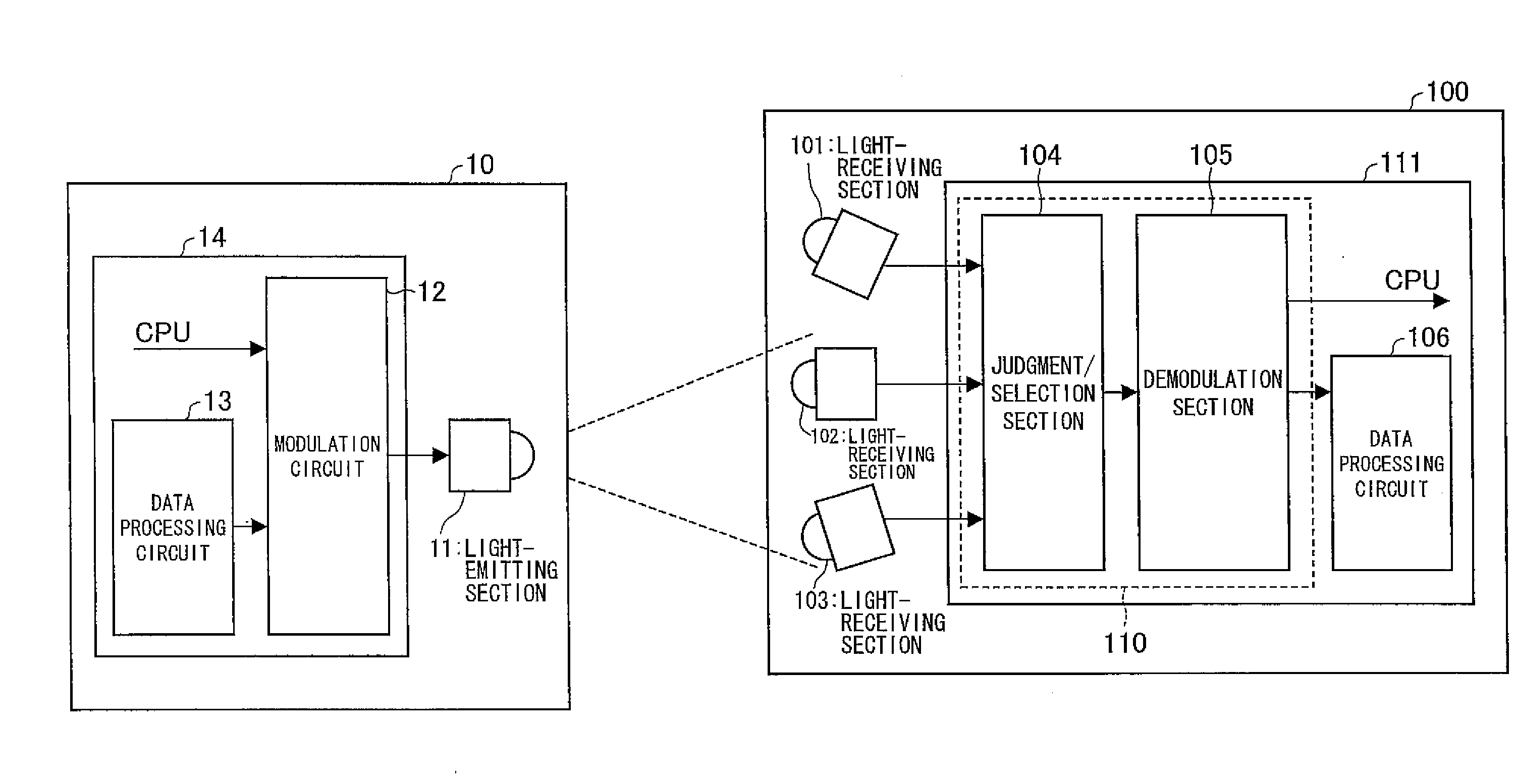

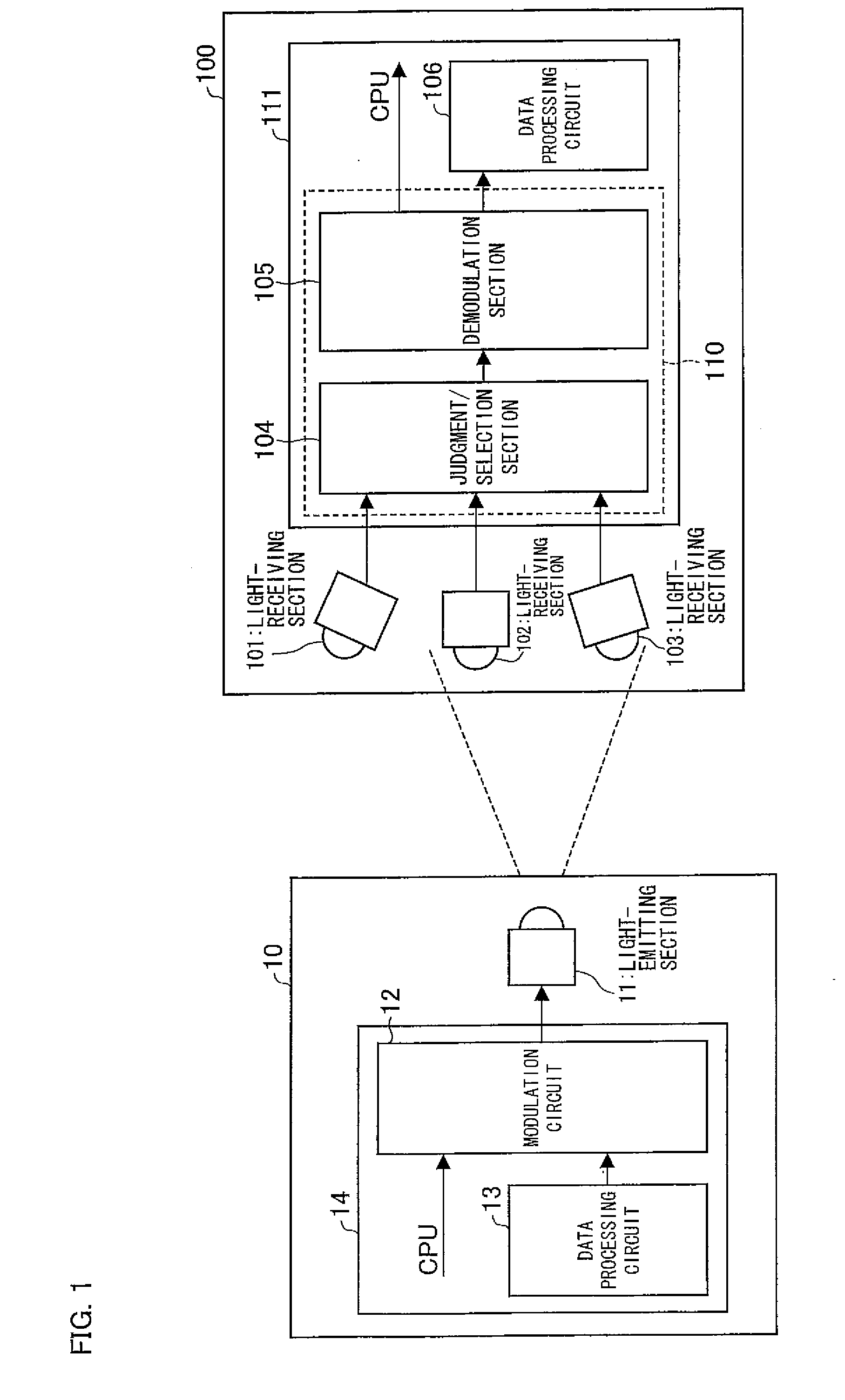

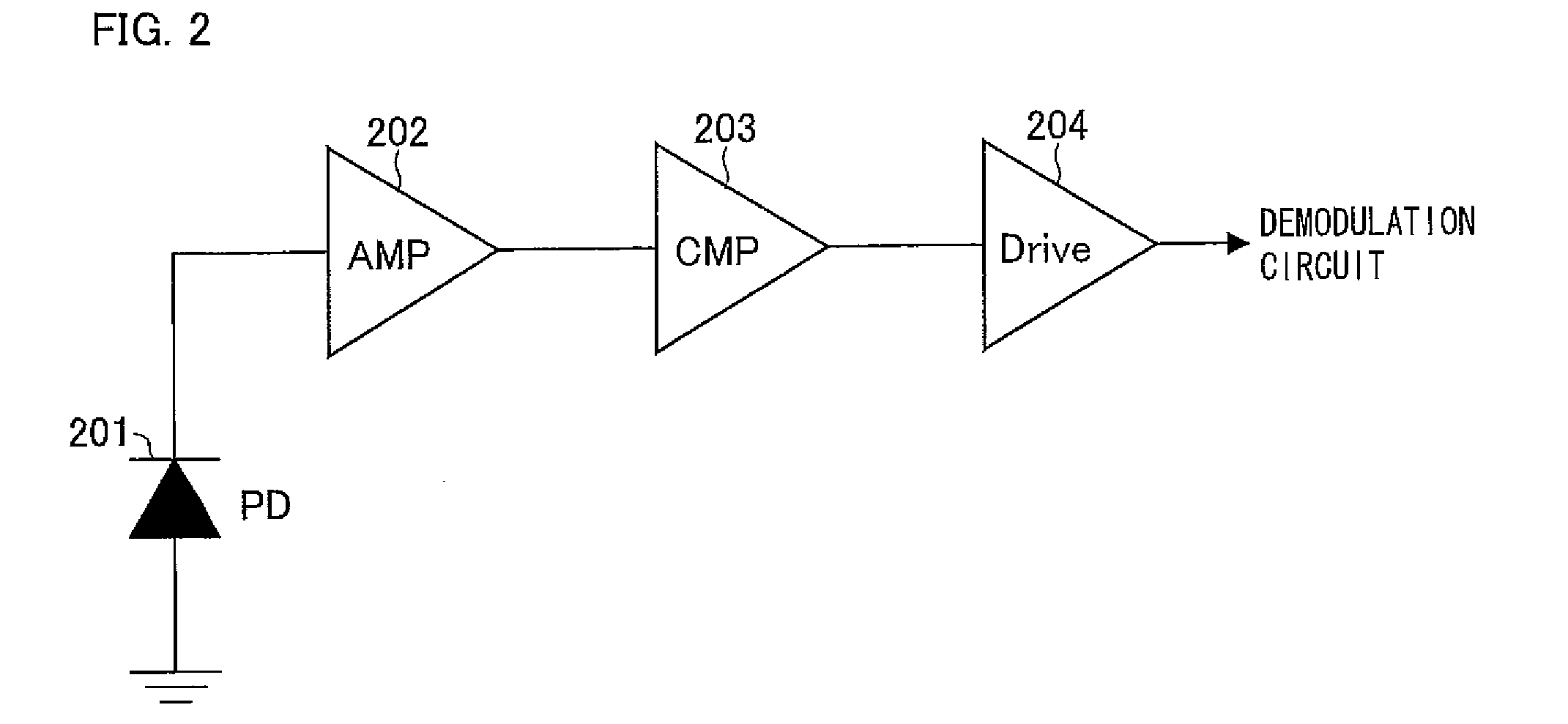

Demodulation circuit, ic, and communication device

InactiveUS20080013963A1Avoid difficult choicesSmall componentLine-faulsts/interference reductionClose-range type systemsDemodulationCommunication device

The demodulation circuit of the present invention is a demodulation circuit, connected with a plurality of light-receiving sections each for receiving an optical signal and converting the signal into a binary pulse signal, operable to select and demodulate a pulse signal out of pulse signals that are supplied from the light-receiving sections, respectively, the demodulation circuit including: a judgment and selection section for detecting timing with which High level and Low level of each of the pulse signals are switched and for selecting at least one pulse signal based on the timing; and a demodulation section for demodulating the pulse signal selected by the judgment and selection section. Consequently, the demodulation circuit easily selects and demodulates a signal whose jitter component is small out of a plurality of supplied signals.

Owner:SHARP KK

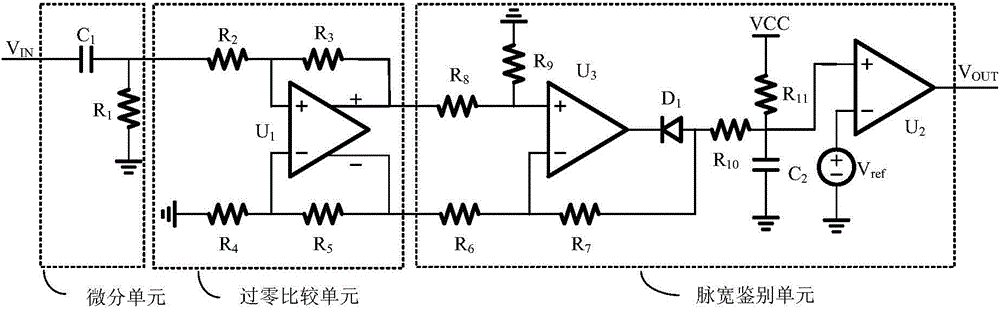

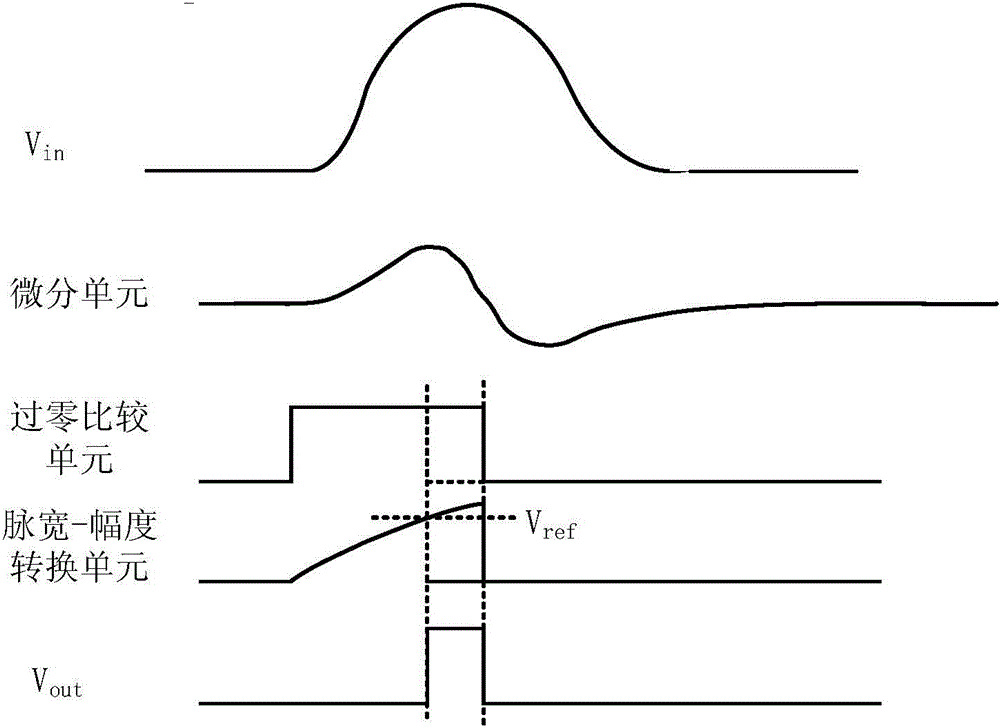

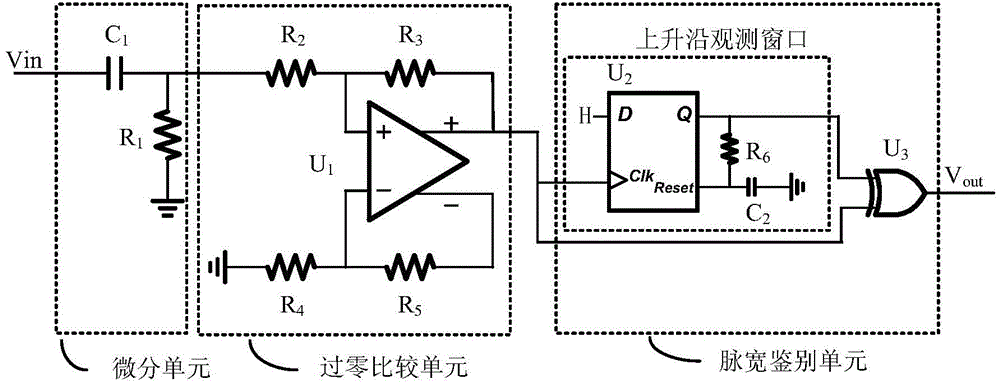

Slow rising edge pulse signal identification circuit

ActiveCN104836553ADoes not affect the zero-crossing time differenceSimple wayPulse descriminationBipolar signalSimple circuit

The invention relates to a slow rising edge pulse signal identification circuit. The slow rising edge pulse signal identification circuit includes a differential unit, a zero crossing comparison unit and a pulse width identification unit; the differential unit performs differential processing on unipolar photon pulse signals inputted from the outside, so that bipolar signals with two zero crossing points can be formed and transmitted to the zero crossing comparison unit; the zero crossing comparison unit converts the bipolar signals into digital pulse signals with a certain pulse width according to a set comparison threshold value, and transmits the digital pulse signals to the pulse width identification unit; and the pulse width identification unit judges whether the width of the digital pulse signals exceeds a set identification threshold value, and judges that the photon pulse signals inputted from the outside are slow rising edge signals and outputs a high-electric level pulse if the width of the digital pulse signals exceeds the set identification threshold value, otherwise, outputs a low-electric level pulse. The slow rising edge pulse signal identification circuit of the invention has the advantages of simple circuit form and high sensitivity.

Owner:BEIJING INST OF CONTROL ENG

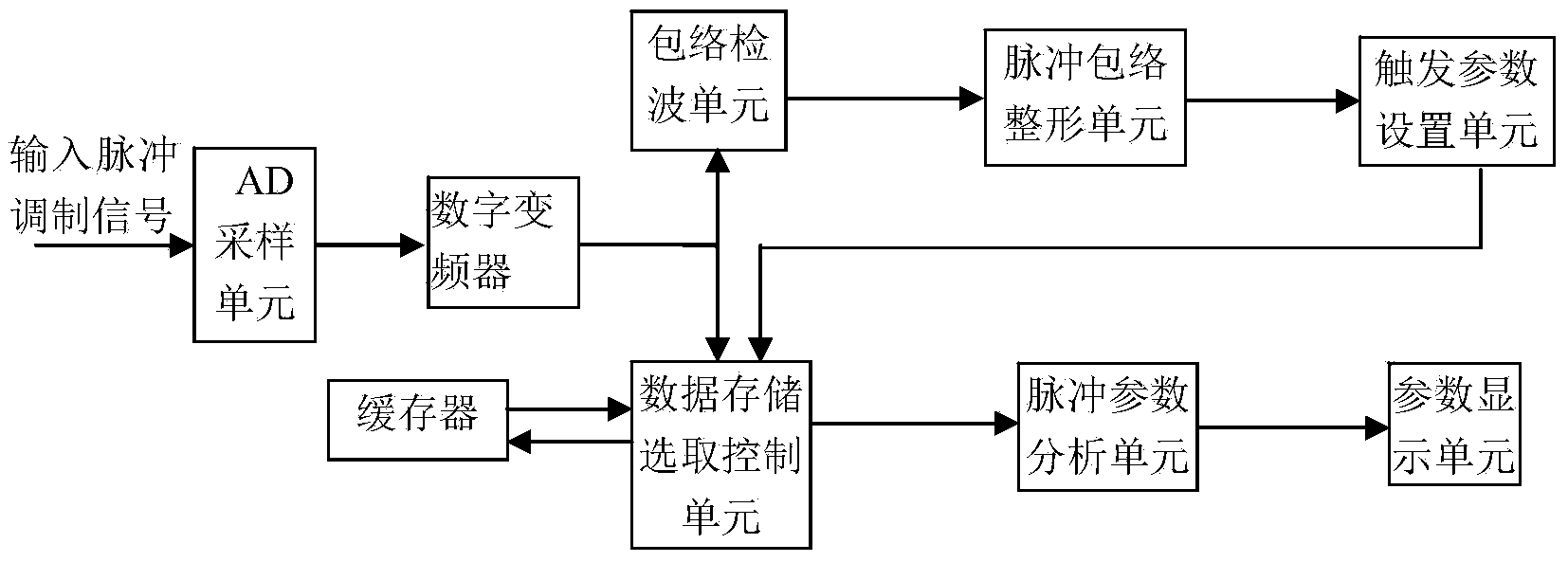

Testing method for pulse modulated signals

ActiveCN104022761ALow data rateEasy to handlePulse shapingPulse descriminationPulse envelopeData segment

The invention discloses a testing method for pulse modulated signals, which comprises the following steps: (1) converting a pulse-modulated signal to a sampled digital signal through an AD sampling unit; (2) converting the sampled digital signal to a pulse baseband signal by a digital frequency converter; and (3) processing the pulse baseband signal in two paths, wherein the first path is used for forming a triggering pulse for controlling and selecting data segments, the second path is stored in a buffer through a data storage / selection control unit; (4) generating a profile envelope of the whole pulse-modulated signal by an envelope demodulating unit; (5) generating a pulse triggering signal from the profile envelope by a pulse envelope shaping unit; (6) generating a triggering data gating signal from the pulse triggering signal by a triggering parameter setting unit; and (7) outputting a corresponding pulse baseband signal to a pulse parameter analyzing unit by a the data storage / selection control unit under control by a gating signal; and performing pulse baseband signal calculation and analysis by the pulse parameter analyzing unit.

Owner:CHINA ELECTRONIS TECH INSTR CO LTD

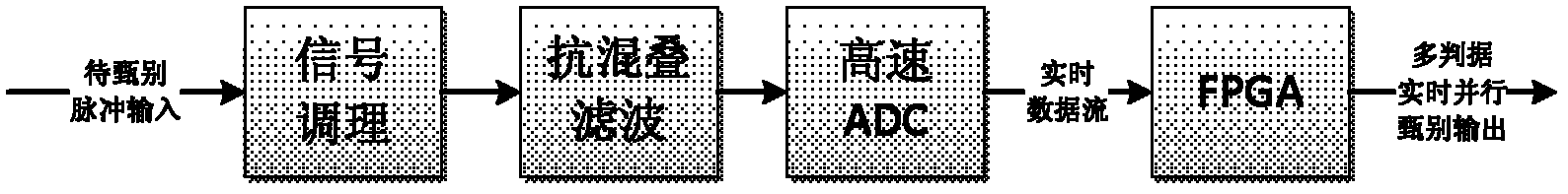

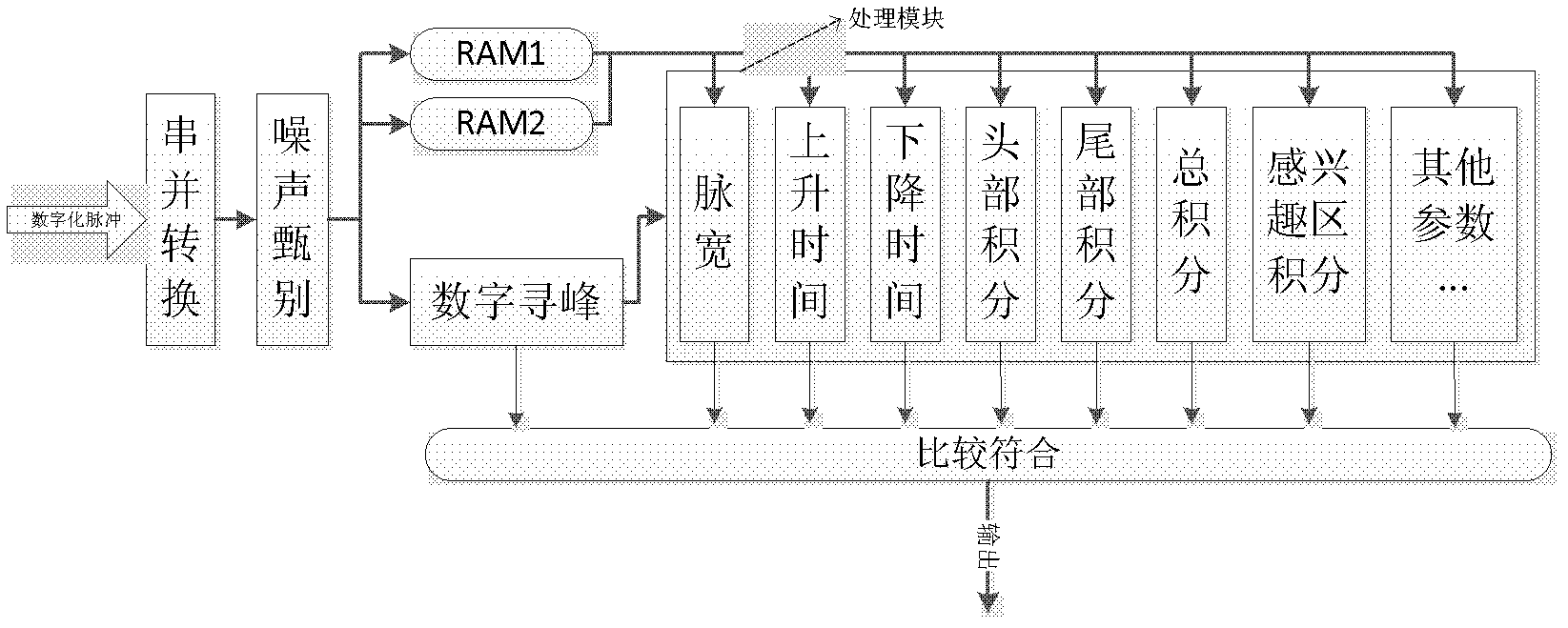

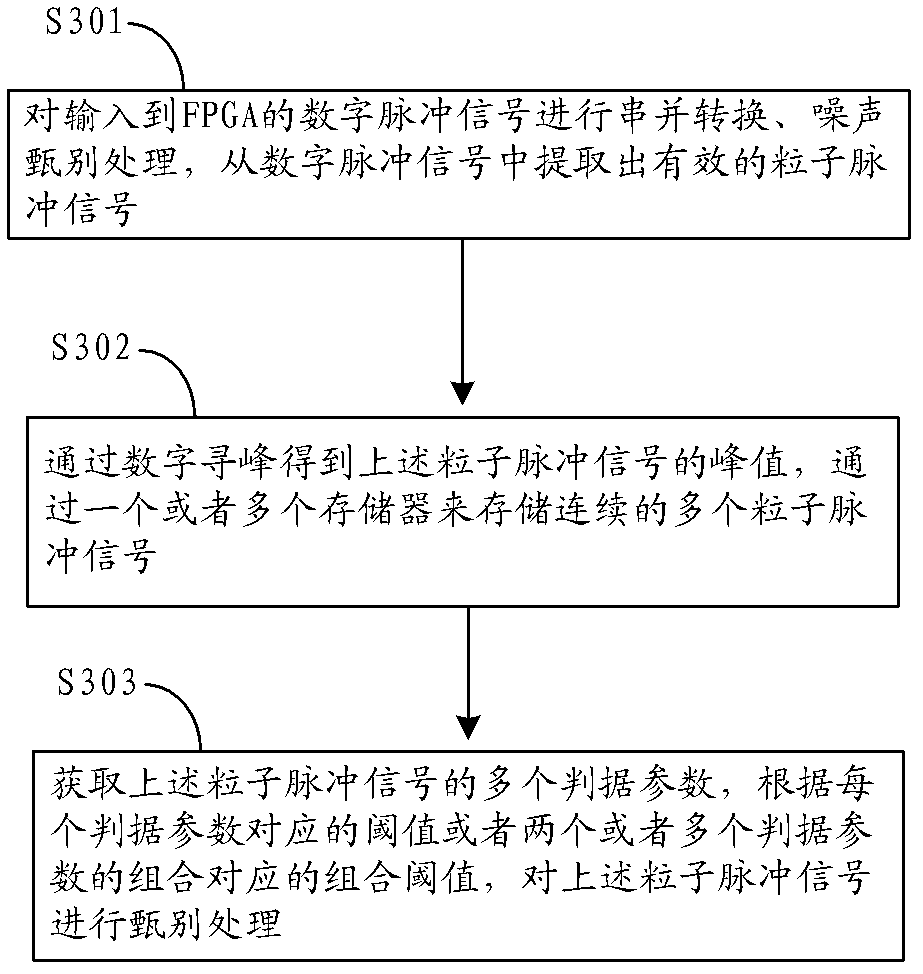

Method and device of screening digital pulse signal

The invention relates to a method and a device of screening digital pulse signal. The method mainly comprises a step of respectively setting a threshold value of each criterion parameter of the digital pulse signal. The method comprises a step of using a parallel stream line working way to capture a plurality of the criterion parameters of the digital pulse signal in real time, a step of judging whether each criterion parameter conforms to the set threshold value, and a step of judging the digital pulse signal as an effective digital pulse signal when each criterion parameter of the plurality of the criterion parameter conforms to the set threshold value. Because of adoption of the real-time dealing method of the multi-criterion parallel stream line, real-time performance can be improved, the digital pulse signal can be regarded as the criterion parameter to conduct grain screening only if wave forms of the digital pulse signal are different, and therefore, pulses with different wave forms can be distinguished to the utmost.

Owner:UNIV OF SCI & TECH OF CHINA

Control interface and protocol

ActiveUS20080224765A1Readily apparentMultiple input and output pulse circuitsInstant pulse delivery arrangementsSignal onComputer science

In one embodiment, a method for a control interface includes: receiving a signal conveying bits of information over a single line; and for each bit of information, comparing the proportion of time that the signal on the single line is low versus the proportion of time that the signal on the single line is high for a respective bit period defined from one operative edge of the signal to the next operative edge of the signal in order to determine a logic value for that bit of information.

Owner:SEMICON COMPONENTS IND LLC