Patents

Literature

1482results about "Electric pulse generator circuits" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

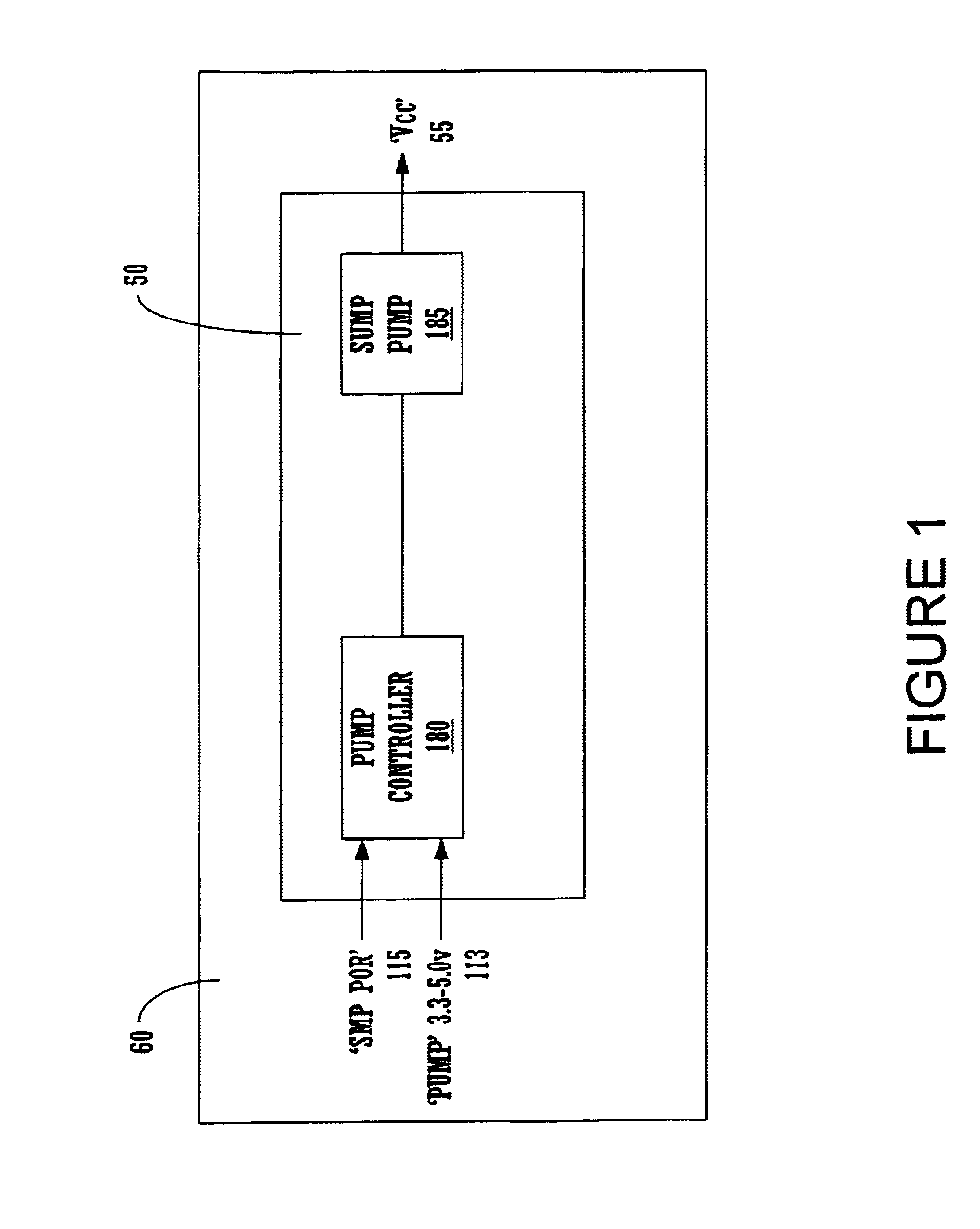

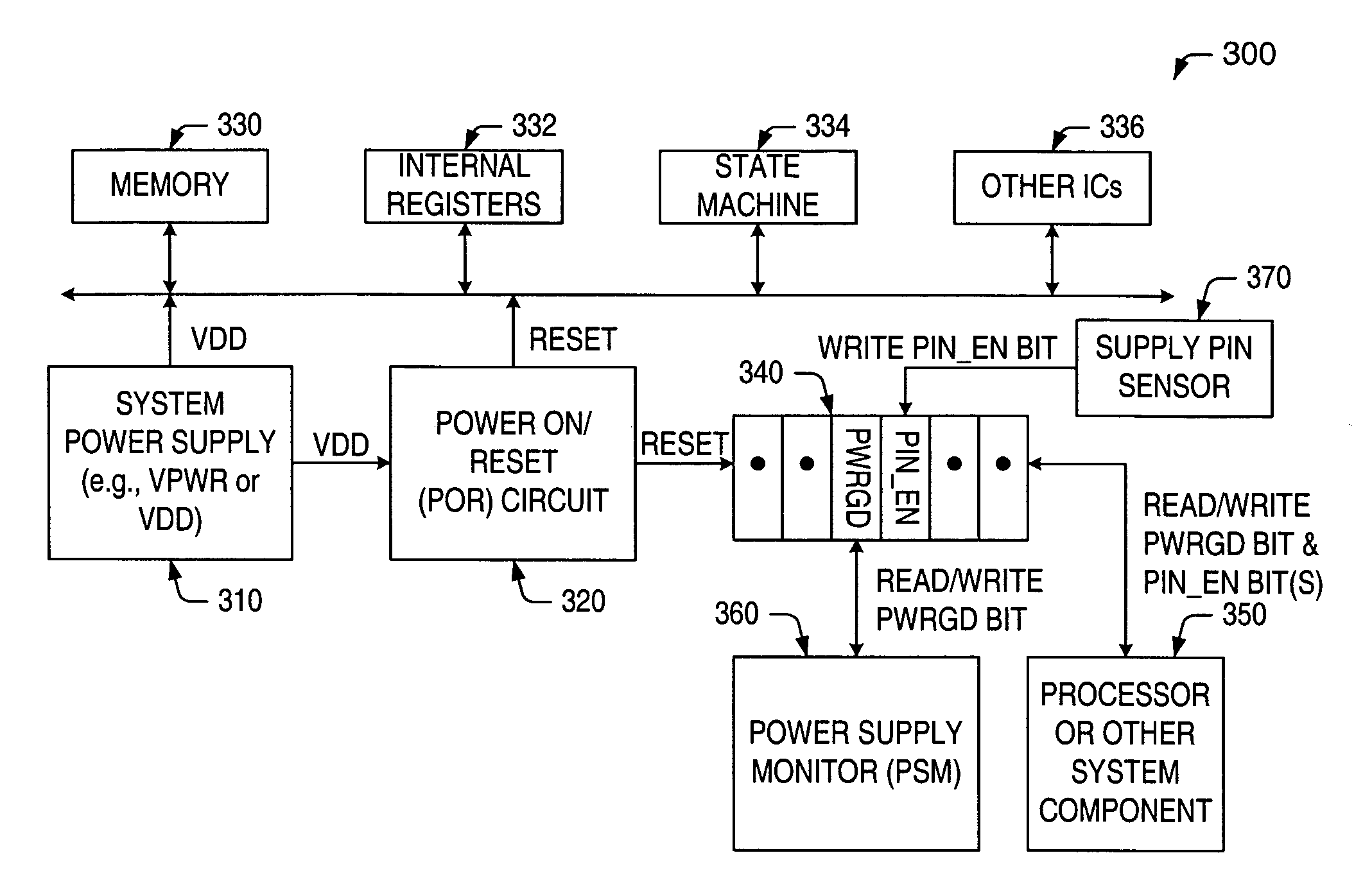

Method and system for interaction between a processor and a power on reset circuit to dynamically control power states in a microcontroller

InactiveUS6854067B1Optimize power stateEfficient workPulse automatic controlVolume/mass flow measurementPower-on resetMicrocontroller

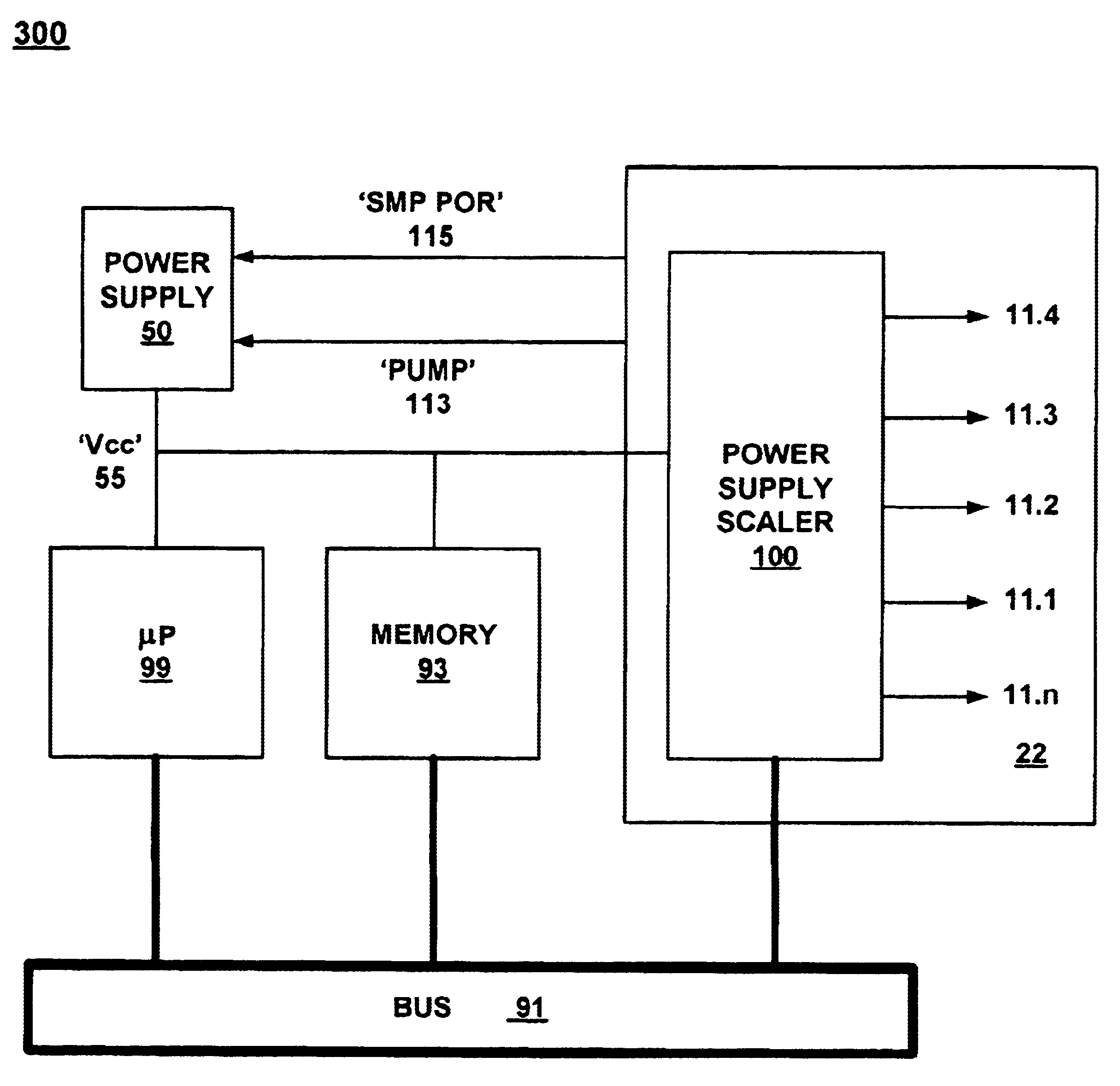

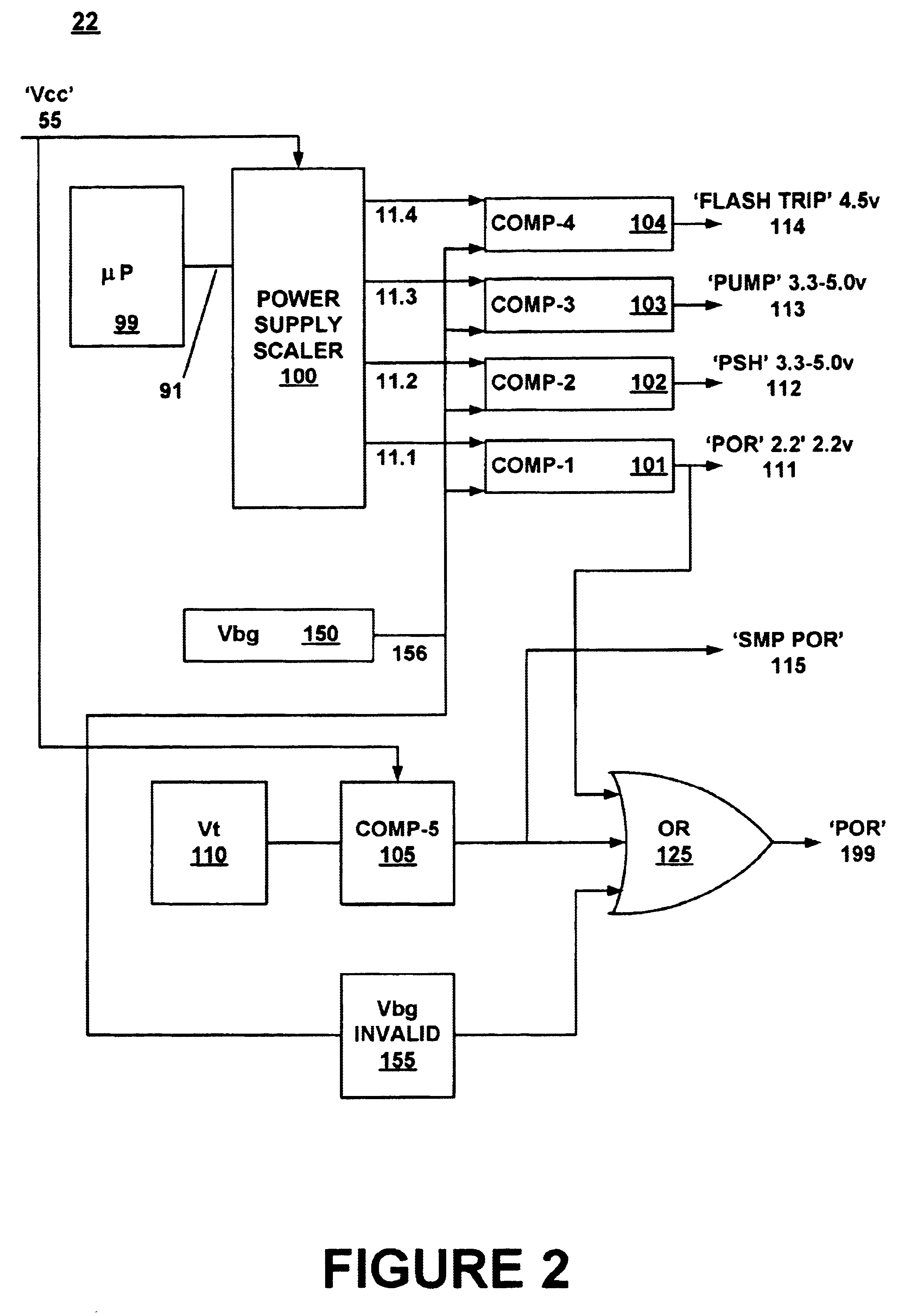

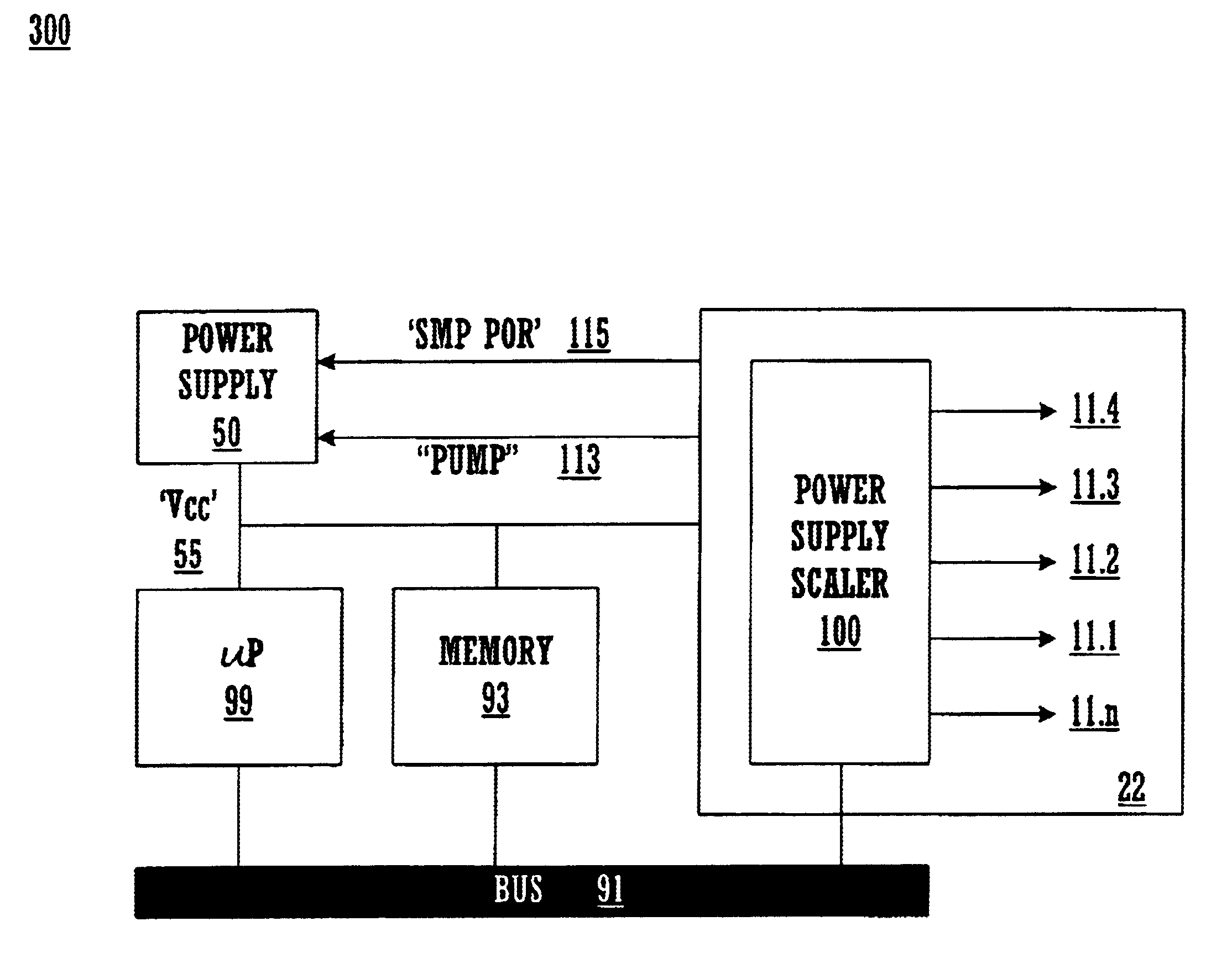

A method and system dynamically controlling microcontroller power. In one embodiment, the method and system configures a microcontroller power state, senses its condition, and determines its suitability status, communicates that status between a POR circuit and a processor, controls certain microcontroller functions accordingly, and dynamically programs power related functions. This is enabled, in one embodiment, by dynamic interaction between the POR circuit and the processor. Microcontroller power status is ascertained, and a corresponding optimal power state determined. Optimal values for programmable independent multiples of a supply voltage is programmatically calculated and set, dynamically adjusting microcontroller power states. In one embodiment, the optimal values are communicated to a scaler in the POR circuit by the processor, and registered within a multiplexer / register matrix within the scaler. The processor commands the matrix to change programmable independent multiples of supply voltage to correspond with the optimal values, and monitors corresponding action and power status.

Owner:HERITAGE IP LLC

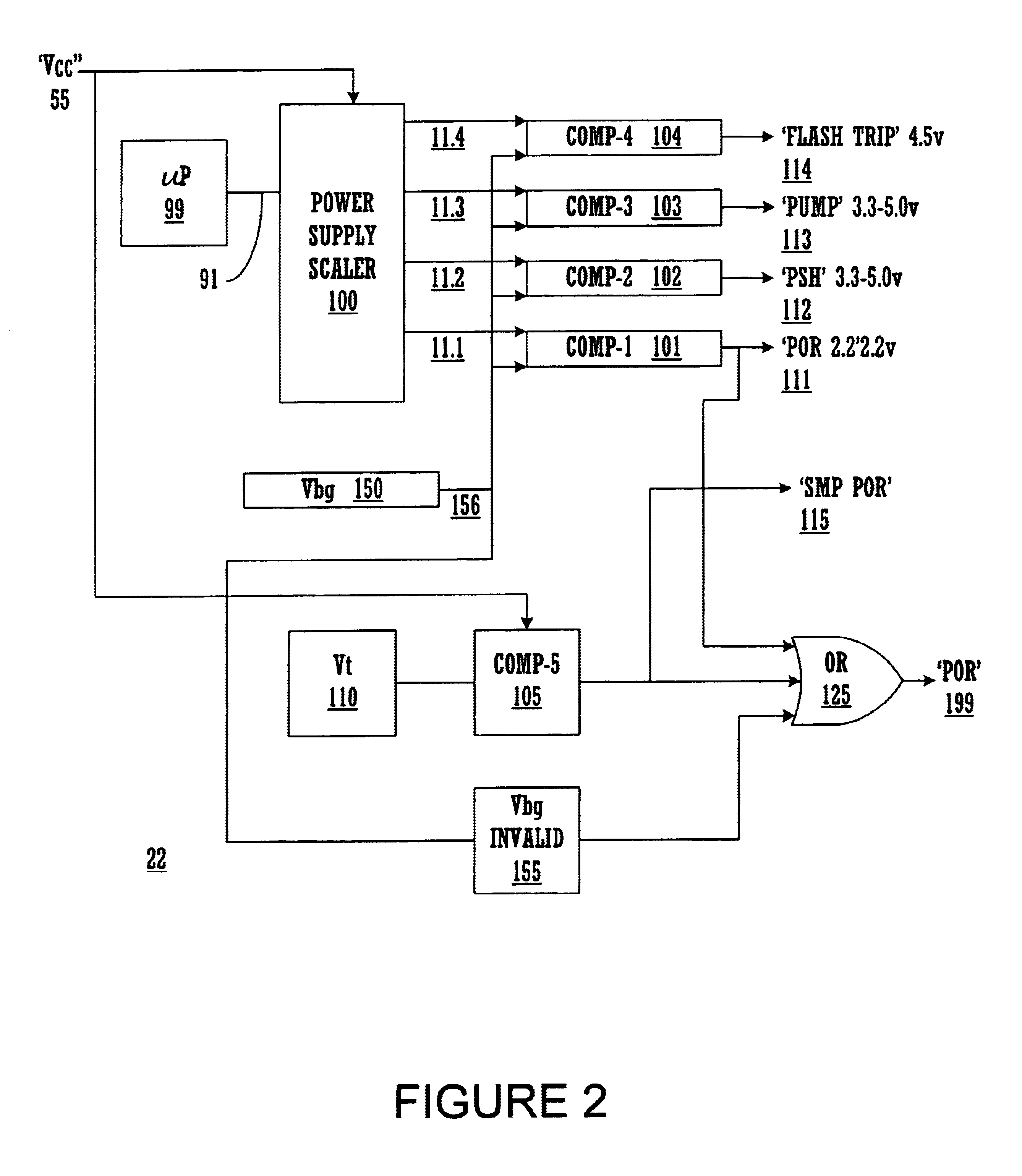

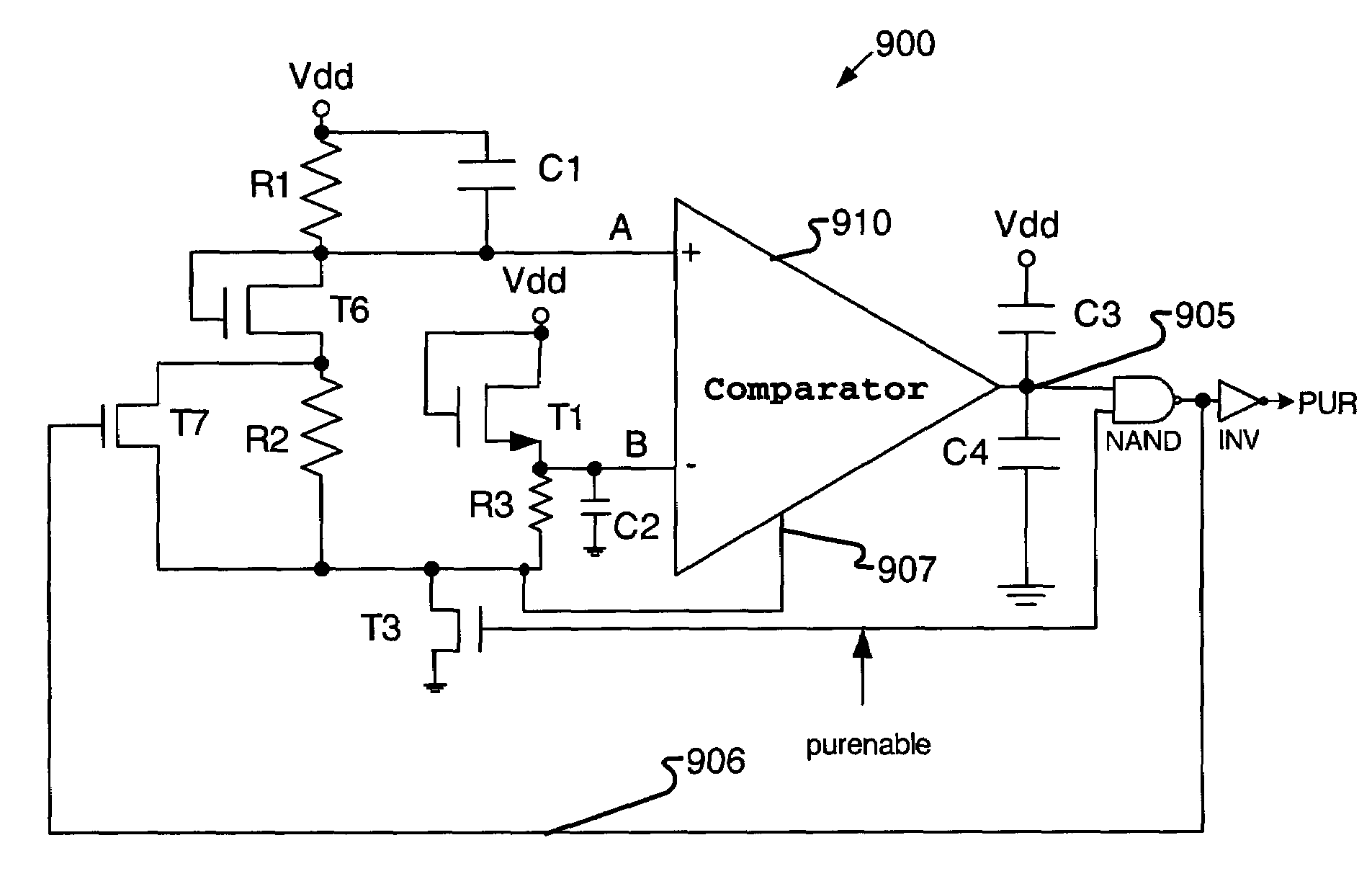

Power on reset circuit for a microcontroller

InactiveUS6868500B1Efficient workProvide functionalityPulse automatic controlVolume/mass flow measurementMicrocontrollerPower-on reset

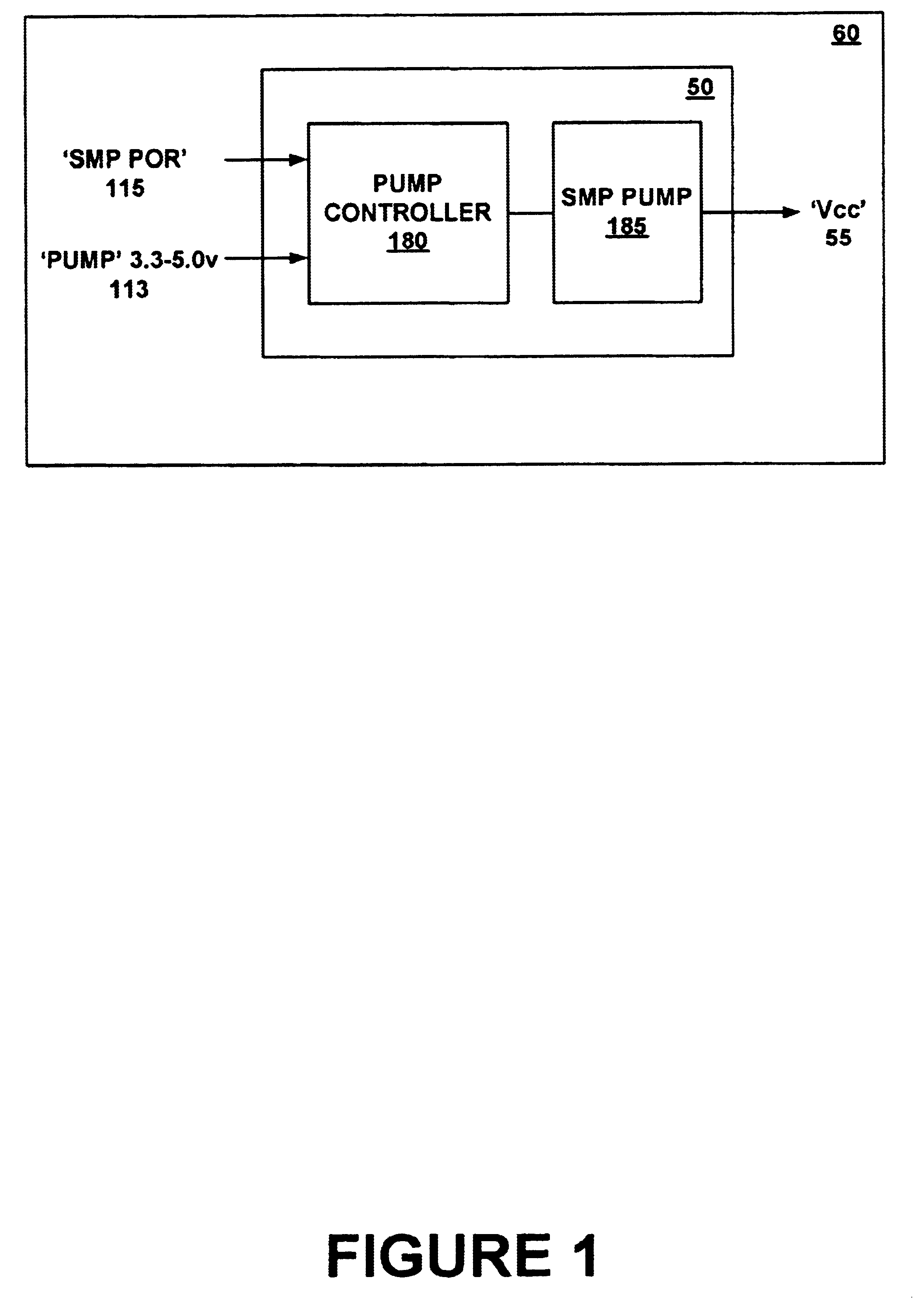

In accordance with one embodiment of the present invention, a circuit provides power stability functions for a microcontroller, during startup and normal operations performing power on reset functions and an array of power stability functions. The power on reset functions hold the microcontroller in a safe reset condition, reinforce the POR hold, and force its switch mode pump to drive up voltage provided to its common supply source. The power stability functions constitute a power on reset function, a power supply health, e.g., power state condition monitoring function, a control function for dynamically controlling the common supply source, and auxiliary functions, which may be protective of a flash memory. The power on reset function operates at a fixed and / or programmably changeable voltage levels. In one embodiment, the POR circuit is interconnected with a processor through a bus, enabling programmatic processor control of microcontroller power through interaction with the POR circuitry.

Owner:MONTEREY RES LLC

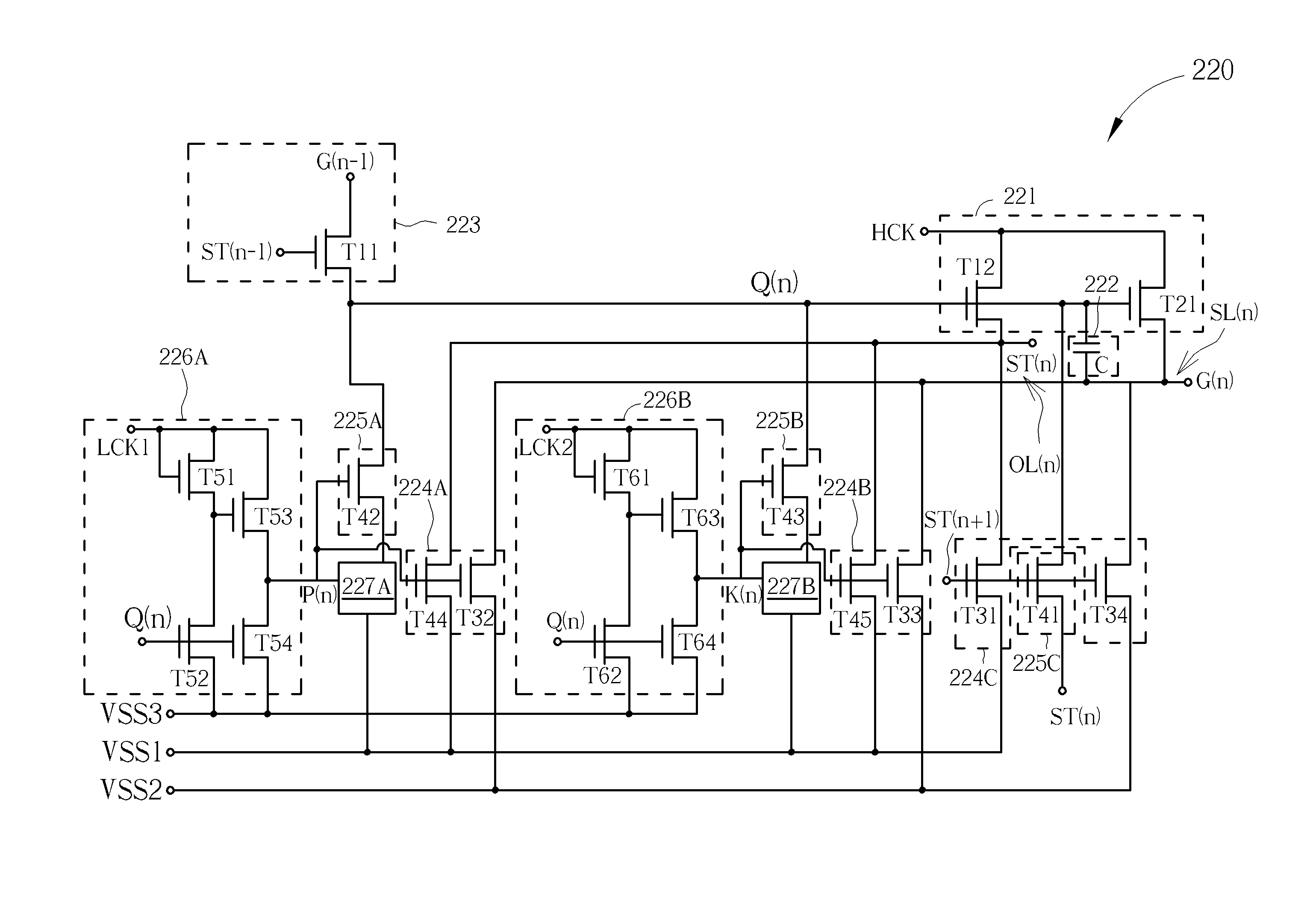

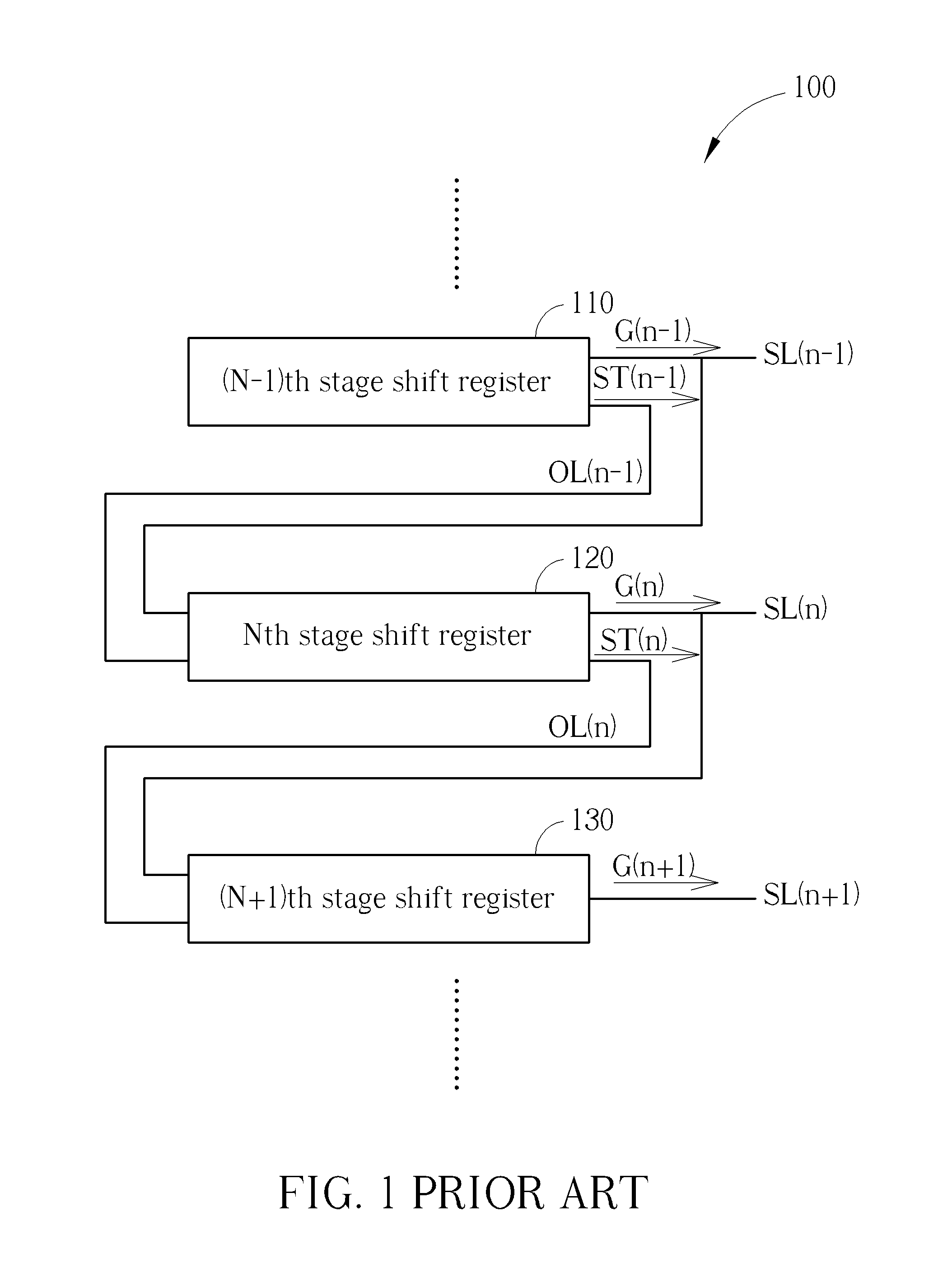

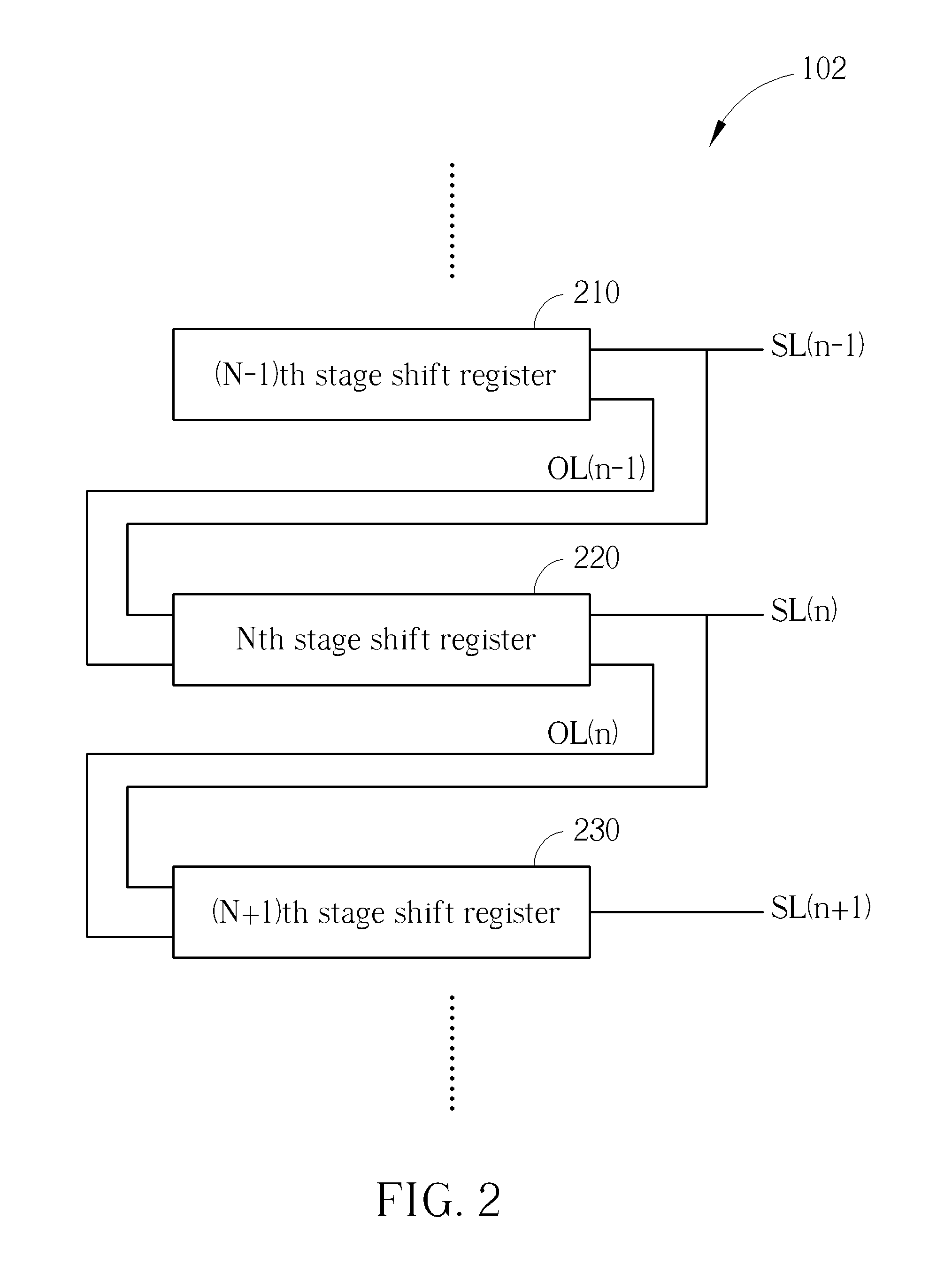

Gate driving circuit

ActiveUS20140103983A1Inhibit currentHigh voltage levelStatic indicating devicesDigital storageDriver circuitShift register

A shift register of a gate driving circuit includes a pull-up unit for pulling up a first output signal and a first gate signal to a high voltage level according to a driving voltage and a high-frequency clock signal, a start-up unit for transmitting a second gate signal, an energy-store unit for providing the driving voltage to the pull-up unit according to the second gate signal, a first discharging unit for pulling down the driving voltage to a first voltage level according to a first control signal, a first leakage-preventing unit for turning off the first discharging unit when the first gate signal reaches the high voltage level, a first pull-down unit for respectively pulling down the first output and first gate signals to the first and a second voltage levels according to the first control signal, and a first control unit for generating the first control signal.

Owner:AU OPTRONICS CORP

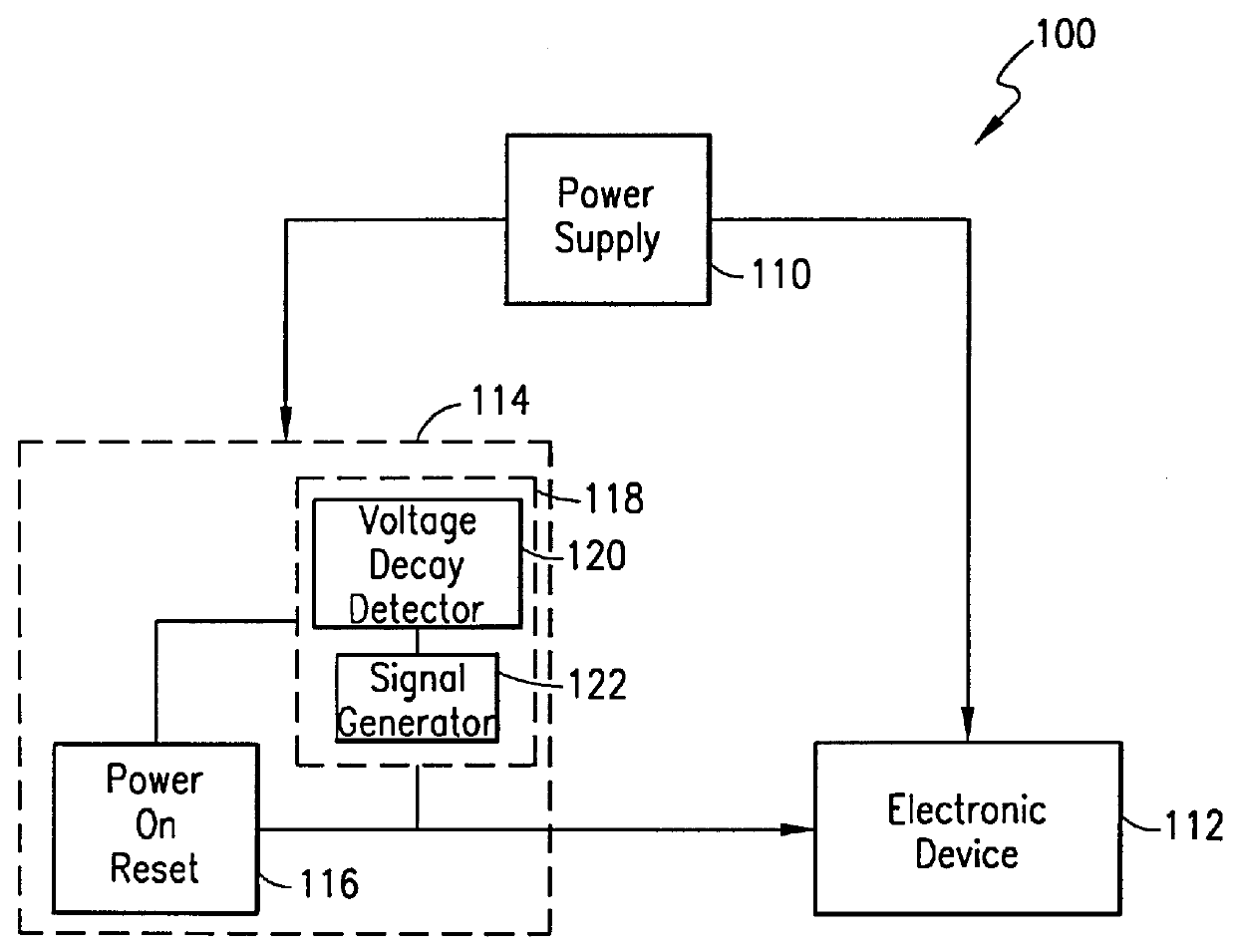

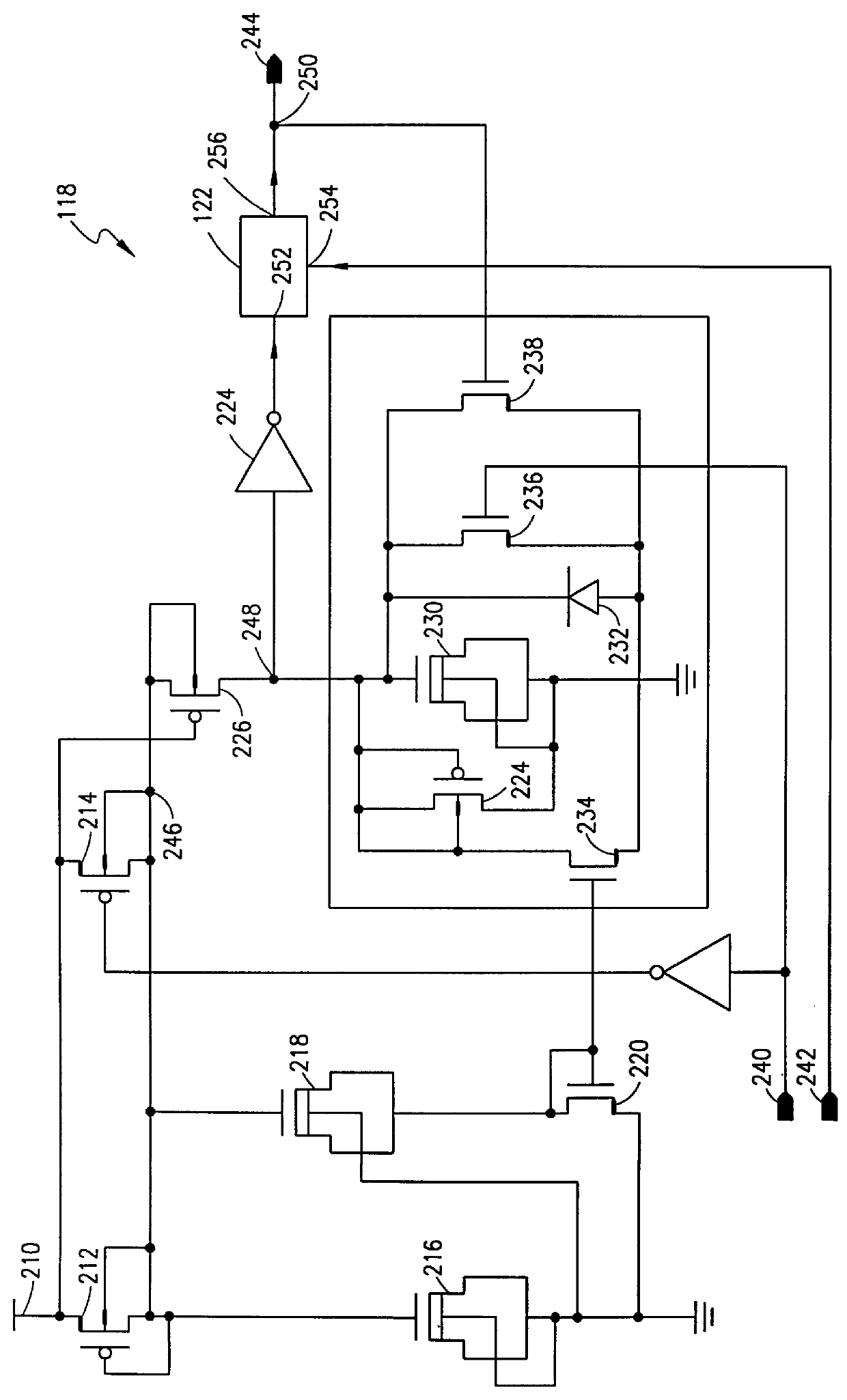

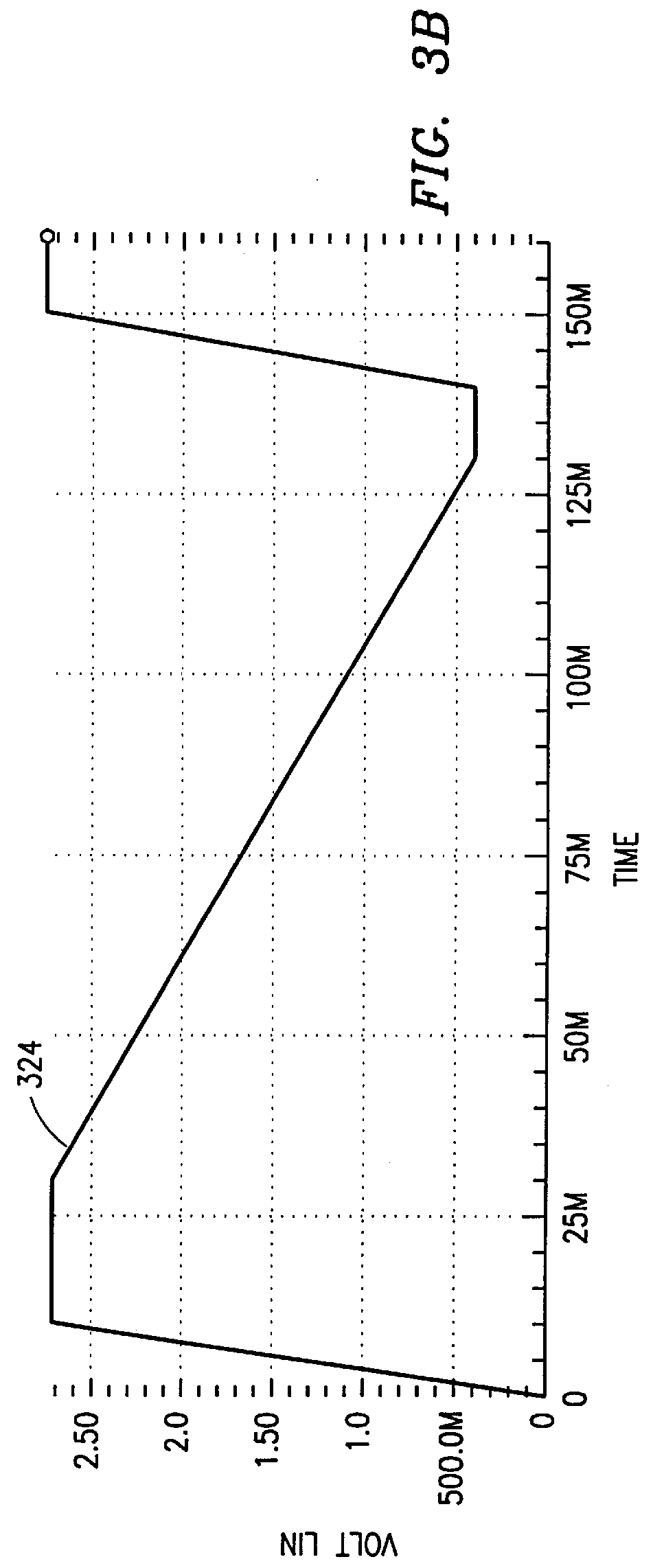

Method for initializing an electronic device using a dual-state power-on-reset circuit

InactiveUS6141764AMinimum power consumptionPulse automatic controlVolume/mass flow measurementPower-on resetElectricity

An initializer that responds to change in a power supply potential level, for generating an initialize signal to initialize a circuit to a select state, the initializer includes a power-on reset circuit that switches between an active and a powered-down state, and is for generating the initialize signal. The initializer also includes a wake-up circuit that monitors the power supply potential level and switches the power-on reset circuit from the powered-down state to the active state when selected change in the power supply potential level occurs.

Owner:MAXIM INTEGRATED PROD INC

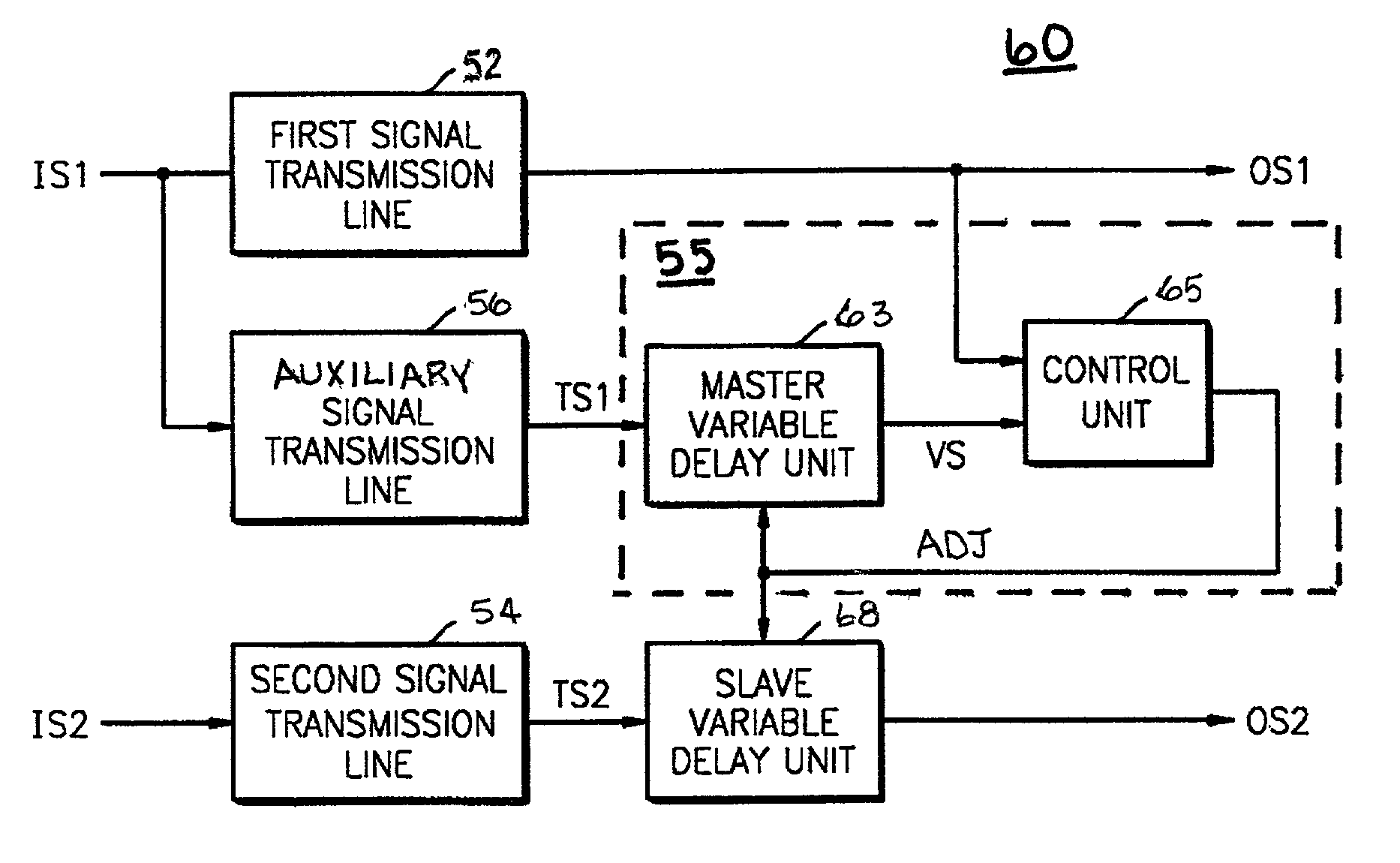

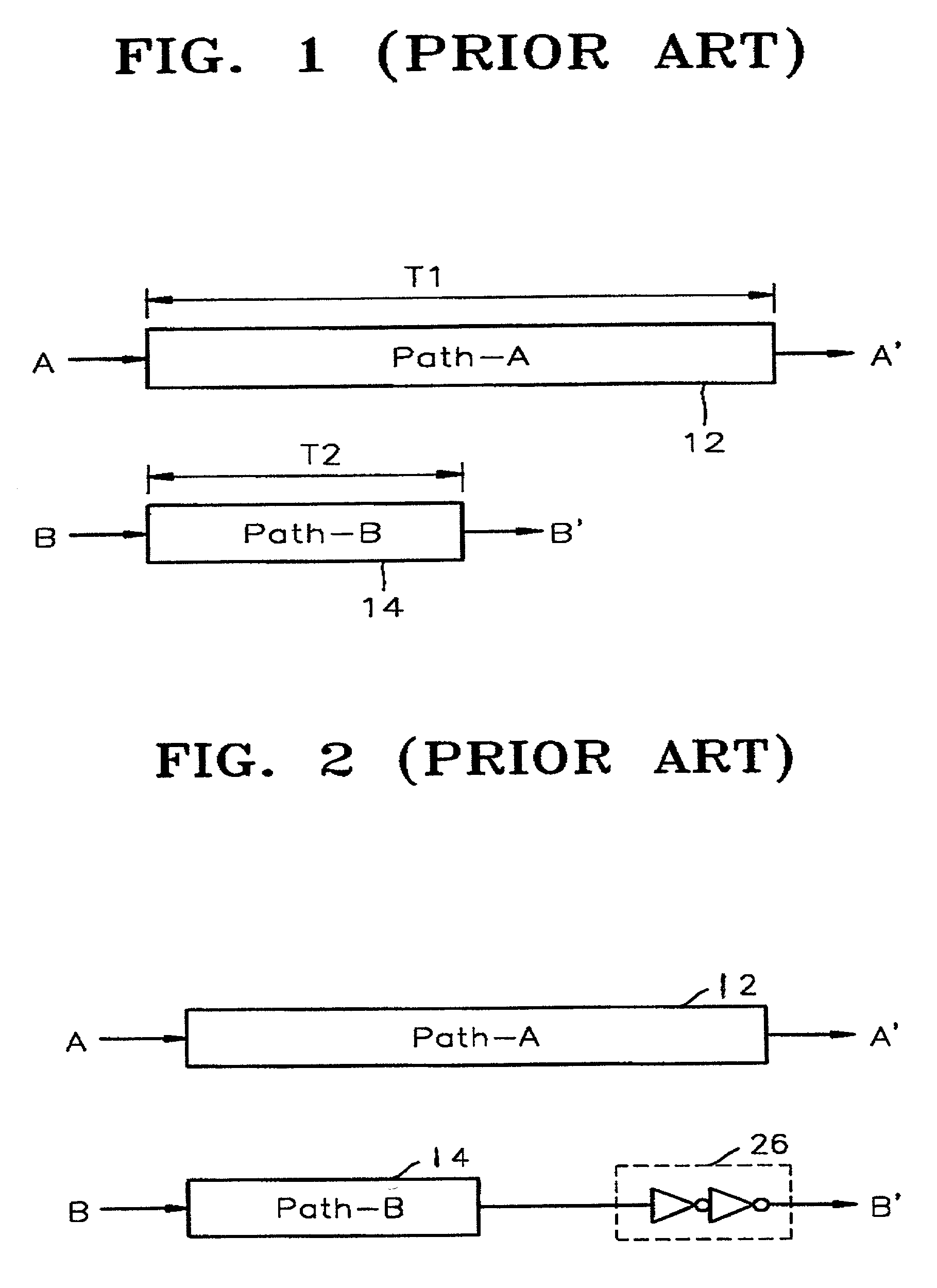

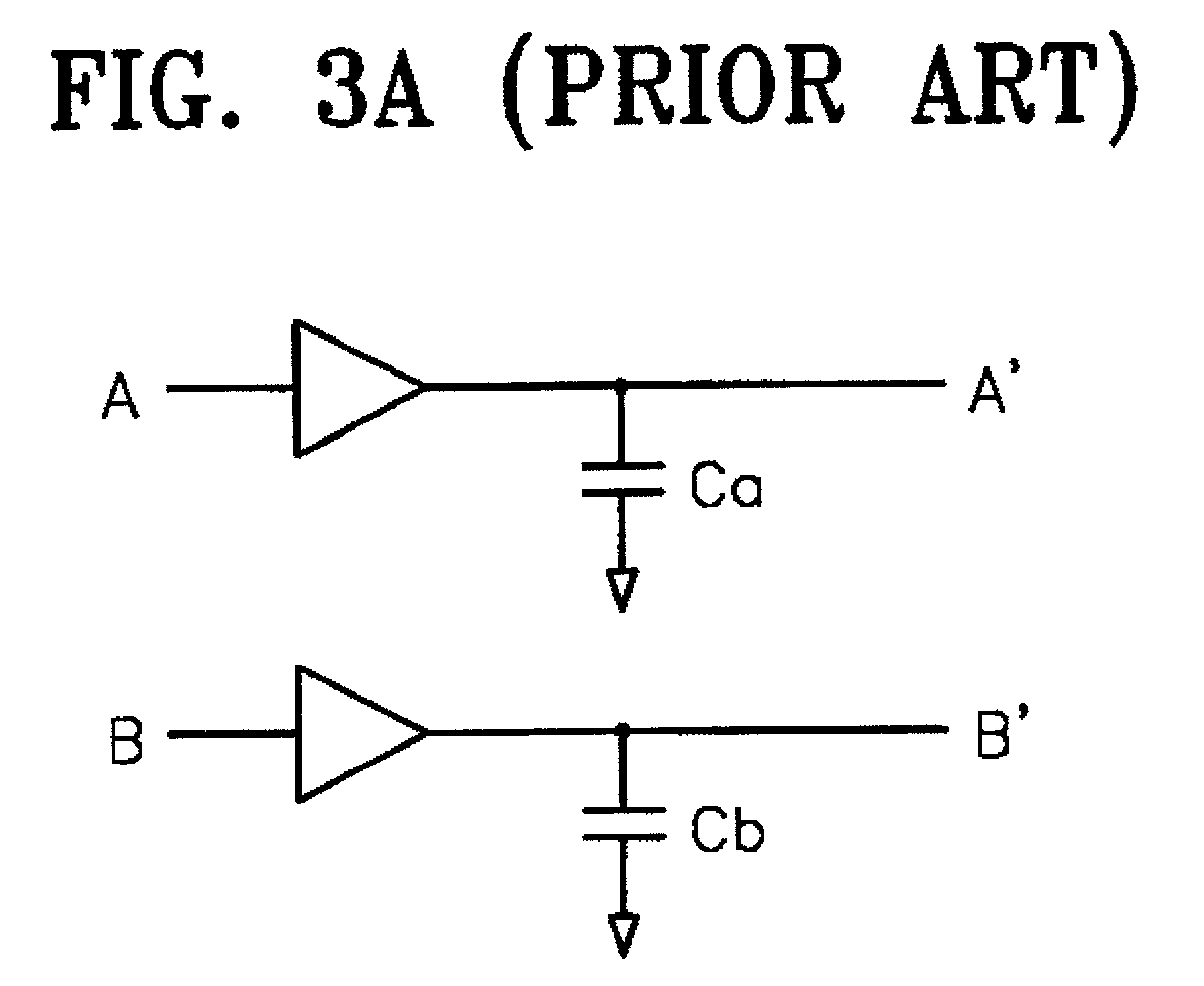

Signal transmission circuit and method for equalizing disparate delay times dynamically, and data latch circuit of semiconductor device implementing the same

InactiveUS7085336B2Accurate compensationKeep in syncChannel dividing arrangementsError preventionDelayed timeDatapath

A signal transmission circuit and a method equalize differential delay characteristics of two signal transmission lines. A controllable delay unit is connected serially to the second line, so as to compensate by adding its internal delay. An auxiliary signal transmission line replicates the second transmission line, while it processes the input signal of the first. A controlling unit compares the output signal of the first transmission line and the of the auxiliary signal transmission line, and adjusts dynamically the internal delay of the controllable delay unit, to attain continuous synchronization. A data latch circuit synchronizes the delays of data paths by having one controllable delay units in each of the data paths.

Owner:SAMSUNG ELECTRONICS CO LTD

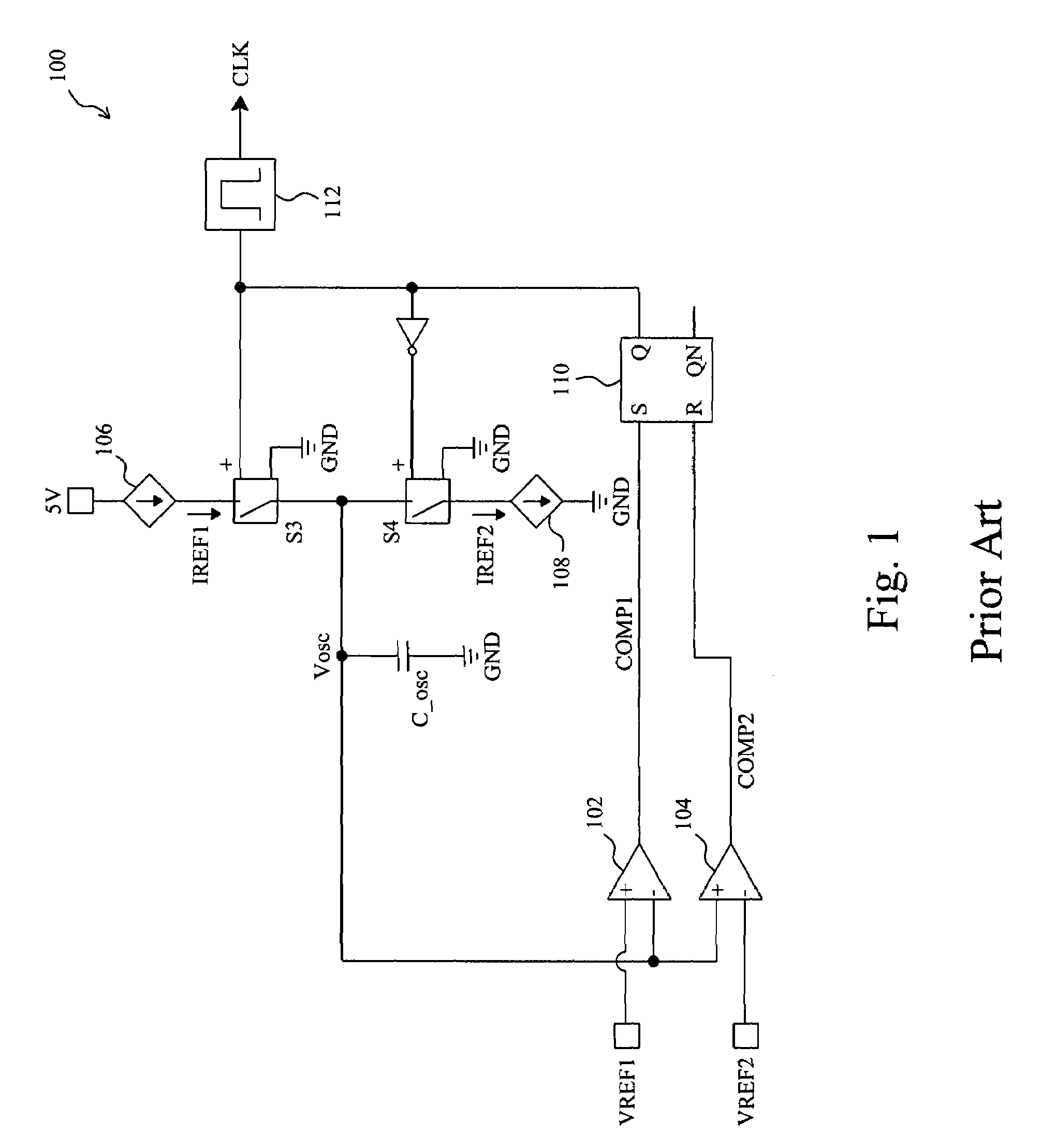

Voltage detector

InactiveUS7030668B1Pulse automatic controlInstant pulse delivery arrangementsDetector circuitsLow voltage

A voltage detector circuit such as a power up and / or brownout detector circuit (100) includes a comparator (102) having at least one of its inputs (104) coupled to a diode-connected transistor (108). The other input can include another diode-connected transistor (110) or a resistor divider (302). Optional compensation capacitors (118 and 120) can be added to the comparator output (116) to provide glitch compensation. Since comparator (102) only needs to output a high or low voltage level, the components that are used to build circuit (100) do not have to have very tight tolerances. Circuit (100) also can operate at very low voltages and consume low amounts of power.

Owner:XILINX INC

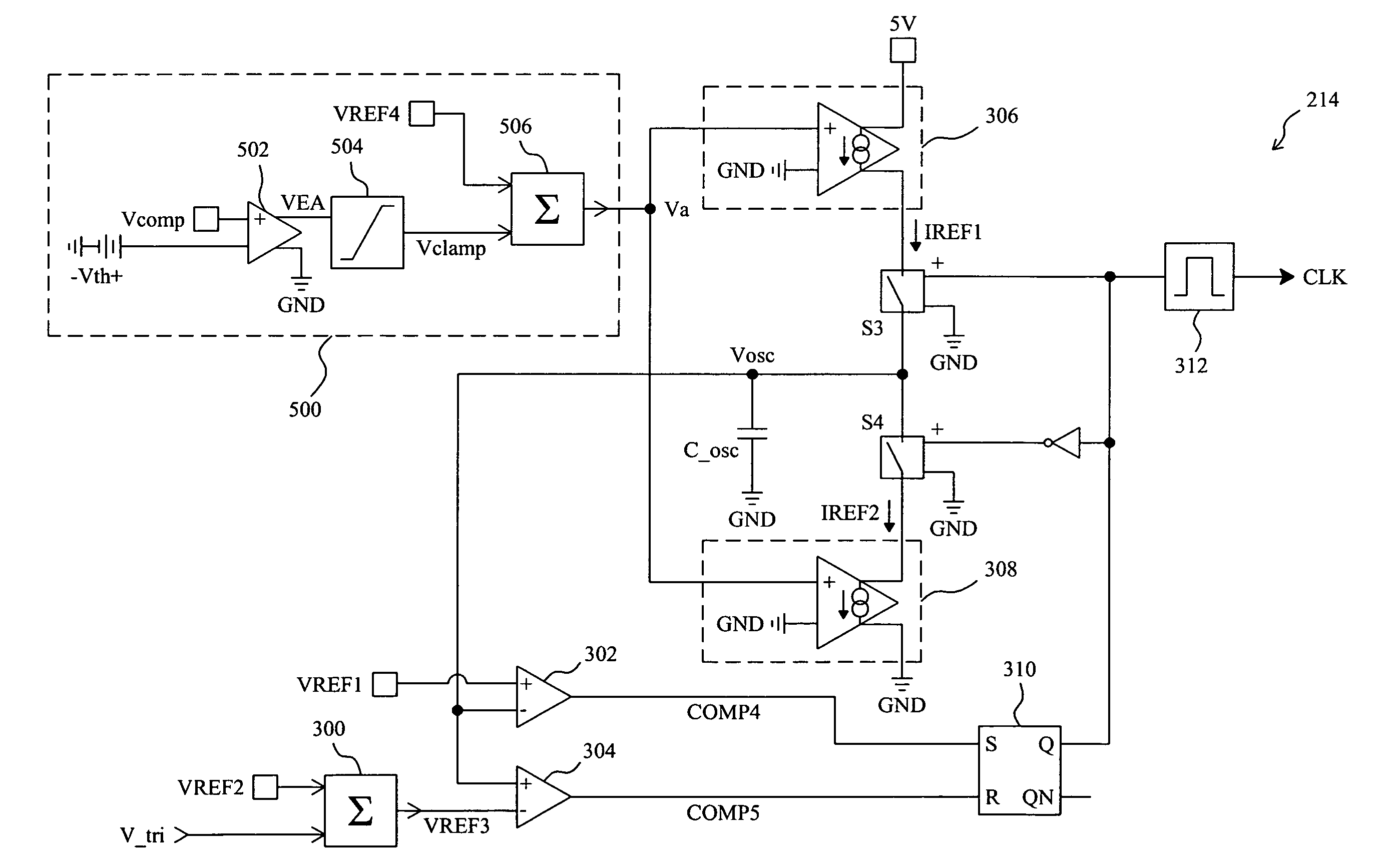

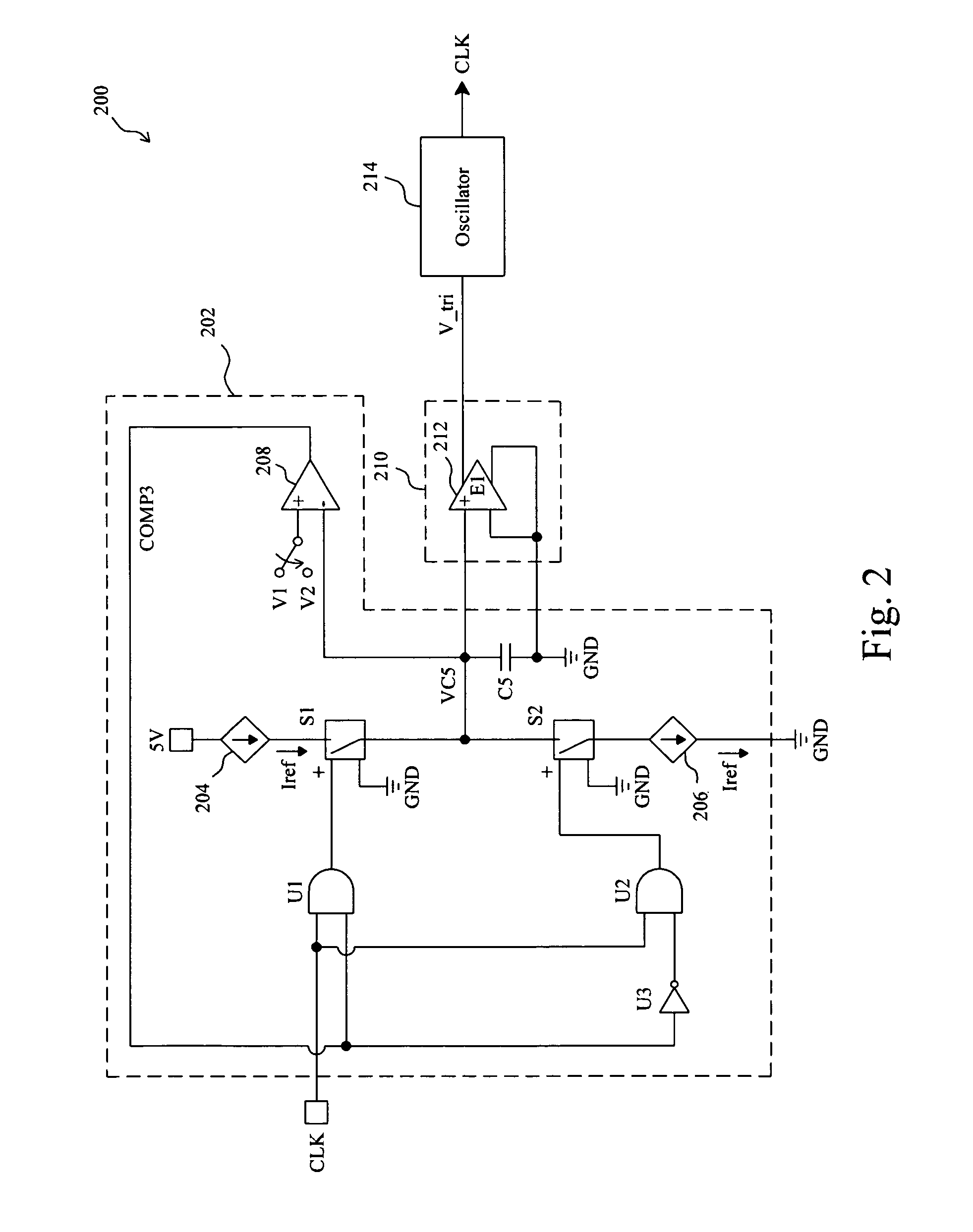

Frequency jittering control for varying the switching frequency of a power supply

ActiveUS7701305B2Digital data processing detailsTransmission noise reductionEngineeringSwitching frequency

Owner:RICHTEK TECH

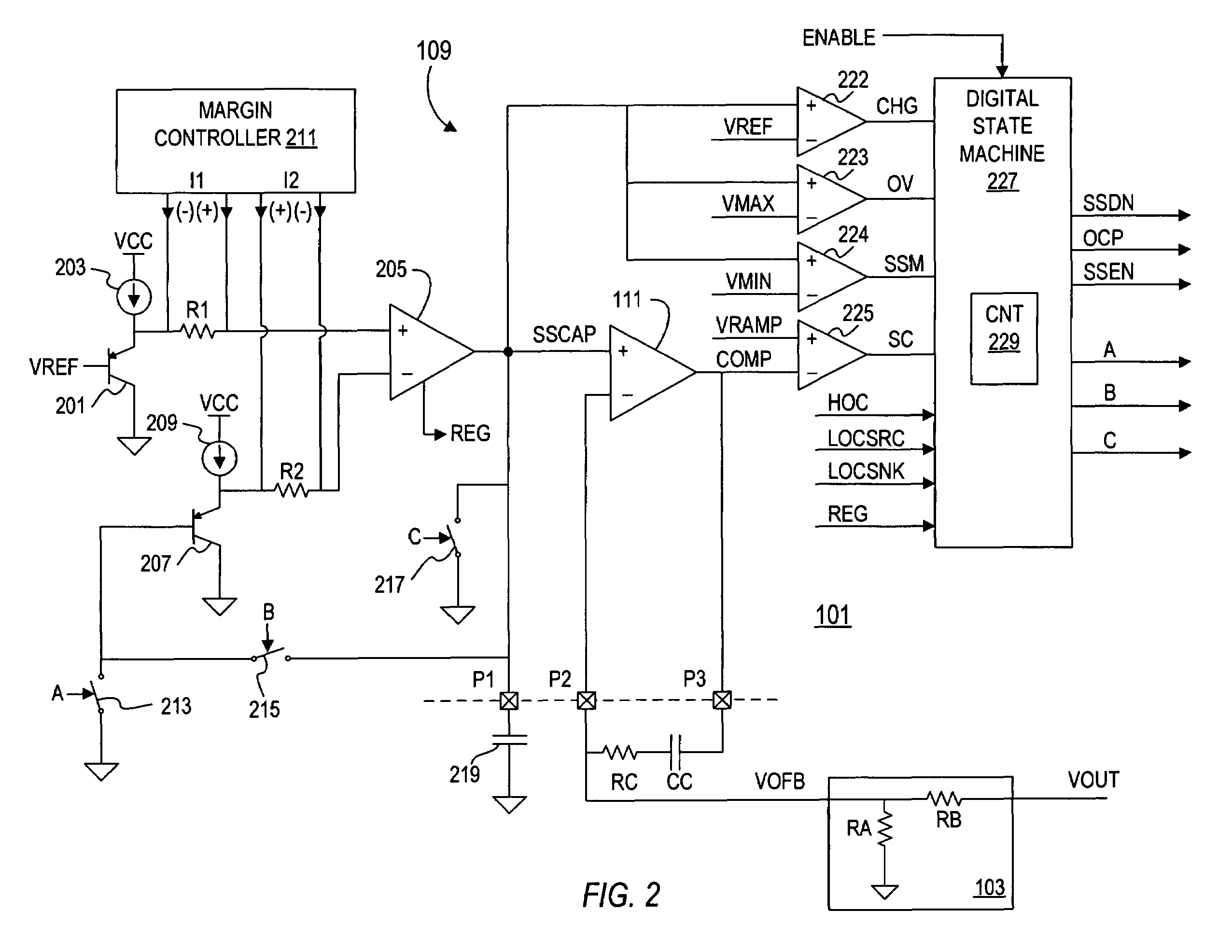

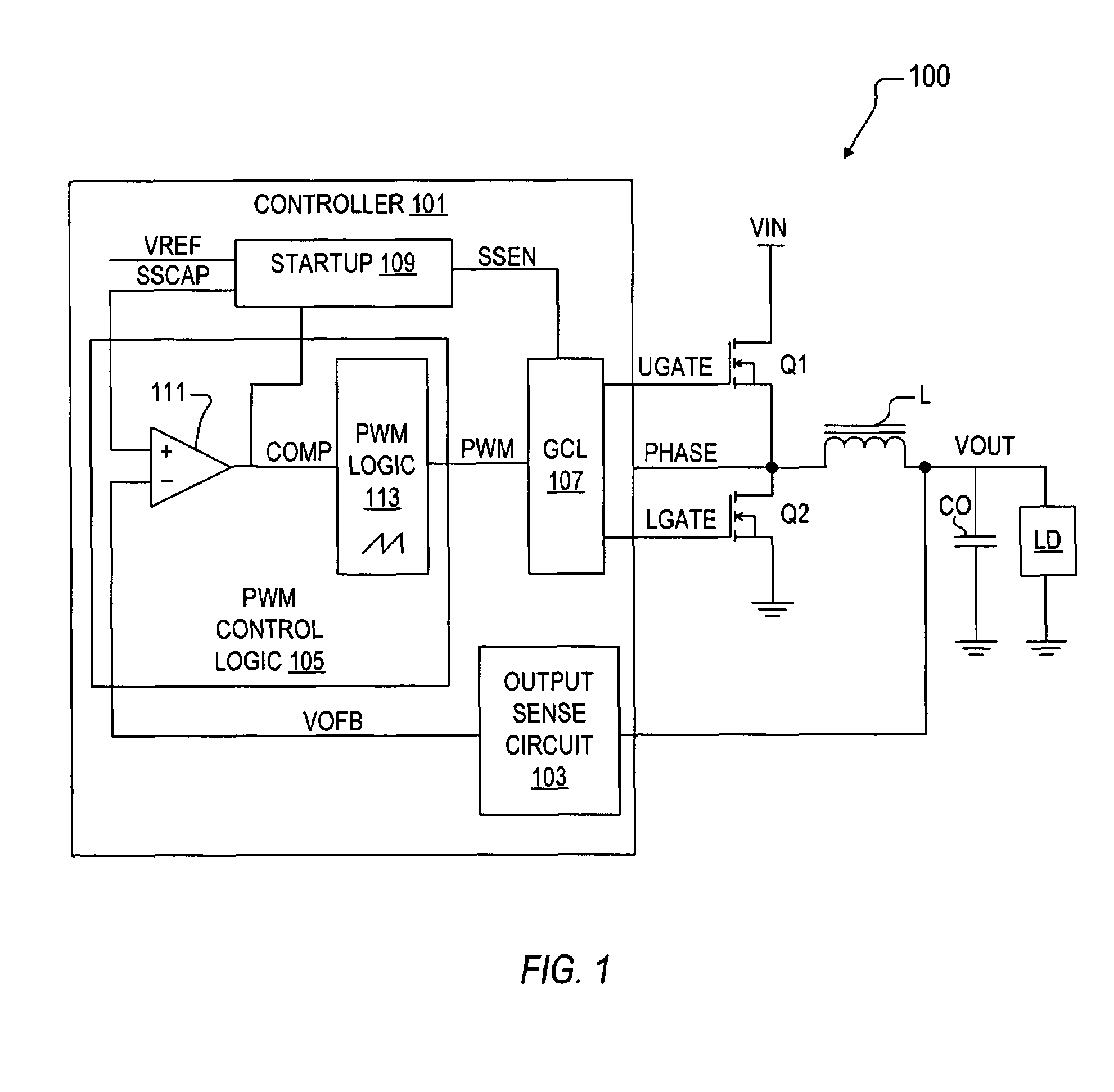

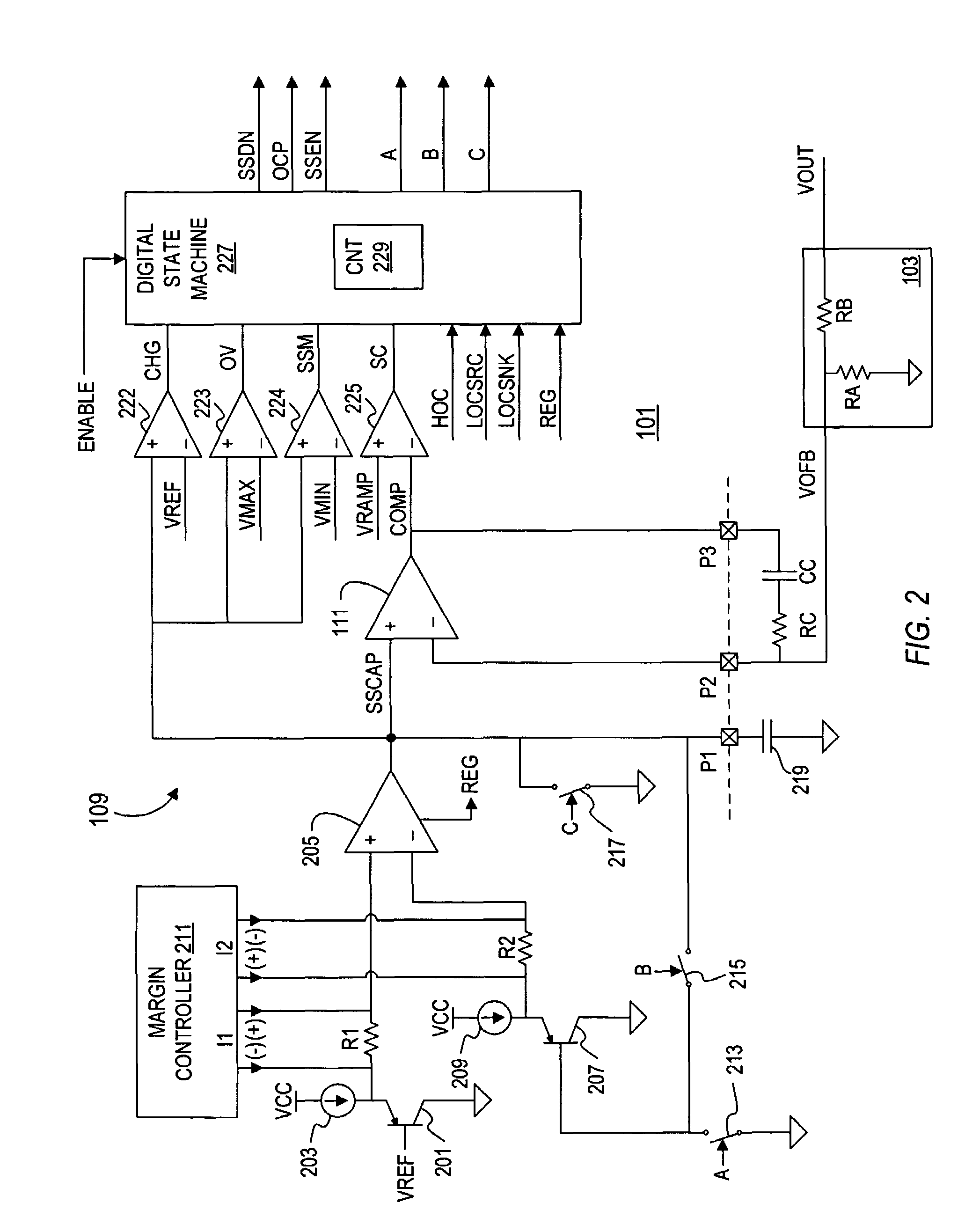

Startup circuit for a DC-DC converter

A startup circuit for a power converter including an amplifier circuit, a comparator, and startup logic. The power converter includes an error amplifier that compares an output sense signal with a startup reference signal and that provides a compensation signal. The amplifier circuit charges the startup reference signal to a predetermined reference level based on a second reference signal in response to a start signal. The comparator determines when the compensation signal reaches a predetermined ramp level and asserts a startup complete signal indicative thereof. The startup logic provides the start signal and provides an output enable signal in response to the startup complete signal. The output enable signal enables output switching to initiate normal regulation operation of the output voltage. In one embodiment, the predetermined ramp level is approximately the center voltage of a sawtooth regulation waveform used for PWM modulation.

Owner:INTERSIL INC

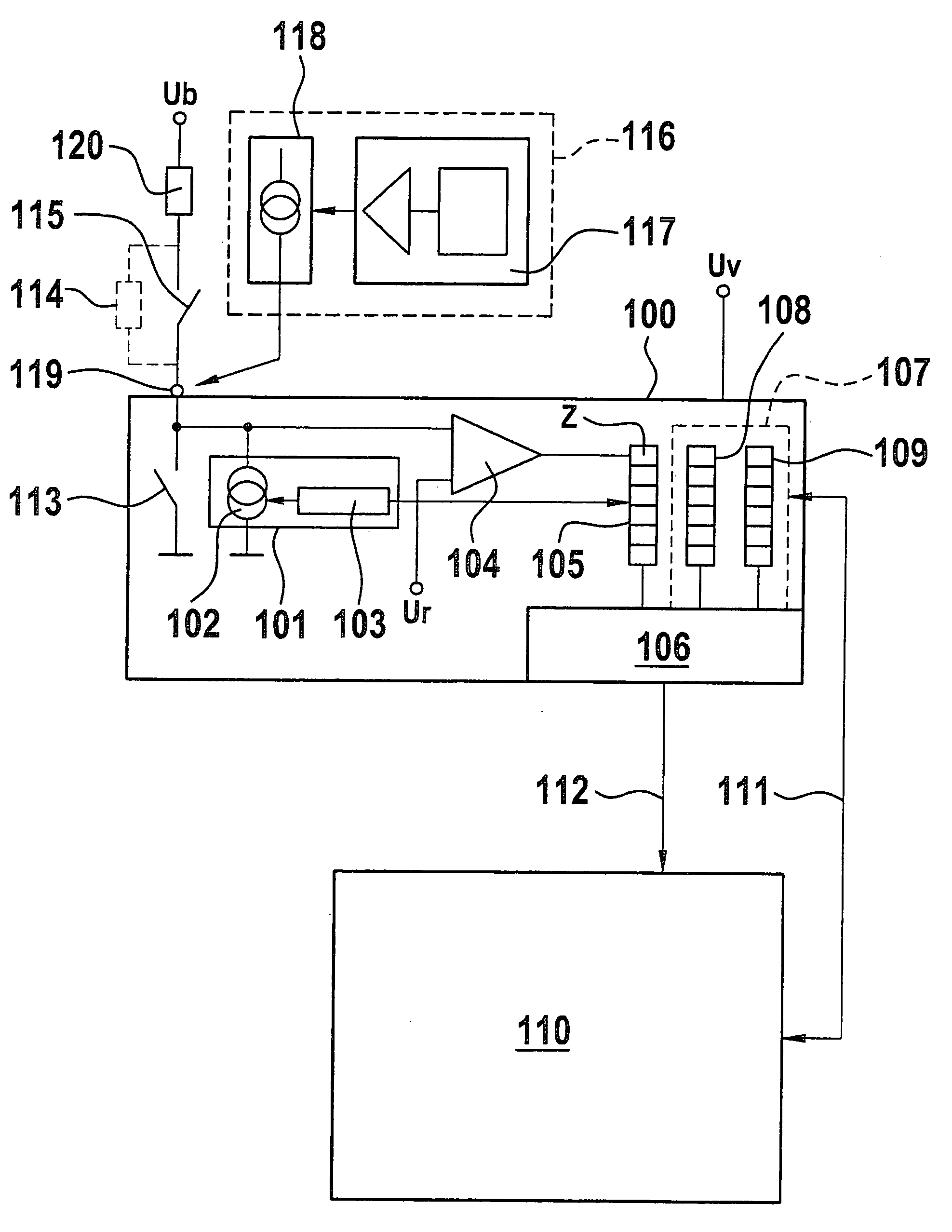

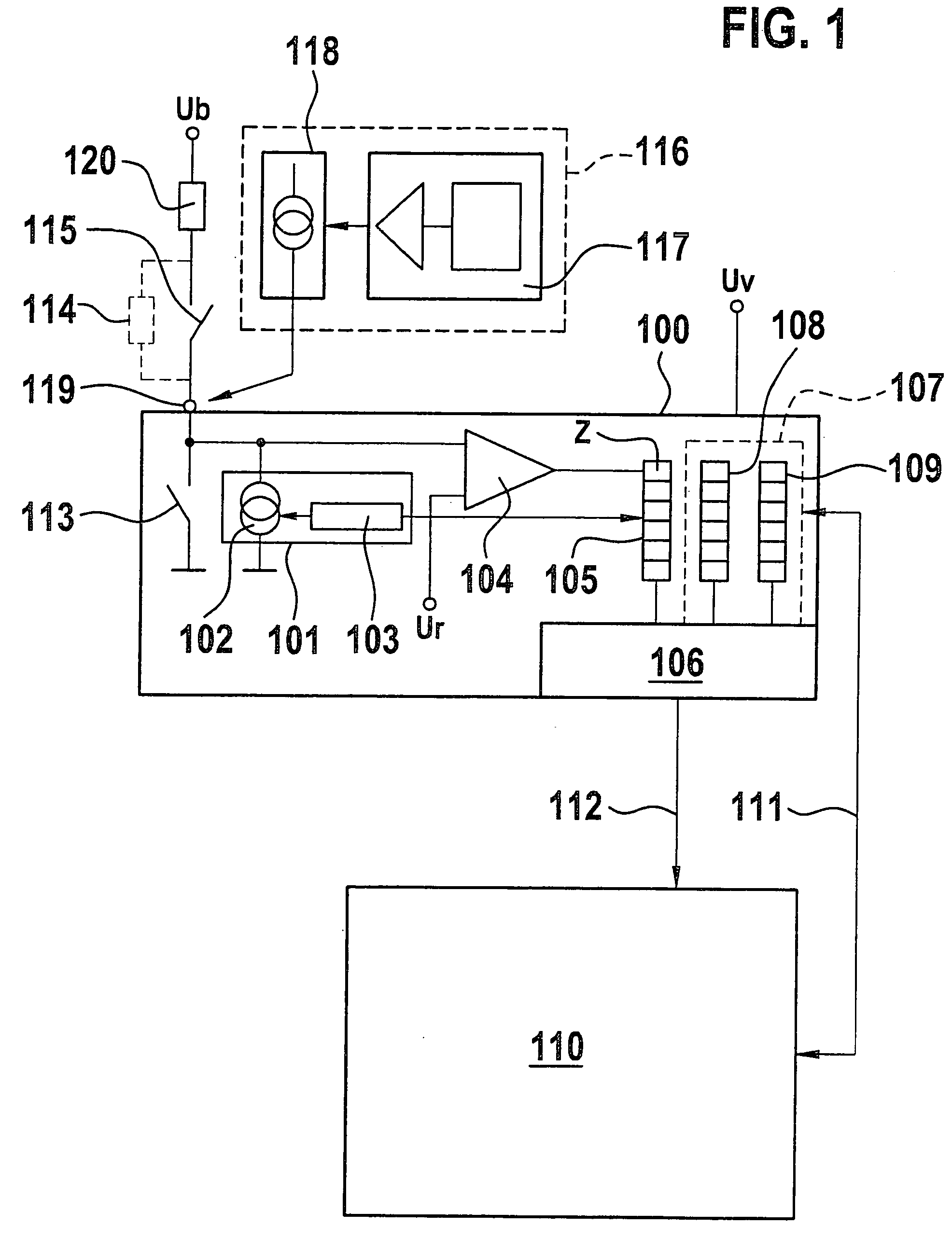

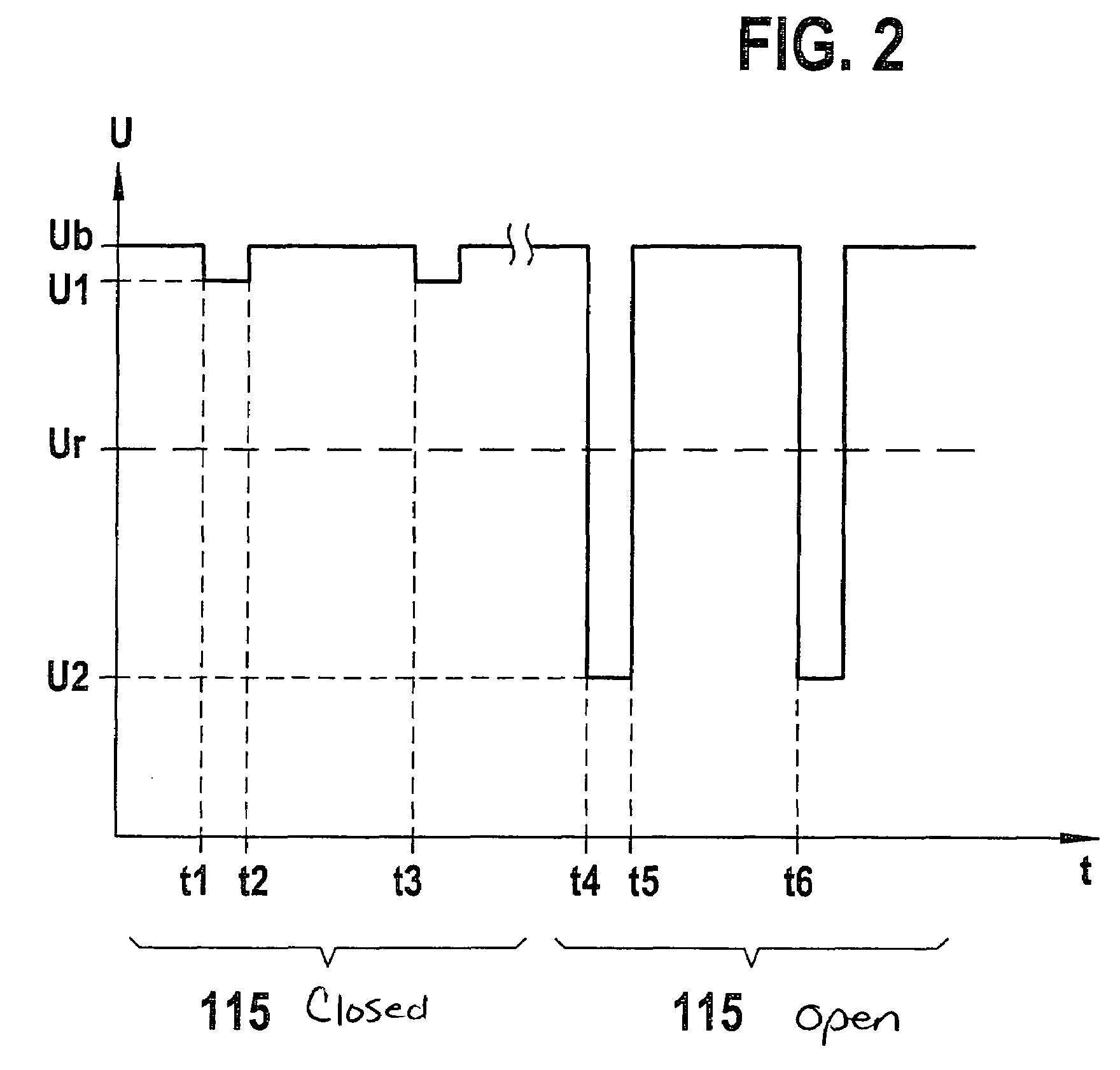

Circuit and method for the input of a start signal for a controller

InactiveUS7114088B2Reduction in no-signal current consumptionReduce necessityEfficient power electronics conversionVolume/mass flow measurementControl engineeringHemt circuits

Owner:ROBERT BOSCH GMBH

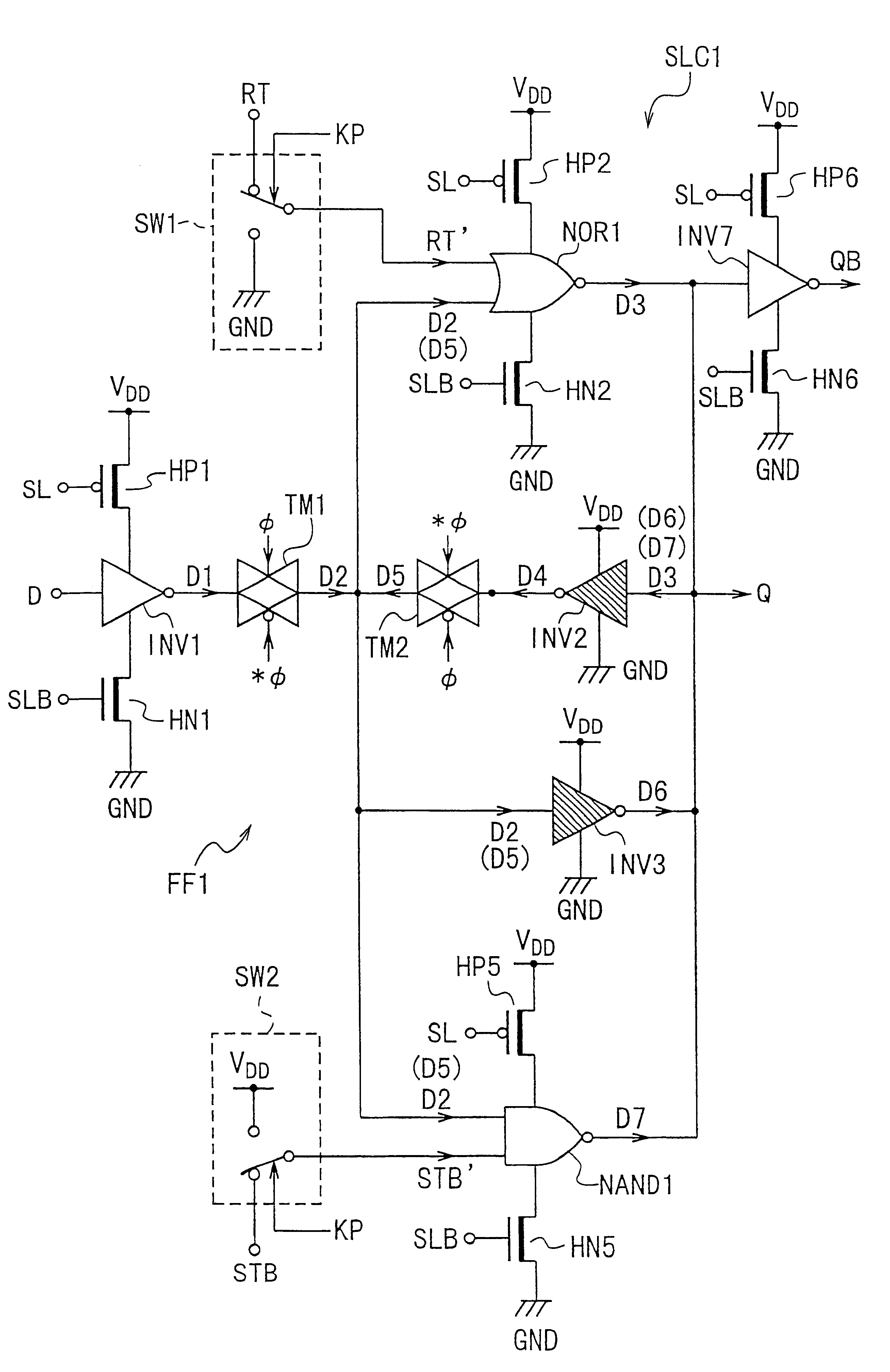

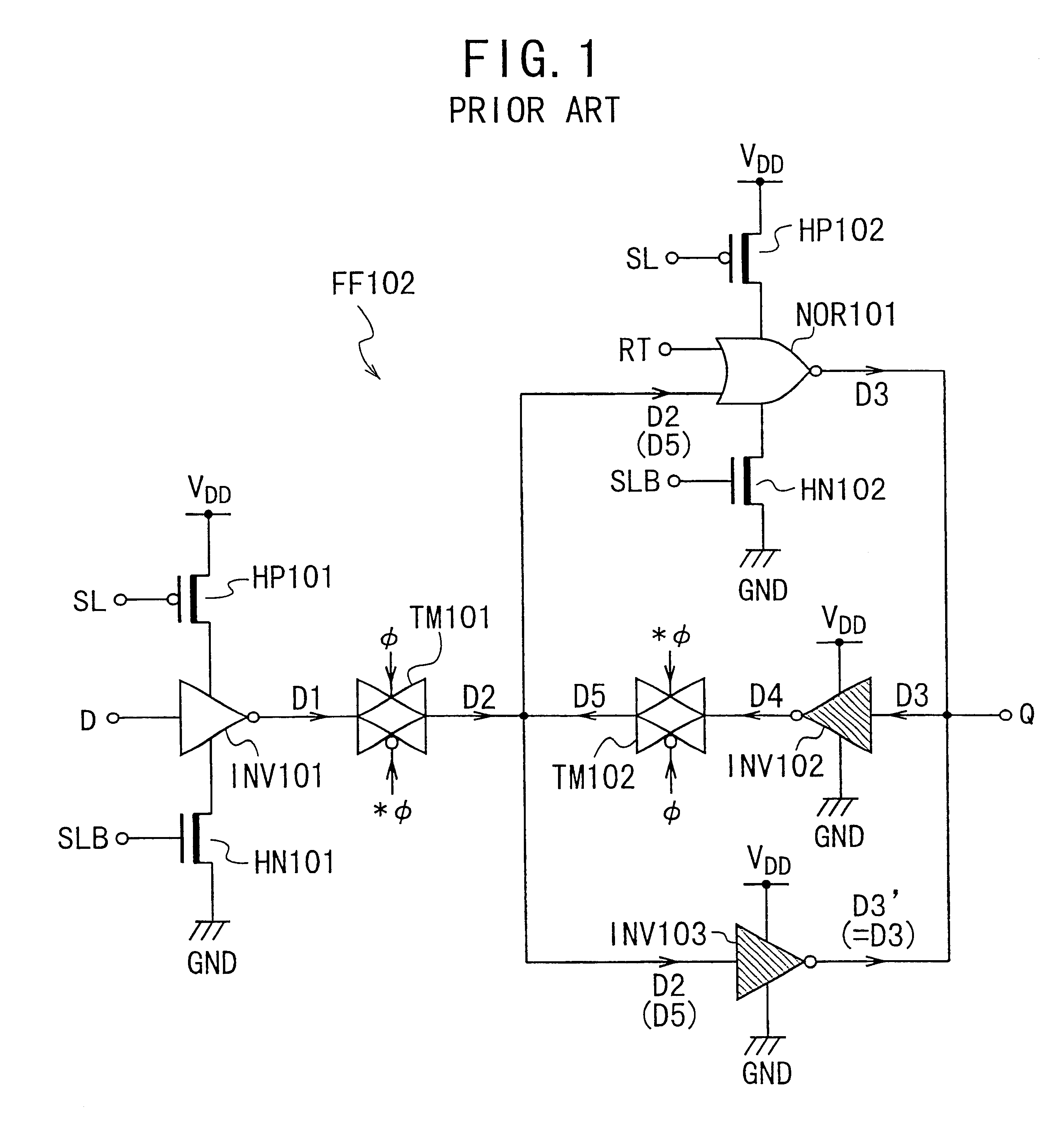

Sequential logic circuit with active and sleep modes

InactiveUS6310491B1Logic circuits characterised by logic functionData resettingLogic stateSequential logic

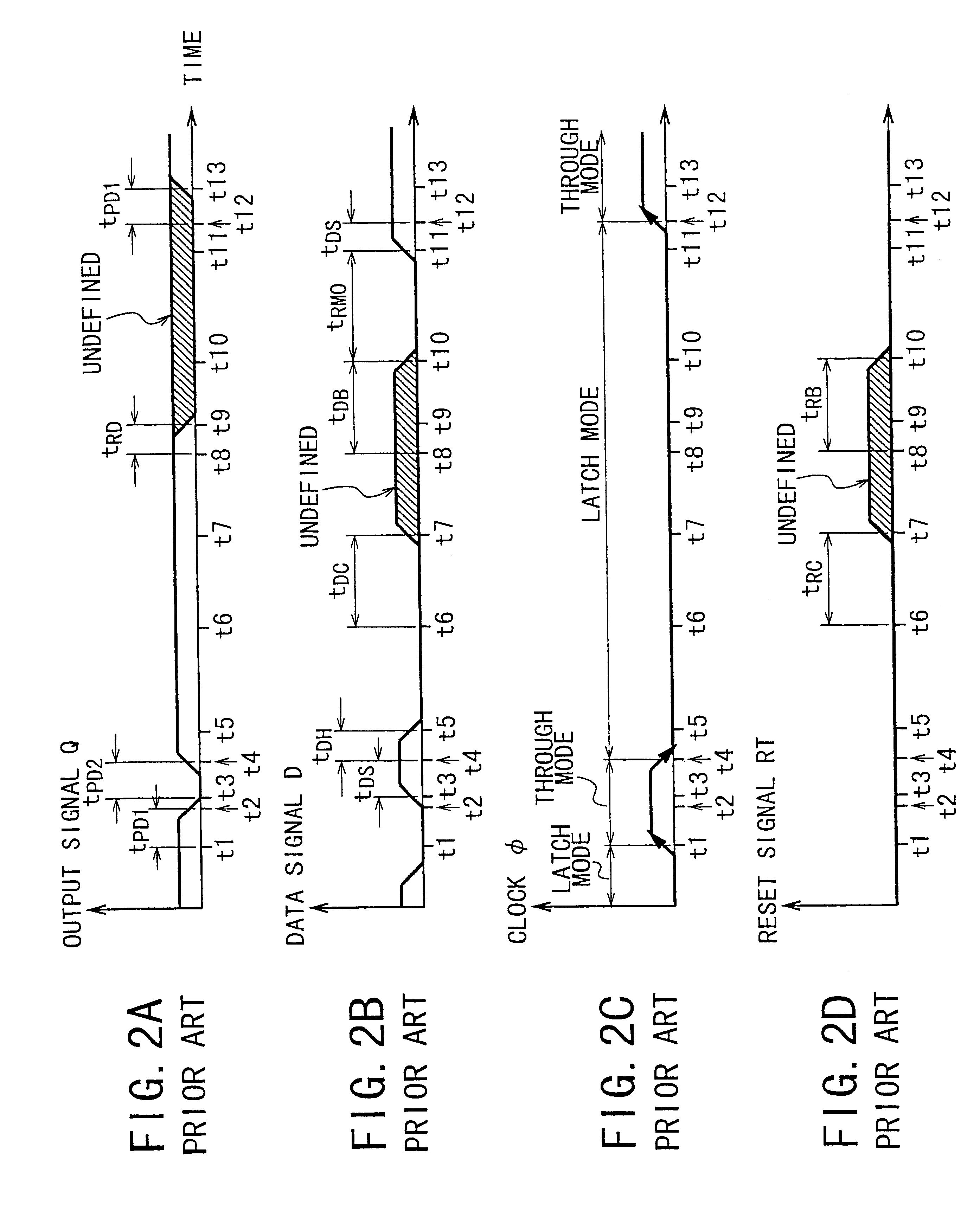

A sequential logic circuit having active and sleep modes prevents stored information from being lost immediately after the transition from a sleep mode to an active mode. This sequential logic circuit includes a latch circuit having an input terminal to which an input signal is applied, an output terminal from which and output signal is derived, and a set and / or reset terminal to which a set and / or reset signal is applied. The latch circuit has an active mode where a latch function is operable and a sleep mode where the latch function is inoperable, one of which is alternatively selected. The output signal is set or reset to have a specific logic state by the set or reset signal having a specific logic level applied to the set or reset terminal in the active mode. The sequential logic circuit further includes circuitry for preventing the set or reset signal from being applied to the set or reset terminal in the sleep mode, thereby avoiding loss of information or data latched in the latch circuit prior to transition to the sleep mode from the active mode. Thus, the information-latch operation in both of the modes is ensured.

Owner:NEC ELECTRONICS CORP

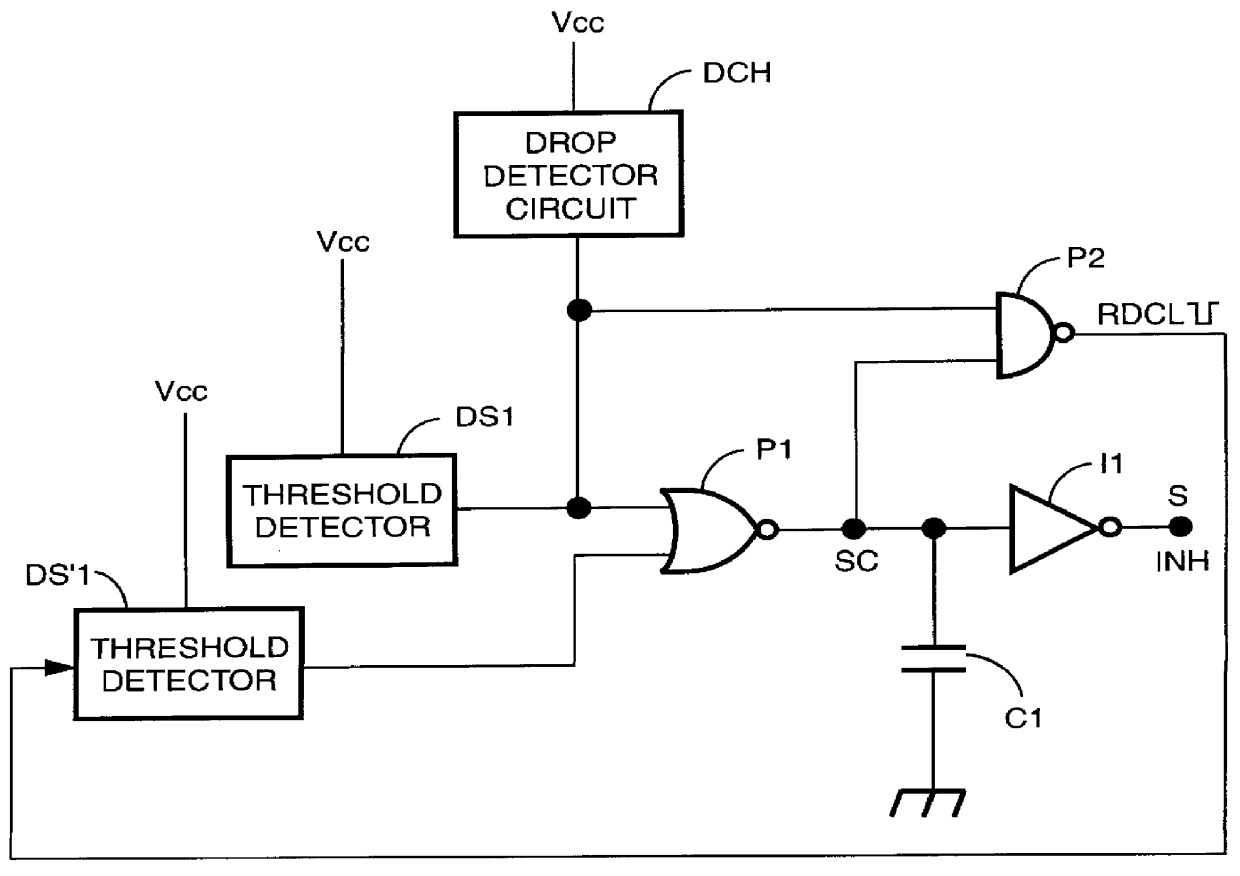

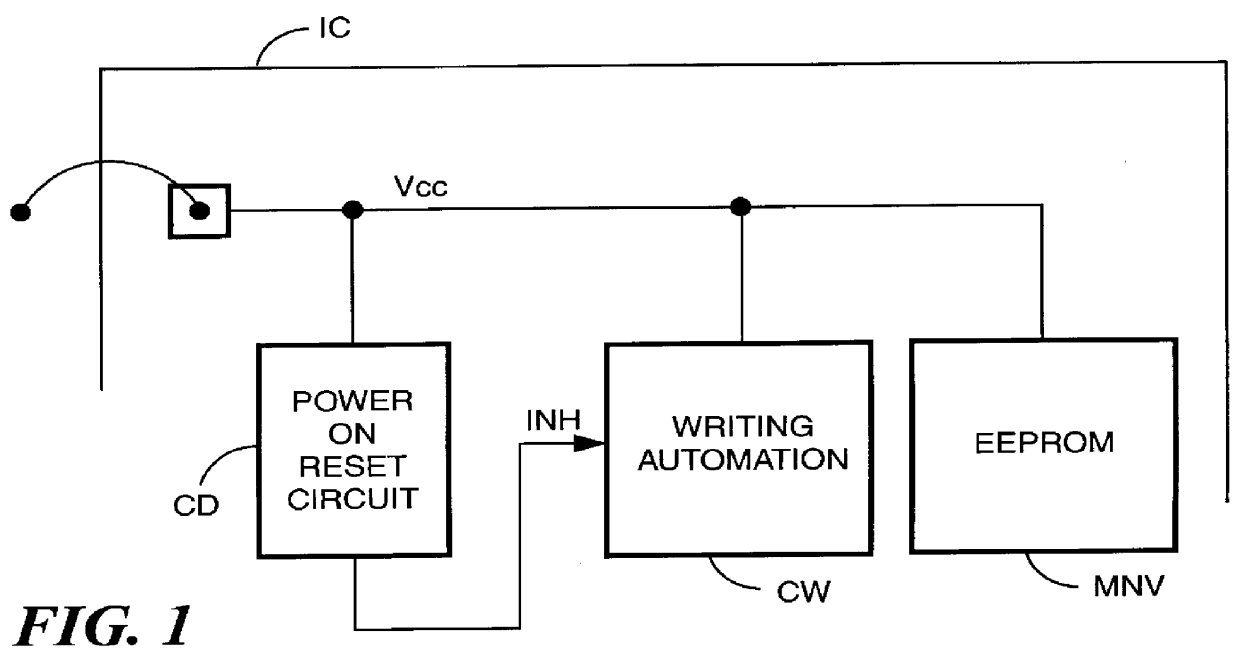

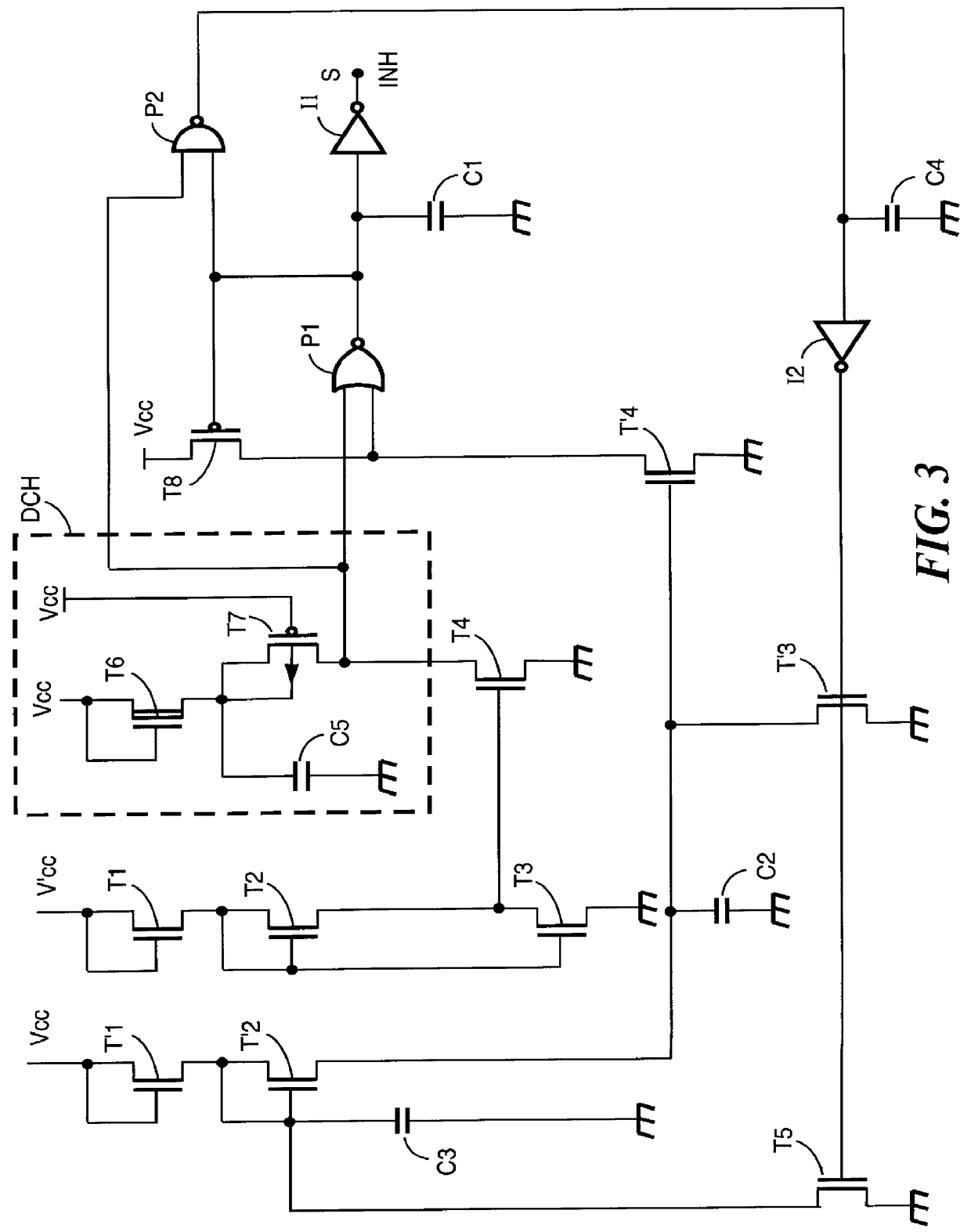

Power-on-reset circuit providing protection against power supply interruptions

The disclosure relates to integrated circuits and, more particularly, to a power-on-reset circuit. The proposed circuit produces an inhibition signal when the power is turned on, this signal being interrupted after the supply voltage Vcc has reached a first threshold (VS1) (VS1). Furthermore, the circuit has means to re-trigger the inhibition signal when the supply voltage drops by a certain value, in doing so even if the supply voltage remains above the first threshold. The reliability of the integrated circuit is improved. The disclosed circuit is particularly applicable to the inhibition of the writing circuit of an EEPROM memory.

Owner:STMICROELECTRONICS SRL

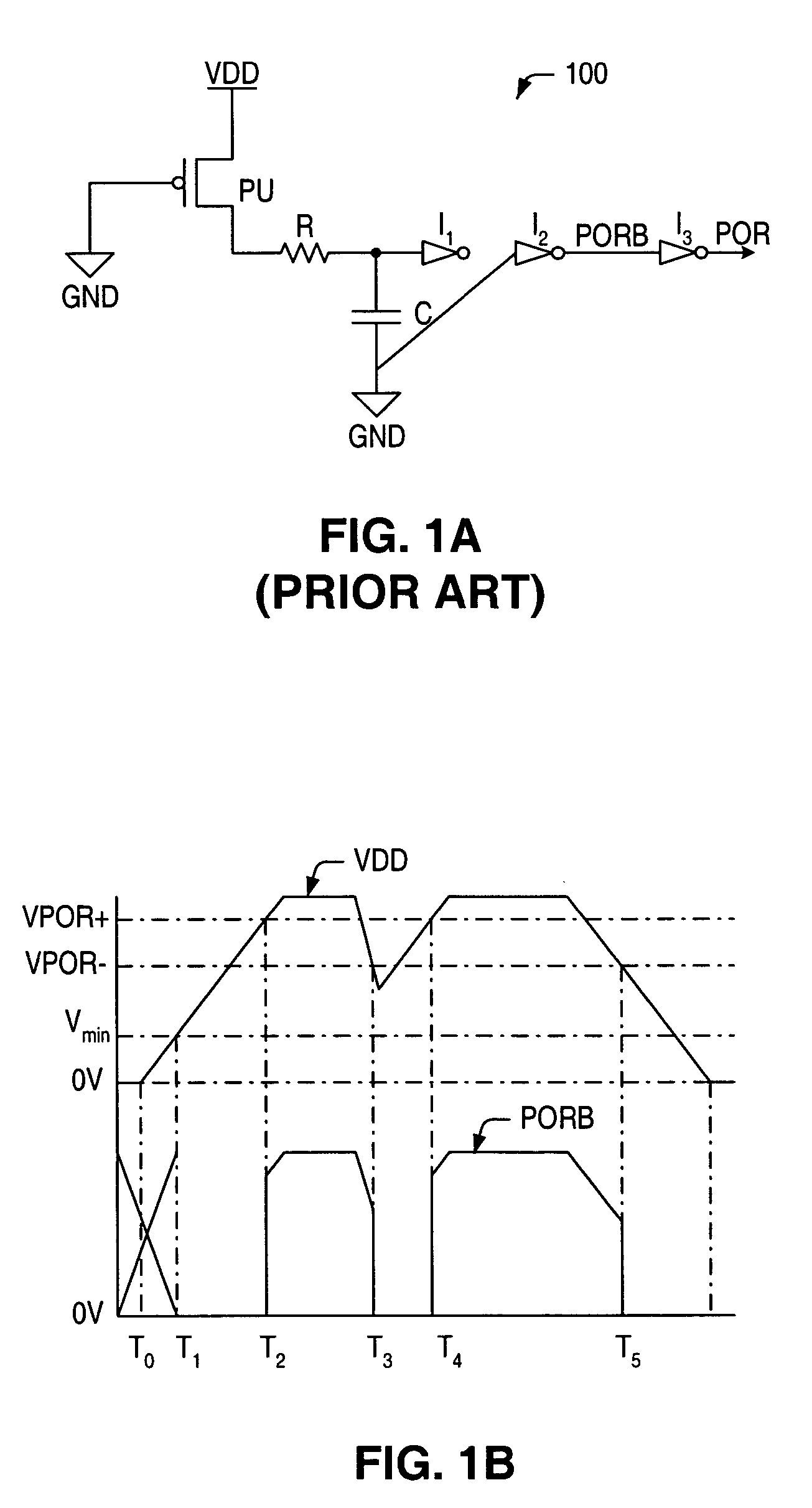

Power on reset circuit

A power on reset (POR) circuit for providing a reset pulse signal to a chip when power supply voltage, VDD, ramps up so that the chip always starts in a known state. The POR circuit generates the reset pulse as soon as VDD exceeds an assertion voltage. The assertion voltage is independent of the ramp rate of VDD. The POR circuit is shut off as soon as the reset signal is generated, thereby drawing zero steady state current from VDD. The re-arm time for the POR circuit is very small. The POR circuit does not reset the chip when there is a dynamic change in VDD.

Owner:SK HYNIX INC

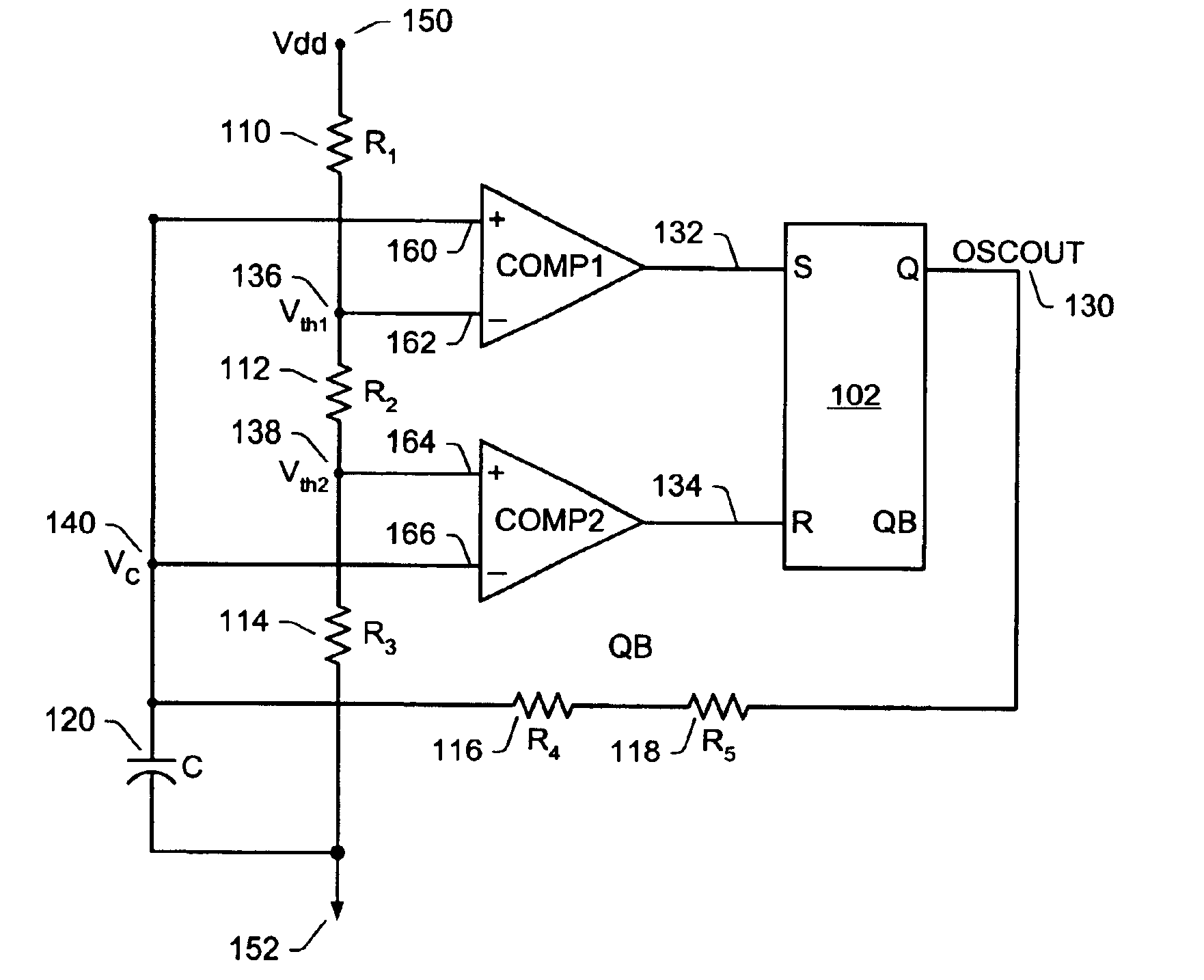

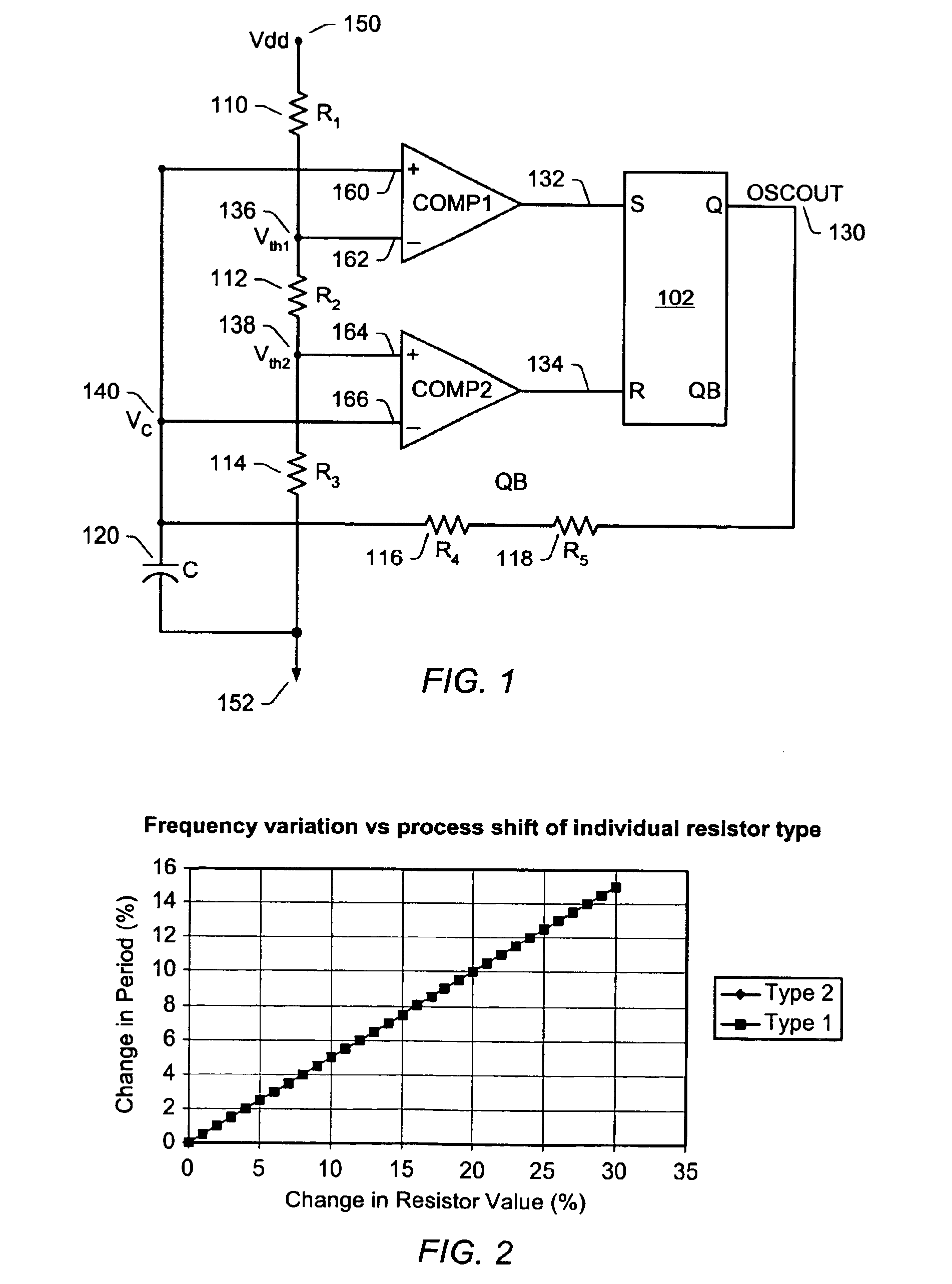

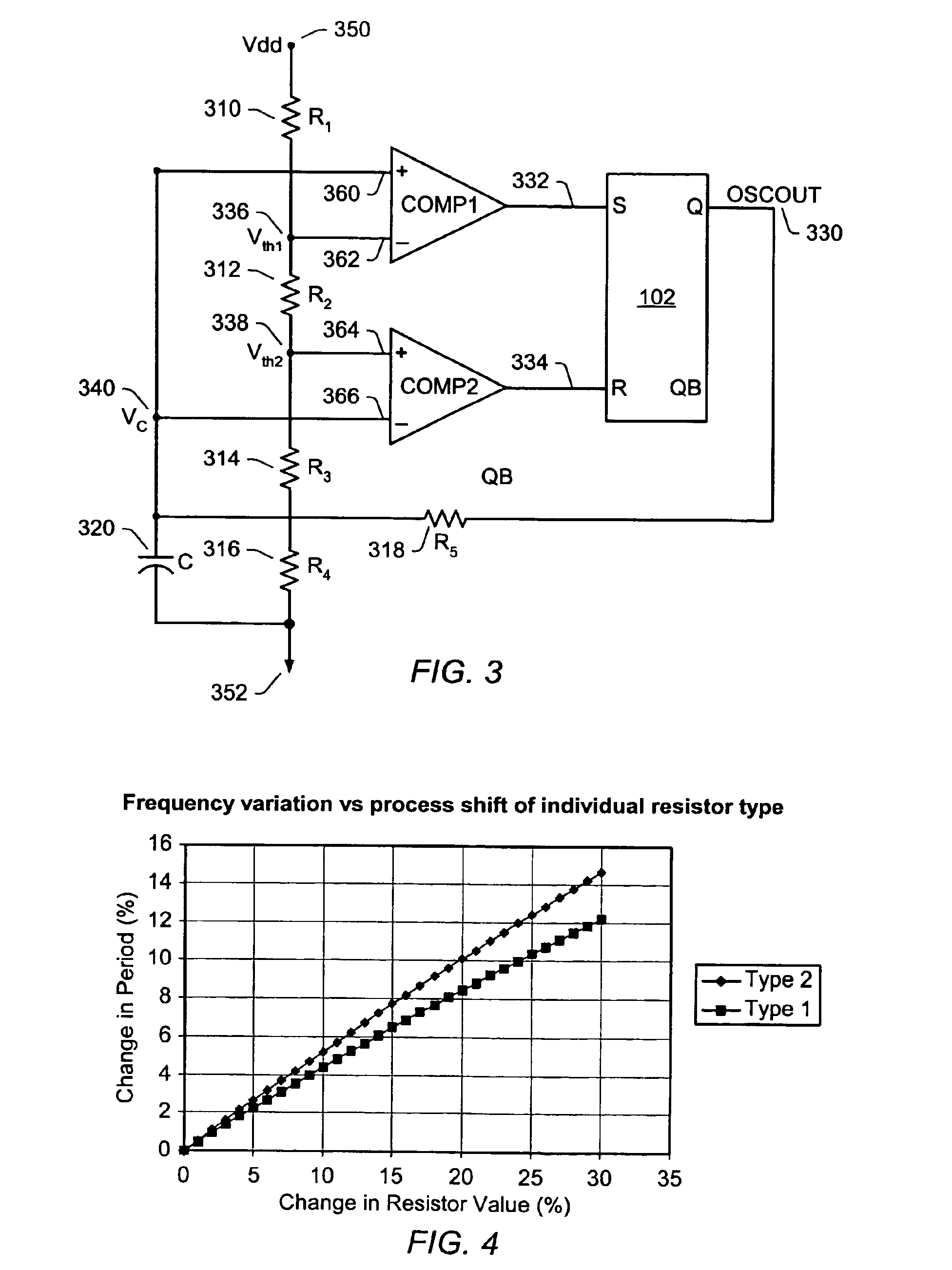

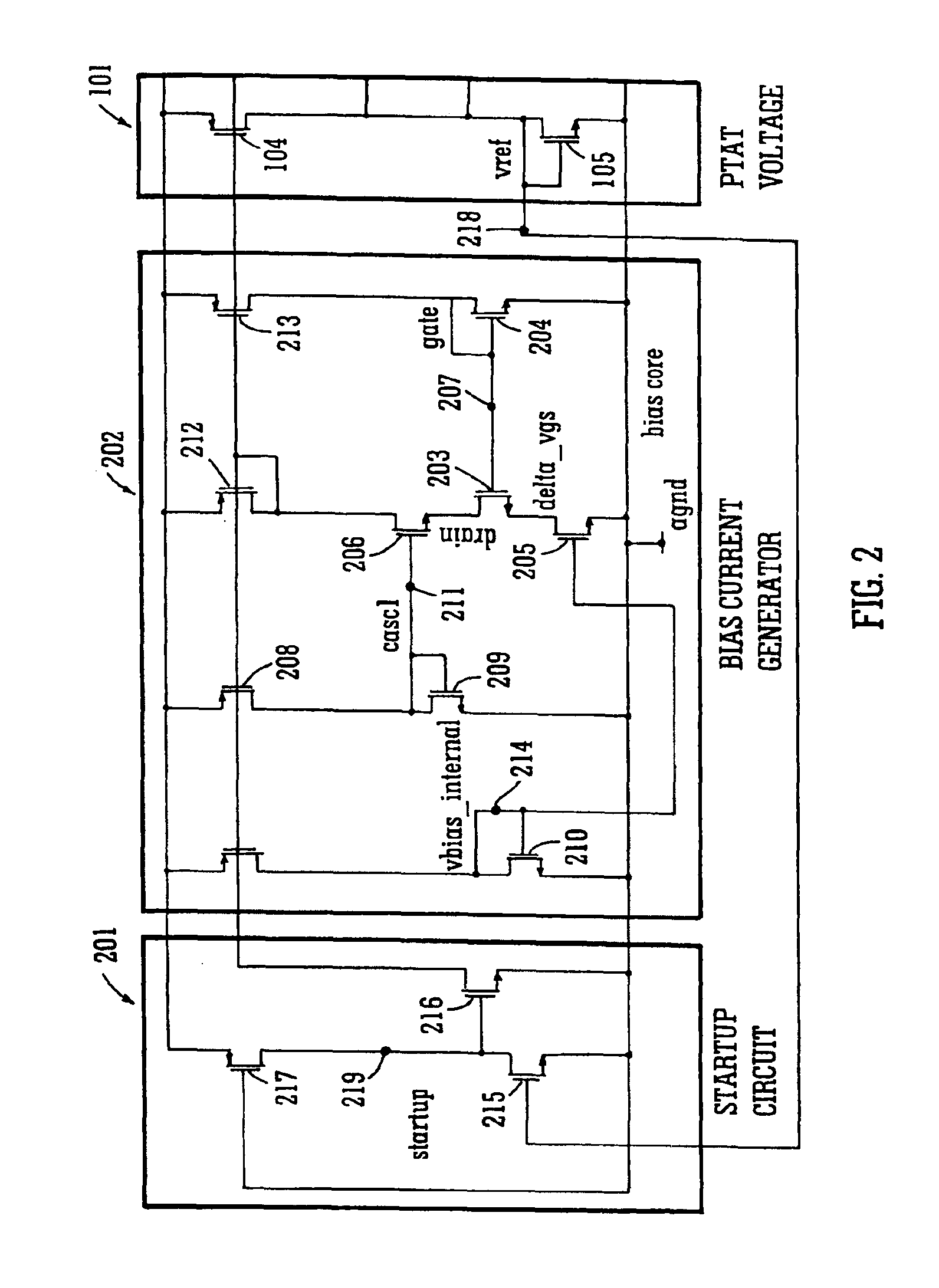

Integrated relaxation oscillator with improved sensitivity to component variation due to process-shift

ActiveUS6924709B2Improve performanceHigh sensitivityGenerator stabilizationElectric pulse generator circuitsDiffusionRC time constant

A system and method for designing an integrated relaxation oscillator that exhibits reduced change in the frequency of oscillation caused by process variation. Improved sensitivity to component variation due to process shift is achieved through using more than one structure type when implementing the resistors affecting the RC time constant and threshold (trip point) voltages of the oscillator. Structure types are related to the fabrication process and for a CMOS process include, but are not limited to n-diffusion, p-diffusion, n-well, p-well, pinched n-well, pinched p-well, poly-silicon and metal. Each structure type exhibits statistically independent process variations, allowing for application of Lyapunov's extension of the Central Limit Theorem for statistically uncorrelated events to desensitize the effect from different possible causes. Thus, improvement in the performance of the oscillator may be achieved with a reduced trim requirement and without using external precision resistors.

Owner:MICROCHIP TECH INC

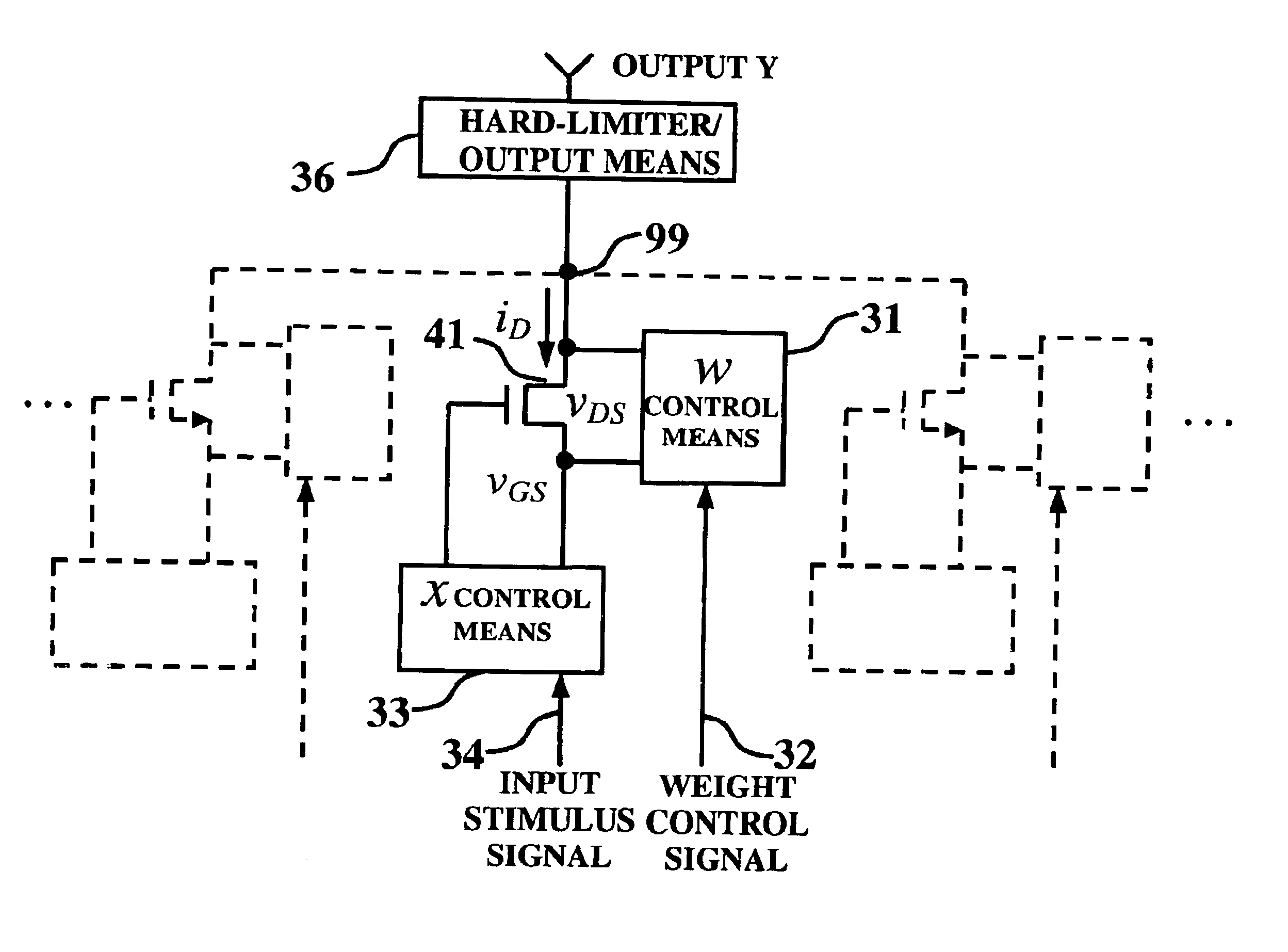

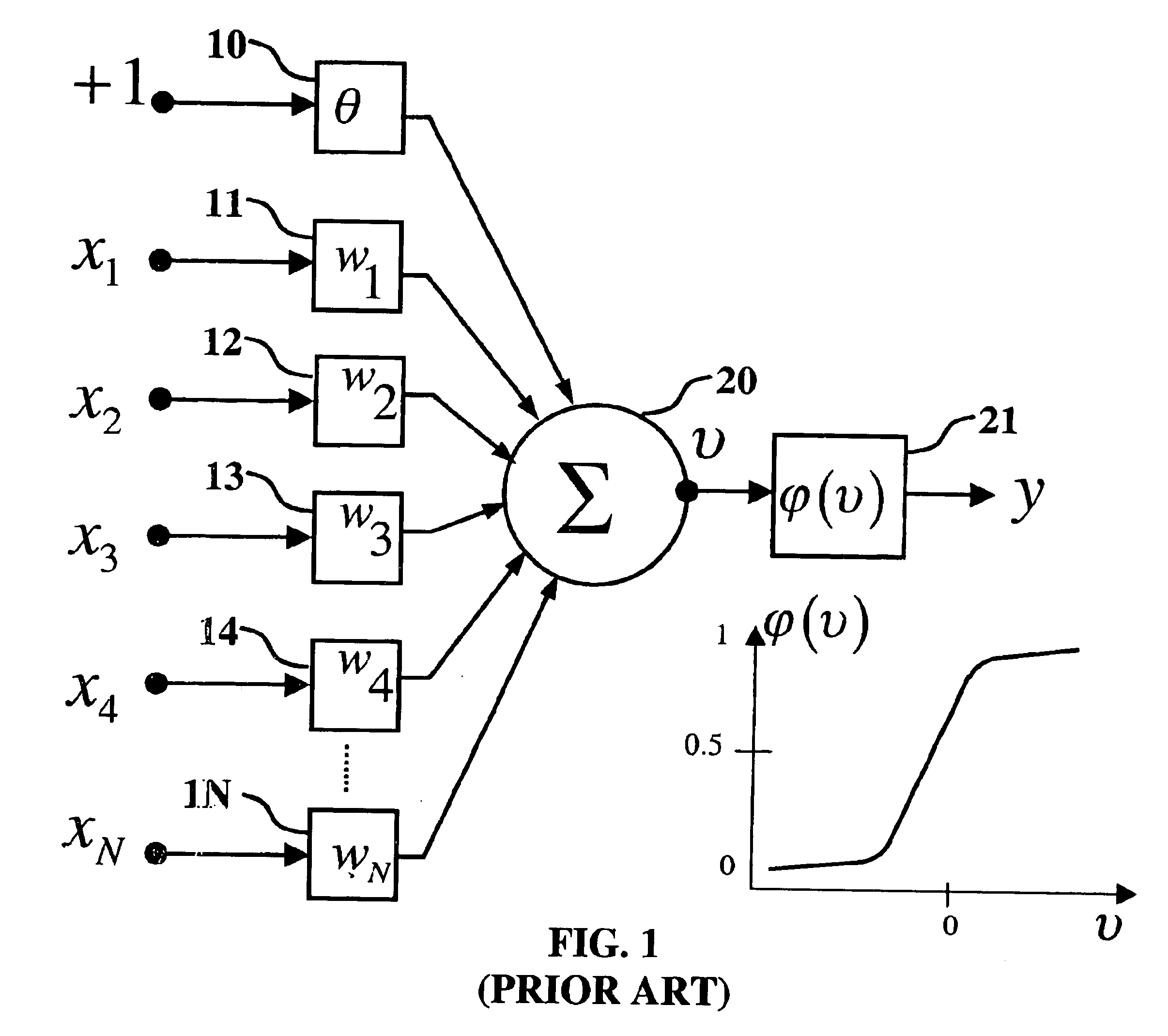

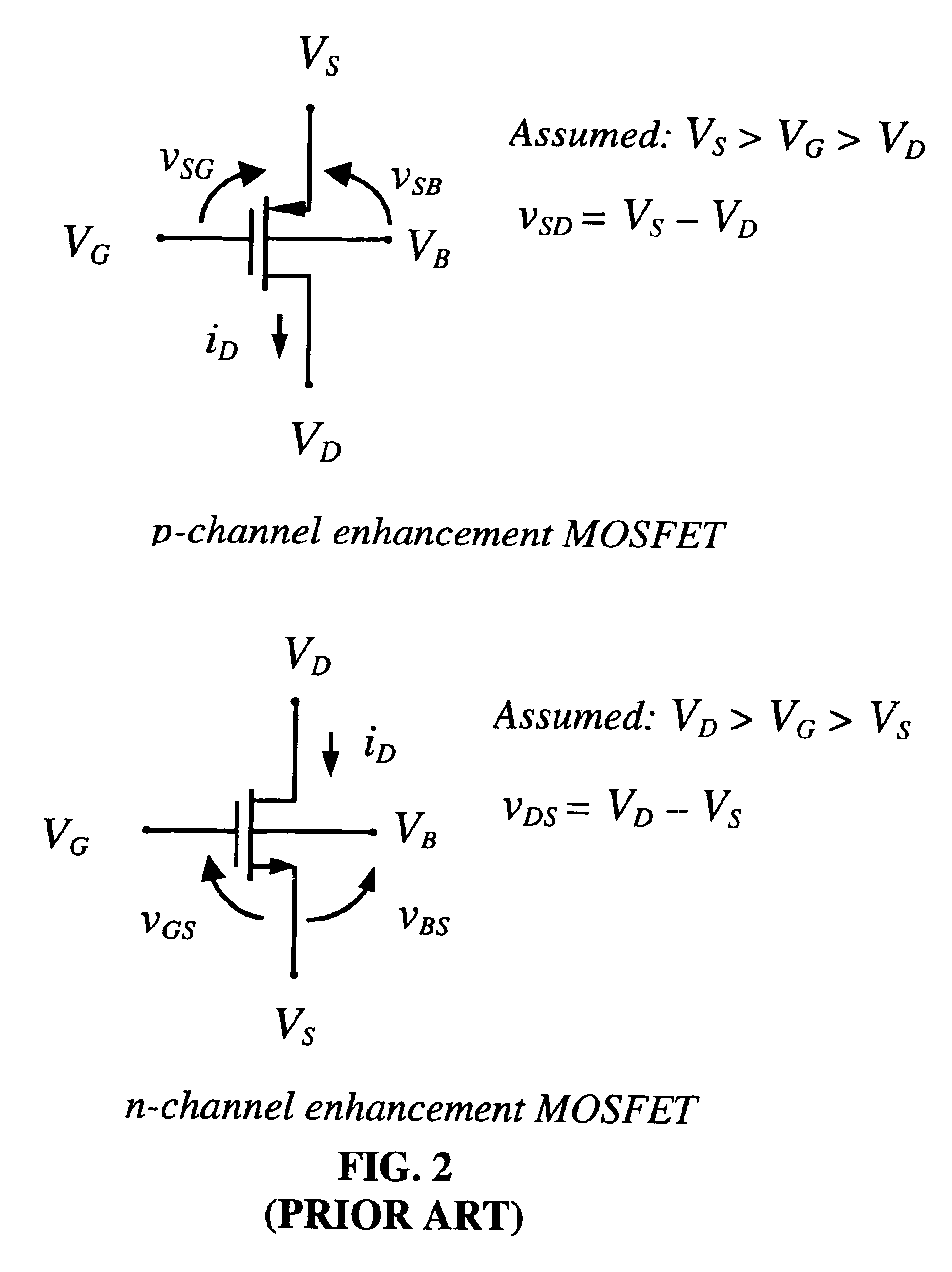

Method and apparatus for modeling a neural synapse function by utilizing a single conventional MOSFET

InactiveUS6829598B2Great potentialSimple methodDigital computer detailsDigital storageMOSFETFunctional modeling

A method and apparatus for modeling a neural synapse function in analog hardware whereby the multiplication function inherent to the operation of a neural synapse is computed by applying a voltage on the gate-source terminals and an independent voltage on drain-source terminals of a MOSFET further using the resultant drain current of the latter device in non-saturation mode as function implementing a computation essentially close to multiplication function between the aforesaid voltages. Analog circuit is provided, capable of generating an output current signal which is proportional in magnitude, within a certain range, to a function computing essentially a sum of weighted input signals-products of corresponding pair of current input signal, and voltage control signal applied to a plurality of inputs thus capable of constructing an artificial neuron model.

Owner:TEXAS INSTR INC

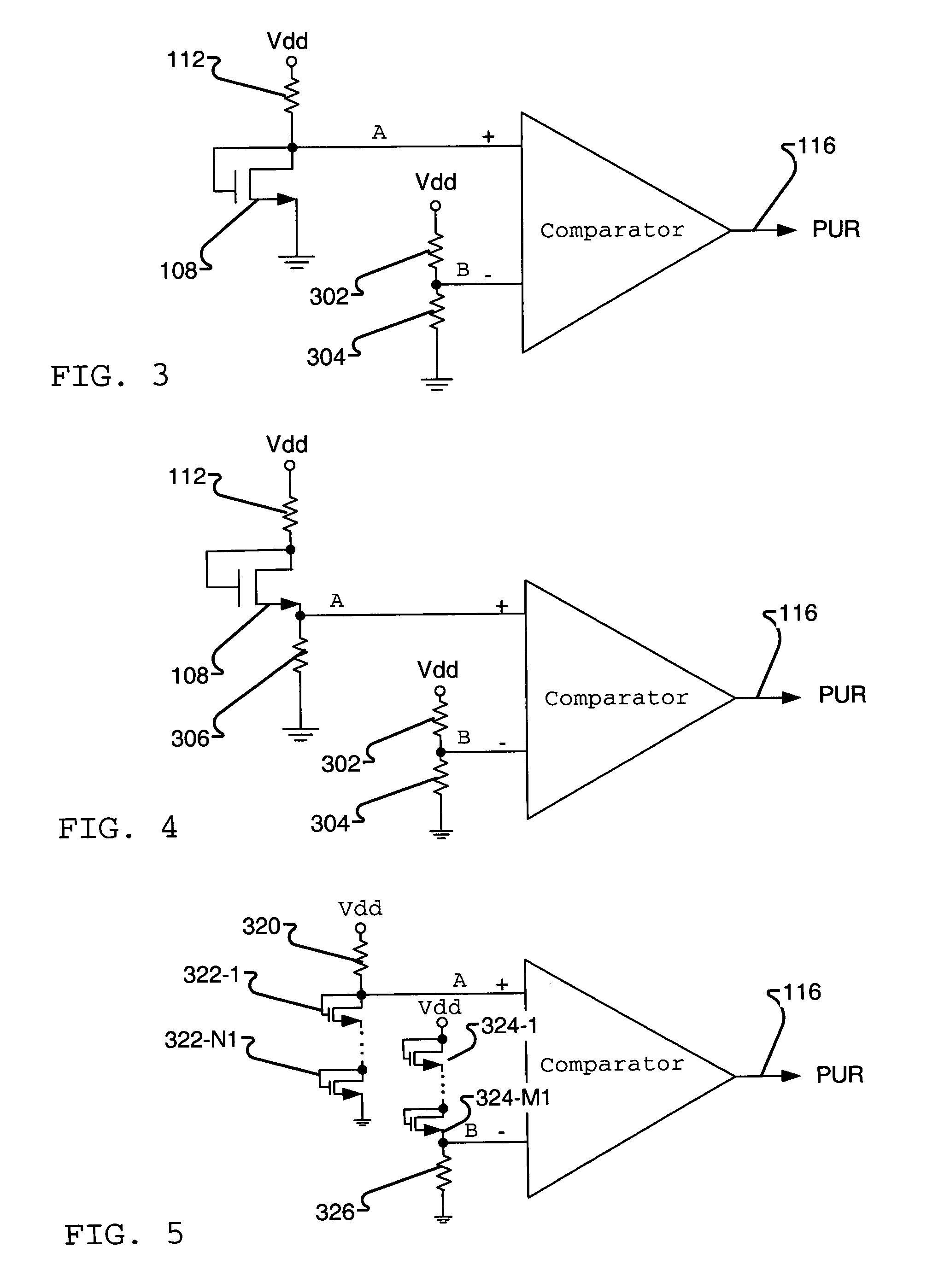

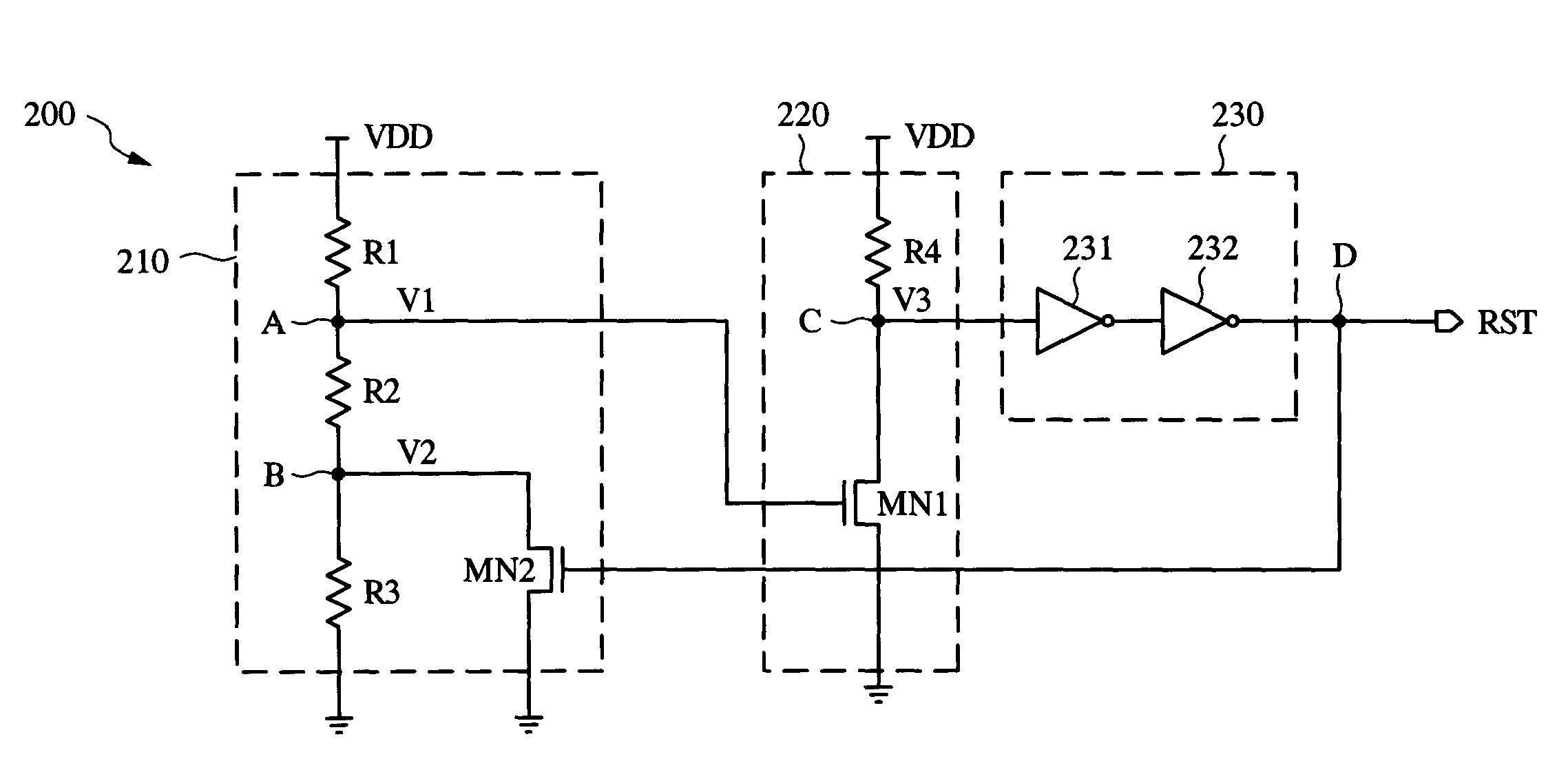

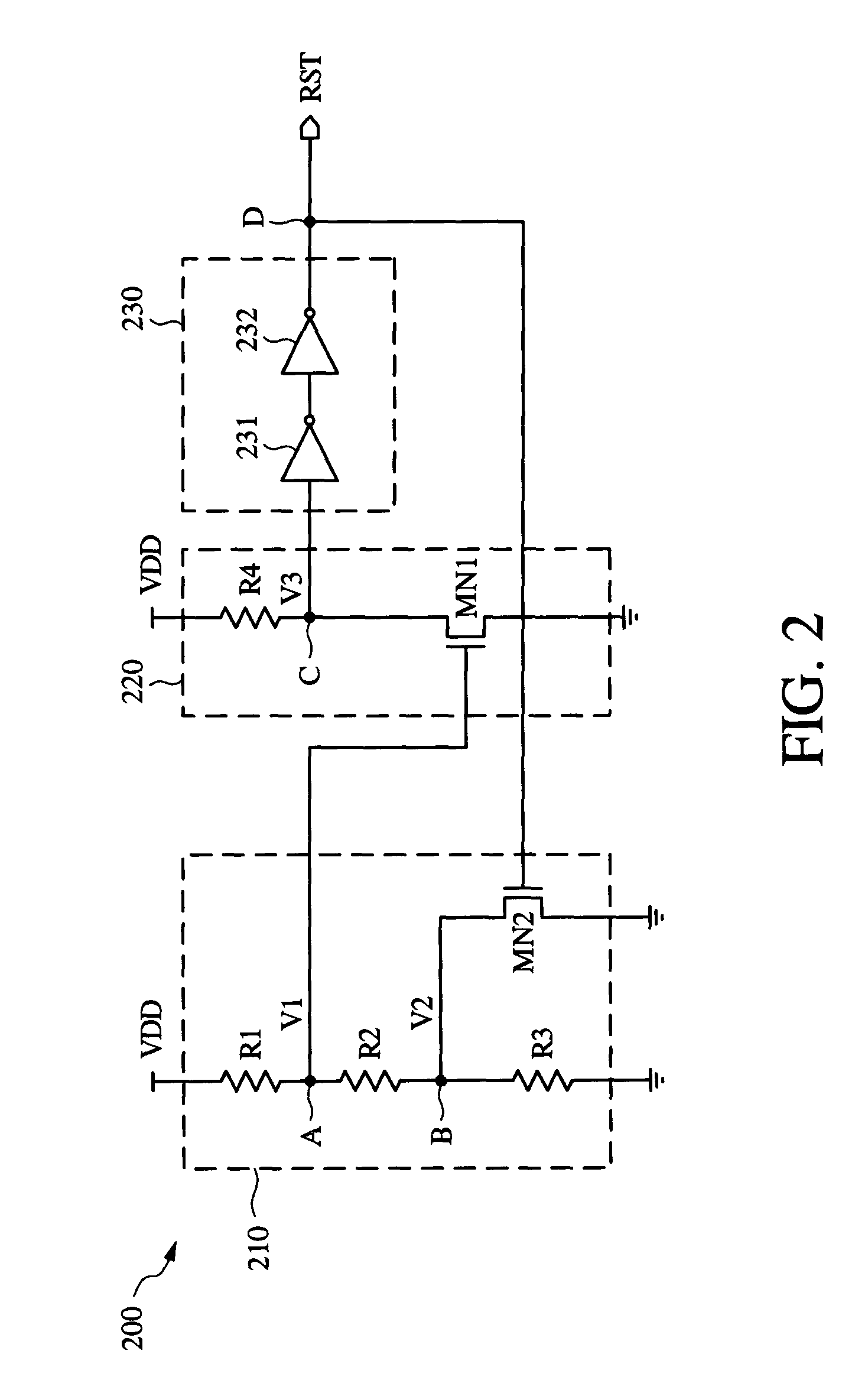

CMOS power on reset circuit

ActiveUS7161396B1Less sensitiveCreates hysteresisPulse automatic controlElectronic switchingPower-on resetCMOS

A power-on reset circuit for generating a reset signal for an associated IC device includes a pull-up resistor connected between a supply voltage and a tracking node, a pull-down transistor connected between the tracking node and ground potential, and a voltage divider circuit connected between the supply voltage and ground potential. The voltage divider circuit has a first ratioed voltage node coupled to the gate of the pull-down transistor. For some embodiments, the voltage divider circuit includes a first resistor connected between the voltage supply and the first ratioed voltage node, a second resistor connected between the first ratioed voltage node and a second ratioed voltage node, a third resistor connected between the second ratioed voltage node and ground potential, and a shunt transistor connected between the second ratioed voltage node and ground potential has a gate responsive to the reset signal.

Owner:XILINX INC

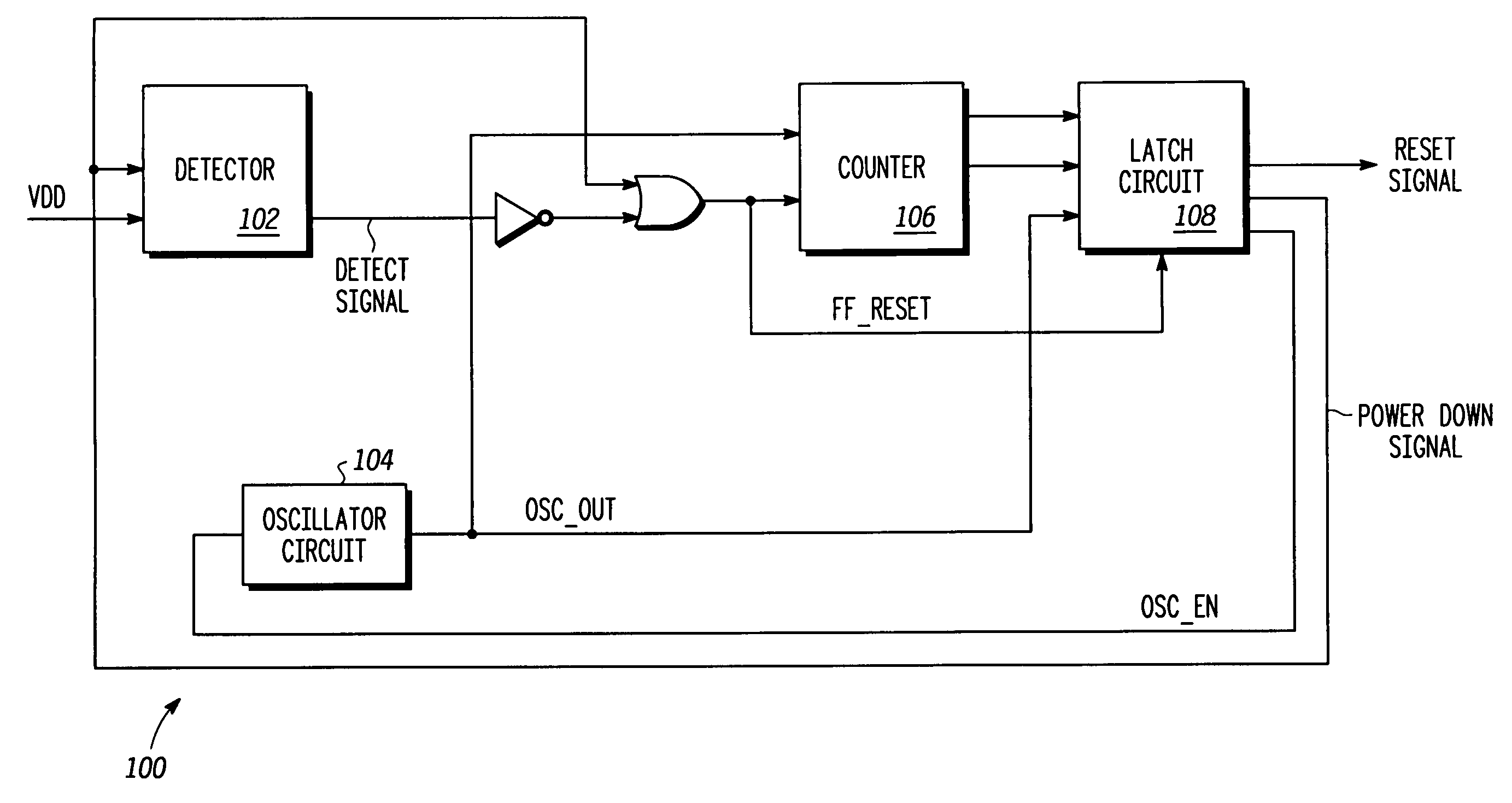

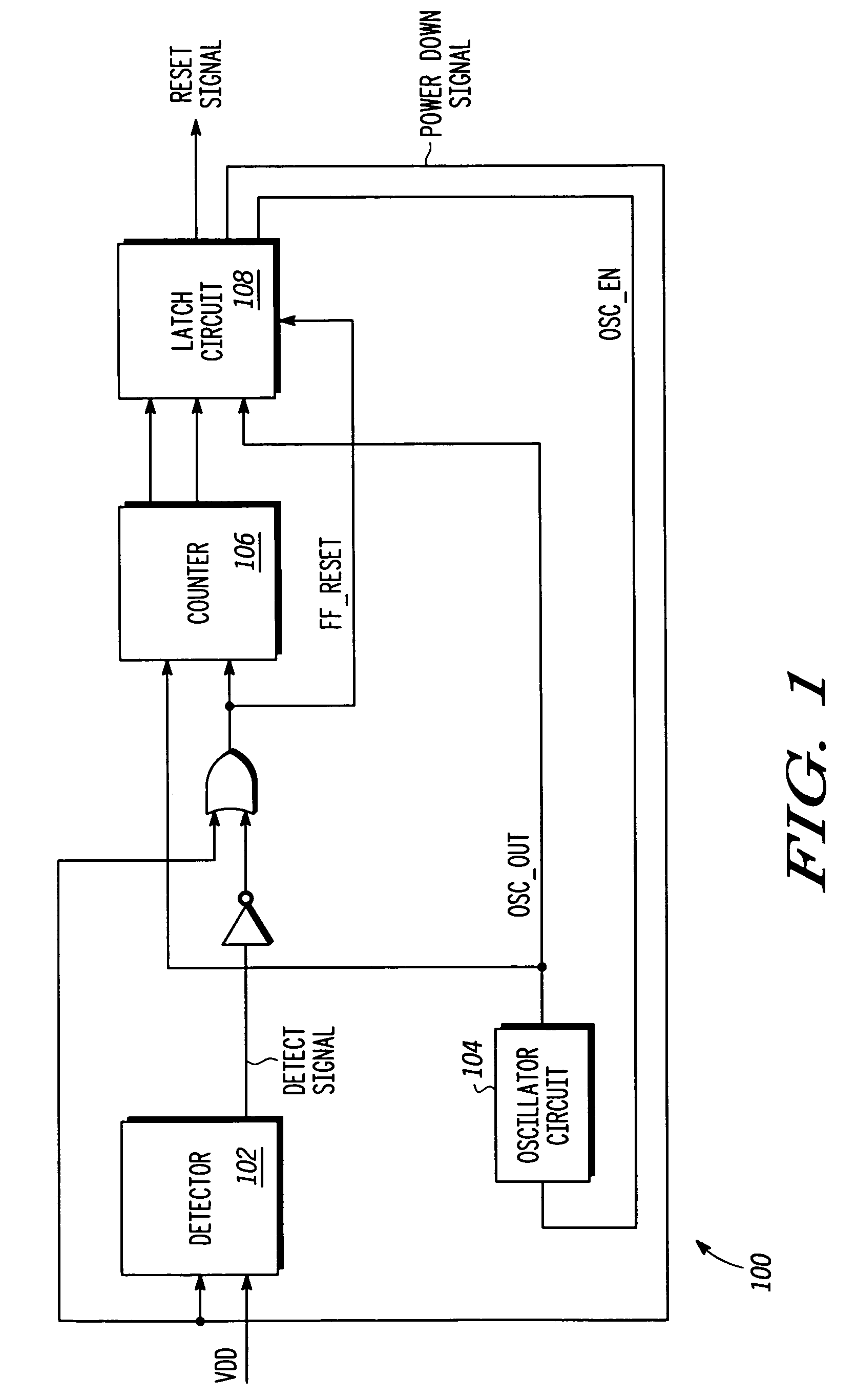

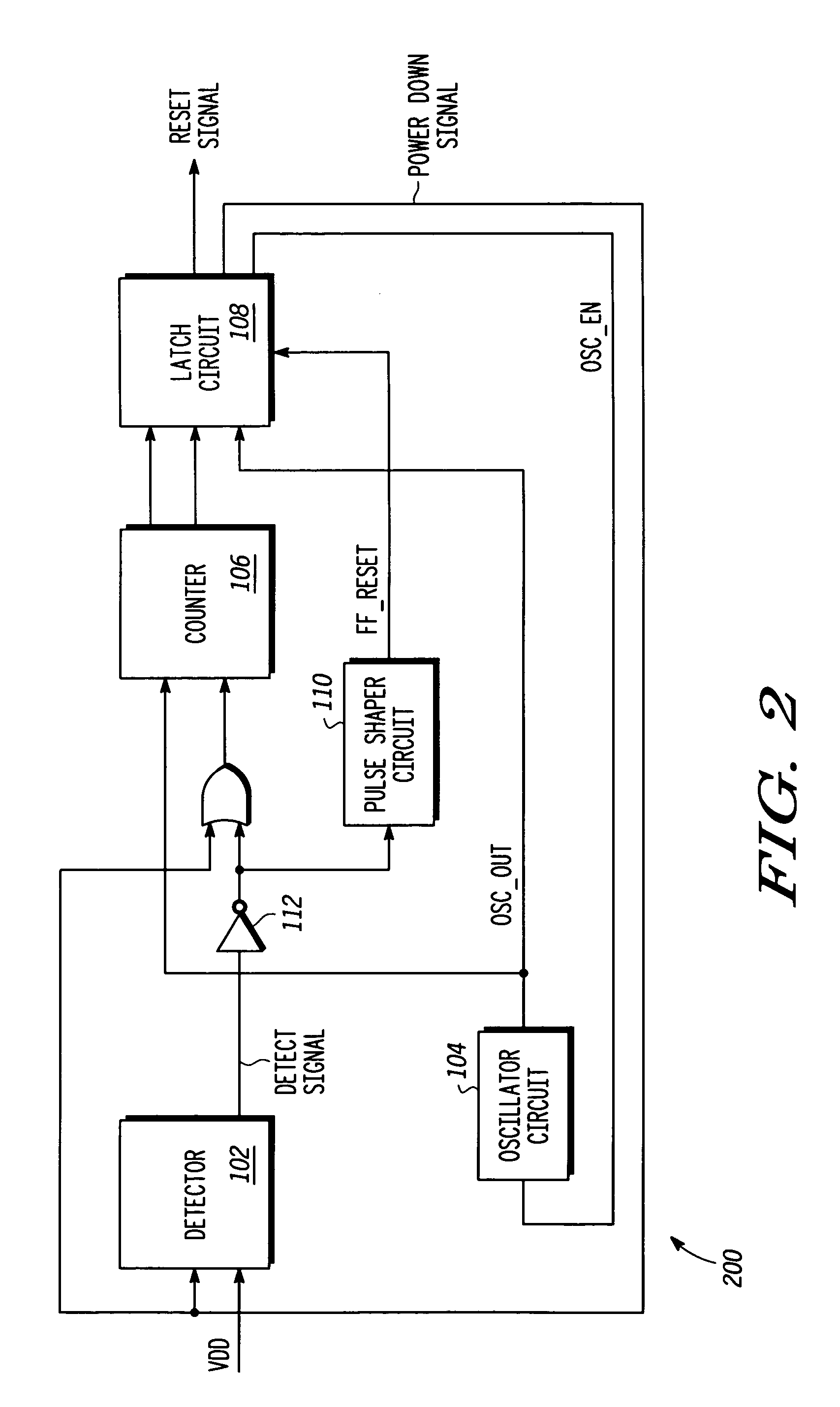

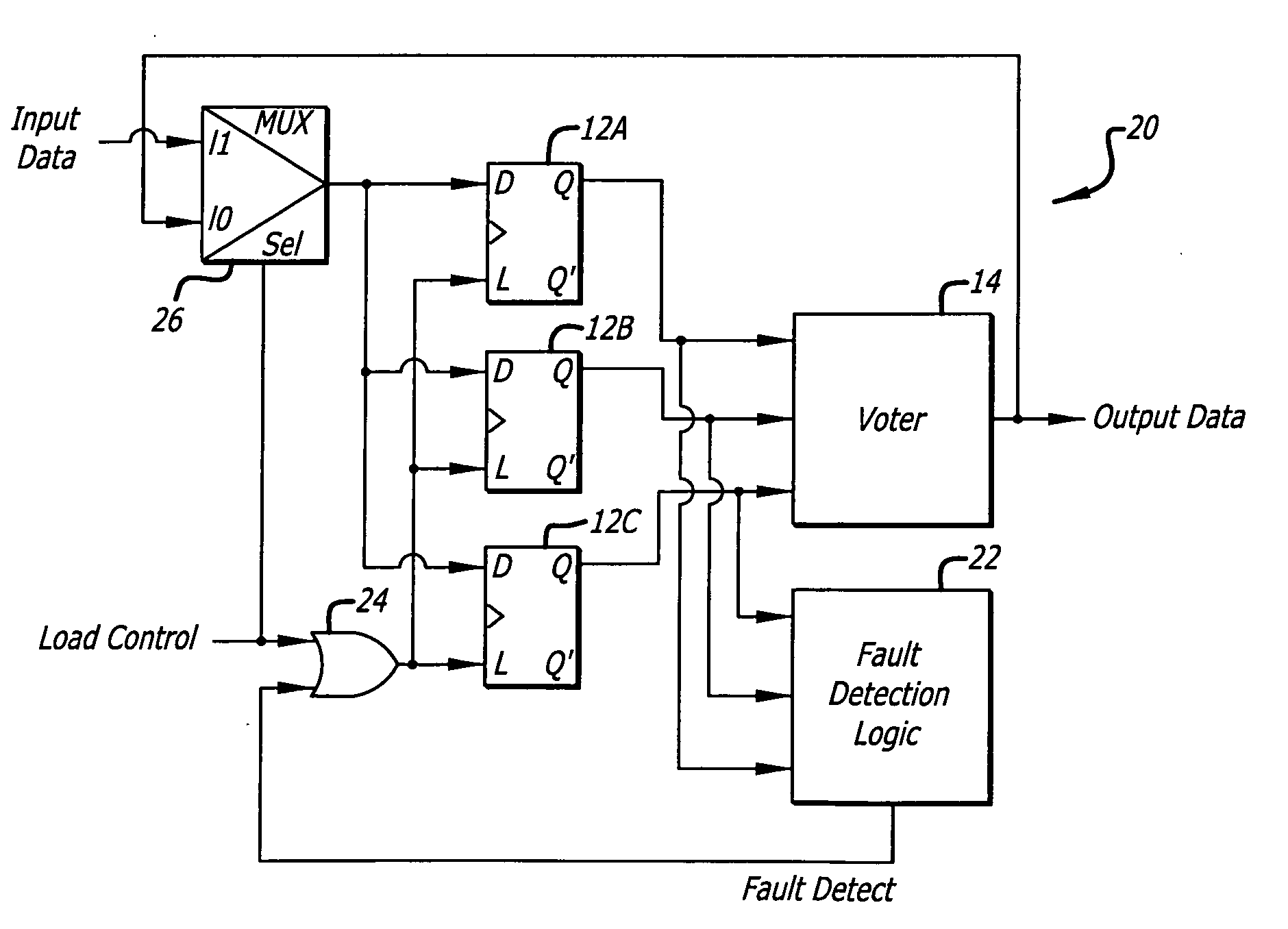

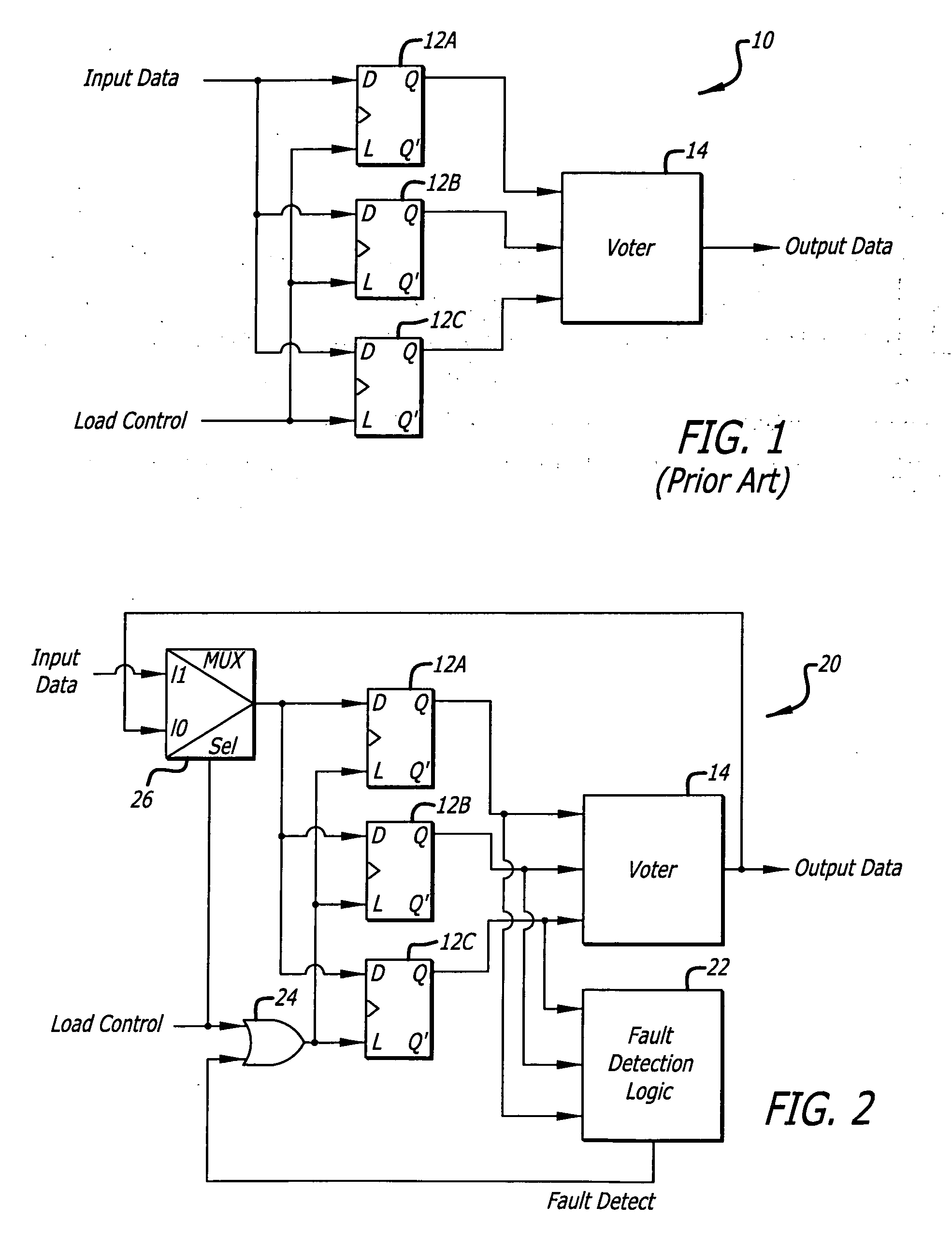

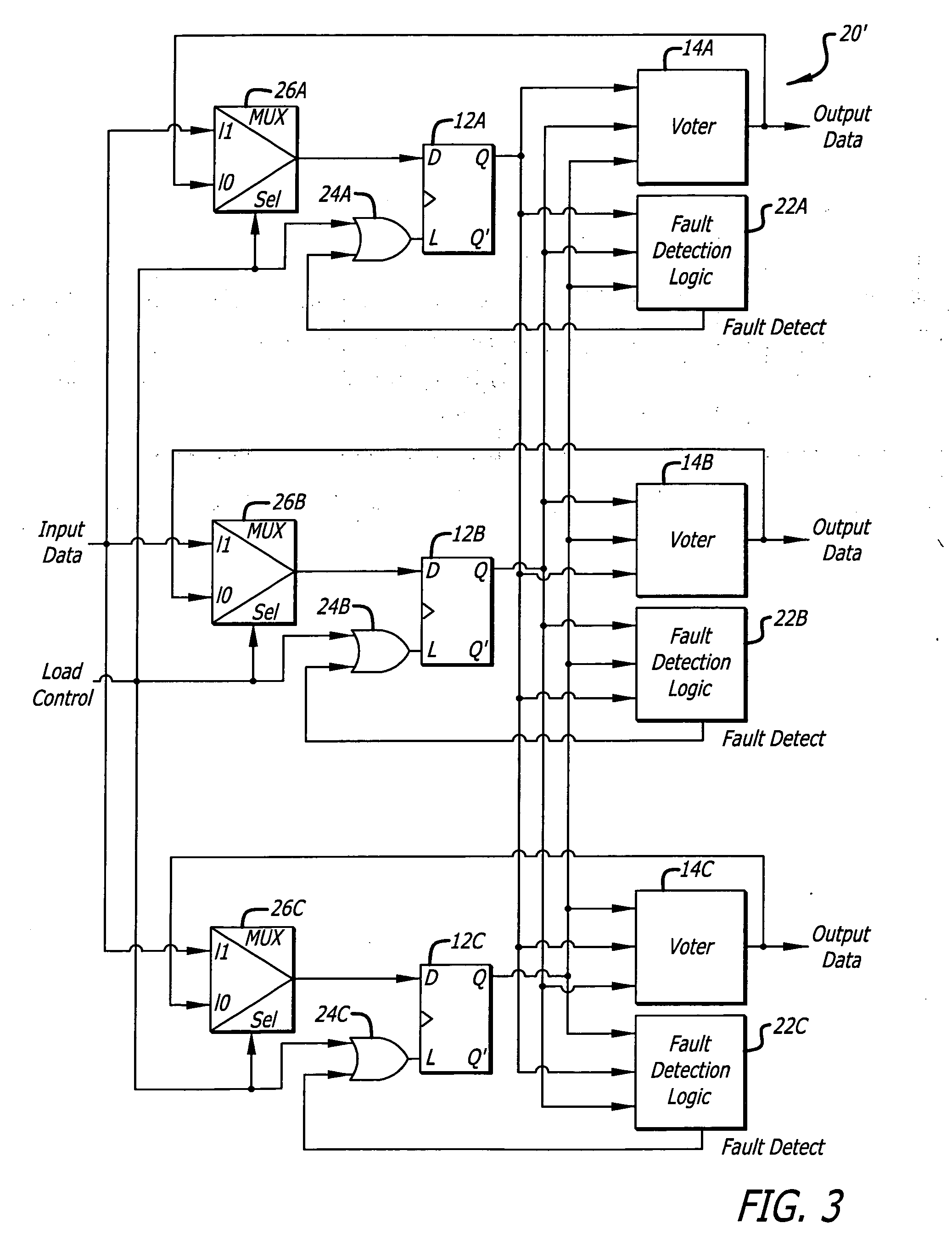

Fault triggerred automatic redundancy scrubber

ActiveUS20100026338A1Reliability increasing modificationsElectric pulse generator circuitsData portScrubber

A redundancy scrubber. The novel scrubber includes fault detection logic for detecting if a circuit has been upset and a mechanism for automatically rewriting data to the circuit when an upset is detected. In an illustrative embodiment, the scrubber corrects for upsets in a circuit comprised of a plurality of redundant circuits, each redundant circuit including a data port for receiving data and a load enable port for controlling when the redundant circuit should load new data. The fault detection logic processes the outputs from each of the redundant circuits and outputs a fault detect signal indicating whether an upset has been detected in one or more of the redundant circuits. The fault detect signal is coupled to the load enable ports, forcing the redundant circuits to immediately reload with corrected data from a voter or with new incoming data when an upset is detected.

Owner:RAYTHEON CO

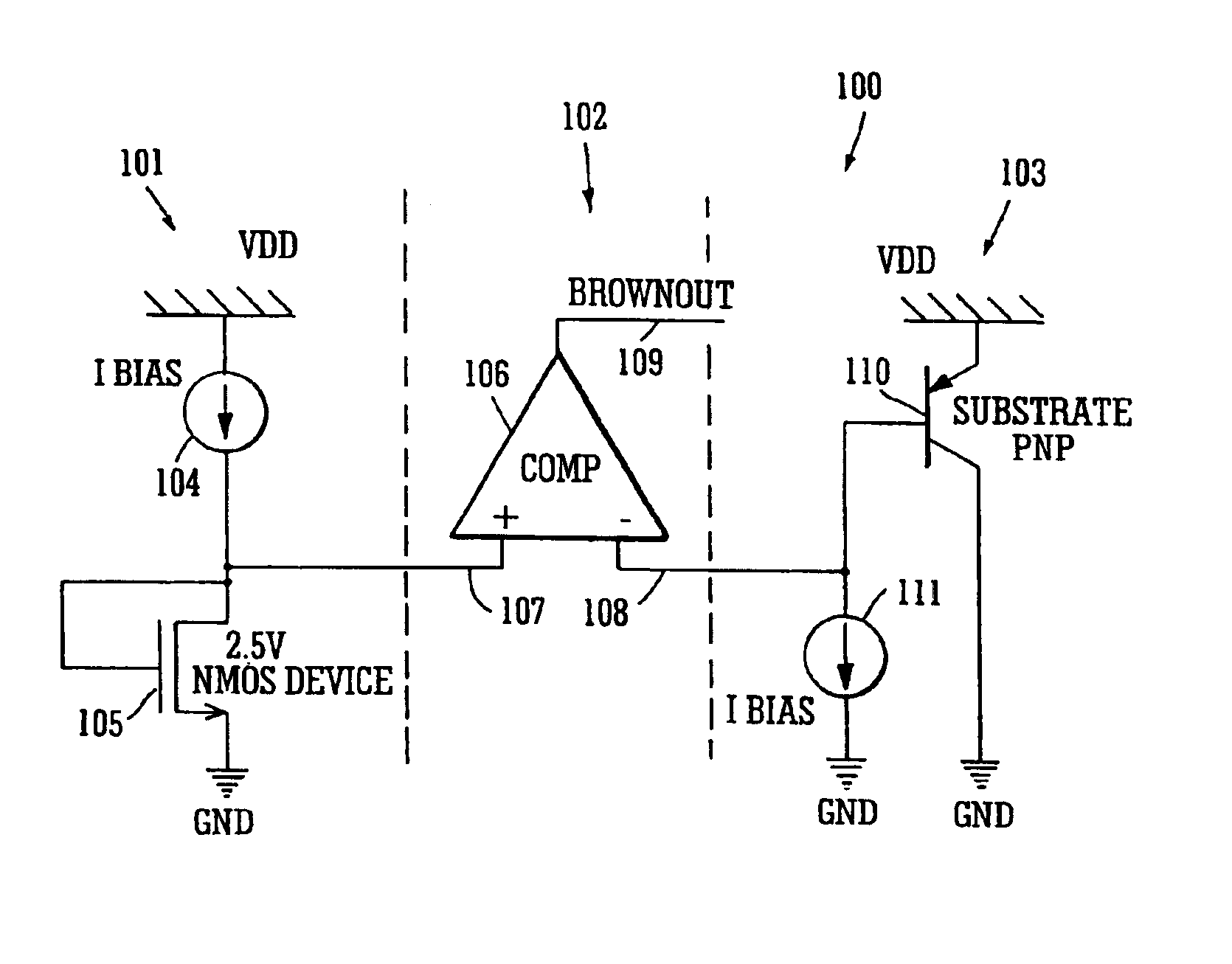

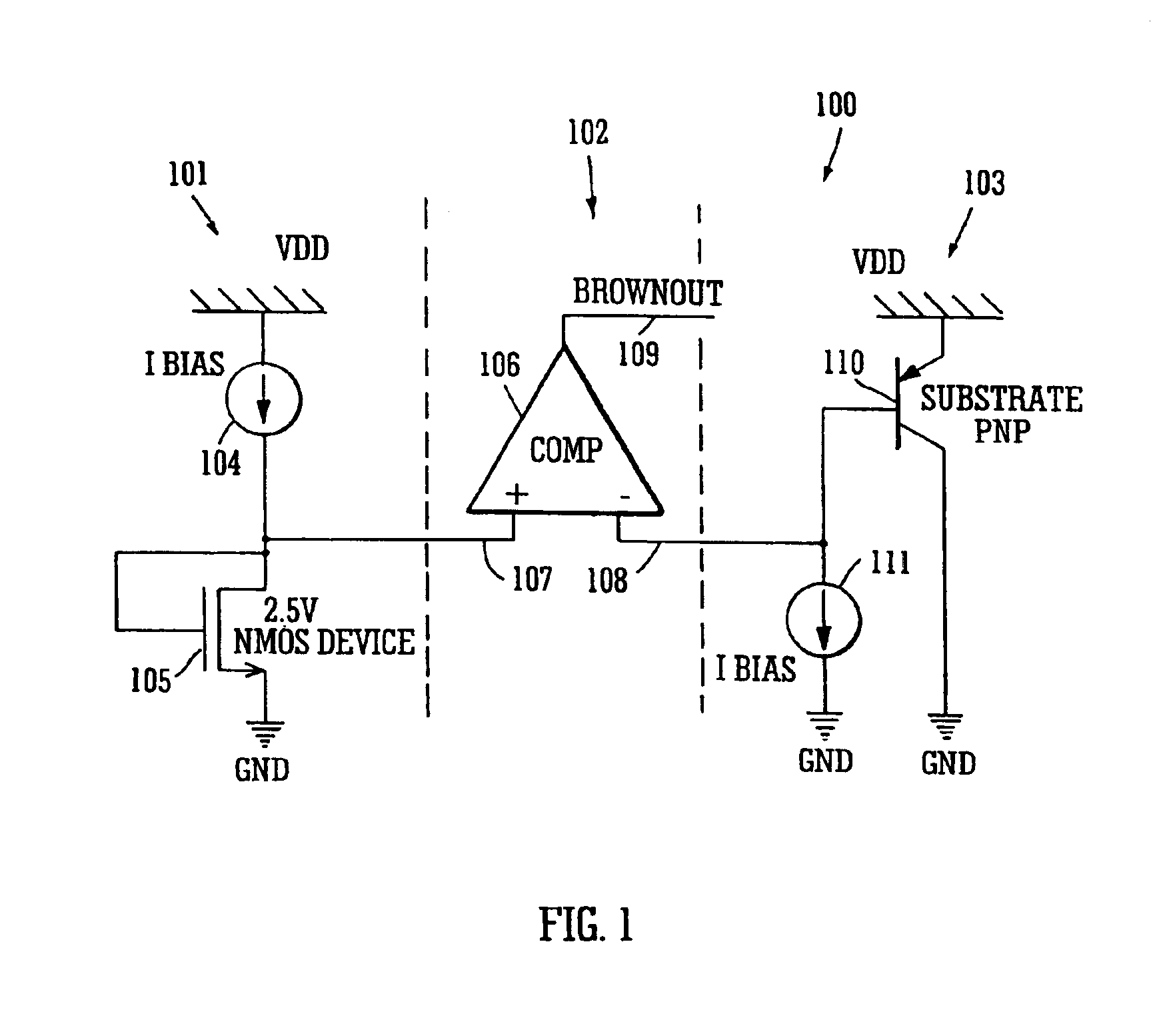

Brown-out detector

InactiveUS6894544B2Satisfies needPulse automatic controlElectronic switchingVoltage referenceComparator

A brown-out detector that continuously monitors power supply voltage and provides an output signal that transitions to a logic HIGH state when the monitored power supply voltage exceeds a predetermined threshold value. One embodiment of the present invention comprises a first voltage reference with respect to ground that varies in direct proportion to absolute temperature, a second voltage reference with respect to the supply voltage that varies inversely with absolute temperature, and a comparator having the first voltage reference coupled to one input, and the second voltage reference coupled to the other input, such that the comparator output changes state when the power supply voltage exceeds a predetermined threshold voltage that is relatively independent of absolute temperature. The circuit may also be configured such that the first voltage reference varies inversely with absolute temperature, while the second voltage reference varies in direct proportion to absolute temperature.

Owner:MEDIATEK INC

System and method for monitoring a power supply level

ActiveUS20070001720A1Pulse automatic controlPower supply for data processingEngineeringElectric power

A system and method are provided herein for monitoring the integrity of a power supply by monitoring a level of the power supply voltage supplied to one or more system components. The method, as described herein, includes setting a bit in a status register after the power supply level reaches a threshold level, and monitoring a state of the bit to determine if the power supply level has dropped below the threshold level. For example, the method may determine that the power supply level has dropped below the threshold level if the state of the bit changes from a set bit to a cleared bit. In addition, the system and method described herein may be used for detecting the occurrence of a power abnormality by providing additional resources / information about a power related event.

Owner:CYPRESS SEMICON CORP

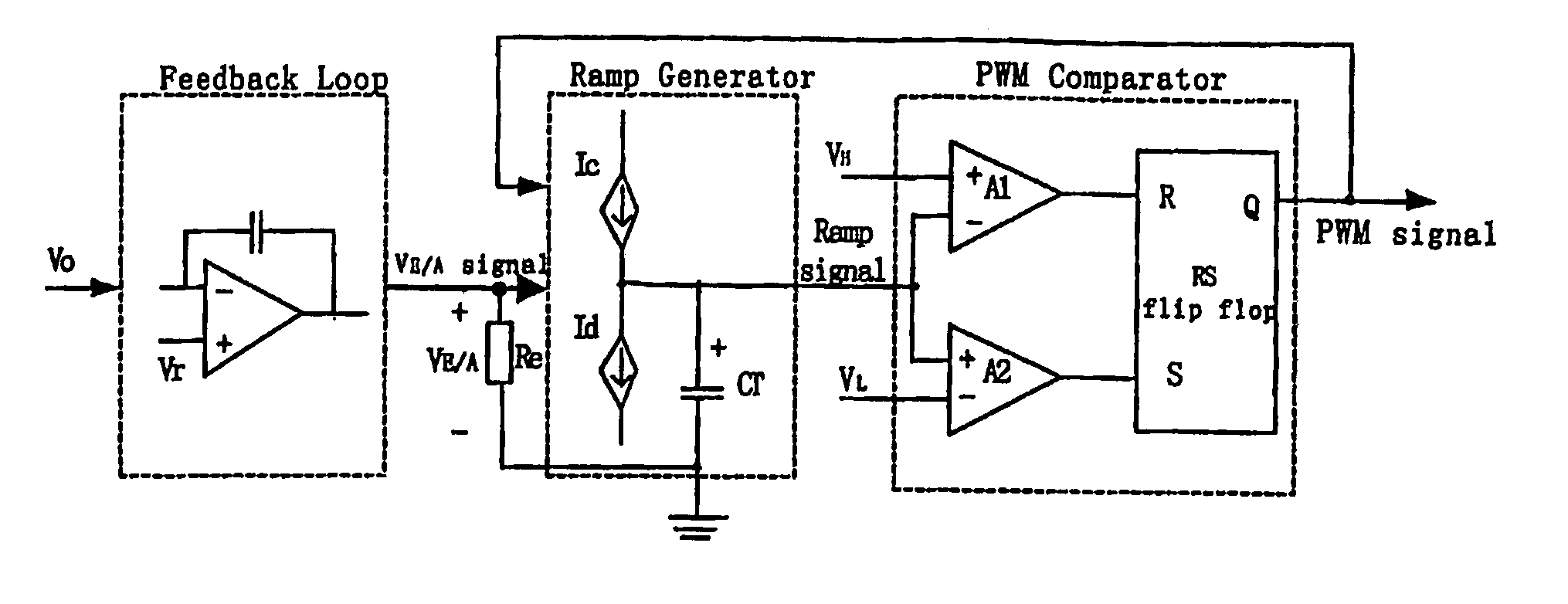

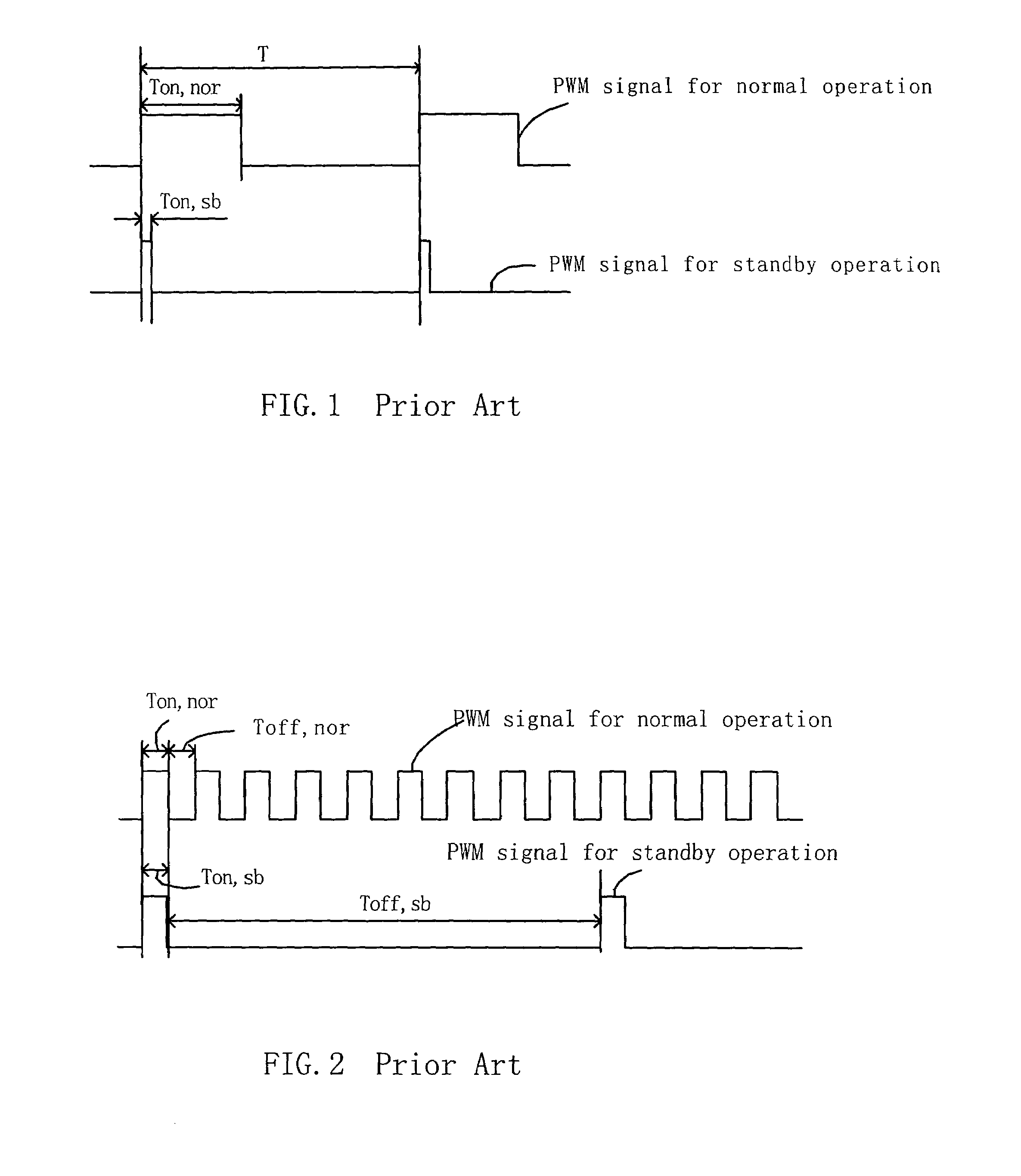

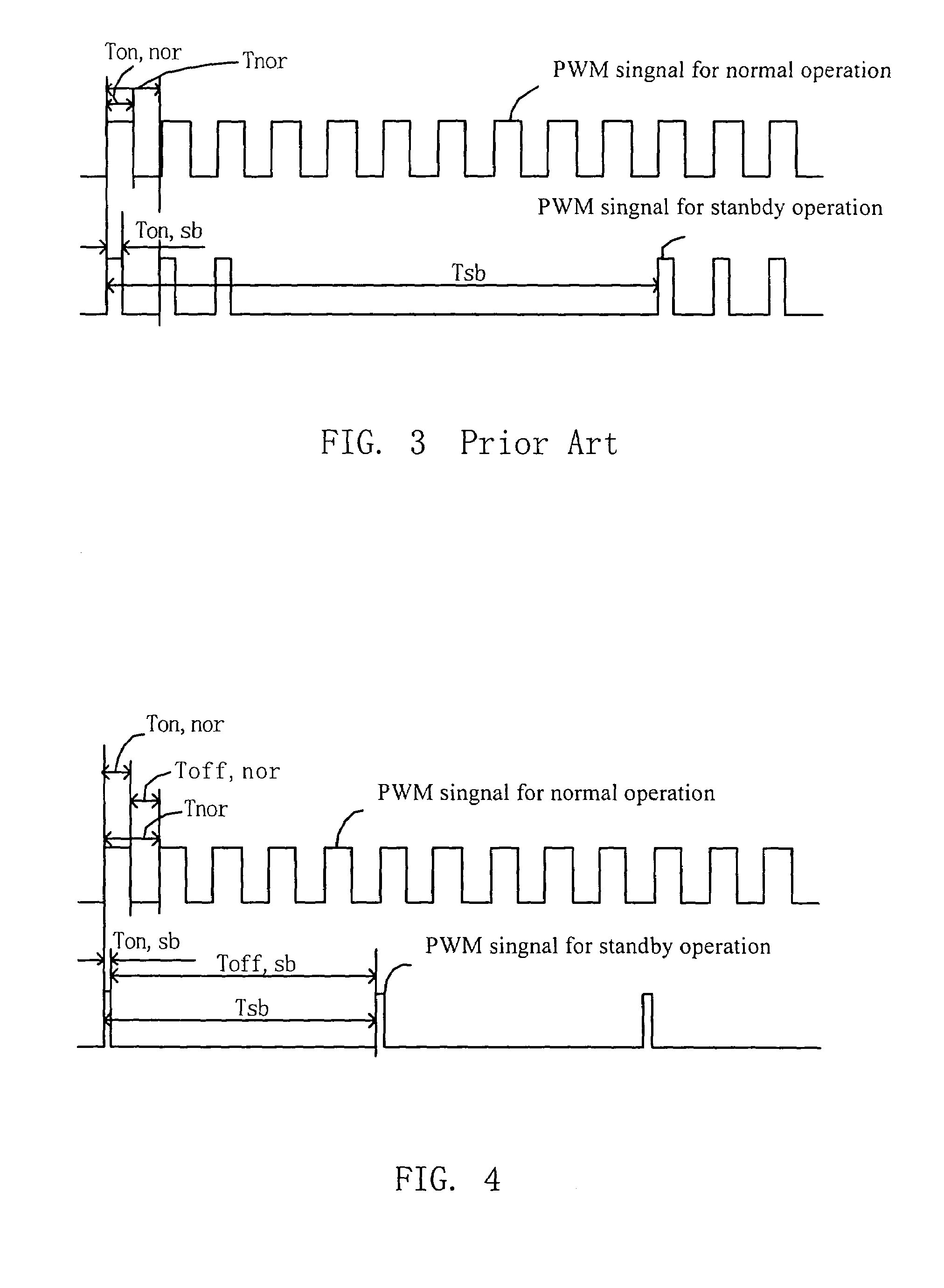

Variable frequency PWM controller circuit

ActiveUS7106130B2Short timeReduce frequencyAc-dc conversion without reversalEfficient power electronics conversionControl theoryPwm signals

The present invention discloses a circuit that generates a variable frequency pulse width modulation (VF PWM) signal. Different from the conventional PWM controller, the frequency and duty cycle of the output PWM signal vary with the error-amplified voltage of the feedback loop simultaneously in this invention. The higher the error-amplified voltage of the feedback loop is, the lower the duty cycle with lower frequency will be. A very low duty cycle PWM signal can be generated stably while its frequency is very low.

Owner:DELTA ELECTRONICS INC

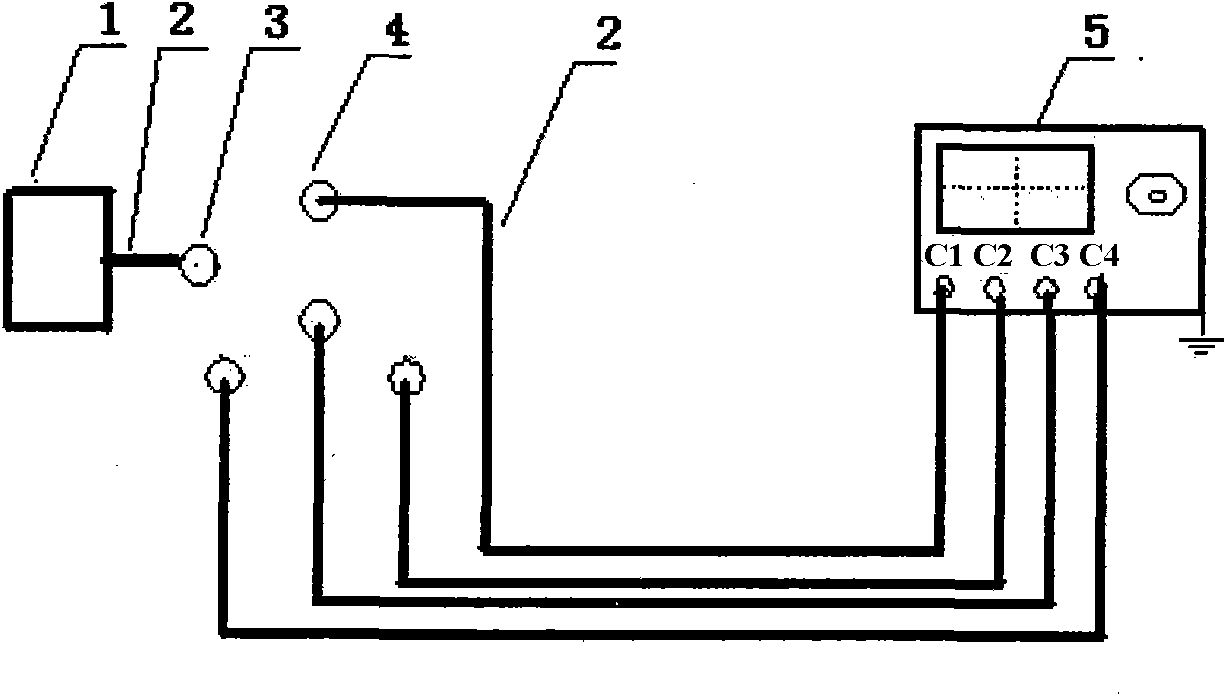

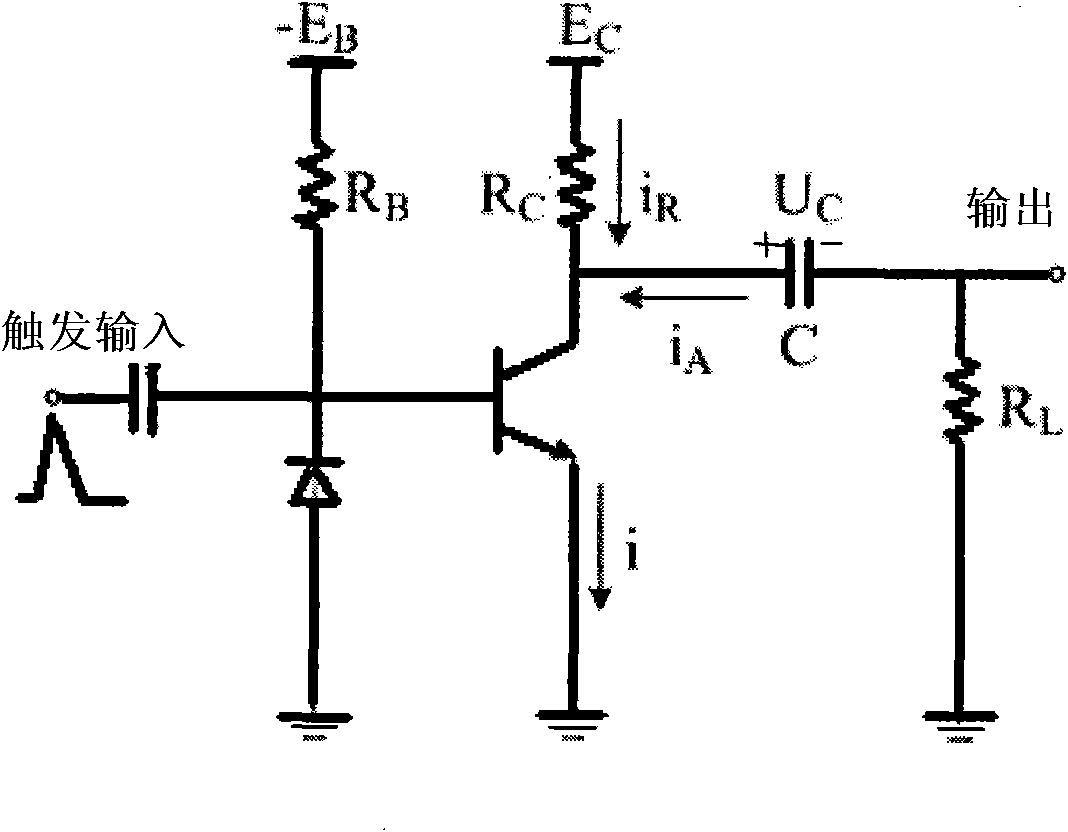

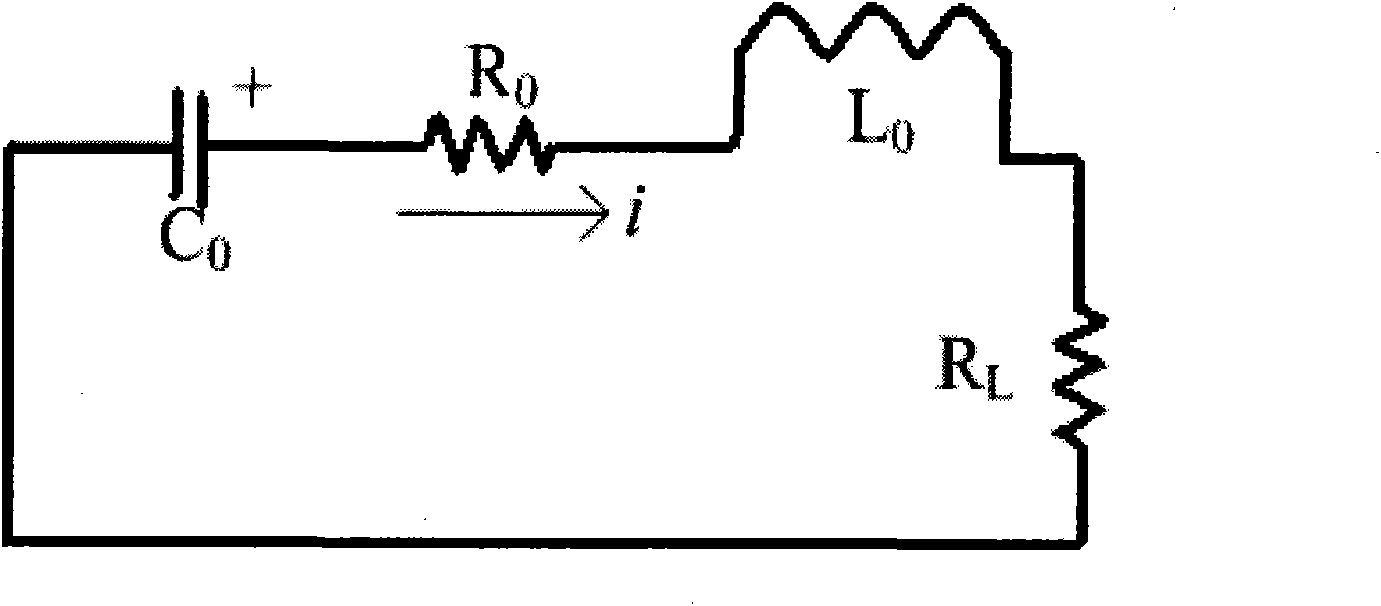

Ultra-high frequency positioning and detection device of local discharge of electrical equipment and method thereof

InactiveCN101620253AWaveform repeatability is goodReduce distractionsTesting dielectric strengthElectric pulse generator circuitsInterference resistanceCoaxial cable

The invention relates to an ultra-high frequency positioning and detection device of local discharge of electrical equipment and a method thereof, belonging to the technical field of experiments of local discharge of the electrical equipment. The device comprises a steep-sided pulse generator, an ultra-high frequency antenna, a high frequency coaxial cable and a high sampling rate oscilloscope. The device is characterized in that the steep-sided pulse generator is a nanosecond pulse generator. The method performs the positioning computation by using the device and a computer through a program and a positioning principle based on the time difference method. The device has simple connection; nanosecond pulse signals generated by the steep-sided pulse generator can really simulate ultra-high frequency signals of the local discharge of the electrical equipment and have strong interference resistance and high accuracy of read time different signals, thereby improving the positioning accuracy. The invention can be widely applied to the experiment of the ultra-high frequency positioning detection of the local discharge of the electrical equipment.

Owner:CHONGQING UNIV

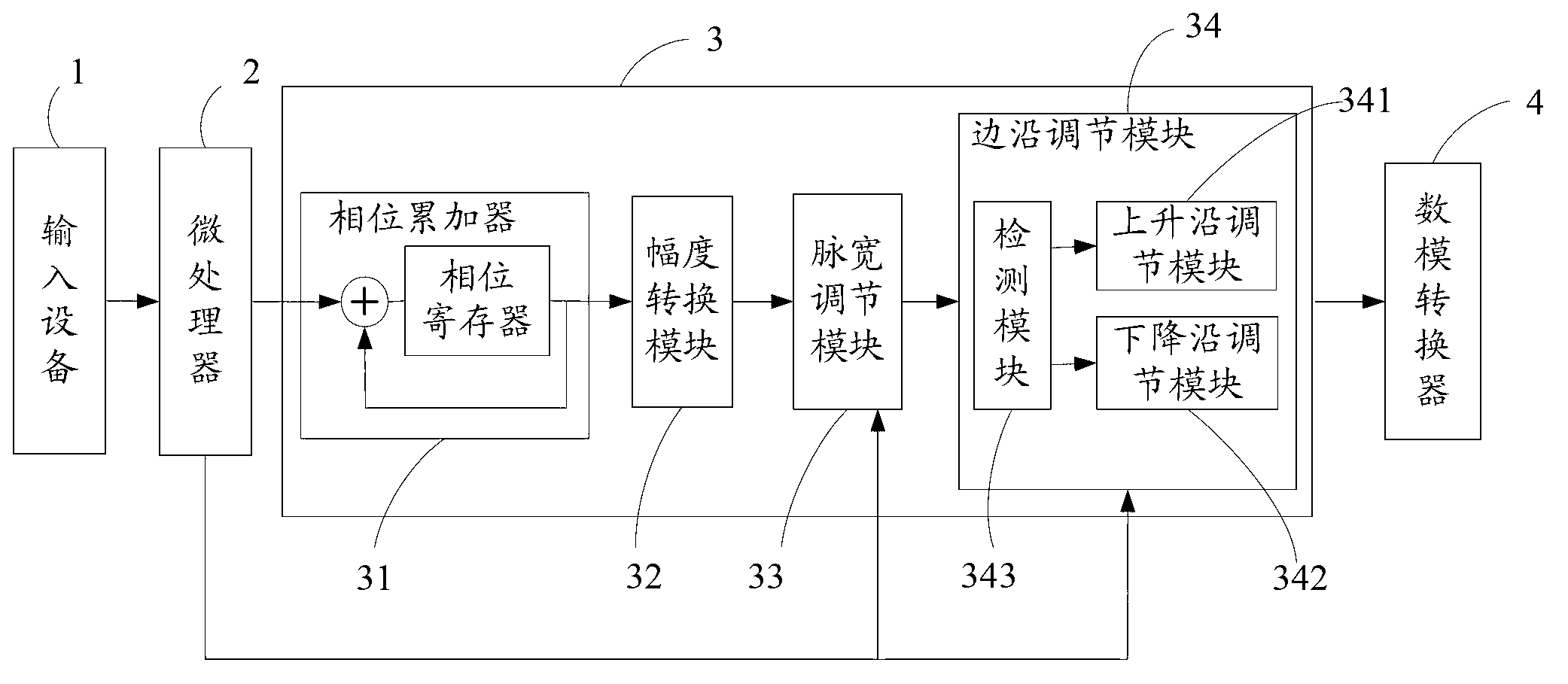

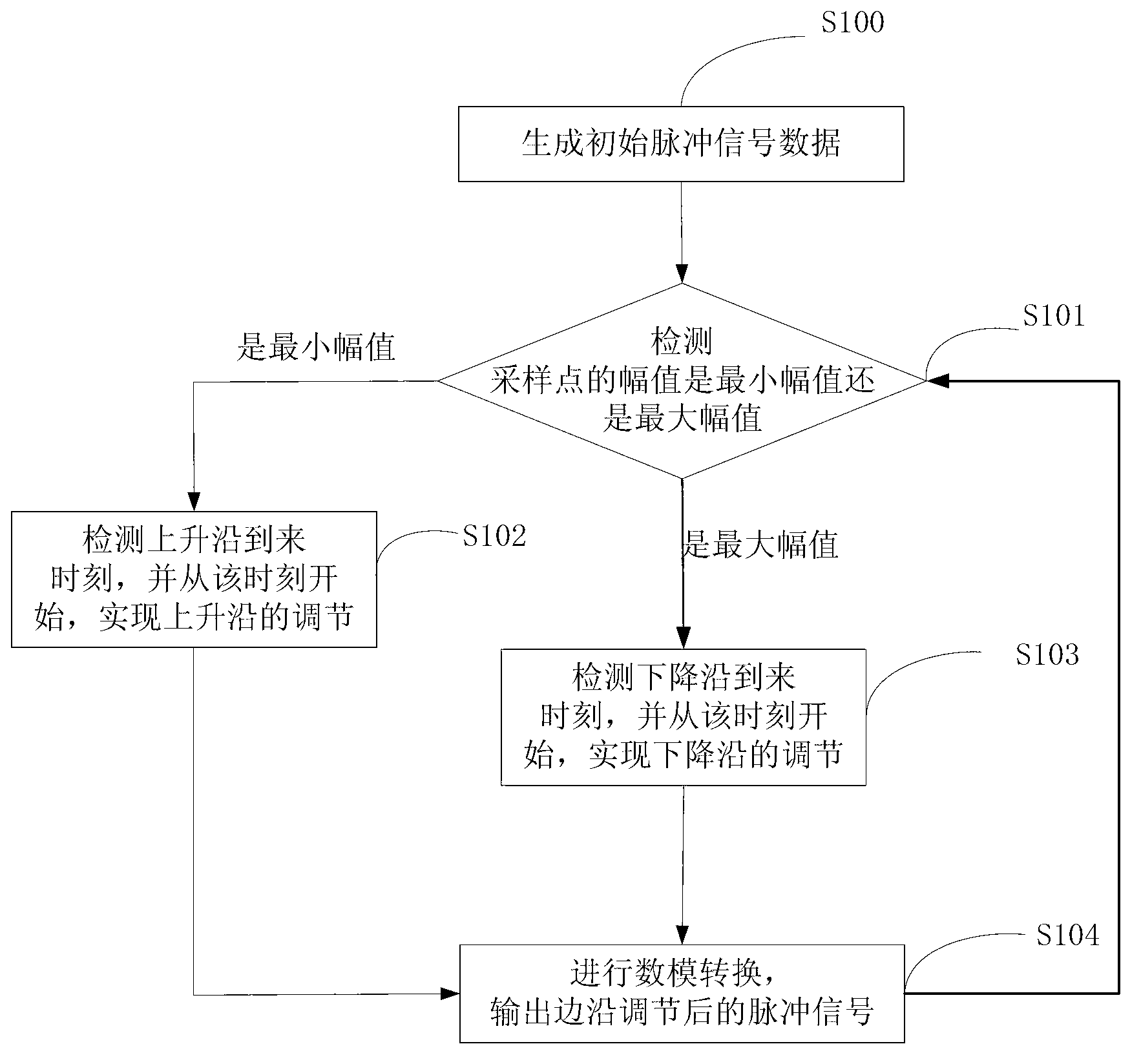

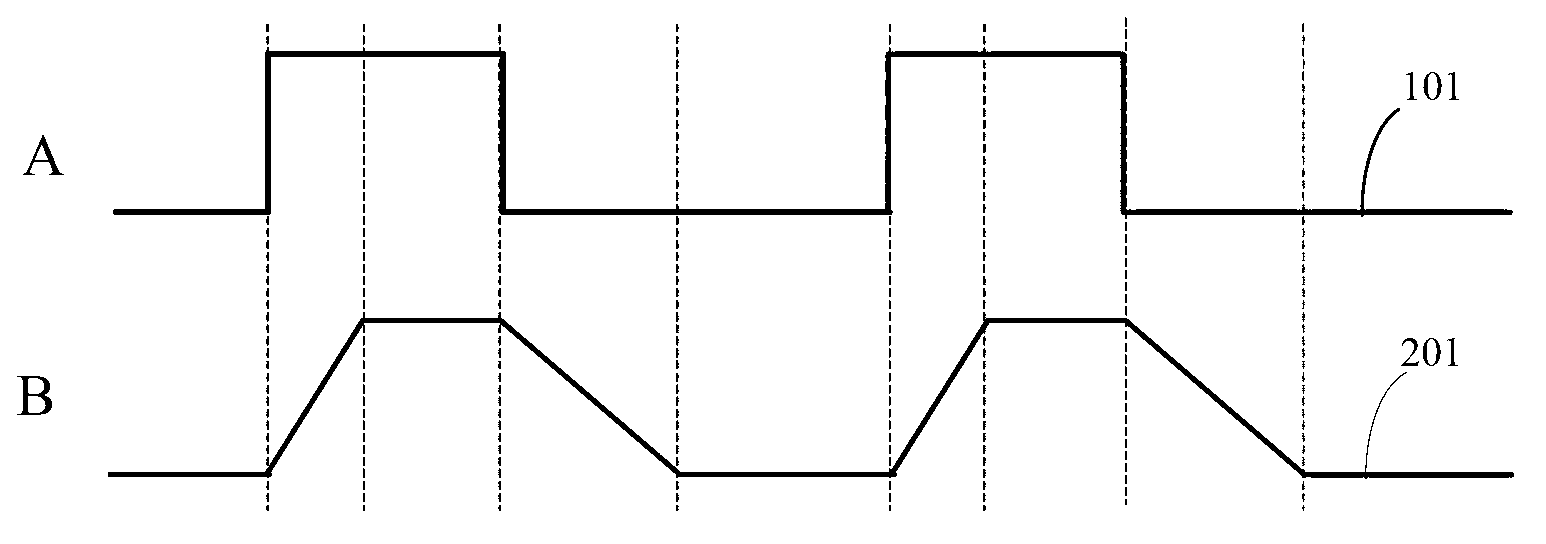

Method and module for DDS (direct digital synthesizer) pulse edge adjusting and pulse signal generator

ActiveCN103178809AEasy to adjustGrow fastElectric pulse generator circuitsPulse manipulationDigital analog converterArrival time

The invention discloses a method and a system for DDS (direct digital synthesizer) pulse edge adjusting and a pulse signal generator. The pulse signal generator comprises input equipment, a microprocessor, a DDS module and a digital-analog converter in sequential connection, the DDS module comprises a phase accumulator, an amplitude converting module, a pulse-width adjusting module and an edge adjusting module, the edge adjusting module comprises a detection module, a rising edge adjusting module and a falling edge adjusting module, the detection module is used for detecting arrival time of a rising edge and arrival time of a falling edge of initial pulse signal data, the rising edge adjusting module is used for realizing rising edge adjusting of the initial pulse signal data according to an upper stepping value, and the falling edge adjusting module is used for realizing falling edge adjusting of the initial pulse signal data according to a lower stepping value. Compared with the prior art, by the technical scheme, quick rising and falling of pulse signal edges can be realized when frequency is low, the duty ratio is extremely low, and large-scale accurate pulse signal edge adjusting can also be realized.

Owner:SHENZHEN CITY SIGLENT TECH

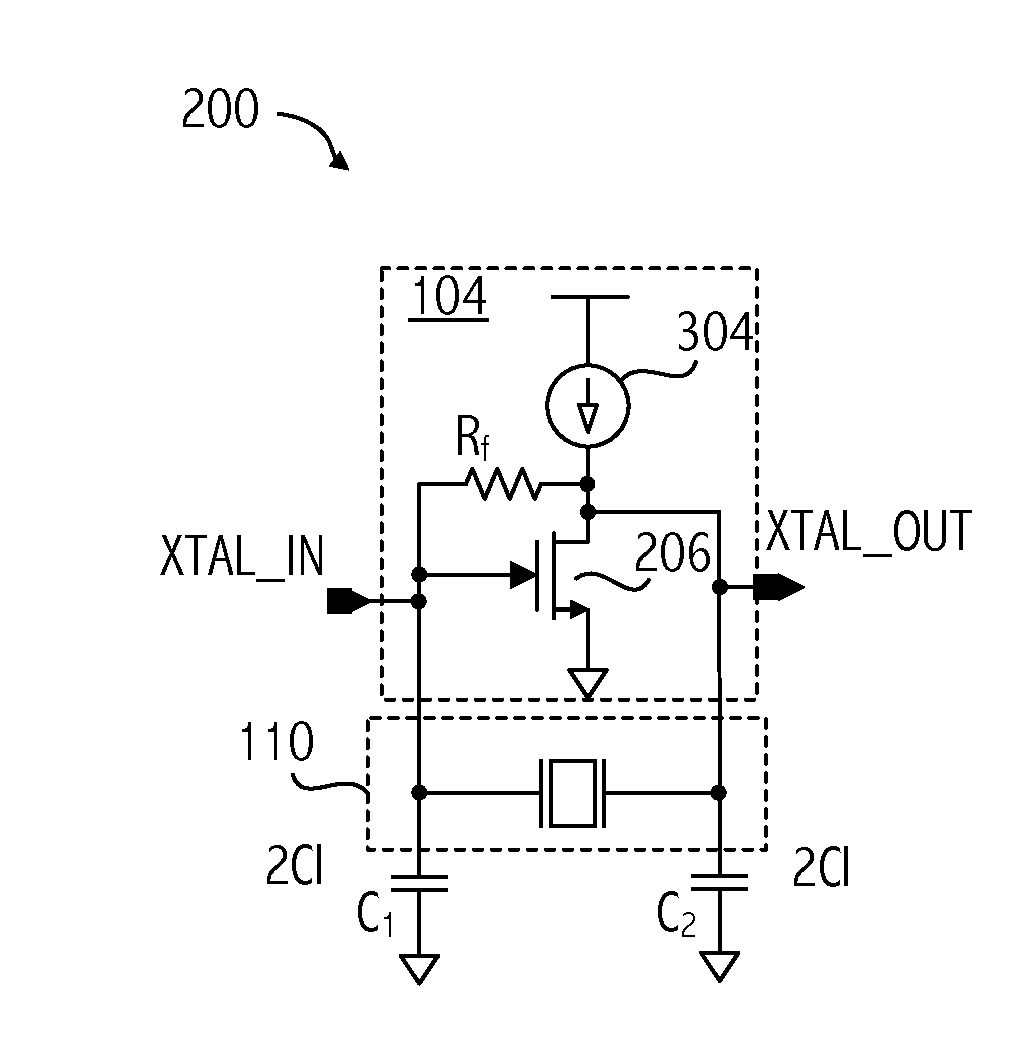

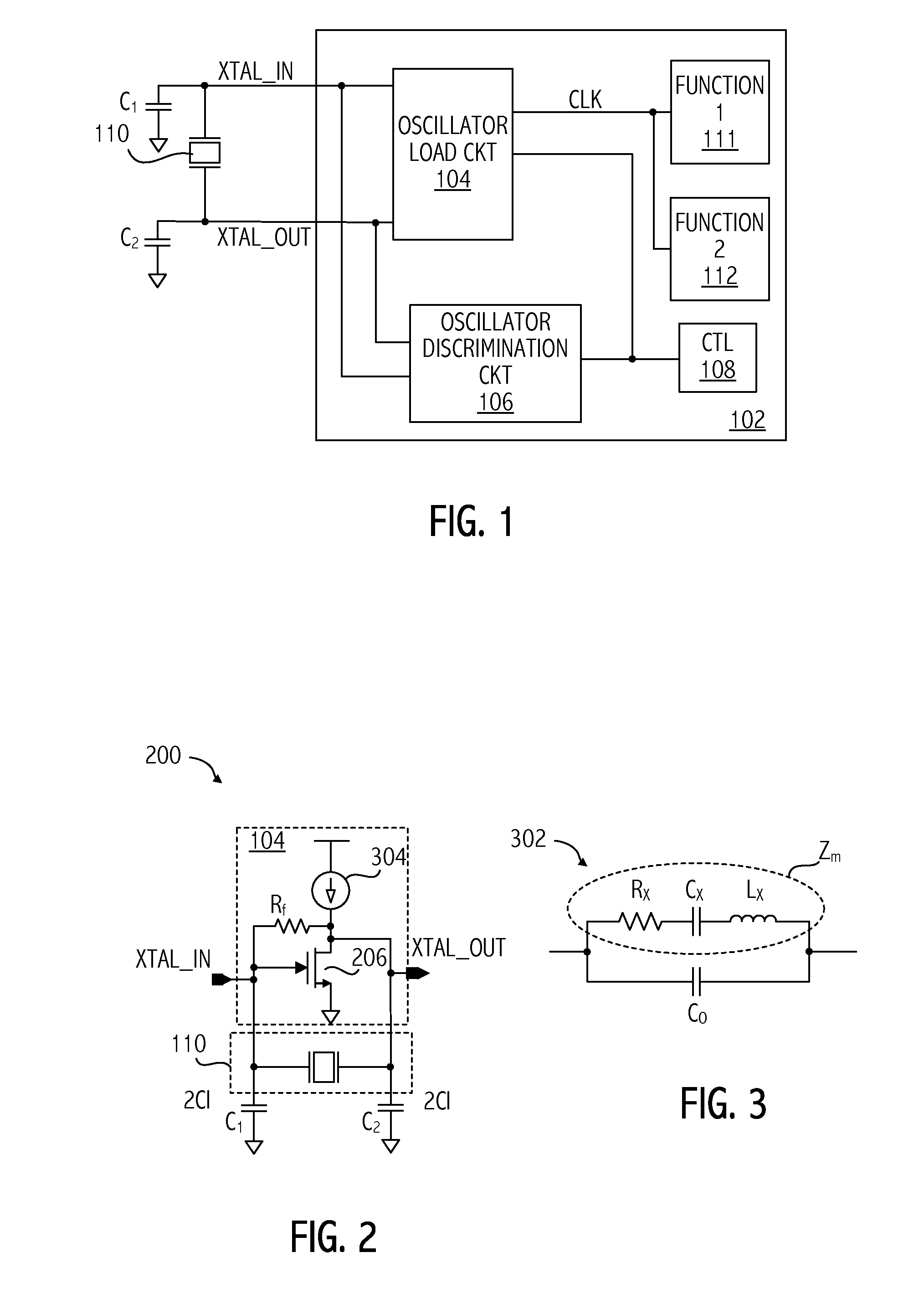

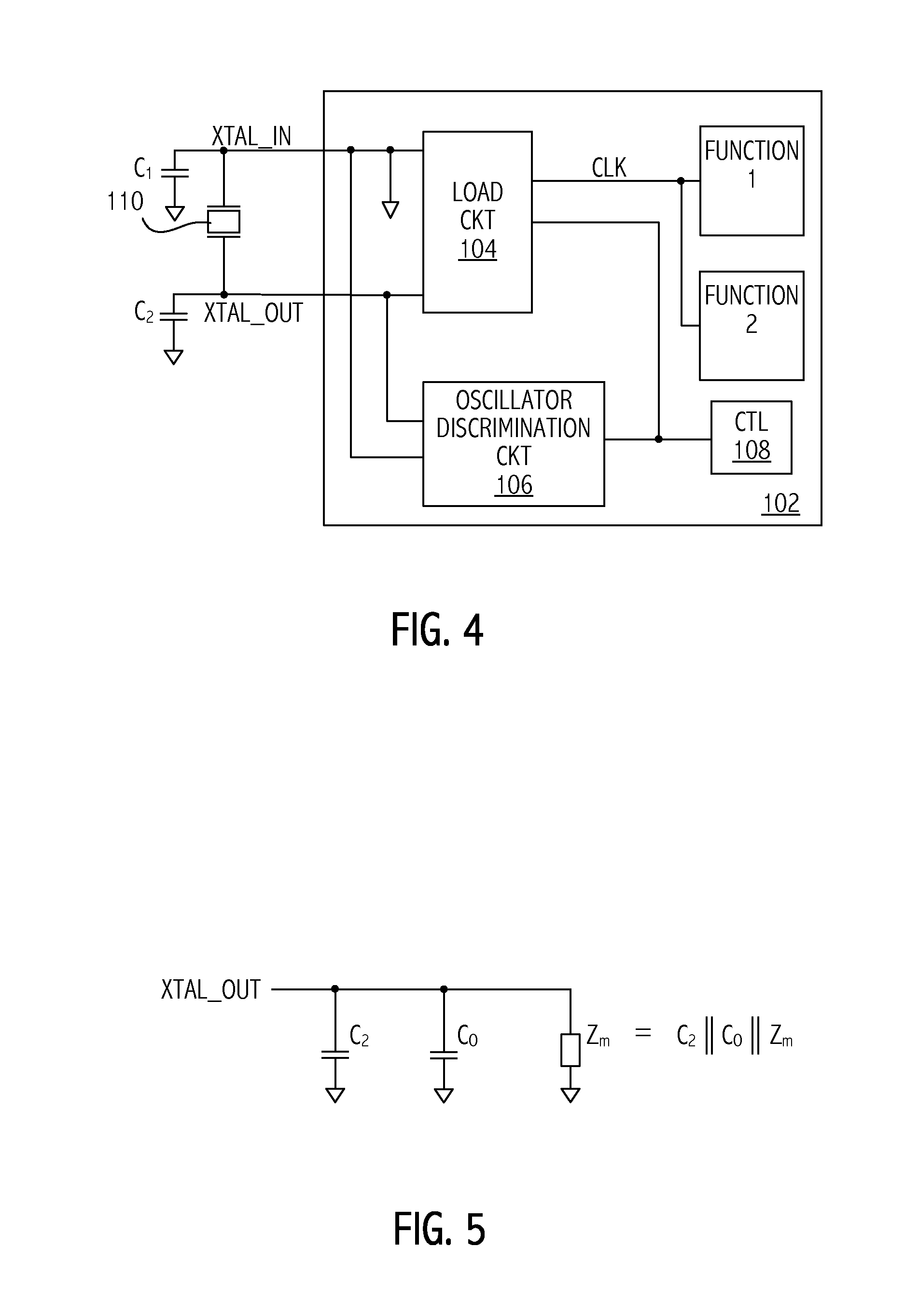

Technique for detecting crystals

In at least one embodiment of the invention, an apparatus includes an integrated circuit, which includes a first oscillator terminal and an oscillator discrimination circuit. The oscillator discrimination circuit is operative to generate an indicator of a capacitance value of a load capacitance external to the integrated circuit and coupled to one of the first and second oscillator terminals. The indicator is generated according to a charge time of a reference node coupled to a reference capacitor and a charge time of a node coupled to the first oscillator terminal. The node and the reference node are charged using substantially matched currents.

Owner:SILICON LAB INC

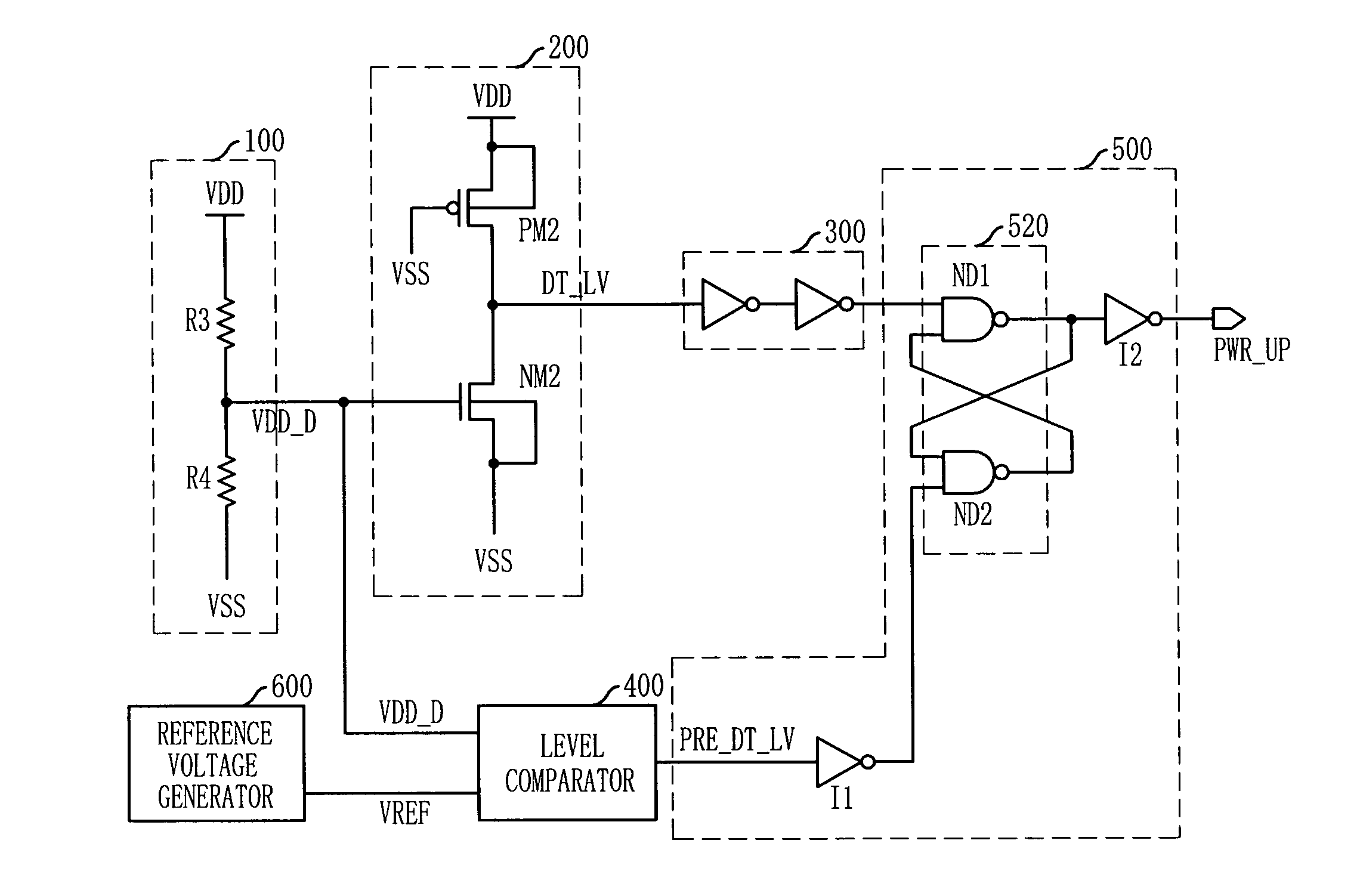

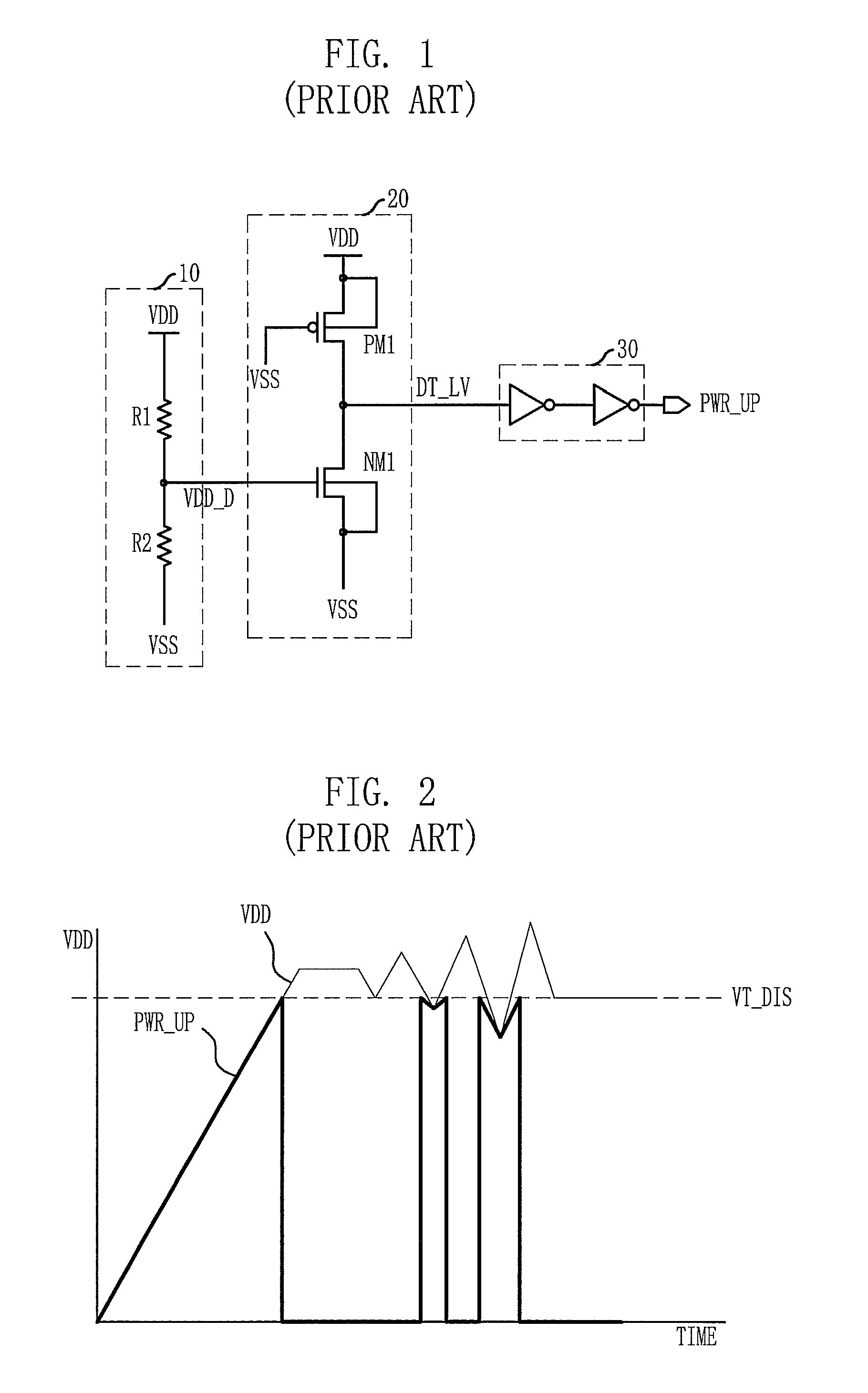

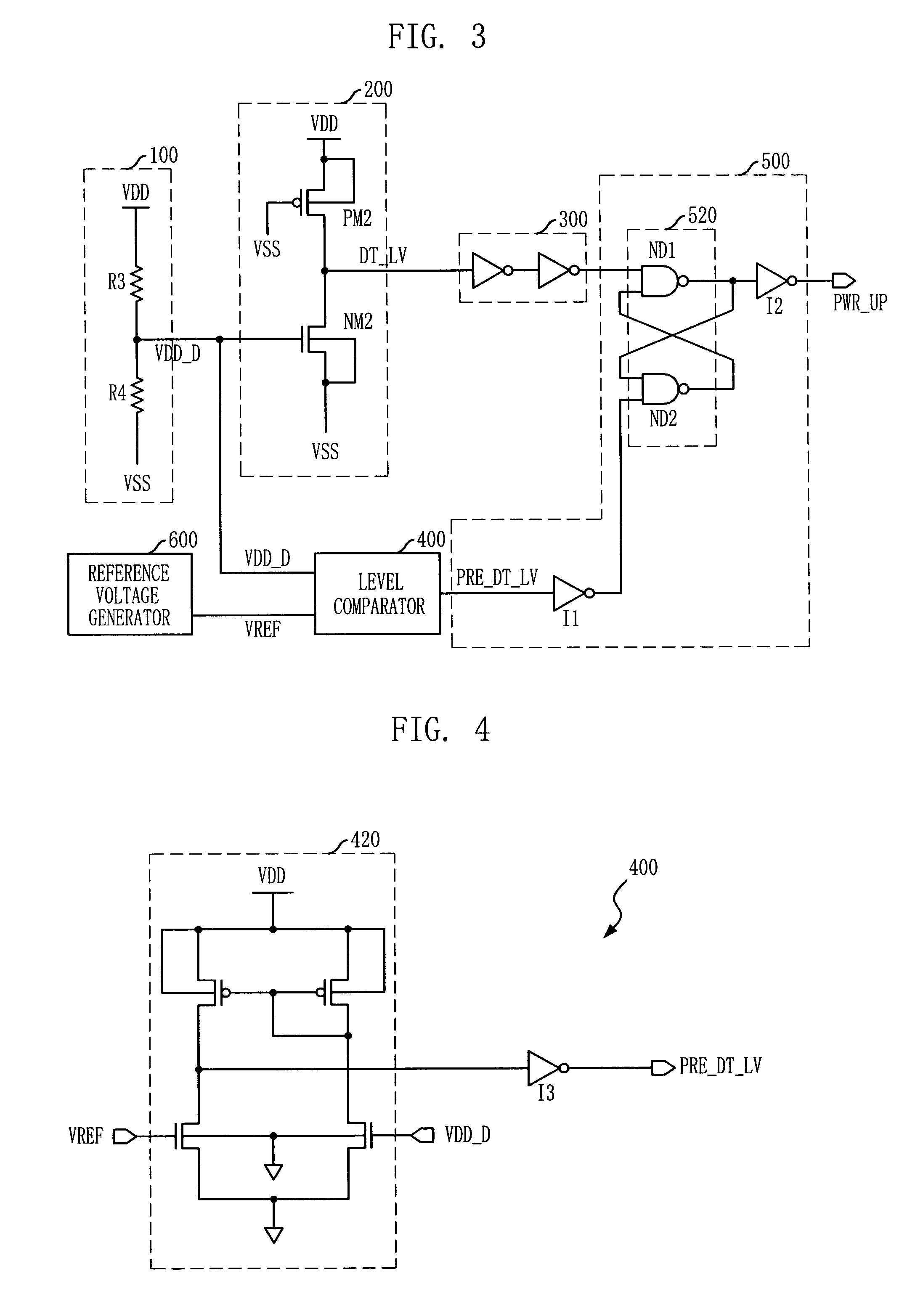

Power-up signal generating circuit and method for driving the same

A power-up signal generating circuit that prevents repeatedly generating a power-up signal even when there is noise on an external voltage. The power-up signal generating circuit includes a level detector, a level comparator, and a reentry protector. The level detector is configured to deactivate a first level detection signal when a level of an external voltage increases above a upper limit reference voltage. The level comparator is configured to deactivate a second level detection signal when the level of the external voltage increases above a lower limit reference voltage. The reentry protector is configured to activate the power-up signal in response to the second level detection signal and deactivate the power-up signal in response to a deactivation of the first level detection signal.

Owner:SK HYNIX INC

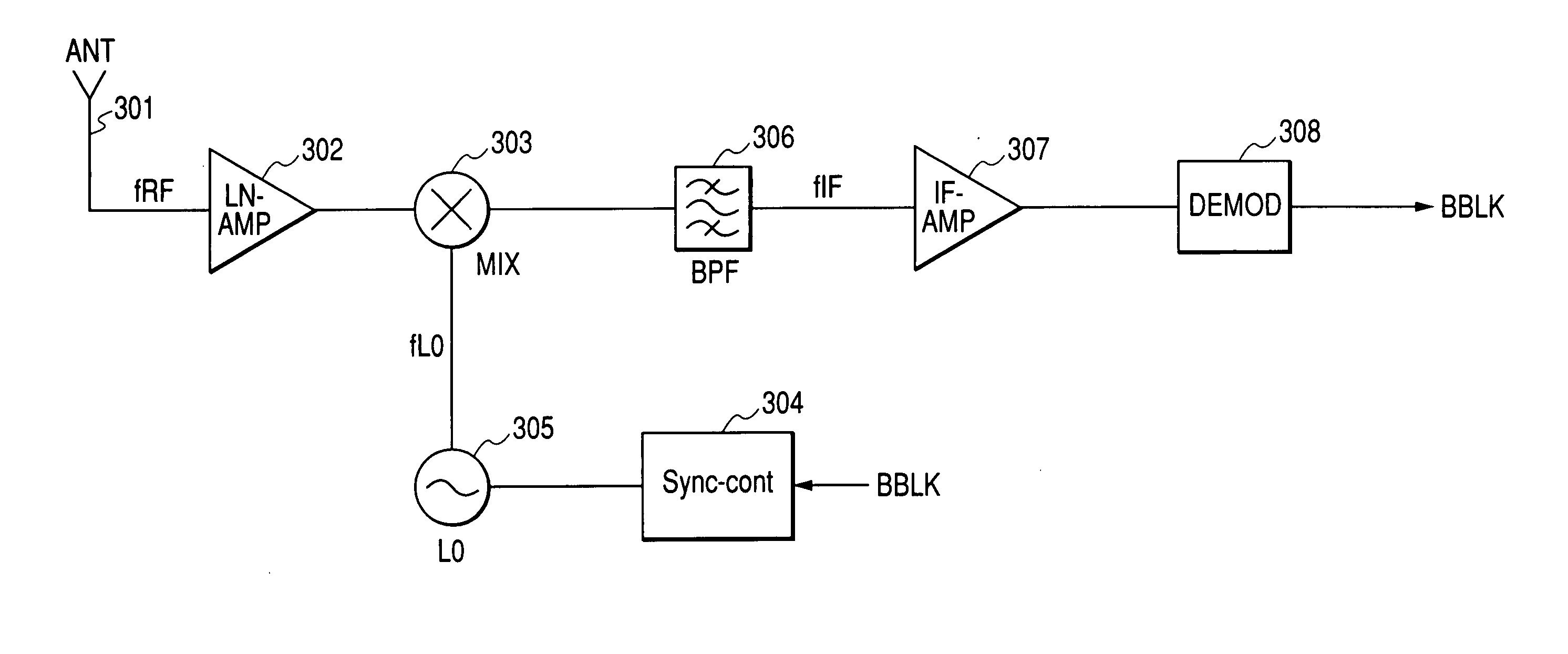

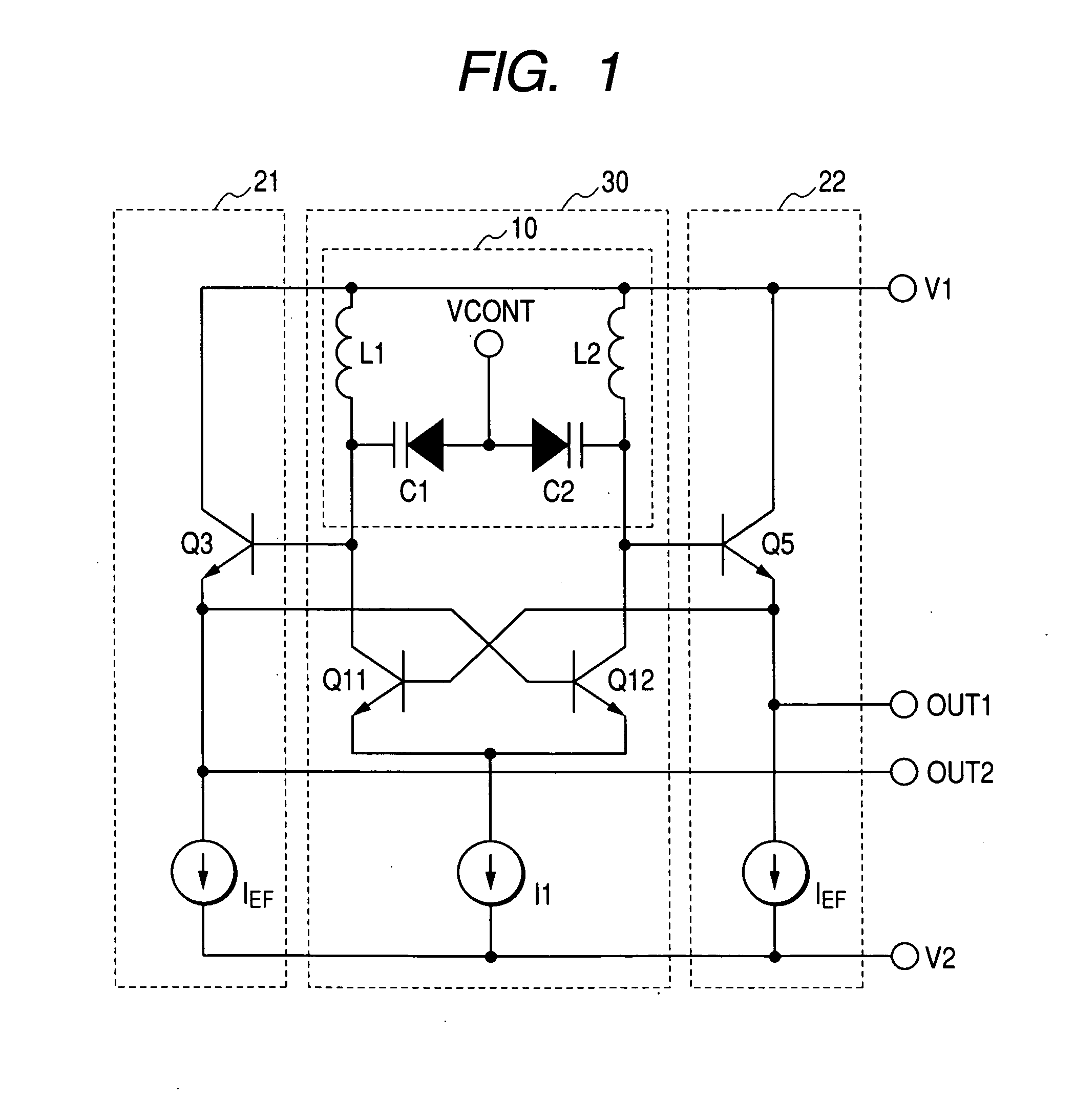

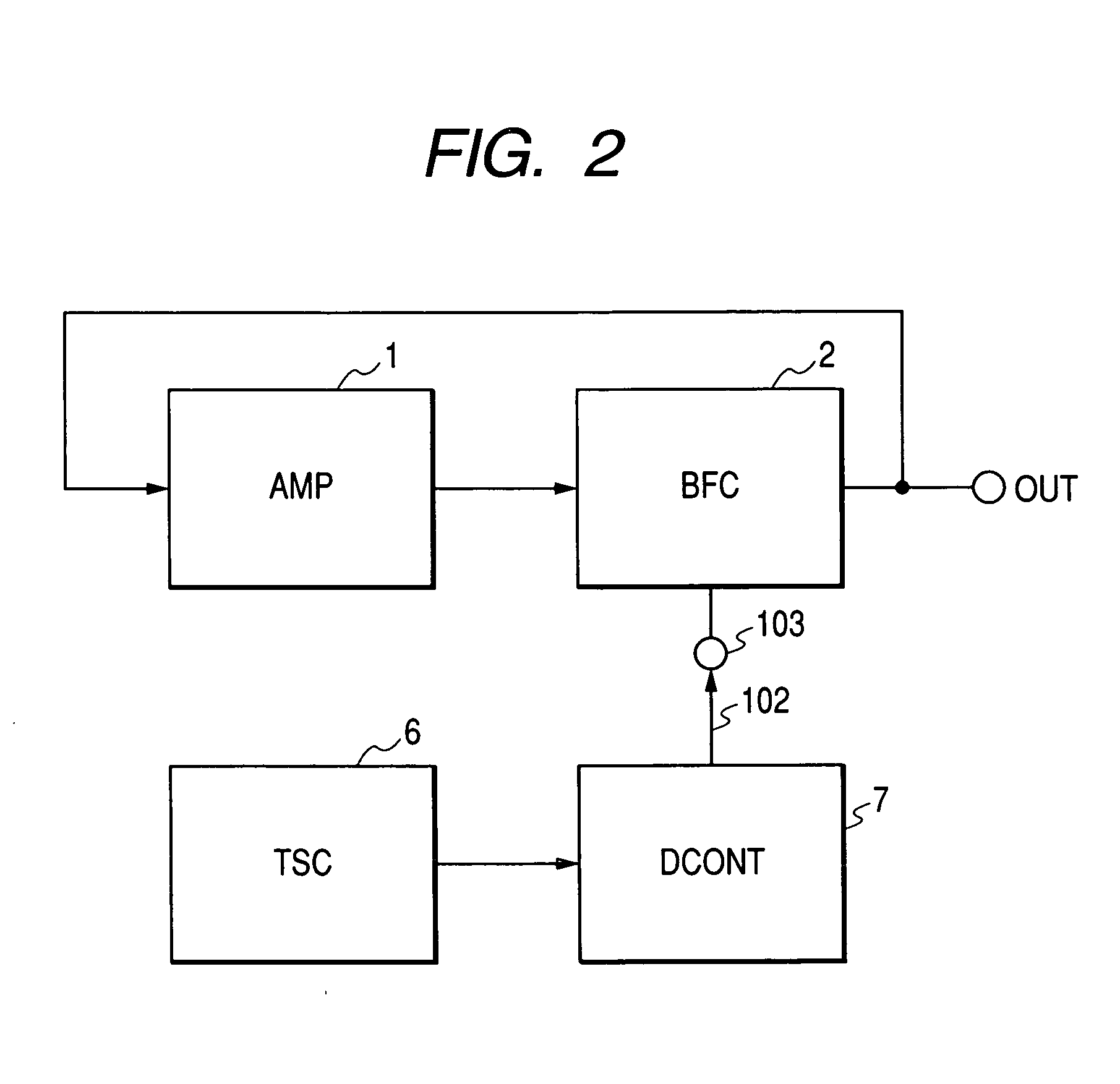

Frequency generator and communication system using the same

InactiveUS20050059373A1Highly stable oscillation frequencyOscillation frequency is stableMultiple-port networksAmplifier modifications to reduce temperature/voltage variationVoltage generatorCommunications system

A frequency generator which can perform stable frequency oscillation unaffected by temperature variation. A frequency generator having a differential amplifier (1) having an LC resonance circuit (10) as a load and buffer circuits (21, 22) feeding back an output of the differential amplifier to its input, wherein a temperature coefficient converter (5) converting an output voltage of a reference voltage generator (4) and its temperature dependence to a voltage having a predetermined voltage and temperature coefficient and outputting it is provided to control bias currents IEF of emitter follower circuits to be in proportion to temperature variation. There are a characteristic in which delay time of the emitter follower circuits constructing the buffer circuits is in inverse proportion to a transconductance of transistors and a characteristic in which the transconductance is in inverse proportion to temperature and is in proportion to the bias currents IEF. An oscillation frequency stable to temperature variation can be obtained.

Owner:RENESAS TECH CORP

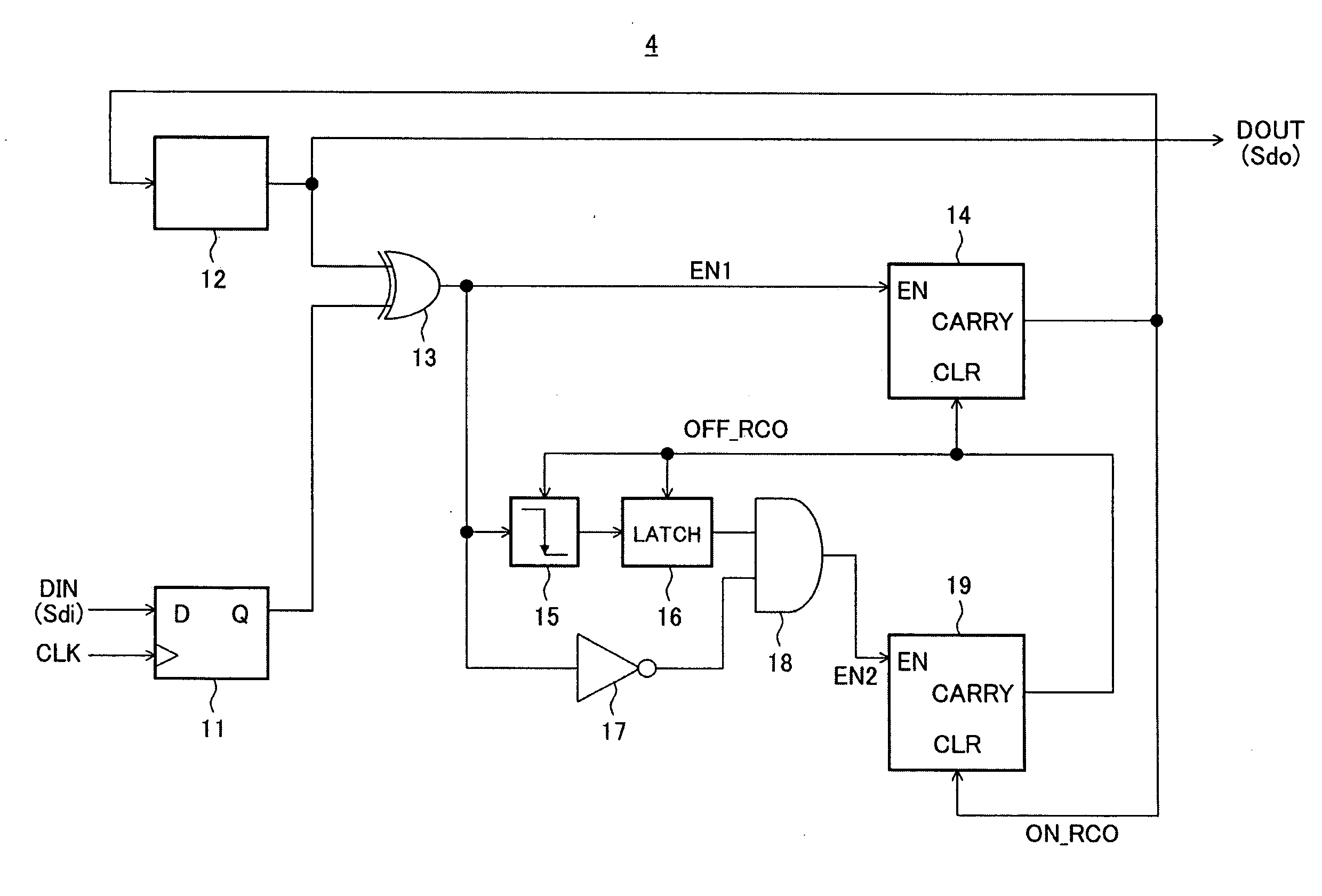

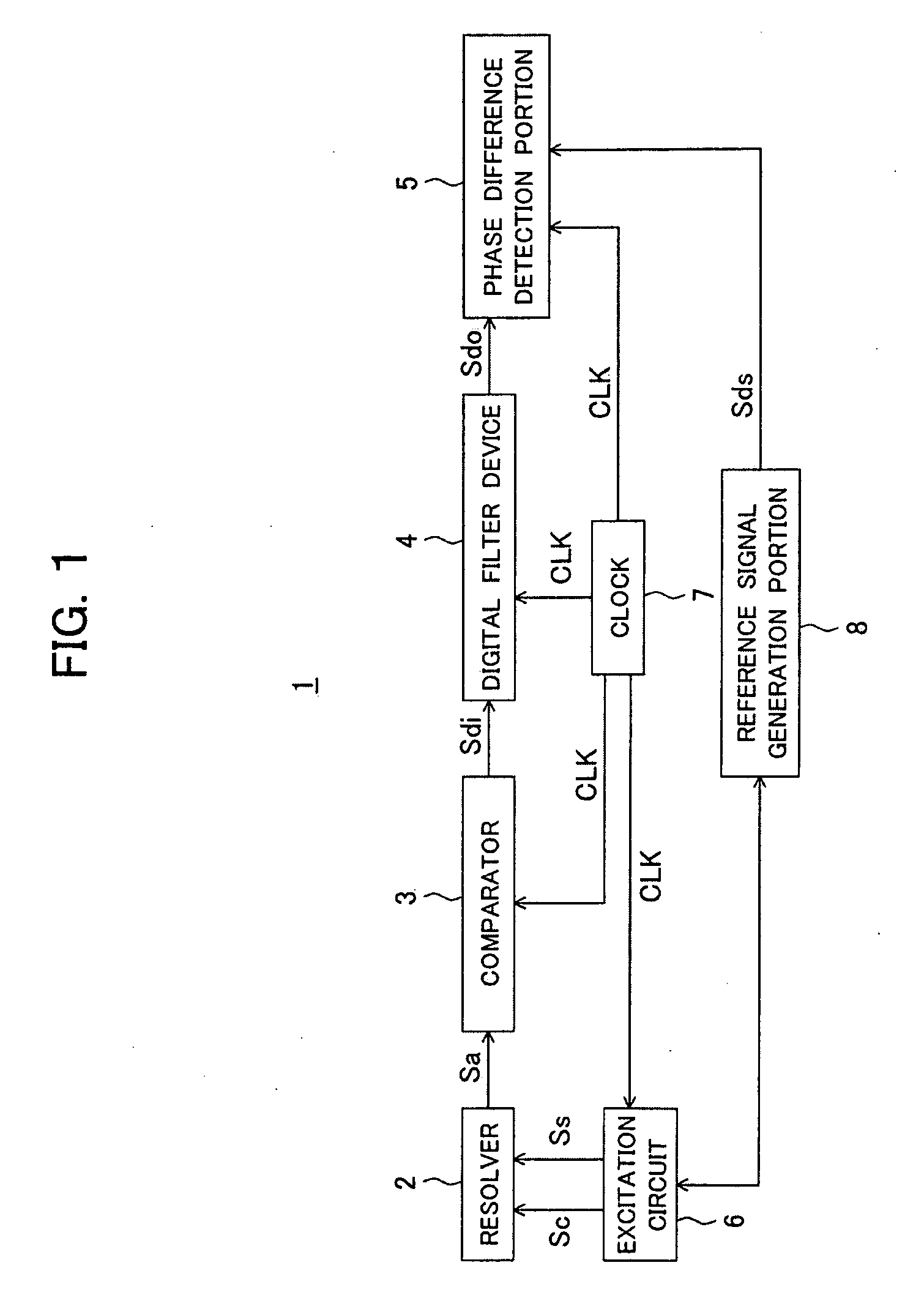

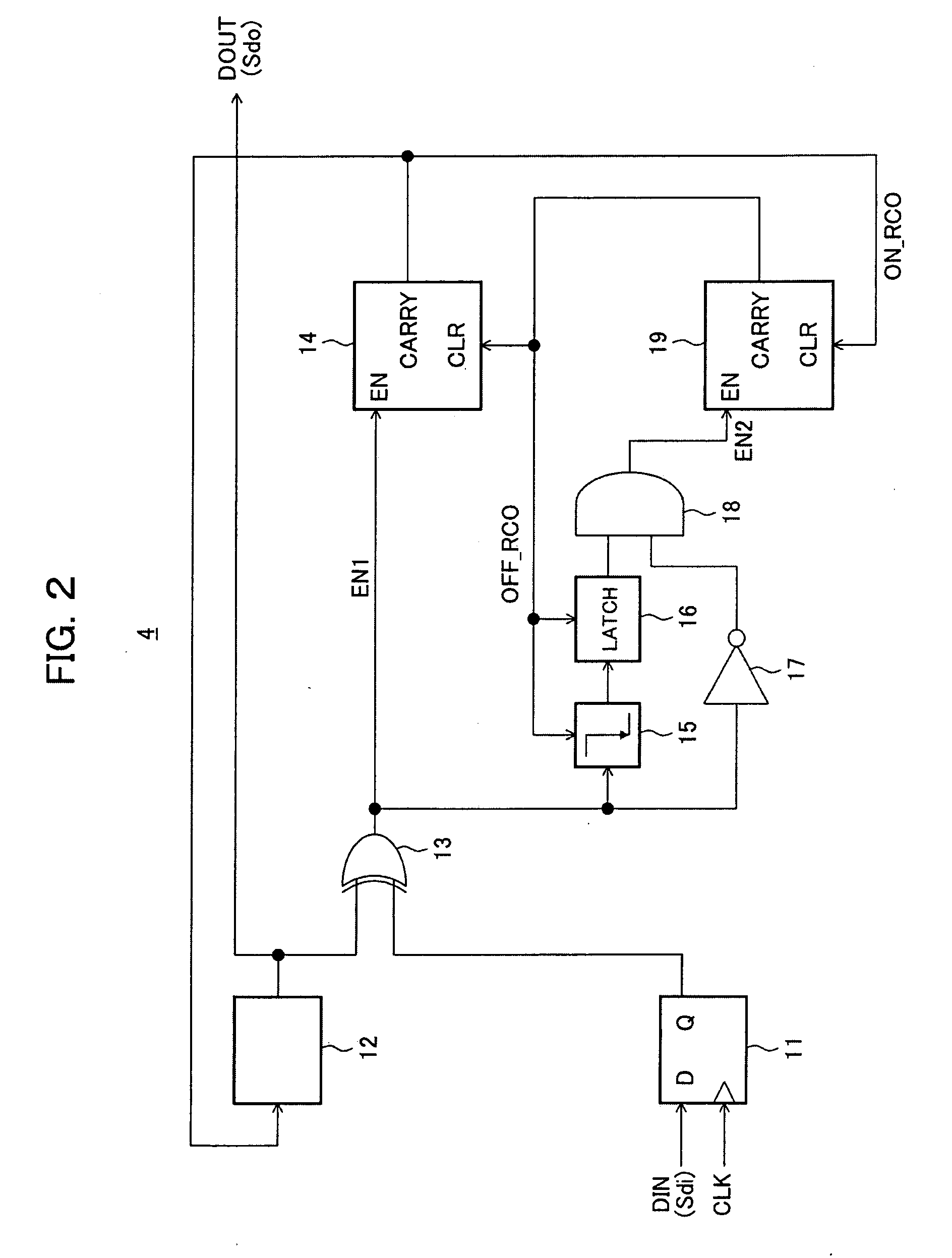

Digital filter device, phase detection device, position detection device, ad conversion device, zero cross detection device, and digital filter program

ActiveUS20090313313A1Eliminate the effects ofDigital variable displayElectric signal transmission systemsLocation detectionDigital filter

A digital filter device capable of removing the effect of noise such as chattering from a zero crossing signal is provided. A digital filter device 4 filtering a binary digital signal DIN and outputting a binary digital signal DOUT is provided with a toggle flip-flop 12 which switches a signal level of the digital signal DOUT each time a trigger signal is input; an XOR circuit 13 which outputs a first enable signal EN1 while a signal level of the digital signal DIN does not match with the signal level of the output digital signal DOUT; and a charge counter 14 which counts in synchronization with a clock signal CLK while the first enable signal EN1 is input and resets the count to an initial value and outputs a carry on signal ON_RCO as the trigger signal to the toggle flip-flop 12 when the count has reached an upper limit value.

Owner:TOSHIBA MASCH CO LTD

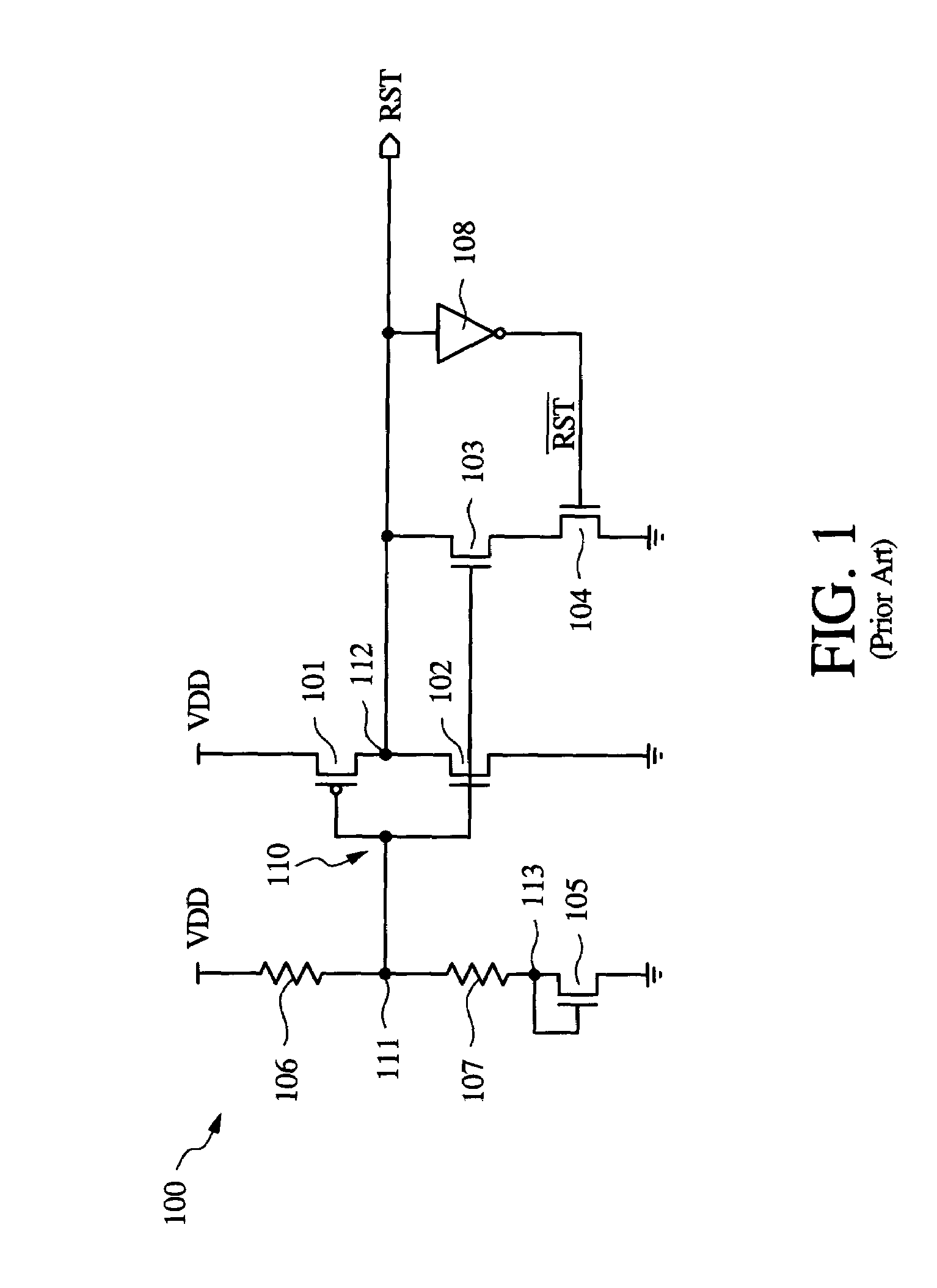

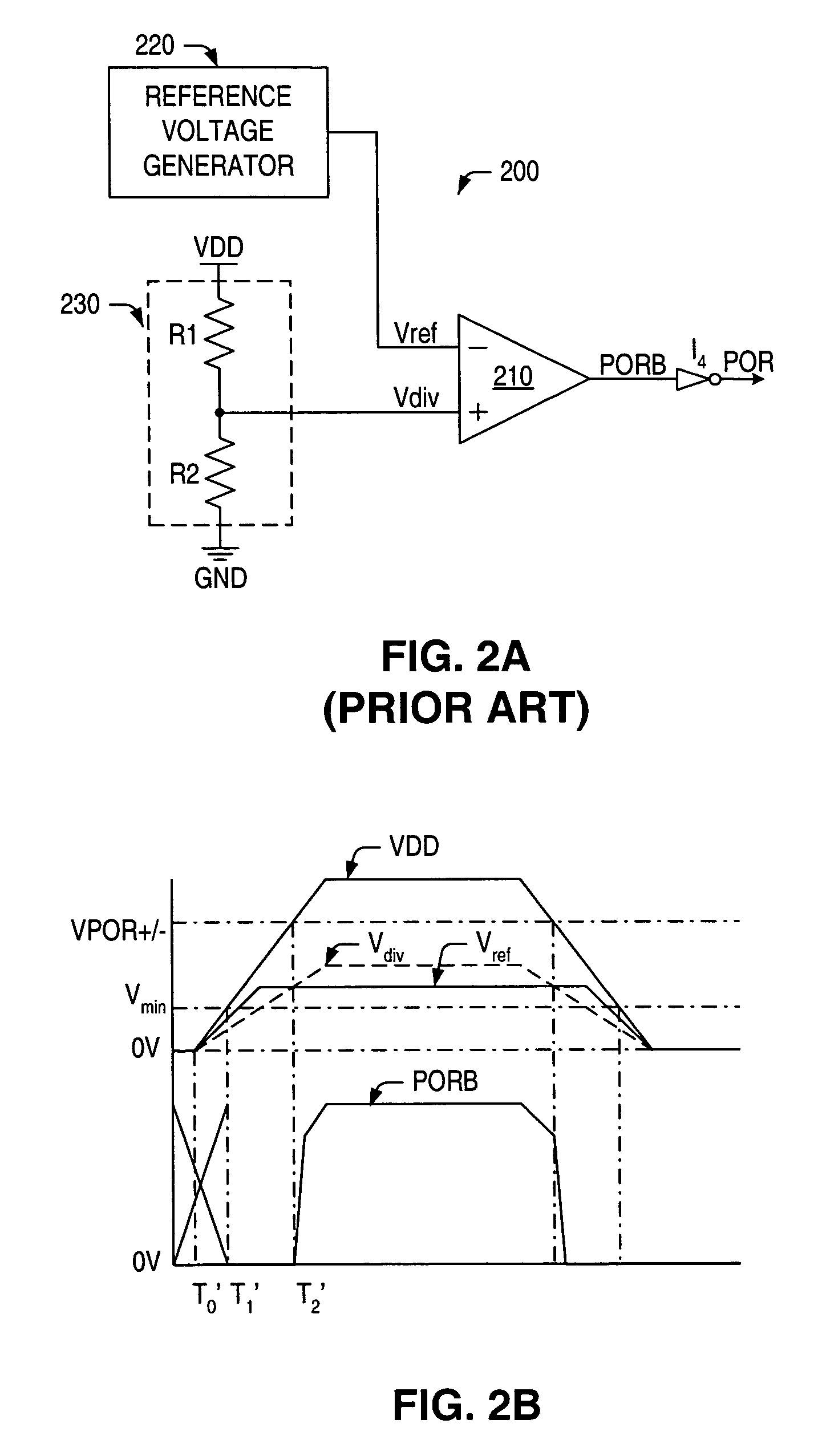

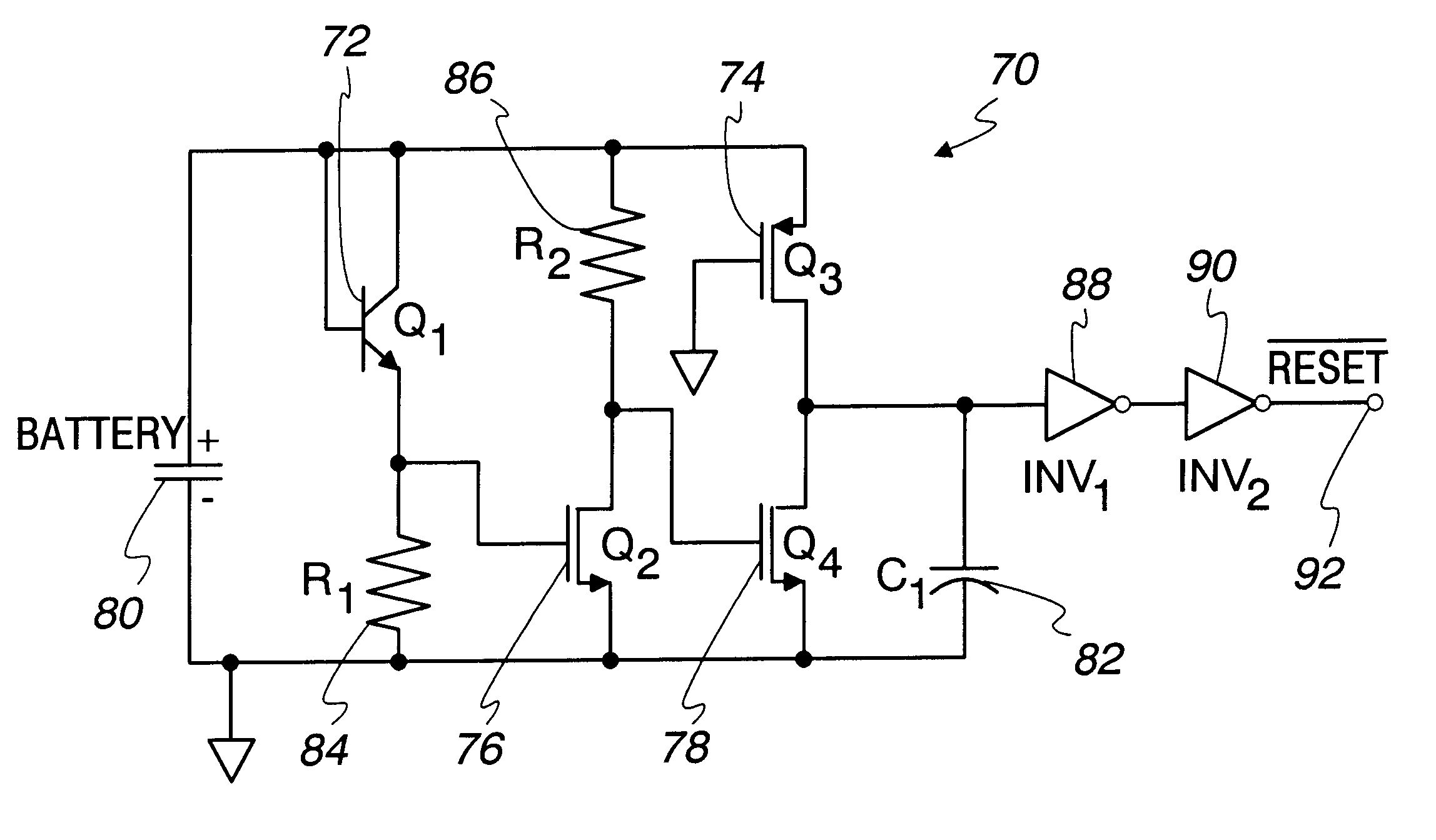

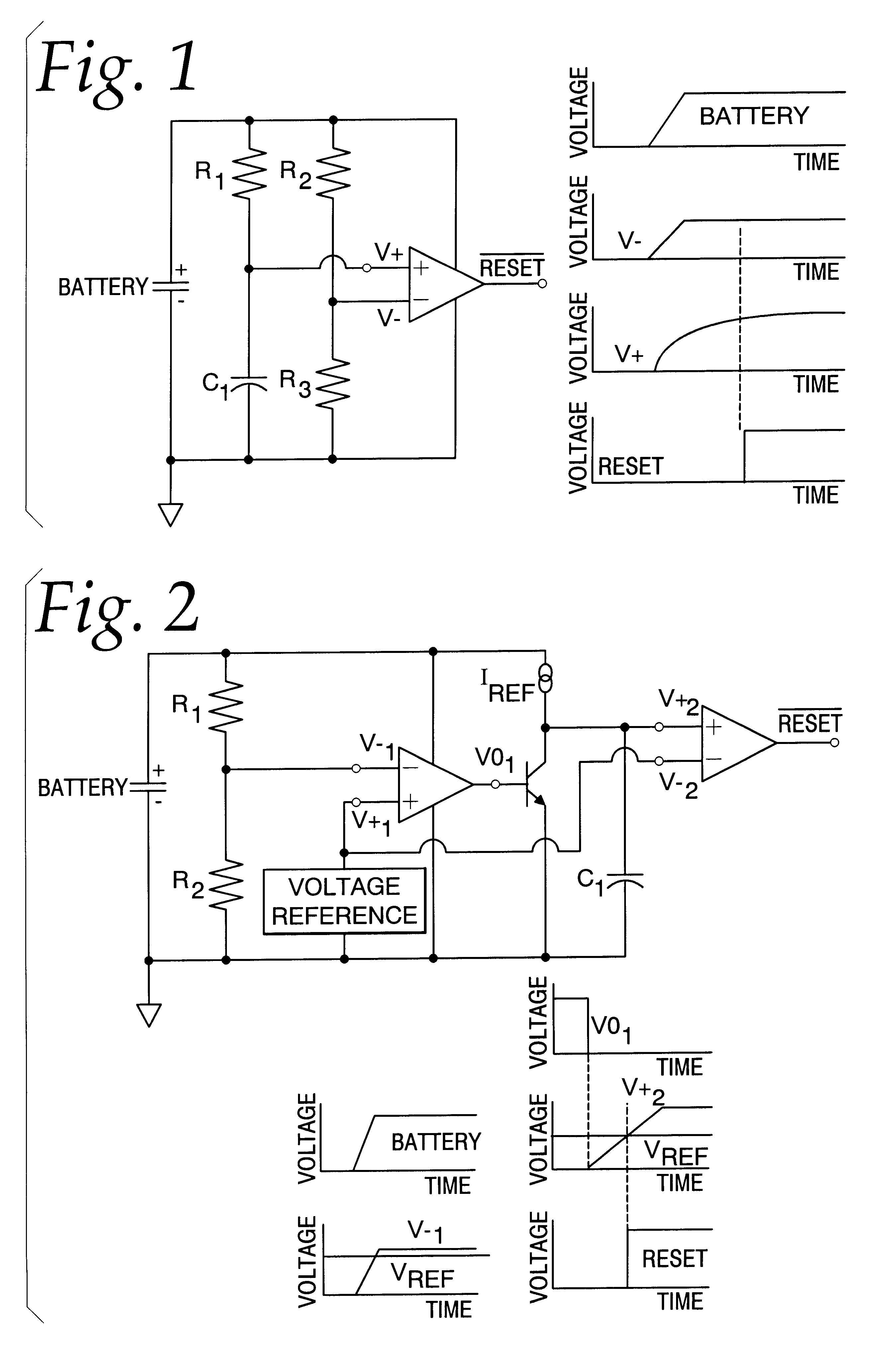

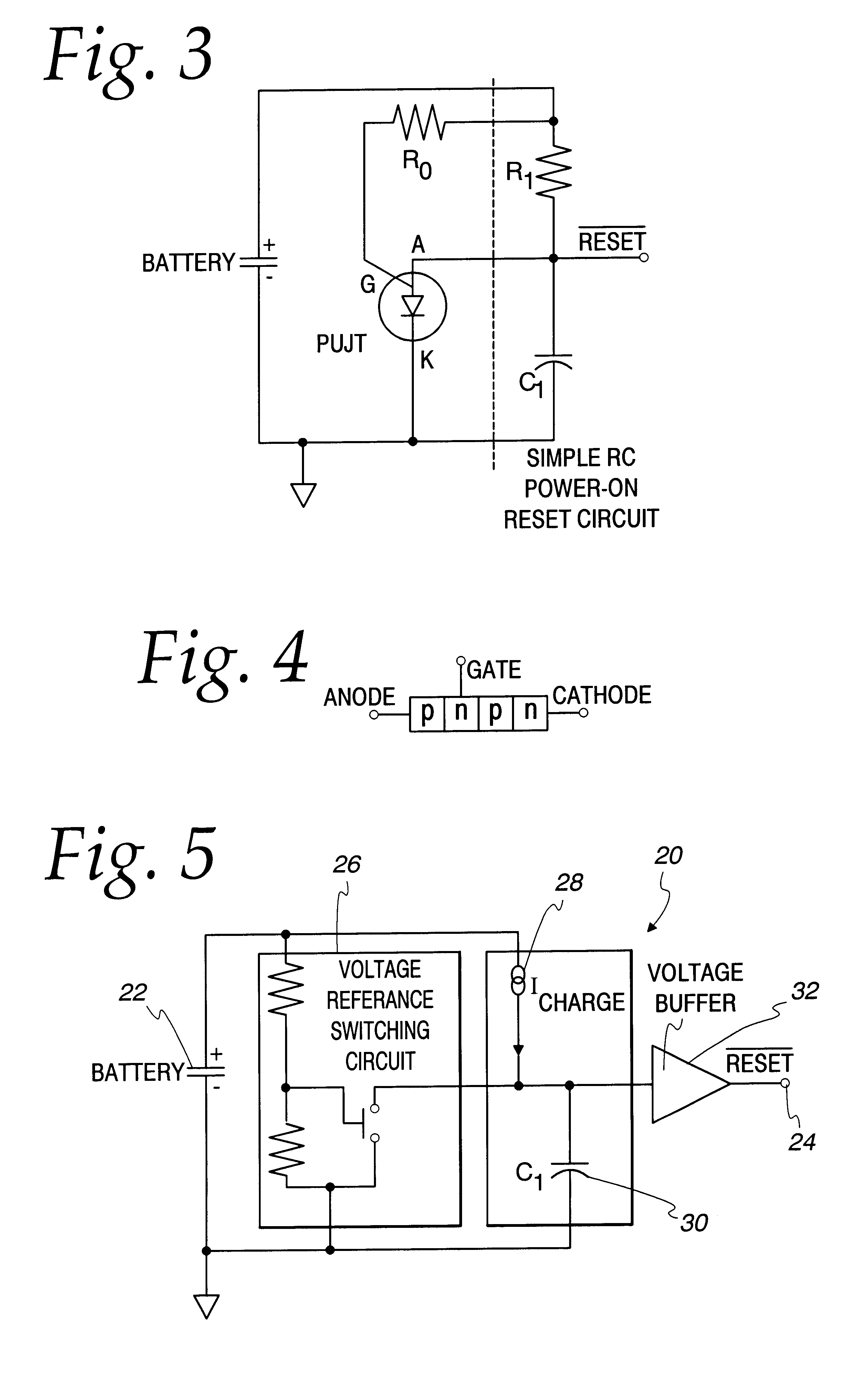

Power-on reset circuit

InactiveUS6181173B1Reduce power consumptionAccurate detectionPulse automatic controlElectronic switchingElectricityPower-on reset

A power-on reset circuit for resetting the register values contained on an integrated circuit upon power-up of the integrated circuit. The power-on reset circuit can be implemented either internal or external to the integrated circuit. The power-on reset circuit generates a reset signal as long as the supply voltage is not in the operational range and maintains the reset signal for a certain time after the supply voltage has returned to its nominal value. The power-on reset circuit also provides accurate detection of a serious supply voltage drop and has low power consumption. The power-on reset circuit comprises a battery, a voltage-referenced switching circuit, a current source, a capacitor and a voltage buffer.

Owner:UNWIRED PLANET

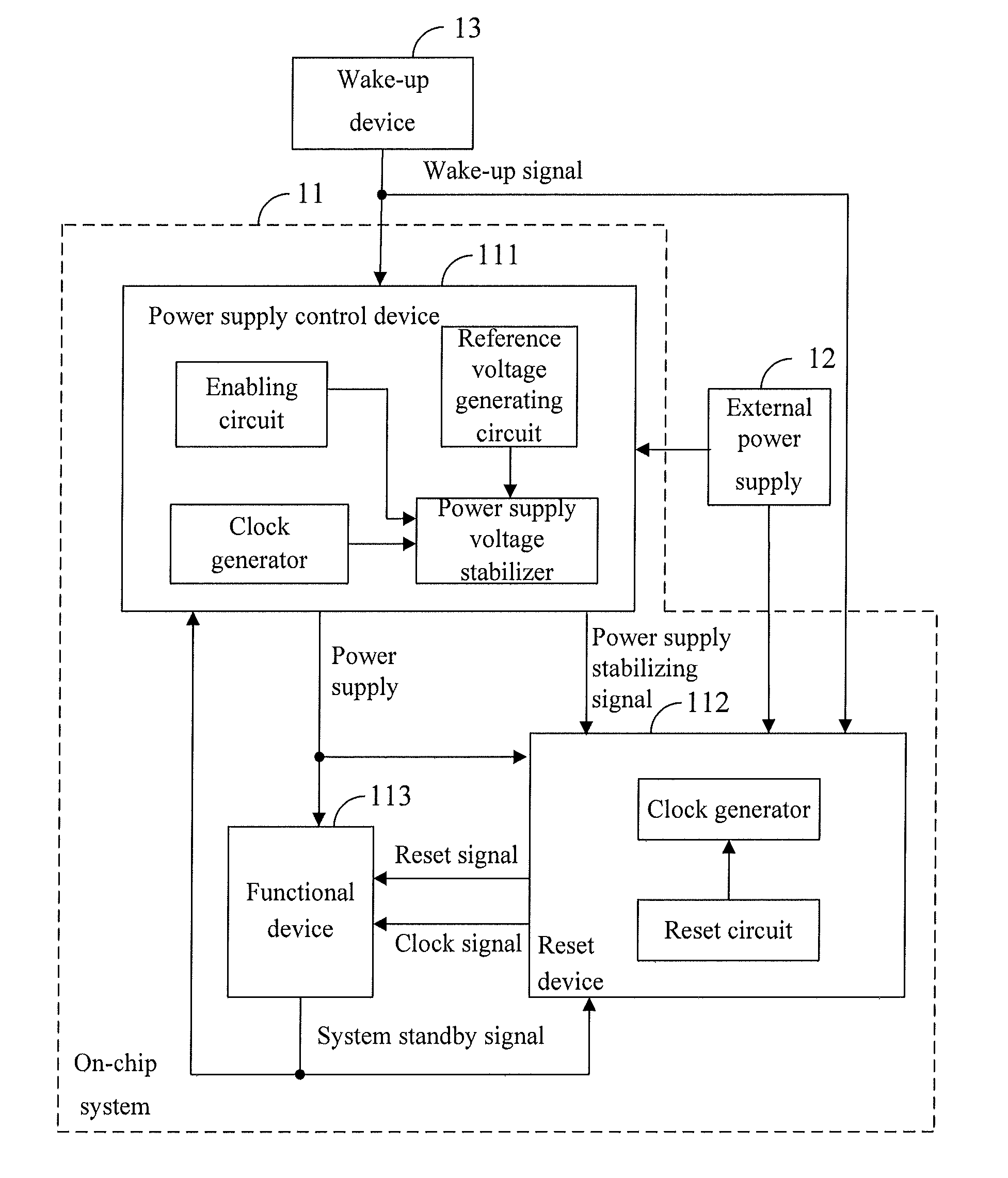

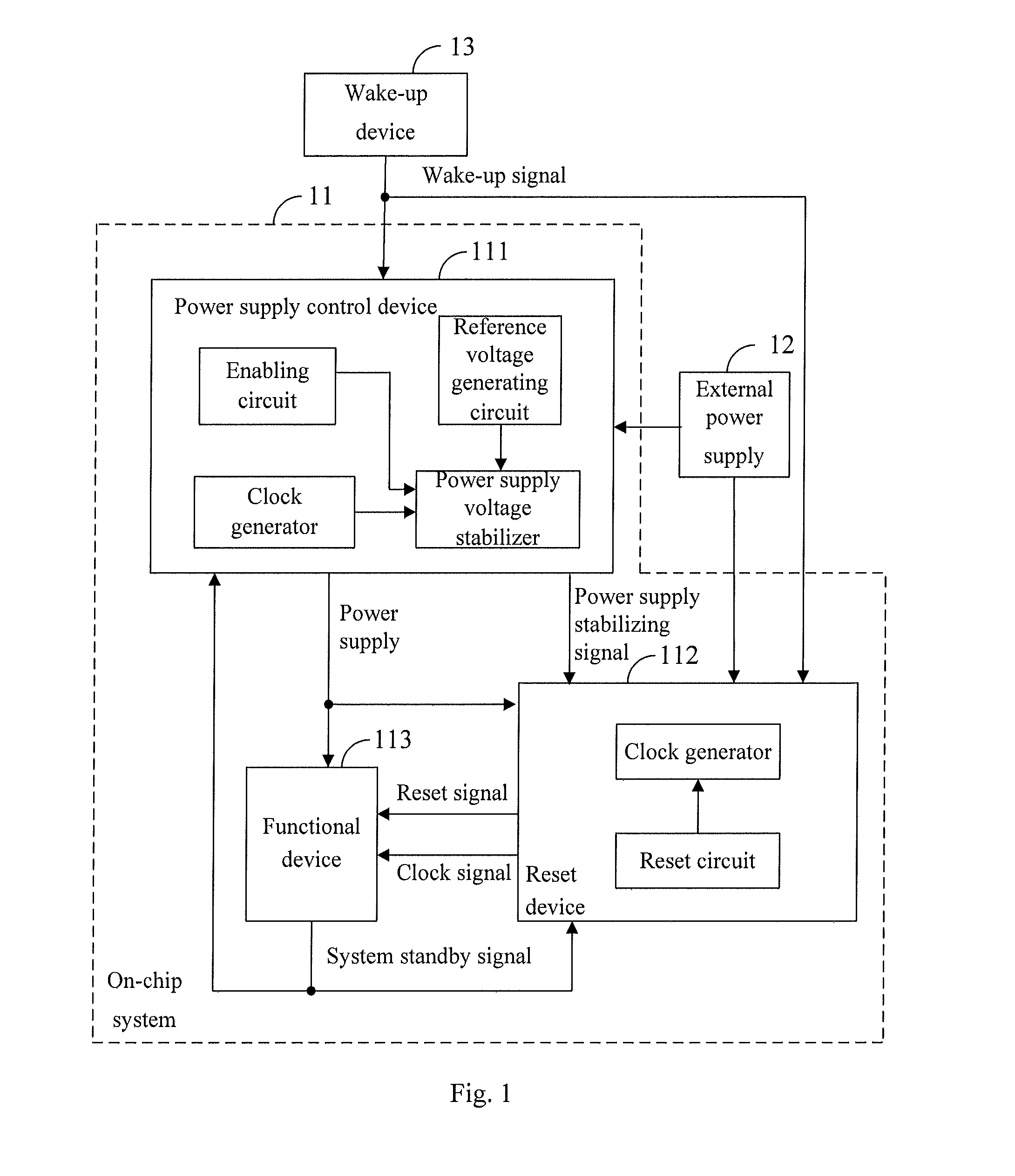

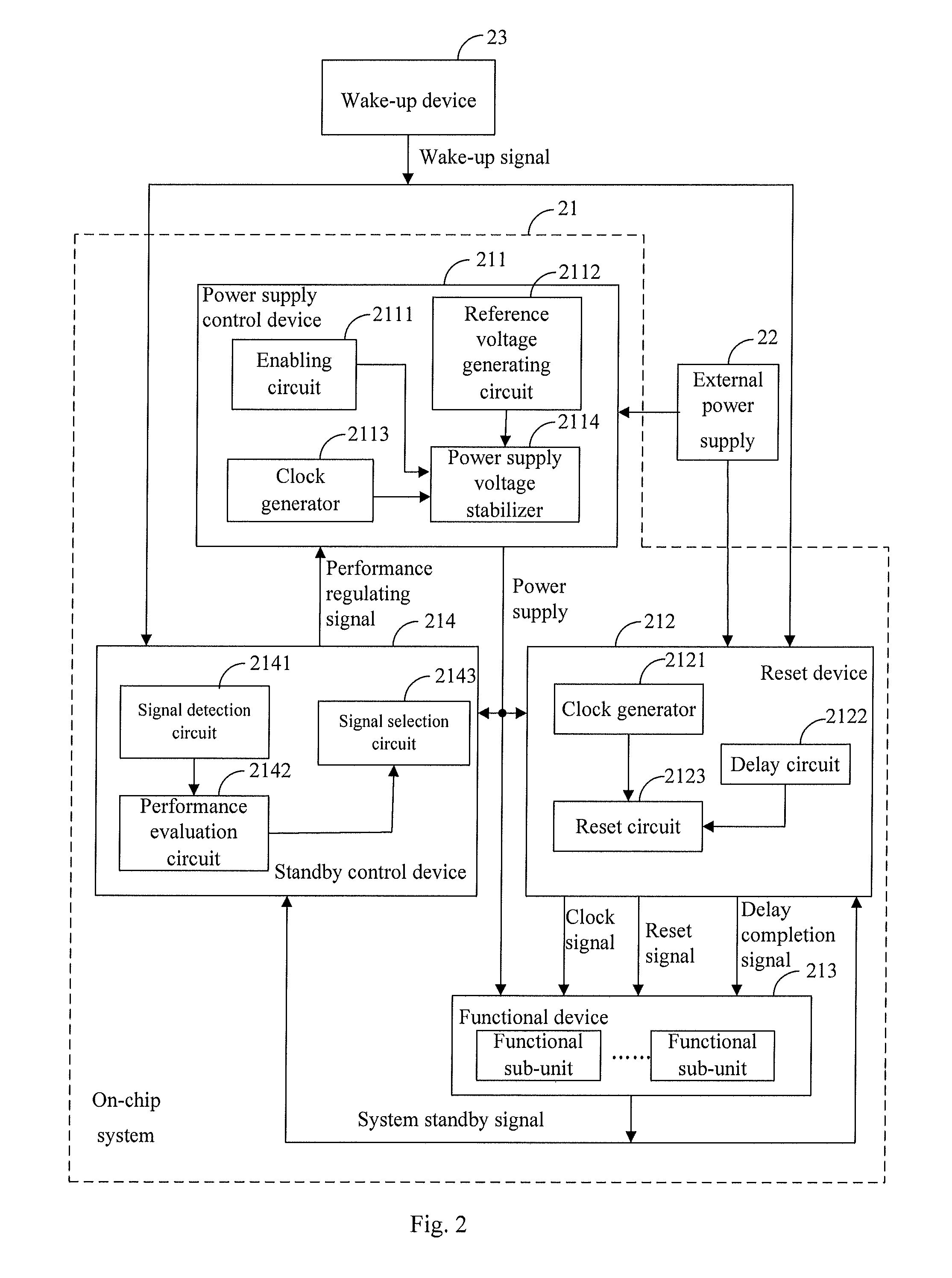

Integrated circuit and standby controlling method thereof

ActiveUS20110221483A1Rapid wake-upReduce standby power consumptionEnergy efficient ICTPulse automatic controlEngineeringControl equipment

The present invention is applicable to the field of electrics and provides an integrated circuit (IC) and a standby controlling method thereof. The IC comprises a reset device, a standby control device, a functional device and a power supply control device. The functional device at least comprises a functional unit that does not operate in a standby mode. The power supply control device is configured to supply power to the functional device, the standby control device and the reset device. The standby control device is configured to control the power supply control device to control a power supply voltage of the functional unit to be within a preset range below a normal operating voltage when a standby status signal is detected, and restore the power supply voltage into the normal operating voltage when a wake-up signal is detected; and the reset device is configured to reset the functional device when the system standby status signal is detected and release the resetting of the functional device when the wake-up signal is detected. The IC of the present invention reduces the time required by the IC to wake up from the standby mode while ensuring that the whole functional device has low static power consumption.

Owner:ARTEK MICROELECTRONICS

Device and control method of device

ActiveUS20100052739A1Pulse automatic controlCounting chain pulse countersEngineeringFrequency divider

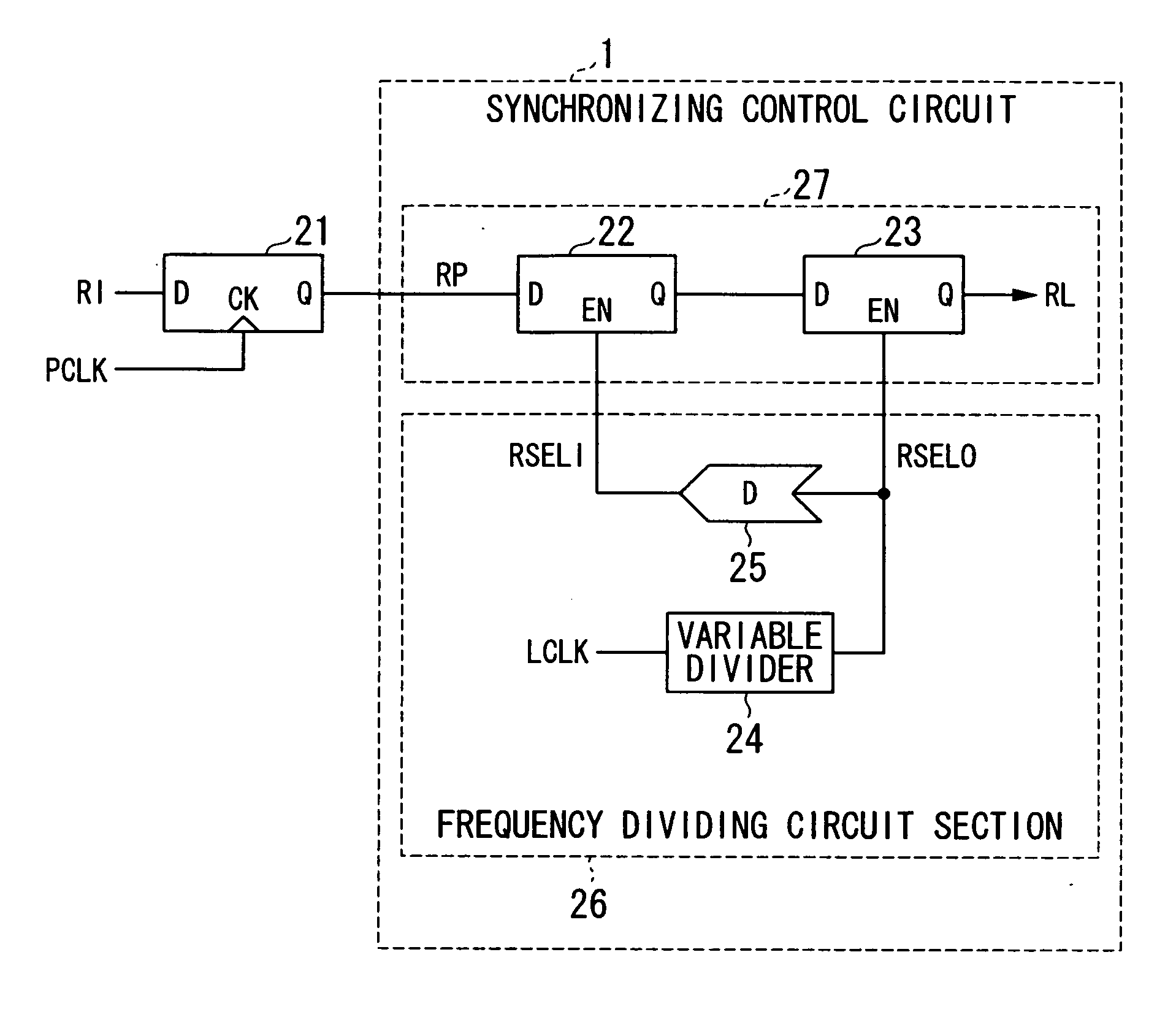

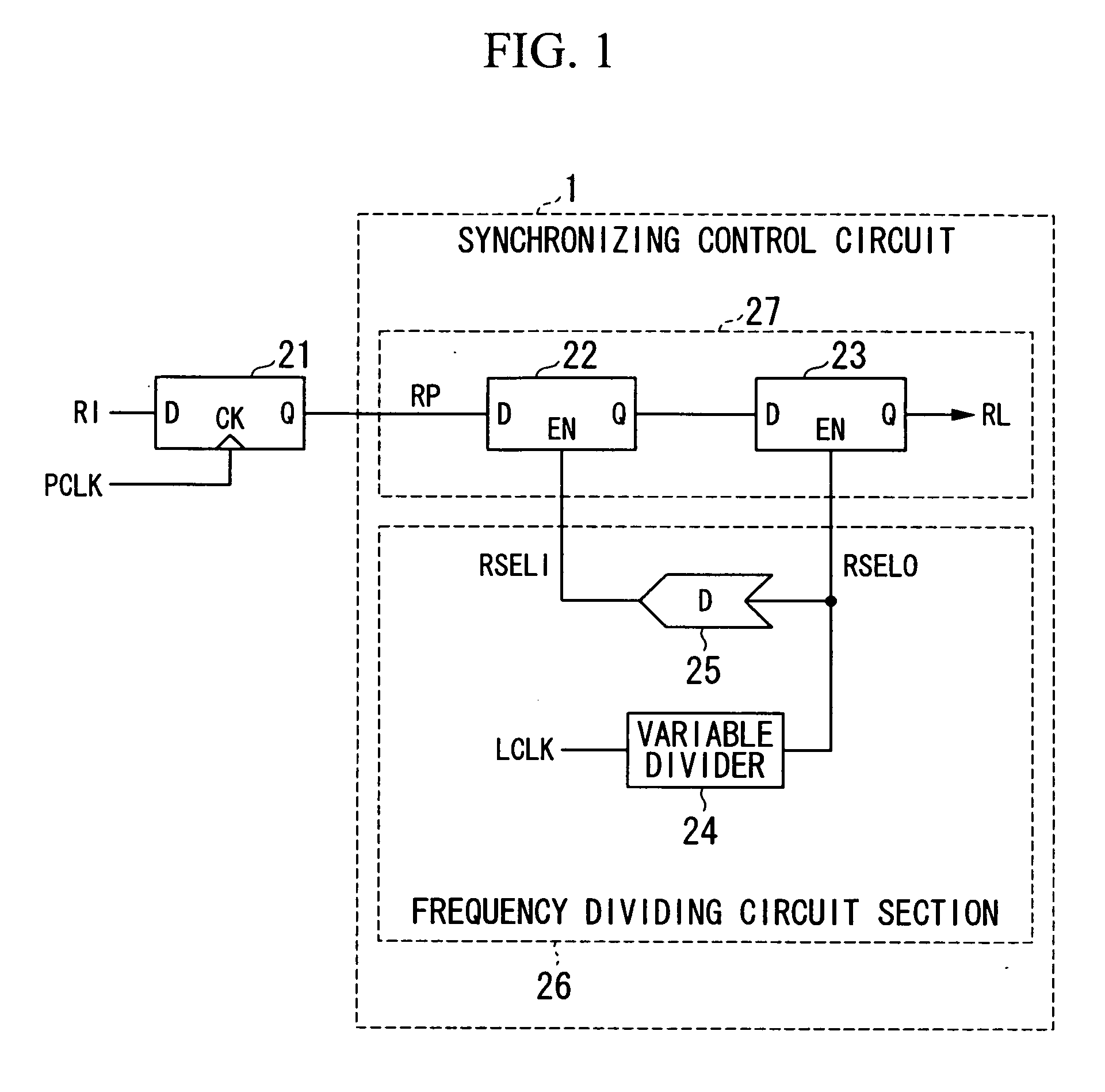

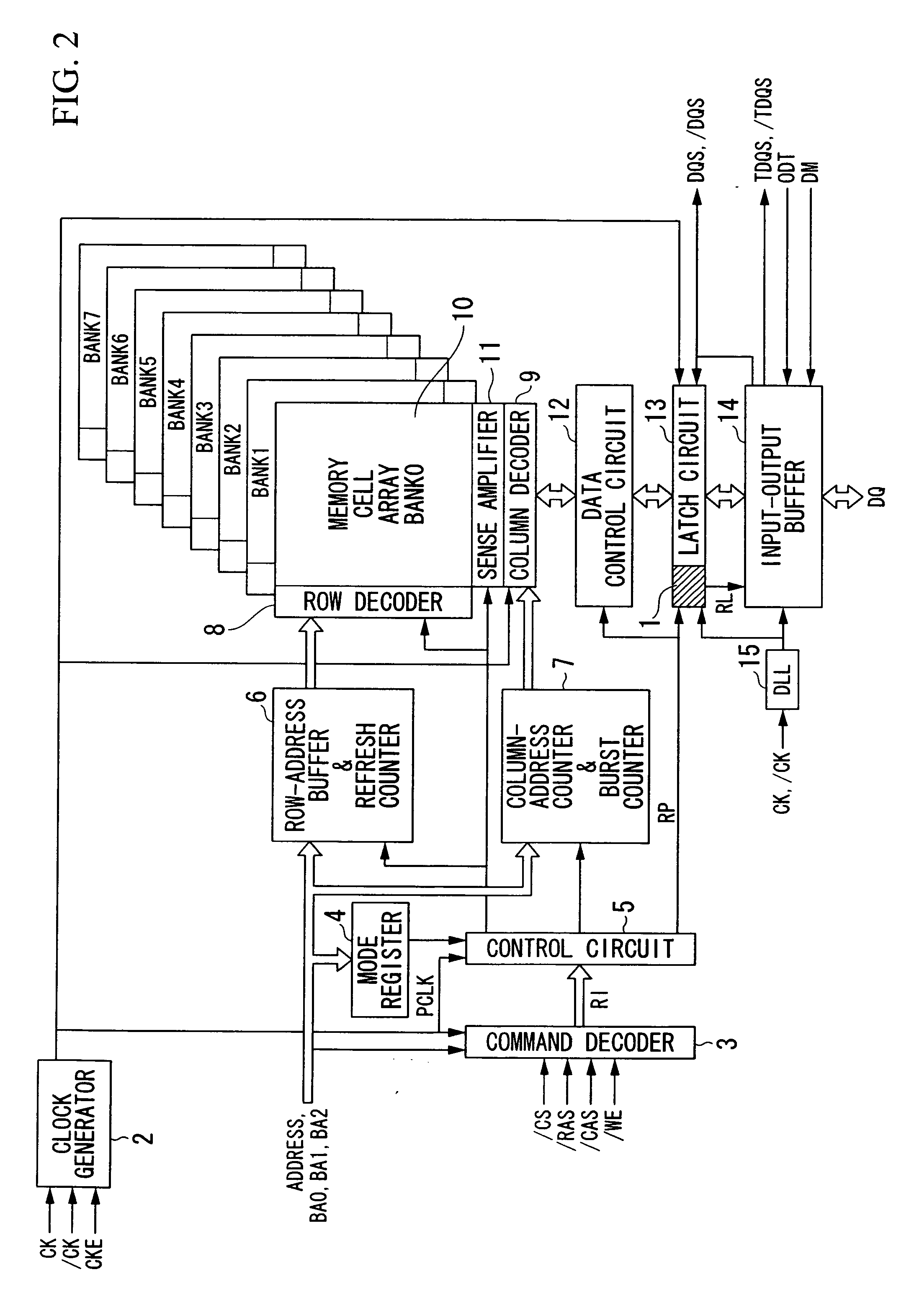

A frequency divider section generates a frequency-divided clock RSELO by dividing the frequency of an internal clock LCLK, which lags behind an external clock in phase, and generates a delayed frequency-divided clock RSELI by delaying the frequency-divided clock RSELO. A signal input from the outside in synchronization with an internal clock PCLK which lags behind the external clock in phase is held in a latch circuit in synchronization with the delayed frequency-divided clock RSELI. Then, an output signal of the latch circuit is read into a latch circuit in synchronization with the frequency-divided clock RSELO and is output as a signal which is synchronized with the internal clock LCLK. In addition, a frequency divider section includes a variable divider which divides the frequency of the internal clock LCLK by a predetermined divide ratio which can be changed.

Owner:LONGITUDE LICENSING LTD

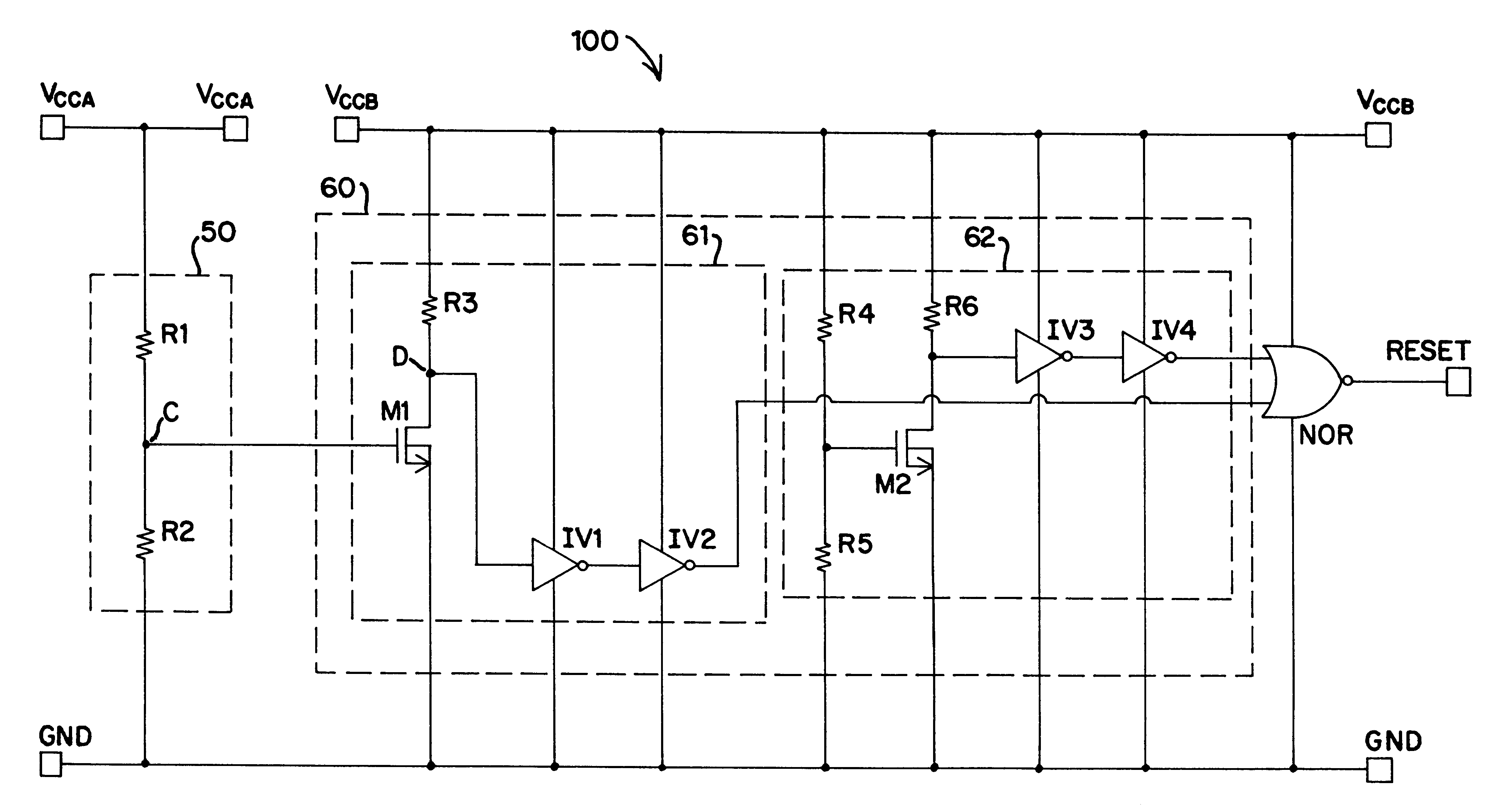

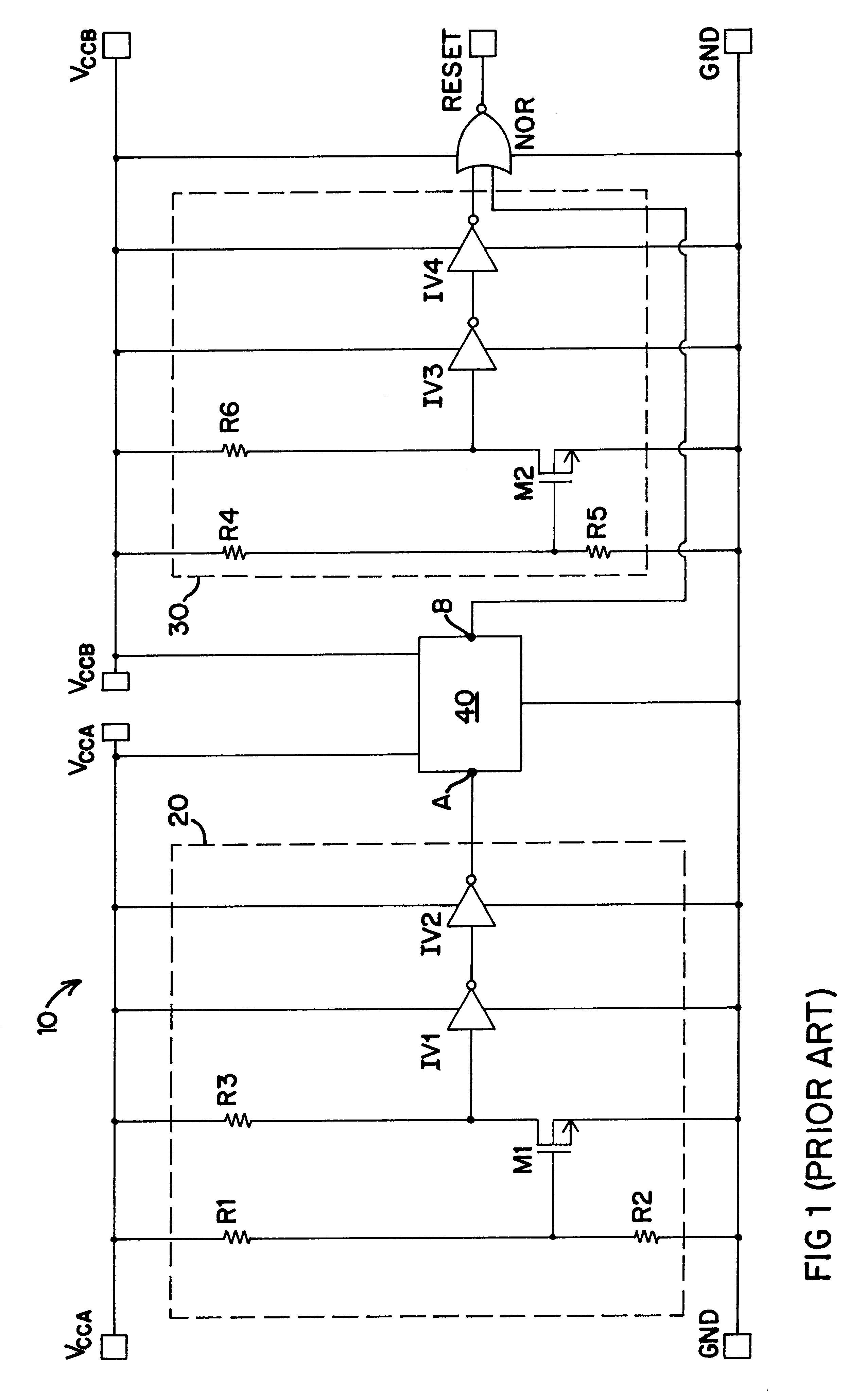

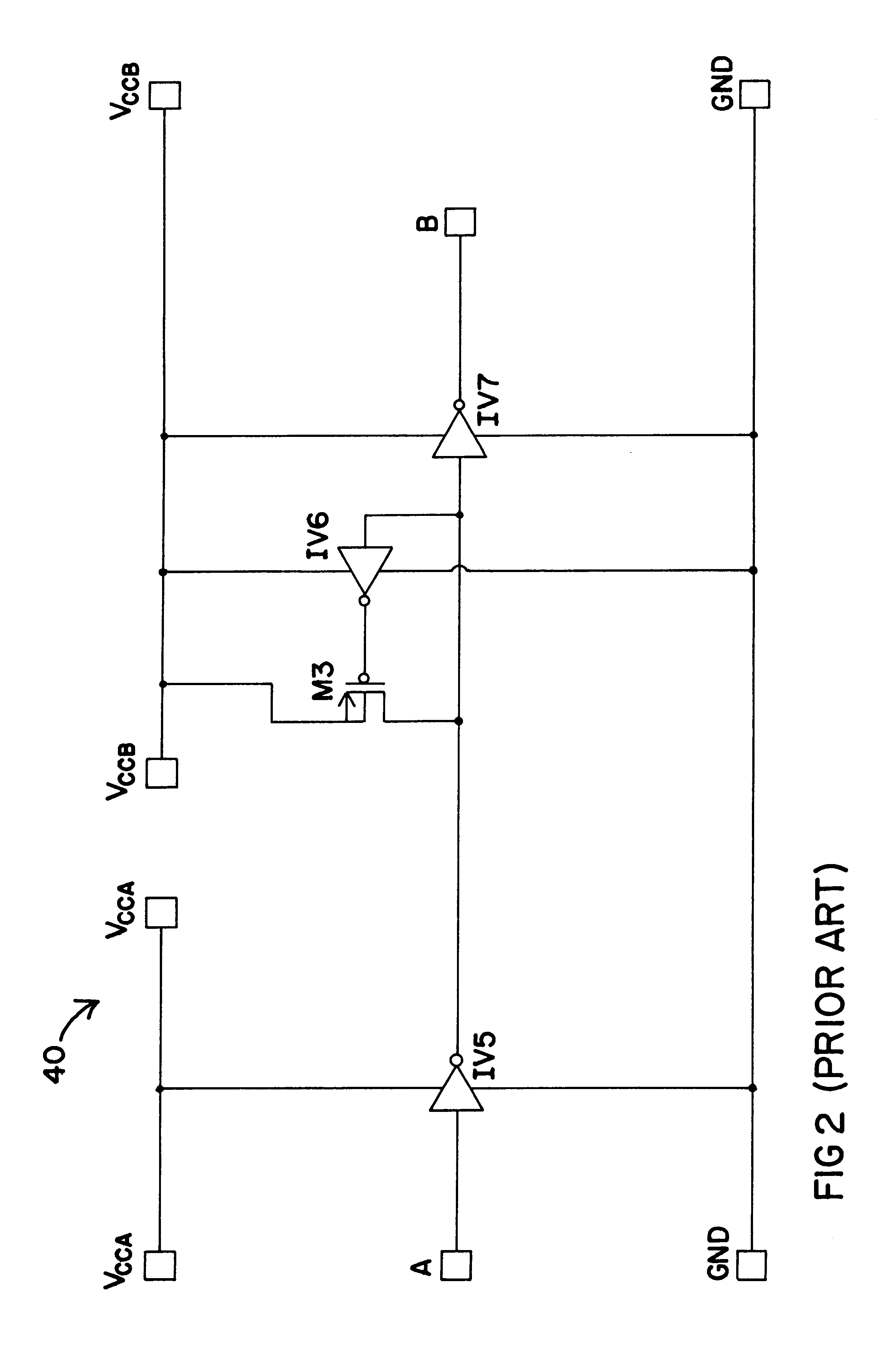

Power-on reset circuit for dual-supply system

A power-on reset circuit for a dual-supply system. The reset circuit includes a voltage divider powered by the first power supply and a sub-circuit supplied by the second power supply. The output of the voltage divider is connected to a control node of the first reset sub-circuit that is otherwise powered by the second power supply. A second reset sub-circuit is strictly regulated and powered by the second power supply. The first reset sub-circuit provides for translation of a signal having a potential limited by the potential of the first supply into a signal having a potential associated with that of the second supply. Only when a control signal from the voltage divider reaches a certain potential, and the second power supply reaches a certain potential, is the first reset sub-circuit activated in a manner that results in a circuit output signaling both supplies are at a suitable potential. This is useful for hot insertion applications in dual-supply systems.

Owner:SEMICON COMPONENTS IND LLC

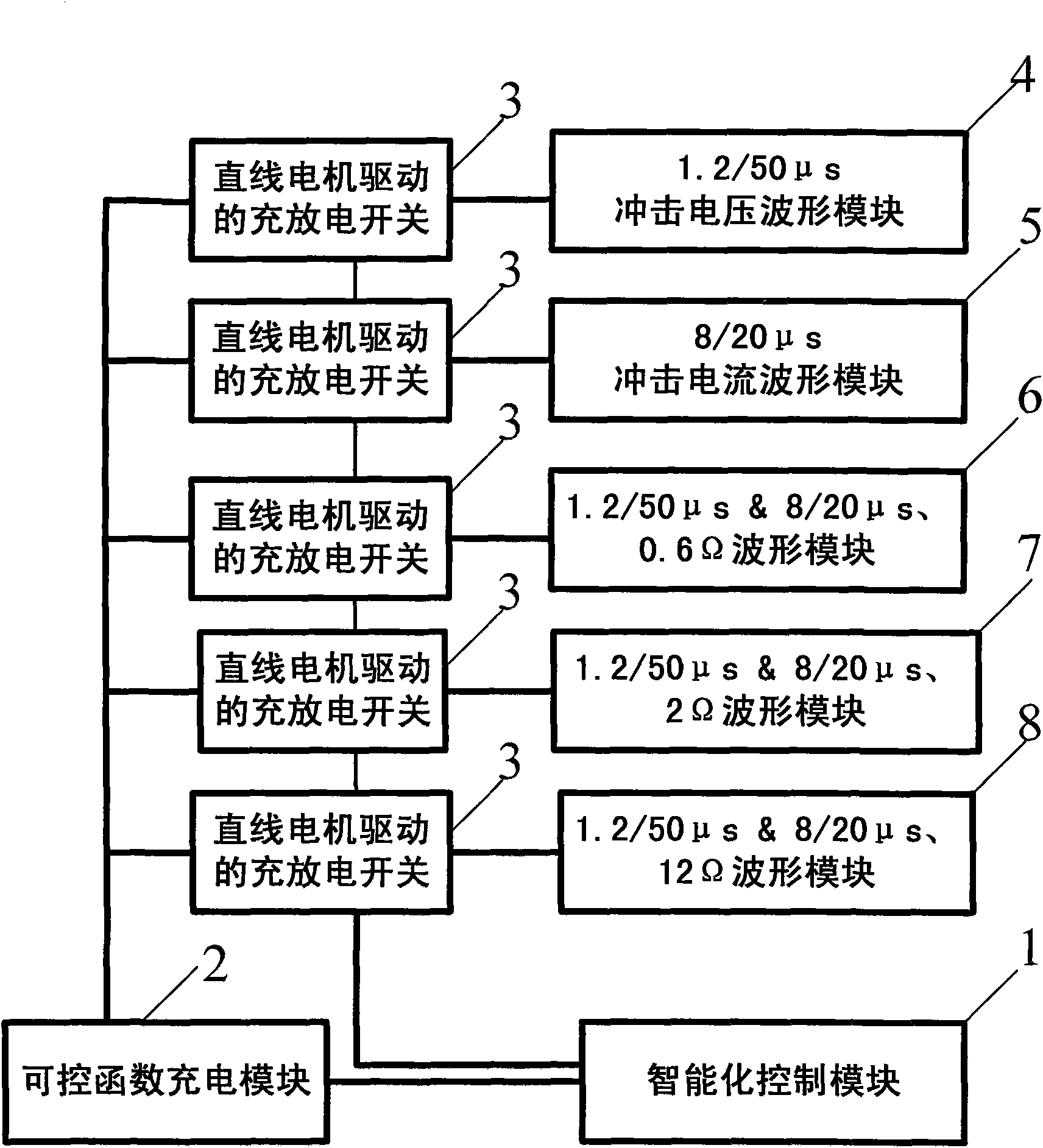

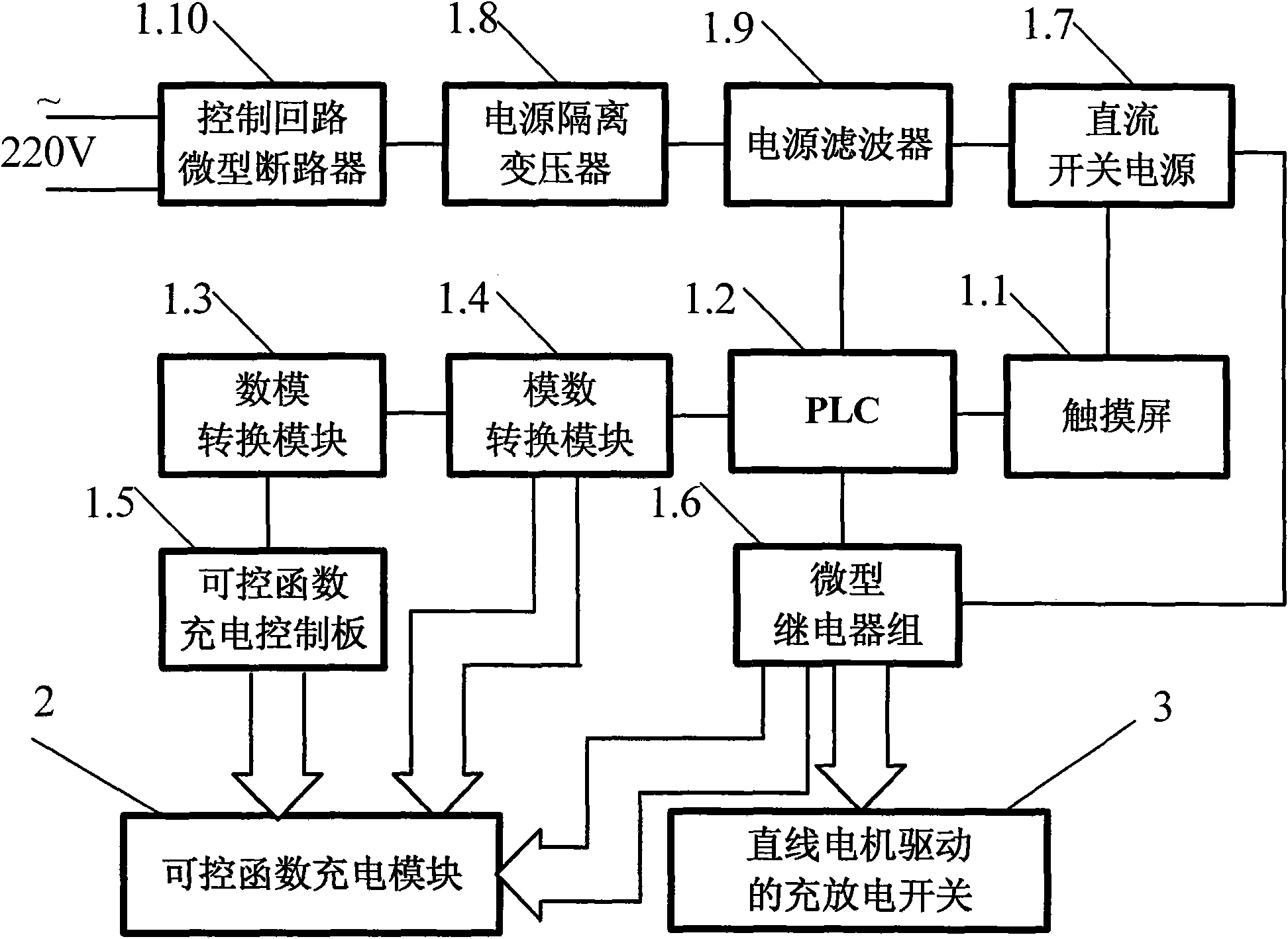

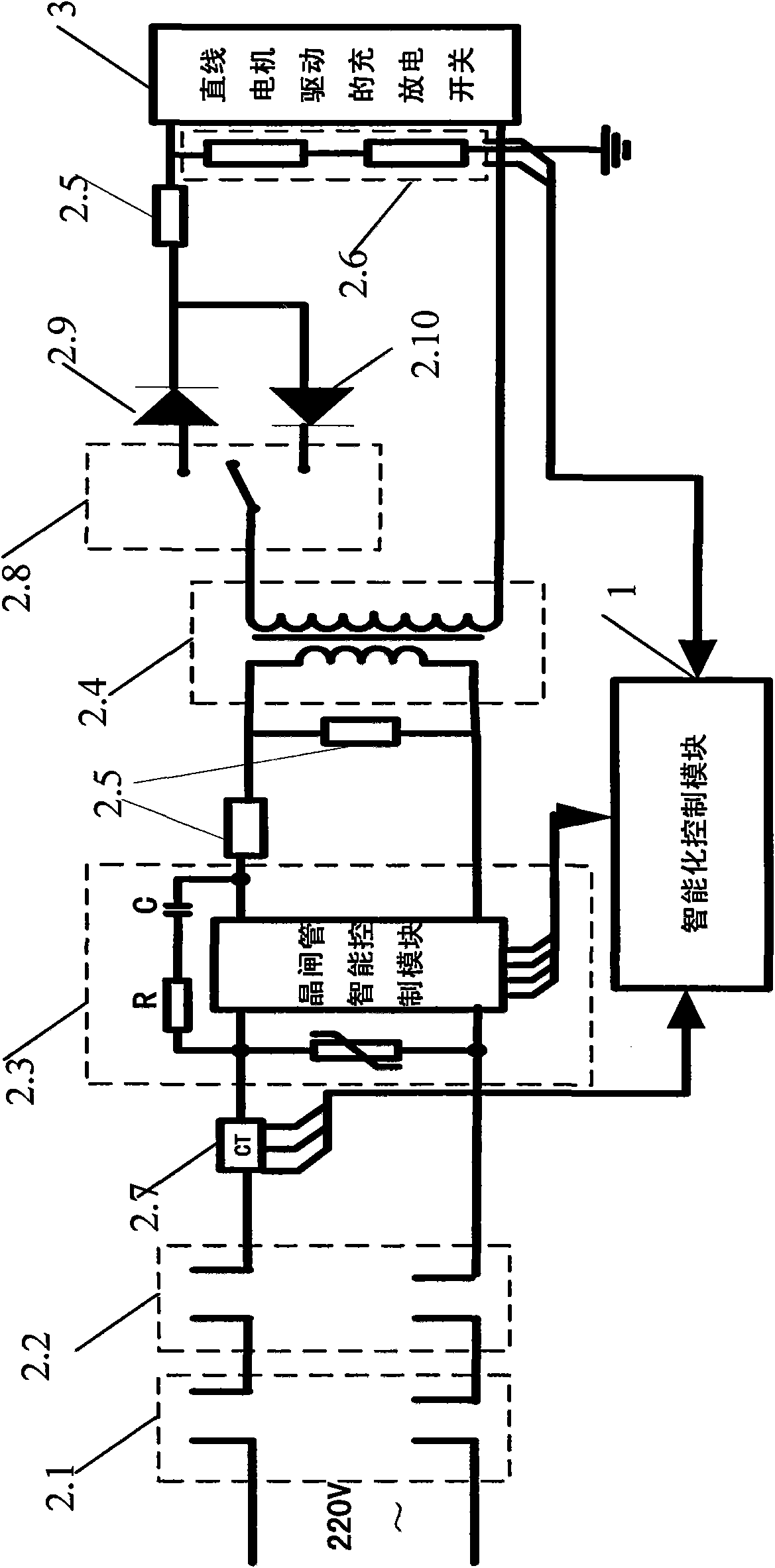

Modularized multiple wave forms impact generator test device

InactiveCN101629981AAccurate and safe charging and dischargingSimple structureElectrical testingElectric pulse generator circuitsElectricityWave form

The invention relates to the technical field of the conversion of power input into surge power output, in particular to a modularized multiple wave forms impact generator test device, comprising a plurality of wave form modules, a plurality of charge and discharge switches driven by linear motors, a controllable function charging module and an intelligent control module, wherein, a plurality of wave form modules are used for generating a plurality of impact wave forms; the multiple charge and discharge switches driven by linear motors are connected with a plurality of wave form modules in one-to-one correspondence manner; the controllable function charging module is electrically connected with each charge and discharge switch driven by linear motors; the intelligent control module is electrically connected with each charge and discharge switch driven by linear motors; the intelligent control module is simultaneously electrically connected with the controllable function charging module and controls the controllable function charging module to charge the specified wave form modules according to the setting charging function. The invention has high degree of automation and strong flexibility of the design of modularized circuit, thus providing a good test device for thunder surging tests, electromagnetic immunity tests and quality control.

Owner:WUHAN UNIV