Patents

Literature

3802results about "Angle demodulation by phase difference detection" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

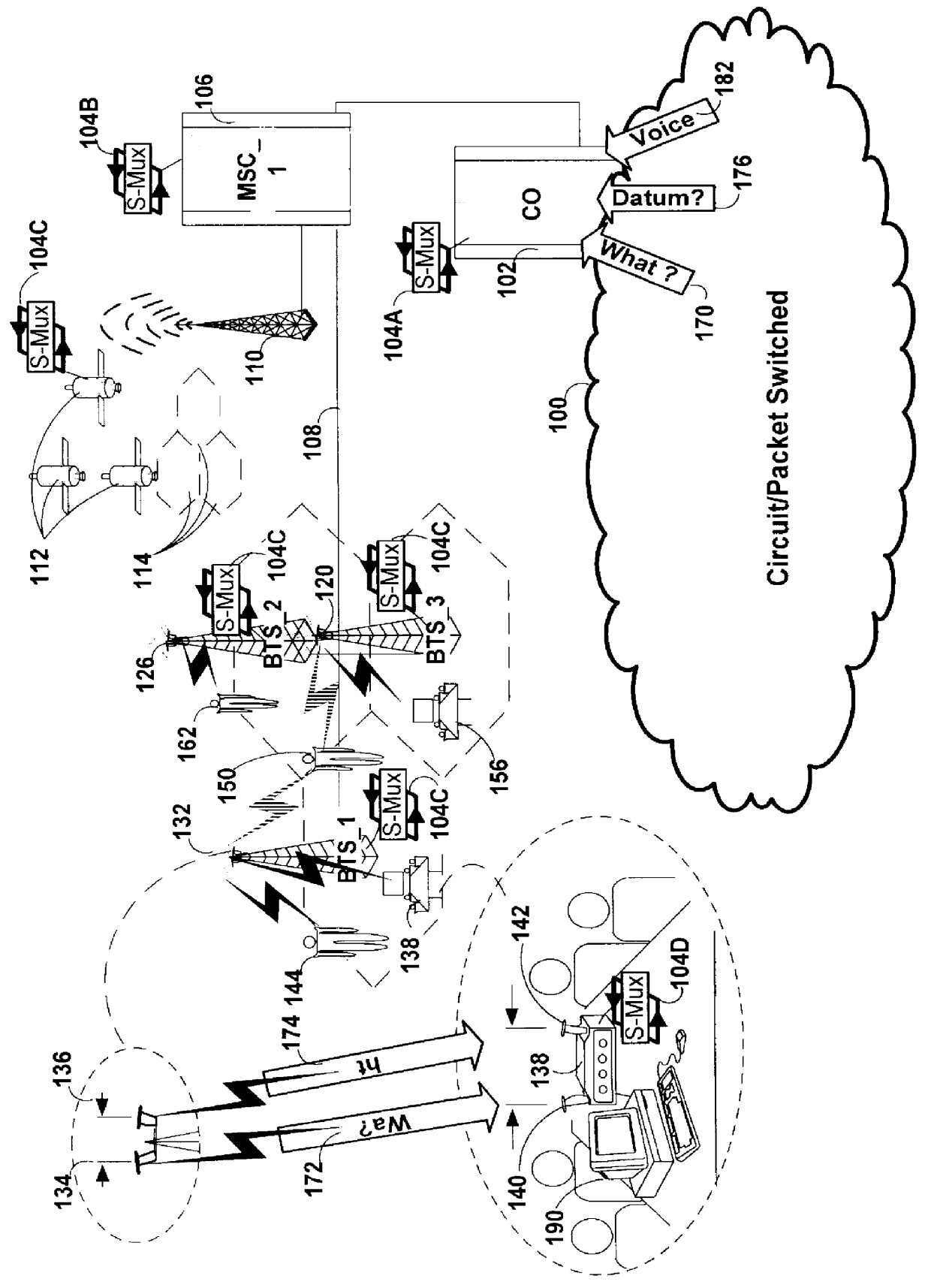

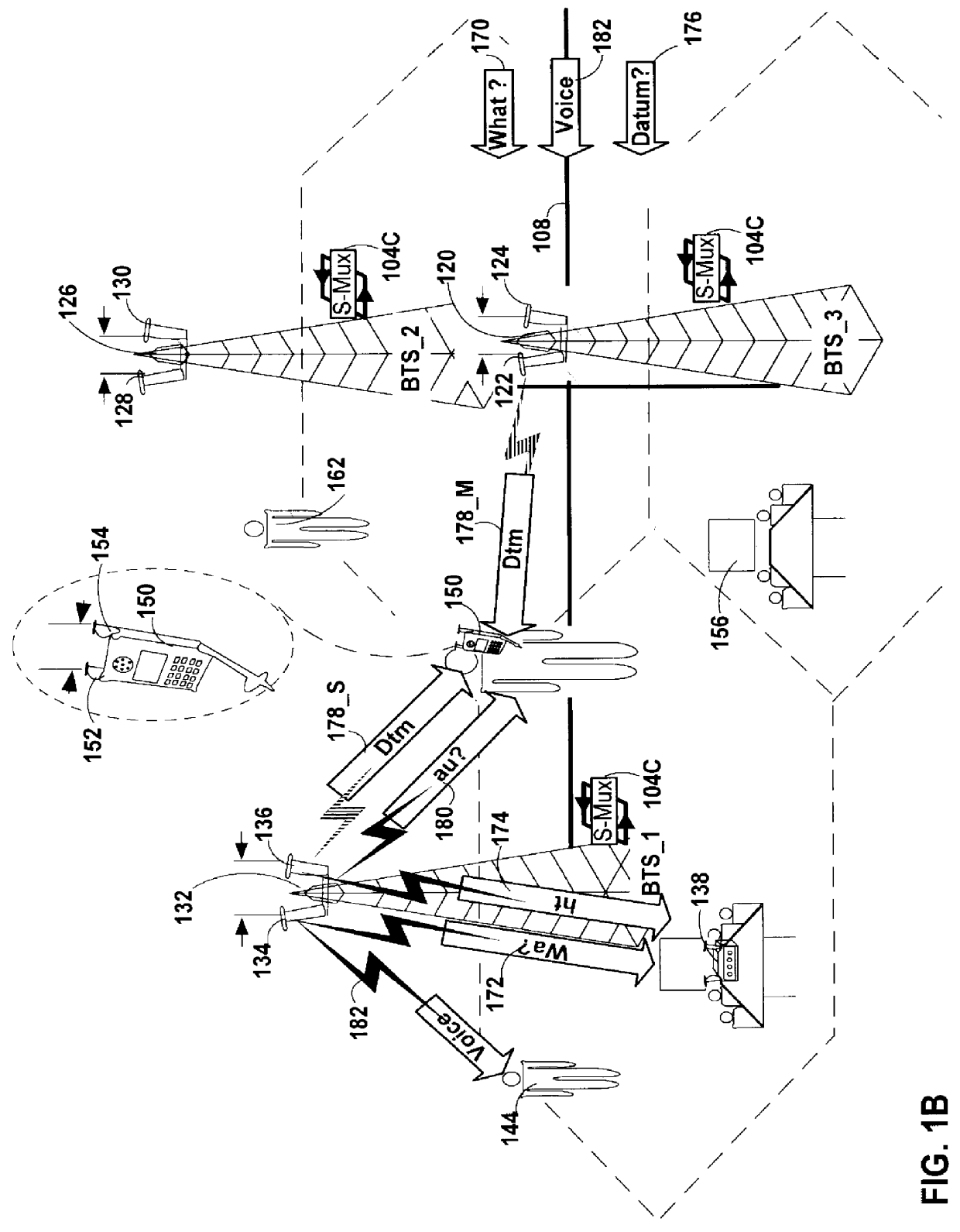

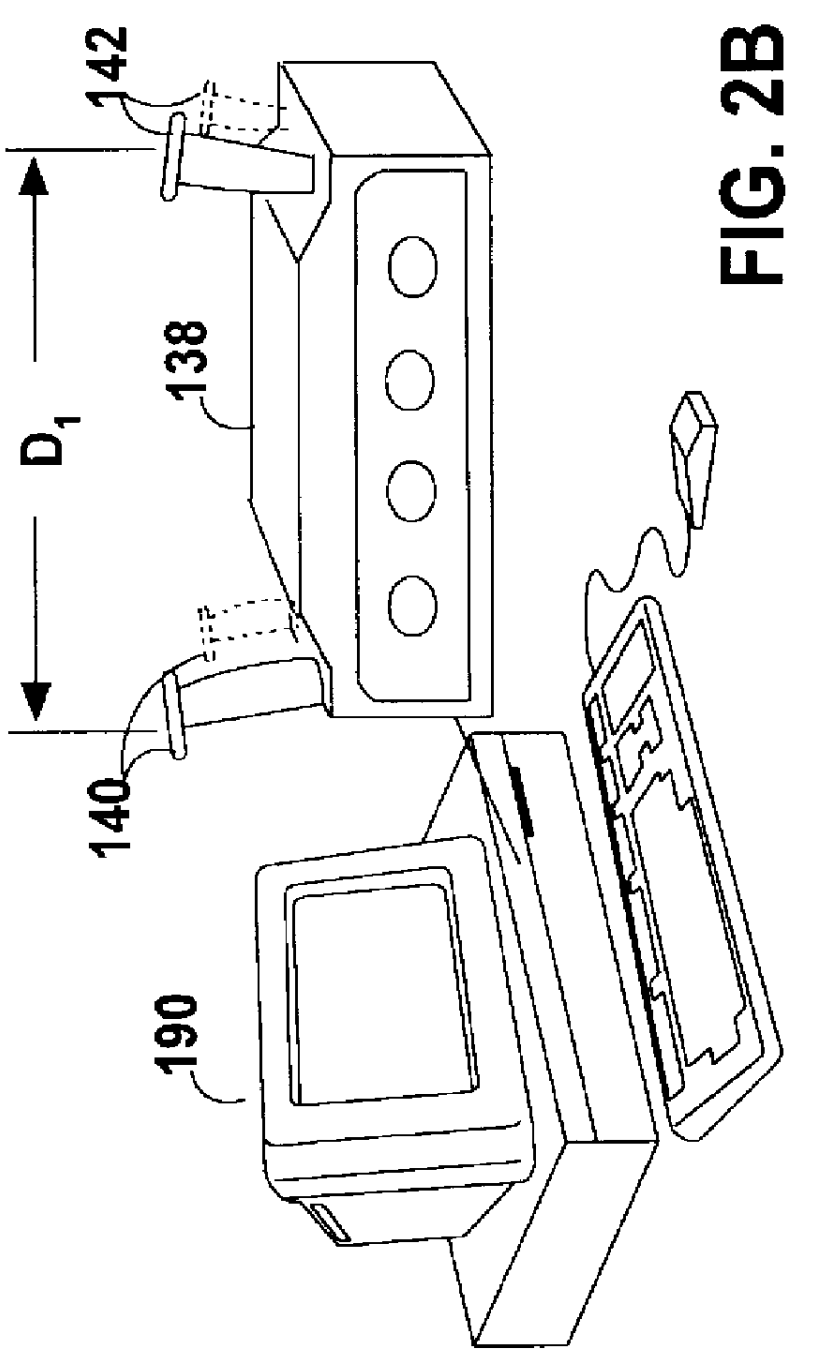

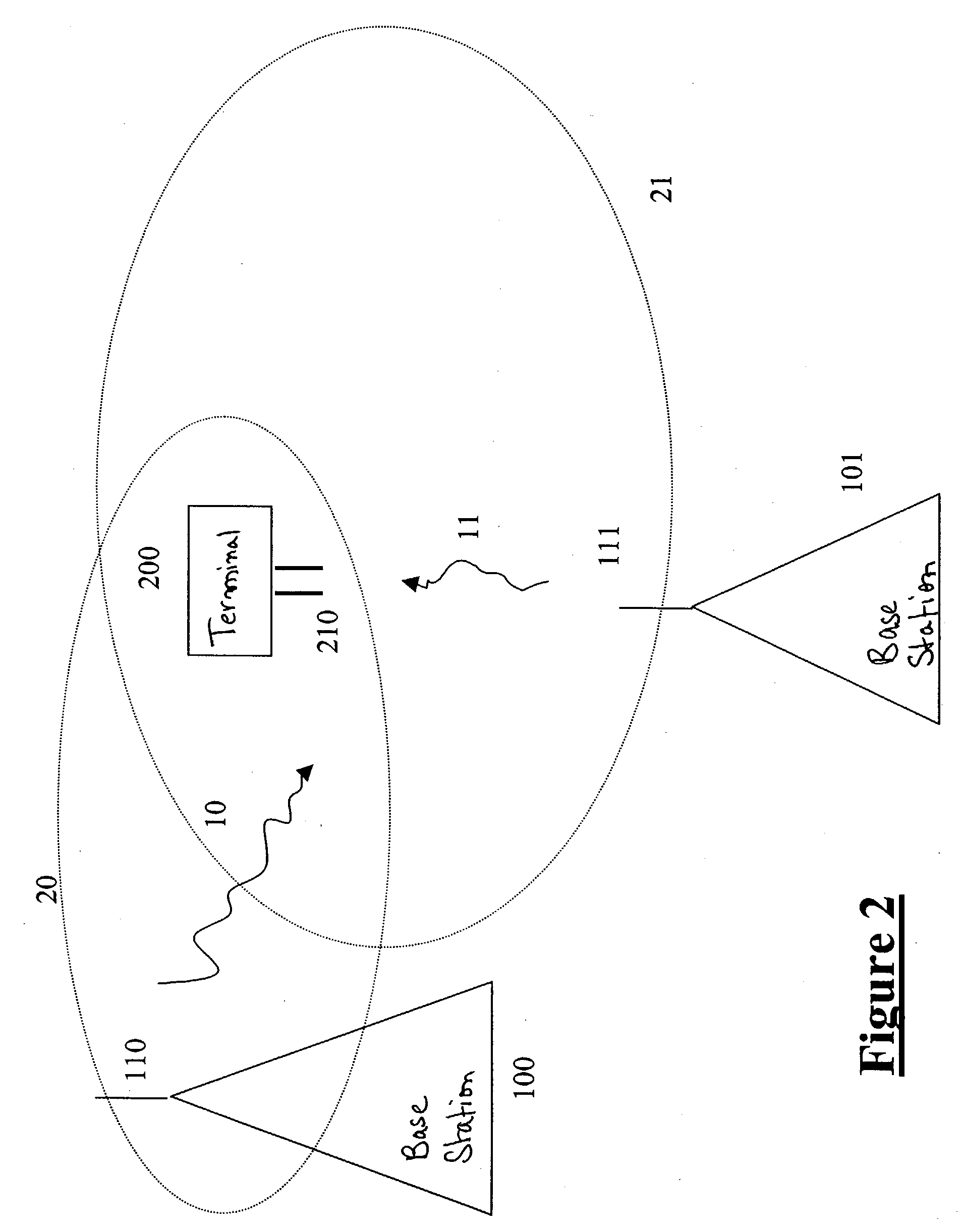

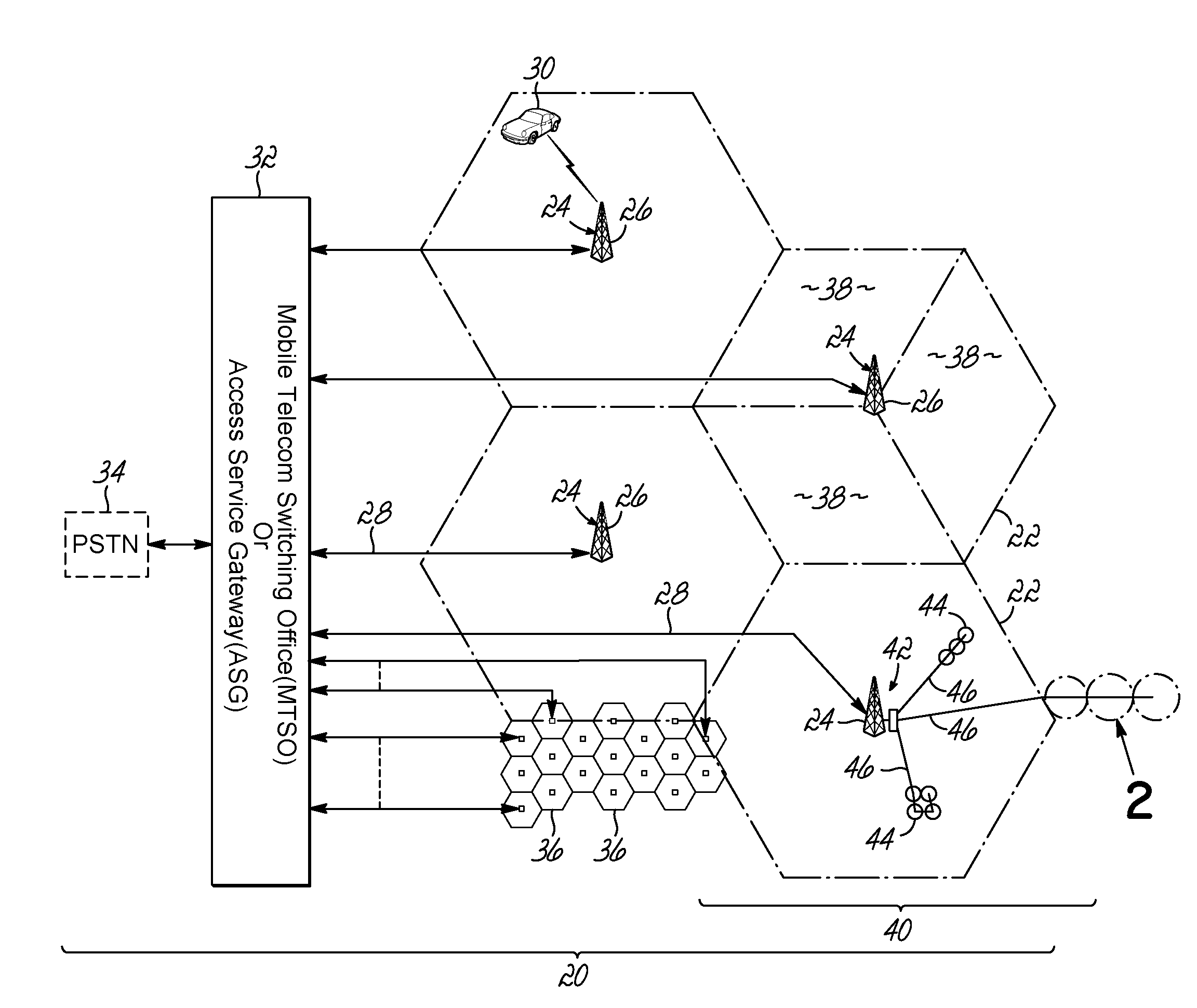

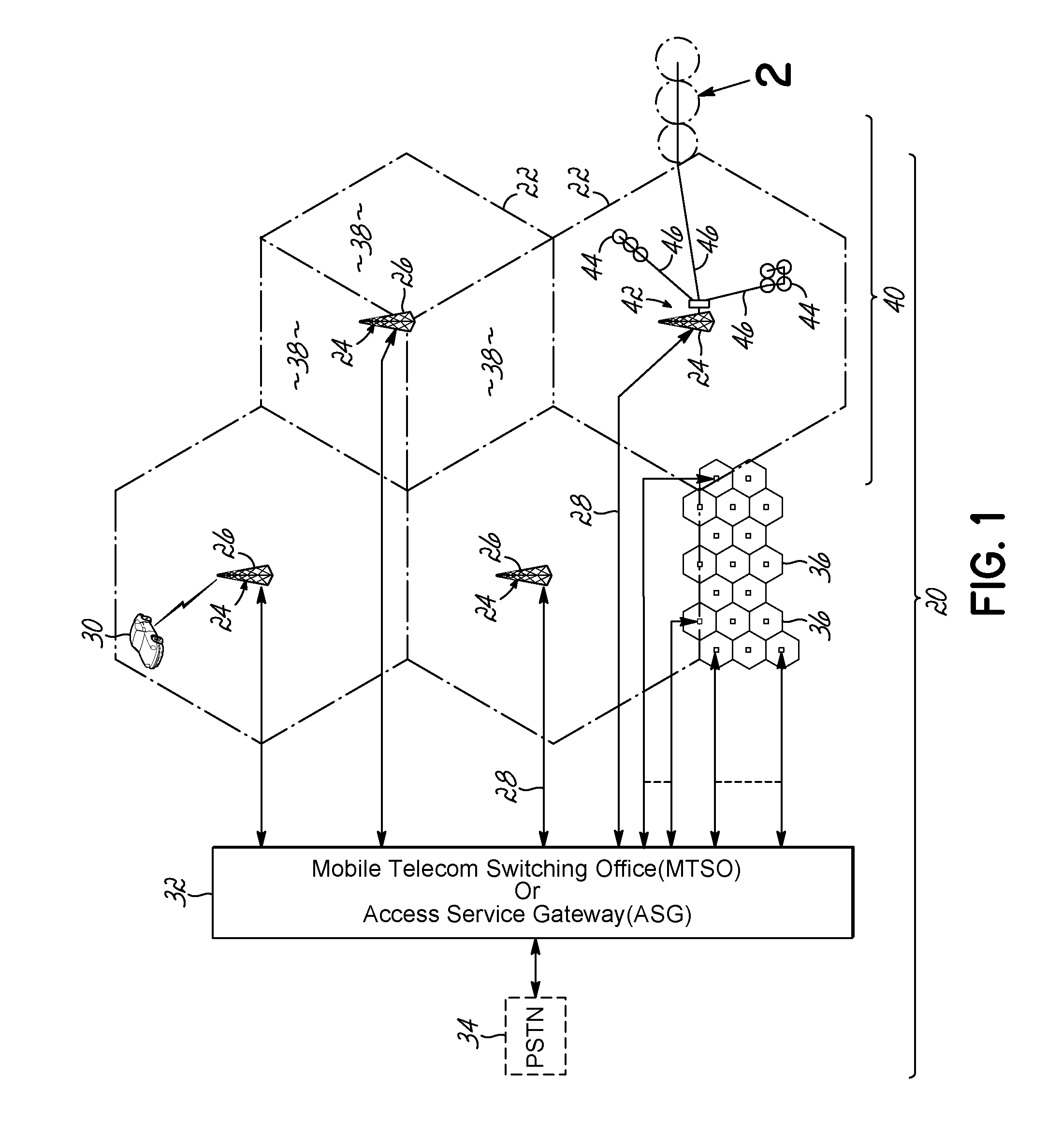

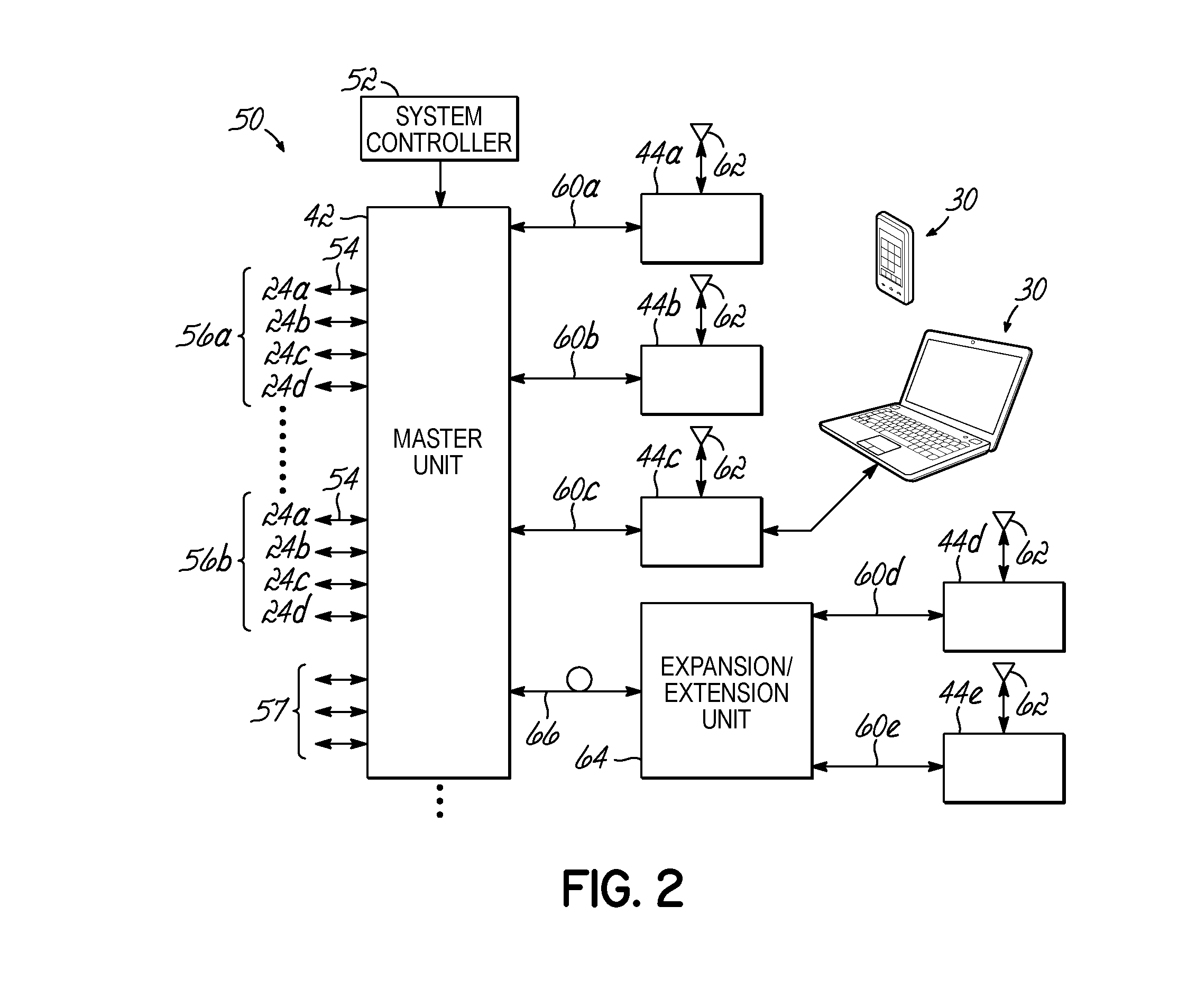

Spatial multiplexing in a cellular network

InactiveUS6067290ASpatial transmit diversityNetwork traffic/resource managementData streamControl signal

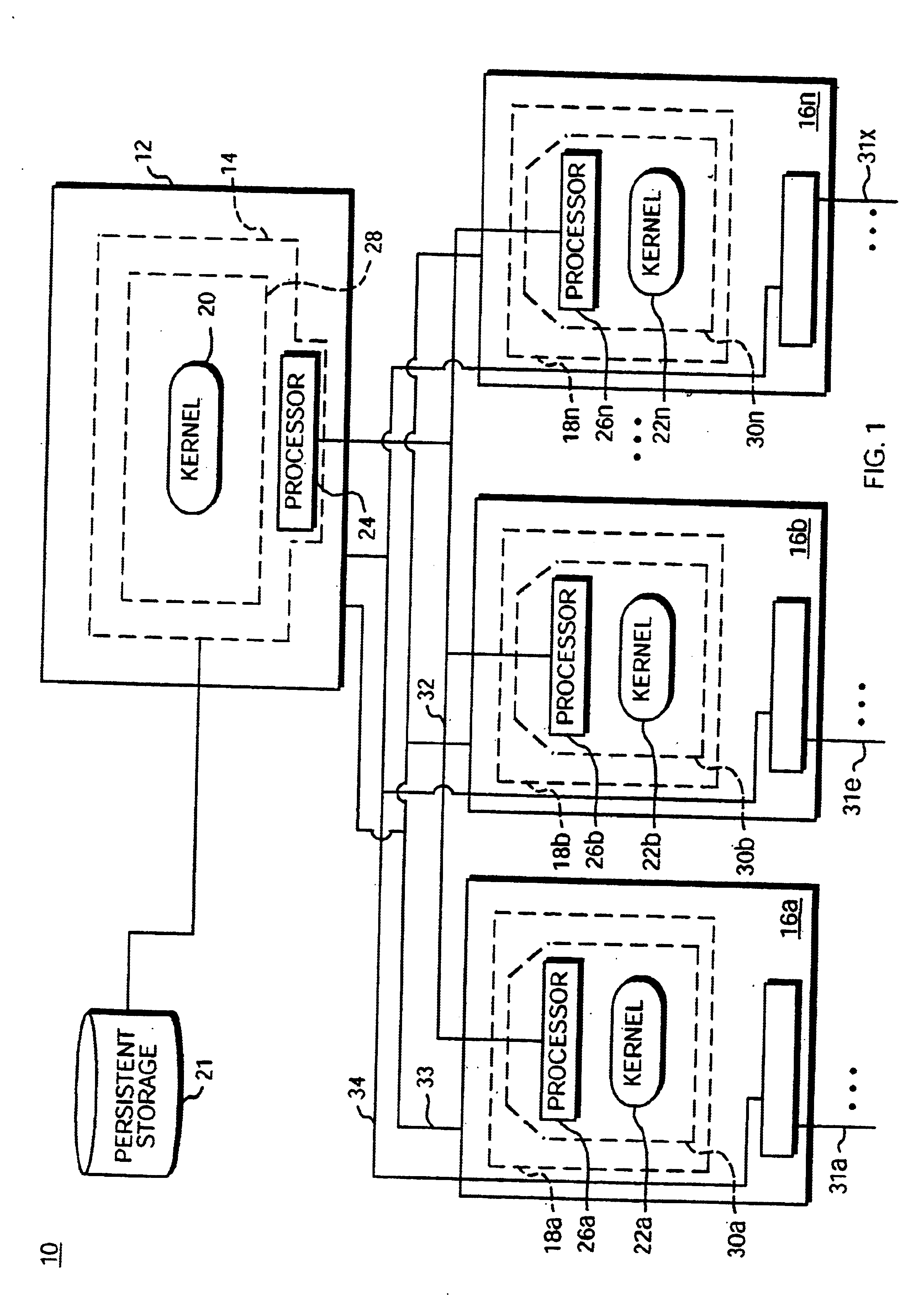

The present invention provides methods and apparatus for implementing spatial multiplexing in conjunction with the one or more multiple access protocols during the broadcast of information in a wireless network. A wireless cellular network for transmitting subscriber datastream(s) to corresponding ones among a plurality of subscriber units located within the cellular network is disclosed. The wireless cellular network includes base stations and a logic. The base stations each include spatially separate transmitters for transmitting, in response to control signals, selected substreams of each subscriber datastream on an assigned channel of a multiple access protocol. The logic communicates with each of the base stations. The logic assigns an available channel on which to transmit each subscriber datastream. The logic routes at least a substream of each datastream to at least a selected one of the base stations. The logic also generates control signals to configure the at least a selected one of the base stations to transmit the selected substreams to a corresponding one among the plurality of subscriber units on the assigned channel. A subscriber unit for use in a cellular system is also disclosed. The subscriber unit includes: spatially separate receivers, a spatial processor, and a combiner. The spatially separate receivers receive the assigned channel composite signals resulting from the spatially separate transmission of the subscriber downlink datastream(s). The spatial processor is configurable in response to a control signal transmitted by the base station to separate the composite signals into estimated substreams based on information obtained during the transmission of known data patterns from at least one of the base stations. The spatial processor signals the base stations when a change of a spatial transmission configuration is required. The combiner combines the estimated substreams into a corresponding subscriber datastream.

Owner:INTEL CORP

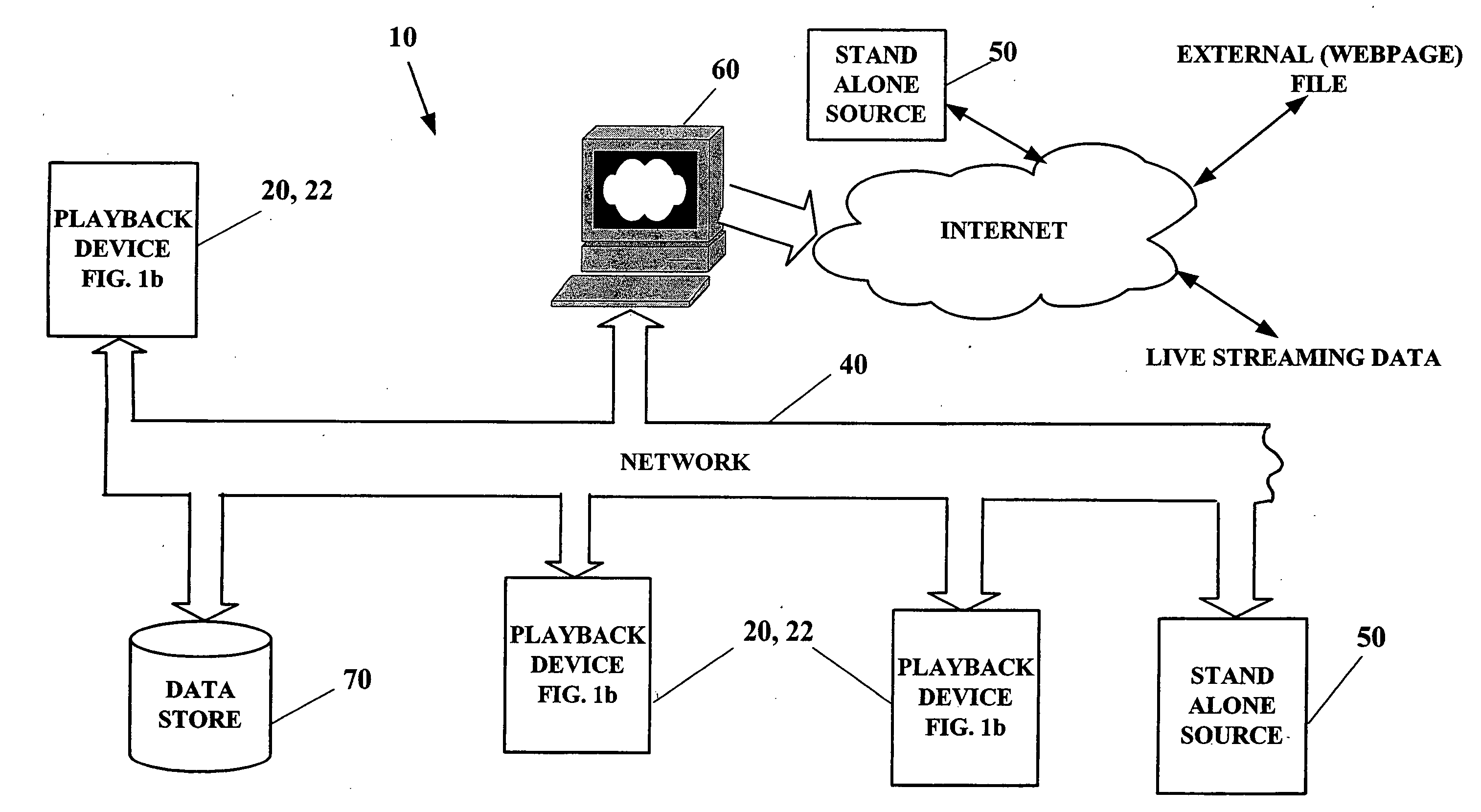

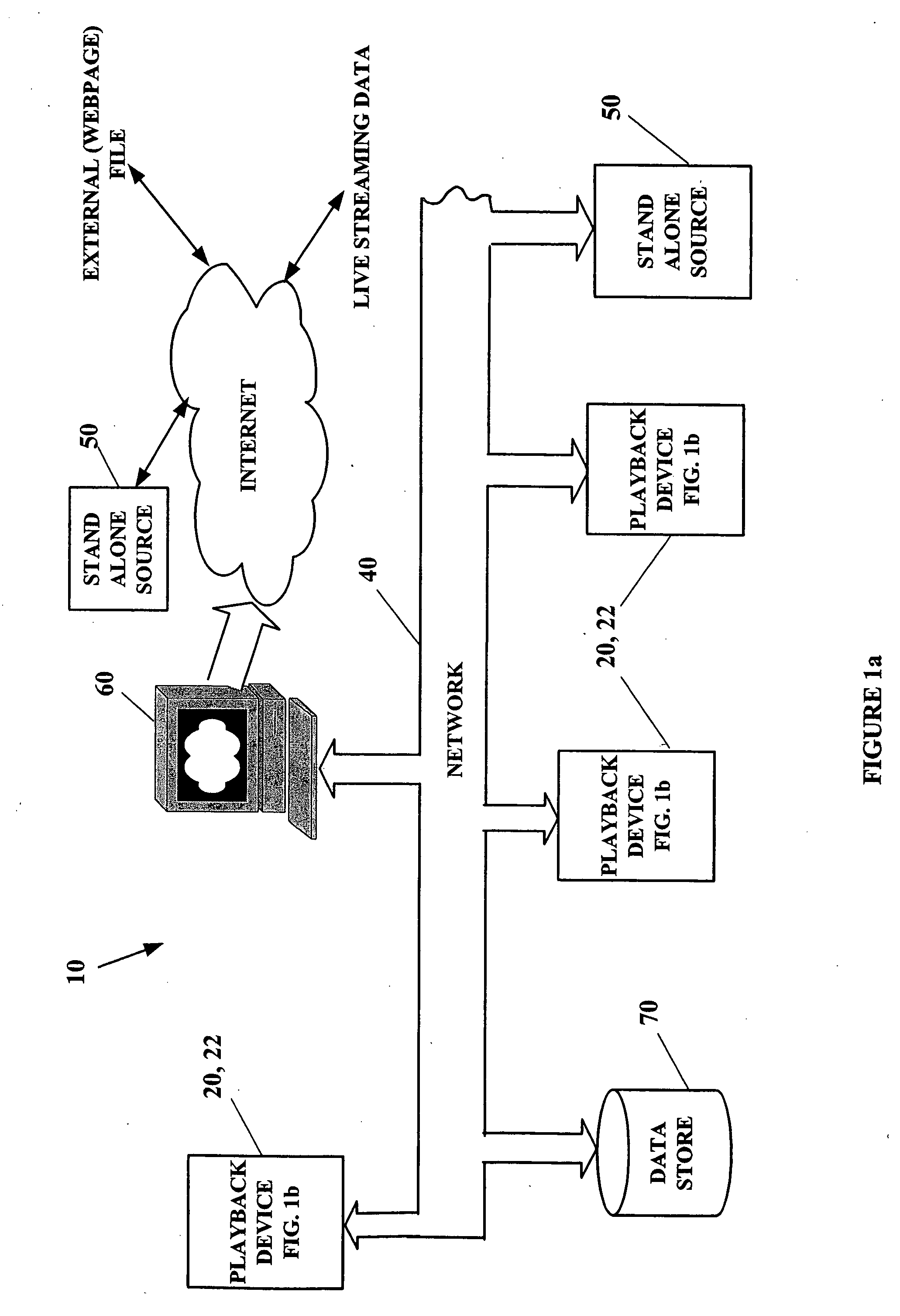

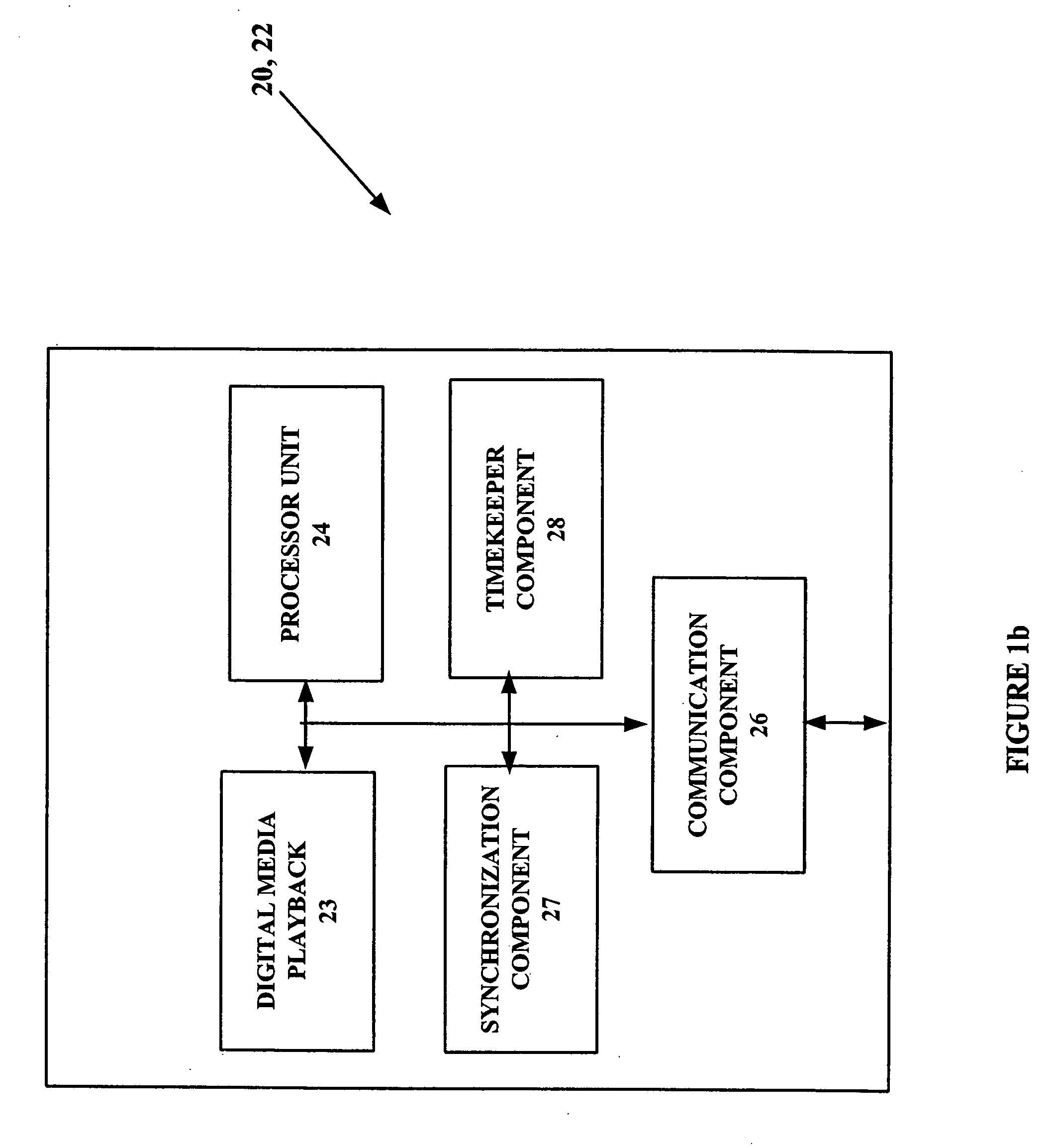

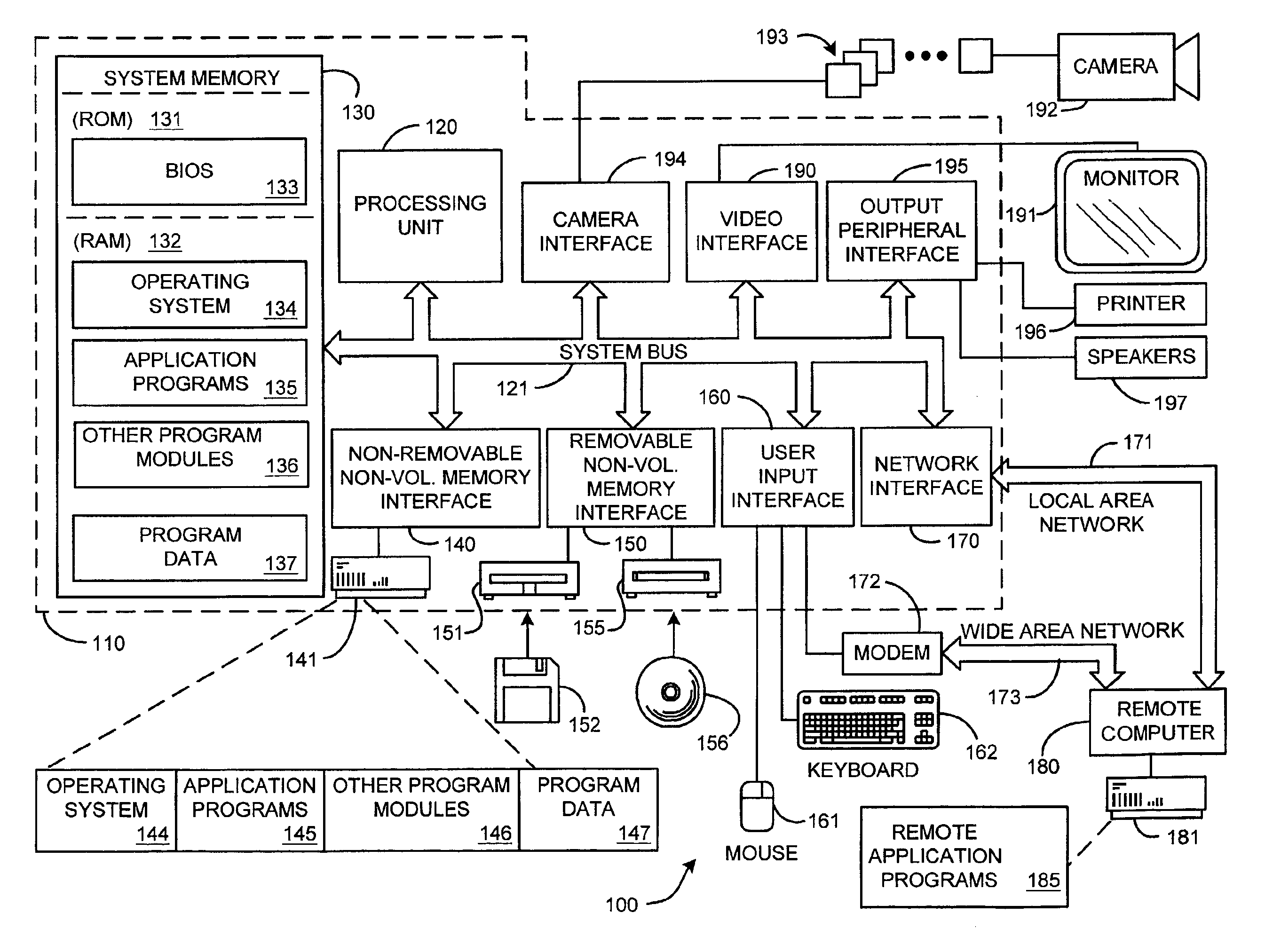

Method and system for synchronization of digital media playback

A system and method for synchronizing digital media playback at multiple digital media playback devices interconnected on a network is provided. A digital media playback device comprising a processor, a synchronization component, a timekeeper component and a digital media source performs synchronization processes to arrange for other players to begin playback at a predetermined position and time in the digital media signal. Synchronization is accomplished by processes which approximate the arrival time of a packet containing audio and / or video digital content across the network and instruct the playback devices as to when playback is to begin, and at what point in the streaming media content signal to begin playback. One method uses a time-stamp packet on the network to synchronize all players. Other methods utilize reiterative processes to narrow approximations of packet arrival time at each playback device.

Owner:ARLO TECH INC

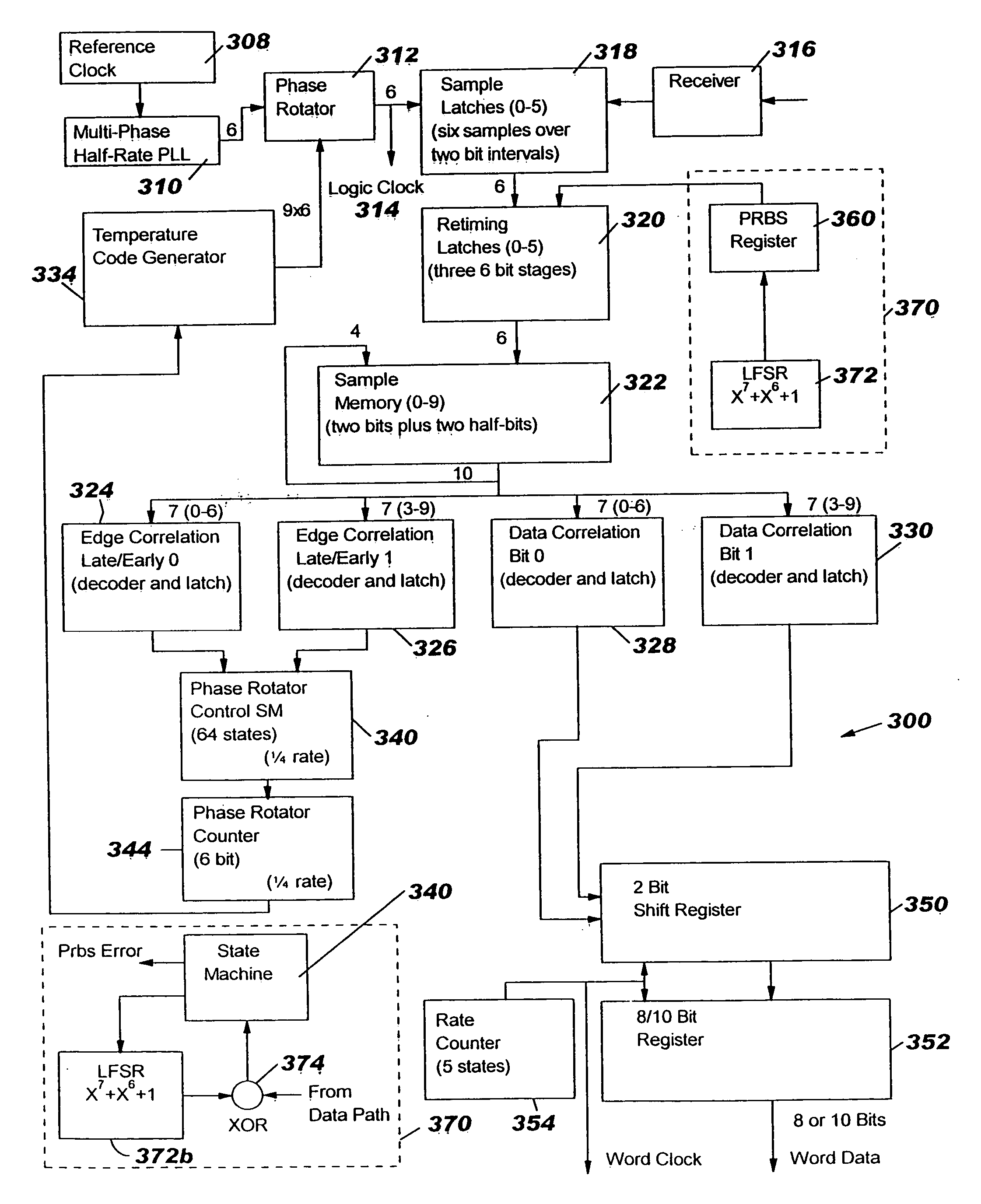

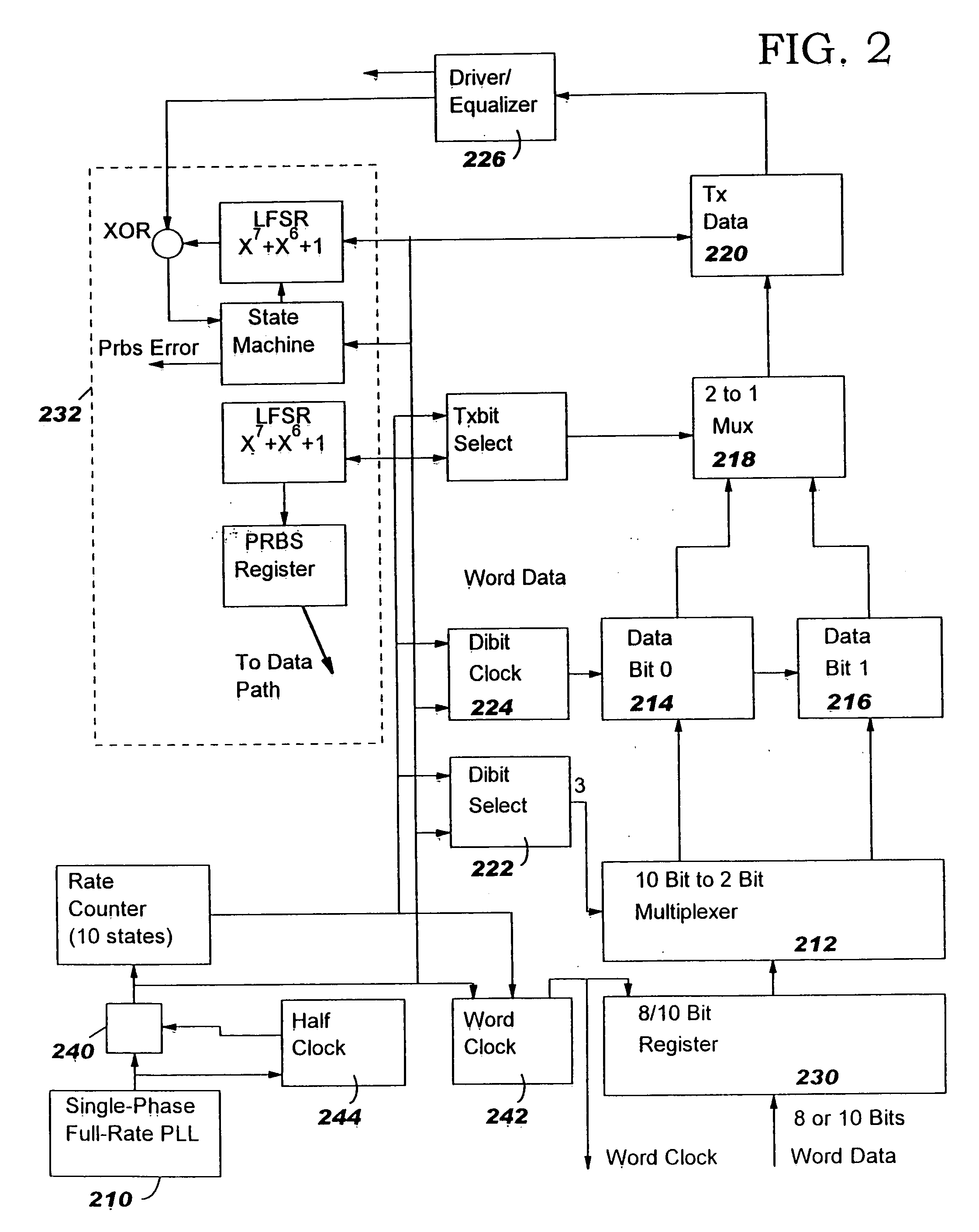

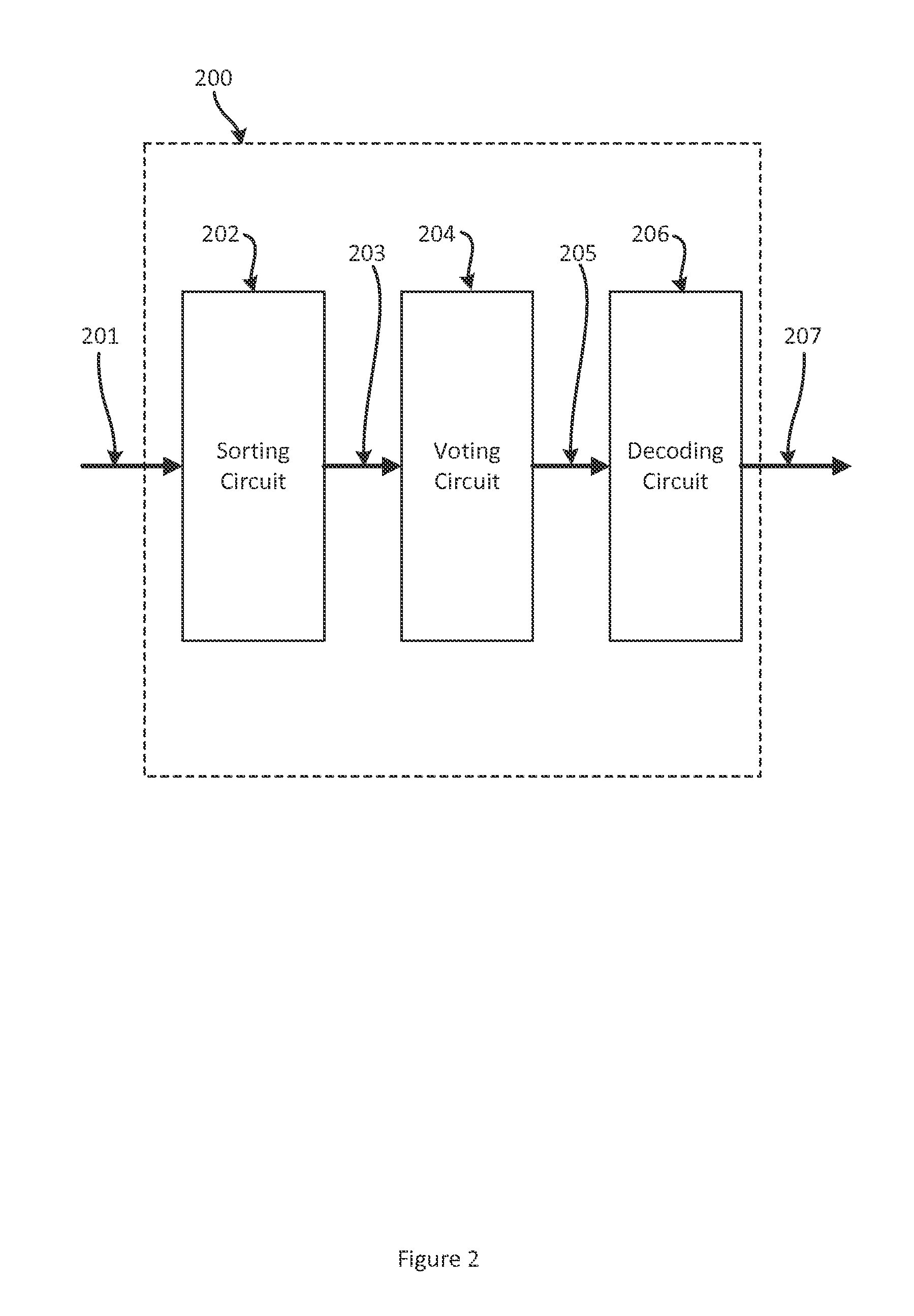

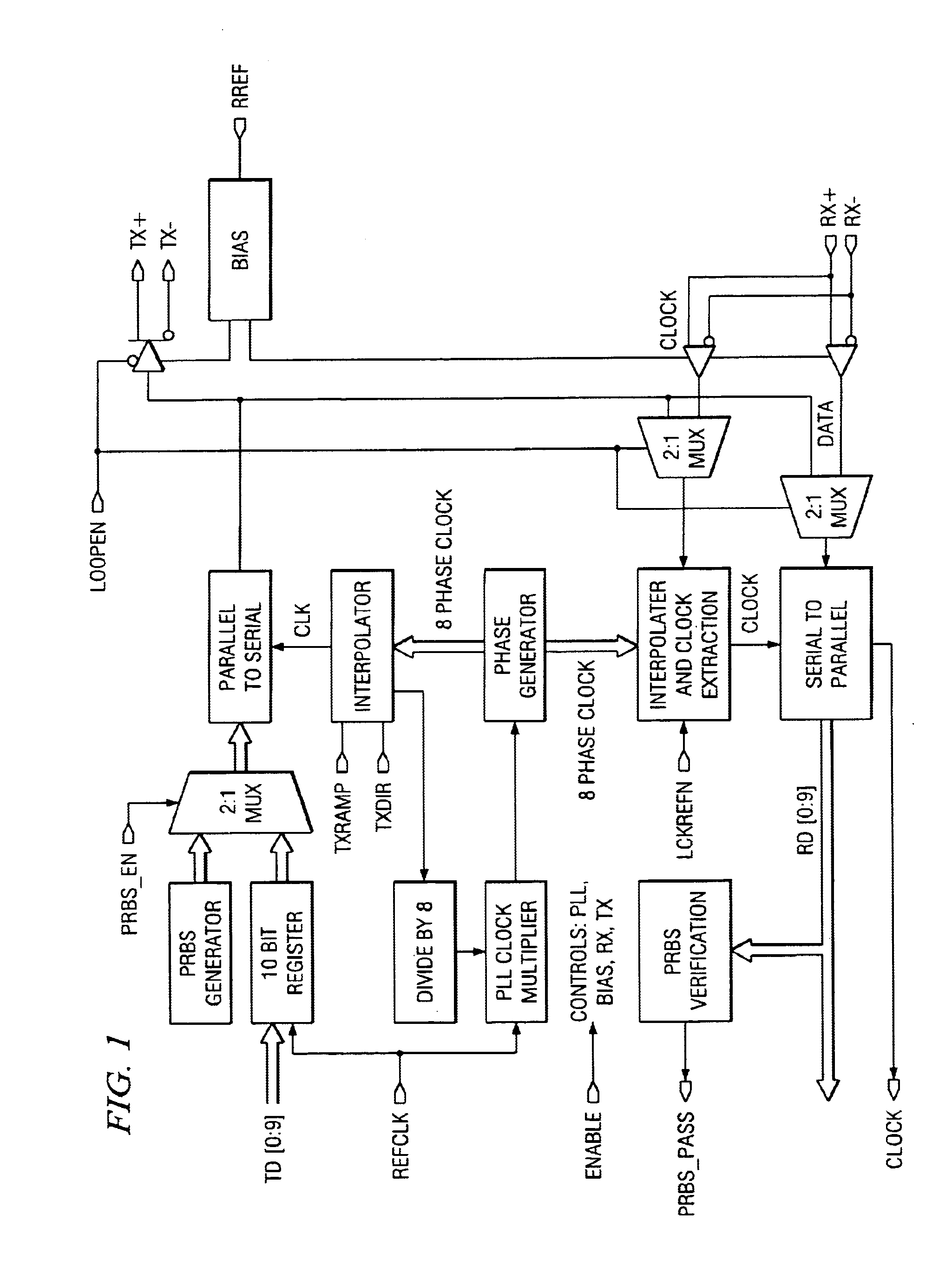

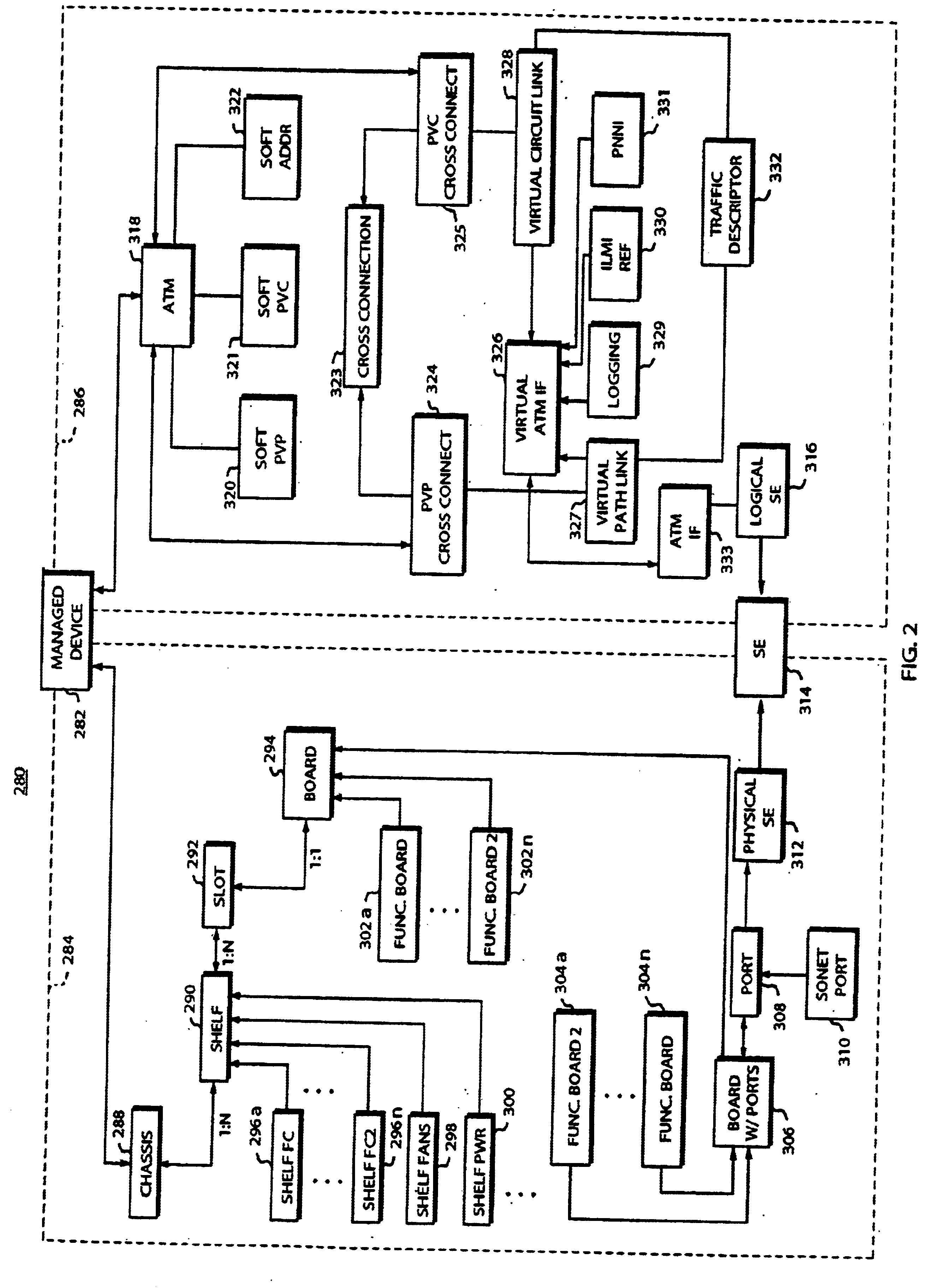

Unified digital architecture

InactiveUS20060029177A1Pulse automatic controlModulated-carrier systemsFinite impulse responseComputer science

A unified, unidirectional serial link is described for providing data across wired media, such as a chip-to chip or a card-to-card interconnect. It consists of a transmit section and a receive section that are operated as pairs to allow the serial data communication. The serial link is implemented as part of a VLSI ASIC module and derives its power, data and clocking requirements from the host modules. The logic transmitter portion contains a phase locked loop (PLL), a dibit data register, a finite impulse response (FIR) filter and a transmit data register. The phase locked loop comprises both a digital coarse loop and an analog fine loop. The digital receiver portion contains a PLL, an FIR phase rotator, a phase rotator control state machine, and a clock buffer. The transmitter and the receiver each preferably utilize a pseudo-random bit stream (PRBS) generator and checker.

Owner:IBM CORP

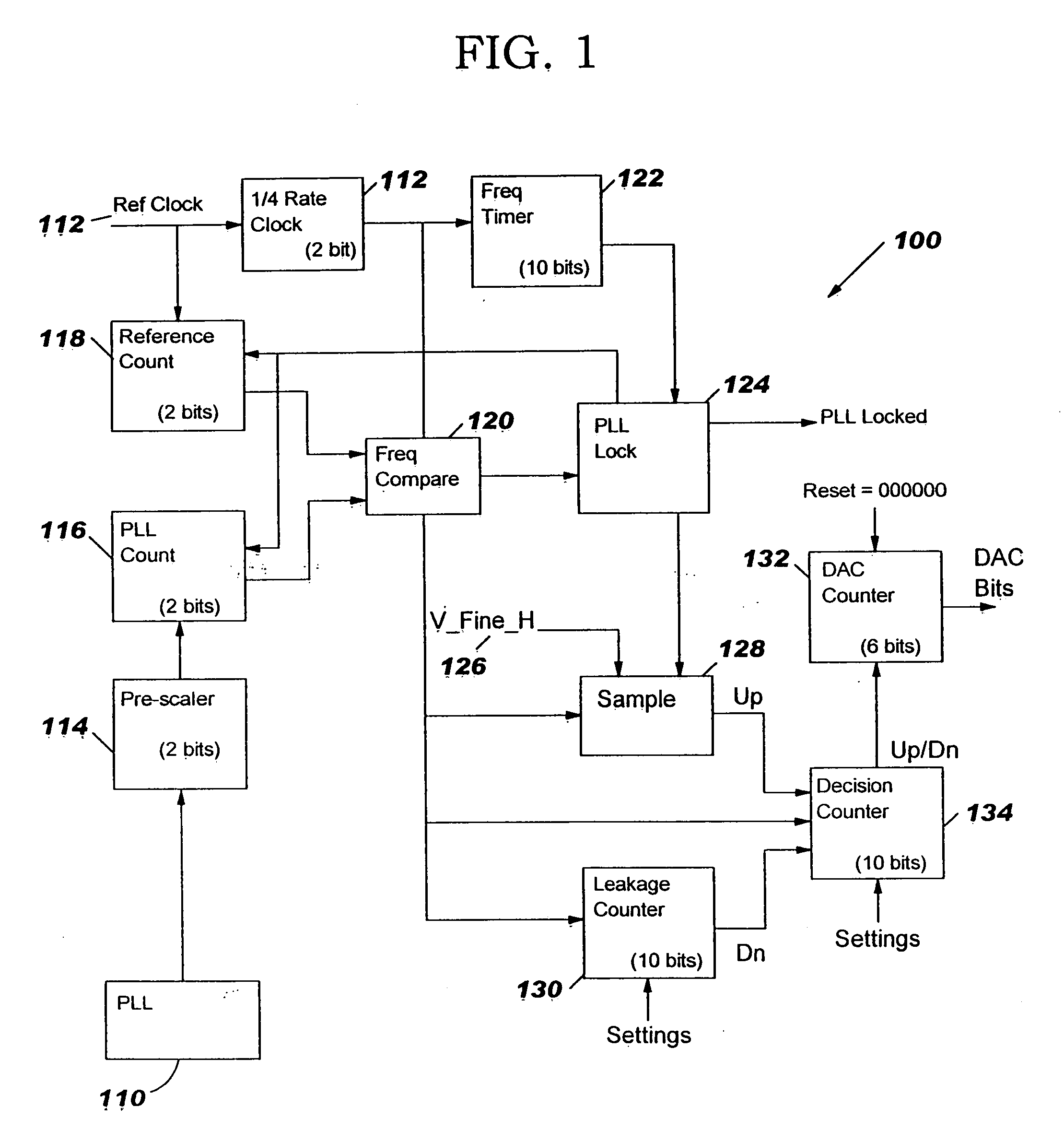

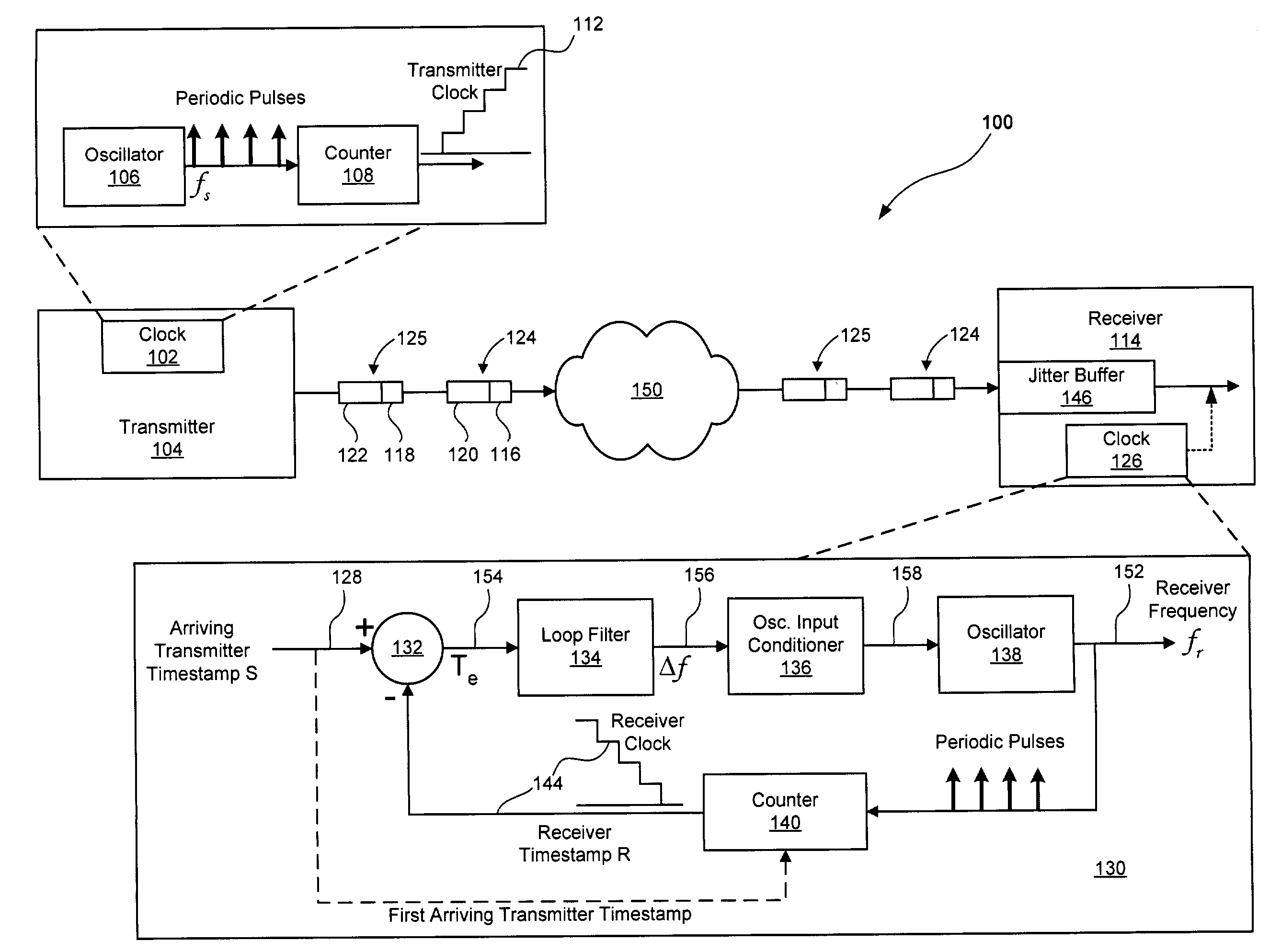

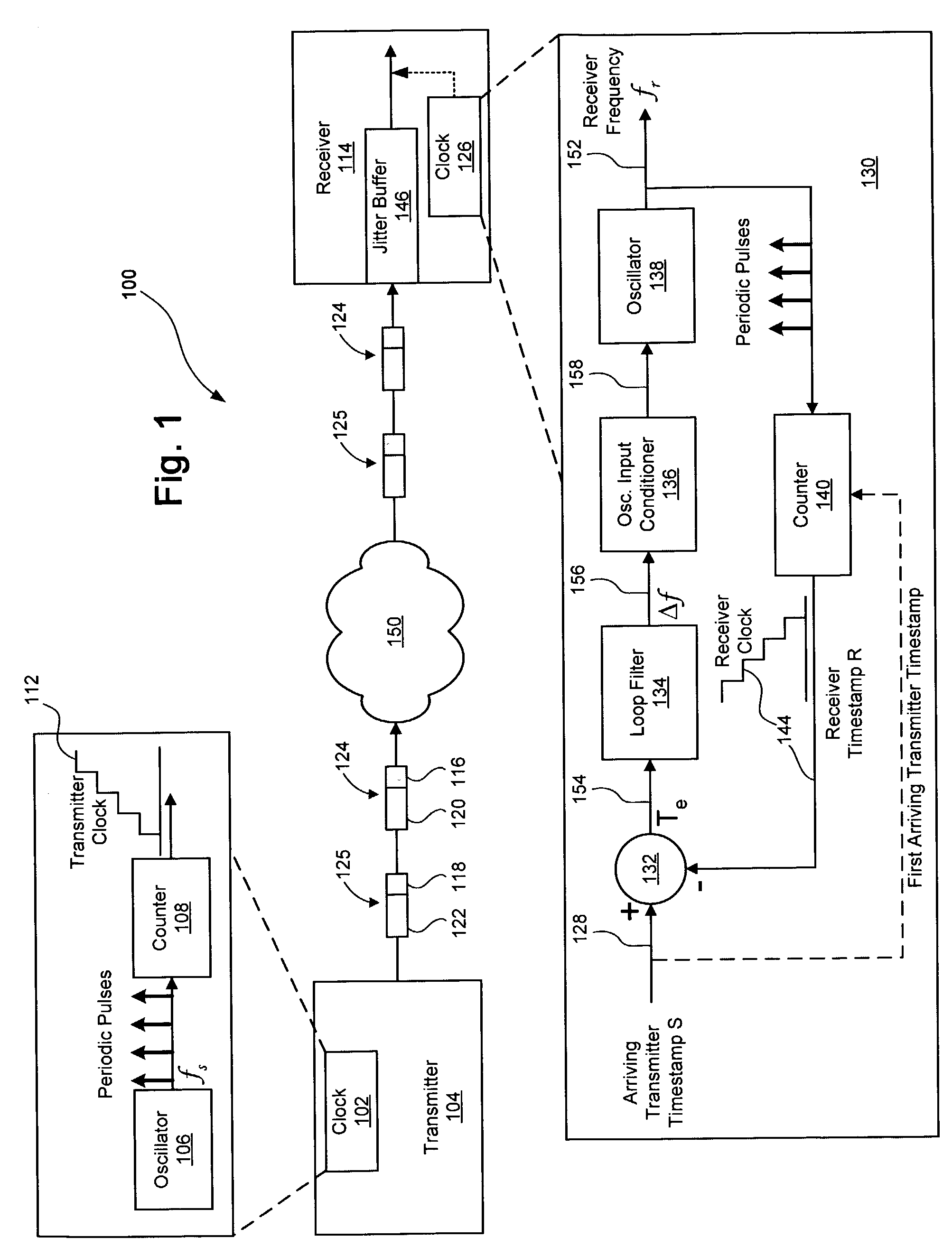

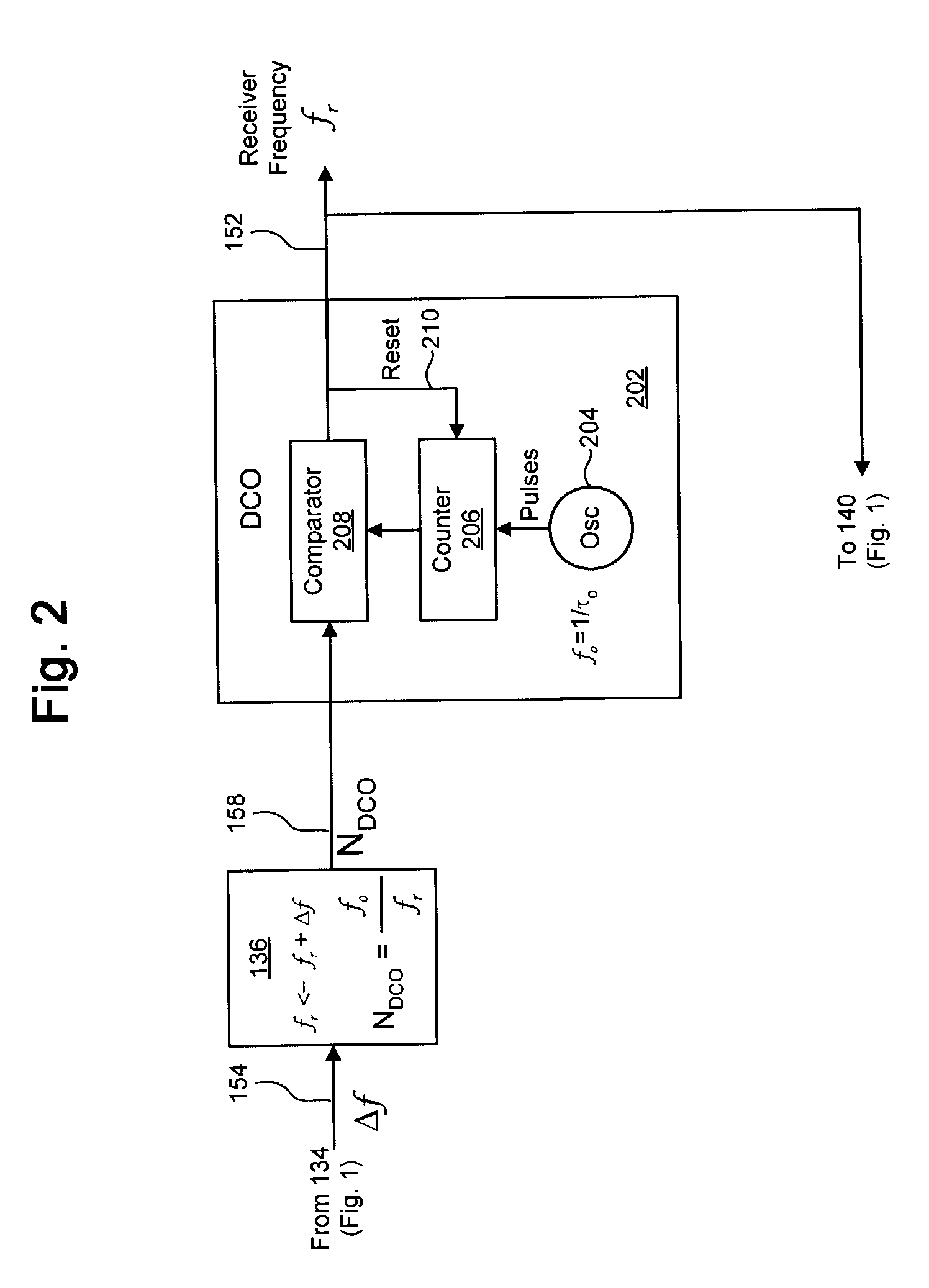

Clock recovery using a direct smoothing process

ActiveUS7130368B1Guaranteed maximum utilizationPulse automatic controlModulated-carrier systemsClock recoveryLinear model

A system and method for synchronizing a local clock to a reference clock using a linear model of the error between the local clock and the reference clock is disclosed. In one embodiment, a direct smoothing process is used in conjunction with the linear model to estimate a frequency offset by which the frequency of an oscillator of the local clock is adjusted. Also disclosed herein is a phased-lock loop (PLL) adapted to synchronize a local clock with a reference clock using the direct smoothing process, as well as a system implementing the PLL for timing the playout of data received from a transmitter.

Owner:CIENA

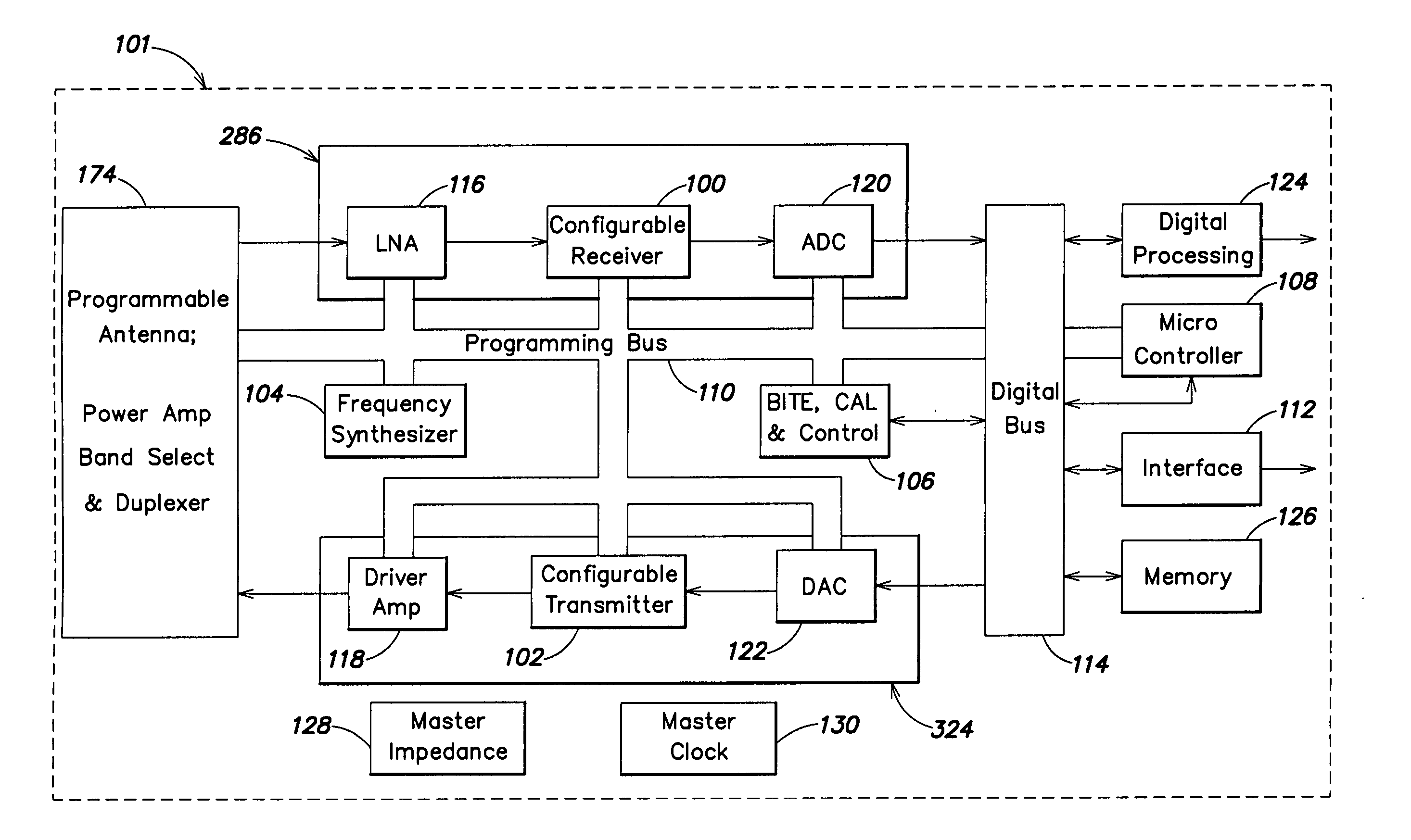

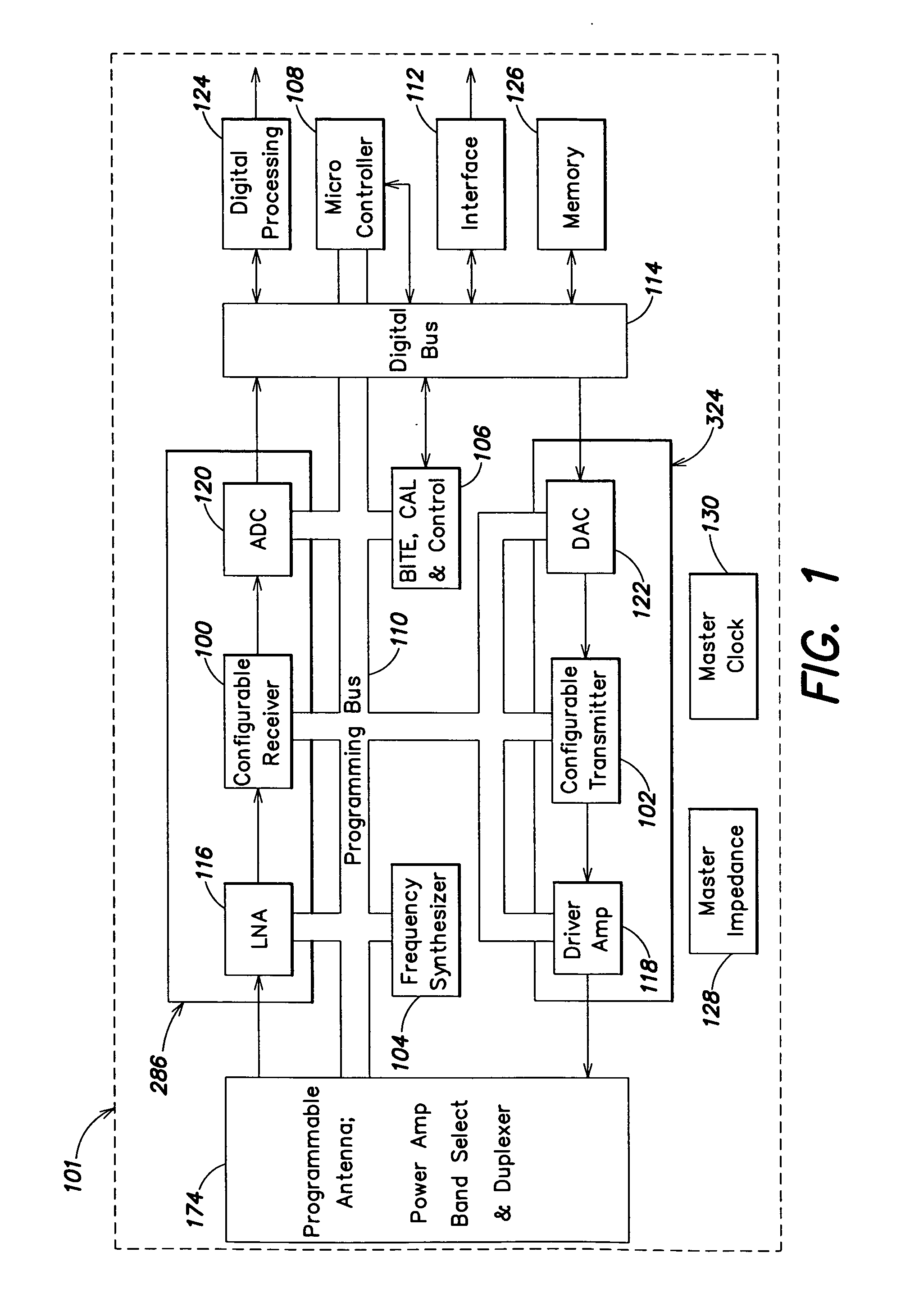

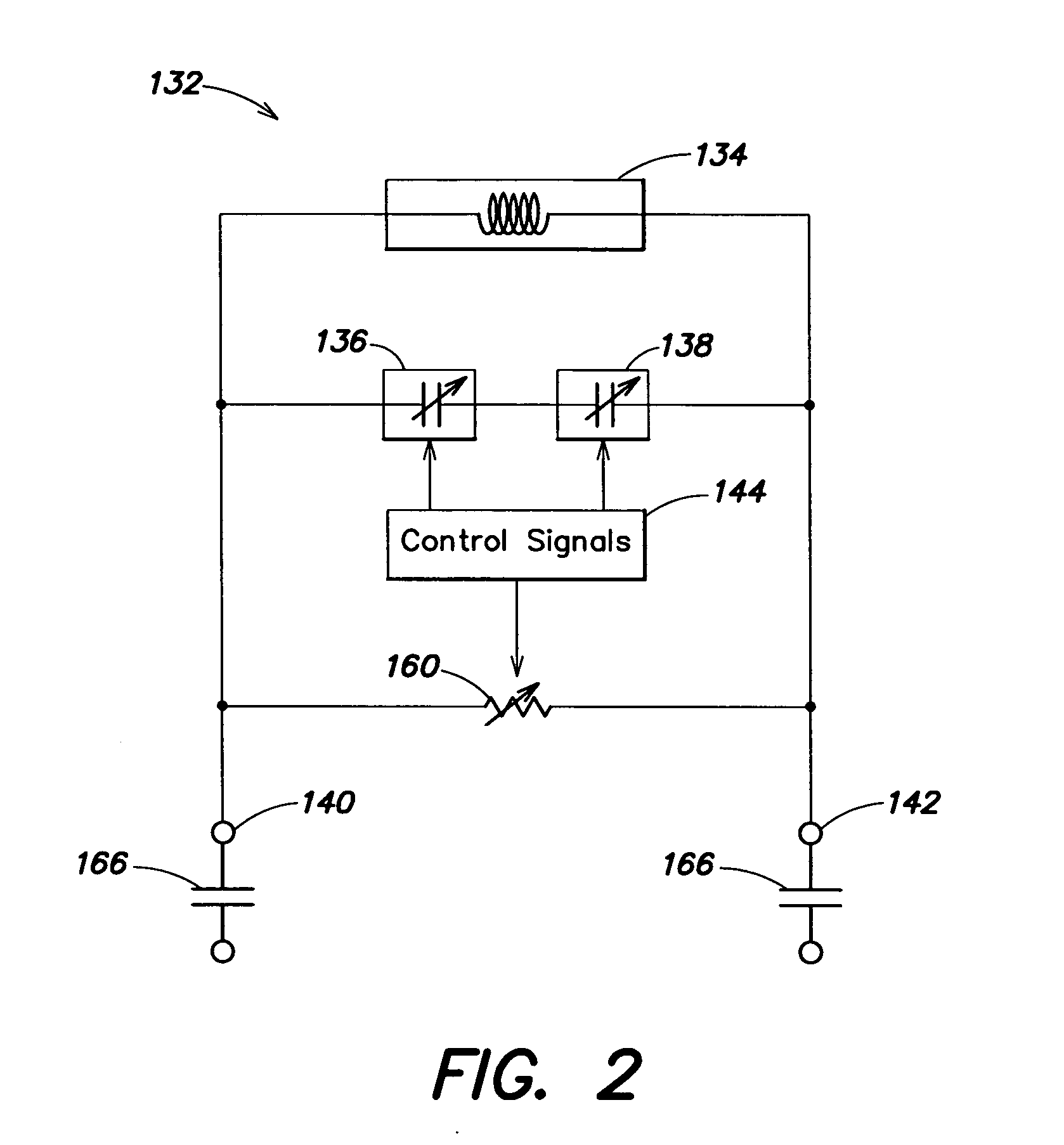

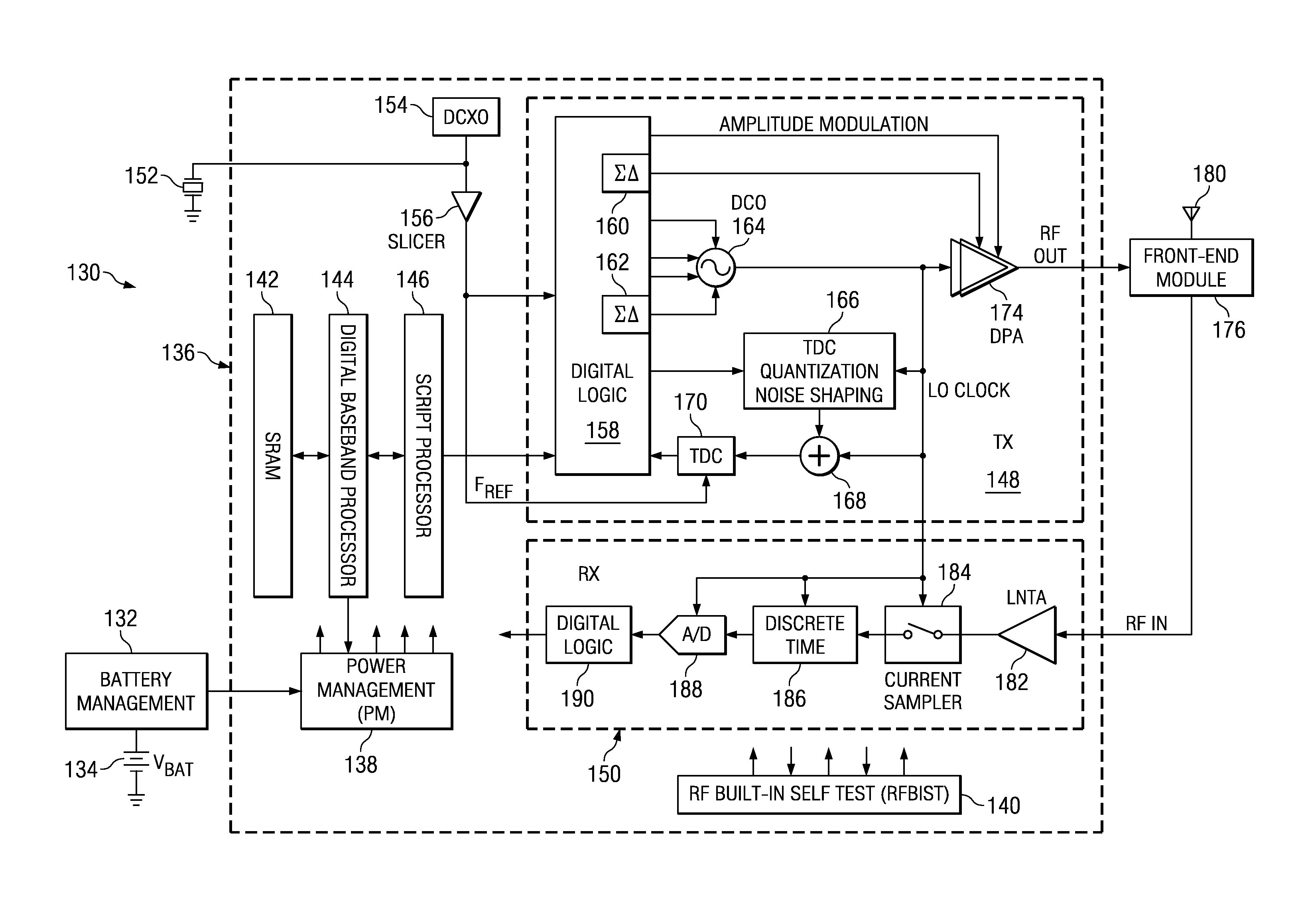

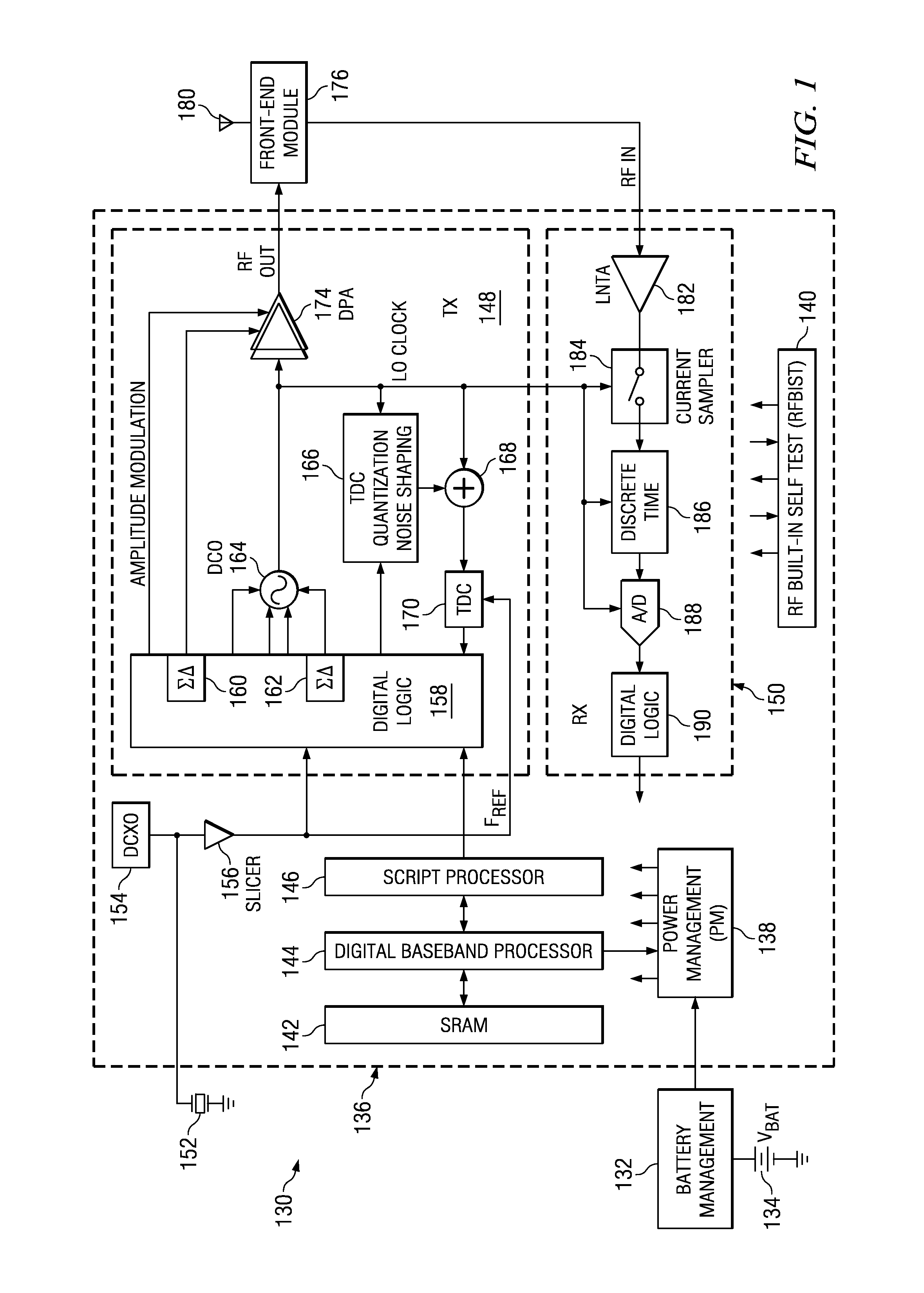

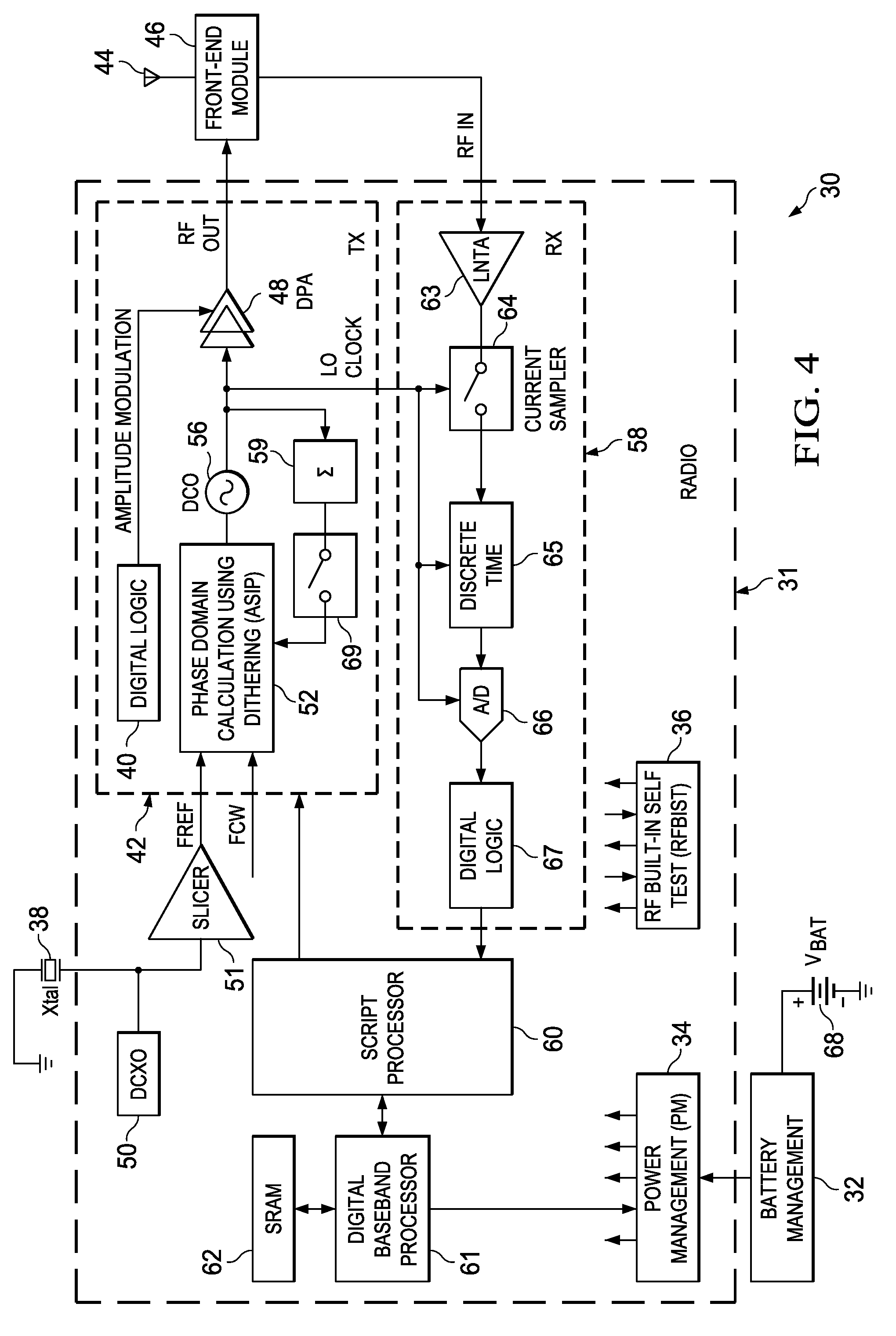

Programmable radio transceiver

ActiveUS20060030277A1Prevent leakageLow noise amplifierSolid-state devicesAmplifier with semiconductor-devices/discharge-tubesExtensibilityTransceiver

A fully integrated, programmable mixed-signal transceiver comprising a radio frequency integrated circuit (RFIC) which is frequency and protocol agnostic with digital inputs and outputs, the transceiver being programmable and configurable for multiple radio frequency bands and standards and being capable of connecting to many networks and service providers. The RFIC does not use spiral inductors and instead includes transmission line inductors allowing for improved scalability. Components of the transceiver are programmable to allow the transceiver to switch between different frequency bands of operating. Frequency switching can be accomplished though the content of digital registers coupled to the components.

Owner:GULA CONSULTING LLC

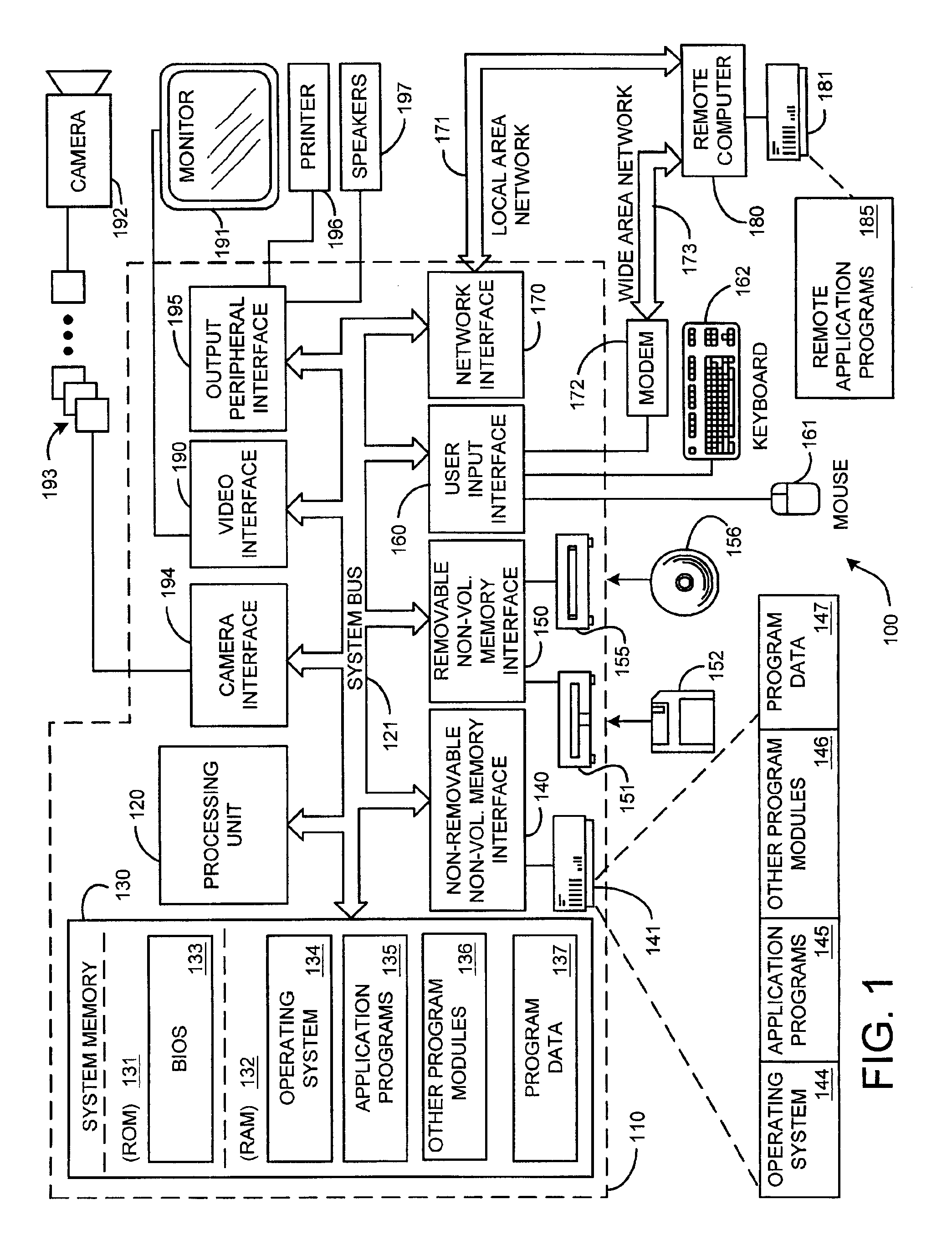

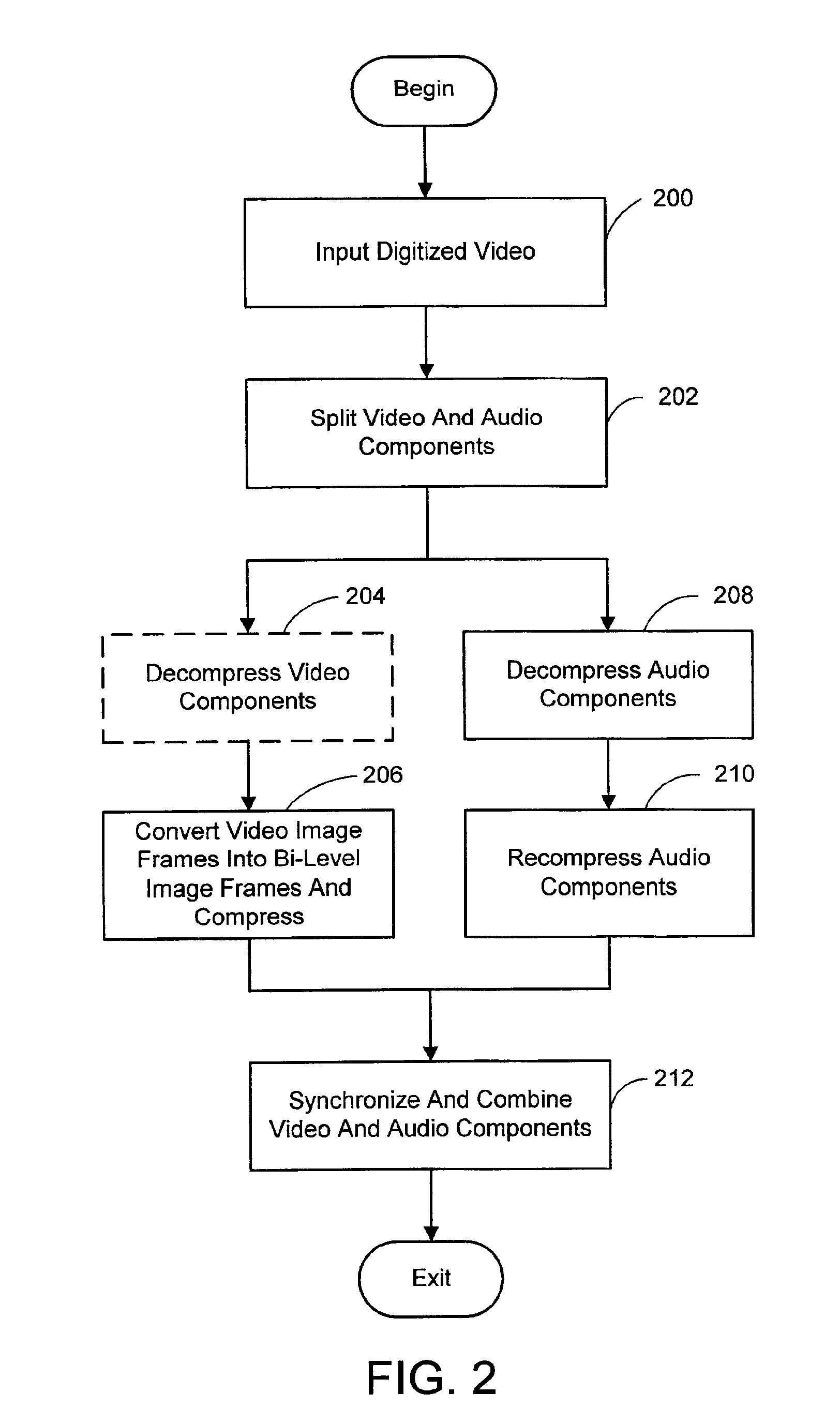

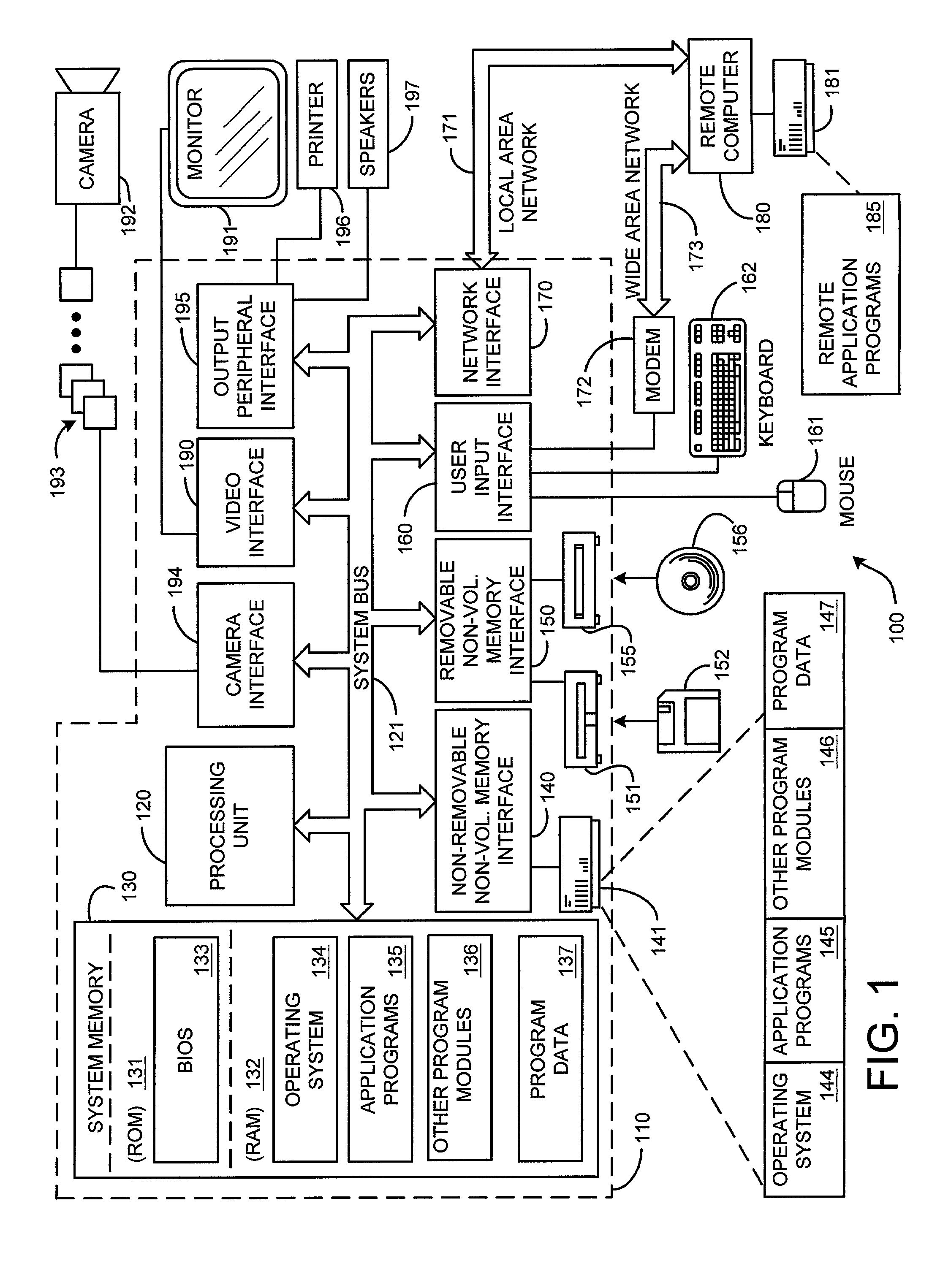

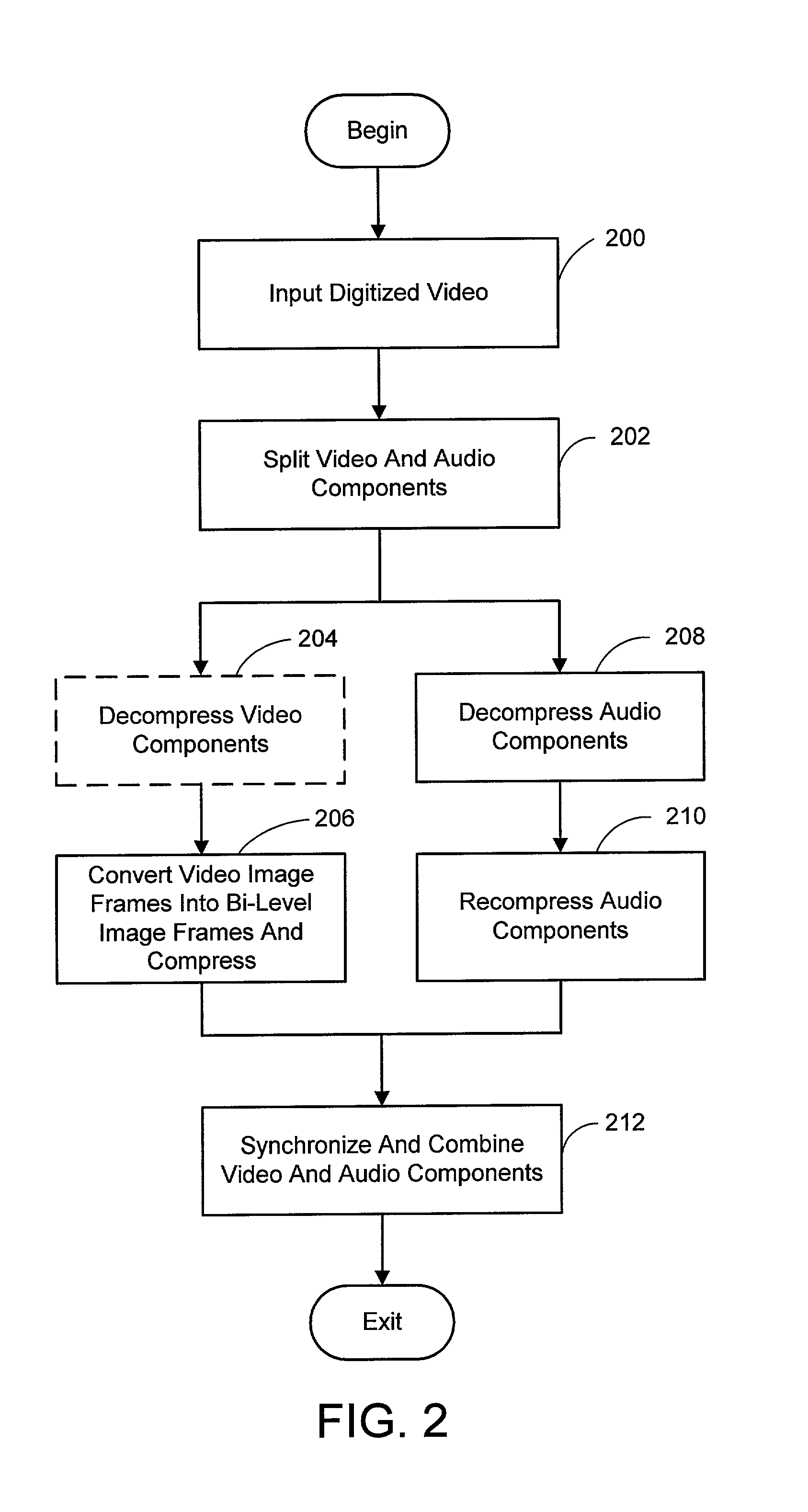

System and process for broadcast and communication with very low bit-rate bi-level or sketch video

InactiveUS6888893B2Clear imagingLow bandwidthPicture reproducers using cathode ray tubesPicture reproducers with optical-mechanical scanningComputer graphics (images)Arithmetic coding

A system and process for broadcast and communication with bi-level or sketch video at extremely low bandwidths is described. Essentially, bi-level and sketch video presents the outlines of the objects in a scene being depicted. Bi-level and sketch video provides a clearer shape, smoother motion, shorter initial latency and cheaper computational cost than do conventional DCT-based video compression methods. This is accomplished by converting each color or gray-scale image frame to bi-level or sketch image frame using adaptive thresholding method, compressing bi-level or sketch image frames into bi-level or sketch video using adaptive context-based arithmetic coding method. Bi-level or sketch video is particularly suitable to such small devices as Pocket PCs and mobile phones that possess small display screen, low bandwidth connection, and light computational power.

Owner:ZHIGU HLDG

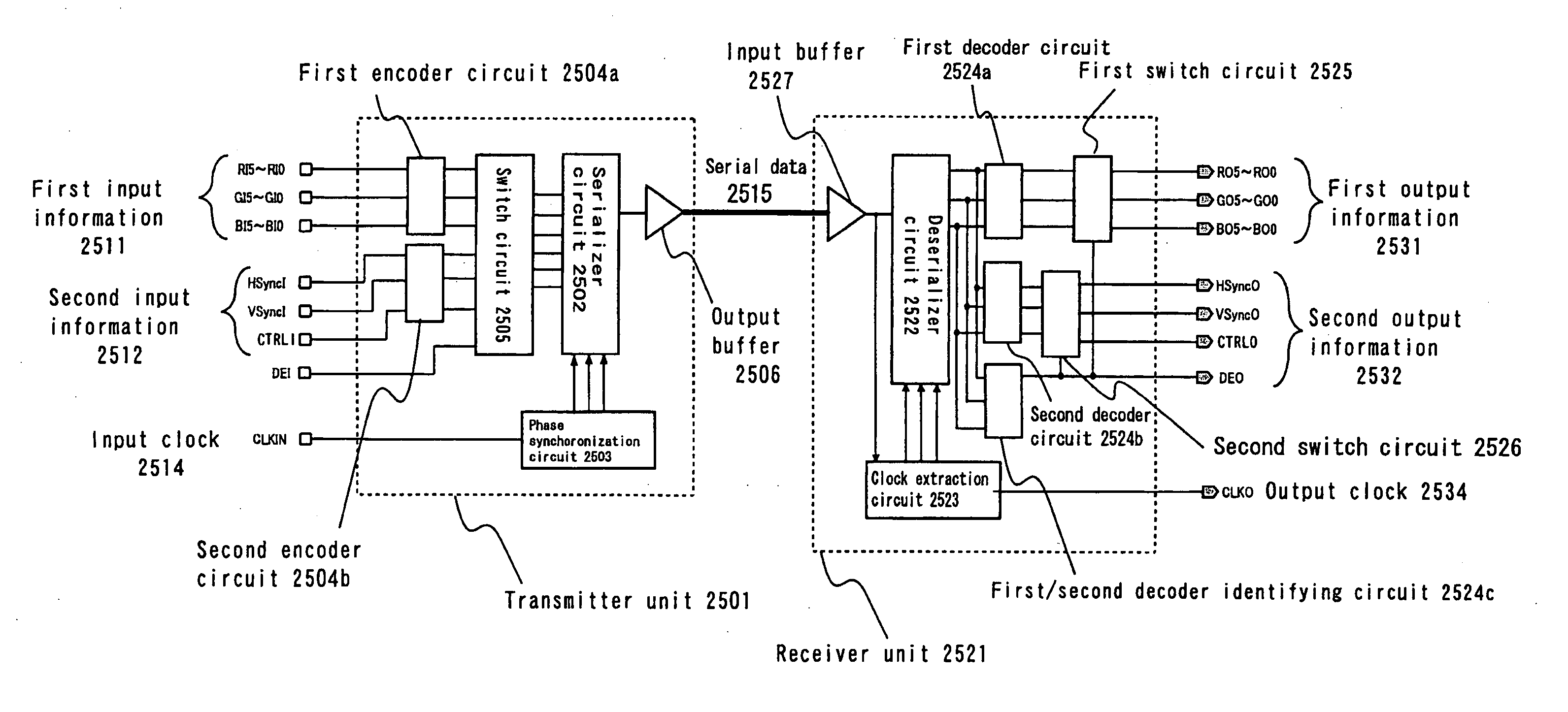

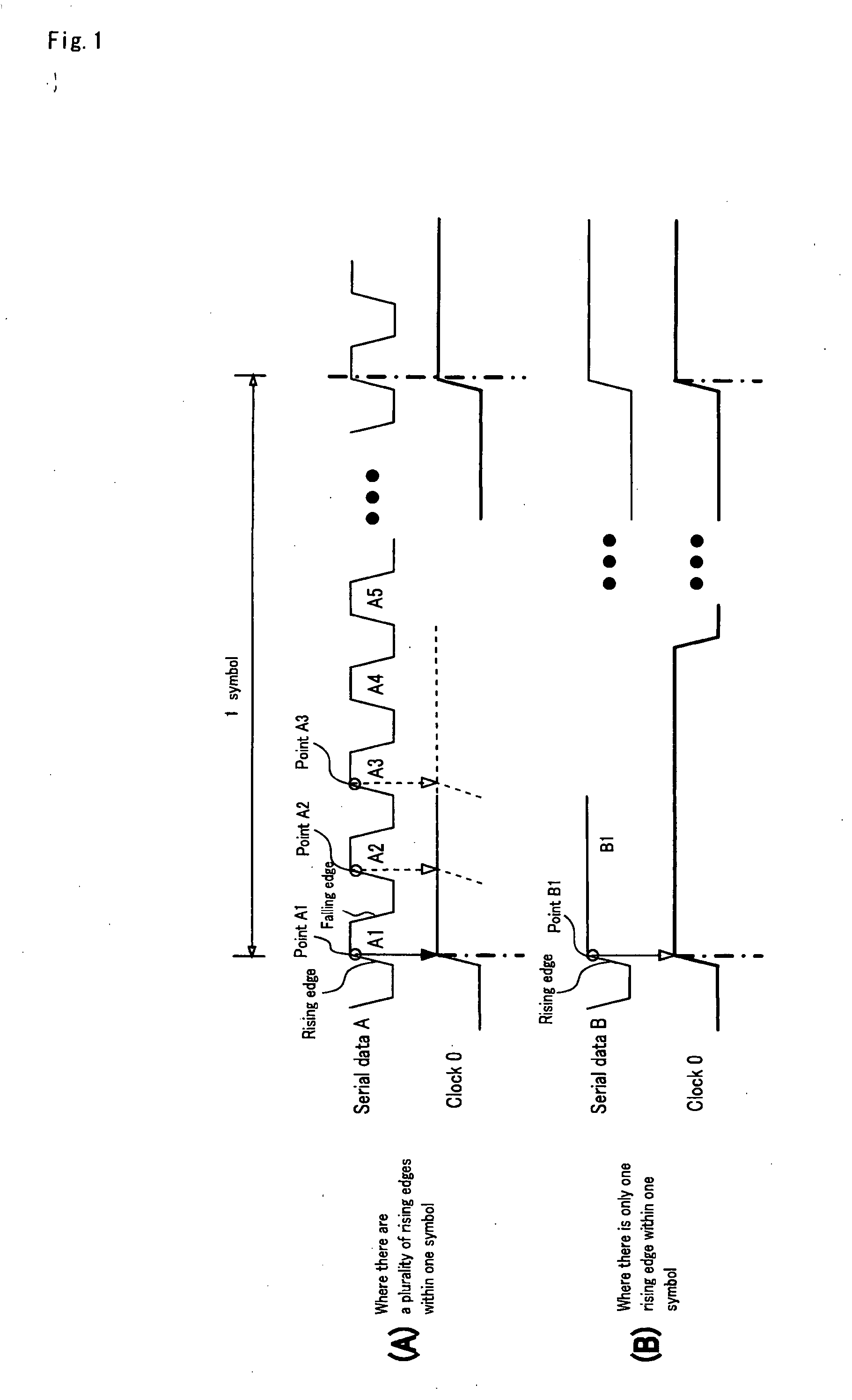

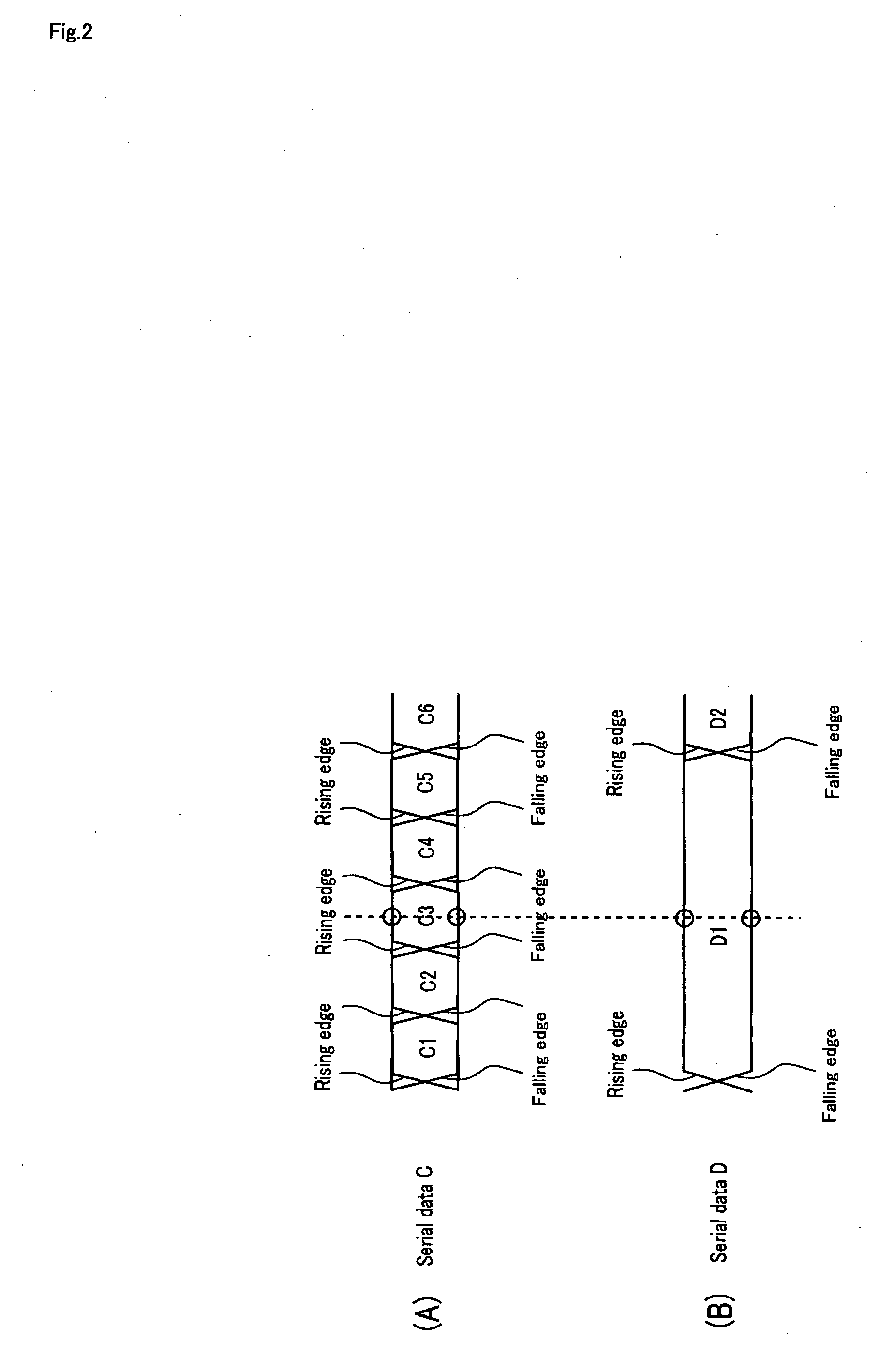

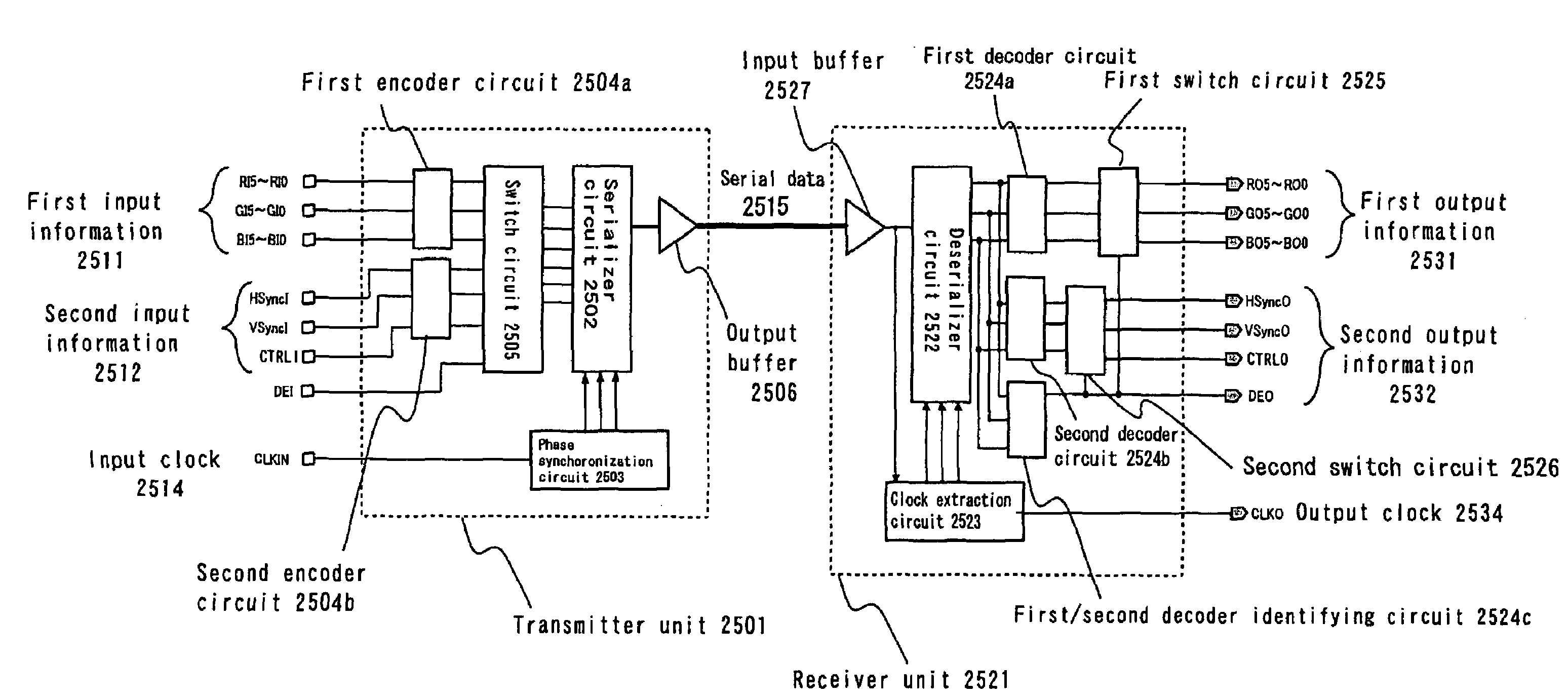

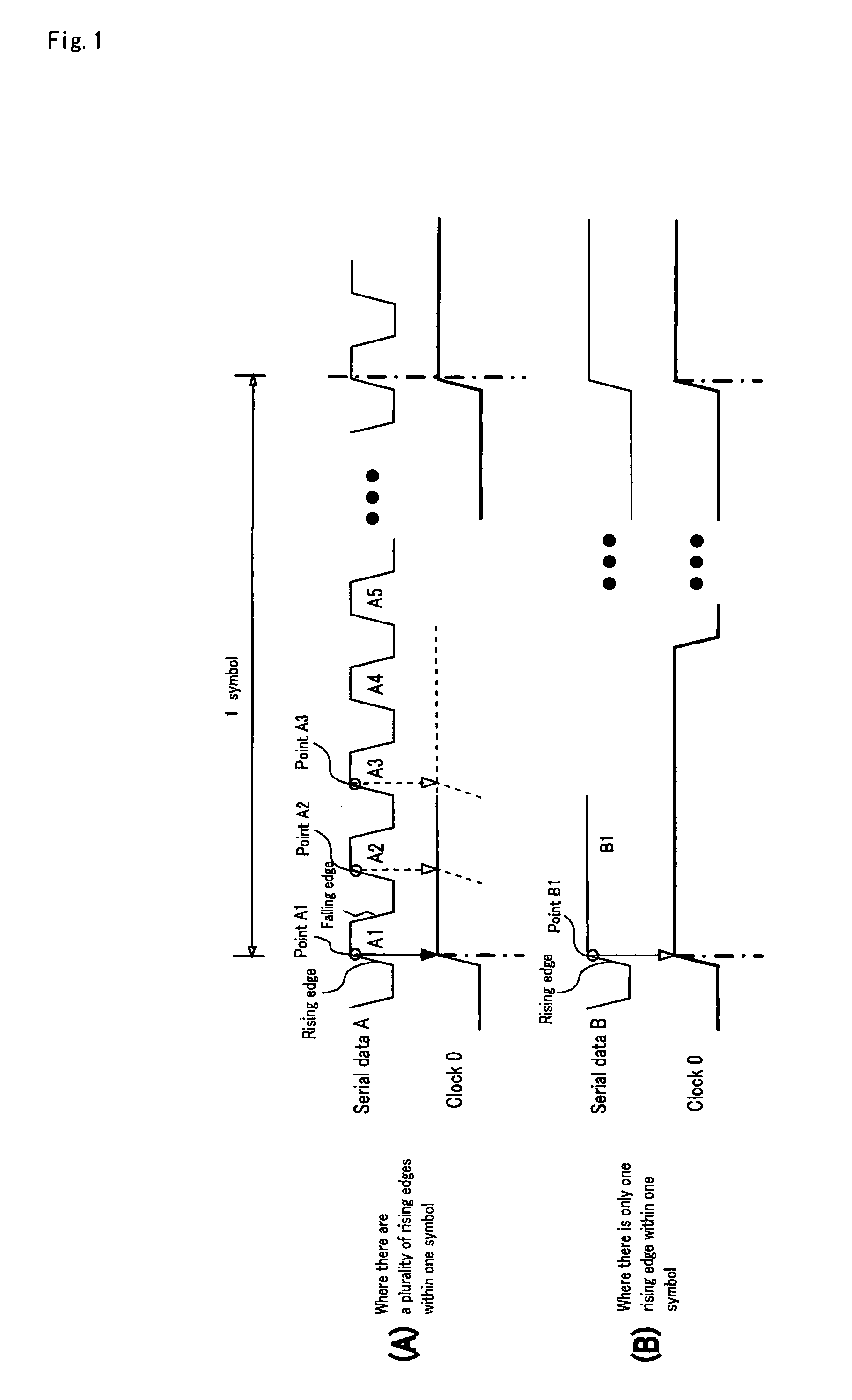

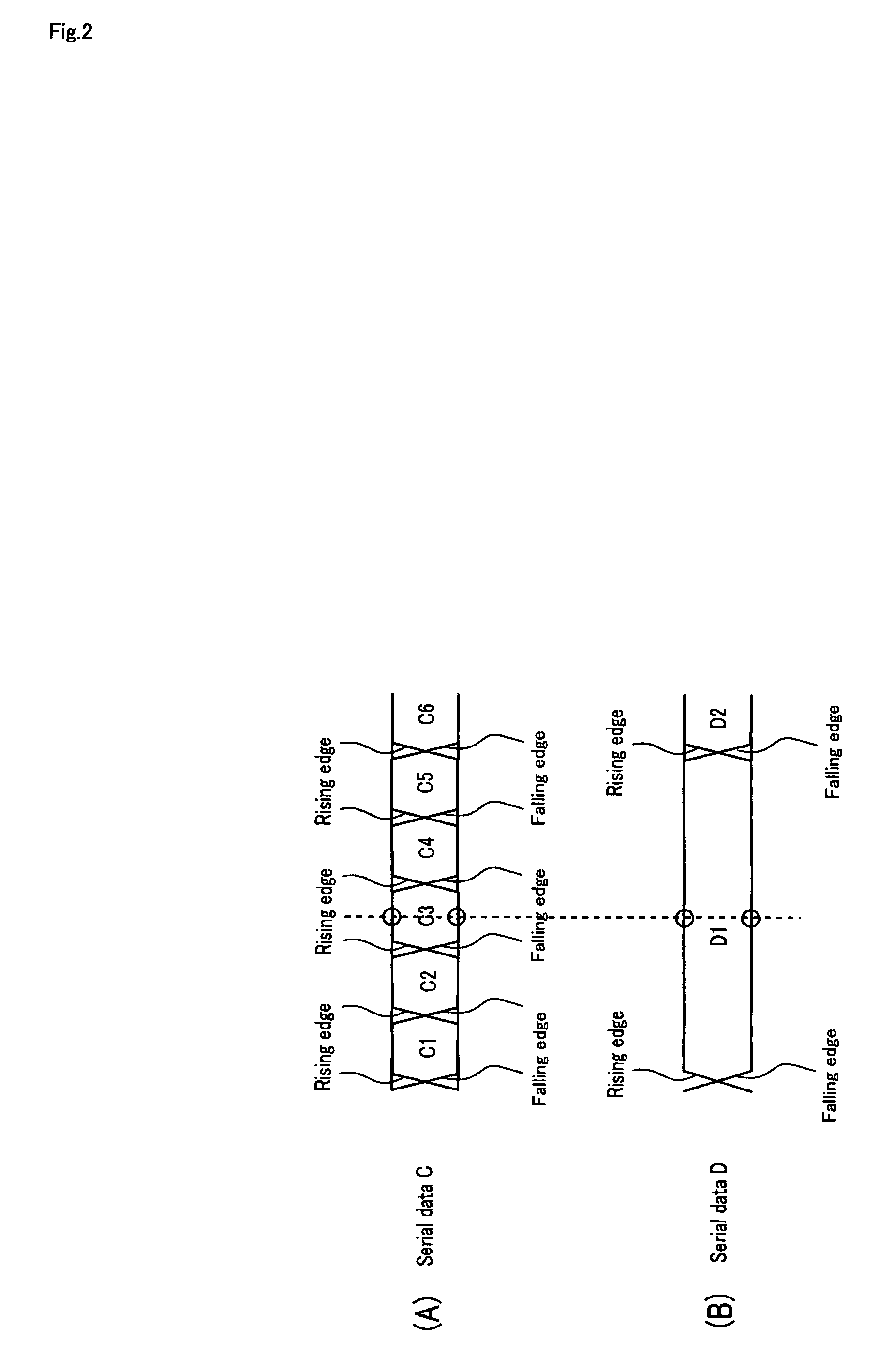

Transmitter circuit, receiver circuit, clock data recovery phase locked loop circuit, data transfer method and data transfer system

ActiveUS20050286643A1Reduce errorsData transmission is stableTelevision system detailsFrequency/rate-modulated pulse demodulationDigital dataPhase locked loop circuit

[Problems] To realize a reliable and stable transfer of digital data that does not require a reference clock and a handshake operation. [Means for Solving the Problem] The present invention provides a digital data transfer method for alternately and periodically transferring first information and second information respectively in a first period and in a second period, wherein: an amount of information of the first information per unit time in the first period is greater than an amount of information of the second information per unit time in the second period; and the second information in the first period is transferred as pulse-width-modulated serial data.

Owner:THINE ELECTRONICS

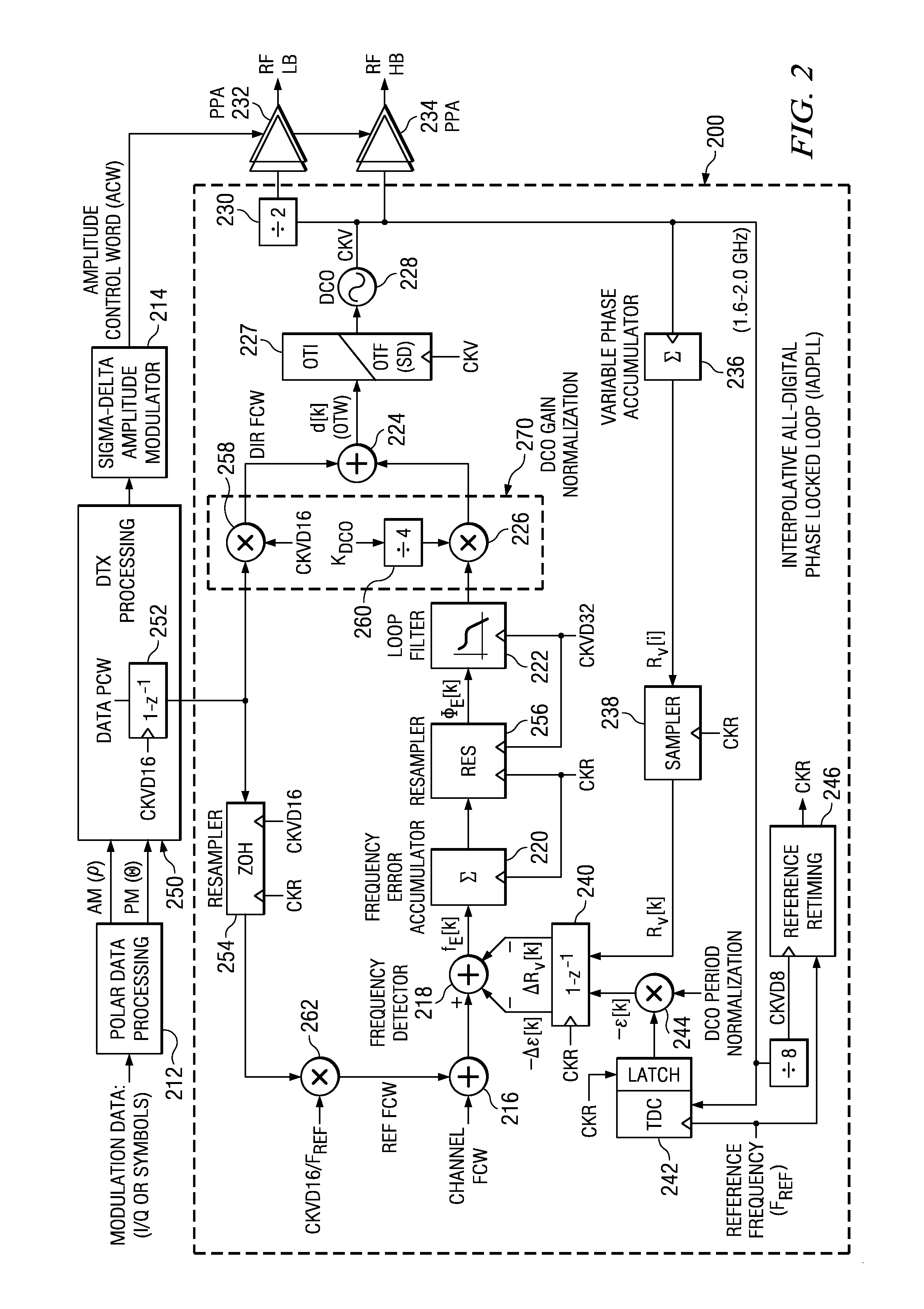

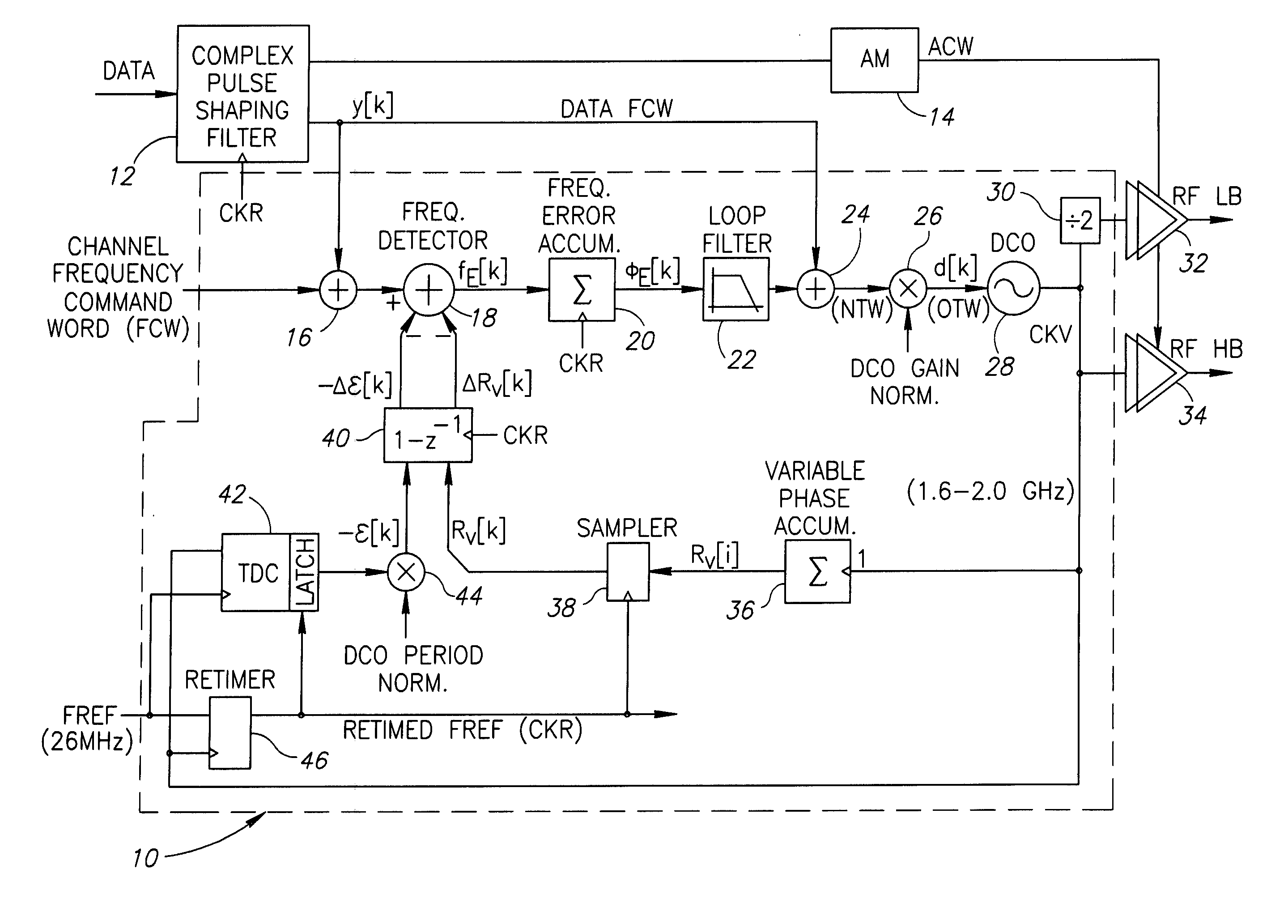

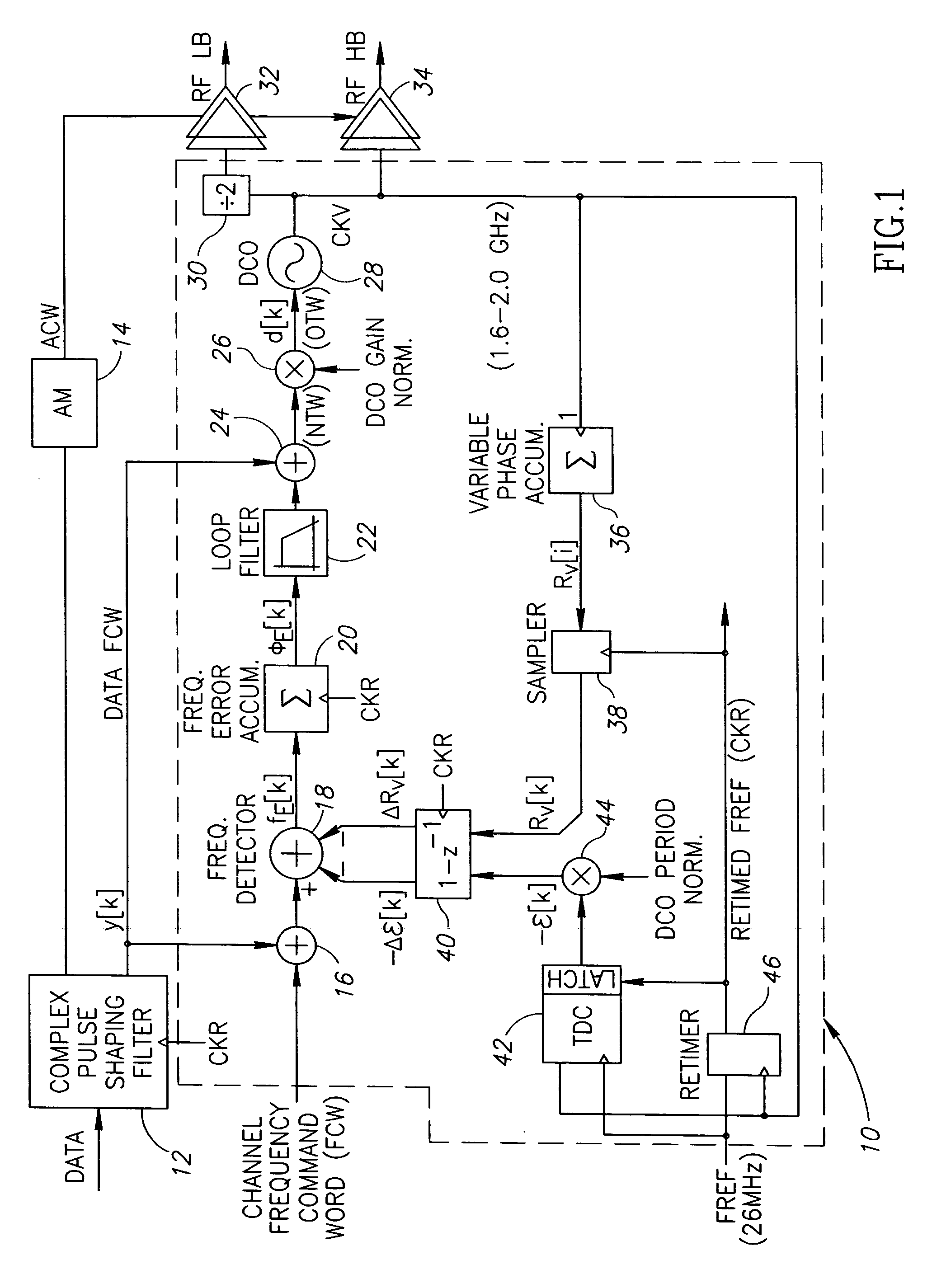

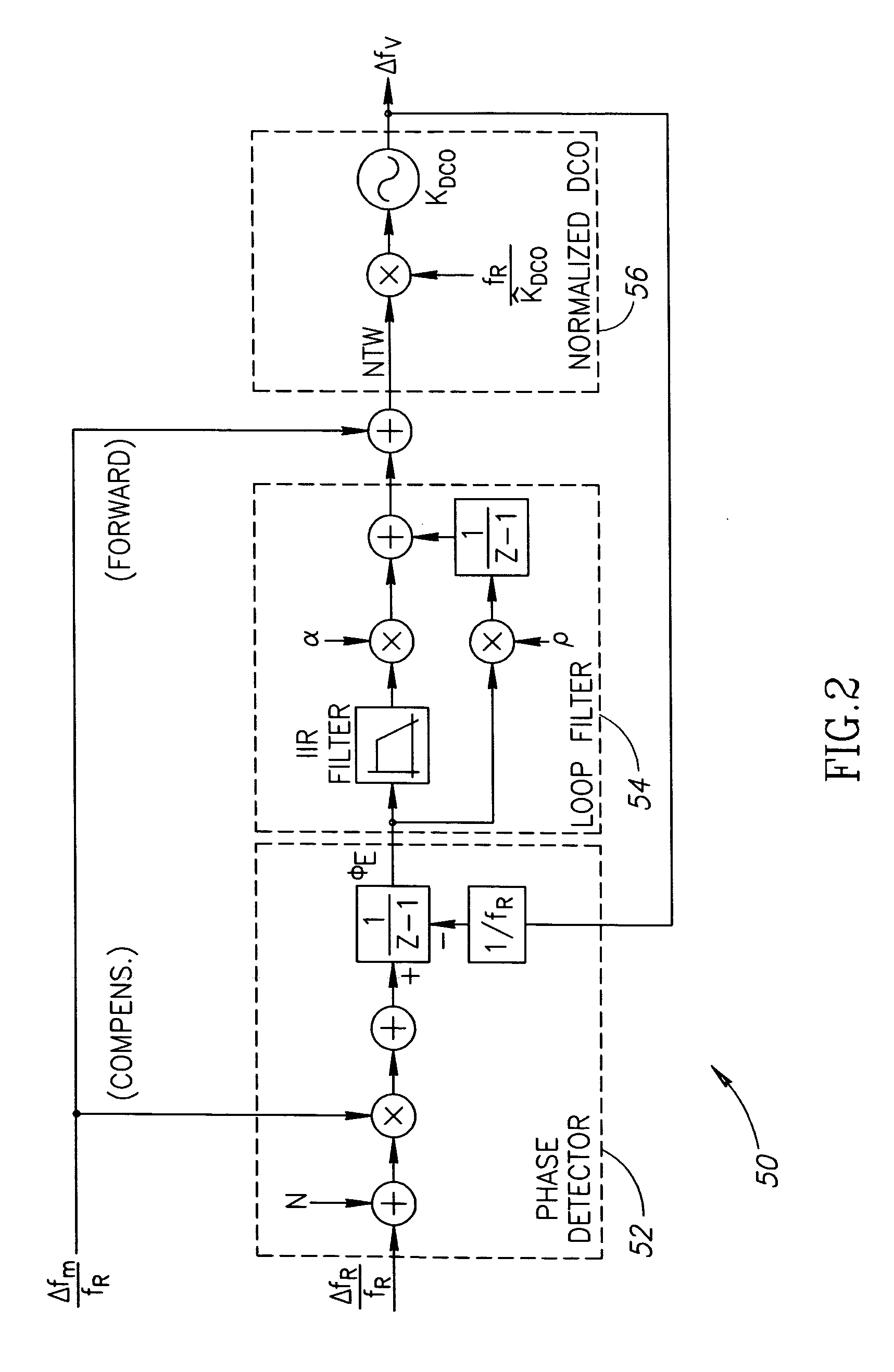

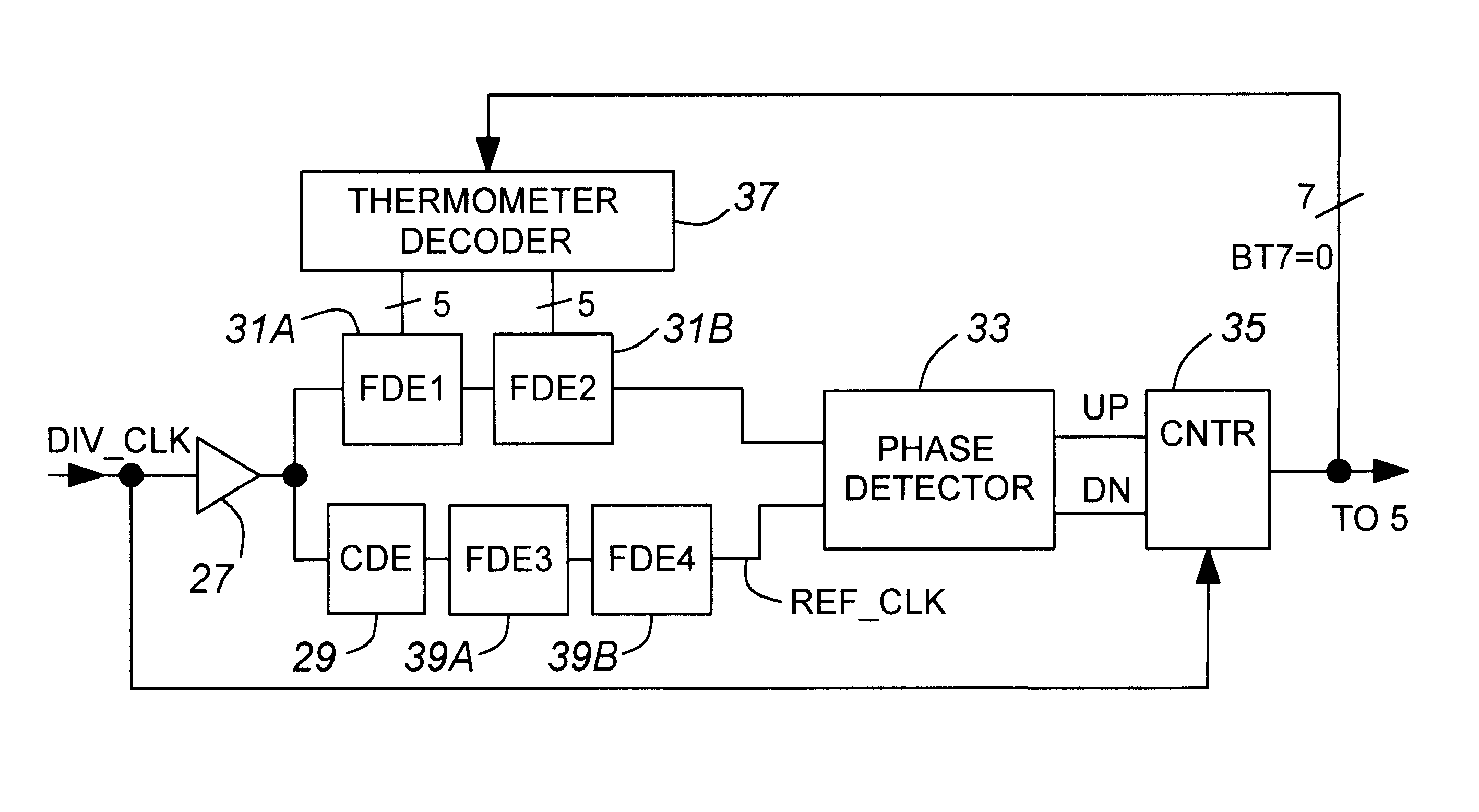

Digital Phase Locked Loop with Integer Channel Mitigation

An embodiment of the present invention provides a phase locked loop that operates on clock signals derived from an RF clock signal generated by the phase locked loop. A frequency reference input provides a reference clock. A controllable oscillator generates the RF clock signal with a plurality of phases. A switch is coupled to receive the RF clock, and is operative to select one of the plurality of phases. A phase detection circuit is coupled to the switch and is operable to receive a selected phase and to provide digital phase error samples indicative of a time difference between the reference clock and the selected phase.

Owner:TEXAS INSTR INC

OFDM communication channel

InactiveUS6985432B1Facilitate communicationImprove performanceFrequency-division multiplexAmplitude-modulated carrier systemsComputer scienceTime synchronization

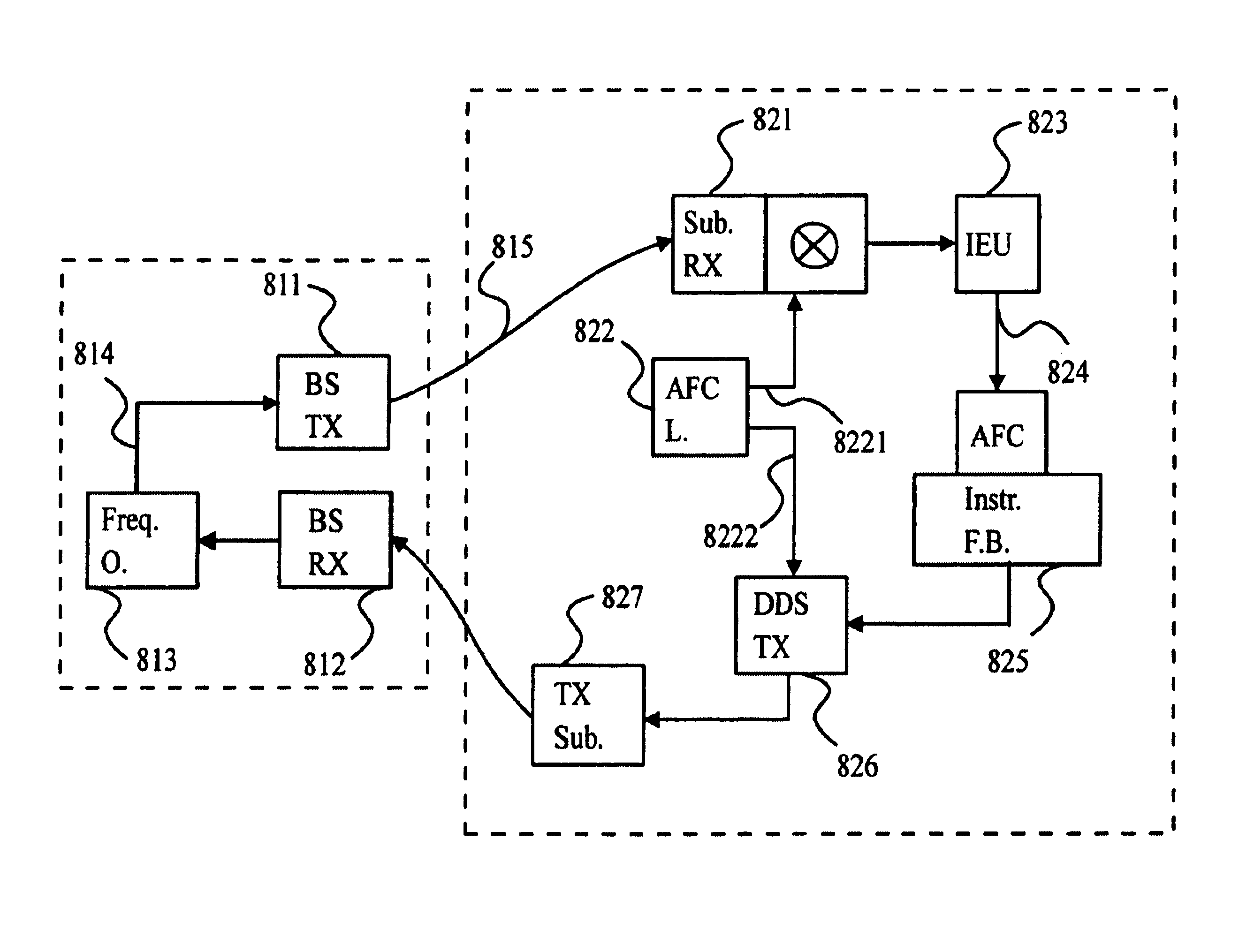

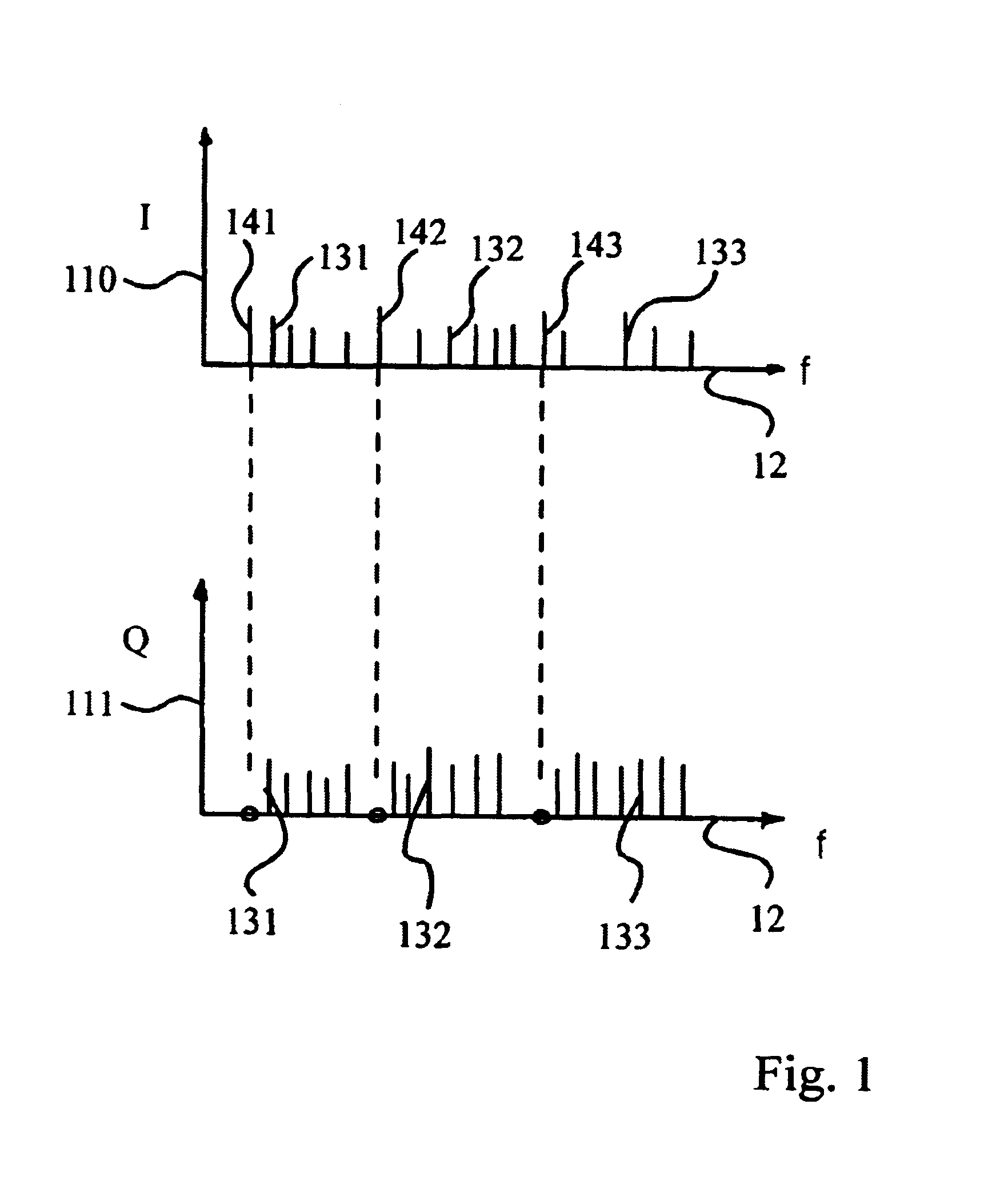

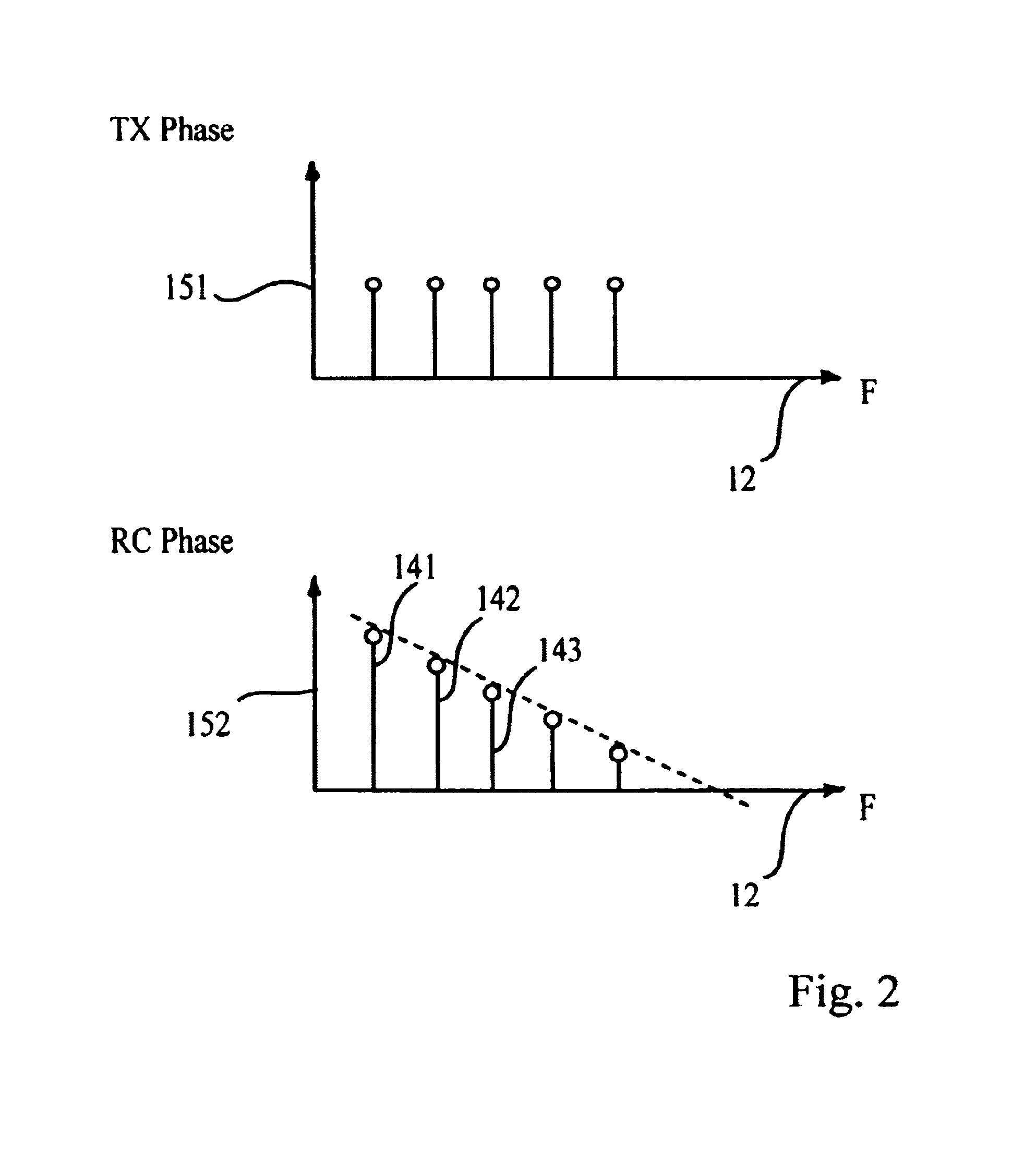

In an OFDM-based receiver, a time synchronization unit comprising: A. a device for extracting pilot signals contained in the OFDM received signal; B. a device for analyzing pilot signals in the frequency domain and for issuing a signal indicative of a synchronization error in the received signal; C. a device for correcting the synchronization error, responsive to the signal indicative of the synchronization error. In an OFDM-based receiver, an automatic frequency correction device in a subscriber unit comprising: A. an inner frequency correction loop for generating a LO frequency related to a frequency of a received signal; B. an outer frequency correction loop for correcting the LO frequency according to instructions received from a base station.

Owner:ZION HADAD COMM

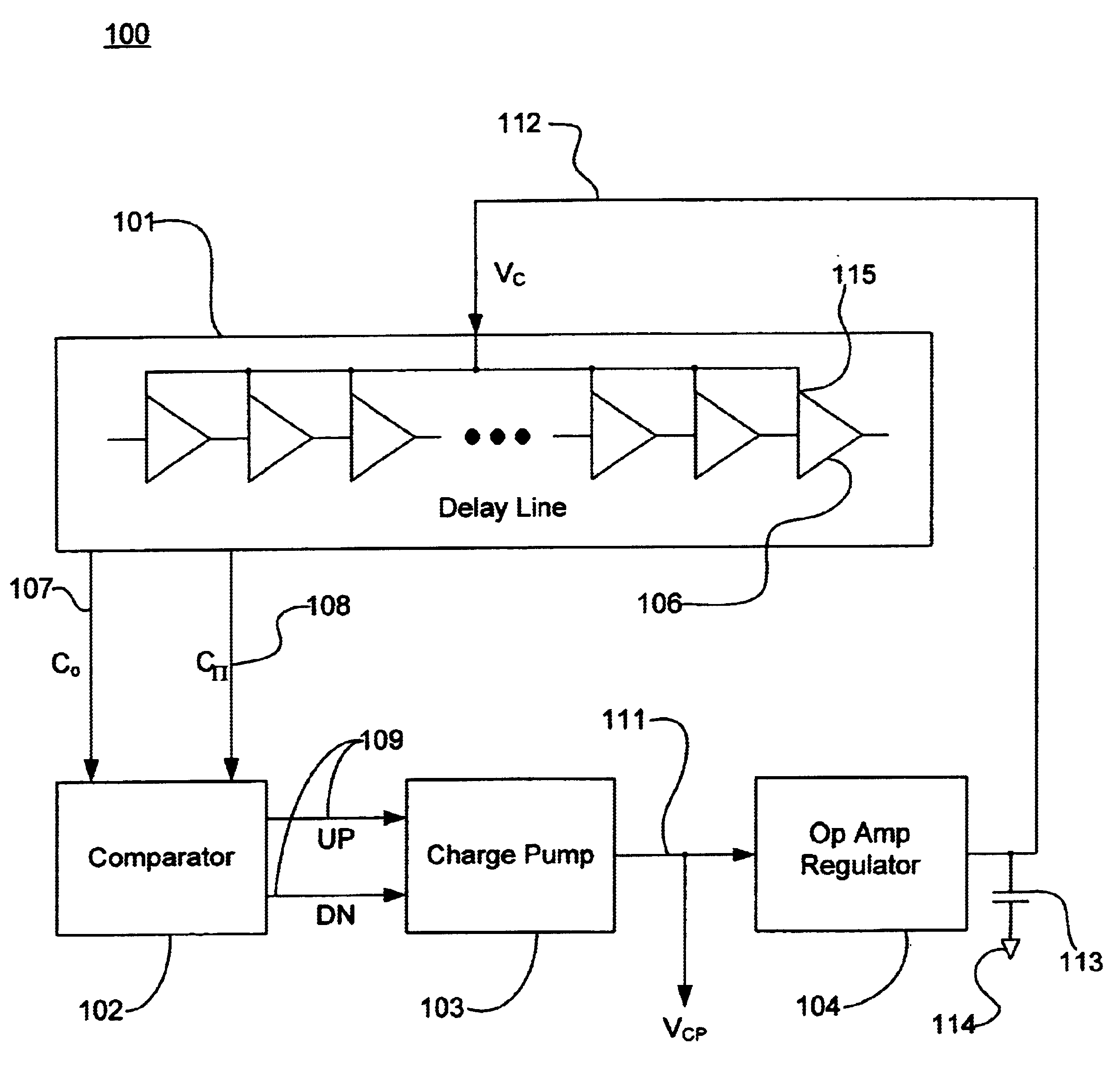

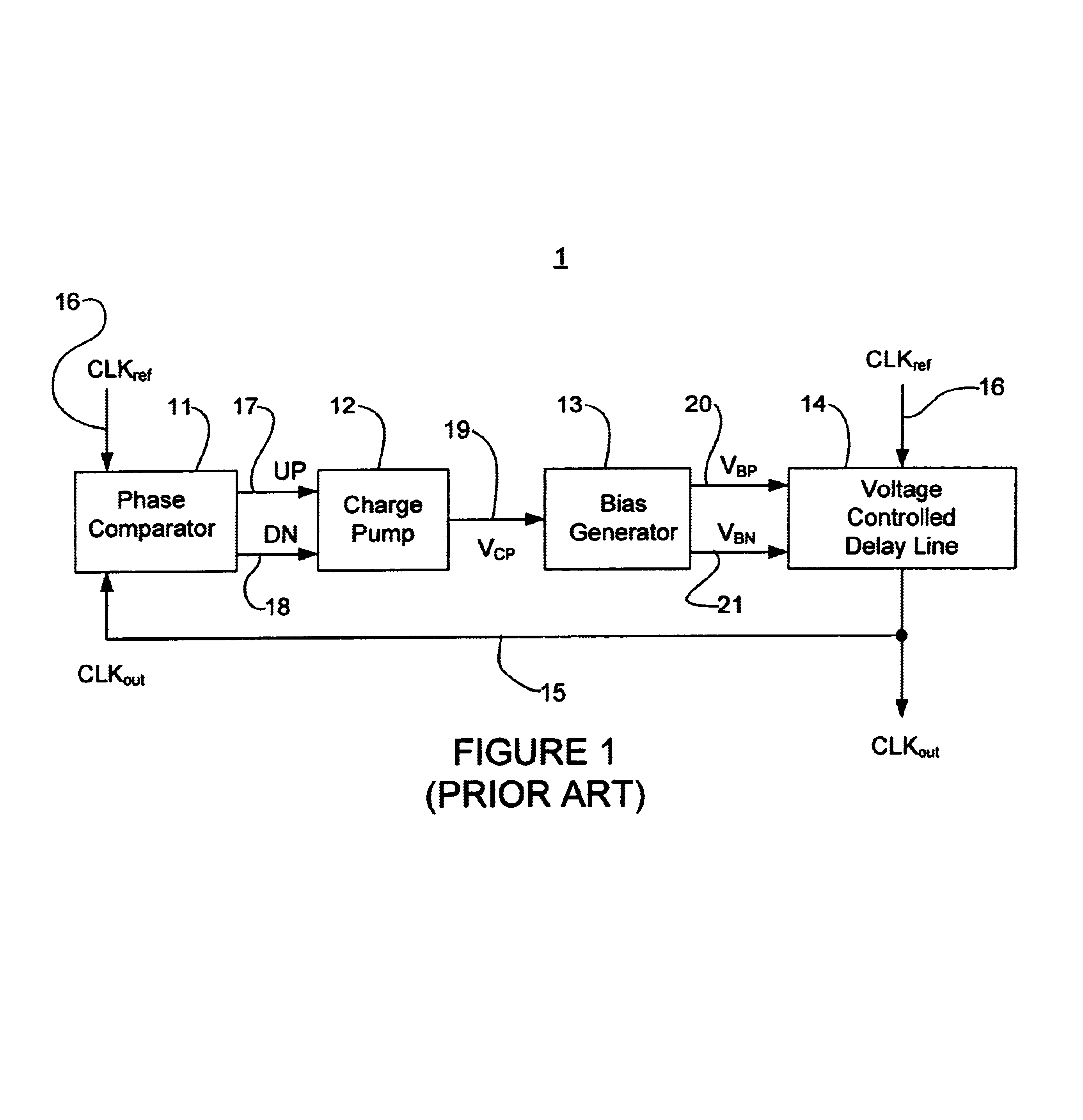

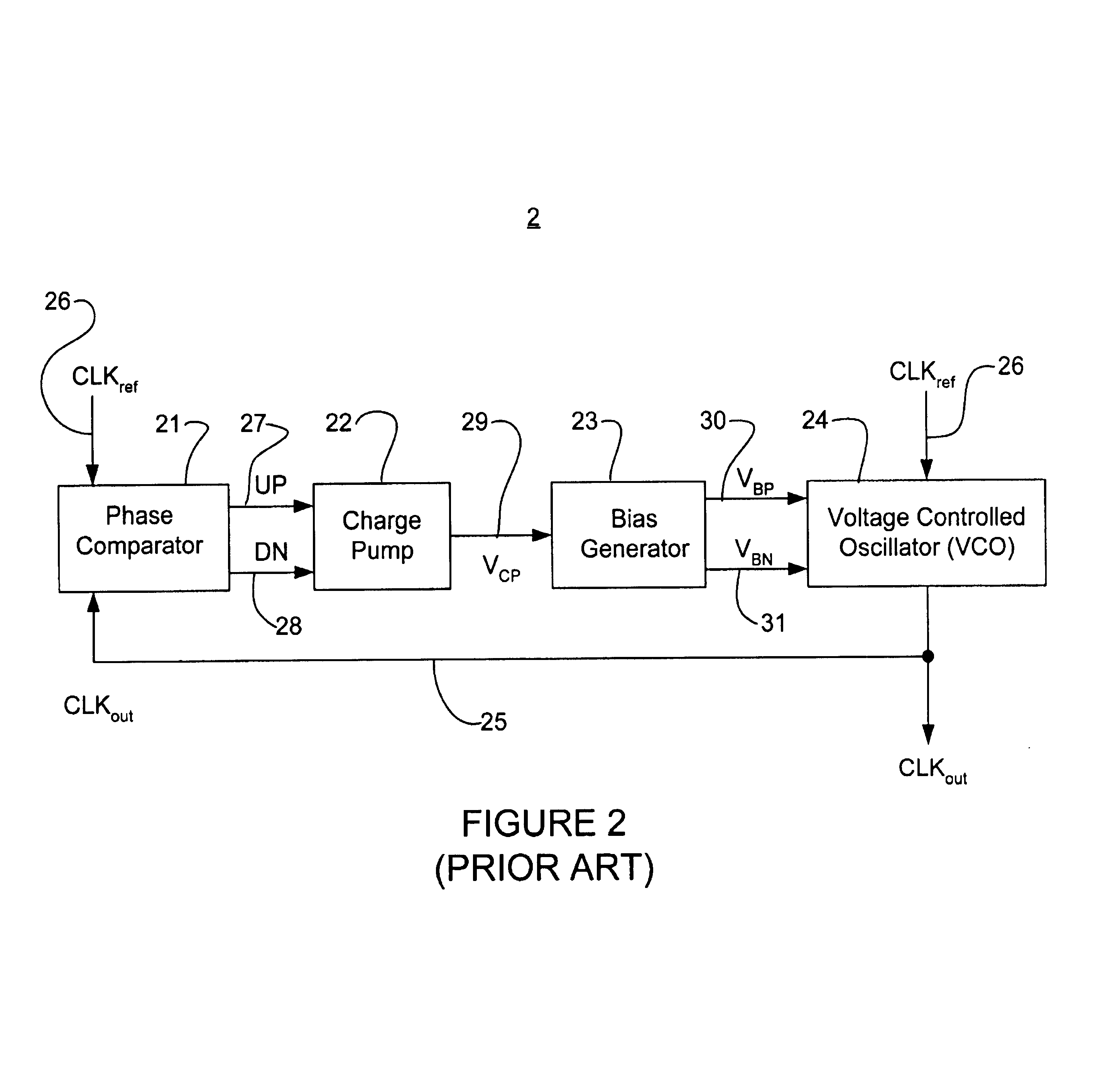

Clock alignment circuit having a self regulating voltage supply

InactiveUS6928128B1Wide range of operationsReduce power consumptionPulse automatic controlDigital data processing detailsAudio power amplifierEngineering

Clock alignment circuits and techniques for reducing power dissipation, increasing power supply noise immunity, decreasing process and temperature variation sensitivity, and providing a wide operating range. A power supply generator generates an isolated supply voltage for a delay line used in a clock alignment circuit. The delay line generates a delayed clock from a reference clock. A comparator detects a correction information (i.e., delay or phase error) between the delayed clock and the reference clock and generates error information representative of the correction information. A charge pump circuit converts the error information into a voltage signal, wherein the voltage signal is a scaled representation of the error information. The power supply generator includes an amplifier having a first input coupled to the voltage signal and an output to provide the supply voltage and a capacitor coupled between the supply voltage and a ground voltage, wherein the amplifier tracks the voltage signal level to regulate the supply voltage.

Owner:RAMBUS INC

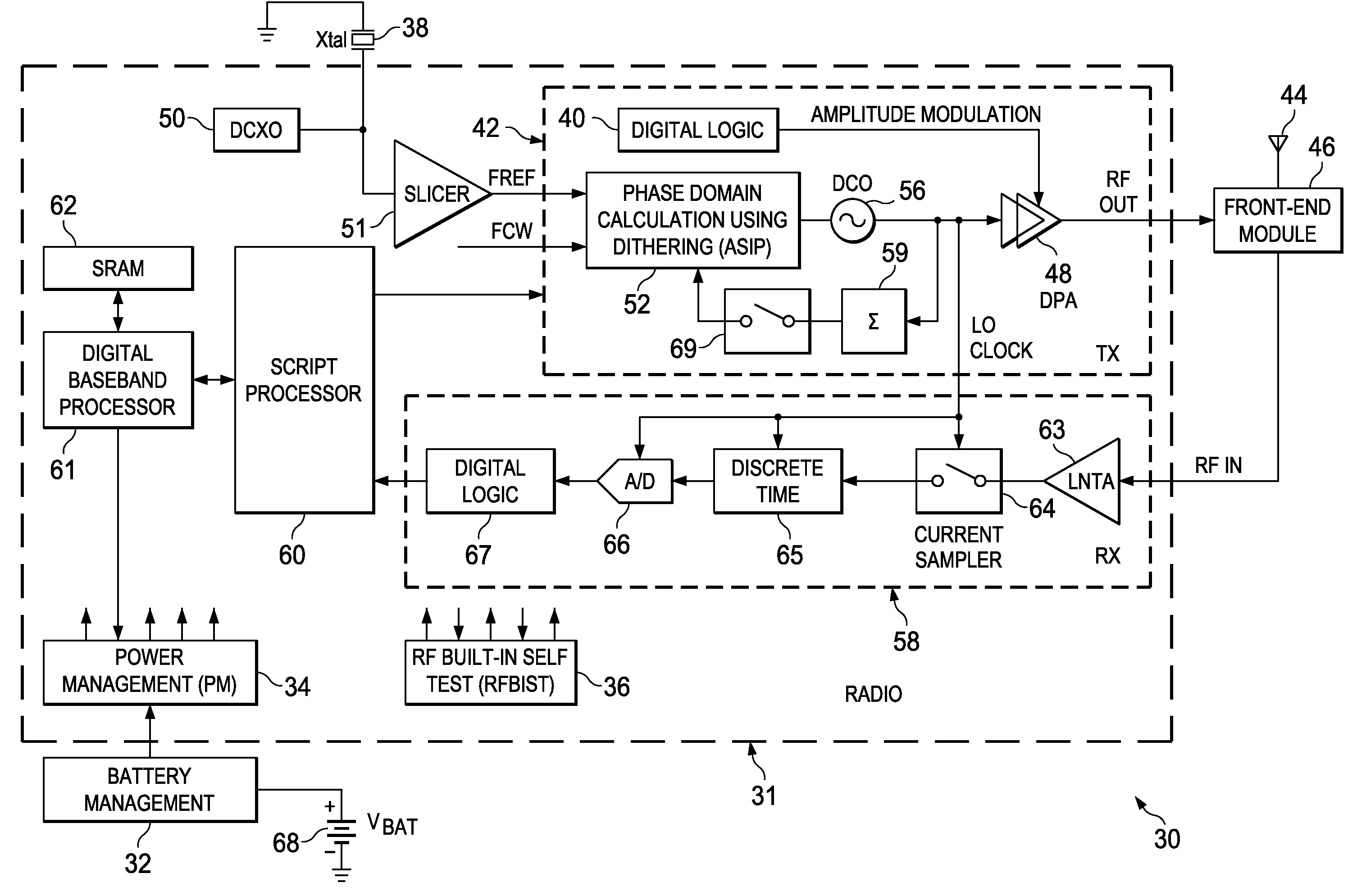

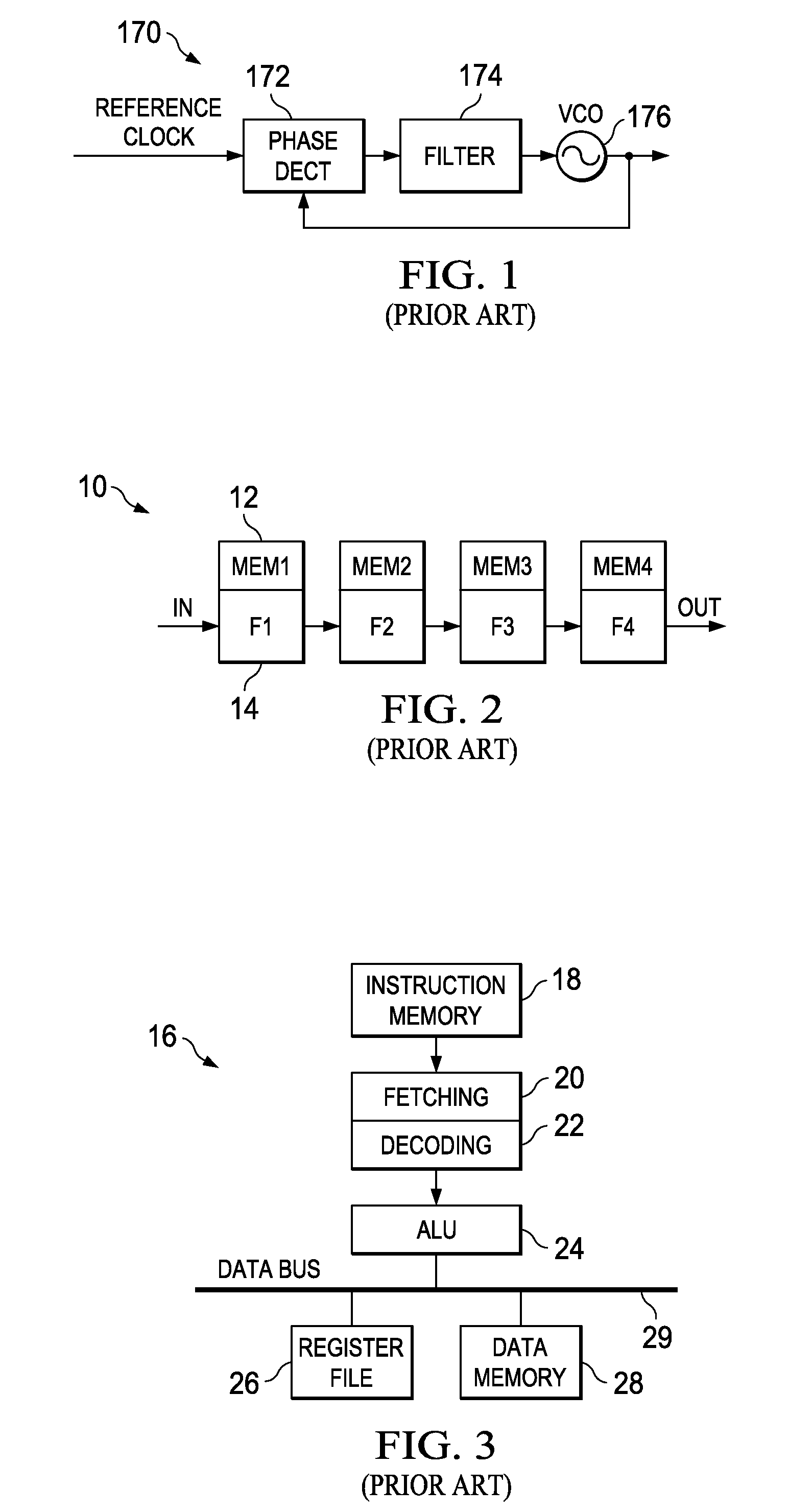

Computation spreading utilizing dithering for spur reduction in a digital phase lock loop

ActiveUS20090262877A1Easy to reconfigureReduce generationPulse automatic controlGenerator stabilizationFrequency spectrumClock rate

A novel and useful apparatus for and method of spur reduction using computation spreading with dithering in a digital phase locked loop (DPLL) architecture. A software based PLL incorporates a reconfigurable calculation unit (RCU) that is optimized and programmed to sequentially perform all the atomic operations of a PLL or any other desired task in a time sharing manner. An application specific instruction-set processor (ASIP) incorporating the RCU is adapted to spread the computation of the atomic operations out over a PLL reference clock period wherein each computation is performed at a much higher processor clock frequency than the PLL reference clock rate. This significantly reduces the per cycle current transient generated by the computations. The frequency content of the current transients is at the higher processor clock frequency which results in a significant reduction in spurs within sensitive portions of the output spectrum. Further reduction in spurs is achieved by dithering the duration of the software loop of atomic operations and / or by randomly shuffling one or more non-data dependent instructions within each iteration of the software loop.

Owner:TEXAS INSTR INC

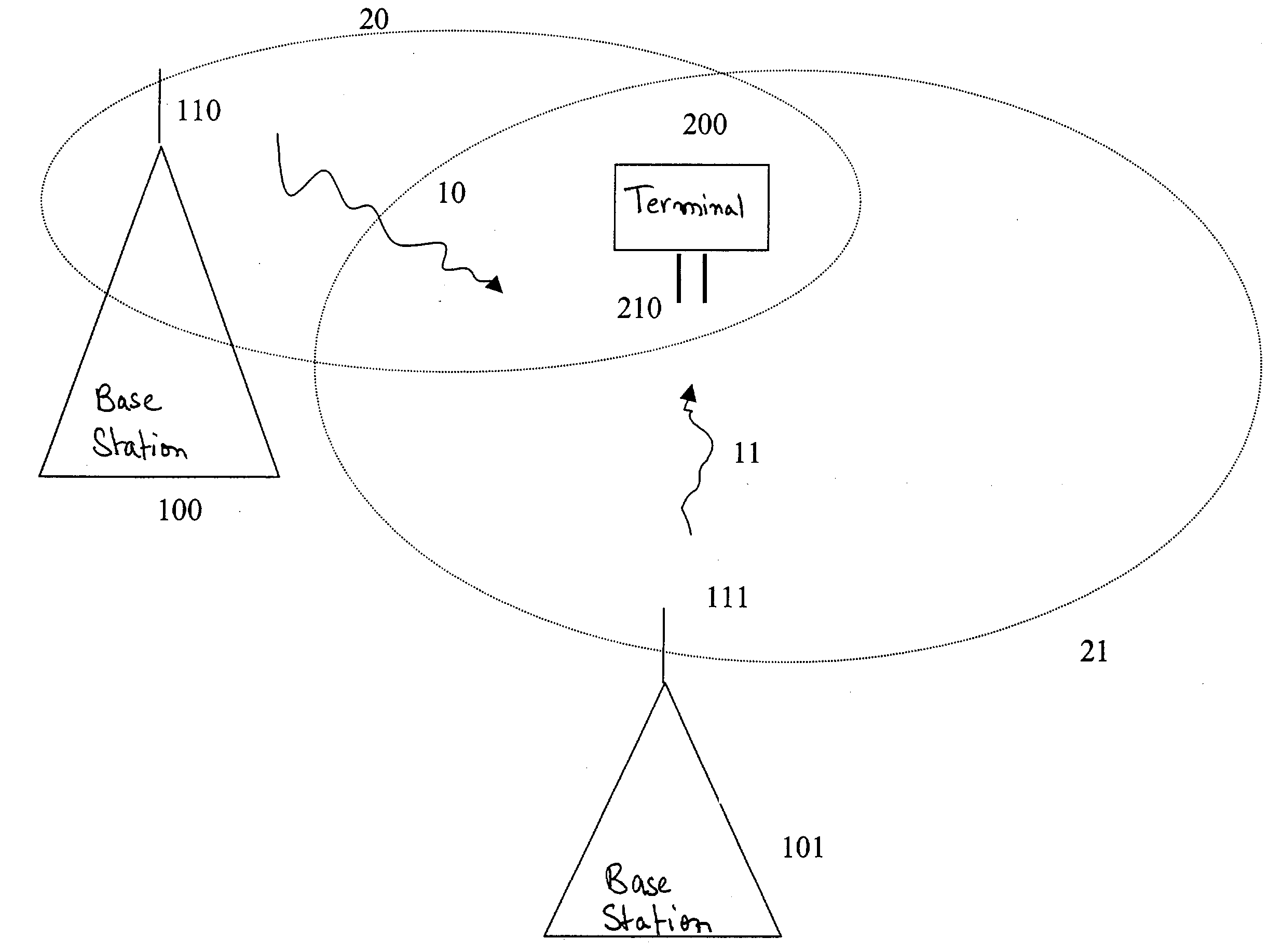

CDMA transceiver techniques for wireless communications

InactiveUS20040120274A1Spatial transmit diversityFrequency diversityWireless transmissionCommunications system

The present invention is related to a method for multi-user wireless transmission of data signals in a communication system having at least one base station and at least one terminal. It comprises, for a plurality of users, the following steps: adding robustness to frequency-selective fading to the data to be transmitted. performing spreading and scrambling of at least a portion of a block of data, obtainable by grouping data symbols by demultiplexing using a serial-to-parallel operation, combining (summing) spread and scrambled portions of the blocks of at least two users, adding transmit redundancy to the combined spread and scrambled portions, and transmitting the combined spread and scrambled portions with transmit redundancy.

Owner:RPX CORP

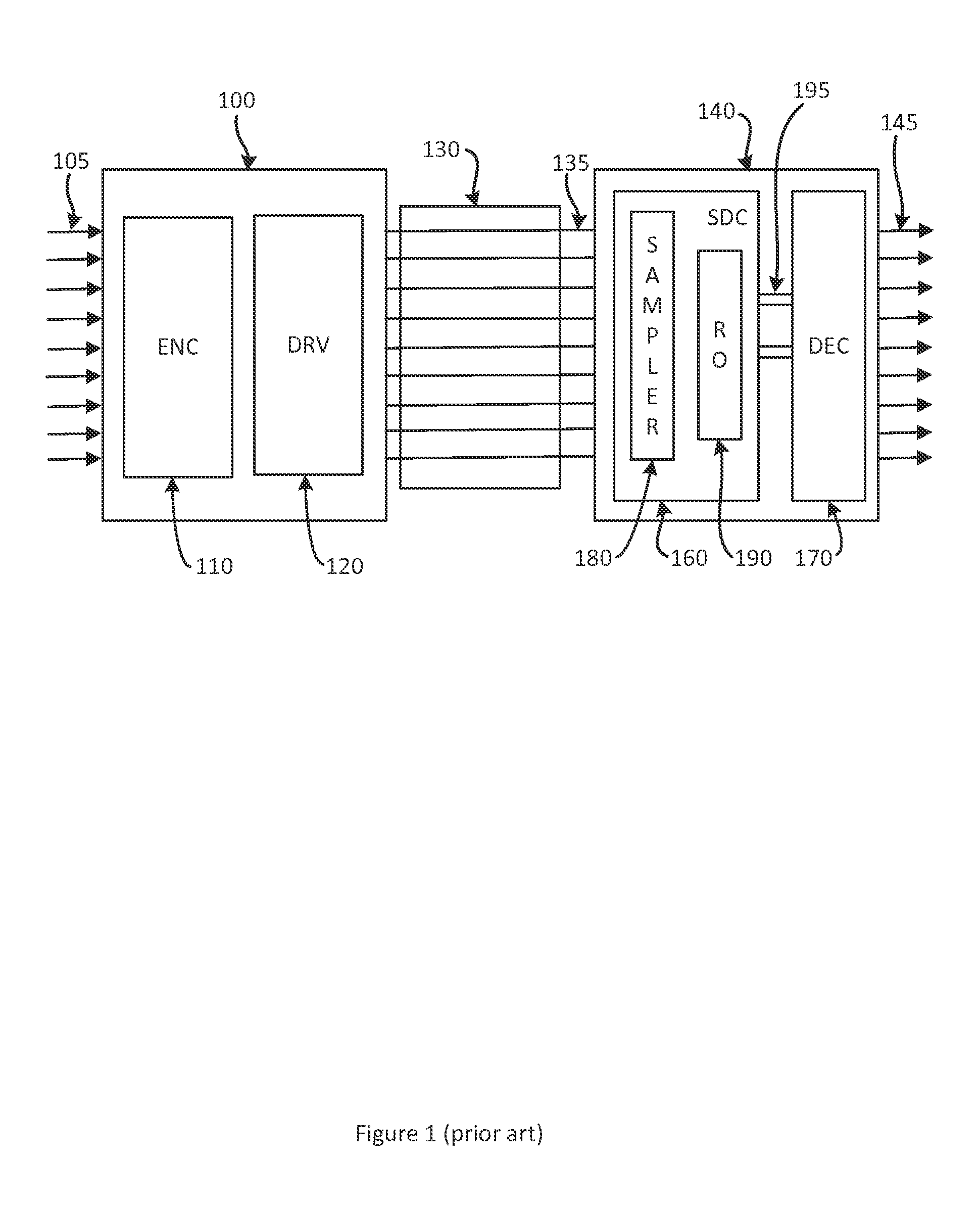

Crossbar switch decoder for vector signaling codes

ActiveUS8989317B1Efficient and effectiveAmplitude demodulation by homodyne/synchrodyne circuitsAmplitude-modulated carrier systemsCrossbar switchData set

An efficient decoding of vector signaling codes is obtained using a circuit that ranks received signal levels, designates ranked values as representing particular code elements, and translates those particular code elements into a decoded result. An optimized ranking circuit combines analog crossbar switching of signal values with comparators that provide digital results. These elements may be repetitively tiled into processing arrays capable of larger ranking operations, or iteratively applied to selected portions of the data set under control of a sequencer or controller.

Owner:KANDOU LABS

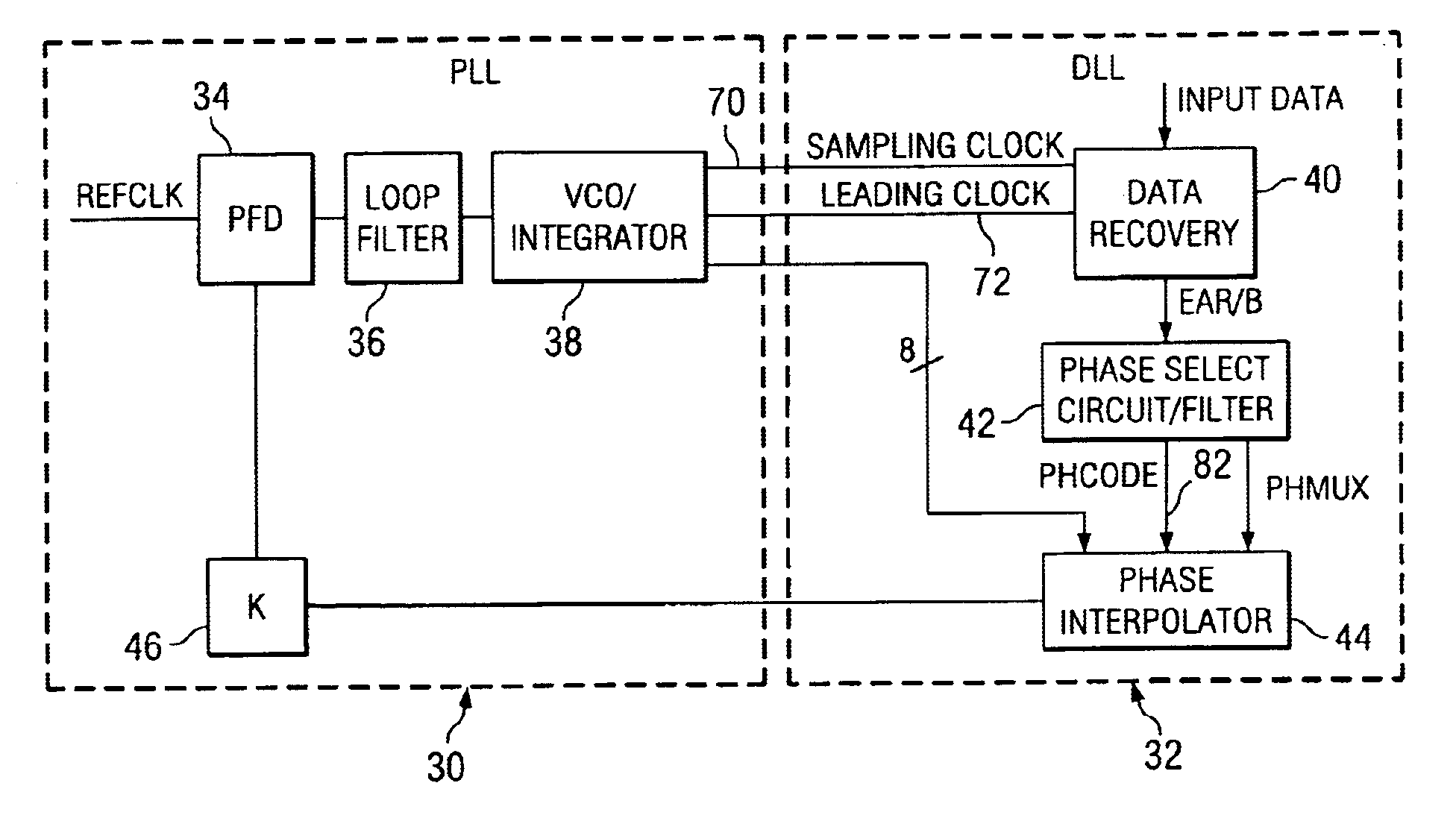

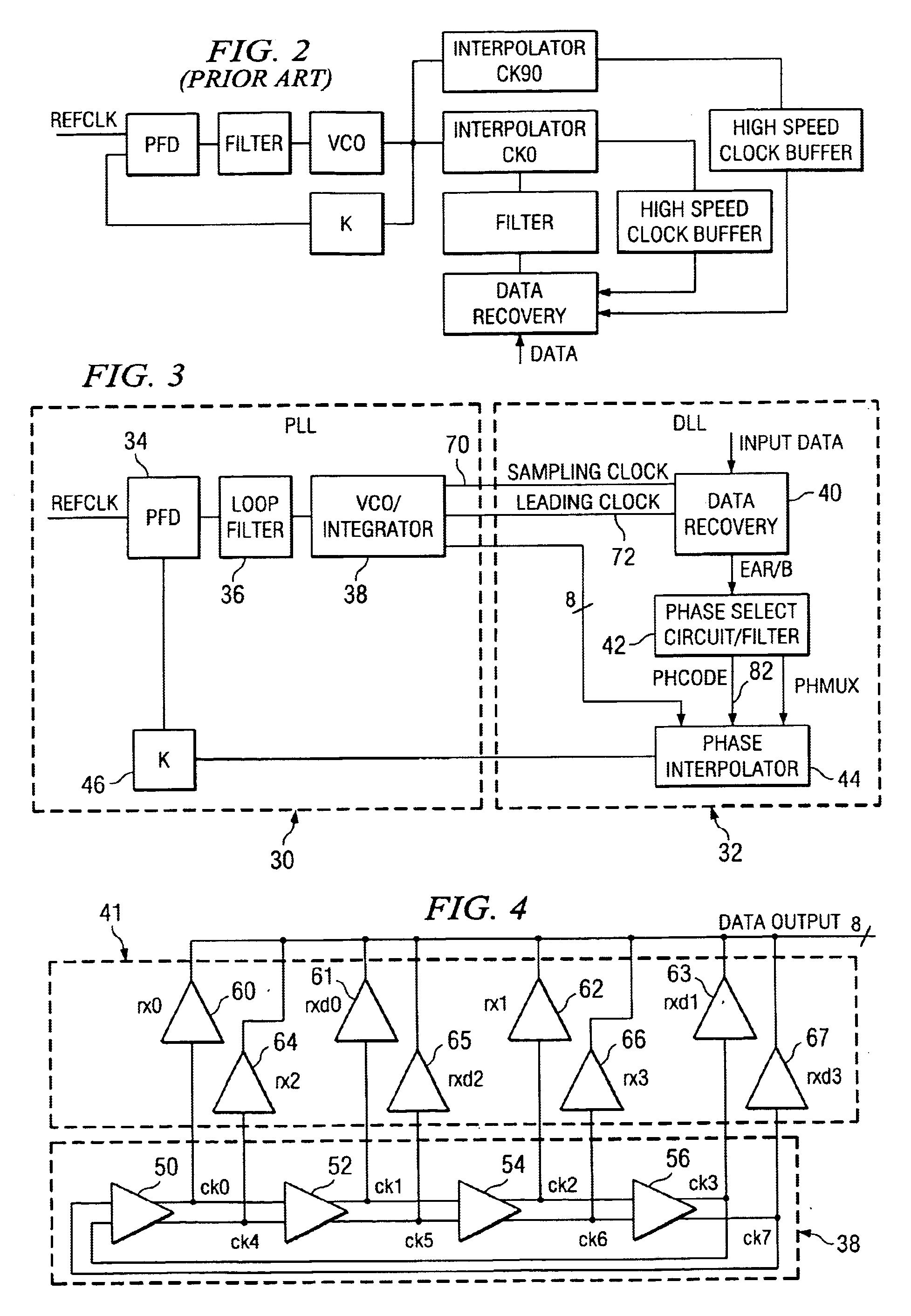

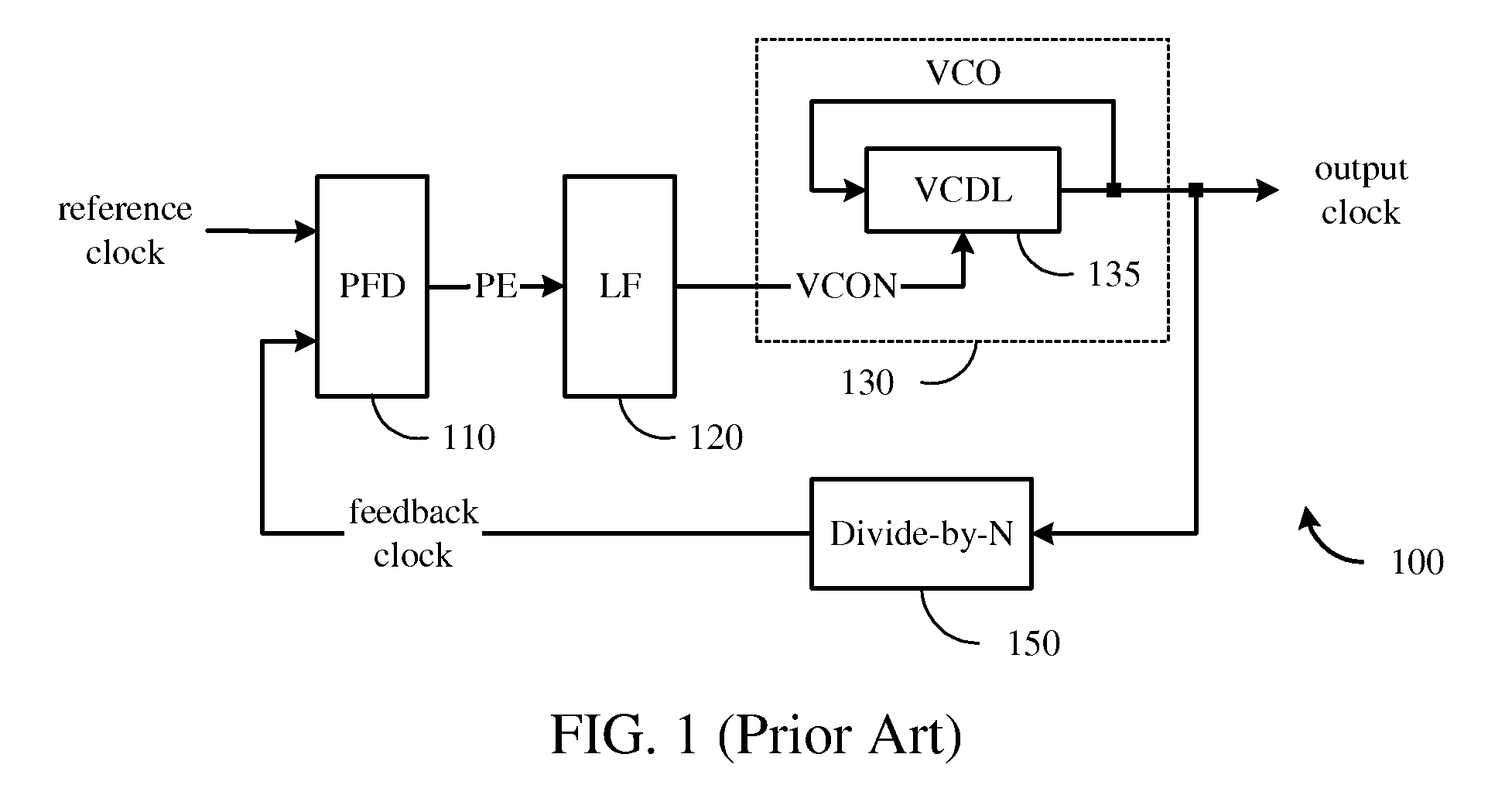

Time division multiplex data recovery system using close loop phase and delay locked loop

InactiveUS6901126B1Alleviate duty cycle issuesHigh bandwidthPulse automatic controlAngle demodulation by phase difference detectionDelay-locked loopClosed loop

A time division multiplex data recovery system using a closed-loop phase lock loop (PLL) and delay locked loop (DLL) is disclosed. In other words, one closed loop comprises both a phase locked loop (PLL) and a delay locked loop (DLL) in a novel time division multiplex data recovery system. This new architecture comprises a 4 stage Voltage Controlled Oscillator (VCO) used to generate 8 clock signals, 45 degrees phase shifted from one another, for 8 receivers to do the oversampling. An interpolator tracks the received data signal and feeds it back to the Phase / Frequency Detector (PFD). The PFD has a second input of the reference clock which the PFD uses along with the interpolator input to correct the frequency of the PLL. The PLL operates at a high bandwidth. The DLL's bandwidth is several orders lower than the PLL. The DLL activates only a multiplexer and an interpolator continuously, thereby drawing a minimum amount of power.

Owner:TEXAS INSTR INC

Transmitter circuit, receiver circuit, clock data recovery phase locked loop circuit, data transfer method and data transfer system

ActiveUS7535957B2Reduce errorsData transmission is stableTelevision system detailsFrequency/rate-modulated pulse demodulationDigital dataPhase locked loop circuit

[Problems] To realize a reliable and stable transfer of digital data that does not require a reference clock and a handshake operation.[Means for Solving the Problem] The present invention provides a digital data transfer method for alternately and periodically transferring first information and second information respectively in a first period and in a second period, wherein: an amount of information of the first information per unit time in the first period is greater than an amount of information of the second information per unit time in the second period; and the second information in the first period is transferred as pulse-width-modulated serial data.

Owner:THINE ELECTRONICS

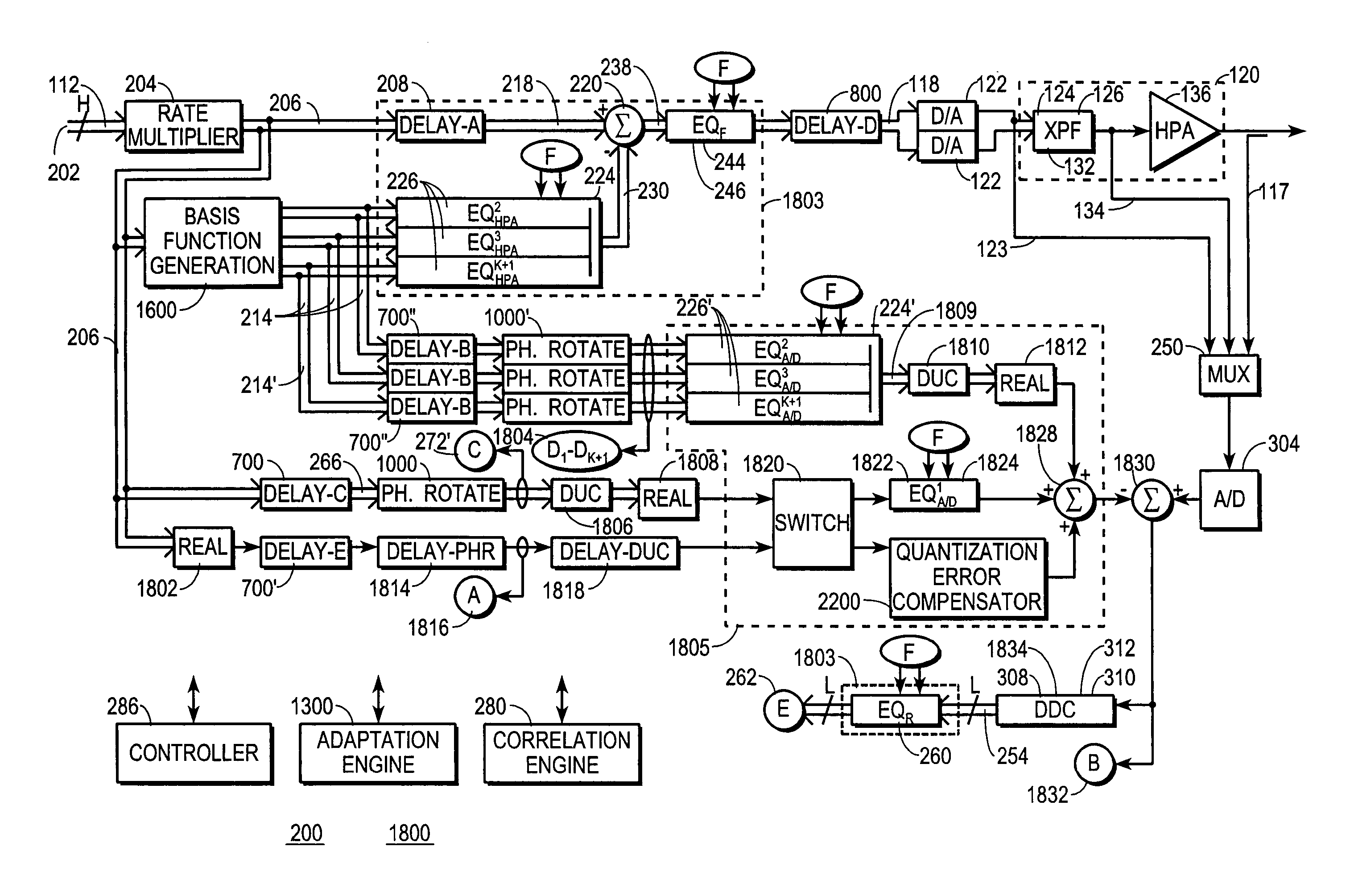

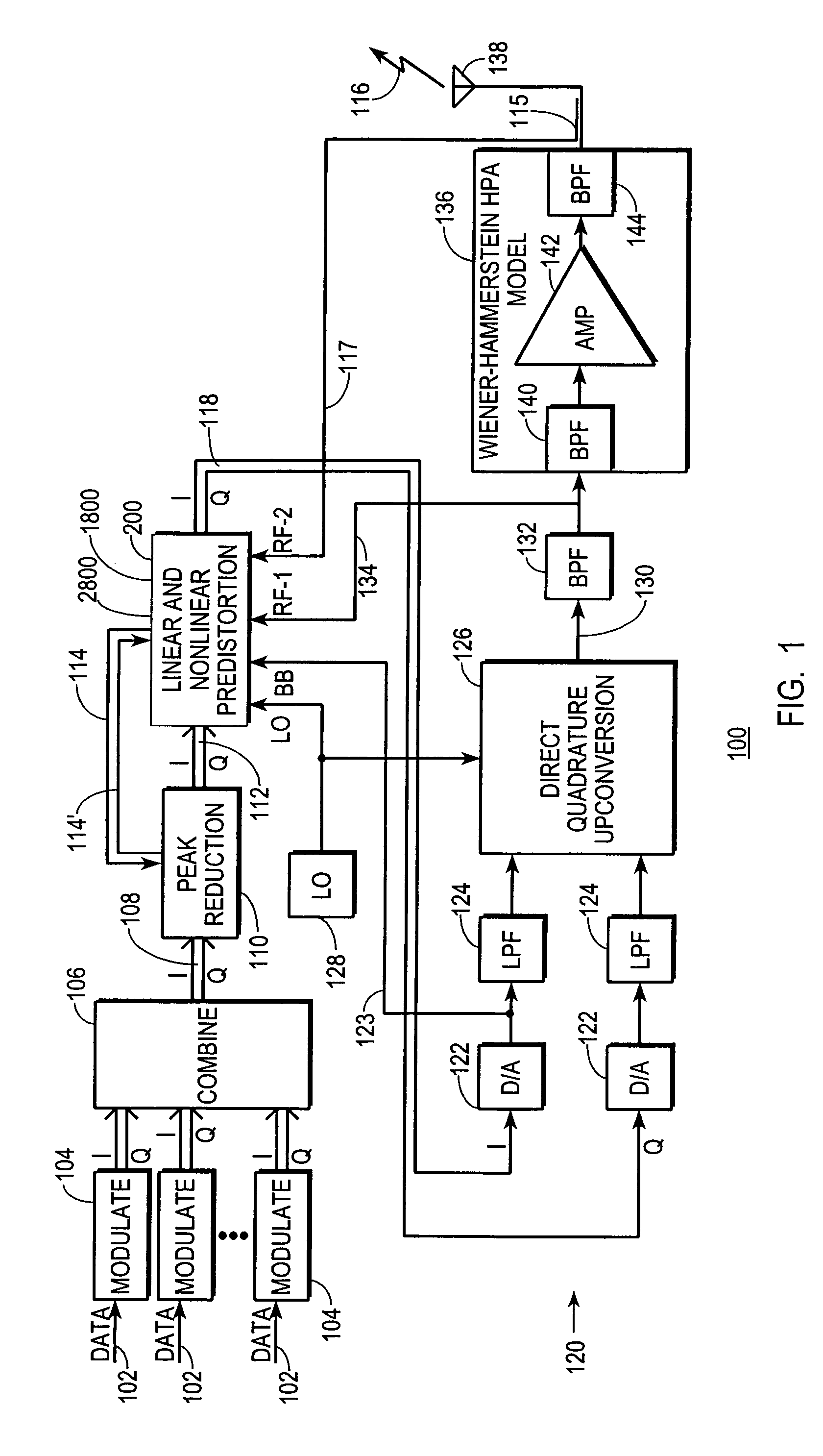

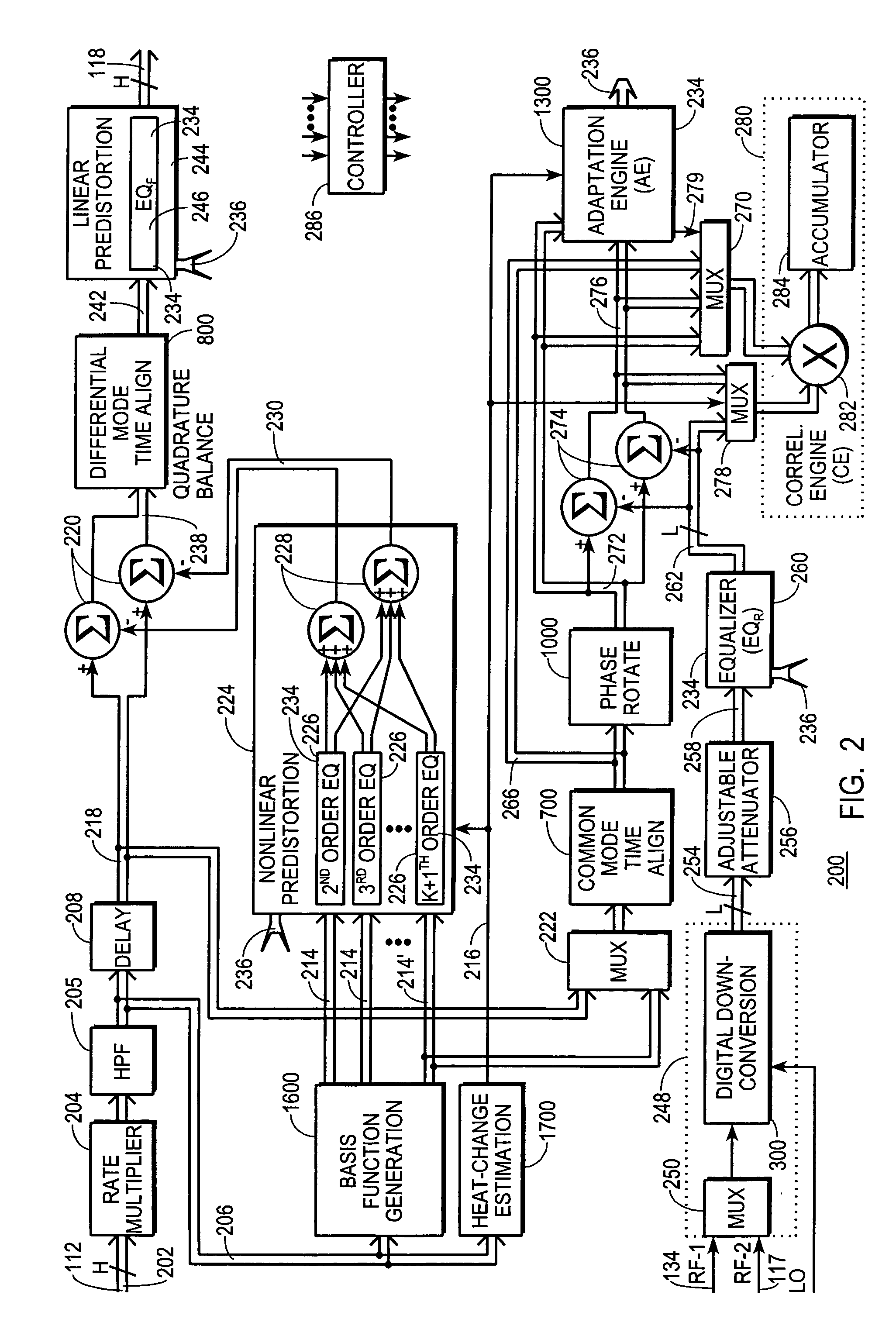

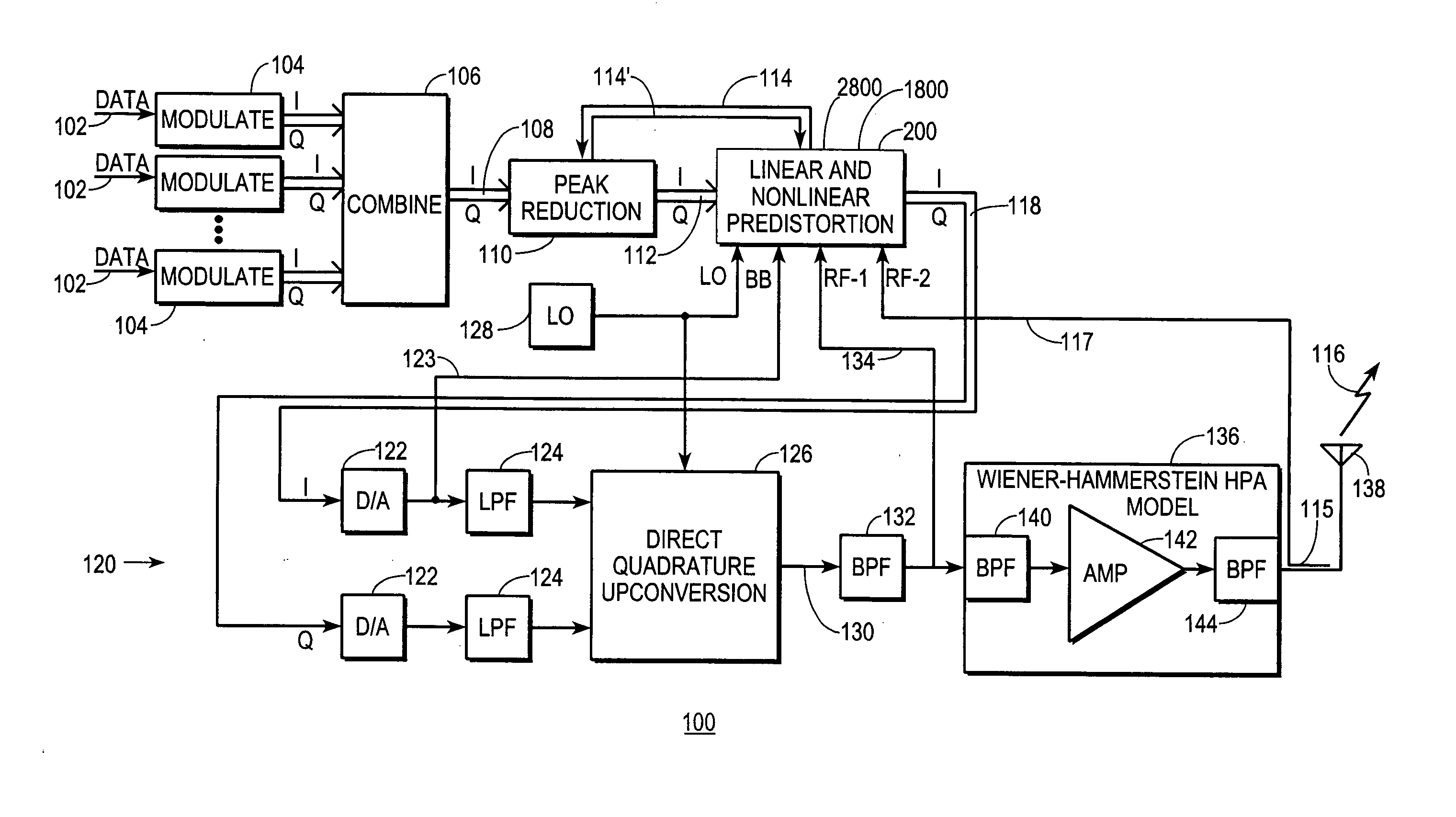

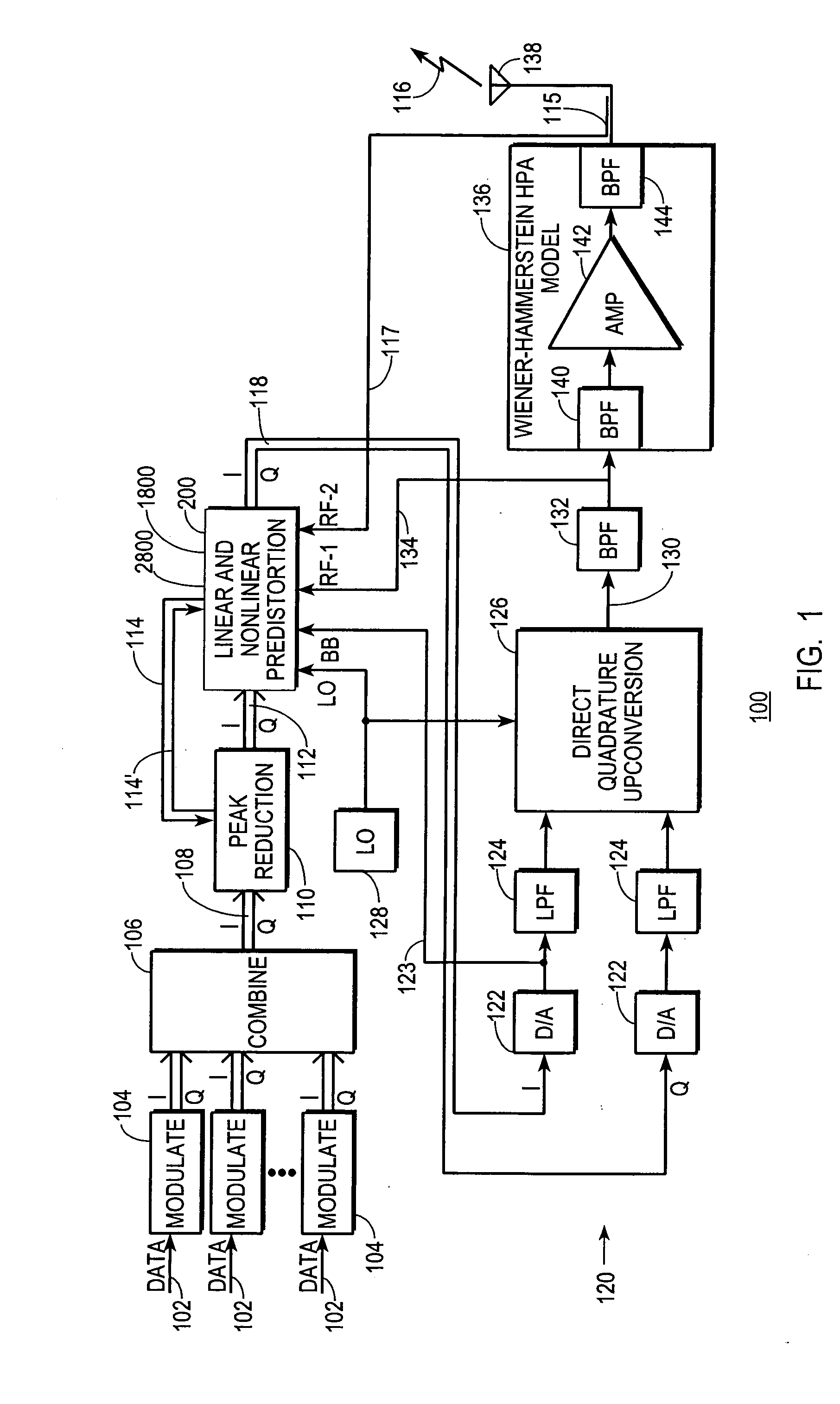

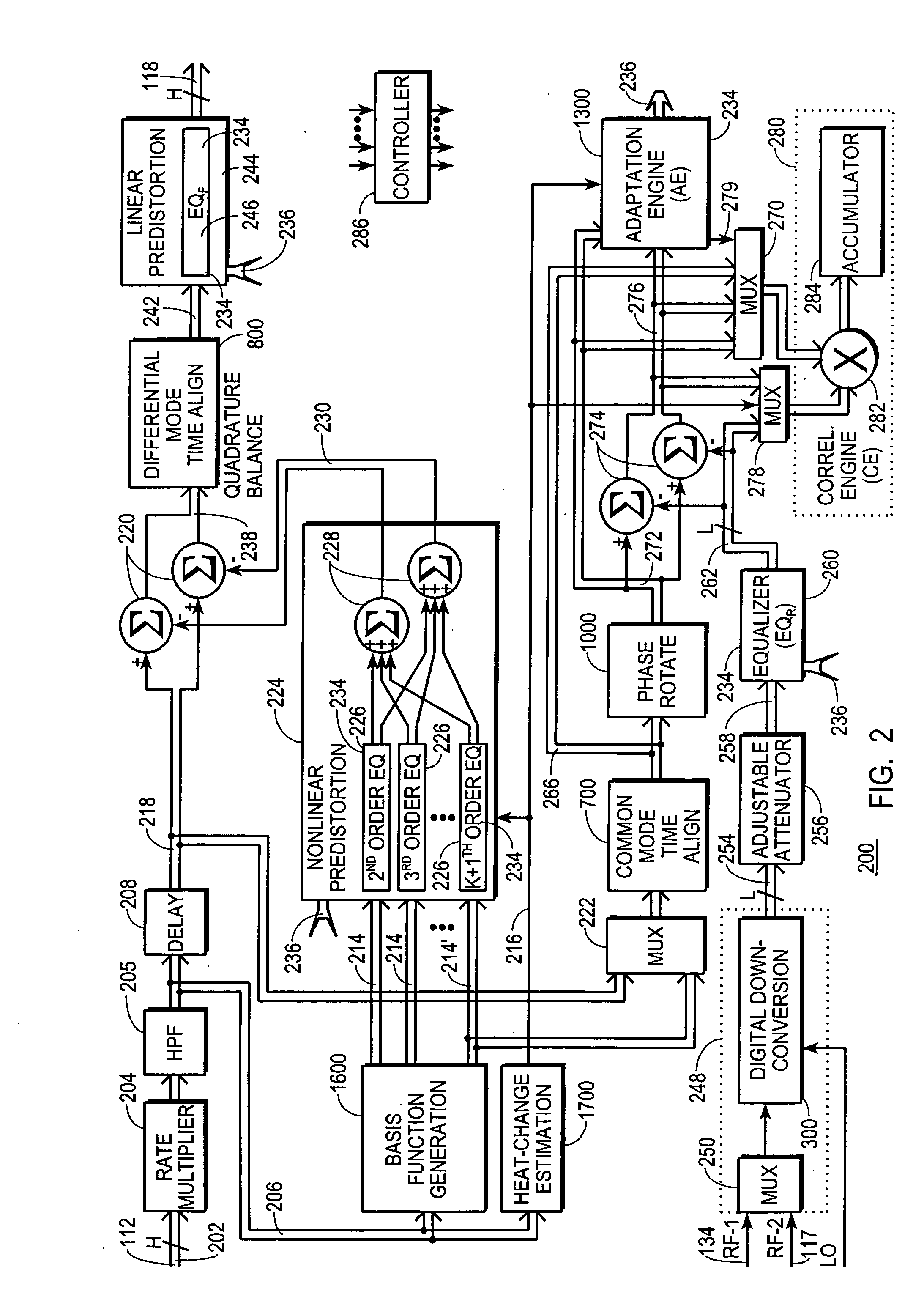

Transmitter predistortion circuit and method therefor

InactiveUS7469491B2Compensation DistortionMultiple-port networksPower amplifiersNonlinear distortionData stream

A digital communications transmitter (100) includes a digital linear-and-nonlinear predistortion section (200, 1800, 2800) to compensate for linear and nonlinear distortion introduced by transmitter-analog components (120). A direct-digital-downconversion section (300) generates a complex digital return-data stream (254) from the analog components (120) without introducing quadrature imbalance. A relatively low resolution exhibited by the return-data stream (254) is effectively increased through arithmetic processing. Distortion introduced by an analog-to-digital converter (304) may be compensated using a variety of adaptive techniques. Linear distortion is compensated using adaptive techniques with an equalizer (246) positioned in the forward-data stream (112). Nonlinear distortion is then compensated using adaptive techniques with a plurality of equalizers (226) that filter a plurality of orthogonal, higher-ordered-basis functions (214) generated from the forward-data stream (112). The filtered-basis functions are combined together and subtracted from the forward-data stream (112).

Owner:CRESTCOM INC

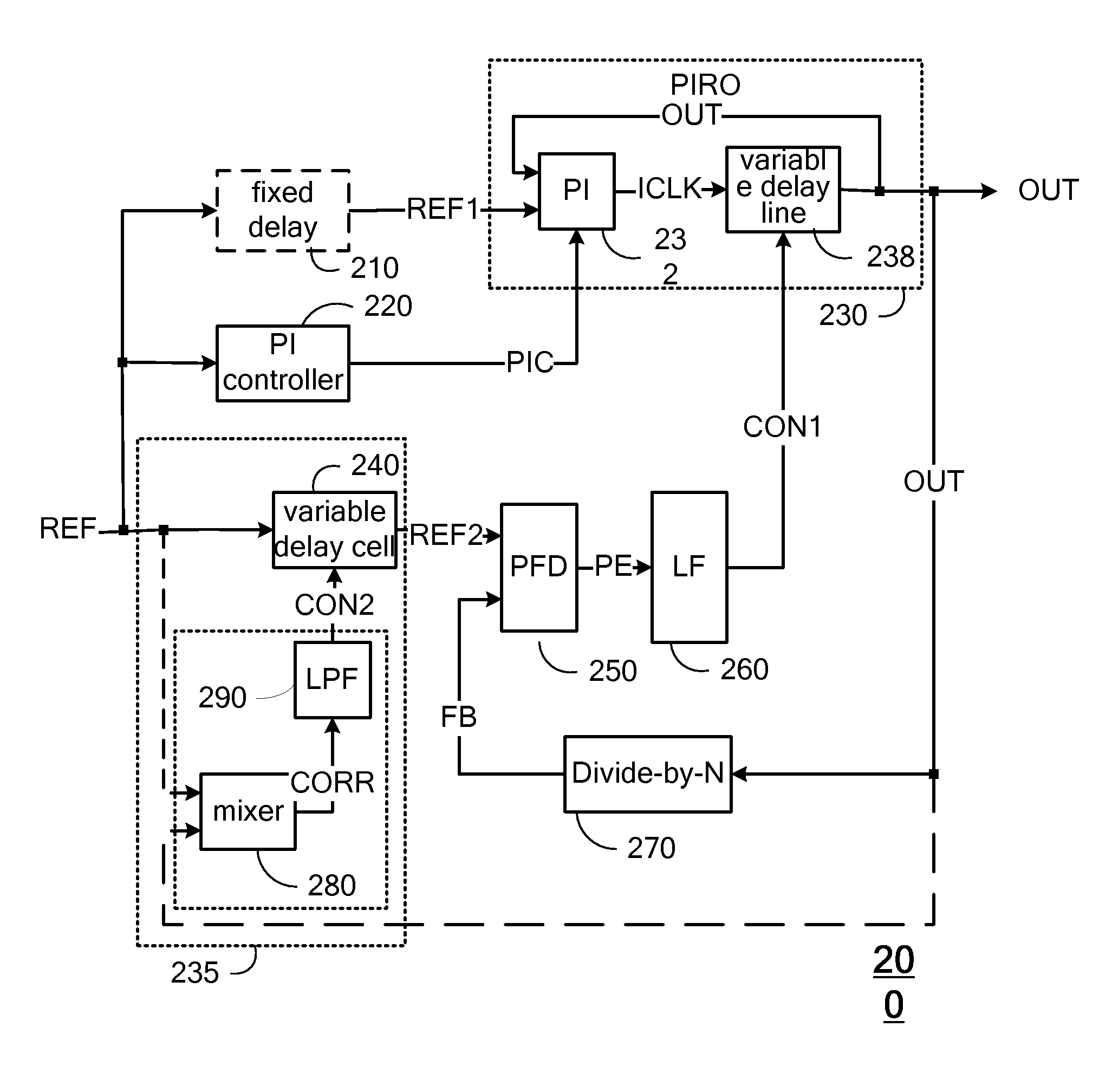

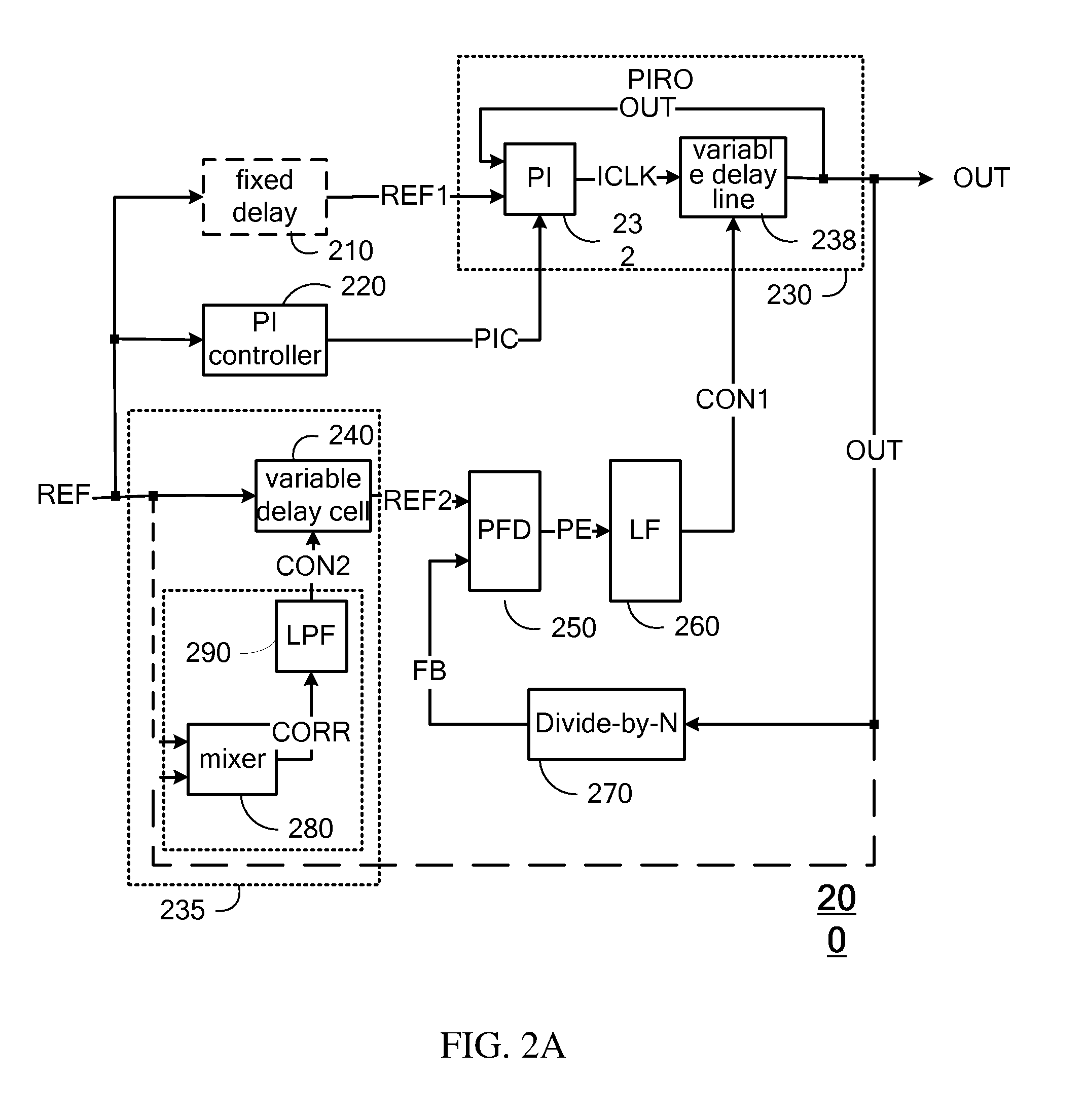

Phase lock loop with phase interpolation by reference clock and method for the same

The present invention relates to a PLL that utilizes a phase interpolation by a reference clock. The PLL includes a phase-interpolated controller for generating a phase-interpolation control signal; a phase / frequency detector for detecting a phase difference between a second reference clock and a feedback clock and outputting a phase error signal to represent the phase difference; a loop filter for filtering the phase error signal to generate a first control signal; a phase-interpolated oscillator for generating an output clock under a control by the phase-interpolation control signal and the first control signal; and a divide-by-N circuit for dividing down the output clock by a factor of N to generate the feedback clock, where N is an integer.

Owner:REALTEK SEMICON CORP

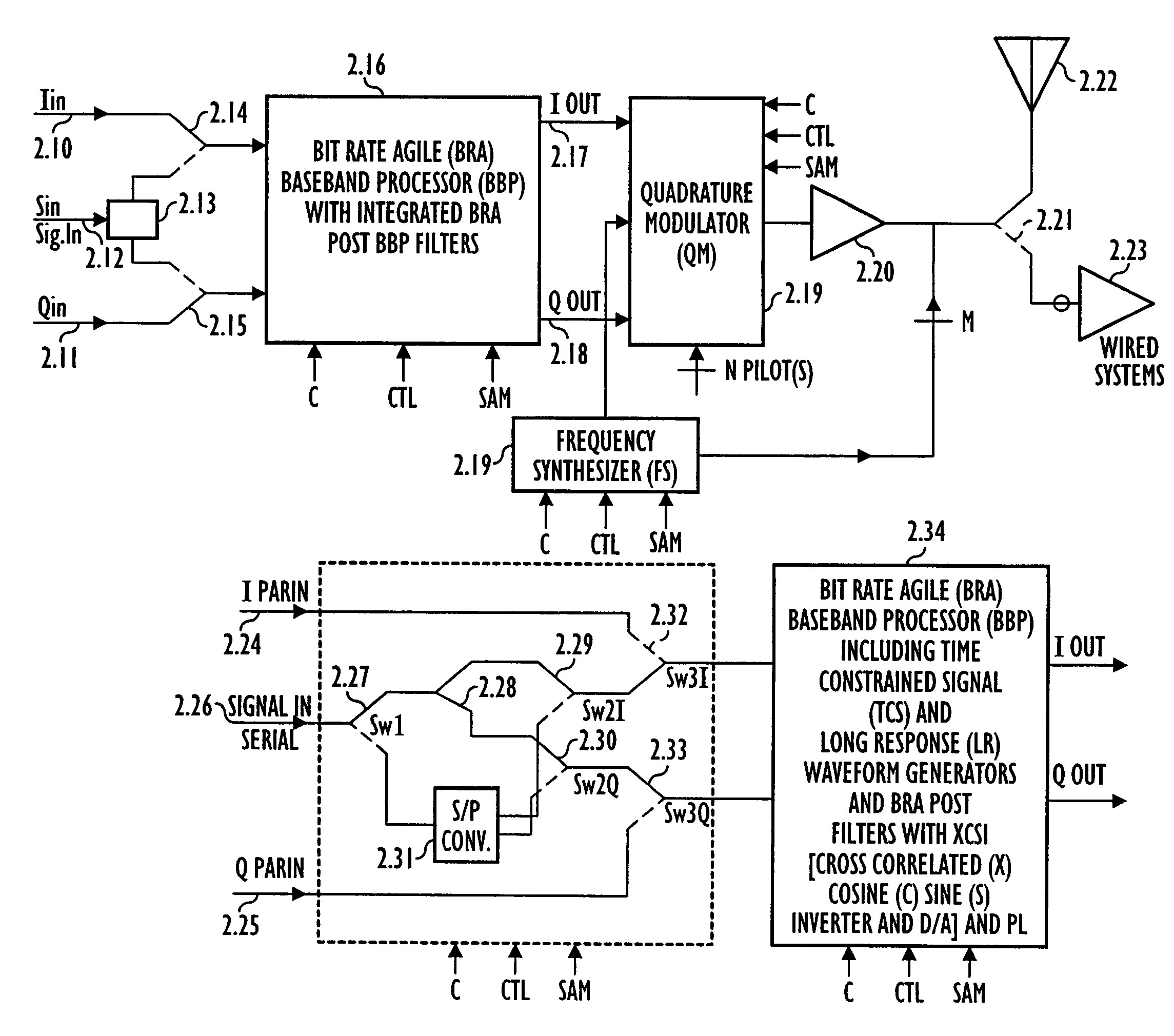

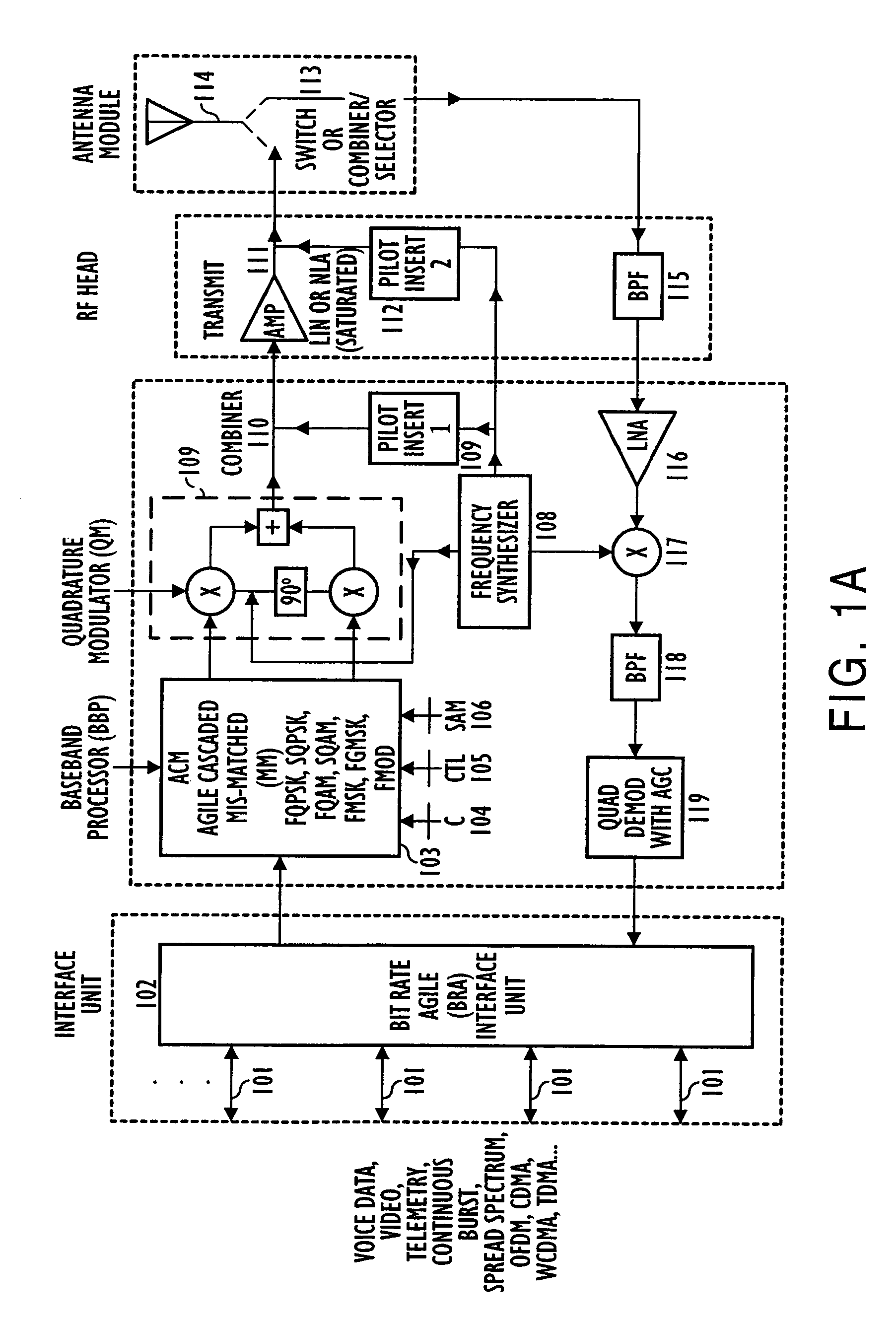

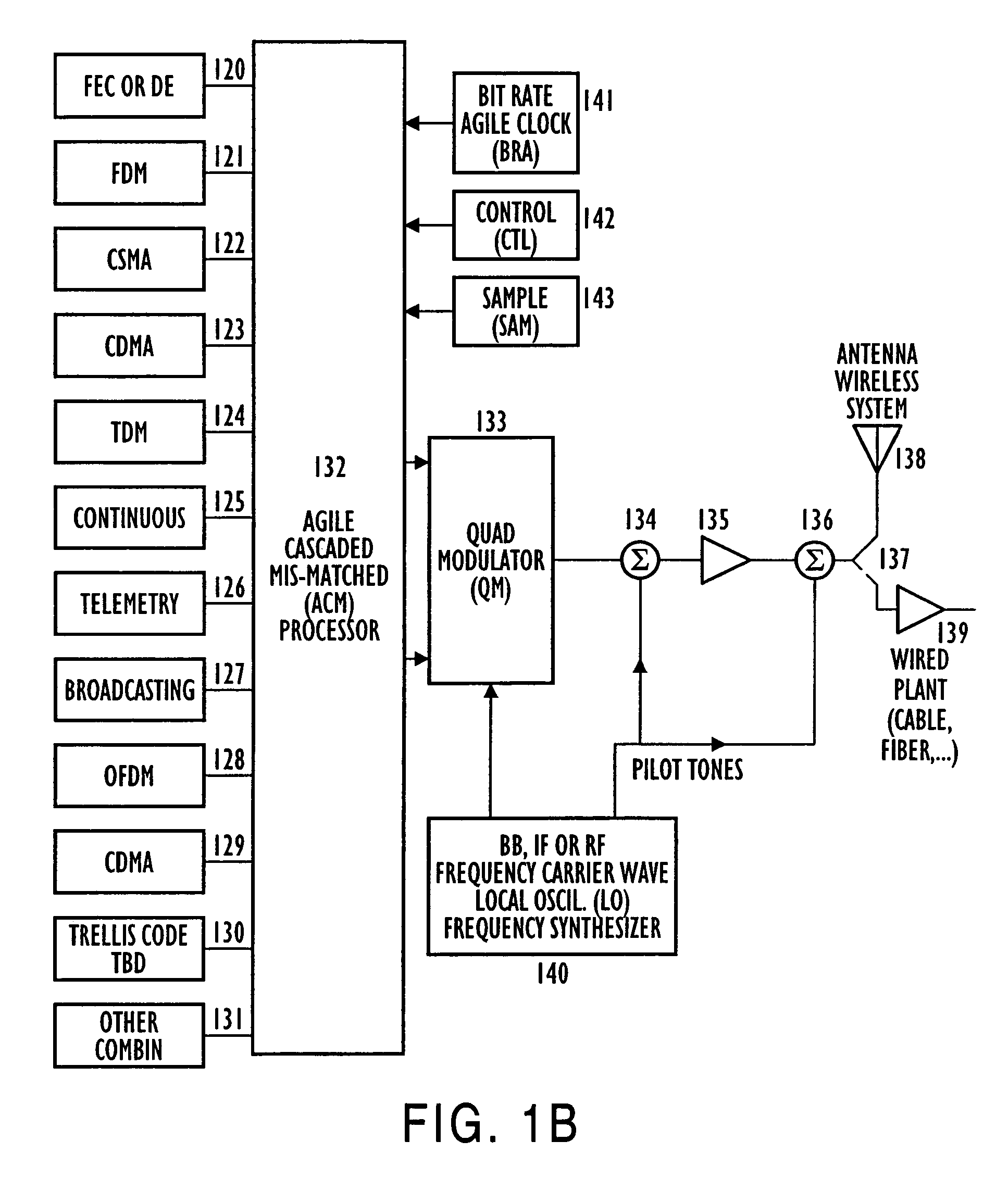

Adaptive receivers for bit rate agile (BRA) and modulation demodulation (modem) format selectable (MFS) signals

InactiveUS7376180B2Improve performanceSignificant spectral saving advantageMultiple-port networksSecret communicationModem deviceThird generation

Systems, apparatus, and methods for new generations of wireless systems, including multiple standard, interoperable Third-Generation (3G) and Second-Generation (2G), Spread Spectrum CDMA, WCDMA, GSM, Enhanced GSM systems and CSMA, TDMA and OFDM. Bit Rate Agile (BRA), Modulation and Code Selectable processing techniques of Gaussian Minimum Shift Keying (GMSK), Quadrature Phase Shift Keying (QPSK), Quadrature Amplitude Modulation (QAM), and of Mis-Matched demodulator filters in which the demodulator filter set is mismatched to the filter set of the signal modulator.

Owner:FEHER KAMILO

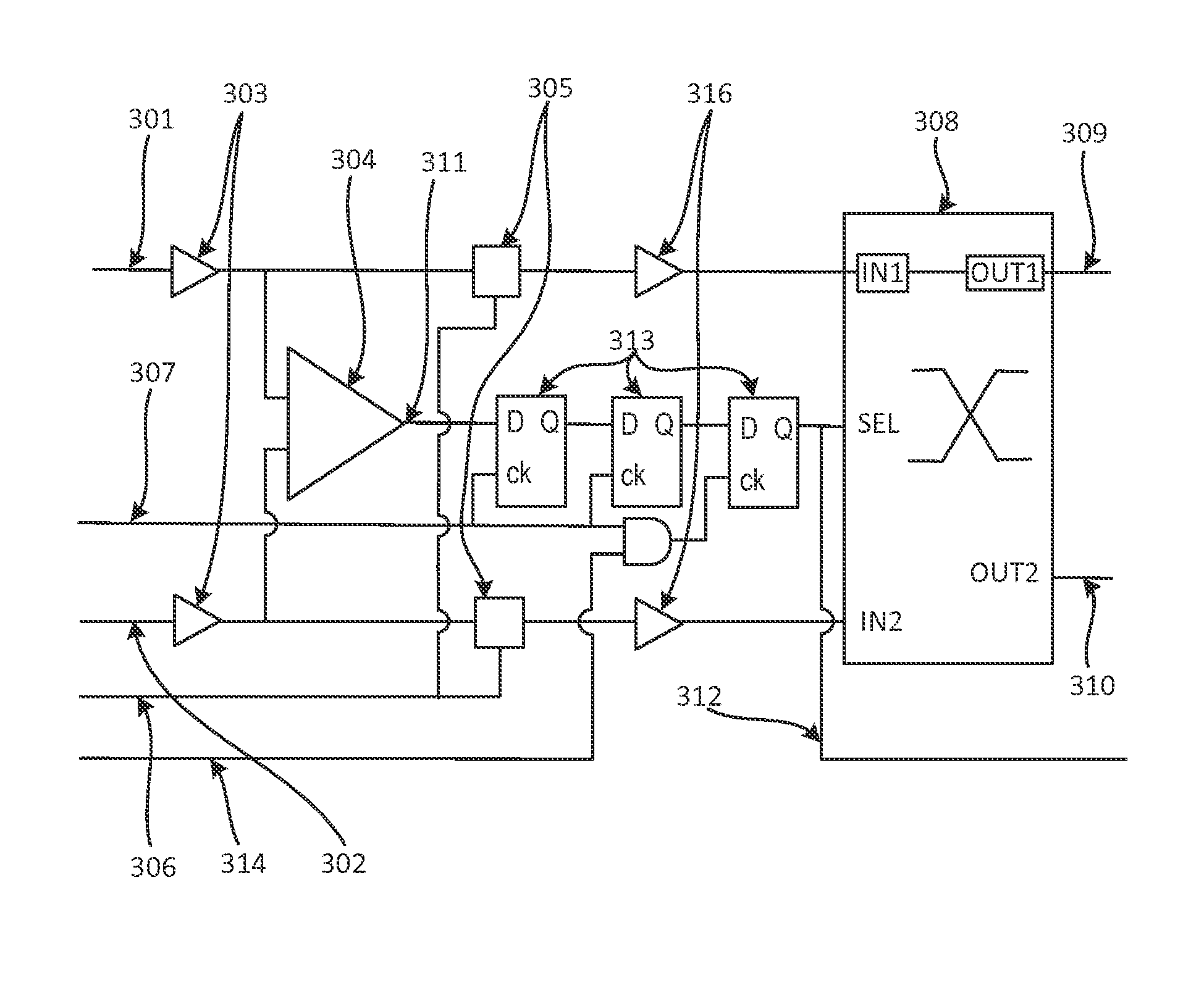

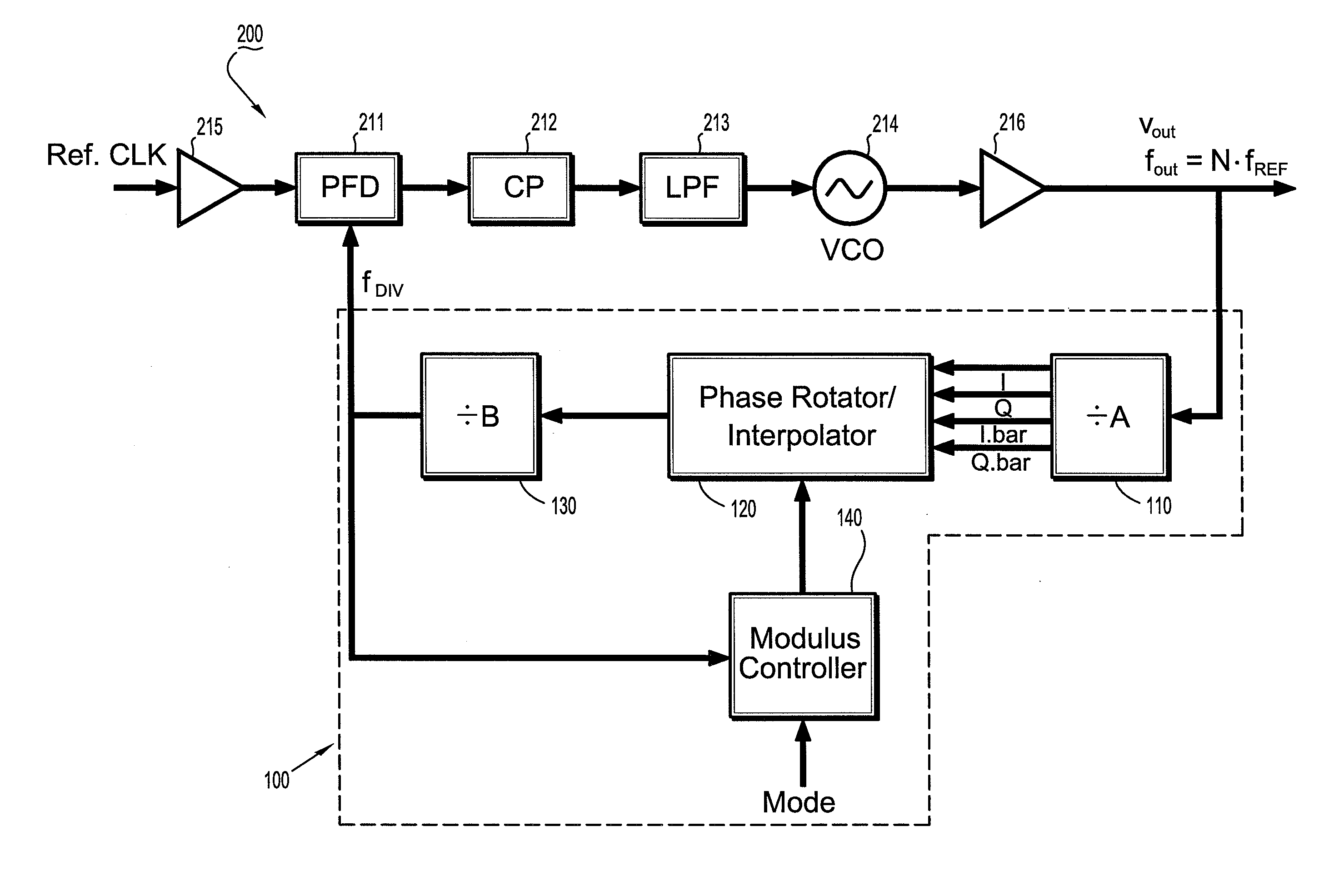

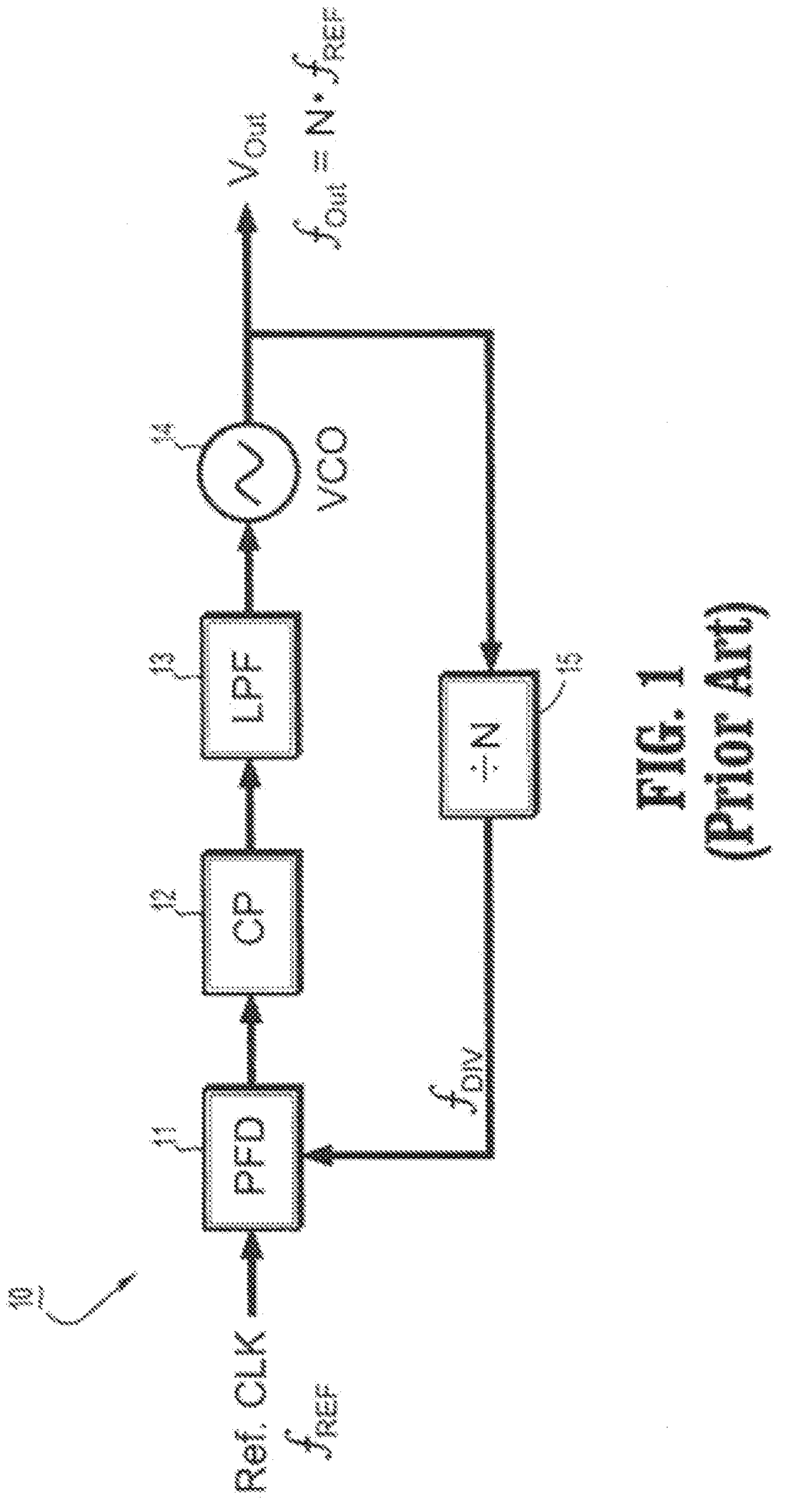

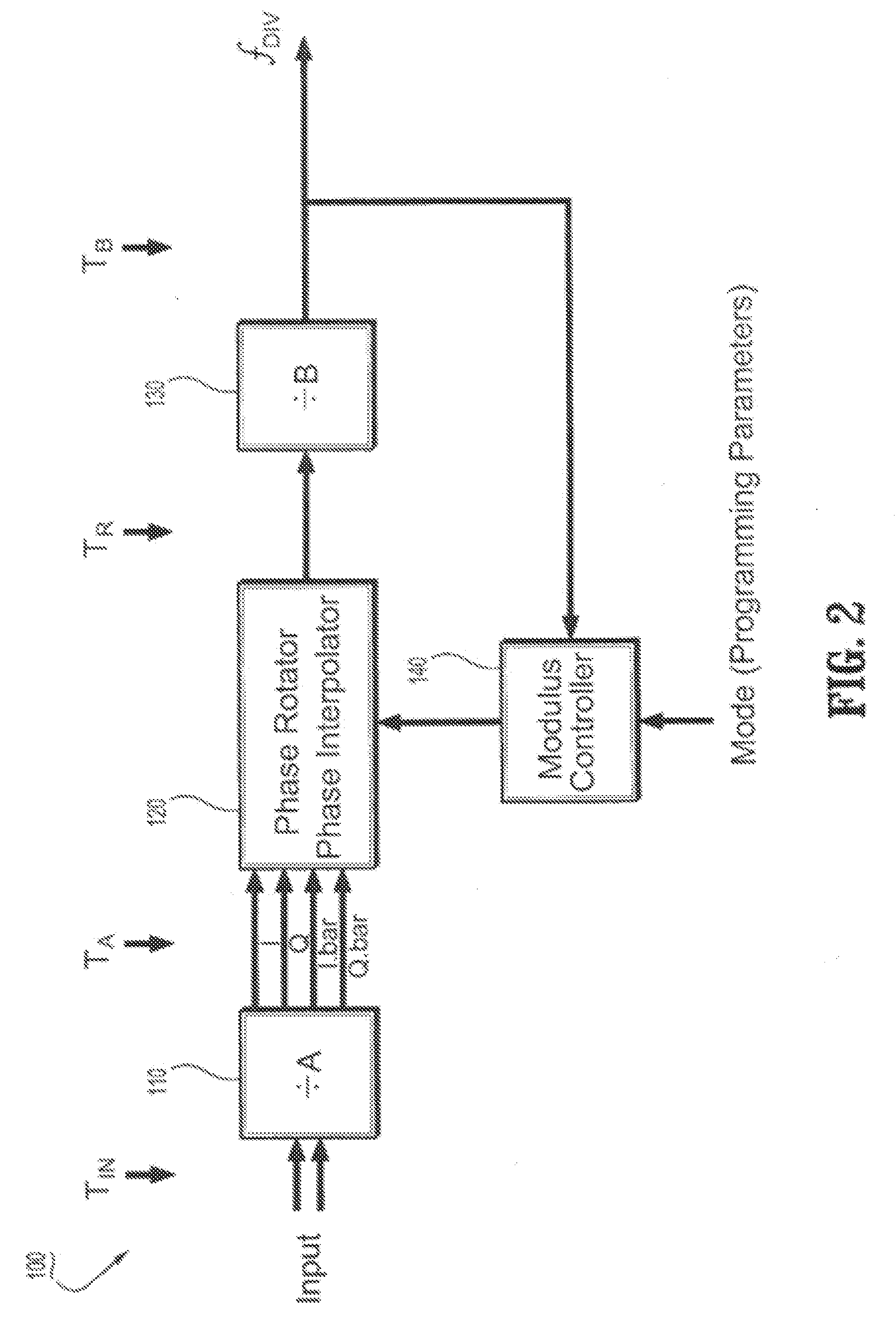

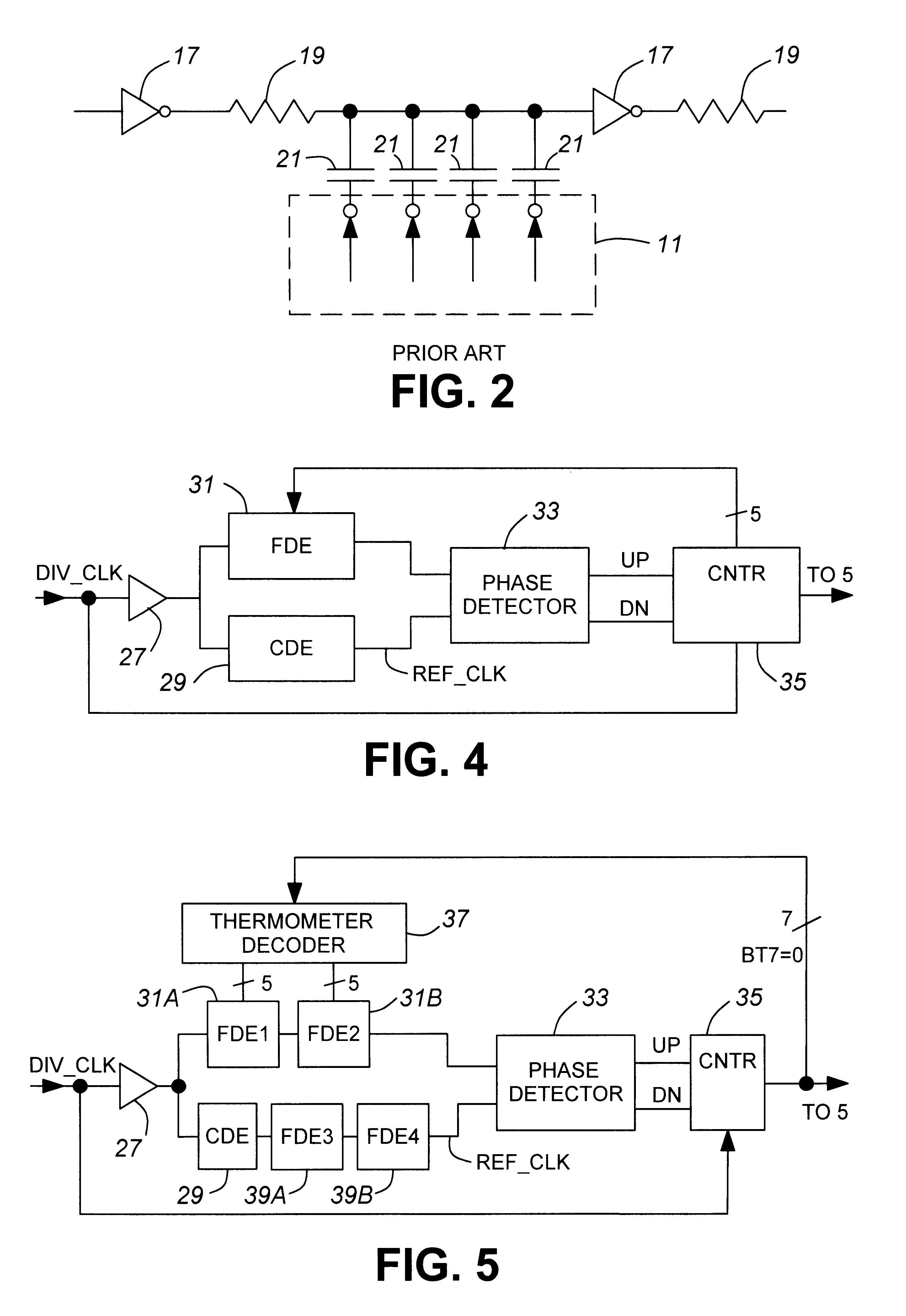

Circuits and methods for implementing sub-integer-n frequency dividers using phase rotators

ActiveUS20080164917A1Reduce and eliminate glitch in output signalPulse automatic controlCounting chain pulse countersFrequency synthesizerFrequency divider

Circuits and methods are provided for implementing programmable sub-integer N frequency dividers for use in, e.g., frequency synthesizer applications, providing glitch free outputs signals with minimal fractional spurs. Phase-rotating sub-integer N frequency dividers are programmable to provide multi-modulus division with a wide range of arbitrary sub-integer division ratios.

Owner:IBM CORP

Transmitter predistortion circuit and method therefor

InactiveUS20050163252A1Easy to optimizeCompensation DistortionMultiple-port networksPower amplifiersNonlinear distortionData stream

A digital communications transmitter (100) includes a digital linear-and-nonlinear predistortion section (200, 1800, 2800) to compensate for linear and nonlinear distortion introduced by transmitter-analog components (120). A direct-digital-downconversion section (300) generates a complex digital return-data stream (254) from the analog components (120) without introducing quadrature imbalance. A relatively low resolution exhibited by the return-data stream (254) is effectively increased through arithmetic processing. Distortion introduced by an analog-to-digital converter (304) may be compensated using a variety of adaptive techniques. Linear distortion is compensated using adaptive techniques with an equalizer (246) positioned in the forward-data stream (112). Nonlinear distortion is then compensated using adaptive techniques with a plurality of equalizers (226) that filter a plurality of orthogonal, higher-ordered-basis functions (214) generated from the forward-data stream (112). The filtered-basis functions are combined together and subtracted from the forward-data stream (112).

Owner:CRESTCOM INC

Gain calibration of a digital controlled oscillator

ActiveUS20060033582A1Good estimateImprove performancePulse automatic controlAngle modulation detailsSteep descentDigital control oscillator

A novel apparatus for and a method of estimating, calibrating and tracking in real-time the gain of a radio frequency (RF) digitally controlled oscillator (DCO) in an all-digital phase locked loop (ADPLL). Precise setting of the inverse DCO gain in the ADPLL modulating path allows direct wideband frequency modulation that is independent of the ADPLL loop bandwidth. The gain calibration technique is based on a steepest descent iterative algorithm wherein the phase ADPLL error is sampled and correlated with the modulating data to generate a gradient. The gradient is then scaled and added to the current value of the DCO gain multiplier.

Owner:TEXAS INSTR INC

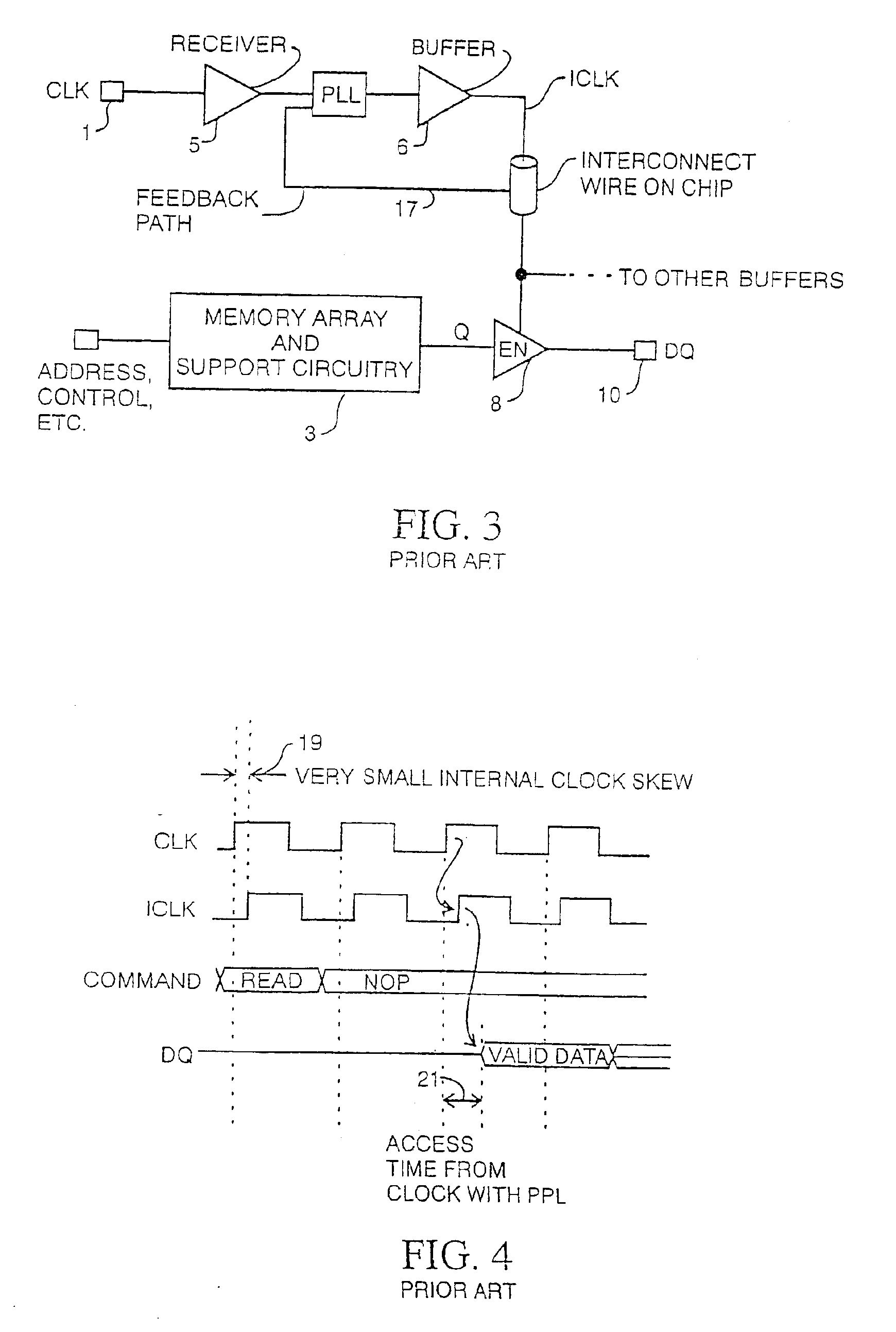

Process, voltage, temperature independent switched delay compensation scheme

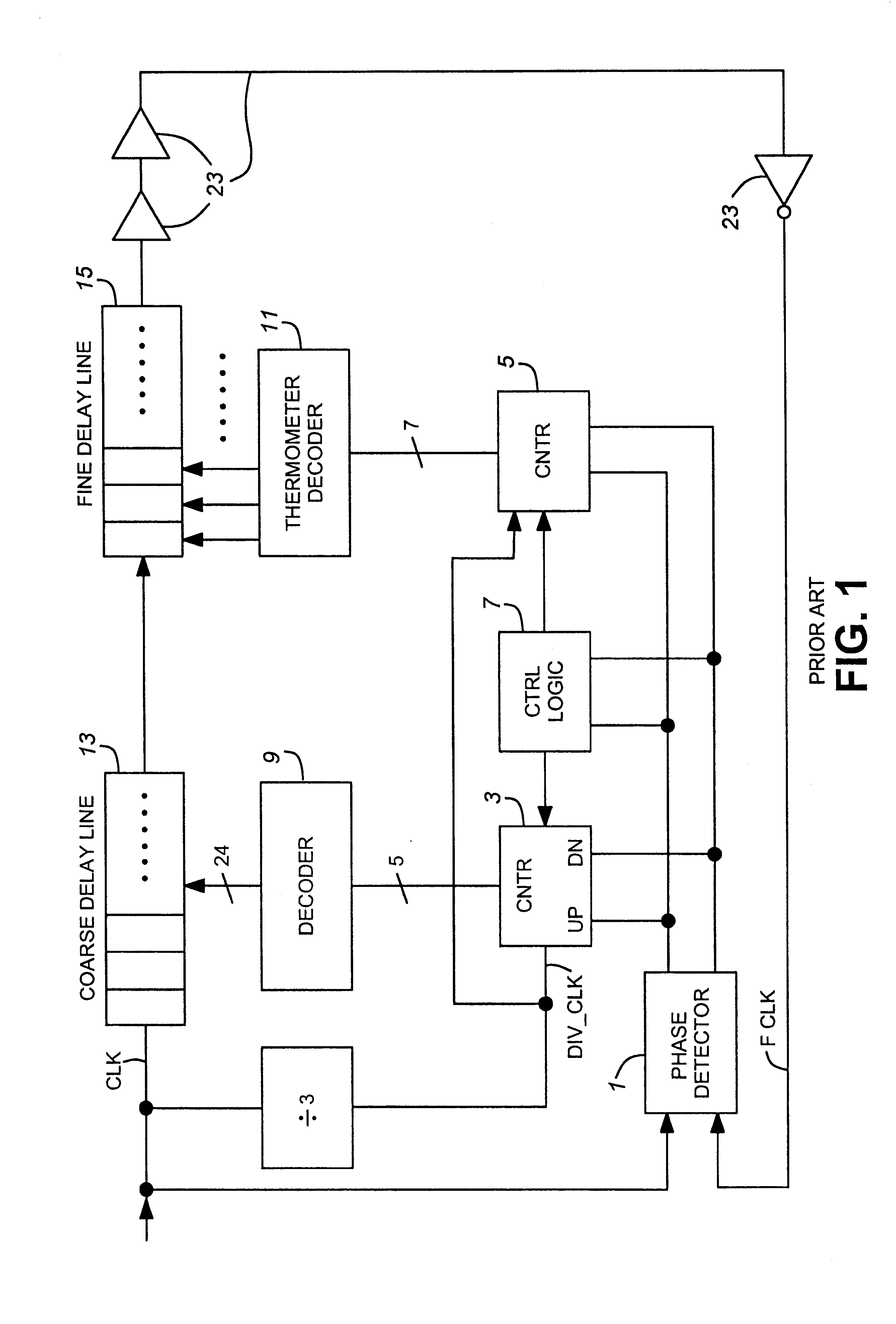

InactiveUS6327318B1Pulse automatic controlAngle demodulation by phase difference detectionDelay-locked loopEngineering

A delay compensation circuit for a delay locked loop which includes a main delay line having a fine delay line comprising fine delay elements and a coarse delay line comprising coarse delay elements, the main delay line being controlled by a controller, the delay compensation circuit comprising: an adjustable fine delay for modeling a coarse delay element, a counter for controlling the adjustable fine delay to a value which is substantially the same as that of a coarse delay element, a circuit for applying a representation of the system clock to the delay compensation circuit, and a circuit for applying the fine delay count from the counter to the controller for adjusting the fine delay line of the main delay line to a value which is substantially the same as that of a coarse delay element of the main delay line.

Owner:CONVERSANT INTPROP MANAGEMENT INC

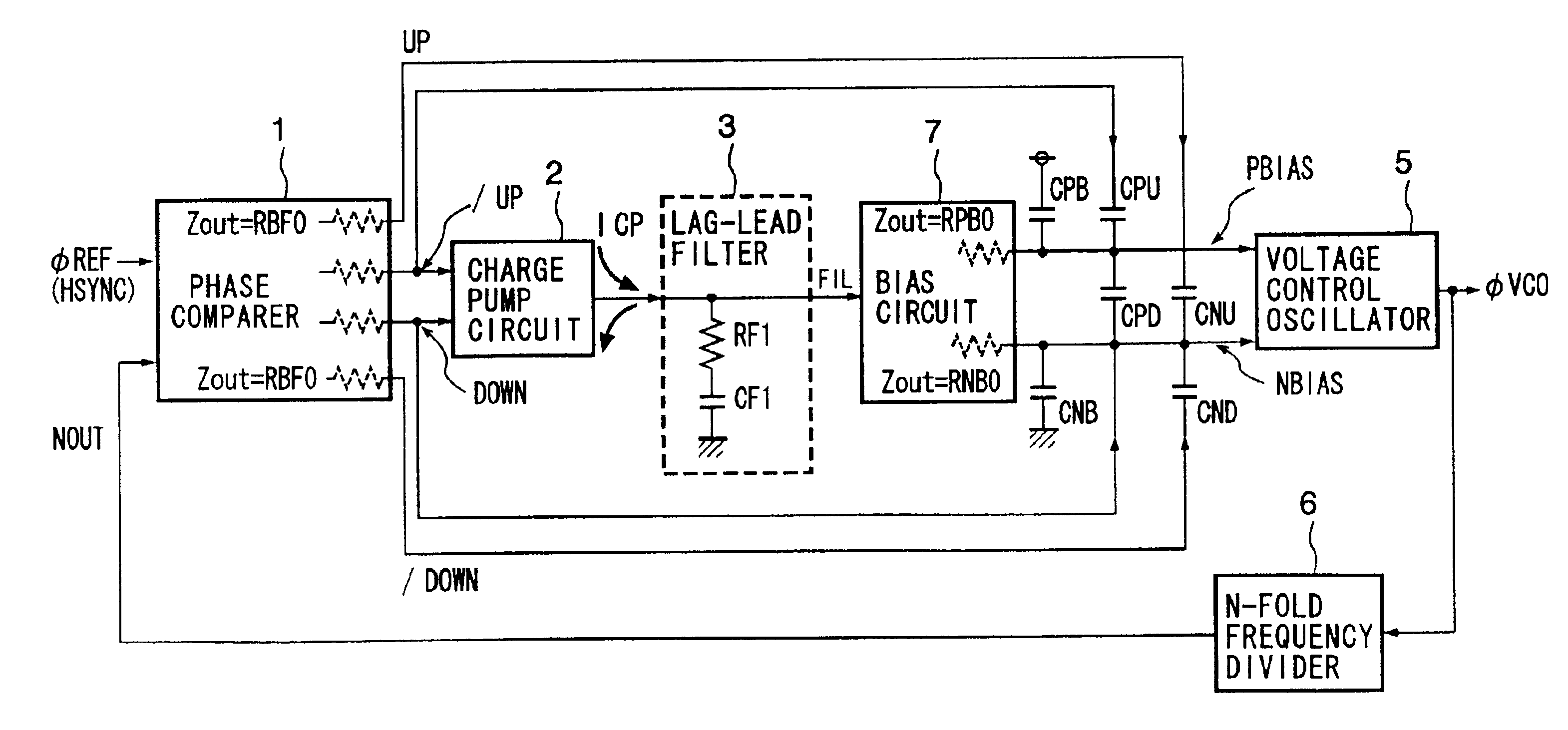

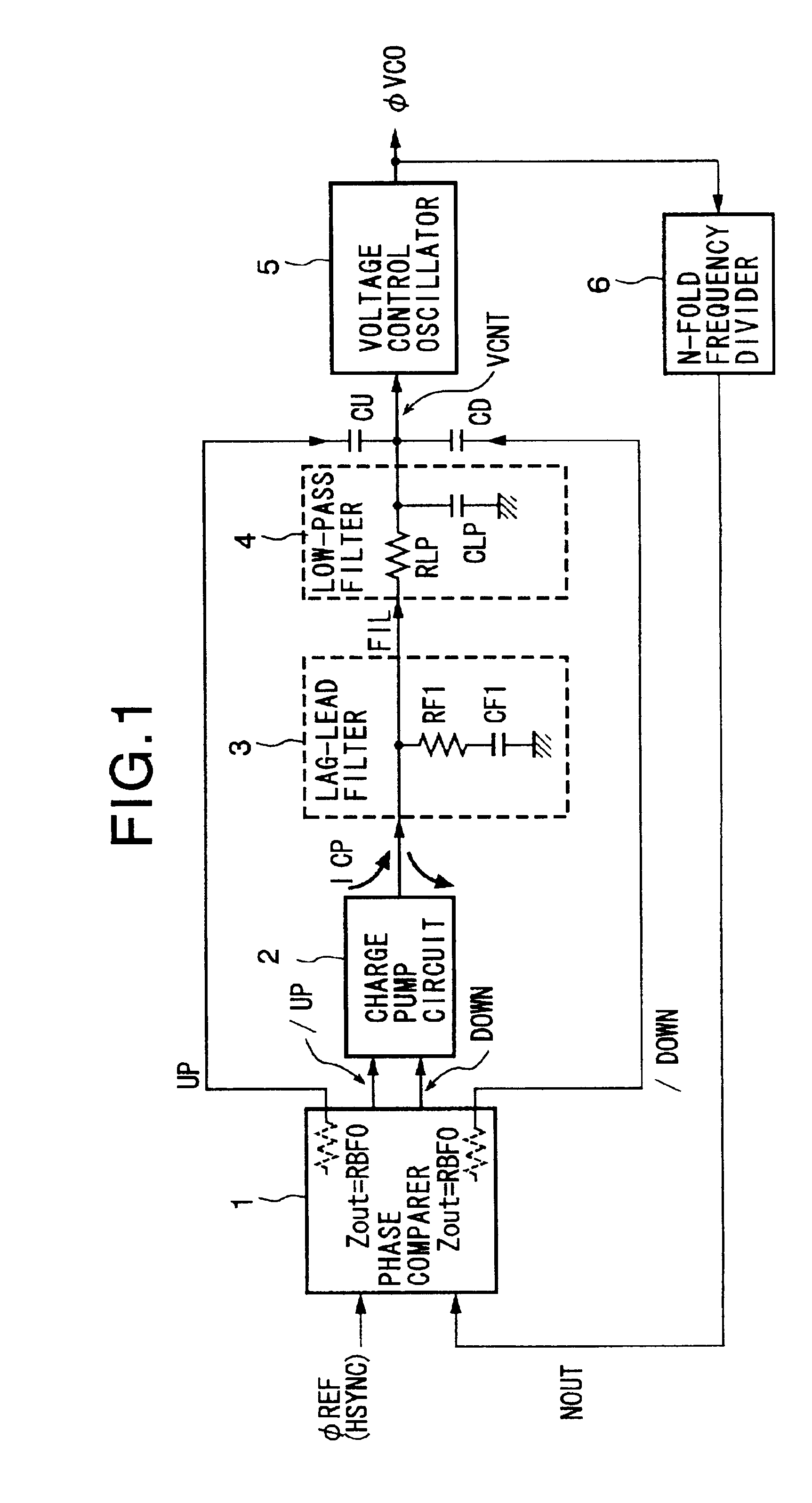

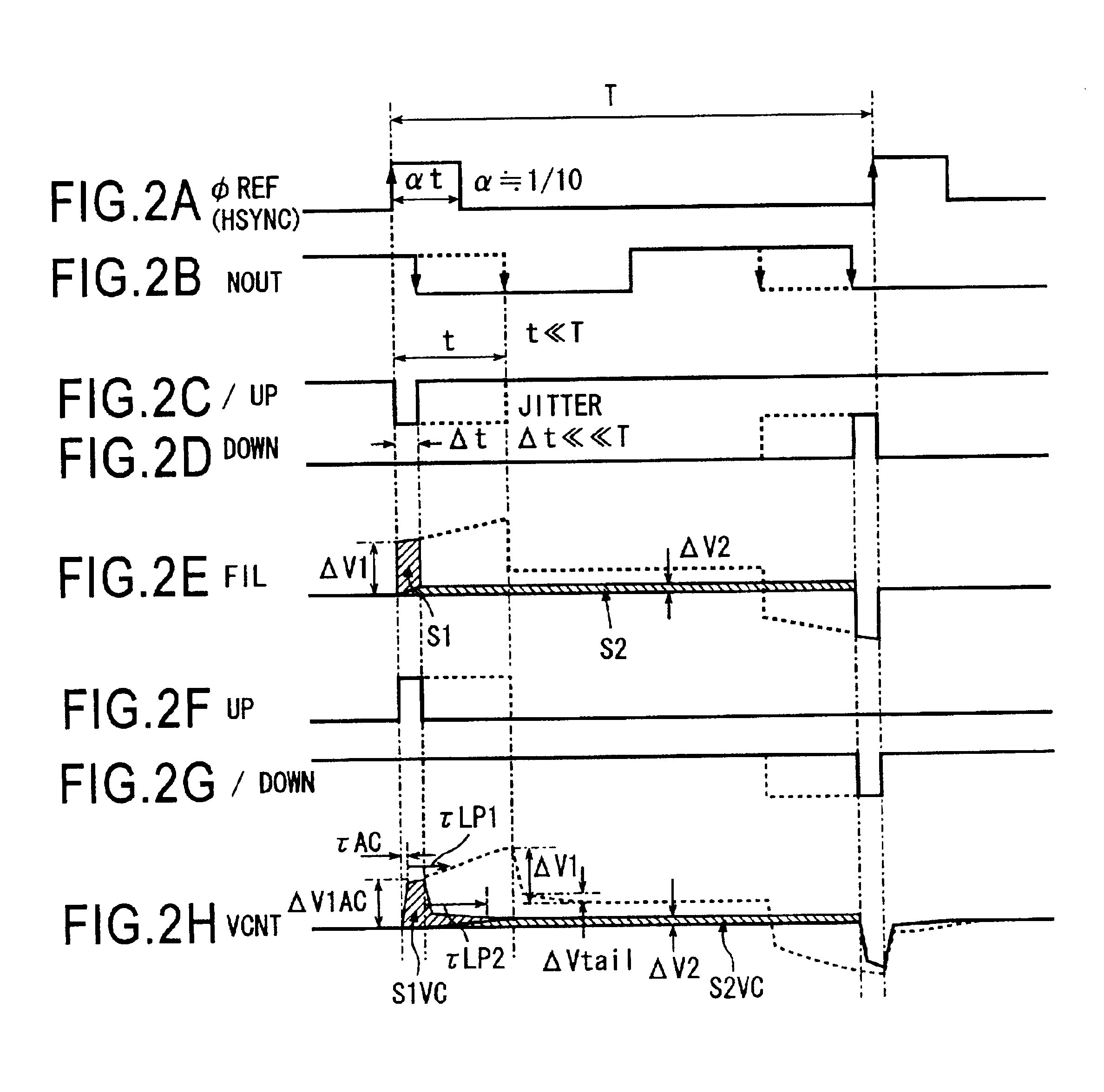

Phase-locked loop circuit and delay-locked loop circuit

InactiveUS6954511B2Reduce changesPulse automatic controlTransmissionPhase locked loop circuitLow-pass filter

A PLL circuit and a DLL circuit able to stabilize a control voltage within a short time after a phase pull-in operation in each cycle of a reference clock. In a phase comparator, the size of a leading phase or a delayed phase of a feedback signal is detected with respect to a reference clock signa, and pulse signals having pulse widths corresponding to the size are output. A current corresponding to the signals is output from a charge pump circuit to a lag-lead filter, and a control voltage obtained by removing noise of the above output is output from a low-pass filter to a voltage-controlled oscillator. Furthermore, through capacitors, pulse signals are superposed on the control voltage, and a sharp waveform is obtained by correcting blunting of the waveform by the low-pass filter. Due to this, the control voltage is stabilized within a short time after a phase pull-in operation in each cycle of the reference clock signal.

Owner:SONY CORP

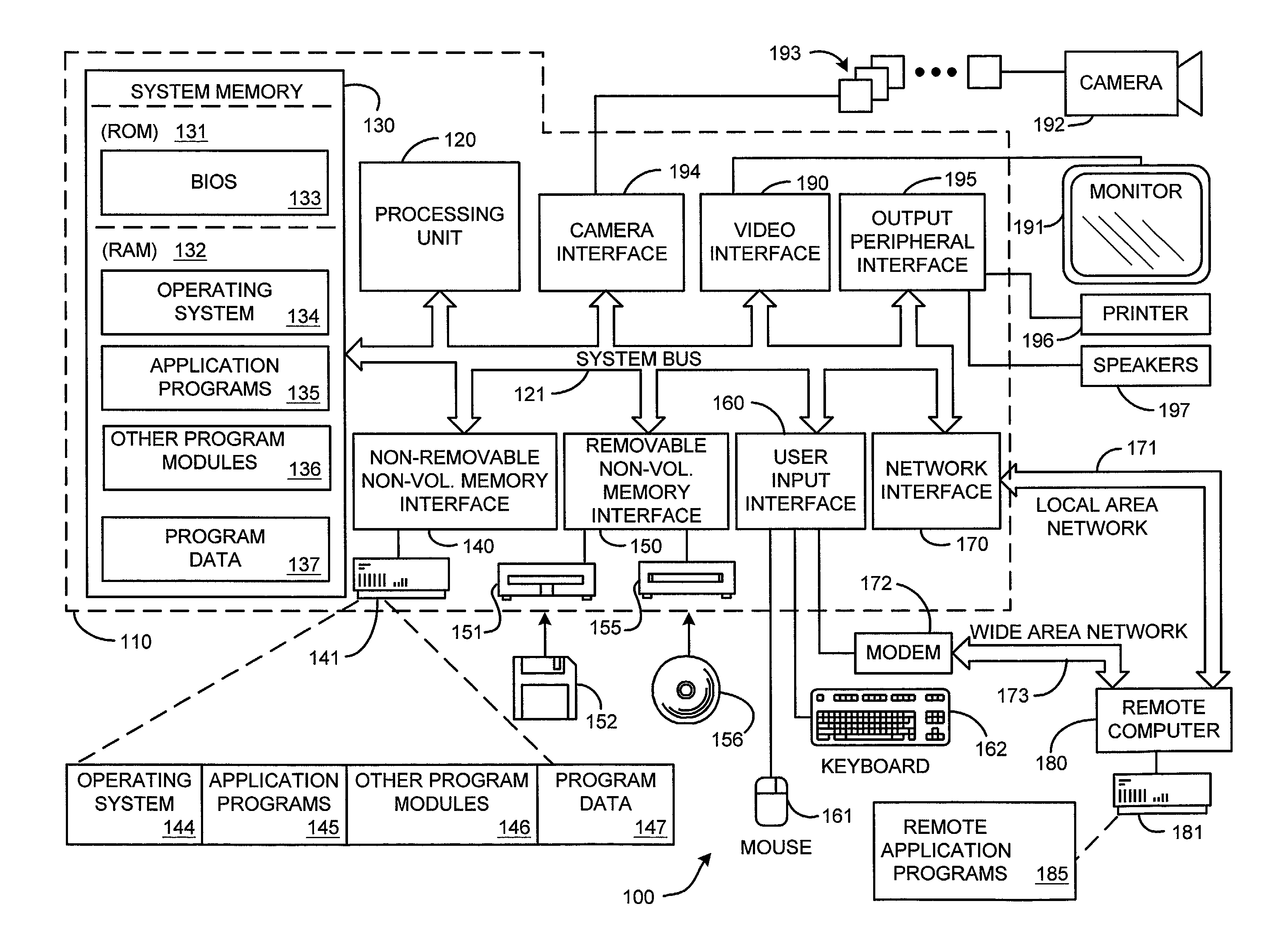

System and process for broadcast and communication with very low bit-rate bi-level or sketch video

InactiveUS20020126755A1Clear imagingLow bandwidthColor television with pulse code modulationColor television with bandwidth reductionComputer graphics (images)Arithmetic coding

A system and process for broadcast and communication with bi-level or sketch video at extremely low bandwidths is described. Essentially, bi-level and sketch video presents the outlines of the objects in a scene being depicted. Bi-level and sketch video provides a clearer shape, smoother motion, shorter initial latency and cheaper computational cost than do conventional DCT-based video compression methods. This is accomplished by converting each color or gray-scale image frame to bi-level or sketch image frame using adaptive thresholding method, compressing bi-level or sketch image frames into bi-level or sketch video using adaptive context-based arithmetic coding method. Bi-level or sketch video is particularly suitable to such small devices as Pocket PCs and mobile phones that possess small display screen, low bandwidth connection, and light computational power.

Owner:ZHIGU HLDG

Linear phase interpolator and phase detector

ActiveUS20090103675A1Pulse automatic controlAngle demodulation by phase difference detectionPhase detectorOperating point

A novel interpolating phase detector for use in a multiphase PLL is described comprising an array of individual phase comparators, all operating at essentially the same operating point which permits the circuits to be designed simultaneously for high speed and for low power consumption. Two adjacent phase outputs of a multi-phase VCO may be selected and interpolated in between, by selectively attaching a variable number of phase comparators to each phase output and summing their phase error outputs. By varying the number of phase comparators attached to each phase output, interpolation can be achieved with high linearity.

Owner:RAMBUS INC

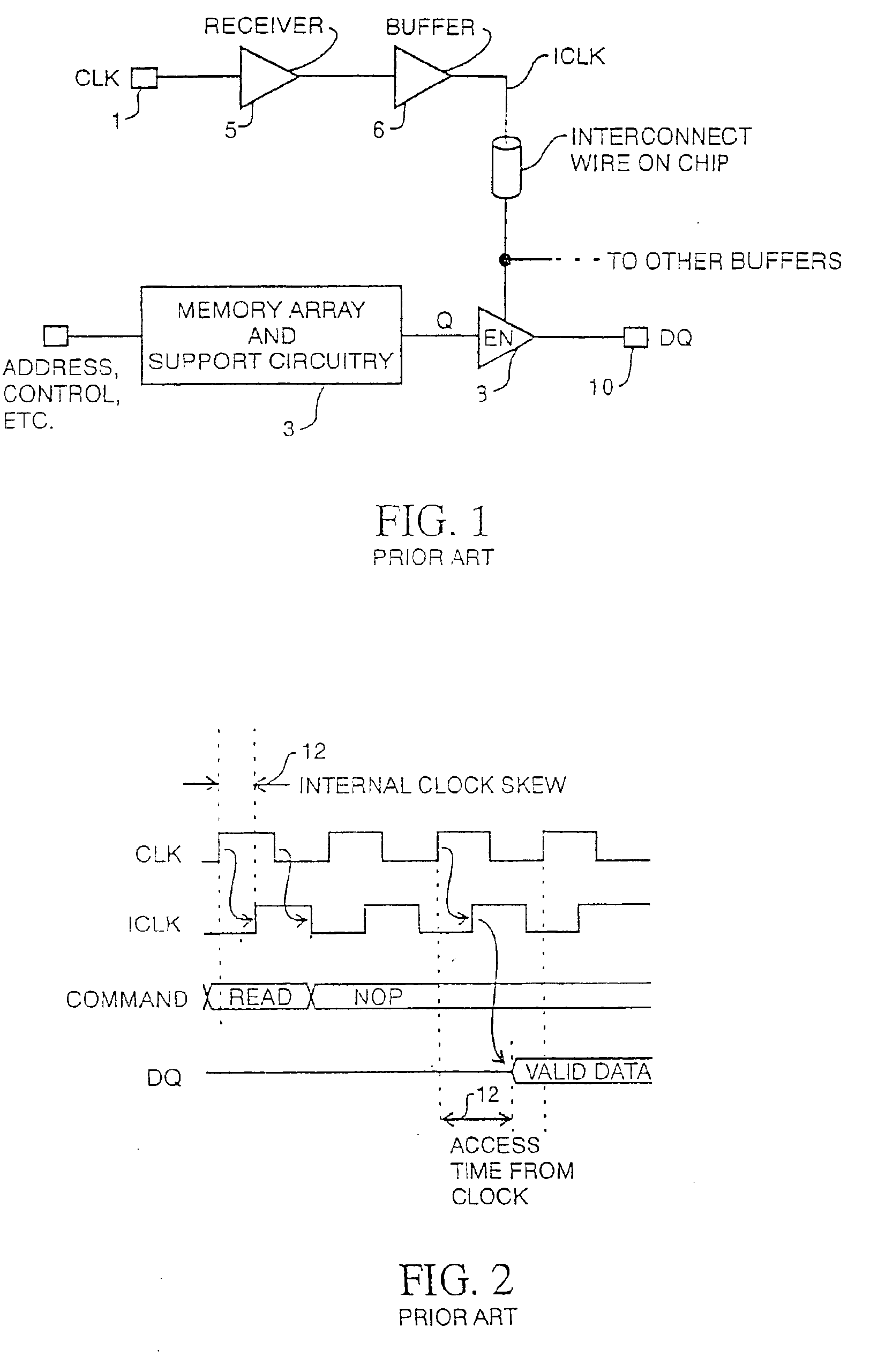

Delay locked loop implementation in a synchronous dynamic random access memory

InactiveUS6992950B2High operating requirementsLess standby current and start-up timePulse automatic controlSingle output arrangementsRandom access memoryDelay-locked loop

Owner:CONVERSANT INTPROP MANAGEMENT INC

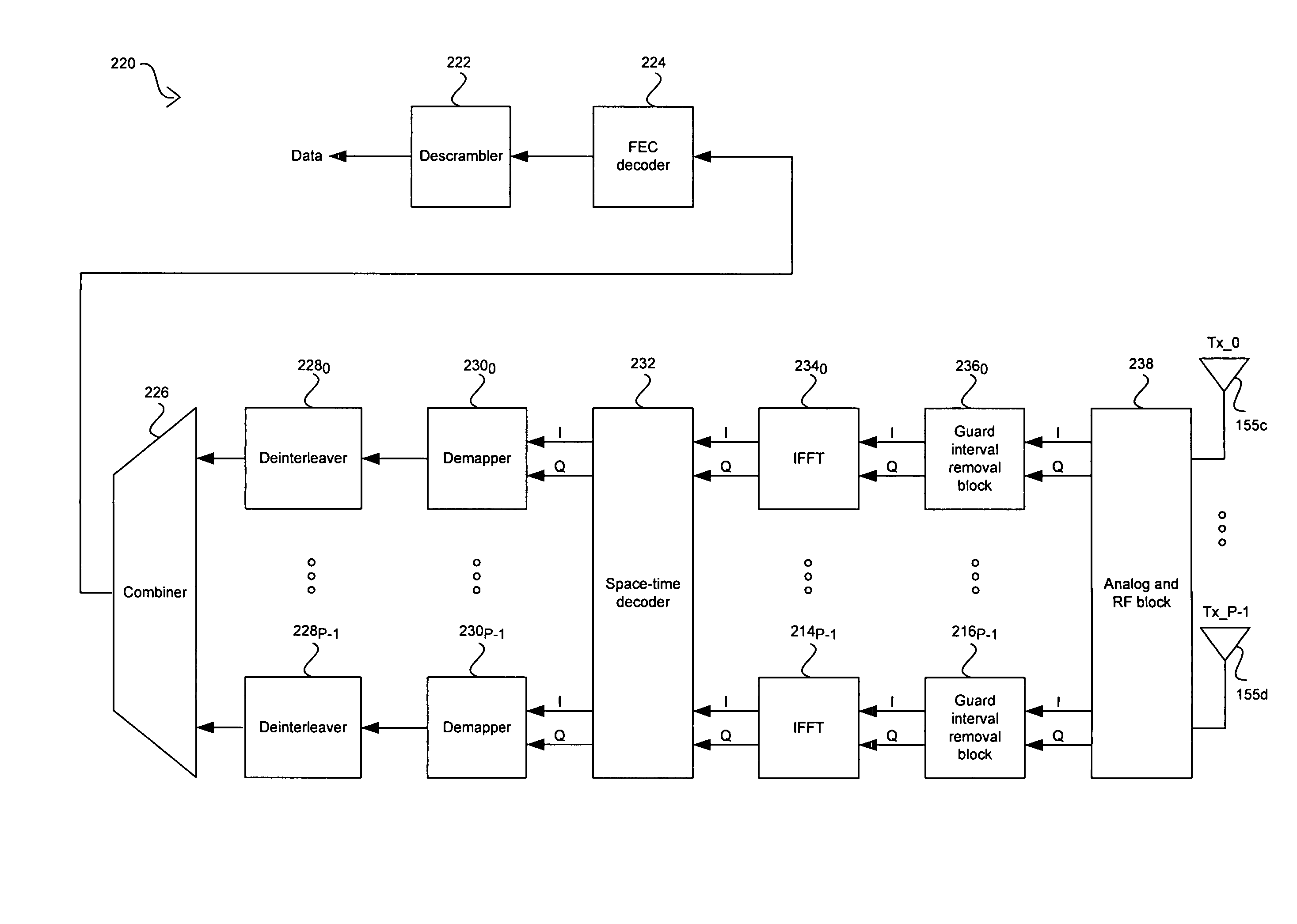

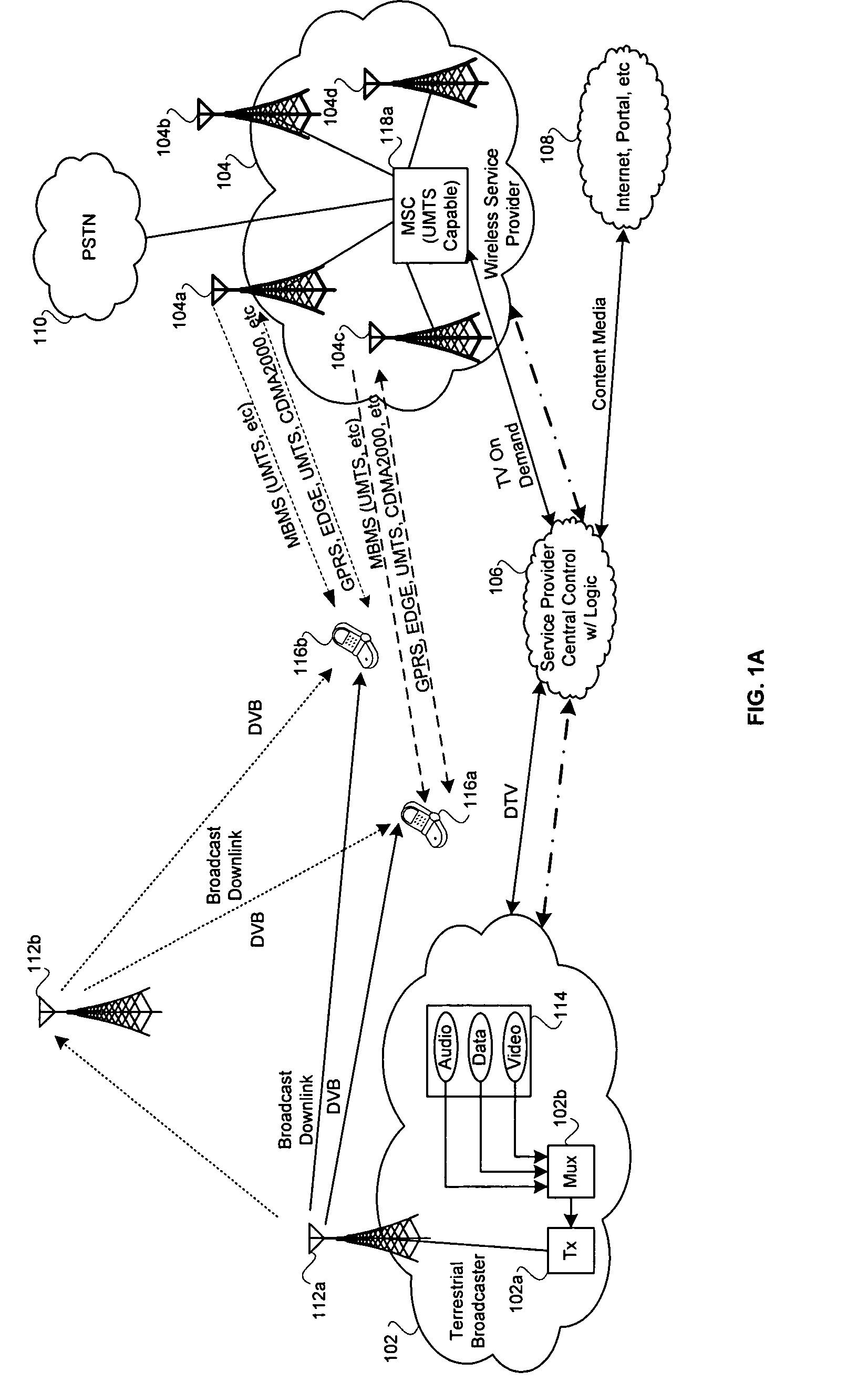

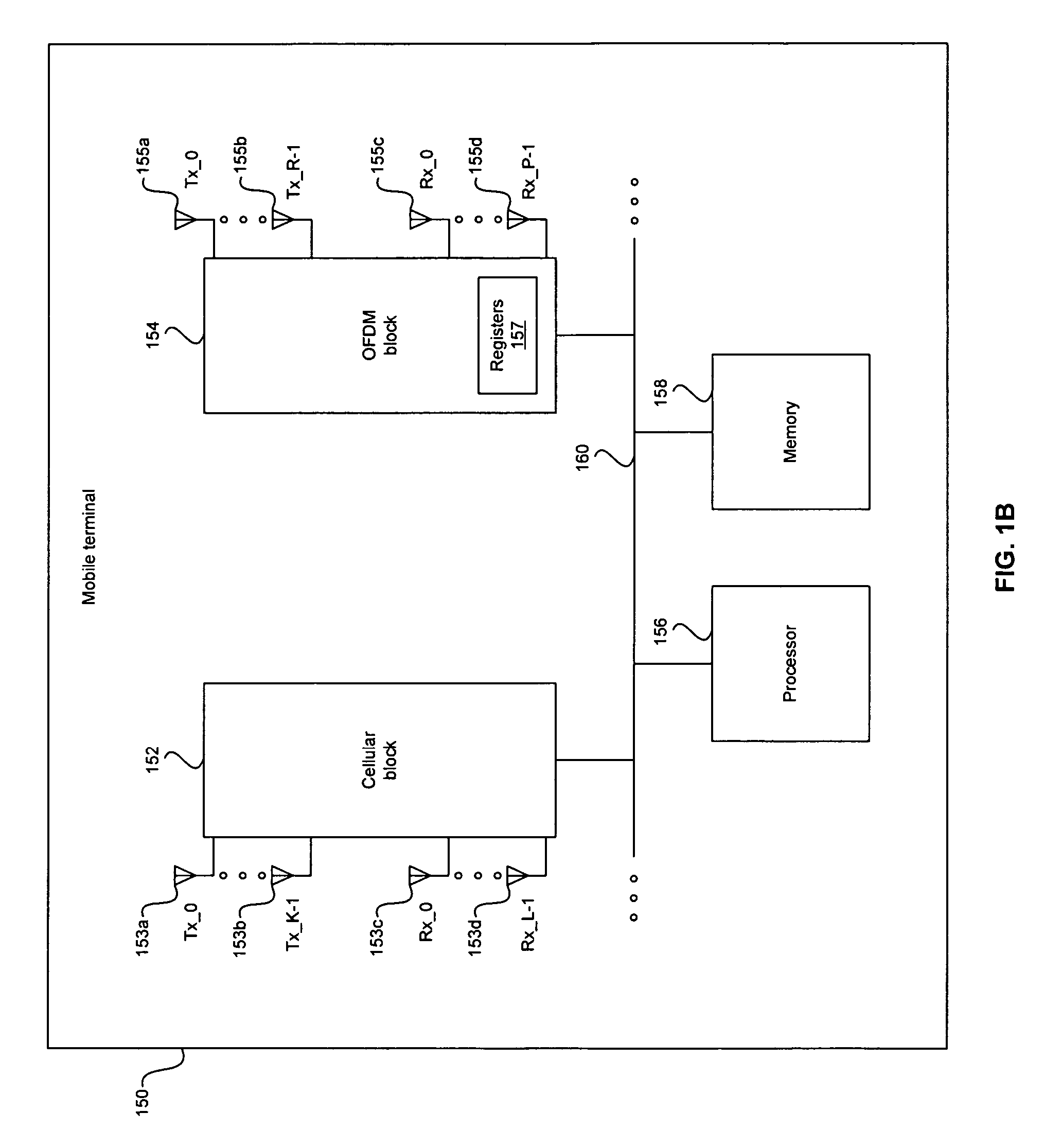

Method and system for increasing data rate in a mobile terminal using spatial multiplexing for DVB-H communication

A method and system for increasing data rate in a mobile terminal using spatial multiplexing for digital video broadcasting for handhelds (DVB-H) communication are provided. A reconfigurable orthogonal frequency division multiplexing (OFDM) chip may be utilized in a mobile terminal to process received spatially multiplexed signals. The mobile terminal may be utilized in a spatially multiplexed multiple-input-multiple-output (SM-MIMO) wireless system. The spatially multiplexed signals may be quadrature phase shift keying (QPSK) modulated and may utilize OFDM subcarries. A processor may be utilized to configure the OFDM chip to process signals such as IEEE 802.11 and 802.16, and DVB. The OFDM chip may generate channel weights to be applied to the spatially multiplexed signals received in multiple receive antennas. The weighted signals may be combined to generate multiple RF received signals from which channel estimates may be generated. Subsequent channel weights may be dynamically generated from generated channel estimates.

Owner:AVAGO TECH INT SALES PTE LTD

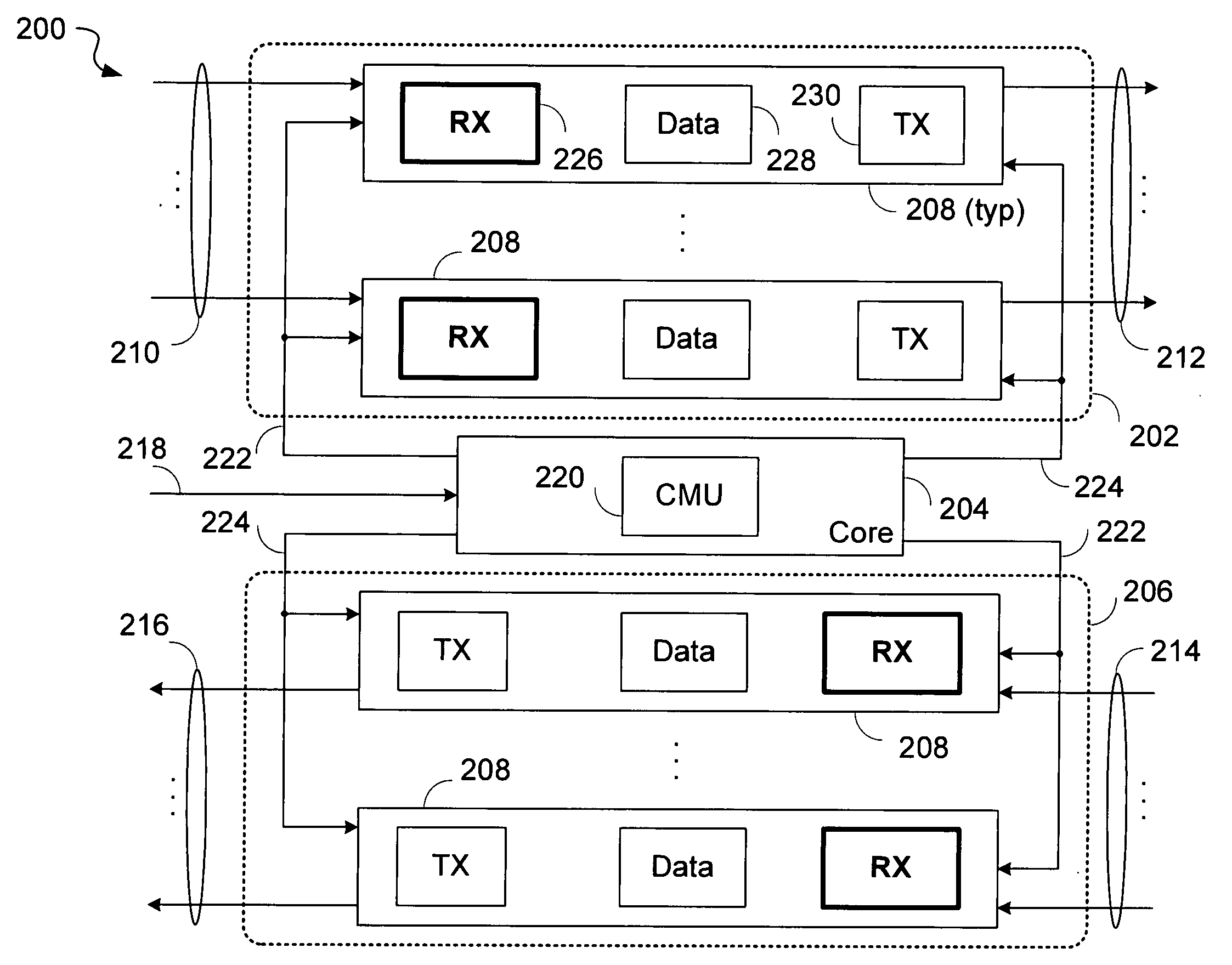

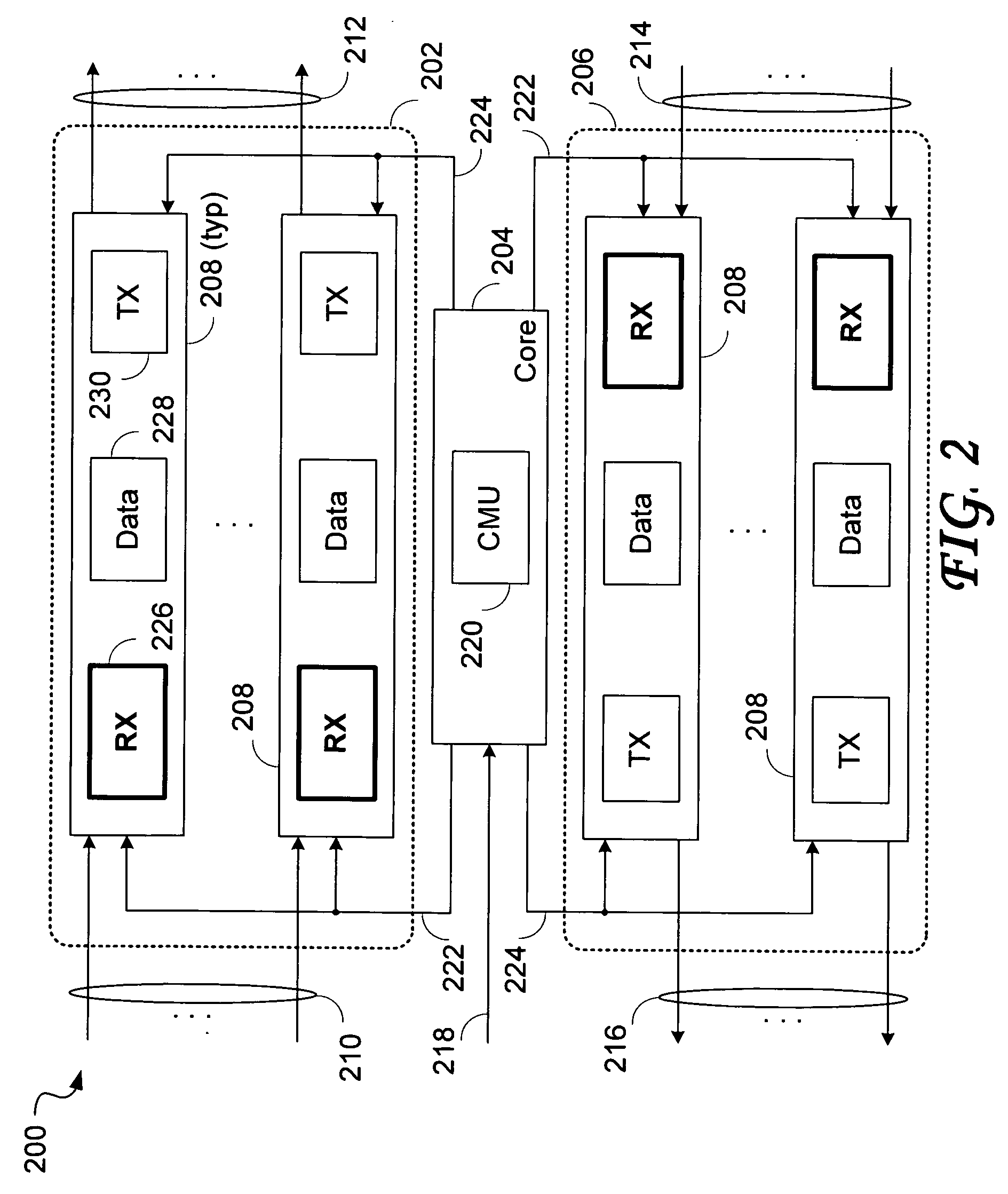

Synchronous transfer of streaming data in a distributed antenna system

Embodiments of the invention provide a method, distributed antenna system, and components that generate a jitter reduced clock signal from a serial encoded binary data stream transmitted over a communication medium. The method comprises receiving a modulated signal that includes the encoded binary data stream and extracting the encoded binary data stream. The method further comprises generating a recovered clock signal that is phase locked to the encoded binary data stream, generating an error signal based on a difference between a phase of the encoded binary data stream and the recovered clock signal, and integrating the error signal to generate a signal to control a voltage controlled oscillator. The method further comprises generating a stable recovered clock signal and producing at least one output clock by scaling the stable recovered clock signal frequency.

Owner:COMMSCOPE TECH LLC

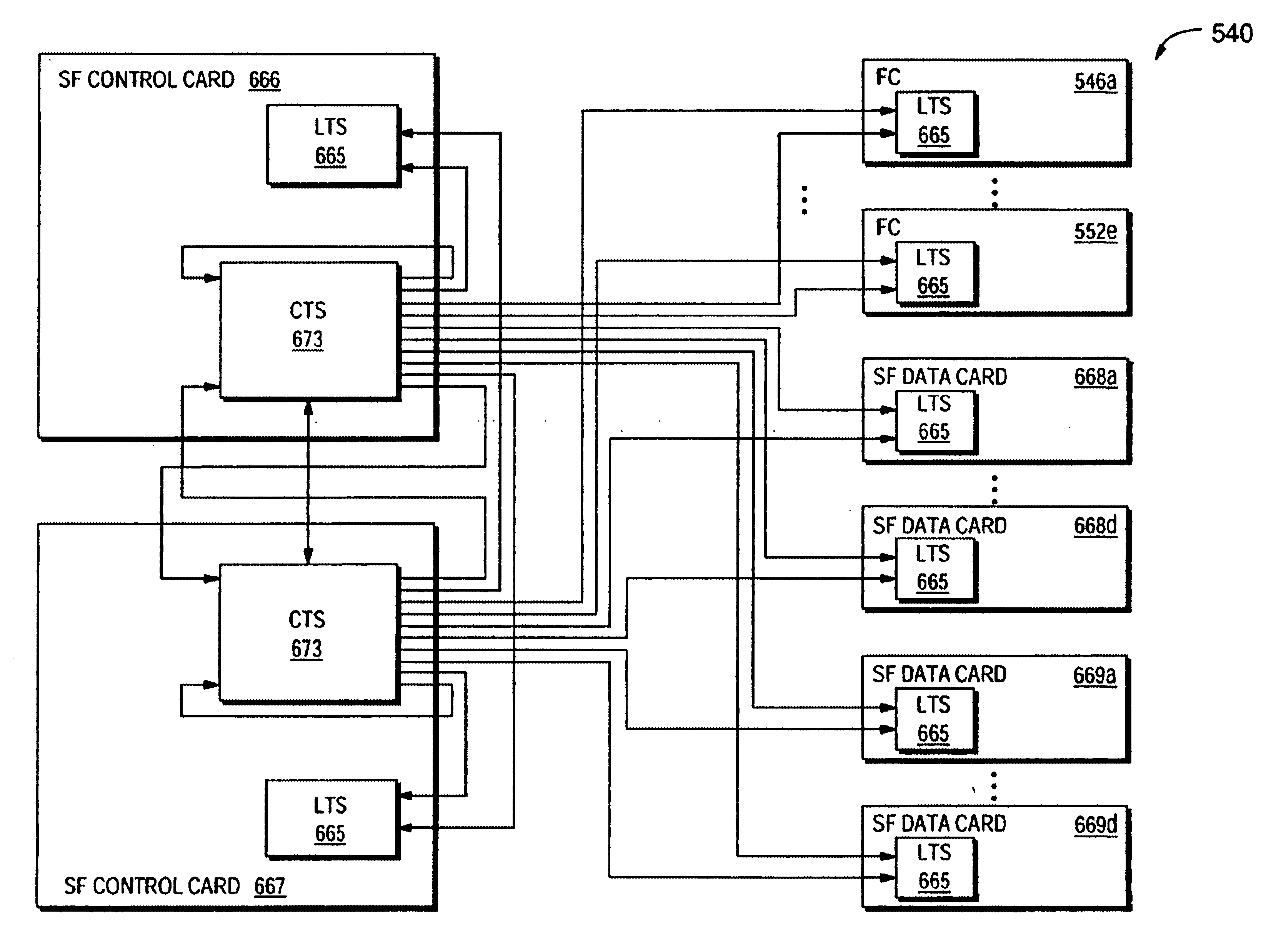

Network device with a distributed switch fabric timing system

InactiveUS6876652B1Low costMultiplex system selection arrangementsSynchronisation information channelsEngineeringTiming system

The present invention provides a central switch fabric timing subsystem and distributed switch fabric timing subsystems. Distributed switch fabric subsystems reduce the cost of a minimally configured network device by providing a network device with a distributed switch fabric. Such a network device locates a portion of the switch fabric functionality on each forwarding card allowing the minimal network device configuration to include less than the entire switch fabric functionality. The cost of the minimal configuration is, therefore, reduced allowing network service providers to more quickly recover the initial cost of the network device. As new services are requested, additional functionality, including both forwarding cards and universal port cards may be added to the network device to handle the new requests, and the fees for the new services may be applied to the cost of the additional functionality. Consequently, the cost of the network device more closely tracks the service fees received by network providers.

Owner:CIENA

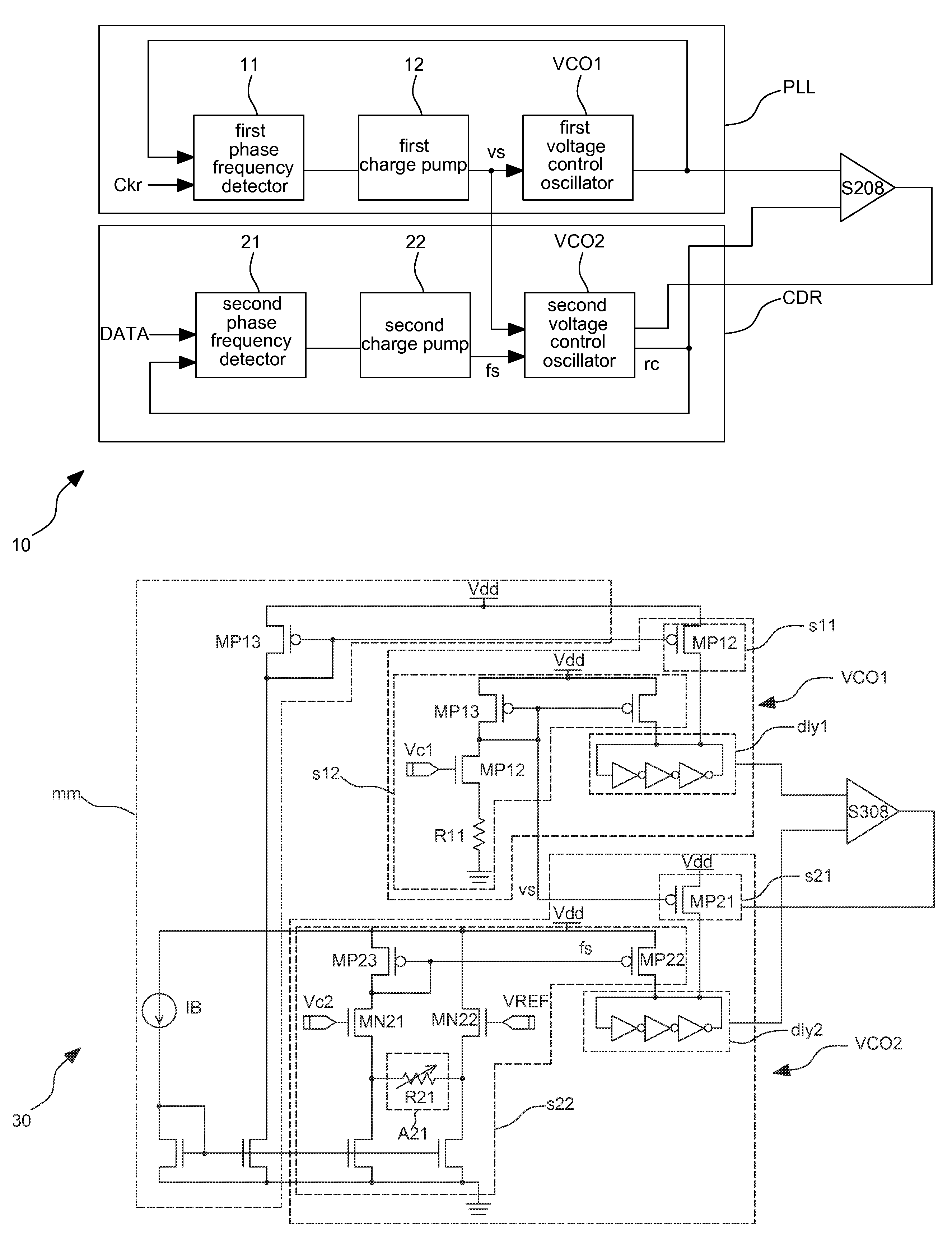

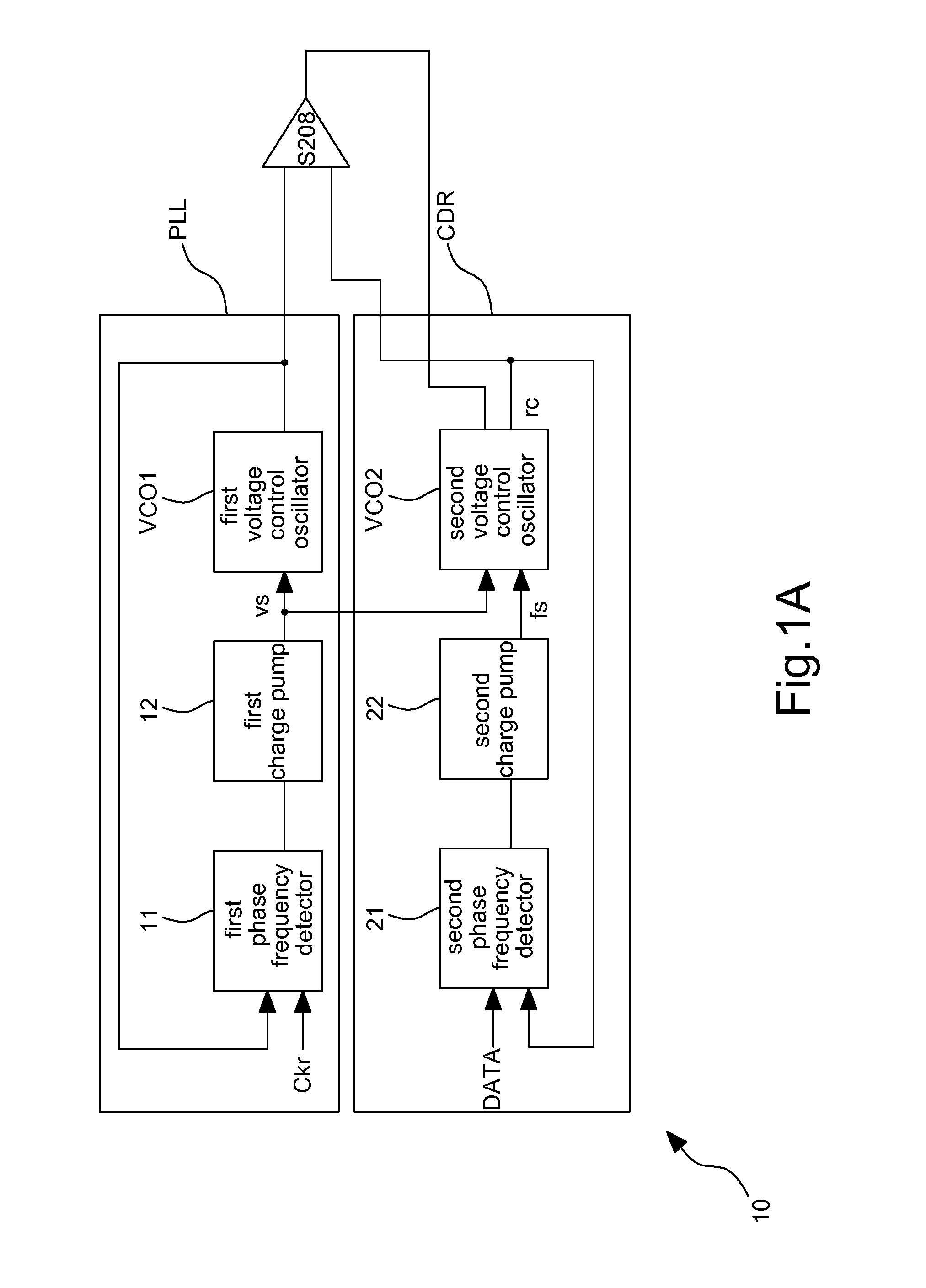

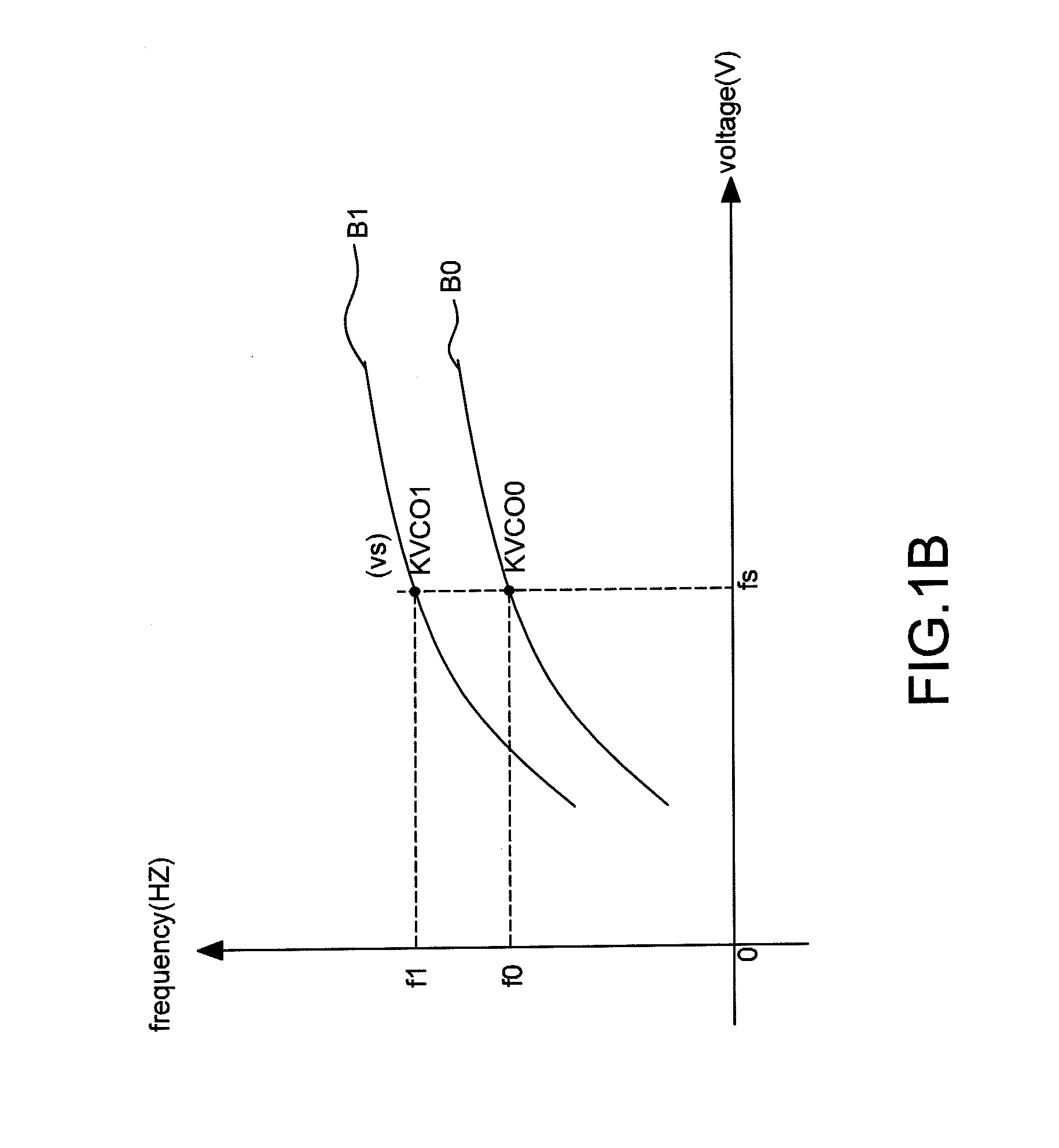

Transceiver, voltage control oscillator thereof and control method thereof

ActiveUS8928416B2Smaller VCO gainLarge rangePulse automatic controlPulse generation by logic circuitsTransceiverControl signal

A transceiver includes a phase lock loop (PLL) and a clock data recovery circuit (CDR). The phase lock loop generates a first level control signal. The clock data recovery circuit, coupled to the phase lock loop, locks an incoming data signal to generate a data recovery clock according to a second level control signal. Wherein the clock data recovery circuit receives the first level control signal to further control a frequency range of the data recovery clock.

Owner:REALTEK SEMICON CORP

Popular searches

Network topologies Data switching by path configuration Wireless network protocols Radio/inductive link selection arrangements Radio transmission for post communication Wireless commuication services Network planning Multiple digital computer combinations Selective content distribution Electric digital data processing