Patents

Literature

1455results about How to "High operating requirements" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

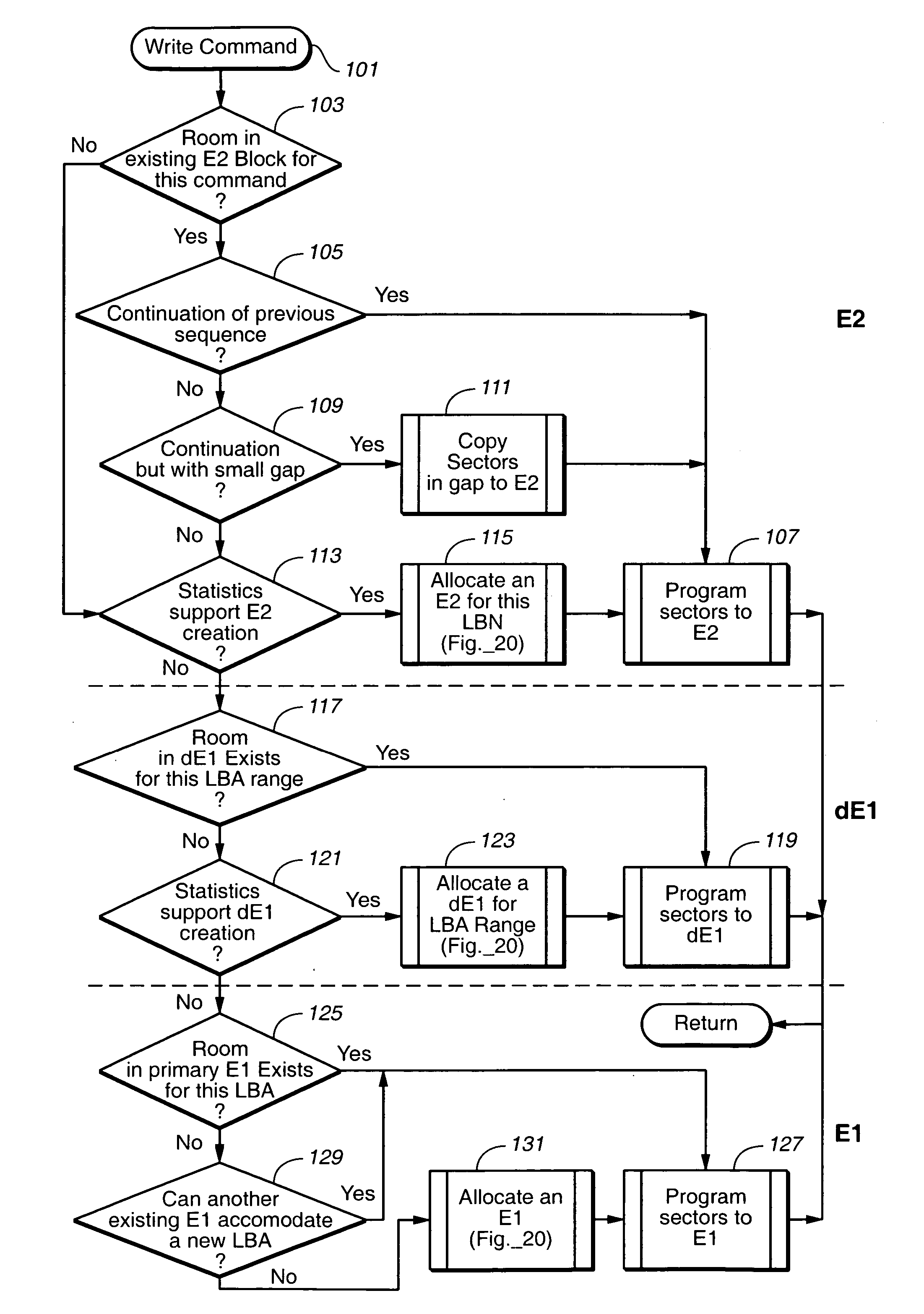

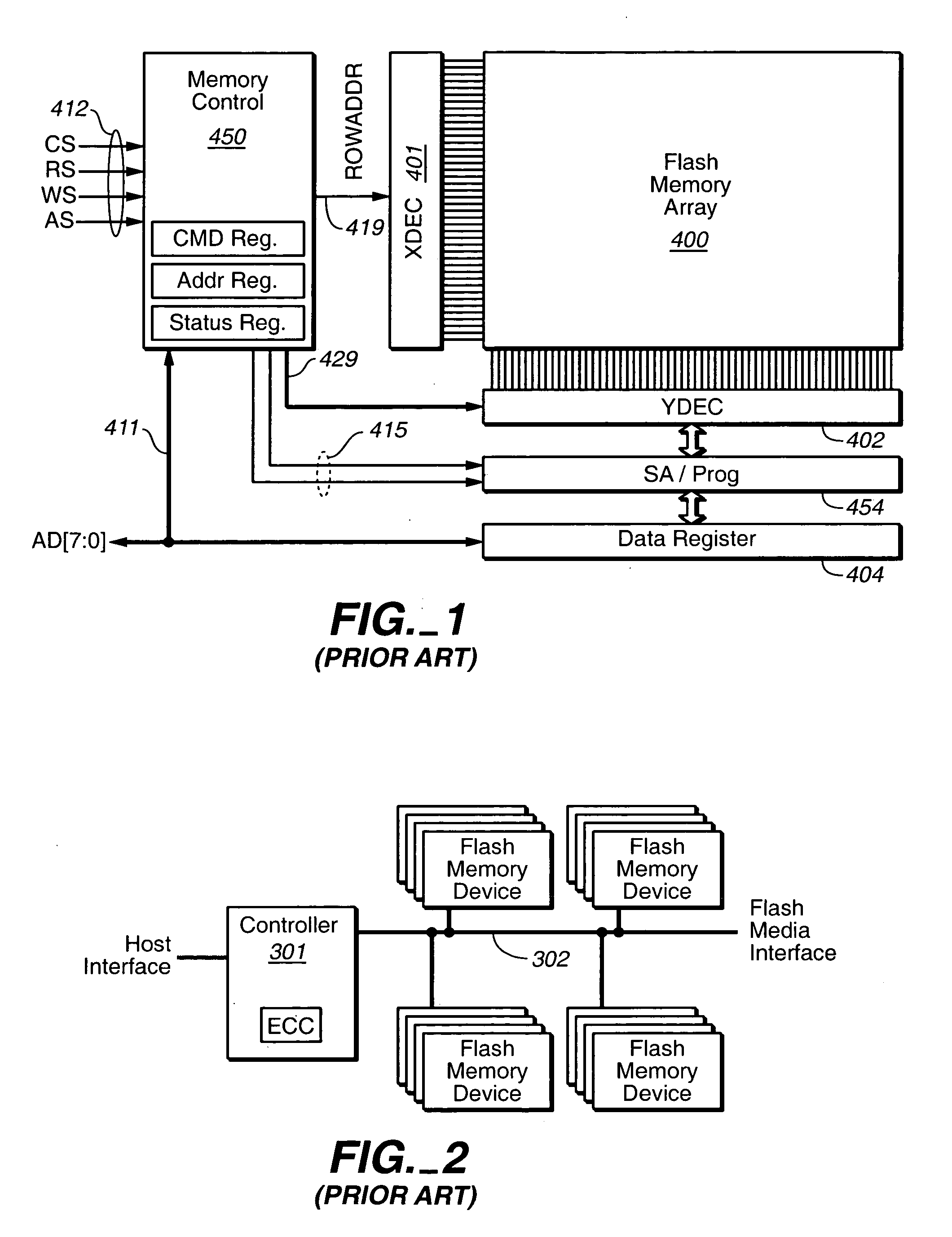

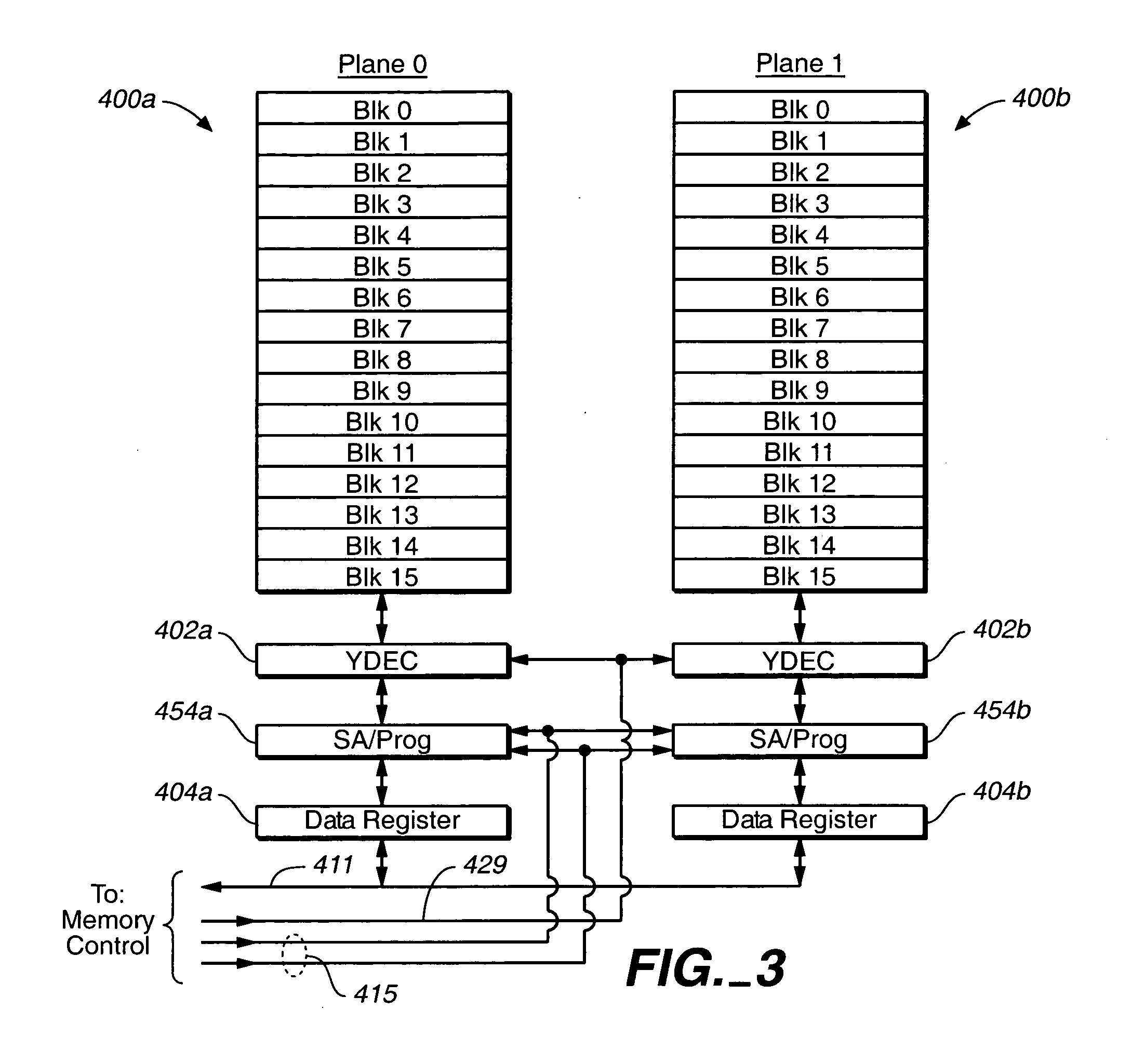

Management of non-volatile memory systems having large erase blocks

ActiveUS20050144358A1Reduce amountImprove system performanceMemory architecture accessing/allocationMemory adressing/allocation/relocationOriginal dataTerm memory

A non-volatile memory system of a type having blocks of memory cells erased together and which are programmable from an erased state in units of a large number of pages per block. If the data of only a few pages of a block are to be updated, the updated pages are written into another block provided for this purpose. Updated pages from multiple blocks are programmed into this other block in an order that does not necessarily correspond with their original address offsets. The valid original and updated data are then combined at a later time, when doing so does not impact on the performance of the memory. If the data of a large number of pages of a block are to be updated, however, the updated pages are written into an unused erased block and the unchanged pages are also written to the same unused block. By handling the updating of a few pages differently, memory performance is improved when small updates are being made. The memory controller can dynamically create and operate these other blocks in response to usage by the host of the memory system.

Owner:SANDISK TECH LLC

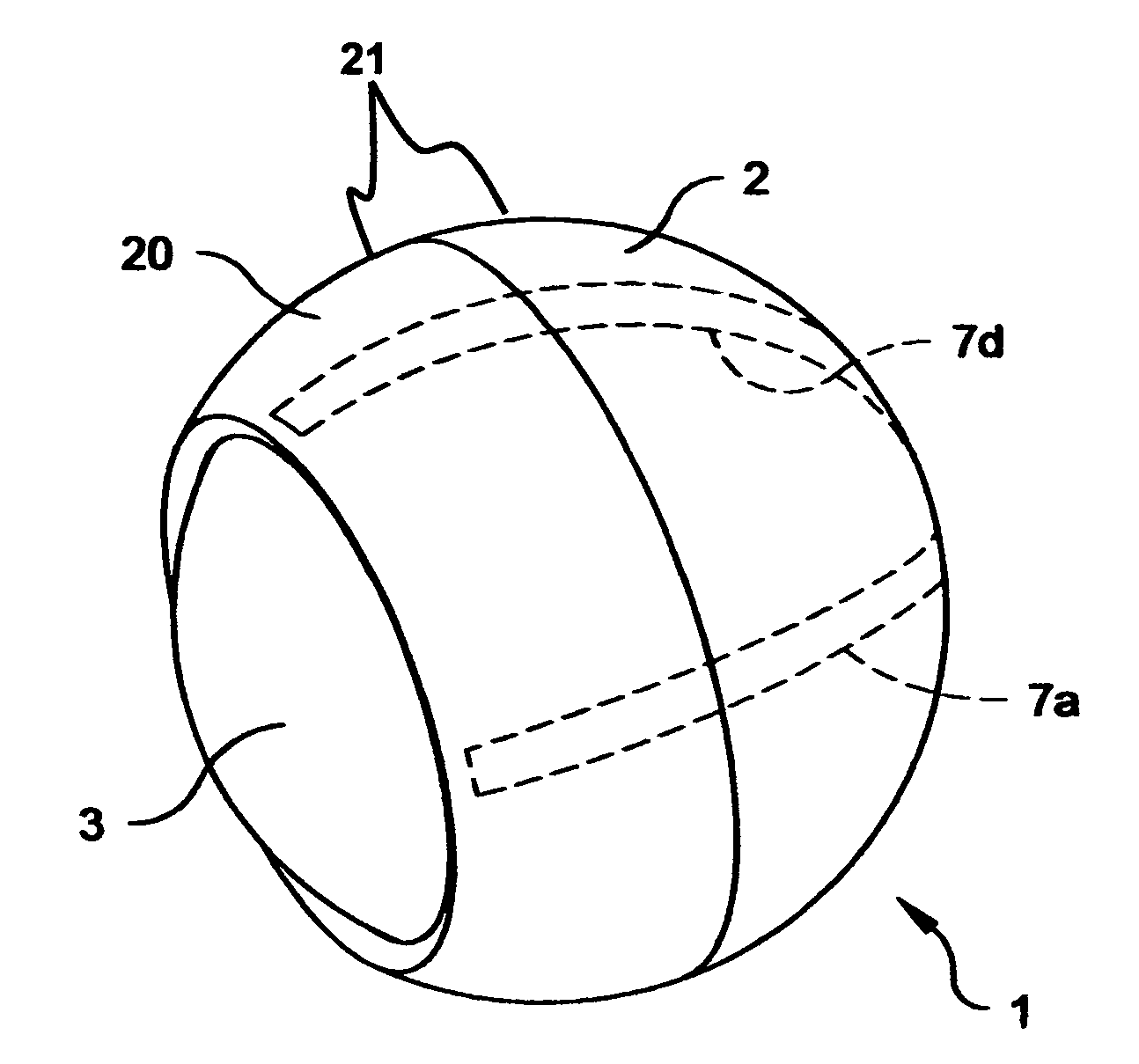

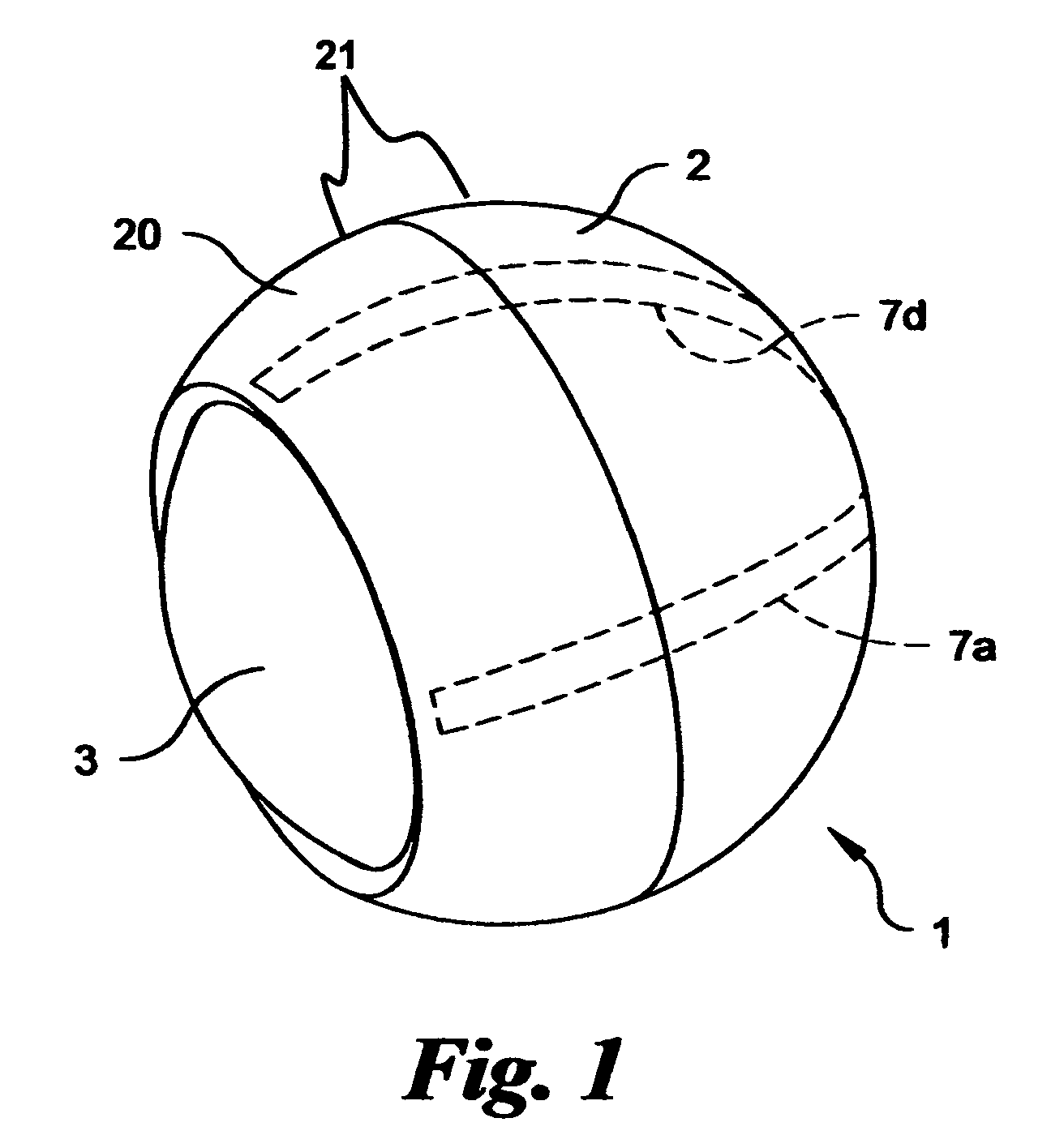

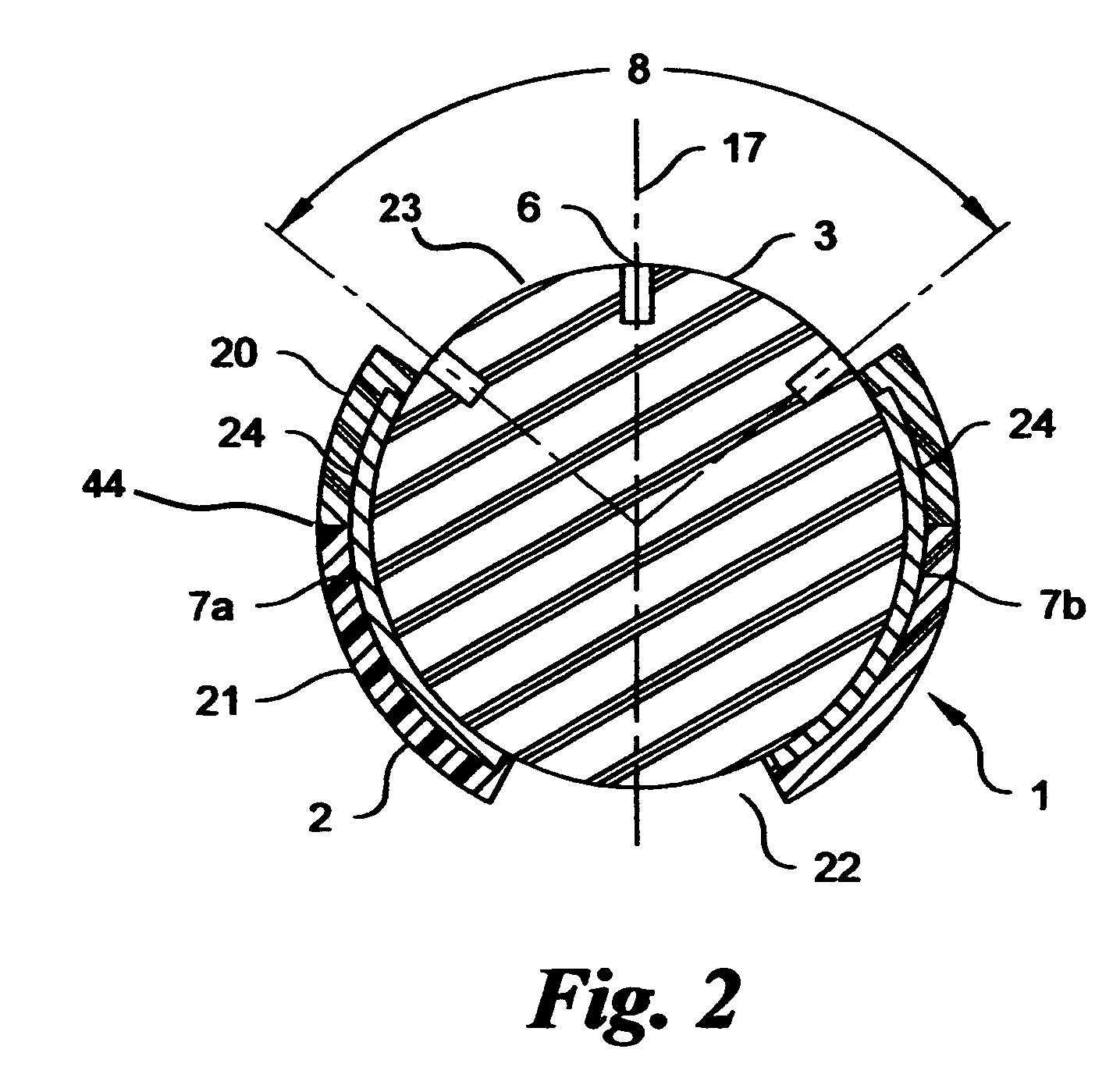

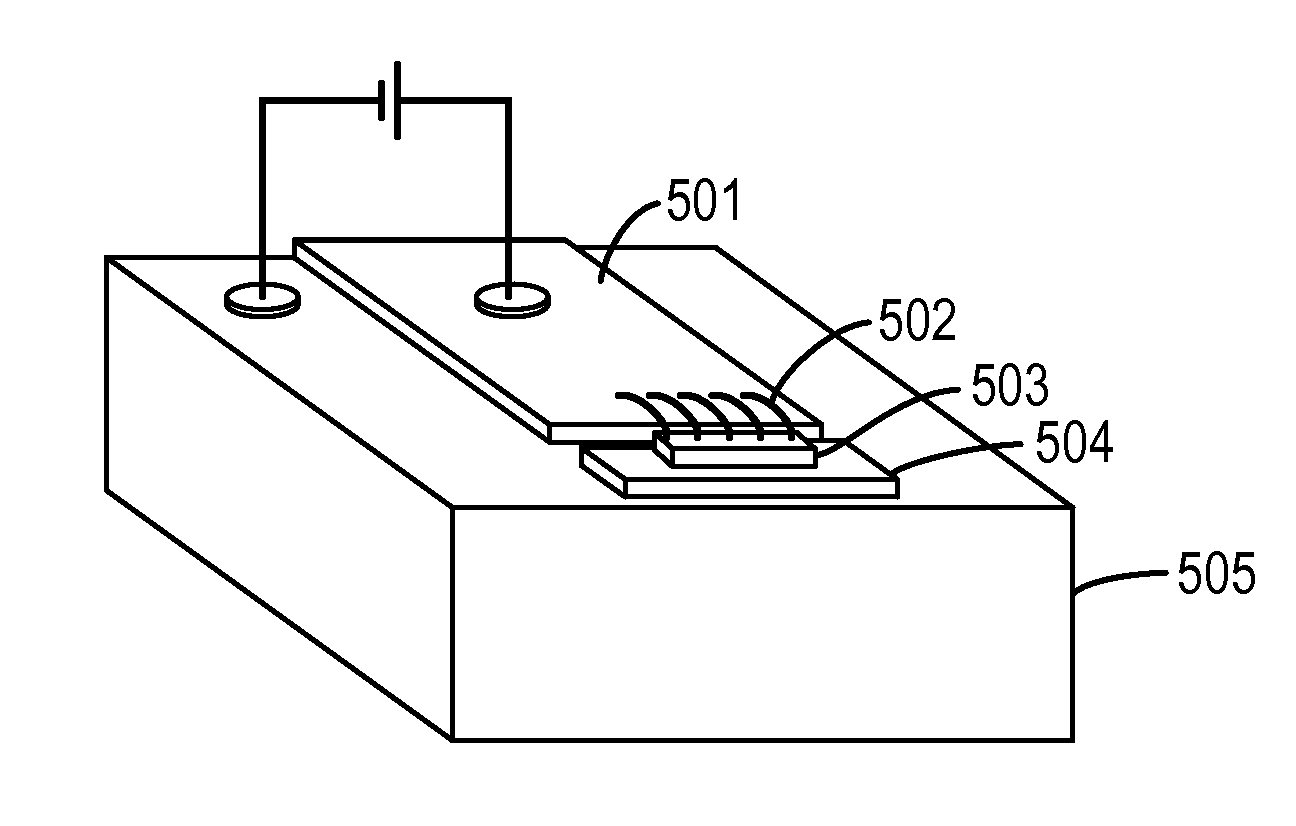

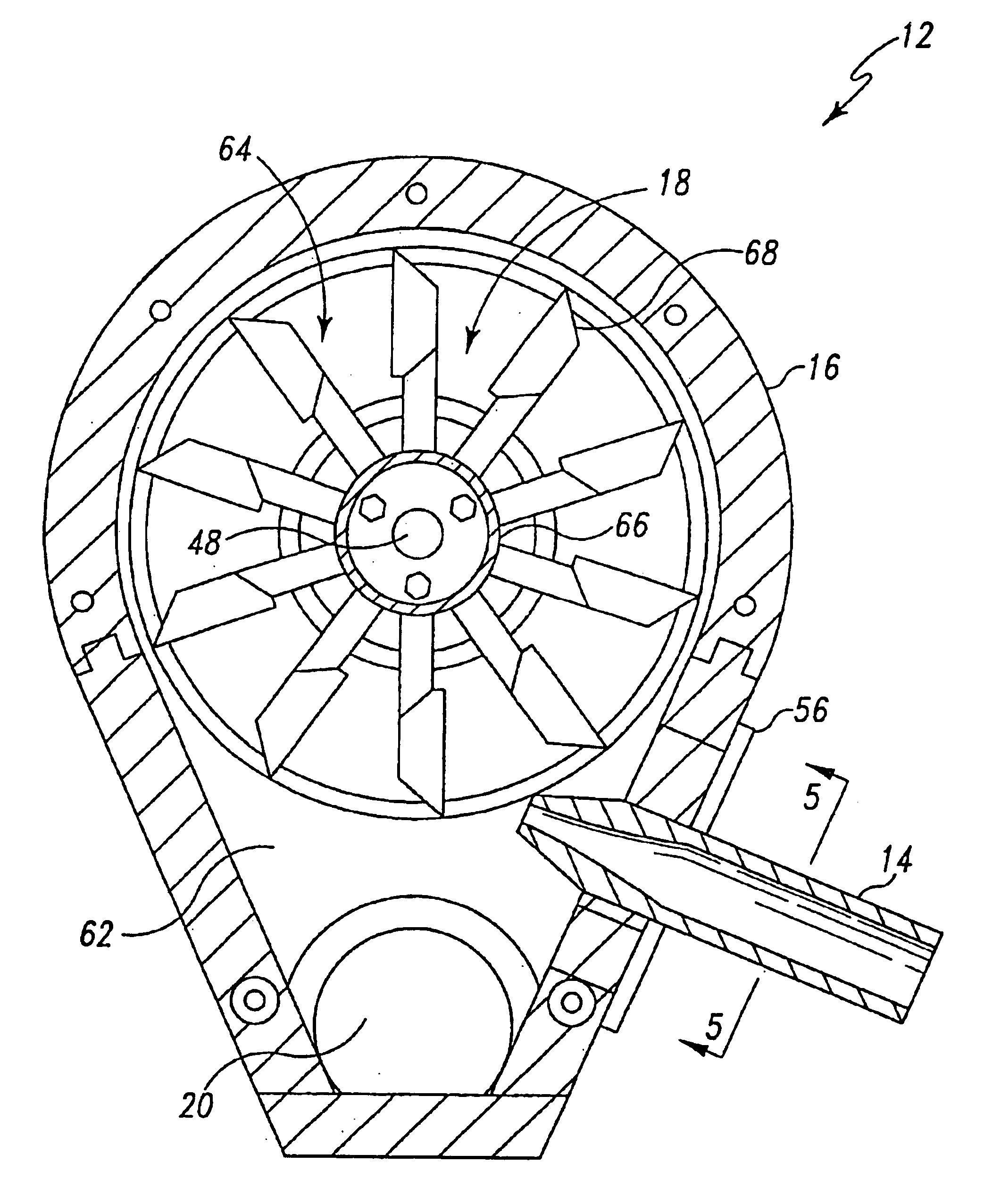

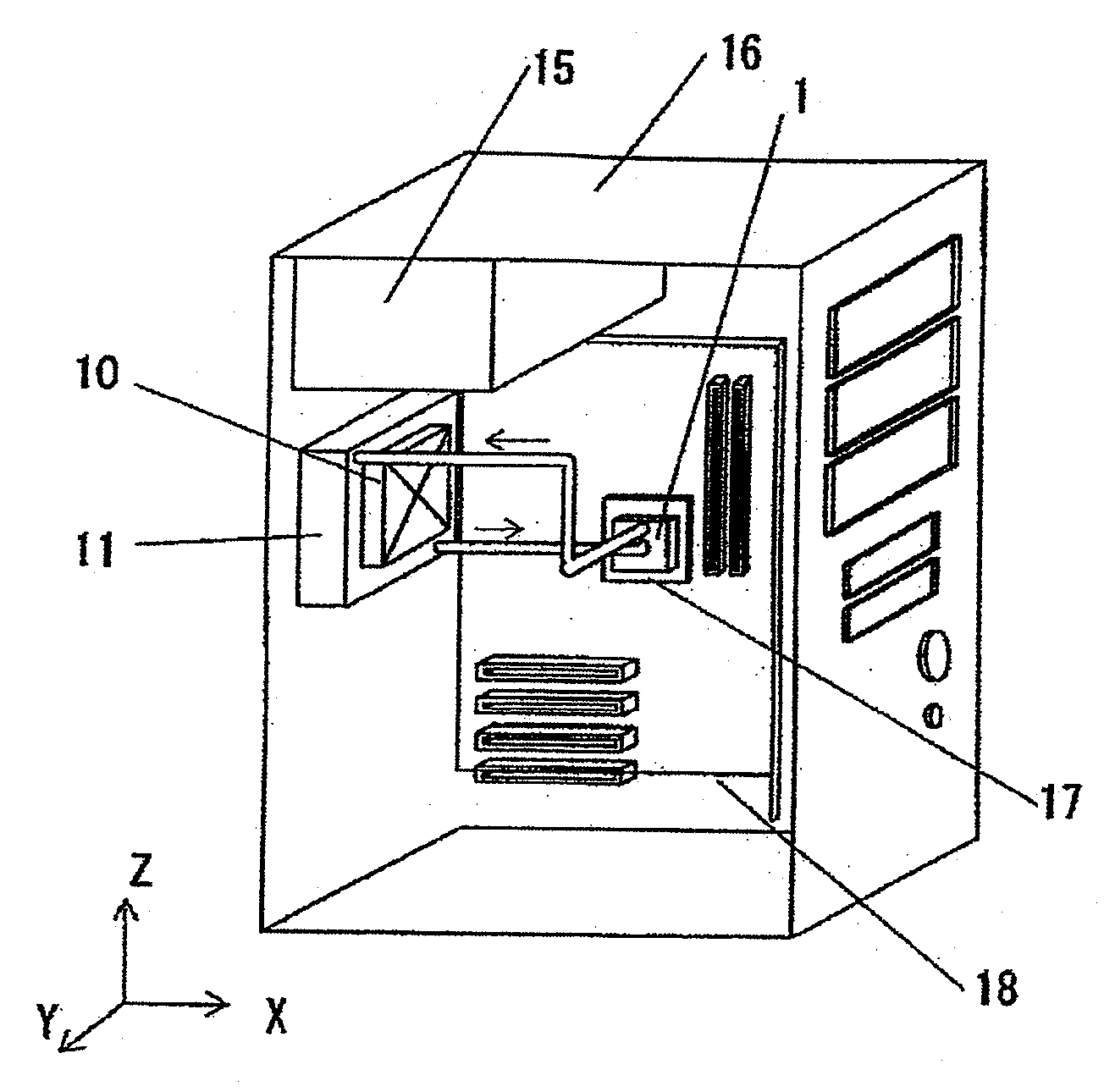

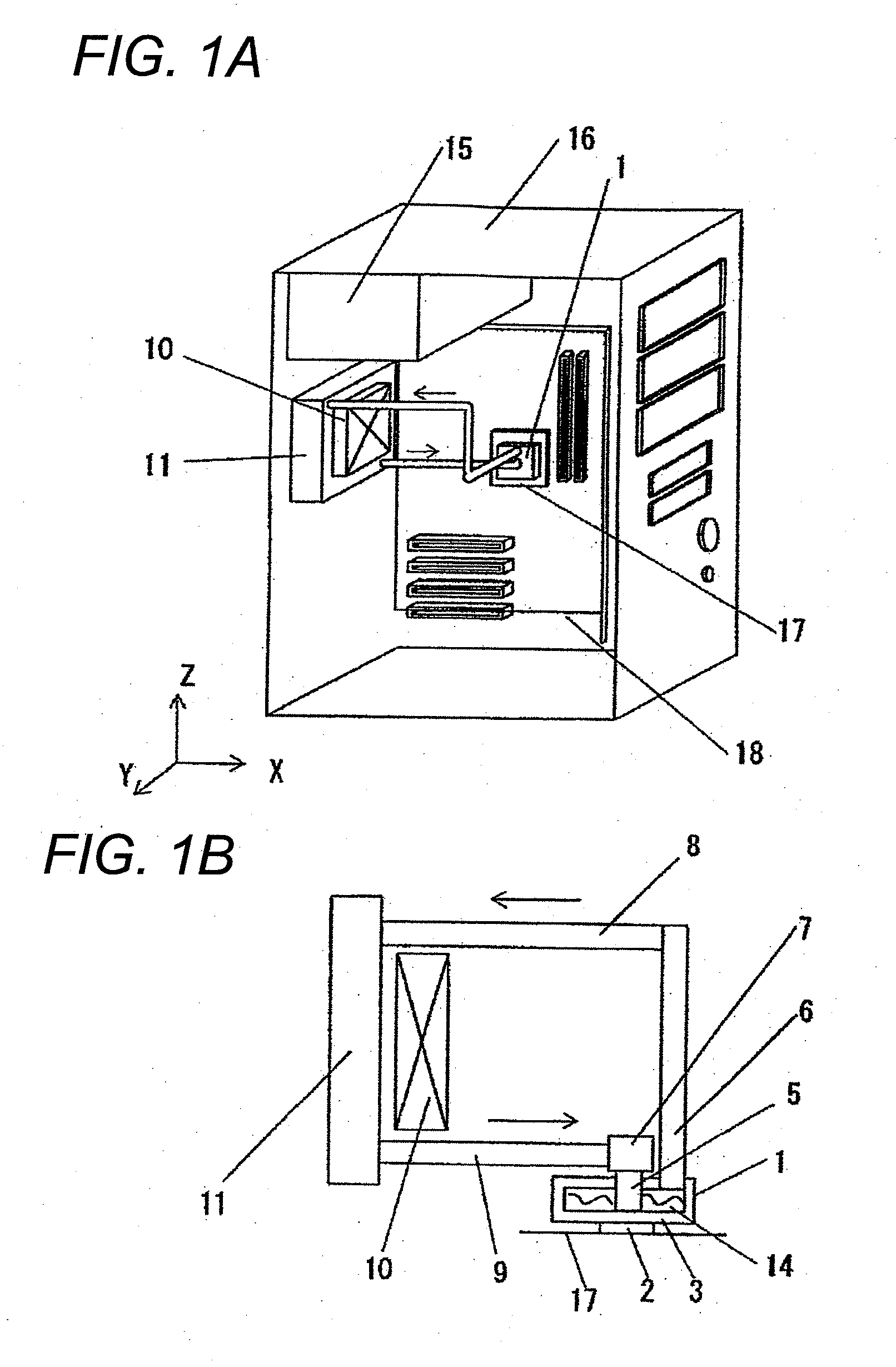

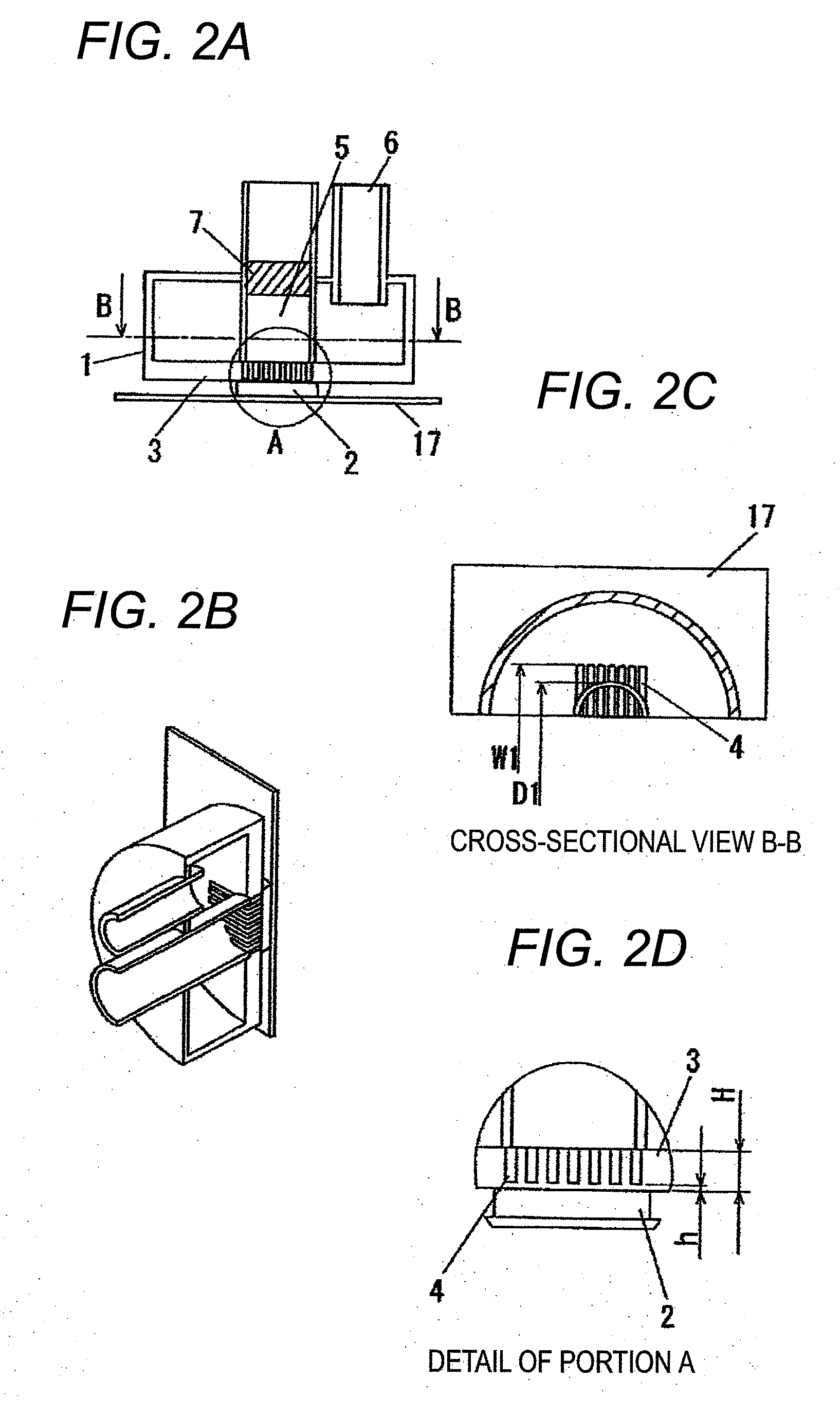

Solid state gimbal system

InactiveUS7459834B2Less powerHigh operating requirementsAdditive manufacturing apparatusPiezoelectric/electrostriction/magnetostriction machinesGuidance systemCommunications system

A non-mechanical gimbal system is presented. The gimbal system includes a gimbal housing, including hemispherical and annular caps, rotatable sphere, and at least two curvilinear actuators. The hemispherical cap is attached to the annular cap in a removable fashion so as to surround the rotatable sphere. The curvilinear actuators are disposed between the rotatable sphere and gimbal housing. Curvilinear actuators rotate the rotatable sphere, via shear induced motion, with respect to the interior surface of the gimbal housing. The present invention has immediate applicability within security devices, games, toys, weapons (including guidance systems and aiming), and communication systems.

Owner:QORTEK

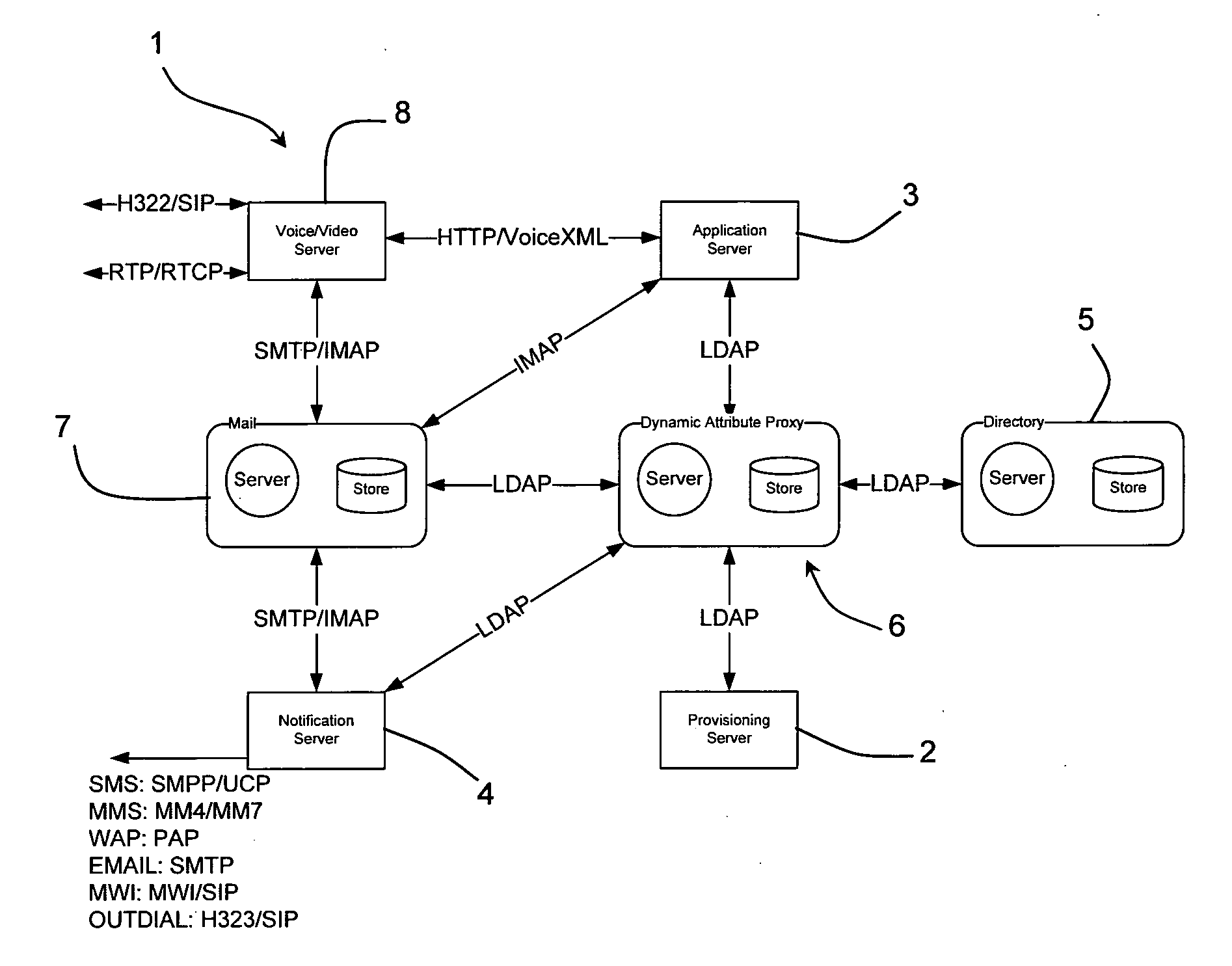

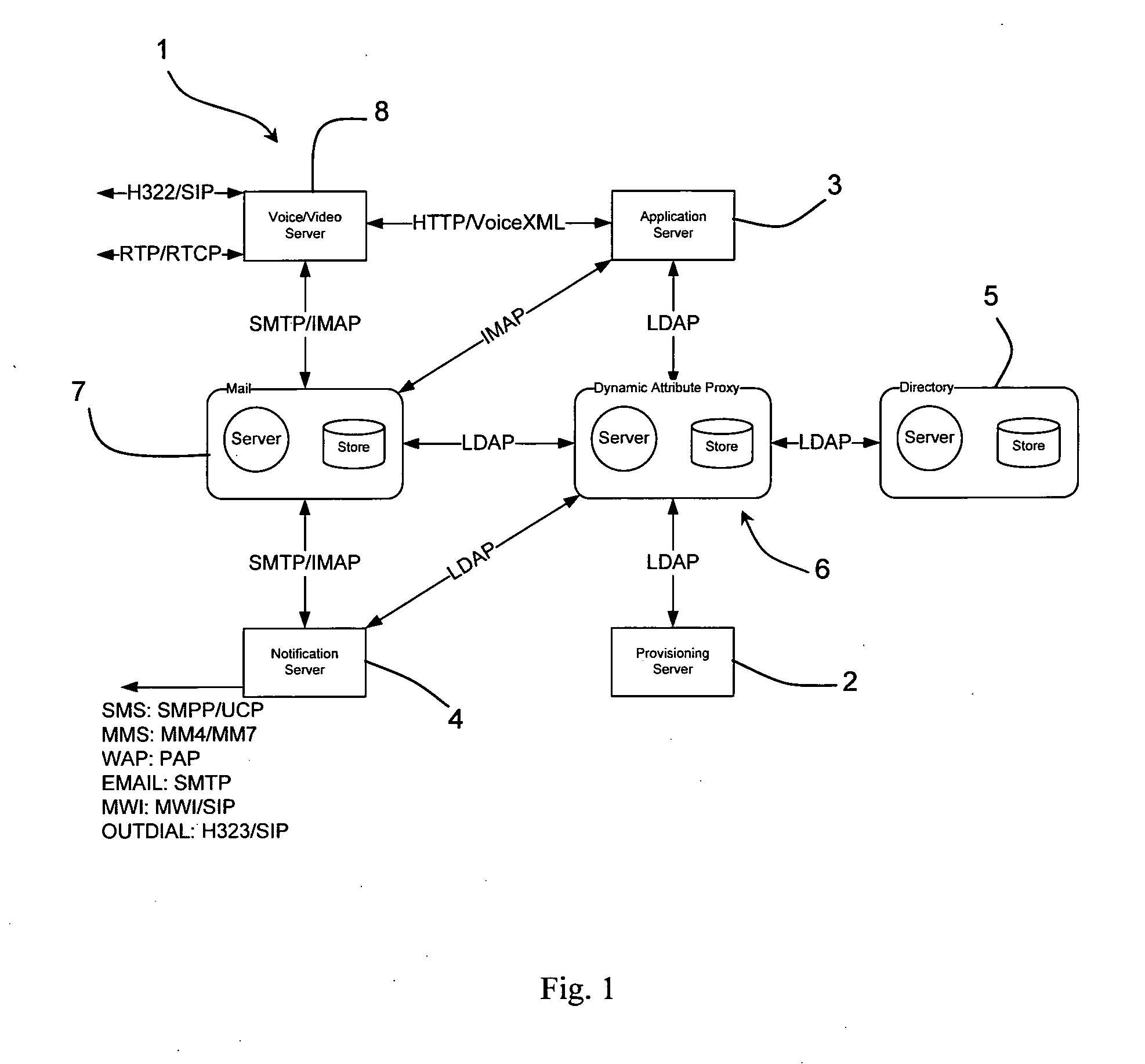

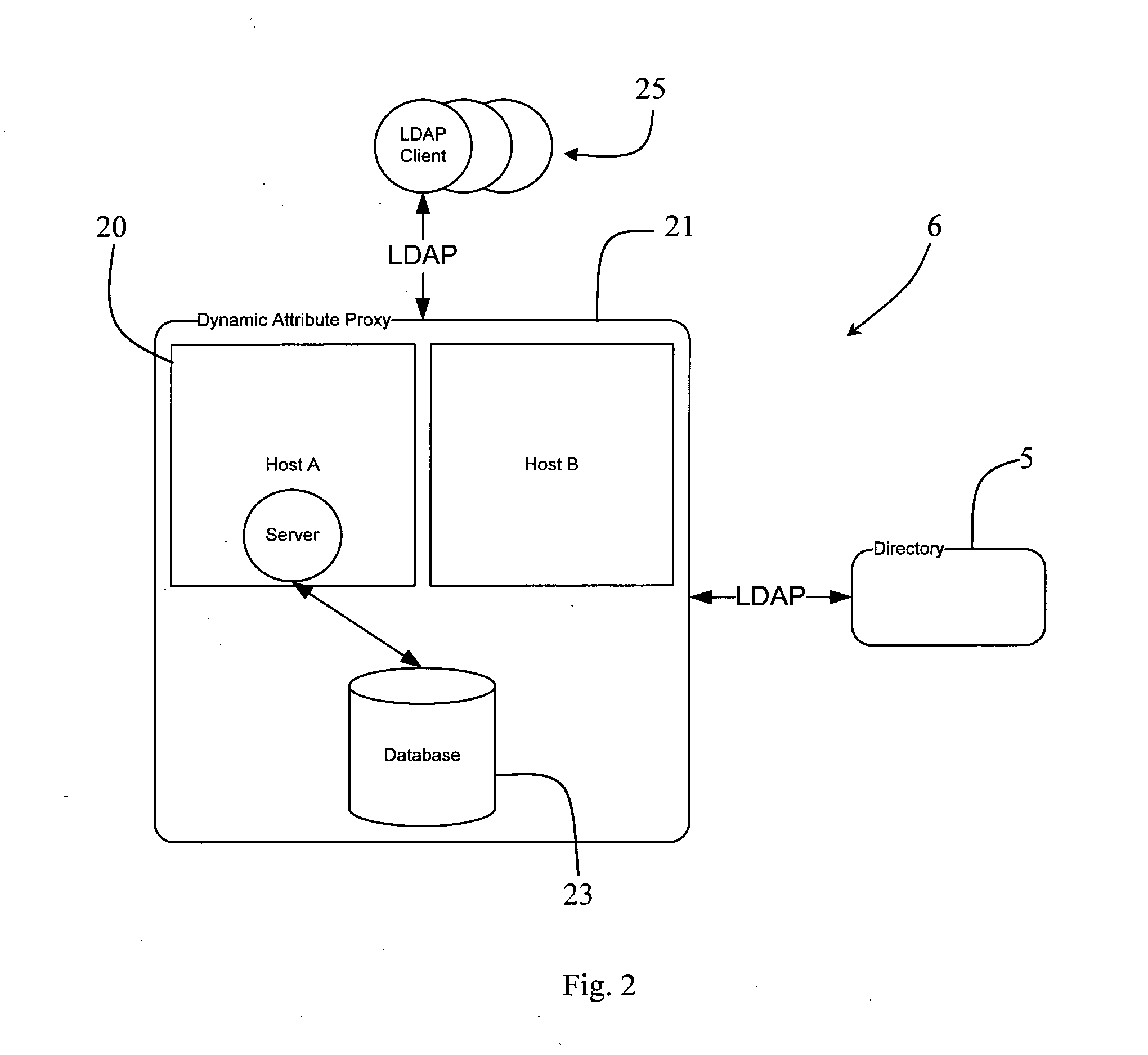

Processing of messaging service attributes in communication systems

InactiveUS20110035434A1Count can be incrementedHigh operating requirementsMultiple digital computer combinationsData switching networksCommunications systemApplication server

A messaging system (1) has a provisioning server (2), an application server (3), a notification server (4), a mail server (7), and a voice / video server (8) which act as clients toward an LDAP directory server (5). A proxy (“DAP”, 6) performs high speed write operations on a subset of attributes which it determines to be dynamic attributes. LDAP client requests that do not involve dynamic attributes are forwarded to the directory server (5) in a conventional manner. The proxy (6) also joins the results of requests that have both high-speed dynamic attributes as well as “static” attributes that are stored in a directory server (5). “Intelligent” services that involve maintaining dynamic attributes for large number of subscribers in a distributed environment can be deployed.

Owner:MARKPORT LTD

Laser package having multiple emitters with color wheel

ActiveUS20120314398A1Simple cost effectiveCost-effectiveNanoopticsSemiconductor lasersLaser transmitterOptoelectronics

Method and devices for emitting electromagnetic radiation at high power using nonpolar or semipolar gallium containing substrates such as GaN, AlN, InN, InGaN, AlGaN, and AlInGaN, are provided. The laser devices include multiple laser emitters integrated onto a substrate (in a module), which emit green or blue laser radiation.

Owner:KYOCERA SLD LASER INC

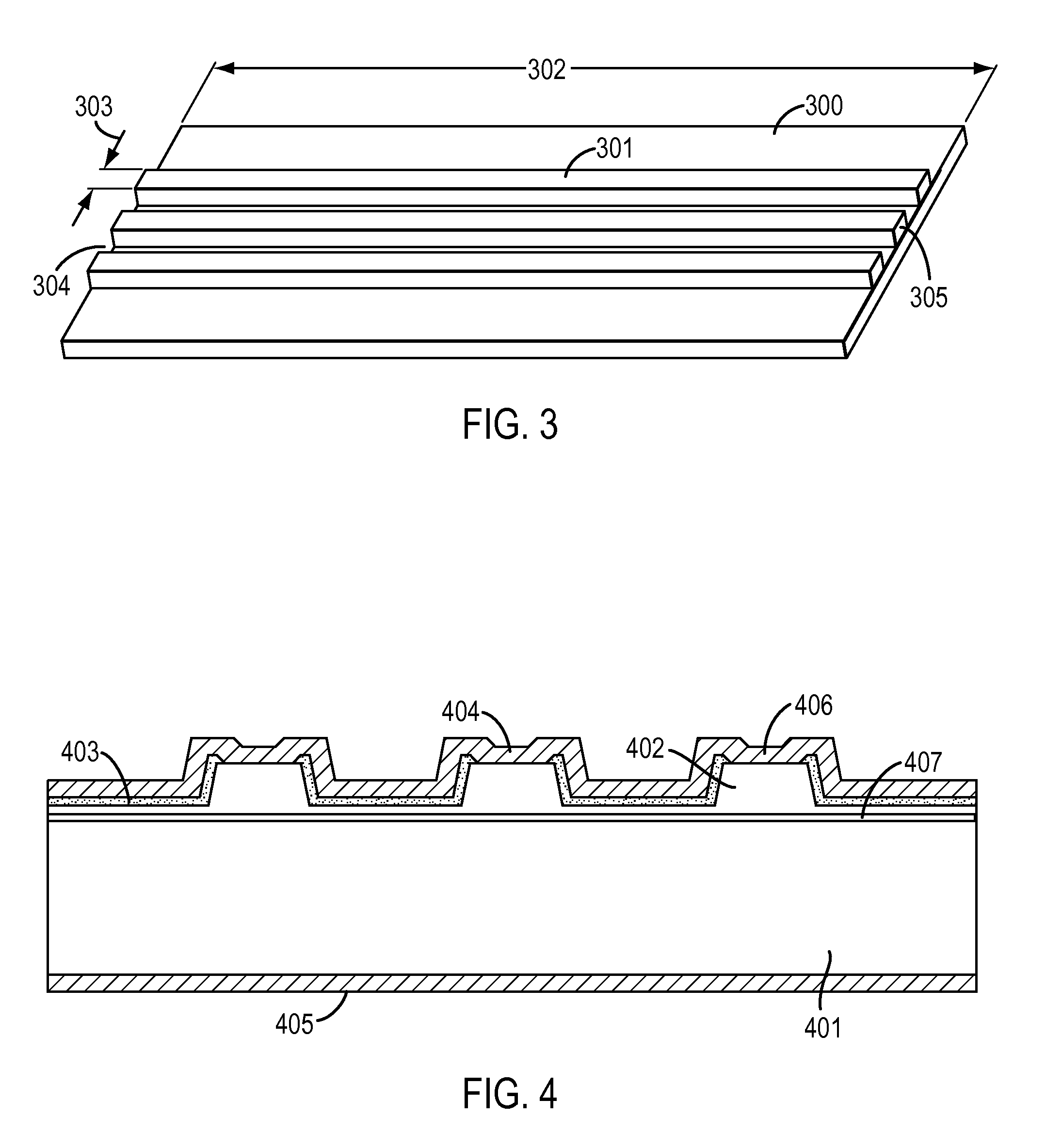

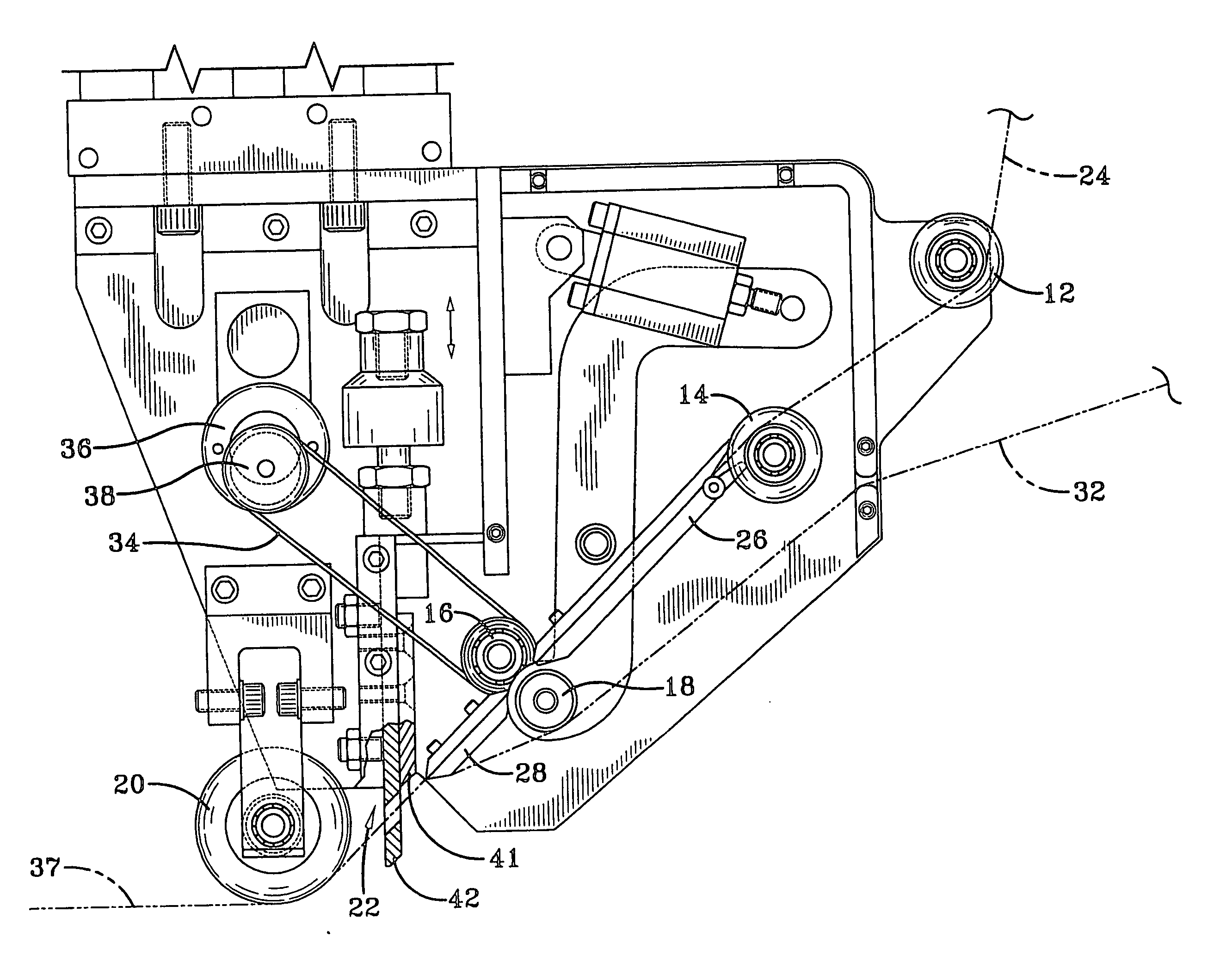

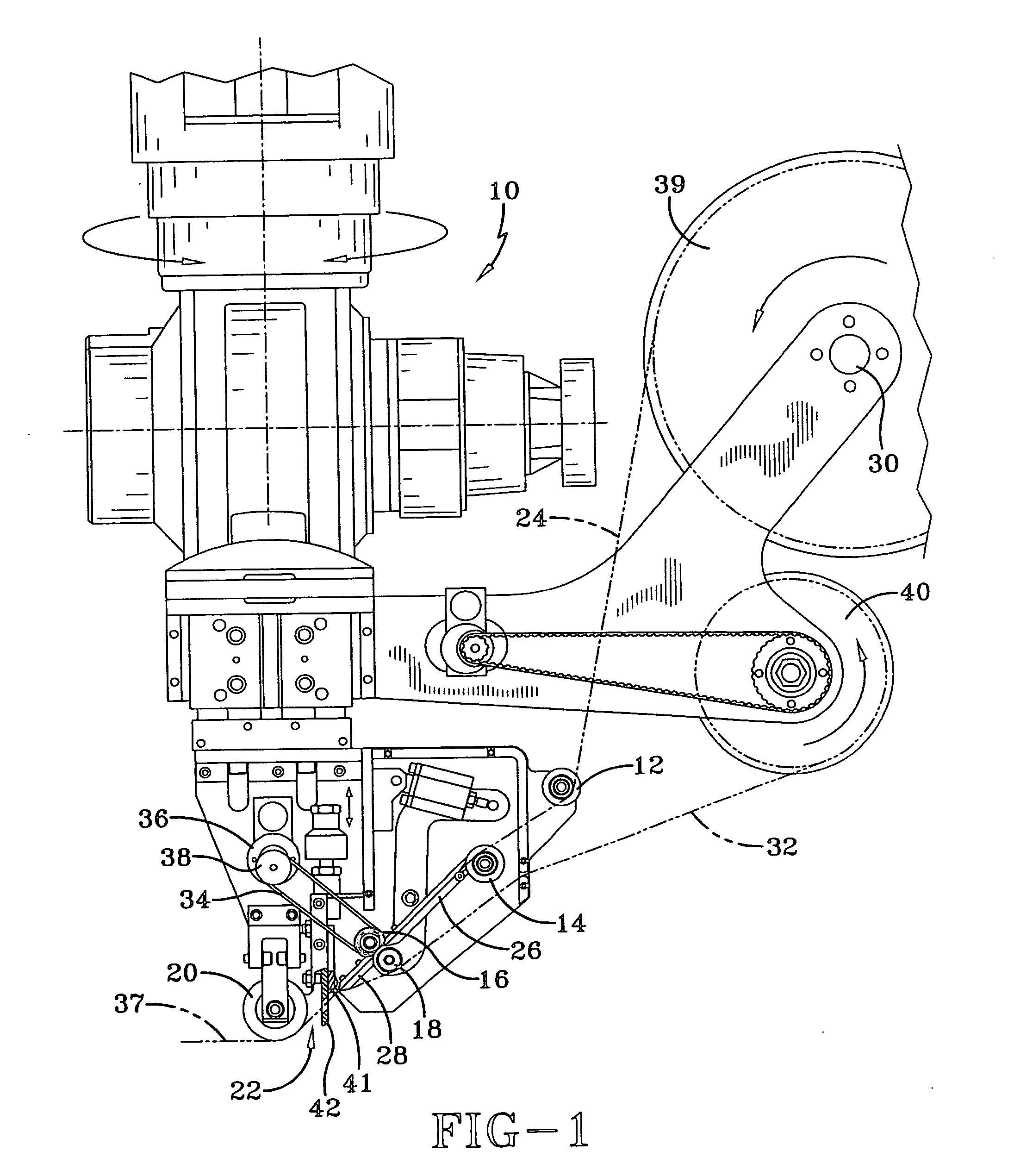

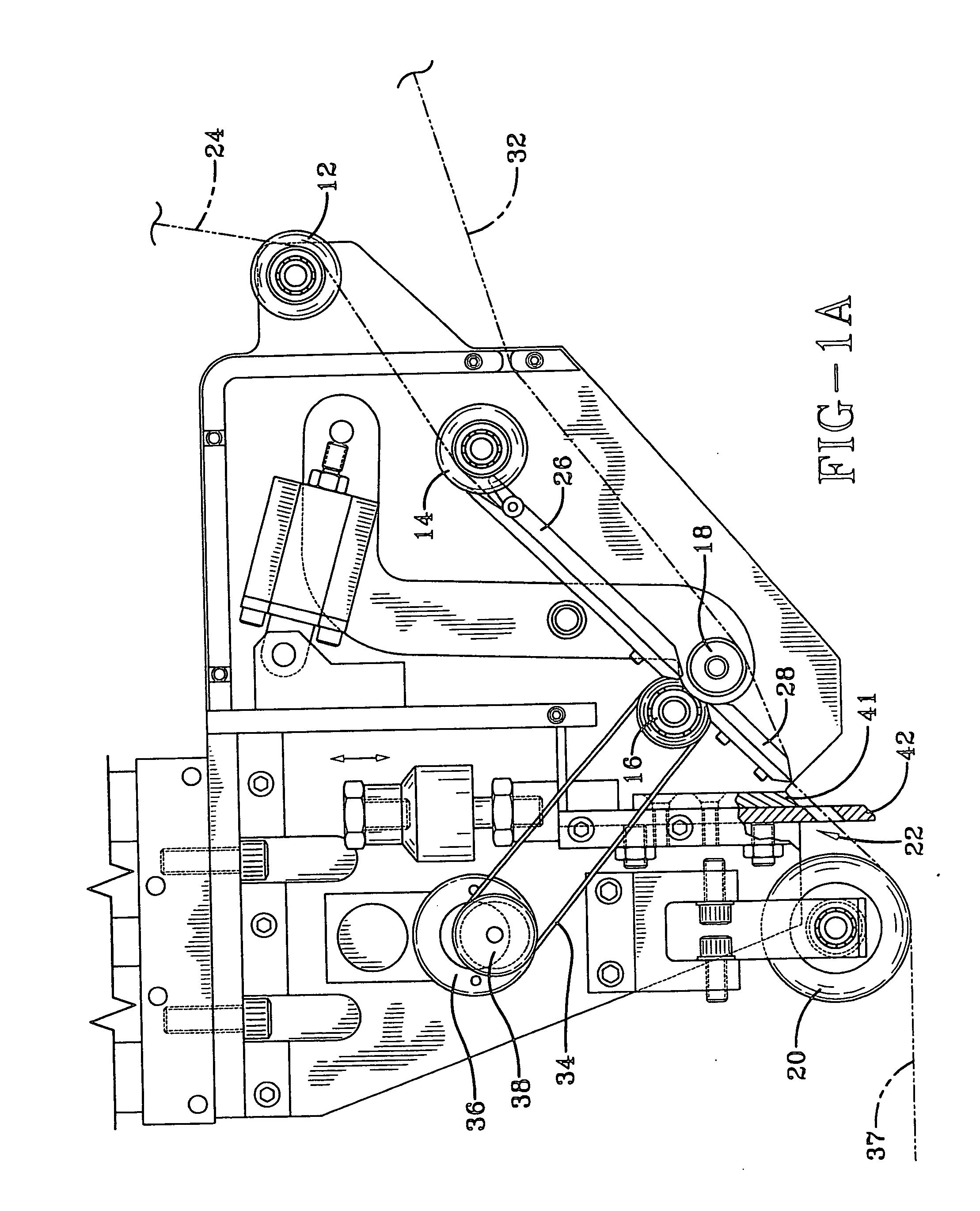

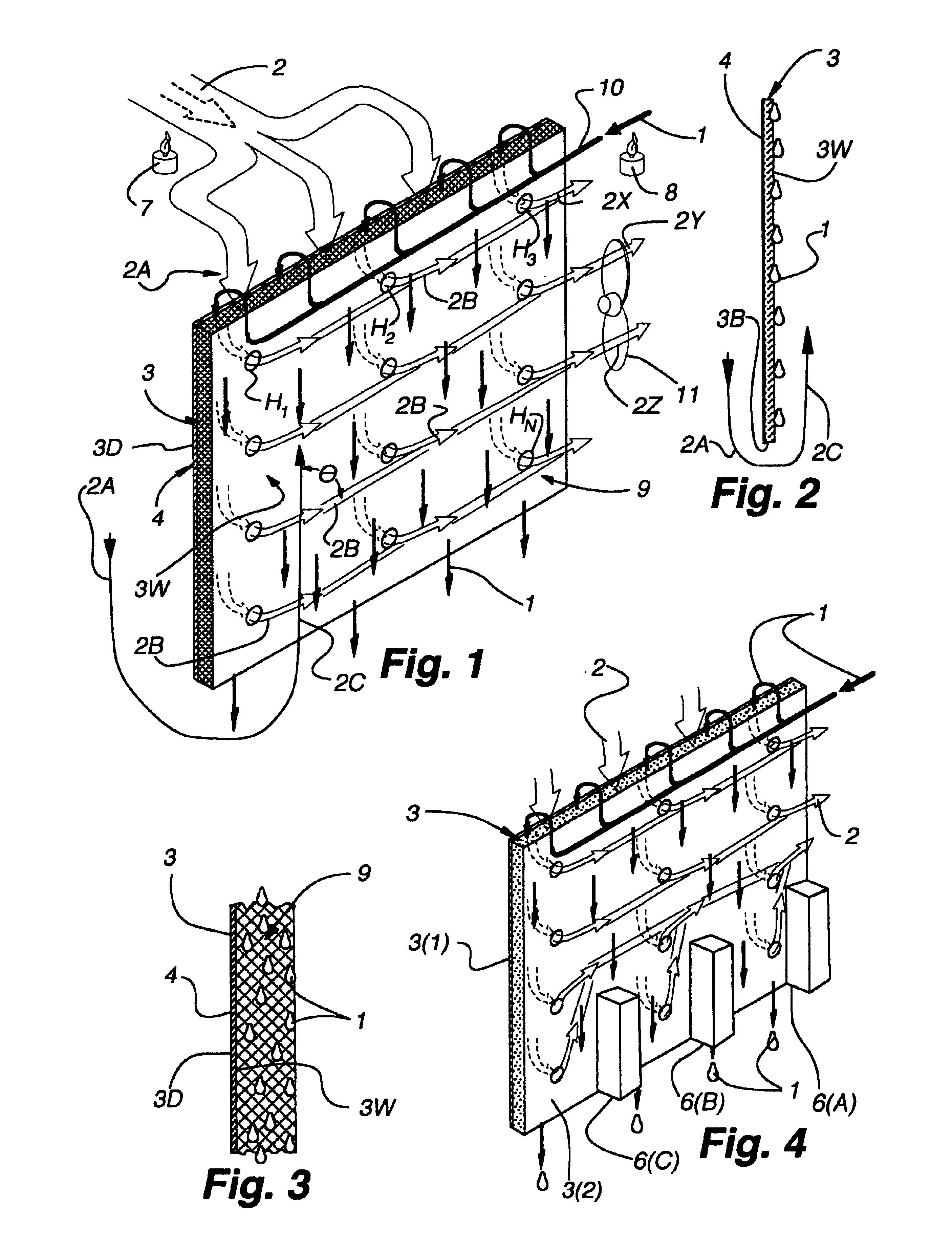

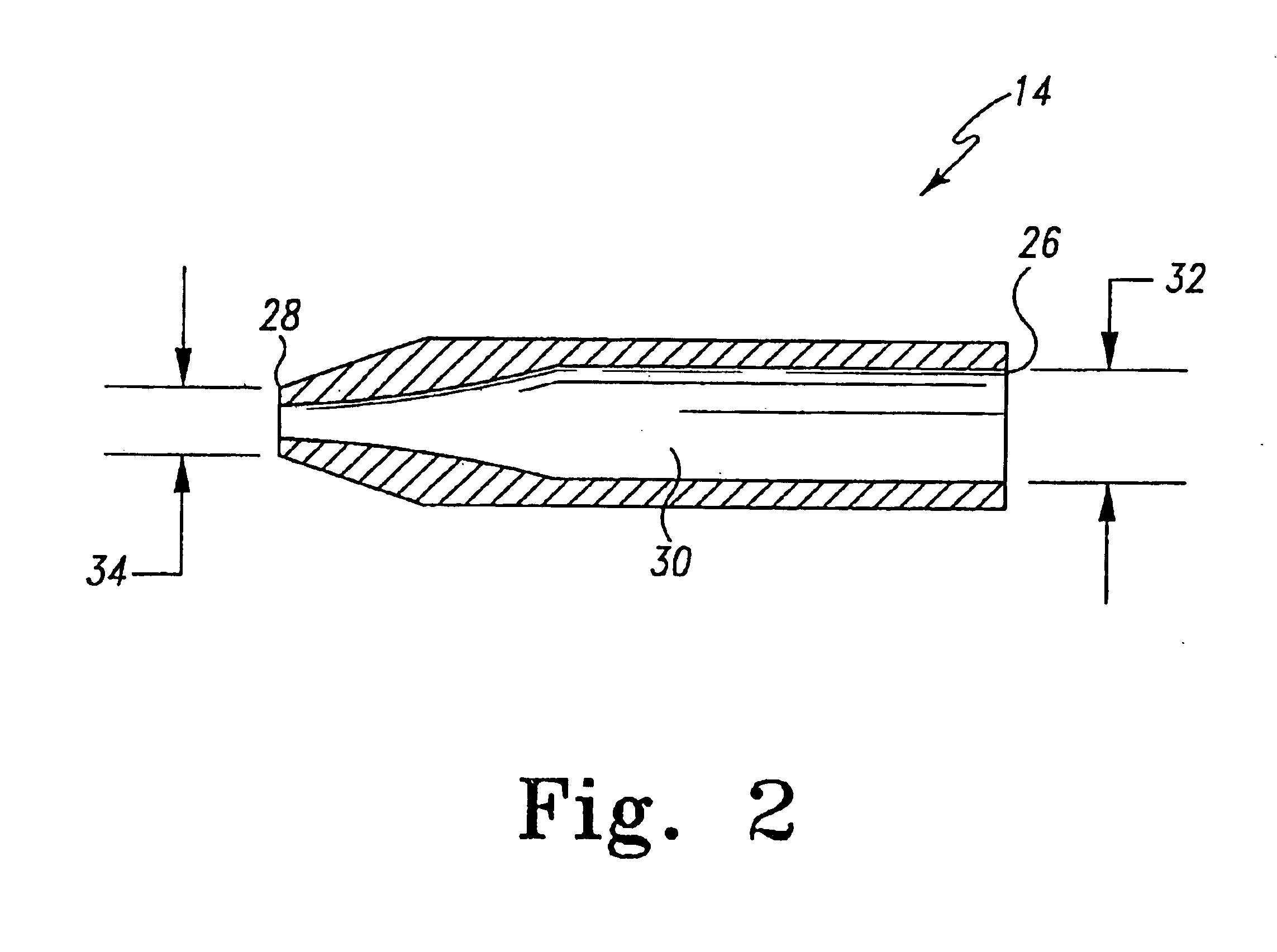

Composite tape laying apparatus and method

ActiveUS20050109451A1Simple procedureMaximizes material throughputLamination ancillary operationsControlling laminationFiberMagnetic tape

A fully automated method and apparatus is disclosed to laminate various structural articles with a layer of resin impregnated fiber tape. The tape laying member removes a releasable backing layer from the tape being employed, then deposits the unbacked tape on the surface of the structural article, and finally severs the end of the tape being deposited. An automated cut and restart procedure is employed in the present tape laying member to increase tape throughput.

Owner:TRELLEBORG SEALING SOLUTIONS GERMANY

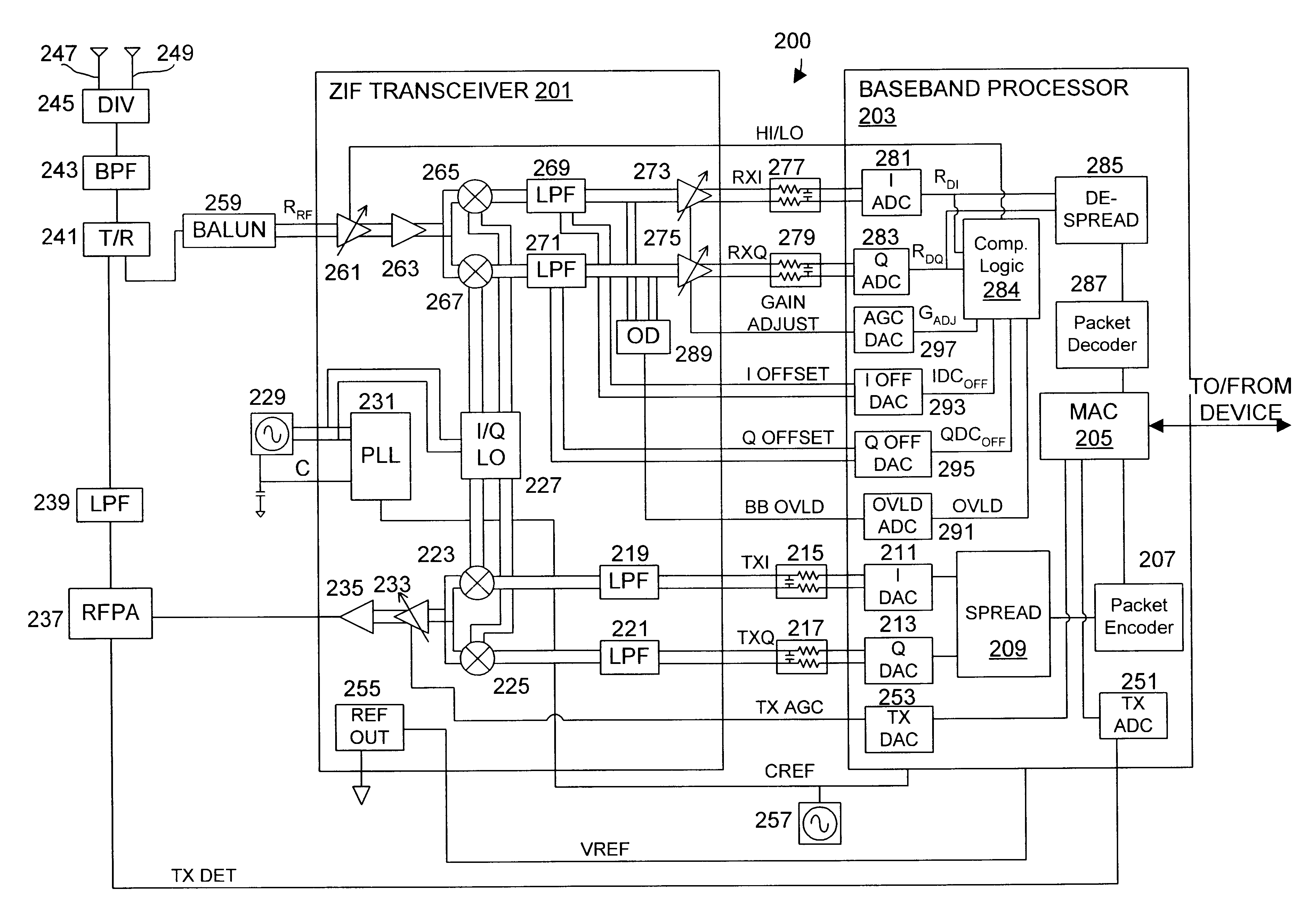

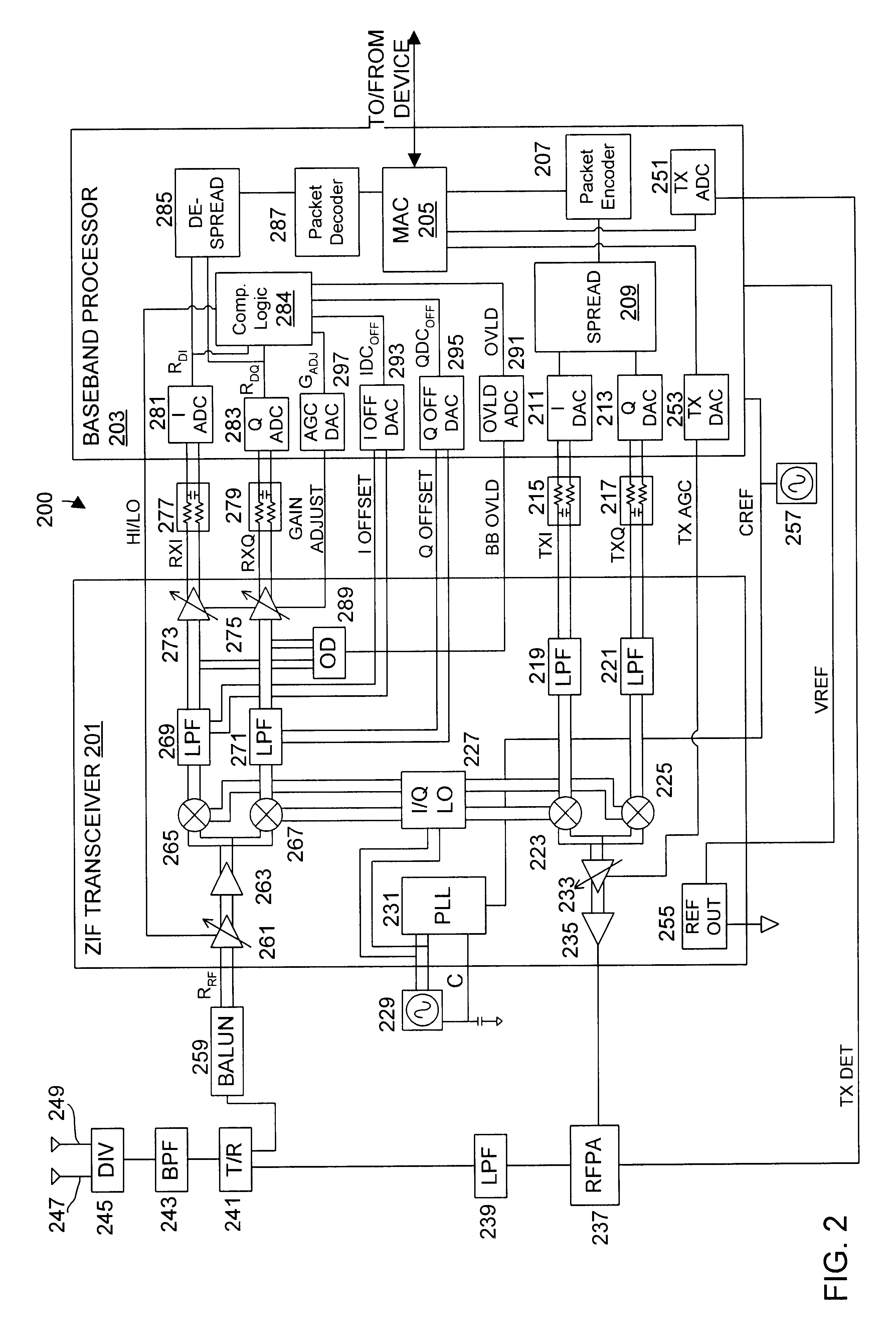

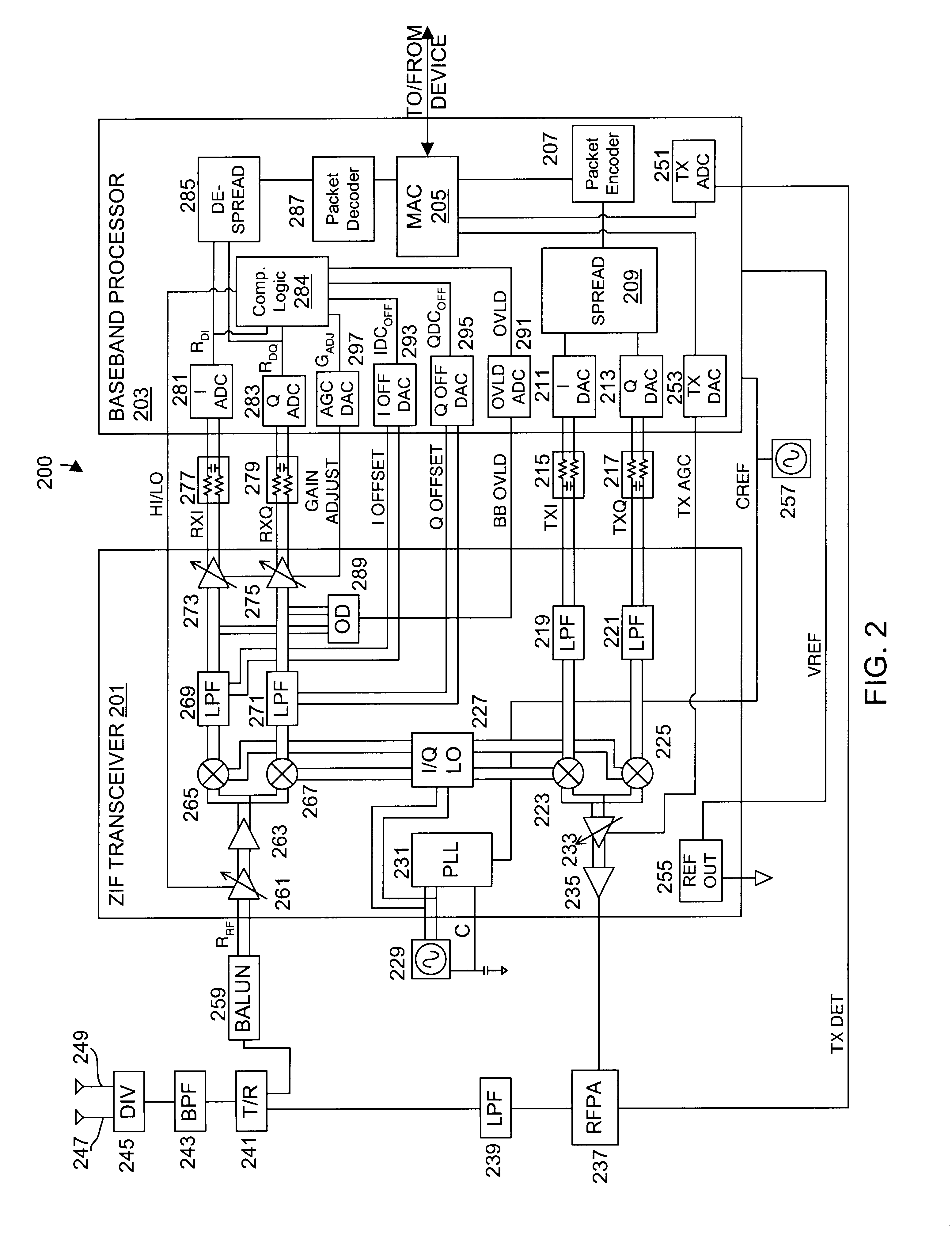

DC compensation system for a wireless communication device configured in a zero intermediate frequency architecture

InactiveUS6560448B1Low costMaximum performanceGain controlAmplitude-modulated carrier systemsTransceiverAudio power amplifier

A wireless communication device including a radio frequency (RF) circuit, a ZIF transceiver and a baseband processor. The ZIF transceiver includes an RF mixer circuit that converts the RF signal to a baseband input signal, a summing junction that subtracts a DC offset from the baseband input signal to provide an adjusted baseband input signal, and a baseband amplifier that receives the adjusted baseband input signal and that asserts an amplified input signal based on a gain adjust signal. The baseband processor includes gain control logic, DC control logic and a gain interface. The gain control logic receives the amplified input signal, estimates input signal power and asserts the gain adjust signal in an attempt to keep the input signal power at a target power level. The DC control logic estimates an amount of DC in the amplified input signal and provides the DC offset in an attempt to reduce DC in the amplified input signal. The gain interface converts gain levels between the gain control logic and the DC control logic. The RF signal may include in-phase (I) and quadrature (Q) portions, where the RF mixer circuit splits I and Q baseband input signals from the RF signal. Operation is substantially identical for both I and Q channels. The DC control logic operates to remove or otherwise eliminate DC from the received signal that is provided to decoders in the baseband processor.

Owner:M RED INC

Thermoplastic polyurethanes comprising polytrimethylene ether soft segments

InactiveUS20070129524A1High breathabilityReduce energy consumptionMonocomponent polyurethanes artificial filamentEtherDi-isocyanate

Thermoplastic polyurethane prepared from reactants comprising: (a) polytrimethylene ether glycol; (b) diisocyanate; (c) diol chain extender; and (d) monofunctional alcohol chain terminator or monofunctional amine chain terminator; and manufacture and use thereof.

Owner:EI DU PONT DE NEMOURS & CO

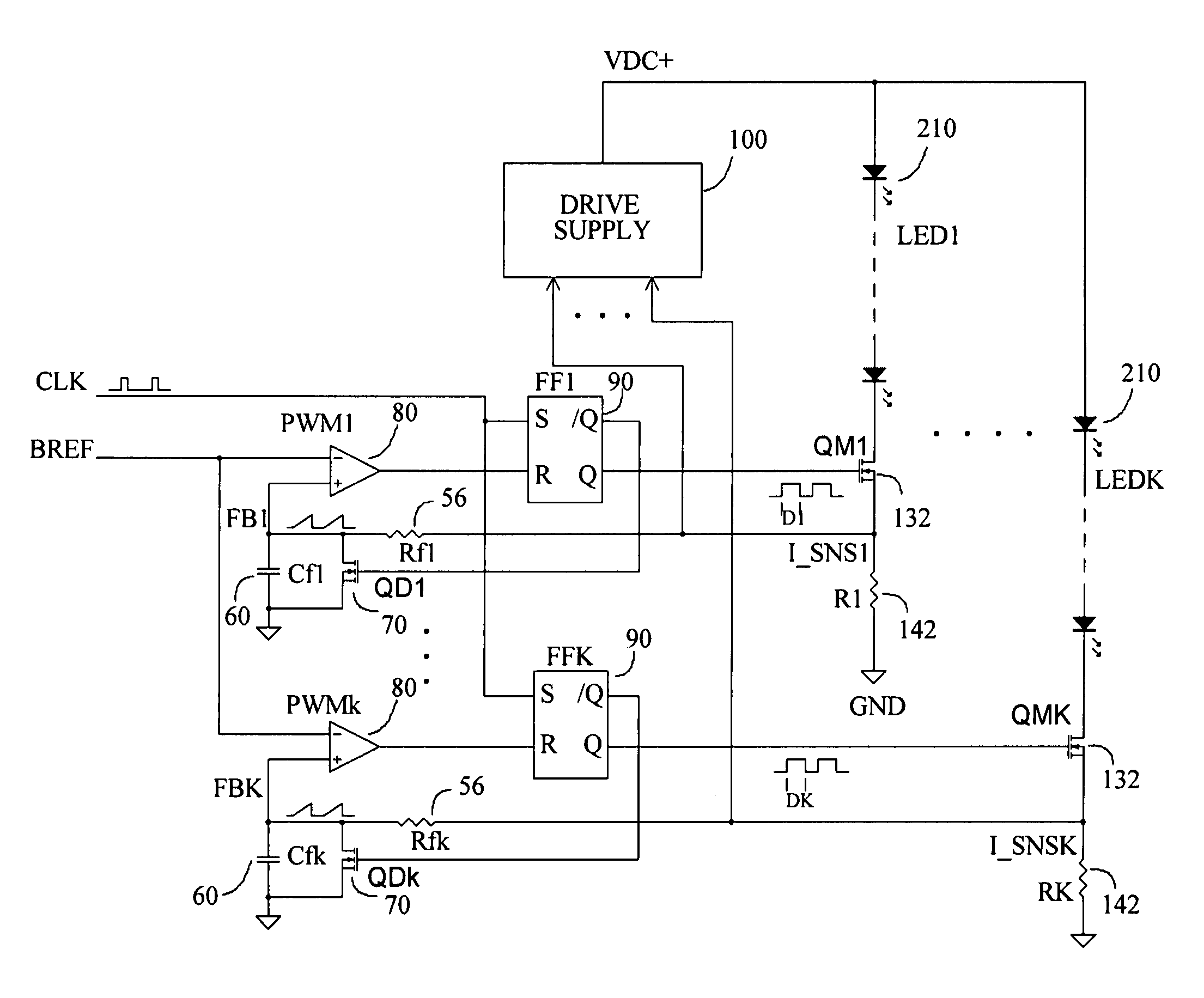

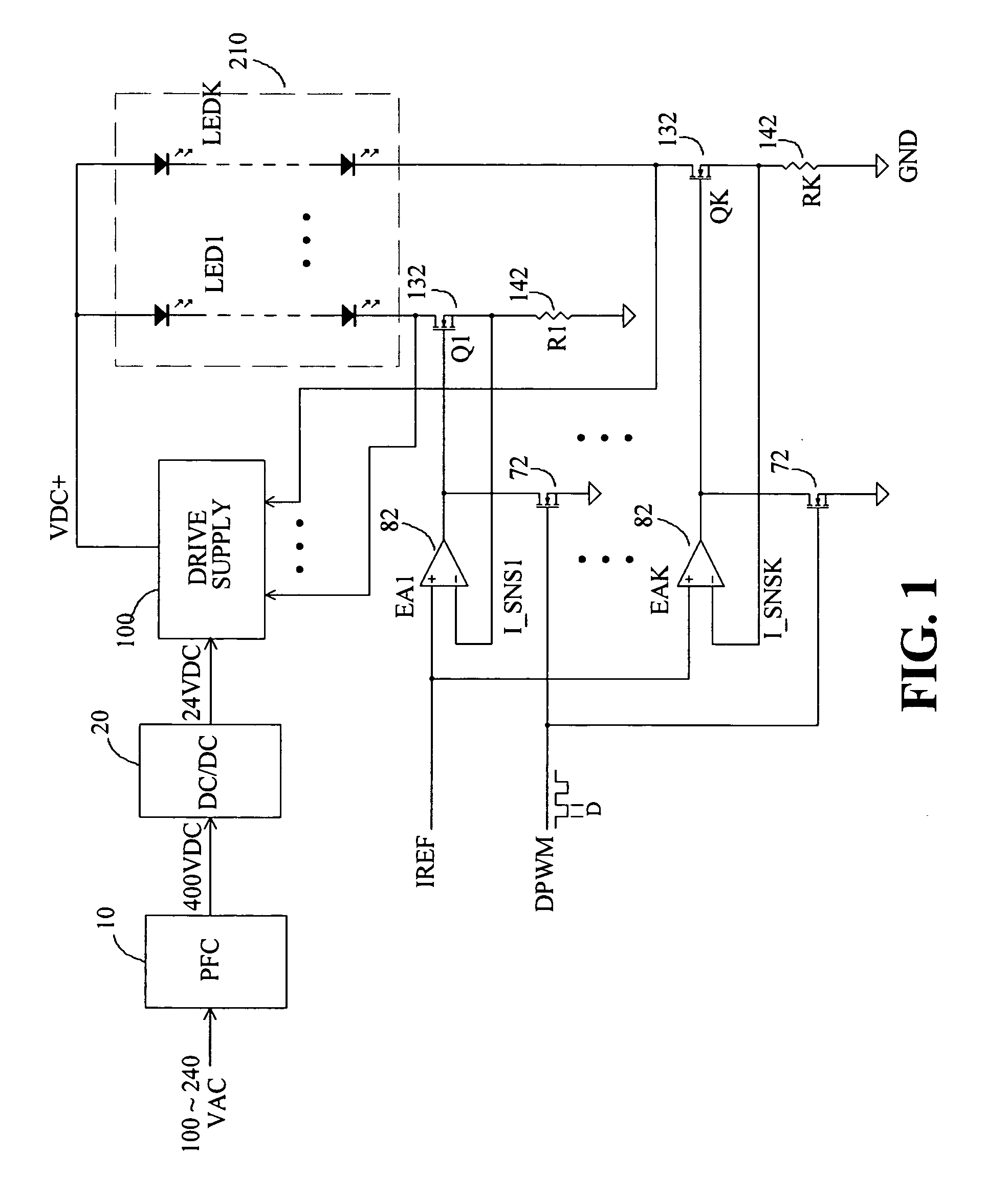

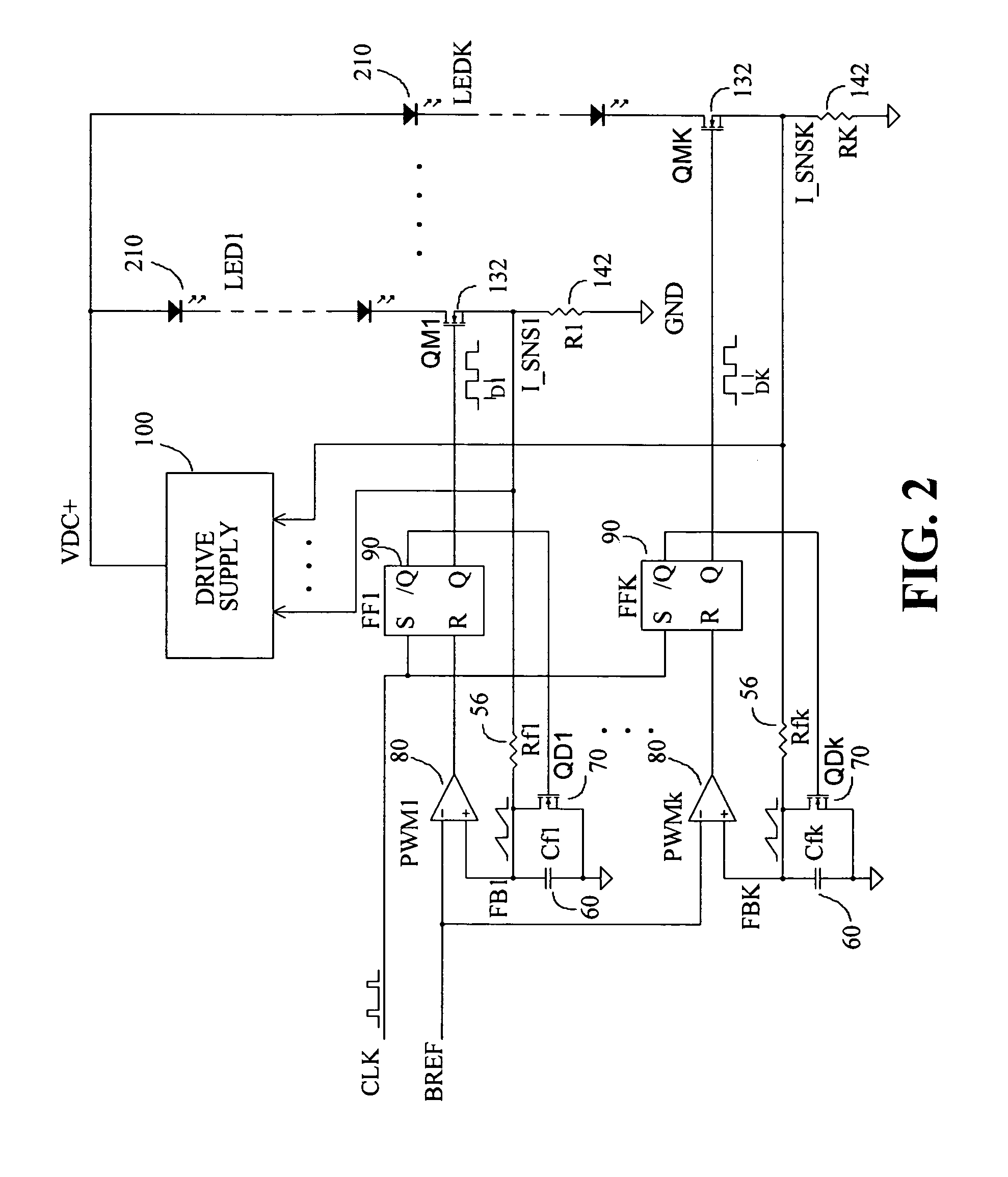

Method and apparatus for driving multiple LED devices

InactiveUS20110068700A1High efficiency circuit operationSimplified power conversion processElectrical apparatusElectroluminescent light sourcesBalancing networkEngineering

A series of methods of driving multiple LED devices with high efficiency balancing technique is disclosed. The regulation of the LED current is accomplished by switching operation to compensate the difference of the LED operating voltage. Reactive components are also employed to construct non-dissipative balancing networks to drive multiple LED strings with low losses. Additionally, a series of concept is presented to drive the LED devices from PFC voltage directly with low cost circuit architecture.

Owner:SUNTEC ENTERPRISES

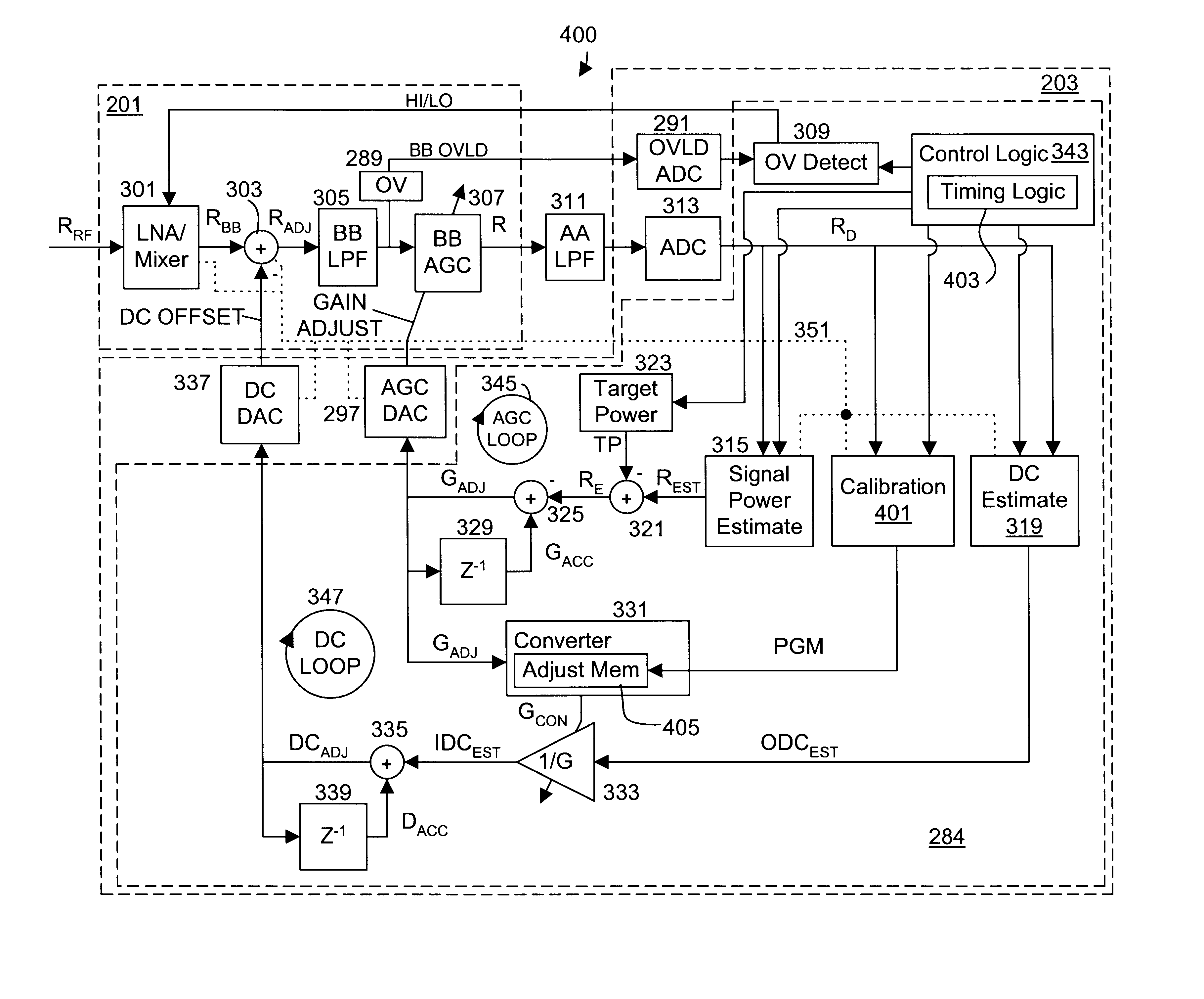

Calibrated DC compensation system for a wireless communication device configured in a zero intermediate frequency architecture

InactiveUS6735422B1Low costMaximum performancePulse automatic controlGain controlTransceiverAudio power amplifier

A calibrated DC compensation system for a wireless communication device configured in a zero intermediate frequency (ZIF) architecture. The device includes a ZIF transceiver and a baseband processor, which further includes a calibrator that periodically performs a calibration procedure. The baseband processor includes gain control logic, DC control logic, a gain converter and the calibrator. The gain converter converts gain between the gain control logic and the DC control logic. The calibrator programs the gain converter with values determined during the calibration procedure. The gain converter may be a lookup table that stores gain conversion values based on measured gain of a baseband gain amplifier of the ZIF transceiver. The gain control logic may further include a gain adjust limiter that limits change of a gain adjust signal during operation based on a maximum limit or on one or more gain change limits. A second lookup table stores a plurality of DC adjust values, which are added during operation to further reduce DC offset. The calibration procedure includes sampling an output signal for each gain step of the baseband amplifier at two predetermined range values and corresponding DC offsets using successive approximation. The data is used to calculate gain, DC offset and DC differential values, which are used to determine the conversion values programmed into the lookup tables or the gain adjust limiter.

Owner:M RED INC

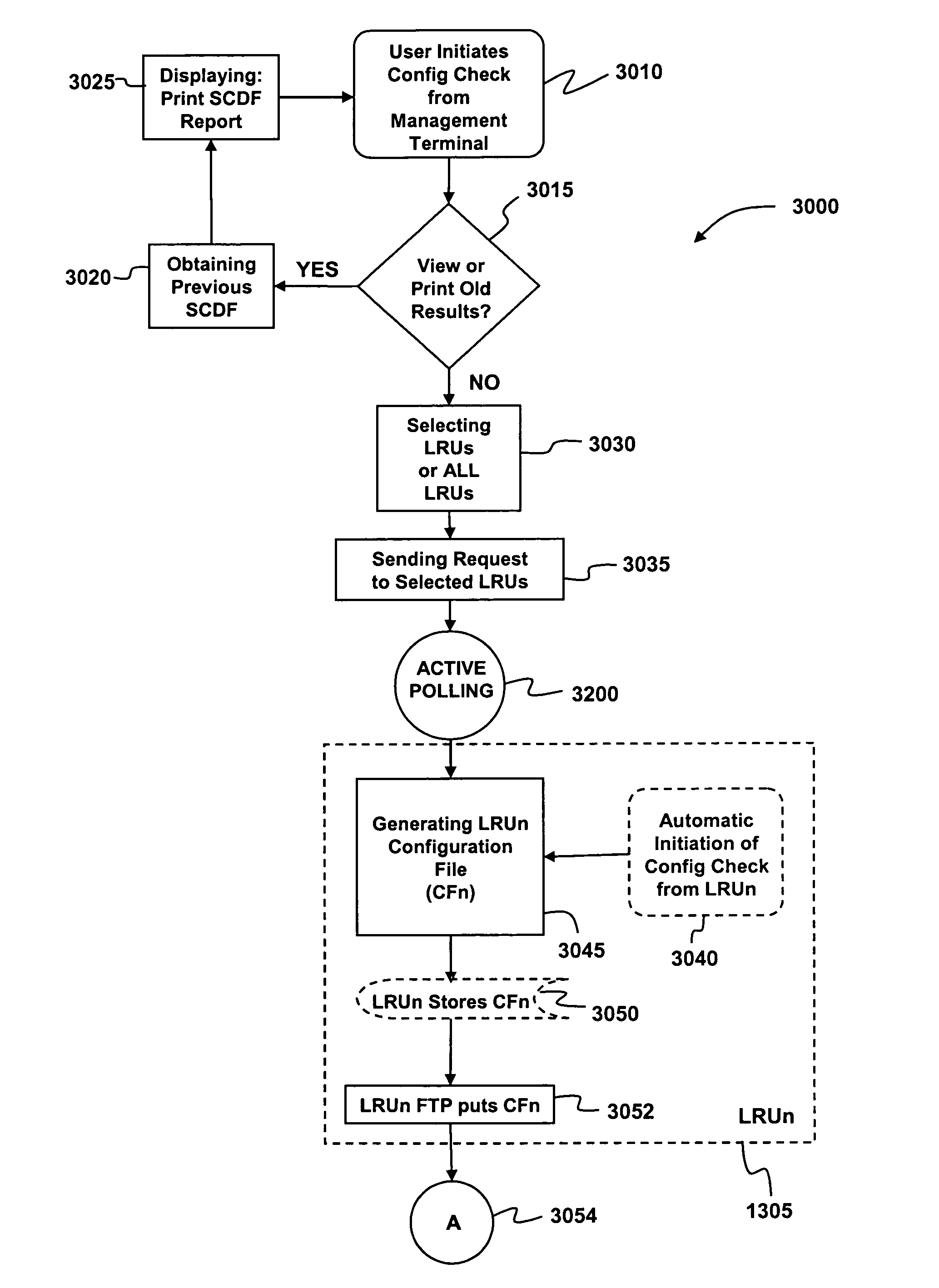

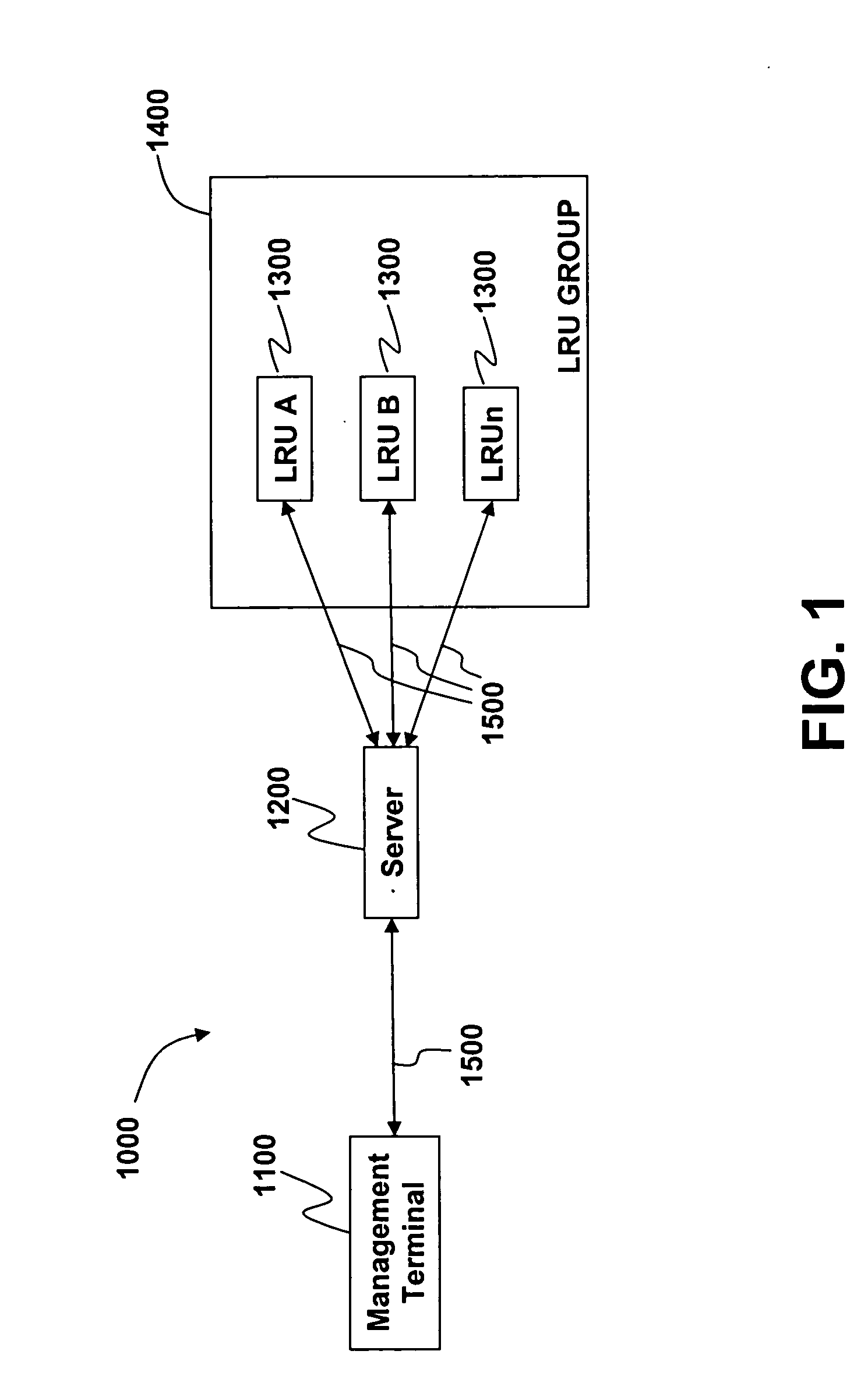

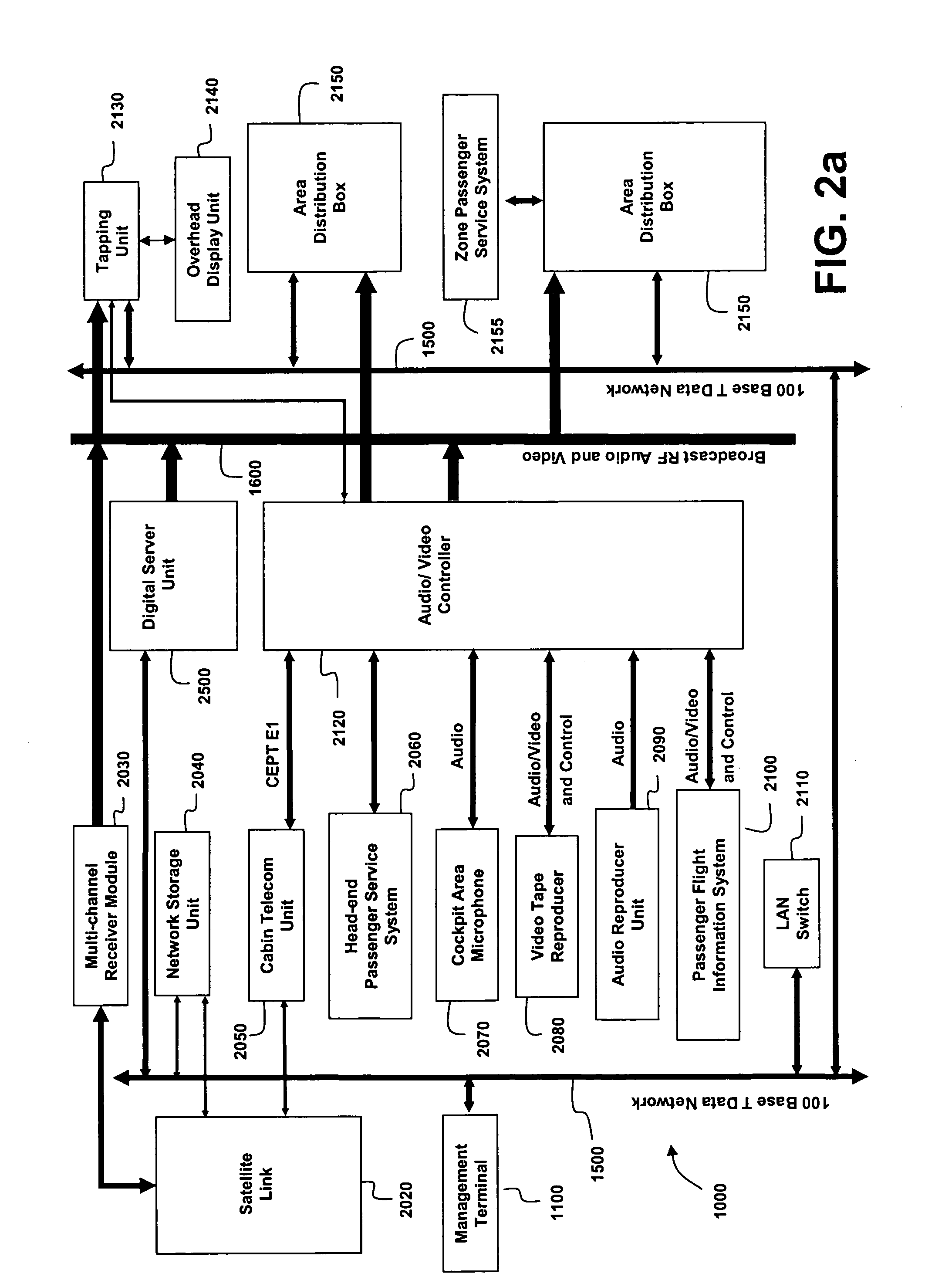

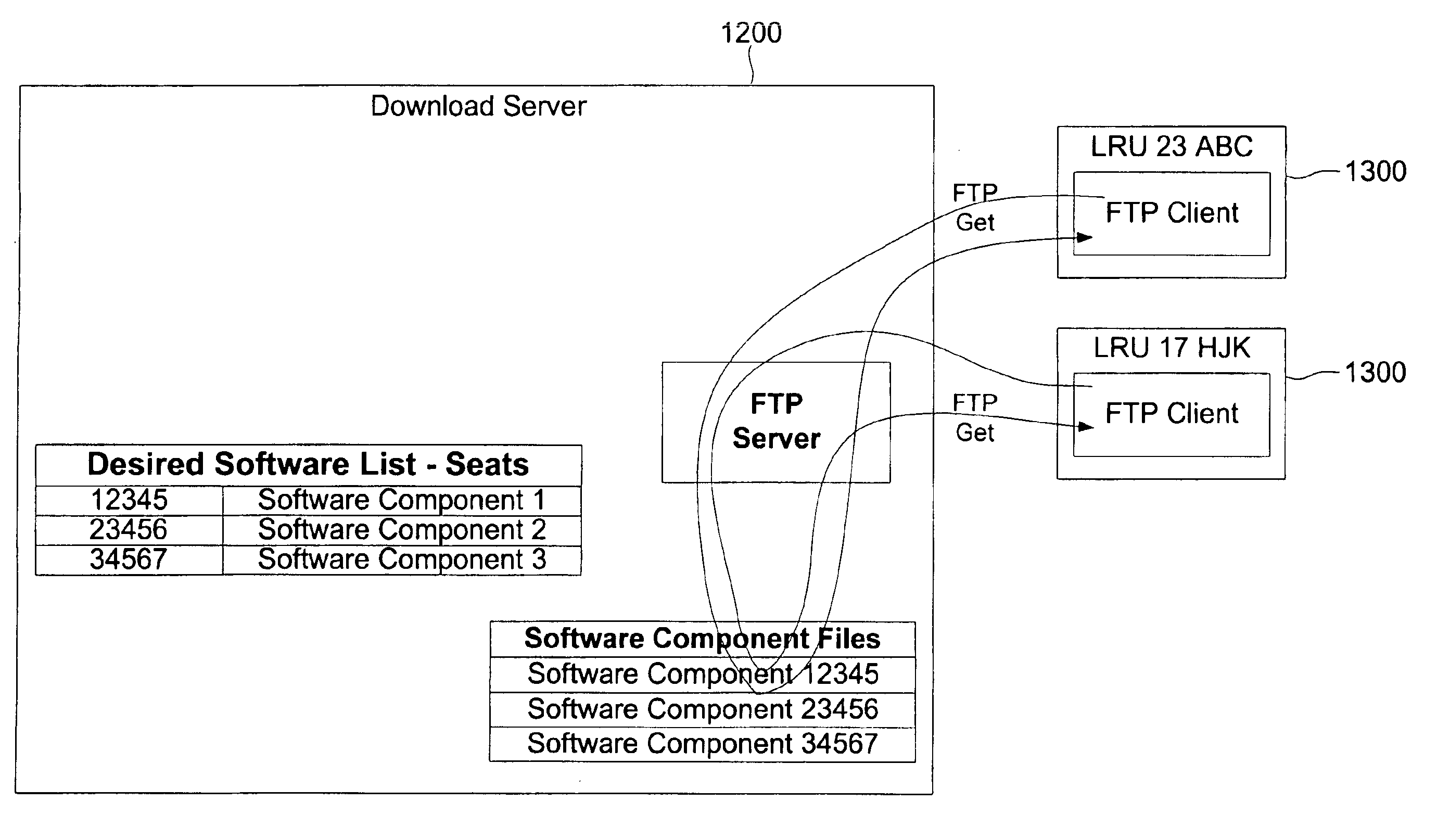

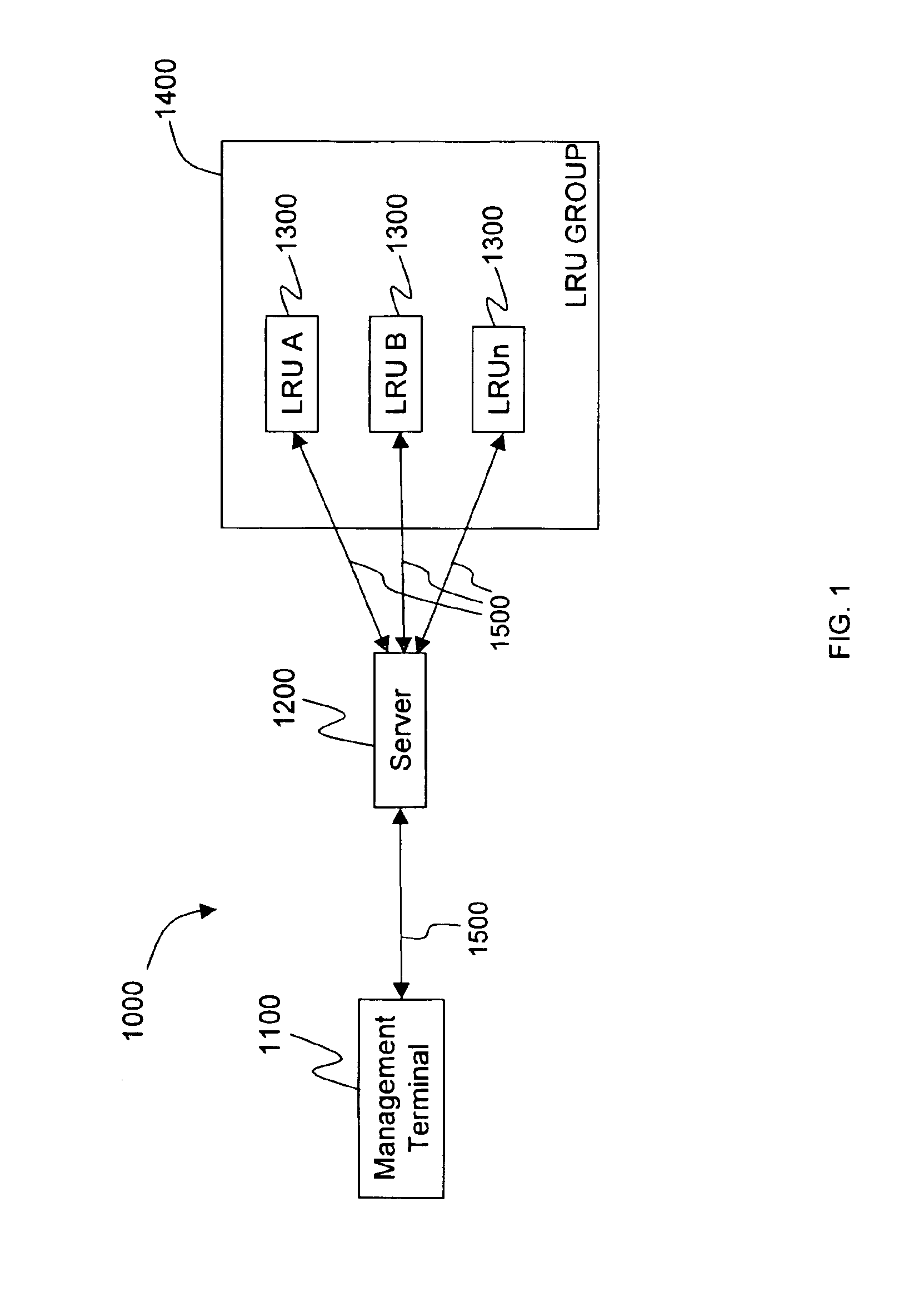

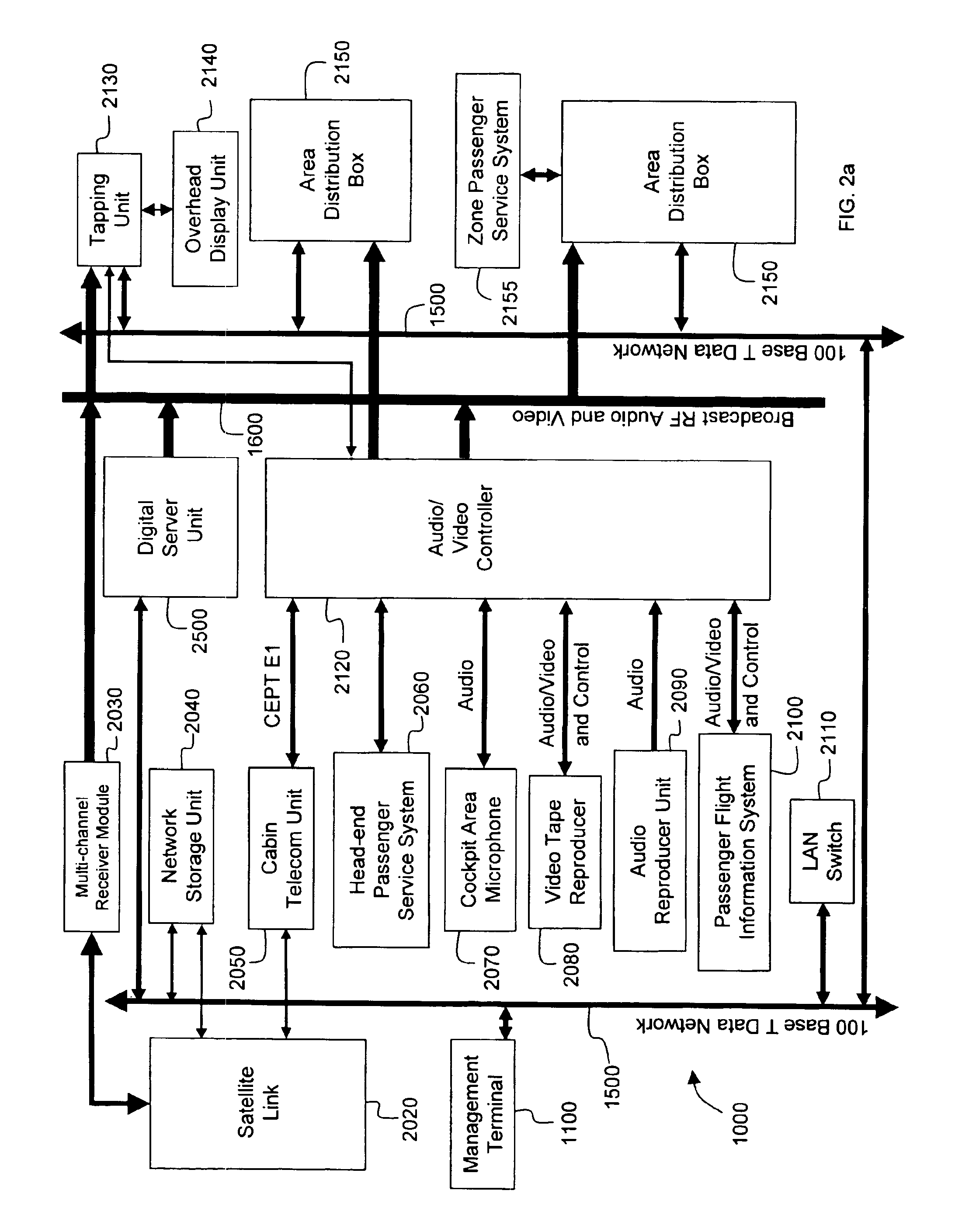

Method and system for configuration and download in a restricted architecture network

ActiveUS20060010438A1Avoids complication and difficultySimplify writingDigital computer detailsData resettingExtensibilityData file

A method and system are provided for updating software configurations of line-replaceable unit (LRU) computers in a restricted architecture network such as an in-flight entertainment system (IFES). Operating in an efficient and parallel manner, each of the LRUs independently creates an individual configuration file that identifies current software components. Each of the LRUs transmits its respective configuration file to a configuration server either automatically upon startup or manually upon request. The configuration server updates a system configuration data file with the current configuration files received from the individual LRUs. In a downloading method, a download server sends a list of desired software components to the LRUs. Each of the LRUs independently and simultaneously transfer (download) the needed software from the download server. The LRU independently requests the download server to download the needed software components. To improve scalability and reliability, the file transfers utilize standard protocols, such as FTP.

Owner:THALES AVIONICS INC

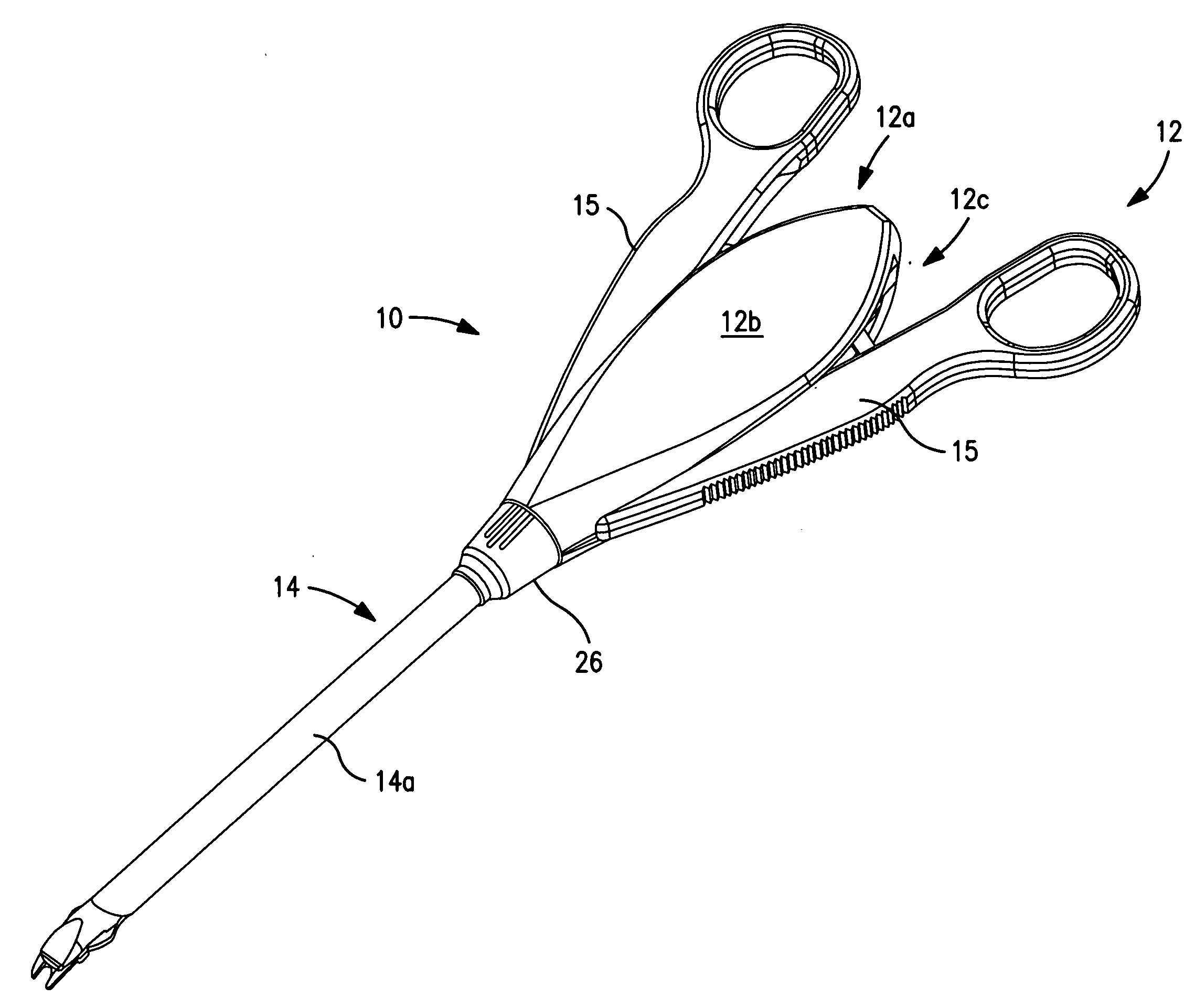

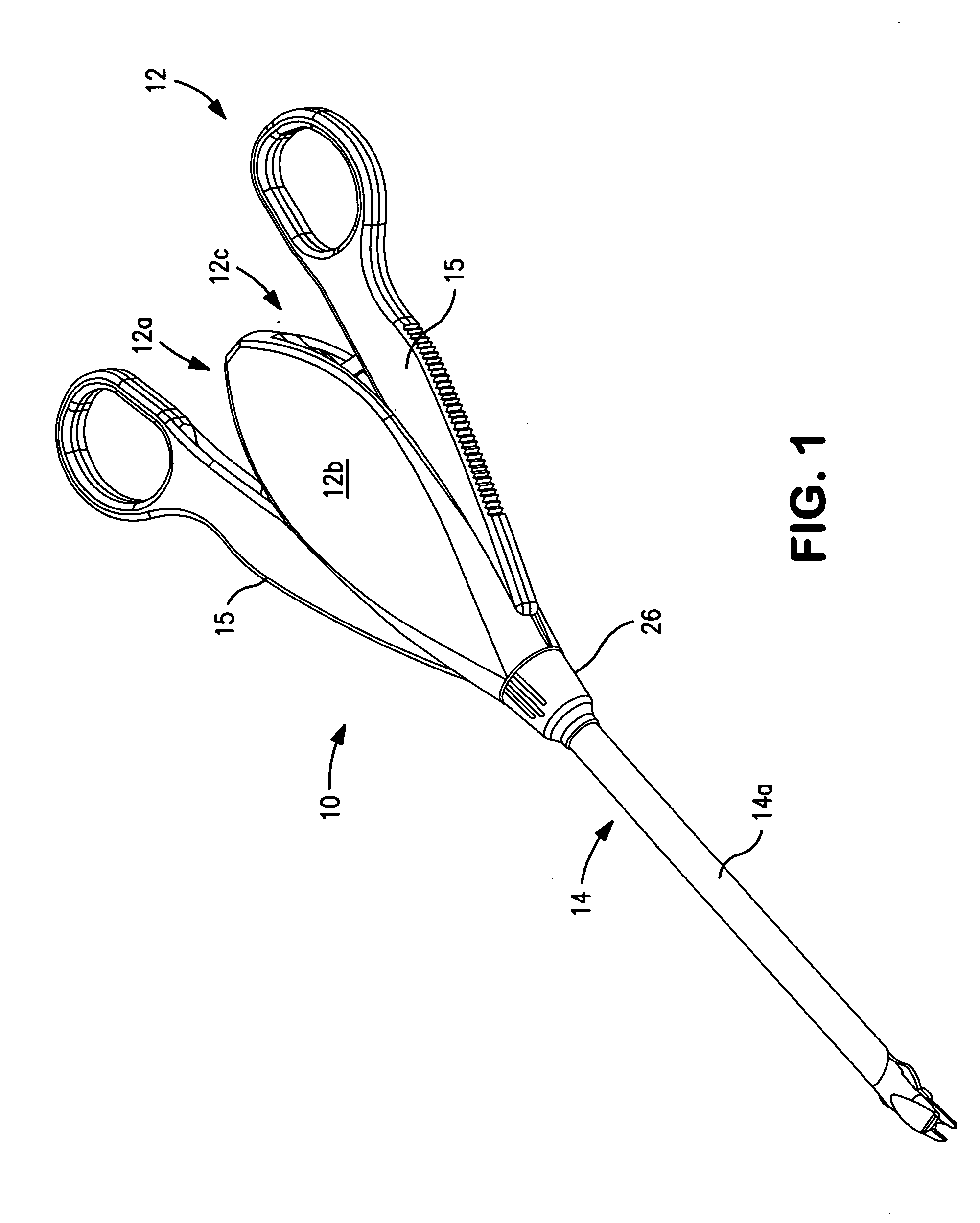

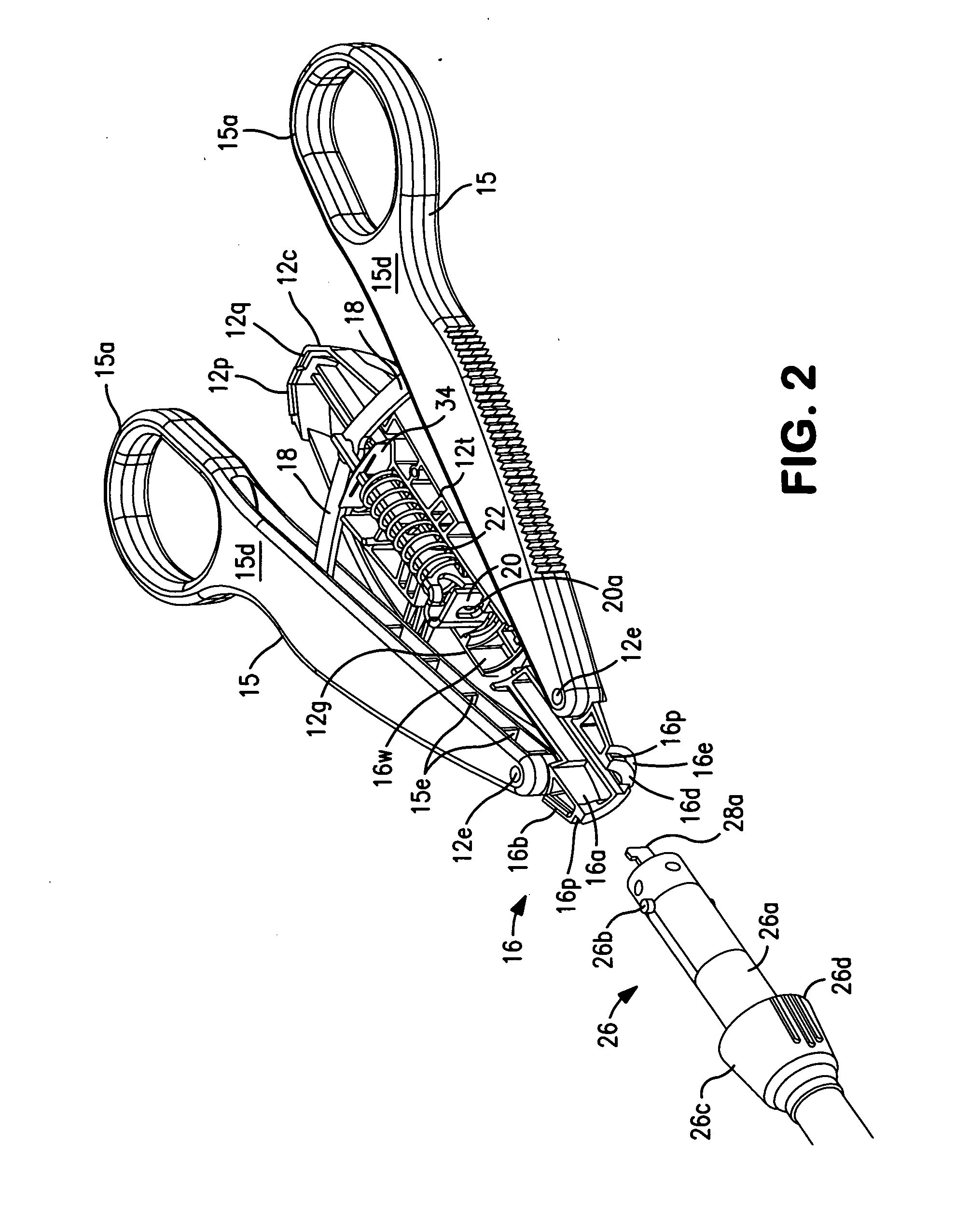

Surgical clip applier

ActiveUS20130165951A1Inhibition releaseMinimal complexityWound clampsJaw operationsReciprocating motion

A surgical clip applier with scissor-type operating handle and clip applying cartridge in which handle has housing of upper and lower shells that defines socket for receiving cartridge, includes a lever arm actuated linear translator for linear reciprocating movement delivered to the cartridge, and an anti-backup mechanism for full forward and release strokes of the handle, and in which cartridge includes jaws for applying clips, safety means to ensure opening of jaws for each cycle, a puller bar for receiving motion from handle and timing of jaw operation to clip feed, a magazine for feeding clips to jaws in proper sequence, and a lockout mechanism to render applier inoperative after using last clip.

Owner:BLAKE III JOSEPH W

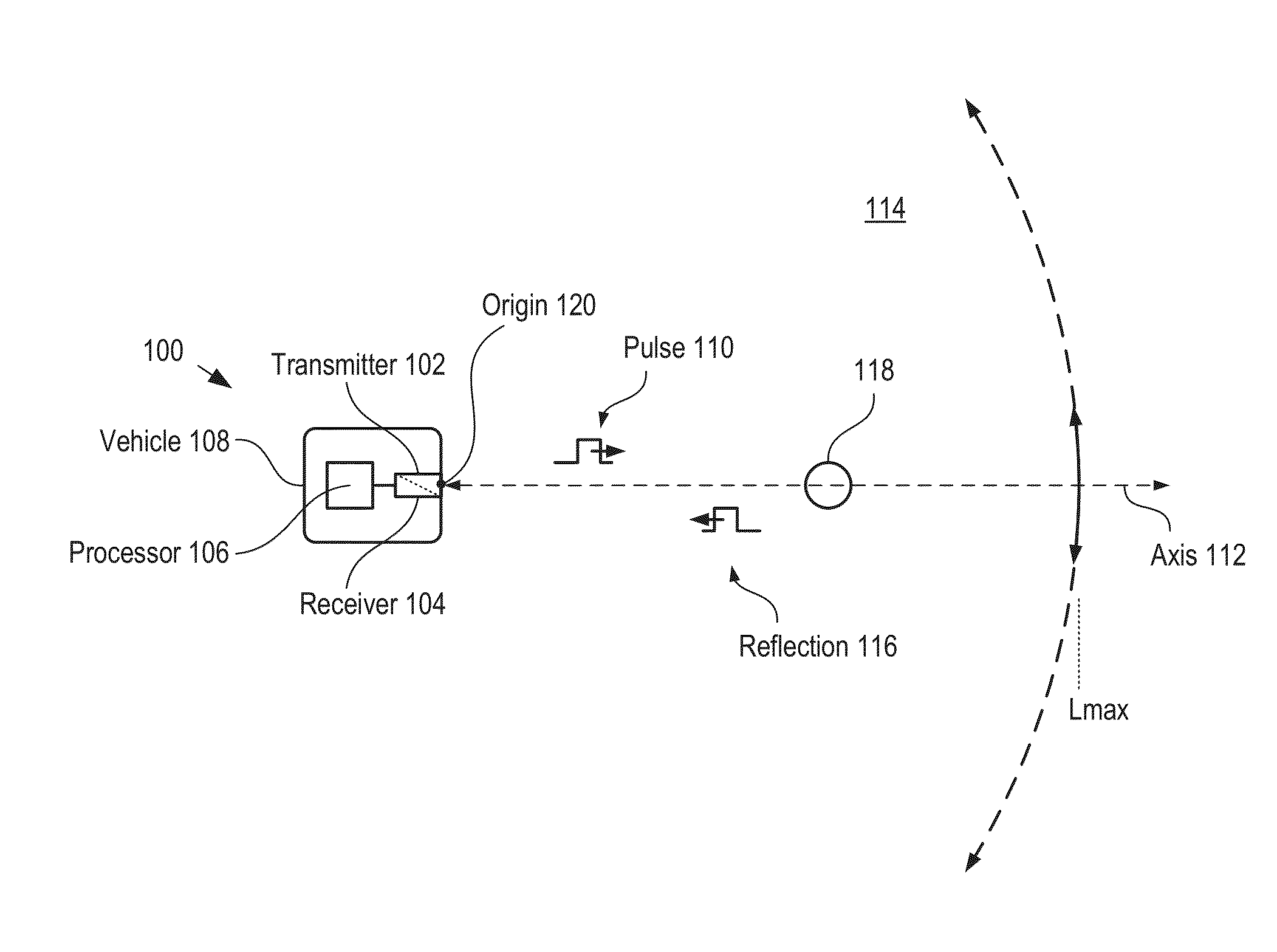

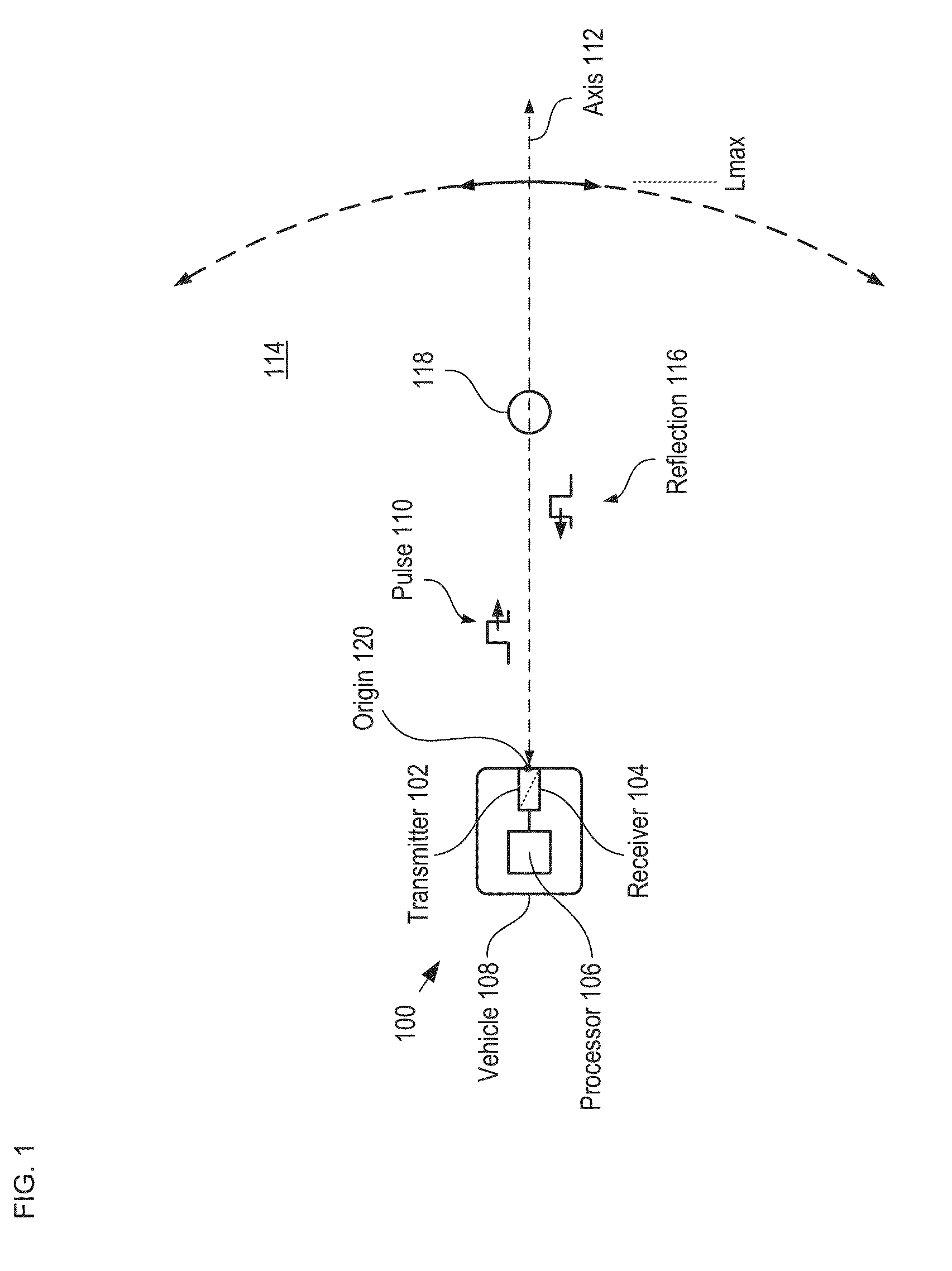

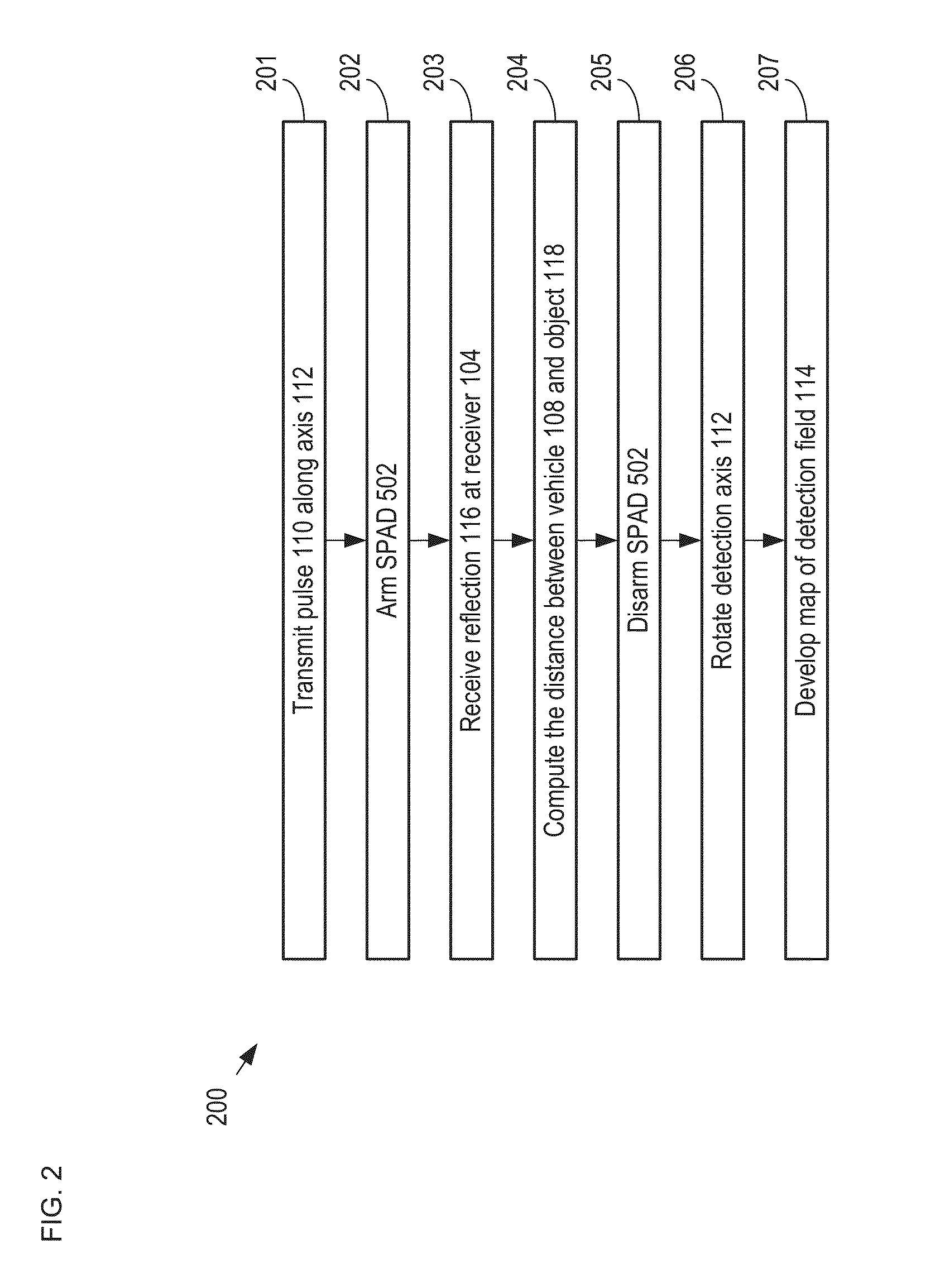

LiDAR System Comprising A Single-Photon Detector

ActiveUS20150192676A1Reduce impactHigh operating requirementsOptical rangefindersElectromagnetic wave reradiationWavelengthMulti dimensional

A method for developing a map of objects in a region surrounding a location is disclosed. The method includes interrogating the region along a detection axis with a series of optical pulses and detecting reflections of the optical pulses that originate at objects located along the detection axis. A multi-dimensional map of the region is developed by scanning the detection axis about the location in at least one dimension. The reflections are detected via a single-photon detector that is armed using a sub-gating scheme such that the single-photon detector selectively detects photons of reflections that originate only within each of a plurality of zones that collectively define the detection field. In some embodiments, the optical pulses have a wavelength within the range of 1350 nm to 1390 nm, which is a spectral range having a relatively high eye-safety threshold and a relatively low solar background.

Owner:LG INNOTEK CO LTD

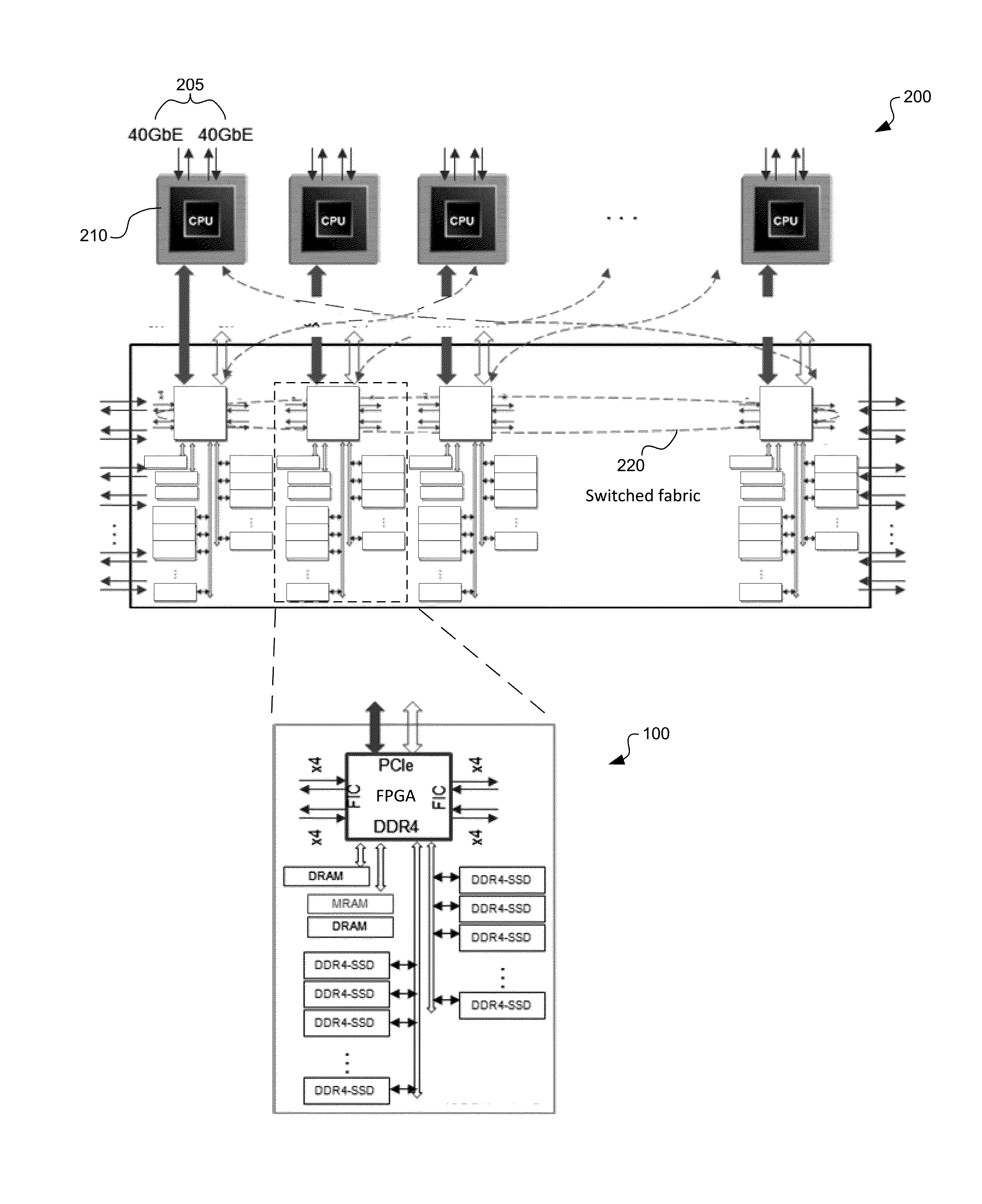

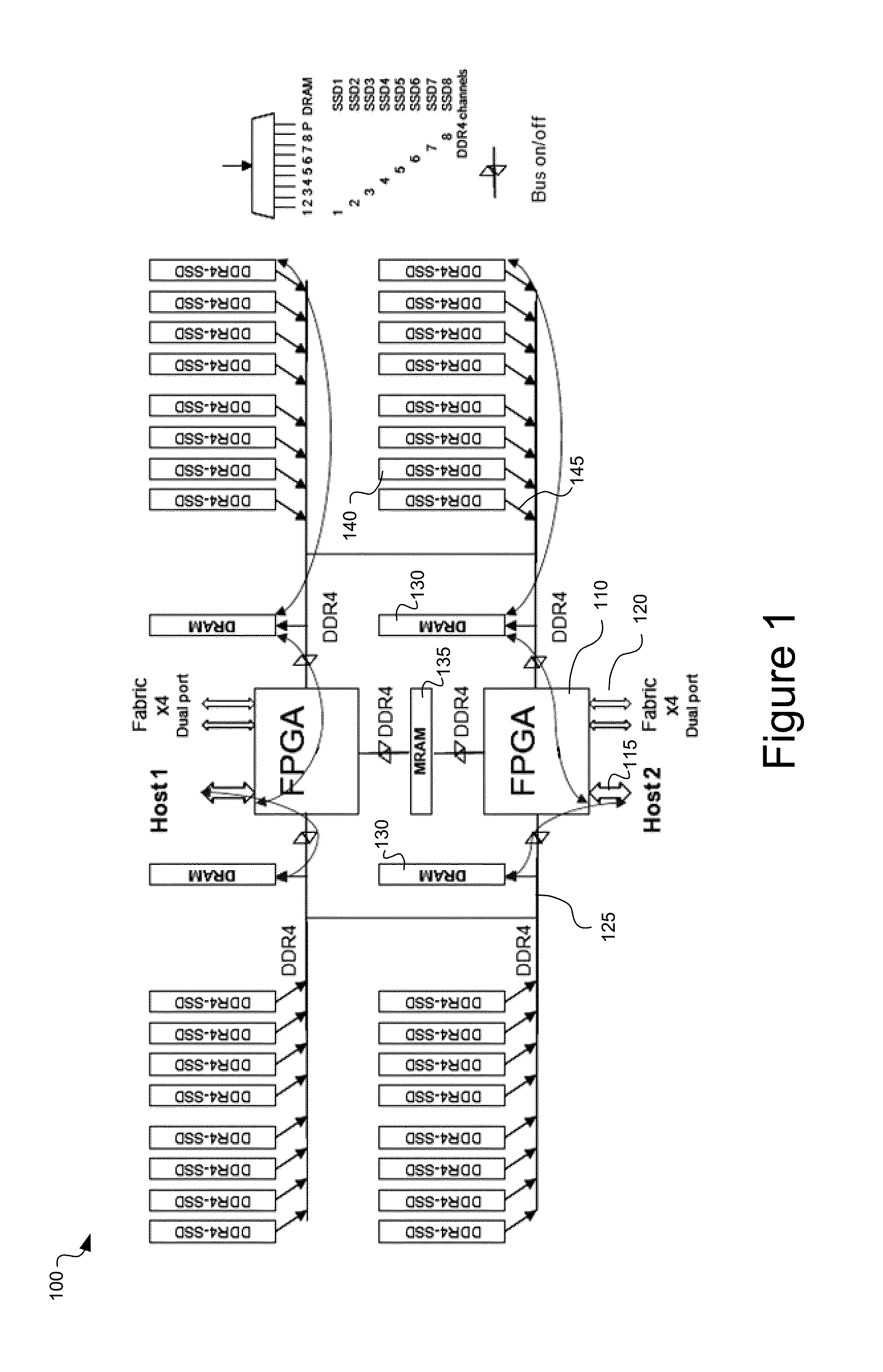

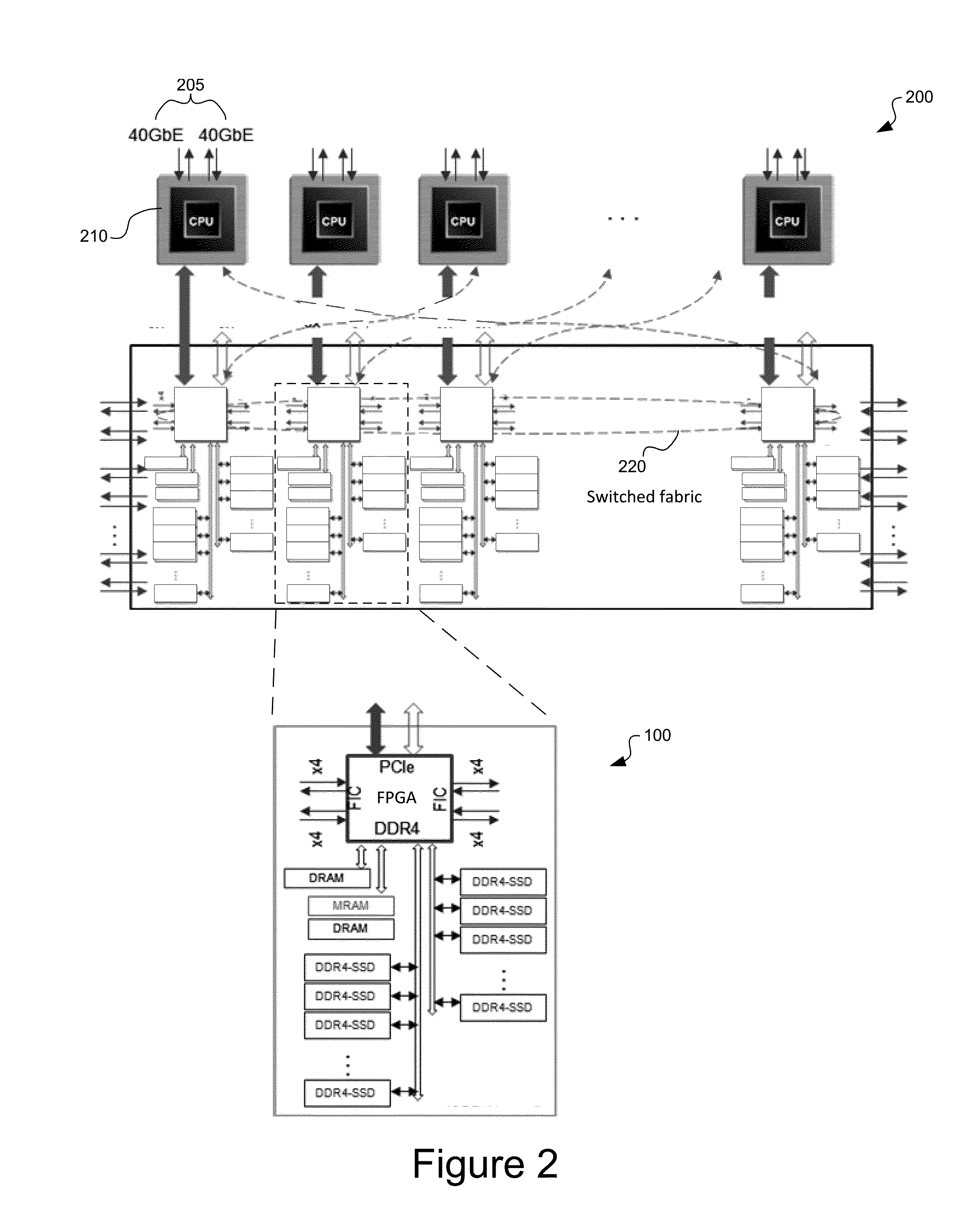

Rdma-ssd dual-port unified memory and network controller

ActiveUS20150254003A1Increase storage capacityLower latencyMemory architecture accessing/allocationInput/output to record carriersMagnetic reluctanceData memory

System and method for a unified memory and network controller for an all-flash array (AFA) storage blade in a distributed flash storage clusters over a fabric network. The unified memory and network controller has 3-way control functions including unified memory buses to cache memories and DDR4-AFA controllers, a dual-port PCIE interconnection to two host processors of gateway clusters, and four switch fabric ports for interconnections with peer controllers (e.g., AFA blades and / or chassis) in the distributed flash storage network. The AFA storage blade includes dynamic random-access memory (DRAM) and magnetoresistive random-access memory (MRAM) configured as data read / write cache buffers, and flash memory DIMM devices as primary storage. Remote data memory access (RDMA) for clients via the data caching buffers is enabled and controlled by the host processor interconnection(s), the switch fabric ports, and a unified memory bus from the unified controller to the data buffer and the flash SSDs.

Owner:FUTUREWEI TECH INC

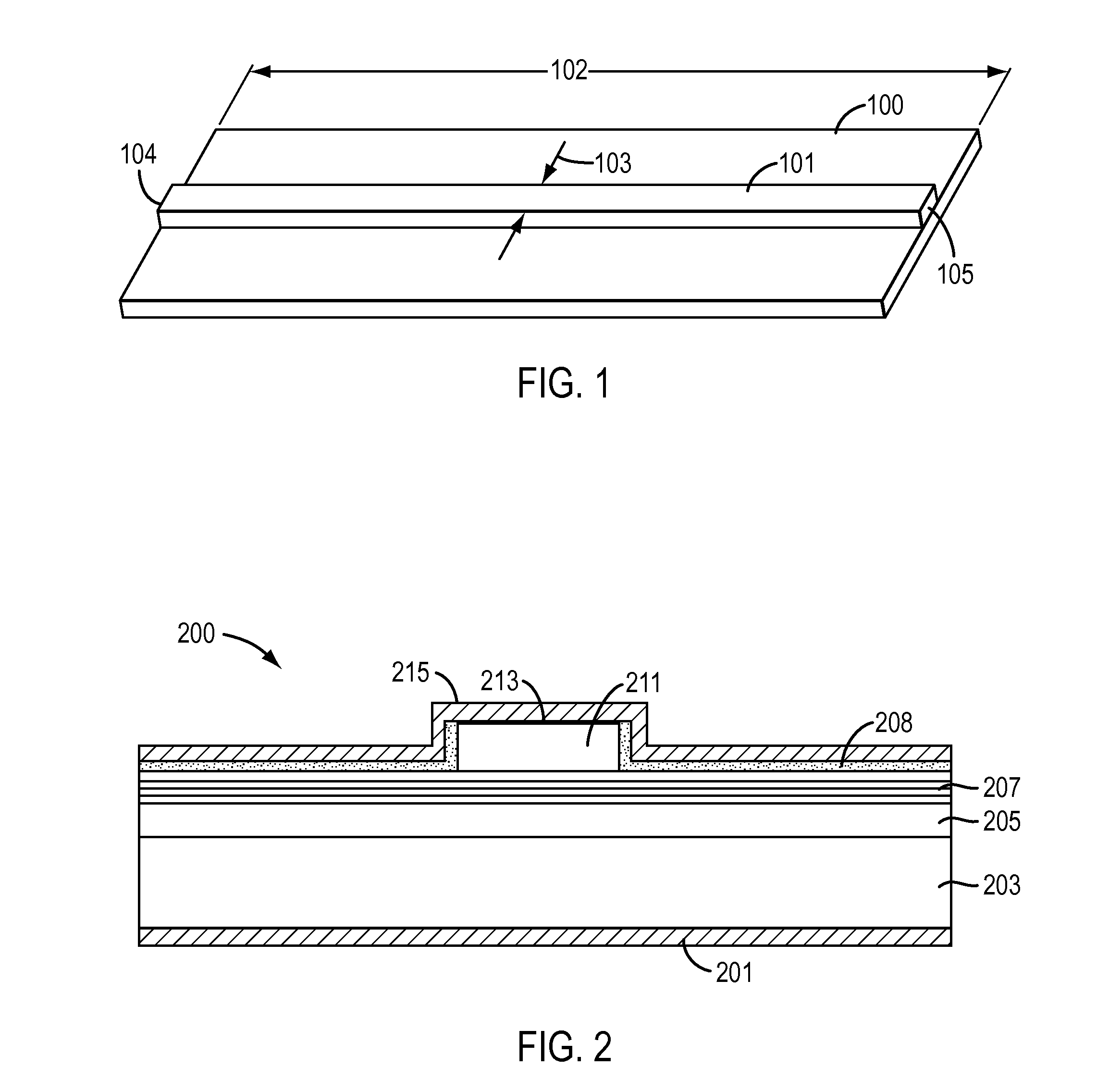

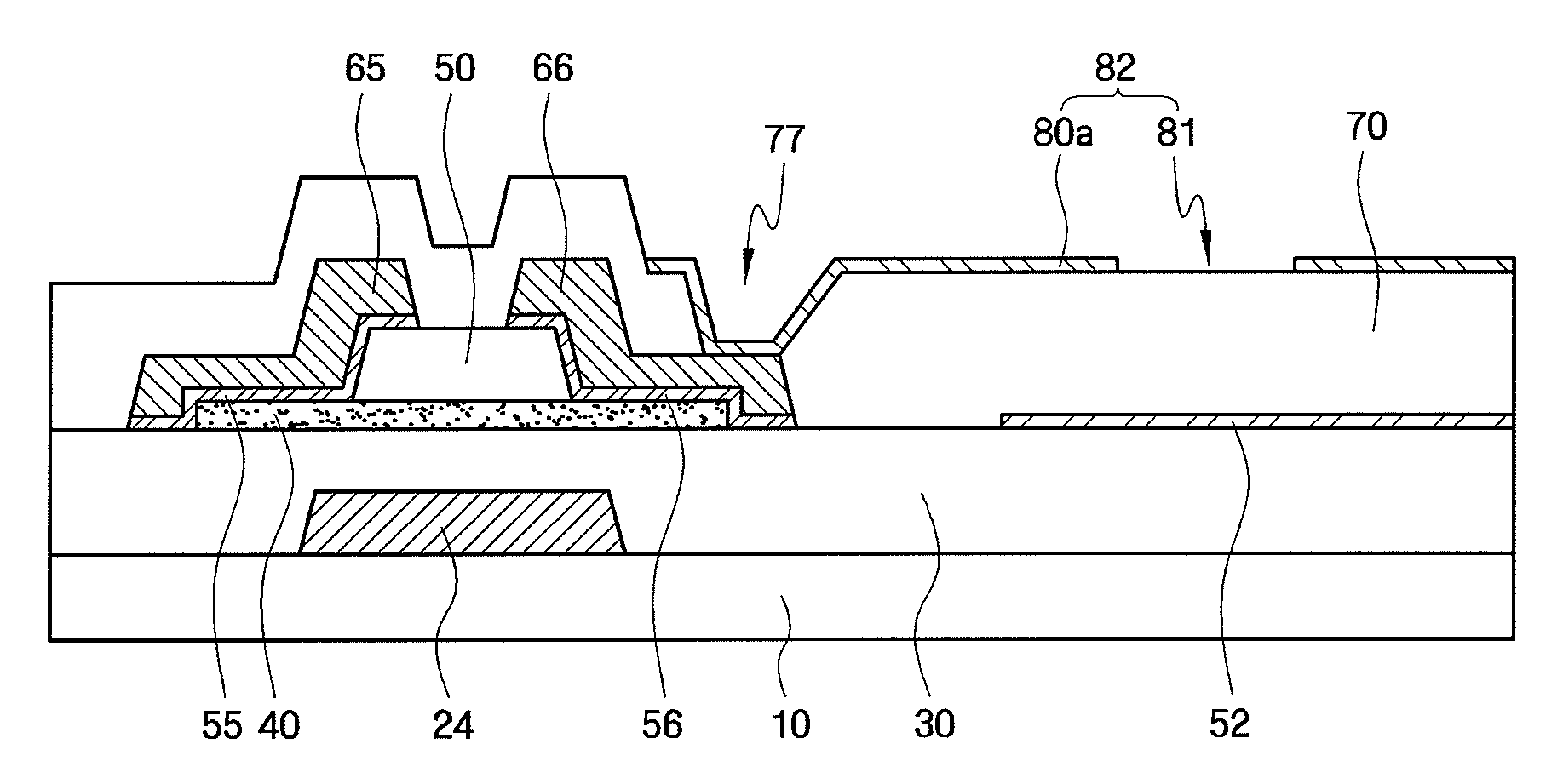

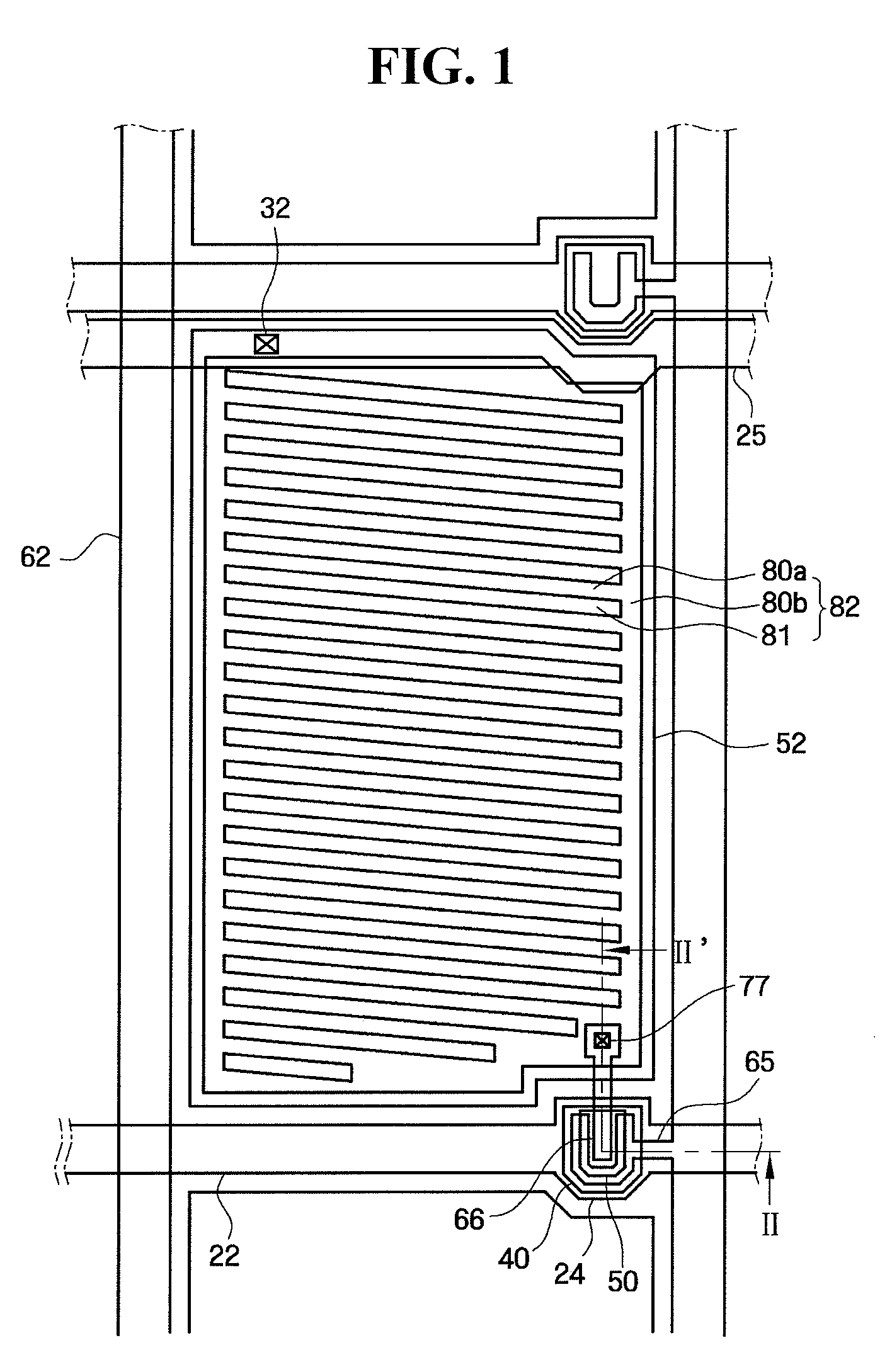

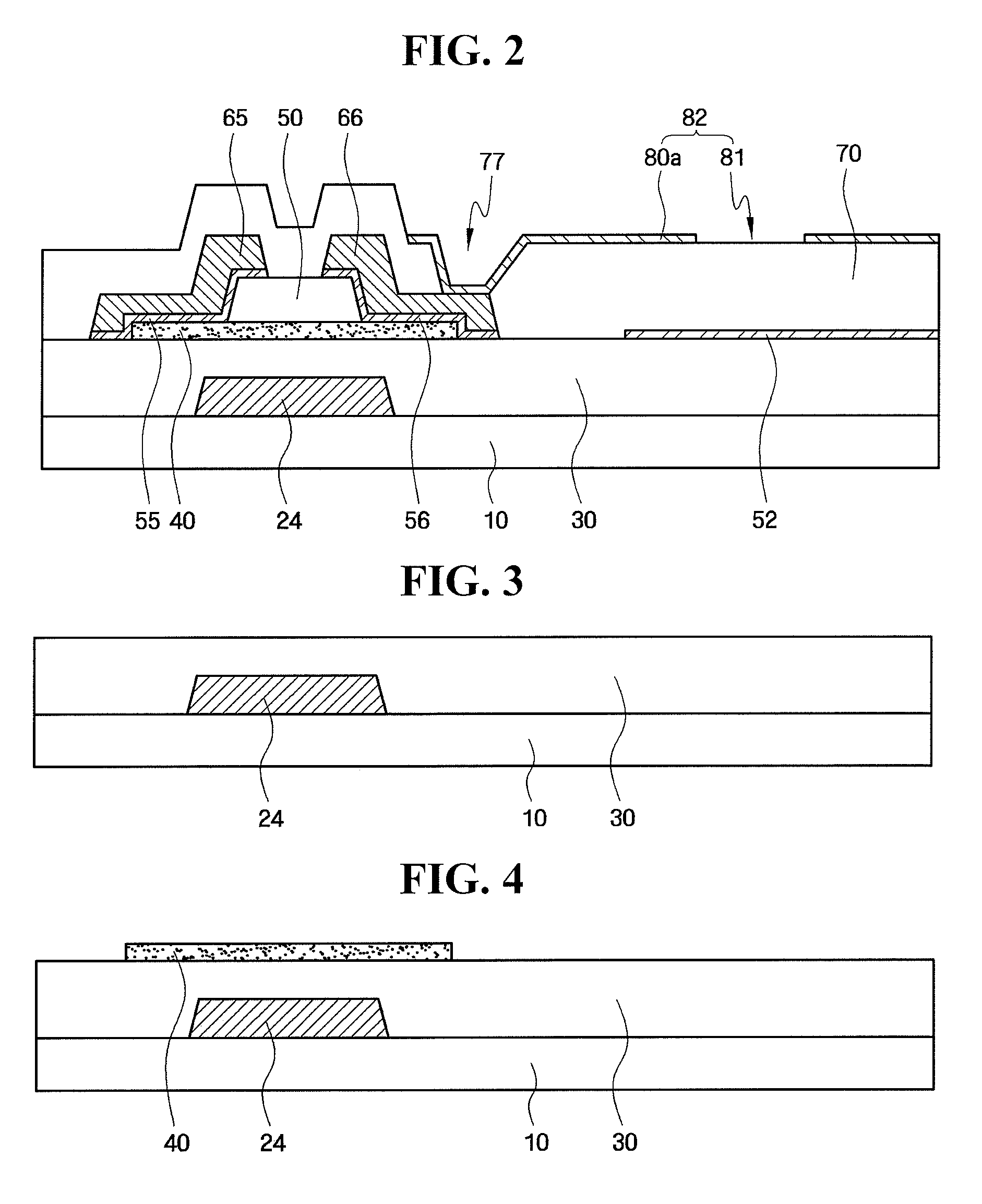

Liquid crystal display and method of manufacturing the same

ActiveUS20100051935A1High operating requirementsHigh transmissionSolid-state devicesSemiconductor/solid-state device manufacturingLiquid-crystal displayEngineering

A liquid crystal display and a method of manufacturing the same are provided. The liquid crystal display includes an insulating substrate, a gate electrode formed on the insulating substrate, an oxide semiconductor layer formed on the gate electrode, an etch stopper formed on the oxide semiconductor layer in a channel area, a common electrode formed on the insulating substrate, source and drain electrodes separated from each other on the etch stopper and extending to an upper portion of the oxide semiconductor layer, a passivation layer formed on the etch stopper, the common electrode, the source and drain electrodes, and a pixel electrode formed on the passivation layer and connected to the drain electrode.

Owner:SAMSUNG DISPLAY CO LTD

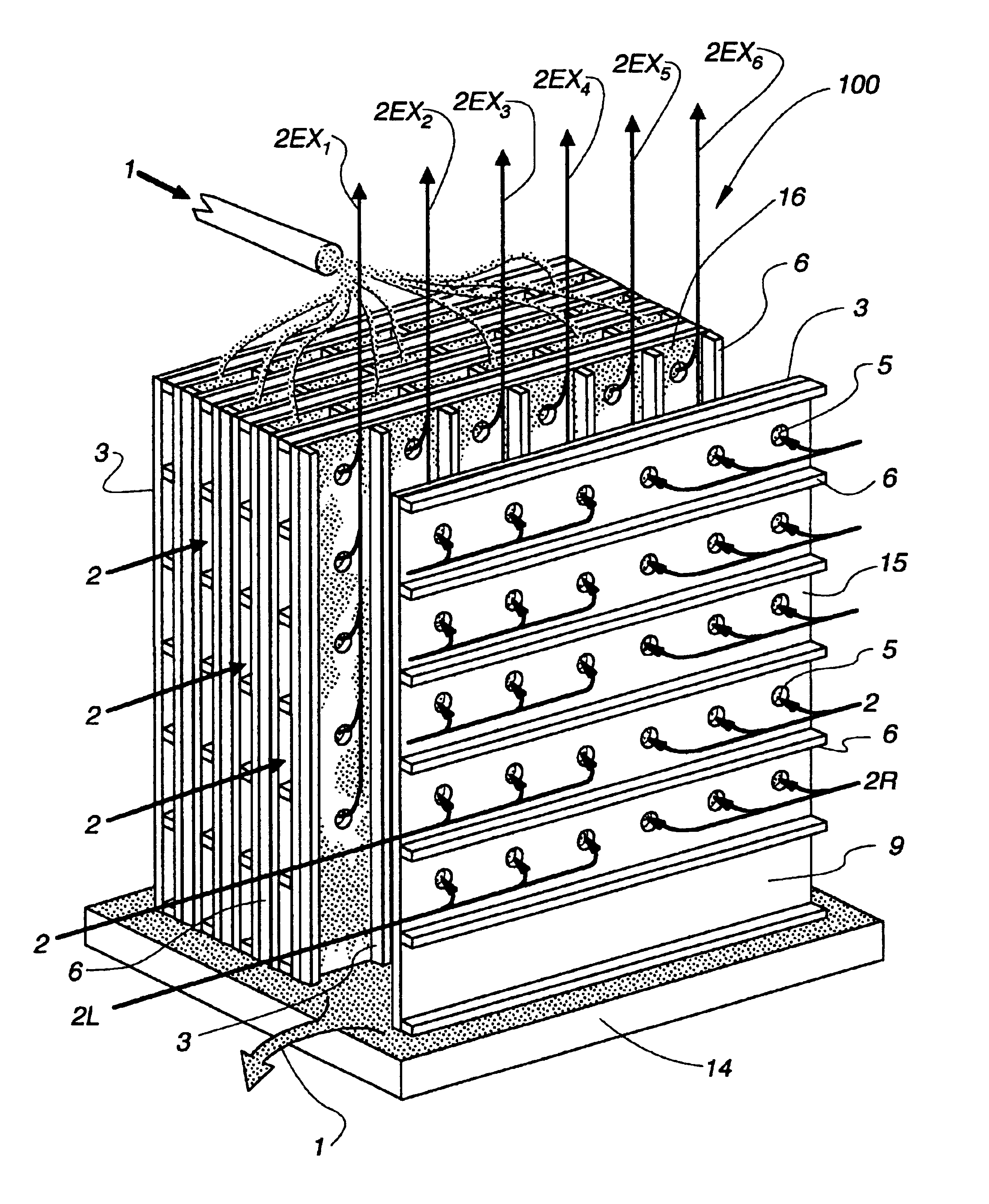

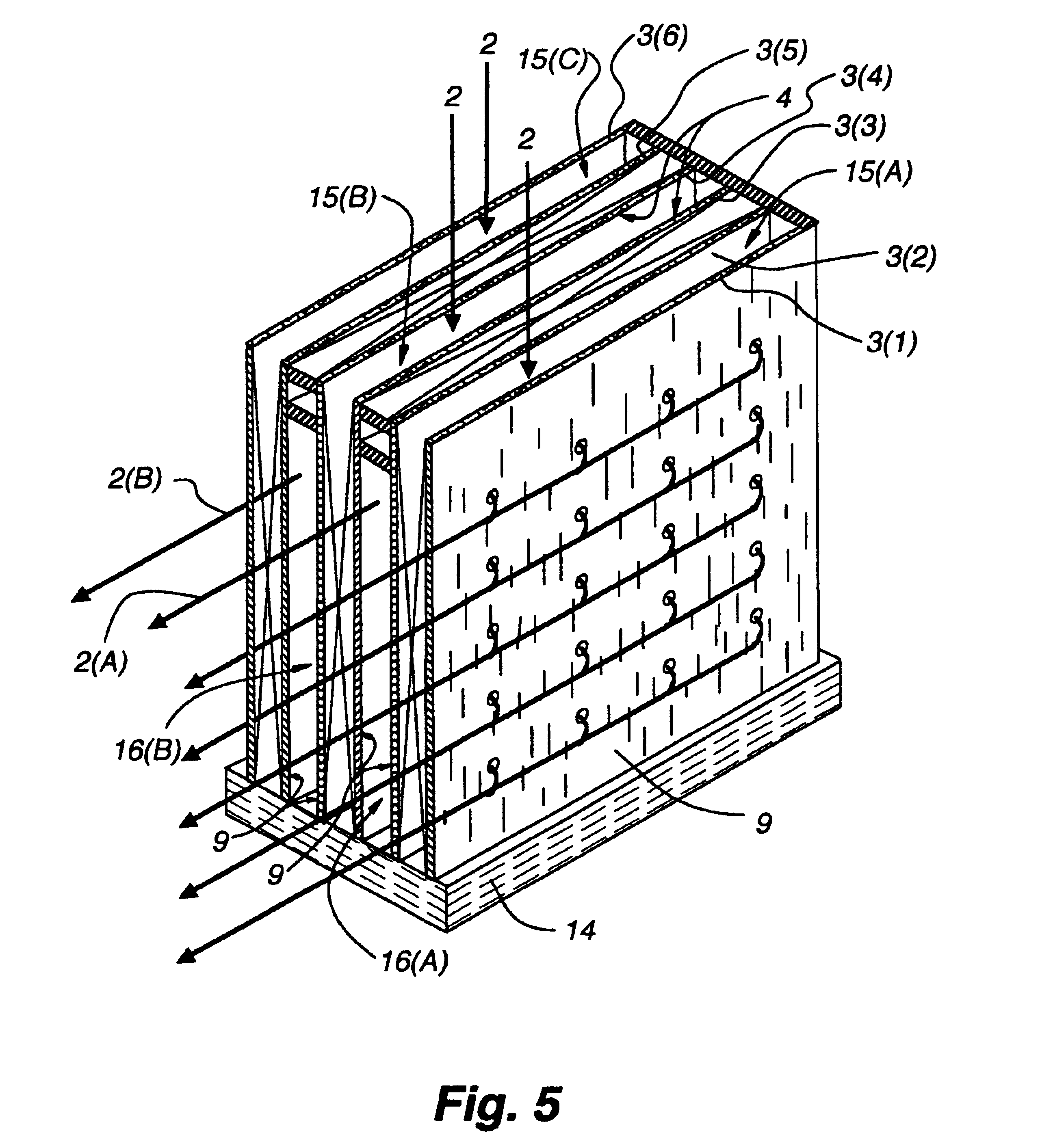

Method of evaporative cooling of a fluid and apparatus therefor

InactiveUS6854278B2Reduce the temperatureLess pressure dropMechanical apparatusSpace heating and ventilation safety systemsDesiccantMechanical engineering

The operating efficiency of indirect evaporative cooling processes and indirect evaporative cooling apparatus employing a dry side channel and a wet side channel separated by a heat exchange plate are improved by placement of holes in the heat exchange plate. Further improvements are obtained when the flow direction in the wet side channel is cross-current to the flow direction in the dry side channel. Placement of desiccant materials in the dry side channel also serve to improve the operating efficiencies of these processes and apparatus.

Owner:IDALEX TECH INC

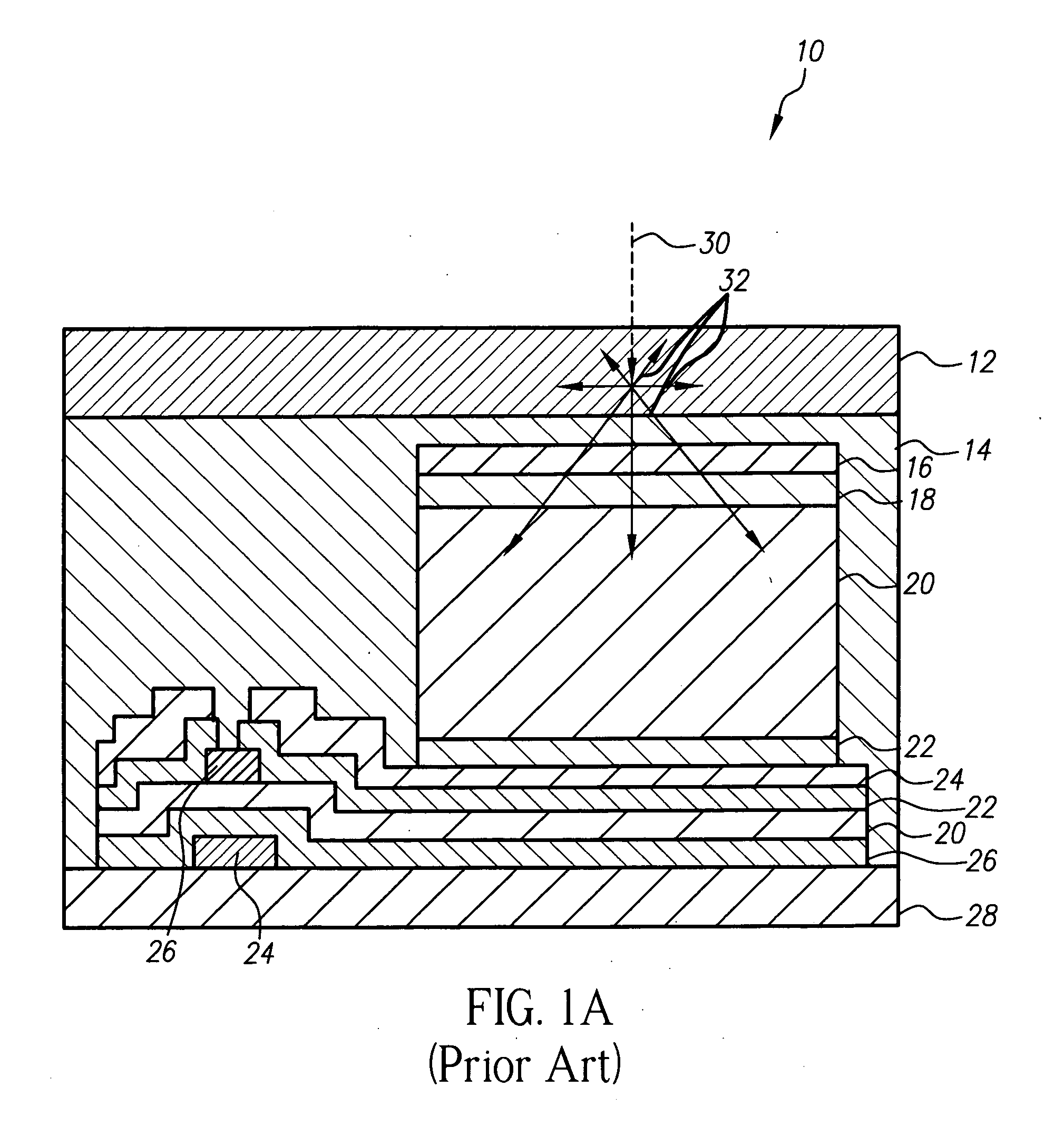

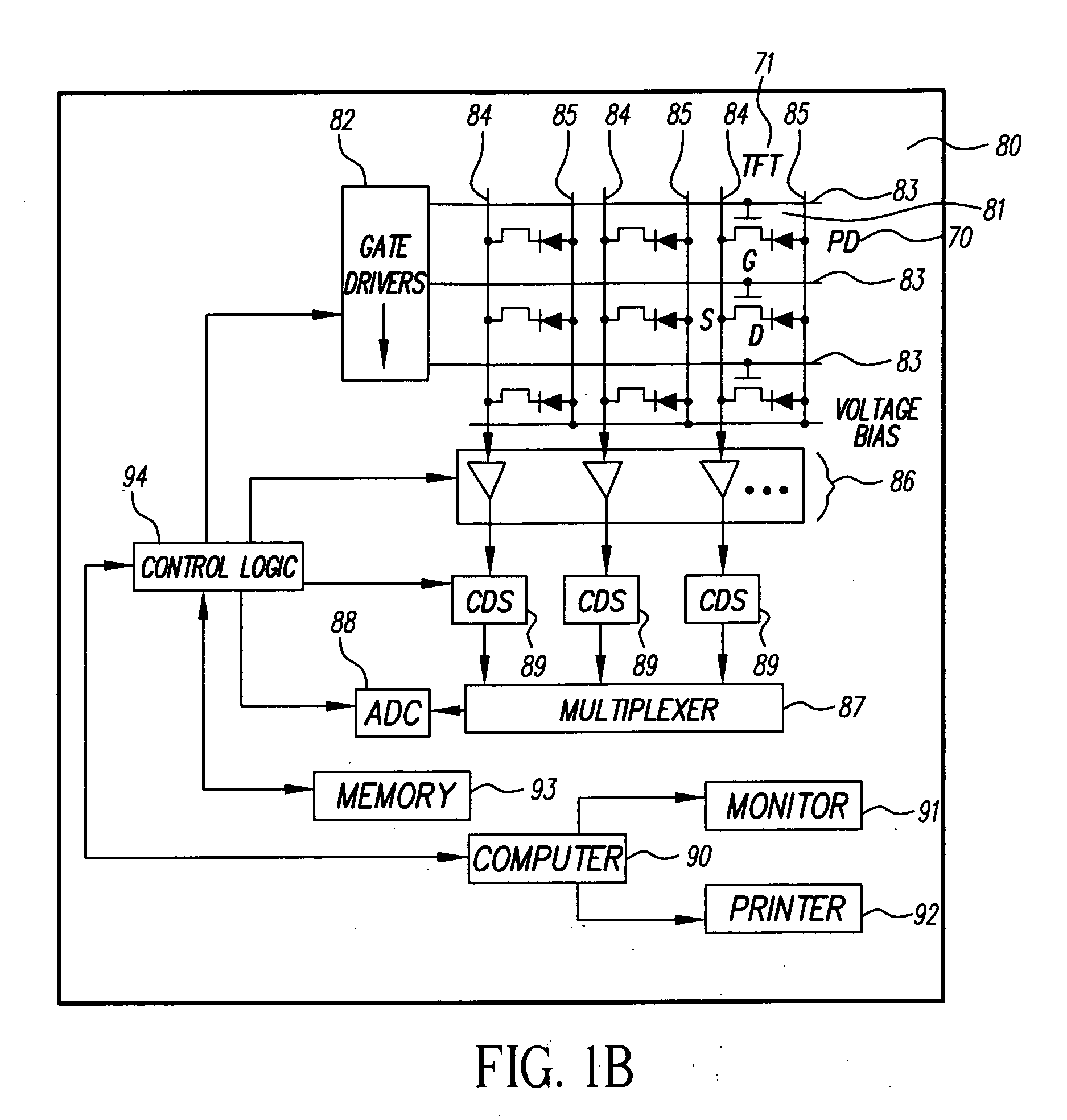

Apparatus for asymmetric dual-screen digital radiography

ActiveUS20080011960A1High detective quantum efficiencyClear imagingSolid-state devicesMaterial analysis by optical meansSoft x rayFluorescence

The present invention relates to radiographic imaging apparatus for taking X-ray images of an object. In various two-panel radiographic imaging apparatus configurations, a front panel and back panel have substrates, arrays of signal sensing elements and readout devices, and passivation layers. The front and back panels have scintillating phosphor layers responsive to X-rays passing through an object produce light which illuminates the signal sensing elements to provide signals representing X-ray images. The X-ray apparatus has means for combining the signals of the X-ray images to produce a composite X-ray image. Furthermore, the composition and thickness of the scintillating phosphor layers are selected, relative to each other, to improve the diagnostic efficacy of the composite X-ray image. Alternatively, a radiographic imaging apparatus has a single panel having arrays of signal sensing elements and readout devices and scintillating phosphor layers that are disposed on both sides of a single substrate. The present invention further relates to various embodiments of indirect dual-screen DR flat-panel imager apparatus that provide single-exposure dual energy imaging.

Owner:CARESTREAM HEALTH INC

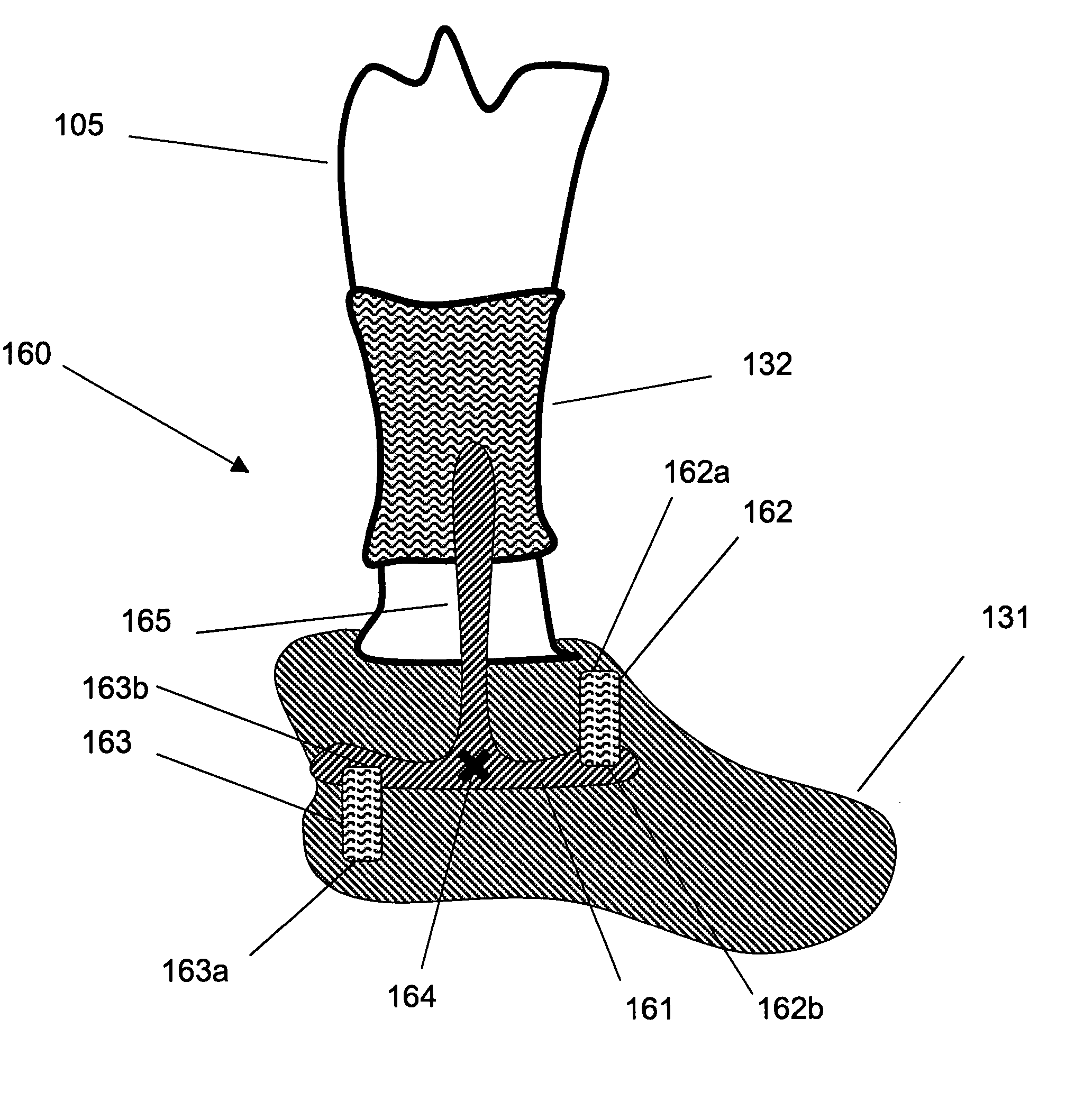

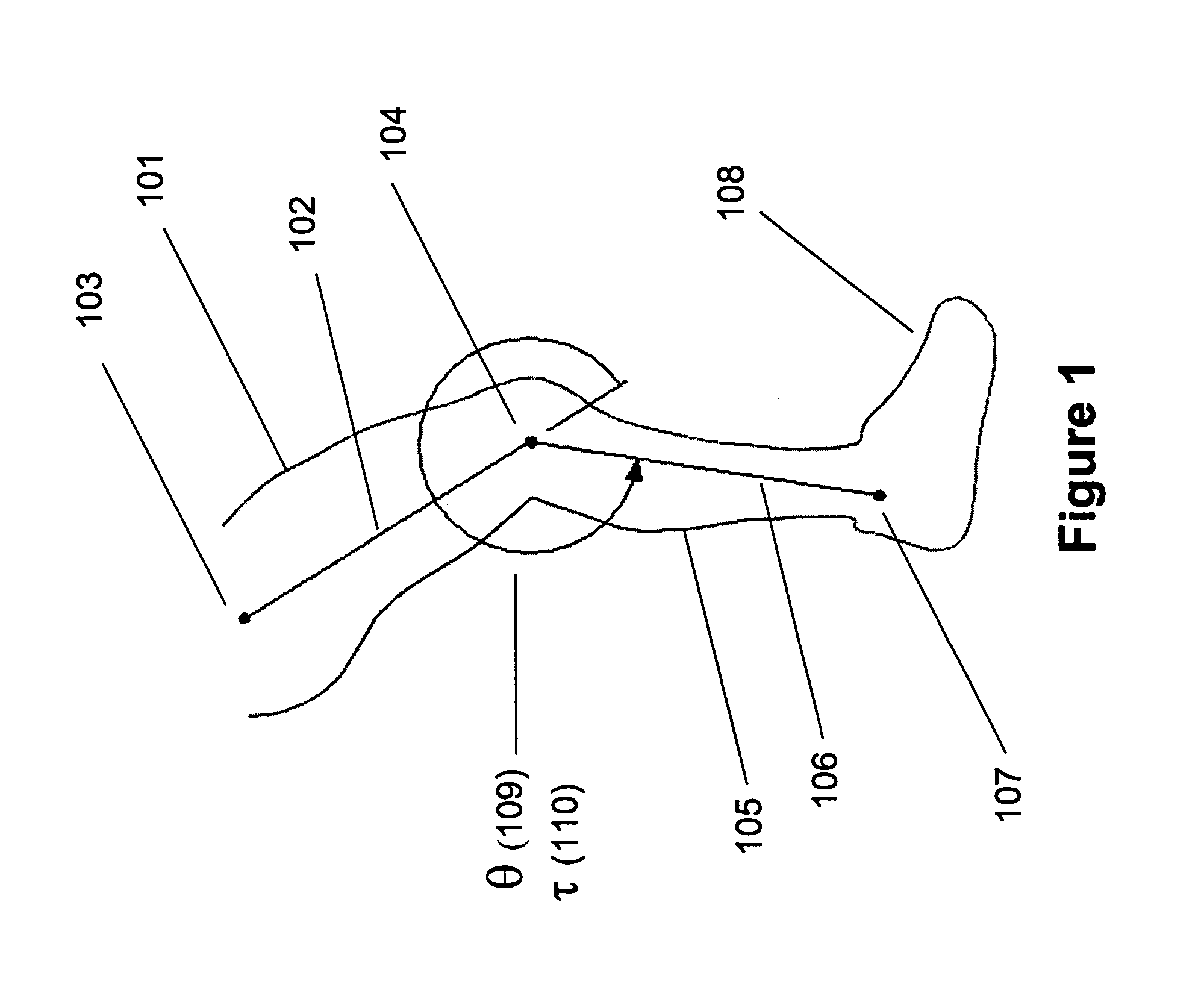

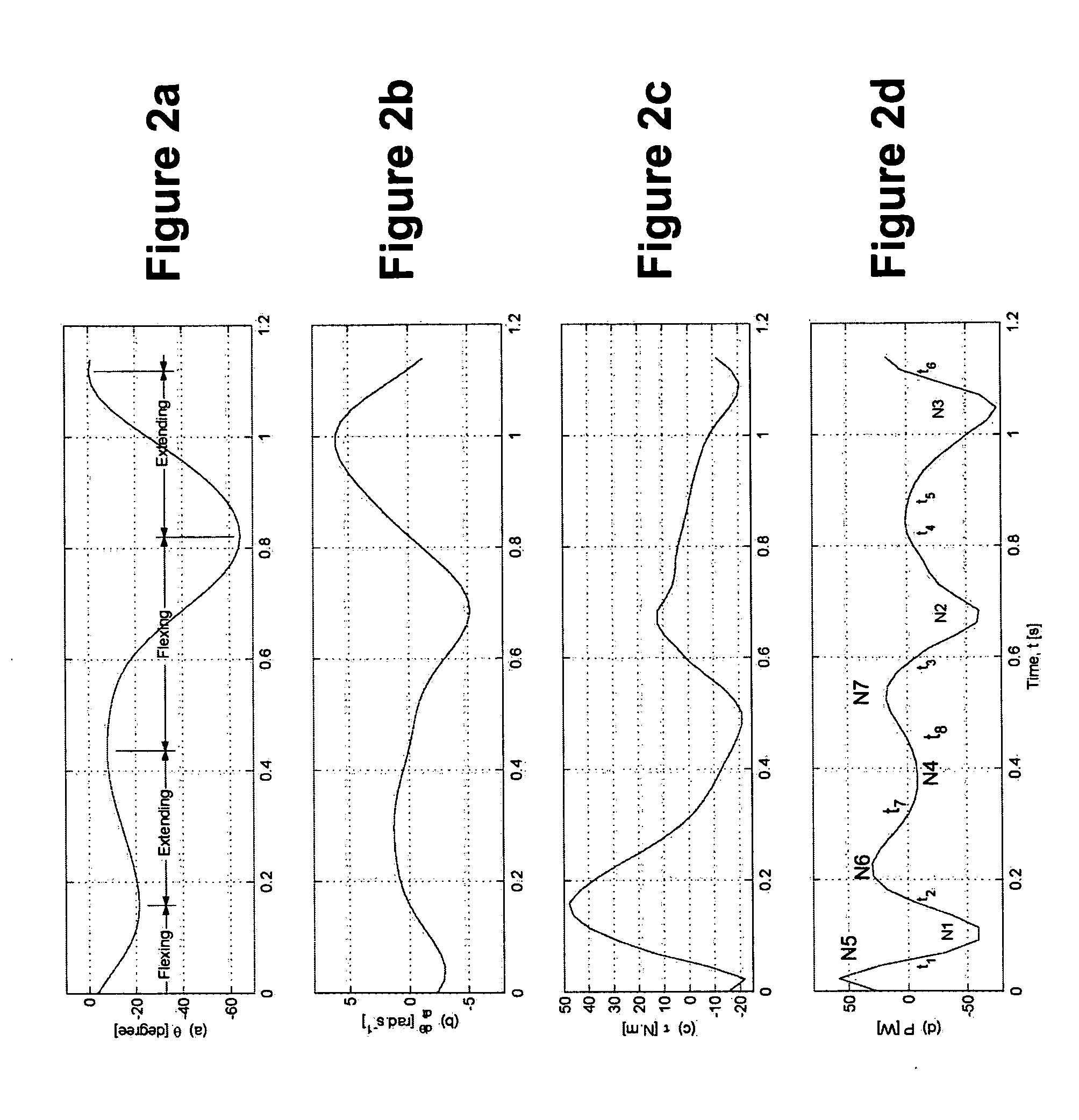

Power generation devices and methods

ActiveUS20060046907A1Reduce “locomotion energyVarying levelSwimming detailsPiezoelectric/electrostriction/magnetostriction machinesEnergy absorbingAutomotive engineering

A method for generating power from an exerted energy associated with muscles acting across a joint is provided. The method including: absorbing energy during one or more periods of a periodic motion of the joint in which energy is absorbed by the muscles; and at least partially returning the absorbed energy to one of an energy storage device or power consuming device.

Owner:OMNITEK PARTNERS LLC

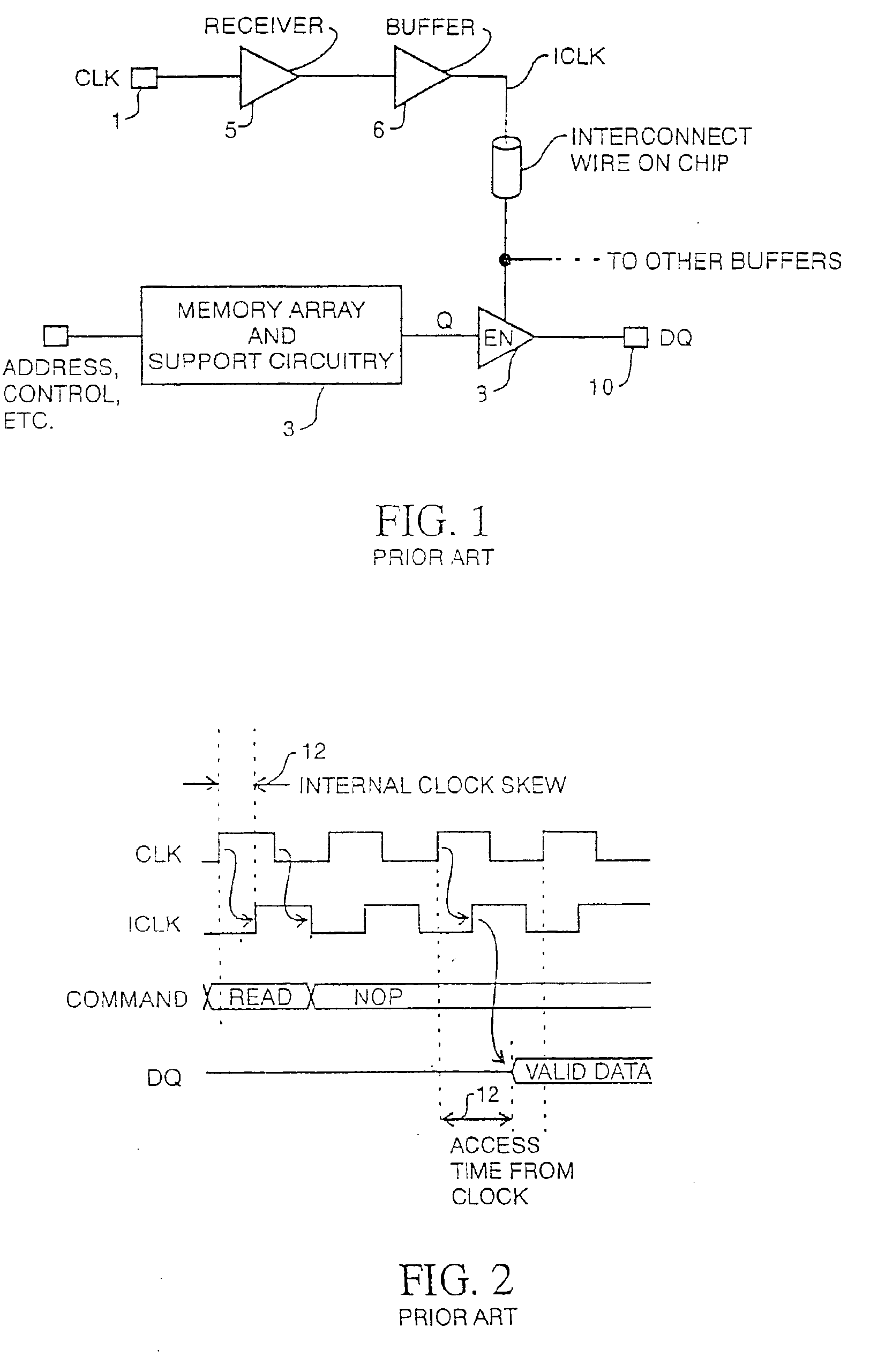

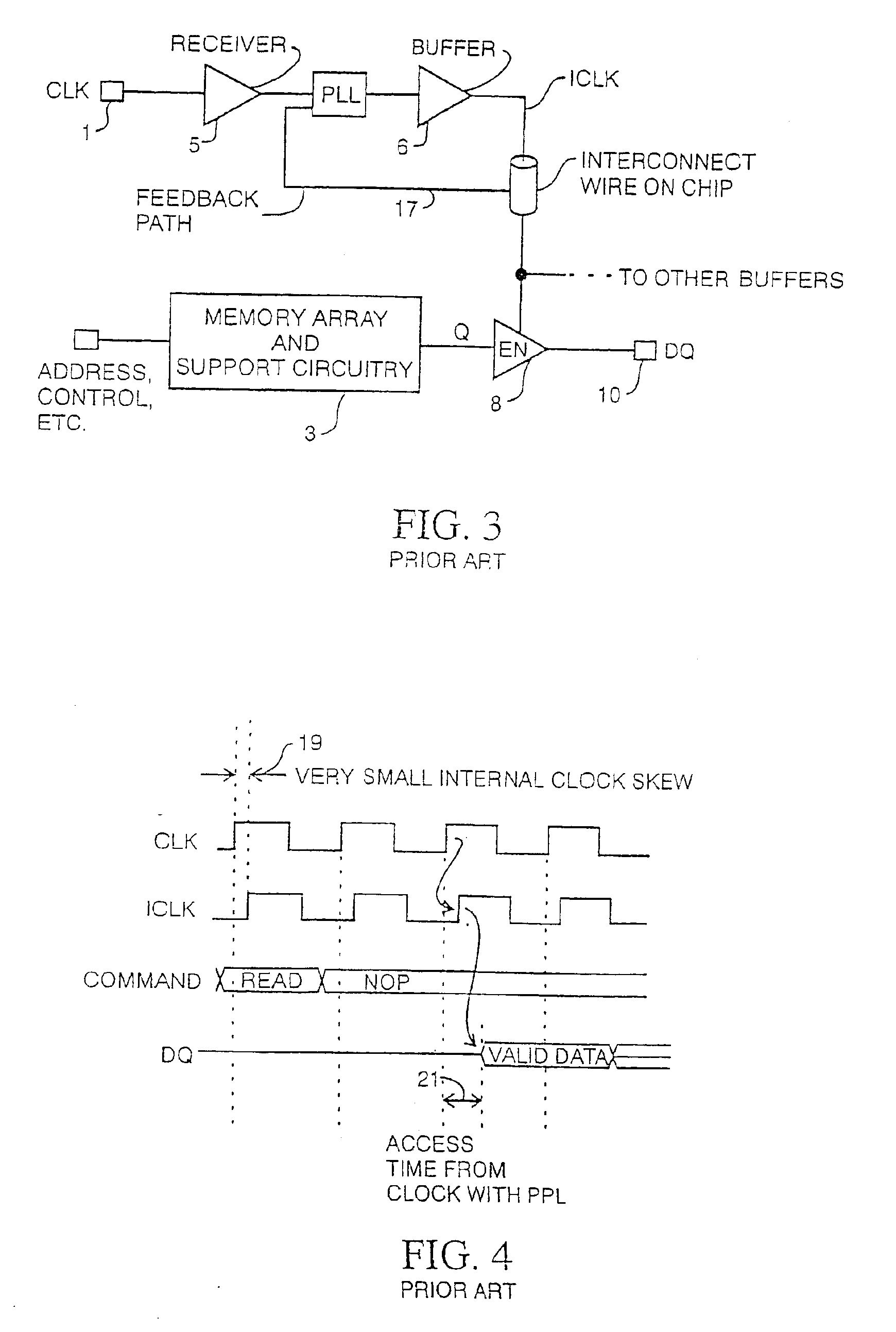

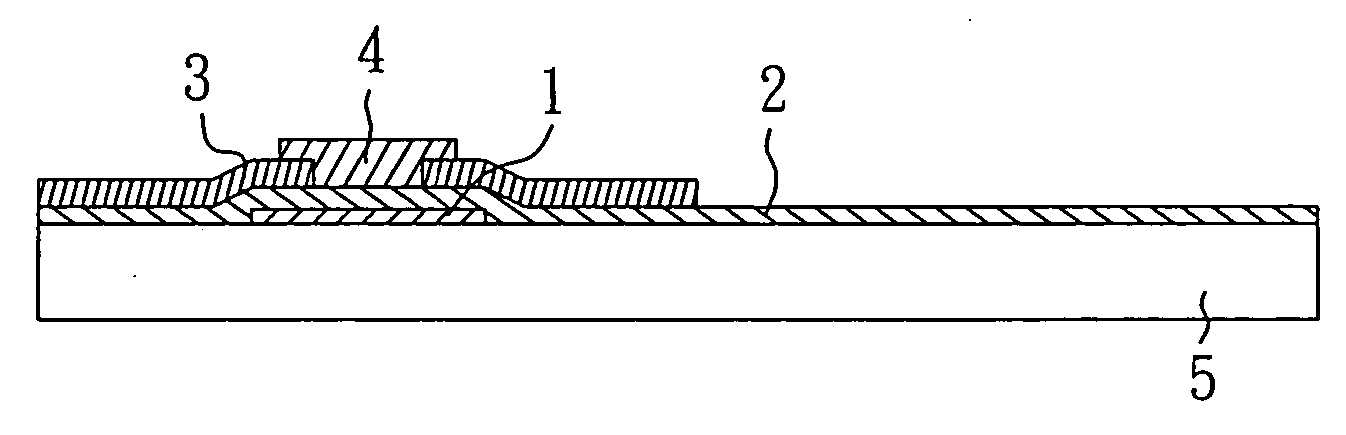

Delay locked loop implementation in a synchronous dynamic random access memory

InactiveUS6992950B2High operating requirementsLess standby current and start-up timePulse automatic controlSingle output arrangementsRandom access memoryDelay-locked loop

Owner:CONVERSANT INTPROP MANAGEMENT INC

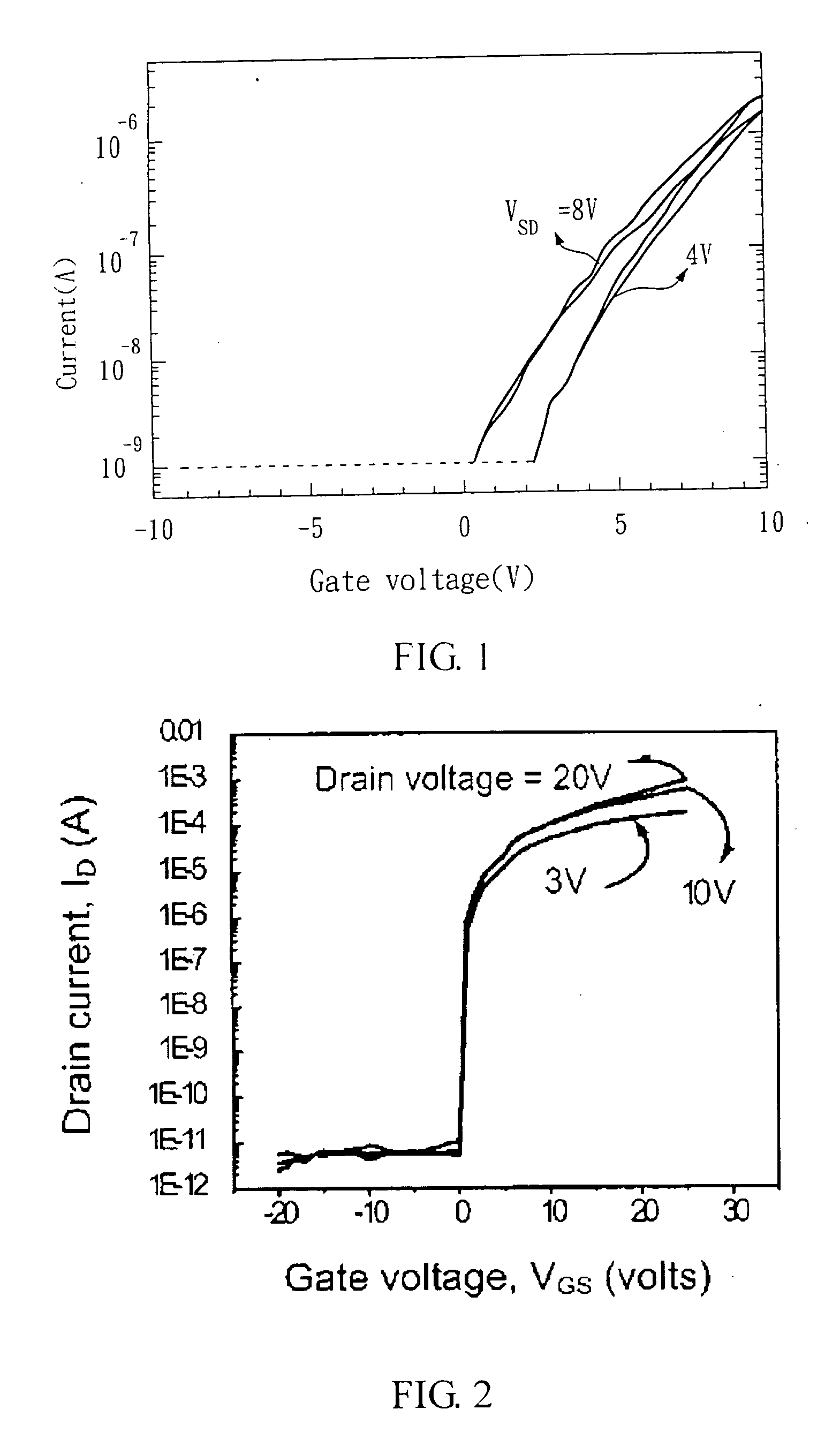

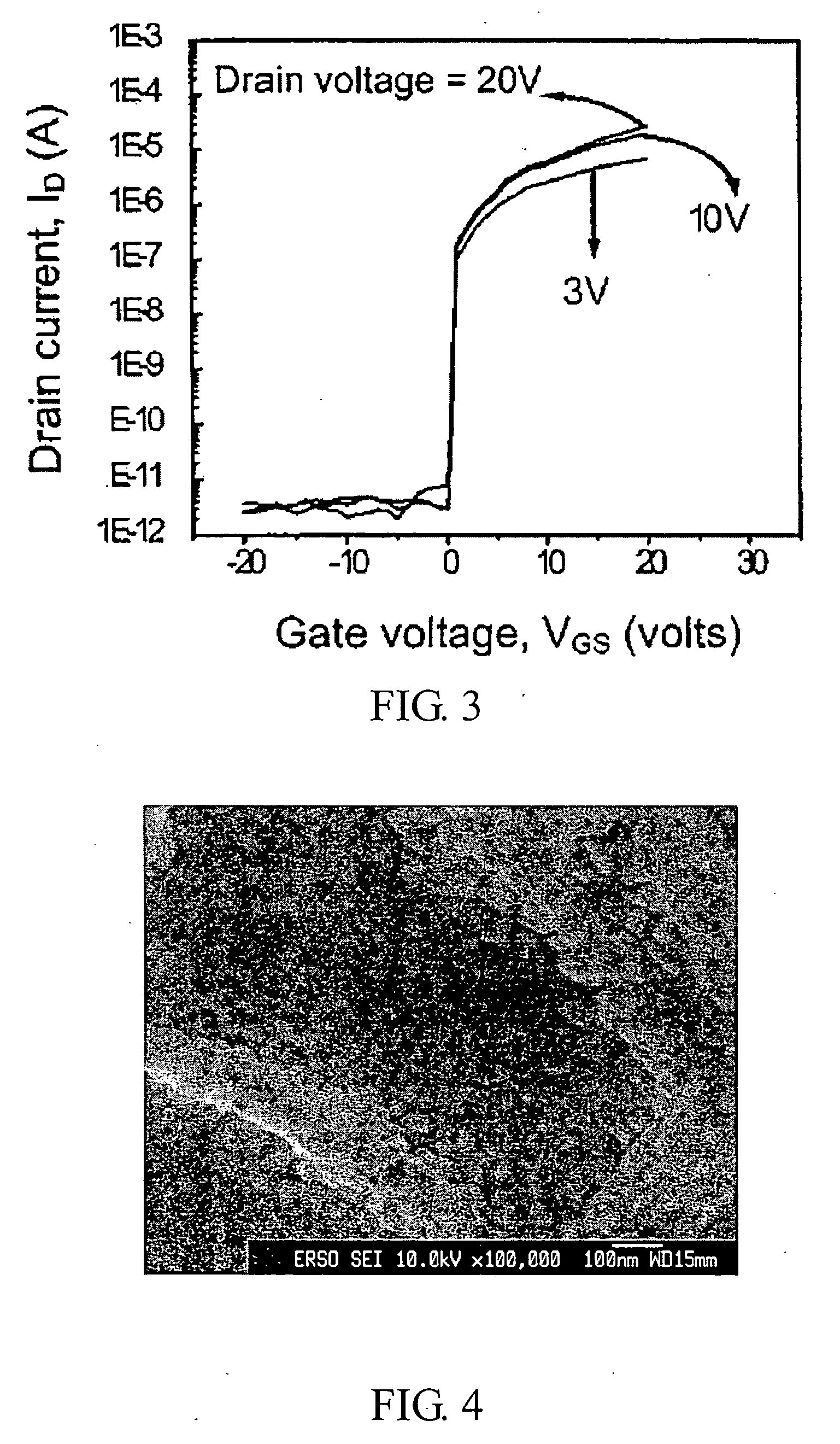

Compound semiconductor material and method for forming an active layer of a thin film transistor device

InactiveUS20050062134A1High voltage-durableImprove device characteristicsTransistorSolid-state devicesDopantAlkaline earth metal

A compound semiconductor material for forming an active layer of a thin film transistor device is disclosed, which has a group II-VI compound doped with a dopant ranging from 0.1 to 30 mol %, wherein the dopant is selected from a group consisting of alkaline-earth metals, group IIIA elements, group IVA elements, group VA elements, group VIA elements, and transitional metals. The method for forming an active layer of a thin film transistor device by using the compound semiconductor material of the present invention is disclosed therewith.

Owner:IND TECH RES INST

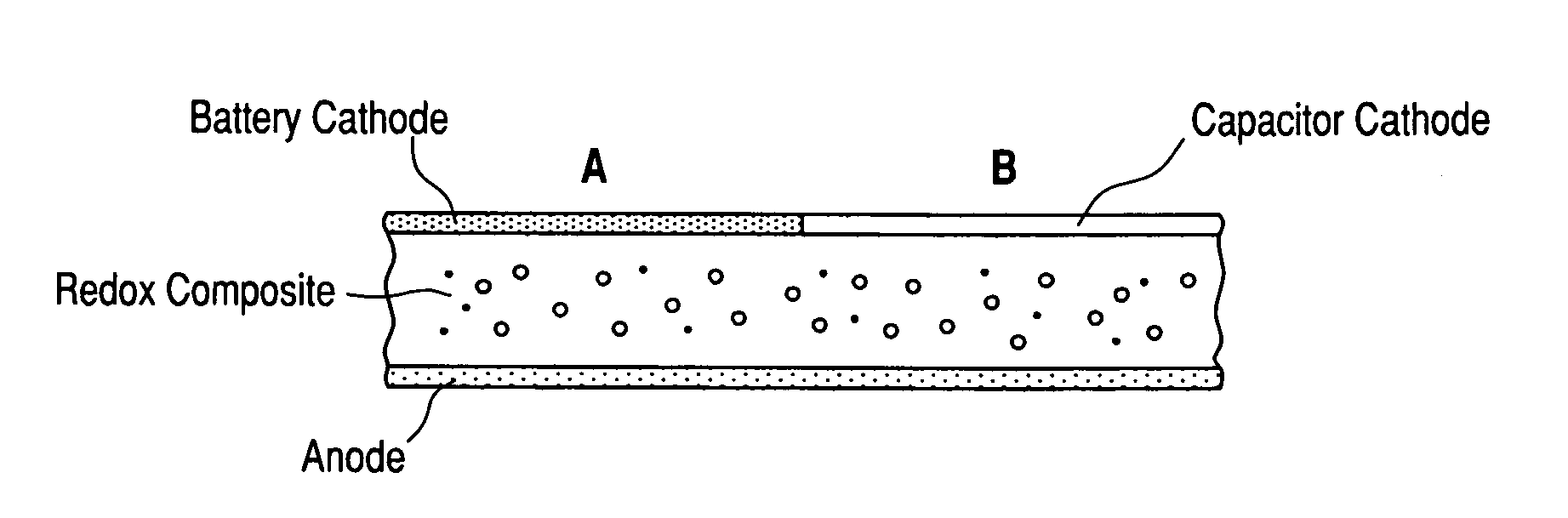

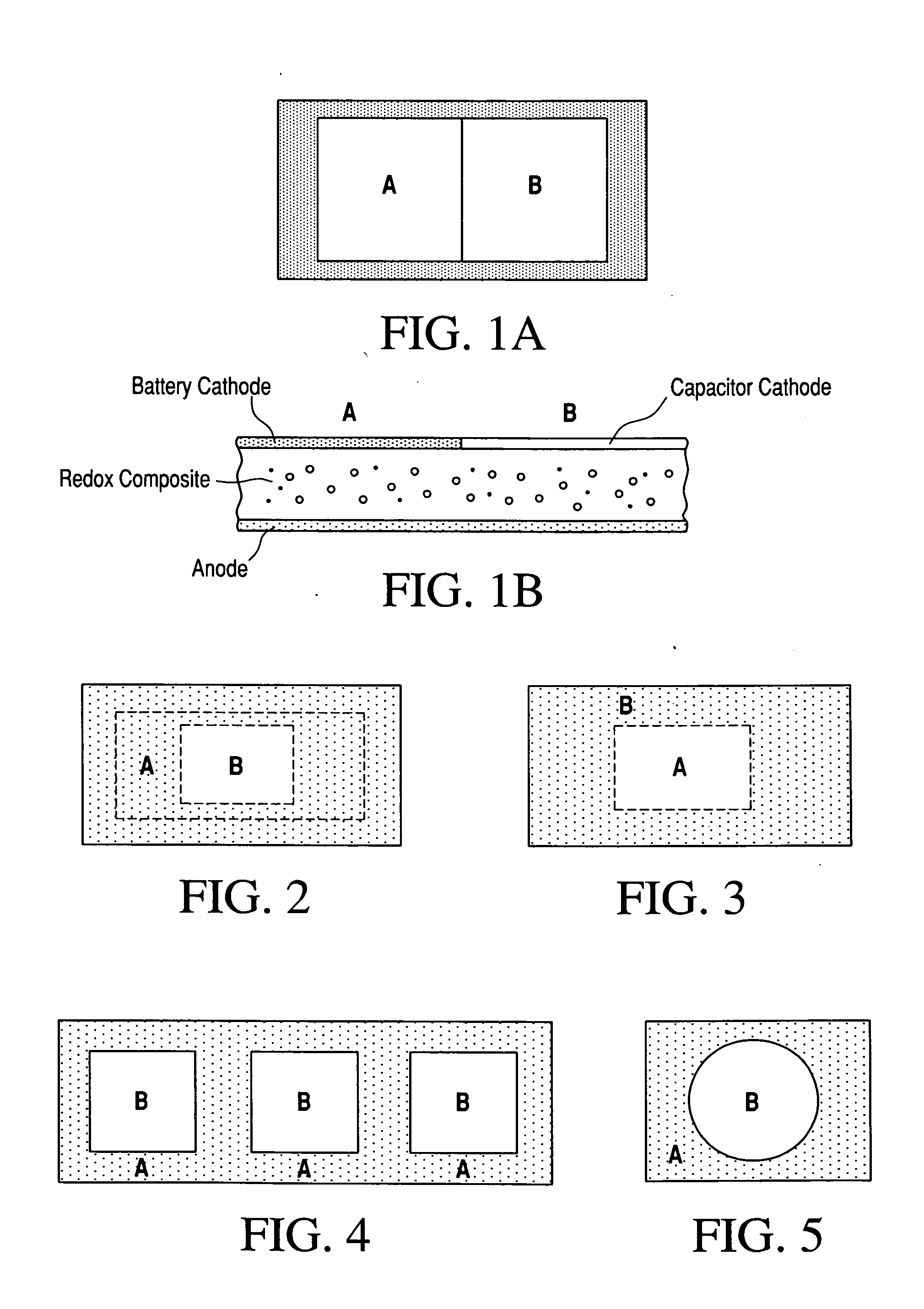

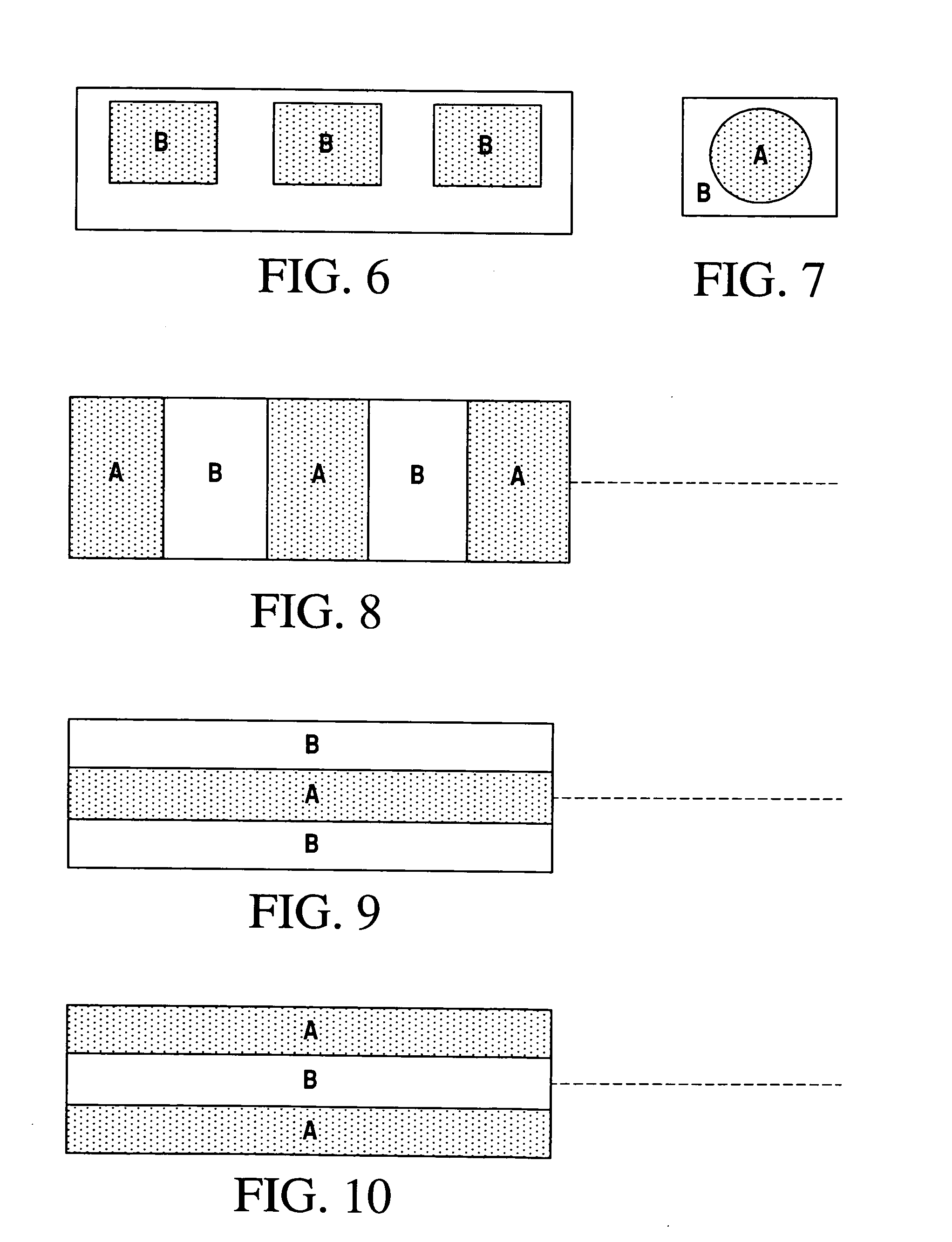

Composite ionic conducting electrolytes

InactiveUS20130026409A1High operating requirementsOptimize volumeFuel and primary cellsHybrid capacitor electrolytesComposite electrolyteConductive polymer

Ionically conducting, redox active additive composite electrolytes are disclosed. The electrolytes include an ionically conductive component and a redox active additive. The ionically conductive component may be an ionically conductive material such as an ionically conductive polymer, ionically conducting glass-ceramic, ionically conductive ceramic, and mixtures thereof. Electrical energy storage devices that employ the ionically conducting, redox active additive composite electrolytes also are disclosed

Owner:RECAPPING +1

Image processing apparatus and storage medium storing image processing program

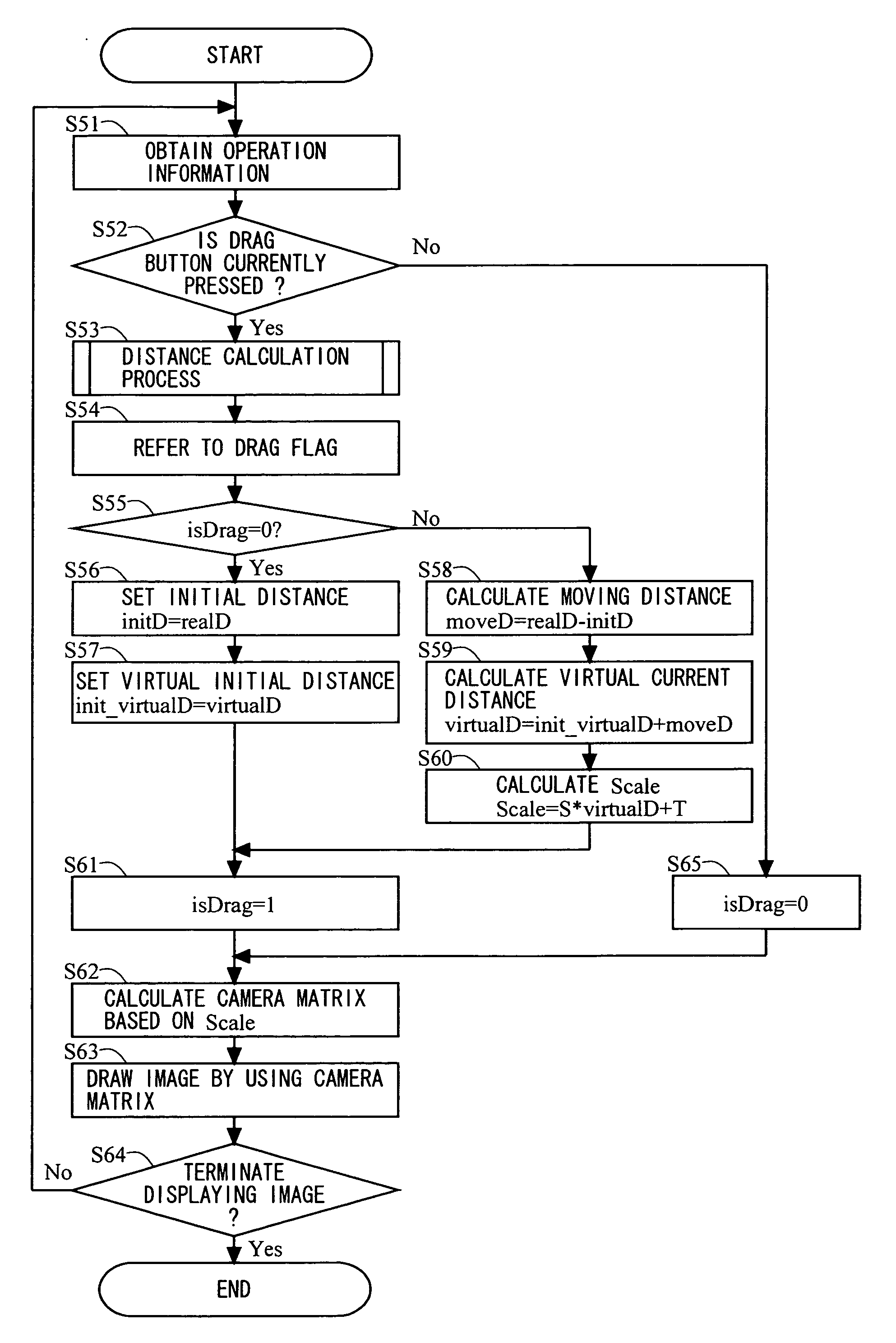

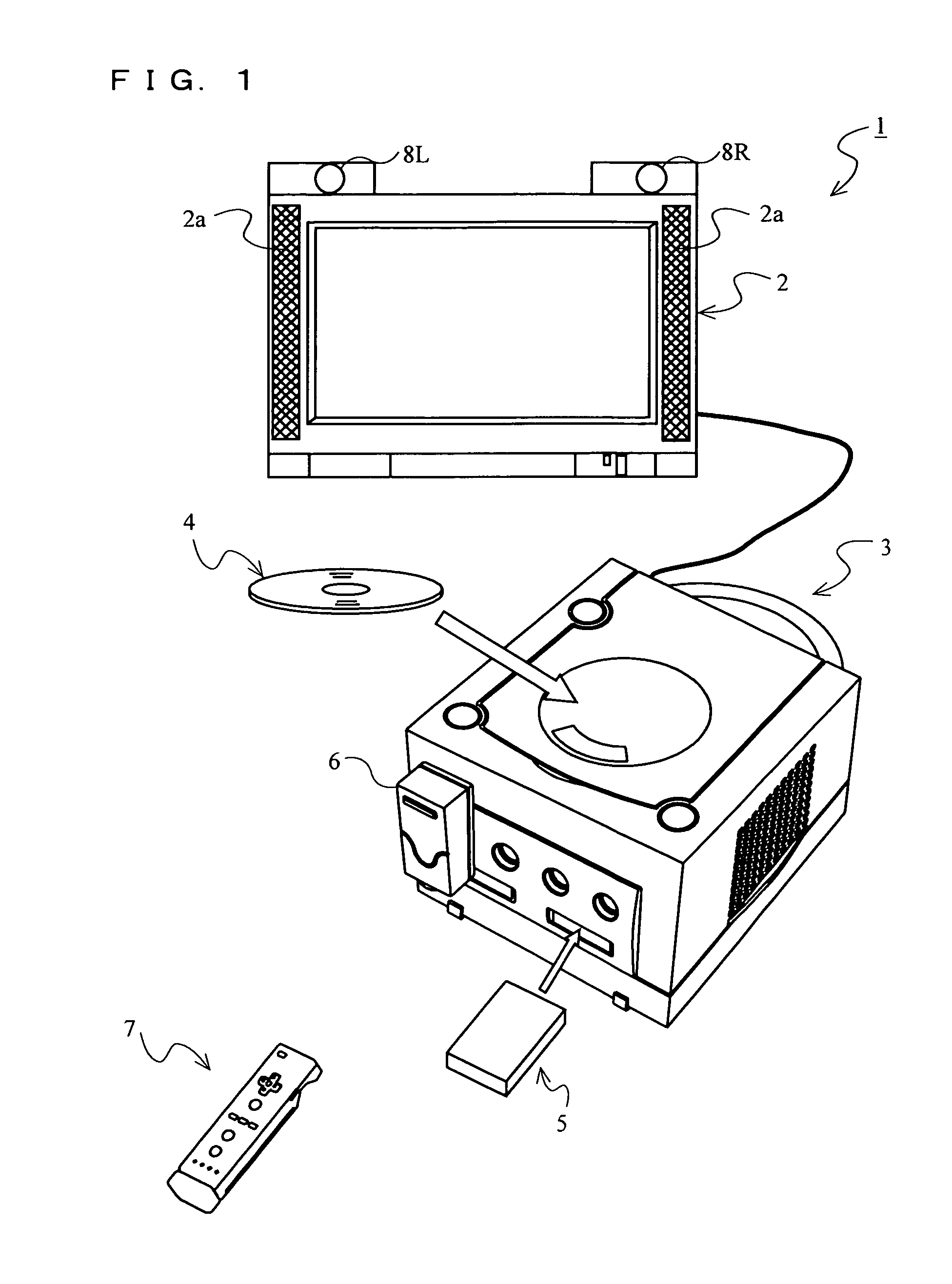

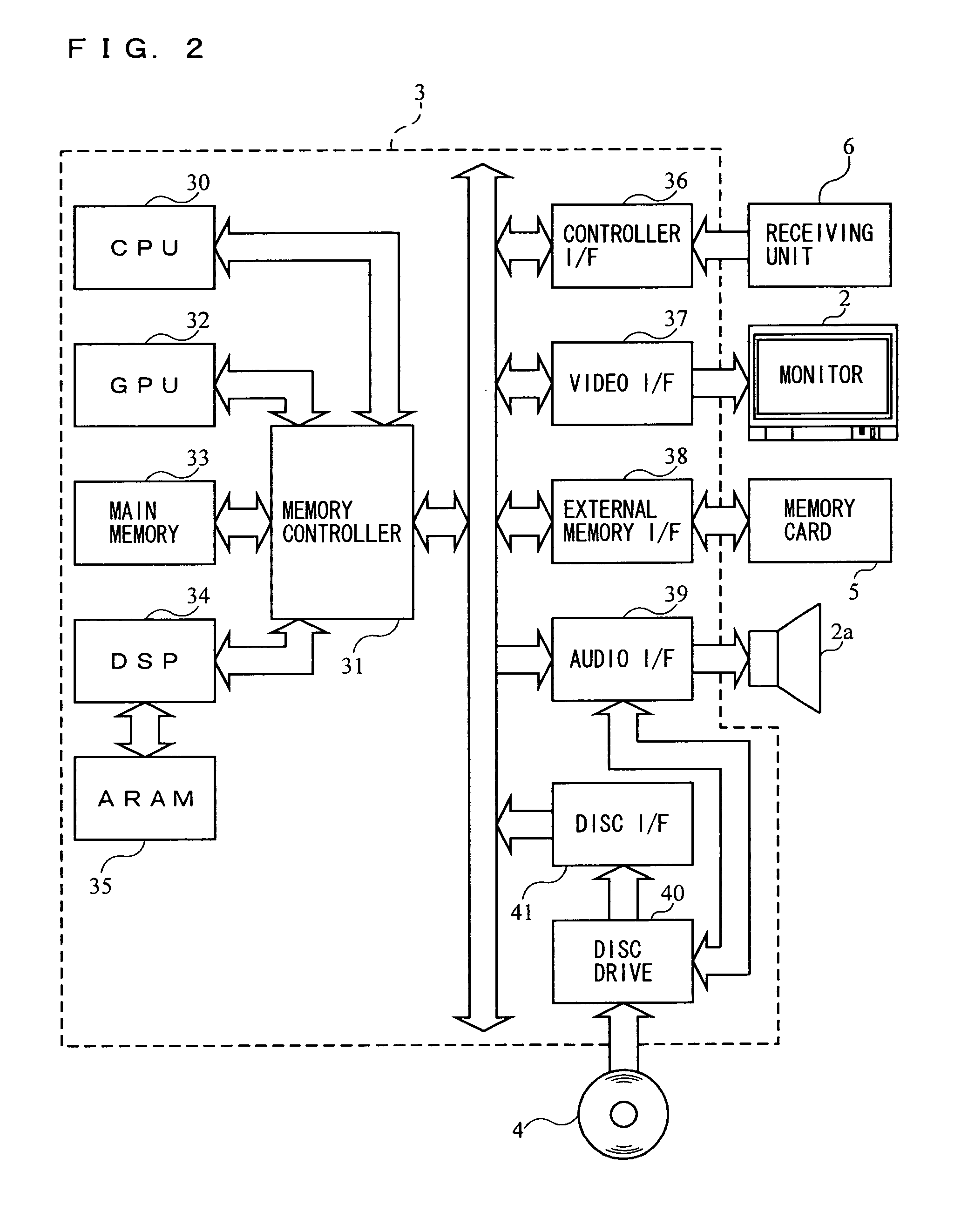

ActiveUS20070211027A1Easy to operateComplicated and intuitive operationCathode-ray tube indicatorsVideo gamesImaging processingDisplay device

Predetermined image processing is performed in accordance with an input operation performed by an input device having image pickup means for taking an image of one or a plurality of imaging targets. Target image data, which is obtained from one target image of the one imaging target or a plurality of target images of the plurality of imaging targets in the image taken by the image pickup means and which indicates a distance between the plurality of target images or a size of the one target image, is sequentially obtained. A display image is enlarged and reduced in accordance with a change in the target image data. Then, the display image processed in such a manner is displayed on a display device.

Owner:NINTENDO CO LTD

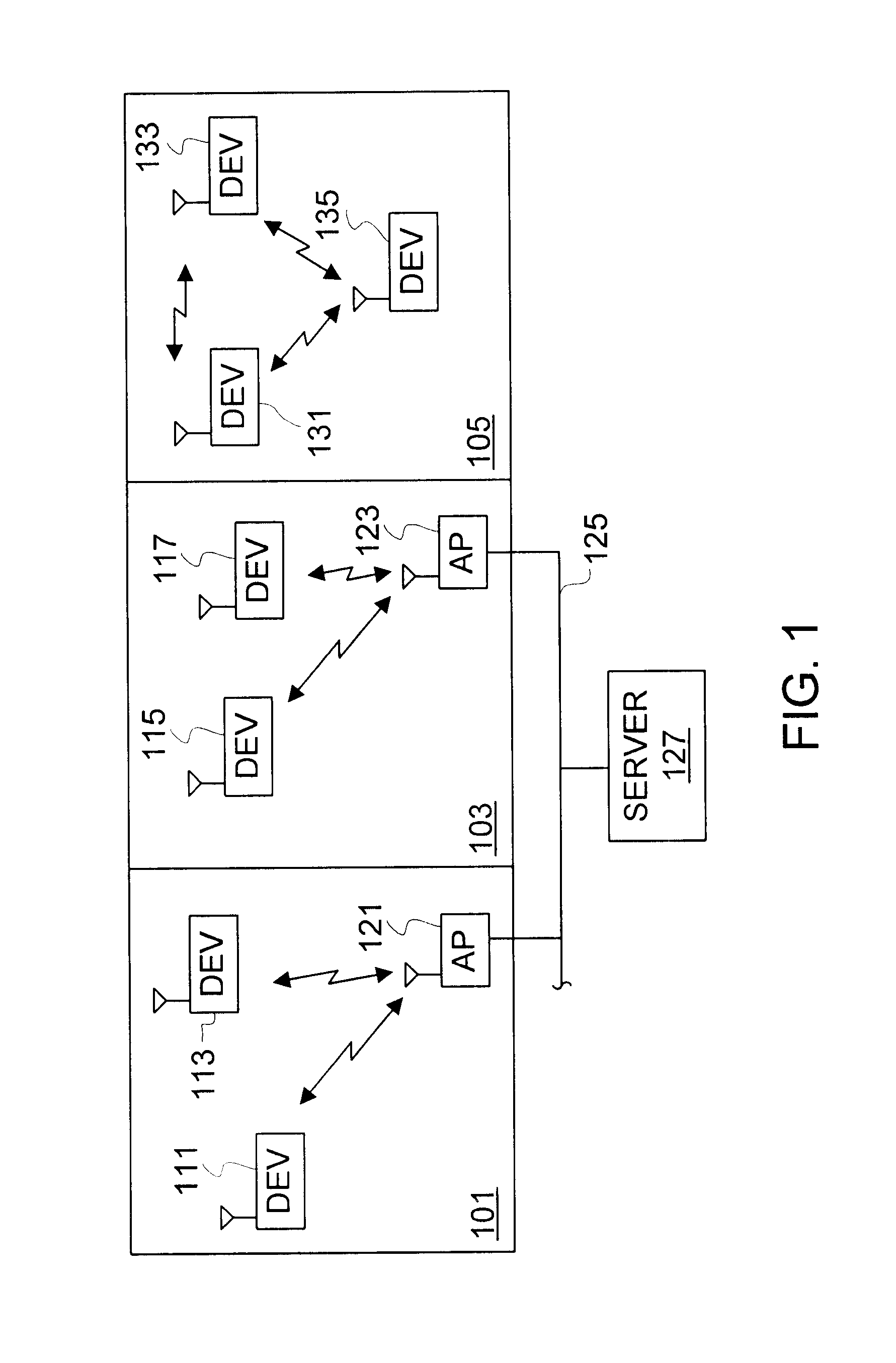

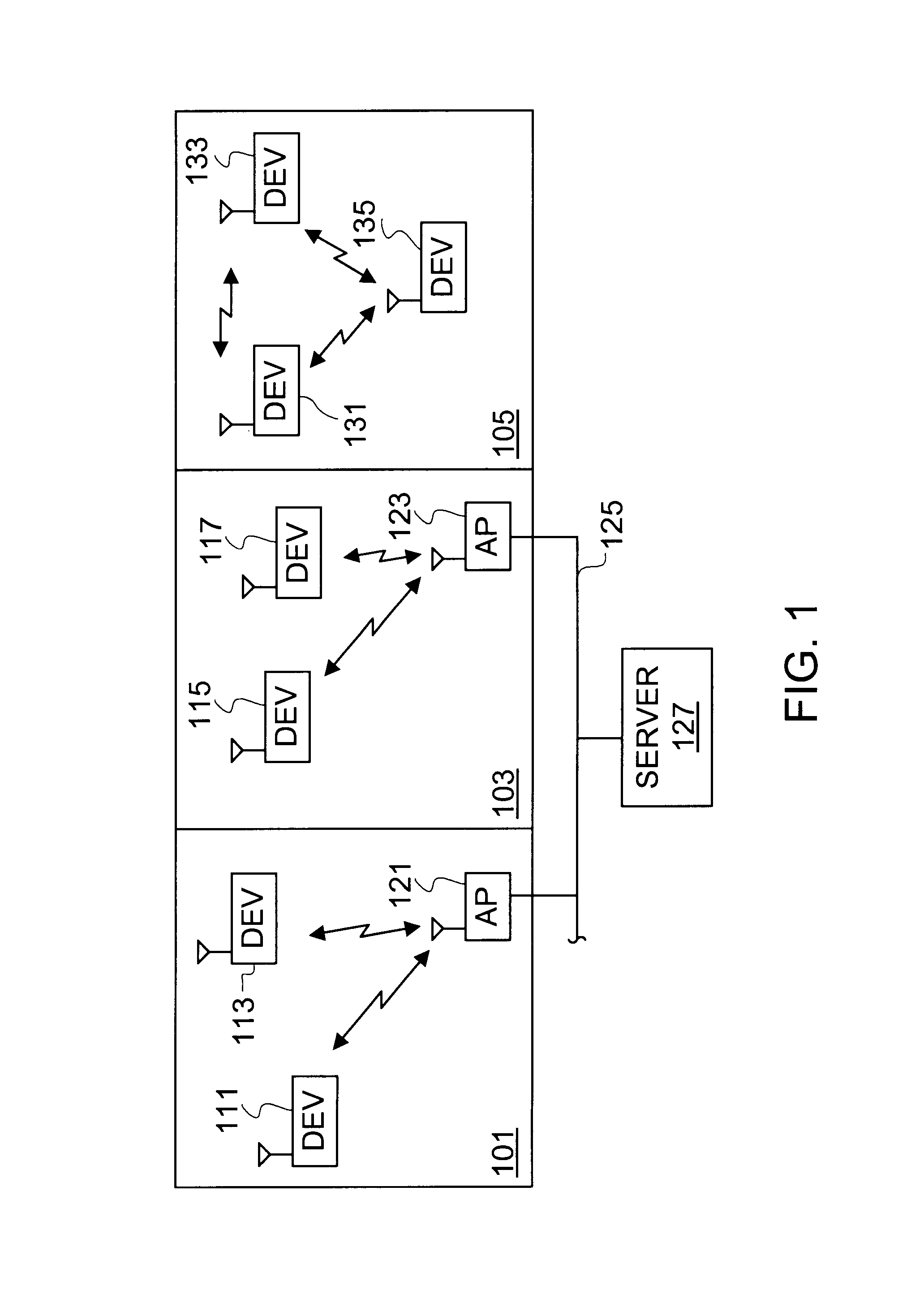

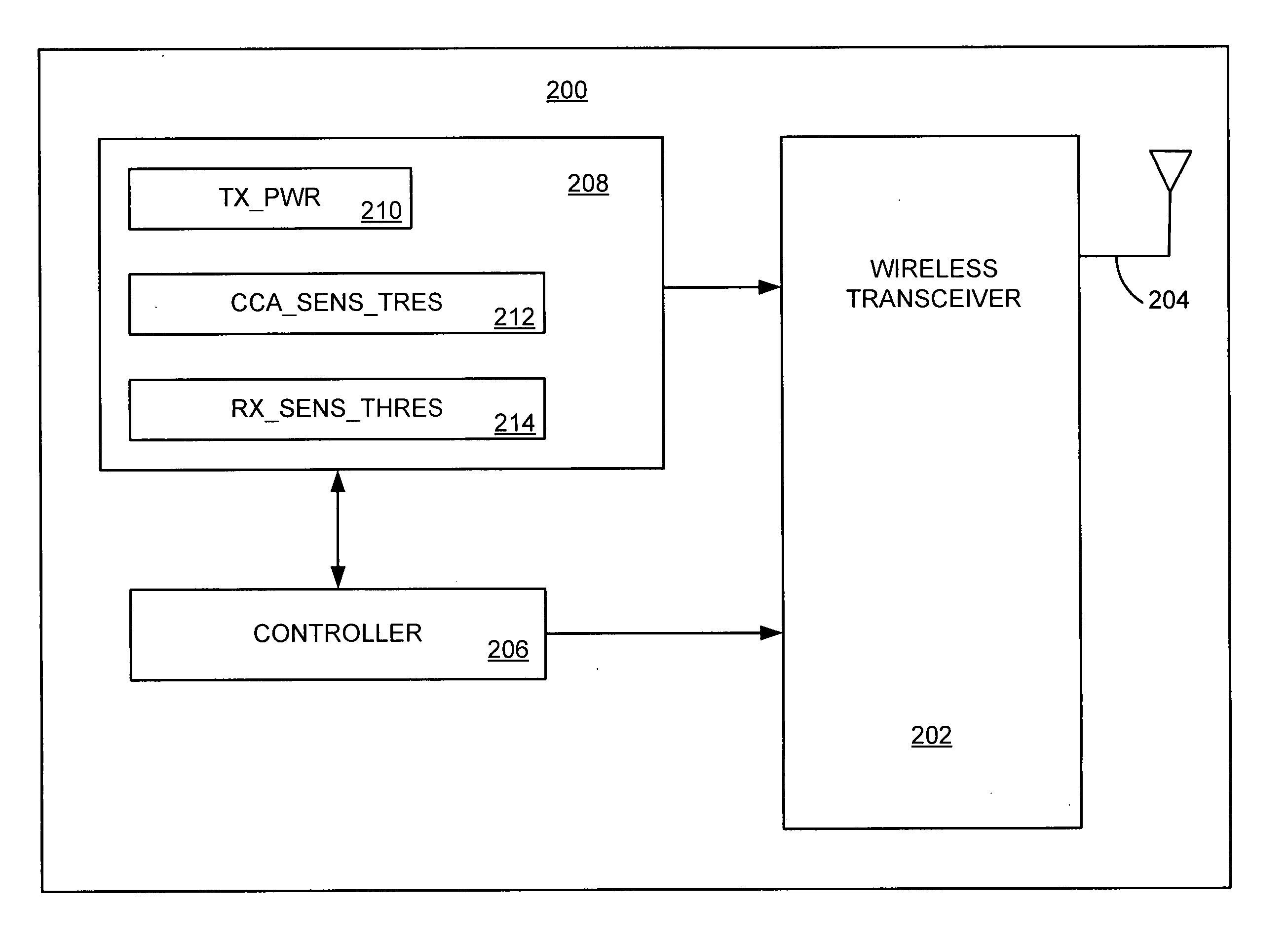

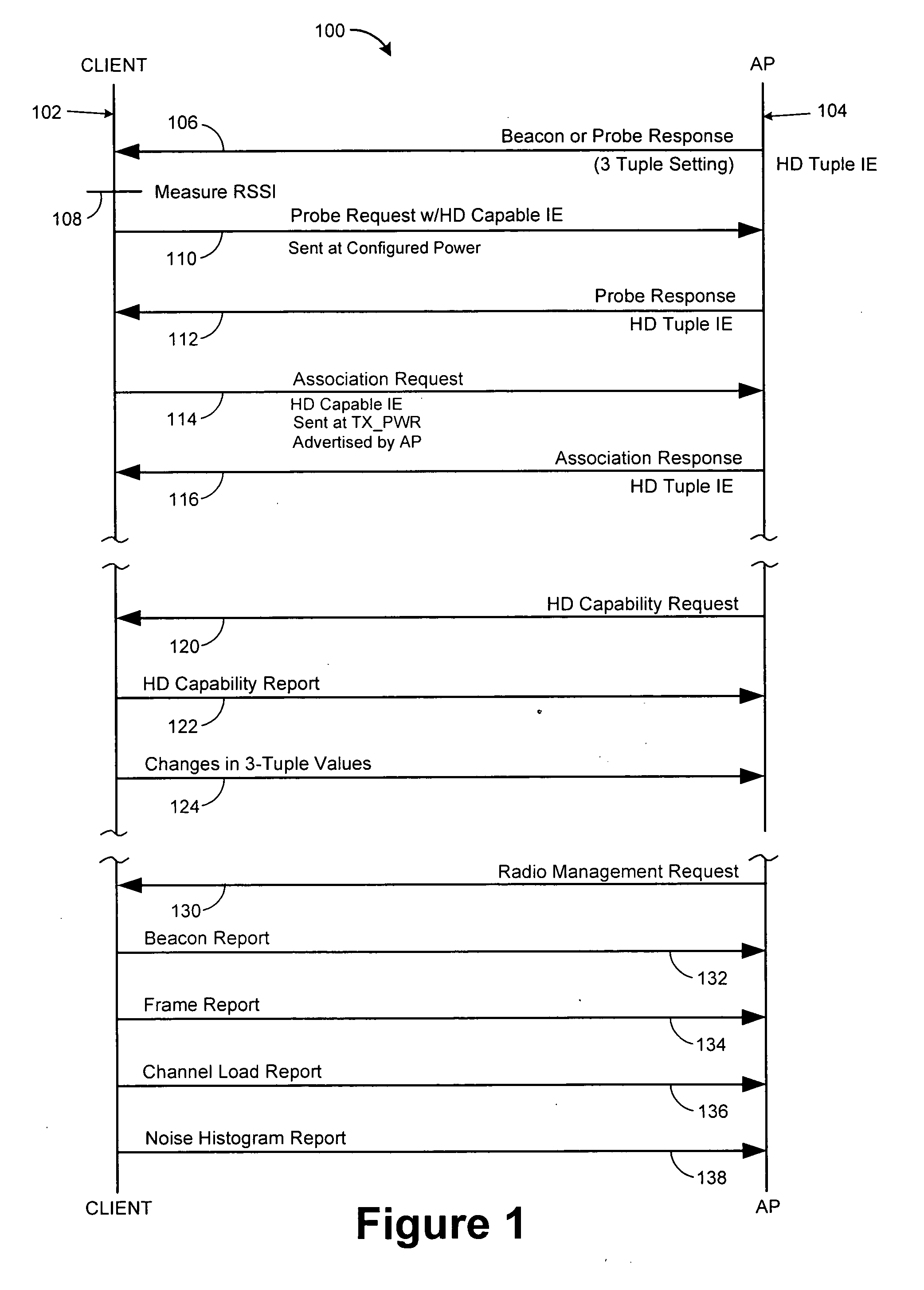

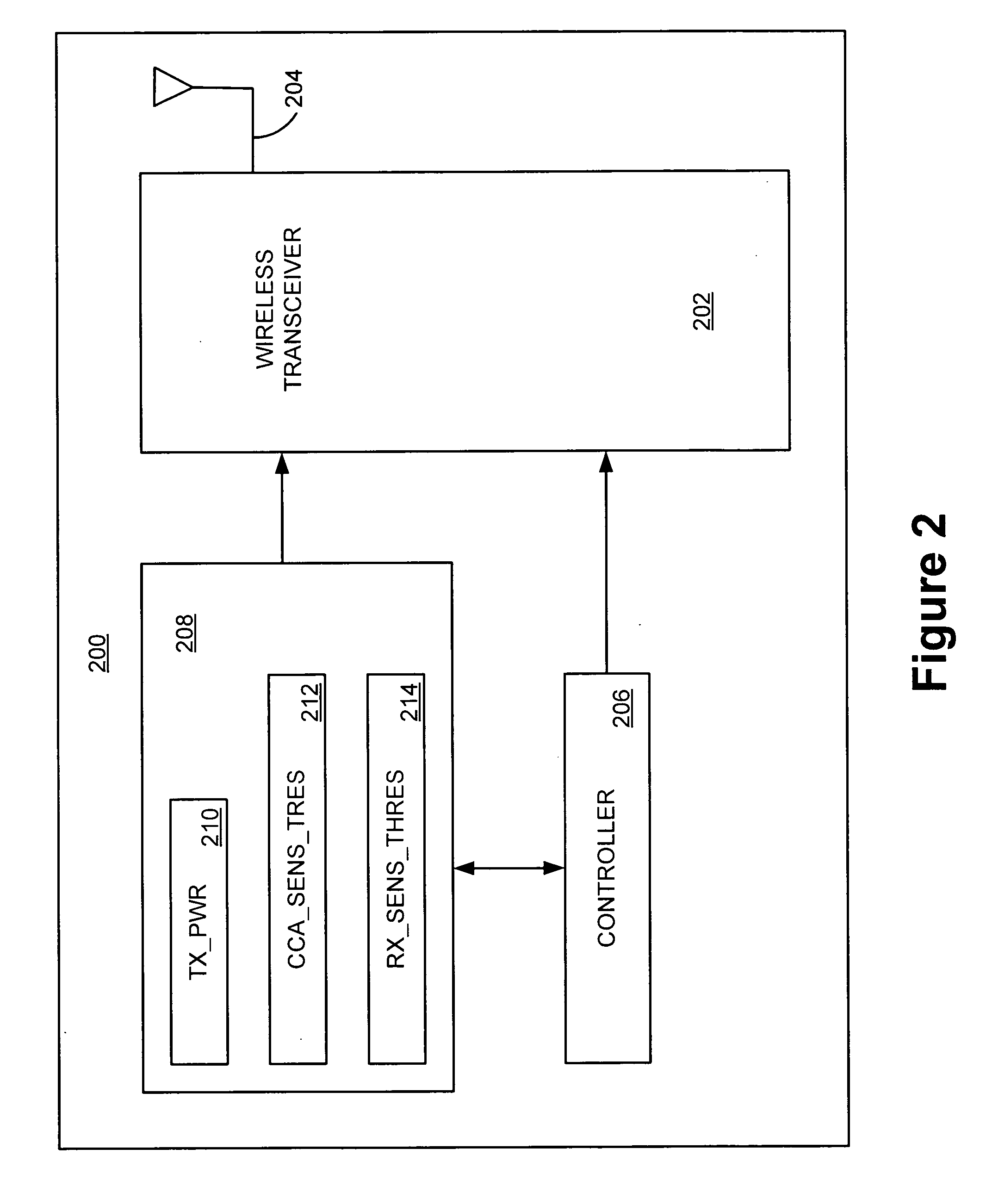

Protocol extension for a high density network

ActiveUS20070072638A1Solve problemsHigh densityPower managementNetwork traffic/resource managementClient-sideHigh density

A set of new information elements are defined that are to be used between an access point and a client that allow an access point to advertise its capabilities, configuration, and / or parameters allowing the client to tune to the parameters prior to, during, or after associating with the access point. If the access point adjusts these parameters, the changes are advertised in subsequent beacons and response frames and the client responsive to receiving a beacon or response frame with changed parameters will change its parameters accordingly. If the station changes its operating parameters it will send a message to the access point informing the access point of the changes.

Owner:CISCO TECH INC

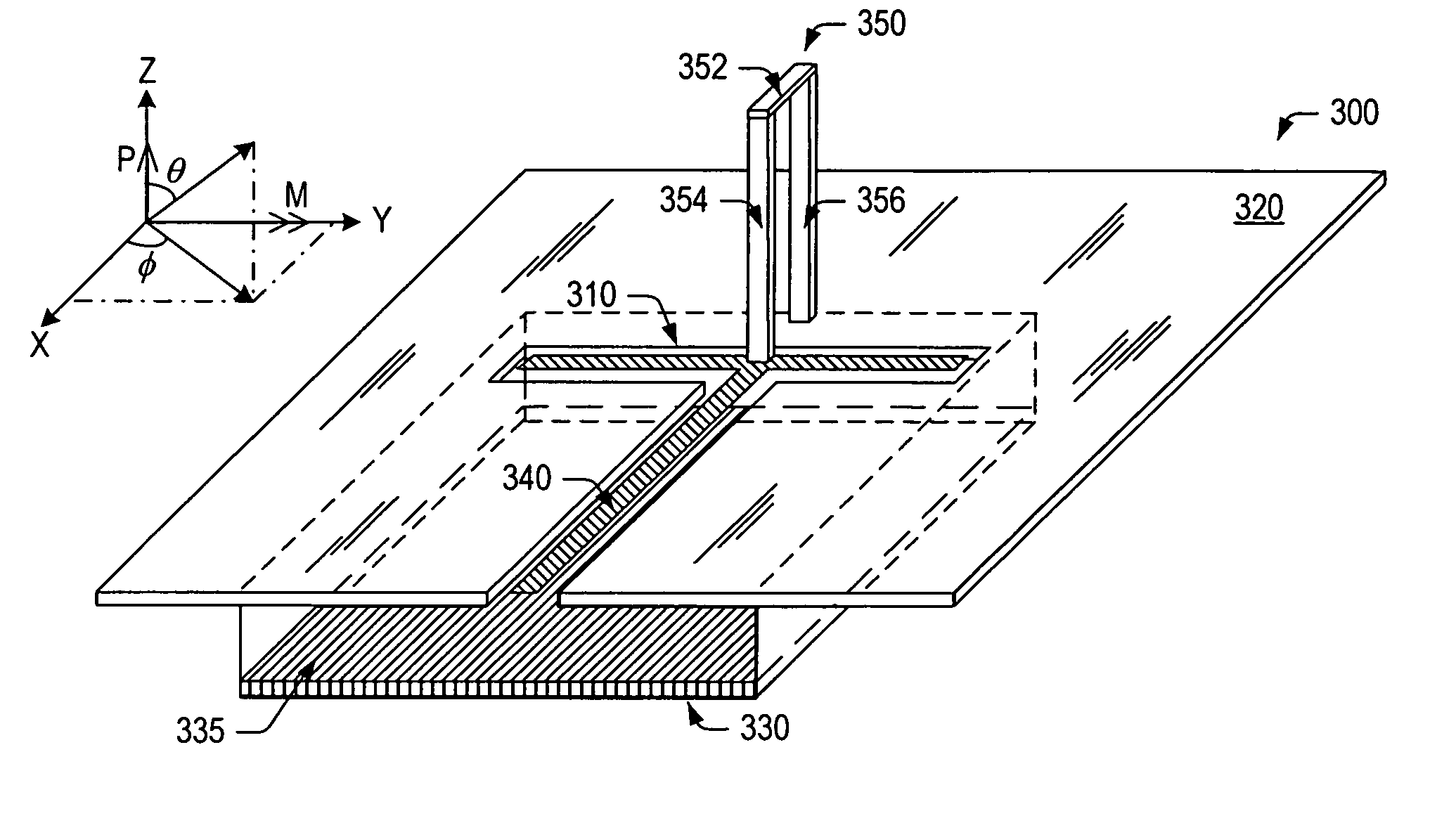

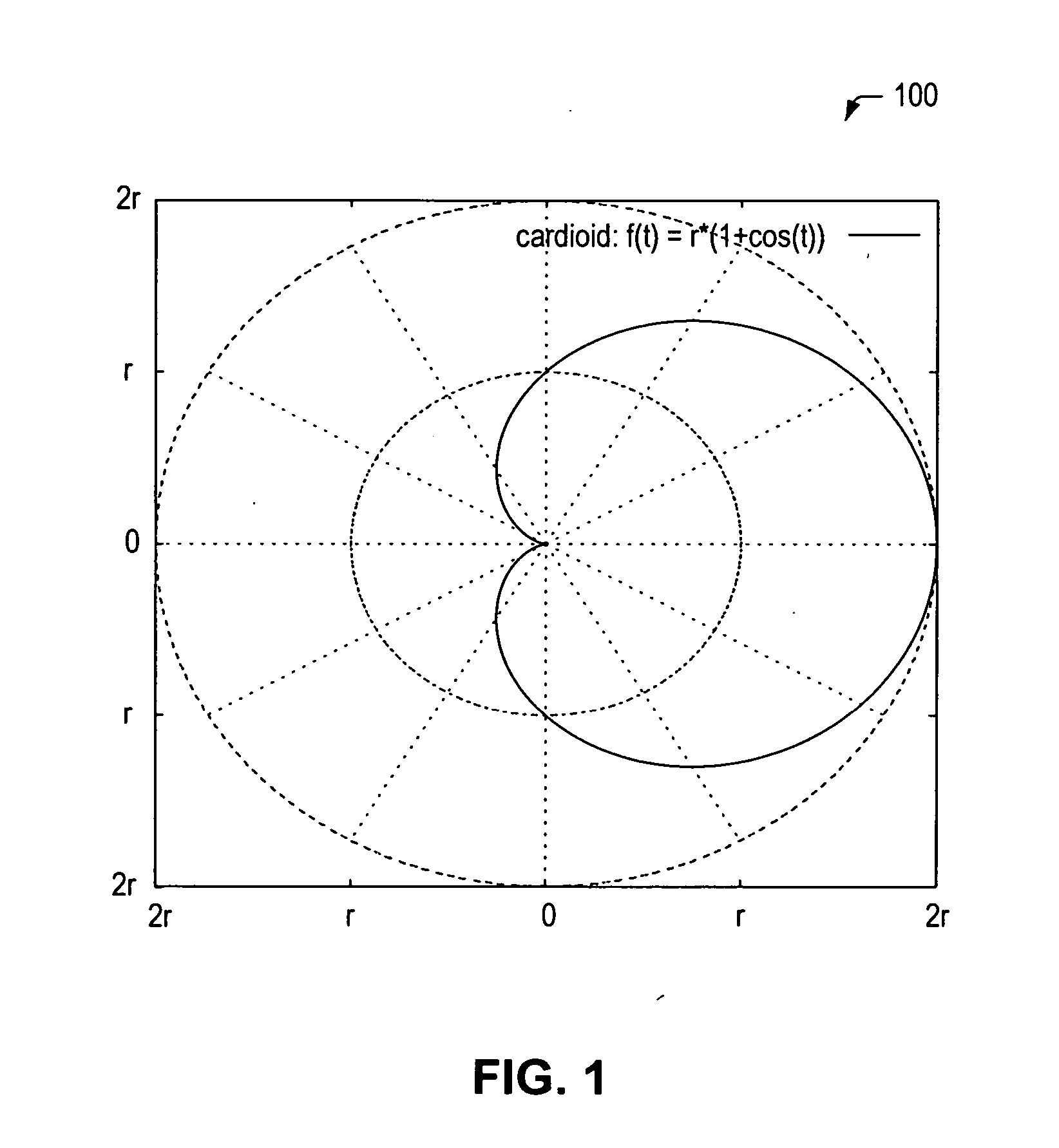

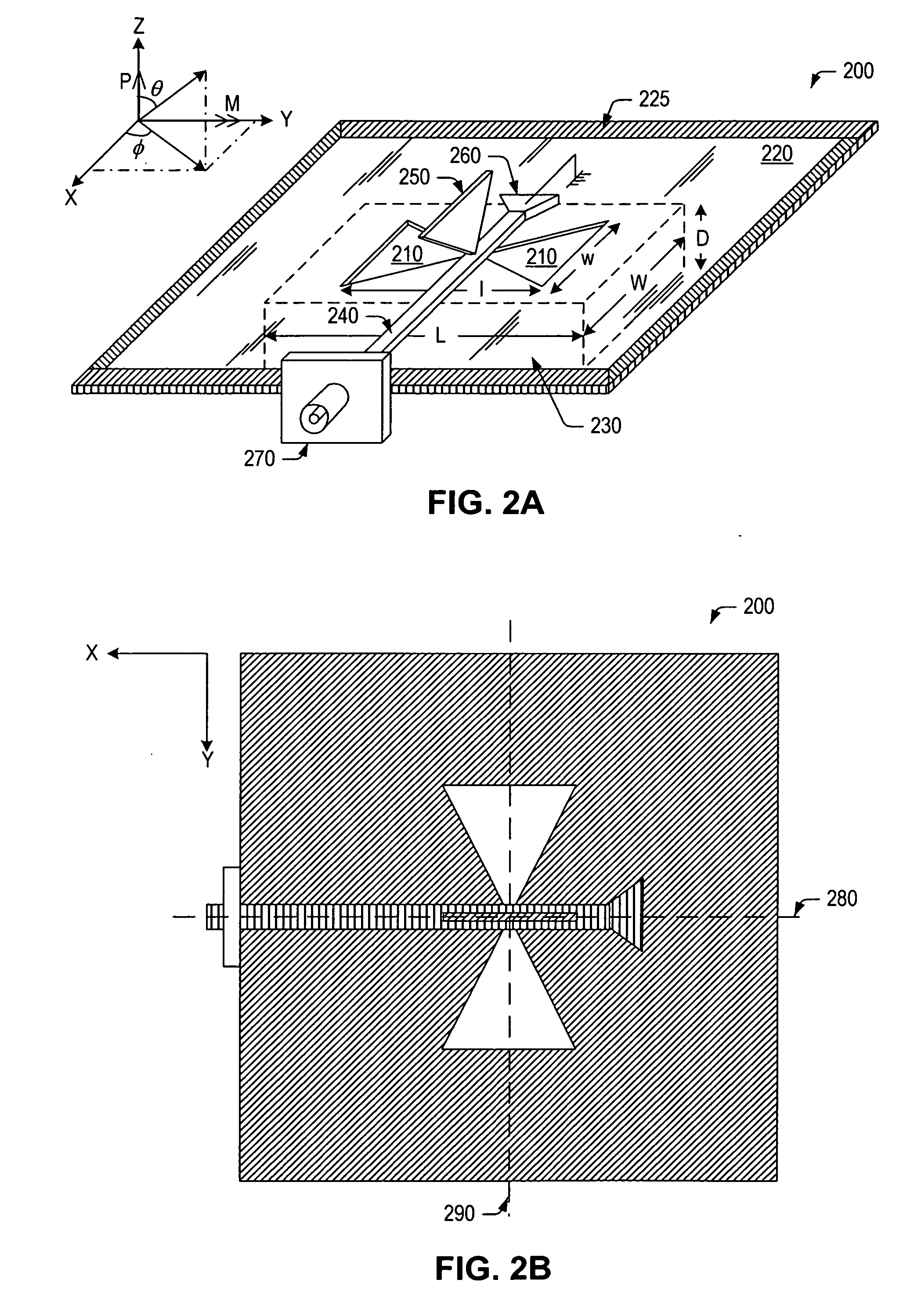

PxM antenna with improved radiation characteristics over a broad frequency range

InactiveUS20070080878A1Reduce lossImprove efficiencyAntenna arraysSimultaneous aerial operationsElectrical resistance and conductanceBroadband

A low-loss, high-efficiency, broadband antenna including both electric and magnetic dipole radiators is provided herein. The broadband antenna may be referred to as a “P×M antenna” and may generally include a ground plane; a magnetic radiator formed within the ground plane; a conductive feed arranged within a first plane, which is parallel to the ground plane; and an electric radiator arranged within a second plane, which is perpendicular to the ground plane and coupled at one end to the conductive feed. According to a particular aspect of the invention, the electric and magnetic radiators are substantially complementary to one another and are coupled for producing a P×M radiation pattern over a broad range of operating frequencies. One advantage of the P×M antenna described herein is that the complementary antenna elements are combined without the use of a lossy, resistive matching network, thereby increasing the efficiency with which the P×M radiation pattern is produced.

Owner:TDK CORPARATION

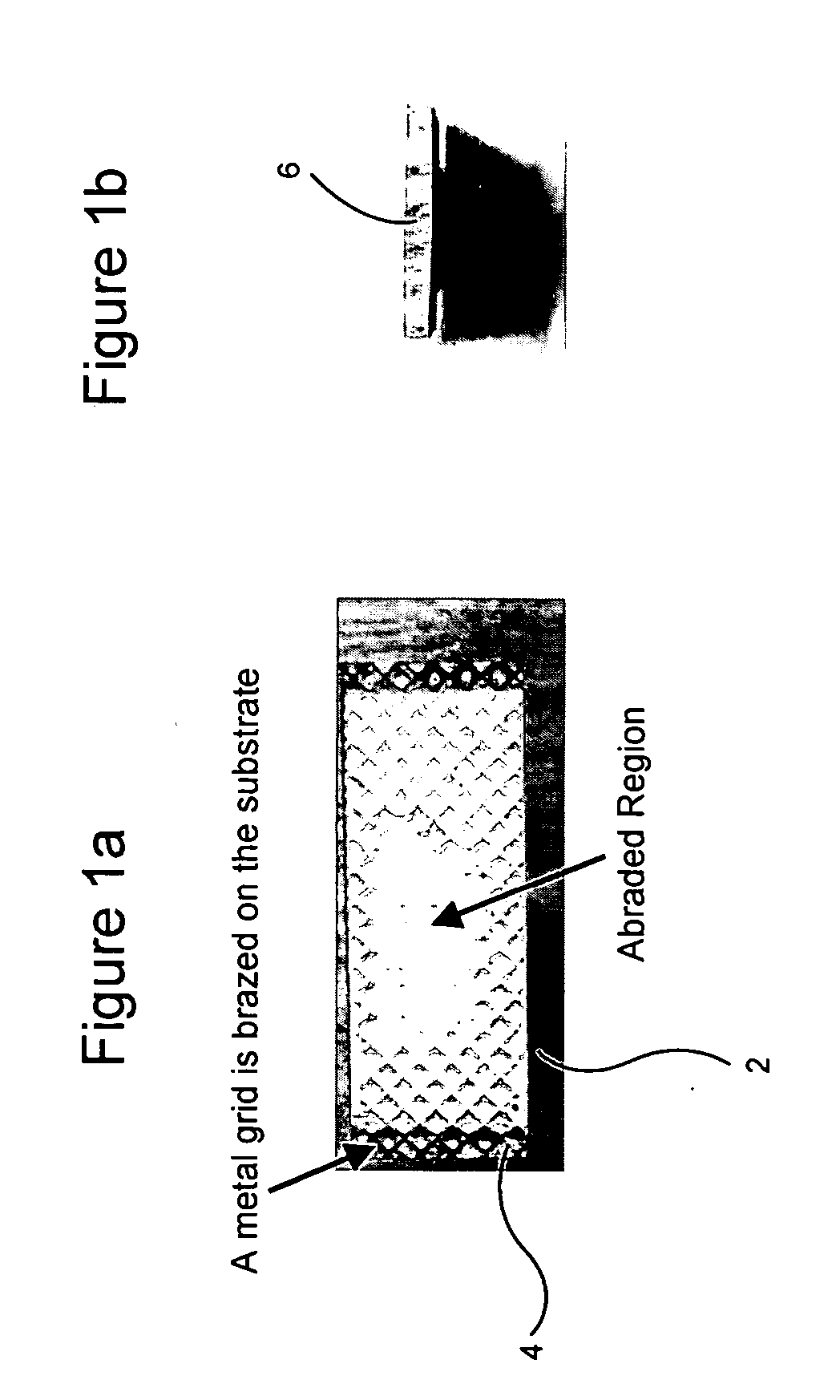

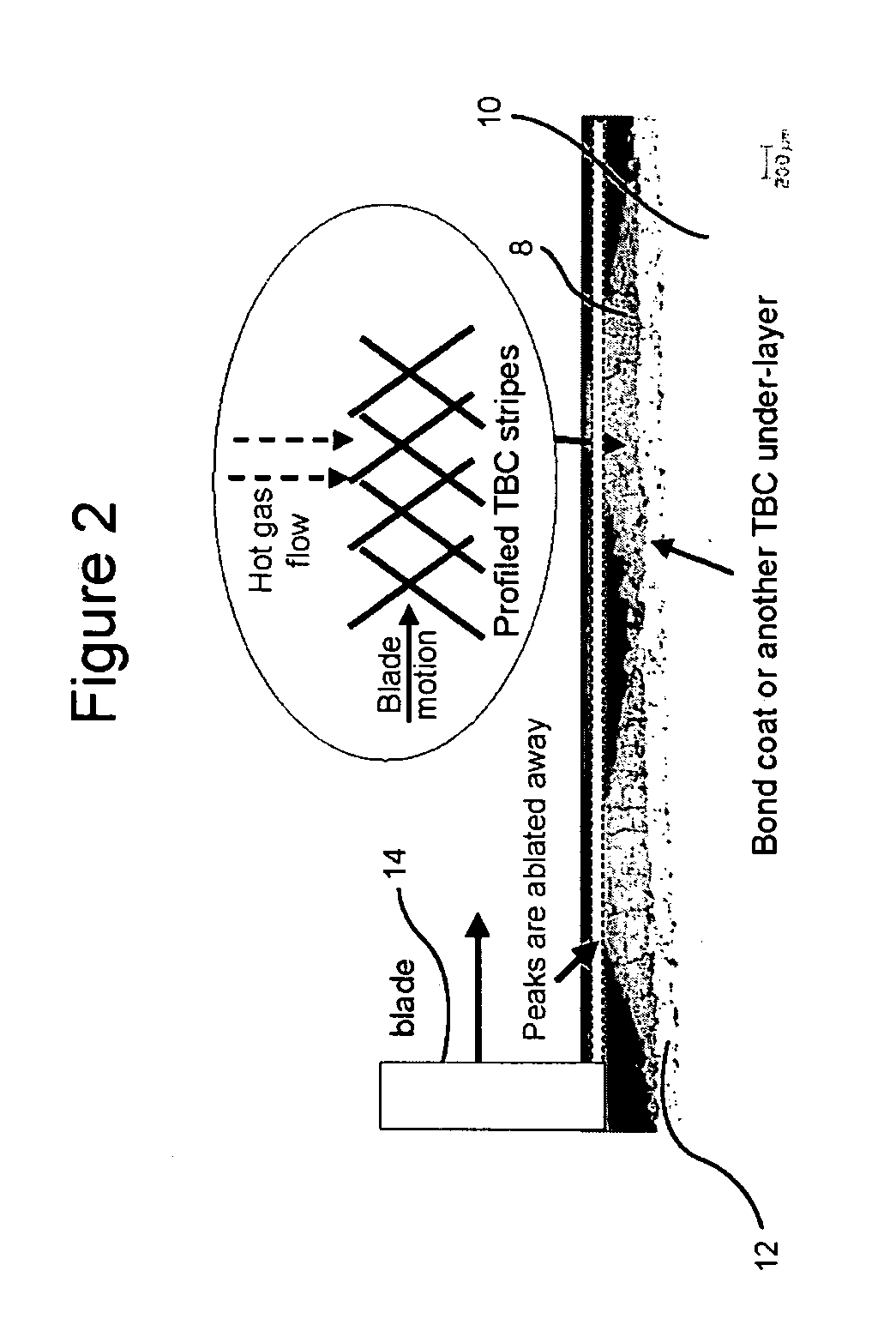

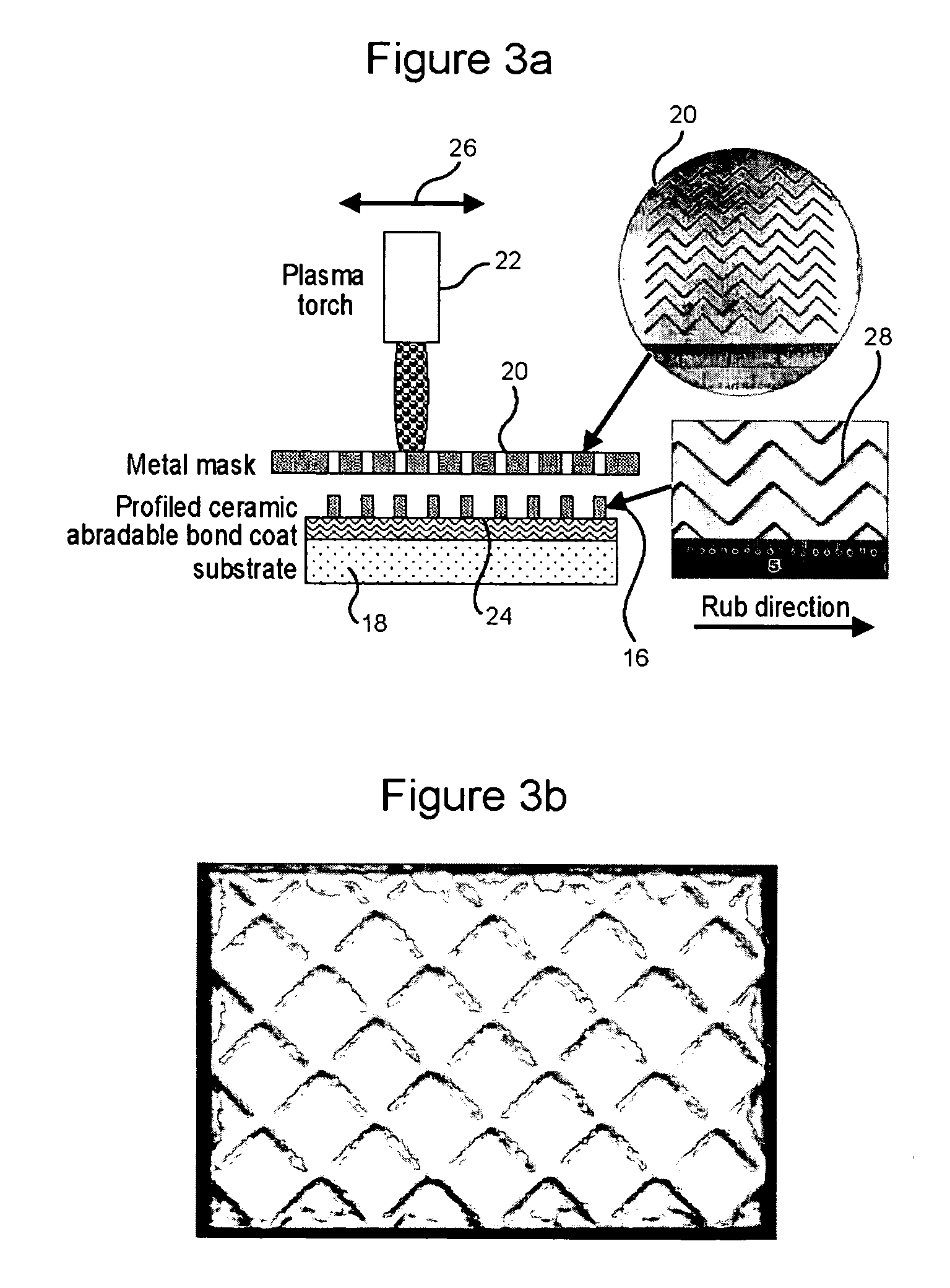

7FAstage 1 abradable coatings and method for making same

InactiveUS20050003172A1Minimal wearReduce gas leakageMolten spray coatingEngine manufactureLeading edgeGrid pattern

A method of applying a profiled abradable coating onto a substrate in which an abradable ceramic coating composition is applied to a metal substrate using one or more coating application techniques to produce a defined ceramic pattern without requiring a separate web or grid to be brazed onto the substrate. The invention is particularly designed to withstand the higher operating temperatures encountered with the stage 1 section of 7FA+e gas turbines to allow for increased coating life without significant deterioration in structural or functional integrity. Typically, the grid pattern coating begins approximately 0.431″ after the leading edge of the shroud, and ends approximately 1.60″ before the trailing edge of the shroud. In the case of diamond-shaped patterns, the grid pattern will be about 0.28″ long and 0.28″ wide, with an overall thickness of about 0.46.″ The coatings thus provide the required levels of abradability and leakage performance and may be applied as a chevron or diamond pattern with the shape oriented such that the diagonals run perpendicular and parallel to the sides of the shroud.

Owner:GENERAL ELECTRIC CO

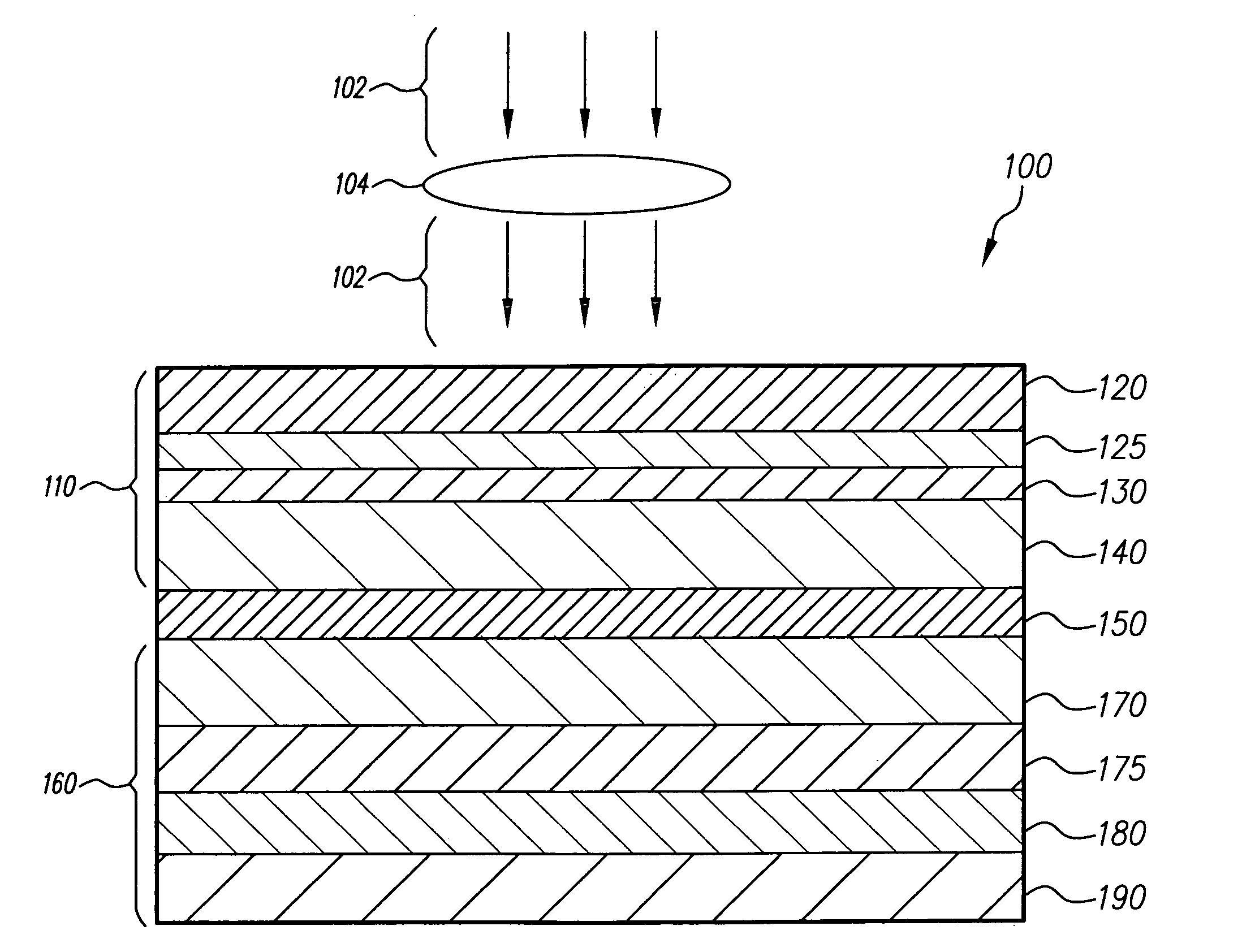

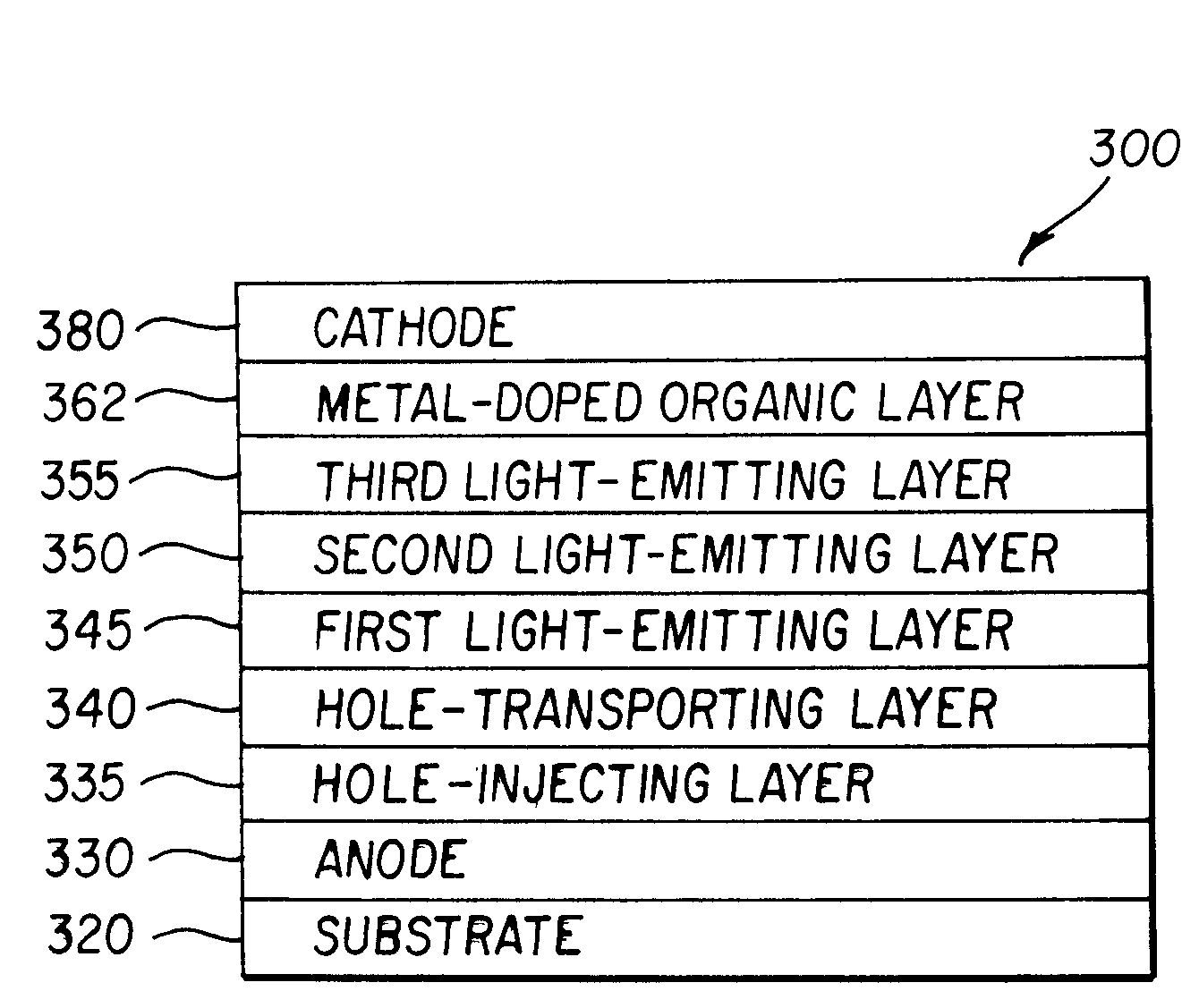

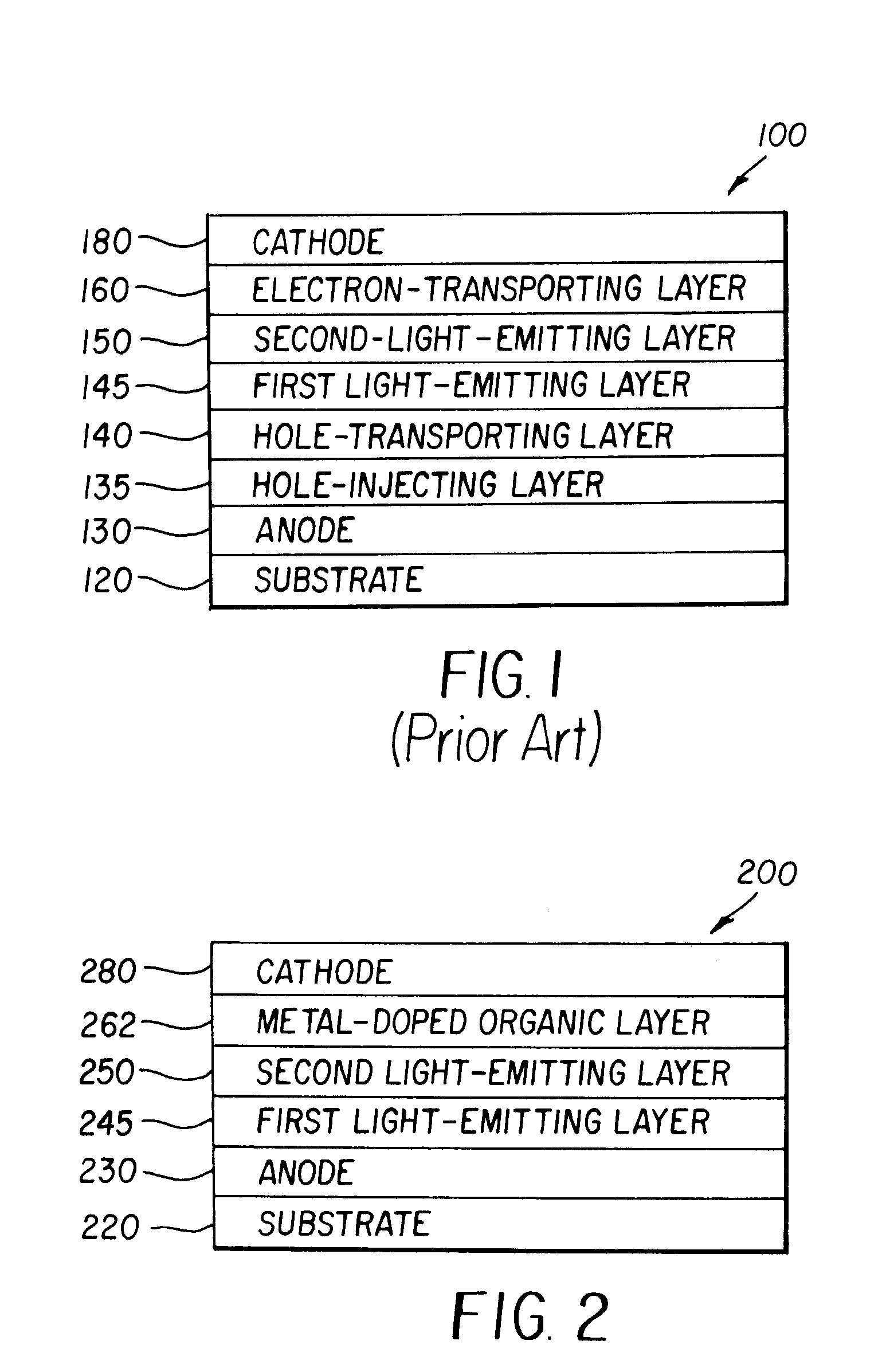

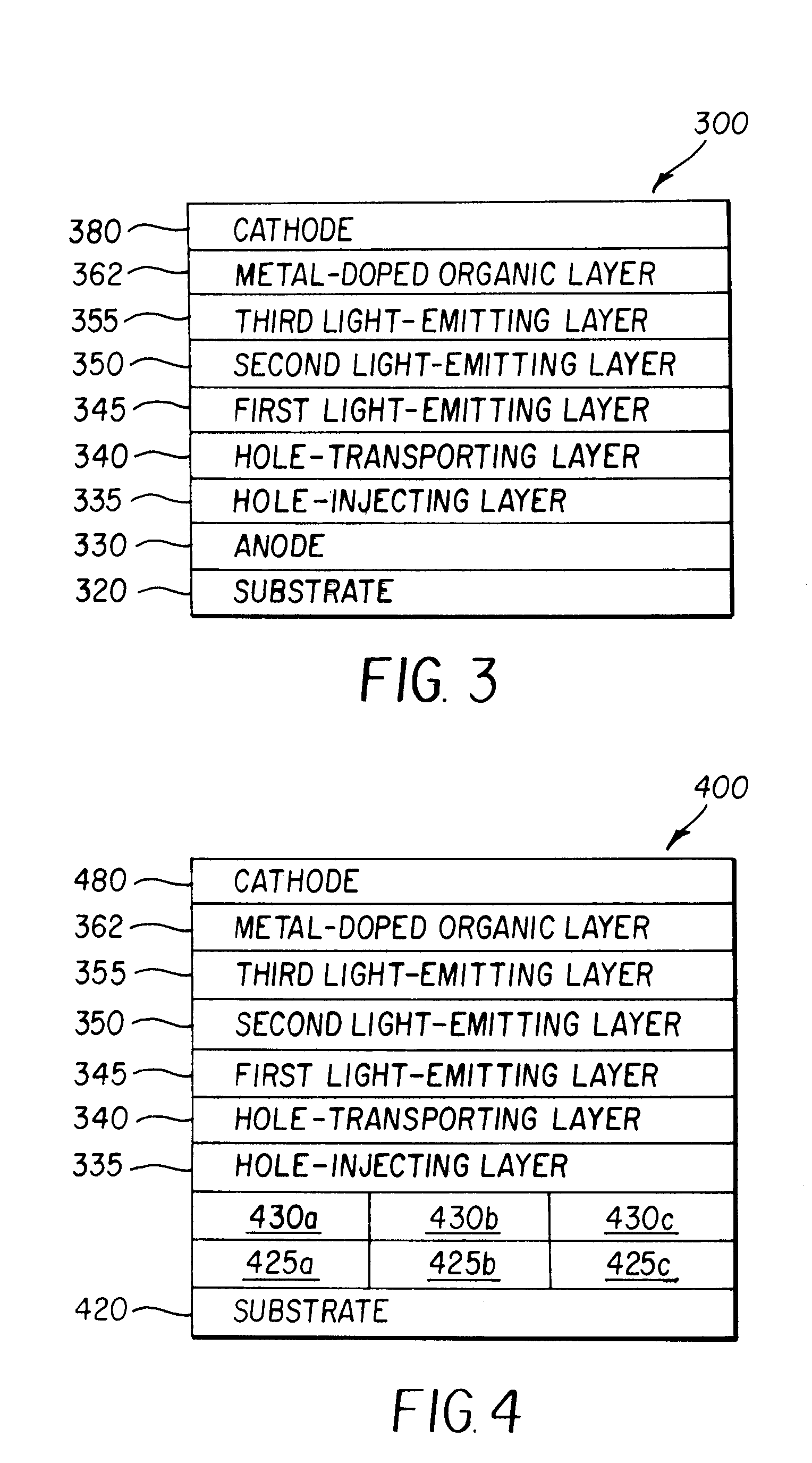

OLED device using reduced drive voltage

ActiveUS7192659B2High luminous efficiencyReduce the driving voltageIncadescent screens/filtersDischarge tube luminescnet screensOrganic layerEngineering

An OLED device includes an anode, a first light-emitting layer disposed over the anode, and a second light-emitting layer disposed over the first light-emitting layer. The device also includes a metal-doped organic layer containing an organic electron-transporting material and a low work function metal disposed over the second light-emitting layer, and a cathode disposed over the metal-doped organic layer.

Owner:GLOBAL OLED TECH

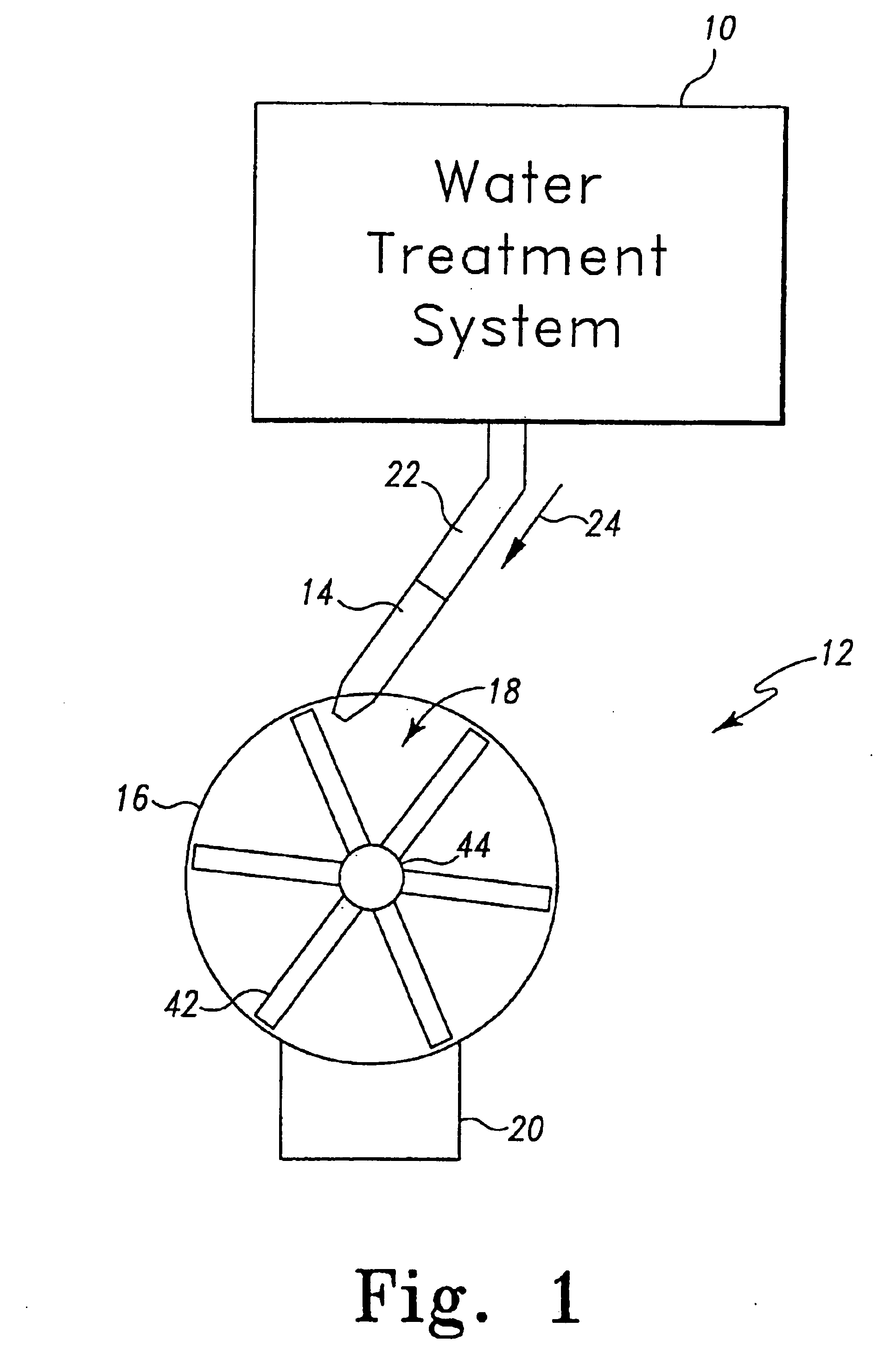

Miniature hydro-power generation system

InactiveUS6885114B2Efficiently provideMaximizing translation of kinetic energyPower plant arrangements/mountingGeneral water supply conservationHydro powerEnergy storage

A miniature hydro-power generation system may produce electric power from a flow of liquid. The miniature hydro-power generation system may include a housing that includes a plurality of paddles positioned to extend outwardly from an outer surface of the housing. The system may also include a nozzle and a centering rod extending through the housing. The housing may rotate around the centering rod when a stream of liquid from the nozzle is directed at the paddles. A generator that includes a rotor and a stator may be positioned within a cavity of the housing. The rotor may be coupled with the housing and the stator may be coupled with the centering rod. The rotor may rotate around the stator at high RPM to generate electric power when the housing rotates. The electric power may supply a load and / or may be stored in an energy storage device.

Owner:ACCESS BUSINESS GRP INT LLC

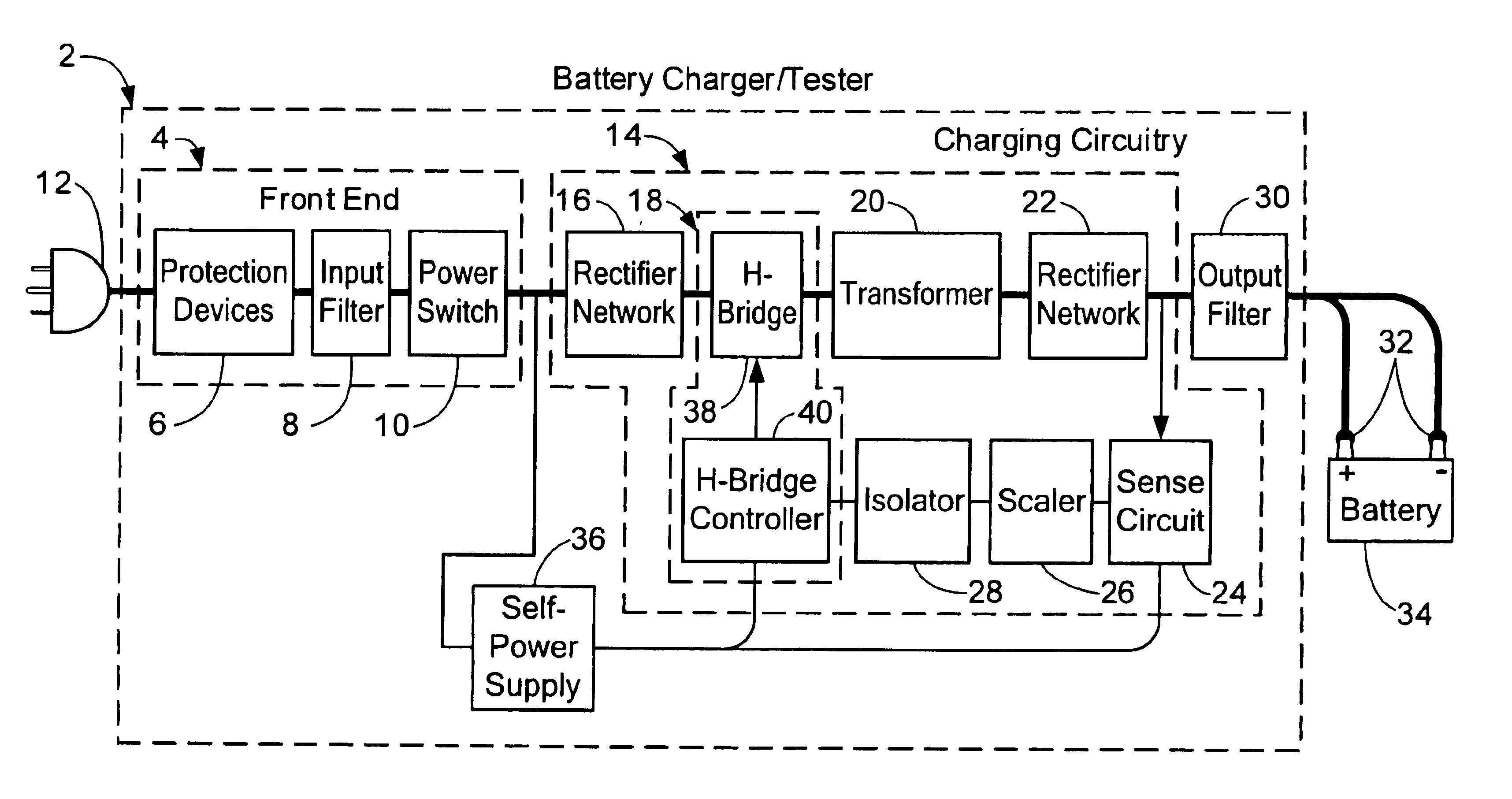

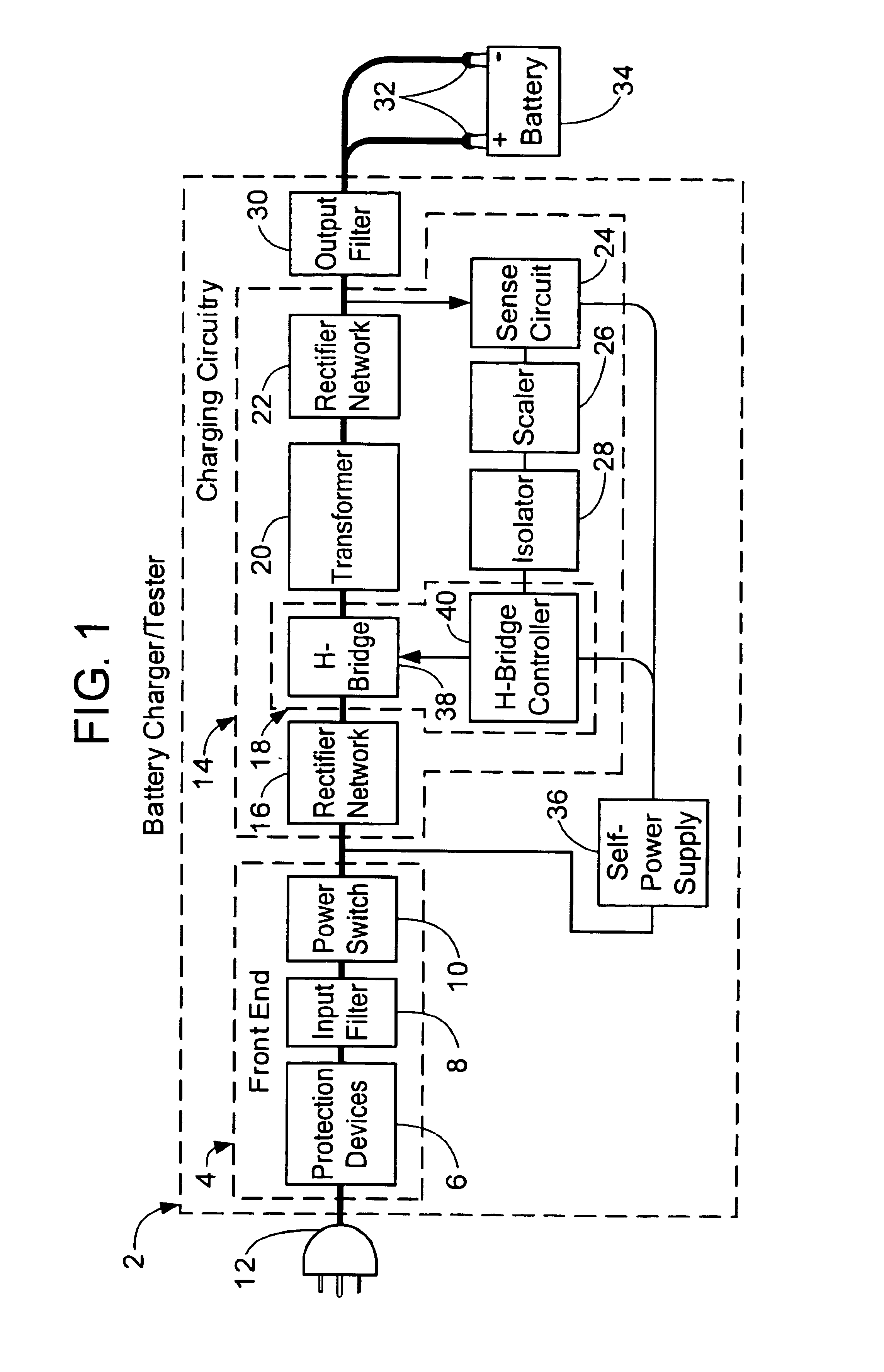

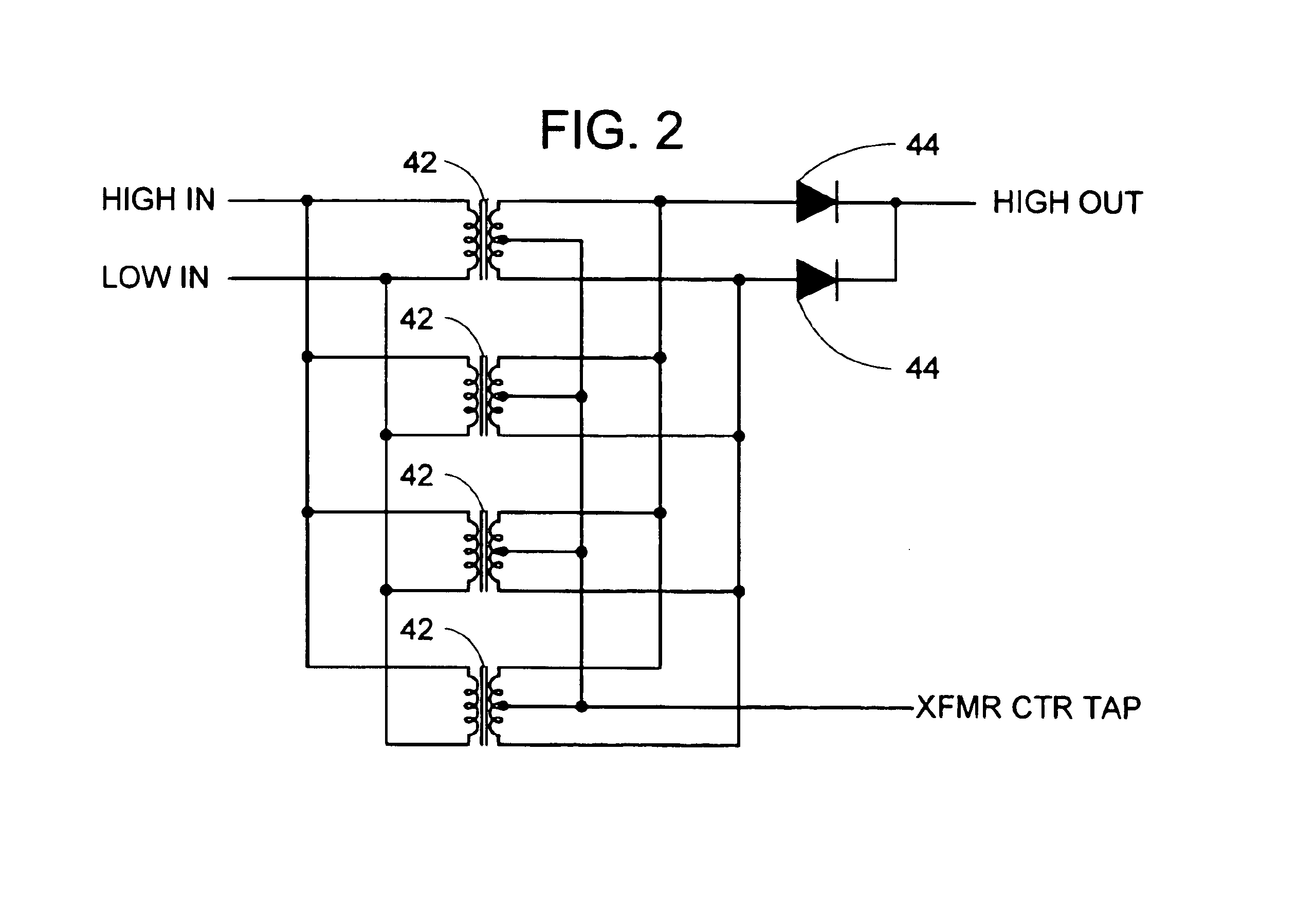

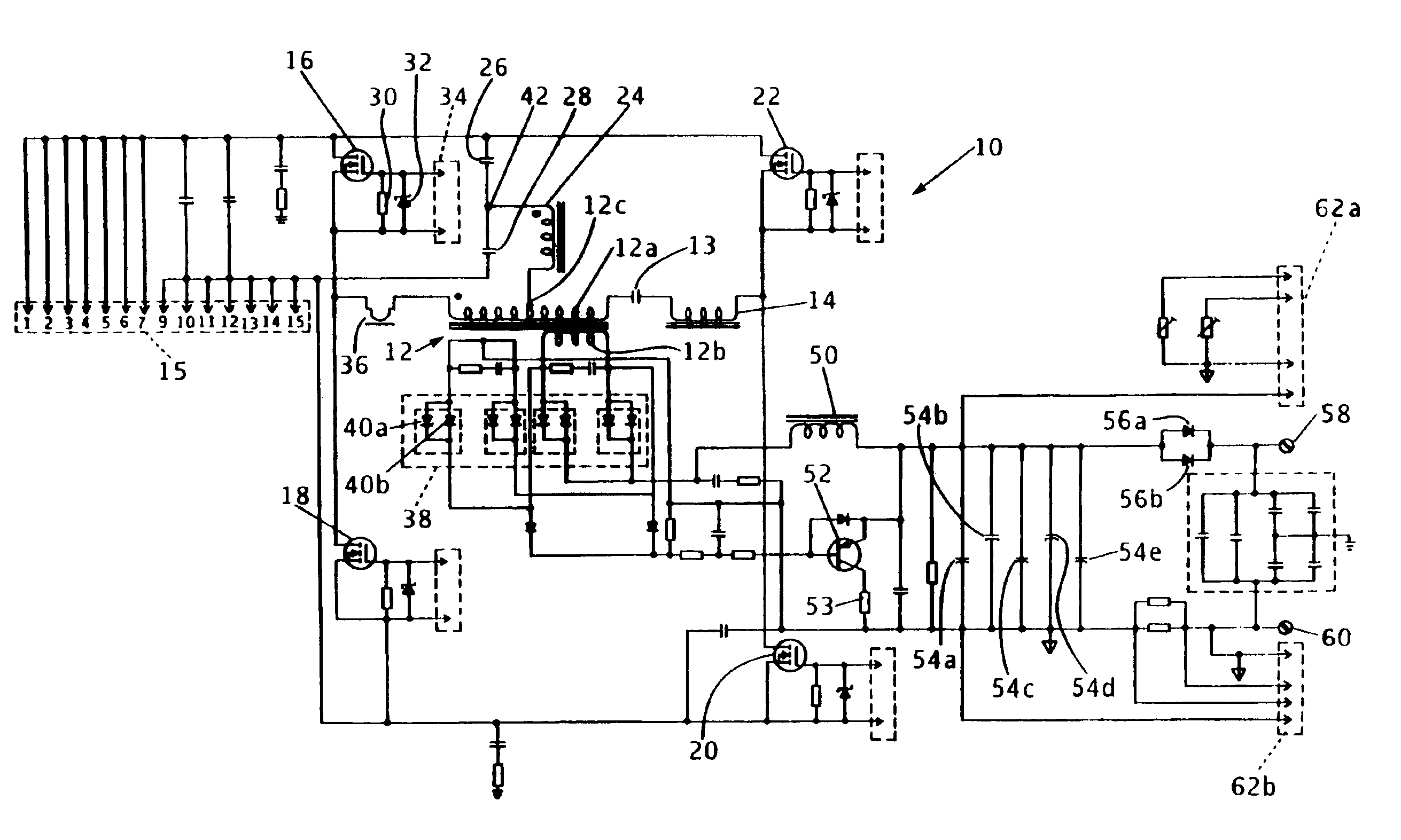

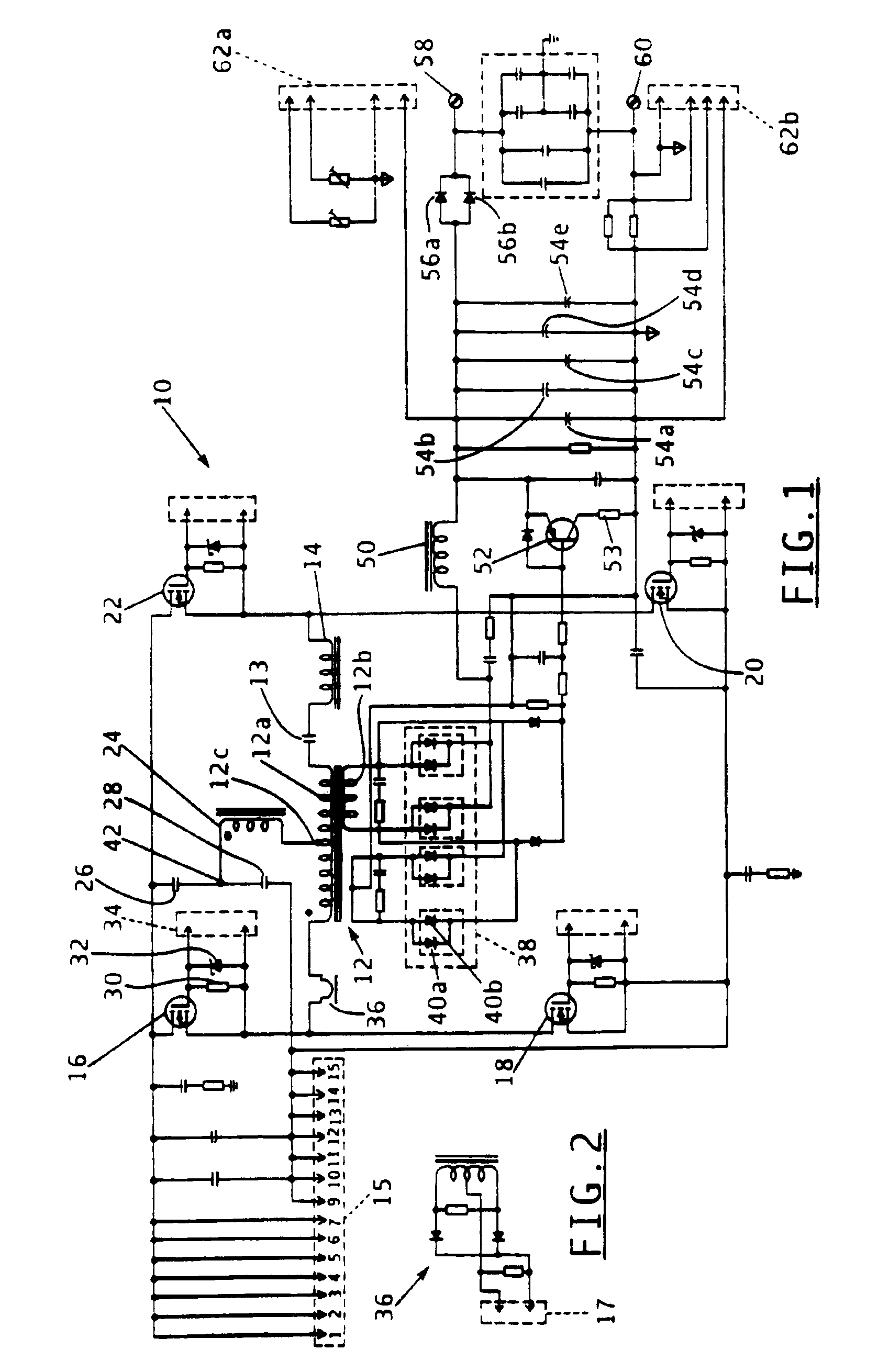

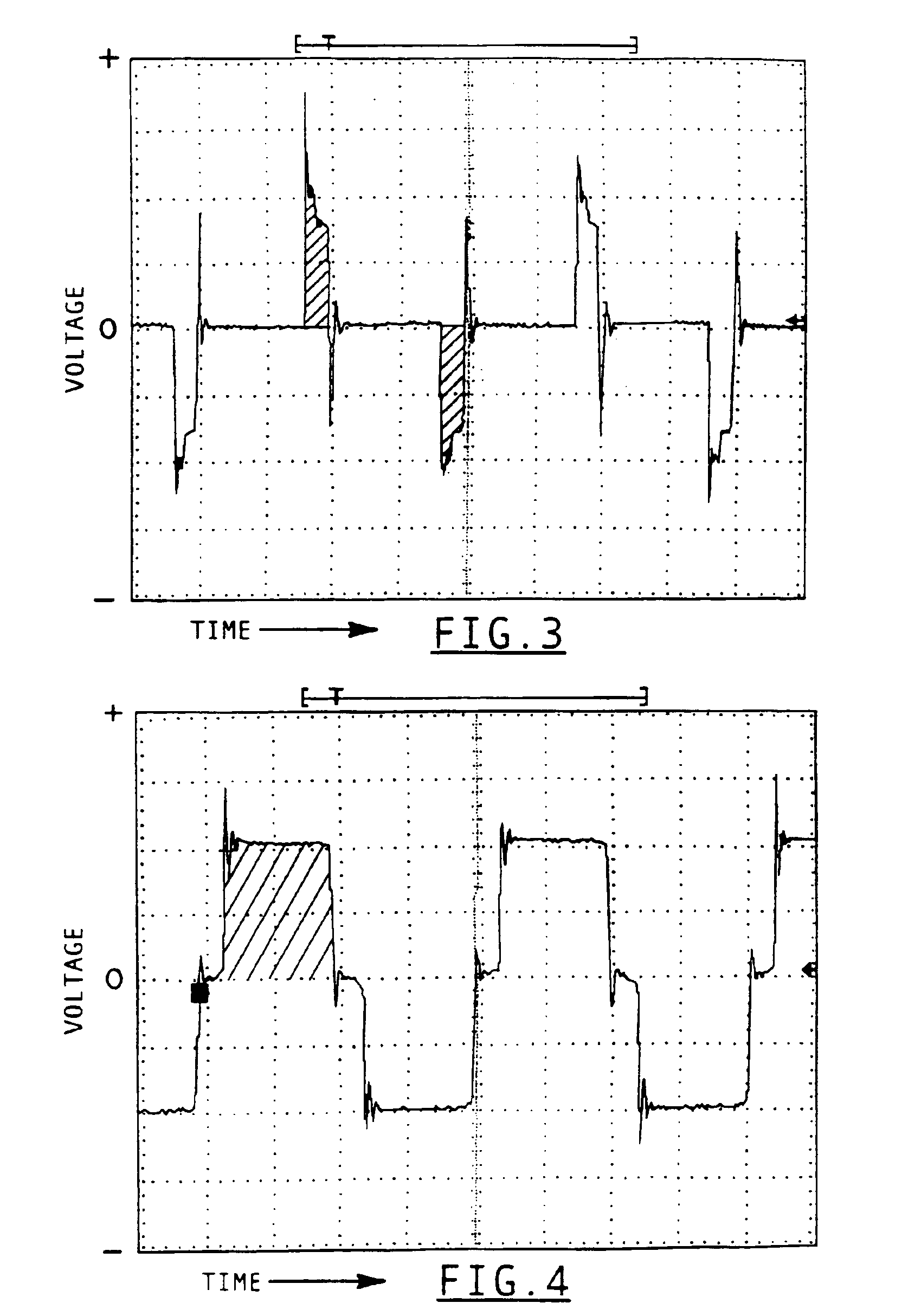

Apparatus and method for high-frequency operation in a battery charger

InactiveUS6838856B2Reduce weight and sizeHigh operating requirementsBatteries circuit arrangementsAc-dc conversion without reversalTransformerAC power

A battery charger includes line-level input rectification, a high-frequency oscillator-controlled chopper circuit, multiple transformers operating in parallel, and controlled output rectification. Use of line-level input rectification reorders the elements of the battery charger compared to previous designs. A chopper frequency several orders of magnitude higher than that of the AC power mains is used. The use of multiple, parallel-wired transformers for voltage and current transformation eases constraints on the physical geometry of a manufactured battery charger product by permitting individual transformers, each smaller than a comparable single transformer, to be employed. Controlled output rectifiers permit power levels to be regulated dynamically.

Owner:SPX CORP

Method and system for configuration and download in a restricted architecture network

InactiveUS6973479B2Avoid complicationsAvoid difficultyMultiple digital computer combinationsProgram loading/initiatingExtensibilityData file

A method and system are provided for updating software configurations of line-replaceable unit (LRU) computers in a restricted architecture network such as an in-flight entertainment system (IFES). Operating in an efficient and parallel manner, each of the LRUs independently creates an individual configuration file that identifies current software components. Each of the LRUs transmits its respective configuration file to a configuration server either automatically upon startup or manually upon request. The configuration server updates a system configuration data file with the current configuration files received from the individual LRUs. In a downloading method, a download server sends a list of desired software components to the LRUs. Each of the LRUs independently and simultaneously transfer (download) the needed software from the download server. The LRU independently requests the download server to download the needed software components. To improve scalability and reliability, the file transfers utilize standard protocols, such as FTP.

Owner:THALES AVIONICS INC

Heatsink apparatus and electronic device having the same

ActiveUS20090084525A1High operation stabilityImprove cooling effectDigital data processing detailsSemiconductor/solid-state device detailsWorking fluidGas phase

A heatsink apparatus performs cooling by circulating a working fluid and causing a phase change between a liquid phase and a gas phase. The heatsink apparatus is provided on an external wall with a heat-generating body. The heatsink apparatus includes a box-shaped heat-receiving unit transferring heat to a heat-receiving plate; an inlet pipe supplying the working fluid to the heat-receiving unit; an outlet pipe discharging vapors into which the working fluid supplied to the heat-receiving plate is evaporated by heat; and a heat dissipater provided at a location higher than the heat-receiving unit and dissipating heat of the vapor passing through the outlet pipe. Slits are provided to the heat-receiving plate on a surface surrounded by an external circumference of the inlet pipe toward outside of the heat-receiving plate.

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

Zero-voltage-switched, full-bridge, phase-shifted DC-DC converter with improved light/no-load operation

InactiveUS6909617B1Operation efficiency is highImprove power supply efficiencyEfficient power electronics conversionConversion with intermediate conversion to dcCapacitanceFull bridge

A zero-voltage-switched, full-bridge, phase-shifted DC-DC converter for use in a DC power supply or battery charger includes a power transformer, four switching transistors connected to form a full bridge, and a decoupling capacitor and resonant inductor connected in series to the primary winding of the power transformer. At high loads, i.e., high output voltages, the resonant inductor charges the stray and internal capacitance of the switching transistors. Under light loads or in a no-load condition, with the current through the resonant inductor insufficient to allow the inductor to recharge these capacitances, the combination of a second inductor connected at one end to the central tap of the power transformer's primary winding and at its second opposed end to the middle point of a capacitive voltage divider, permits the second inductor to store enough energy to effectively recharge the stray and internal capacitance of the switching transistors for improved operating efficiency.

Owner:LA MARCHE MFG