Patents

Literature

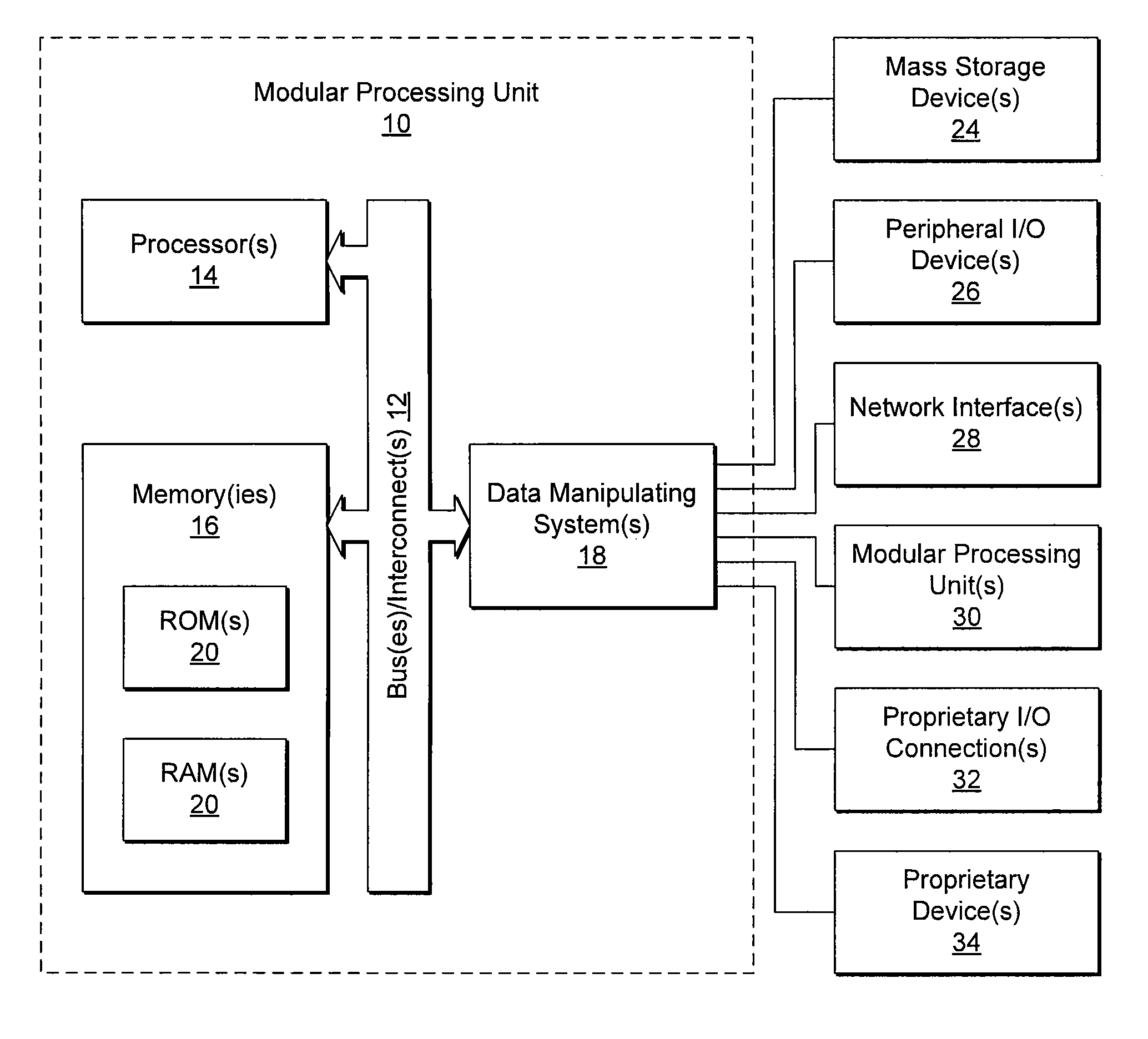

368 results about "Memory performance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Memory performance information is available from the memory manager through the system performance counters and through functions such as GetPerformanceInfo, GetProcessMemoryInfo, and GlobalMemoryStatusEx.

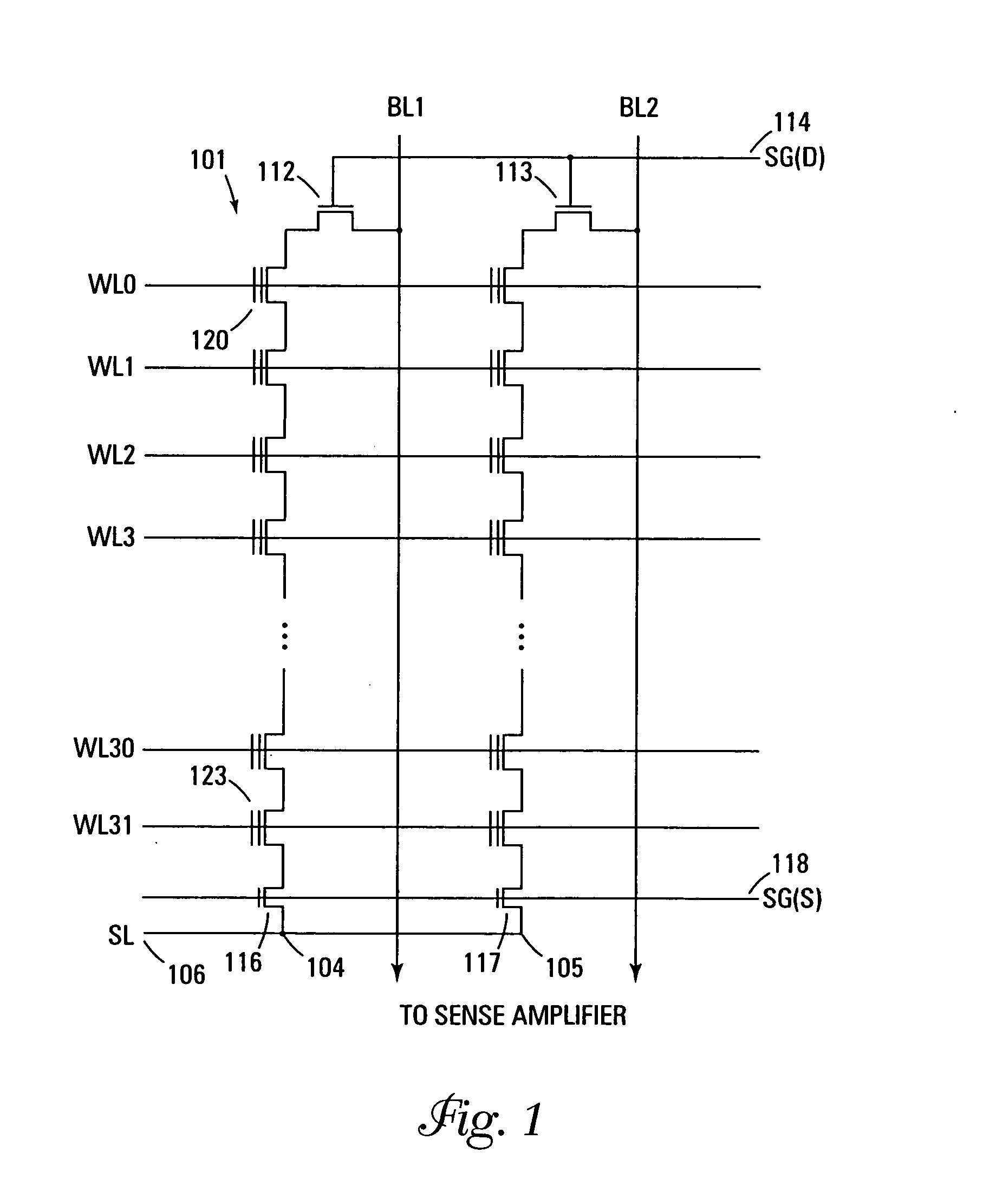

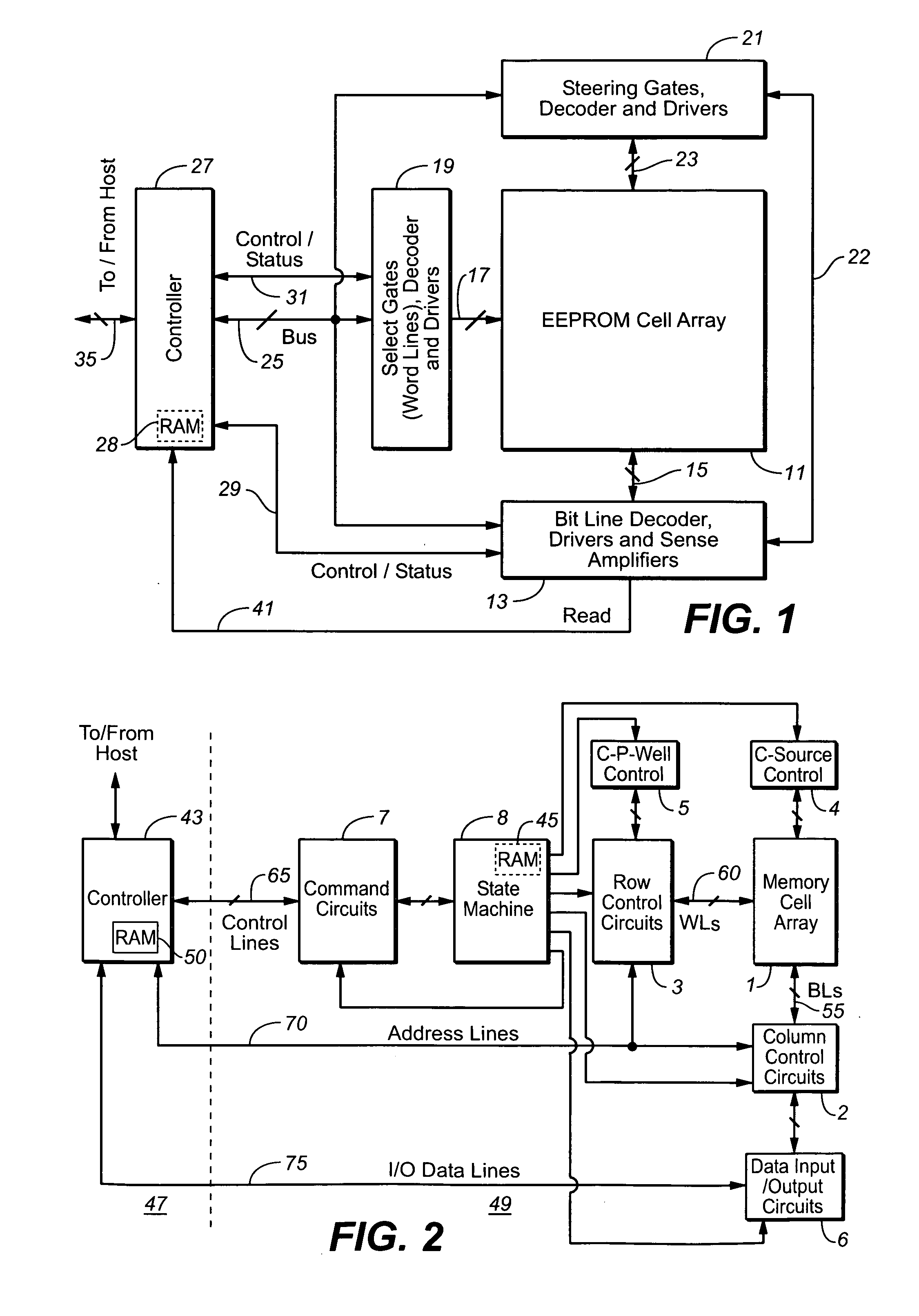

Management of non-volatile memory systems having large erase blocks

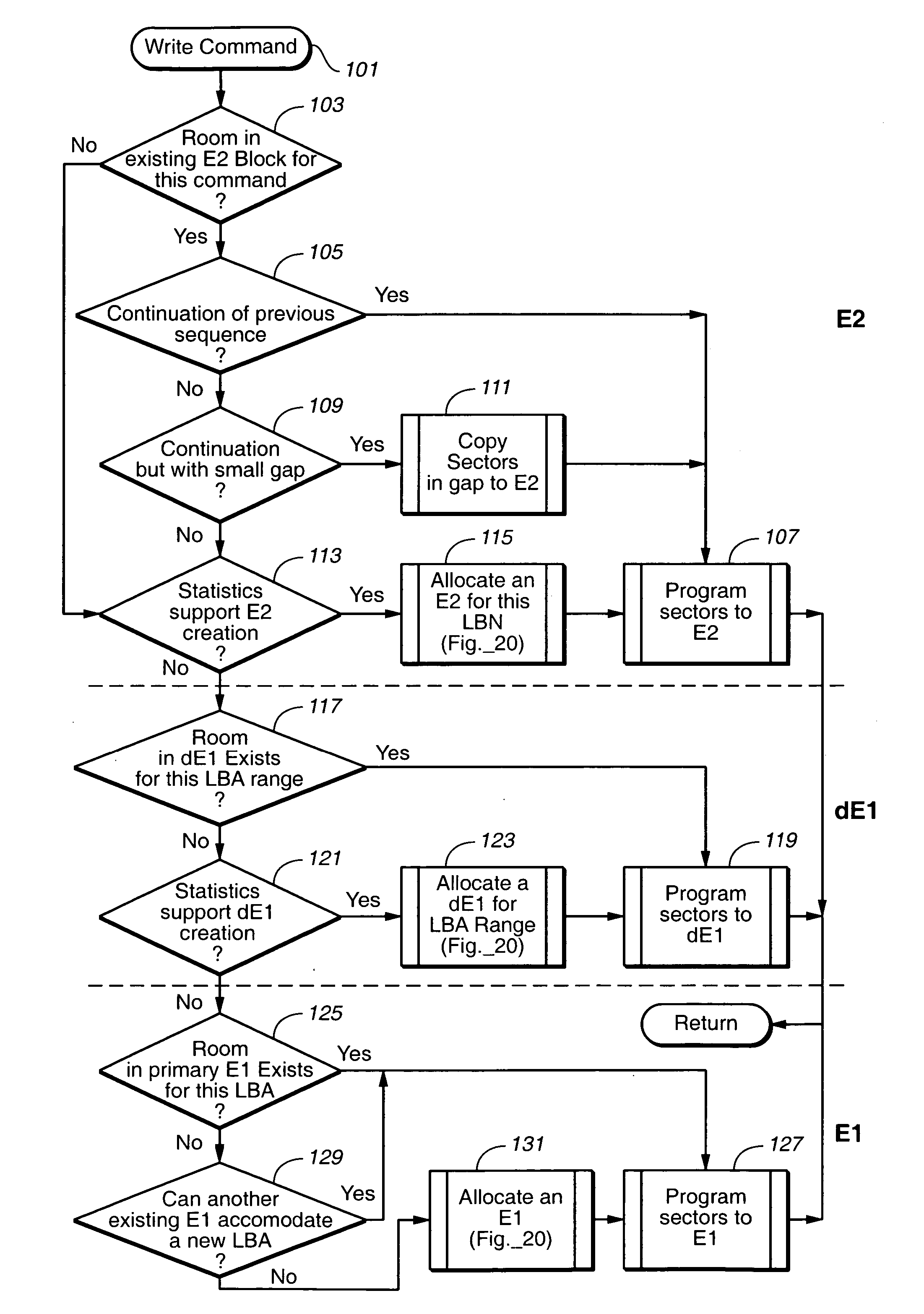

ActiveUS20050144358A1Reduce amountImprove system performanceMemory architecture accessing/allocationMemory adressing/allocation/relocationOriginal dataTerm memory

A non-volatile memory system of a type having blocks of memory cells erased together and which are programmable from an erased state in units of a large number of pages per block. If the data of only a few pages of a block are to be updated, the updated pages are written into another block provided for this purpose. Updated pages from multiple blocks are programmed into this other block in an order that does not necessarily correspond with their original address offsets. The valid original and updated data are then combined at a later time, when doing so does not impact on the performance of the memory. If the data of a large number of pages of a block are to be updated, however, the updated pages are written into an unused erased block and the unchanged pages are also written to the same unused block. By handling the updating of a few pages differently, memory performance is improved when small updates are being made. The memory controller can dynamically create and operate these other blocks in response to usage by the host of the memory system.

Owner:SANDISK TECH LLC

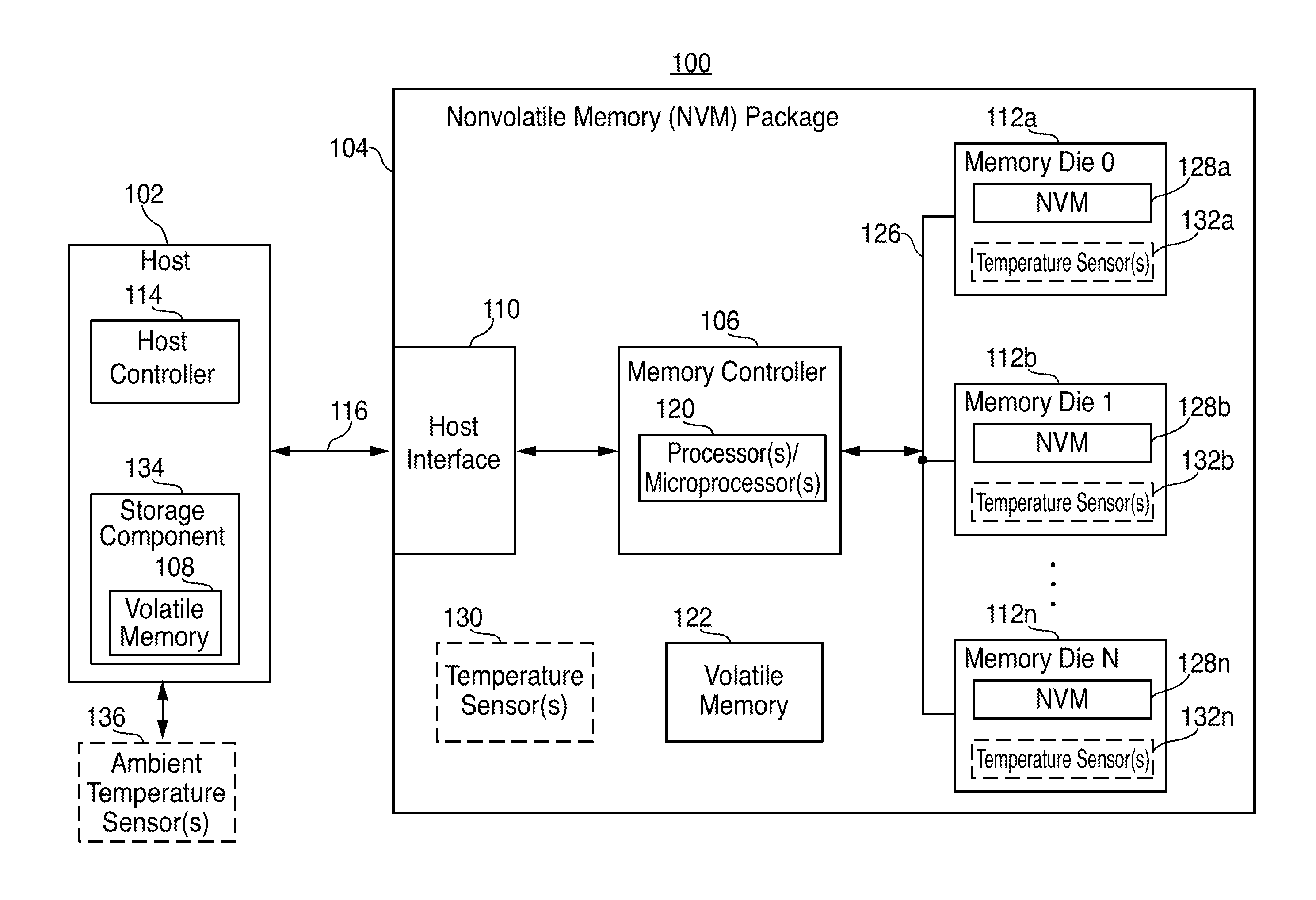

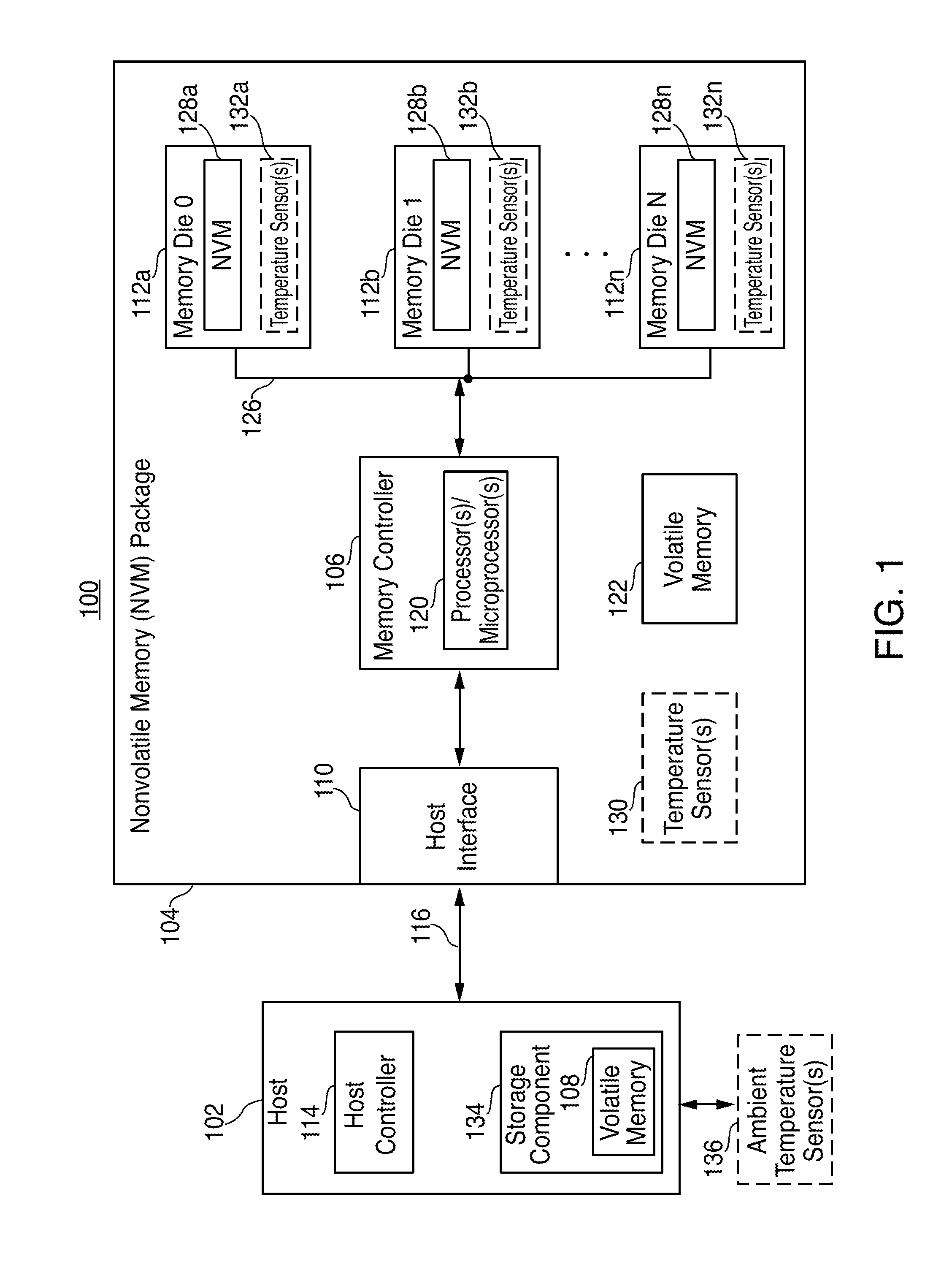

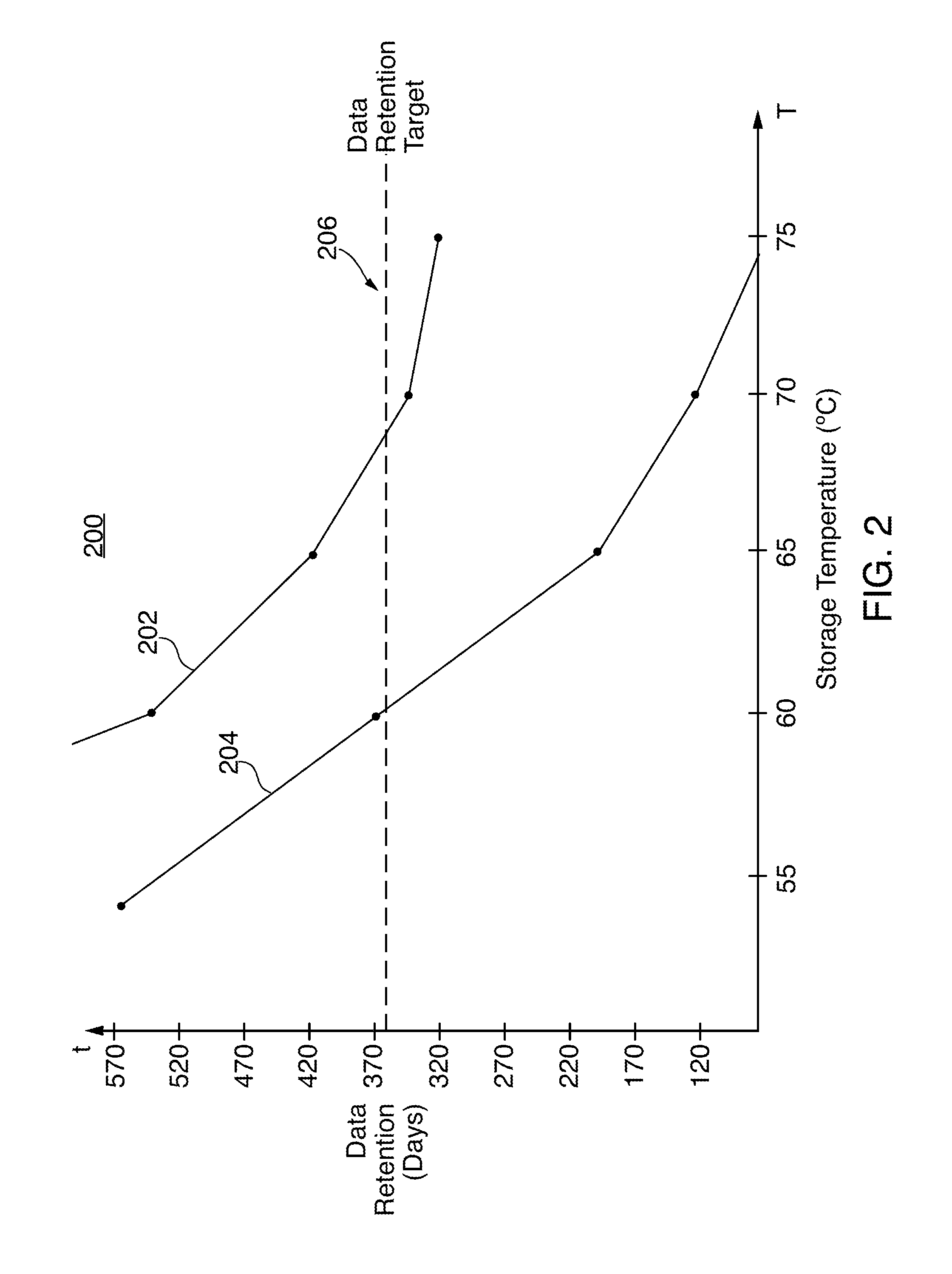

Systems and methods for nonvolatile memory performance throttling

ActiveUS20140101371A1Safe storageMemory architecture accessing/allocationError detection/correctionComputer scienceMemory performance

Systems and methods for nonvolatile memory (“NVM”) performance throttling are disclosed. Performance of an NVM system may be throttled to achieve particular data retention requirements. In particular, because higher storage temperatures tend to reduce the amount of time that data may be reliably stored in an NVM system, performance of the NVM system may be throttled to reduce system temperatures and increase data retention time.

Owner:APPLE INC

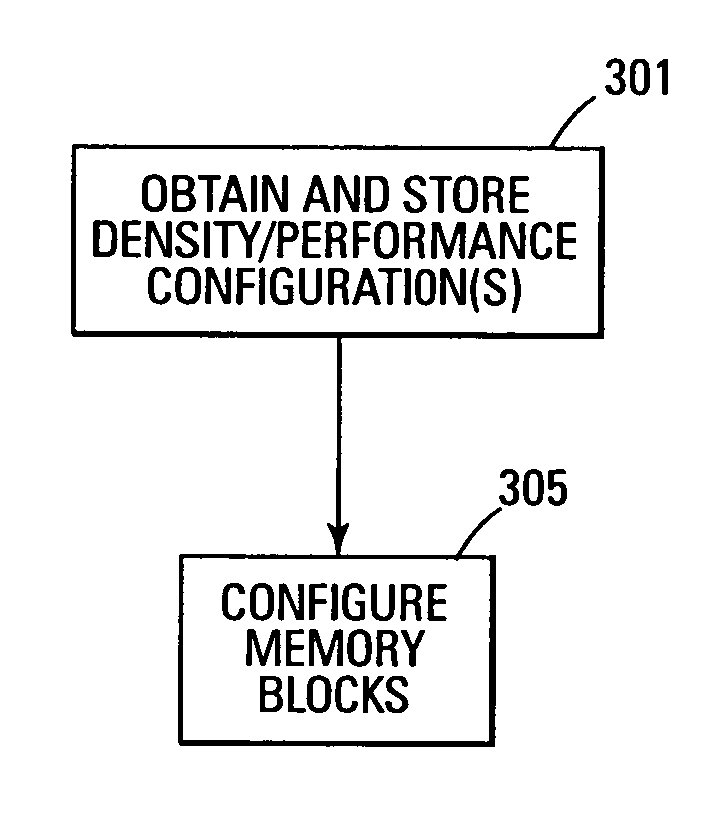

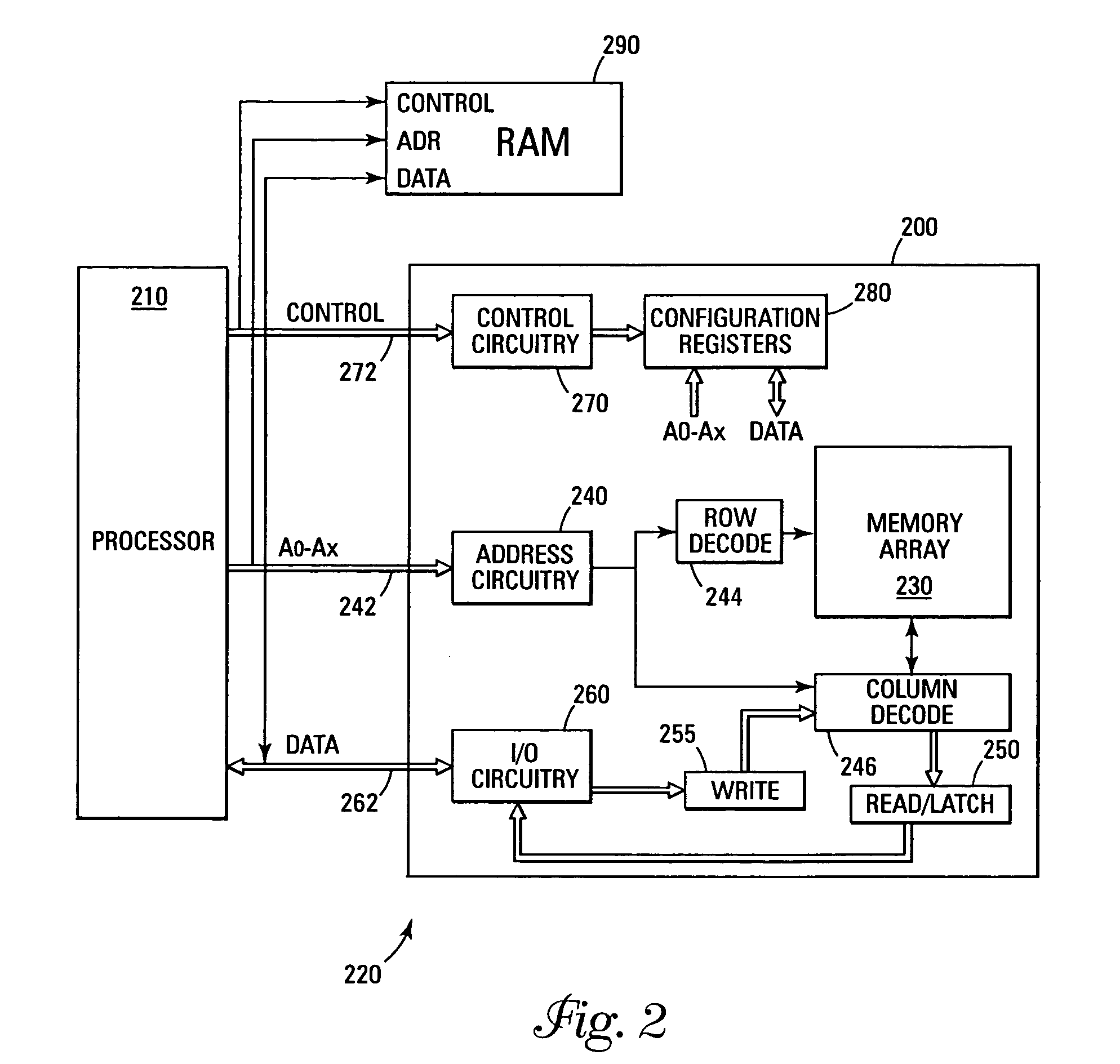

Memory system with user configurable density/performance option

The memory system has one or more memory dies coupled to a processor or other system controller. Each die has a separate memory array organized into multiple memory blocks. The different memory blocks of each die can be assigned a different memory density by the end user, depending on the desired memory performance and / or memory density. The user configurable density / performance option can be adjusted with special read / write operations or a configuration register having a memory density configuration bit for each memory block.

Owner:MICRON TECH INC

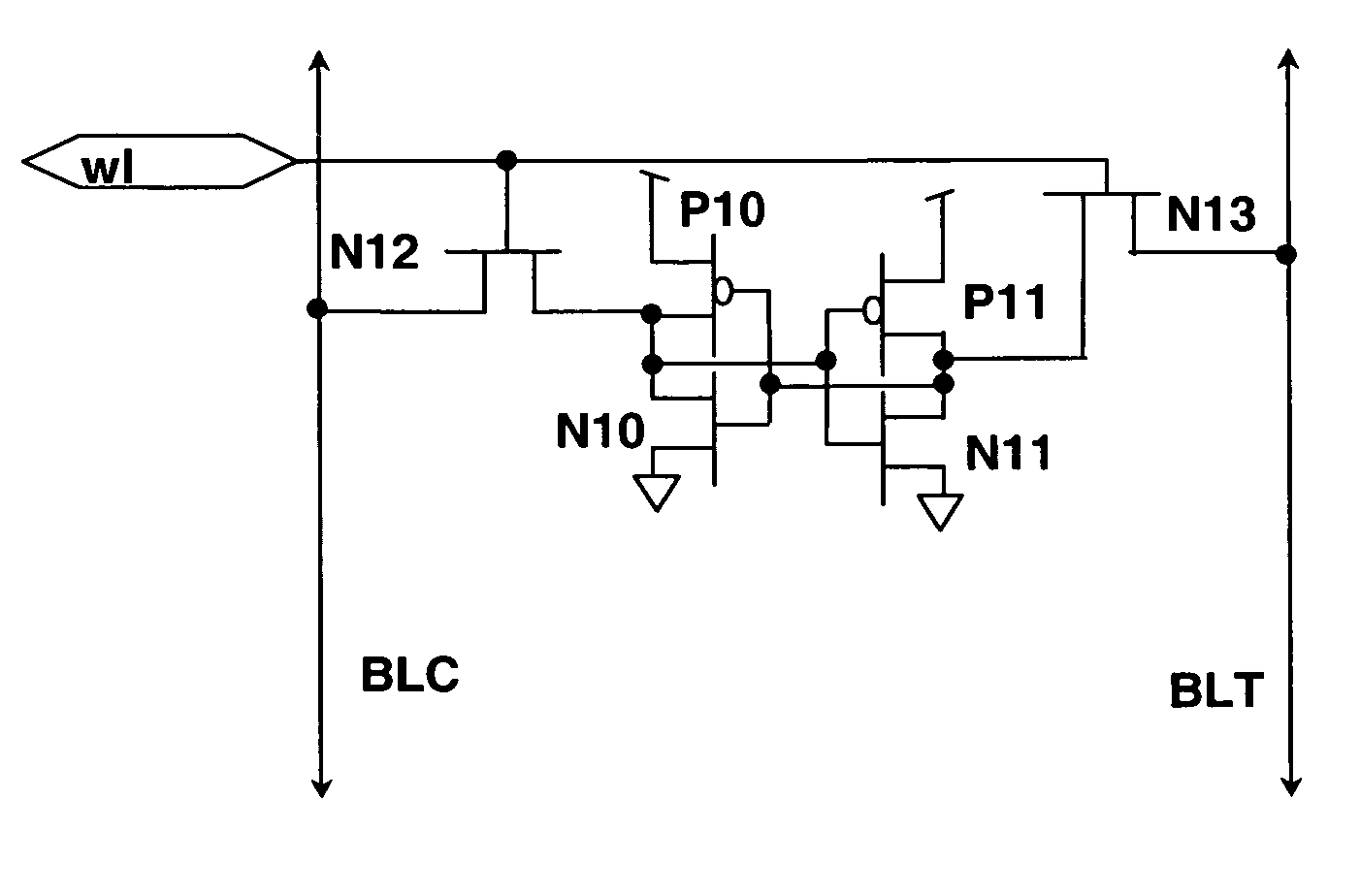

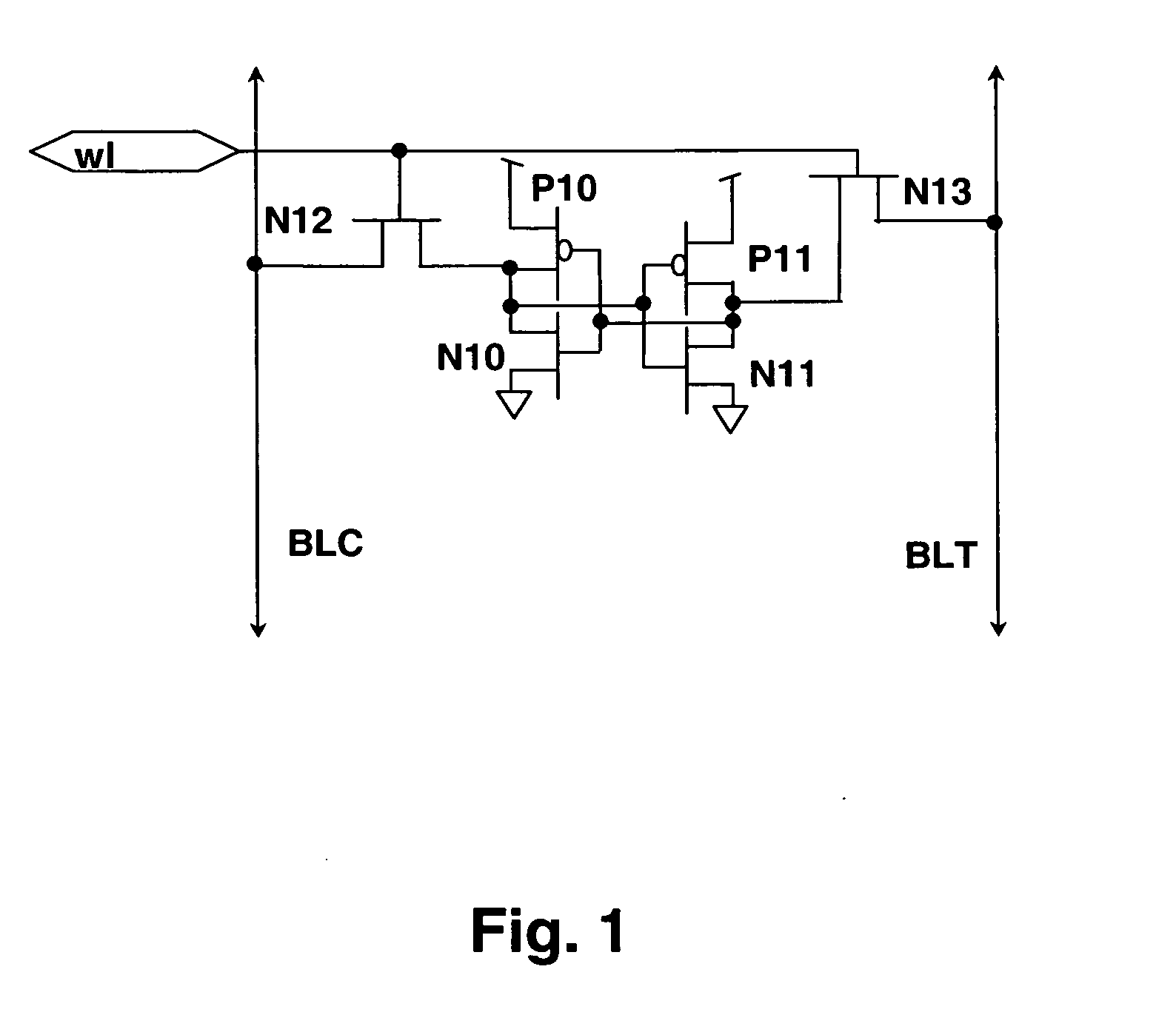

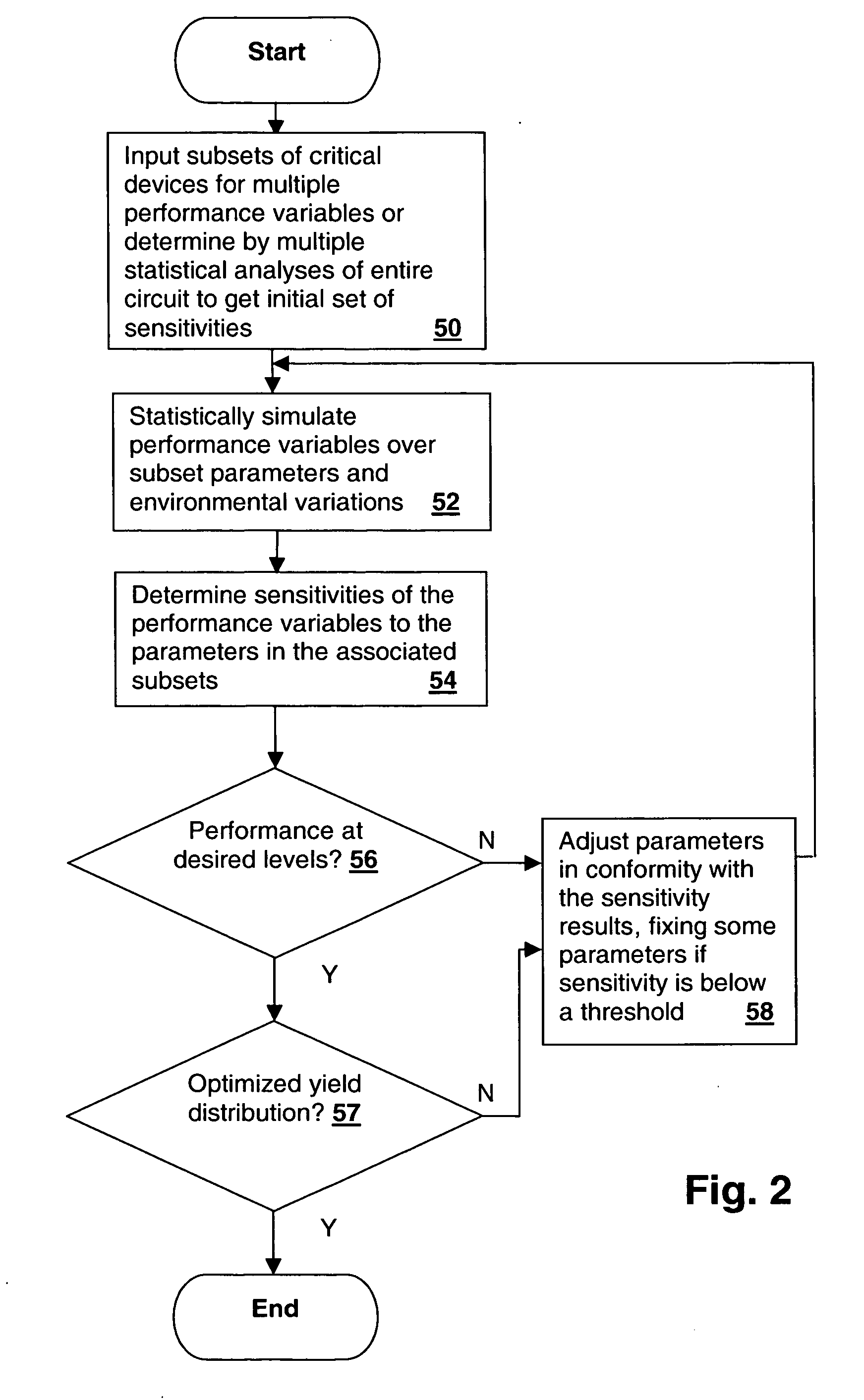

Efficient method and computer program for modeling and improving static memory performance across process variations and environmental conditions

InactiveUS20060203581A1Simple designImprove device yieldDigital storageCAD circuit designParallel computingCell design

An efficient method and computer program for modeling and improving stating memory performance across process variations and environmental conditions provides a mechanism for raising the performance of memory arrays beyond present levels / yields. Statistical (Monte-Carlo) analyses of subsets of circuit parameters are performed for each of several memory performance variables and then sensitivities of each performance variable to 15 each of the circuit parameters are determined. The memory cell design parameters and / or operating conditions of the memory cells are then adjusted in conformity with the sensitivities, resulting in improved memory yield and / or performance. Once a performance level is attained, the sensitivities can then be used to alter the probability distributions of the performance variables to achieve a higher yield. Multiple cell designs can be compared for performance, yield and sensitivity of performance variables to circuit parameters over particular environmental conditions in order to select the best cell design.

Owner:GLOBALFOUNDRIES INC

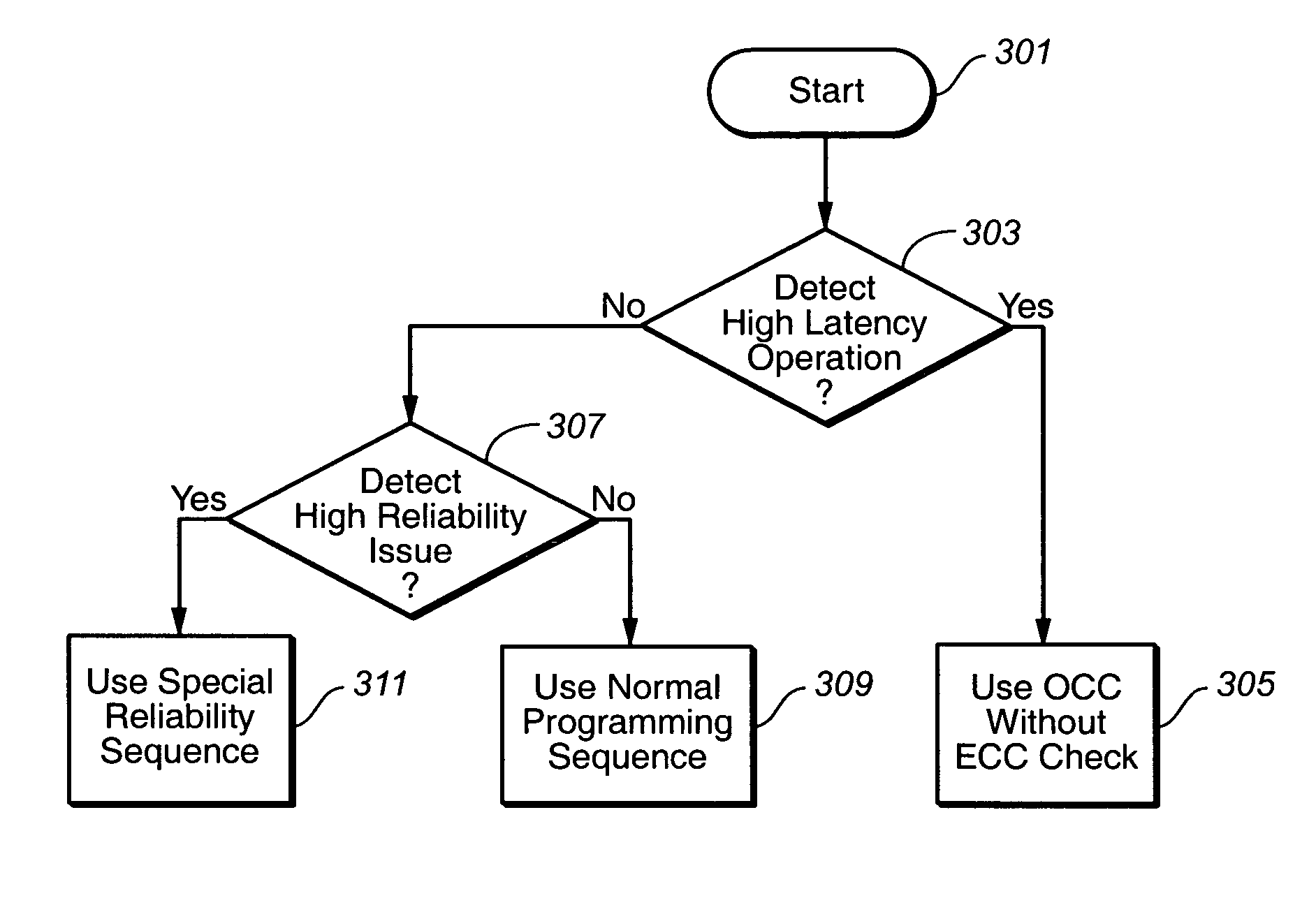

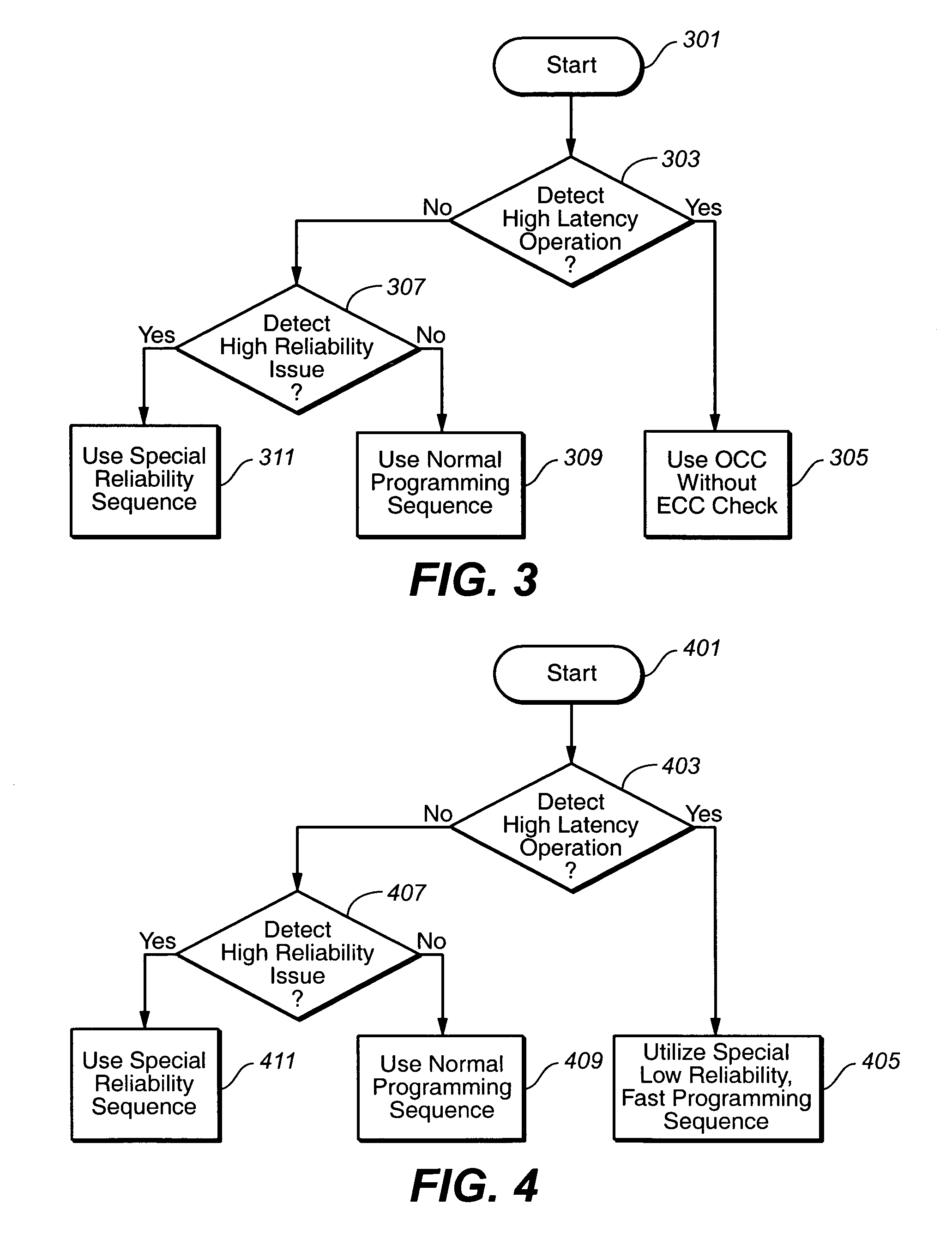

Situation sensitive memory performance

ActiveUS20070033581A1Avoid timeoutImprove programming speedEnergy efficient ICTVolume/mass flow measurementTerm memoryComputer science

The present invention presents a non-volatile memory system that adapts its performance to one or more system related situation. If a situation occurs where the memory will require more than the allotted time for completing an operation, the memory can switch from its normal operating mode to a high performance mode in order to complete the operation quickly enough. Conversely, if a situation arises where reliability could be an issue (such as partial page programming), the controller could switch to a high reliability mode. In either case, once the trigging system situation has returned to normal, the memory reverts to the normal operation. The detection of such situations can be used both for programming and data relocation operations. An exemplary embodiment is based on firmware programmable performance.

Owner:SANDISK TECH LLC

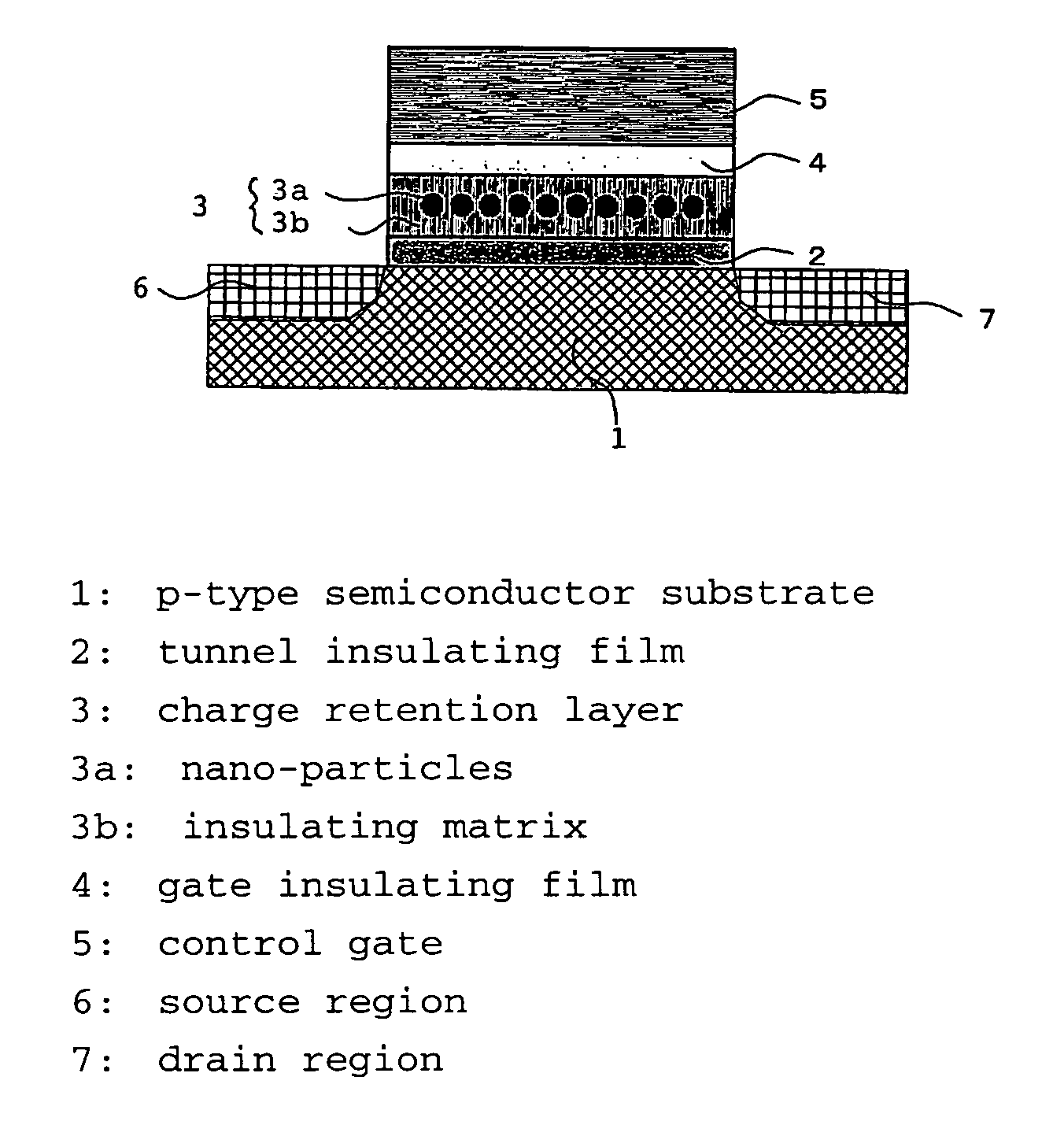

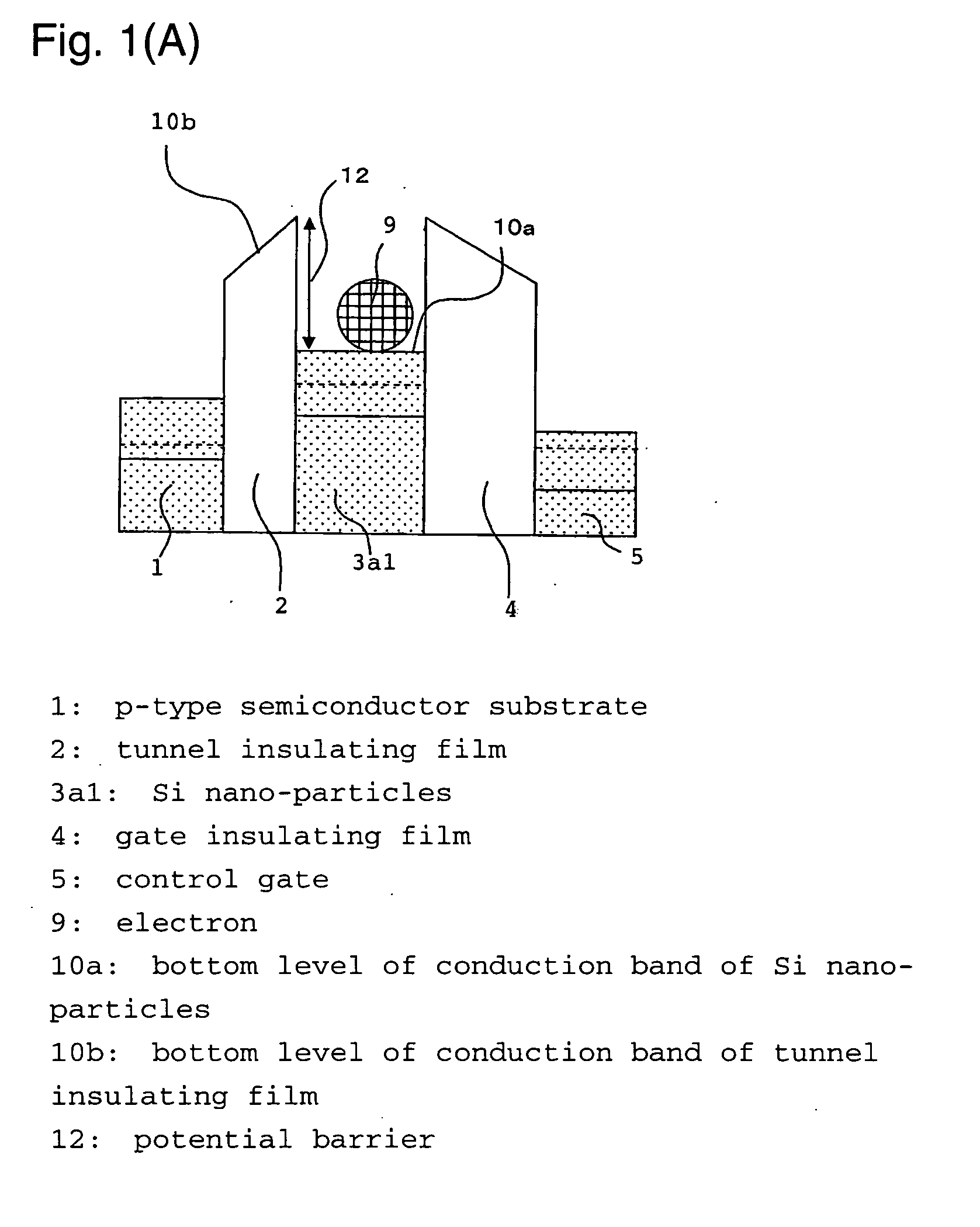

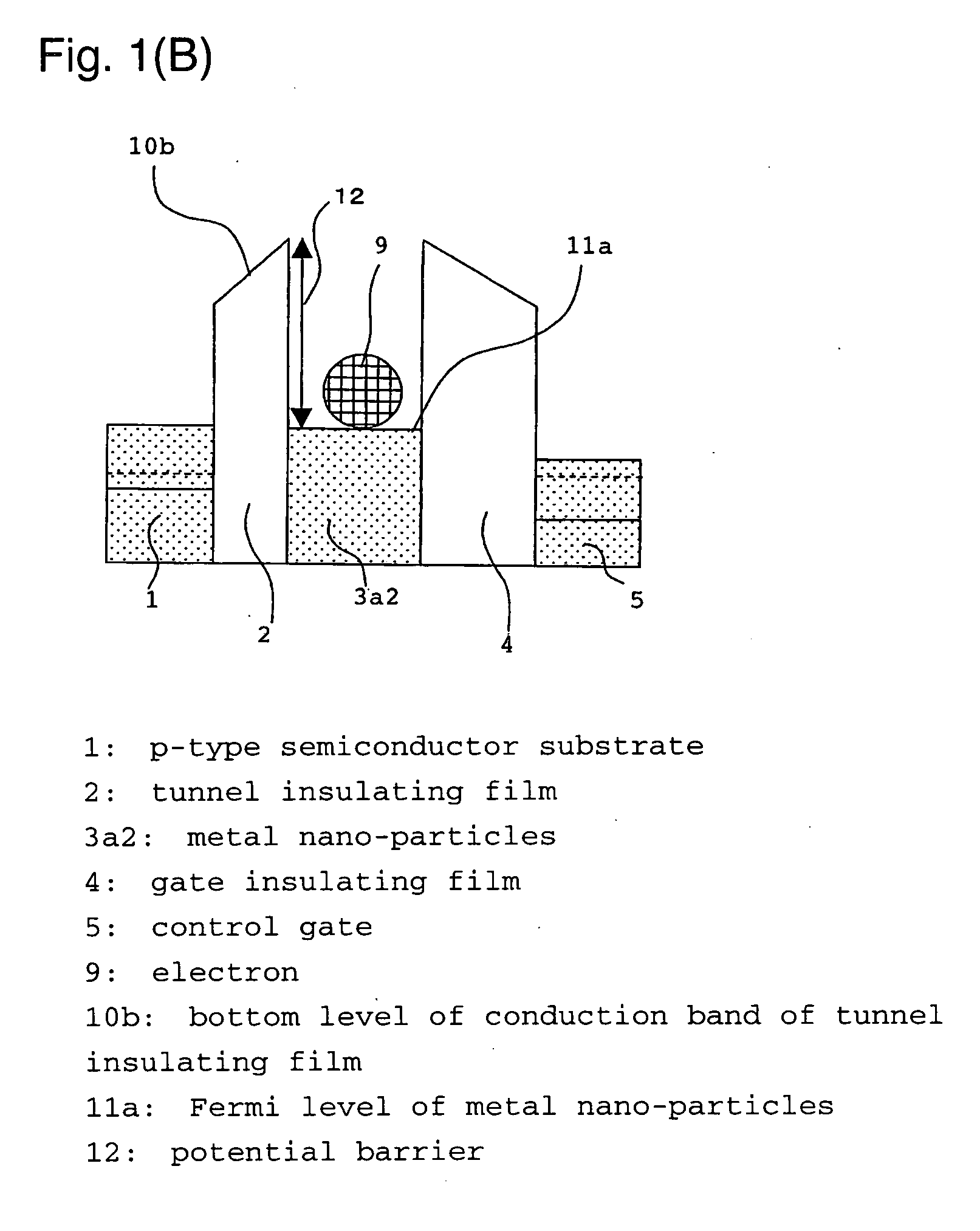

Nonvolatile semiconductor memory device having excellent charge retention and manufacturing process of the same

InactiveUS20060118853A1Improve adhesionIncrease production capacityNanotechRead-only memoriesCharge retentionManufacturing technology

There has been a problem in conventional Si-type floating-gate type nonvolatile semiconductor memory devices that the charge retention characteristic is low due to insufficiently large electron affinity of Si, therefore improvement of the memory performances, such as scaling down of a memory cell and increasing operation speed, have been difficult to be achieved due to the essential problem. In order to solve the above problem, in the nonvolatile semiconductor memory device of the present invention, a material having large work function or large electron affinity or a material having a work function close to that of semiconductor substrate or of a control gate, is employed for a floating gate retaining charges. Further, an amorphous material having small electron affinity for an insulating matrix is used. Further, at a time of deposition of charge retention layer, the supply ratio of the nano-particle material and the insulating matrix material, such as the mixture ratio of materials of both phases in a target in a sputtering method, is adjusted. By these methods, the charge retention characteristic of the floating-gate type nonvolatile semiconductor memory device can be improved, and the above-mentioned problem of the nonvolatile semiconductor memory device can be solved.

Owner:ASAHI GLASS CO LTD +1

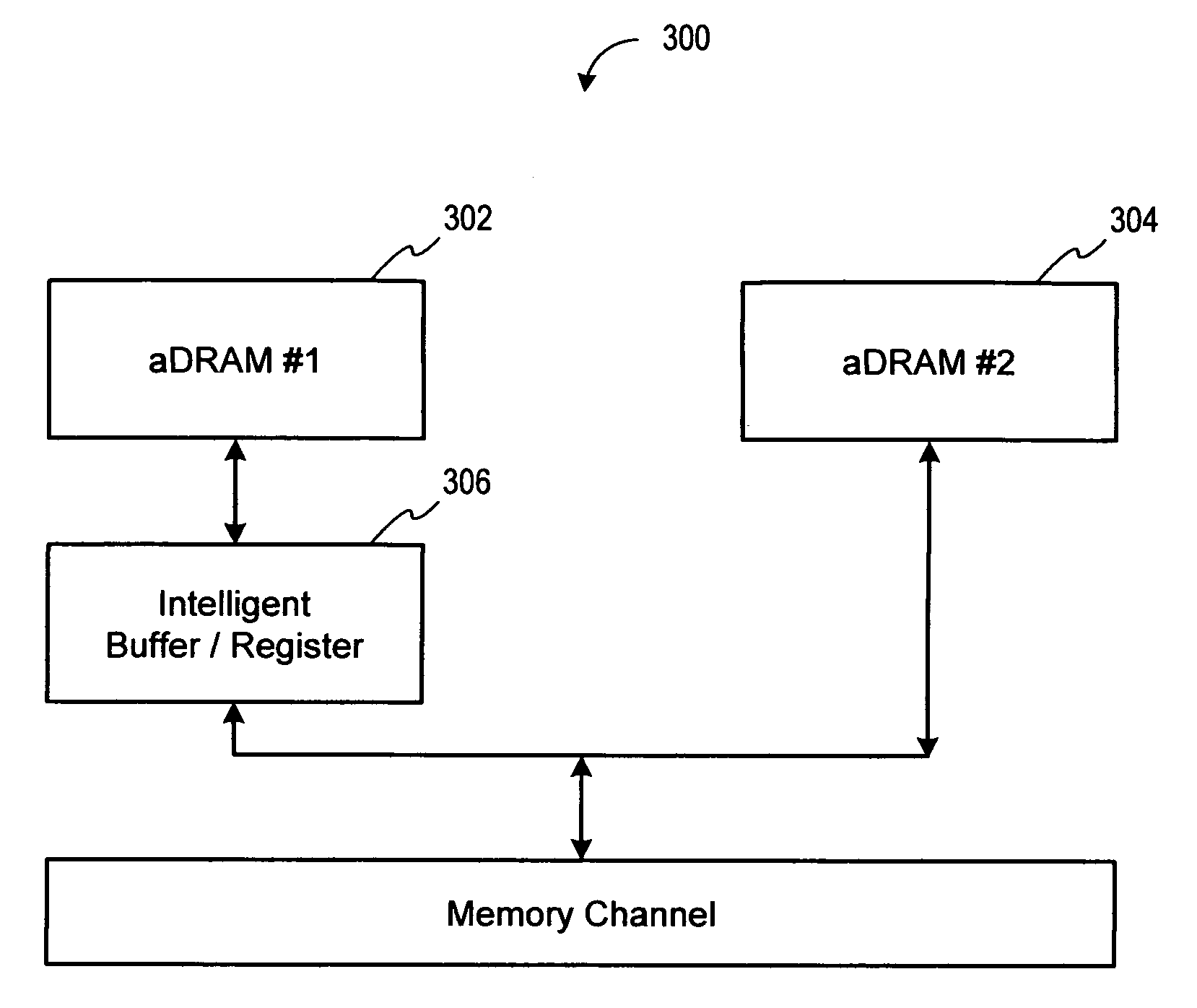

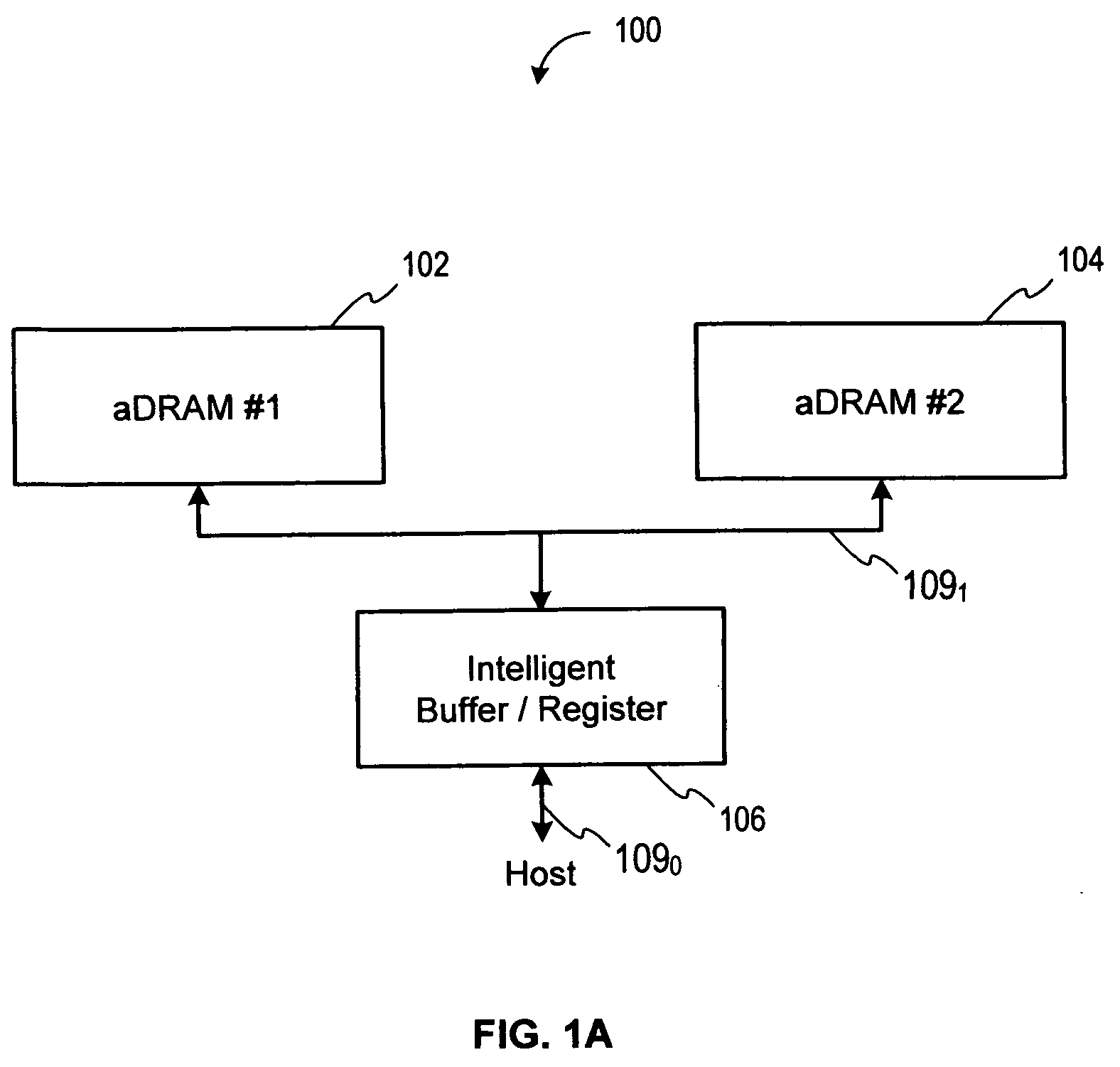

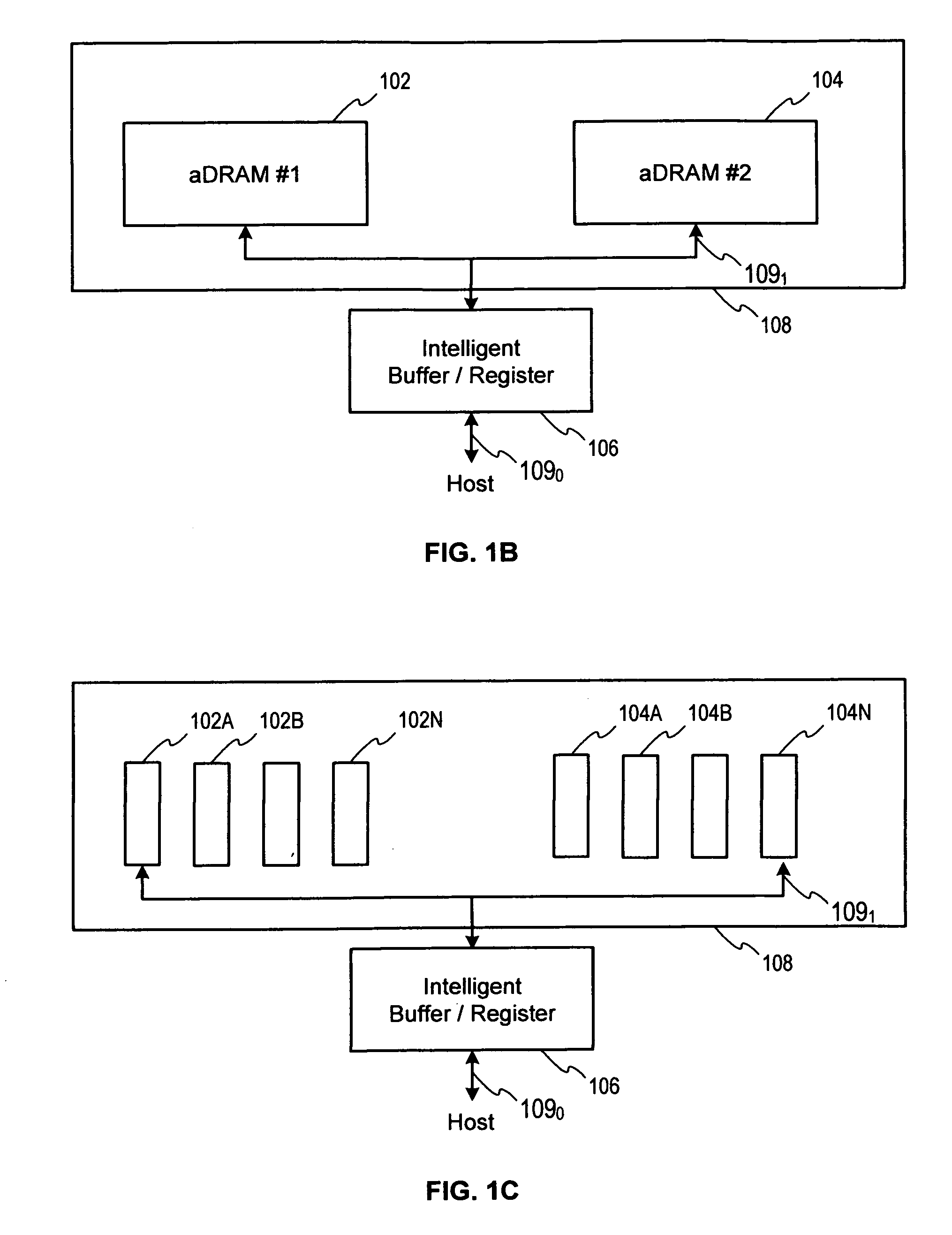

Emulation of abstracted DIMMs using abstracted DRAMs

ActiveUS20090216939A1Memory performanceEnergy efficient ICTMemory adressing/allocation/relocationMemory typeRelevant feature

One embodiment of the present invention sets forth an abstracted memory subsystem comprising abstracted memories, which each may be configured to present memory-related characteristics onto a memory system interface. The characteristics can be presented on the memory system interface via logic signals or protocol exchanges, and the characteristics may include any one or more of, an address space, a protocol, a memory type, a power management rule, a number of pipeline stages, a number of banks, a mapping to physical banks, a number of ranks, a timing characteristic, an address decoding option, a bus turnaround time parameter, an additional signal assertion, a sub-rank, a number of planes, or other memory-related characteristics. Some embodiments include an intelligent register device and / or, an intelligent buffer device. One advantage of the disclosed subsystem is that memory performance may be optimized regardless of the specific protocols used by the underlying memory hardware devices.

Owner:GOOGLE LLC

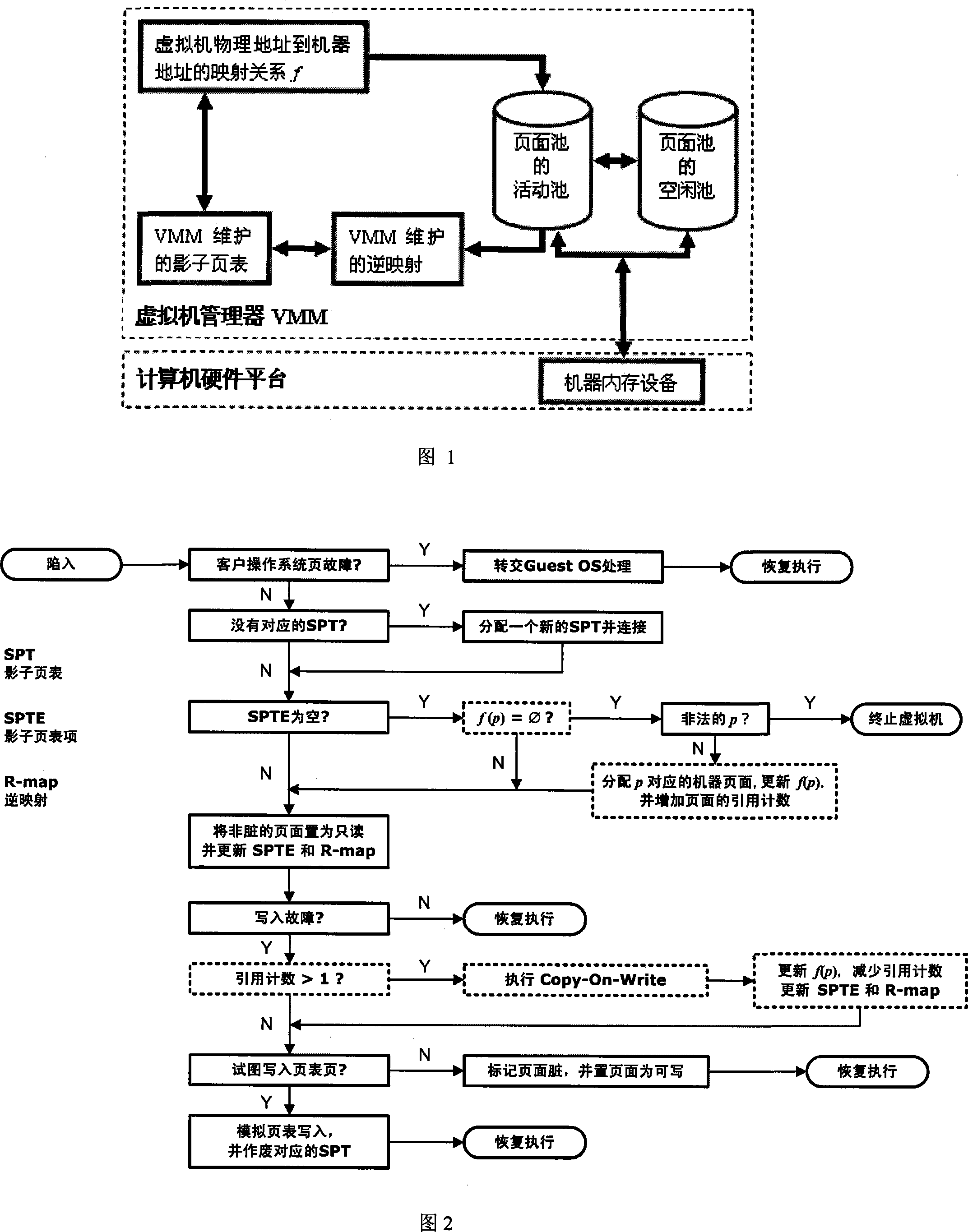

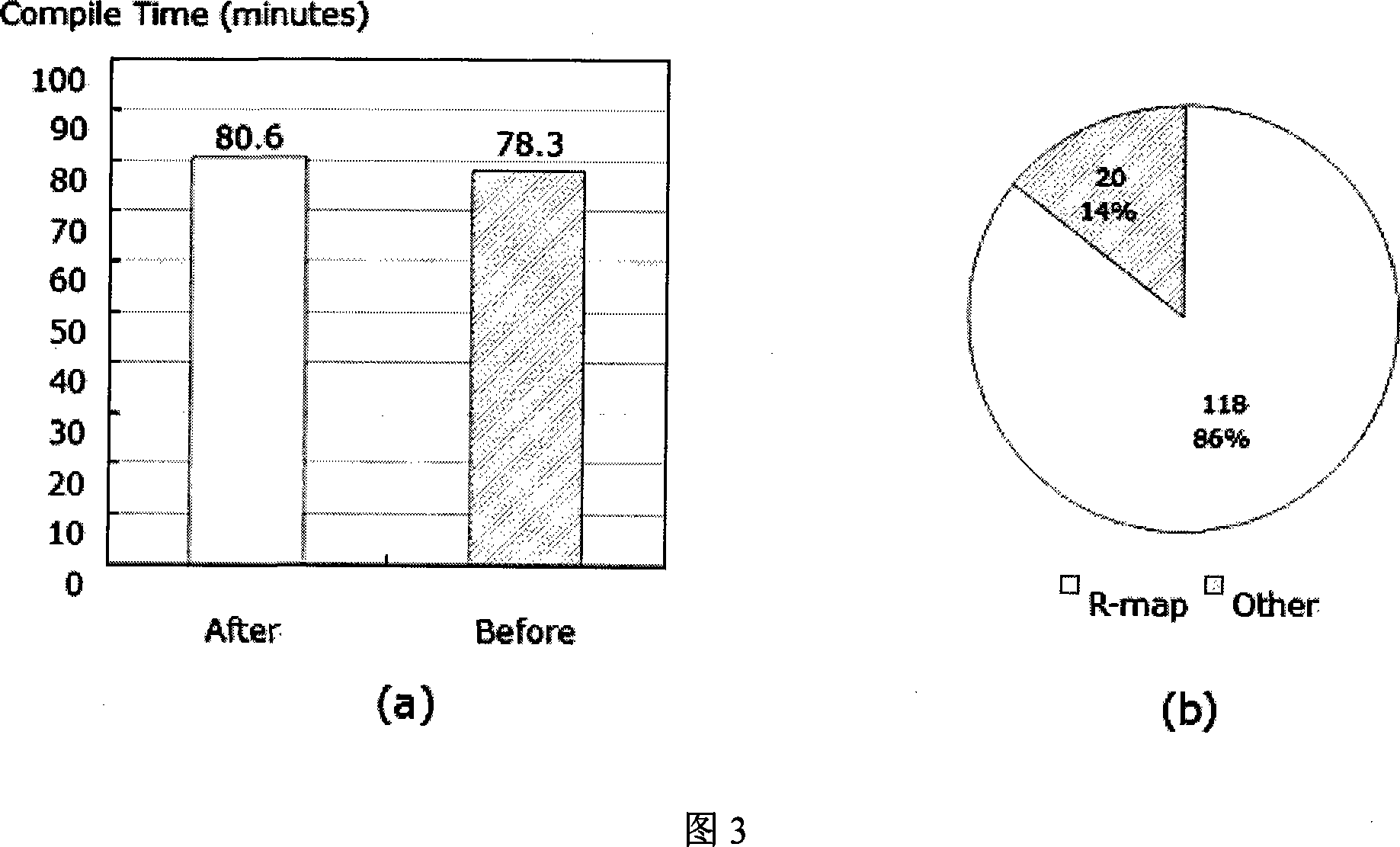

Dynamic EMS memory mappings method of virtual machine manager

InactiveCN101158924ARealize page fetching on demandImplement memory sharingMemory adressing/allocation/relocationSoftware simulation/interpretation/emulationDynamic managementMemory sharing

The invention discloses a dynamic memory mapping method of a virtual machine manager, the steps are that: separately establish a virtual machine page pool and a virtual machine manager page pool; when the virtual machine access is violated, the virtual machine manager dynamically establishes and updates the mapping relations f(p) form a physical memory collection P to a machine memory collection M in the virtual machine manager page pool; the inventive method can simultaneously support obtaining pages according to the requirements at upper layer, virtual storage, as well as memory shared functions, so as to make the virtual machine manager realize dynamic management and allocation of the virtual machine memory on the premise that the virtual machine manager sufficiently guarantees the virtual machine access memory performance.

Owner:PEKING UNIV

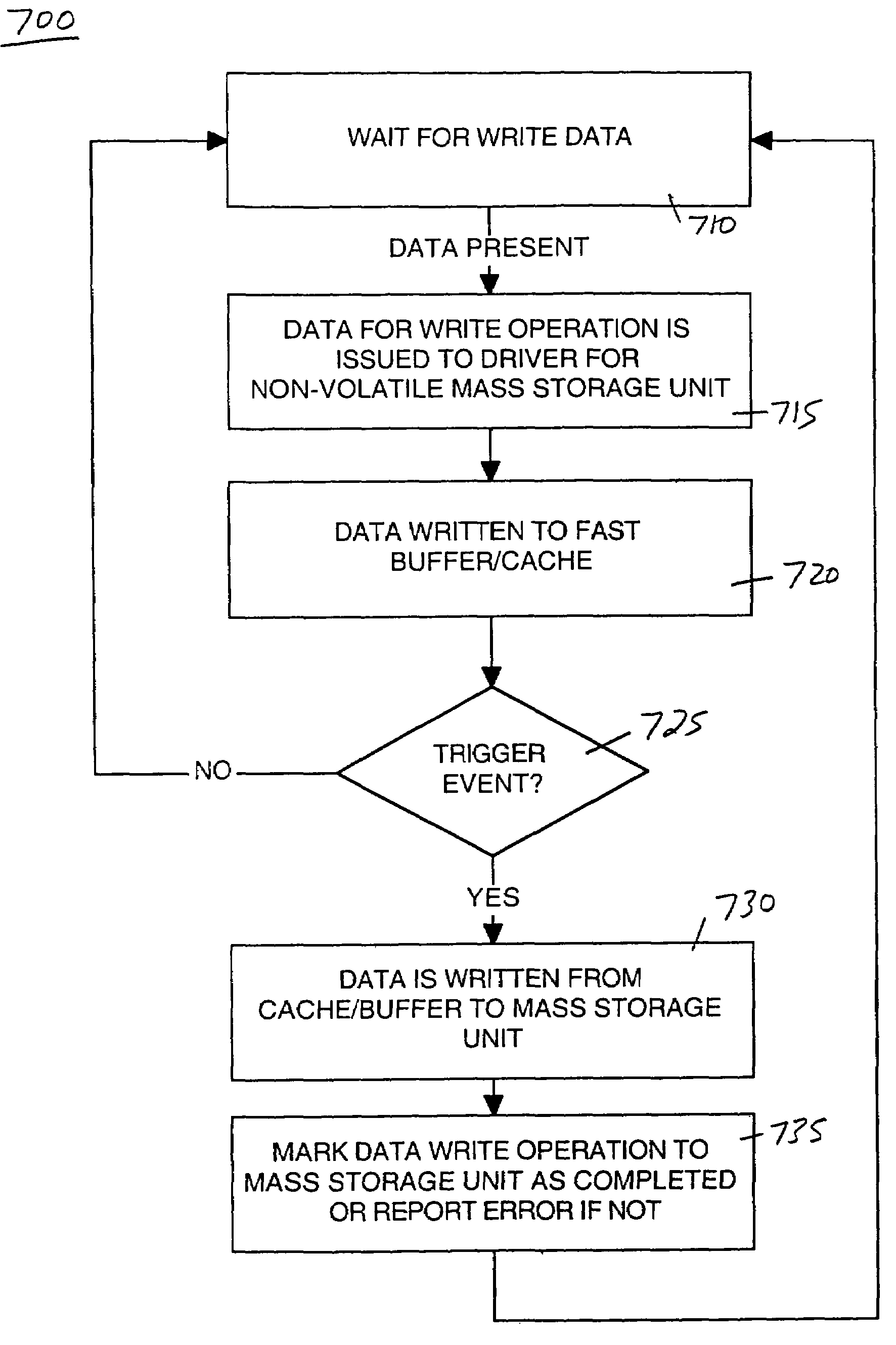

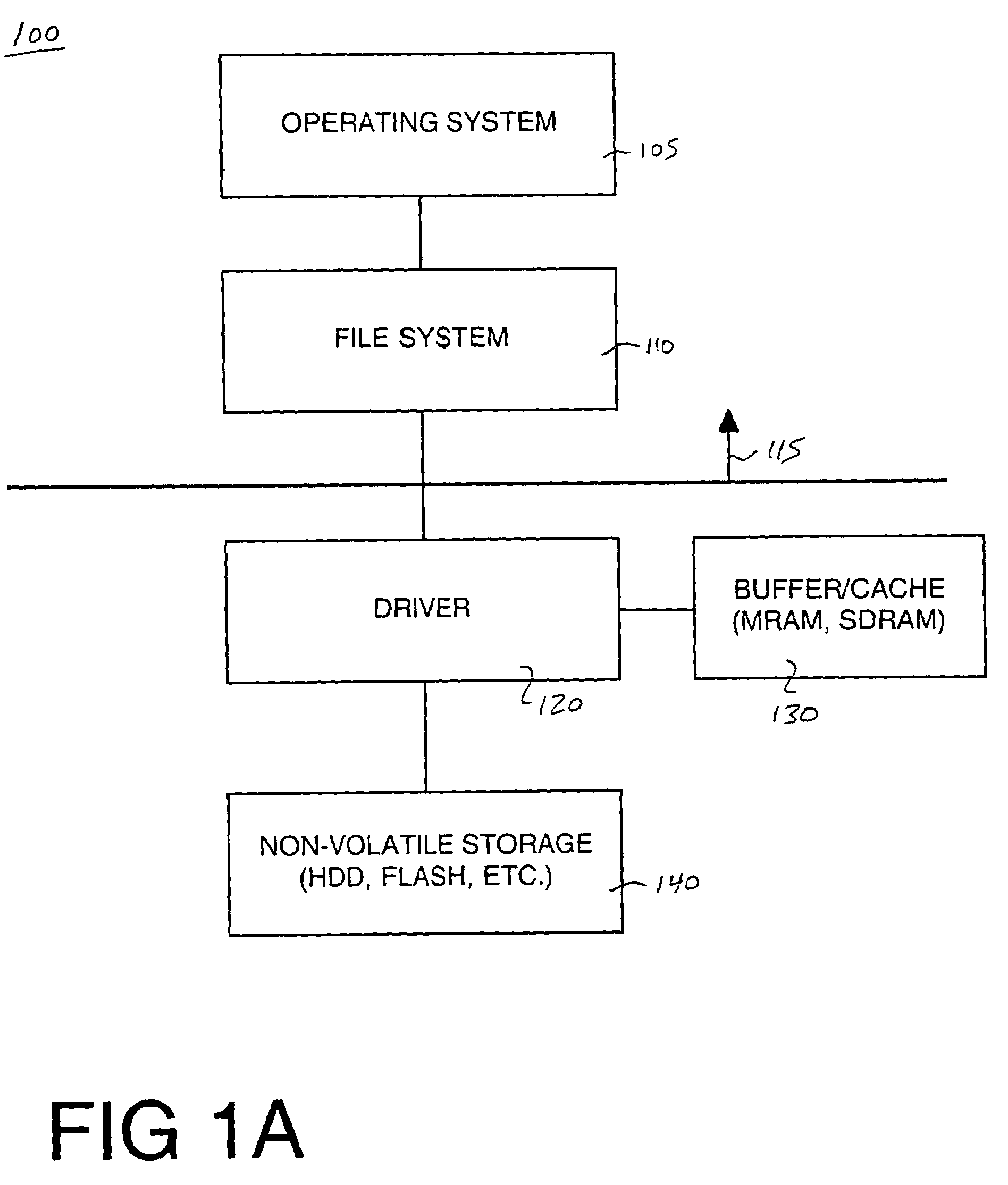

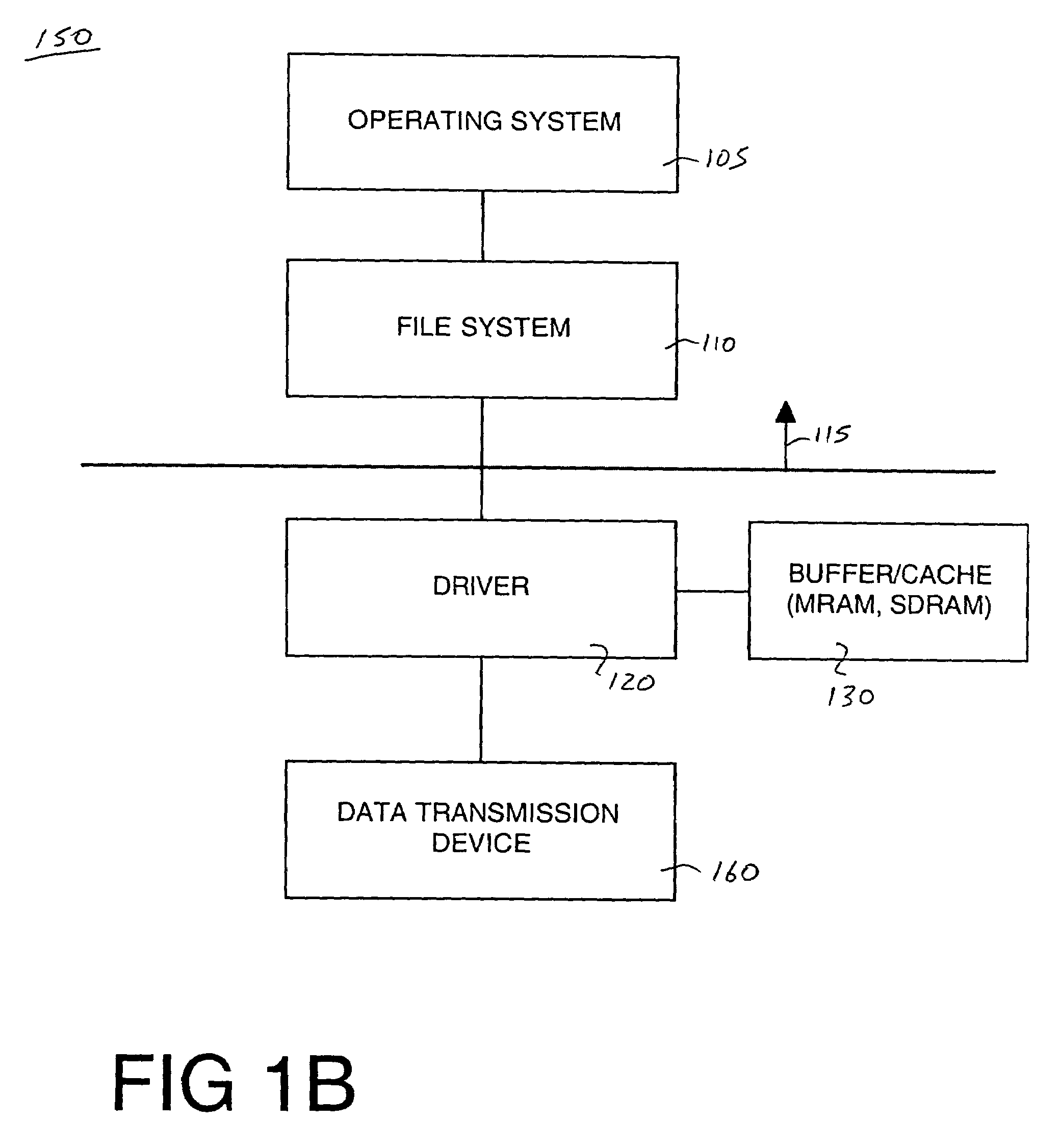

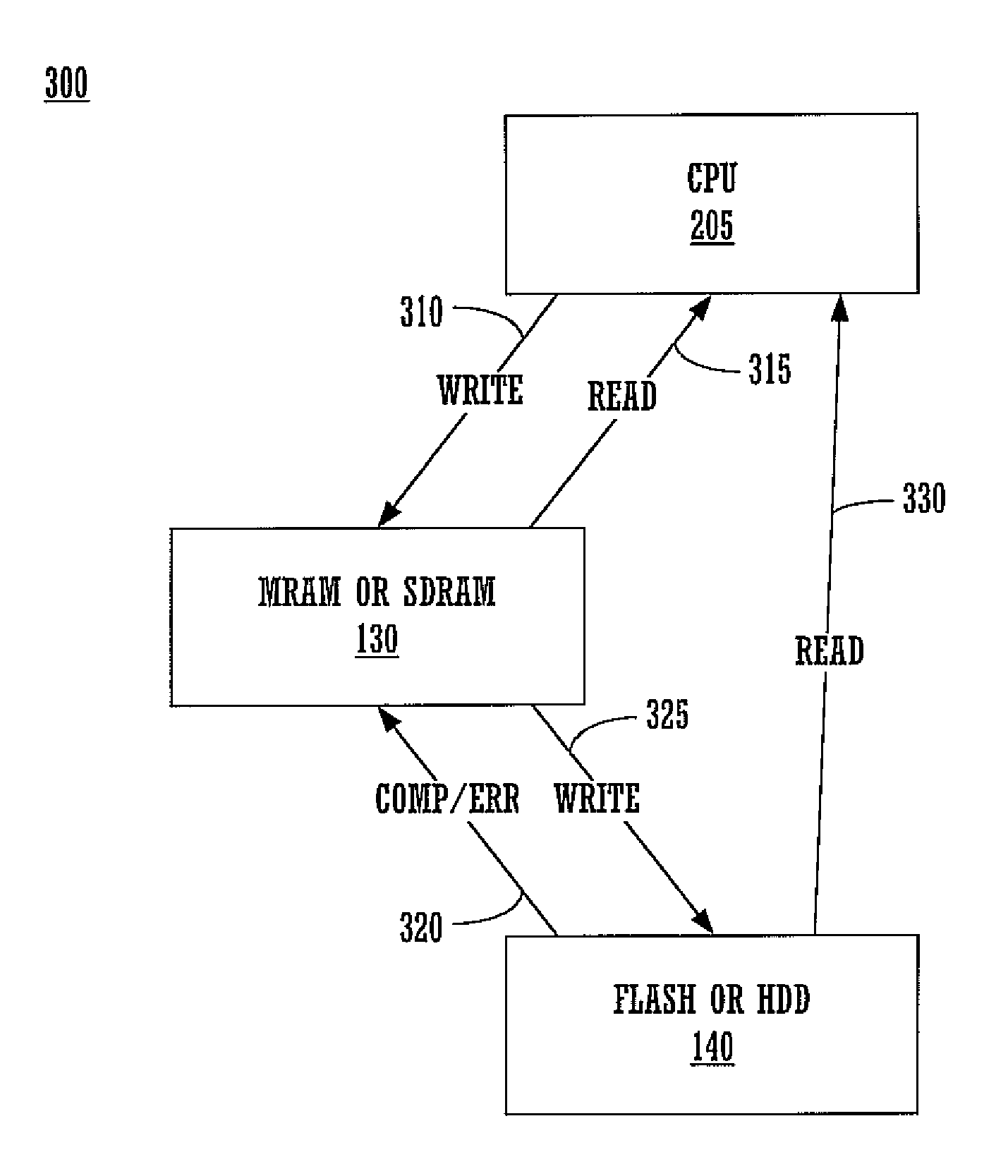

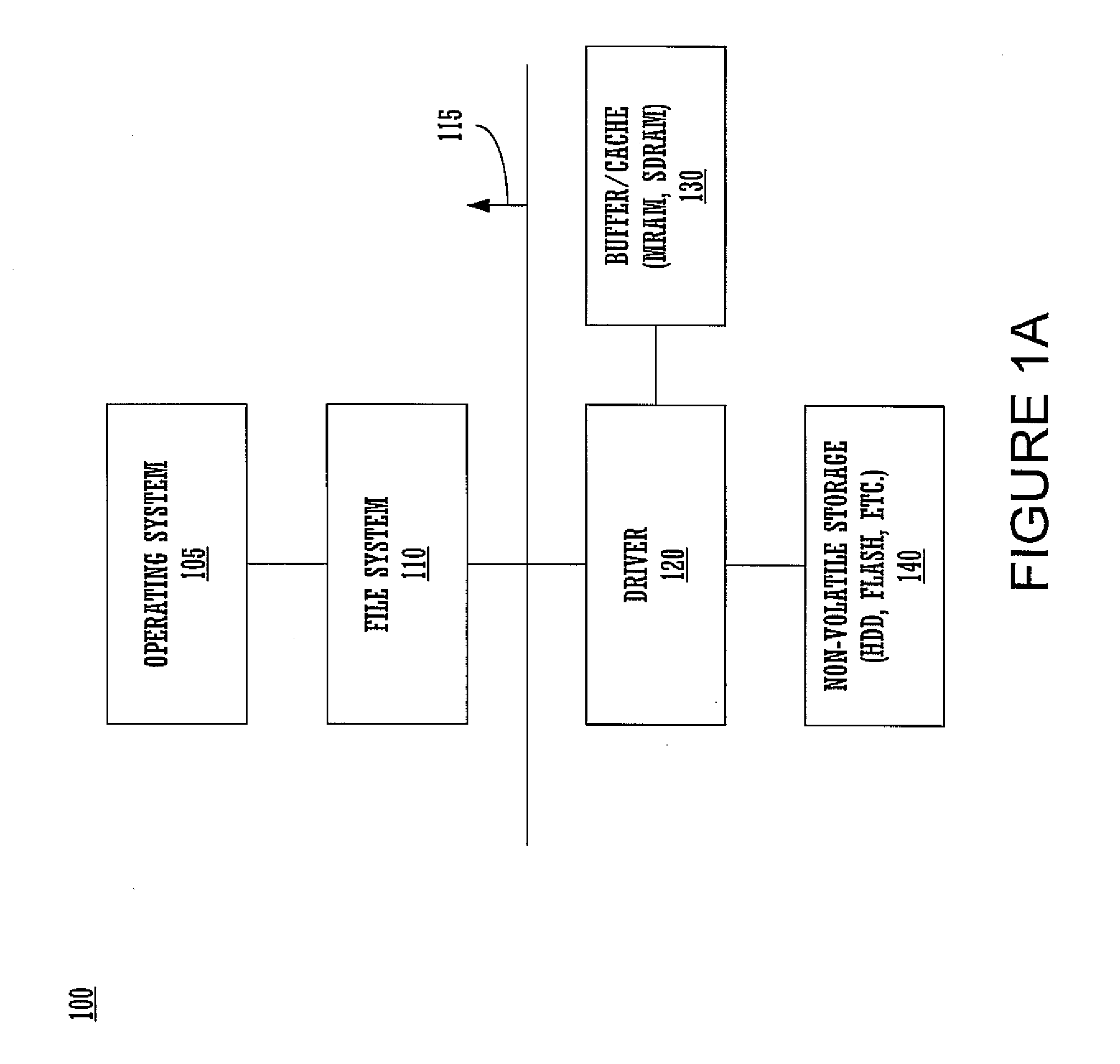

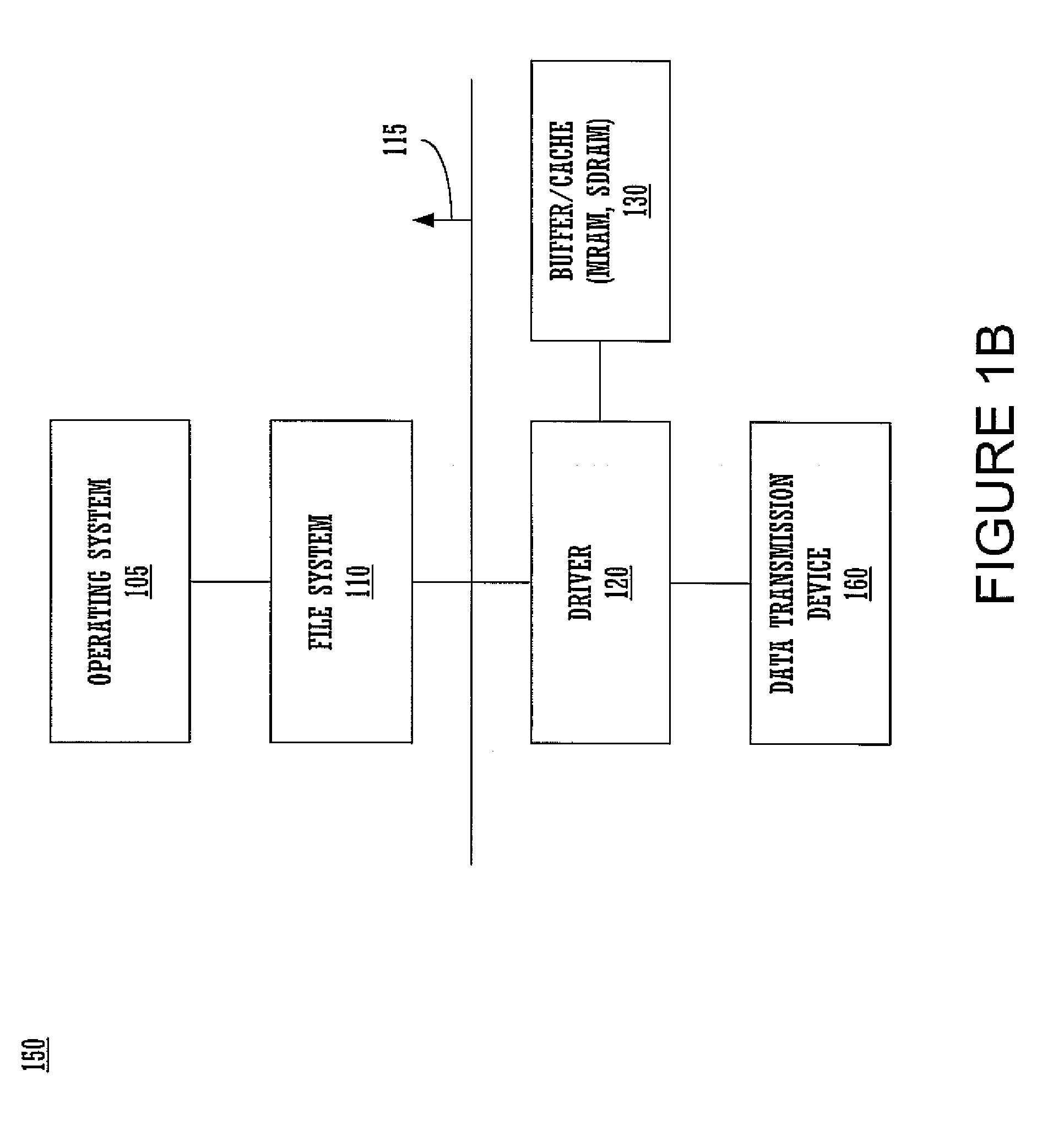

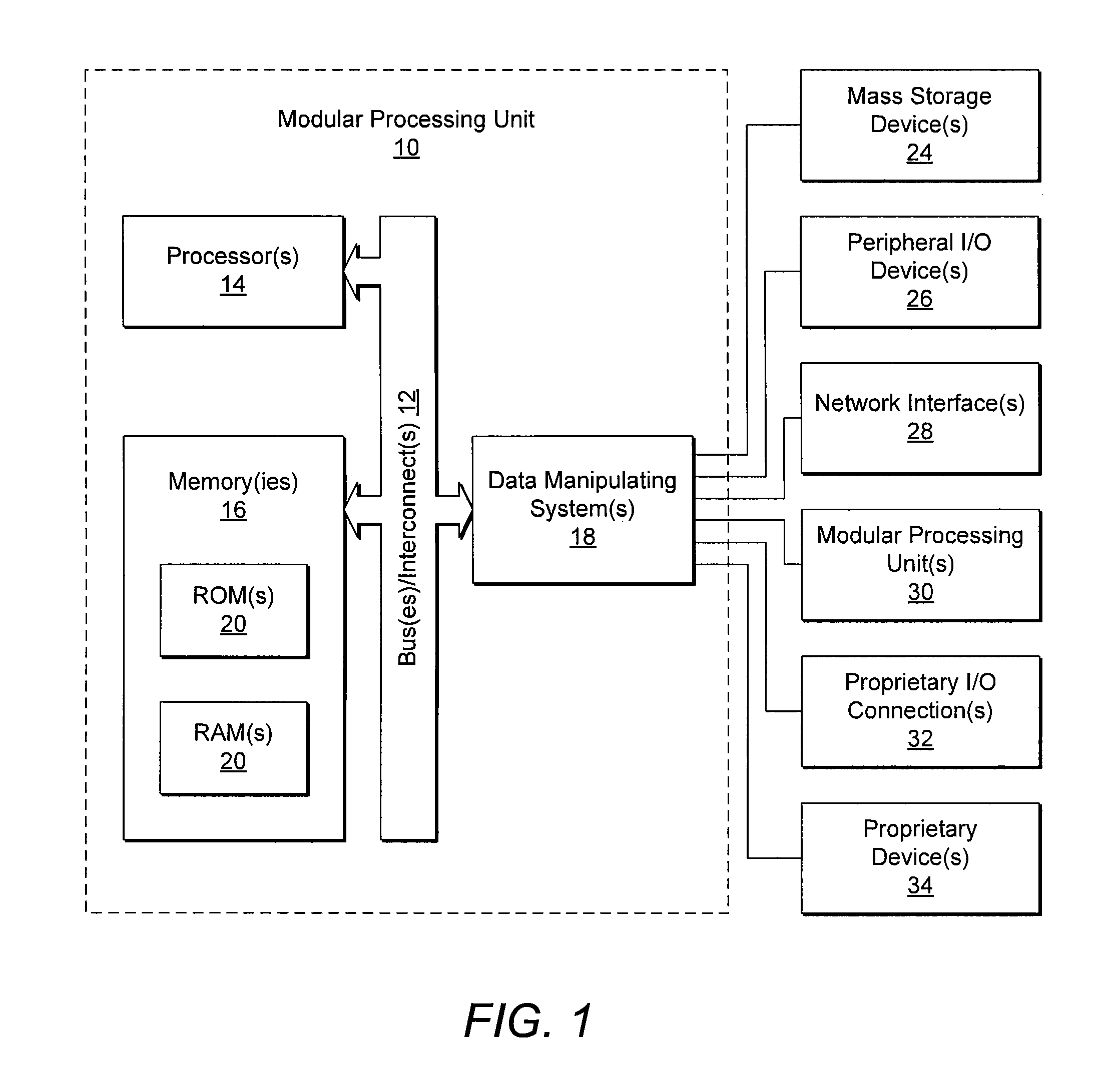

System and method for improving data integrity and memory performance using non-volatile media

A system and computer system for improving data integrity and memory performance using non-volatile media. A system includes a non-volatile mass storage unit, e.g., a flash memory device and / or a hard drive unit for instance. A memory device is used as a high speed data buffer and / or cache for the non-volatile storage unit. The memory device may be non-volatile, e.g., magnetic random access memory (MRAM) or volatile memory, e.g., synchronous dynamic random access memory (SDRAM). By buffering and / or caching the write data, fewer accesses are required to the mass storage device thereby increasing system performance. Additionally, mechanical and electrical degradation of the mass storage device is reduced. Certain trigger events can be programmed to cause data from the memory device to be written to the mass storage device. In one embodiment, the write buffer contents are preserved across reset or power loss events. In one embodiment, the mass storage unit may be a data transport layer, e.g., Ethernet, USB, Bluetooth, etc.

Owner:QUALCOMM INC

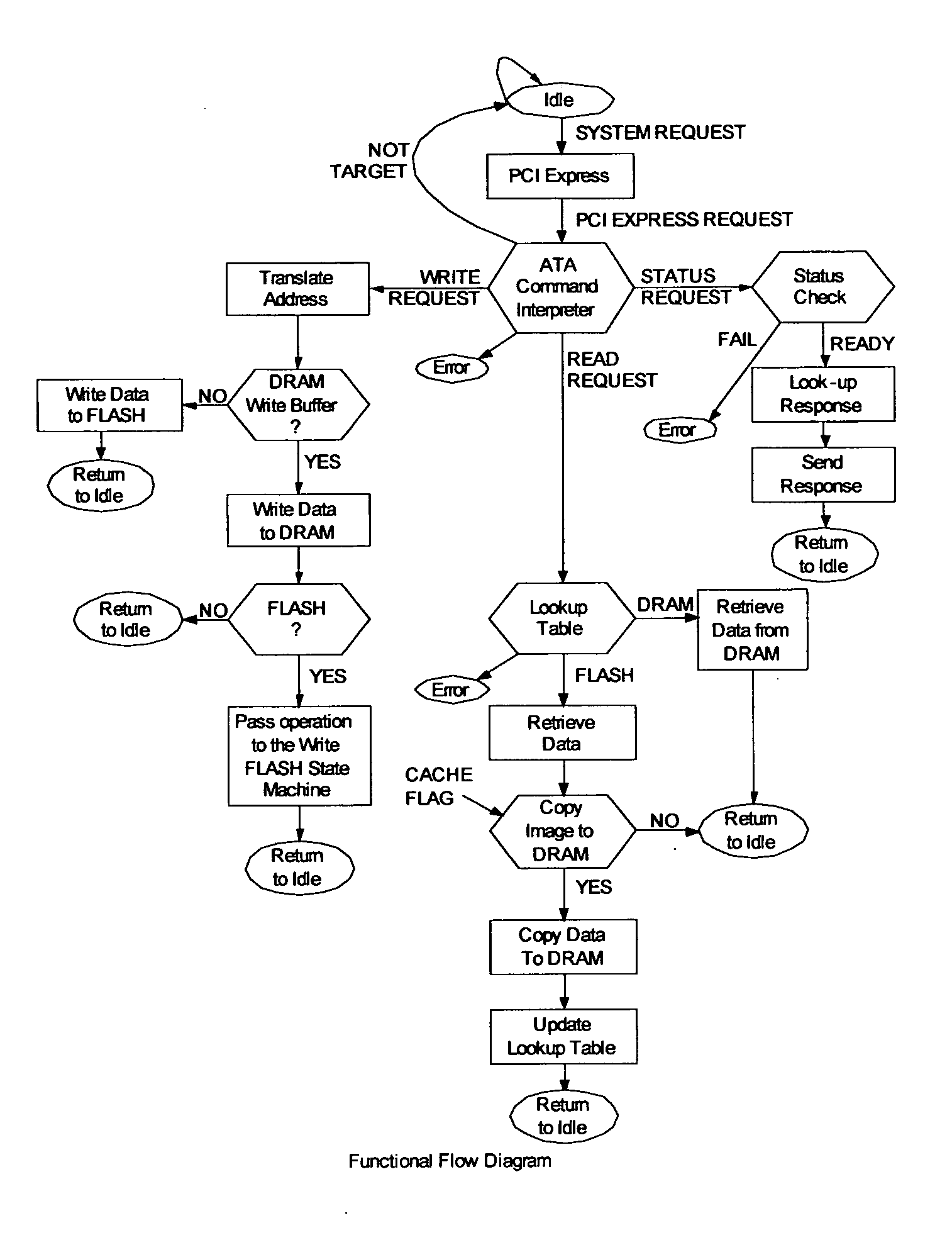

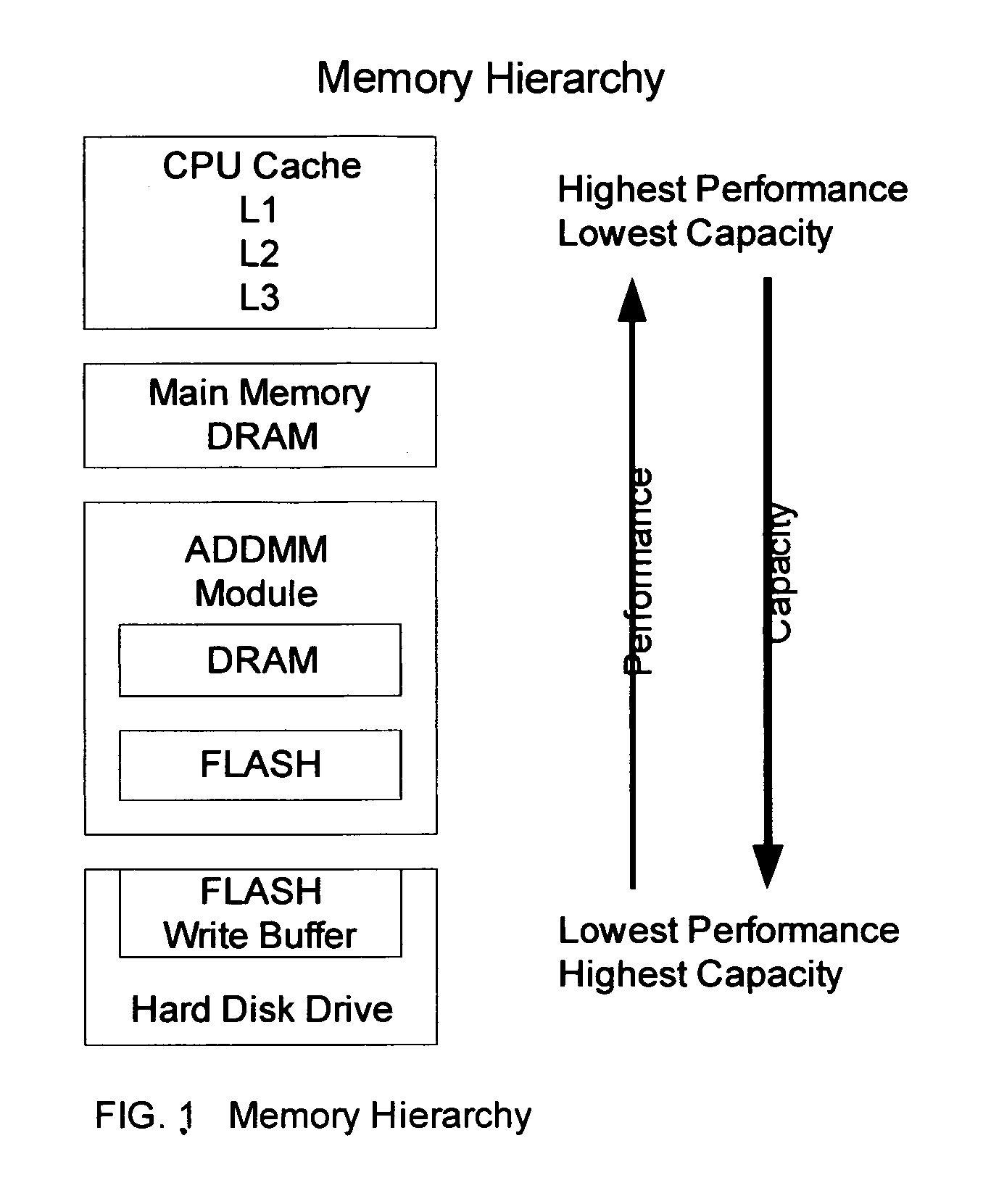

Advanced dynamic disk memory module

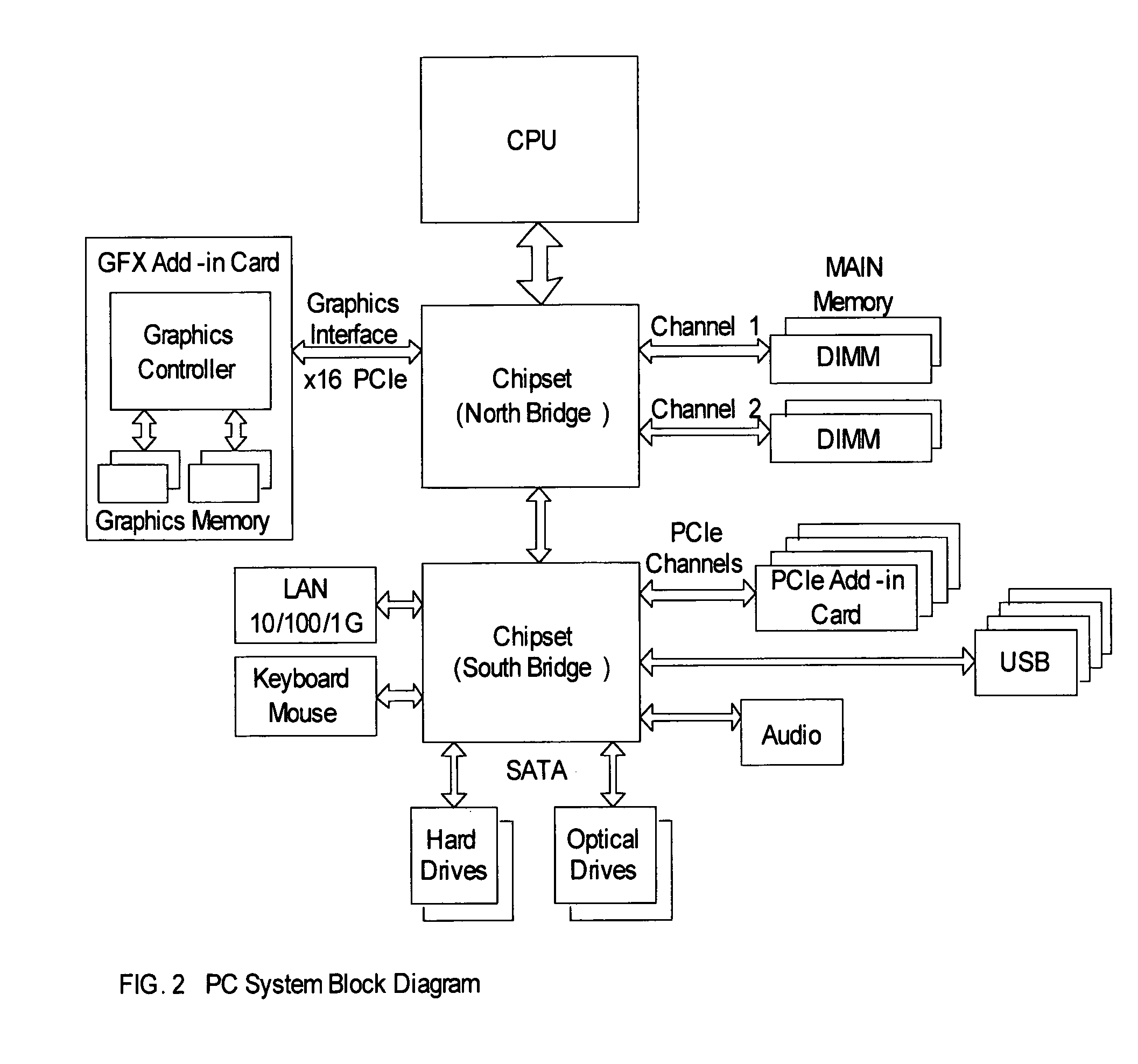

InactiveUS20070079065A1Memory systemsMicro-instruction address formationParallel computingPersonal computer

Memory modules address the growing gap between main memory performance and disk drive performance in computational apparatus such as personal computers. Memory modules disclosed herein fill the need for substantially higher storage capacity in end-user add-in memory modules. Such memory modules accelerate the availability of applications, and data for those applications. An exemplary application of such memory modules is as a high capacity consumer memory product that can be used in Hi-Definition video recorders. In various embodiments, memory modules include a volatile memory, a non-volatile memory, and a command interpreter that includes interfaces to the memories and to various busses. The first memory acts as an accelerating buffer for the second memory, and the second memory provides non-volatile backup for the first memory. In some embodiments data transfer from the first memory to the second memory may be interrupted to provide read access to the second memory.

Owner:ADDMM

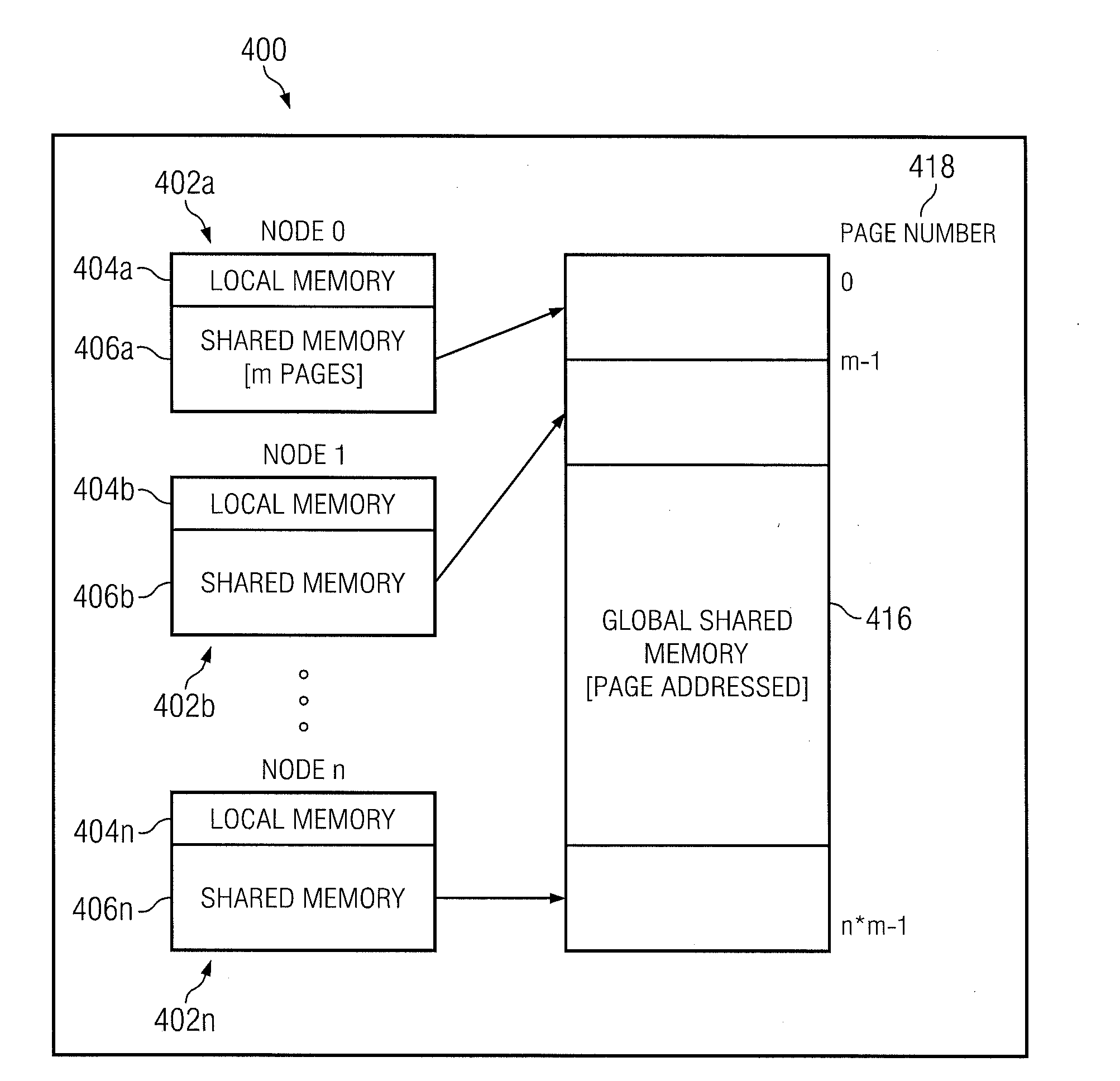

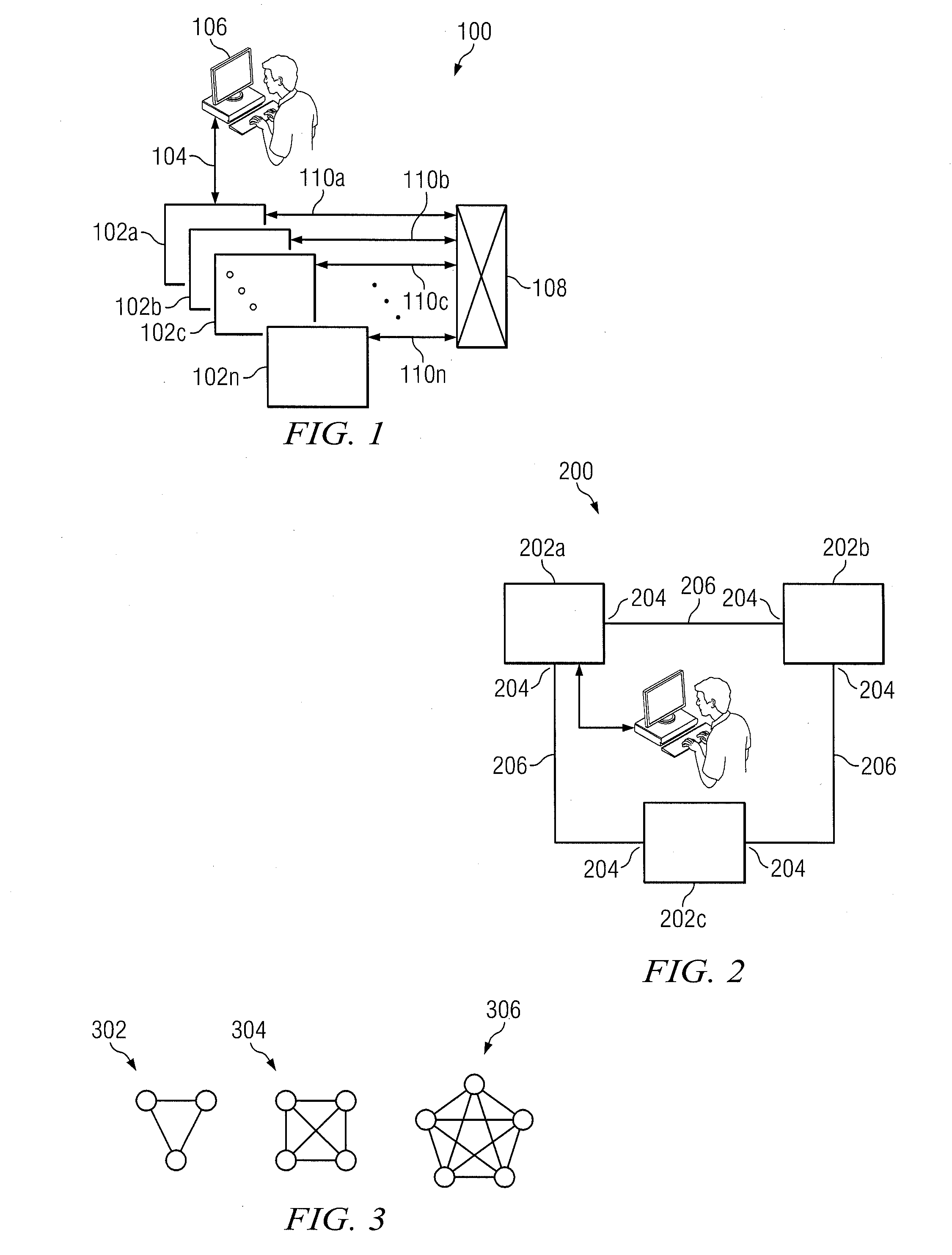

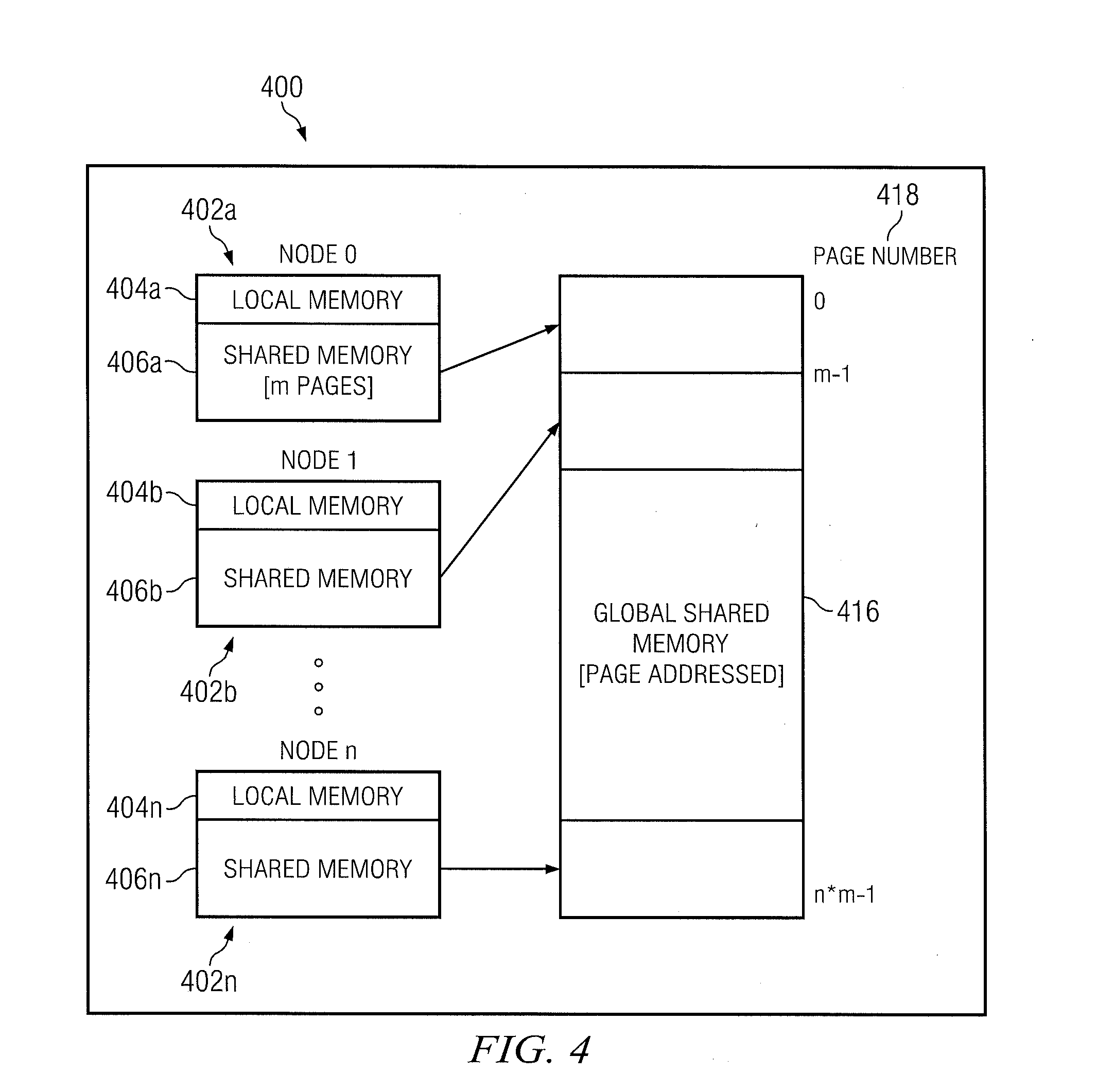

Distributed symmetric multiprocessing computing architecture

ActiveUS20110125974A1Shorten the progressMemory adressing/allocation/relocationDigital computer detailsSupercomputerGlobal address space

Example embodiments of the present invention includes systems and methods for implementing a scalable symmetric multiprocessing (shared memory) computer architecture using a network of homogeneous multi-core servers. The level of processor and memory performance achieved is suitable for running applications that currently require cache coherent shared memory mainframes and supercomputers. The architecture combines new operating system extensions with a high-speed network that supports remote direct memory access to achieve an effective global distributed shared memory. A distributed thread model allows a process running in a head node to fork threads in other (worker) nodes that run in the same global address space. Thread synchronization is supported by a distributed mutex implementation. A transactional memory model allows a multi-threaded program to maintain global memory page consistency across the distributed architecture. A distributed file access implementation supports non-contentious file I / O for threads. These and other functions provide a symmetric multiprocessing programming model consistent with standards such as Portable Operating System Interface for Unix (POSIX).

Owner:ANDERSON RICHARD S

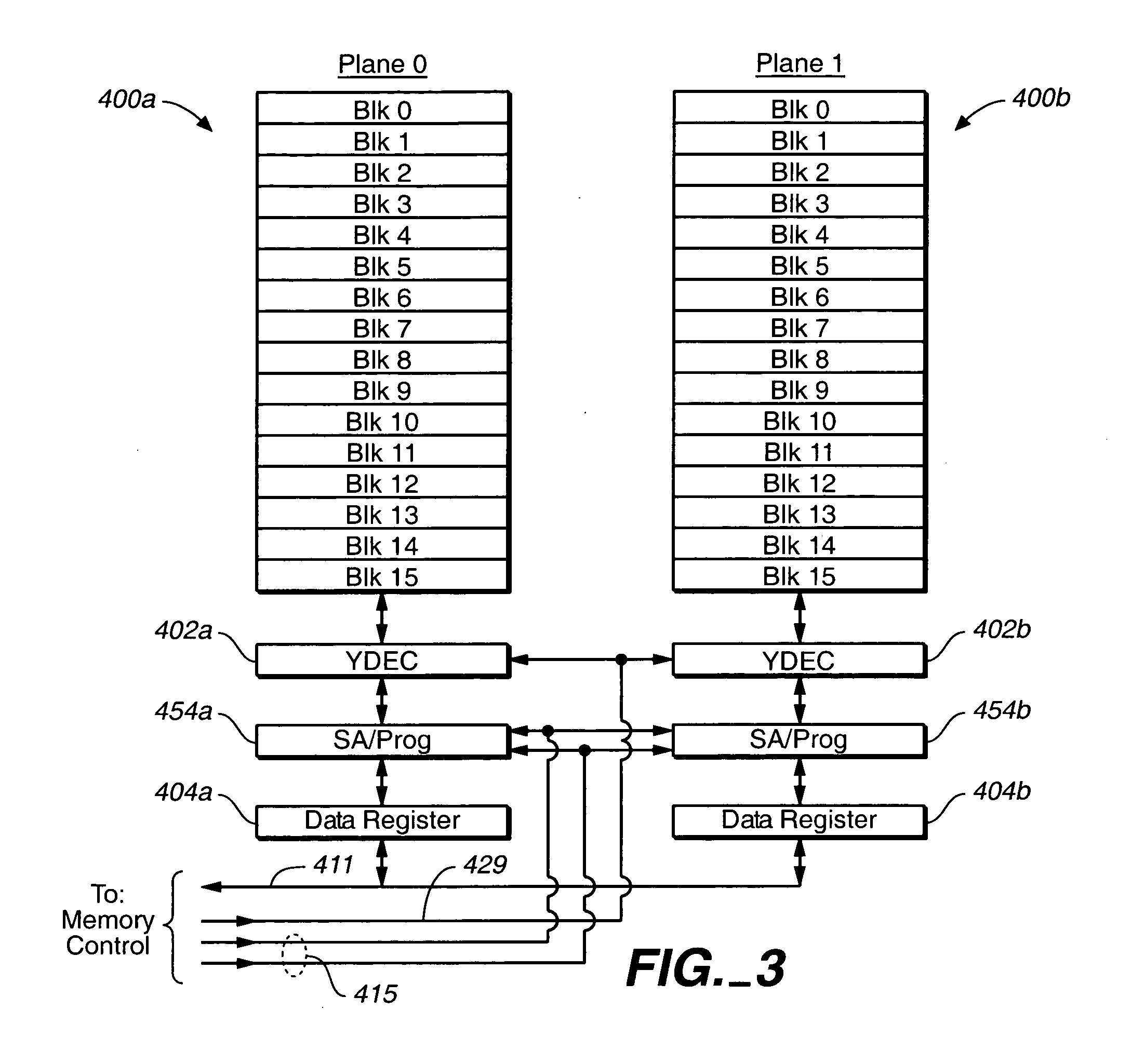

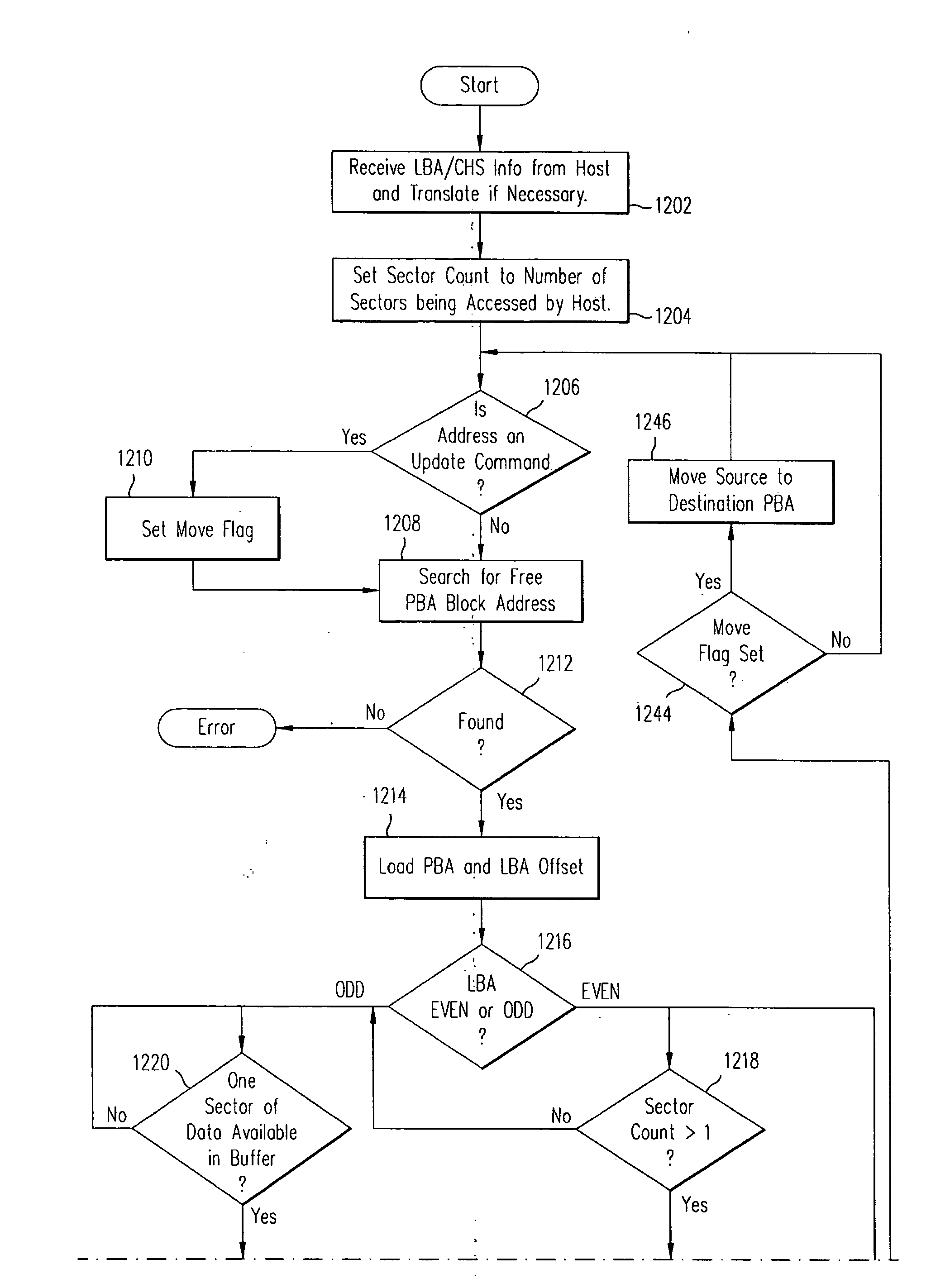

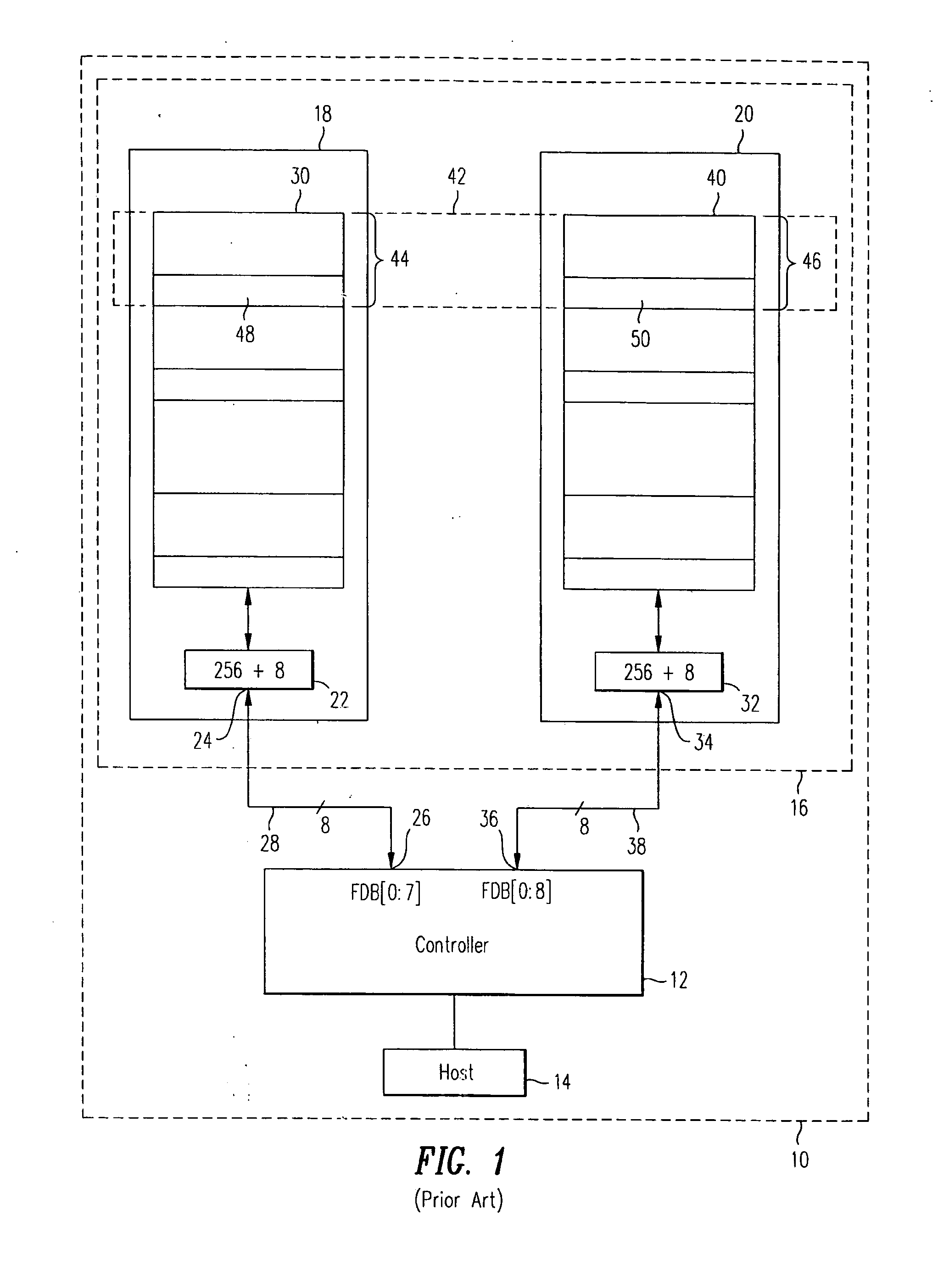

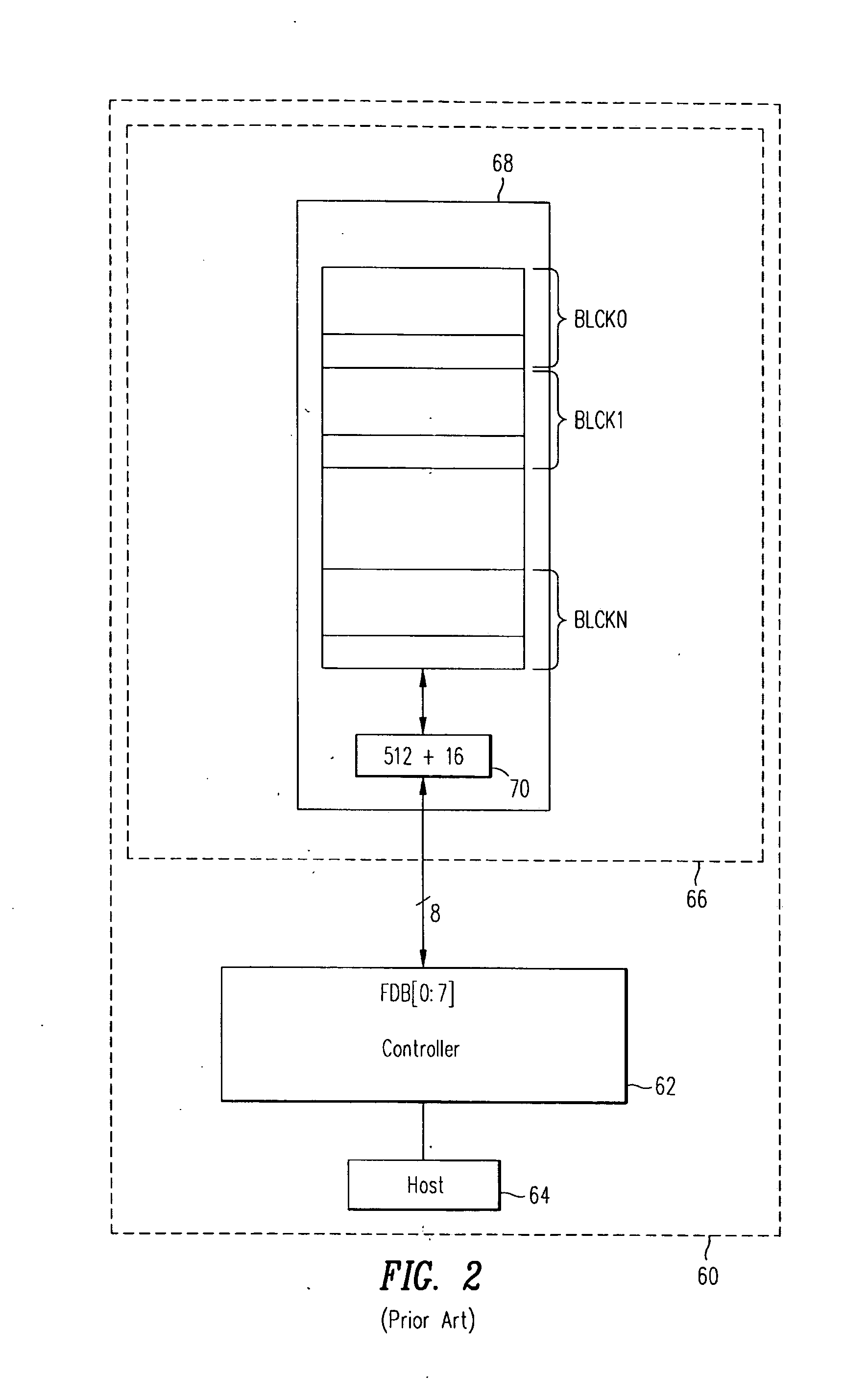

Increasing the memory performance of flash memory devices by writing sectors simultaneously to multiple flash memory devices

InactiveUS20060195651A1Improve performanceShorten the timeInput/output to record carriersMemory adressing/allocation/relocationControl storeTerm memory

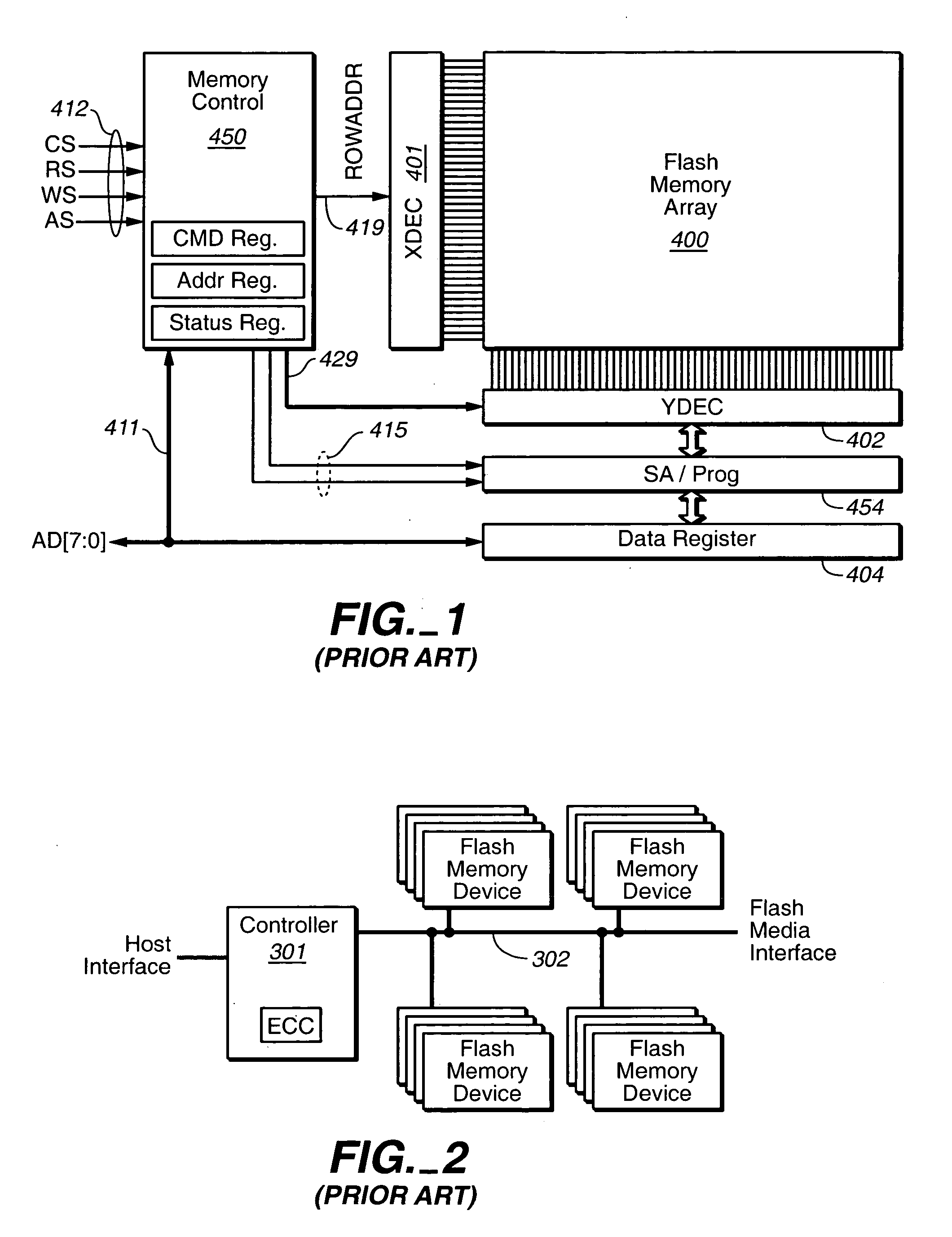

In one embodiment of the present invention, a memory storage system for storing information organized in sectors within a nonvolatile memory bank is disclosed. The memory bank is defined by sector storage locations spanning across one or more rows of a nonvolatile memory device, each the sector including a user data portion and an overhead portion. The sectors being organized into blocks with each sector identified by a host provided logical block address (LBA). Each block is identified by a modified LBA derived from the host-provided LBA and said virtual PBA, said host-provided LBA being received by the storage device from the host for identifying a sector of information to be accessed, the actual PBA developed by said storage device for identifying a free location within said memory bank wherein said accessed sector is to be stored. The storage system includes a memory controller coupled to the host; and a nonvolatile memory bank coupled to the memory controller via a memory bus, the memory bank being included in a non-volatile semiconductor memory unit, the memory bank has storage blocks each of which includes a first row-portion located in said memory unit, and a corresponding second row-portion located in each of the memory unit, each of the memory row-portions provides storage space for two of said sectors, wherein the speed of performing write operations is increased by writing sector information to the memory unit simultaneously.

Owner:MICRON TECH INC

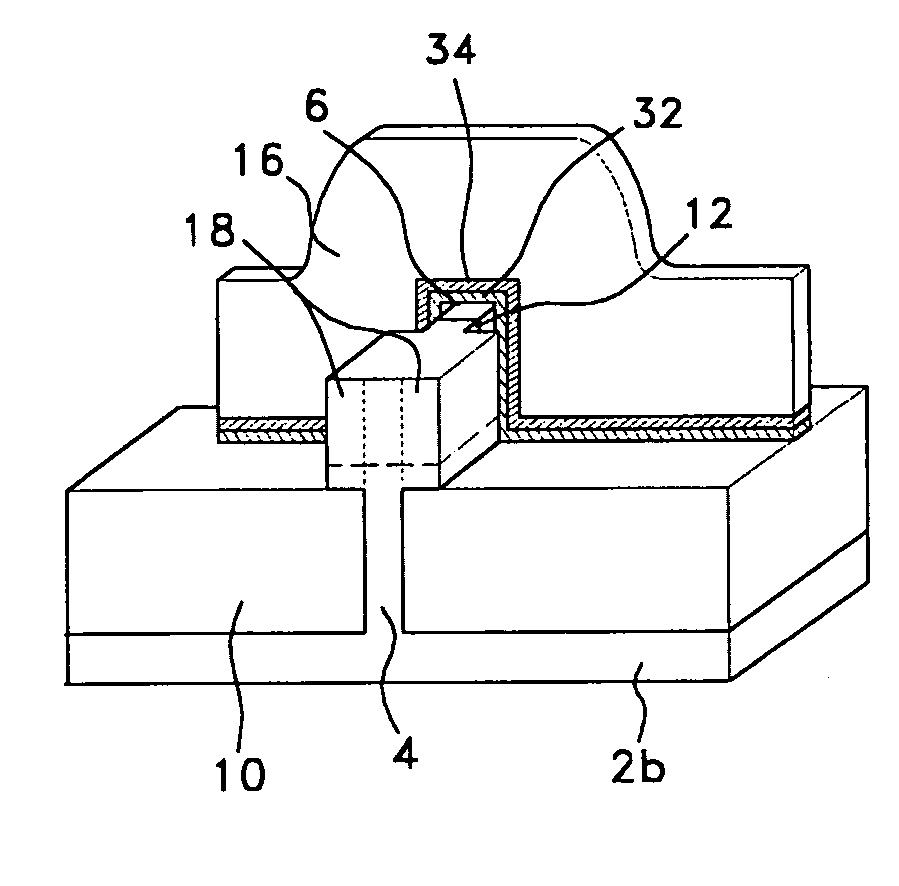

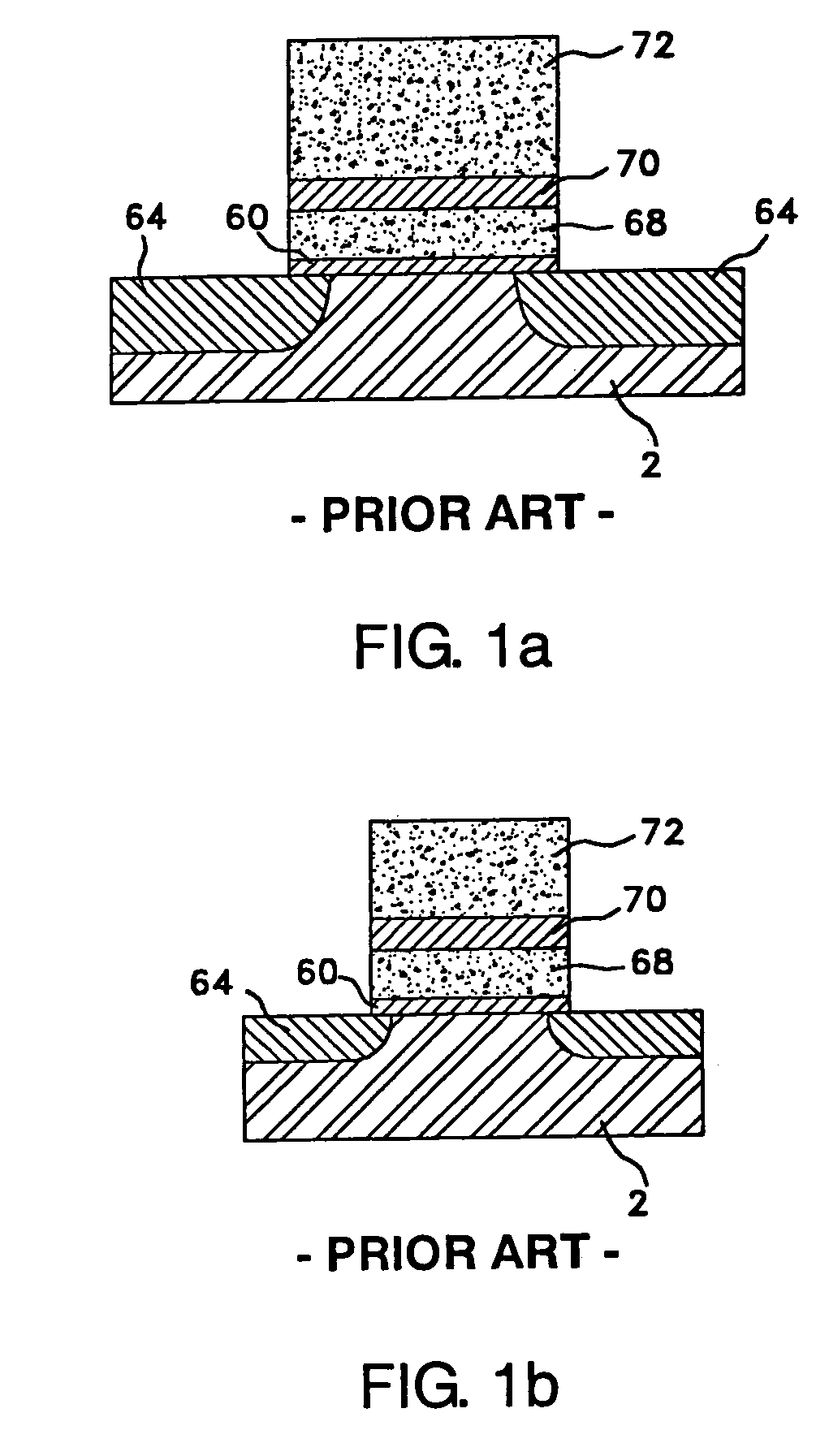

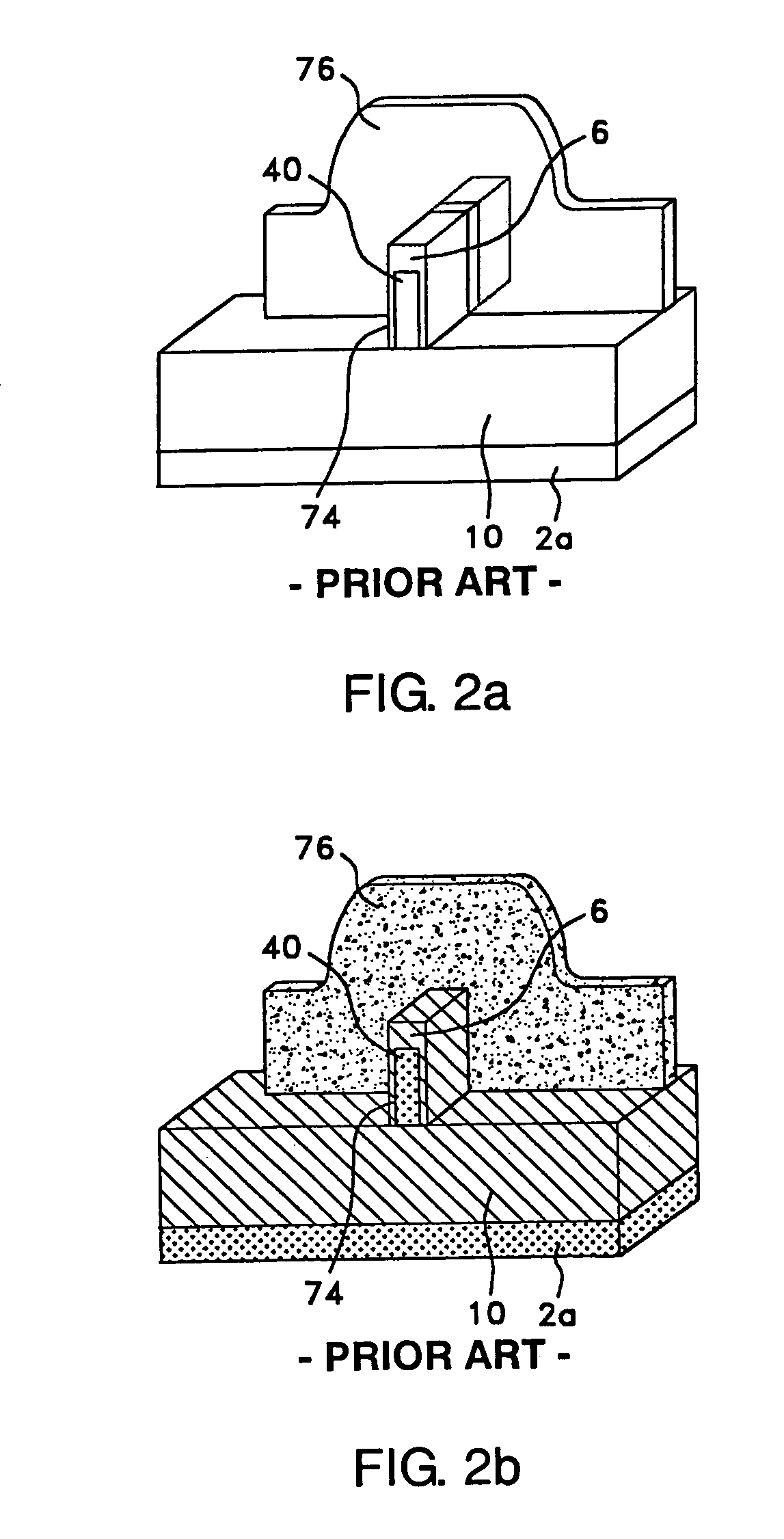

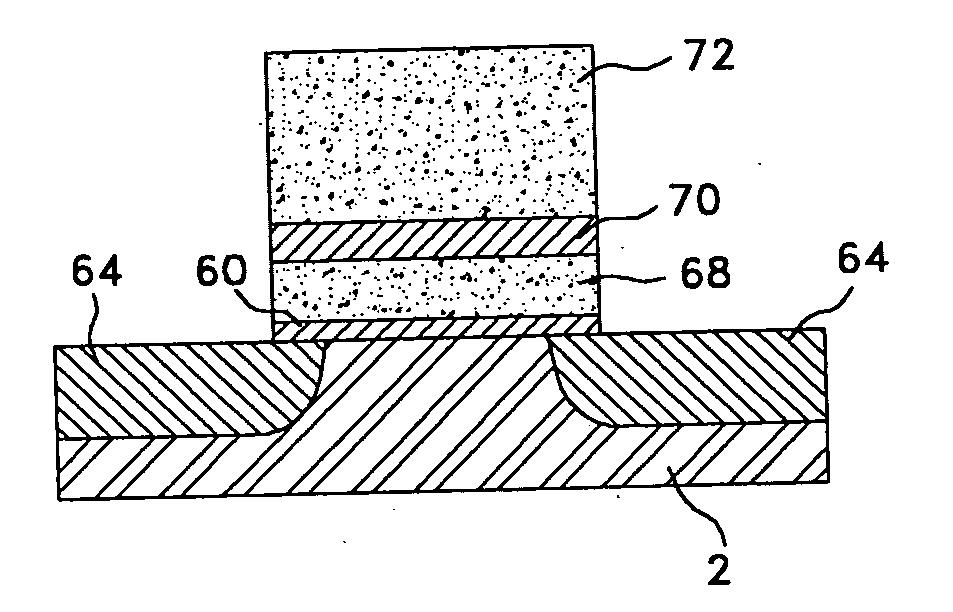

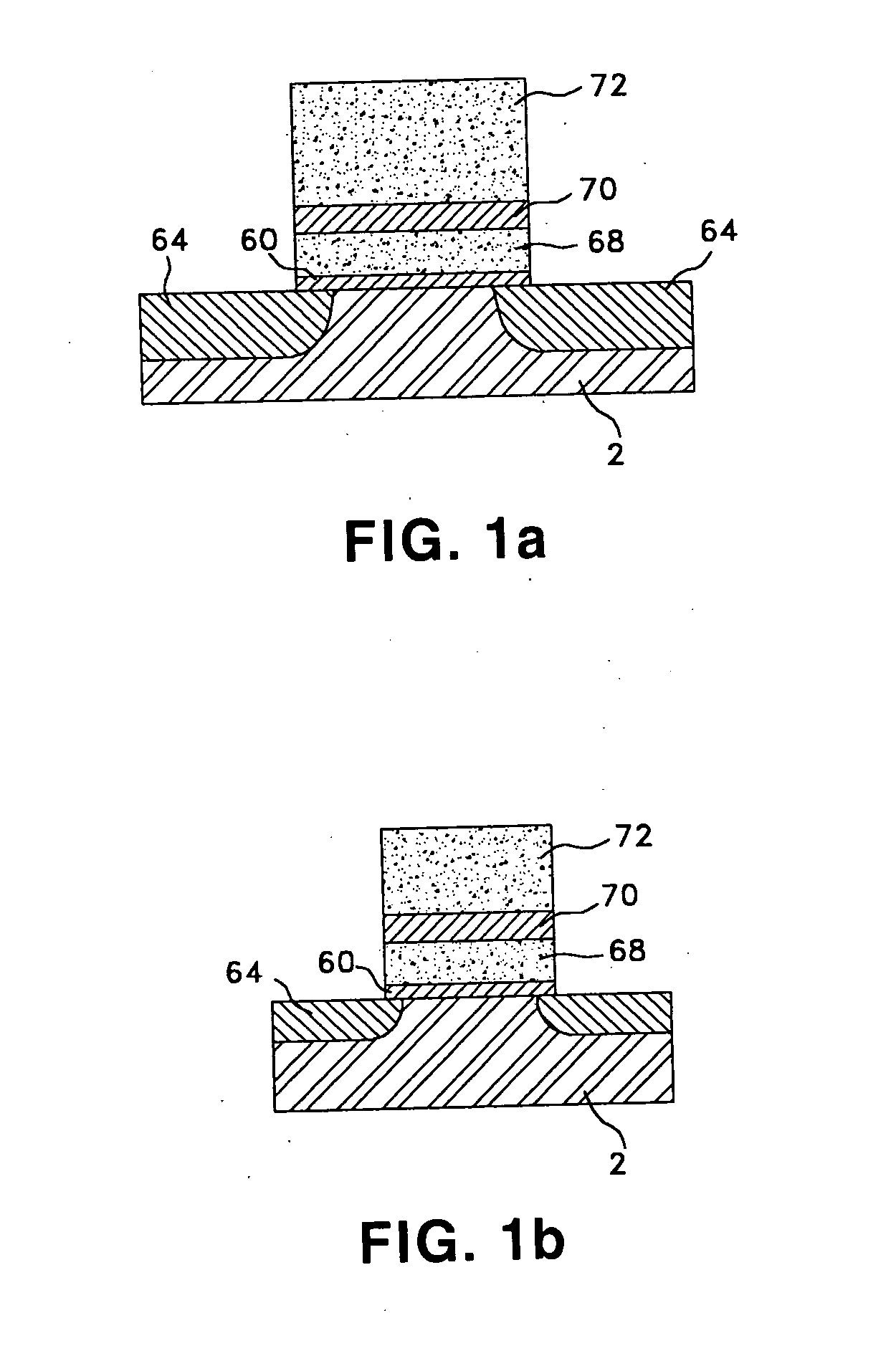

Double-gate flash memory device

The conventional flash memory device is fabricated by the MOS processing technology on a bulk substrate and has a similar configuration to an MOS device.While the conventional CMOS device has a superior scaling down characteristic, the scaling down characteristic of a flash memory device is poor due to the inability to reduce the thickness below 7 nm or 8 nm for the tunneling oxide film where the charges in the channel are tunneled into the floating electrode through the tunneling oxide.In order to resolve this problem, the present invention, instead of a SOI wafer, uses a cheaper bulk silicon wafer with lower defect density. A wall shape Fin active region where the channel and the source / drain are formed is connected to the bulk silicon substrate by which floating body effect and heat conduction problem are resolved. a flash memory device is fabricated by forming a tunneling oxide film on side surfaces of the Fin active and a floating (storage) electrode where the charges could be stored.The above structure has a superior scaling down characteristic and enhanced memory performance due to a double-gate flash memory device structure.

Owner:SEOUL NAT UNIV R&DB FOUND

Double-gate flash memory device and fabrication method thereof

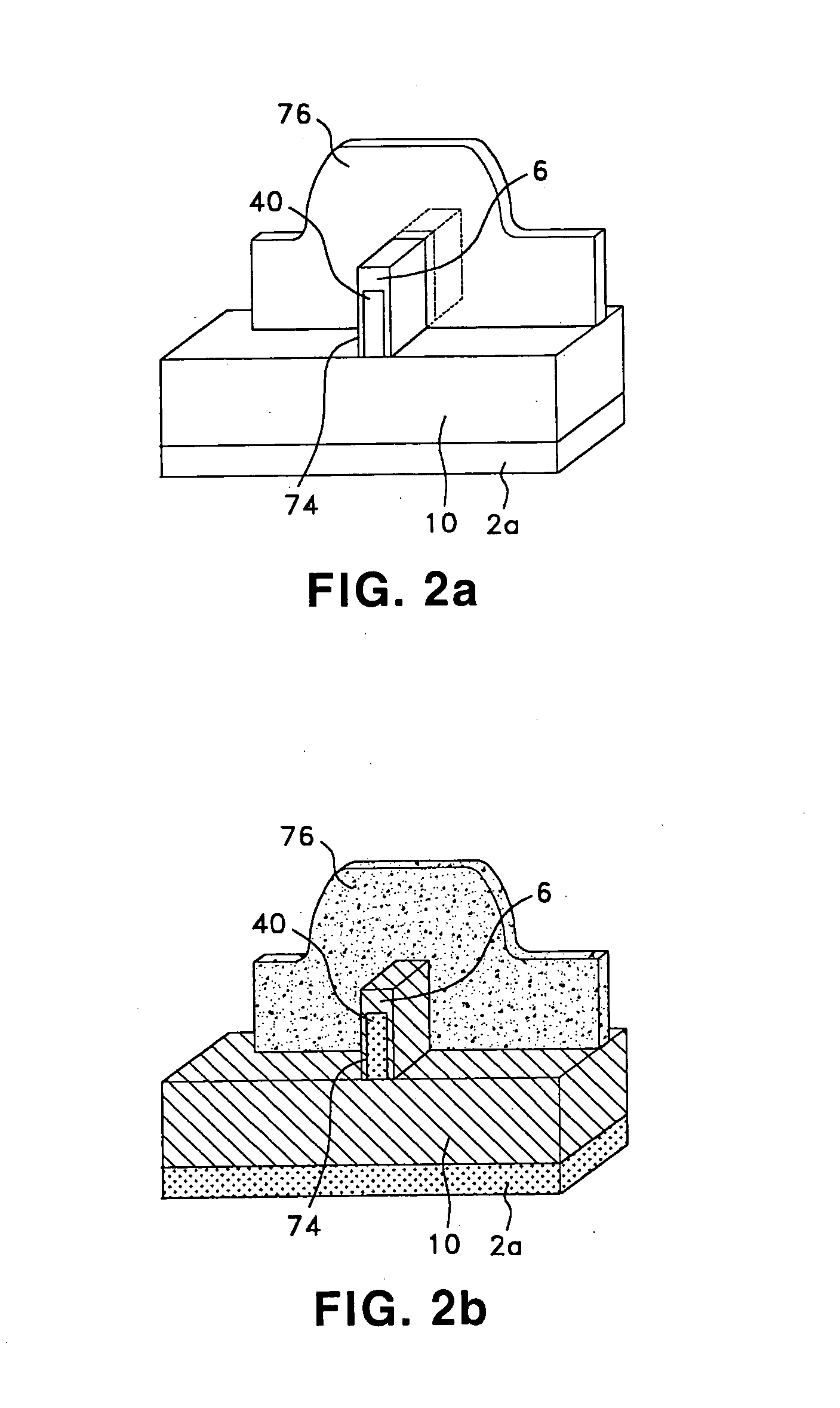

ActiveUS20050145926A1Improve featuresImprove integration densityTransistorNanoinformaticsFloating body effectEngineering

The conventional flash memory device is fabricated by the MOS processing technology on a bulk substrate and has a similar configuration to an MOS device. While the conventional CMOS device has a superior scaling down characteristic, the scaling down characteristic of a flash memory device is poor due to the inability to reduce the thickness below 7 nm or 8 nm for the tunneling oxide film where the charges in the channel are tunneled into the floating electrode through the tunneling oxide. In order to resolve this problem, the present invention, instead of a SOI wafer, uses a cheaper bulk silicon wafer with lower defect density. A wall shape Fin active region where the channel and the source / drain are formed is connected to the bulk silicon substrate by which floating body effect and heat conduction problem are resolved. a flash memory device is fabricated by forming a tunneling oxide film on side surfaces of the Fin active and a floating (storage) electrode where the charges could be stored. The above structure has a superior scaling down characteristic and enhanced memory performance due to a double-gate flash memory device structure.

Owner:SEOUL NAT UNIV R&DB FOUND

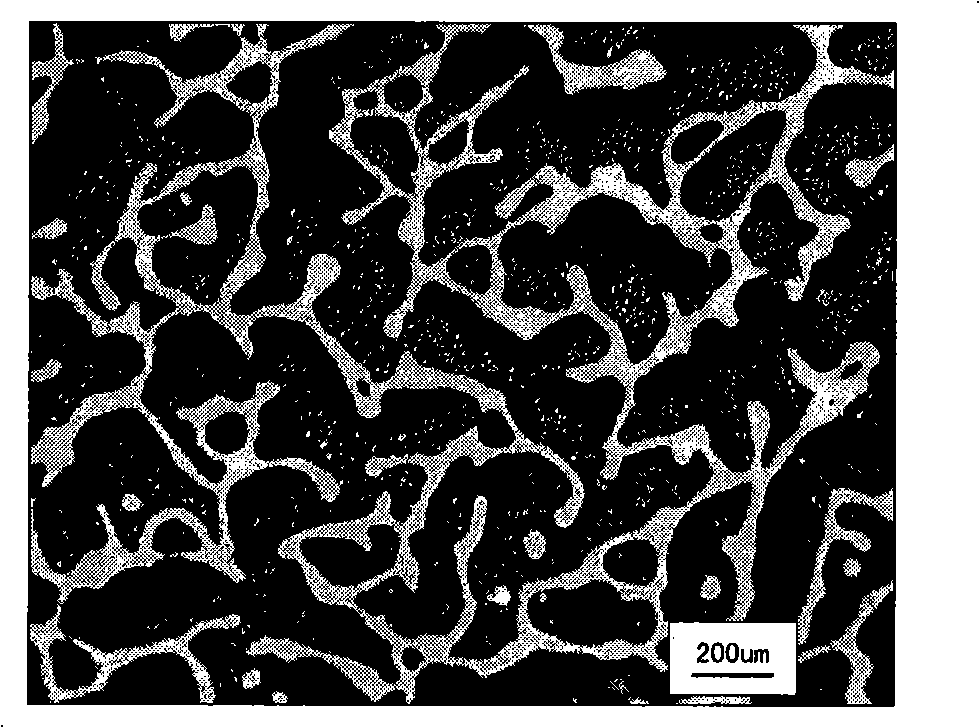

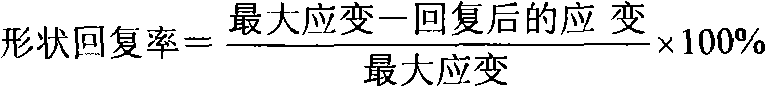

Blending polymer shape memory material and preparation method thereof

The invention belongs to the industrial and medical technical field, and particularly relates to a shape memory material and a preparation method thereof. The shape memory material is a macromolecular blend based on the incompletely compatibility between components, and comprises at least one sort of elastomer polymer and at least one sort of phase-transformation polymer, wherein the elastomer polymer component comprises any thermosetting or thermoplastic elastomer with excellent tension performance and rebound performance; and the phase-transformation polymer component comprises any polymer capable of crystallization or having obvious vitrification transformation. The preparation of the shape memory material adopts a milling method of solution or fused mass so as to ensure that the material has a uniform phase structure. Moreover, the shape memory material has excellent shape memory performance, and the shape recovery rate and the shape fixation rate of the material can be controlled through adjusting the contents of both components.

Owner:FUDAN UNIV

System and method for improving data integrity and memory performance using non-volatile media

ActiveUS20100115193A1Reduce accessImprove system performanceMemory adressing/allocation/relocationMass storageHard disc drive

A system and computer system for improving data integrity and memory performance using non-volatile media. A system includes a non-volatile mass storage unit, e.g., a flash memory device and / or a hard drive unit for instance. A memory device is used as a high speed data buffer and / or cache for the non-volatile storage unit. The memory device may be non-volatile, e.g., magnetic random access memory (MRAM) or volatile memory, e.g., static dynamic random access memory (SDRAM). By buffering and / or caching the write data, fewer accesses are required to the mass storage device thereby increasing system performance. Additionally, mechanical and electrical degradation of the mass storage device is reduced. Certain trigger events can be programmed to cause data from the memory device to be written to the mass storage device. In one embodiment, the write buffer contents are preserved across reset or power loss events. In one embodiment, the mass storage unit may be a data transport layer, e.g., Ethernet, USB, Bluetooth, etc.

Owner:QUALCOMM INC

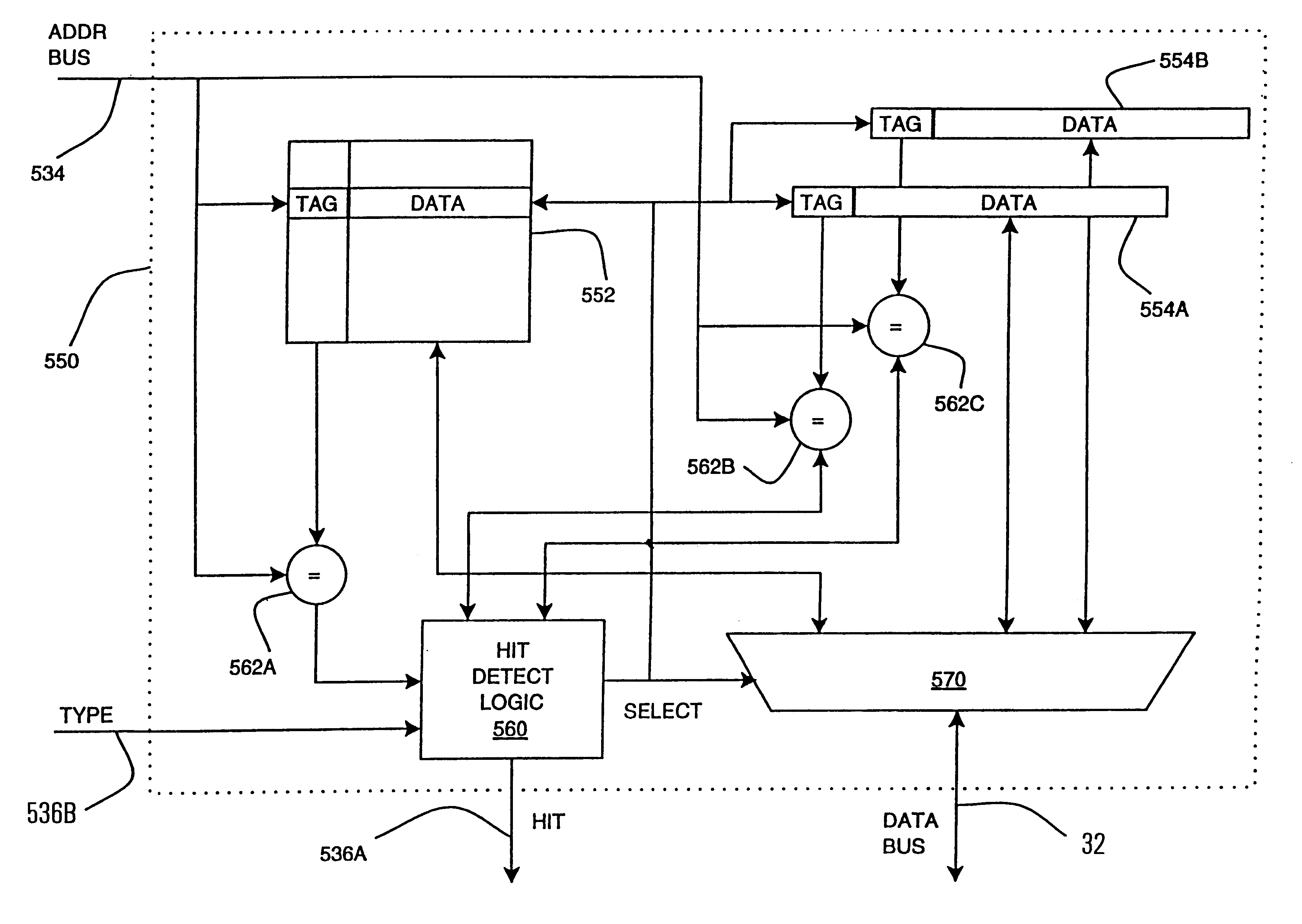

Method and architecture for data coherency in set-associative caches including heterogeneous cache sets having different characteristics

A processor architecture and method are shown which involve a cache having heterogeneous cache sets. An address value of a data access request from a CPU is compared to all cache sets within the cache regardless of the type of data and the type of data access indicated by the CPU to create a unitary interface to the memory hierarchy of the architecture. Data is returned to the CPU from the cache set having the shortest line length of the cache sets containing the data corresponding to the address value of the data request. Modified data replaced in a cache set having a line length that is shorter than other cache sets is checked for matching data resident in the cache sets having longer lines and the matching data is replaced with the modified data. All the cache sets at the cache level of the memory hierarchy are accessed in parallel resulting in data being retrieved from the fastest memory source available, thereby improving memory performance. The unitary interface to a memory hierarchy having multiple cache sets maintains data coherency, simplifies code design and increases resilience to coding errors.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

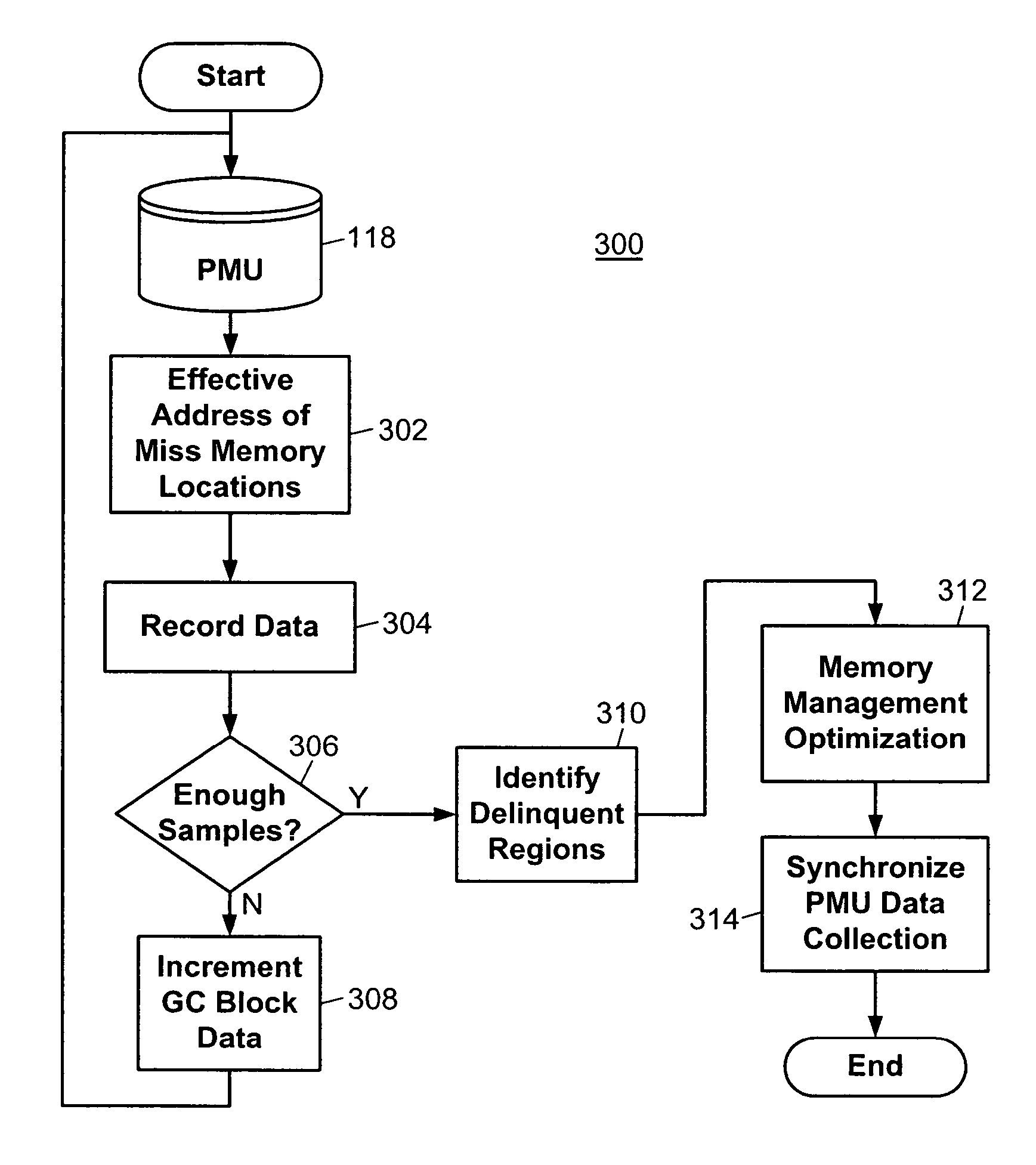

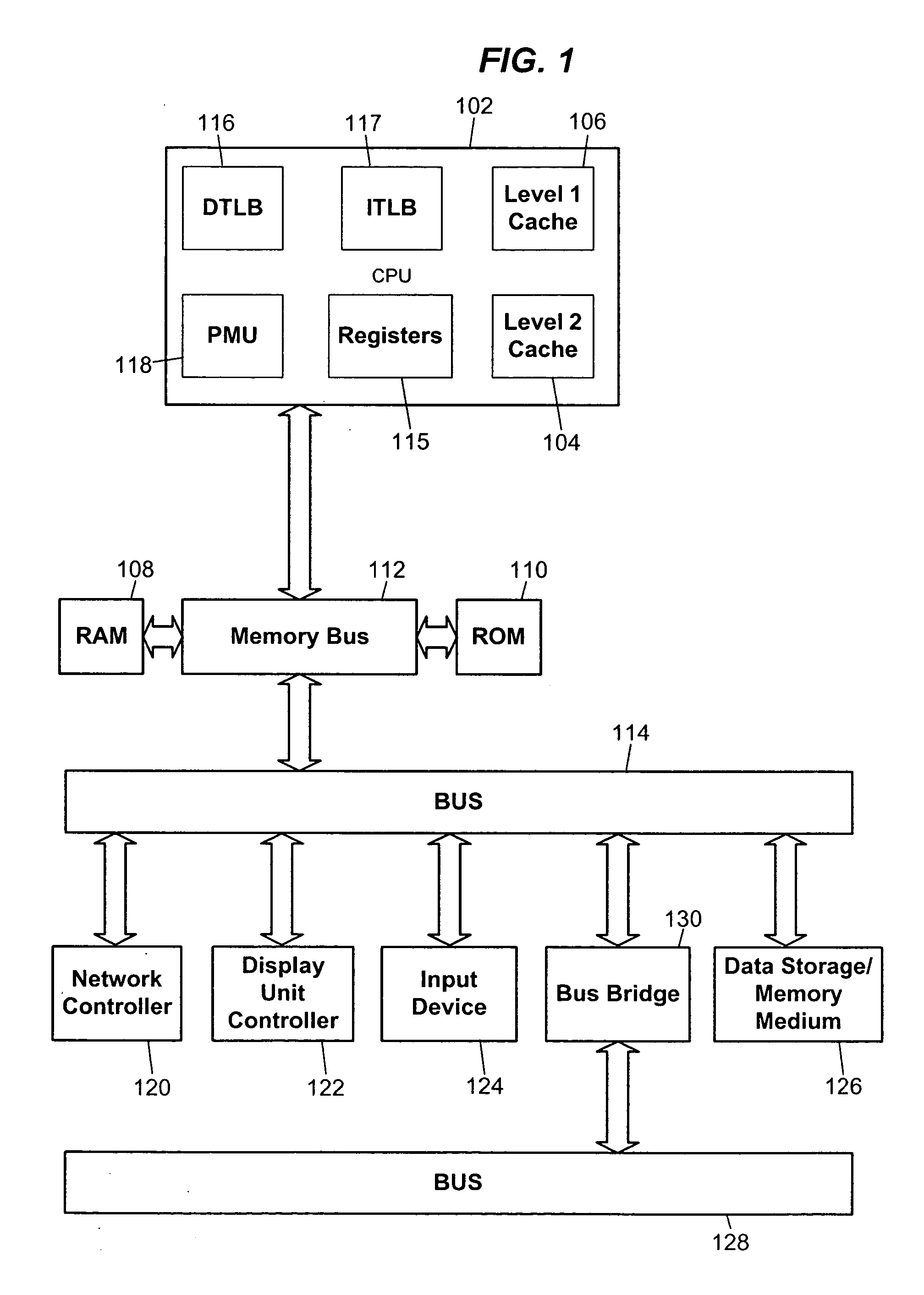

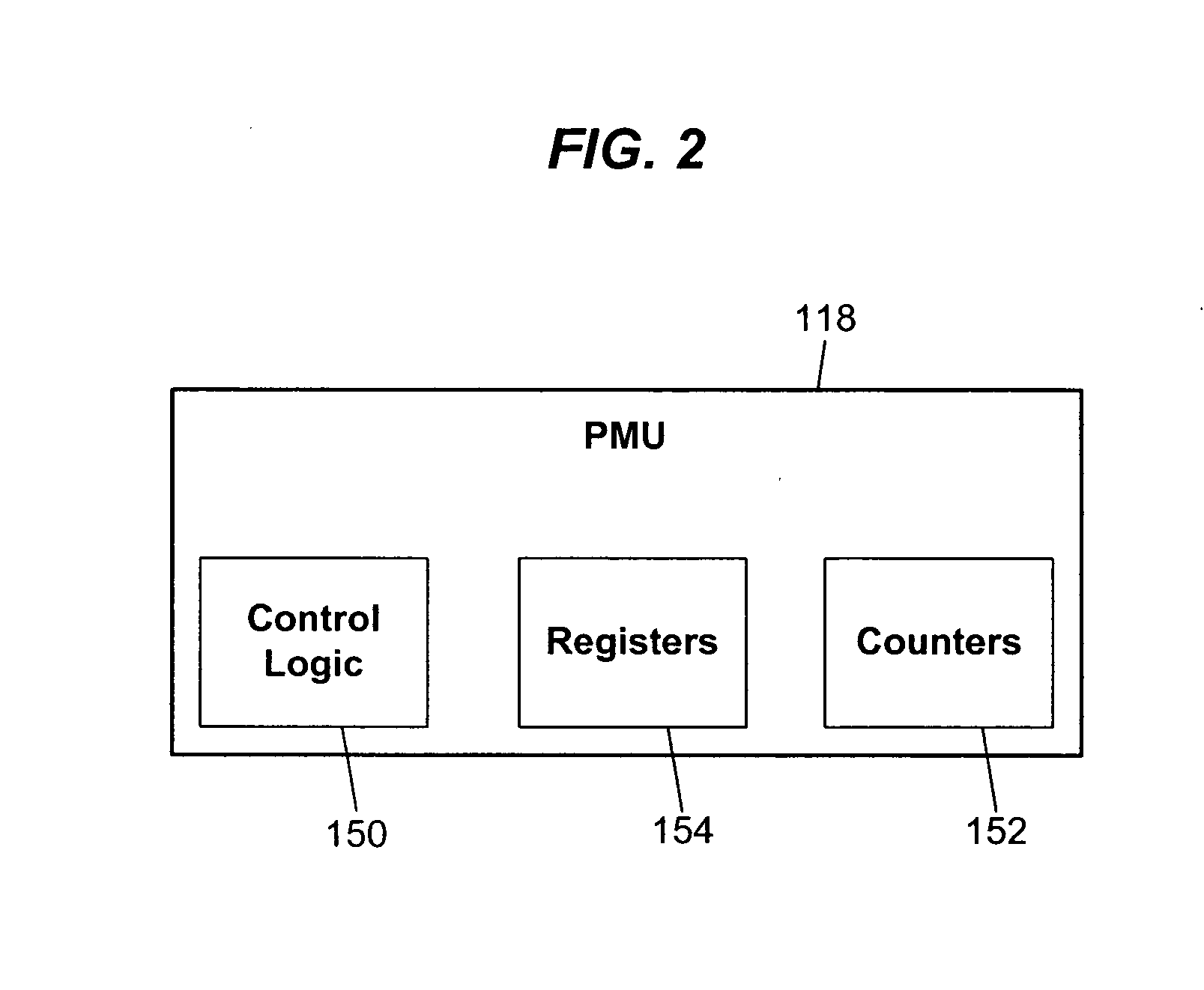

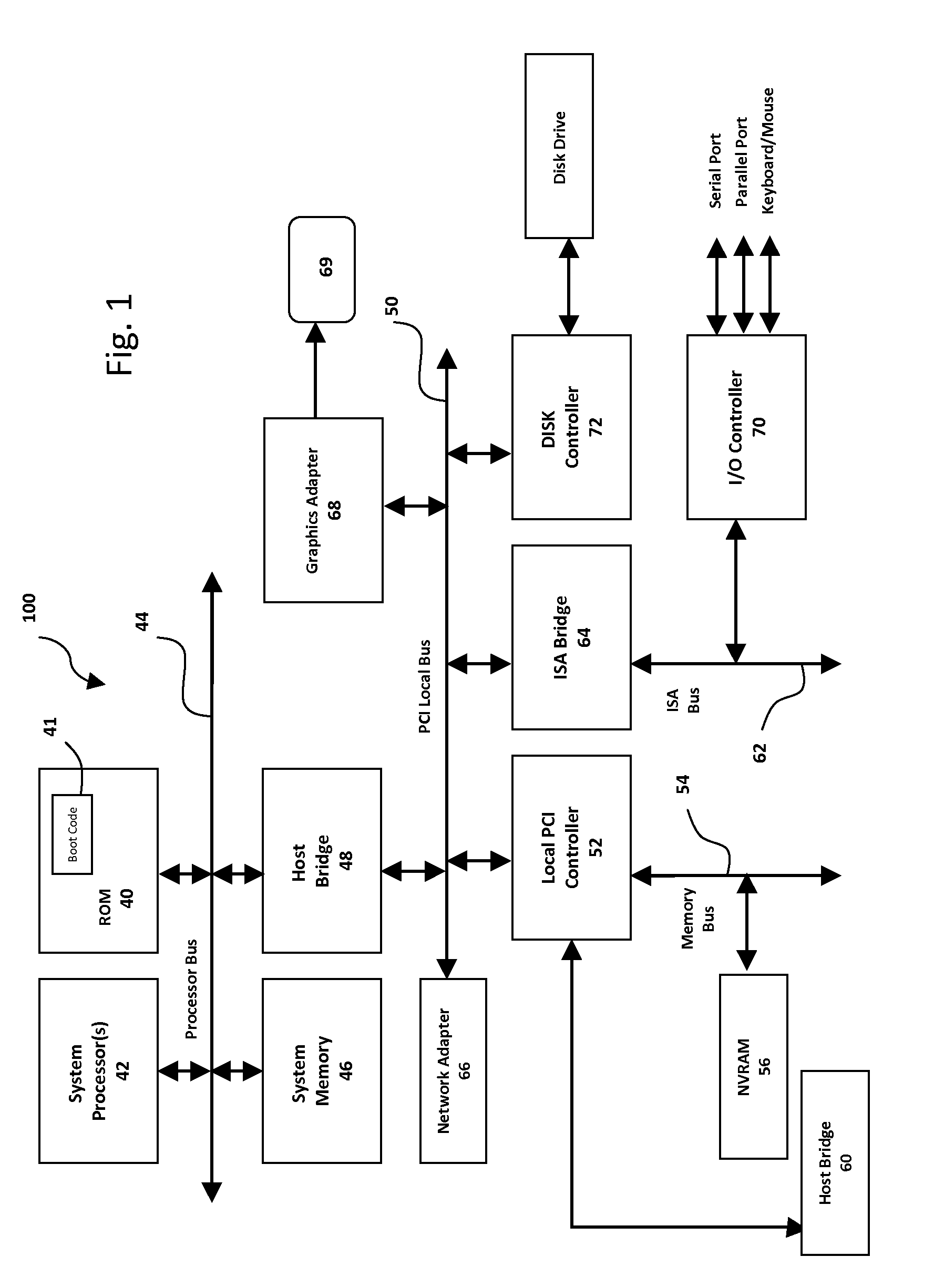

Dynamic performance monitoring-based approach to memory management

InactiveUS20060143421A1Data processing applicationsMemory adressing/allocation/relocationParallel computingTerm memory

Techniques are described for optimizing memory management in a processor system. The techniques may be implemented on processors that include on-chip performance monitoring and on systems where an external performance monitor is coupled to a processor. Processors that include a Performance Monitoring Unit (PMU) are examples. The PMU may store data on read and write cache misses, as well as data on translation lookaside buffer (TLB) misses. The data from the PMU is used to determine if any memory regions within a memory heap are delinquent memory regions, i.e., regions exhibiting high numbers of memory problems or stalls. If delinquent memory regions are found, the memory manager, such as a garbage collection routine, can efficiently optimize memory performance as well as the mutators performance by improving the layout of objects in the heap. In this way, memory management routines may be focused based on dynamic and real-time memory performance data.

Owner:INTEL CORP

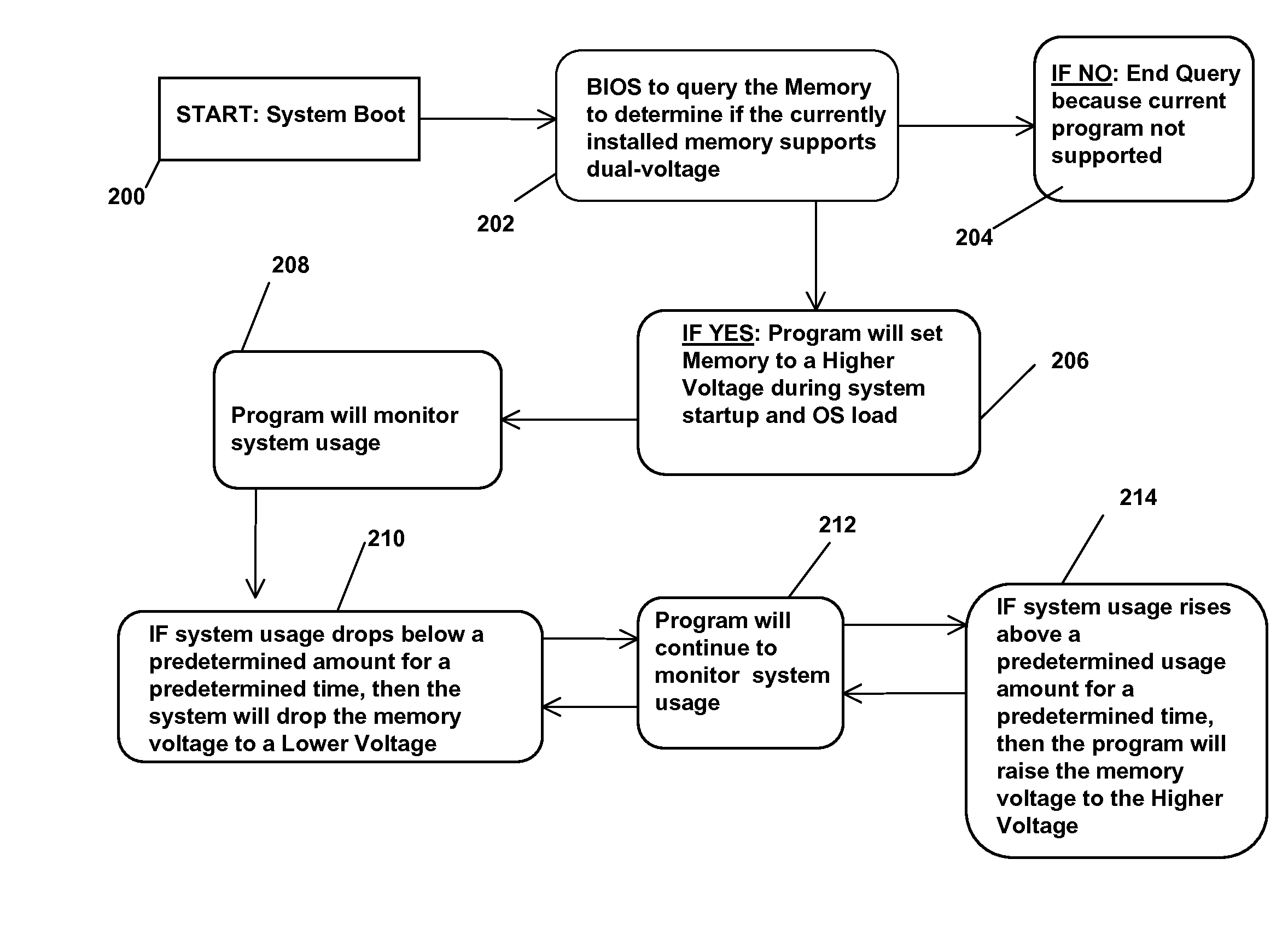

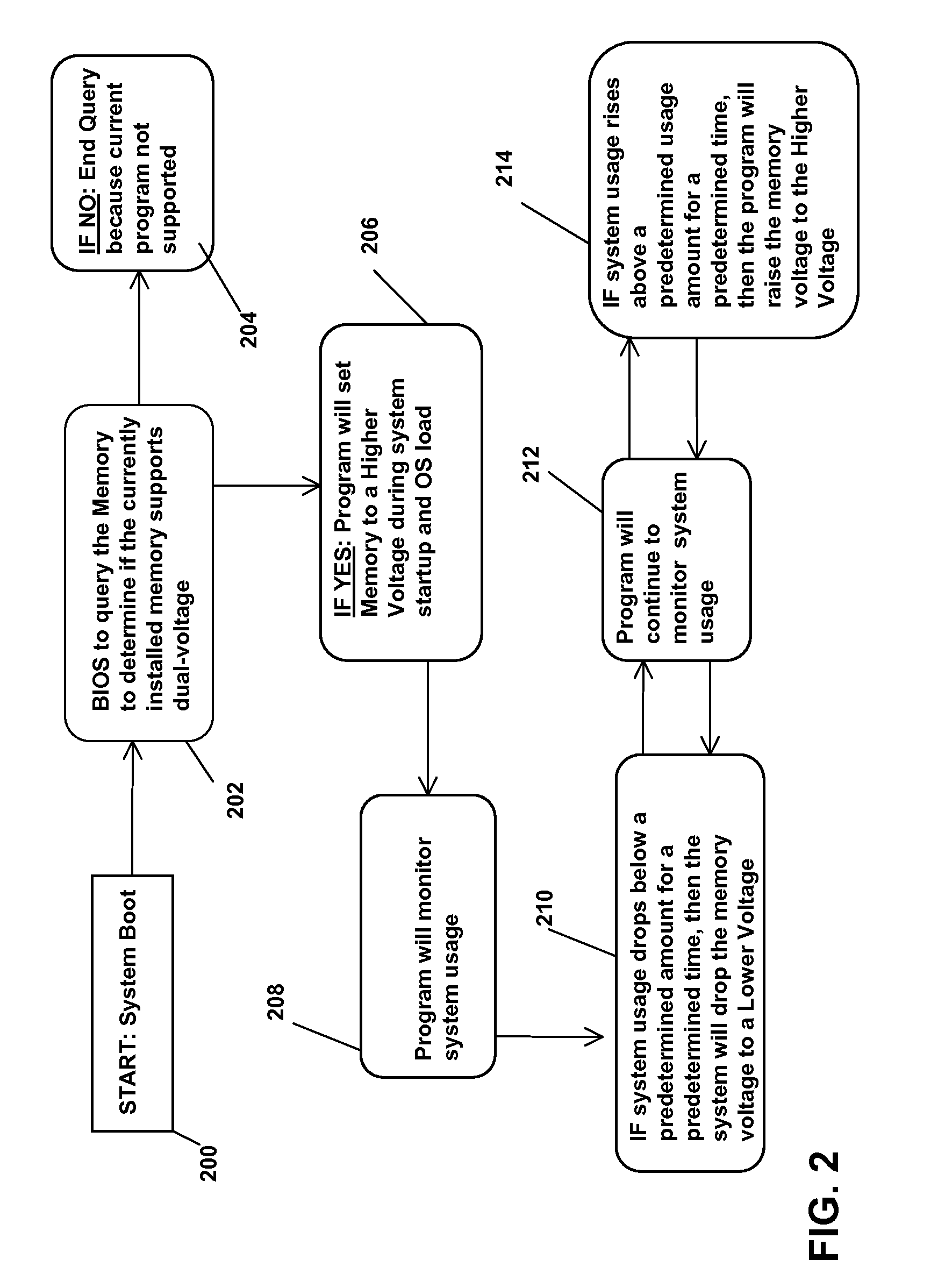

Dynamic memory voltage scaling for power management

ActiveUS20100250981A1Save powerFull memory performanceEnergy efficient ICTVolume/mass flow measurementDram memoryComputerized system

In the context of computer systems, the present invention broadly contemplates the ability to dynamically adjust the voltage and frequency of DRAM memory modules that are dual-voltage tolerant based on system performance. The invention allows a computer system to dynamically scale the memory voltage between a lower and a higher voltage, thereby allowing the system to save power when the system is idle or in low usage, but also allowing the system to realize the full memory performance when running more intensive applications.

Owner:LENOVO PC INT

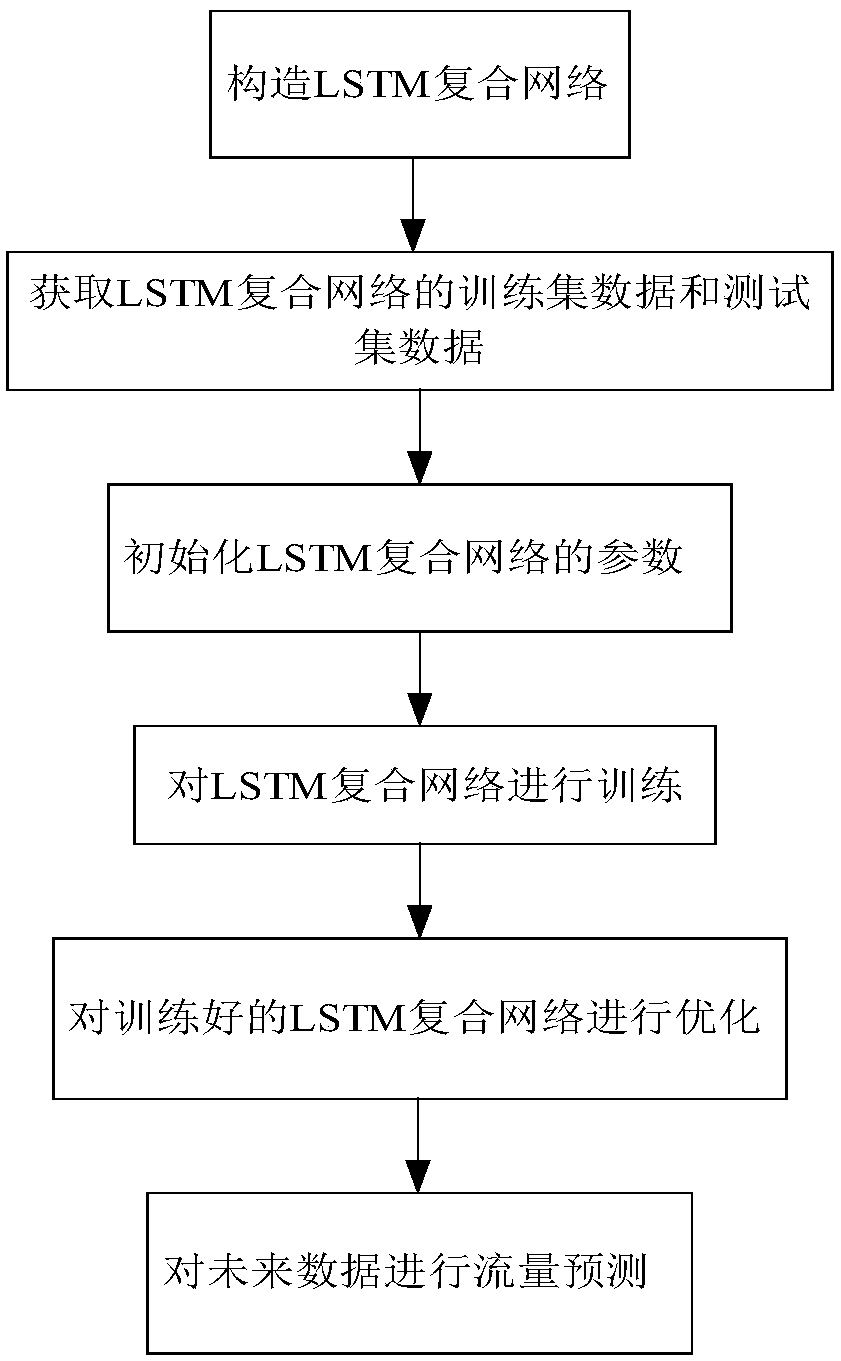

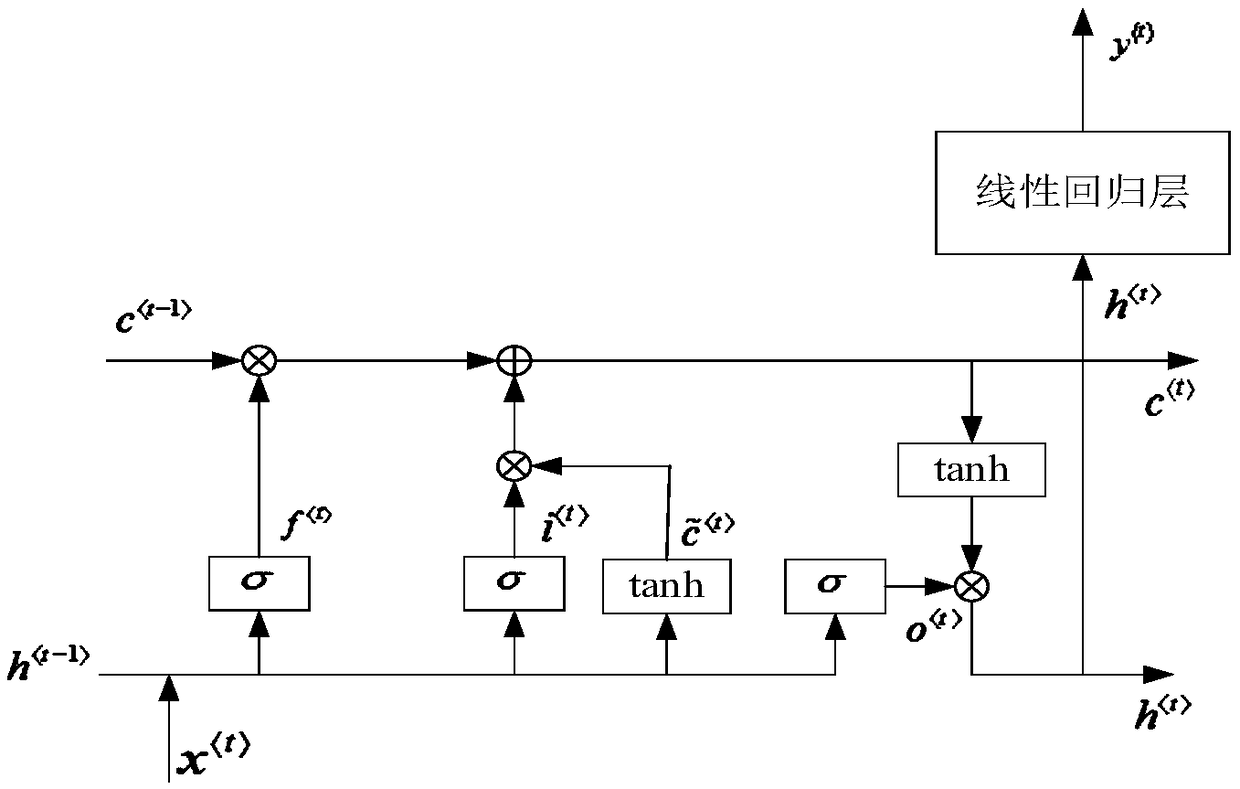

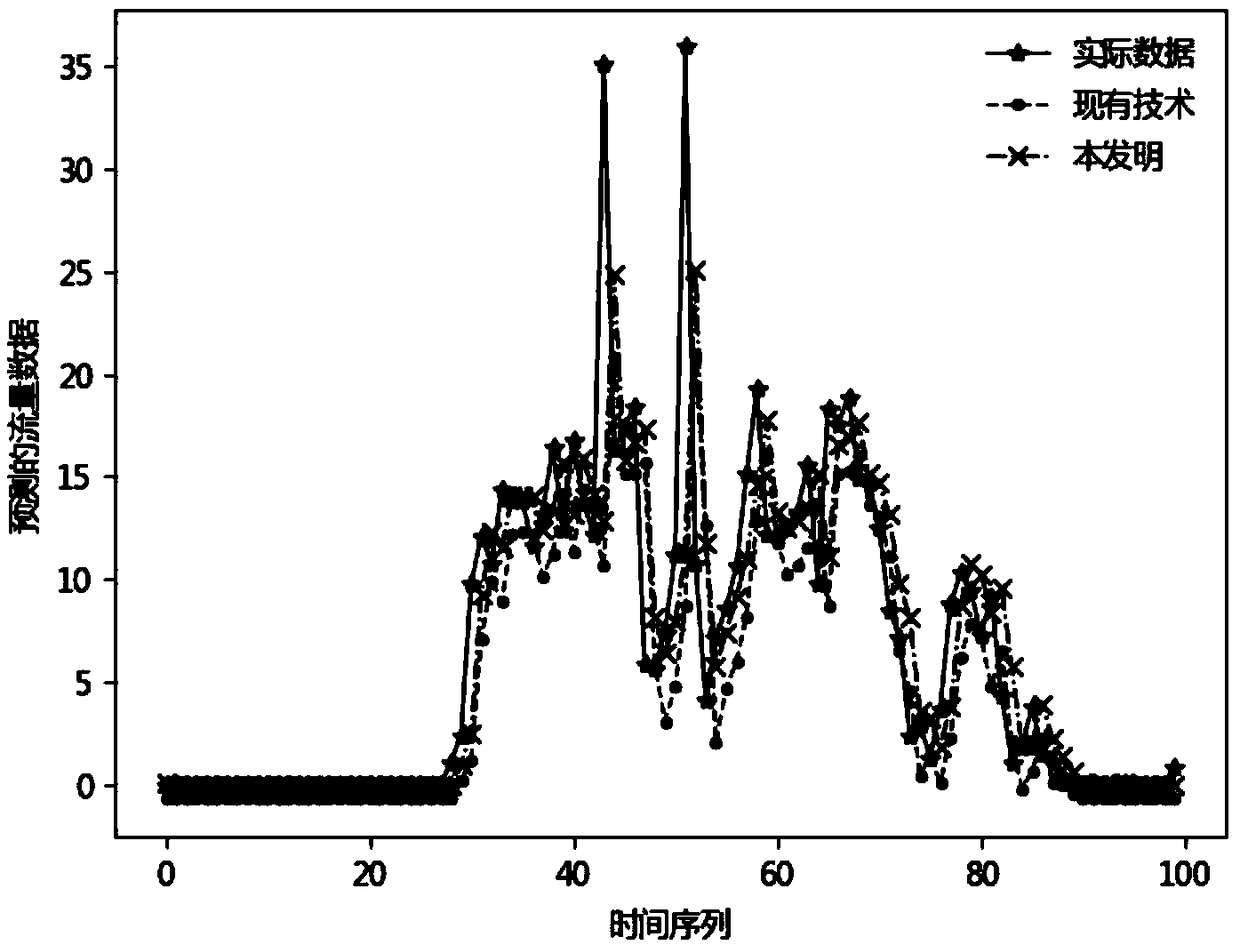

Wireless network flow rate prediction method based on LSTM network

ActiveCN108900346AHigh precisionAvoid the pitfalls of poor long-term memoryData switching networksTraffic predictionLTM - Long-term memory

The invention provides a wireless network flow rate prediction method based on an LSTM network. The method is used for solving the technical problem of low prediction precision in the prior art. The method has the realization steps of constructing an LSTM composite network; obtaining a training set data and test set data of the LSTM composite network; initializing the parameter of an LSTM composite network; training the LSTM composite network; optimizing the trained LSTM composite network; predicting the flow rate on the future data. The long-period memory performance of the LSTM network on the flow rate data is sufficiently utilized; the contribution of the historical information on the current prediction can be automatically regulated according to the current state; the wireless networkflow rate prediction precision is improved; the method can be used in the fields of internet of vehicles, finance and the like.

Owner:XIDIAN UNIV

Defect gradient to boost nonvolatile memory performance

ActiveUS20130056700A1Reduce distanceSolid-state devicesBulk negative resistance effect devicesDigital dataEngineering

Embodiments of the present invention generally relate to a resistive switching nonvolatile memory element that is formed in a resistive switching memory device that may be used in a memory array to store digital data. The memory element is generally constructed as a metal-insulator-metal stack. The resistive switching portion of the memory element includes a getter portion and / or a defect portion. In general, the getter portion is an area of the memory element that is used to help form, during the resistive switching memory device's fabrication process, a region of the resistive switching layer that has a greater number of vacancies or defects as compared to the remainder of resistive switching layer. The defect portion is an area of the memory element that has a greater number of vacancies or defects as compared to the remainder of the resistive switching layer, and is formed during the resistive switching memory device's fabrication process. The addition of the getter or defect portions in a formed memory device generally improves the reliability of the resistive switching memory device, improves the switching characteristics of the formed memory device and can eliminate or reduce the need for the time consuming additional post fabrication “burn-in” or pre-programming steps.

Owner:KIOXIA CORP +1

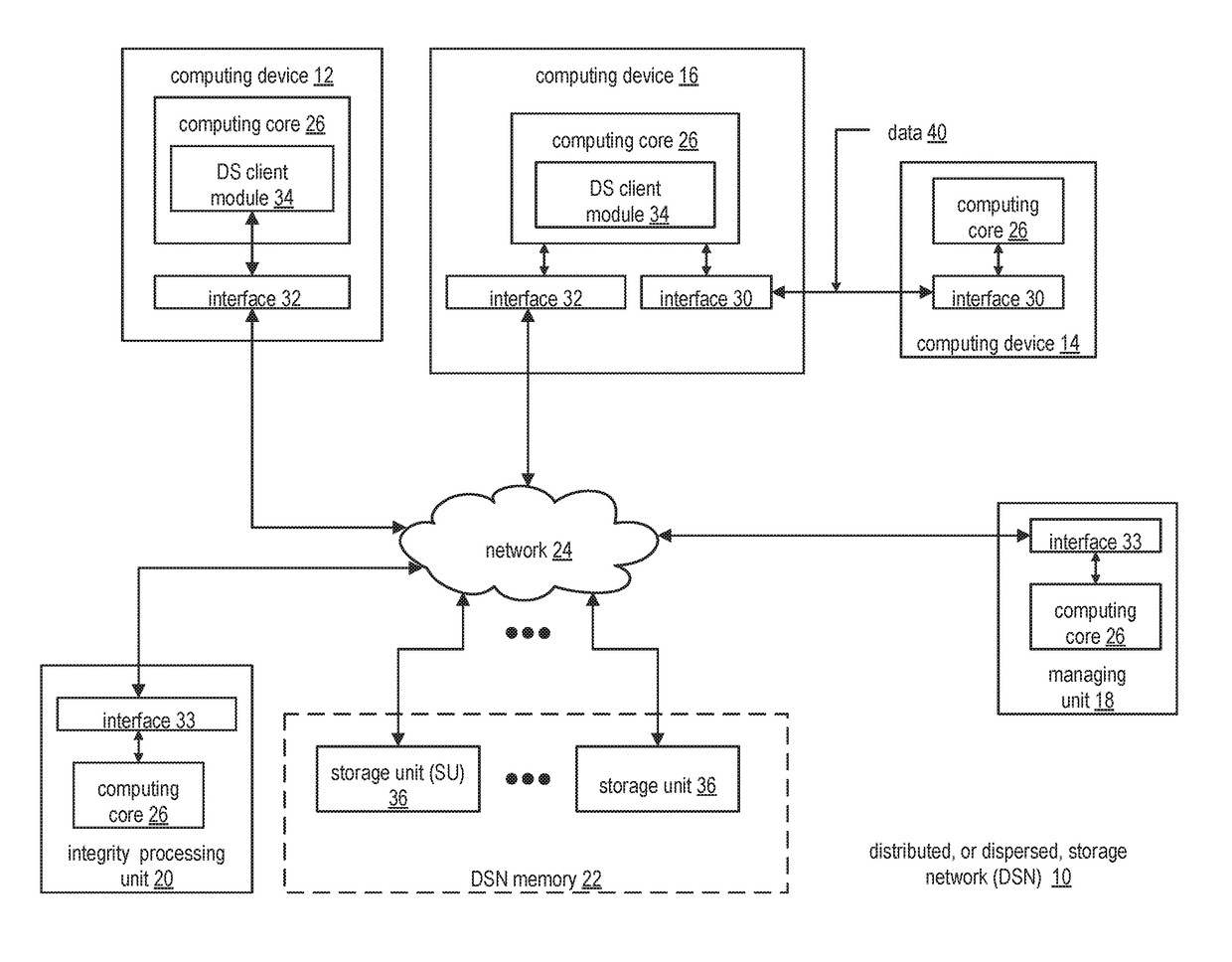

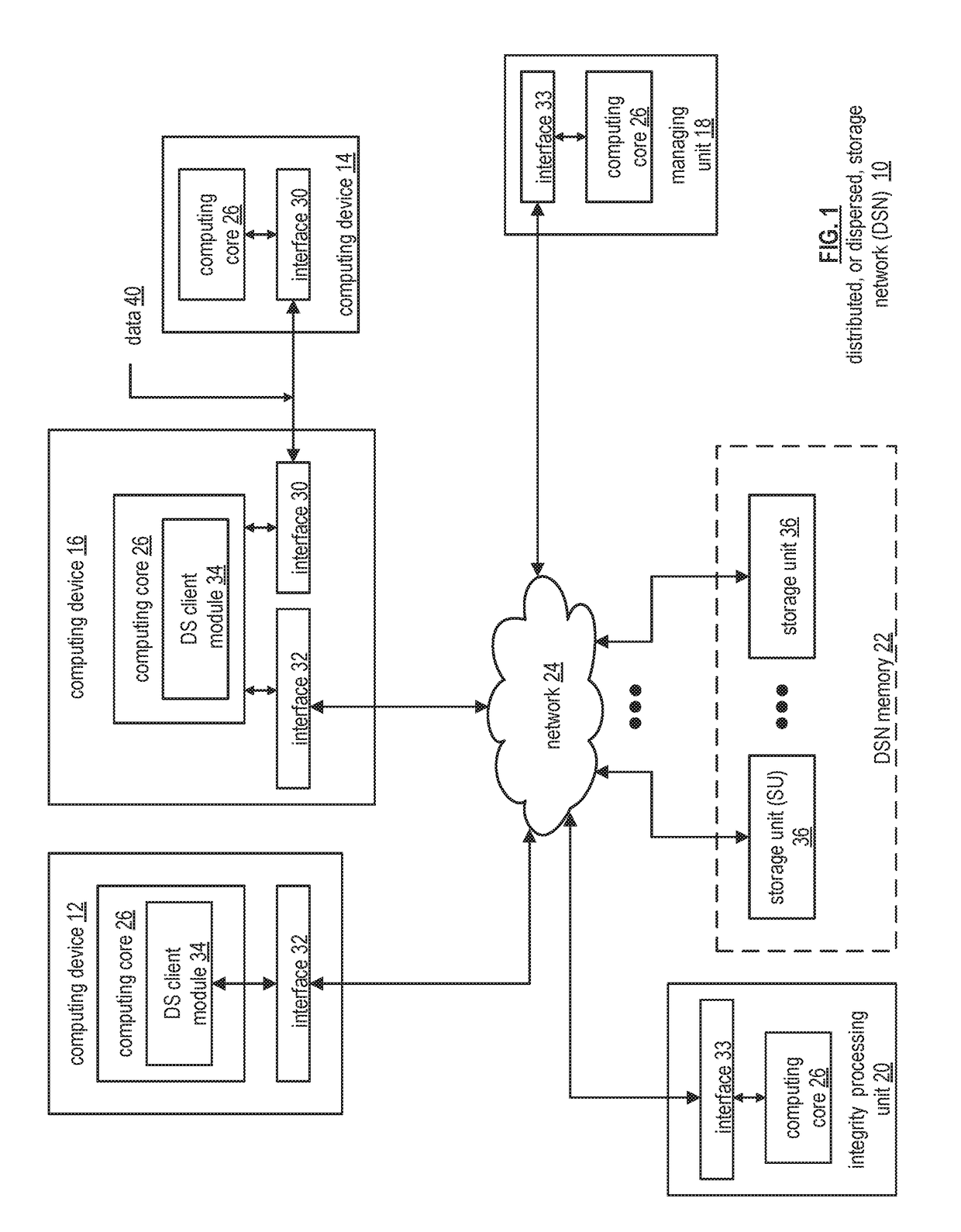

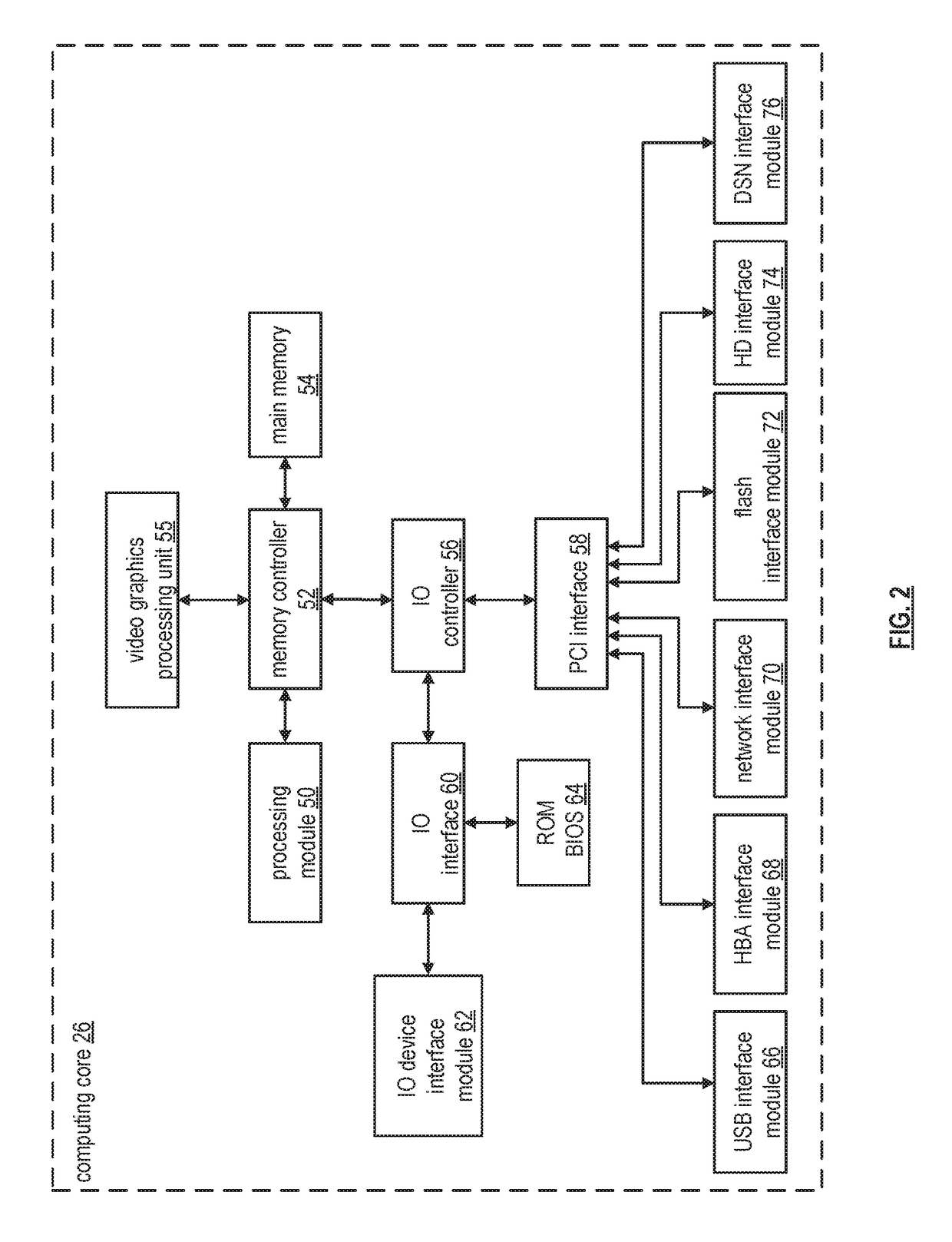

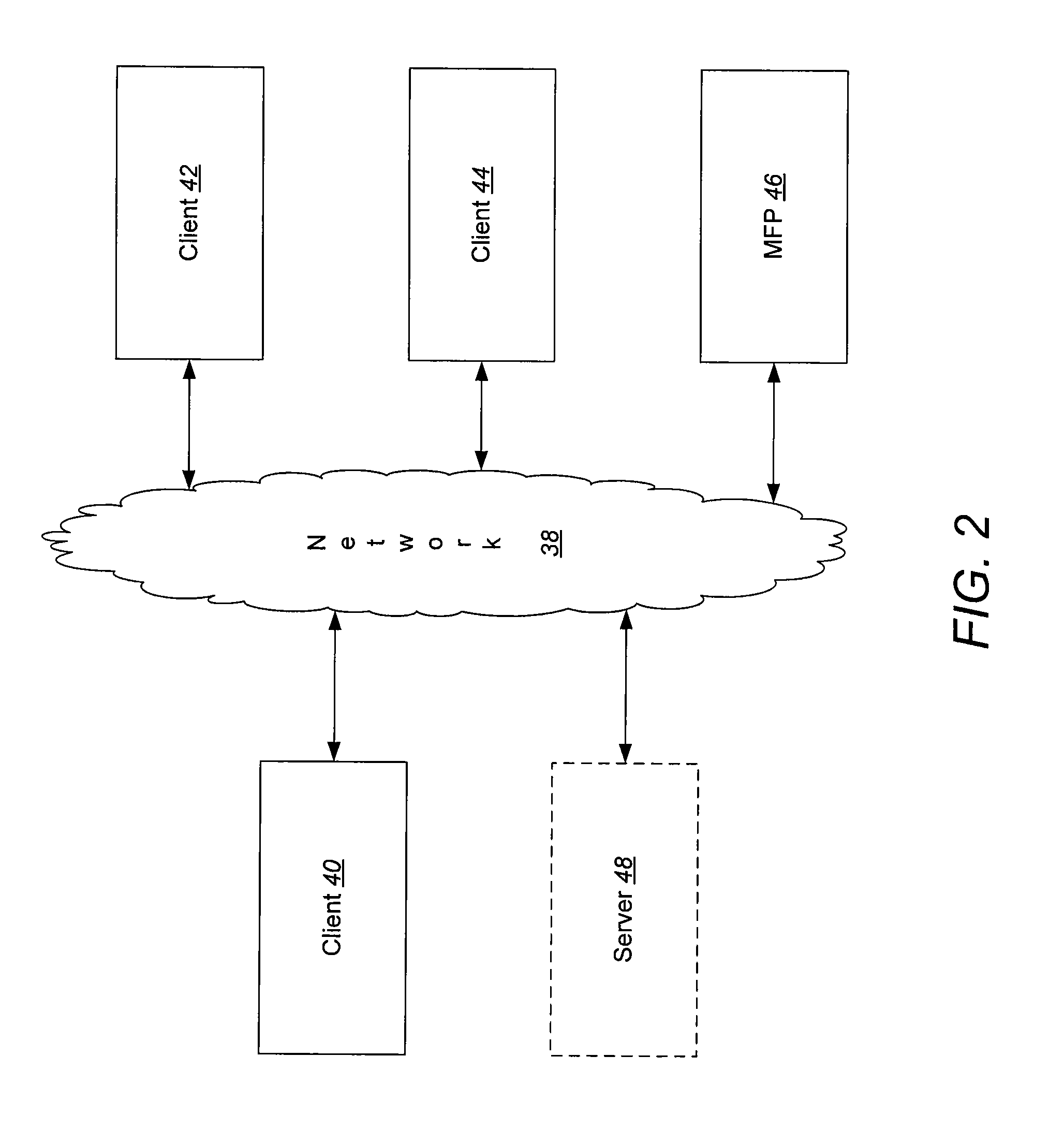

Developing an accurate dispersed storage network memory performance model through training

ActiveUS20170249551A1Input/output to record carriersMultiple keys/algorithms usageAlgorithmNetwork model

A computing device includes an interface configured to interface and communicate with a dispersed or distributed storage network (DSN), a memory that stores operational instructions, and a processing module operably coupled to the interface and memory such that the processing module, when operable within the computing device based on the operational instructions, is configured to perform various operations. The computing device receives first samples corresponding to inputs that characterize configuration of the DSN and receives second samples corresponding to outputs that characterize system behavior of the DSN. The computing device then processes the first and samples to generate a DSN model to generate predictive performance of the outputs based on various values of the inputs. In some instances, the DSN model is based on a neural network model that employs the inputs that characterize the configuration of the DSN and generates the outputs that characterize system behavior of the DSN.

Owner:PURE STORAGE

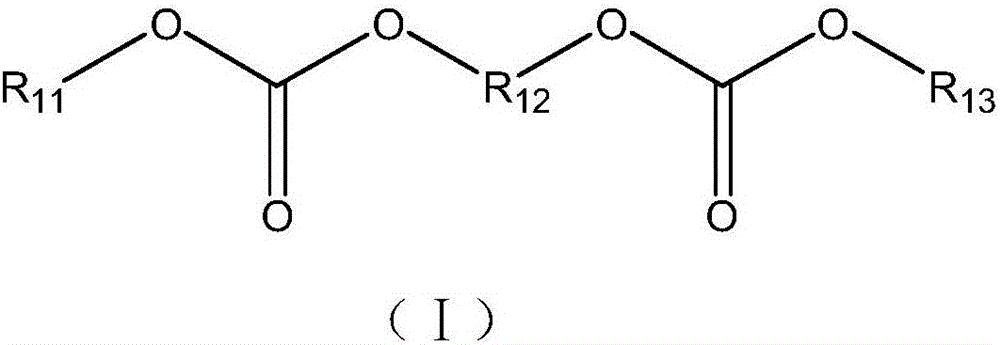

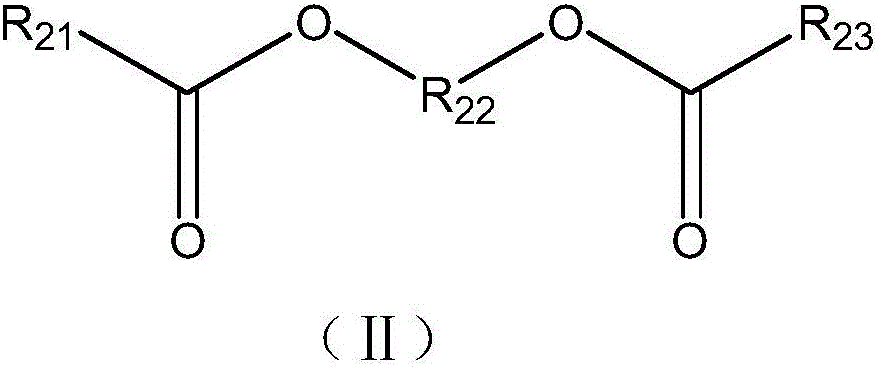

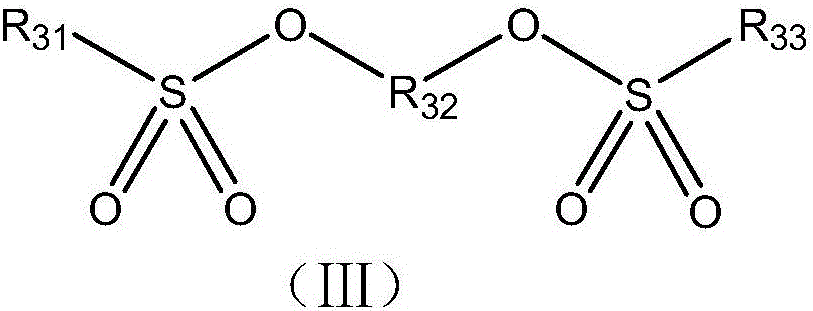

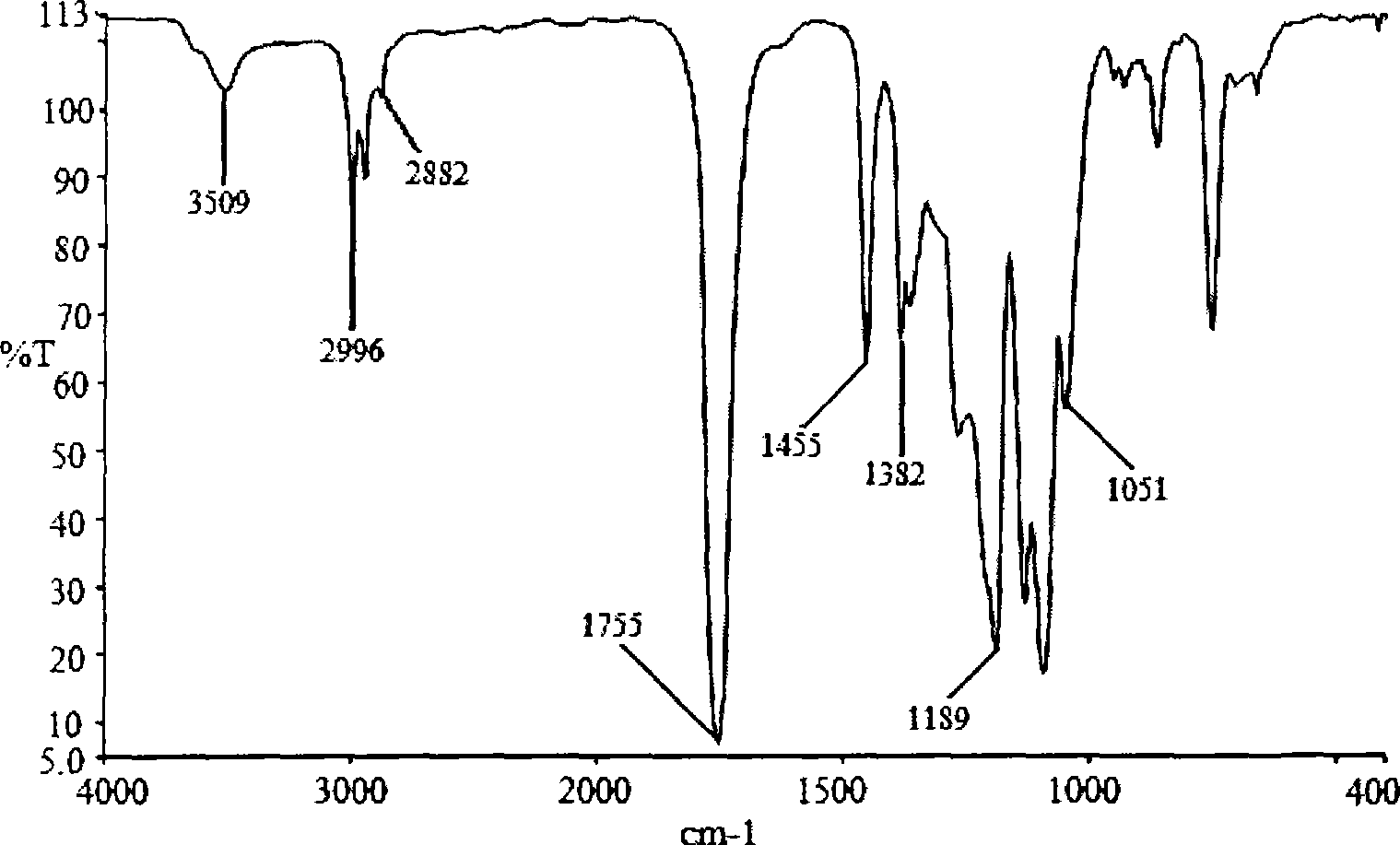

Electrolyte and lithium ion battery containing electrolyte

InactiveCN105826608AImprove cycle performanceImproved magnification performanceSecondary cellsOrganic solventEther

The invention relates to the technical field of lithium ion batteries, in particular to an electrolyte and a lithium ion battery containing the electrolyte .The electrolyte comprises lithium salt, organic solvent and additives, wherein the additives include a dimerization ester compound and a dinitrile compound containing an ether bond, and the dimerization ester compound includes carbonic acid ester dimer, carboxylic acid ester dimer and sulfonated lactone dimer .The electrolyte can improve the cycle performance, rate capability and high-temperature memory performance of the lithium ion battery on high voltage.

Owner:NINGDE AMPEREX TECH

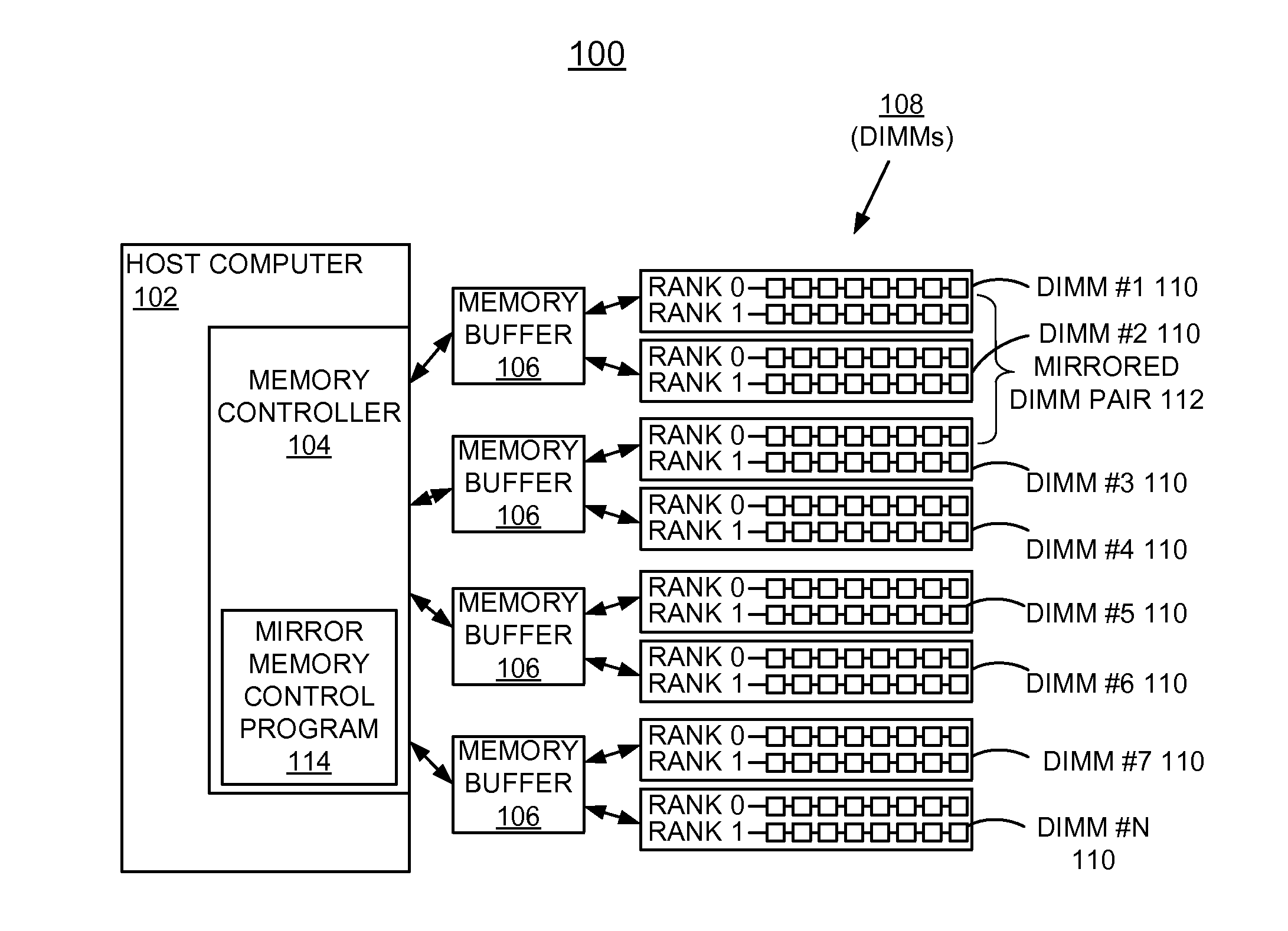

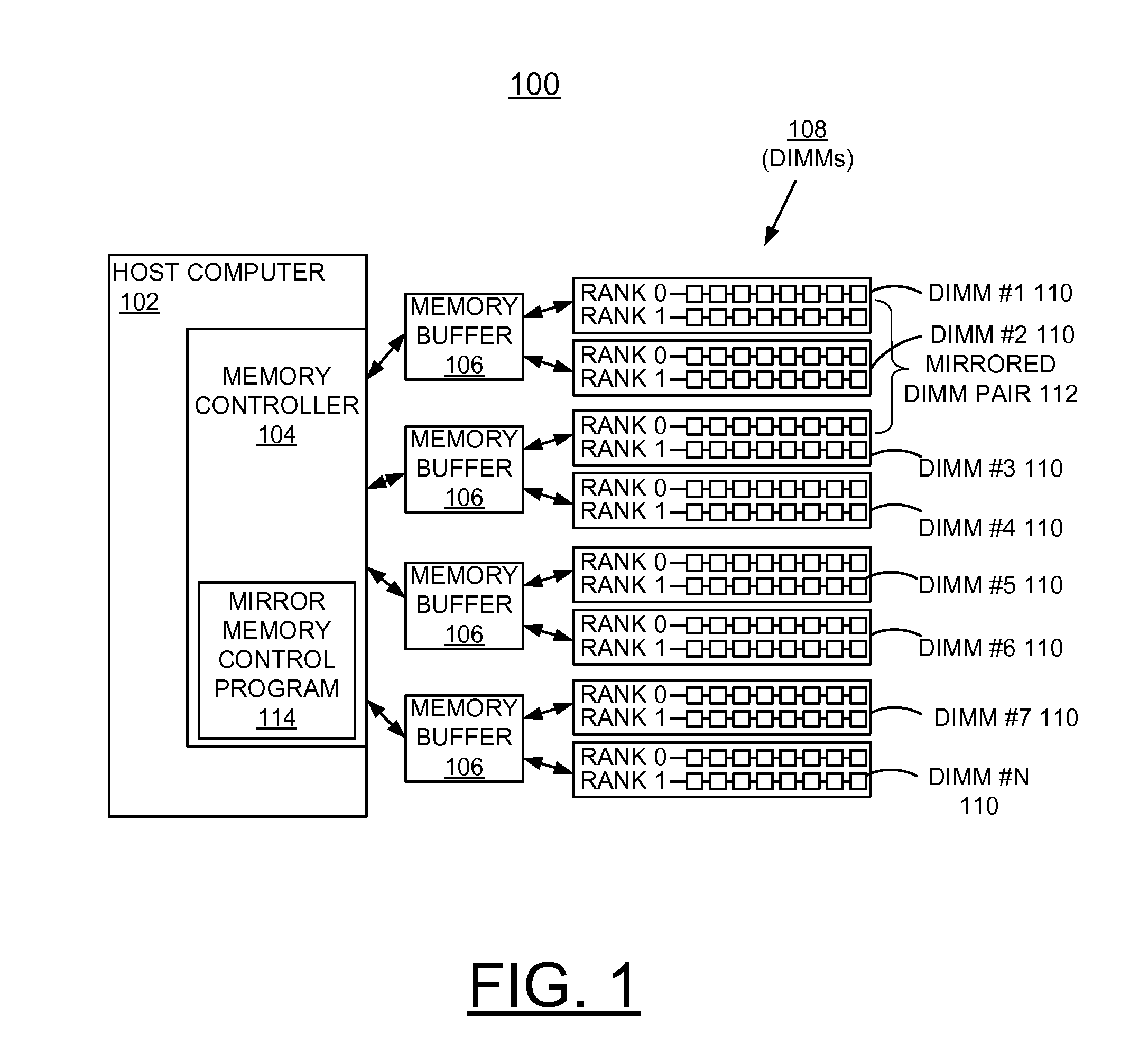

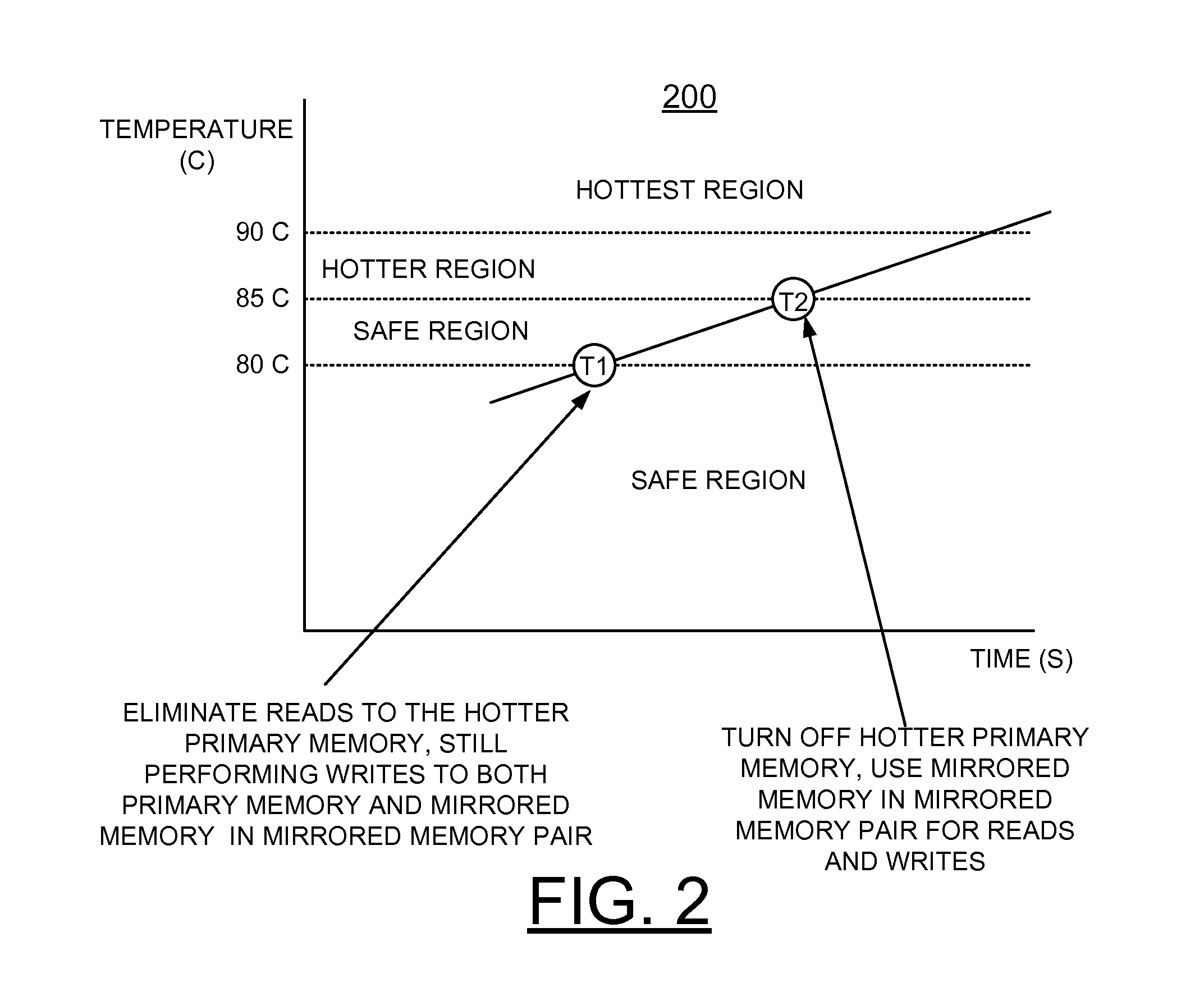

Iimplementing memory performance management and enhanced memory reliability accounting for thermal conditions

InactiveUS20130138901A1Improve reliabilityWithout negative effectMemory loss protectionError detection/correctionComputerized systemDependability

Owner:IBM CORP

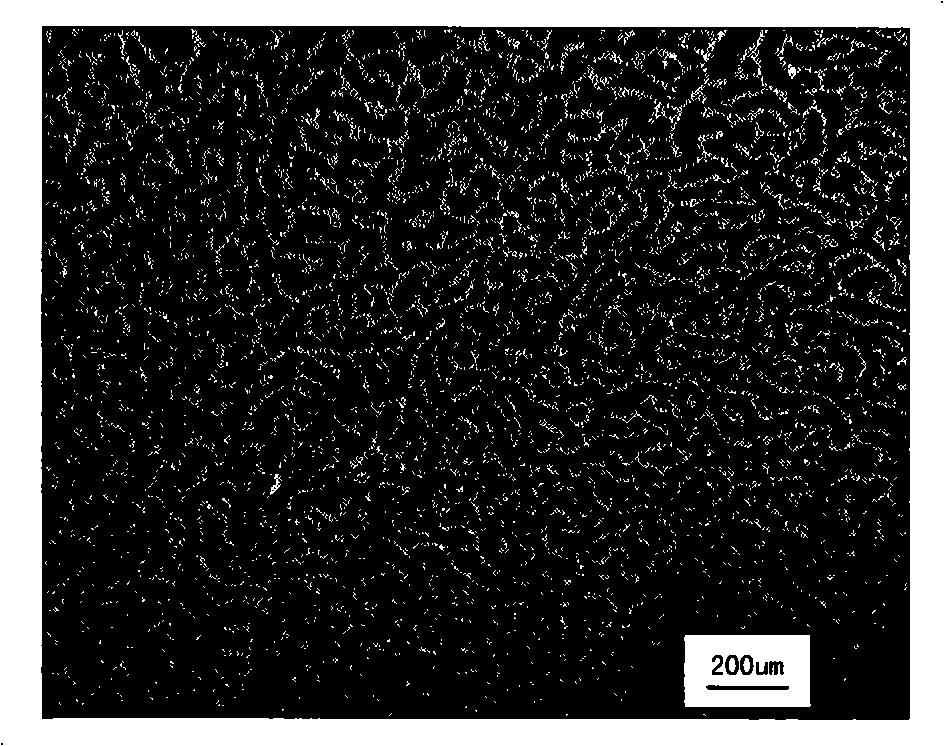

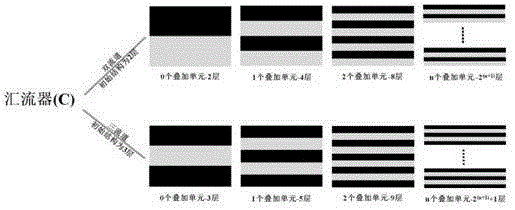

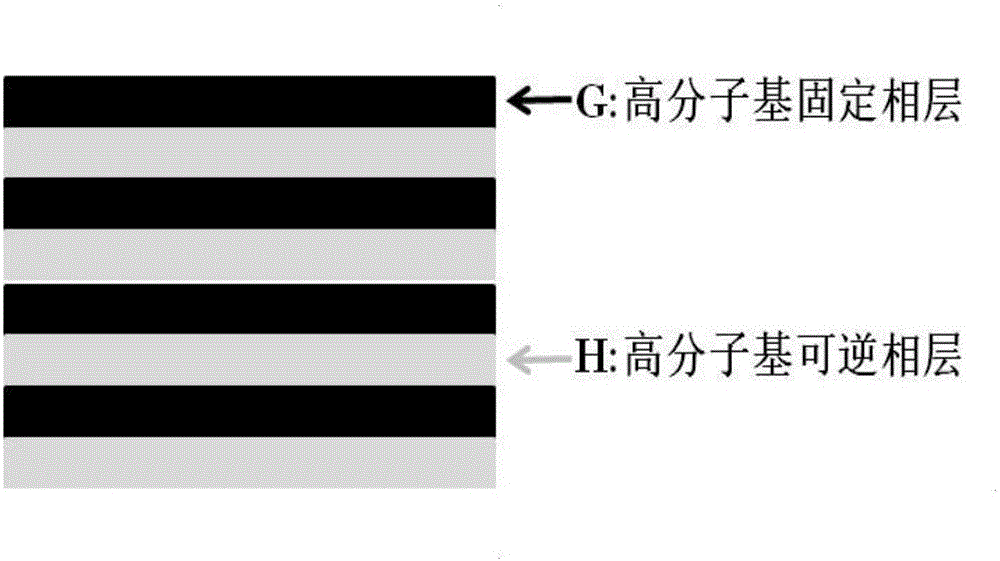

Preparation method of novel polymer-based multilayer shape memory material

ActiveCN106379011AExcellent shape memory performanceEasy to fixSynthetic resin layered productsRubber layered productsPolymer scienceRubber elasticity

The invention discloses a preparation method of a novel polymer-based multilayer shape memory material. The multilayer shape memory material prepared through the preparation method is formed by a polymer-based fixed phase layer and a polymer-based revertible phase layer, and has a two phase alternate multilayer bicontinuous structure, wherein the polymer-based fixed phase layer is a polymer having rubber elasticity at room temperature, and the polymer-based revertible phase layer is a polymer having obvious melt transition or glass transition in the heating process. The multilayer material deforms at a melting point or a glass transition temperature or above, then is cooled to room temperature in order to obtain a temporary shape, and then is heated to the melting point or the glass transition temperature or above in order to recover to an initial shape. The polymer-based multilayer shape memory material prepared through the preparation method has the advantages of controllable layer quantity, layer thickness and layer structure, adjustable raw material formula, excellent shape memory performance, commercial raw materials, and low production cost; and the preparation method has the advantages of simplicity, high production efficiency, and realization of continuous batch production.

Owner:SICHUAN UNIV

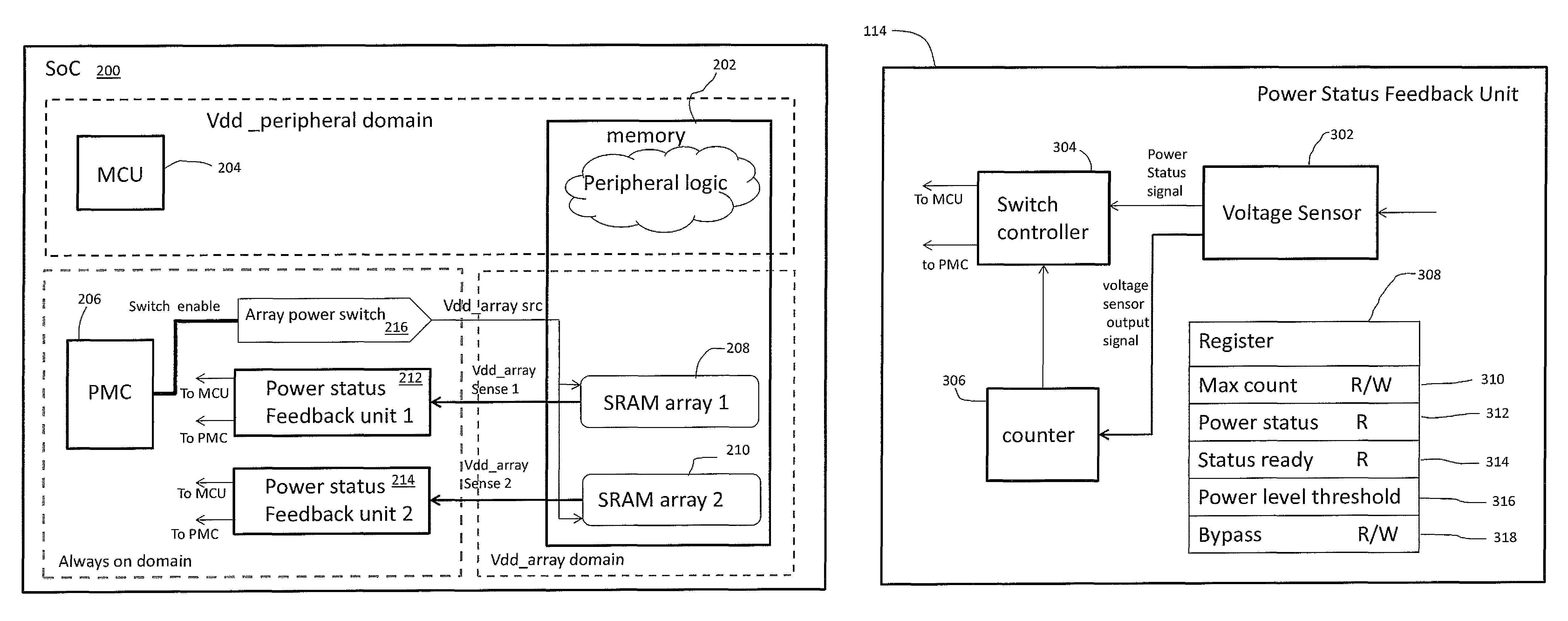

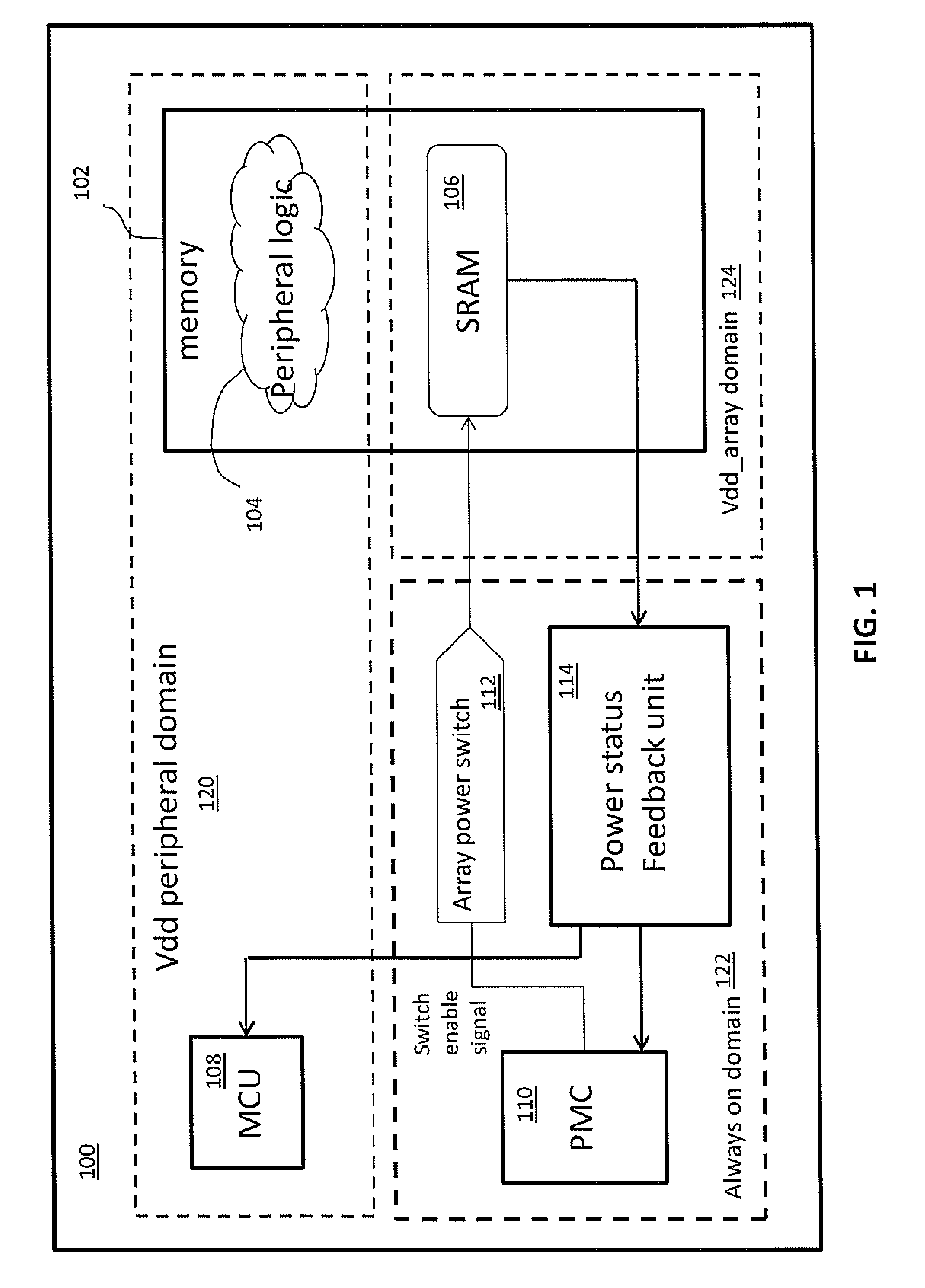

Performance based power management of a memory and a data storage system using the memory

ActiveUS9189053B2Input/output to record carriersPulse automatic controlData treatmentVoltage sensing

Power control circuitry for a data processor supplies a memory array with a supply voltage corresponding to a memory performance level. The performance levels include a full performance level and a power-saving performance level. Voltage sensing circuitry senses a voltage level of the memory array and outputs a power status signal. The power status signal is used to determine when the memory array is awake and can be accessed.

Owner:NXP USA INC

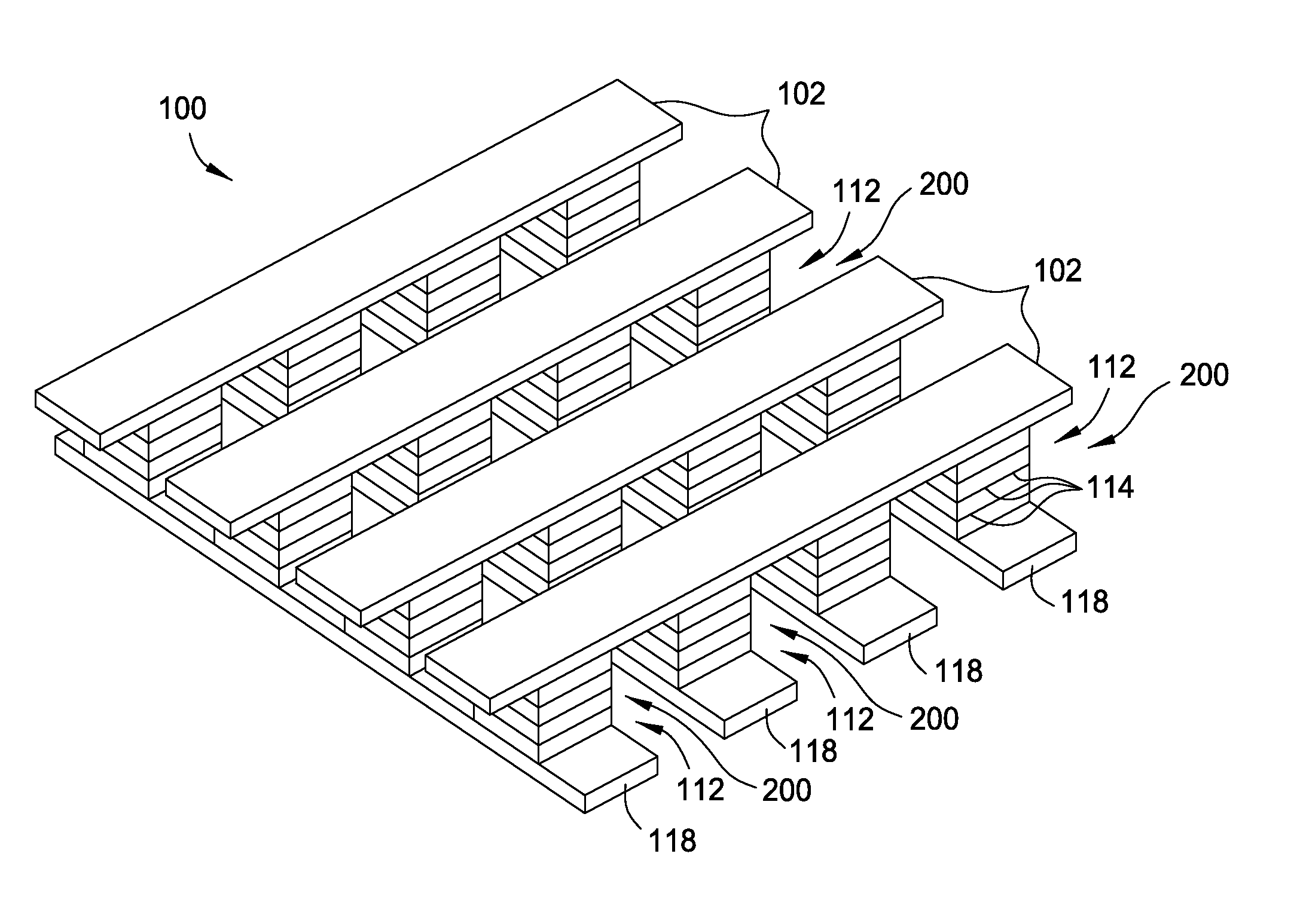

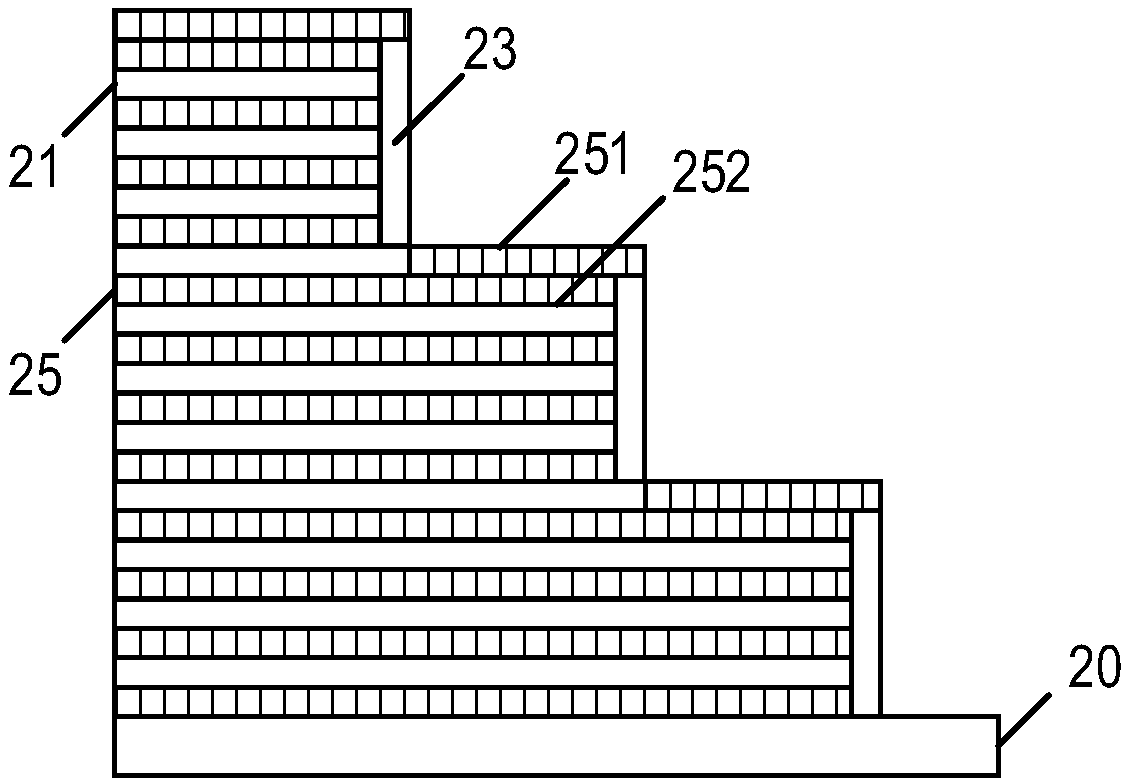

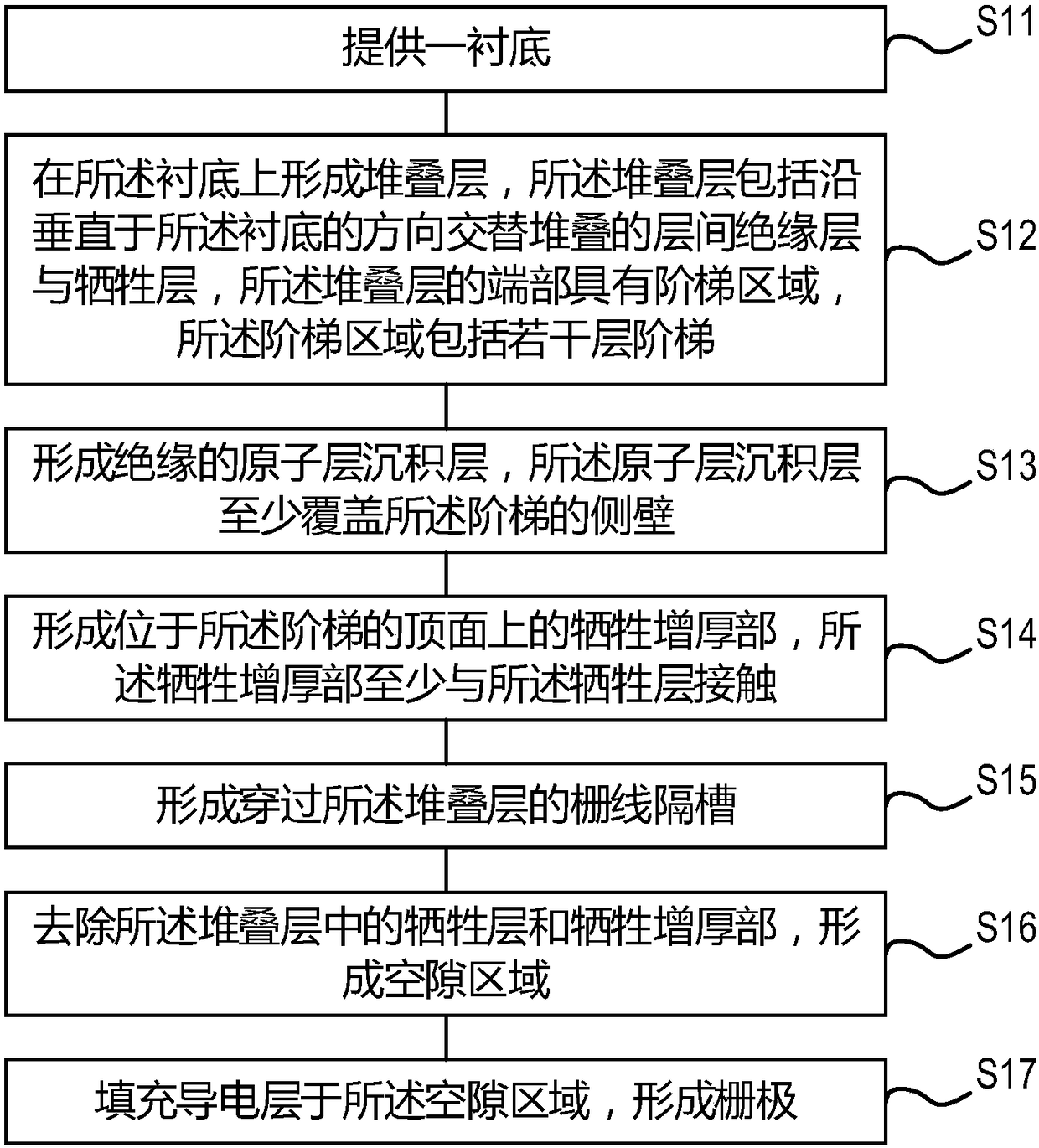

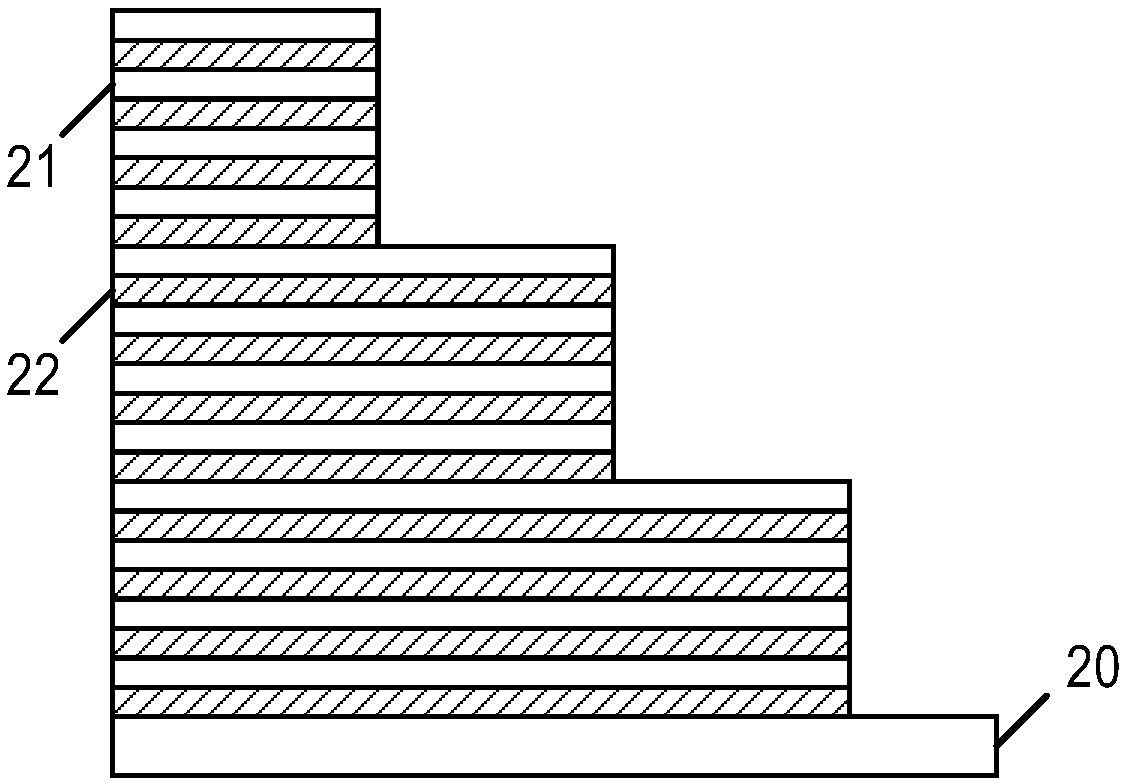

Three-dimensional memory and manufacturing method thereof

PendingCN108493192AIncrease storage capacityStable storageSolid-state devicesSemiconductor devicesEngineeringAtomic layer deposition

The invention relates to the technical field of semiconductor manufacturing and particularly relates to a three-dimensional memory and a manufacturing method thereof. The three-dimensional memory comprises a substrate, a stacking structure and an insulated atom layer settling layer, wherein the stacking structure is formed on the substrate and comprises grid electrodes, interlayer insulating layers and multiple layers of steps, the grid electrodes and the interlayer insulating layers are alternately stacked along the direction vertical to the substrate, and the steps are located at the end part of the substrate; the grid electrodes comprise thickened parts, and the thickened parts protrude along the direction, towards the stacking structure, of the substrate and are located on the top surfaces of the steps; and the insulated atom layer settling layer is in contact with the side walls of the steps and is used for electrically isolating the grid electrode between two layers of the steps.According to the three-dimensional memory, the problem that a three-dimensional memory easily malfunctions is avoided, and the memory performance of the three-dimensional memory is improved.

Owner:YANGTZE MEMORY TECH CO LTD

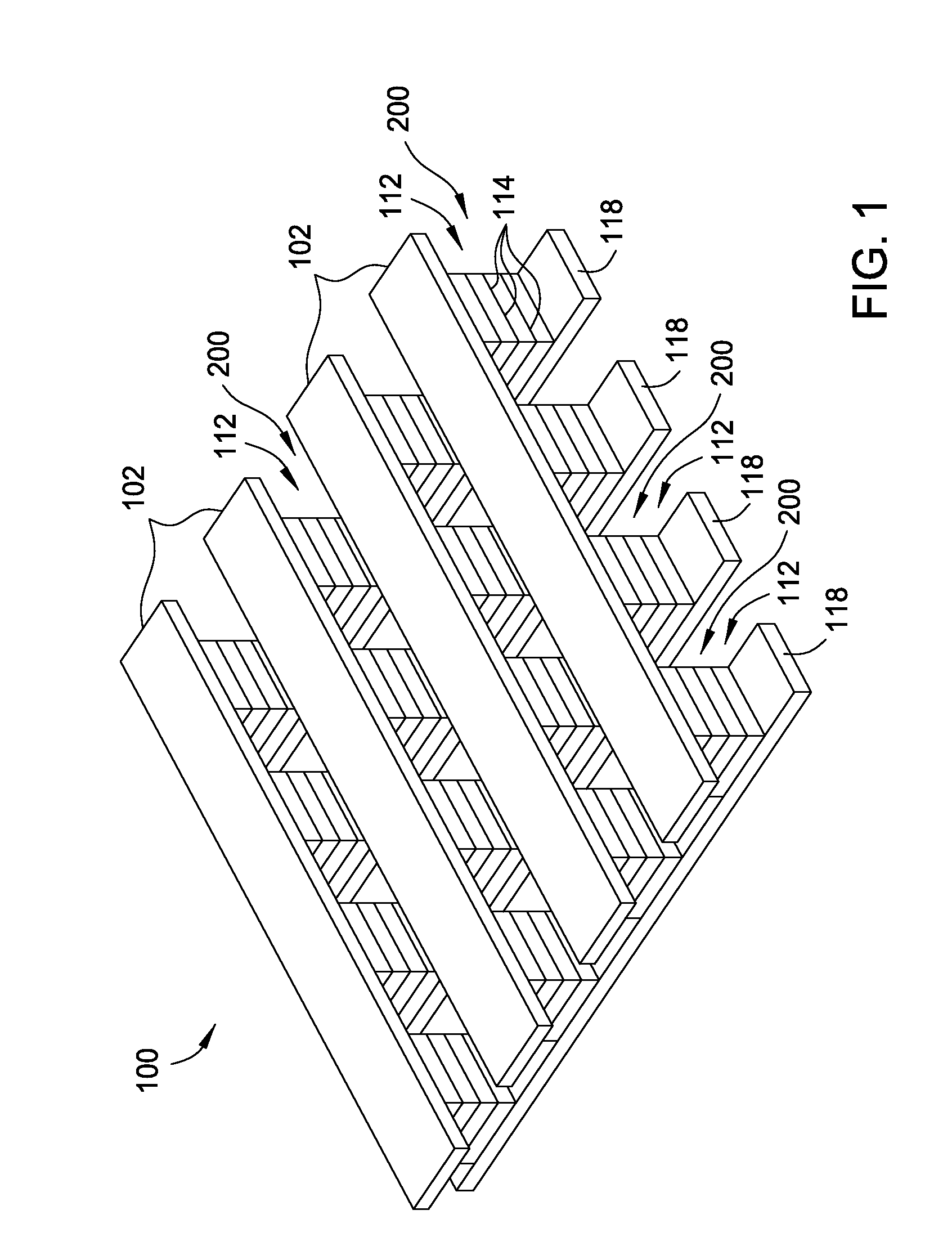

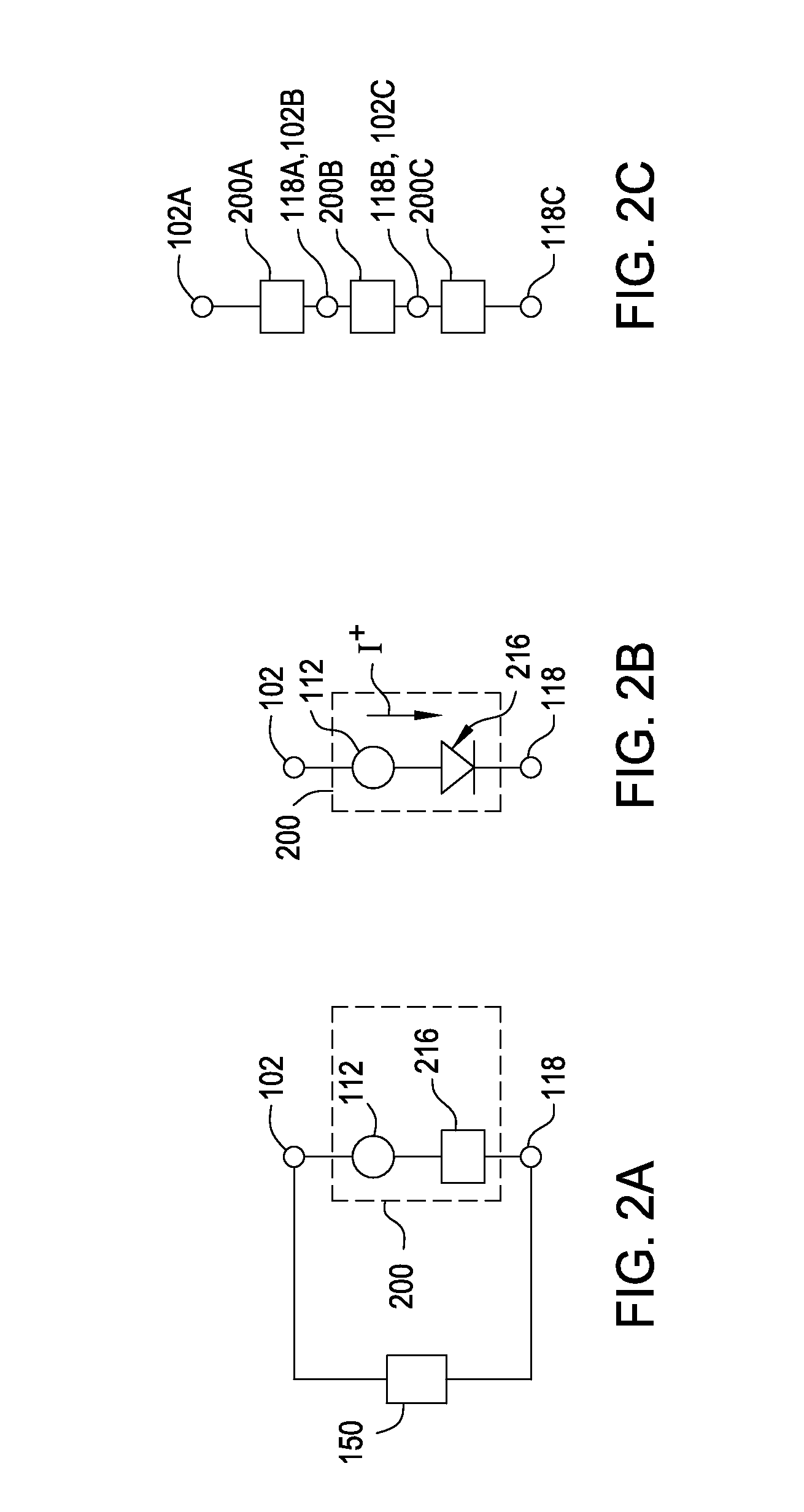

Miniturization techniques, systems, and apparatus relatng to power supplies, memory, interconnections, and leds

InactiveUS20120002455A1Improve performanceMiniaturized layoutCoupling device connectionsFinal product manufactureElectricityMiniaturization

Miniaturization techniques, systems, and apparatus relating to power supplies, memory, interconnections, and LEDS are described herein. Specifically, some aspects of the invention relate to techniques for miniaturization of power supplies. Other aspects relate to systems and methods for optimizing memory performance in a computer device or system. Still further, some aspects relate to systems and methods for miniaturizing and optimizing memory layout on a circuit board. Other aspects relate to systems and methods for attaching an integrated circuit, which comprises an array of pins, to a circuit board through the use of an adaptor that comprises a BGA, and which is configured to electrically and physically attach to the circuit board. Furthermore, some aspects relate to systems and methods for achieving activation of at least one multi-color LED, such as a bi-color or tri-color LED, using multiple electrical ground outputs or signals intended to activate only a single unicolor LED.

Owner:ATD VENTURES

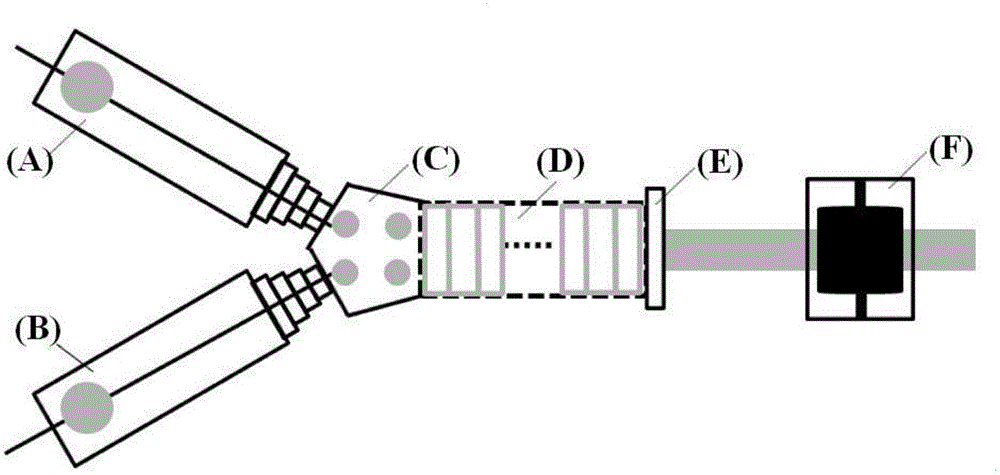

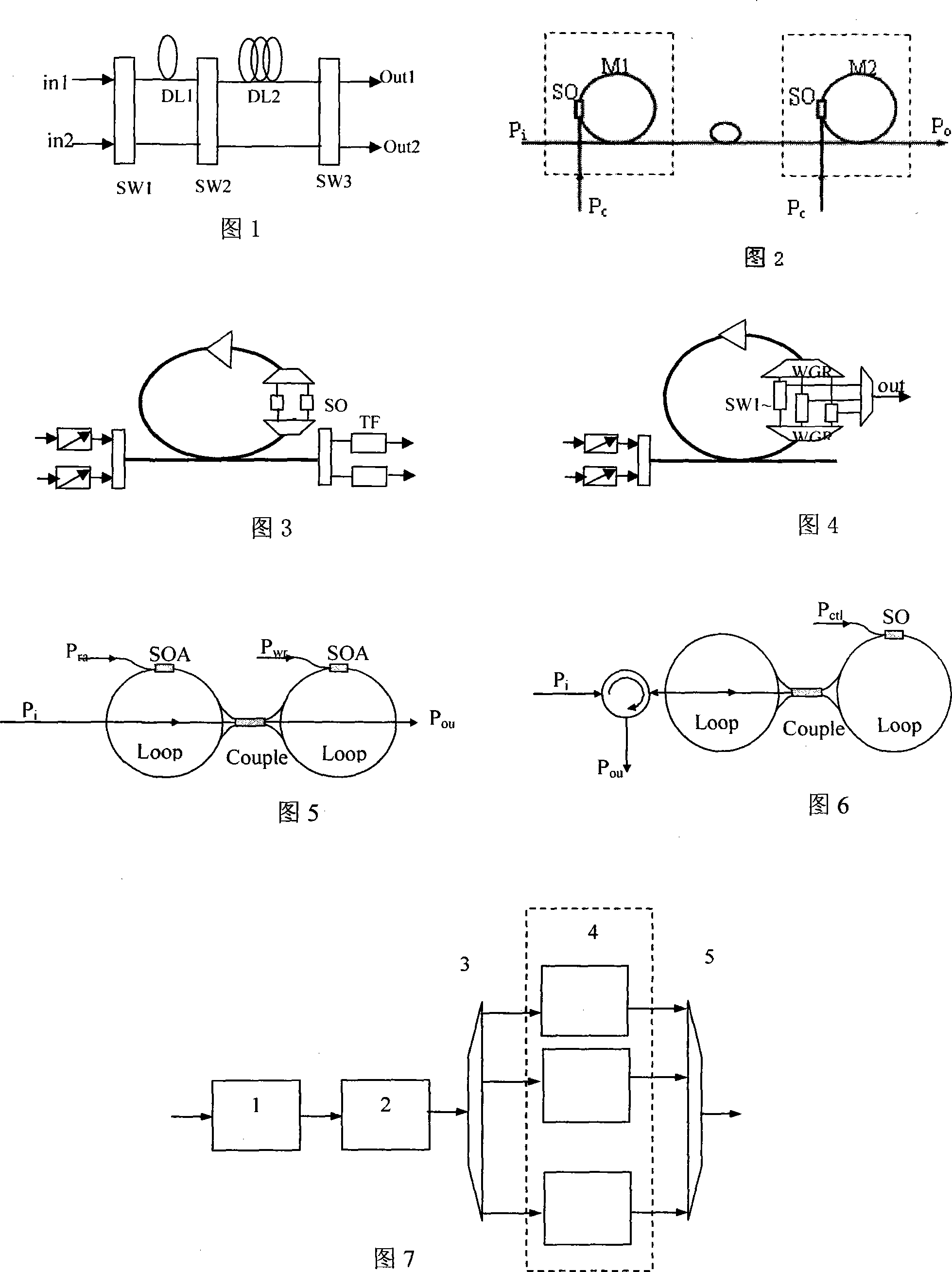

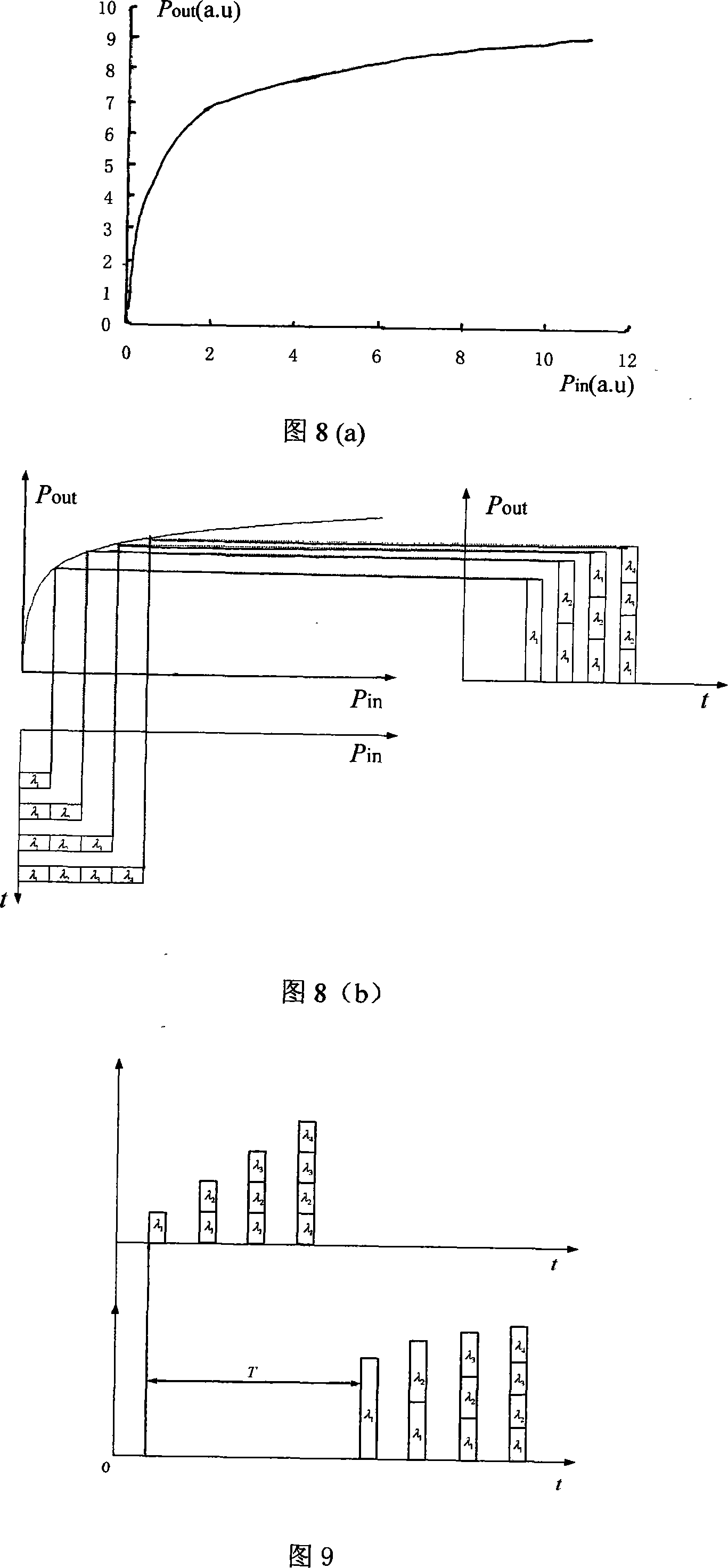

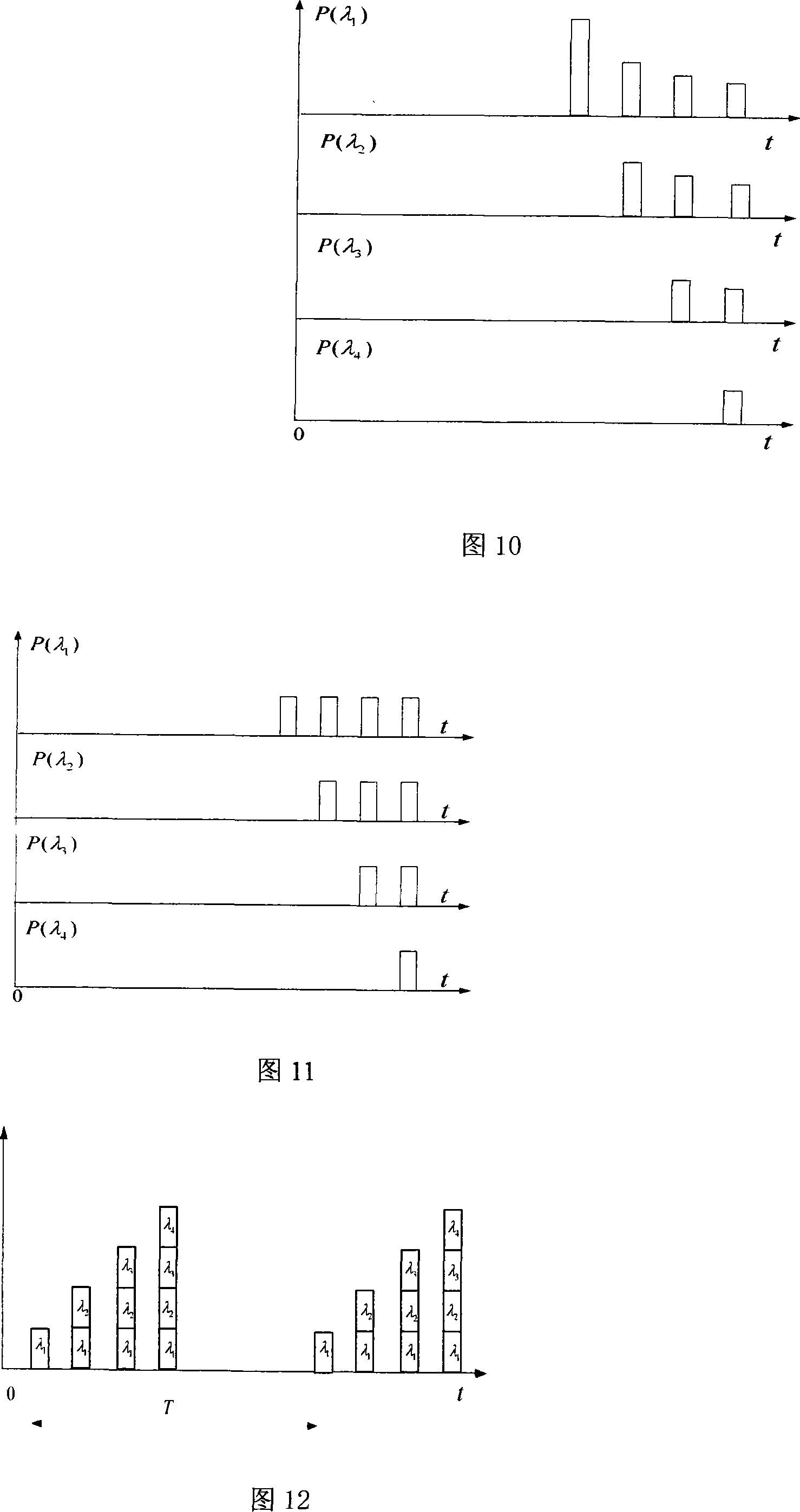

Multi-wave length parallel buffer full optical buffer

InactiveCN101127570AOvercoming cross modulationImprove signal-to-noise ratioWavelength-division multiplex systemsCoupling light guidesSignal-to-noise ratio (imaging)Multiplexer

The utility model relates to an all-optical buffer of multiple wavelength parallel storage to solve parallel buffer problem of dense wave-division multiplex signal and consists of an input power equalizer, a light buffer unit, a wave-division multiplex-de-multiplexer, an output power equalizer set and a wave-division multiplexer. The utility model adopts the multiple wavelength parallel storage technique of power equalization - parallel buffer - de-multiplex - power equalization - re-multiplex to maintain the synchronous buffering of multiple wavelength signals, so that the cross modulation among multiple wavelength signals can be effectively overcome, the signal-to-noise ratio can be promoted and the good buffer memory performance can be gained. Free adjustment on the cycle multiple of multiple wavelength signals buffer period can be realized in the utility model and the reading and writing time can be controlled with light signal writing and reading. The reading time can be started as required after storing signals; the event triggering can be realized without preset in the buffer. With great flexibility, the utility model is a real all-optical buffer suitable to all-optical routers or all-optical exchangers.

Owner:BEIJING JIAOTONG UNIV

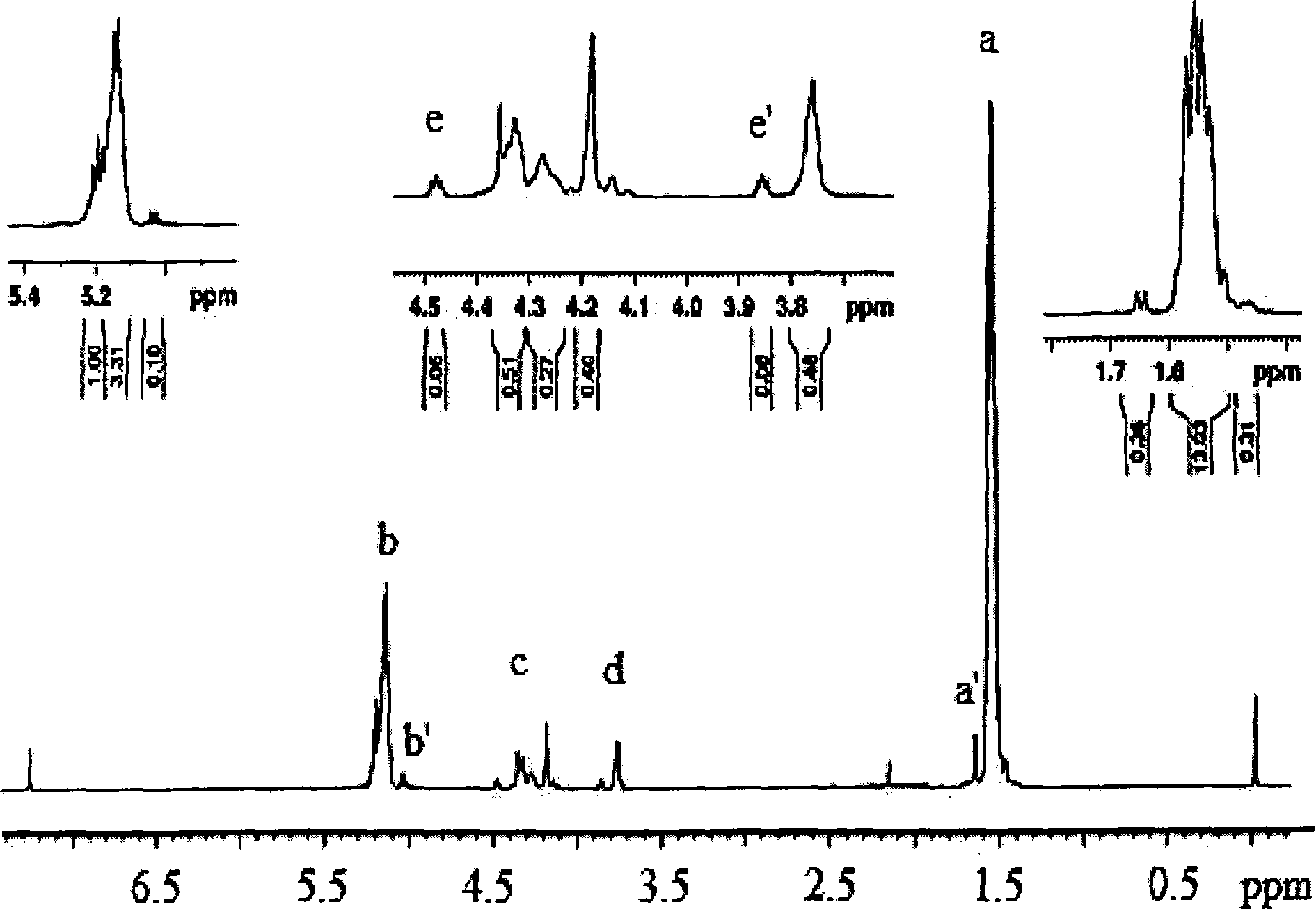

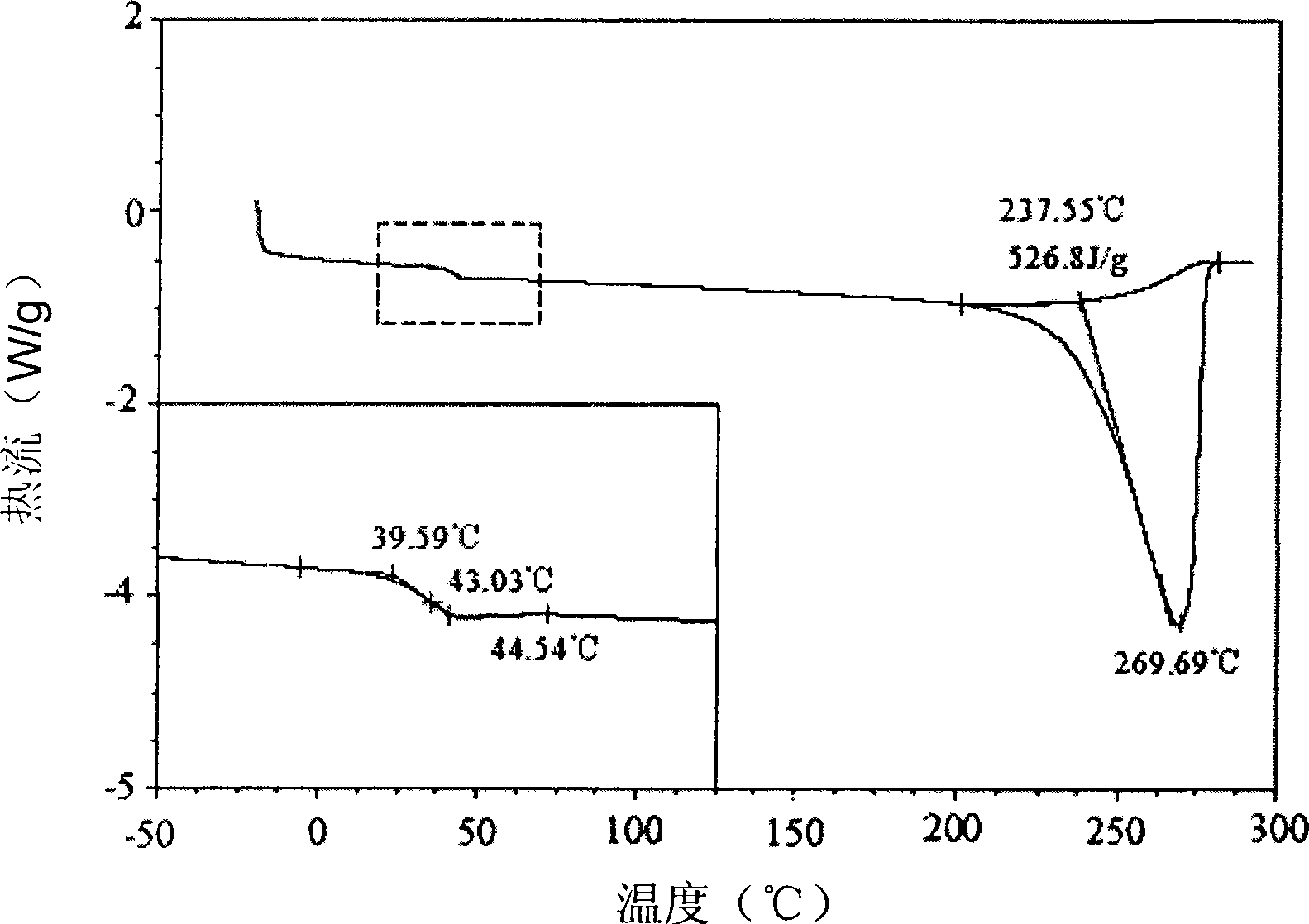

Multi-block polyurethane shape memory high molecule material and preparation method thereof

The invention provides a multi-block polyurethane shape memory polymer material based on lactide and 1, 4-dioxegy cyclohexanone. The polymer material takes hydroxyl terminated poly (lactide-co-1, 4-dioxegy cyclohexanone) as a soft block; a PUU chain segment or uramido chain segment product which is formed by vulcabond and bifunctional micromolecules containing active hydrogen is chosen as a hard block. The temperature of the shape memory is within 20-55 DEG C. The invention further provides the preparation method of the material. The shape memory polymer material based on lactide and 1, 4-dioxegy cyclohexanone provided by the invention integrates good odegradability, biocompatibility, high mechanical strength, flexility and the shape memory performance together. The deformation temperature of the polymer material can be adjusted to be close to human body temperature; therefore, the polymer material is applied to surgical operations or medical appliance implantation materials.

Owner:CHONGQING UNIV +1