Patents

Literature

1252 results about "Voltage sensing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A voltage sensing circuit is a circuit intended to carry minimal to no current so there is minimal voltage drop in this measurement circuit. The voltage sensing circuit should really be considered a voltage correction circuit or a voltage drop compensation circuit.

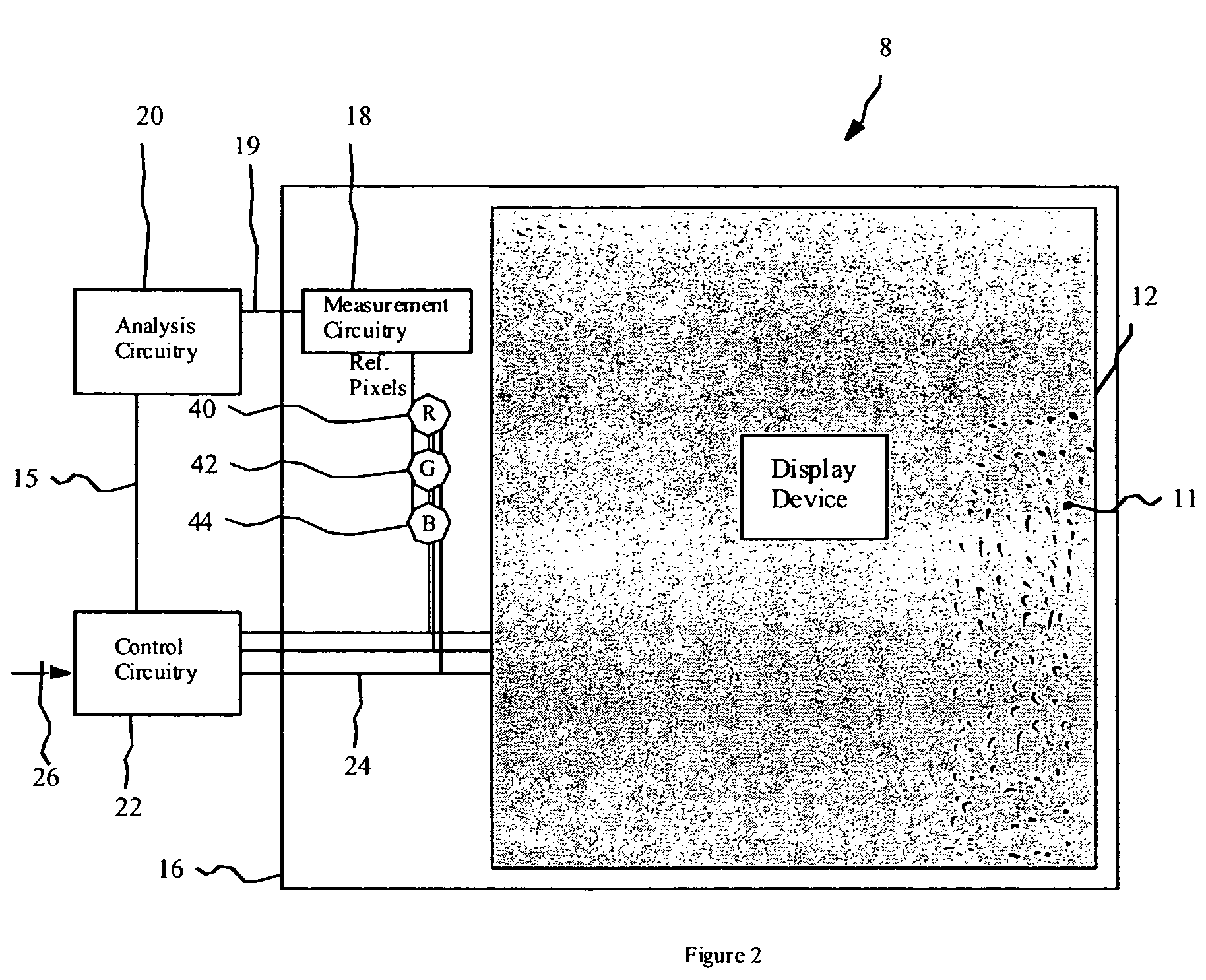

OLED display with aging compensation

Owner:GLOBAL OLED TECH

OLED display with aging compensation

ActiveUS20050110420A1Simple voltage measurementEasy to measureHeater elementsCathode-ray tube indicatorsDisplay deviceHemt circuits

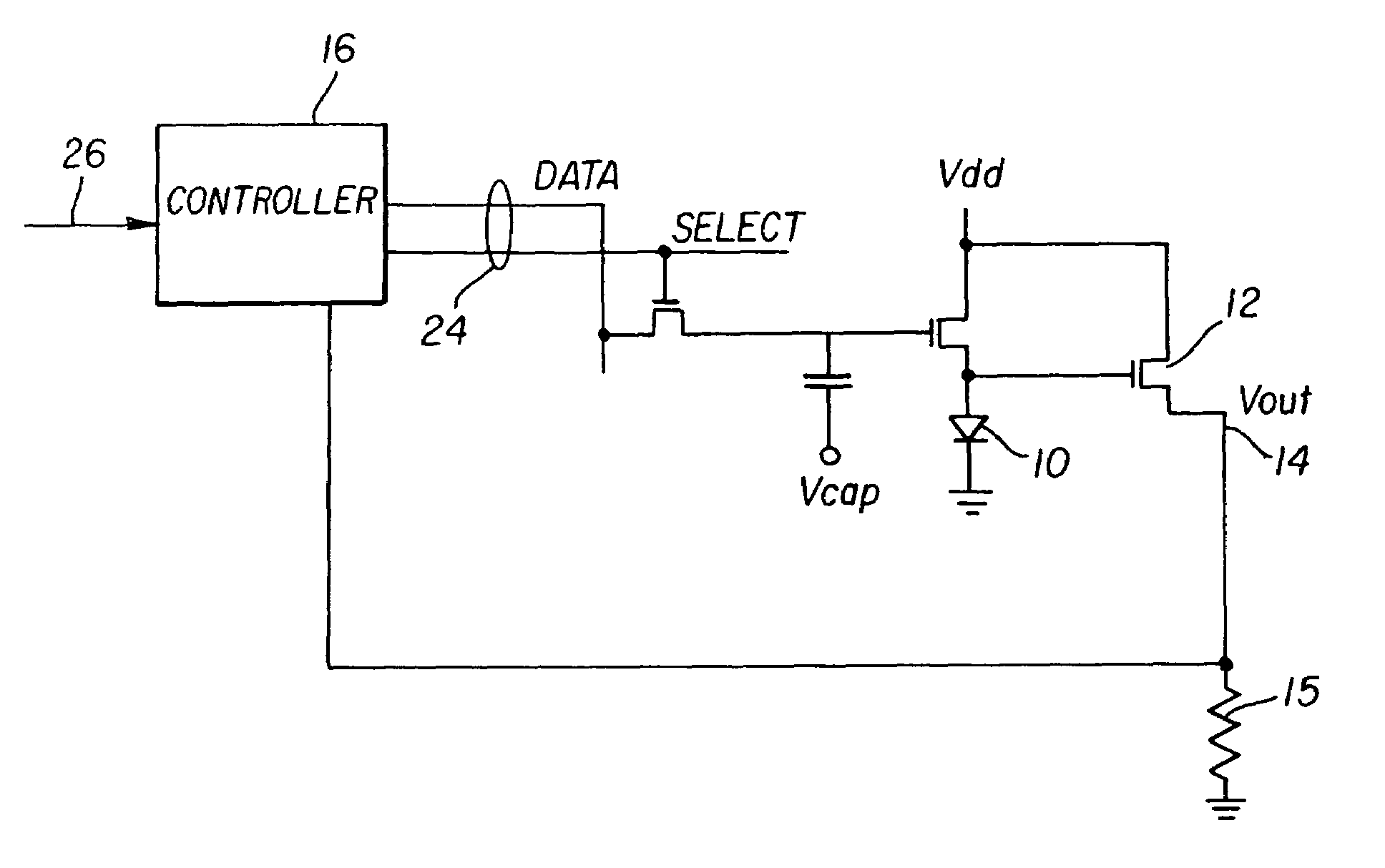

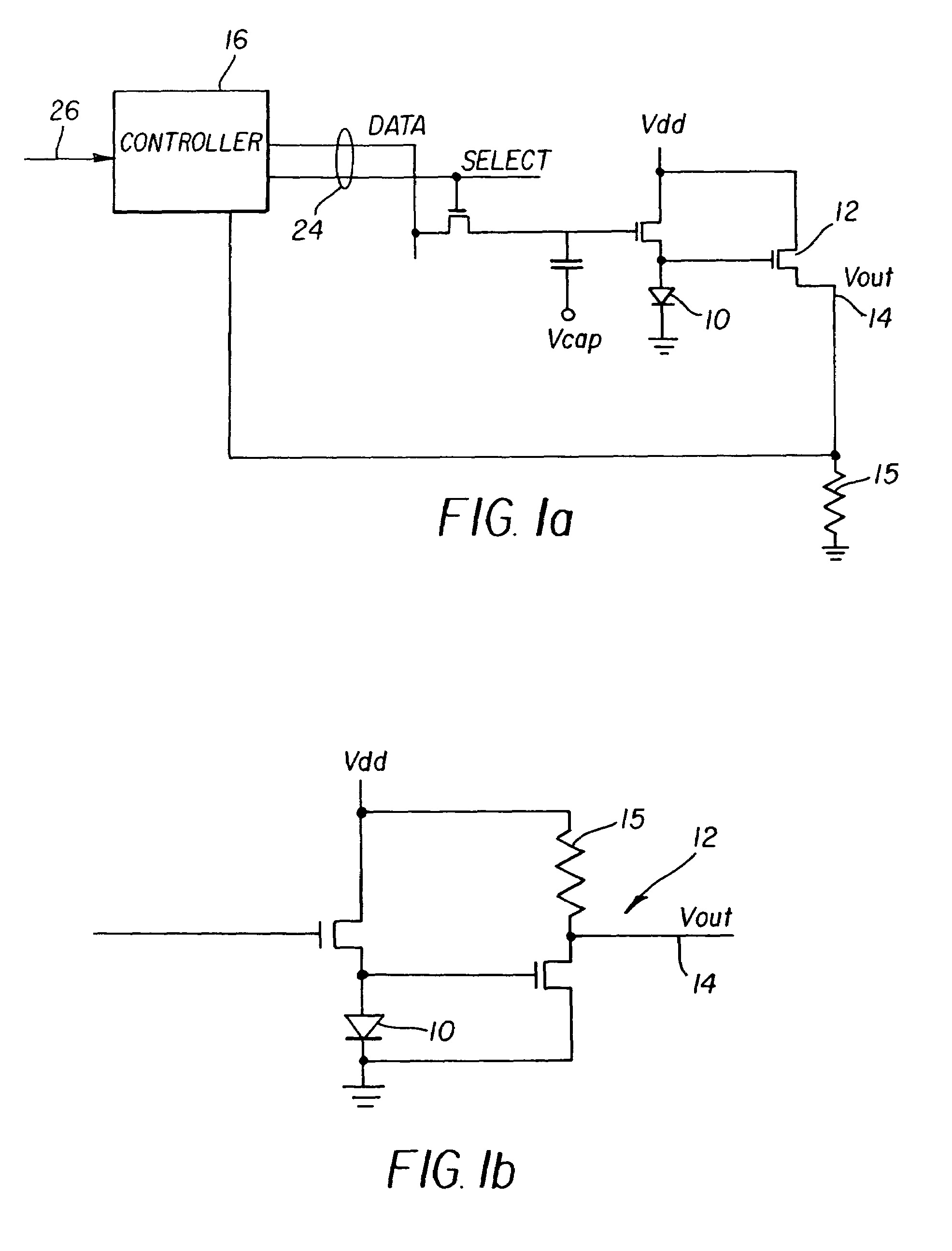

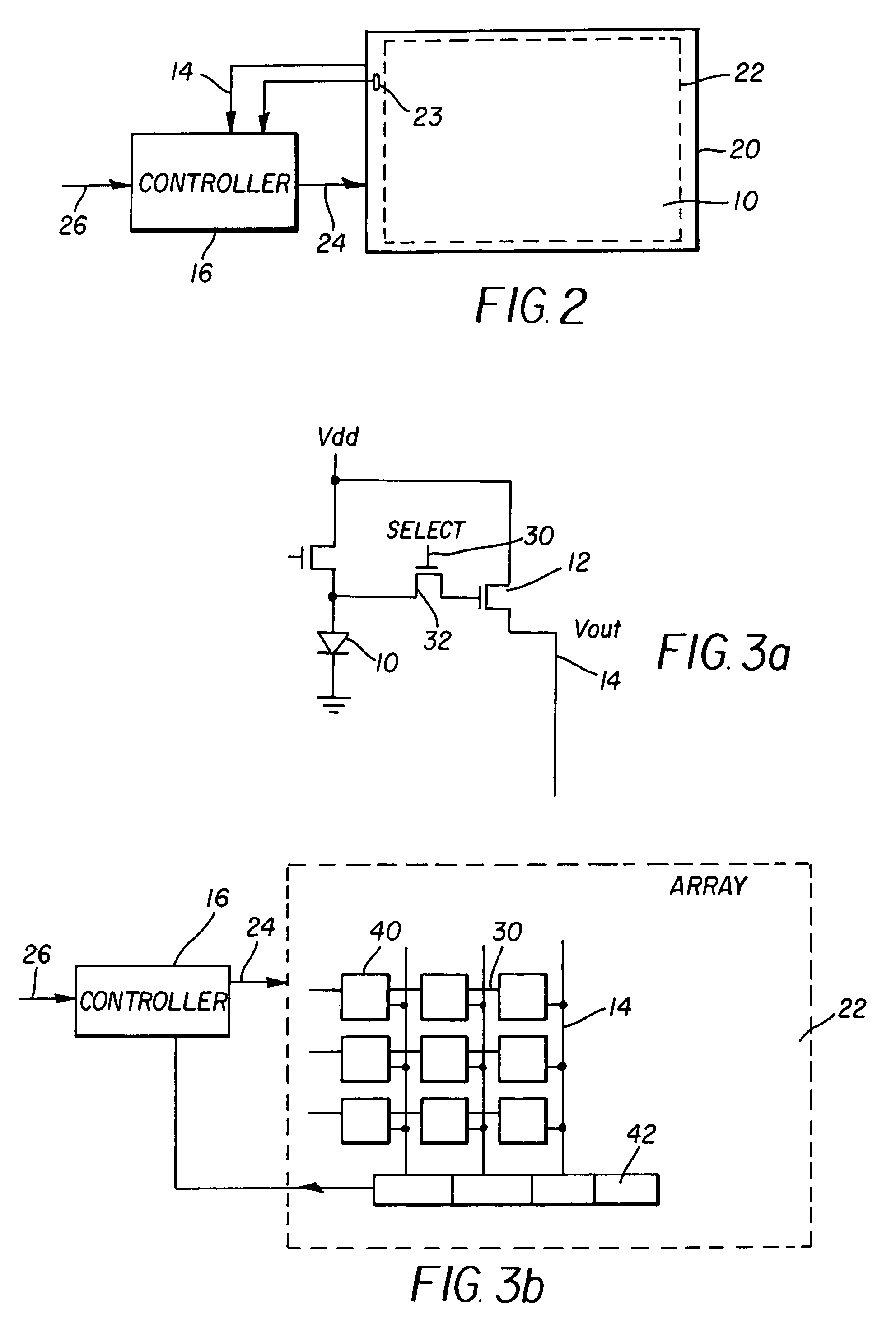

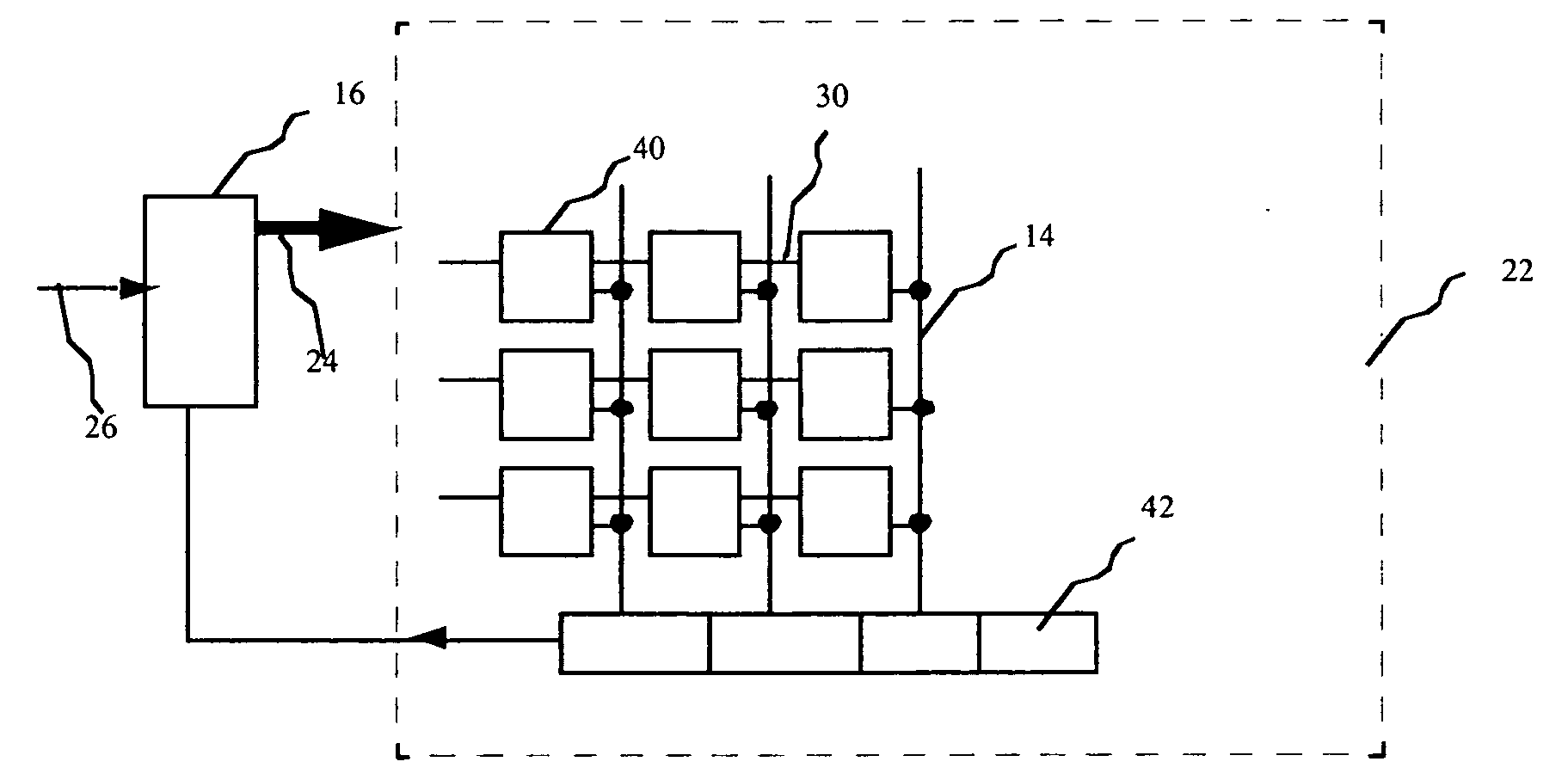

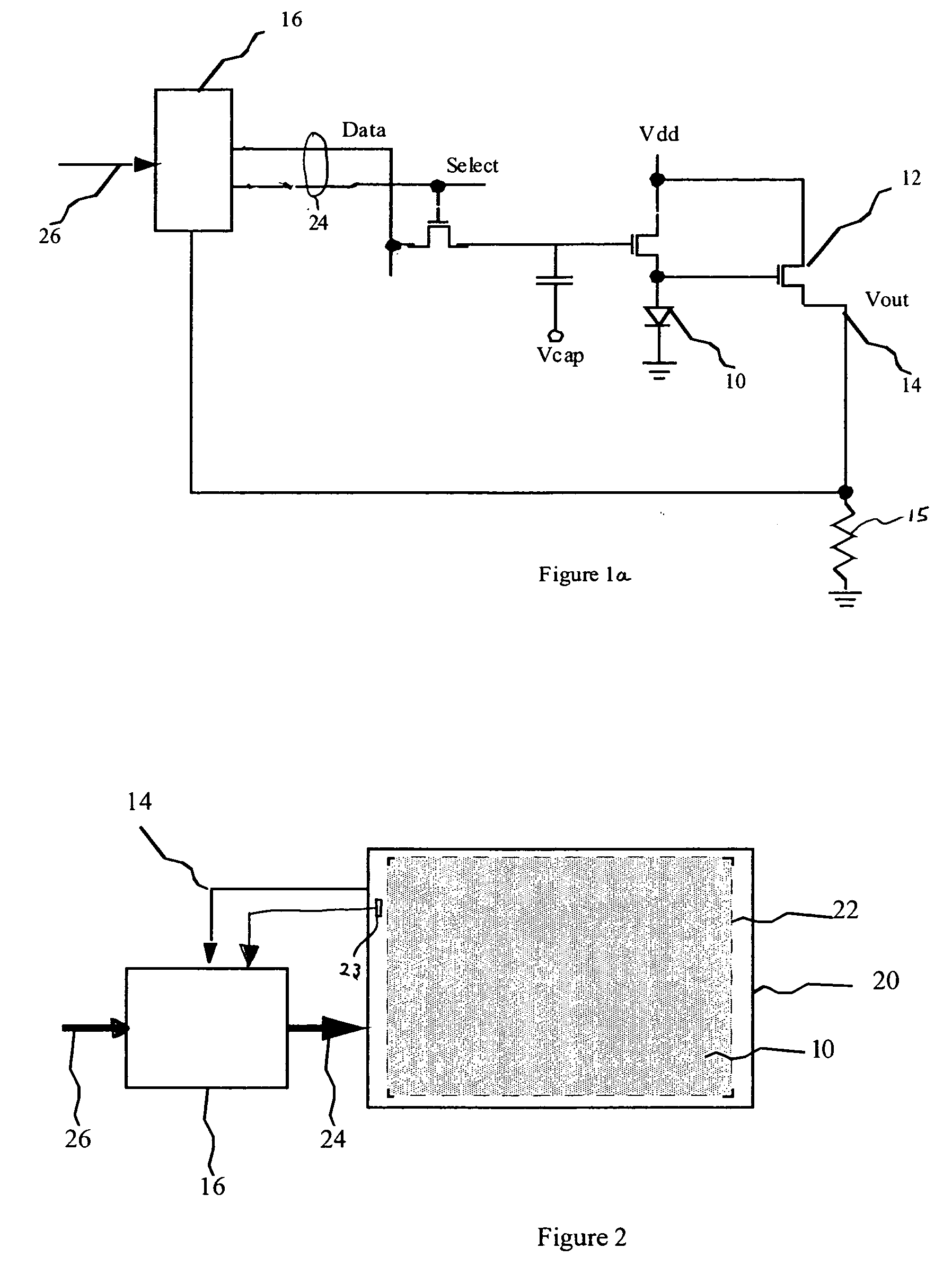

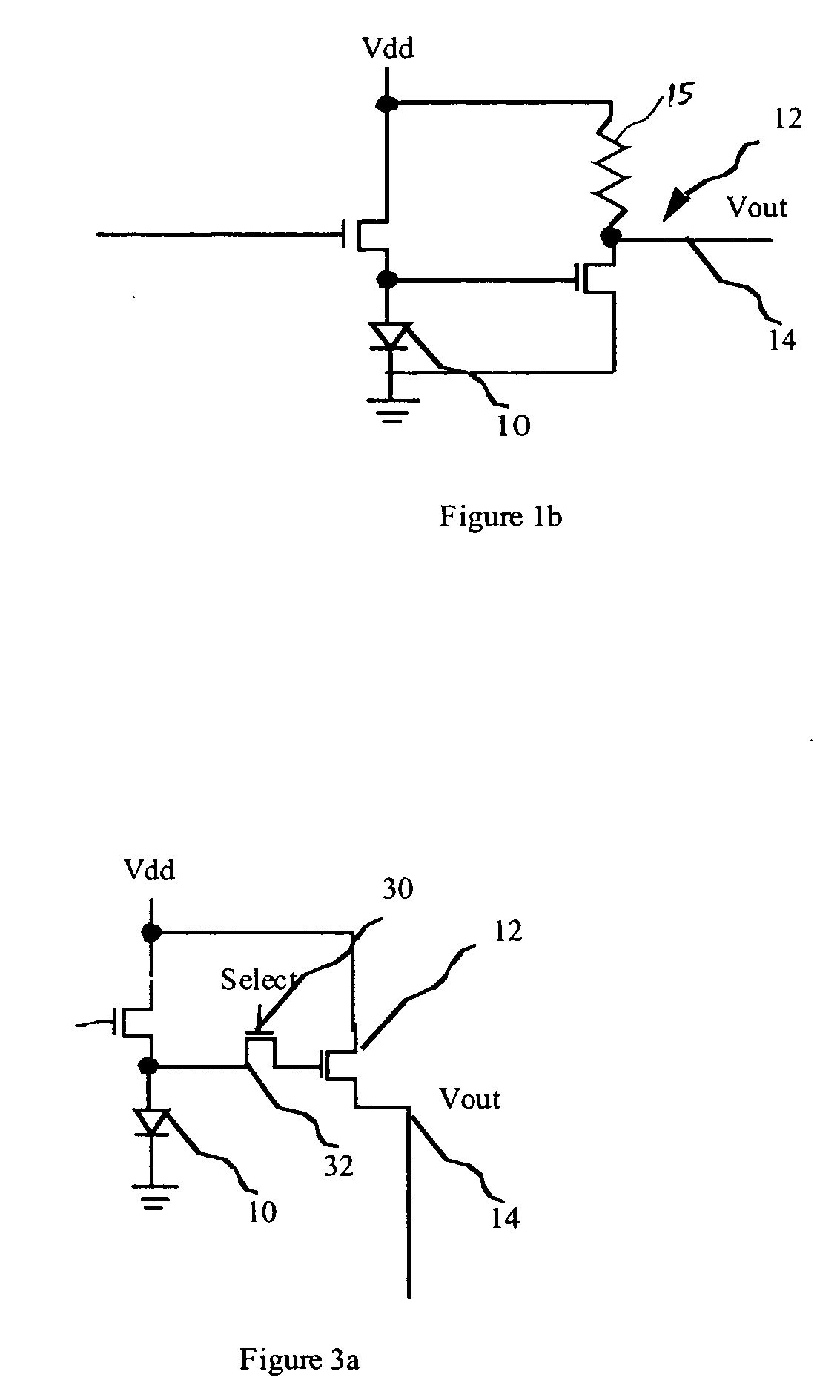

An organic light emitting diode (OLED) display includes an array of OLEDs, each OLED having two terminals; a voltage sensing circuit for each OLED including a transistor in each circuit connected to one of the terminals of a corresponding OLED for sensing the voltage across the OLED to produce feedback signals representing the voltage across the OLEDs; and a controller responsive to the feedback signals for calculating a correction signal for each OLED and applying the correction signal to data used to drive each OLED to compensate for the changes in the output of each OLED.

Owner:GLOBAL OLED TECH

OLED display with aging compensation

InactiveUS7321348B2Simple voltage measurementSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceControl circuit

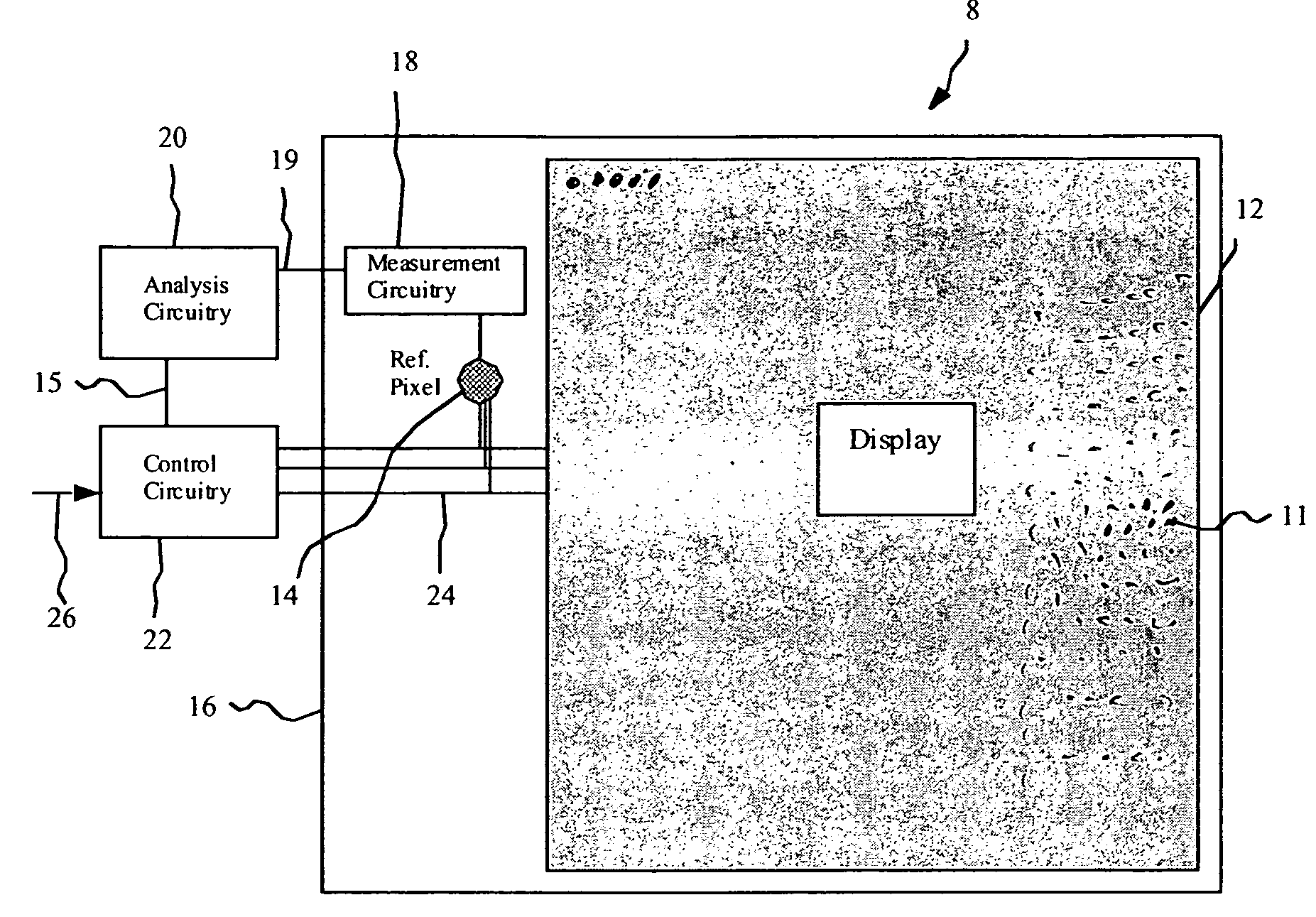

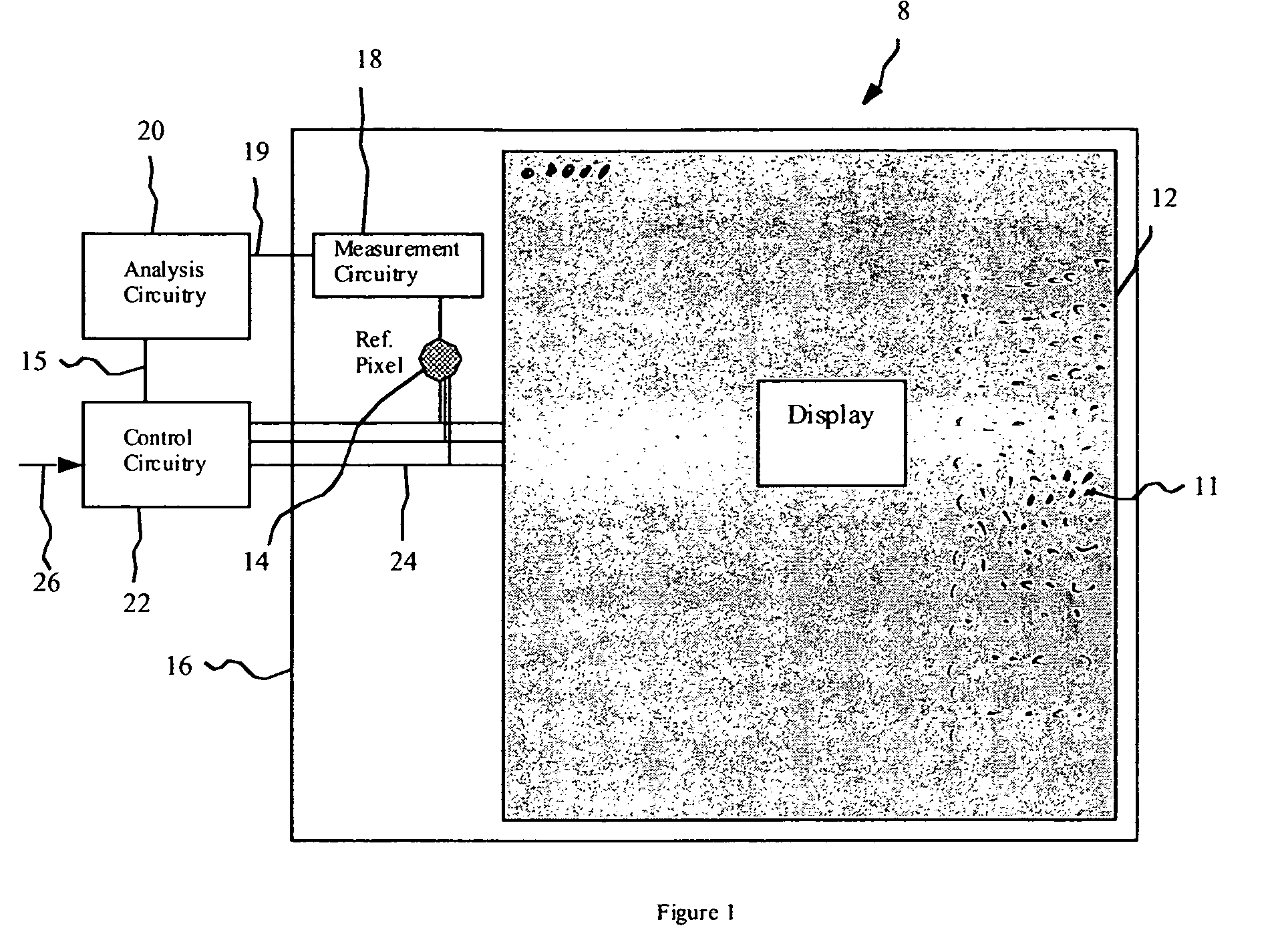

An organic light-emitting diode (OLED) display having addressable pixels on a substrate, the pixels having performance attributes, and a control circuit for controlling the pixels of the display device, includes one or more OLED pixels; an OLED reference pixel located on a substrate and connected to the control circuit, the OLED reference pixel having the same performance attributes as the one or more OLED pixels, the OLED reference pixel having a voltage sensing circuit including a transistor connected to one of the terminals of the OLED reference pixel for sensing the voltage across the OLED reference pixel to produce a voltage signal representing the voltage across the OLED reference pixel; a measurement circuit connected to the voltage signal to produce an output signal representative of the performance attributes of the OLED reference pixel; an analysis circuit connected to the measurement circuit to receive the output signal, compare the performance attributes with predetermined performance attributes, and produce a feedback signal in response thereto; and the control circuit being responsive to the feedback signal to compensate for changes in the output of the OLED pixels.

Owner:GLOBAL OLED TECH

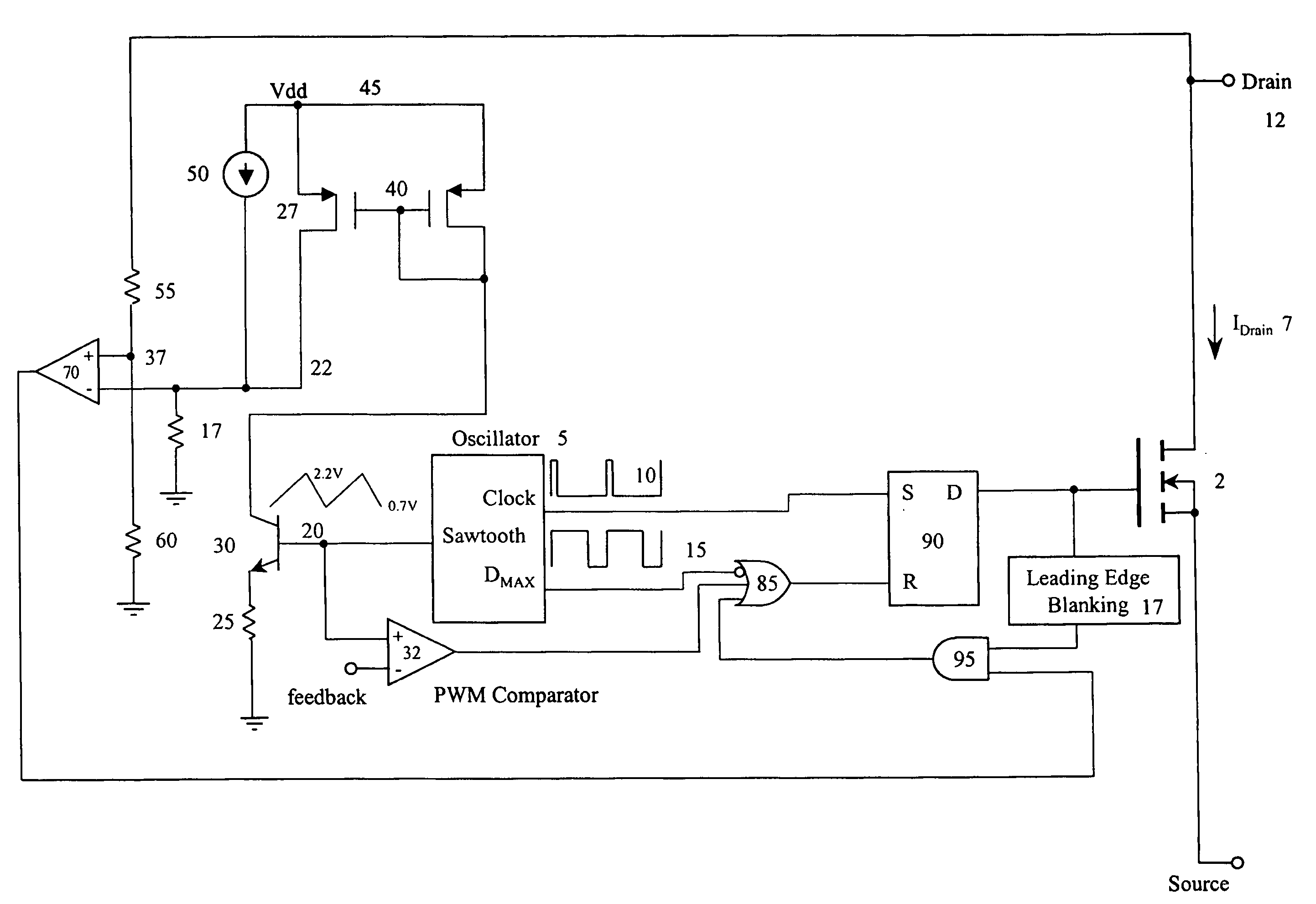

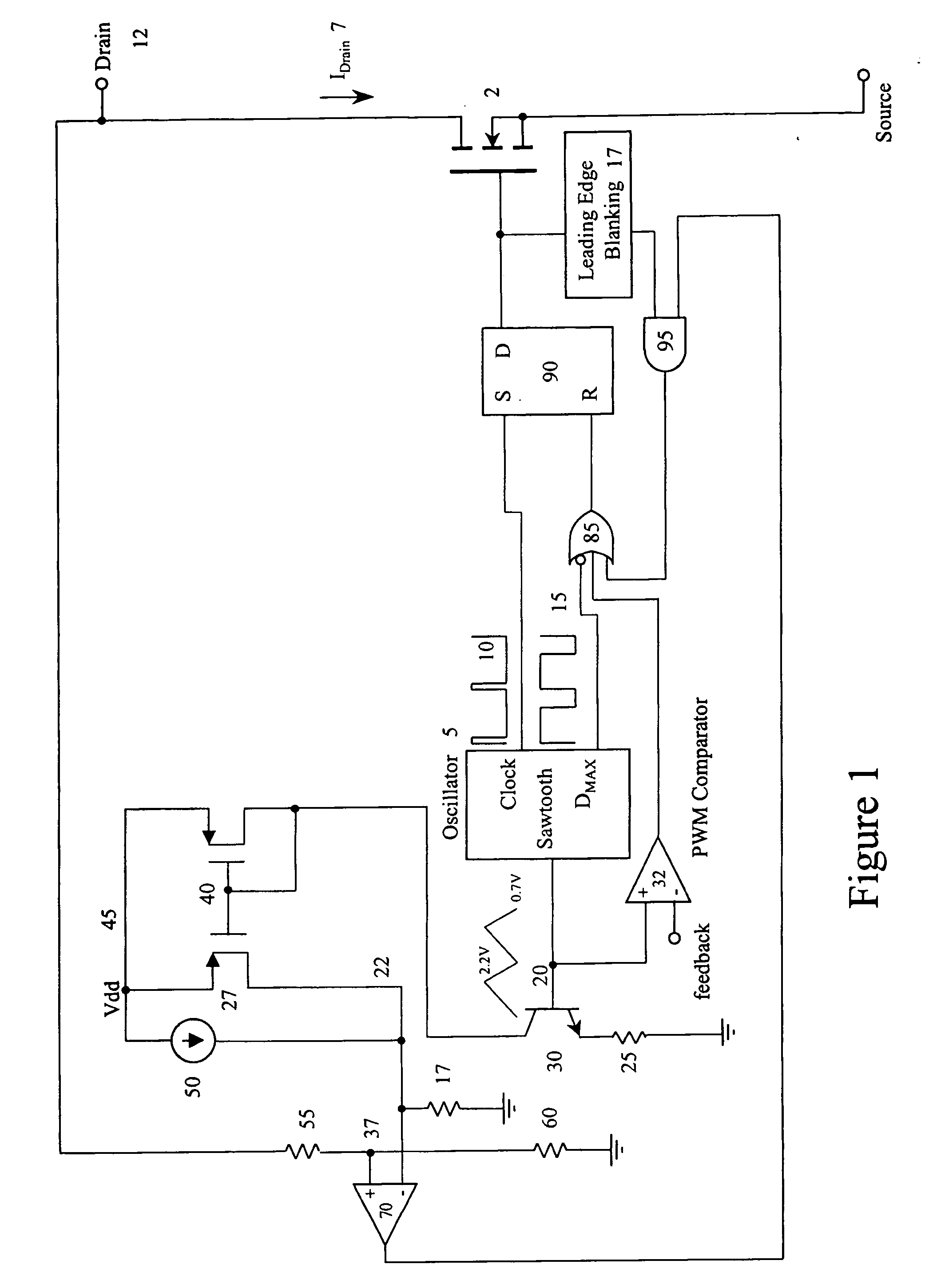

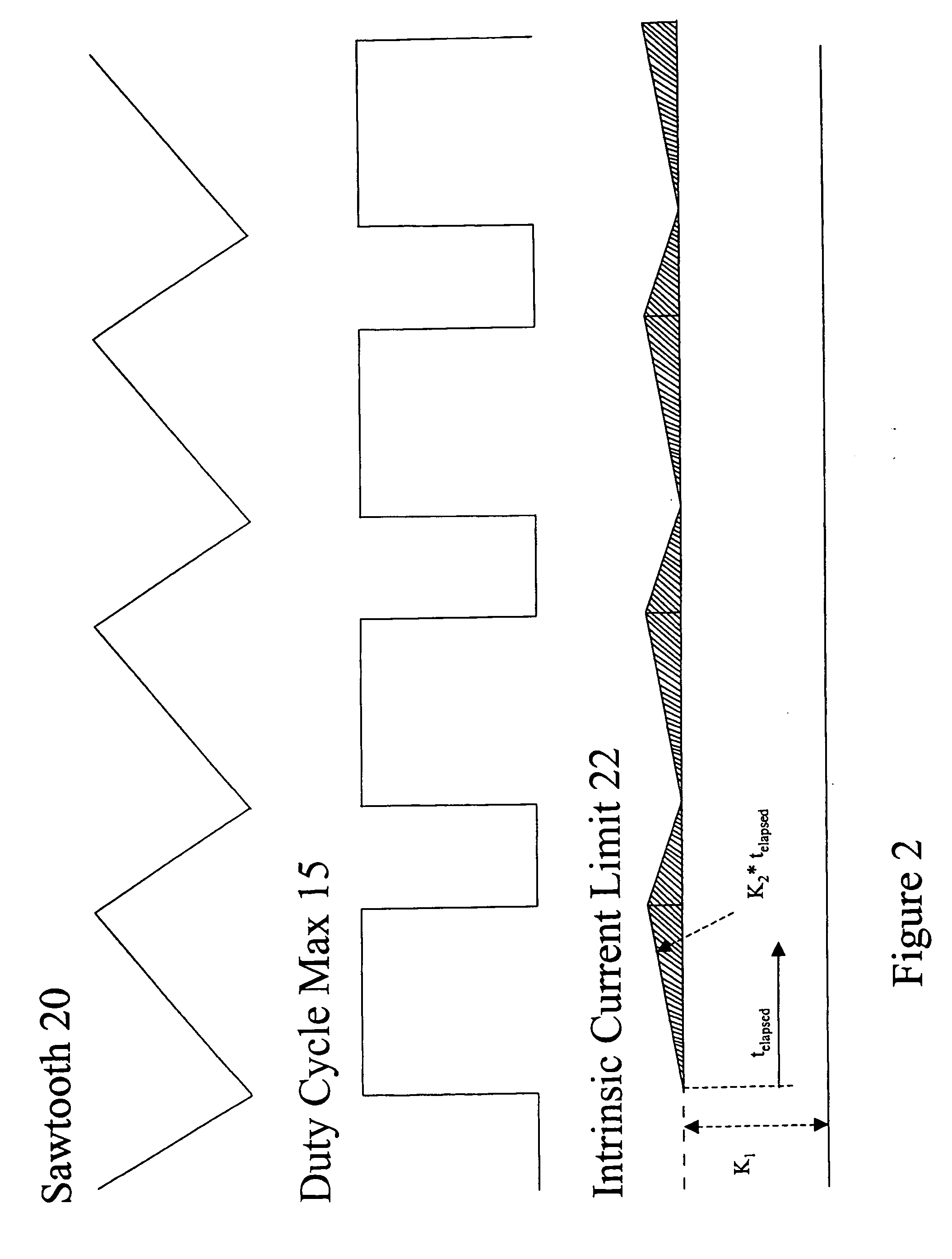

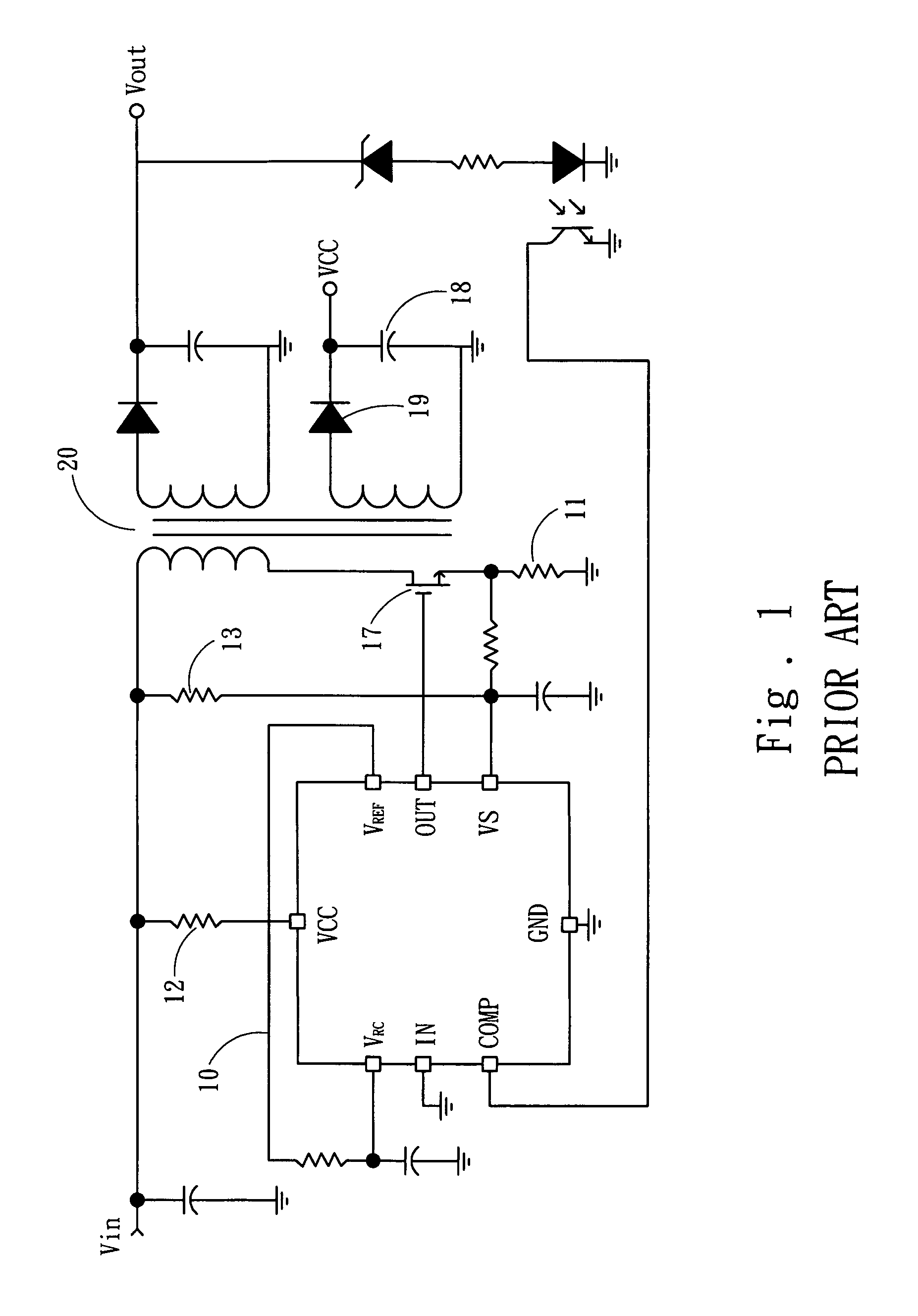

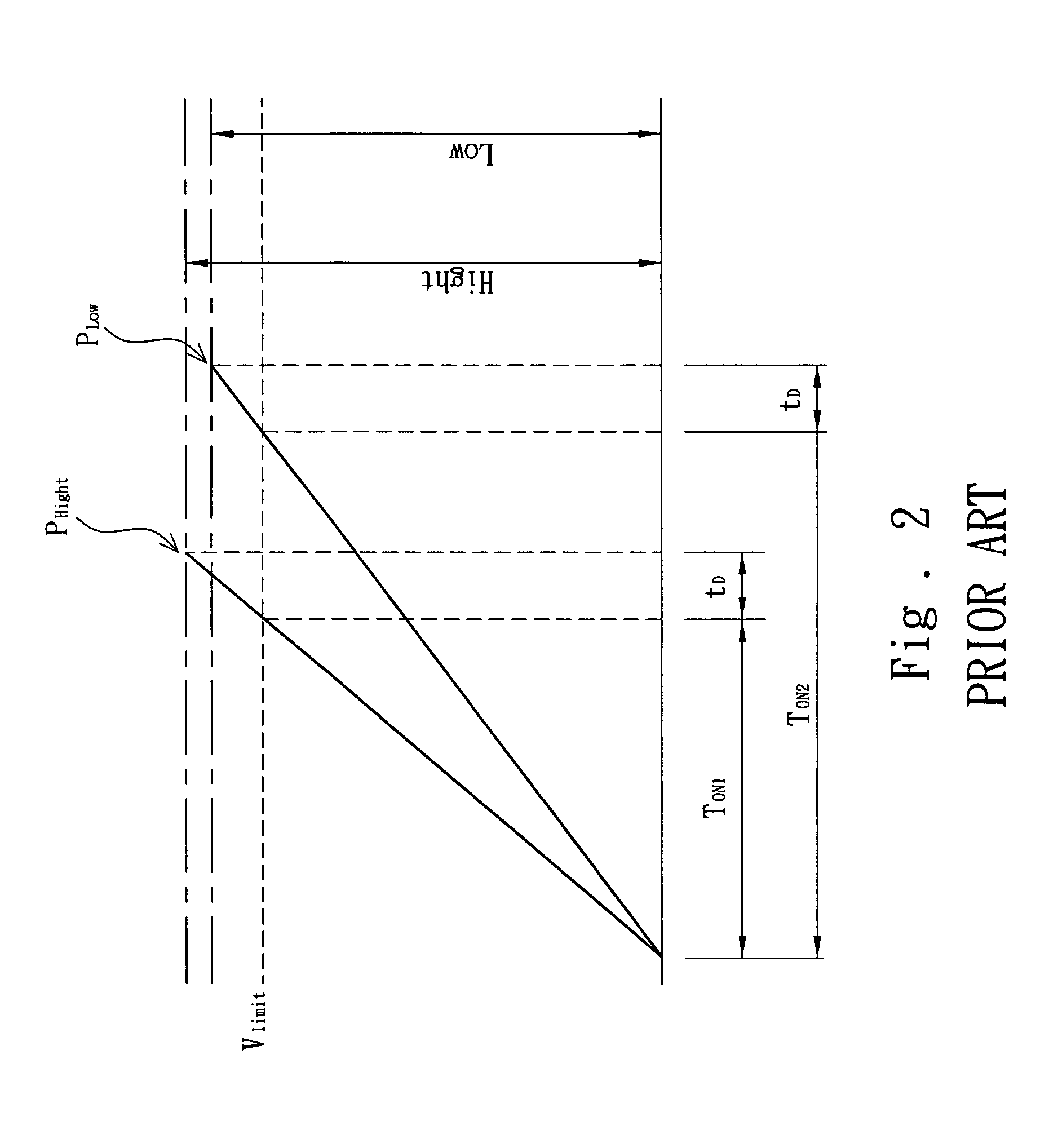

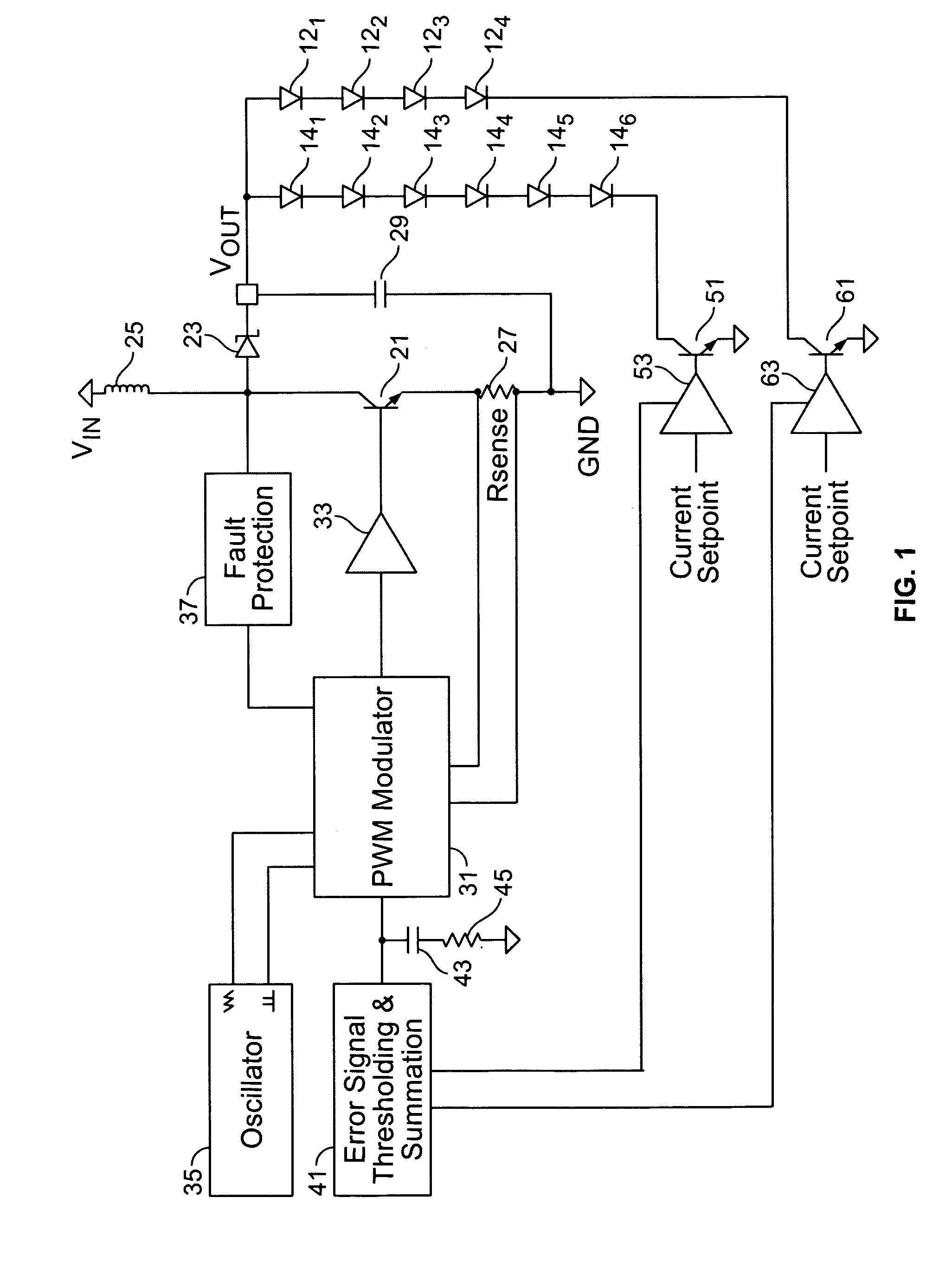

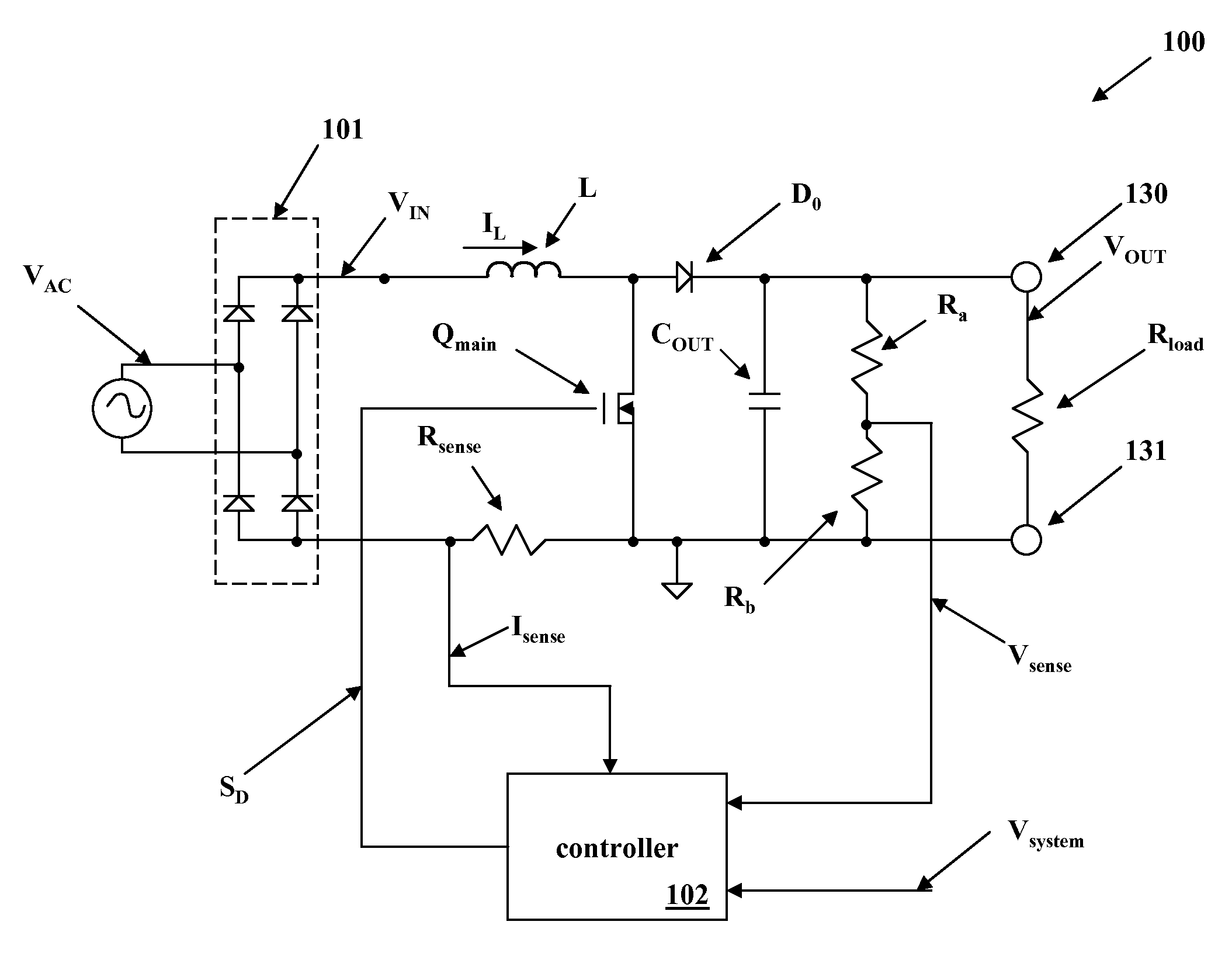

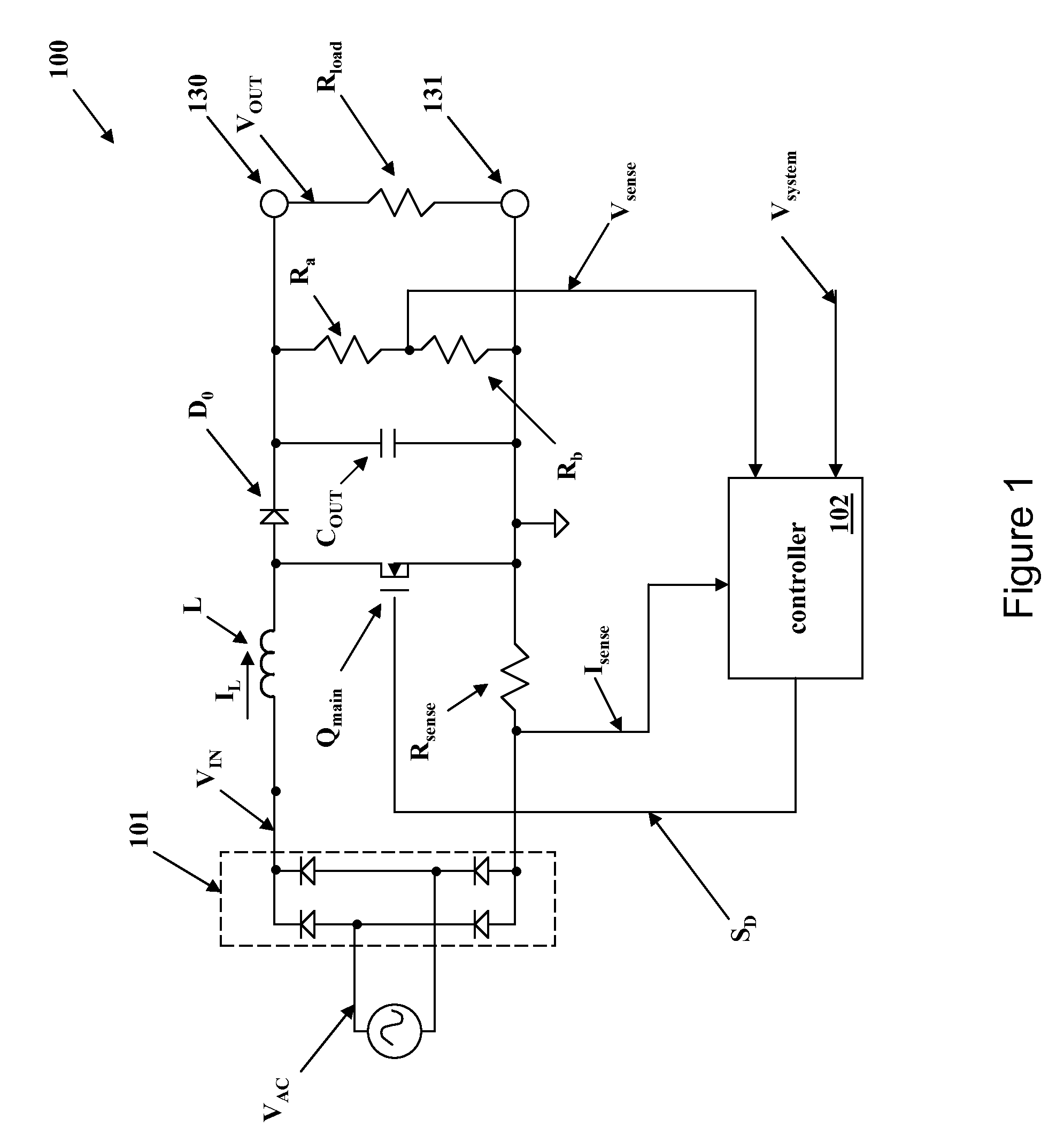

Method and apparatus for maintaining a constant load current with line voltage in a switch mode power supply

InactiveUS20060176716A1TransistorConversion with intermediate conversion to dcConstant loadSignal response

A power supply including a regulation circuit that maintains an approximately constant load current with line voltage. An example circuit includes a switch including first, second and third terminals. The first terminal is coupled or decoupled to the second terminal in response to a control signal received at the third terminal. Voltage sense circuitry is included and is coupled to sense a voltage drop across the switch. The voltage drop is representative of a current in the switch during an on time of the switch. The voltage sense circuitry has a variable current limit threshold that increases between a first level and a second level during the on time of the switch. The control signal is responsive to the variable current limit threshold to regulate a power supply with an output characteristic having an approximately constant output voltage below an output current threshold and an approximately constant output current below an output voltage threshold.

Owner:POWER INTEGRATIONS INC

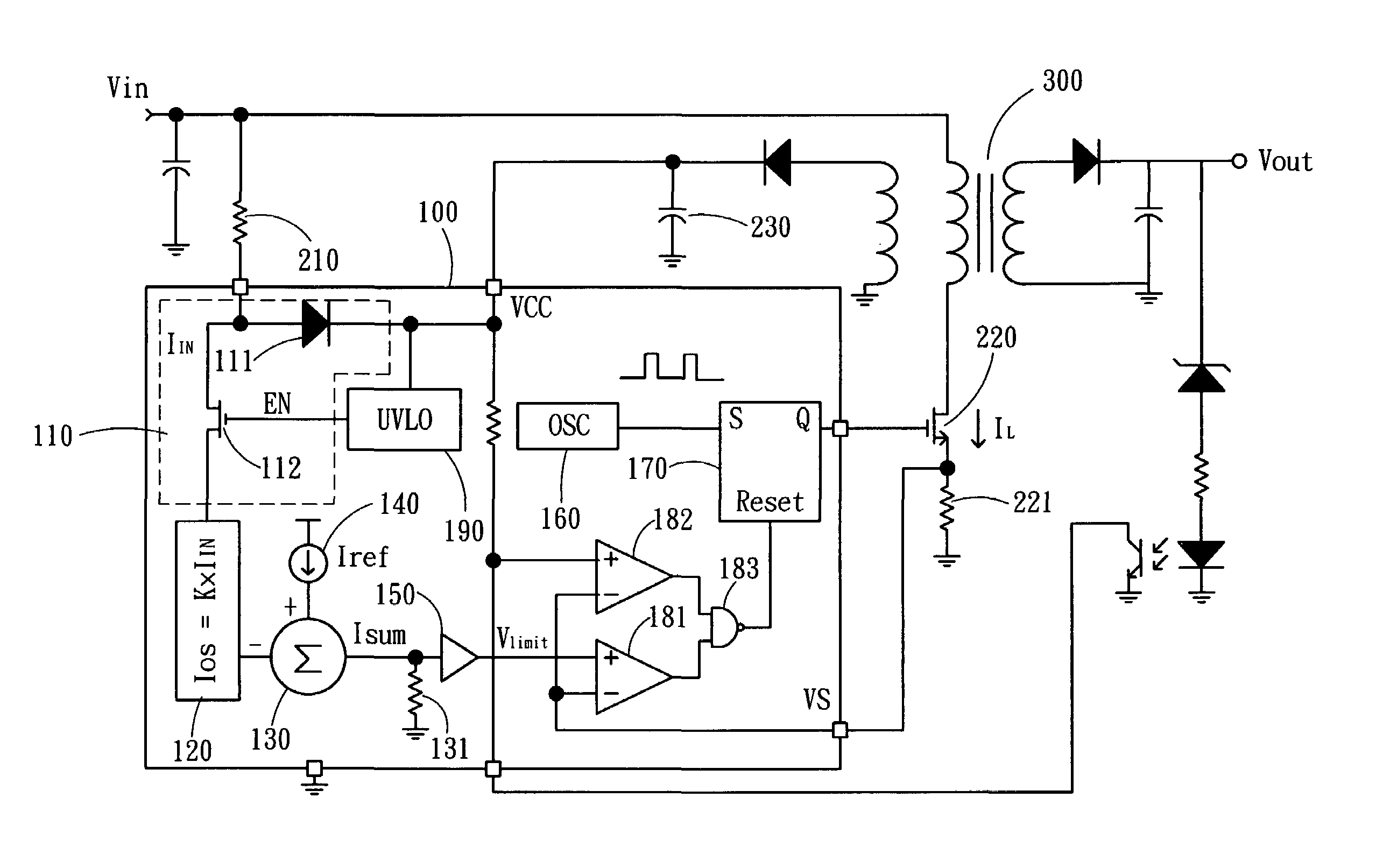

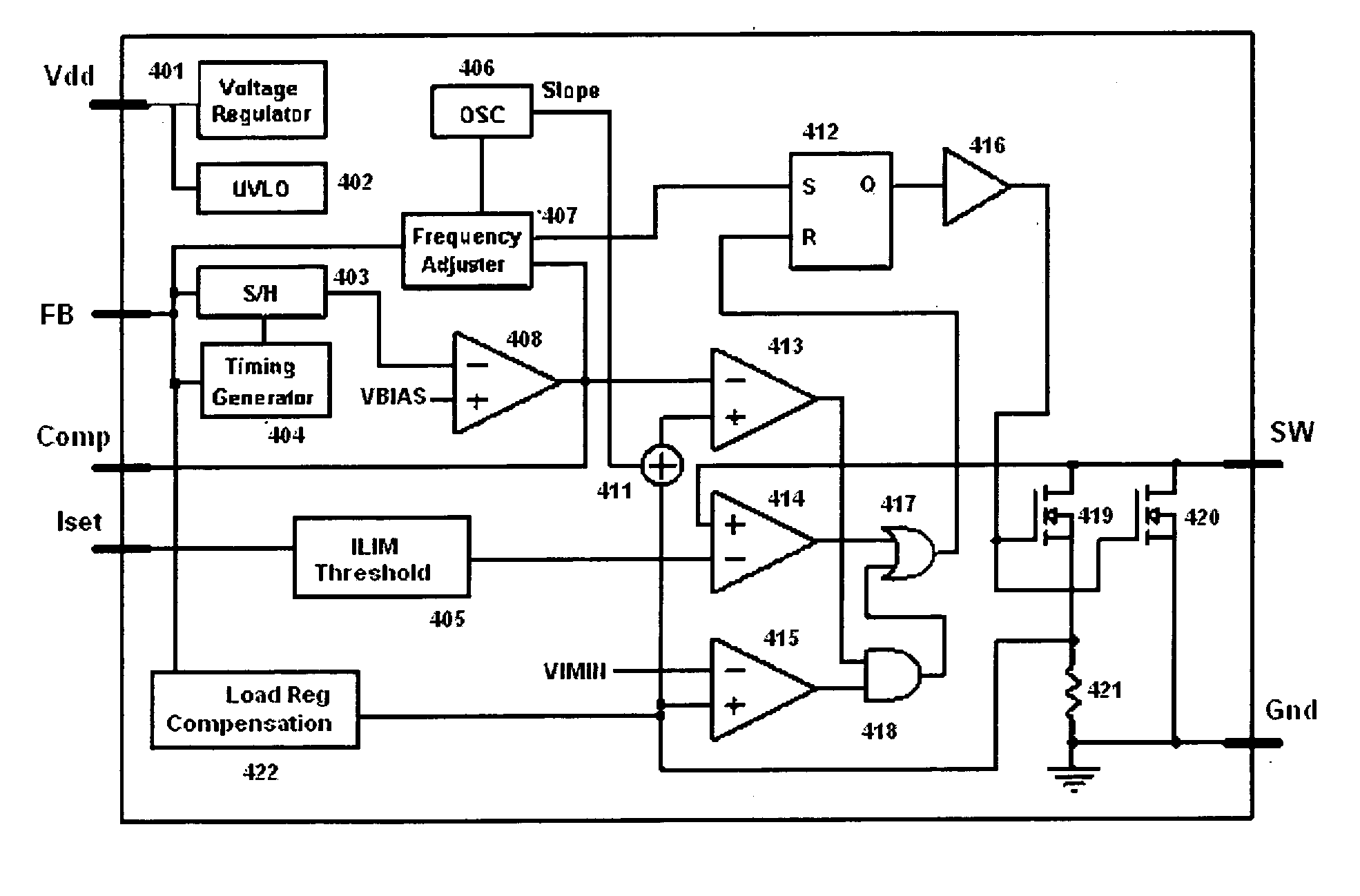

PWM controller with constant output power limit for a power supply

ActiveUS7099163B1Save power consumptionEase PCB layoutDc-dc conversionElectric variable regulationReference currentEngineering

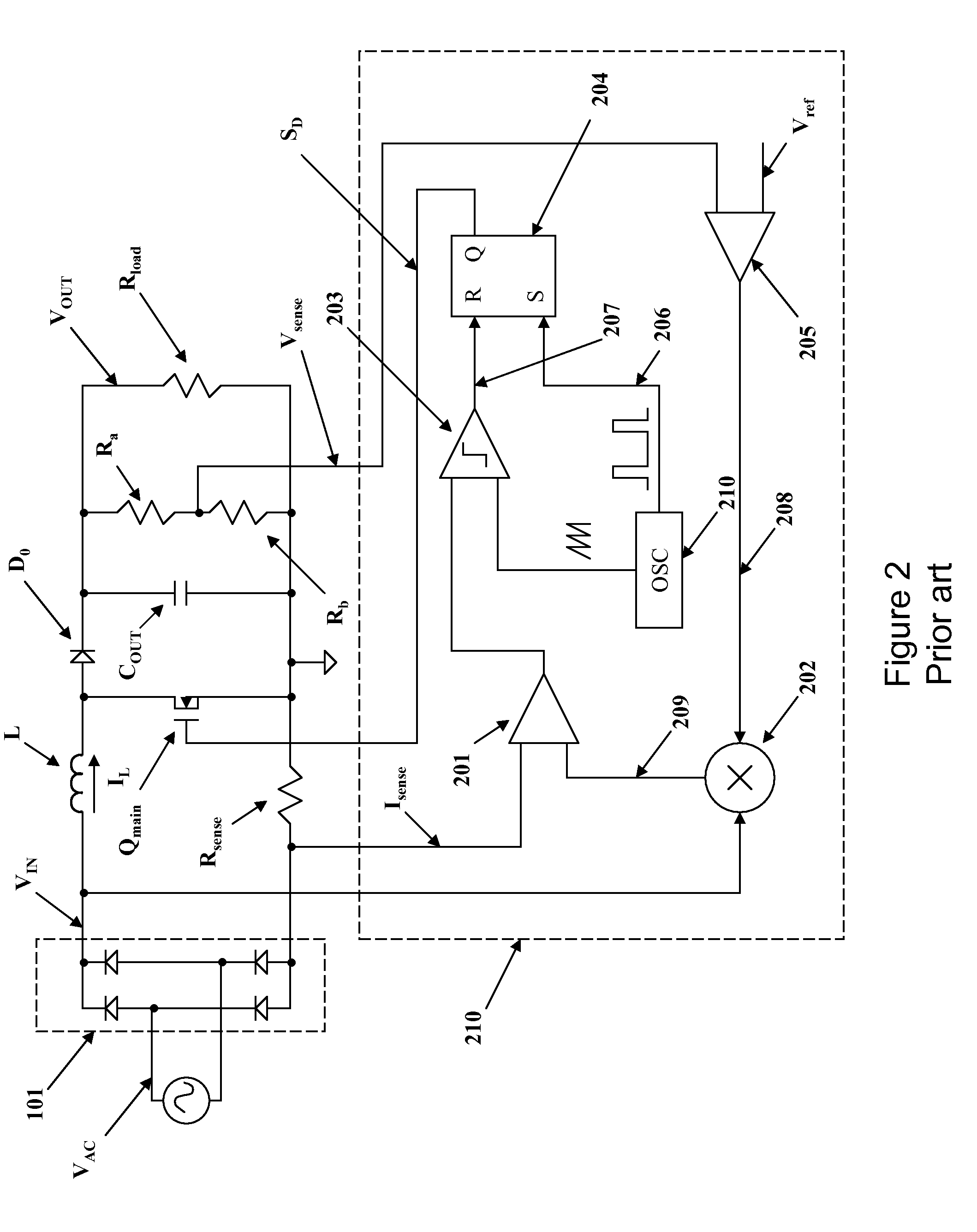

A PWM controller has a line voltage input that allows using a start-up resistor for both start-up and power-limit compensations so that it can save the power consumption, ease the PCB layout, and shrink the power supply size. In the integrated circuit, a current switch used for both start-up and line voltage sensing is composed of a diode and a switch transistor. A current multiplier is used to improve the precise by canceling the impact of the integrated resistor's absolute value, which is composed of a transistor loop, a constant current and a reference current. Thus, by properly selecting the value of the start-up resistor, an identical output power limit for low line and high line voltage input can be achieved.

Owner:BCD SHANGHAI MICRO ELECTRONICS CO LTD

Utilization of a multifunctional pin combining voltage sensing and zero current detection to control a switched-mode power converter

InactiveUS8670255B2Ac-dc conversion without reversalEfficient power electronics conversionOvervoltagePower flow

Owner:INFINEON TECH AUSTRIA AG

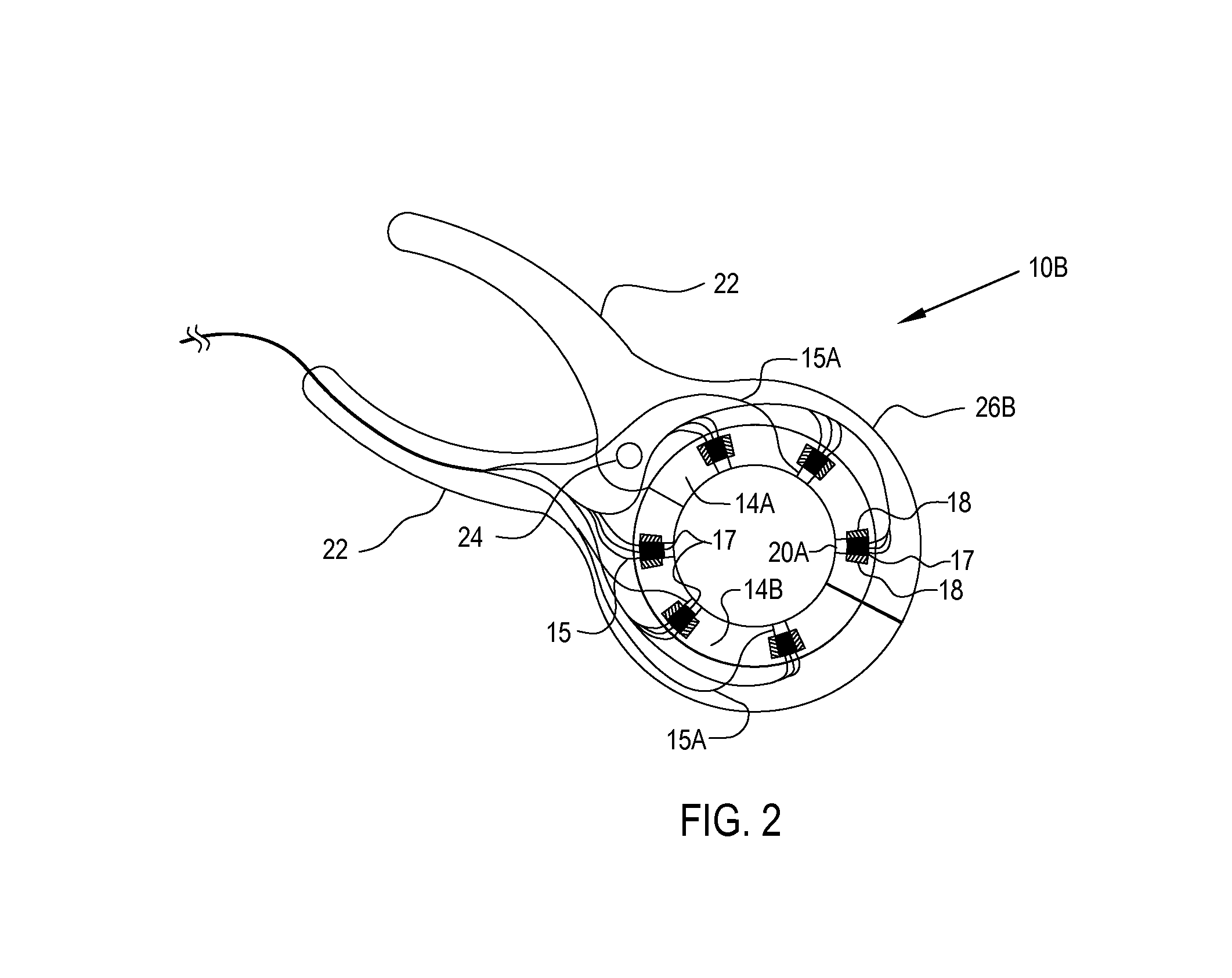

Non-contact current and voltage sensing clamp

InactiveUS20130076343A1Computing powerCurrent/voltage measurementBase element modificationsVoltage amplitudeElectrical conductor

A clamping current and voltage sensor provides an isolated and convenient technique for measuring current passing through a conductor such as an AC branch circuit wire, as well as providing an indication of an electrostatic potential on the wire, which can be used to indicate the phase of the voltage on the wire, and optionally a magnitude of the voltage. The device includes a body formed from two handle portions that contain the current and voltage sensors within an aperture at the distal end, which may be a ferrite cylinder with a hall effect sensor disposed in a gap along the circumference to measure current, or alternatively a winding provided through the cylinder along its axis and a capacitive plate or wire disposed adjacent to, or within, the ferrite cylinder to provide the indication of the voltage. When the handles are compressed the aperture is opened to permit insertion of a wire for measurement.

Owner:IBM CORP

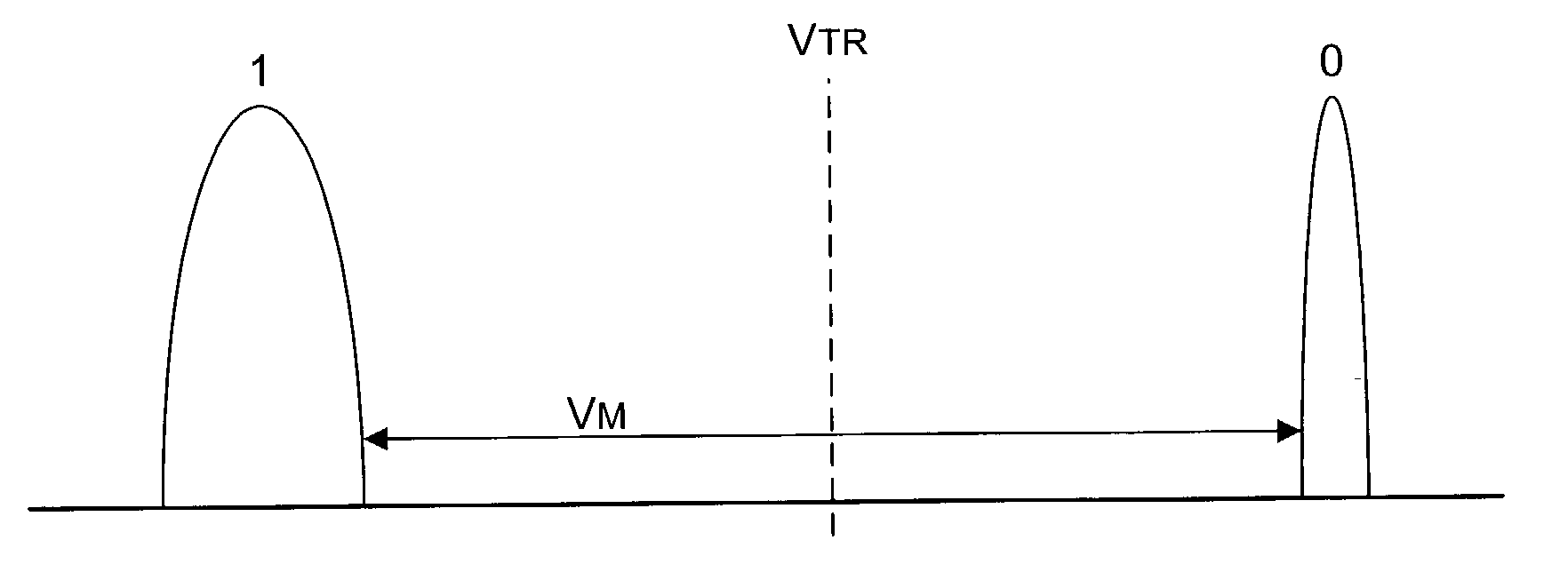

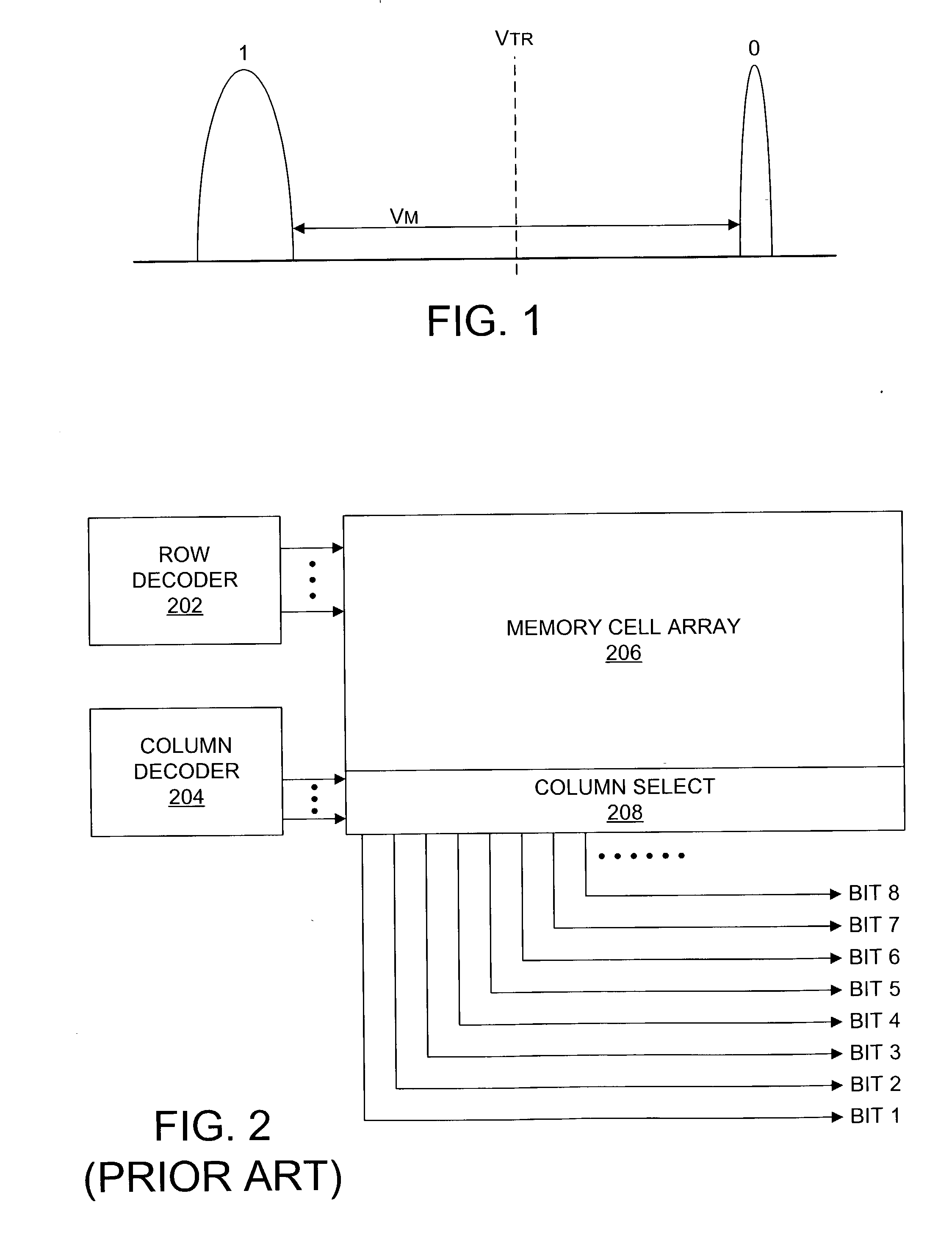

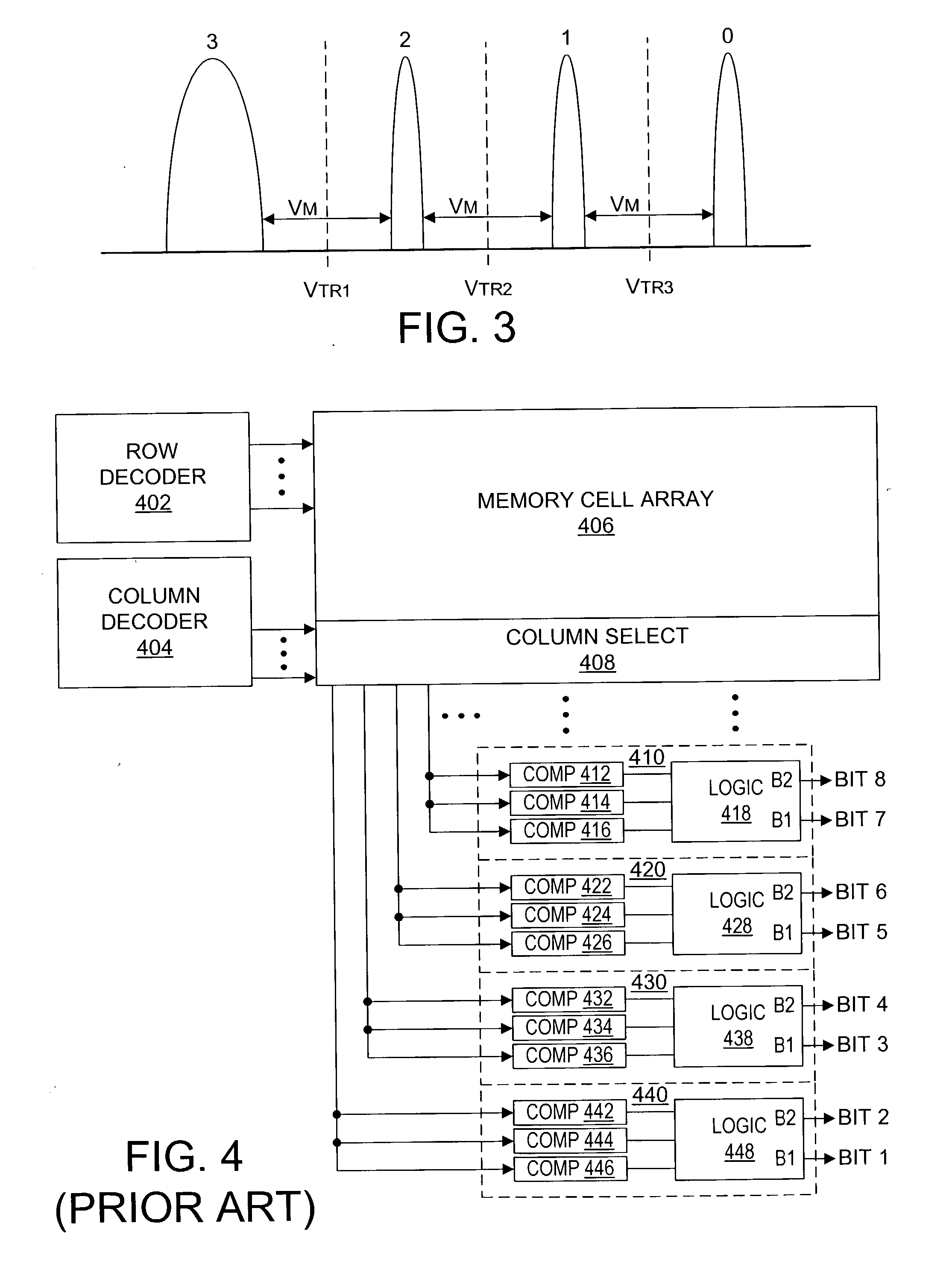

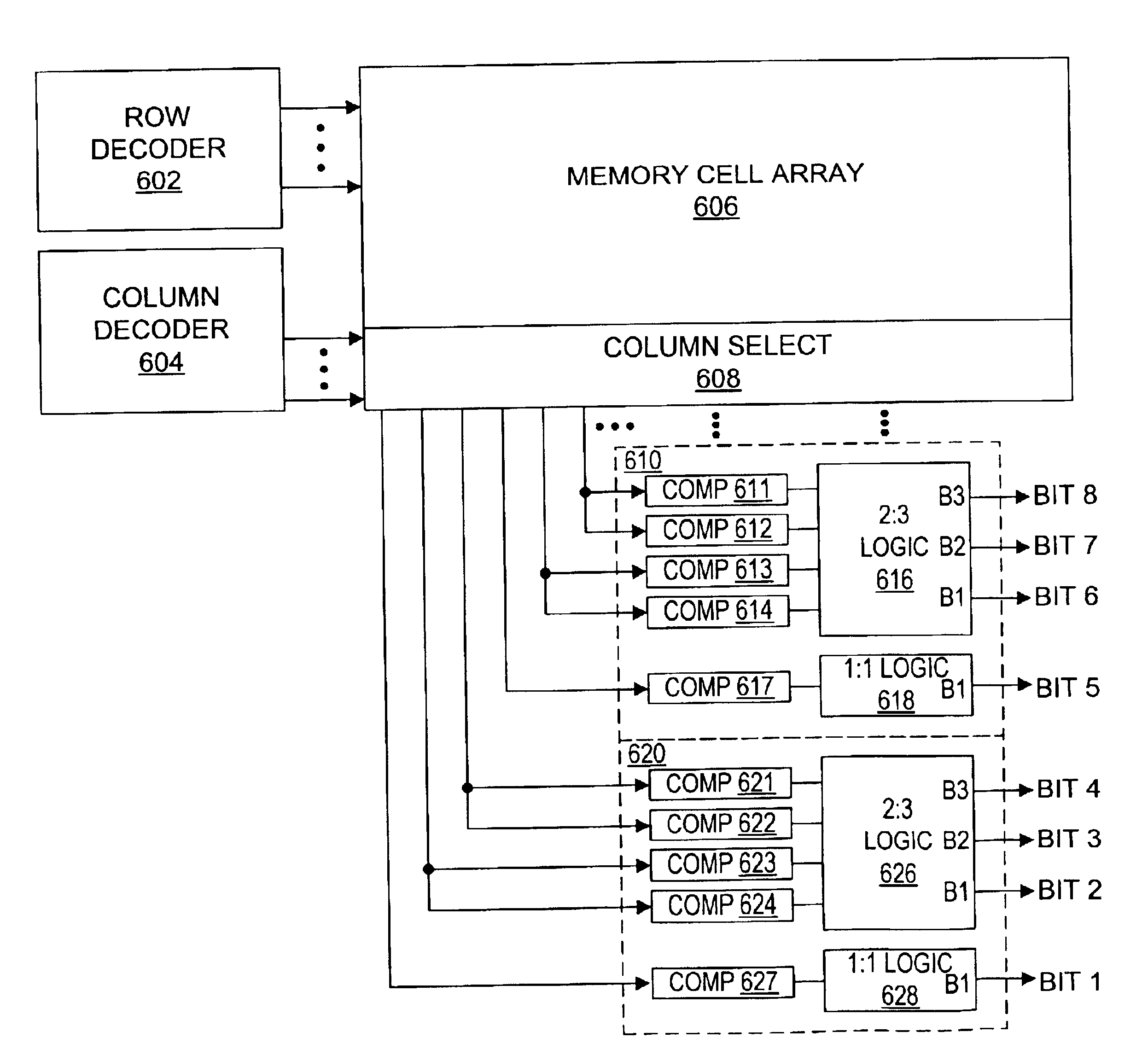

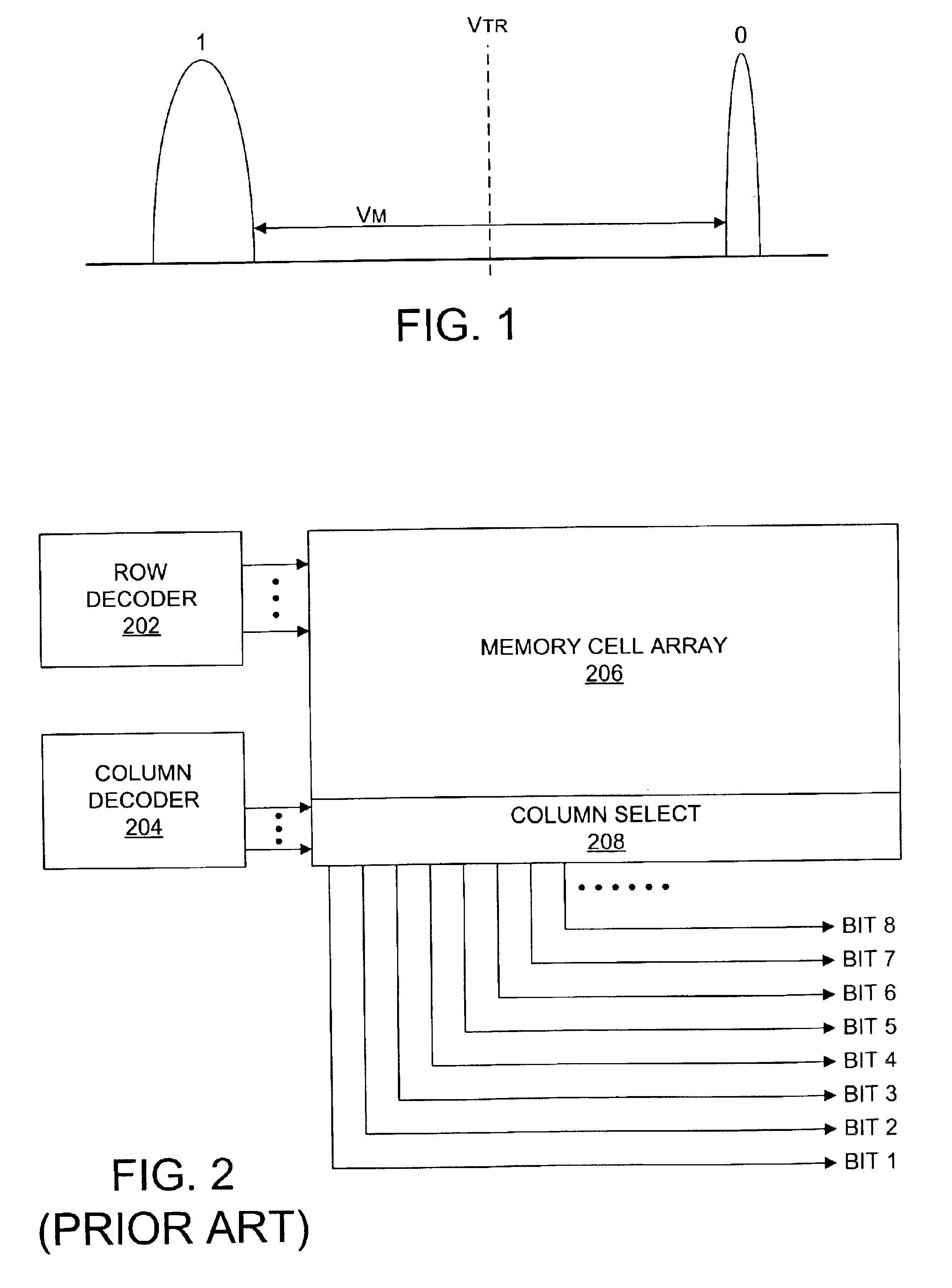

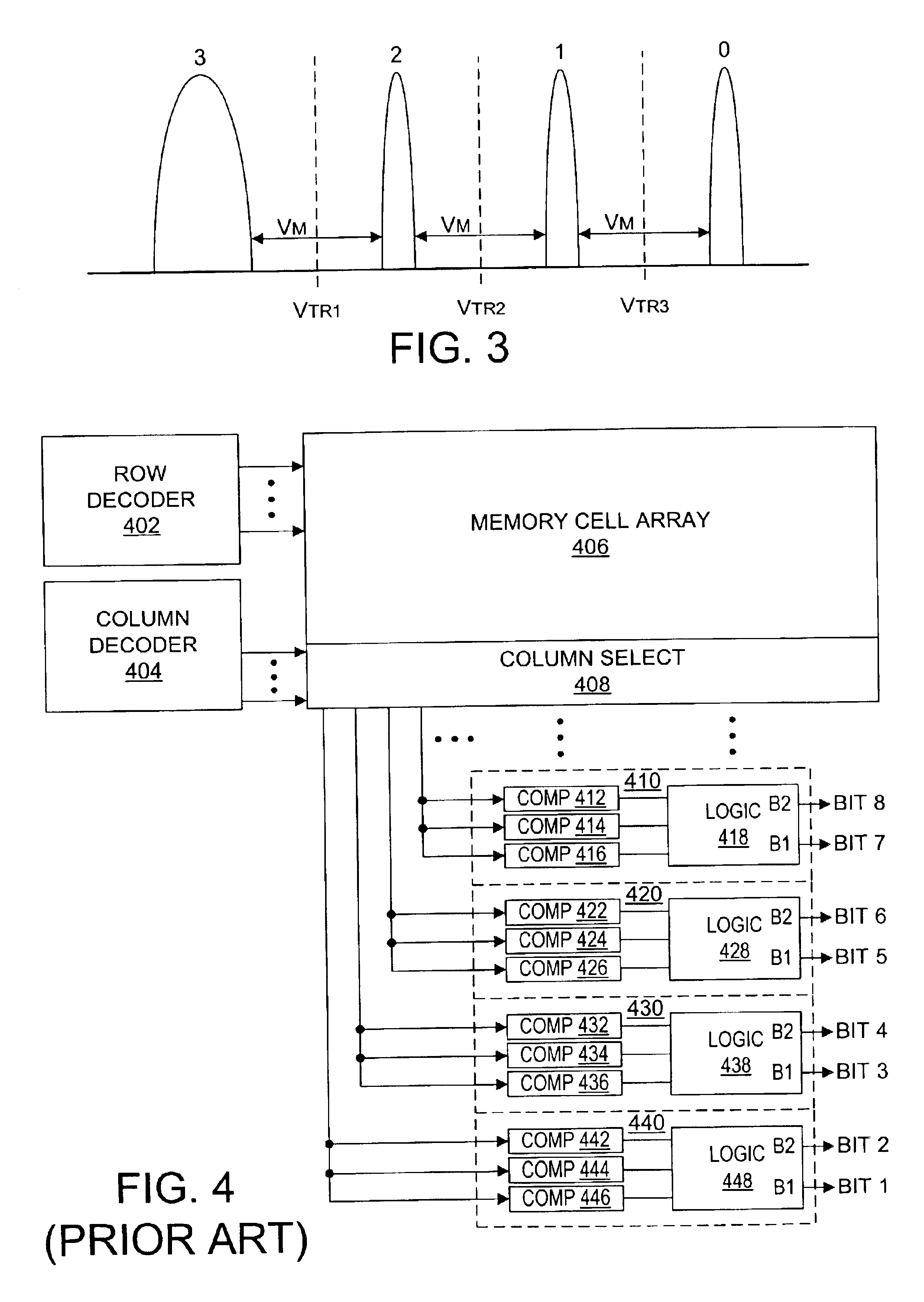

Nonvolatile semiconductor memory having three-level memory cells and program and read mapping circuits therefor

A memory uses multiple threshold levels in a memory cell that are not a power of two, and further uses a cell mapping technique wherein the read mapping is only a partial function The domain of read states for a single three-level memory cell, for example, has three states, but only two of them can be uniquely mapped to a bit. The domain of read states for two three-level memory cell, for example, has nine states, but only eight of them can be uniquely mapped to three bits. Although the read mapping is only partial, the voltage margin for the three-level memory cells is larger that the voltage margin available in the commonly used four-level memory cells. This increased voltage margin facilitates memory cell threshold voltage sensing, thereby increasing the reliability of the memory. Memory reliability may be further improved by increasing the voltage margin between the memory cell 0 state and the 1 state relative to the voltage margin between the 1 state and the 2 state, which more effectively accommodates charge loss from the 0 state through electron leakage. Asymmetrical read and program mapping may also be used to improve read reliability in the presence of ground noise or VCC noise.

Owner:WINBOND ELECTRONICS CORP

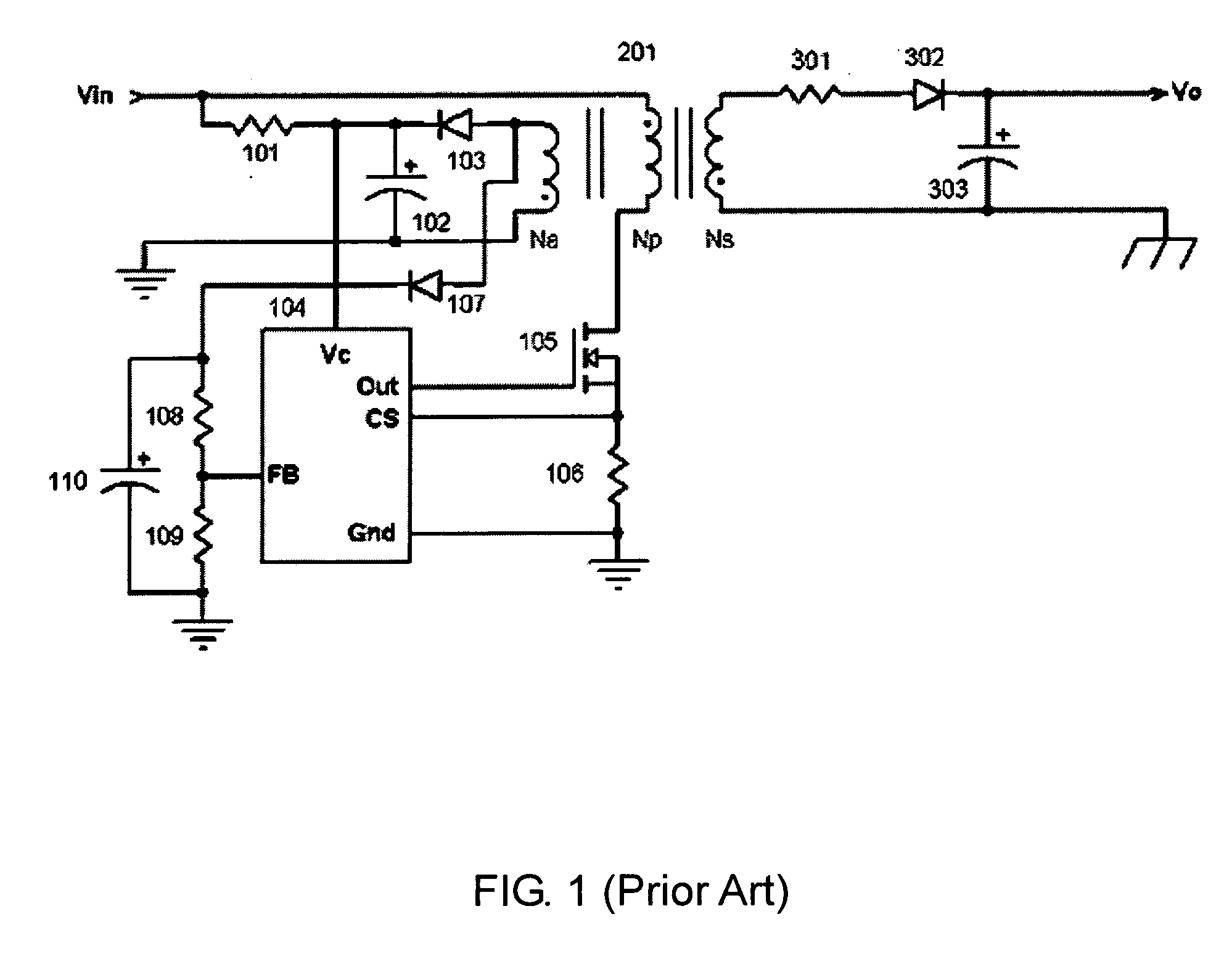

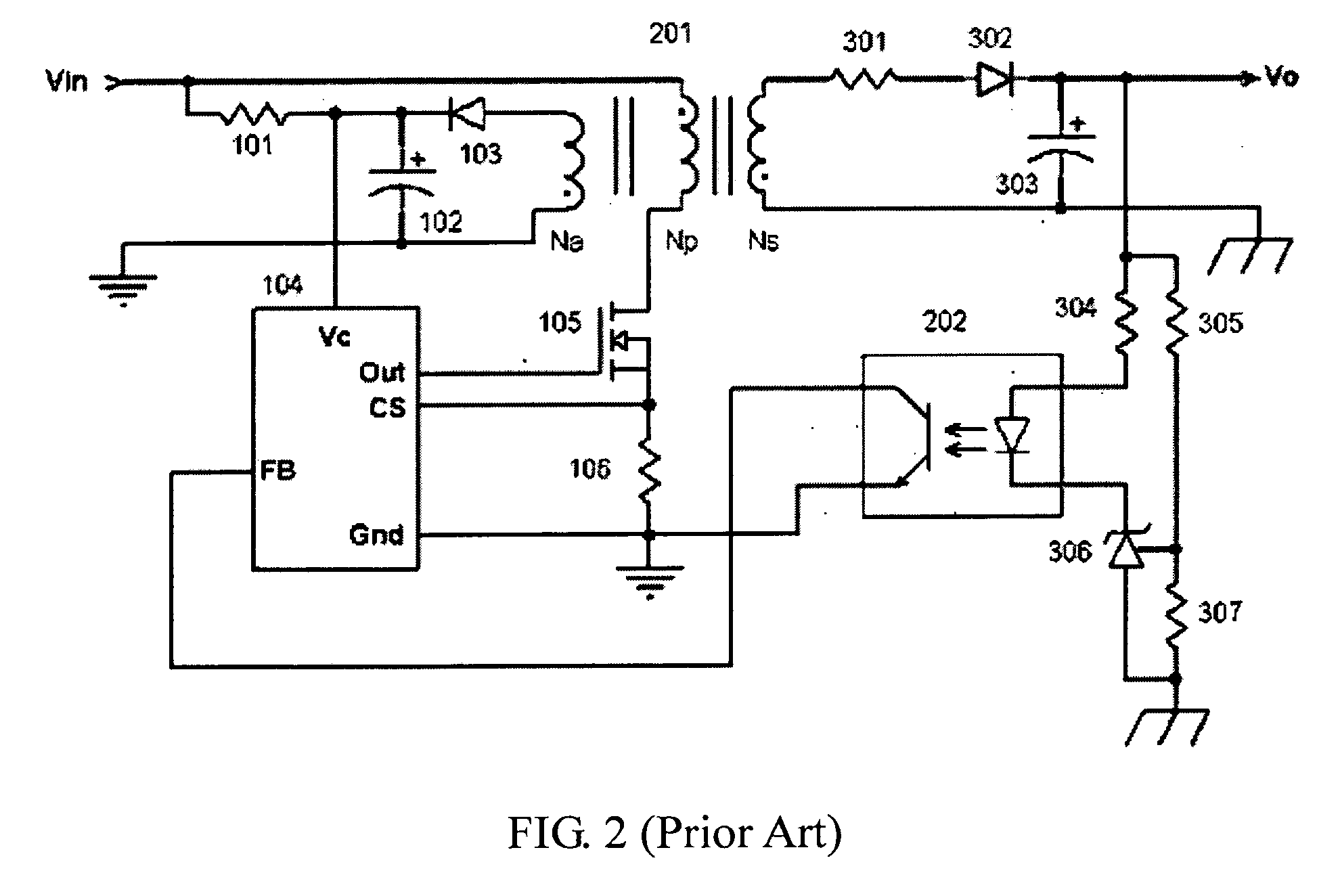

System and method for a primary feedback switched mode power supply

ActiveUS20070133234A1Reduce electromagnetic interference emissionReducing electromagnetic interference emissionDc-dc conversionElectric variable regulationAudio power amplifierControl power

A primary side controlled power converter having a voltage sensing means coupled to a transformer of the power converter and configured to provide a voltage feedback waveform representative of an output of the transformer is provided. A primary switching circuit operates to control energy storage of a primary side of the transformer. The primary switching circuit is operable during an on time and inoperable during an off time. The on and off time is switched at a system frequency. A feedback amplifier generates an error signal indicative of a difference between the voltage feedback waveform and a reference voltage. A sample and hold circuit samples the error signal at a periodic frequency during the off time. An error signal amplifier is configured to provide the sampled value to the primary switching circuit wherein the primary switching circuit controls the transformer and thereby regulates an output of the power converter.

Owner:ACTIVE SEMI

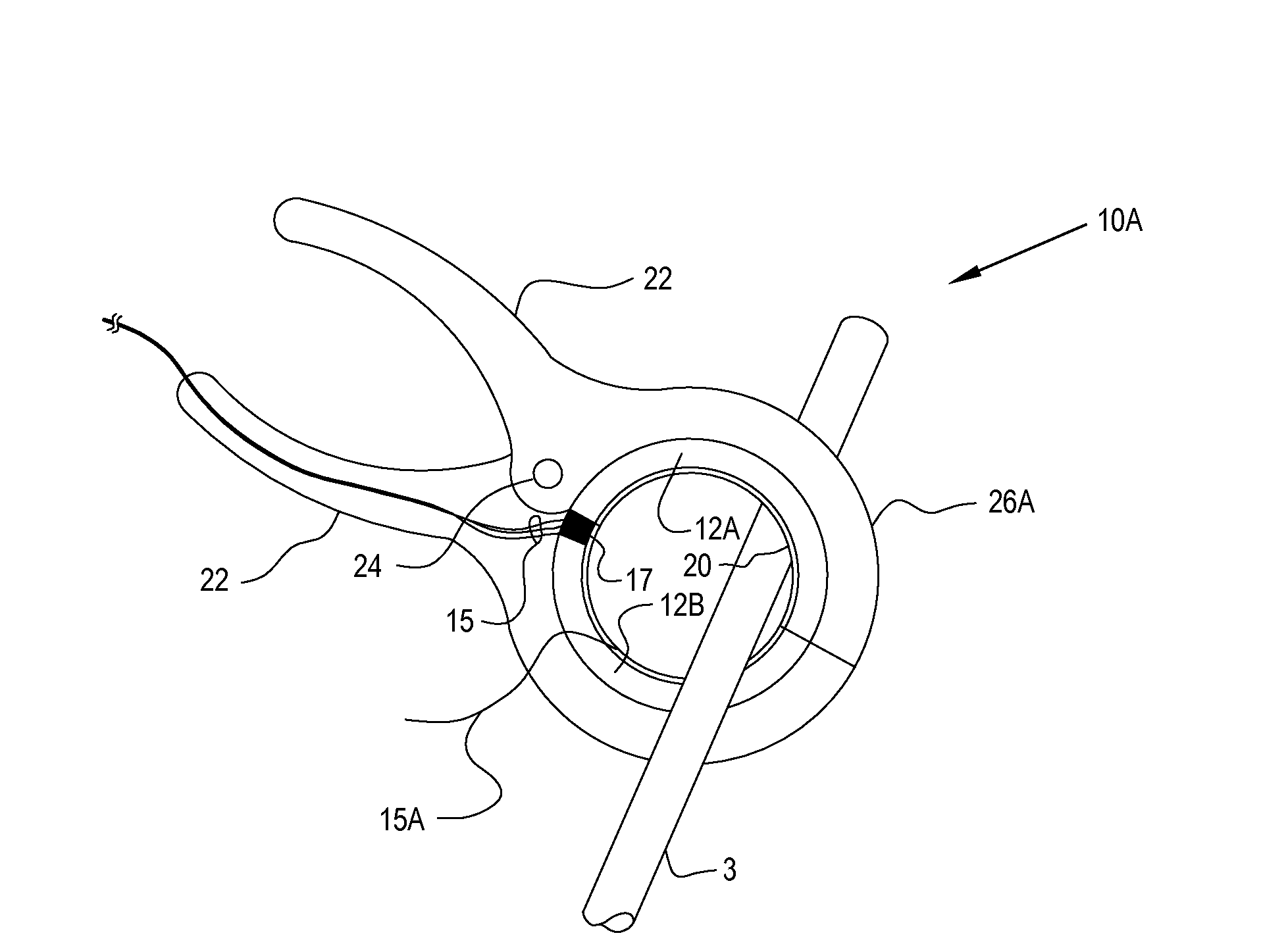

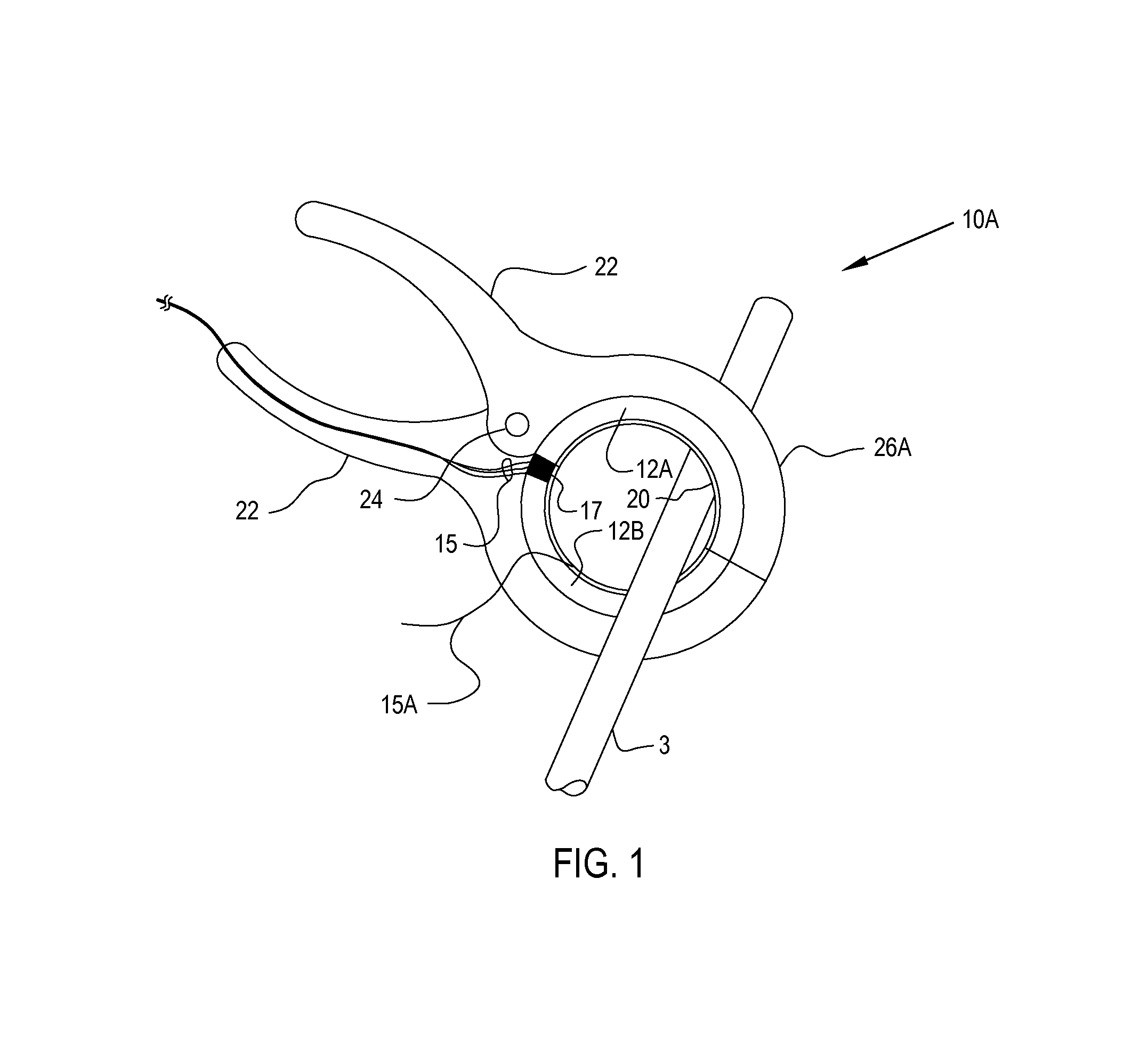

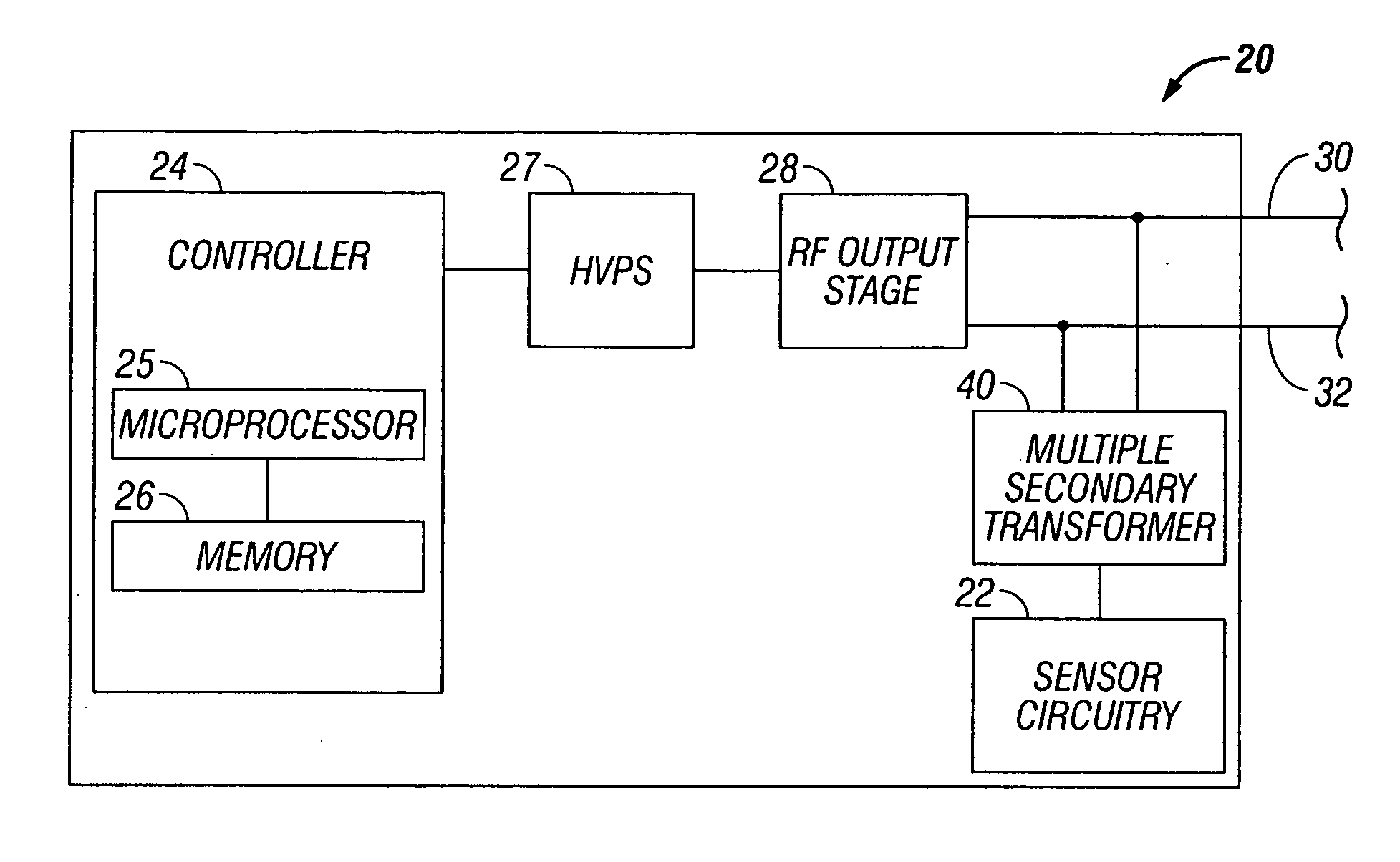

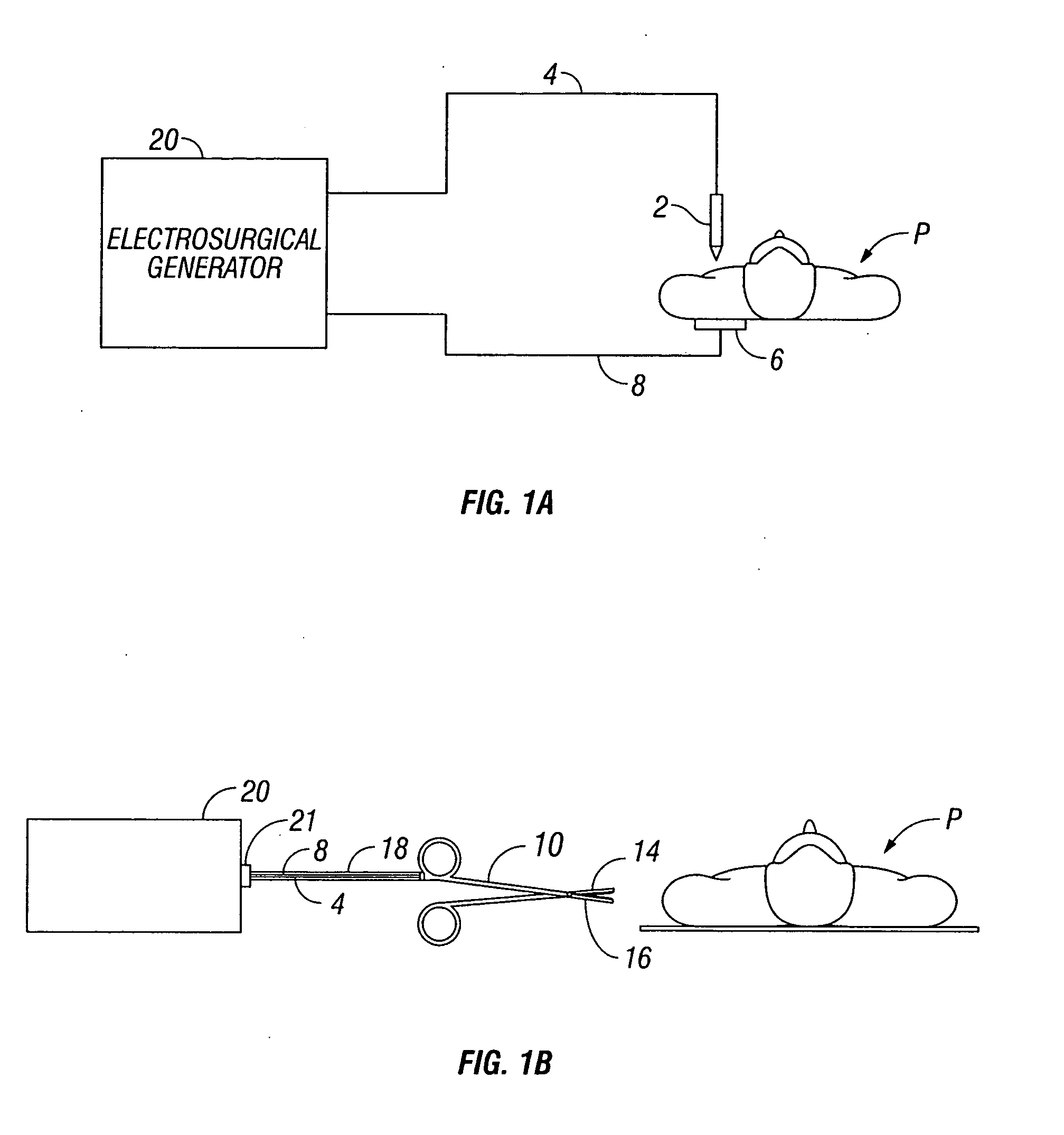

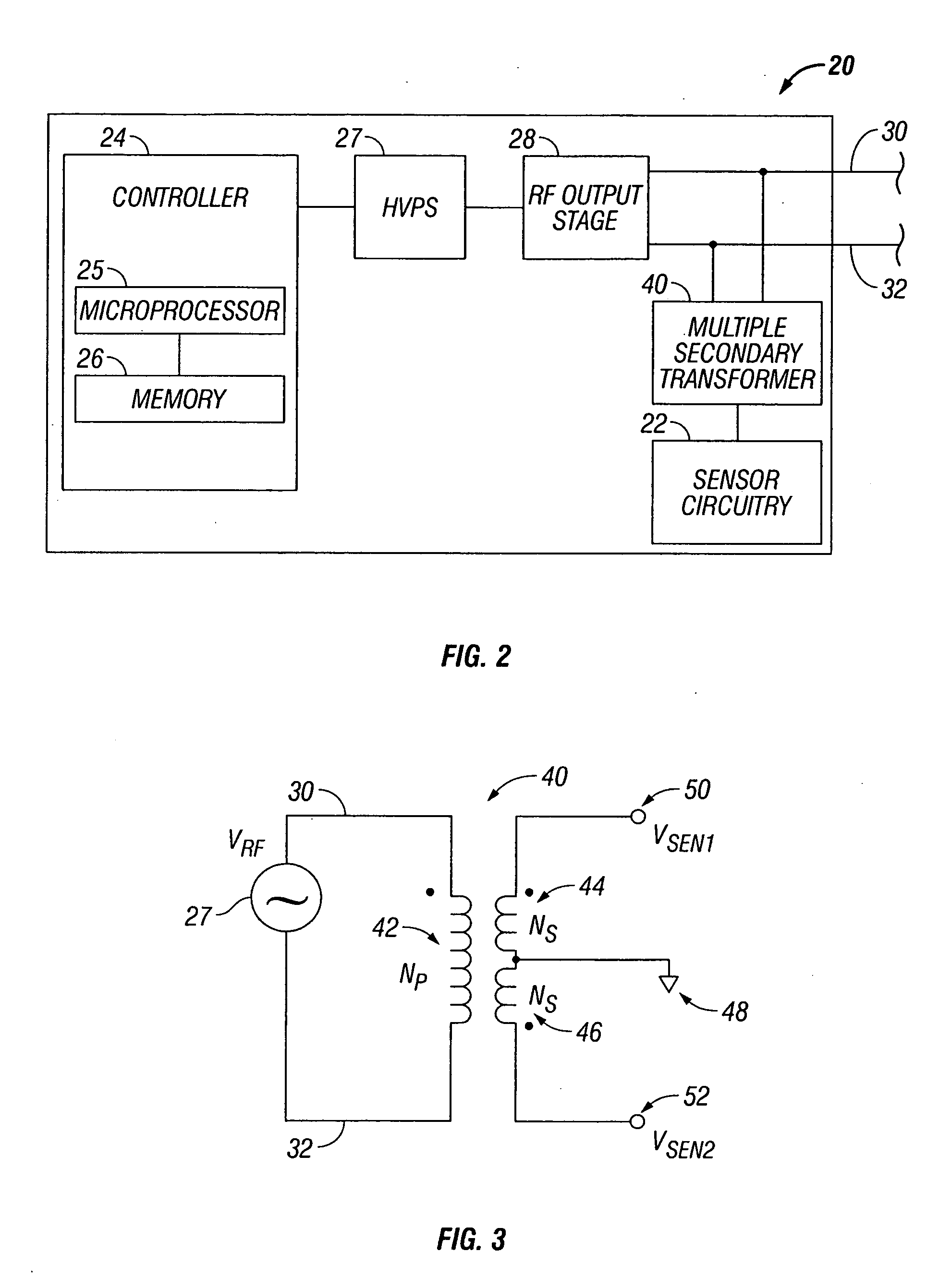

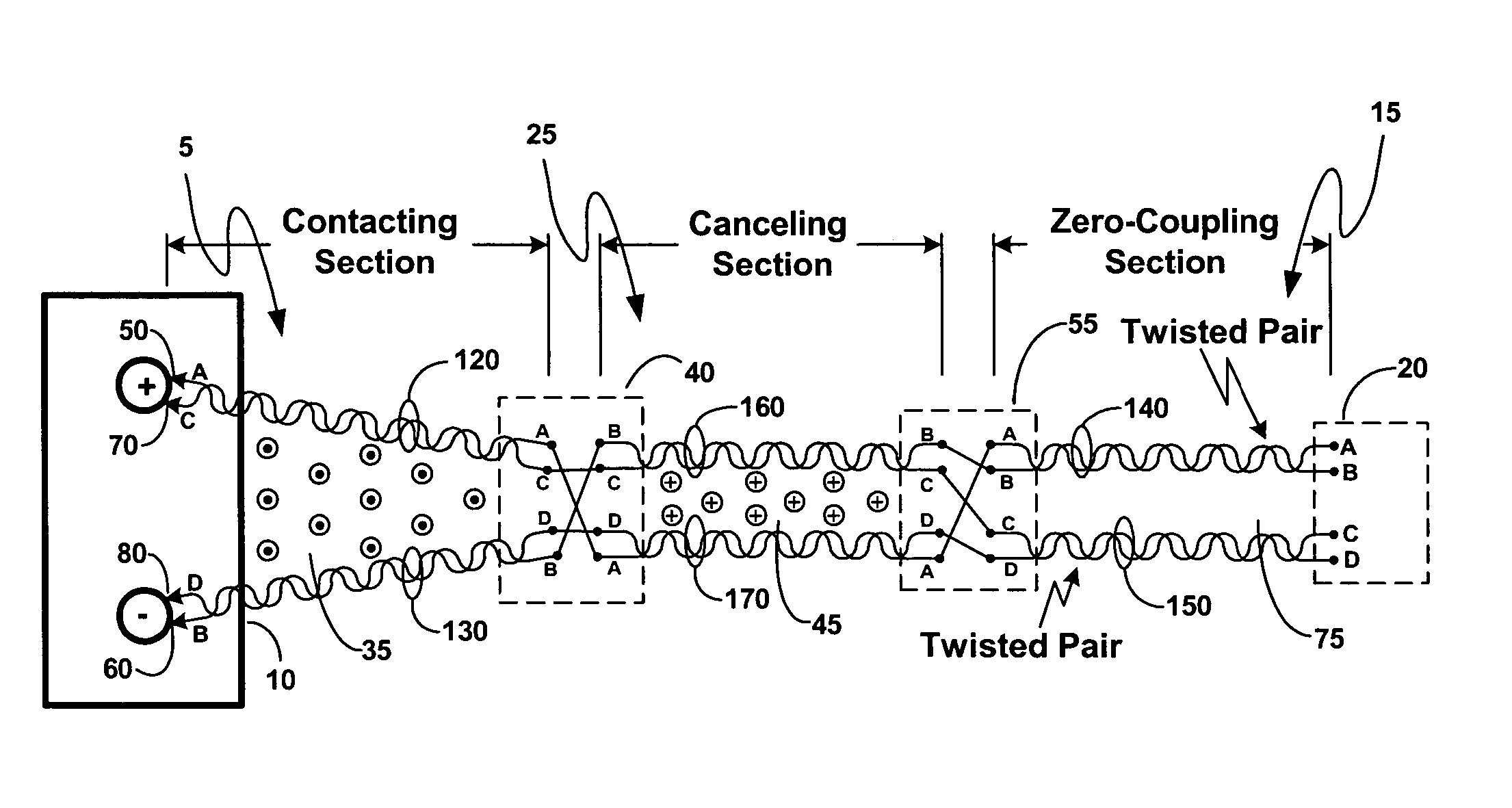

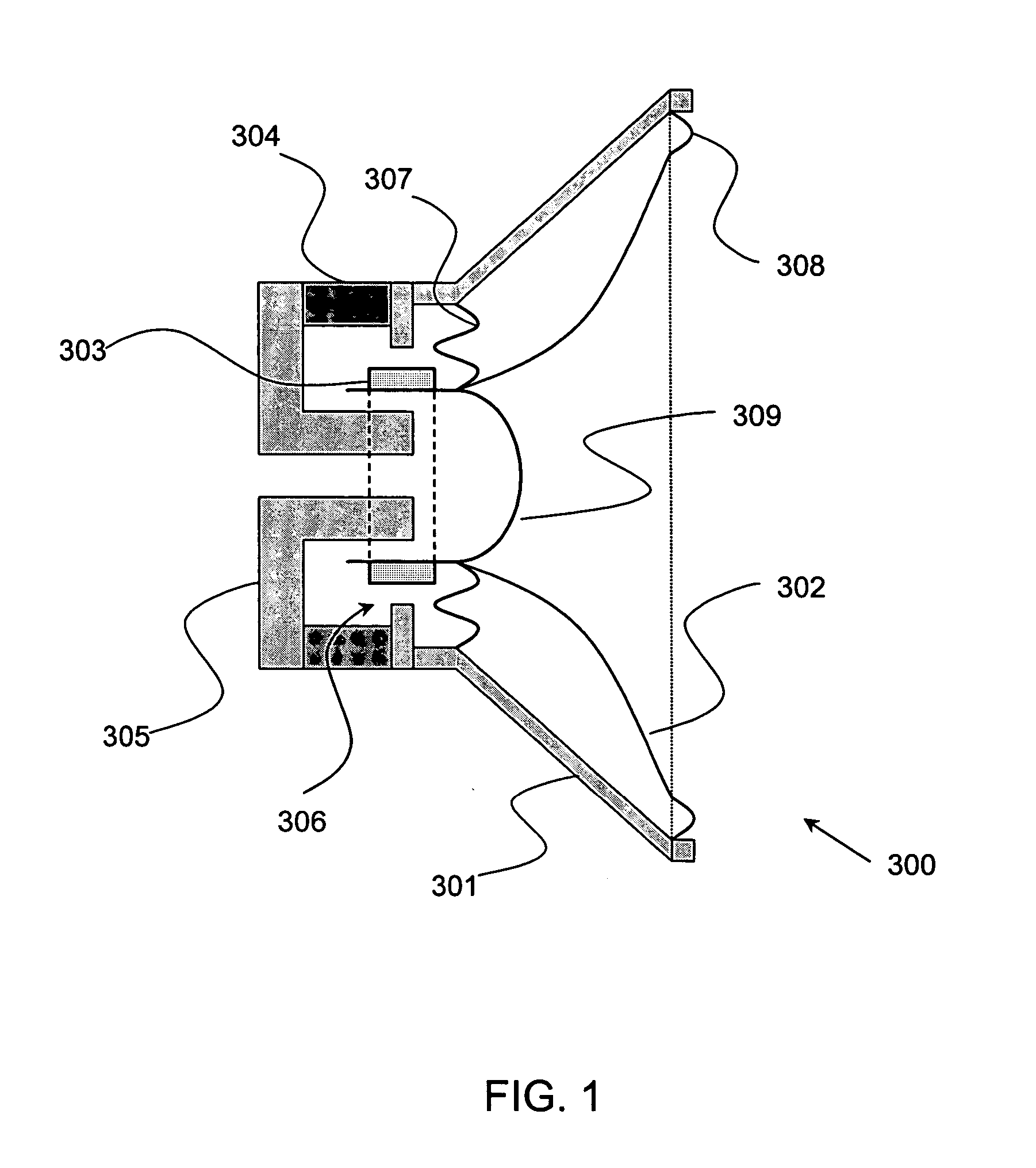

Transformer for RF voltage sensing

ActiveUS20080082094A1Transformers/inductances coils/windings/connectionsSurgical instruments for heatingElectricityTransformer

An electrosurgical system is disclosed. The electrosurgical system includes a multiple-secondary transformer configured for sensing voltage. The multiple-secondary transformer includes a primary winding coupled to an active terminal and a return terminal of the electrosurgical system and a plurality of secondary windings. Each of the secondary windings is configured to transform the radio frequency voltage into a sensed voltage. Each of the secondary windings includes an output coupled to a sensor circuit and configured to transmit the sensed voltage to the sensor circuit.

Owner:COVIDIEN AG

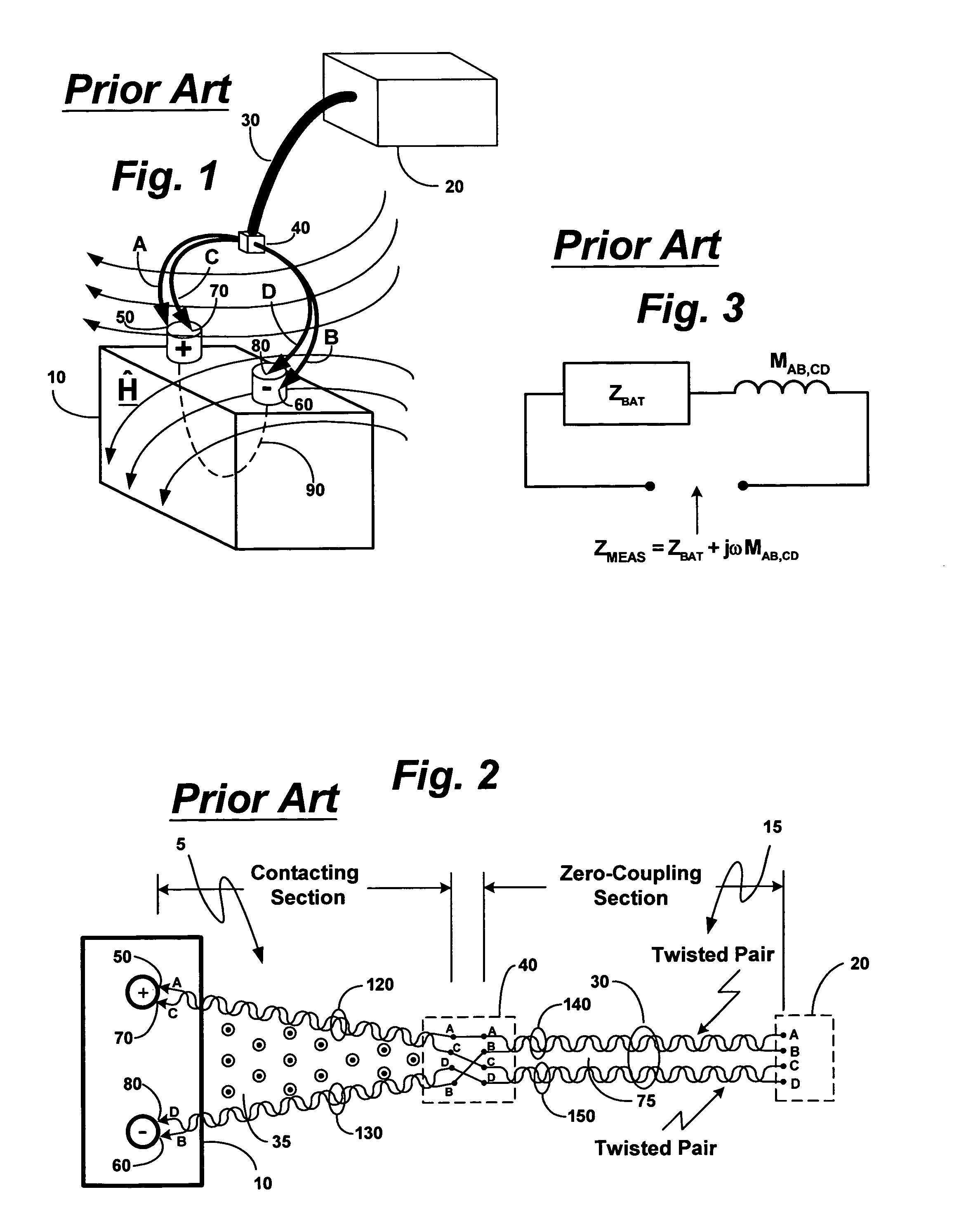

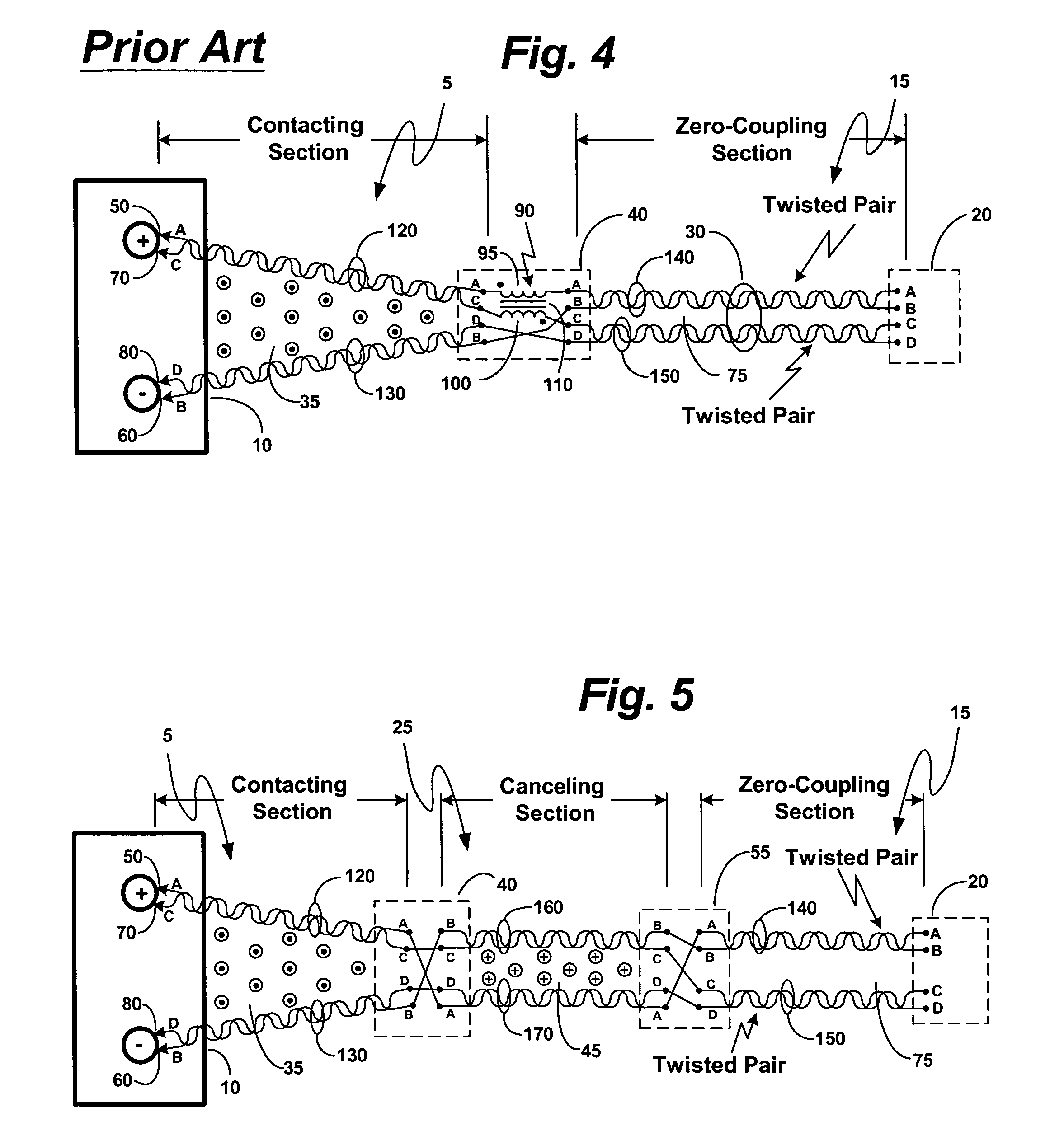

Broad-band low-inductance cables for making Kelvin connections to electrochemical cells and batteries

ActiveUS7106070B2Effectively cancellingResistance/reactance/impedenceElectrical testingElectrical conductorCoaxial cable

A broad-band technique for reducing the distributed inductance of a four-conductor Kelvin cable is disclosed. A special inductance-canceling cable section is connected in tandem with the cable section contacting the cell / battery. Connections between the two cable sections are transposed such that conductors in each conductor pair of the canceling section connect to current-carrying and voltage-sensing conductors from different conductor pairs in the contacting section. The canceling section thereby exhibits a distributed negative mutual inductance between its current-carrying and voltage-sensing conductors that can effectively cancel the distributed positive mutual inductance introduced by the contacting section.In one embodiment, conductor pairs comprise pairs of insulated wires which may be twisted together. In other disclosed embodiments, conductor pairs comprise shielded coaxial cables.

Owner:MIDTRONICS

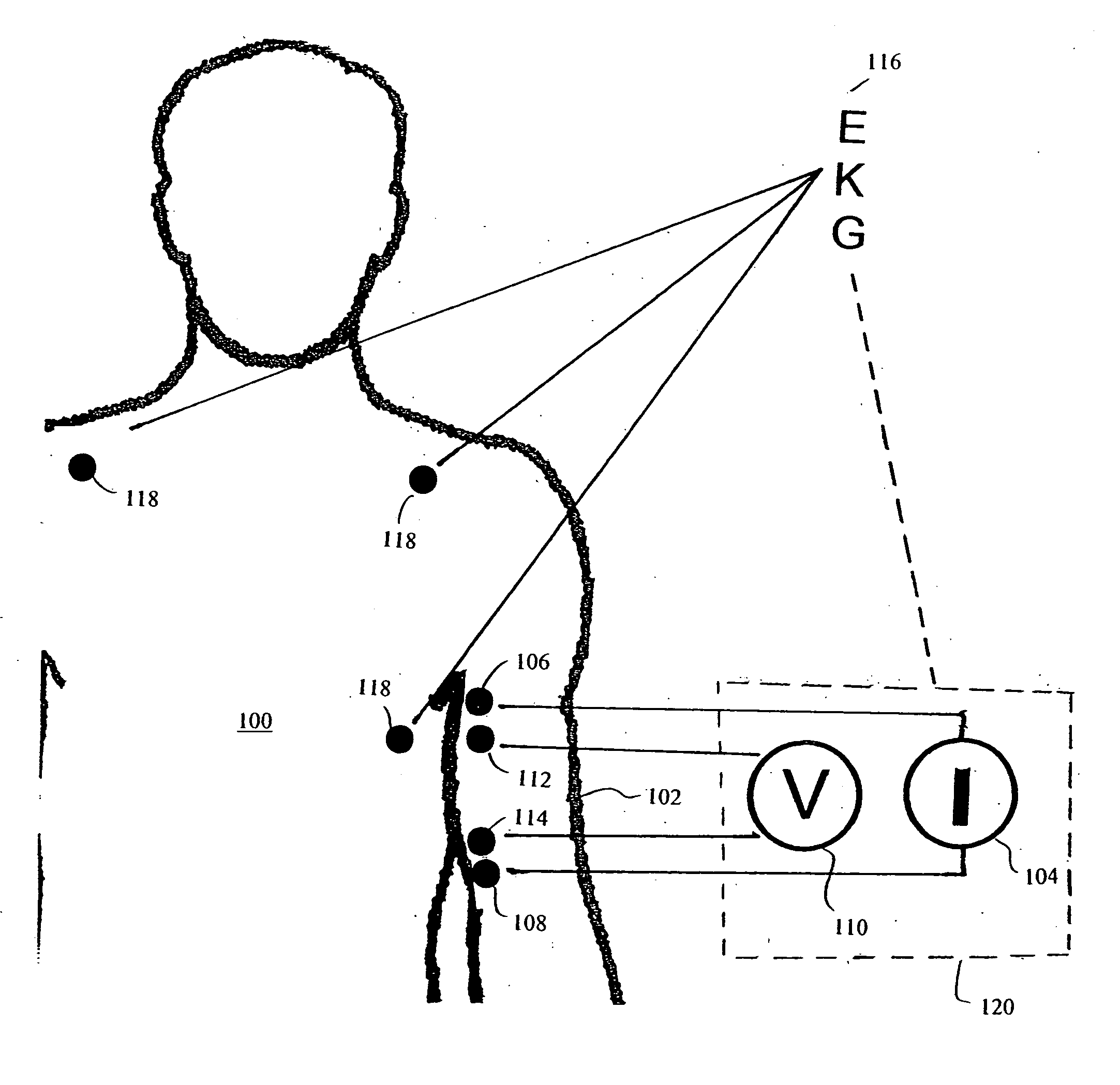

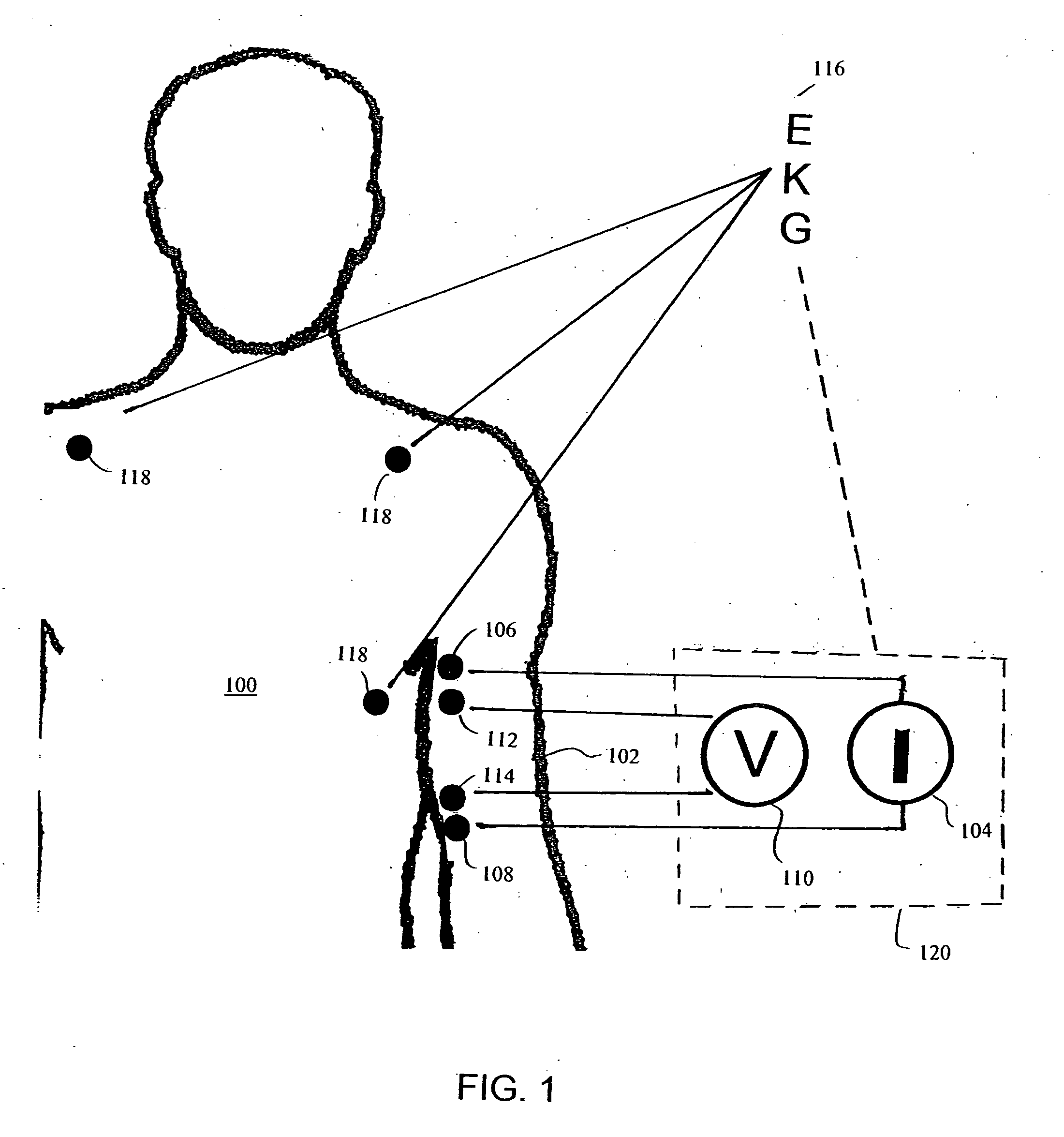

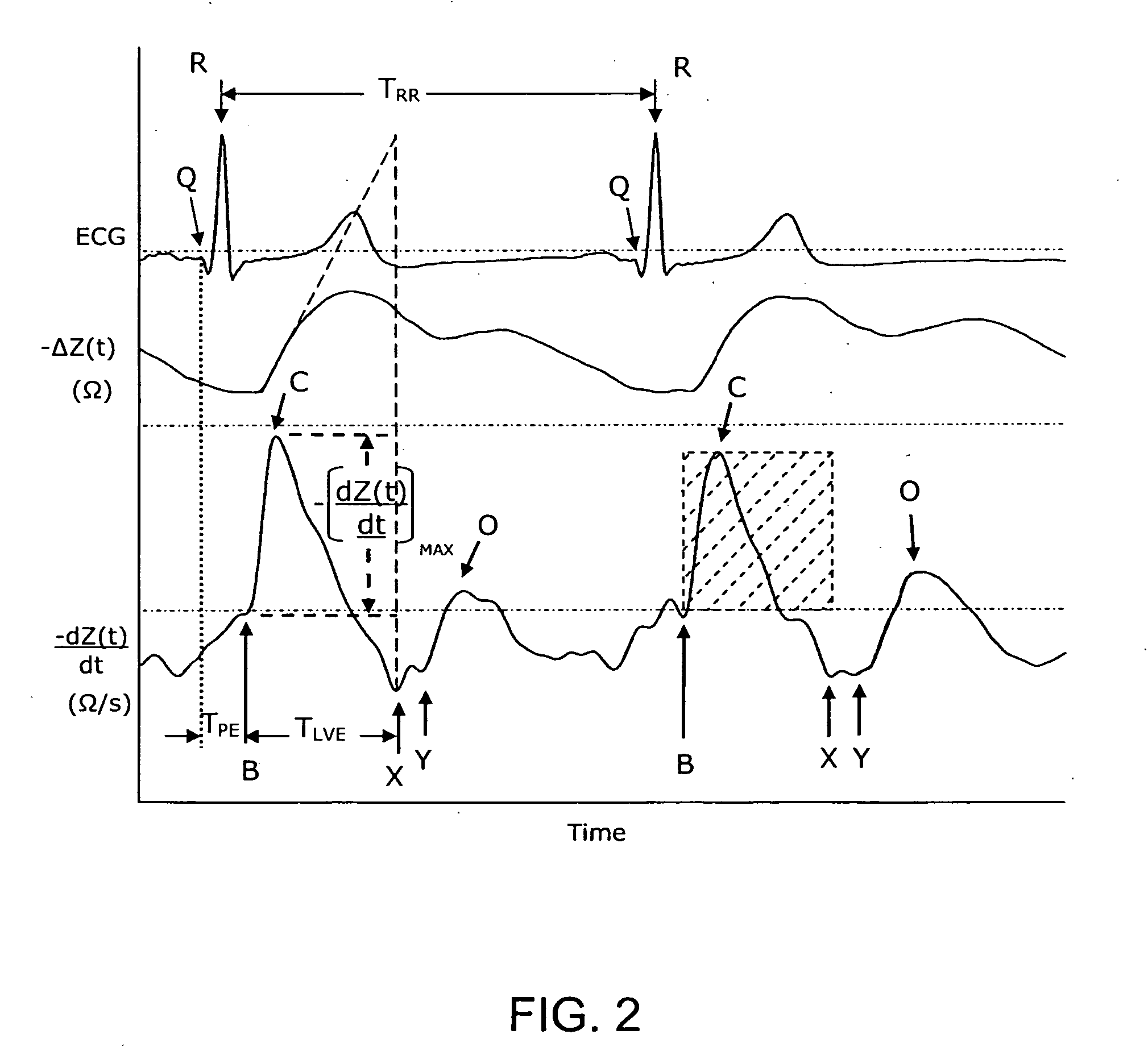

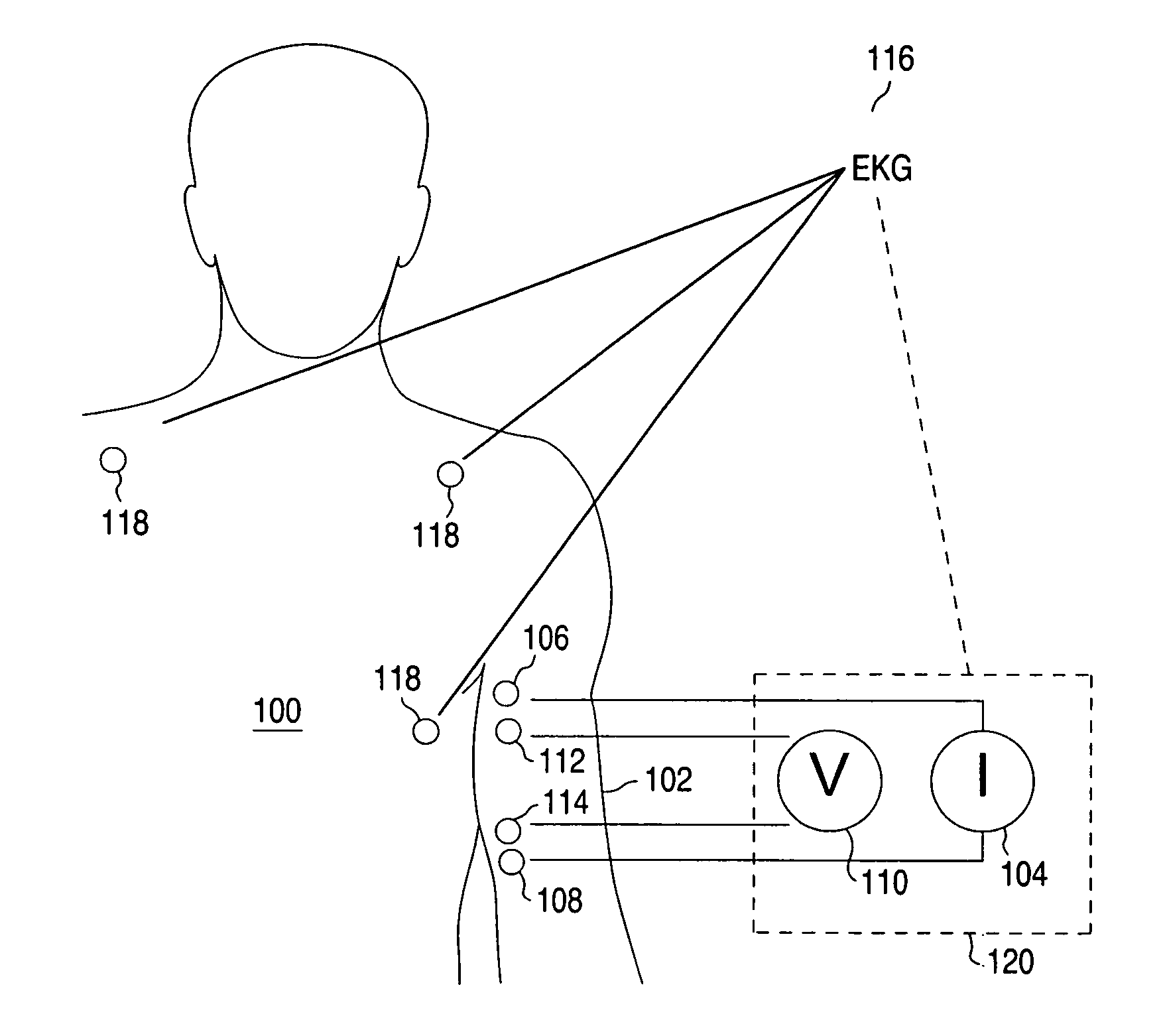

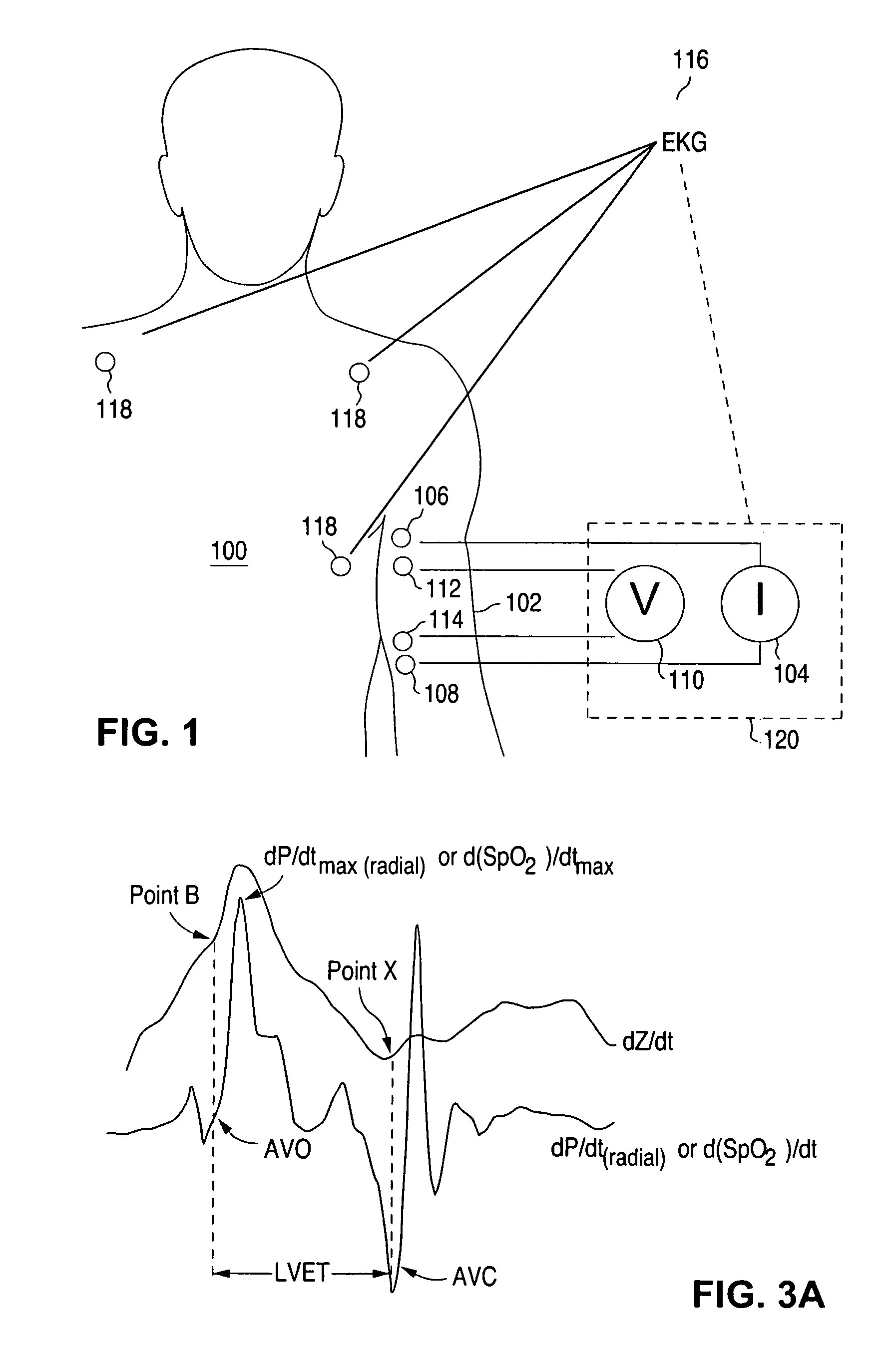

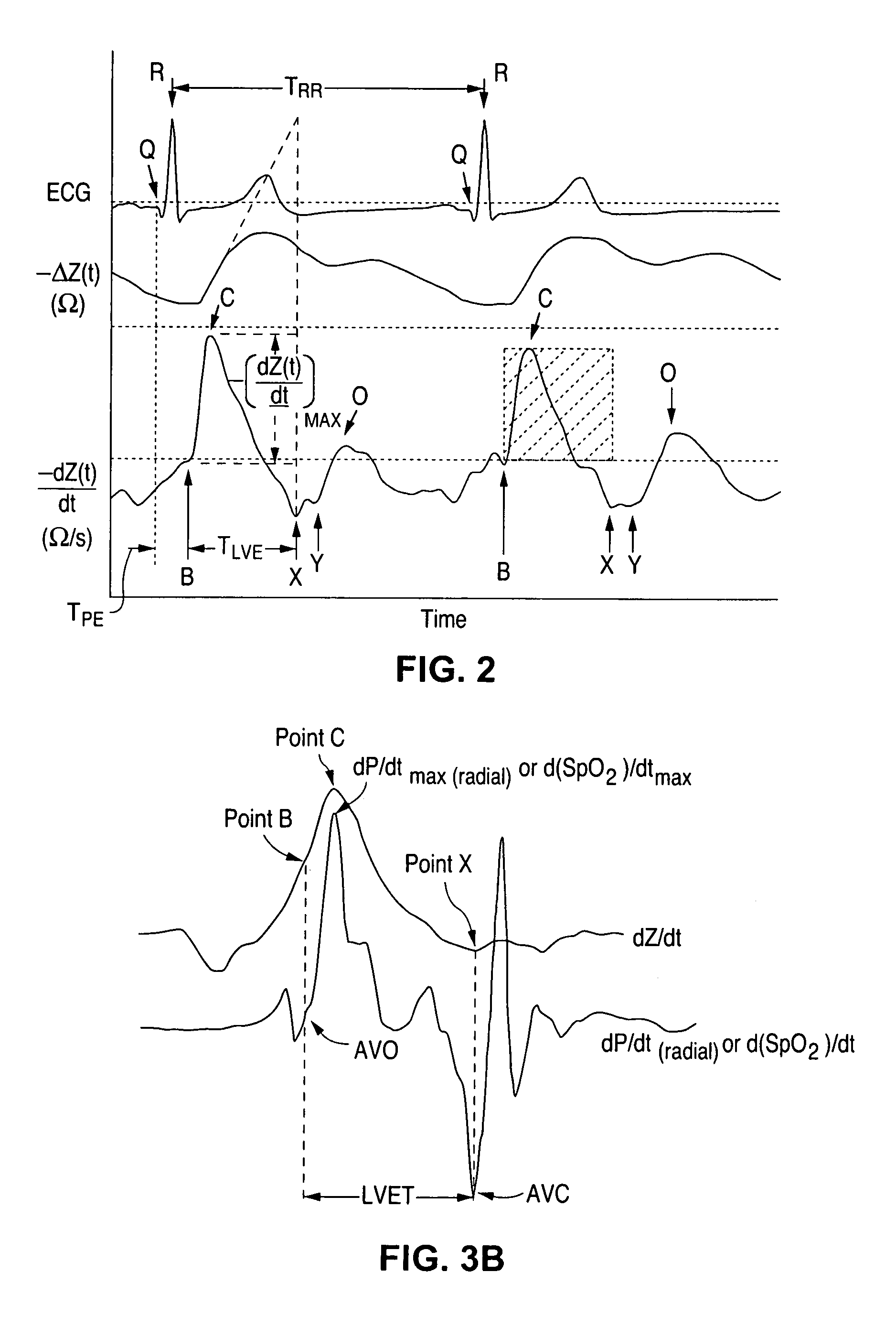

Apparatus and method for determination of stroke volume using the brachial artery

Provided herein are methods and apparatus for stroke volume determination by bioimpedance from a patient's upper arm, or brachium, utilizing pulsations of the brachial artery contained therein. The apparatus includes two or more spaced apart alternating current flow electrodes positioned on the patient's arm proximate the brachial artery and two or more spaced apart voltage sensing electrodes positioned on the patient's arm proximate the brachial artery. The voltage sensing electrodes are positioned between the alternating current flow electrodes on the arm. An alternating current source is electrically connected to the alternating current flow electrodes and a voltmeter electrically is connected to the voltage sensing electrodes. A data input device is provided along with a processing unit in communication with the data input device, the alternating current source, alternating current flow electrodes, the voltmeter, and voltage sensing electrodes. The processing unit is capable of using data from the data input device and voltage sensing electrodes to calculate the stroke volume of the patient.

Owner:BERSTEIN DONALD P

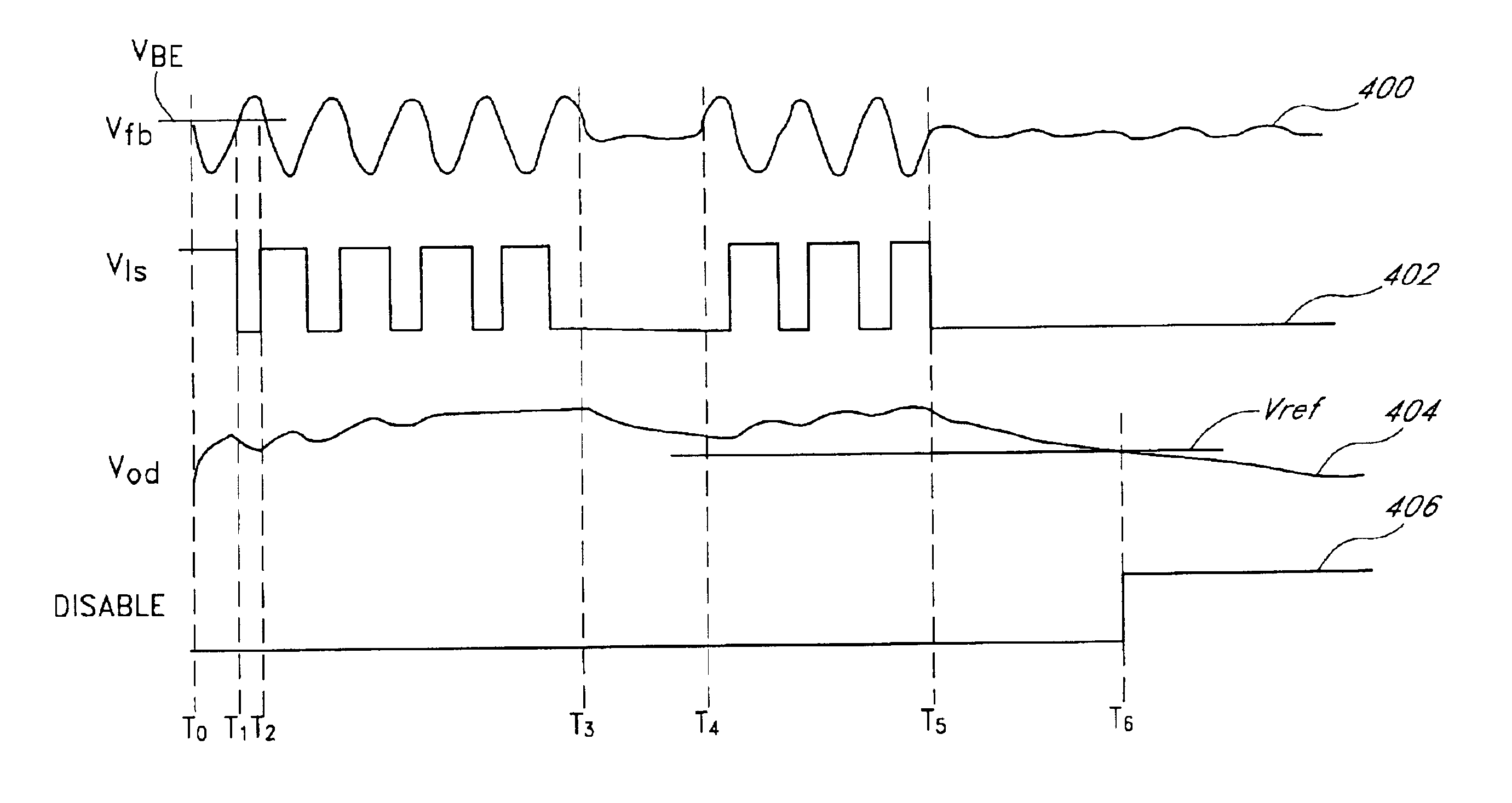

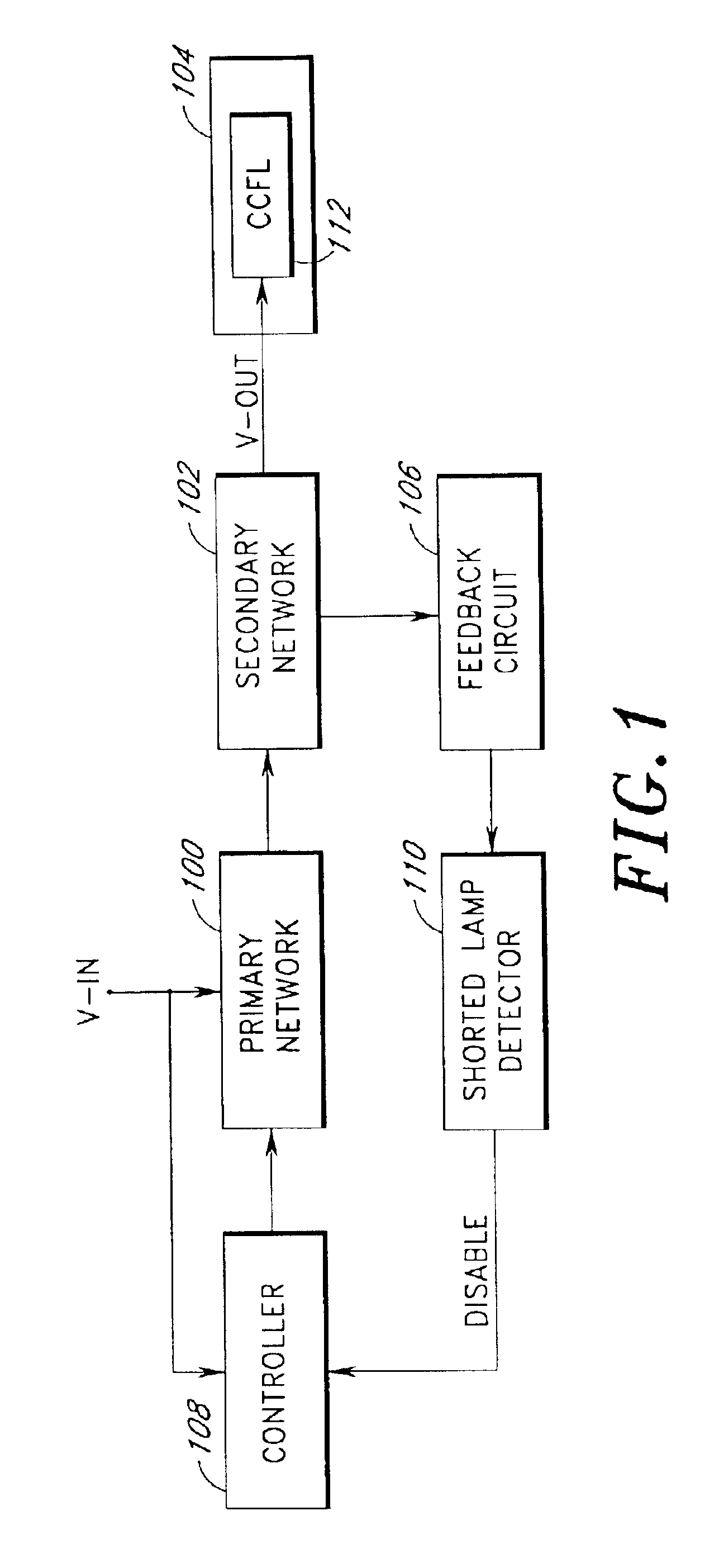

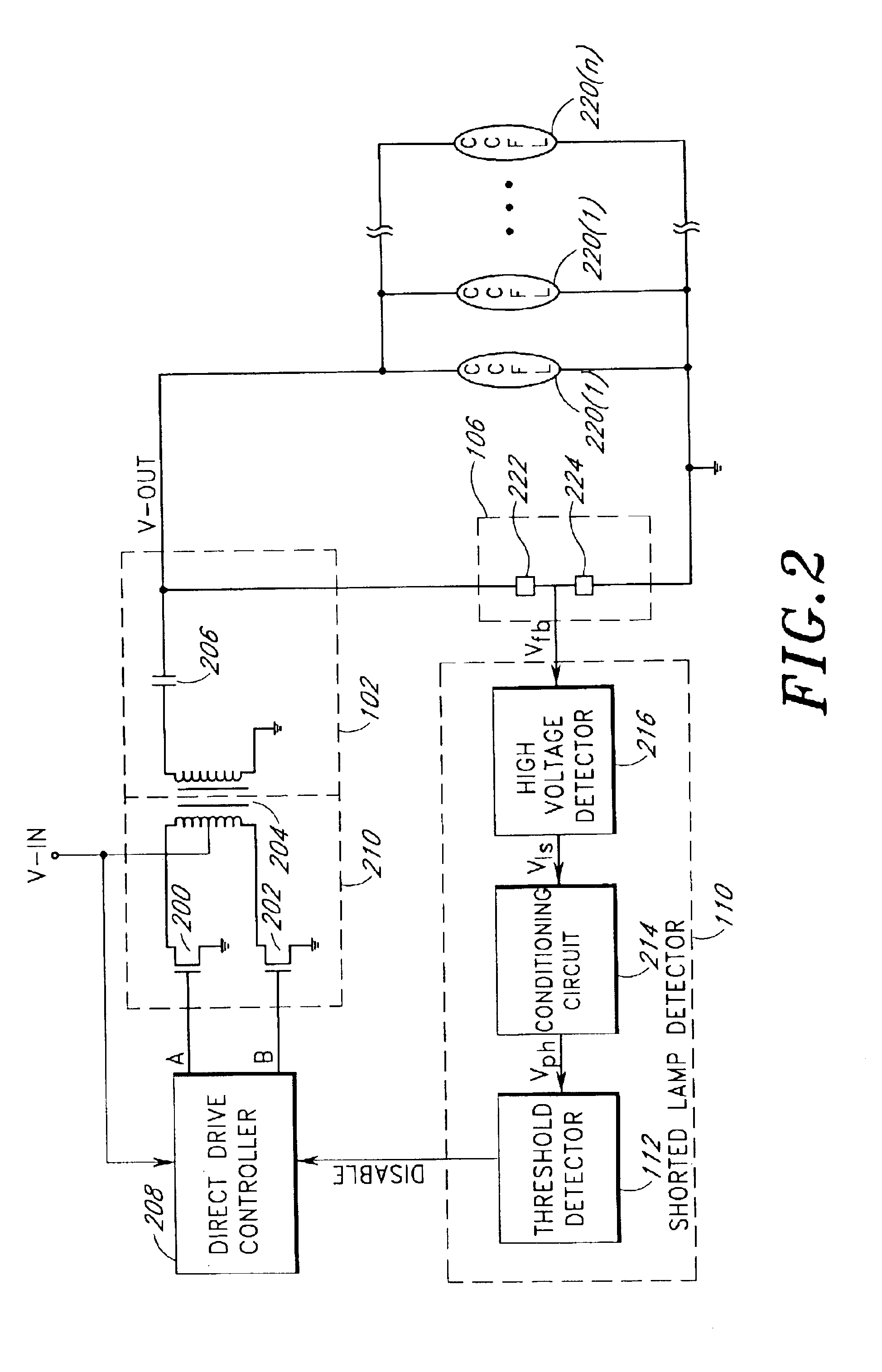

Shorted lamp detection in backlight system

InactiveUS6870330B2Affect operationElectrical apparatusElectric light circuit arrangementCapacitive voltage dividerFeedback circuits

A power conversion circuit senses an output voltage to detect shorted lamp conditions in a backlight system. The power conversion circuit can drive at least one fluorescent lamp. A voltage sensing feedback circuit, such as a capacitive voltage divider or a resistive voltage divider, senses the output voltage at an output of the power conversion circuit and generates a voltage feedback signal for a shorted lamp detector. The shorted lamp detector reliably detects a shorted lamp condition of one fluorescent lamp in a multi-lamp configuration or detects a short circuit condition of the output voltage line coupling the output voltage of the power conversion circuit to the fluorescent lamps.

Owner:MICROSEMI

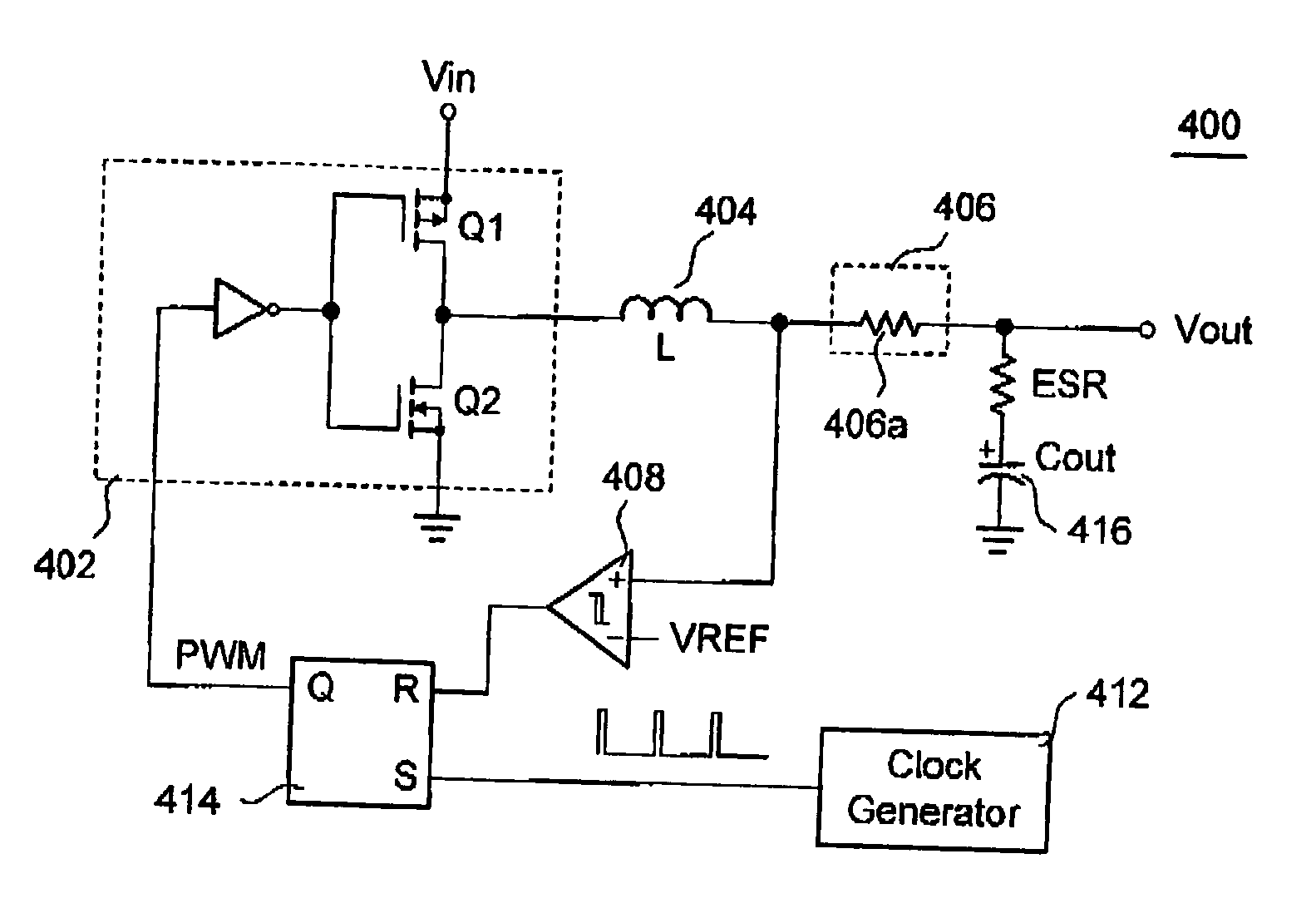

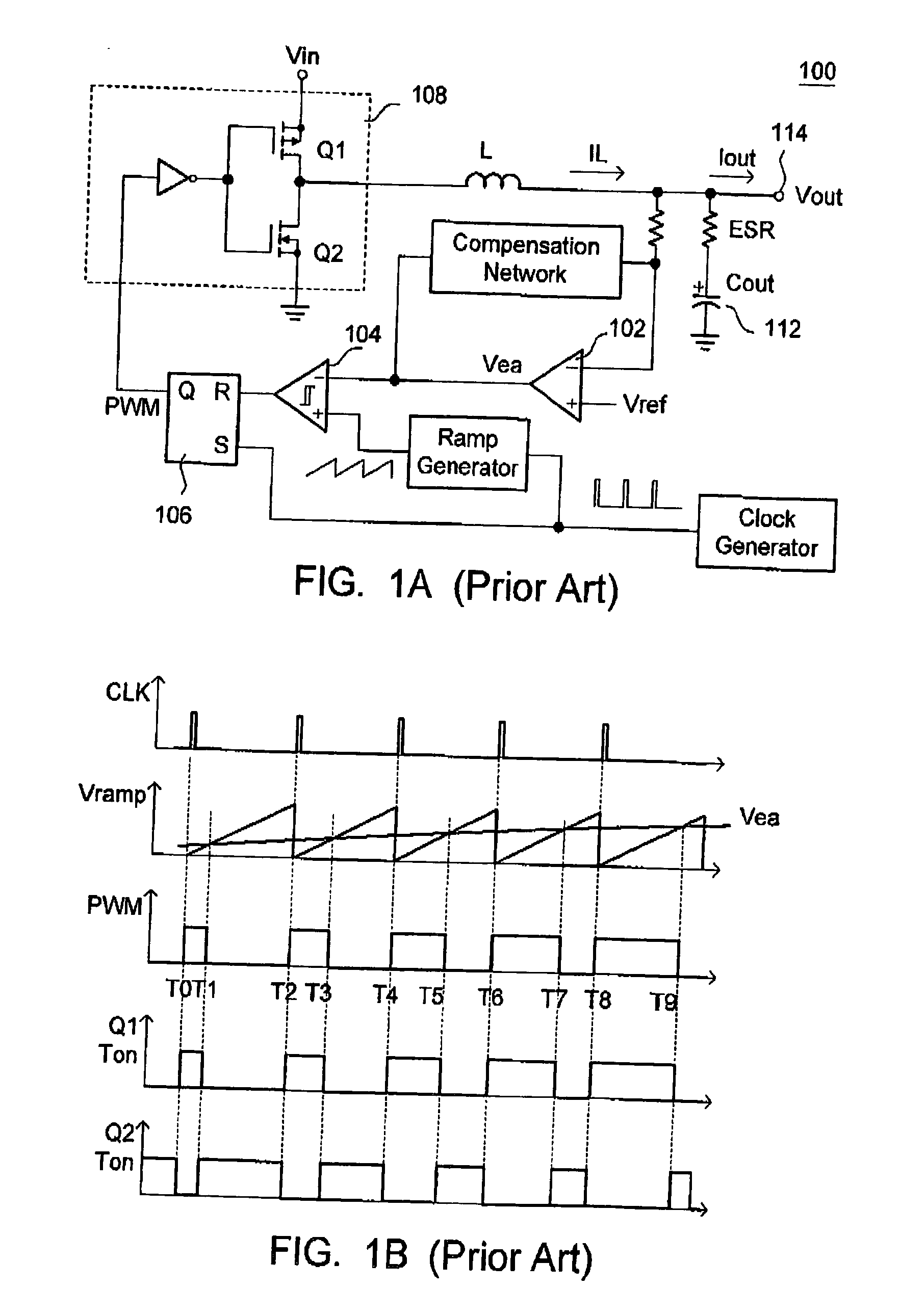

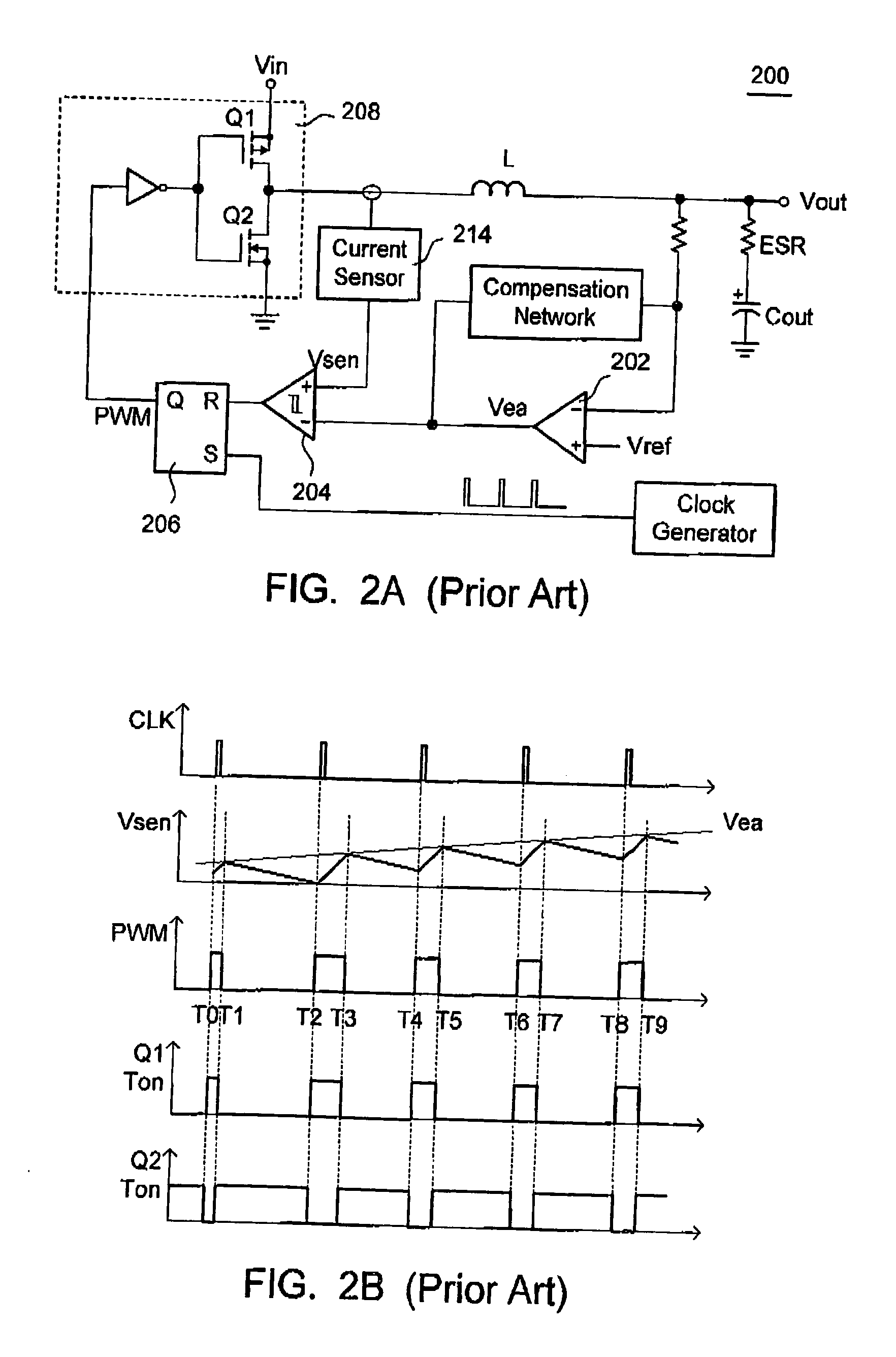

Direct mode pulse width modulation for DC to DC converters

InactiveUS20070063681A1Simple control circuitFast transient responseEfficient power electronics conversionDc-dc conversionCapacitanceEngineering

A DC to DC converter has an inverter, an inductor, a voltage sensor, a comparator, a clock generator, a driver and an output capacitor. The inverter converts an input voltage into a square-wave voltage. The inductor is electrically connected to an output of the inverter. The voltage sensor is electrically connected to the inductor and derives a sense voltage. The comparator compares the sense voltage and a reference voltage. The clock generator generates a reference clock pulse. The driver is triggered by the reference clock pulse and switches the inverter according to an output of the comparator. The output capacitor is electrically connected between the voltage sensor and the ground.

Owner:AMAZION ELECTRONICS

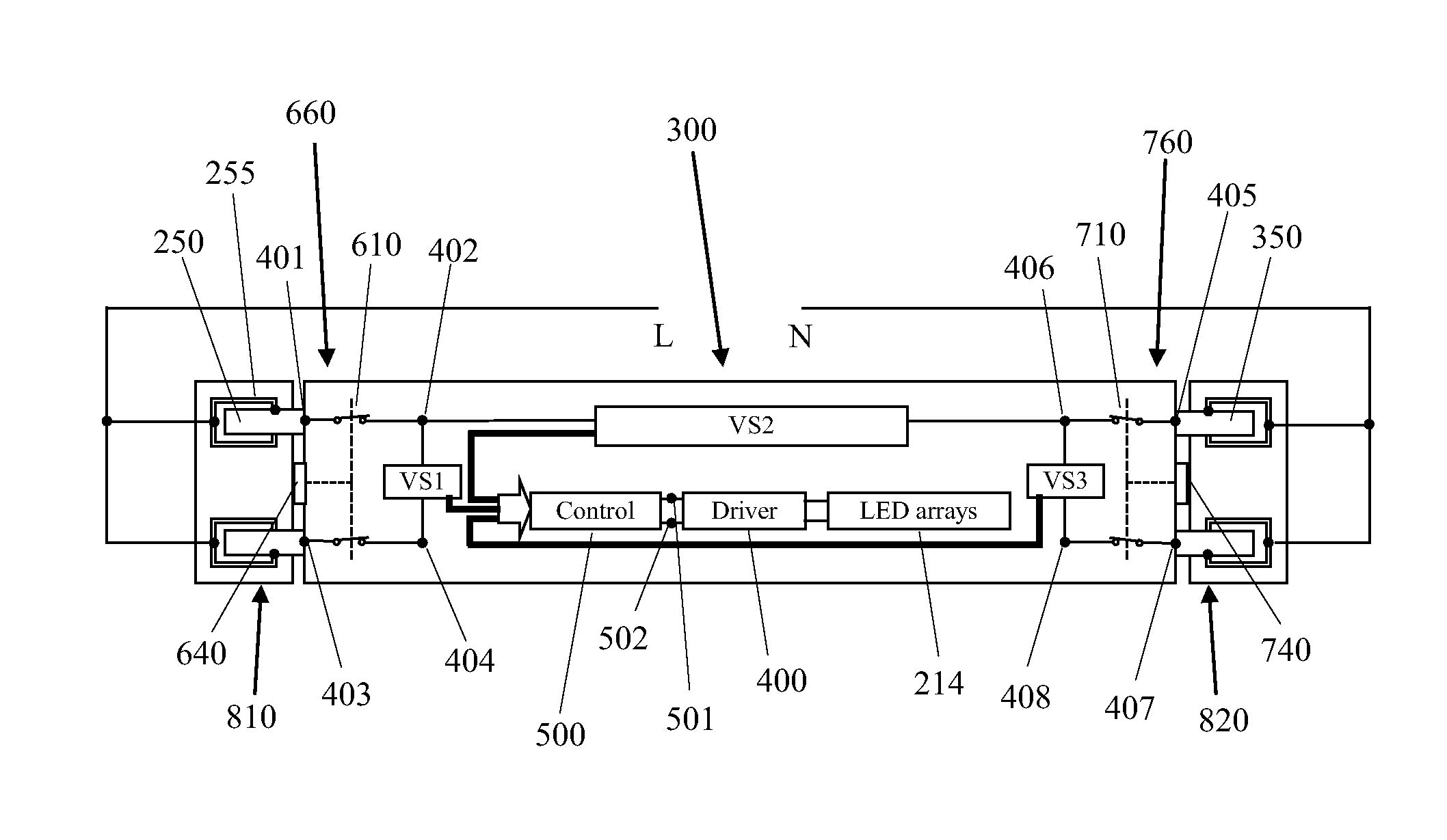

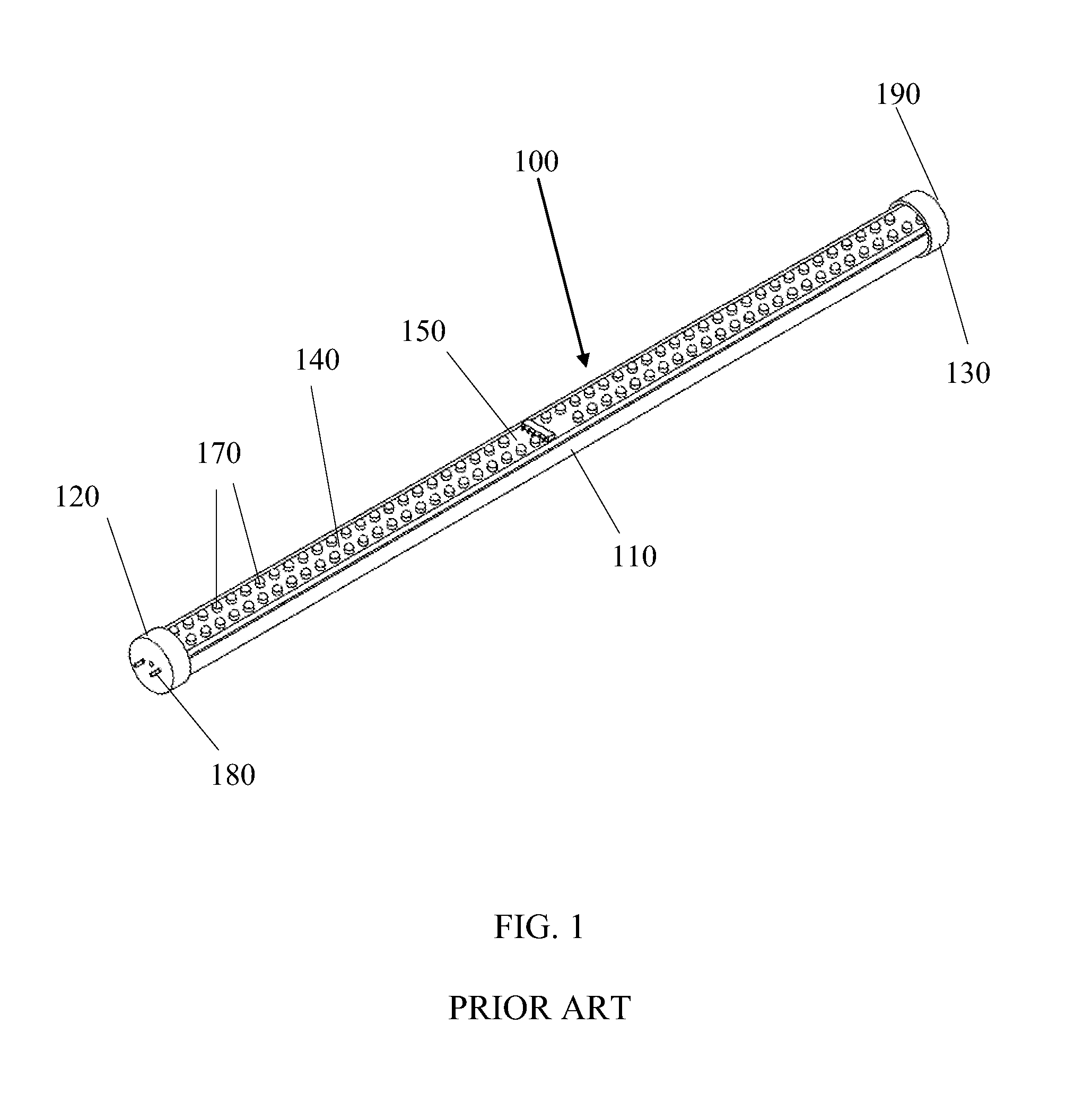

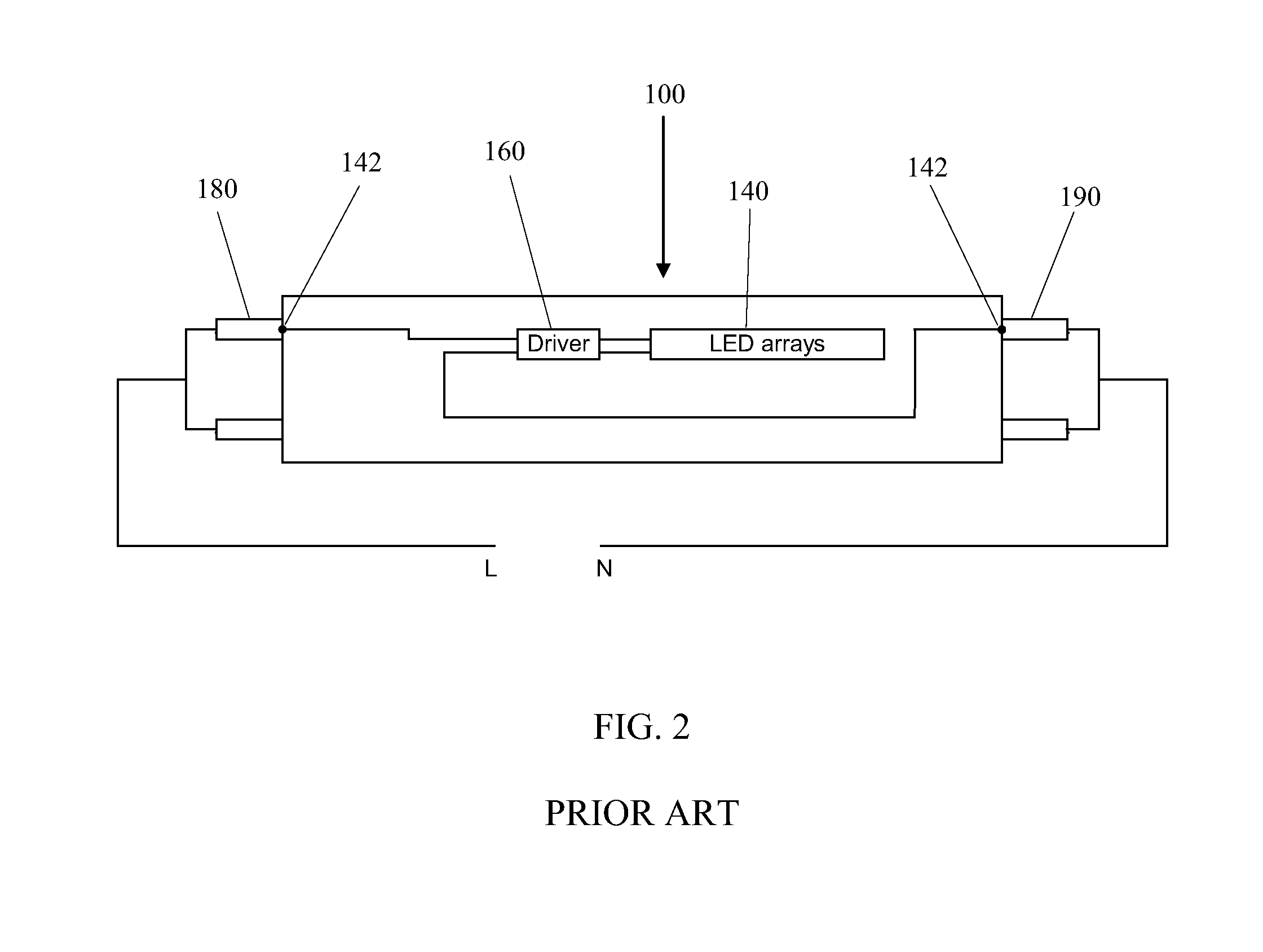

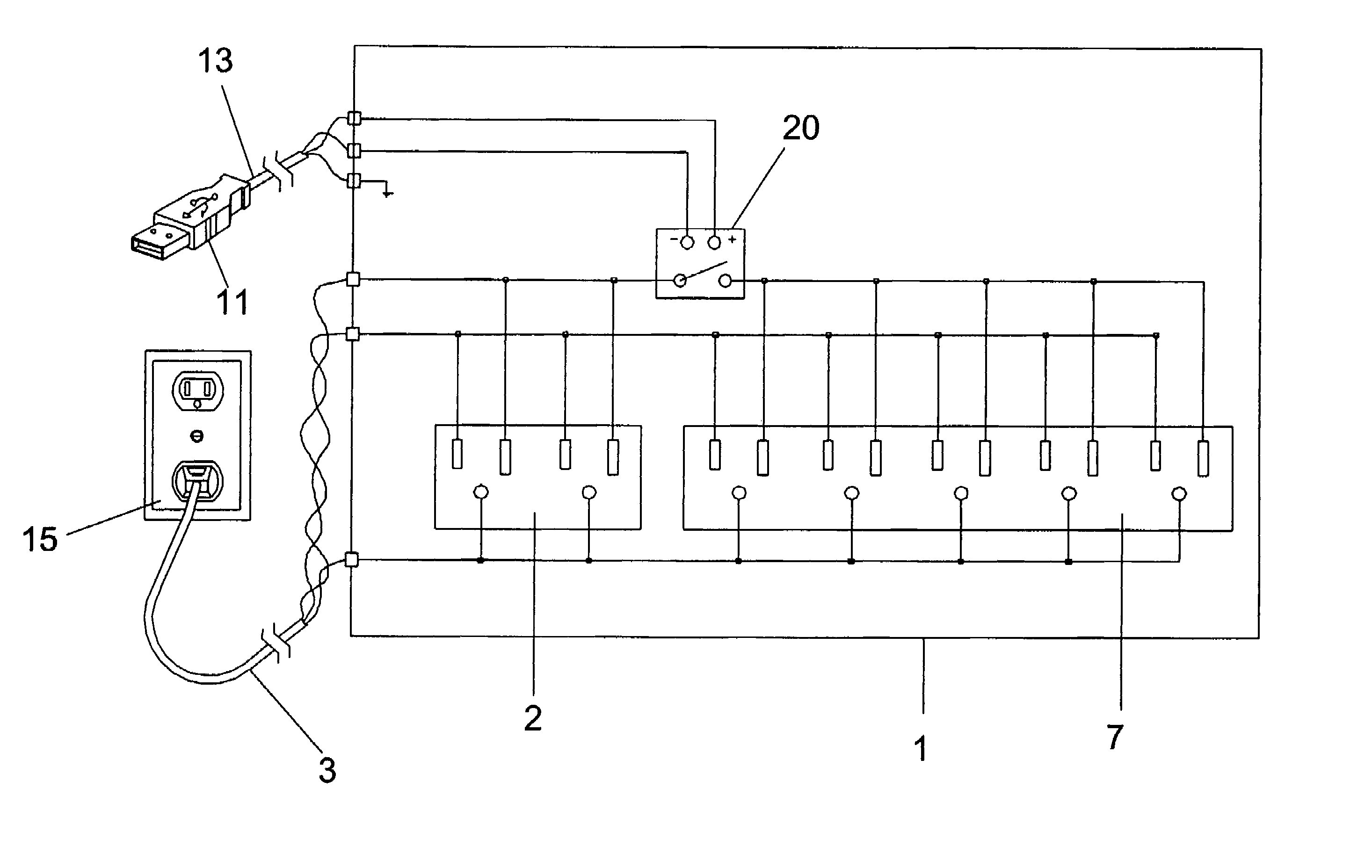

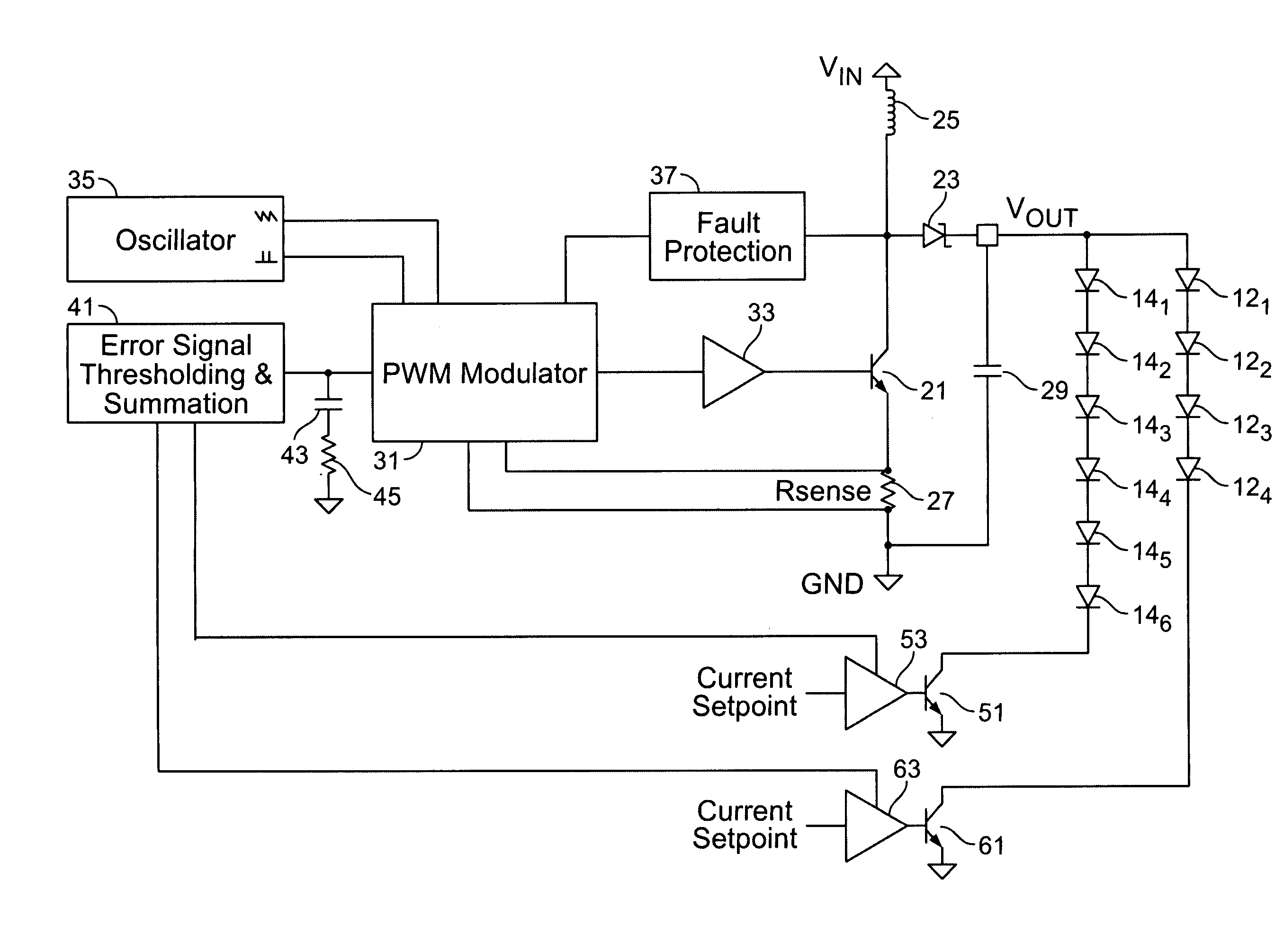

Linear solid-state lighting with voltage sensing mechanism free of fire and shock hazards

ActiveUS20130335959A1Risk of fire and shockElectrical apparatusPoint-like light sourceSmart lightingEngineering

A linear light-emitting diode (LED)-based solid-state lamp using a novel voltage sensing and control mechanism operates normally in both single-ended and double-ended luminaire fixtures. The voltage sensing and control mechanisms automatically detect supply source configuration in the fixture and make proper management so that the linear LED lamp works in any fixtures without operational uncertainty or risk of fire. When used with shock protection switches on the two lamp bases at two opposite ends, the universal lamp fully protects a person from possible electric shock during initial installation and re-lamping.

Owner:ALEDDRA INC

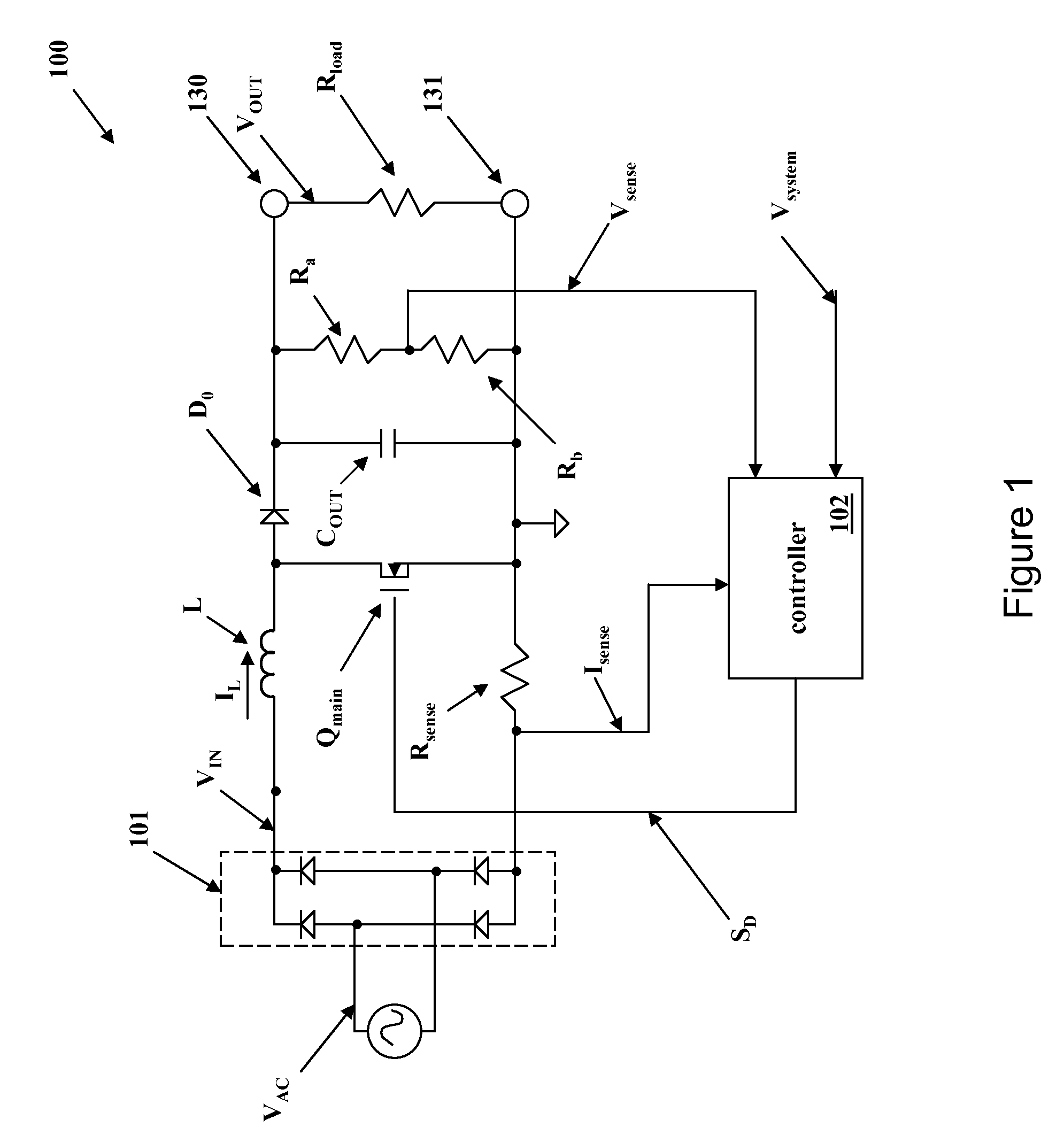

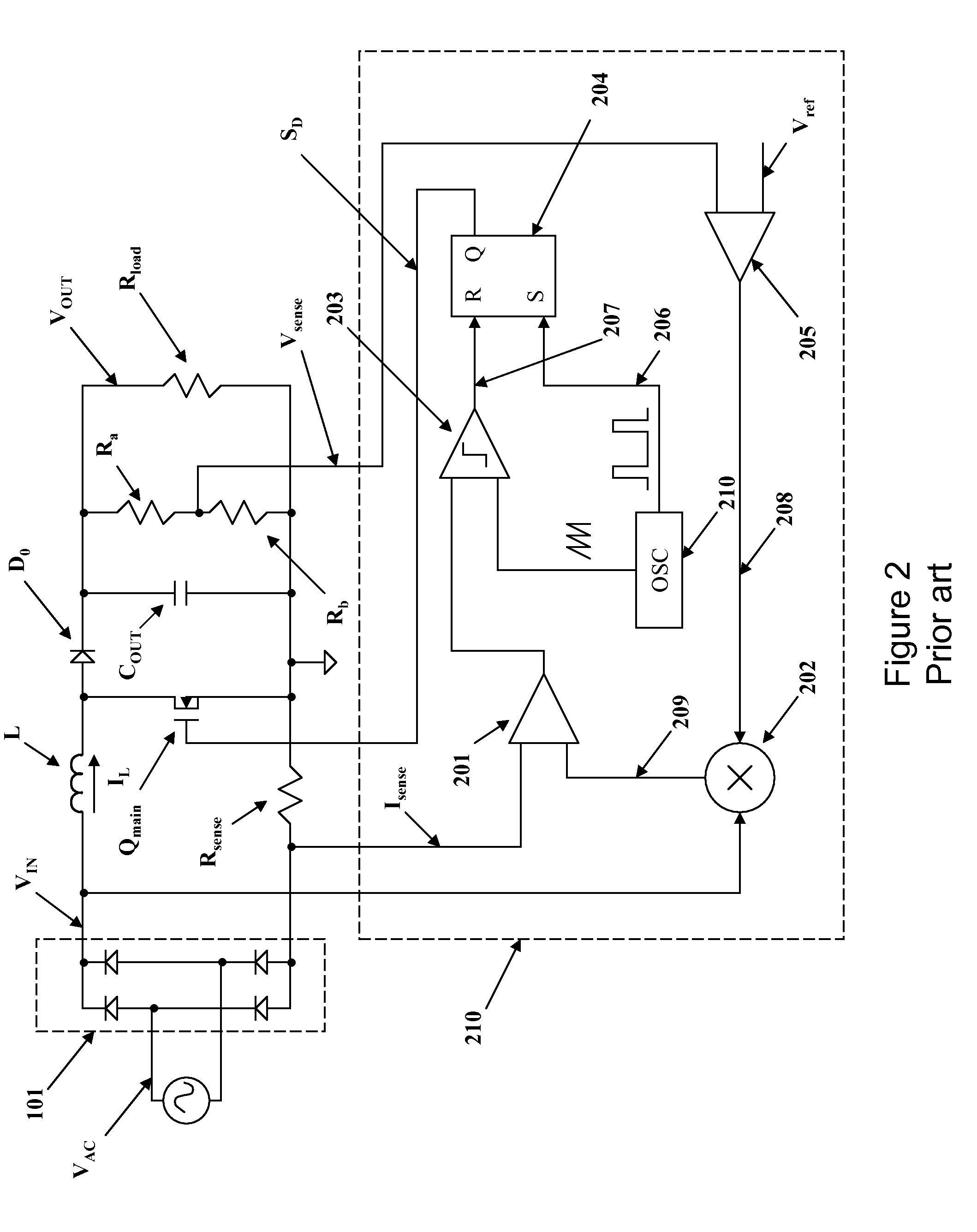

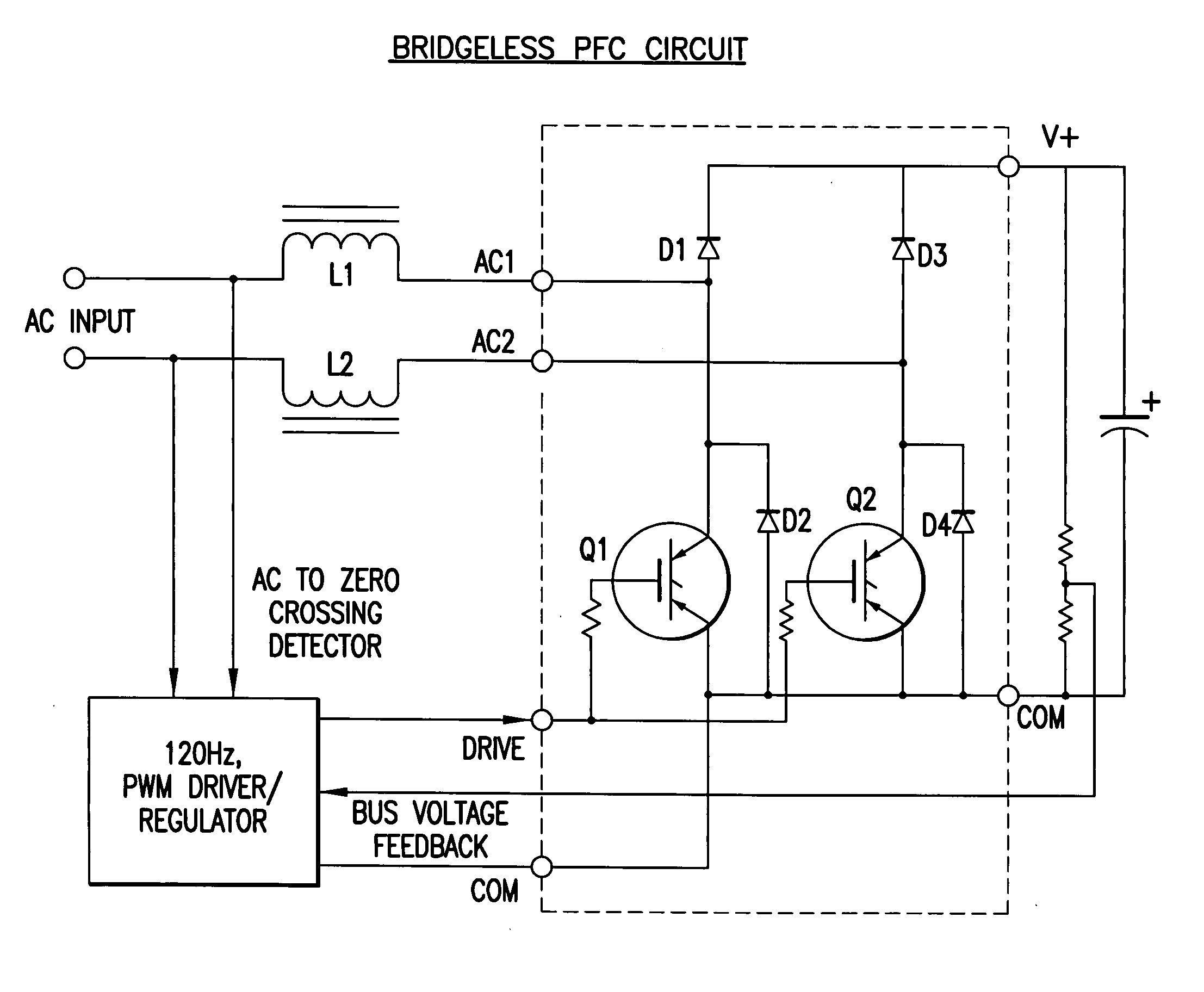

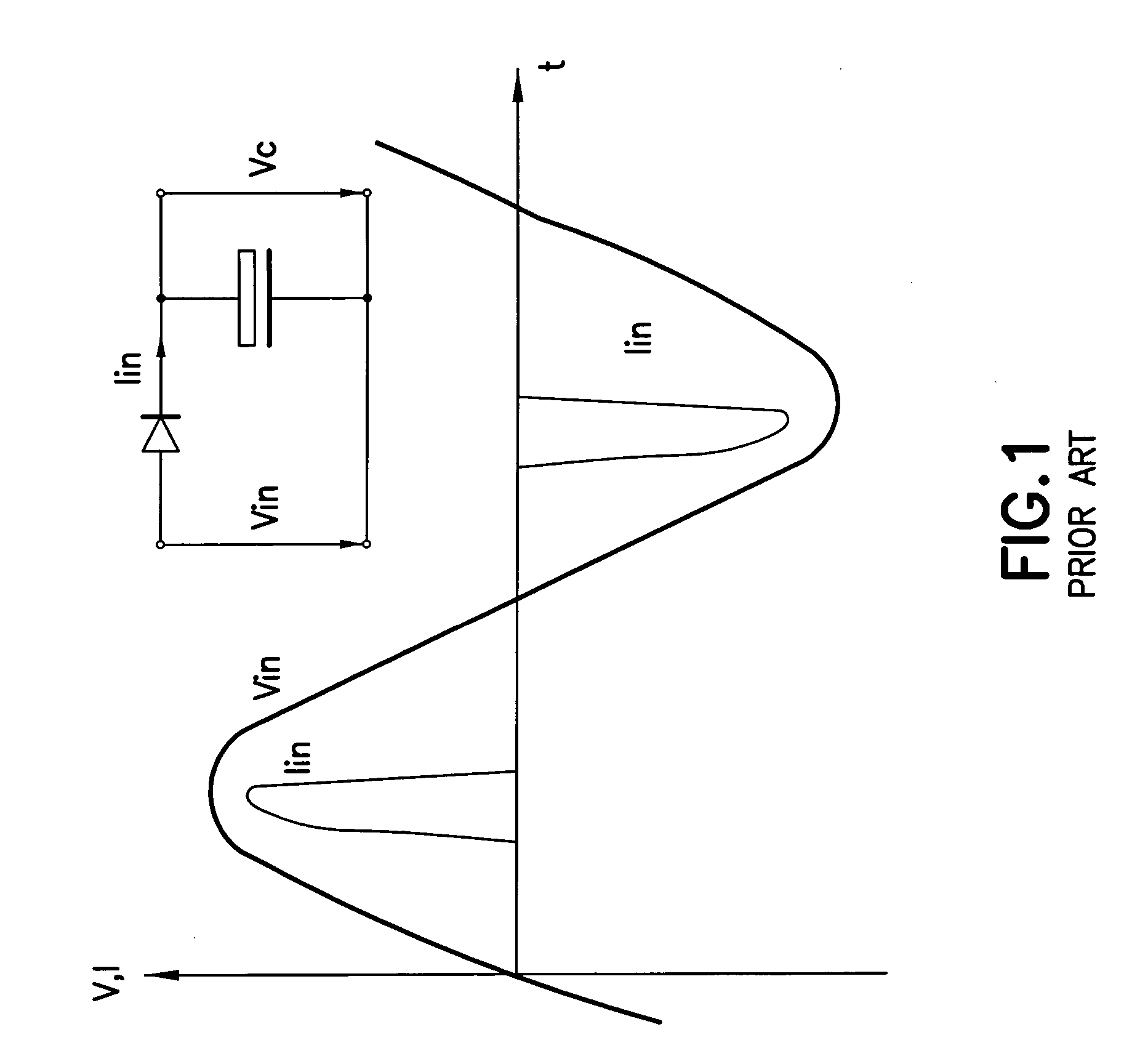

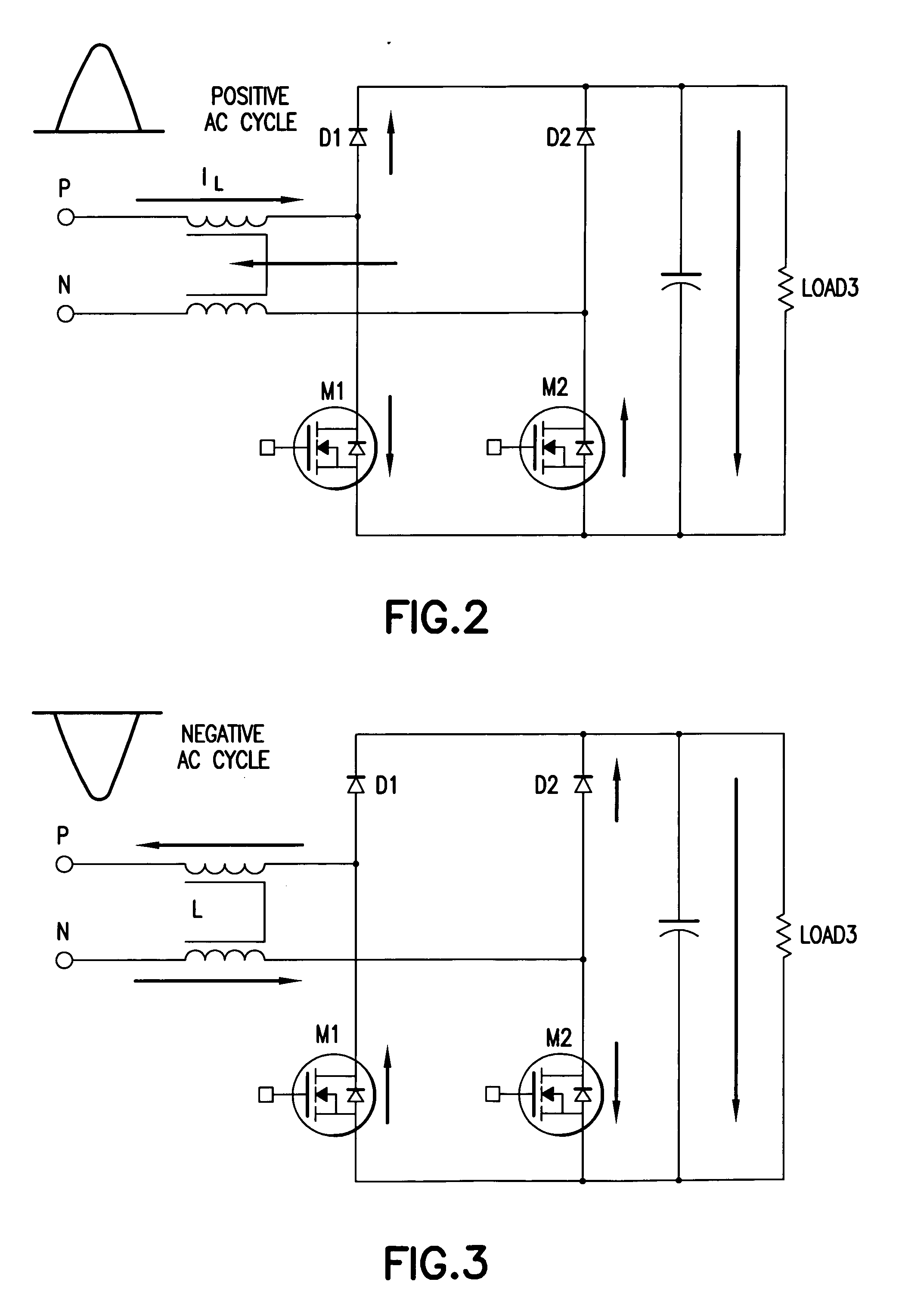

Bridgeless boost converter with PFC circuit

InactiveUS20060198172A1Improve efficiencyLow costAc-dc conversion without reversalEfficient power electronics conversionControl signalEngineering

A boost type power supply circuit for providing a DC output voltage comprising first and second semiconductor switches coupled between respective input lines and a common connection; an AC input voltage from an AC source being supplied across the input lines; first and second diodes coupled in series with respective ones of the switches; third and fourth diodes coupled across respective ones of the switches in a free-wheeling relationship with the switches; an inductance coupled in at least one of the input lines; a controller for controlling the conduction times of the switches by providing a pulse width control signal to each of the switches; wherein the controller turns on at least one of the switches during a positive half cycle of the AC voltage to allow energy storage in the inductance and turns off the at least one switch to allow the energy stored in the inductance to be supplied to an attached load through one of the first and second diodes and one of the third or fourth diodes; and the controller turns on at least one of the switches during a negative half cycle of the AC voltage to allow energy storage in the inductance and turns off at least one switch to allow the energy stored in the inductance to be supplied to the attached load through one of the first and second diodes and one of the third and fourth diodes. The controller determines an on-time and an off-time of a pulse of the pulse width modulated control signal during each half cycle of the AC voltage, the on-time and off-time of the pulse being controlled to regulate said output voltage and to provide power factor correction of said AC input voltage, based on either voltage sensing or current sensing.

Owner:INTERNATIONAL RECTIFIER COEP

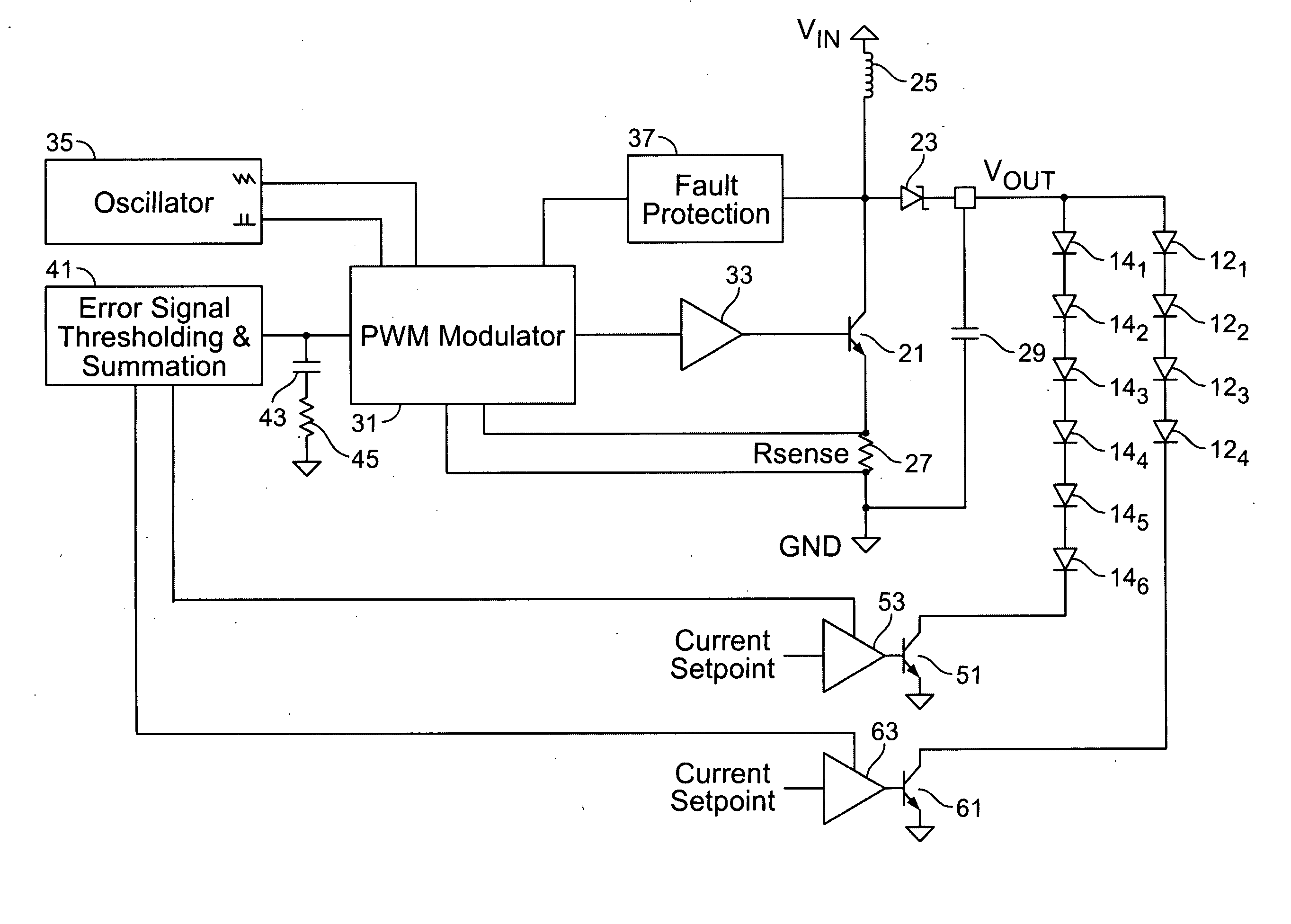

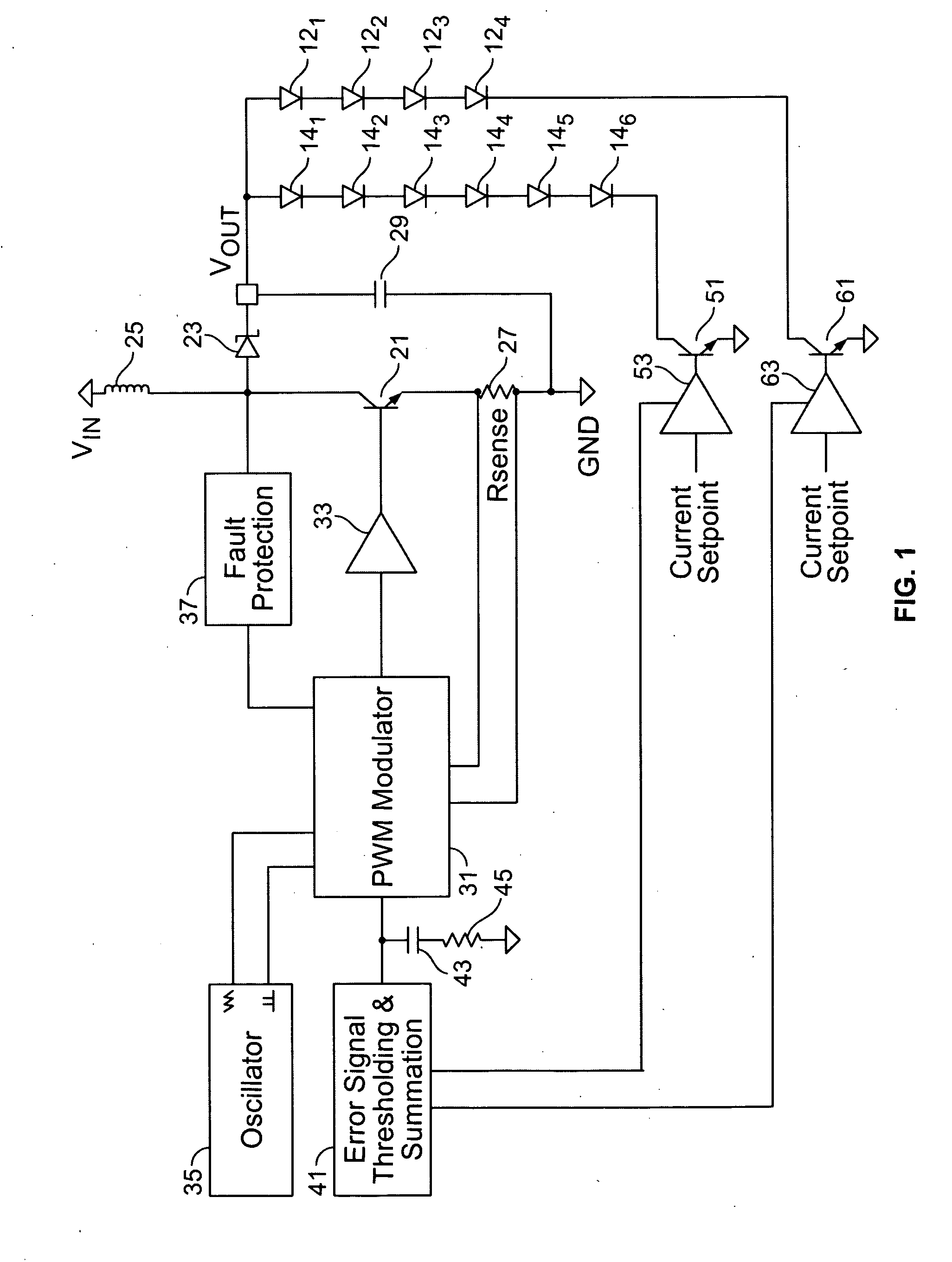

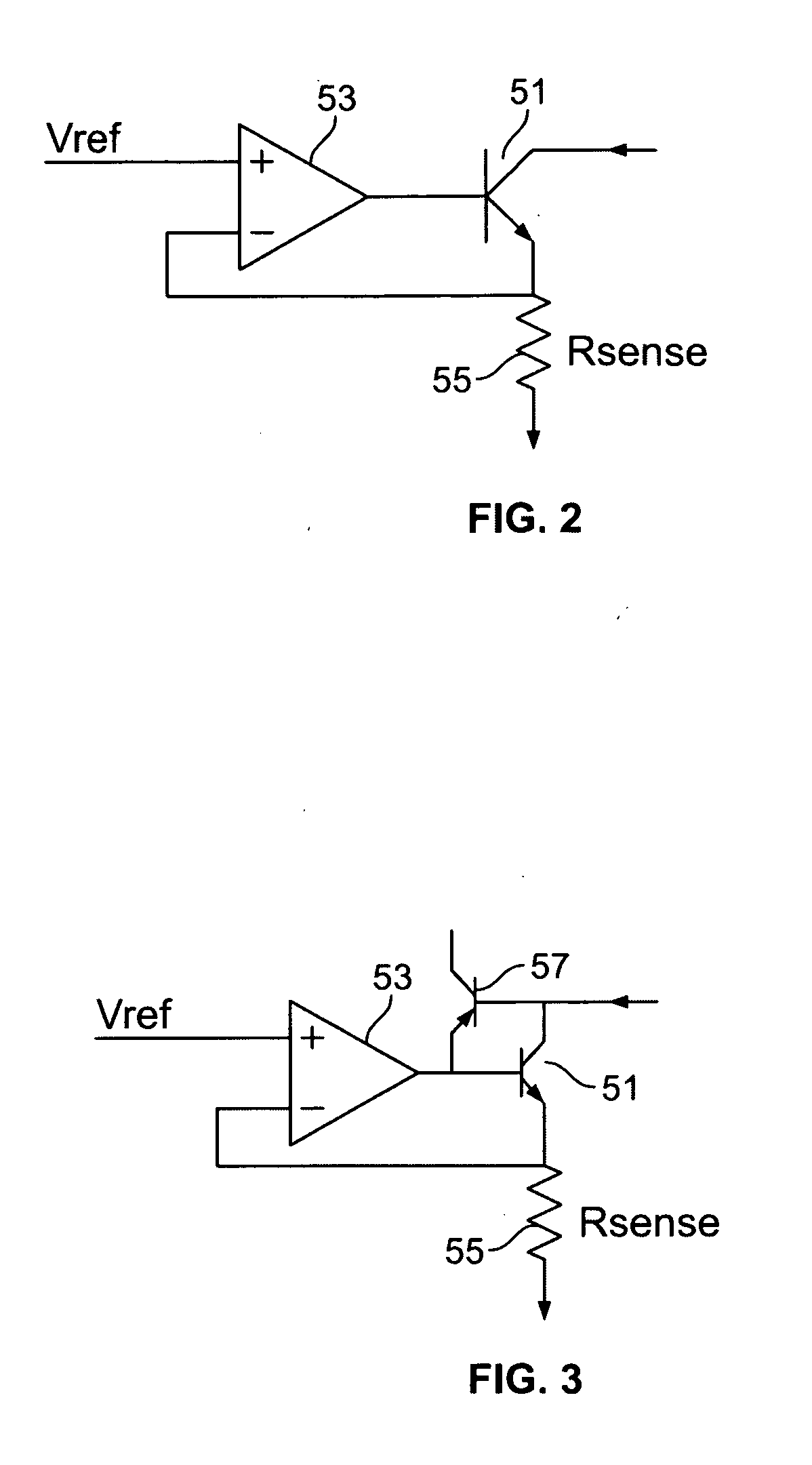

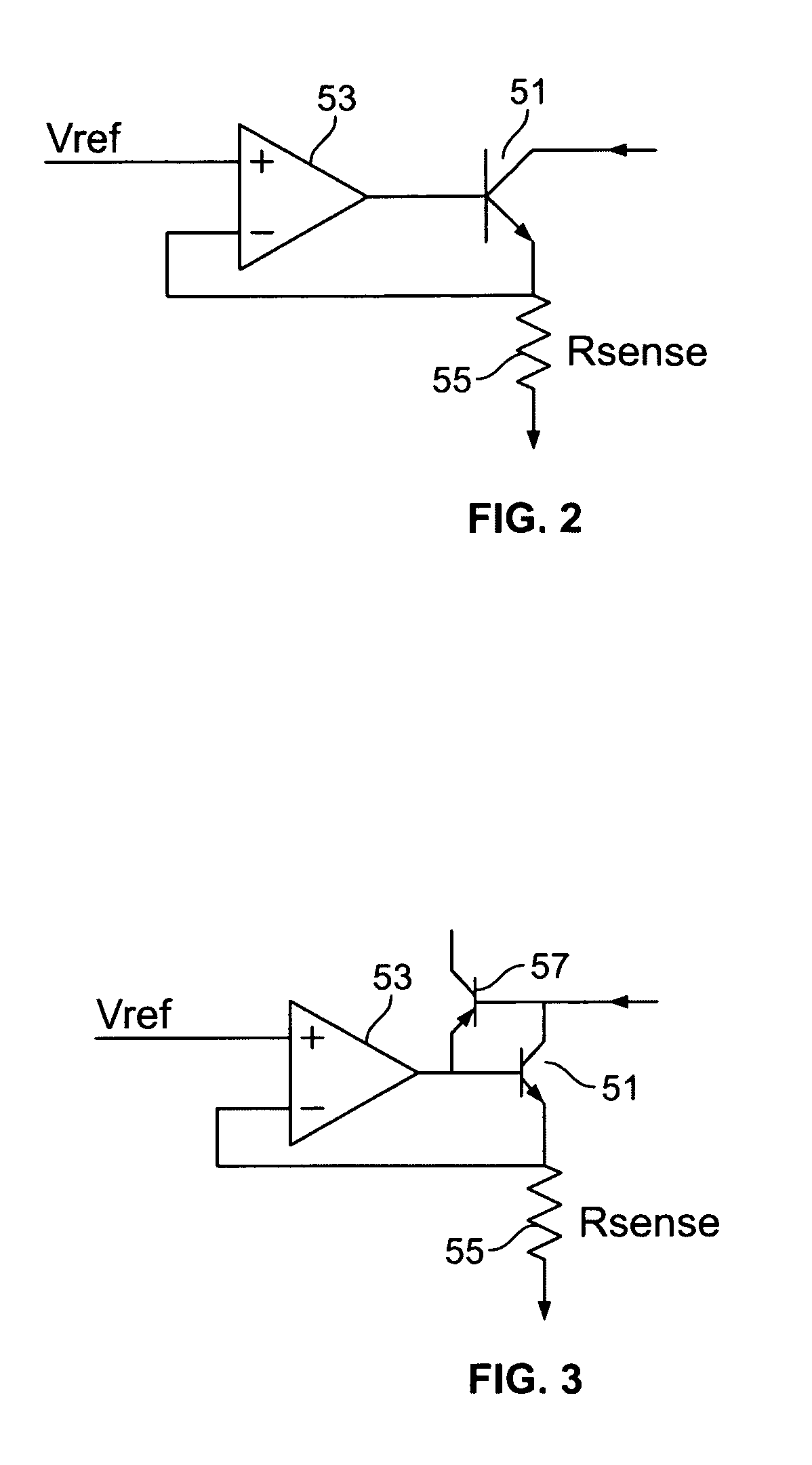

High efficiency power supply for LED lighting applications

InactiveUS20070120506A1Accurate current regulationHigh efficiency operating pointElectrical apparatusElectroluminescent light sourcesVoltage regulationEffect light

A power supply for plural loads coupled in parallel comprises a voltage regulator, a plurality of current regulators, and an error control circuit. The voltage regulator provides a common output voltage to the plural loads. The voltage regulator comprises a sensor circuit providing a voltage sense signal corresponding to the output voltage, which provides feedback to regulate the output voltage at a selected level. The plurality of current regulators are coupled to respective ones of the plural loads. Each of the plurality of current regulators regulates current drawn by respective ones of the plural loads to within a desired regulation range. The plurality of current regulators each further provide a respective error signal corresponding to an ability to remain within the desired regulation range. The error control circuit is operatively coupled to the voltage regulator and to the plurality of current regulators. The error control circuit receives the error signals from the plurality of current regulators and provides a common error signal to the voltage regulator. The voltage regulator thereby changes the selected level of the output voltage in response to the common error signal. Accordingly, the selected level of the output voltage remains at a minimum voltage necessary to keep the plural loads in the desired regulation range.

Owner:SEMTECH CORP

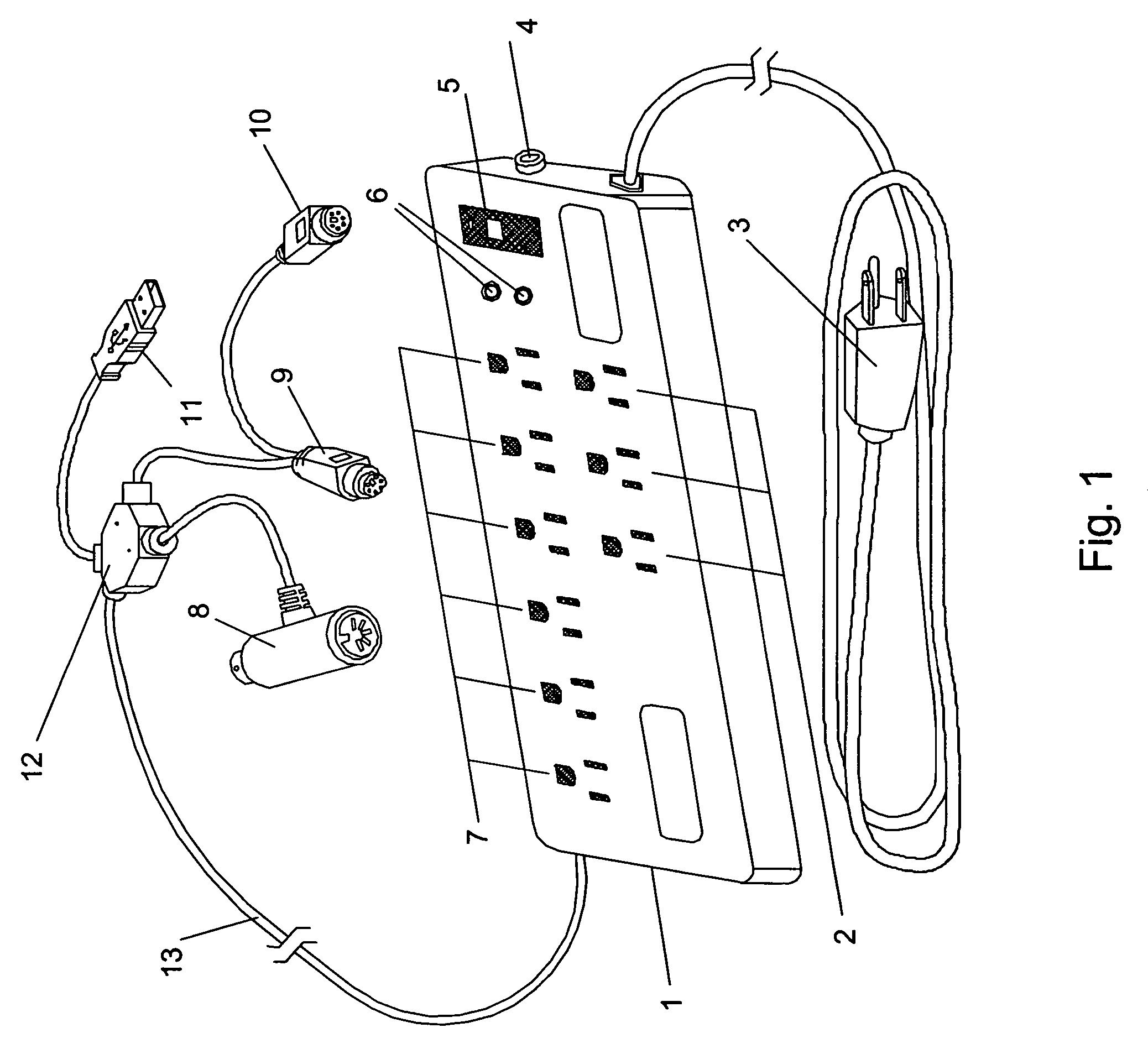

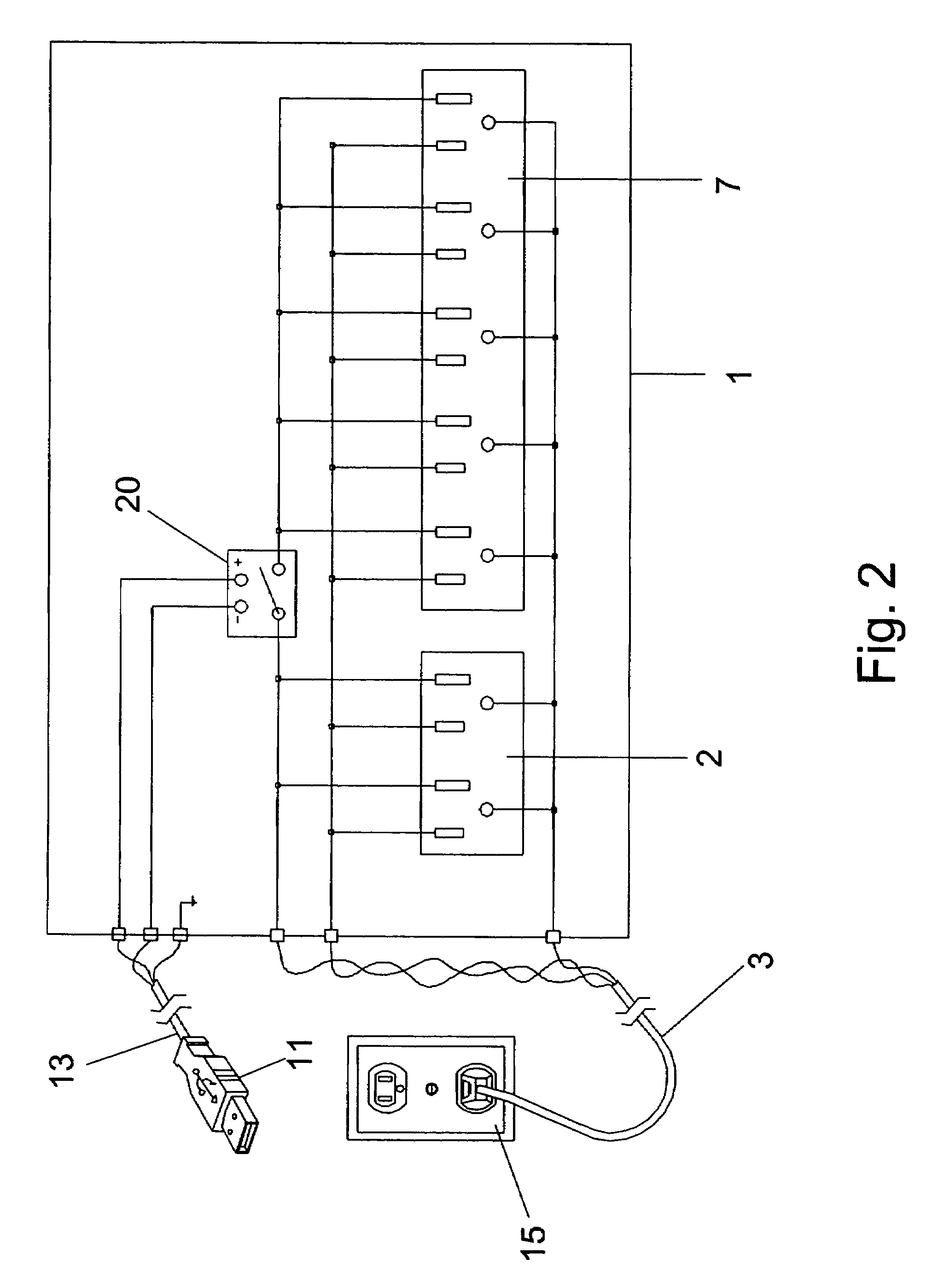

System and method for automatically interrupting power to a secondary device upon the extinguishing of power to a primary device

InactiveUS7132763B2Dc network circuit arrangementsVolume/mass flow measurementPower stripElectric power

The present invention encompasses a system and method for automatically interrupting a flow of power from an external electrical energy source to at least one device upon the extinguishing of power to another device. The system includes a power strip, a voltage sensing device (e.g., a 5 Volt power tap), and a switch. The power strip has at least one switched outlet adapted to receive an electrical power cord plug from at least one secondary or peripheral device. The voltage sensing device selectively detects an operating voltage of a primary device, wherein the operating voltage is less than a voltage associated with power supplied by the energy source. The switch is coupled to the voltage sensing device and selectively supplies electrical energy from the energy source to the switched outlet(s) depending upon whether or not the voltage sensing device detects the operating voltage of the primary device.

Owner:RENDIC NEVEN V

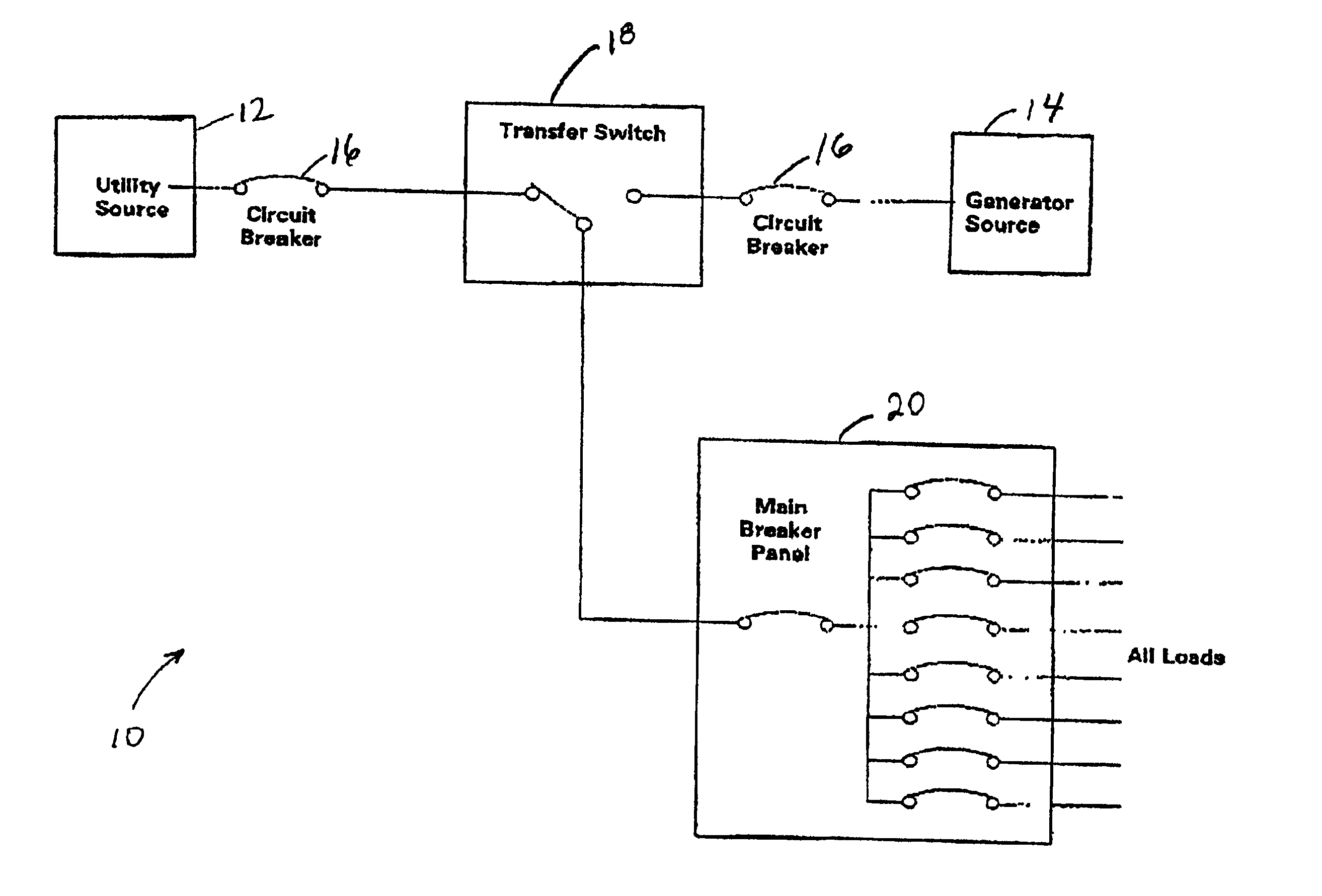

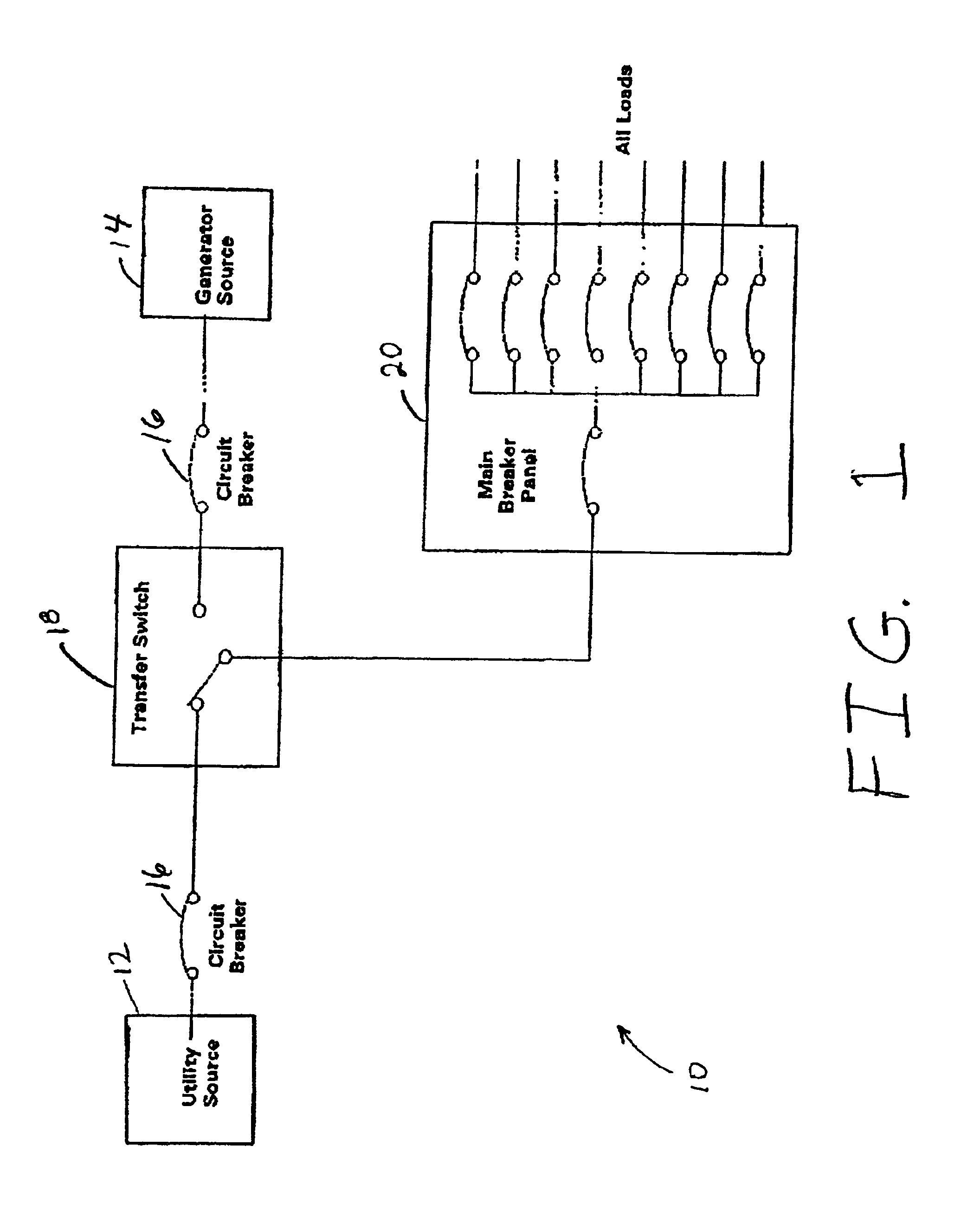

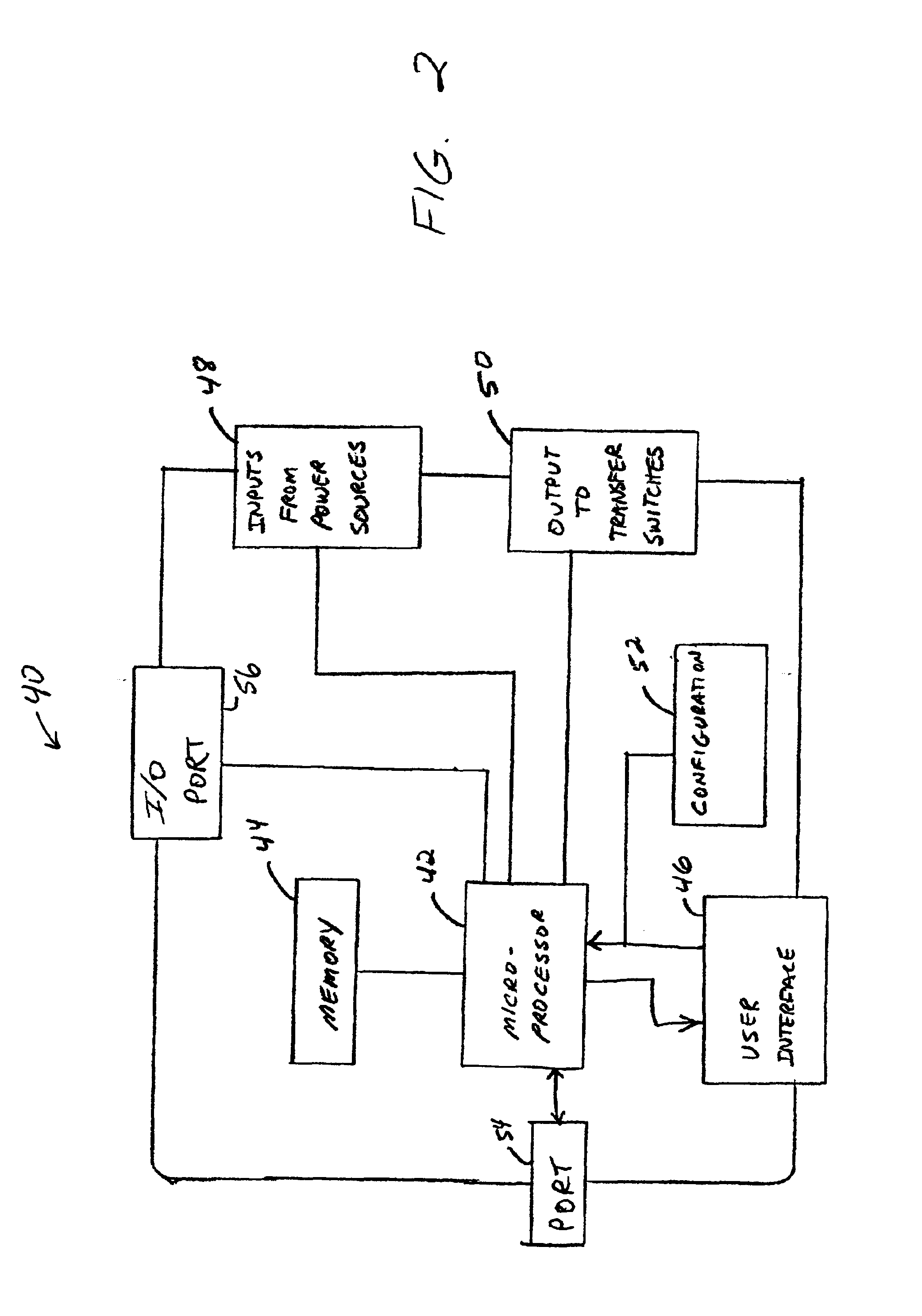

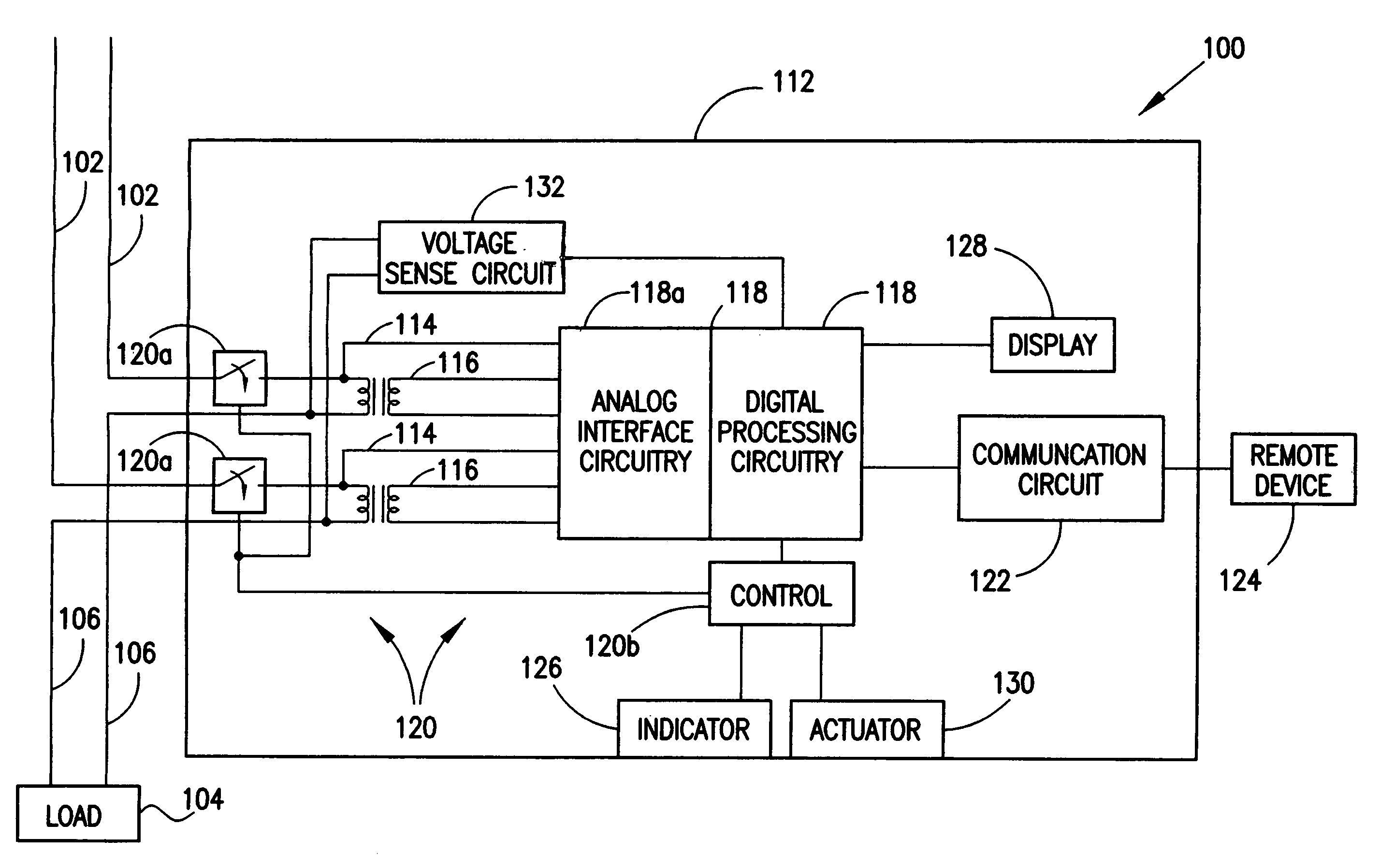

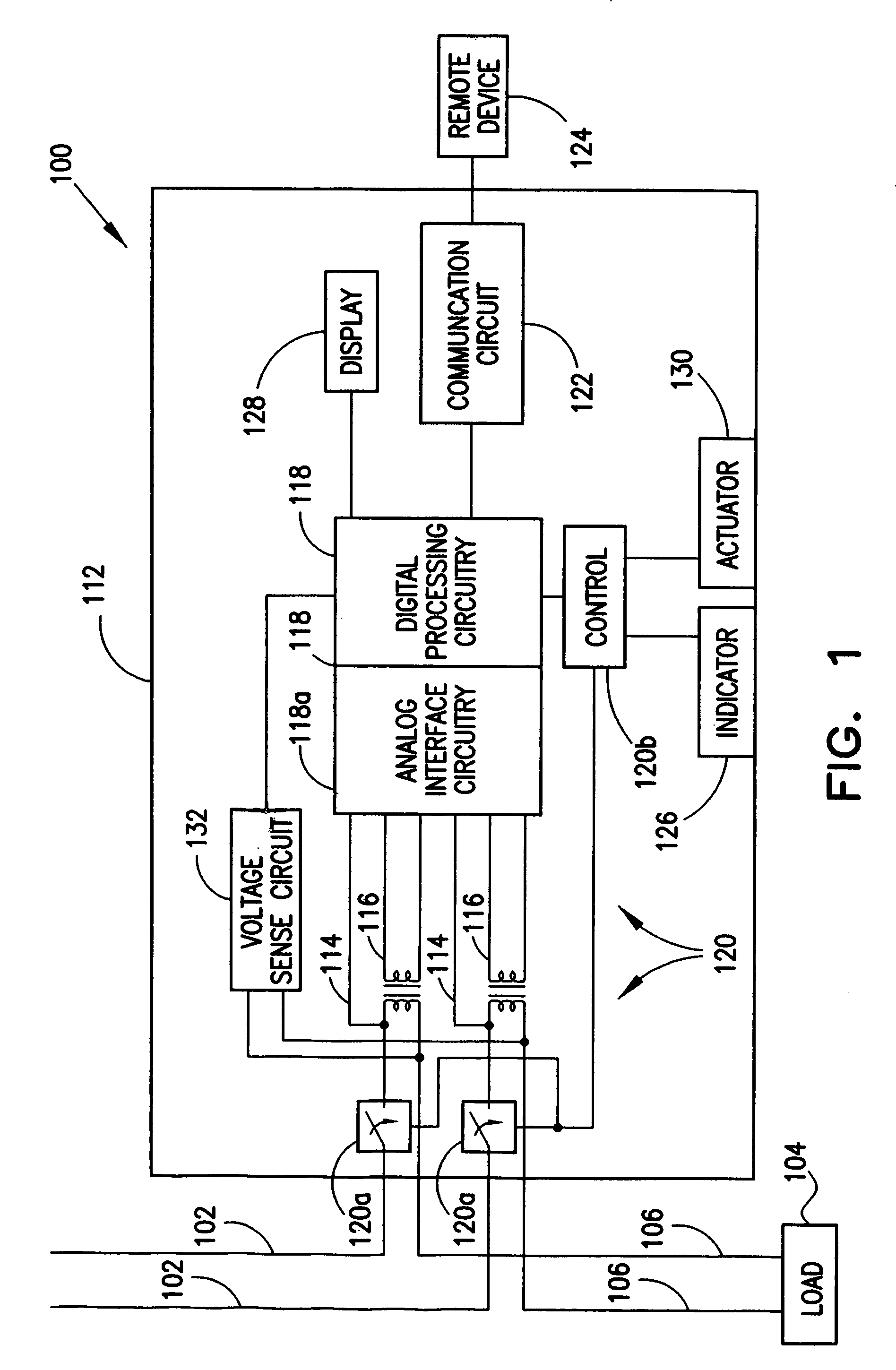

Automatic transfer switch systems and controllers

InactiveUS6876103B2Batteries circuit arrangementsBoards/switchyards circuit arrangementsMicrocontrollerDriver circuit

An automatic transfer switch (ATS) controller is disclosed which includes a power supply circuit to regulate and filter input power, a transformer to convert utility and generator power sources into power supply voltages and voltage sensing sources and a voltage sense signal conditioning circuit. Controller further implements a solenoid driver circuit to drive automatic transfer switch solenoids, an embedded microcontroller configured to monitor utility and generator voltages and a user interface interfaced to said microcontroller for operator entry of instructions. A LED indicator is included and is configured to verify user interface entries and overall operation of the controller and ATS system.

Owner:GENERAL ELECTRIC CO

Nonvolatile semiconductor memory having three-level memory cells and program and read mapping circuits therefor

InactiveUS6847550B2Improve reliabilityHigh voltageRead-only memoriesDigital storageThree levelNon symmetric

A memory uses multiple threshold levels in a memory cell that are not a power of two, and further uses a cell mapping technique wherein the read mapping is only a partial function The domain of read states for a single three-level memory cell, for example, has three states, but only two of them can be uniquely mapped to a bit. The domain of read states for two three-level memory cell, for example, has nine states, but only eight of them can be uniquely mapped to three bits. Although the read mapping is only partial, the voltage margin for the three-level memory cells is larger that the voltage margin available in the commonly used four-level memory cells. This increased voltage margin facilitates memory cell threshold voltage sensing, thereby increasing the reliability of the memory. Memory reliability may be further improved by increasing the voltage margin between the memory cell 0 state and the 1 state relative to the voltage margin between the 1 state and the 2 state, which more effectively accommodates charge loss from the 0 state through electron leakage. Asymmetrical read and program mapping may also be used to improve read reliability in the presence of ground noise or VCC noise.

Owner:WINBOND ELECTRONICS CORP

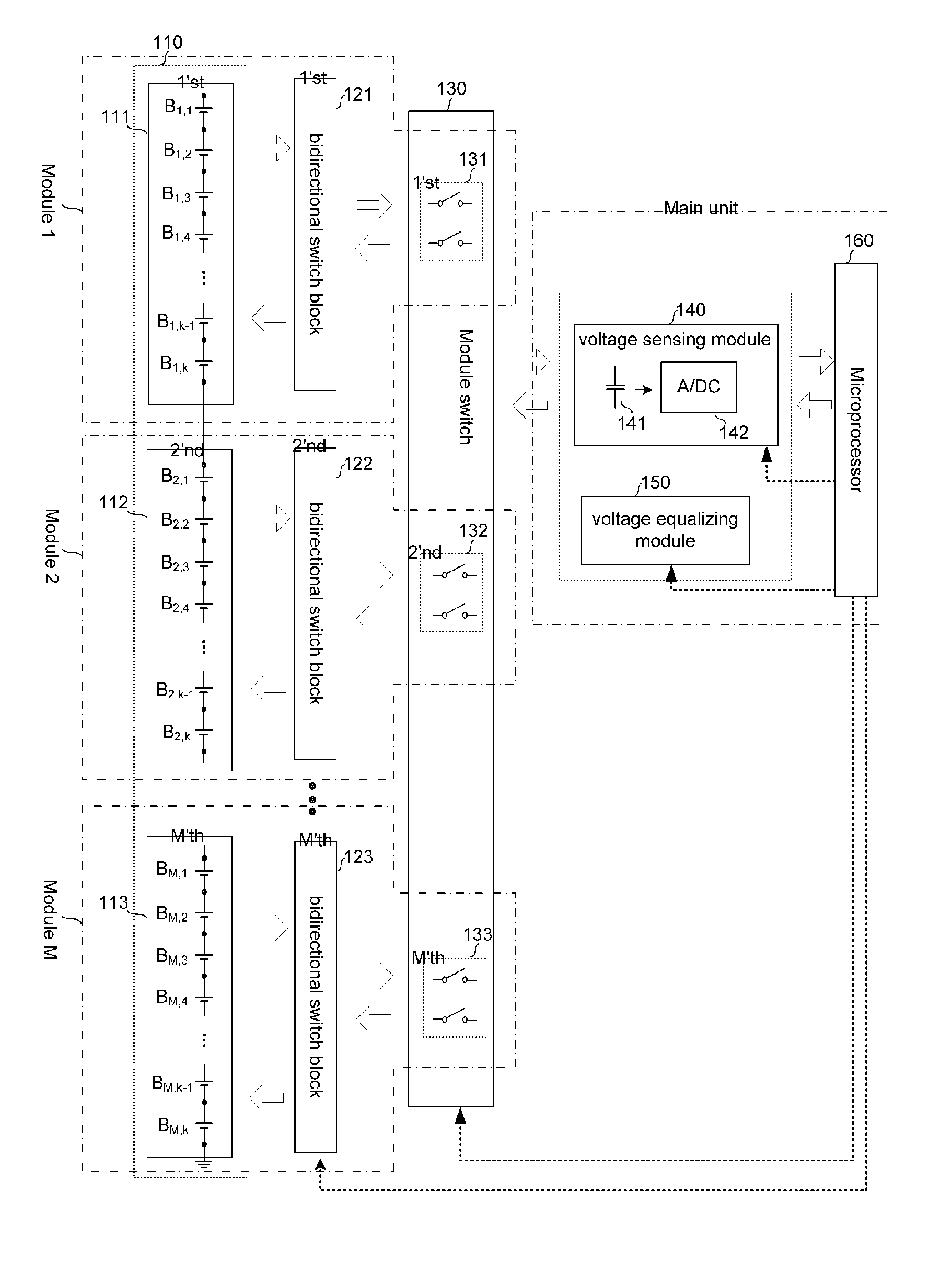

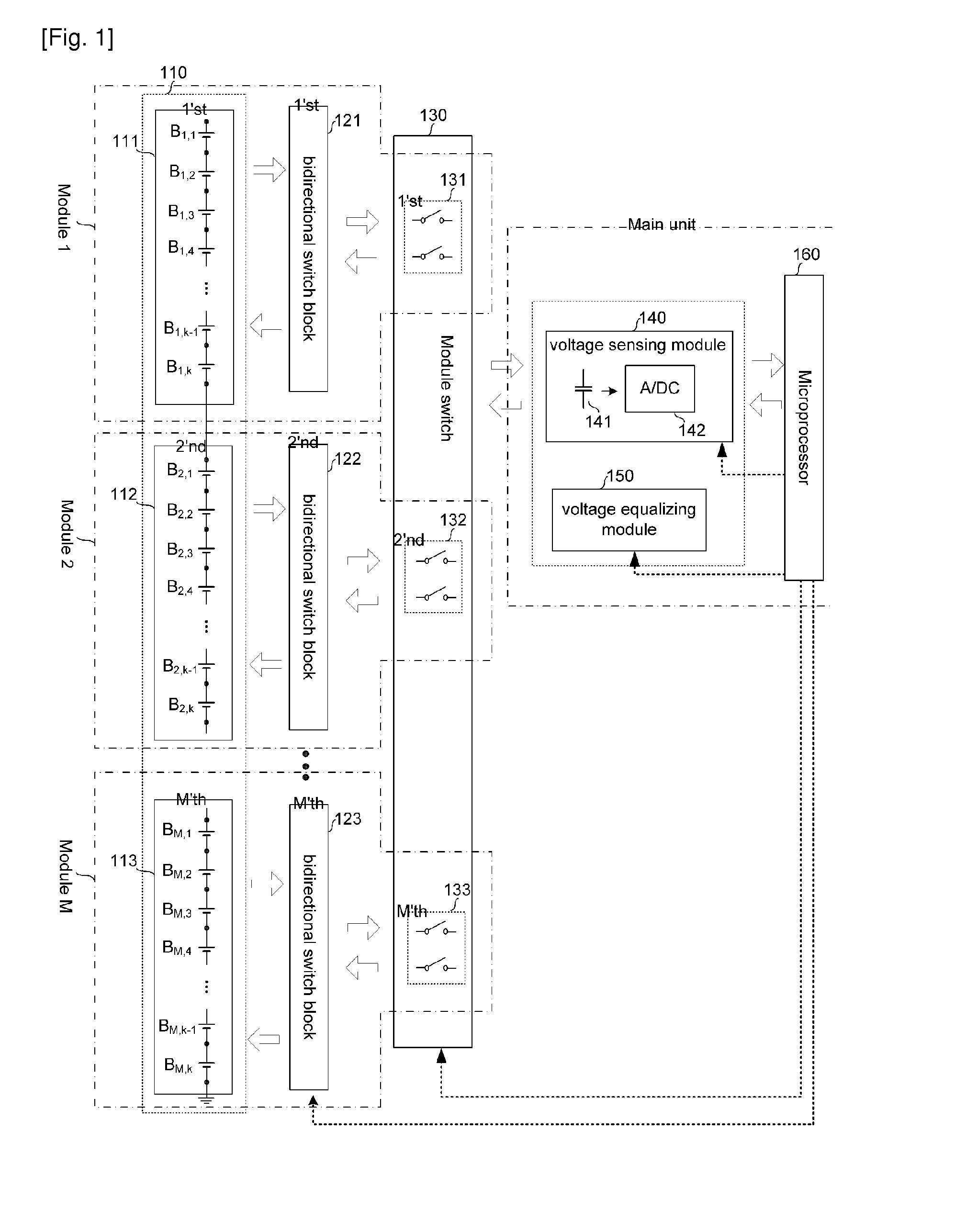

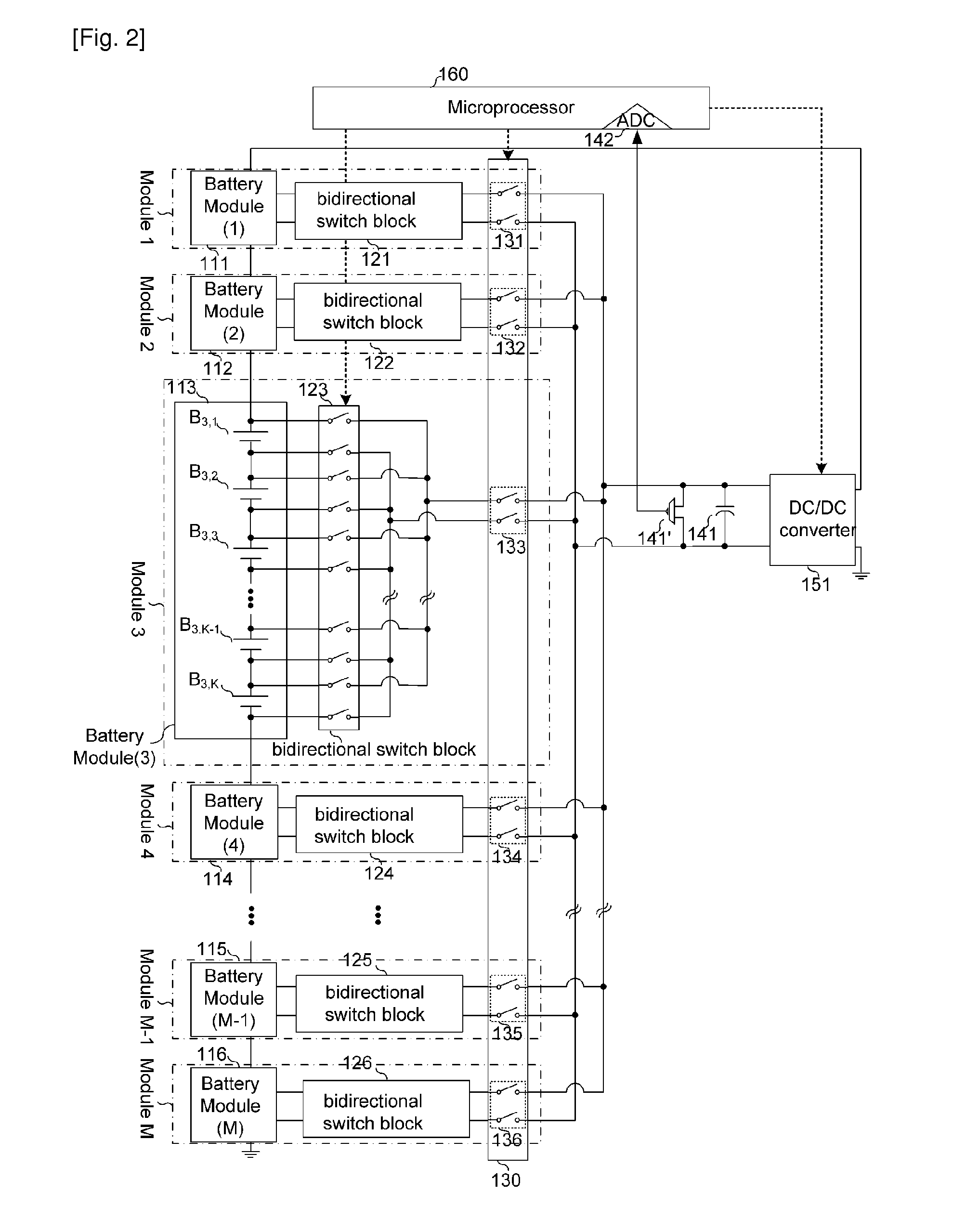

Charge Equalization Apparatus And Method For Series-Connected Battery String

ActiveUS20120086390A1Reduce complexityReduce volumeCharge equalisation circuitCircuit monitoring/indicationEngineeringEqualization

Provided are a charge equalization apparatus and method for a battery string connected in series, and more particularly, are a charge equalization apparatus and method that efficiently perform charge equalization while reducing entire complexity and volume and lowering production costs through a configuration that an individual battery included in a battery string shares a single voltage sensing module and a single charge equalizing module; a switch block of a two-stage structure forms a current path for measuring voltage of individual batteries included in the battery string, and at the same time, forms a charging or discharding path of a low-charged or over-charged battery among the battery strings; and a switch device having low withstand voltage is used.

Owner:KOREA ADVANCED INST OF SCI & TECH +1

Electrical service disconnect having tamper detection

InactiveUS7091878B2Readily apparentElectric signal transmission systemsElectrical measurement instrument detailsElectricityVoltage sensing

A tamper detection arrangement in a meter having a service disconnect switch employs a voltage sense circuit that requires only a single connection to digital processing circuitry for the feeder lines of typical residential service. In one embodiment, the voltage sense circuit includes an isolation device that electrically isolates the processing device from the line voltages. The voltage sense circuit senses a voltage on the feeder lines and is operable to generate a voltage detection signal having a characteristic representative of whether line voltage from the electrical power lines is present on the feeder lines. A processing circuit is operably connected to the voltage sense circuit to receive the voltage detection signal and to selectively generate a tamper flag based on whether the characteristic of the voltage detection signal indicates the presence of voltage on the first and second feeder lines when the service disconnect switch has disconnected the electrical power lines from the first and second feeder lines.

Owner:LANDIS GYR LLC

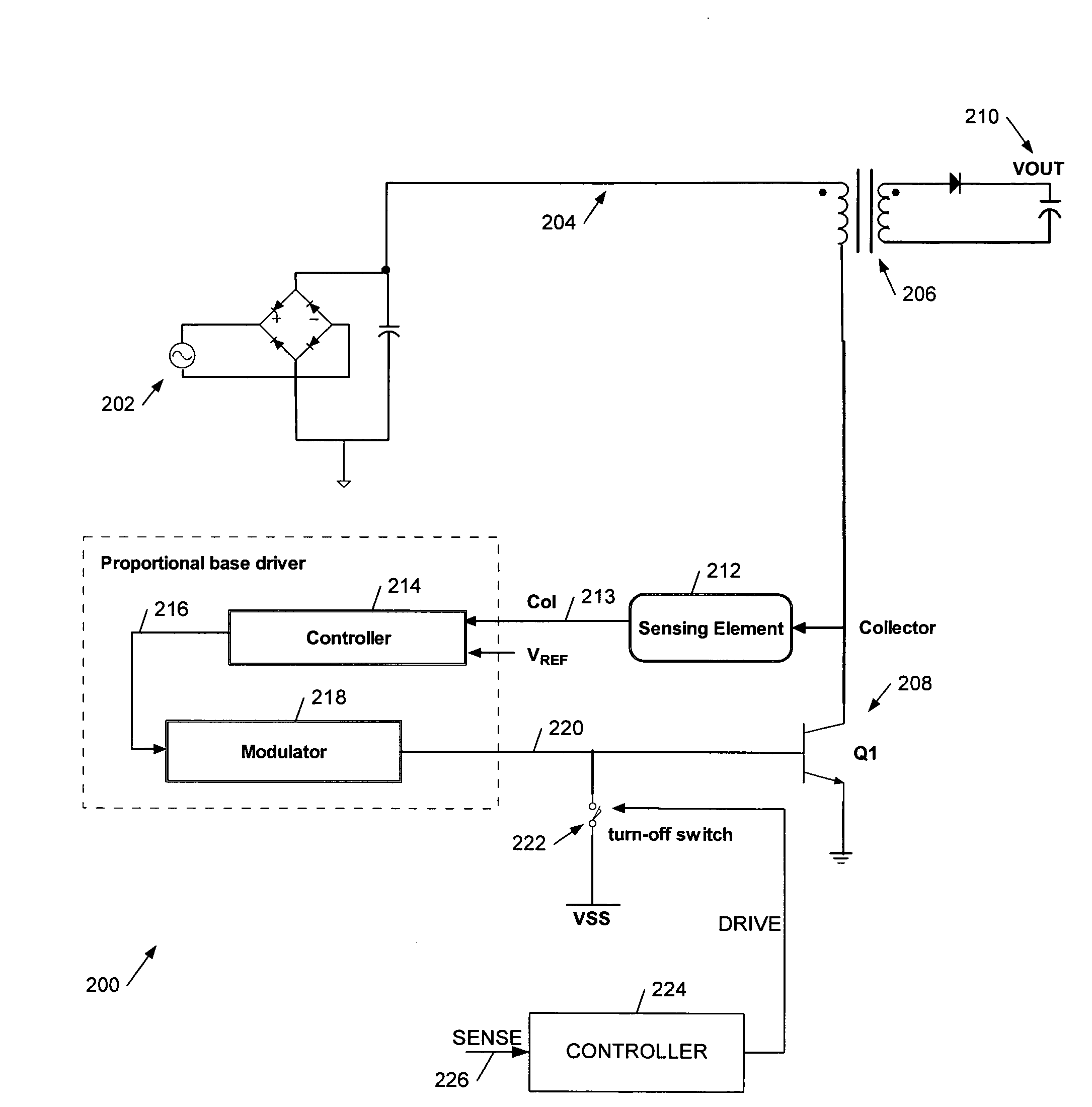

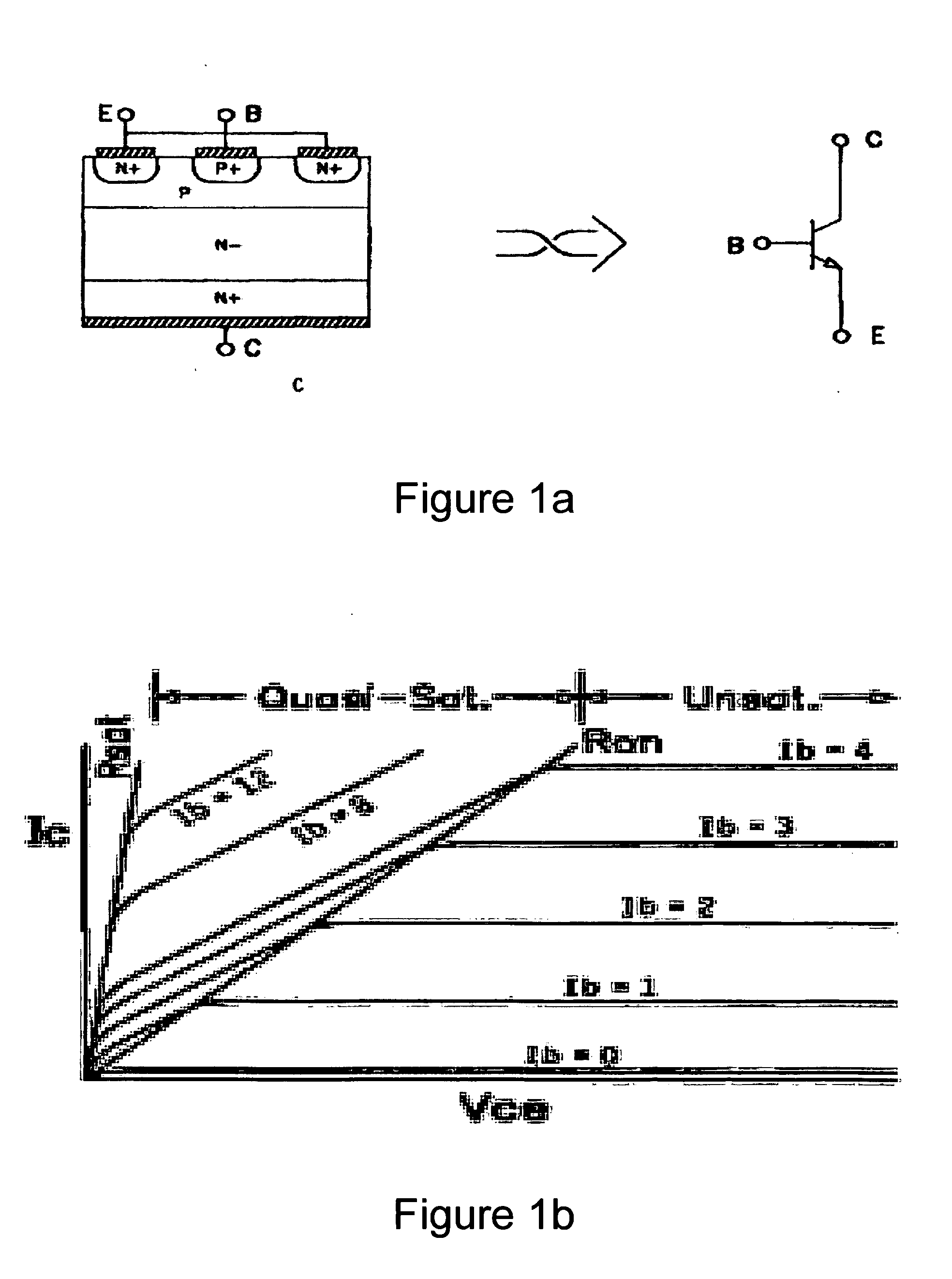

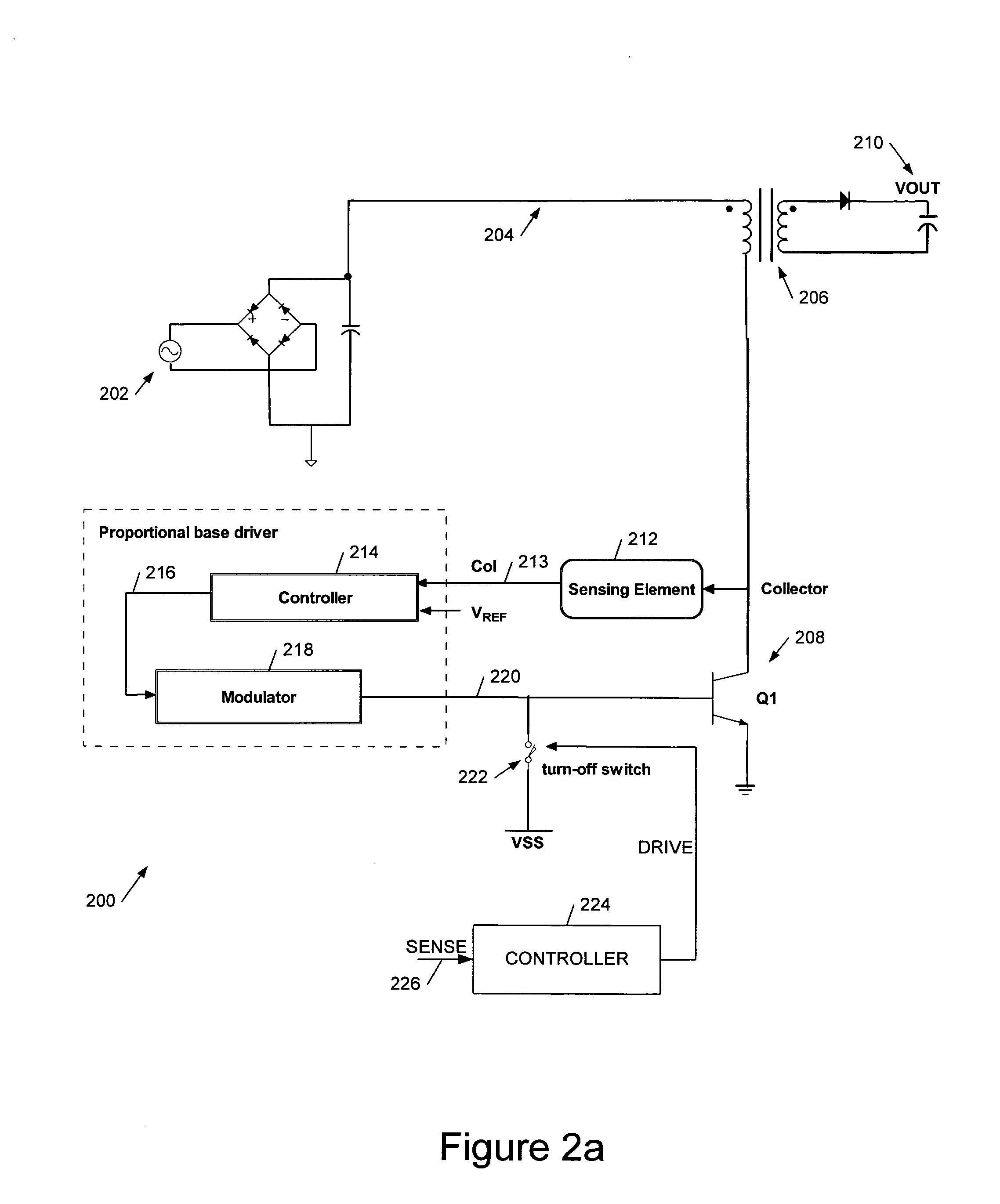

Bipolar transistor drivers

InactiveUS20090040796A1Reduce impactEffectively allows the sensed voltage to be scaledTransistorEfficient power electronics conversionControl signalControl system

We describe a switching power converter comprising a bipolar switching device (BJT or IGBT) switching an inductive load, and including a closed-loop control system. The control system comprises a voltage sensing system to sense a voltage on a collector terminal of the switching device and provide a voltage sense signal; a controller; and a drive modulation system coupled to an output of the controller for modulating a drive to the control terminal of said bipolar switching device responsive to a controller control signal; wherein said controller is configured to monitor changes in the sensed voltage during a period when said switching device is switched on and to control said drive modulation system to control the degree of saturation of said bipolar switching device when the device is switched on and hence improve turn-off times.

Owner:POWER INTEGRATIONS INC

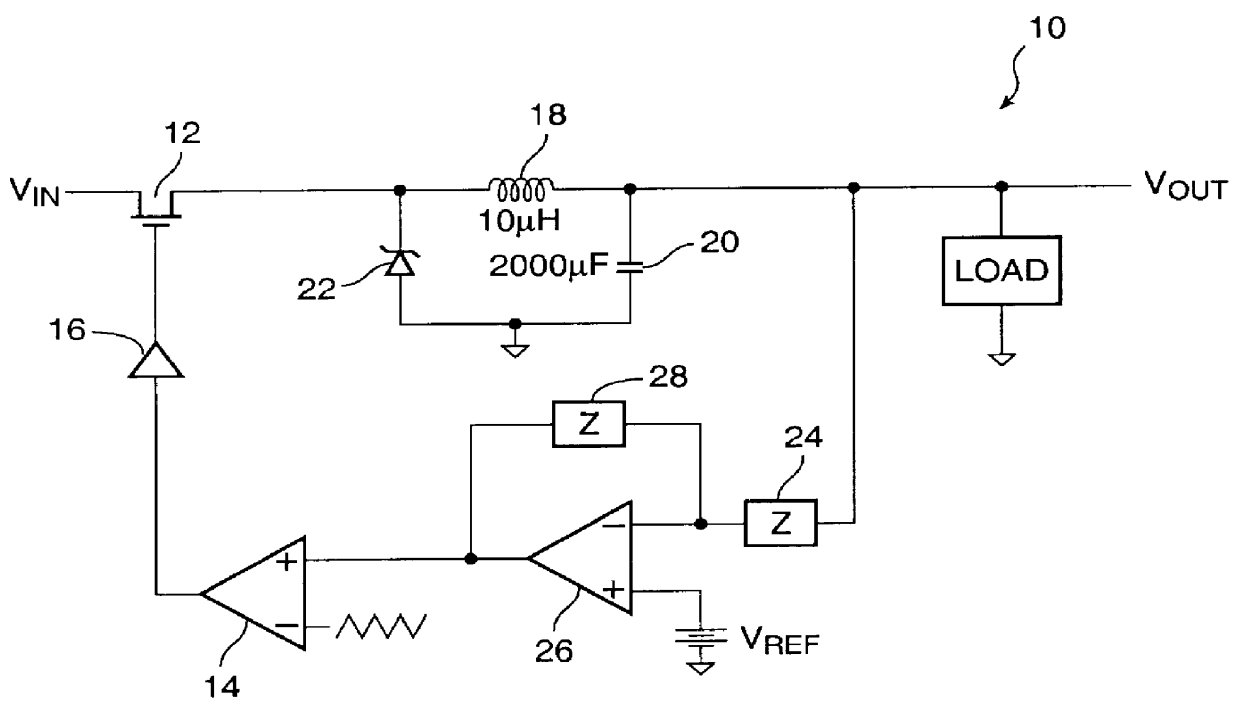

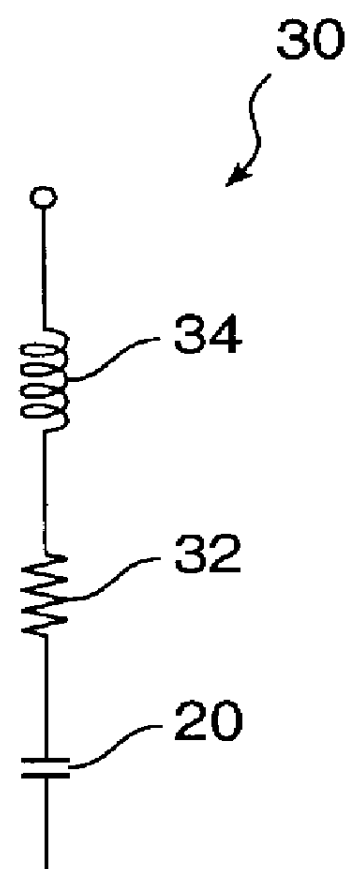

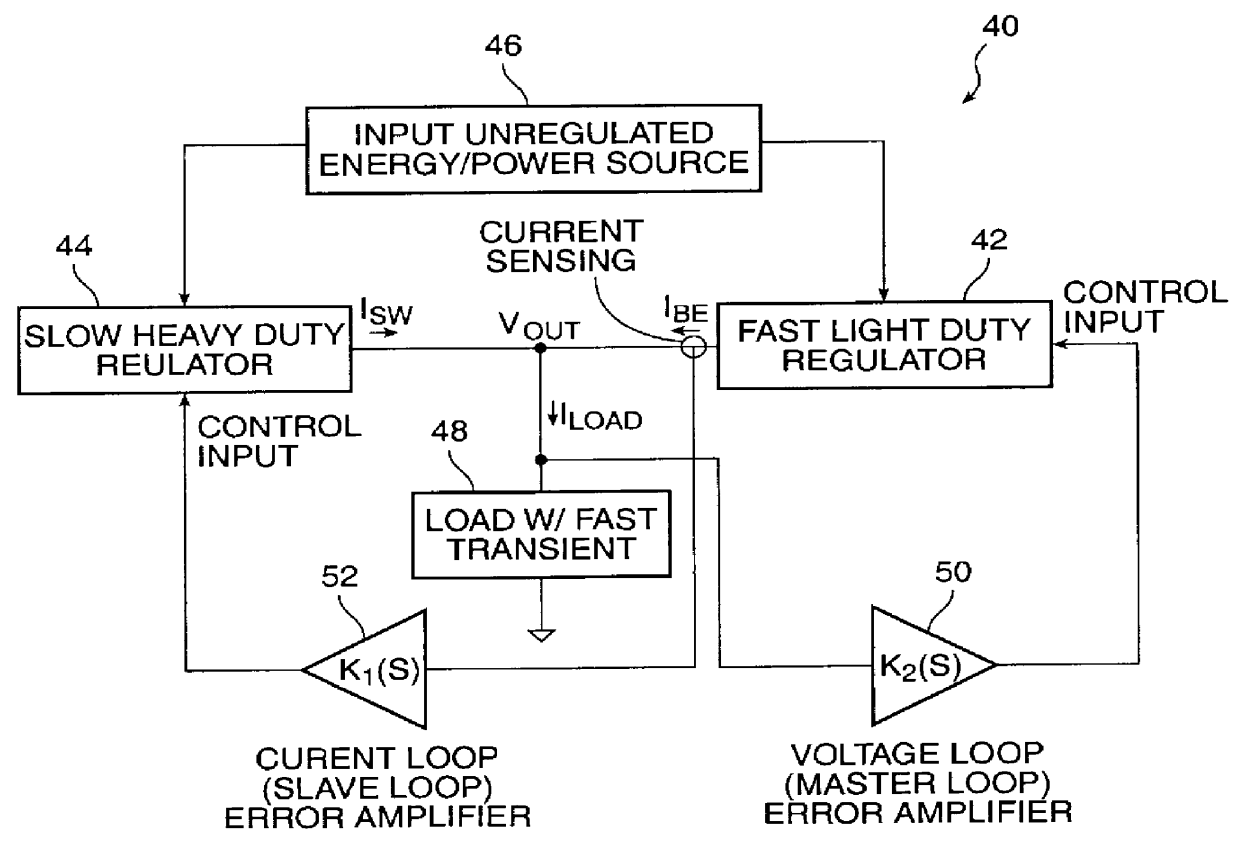

Voltage regulator with wide control bandwidth

A fast buffer and switching regulator are combined in parallel in a master-slave loop topology to form a voltage regulator. The buffer circuit has a voltage sensing amplifier that senses the difference between the voltage at the output of the voltage regulator and a reference voltage. This voltage difference is amplified, and then input to a buffer that sources current to or sinks current from the output of the voltage regulator. The output of the buffer circuit is coupled to the switching converter which senses the changing buffer circuit output current. The switching converter changes its duty cycle to oppose the current from the buffer circuit. This is a master-slave loop topology wherein the buffer circuit is the master loop that quickly provides high levels of current to compensate for a voltage transient at the output of the voltage regulator, and the switching converter is the slave loop which eventually takes over from the master loop to meet the current output requirements of the voltage regulator.

Owner:SEMTECH CORP

High efficiency power supply for LED lighting applications

InactiveUS7265504B2Accurate currentEffective pointingElectrical apparatusElectroluminescent light sourcesEffect lightVoltage regulation

A power supply for plural loads coupled in parallel comprises a voltage regulator, a plurality of current regulators, and an error control circuit. The voltage regulator provides a common output voltage to the plural loads. The voltage regulator comprises a sensor circuit providing a voltage sense signal corresponding to the output voltage, which provides feedback to regulate the output voltage at a selected level. The plurality of current regulators are coupled to respective ones of the plural loads. Each of the plurality of current regulators regulates current drawn by respective ones of the plural loads to within a desired regulation range. The plurality of current regulators each further provide a respective error signal corresponding to an ability to remain within the desired regulation range. The error control circuit is operatively coupled to the voltage regulator and to the plurality of current regulators. The error control circuit receives the error signals from the plurality of current regulators and provides a common error signal to the voltage regulator. The voltage regulator thereby changes the selected level of the output voltage in response to the common error signal. Accordingly, the selected level of the output voltage remains at a minimum voltage necessary to keep the plural loads in the desired regulation range.

Owner:SEMTECH CORP

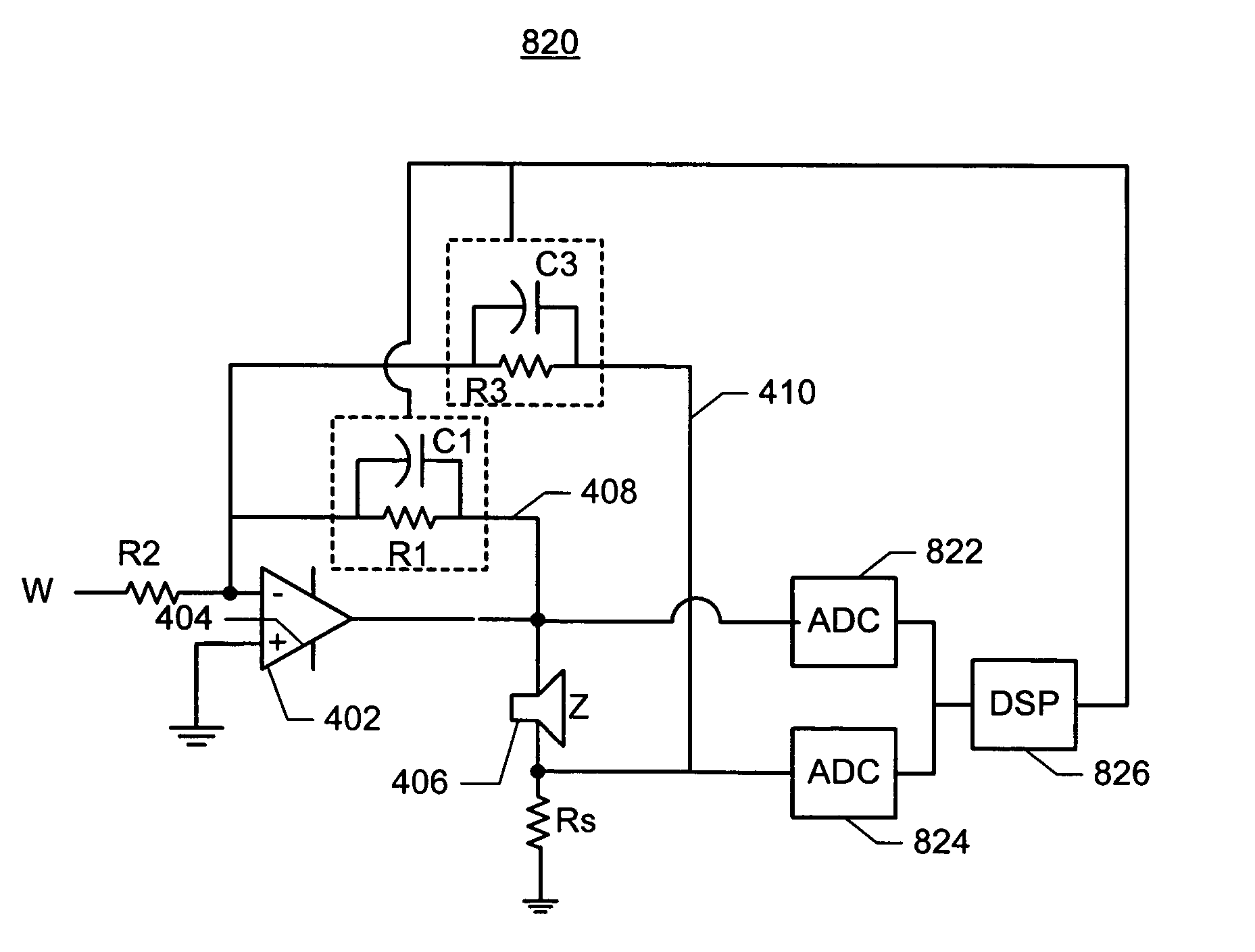

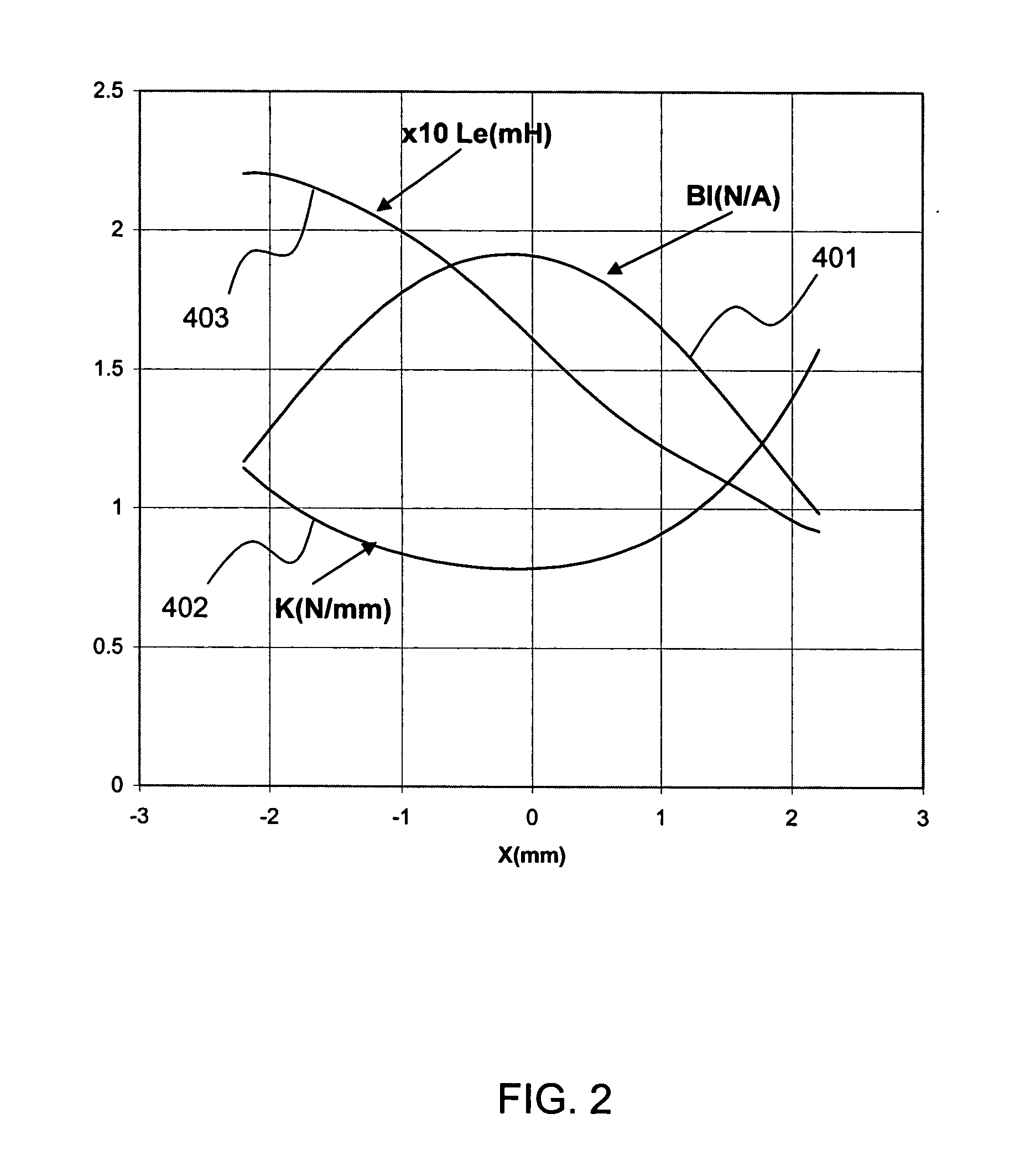

Mixed-mode (current-voltage) audio amplifier

ActiveUS20050134374A1Total current dropReduce voltageNegative-feedback-circuit arrangementsLow frequency amplifiersAudio power amplifierCurrent voltage

A method and system for providing a mixed-mode (current- and voltage-source) audio amplifier is disclosed. The mixed-mode amplifier includes a voltage sensing feedback path including a first network comprising at least one circuit; and a current sensing feedback path including a second network comprising at least one circuit. According to the method and system disclosed herein, the first and second networks vary an output impedance or transconductance of the amplifier as a function of frequency of the input voltage signal, such that at a first frequency range, the amplifier operates substantially as a current amplifier, and at a second frequency range, the amplifier operates substantially as a voltage amplifier, thereby inheriting distortion reduction of the current amplifier and stability of the voltage amplifier.

Owner:TYMPHANY HK

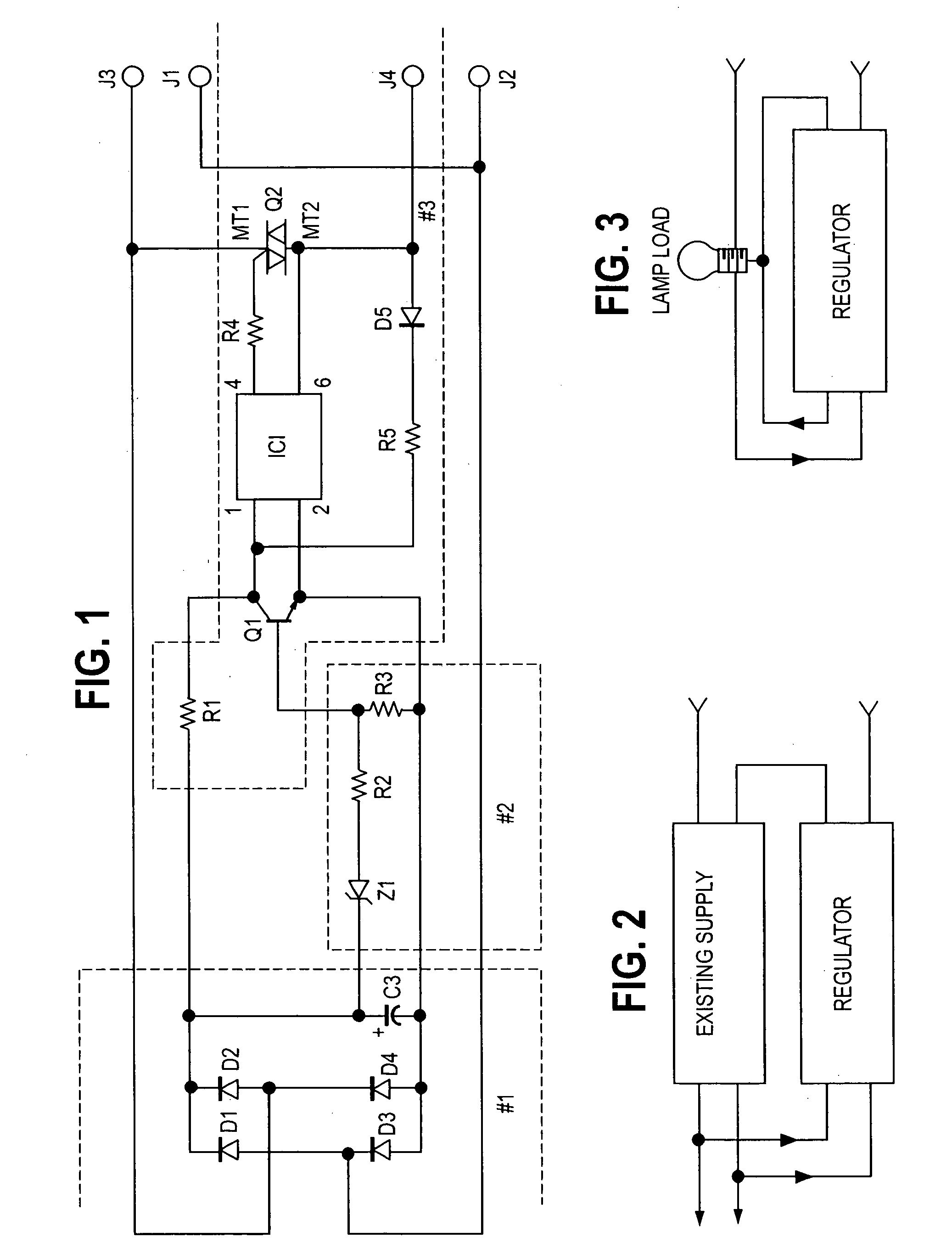

Low voltage regulator for in-line powered low voltage power supply

The invented voltage regulator is a solid state low voltage regulator for in-line power lines for LED arrays and incandescent lamps, preferably low-voltage halogen lamps. The invented voltage regulator comprises, in combination, a full-wave bridge rectifier circuit, a voltage sensing circuit across the output of the full wave bridge rectifier circuit, and an AC power line voltage control circuit across the output of the voltage sensing circuit, the output of the AC power line voltage control circuit controlled by a switching power control circuit to provide a regulated 11.0 to 12.5 V AC output regardless of line voltage variations.

Owner:TROY CSL LIGHTING +1

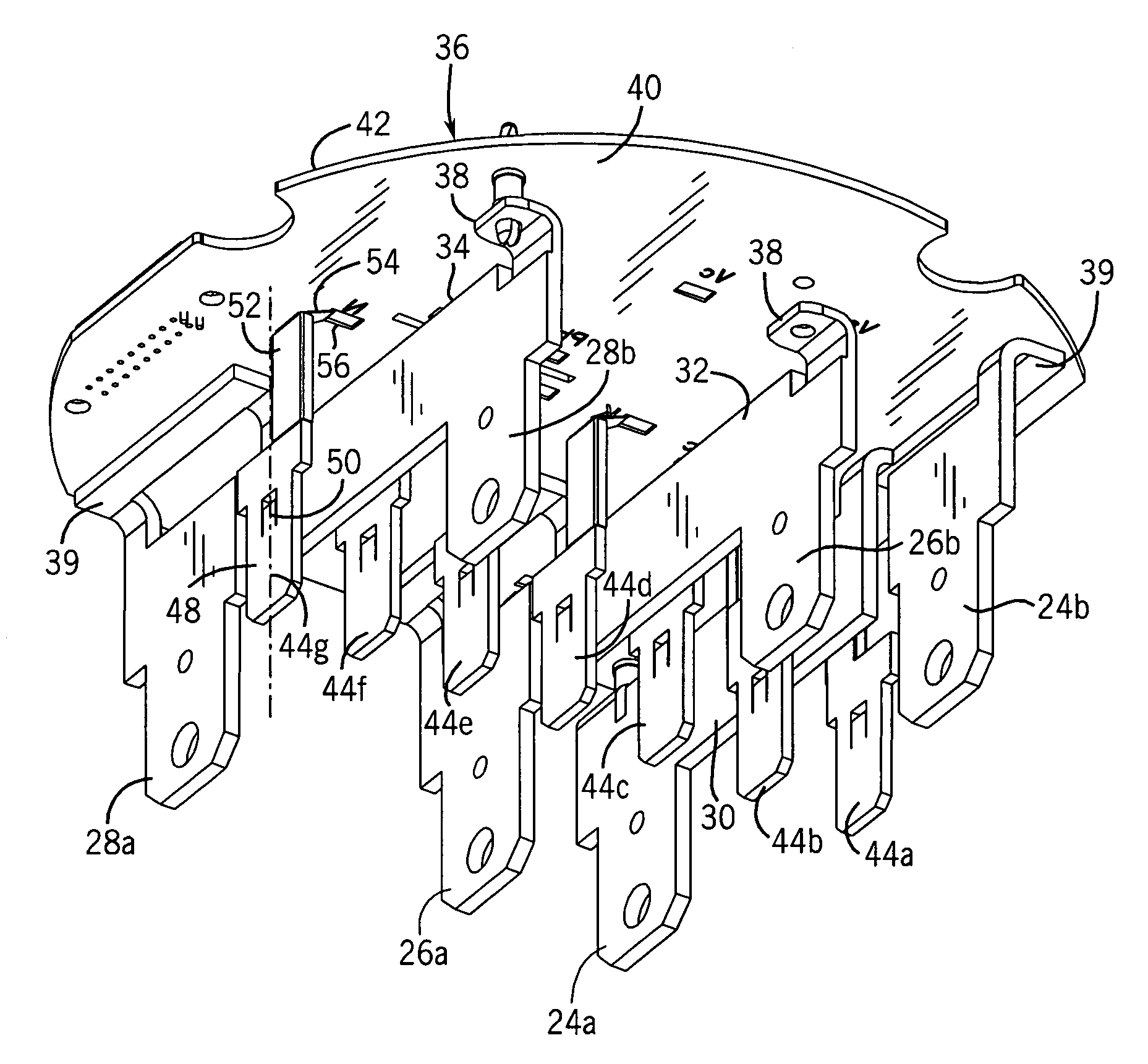

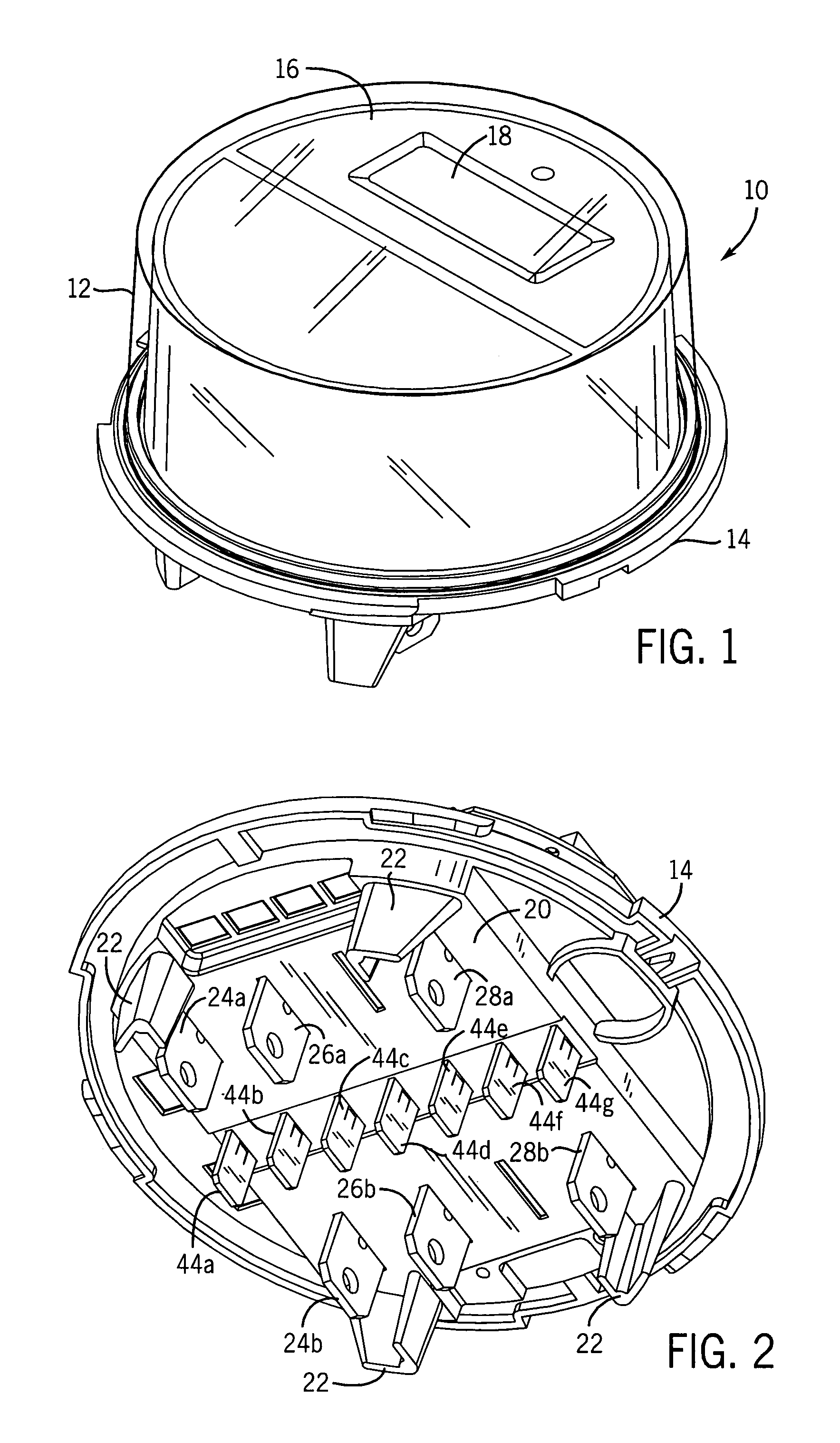

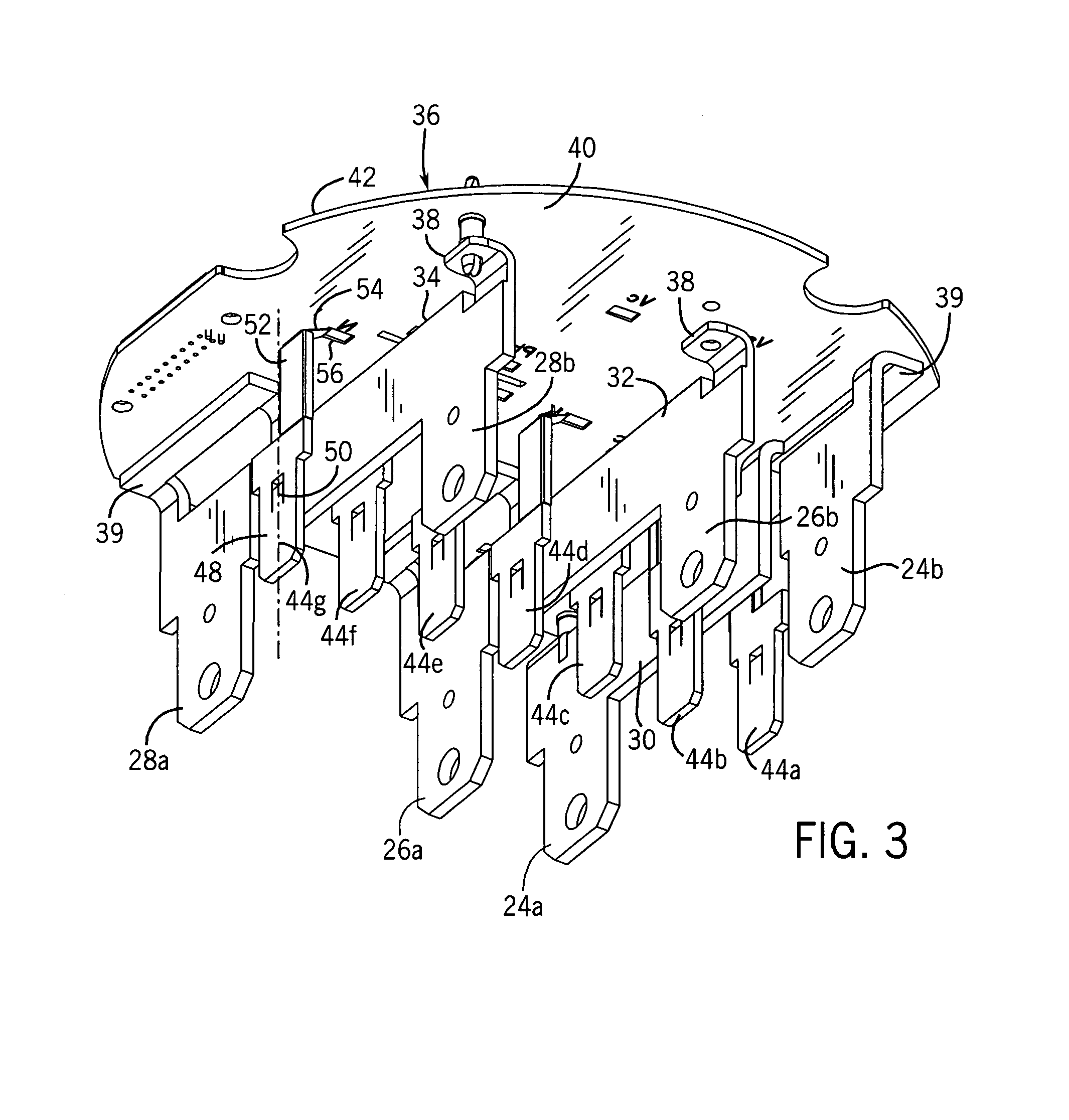

Electronic electricity meter having configurable contacts

ActiveUS6972555B2Protect environmentEliminate needCurrent/voltage measurementSpecial tariff metersMeter-BusEngineering

A three-phase electronic electricity meter that includes configurable voltage sensing blades such that the electricity meter can be configured for use with various electrical service types. The electricity meter includes a base having a configuration to correspond to standard ANSI-type sockets. The meter base includes a plurality of individual voltage sensing blades that are received by the ANSI socket. At least one of the voltage sensing blades is movable between a first and a second position such that the voltage sensing blade contacts different areas on a meter circuit board in the first and second positions. A common circuit board can be utilized for different electrical service types and the contact arrangement can be selectively configured by moving the voltage sensing blades between their first and second positions.

Owner:SENSUS SPECTRUM LLC

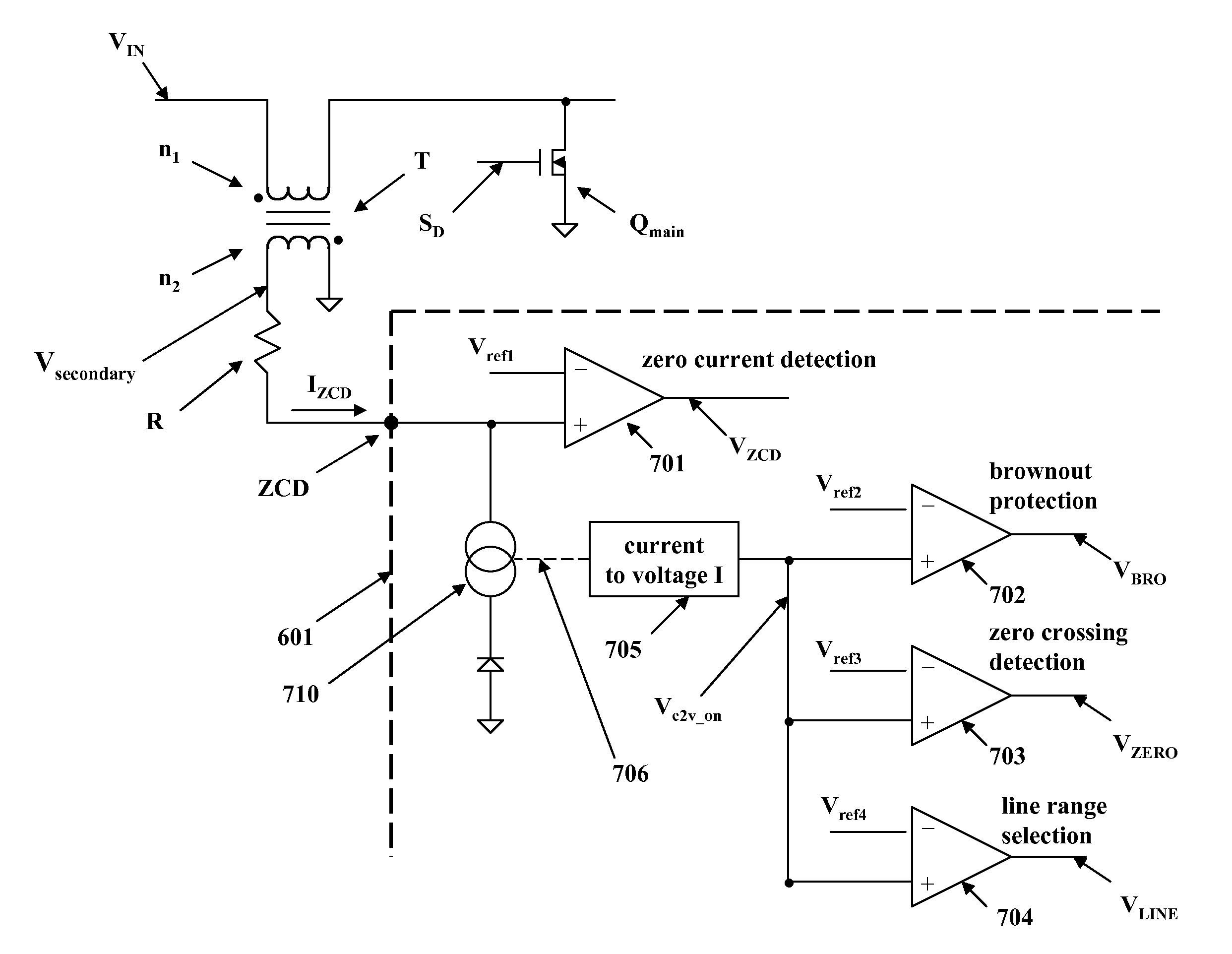

Novel Utilization of a Multifunctional Pin Combining Voltage Sensing and Zero Current Detection to Control a Switched-Mode Power Converter

InactiveUS20100066337A1Efficient power electronics conversionElectric variable regulationOvervoltageInductor

An embodiment of the invention relates to a power converter including an inductor coupled in series with a power switch and a resistor coupled to a winding of the inductor. Input and output power converter voltages including an input brownout condition or an output overvoltage condition are estimated, and the output voltage may be regulated, by sensing a current in the resistor. An input current waveform can thereby be controlled to replicate substantially the input voltage waveform. The controller adjusts an on time and terminates an off time of the power switch by sensing respectively a current and a change of current in the resistor. The controller may sense a current flowing in the resistor to select a line voltage range of the input voltage to the power converter. The controller may estimate an input current to the power converter employing the current flowing in the resistor.

Owner:INFINEON TECH AUSTRIA AG

Apparatus for determination of stroke volume using the brachial artery

Provided herein are methods and apparatus for stroke volume determination by bioimpedance from a patient's upper arm, or brachium, utilizing pulsations of the brachial artery contained therein. The apparatus includes two or more spaced apart alternating current flow electrodes positioned on the patient's arm proximate the brachial artery and two or more spaced apart voltage sensing electrodes positioned on the patient's arm proximate the brachial artery. The voltage sensing electrodes are positioned between the alternating current flow electrodes on the arm. An alternating current source is electrically connected to the alternating current flow electrodes and a voltmeter electrically is connected to the voltage sensing electrodes. A data input device is provided along with a processing unit in communication with the data input device, the alternating current source, alternating current flow electrodes, the voltmeter, and voltage sensing electrodes. The processing unit is capable of using data from the data input device and voltage sensing electrodes to calculate the stroke volume of the patient.

Owner:BERSTEIN DONALD P