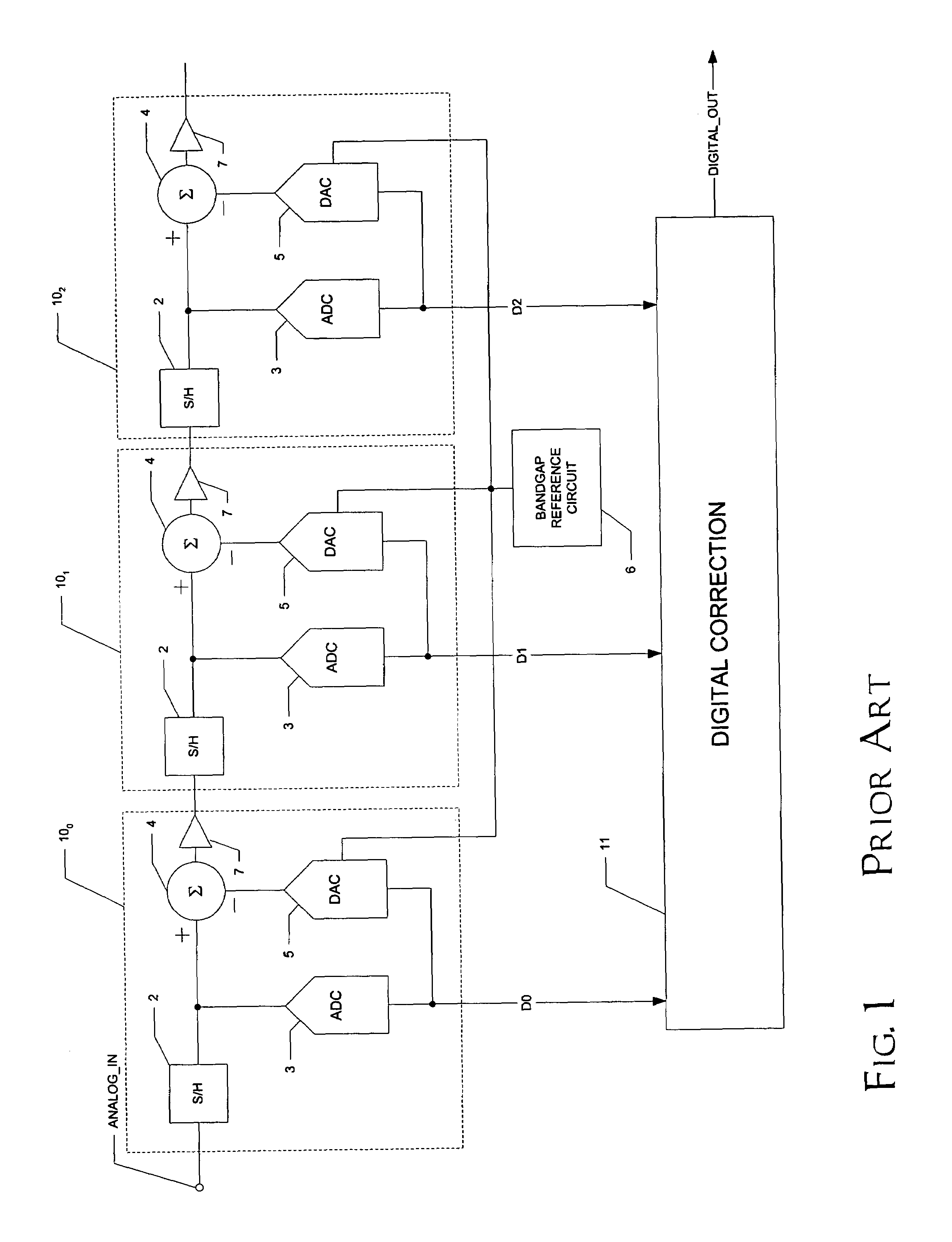

Patents

Literature

1305 results about "Sample and hold" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In electronics, a sample and hold (also known as sample and follow) circuit is an analog device that samples (captures, takes) the voltage of a continuously varying analog signal and holds (locks, freezes) its value at a constant level for a specified minimum period of time. Sample and hold circuits and related peak detectors are the elementary analog memory devices. They are typically used in analog-to-digital converters to eliminate variations in input signal that can corrupt the conversion process. They are also used in electronic music, for instance to impart a random quality to successively-played notes.

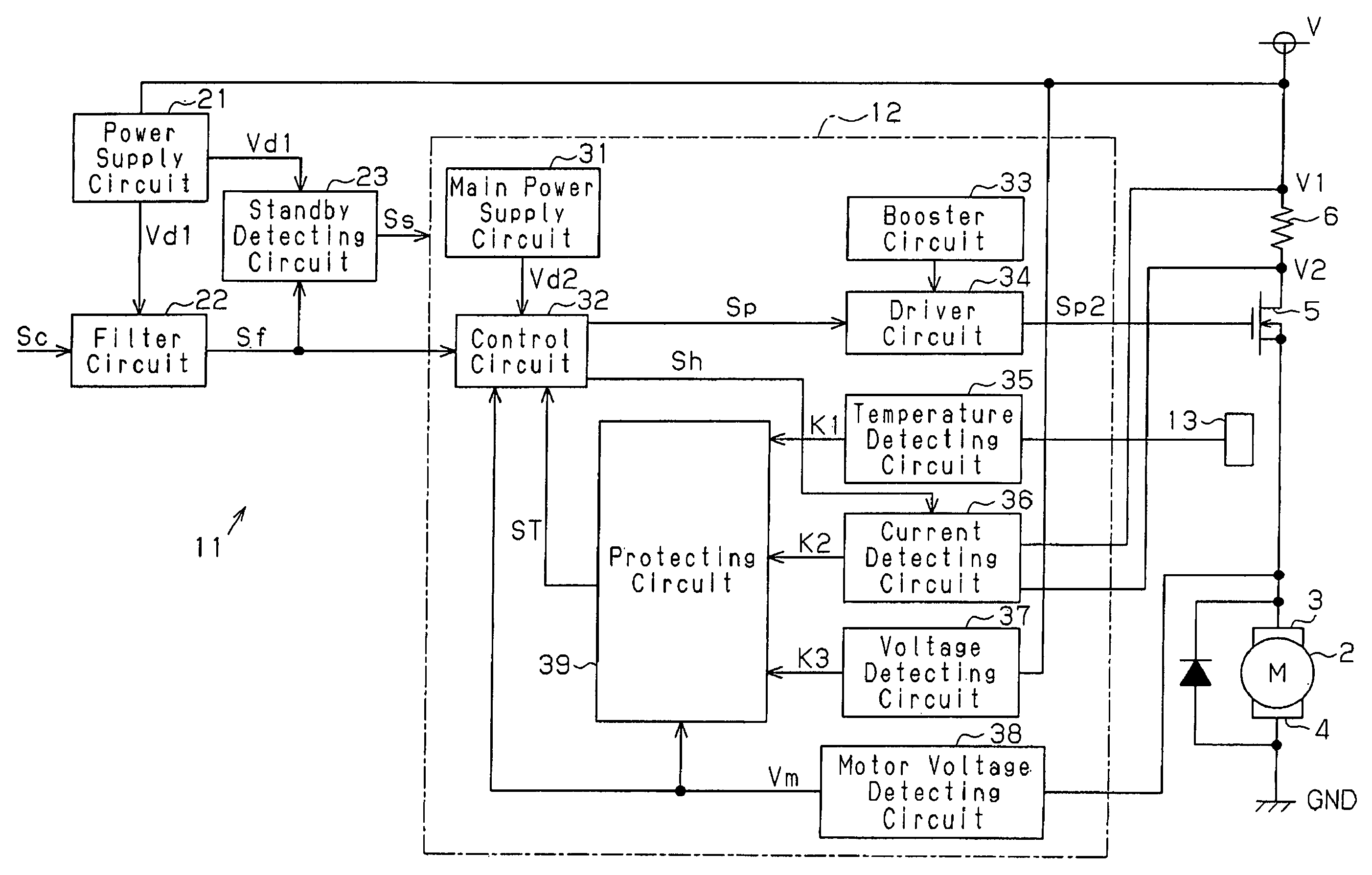

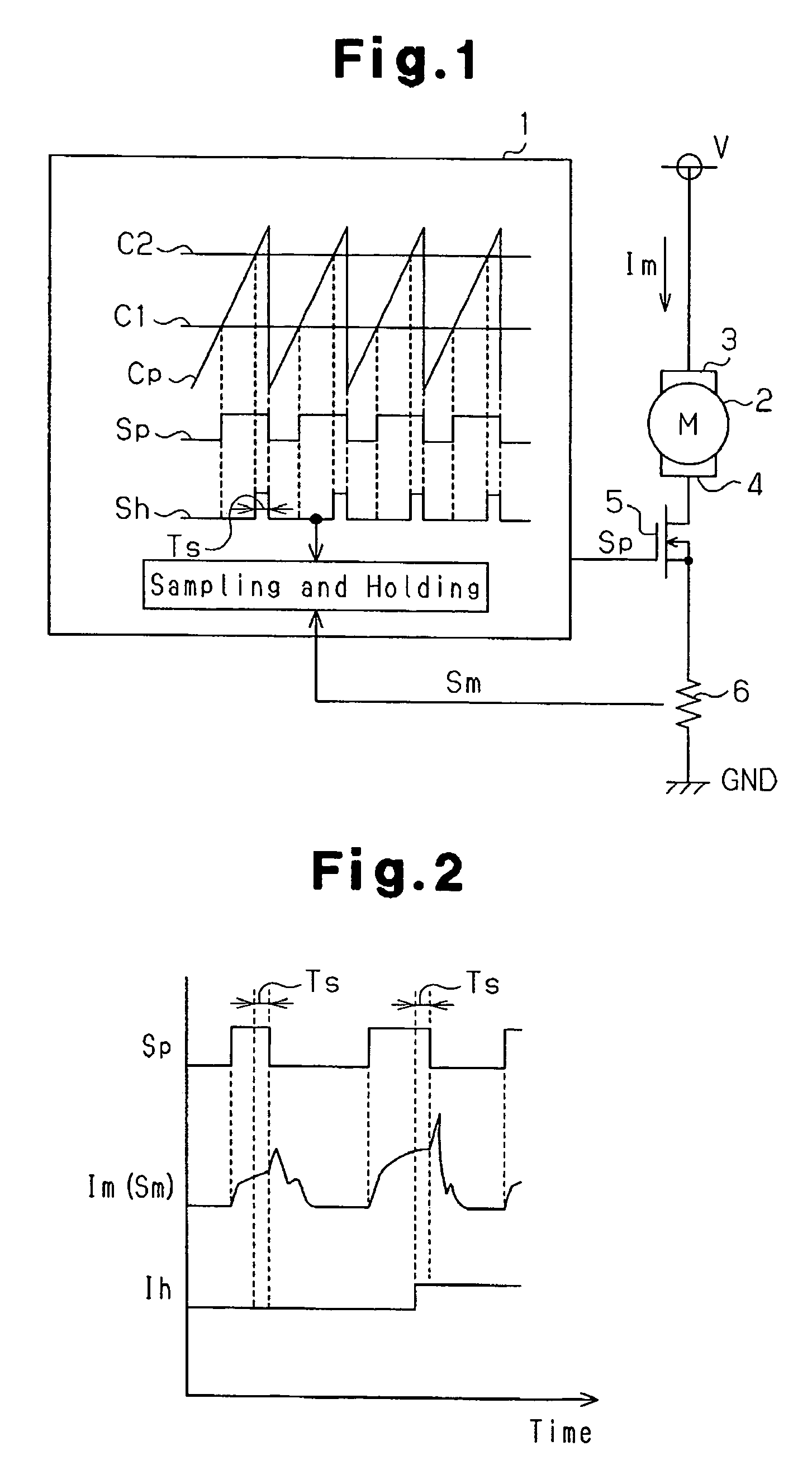

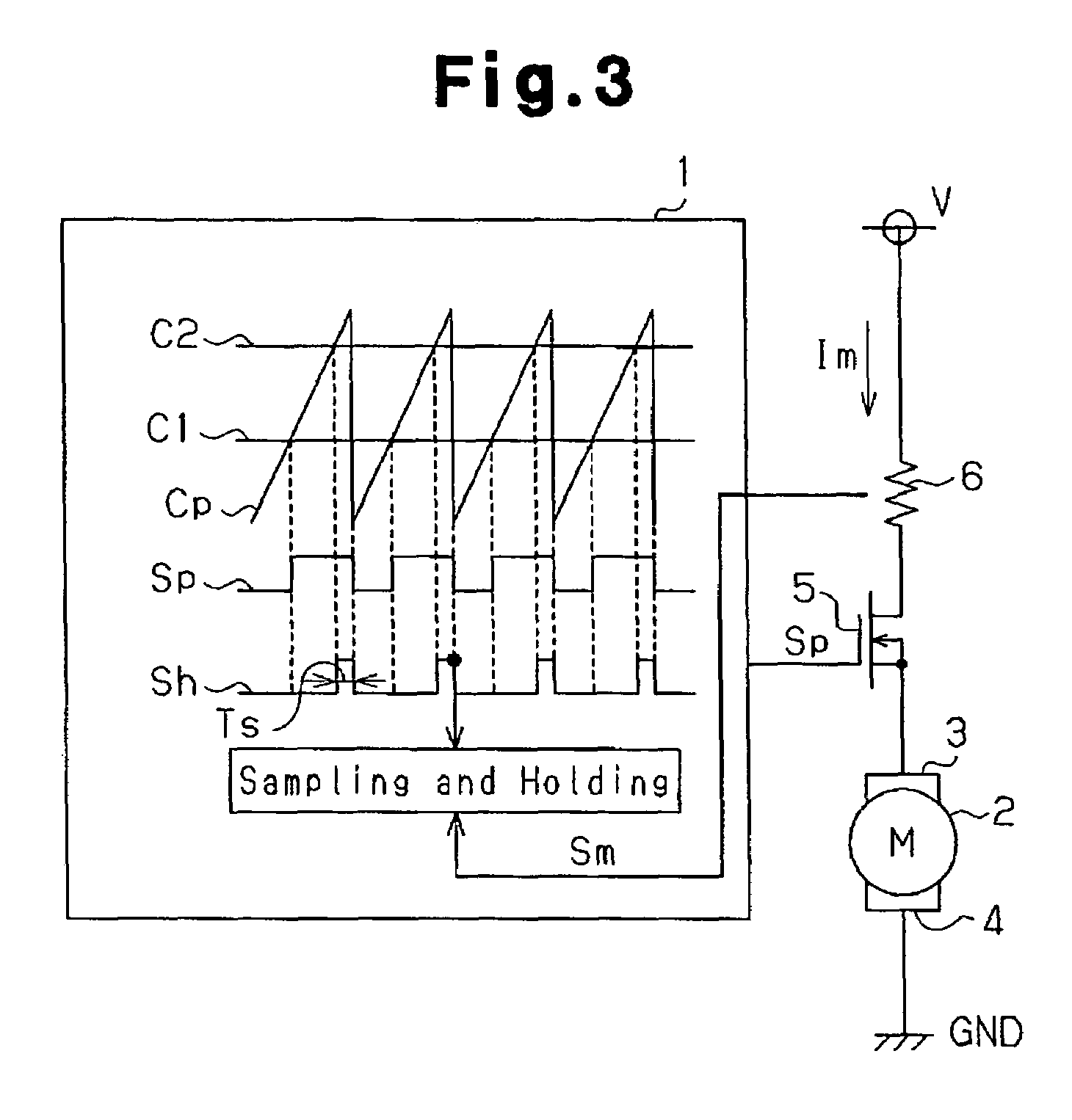

Motor control device and motor control method

InactiveUS7183737B2Improve accuracyCurrent detectionAC motor controlElectric motor controlDriving currentControl signal

A motor control device selectively turns on or off a drive transistor in-accordance with a PWM control signal Sp, such that a drive current Im supplied to a motor is adjusted. The device also samples and holds a motor current Sm for obtaining a motor current value Ih. With reference to the motor current value Ih, the device protects the motor from an overcurrent. Sampling and holding of the motor current Sm is performed for a sampling and holding time Ts. The sampling and holding time Ts corresponds to a time period between a first point in time when the level of the PWM control signal Sp is switched for turning off the drive transistor and a second point in time that precedes the first point in time by a predetermined period. As a result, the motor current value Ih is detected with high accuracy.

Owner:ASMO CO LTD

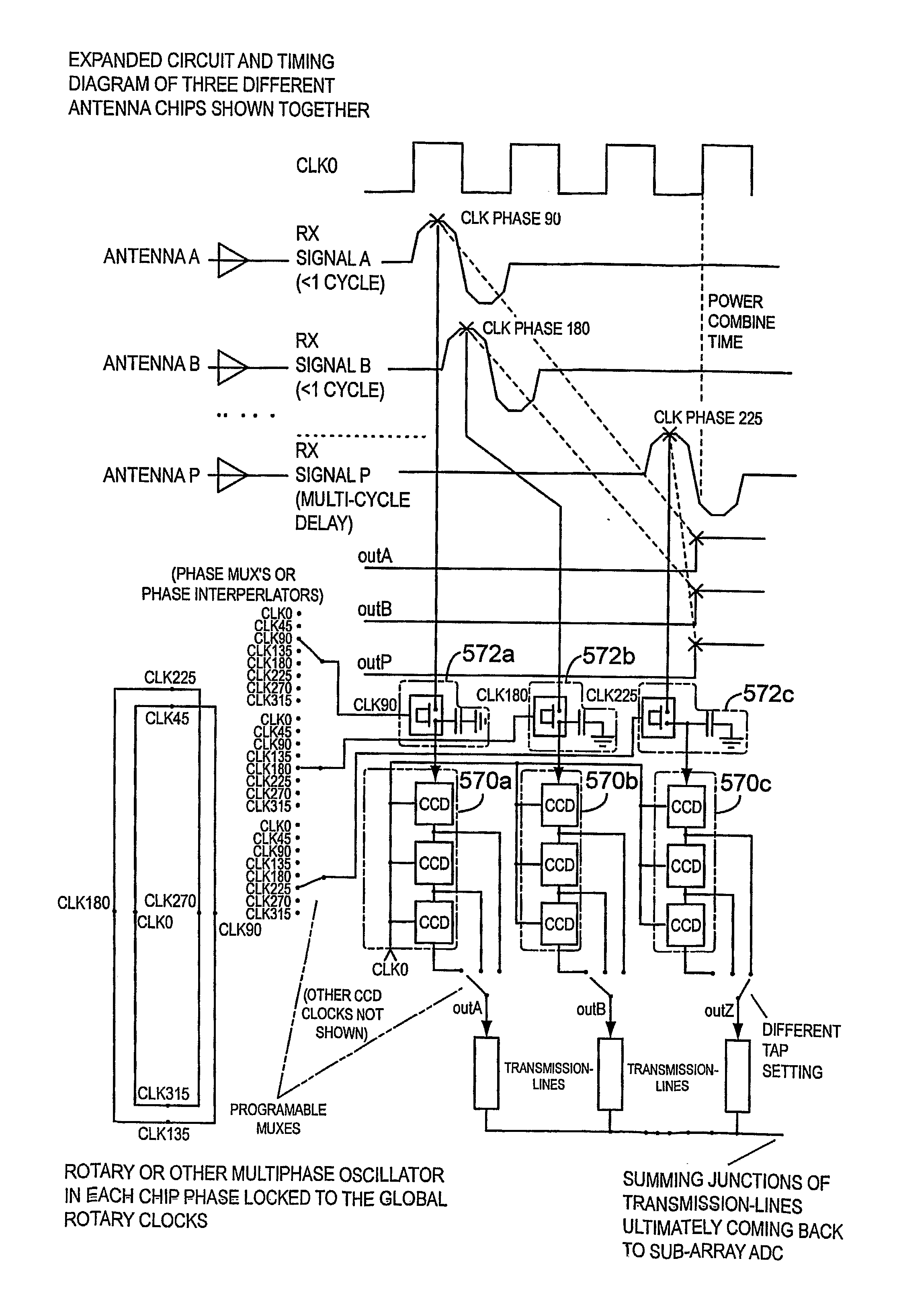

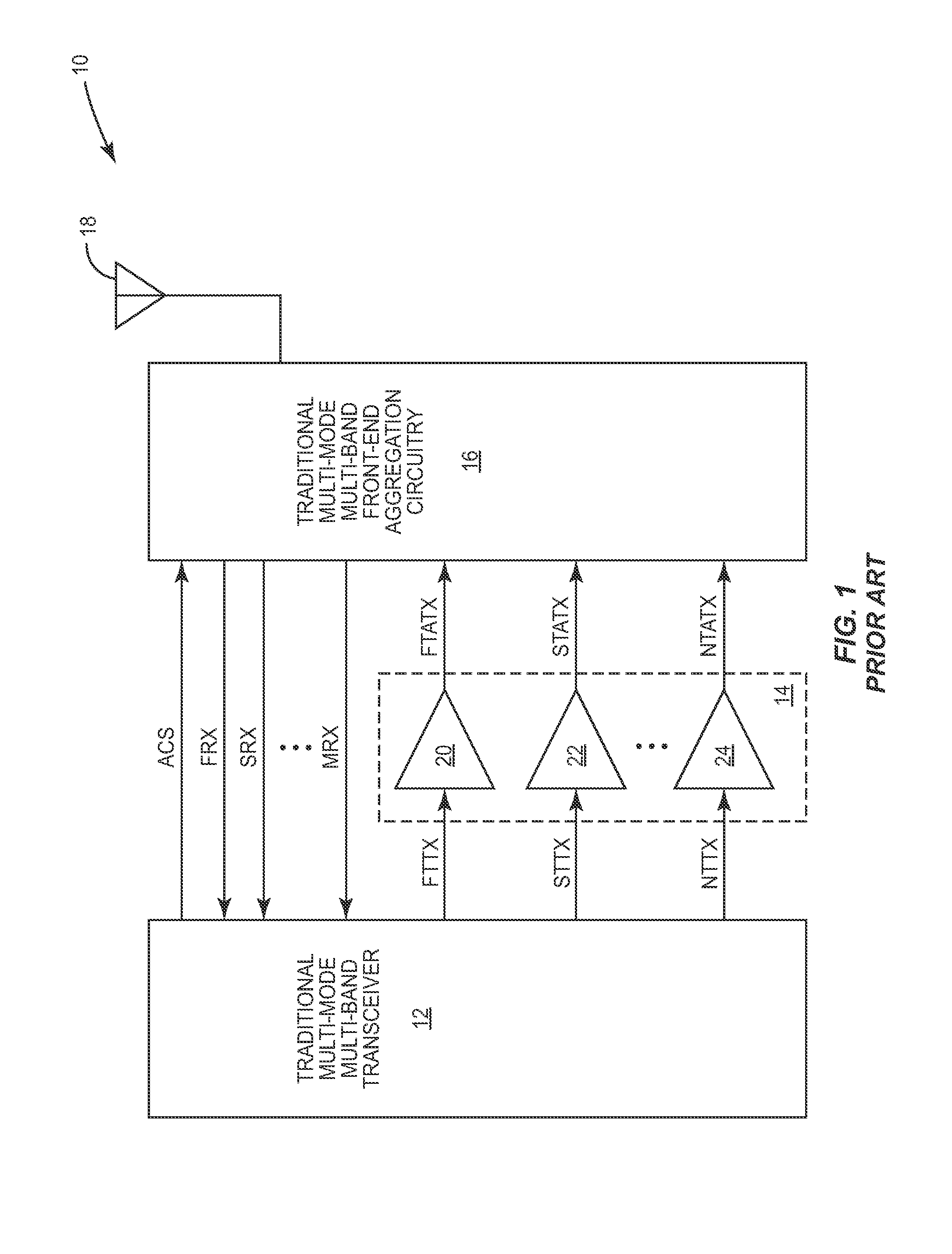

True time delay phase array radar using rotary clocks and electronic delay lines

ActiveUS20120039366A1Forming accuratelyEasy to moveAntenna arraysPulse automatic controlTime delaysAnalog delay line

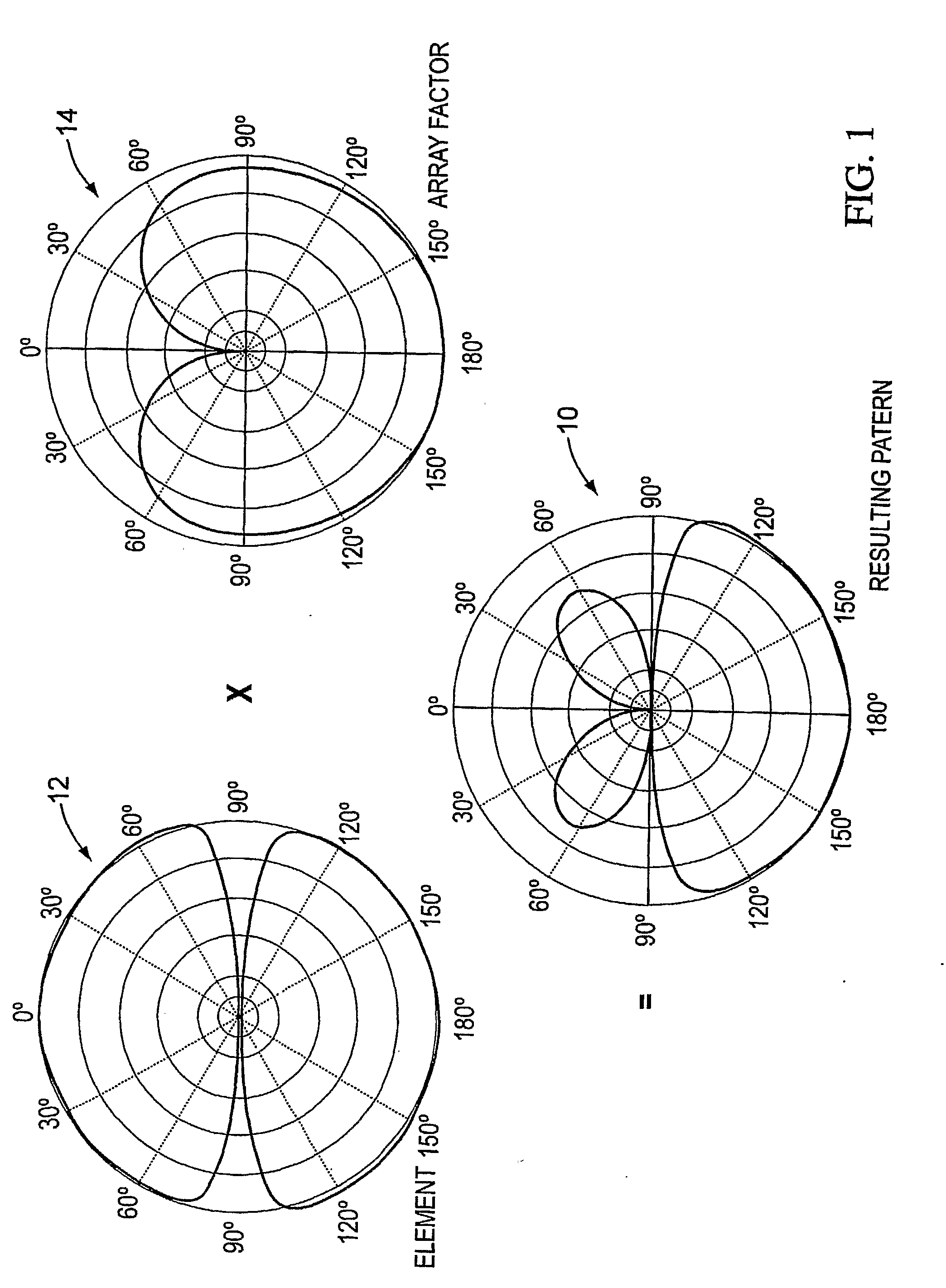

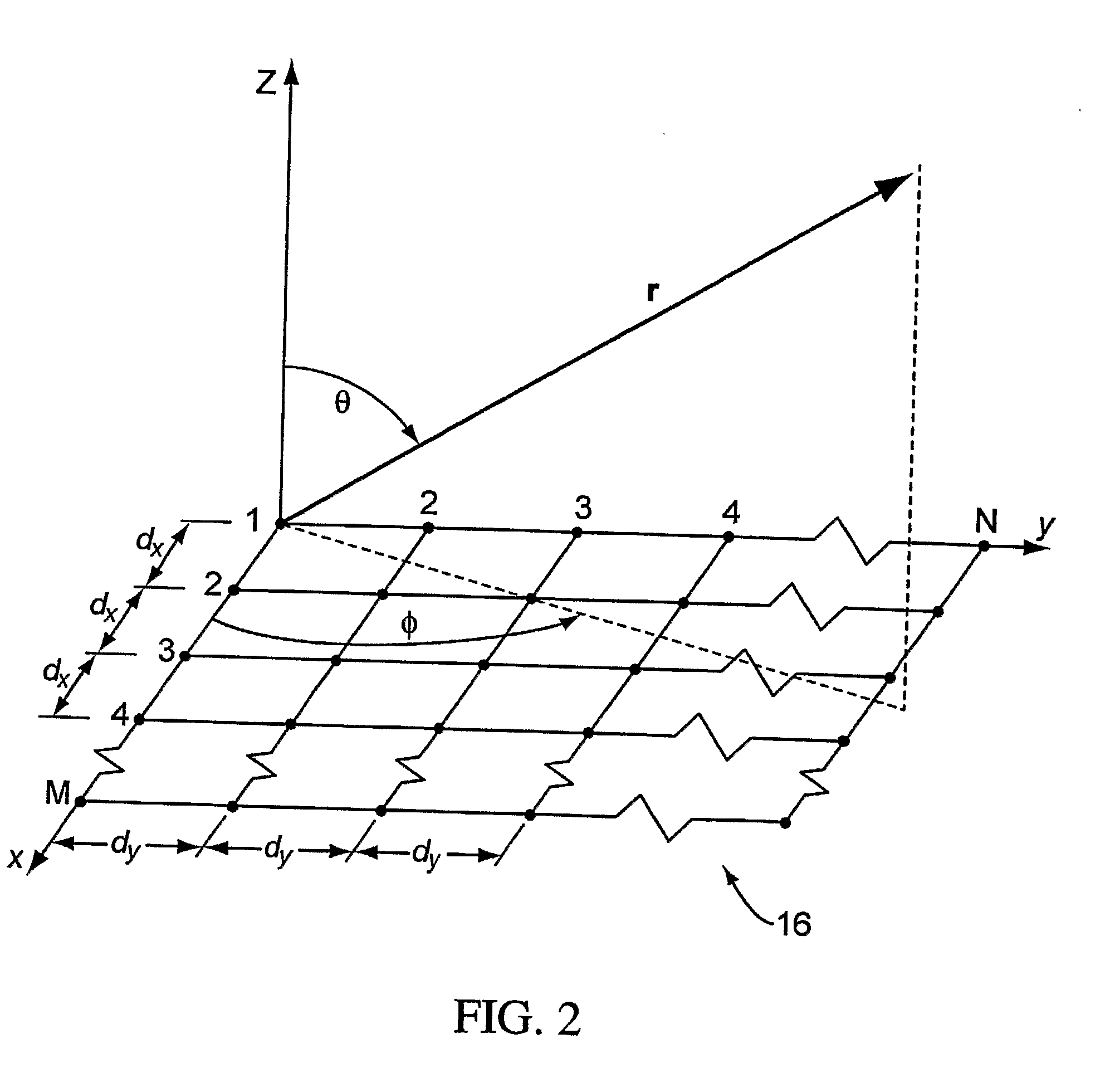

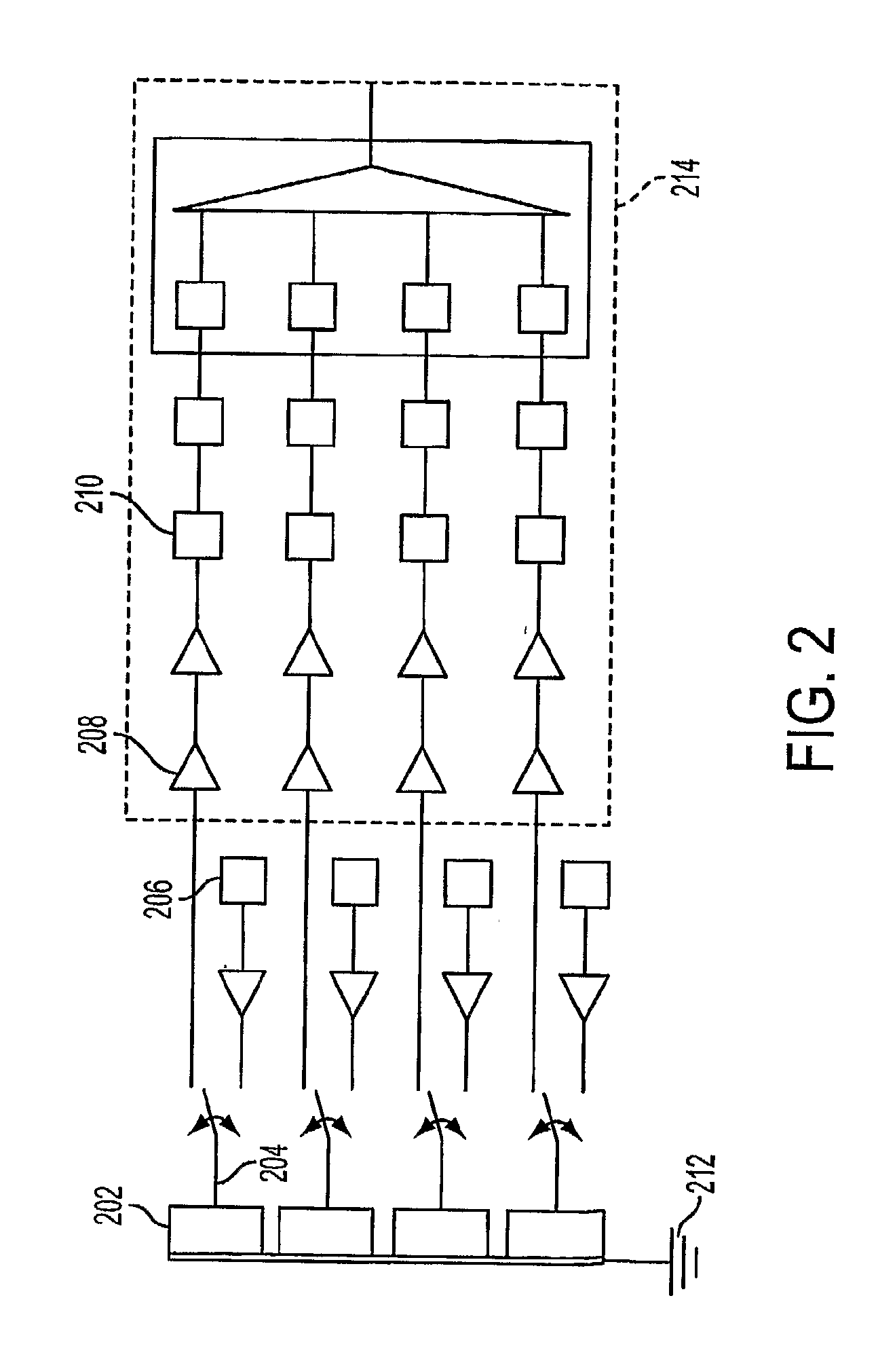

Local oscillator circuitry for an antenna array is disclosed. The circuitry includes an array of rotary traveling wave oscillators which are arranged in a pattern over an area and coupled so as to make them coherent. This provides for a set of phase synchronous local oscillators distributed over a large area. The array also includes a plurality of phase shifters each of which is connected to one of the rotary oscillators to provide a phase shifted local oscillator for the array. The phase shifter optionally includes a cycle counter that is configured to count cycles of the rotary oscillator to which it is connected and control circuitry that is then operative to provide a shifted rotary oscillator output based on the count from the cycle counter. A system and method for operating a true-time delay phased array antenna system. The system includes a plurality of antenna element circuits for driving or receiving an rf signal from the elements of the array. Each element circuit has a transmit and a receive path and a local multiphase oscillator, such as a rotary traveling wave oscillator. Each path has an analog delay line for providing a true-time delay for the antenna element. Preferably, the analog delay line is a charge coupled device whose control nodes are connected to phases of the local multiphase oscillator to implement a delay that is an integer number local multiphase oscillator periods. A fractional delay is also included in the path by using a sample and hold circuit connected to a particular phase of the oscillator. By delaying each antenna element by a true time delay, broadband operation of the array is possible.

Owner:ANALOG DEVICES INC

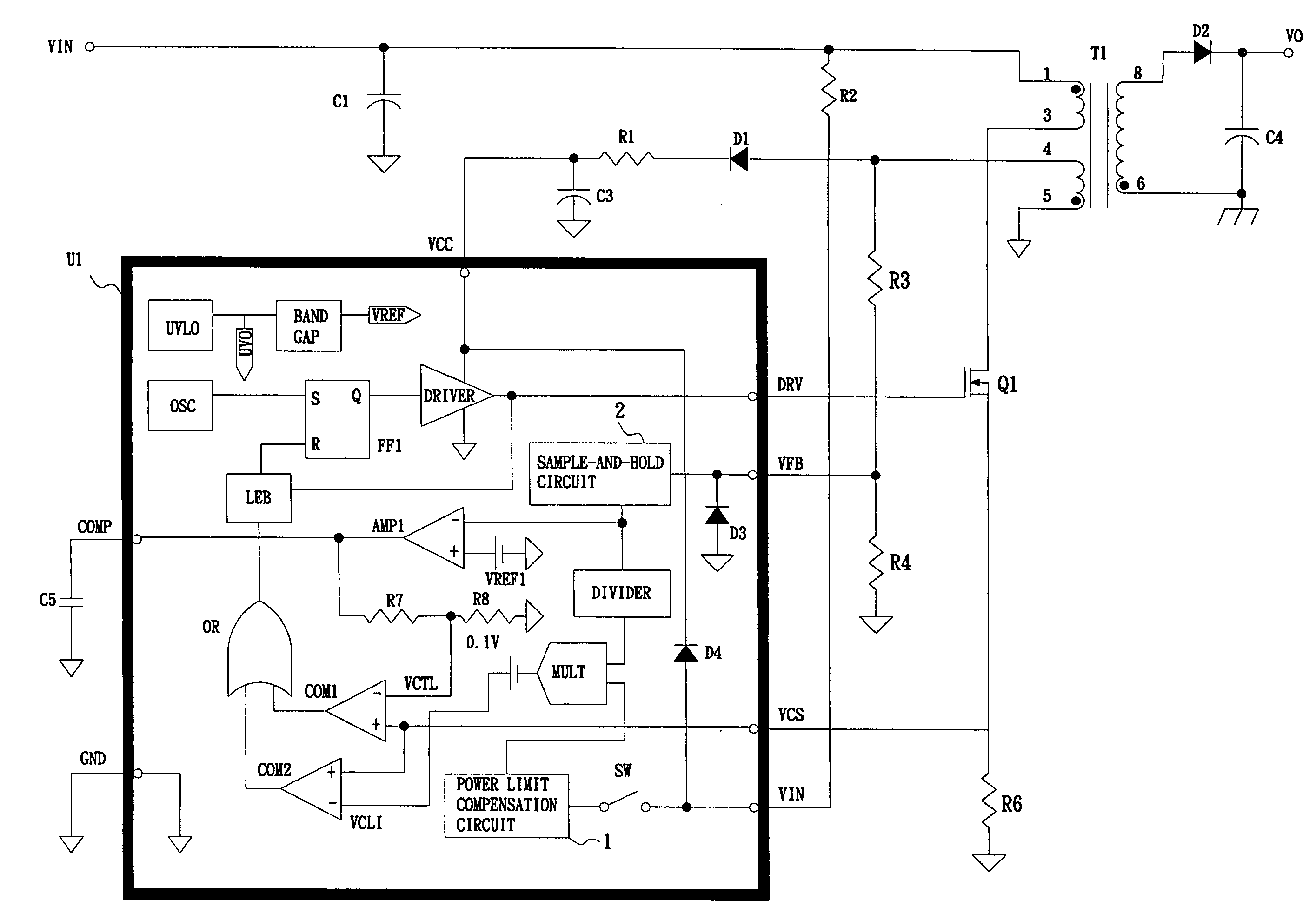

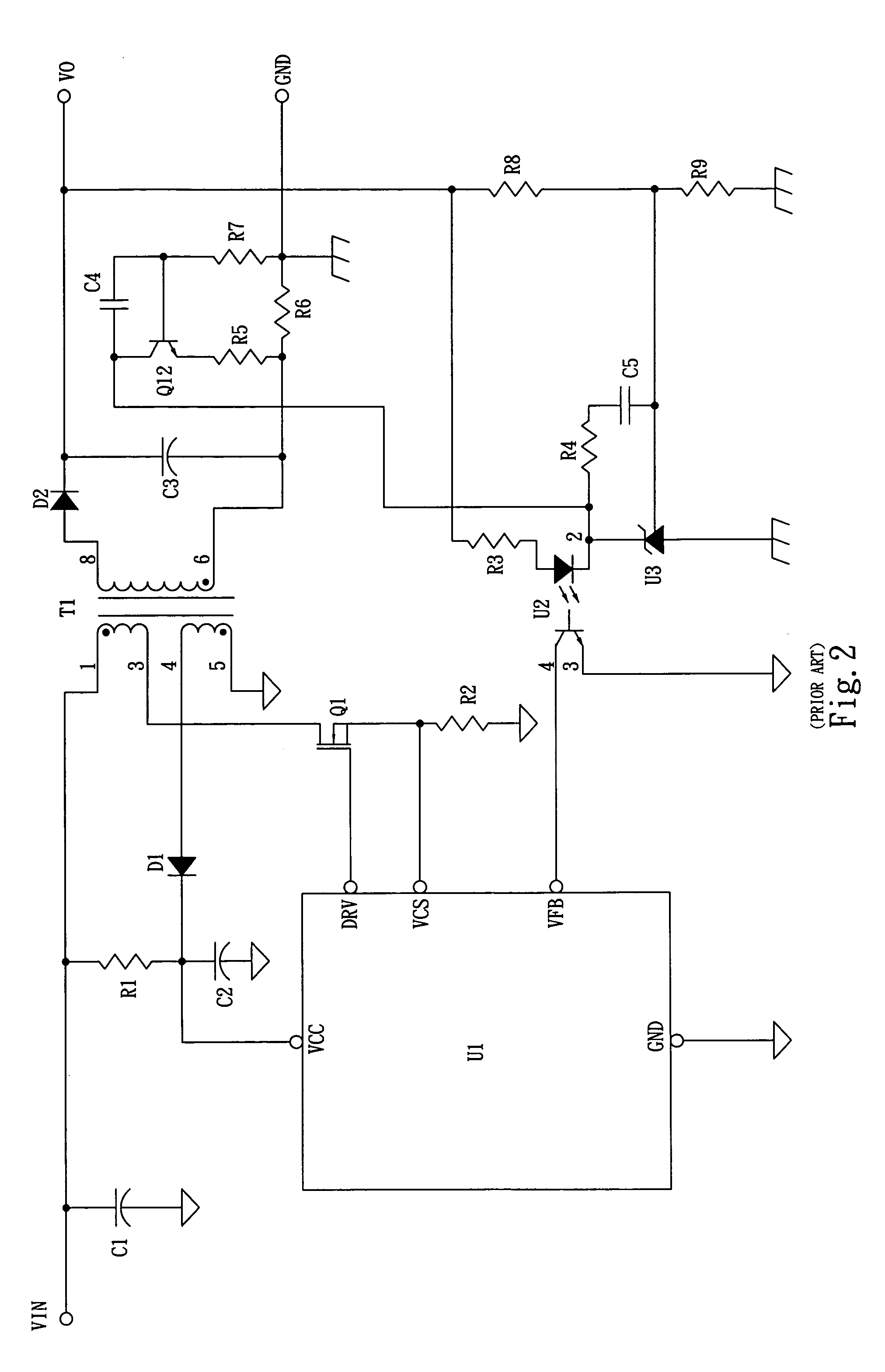

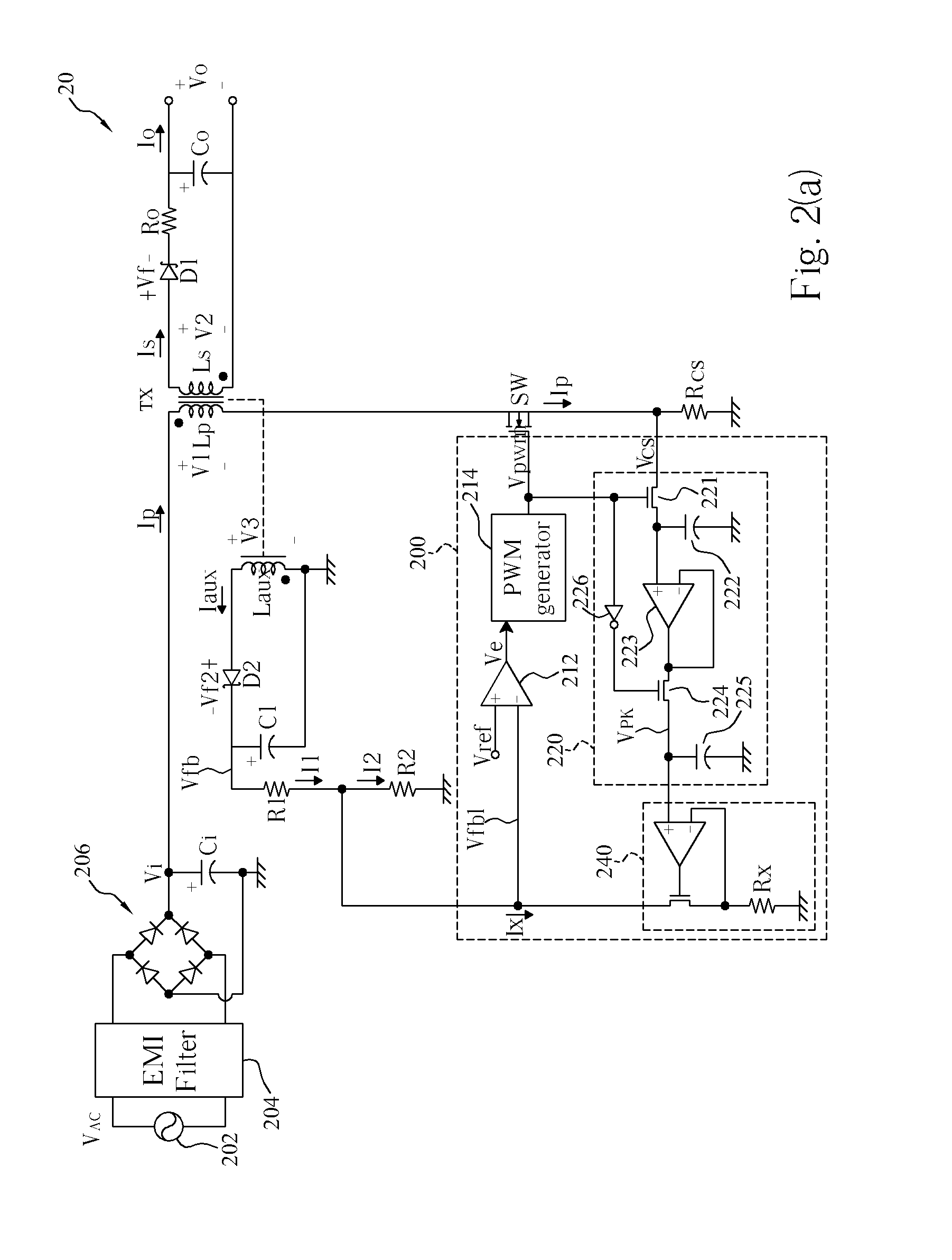

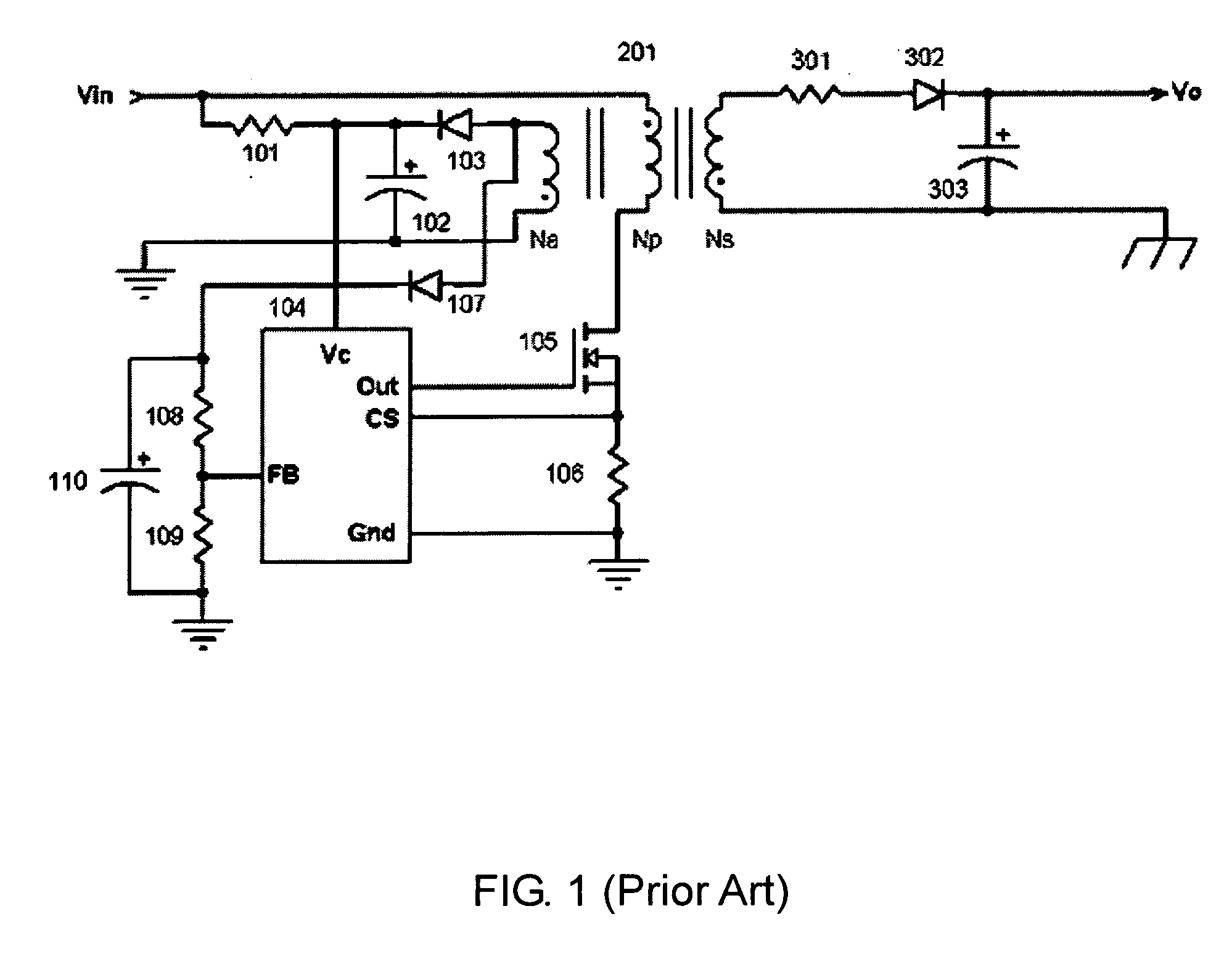

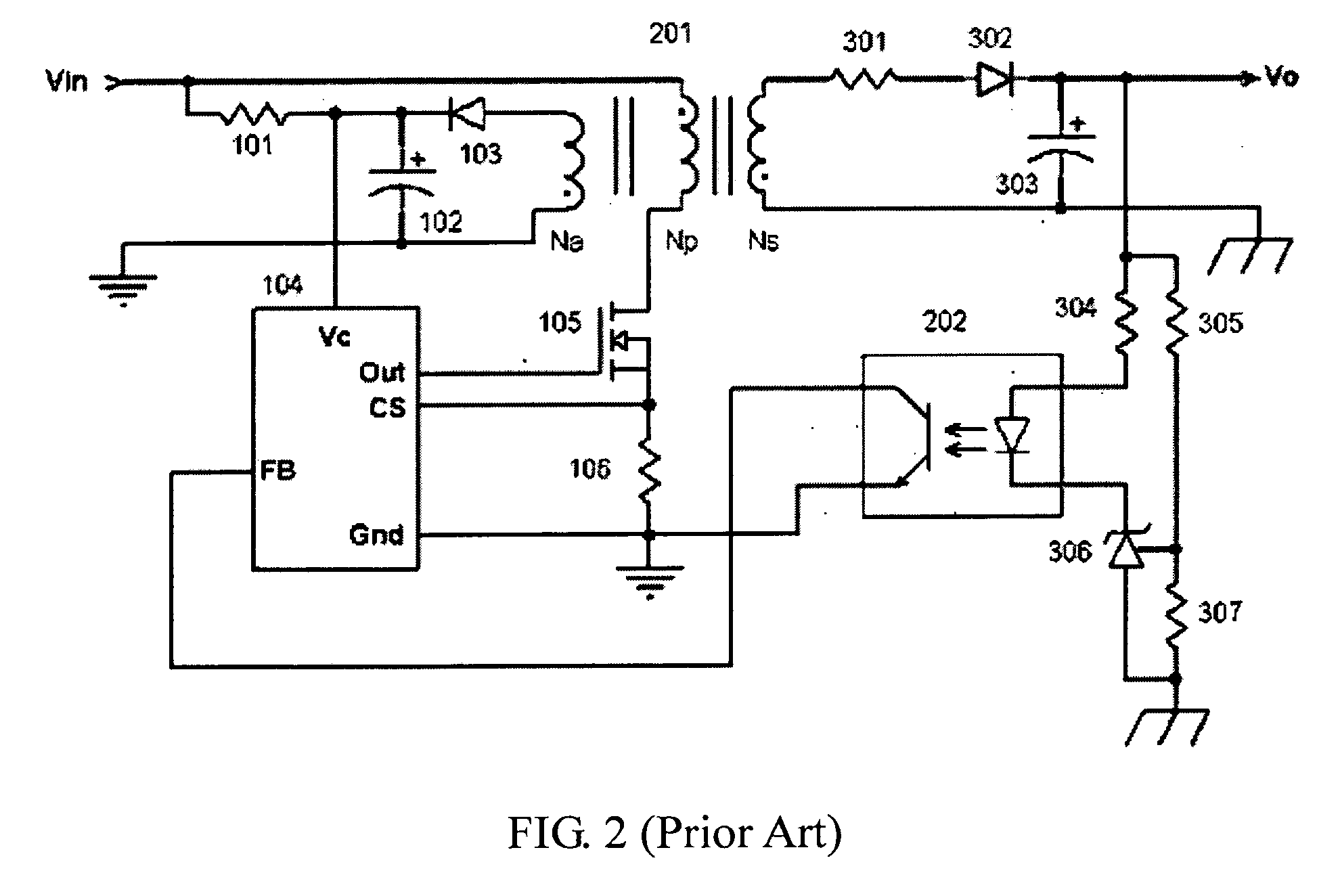

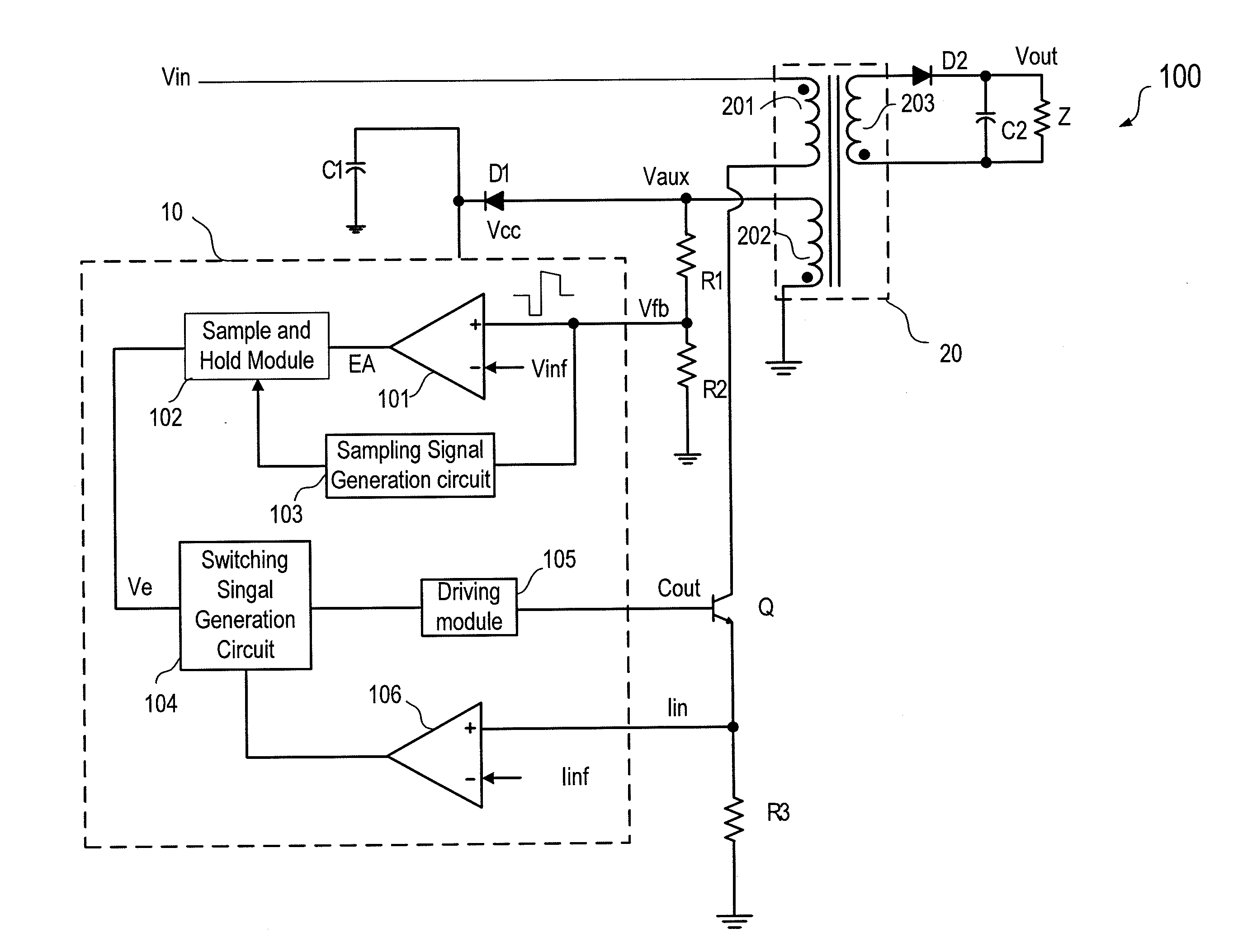

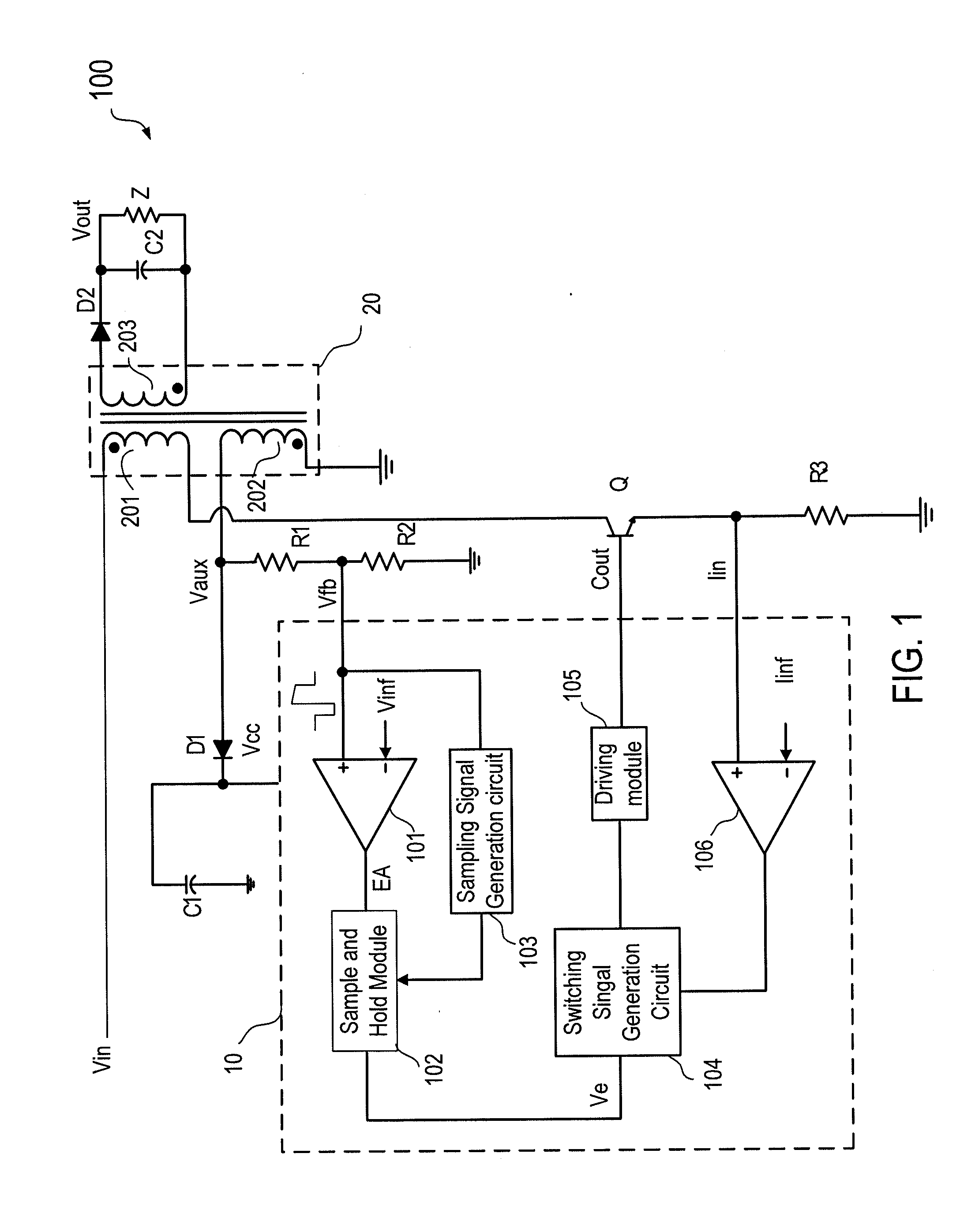

Primary-side feedback switching power supply

The present invention discloses a primary-side feedback switching power supply that uses a sample-and-hold circuit to obtain a corner voltage of a harmonic wave voltage while the primary-side auxiliary winding is operating at a discontinuous mode as a feedback control, and provides both voltage regulation and current limit functions. A stable voltage output is provided within the nominal input voltage and nominal output load, such that when the output reaches a current limit, the output voltage drops but the output current is controlled to remain unchanged, so as to provide an over-current protection.

Owner:NIKO SIMICONDUCTOR CO LTD

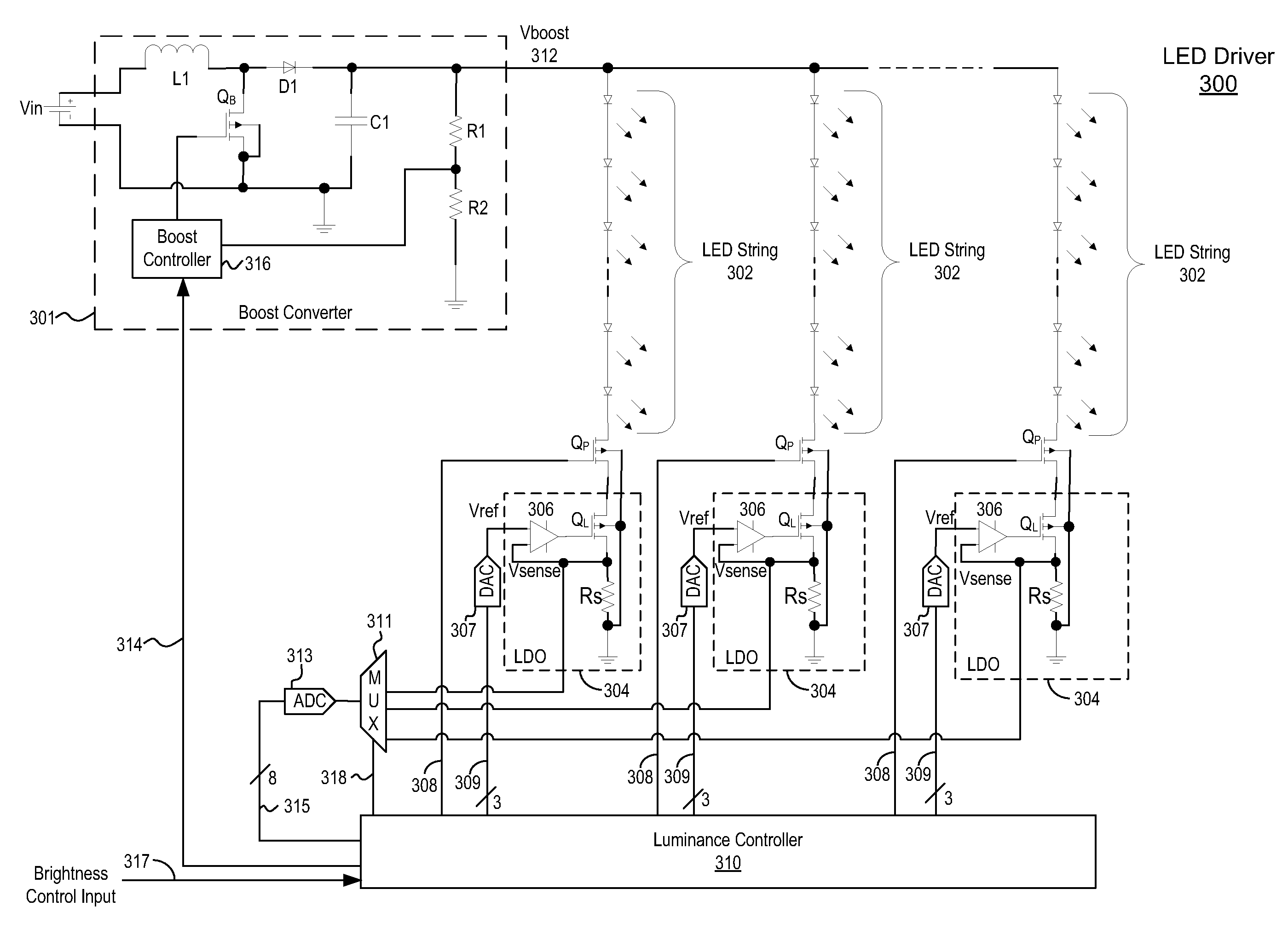

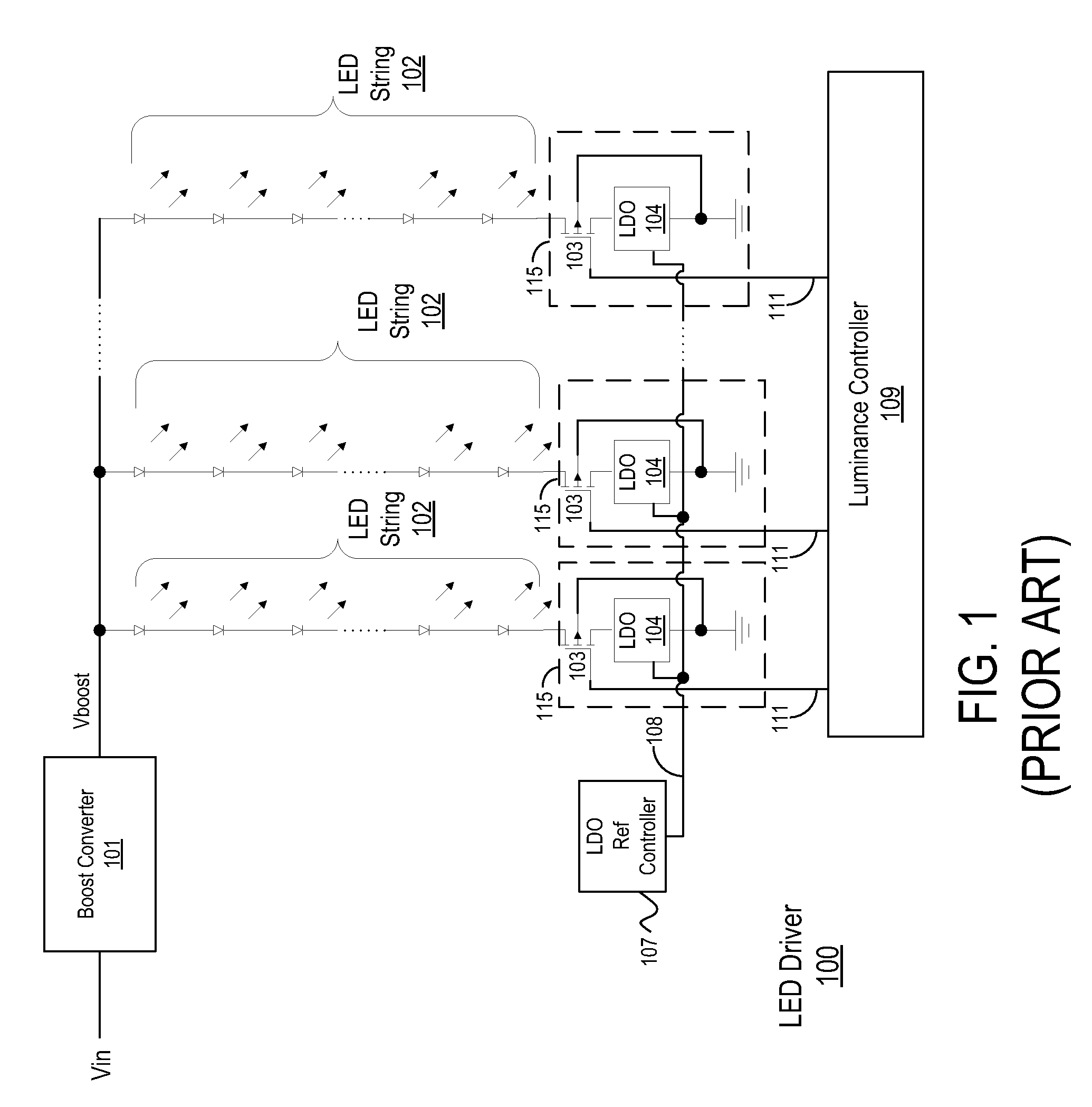

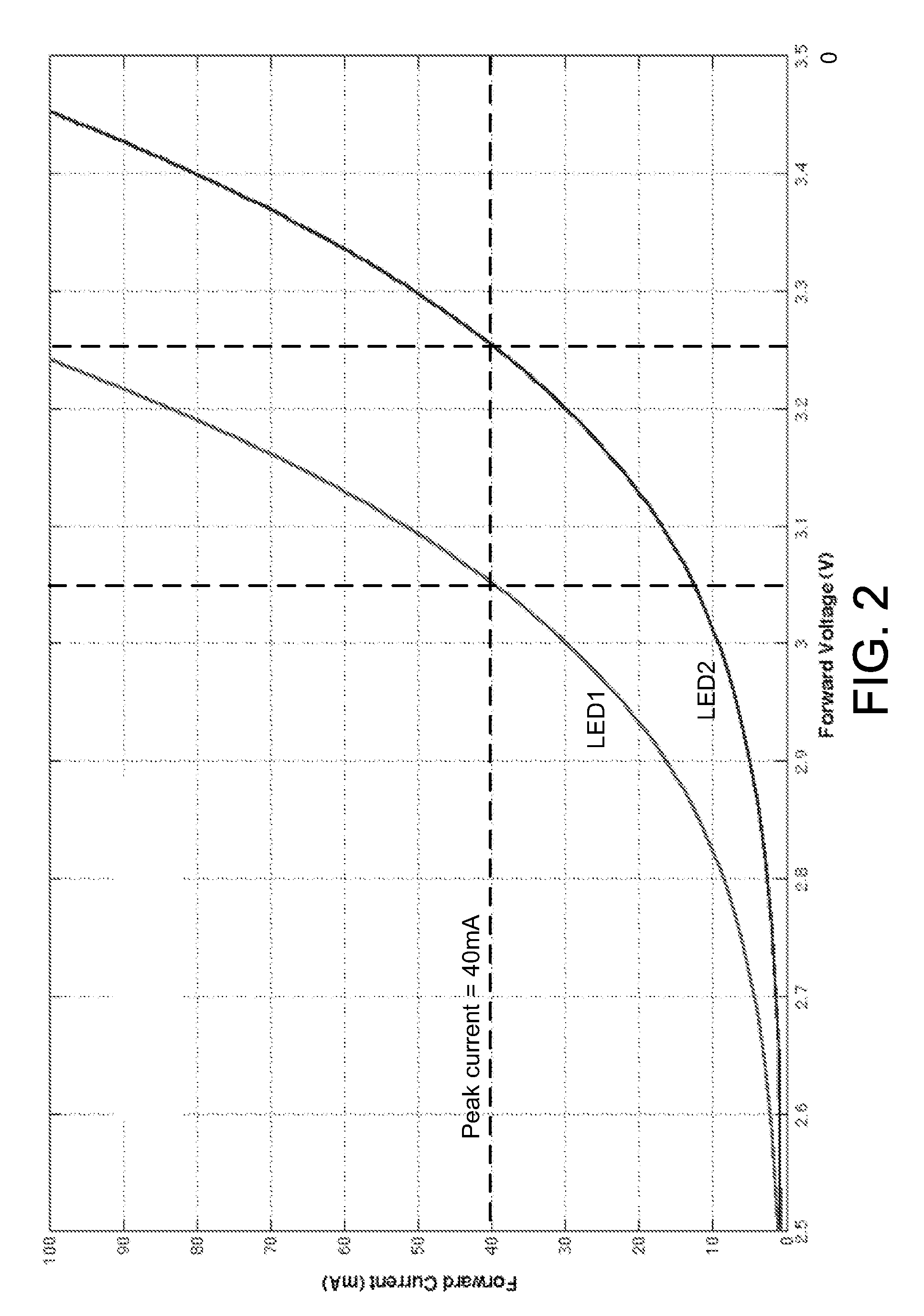

Adaptive Switch Mode LED Driver

ActiveUS20110062872A1Exact matchFast dynamic responseSemiconductor/solid-state device testing/measurementElectroluminescent light sourcesPower flowEngineering

An adaptive switch mode LED driver provides an intelligent approach to driving multiple strings of LEDs. The LED driver determines an optimal current level for each LED channel from a limited set of allowed currents. The LDO driver then determines a PWM duty cycle for driving the LEDs in each LED channel to provide precise brightness control over the LED channels. Beneficially, the LED driver minimizes the power dissipation in the LDO circuits driving each LED string, while also ensuring that the currents in each LED string are maintained within a limited range. A sample and hold LDO allows PWM control over extreme duty cycles with very fast dynamic response. Furthermore, fault protection circuitry ensures fault-free startup and operation of the LED driver.

Owner:DIALOG SEMICONDUCTOR INC

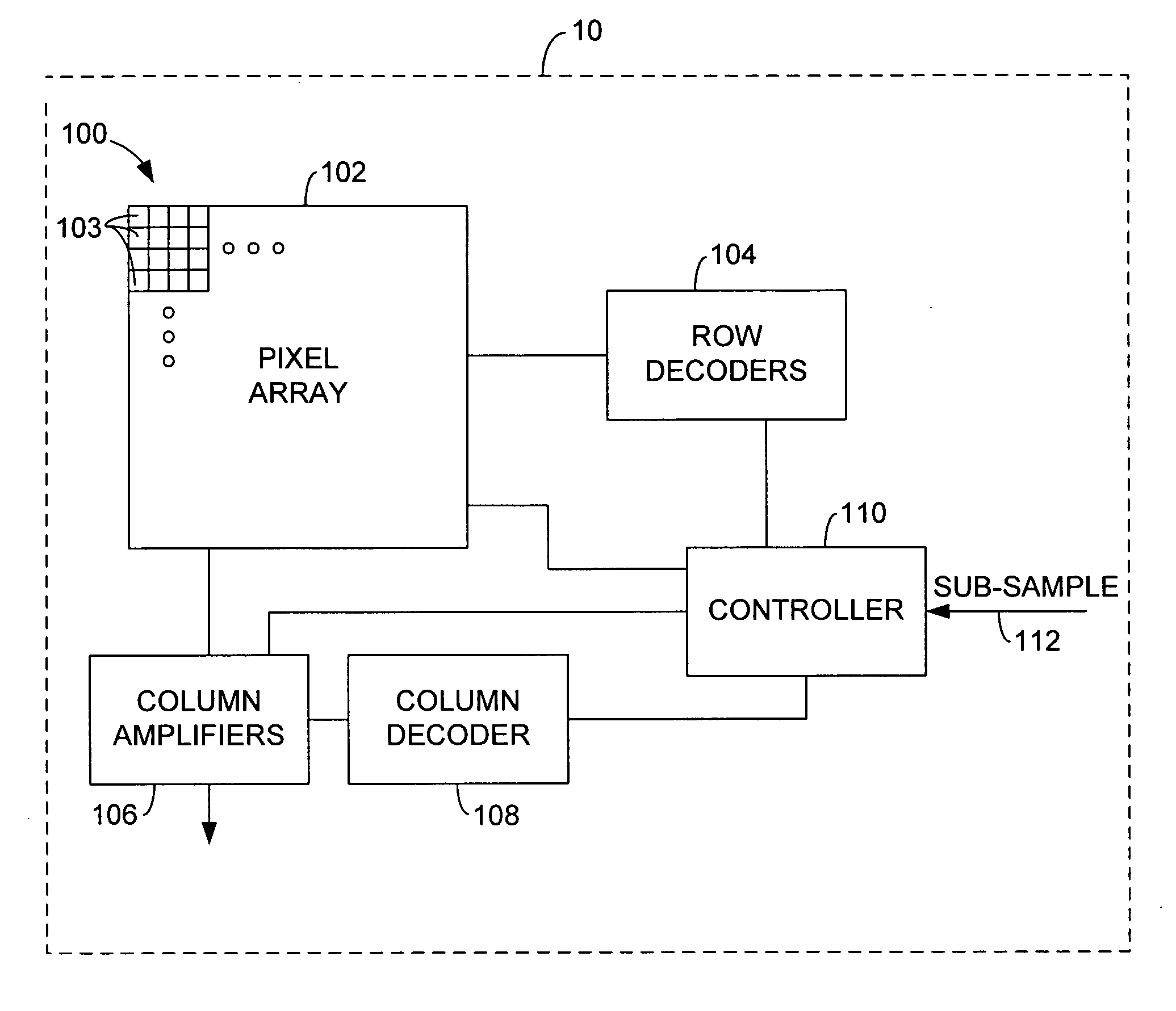

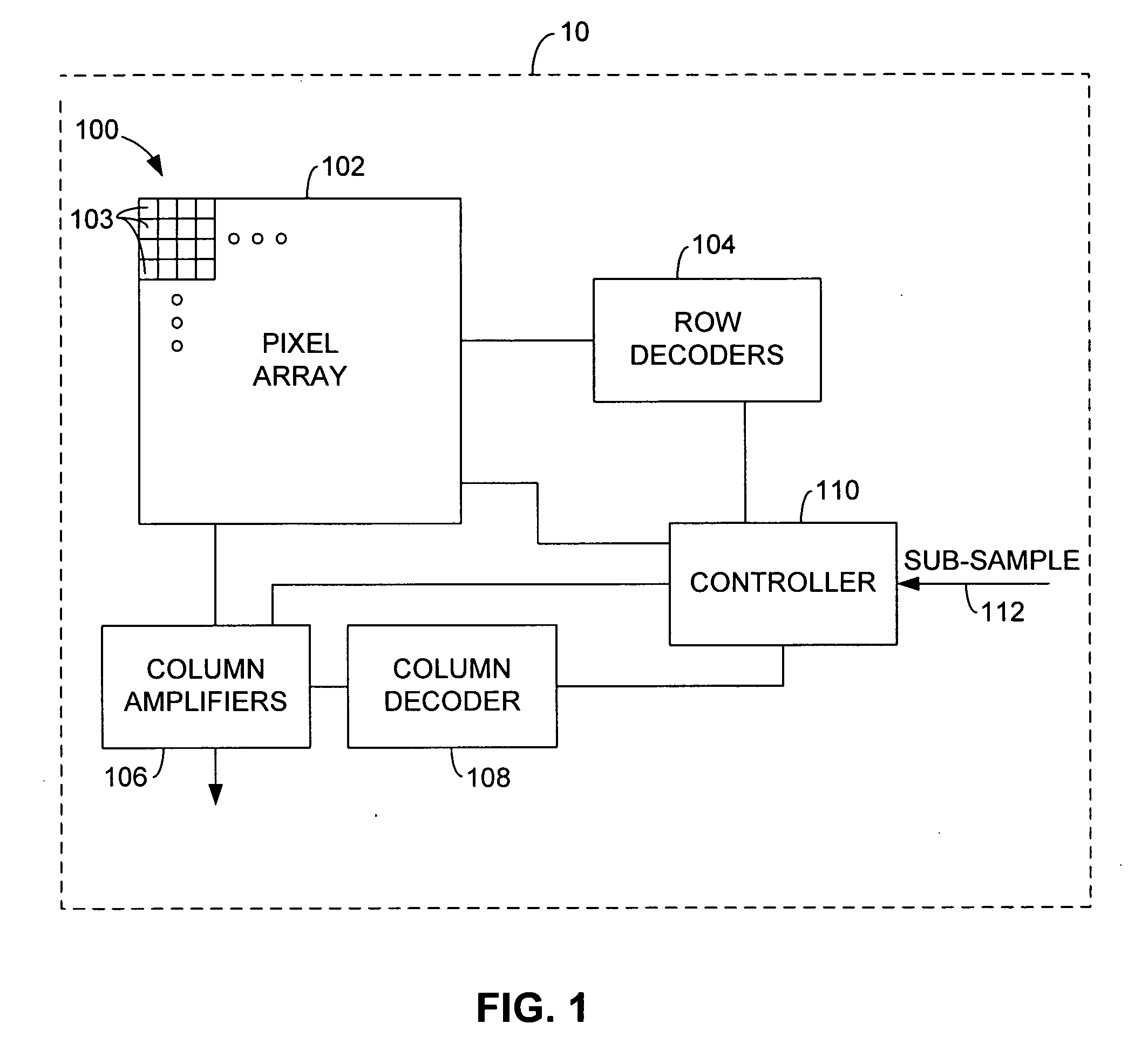

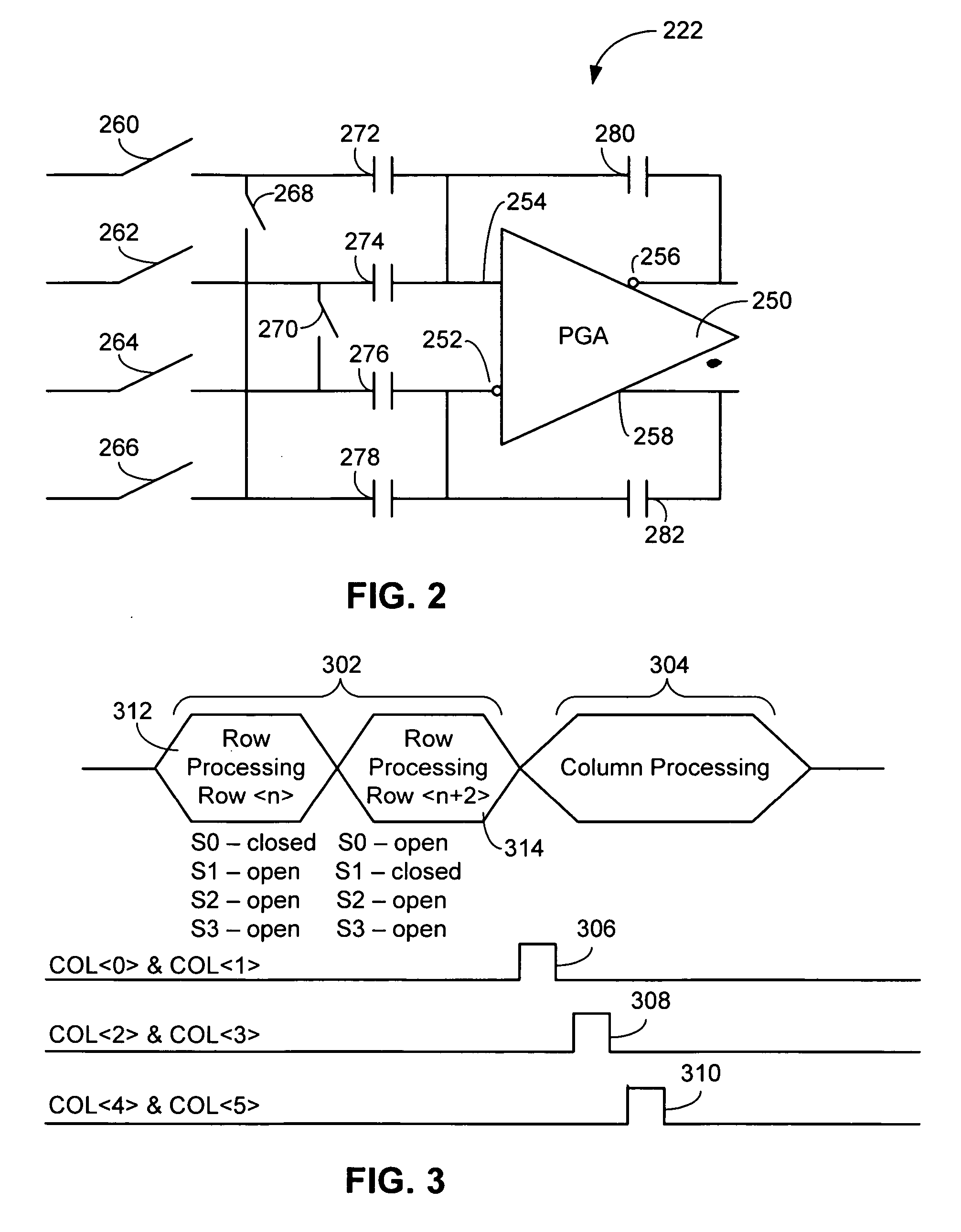

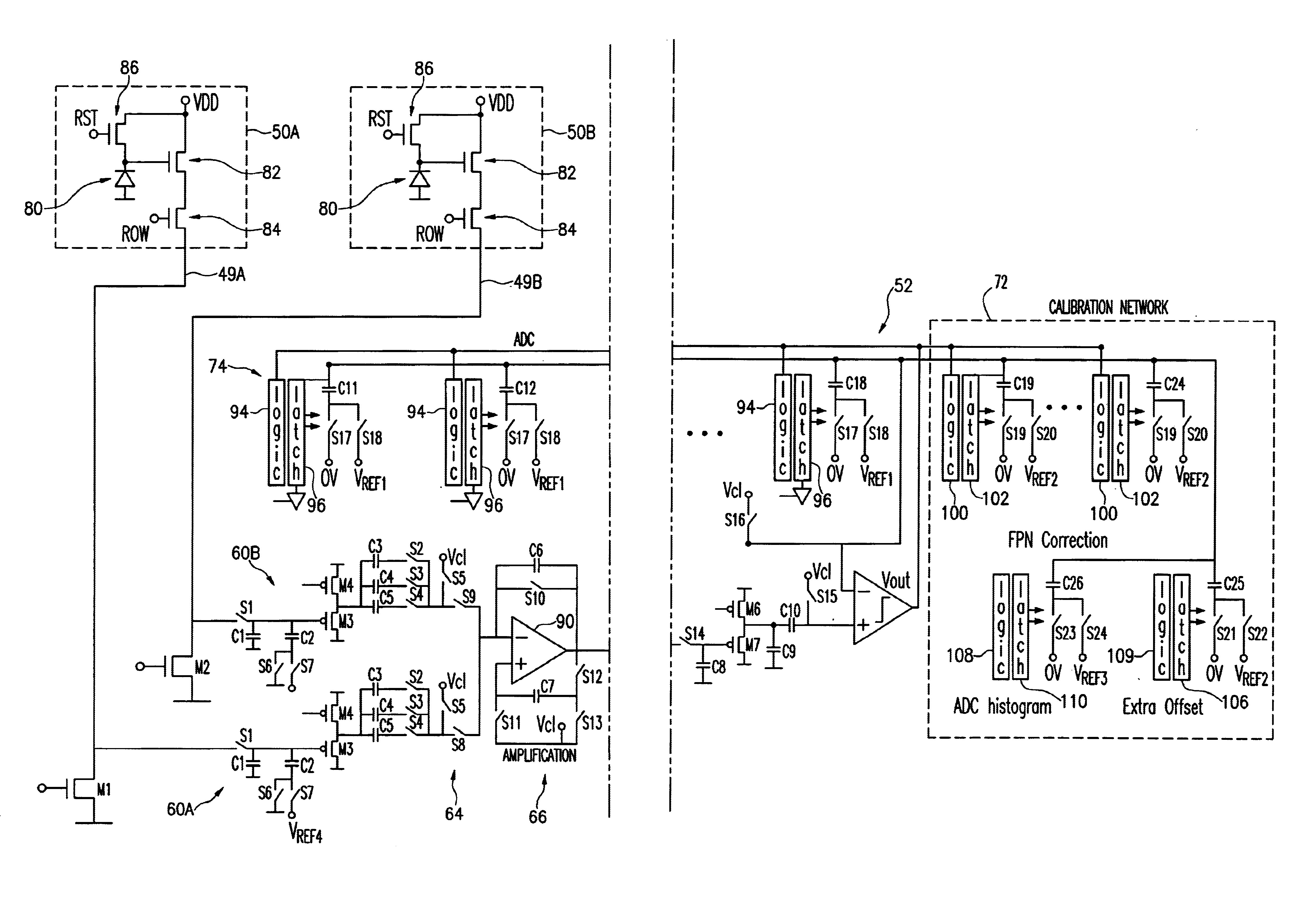

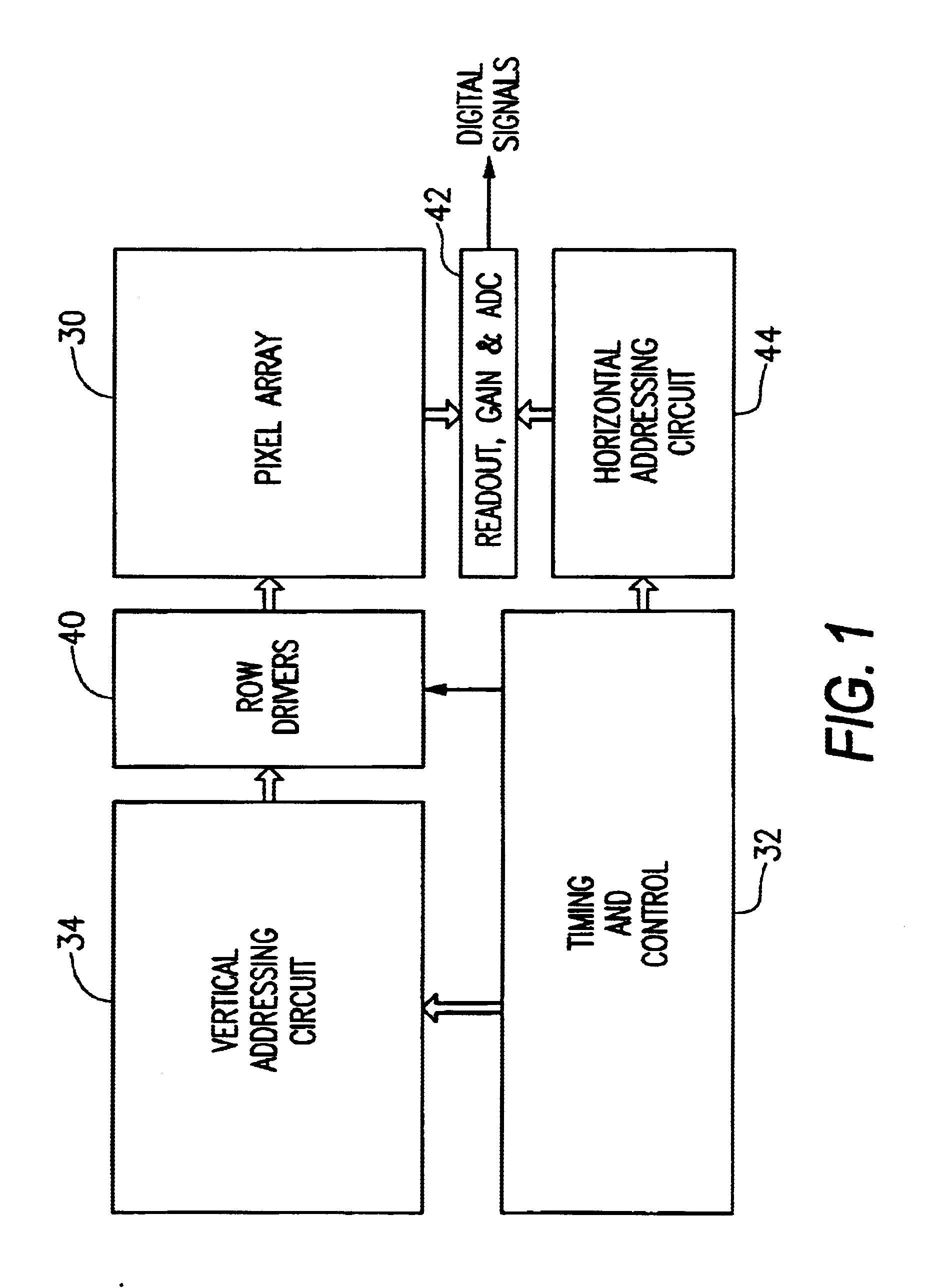

Analog vertical sub-sampling in an active pixel sensor (APS) image sensor

ActiveUS20070228256A1Television system detailsTelevision system scanning detailsCMOS sensorAudio power amplifier

An active pixel sensor (APS) image sensor comprises an array of pixel circuits corresponding to rows and columns of pixels, a plurality of amplifiers that buffer signals output by the array of pixel circuits, and a plurality of sample and hold circuits that read the buffered signals. A routing mechanism is positioned between the array of pixel circuits and the plurality of amplifiers. A controller selects a set of the pixel circuits for sampling and is configured to control the routing mechanism to couple each pixel circuit in the set to a different one of the amplifiers during a normal mode of operation and to couple each pixel circuit of a subset of pixel circuits in a first set of pixel circuits to a different amplifier of a first subset of the amplifiers, to couple each pixel circuit of a subset of pixel circuits in a second set of pixel circuits to a different amplifier of a second subset of the amplifiers, and to connect the amplifiers of the first and second subsets of amplifiers in pairs to a common one of the sample and hold circuits during a sub-sampling mode of operation.

Owner:APTINA IMAGING CORP +1

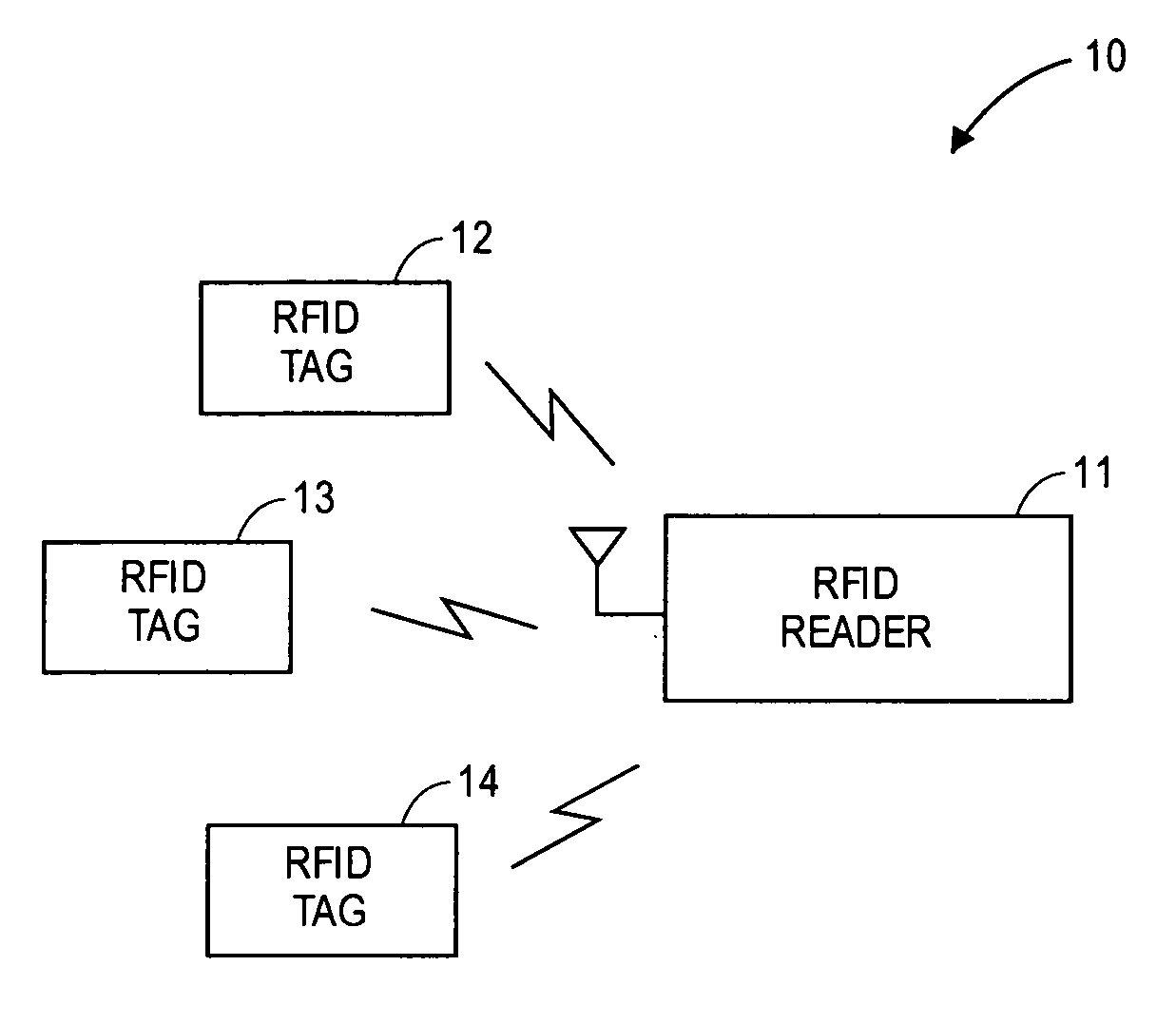

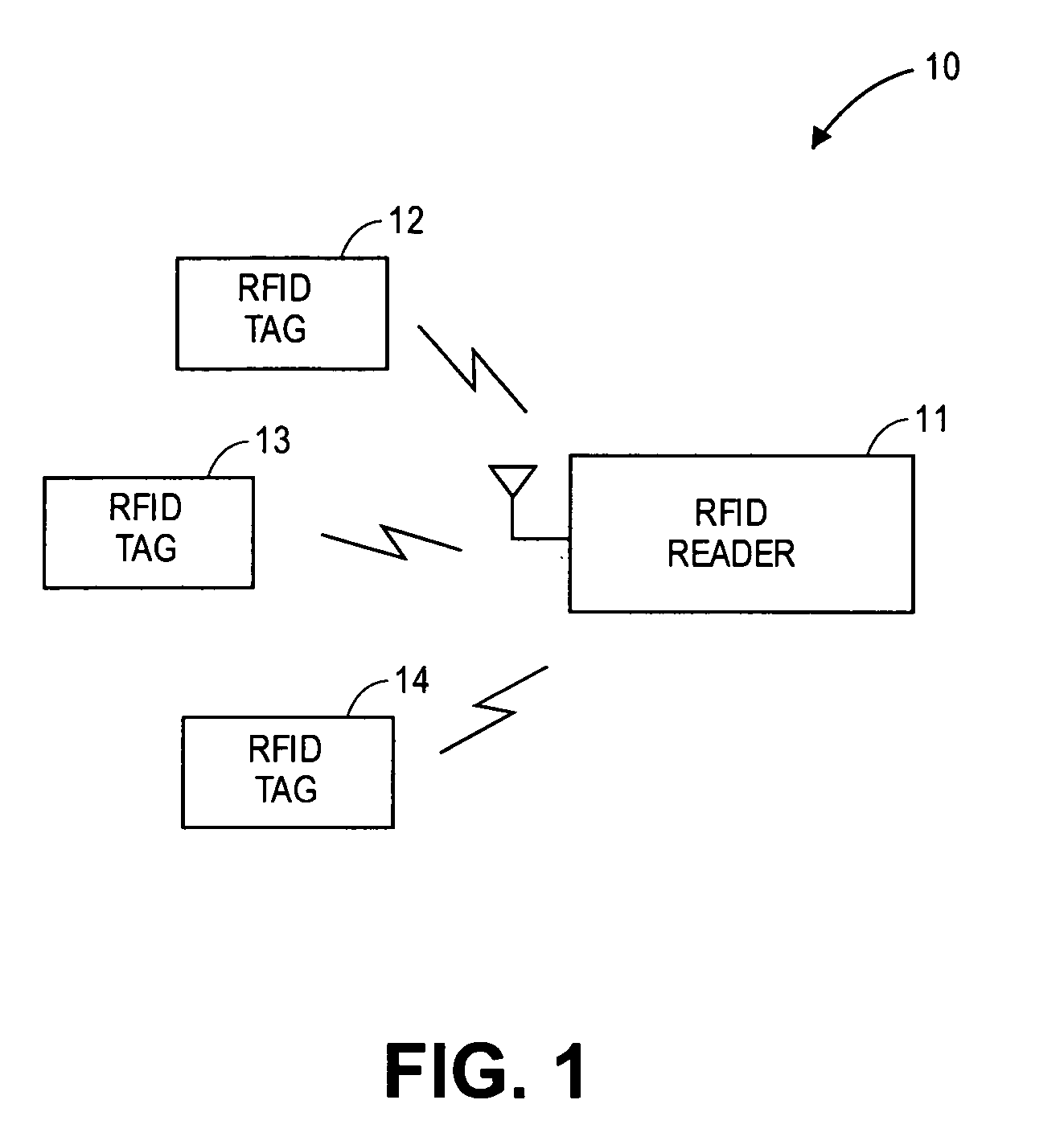

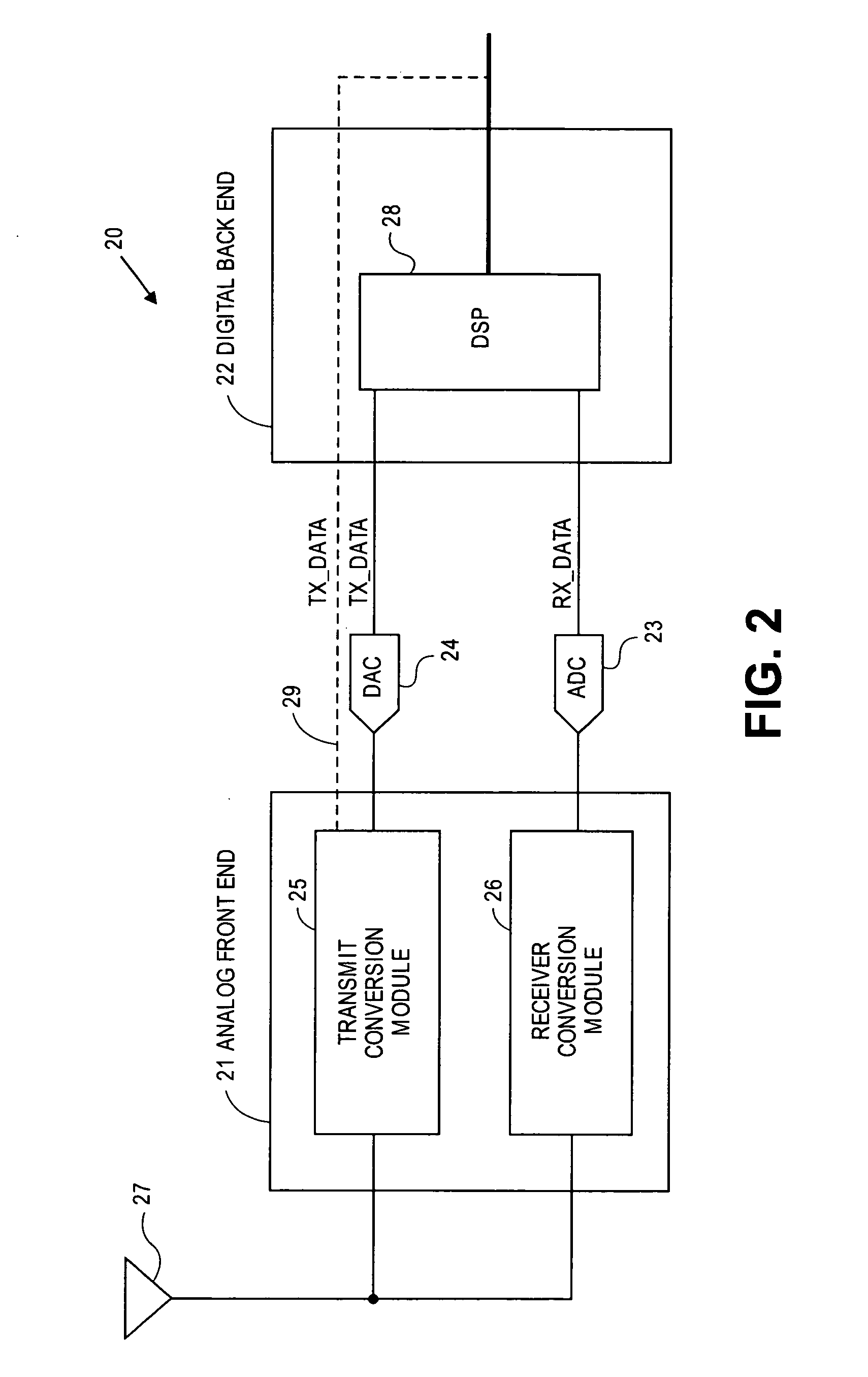

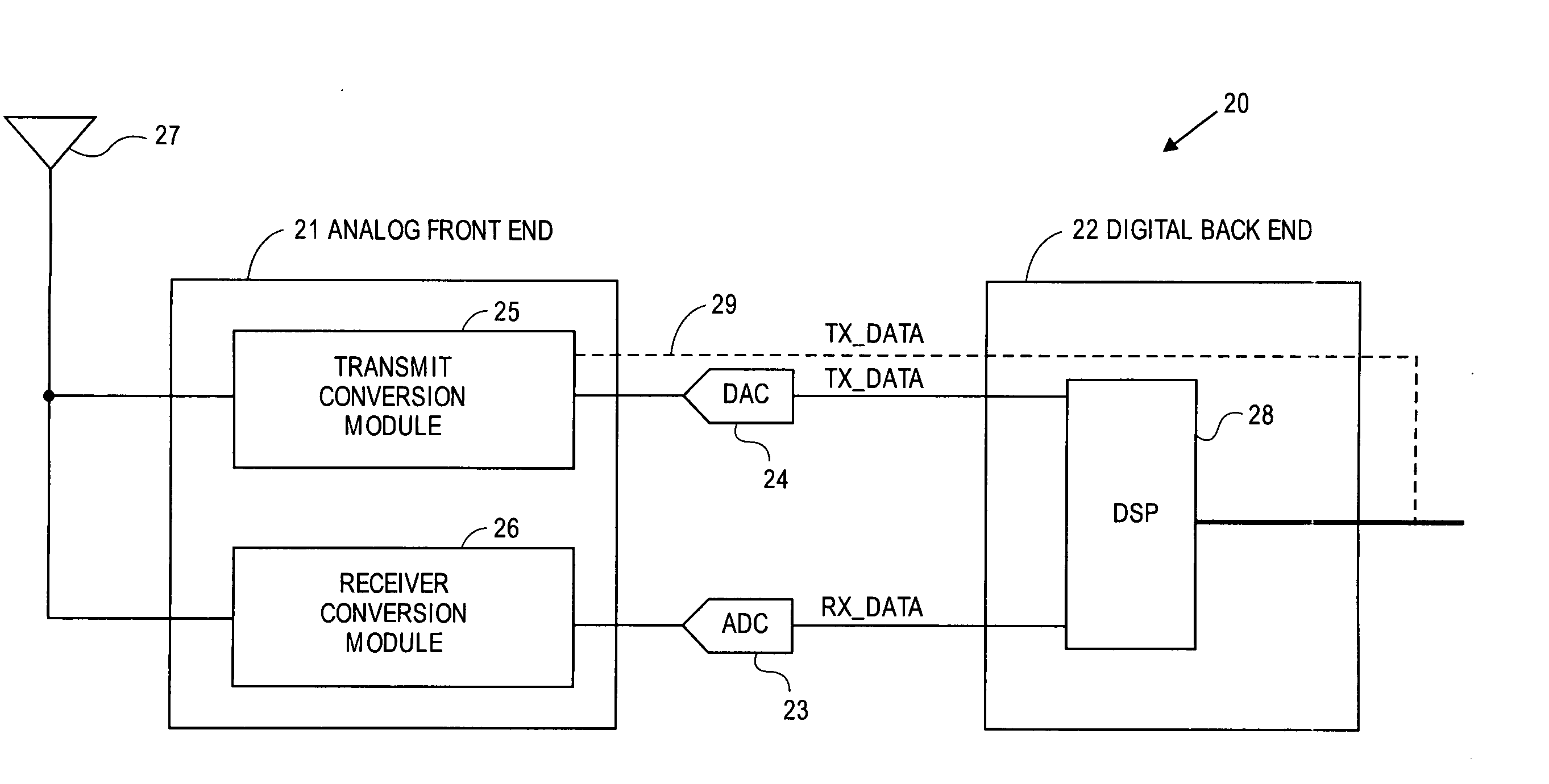

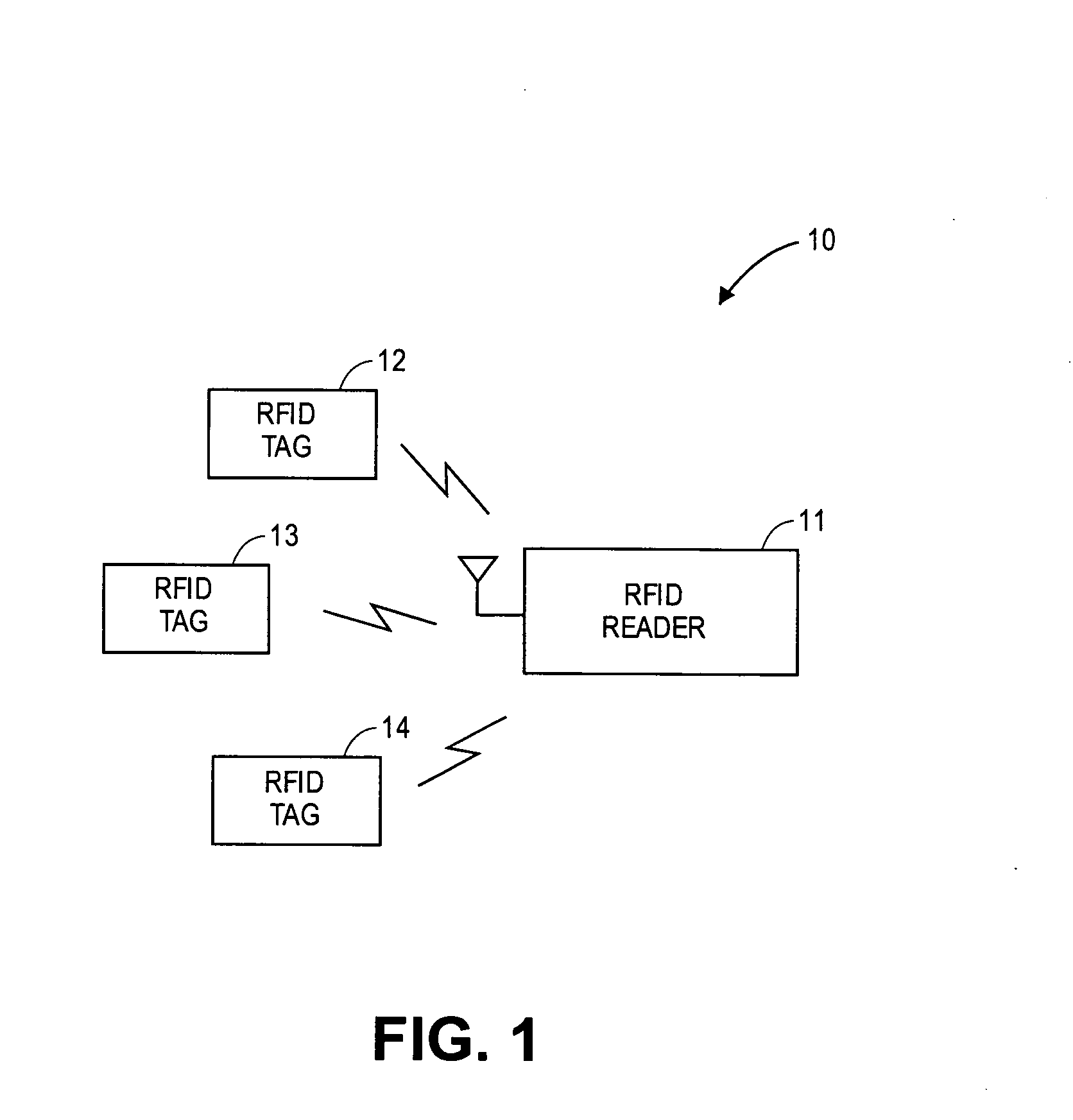

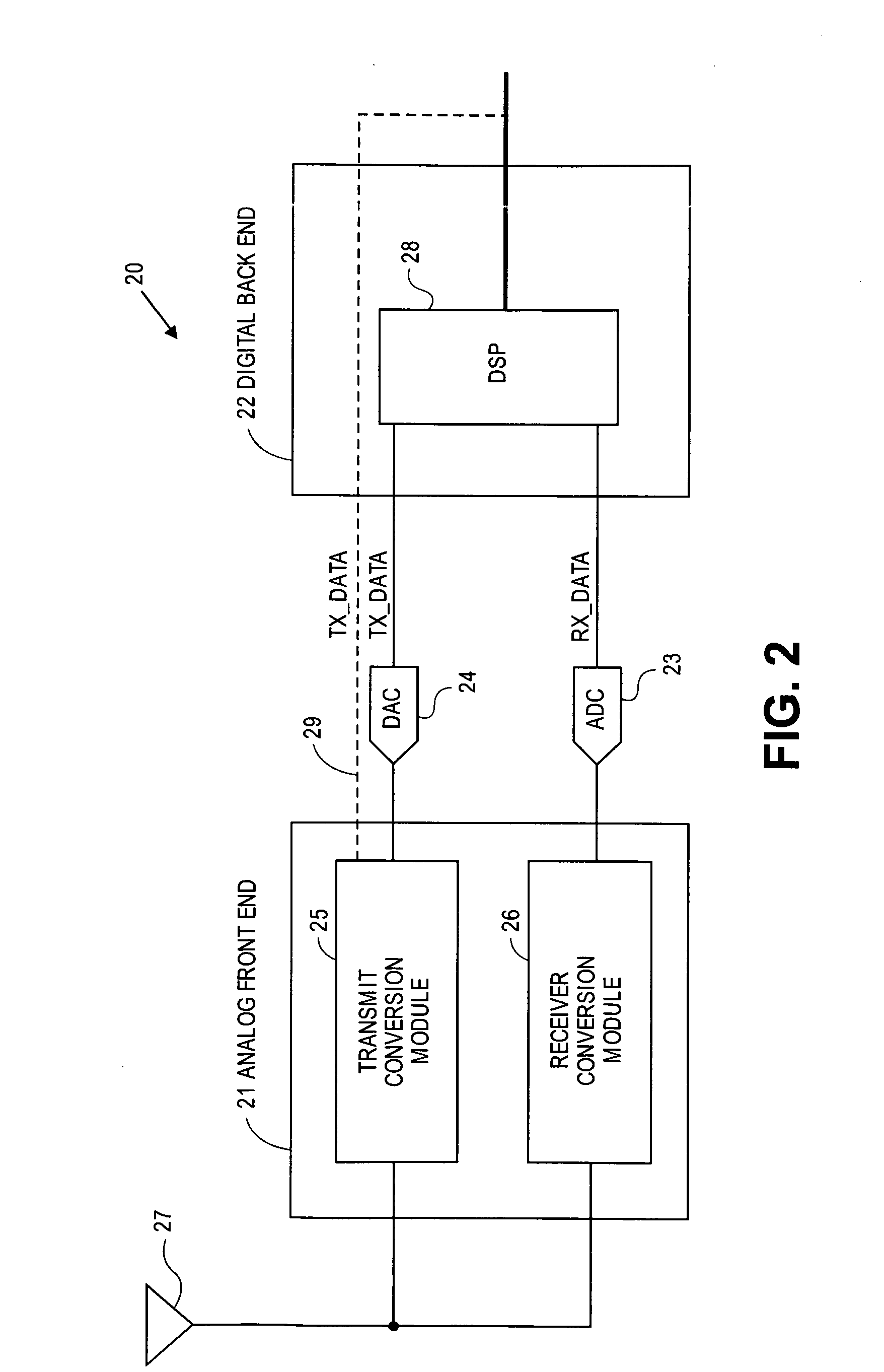

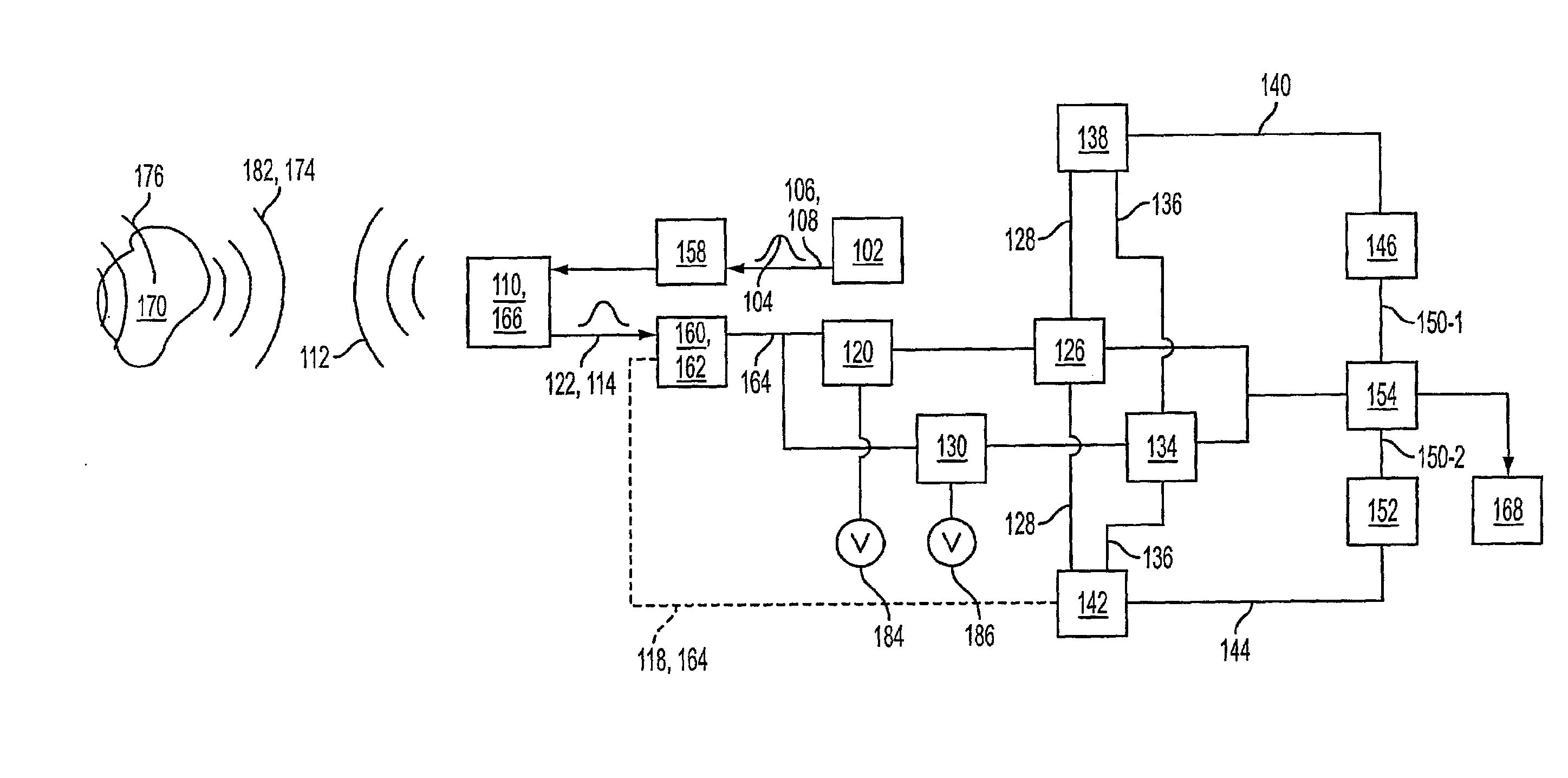

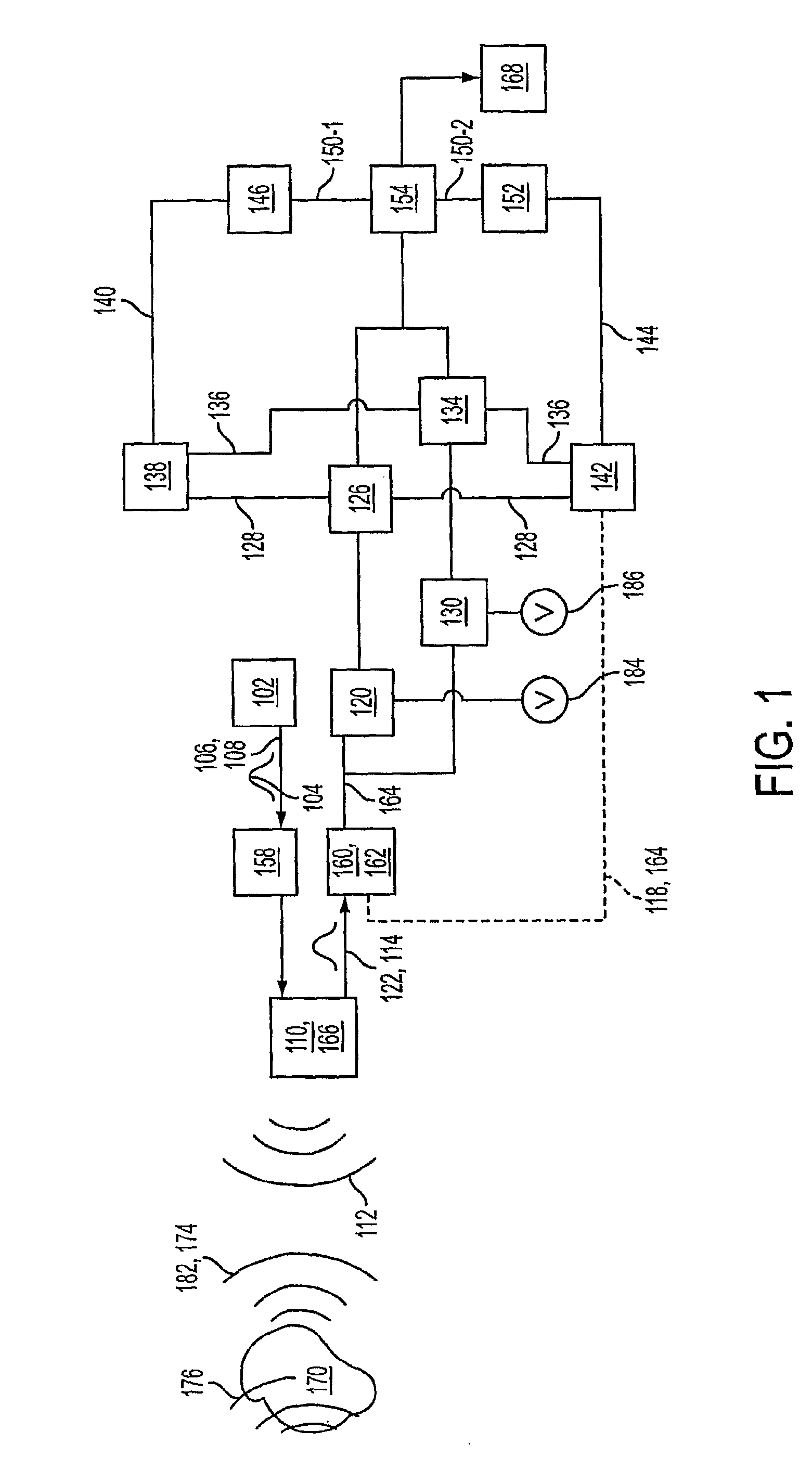

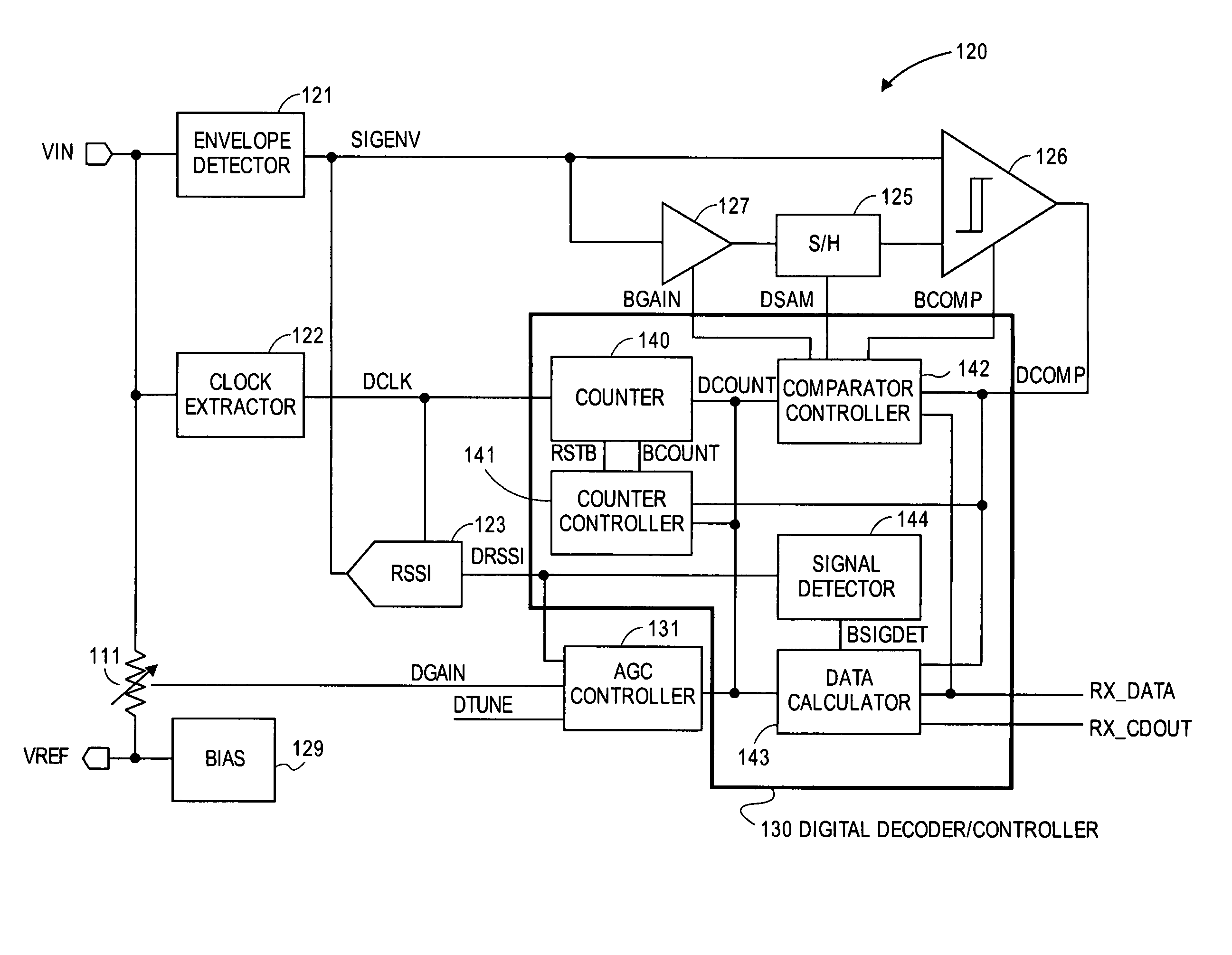

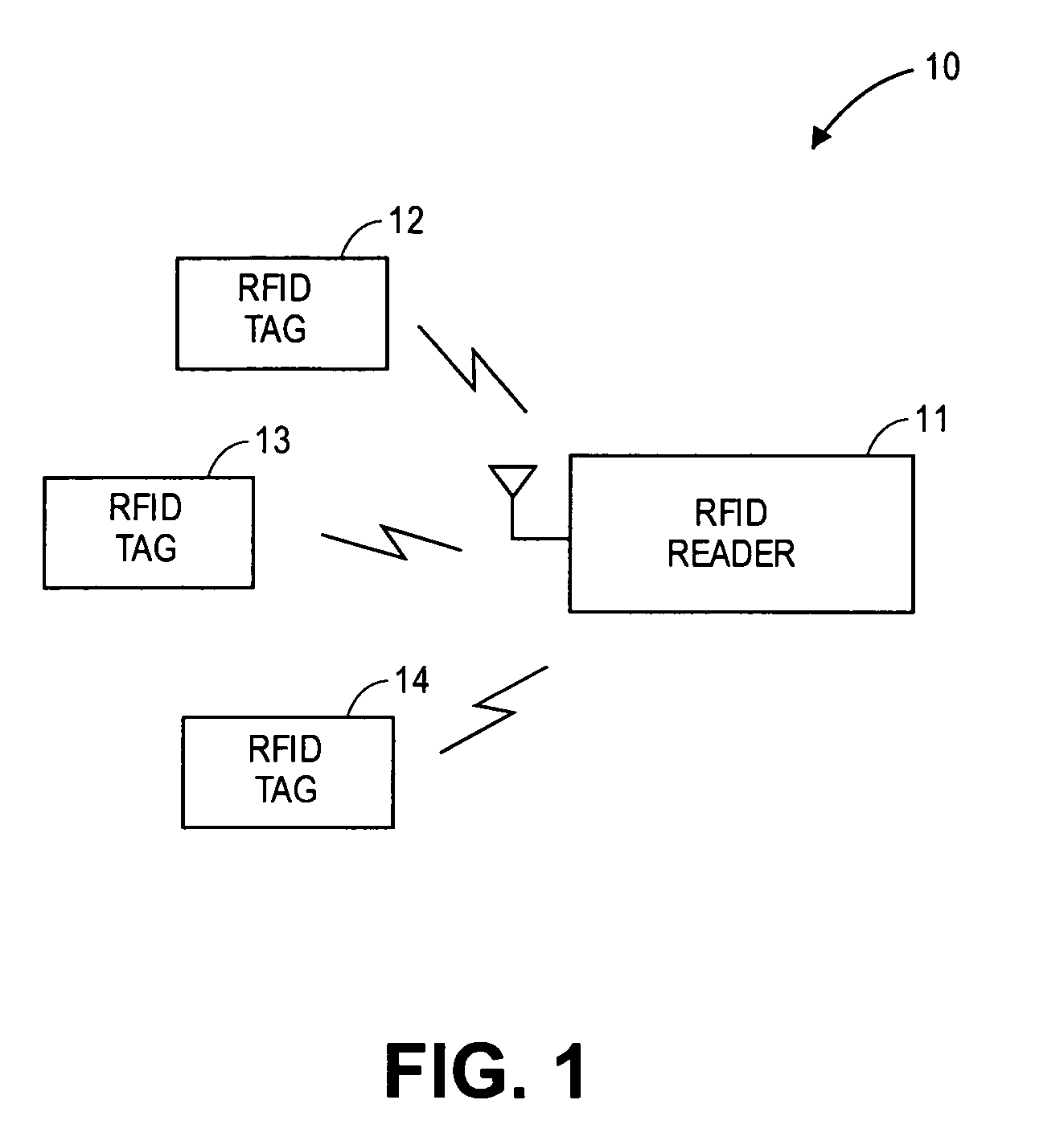

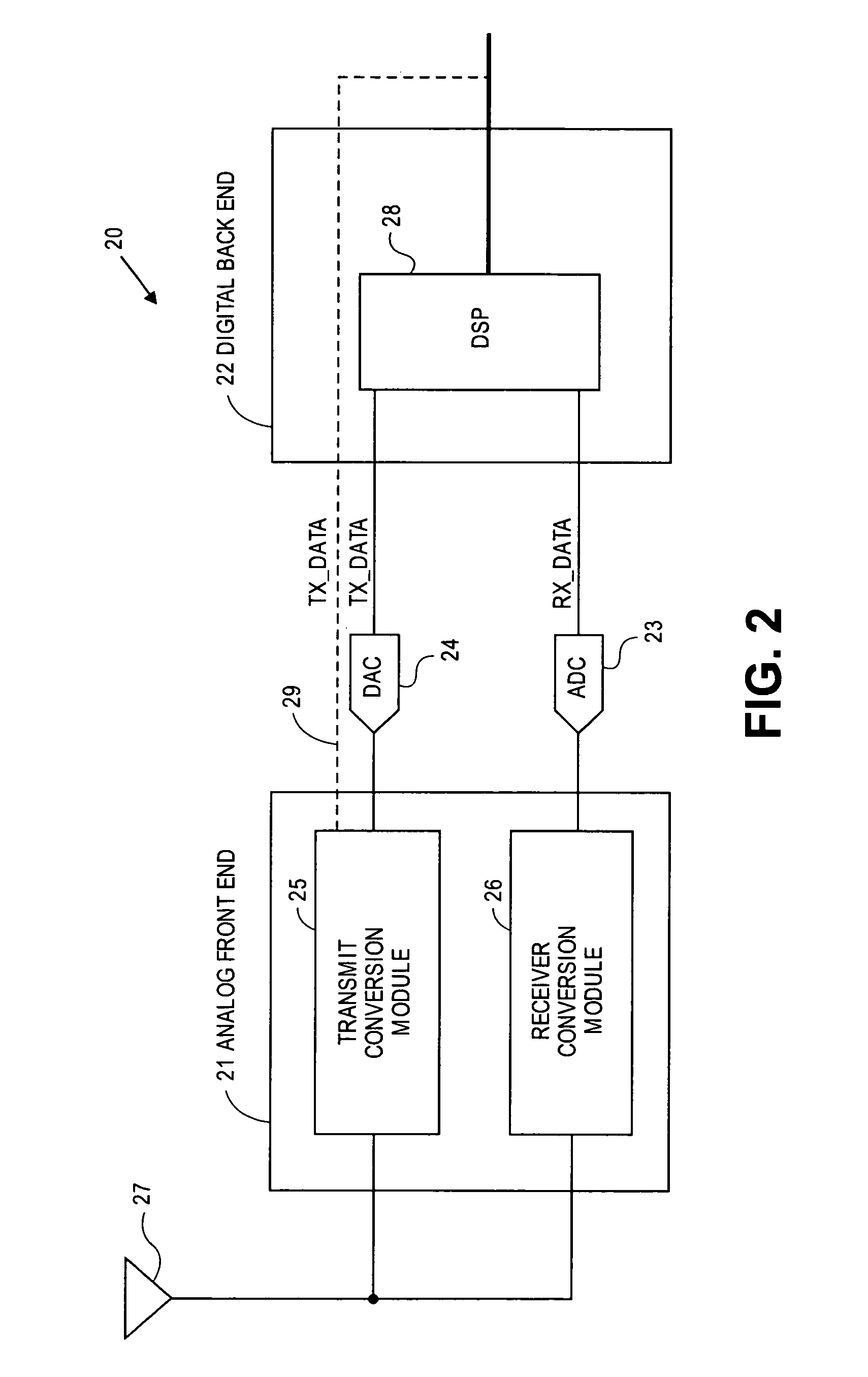

Multi-protocol radio frequency identification transponder transceiver

ActiveUS20060238301A1Memory record carrier reading problemsNear-field in RFIDTransceiverIn-phase and quadrature components

A transceiver for a RFID reader and a transceiver for a RFID transponder (tag) allow communication between the two devices. The RFID reader utilizes an analog front end and a digital backend. In the receiver portion of the transceiver, the front end of the RFID reader uses a pair of down-conversion mixers to demodulate a received signal into in-phase (I) and quadrature (Q) components and analog-to-digital converters (ADC) digitize the signal. A digital signal processor (DSP) in the back end processes the digital signal and uses a matched filter for data detection. The RFID tag receives an inductively coupled signal from the reader and the receiver portion of the tag uses a pulse / level detector that employs an analog comparator and a sample and hold circuit to detect the received signal. A digital decoder / controller is used to decode the incoming data and to establish a sampling clock for the pulse / level detector. An automatic gain control (AGC) circuit adjusts a receiver gain according to the received signal strength and controls tuning of magnetic coupling circuitry.

Owner:NXP USA INC

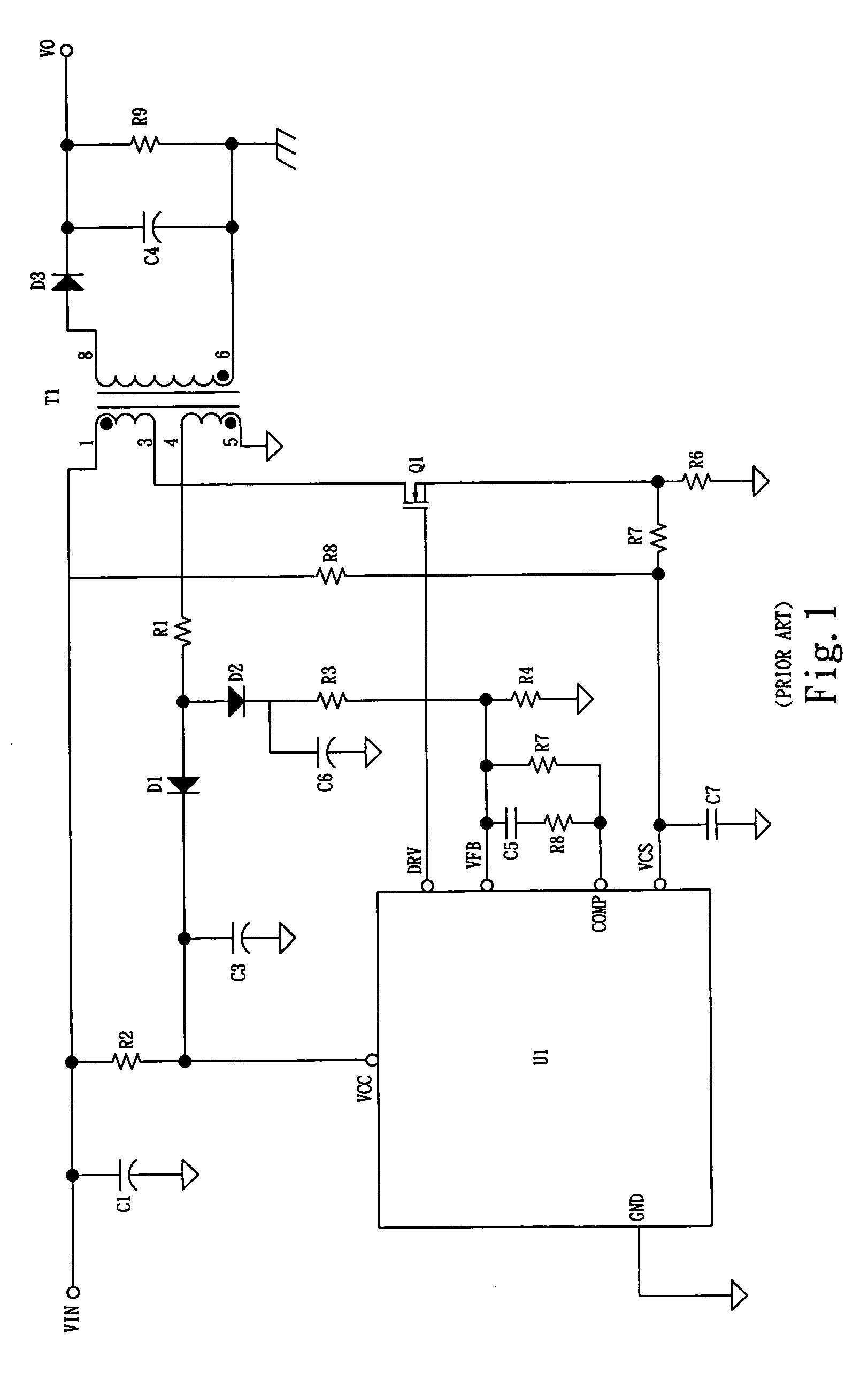

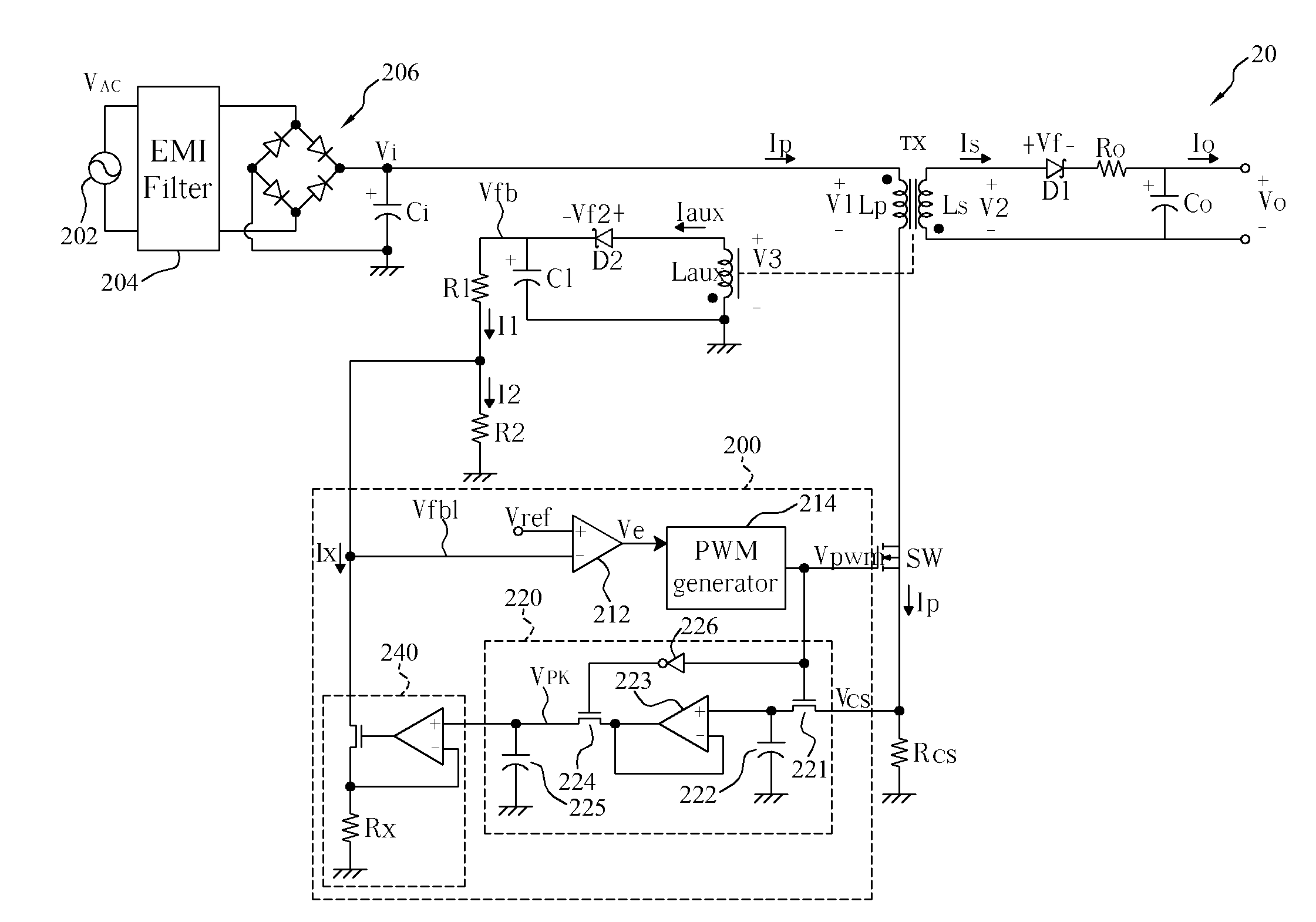

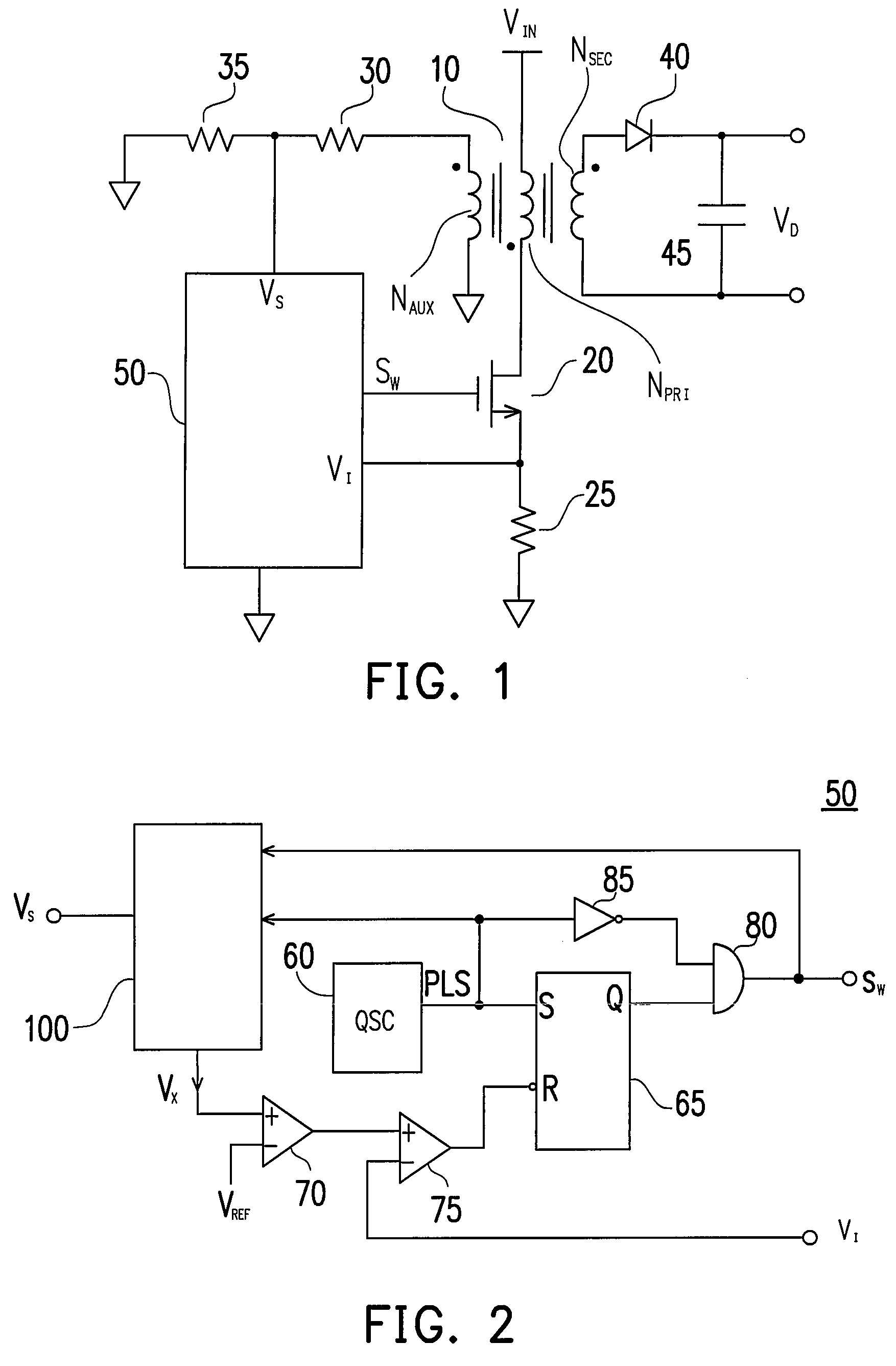

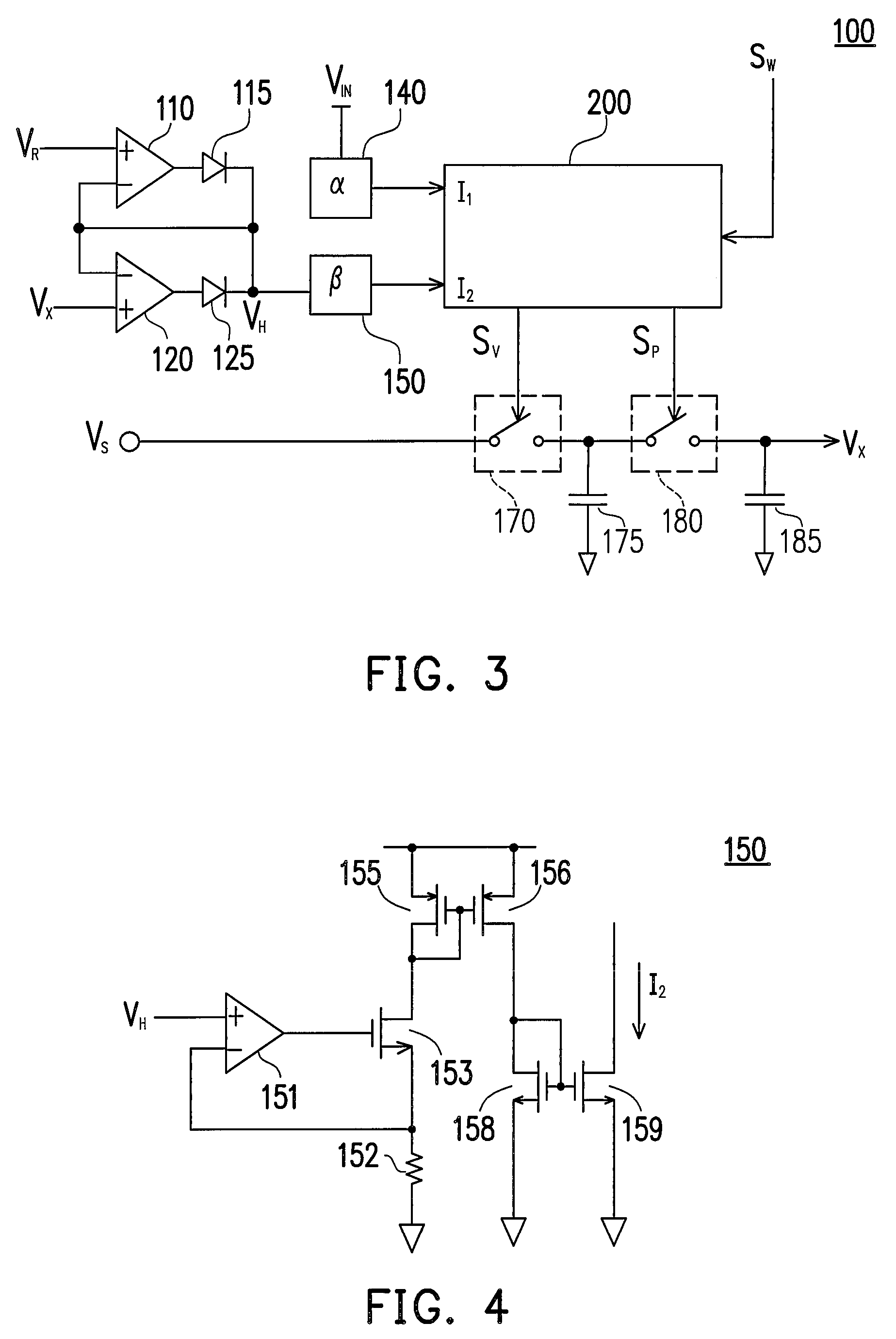

Switching-mode power converter and pulse-width-modulation control circuit with primary-side feedback control

A pulse-width-modulation control circuit of a switching-mode power converter with a primary-side feedback control is disclosed. The switching-mode power converter includes a transformer, a power switch, a current sensing resistor and the pulse-width-modulation control circuit. The transformer includes a primary-side winding, a secondary-side winding and an auxiliary winding. The pulse-width-modulation control circuit includes a sample and hold circuit, a transconductor circuit, an error amplifier and a pulse-width-modulation generator.

Owner:LEADTREND TECH

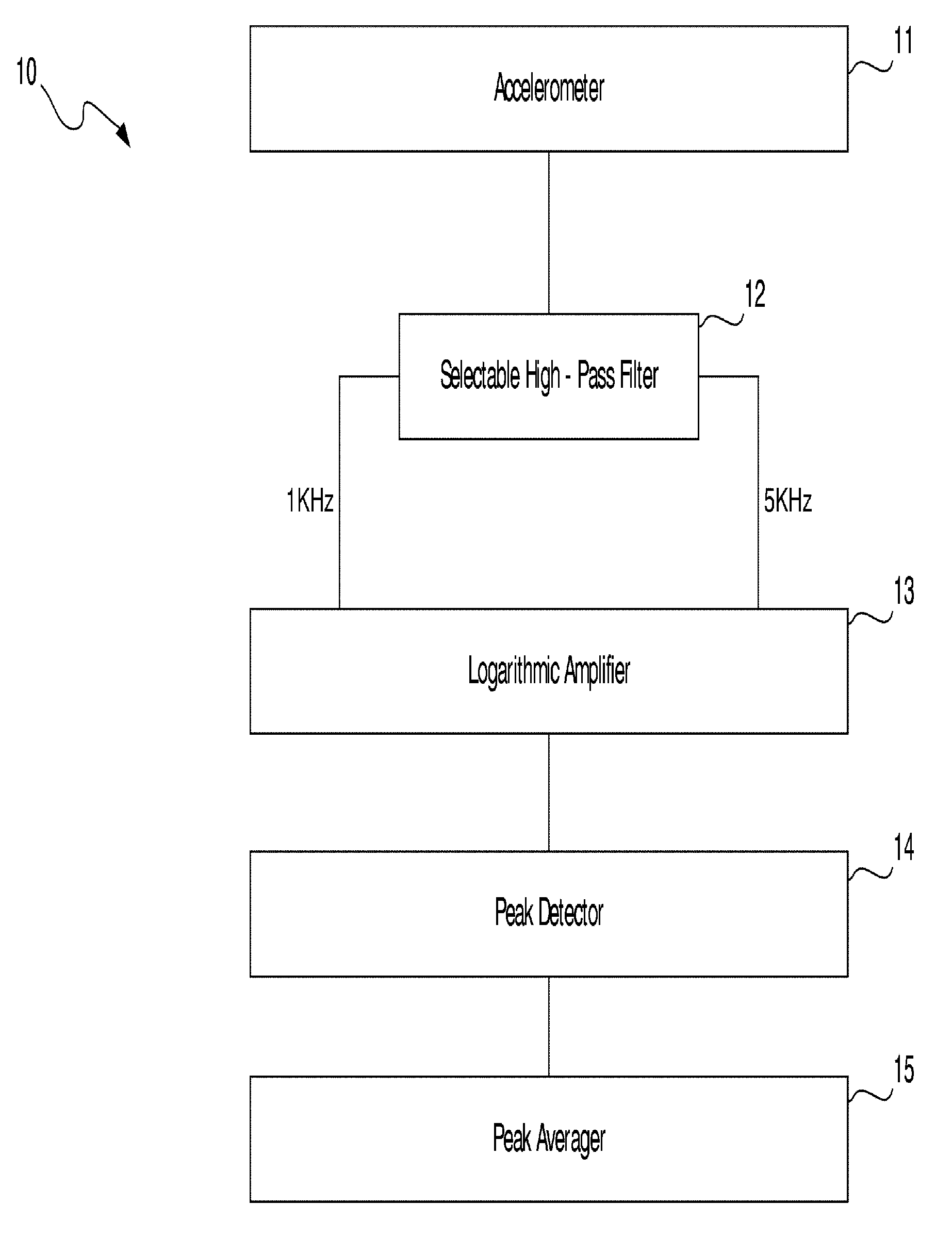

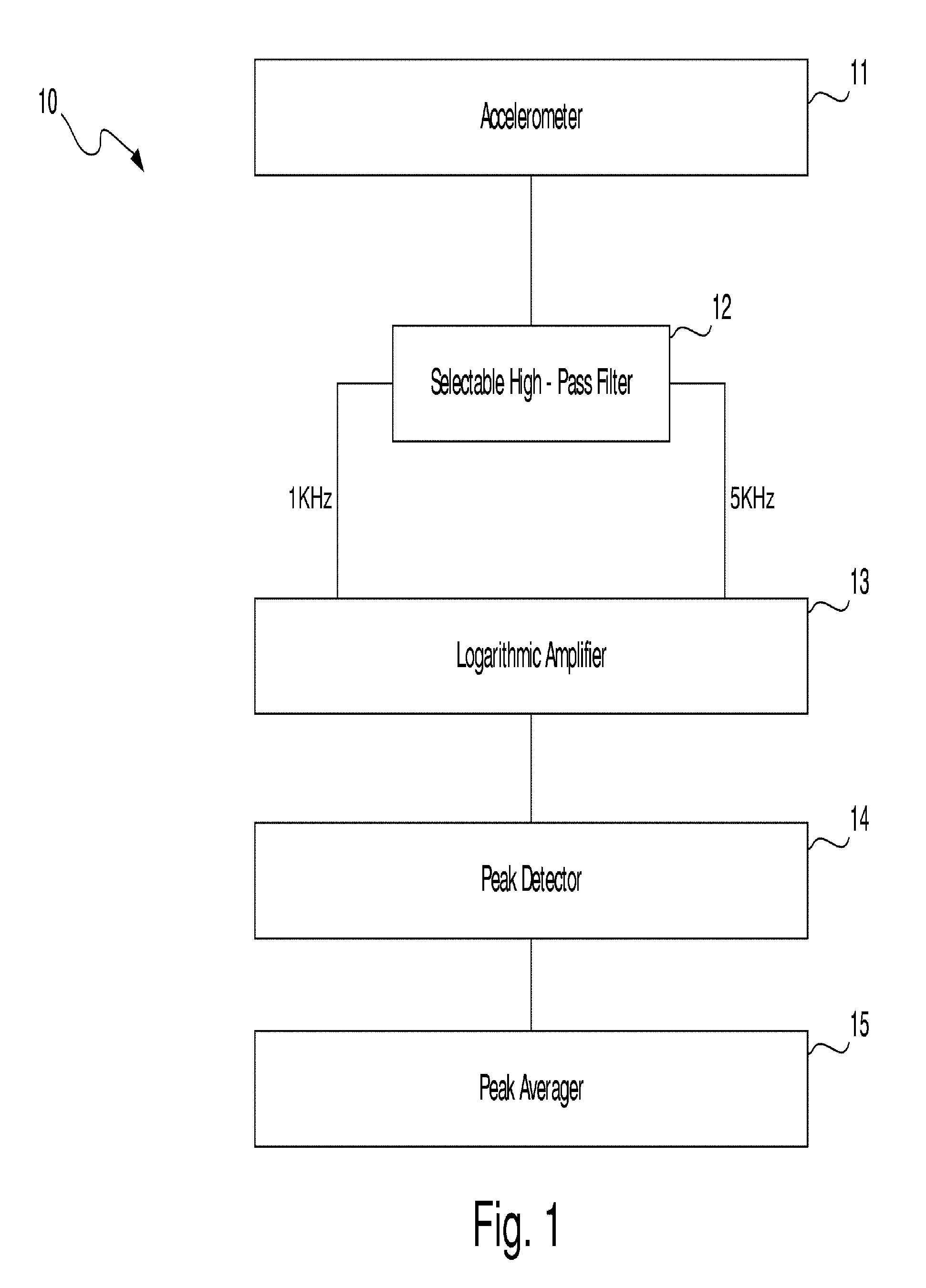

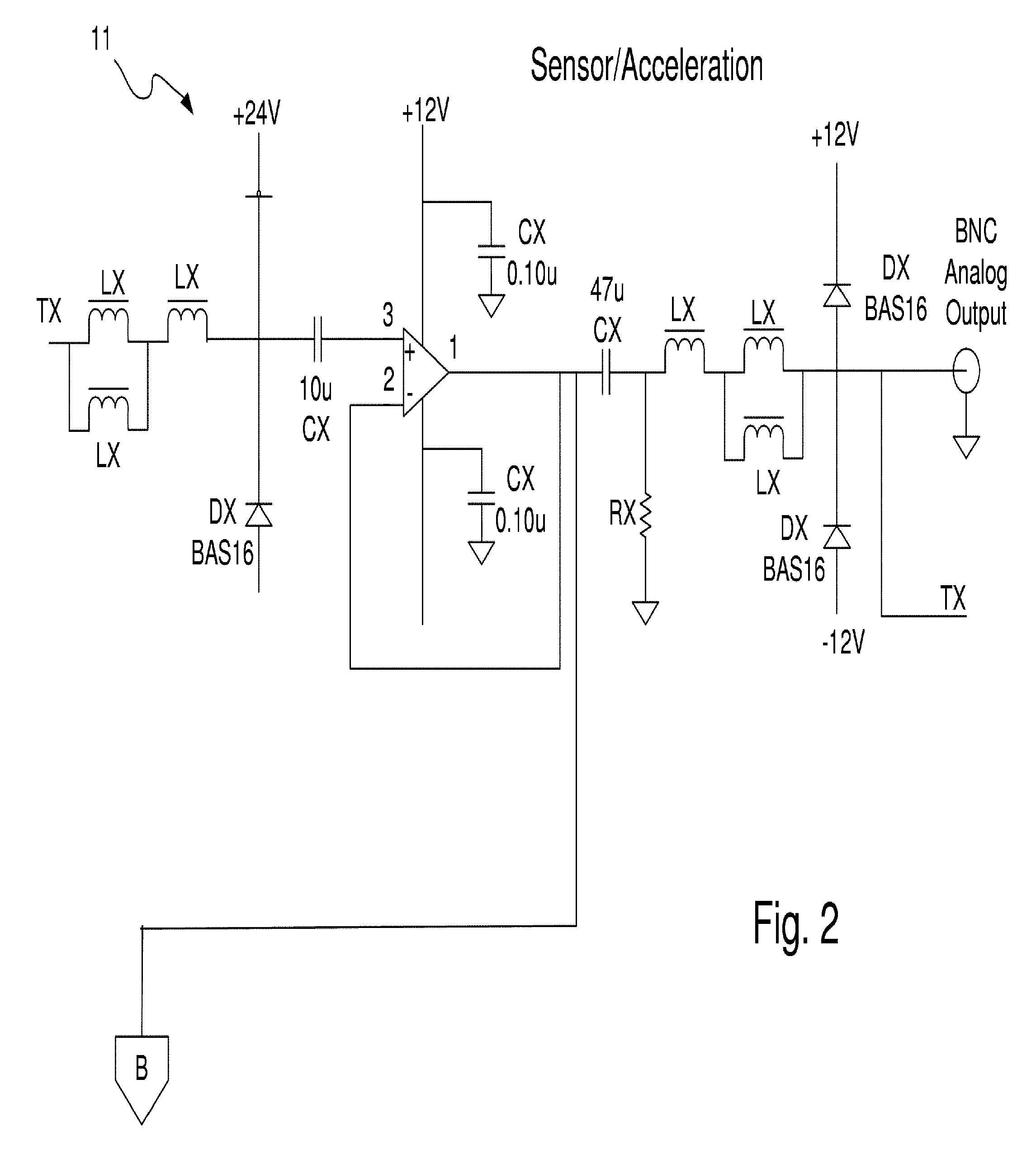

Method and apparatus for vibration sensing and analysis

InactiveUS20050011266A1Readily apparentVibration measurement in solidsMachine part testingPeak valueAcoustics

A method and apparatus for sensing and measuring stress waves. The method comprises the steps of: a.) sensing motion, where the motion comprises a stress wave component and a vibration component; b.) separating the stress wave component from the vibration component with a high pass filter to create a signal proportional to the stress wave; c.) amplifying the signal to create an amplified signal; d.) processing the amplified signal with a sample and hold peak detector over a predetermined interval of time to determine peaks of the amplified signal over said predetermined period of time; e.) creating an output signal proportional to the determined peaks of the amplified signal; and, f.) repeating steps d.) and e.). The invention also includes an apparatus for implementing the method of the invention.

Owner:PCB PIEZOTRONICS IMI SENSORS +1

Multi-protocol radio frequency identification reader transceiver

ActiveUS20060186995A1Electric signal transmission systemsError preventionTransceiverDown conversion mixer

A transceiver for a RFID reader and a transceiver for a RFID transponder (tag) allow communication between the two devices. The RFID reader utilizes an analog front end and a digital backend. In the receiver portion of the transceiver, the front end of the RFID reader uses a pair of down-conversion mixers to demodulate a received signal into in-phase (I) and quadrature (Q) components and analog-to-digital converters (ADC) digitize the signal. A digital signal processor (DSP) in the back end processes the digital signal and uses a matched filter for data detection. The RFID tag receives an inductively coupled signal from the reader and the receiver portion of the tag uses a pulse / level detector that employs an analog comparator and a sample and hold circuit to detect the received signal. A digital decoder / controller is used to decode the incoming data and to establish a sampling clock for the pulse / level detector. An automatic gain control (AGC) circuit adjusts a receiver gain according to the received signal strength and controls tuning of magnetic coupling circuitry.

Owner:NXP USA INC

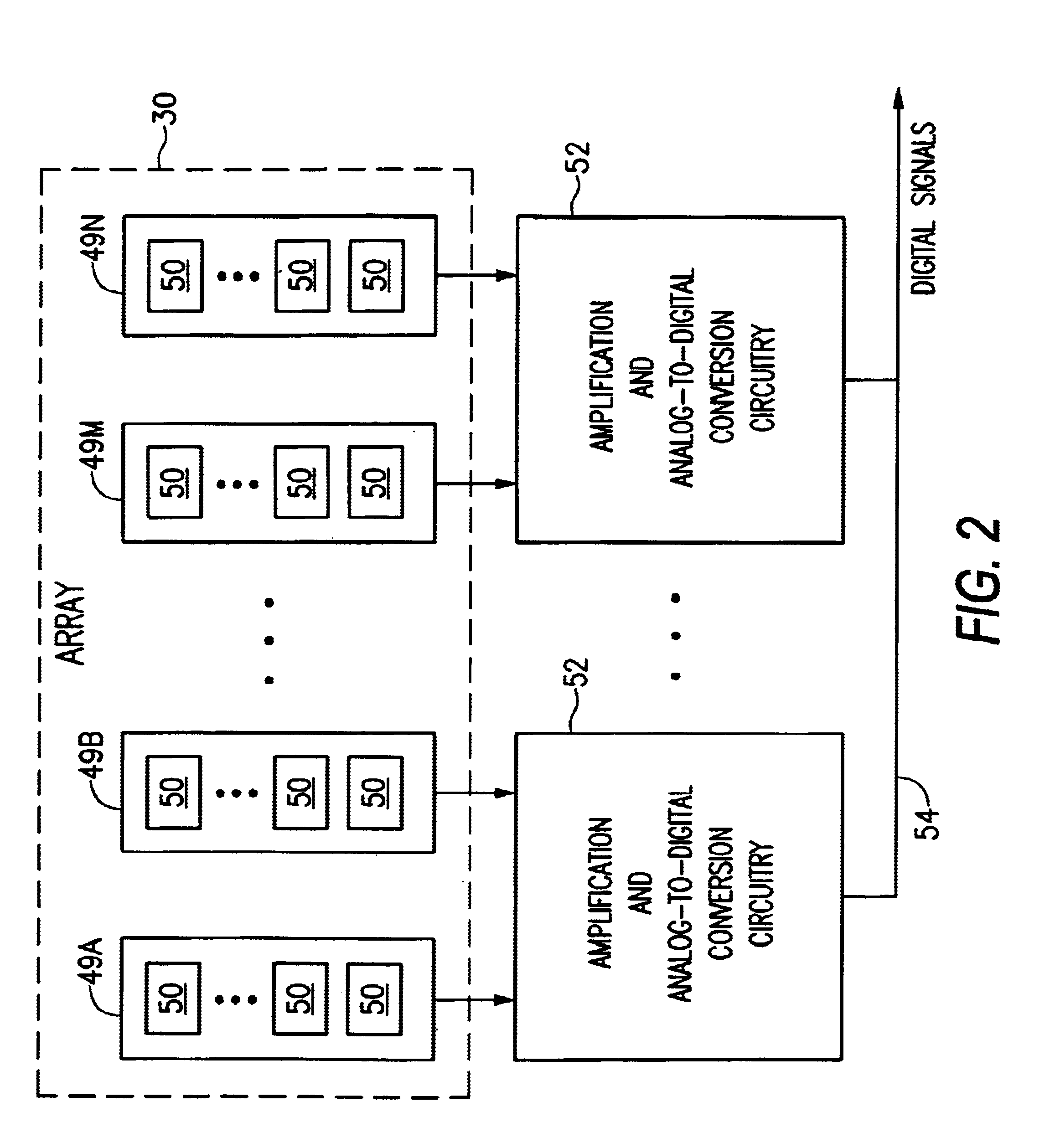

Readout circuit with gain and analog-to-digital a conversion for image sensor

InactiveUS6885396B1Increase parallel structureAttenuation bandwidthTelevision system detailsElectric signal transmission systemsSensor arrayCMOS sensor

A CMOS imager includes an array of active pixel sensors, wherein each pixel is associated with a respective column in the array. The imager also includes multiple circuits for reading out values of pixels from the active sensor array. Each readout circuit can be associated with a respective pair of columns in the array and can include first and second sample-and-hold circuits. The first and second sample-and-hold circuits are associated, respectively, with first and second columns of pixels in the array. Each readout circuit also includes an operational amplifier-based charge sensing circuit that selectively provides an amplified differential output signal based on signals sampled either by the first sample-and-hold circuit or the second sample-and-hold circuit. The readout circuit also has an analog-to-digital converter for converting the differential output to a corresponding digital signal using a successive approximation technique. Use of the readout circuit can increase the parallel structure of the overall chip, thereby reducing the bandwidth which each readout circuit must be capable of handling.

Owner:APTINA IMAGING CORP

Ultrasound imaging beam-former apparatus and method

InactiveUS20070016022A1Ultrasonic/sonic/infrasonic diagnosticsInfrasonic diagnosticsUltrasound imagingIlluminance

In some illustrative embodiments, an incoming signal from a transducer in an ultrasound imaging beam-former apparatus is applied to an in-phase sample-and-hold and a quadrature sample-and-hold. The quadrature sample-and-hold may be clocked a quarter period behind the in-phase sample-and-hold. The output of the sample-and-holds are applied to in-phase and quadrature analog-to-digital converters. A magnitude calculator receives the in-phase and quadrature digital values, and outputs a magnitude. A phase calculator receives the in-phase and quadrature digital values, and outputs a phase. An apodizer applies a difference between an amplitude of the outgoing signal and the magnitude and applies a first illumination to a image point in substantial proportion to the difference, and a phase rotator applies a second illumination to the image point in substantial proportion to the phase.

Owner:UNIV OF VIRGINIA ALUMNI PATENTS FOUND

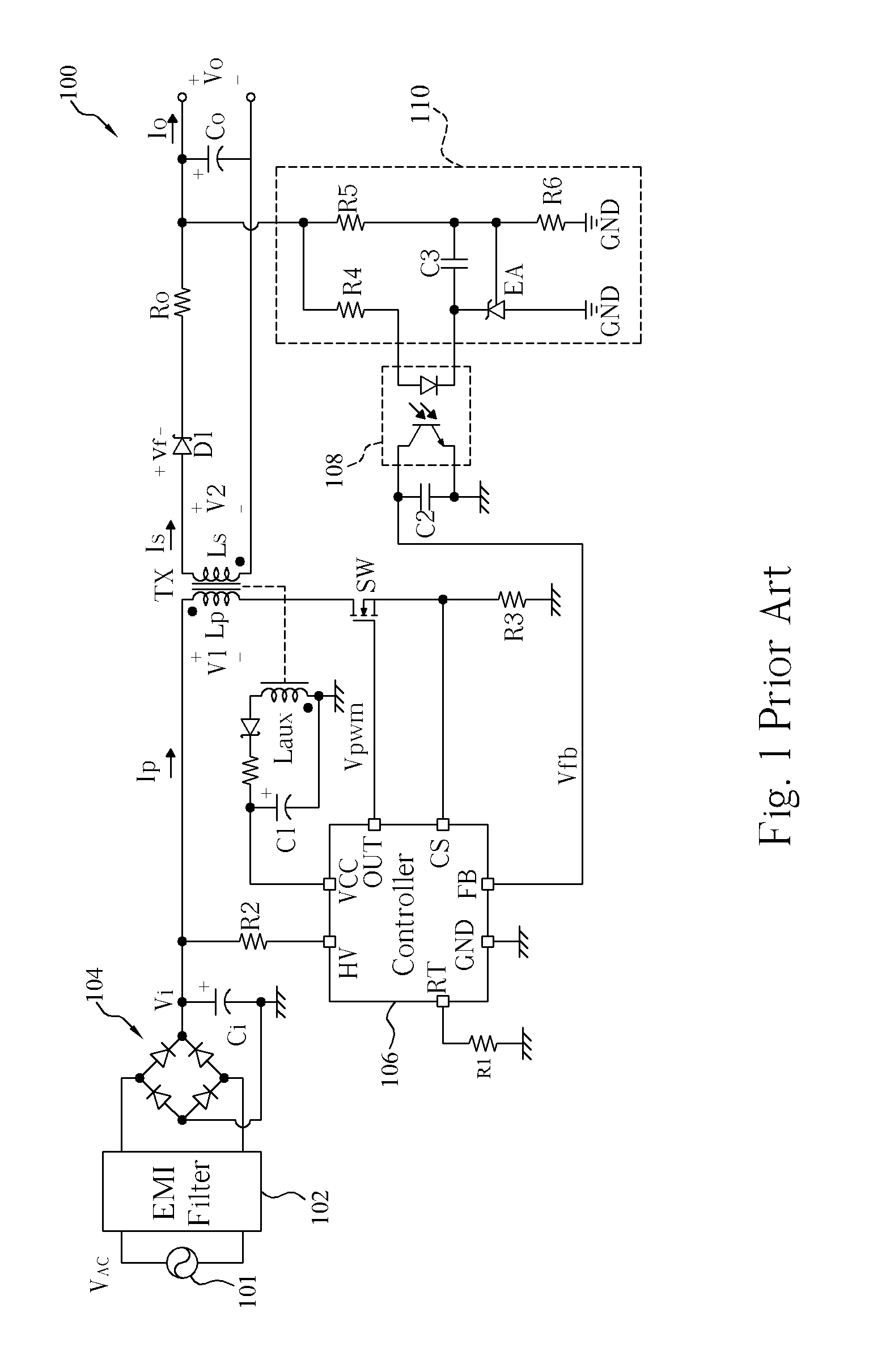

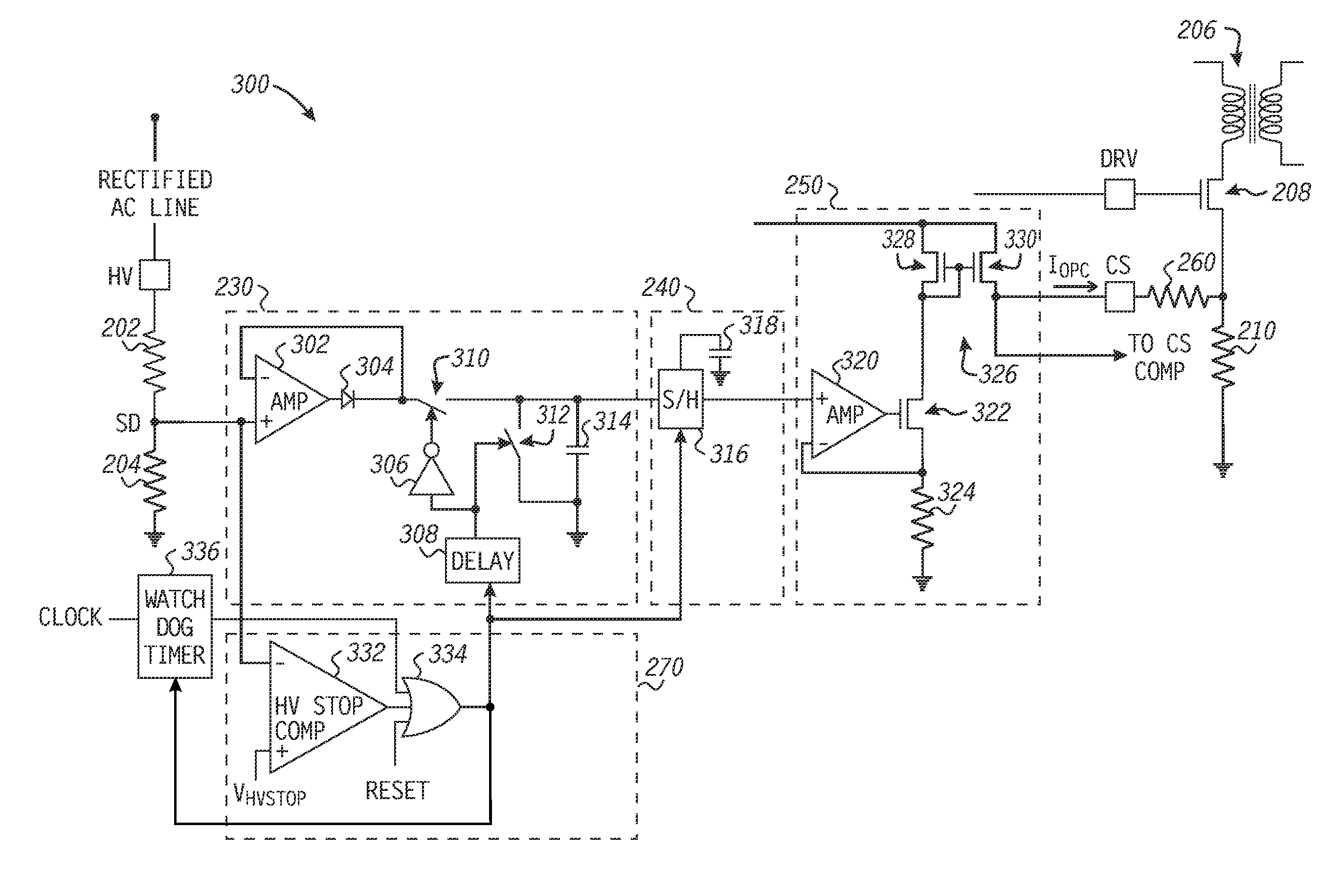

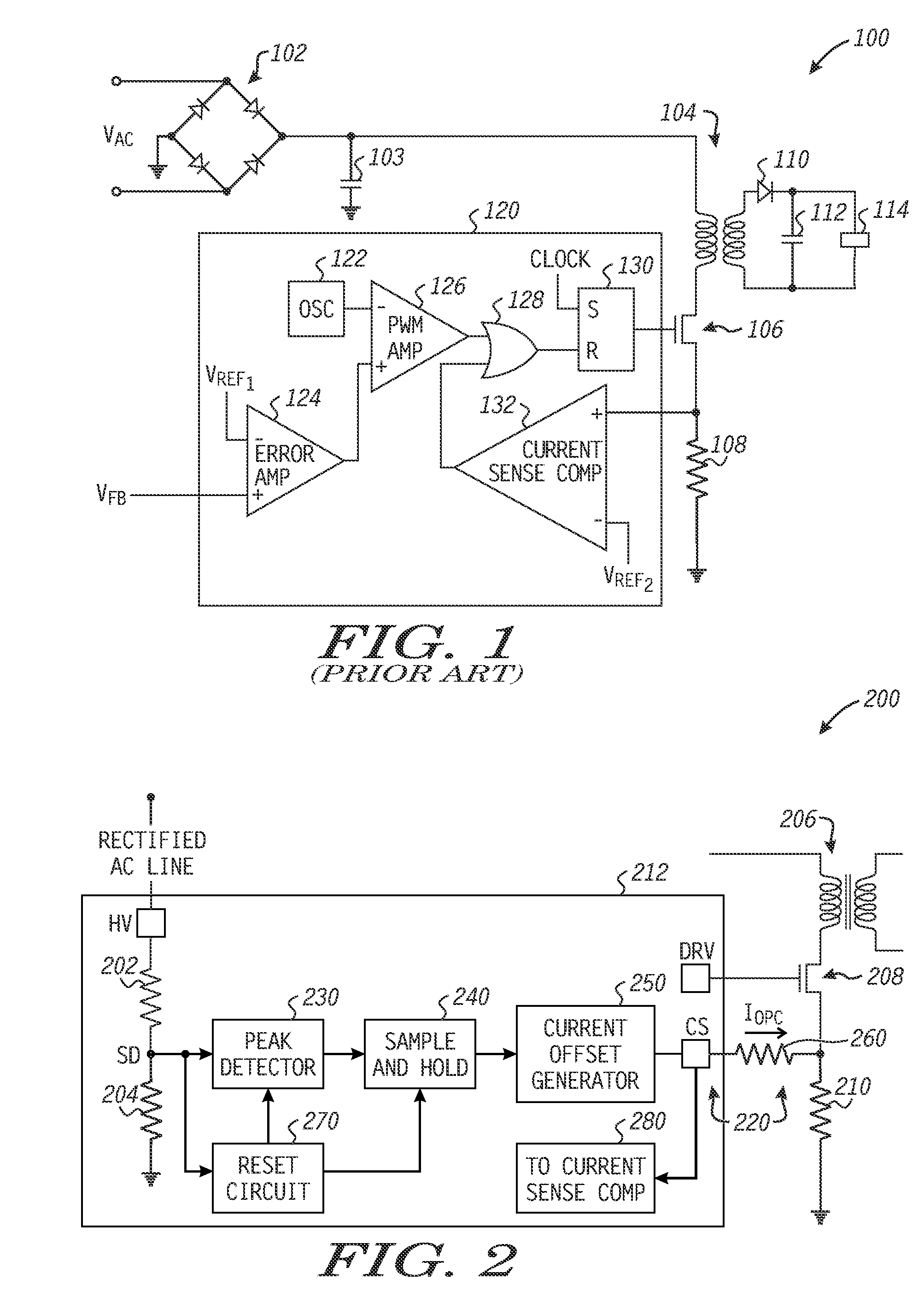

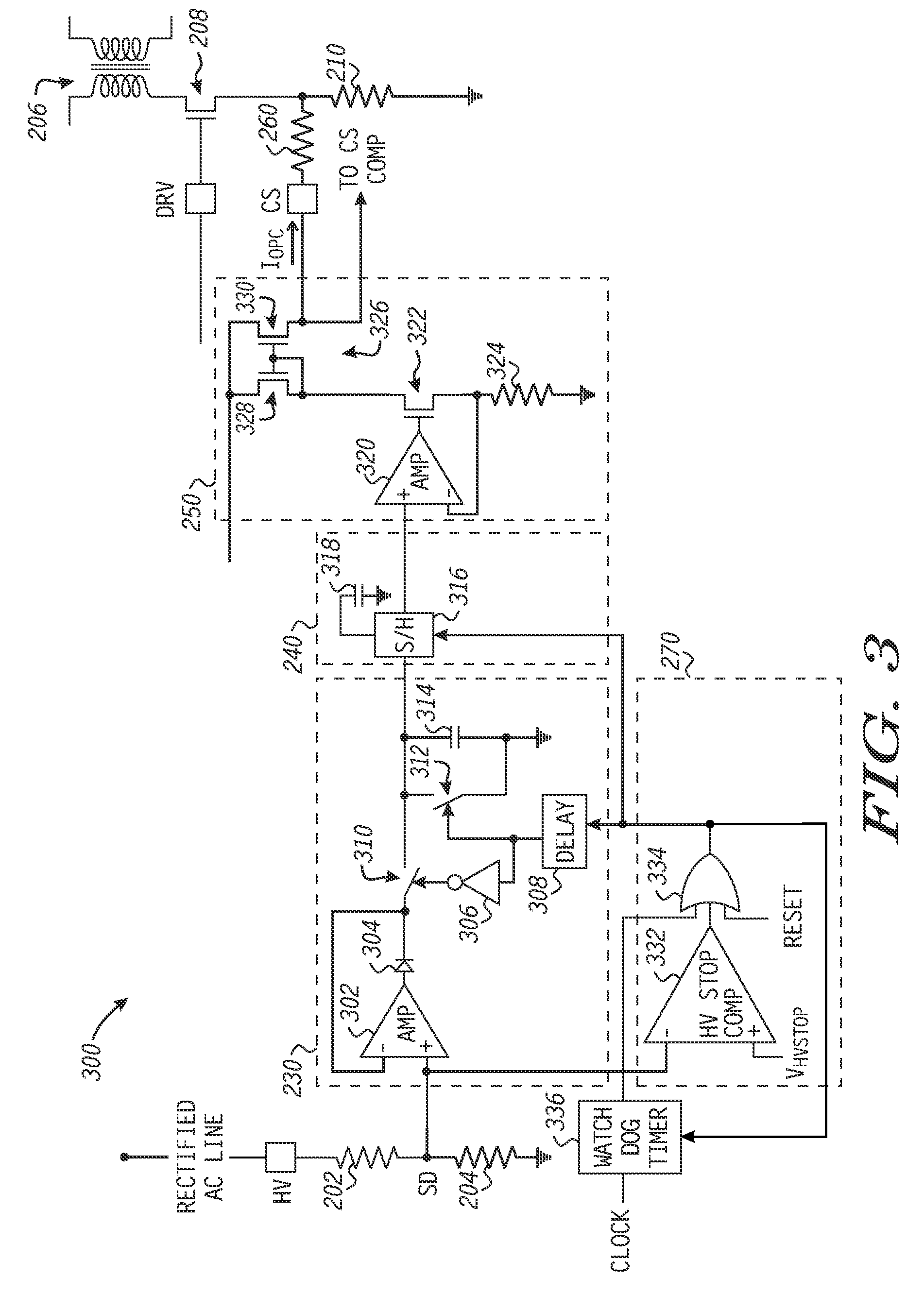

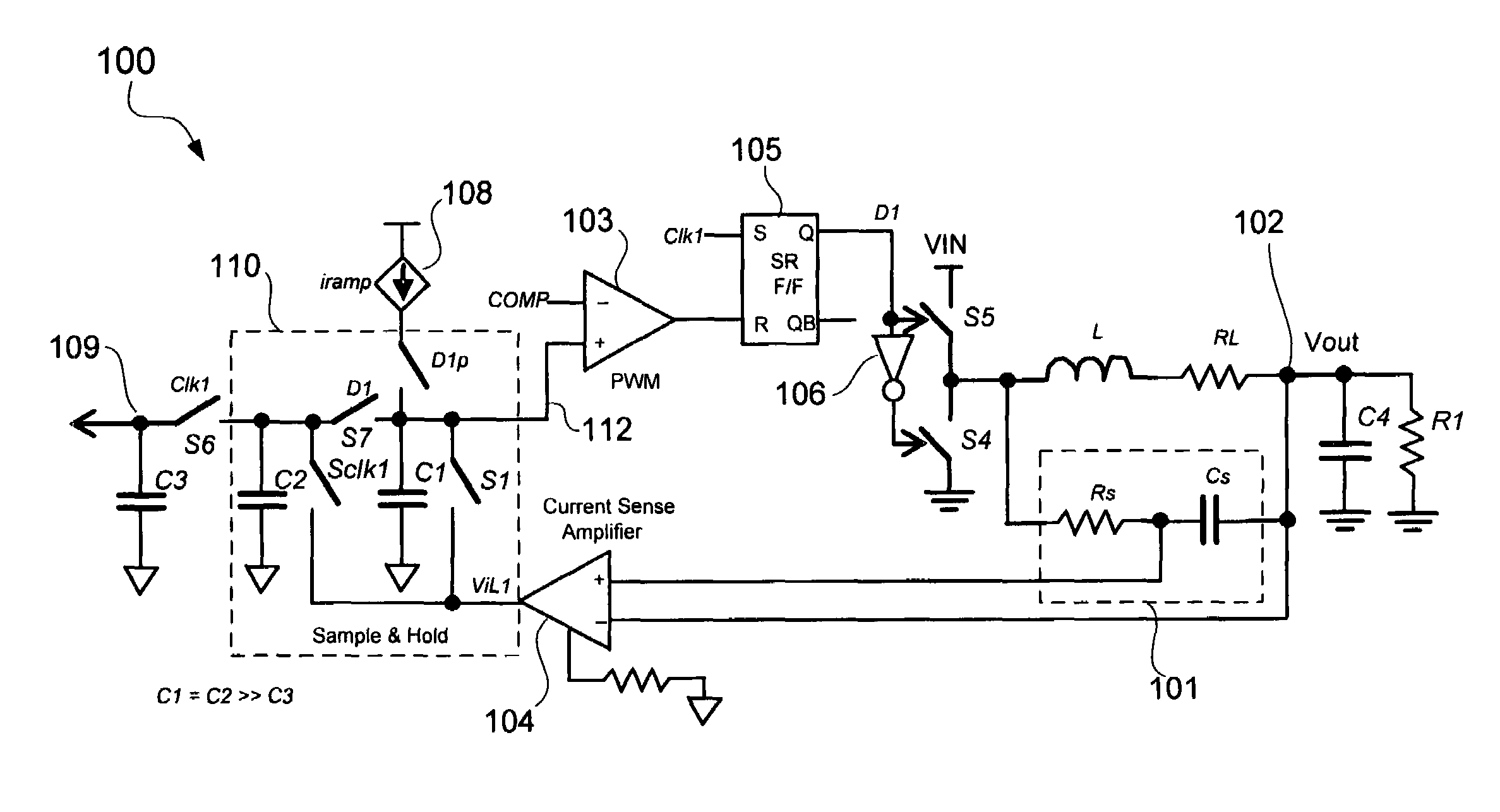

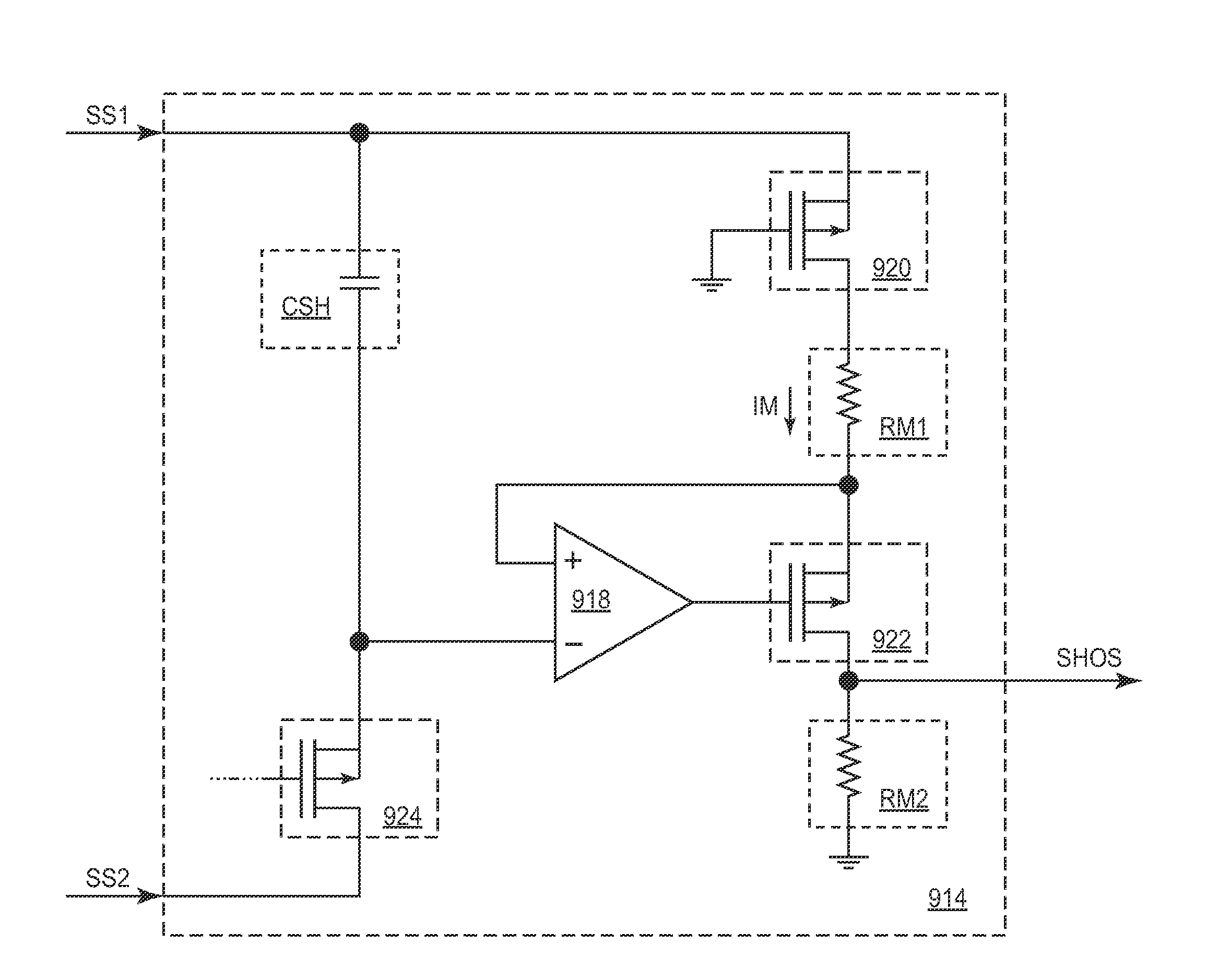

Over power compensation in switched mode power supplies

ActiveUS20100123447A1Dc-dc conversionElectric variable regulationPower compensationElectrical resistance and conductance

An over-power compensation circuit for use in a switched mode power supply having a current sense circuit for sensing a current flowing through a power transistor of the switched mode power supply. The over-power compensation circuit includes a peak detector, a sample-and-hold circuit, a current offset generator, and an offset resistor. The peak detector has an input for receiving an input voltage derived from the input line, and an output. The sample-and-hold circuit has an input connected to the output of the peak detector, and an output. The current offset generator has an input connected to the output of the sample-and-hold circuit, and an output for providing an offset current. The offset resistor has a first terminal connected to the output of the current offset generator, and a second terminal adapted to be connected to a current conducting electrode of the power transistor.

Owner:SEMICON COMPONENTS IND LLC

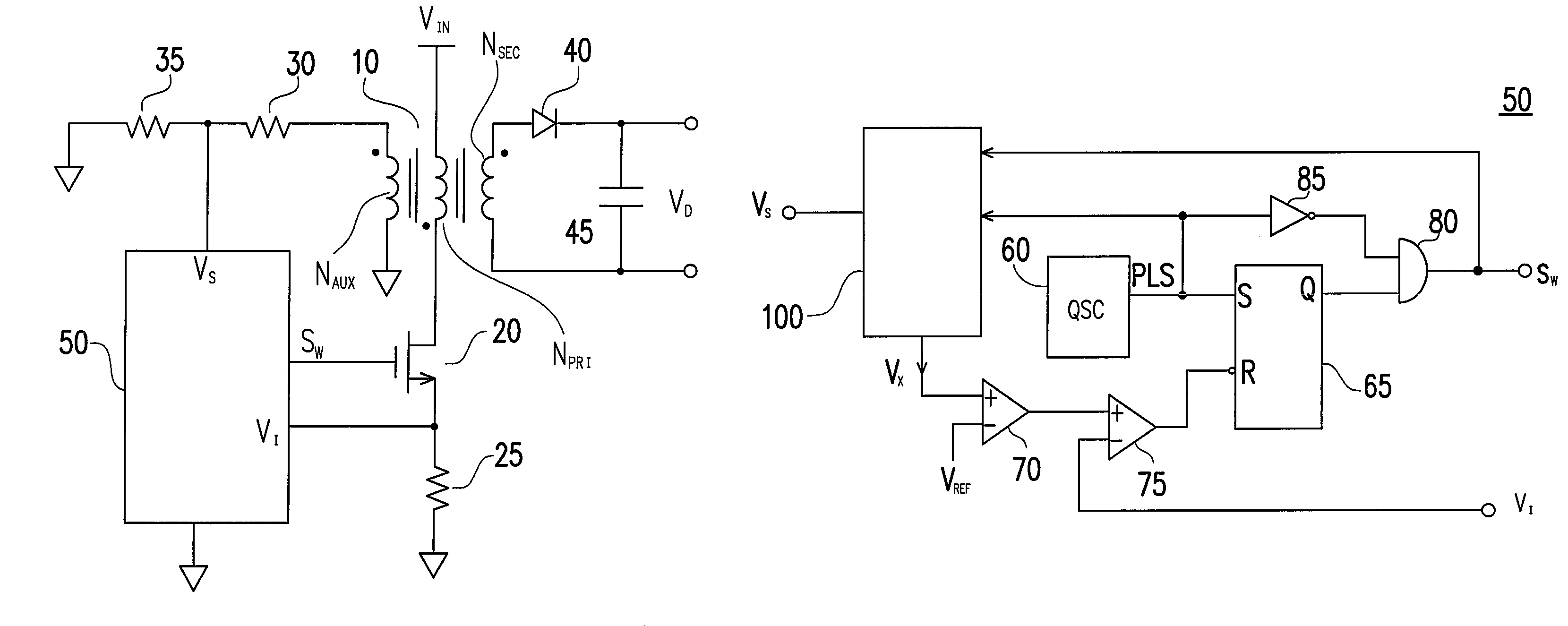

System and method for a primary feedback switched mode power supply

ActiveUS20070133234A1Reduce electromagnetic interference emissionReducing electromagnetic interference emissionDc-dc conversionElectric variable regulationAudio power amplifierControl power

A primary side controlled power converter having a voltage sensing means coupled to a transformer of the power converter and configured to provide a voltage feedback waveform representative of an output of the transformer is provided. A primary switching circuit operates to control energy storage of a primary side of the transformer. The primary switching circuit is operable during an on time and inoperable during an off time. The on and off time is switched at a system frequency. A feedback amplifier generates an error signal indicative of a difference between the voltage feedback waveform and a reference voltage. A sample and hold circuit samples the error signal at a periodic frequency during the off time. An error signal amplifier is configured to provide the sampled value to the primary switching circuit wherein the primary switching circuit controls the transformer and thereby regulates an output of the power converter.

Owner:ACTIVE SEMI

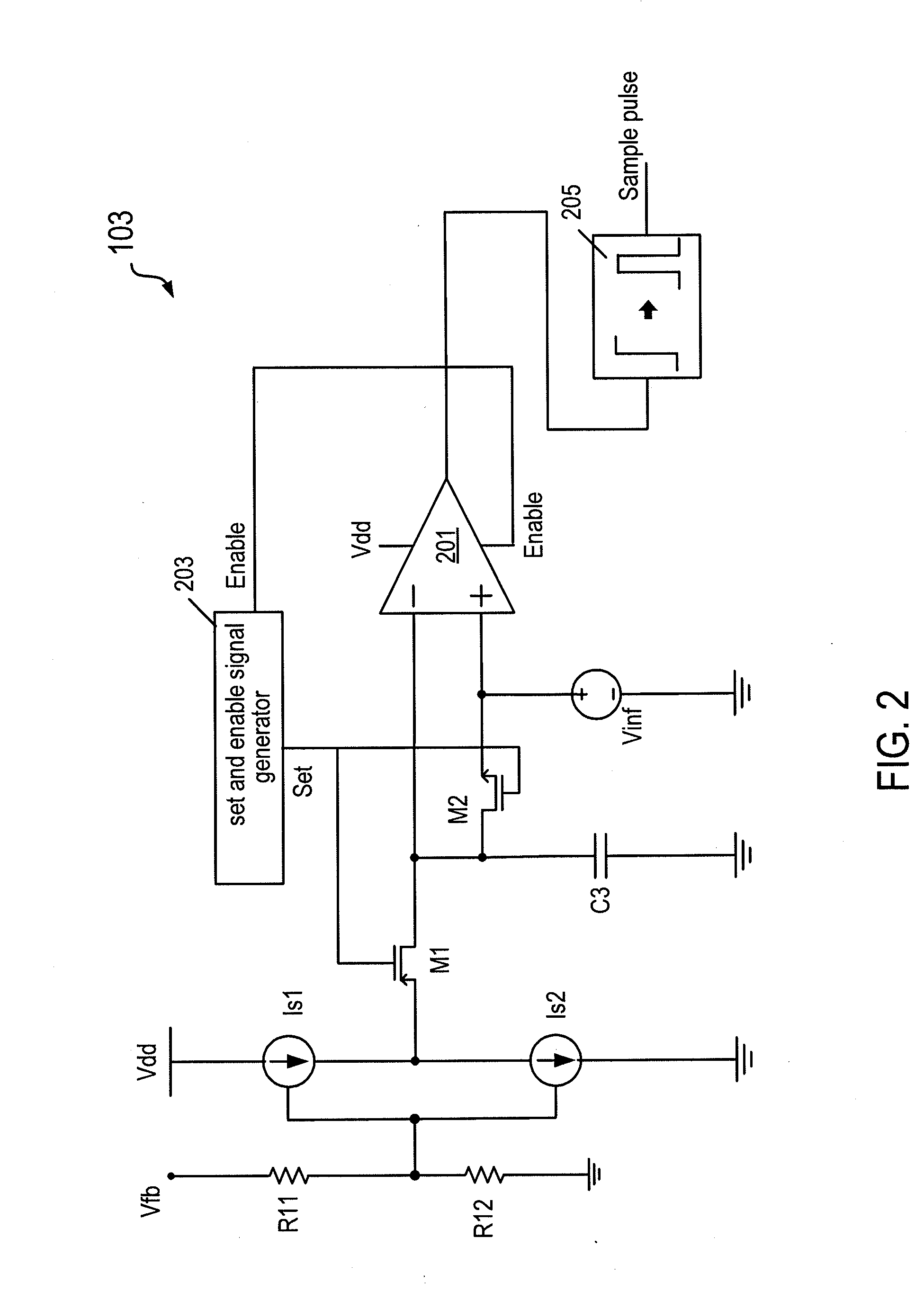

Linear-predict sampling for measuring demagnetized voltage of transformer

ActiveUS7486528B2Conversion with intermediate conversion to dcDc-dc conversionTransformerSwitching signal

A linear-predict sampling circuit is developed to generate a feedback signal by detecting a demagnetized voltage of the transformer. A switching signal is generated in response to the feedback signal for regulating the output of the power converter. A signal-generation circuit is used to generate a sample signal in response to a first signal, a second signal, and the switching signal. The first signal is correlated to a magnetized voltage of the transformer. The second signal is correlated to the demagnetized voltage of the transformer. A sample-and-hold circuit is coupled to the transformer to generate the feedback signal by sampling the demagnetized voltage of the transformer in response to the sample signal. The feedback signal is correlated to the output voltage of the power converter.

Owner:FAIRCHILD SEMICON CORP

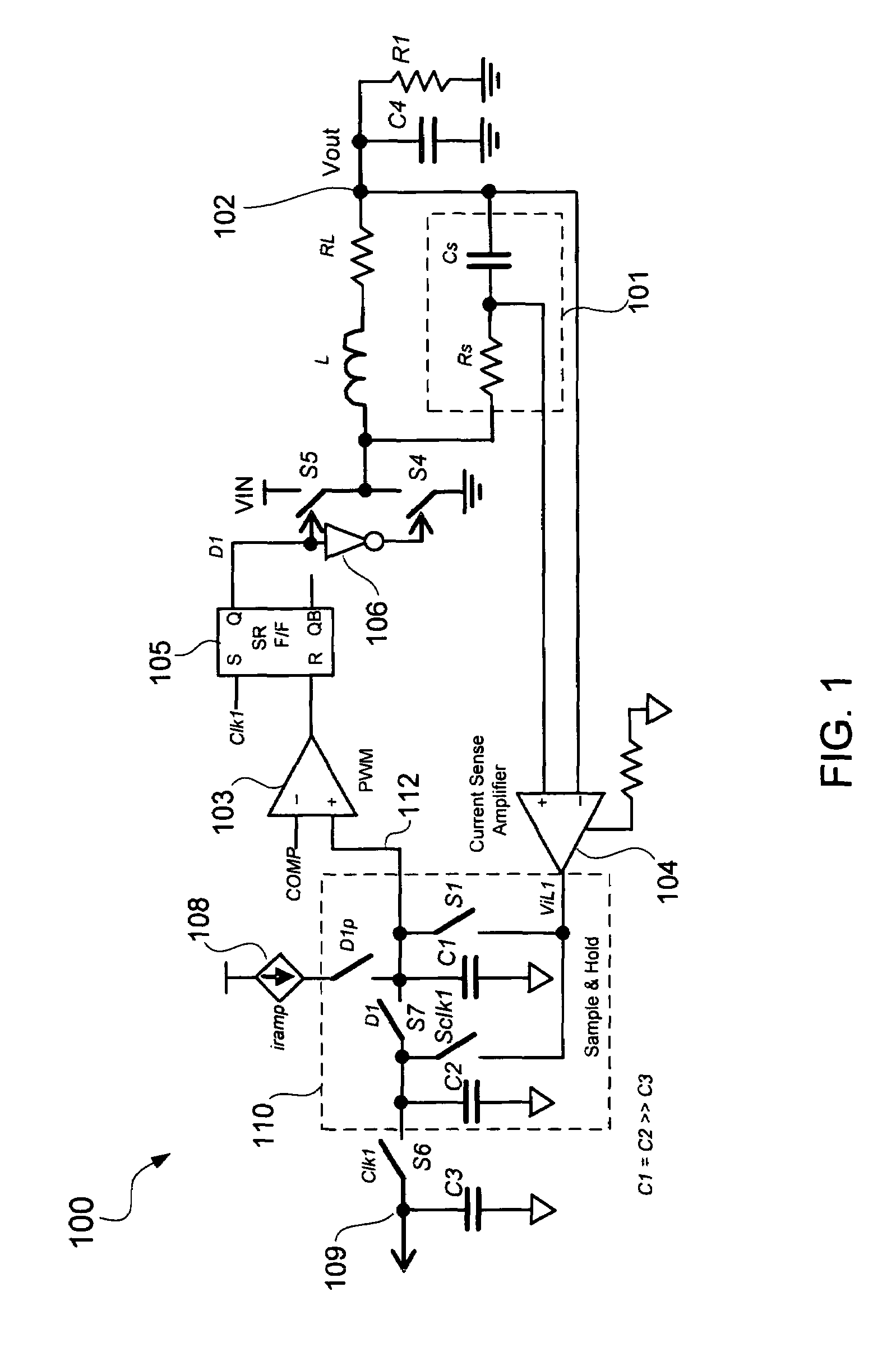

Sample and hold technique for generating an average of sensed inductor current in voltage regulators

A sample and hold inductor current sense configuration senses inductor current flowing through an output inductor of a voltage regulator and generates an average of the sensed inductor current. The average of the sensed inductor current may be generated from samples of peaks and valleys of the sensed inductor current. For example, the peak of the sensed inductor current may be stored in a first capacitor and the valley of the sensed inductor current may be stored in a second capacitor. The first and second capacitors may be coupled together to generate the average of the sensed inductor current. The average of the sensed inductor current may be provided to a droop control circuit to control droop of an output voltage of the voltage regulator. An input offset voltage of a current sense amplifier sensing the inductor current may be calibrated between samplings of the sensed inductor current.

Owner:SEMICON COMPONENTS IND LLC

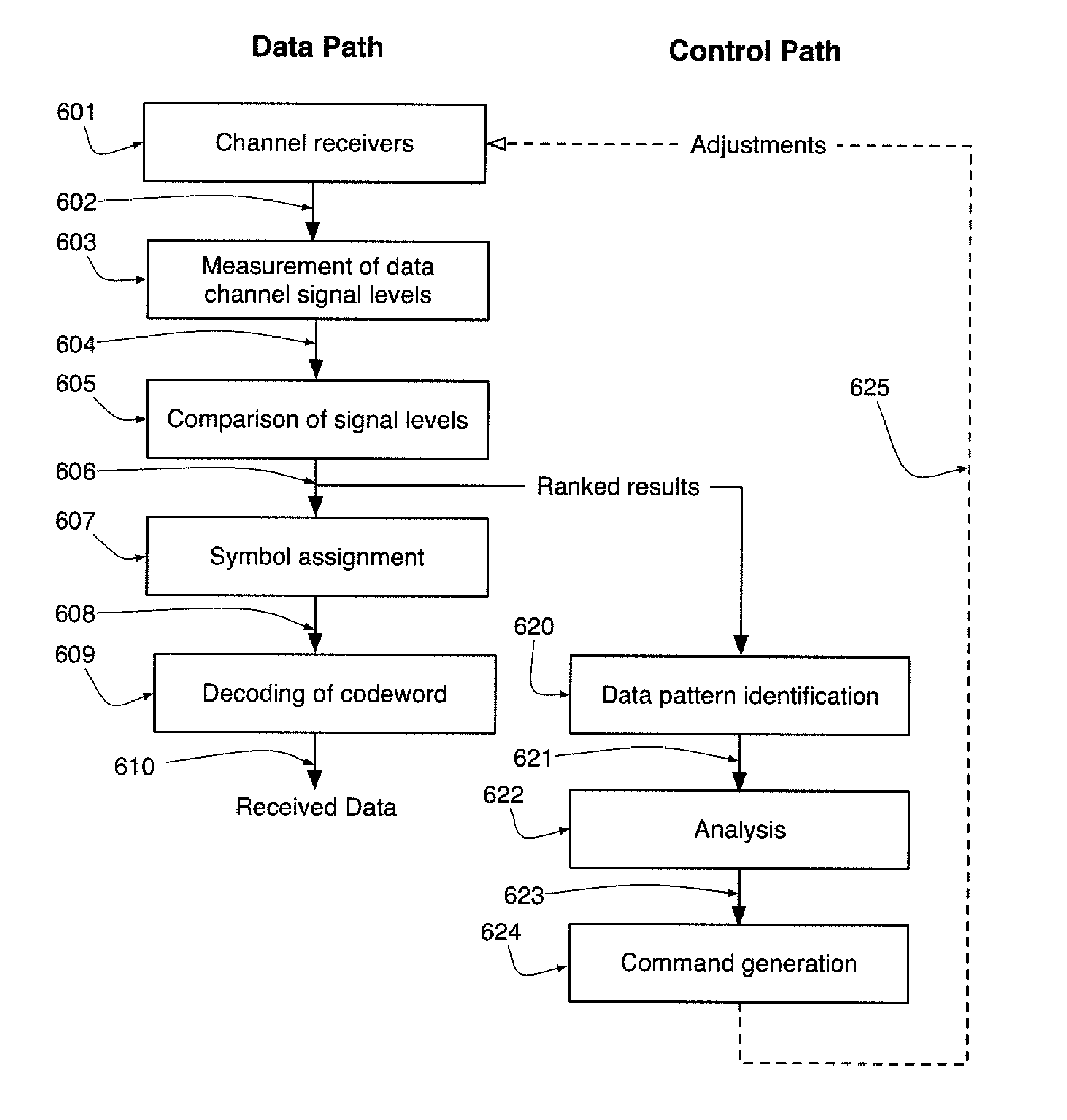

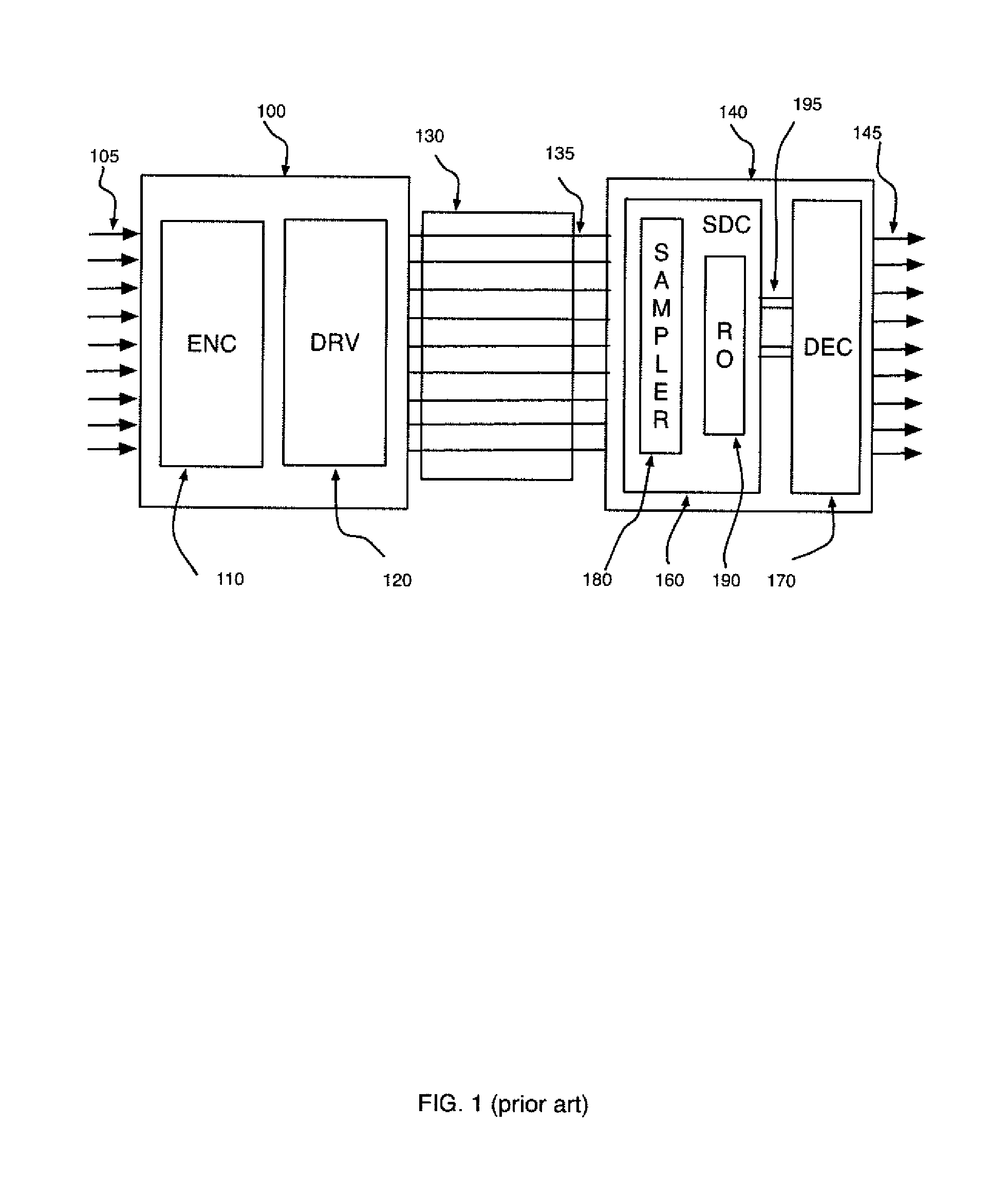

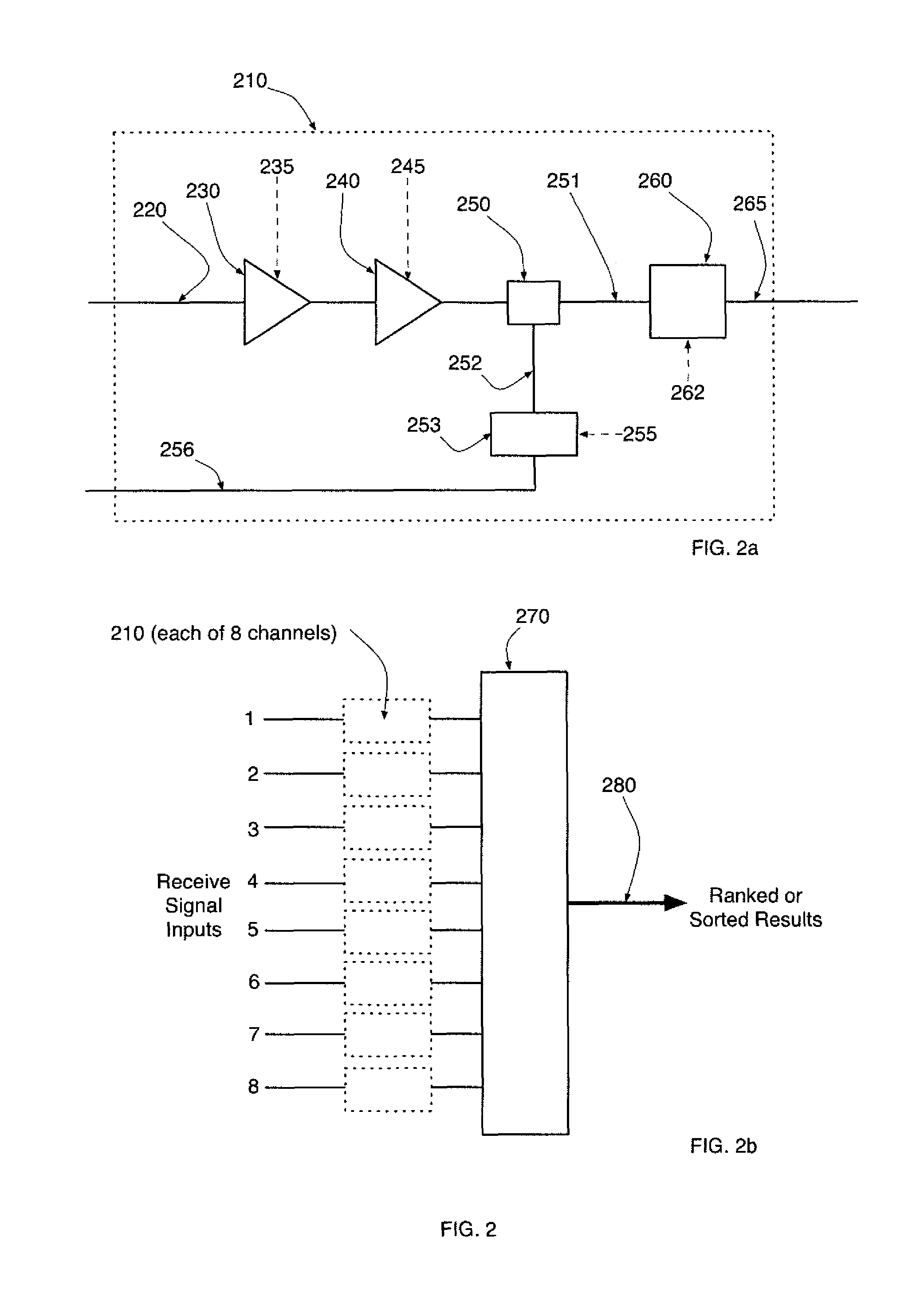

Control loop management and differential delay correction for vector signaling code communications links

ActiveUS9059816B1Exact reproductionTransmitter/receiver shaping networksLink quality based transmission modificationCommunications systemTelecommunications link

Vector signaling code communications systems rely on group transmission of code symbols using multiple signaling channels that may have differing propagation characteristics, resulting in differing received signal levels, waveforms, and symbol arrival times, and thus that should be actively monitored and adjusted to minimize differential signal characteristics. Information obtained during symbol decode may be analyzed to identify channel operational characteristics during normal operation and perform non-disruptive channel adjustments, including per-channel adjustment of sample-and-hold timing to realign code symbol groups. Initialization or start-up adjustment may also be performed using intentionally-transmitted training patterns.

Owner:KANDOU LABS

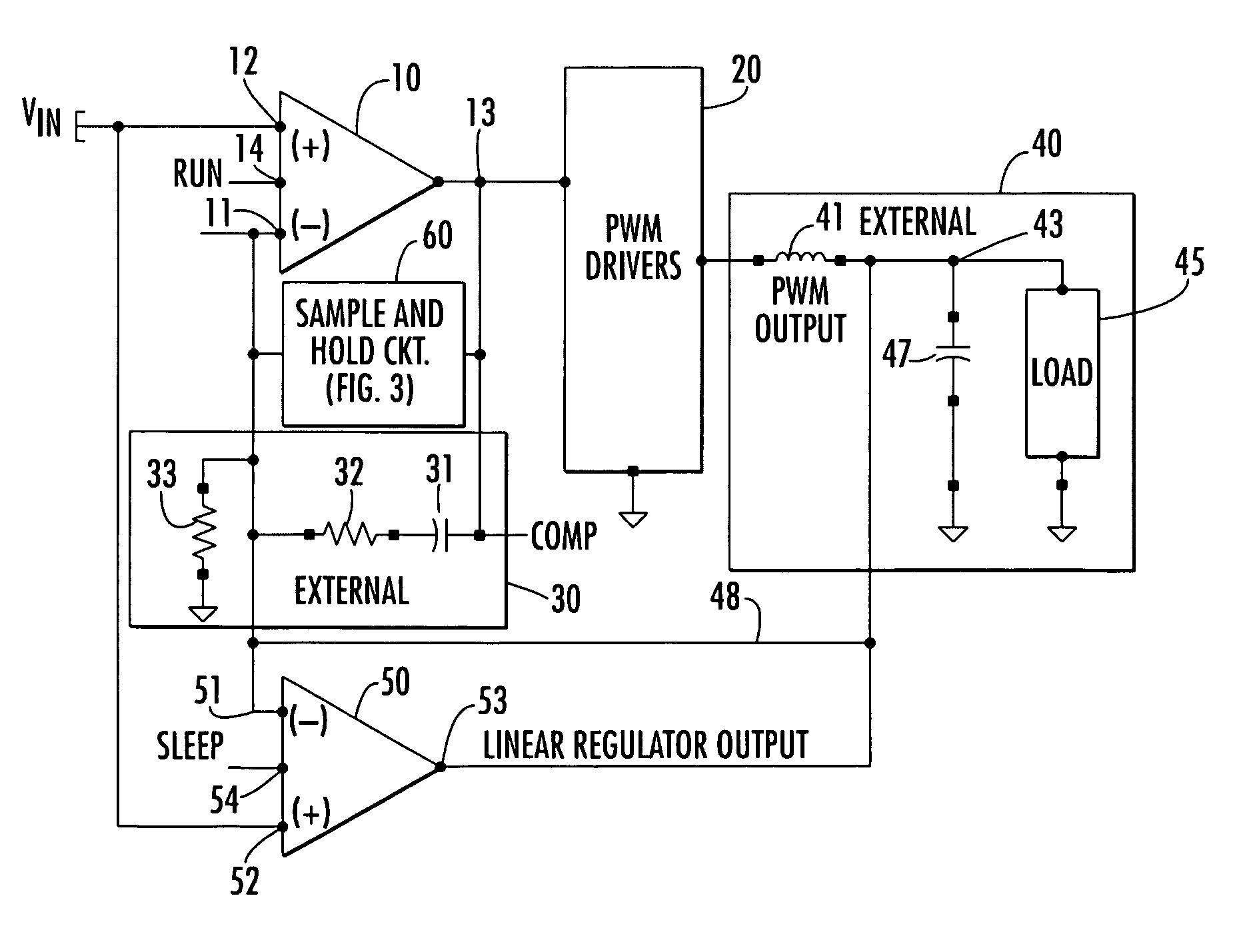

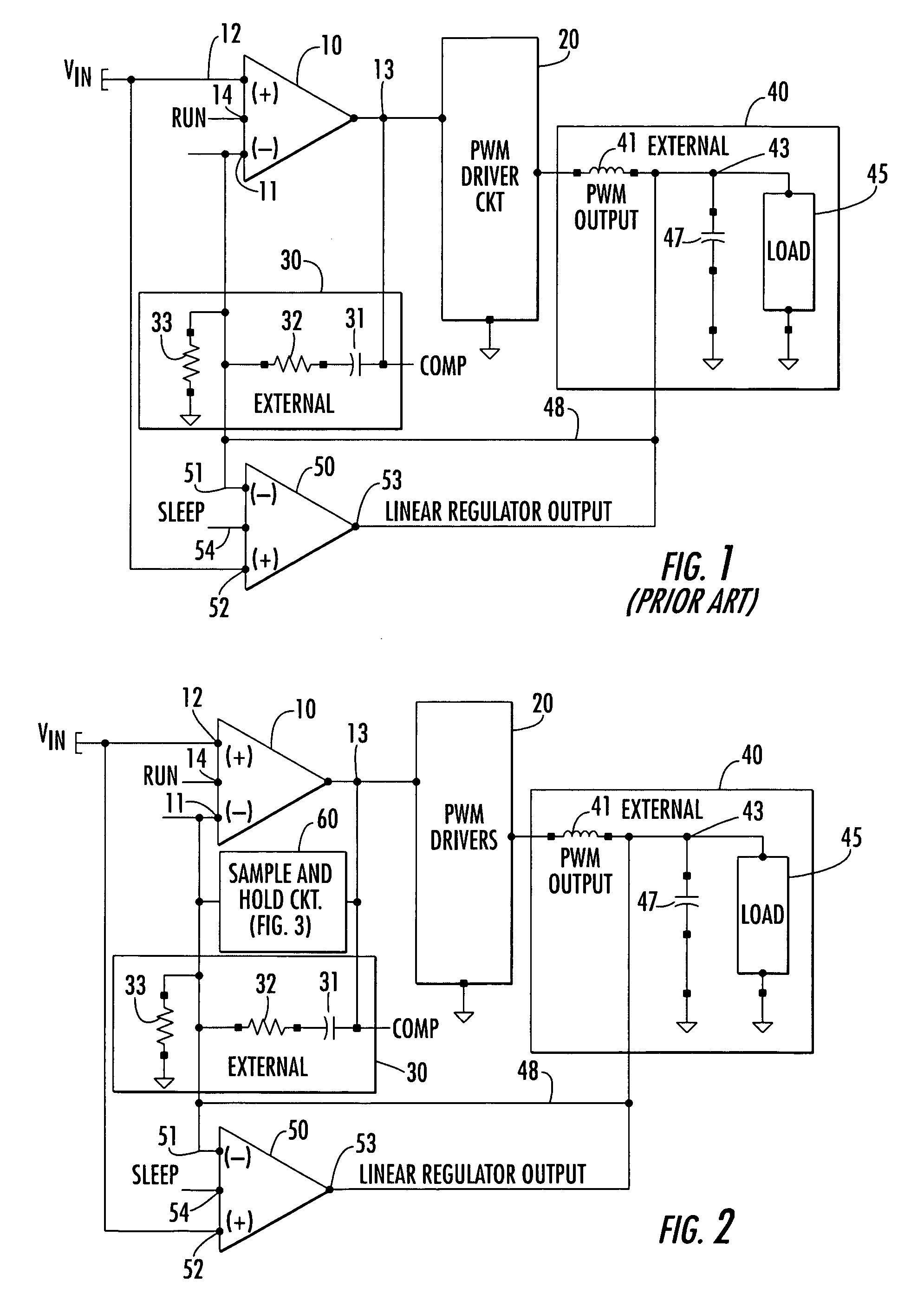

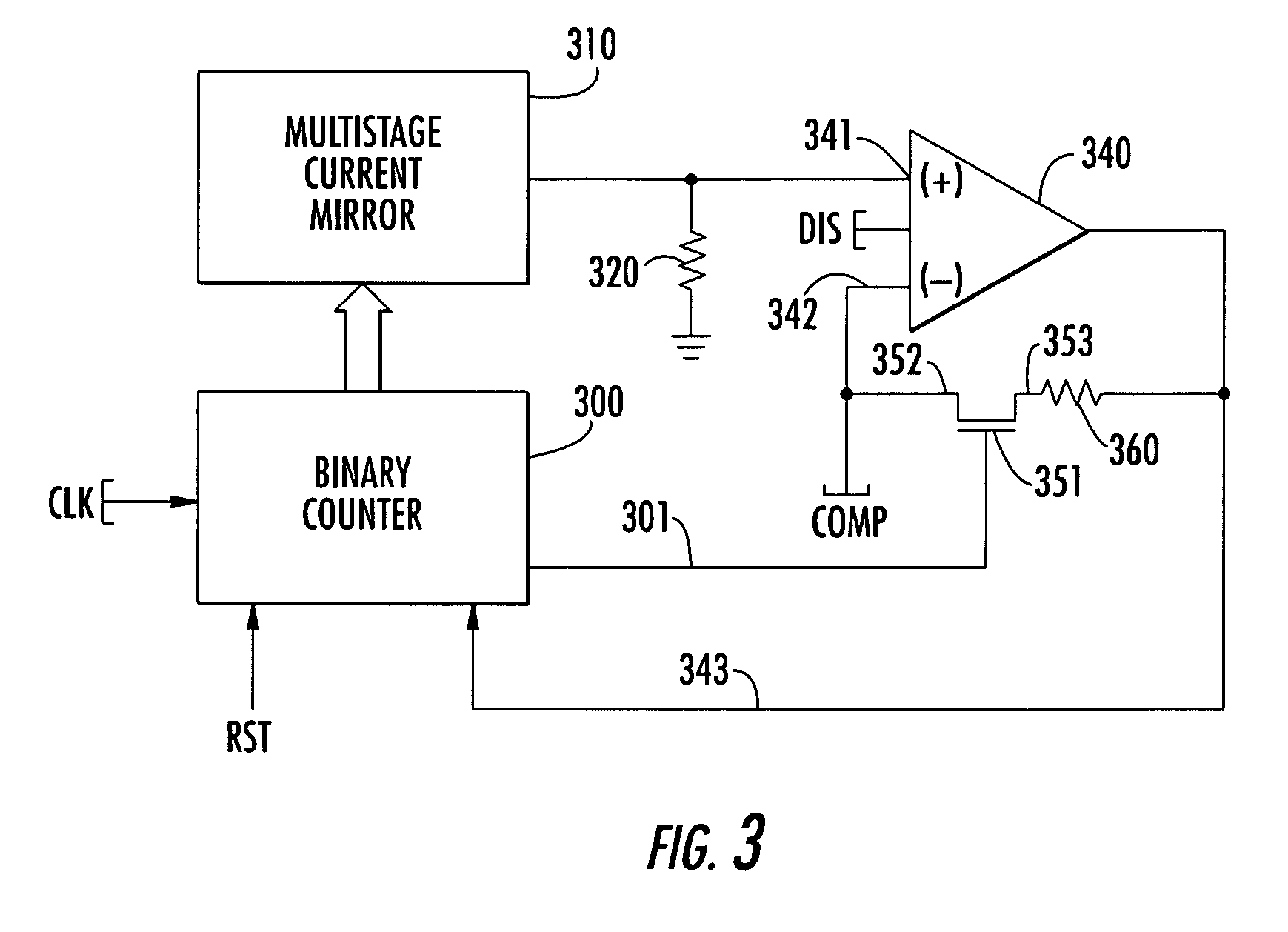

Compensation sample and hold for voltage regulator amplifier

ActiveUS6958596B1Smooth transitionSmooth supplyElectric variable regulationPower conversion systemsLow noisePulse-code modulation

The problem of charge leakage in the AC compensation filter for the error amplifier of a pulse width modulation (PWM)-based DC—DC converter is effectively obviated by controllably sampling and storing the voltage across the AC compensation filter, in response to a transition of the operation of a DC power supply from run or active mode to quiescent or sleep mode. The sampled voltage is retained as a compensation voltage throughout the quiescent mode, so that it will be immediately available to the PWM circuitry at the termination of the quiescent interval. This serves to ensure a relatively smooth (low noise) power supply switch-over during a subsequent transition from quiescent to active mode.

Owner:INTERSIL INC

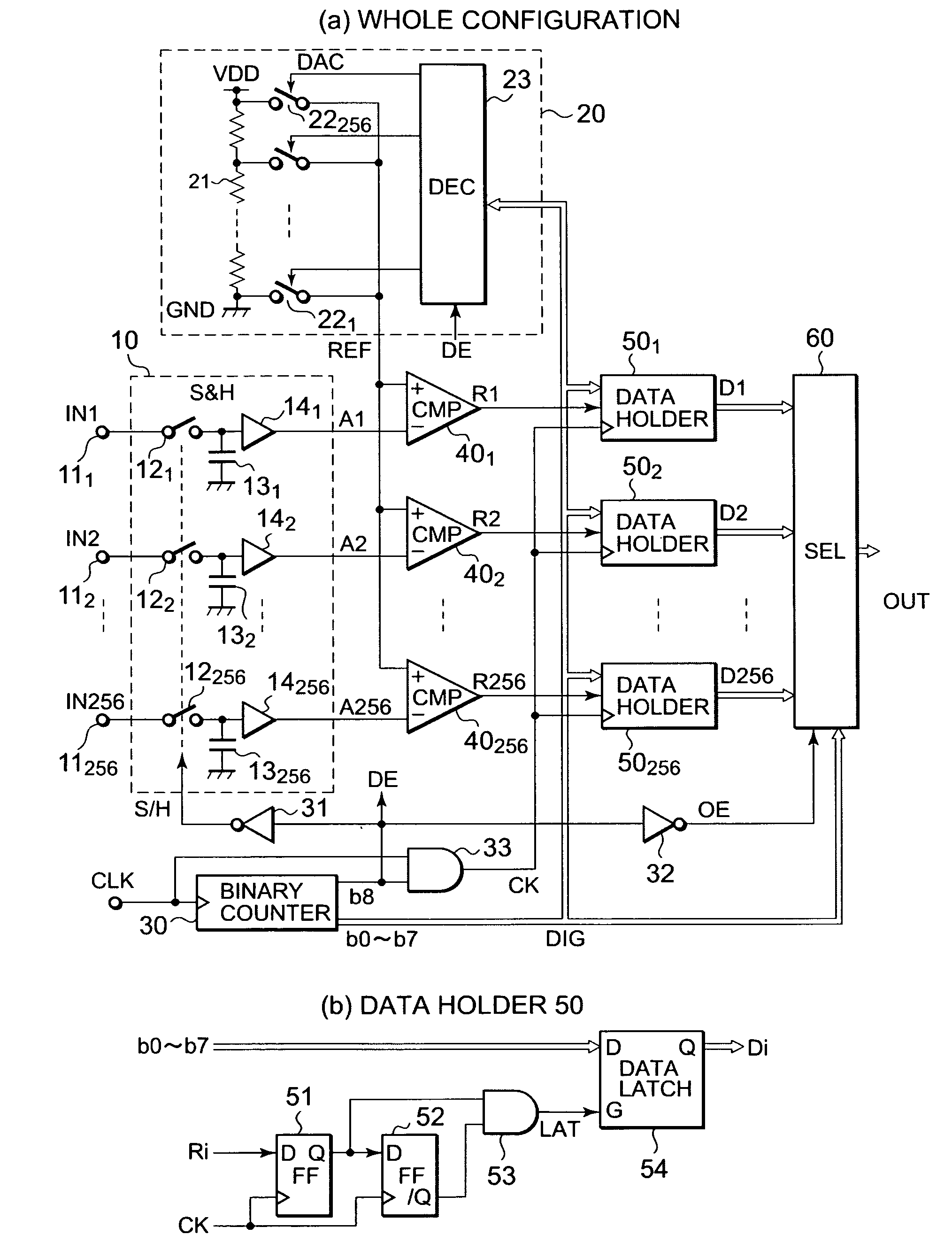

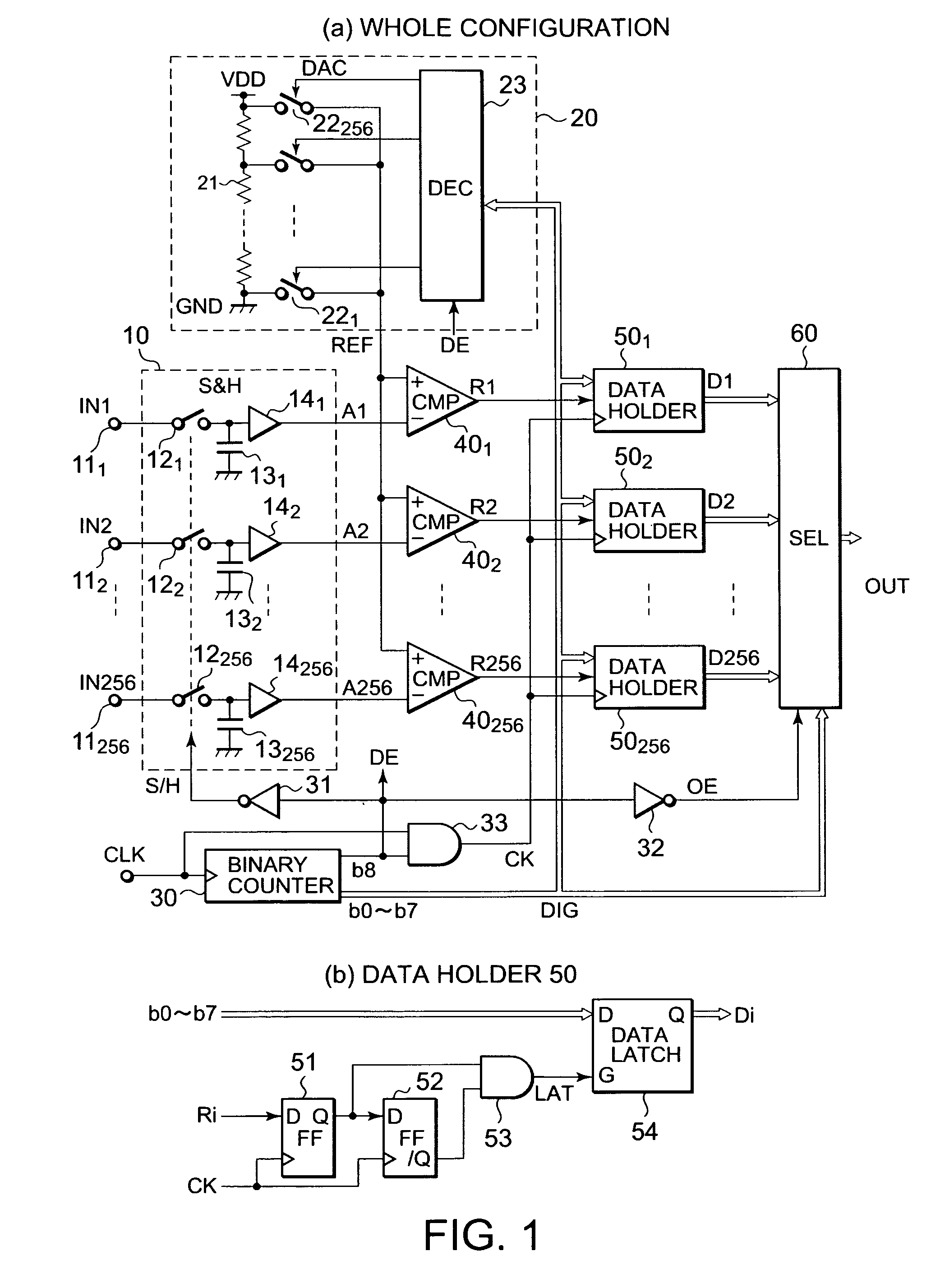

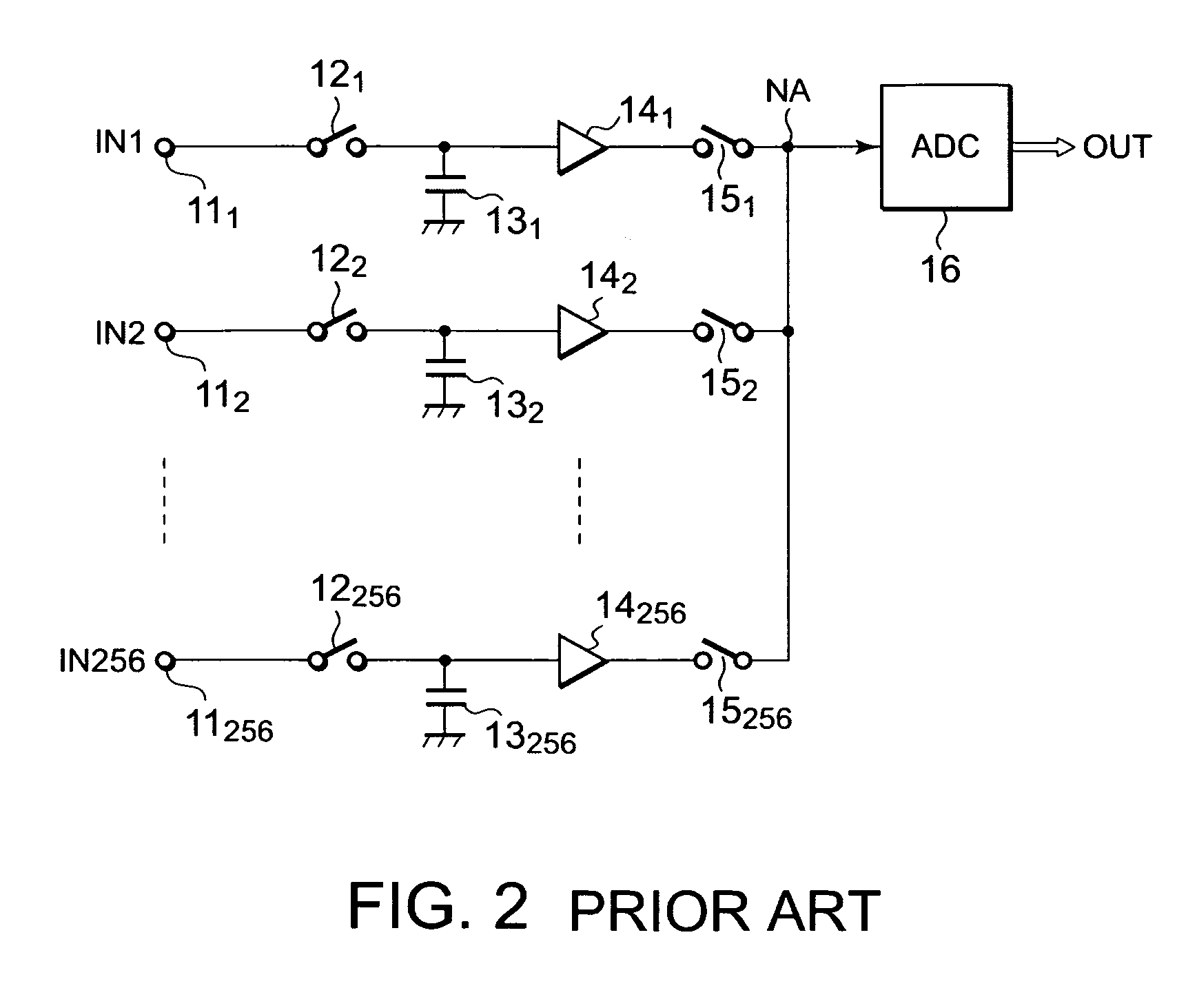

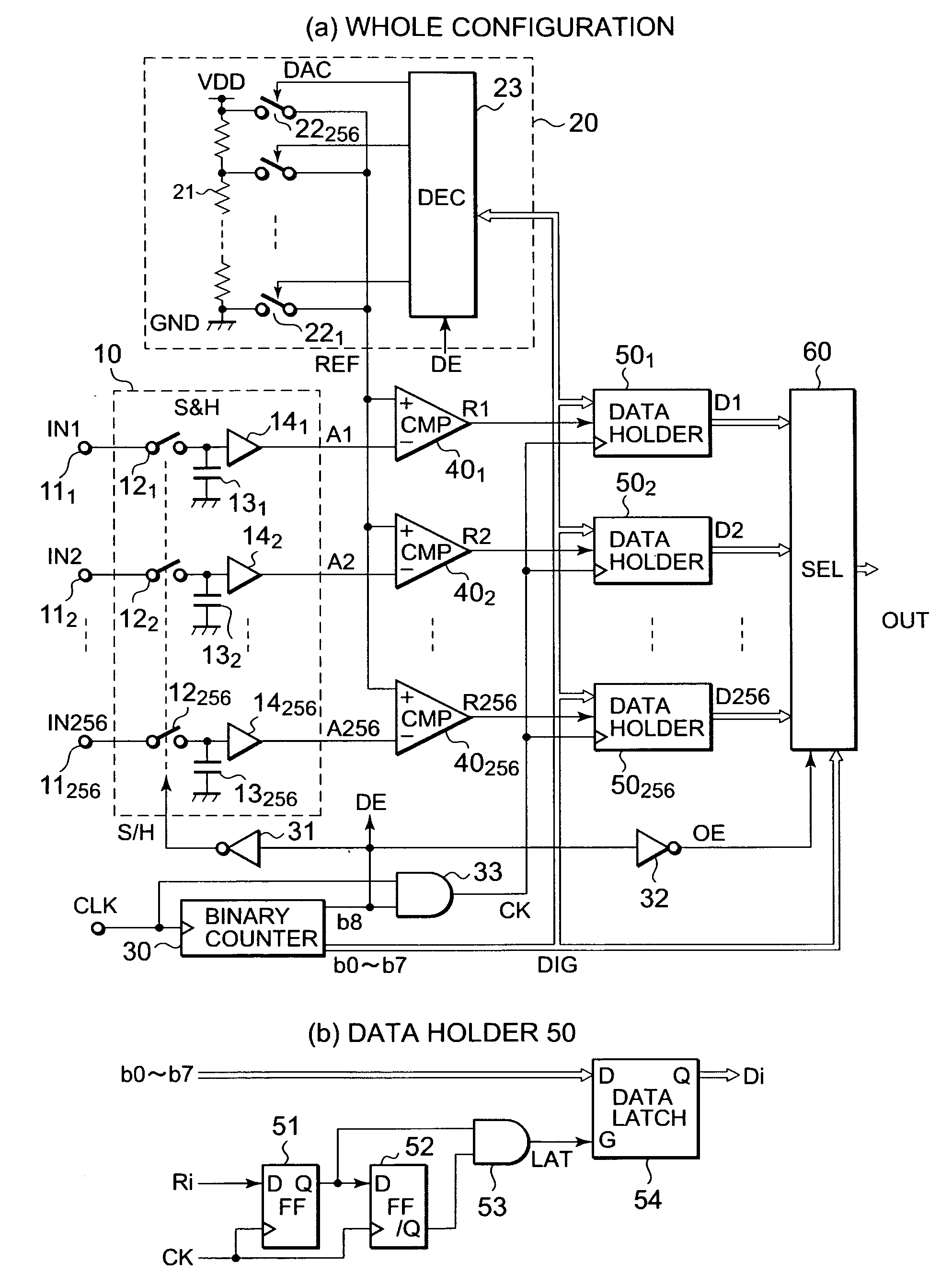

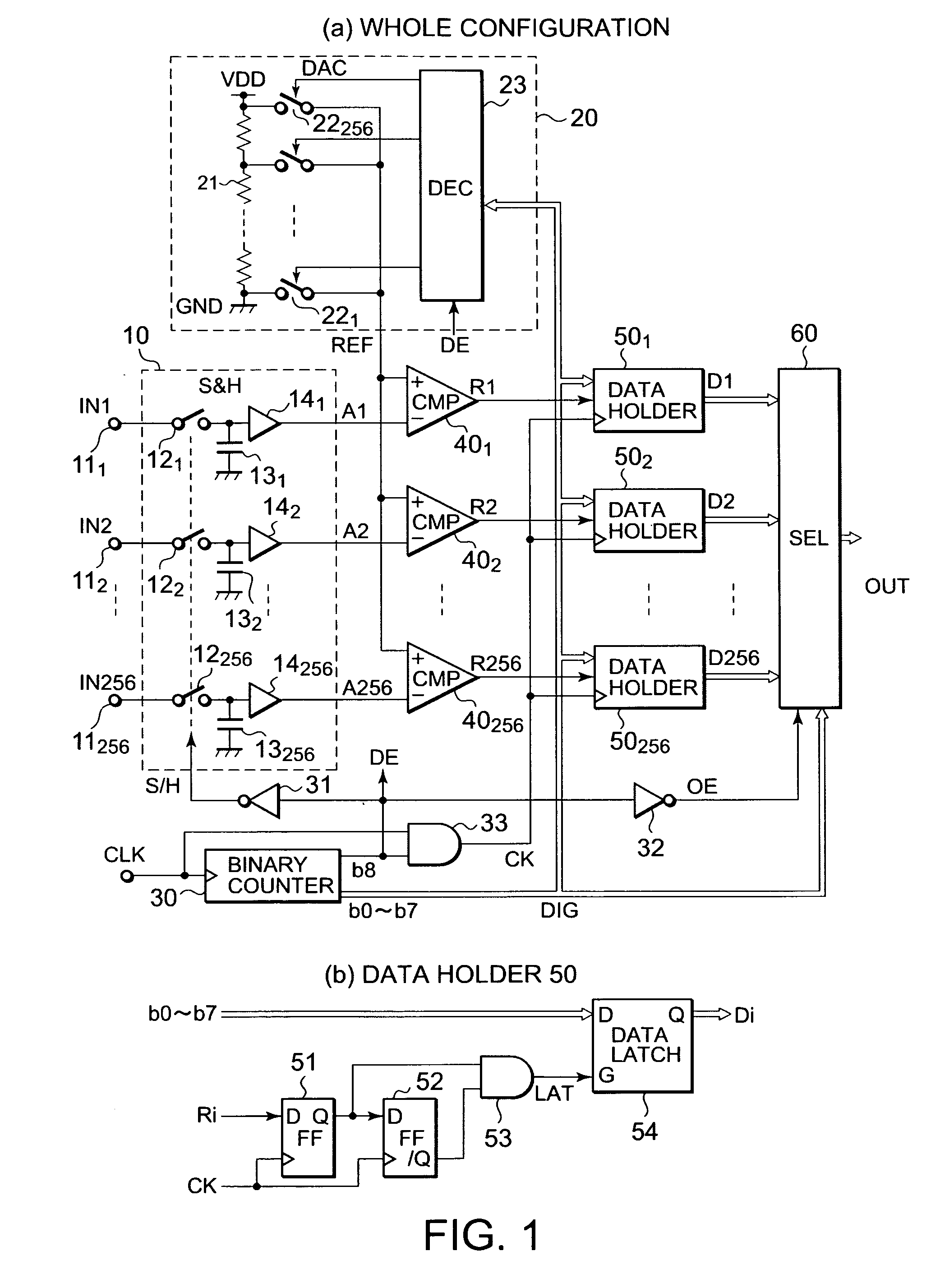

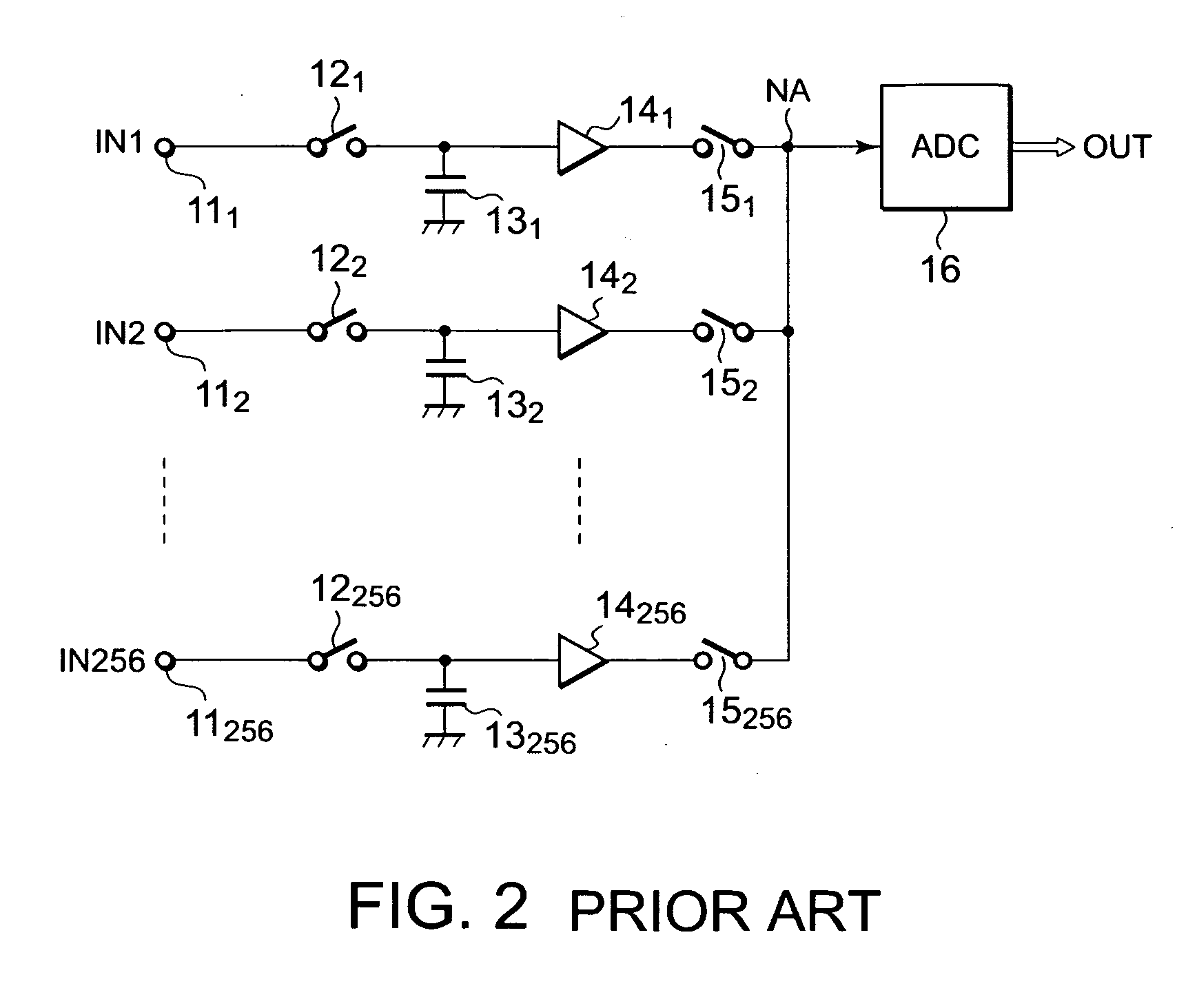

Analog-digital converter circuit

ActiveUS7372390B2Reduced conversion timeSimple circuit configurationElectric signal transmission systemsAnalogue-digital convertersMulti inputCurrent consumption

The present invention provides a multi-input A / D converter circuit capable of shorting a conversion time without increasing its layout area and current consumption. When a most significant bit of a binary counter is “L”, individual input signals are sampled by a sample and hold unit, and digital signals held in respective data holders are sequentially selected by a selector. When the most significant bit is brought to “H”, the respective input signals are held as analog signals and compared with each of reference voltages produced corresponding to a digital signal by a DAC. When decision signals outputted from comparators are changed from “L” to “H”, the digital signal at that time is held in the individual data holders as digital signals.

Owner:LAPIS SEMICON CO LTD

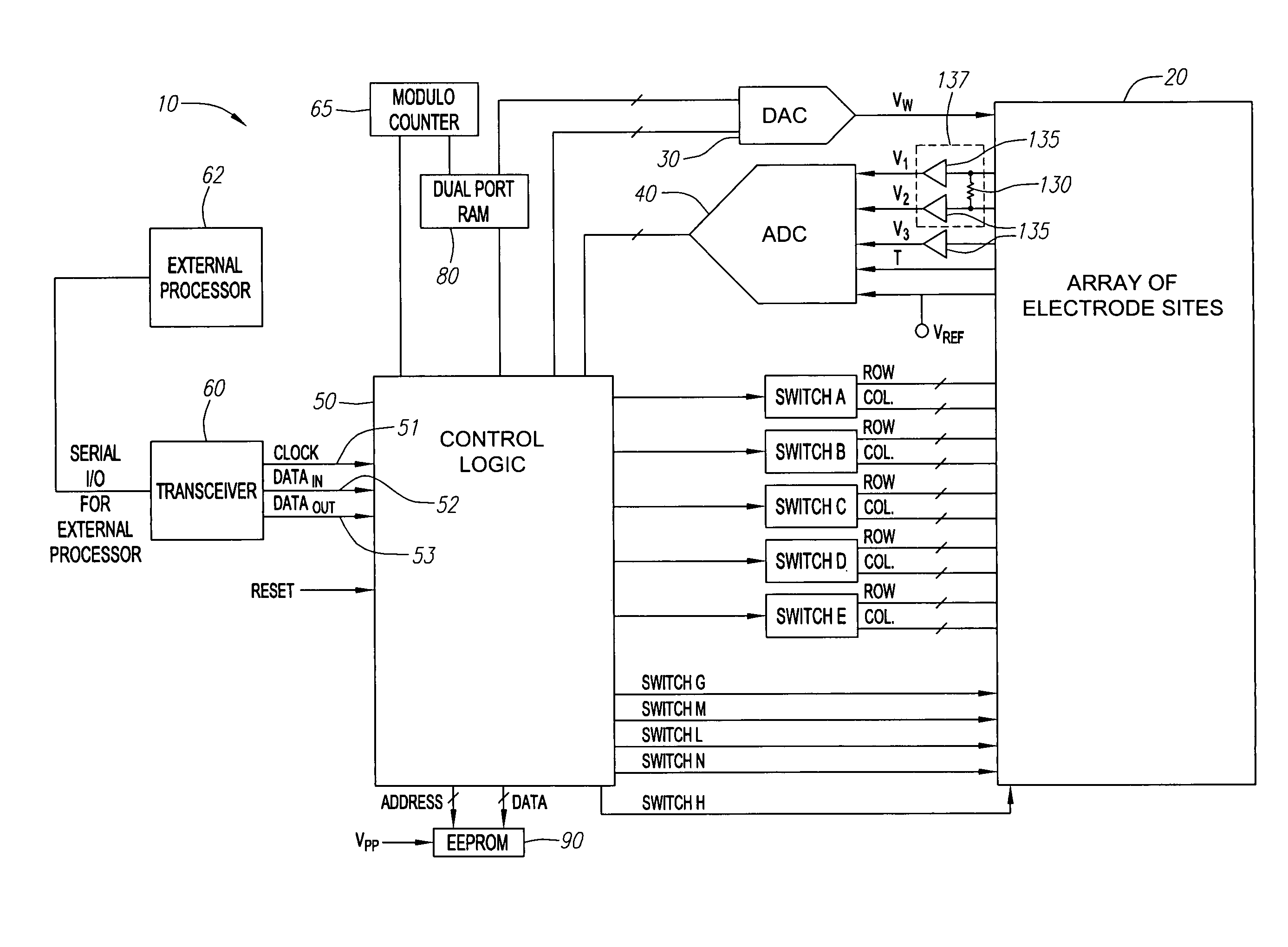

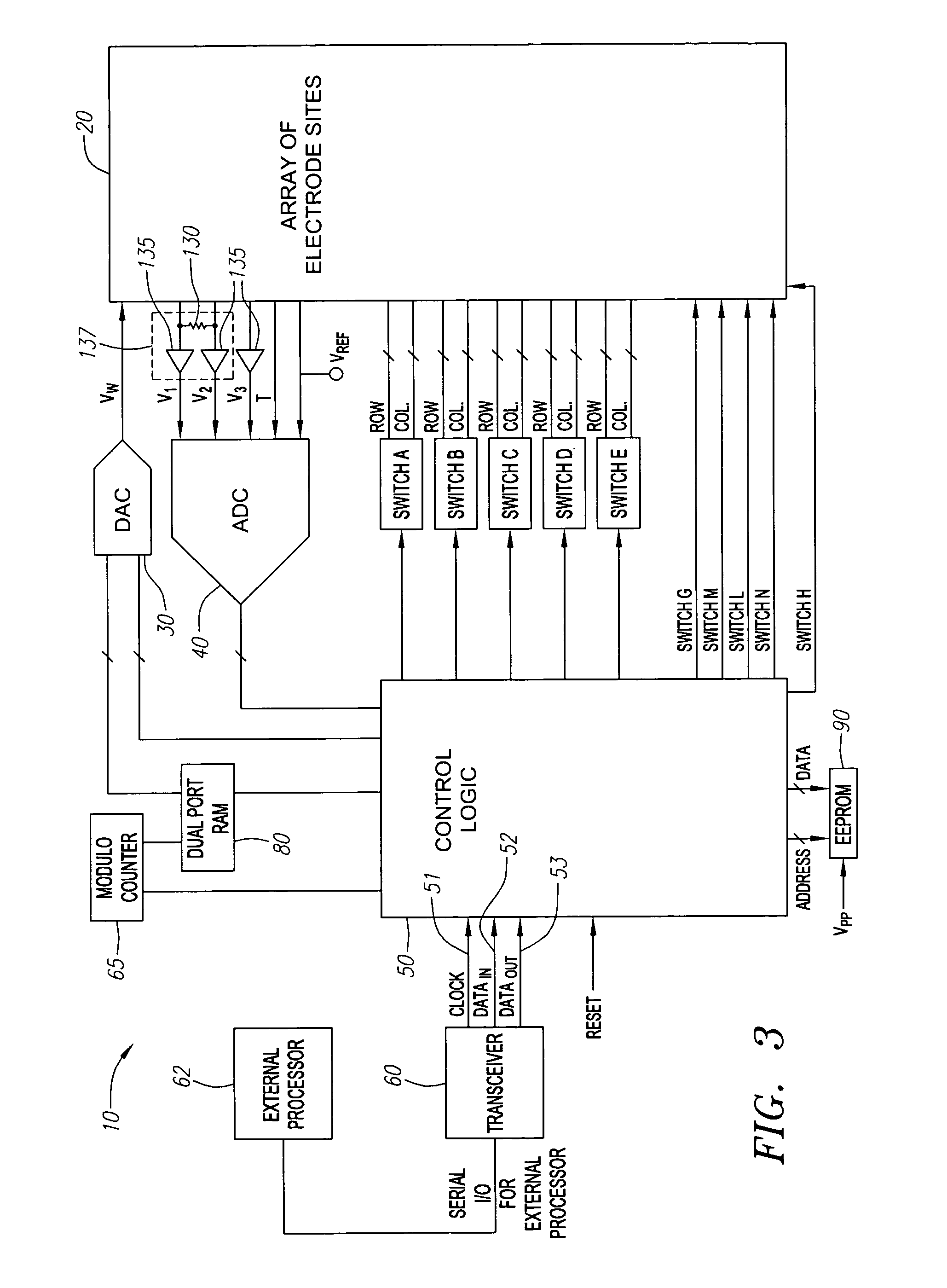

Programmable multiplexed active biologic array

The present invention is directed to devices and methods for carrying out and / or monitoring biological reactions in response to electrical stimuli. A programmable multiplexed active biologic array includes an array of electrodes coupled to sample-and-hold circuits. The programmable multiplexed active biologic array includes a digital interface that allows external control of the array using an external processor. The circuit may monitor, digitally control, and deliver electrical stimuli to the electrodes individually or in selected groups.

Owner:ADOR DIAGNOSTICS SRL +1

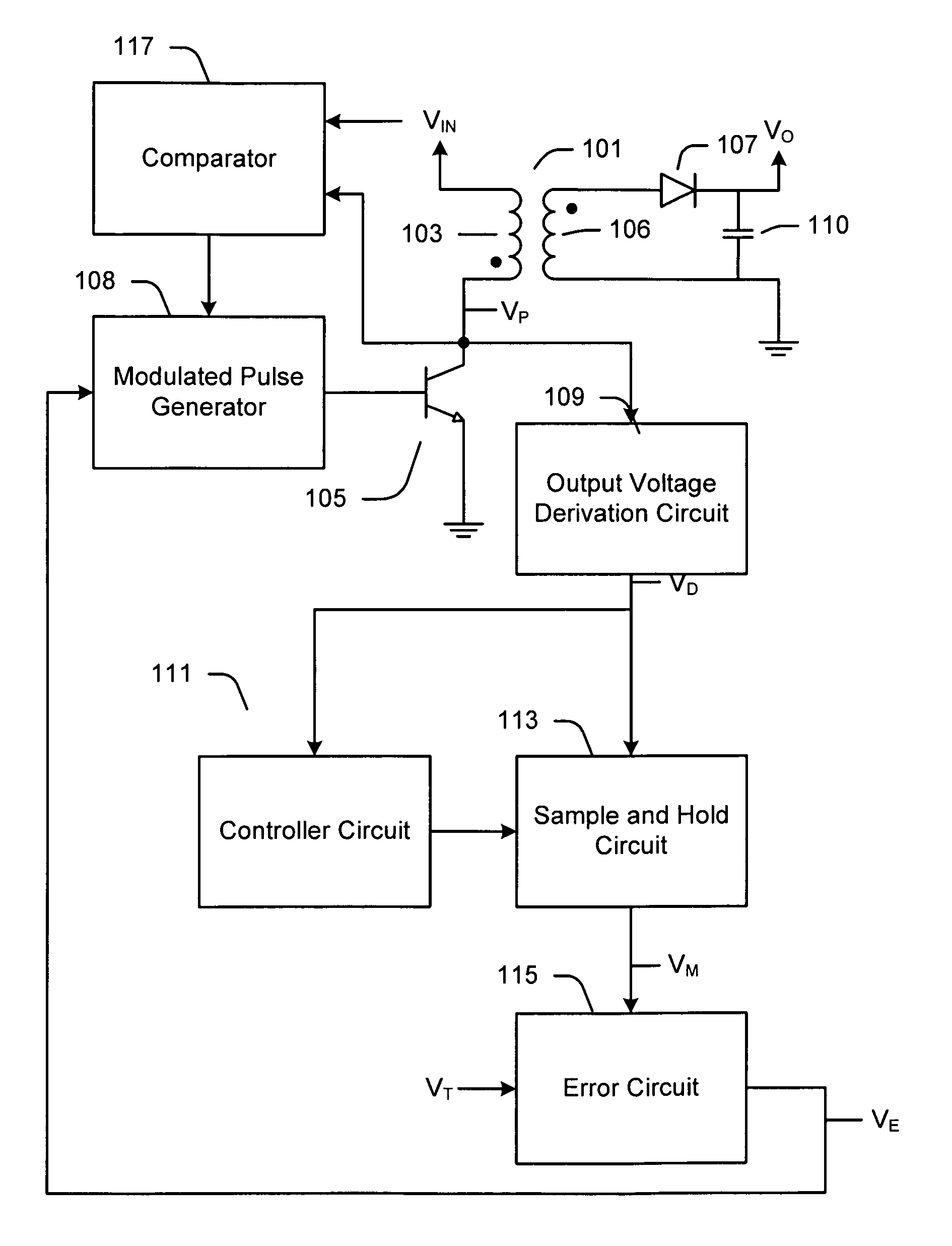

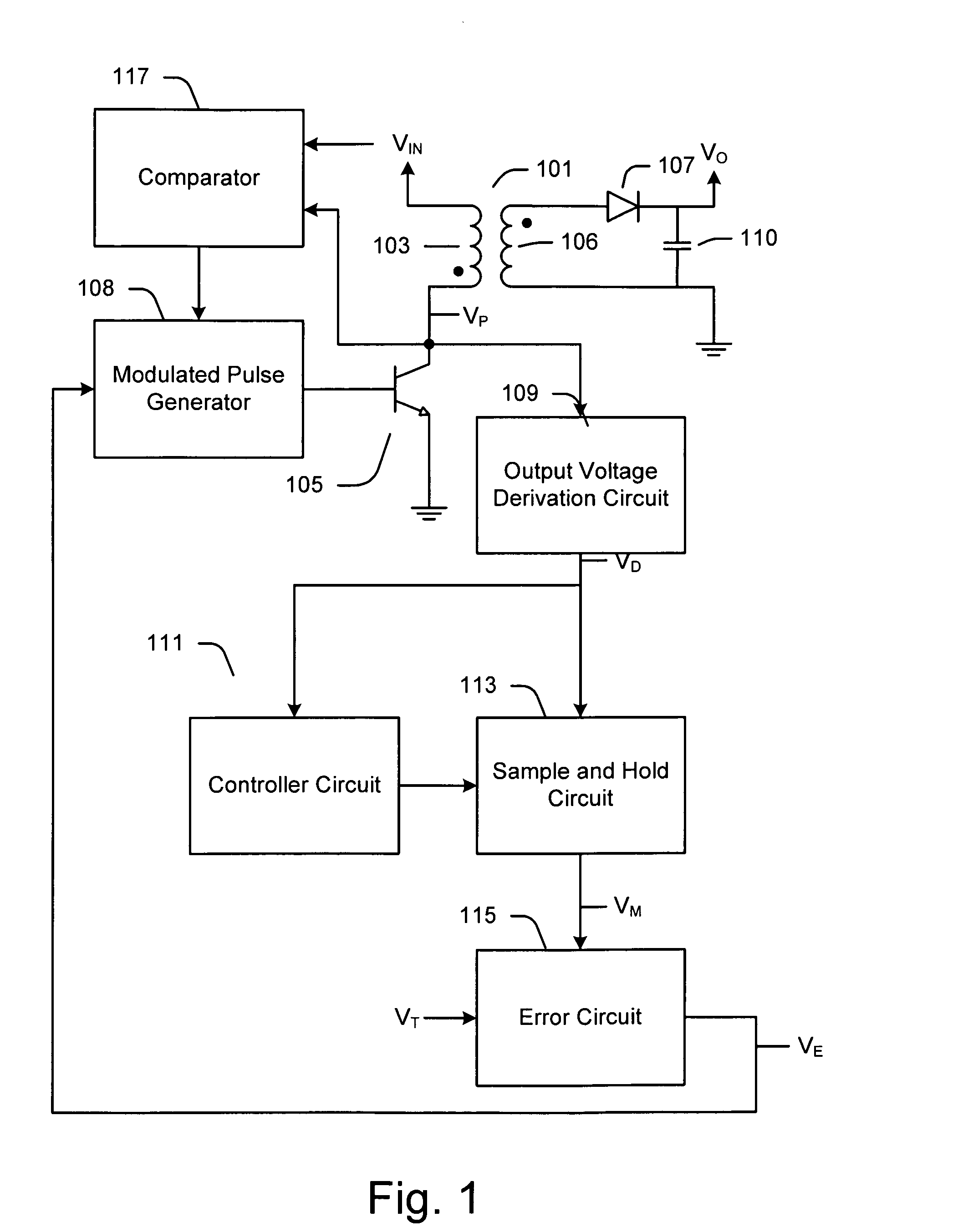

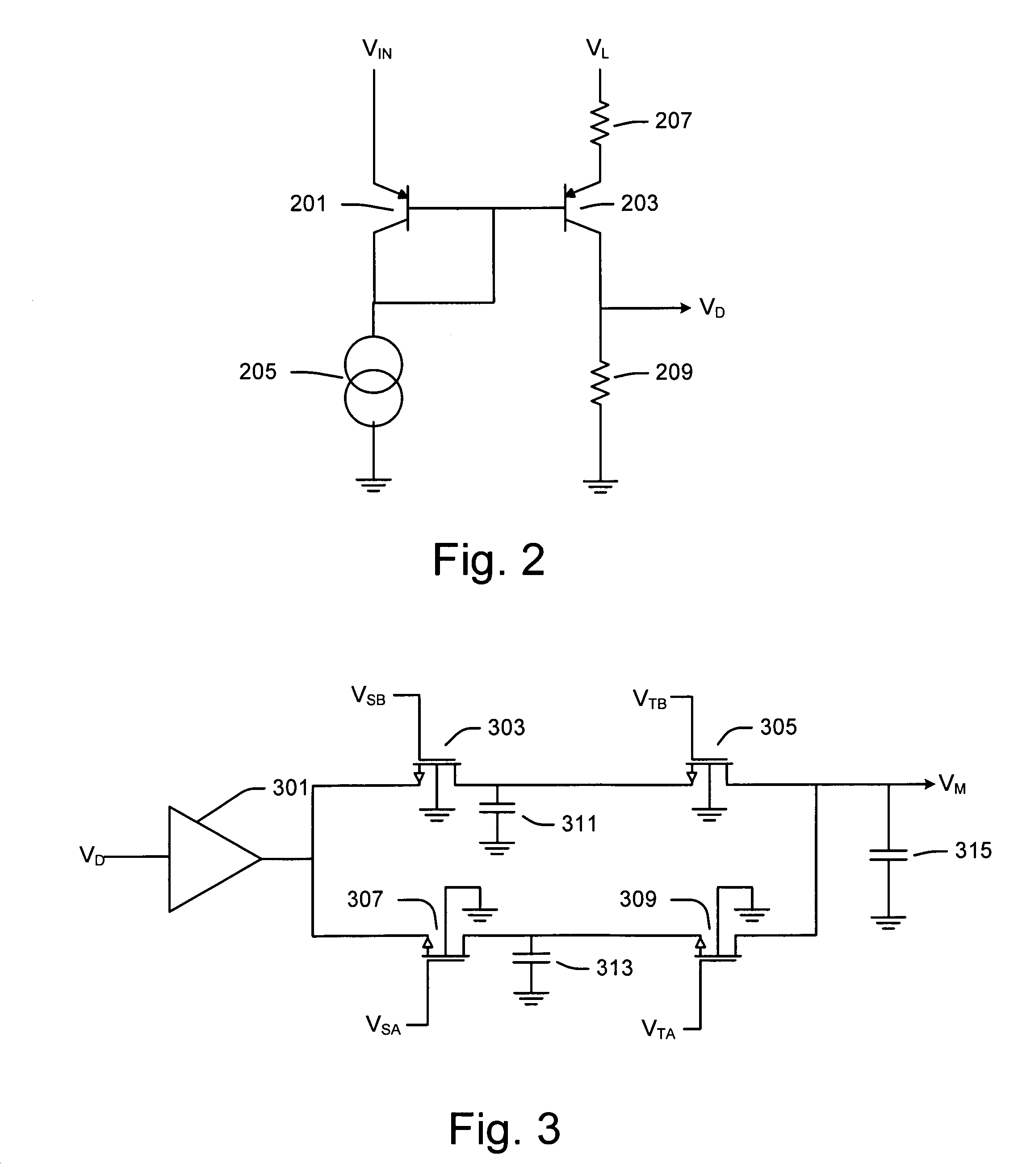

Regulator for isolated flyback power supply using primary side sensing

A regulator for an isolated flyback power supply using primary side sensing. The regulator may include an error circuit configured to generate an error signal representative of the difference between a target value and a measured value, a sample and hold circuit, and a controller circuit. The controller circuit may be configured to cause the sample and hold circuit to sample the value of a derived signal that is derived from a connection to the primary winding at a time when the primary winding is decoupled from the energy-supplying circuit and the diode is conducting current, and to hold the sampled value at least until the diode stops conducting current. The controller circuit may also be configured to cause the held value to be the measured value used by the error circuit.

Owner:ANALOG DEVICES INT UNLTD

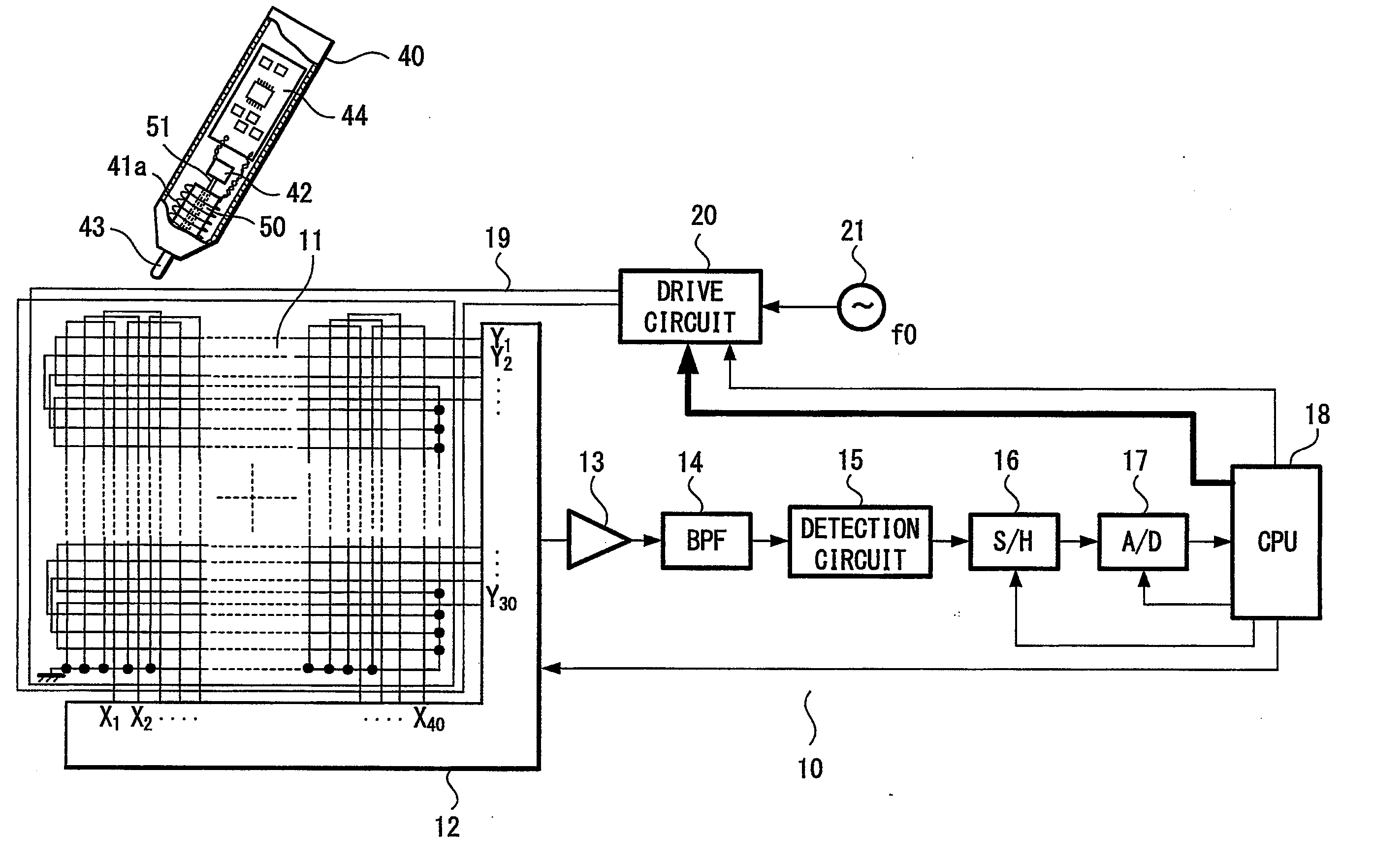

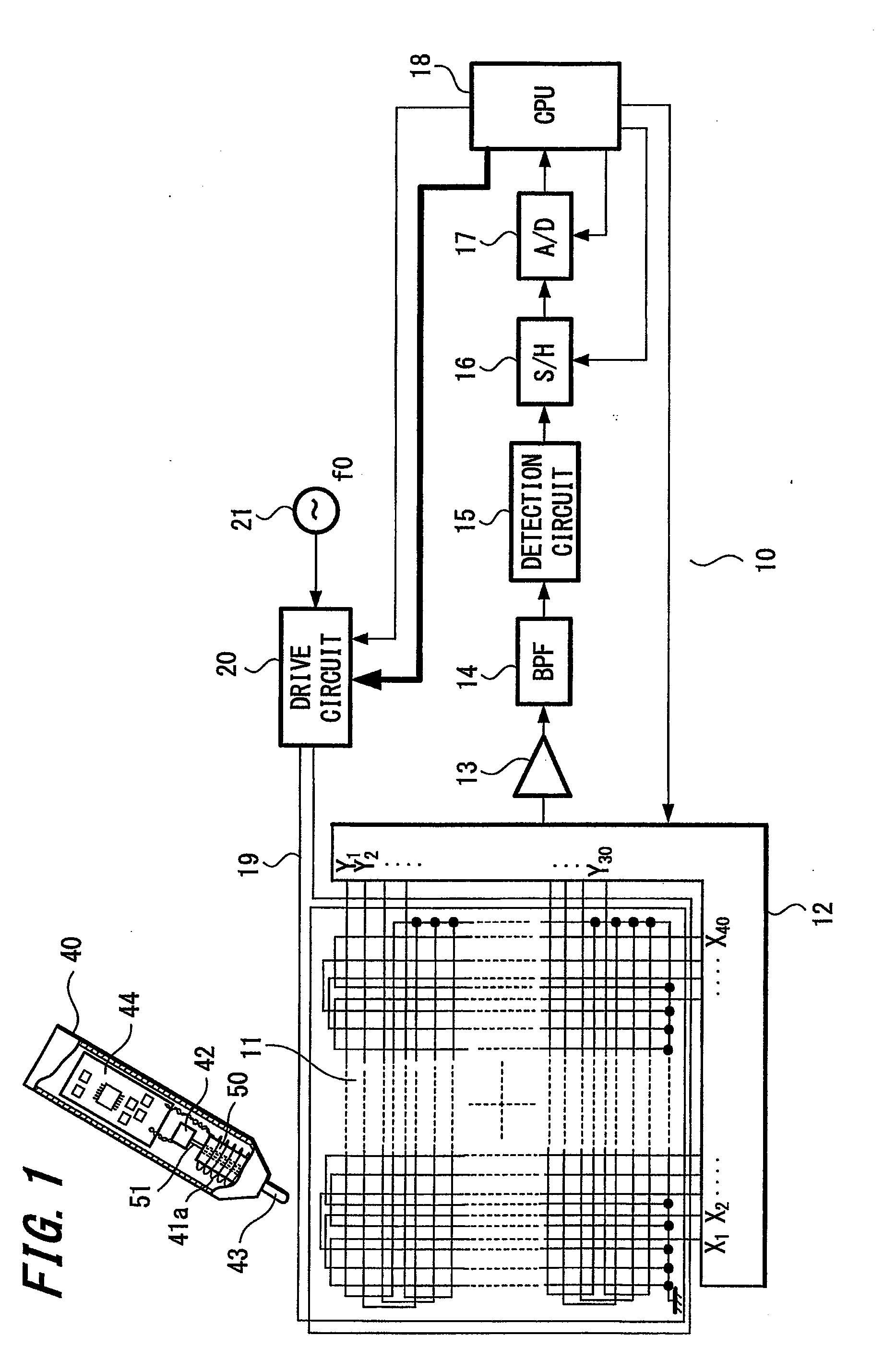

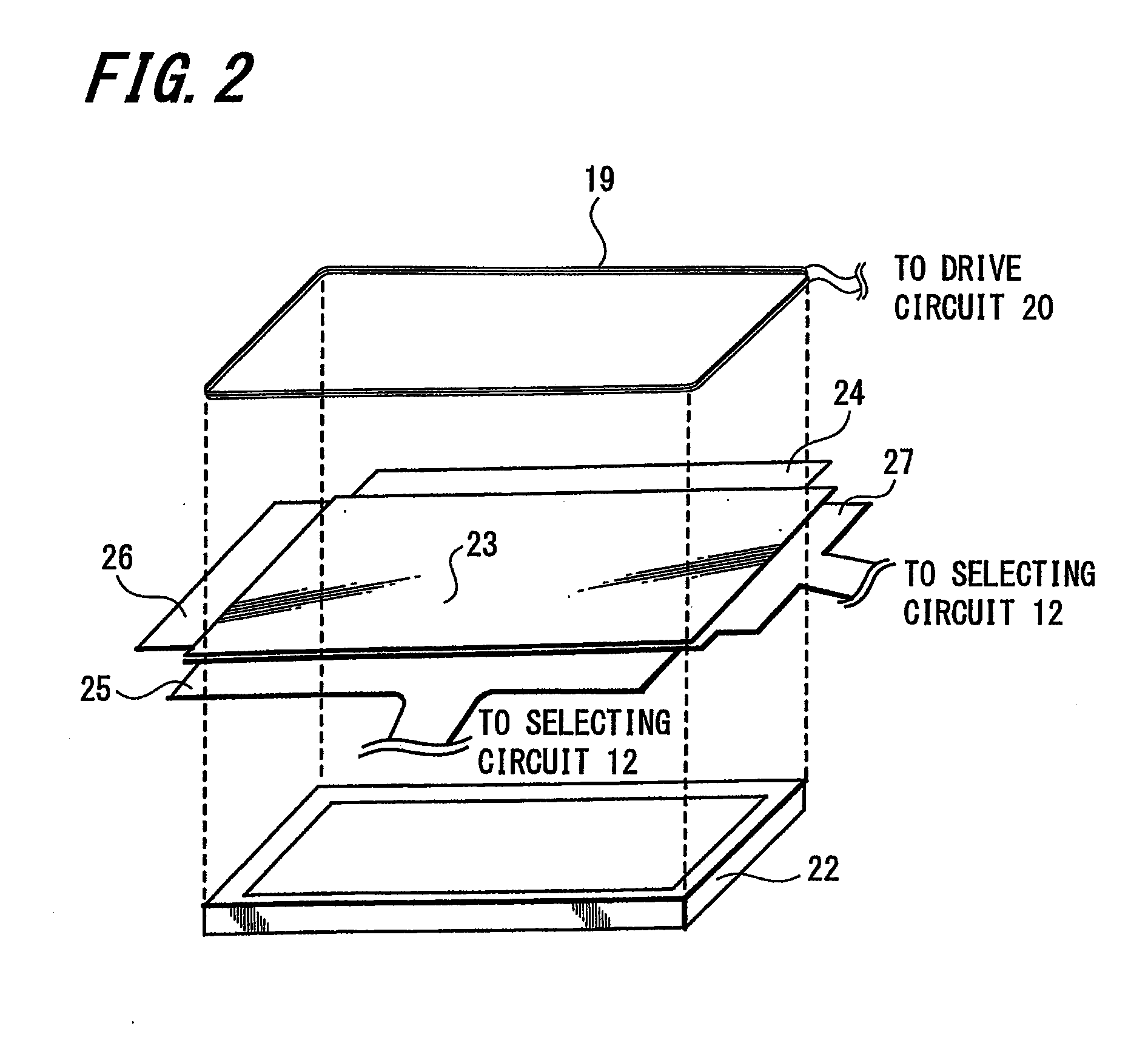

Position detecting device and position detecting method

ActiveUS20090065269A1Reduce power consumptionExtend battery lifeTransmission systemsElectric/electromagnetic visible signallingControl signalExcitation signal

An excitation coil (19) surrounding the periphery of the position detecting area is connected to an oscillating circuit (21), which oscillates at a frequency f0, through a drive circuit (20). A CPU (18) supplies control signals to a selecting circuit (12), a sample-and-hold circuit (16), an A / D conversion circuit (17), and the drive circuit (20). Based on the control signal output from the CPU (18), the drive circuit (20) controls the power of the signal output from the excitation coil (19) to ON or OFF. Further, the strength of the excitation signal supplied from the excitation coil (19) is controlled based on information obtained by analyzing a signal received from a position indicator (40), such as the position indicated by the position indicator on the position detecting area and / or a strength of the signal received from the position indicator.

Owner:WACOM CO LTD

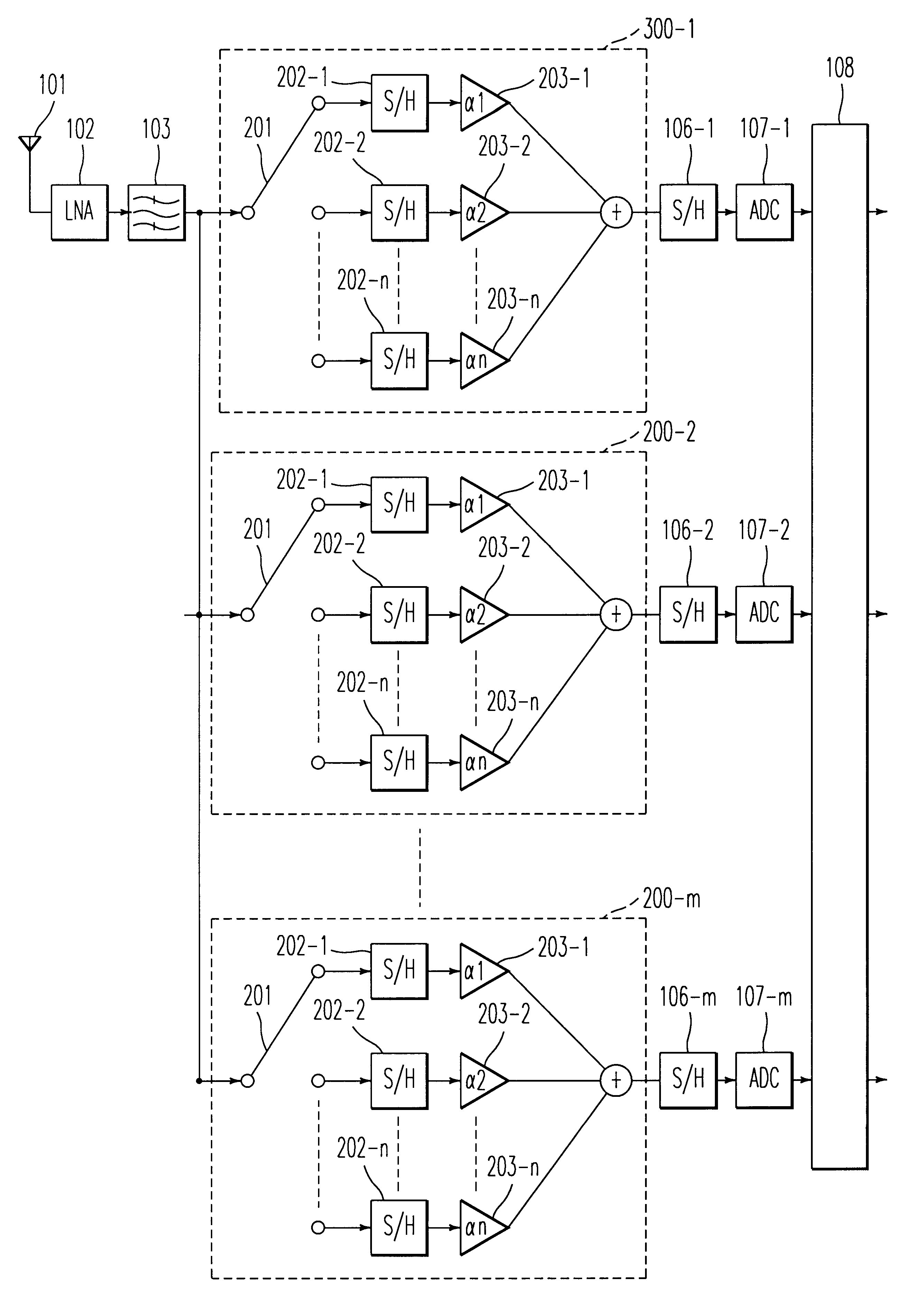

Sampling system

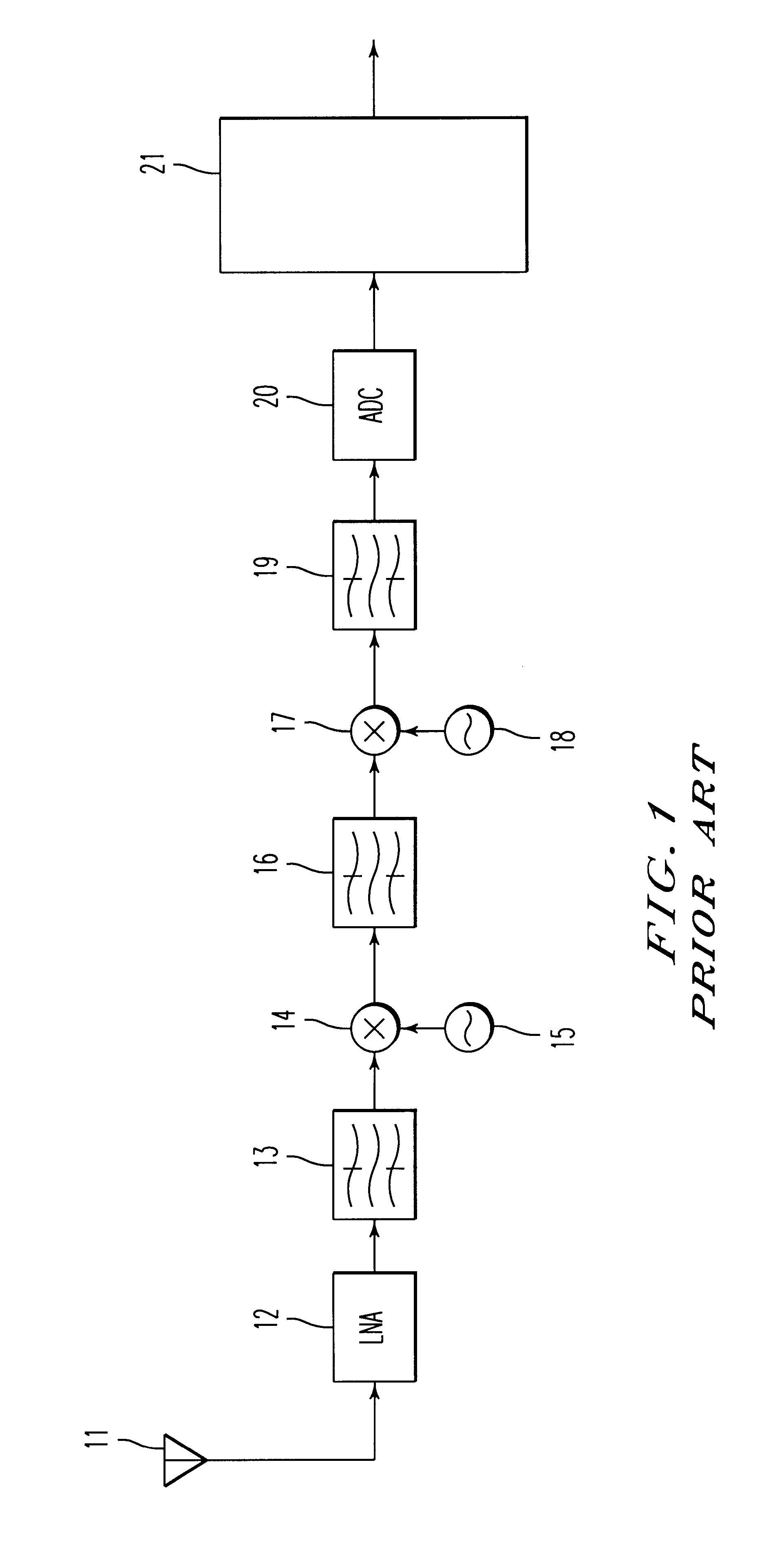

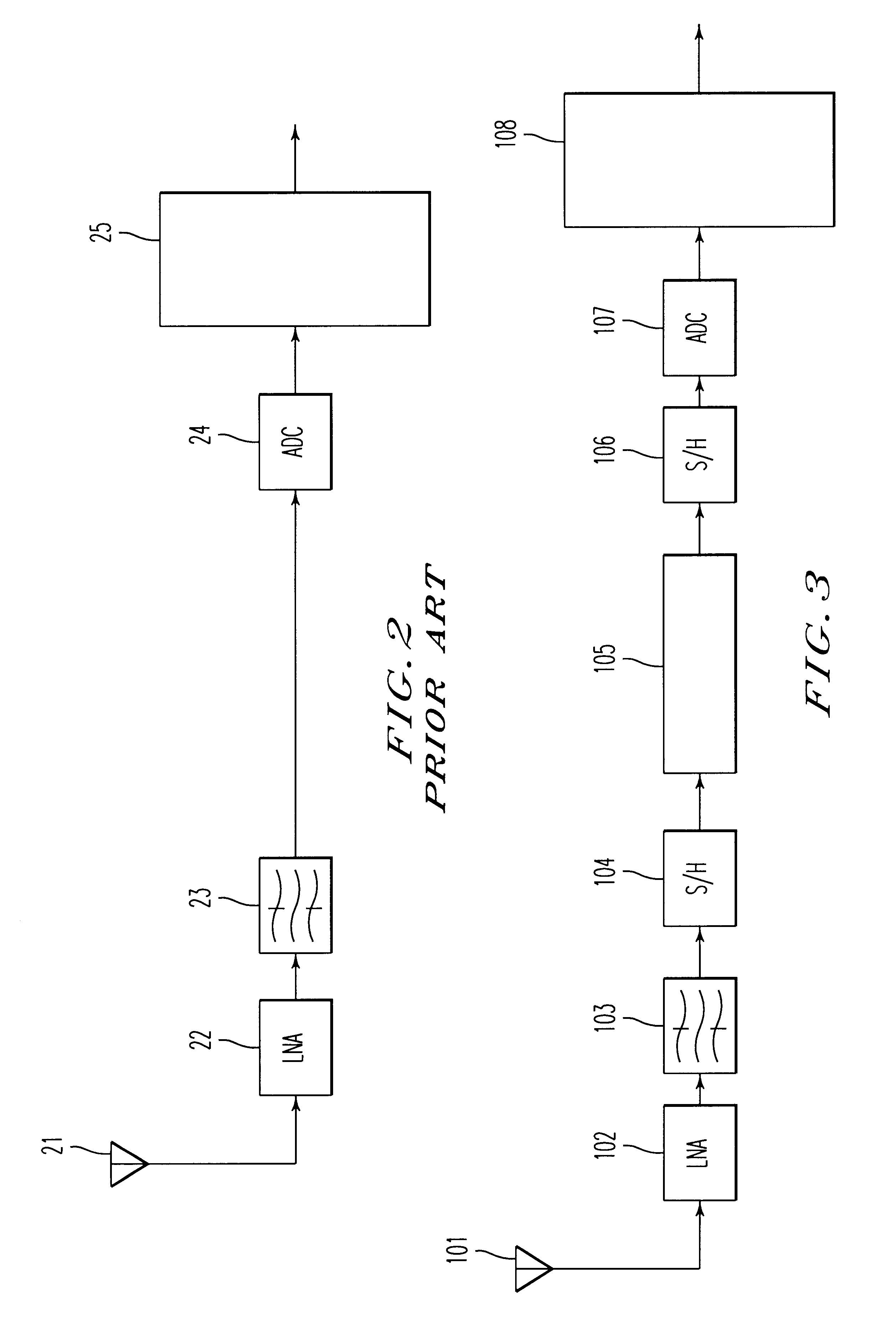

A sampling system arranged such that a modulated signal received by an antenna and input via a low noise amplifier and a band-pass filter is sampled at a sampling frequency higher than the signal band of the modulated signal by a first sample and hold circuit and is input to an analog decimation filter to remove a frequency component which may turn out to be aliasing noise. The output of the analog decimation filter is sampled with a sampling frequency lower than the sampling frequency of the first sample and hold circuit by a second sample and hold circuit and is digitized by an A / D converter to be demodulated by a demodulator. The sampling system which can convert the modulated signal into a low frequency without using the highly precision mixer circuit or a filter having sharp characteristics may be provided by constructing as described above.

Owner:KK TOSHIBA

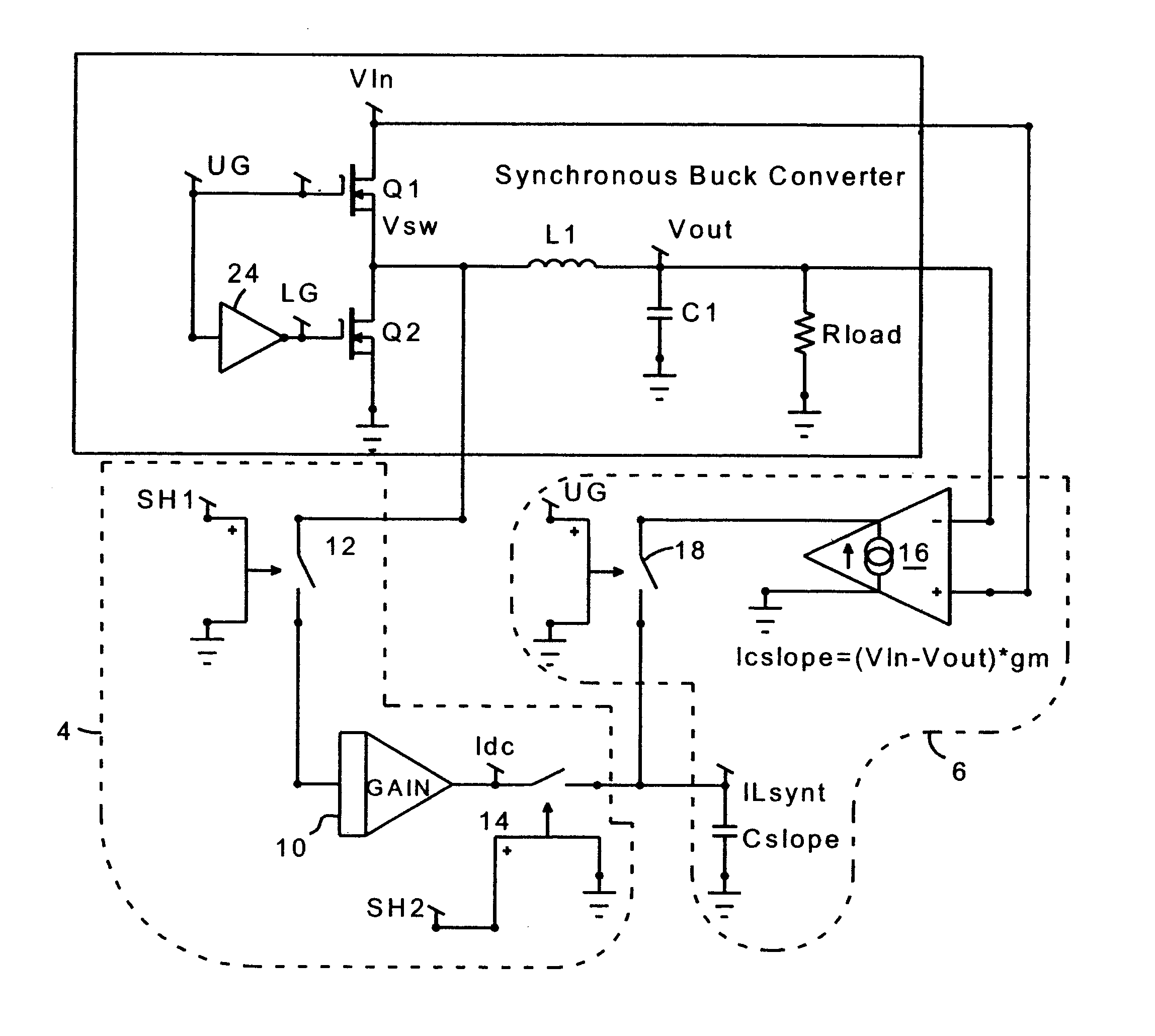

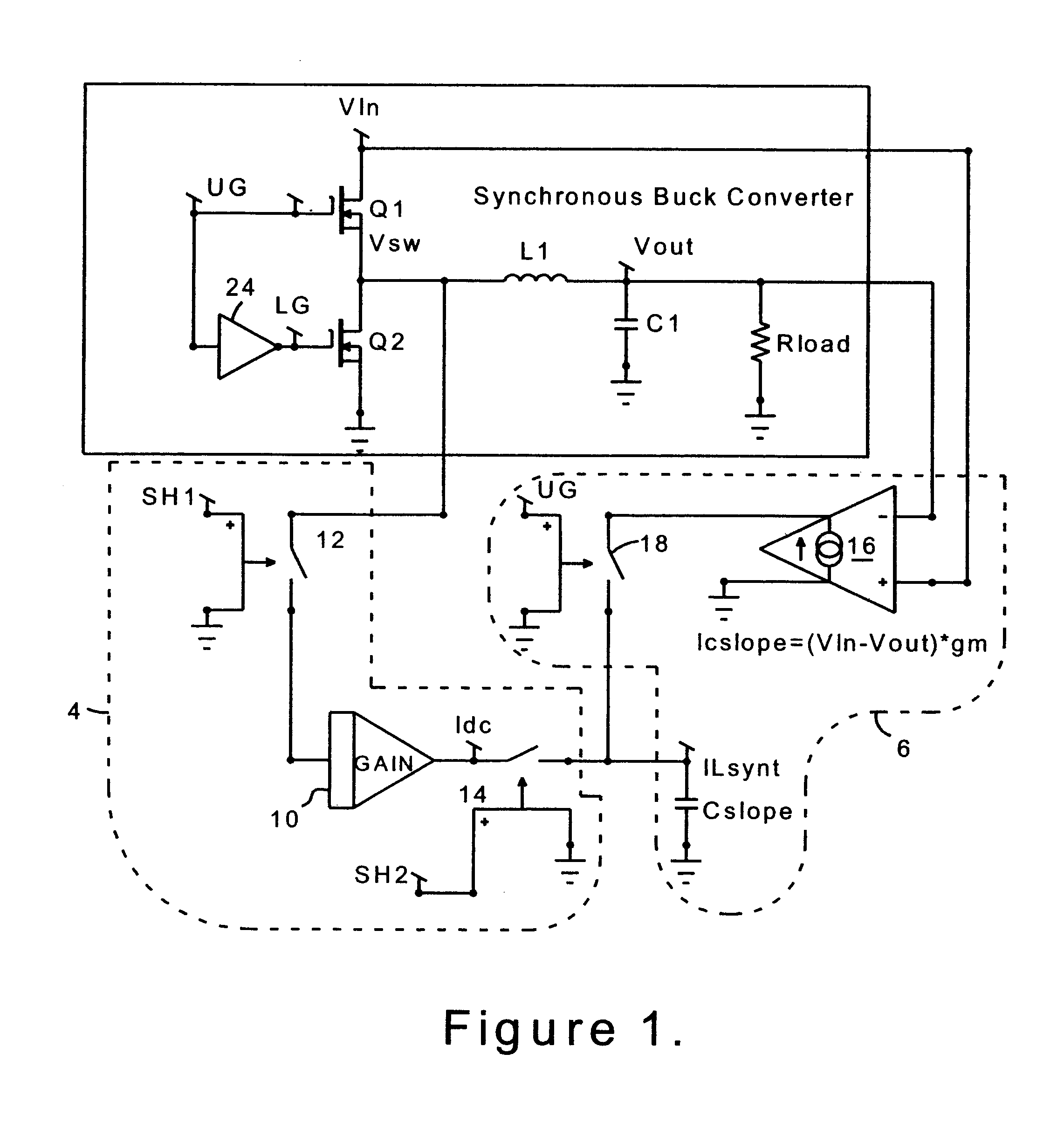

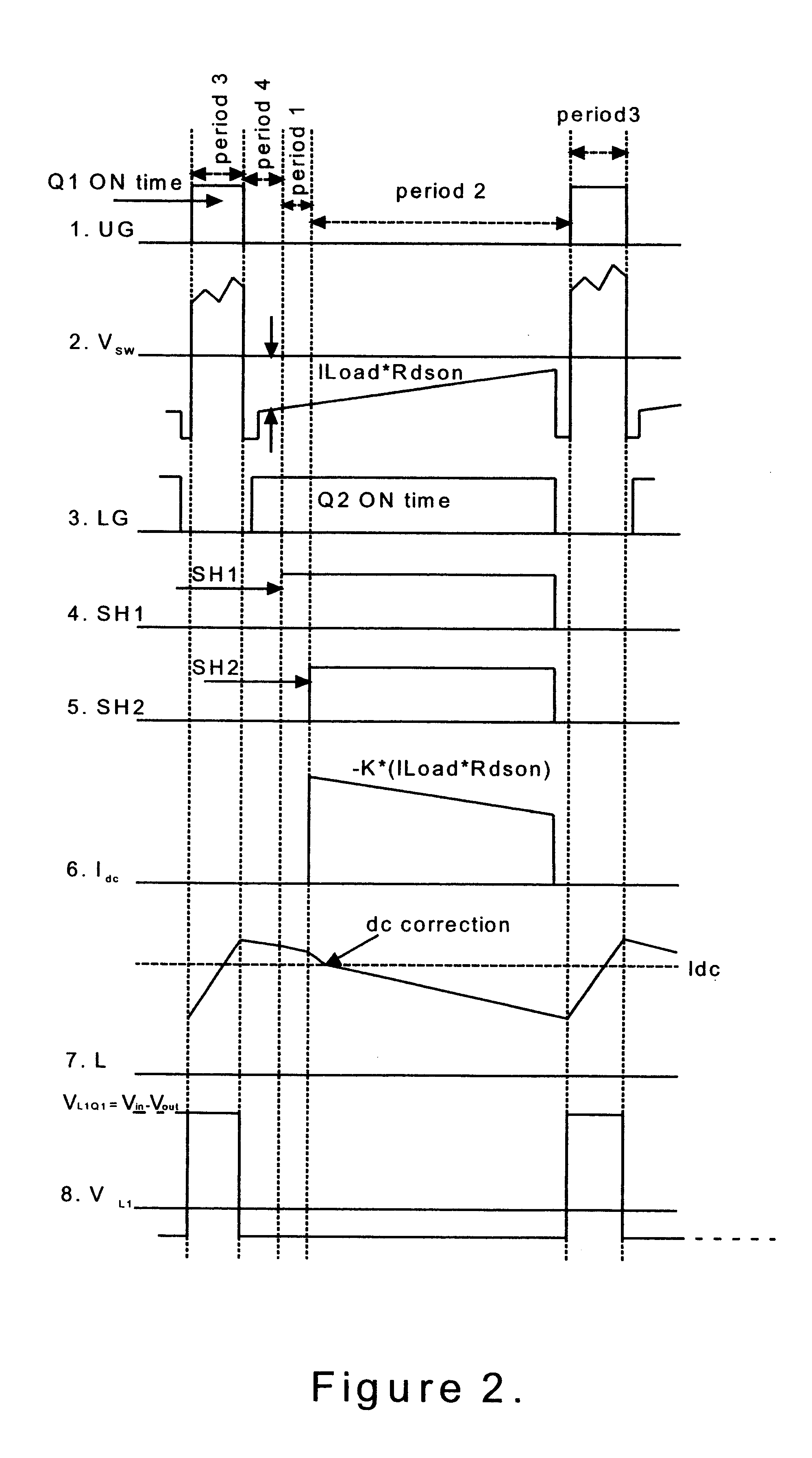

Inductor current synthesizer for switching power supplies

InactiveUS6381159B2Ac-dc conversion without reversalEfficient power electronics conversionMOSFETSwitching cycle

A circuit and method for sensing the inductor current flowing to a load from a switching power supply without using a sense resistor in the path of the inductor current. In a synchronous buck converter topology, the inductor current is derived by sensing the voltage drop across the synchronous MOSFET of the half-bridge and reconstructing the current using a sample and hold technique. A ripple current synthesizer is employed to reconstruct inductor current outside the sample and hold window. The sampled product ILoadxRDSon is used to update the ripple current estimator with dc information every switching cycle. The resulting voltage waveform is directly proportional to the inductor current. The inductor current synthesizer of the present invention can also be used in boost converter, flyback converter and forward converter topologies.

Owner:INFINEON TECH AMERICAS CORP

Analog-digital converter circuit

ActiveUS20070188367A1Reduced conversion timeSimple circuit configurationElectric signal transmission systemsAnalogue-digital convertersMulti inputA d converter

The present invention provides a multi-input A / D converter circuit capable of shorting a conversion time without increasing its layout area and current consumption. When a most significant bit of a binary counter is “L”, individual input signals are sampled by a sample and hold unit, and digital signals held in respective data holders are sequentially selected by a selector. When the most significant bit is brought to “H”, the respective input signals are held as analog signals and compared with each of reference voltages produced corresponding to a digital signal by a DAC. When decision signals outputted from comparators are changed from “L” to “H”, the digital signal at that time is held in the individual data holders as digital signals.

Owner:LAPIS SEMICON CO LTD

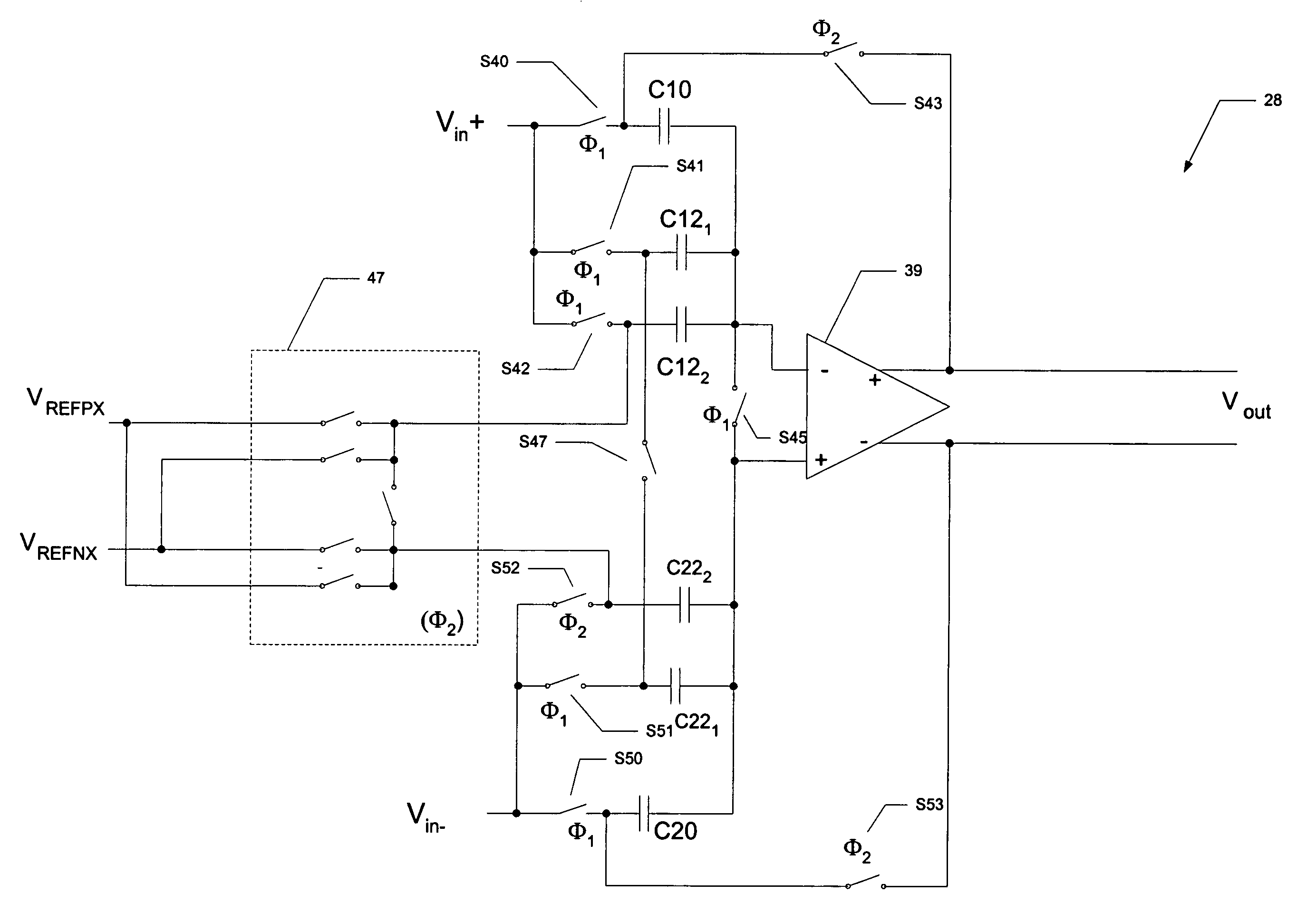

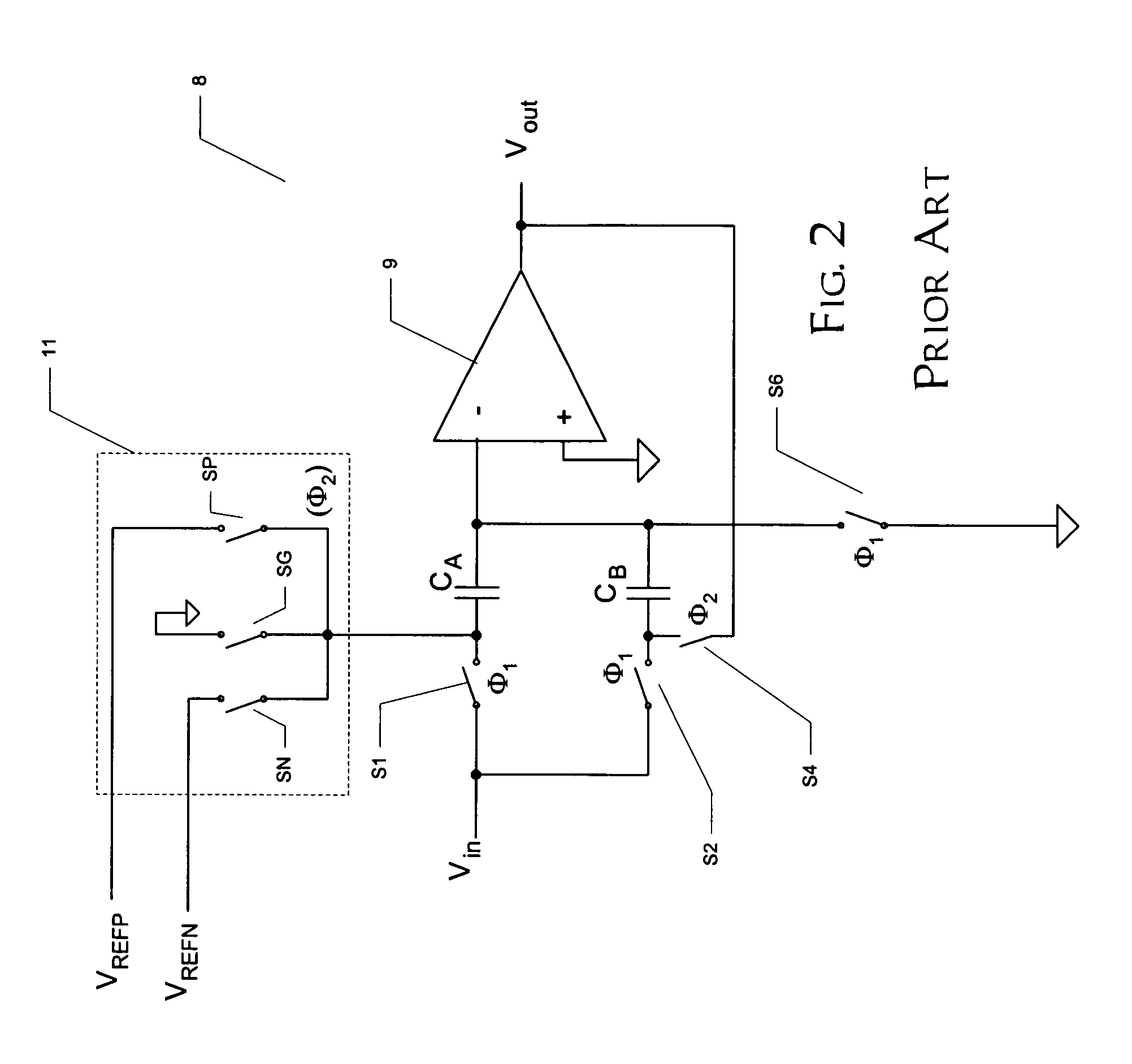

Switched-capacitor circuit with scaled reference voltage

ActiveUS7009549B1Improve precisionImprove stabilityElectric signal transmission systemsAnalogue-digital convertersCapacitanceAudio power amplifier

A pipelined analog-to-digital converter (ADC) (30) with improved precision is disclosed. The pipelined ADC (30) includes a sequence of stages (20), each of which includes a sample-and-hold circuit (22), an analog-to-digital converter (23), and the functions of a digital-to-analog converter (DAC) (25), an adder (24), and a gain stage (27) at which a residue signal (RES) is generated for application to the next stage (20) in the sequence. A multiplying DAC (28) performs the functions of the DAC (25), adder (24), and gain stage (27) in the stage (20), and is based on an operational amplifier (29). Sample capacitors (C10, C20) and reference capacitors (C122, C222) receive the analog input from the sample-and-hold circuit (22) in a sample phase; parallel capacitors (C121, C221) are provided to maintain constant circuit gain. Extended reference voltages (VREFPX, VREFNX) at levels that exceed the output range (V0+, V0−) of the operational amplifier (29) are applied to the reference capacitors, in response to the digital output of the analog-to-digital converter (23) in its stage (20). The reference capacitors (C12, C22) are scaled according to the extent to which the extended reference voltages (VREFPX, VREFNX) exceed the op amp output levels (V0+, V0−). The effects of noise on the reference voltages (VREFPX, VREFNX) on the residue signal (RES) are thus greatly reduced.

Owner:TEXAS INSTR INC

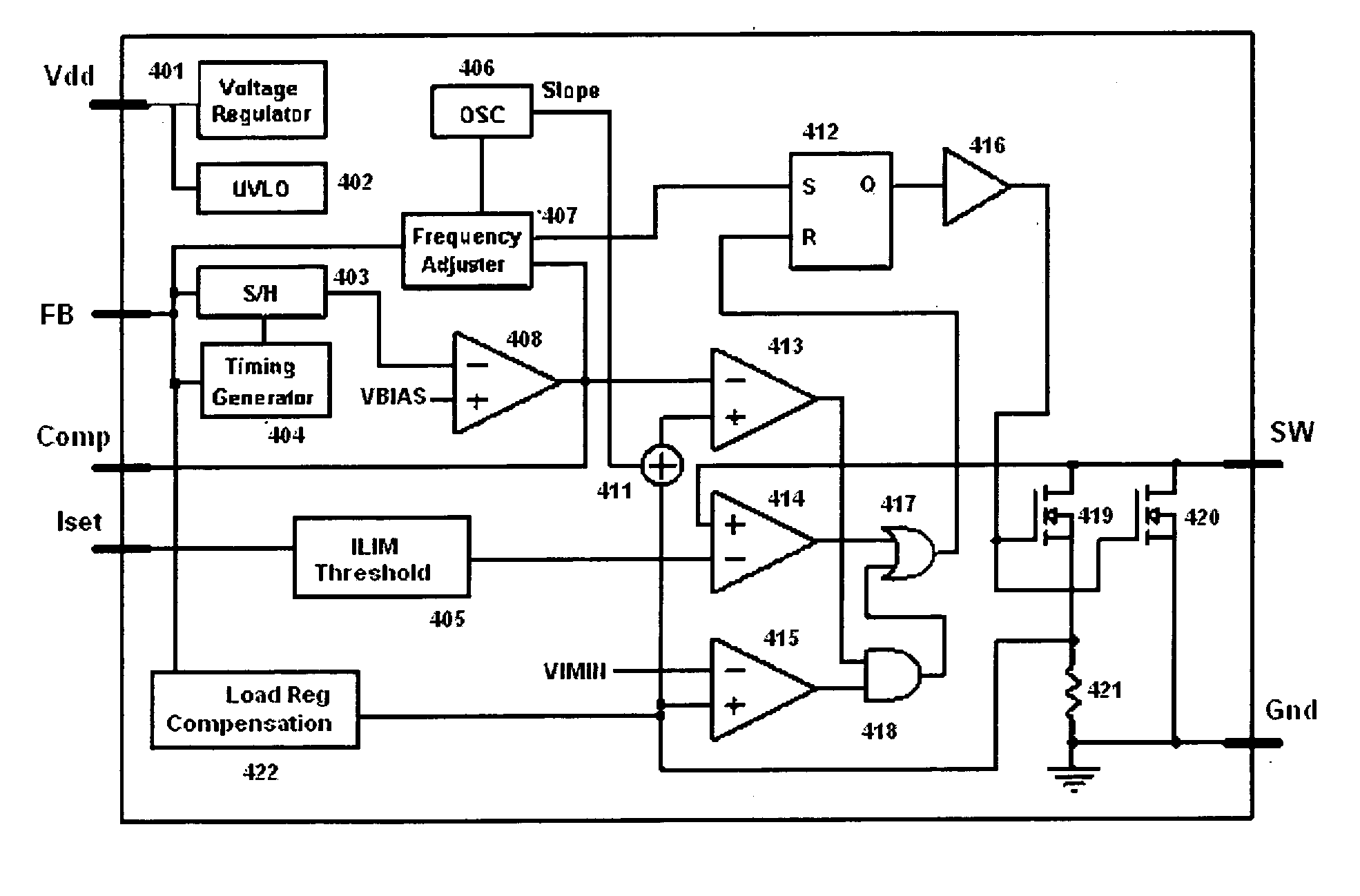

Control circuit for primary side control of switching power supply

A switched mode power supply (SMPS) includes a transformer with a primary winding, a secondary winding, an auxiliary winding, and a power switch coupled to the primary winding. During one switching cycle, the auxiliary winding provides a feedback signal which includes a first voltage pulse that is induced after the power switch is turned on and a second voltage pulse that is induced after the power switch is turned off. A control circuit includes a circuit for generating a sampling signal for sampling the second voltage pulse in a switching cycle at a time that is determined based on the first voltage pulse in the same switching cycle. A sample-and-hold circuit is configured for sampling and storing the second voltage pulse in response to the sampling signal. A switching signal generating circuit is configured to generate a switching signal for controlling the power switch based on an output of the sample-and-hold circuit.

Owner:BCD SHANGHAI MICRO ELECTRONICS CO LTD

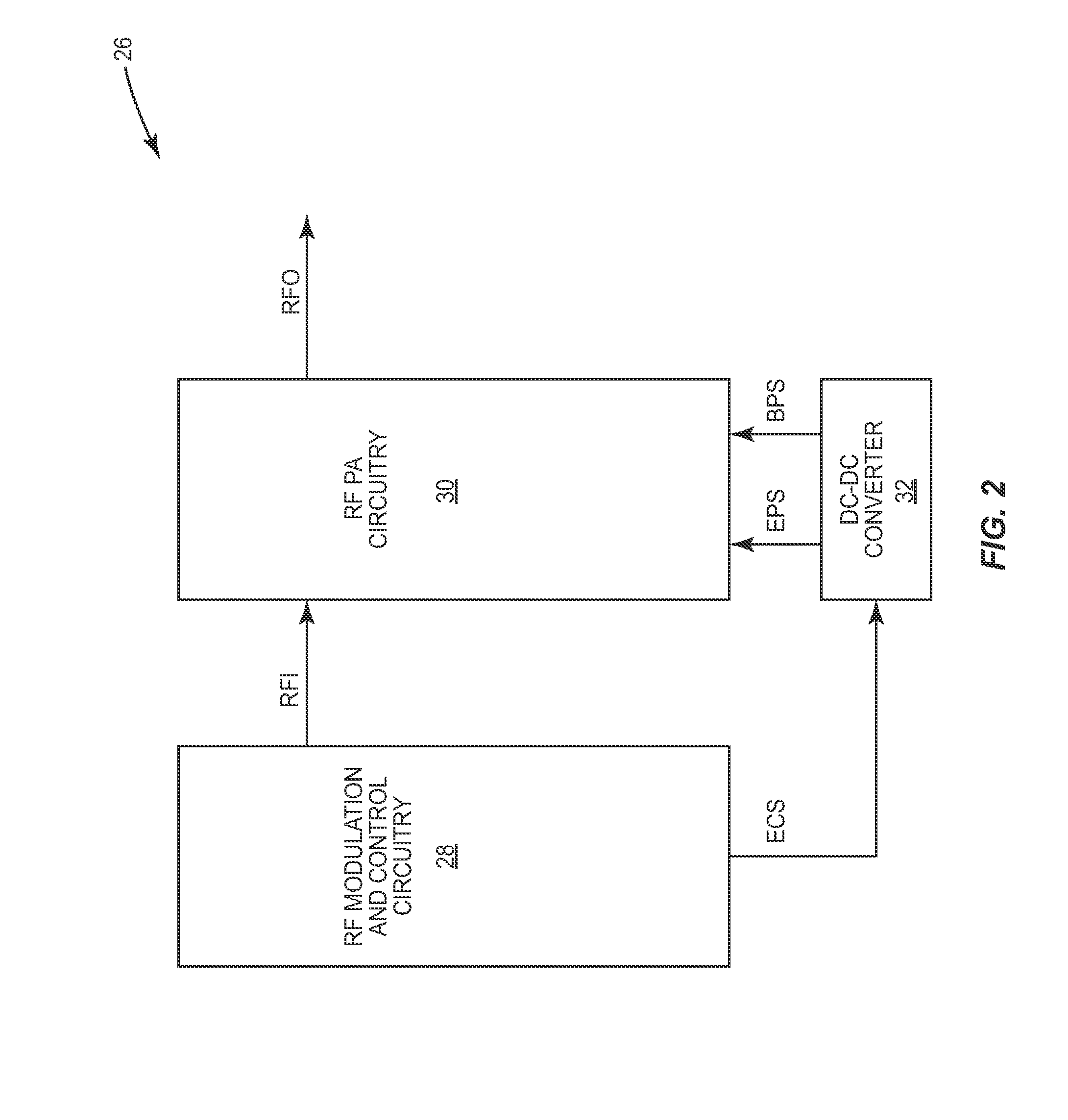

Dc-dc converter current sensing

A sample-and-hold (SAH) current estimating circuit and a first switching power supply are disclosed. The first switching power supply provides a first switching power supply output signal based on a series switching element and a setpoint. The SAH current estimating circuit samples a voltage across the series switching element of the first switching power supply during an ON state of the series switching element and during a ramping signal peak to provide an SAH output signal based on an estimate of an output current of the first switching power supply output signal. The first switching power supply selects the ON state of the series switching element, such that during the ramping signal peak, the series switching element has a series current having a magnitude, which is about equal to a magnitude of the output current of the first switching power supply output signal.

Owner:QORVO US INC

Multi-protocol radio frequency identification transponder transceiver

ActiveUS7689195B2Electric signal transmission systemsMemory record carrier reading problemsDigital signal processingTransceiver

A transceiver for a RFID reader and a transceiver for a RFID transponder (tag) allow communication between the two devices. The RFID reader utilizes an analog front end and a digital backend. In the receiver portion of the transceiver, the front end of the RFID reader uses a pair of down-conversion mixers to demodulate a received signal into in-phase (I) and quadrature (Q) components and analog-to-digital converters (ADC) digitize the signal. A digital signal processor (DSP) in the back end processes the digital signal and uses a matched filter for data detection. The RFID tag receives an inductively coupled signal from the reader and the receiver portion of the tag uses a pulse / level detector that employs an analog comparator and a sample and hold circuit to detect the received signal. A digital decoder / controller is used to decode the incoming data and to establish a sampling clock for the pulse / level detector. An automatic gain control (AGC) circuit adjusts a receiver gain according to the received signal strength and controls tuning of magnetic coupling circuitry.

Owner:NXP USA INC

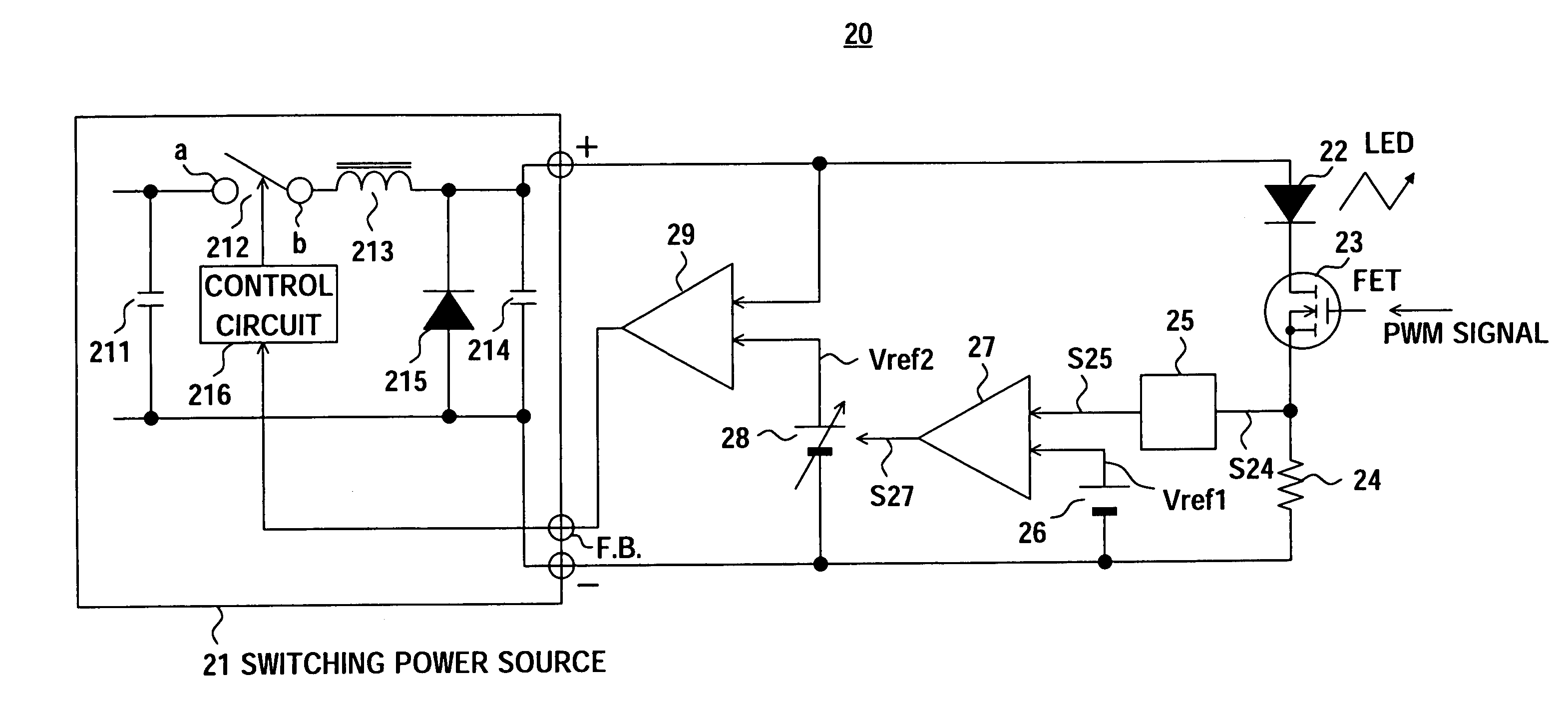

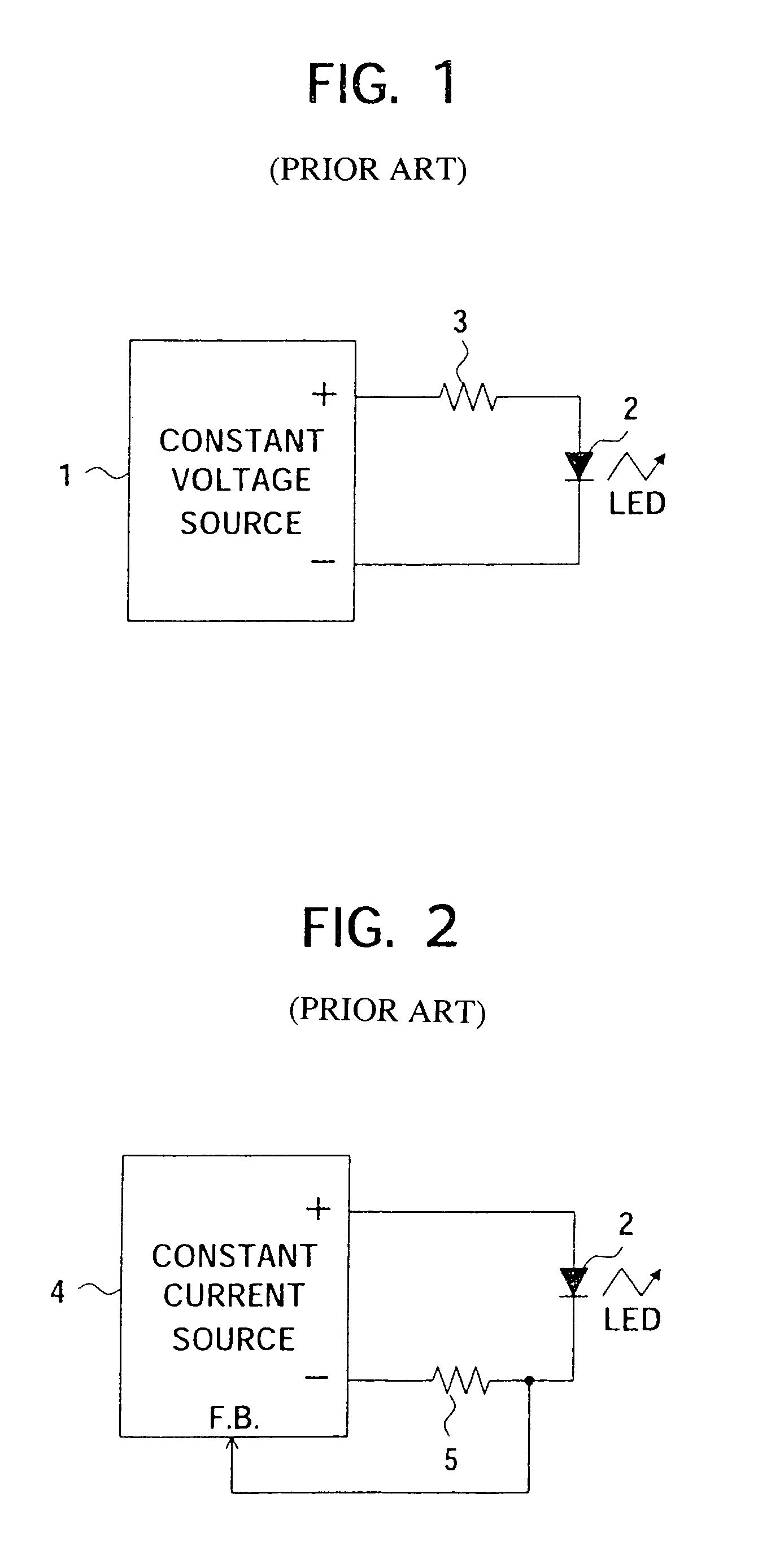

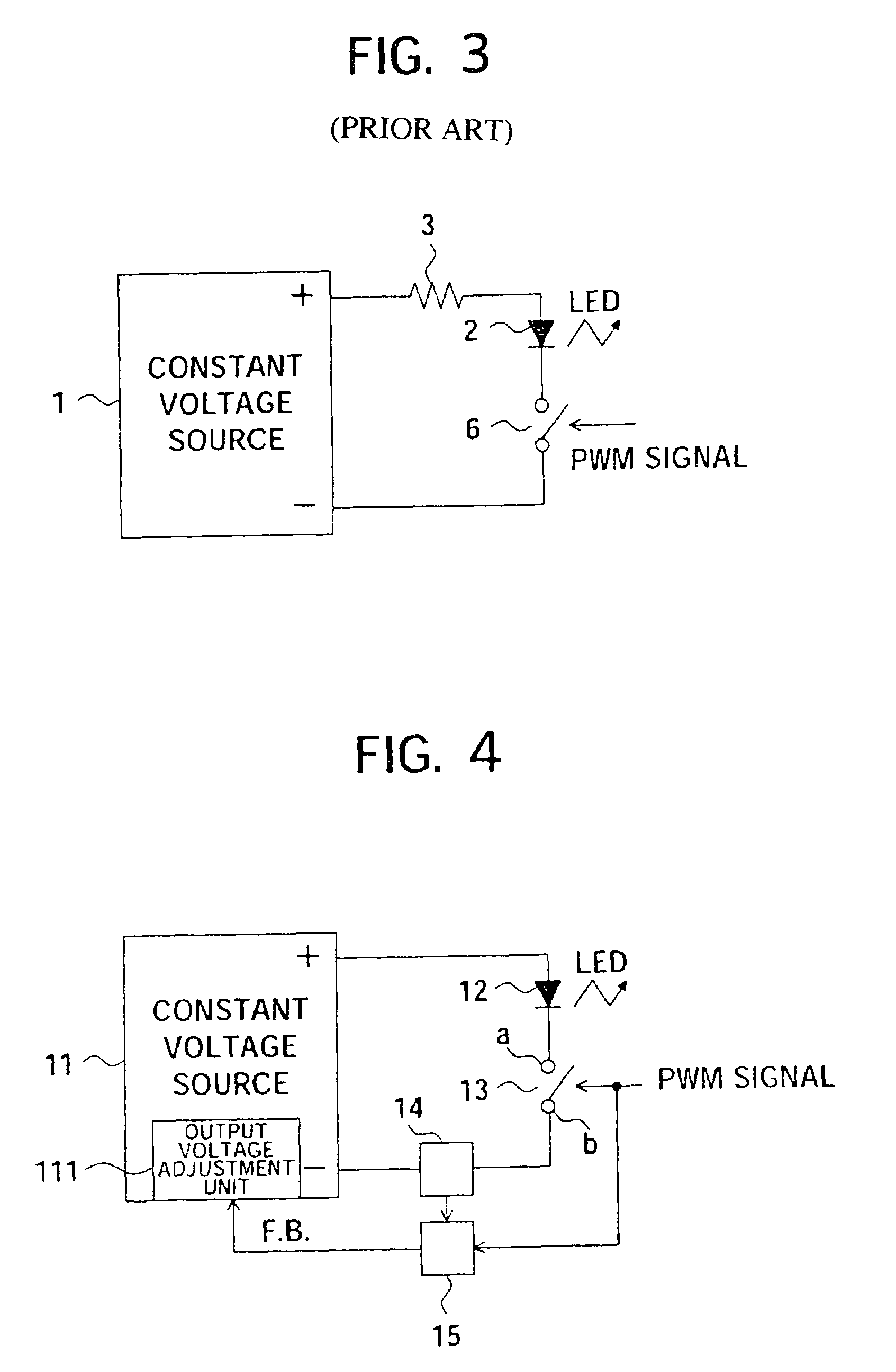

Light emitting element drive device and display apparatus

ActiveUS7312783B2Regulation stabilityBrightness adjustableElectroluminescent light sourcesDc-dc conversionVoltage regulationEngineering

A light emitting element drive circuit and a display system able to simultaneously perform constant current control and PWM control and able to perform a stable adjustment of luminance over a wide dynamic range, including a constant voltage source having an output voltage adjustment unit able to be changed in output voltage according to a signal from the outside, a switch circuit connected to the cathode side of the LED and ON / OFF controlled in accordance with a PWM signal from the outside, a current detection unit for detecting the current flowing in the circuit, and a sample and hold circuit for maintaining the current input value from the current detection unit for a constant period, and the output voltage adjustment unit receives as input the output of the sample and hold circuit, that is, the current value when the switch circuit is ON, and adjusts the output of the constant voltage source so that this value becomes a previously determined set value, to thereby make the current flowing in the LED constant.

Owner:SATURN LICENSING LLC

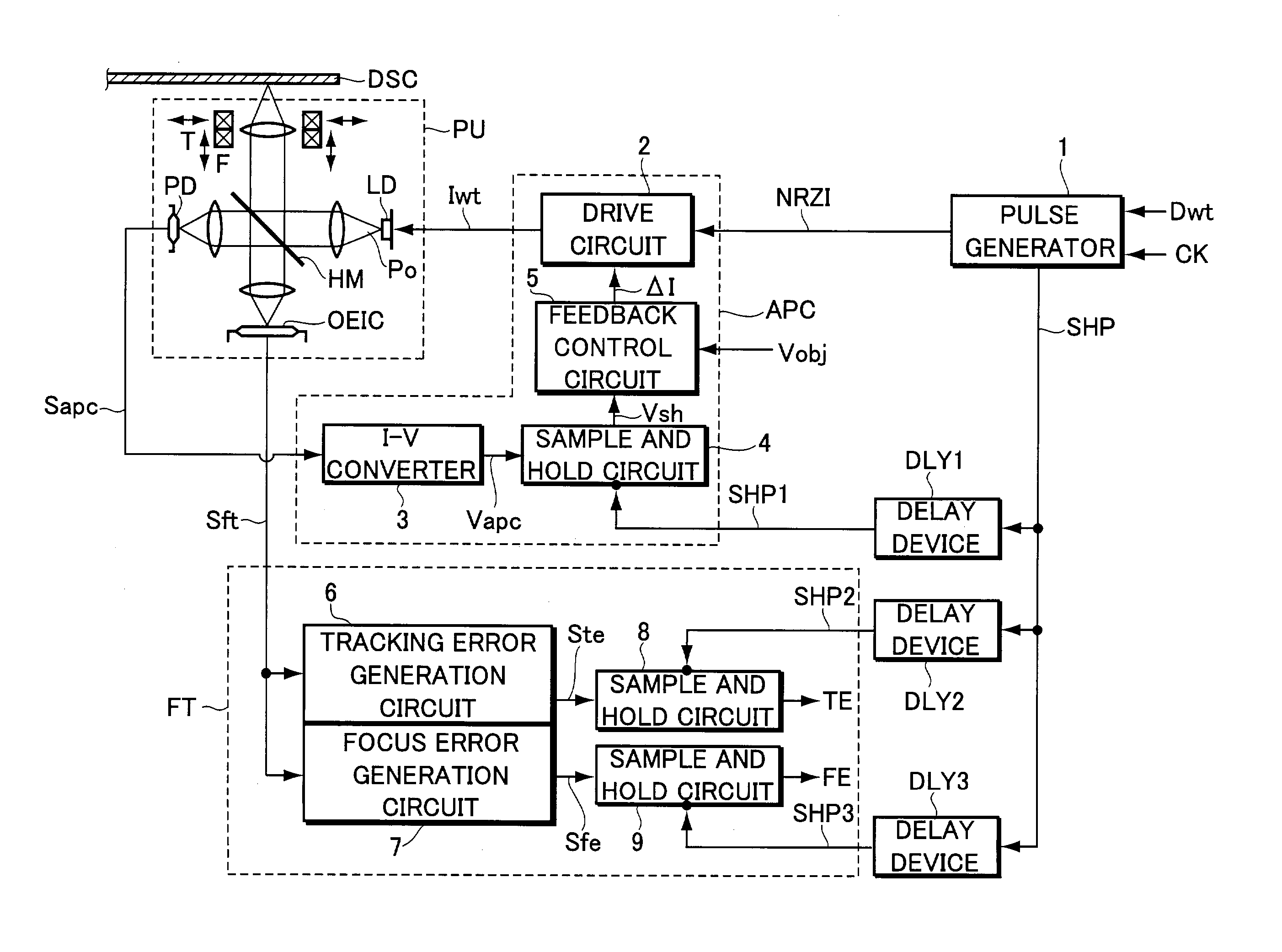

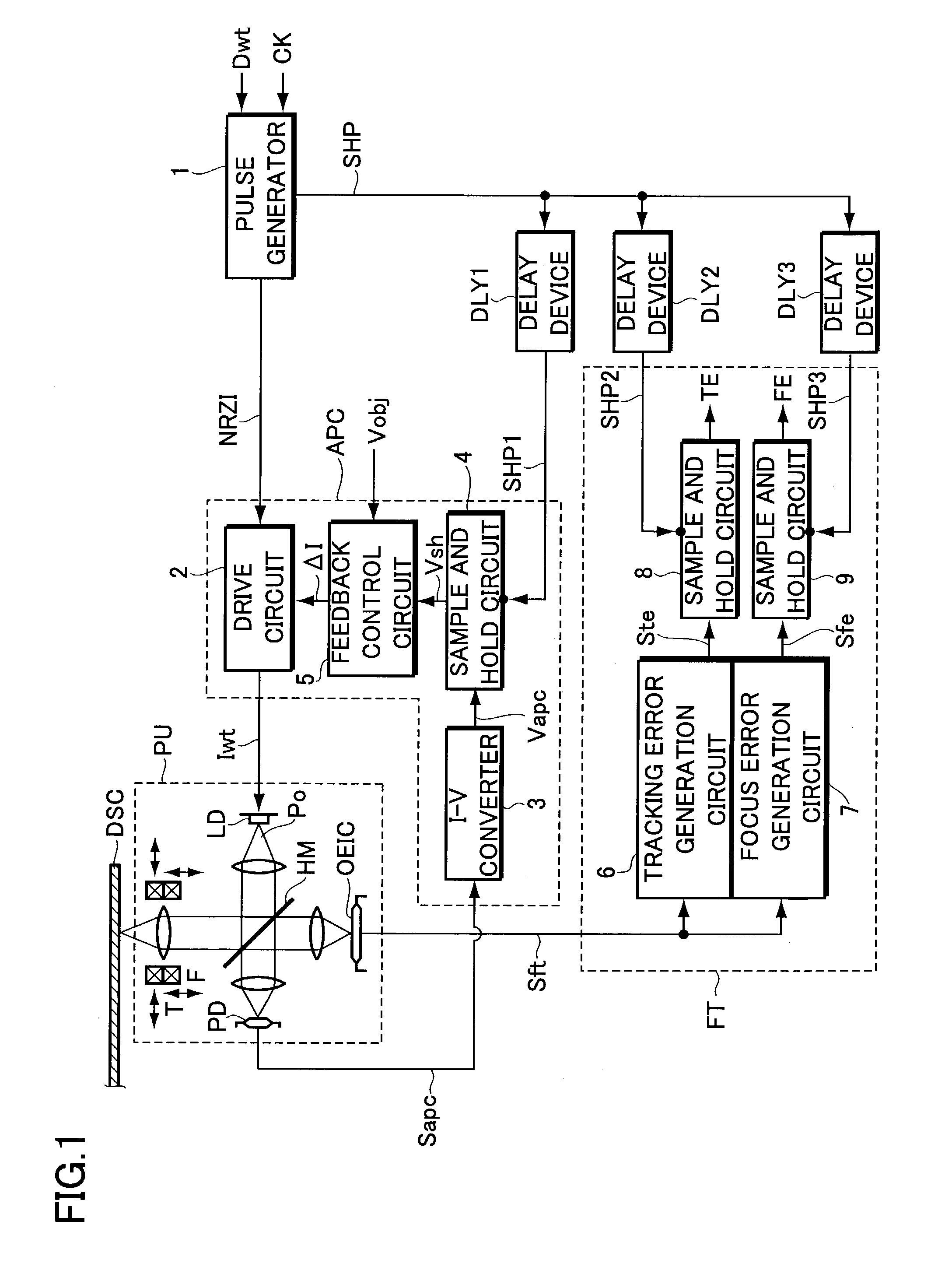

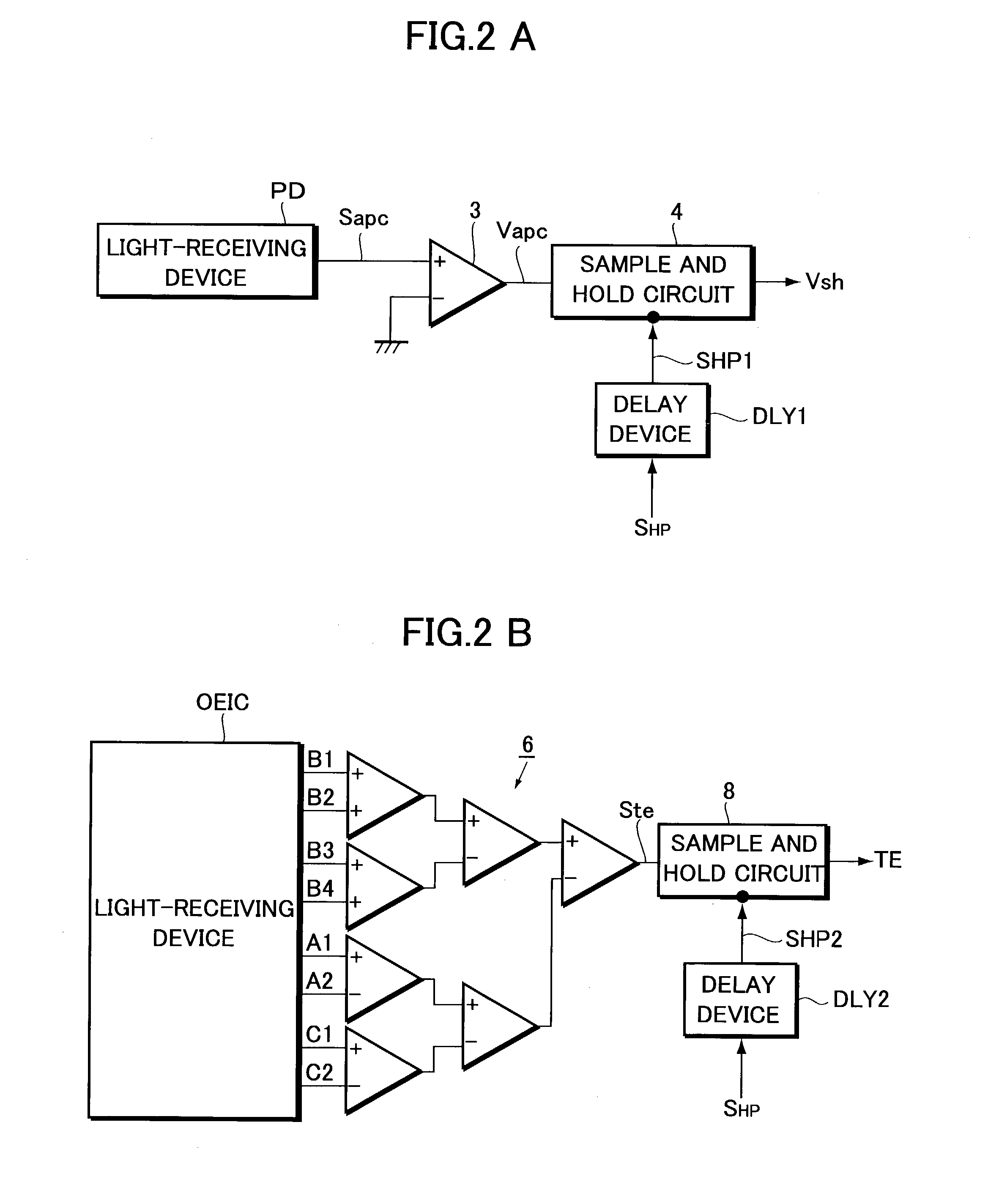

Information recording apparatus

InactiveUS7164631B2Improve accuracyAccurate power adjustmentCombination recordingOptical beam sourcesTime delaysDelayed time

An information recording apparatus is provided, which can control over the power of light beams emitted from a light source and various types of servo control with higher accuracy. A laser beam is emitted from a semiconductor laser to write information onto an optical disc. A detection signal indicative of the power of the laser beam output from a light-receiving device is sampled and held with a sample and hold circuit via an I-V converter at a timing delayed by the time corresponding to the delay time of the I-V converter. A tracking error generation circuit and a focus error generation circuit generate a tracking error signal and a focus error signal, respectively, on the basis of a detection signal having information about tracking error and focus error and output from a light-receiving device. Sample and hold circuits sample and hold the tracking error signal and the focus error signal at a timing delayed by the time corresponding to the delay time of each of the generation circuits, respectively. Power control, tracking servo, and focus servo are performed using each of the signals held by the sample and hold circuits, respectively.

Owner:PIONEER CORP