Patents

Literature

1539results about "Electric analogue stores" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

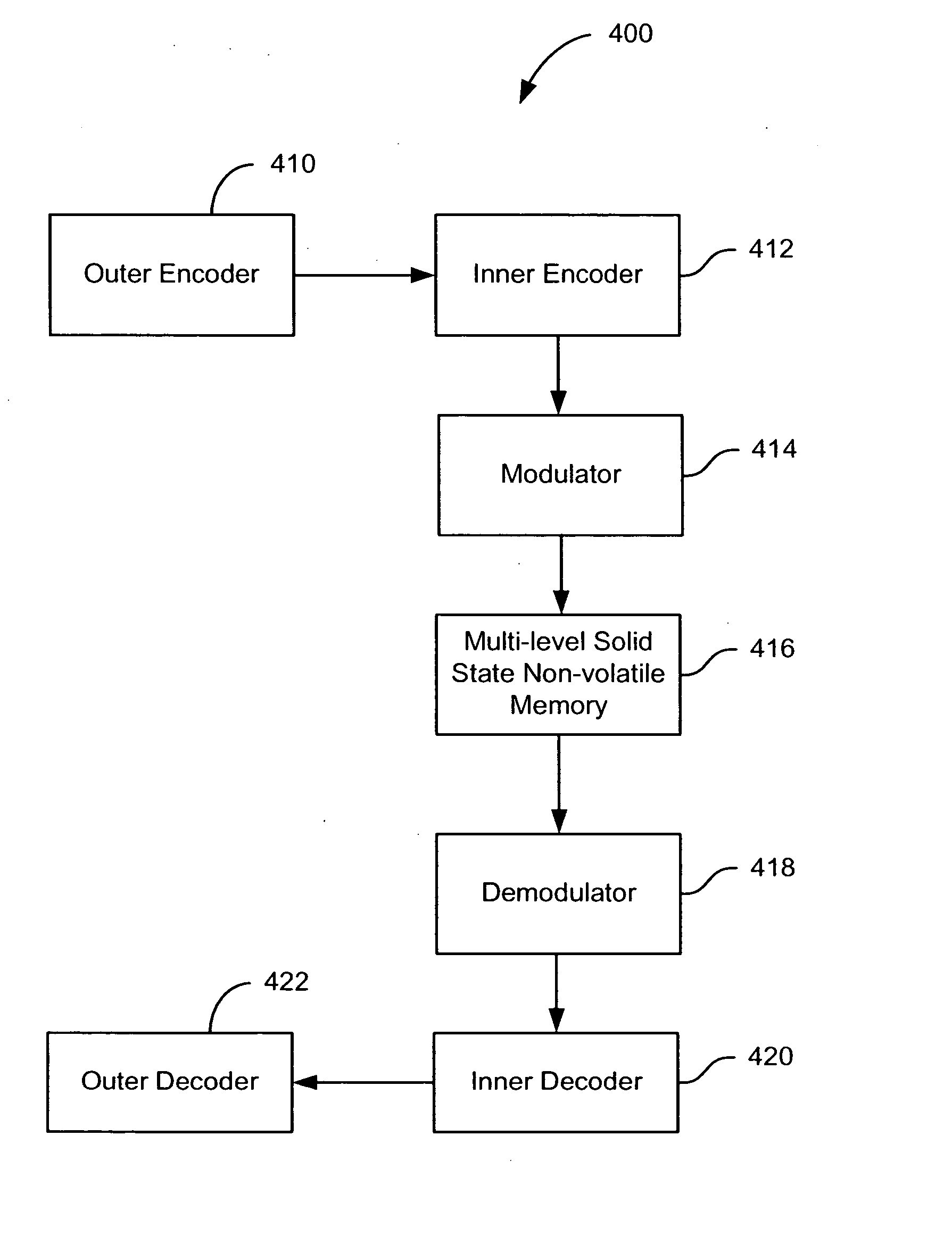

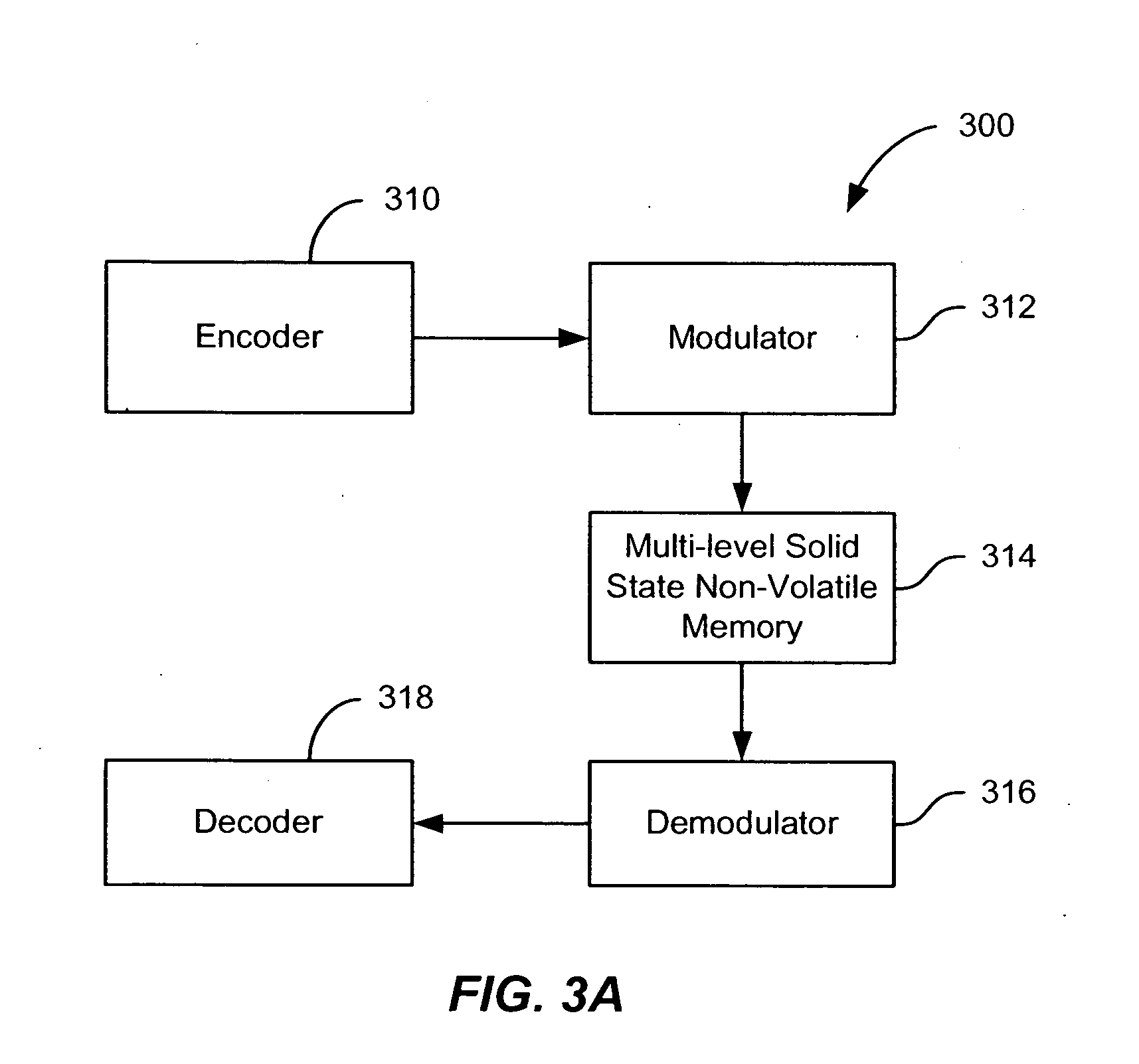

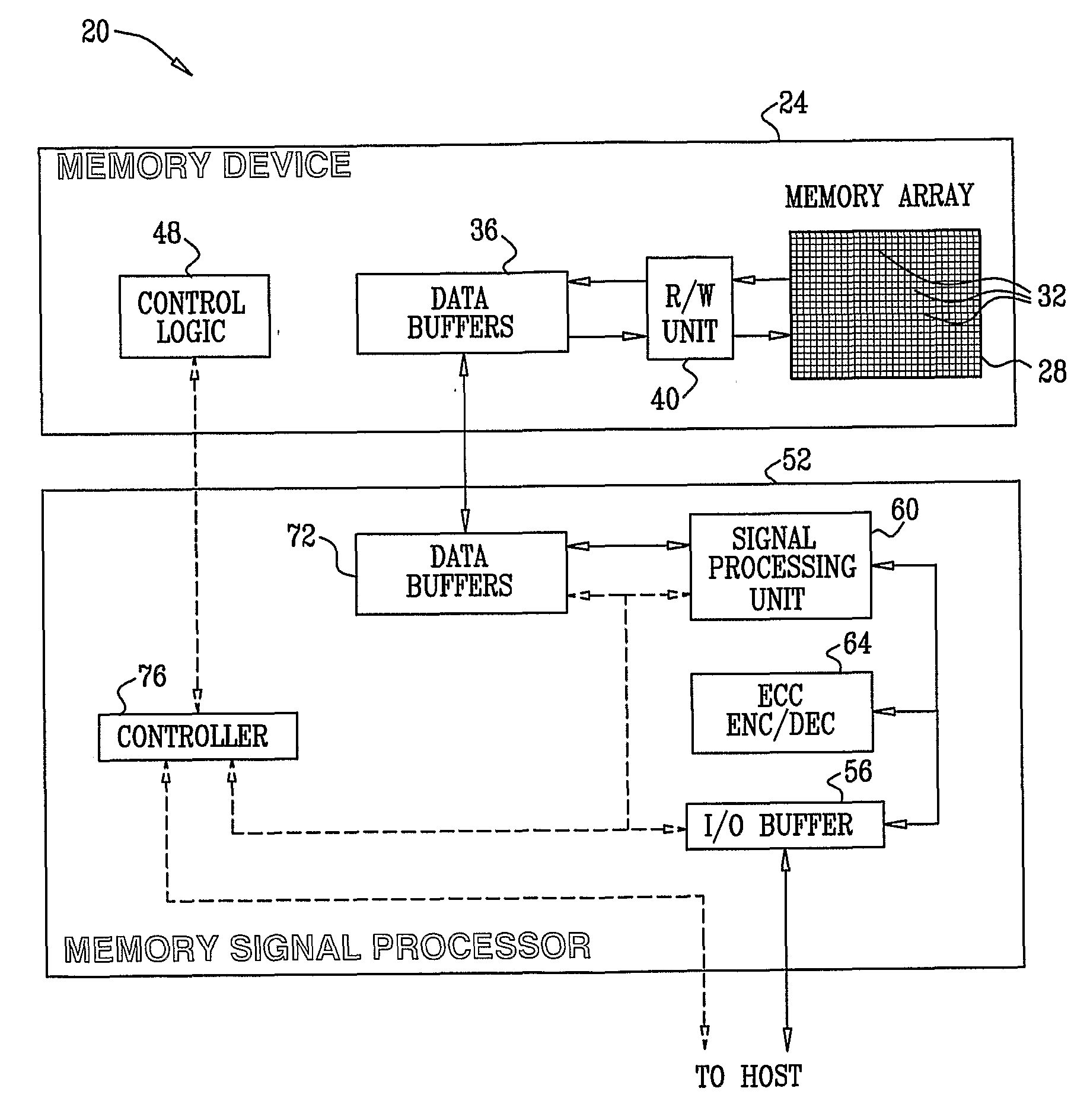

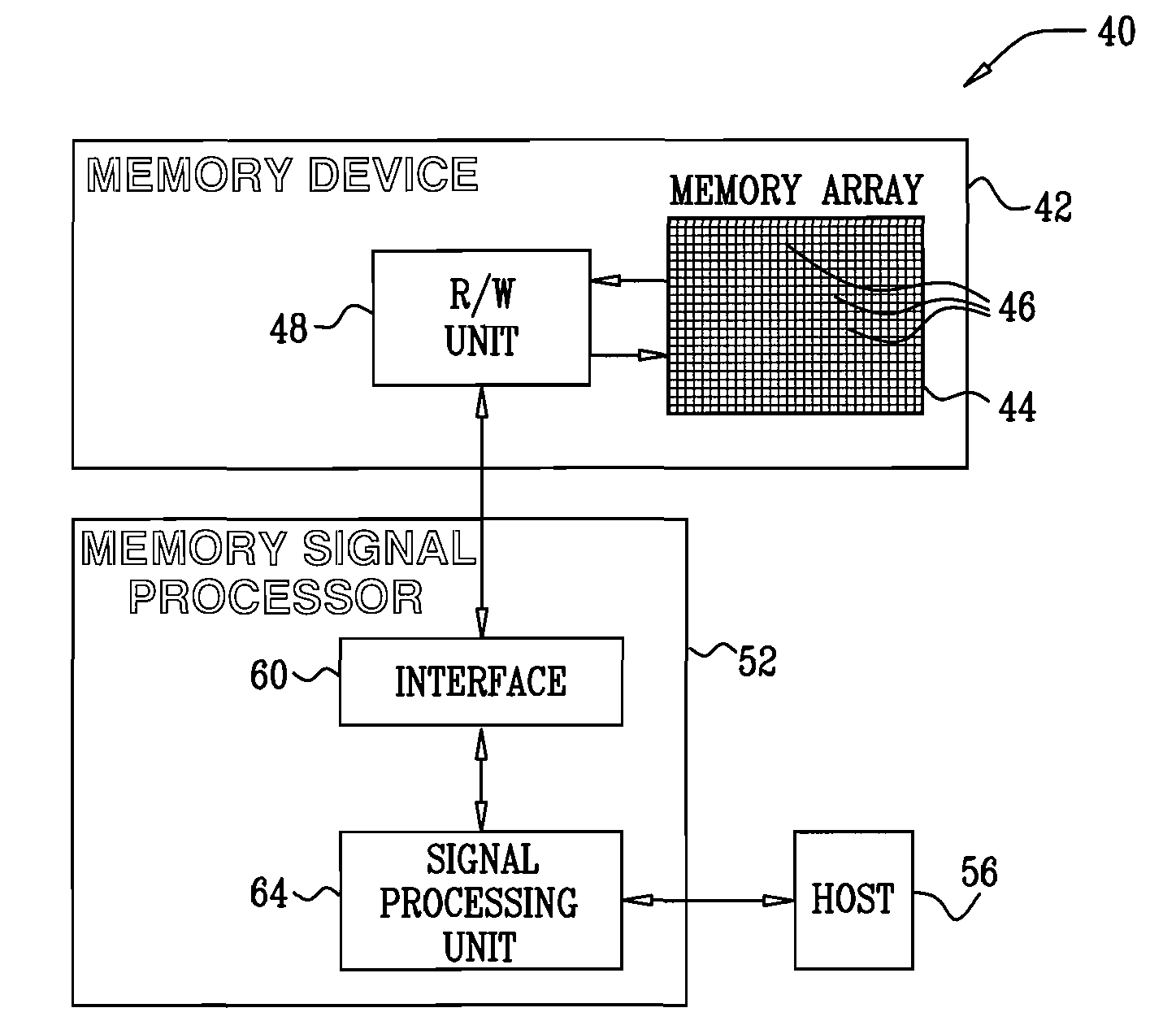

Method and system for error correction in flash memory

ActiveUS20070171730A1Improve storage densityImprove reliabilityMemory architecture accessing/allocationError detection/correctionA d converterData memory

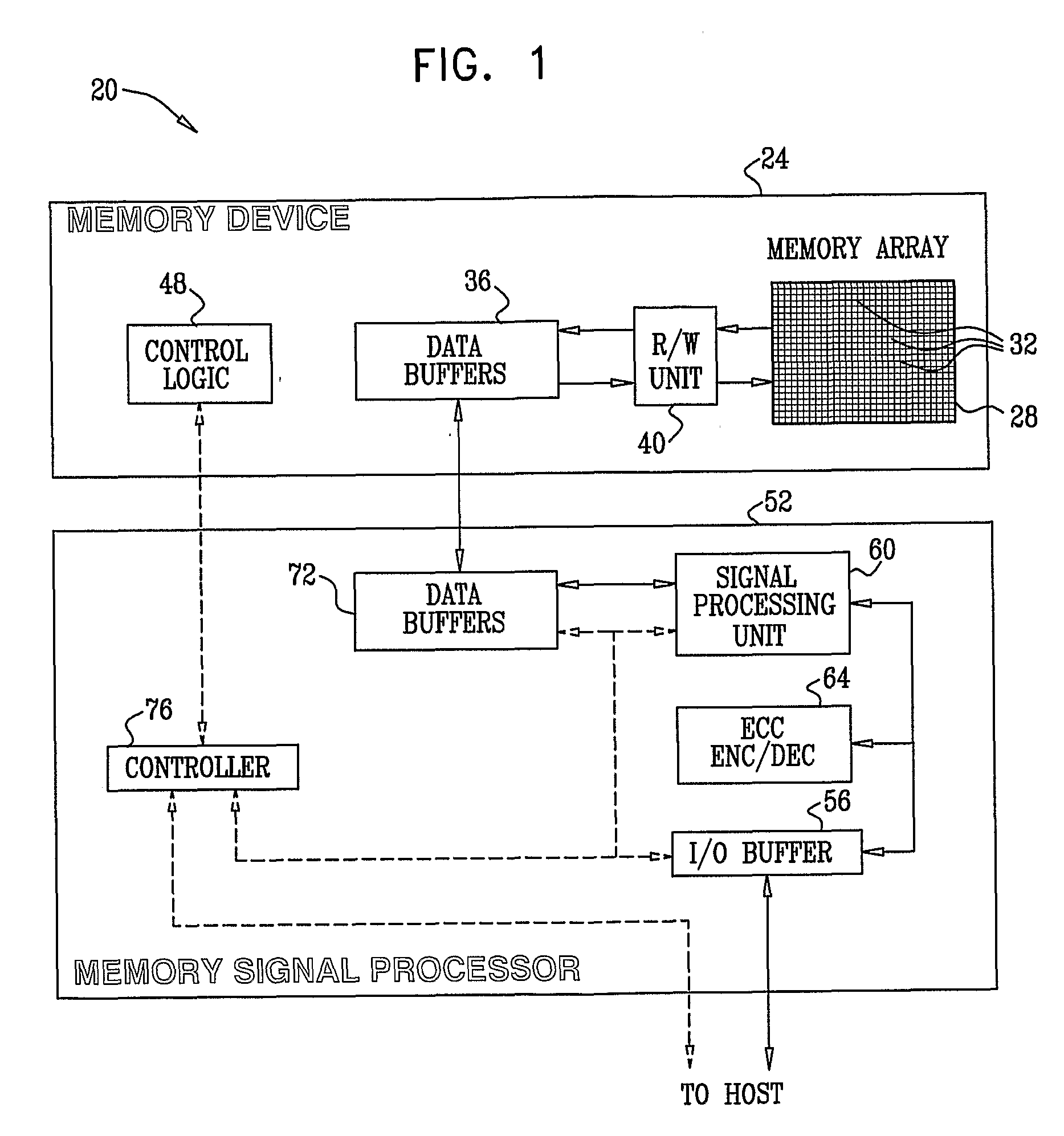

A solid state non-volatile memory unit. The memory unit includes a multi-level solid state non-volatile memory array adapted to store data characterized by a first number of digital levels. The memory unit also includes an analog-to-digital converter having an input and an output. The input of the analog-to-digital converter is adapted to receive data from the multi-level solid state non-volatile memory array. The output of the analog-to-digital converter is adapted to output a digital signal characterized by a second number of digital levels greater than the first number of digital levels.

Owner:MARVELL ASIA PTE LTD

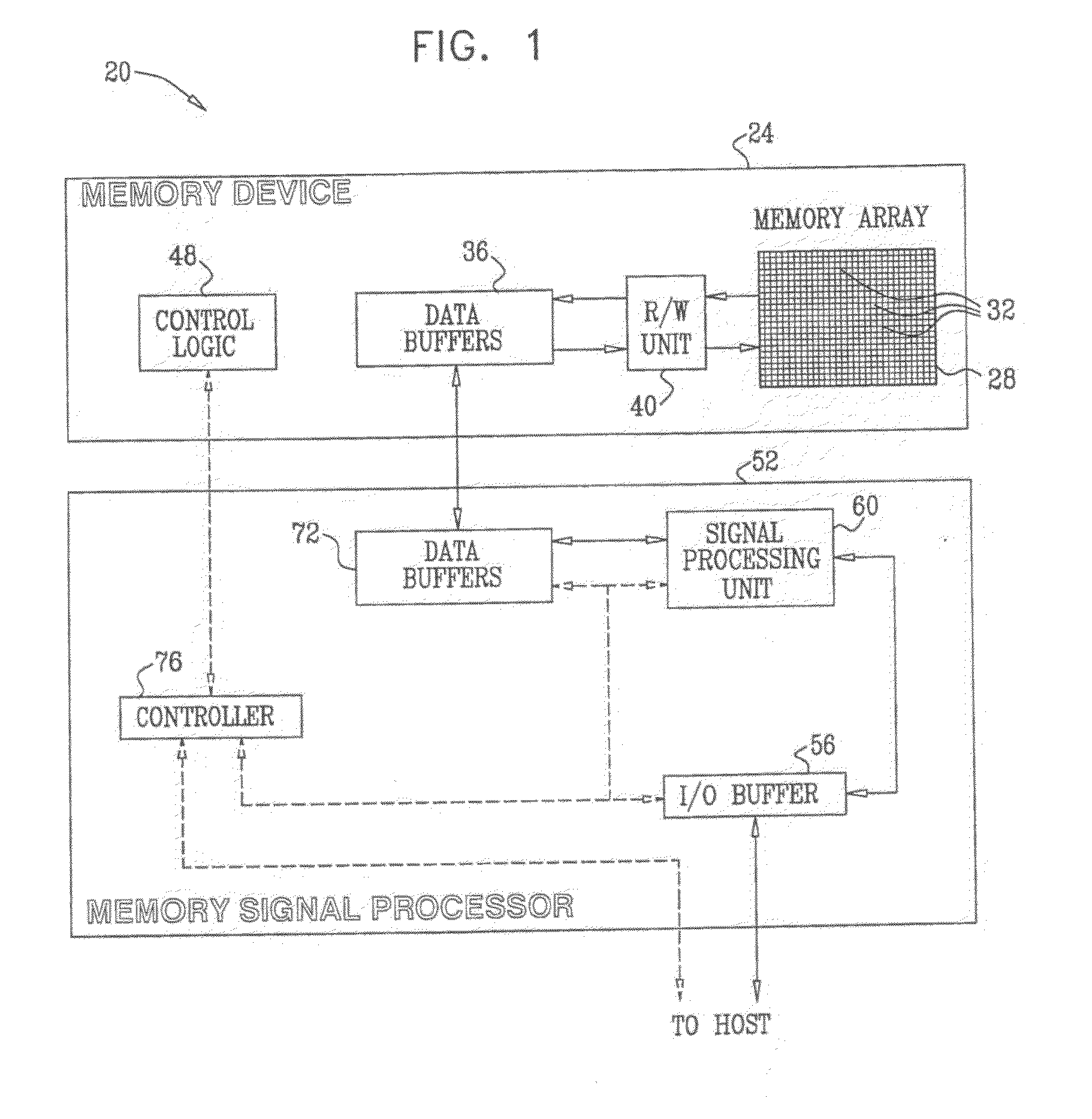

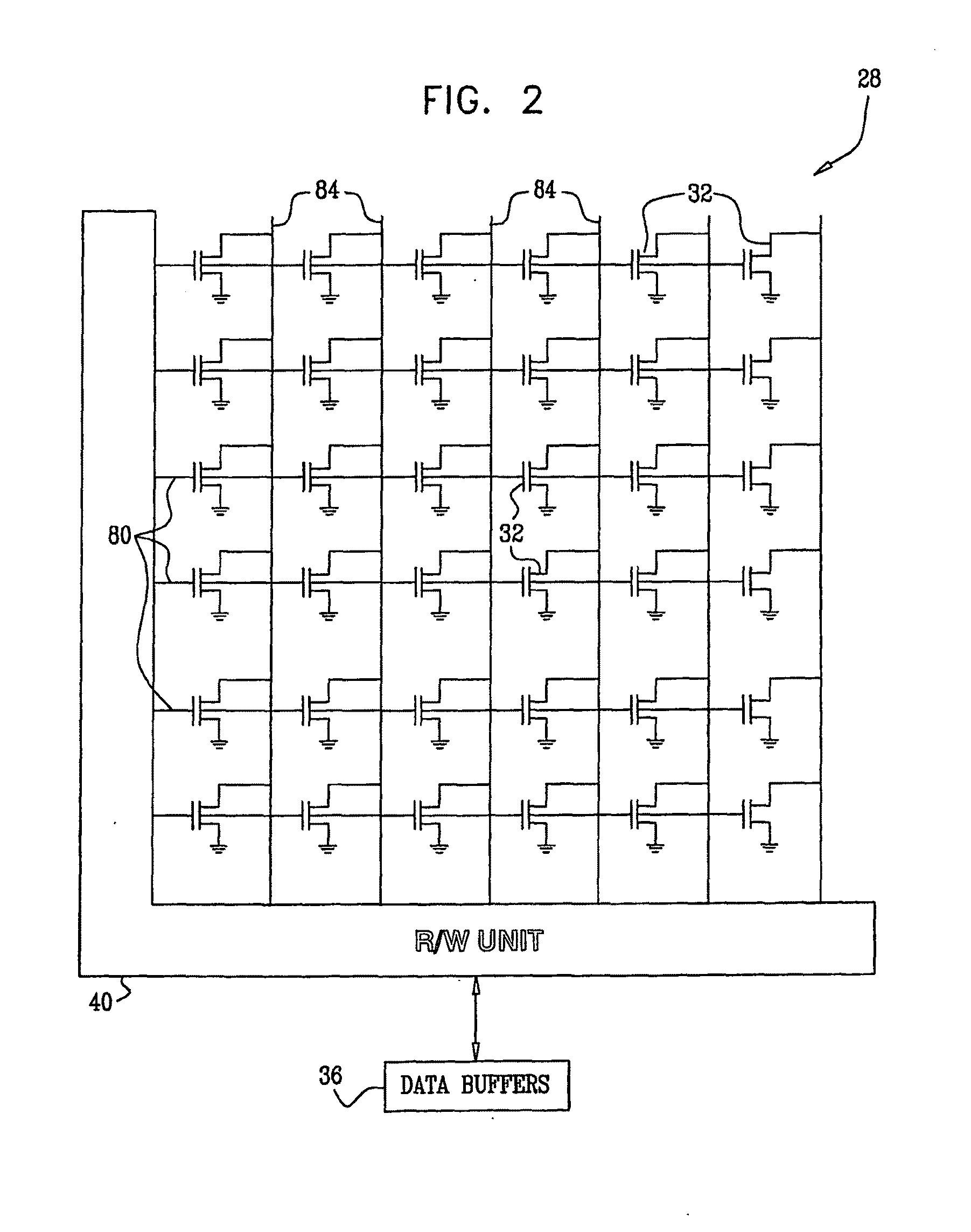

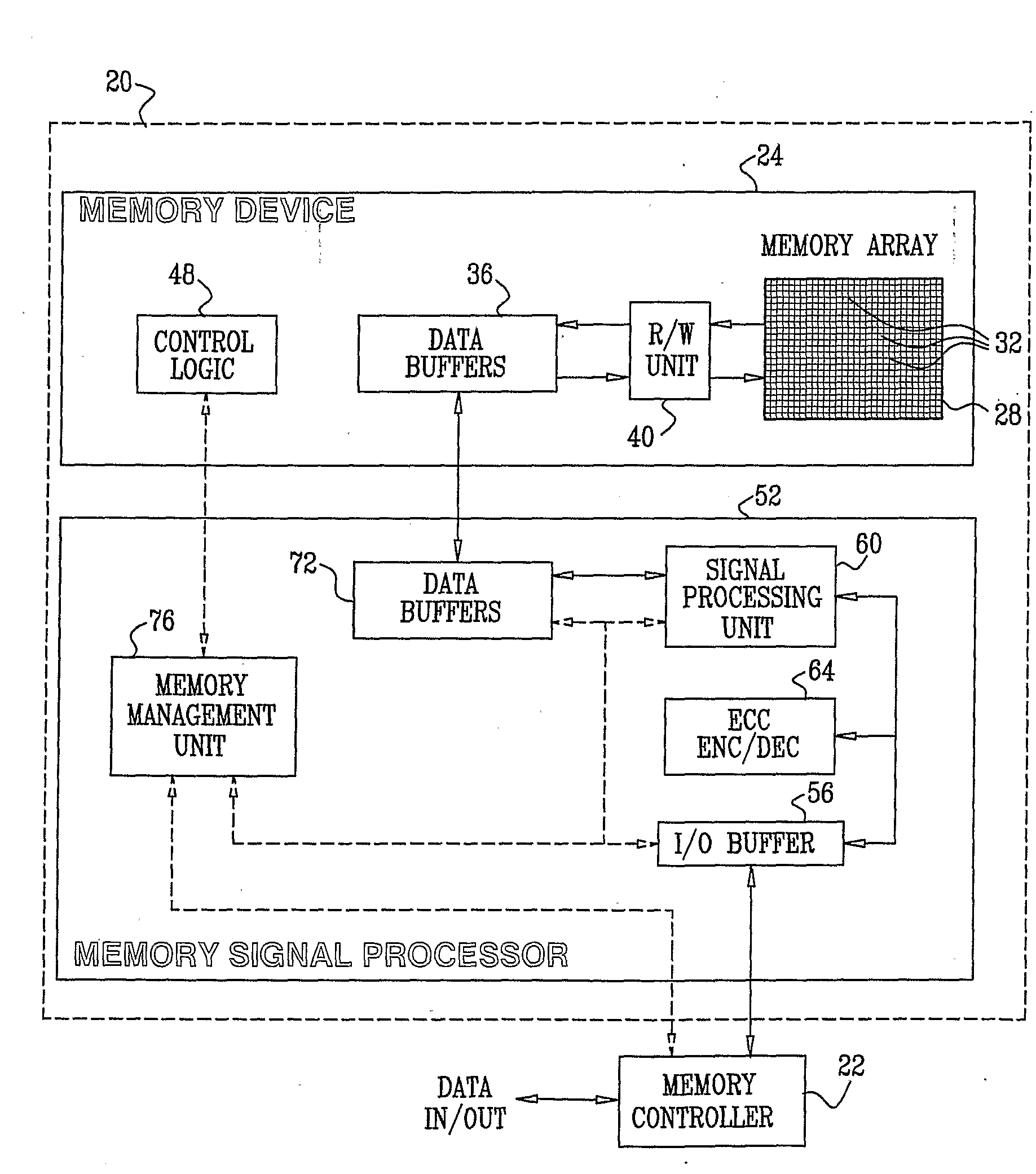

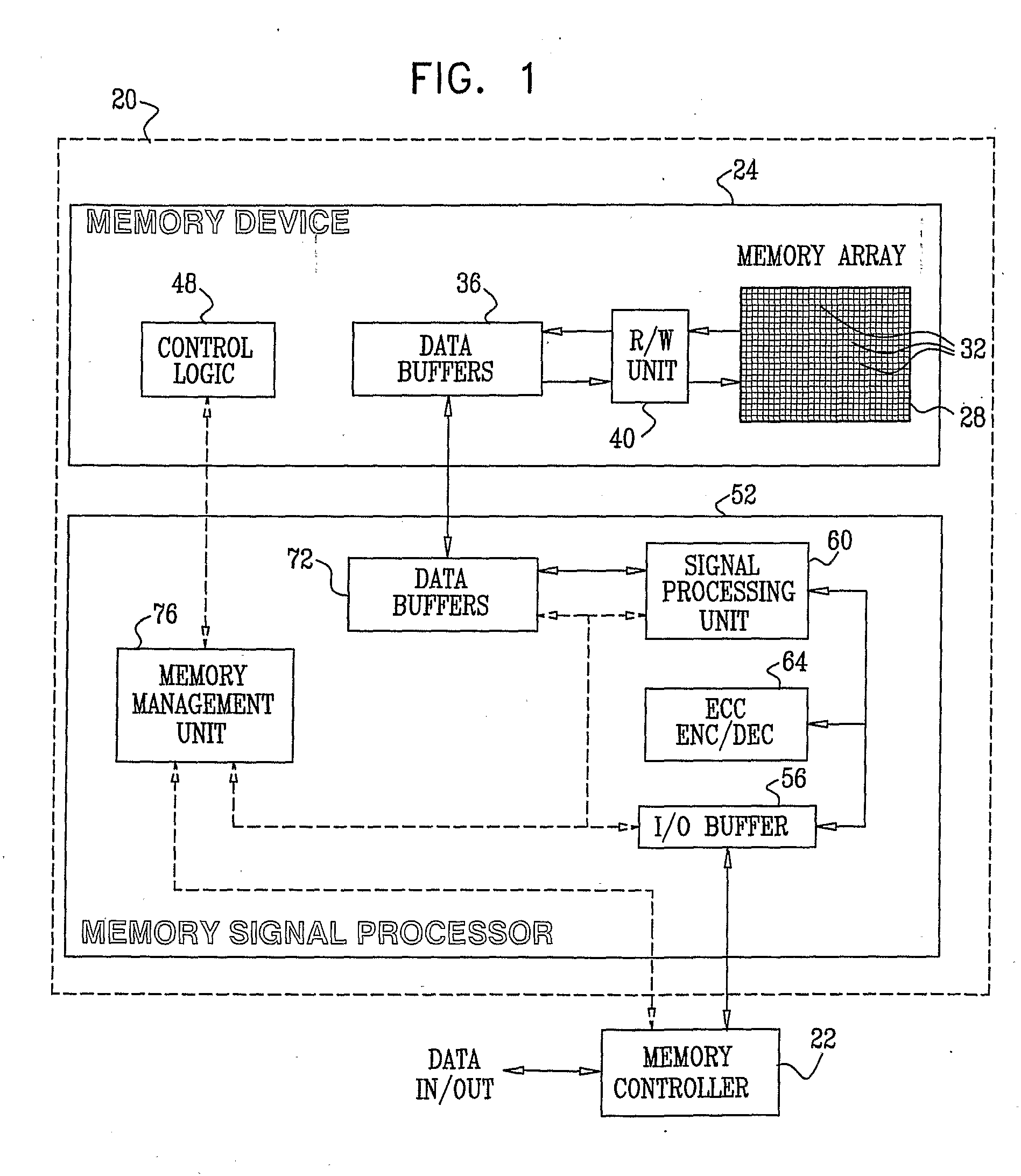

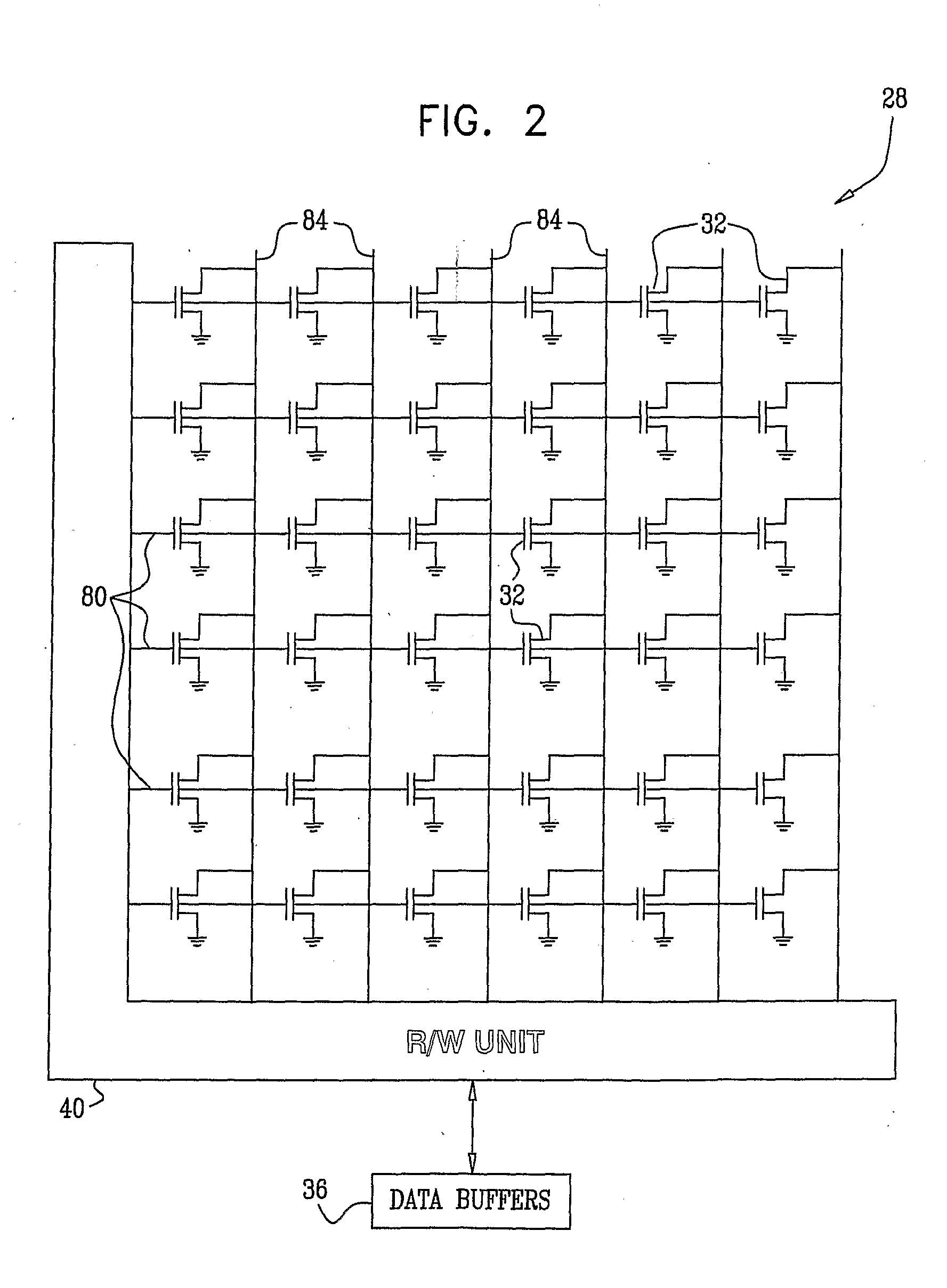

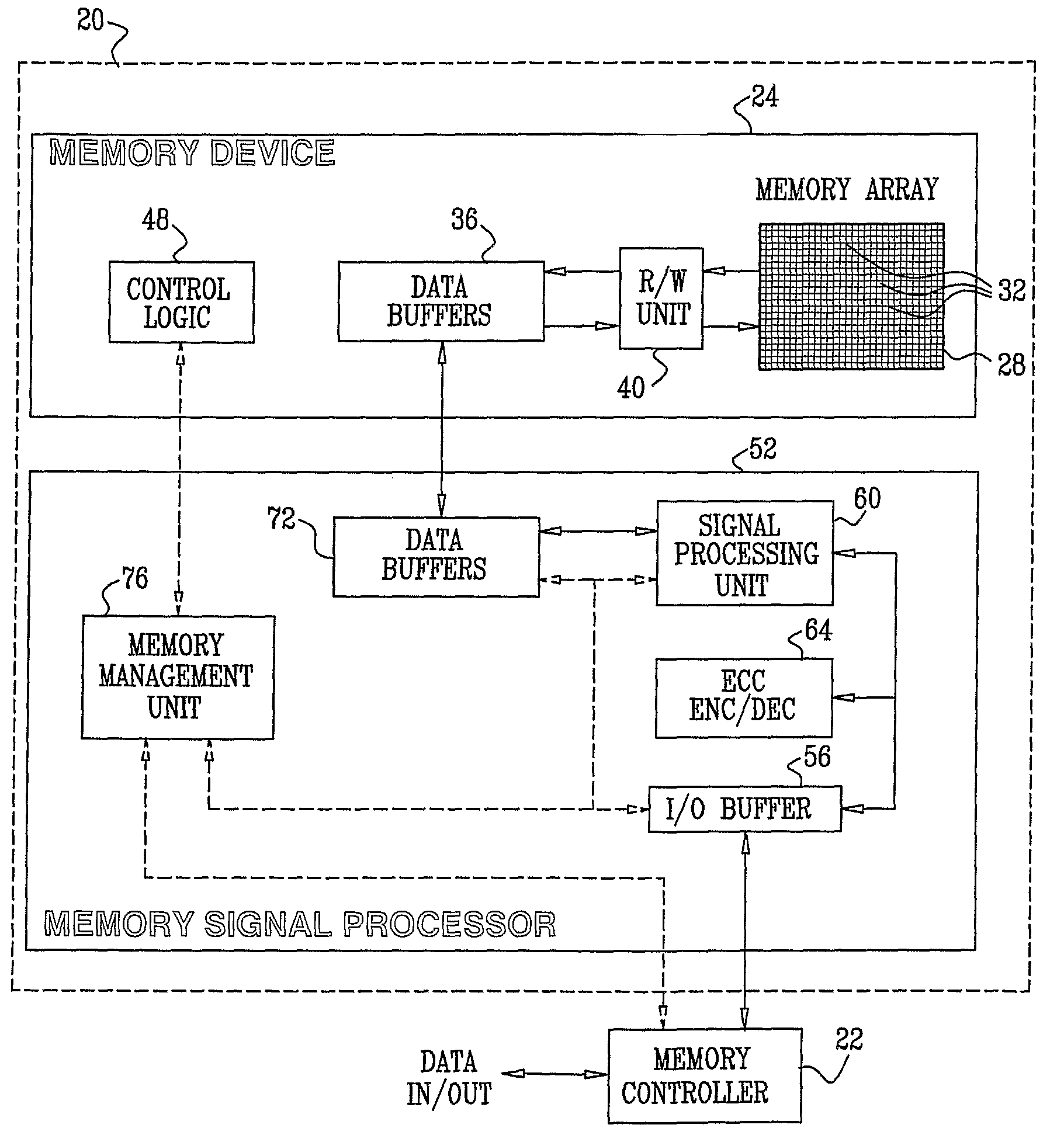

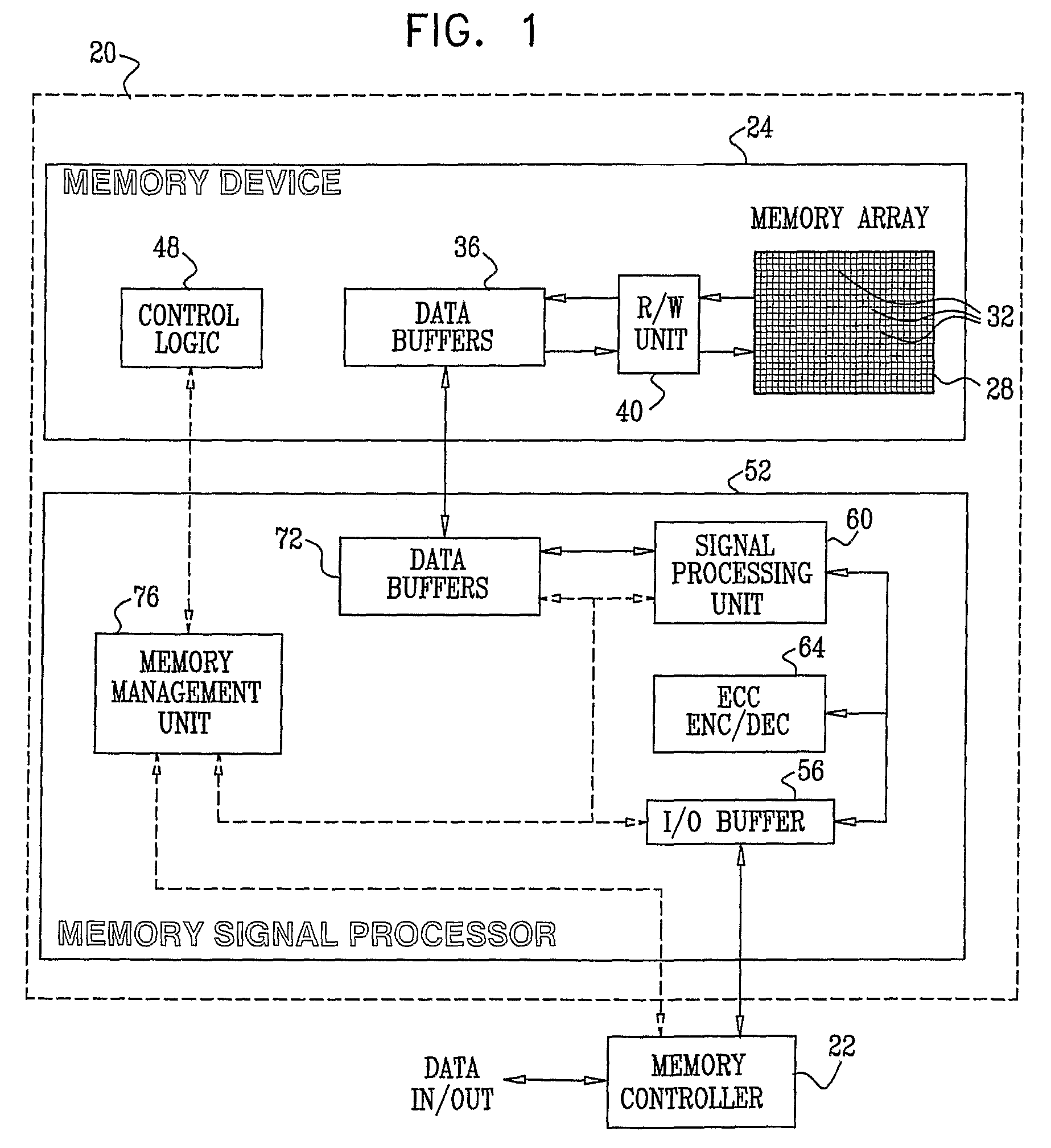

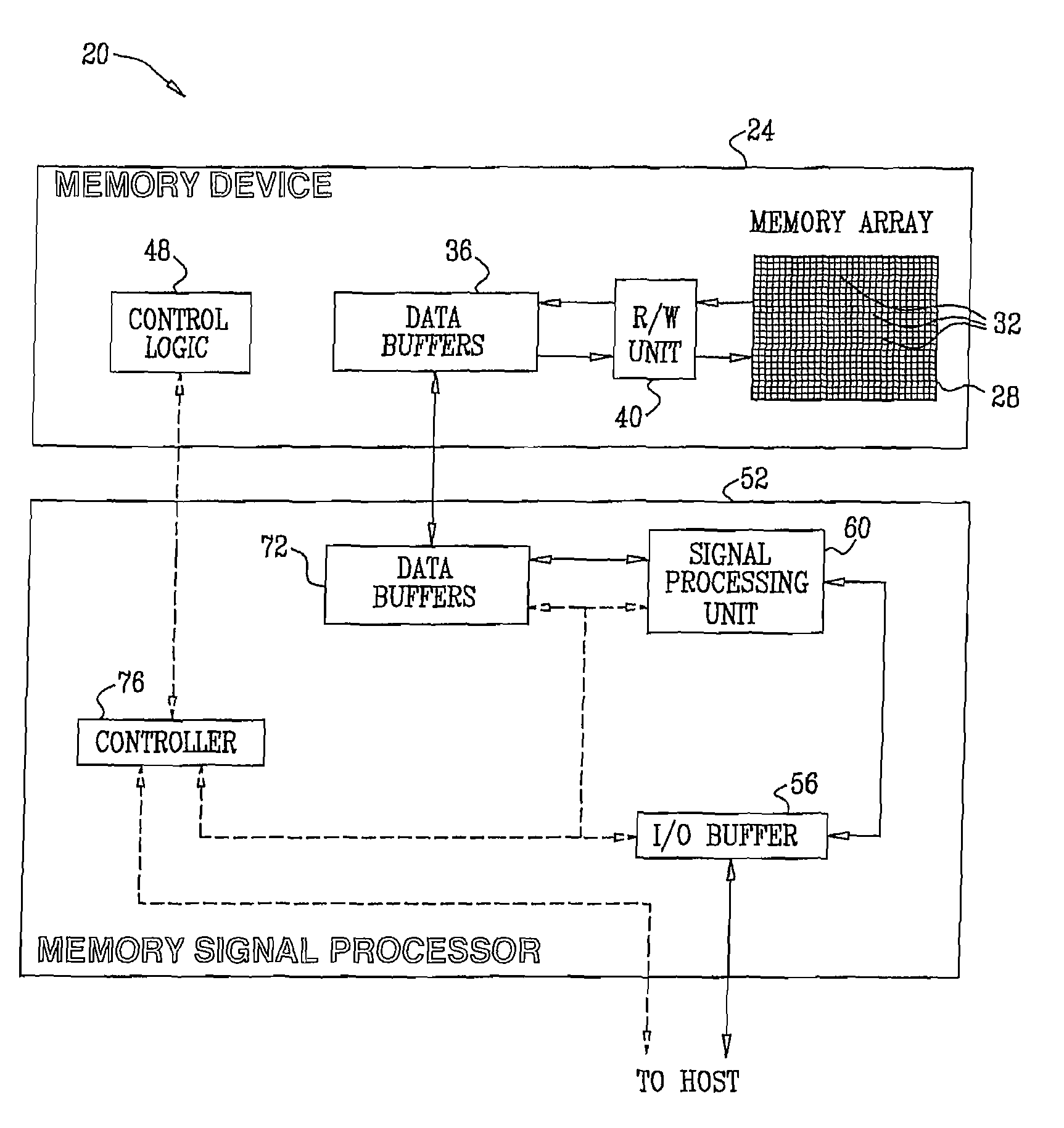

Distortion Estimation And Cancellation In Memory Devices

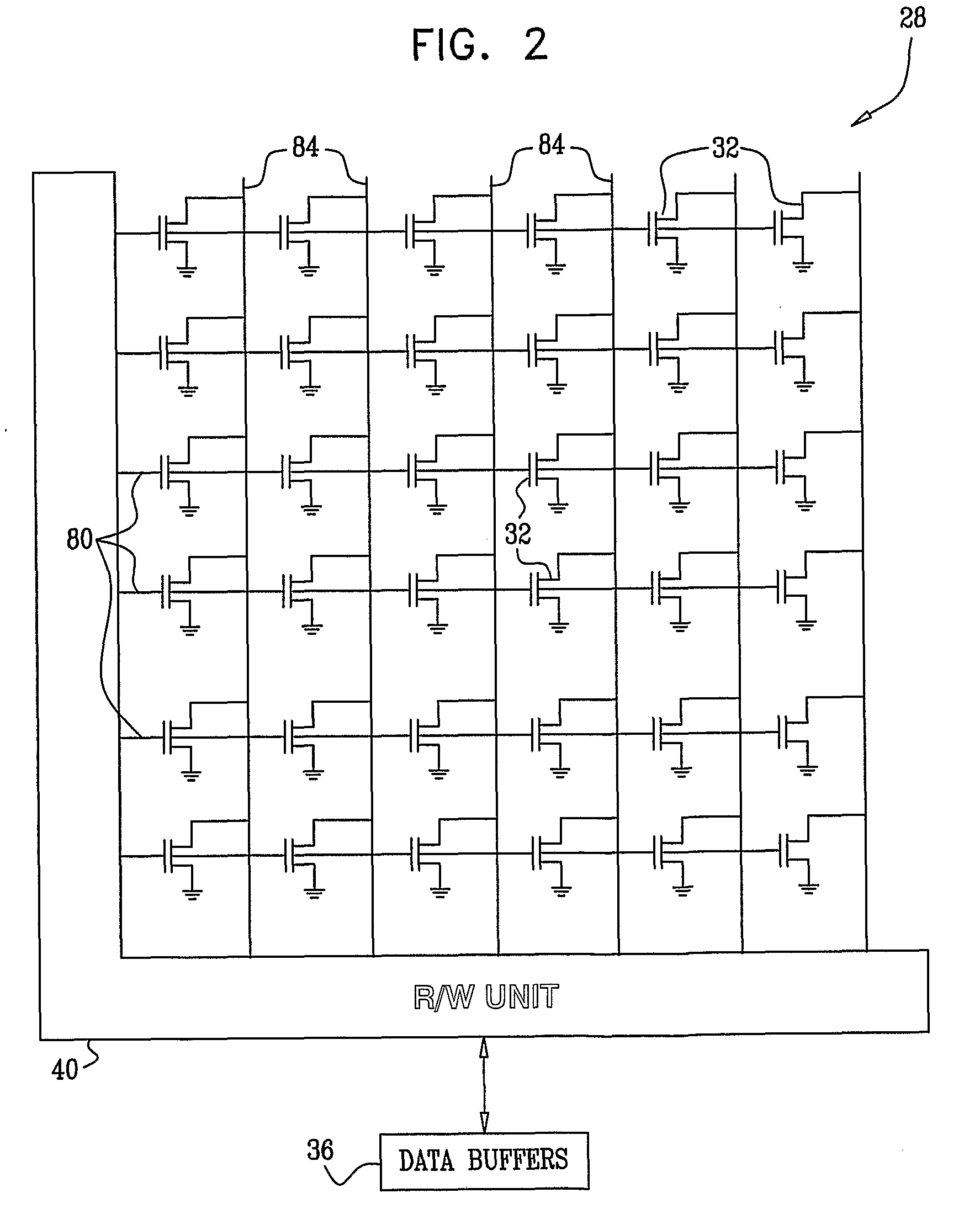

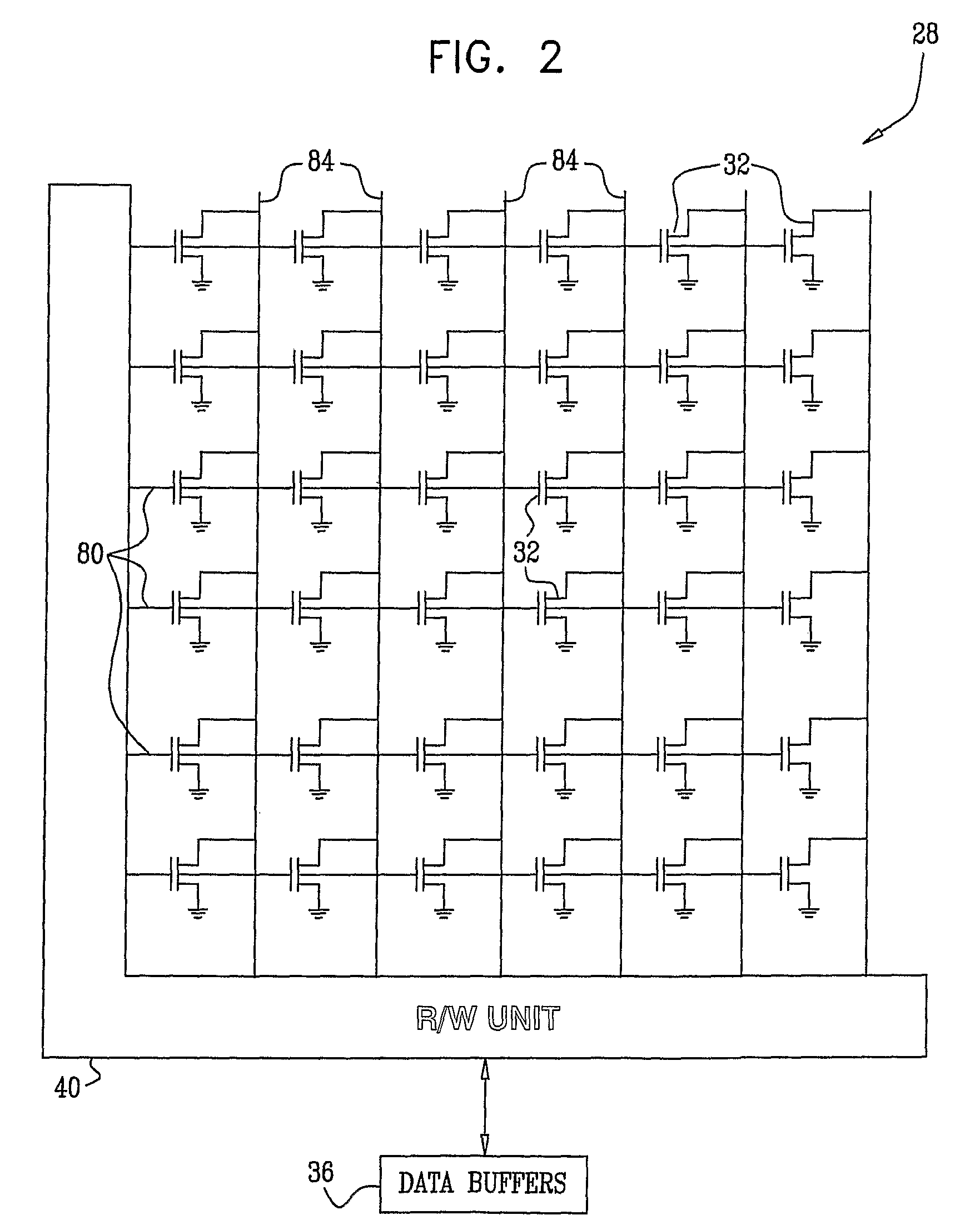

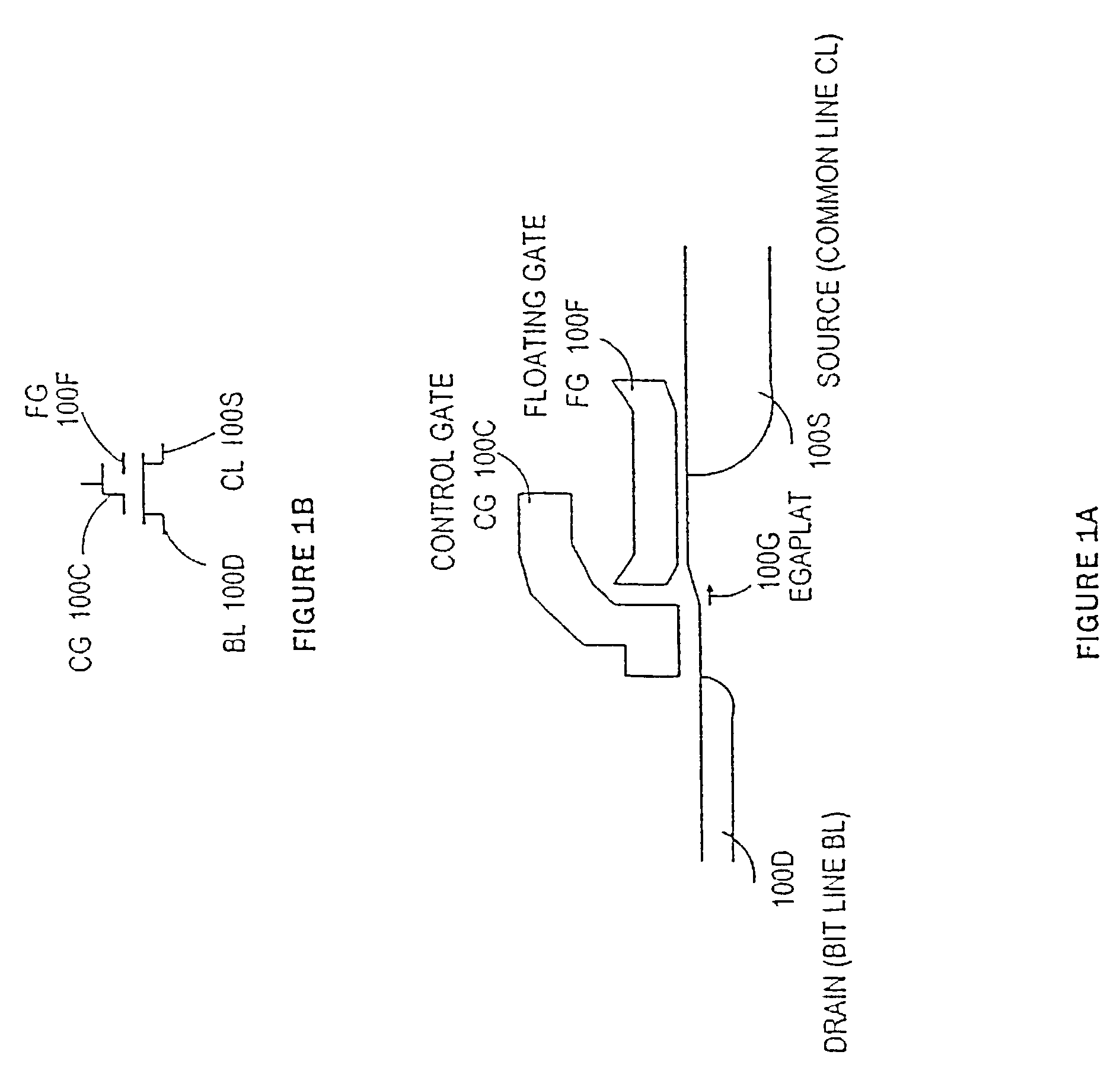

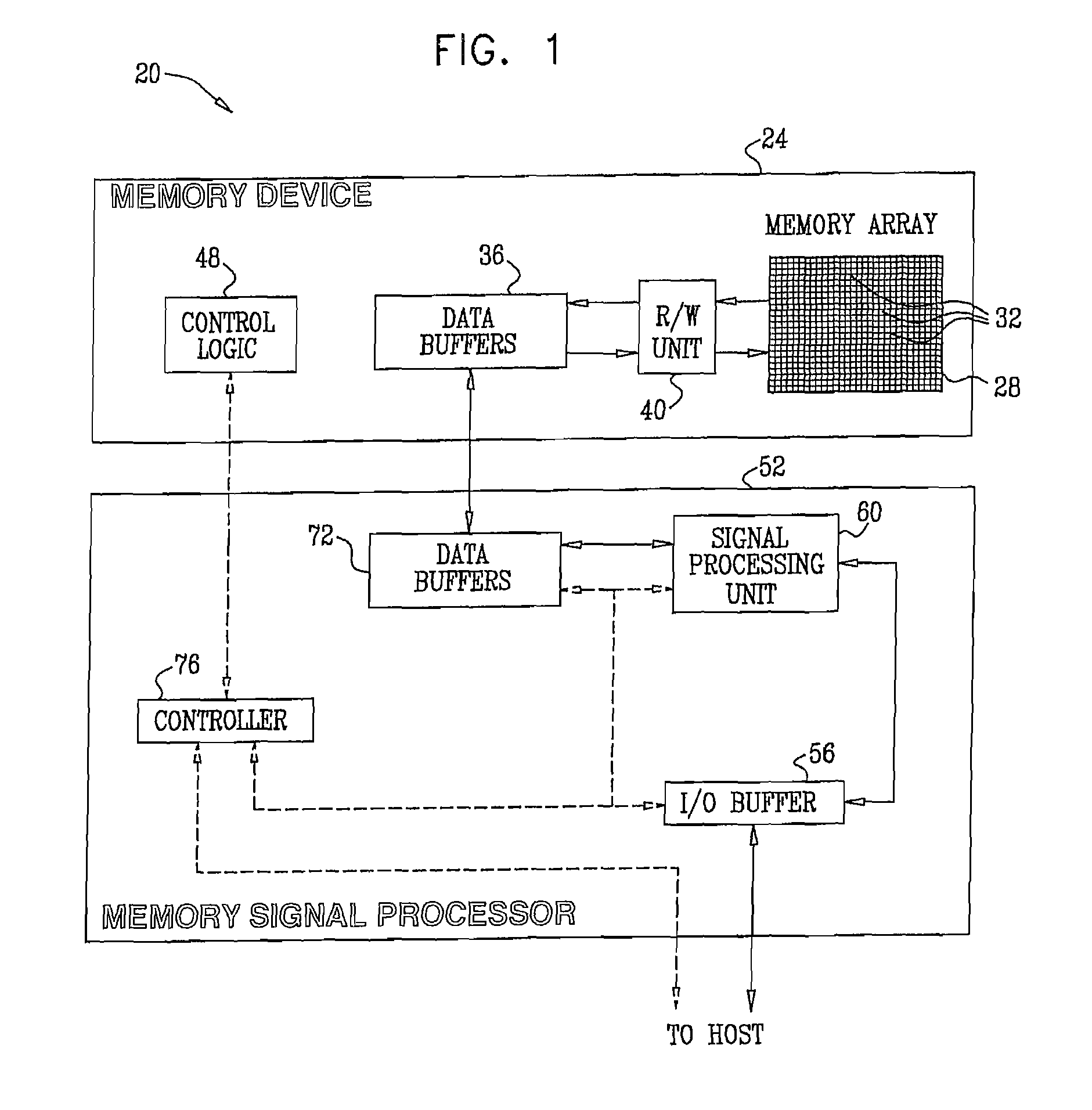

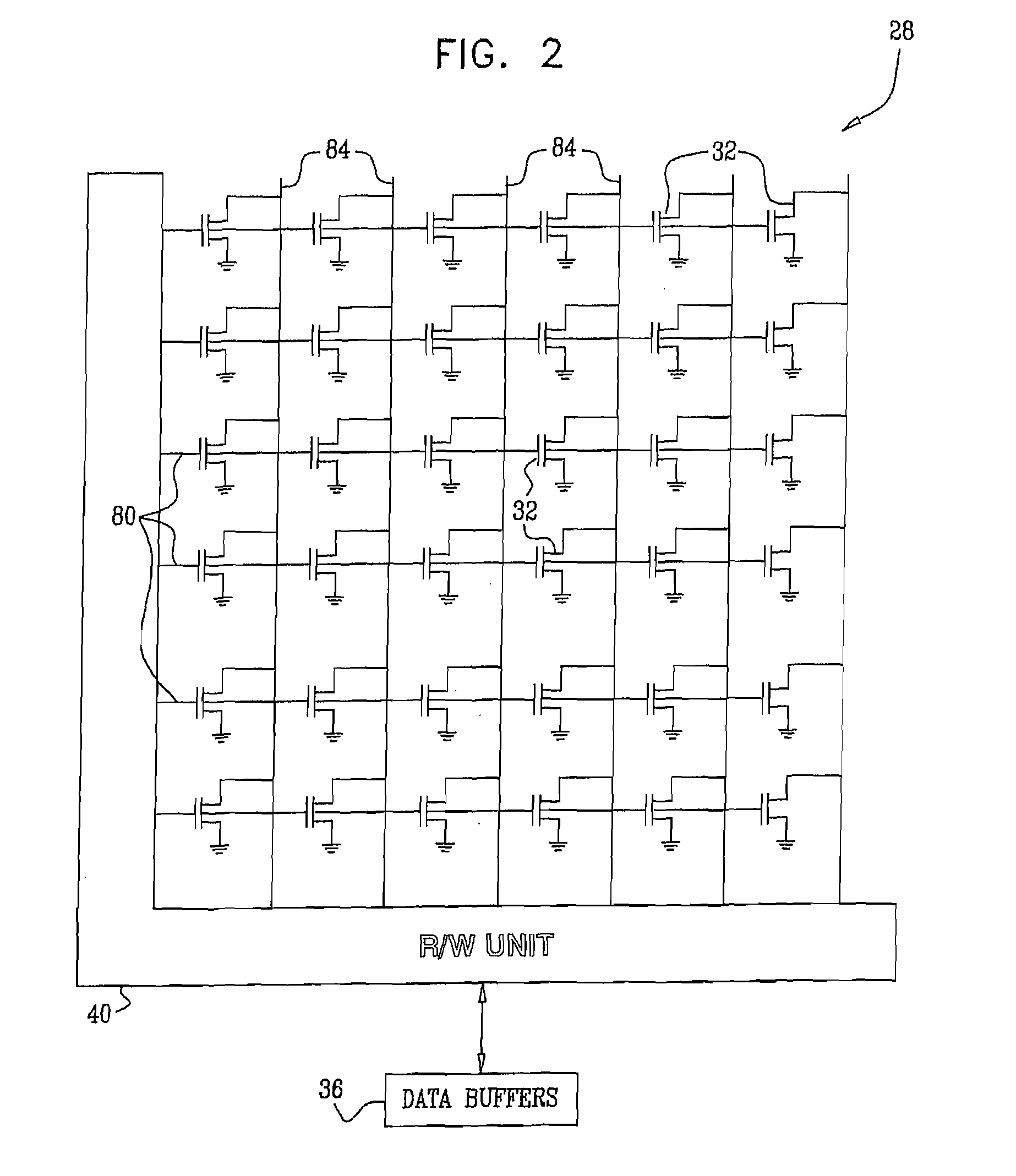

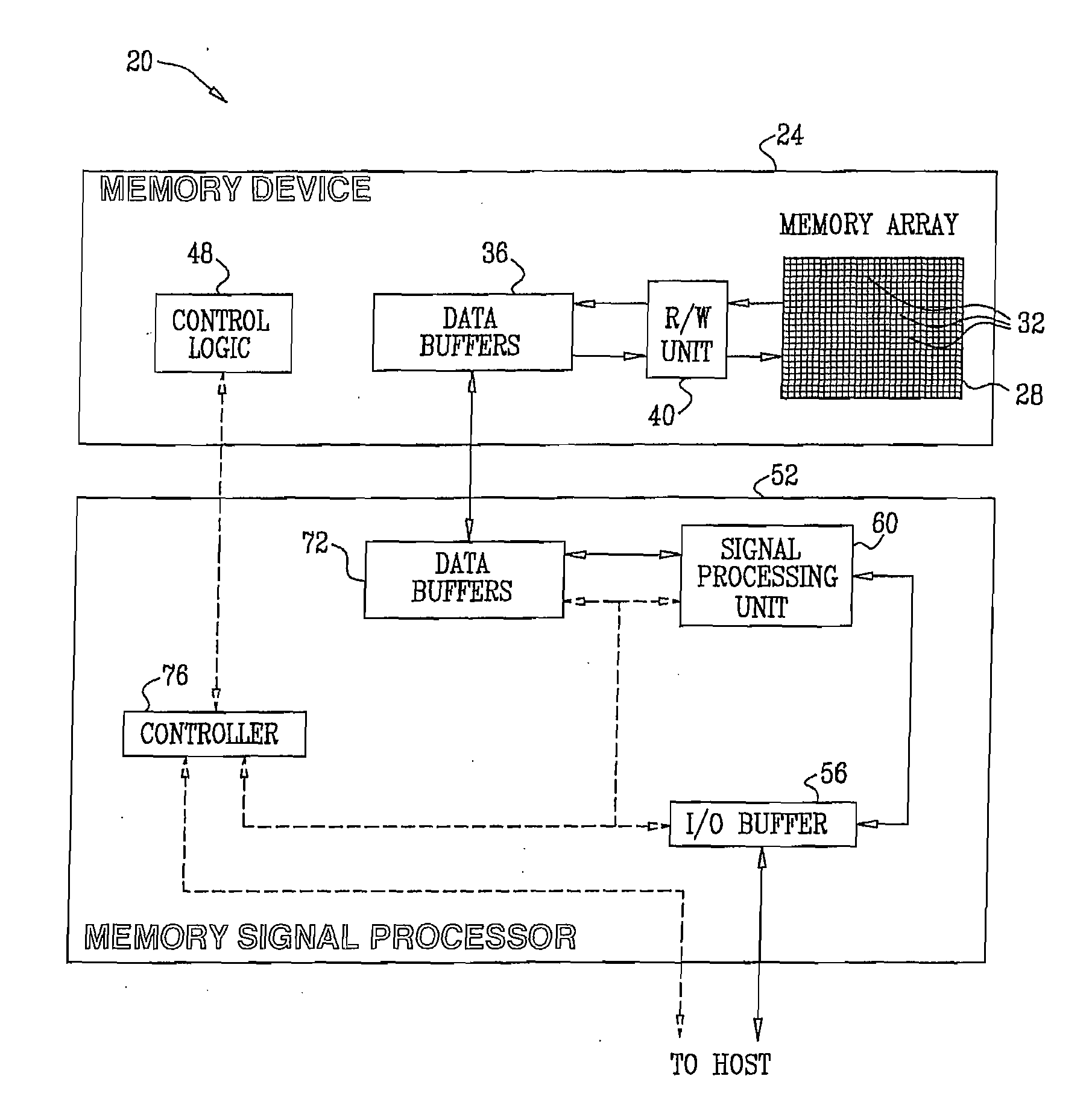

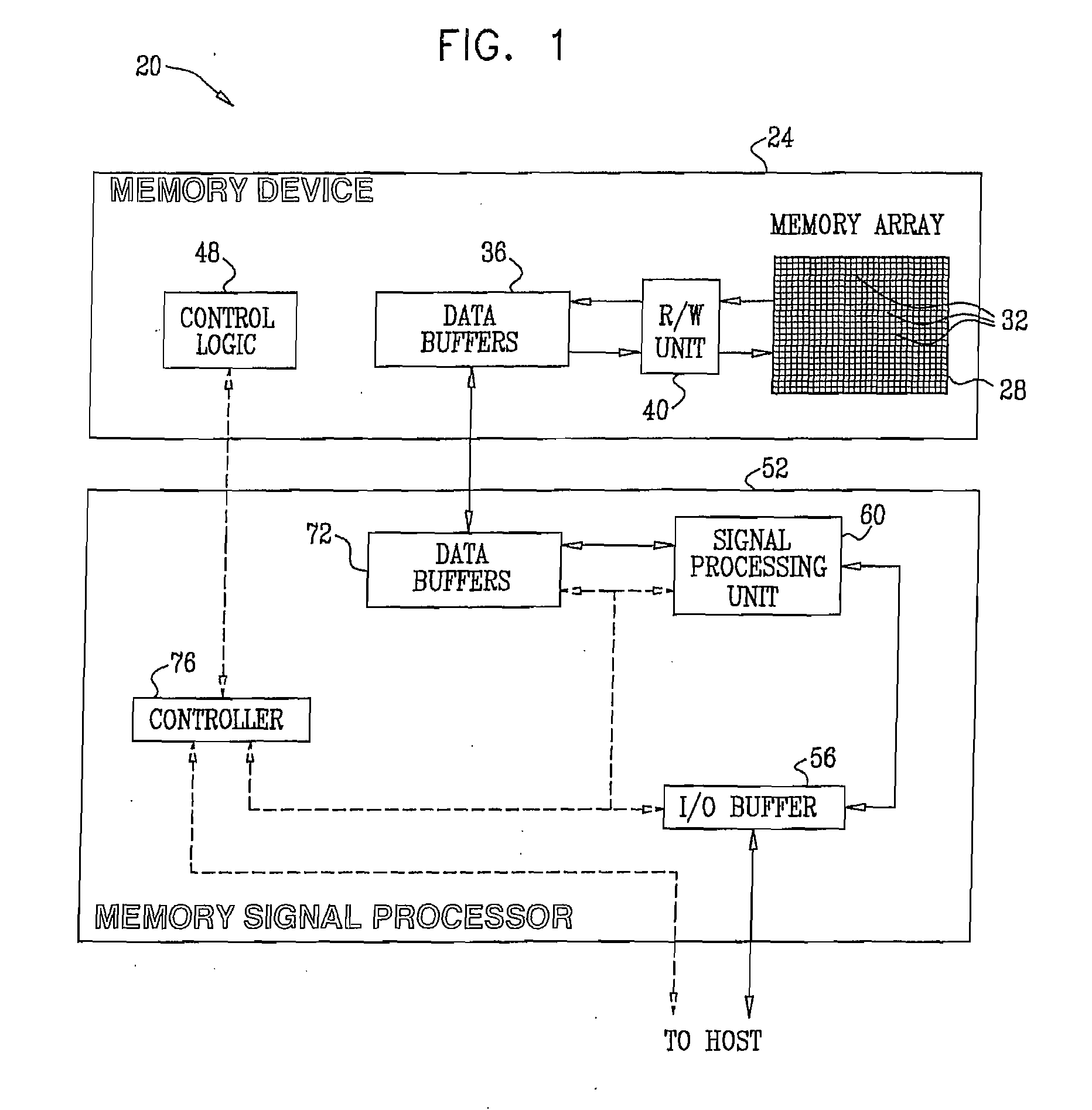

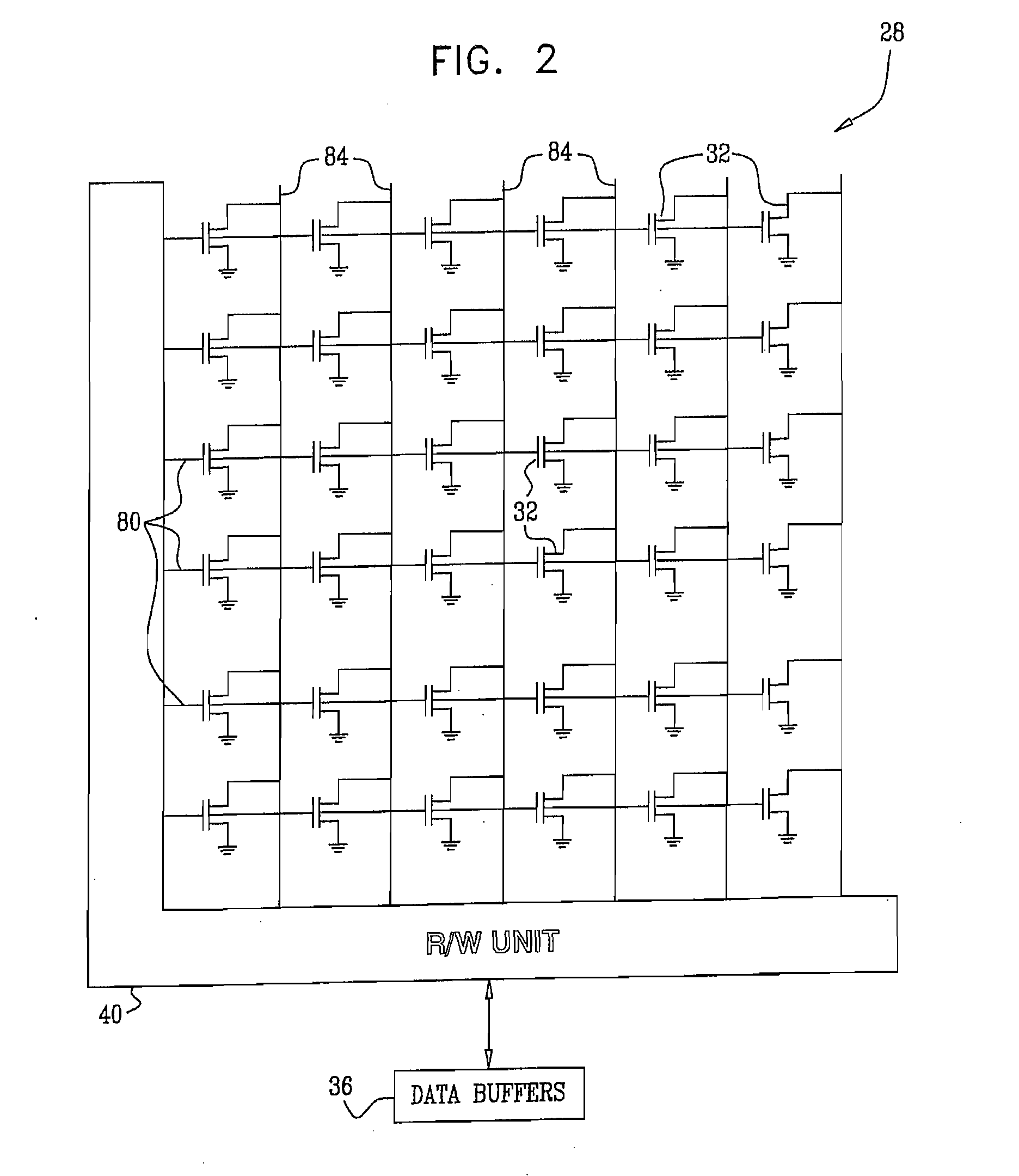

A method for operating a memory (28) includes storing data in a group of analog memory cells (32) of the memory as respective first voltage levels. After storing the data, second voltage levels are read from the respective analog memory cells. The second voltage levels are affected by cross-coupling interference causing the second voltage levels to differ from the respective first voltage levels. Cross-coupling coefficients, which quantify the cross-coupling interference among the analog memory cells, are estimated by processing the second voltage levels. The data stored in the group of analog memory cells is reconstructed from the read second voltage levels using the estimated cross-coupling coefficients.

Owner:APPLE INC

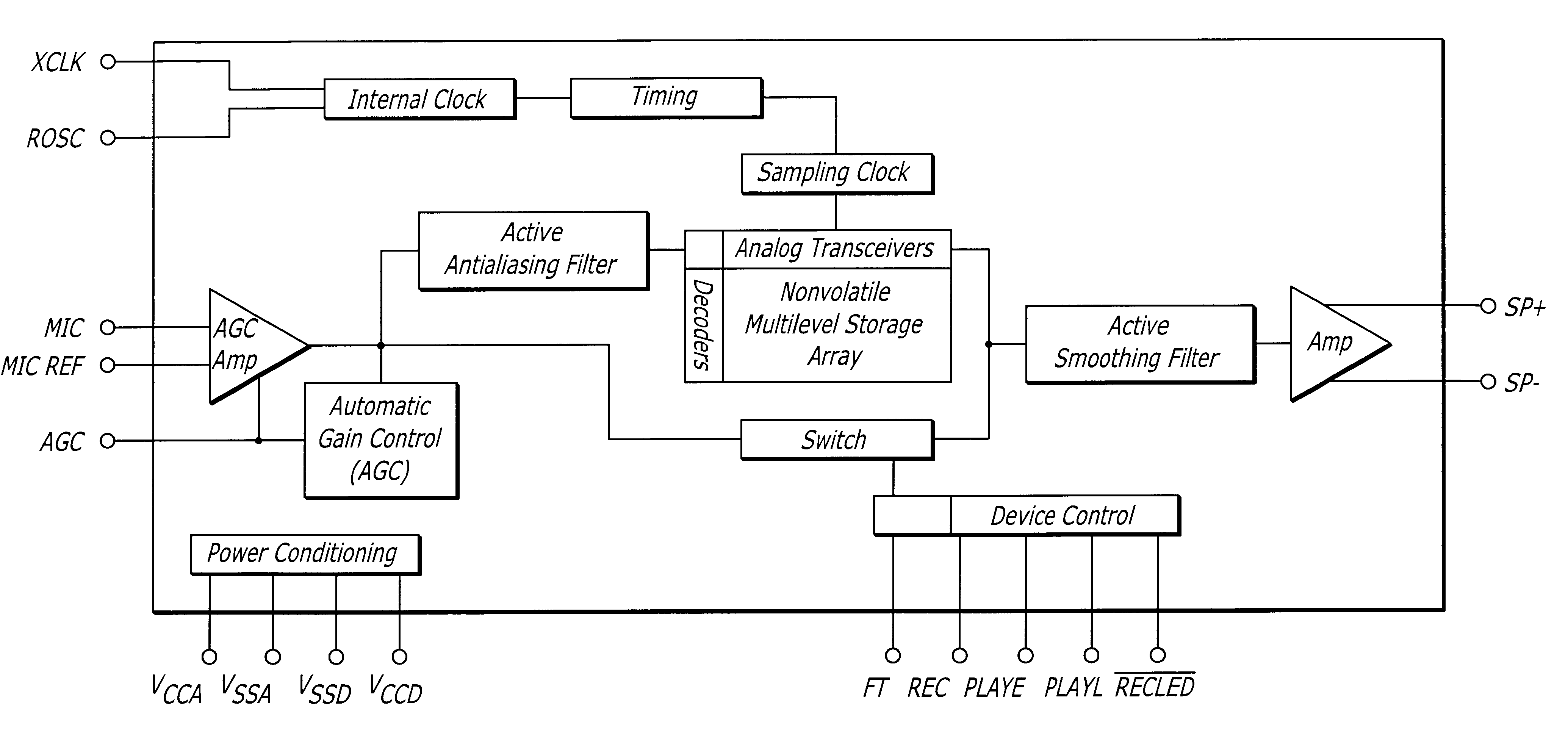

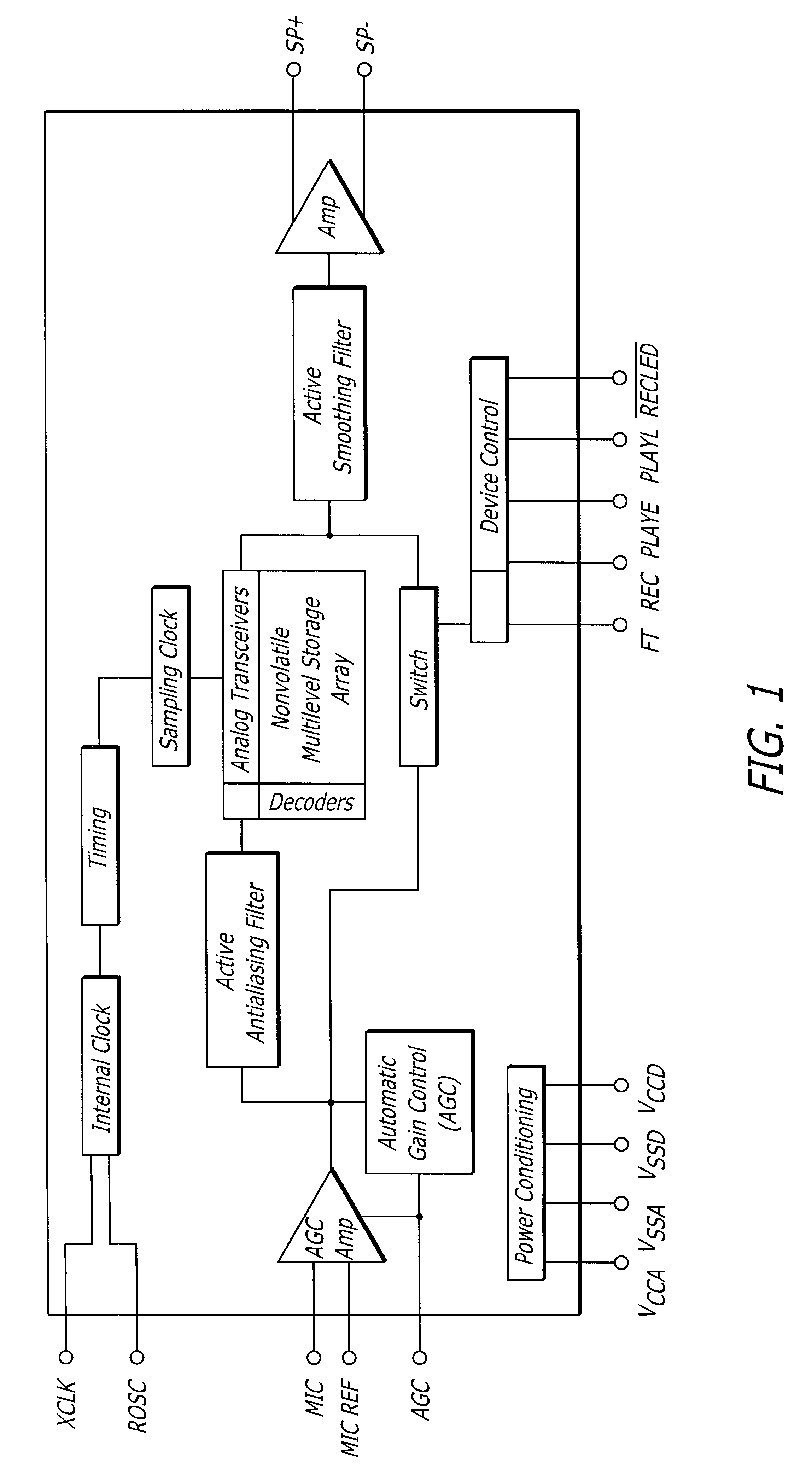

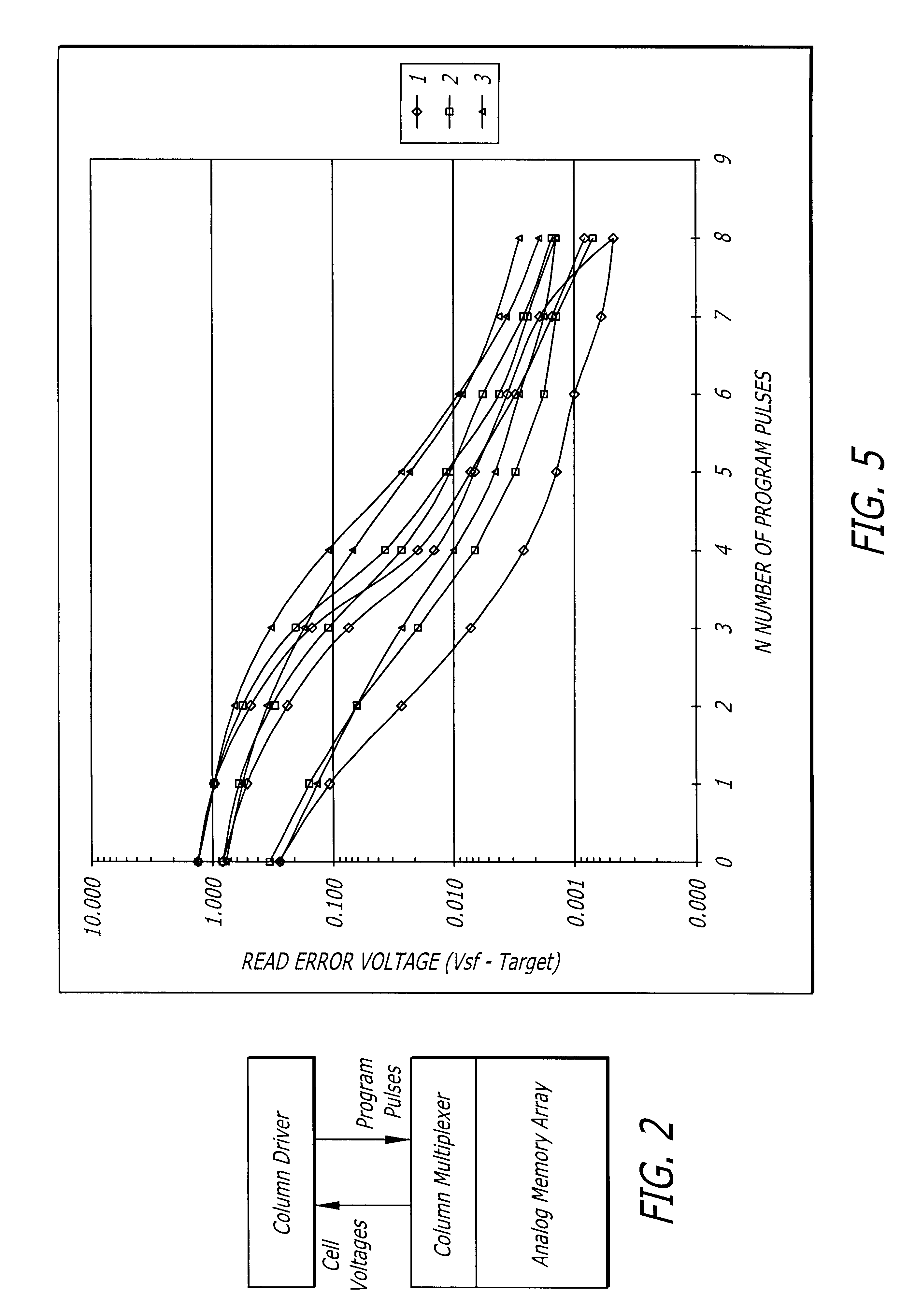

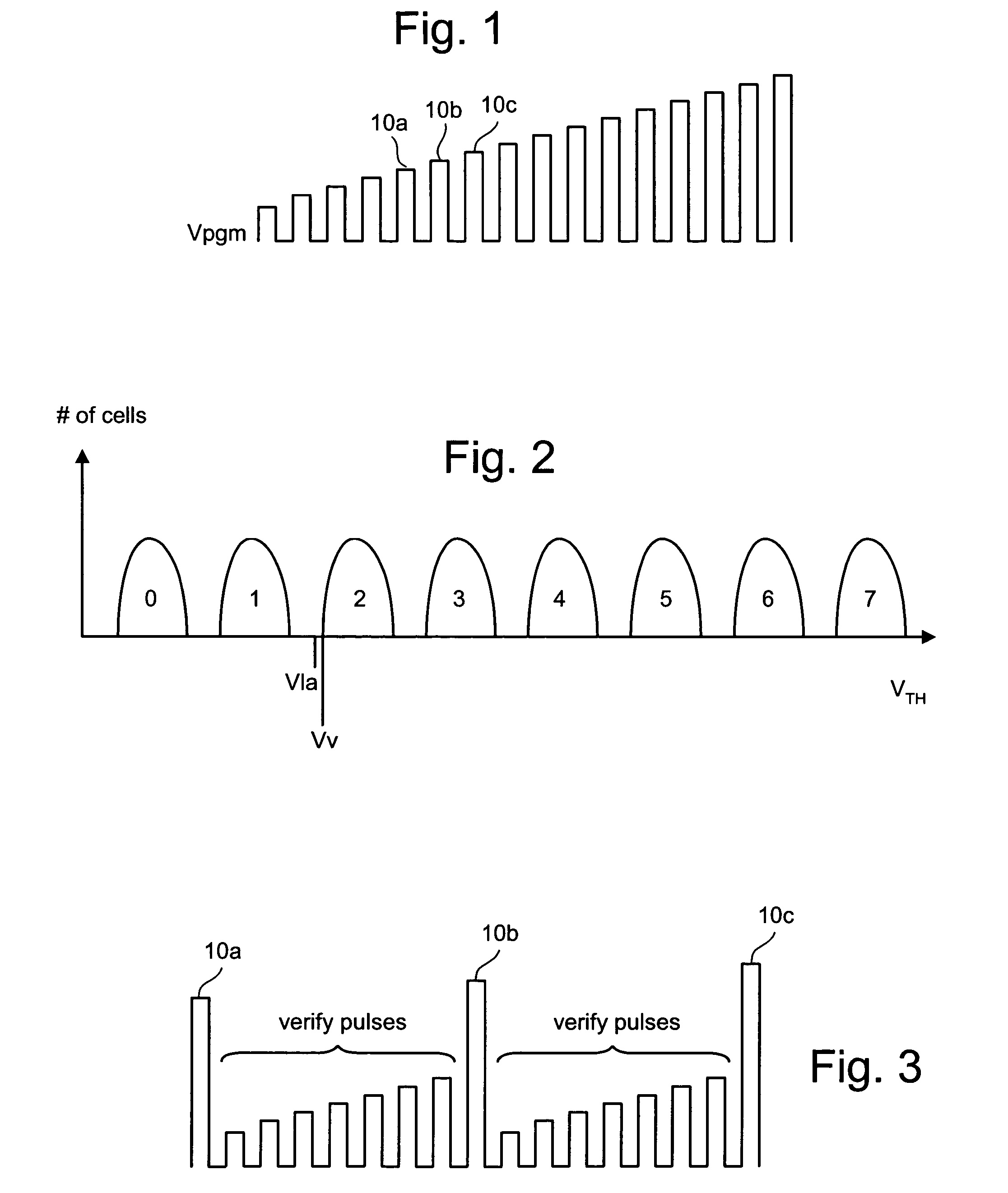

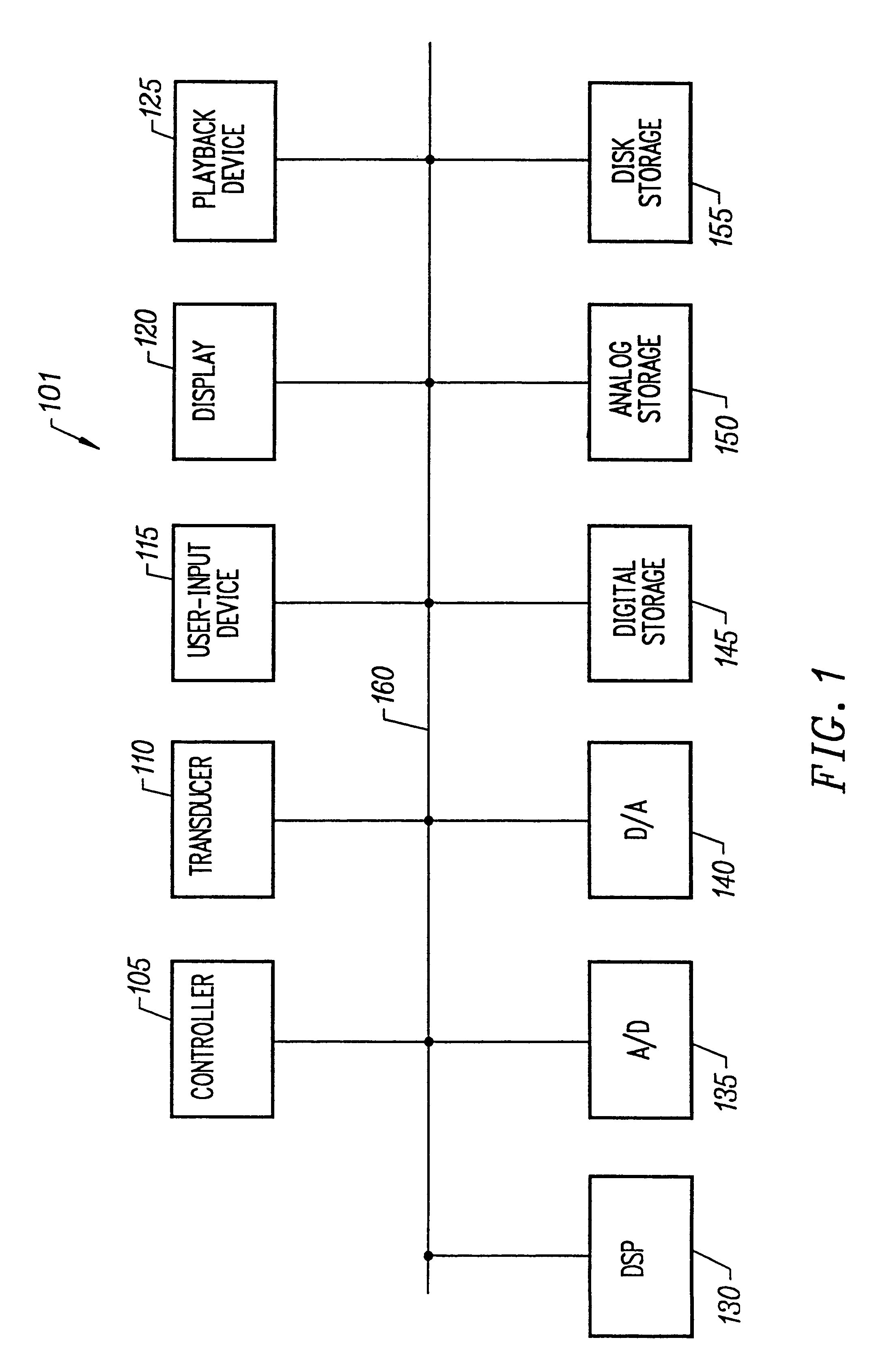

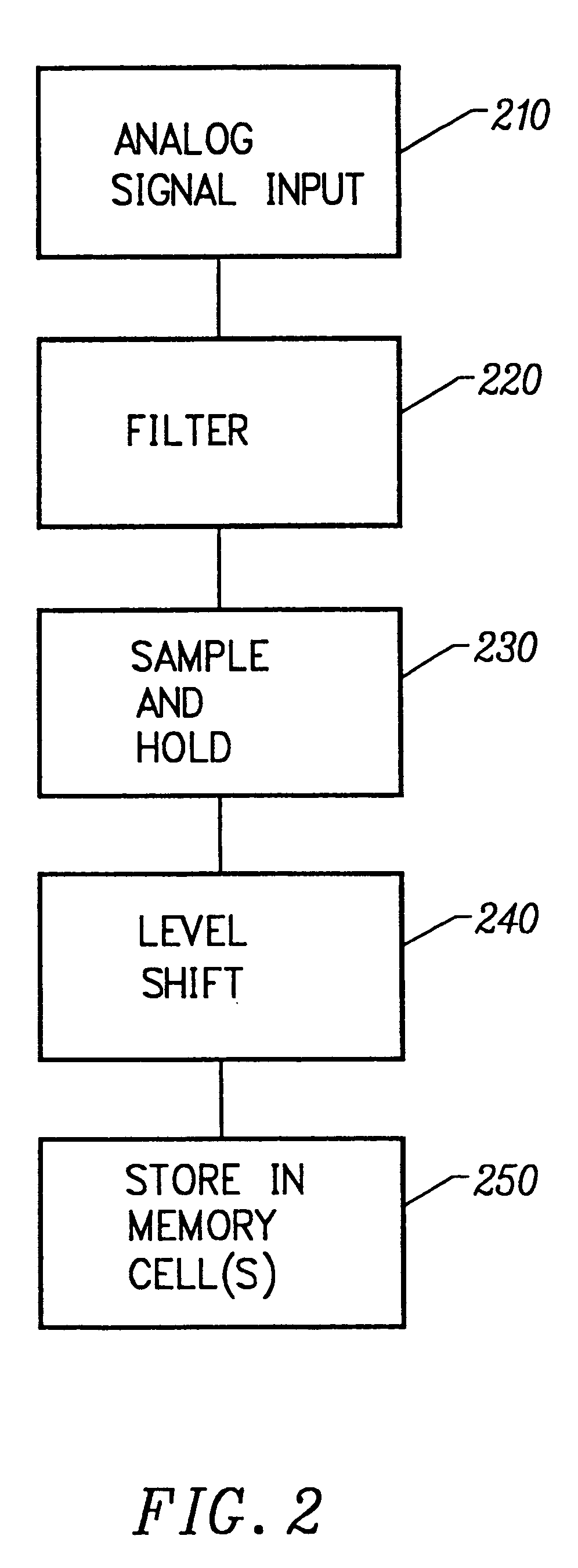

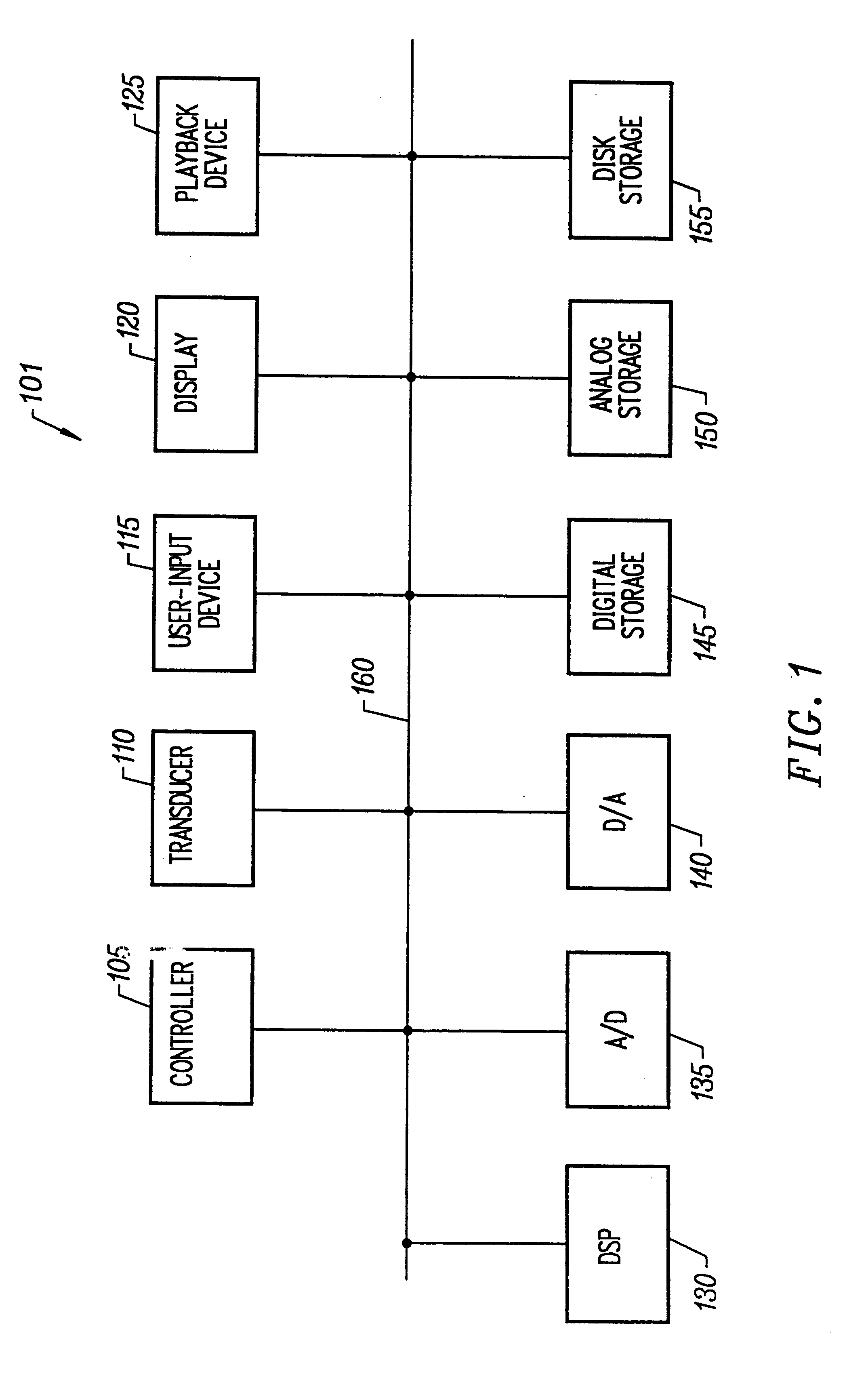

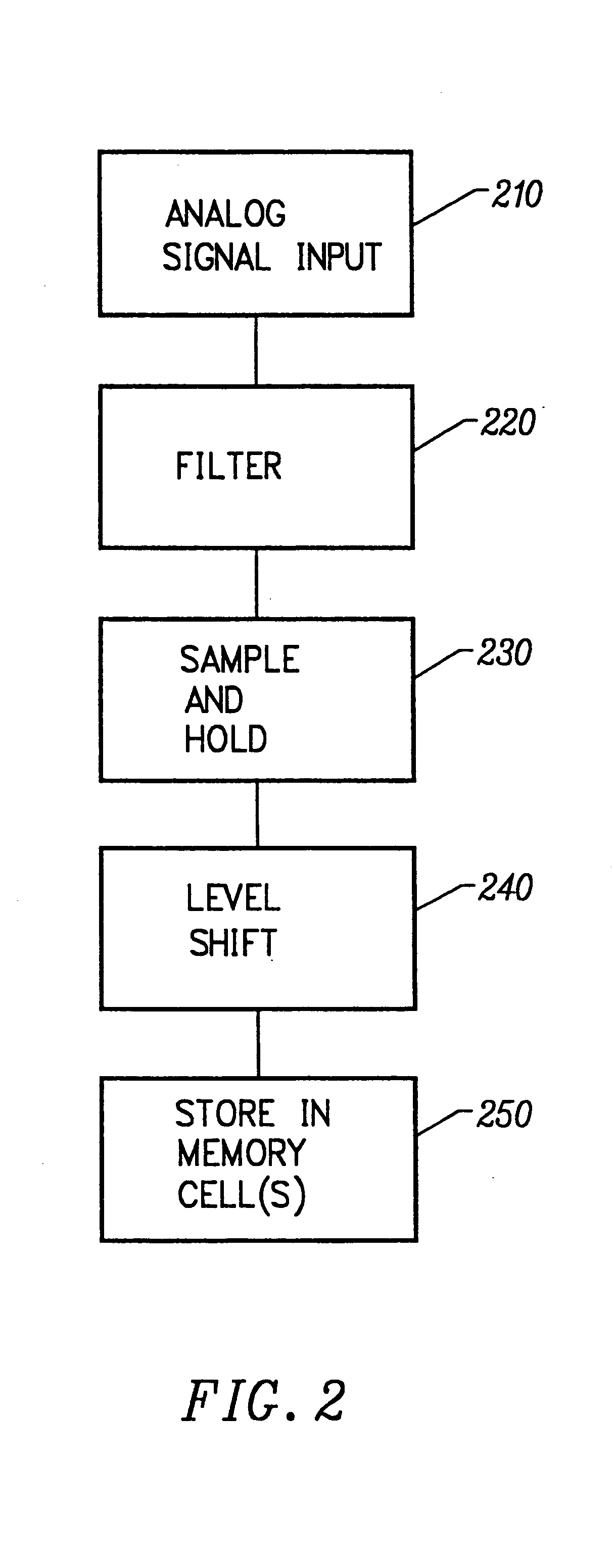

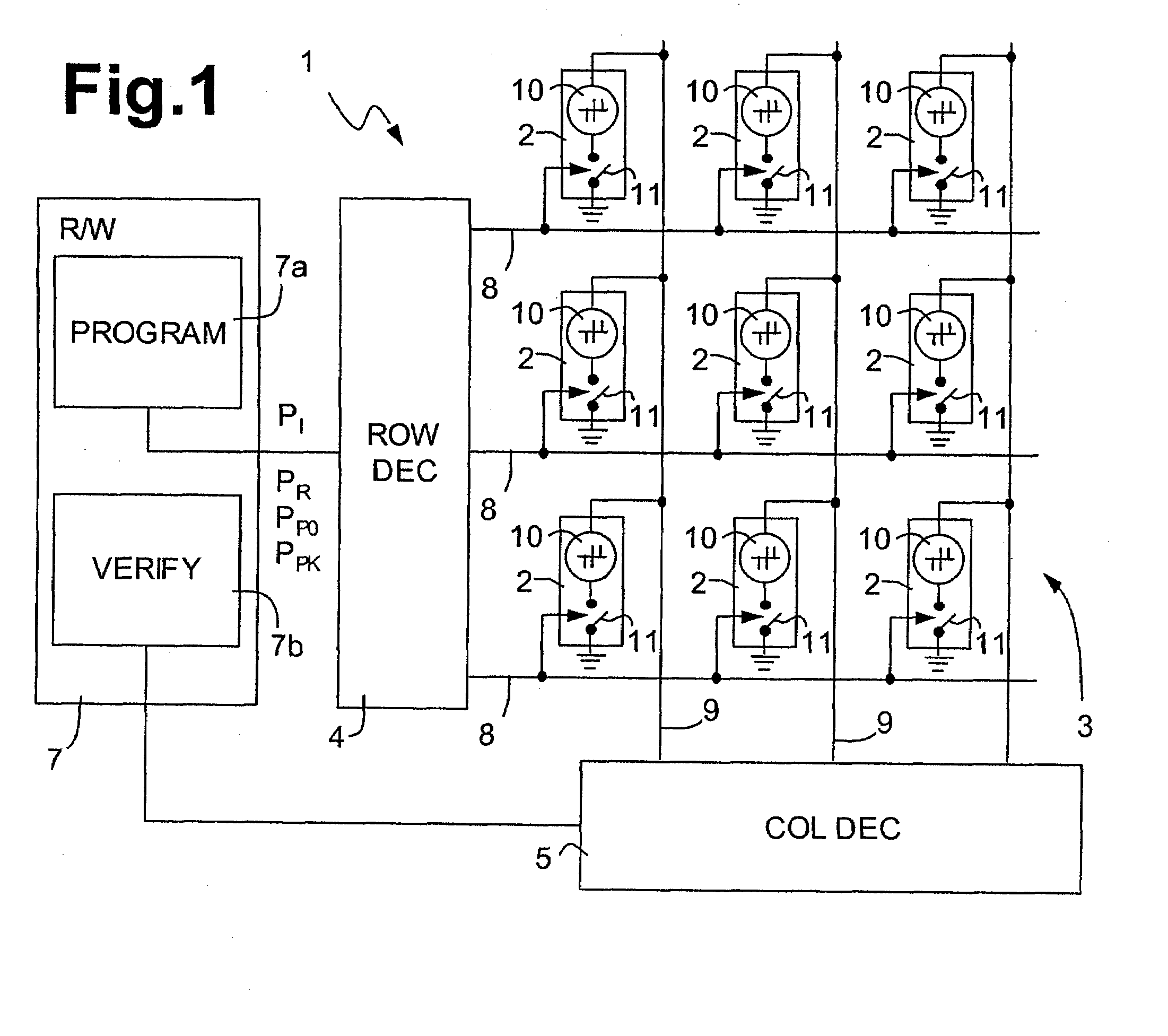

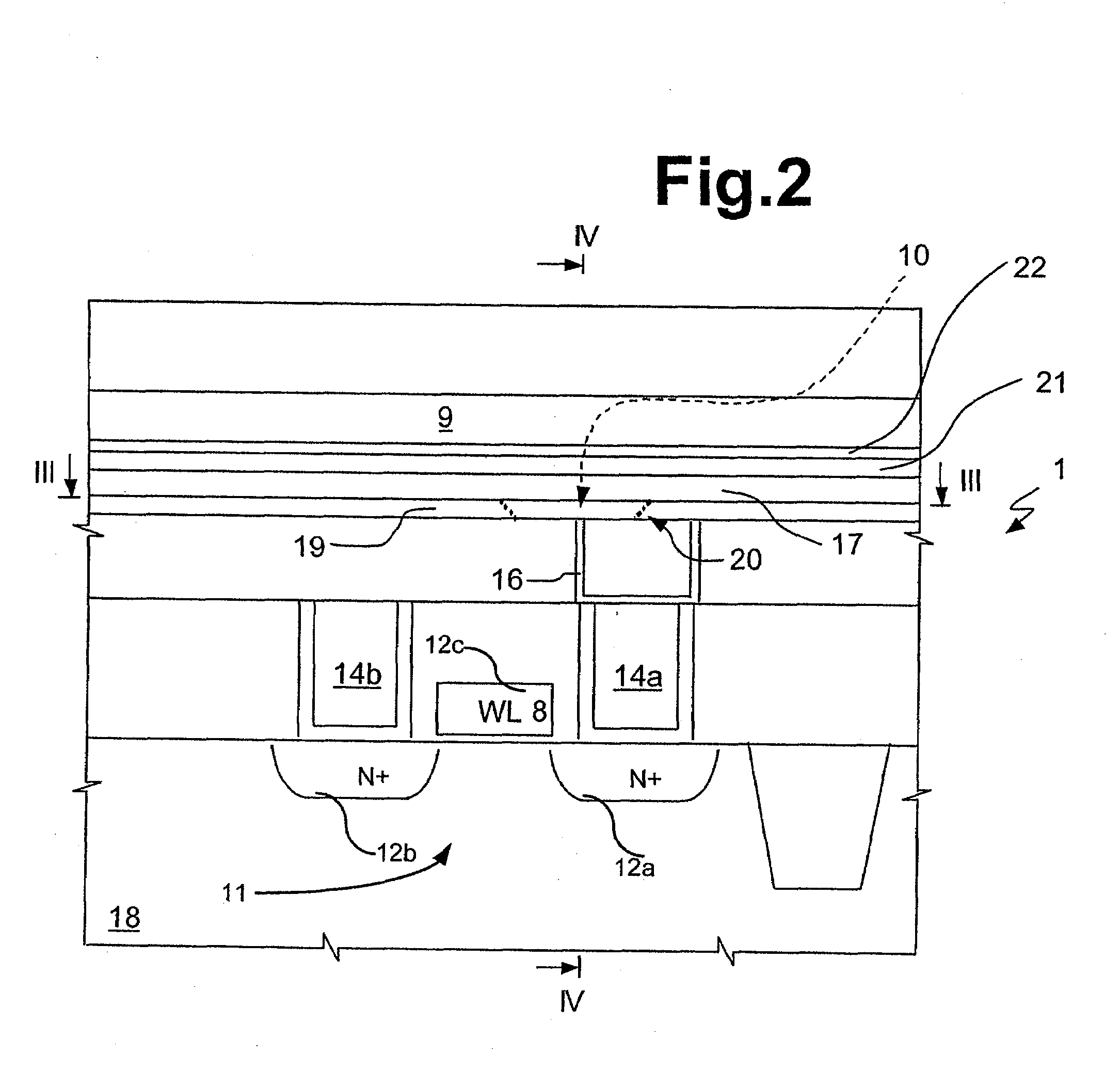

Adaptive programming method and apparatus for flash memory analog storage

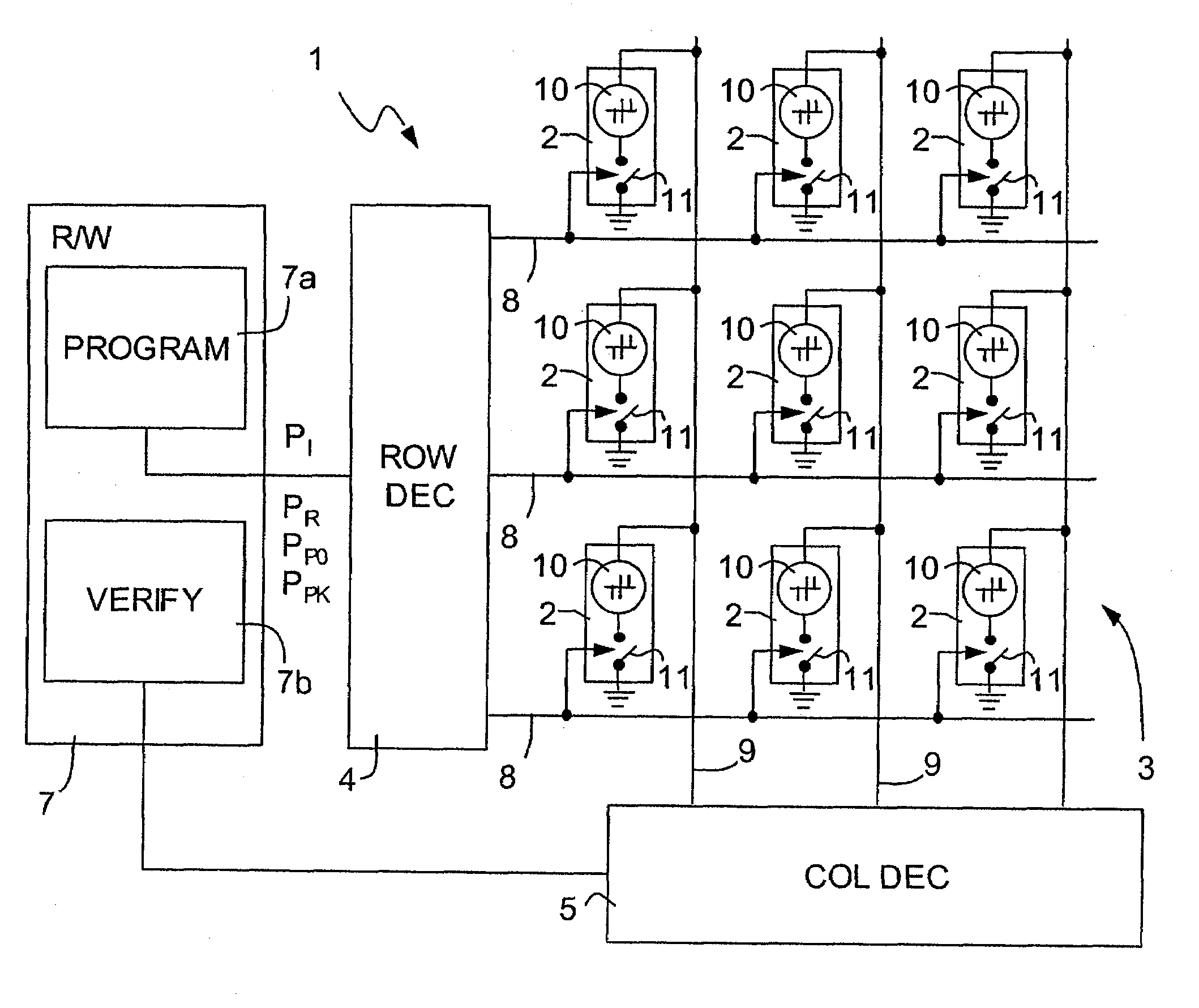

Adaptive programming method and apparatus for flash memory analog storage. The present invention method is to adjust the voltage of the programming pulse each time based on the result of the previous pulse. The expected change in the programmed value is compared to the measured change, and the difference used to improve the model of that cell after each programming pulse. The algorithm is "adaptive" because the voltage of each pulse is adapted to whatever the cell needs. If the cell is programming too slowly, the voltage is increased dramatically to make it faster. Conversely if the results show that a particular cell is programming too fast, the next voltage pulse is increased by only a small amount (or even decreased if necessary). Because the response of the cell is non-linear, a special analog circuit is used to calculate the optimum voltage for each pulse. As one alternative, a digital calculation may also be used to program the cells. Because of the programming speed of the exemplary method, a voice signal may be sampled and stored in flash memory one cell at a time. Variable programming parameters other than voltage may be used if desired.

Owner:WINBOND ELECTRONICS CORP

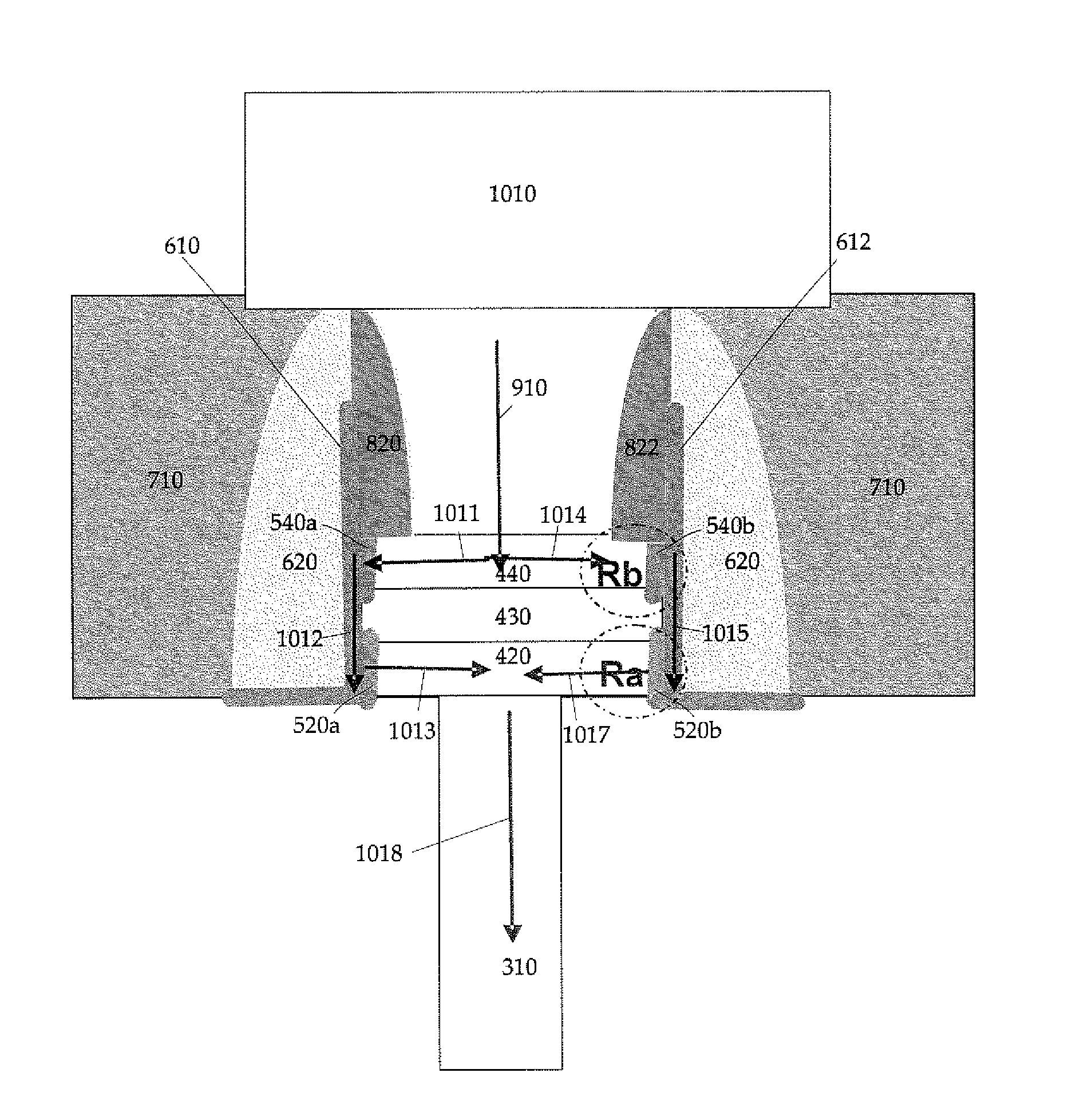

Multi-level cell resistance random access memory with metal oxides

ActiveUS7697316B2High densityElectrical apparatusElectric analogue storesRandom access memoryElectrical battery

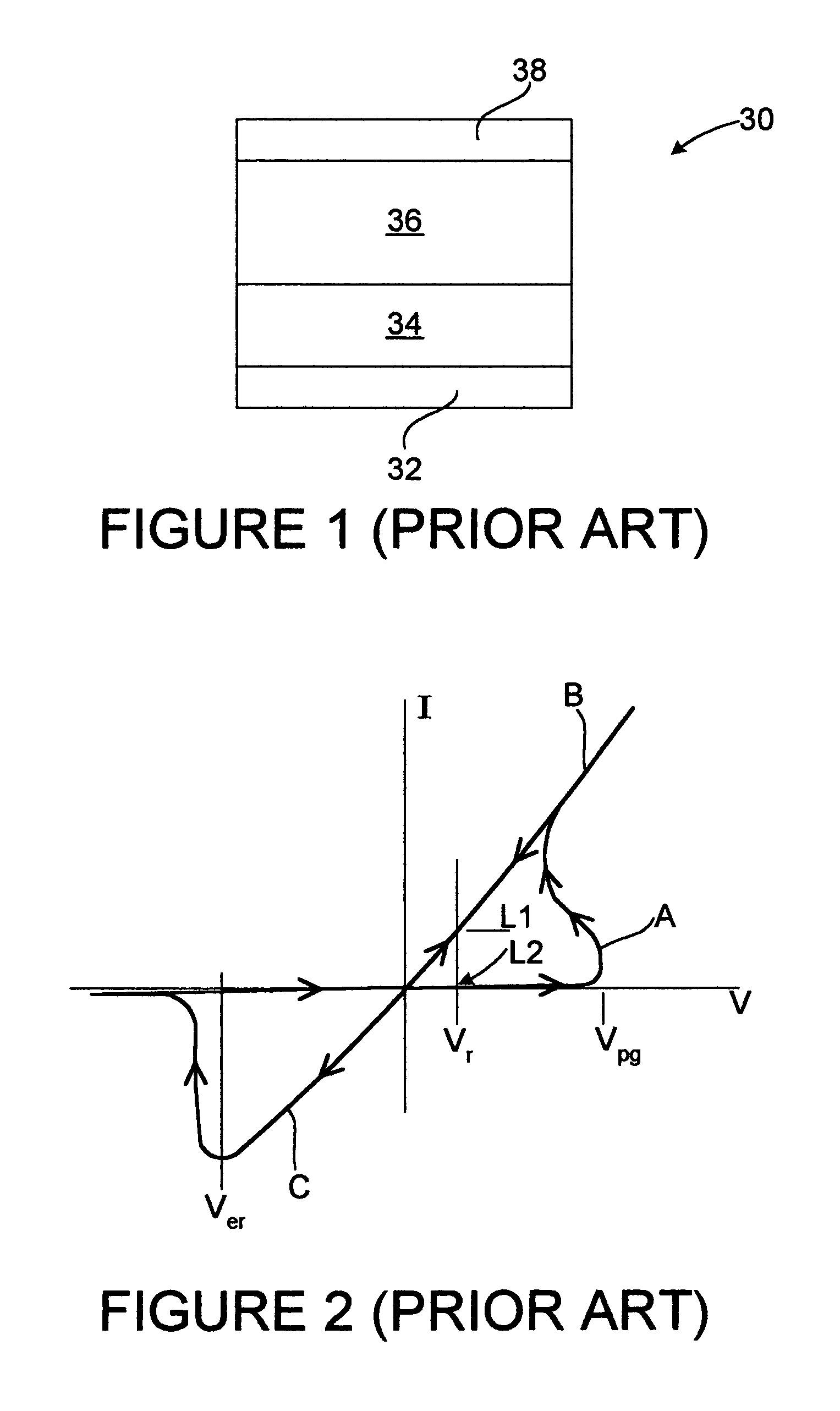

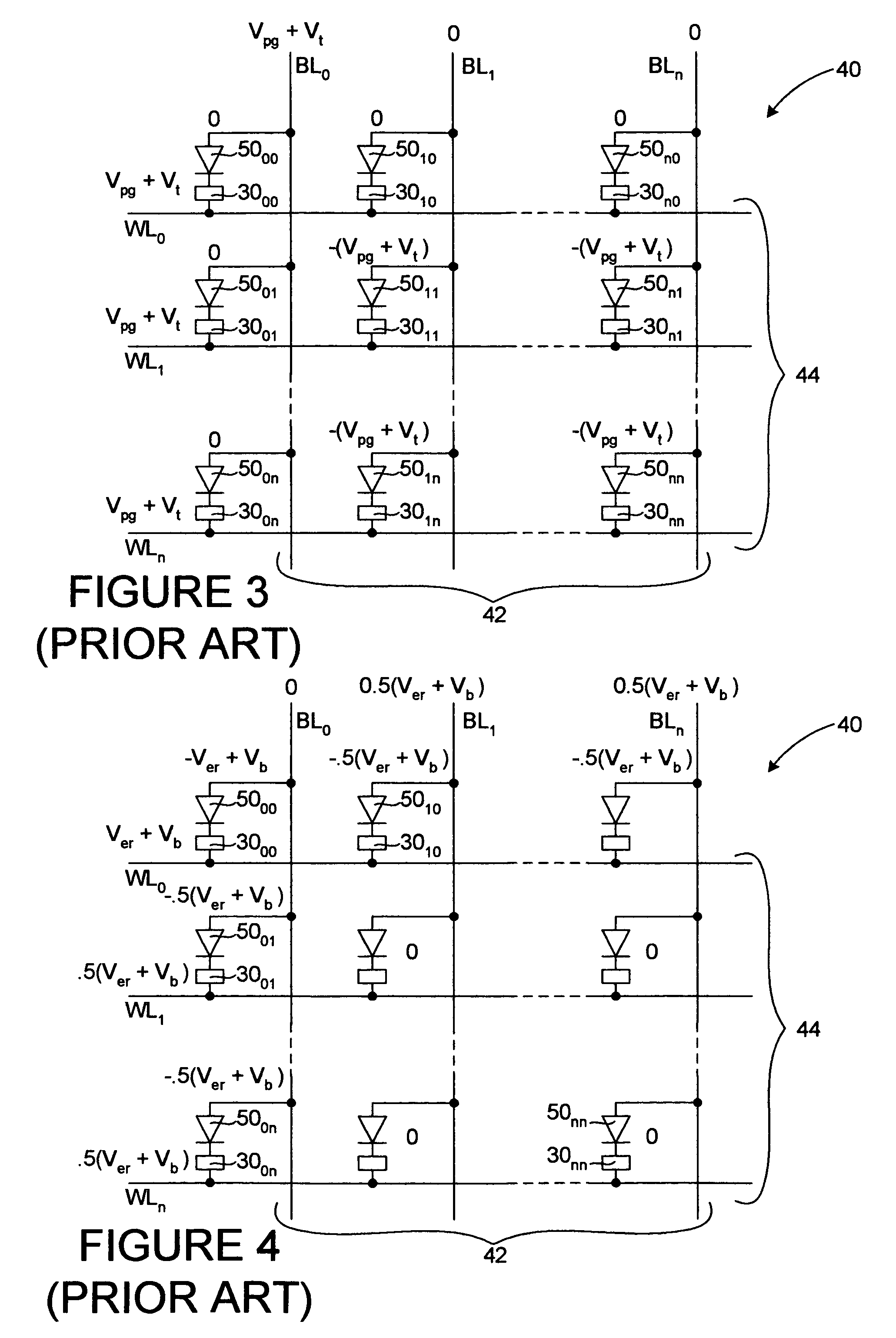

A bistable resistance random access memory comprises a plurality of programmable resistance random access memory cells where each programmable resistance random access memory cell includes multiple memory members for performing multiple bits for each memory cell. The bistable RRAM includes a first resistance random access member connected to a second resistance random access member through interconnect metal liners and metal oxide strips. The first resistance random access member has a first resistance value Ra, which is determined from the thickness of the first resistance random access member based on the deposition of the first resistance random access member. The second resistance random access member has a second resistance value Rb, which is determined from the thickness of the second resistance random access member based on the deposition of the second resistance random access member.

Owner:MACRONIX INT CO LTD

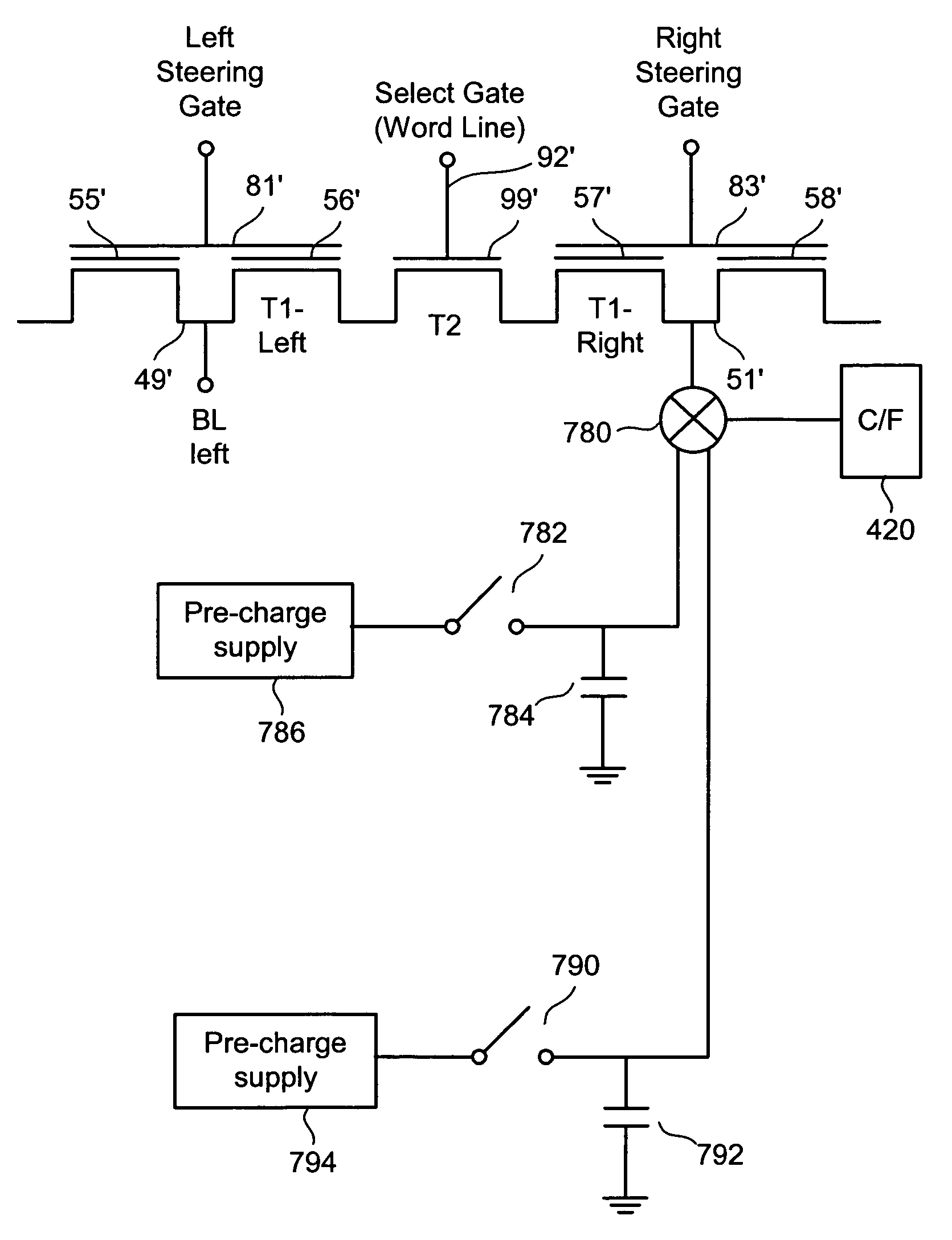

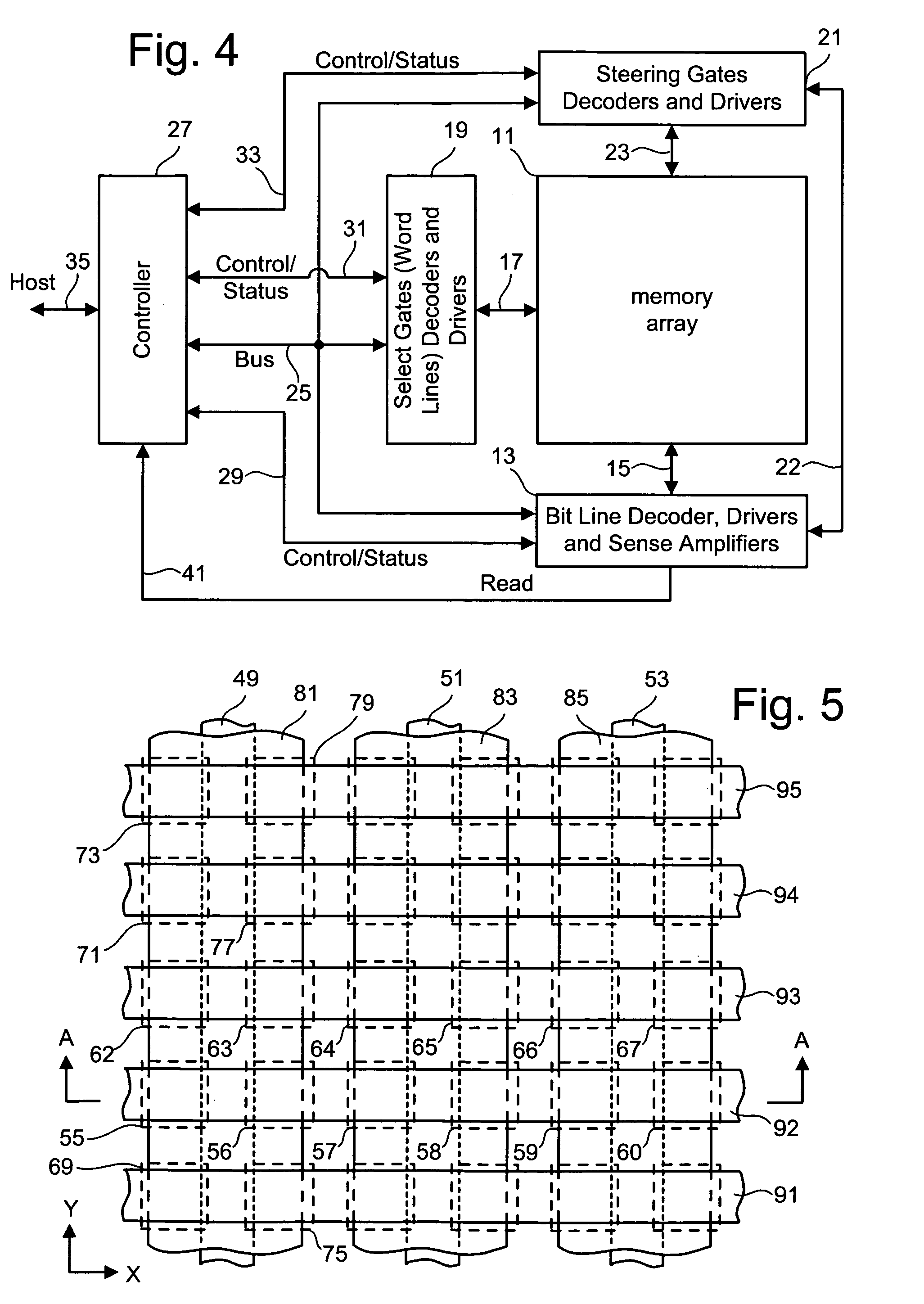

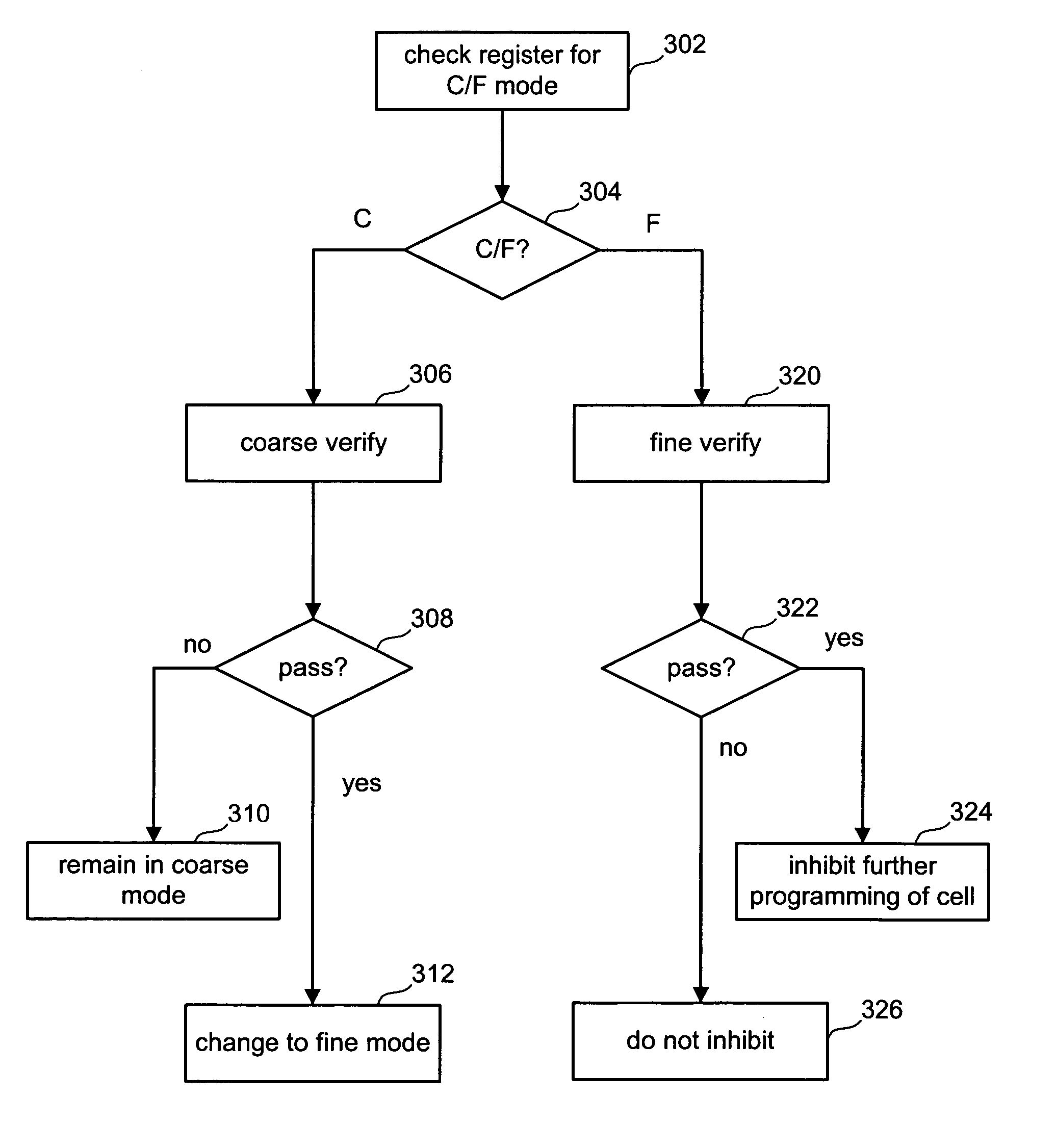

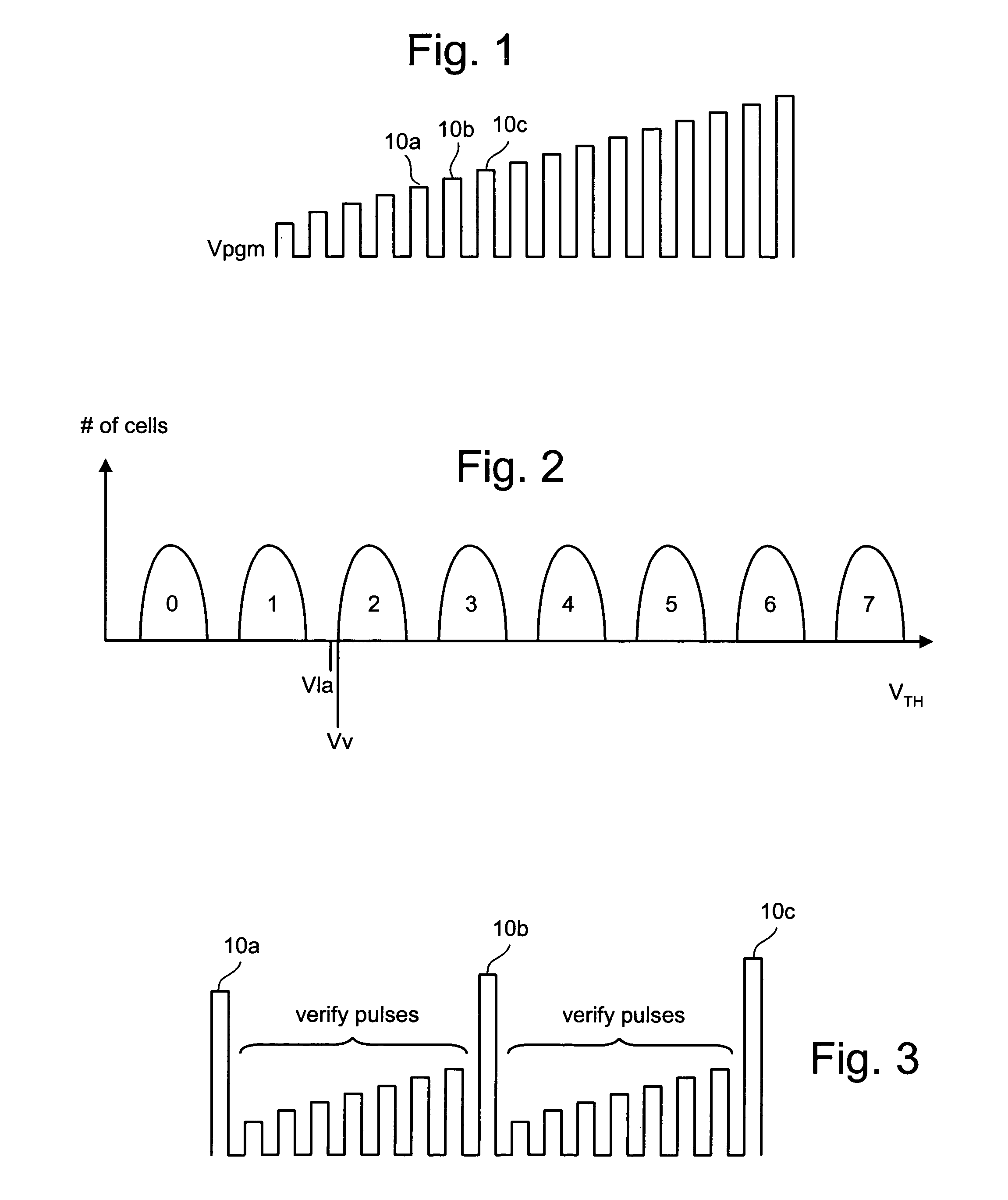

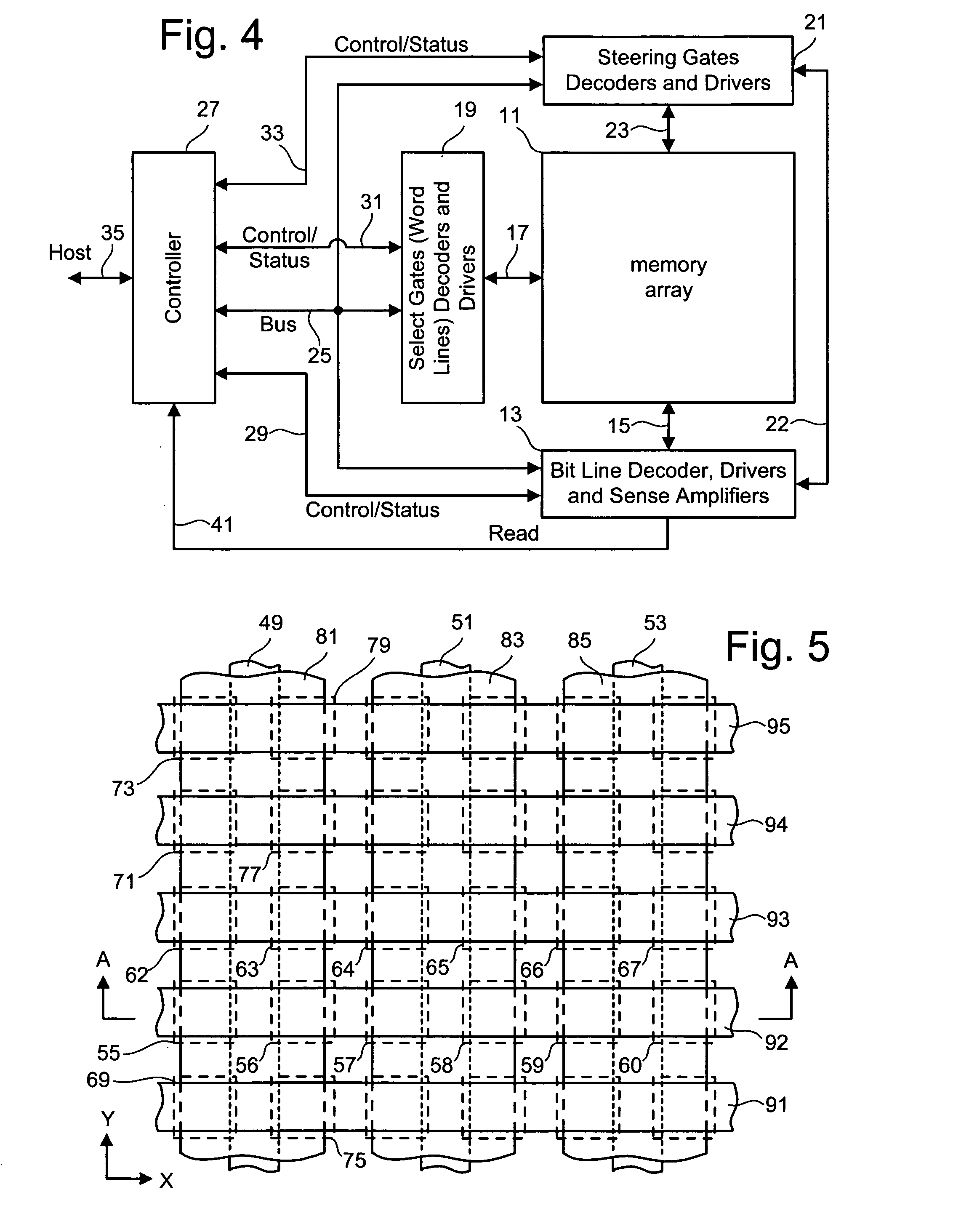

Charge packet metering for coarse/fine programming of non-volatile memory

A non-volatile memory device is programmed by first performing a coarse programming process and subsequently performing a fine programming process. The coarse / fine programming methodology is enhanced by using an efficient verification scheme that allows some non-volatile memory cells to be verified for the coarse programming process while other non-volatile memory cells are verified for the fine programming process. The fine programming process can be accomplished using current sinking, charge packet metering or other suitable means.

Owner:SANDISK TECH LLC

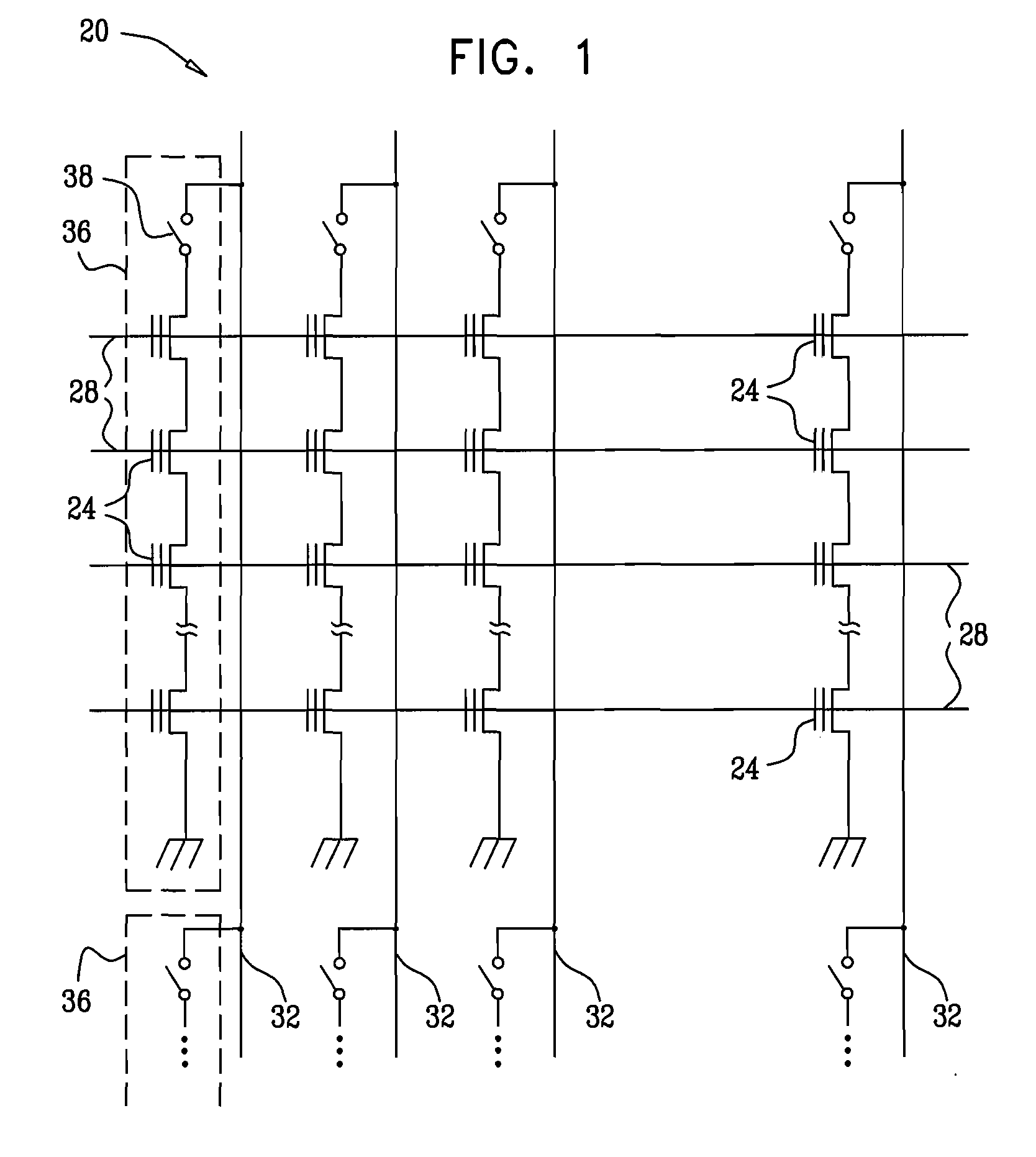

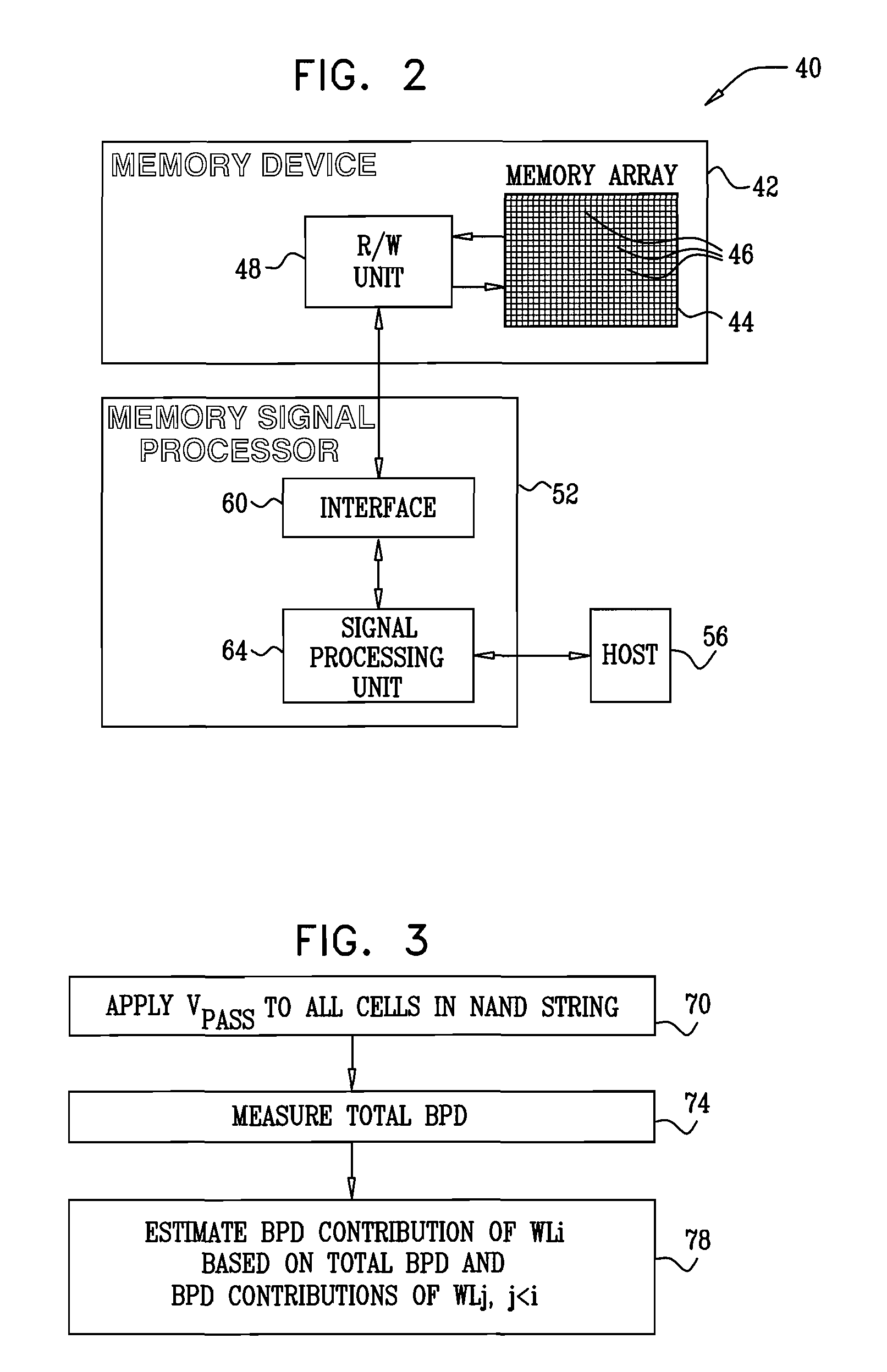

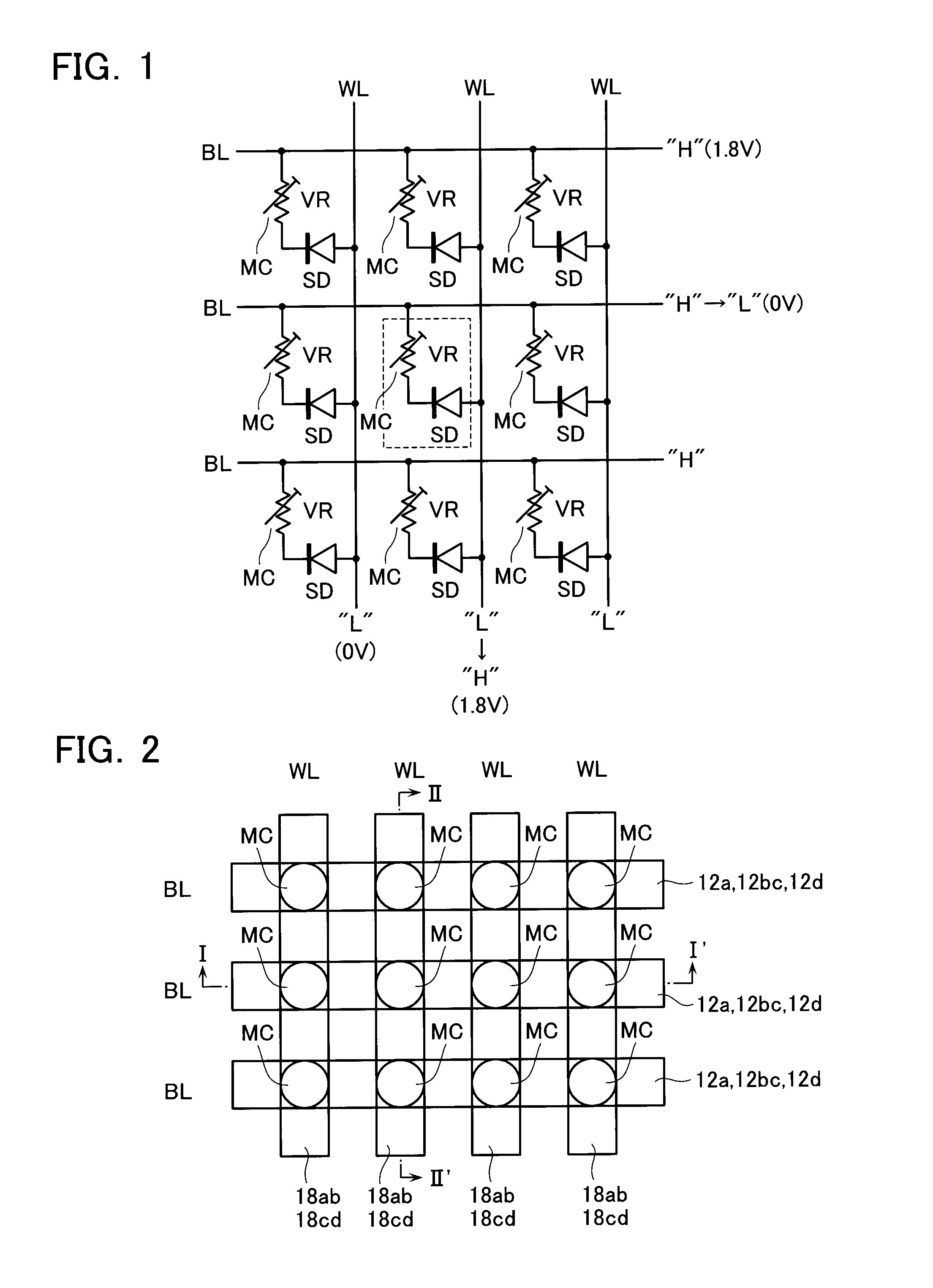

Reduction of back pattern dependency effects in memory devices

ActiveUS20080219050A1High voltageError detection/correctionElectric analogue storesParallel computingDistortion

A method for operating a memory that includes multiple analog memory cells includes storing data in the memory by writing first storage values to the cells, so as to cause the cells to hold respective electrical charge levels. After storing the data, second storage values are read from at least some of the cells, including at least one interfered cell that belongs to a group of cells. A Back Pattern Dependency (BPD) distortion caused by the electrical charge levels of one or more interfering cells in the group to at least one of the second storage values read from the at least one interfered cell is detected and canceled. The second storage values, including the at least one of the second storage values in which the BPD distortion was canceled, are processed so as to reconstruct the data.

Owner:APPLE INC

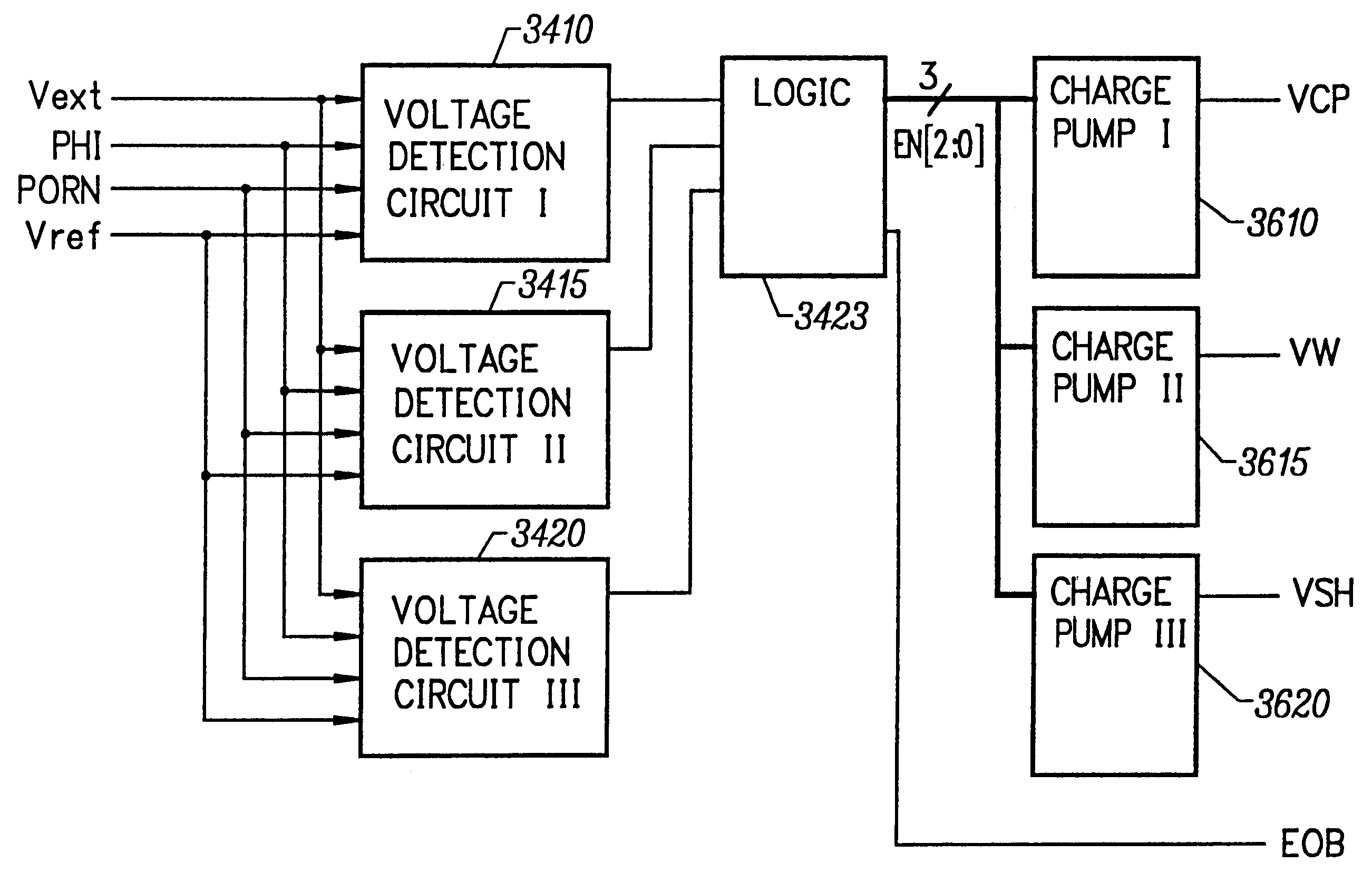

Charge pump circuit adjustable in response to an external voltage source

InactiveUS6370075B1Prolong lifeImprove reliabilityElectric analogue storesRead-only memoriesEngineeringVoltage source

An integrated circuit detects the voltage level of the supply voltage to the integrated circuit. Circuity on the integrated circuit including the charge pump circuity adjusts to operate more effectively or efficiently at the voltage level of the supply voltage.

Owner:SANDISK TECH LLC

Variable current sinking for coarse/fine programming of non-volatile memory

A non-volatile memory device is programmed by first performing a coarse programming process and subsequently performing a fine programming process. The coarse / fine programming methodology is enhanced by using an efficient verification scheme that allows some non-volatile memory cells to be verified for the coarse programming process while other non-volatile memory cells are verified for the fine programming process. The fine programming process can be accomplished using current sinking, charge packet metering or other suitable means.

Owner:SANDISK TECH LLC

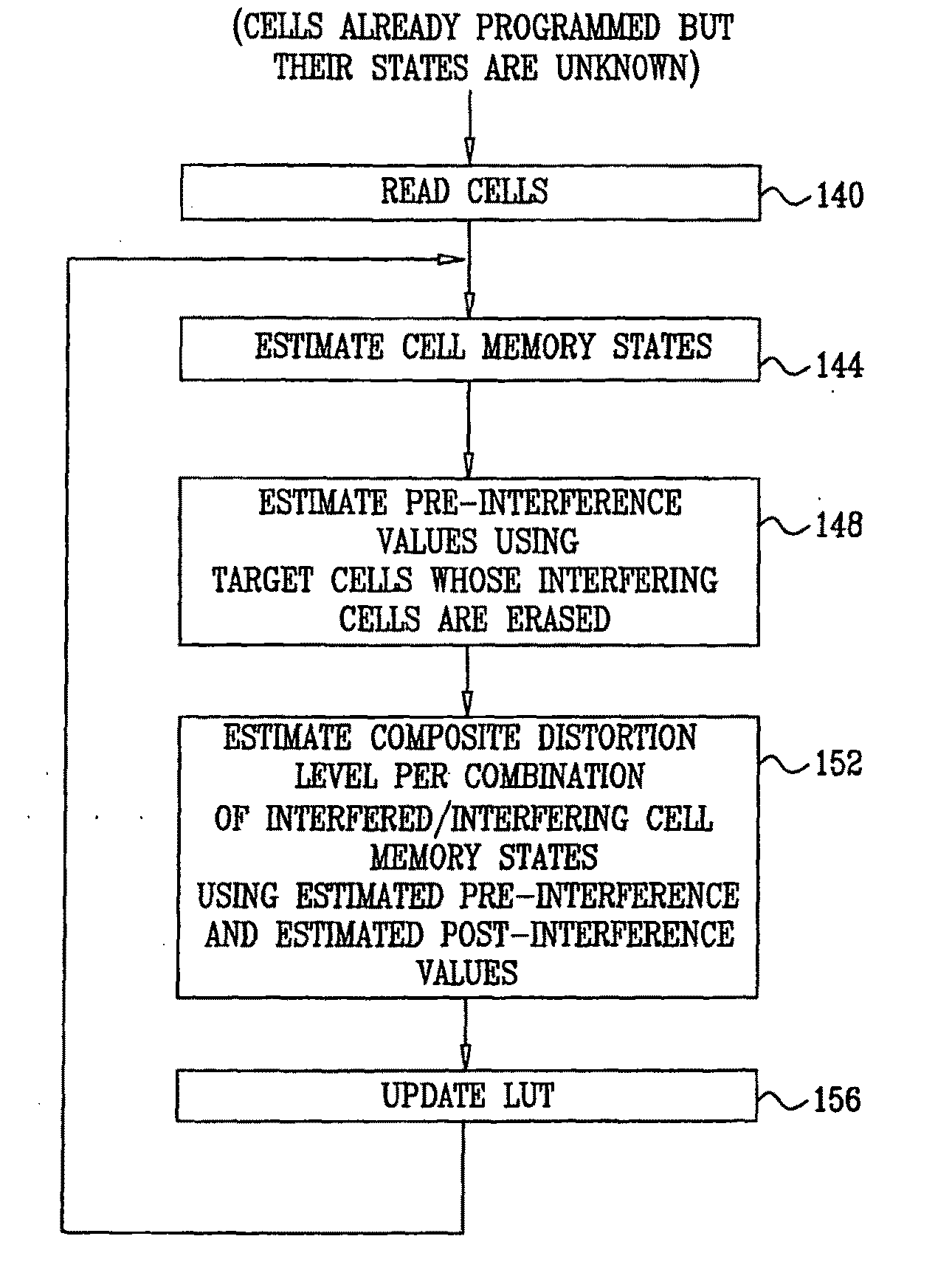

Estimation of non-linear distortion in memory devices

A method for operating a memory (24) includes storing data in analog memory cells (32) of the memory by writing respective analog values to the analog memory cells. A set of the analog memory cells is identified, including an interfered cell having a distortion that is statistically correlated with the respective analog values of the analog memory cells in the set. A mapping is determined between combinations of possible analog values of the analog memory cells in the set and statistical characteristics of composite distortion levels present in the interfered memory cell. The mapping is applied so as to compensate for the distortion in the interfered memory cell.

Owner:APPLE INC

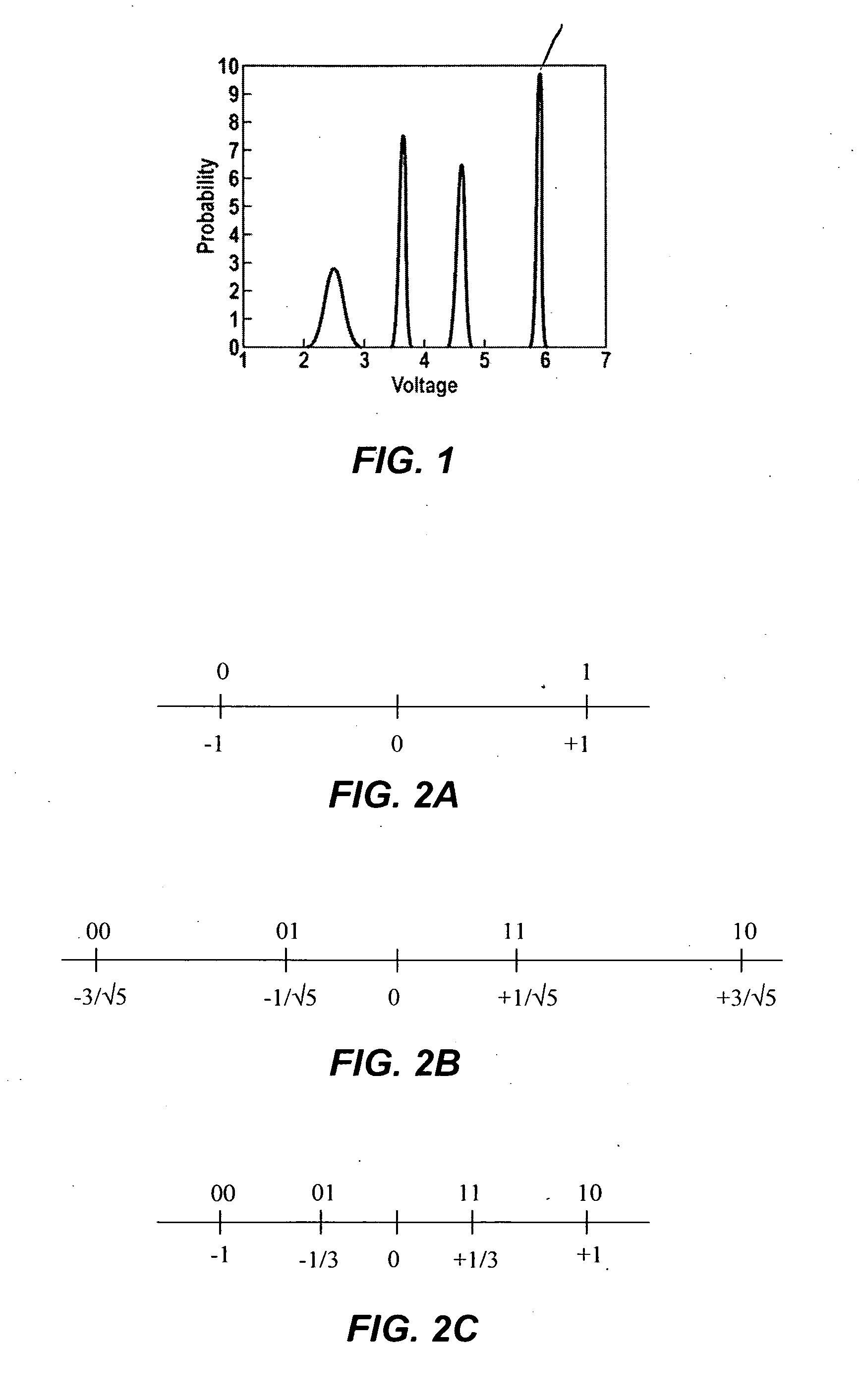

Reducing programming error in memory devices

InactiveUS20090103358A1Multiplex system selection arrangementsElectric analogue storesComputer scienceVoltage

A method for storing data in an array (28) of analog memory cells (32) includes defining a constellation of voltage levels (90A, 90B, 90C, 90D) to be used in storing the data. A part of the data is written to a first analog memory cell in the array by applying to the analog memory cell a first voltage level selected from the constellation. After writing the part of the data to the first analog memory cell, a second voltage level that does not belong to the constellation is read from the first analog memory cell. A modification to be made in writing to one or more of the analog memory cells in the array is determined responsively to the second voltage level, and data are written to the one or more of the analog memory cells subject to the modification.

Owner:APPLE INC

Reducing programming error in memory devices

InactiveUS7697326B2Multiplex system selection arrangementsElectric analogue storesComputer scienceVoltage

A method for storing data in an array (28) of analog memory cells (32) includes defining a constellation of voltage levels (90A, 90B, 90C, 90D) to be used in storing the data. A part of the data is written to a first analog memory cell in the array by applying to the analog memory cell a first voltage level selected from the constellation. After writing the part of the data to the first analog memory cell, a second voltage level that does not belong to the constellation is read from the first analog memory cell. A modification to be made in writing to one or more of the analog memory cells in the array is determined responsively to the second voltage level, and data are written to the one or more of the analog memory cells subject to the modification.

Owner:APPLE INC

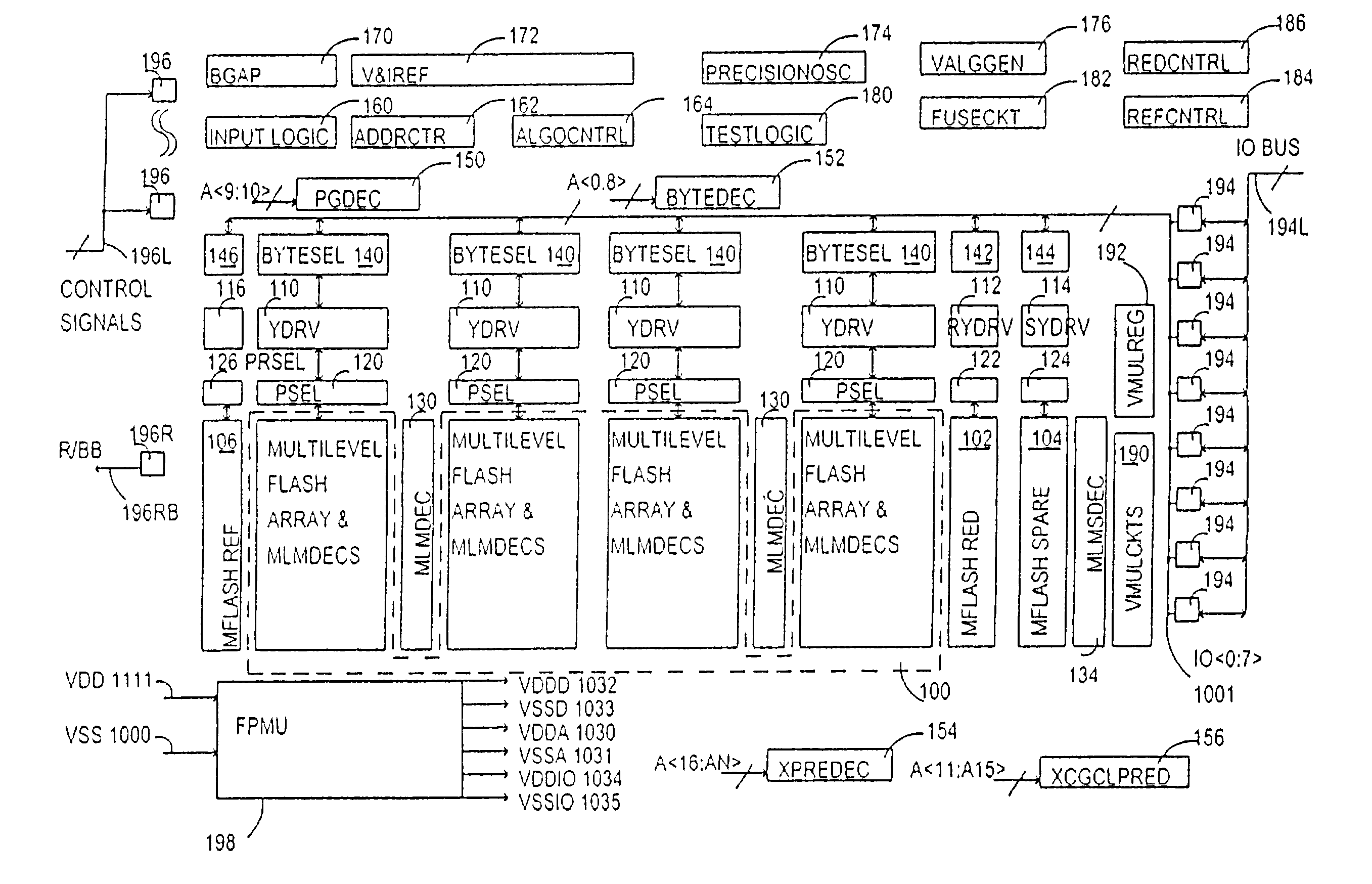

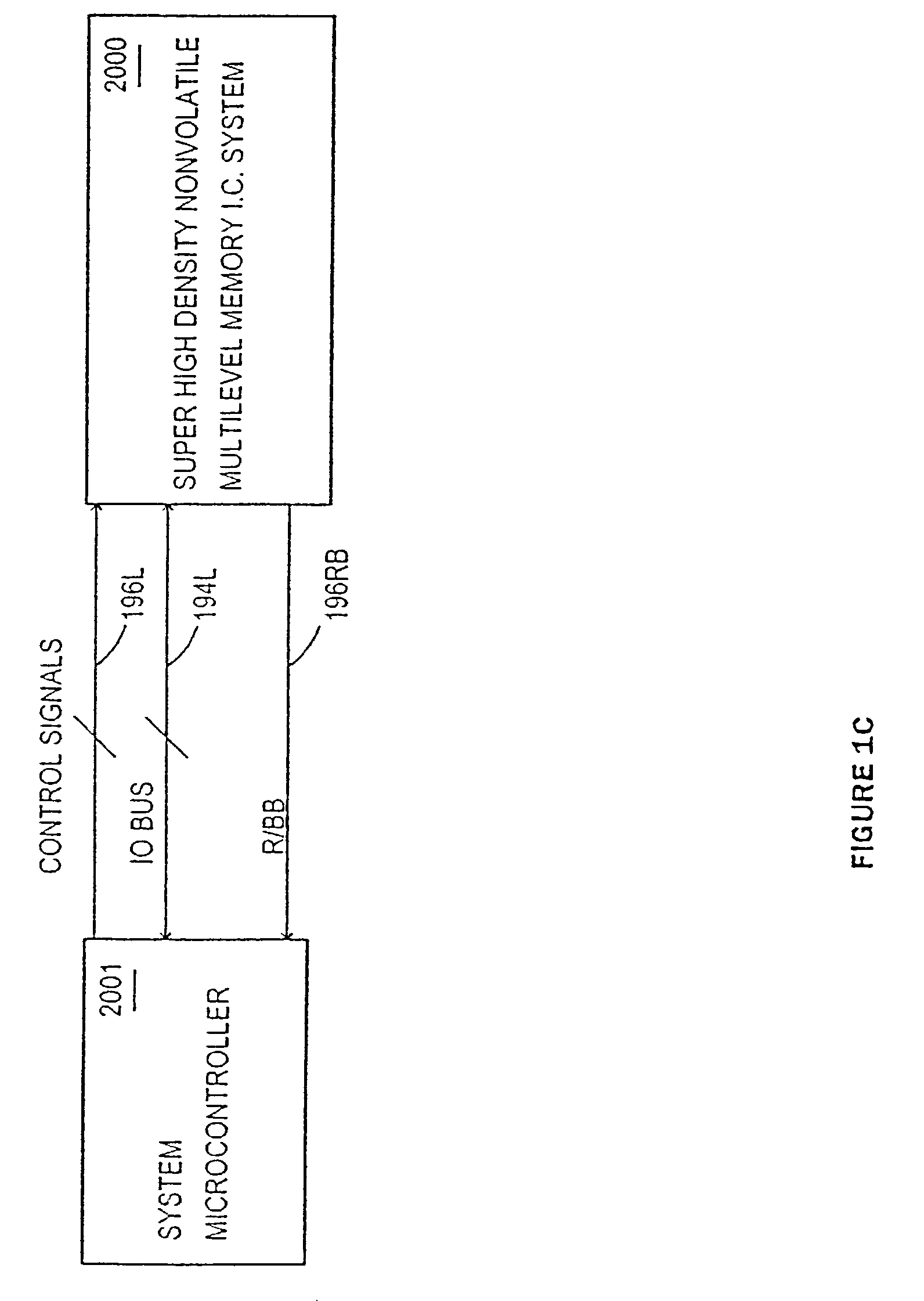

Digital multilevel memory system having multistage autozero sensing

A digital multibit non-volatile memory integrated system includes autozero multistage sensing. One stage may provide local sensing with autozero. Another stage may provide global sensing with autozero. A twisted bitline may be used for array arrangement. Segment reference may be used for each segment. The system may read data cells using a current sensing one or two step binary search. The system may use inverse voltage mode or inverse current mode sensing. The system may use no current multilevel sensing. The system may use memory cell replica sensing. The system may use dynamic sensing. The system may use built-in byte redundancy. Sense amplifiers capable of sub-volt (<<1V) sensing are described.

Owner:SILICON STORAGE TECHNOLOGY

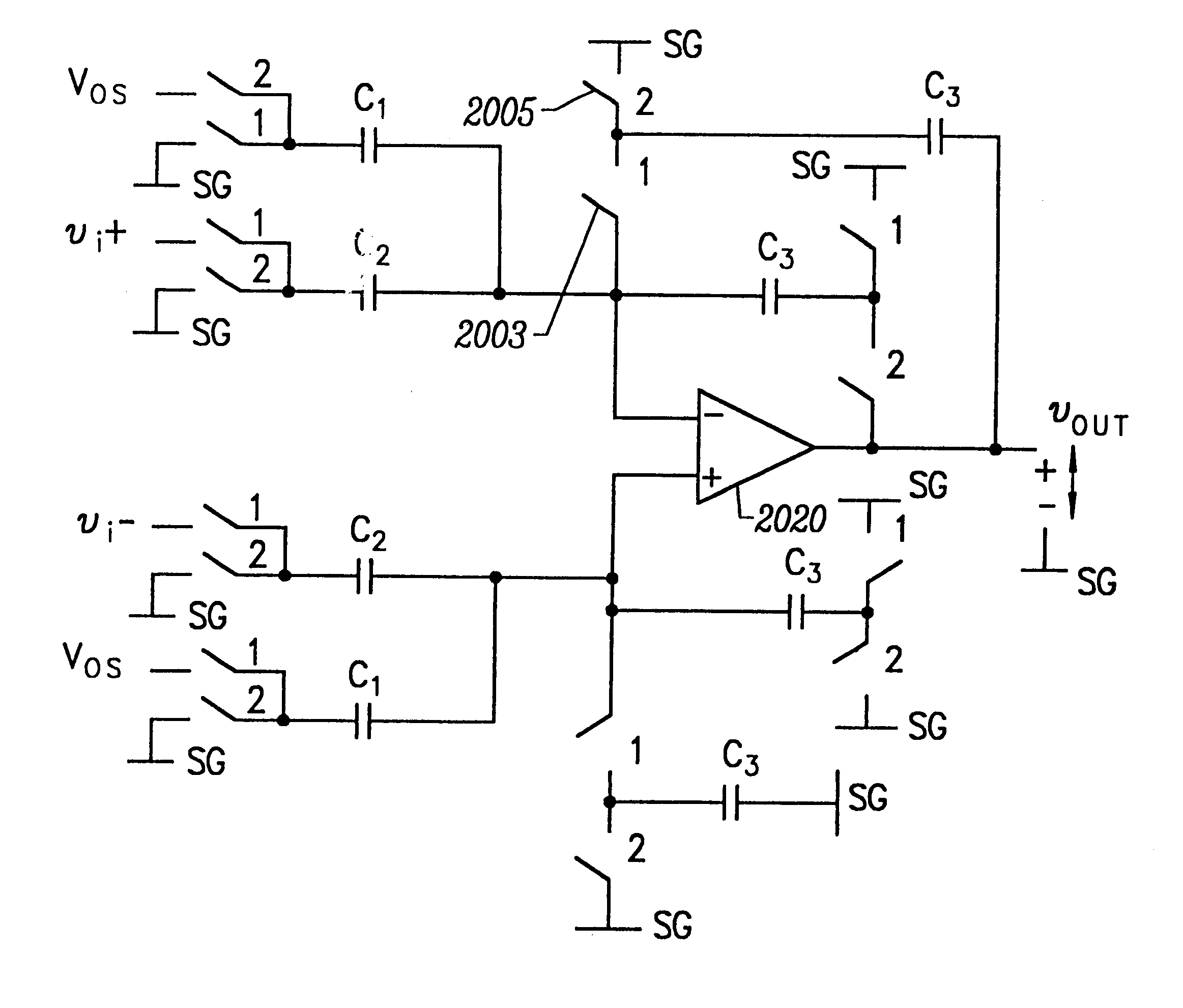

Adjustable level shifter circuits for analog or multilevel memories

InactiveUS6184726B1Prolong lifeImprove reliabilityPulse automatic controlElectric analogue storesMultilevel memoryEngineering

Level shifter circuits are used to configure analog or multilevel memory cells. A level shifter circuit generates an output voltage that is above the input voltage by an offset voltage value. The magnitude of this offset voltage or the relationship between the input and output voltages of the level shifter is adjustable or programmably selectable. Adjustments can be made after the integrated circuits is fabricated and packaged. Adjustments are made by configuring bits of data in the integrated circuit to indicate the offset voltage or other parameters. These configuration bits are implemented using latches, flip-flops, registers, memory cells, or other storage circuits.

Owner:SANDISK CORP

Reading memory cells using multiple thresholds

A method for operating a memory (28) includes storing data, which is encoded with an Error Correction Code (ECC), in analog memory cells (32) of the memory by writing respective analog input values selected from a set of nominal values to the analog memory cells. The stored data is read by performing multiple read operations that compare analog output values of the analog memory cells to different, respective read thresholds so as to produce multiple comparison results for each of the analog memory cells. At least two of the read thresholds are positioned between a pair of the nominal values that are adjacent to one another in the set of the nominal values. Soft metrics are computed responsively to the multiple comparison results. The ECC is decoded using the soft metrics, so as to extract the data stored in the analog memory cells.

Owner:APPLE INC

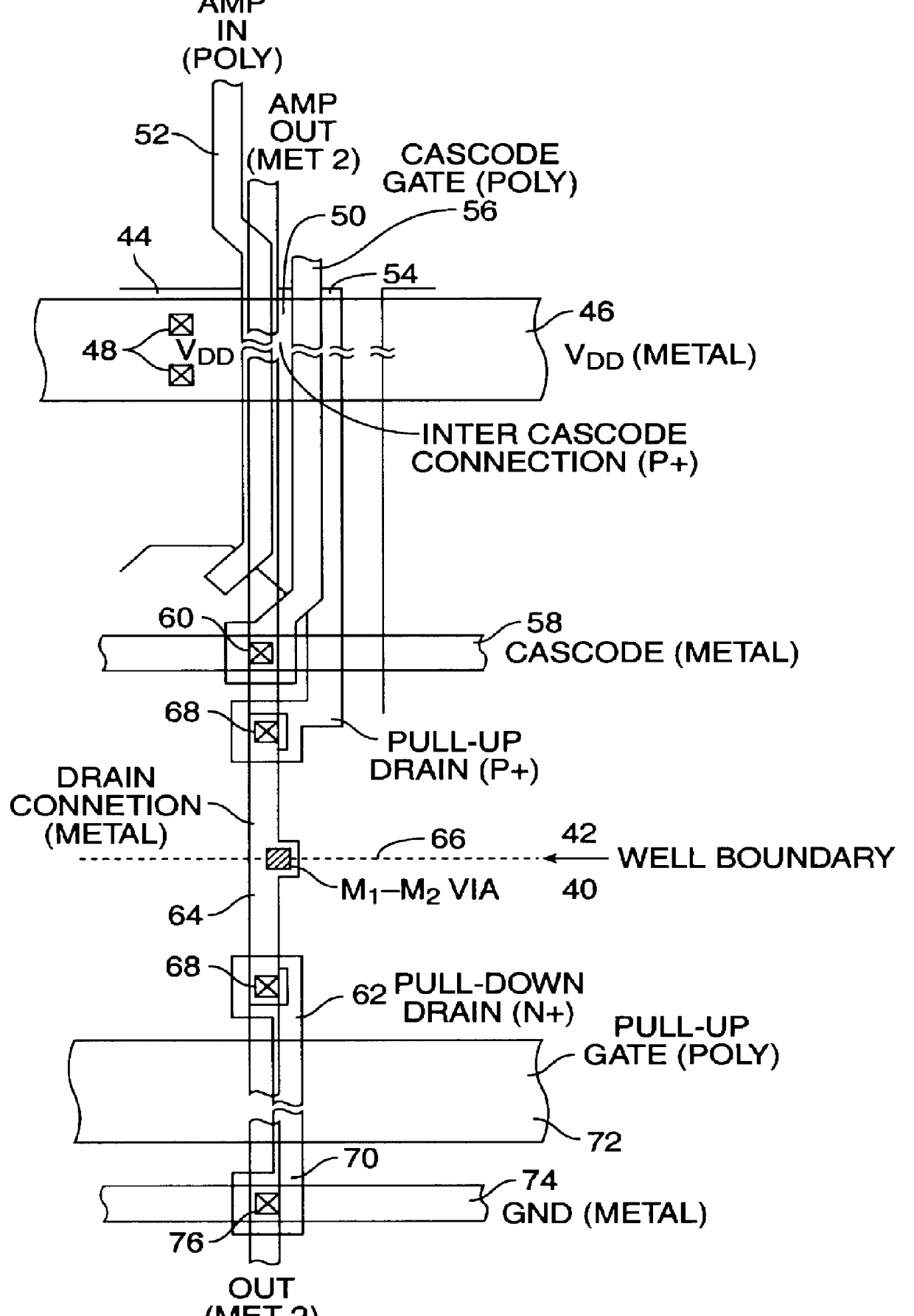

Sense amplifier for high-density imaging array

InactiveUS6097432ATelevision system detailsTelevision system scanning detailsHigh densityAudio power amplifier

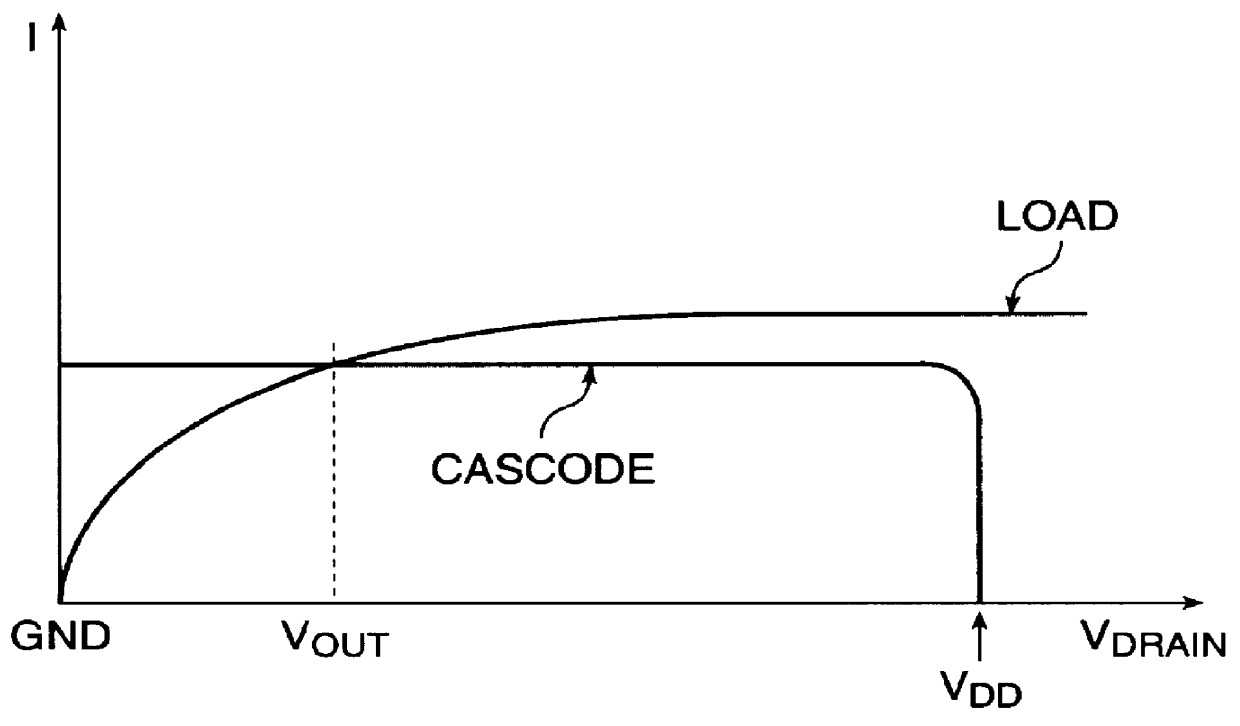

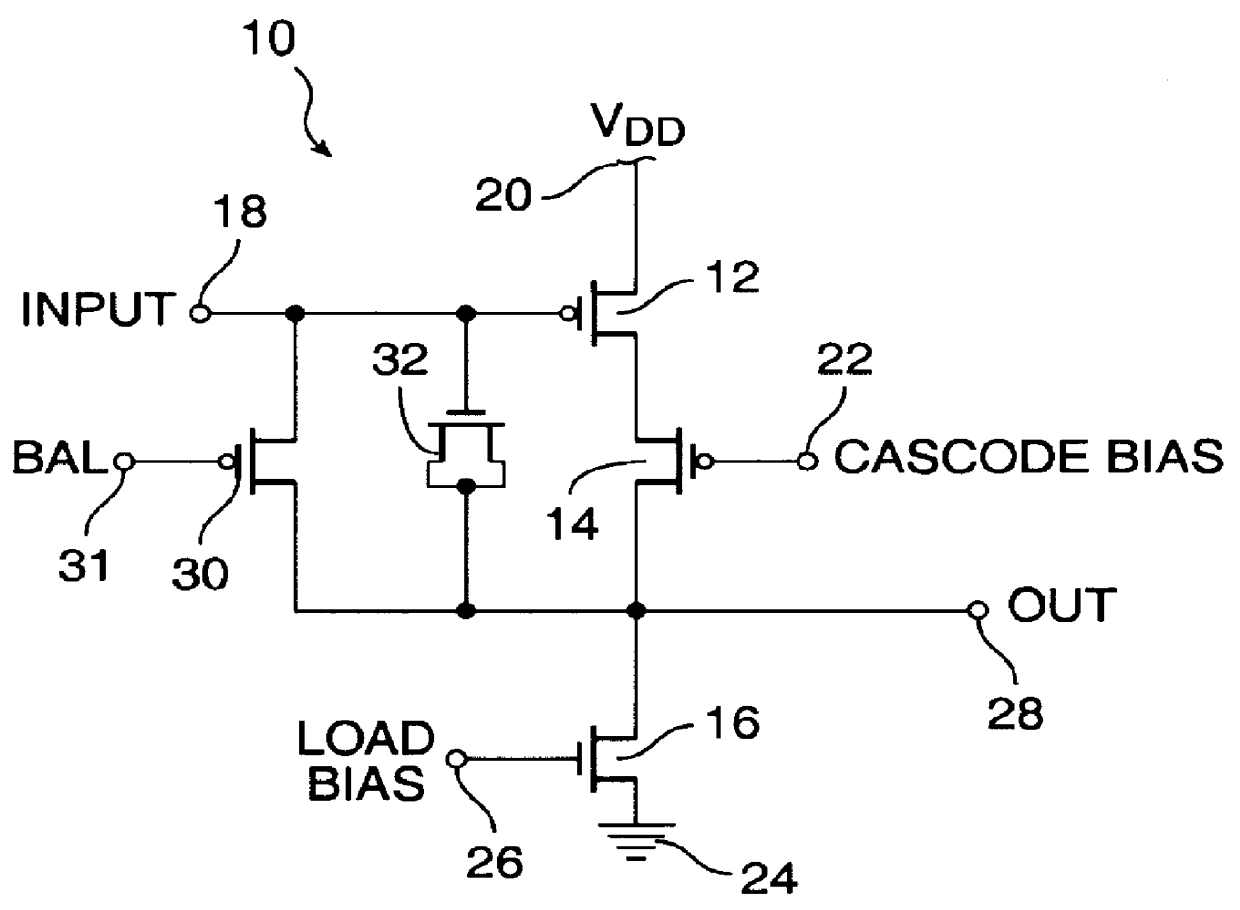

A sense amplifier comprises an input node and an output node. An input transistor has a gate connected to the input node, a source connected to a first supply voltage rail, and a drain. A cascode transistor has a gate connected to a cascode node, a source connected to the drain of the input transistor, and a drain connected to the output node. A load transistor has a gate connected to a bias node, a drain connected to the output node, and a source connected to a second supply voltage rail. The gates of the cascode transistor and the load transistor are biased such that the input transistor and the cascode transistor are operated near their threshold and the load transistor is operated above threshold. In a presently preferred embodiment of the present invention, the input transistor and the cascode transistor of the sense amplifier are wide and short, such that they operate in below threshold, whereas the load transistor is made long and relatively narrow, so that it operates above threshold.

Owner:FOVEON

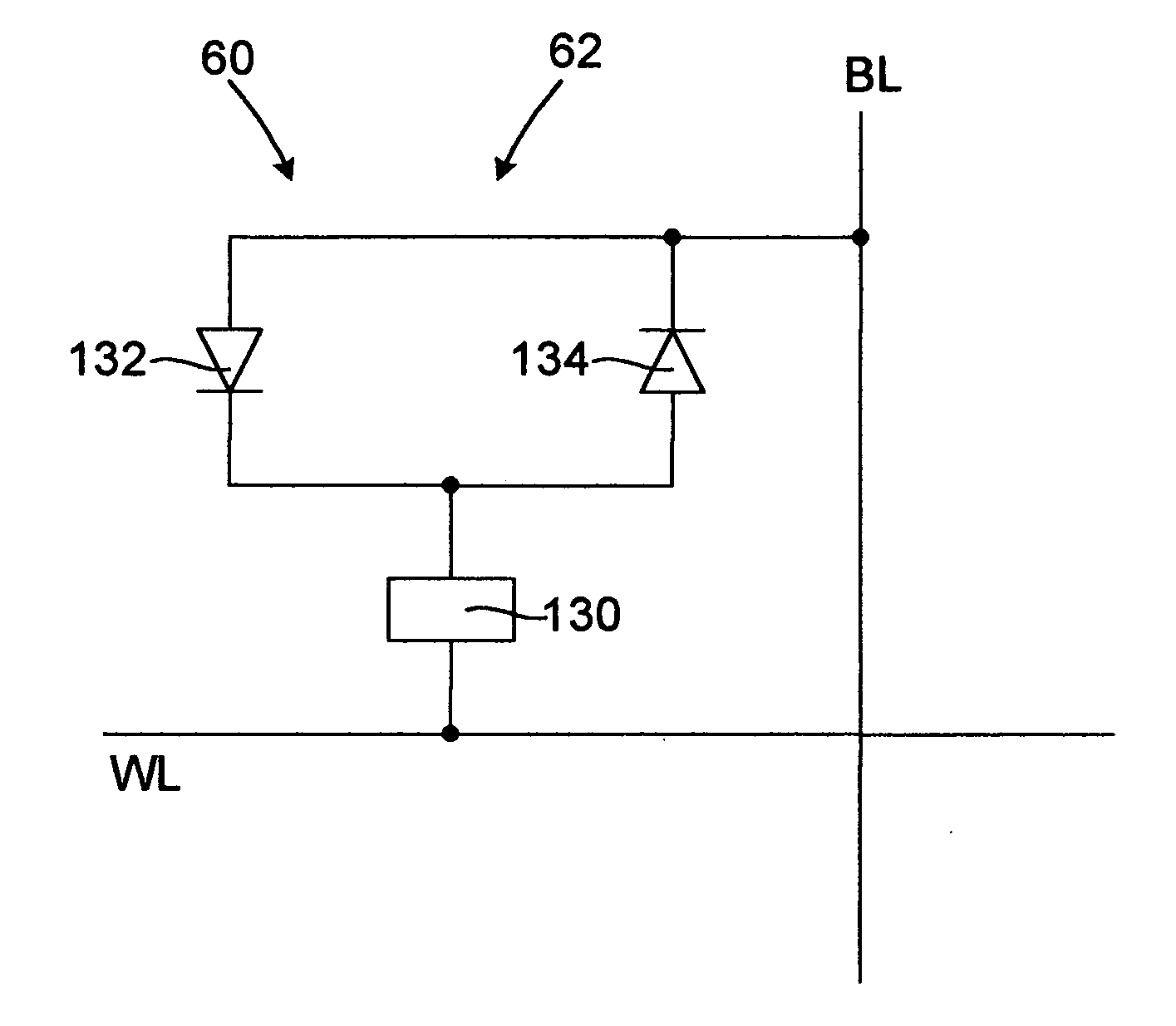

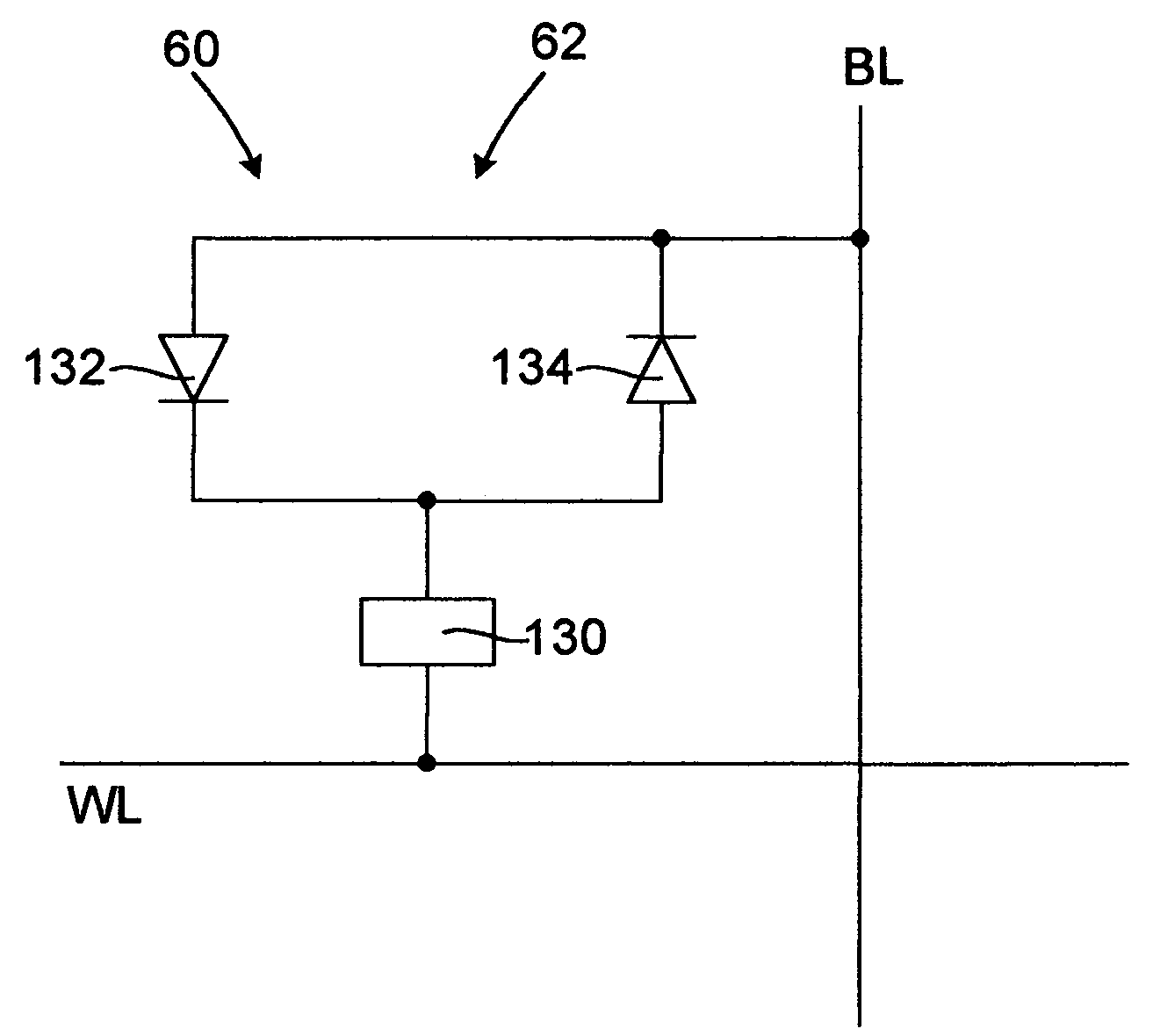

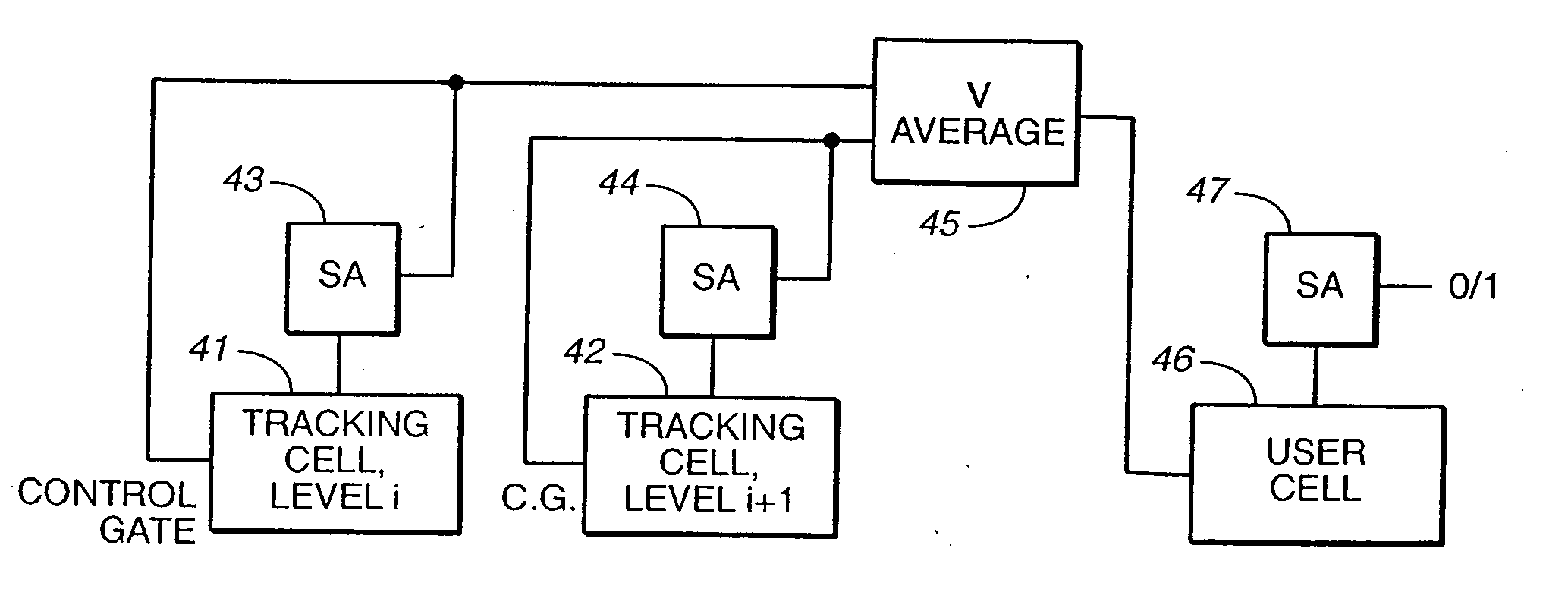

Diode array architecture for addressing nanoscale resistive memory arrays

The present memory structure includes thereof a first conductor, a second conductor, a resistive memory cell connected to the second conductor, a first diode connected to the resistive memory cell and the first conductor, and oriented in the forward direction from the resistive memory cell to the first conductor, and a second diode connected to the resistive memory cell and the first conductor, in parallel with the first diode, and oriented in the reverse direction from the resistive memory cell to the first conductor. The first and second diodes have different threshold voltages

Owner:MONTEREY RES LLC

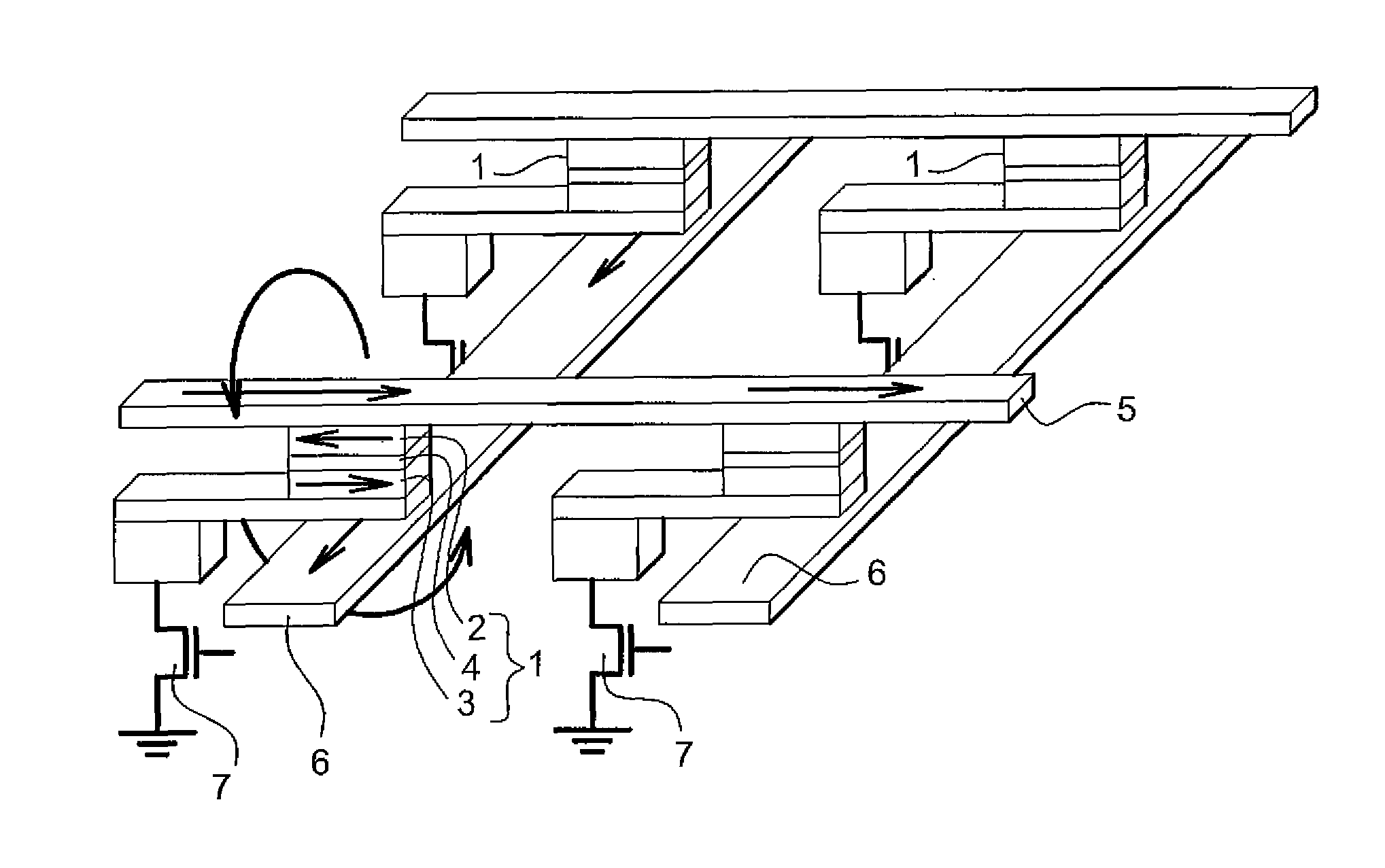

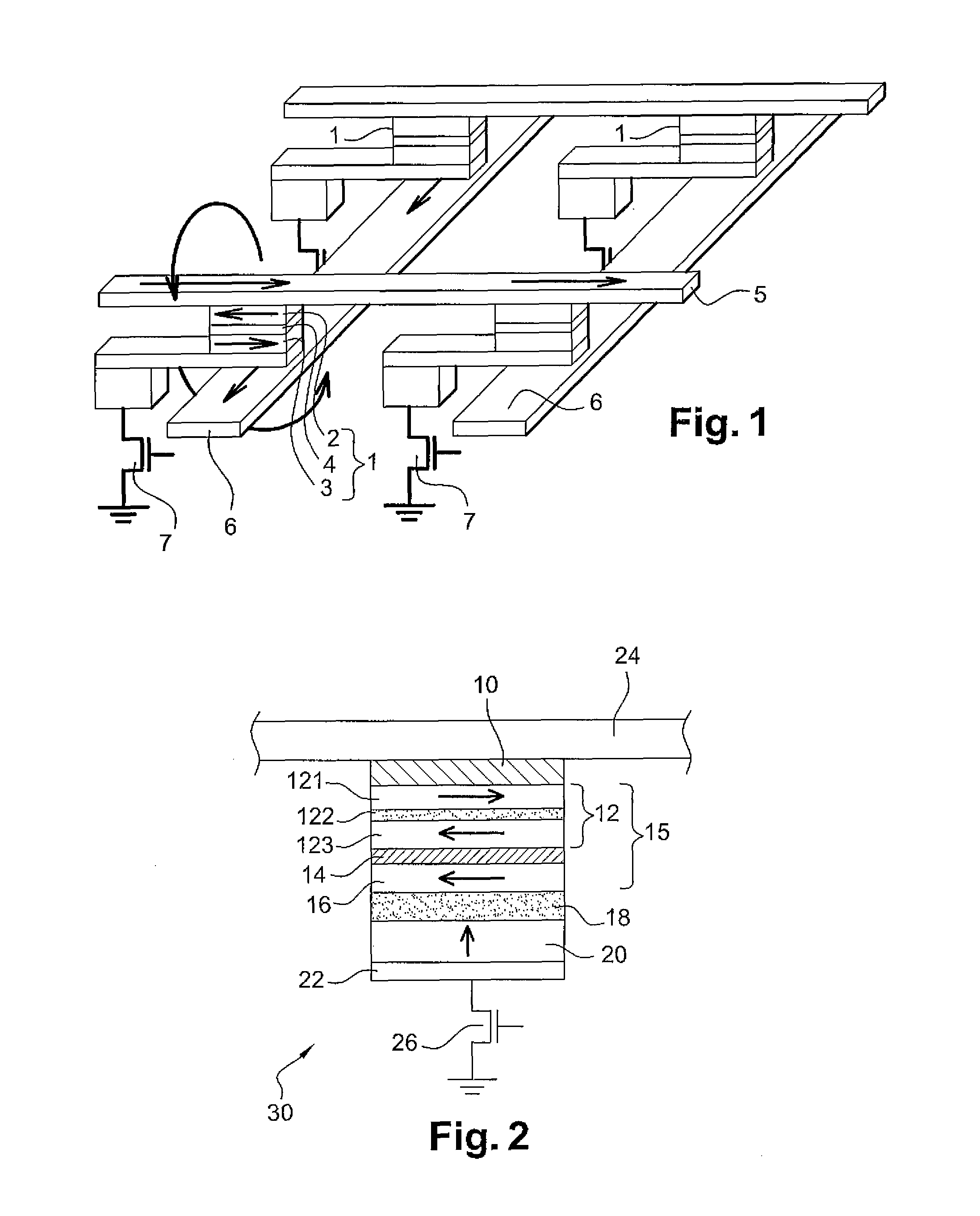

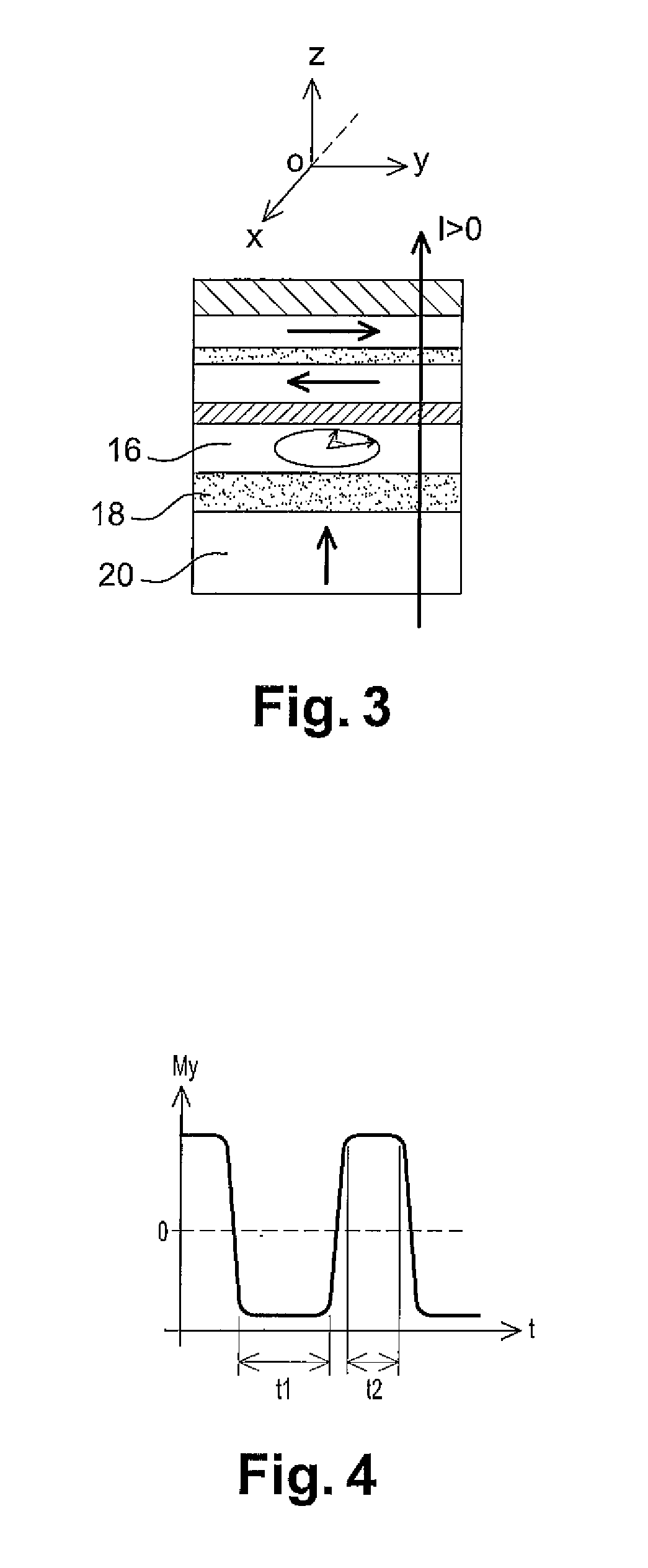

Spin polarised magnetic device

ActiveUS8279666B2Reducing the stochastic fluctuations in the magnetisation reversal timeTotal current dropNanomagnetismMagnetic measurementsMagnetic storageSpins

A magnetic device includes a magnetic reference layer with a fixed magnetization direction located either in the plane of the layer or perpendicular to the plane of the layer, a magnetic storage layer with a variable magnetization direction, a non-magnetic spacer separating the reference layer and the storage layer and a magnetic spin polarizing layer with a magnetization perpendicular to that of the reference layer, and located out of the plane of the spin polarizing layer if the magnetization of the reference layer is directed in the plane of the reference layer or in the plane of the spin polarizing layer if the magnetization of the reference layer is directed perpendicular to the plane of the reference layer. The spin transfer coefficient between the reference layer and the storage layer is higher than the spin transfer coefficient between the spin polarizing layer and the storage layer.

Owner:INSTITUT NAT POLYTECHN DE GRENOBLE +2

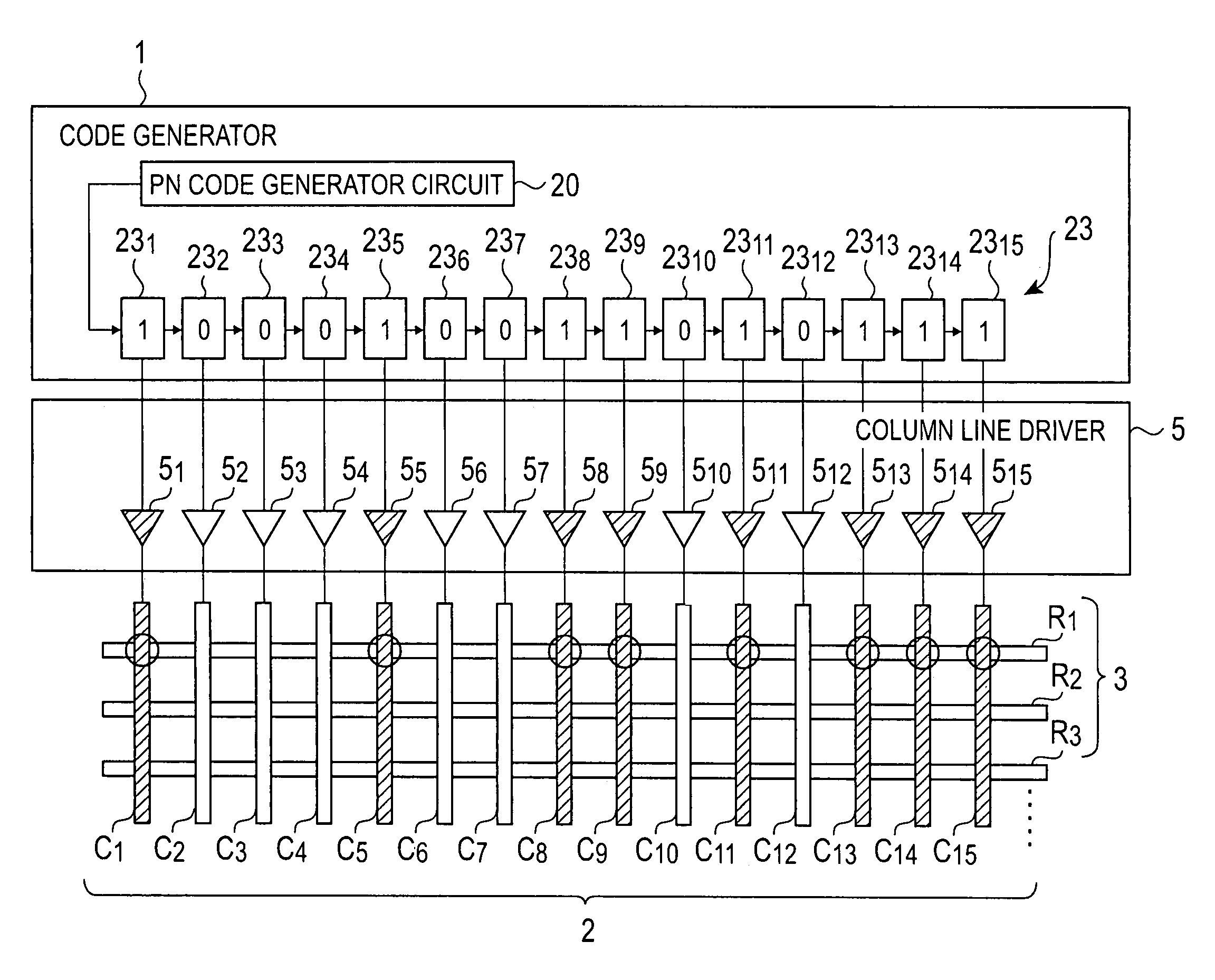

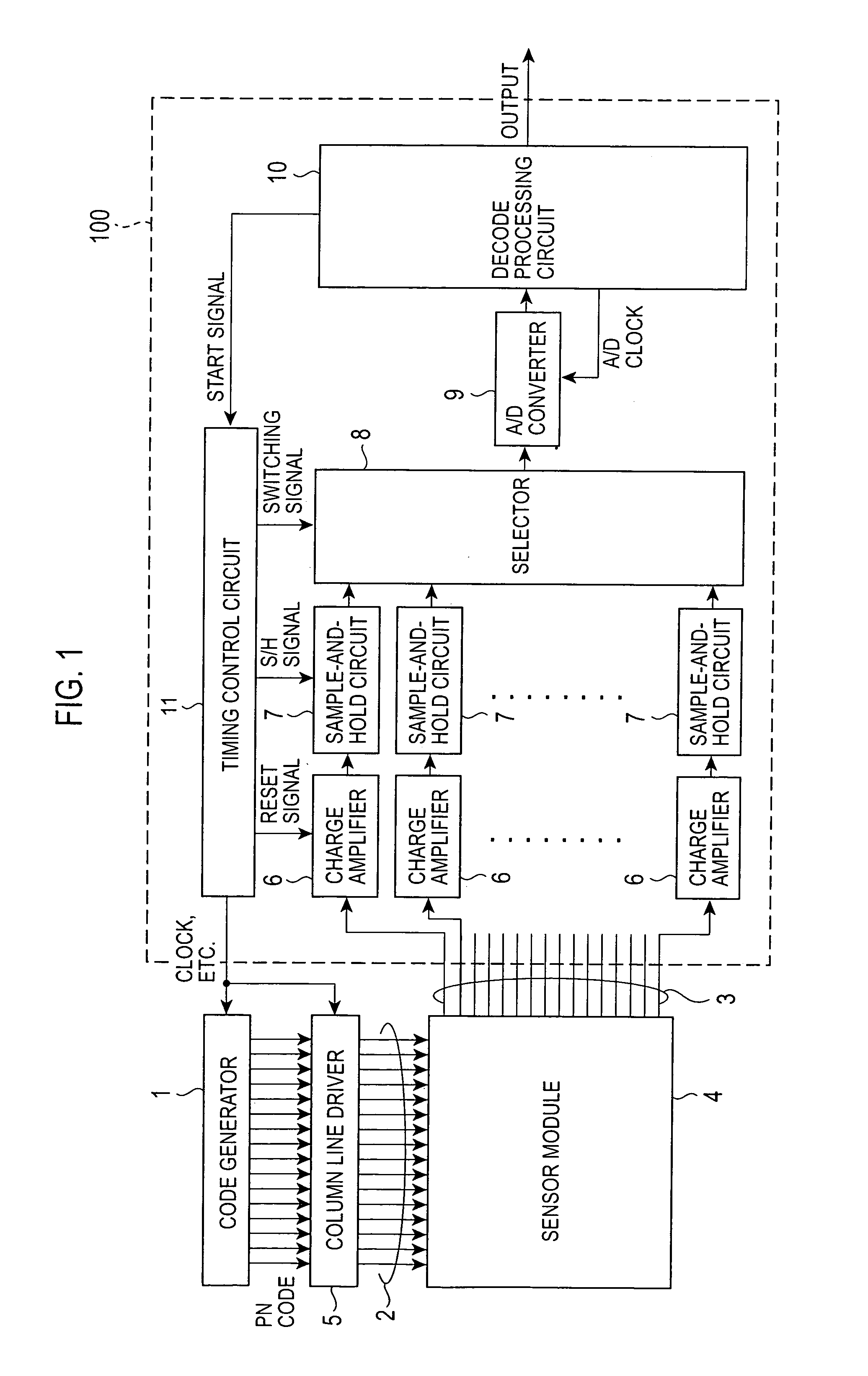

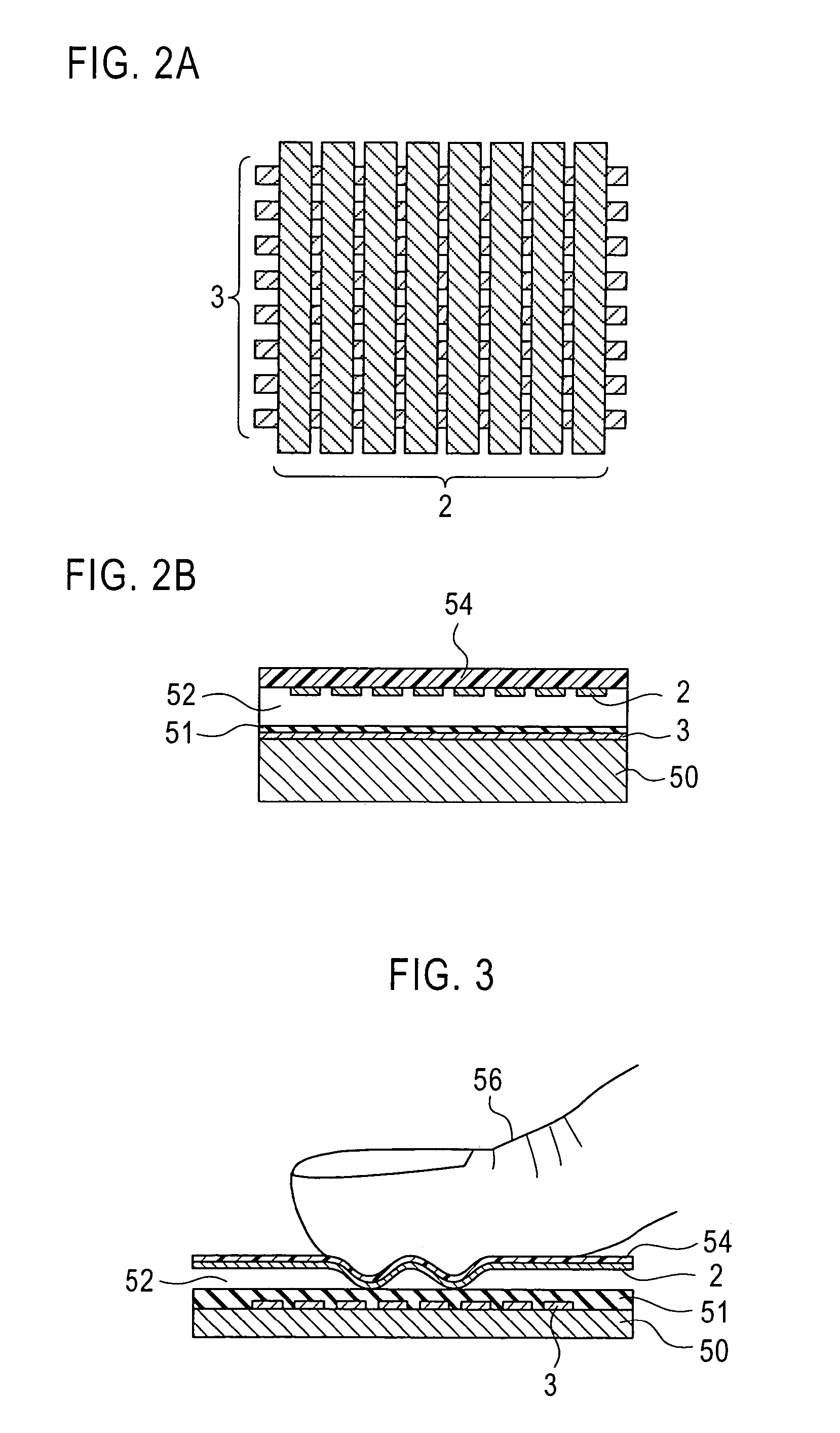

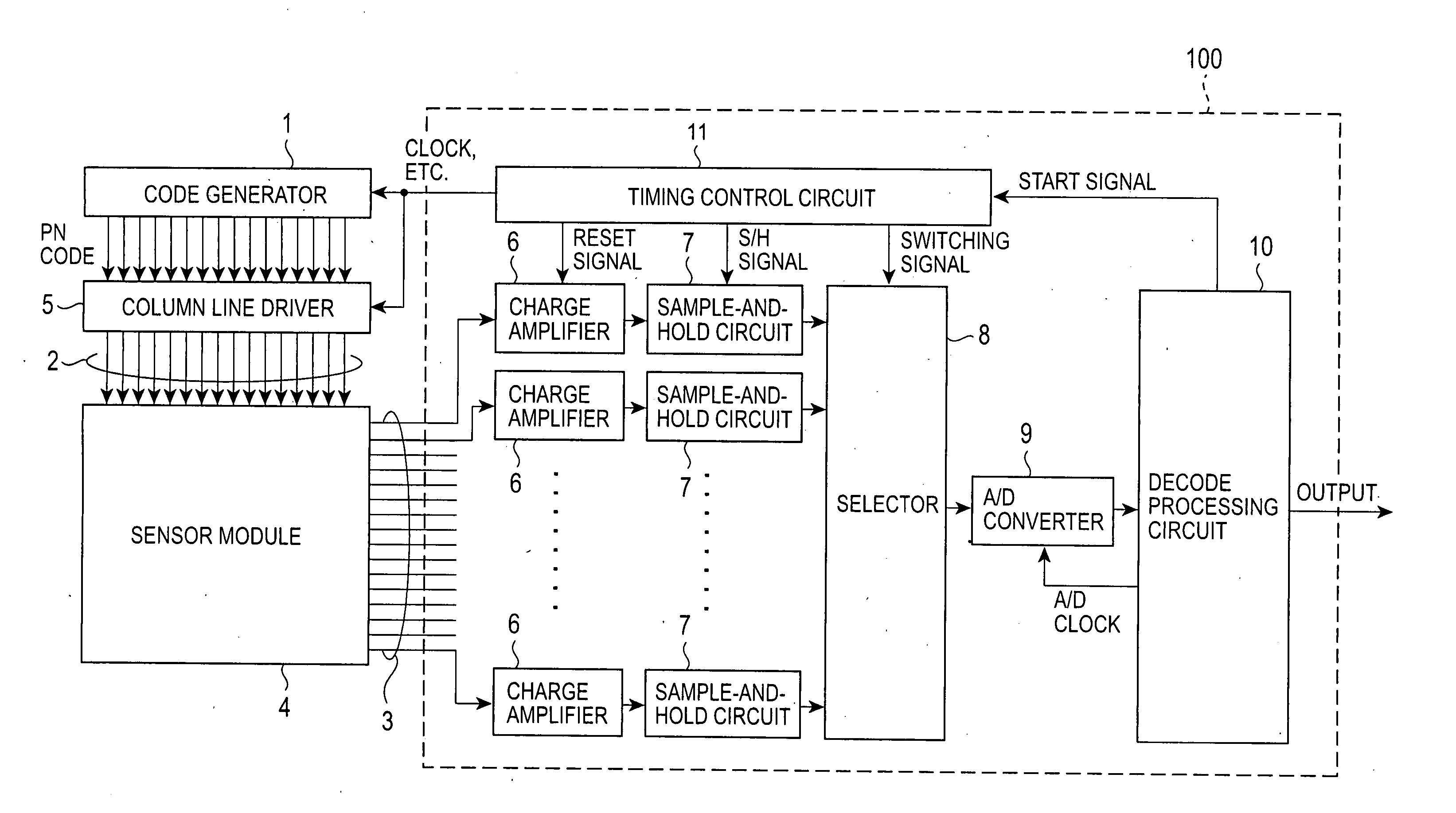

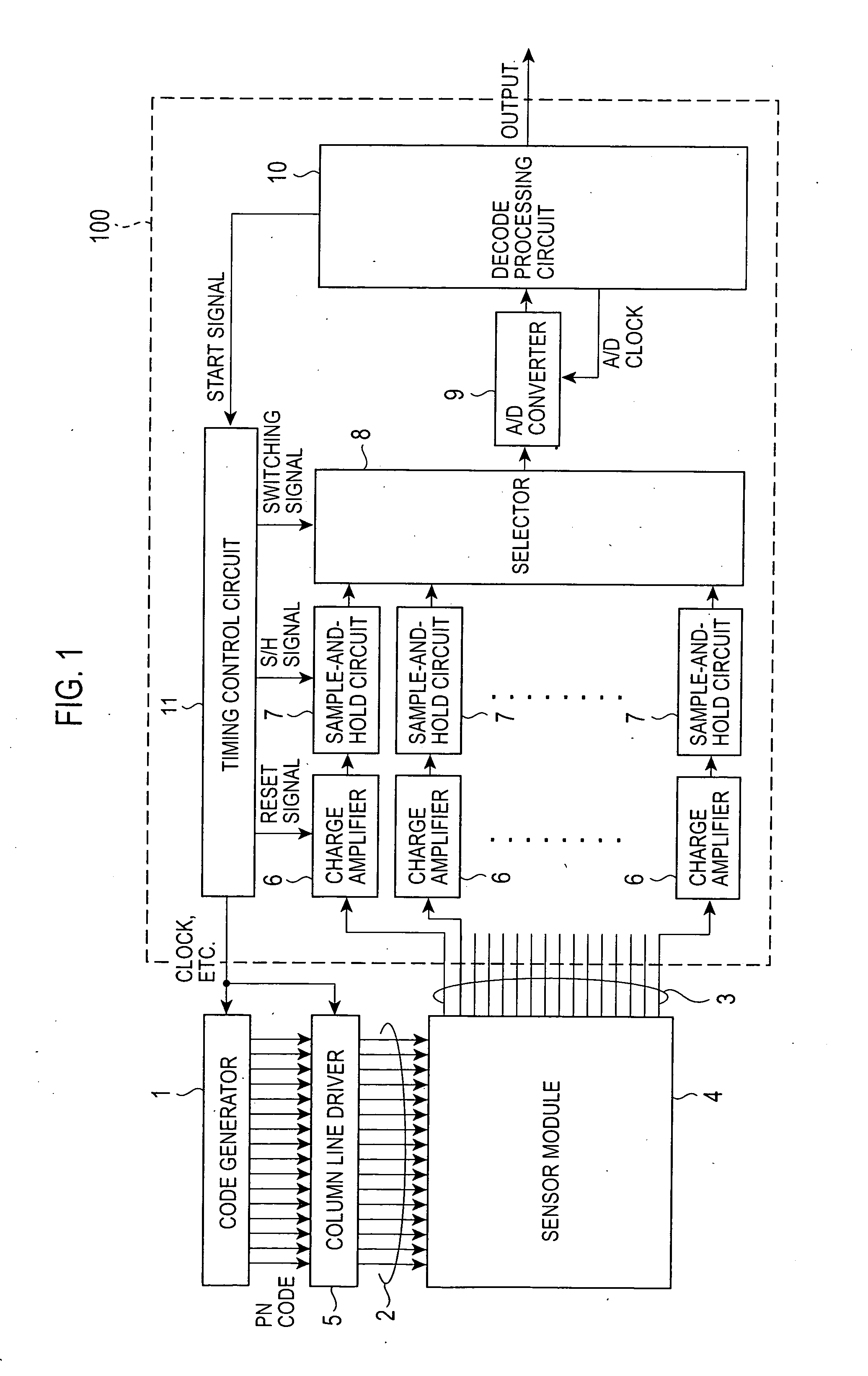

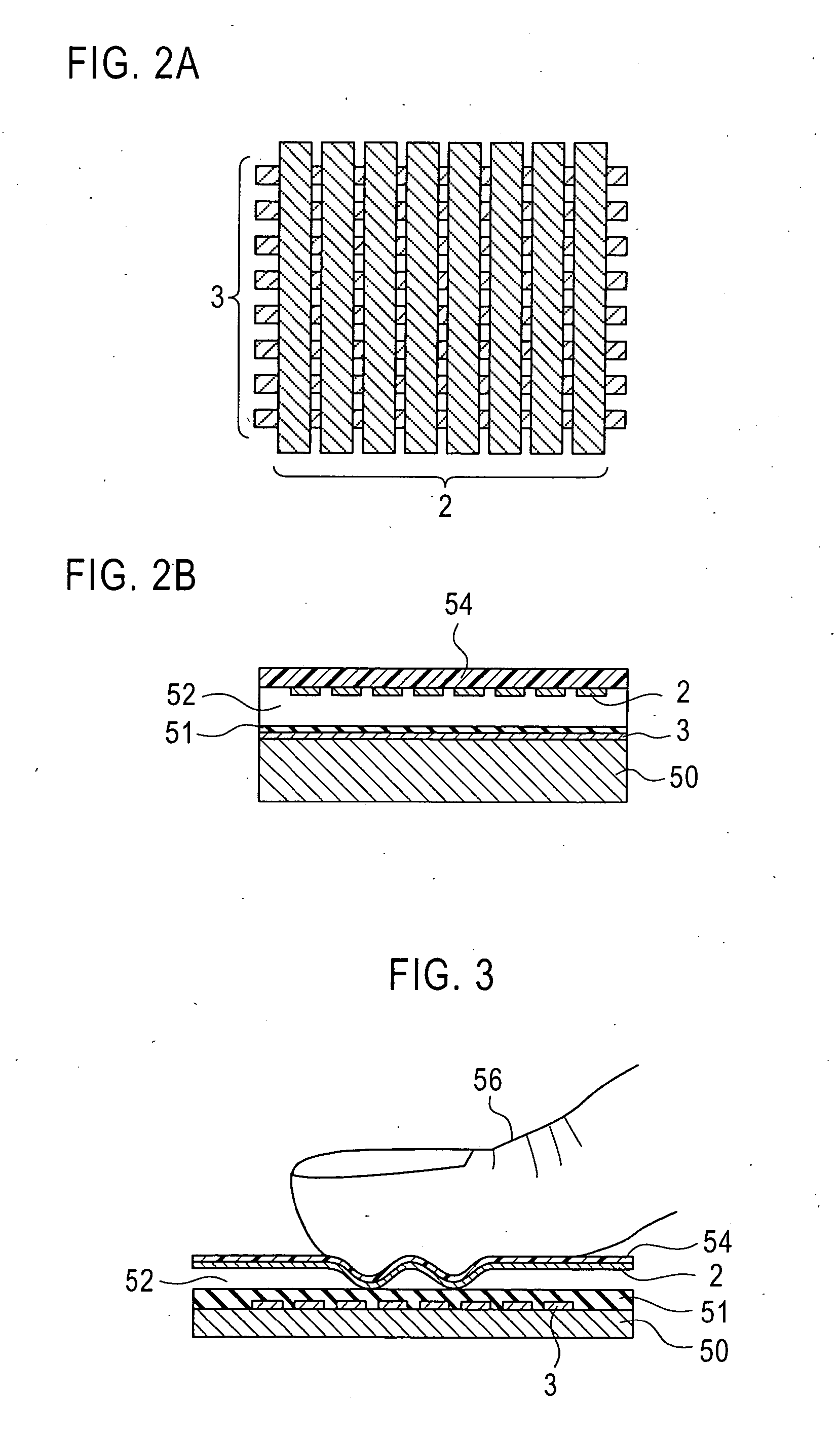

Capacitance detector circuit, capacitance detection method, and fingerprint sensor using the same

ActiveUS7075316B2Improve signal-to-noise ratioCapacitance measurementsElectric analogue storesDetector circuitsCapacitance transducer

A capacitance detecting circuit of a capacitive sensor having a plurality of column lines and a row line intersecting the column lines detects a change in capacitance at an intersection of a column line and a row line. The circuit includes a PN code generating unit for generating a code having orthogonality in time sequence to output the generated code as a column drive signal, a column line drive unit for driving a predetermined one of the column lines which are selected in response to the code, a capacitance detecting unit, connected to the row line, for detecting a voltage by converting a total sum of changes in capacitance at intersections of the selected column lines into the voltage to output the detected voltage, and a decode processing unit for performing a predetermined calculation on the detected voltage output from the capacitance detecting unit and the code to determine a voltage value responsive to the capacitance change at the intersection.

Owner:SYNAPTICS INC

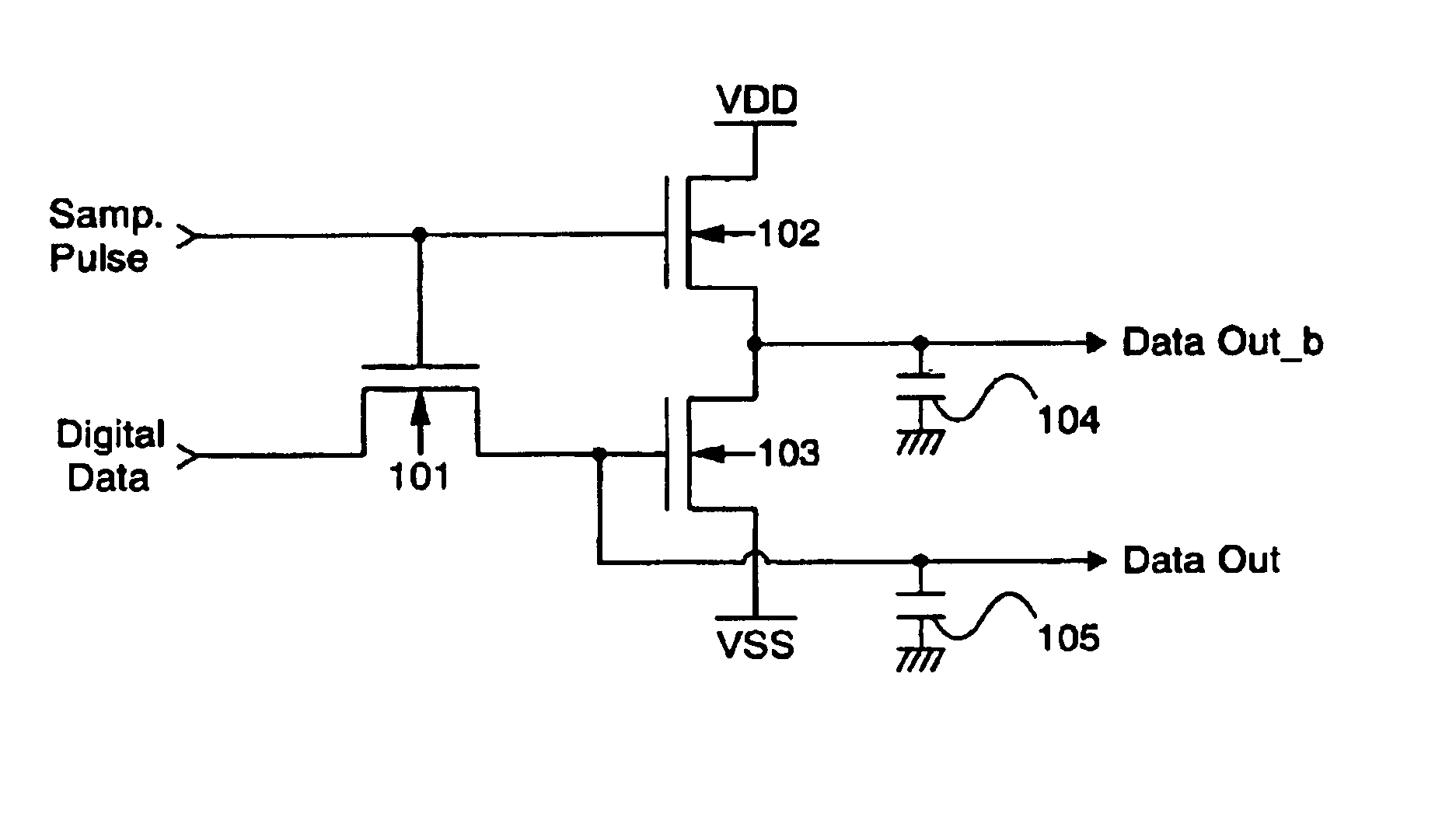

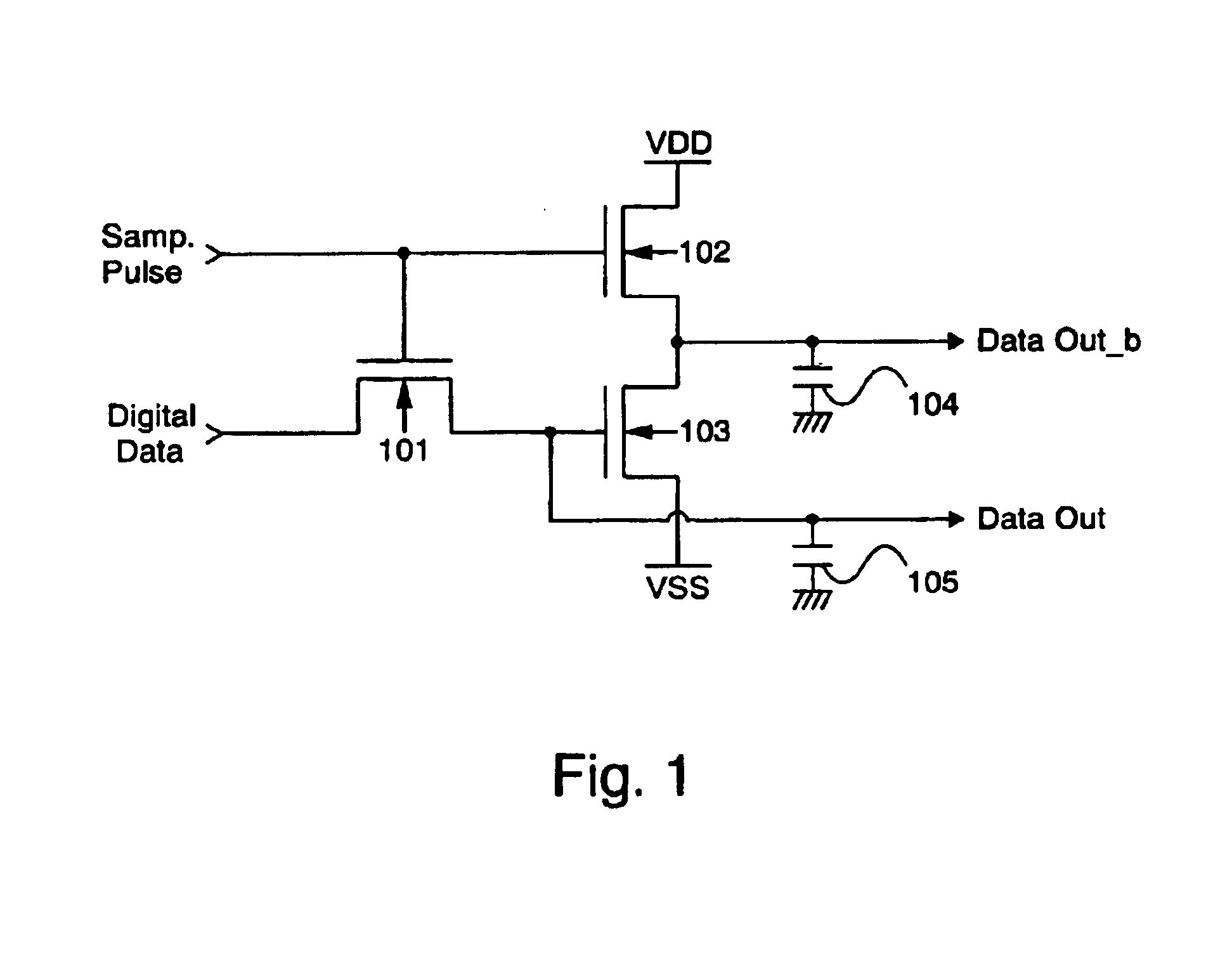

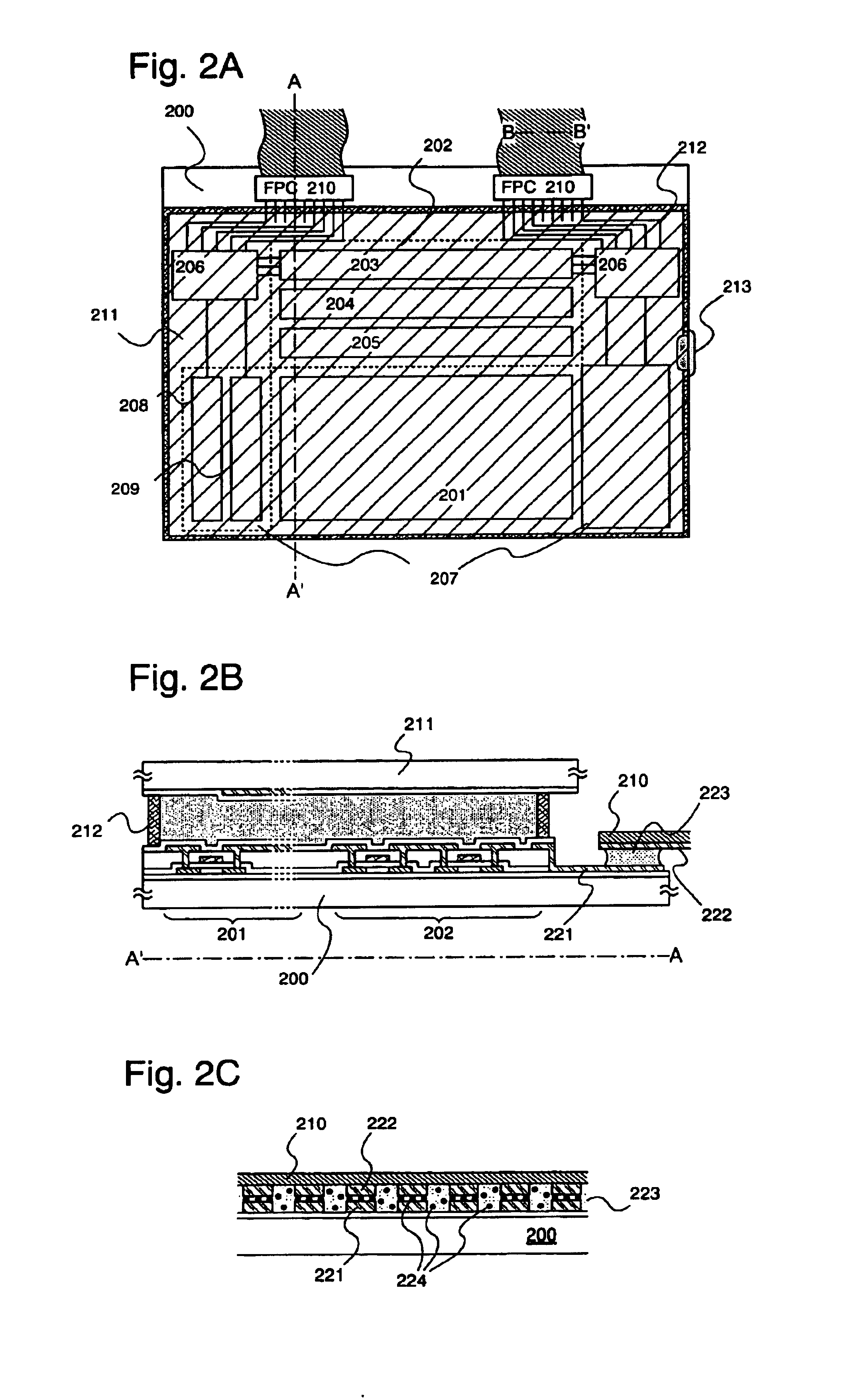

Semiconductor device and display device

InactiveUS7068076B2Obstruction is producedPower reduction in field effect transistorsLogic circuits characterised by logic functionDigital videoDevice material

A circuit capable of reducing a consumption current is provided for a digital display device composed of unipolar TFTs. There is provided a latch circuit for holding a digital video signal. According to the latch circuit, when the digital video signal is inputted to an input electrode of a TFT (101), a non-inverting output signal is outputted from an output electrode of the TFT (101) and an inverting output signal is outputted from output electrodes of TFTs (102 and 103). Two line outputs of non-inversion and inversion are obtained. Thus, when a buffer located in a subsequent stage is operated, a period for which a direct current path is produced between a high potential and a low potential of a power source can be shortened, thereby contributing to reduction in a consumption current.

Owner:SEMICON ENERGY LAB CO LTD

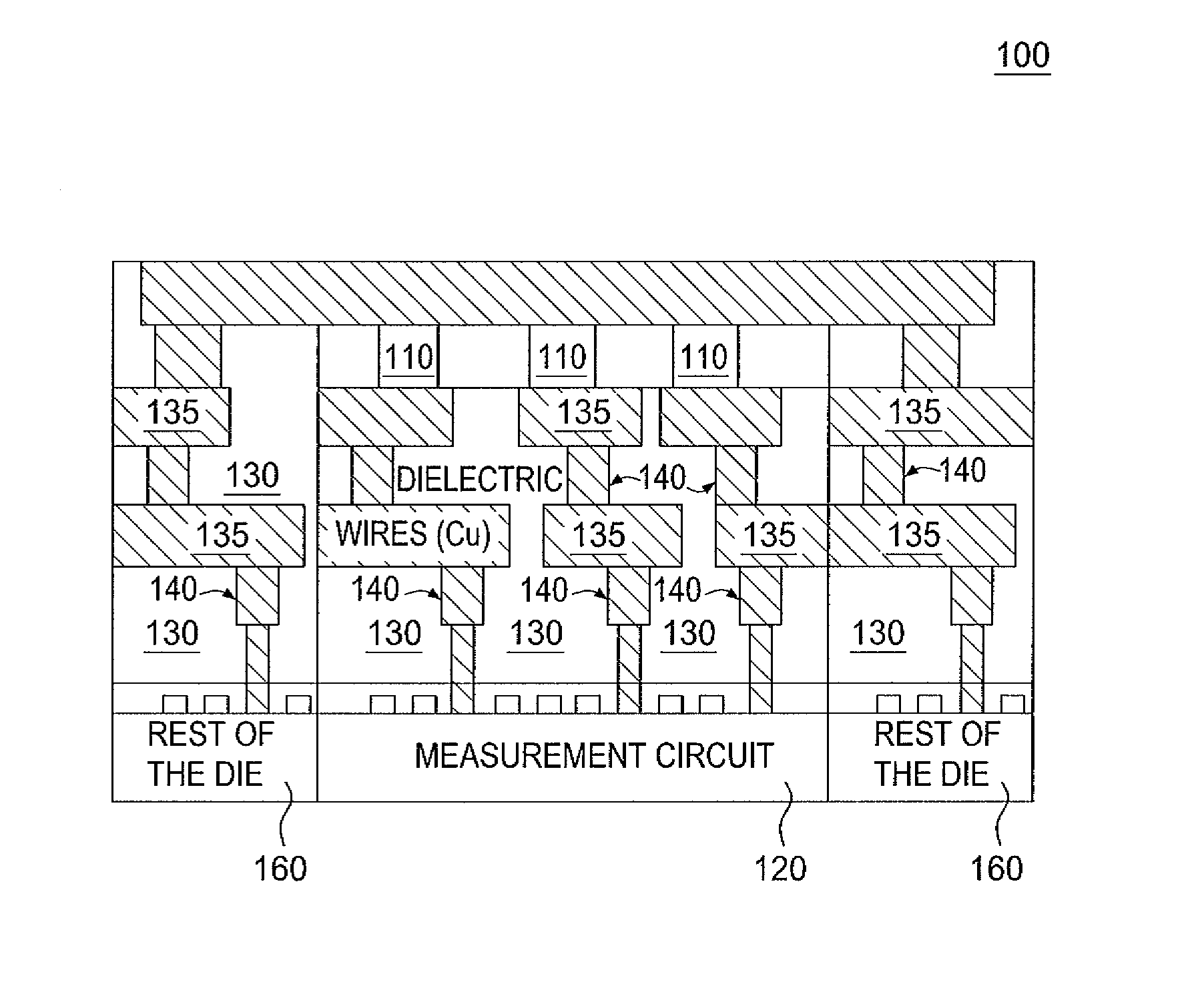

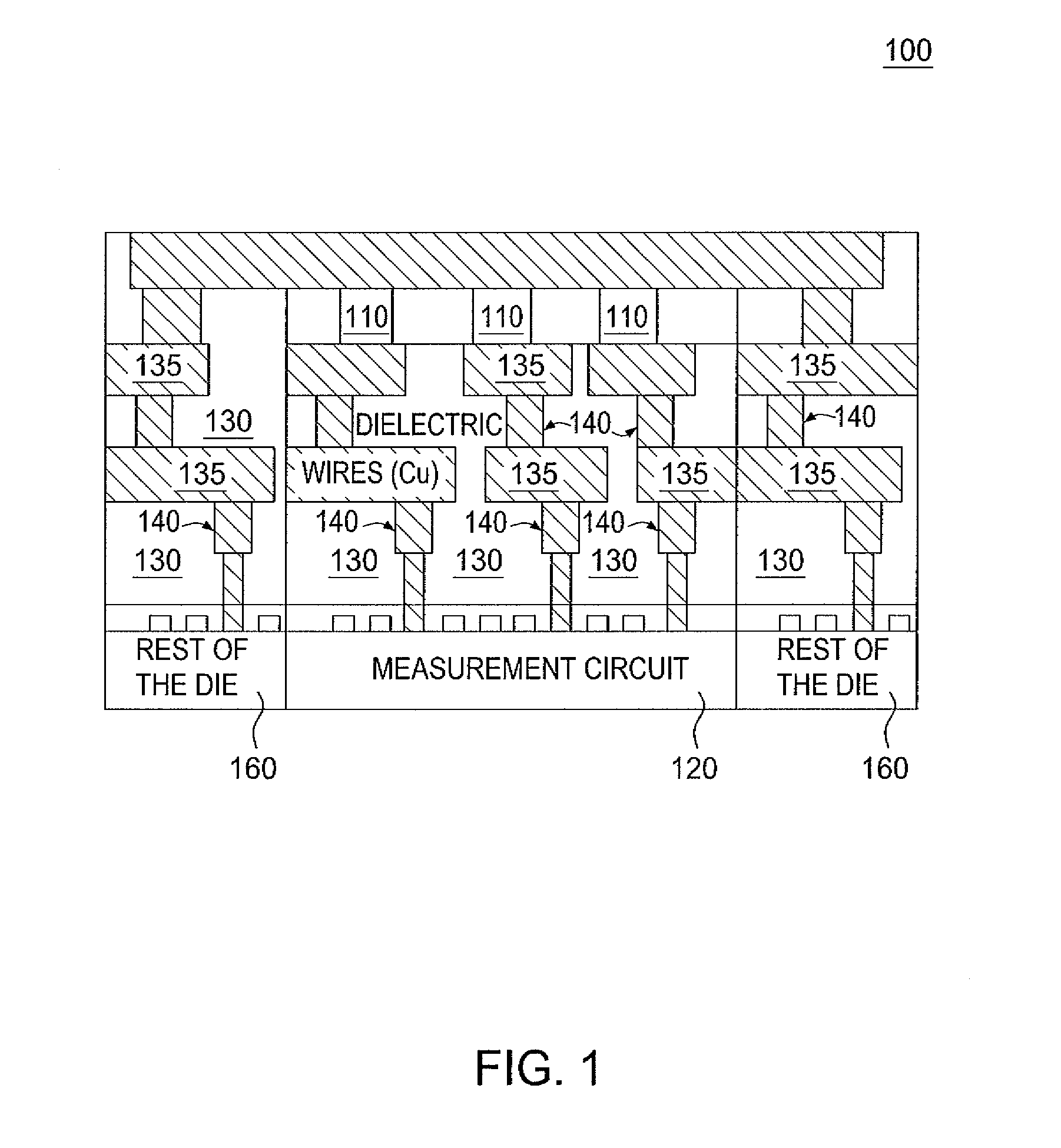

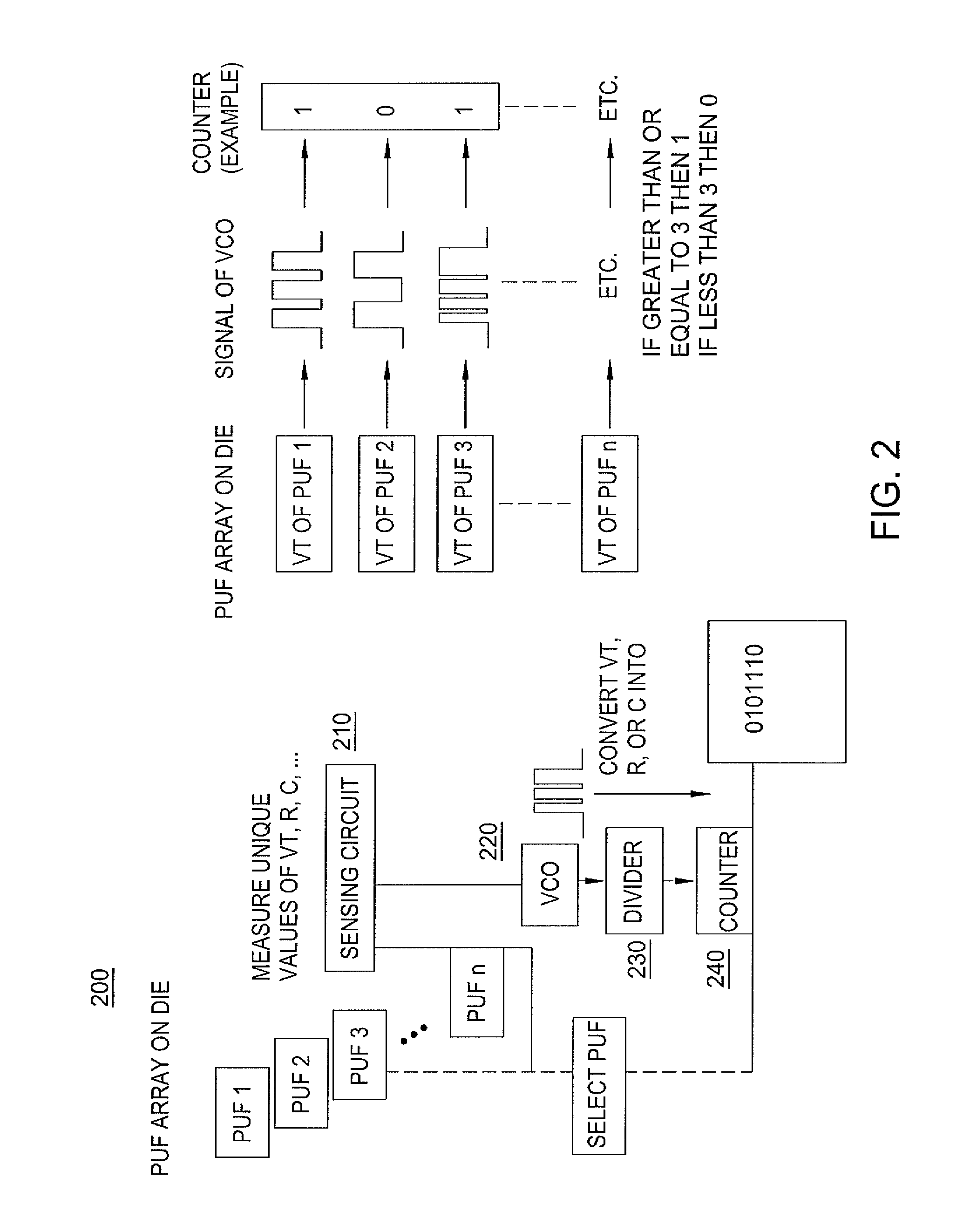

Reliable physical unclonable function for device authentication

ActiveUS8525169B1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsComputer hardwareSemiconductor materials

The present disclosure relates to a secure device having a physical unclonable function. The device includes an integrated circuit having a semiconducting material in at least one via in a backend of the integrated circuit. The present disclosure also relates to a method for manufacturing a secure device having a physical unclonable function. The method includes providing an integrated circuit and adding a semiconducting material to at least one via in a backend of the integrated circuit. In some instances a property of the semiconducting material in the at least one via is measured to derive a signature.

Owner:GLOBALFOUNDRIES US INC

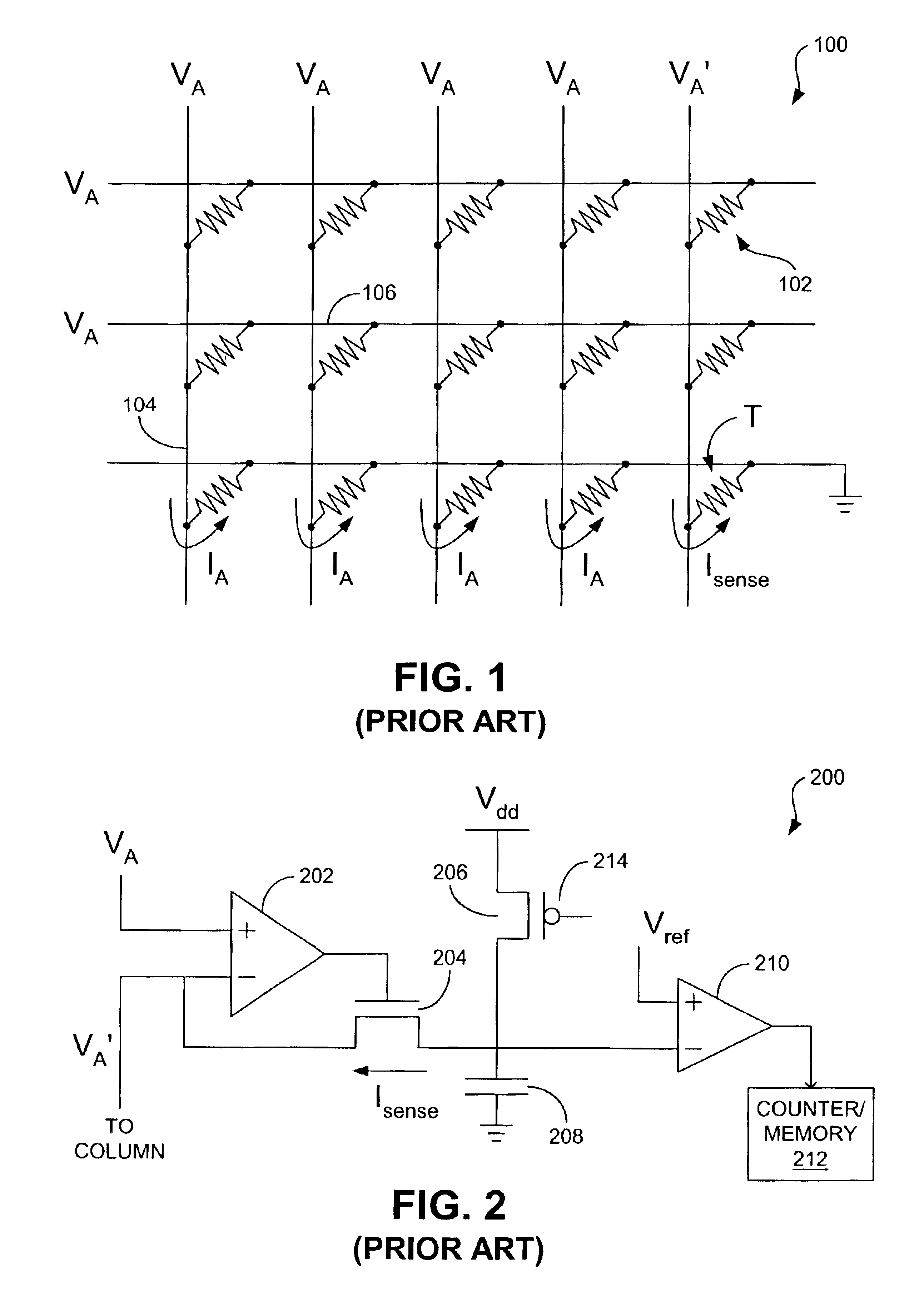

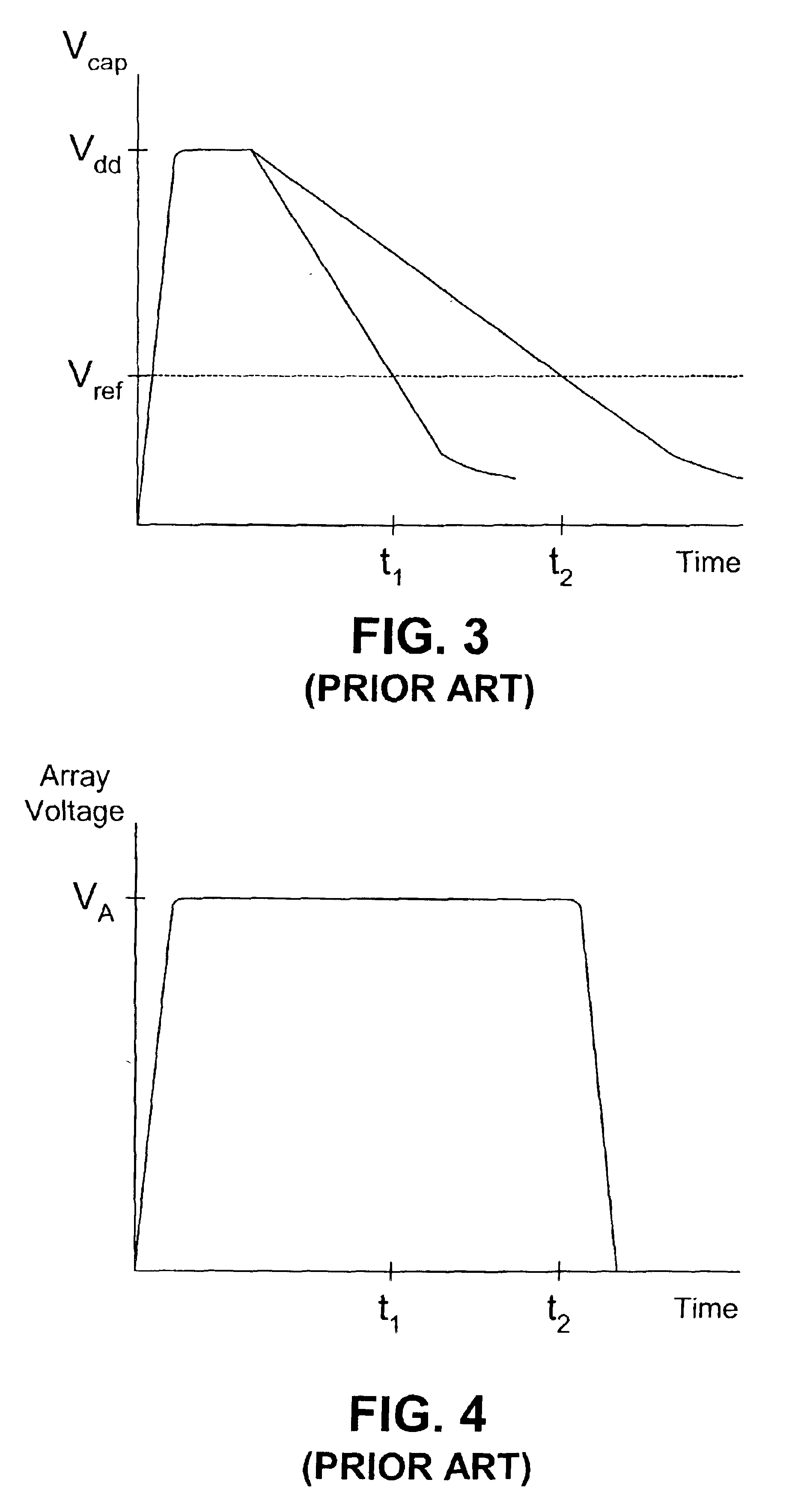

Power-saving reading of magnetic memory devices

Power-saving reading of magnetic memory devices. In one arrangement, a method includes pulsing a voltage on the array, and obtaining a voltage value indicative of a memory state of the target memory cell from the voltage pulse using a sensing circuit that is electrically connected to the target memory cell. In another arrangement, a method includes pulsing an array voltage on a plurality of row and column conductors of the array, connecting a sensing circuit to a conductor that is electrically coupled to the target memory cell, the sensing circuit including a sense element, and determining the voltage drop across the sense element of the sensing circuit during the voltage pulse, the voltage drop being indicative of a memory state of the target memory cell.

Owner:SAMSUNG ELECTRONICS CO LTD

Diode array architecture for addressing nanoscale resistive memory arrays

The present memory structure includes thereof a first conductor, a second conductor, a resistive memory cell connected to the second conductor, a first diode connected to the resistive memory cell and the first conductor, and oriented in the forward direction from the resistive memory cell to the first conductor, and a second diode connected to the resistive memory cell and the first conductor, in parallel with the first diode, and oriented in the reverse direction from the resistive memory cell to the first conductor. The first and second diodes have different threshold voltages.

Owner:MONTEREY RES LLC

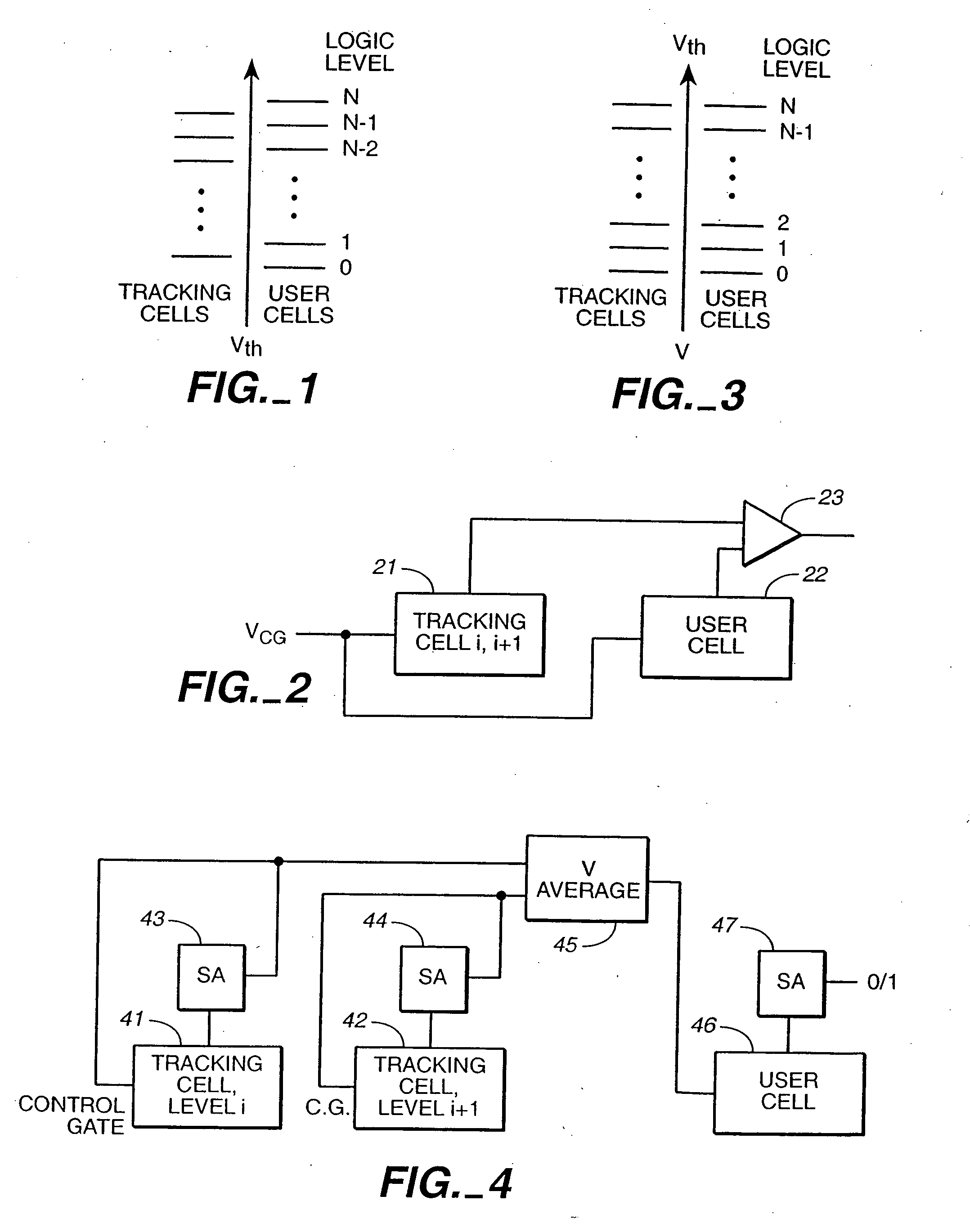

Writable tracking cells

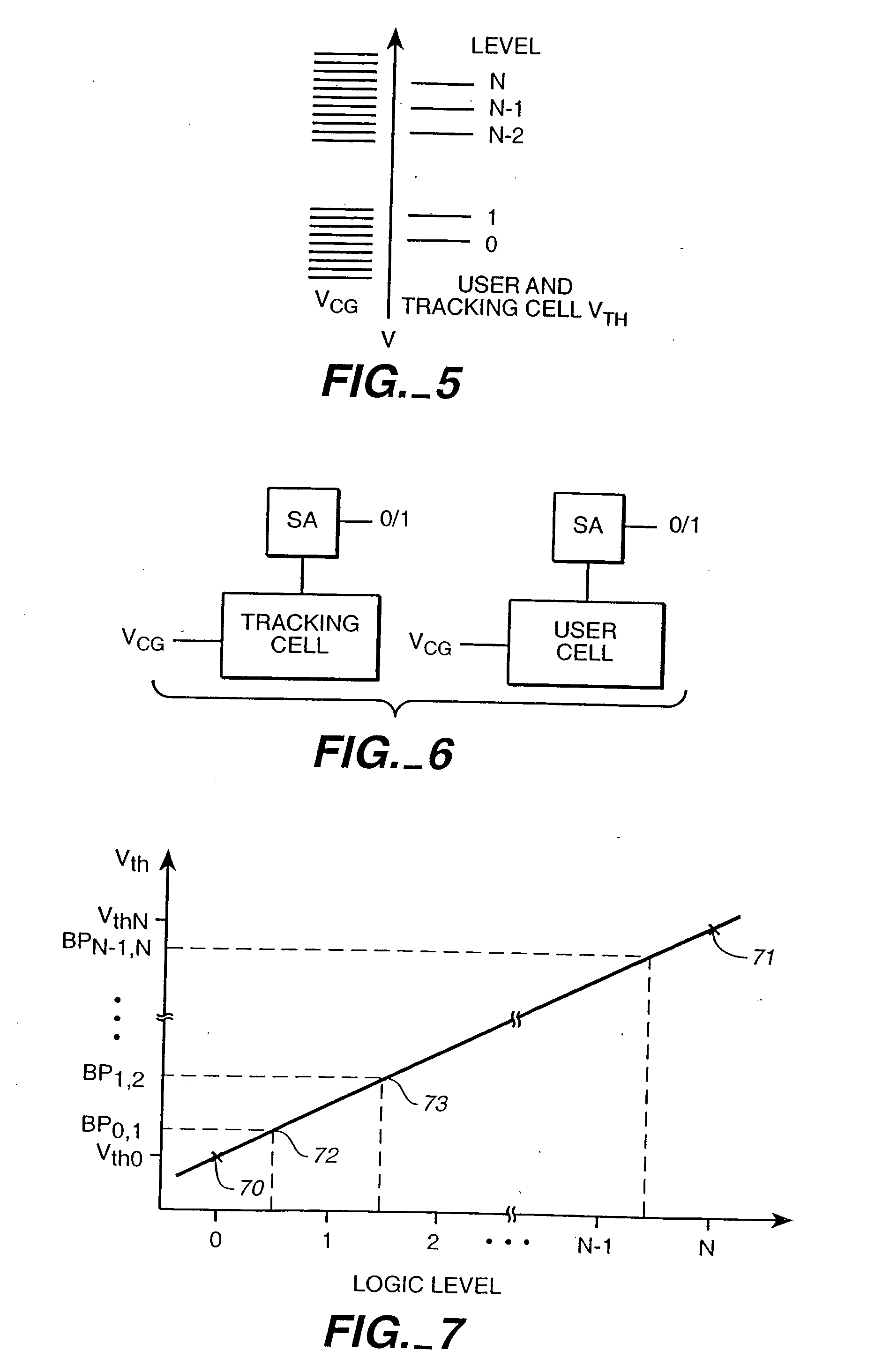

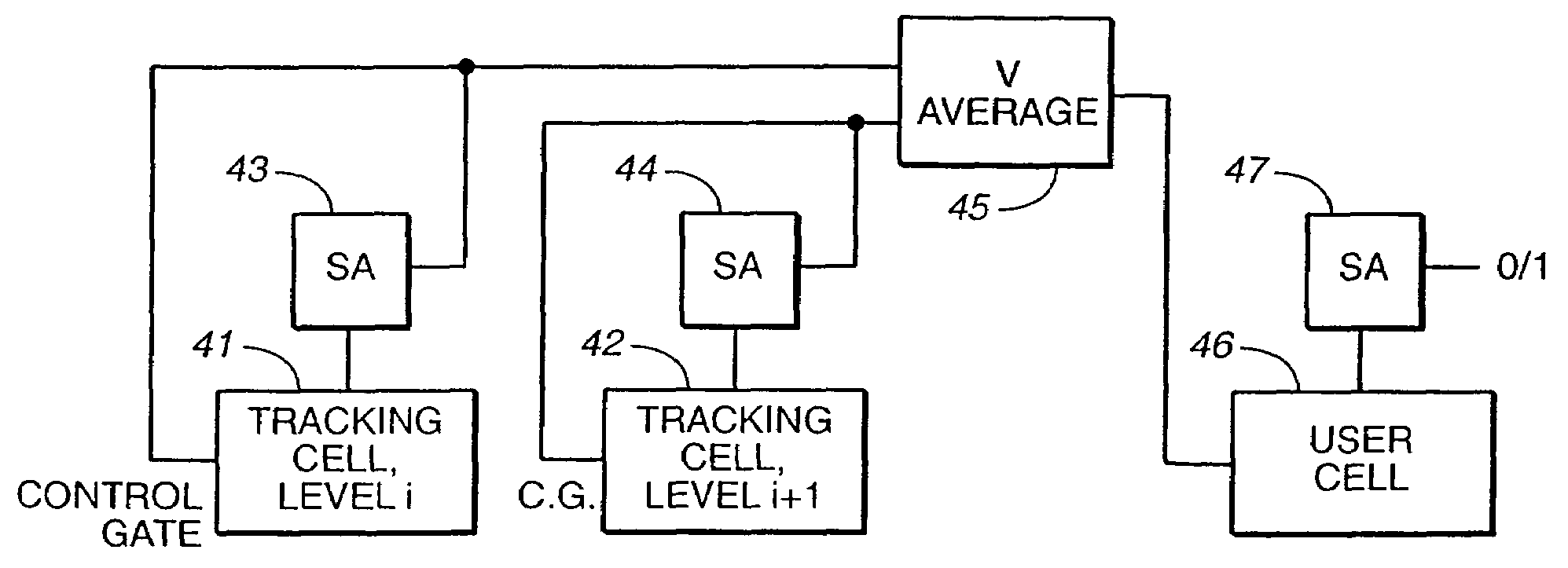

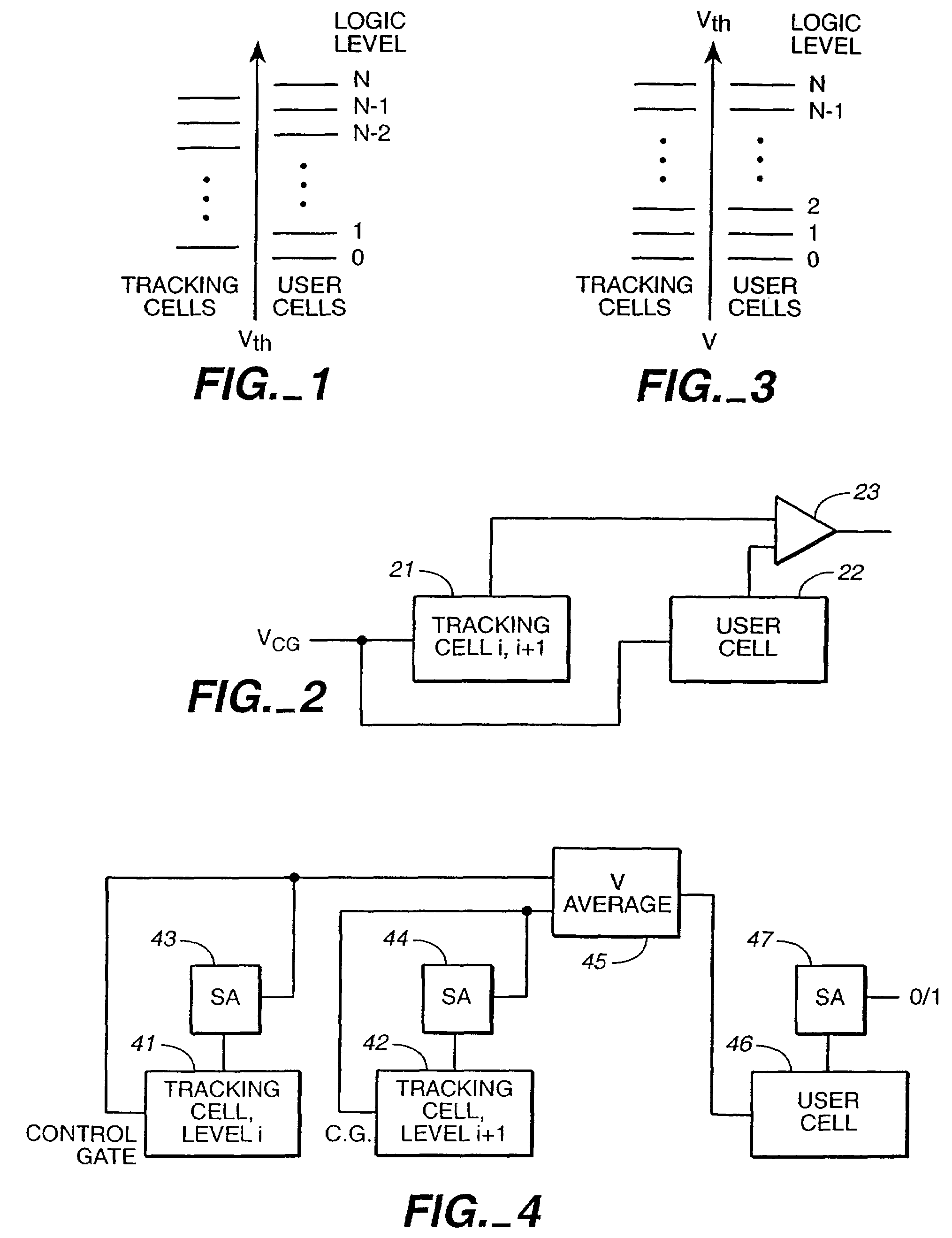

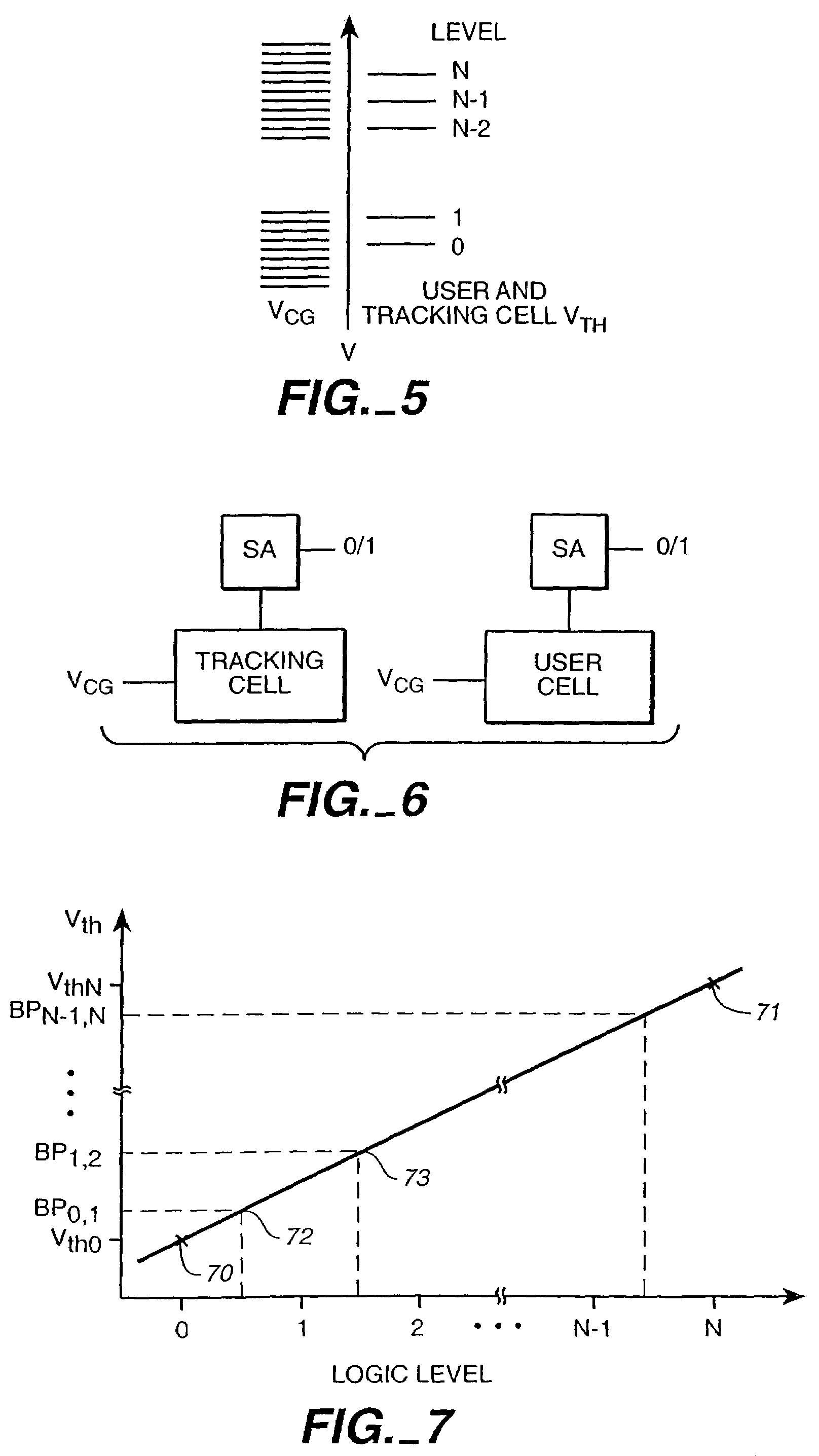

ActiveUS20050169051A1Less uncertaintyReduce reference cell threshold uncertaintyElectric analogue storesRead-only memoriesComputer scienceThreshold voltage

The present invention presents several techniques for using writable tracking cells. Multiple tracking cells are provided for each write block of the memory. These cells are re-programmed each time the user cells of the associated write block are written, preferably at the same time, using the same fixed, global reference levels to set the tracking and user cell programmed thresholds. The threshold voltages of the tracking cells are read every time the user cells are read, and these thresholds are used to determine the stored logic levels of the user cells. In one set of embodiments, populations of one or more tracking cells are associated with different logic levels of a multi-state memory. These tracking cell populations may be provided for only a subset of the logic levels. The read points for translating the threshold voltages are derived for all of the logic levels based upon this subset. In one embodiment, two populations each consisting of multiple tracking cells are associated with two logic levels of the multi-bit cell. In an analog implementation, the user cells are read directly using the analog threshold values of the tracking cell populations without their first being translated to digital values. A set of alternate embodiments provide for using different voltages and / or timing for the writing of tracking cells to provide less uncertainty in the tracking cells' final written thresholds.

Owner:SANDISK TECH LLC

Writable tracking cells

InactiveUS7301807B2Less uncertaintyReduced referenceElectric analogue storesRead-only memoriesComputer scienceThreshold voltage

The present invention presents several techniques for using writable tracking cells. Multiple tracking cells are provided for each write block of the memory. These cells are re-programmed each time the user cells of the associated write block are written, preferably at the same time, using the same fixed, global reference levels to set the tracking and user cell programmed thresholds. The threshold voltages of the tracking cells are read every time the user cells are read, and these thresholds are used to determine the stored logic levels of the user cells. In one set of embodiments, populations of one or more tracking cells are associated with different logic levels of a multi-state memory. These tracking cell populations may be provided for only a subset of the logic levels. The read points for translating the threshold voltages are derived for all of the logic levels based upon this subset. In one embodiment, two populations each consisting of multiple tracking cells are associated with two logic levels of the multi-bit cell. In an analog implementation, the user cells are read directly using the analog threshold values of the tracking cell populations without their first being translated to digital values. A set of alternate embodiments provide for using different voltages and / or timing for the writing of tracking cells to provide less uncertainty in the tracking cells' final written thresholds.

Owner:SANDISK TECH LLC

Capacitance detector circuit, capacitance detection method, and fingerprint sensor using the same

ActiveUS20050073324A1Reduce the impact of interferenceEasy to detectCapacitance measurementsElectric analogue storesDetector circuitsEngineering

A capacitance detecting circuit of a capacitive sensor having a plurality of column lines and a row line intersecting the column lines detects a change in capacitance at an intersection of a column line and a row line. The circuit includes a PN code generating unit for generating a code having orthogonality in time sequence to output the generated code as a column drive signal, a column line drive unit for driving a predetermined one of the column lines which are selected in response to the code, a capacitance detecting unit, connected to the row line, for detecting a voltage by converting a total sum of changes in capacitance at intersections of the selected column lines into the voltage to output the detected voltage, and a decode processing unit for performing a predetermined calculation on the detected voltage output from the capacitance detecting unit and the code to determine a voltage value responsive to the capacitance change at the intersection.

Owner:SYNAPTICS INC

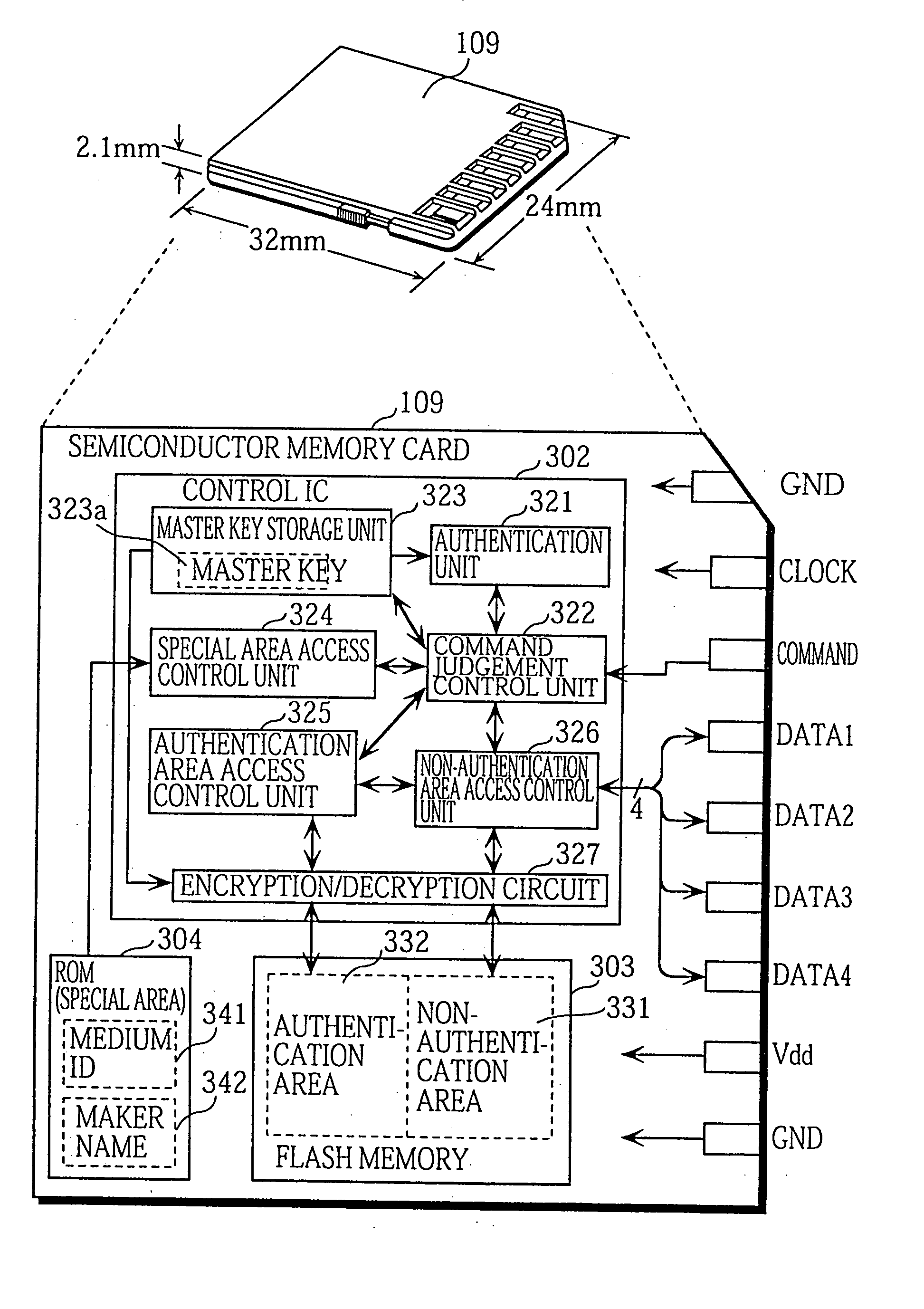

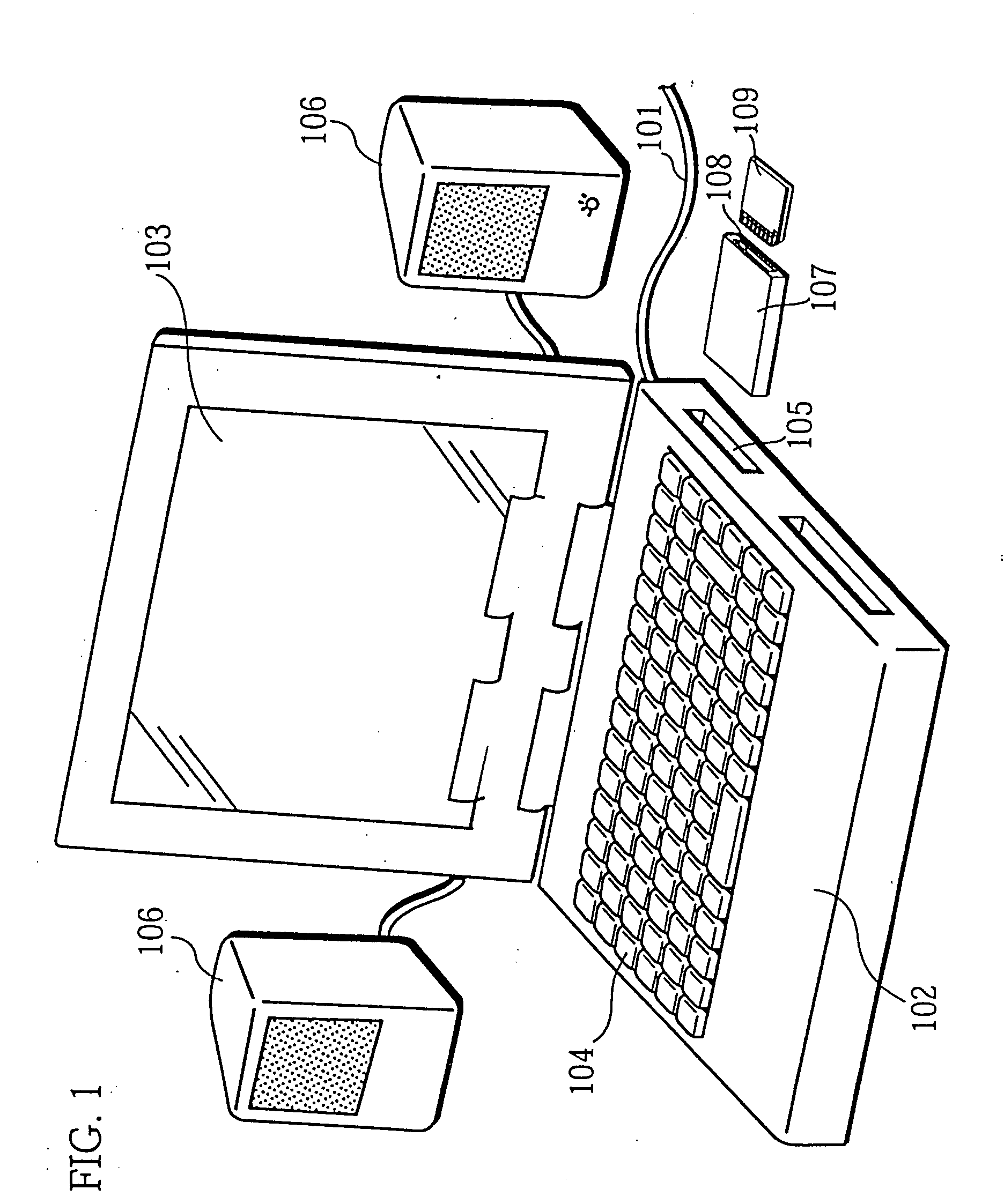

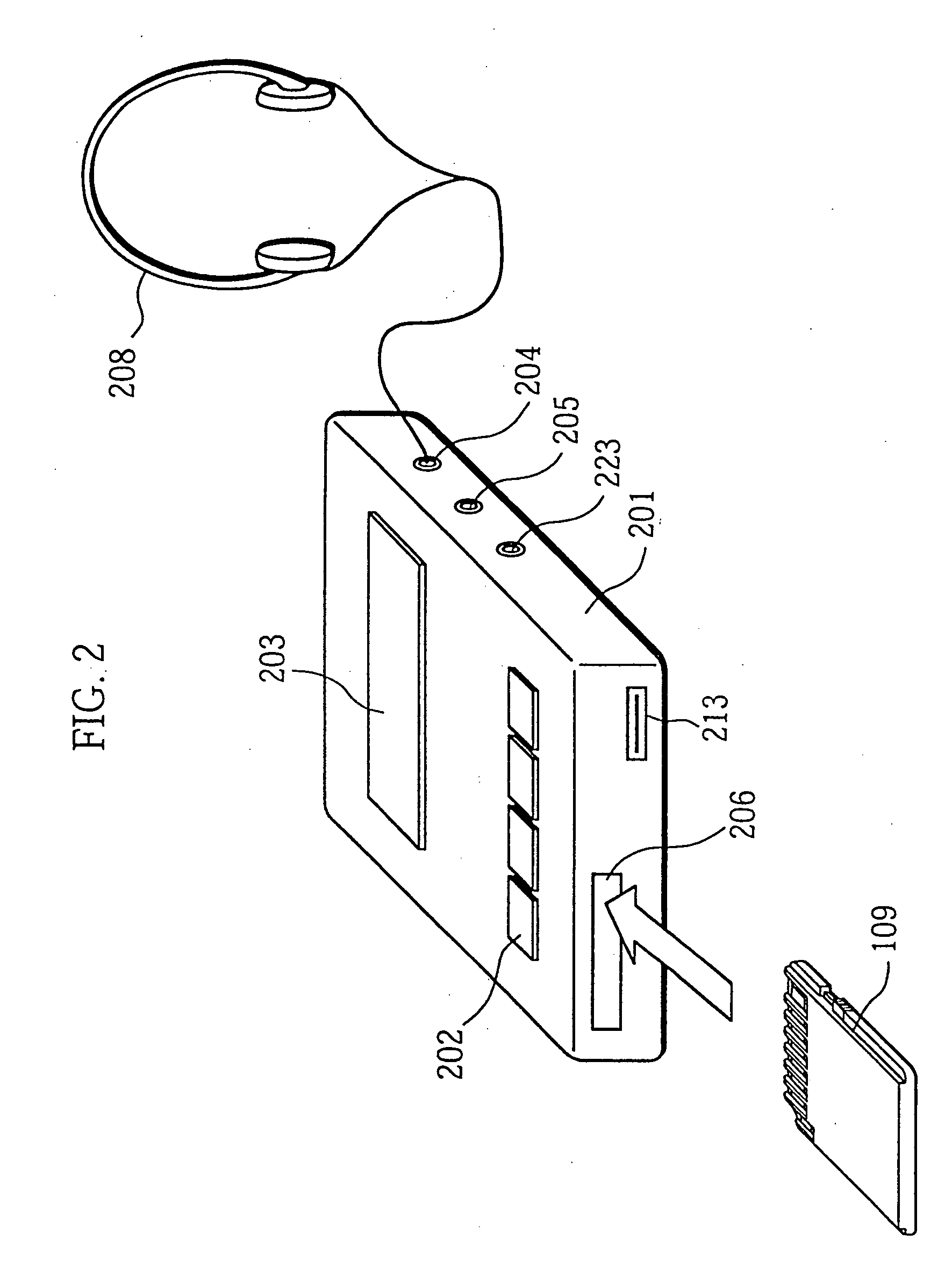

Semiconductor memory card and data reading apparatus

InactiveUS20050005149A1Secures healthy distribution of digital contentKey distribution for secure communicationDigital data processing detailsRead-only memorySemiconductor

A semiconductor memory card comprising a control IC 302, a flash memory 303, and a ROM 304. The ROM 304 holds information such as a medium ID 341 unique to the semiconductor memory card. The flash memory 303 includes an authentication memory 332 and a non-authentication memory 331. The authentication memory 332 can be accessed only by external devices which have been affirmatively authenticated. The non-authentication memory 331 can be accessed by external devices whether the external devices have been affirmatively authenticated or not. The control IC 302 includes control units 325 and 326, an authentication unit 321 and the like. The control units 325 and 326 control accesses to the authentication memory 332 and the non-authentication memory 331, respectively. The authentication unit 321 executes a mutual authentication with an external device.

Owner:PANASONIC CORP

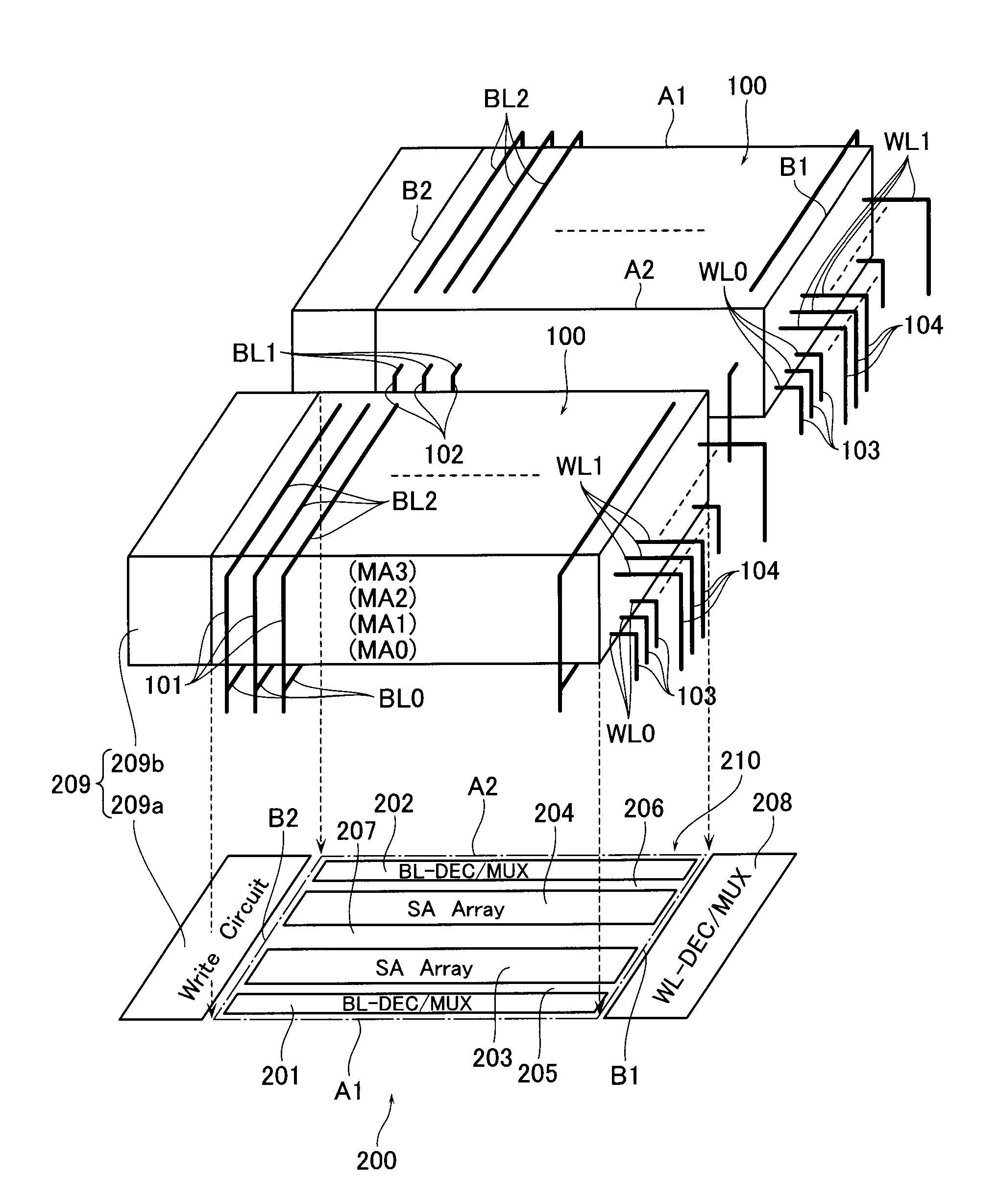

Resistance change memory device

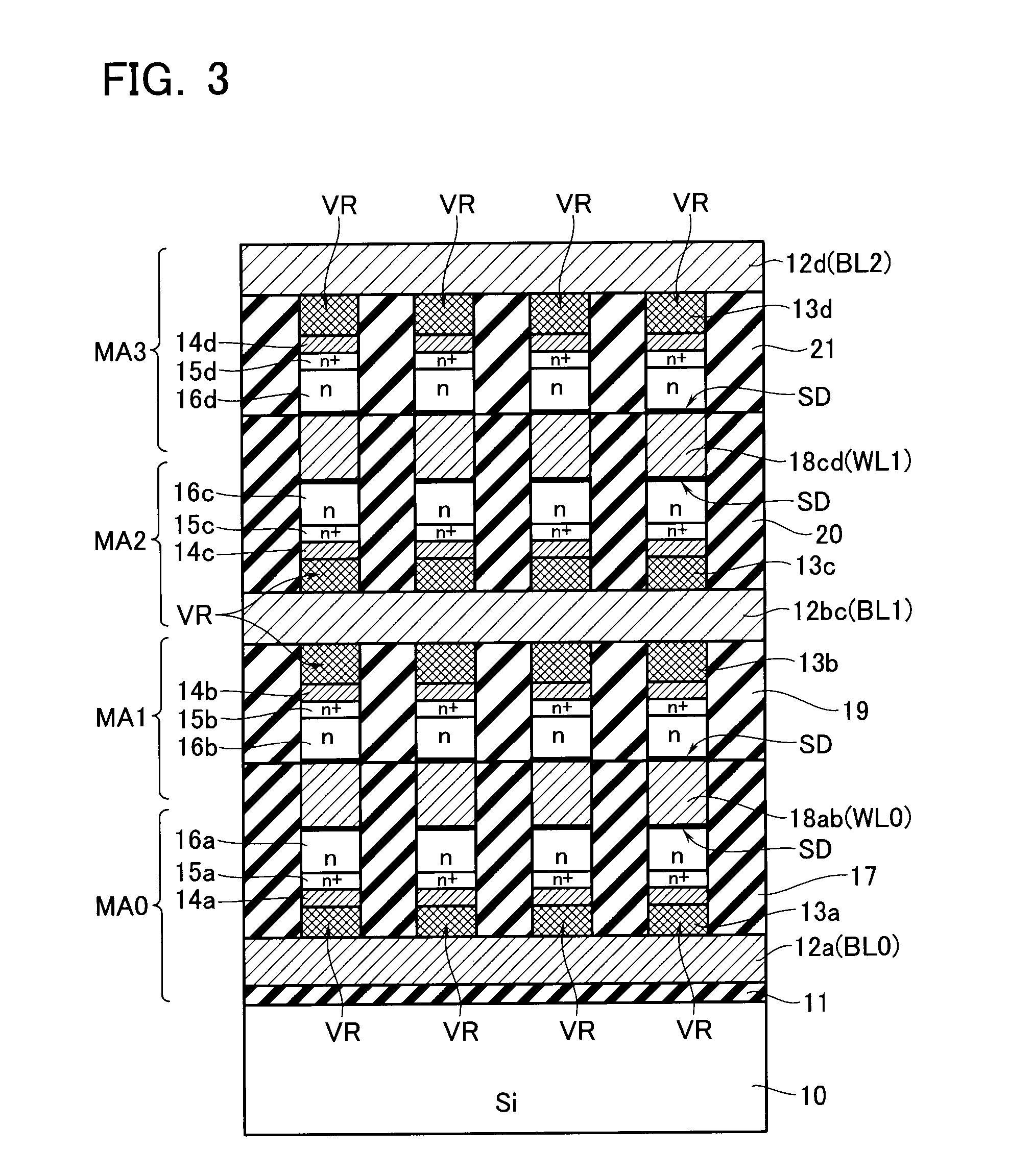

A resistance change memory device including: a semiconductor substrate; cell arrays stacked above the substrate, each having memory cells, bit lines and word lines; a read / write circuit formed on the semiconductor substrate; first and second vertical wirings disposed to connect the bit lines to the read / write circuit; and third vertical wirings disposed the word lines to the read / write circuit. The memory cell includes a variable resistance element for storing as information a resistance value, which has a recording layer composed of a composite compound containing at least two types of cation elements, at least one type of the cation element being a transition element having “d” orbit, in which electrons are incompletely filled, the shortest distance between adjacent cation elements being 0.32 nm or less.

Owner:TOSHIBA MEMORY CORP

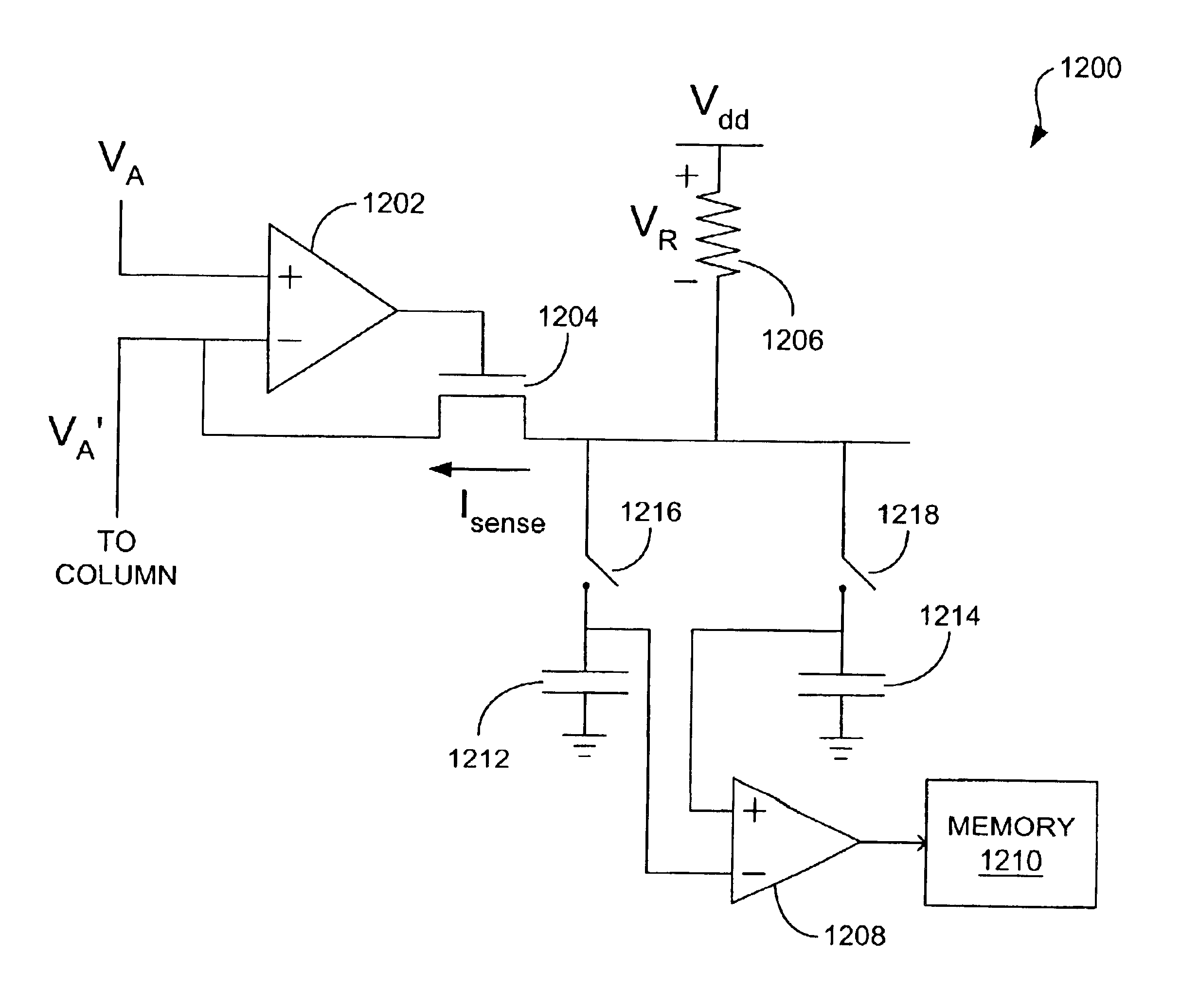

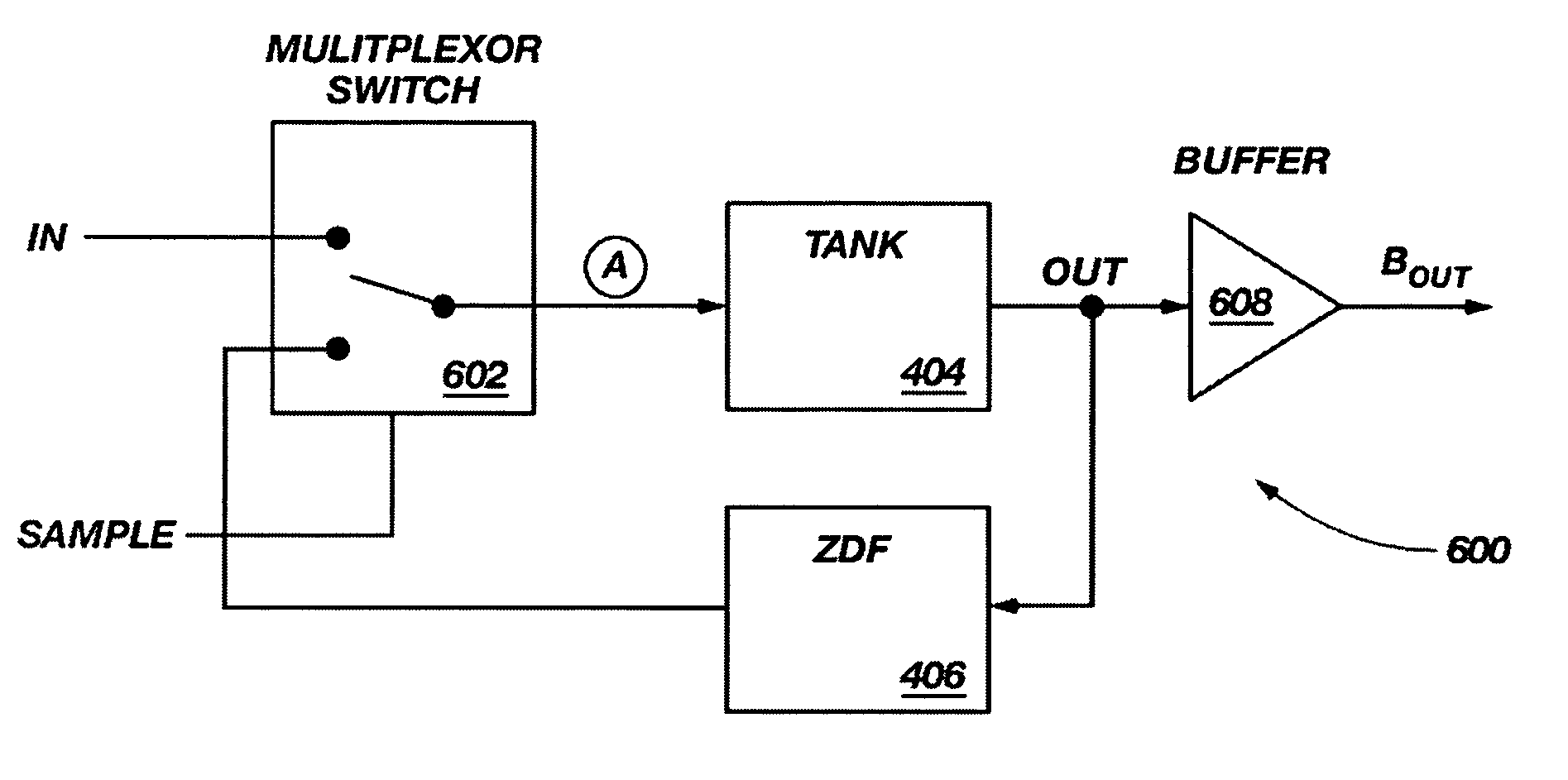

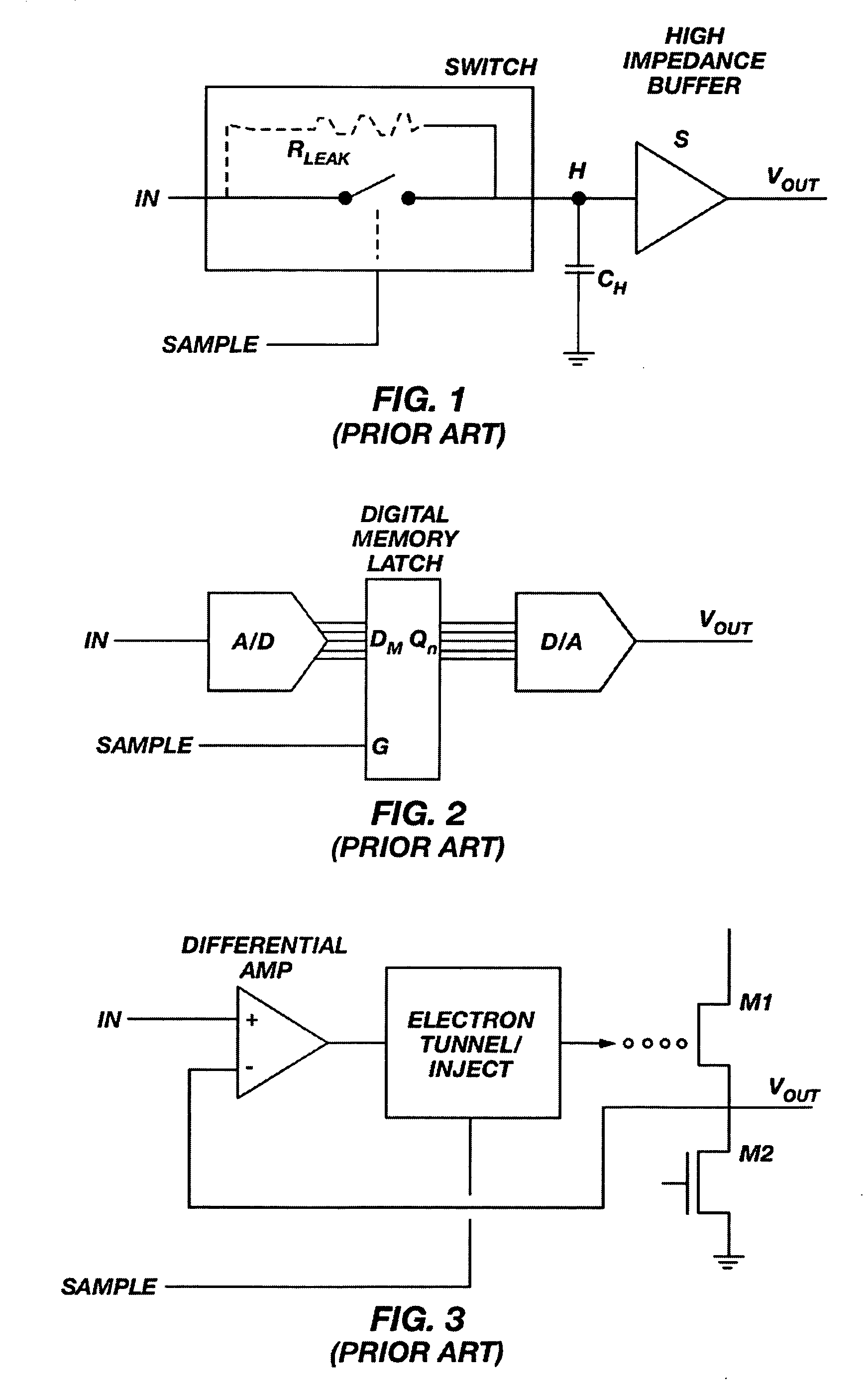

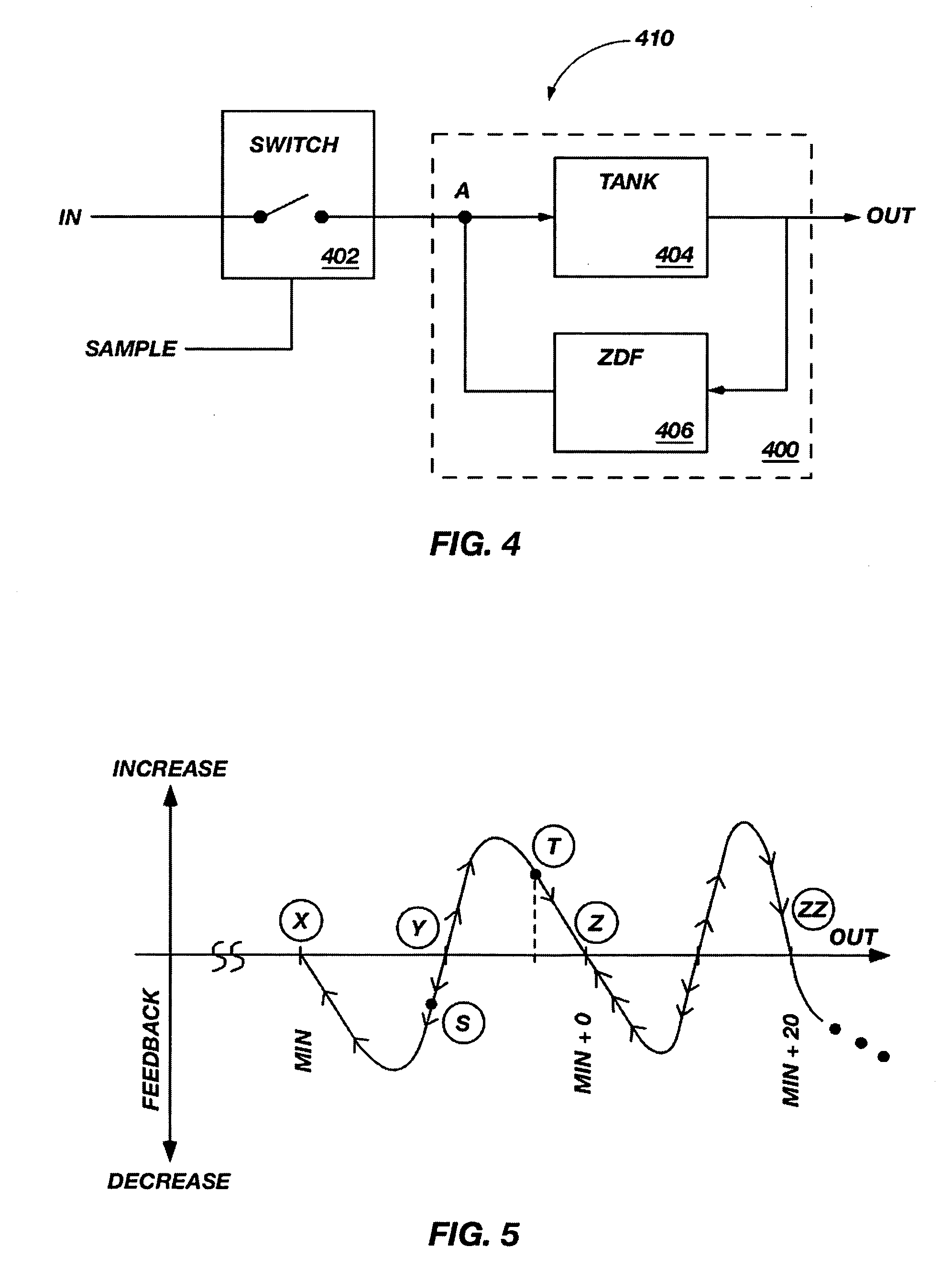

Zero drift analog memory cell, array and method of operation

A zero-drift analog memory (ZDAM) cell that indefinitely maintains an output signal at a discrete voltage while the memory circuit is powered, wherein the memory circuit receives an input signal, passes the input signal to a storage element upon receiving an assertion signal, maintains an output signal at a level of the input signal when the assertion signal is removed, and utilizes a zero-drift transfer function feedback loop on the output signal to maintain the output signal. A memory array including a plurality of ZDAM cells and method of operation are also disclosed.

Owner:VODAFONE AG

Reading memory cells using multiple thresholds

A method for operating a memory (28) includes storing data, which is encoded with an Error Correction Code (ECC), in analog memory cells (32) of the memory by writing respective analog input values selected from a set of nominal values to the analog memory cells. The stored data is read by performing multiple read operations that compare analog output values of the analog memory cells to different, respective read thresholds so as to produce multiple comparison results for each of the analog memory cells. At least two of the read thresholds are positioned between a pair of the nominal values that are adjacent to one another in the set of the nominal values. Soft metrics are computed responsively to the multiple comparison results. The ECC is decoded using the soft metrics, so as to extract the data stored in the analog memory cells.

Owner:APPLE INC

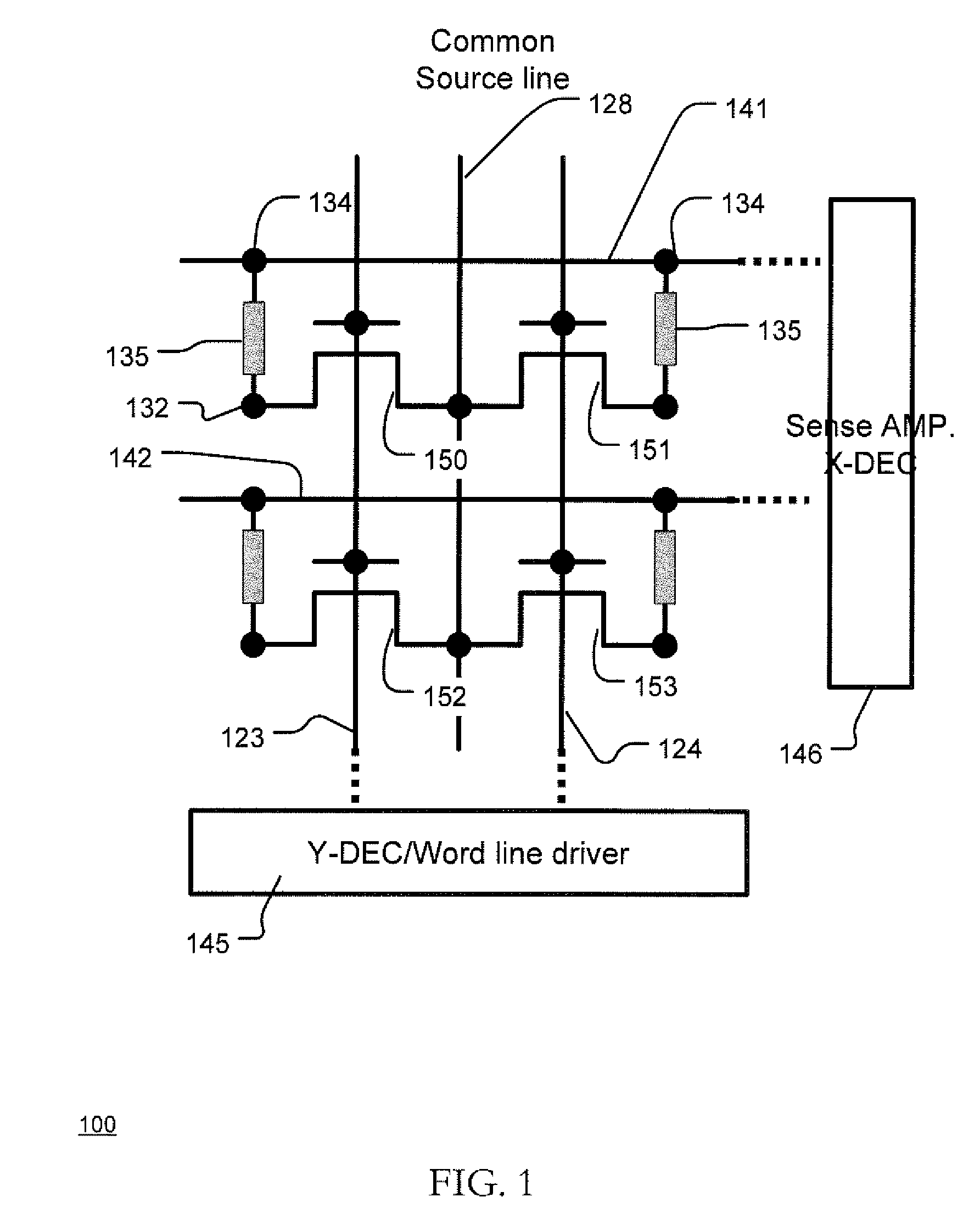

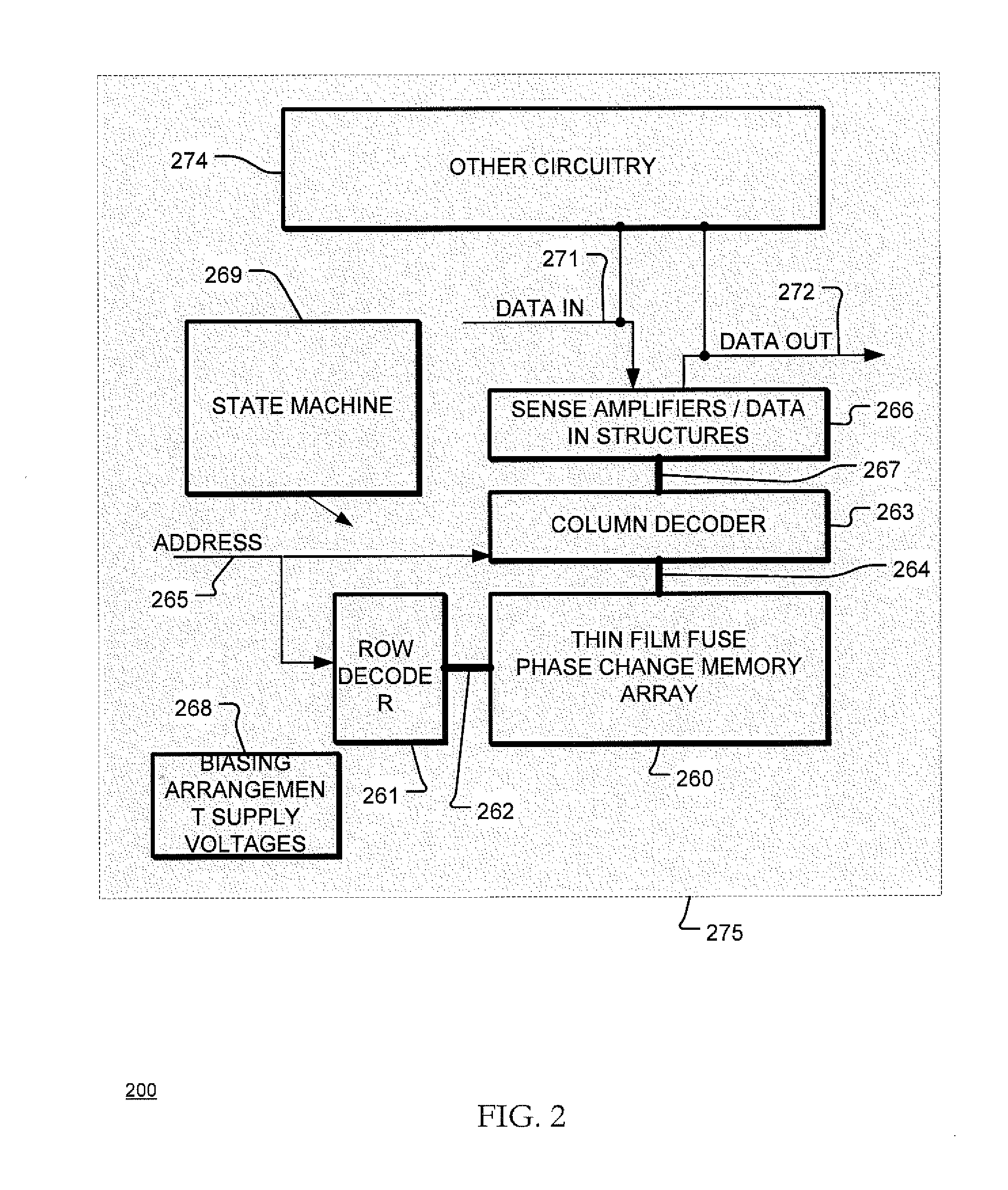

Method for multilevel programming of phase change memory cells using a percolation algorithm

ActiveUS20080151612A1Increase resistanceReduce resistanceElectric analogue storesRead-only memoriesPhase-change memoryAmorphous phase

A method and apparatus for programming a phase change memory cell is disclosed. A phase change memory cell includes a memory element of a phase change material having a first state, in which the phase change material is crystalline and has a minimum resistance level, a second state in which the phase change material is amorphous and has a maximum resistance level, and a plurality of intermediate states with resistance levels there between. The method includes using programming pulses to program the phase change memory cell in either the set, reset, or one of the intermediate states. To program in the intermediate states, a programming pulse creates a crystalline percolation path having an average diameter through amorphous phase change material and a second programming pulse modifies the diameter of the crystalline percolation path to program the phase change memory cell to the proper current level.

Owner:MICRON TECH INC