Patents

Literature

54results about How to "Reduced reference" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

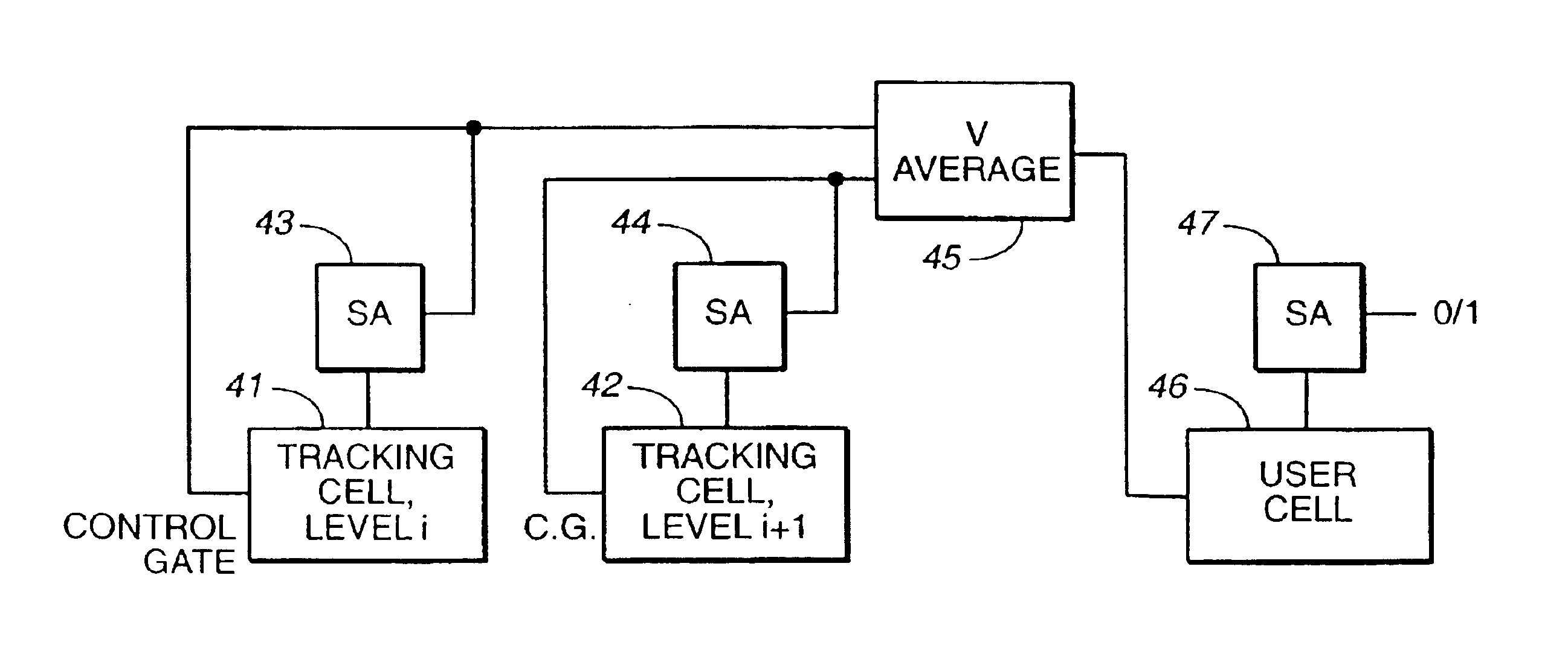

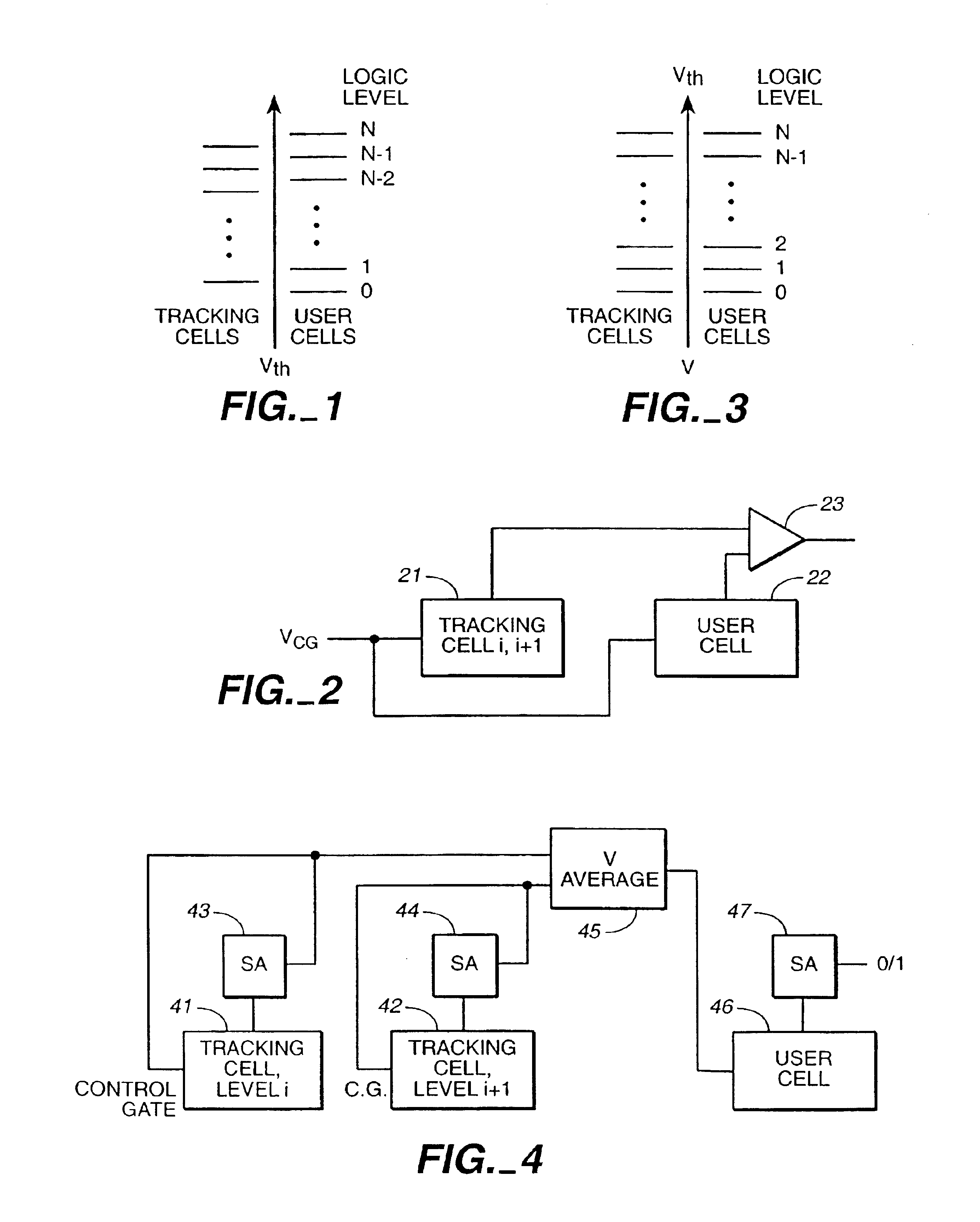

Writable tracking cells

ActiveUS20050169051A1Less uncertaintyReduce reference cell threshold uncertaintyElectric analogue storesRead-only memoriesComputer scienceThreshold voltage

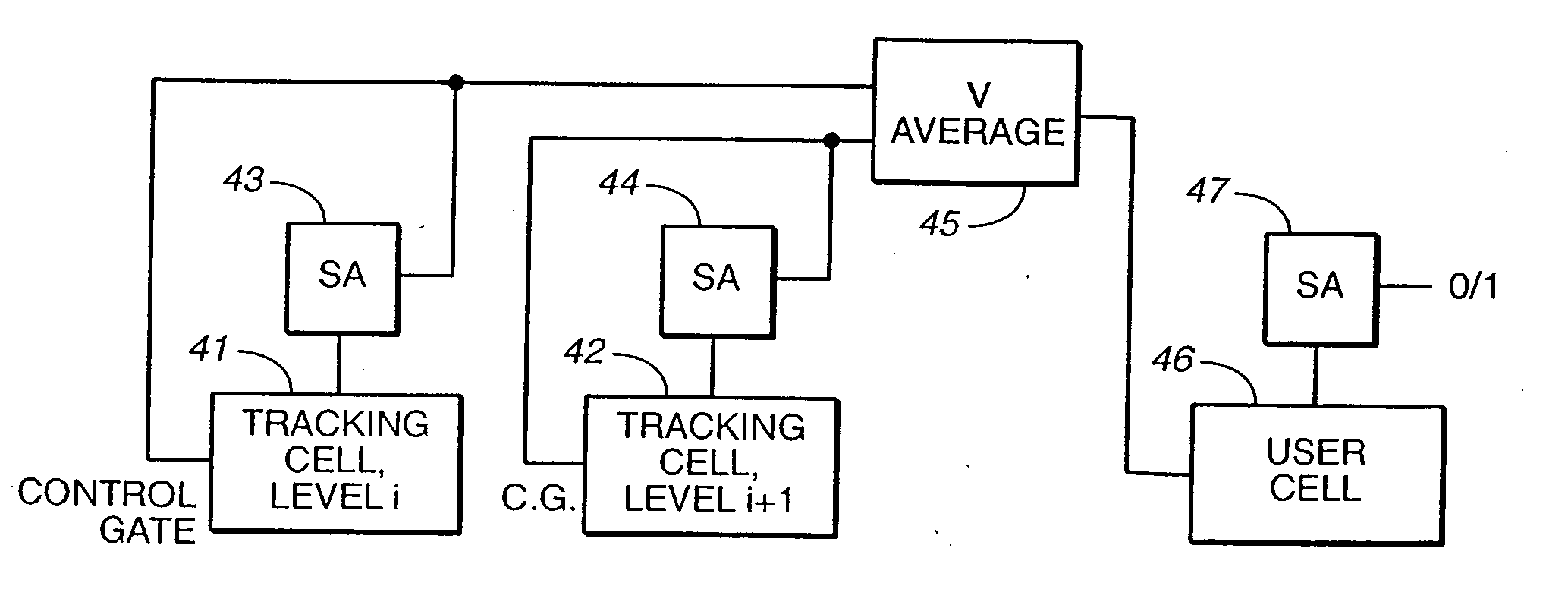

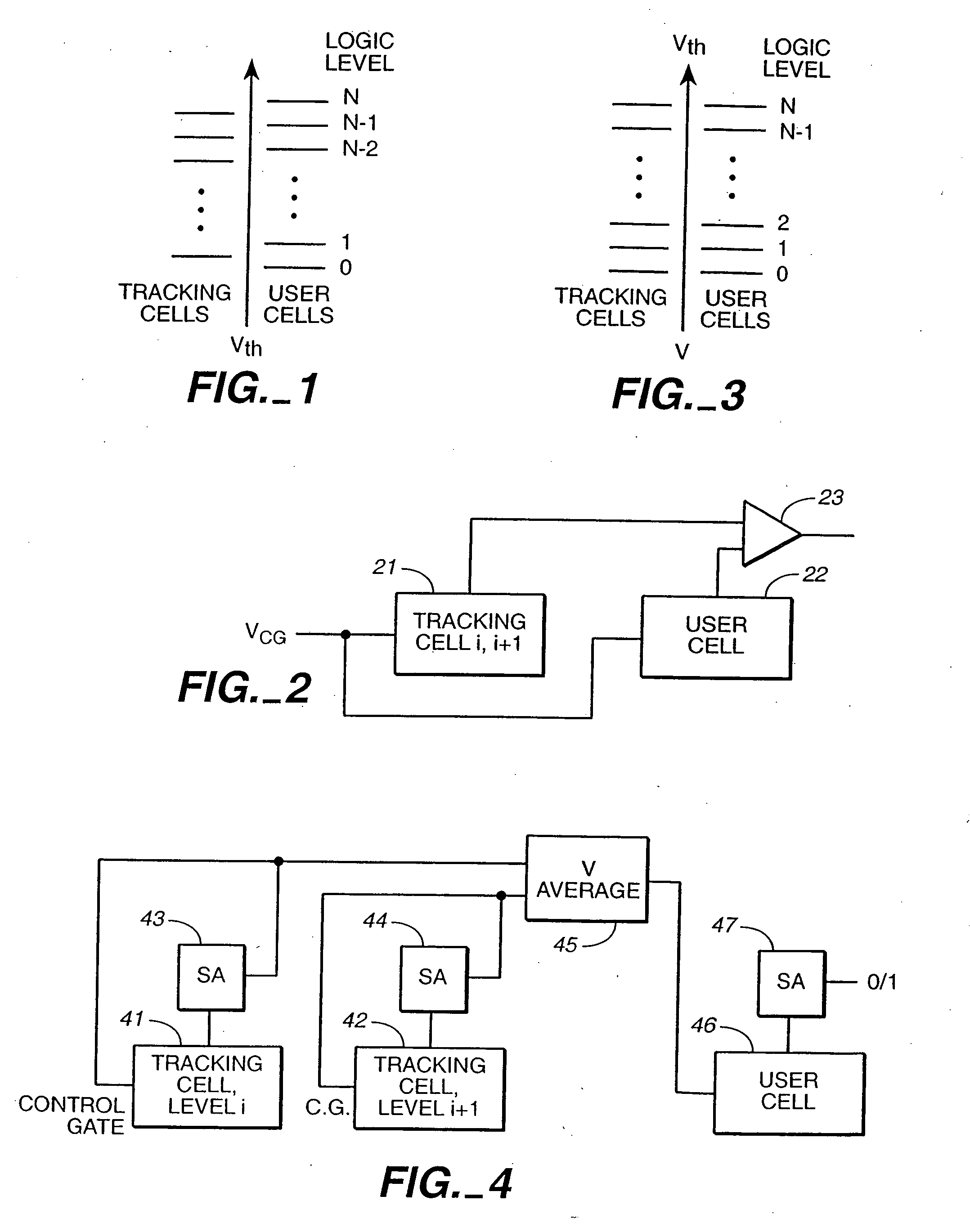

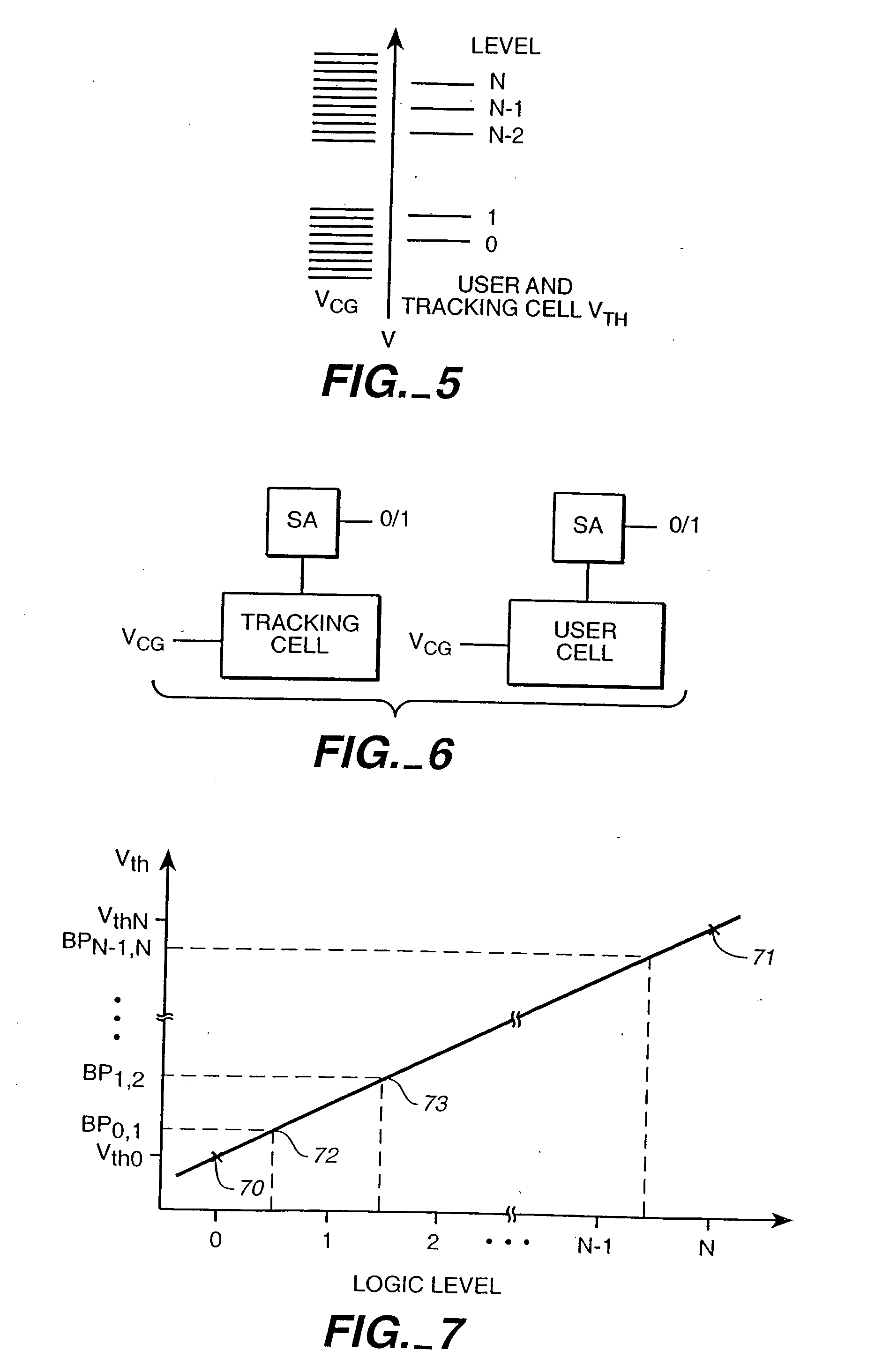

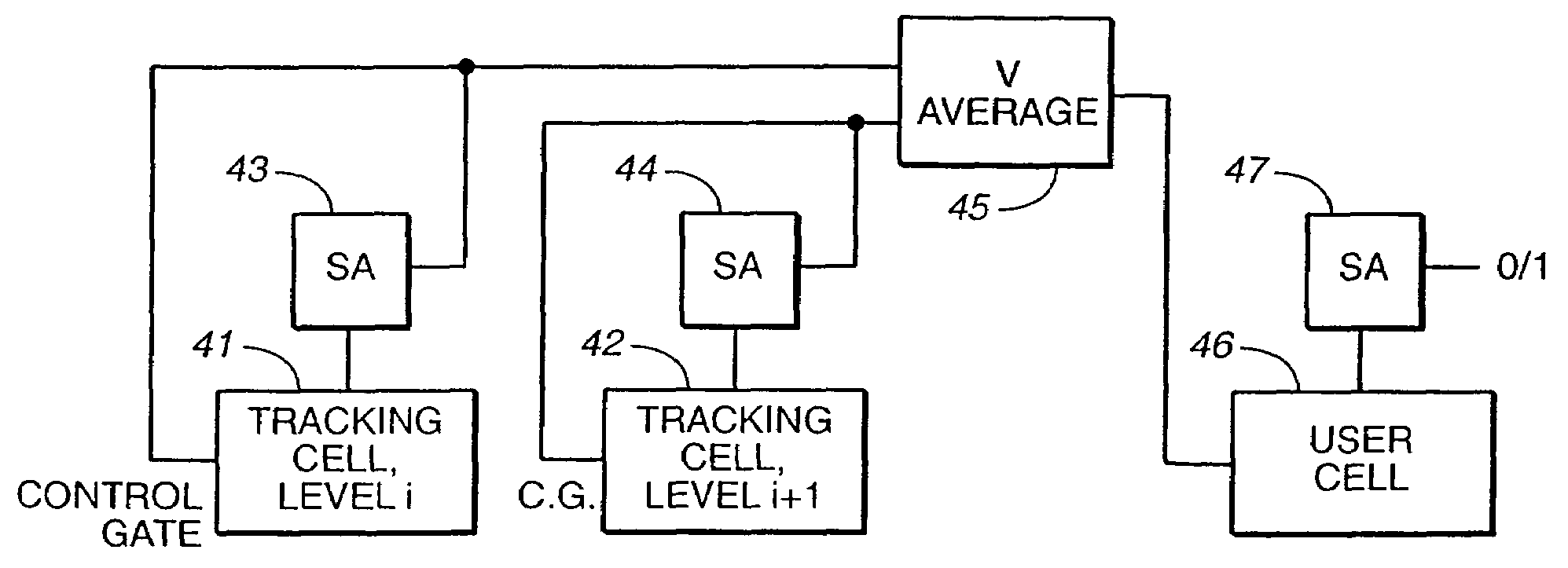

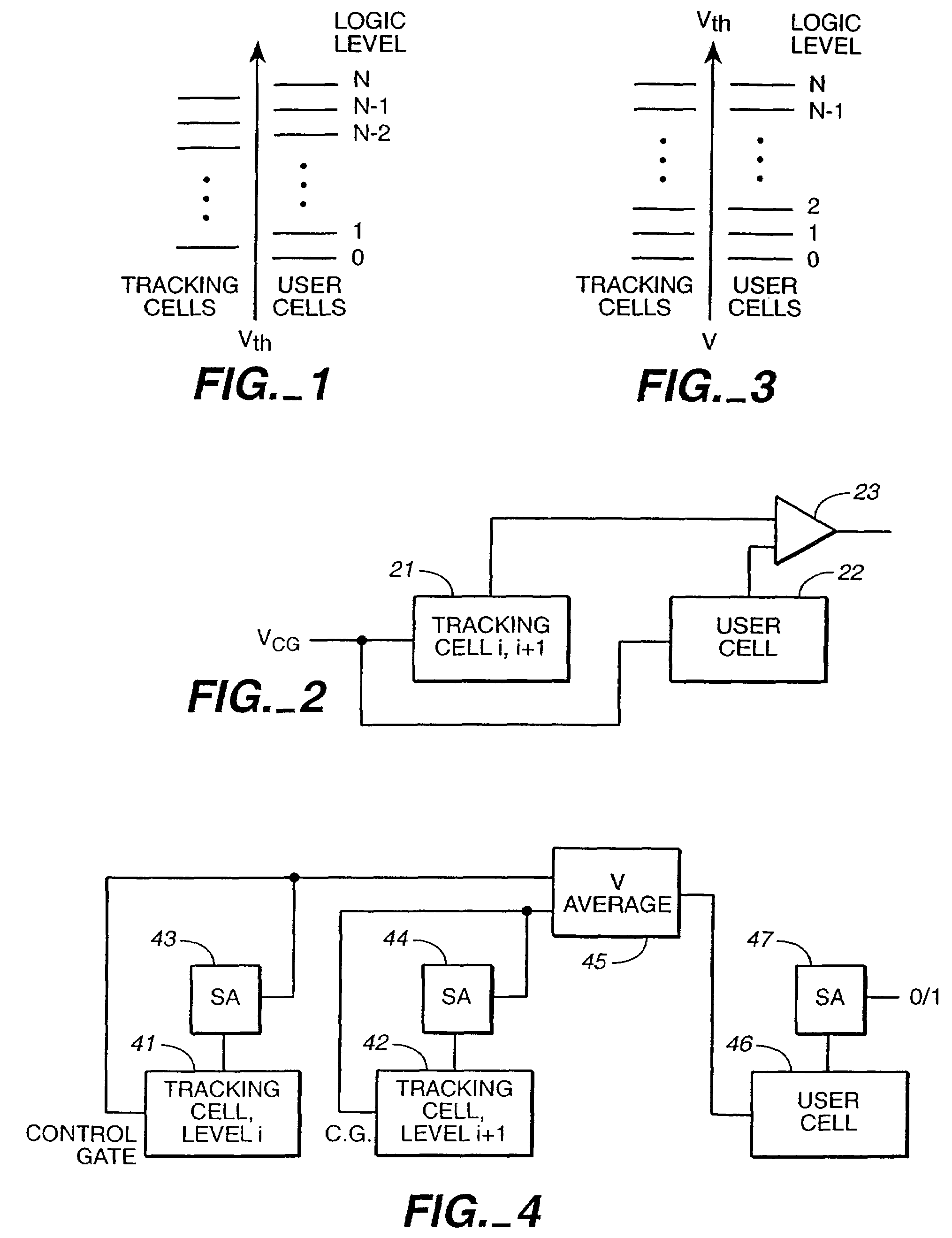

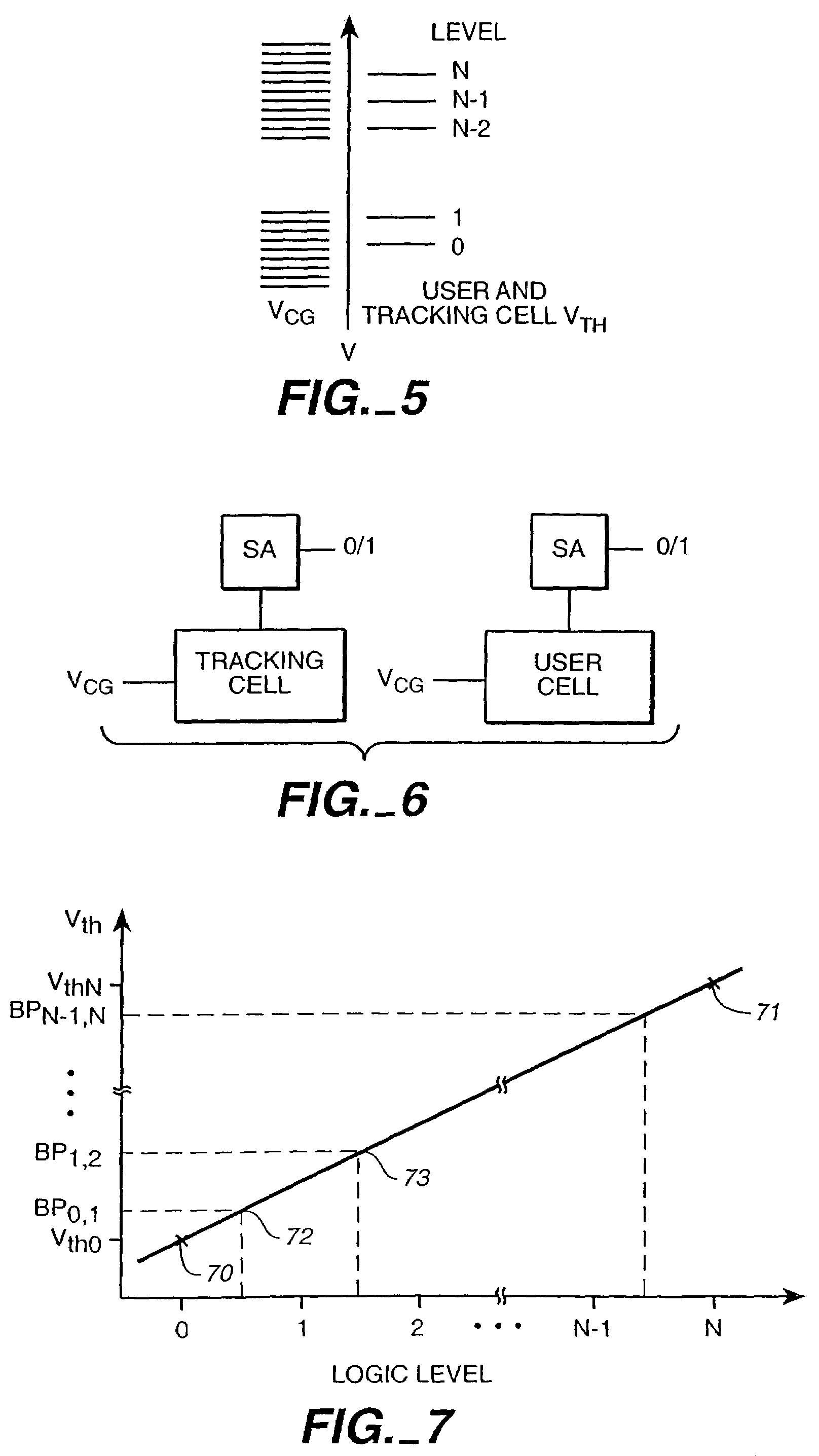

The present invention presents several techniques for using writable tracking cells. Multiple tracking cells are provided for each write block of the memory. These cells are re-programmed each time the user cells of the associated write block are written, preferably at the same time, using the same fixed, global reference levels to set the tracking and user cell programmed thresholds. The threshold voltages of the tracking cells are read every time the user cells are read, and these thresholds are used to determine the stored logic levels of the user cells. In one set of embodiments, populations of one or more tracking cells are associated with different logic levels of a multi-state memory. These tracking cell populations may be provided for only a subset of the logic levels. The read points for translating the threshold voltages are derived for all of the logic levels based upon this subset. In one embodiment, two populations each consisting of multiple tracking cells are associated with two logic levels of the multi-bit cell. In an analog implementation, the user cells are read directly using the analog threshold values of the tracking cell populations without their first being translated to digital values. A set of alternate embodiments provide for using different voltages and / or timing for the writing of tracking cells to provide less uncertainty in the tracking cells' final written thresholds.

Owner:SANDISK TECH LLC

Writable tracking cells

InactiveUS7301807B2Less uncertaintyReduced referenceElectric analogue storesRead-only memoriesComputer scienceThreshold voltage

The present invention presents several techniques for using writable tracking cells. Multiple tracking cells are provided for each write block of the memory. These cells are re-programmed each time the user cells of the associated write block are written, preferably at the same time, using the same fixed, global reference levels to set the tracking and user cell programmed thresholds. The threshold voltages of the tracking cells are read every time the user cells are read, and these thresholds are used to determine the stored logic levels of the user cells. In one set of embodiments, populations of one or more tracking cells are associated with different logic levels of a multi-state memory. These tracking cell populations may be provided for only a subset of the logic levels. The read points for translating the threshold voltages are derived for all of the logic levels based upon this subset. In one embodiment, two populations each consisting of multiple tracking cells are associated with two logic levels of the multi-bit cell. In an analog implementation, the user cells are read directly using the analog threshold values of the tracking cell populations without their first being translated to digital values. A set of alternate embodiments provide for using different voltages and / or timing for the writing of tracking cells to provide less uncertainty in the tracking cells' final written thresholds.

Owner:SANDISK TECH LLC

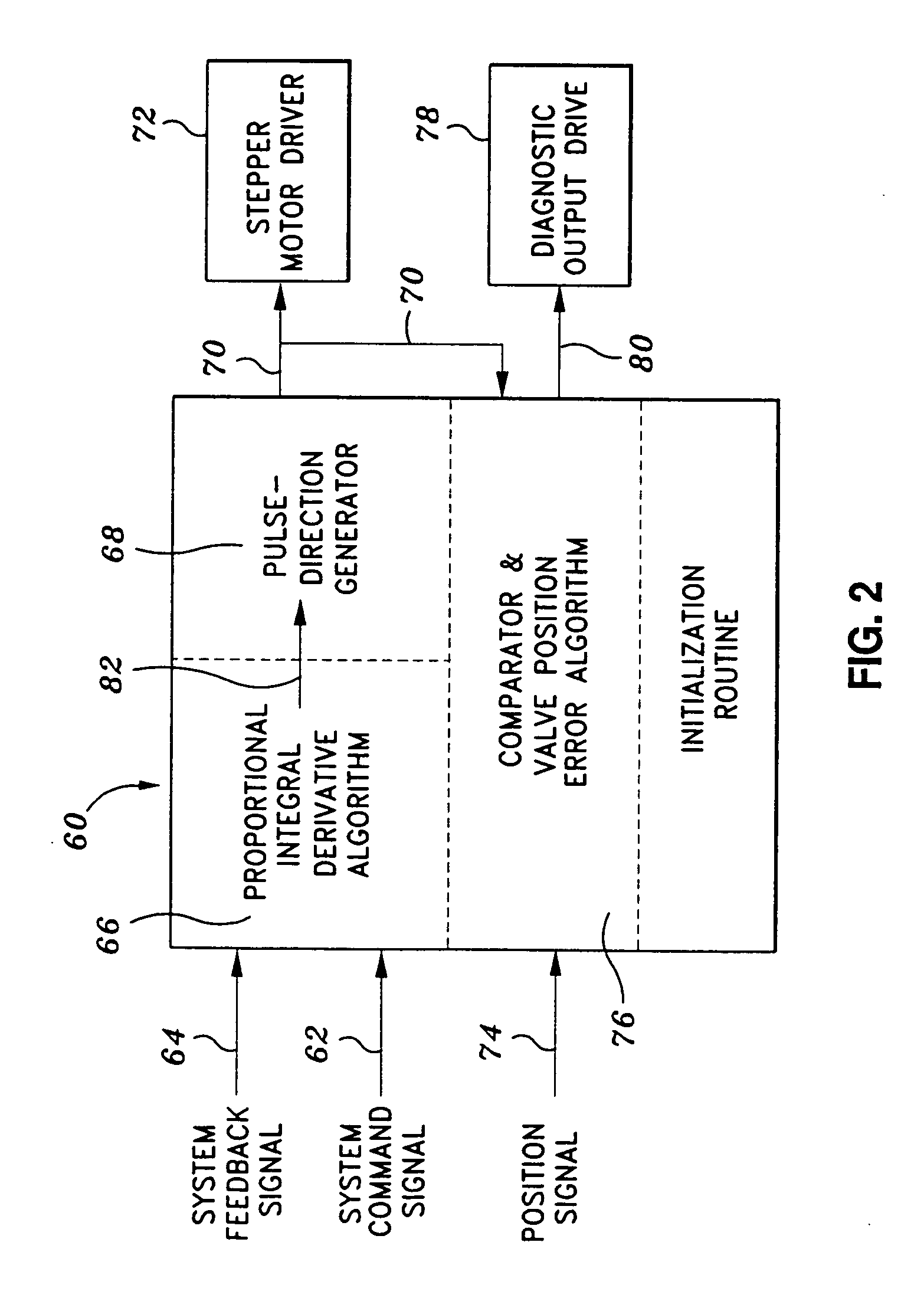

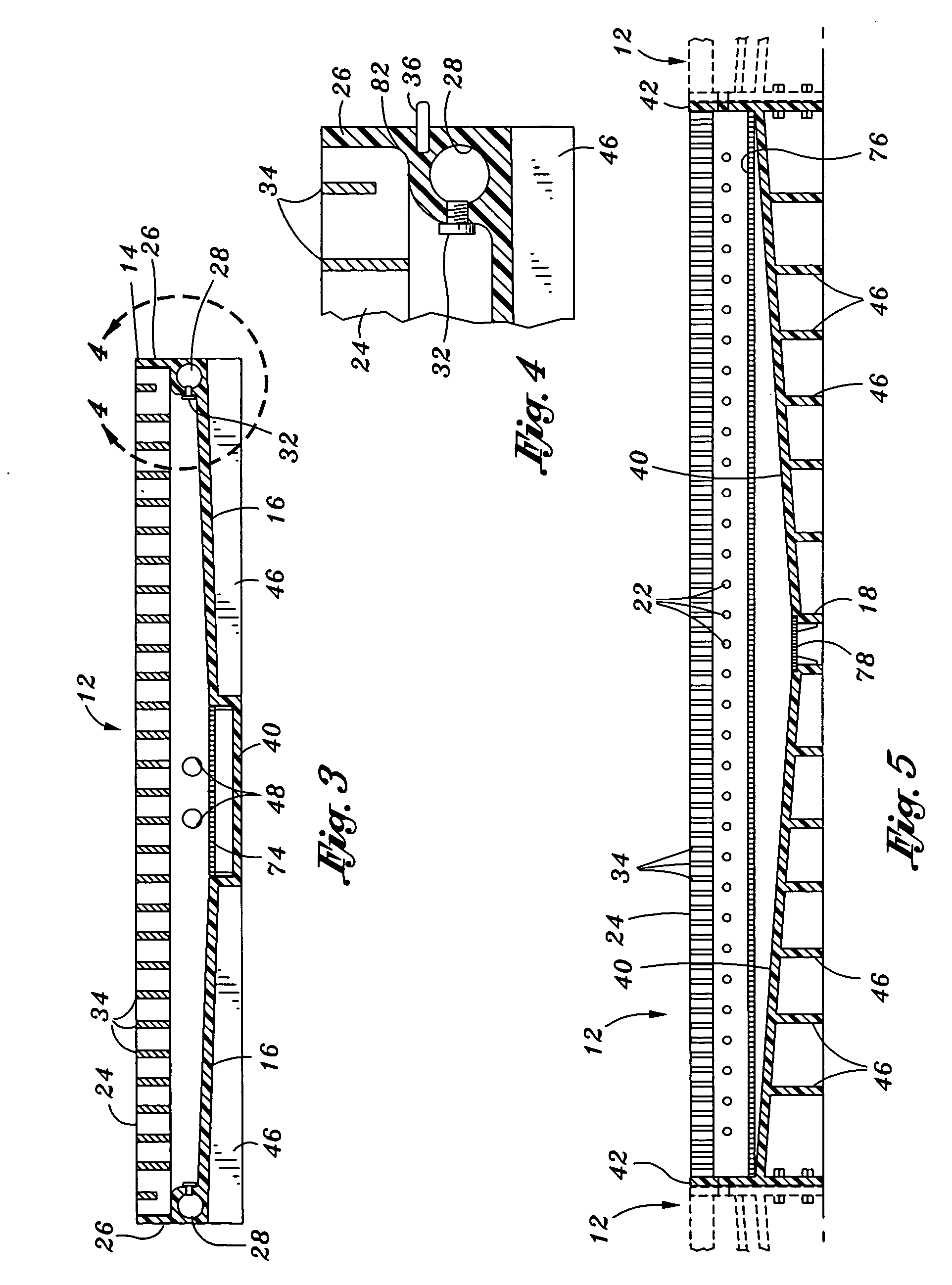

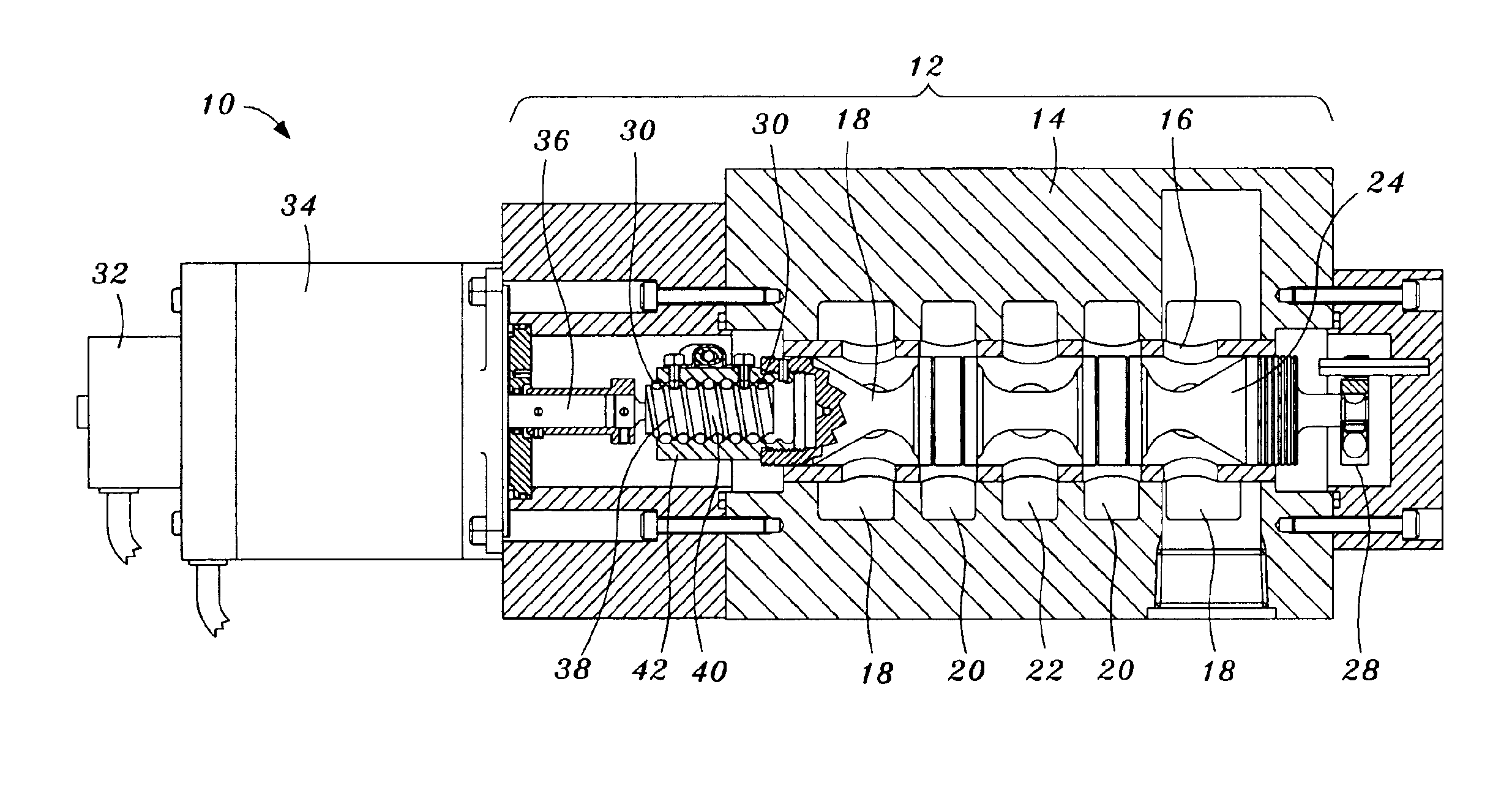

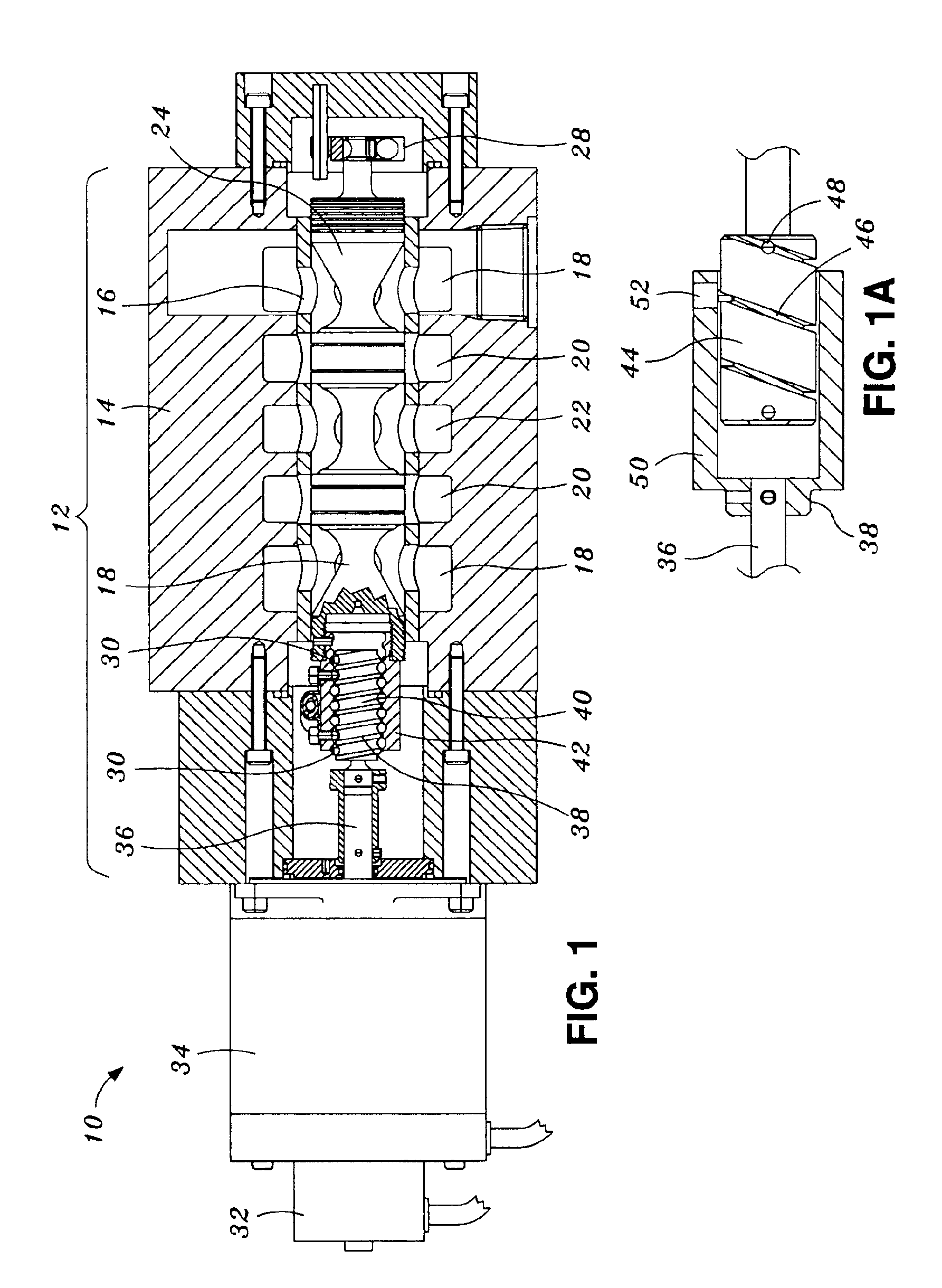

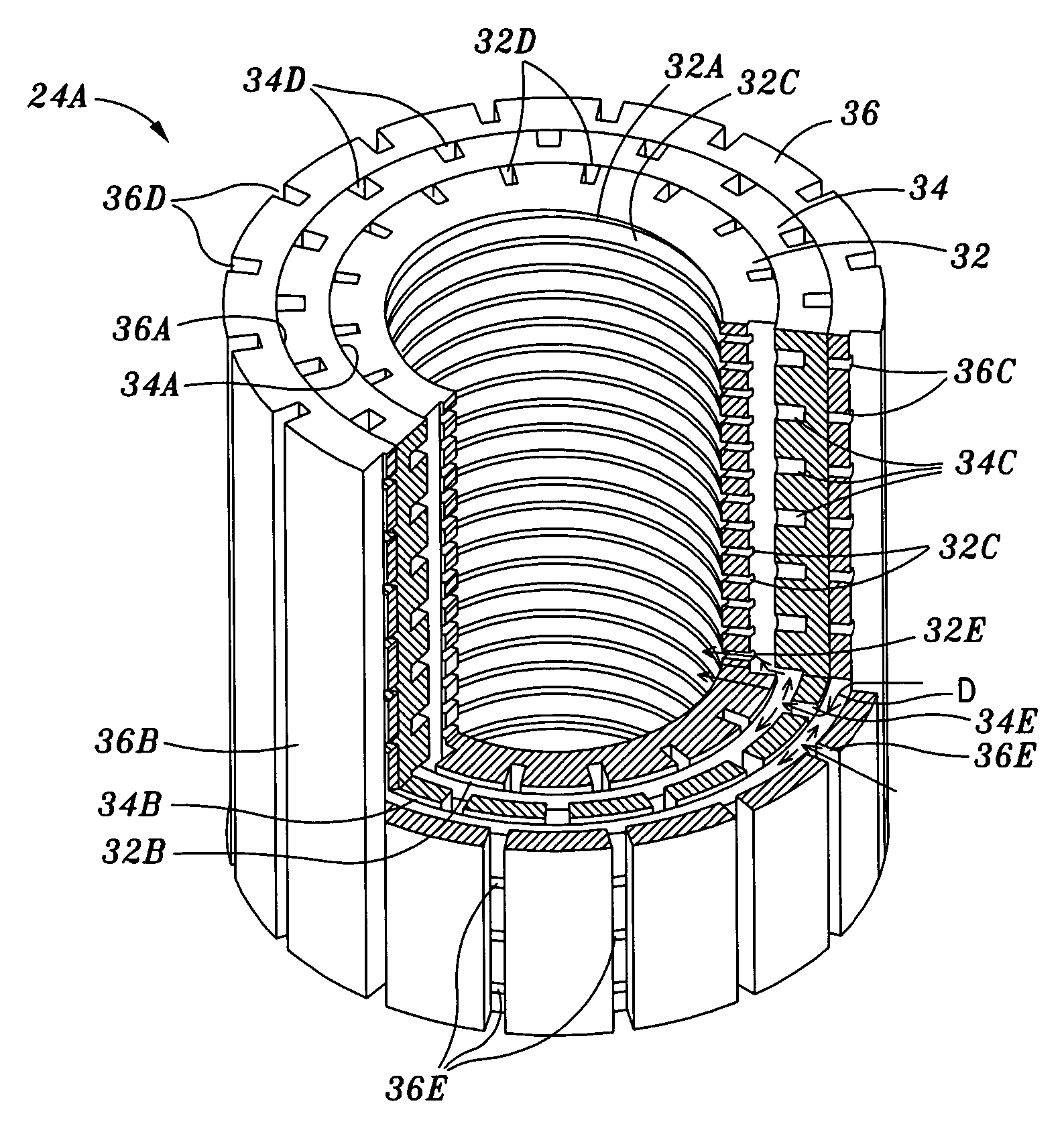

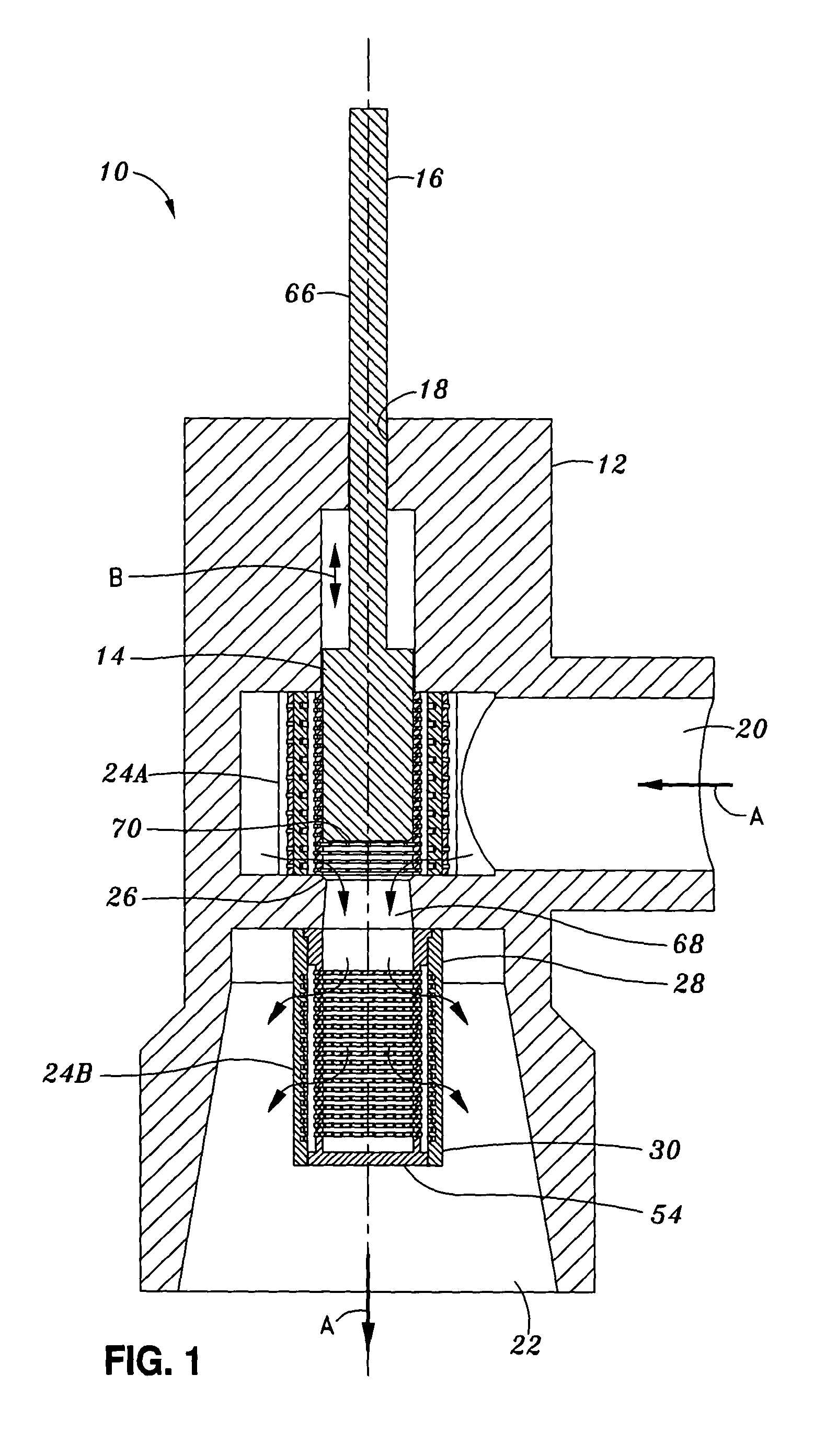

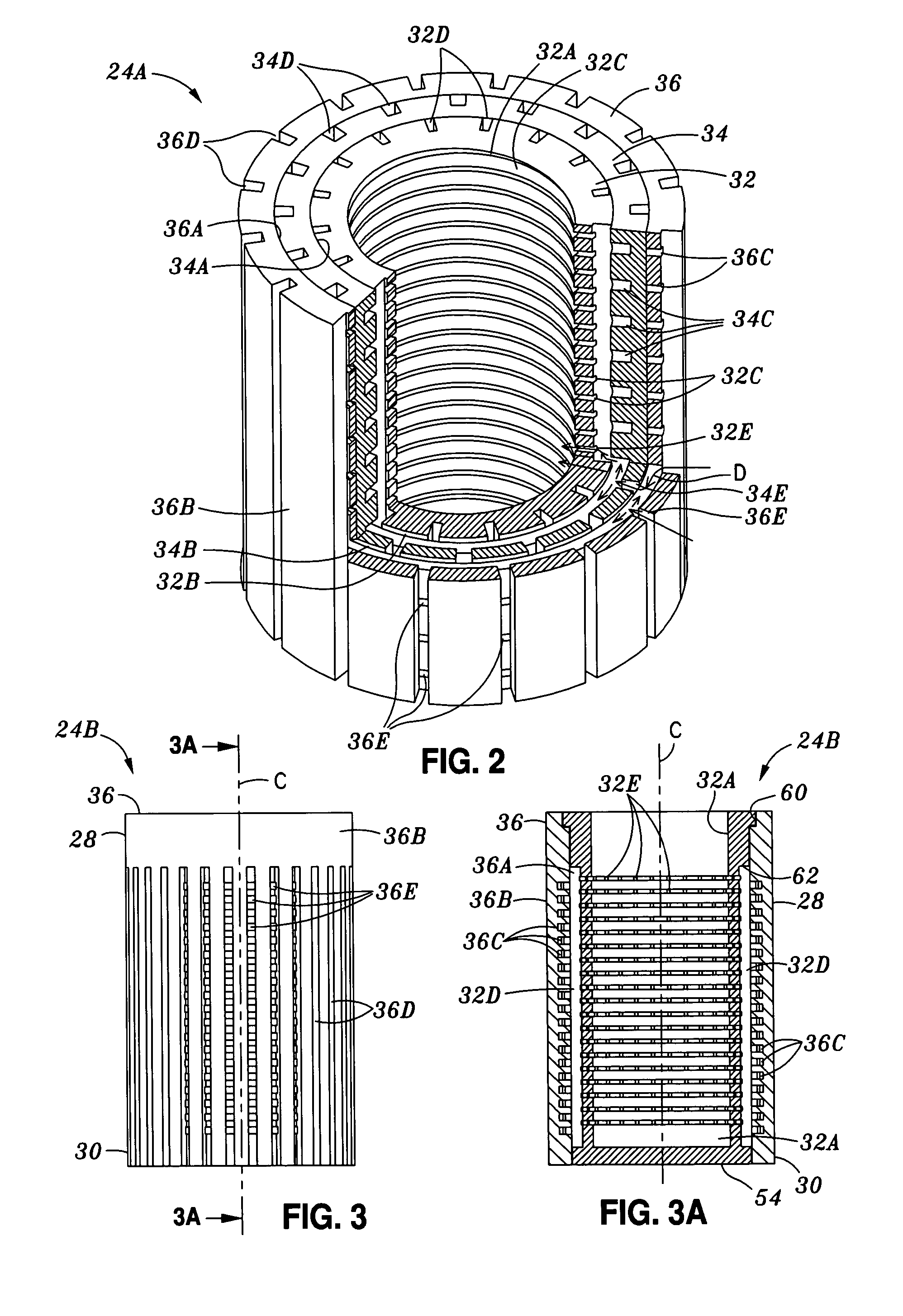

Predictive maintenance and initialization system for a digital servovalve

ActiveUS20050000580A1Simple and reliable initializationReduced referenceFluid-pressure actuator testingOperating means/releasing devices for valvesMechanical resistanceEngineering

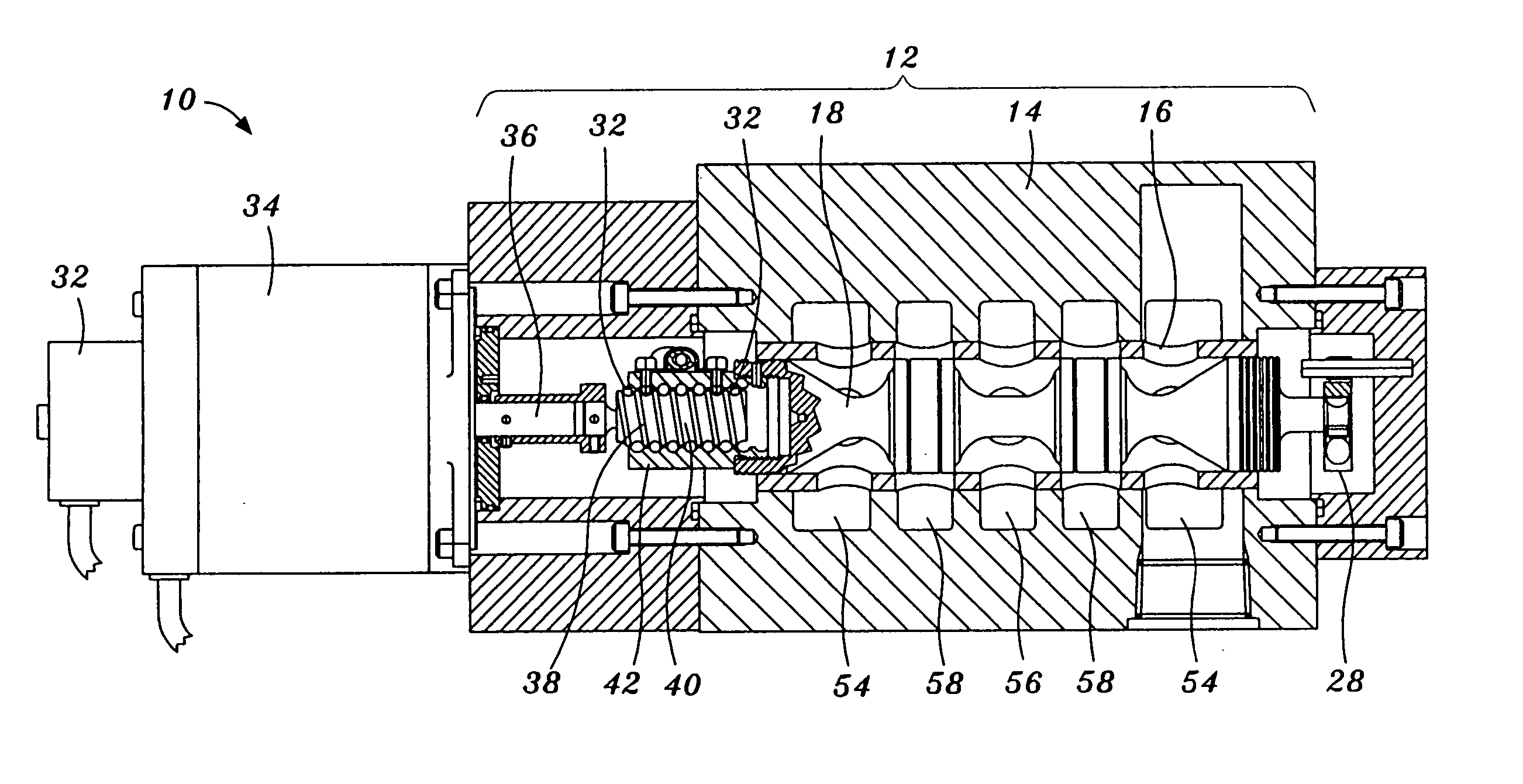

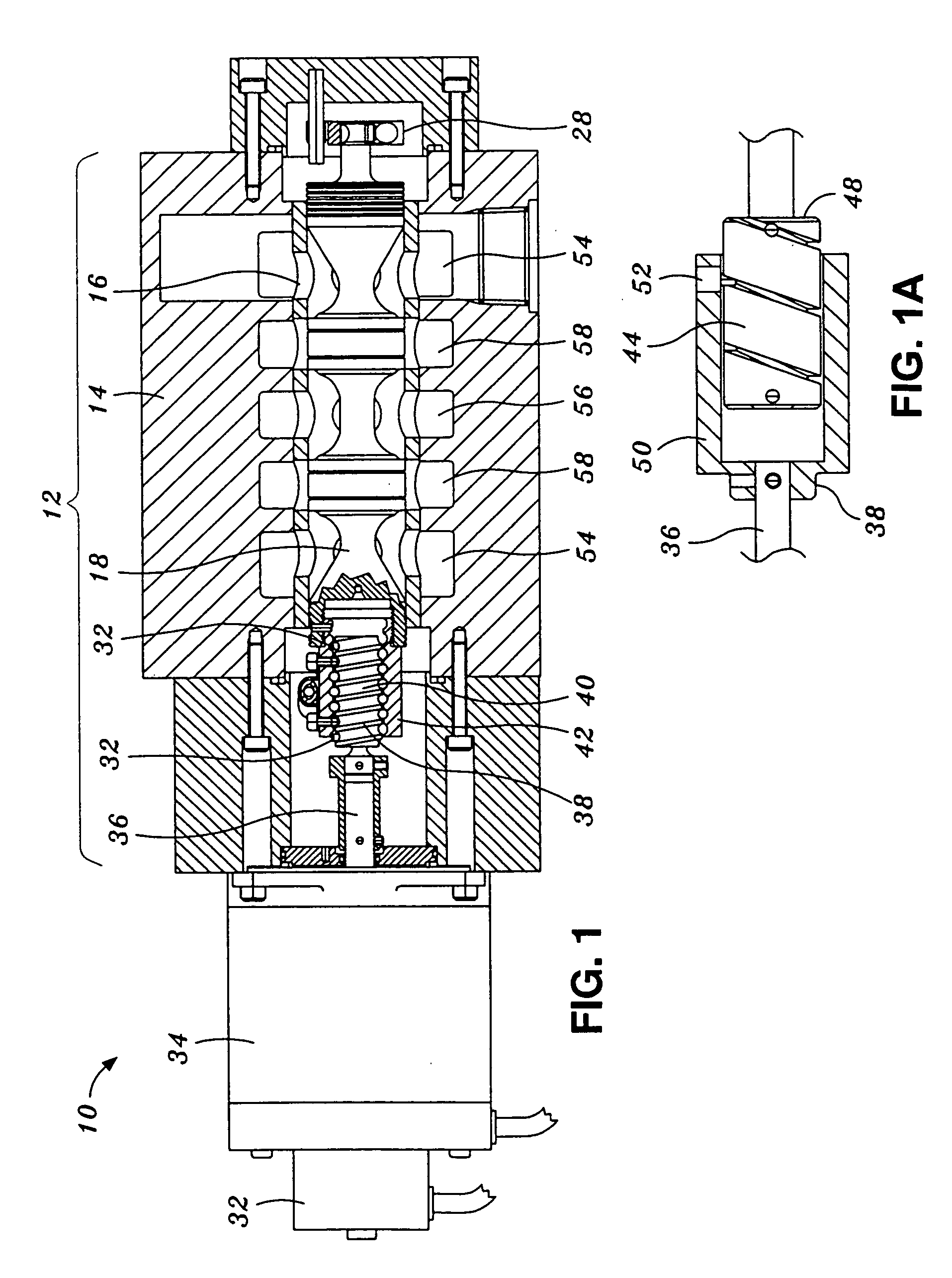

Provided is a servovalve system for regulating fluid flowing within a fluid circuit. The servovalve system comprises a housing, a spool slidably disposed within the housing, a stepper motor operatively connected to the spool, and a controller and a position sensor electronically connected to the stepper motor. The controller generates driver signals representative of a desired amount of stepper motor rotation in order to cause the stepper motor to effectuate spool motion relative to the housing. The position sensor senses an actual amount of stepper motor rotation and generates a quantity of position signals representative thereof. The controller determines a signal ratio of the quantity of the position signals to the quantity of the driver signals and generates a diagnostic signal when the signal ratio reaches a threshold value representative of a predetermined level of mechanical resistance of spool motion relative to the housing.

Owner:CONTROL COMPONENTS INC

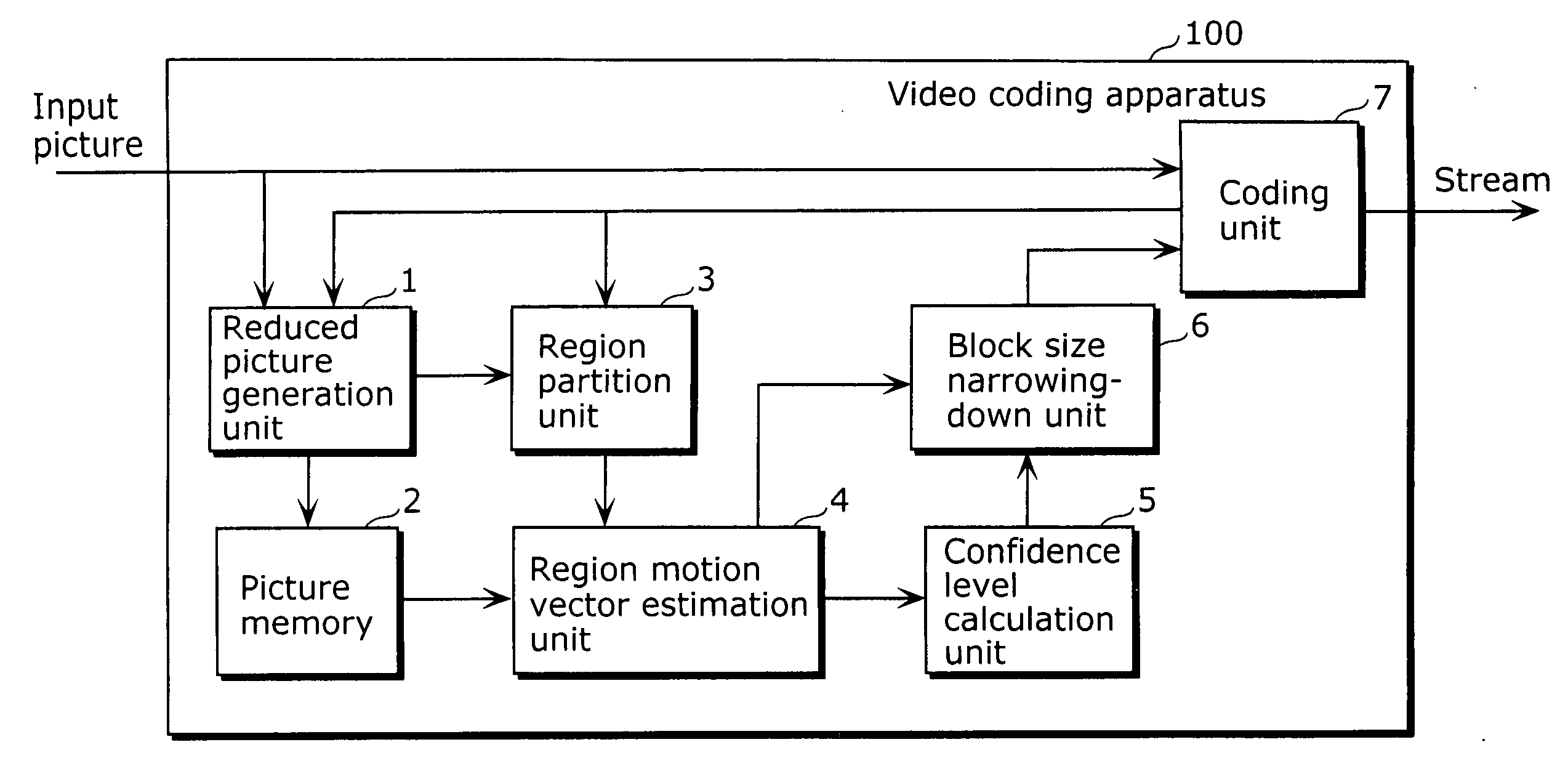

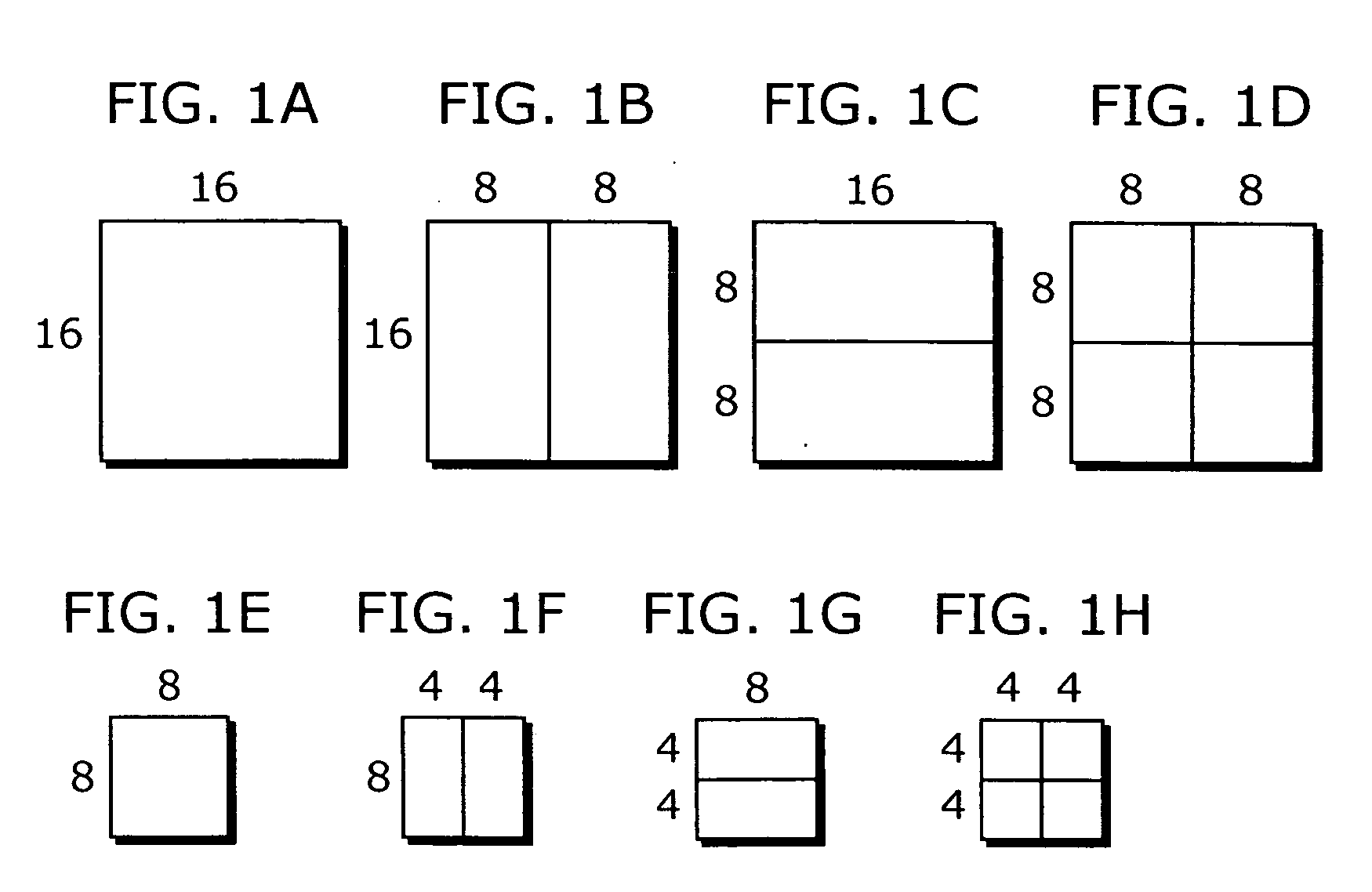

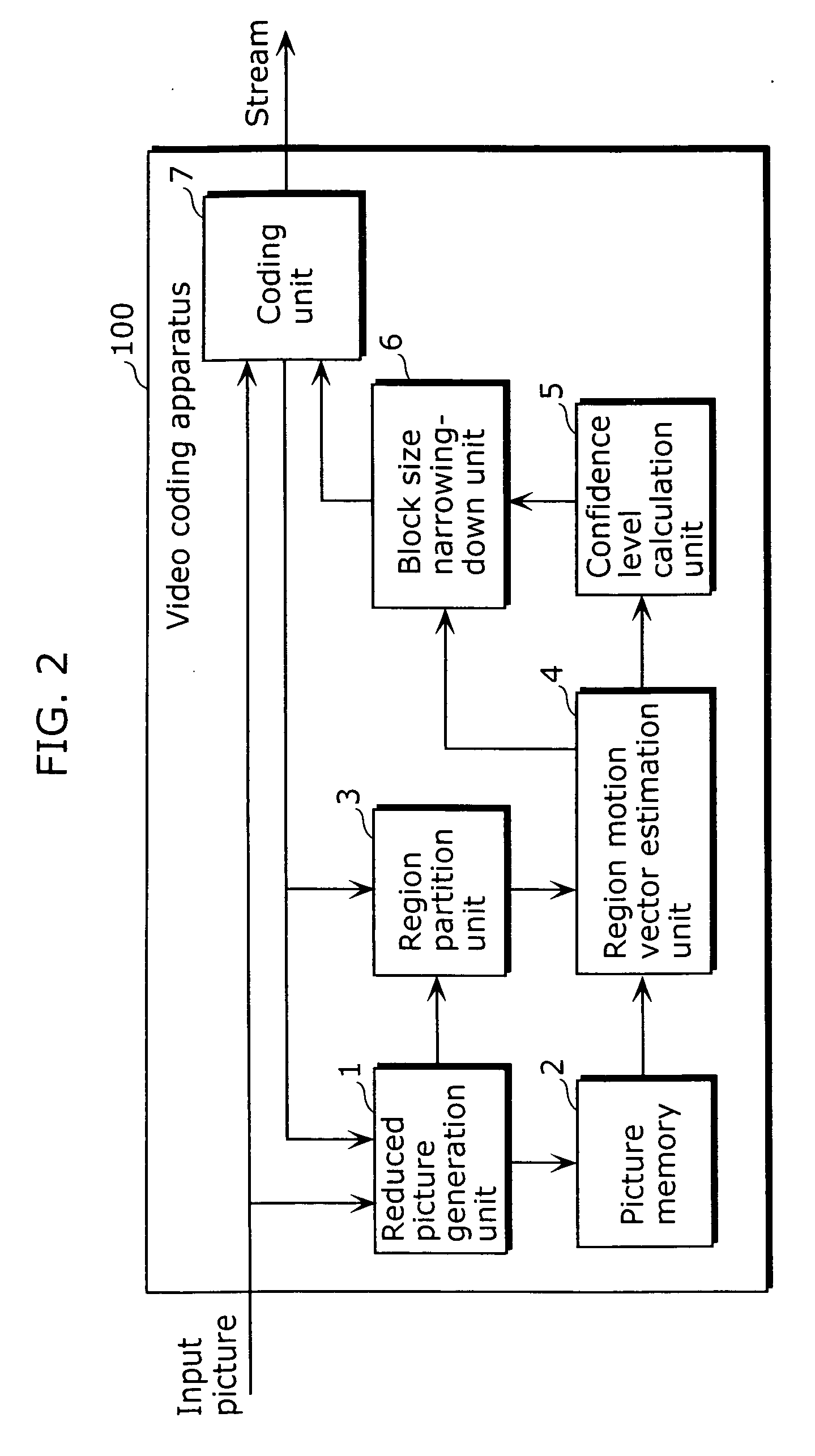

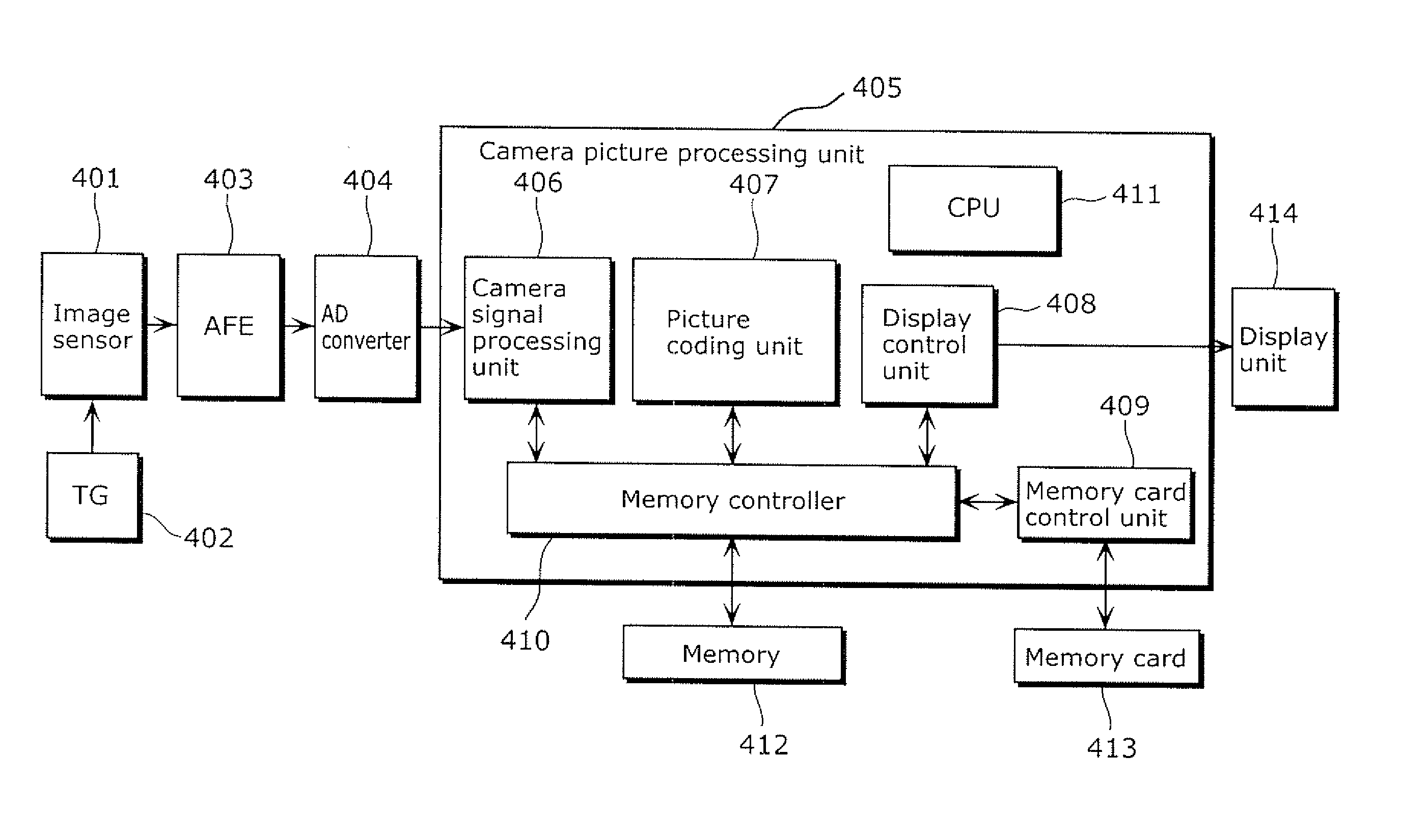

Motion vector estimation apparatus and motion vector estimation method

ActiveUS20070047652A1Reduce the amount of calculationIncrease bitrateTelevision system detailsPicture reproducers using cathode ray tubesMotion vectorEstimation methods

A motion vector estimation apparatus that can reduce an amount of calculation for video coding processing and thus achieve a higher bit rate and lower consumption power, while contributing to improvement in image quality and coding efficiency include: a reduced picture generation unit which generates a reduced current picture to be coded and a reduced reference picture; a region partition unit which partitions a reduced current picture to be coded into regions and generates reduced region images; a region motion vector estimation unit which estimates a region motion vector of a reduced region image; a confidence level calculation unit which calculates a confidence level of a region motion vector; and a block size narrowing-down unit which narrows down candidate block sizes so as to determine a block size to be used for coding a current block to be coded, based on a region motion vector and a confidence level of the region motion vector.

Owner:PANASONIC CORP

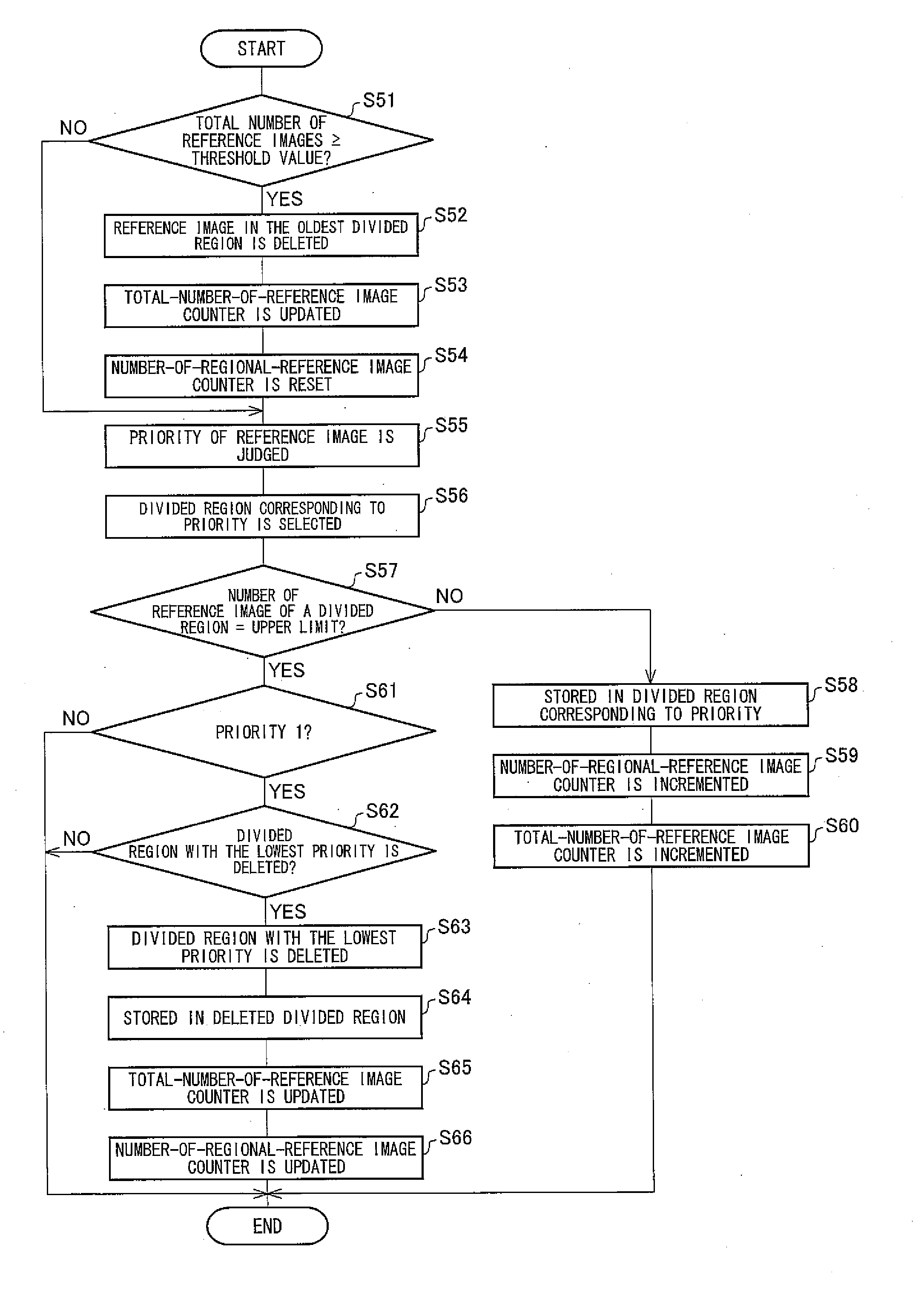

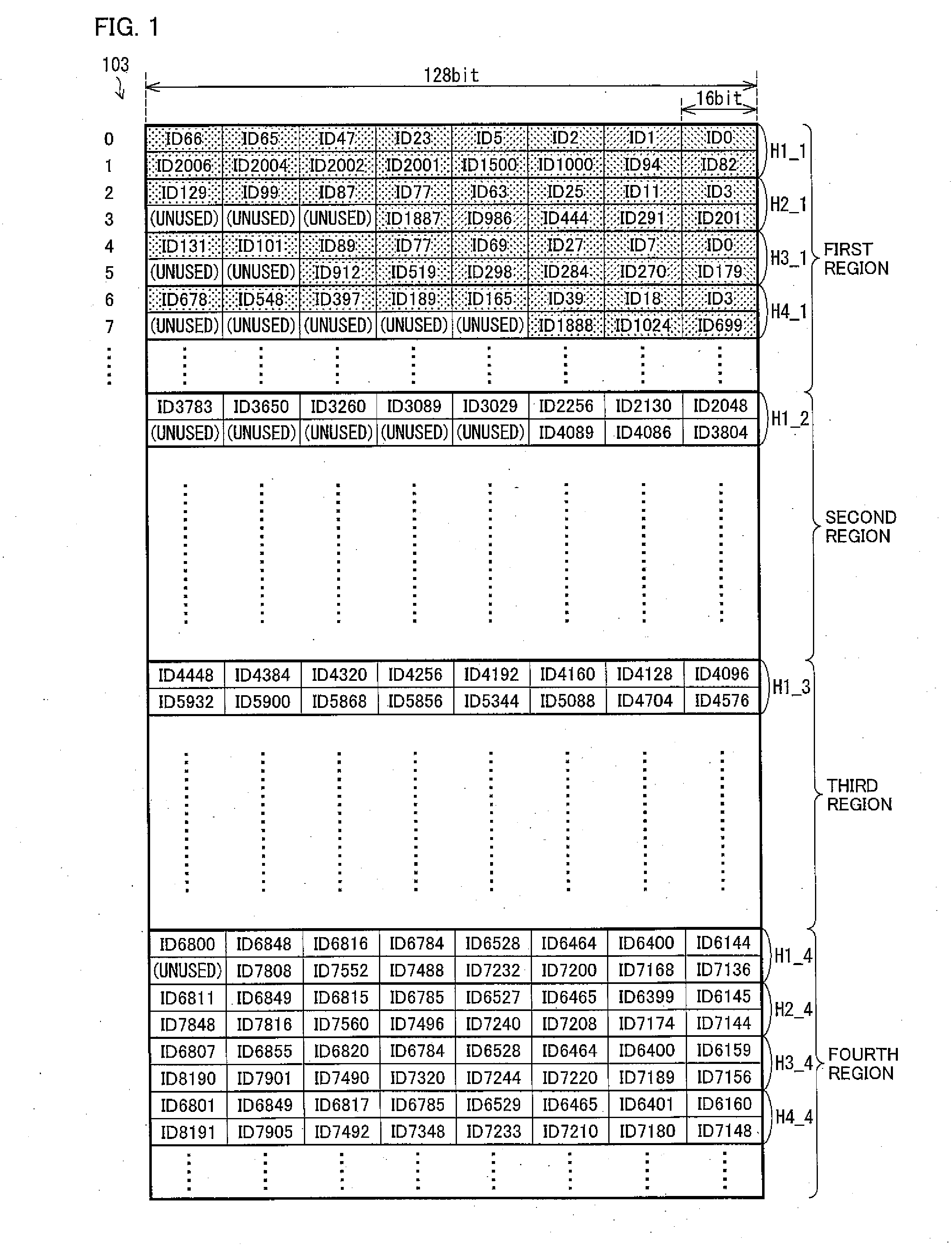

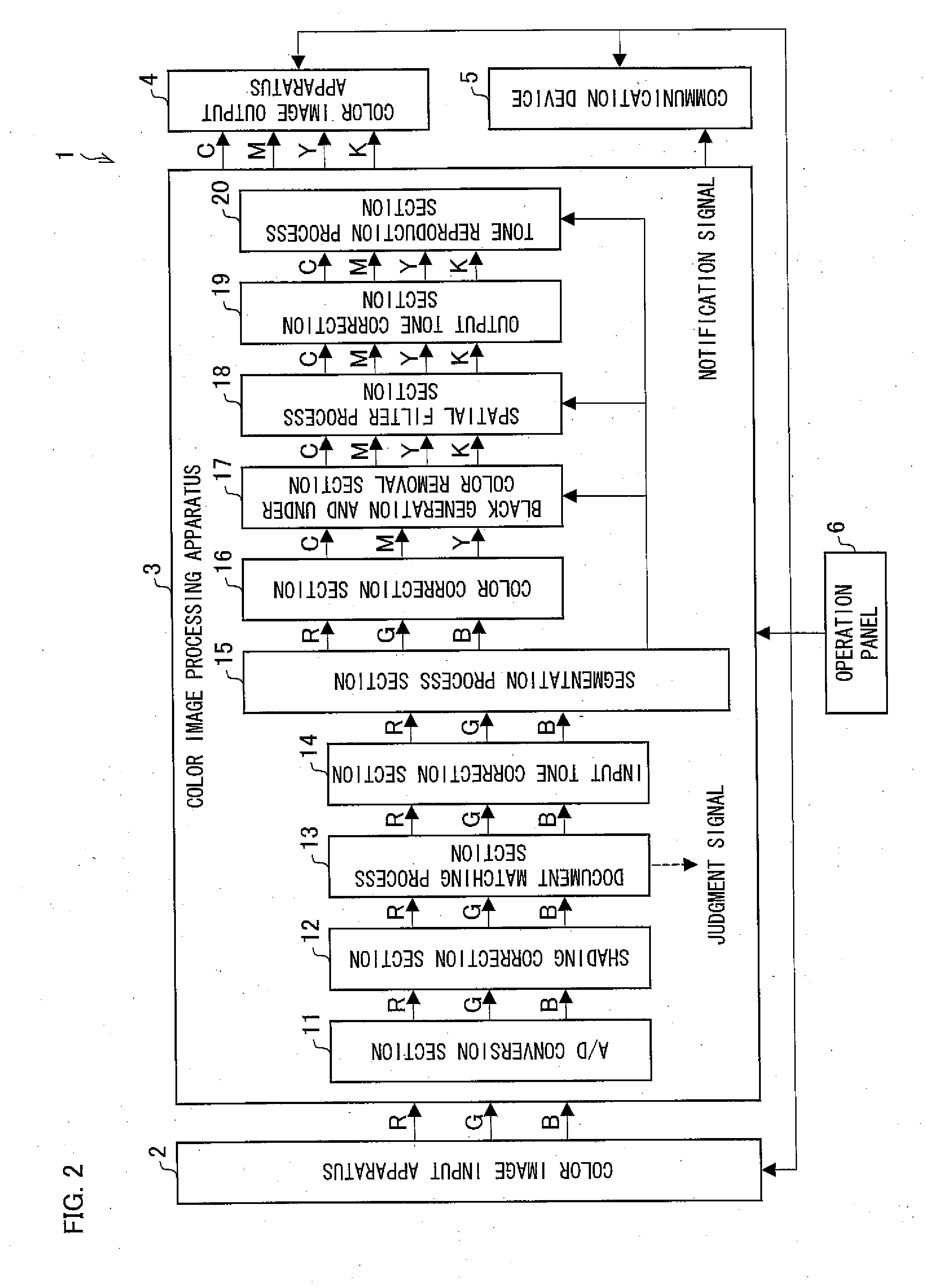

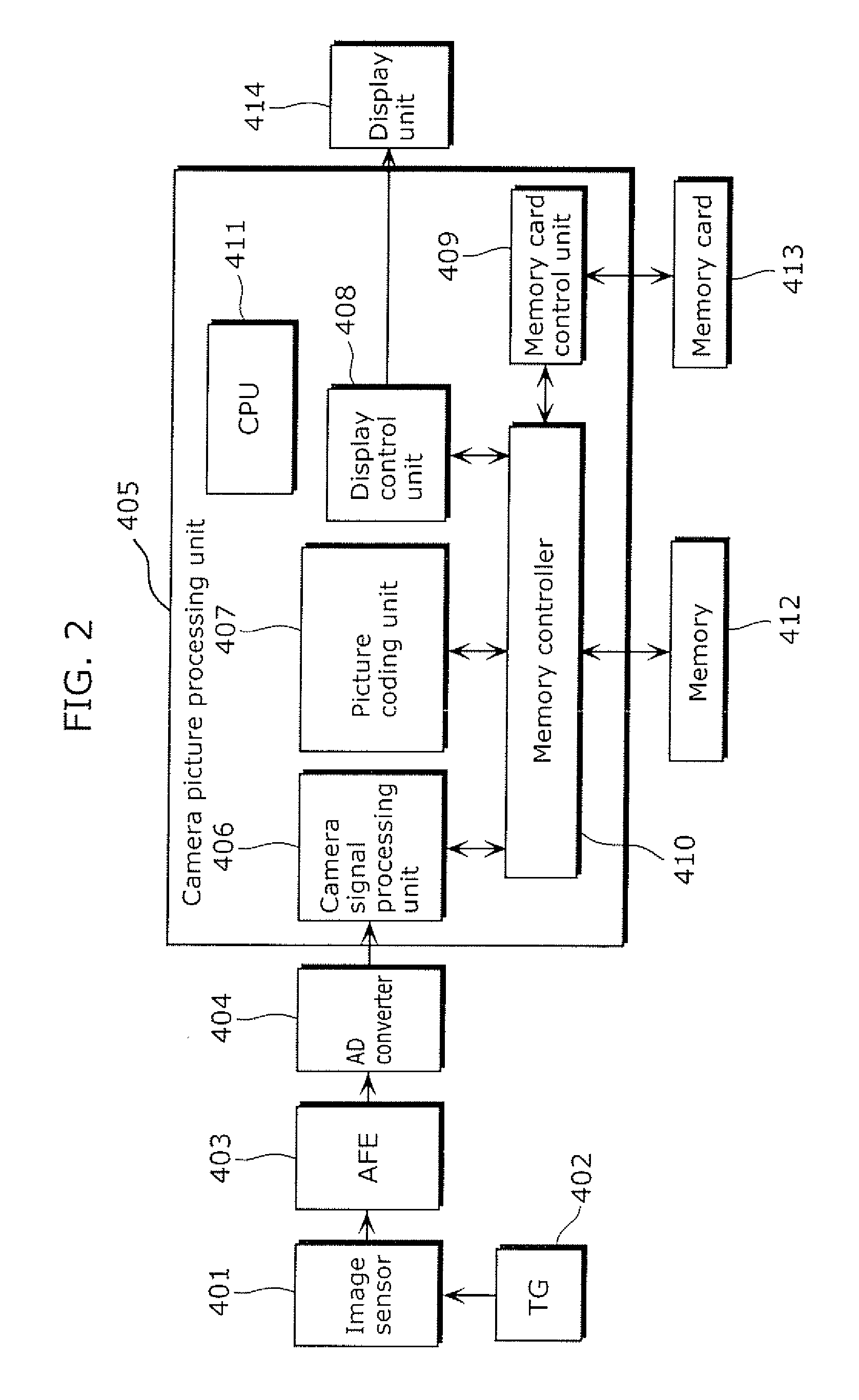

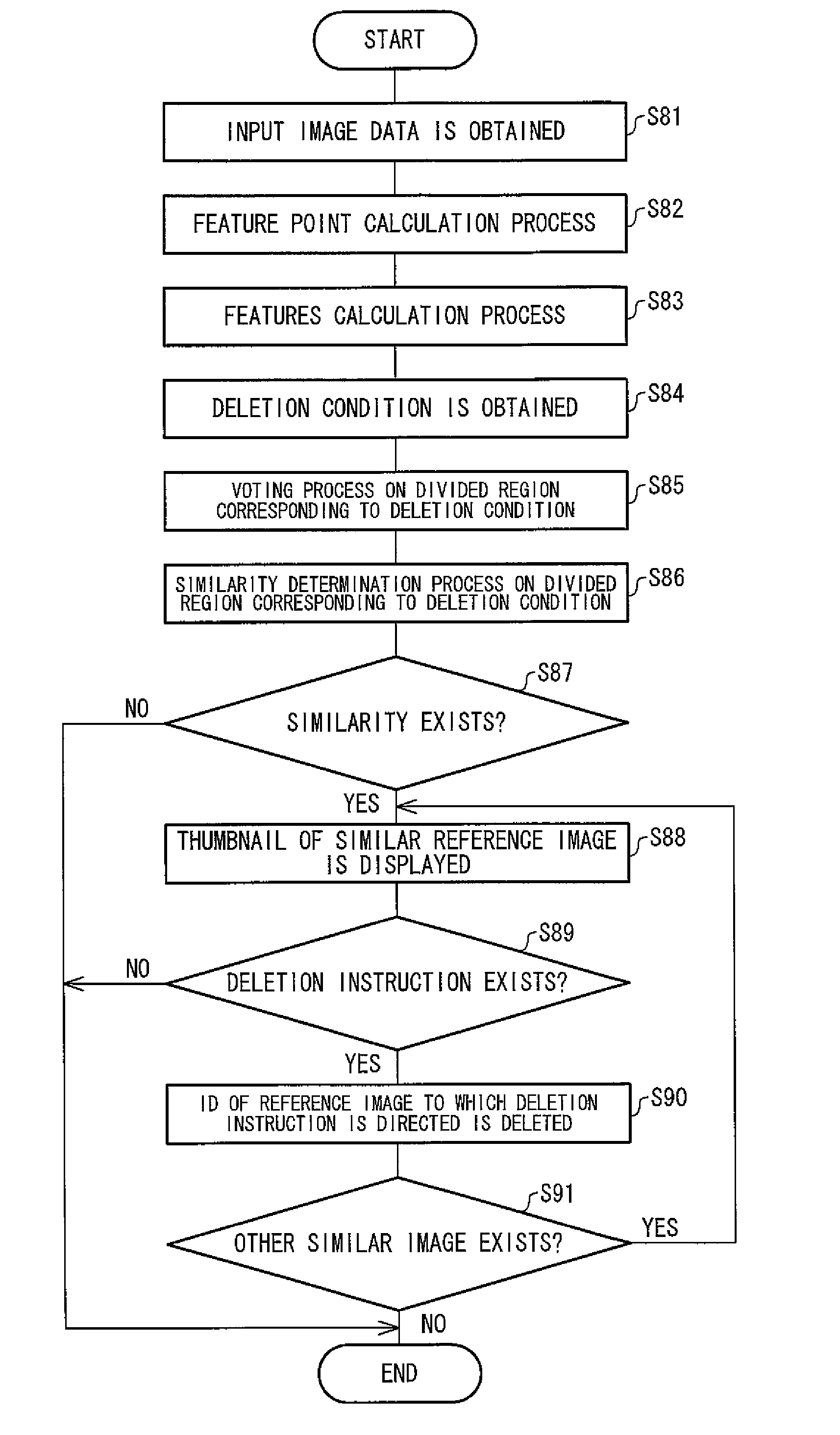

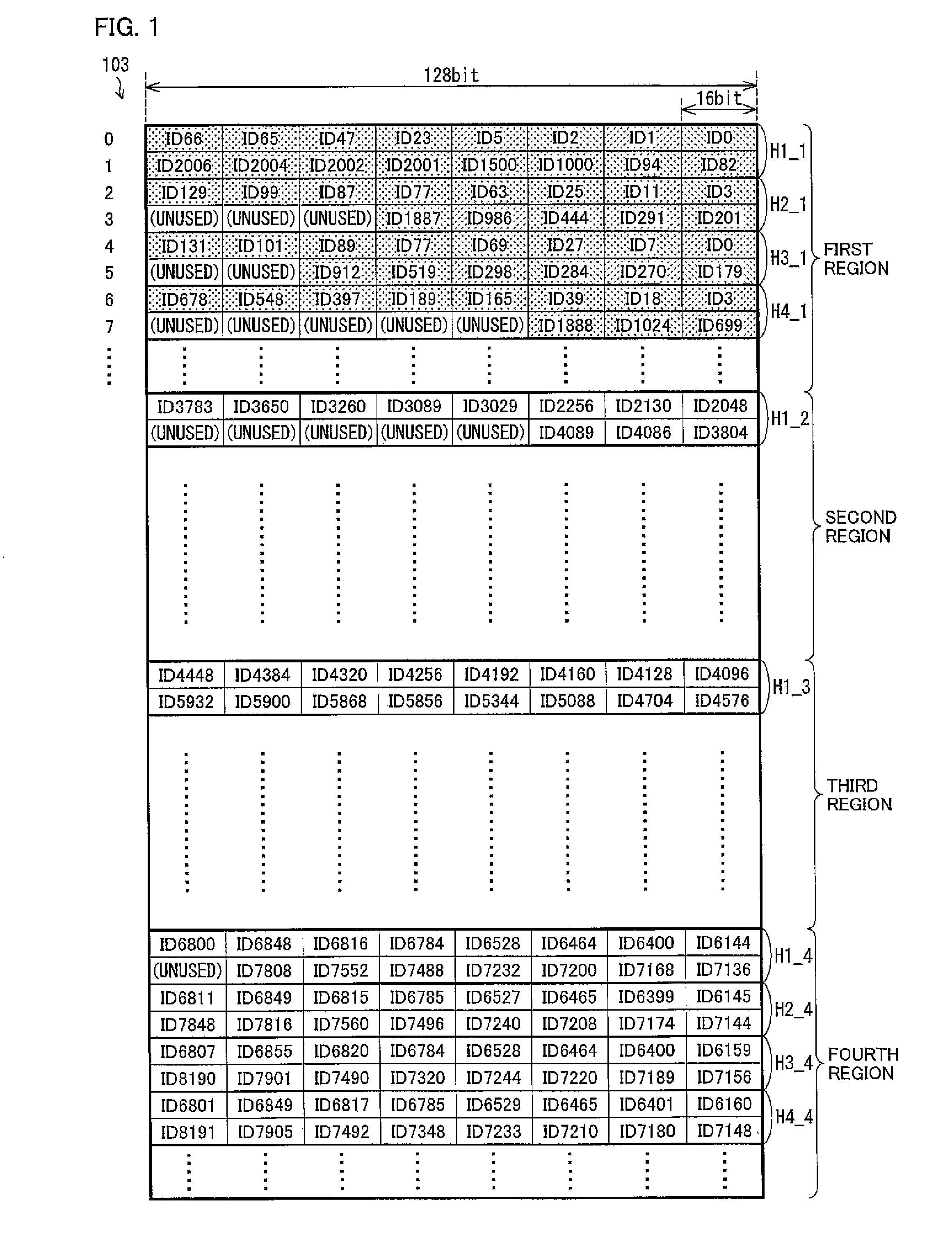

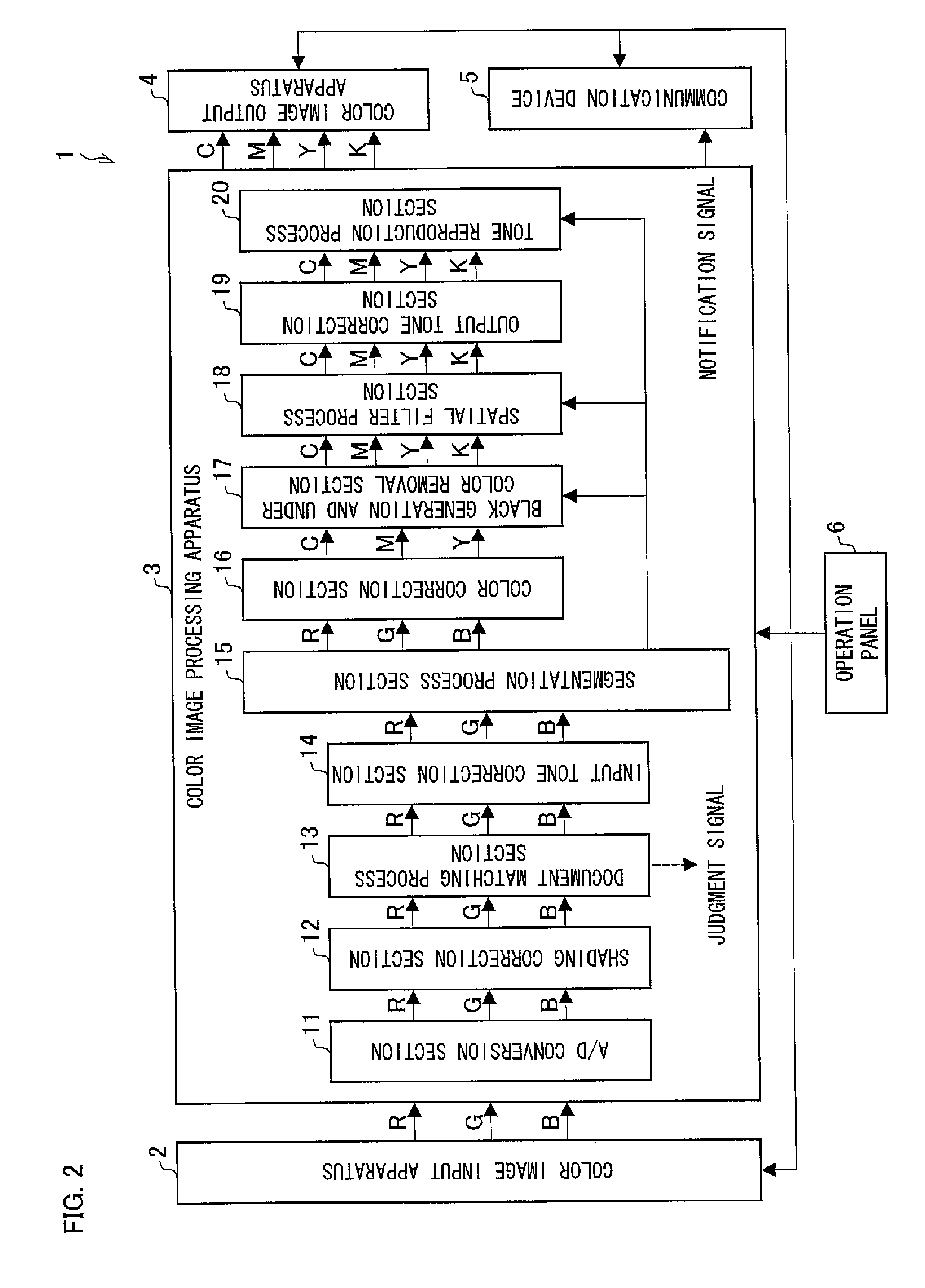

Image processing apparatus, image forming apparatus, image processing system, and image processing method

ActiveUS20080247677A1Shorten the timeReduce workloadDigital data information retrievalDigital data processing detailsImaging processingComputer graphics (images)

A reference image and features of the reference image are stored in a hash table in such a manner that the reference image and the features are related to each other. A storage region of the hash table is divided into a plurality of divided regions, and each divided region is related to a storage condition under which a reference image is stored in the divided region. When a reference image is stored in the hash table, a storage region where the reference image is to be stored is selected out of the plurality of divided regions in accordance with the storage condition. This allows shortening a time for updating a reference image, and reducing a workload on means for updating the reference image.

Owner:SHARP KK

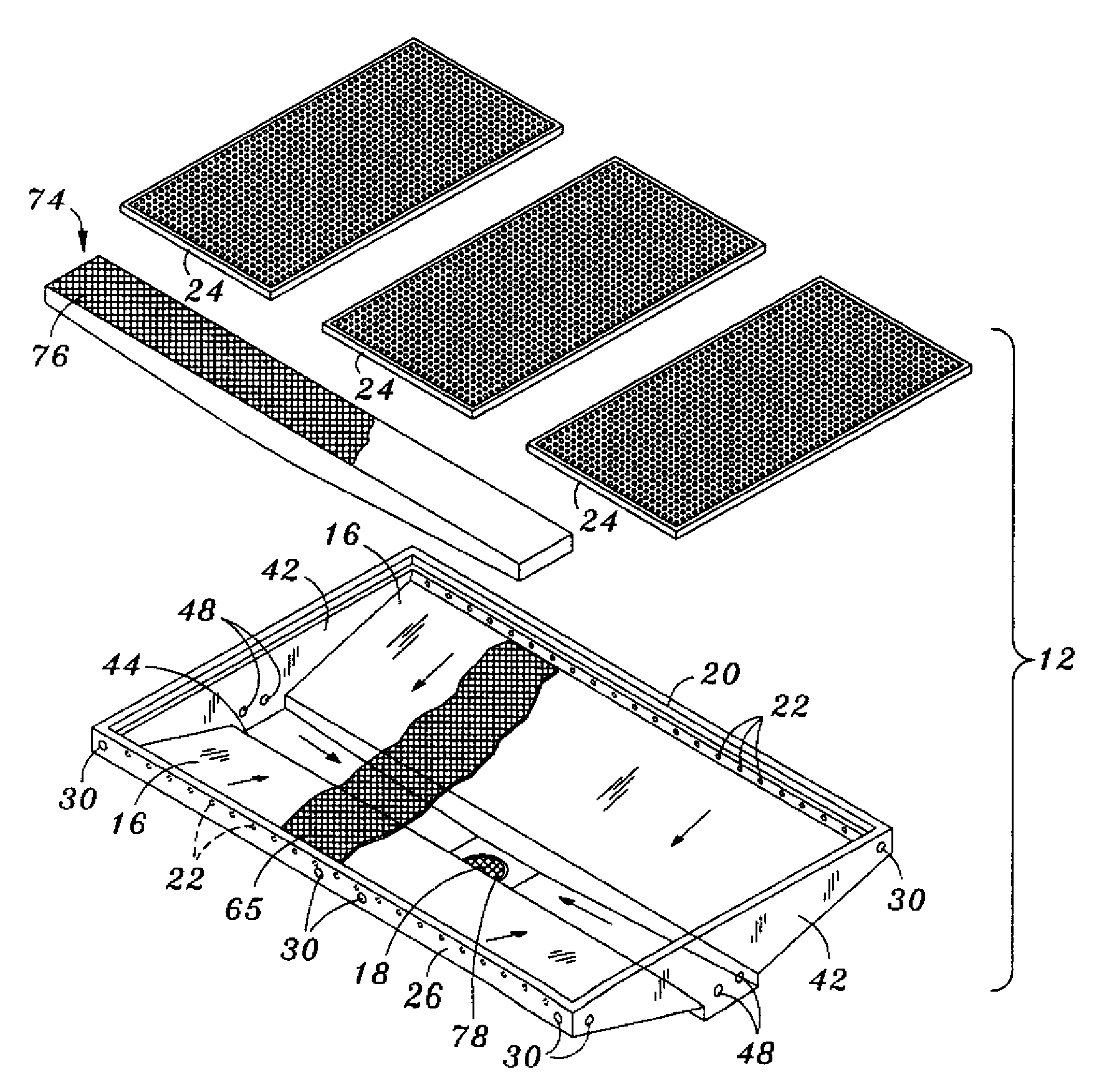

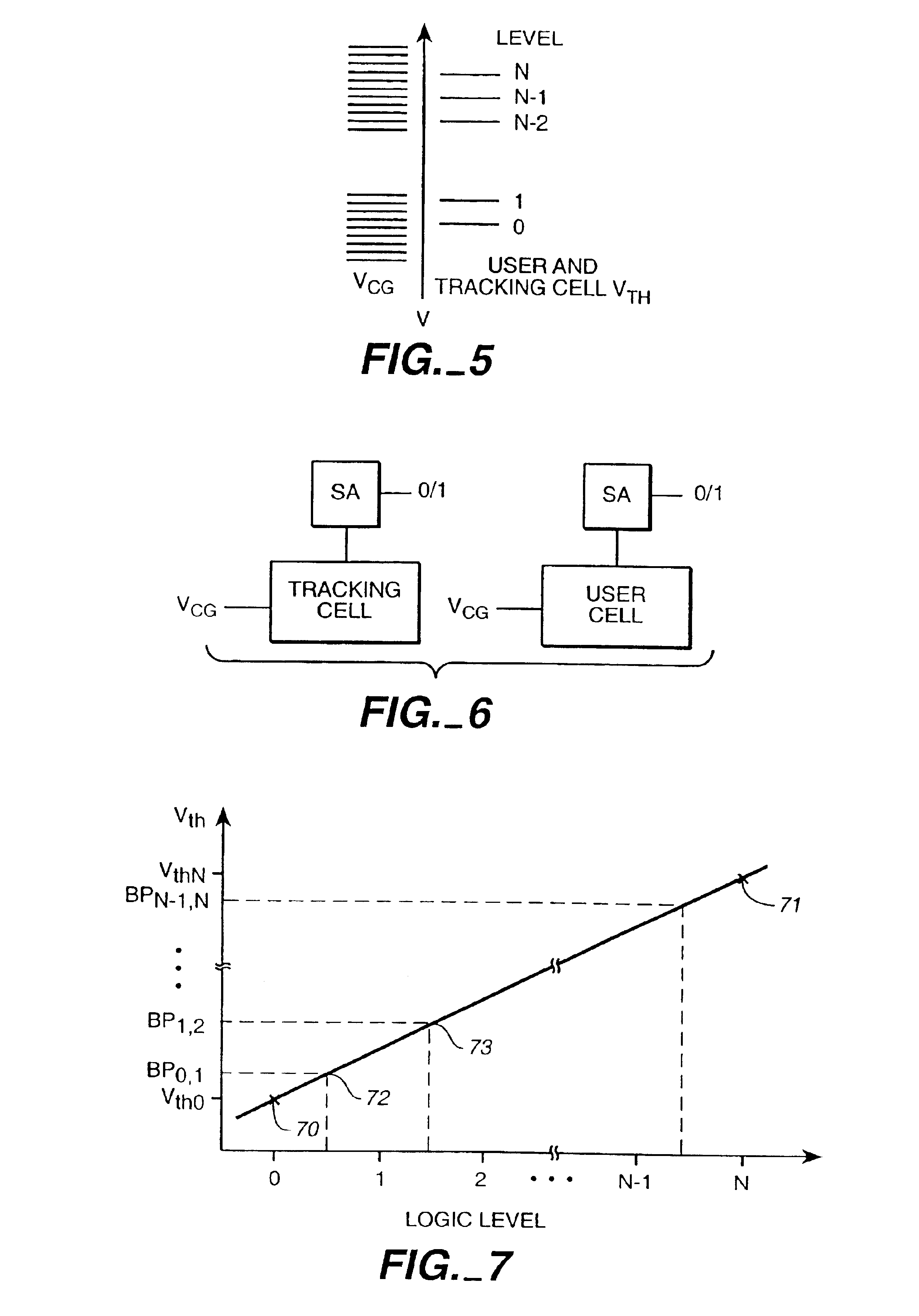

Self-cleaning flooring system

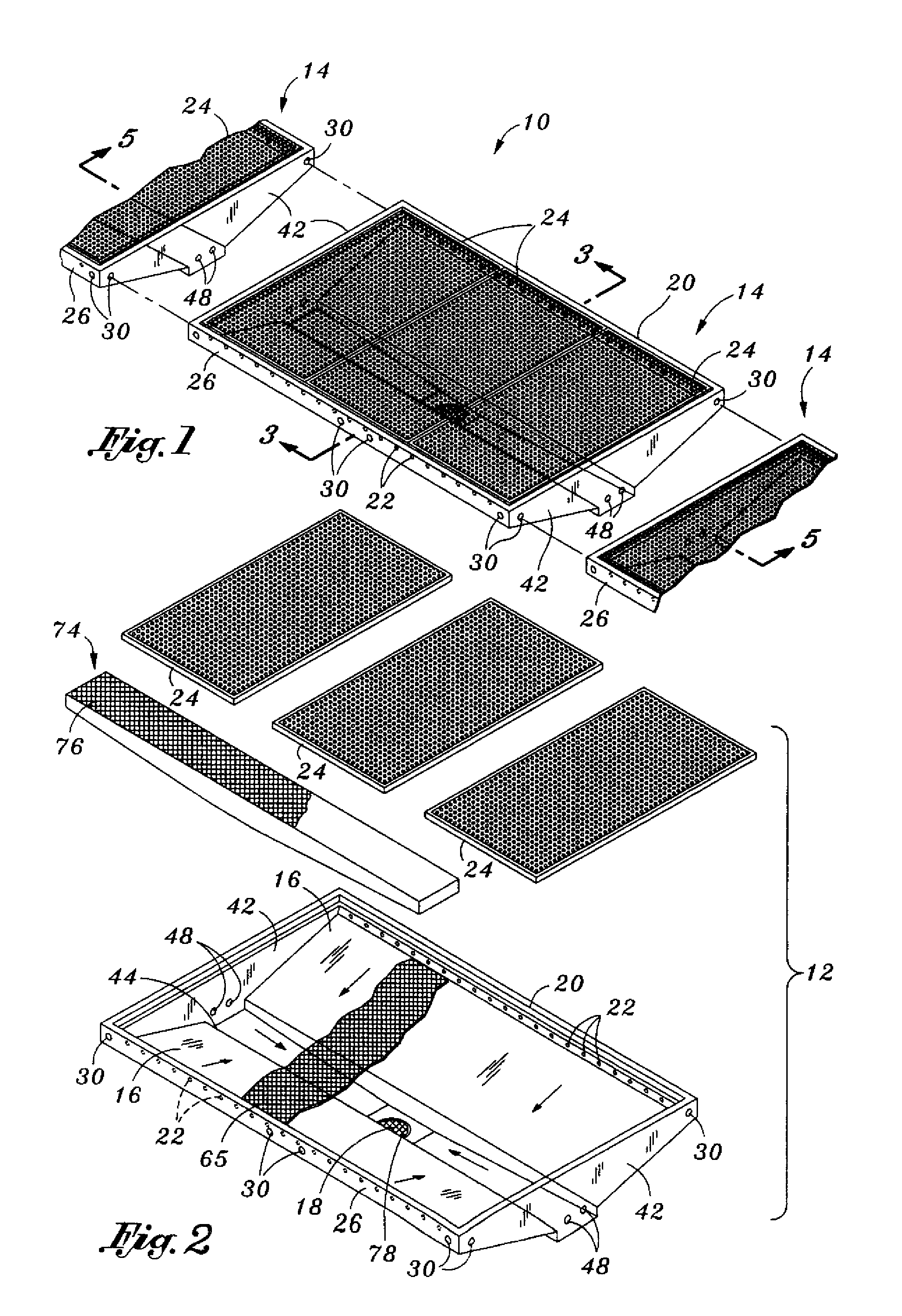

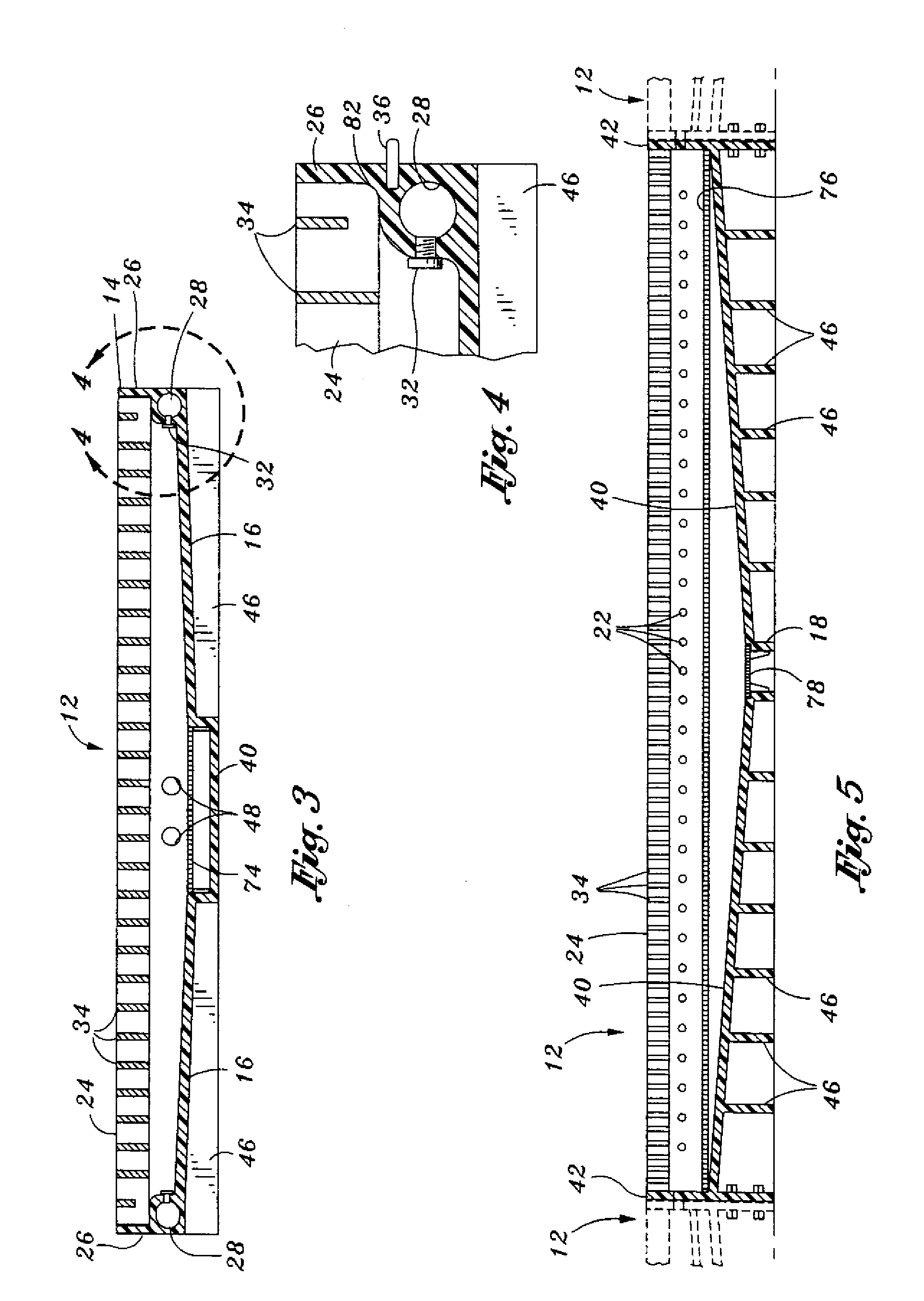

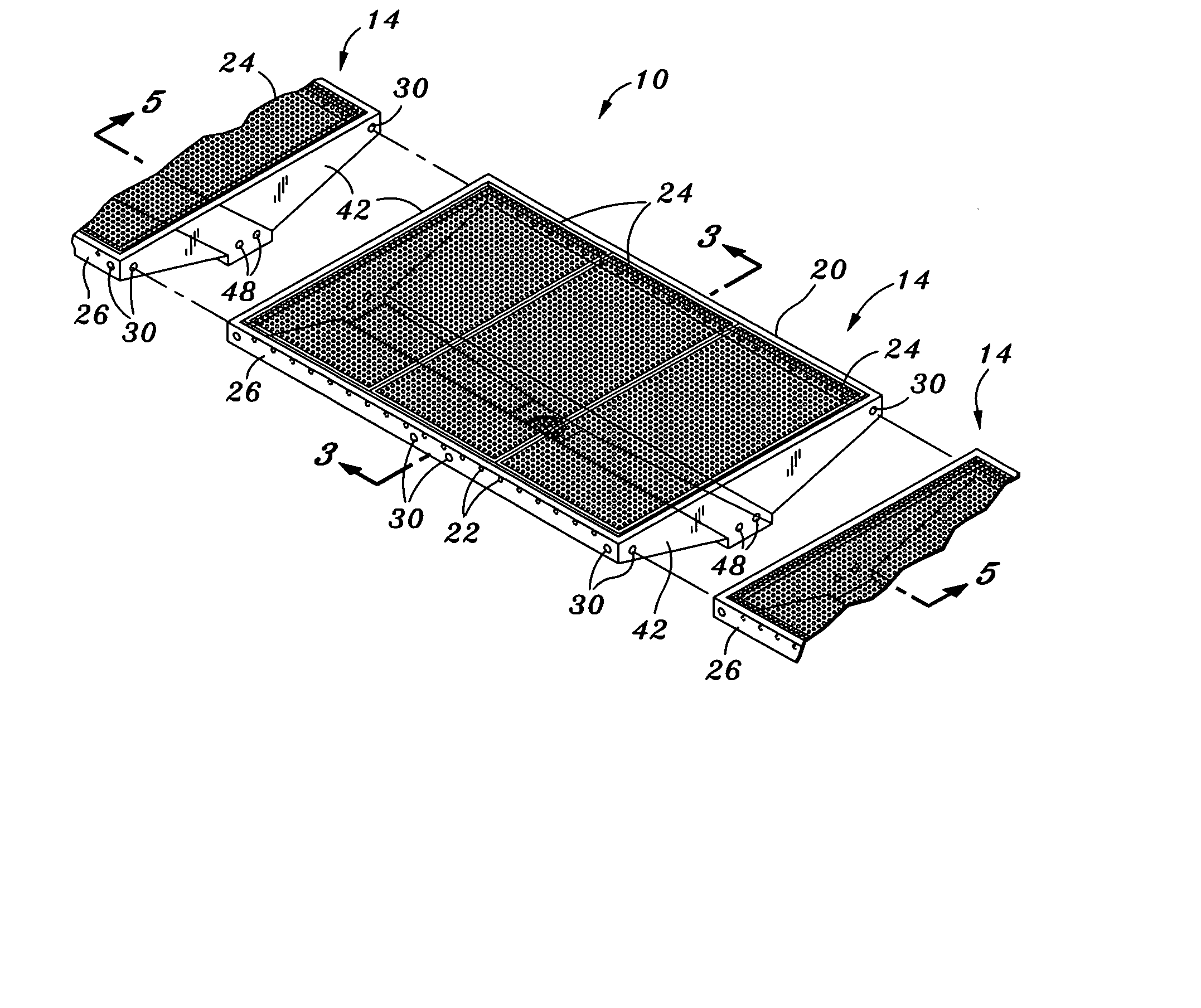

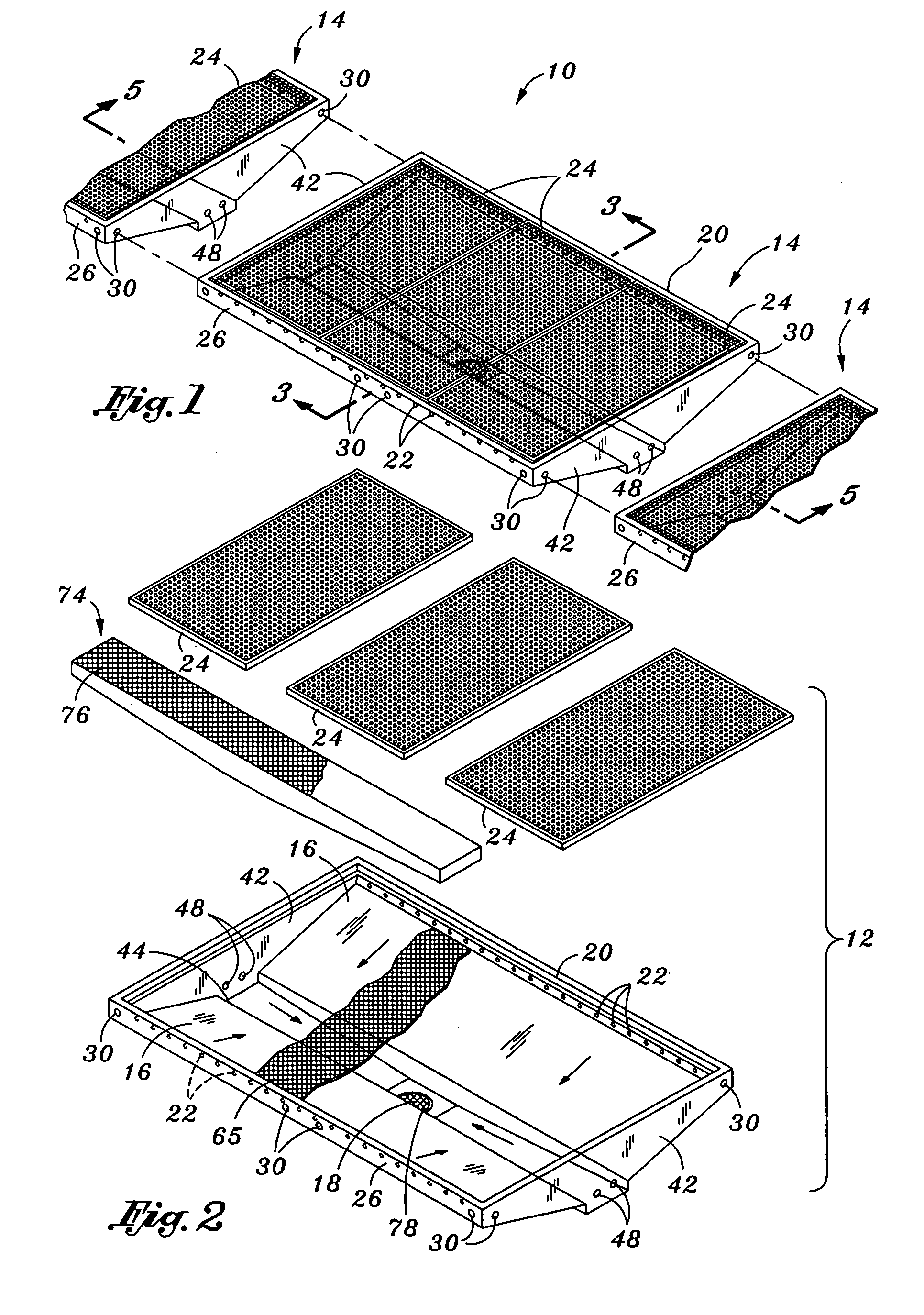

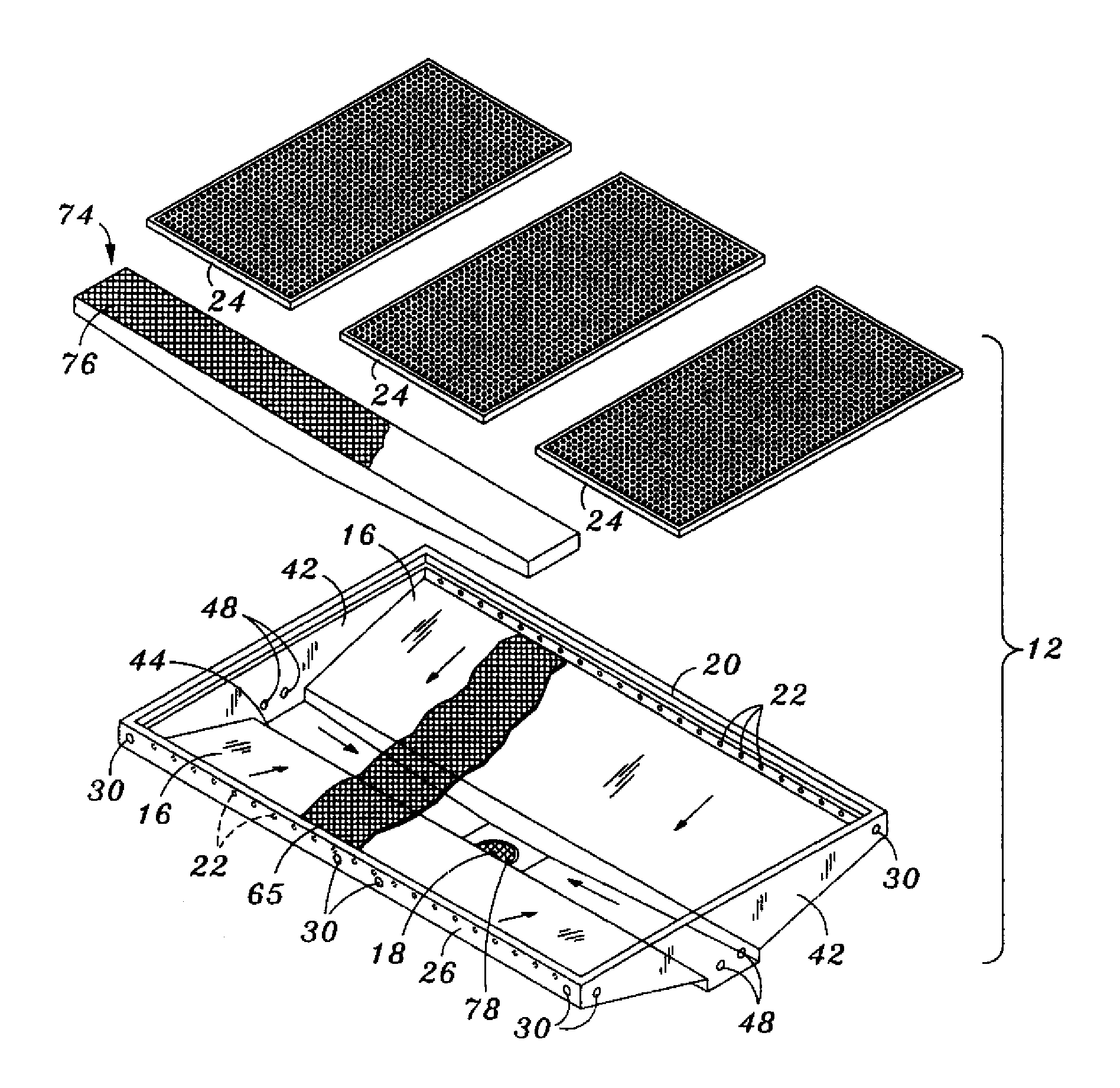

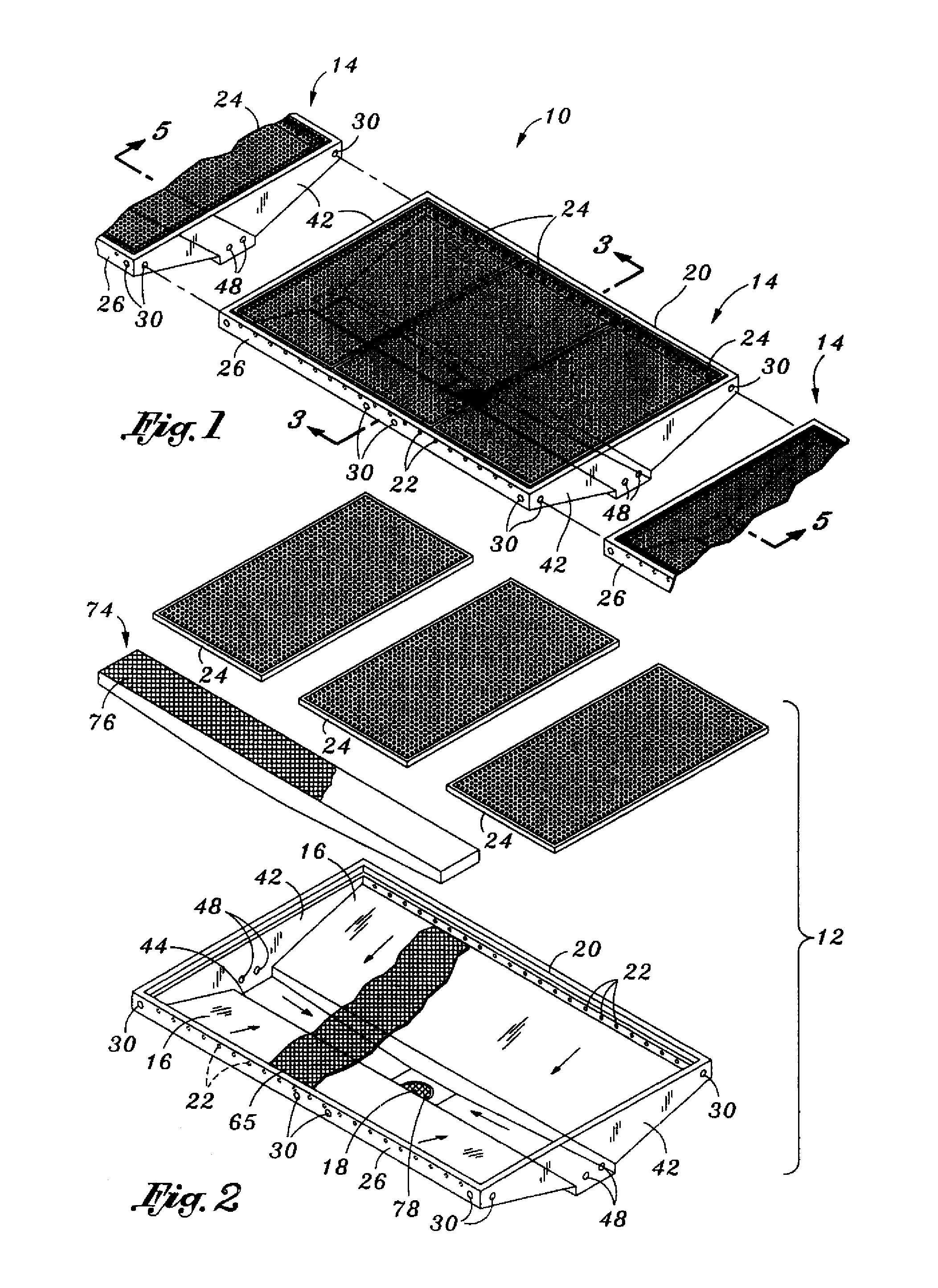

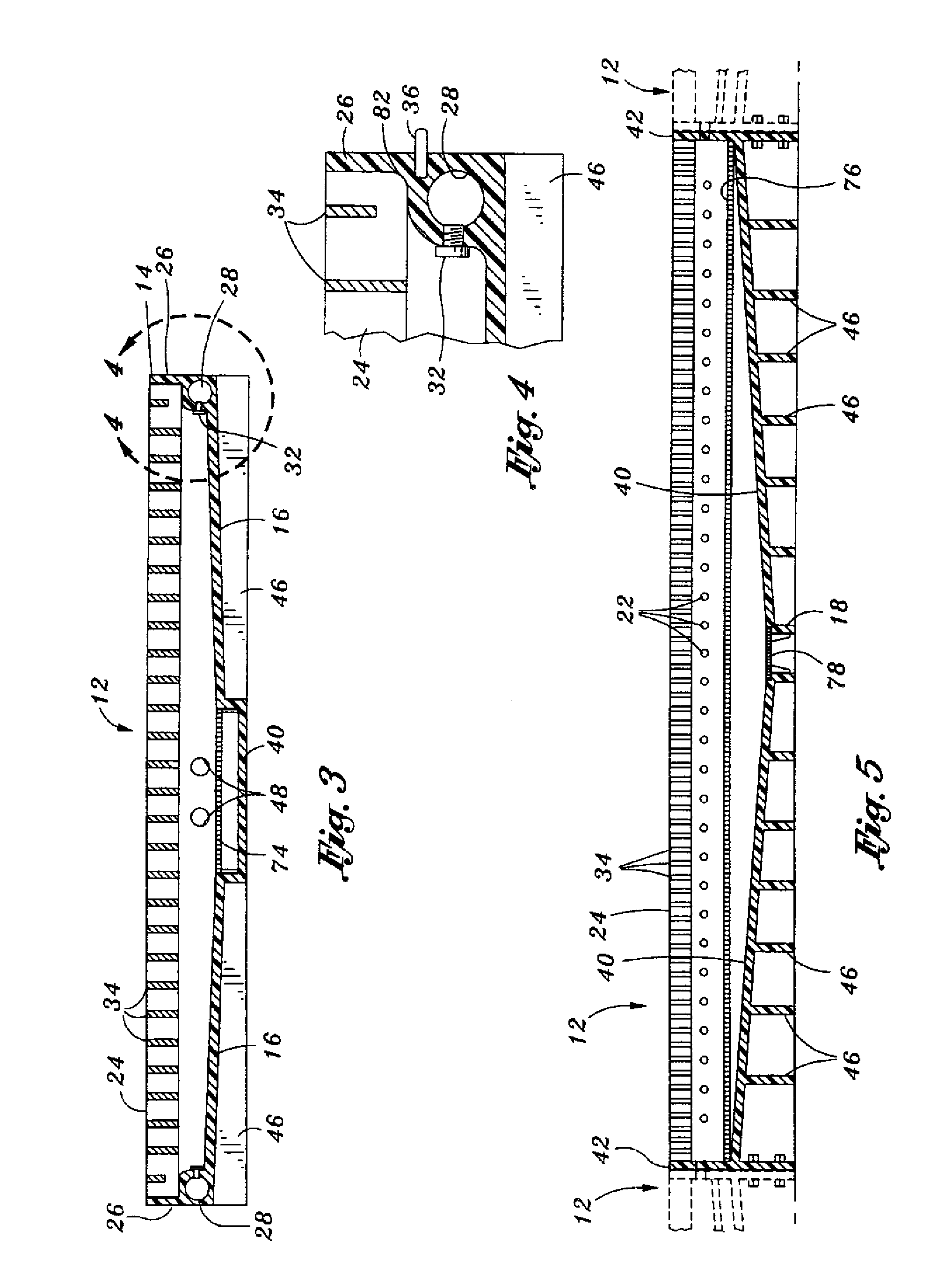

InactiveUS20090241442A1Reduced referenceDurable flooring systemConstruction materialAnimal housingSelf cleaningWaste management

A self-cleaning flooring system is provided that includes at least one module. The module comprises a drain pan, a plurality of discharge ports, and at least one side wall. The drain pan may have a ramp and a drain outlet. The ramp may slope downward towards the drain outlet. The discharge ports may be disposed about a periphery of the drain pan and may be directed towards the drain outlet to direct flushing fluid towards the drain outlet. The side wall may circumscribe a portion of the periphery of the drain pan and include a hollow passage and at least one fluid inlet. The fluid inlet may be in fluid communication with the hollow passage for delivering flushing fluid to the discharge ports.

Owner:SANI FLOOR INC

Self-cleaning flooring system

InactiveUS20060048469A1Reduced referenceDurable flooring systemSewerage structuresClimate change adaptationDrain tubeWaste management

A self-cleaning flooring system is provided that includes at least one module. The module comprises a drain pan, a plurality of discharge ports, and at least one side wall. The drain may have a ramp and a drain outlet. The ramp may slope downward towards the drain outlet. The discharge ports may be disposed about a periphery of the drain pan and may be directed towards the drain outlet to direct flushing fluid towards the drain outlet. The side wall may circumscribe a portion of the periphery of the drain pan and include a hollow passage and at least one fluid inlet. The fluid inlet may be in fluid communication with the hollow passage for delivering flushing fluid to the discharge ports.

Owner:SANI FLOOR INC

Writable tracking cells

InactiveUS6873549B2Less uncertaintyReduce reference cell threshold uncertaintyElectric analogue storesRead-only memoriesComputer scienceThreshold voltage

The present invention presents several techniques for using writable tracking cells. Multiple tracking cells are provided for each write block of the memory. These cells are re-programmed each time the user cells of the associated write block are written, preferably at the same time, using the same fixed, global reference levels to set the tracking and user cell programmed thresholds. The threshold voltages of the tracking cells are read every time the user cells are read, and these thresholds are used to determine the stored logic levels of the user cells. In one set of embodiments, populations of one or more tracking cells are associated with different logic levels of a multi-state memory. These tracking cell populations may be provided for only a subset of the logic levels. The read points for translating the threshold voltages are derived for all of the logic levels based upon this subset. In one embodiment, two populations each consisting of multiple tracking cells are associated with two logic levels of the multi-bit cell. In an analog implementation, the user cells are read directly using the analog threshold values of the tracking cell populations without their first being translated to digital values. A set of alternate embodiments provide for using different voltages and / or timing for the writing of tracking cells to provide less uncertainty in the tracking cells' final written thresholds.

Owner:SANDISK TECH LLC

Predictive maintenance and initialization system for a digital servovalve

ActiveUS7066189B2Simple and reliable initializationReduced referenceFluid-pressure actuator testingOperating means/releasing devices for valvesMechanical resistanceEngineering

Provided is a servovalve system for regulating fluid flowing within a fluid circuit. The servovalve system comprises a housing, a spool slidably disposed within the housing, a stepper motor operatively connected to the spool, and a controller and a position sensor electronically connected to the stepper motor. The controller generates driver signals representative of a desired amount of stepper motor rotation in order to cause the stepper motor to effectuate spool motion relative to the housing. The position sensor senses an actual amount of stepper motor rotation and generates a quantity of position signals representative thereof. The controller determines a signal ratio of the quantity of the position signals to the quantity of the driver signals and generates a diagnostic signal when the signal ratio reaches a threshold value representative of a predetermined level of mechanical resistance of spool motion relative to the housing.

Owner:CONTROL COMPONENTS INC

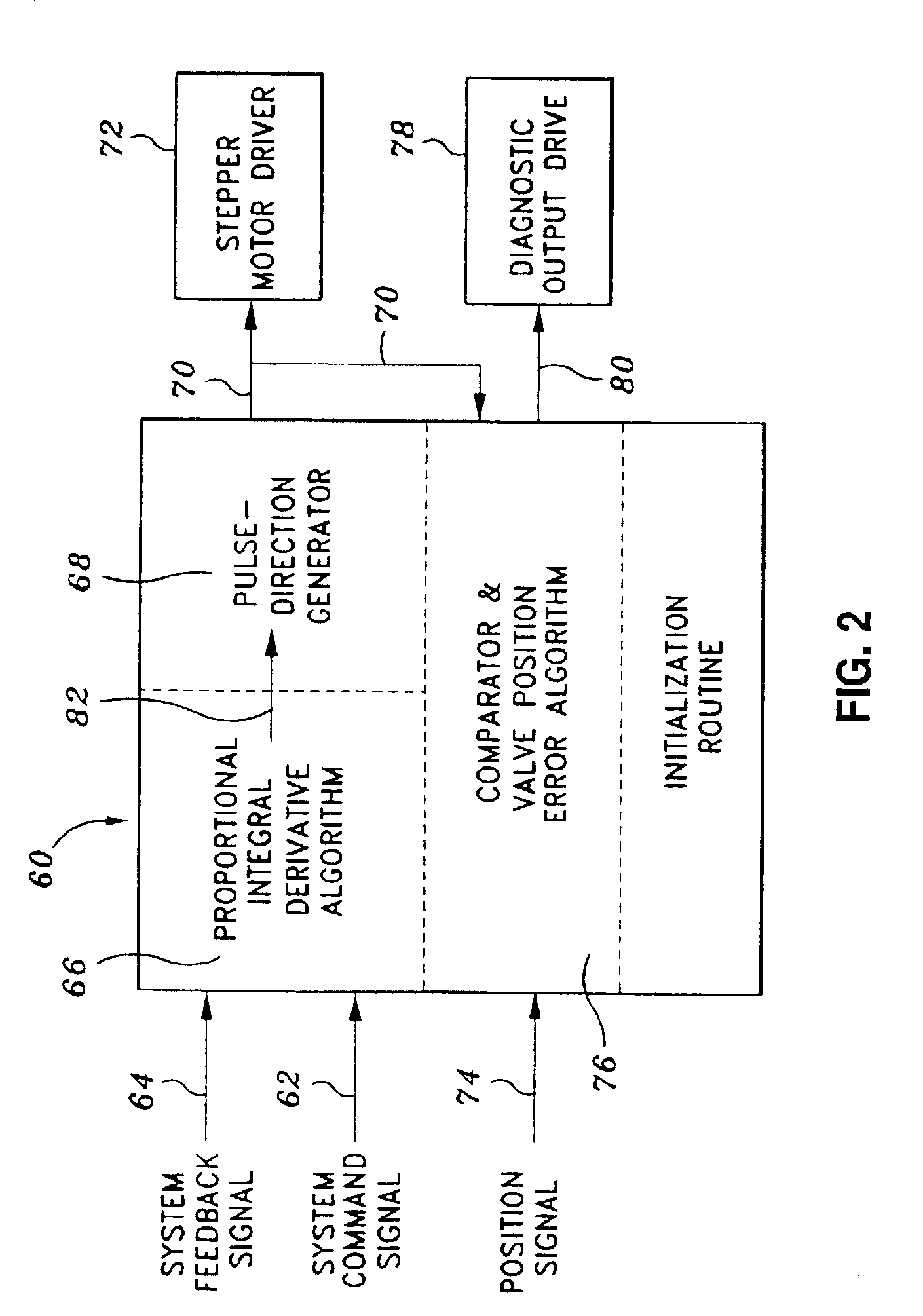

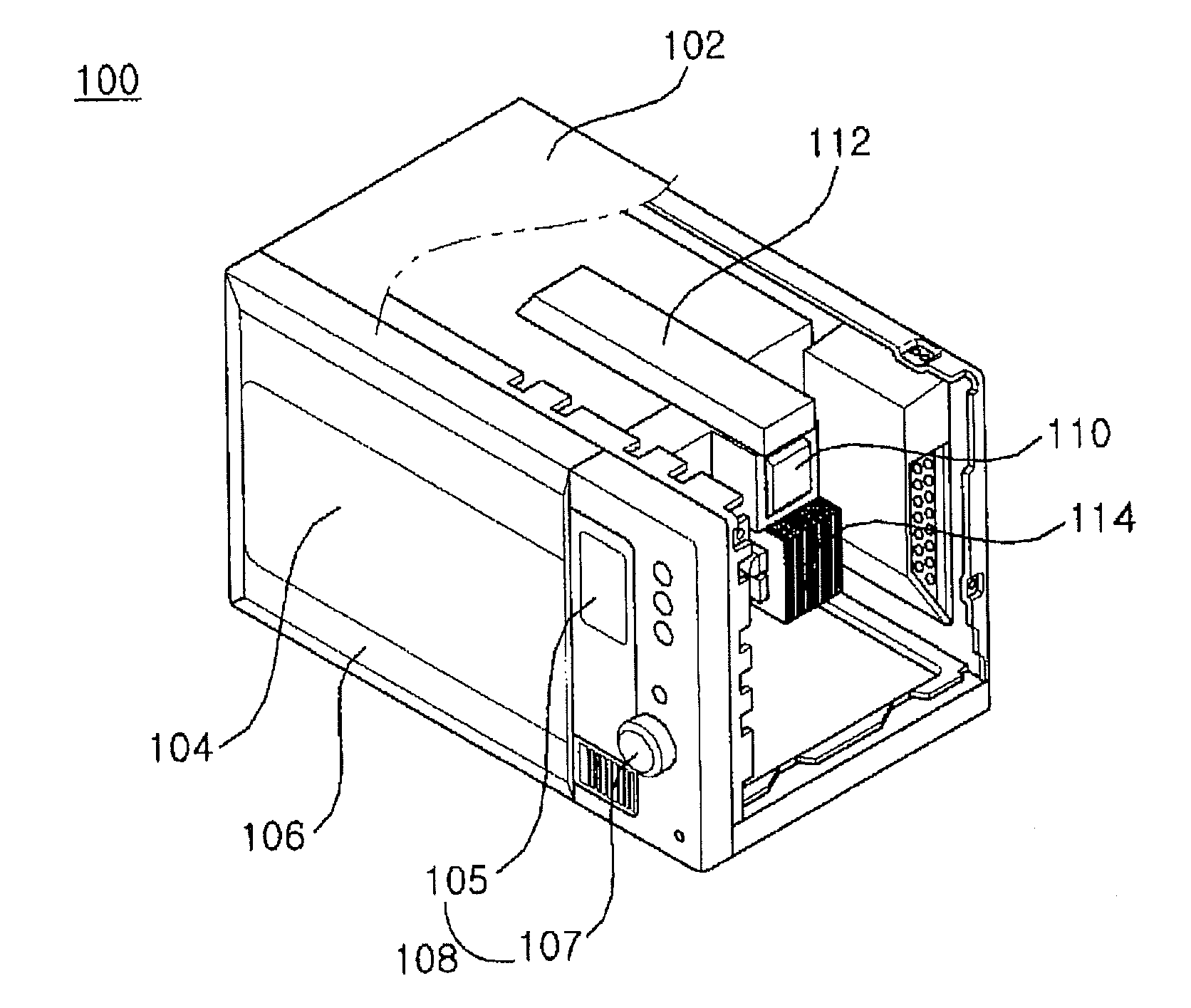

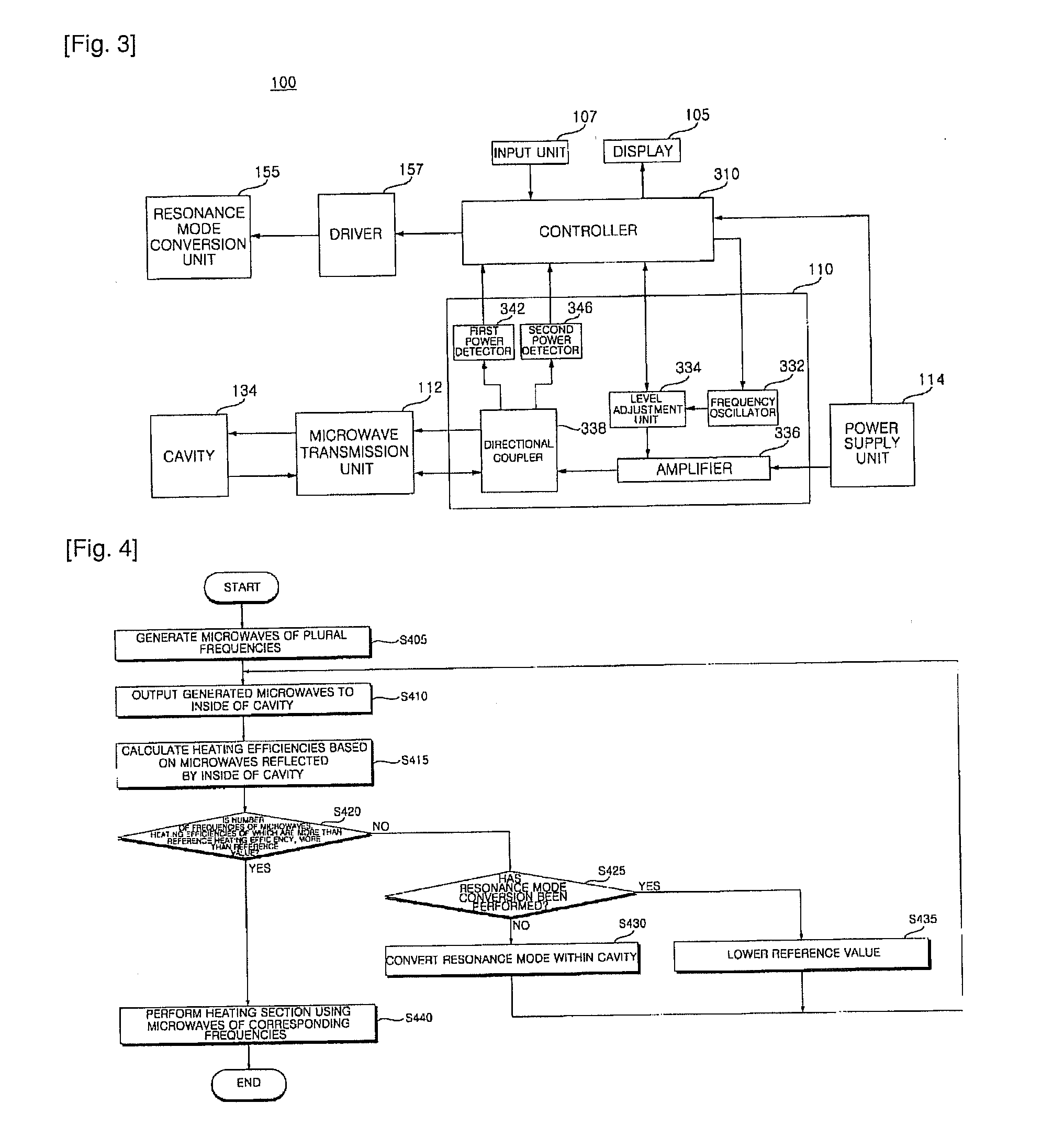

Cooking apparatus

InactiveUS20130206752A1Effectively enter heating sessionPerforming heatingMicrowave heatingDomestic cooking appliancesMicrowaveResonance

Provided herein are a cooking apparatus and an operating method thereof. The cooking apparatus includes a microwave generator to generate and output microwaves of a plurality of frequencies to heat an object within a cavity, a resonance mode conversion unit to convert a resonance mode by varying at least one of progressing direction, power or frequency of the microwaves output to the inside of the cavity, and a controller to operate the resonance mode conversion unit, if the number of frequencies of microwaves, the heating efficiencies of which are more than a reference heating efficiency, is below a reference value, based on heating efficiencies calculated according to microwaves reflected by the inside of the cavity from among the output microwaves. Thereby, operating efficiency of the cooking apparatus is improved.

Owner:LG ELECTRONICS INC

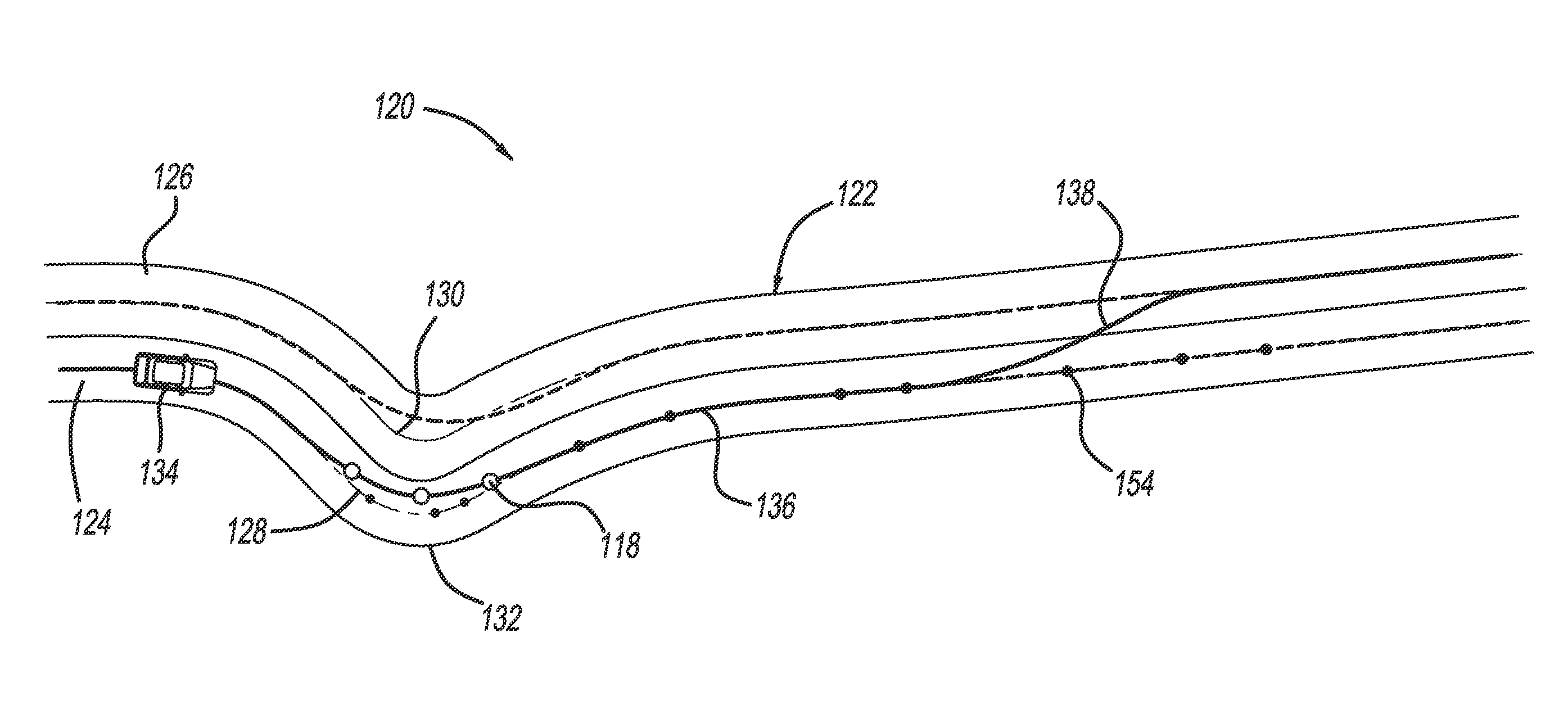

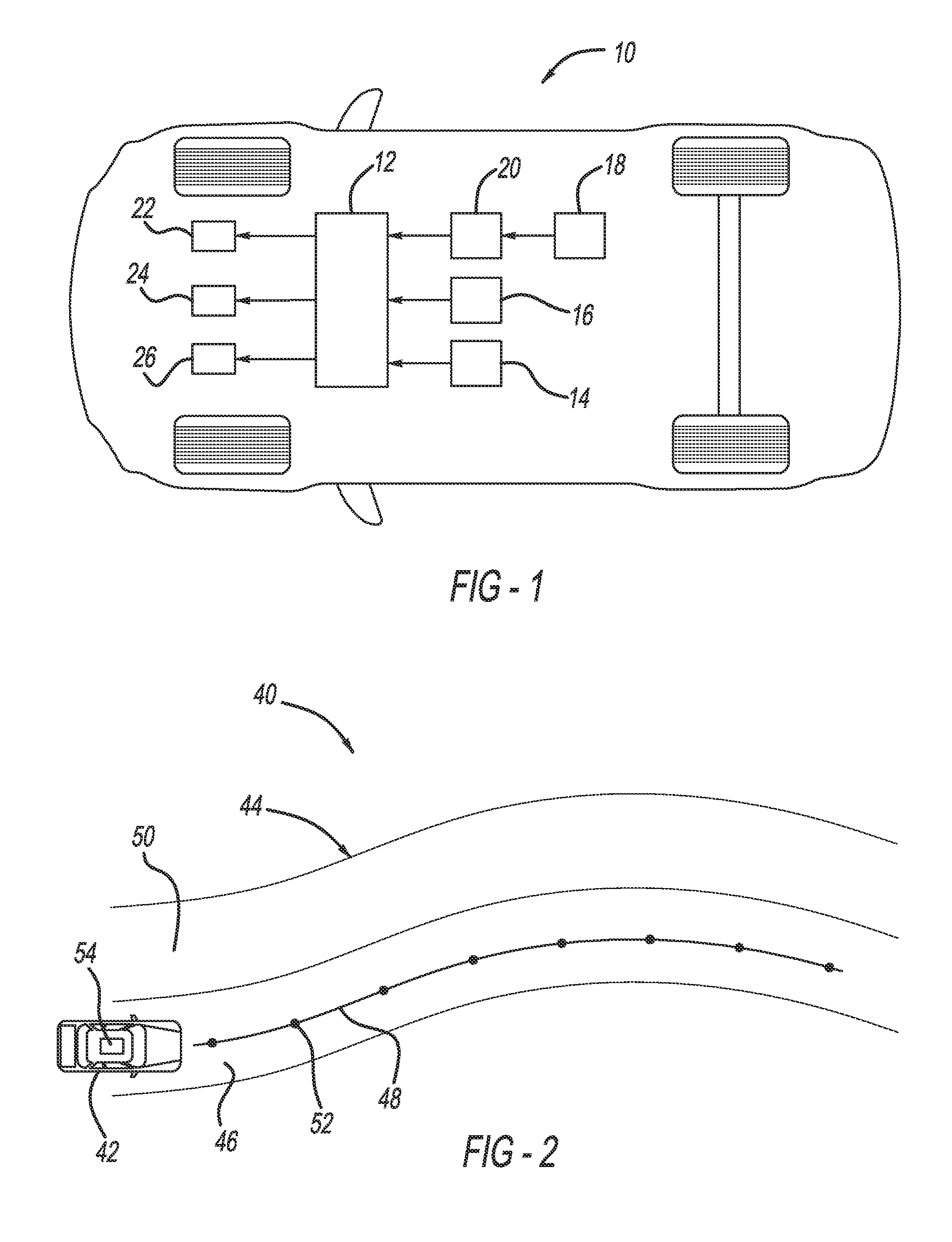

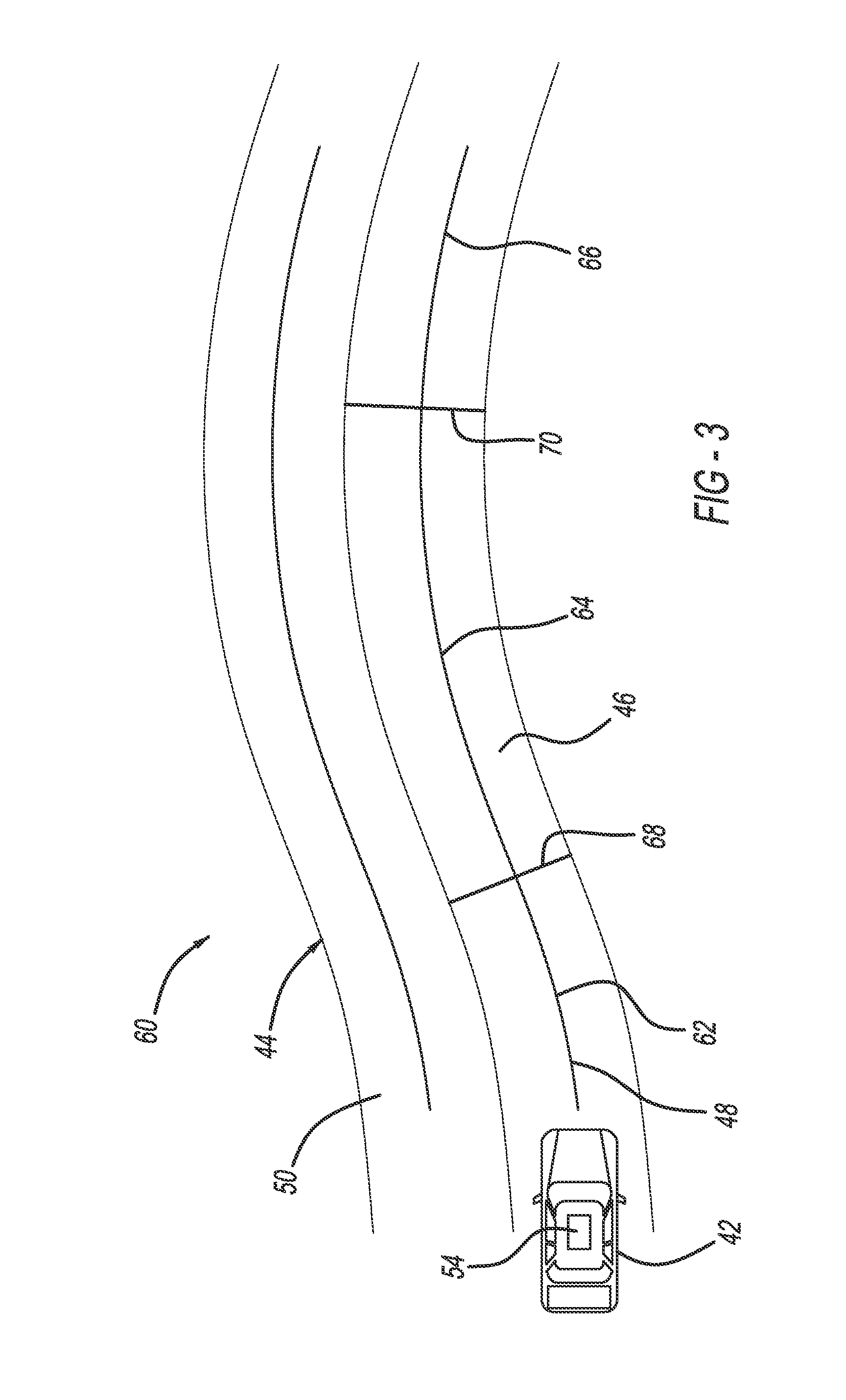

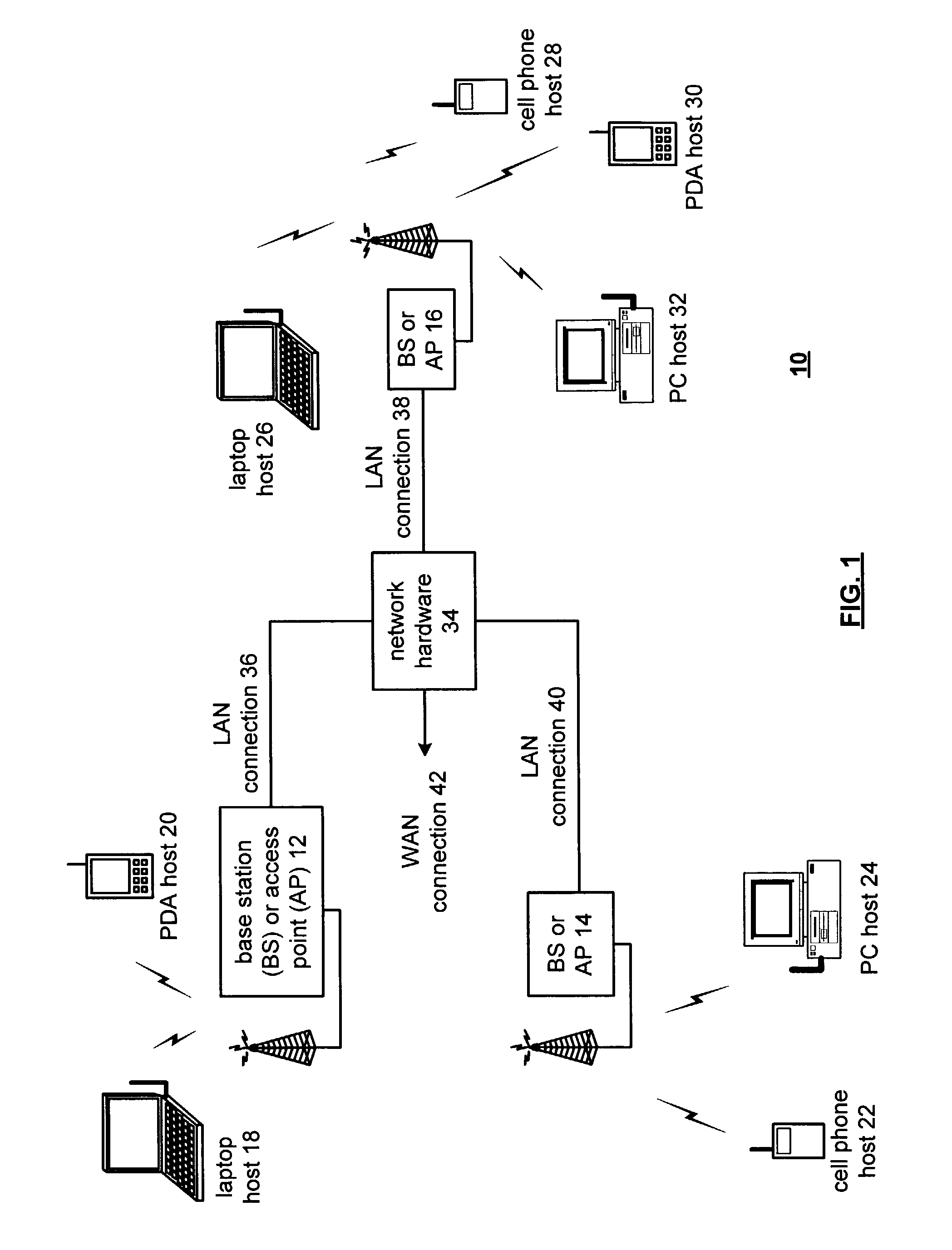

Unified motion planning algorithm for autonomous driving vehicle in obstacle avoidance maneuver

ActiveUS9457807B2Reduces turning requirementReduced referenceExternal condition input parametersEngineeringObstacle avoidance

A method for automated lane centering and / or lane changing purposes for a vehicle traveling on a roadway that employs roadway points from a map database to determine a reference vehicle path and sensors on the vehicle for detecting static and moving objects to adjust the reference path. The method includes reducing the curvature of the reference path to generate a reduced curvature reference path that reduces the turning requirements of the vehicle and setting the speed of the vehicle from posted roadway speeds from the map database. The method also includes providing multiple candidate vehicle paths and vehicle speeds to avoid the static and moving objects in front of the vehicle.

Owner:CARNEGIE MELLON UNIV +1

Self-cleaning flooring system

InactiveUS20120198778A1Reduced referenceDurable flooring systemRoof covering using slabs/sheetsRoof covering using tiles/slatesWaste managementSelf cleaning

A self-cleaning flooring system is provided that includes at least one module. The module comprises a drain pan, a plurality of discharge ports, and at least one side wall. The drain pan may have a ramp and a drain outlet. The ramp may slope downward towards the drain outlet. The discharge ports may be disposed about a periphery of the drain pan and may be directed towards the drain outlet to direct flushing fluid towards the drain outlet. The side wall may circumscribe a portion of the periphery of the drain pan and include a hollow passage and at least one fluid inlet. The fluid inlet may be in fluid communication with the hollow passage for delivering flushing fluid to the discharge ports.

Owner:SANI FLOOR INC

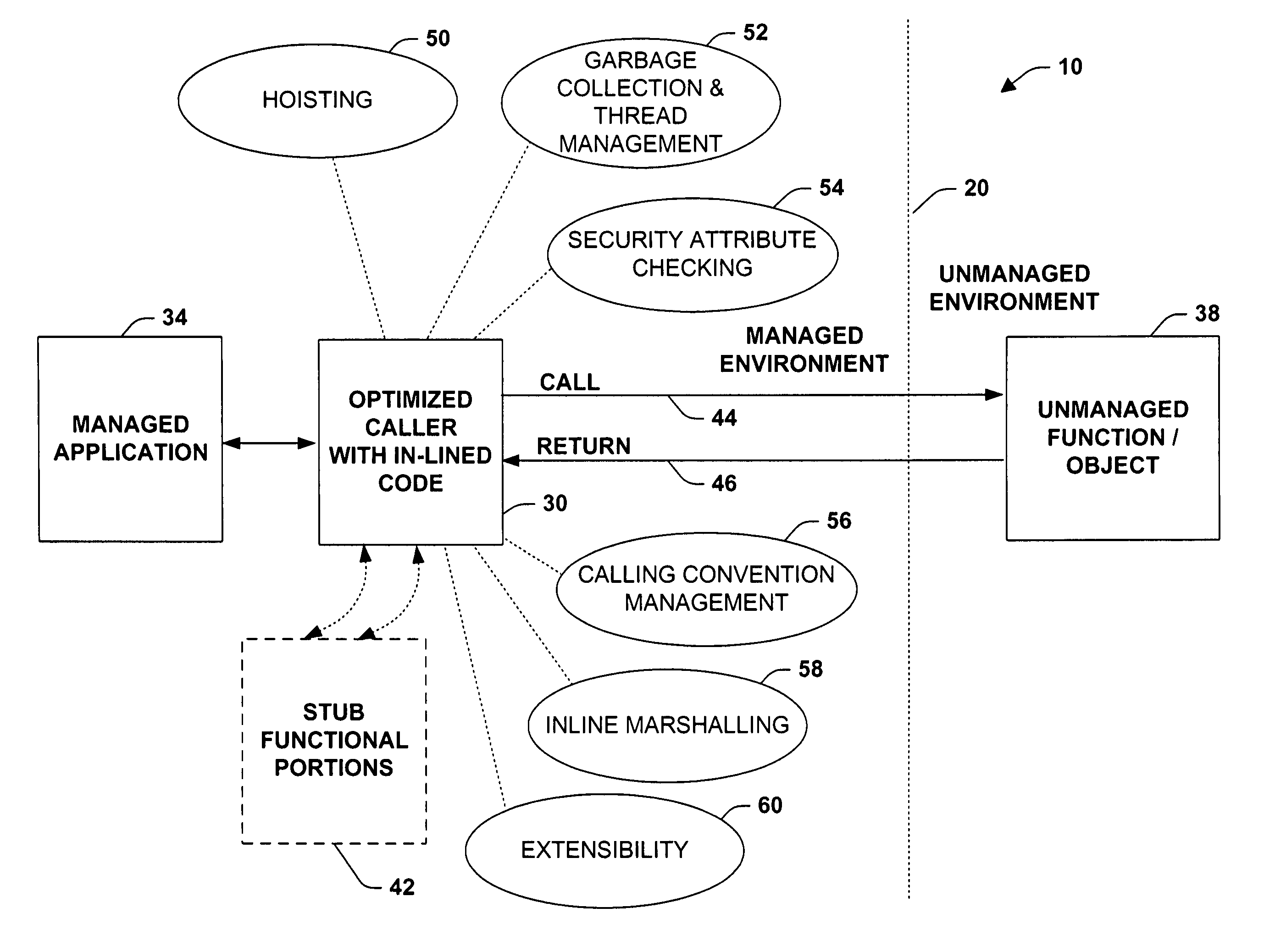

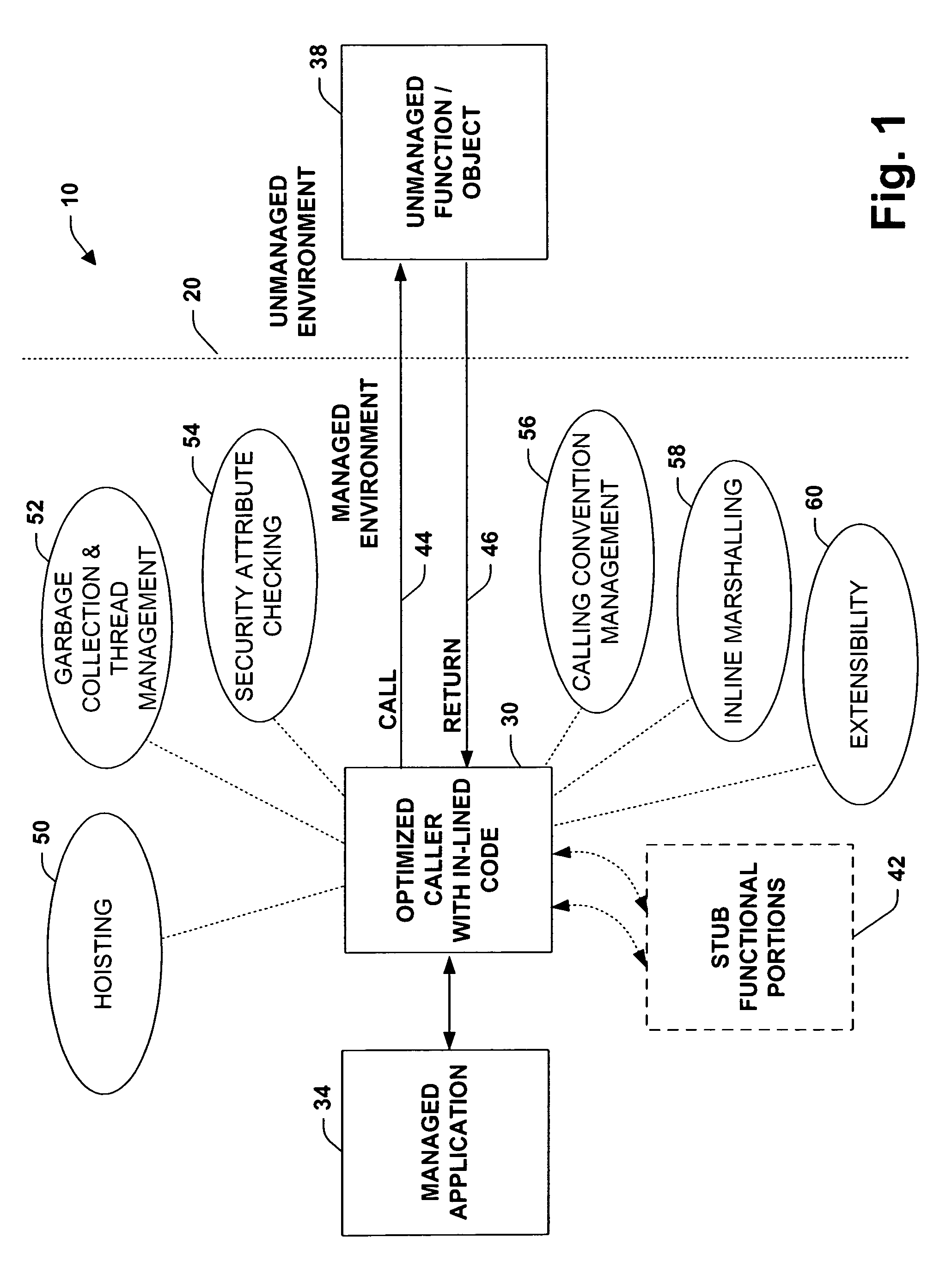

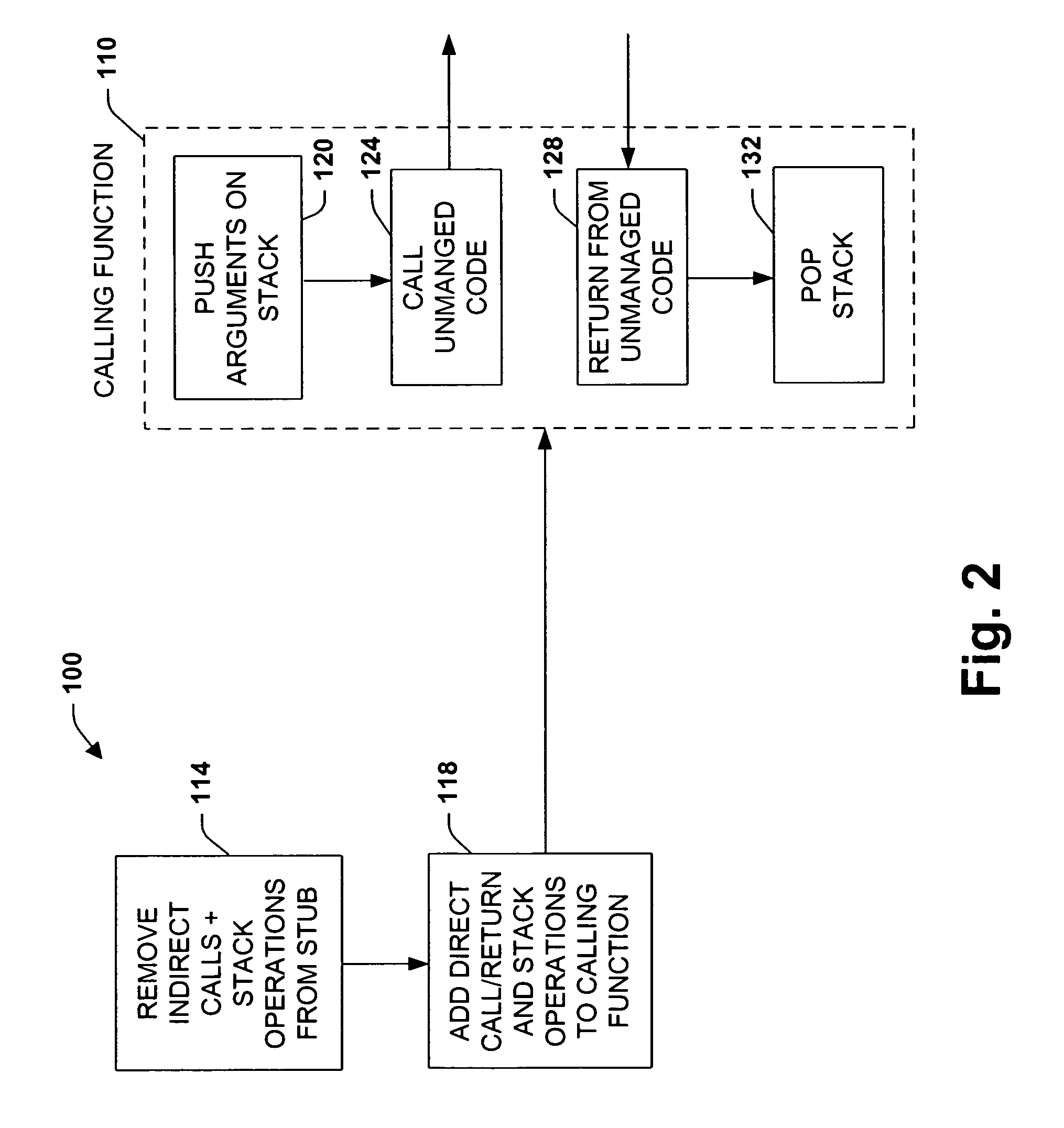

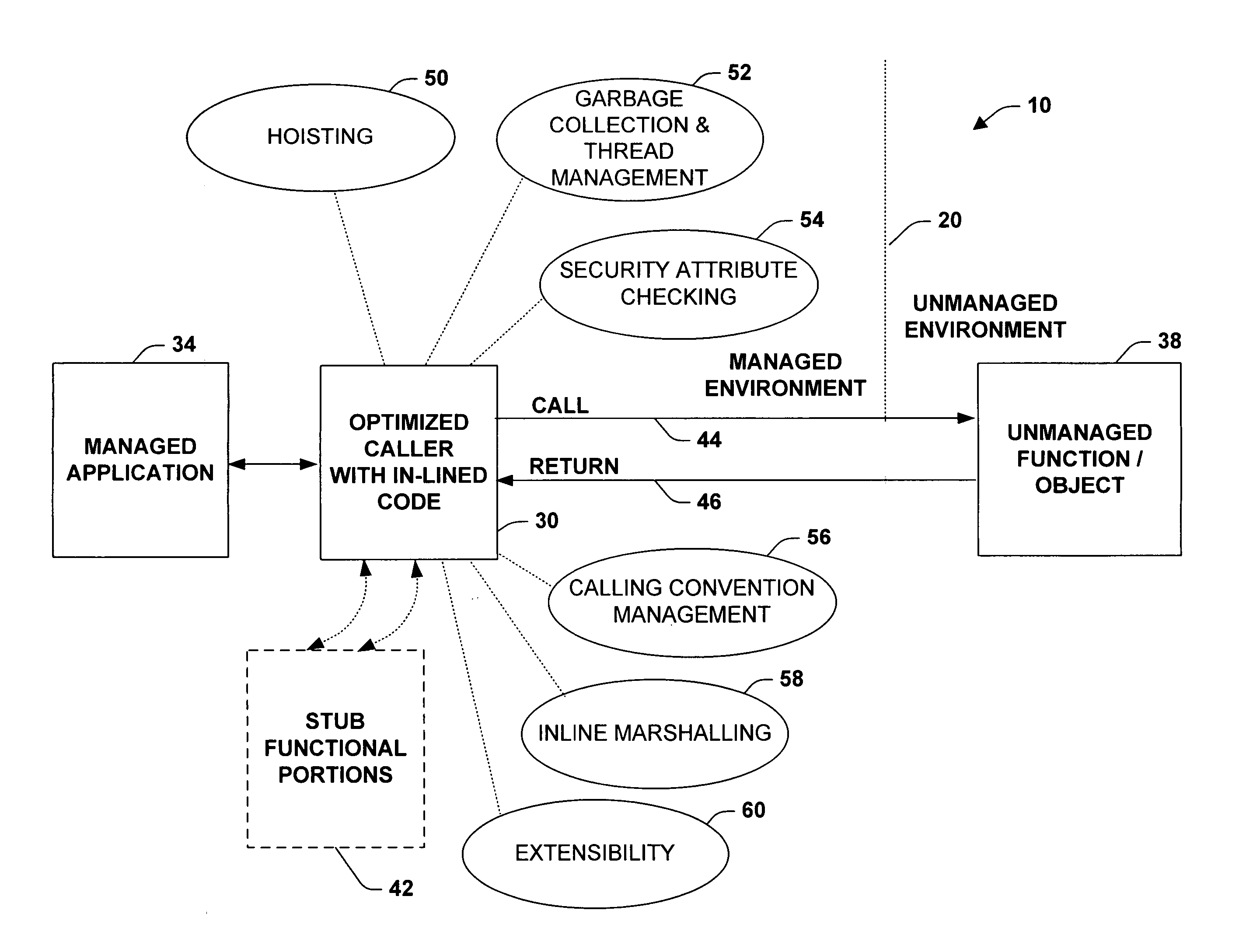

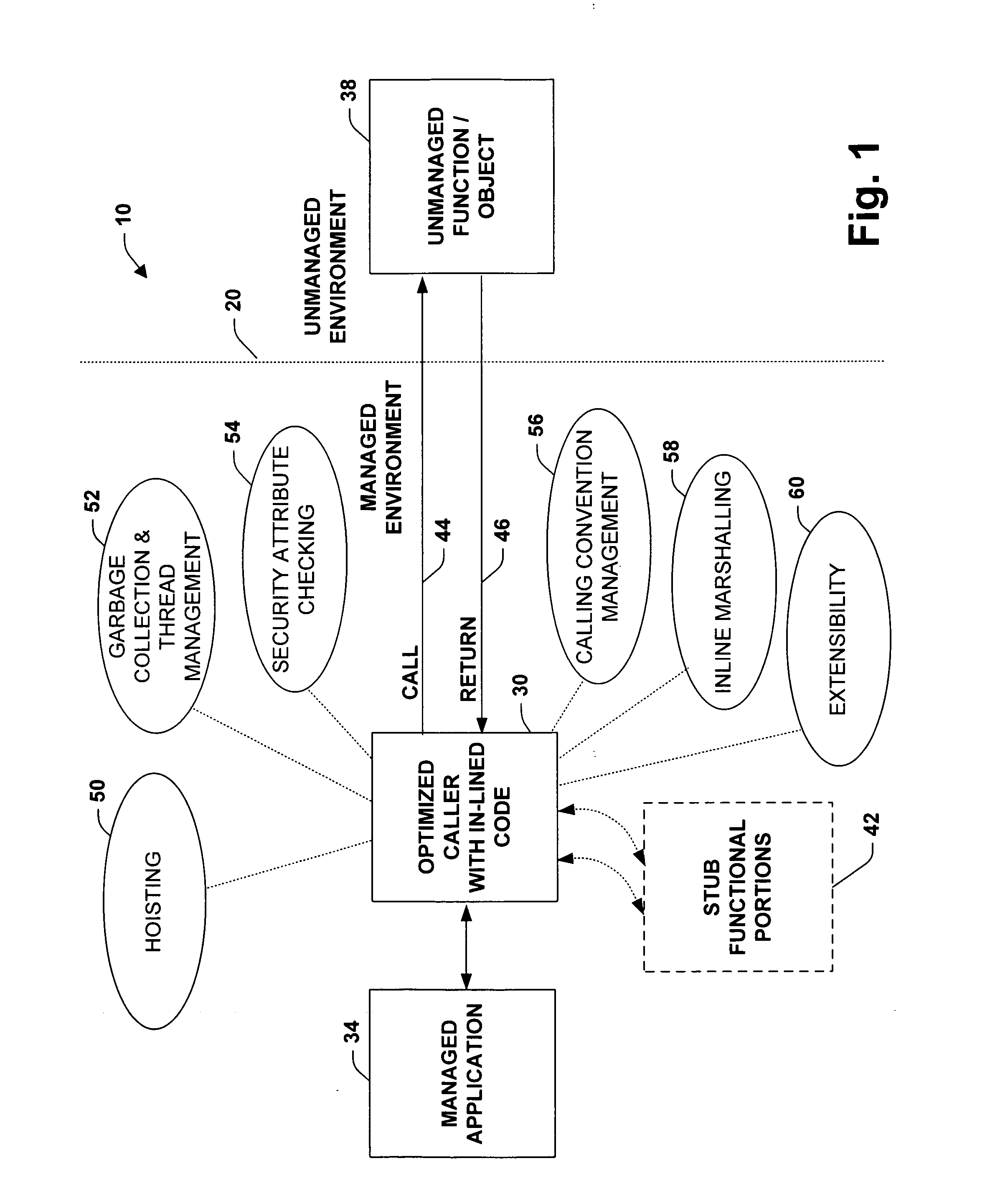

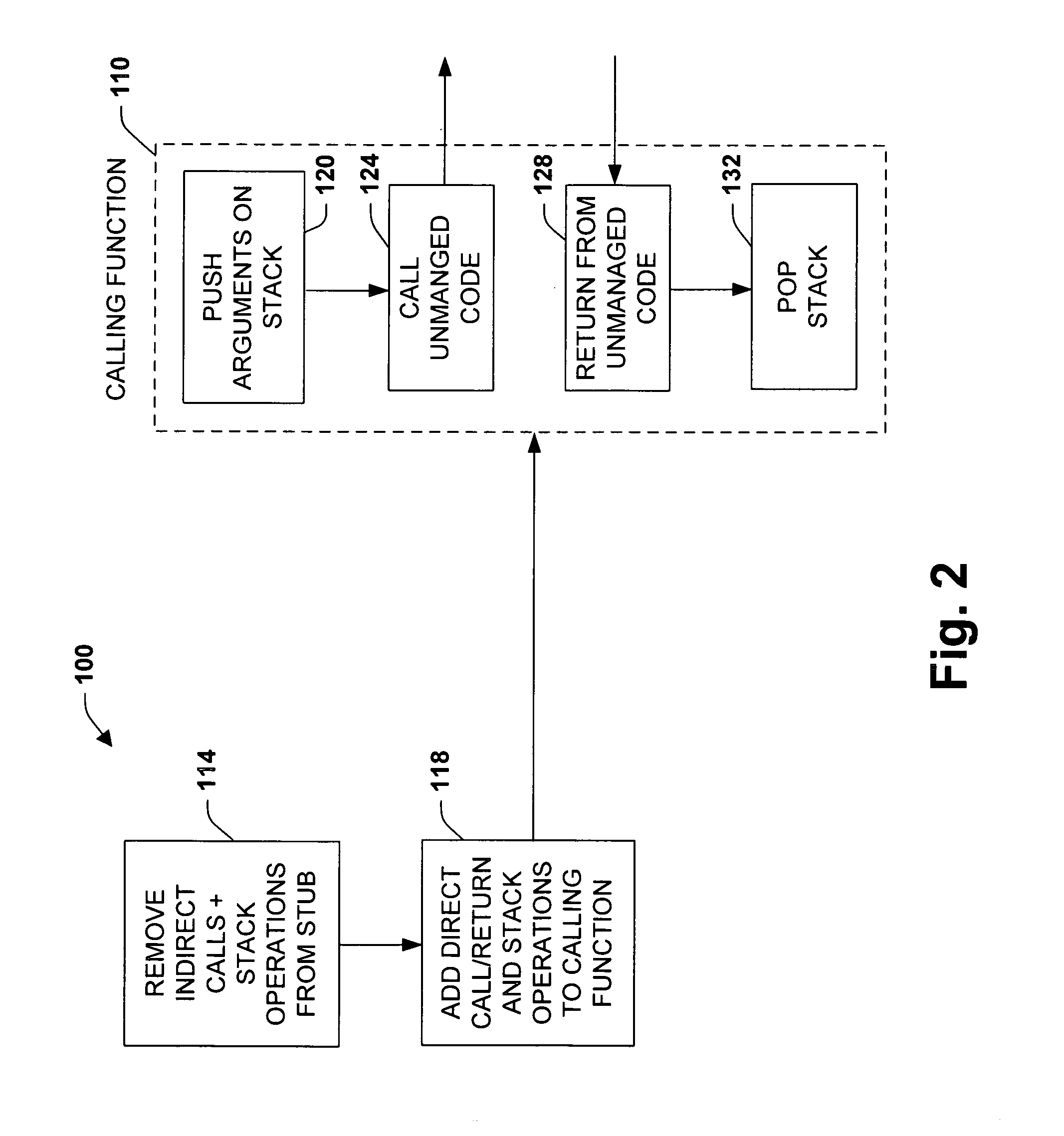

System and method providing inlined stub

InactiveUS6980997B1Facilitates communication and execution performanceReduce copyData processing applicationsSpecific program execution arrangementsRemote function callExtensibility

A system and method is provided to facilitate communications between object systems. A caller is provided having optimized in-lined functionality when initiating a remote function call between managed and unmanaged object systems, for example. The in-lined functionality includes utilizing direct calls and returns within a calling function. In this manner, pushing additional arguments onto an execution stack because of an external stub reference is mitigated. In addition, one or more code loops can be analyzed to enable stack markers to be “hoisted” and thus pushed a single time instead of each time the calling function executes. Other aspects of the optimized caller provide garbage collection and thread management, security attribute checking on outgoing calls, calling convention considerations, wherein arguments and return values are organized according to the convention utilized by the remote object system, and in-lined marshalling to provide enhanced performance over external stub code references. Code extensibility options can be included enabling functions to be generalized thereby insulating object systems from implementation details of the called functions.

Owner:MICROSOFT TECH LICENSING LLC

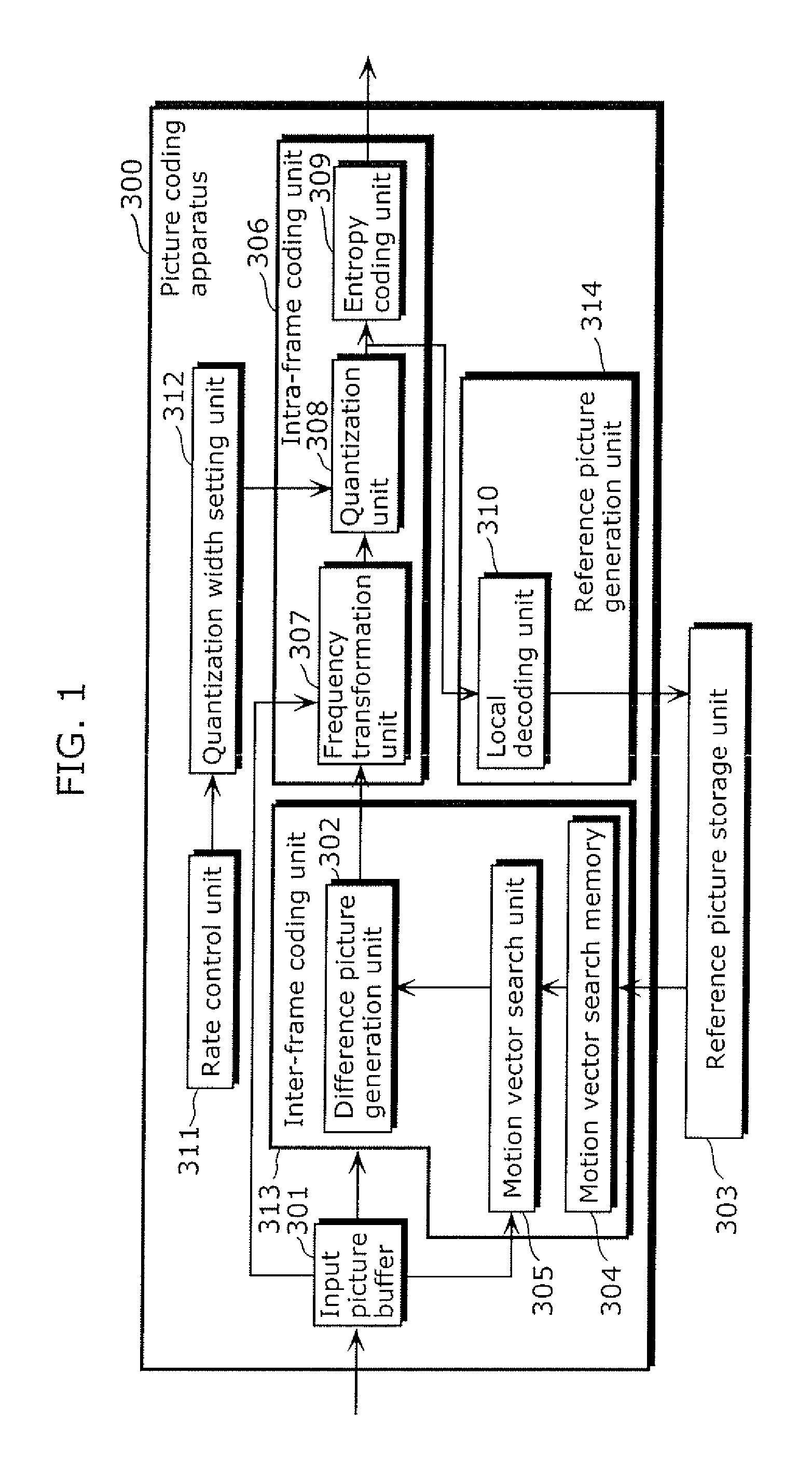

Moving picture coding apparatus, method and program

InactiveUS20070025443A1Reduce memory capacityIncrease probabilityTelevision system detailsPicture reproducers using cathode ray tubesComputer graphics (images)Interframe coding

A moving picture coding apparatus, for optimizing a handling of a reference picture with the view to reducing the data amount of the reference picture to be stored for use in motion prediction coding, which is configured of: a local decoding unit which obtains a reference picture by decoding a first code representing a first input picture; a reference picture reduction unit which obtains a reduced reference picture by reducing the size of the reference picture; a reference picture storage unit which stores the reduced reference picture; an inter-frame coding unit which generates a difference picture between a second input picture and a reconstructed reference picture obtained by expanding the size of the reduced reference picture obtained from the reference picture storage unit; and an intra-frame coding unit which codes the difference picture.

Owner:PANASONIC CORP

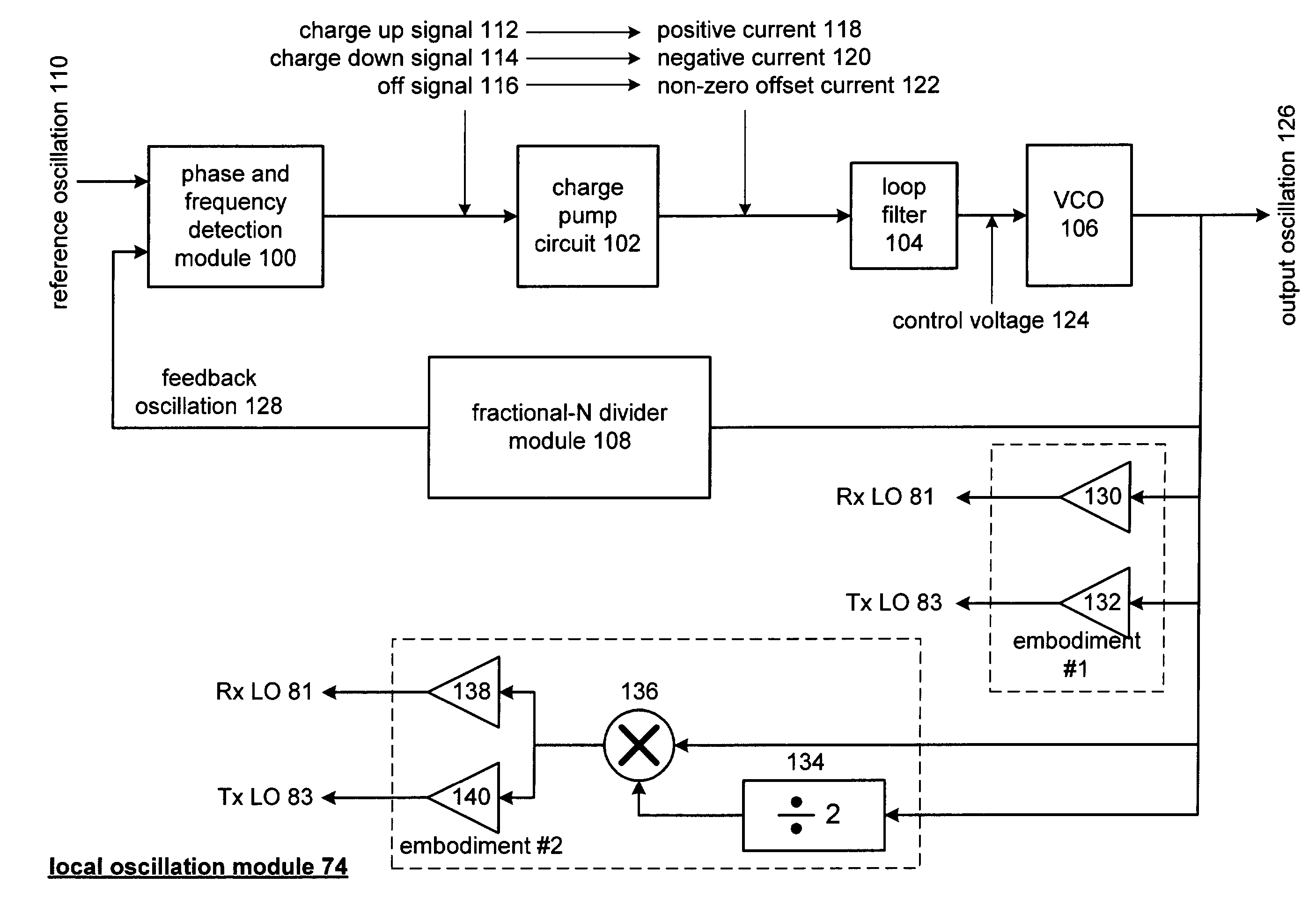

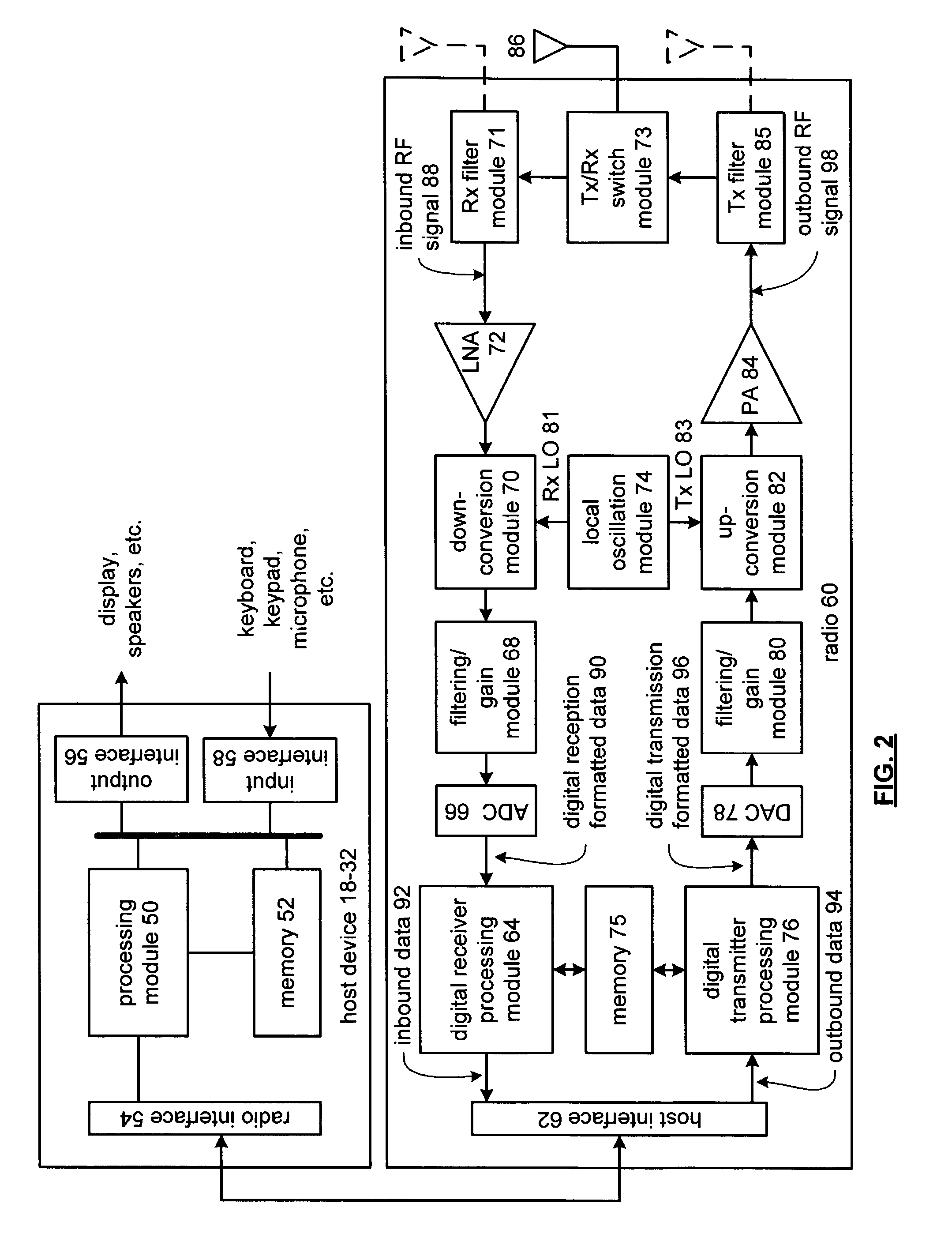

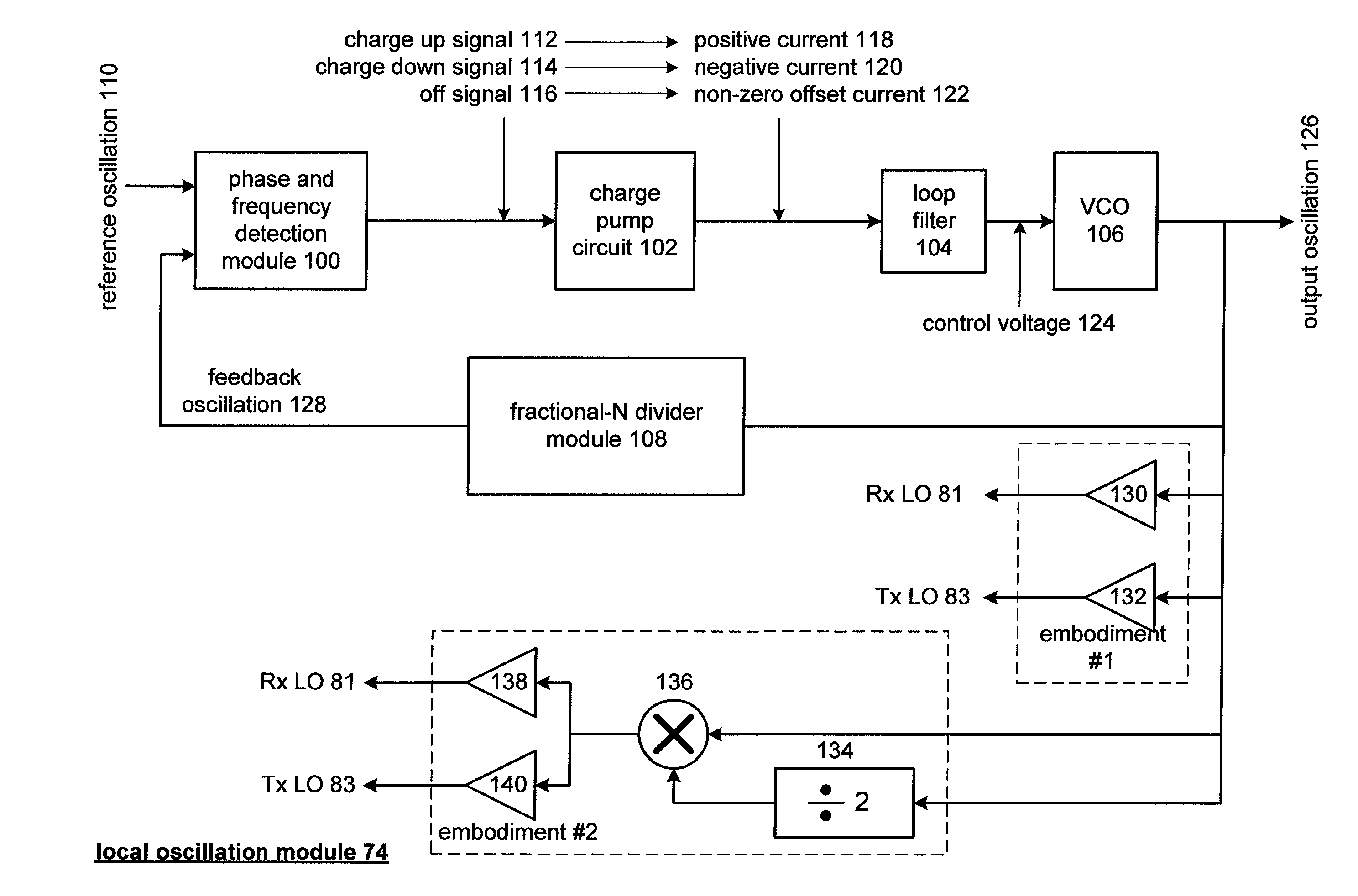

Linearized fractional-N synthesizer having a gated offset

ActiveUS6985708B2Good effectReduced referencePulse automatic controlNetwork topologiesLow-pass filterVoltage control

A linearized oscillation synthesizer includes a phase and frequency detection module, charge pump circuit, low pass filter, voltage control oscillator, and a feedback module. The phase and frequency detection module is operably coupled to produce a charge-up signal, a charge-down signal, and an off signal based on phase and / or frequency differences between a reference oscillation and a feedback oscillation. The reference oscillation is generated by a clock source such as a crystal oscillator while the divider module generates the feedback oscillation by dividing the output oscillation by a divider value. The charge pump circuit produces a positive current in response to the charge-up signal, a negative current in response to the charge-down signal and also produces a non-zero offset current. The non-zero offset current shifts the steady state operating condition, and other operating conditions, of the charge pump into a linear region of charge pump performance curve.

Owner:QUALCOMM INC

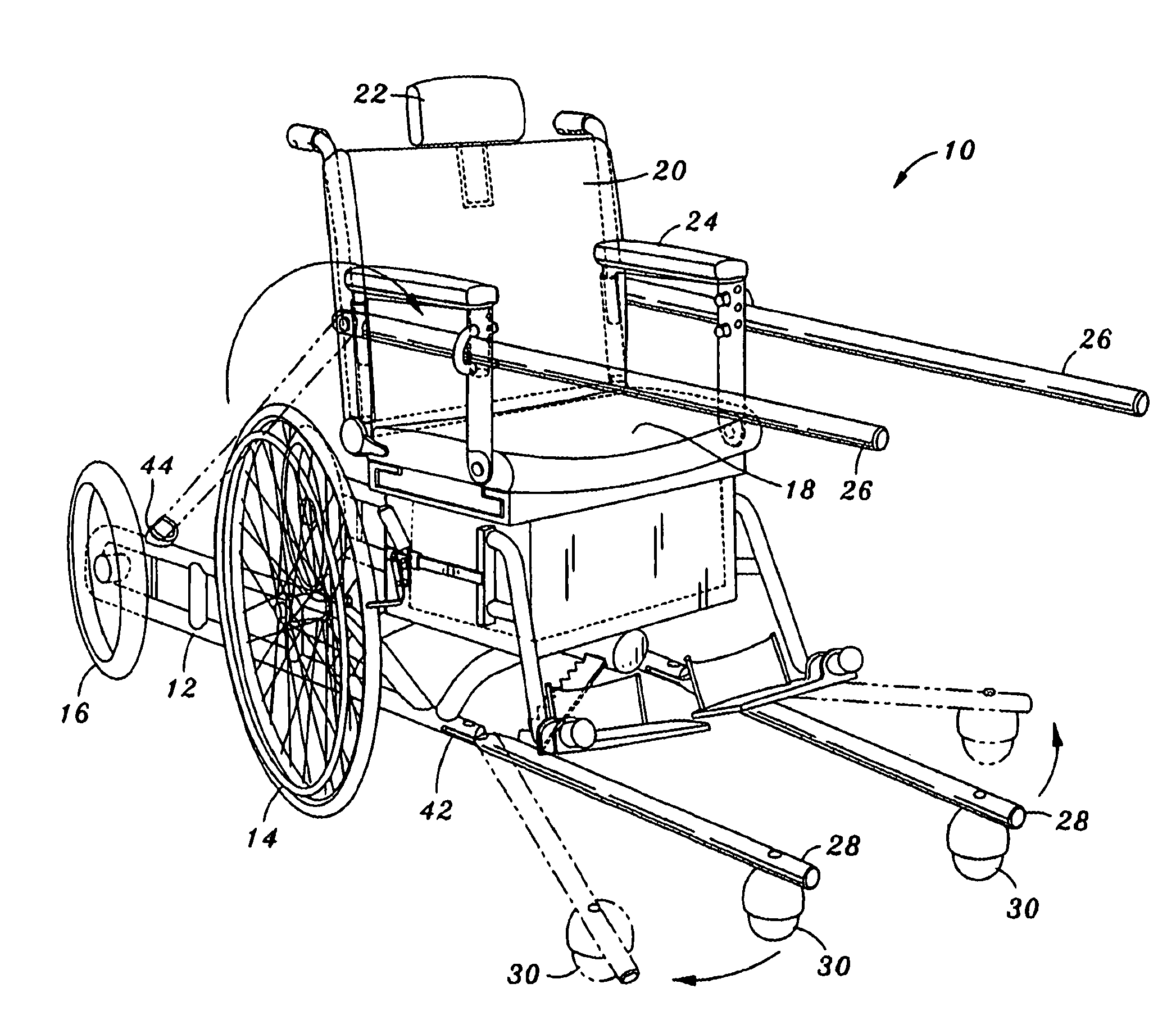

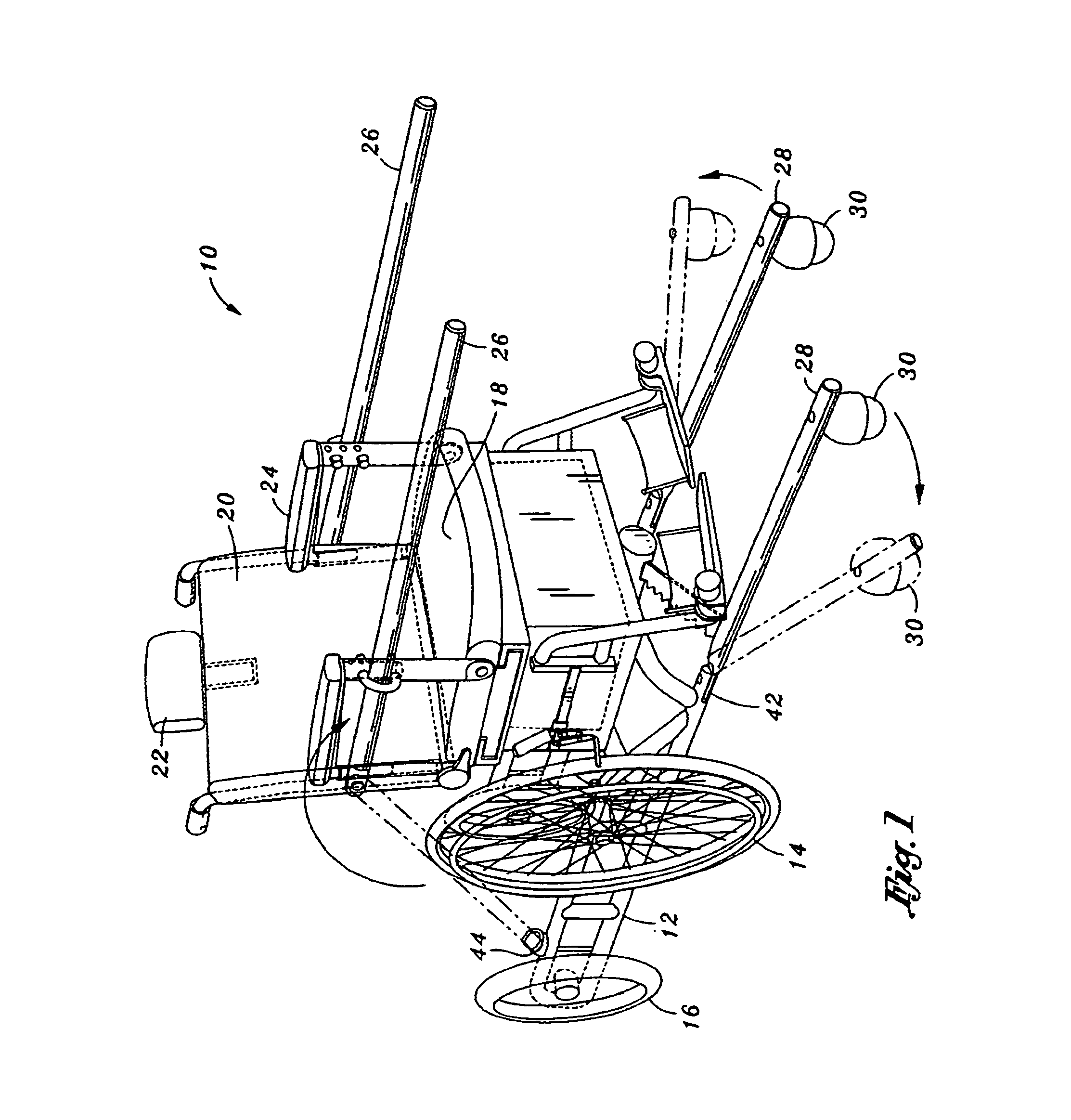

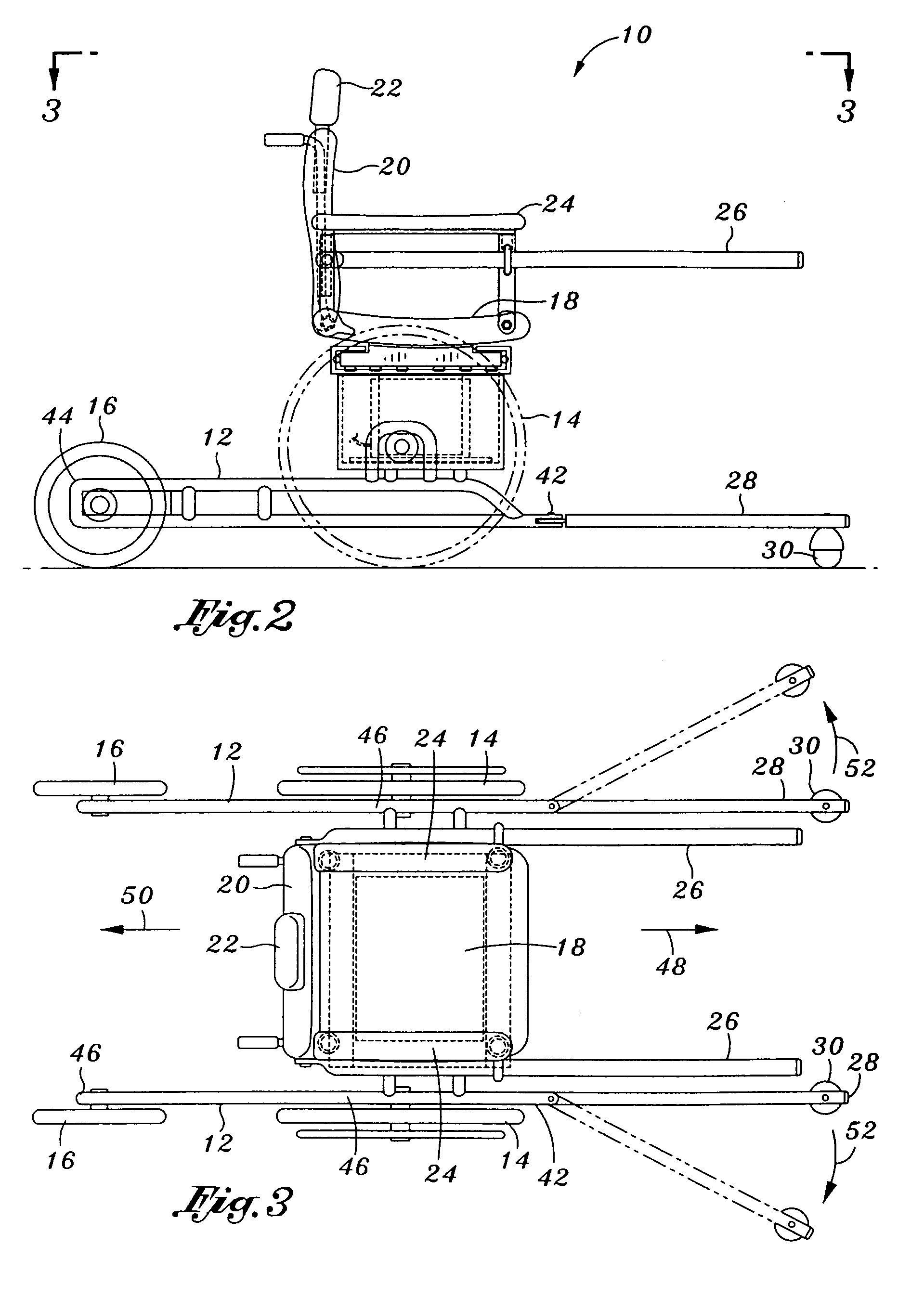

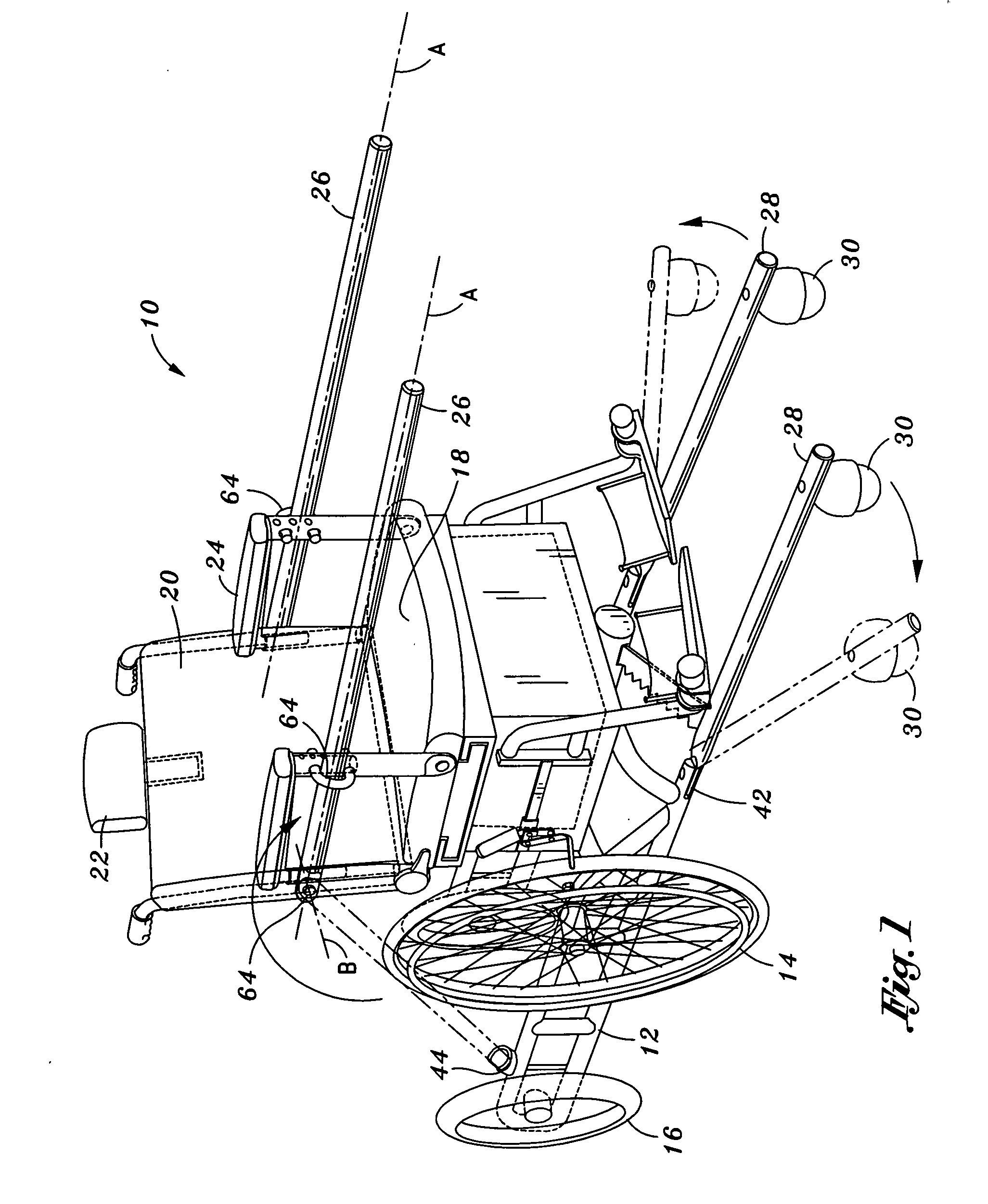

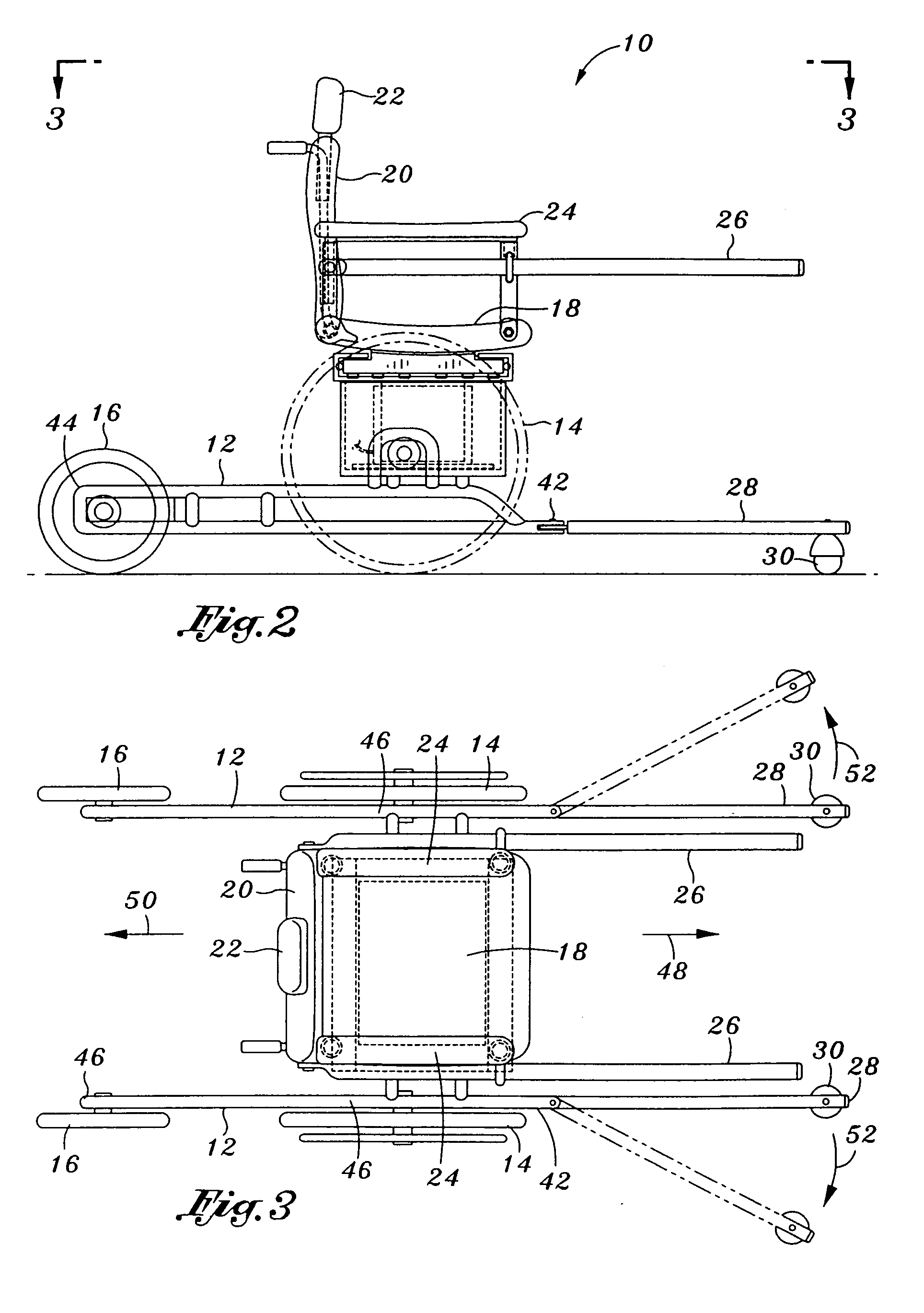

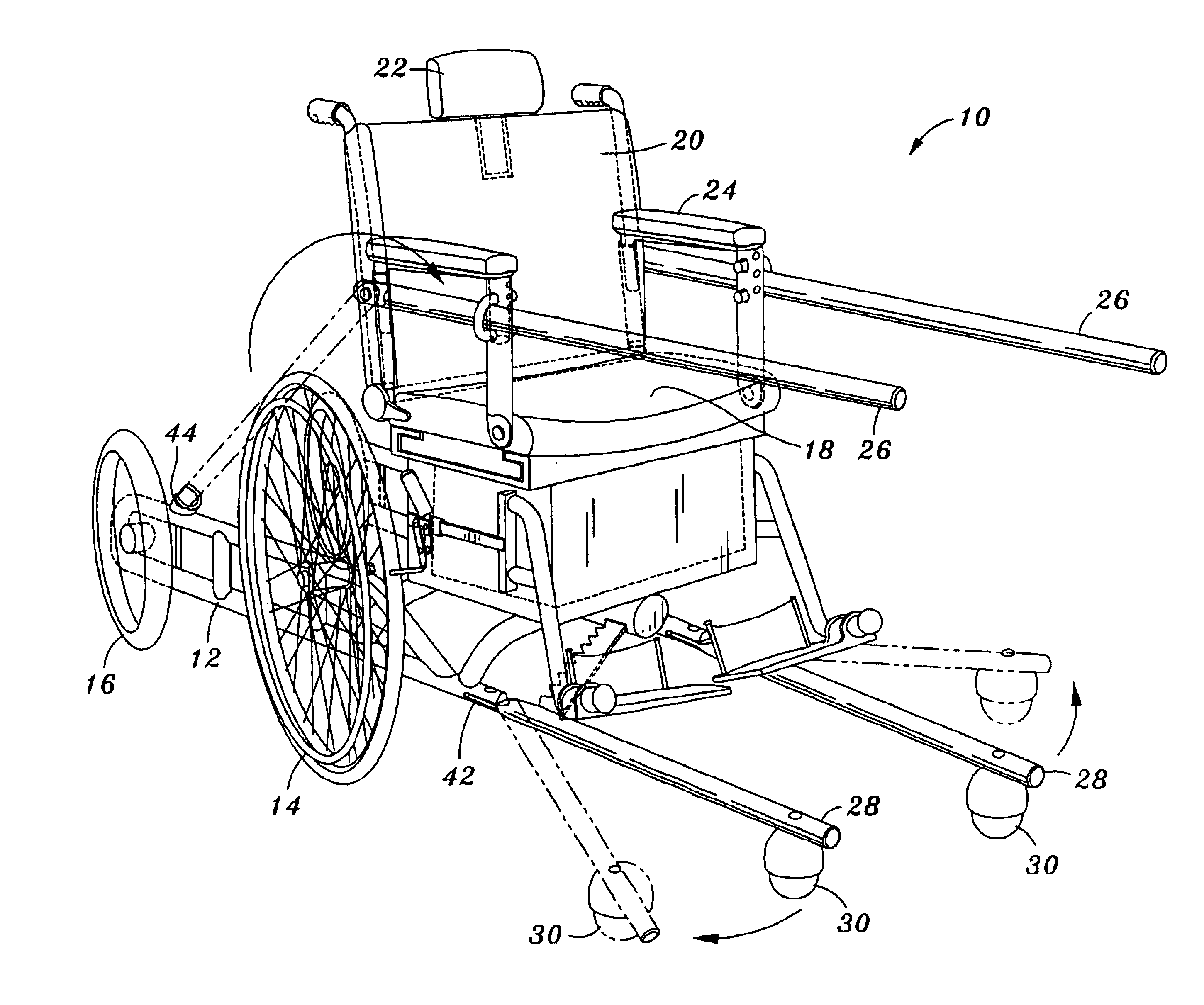

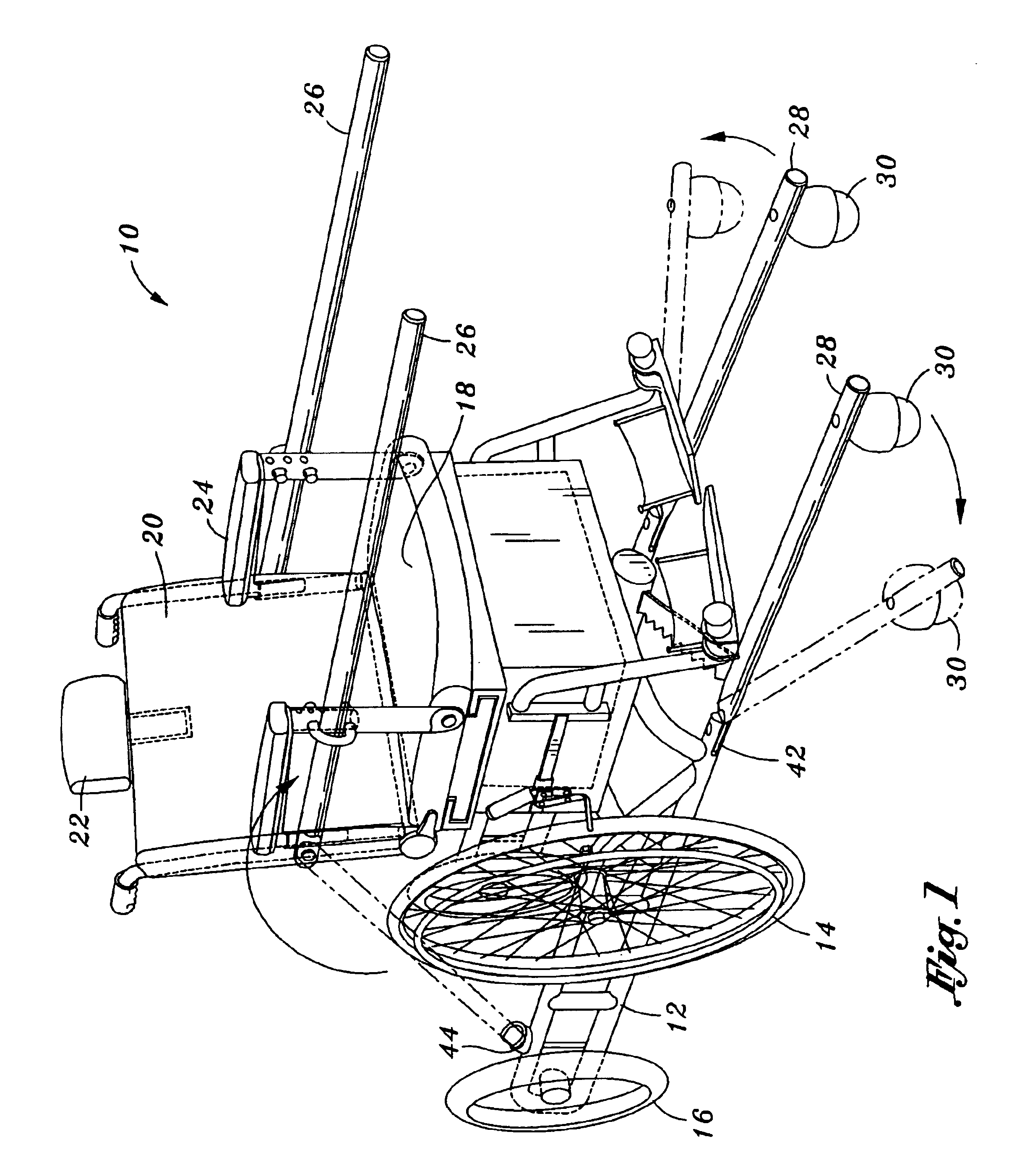

Transport chair for a patient

InactiveUS7040641B2Reduced referenceEasy transferVehicle seatsCycle safety equipmentsWheelchairHand held

Disclosed is a wheelchair for transporting a patient. The wheelchair comprises a support frame having a front, a rear, and opposing sides with the front and rear facing in respective forward and aft directions and the opposing sides facing in opposing lateral directions. The wheelchair further comprises at least two main wheels mounted on the support frame and a seat base disposed upon the support frame between the main wheels. The seat base is configured for selectively raising and lowering the patient between a first level and a second level with the aid of at least one security beam disposed adjacent one of the main wheels. The security beam may have a substantially vertical orientation and may be configured as a hand hold for steadying the patient when transferring onto and off of the seat base.

Owner:WING THOMAS W

System and method providing inlined stub

InactiveUS20060085460A1Facilitates communication and execution performanceReduce copyData processing applicationsDigital data processing detailsExtensibilityRemote function call

A system and method is provided to facilitate communications between object systems. A caller is provided having optimized in-lined functionality when initiating a remote function call between managed and unmanaged object systems, for example. The in-lined functionality includes utilizing direct calls and returns within a calling function. In this manner, pushing additional arguments onto an execution stack because of an external stub reference is mitigated. In addition, one or more code loops can be analyzed to enable stack markers to be “hoisted” and thus pushed a single time instead of each time the calling function executes. Other aspects of the optimized caller provide garbage collection and thread management, security attribute checking on outgoing calls, calling convention considerations, wherein arguments and return values are organized according to the convention utilized by the remote object system, and in-lined marshalling to provide enhanced performance over external stub code references. Code extensibility options can be included enabling functions to be generalized thereby insulating object systems from implementation details of the called functions.

Owner:MICROSOFT TECH LICENSING LLC

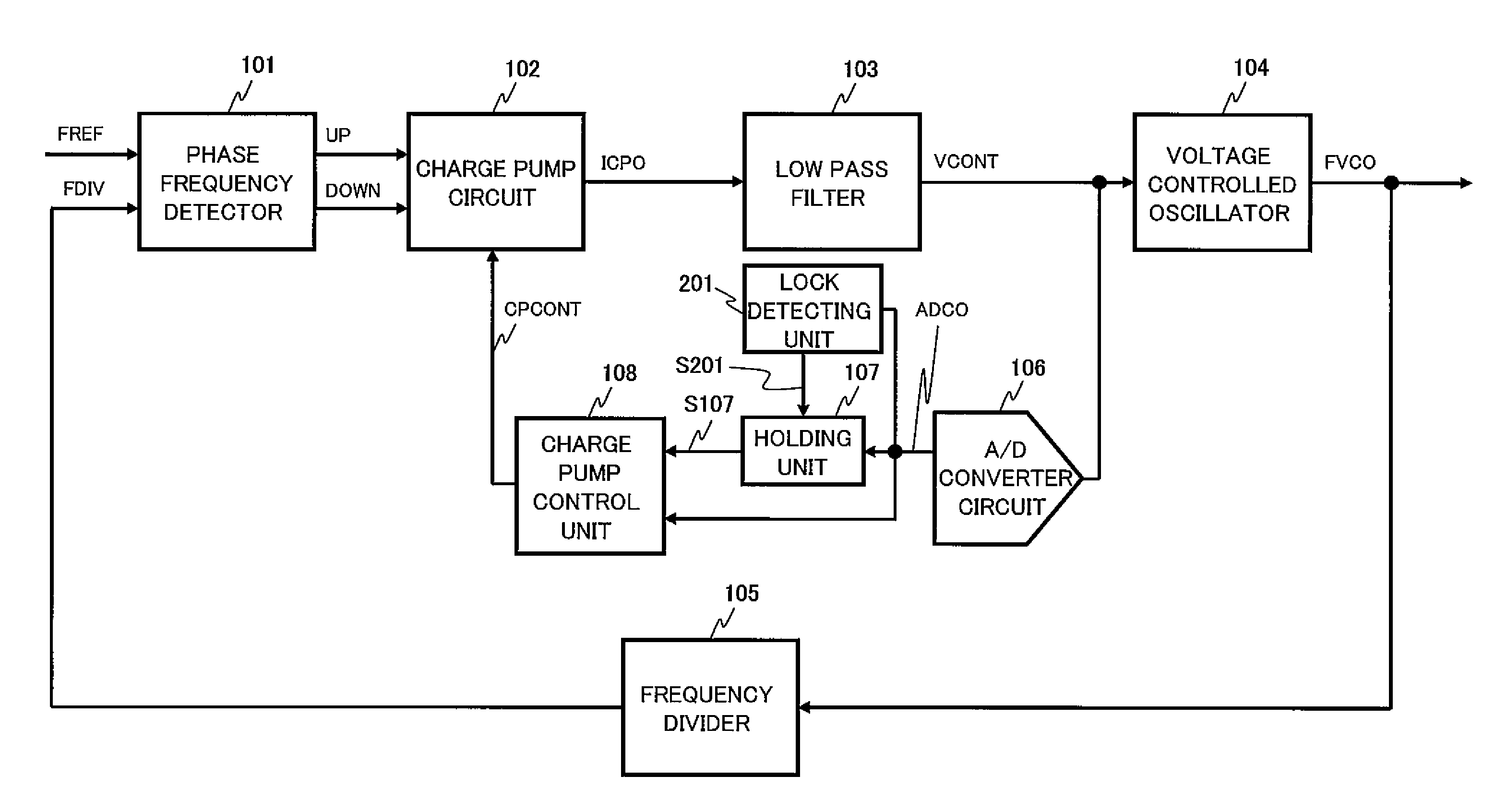

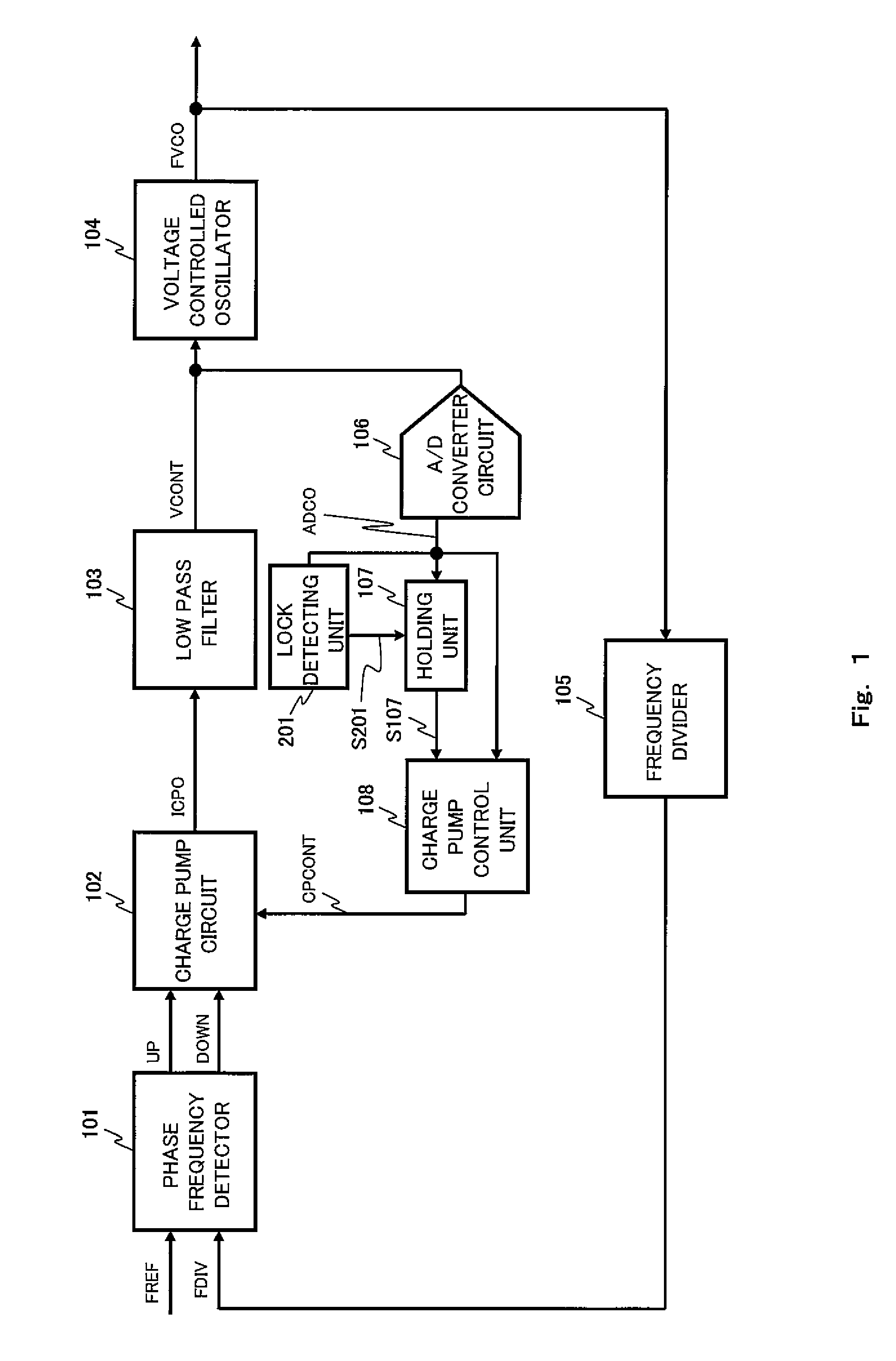

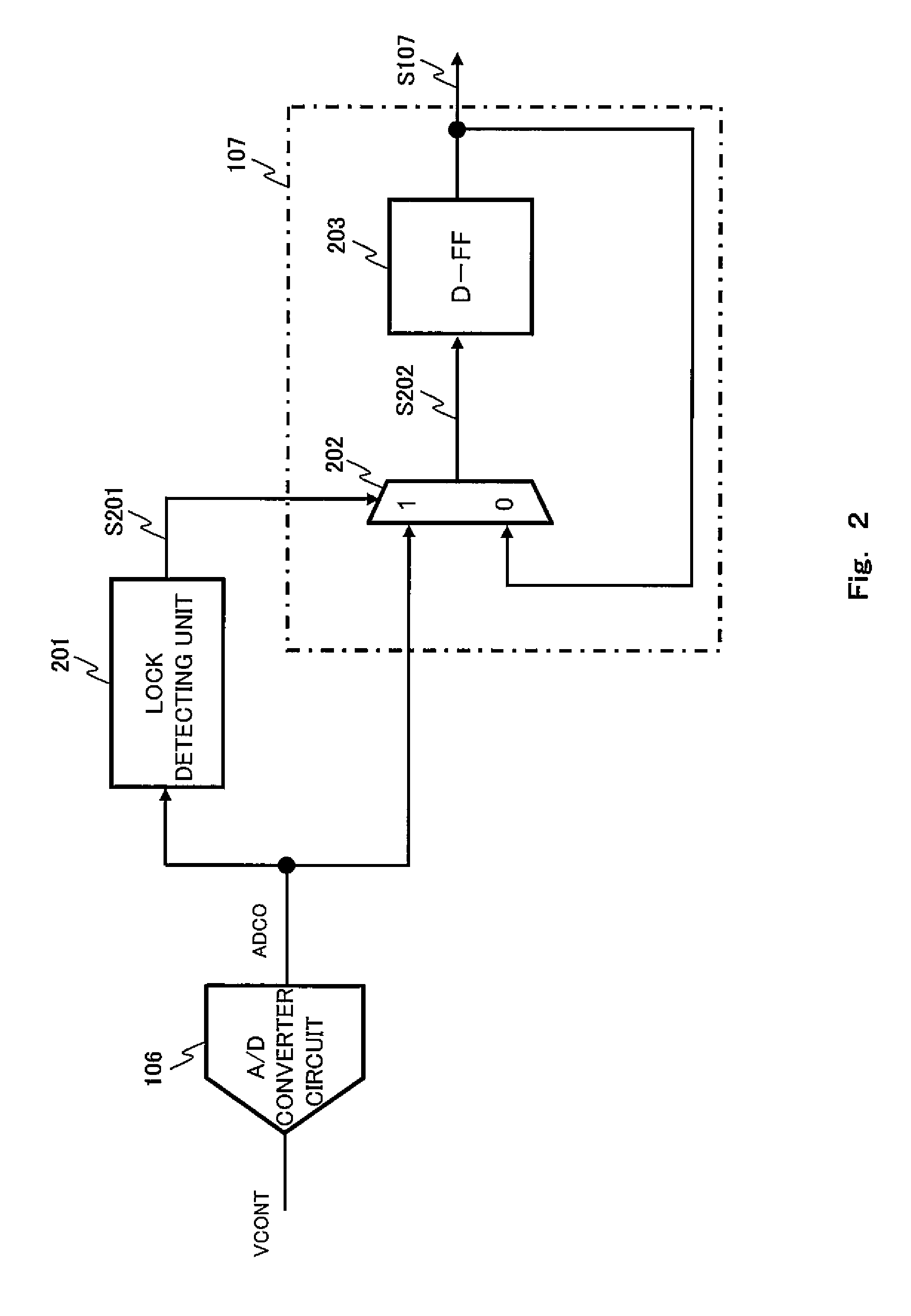

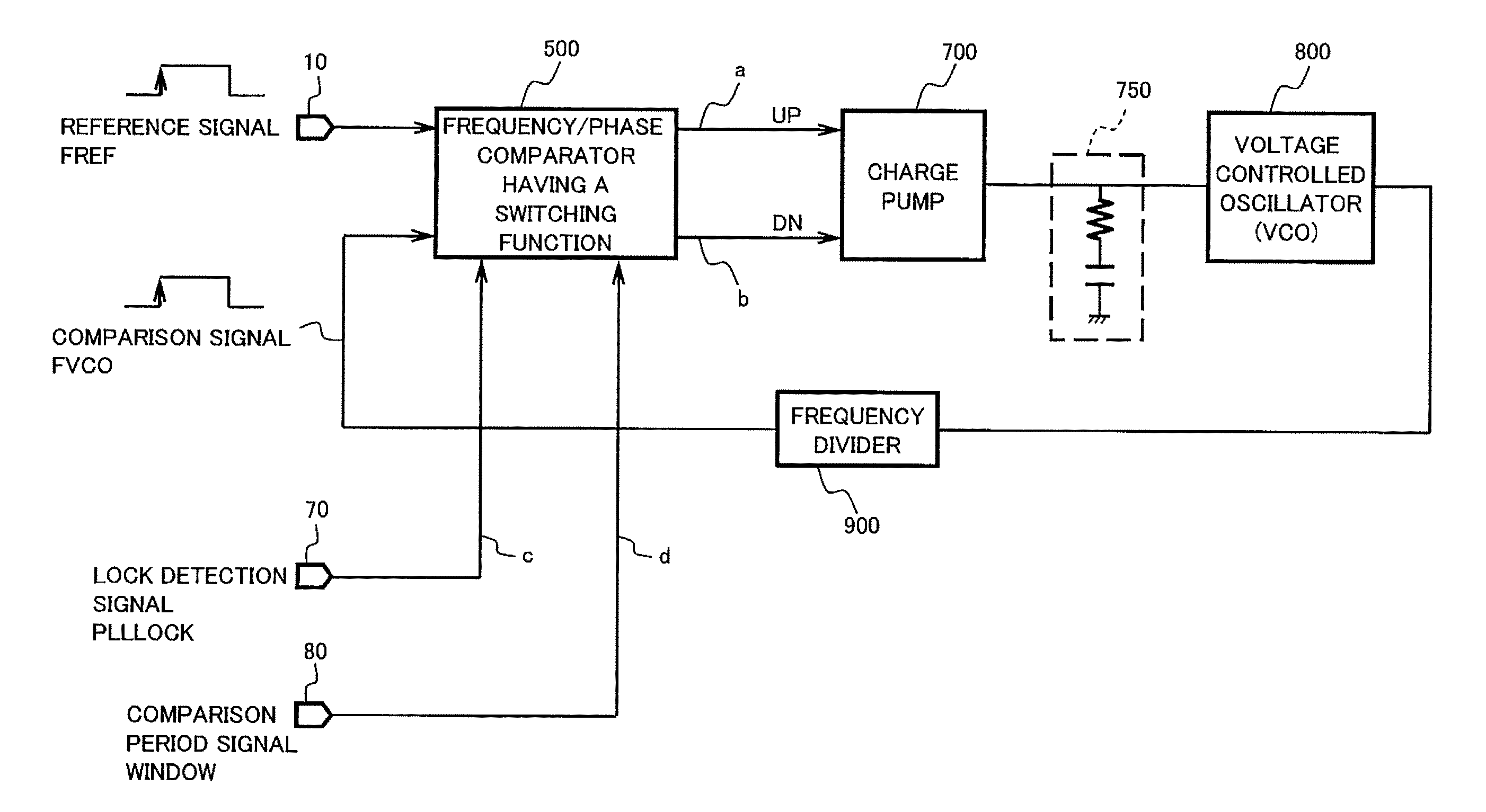

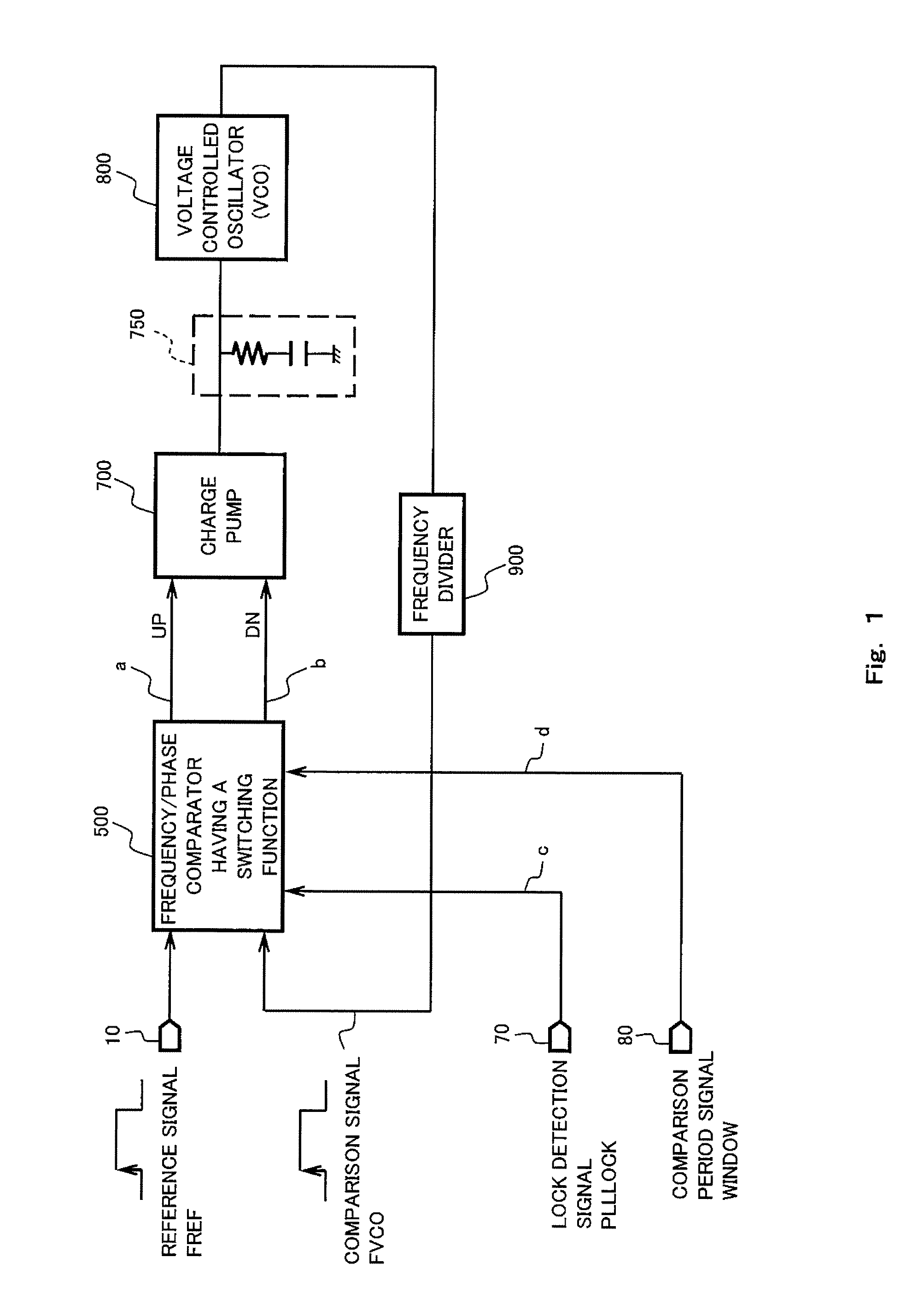

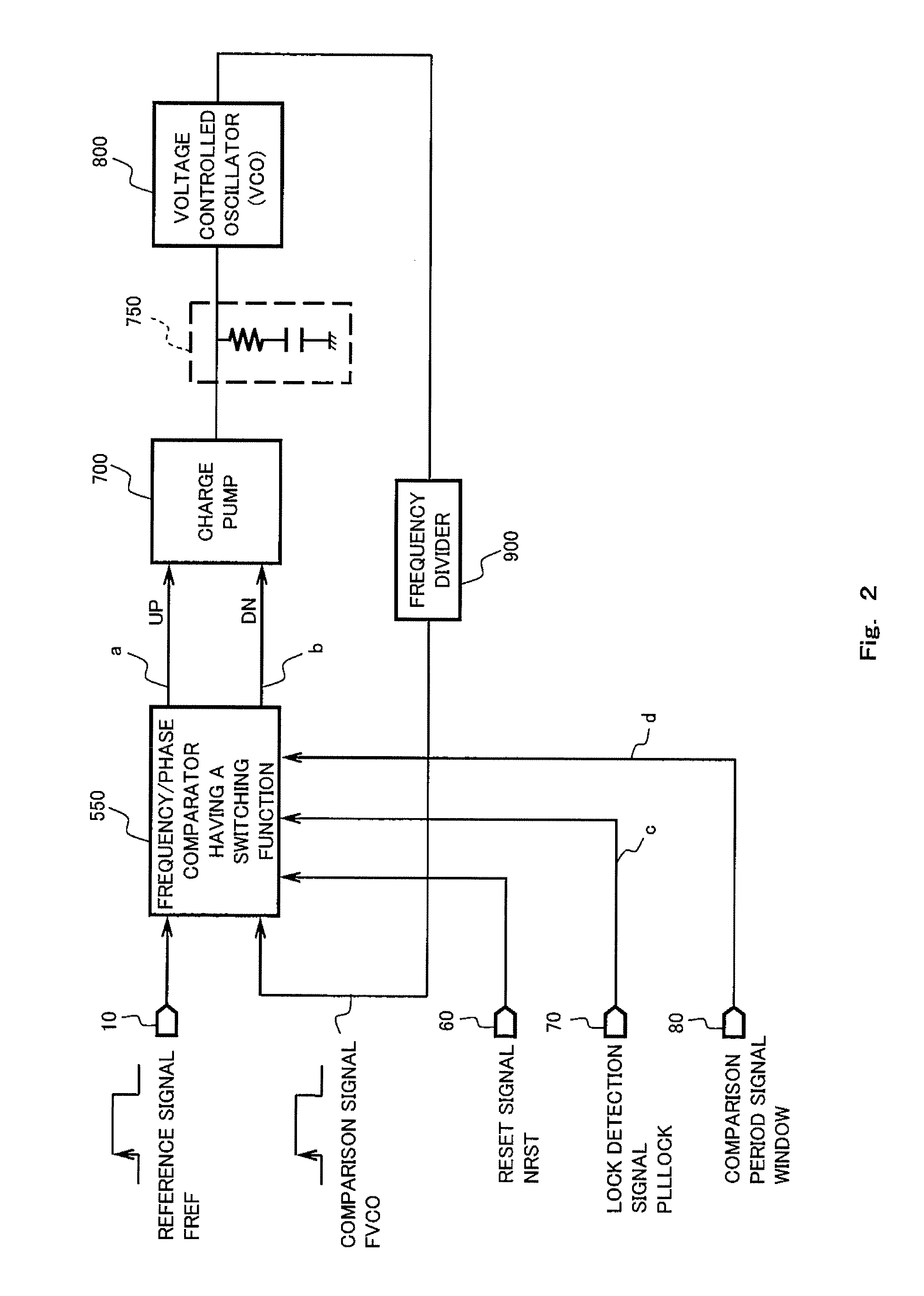

Pll circuit

InactiveUS20110304366A1Shorten lock timeReduced referencePulse automatic controlControl signalPhase difference

A PLL circuit comprises a phase frequency detector configured to output a phase frequency difference signal with a pulse duration according to a phase difference and a frequency difference between a reference clock signal and a feedback clock signal according to an output clock signal; a charge pump circuit configured to output a charge pump current which is an output current according to the phase frequency difference signal and reduce a charge pump current amount in accordance with a charge pump current amount control signal for reducing the charge pump current amount stepwisely; and a lock detecting unit configured to detect whether or not the feedback clock signal is locked to the reference clock signal and output a lock detection signal when detecting a lock of the reference clock signal and the feedback clock signal

Owner:PANASONIC CORP

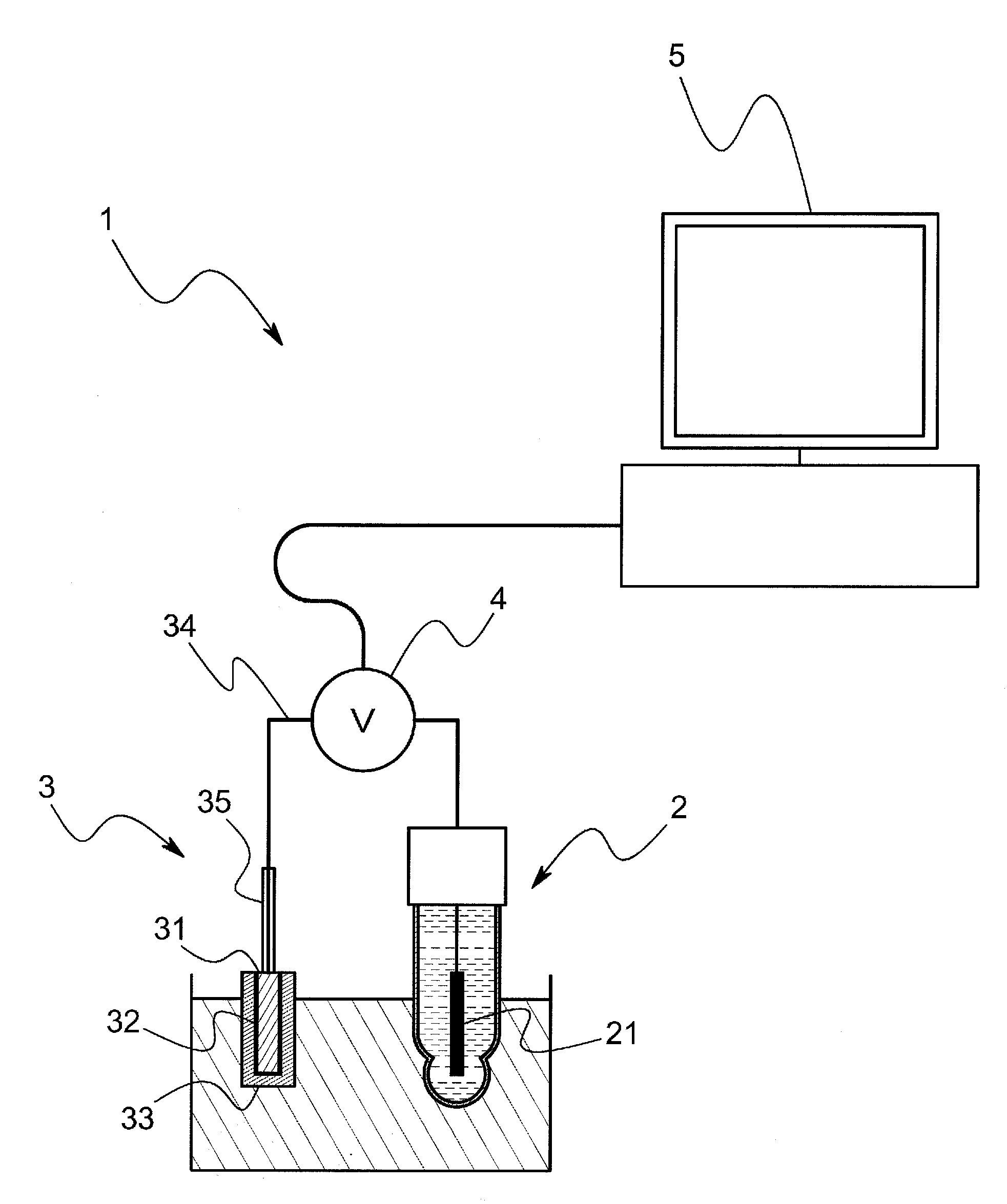

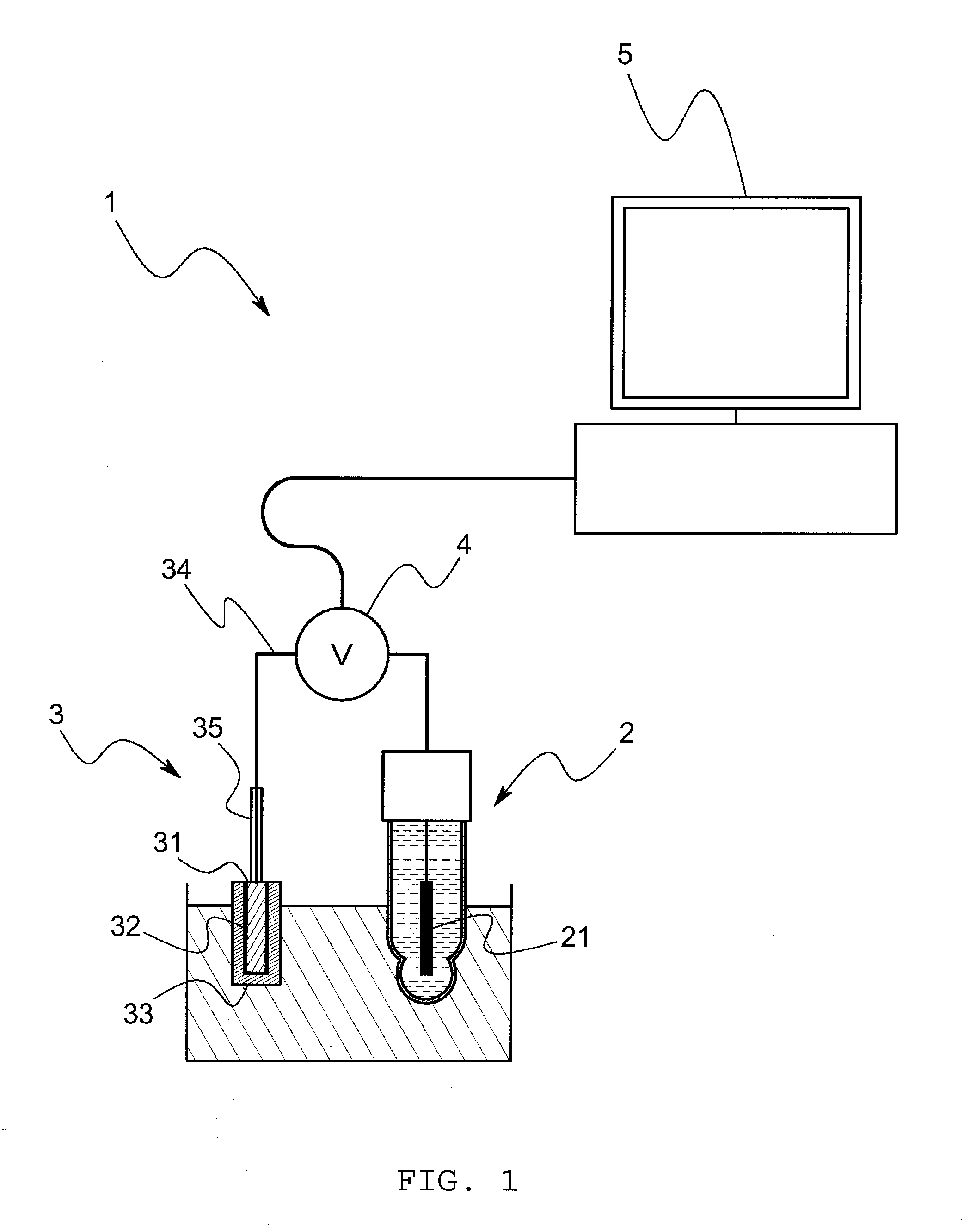

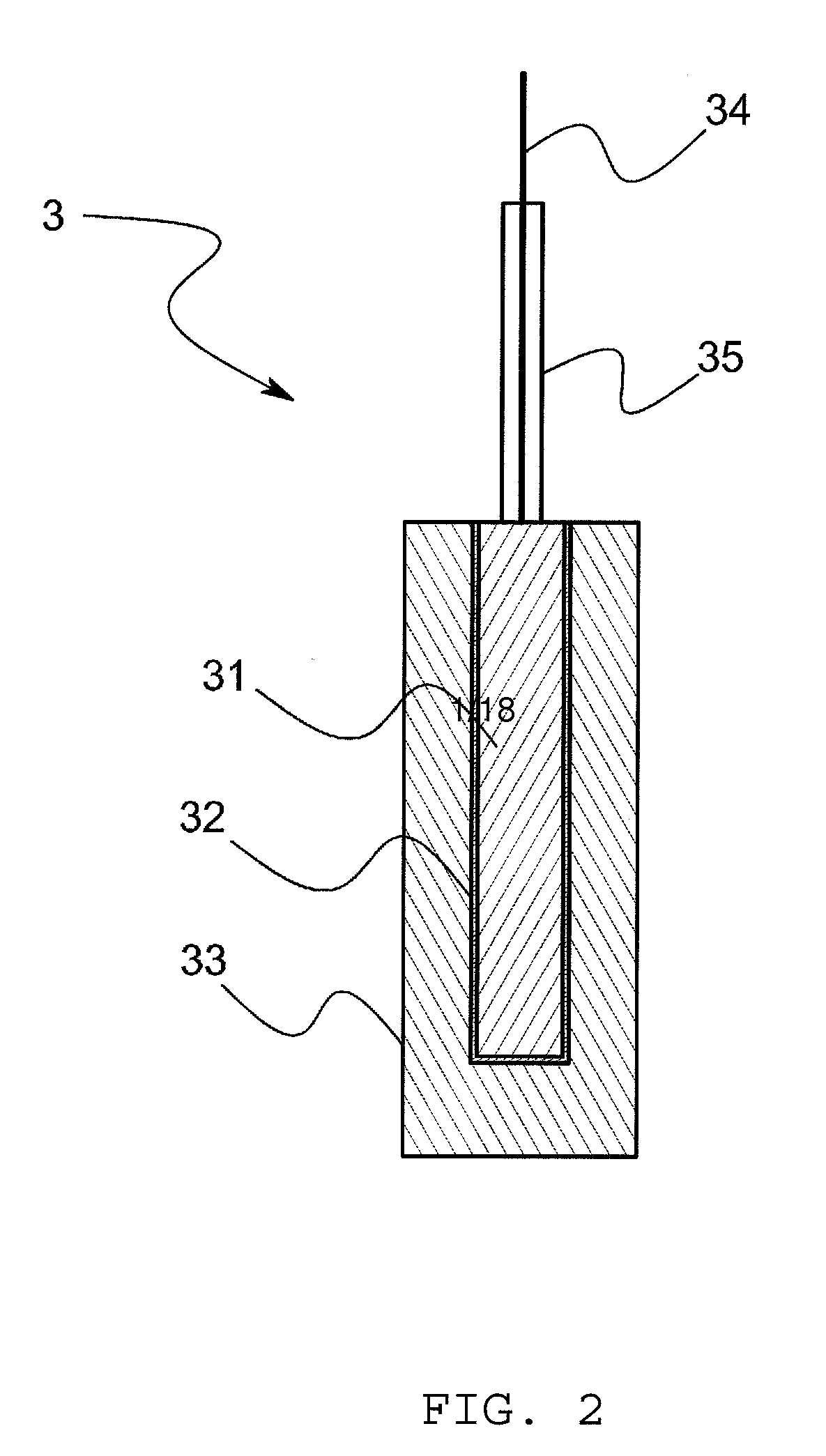

Reference Electrode Coated with Ionic Liquid and Electrochemical Measurement System Using the Reference Electrode

ActiveUS20090283404A1Eliminate fluctuationsSpeed blockMaterial electrochemical variablesAqueous solutionIonic liquid

This invention provides a reference electrode (3) that can be downsized and stable in voltage. The reference electrode (3) in accordance with this invention is a reference electrode (3) that does not require an internal aqueous solution such as a KCl aqueous solution and comprises a metal body (31), a slightly soluble salt film (32) that comprises a slightly soluble salt of the metal body (31) and that coats the metal body (31) and a hydrophobic ionic liquid (33) that is arranged to make contact with both the slightly soluble salt film (32) and a sample to be measured.

Owner:HORIBA LTD

Method and terminal of transmitting an uplink signal with fewer transmission resource blocks to prevent a lowering in reference sensitivity in intra-band non-contiguous uplink carrier aggregation

ActiveUS20140204867A1Avoid desensitizationReduced referenceTransmission path divisionOrthogonal multiplexTelecommunicationsResource block

There is provided a method of transmitting an uplink for reference sensitivity test for intra-band non-contiguous CA in LTE-A system. The method may comprise: if a carrier aggregation (CA) is configured, if the configured CA corresponds to an intra-band CA, and if the configured CA corresponds to non-contiguous CA, transmitting an uplink on a primary component carrier using allocated resource blocks (RBs). if a channel bandwidth by an aggregation of the primary component carrier and a secondary component carrier is at least one of 25 RBs, 50 RBs, 75 RBs and 100 RBs and if a gap between two sub-blocks corresponds to a predetermined range, the number of the allocated resource block (RB) in the primary component carrier may be limited to 10 to meet a requirement for a reference sensitivity on a downlink of the secondary component carrier.

Owner:LG ELECTRONICS INC

Linearized fractional-N synthesizer with fixed charge pump offset

ActiveUS7082176B2Improve radio performanceImprove performancePulse automatic controlAngle demodulation by phase difference detectionLow-pass filterVoltage control

A linearized oscillation synthesizer includes a phase and frequency detection module, charge pump circuit, low pass filter, voltage control oscillator, and a feedback module. The phase and frequency detection module is operably coupled to produce a charge-up signal, a charge-down signal, and an off signal based on phase and / or frequency differences between a reference oscillation and a feedback oscillation. The reference oscillation is generated by a clock source such as a crystal oscillator while the divider module generates the feedback oscillation by dividing the output oscillation by a divider value. The charge pump circuit produces a positive current in response to the charge-up signal, a negative current in response to the charge-down signal and also produces a non-zero offset current. The non-zero offset current shifts the steady state operating condition, and other operating conditions, of the charge pump into a linear region of charge pump performance curve.

Owner:QUALCOMM INC

Pll circuit for reducing reference leak and phase noise

A phase locked loop circuit comprises a charge pump fed with a phase error output signal; a loop filter charged or discharged with an output of the charge pump; an oscillator, an oscillating frequency of which is controlled by a voltage of the loop filter; and a frequency / phase comparator having a switching function which is fed with a reference signal and an output signal of the oscillator and outputs the phase error output signal; the frequency / phase comparator being configured to, based on a lock detection signal, switch between comparing frequencies by detecting rising edges of the reference signal and the comparison signal to detect a phase difference between the reference signal and the comparison signal, and comparing phases by detecting voltage levels of the reference signal and the comparison signal to detect a phase difference between the reference signal and the comparison signal.

Owner:PANASONIC CORP

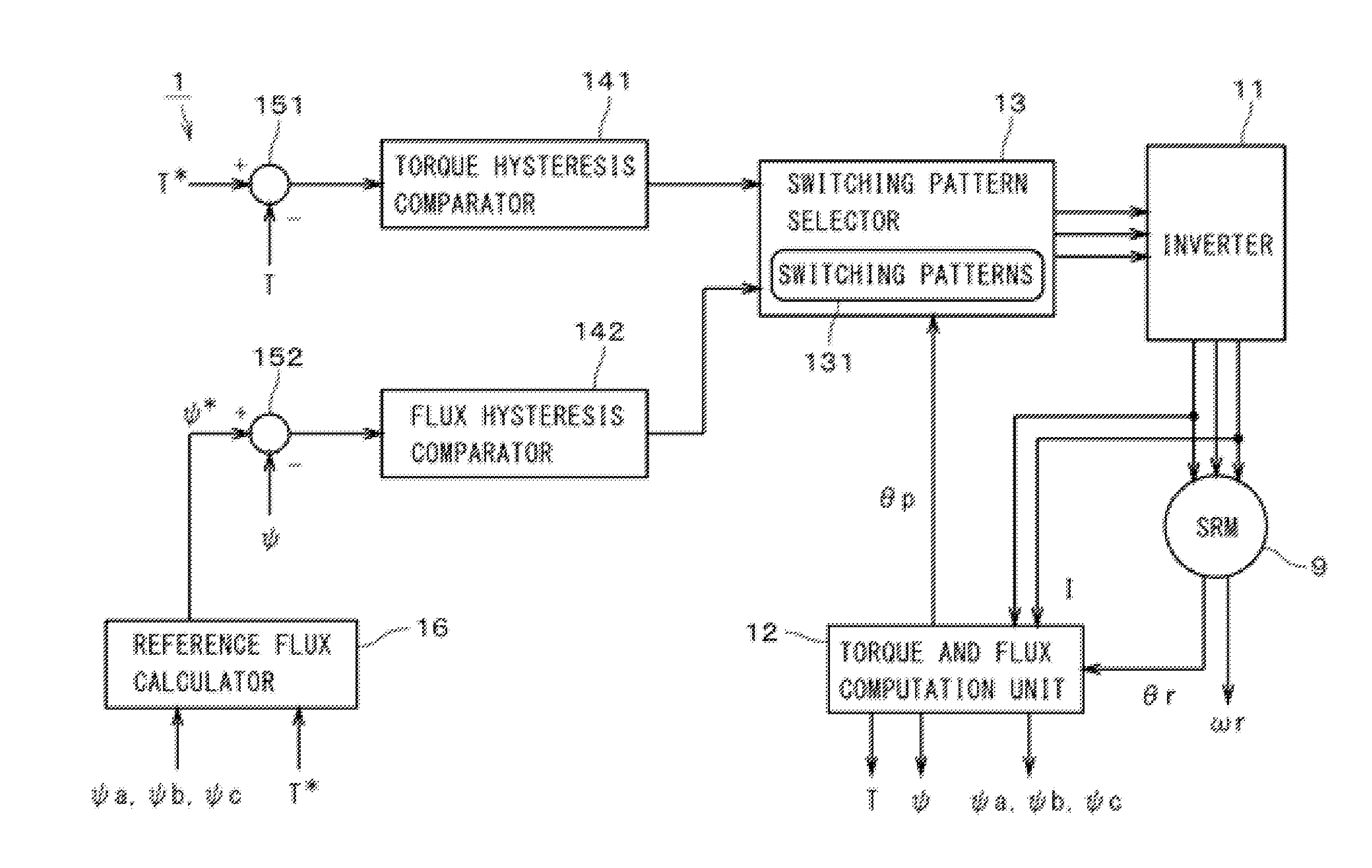

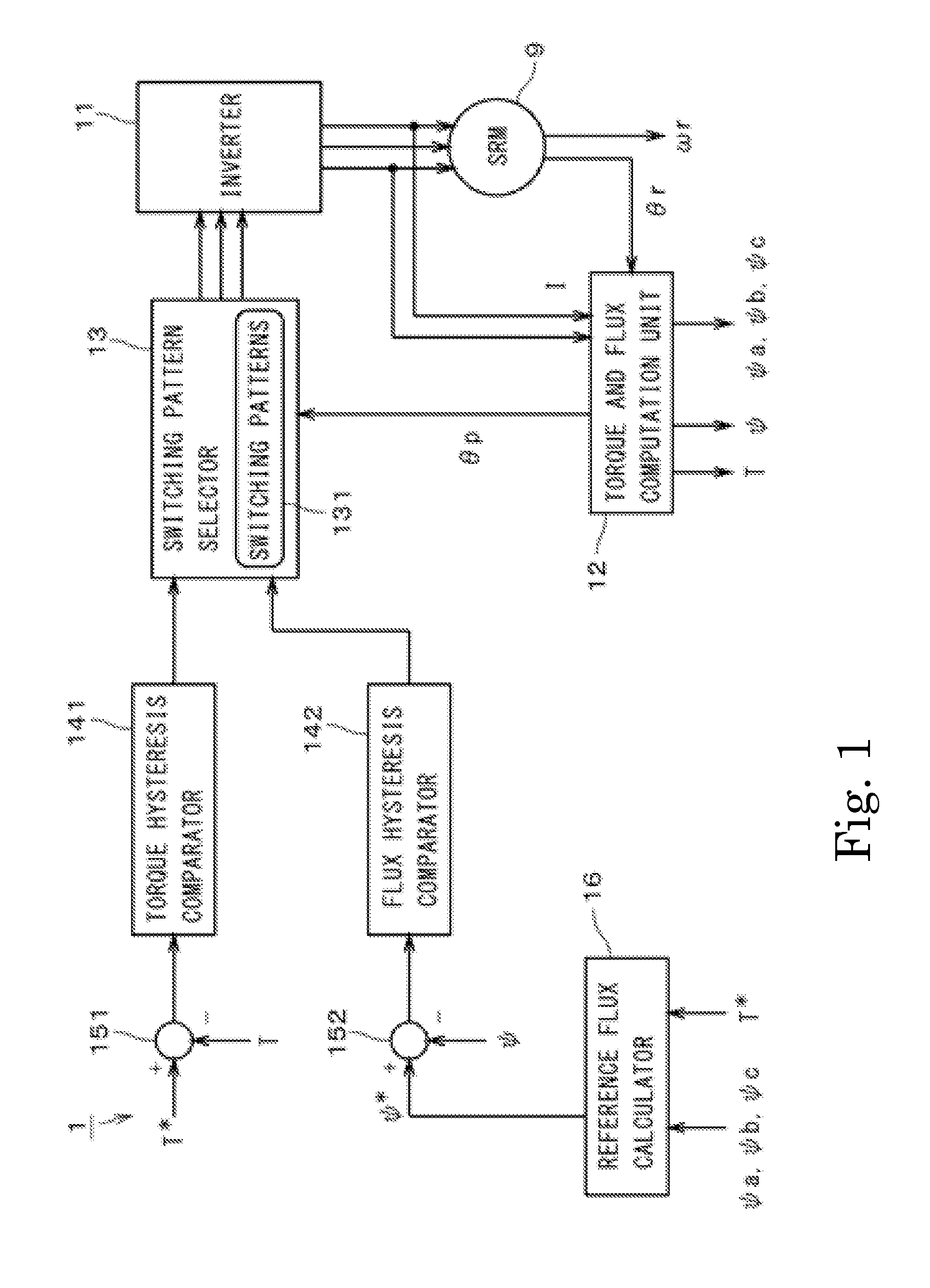

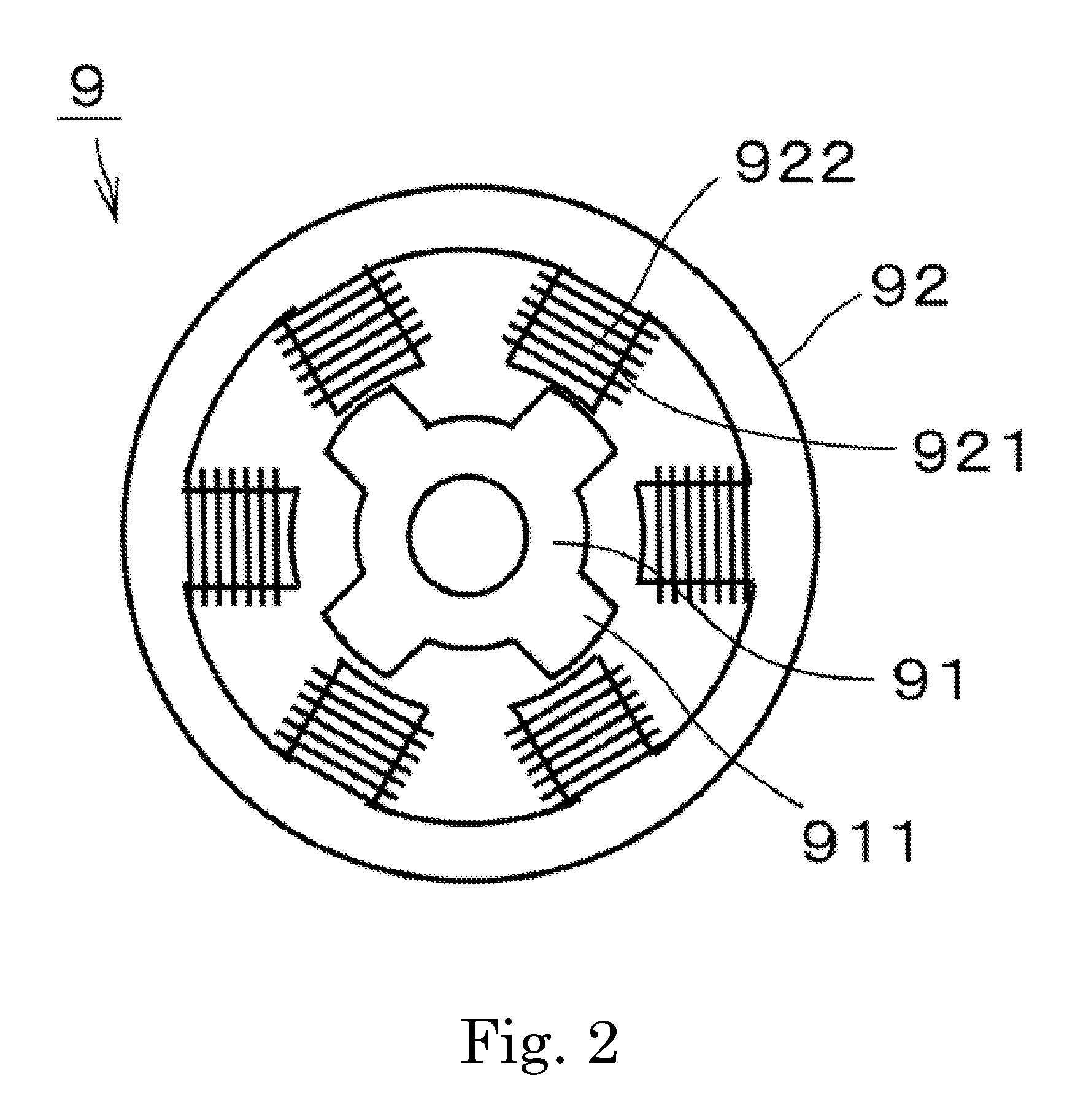

Motor controller

ActiveUS20150180399A1Reduce reference fluxReduce and prevent torque rippleElectronic commutation motor controlMotor/generator/converter stoppersMotor controllerThree-phase

A motor controller of a switched reluctance motor includes an inverter, a torque and flux calculator configured to estimate or measure torque and flux generated in the switched reluctance motor as calculated torque flux, based on an output from the inverter and a rotor angle of the switched reluctance motor, a switching pattern selector configured to input a signal to the inverter to select one of a plurality of switching patterns based on comparison results of a reference torque and the calculated torque and a reference flux and the calculated flux, and a flux phase angle, and a reference flux calculator configured to compare a highest phase flux out of three phase fluxes obtained by the torque and flux calculator with a flux limit and to reduce the reference flux when the maximum phase flux is higher than the flux limit.

Owner:NIPPON DENSAN CORP

Transport chair for a patient

InactiveUS20050104319A1Reduced referenceEasy transferVehicle seatsCycle safety equipmentsWheelchairBraced frame

Disclosed is a wheelchair for transporting a patient. The wheelchair comprises a support frame having a front, a rear, and opposing sides with the front and rear facing in respective forward and aft directions and the opposing sides facing in opposing lateral directions. The wheelchair further comprises at least two main wheels mounted on the support frame and a seat base disposed upon the support frame between the main wheels. The seat base is configured for selectively raising and lowering the patient between a first level and a second level with the aid of at least one security beam disposed adjacent one of the main wheels. The security beam may have a substantially vertical orientation and may be configured as a hand hold for steadying the patient when transferring onto and off of the seat base.

Owner:WING THOMAS W

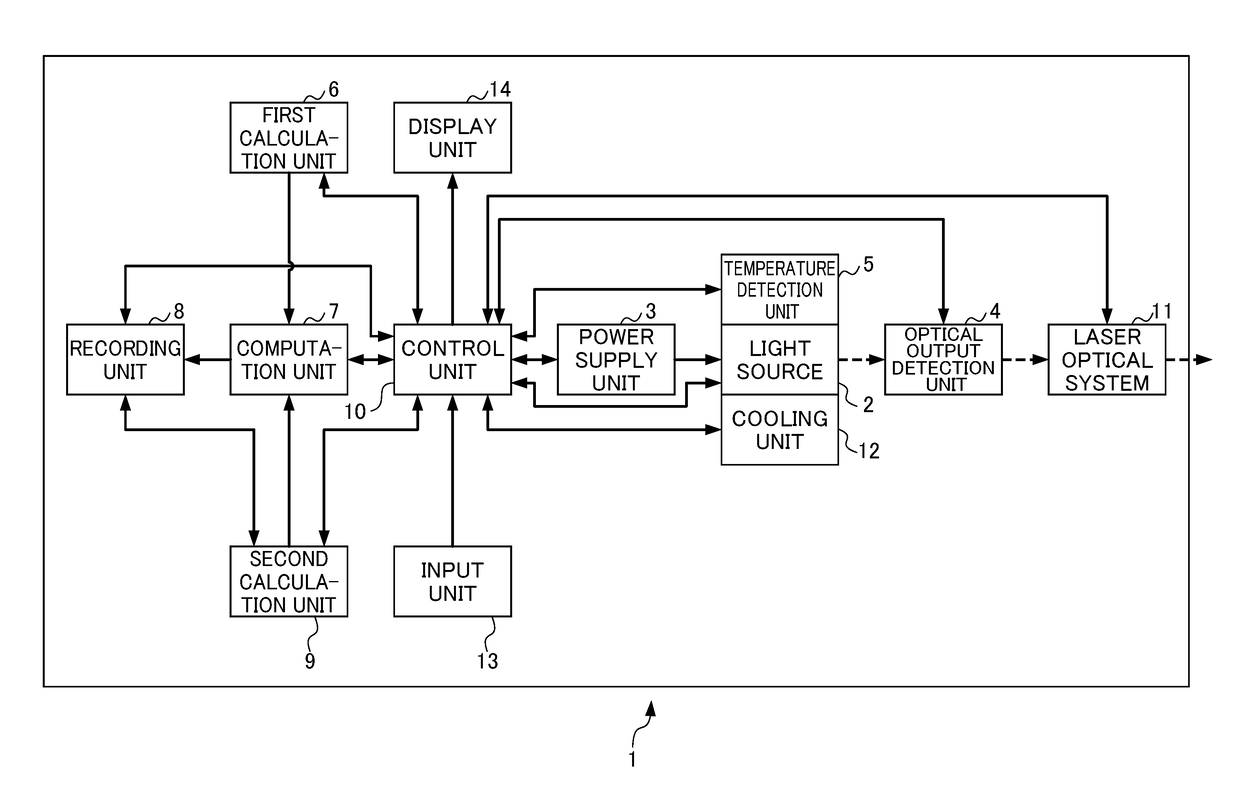

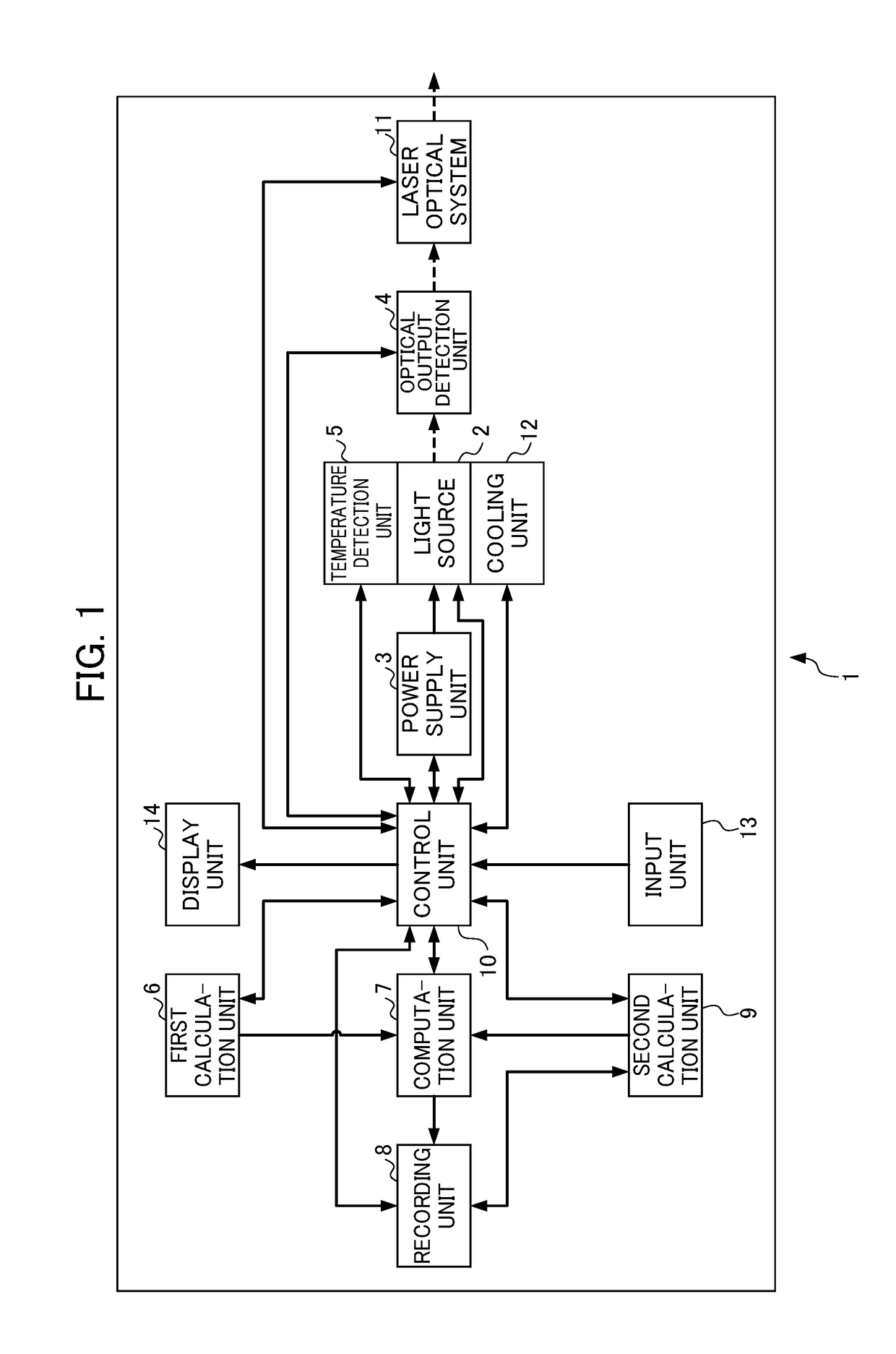

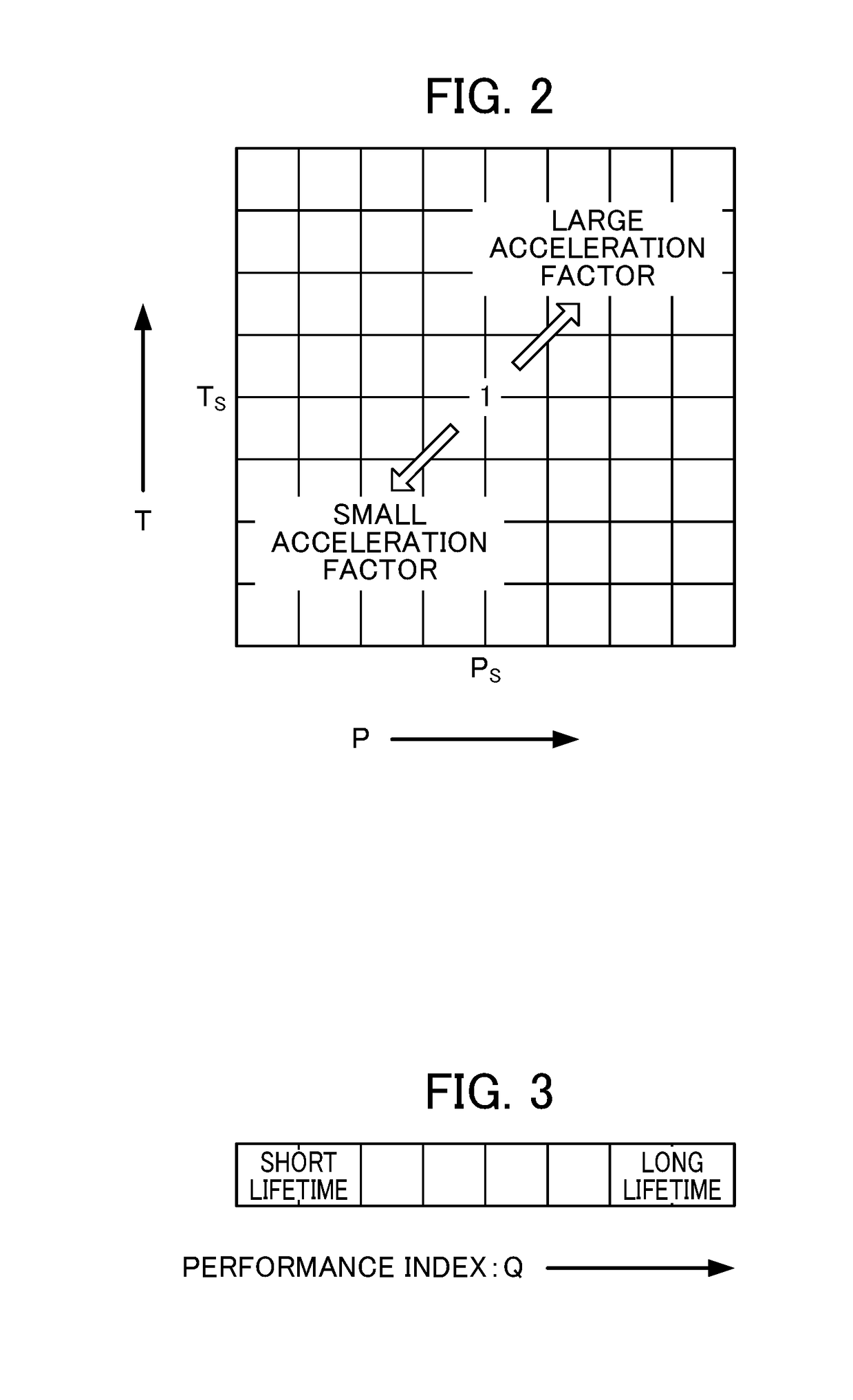

Laser apparatus enabling calculation of effective driving time and remaining lifetime taking account of drive conditions including temperature

ActiveUS20180013259A1Reduced referenceReduce dataLaser detailsAnalysis by electrical excitationAcceleration factorPerformance index

A first calculation unit calculates an acceleration factor of lifetime consumption of the light source with as case of a standard temperature and standard drive condition as a reference, a second calculation unit calculates a whole lifetime or remaining lifetime of individual light sources relative to a performance index of the individual light sources or a change rate of the performance index, a computation unit obtains an effective cumulative driving time at which the magnitude of influence imparted on the lifetime is equivalent with a case of driving at the standard temperature and standard drive condition, by calculating a time integral of the acceleration factor, and a recording unit records the effective cumulative driving time and the whole lifetime or remaining lifetime together with an optical output characteristic of the light source.

Owner:FANUC LTD

Transport chair for a patient

InactiveUS6902178B2Reduced referenceEasy transferOperating chairsWheelchairs/patient conveyanceWheelchairBraced frame

Disclosed is a wheelchair for transporting a patient. The wheelchair comprises a support frame having a front, a rear, and opposing sides with the front and rear facing in respective forward and aft directions and the opposing sides facing in opposing lateral directions. The wheelchair further comprises at least two main wheels mounted on the support frame and a seat base disposed upon the support frame between the main wheels. The seat base is configured for selectively raising and lowering the patient between a first level and a second level with the aid of at least one security beam disposed adjacent one of the main wheels. The security beam may have a substantially vertical orientation and may be configured as a hand hold for steadying the patient when transferring onto and off of the seat base.

Owner:O MATIC CORP

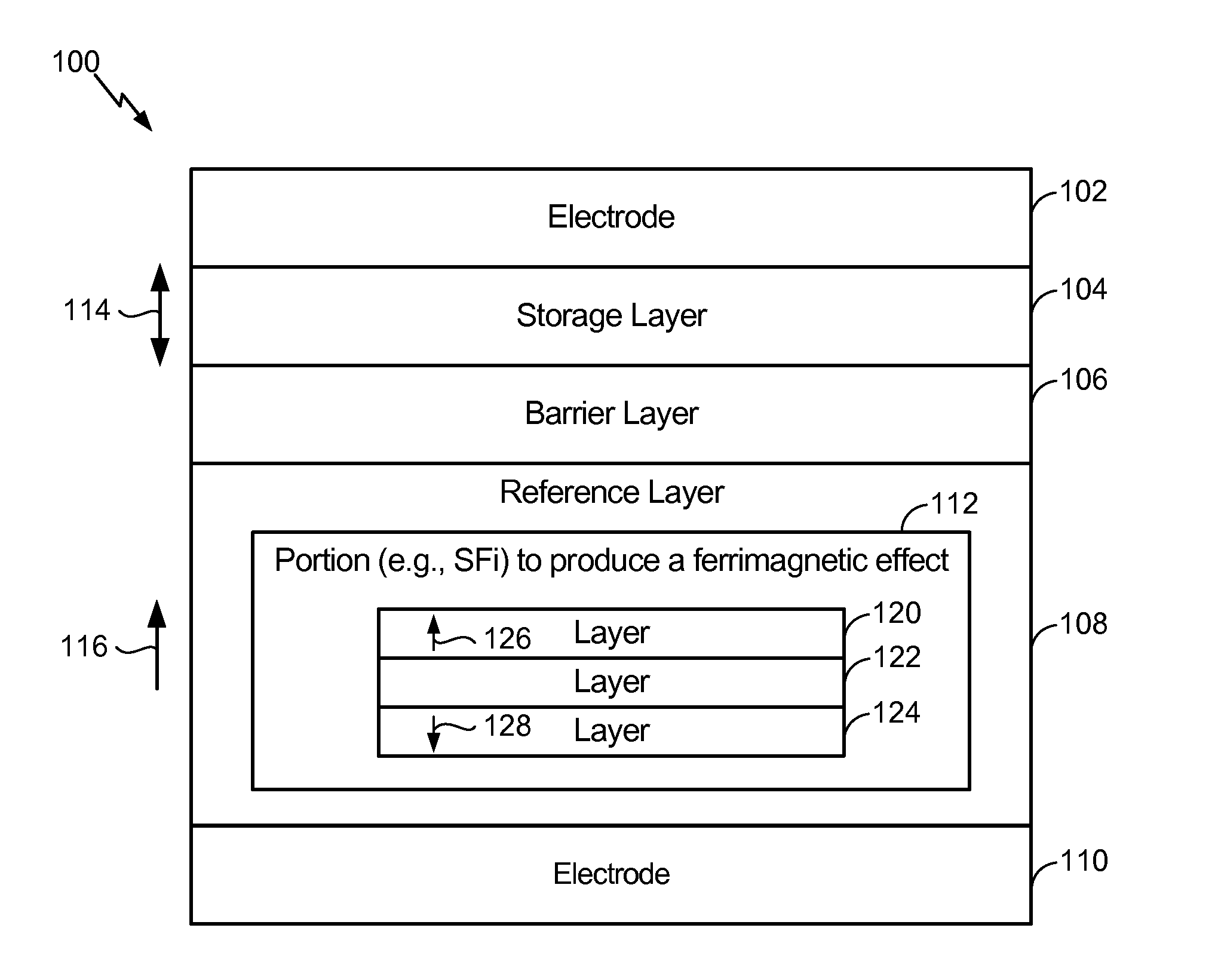

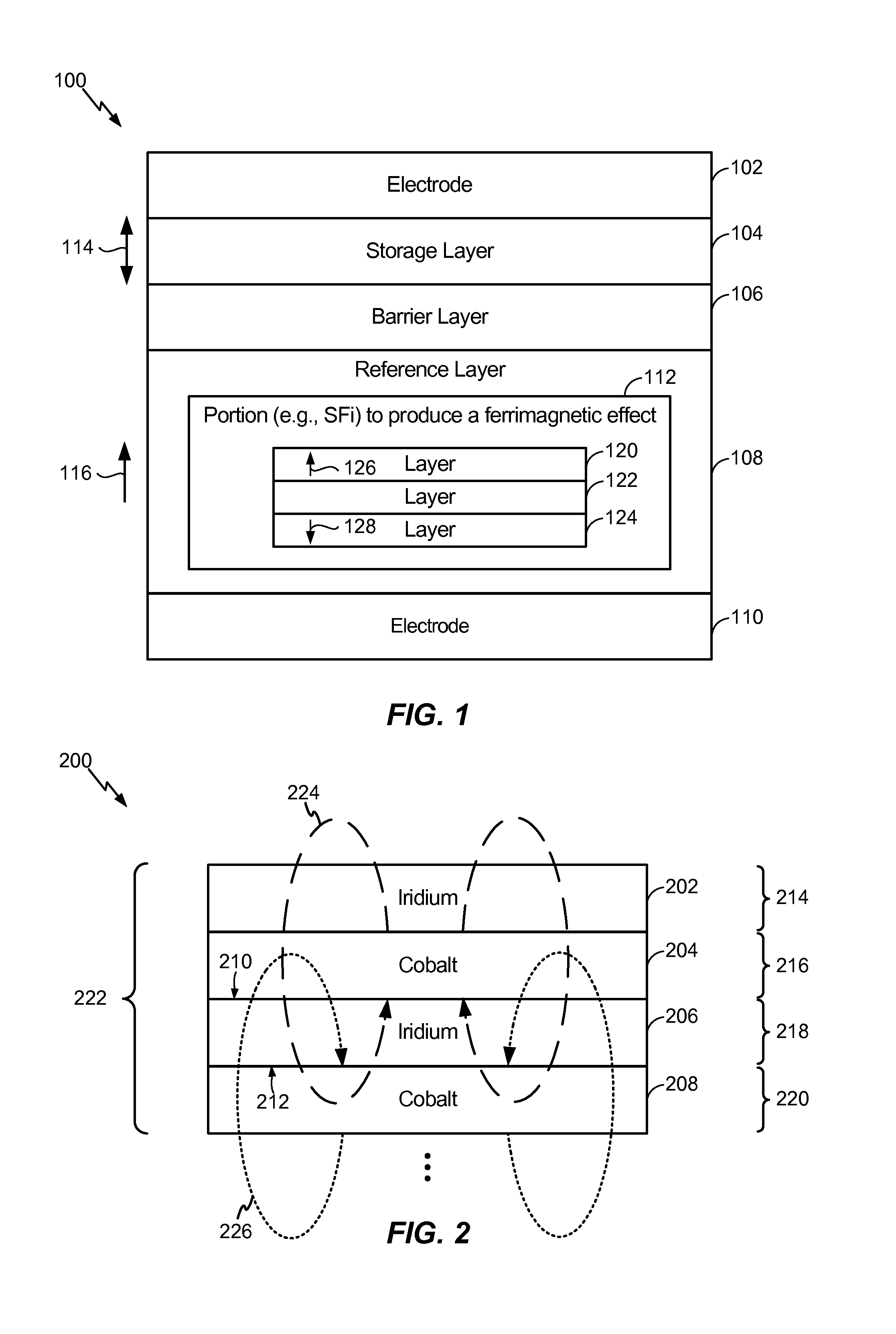

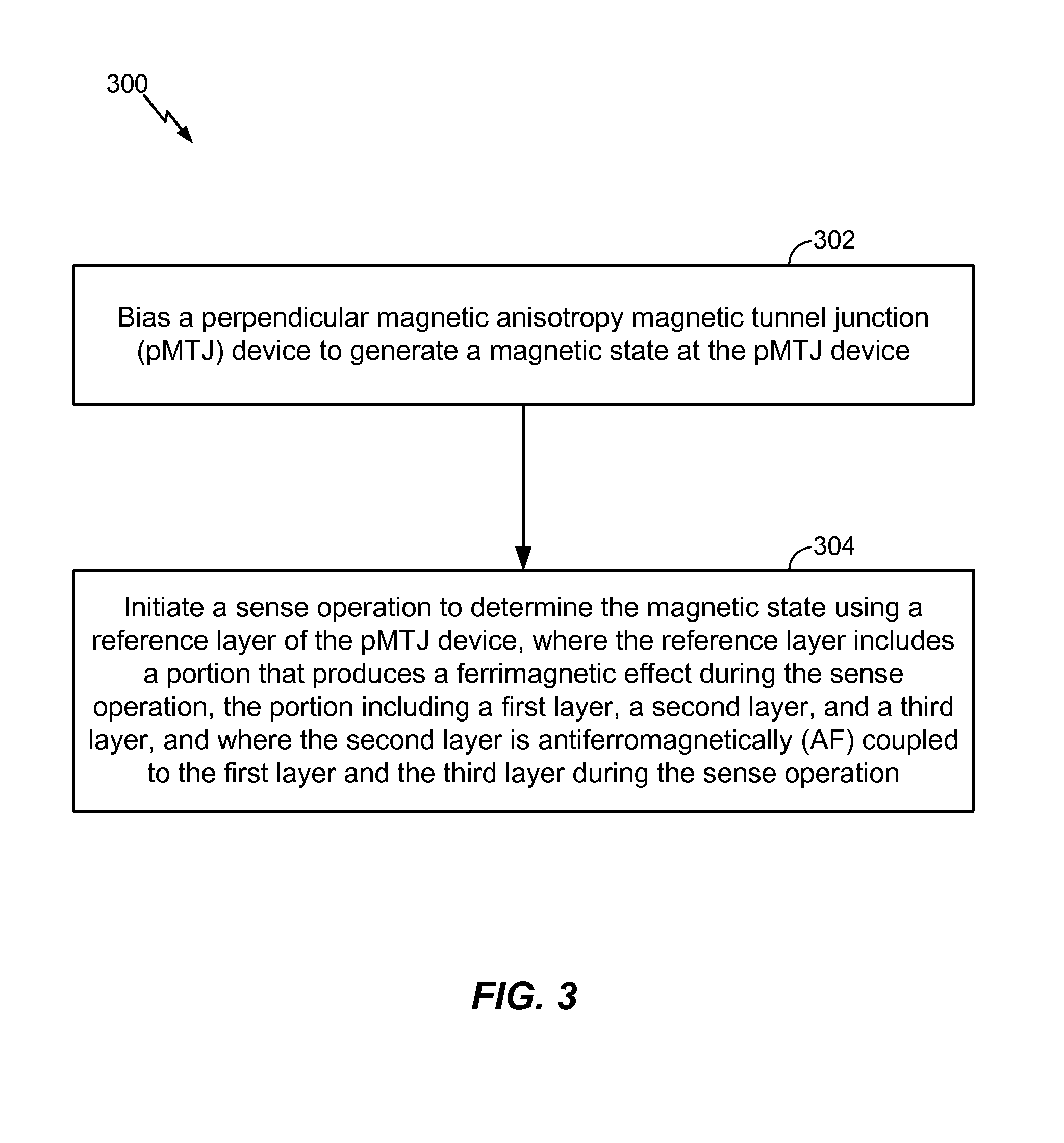

Reference layer for perpendicular magnetic anisotropy magnetic tunnel junction

ActiveUS20150263266A1Lower performance requirementsWeakening rangeMagnetic-field-controlled resistorsDigital storageTunnel junctionNuclear magnetic resonance

An apparatus includes a perpendicular magnetic anisotropy magnetic tunnel junction (pMTJ) device. The pMTJ device includes a storage layer and a reference layer. The reference layer includes a portion configured to produce a ferrimagnetic effect. The portion includes a first layer, a second layer, and a third layer. The second layer is configured to antiferromagnetically (AF) couple the first layer and the third layer during operation of the pMTJ device.

Owner:QUALCOMM INC

Image processing apparatus, image forming apparatus, image processing system, and image processing method having storage section, divided into a plurality of regions, for storing identification information for identifying reference image

ActiveUS8131083B2Shorten the timeReduce workloadDigital data information retrievalDigital data processing detailsImaging processingComputer graphics (images)

A reference image and features of the reference image are stored in a hash table in such a manner that the reference image and the features are related to each other. A storage region of the hash table is divided into a plurality of divided regions, and each divided region is related to a storage condition under which a reference image is stored in the divided region. When a reference image is stored in the hash table, a storage region where the reference image is to be stored is selected out of the plurality of divided regions in accordance with the storage condition. This allows shortening a time for updating a reference image, and reducing a workload on means for updating the reference image.

Owner:SHARP KK

Throttle device for high fluid pressures

ActiveUS7013919B2Increased energy lossWeaken energyOperating means/releasing devices for valvesValve members for absorbing fluid energyHigh pressureBiomedical engineering

A throttle device comprises a tubular outer sleeve having a plurality of outer sleeve circumferential grooves formed on an outer sleeve inner surface and intersecting a plurality of outer sleeve axial grooves formed on an outer sleeve outer surface to form outer sleeve orifices. Also included is a tubular inner sleeve concentrically disposed within the outer sleeve and having a plurality of inner sleeve circumferential grooves formed on an inner sleeve inner surface. A plurality of inner sleeve axial grooves are formed on the inner sleeve outer surface and intersect the inner sleeve circumferential grooves to form inner sleeve orifices. The offset inner and outer sleeve orifices define tortuous flow paths wherein fluid flows into the outer sleeve axial grooves, through the outer sleeve orifices, through the outer sleeve circumferential grooves, through the inner sleeve axial grooves, through the inner sleeve orifices before exiting the inner sleeve circumferential grooves.

Owner:CONTROL COMPONENTS INC

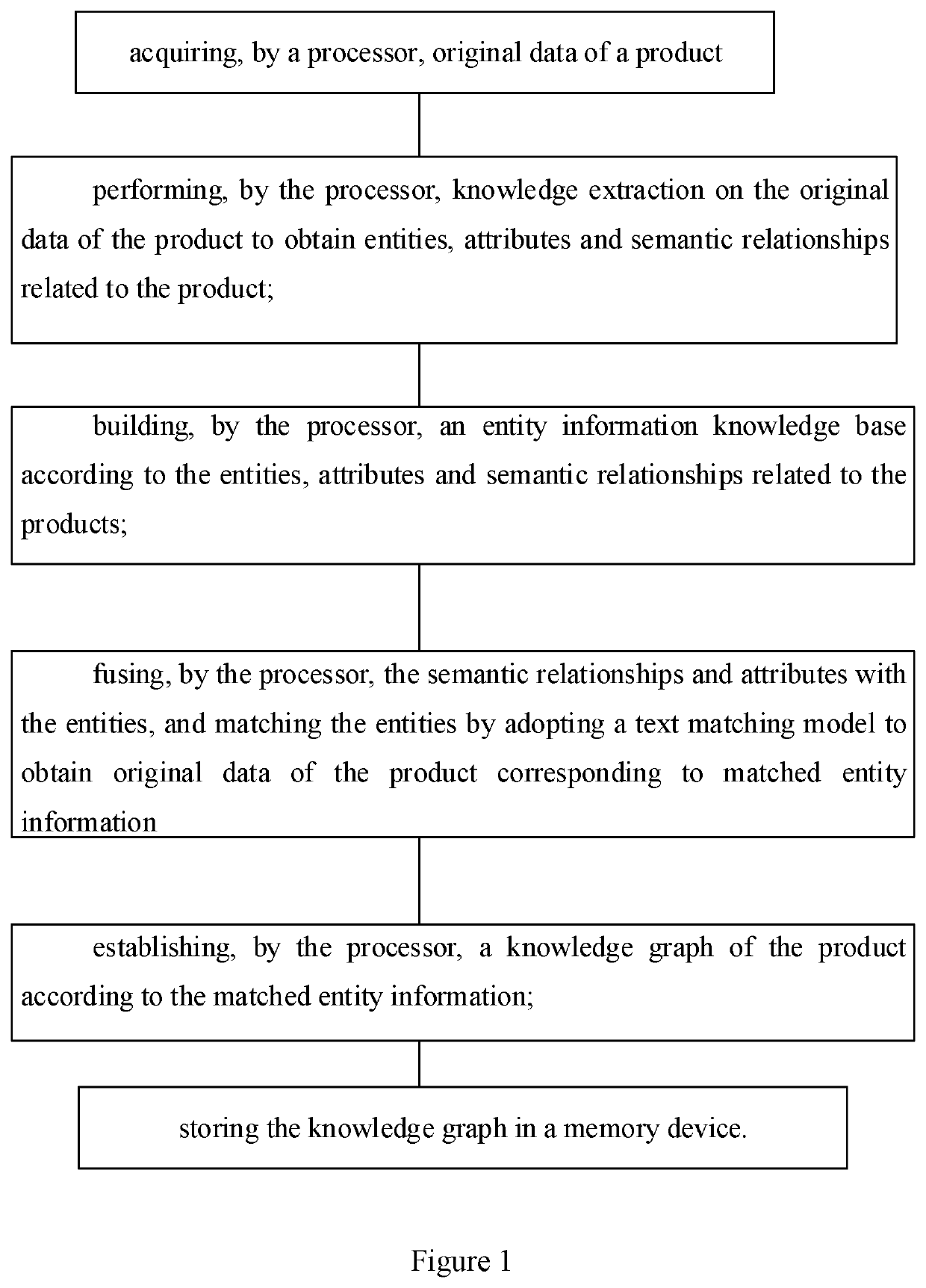

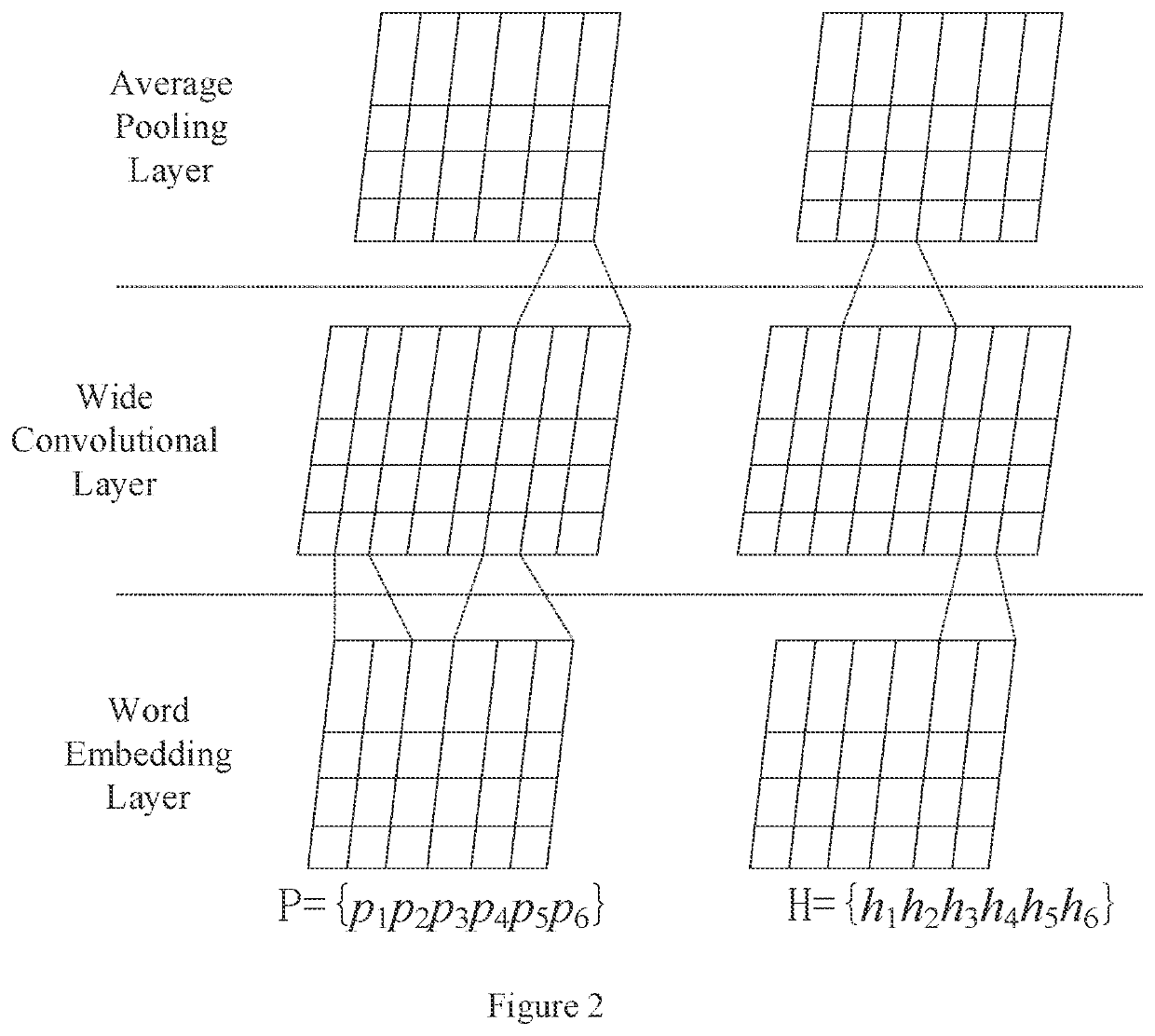

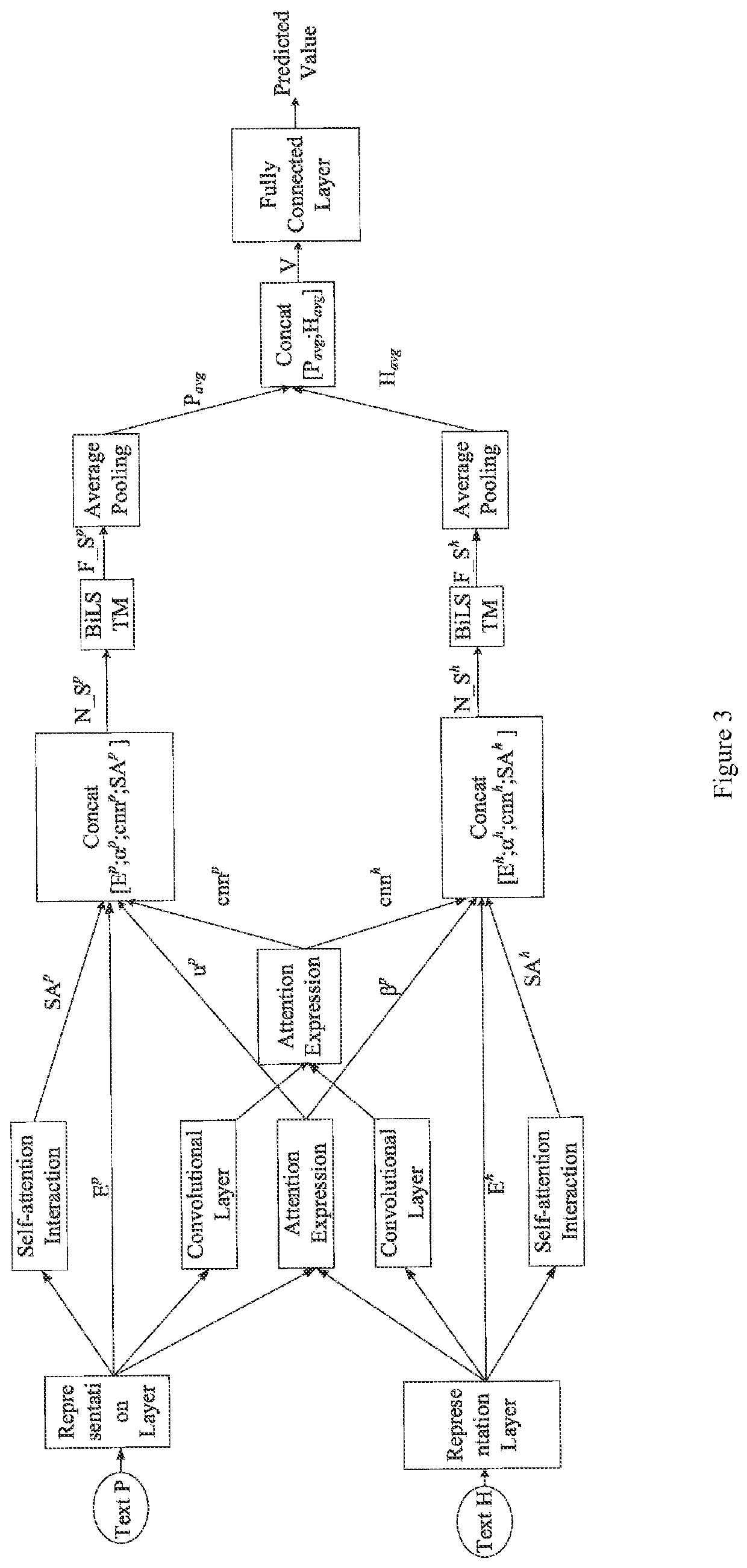

Method and system for product knowledge fusion

PendingUS20220309248A1Improve matching accuracyReduced referenceNatural language translationSemantic analysisPolysemyKnowledge extraction

A method and system for product knowledge fusion are discloses. The method includes following steps: acquiring original data of a product; performing knowledge extraction on the original data of the product to obtain entities, attributes and semantic relationships related to the product; building an entity information knowledge base according to the entities, attributes and semantic relationships related to the products; fusing the semantic relationships and attributes with the entities and matching the entities by adopting a text matching model to obtain original data of the product corresponding to matched entity information; and establishing a knowledge graph of the product according to the matched entity information. The method and system standardize multi-source heterogeneous data with a knowledge fusion method, thus effectively reducing polysemy and unclear references of knowledge caused by different data structures and sources.

Owner:CHINA ACAD OF ART