Patents

Literature

315 results about "Mechanical resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Mechanical resistance is a property of some materials, representing the difficulty of working with them. Mechanical strength is the property of consumables and other objects that overcomes it. The total mechanical strength must equal or exceed the mechanical resistance of the materials or the crafting task is not possible.

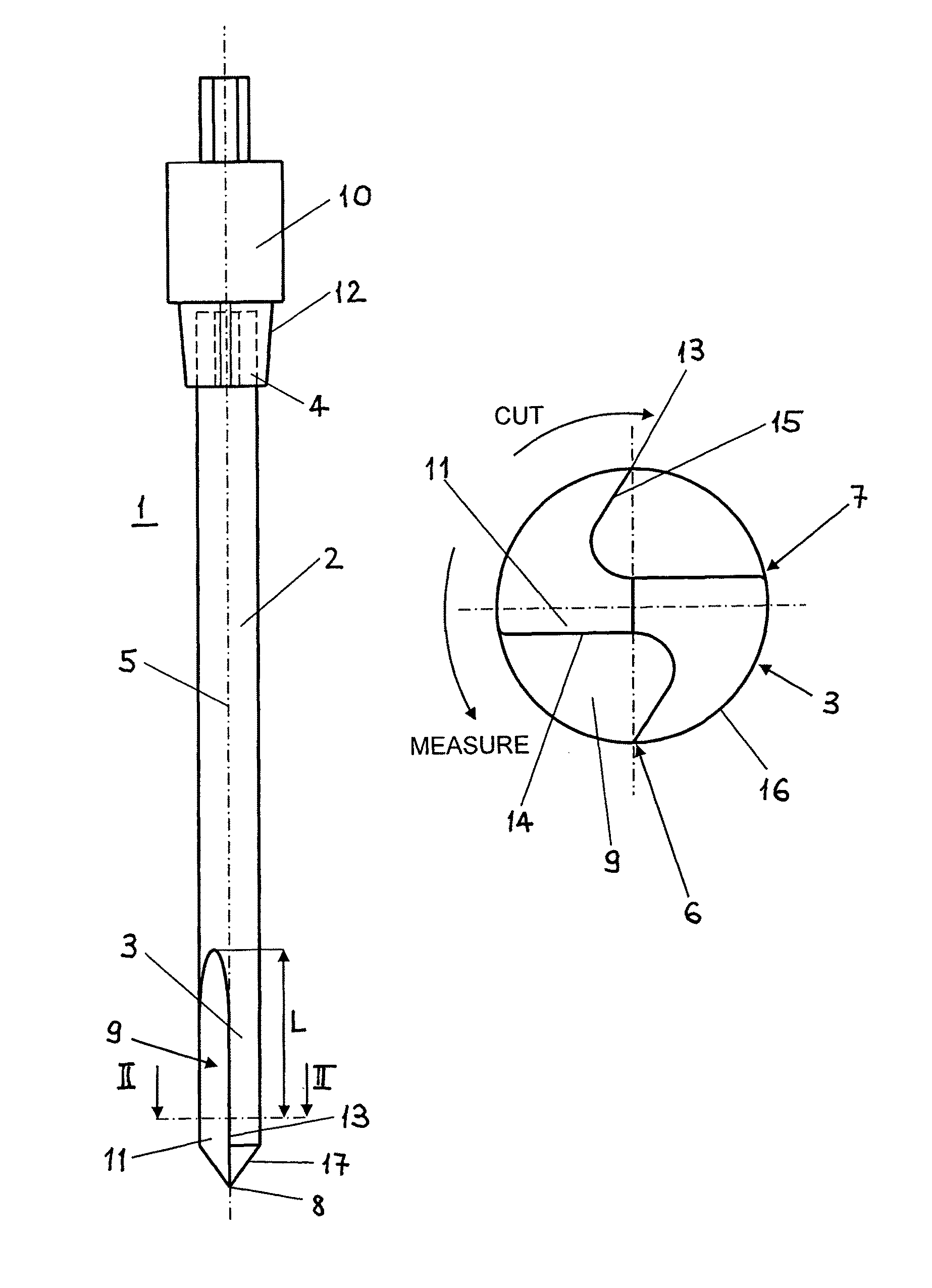

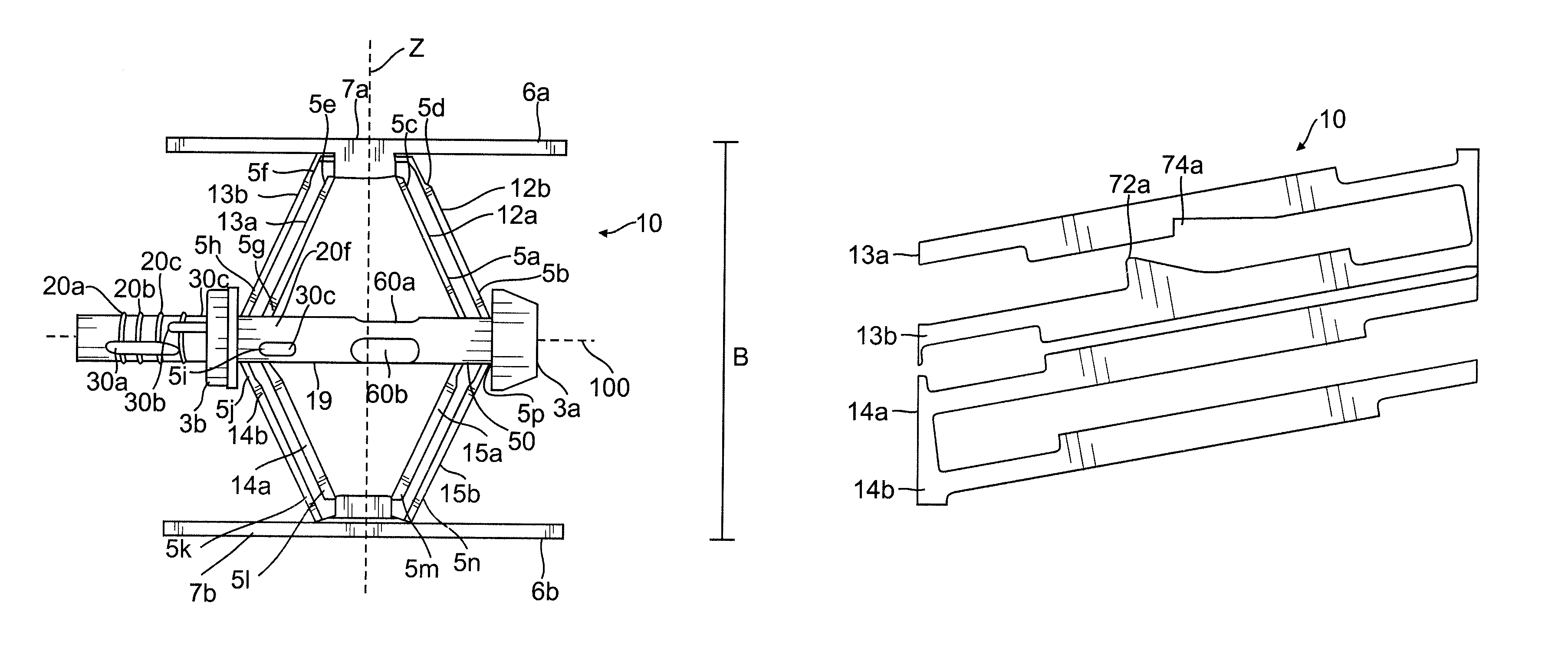

Surgical instrument

ActiveUS9579158B2Reduce usageReduce frictionDiagnostic recording/measuringSensorsMechanical resistanceBone tissue

Owner:AO TECH AG

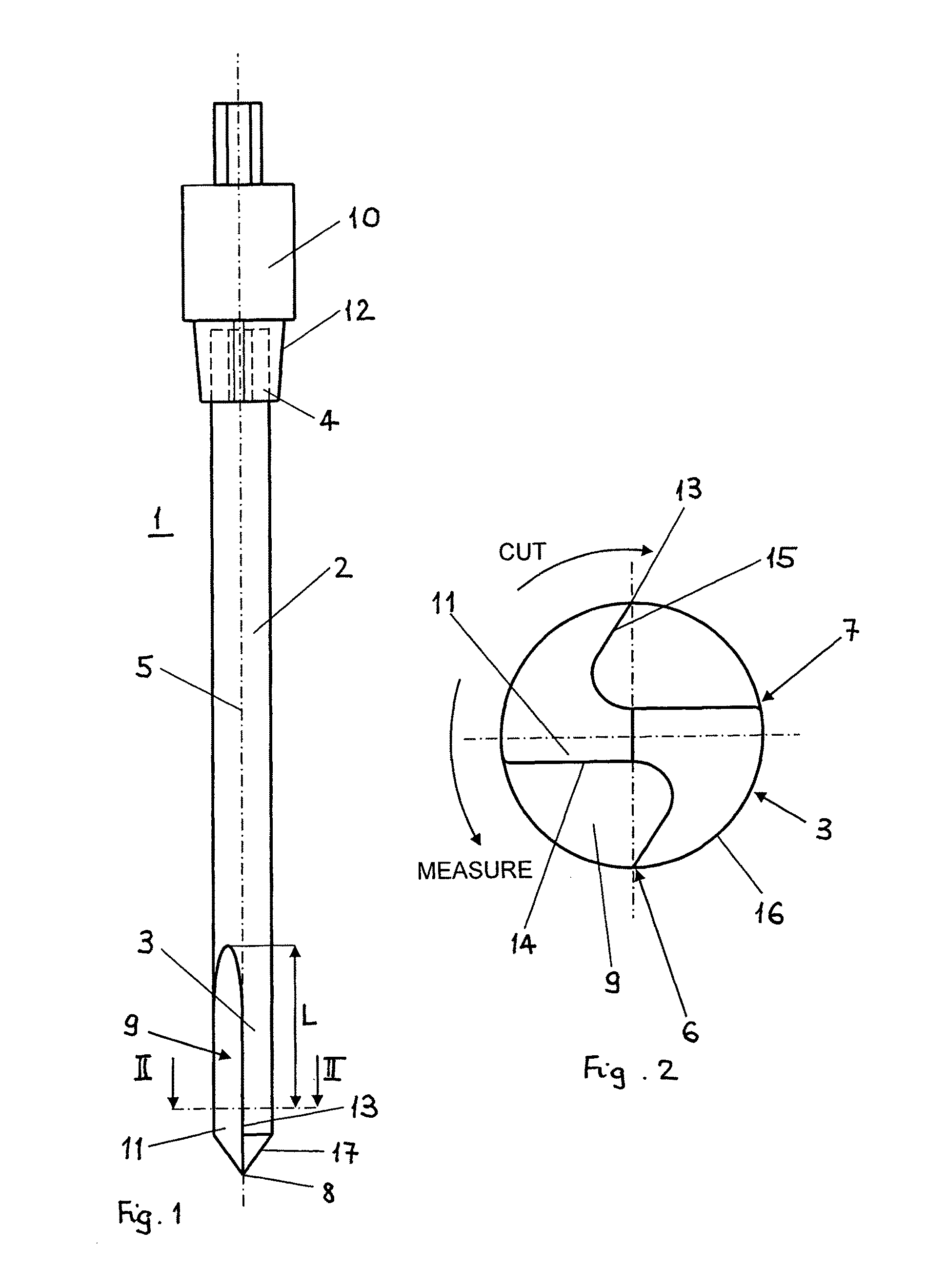

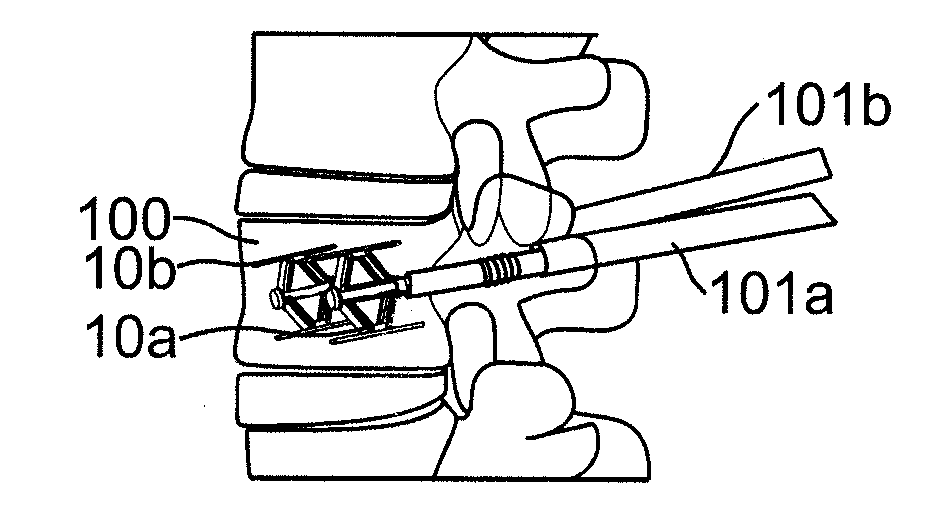

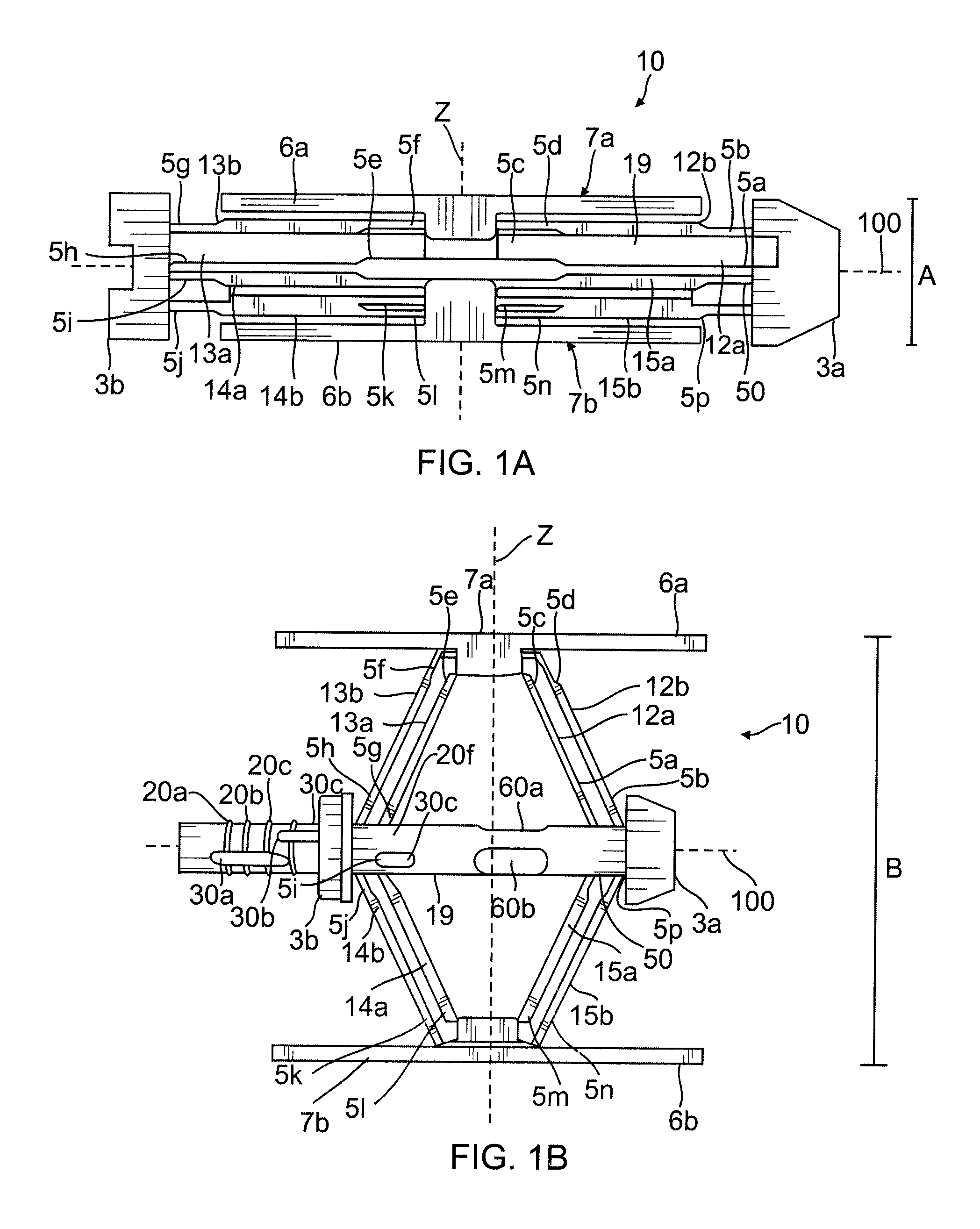

Apparatus for Bone Restoration of the Spine and Methods of Use

ActiveUS20120071977A1Inhibition of contractionInternal osteosythesisBone implantMechanical resistanceBack pain

The subject disclosure is directed to systems, apparatuses, devices and methods for vertebral and spinal correction. In some embodiments, an expandable implant is provided which may be inserted inside the vertebral body and / or between two vertebrae, for instance, for maintenance and / or restoration of a space therein or there between. In certain embodiments, the implant includes a mechanical resistance that prevents the expandable implant from contracting once it has been expanded. Methods of treatment and methods of use of such implants for the alleviation of back pain (for example) are also provided herein.

Owner:STRYKER EUROPEAN OPERATIONS LIMITED

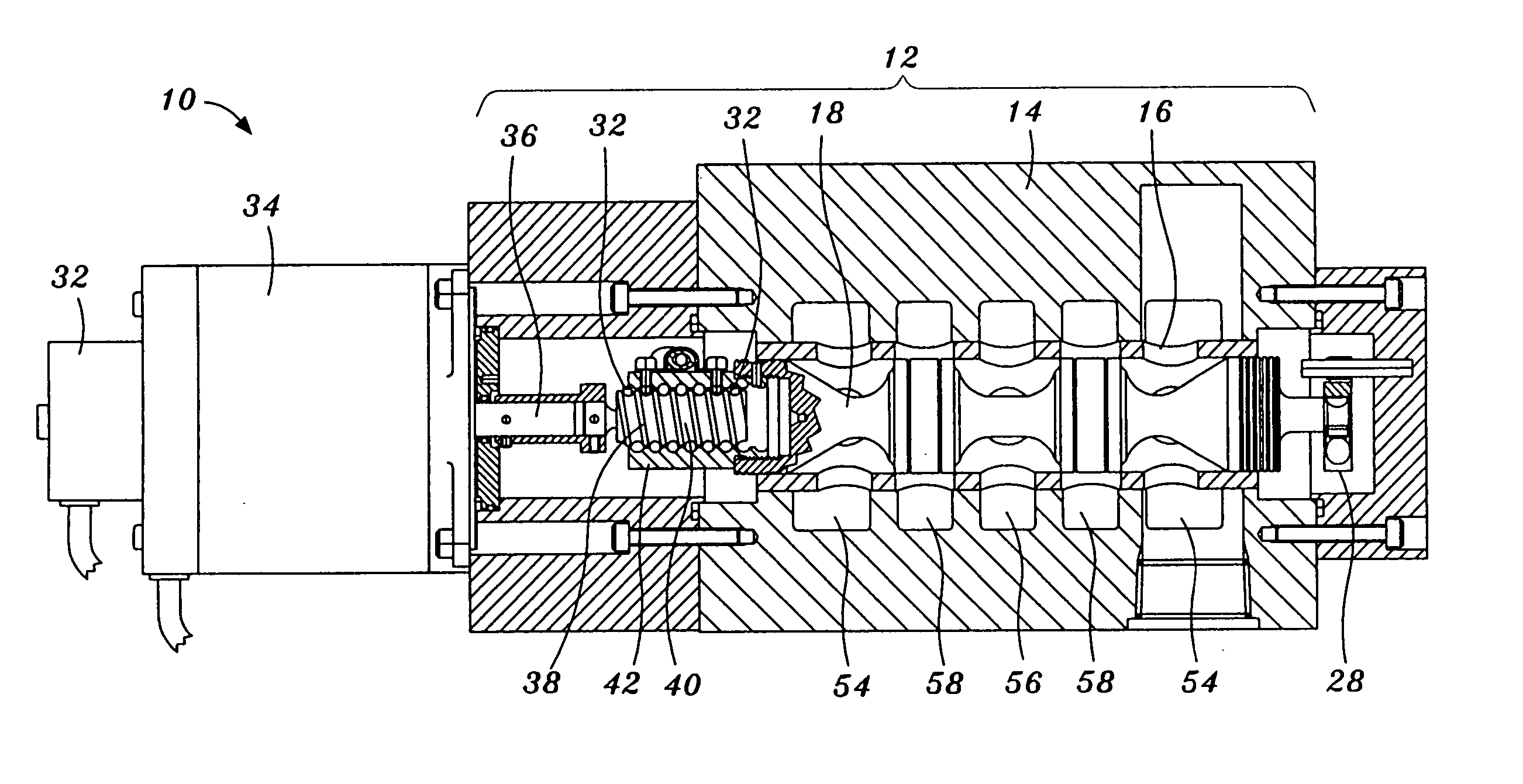

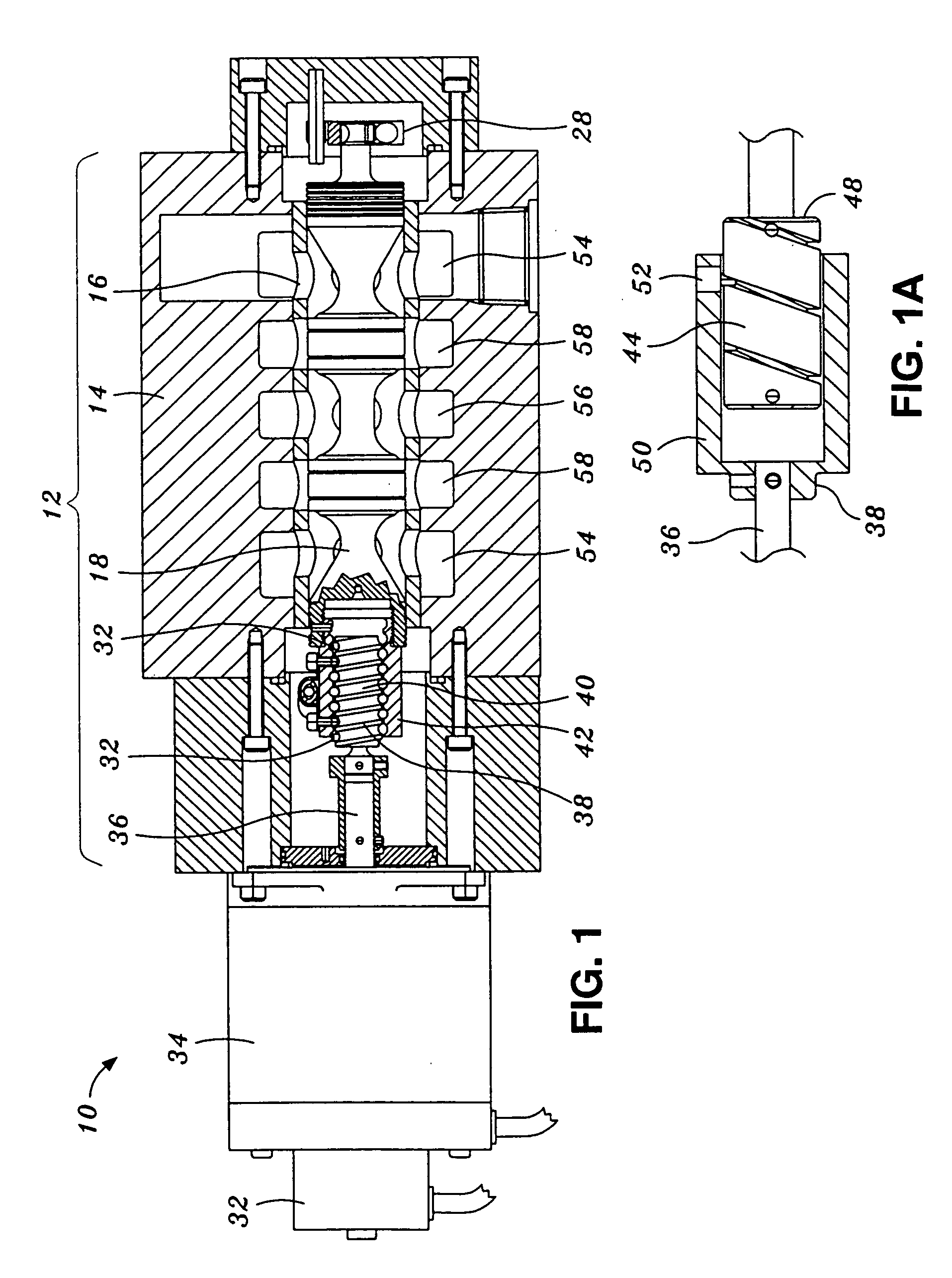

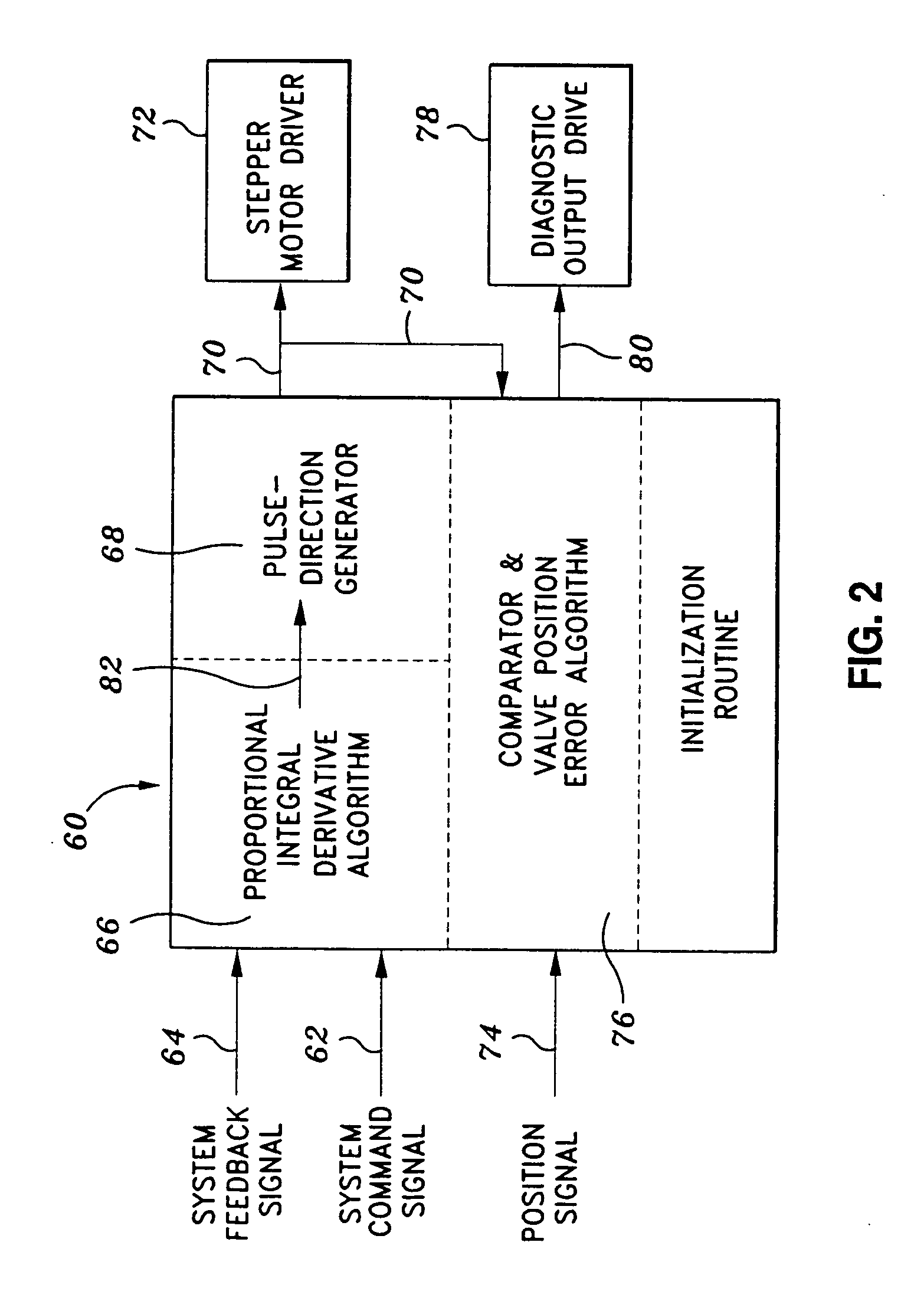

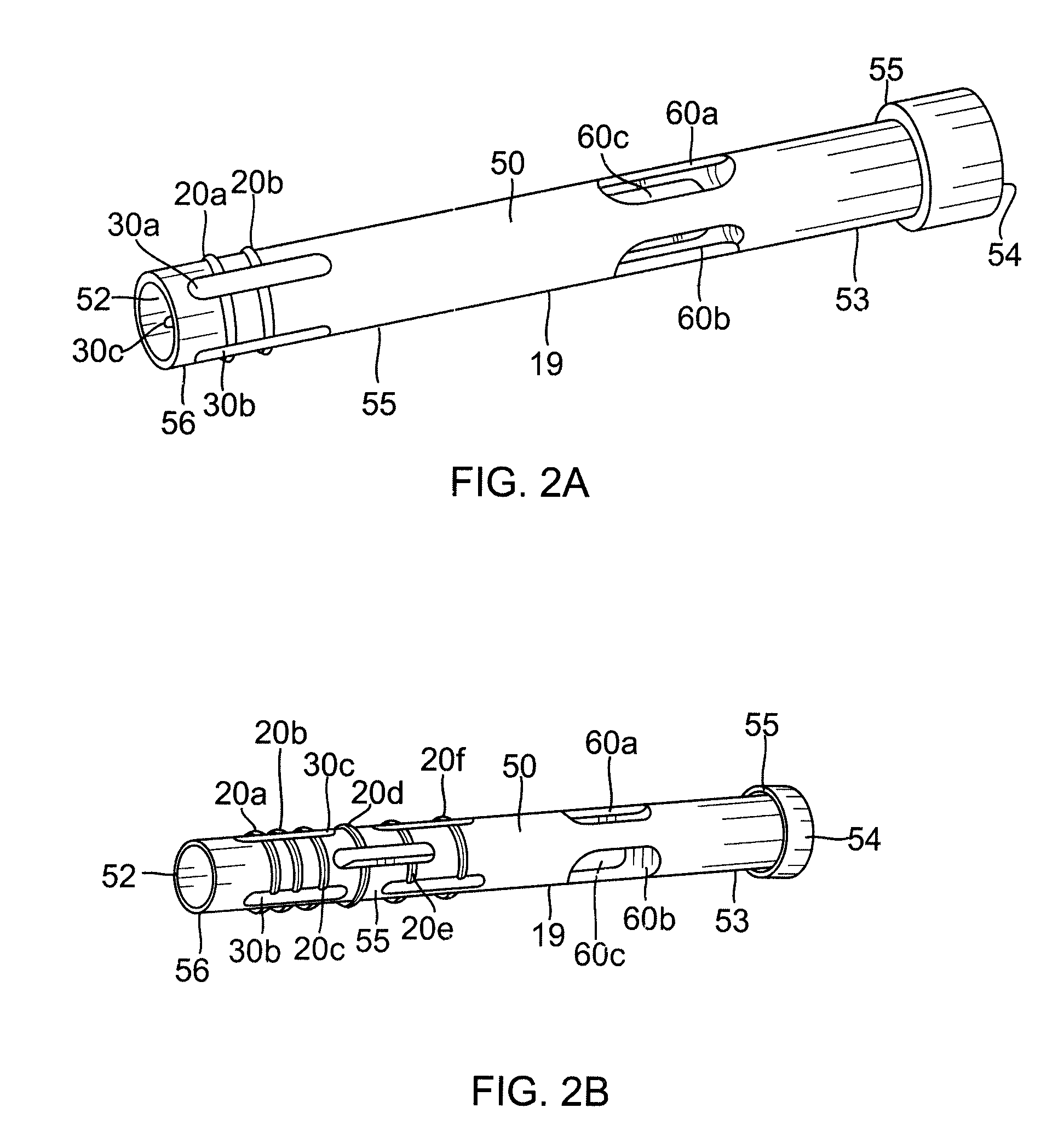

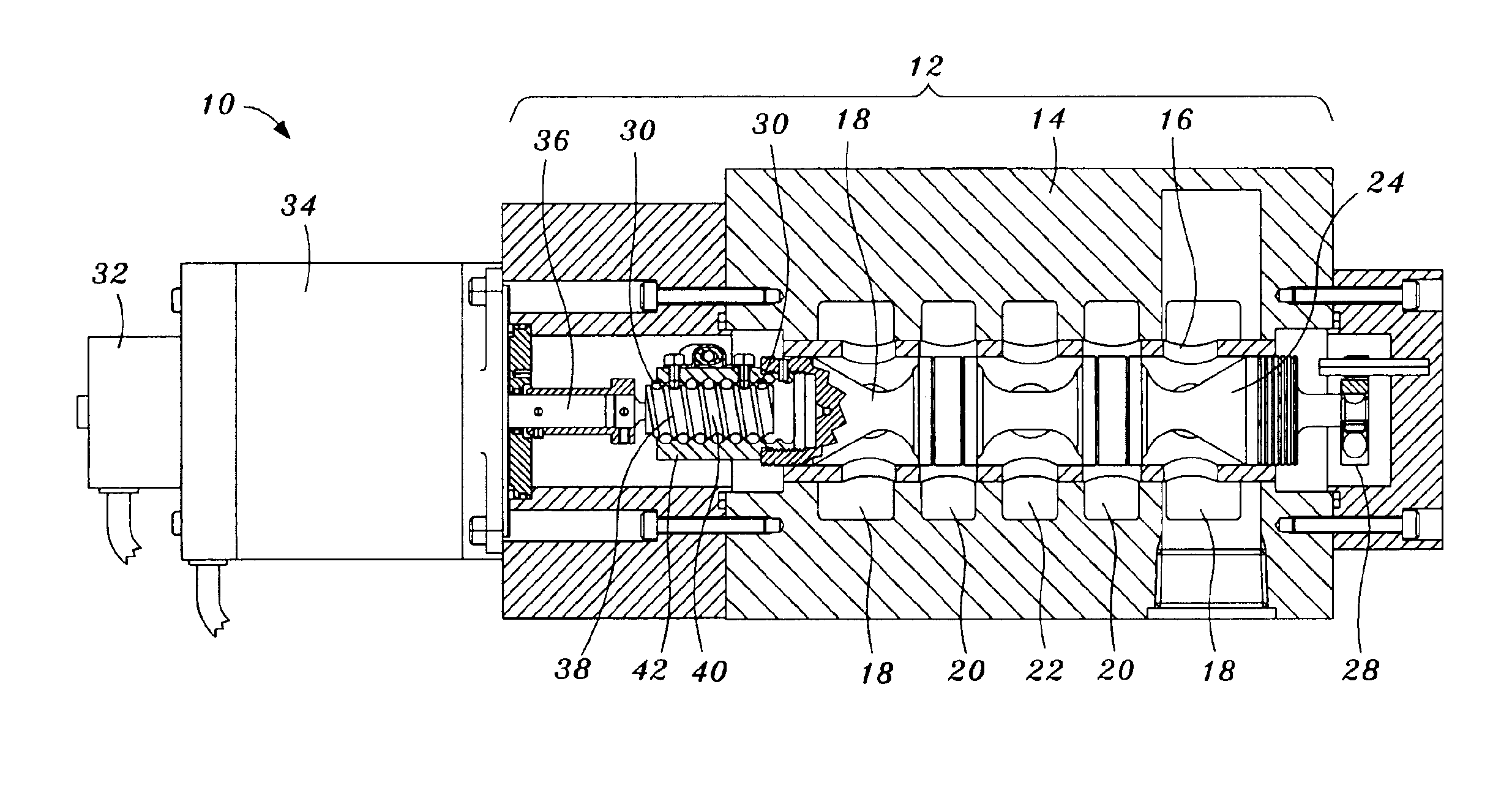

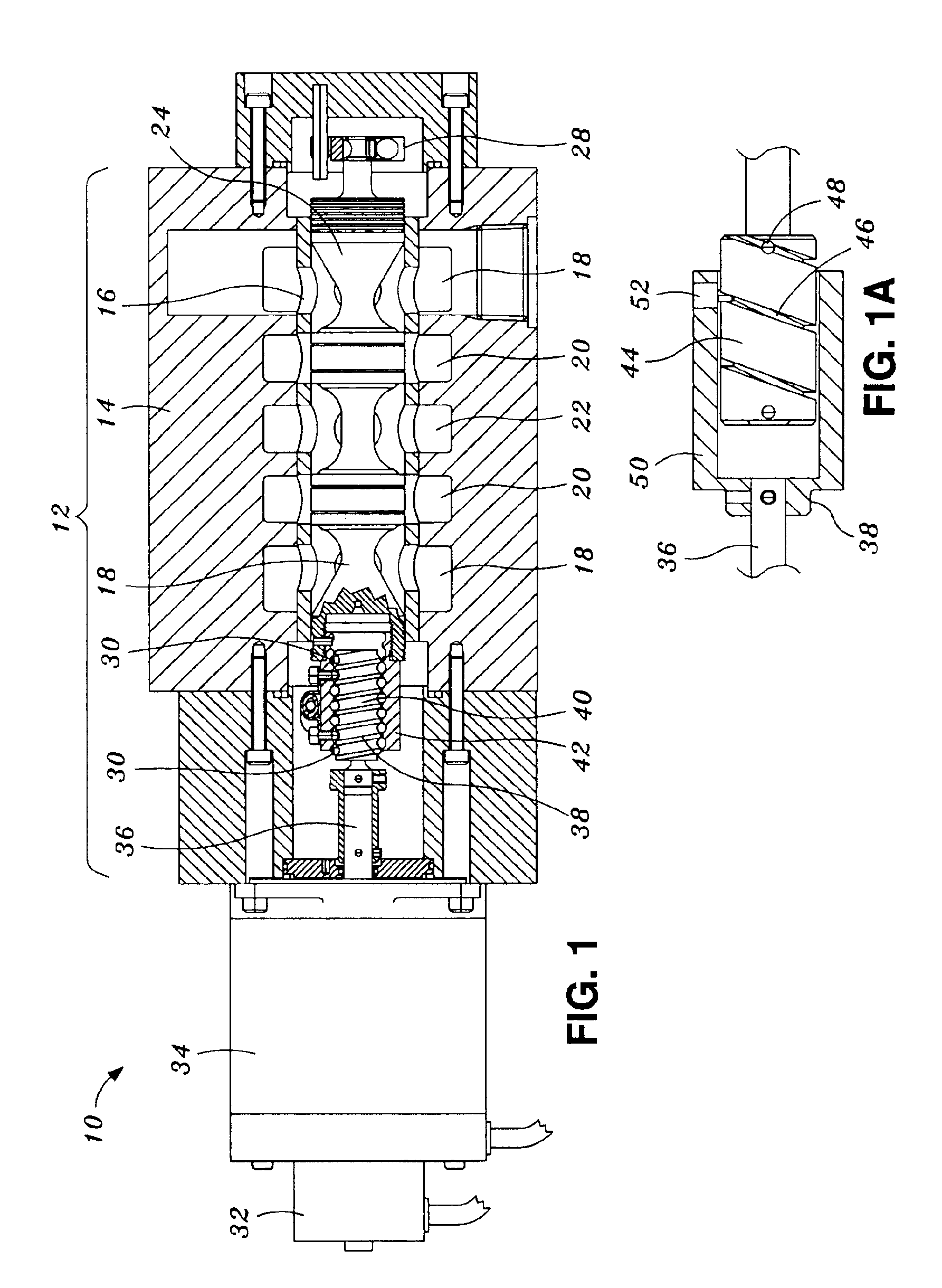

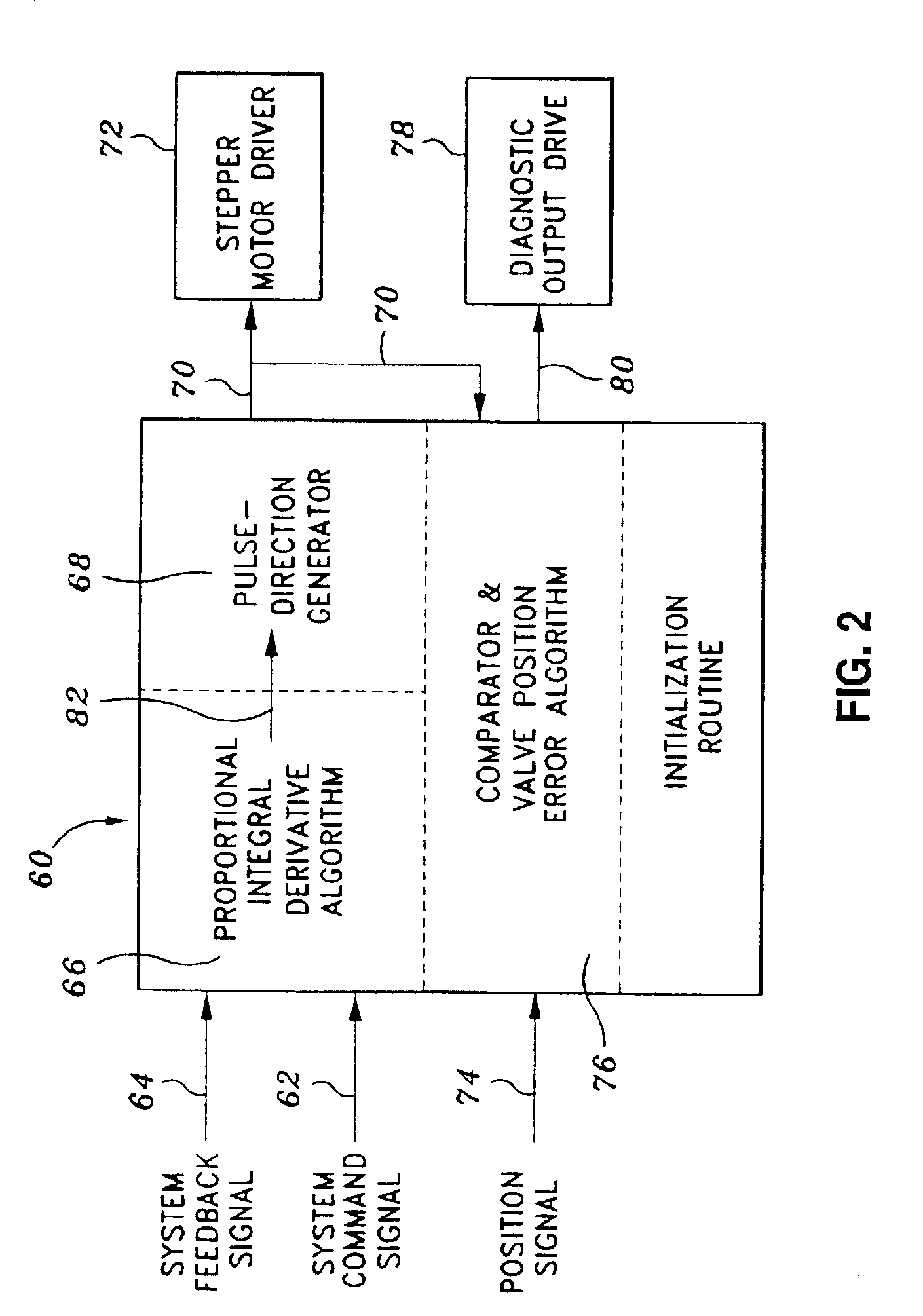

Predictive maintenance and initialization system for a digital servovalve

ActiveUS20050000580A1Simple and reliable initializationReduced referenceFluid-pressure actuator testingOperating means/releasing devices for valvesMechanical resistanceEngineering

Provided is a servovalve system for regulating fluid flowing within a fluid circuit. The servovalve system comprises a housing, a spool slidably disposed within the housing, a stepper motor operatively connected to the spool, and a controller and a position sensor electronically connected to the stepper motor. The controller generates driver signals representative of a desired amount of stepper motor rotation in order to cause the stepper motor to effectuate spool motion relative to the housing. The position sensor senses an actual amount of stepper motor rotation and generates a quantity of position signals representative thereof. The controller determines a signal ratio of the quantity of the position signals to the quantity of the driver signals and generates a diagnostic signal when the signal ratio reaches a threshold value representative of a predetermined level of mechanical resistance of spool motion relative to the housing.

Owner:CONTROL COMPONENTS INC

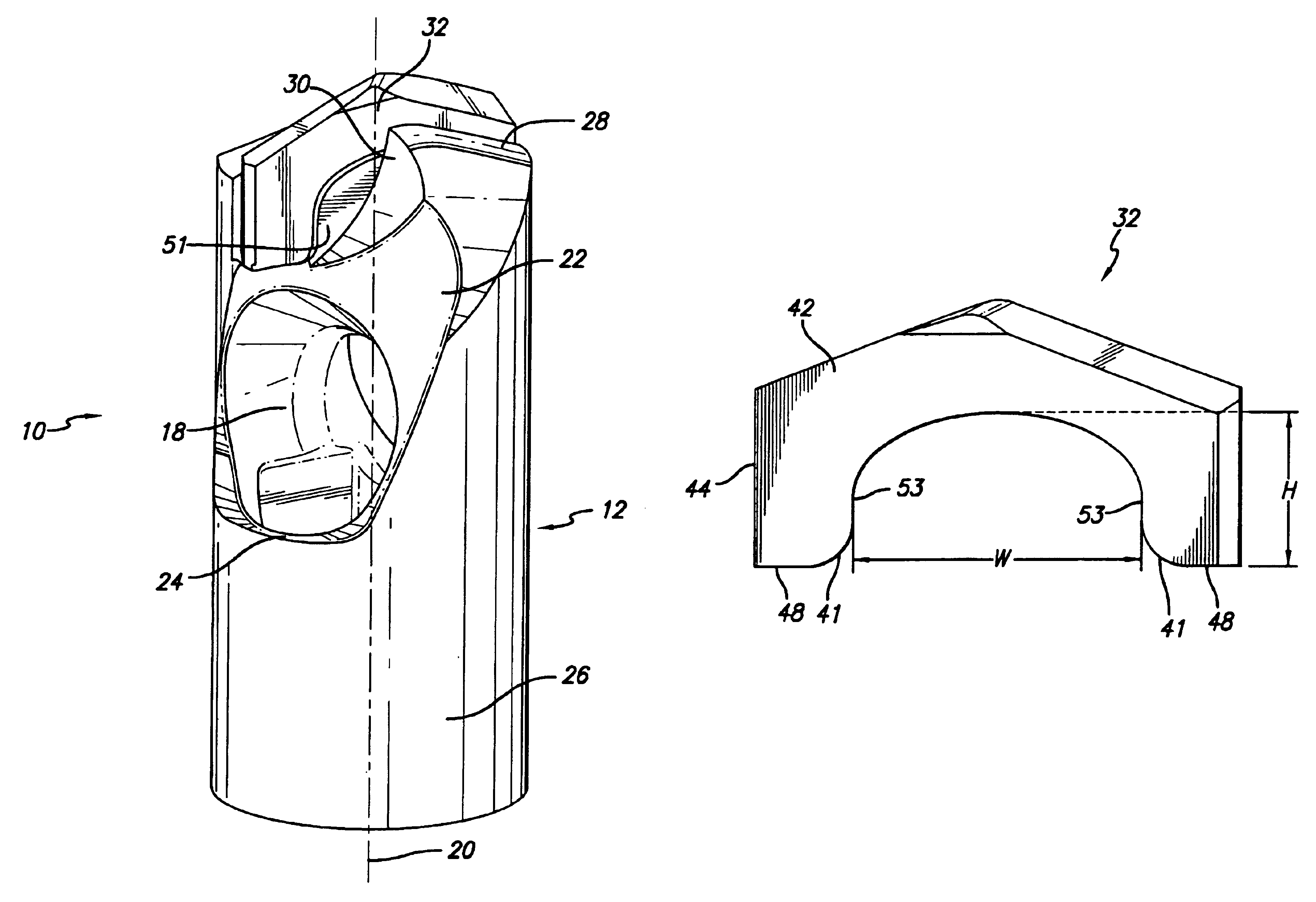

Apparatus for bone restoration of the spine and methods of use

ActiveUS8986386B2Inhibition of contractionInternal osteosythesisJoint implantsMechanical resistanceBack pain

The subject disclosure is directed to systems, apparatuses, devices and methods for vertebral and spinal correction. In some embodiments, an expandable implant is provided which may be inserted inside the vertebral body and / or between two vertebrae, for instance, for maintenance and / or restoration of a space therein or there between. In certain embodiments, the implant includes a mechanical resistance that prevents the expandable implant from contracting once it has been expanded. Methods of treatment and methods of use of such implants for the alleviation of back pain (for example) are also provided herein.

Owner:STRYKER EUROPEAN OPERATIONS LIMITED

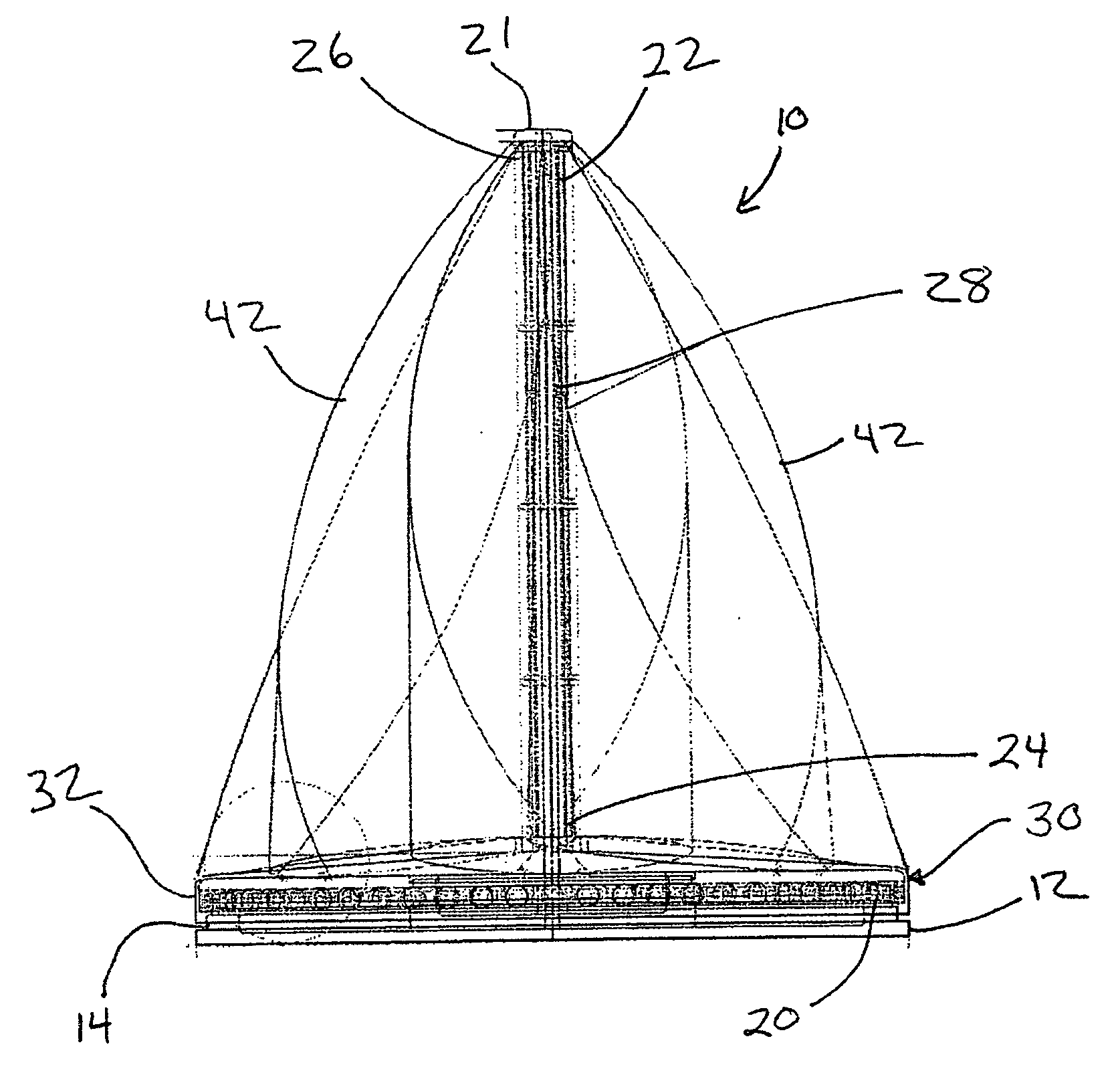

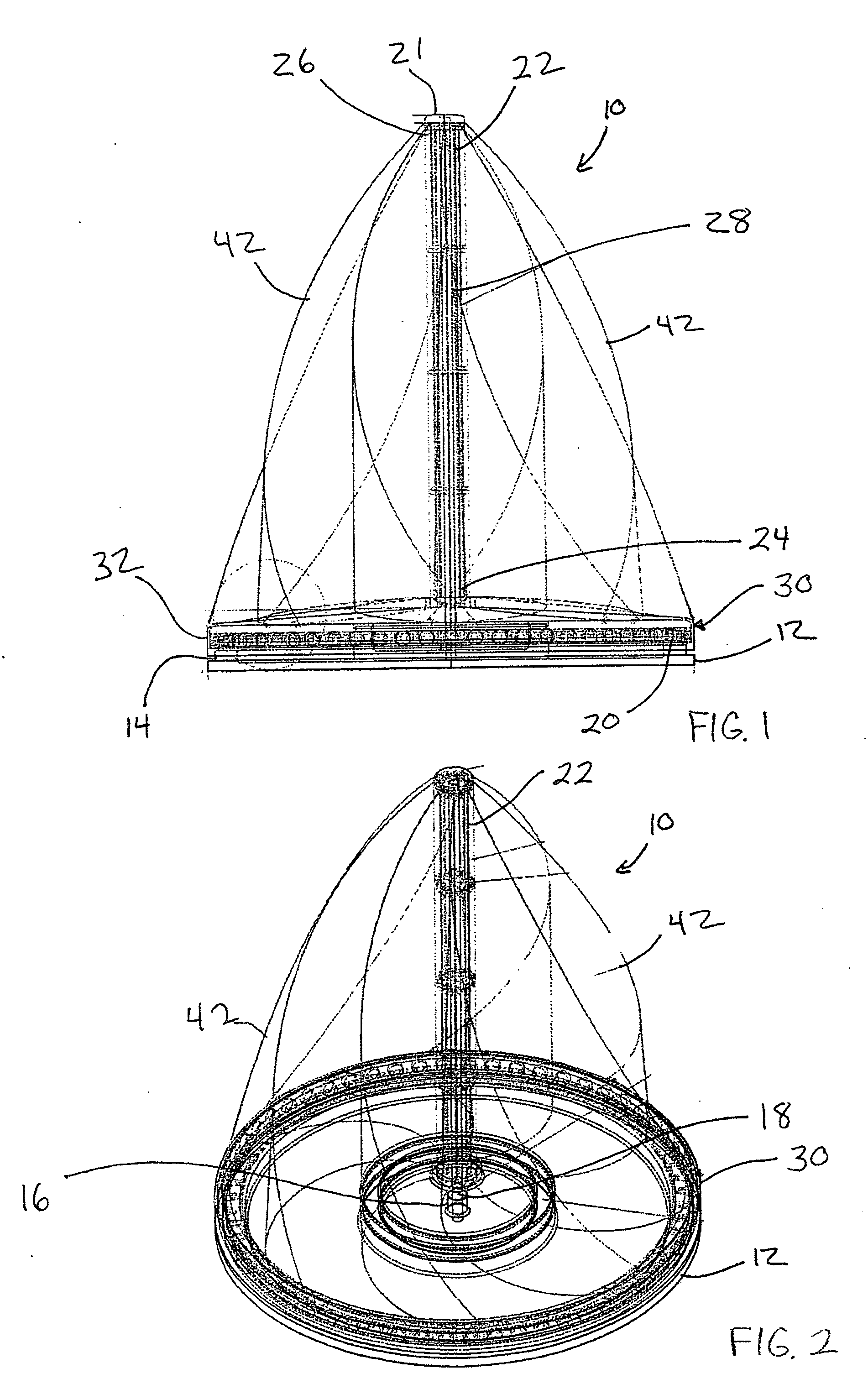

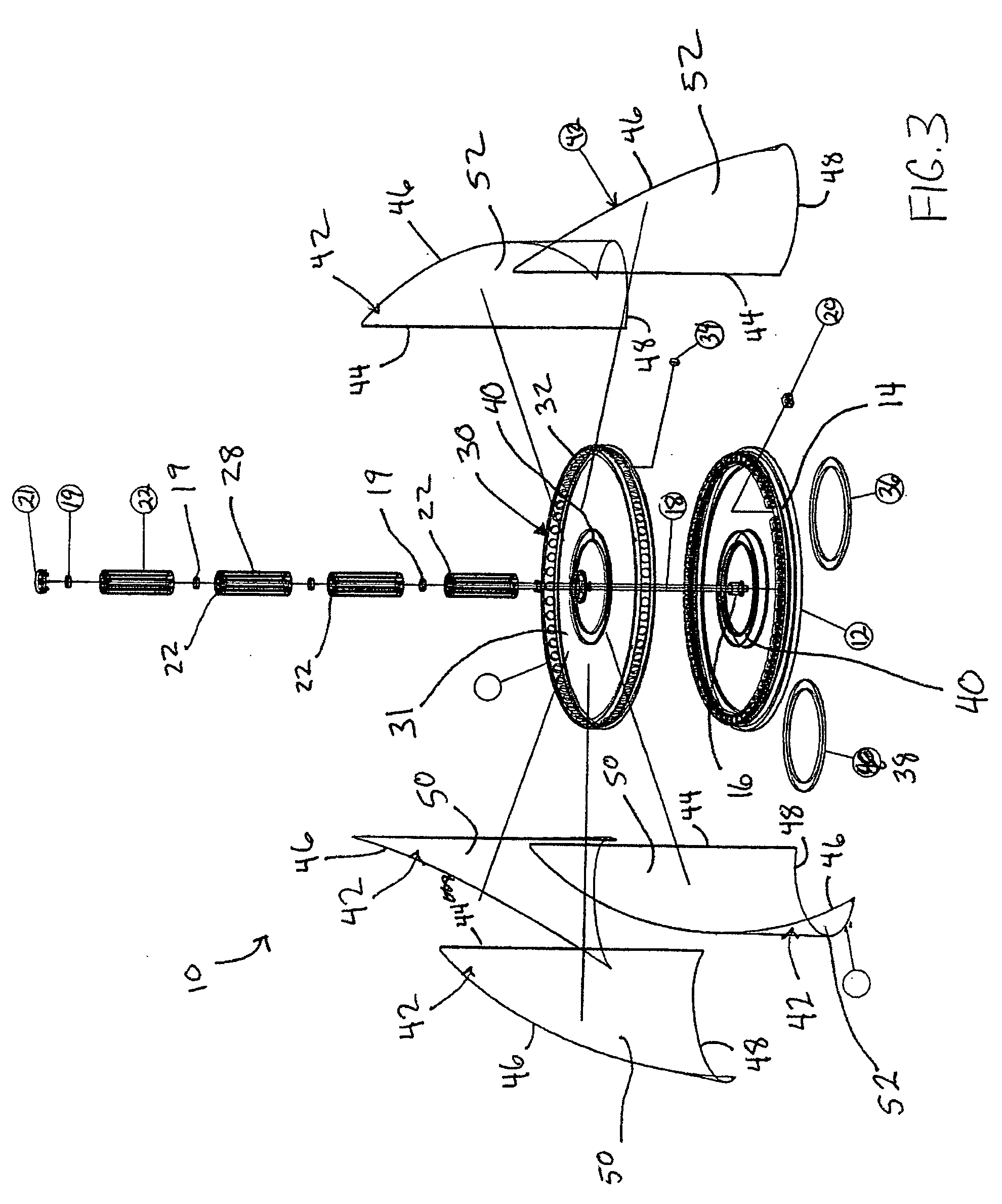

Magnetic vertical axis wind turbine

InactiveUS20070098563A1Reduce frictionMaximize operation of systemOther chemical processesPump componentsElectricityAlternator

A lift and drag-based vertical axis wind turbine in which the vertical axis and foils mounted thereon are magnetically levitated above the turbine's base, thereby reducing friction within the system. The foils or vanes are three-dimensionally shaped about the vertical axis so as to resemble the billowed sail of a sailing ship and capture wind through 360 degrees of rotation under any wind condition. The system has an axial flux alternator using variable resistance coils which can be individually and selectively turned on or off depending on wind conditions and electrical draw requirements. The coils can also be used to produce mechanical drag on the system as desired to brake the turbine in high wind conditions or for maintenance. The system may be programmed to assess whether electricity generated by the system can be or should be transmitted to a public grid or stored locally on a chargeable battery system.

Owner:NIAGARA CENT RES

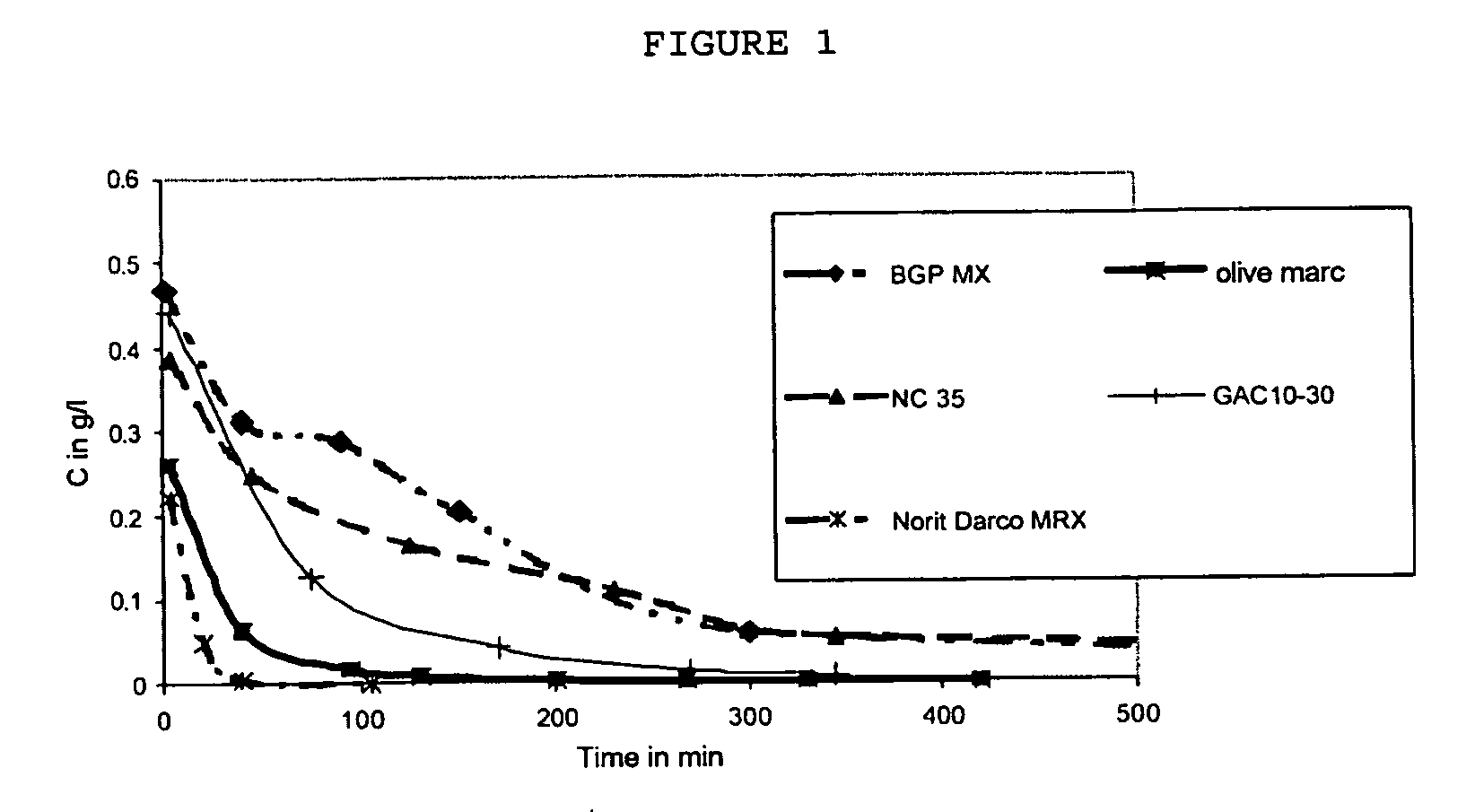

Activated carbon with improved mechanical resistance, and the uses thereof, especially as a catalyst carrier

InactiveUS20070123419A1Strong mechanical propertiesRapidly impregnated with oxidation catalystCarbon compoundsOther chemical processesGas phaseSolvent

The present invention relates to active charcoals with improved mechanical properties. They can advantageously be used in the sweetening of petroleum fractions, as oxidation catalyst support in the conversion of mercaptans to disulphides, but also in any other type of reaction, such as, for example, for the oxidation of cyanide present in water or in the synthesis of glyphosate, and in processes for purification and / or separation by selective adsorption in a liquid phase and / or in a gas phase (decolouration of liquid foodstuffs, water treatment, air treatment, recovery of solvents, and the like).

Owner:LE BEC REMY

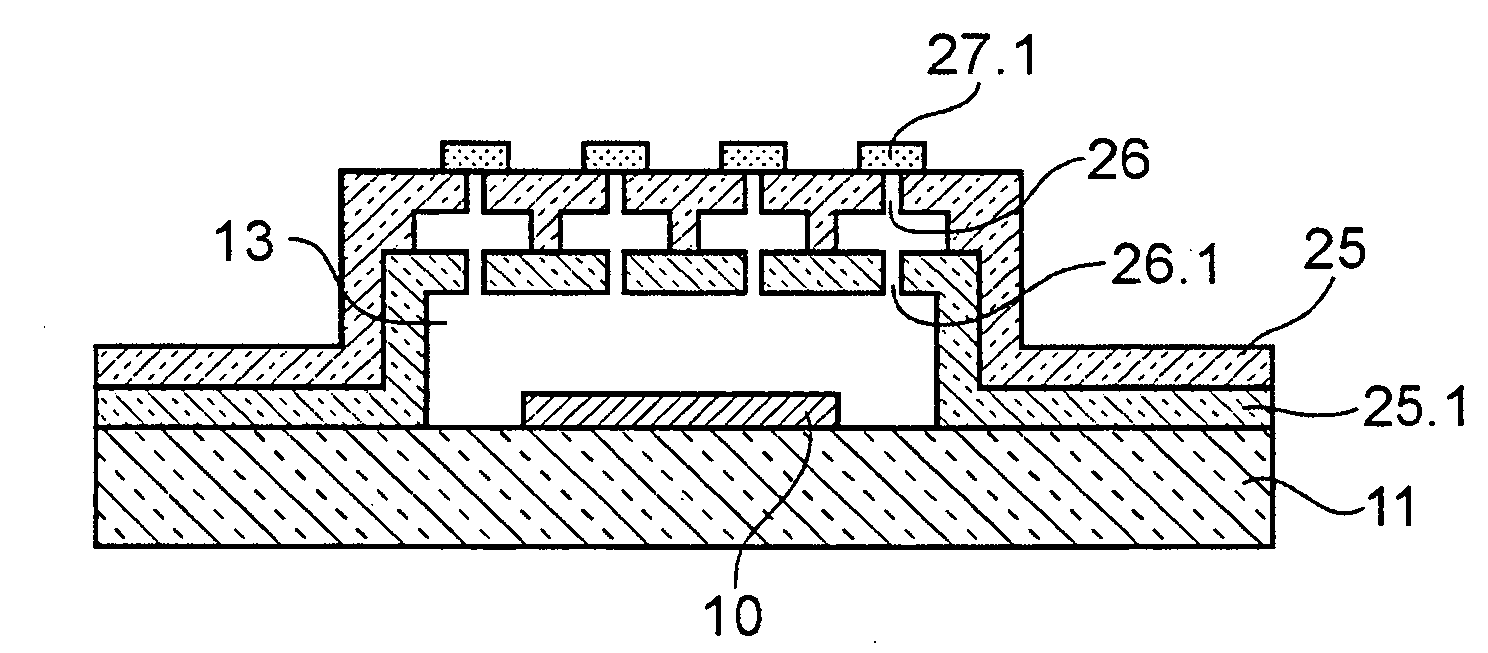

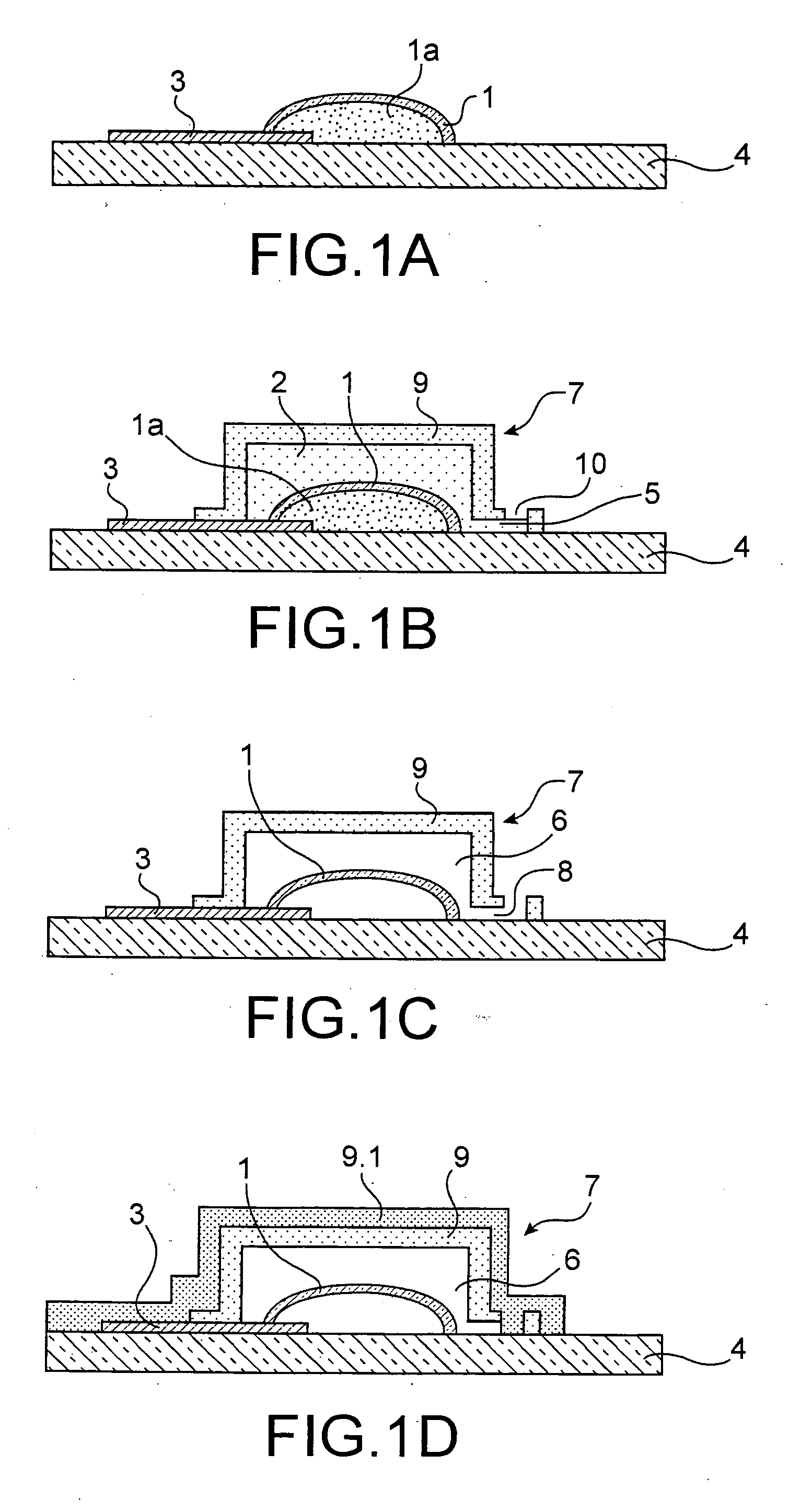

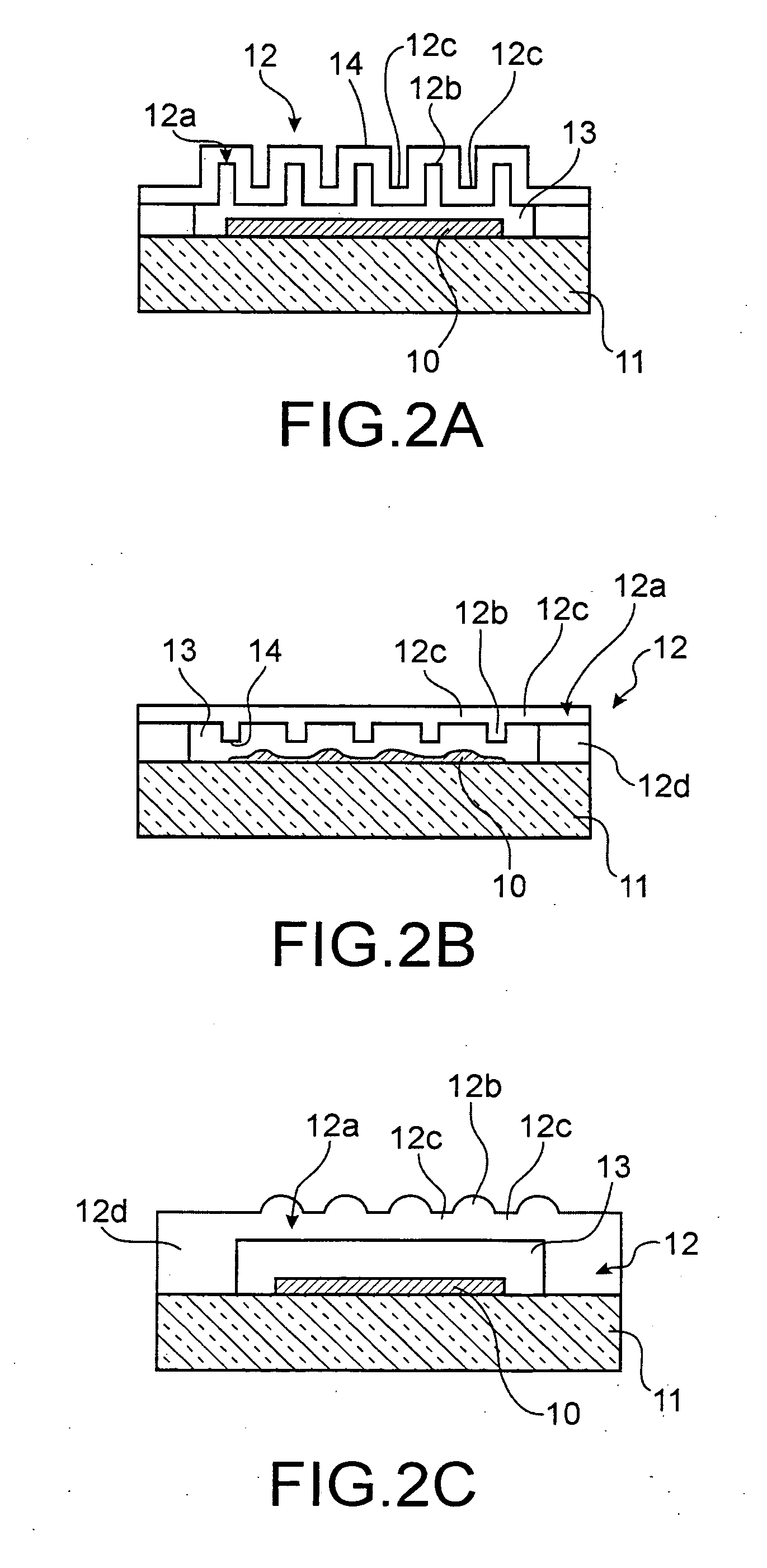

Microcomponent Provided with a Cavity Delimited by a Cap with Enhanced Mechanical Resistance

ActiveUS20090194309A1Easy to manufactureGood mechanical resistanceForming microstructural systemsPrinted circuit manufactureMechanical resistanceMechanical engineering

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

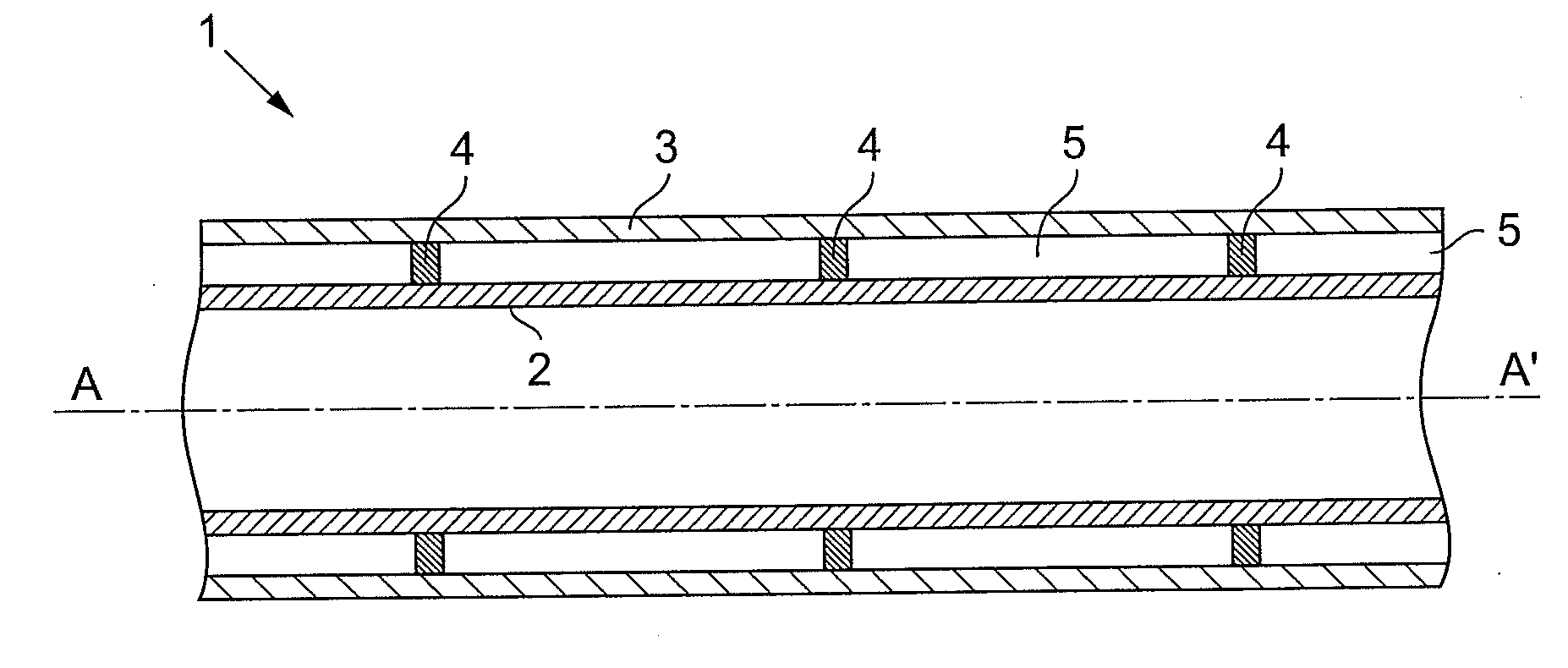

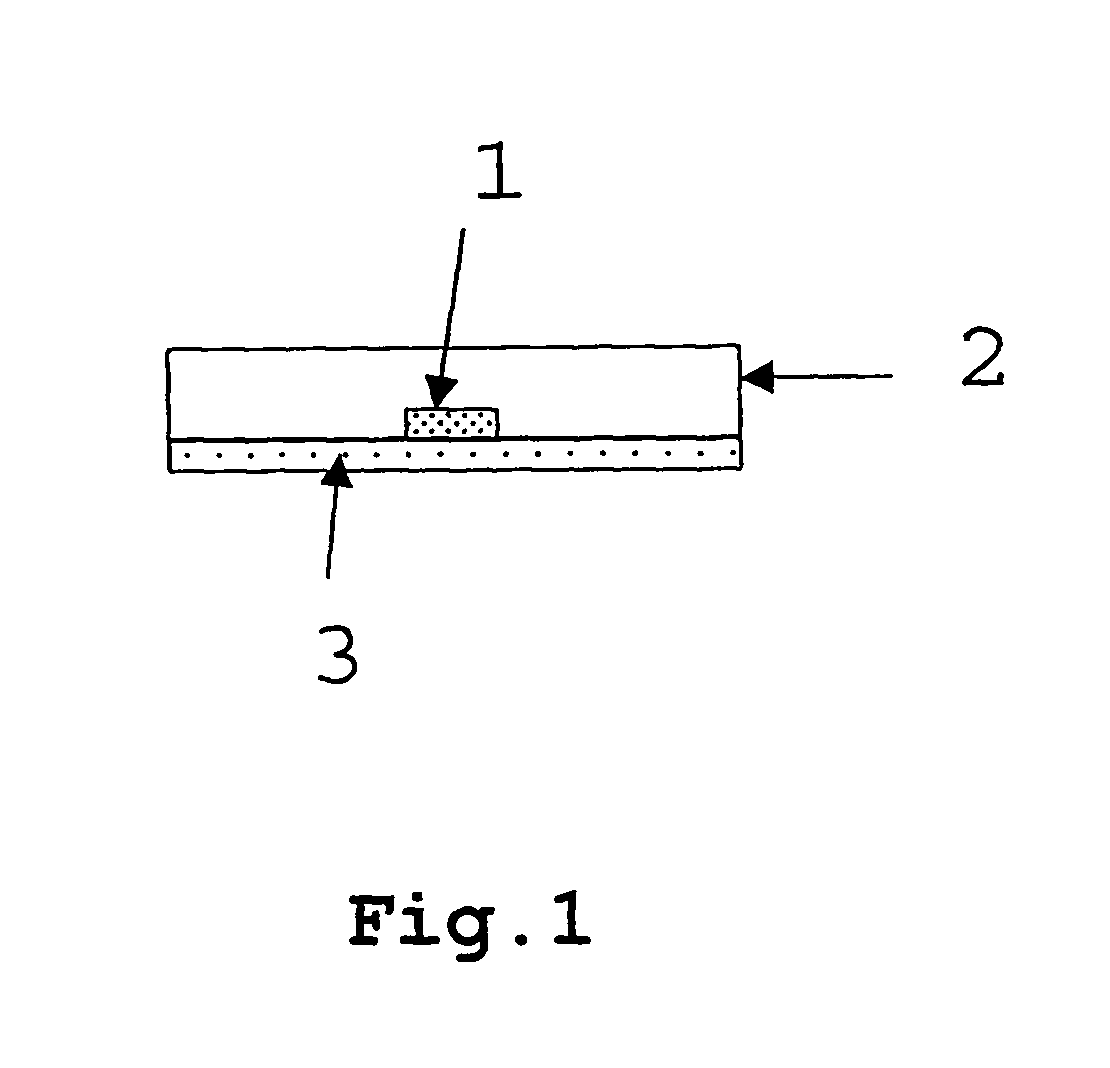

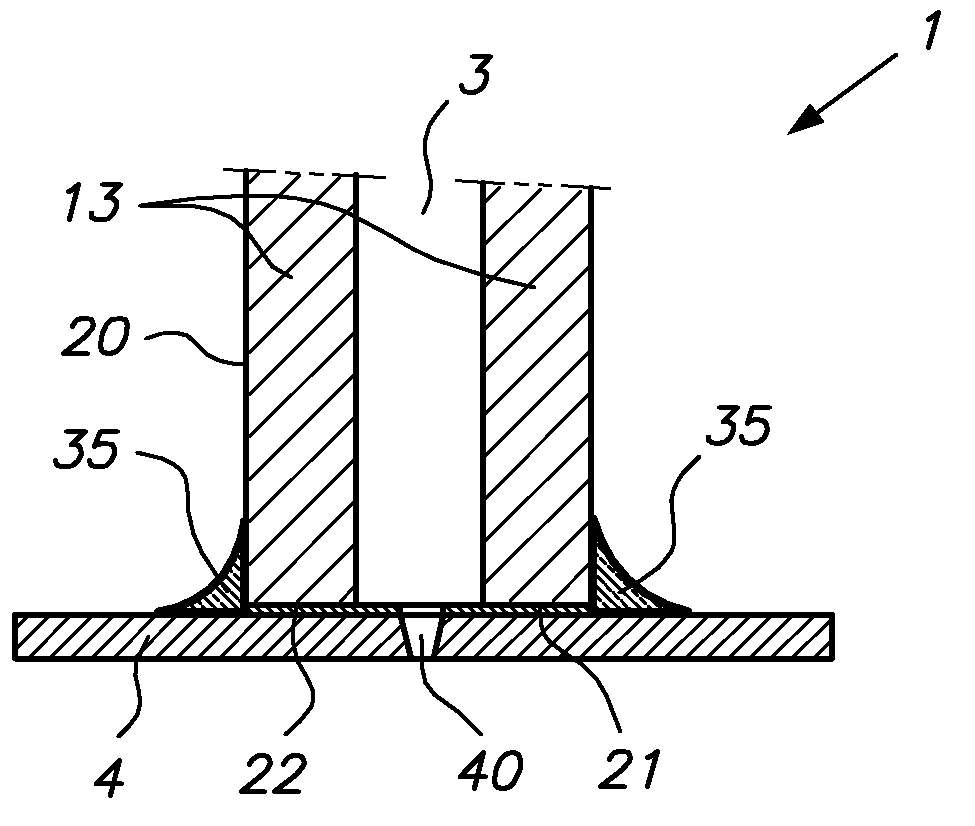

Reinforced double-walled pipe and manufacturing method

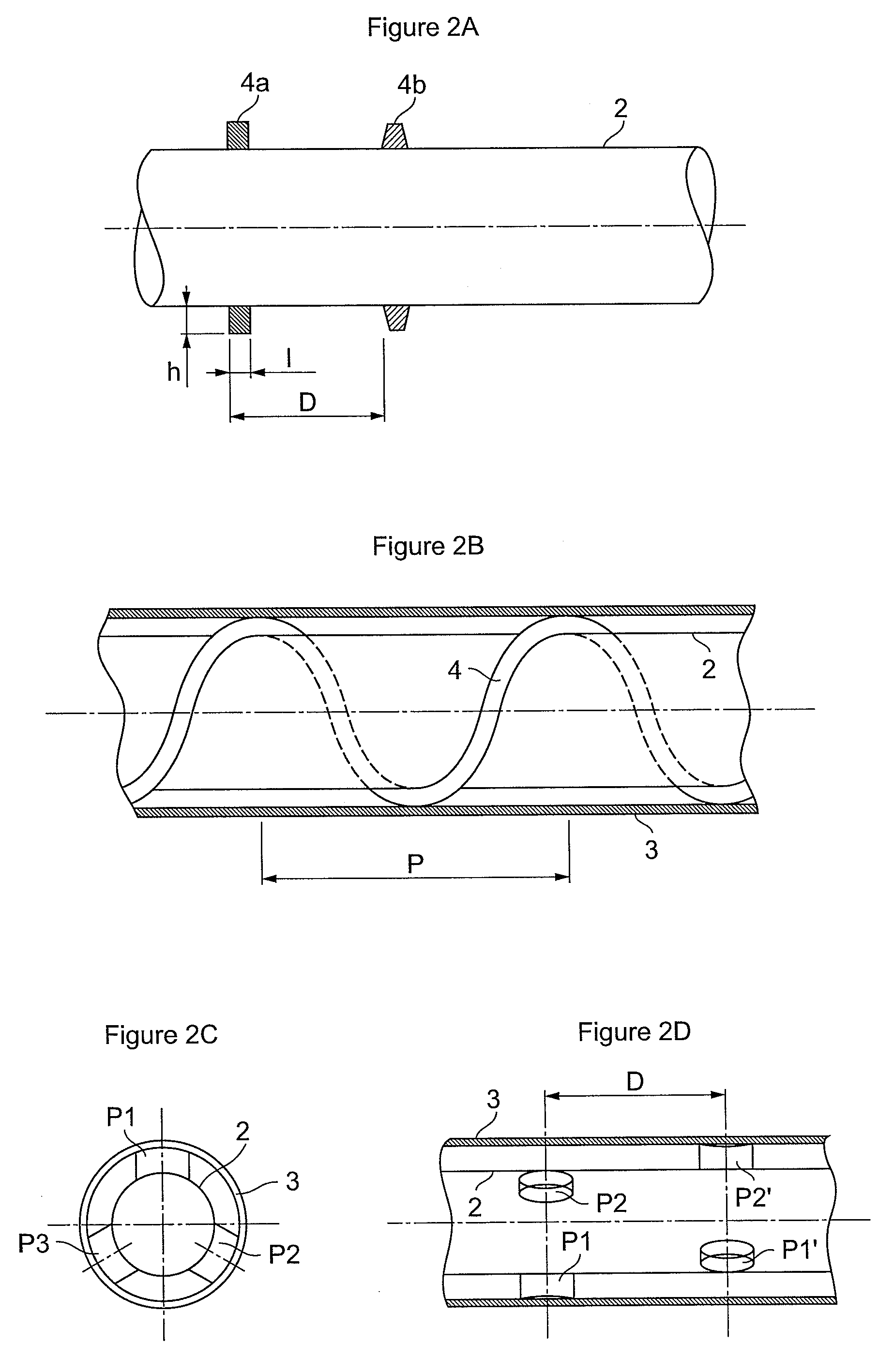

InactiveUS20090000681A1Good mechanical resistanceReduce steel thicknessThermal insulationMetal-working apparatusMechanical resistanceDouble-walled pipe

The double-walled pipe comprises a rigid internal tube 2 arranged in a rigid external tube 3, the tubes being separated by an annular space, centering elements holding the internal tube in position in relation to the external tube.External tube 3 withstands alone an external pressure at least above 50 bars.The mechanical resistance of the pipe to the external pressure is reinforced by placing centering elements 4 in contact with internal tube 2 and with external tube 3.

Owner:INST FR DU PETROLE

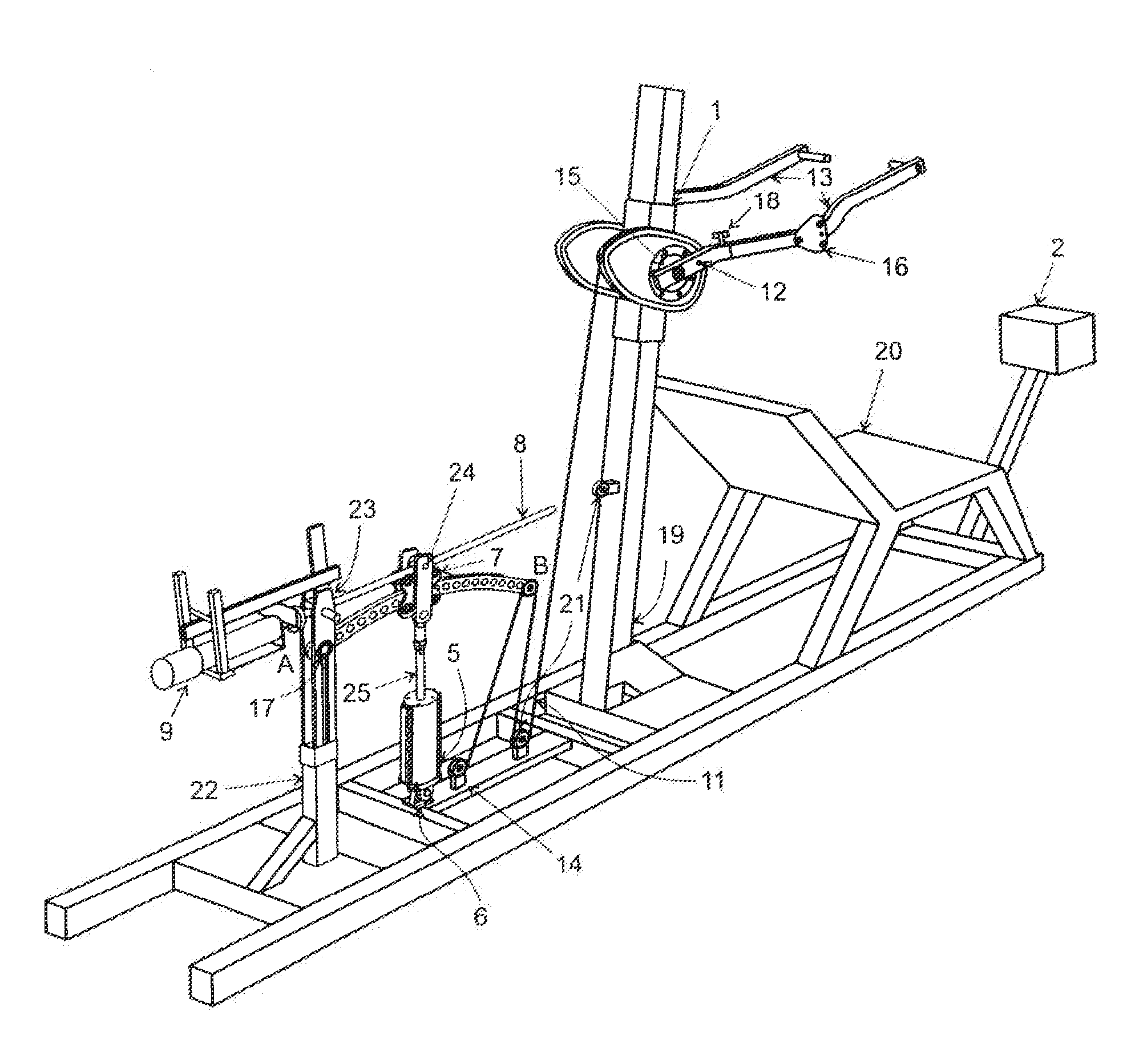

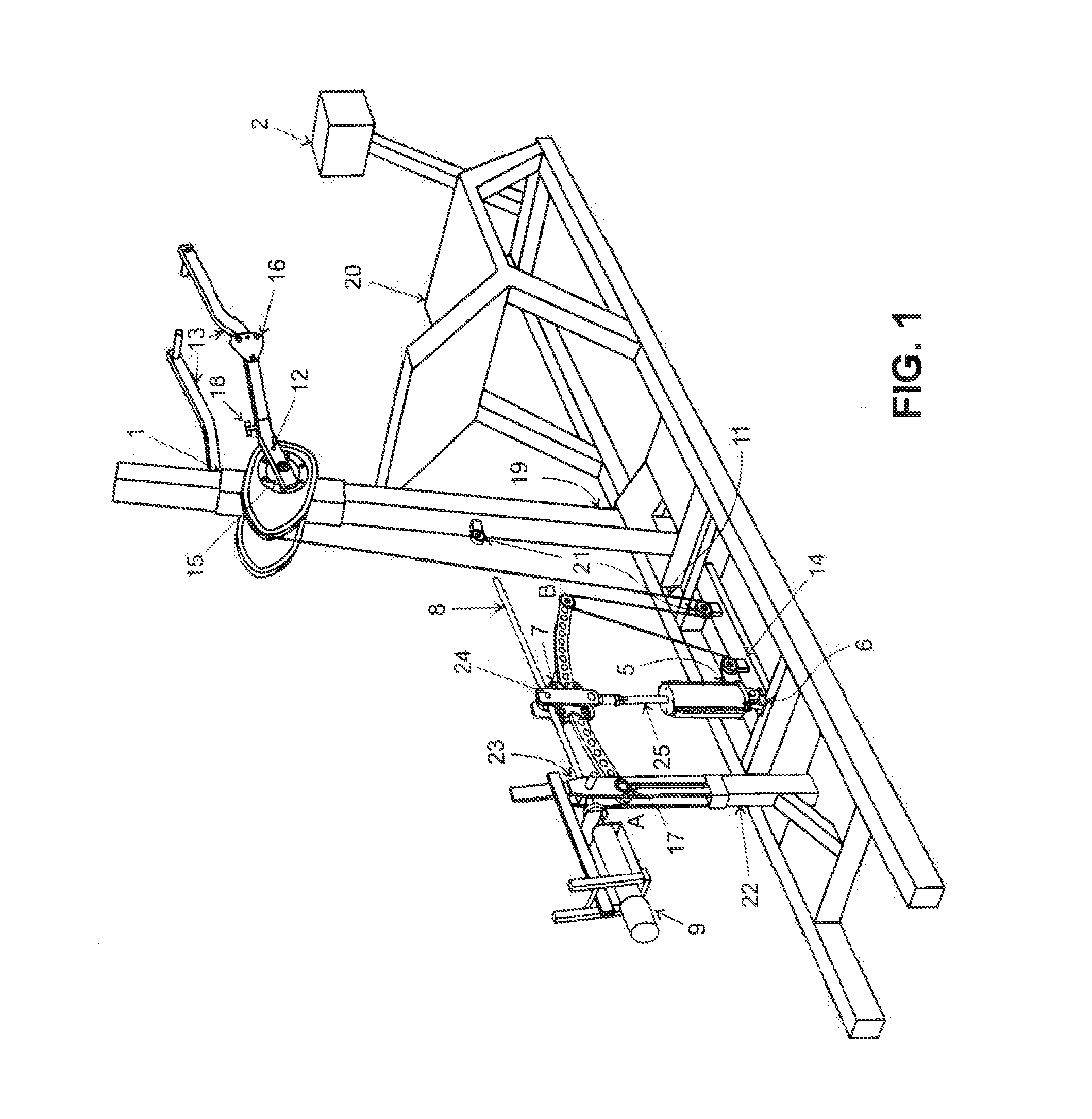

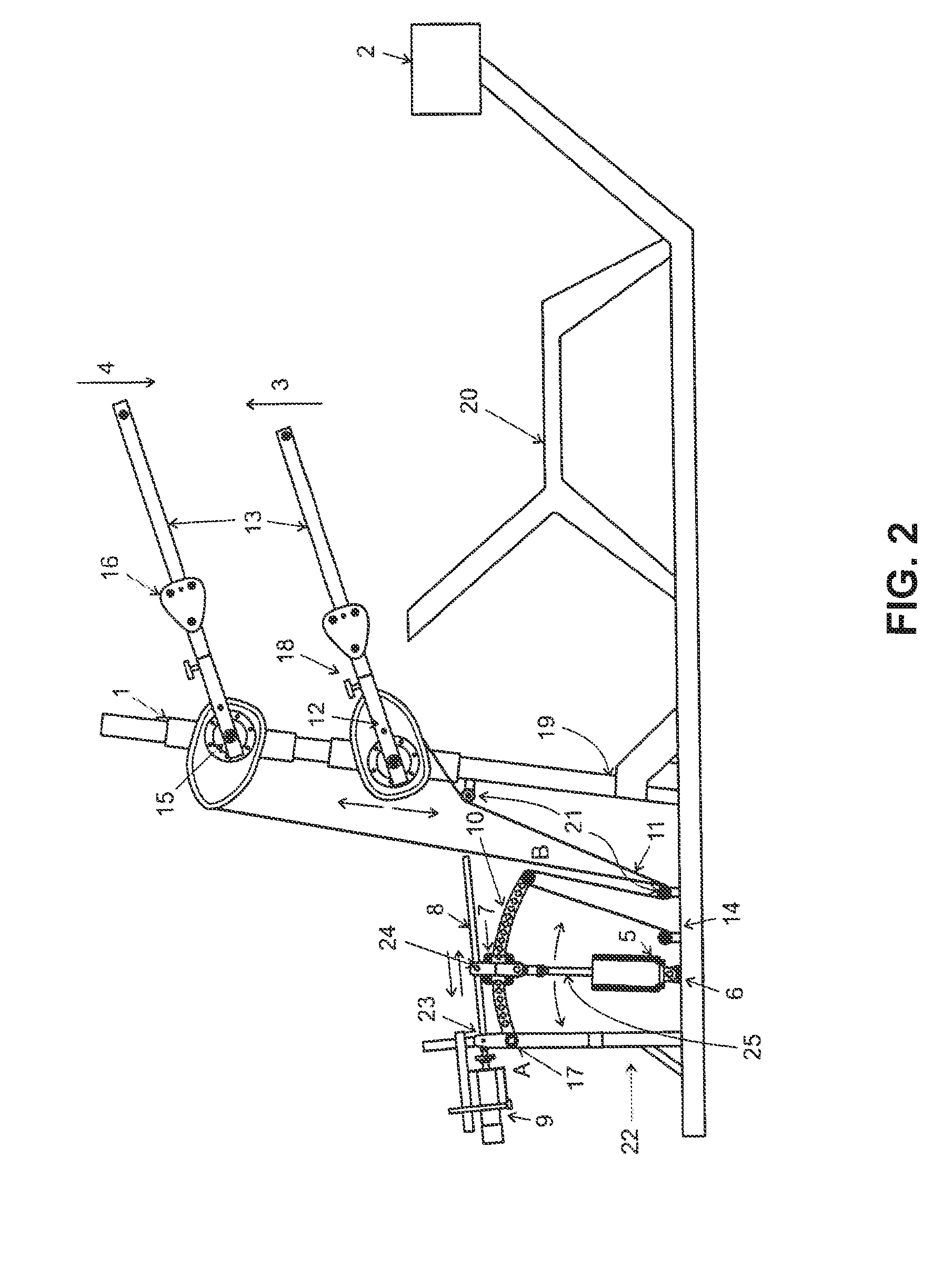

Resisting system for making variable mechanical resistance exercises

The present invention relates to equipment, apparatus and systems used for exercising muscle groups of the body, more specifically, a resistance system for making variable mechanical resistance exercises, which receive voice commands, changes in brain waves and / or any body movement.

Owner:BISSU MOISES BUCAY

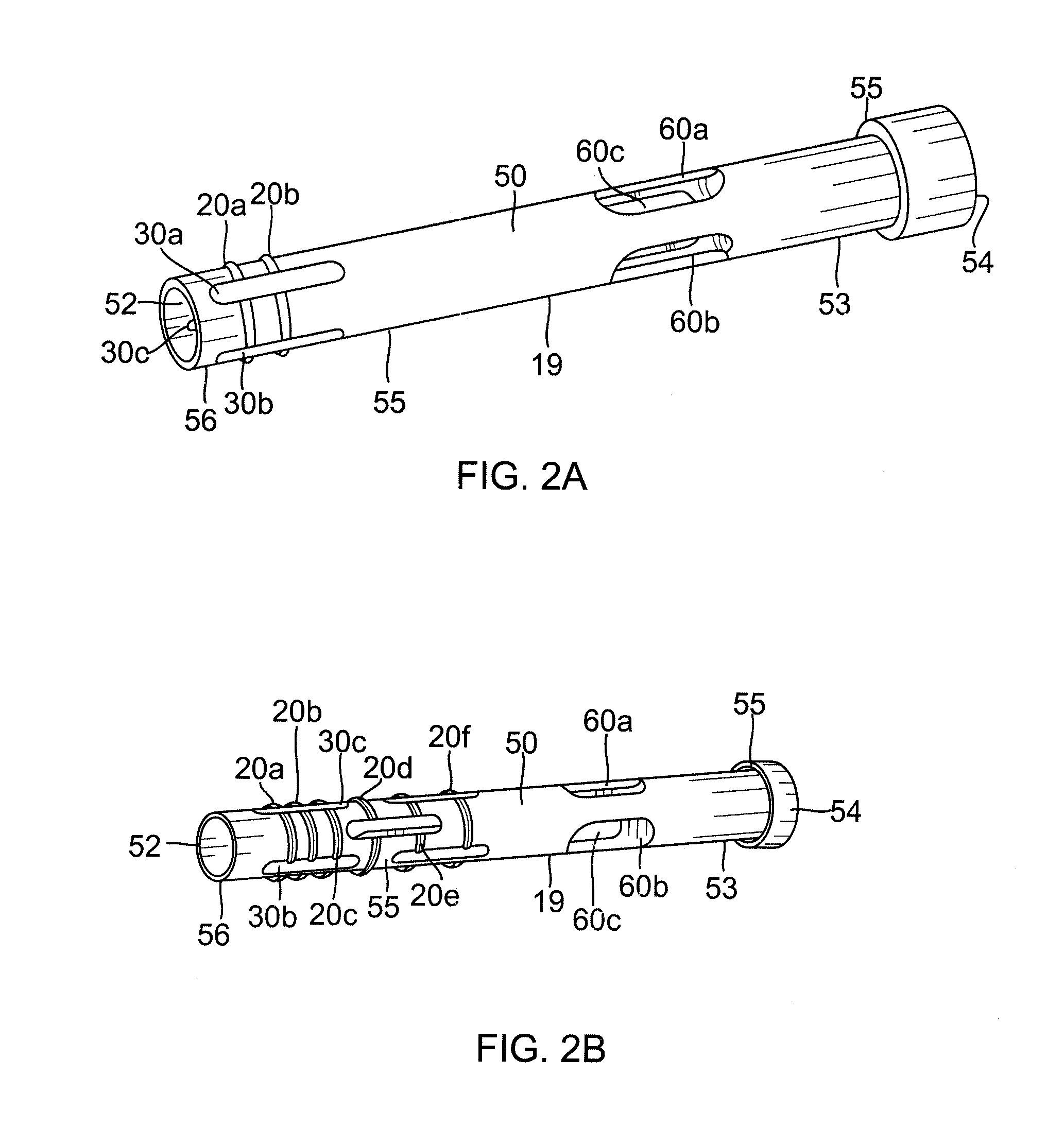

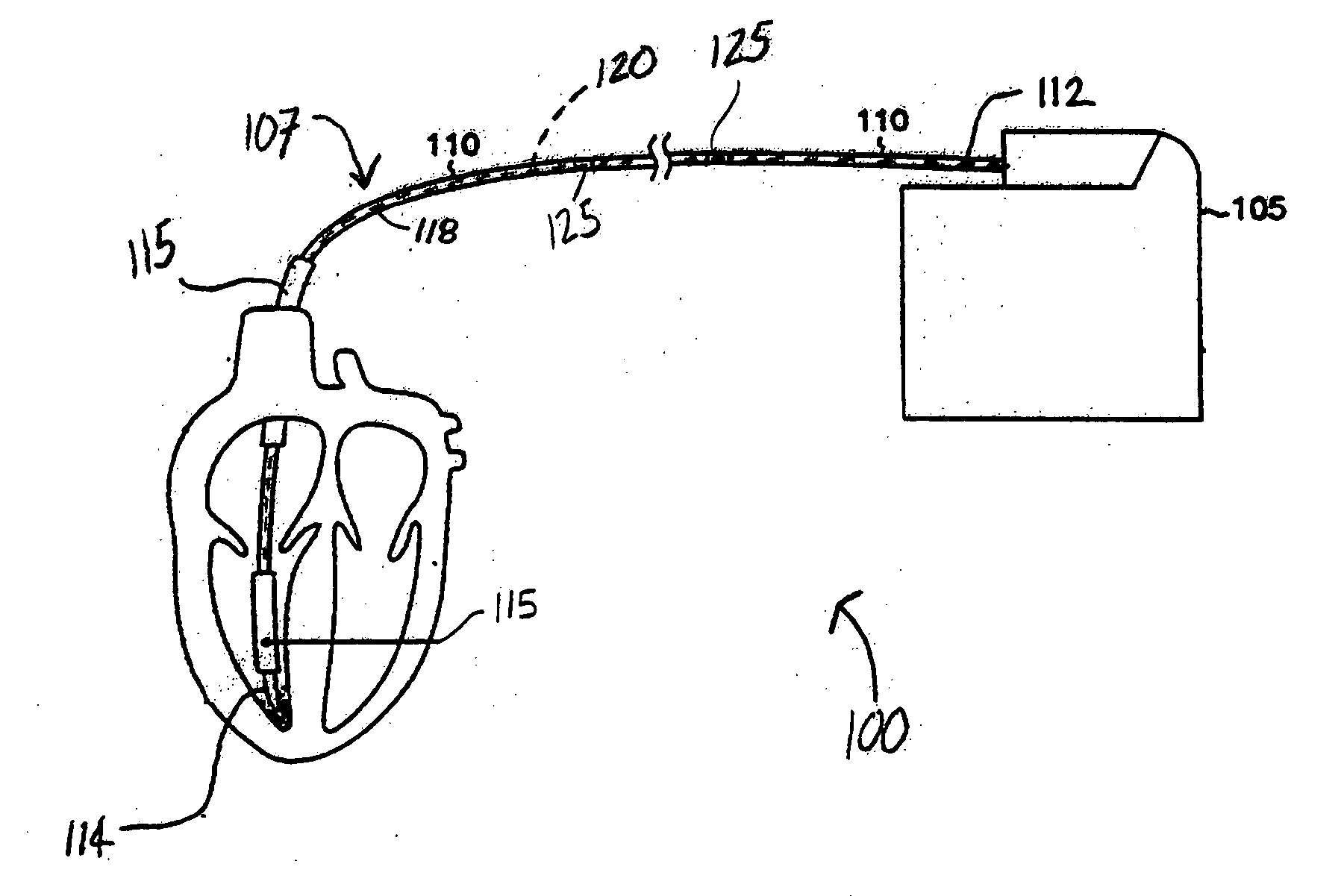

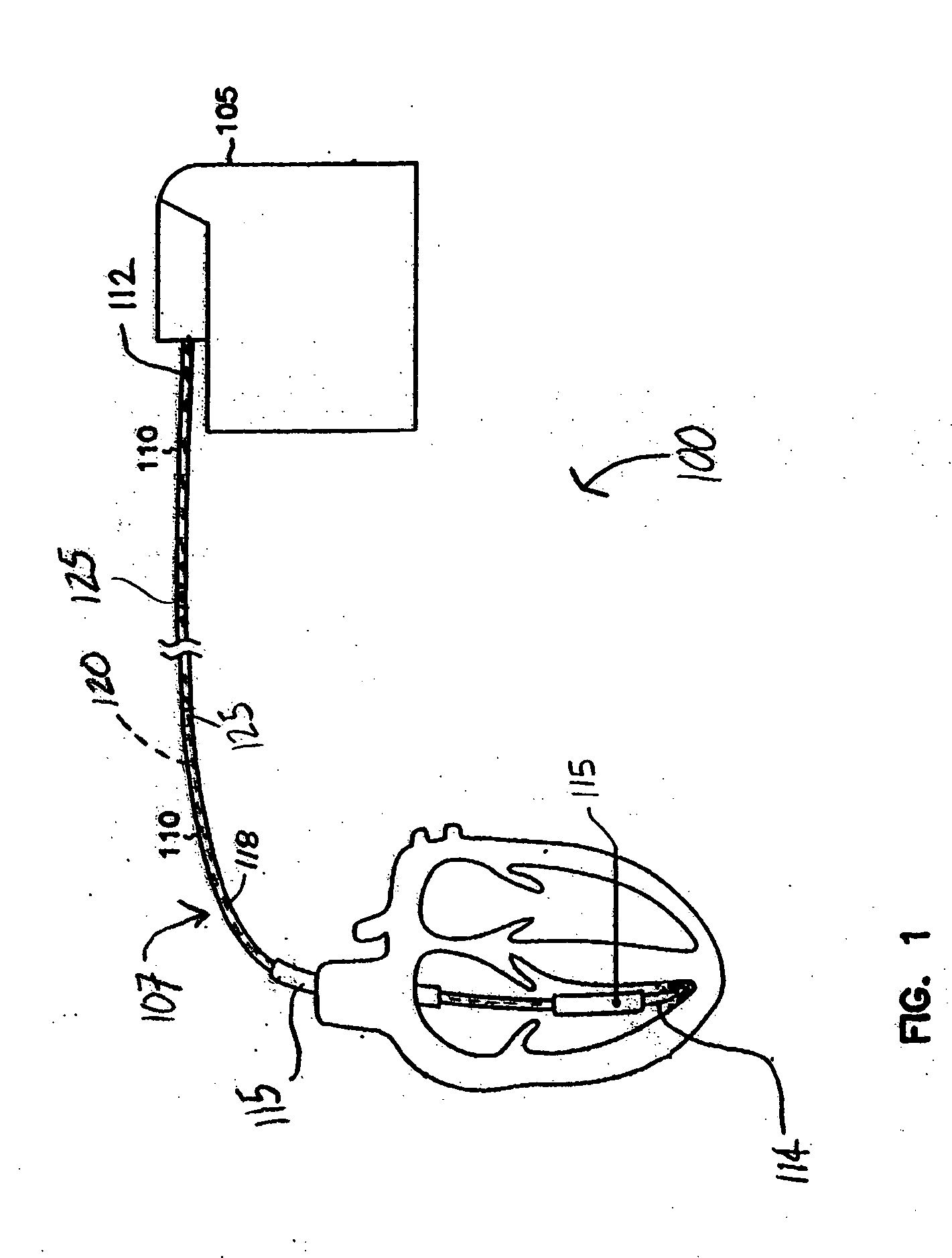

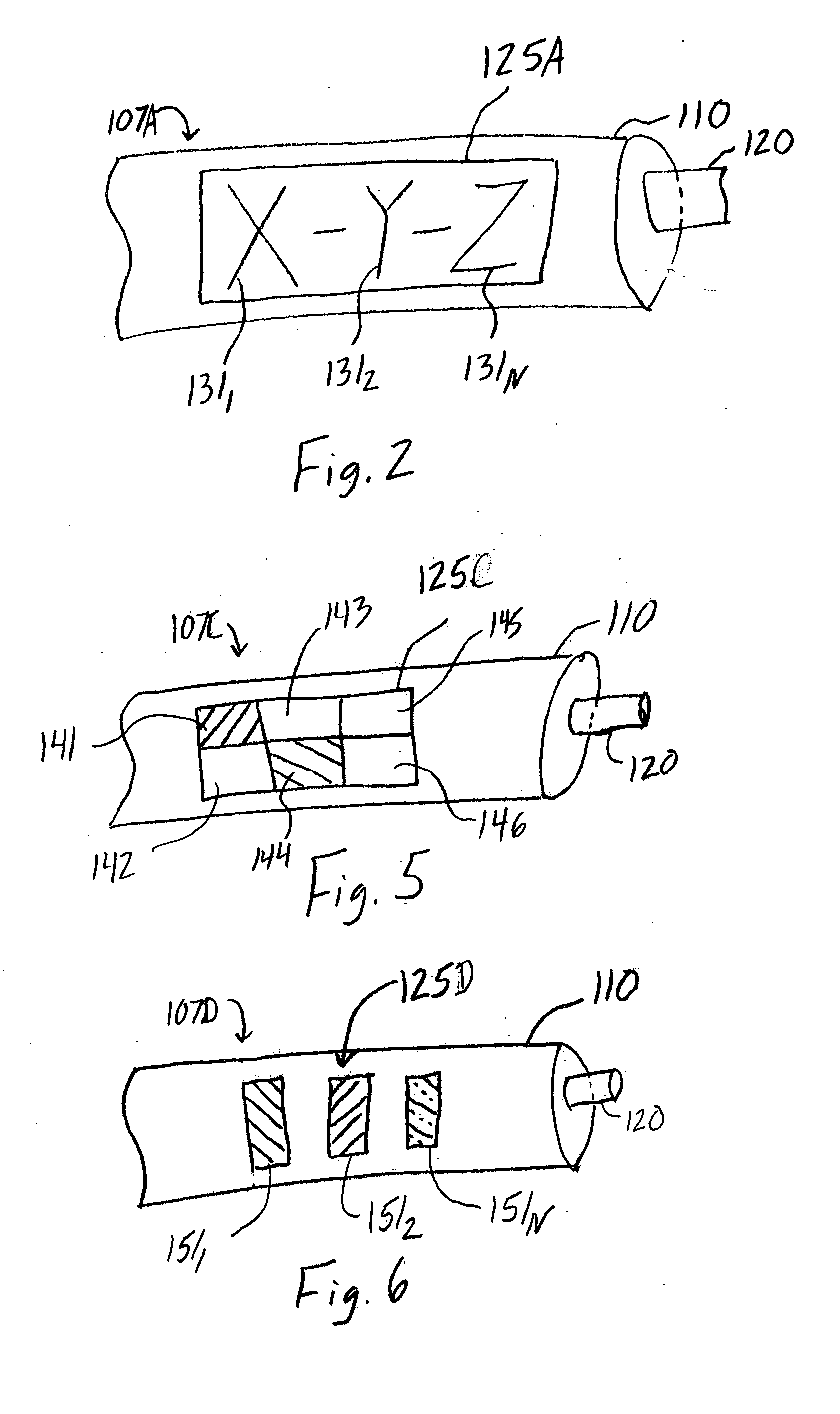

Systems and methods for characterizing leads

InactiveUS20060020314A1Easy to understandImprove featuresInternal electrodesExternal electrodesGraphicsMechanical resistance

Indicia represent characteristics of an implantable lead. The characteristics include at least one of stiffness, bending stiffness, torsional stiffness, weight, mass per unit length, electrical properties, lubricity, mechanical resistance, and pushability. The indicia include a plurality of alpha-numeric characters and / or graphics, which represent a corresponding plurality of lead characteristics.

Owner:CARDIAC PACEMAKERS INC

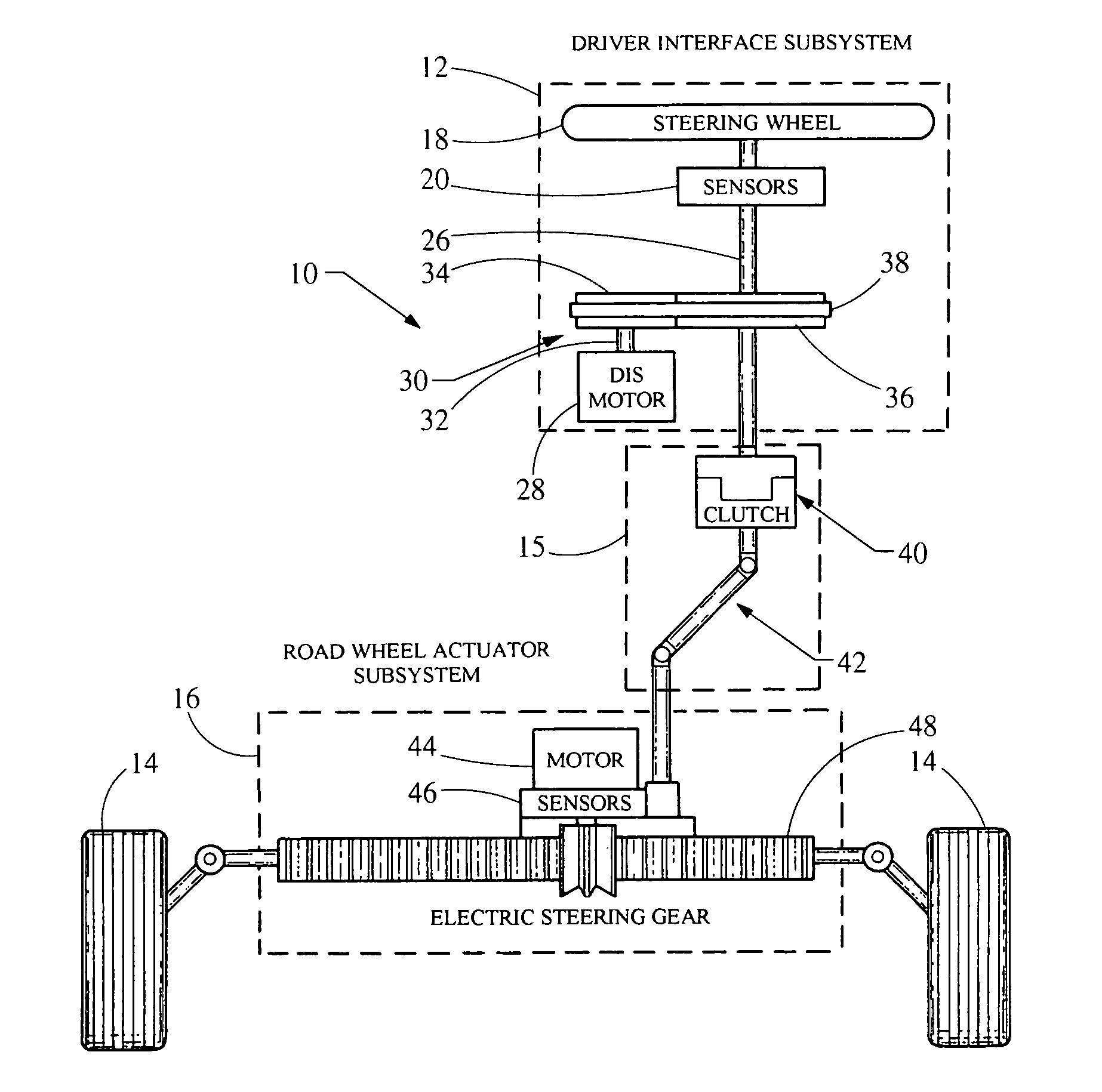

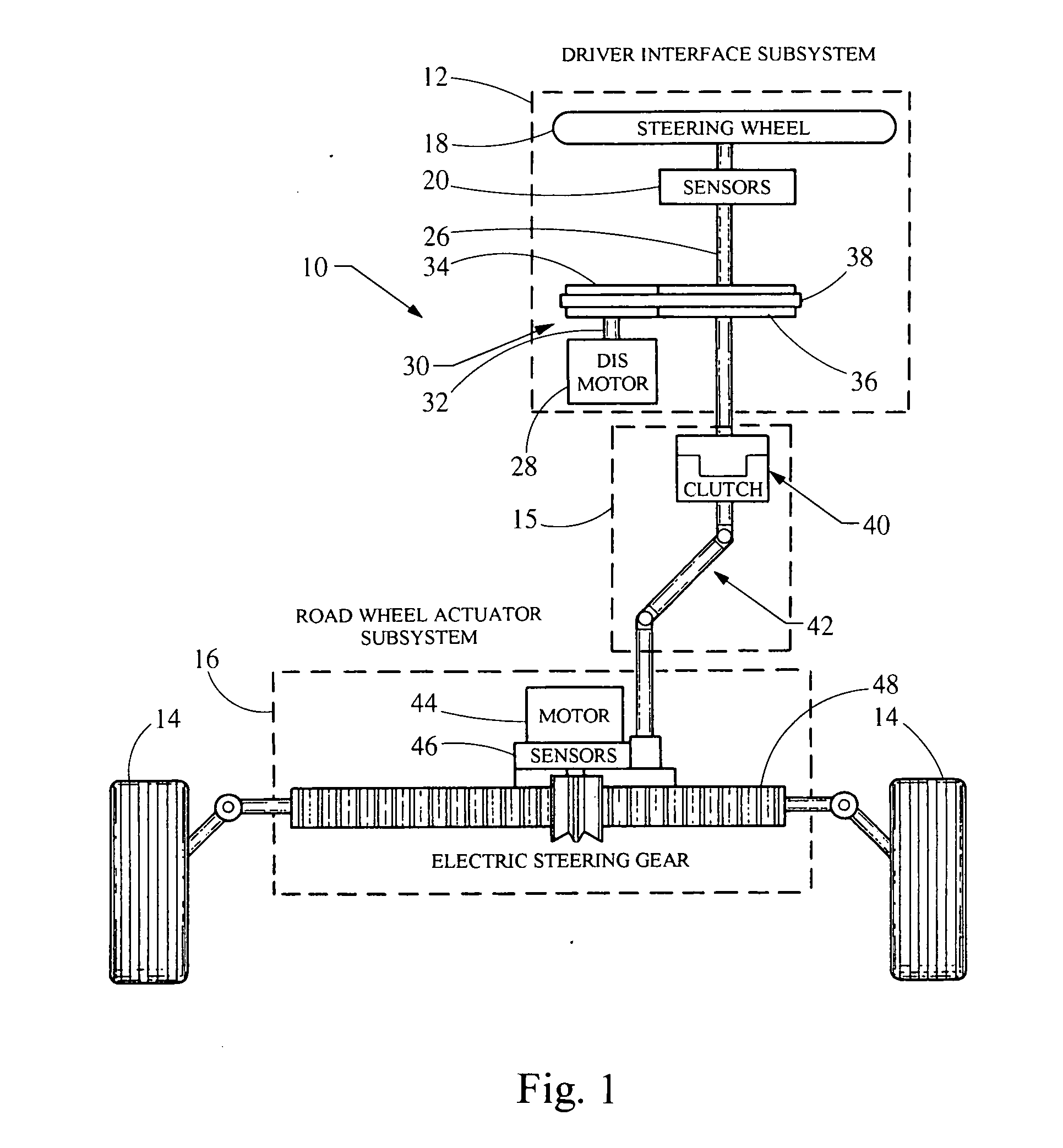

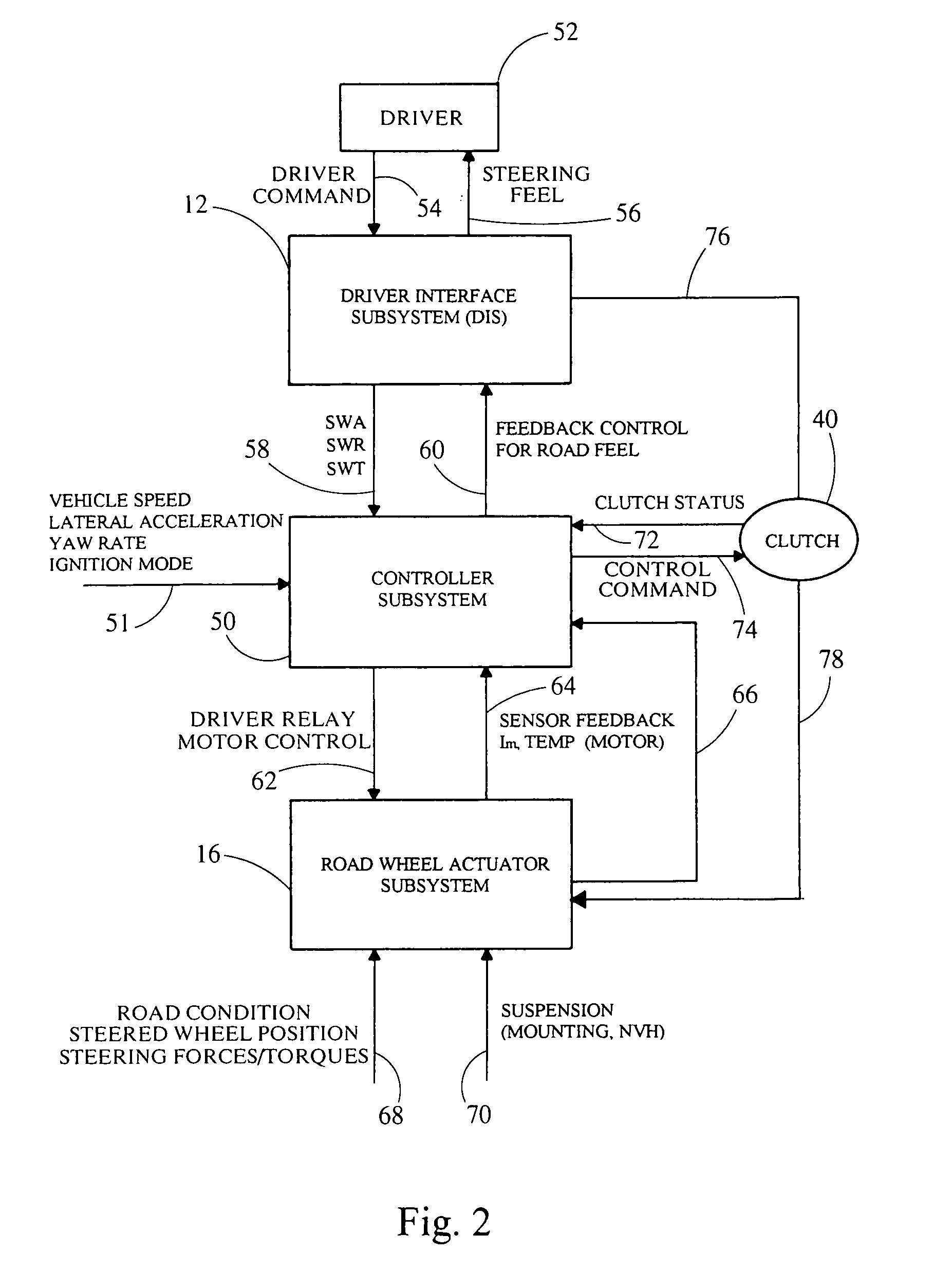

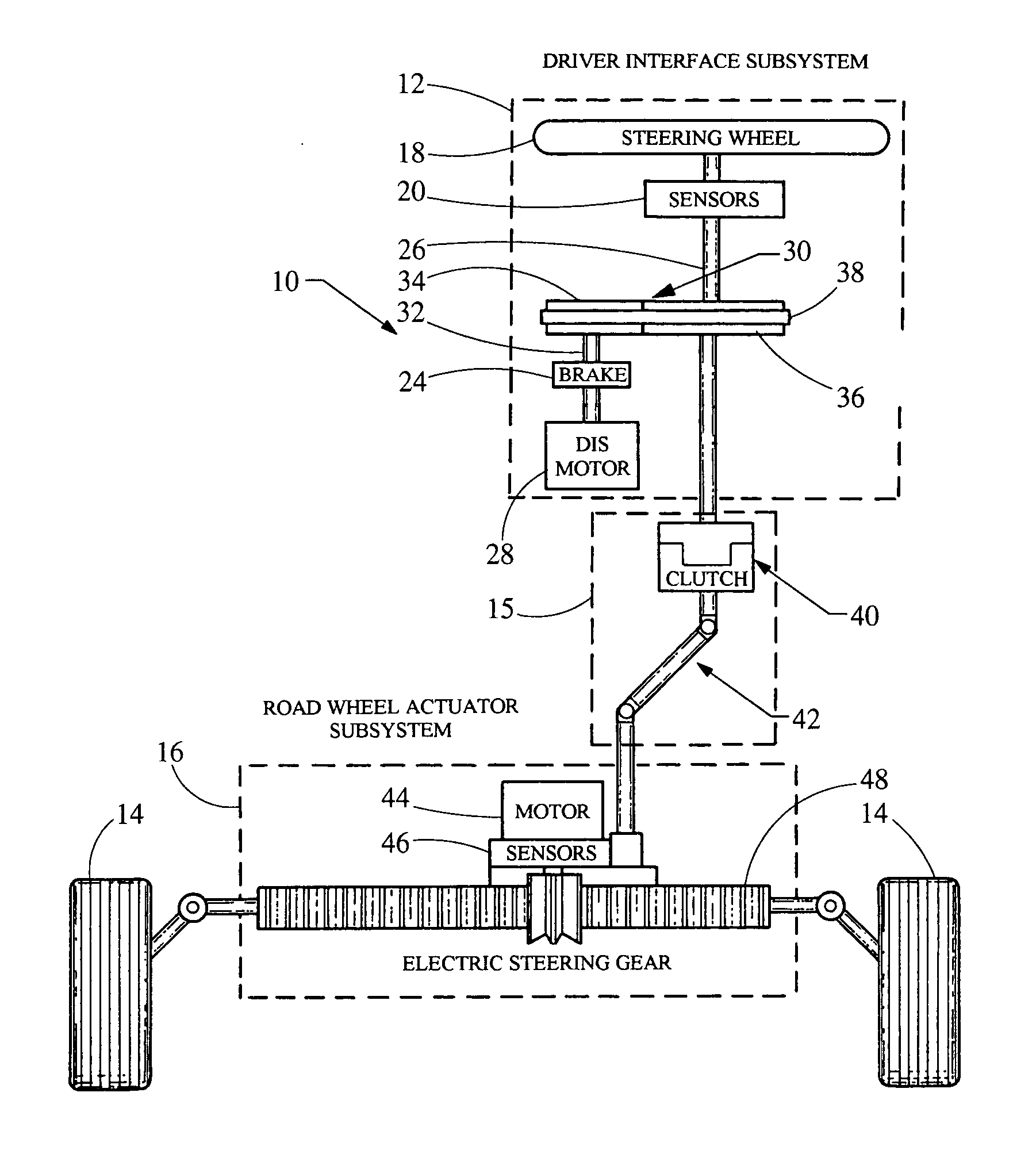

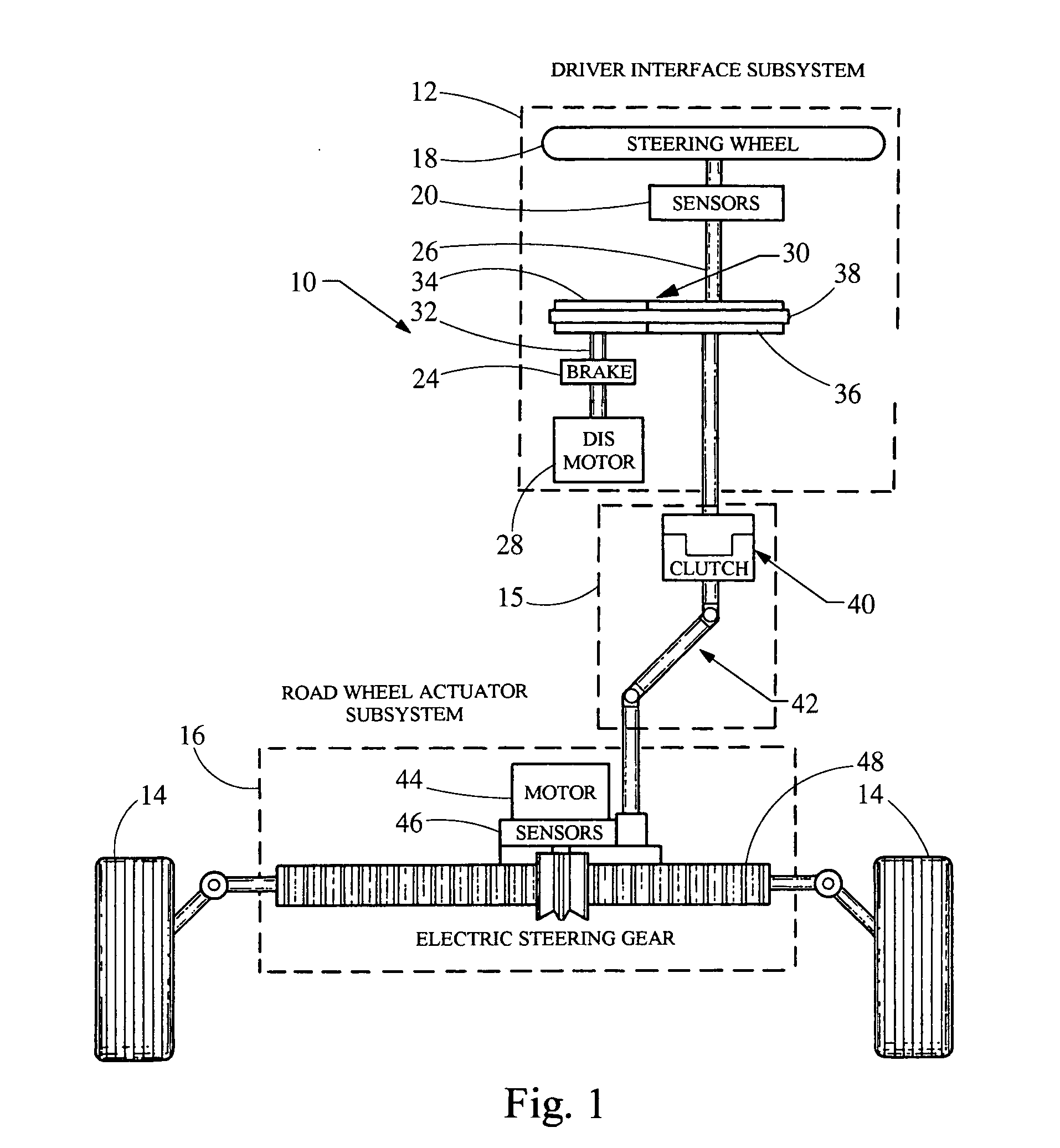

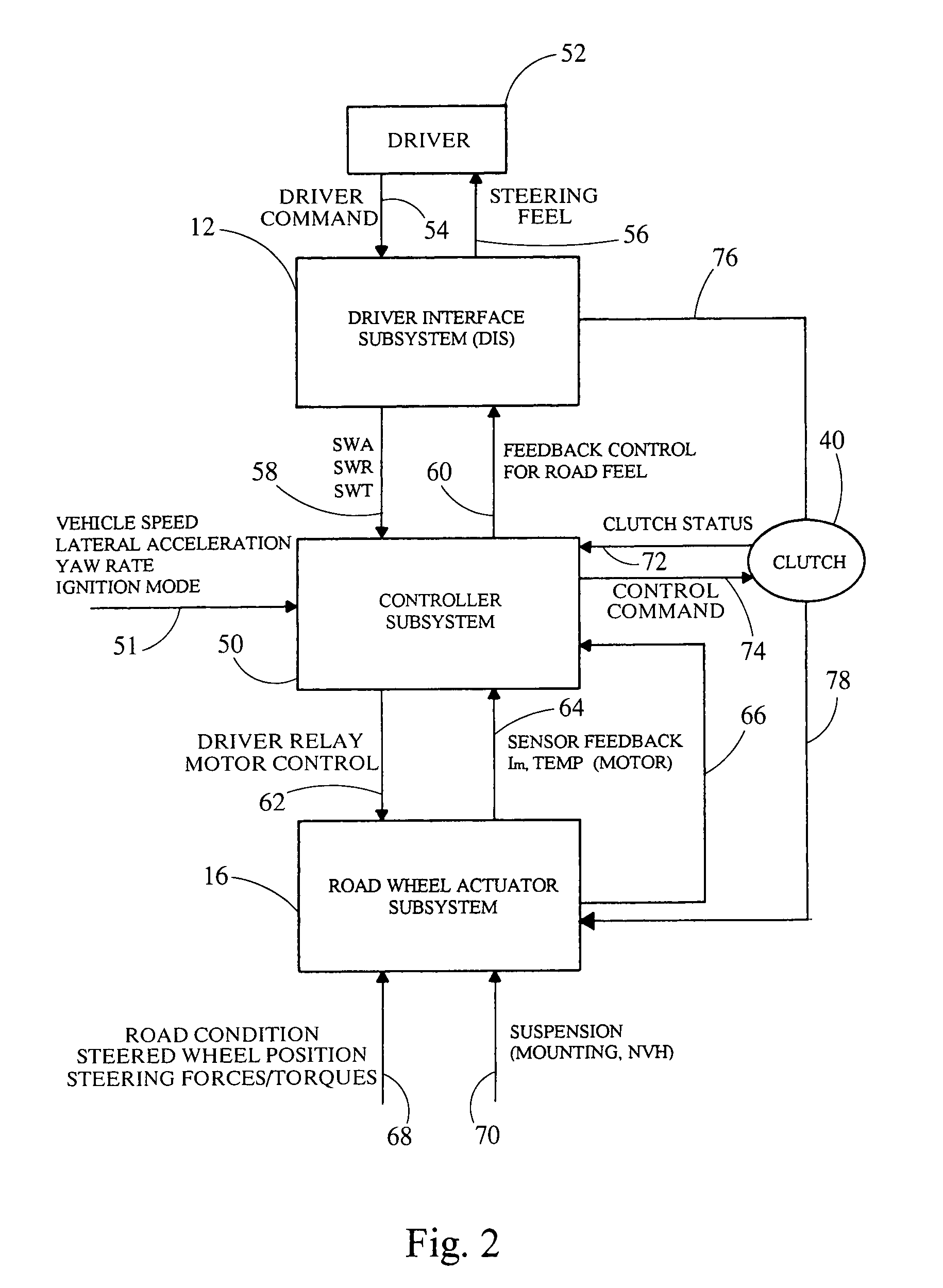

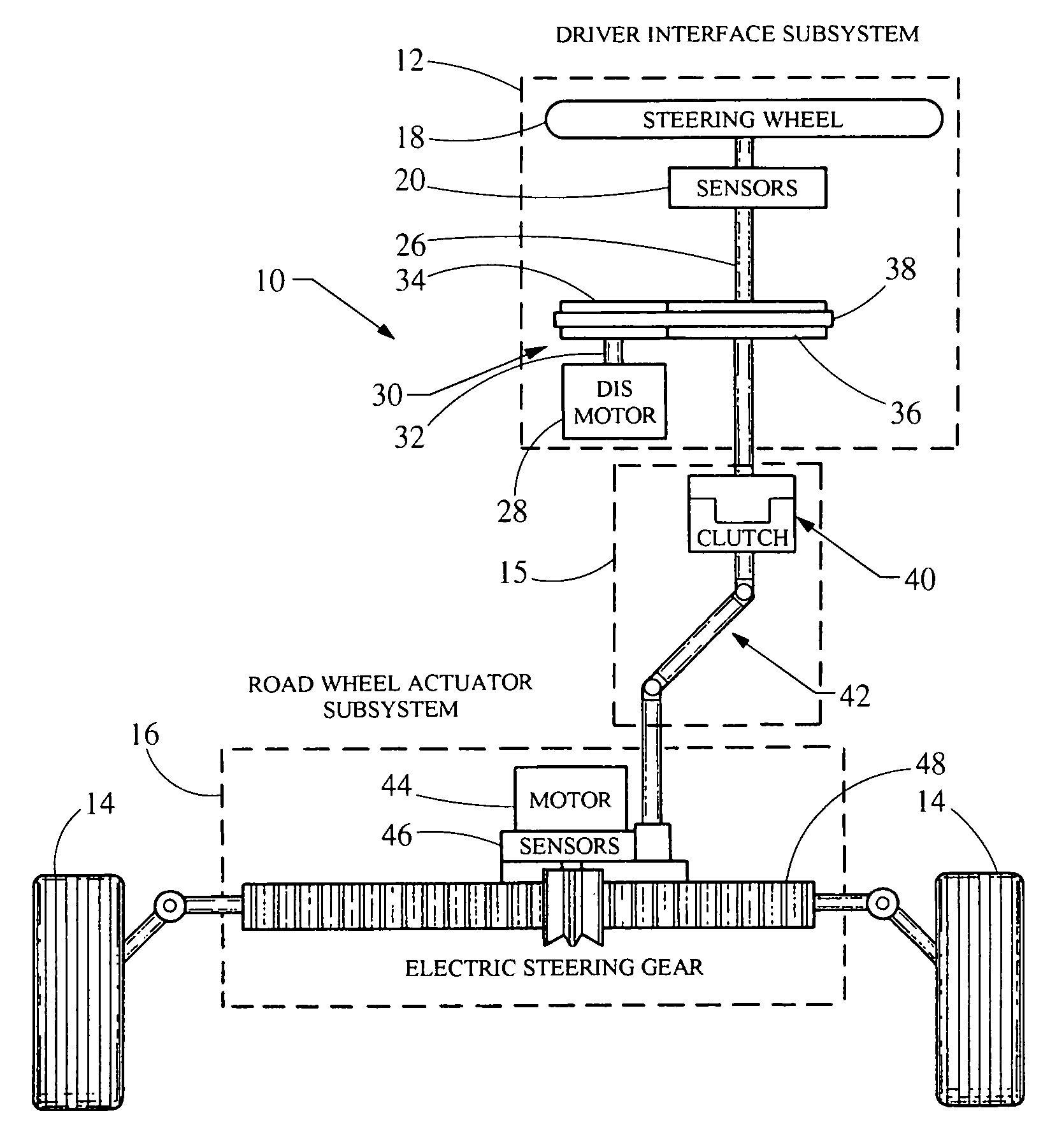

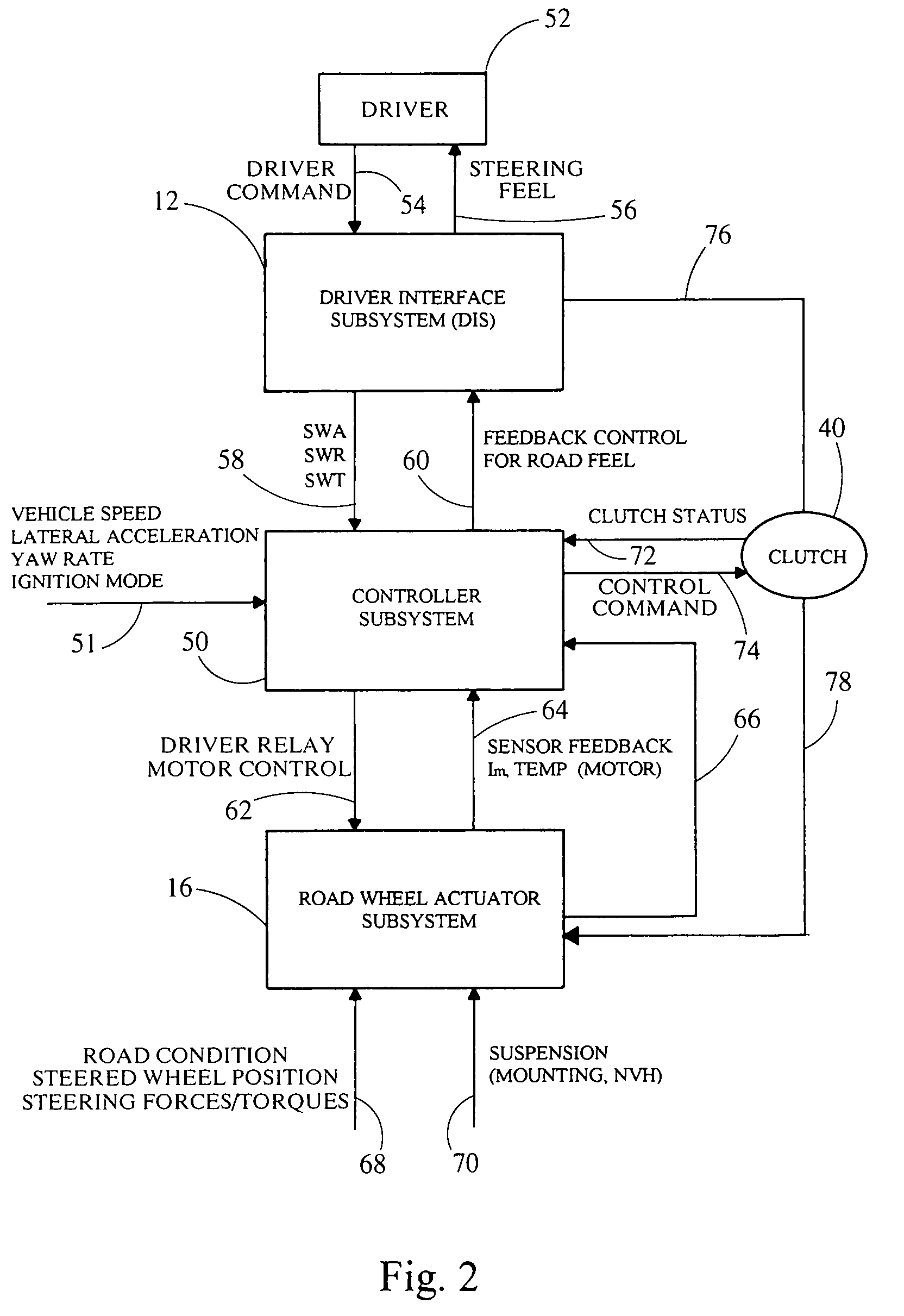

End of travel feature for steer by wire vehicle

The present invention provides a system for generating an end of travel feedback to the driver of a vehicle where the vehicle includes a steer by wire system. The system includes a steering wheel, a steering shaft, a motor, and a clutch. The steering wheel is configured to control the steer by wire system. The steering shaft is coupled to the steering wheel and rotates in conjunction with the steering wheel. To provide road feel resistance to the driver, the motor is coupled to the steering shaft. Further, the clutch is configured to mechanically couple the steering shaft to the road wheel to provide mechanical resistance when the road wheel is at an end of travel position.

Owner:VISTEON GLOBAL TECH INC

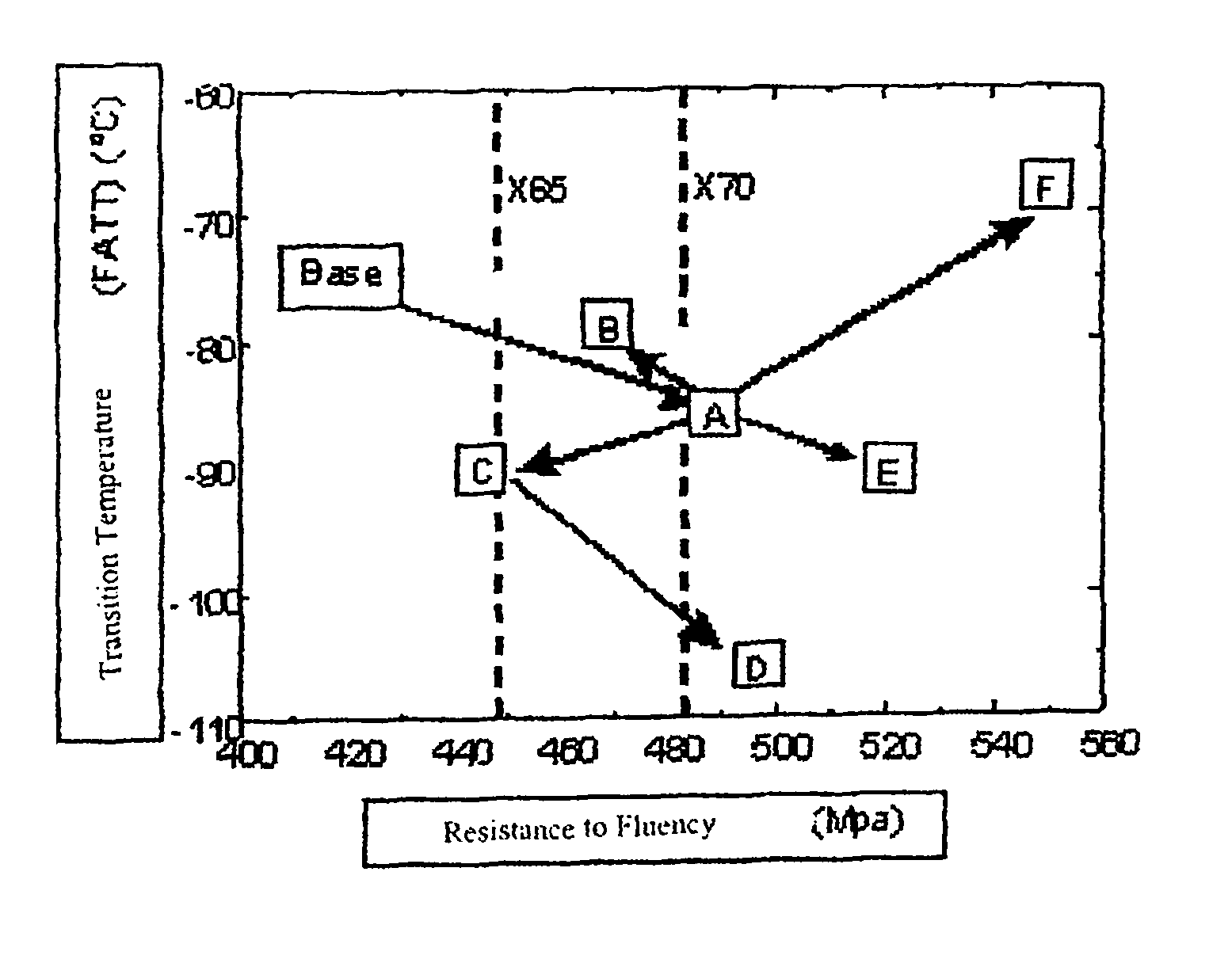

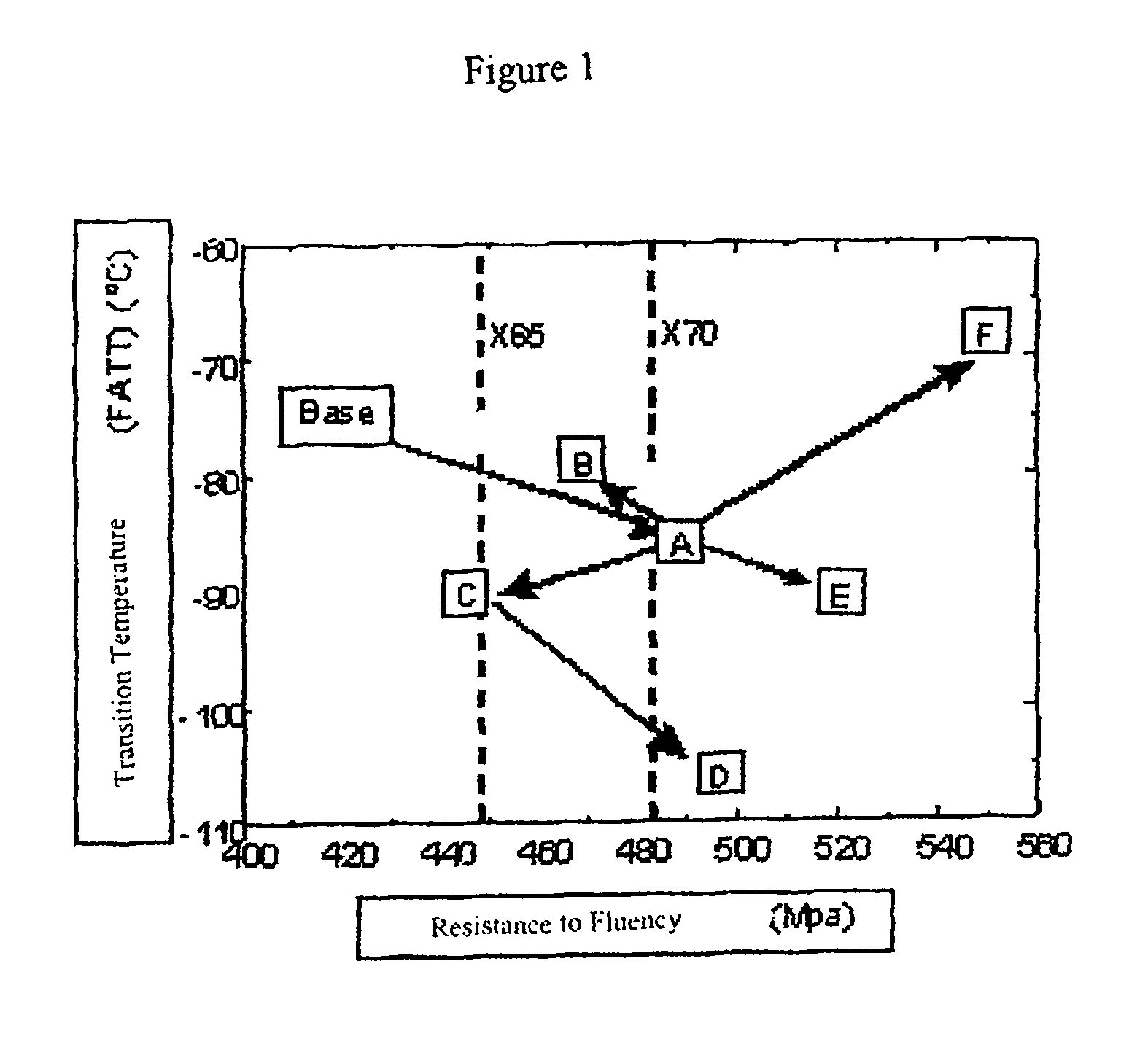

Seamless steel tube which is intended to be used as a guide pipe and production method thereof

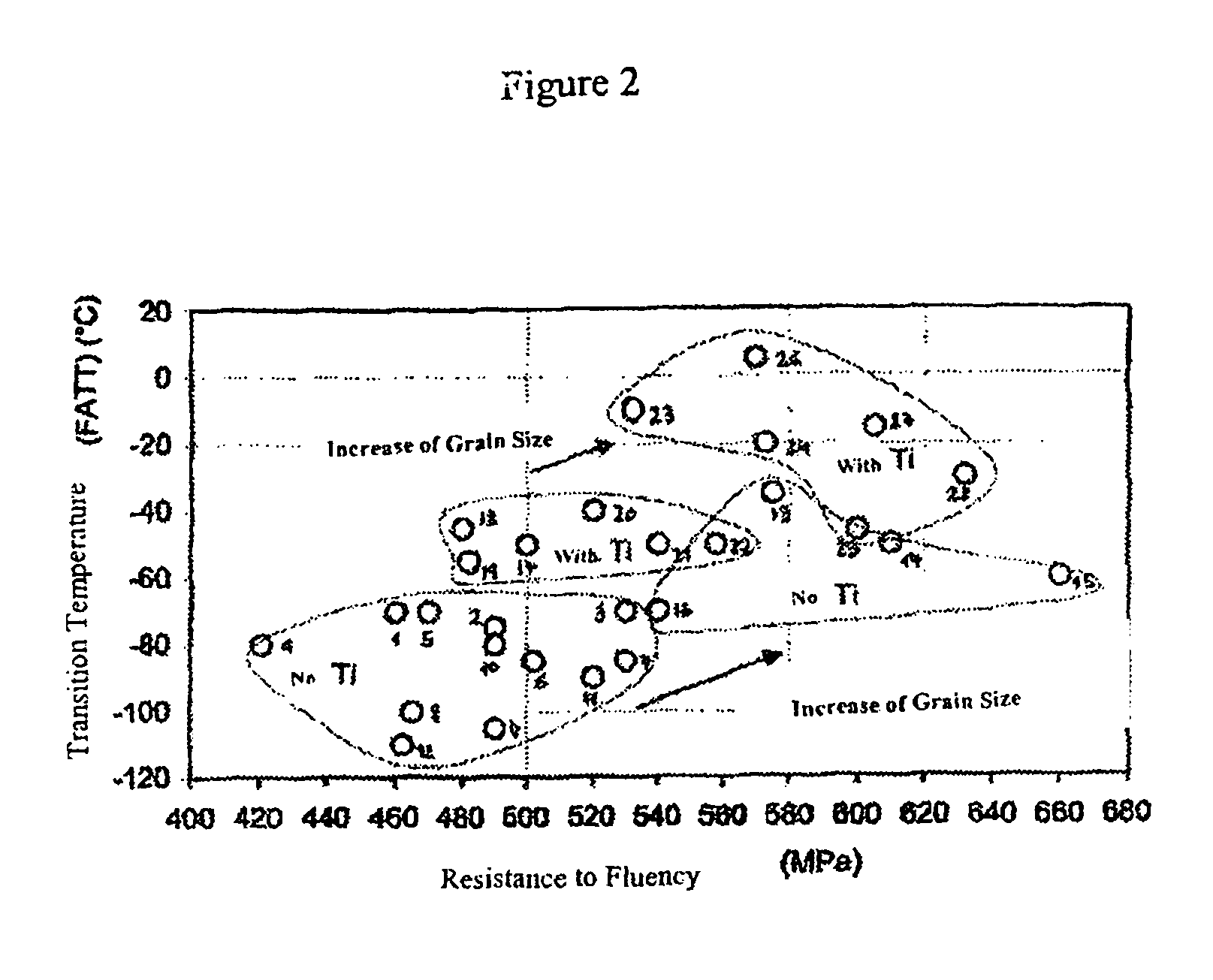

ActiveUS8002910B2Good mechanical resistanceImprove toughnessFurnace typesHeat treatment furnacesHeat-affected zoneCrack resistance

The present invention pertains to steel with high mechanical resistance at room temperature and up to 130° C., good toughness and good corrosion resistance in the metal base as well as good resistance to cracking in the heat affected zones (HAZ) once the tubing is welded together, and more specifically to heavy gauge seamless steel tubing with high mechanical resistance, good toughness and good corrosion resistance called catenary conduit. The advantages of the present invention with respect to those of an the state of technology reside in providing a chemical composition for steel used to manufacture heavy gauge seamless steel tubing with high mechanical resistance, good toughness, good fissure resistance in the HAZ and good corrosion resistance and a process for manufacturing this product. These advantages are obtained by using a composition made up basically of Fe and a specific chemical composition.

Owner:TUBOS DE ACERO DE MEXICO +1

Orally disintegrating tablets and process for obtaining them

InactiveUS20060165781A1High dissolution rateImprove compression performancePill deliveryPharmaceutical non-active ingredientsMANNITOL/SORBITOLOrally disintegrating tablet

The tablets comprise: at least 59.5% spray-dried mannitol; active ingredient below or equal to 10%, where at least 90% in weight of the active ingredient has a particle size below 100 μm; microcrystalline cellulose 10-18%, with an average particle size of 50 μm and where at least 99% in weight of microcrystalline cellulose has a particle size below 250 μm; sodium croscarmellose 14%; and a lubricant agent 0.5-2%; where, unless specified otherwise, the percentages are expressed in weight of the total weight of the tablet. And also a process comprising: sieving and mixing of components except for the lubricant agent; mixing of all components; and direct compression of the final mixture. The tablets of the invention give lower disintegration times as well as good perception on the tongue after disintegration, and overcome the problem of insufficient mechanical resistance for packaging and transport operations.

Owner:WARNER CHILCOTT IBERIA

High temperature-resistant and wear-resistant heavy-duty anticorrosive paint and preparation method thereof

The invention relates to anticorrosive paint and a preparation method of the paint, in particular to high temperature-resistant and wear-resistant heavy-duty anticorrosive paint and a preparation method of the paint. The high temperature-resistant and wear-resistant heavy-duty anticorrosive paint comprises component A and component B, wherein the component A comprises the raw materials by mass percent: 13-31% of epoxy resin or 14-16% of phenolic epoxy resin, 0-6% of boron-containing phenolic resin, 4-7% of titanium dioxide, 5-8% of barium sulfate, 3-5% of silicon carbide, 5-8% of talcum powder, 0.3-0.5% of white carbon black, 0.9-2% of nano titanium slurry, 6-8% of liquid nitrile butadiene rubber, 0.9-2% of organobentonite, 0.02% of defoaming agent and 30-54% of mixed solvent; and the component B comprises modified amine cured substance or dicyandiamide. The preparation method comprises the steps of: dispersing for 2h by ball milling according to the proportion, and then preparing the component A; and adding the component B into the component A at the room temperature to obtain the high temperature-resistant and wear-resistant heavy-duty anticorrosive paint. The heavy-duty anticorrosive paint is good in high temperature resistance, high in mechanical resistance and ideal in effects of resisting acid, alkali and salt, and can be used for protecting metal material for a long time in the high-temperature environment with acid gas and impurities.

Owner:NANTONG JUNQI MACHINERY

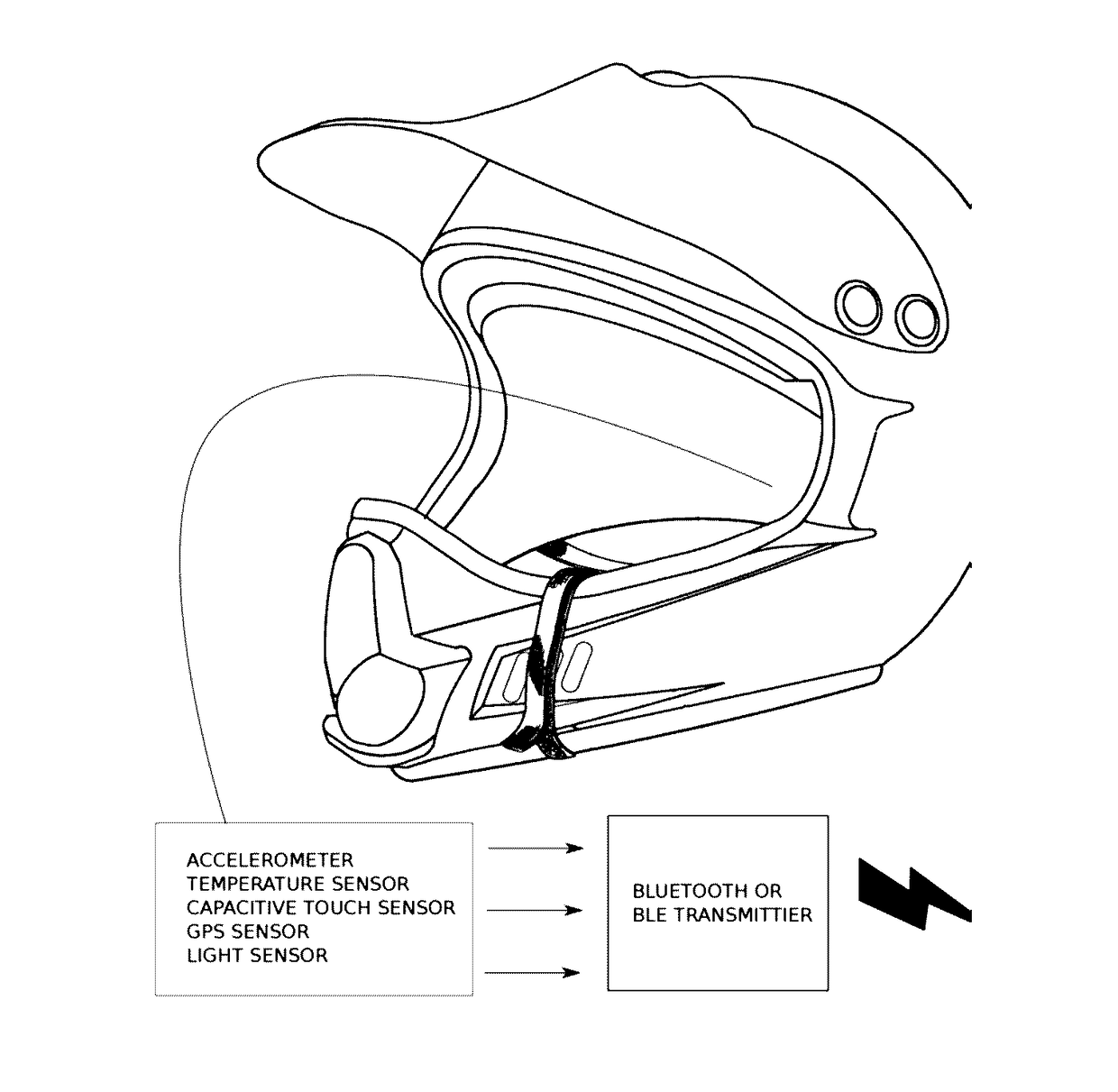

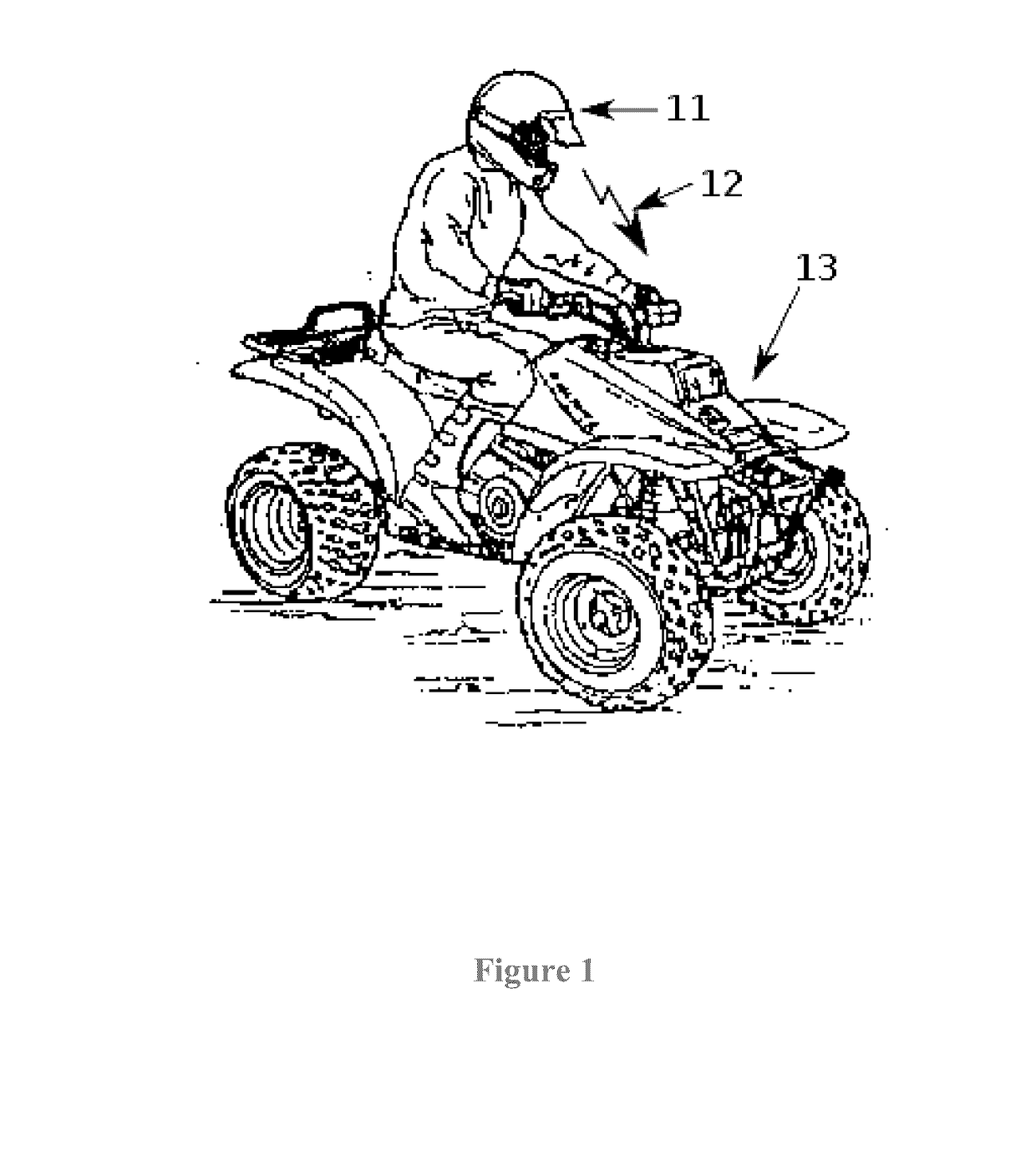

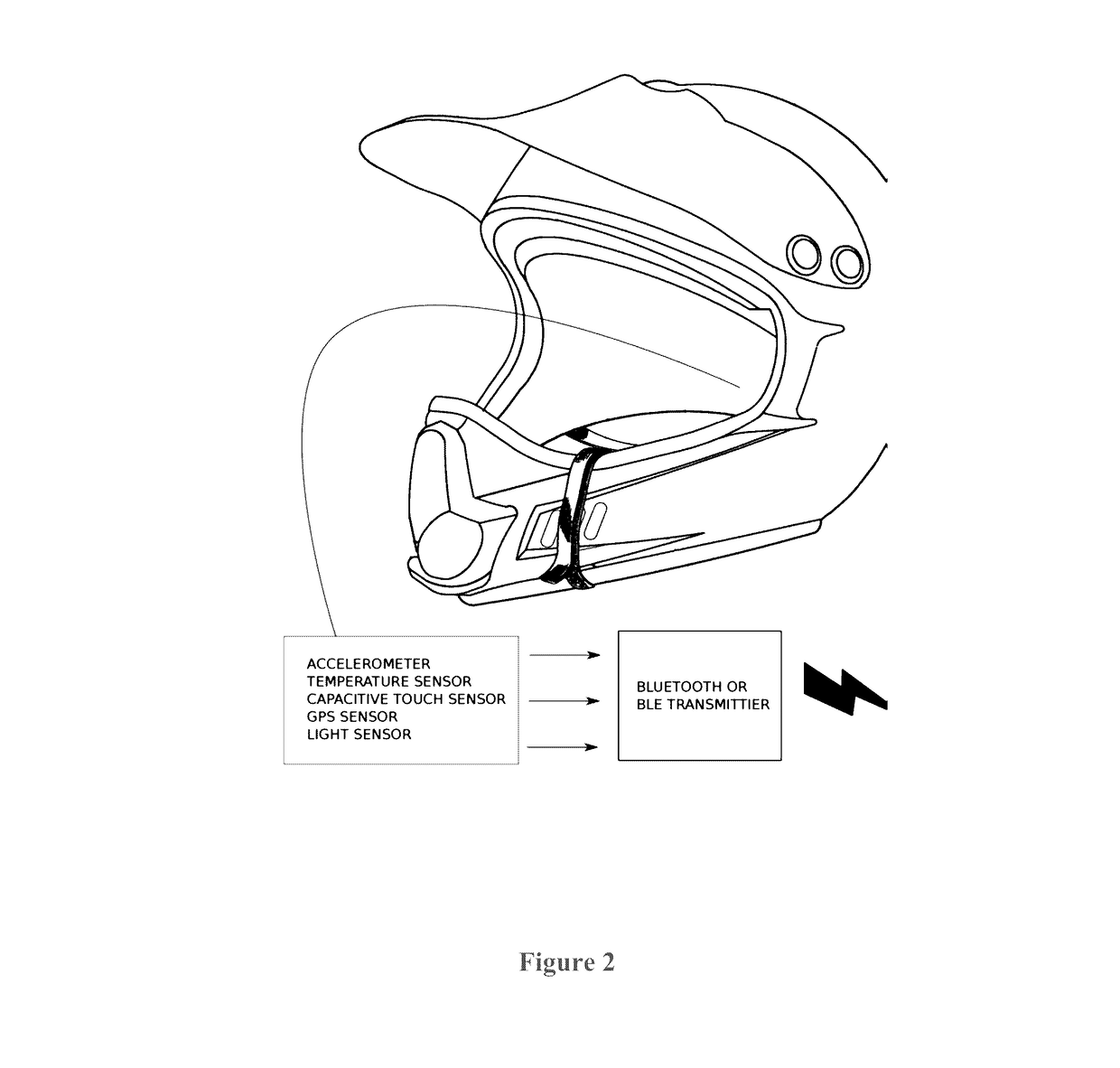

Travel Safety Control

InactiveUS20170136875A1Accurate operationEfficient use ofVehicle fittingsOff-road vehiclesMechanical resistanceSafety control

A system and method for encouraging a user of a recreational vehicle to wear safety equipment is described. The helmet contains a microprocessor and sensors to determine if the helmet is worn. The helmet communicates with the vehicle and the vehicle either disables operation or allows limited operation if the helmet is not worn. On motorized vehicles, the motor operation is restricted. On human powered vehicles mechanical resistance may limit operation.

Owner:TWIN HARBOR LABS

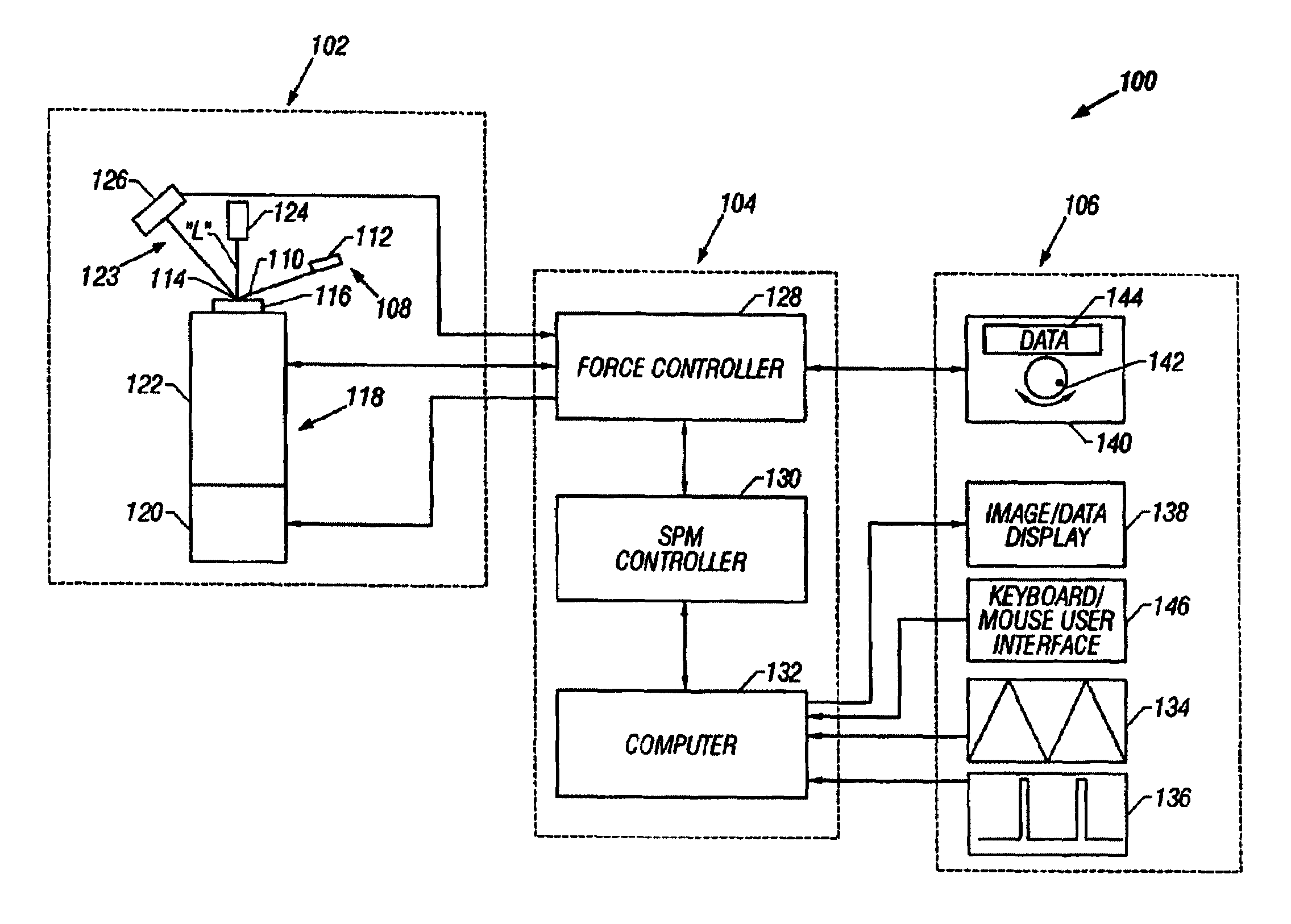

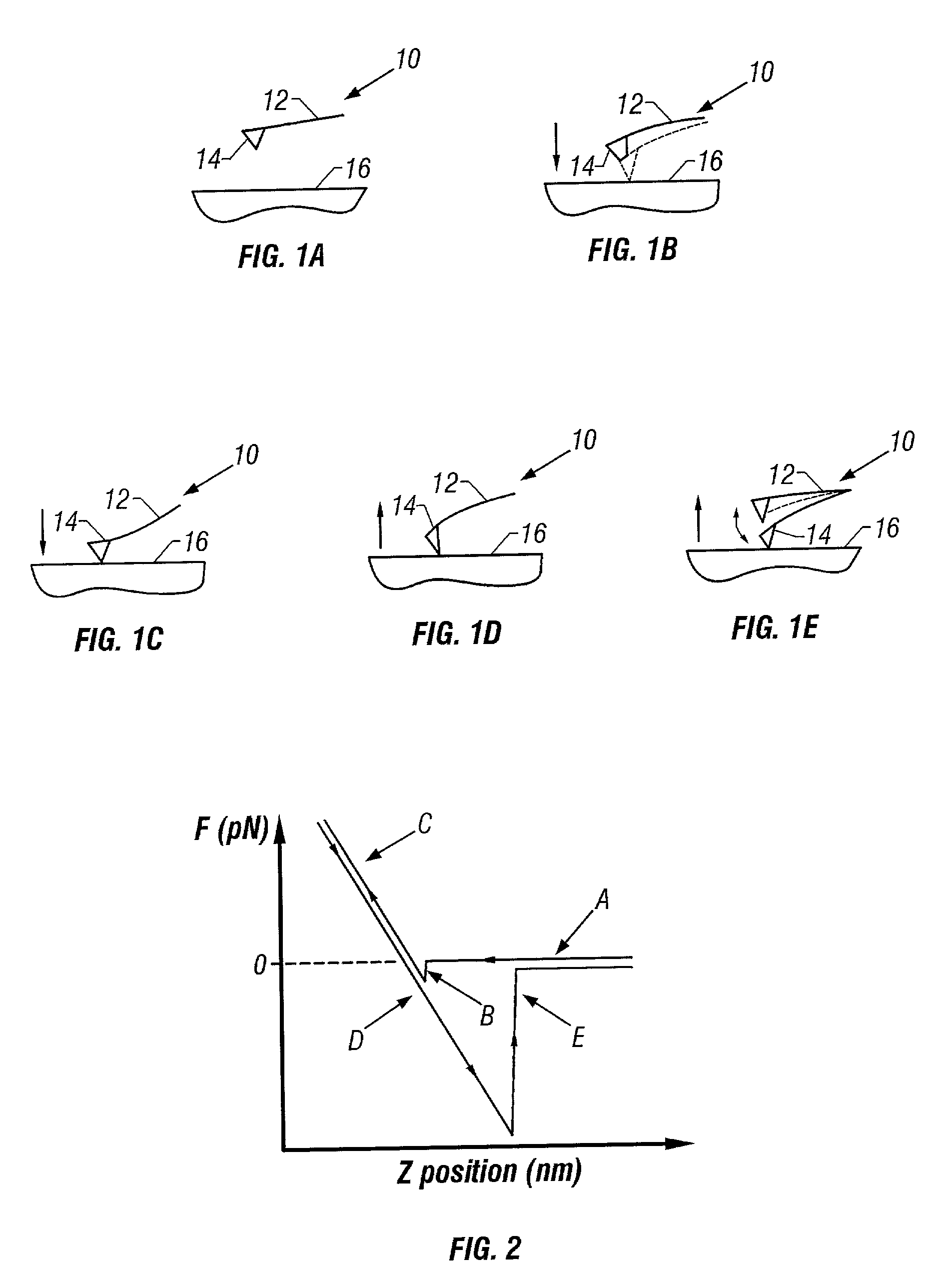

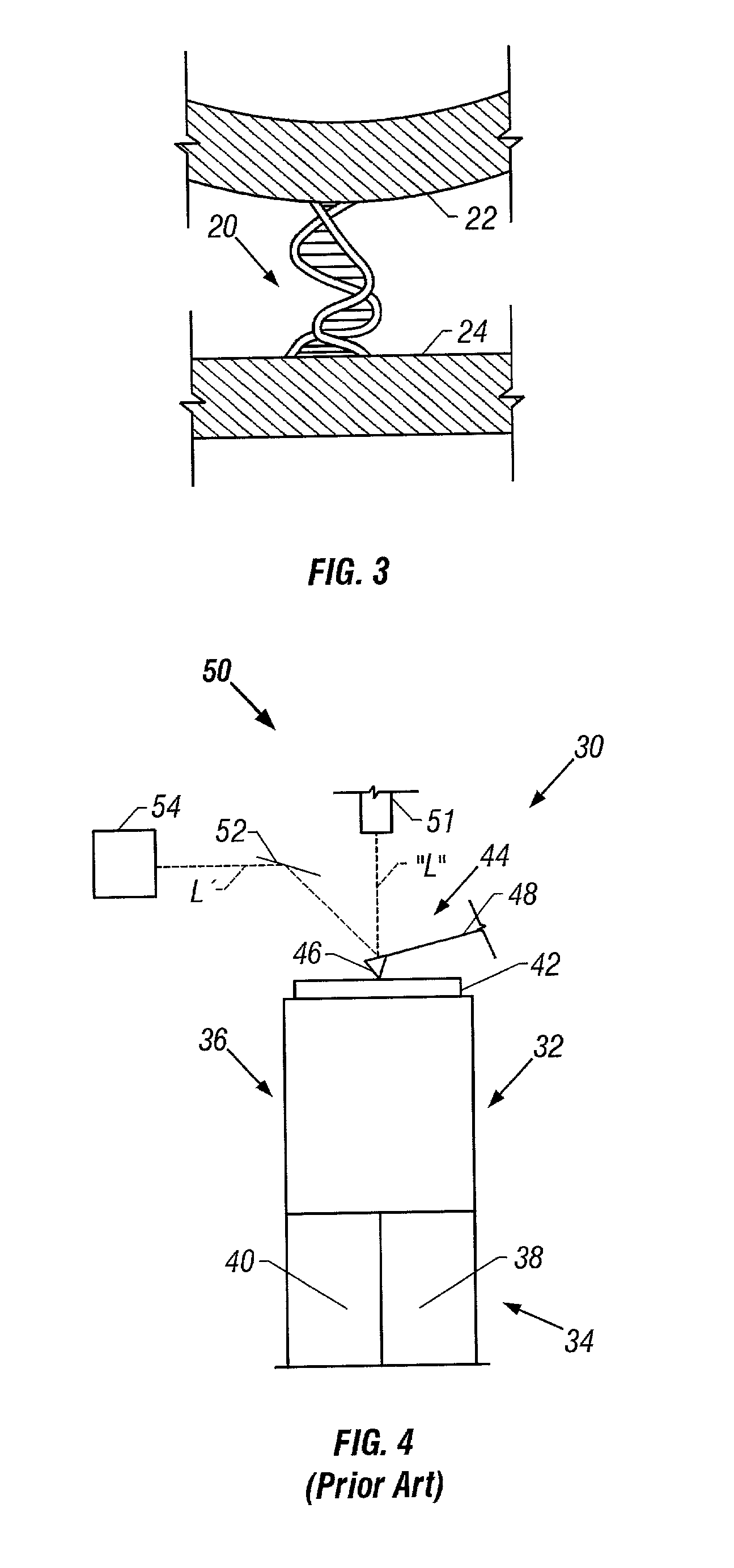

Manual control with force-feedback for probe microscopy-based force spectroscopy

InactiveUS7013717B1Overcomes drawbackSurface/boundary effectNanotechnologyMechanical resistanceRelative motion

A probe microscope includes a probe and a scanner, the scanner generating relative motion between a probe and a sample. In addition, a manual input device is provided to control a separation between a sample and a probe. The detector is used to generate a signal related to movement of the probe (for example, deflection). Moreover, the microscope has an alerting device that is responsive to the signal to provide feedback to an operator, the feedback being indicative of interaction between the sample and the probe. Preferably, the manual input device is a rotatable knob. Also, the alerting device is preferably a mechanical resistance device coupled to the knob to provide the feedback to the user.

Owner:BRUKER NANO INC

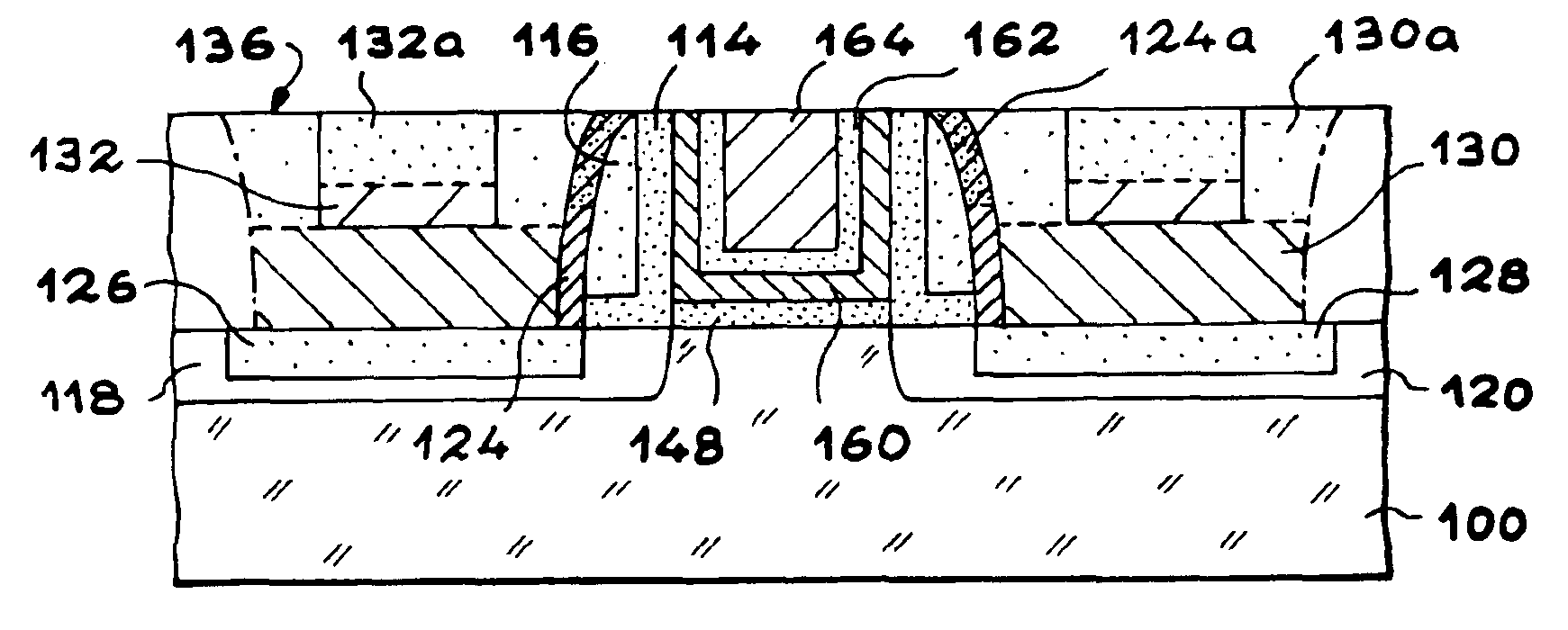

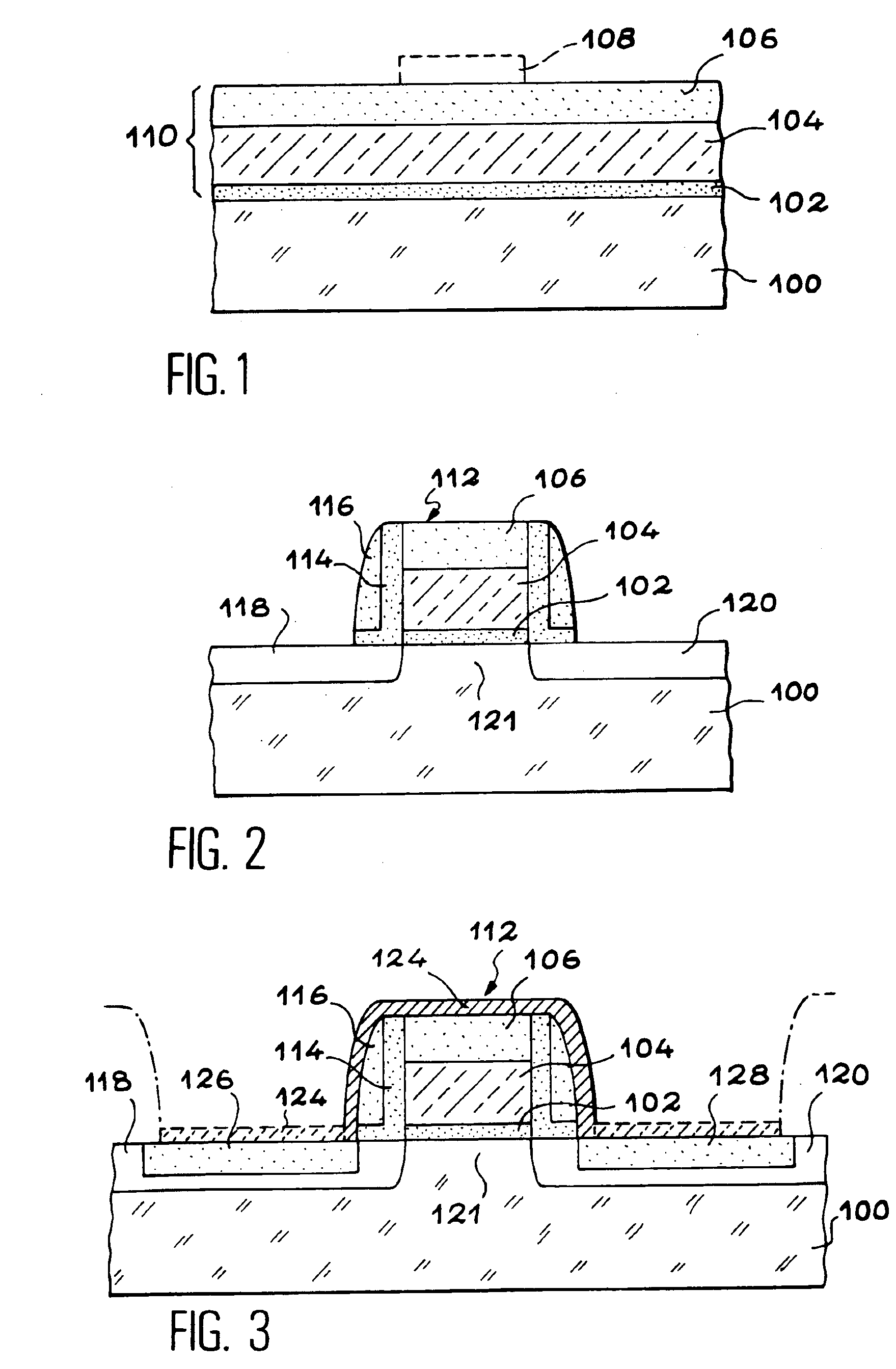

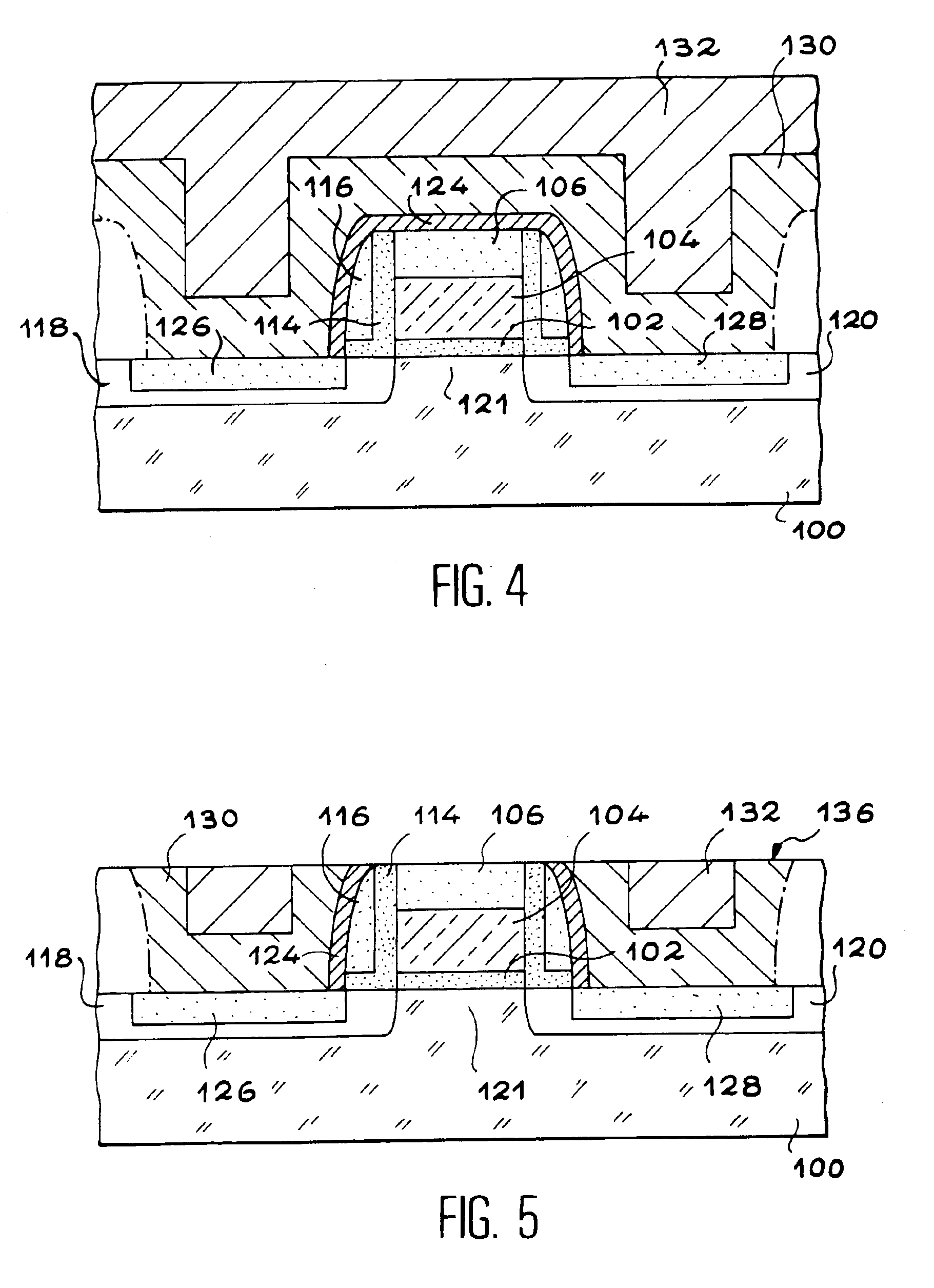

Method for making an electronic component with self-aligned drain and gate, in damascene architecture

InactiveUS6867128B2Reduce resistanceLow resistivitySolid-state devicesSemiconductor/solid-state device manufacturingMechanical resistanceTitanium

A method for fabricating an electronic component with a self-aligned source, drain and gate. The method includes forming a dummy gate on a silicon substrate, in which the dummy gate defines a position for a channel of the component. The method also includes at least one implantation of doping impurities in the substrate, to form a source and a drain on either side of the channel, using the dummy gate as an implanting mask, superficial, self-aligned siliciding of the source and drain, depositing at least one contact metal layer having a total thickness greater than a height of the dummy gate, polishing the at least one contact metal layer stopping at the dummy gate, and replacing the dummy gate by at least one final gate separated from the substrate by a gate insulating layer, and electrically insulated from the source and drain. Further, depositing the at least one contact metal layer includes depositing a first metal layer and, above the first metal layer, a second metal layer having a greater mechanical resistance to polishing than the first metal layer. In addition, a thickness of the first metal layer is less than the height of the dummy gate, and a total thickness of the first and second layers is greater than the height of the dummy gate. Further, the first metal is chosen from among tungsten and titanium, and the second metal is chosen from among TaN, Ta and TiN.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

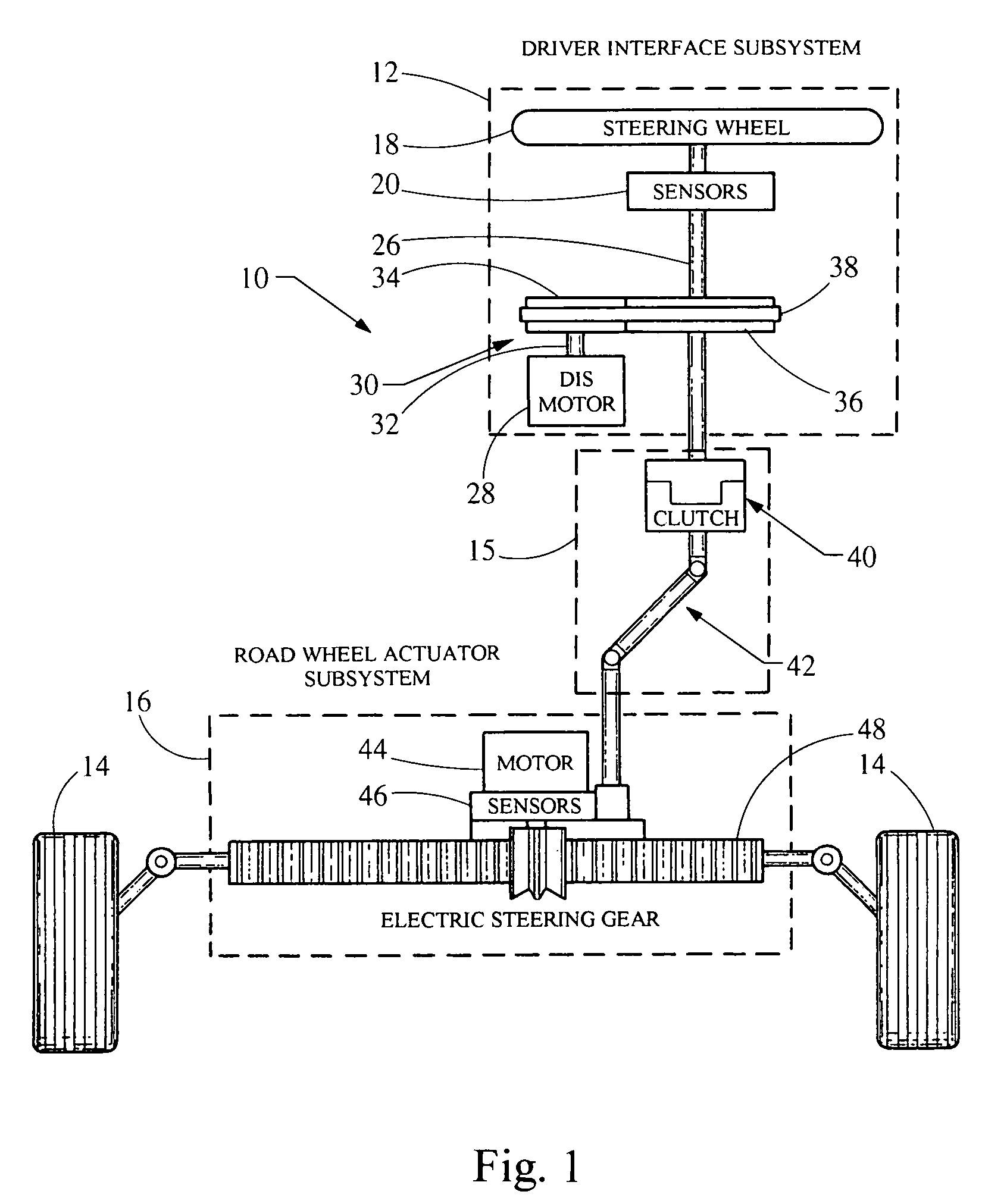

End of travel system and method for steer by wire systems

The present invention provides a system for generating an end of travel feedback to the driver of a vehicle where the vehicle includes a steer by wire system. The system includes a steering wheel, a steering shaft, a motor, and a brake. The steering wheel is configured to control the steer by wire system. The steering shaft is coupled to the steering wheel and rotates in conjunction with the steering wheel. To provide road feel resistance to the driver, the motor is coupled to the steering shaft. Further, the brake is coupled to a shaft of the motor and is adapted to provide mechanical resistance when the road wheel is at an end of travel position.

Owner:NISSAN MOTOR CO LTD

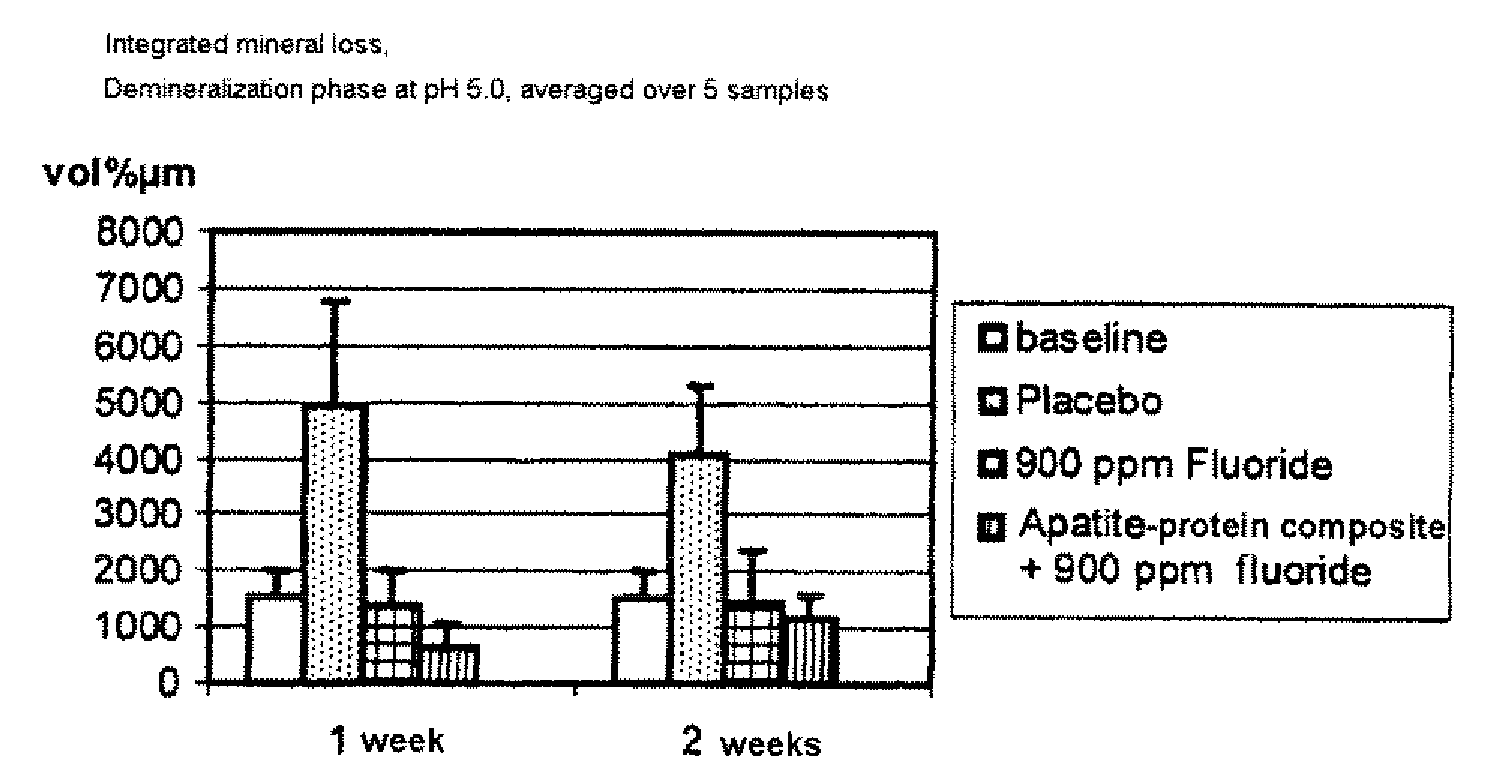

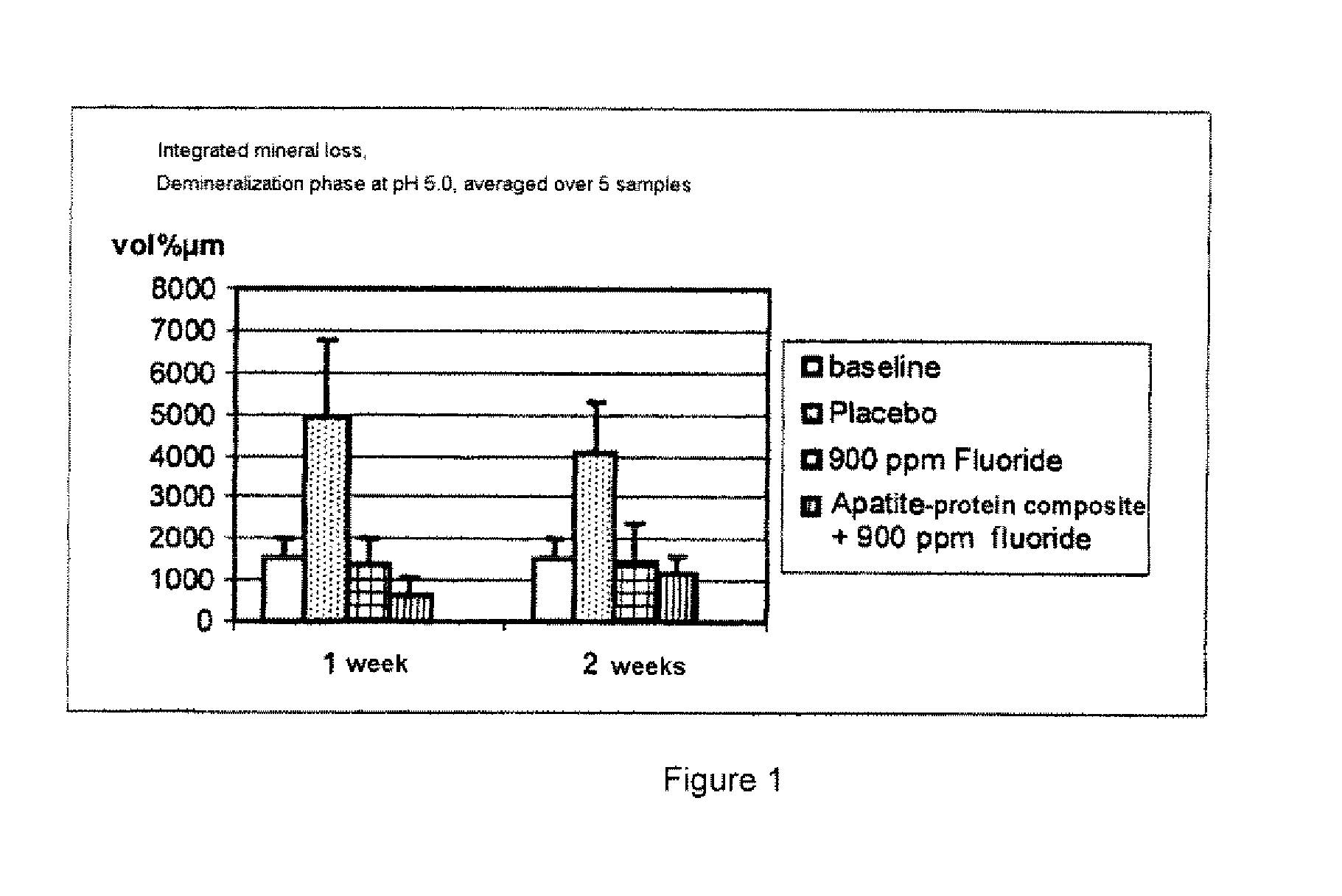

Use of poorly water-soluble calcium salts and/or the composites thereof

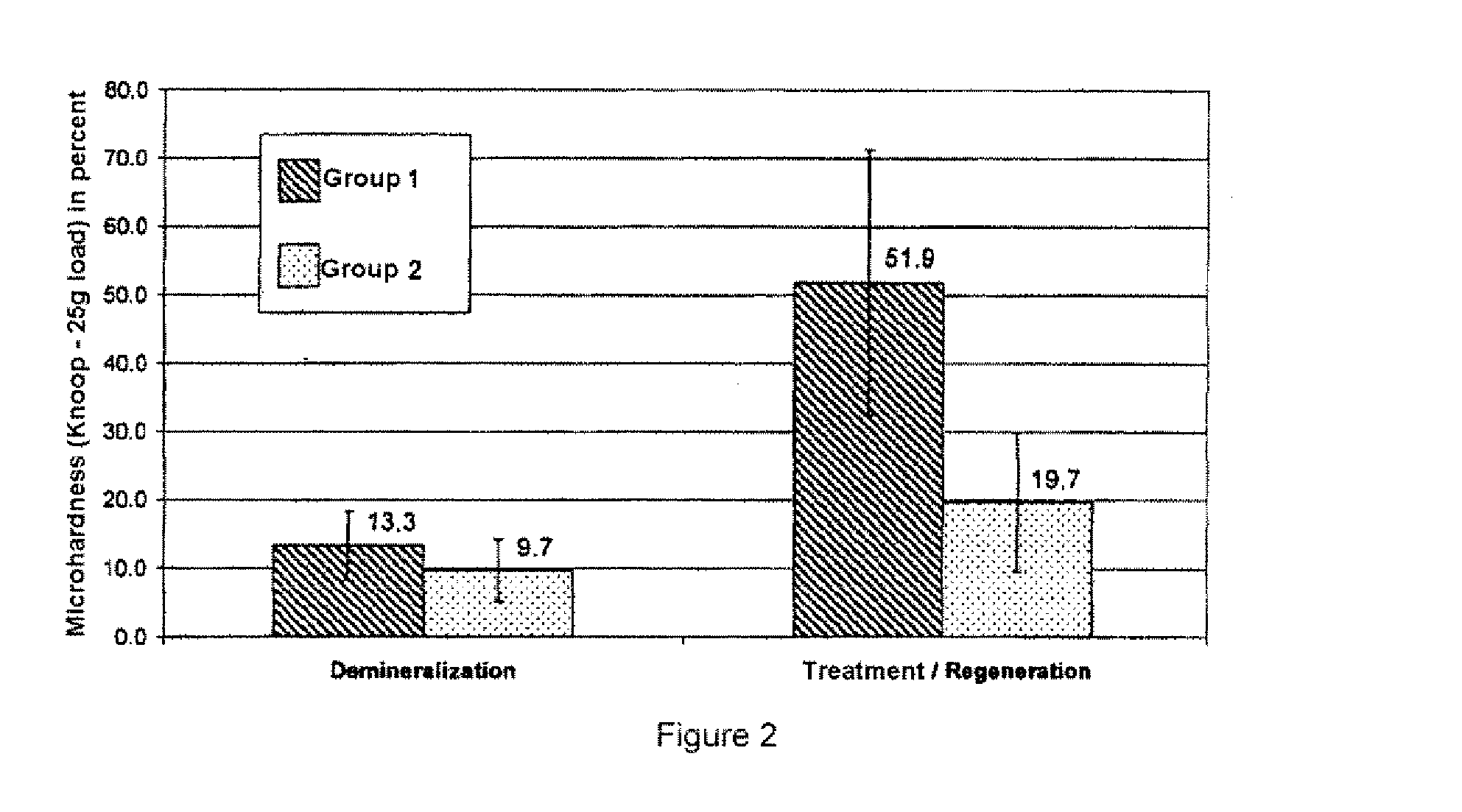

InactiveUS20080226566A1Good biocompatibilityCosmetic preparationsImpression capsTeeth erosionProphylactic treatment

The use of a composition containing at least one not easily water-soluble calcium salt and / or the composite material thereof, to protect and / or therapeutically treat and / or preventively treat teeth and / or bones in case of damage or prevent damage resulting from external influences, especially biological, chemical, physical, and / or microbiological influences, particularly to prevent and repair bone and tooth erosion, especially the enamel, maintain the enamel, protect teeth from aggressive acids, particularly caused by bacterial activity or the effect of acids contained in food, protect teeth from demineralizing, seal cracks, provide protection against and / or repair primary lesions and / or initial cavities in the enamel, smooth the tooth surface, prevent cavities make it easier to clean teeth, improve the mechanical resistance of teeth, and generally keep teeth healthy.

Owner:HENKEL KGAA

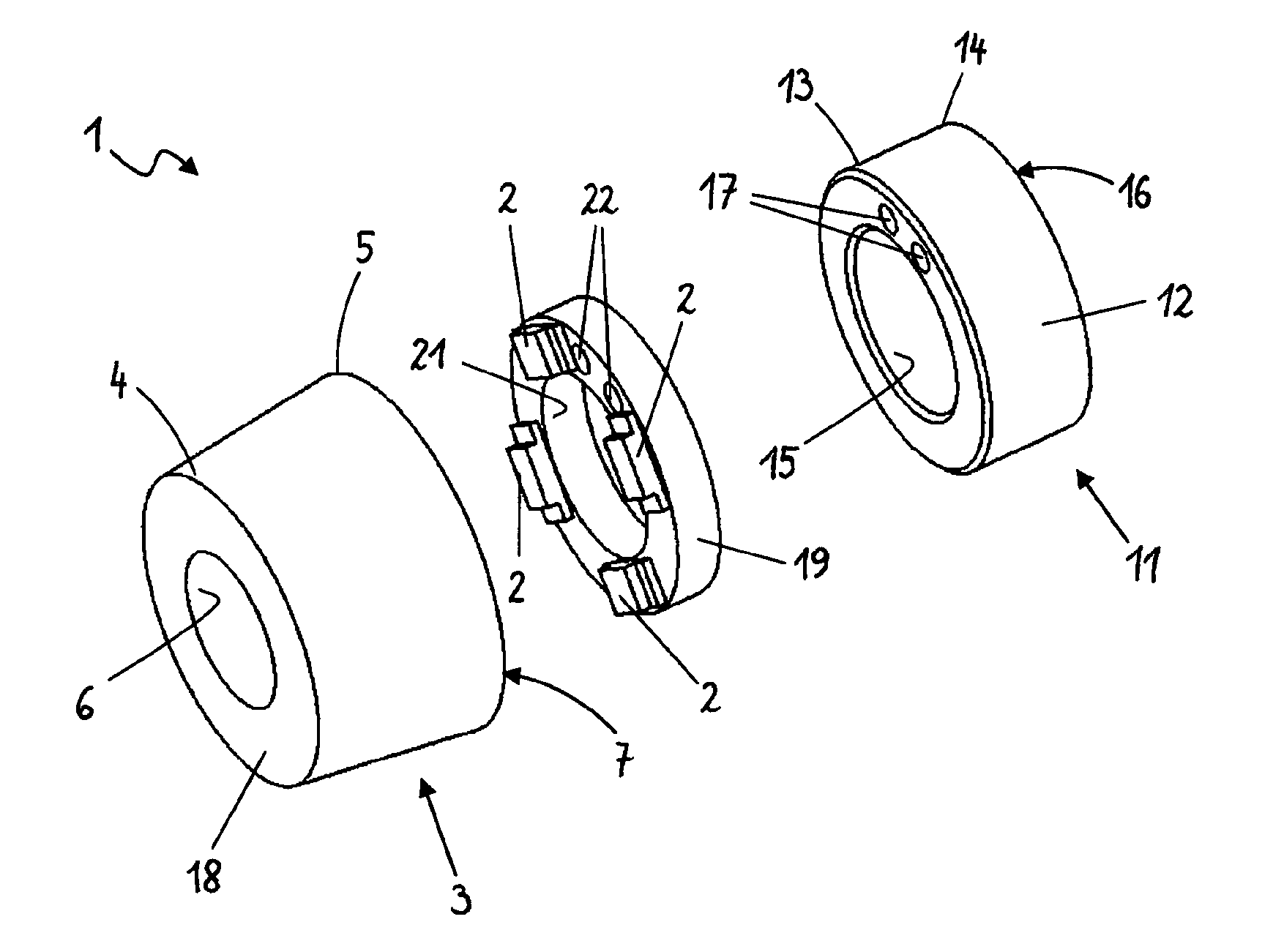

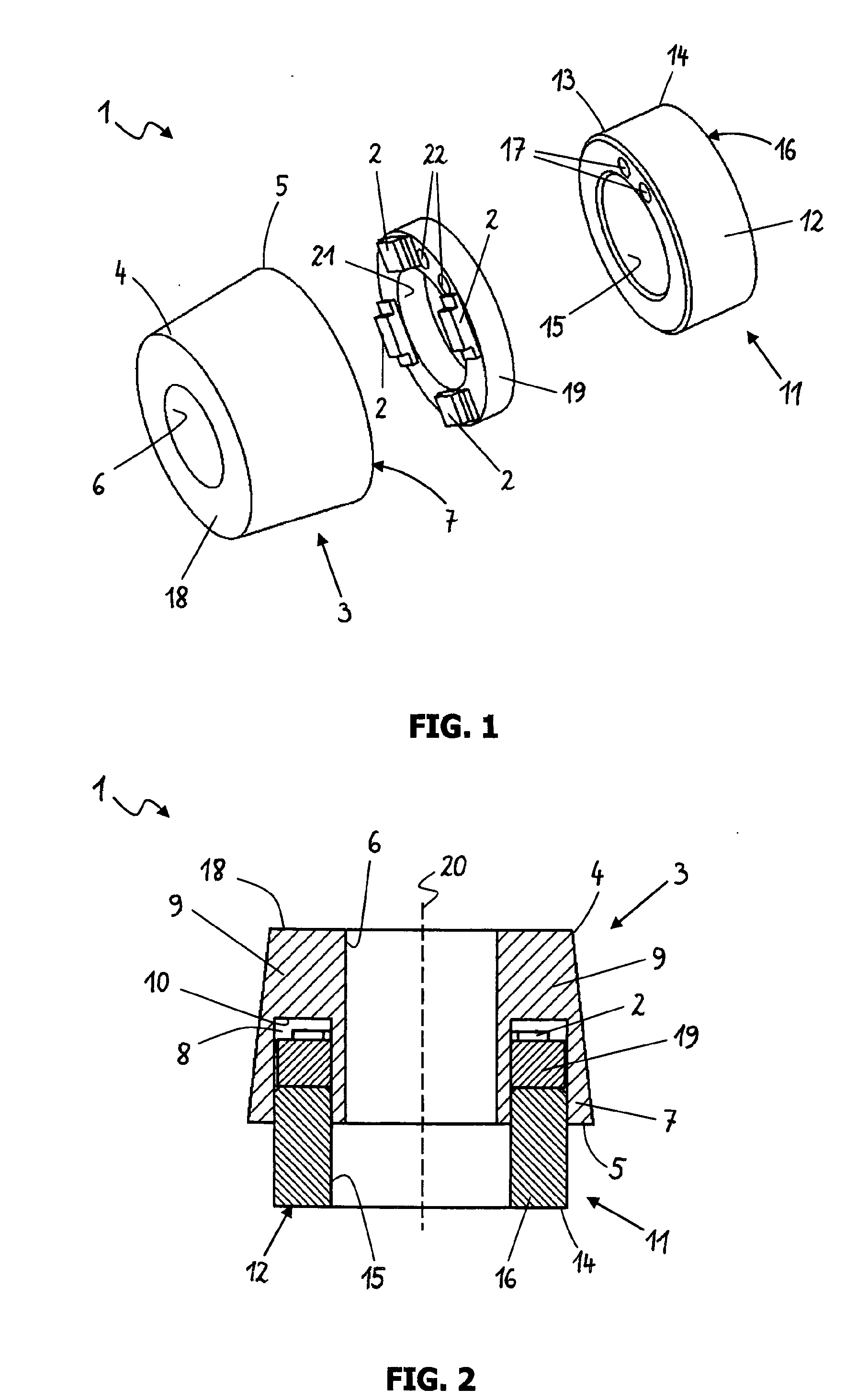

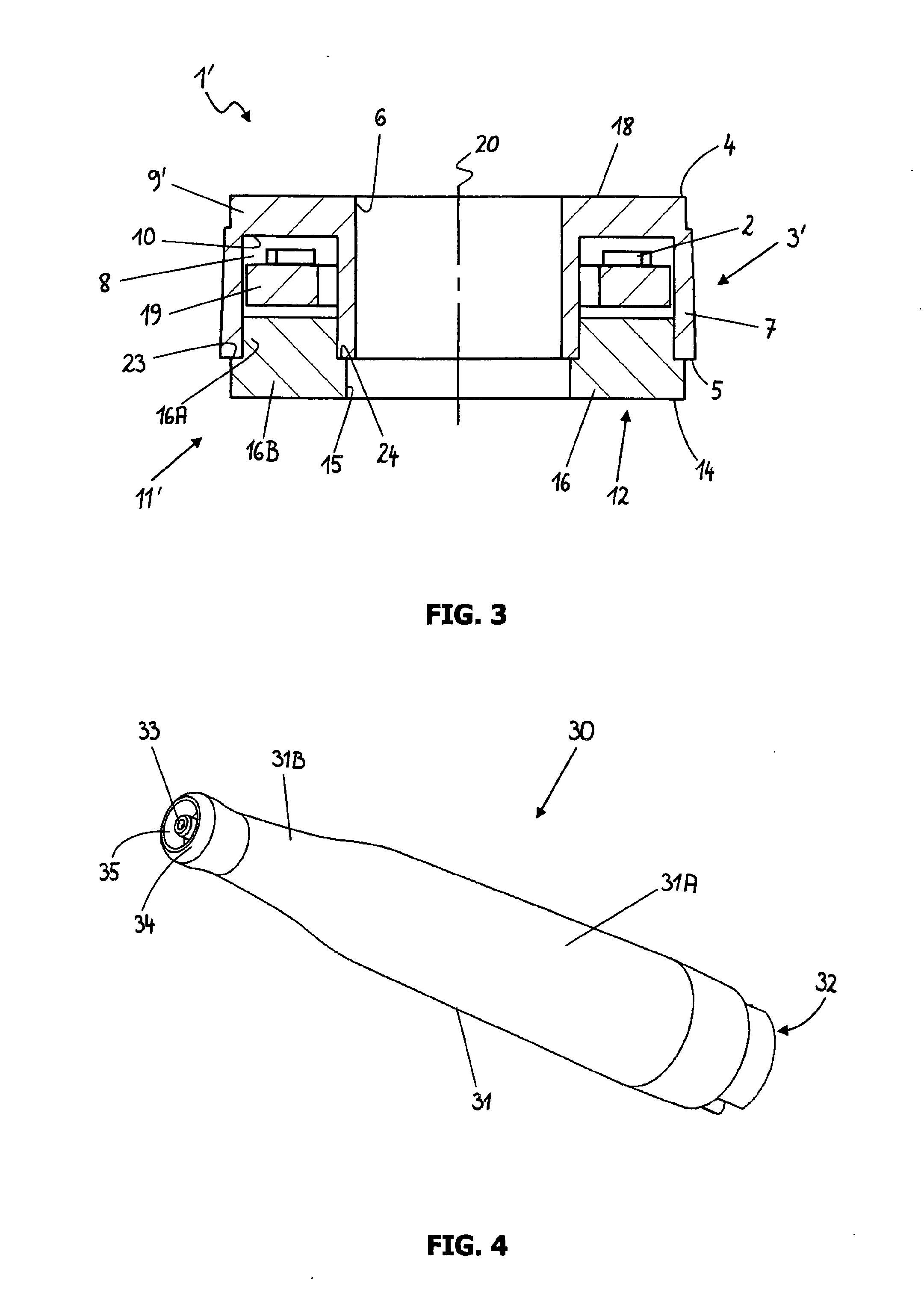

Medical handle device and illumination apparatus

InactiveUS20080045802A1Resistance to mechanical damageFirmly connectedBronchoscopesCoupling device connectionsMechanical resistanceHand held

A medical handle device having an illumination apparatus with at least one optical semiconductor component and a method for manufacturing such a hand-held device are displayed. It is proposed that in order to adapt the hand-held device to the specific requirements of a medical application such as uniformly high light emission, high mechanical resistance, sterilizability and electric safety, the illumination apparatus is provided with a base body, at least one blind hole arranged in the base body, a light-emitting window which is formed by the part of the base body extending from the bottom of the blind hole to the first end of the base body and is connected to a cover device which is connected to the base body and with which the blind hole forms a hermetically sealed interior, whereby the at least one optical semiconductor component is arranged in the hermetically sealed interior and the base body and the cover device are made of an electrically non-conducting material that can withstand sterilization. In some embodiments, at least one optical semiconductor component is encased in a transparent thermoplastic material.

Owner:W&H DENTALWERK

Predictive maintenance and initialization system for a digital servovalve

ActiveUS7066189B2Simple and reliable initializationReduced referenceFluid-pressure actuator testingOperating means/releasing devices for valvesMechanical resistanceEngineering

Provided is a servovalve system for regulating fluid flowing within a fluid circuit. The servovalve system comprises a housing, a spool slidably disposed within the housing, a stepper motor operatively connected to the spool, and a controller and a position sensor electronically connected to the stepper motor. The controller generates driver signals representative of a desired amount of stepper motor rotation in order to cause the stepper motor to effectuate spool motion relative to the housing. The position sensor senses an actual amount of stepper motor rotation and generates a quantity of position signals representative thereof. The controller determines a signal ratio of the quantity of the position signals to the quantity of the driver signals and generates a diagnostic signal when the signal ratio reaches a threshold value representative of a predetermined level of mechanical resistance of spool motion relative to the housing.

Owner:CONTROL COMPONENTS INC

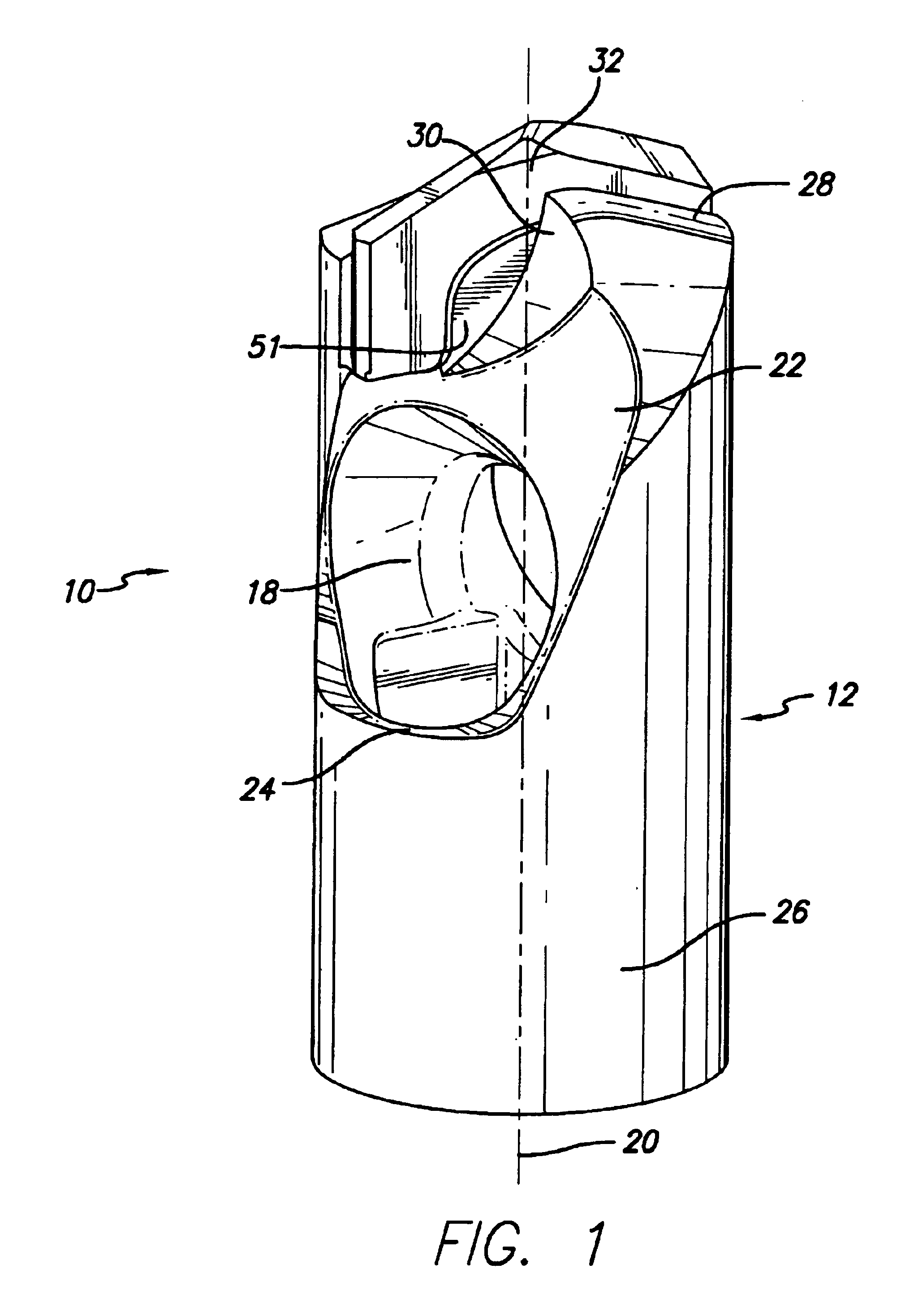

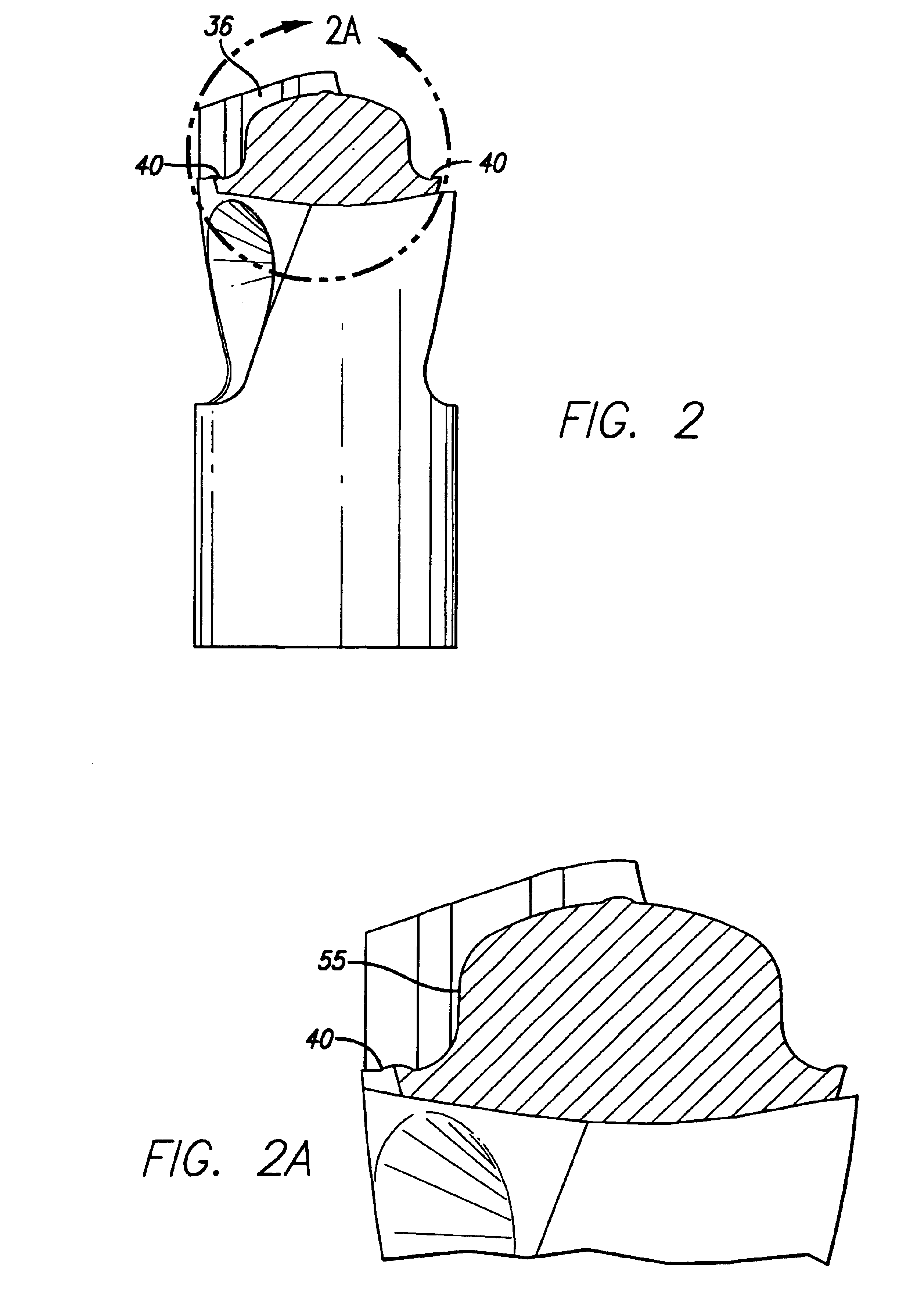

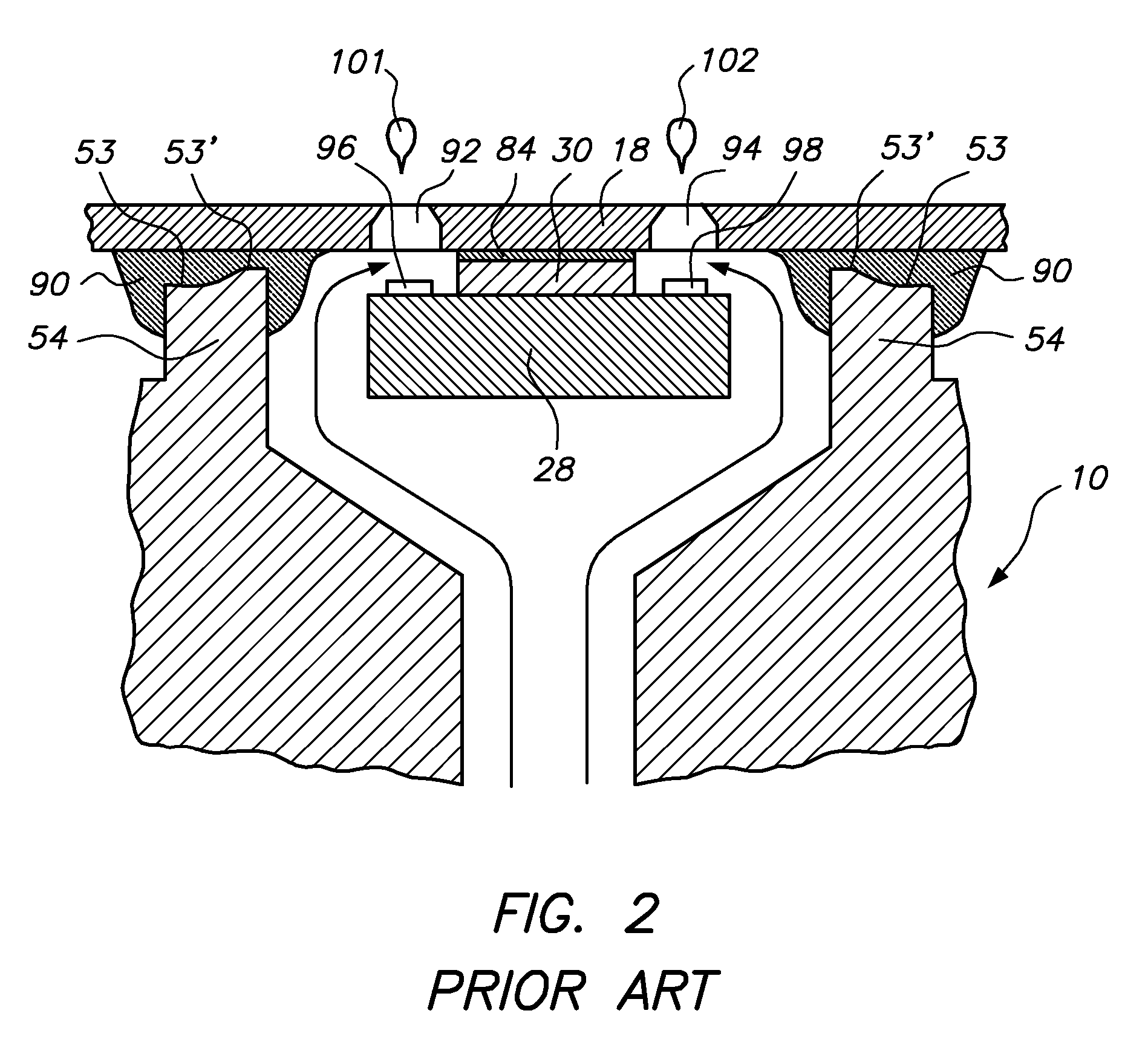

Roof bit and insert assembly

InactiveUS6945340B2Reduce displacementQuality improvementDrill bitsConstructionsMechanical resistanceCarbide

A center vacuum rotary drill bit including a rotary drill bit body and an insert. The bottom surface of the slot has a projecting key that cooperates with a depression keyway of the insert. Generally vertical sidewall surfaces of a depression keyway and vertical surfaces of a projection key provide mechanical resistance against lateral movement of the cutting insert. This mechanical resistance reduces displacement of the insert with respect to the bit body during brazing and thus a high quality, accurately aligned drill bit assembly is provided by applicants' invention. The depression keyway is designed so as to minimize the effect of the axial load on the insert by avoiding sharp corners which tend to amplify nominal stress and provides an insert of a proper carbide density after pressing. Integral bit body protuberance means adequately separate the insert within the slot and permit braze flow between the insert and slot. The protuberance means enhance braze flow when braze is fed between the insert body and bit body.

Owner:KENNAMETAL INC

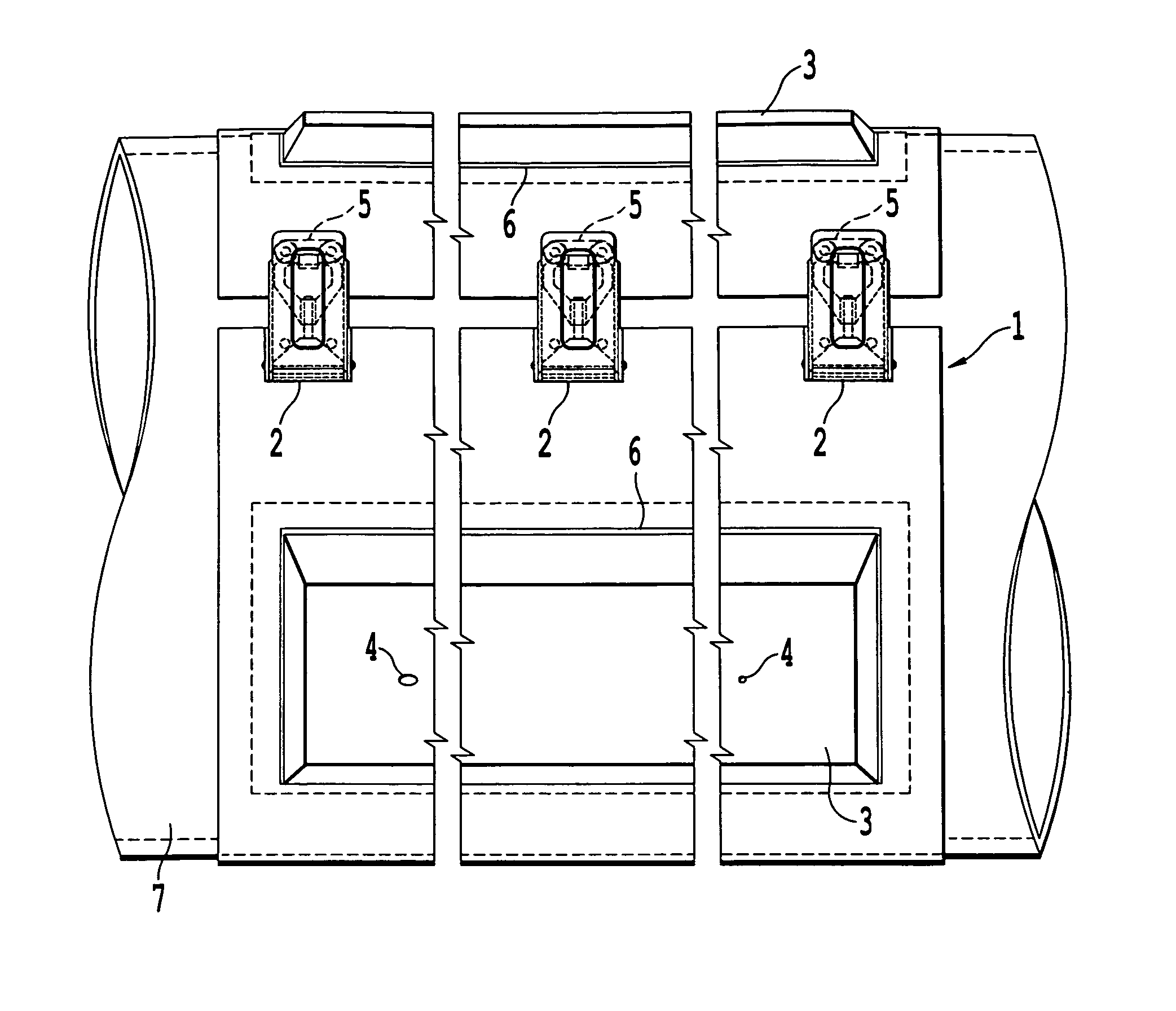

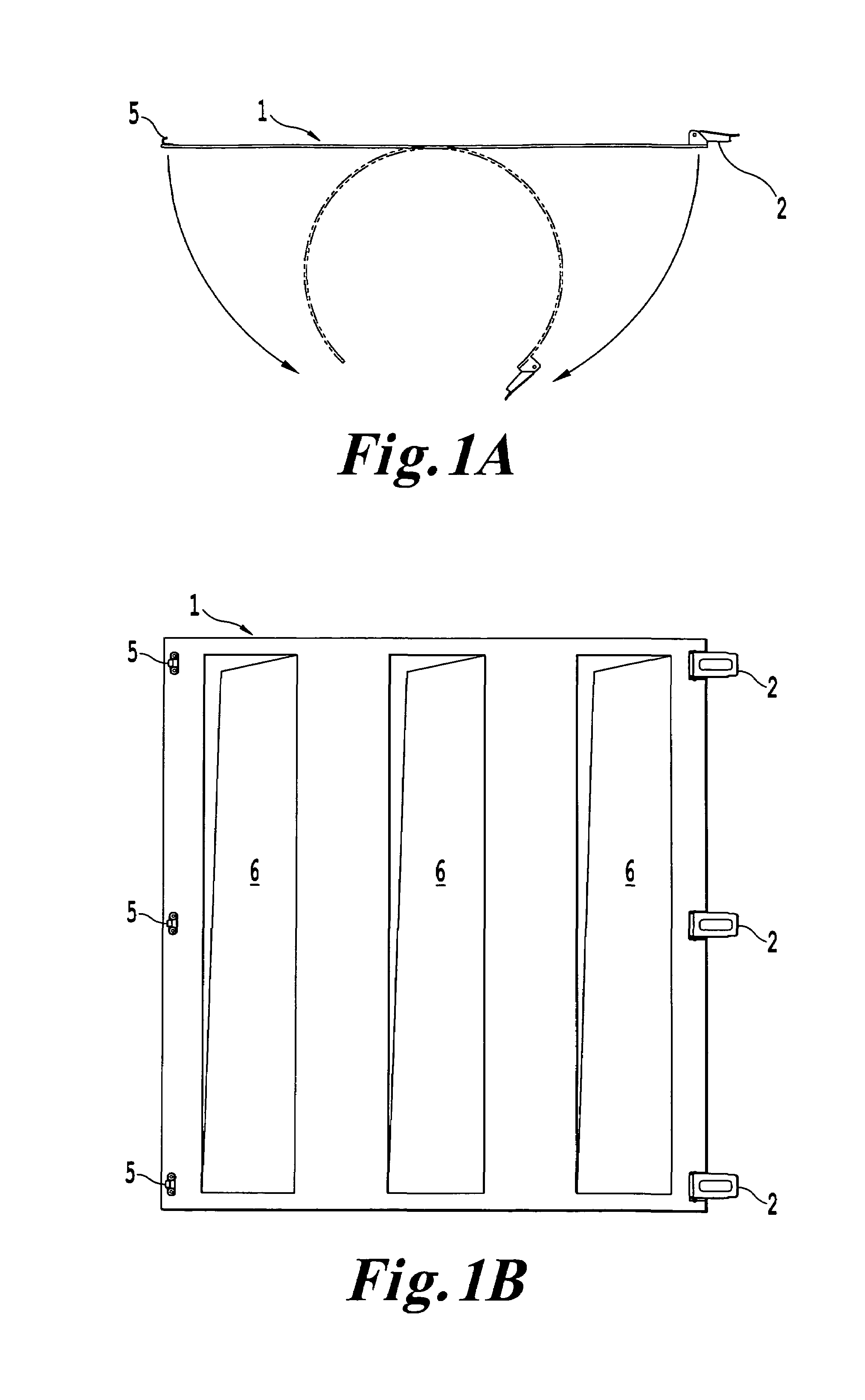

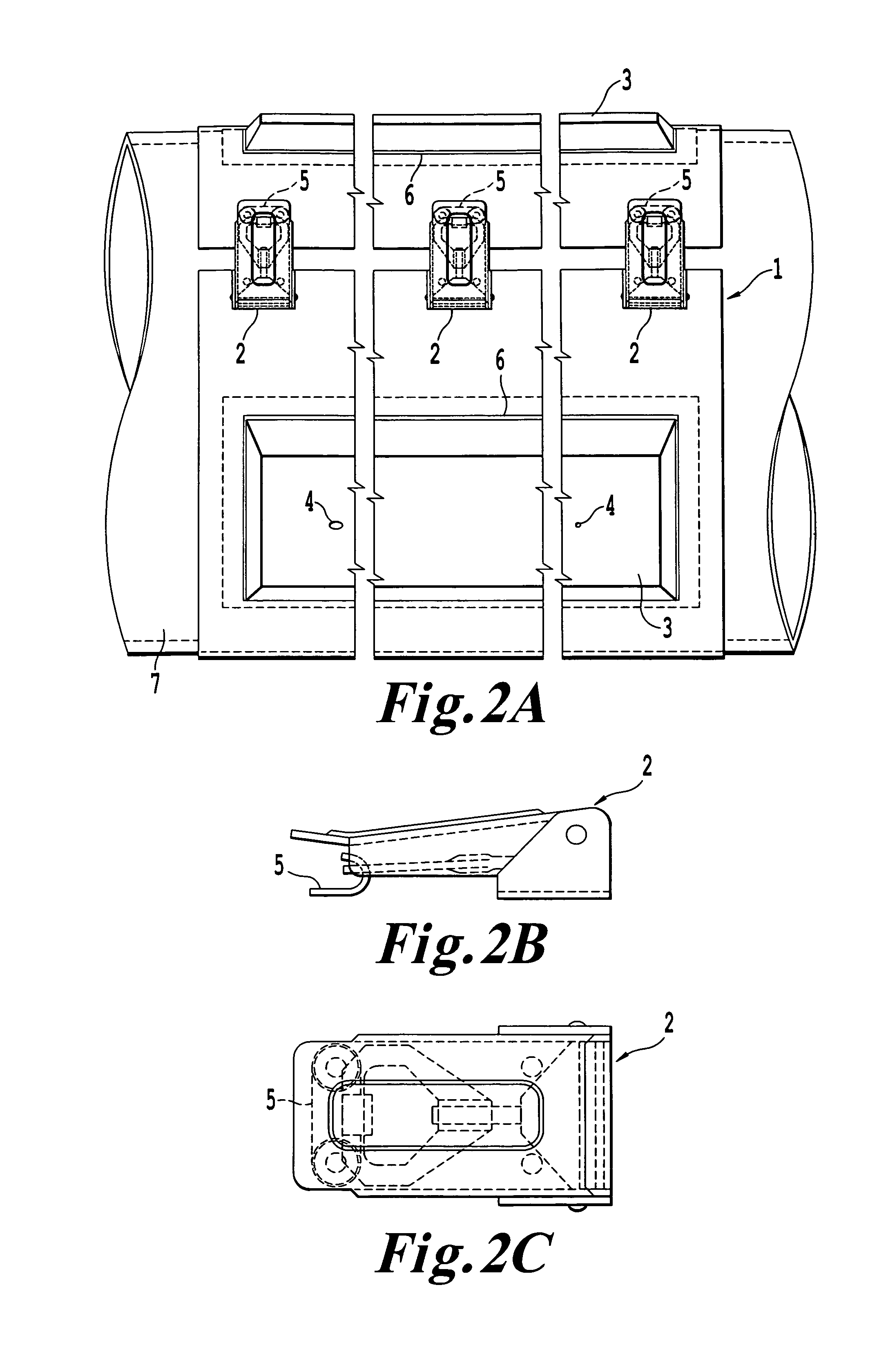

Method Of Bonding A Nozzle Plate To An Inkjet Printhead

InactiveUS20070279453A1Improved mechanical peel-off resistanceImprove the immunityDecorative surface effectsPrintingMechanical resistanceAdhesive bonding

A nozzle plate is affixed to an inkjet printhead body by application of a first adhesive bonding step that hydraulically seals the ink chambers to the nozzle plate, followed by a second adhesive bonding step that strengthens the junction between the printhead body and the nozzle plate. The second adhesive bond may be created by capillary propagation of the second adhesive along the junction. The nozzle plate affixing method enhances the mechanical resistance of nozzle plates against peeling from the printhead body by the influence of wiper blades onto the nozzle plate during wiping.

Owner:XAAR PLC

Method for making centralizers for centralising a tight fitting casing in a borehole

Method for the centralization of drill casings in a tight borehole, both vertical and deviated, comprising the following operations: Application on the casing section in question, of an adherence strip equipped with one or more housings and rapid adjustable lever closure; Insertion of suitable molds in the housings of which the strip is equipped; Injection into the molds of plastic material characterized by a high mechanical resistance, a high degree of surface adhesion and resistance to abrasion by friction, and also in-place elasticity, higher than the elasticity of the casings; Removal of the adherence strip once the hardening of the plastic material in the shape of the mold, has been completed.

Owner:ENI SPA

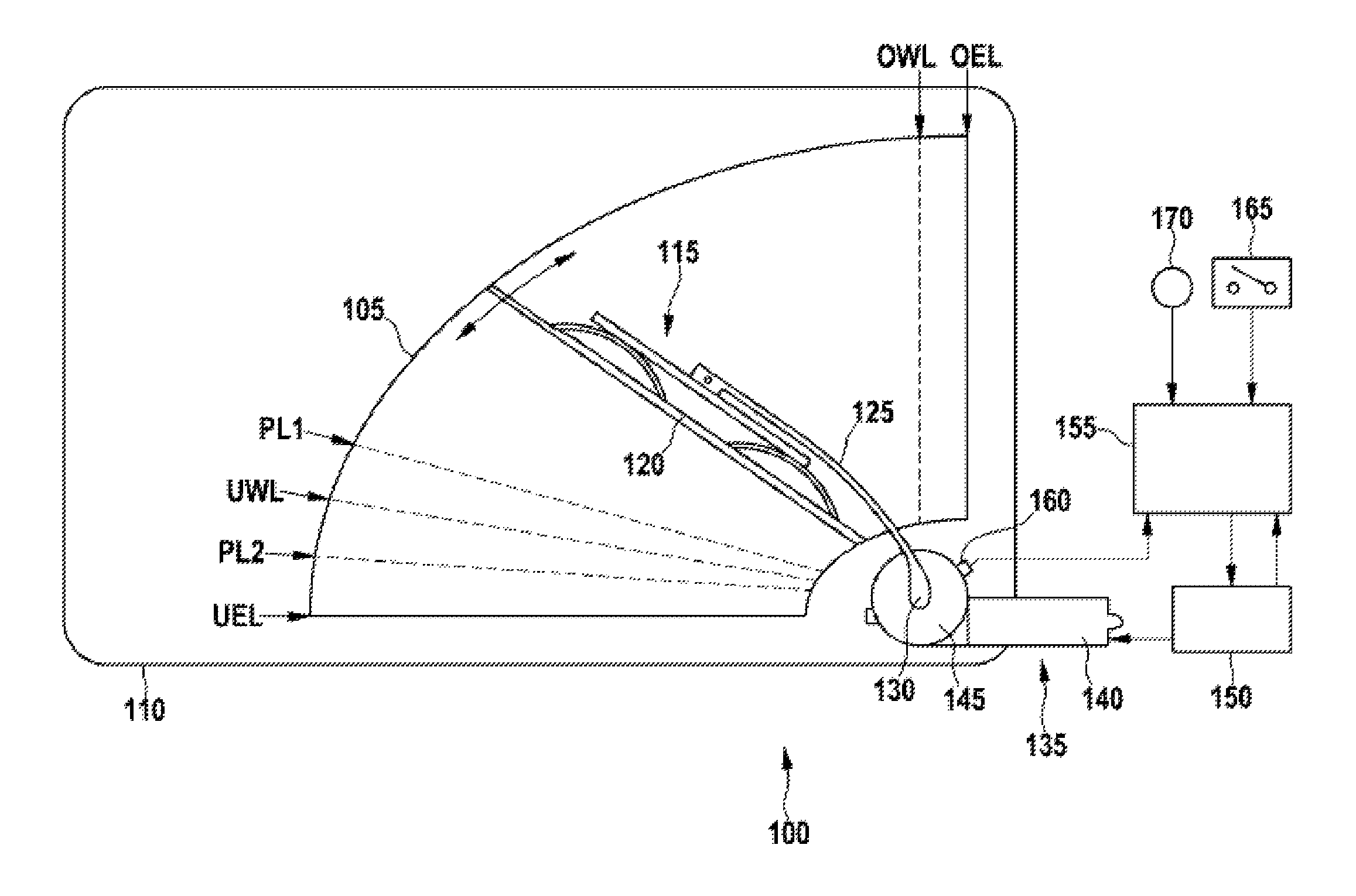

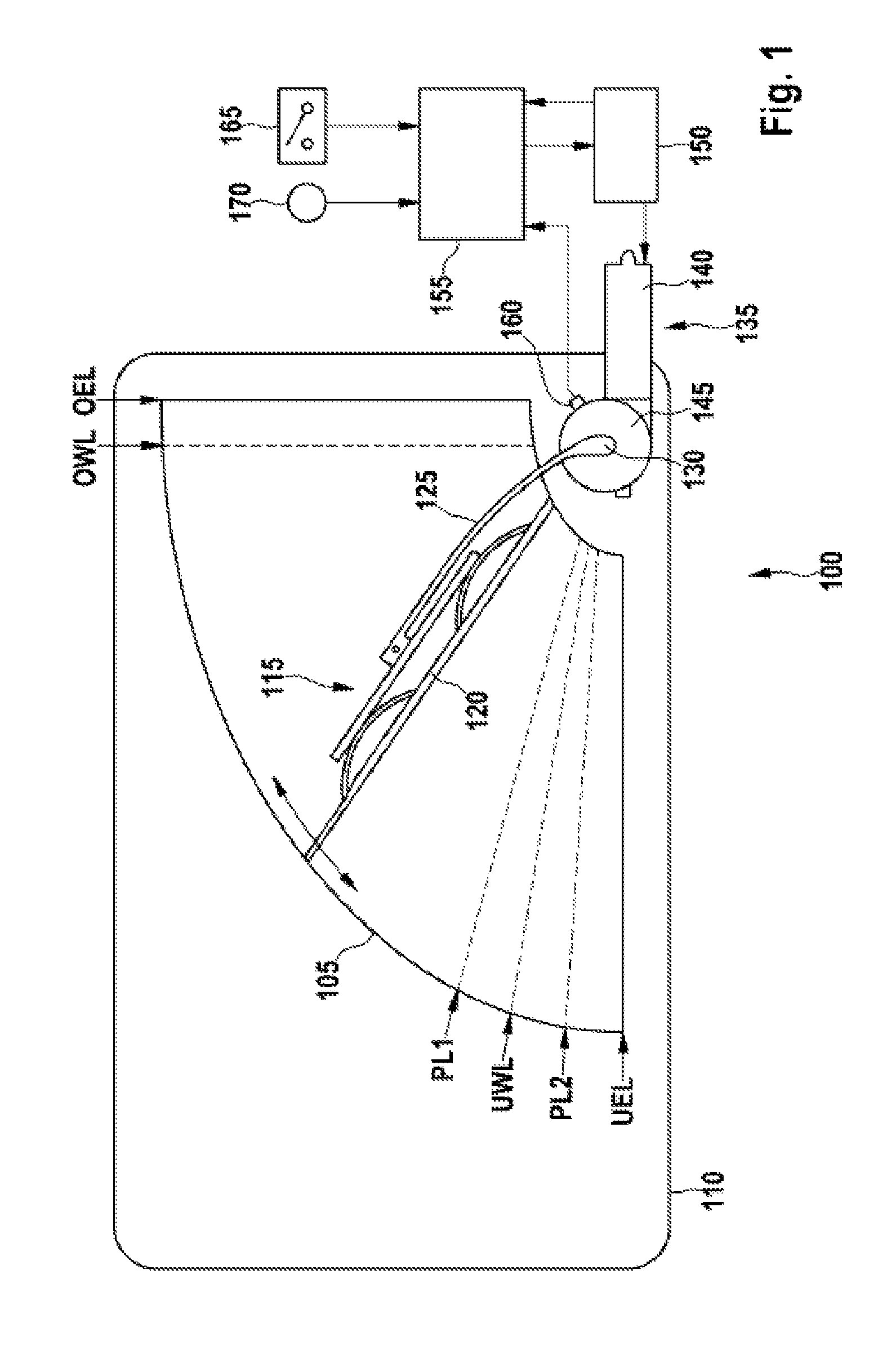

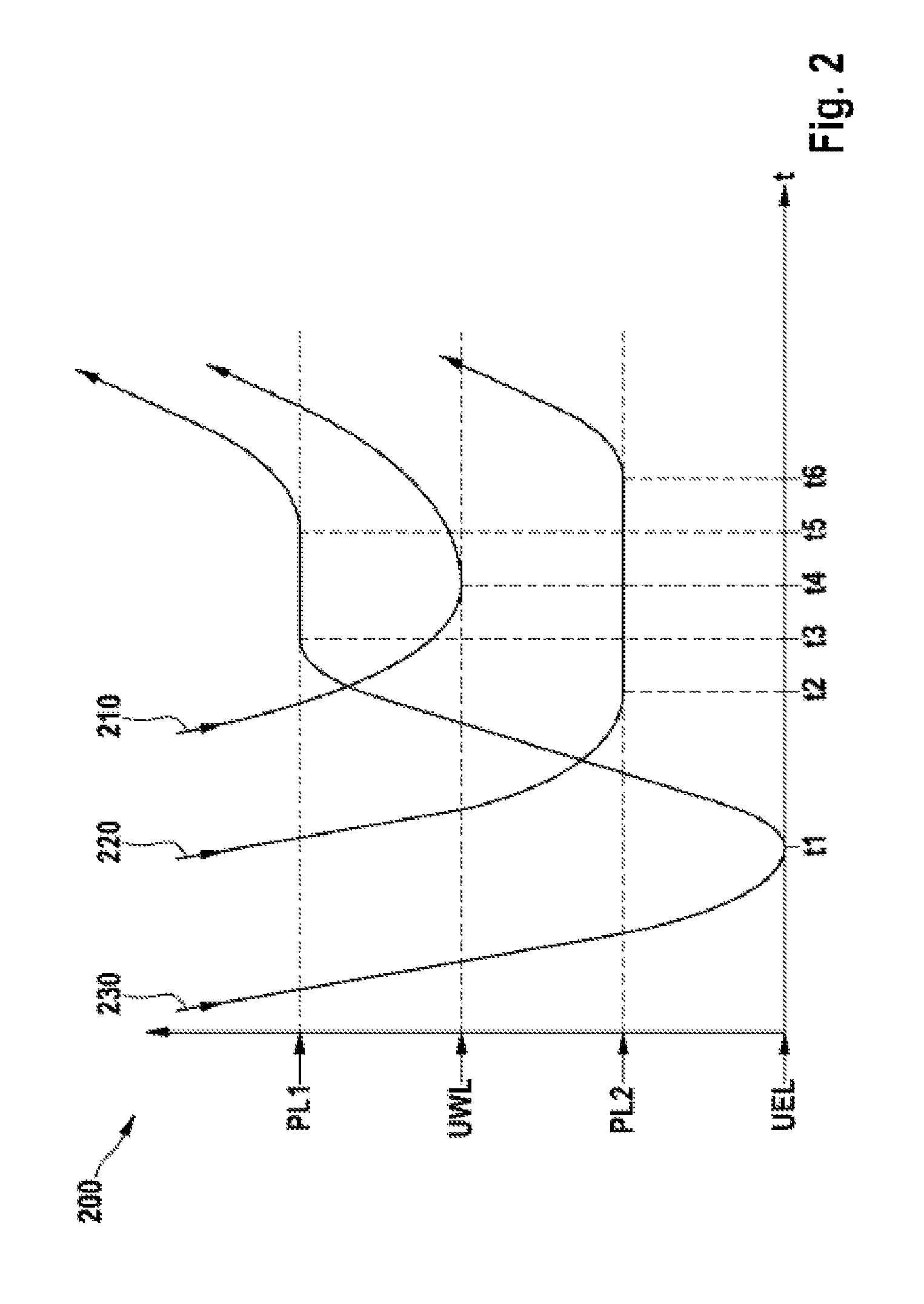

Wiper control

InactiveUS8957619B2Improve noiseAvoid turningMotor/generator/converter stoppersDC motor speed/torque controlMechanical resistanceEngineering

The invention relates to a method for controlling the movement of a wiper blade over a wiping surface, including the steps of moving the wiper blade up and down over the wiping surface between a lower turning position and an upper turning position, detecting a requirement to stop the wiper blade, moving the wiper blade downward into a lower end position and from there upward into a first parking position in the event that a reversing signal is present, and stopping the wiper blade. To this end, the wiper blade is moved into the lower end position only if previously thereto low mechanical resistance against the movement of the wiper blade over the wiping surface was determined.

Owner:ROBERT BOSCH GMBH

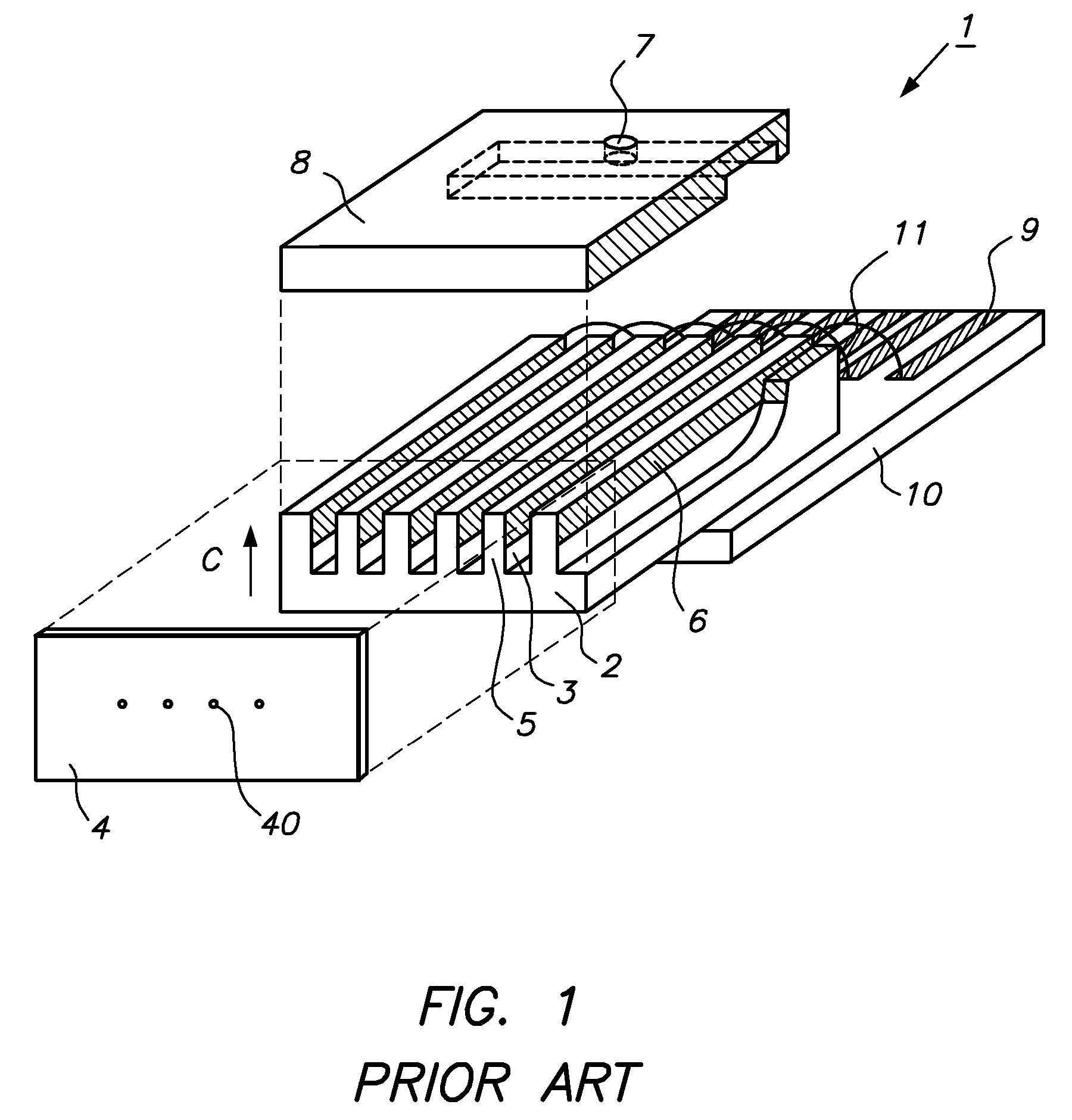

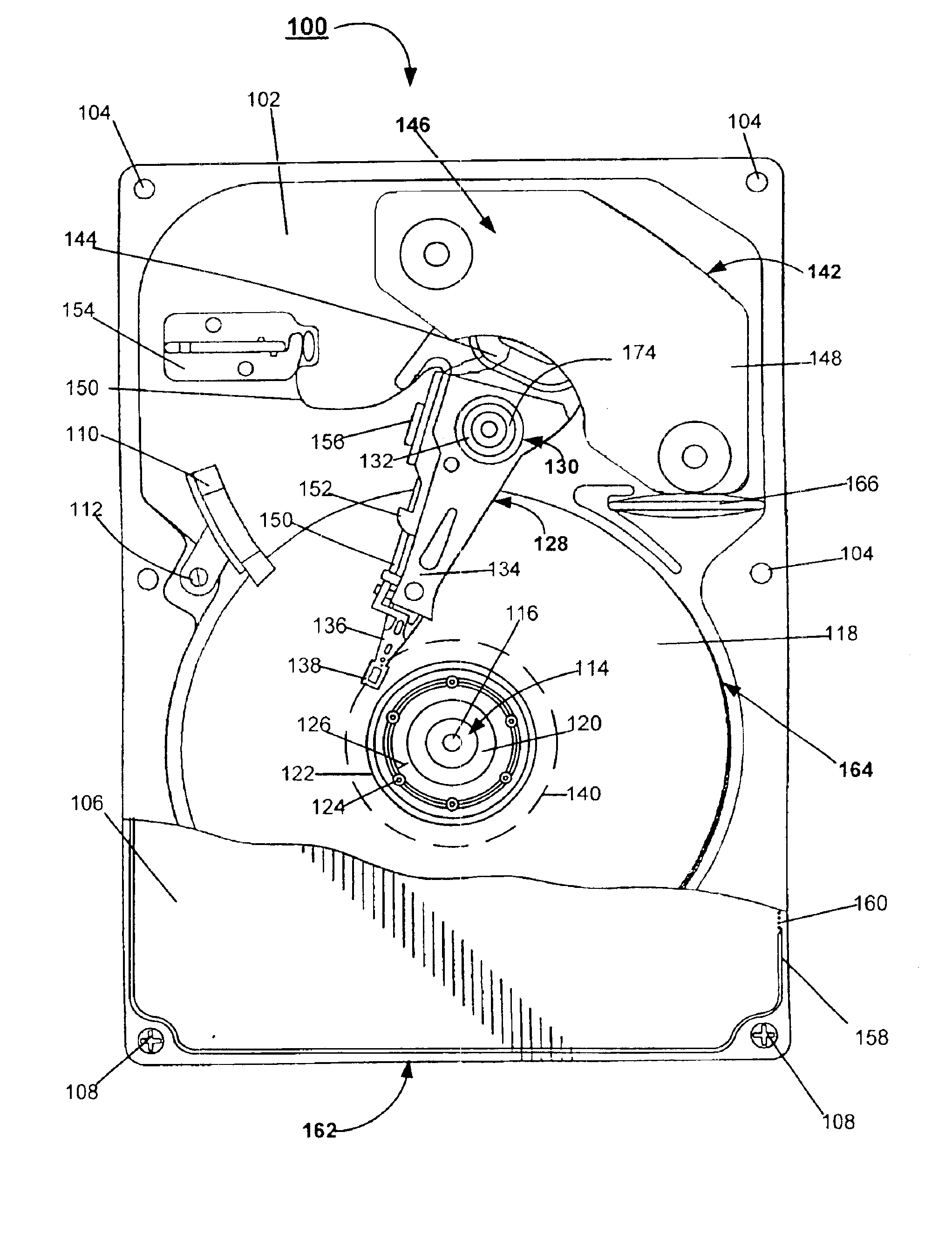

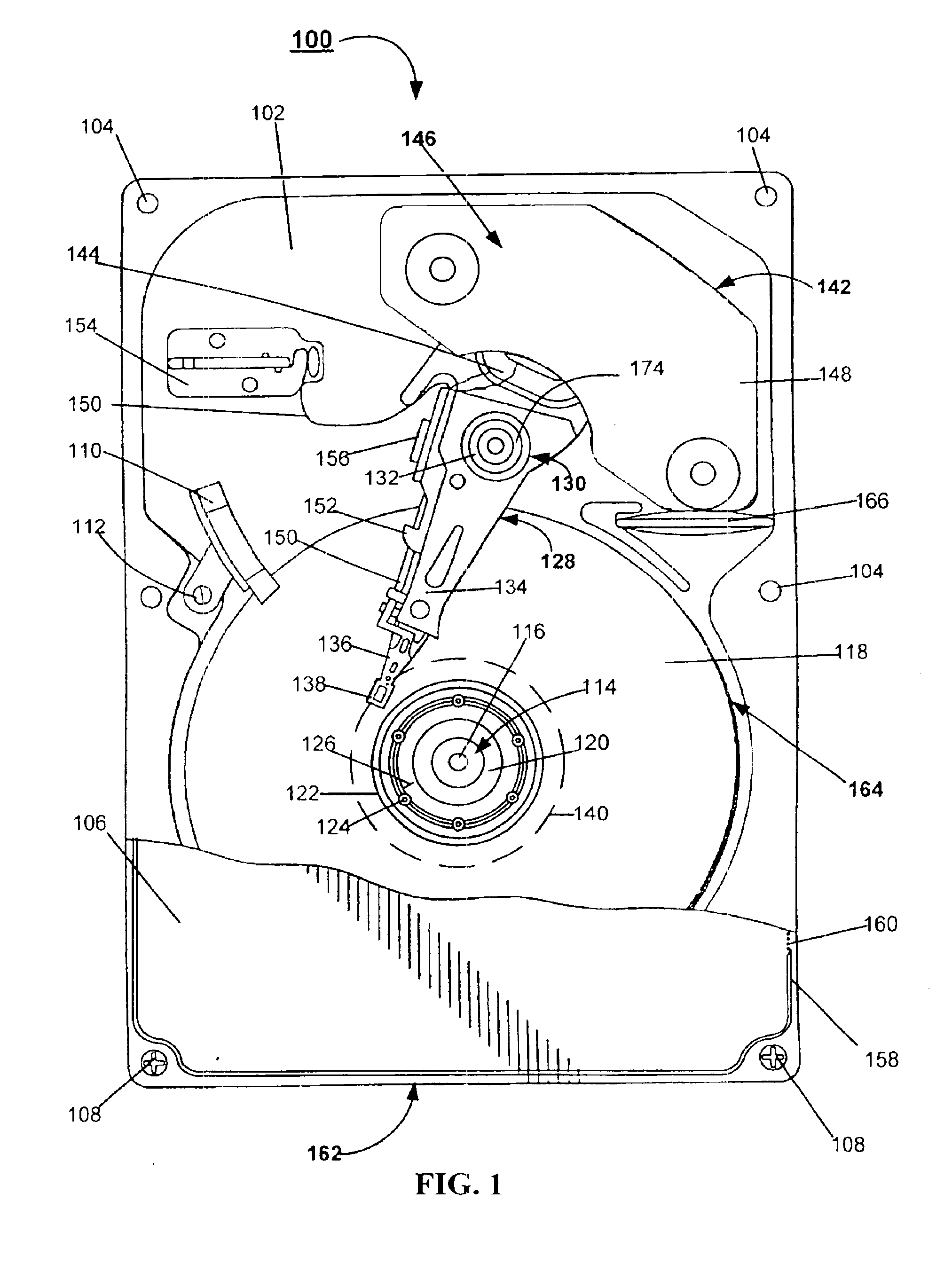

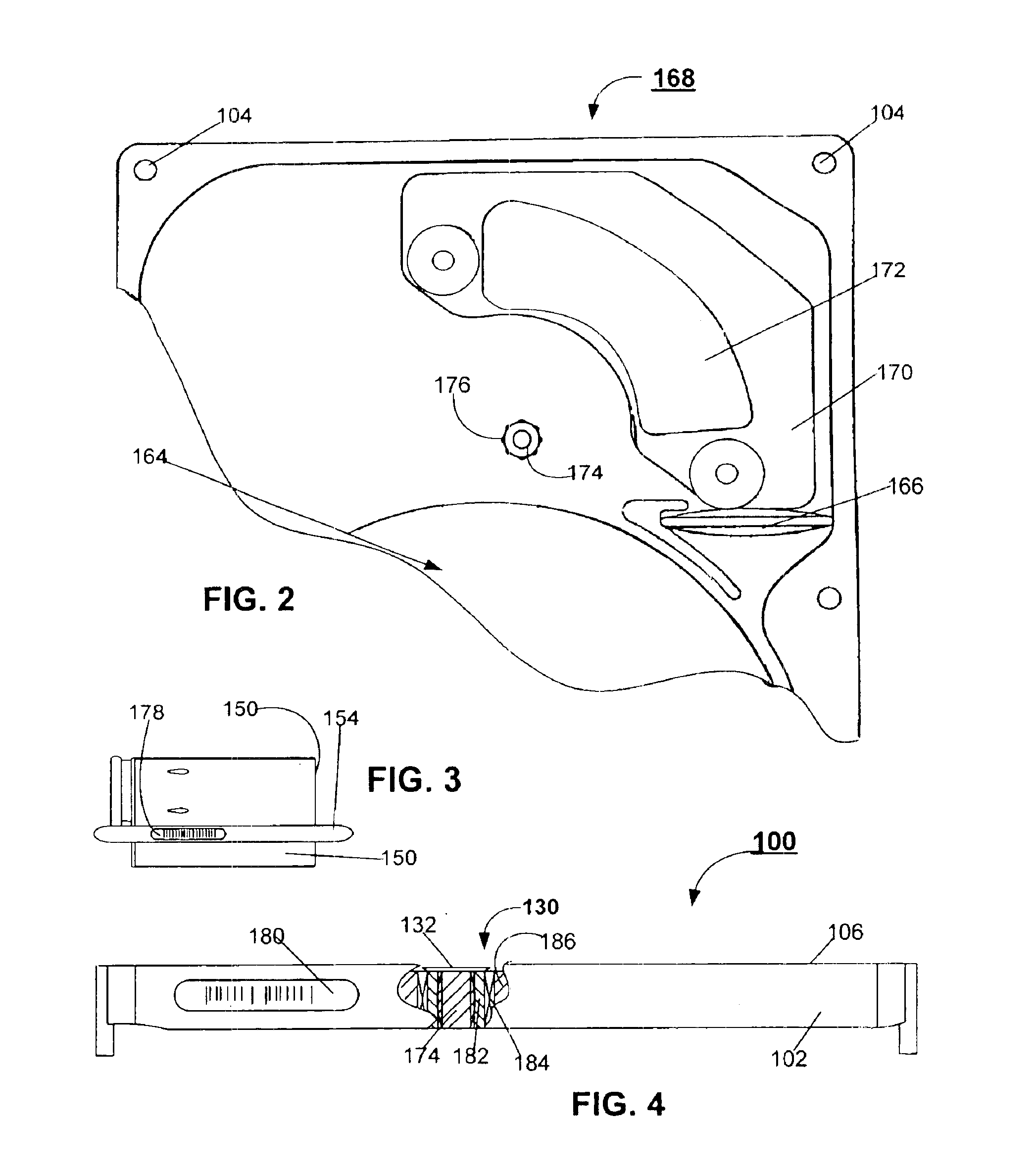

Computer directed head stack assembly installation system

The present invention provides a computer directed head stack assembly installation system with an installation software stored on recordable media directing the controlling a sequence of head stack installation assembly steps executed by a robotic assembly to pick and place a head stack assembly into a basedeck. The installation software program monitors compliance of the placement operation regarding mechanical resistance encountered by the head stack assembly engaging the basedeck compared to a dynamic force threshold F determined by the equation [F=(f(p)+ / −x)] and against the dynamic slope V determined by the equation [V=V=(fn−fn−1) / (pn−pn−1). Upon successful installation of the head stack assembly into the basedeck forming the head disc assembly, the head disc assembly is released from the head stack assembly installation station.

Owner:SEAGATE TECH LLC

Coated product

InactiveCN102529212AUniform growthReduce corrosionGlass/slag layered productsMetal layered productsInfraredCoating system

The invention discloses a coated product and particularly relates to coated glass which can be processed at a high temperature. The material of a reflective infrared film layer of the coated product is changed from the traditional pure silver material to an alloy material Ag1-aSba including silver (Ag) and stibium (Sb) metals, wherein a is greater than 0 and is less than or equal to 9wt%, and Sb is used as a wetting agent in the deposition process of a silver layer and enables the silver layer to grow in a two-dimensional shape; meanwhile, Sb can prevent Ag to interact with the adjacent oxide layer, improve the stability of a coating system in a high-temperature heat treatment and further improve the chemical stability as well as mechanical property of the silver layer. The coated product disclosed by the invention has high visible light transmittance, favorable mechanical resistance and chemical stability and is mainly applied to automobile windshields.

Owner:FUYAO GLASS IND GROUP CO LTD +1

End of travel feature for steer by wire vehicle

The present invention provides a system for generating an end of travel feedback to the driver of a vehicle where the vehicle includes a steer by wire system. The system includes a steering wheel, a steering shaft, a motor, and a clutch. The steering wheel is configured to control the steer by wire system. The steering shaft is coupled to the steering wheel and rotates in conjunction with the steering wheel. To provide road feel resistance to the driver, the motor is coupled to the steering shaft. Further, the clutch is configured to mechanically couple the steering shaft to the road wheel to provide mechanical resistance when the road wheel is at an end of travel position.

Owner:VISTEON GLOBAL TECH INC

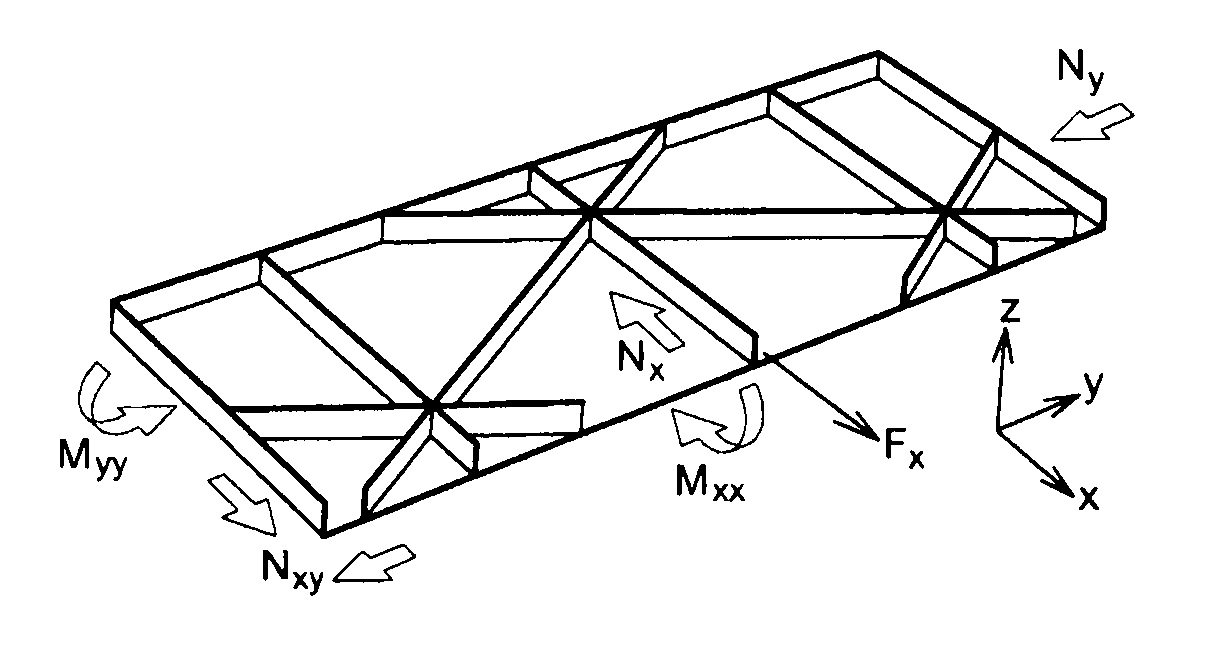

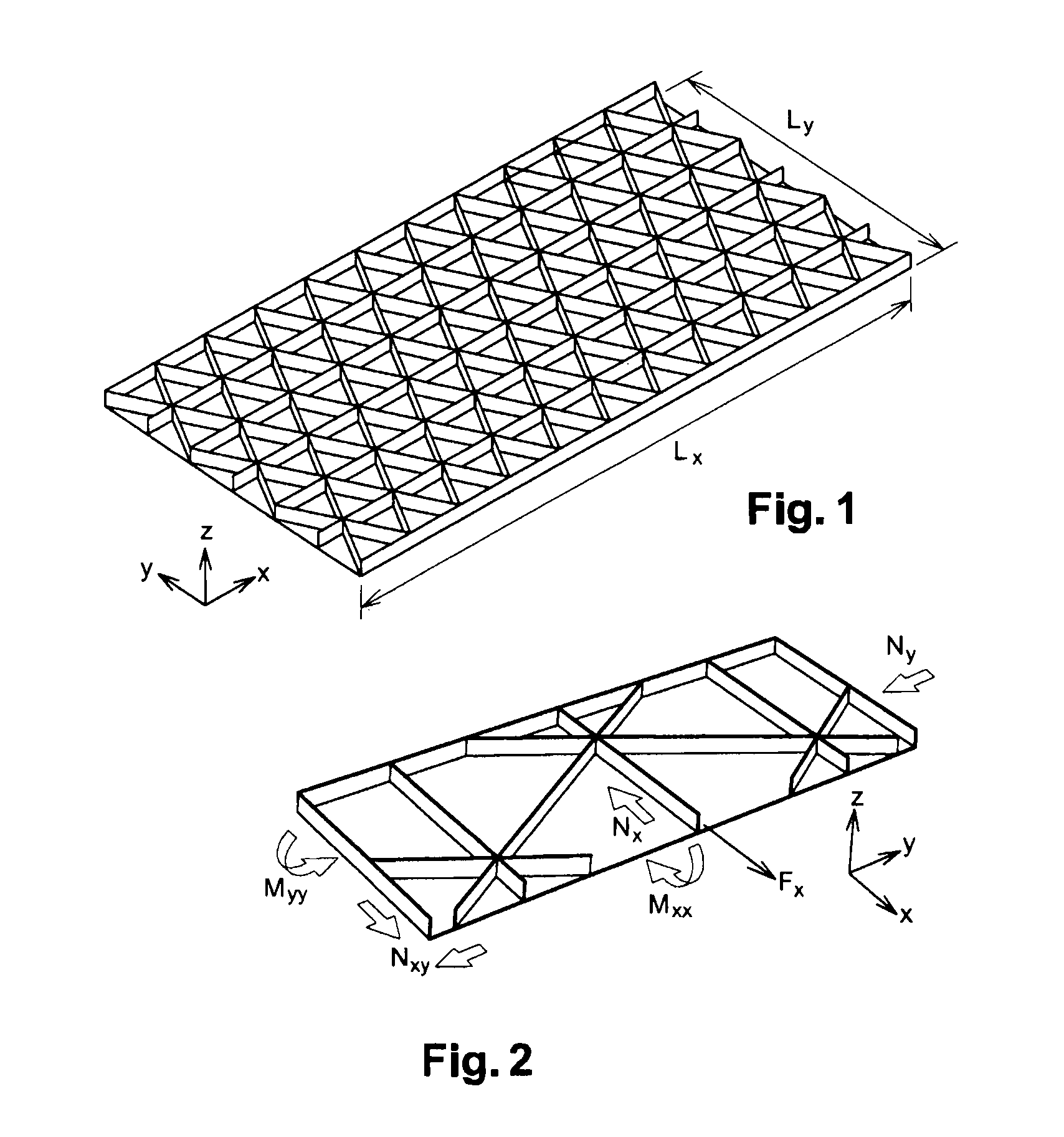

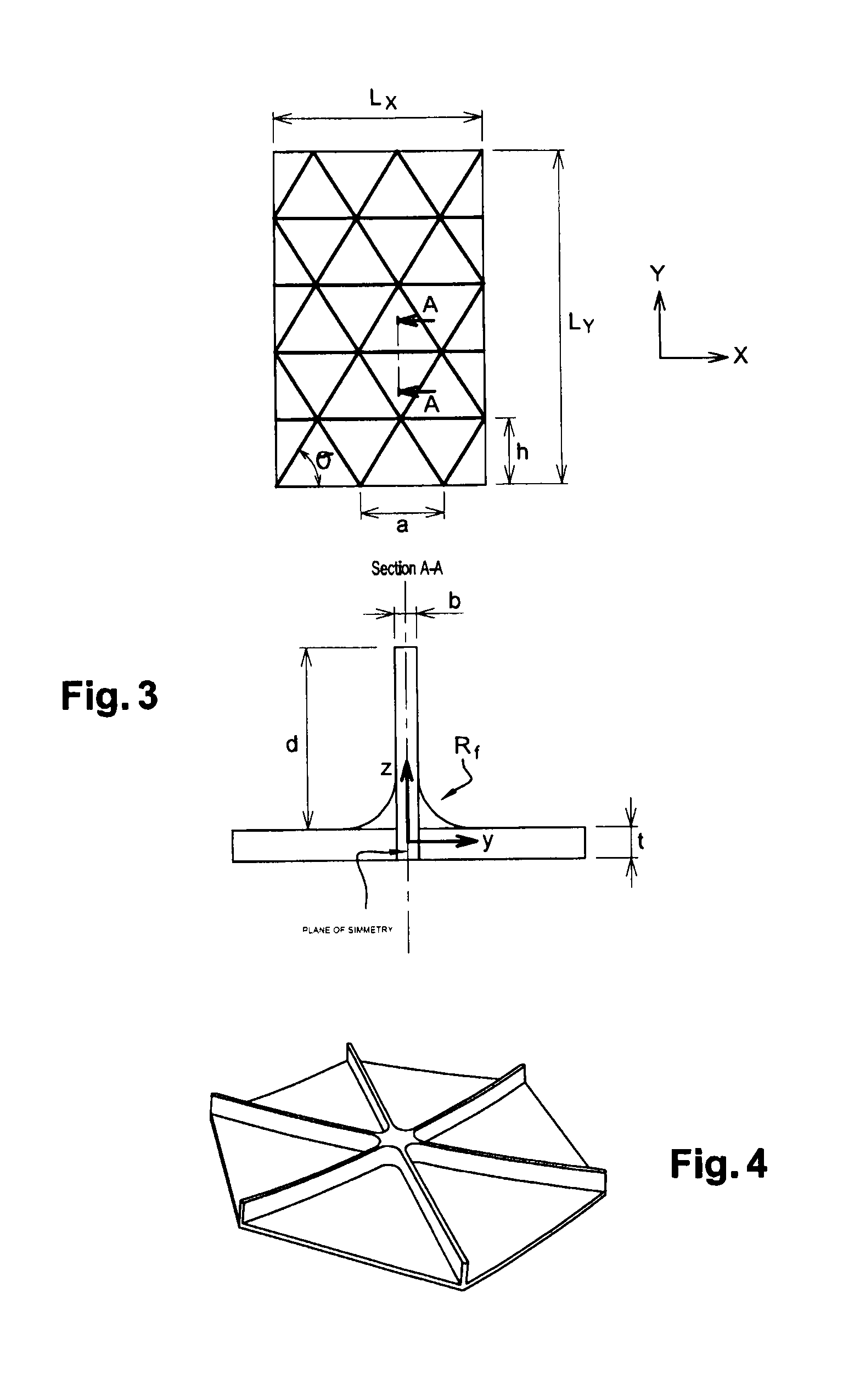

Method for the structural analysis of panels consisting of an isotropic material and stiffened by triangular pockets

The invention relates to a method for dimensioning, by an analytical method, of an essentially plane panel consisting of a homogenous and isotropic material, said panel consisting of a skin reinforced by a set of three parallel bundles of stiffeners built into the panel. The pockets determined on the skin by said groups of stiffeners are triangular, the stiffeners are blade shaped and the stiffened panel must comply with specifications for mechanical resistance to predetermined external loads, the angles between bundles of stiffeners being such that the triangular pockets have any kind of isosceles form.

Owner:AIRBUS OPERATIONS (SAS)

Medical handle device and illumination apparatus

InactiveUS7726863B2Resistance to mechanical damageFirmly connectedBronchoscopesCoupling device connectionsMechanical resistanceHand held

A medical handle device having an illumination apparatus with at least one optical semiconductor component and a method for manufacturing such a hand-held device are displayed. It is proposed that in order to adapt the hand-held device to the specific requirements of a medical application such as uniformly high light emission, high mechanical resistance, sterilizability and electric safety, the illumination apparatus is provided with a base body, at least one blind hole arranged in the base body, a light-emitting window which is formed by the part of the base body extending from the bottom of the blind hole to the first end of the base body and is connected to a cover device which is connected to the base body and with which the blind hole forms a hermetically sealed interior, whereby the at least one optical semiconductor component is arranged in the hermetically sealed interior and the base body and the cover device are made of an electrically non-conducting material that can withstand sterilization. In some embodiments, at least one optical semiconductor component is encased in a transparent thermoplastic material.

Owner:W&H DENTALWERK