Patents

Literature

1974 results about "Frequency detection" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Multiple simultaneous frequency detection

ActiveUS20080309625A1Wireless commuication servicesTransducer casings/cabinets/supportsFrequency mixerFrequency detection

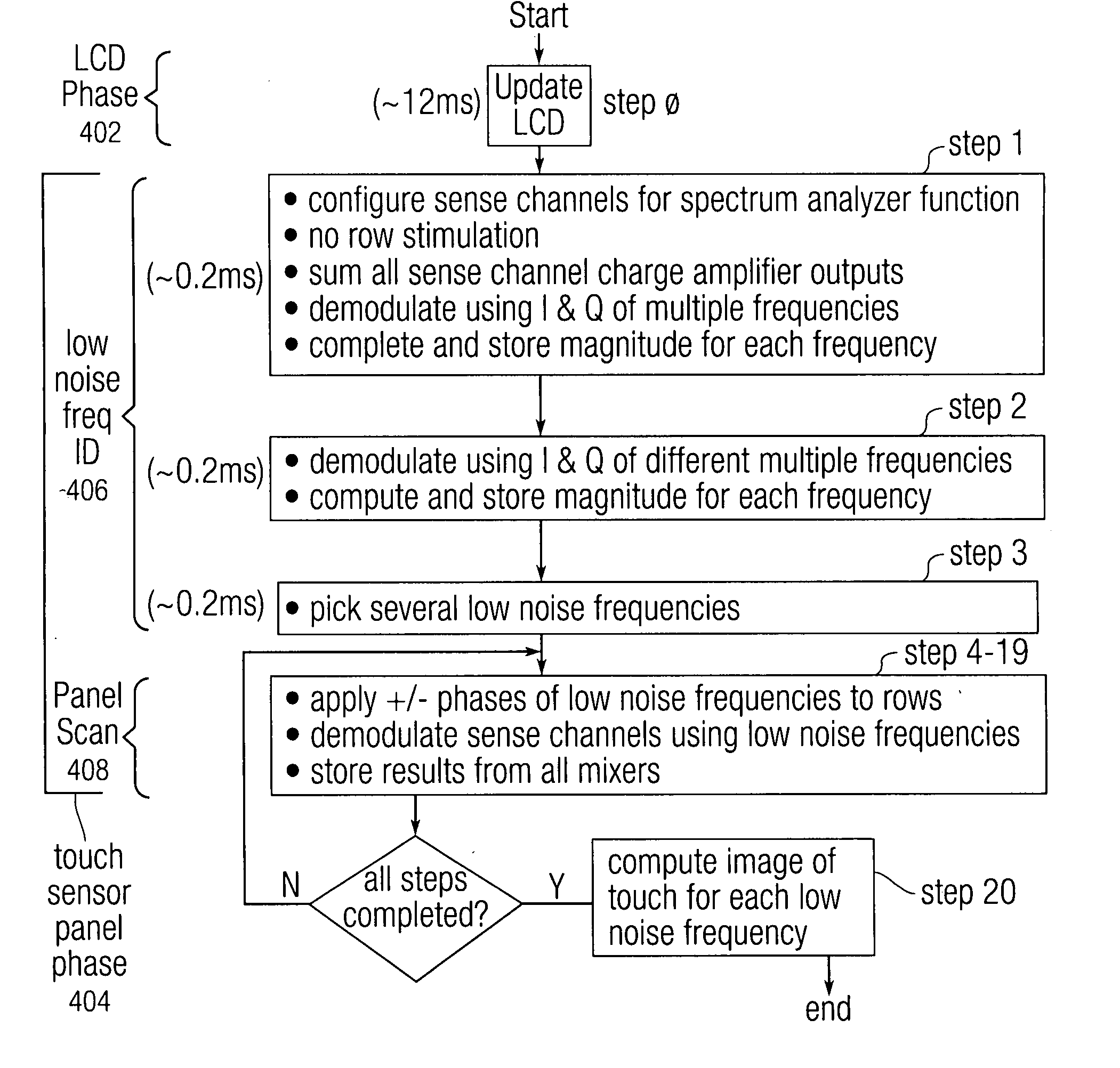

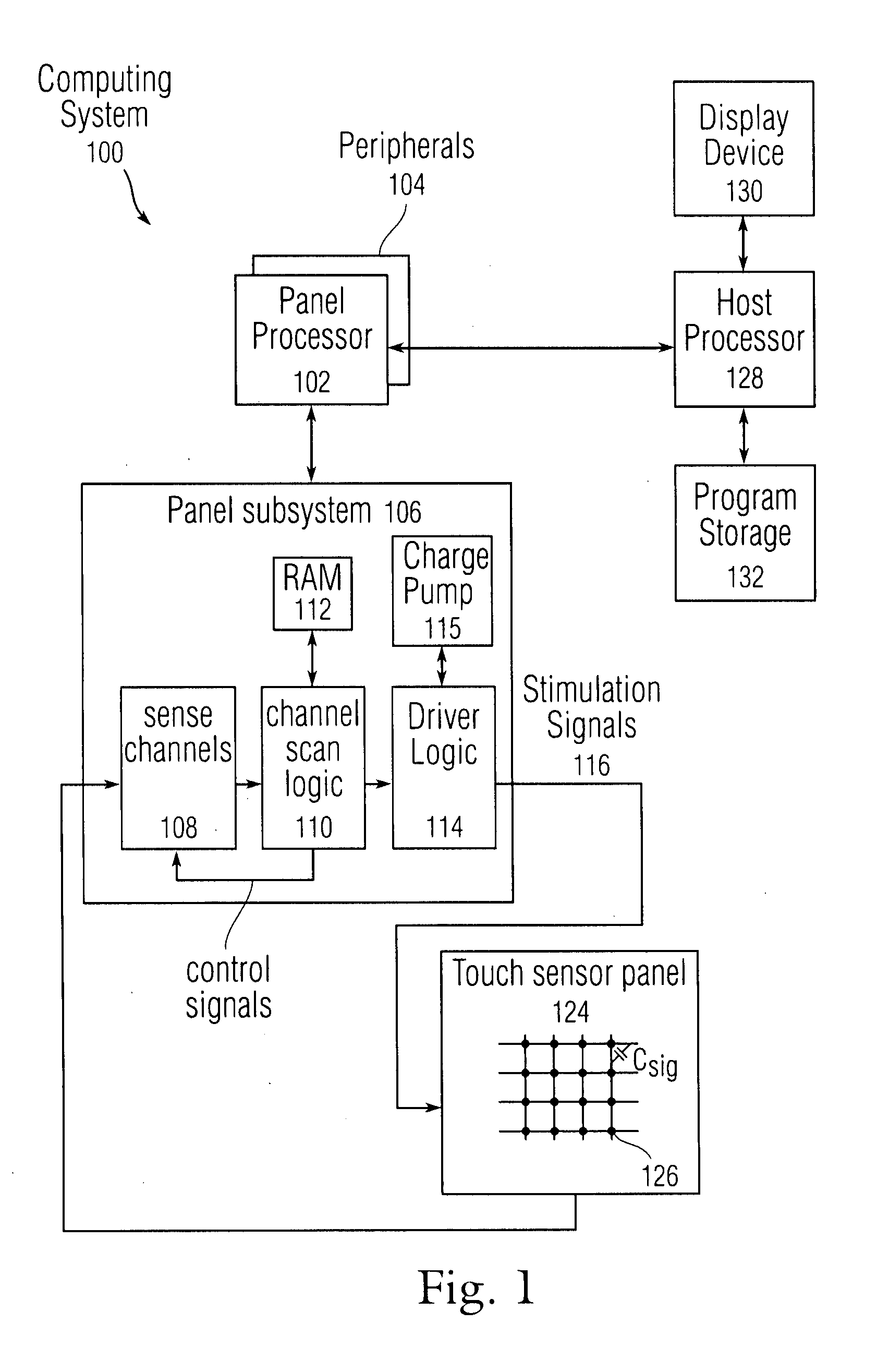

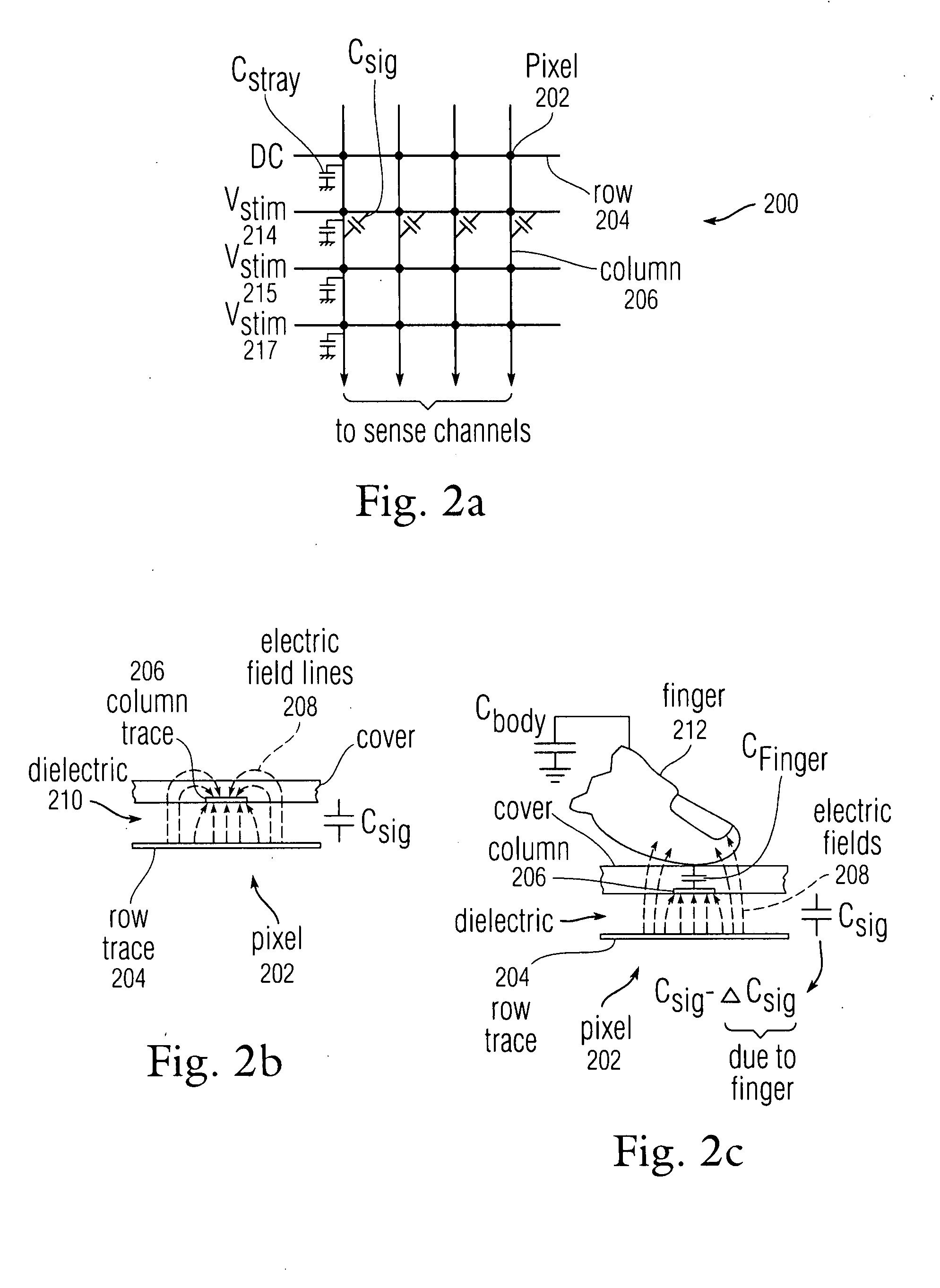

The use of multiple stimulation frequencies and phases to generate an image of touch on a touch sensor panel is disclosed. Each of a plurality of sense channels can be coupled to a column in a touch sensor panel and can have multiple mixers. Each mixer in the sense channel can utilize a circuit capable generating a demodulation frequency of a particular frequency. At each of multiple steps, various phases of selected frequencies can be used to simultaneously stimulate the rows of the touch sensor panel, and the multiple mixers in each sense channel can be configured to demodulate the signal received from the column connected to each sense channel using the selected frequencies. After all steps have been completed, the demodulated signals from the multiple mixers can be used in calculations to determine an image of touch for the touch sensor panel at each frequency.

Owner:APPLE INC

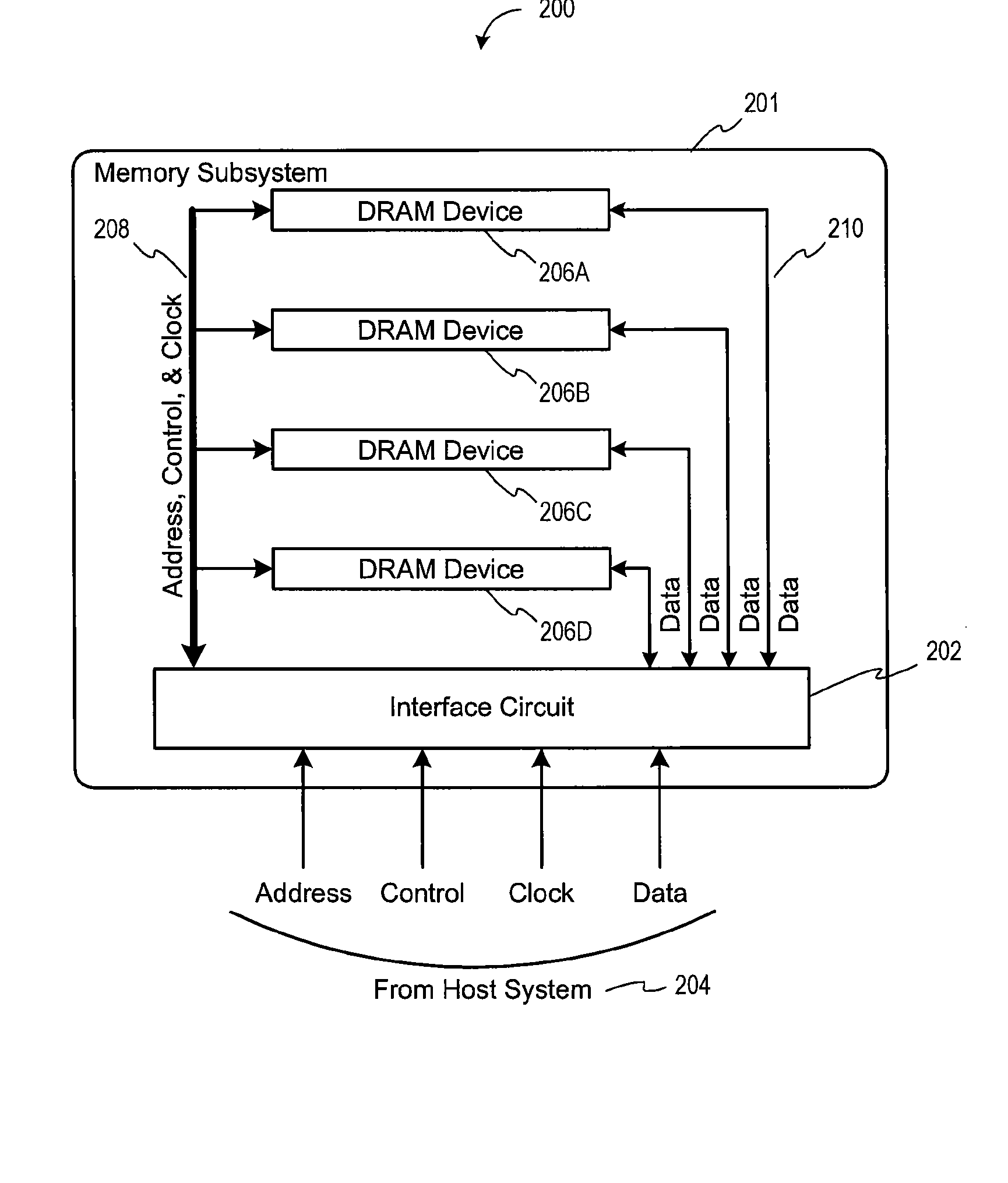

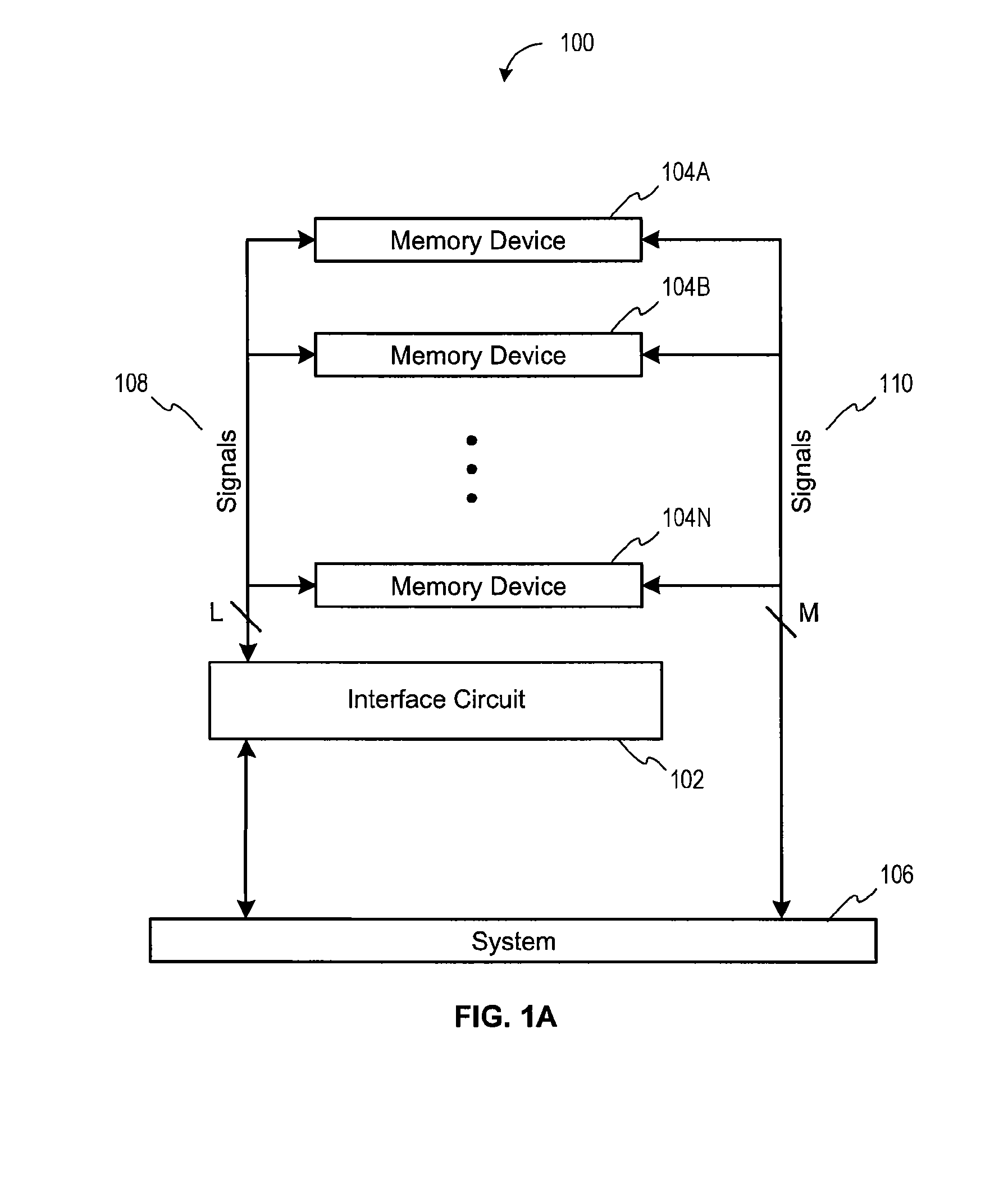

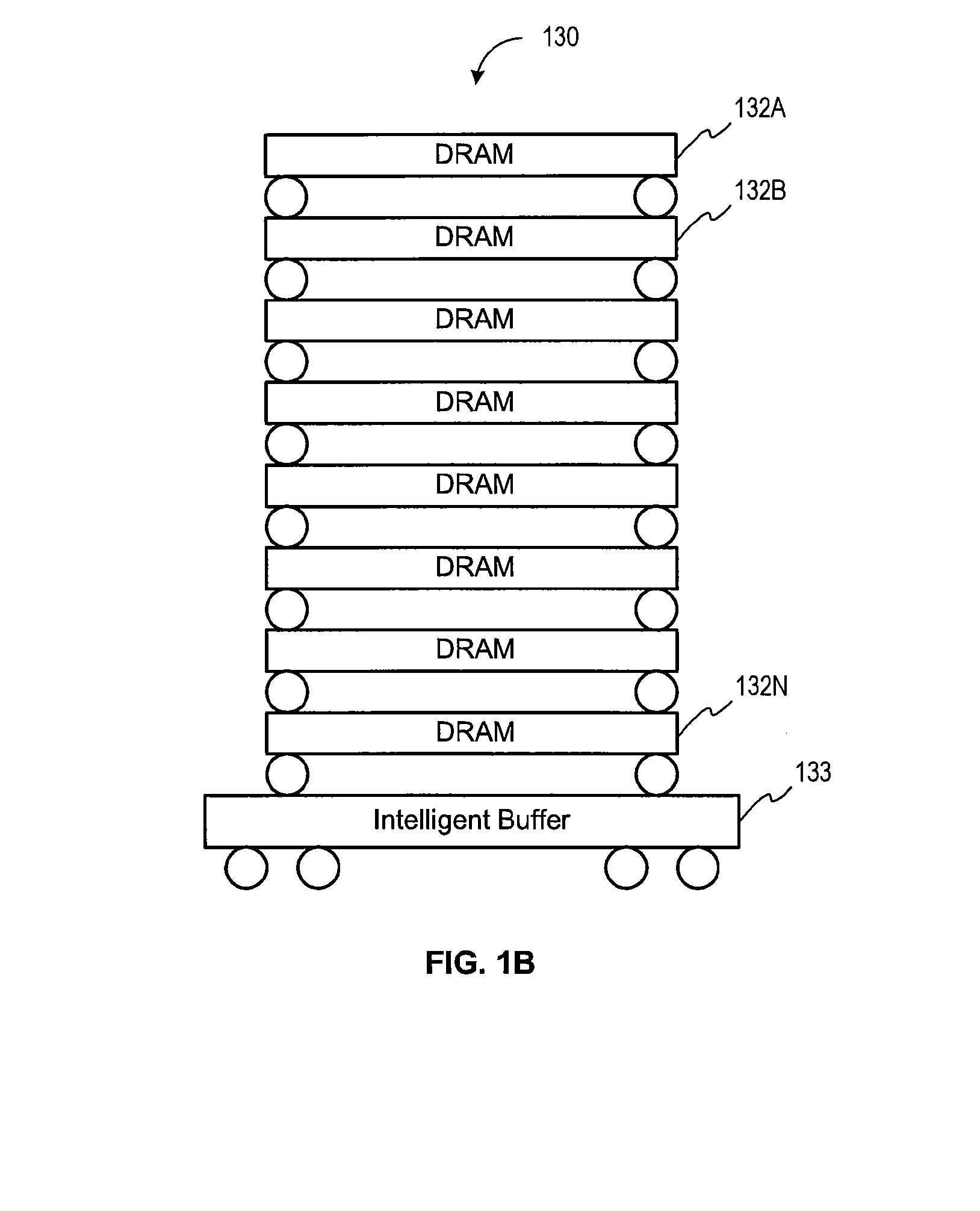

Method and Apparatus For Refresh Management of Memory Modules

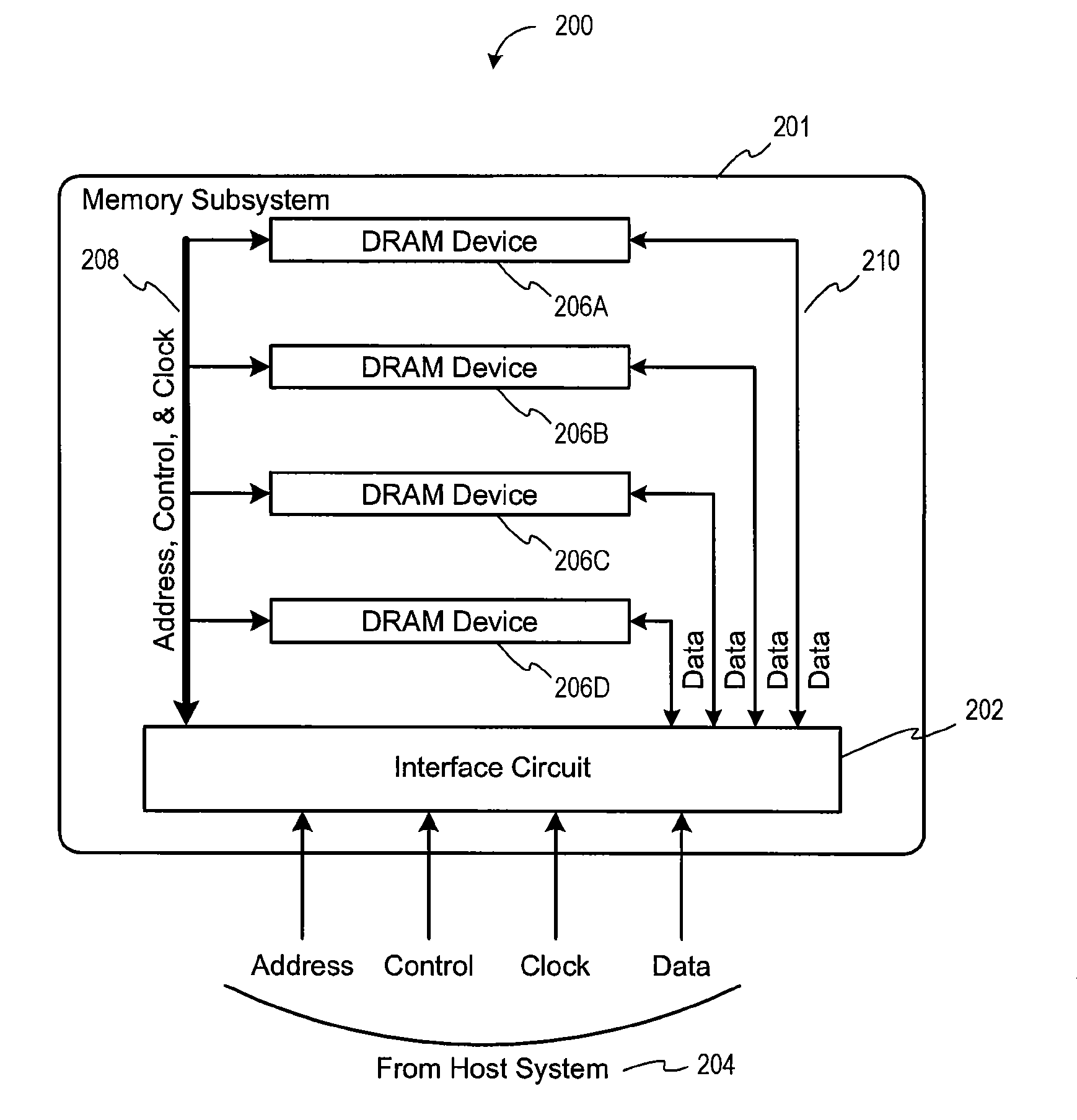

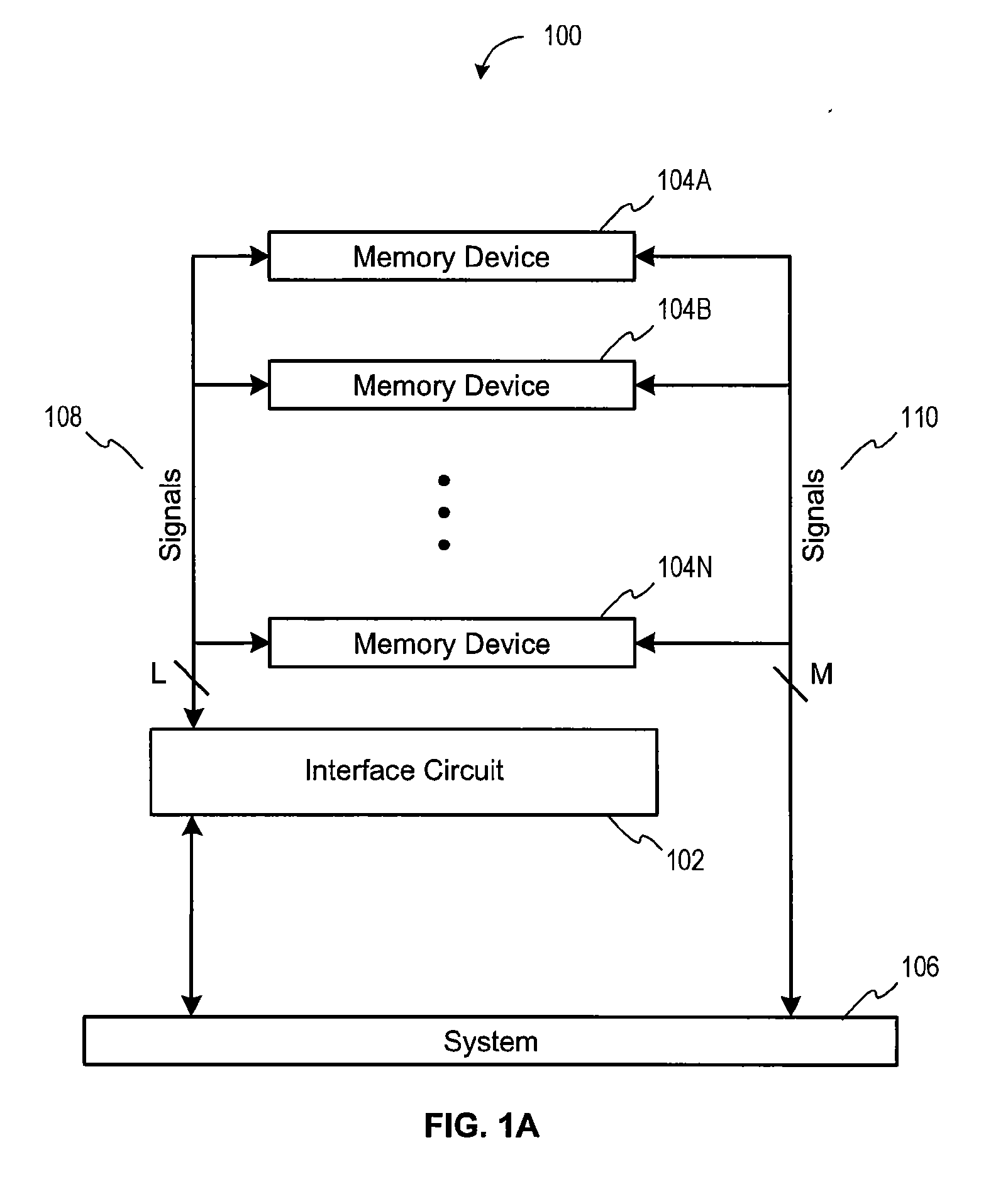

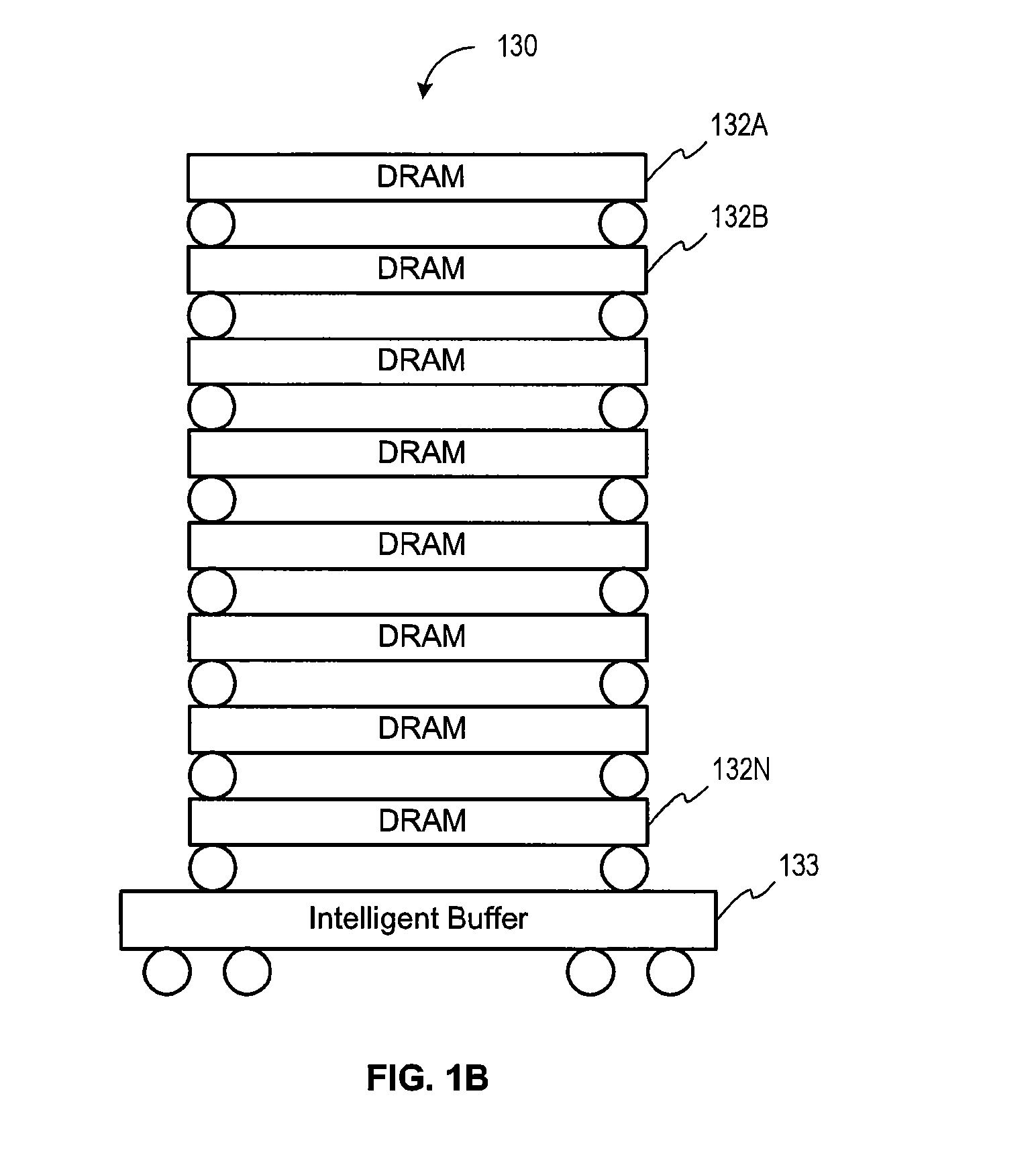

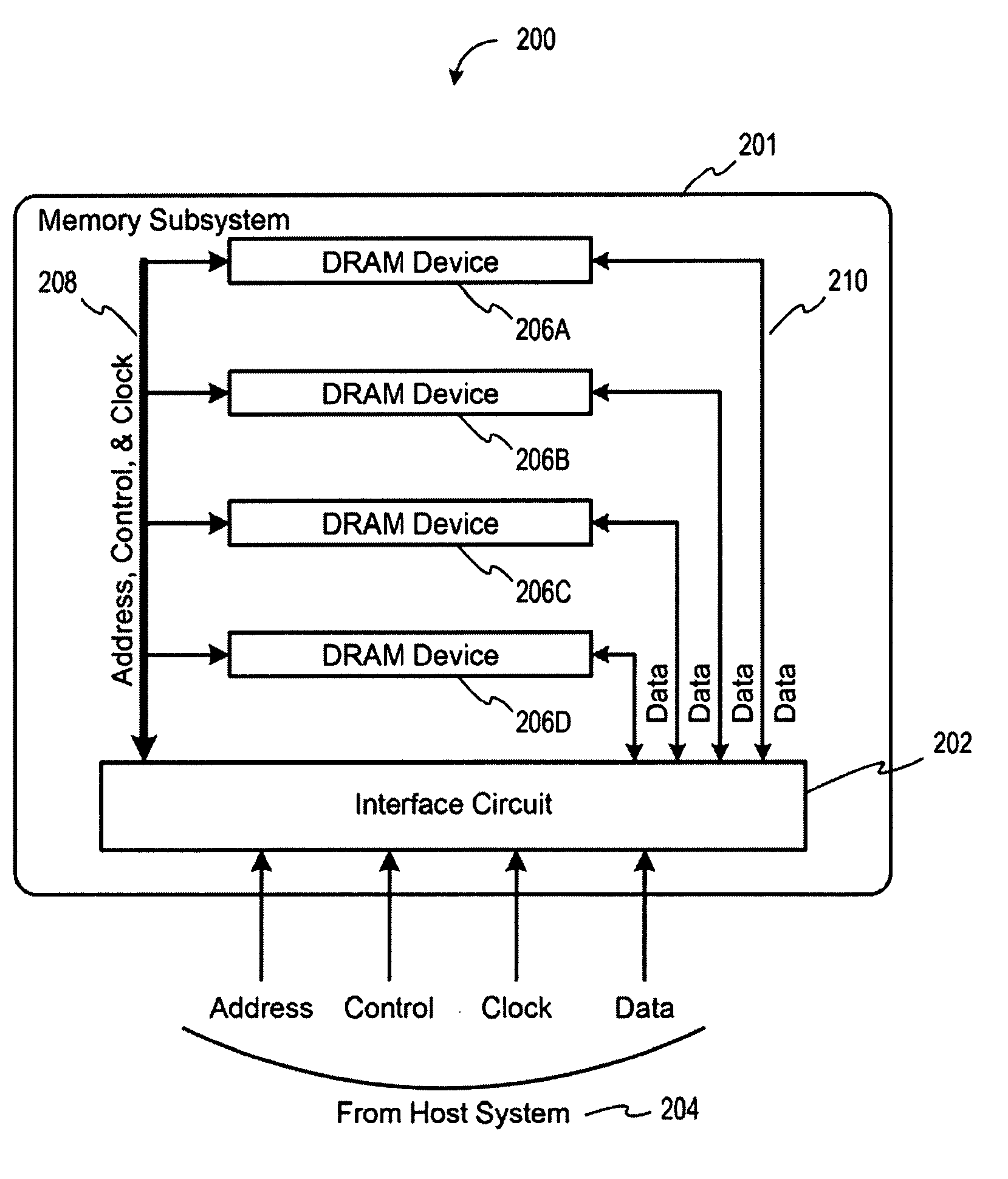

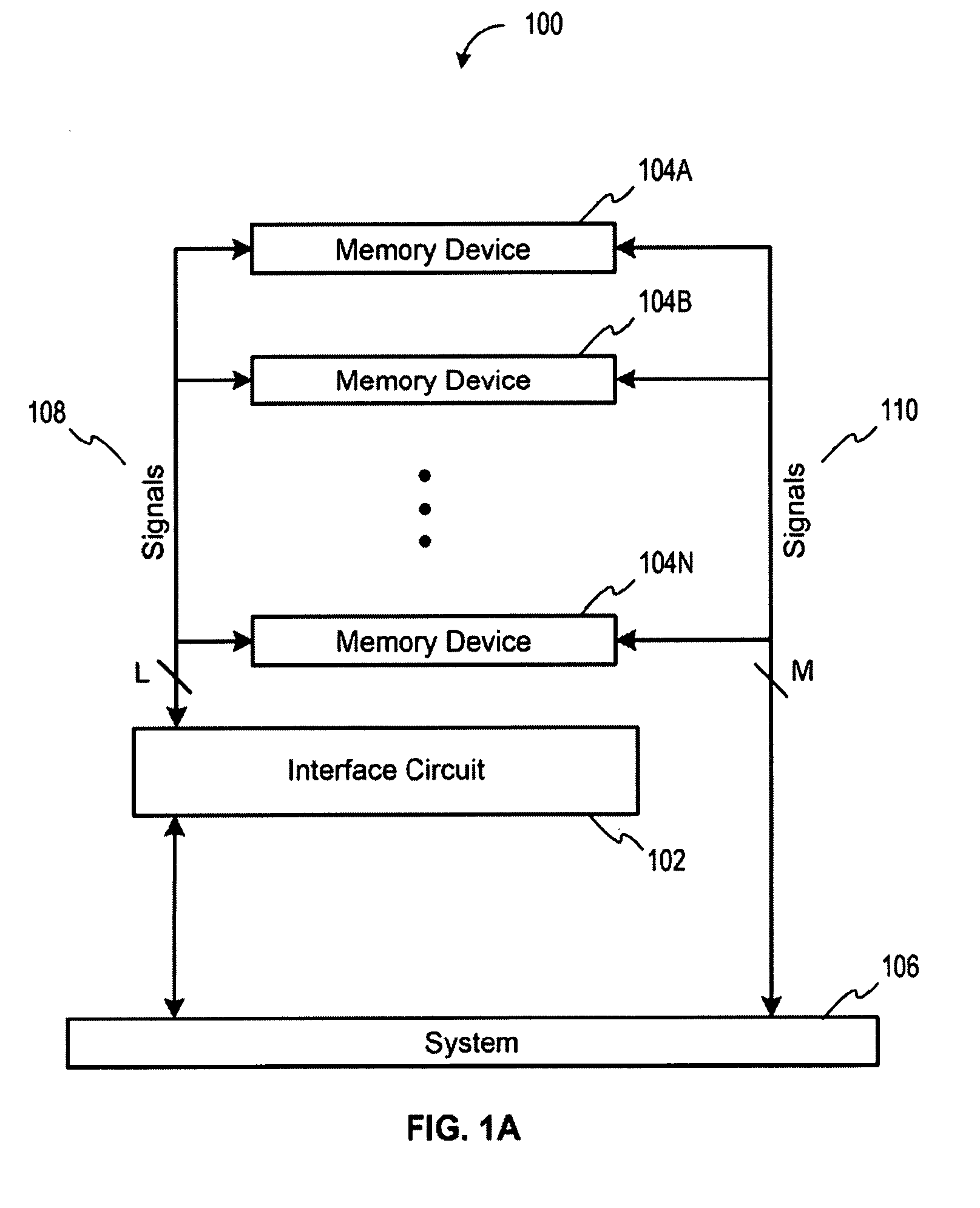

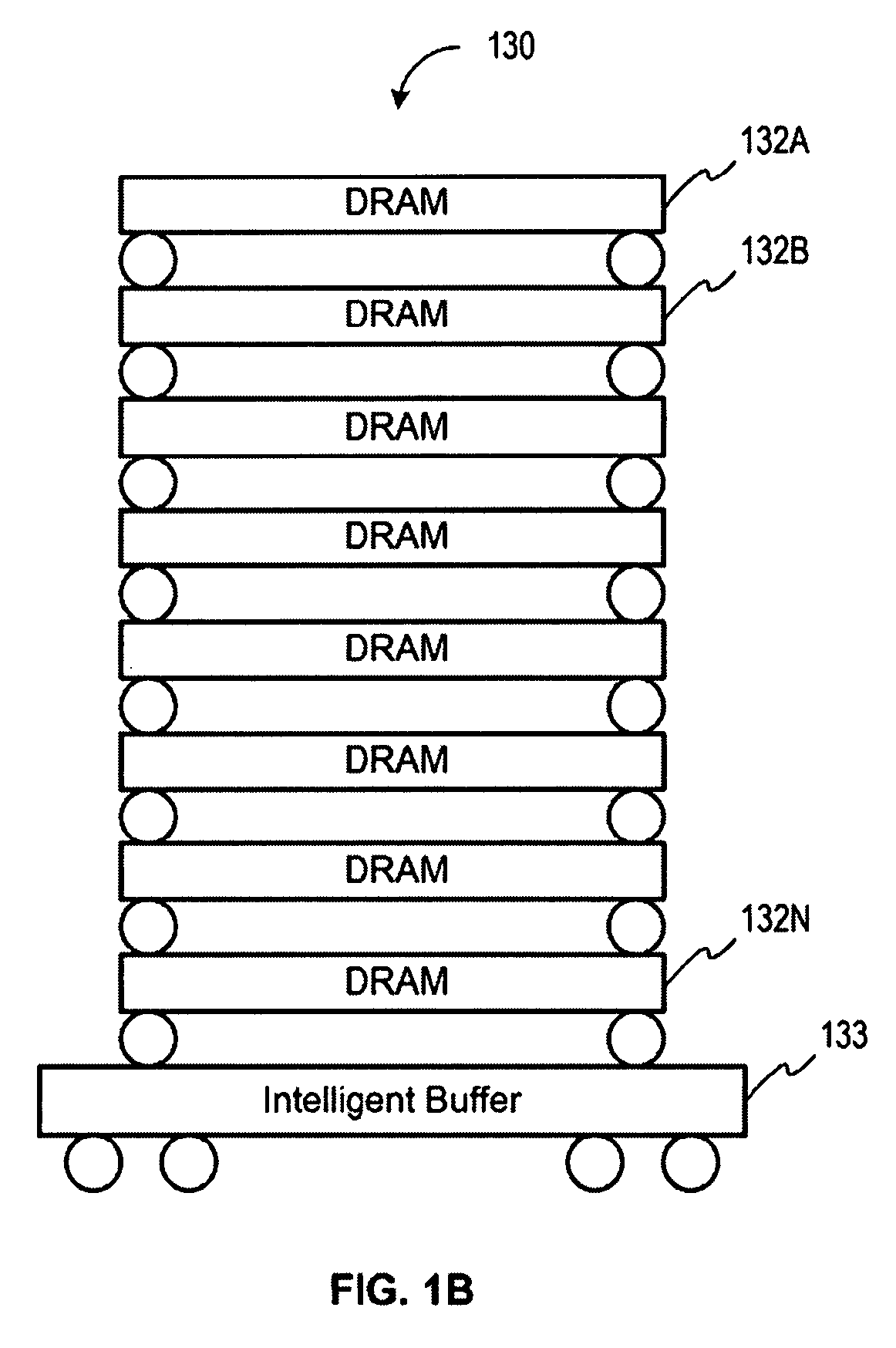

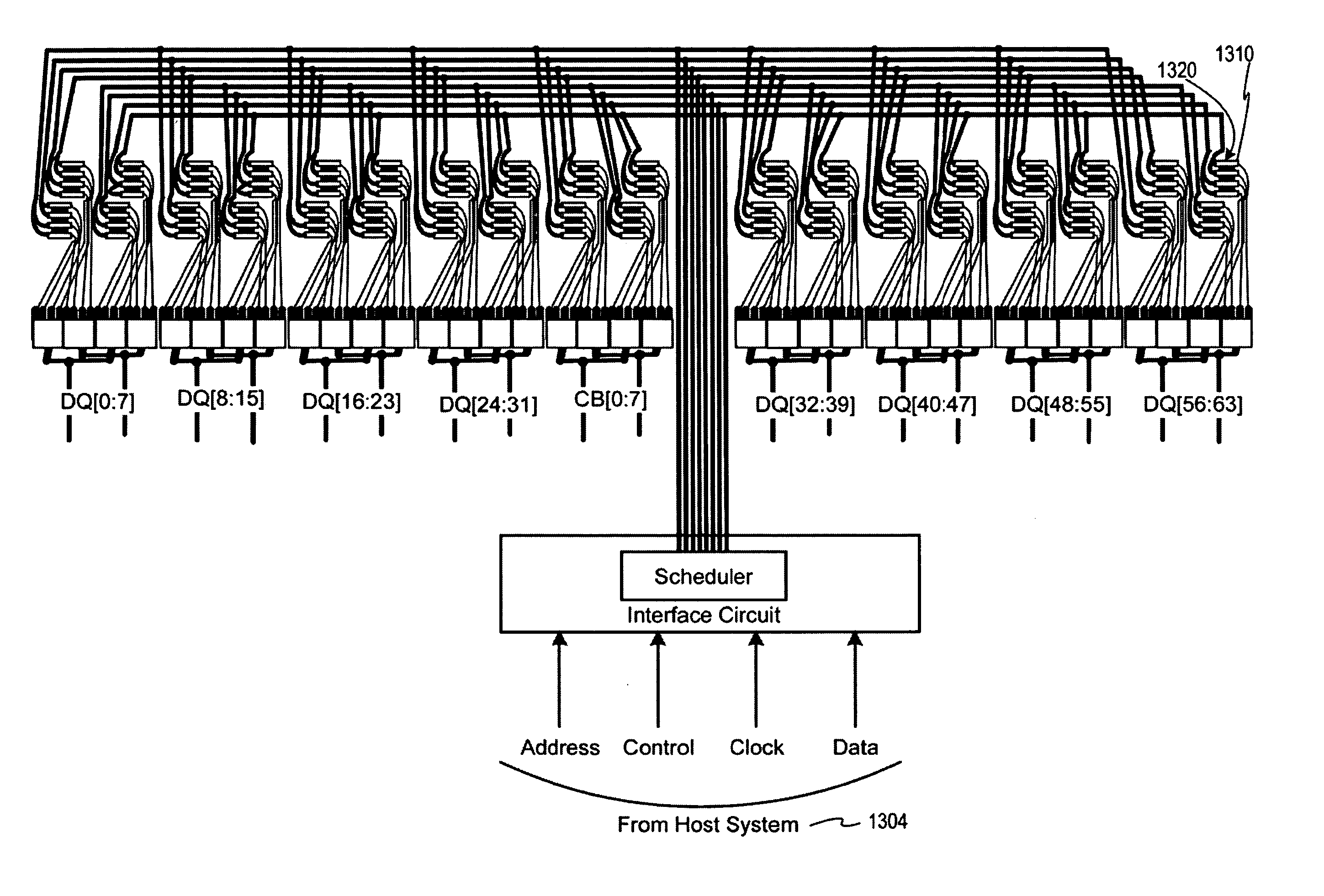

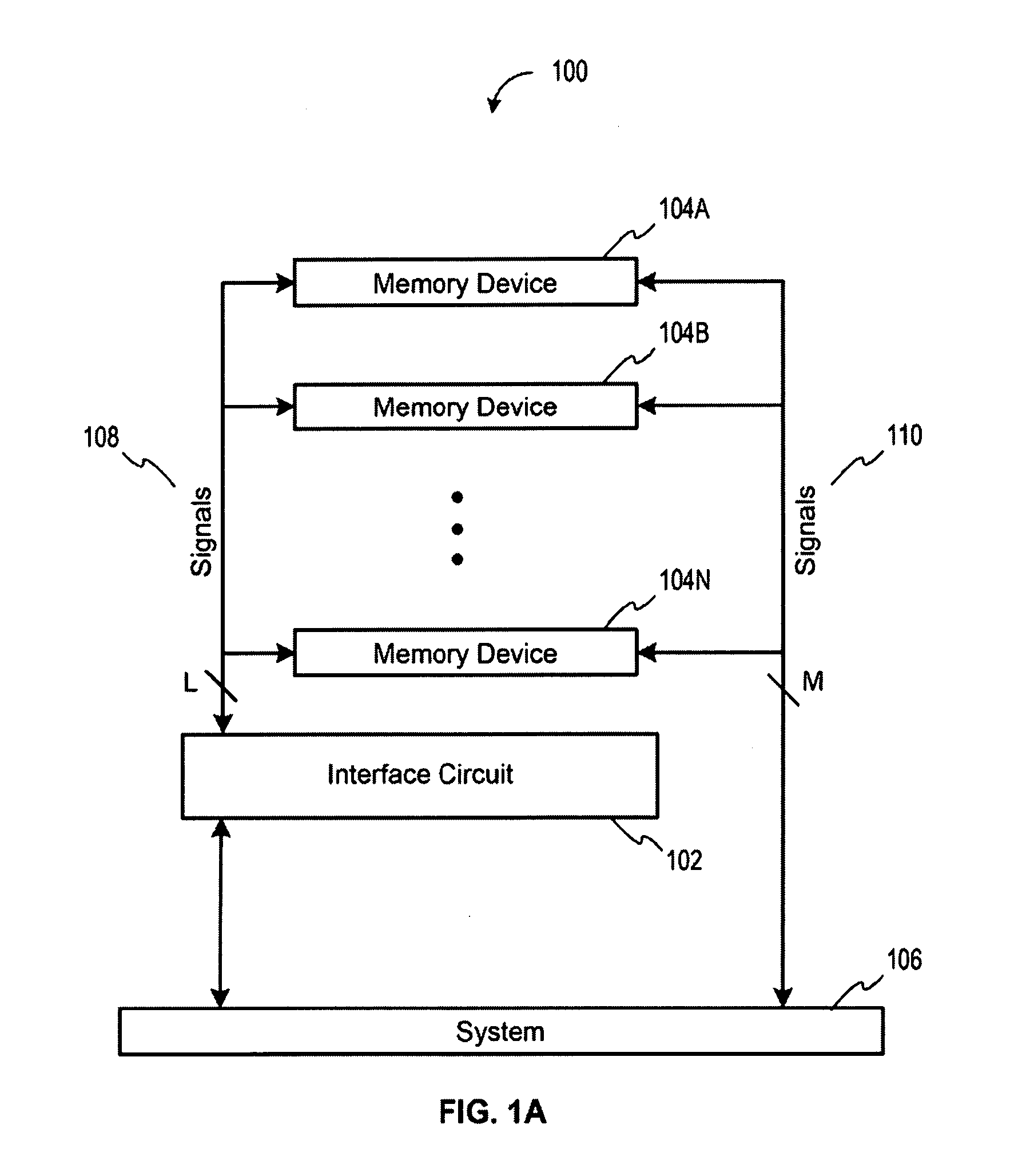

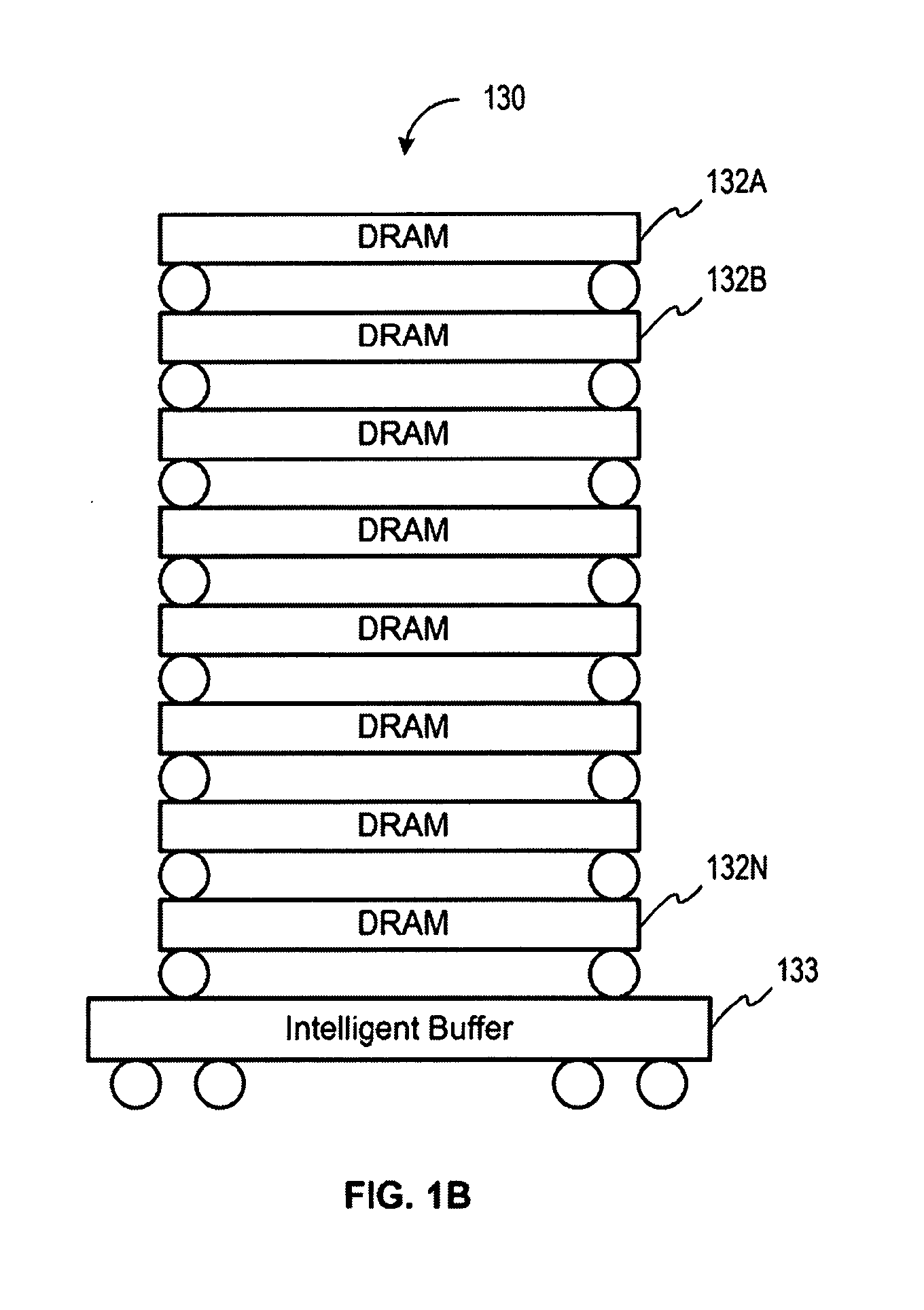

One embodiment sets forth an interface circuit configured to manage refresh command sequences that includes a system interface adapted to receive a refresh command from a memory controller, clock frequency detection circuitry configured to determine the timing for issuing staggered refresh commands to two or more memory devices coupled to the interface circuit based on the refresh command received from the memory controller, and at least two refresh command sequence outputs configured to generate the staggered refresh commands for the two or more memory devices

Owner:GOOGLE LLC

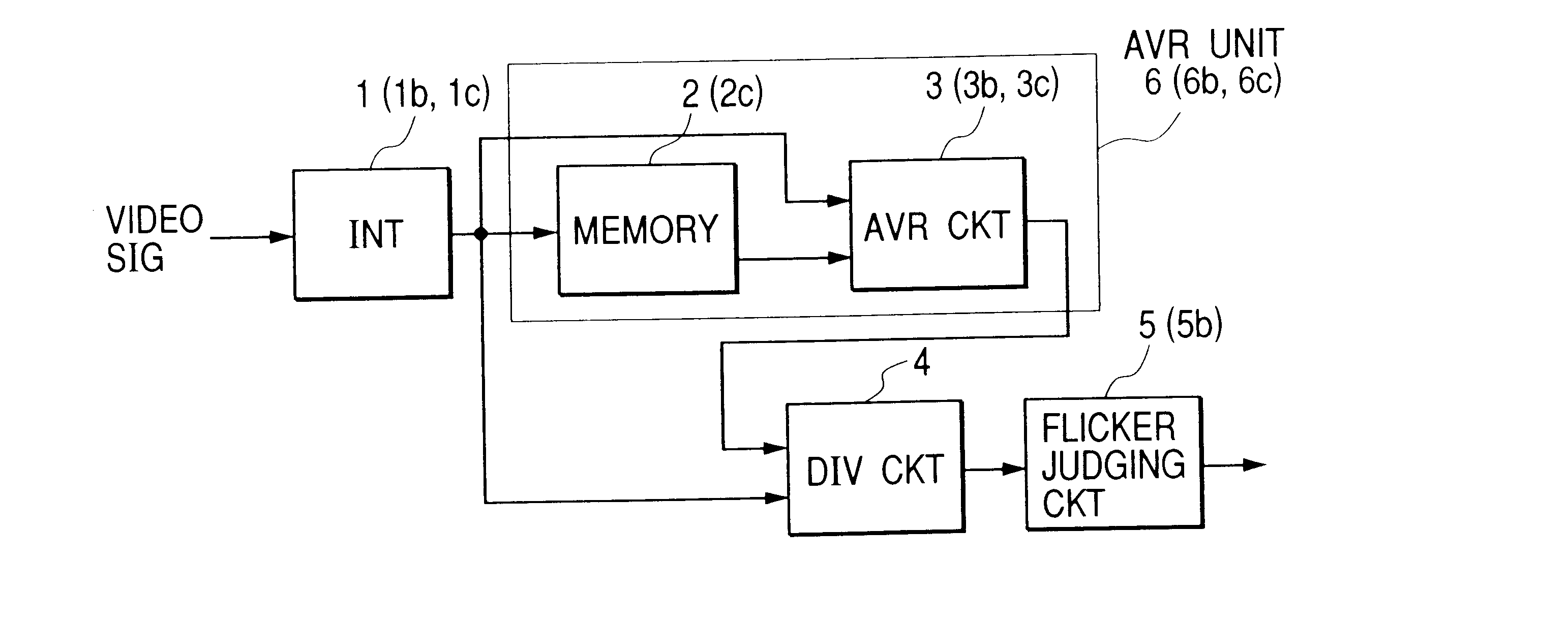

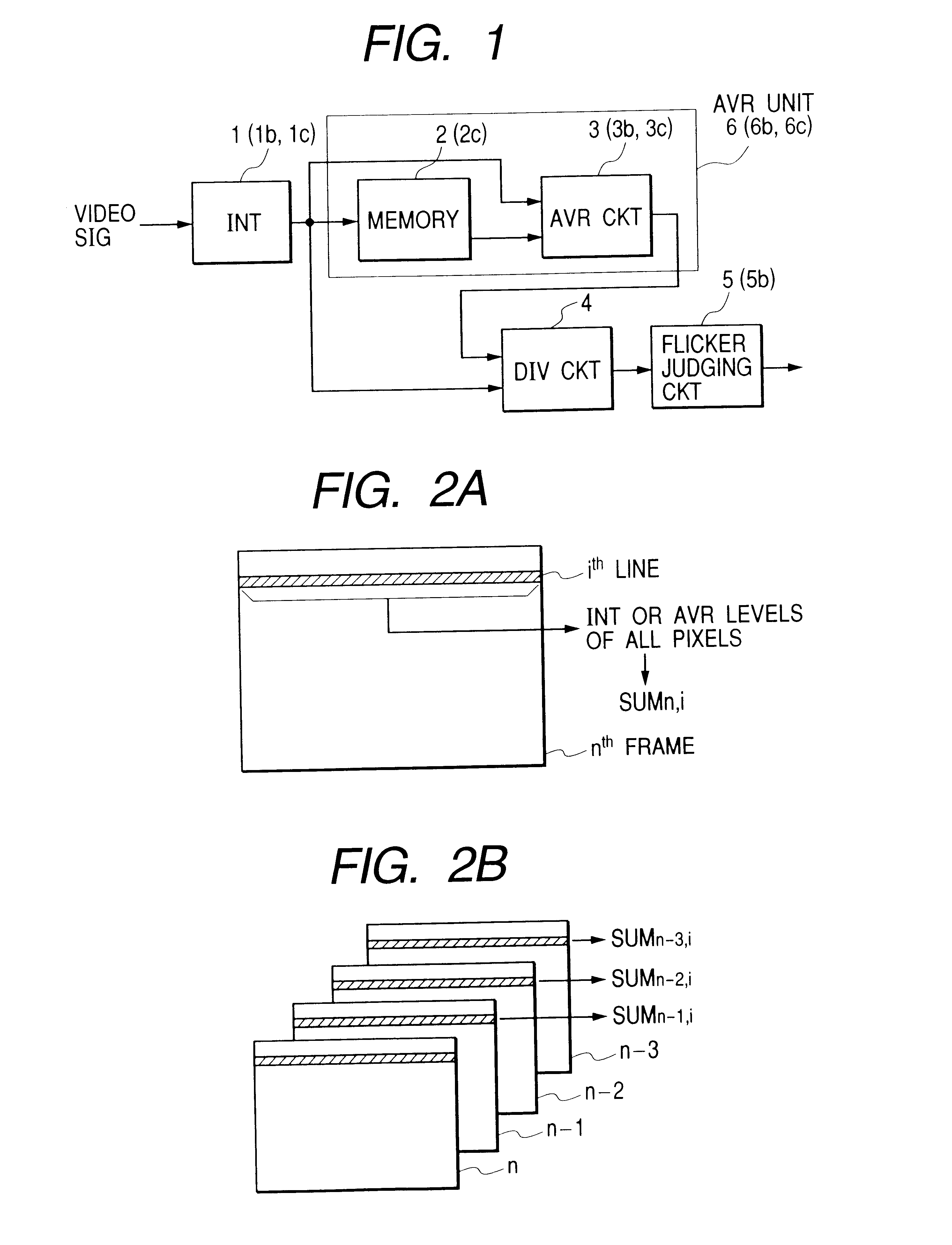

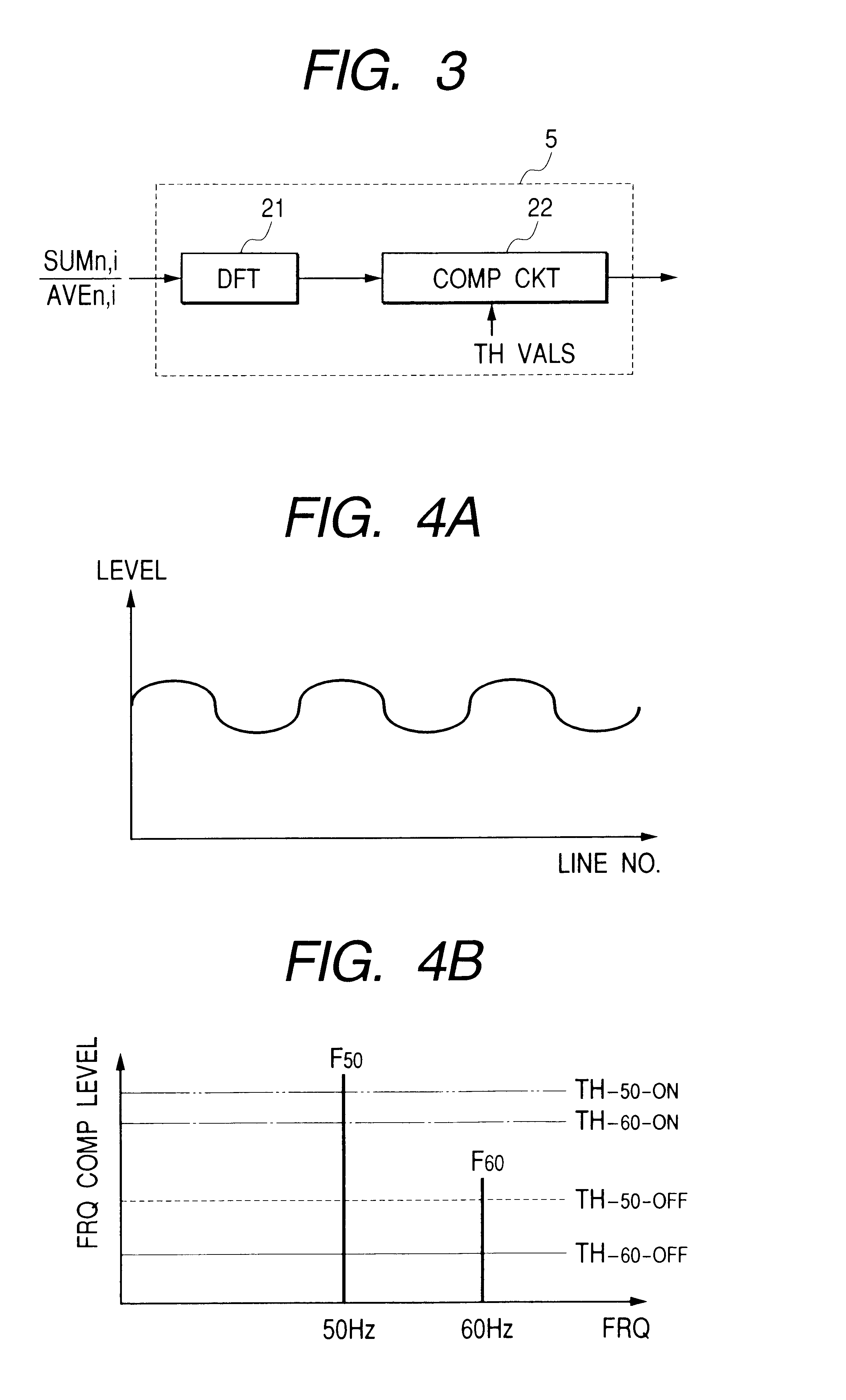

Illumination flicker detection apparatus, an illumination flicker compensation apparatus, and an ac line frequency detection apparatus, methods of detecting illumination flicker, compensating illumination flicker, and measuring ac line frequency

A video signal including illumination flicker component is integrated at each of unit areas (horizontal lines) in a frame (field) of the video signal. The integrated level at each of the unit areas at the frame and the integrated level at the corresponding unit area of an adjacent frame are averaged. Dividing is effected between results of the averaging and integrating every unit area. It is judged whether flicker exists in the video signal by frequency-analyzing results of the dividing result at the unit areas. The unit area may be plural adjacent lines where flickering are negligible. The averaging circuit may be circulation type of or FIR filter. Threshold level for judging the flicker is changed according to a shutter speed control signal. Flicker compensation may be executed by controlling shutter speed or the AGC according to flicker judging result. A still condition at a block in a frame may be detected from the integration result at plural frames. When the block is judged to be still, the flicker is judged. An ac line frequency detection is also disclosed to detect the frequency of the ac line from a video signal generated under illumination including flicker. An imaging circuit may be provided to generate the video signal therein.

Owner:PANASONIC CORP

Method and apparatus for refresh management of memory modules

One embodiment sets forth an interface circuit configured to manage refresh command sequences that includes a system interface adapted to receive a refresh command from a memory controller, clock frequency detection circuitry configured to determine the timing for issuing staggered refresh commands to two or more memory devices coupled to the interface circuit based on the refresh command received from the memory controller, and at least two refresh command sequence outputs configured to generate the staggered refresh commands for the two or more memory devices

Owner:GOOGLE LLC

Method and apparatus for refresh management of memory modules

One embodiment sets forth an interface circuit configured to manage refresh command sequences that includes a system interface adapted to receive a refresh command from a memory controller, dock frequency detection circuitry configured to determine the timing for issuing staggered refresh commands to two or more memory devices coupled to the interface circuit based on the refresh command received from the memory controller. and at least two refresh command sequence outputs configured to generate the staggered refresh commands for the two or more memory devices

Owner:GOOGLE LLC

Method and apparatus for refresh management of memory modules

One embodiment sets forth an interface circuit configured to manage refresh command sequences that includes a system interface adapted to receive a refresh command from a memory controller, clock frequency detection circuitry configured to determine the timing for issuing staggered refresh commands to two or more memory devices coupled to the interface circuit based on the refresh command received from the memory controller, and at least two refresh command sequence outputs configured to generate the staggered refresh commands for the two or more memory devices

Owner:GOOGLE LLC

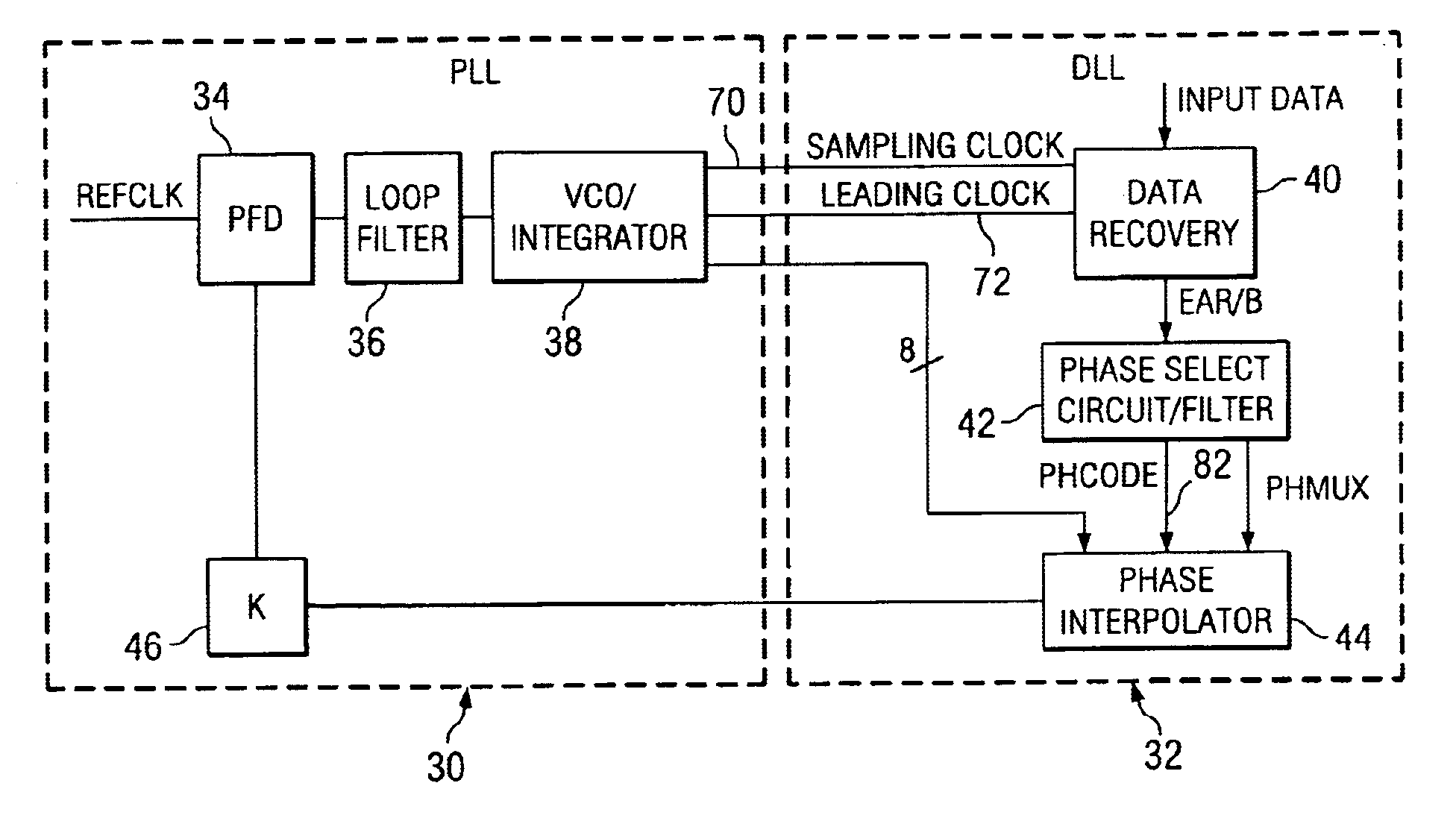

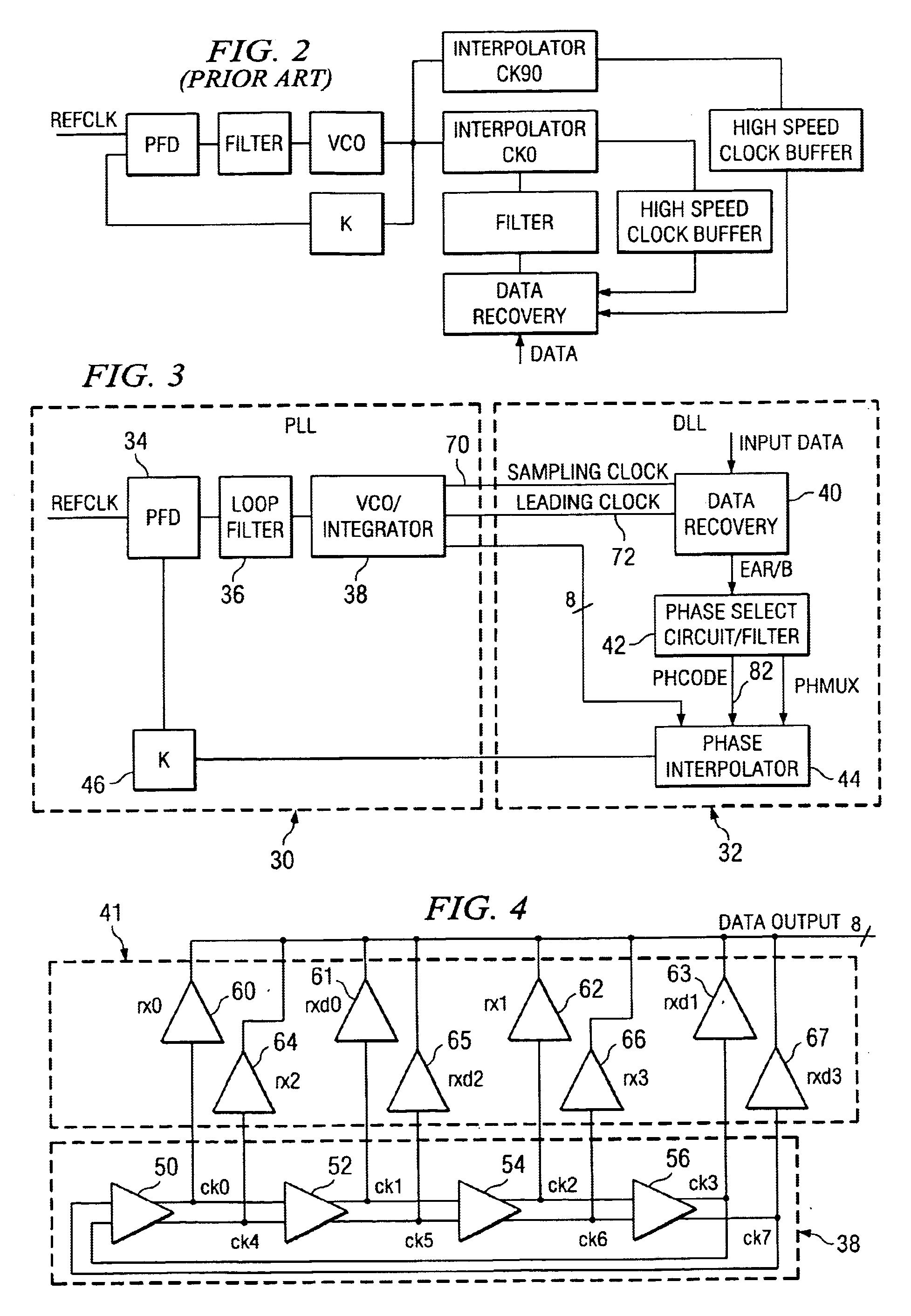

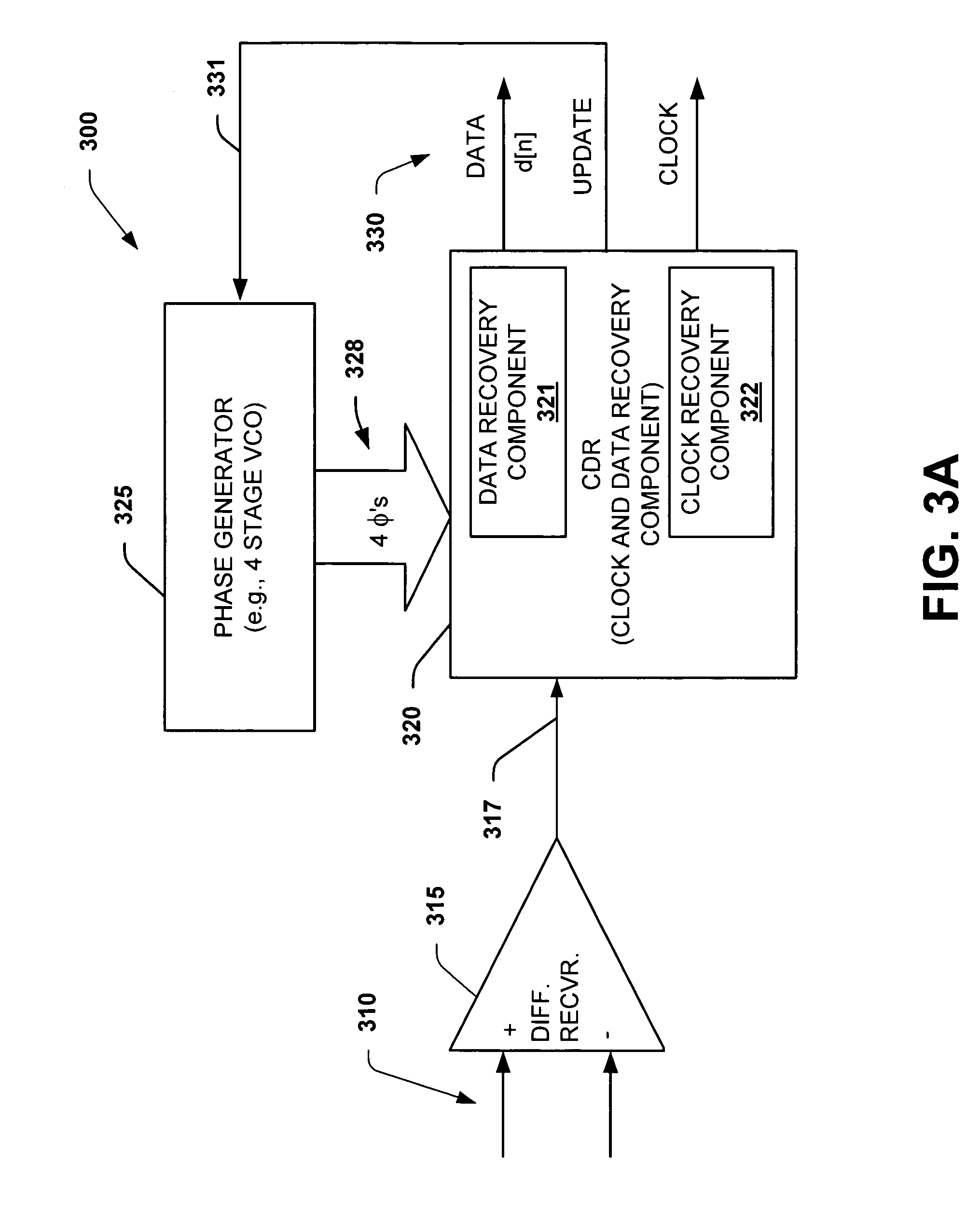

Time division multiplex data recovery system using close loop phase and delay locked loop

InactiveUS6901126B1Alleviate duty cycle issuesHigh bandwidthPulse automatic controlAngle demodulation by phase difference detectionDelay-locked loopClosed loop

A time division multiplex data recovery system using a closed-loop phase lock loop (PLL) and delay locked loop (DLL) is disclosed. In other words, one closed loop comprises both a phase locked loop (PLL) and a delay locked loop (DLL) in a novel time division multiplex data recovery system. This new architecture comprises a 4 stage Voltage Controlled Oscillator (VCO) used to generate 8 clock signals, 45 degrees phase shifted from one another, for 8 receivers to do the oversampling. An interpolator tracks the received data signal and feeds it back to the Phase / Frequency Detector (PFD). The PFD has a second input of the reference clock which the PFD uses along with the interpolator input to correct the frequency of the PLL. The PLL operates at a high bandwidth. The DLL's bandwidth is several orders lower than the PLL. The DLL activates only a multiplexer and an interpolator continuously, thereby drawing a minimum amount of power.

Owner:TEXAS INSTR INC

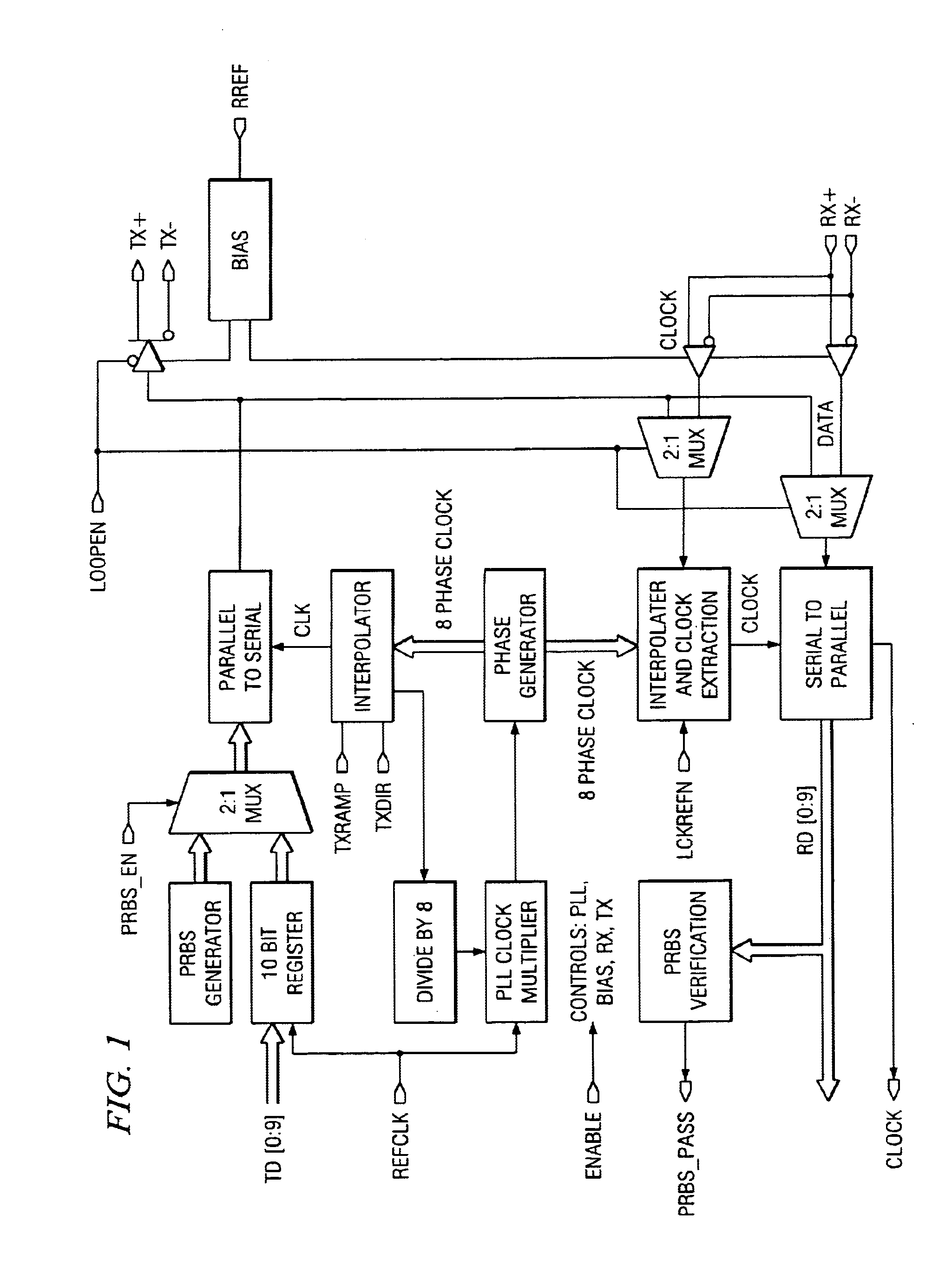

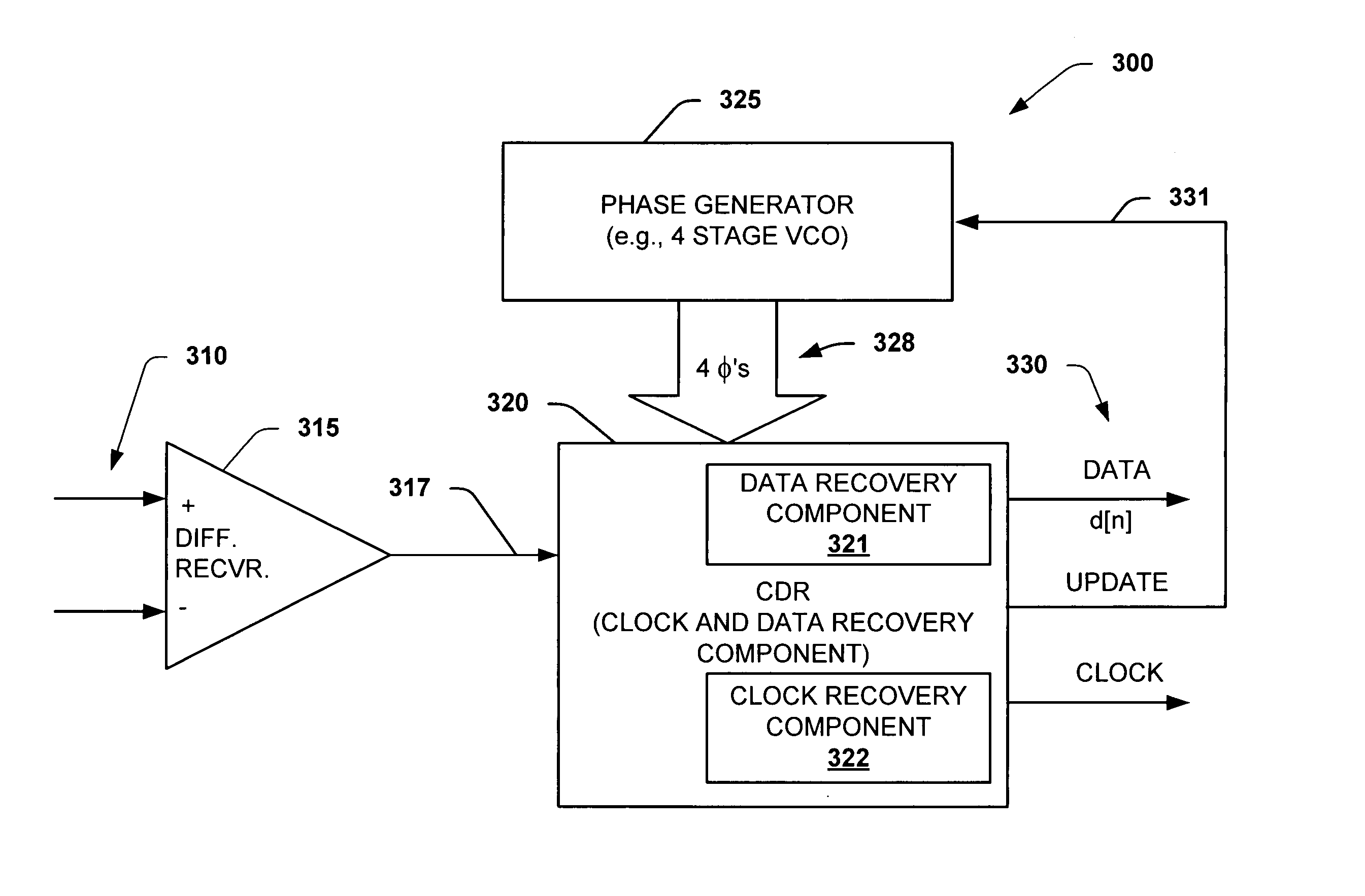

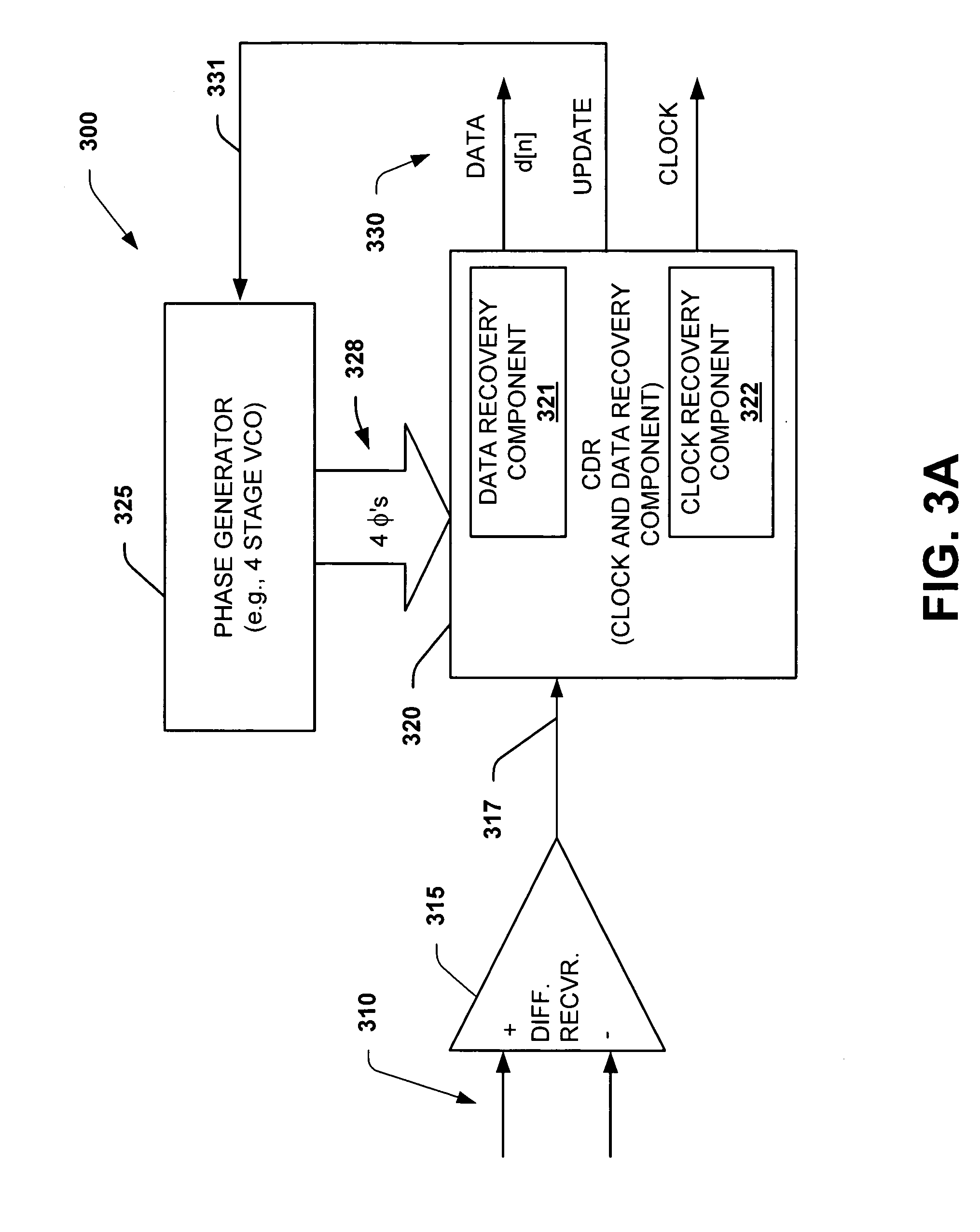

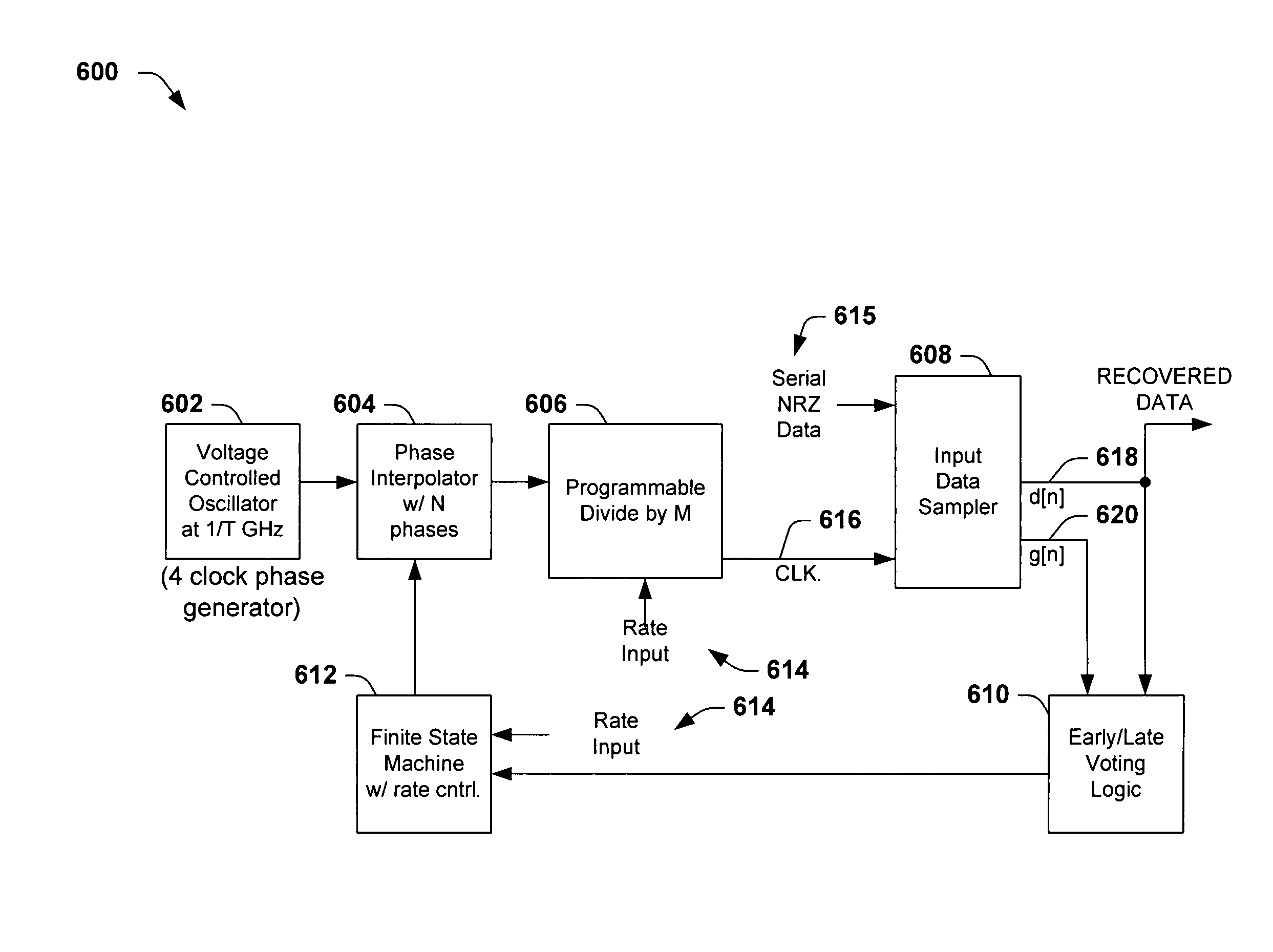

Interpolator based clock and data recovery (CDR) circuit with digitally programmable BW and tracking capability

ActiveUS20050180536A1High bandwidthLower latencyPulse automatic controlSynchronising arrangementPhase correctionData stream

The present invention facilitates clock and data recovery (330,716 / 718) for serial data streams (317,715) by providing a mechanism that can be employed to maintain a fixed tracking capability of an interpolator based CDR circuit (300,700) at multiple data rates (e.g., 800). The present invention further provides a wide data rate range CDR circuit (300,700), yet uses an interpolator design optimized for a fixed frequency. The invention employs a rate programmable divider circuit (606,656,706) that operates over a wide range of clock and data rates (e.g., 800) to provide various phase correction step sizes (e.g., 800) at a fixed VCO clock frequency. The divider (606,656,706) and a finite state machine (FSM) (612,662,712) of the exemplary CDR circuit (600,650,700) are manually programmed based on the data rate (614,667). Alternately, the data rate may be detected from a recovered serial data stream (718) during CDR operations (on-the-fly) utilizing a frequency detection circuit (725) to automatically program the divider (706) and FSM (712) to provide CDR circuit operation at the nearest base clock rate (716).

Owner:TEXAS INSTR INC

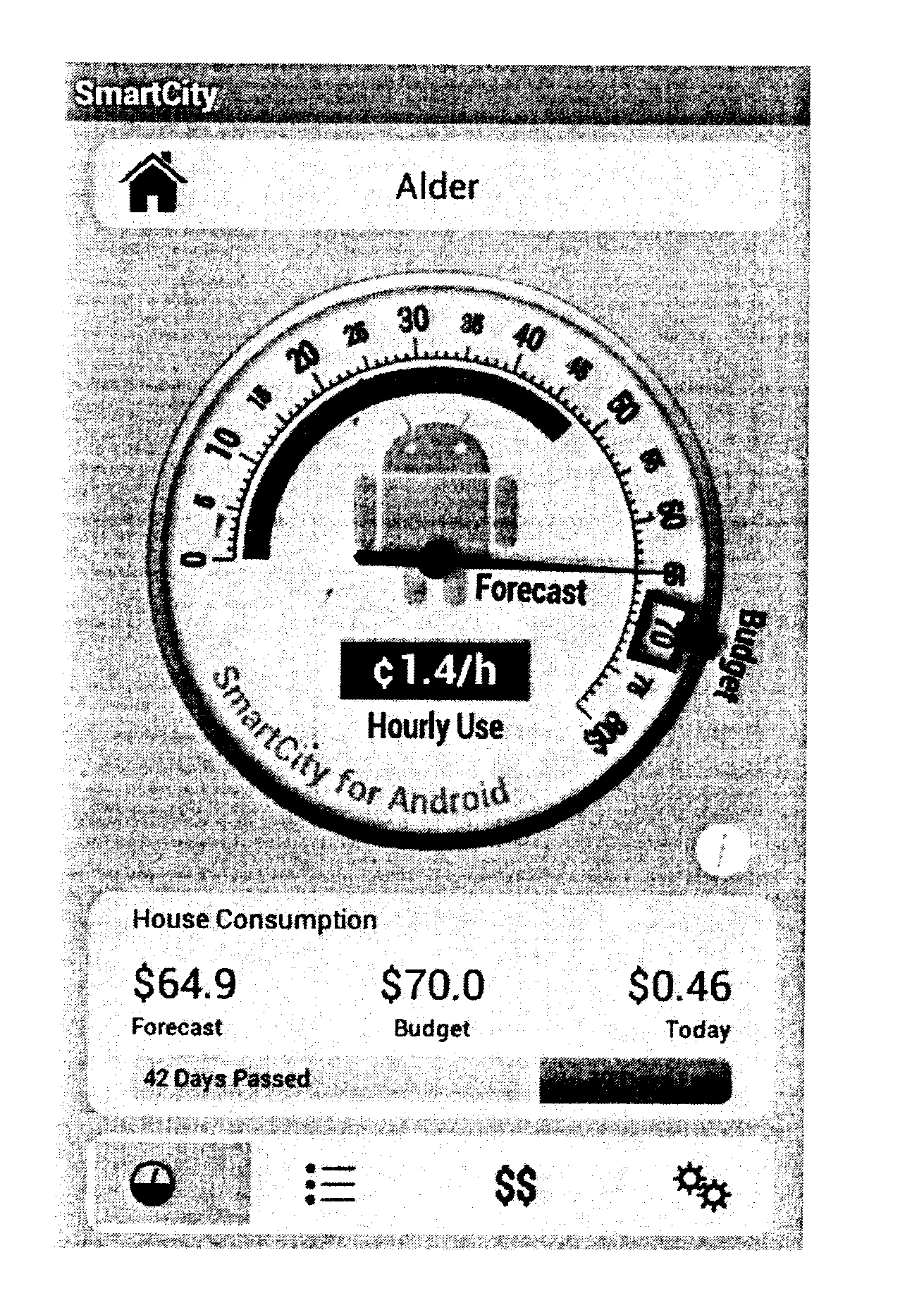

System and method of compiling and organizing power consumption data and converting such data into one or more user actionable formats

InactiveUS20150012147A1Superior demand forecastIncrease data granularityProgramme controlMechanical power/torque controlData transformationUtility industry

A method and system for use in creating a profile of, managing and understanding power consumption in a premise of a user, wherein said premise comprises two or more power consuming devices comprises measuring, via at least one sensor, aggregate energy consumption at the premise, receiving at a mobile computing device comprising a data processor, said aggregated signal from the sensor, collecting and recording the aggregate signal over a plurality of time resolutions and frequencies, therein to create a predicted aggregate signal for each time x and frequency y, detecting changes in the predicted aggregate signal at time x an frequency y (detected consumption pattern changes) and conveying to at least one of the user, a utility company, and other third party a notification of detected consumption pattern changes.

Owner:NEURIO TECH

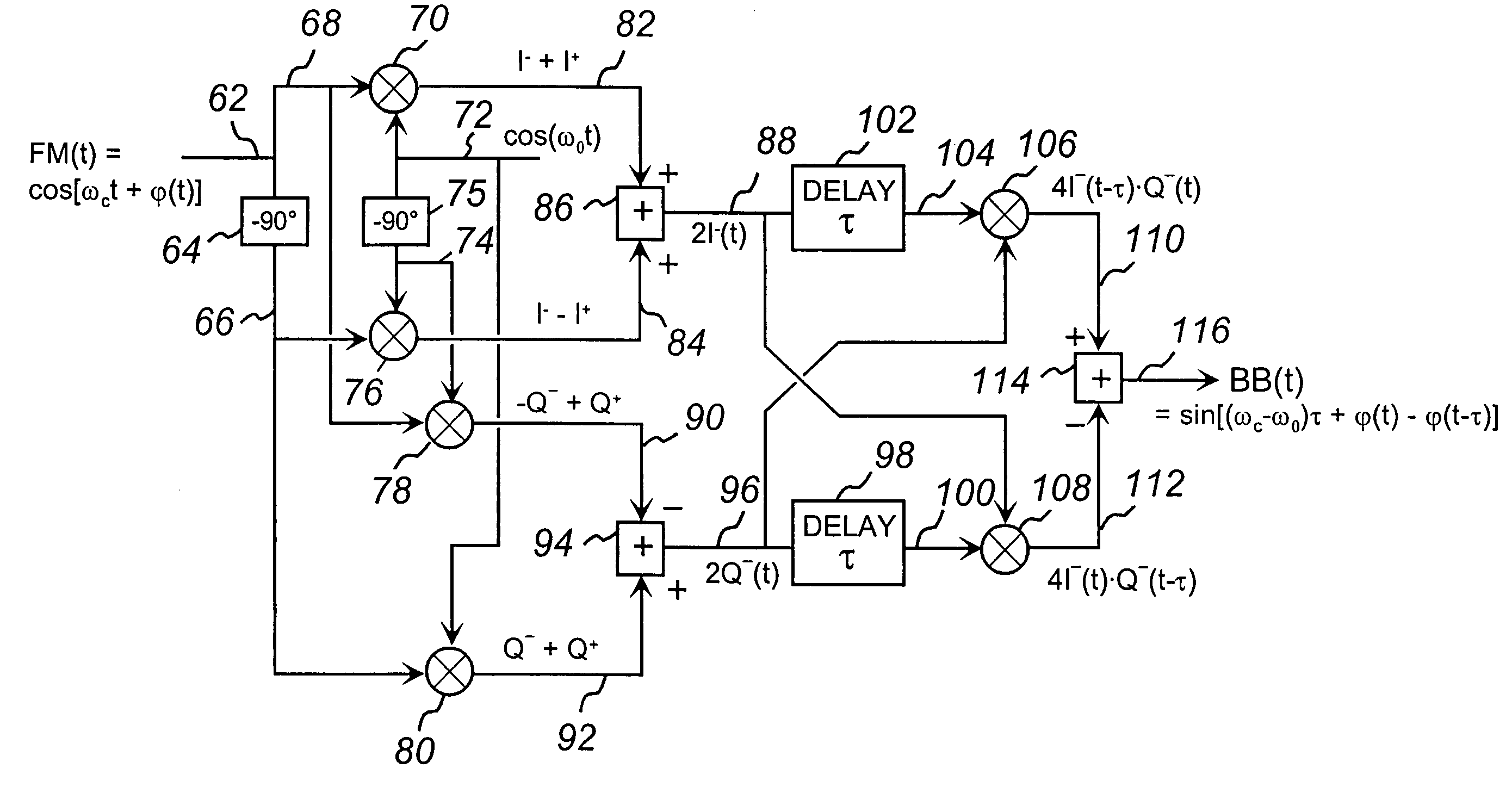

High frequency low noise phase-frequency detector and phase noise reduction method and apparatus

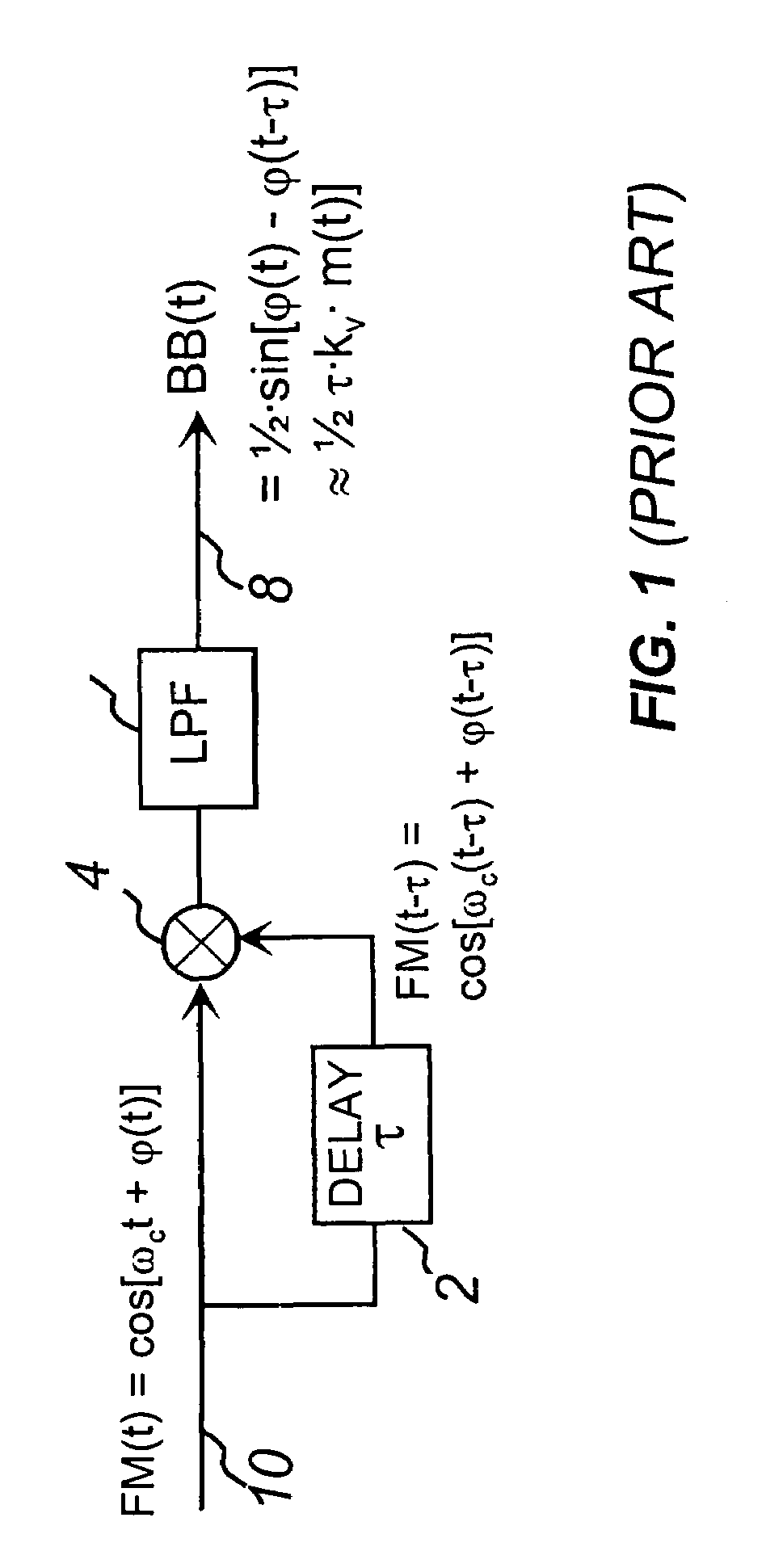

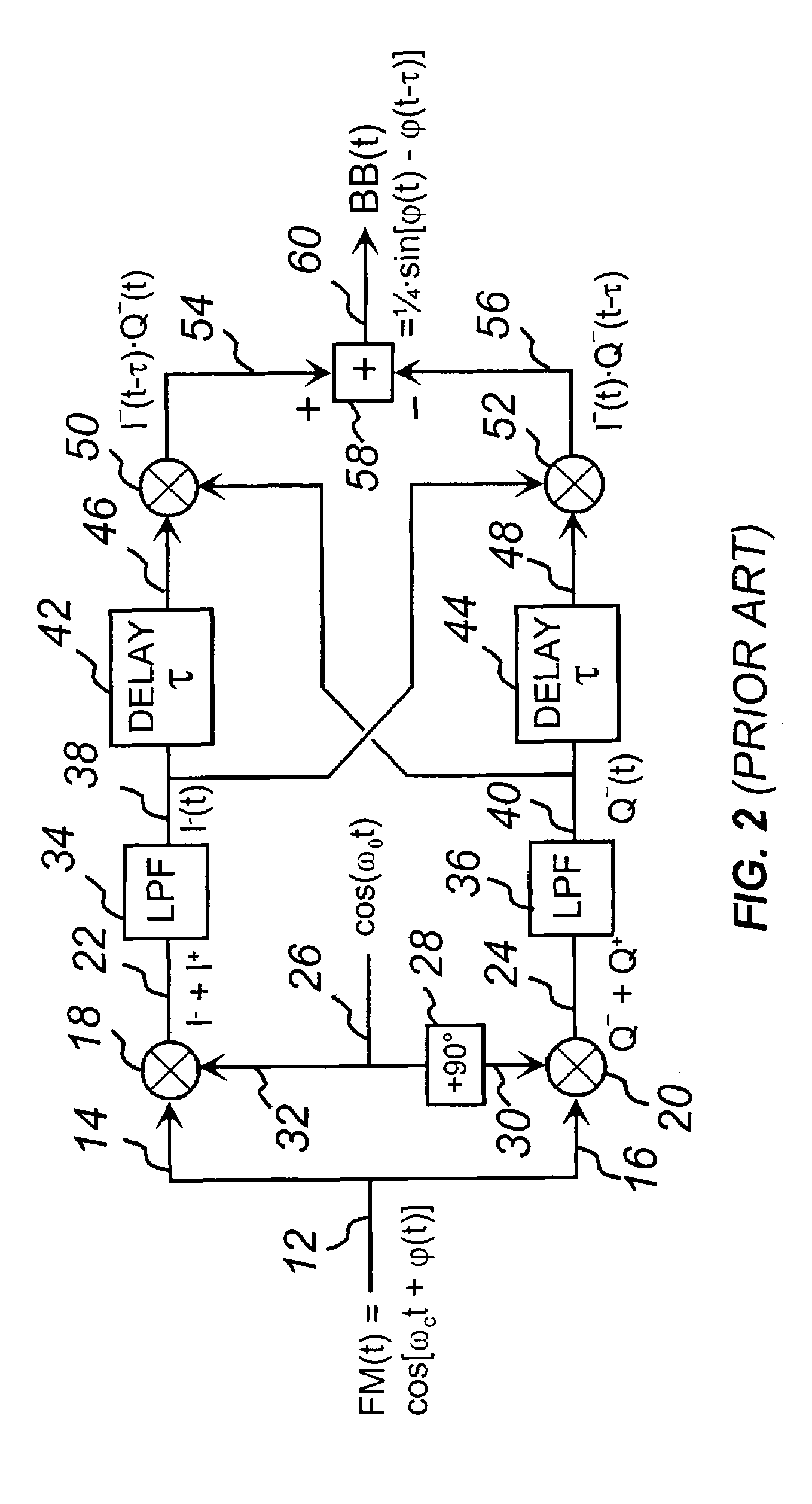

The present invention discloses a new type of extremely low-noise phase-frequency detector (PFD) 500, broadband from DC to multi-GHz RF frequencies for PLL synthesizer applications. Free of any feedback mechanisms, thus inherently fast, it operates close to transition frequency fT of IC processes or frequency limits of discrete mixers. The PFD 500 utilizes complex SSB conversion in both the in-phase and quadrature arms, delaying the in-phase arm in 530, beating the delayed signal 124 with the un-delayed quadrature signal 122 in mixer 126. The output 128 contains both the frequency difference and the phase difference information between the two signals 118 and 520, providing both the frequency-discrimination (FD) and the phase detection (PD) functions. Utilizing standard mixers the PFD 500 can achieve superior CNRs of 180 dBc / Hz at multi-GHz RF. Additionally, utilizing the FD / FM demodulation capability, the present invention improves phase noise of various signals and linearity of FM modulators.

Owner:ARRIS ENTERPRISES LLC

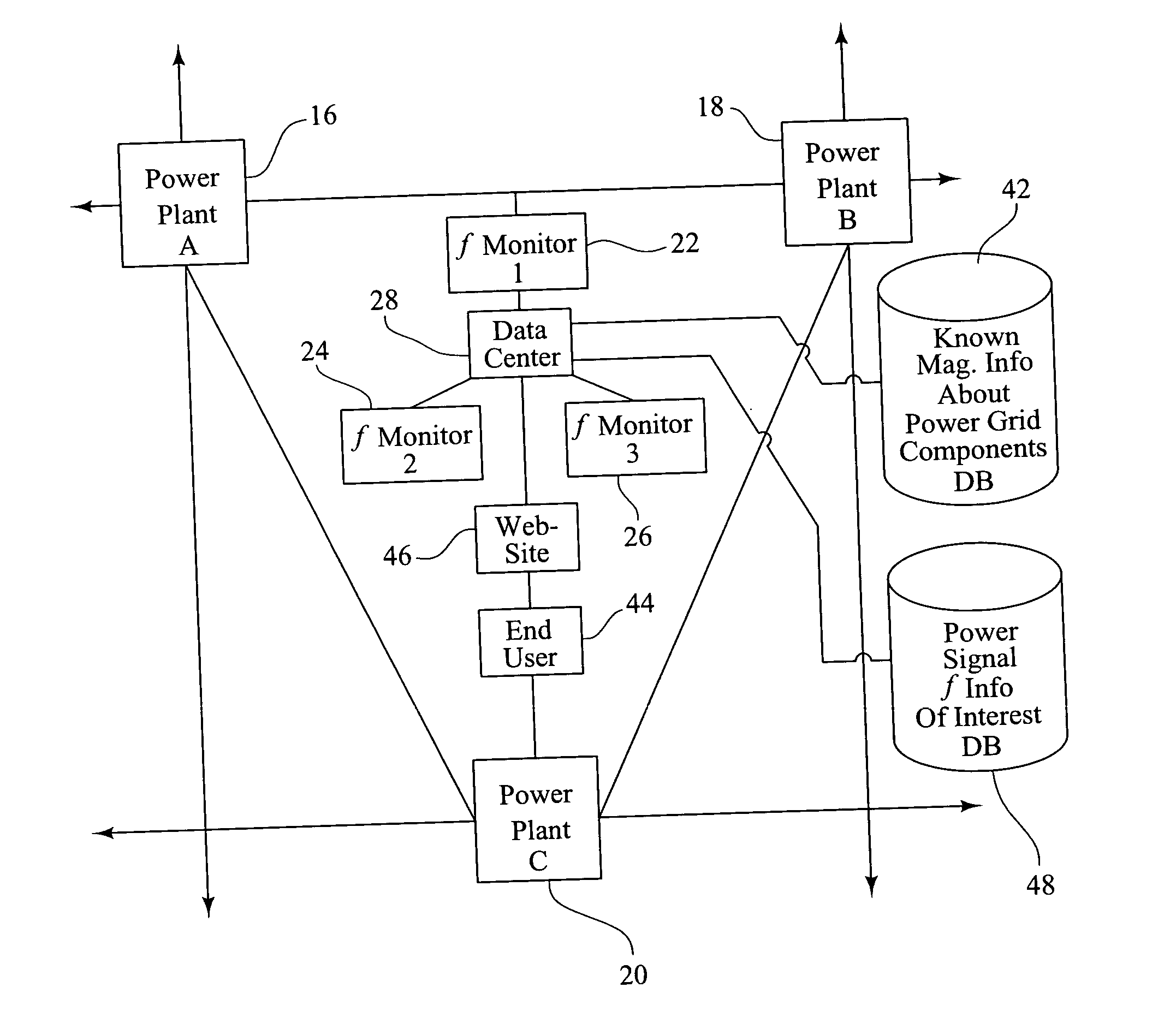

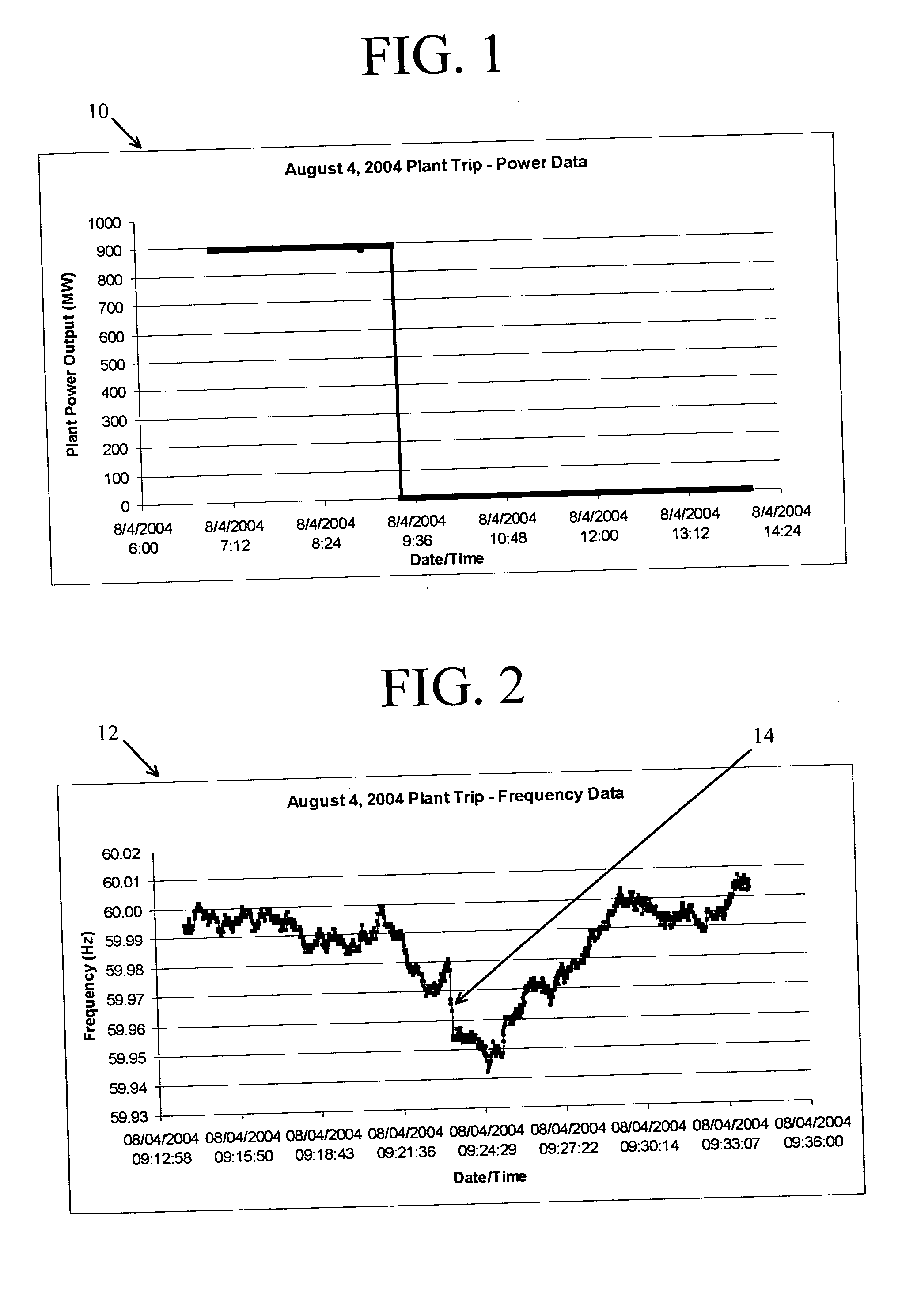

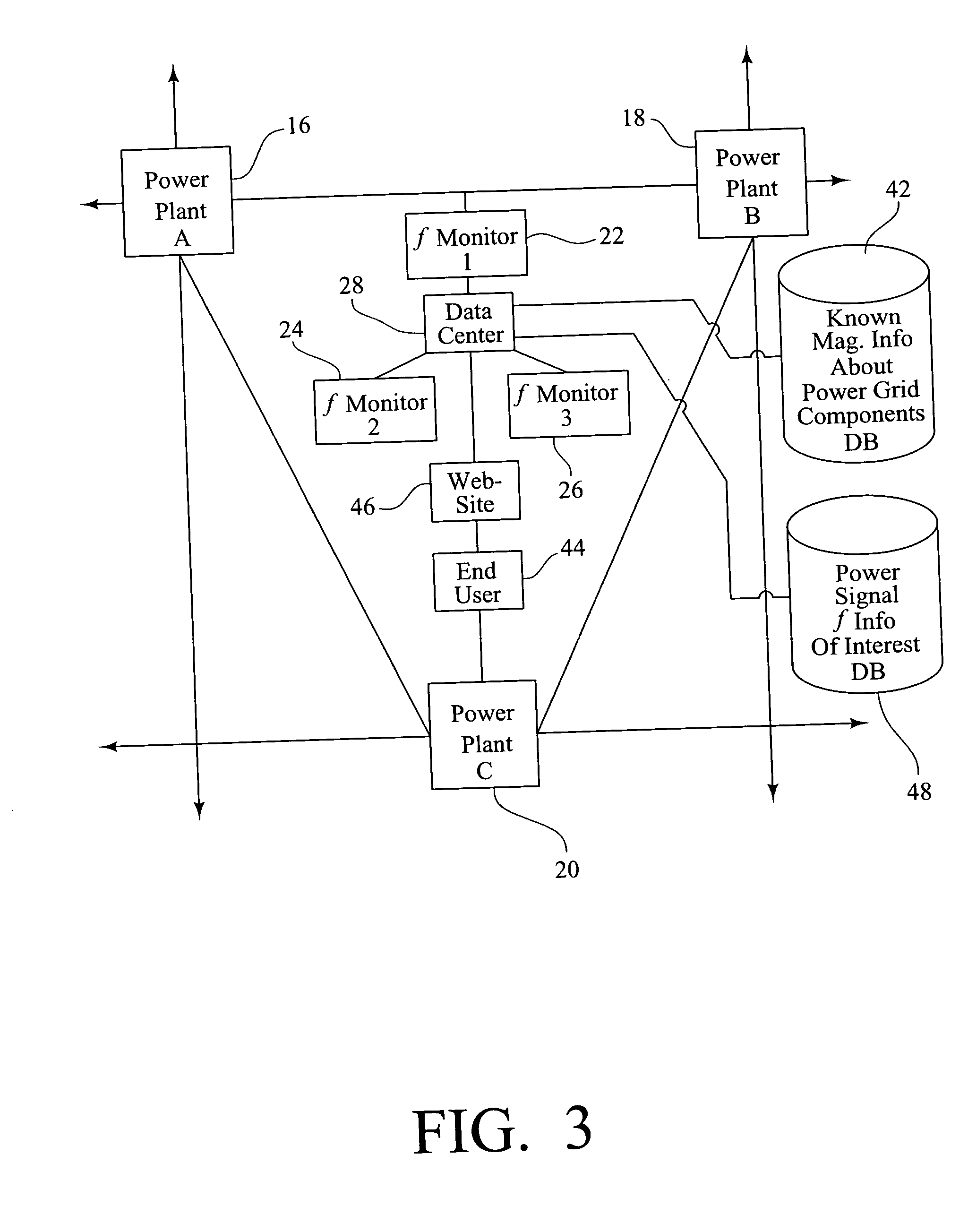

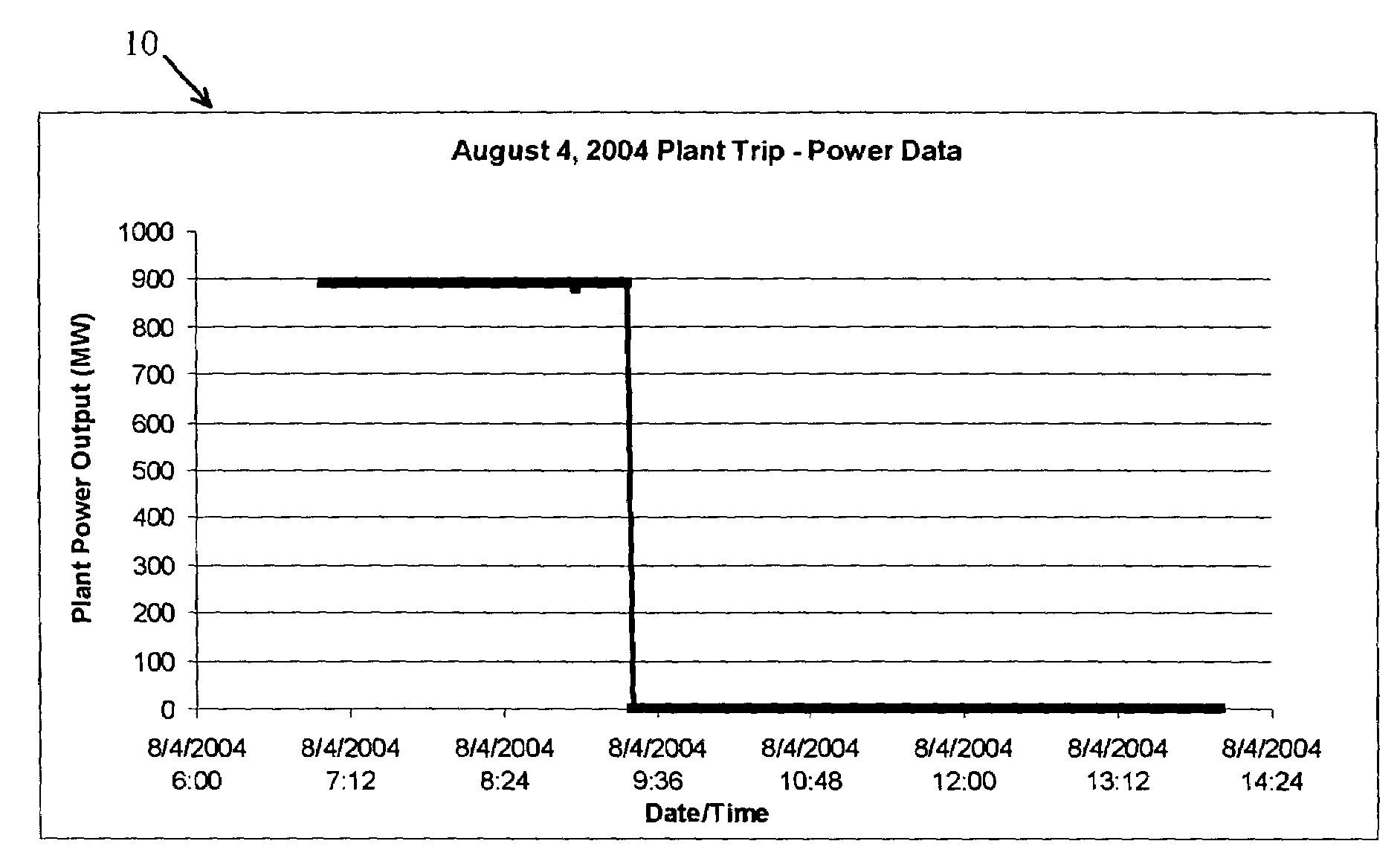

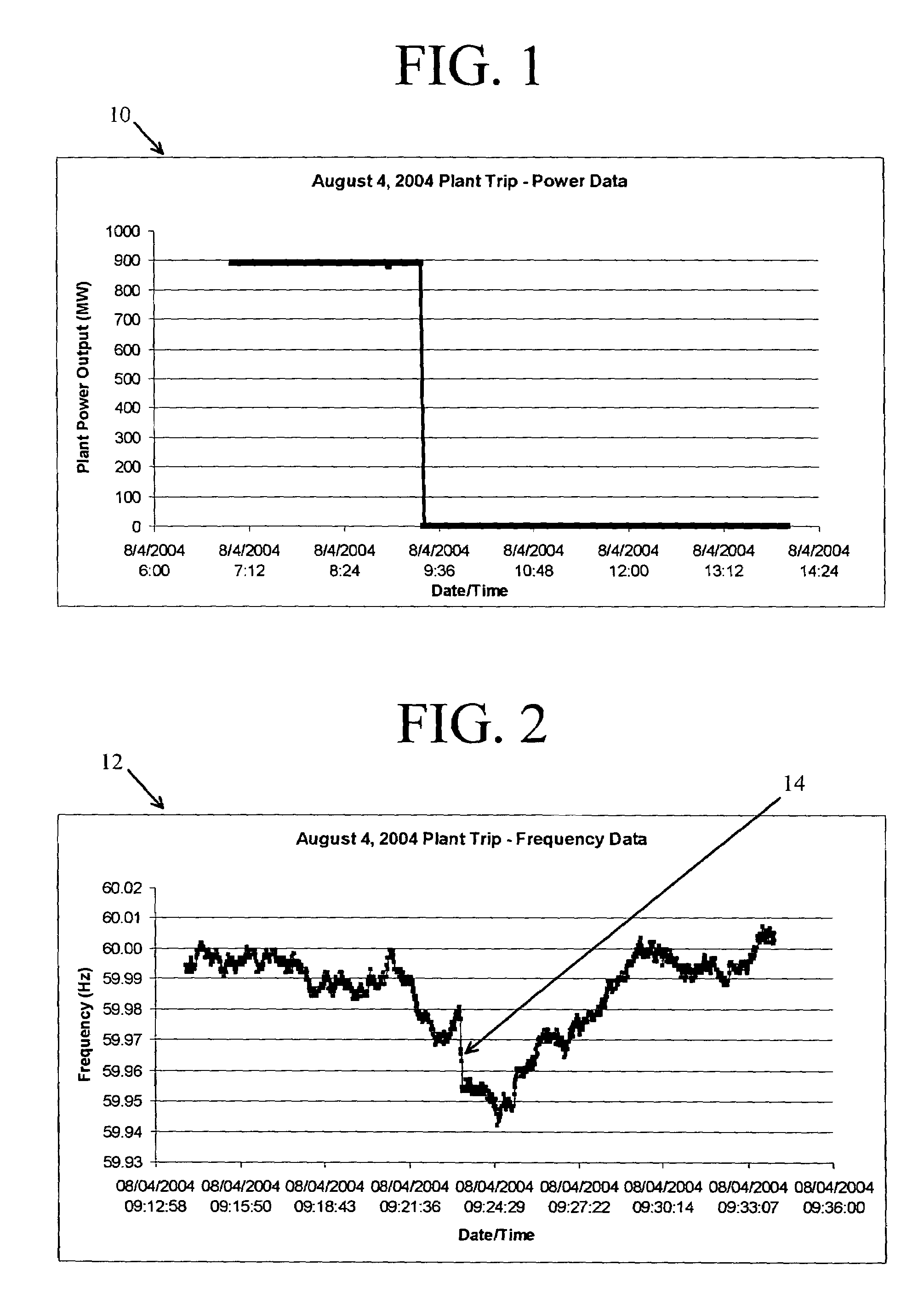

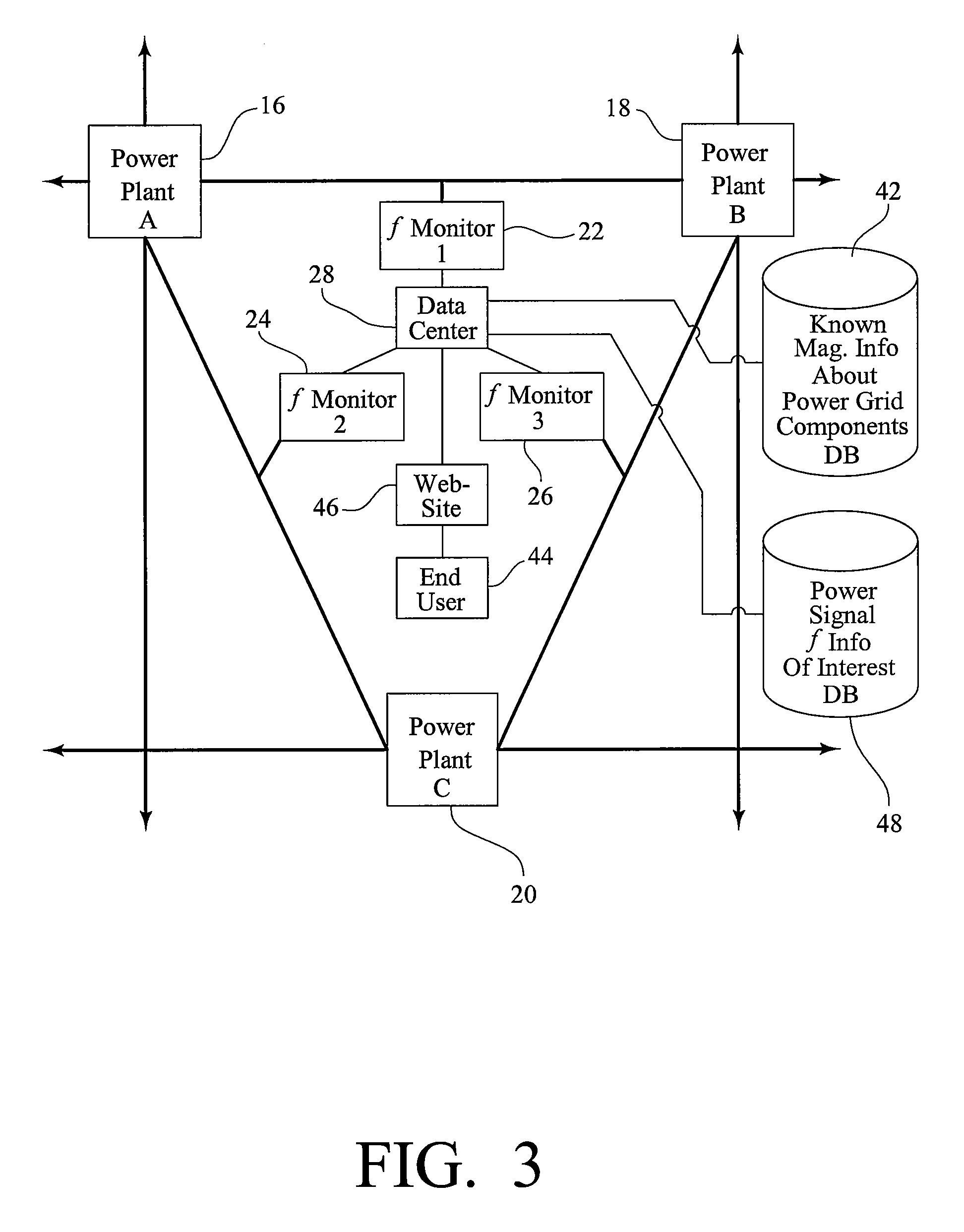

Method and system for AC power grid monitoring

ActiveUS20060235574A1High economic valueEasy to operateMechanical power/torque controlLevel controlPower stationFrequency detection

A method and system allows for substantially real-time monitoring of the operational dynamics of power plants and other components comprising an AC power grid, by using information collected from a network of power grid frequency detection and reporting devices. The invention allows for the substantially real-time detection and reporting of certain power grid events such as power plant trips.

Owner:GENSCAPE

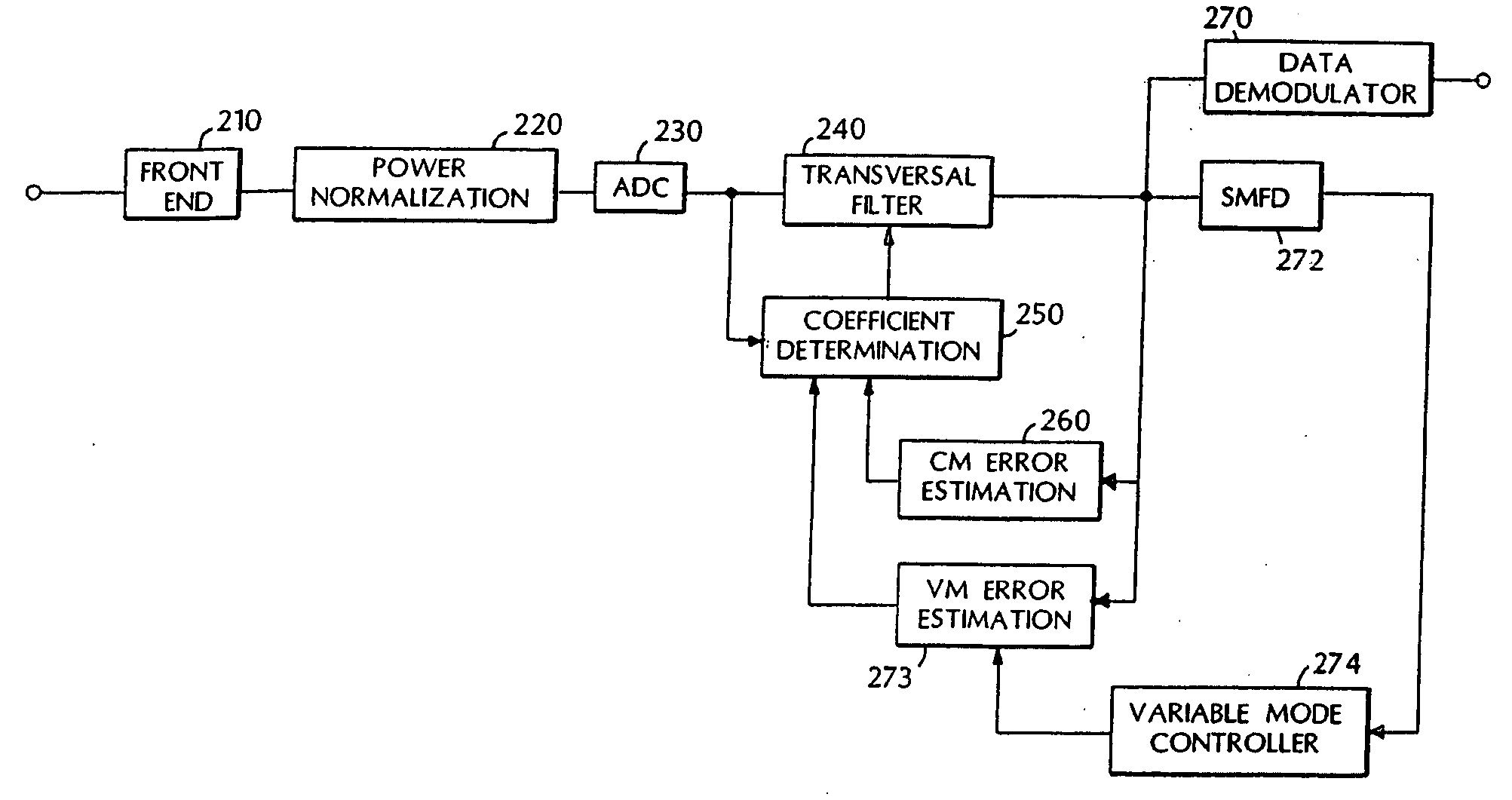

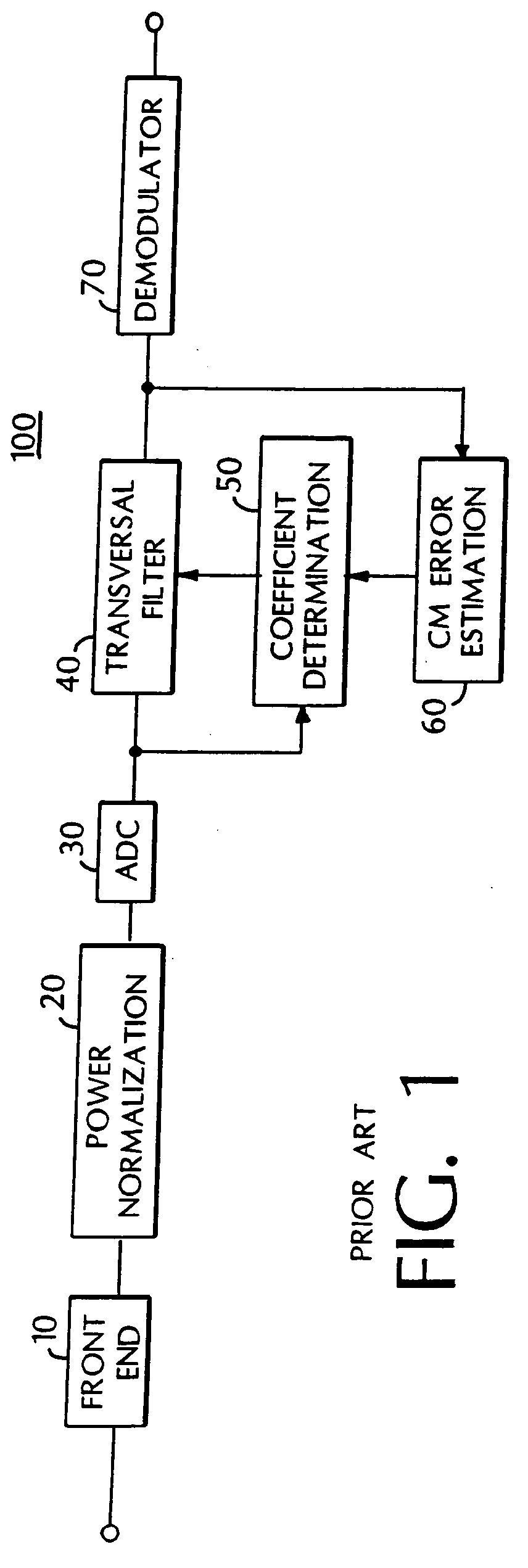

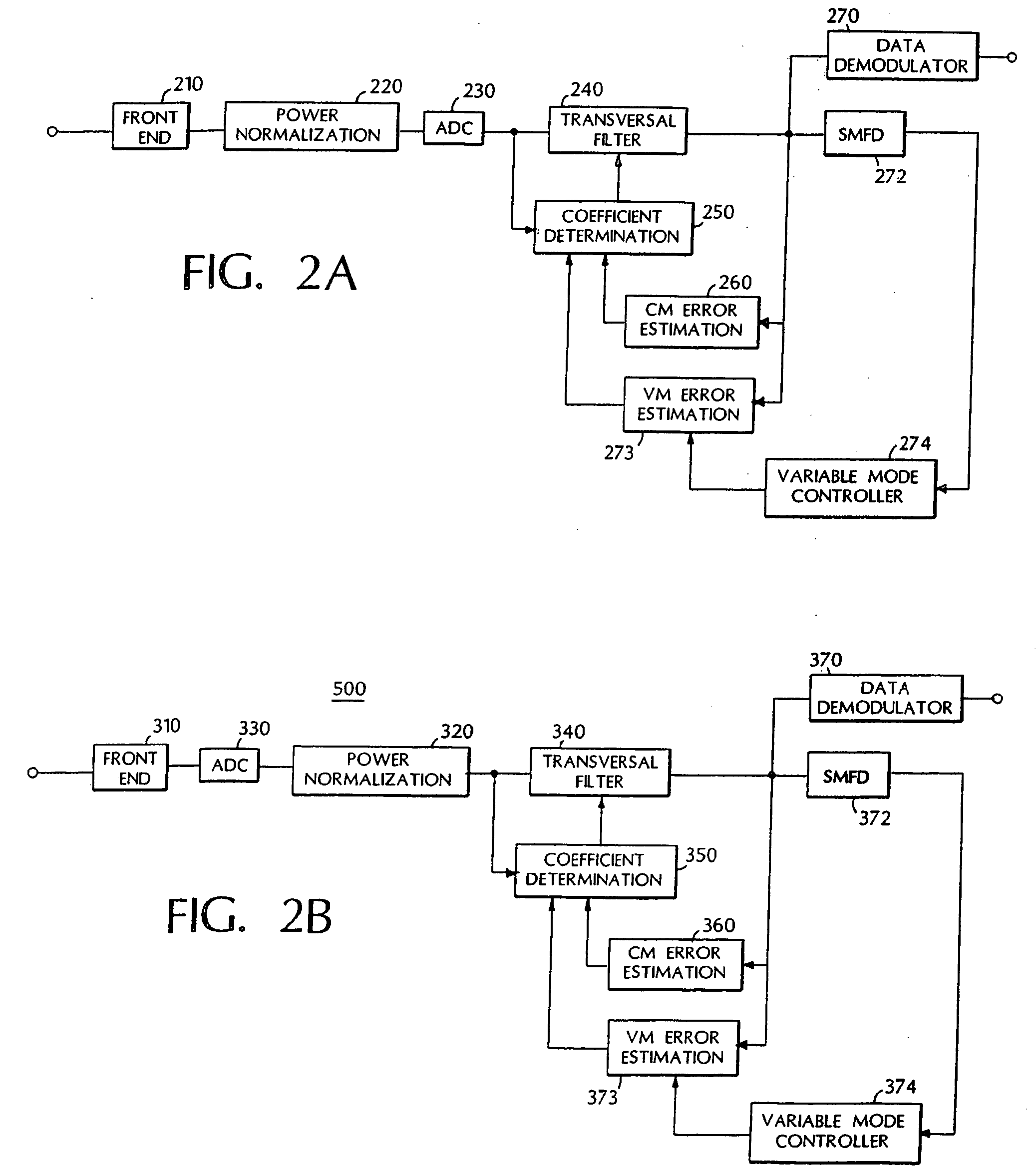

Demodulation

InactiveUS20060152276A1Improve filtering effectImprove adaptabilityMultiple-port networksTransmission control/equlisationFrequency spectrumFrequency detection

Demodulation apparatus includes a transversal filter characterized by coefficients adjusted by a coefficient determiner responsive to a constant modulus error signal and variable mode error signal related to the output of a spectral mean frequency detector having its input coupled to the output of the transversal filter.

Owner:BOSE CORP

Method and system for AC power grid monitoring

ActiveUS7571028B2High economic valueMechanical power/torque controlLevel controlPower stationEngineering

A method and system allows for substantially real-time monitoring of the operational dynamics of power plants and other components comprising an AC power grid, by using information collected from a network of power grid frequency detection and reporting devices. The invention allows for the substantially real-time detection and reporting of certain power grid events such as power plant trips.

Owner:GENSCAPE

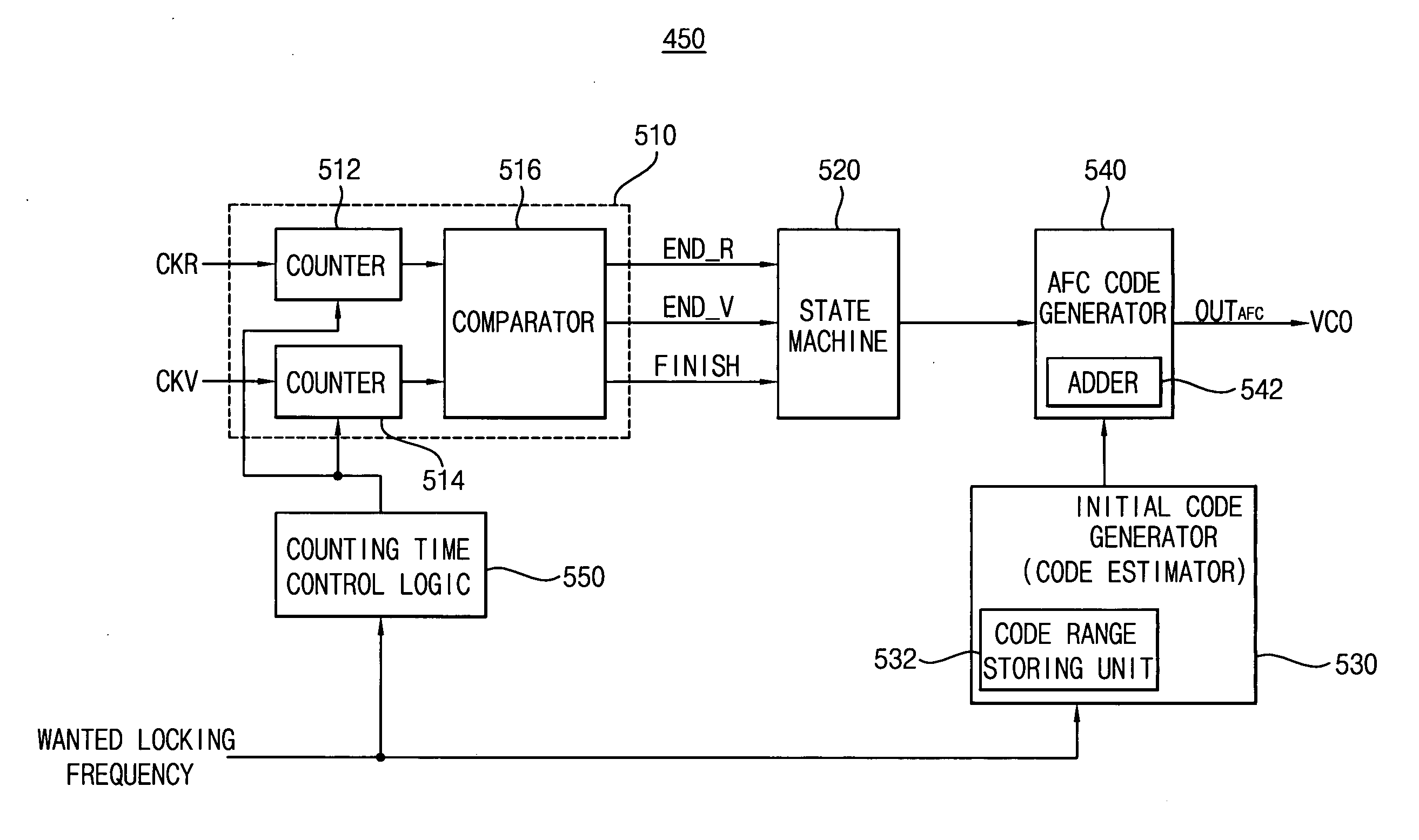

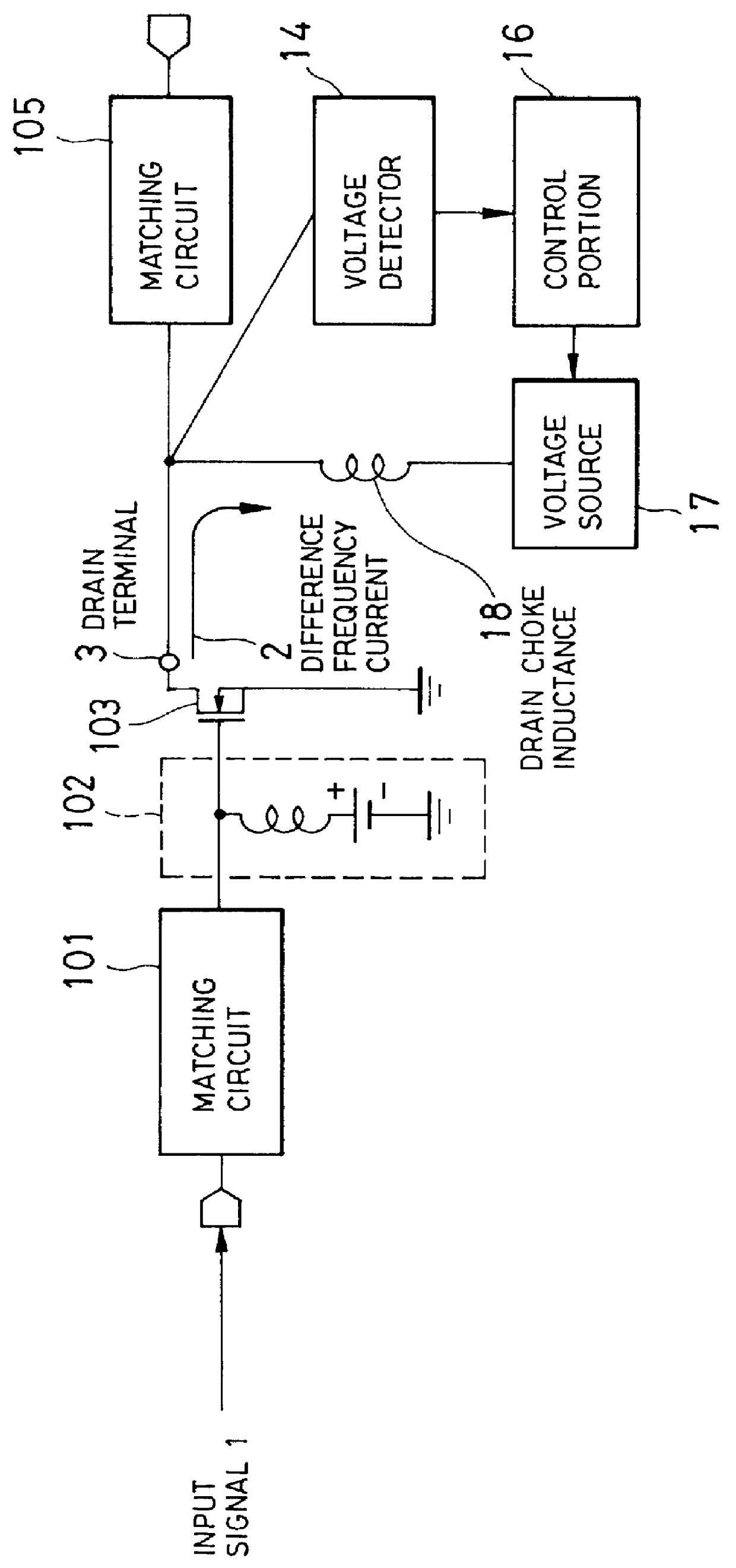

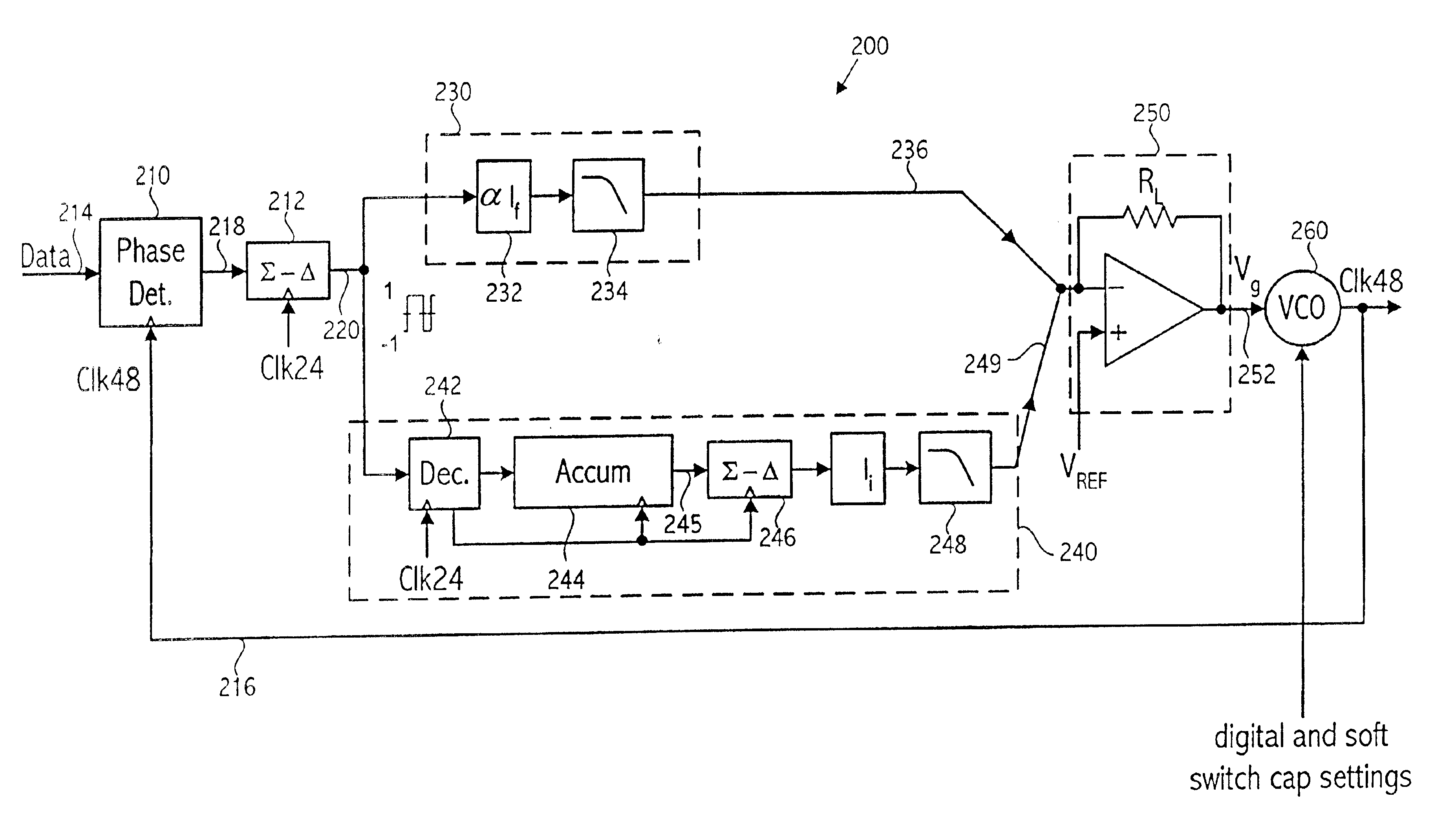

Adaptive frequency controller, a phase-locked loop including the same, and an adaptive frequency controlling method

InactiveUS20060120489A1Shorten lock timePulse automatic controlAmplitude-modulated carrier systemsEngineeringFrequency detection

An adaptive frequency controller, a phase-locked loop including the same and an adaptive frequency controlling method are provided. In an adaptive frequency controller, a frequency detector compares a frequency of a first signal with a frequency of a second signal. A state machine adjusts a code position based on a lo result of the comparison of the frequencies of the first and second signals. An initial code generator receives a locking frequency, determines an estimation code, and sets a code range to be searched. An AFC code generator generates a code value from the determined estimation code based on the code position of the state machine.

Owner:SAMSUNG ELECTRONICS CO LTD

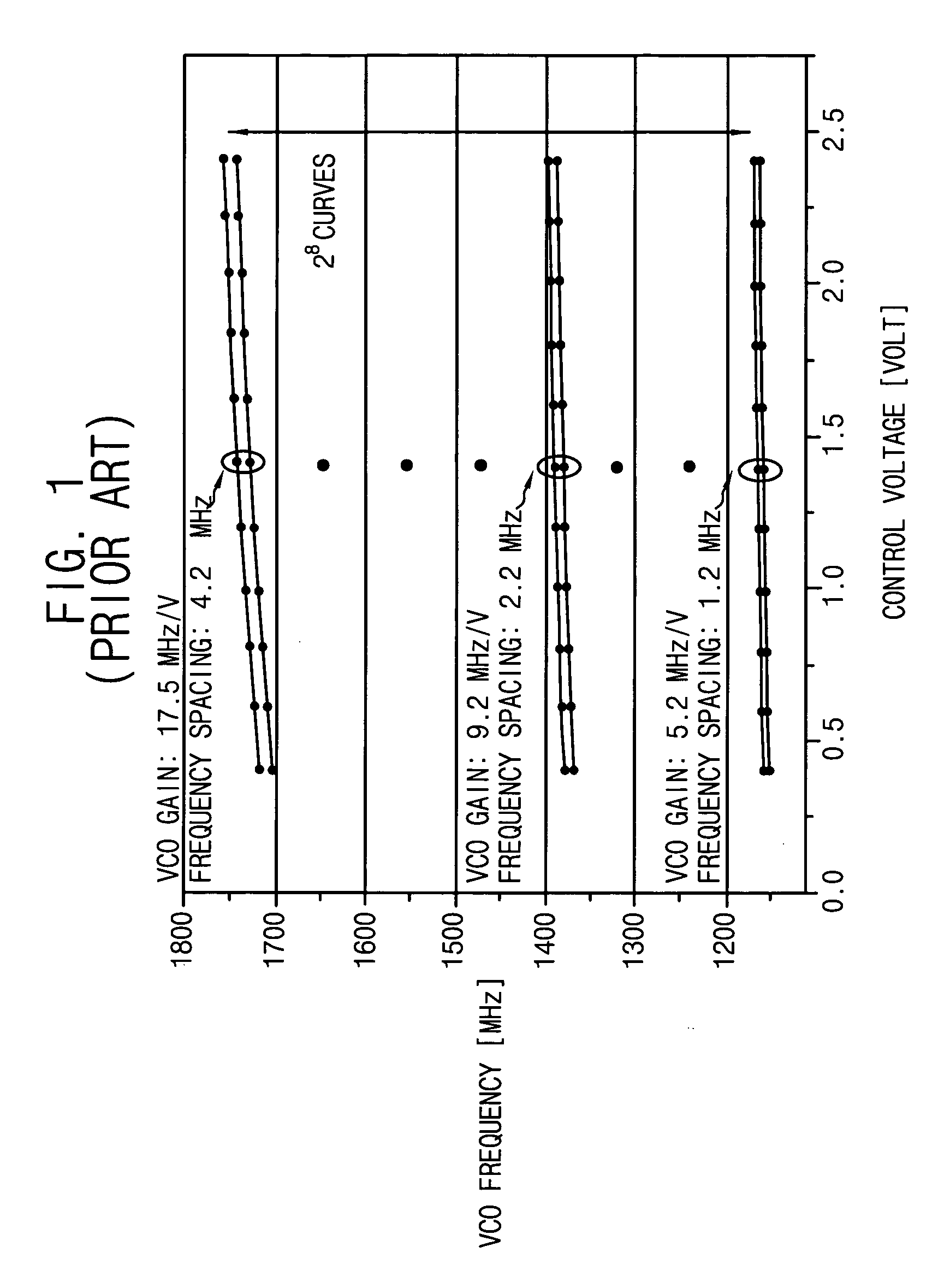

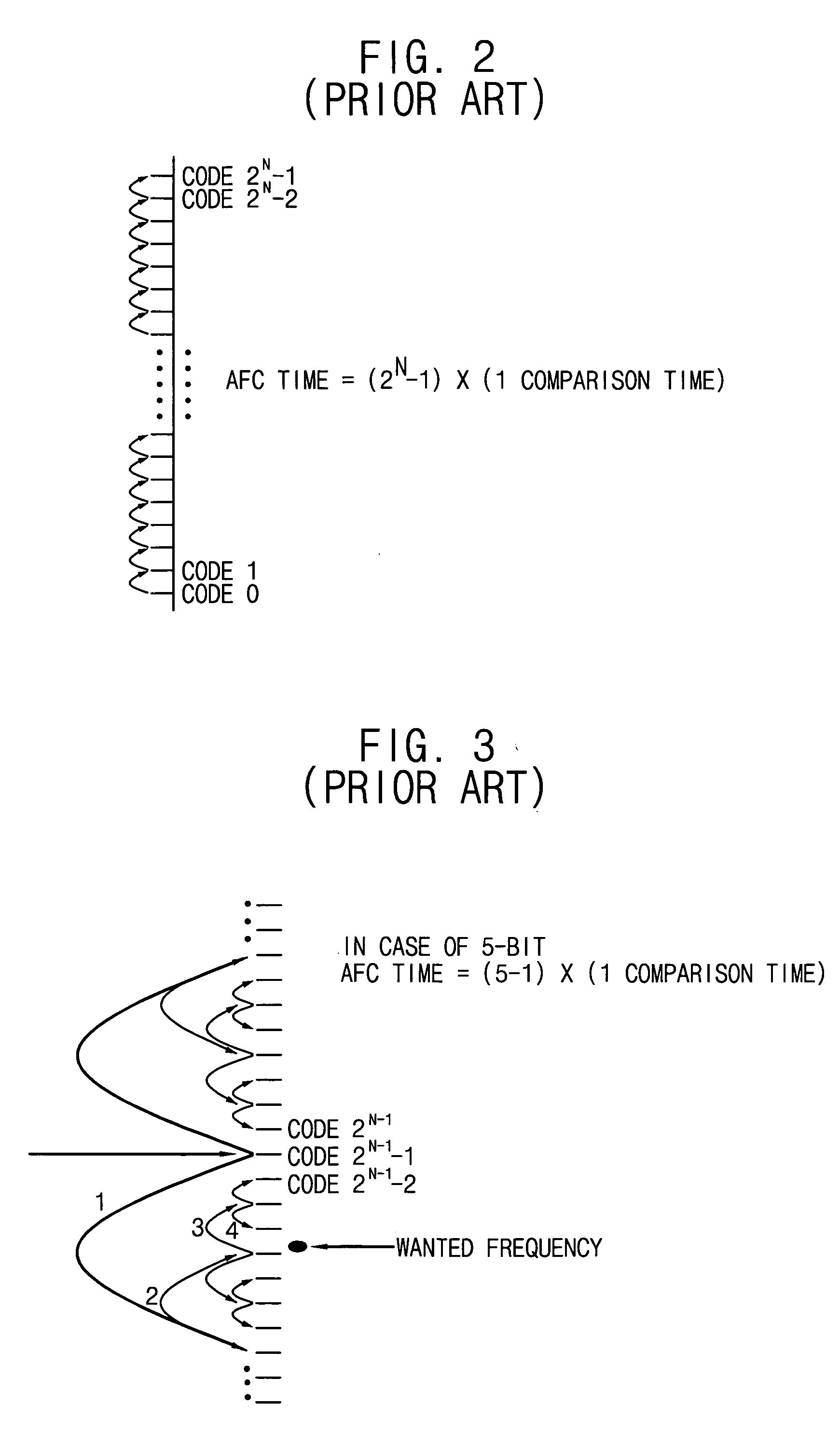

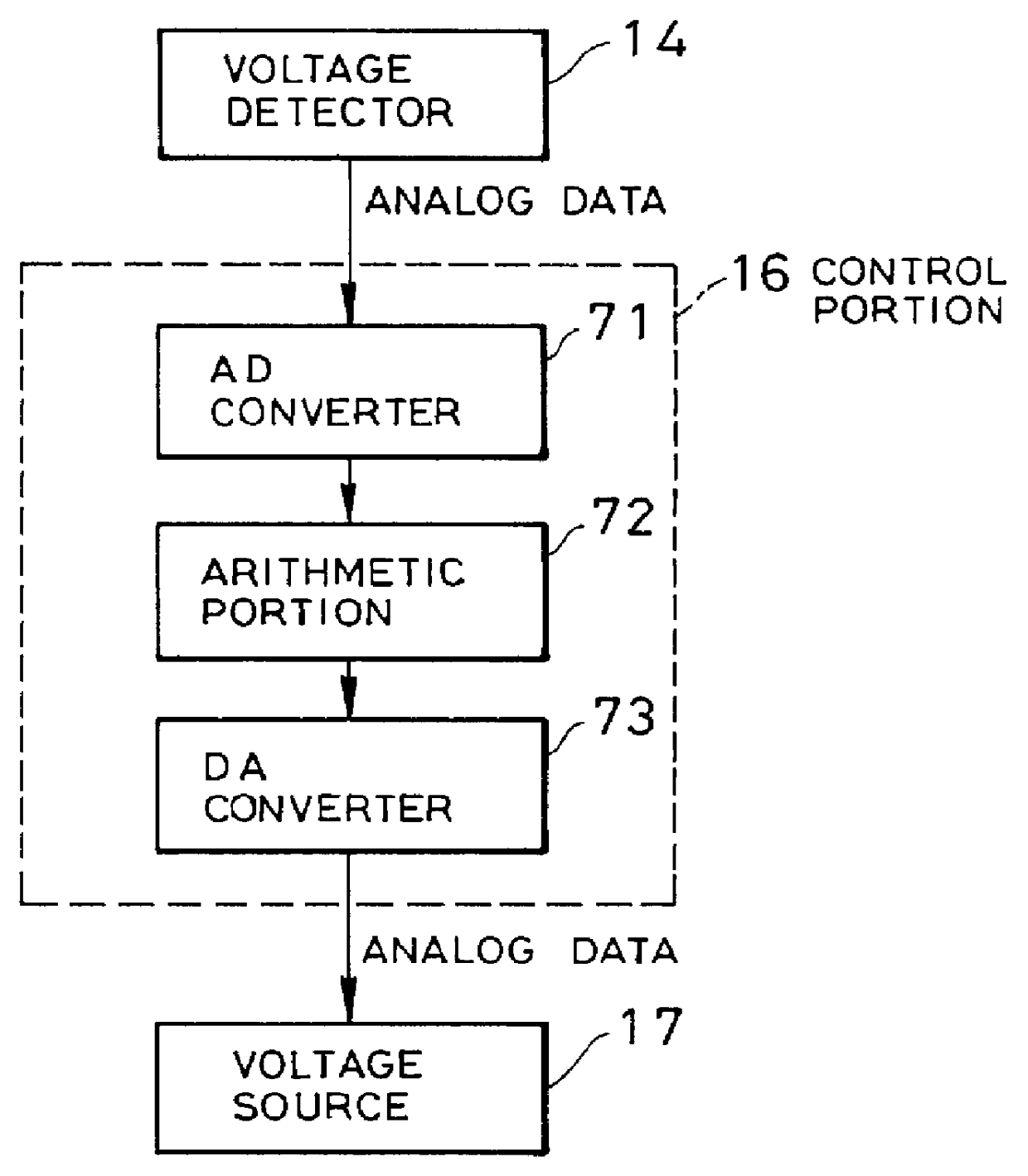

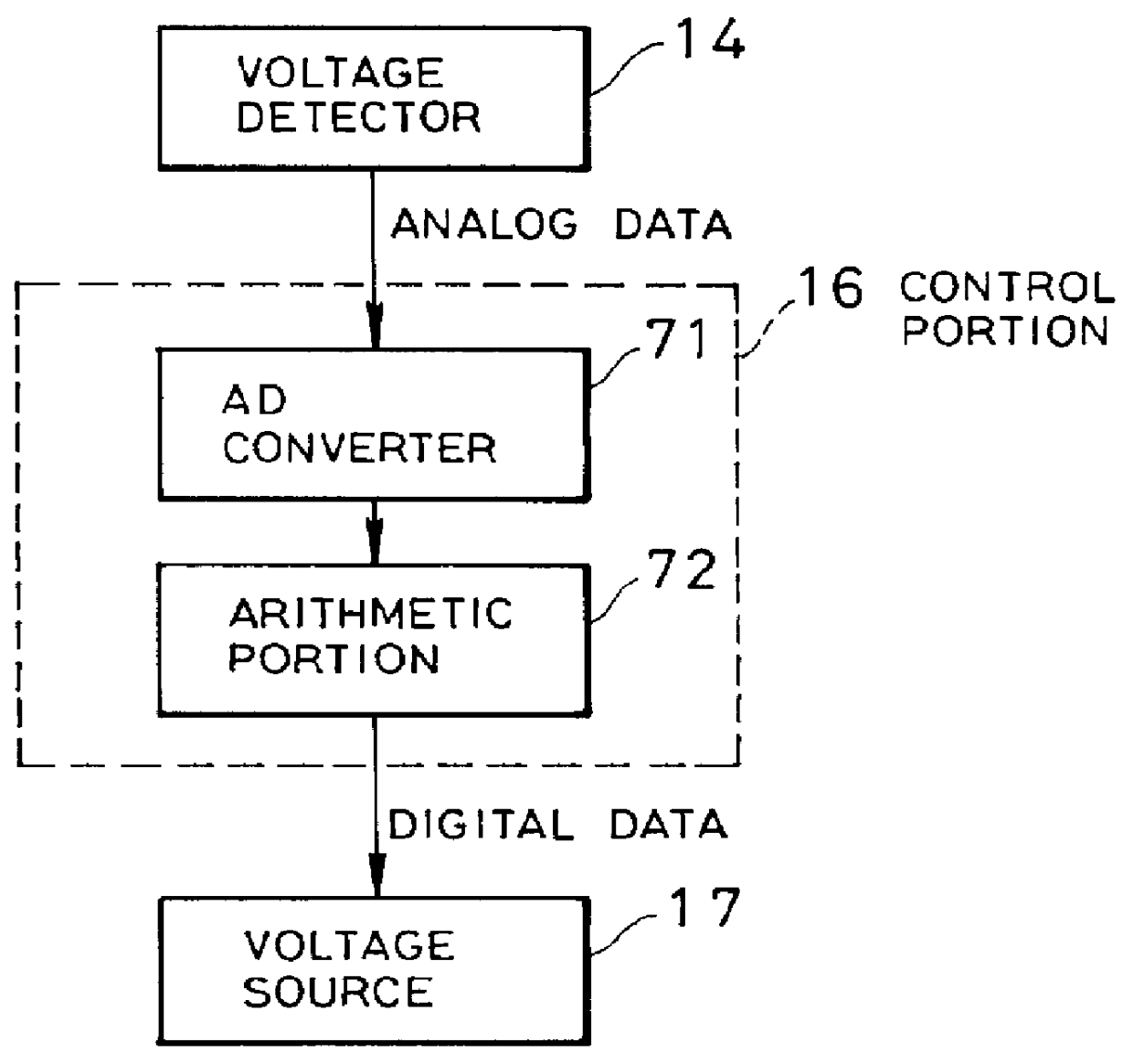

High frequency amplifier circuit

InactiveUS6111461AAmplifier modifications to reduce non-linear distortionAmplifier modifications to reduce noise influenceAudio power amplifierEngineering

A high frequency amplifier circuit includes the voltage source supplying the power source voltage on the output side of the high frequency amplifying active element. The high frequency amplifier is constructed with a voltage detector detecting a difference frequency voltage of the input signal at a frequency lower than the input signal of the high frequency amplifier circuit and control portion for attenuating the difference frequency voltage from the output signal by controlling the power source voltage on the basis of the difference frequency voltage detected by the voltage detector. Therefore, distortion due to modulating the input signal with the difference frequency component of the input signal can be reduced.

Owner:NEC CORP

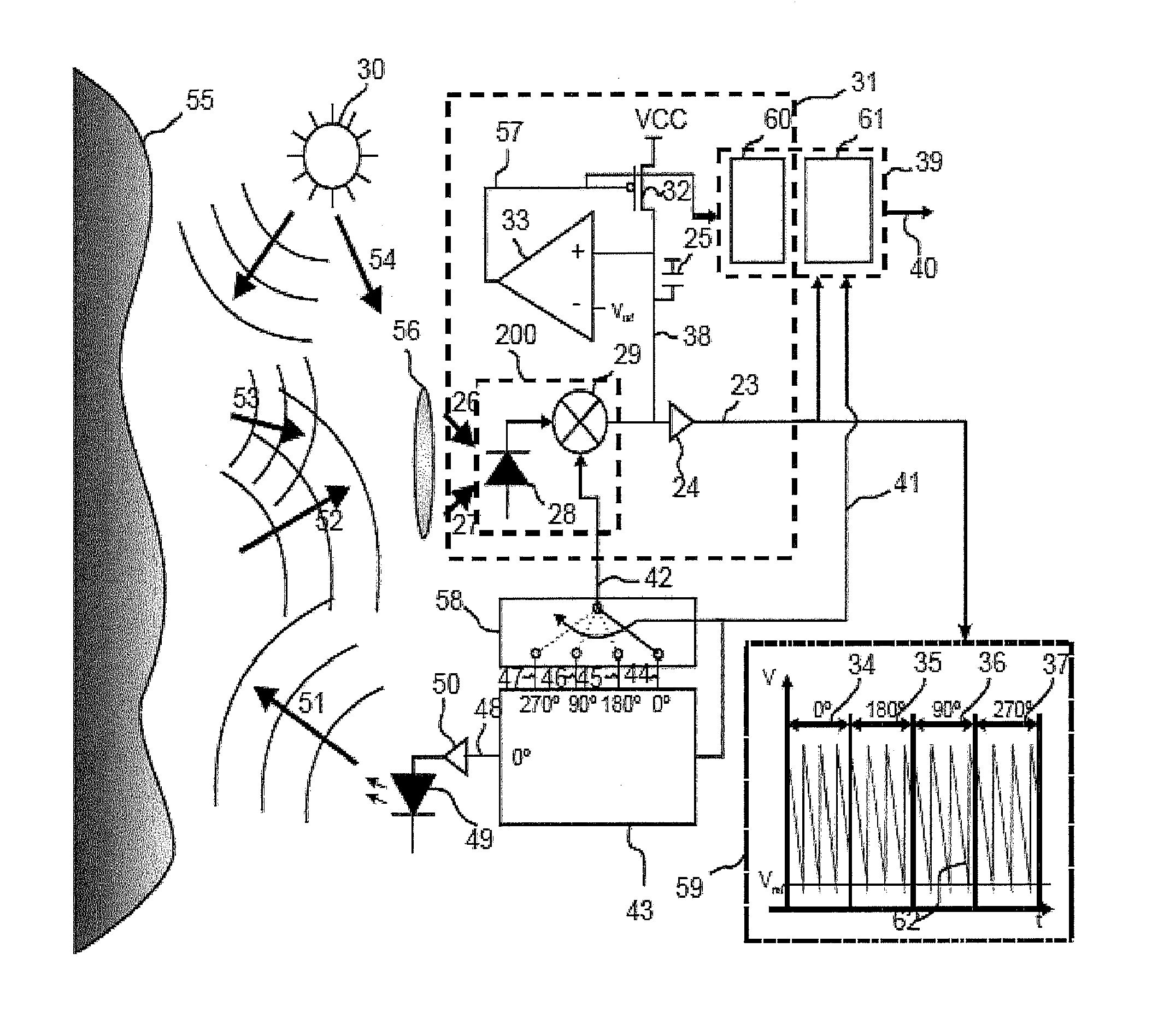

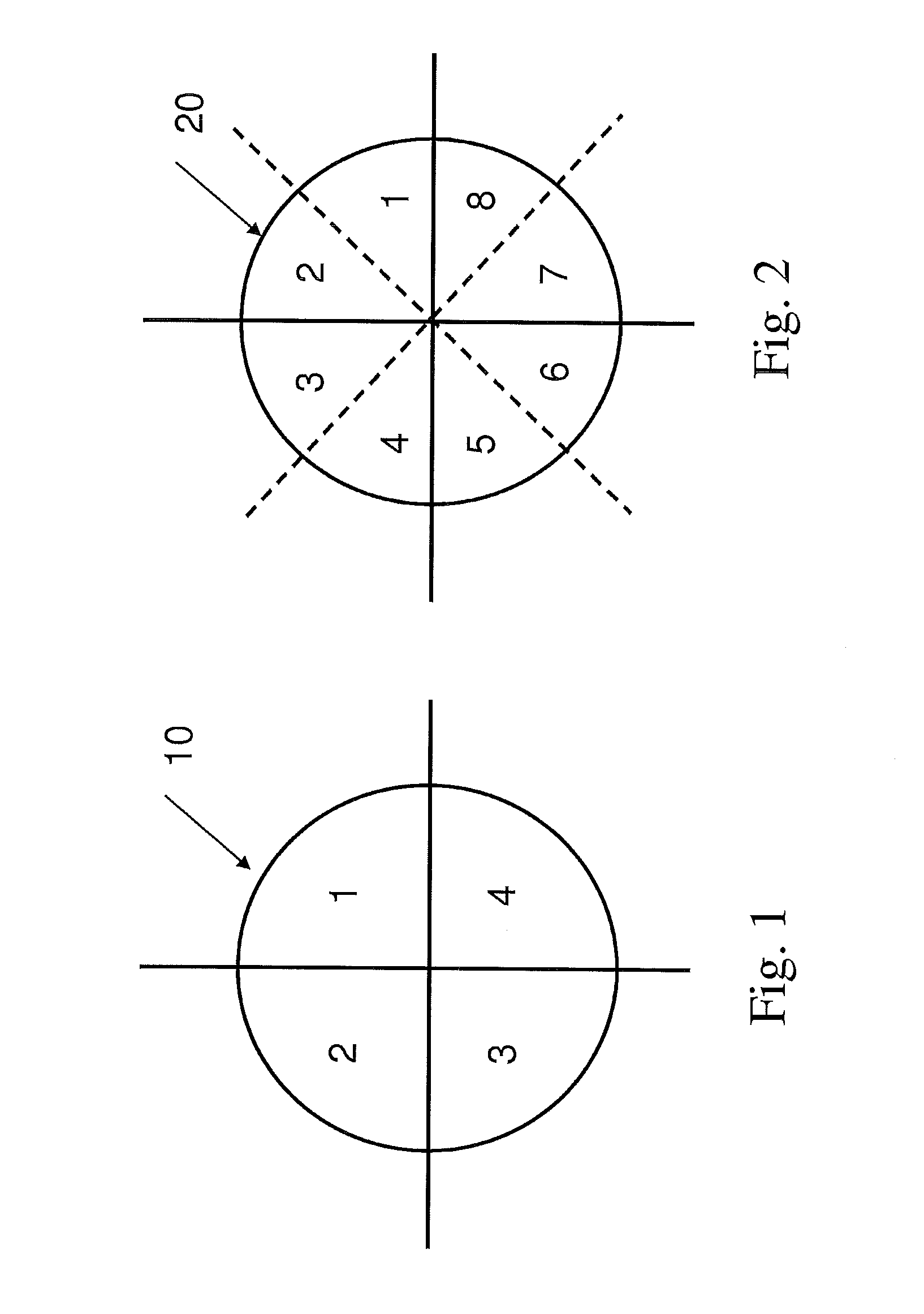

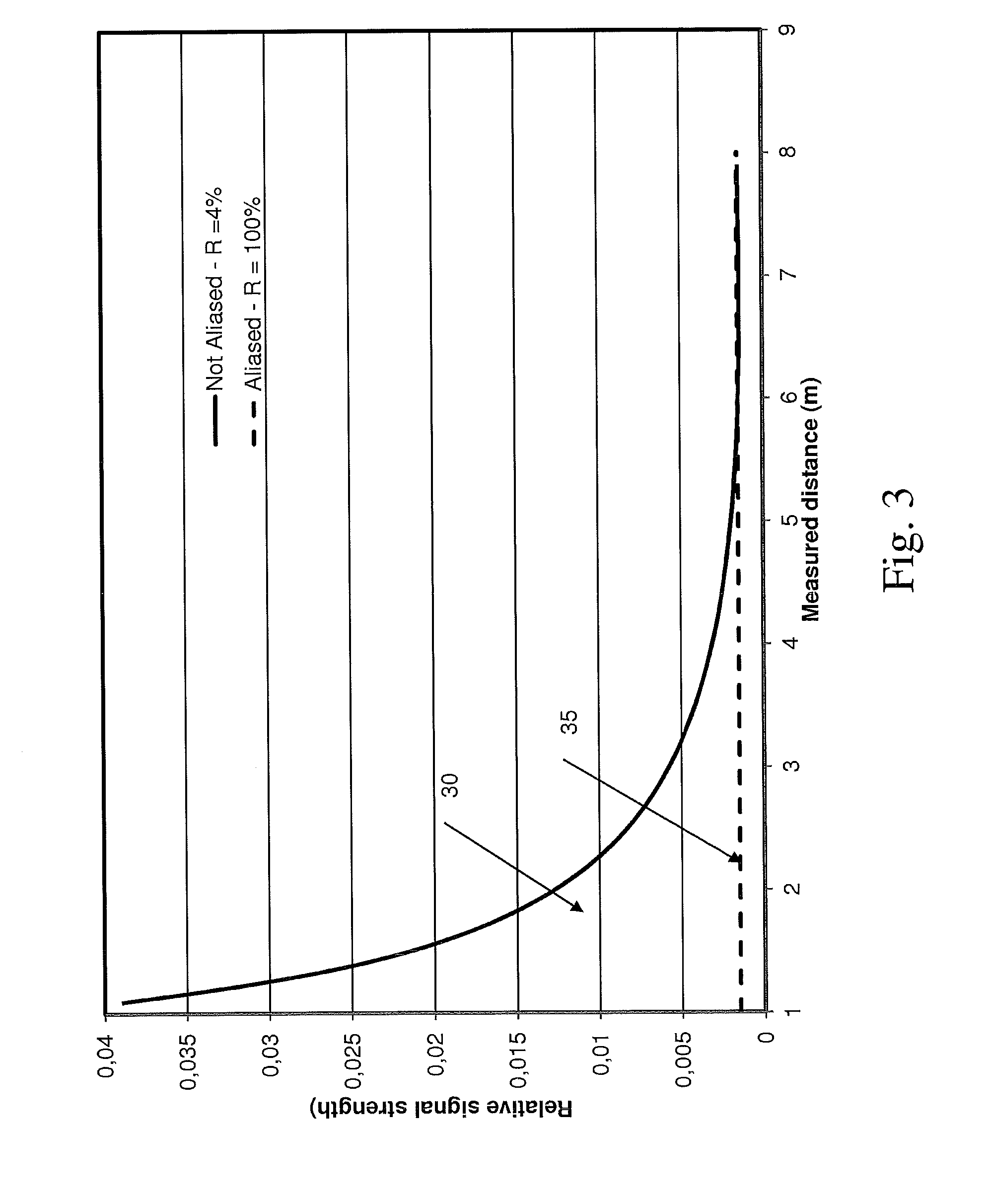

Processing of time-of-flight signals

ActiveUS20140313376A1Efficient executionAvoid aliasingTelevision system detailsColor television detailsFrequency detectionTime of flight

Described herein is a method and sensor of processing time-of-flight (TOF) signals in a TOF camera system including an illumination unit and an imaging sensor. The method comprises illuminating the scene with light at a first frequency, detecting reflected light from at least one object in the scene at the first frequency, and determining a phase measurement using I and Q values. In addition, the scene is illuminated with light at a second frequency, the second frequency being 2−n of the first frequency where n=1, 2, . . . , etc., and the signs of I and Q values for both the first and second frequencies is used to determine the presence of aliasing in the phase measurement so that it can be corrected. The phase measurement is then corrected for aliasing and the effective range of the TOF camera system is extended by multiples of 2n. In addition, relative signal strength needs to be considered in accordance with the reflectivity of objects within the scene. For a reflectivity of 4% and no aliasing, the ability to detect an object decreases with distance (30). For an aliased phase measurement for an object with a reflectivity of 100%, the ability to detect the object is substantially constant (35).

Owner:SOFTKINETIC SENSORS

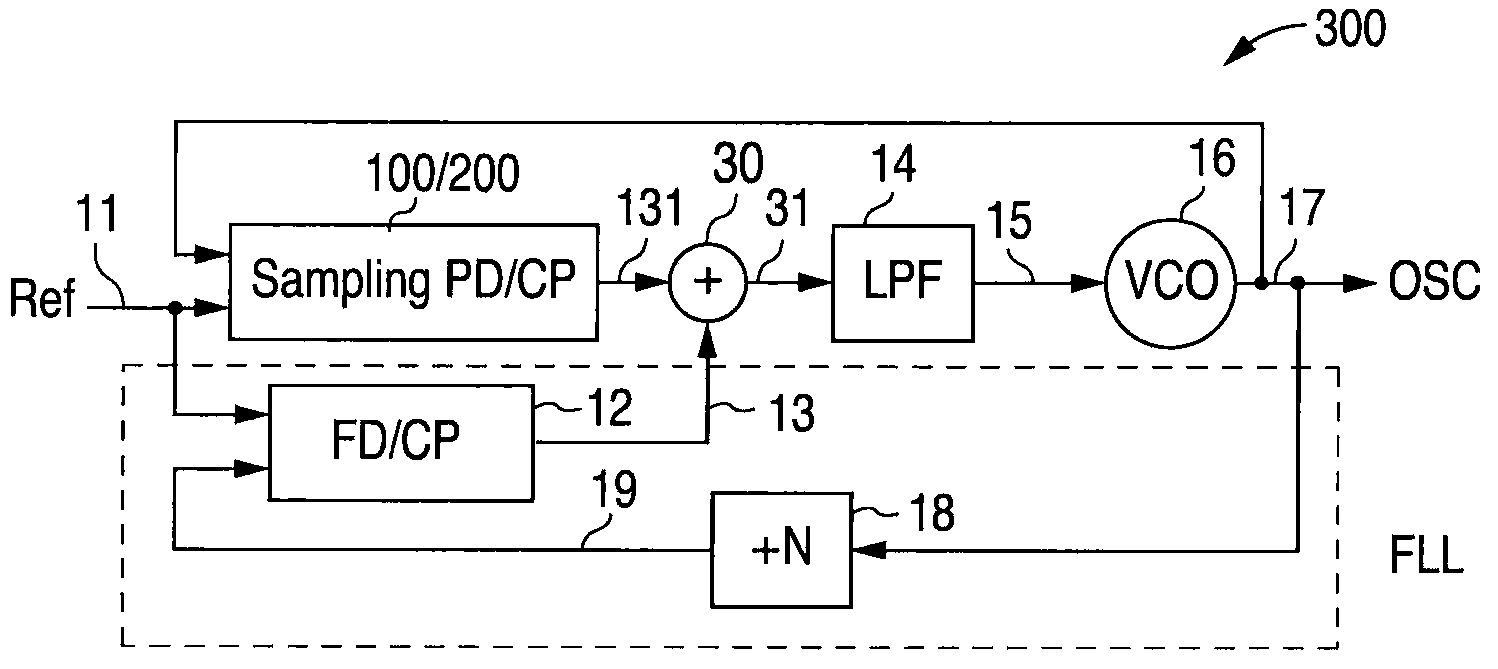

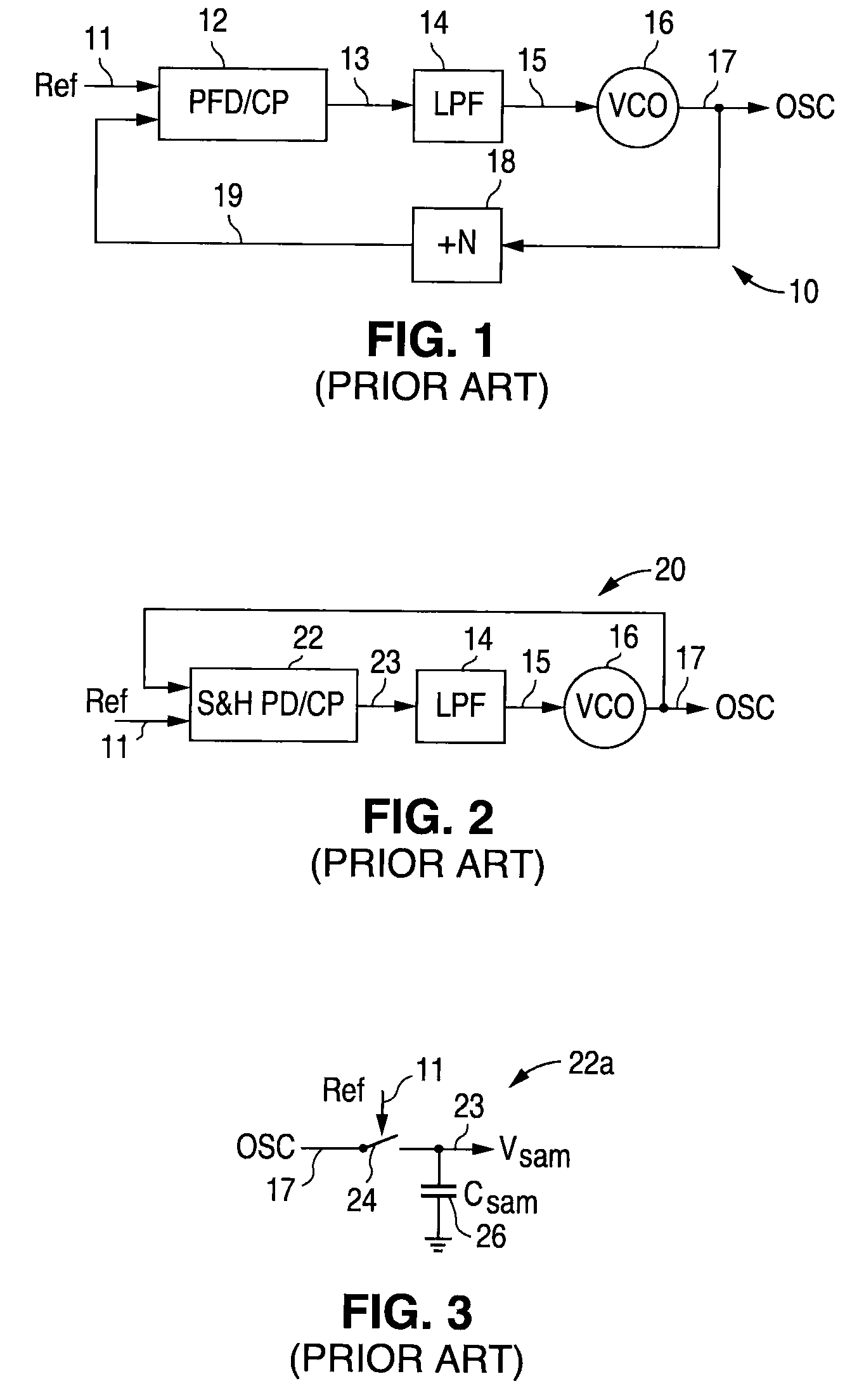

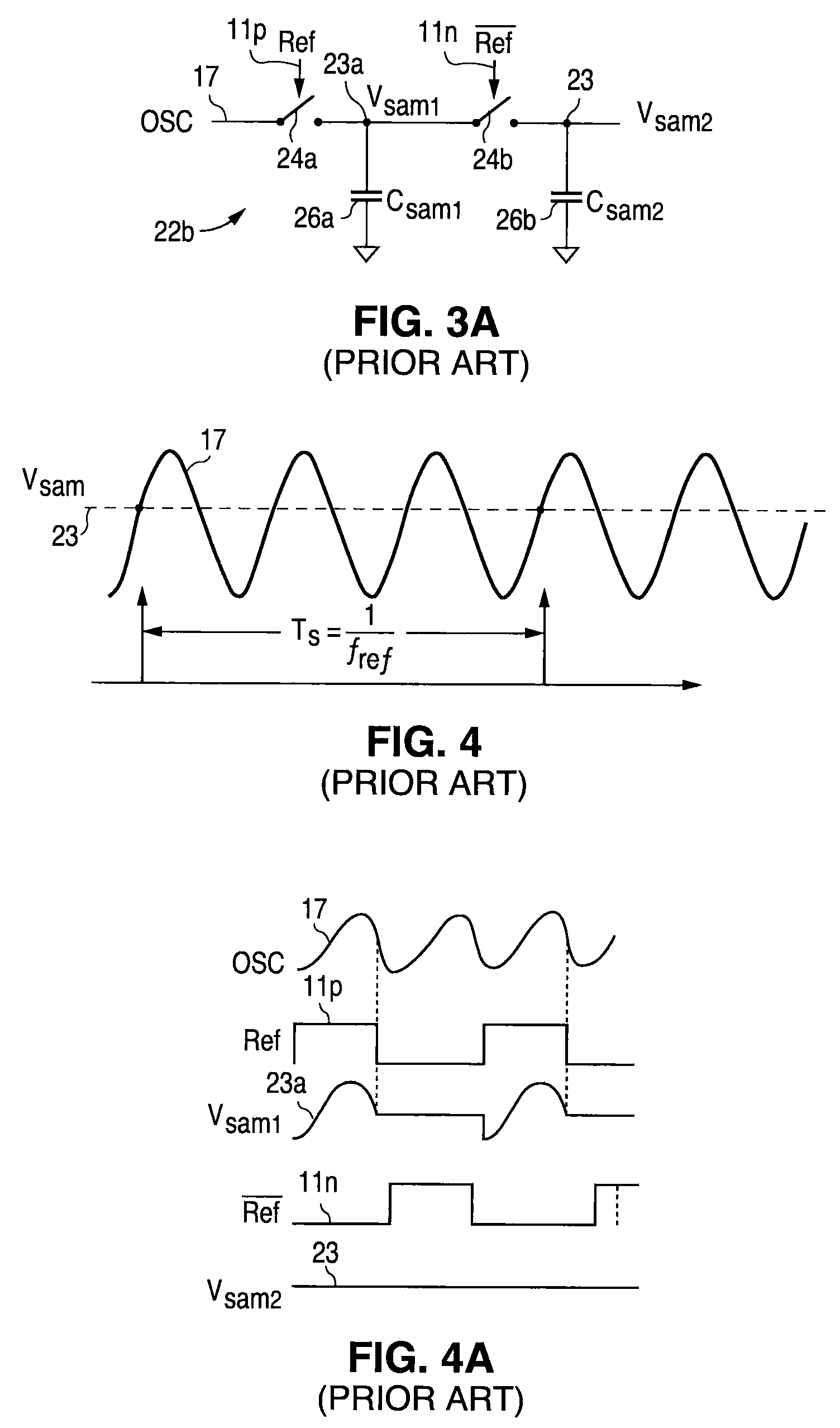

Phase-locked loop including sampling phase detector and charge pump with pulse width control

ActiveUS7737743B1Pulse automatic controlAngle demodulation by phase difference detectionPhase detectorFrequency detection

Phase-locked loop (PLL) circuitry in which a sampling phase detector samples the output signal in accordance with the reference signal and a frequency detector detects the output signal frequency in accordance with the reference signal.

Owner:NAT SEMICON CORP

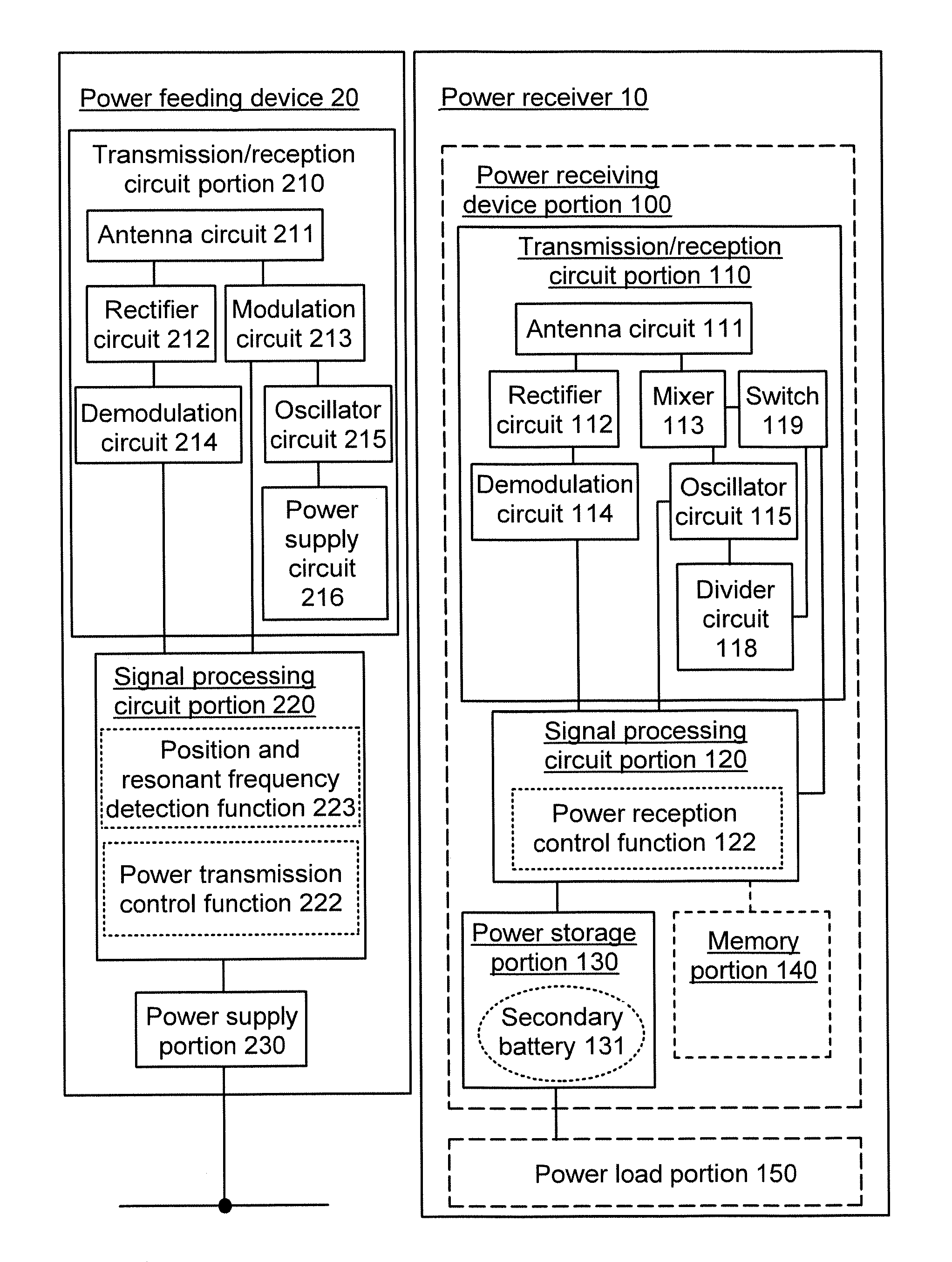

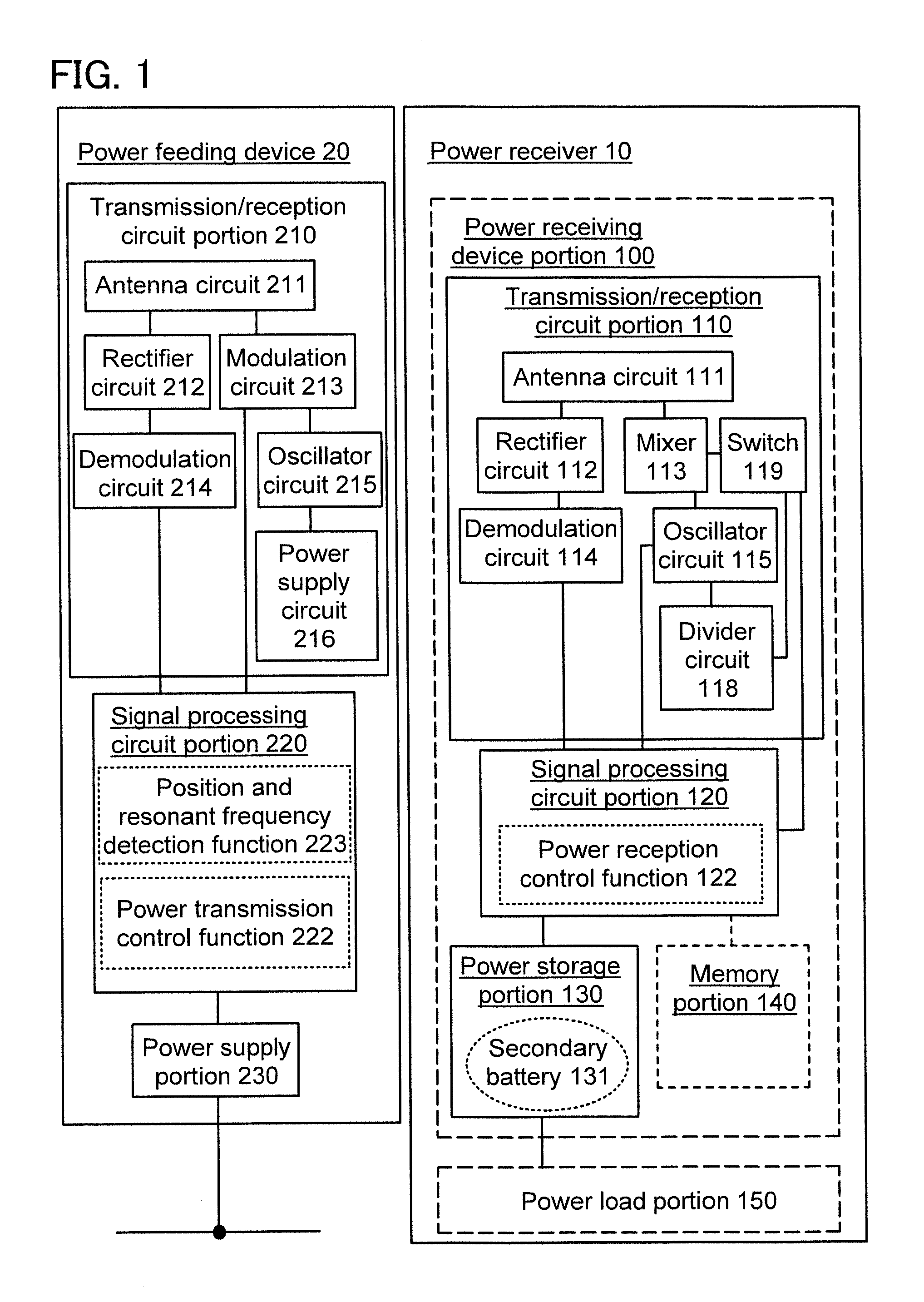

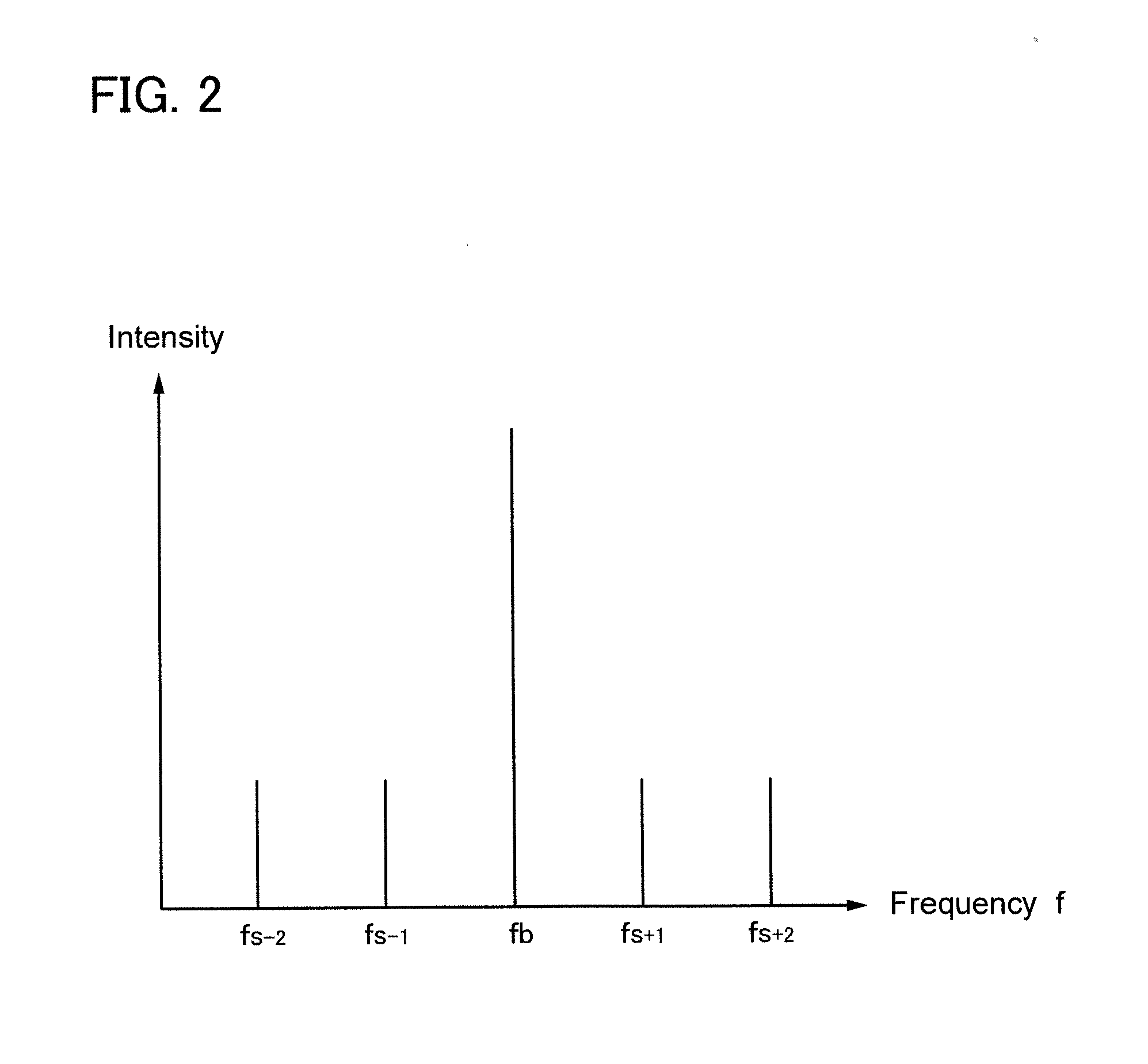

Wireless power feeding system and wireless power feeding method

InactiveUS20120025631A1Improve transmission efficiencyConvenient power supplyCircuit authenticationElectromagnetic wave systemCarrier signalEngineering

An object is to provide a power feeding system and a power feeding method which are more convenient for a power feeding user at the power receiving end, without causing increases in complexity and size of devices. An object is to provide a power feeding system and a power feeding method which also allow a power feeding provider (a company) which feeds power (at the power transmitting end) to supply power without waste. A power feeding device which wirelessly supplies power to a power receiver detects the position and the resonant frequency of the power receiver by receiving a position and resonant frequency detection signal using a plurality of sub-carriers having different frequencies from the power receiver, and controls the frequency of a power signal to be transmitted to the power receiver on the basis of the information. An efficient power feeding service can be offered by transmitting a power signal to the power receiver at an optimum frequency for high power transmission efficiency.

Owner:SEMICON ENERGY LAB CO LTD

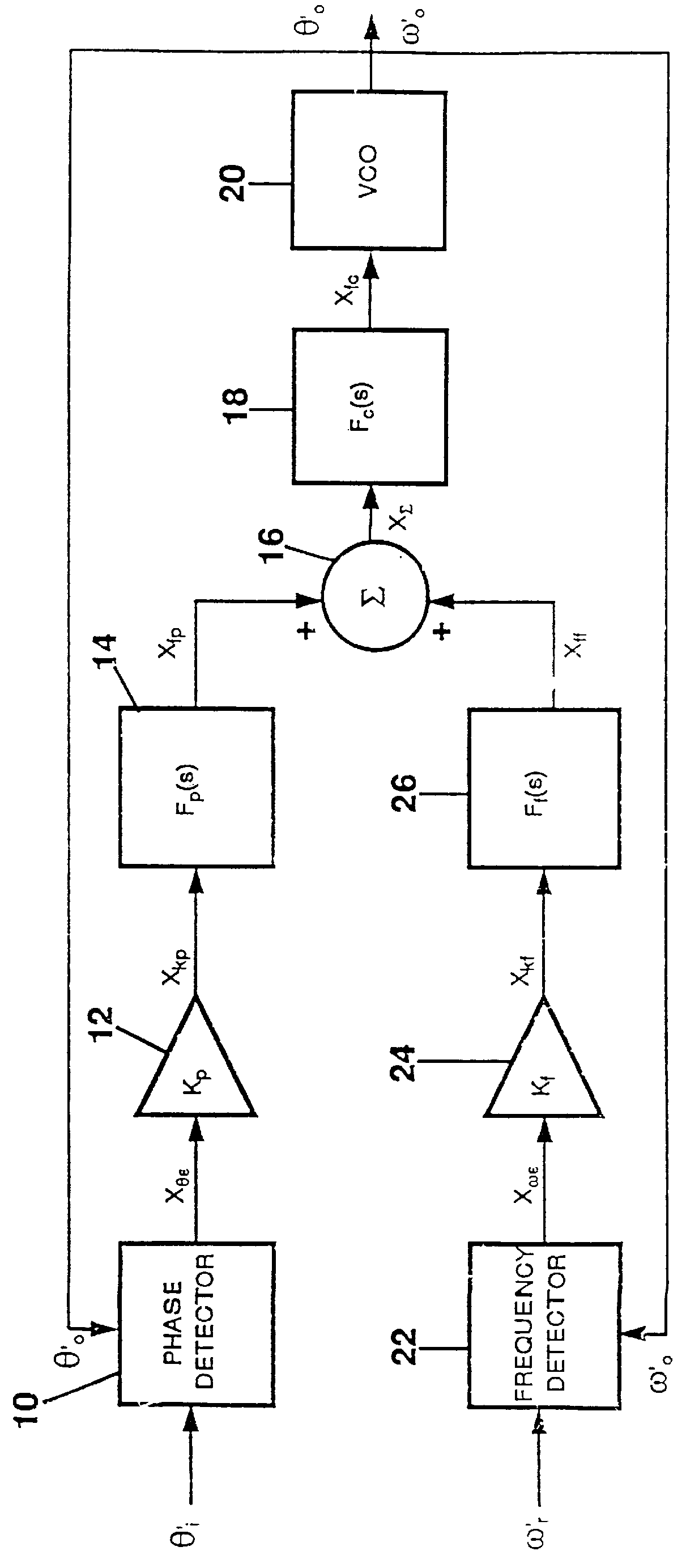

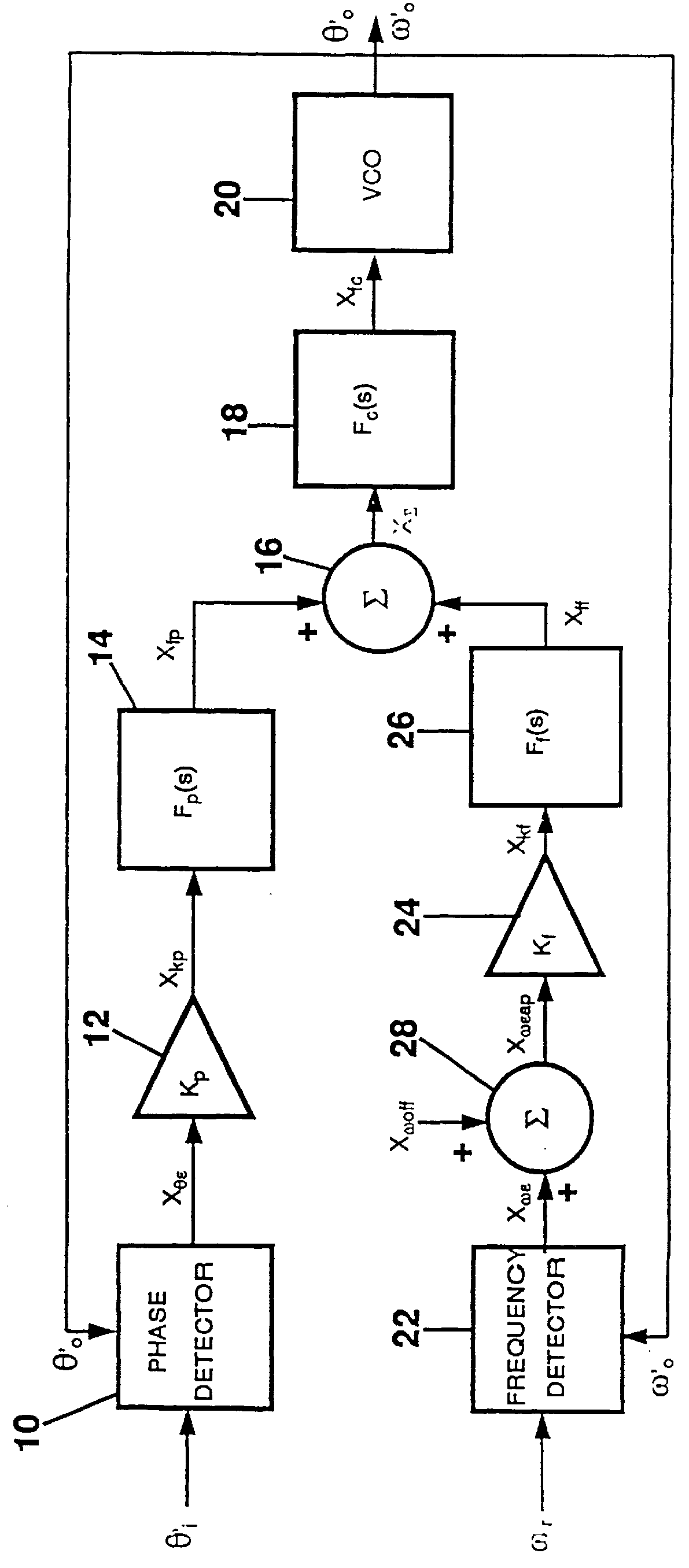

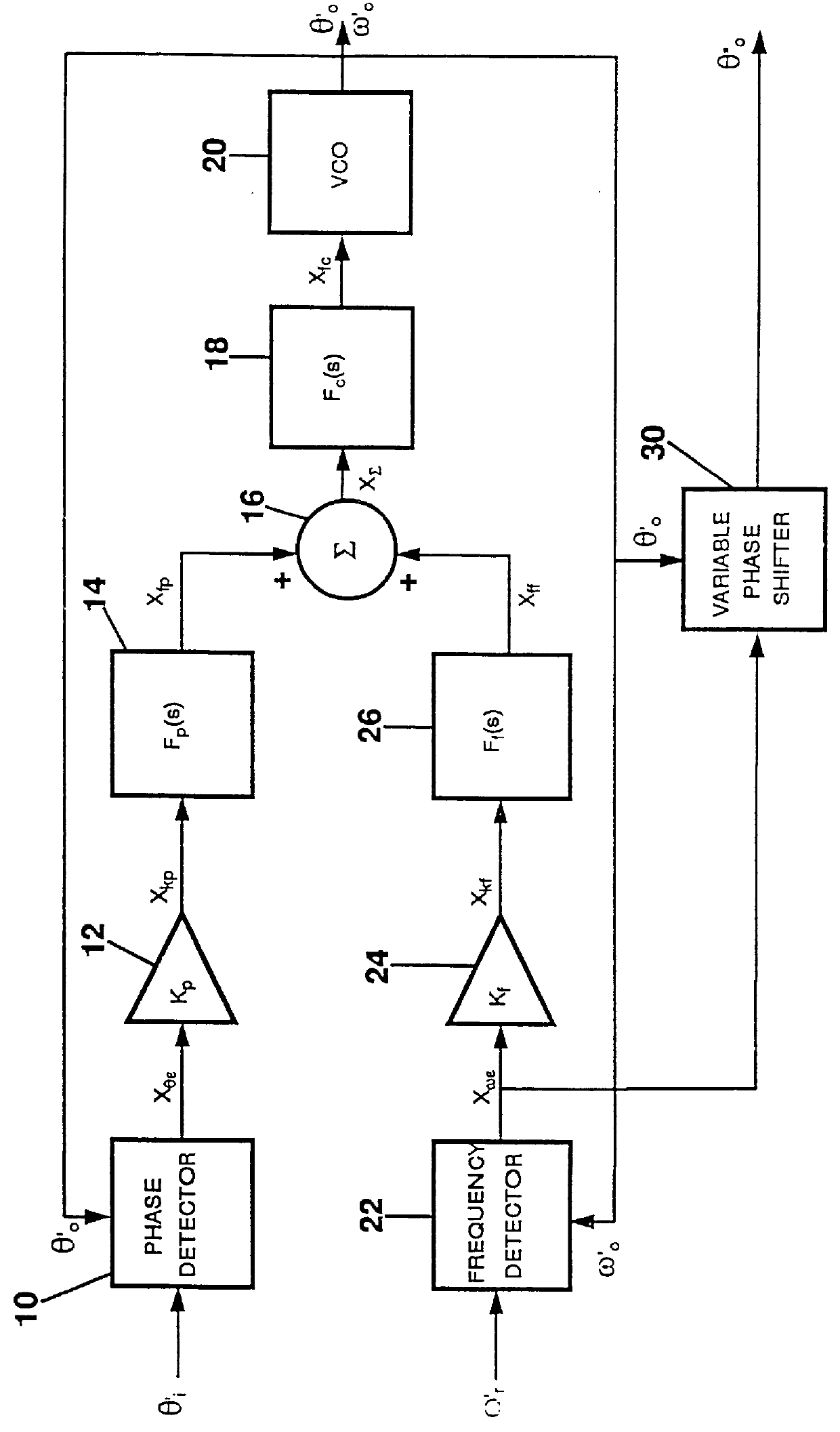

Steered frequency phase locked loop

InactiveUS6031428APulse automatic controlFrequency-modulated carrier systemsPhase detectorFrequency detection

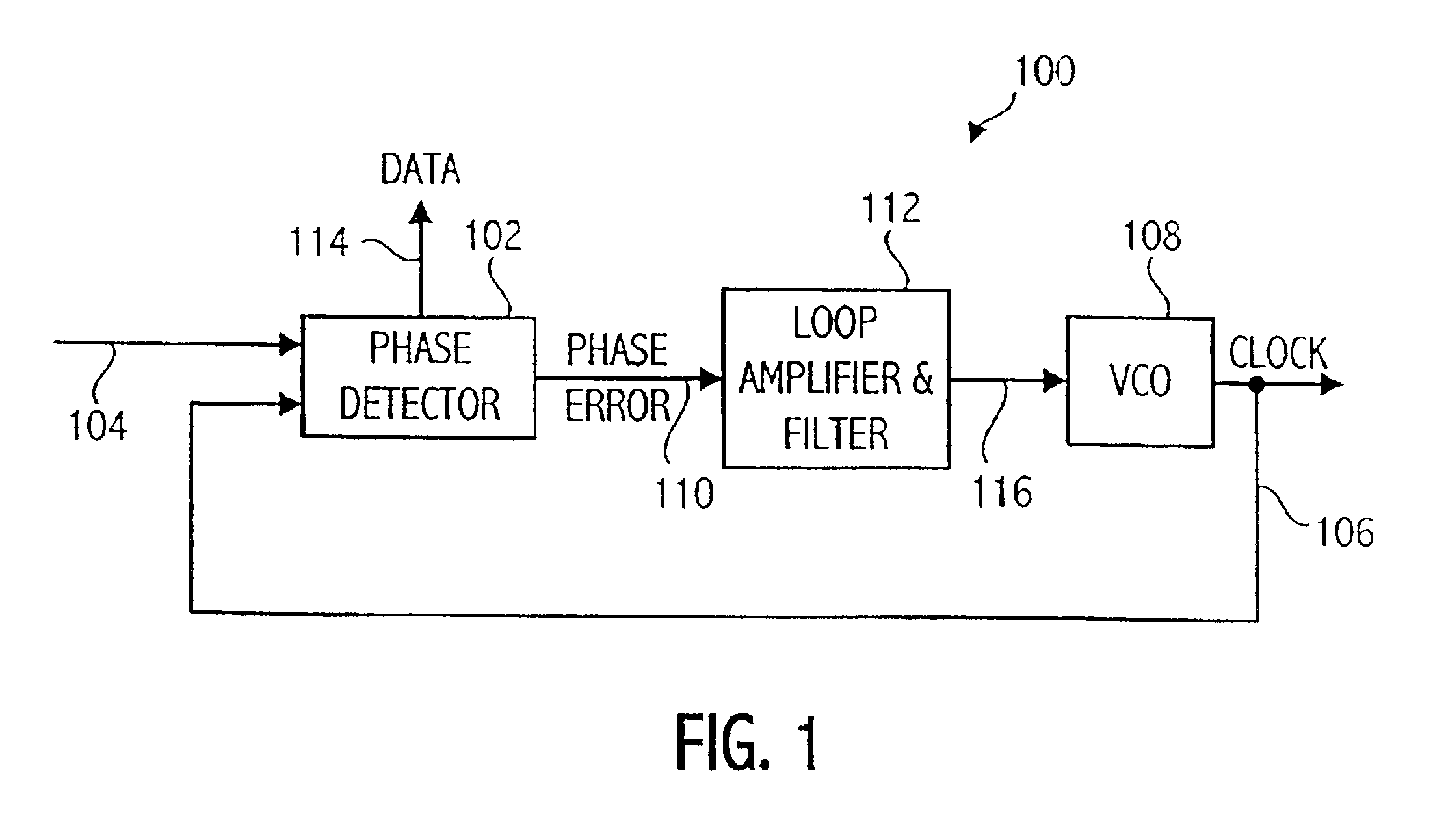

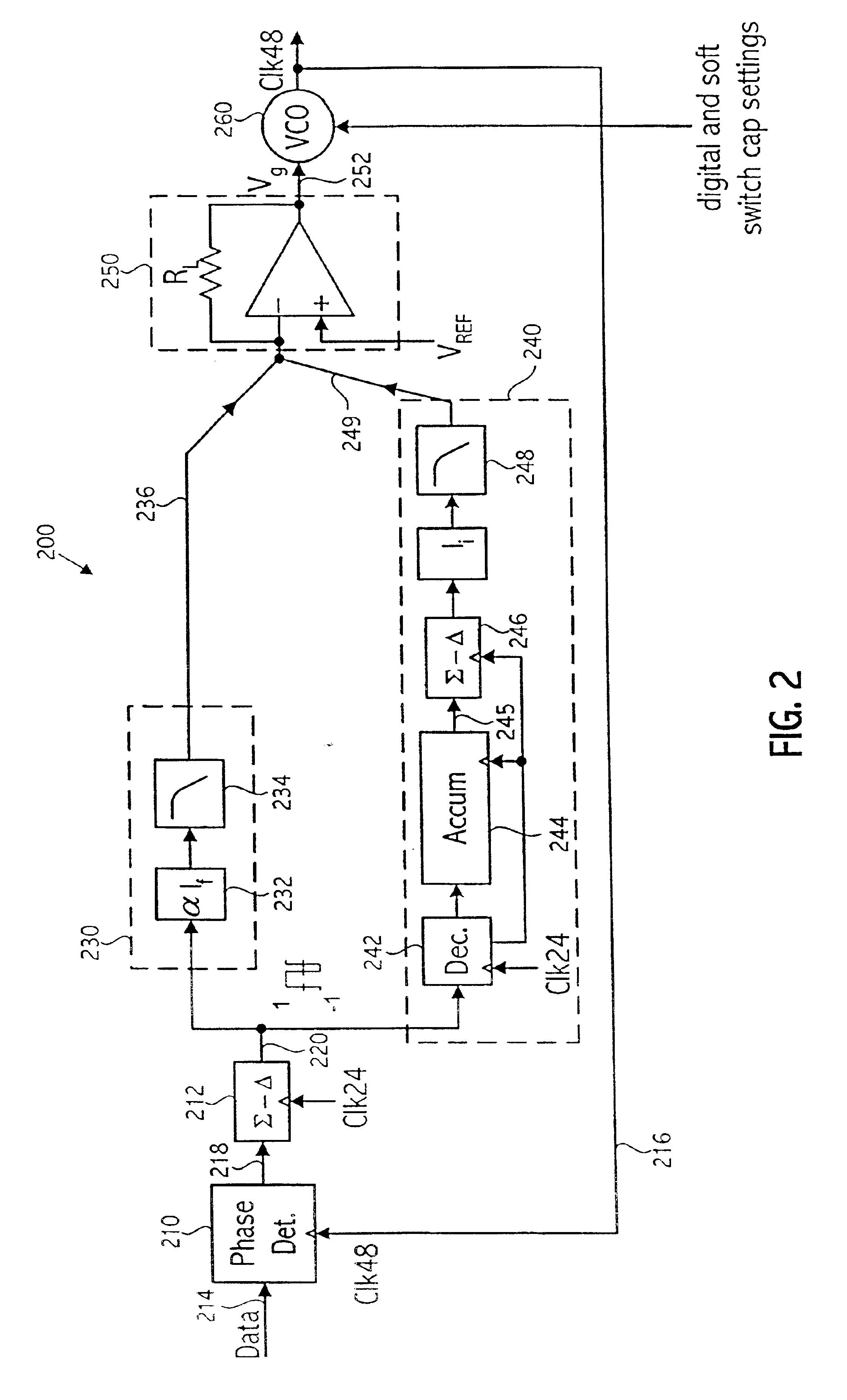

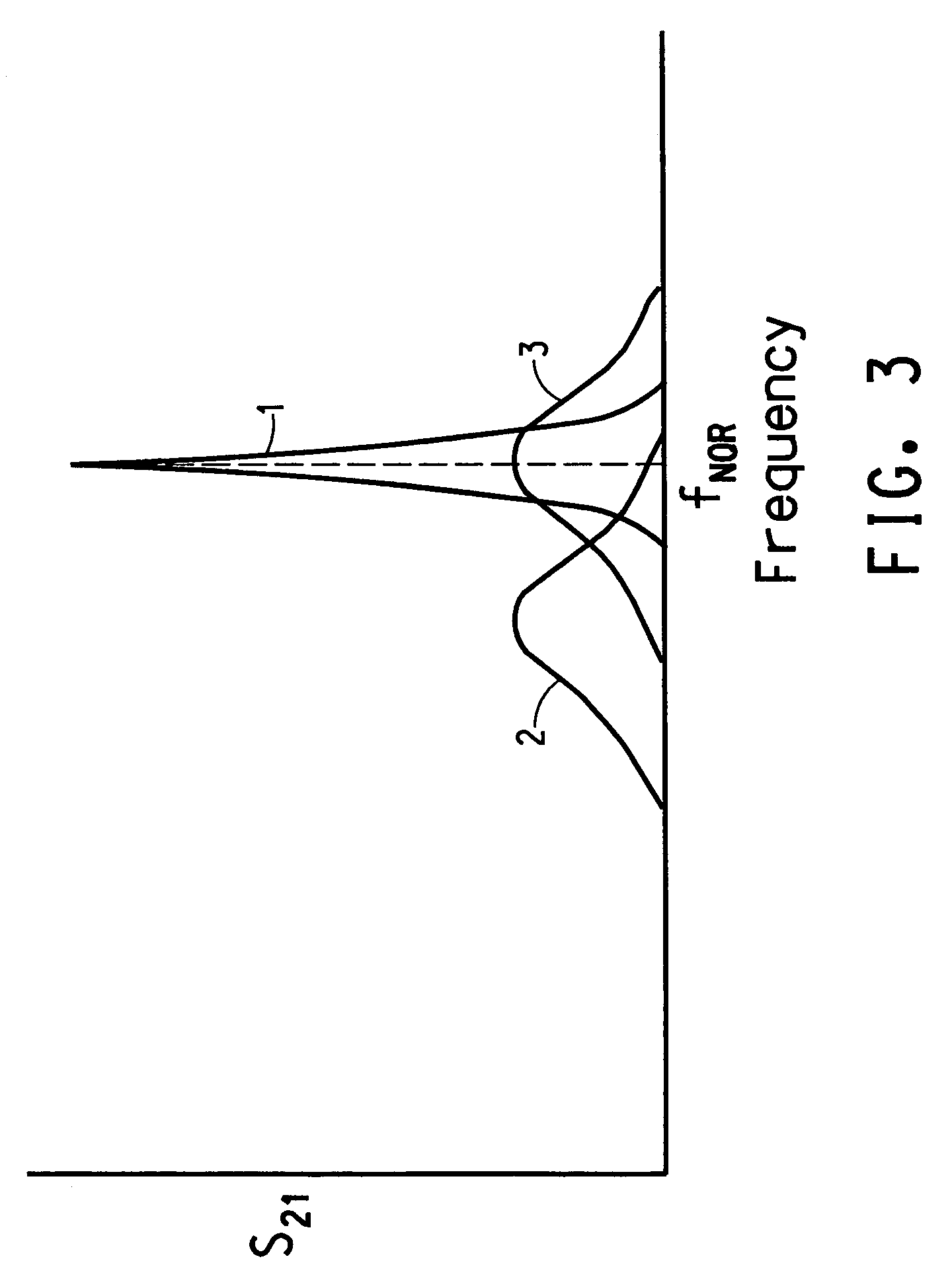

PCT No. PCT / AU95 / 00793 Sec. 371 Date Sep. 30, 1997 Sec. 102(e) Date Sep. 30, 1997 PCT Filed Nov. 28, 1995 PCT Pub. No. WO96 / 17435 PCT Pub. Date Jun. 6, 1996A Steered Frequency Phase Lock Loop (SFPLL) comprises a phase loop that functions like a normal phase locked loop (PLL) and locks to the input signal, and a frequency loop that uses a reference frequency to influence the phase loop and effectively confines the output frequency of the phase loop and the SFPLL to be in a range of frequencies close to the reference frequency. The reference frequency is chosen to be very close to the input signal frequency that it is desired the SFPLL lock to. The SFPLL comprises a phase detector (10), a frequency detector (22), first and second gain components (12, 24), first, second and third filter components (14, 18, 26), a summer (16) and a voltage controlled oscillator (VCP)(20). By a judicious choice of the gains in the phase and frequency loops the SFPLL can be designed so that the range of frequencies to which the SFPLL will lock can be confined to an arbitrarily small region around the reference frequency ( omega 'r). Applications of the SFPLL include demodulation in CW modulation systems and timing recovery from NRZ data. Three advantages of the SFPLL are that the output frequency is equal or close to the reference frequency when no input signal is present, and the range of frequencies to which the SFPLL can lock is confined to a region around the reference frequency, and the phase and frequency instabilities of the VCO can be reduced.

Owner:CURTAIN UNIV OF TECH

Interpolator based clock and data recovery (CDR) circuit with digitally programmable BW and tracking capability

ActiveUS7315596B2Easy to operateWide data rate rangePulse automatic controlSynchronising arrangementPhase correctionData stream

Owner:TEXAS INSTR INC

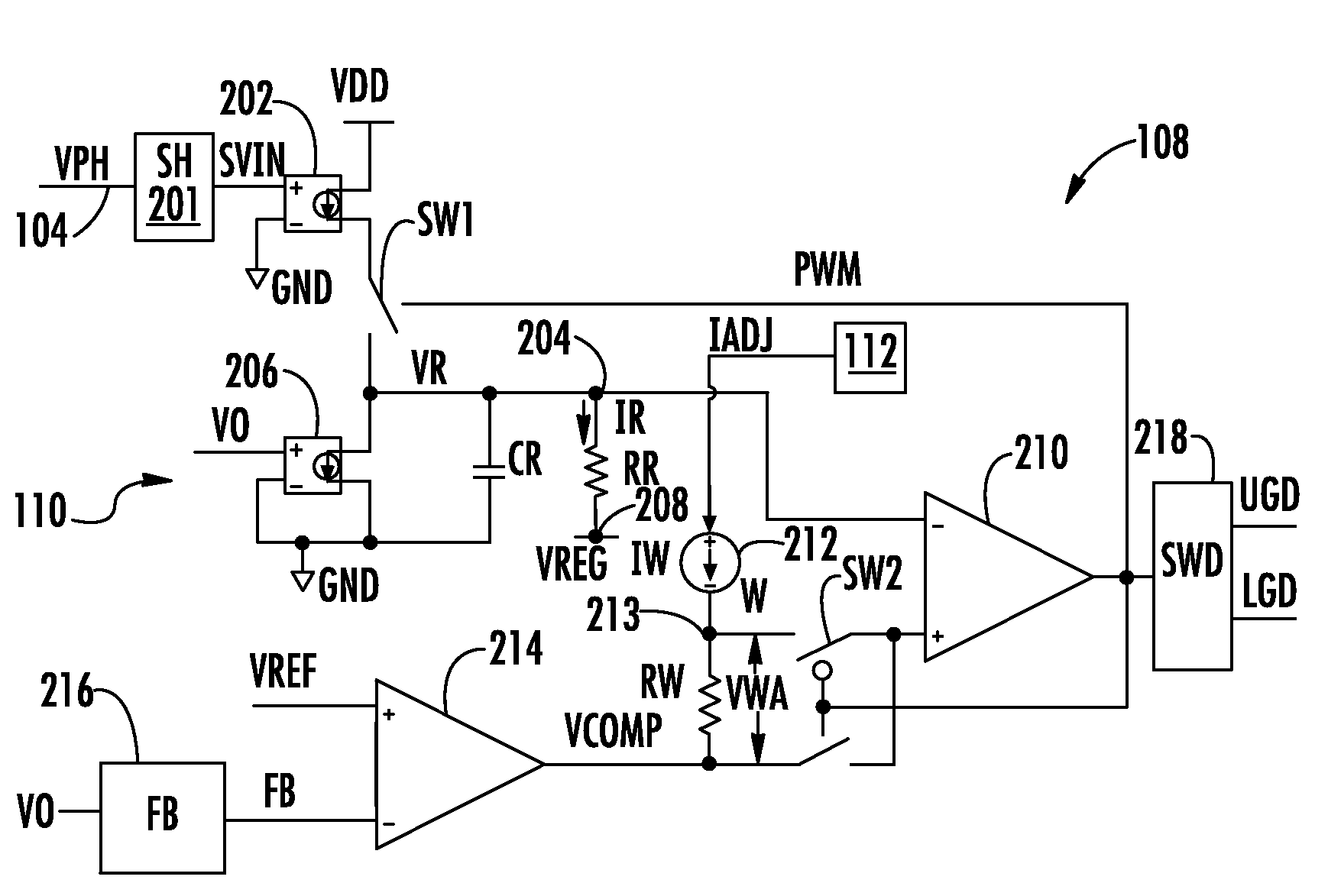

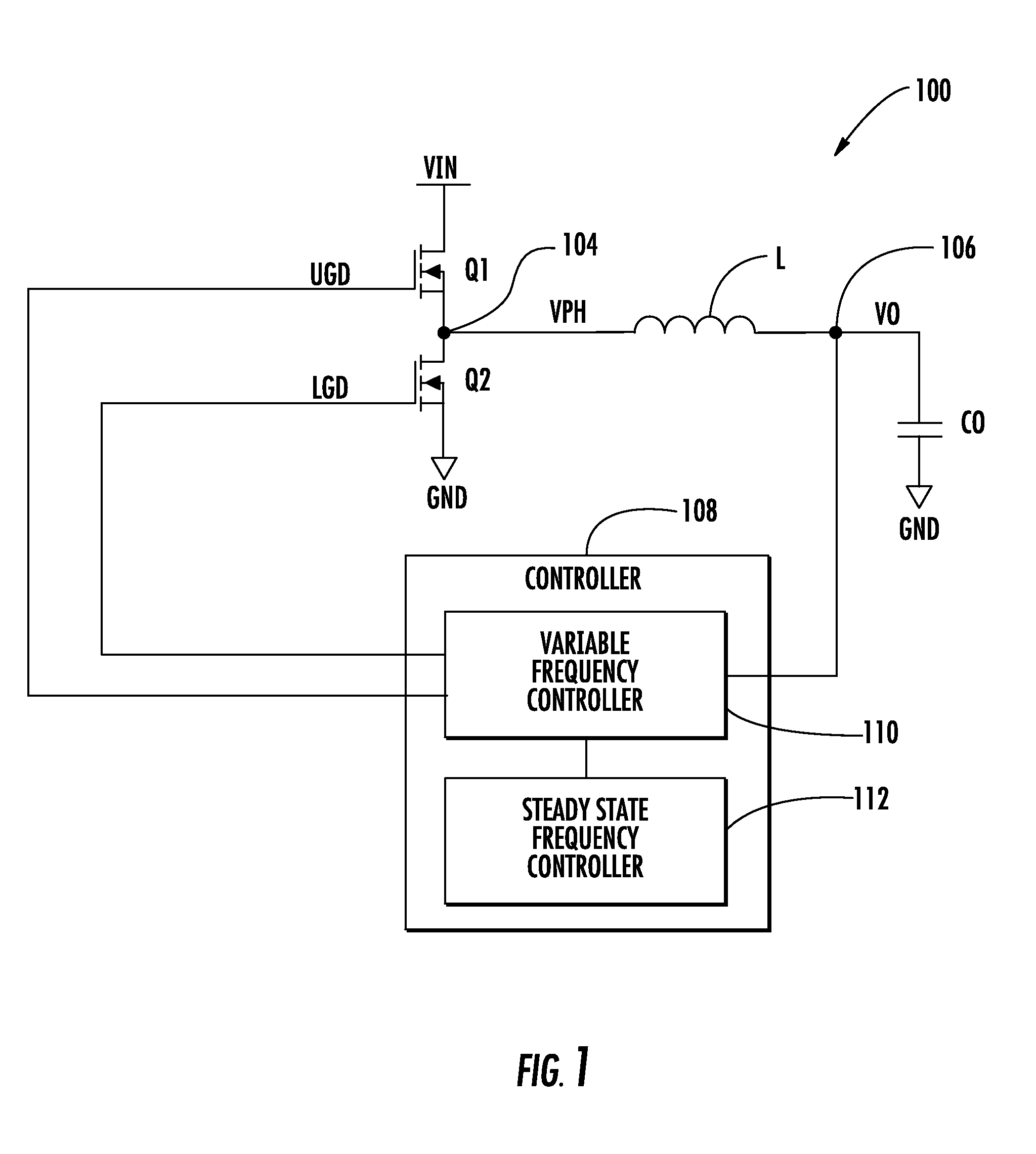

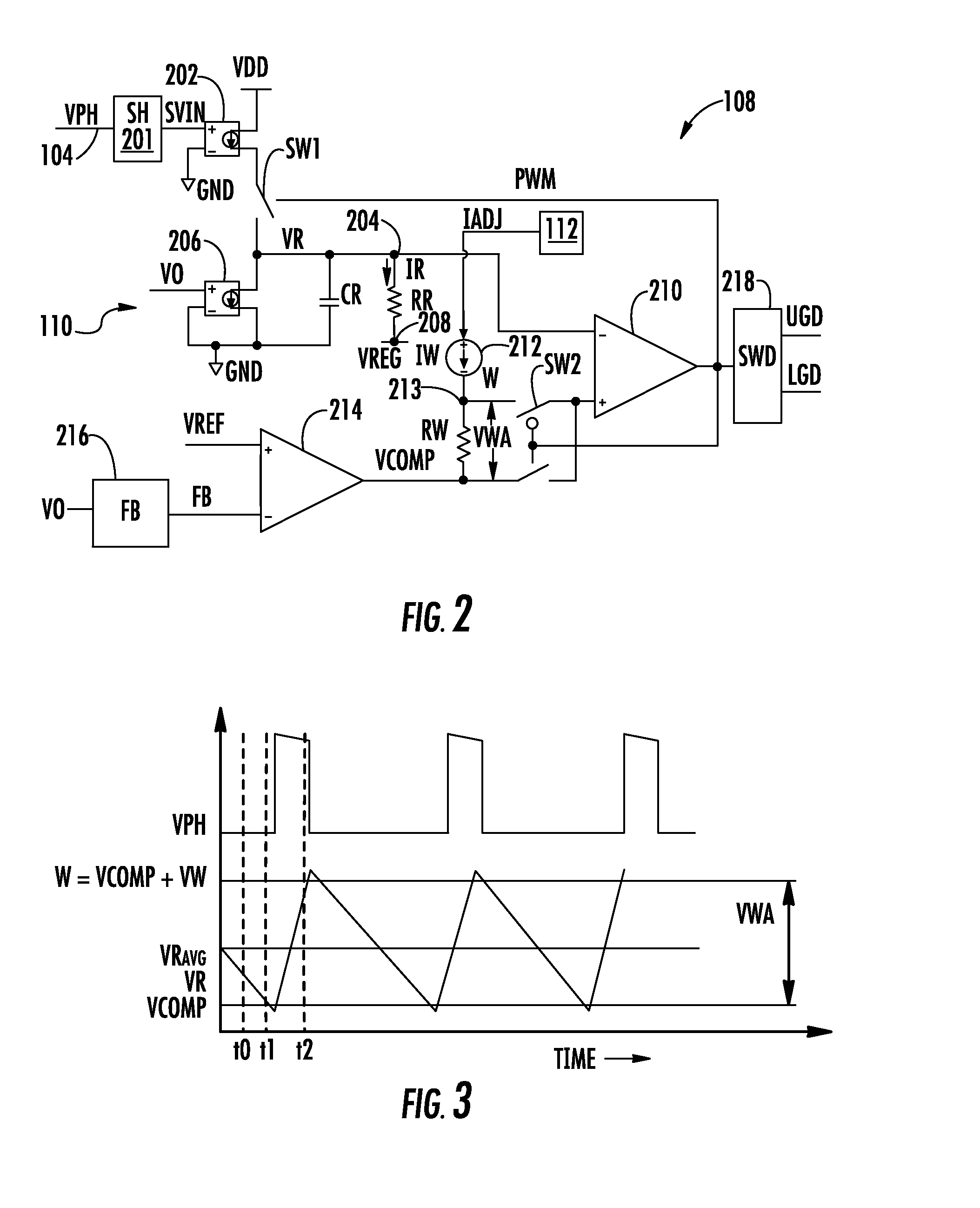

Steady state frequency control of variable frequency switching regulators

A steady state frequency control circuit for a variable frequency regulator including an open loop frequency control circuit, a frequency detector and a comparator circuit. The variable frequency regulator provides a clock signal indicating actual operating frequency and has a frequency control parameter for adjusting steady state operating frequency. The frequency detector receives the clock signal and provides a frequency sense signal which is compared with a steady state frequency reference signal to provide a frequency adjust signal. The frequency control parameter is adjusted by the frequency adjust signal to control steady state frequency. A method of controlling steady state frequency of a variable frequency regulator includes using open loop frequency control, determining the operating frequency and providing a frequency sense signal, comparing the frequency sense signal with frequency reference signal and providing a frequency adjust signal, and adjusting the frequency control parameter based on the frequency adjust signal.

Owner:INTERSIL INC

Auto-detection between referenceless and reference clock mode of operation

An internal frequency reference, such as a VCO used in a PLL, having a free-running frequency fairly well controlled within a predictable range, is used to determine which of two possible modes of operation, a referenceless or reference clock mode of operation, is used based on a detected frequency of an externally-provided frequency reference signal. The frequency is detected without any additional externally provided signal to indicate the mode of operation or the frequency of the reference clock. If the frequency detection circuit detects a frequency below a predetermined threshold, referenceless mode of operation is indicated. Otherwise, reference clock mode of operation is indicated. In referenceless mode of operation such operations as frequency acquisition and lock detect are performed without the use of a reference clock. In reference clock mode the reference clock is used for such operations as frequency acquisition and lock detect.

Owner:SKYWORKS SOLUTIONS INC

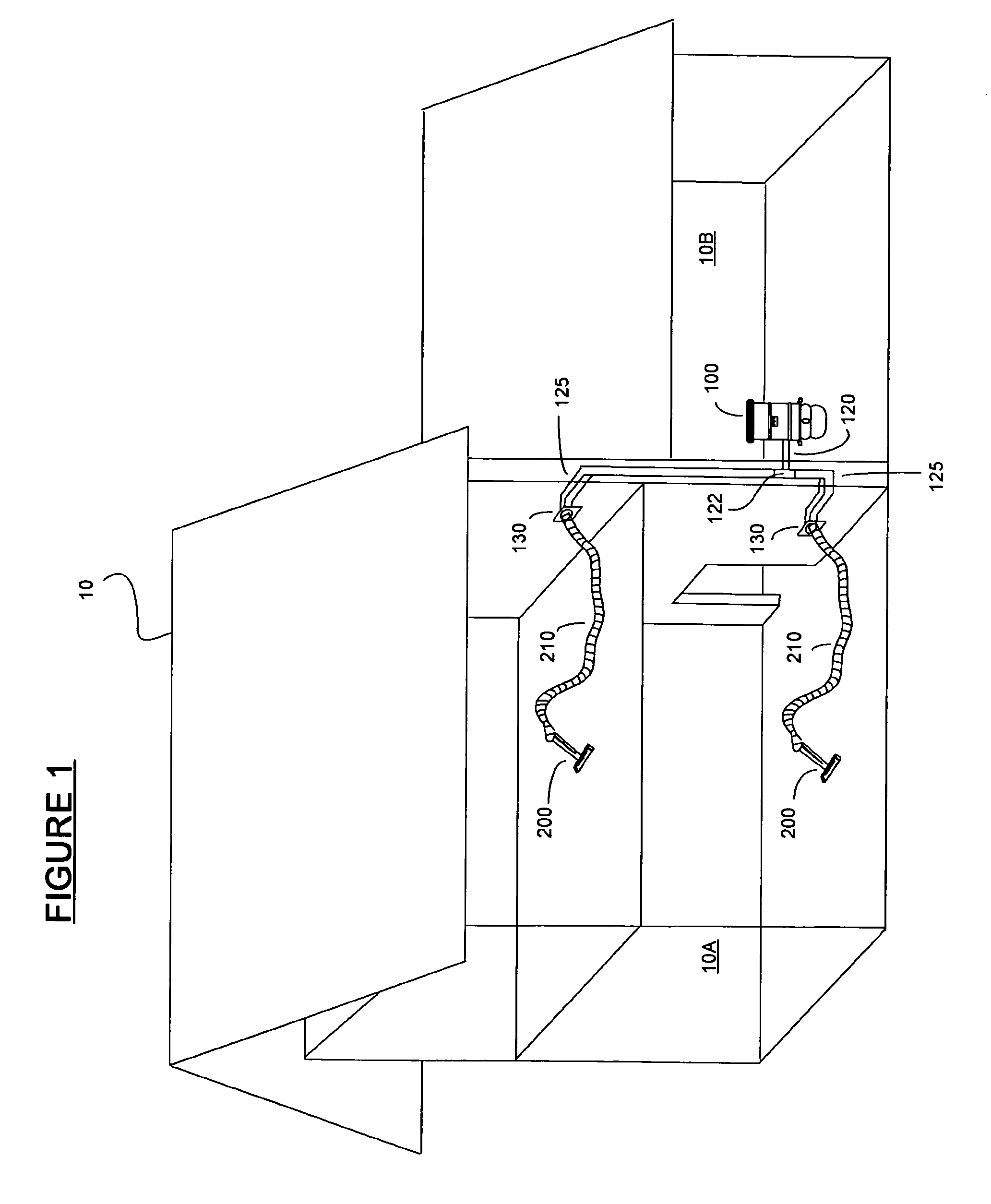

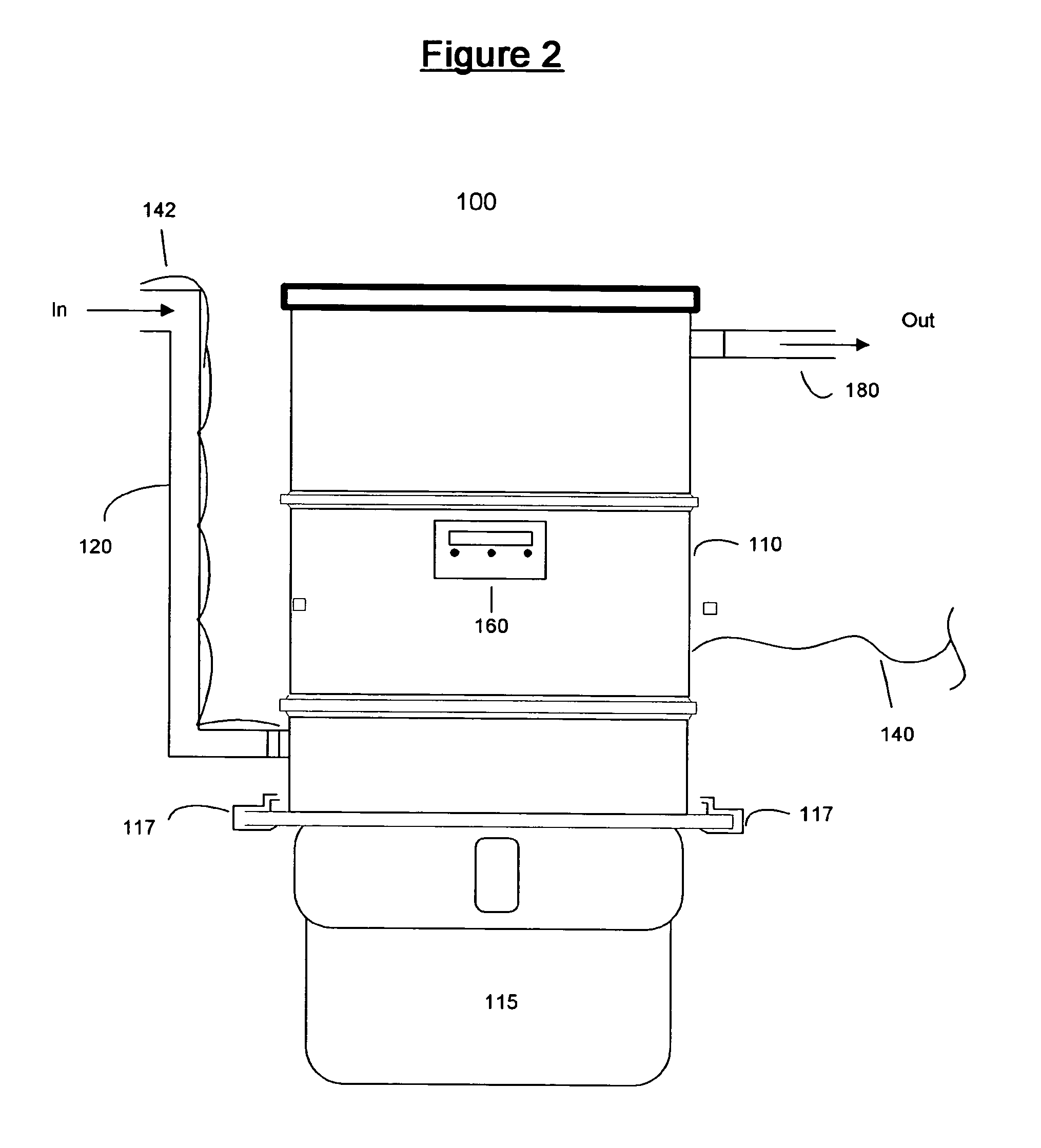

Electronic control system for a vacuum system

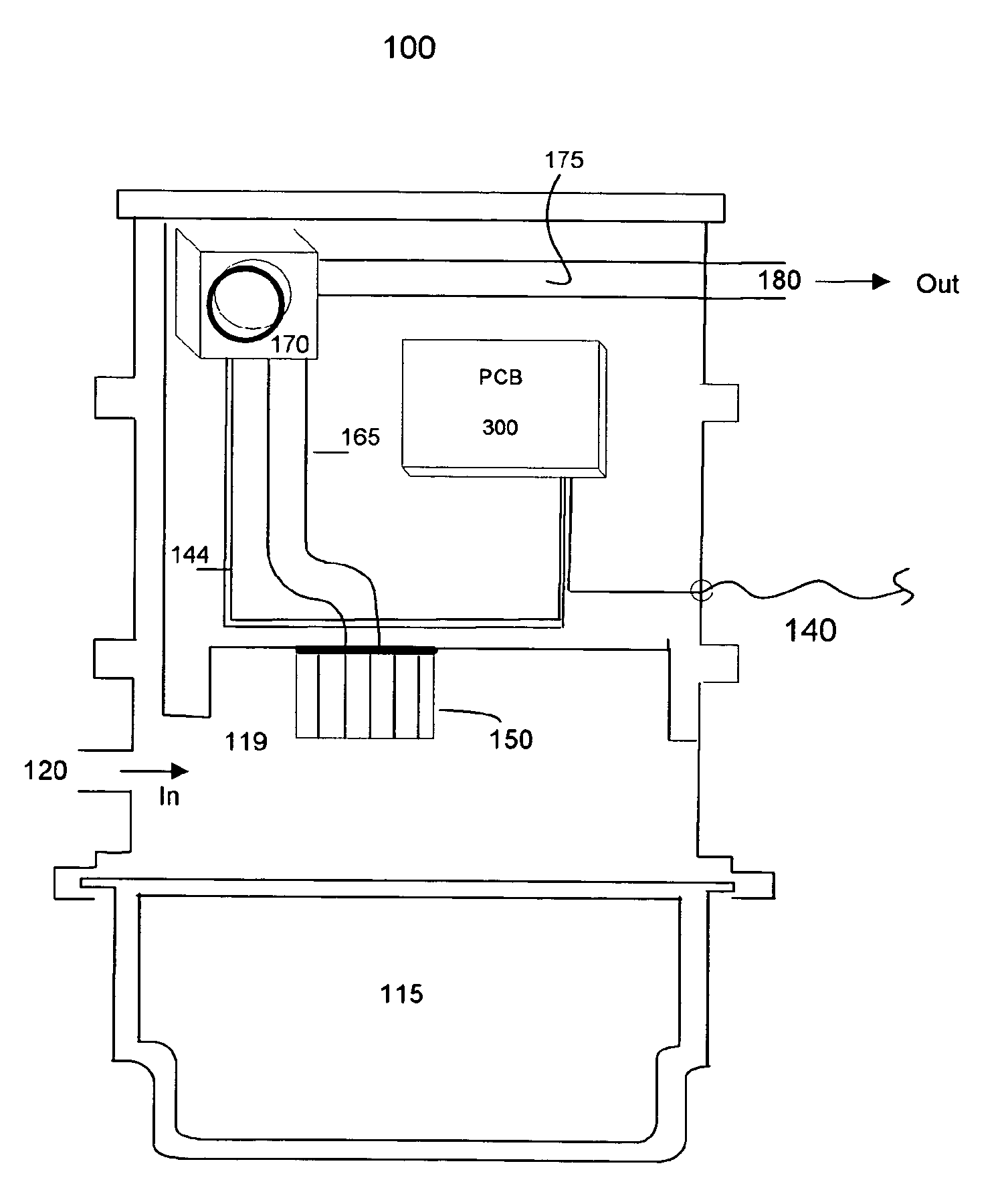

A programmable control unit for a vacuum cleaning system, such as central vacuum cleaning system. A control unit is programmed after manufacture to execute a particular control program for performing various diagnostic and operational functions including user interface, voltage level detecting, voltage monitoring, current monitoring, user interface, power supply control, temperature monitoring, AC line frequency detection, operation data recording, speed control program selection, expansion bus interface and service tool interface. Power control to the vacuum motor is facilitated by the control unit directly through a triode for alternating current (TRIAC). Manufacturing costs are reduced by producing a single programmable control unit that can be programmed with a control program corresponding to a variety of different vacuum cleaning devices across a manufacturer's product line.

Owner:ELECTROLUX HOME CARE PRODS

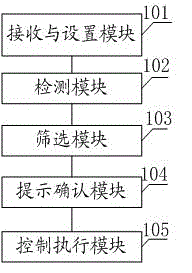

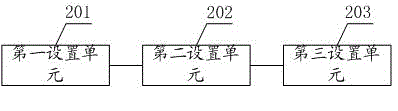

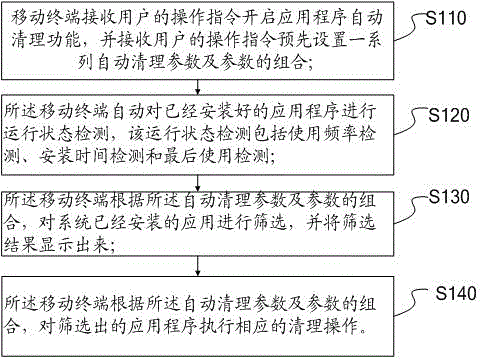

Automatic application program cleaning method and system based on mobile terminal

InactiveCN102945159AWith automatic cleaning functionProgram loading/initiatingControl engineeringApplication procedure

The invention discloses an automatic application program cleaning method and system based on a mobile terminal. The method comprises the following steps: a mobile terminal receives an operation instruction of a user, starts the automatic application program cleaning function, receives the operation construction of user and sets a series of automatic cleaning parameters and a combination of parameters in advance; the mobile terminal executes the operation state detection to the installed application program, wherein the operation state detection comprises using frequency detection, installing time detection and final-using detection; and the mobile terminal screens the application program installed in the system according to the automatic cleaning parameters and the combination of the parameters, displays a screen result, and executes associated cleaning operation to the screened-out application programs according to the result confirmed by the user. According to the invention, the operation state of the application programs in the mobile terminal can be automatically detected out by adding the automatic application program cleaning function in the mobile terminal.

Owner:SHENZHEN WONKATEK NETWORK

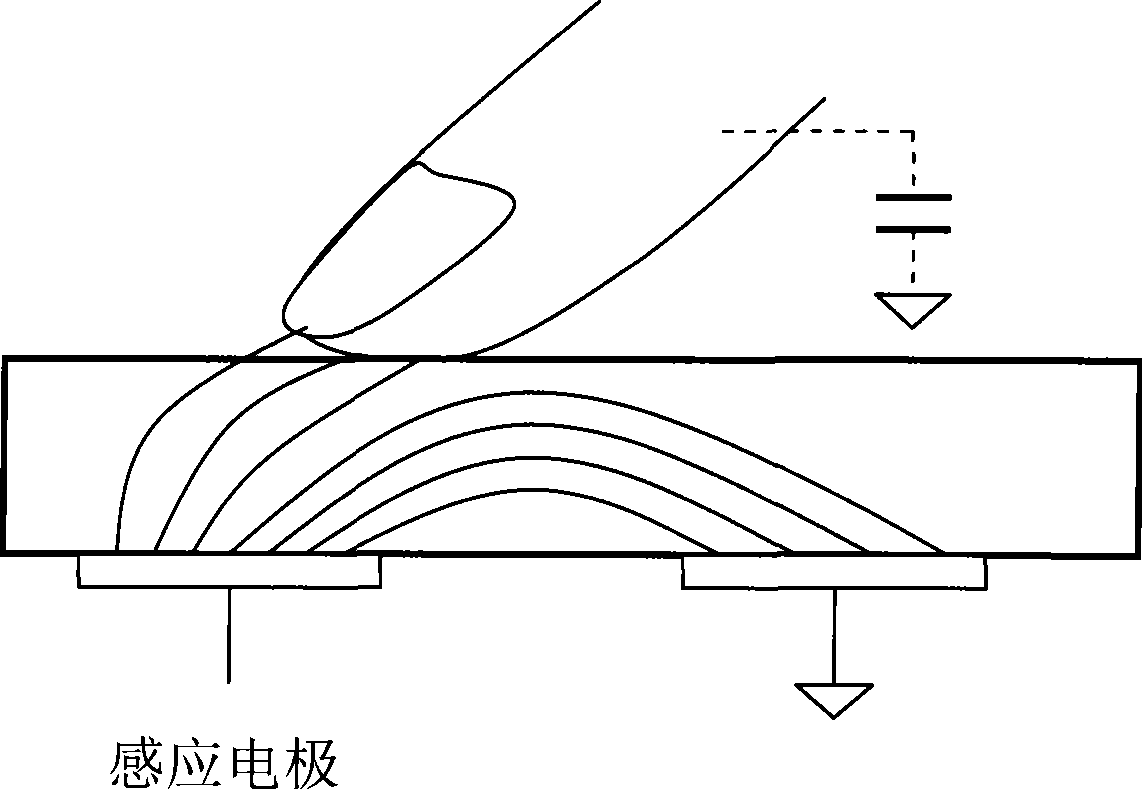

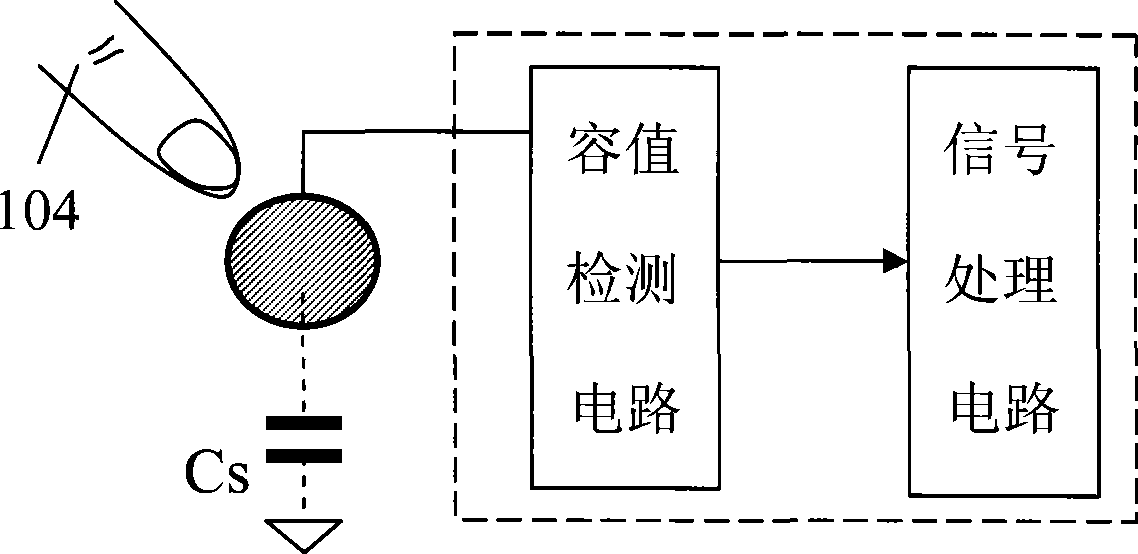

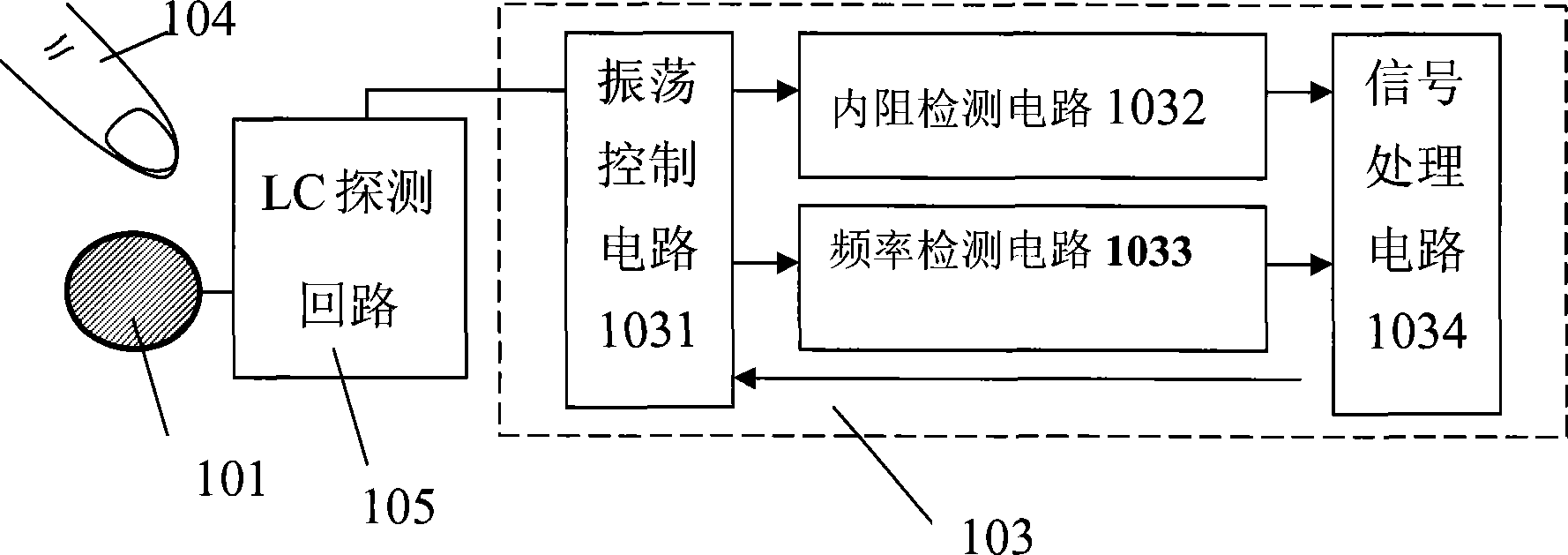

Capacitance touch detection device and detection method thereof

ActiveCN101419522AImprove signal-to-noise ratioSolve the problem of poor water resistance coverageInput/output processes for data processingCapacitanceSignal processing circuits

The invention discloses a capacitance touch detection device; an LC probing loop including an inductive electrode is connected with a touch detection circuit; the touch detection circuit comprises an oscillation control circuit, a frequency detection circuit, an internal resistance detection circuit and a signal processing circuit; the LC probing loop formed by combining the inductive electrode and a sensitive element is connected with the oscillation control circuit; the touch detection circuit is used for probing approach or contact response of the electrode on human body by detecting the resonance frequency and the internal resistance of the LC probing loop. The invention has good capability of anti-water coverage and anti-electromagnetic interference, and can probe the touch action reliably under complicated and rigorous environment.

Owner:SHENZHEN GOODIX TECH CO LTD

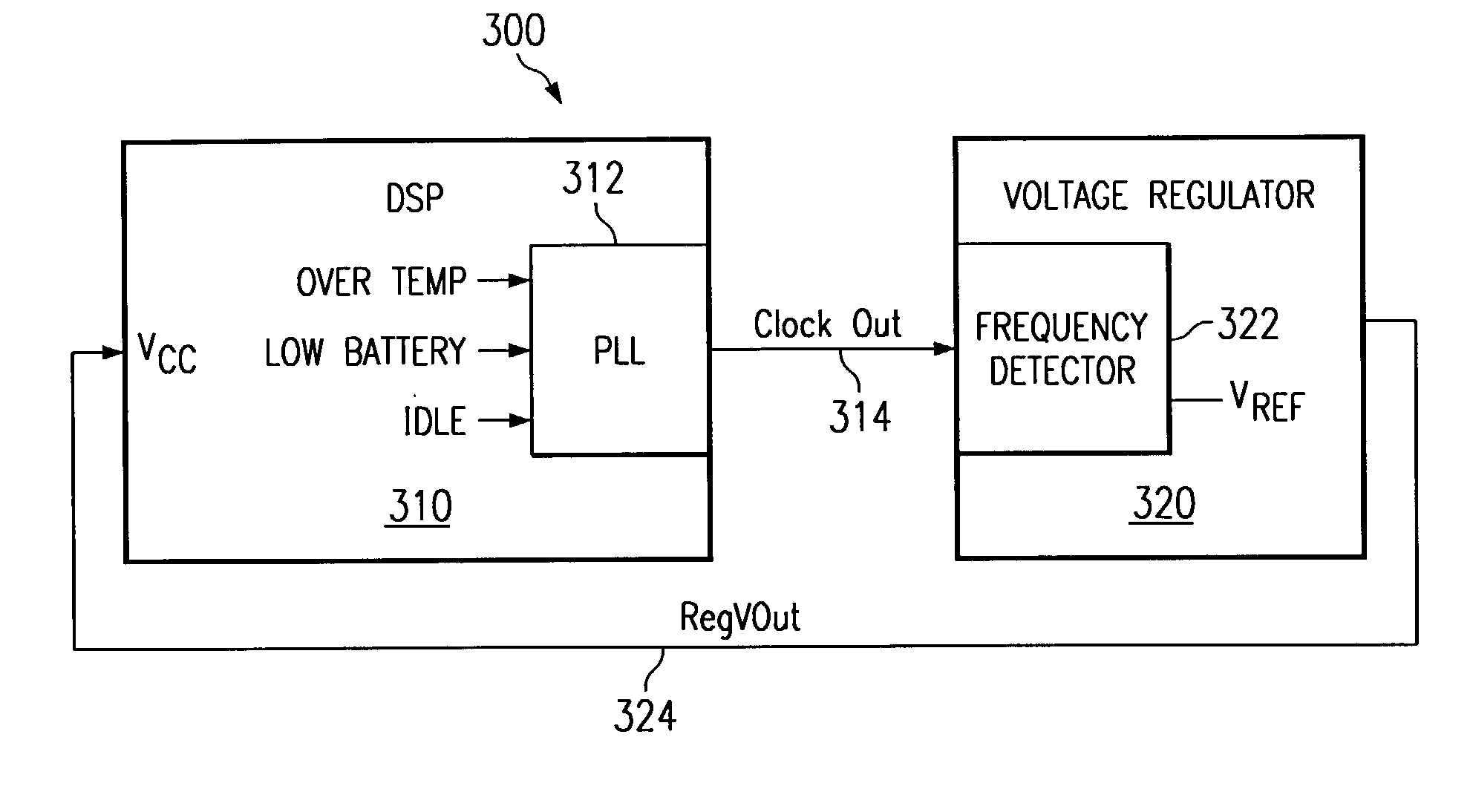

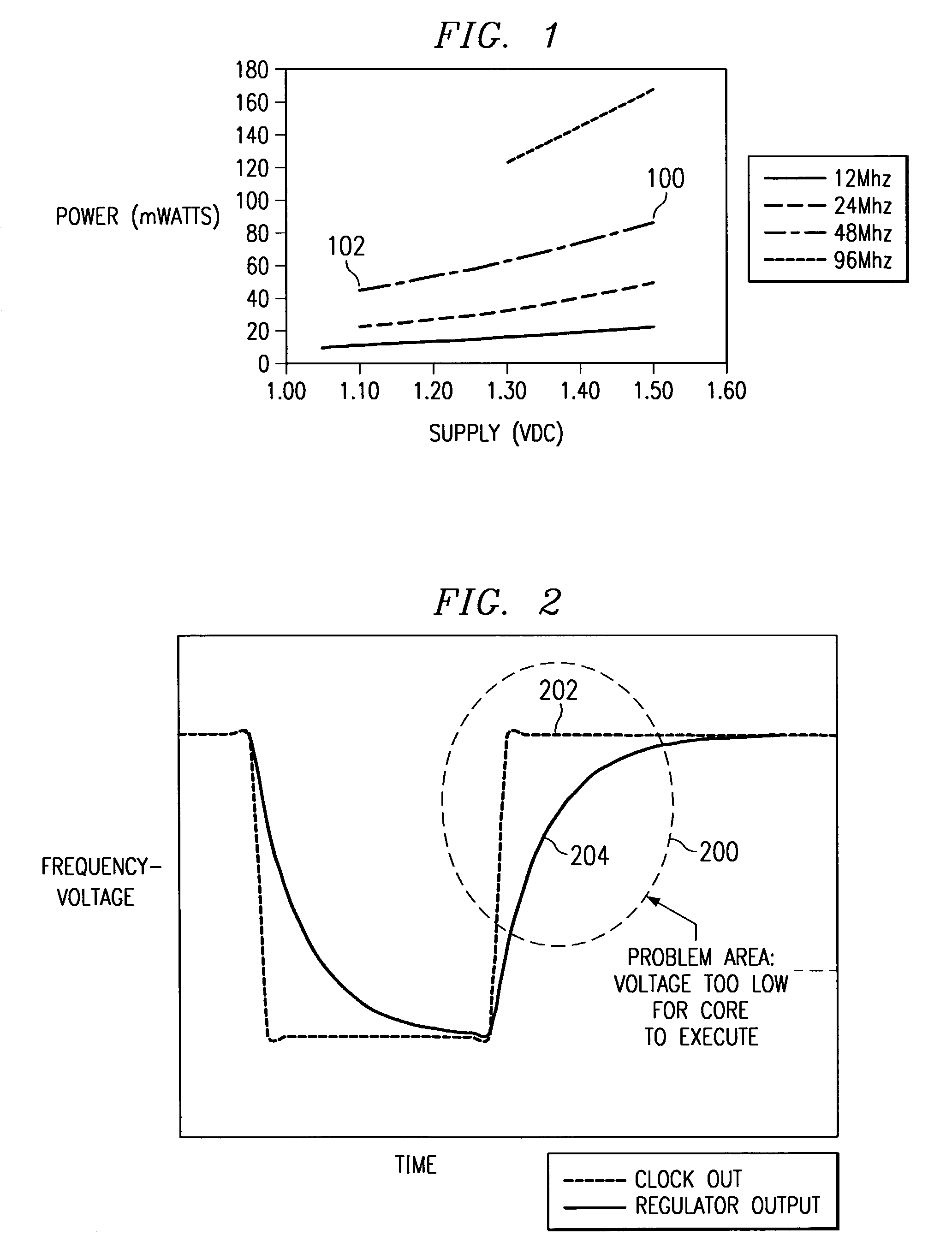

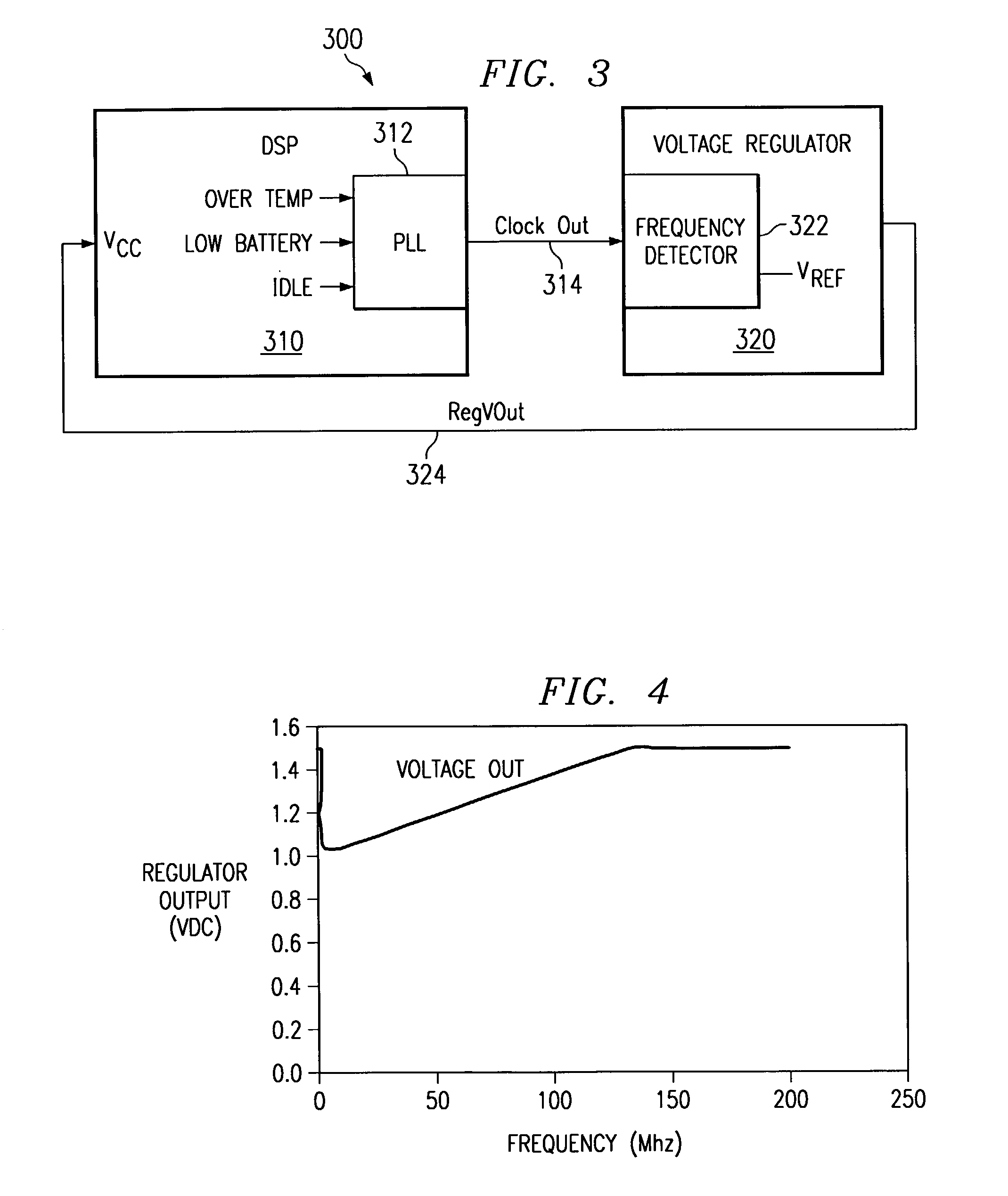

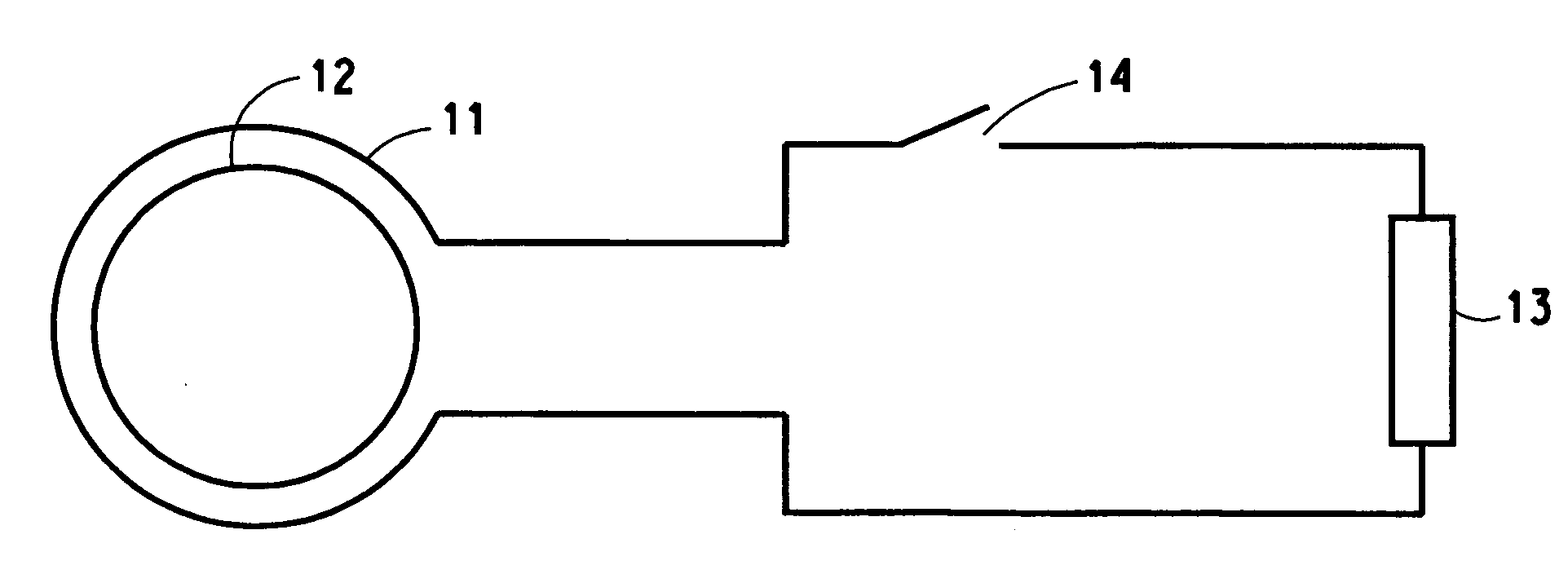

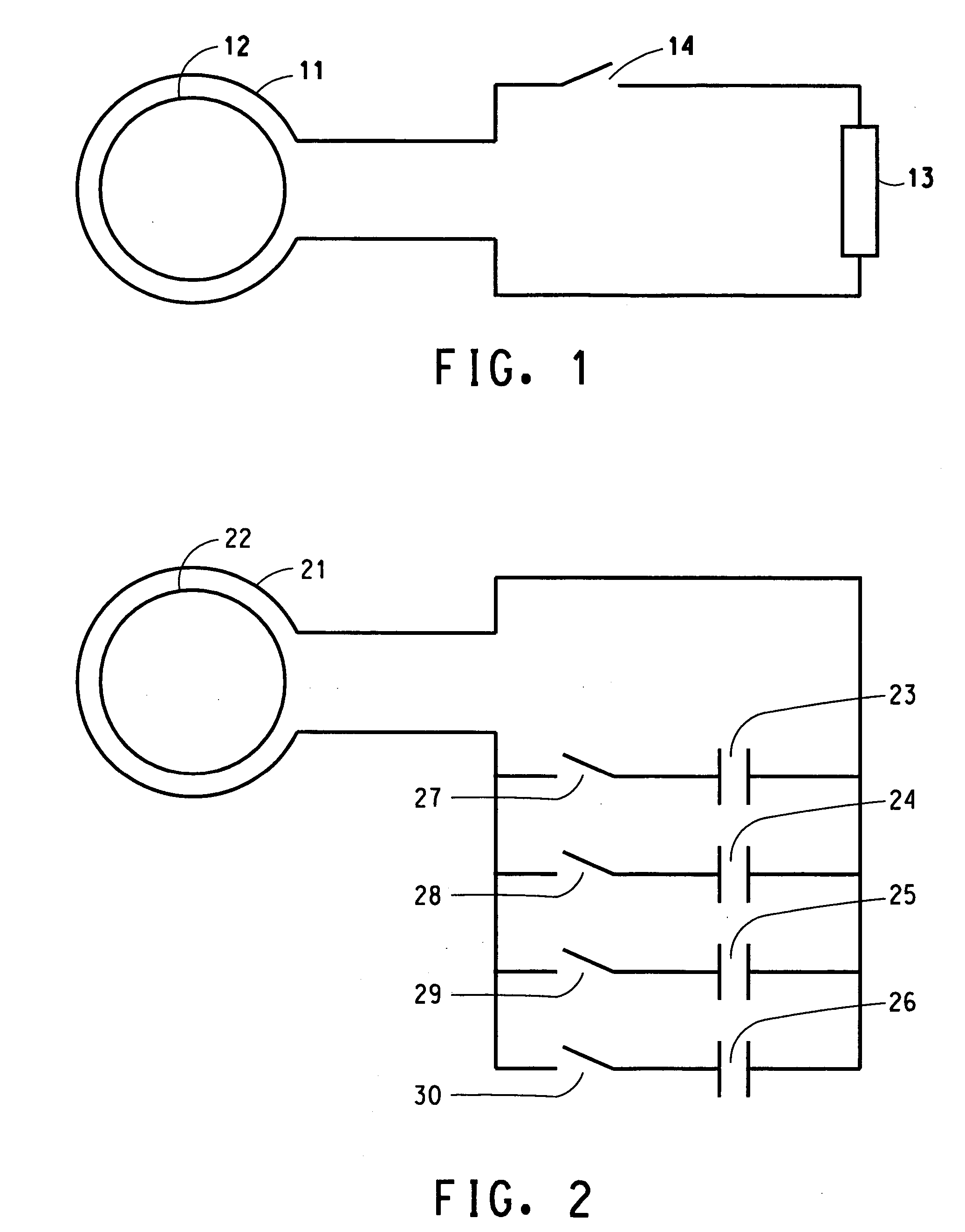

Adjusting voltage supplied to a processor in response to clock frequency

ActiveUS6996730B2Simple methodReduce clock frequencyEnergy efficient ICTVolume/mass flow measurementClock rateVoltage regulation

A method and apparatus for adjusting the clock frequency and voltage supplied to an integrated circuit is provided. A request signal is sent to the clock, and in response, the clock lowers the clock frequency supplied to the integrated circuit. A frequency detection circuit monitors the clock signal and causes a voltage regulator to reduce the voltage supplied to the integrated circuit in response to the reduced clock frequency. Similarly, a request signal is sent to the clock, and in response, the clock raises the clock frequency supplied to the integrated circuit. The frequency detection circuit monitors the clock signal and causes a voltage regulator to raise the voltage supplied to the integrated circuit in response to the increased clock frequency. The slew rate of the clock is controlled so that at least a minimum required voltage for each operating frequency is provided while the clock frequency is being changed. In this manner, reliable operation of the processor is assured while the clock speed and operating voltage are being changed.

Owner:TEXAS INSTR INC

Frequency detection system comprising circuitry for adjusting the resonance frequency of a high temperature superconductor self-resonant coil

InactiveUS20060012371A1Magnetic field measurement using superconductive devicesElectric/magnetic detectionElectrical conductorResonance

The use of a circuit to adjust the resonance frequency of a high temperature superconductor self-resonant transmit, receive, or transmit and receive coil results in improved performance. The circuit is useful in a frequency detection system, especially in a nuclear quadrupole resonance detection system.

Owner:PENN STATE RES FOUND

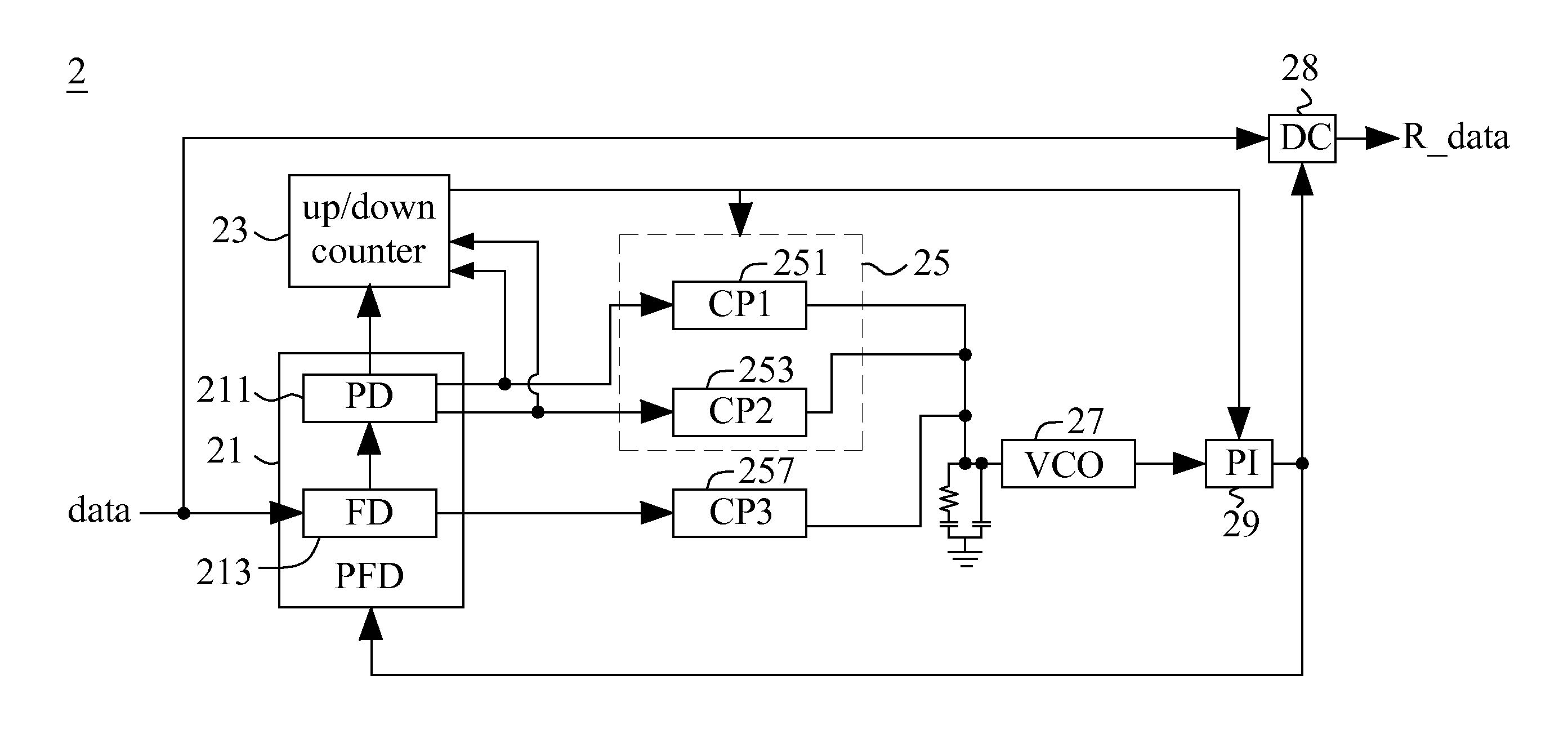

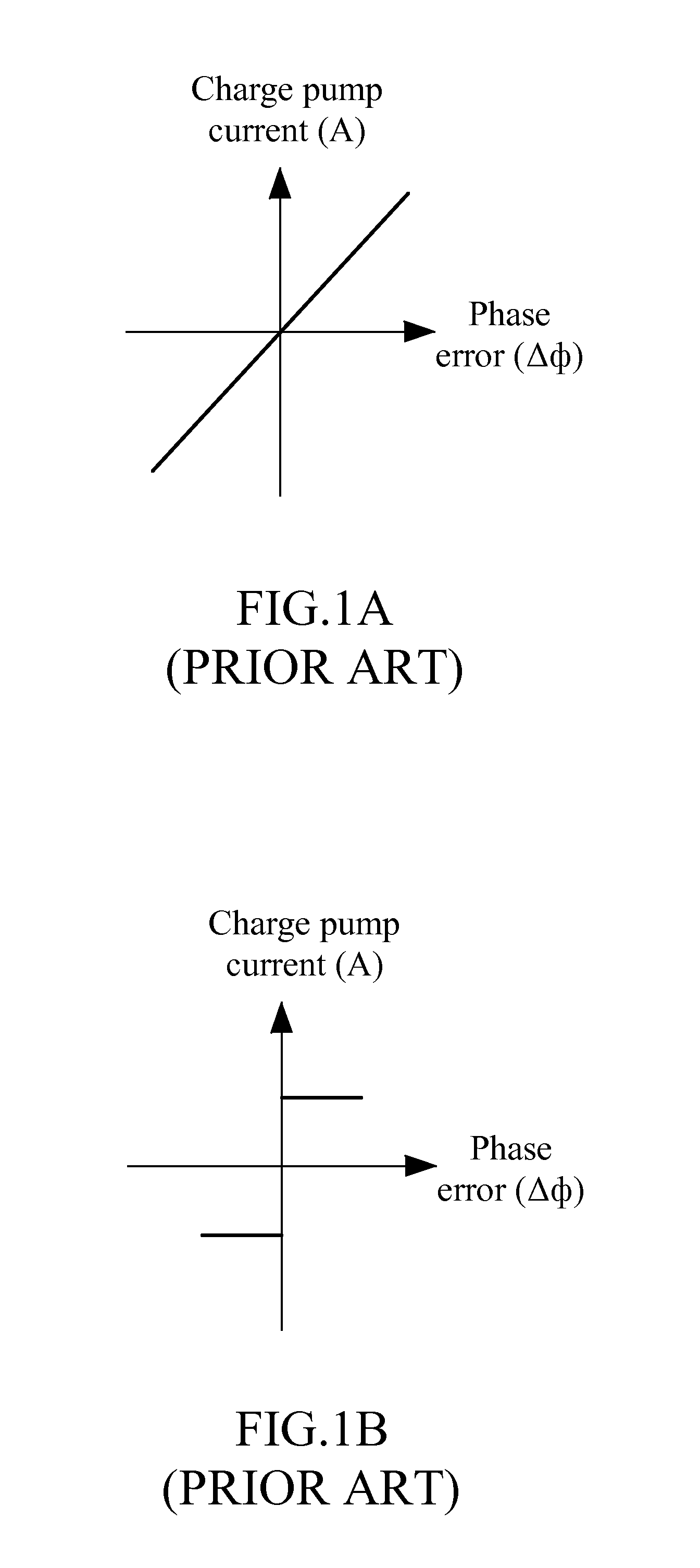

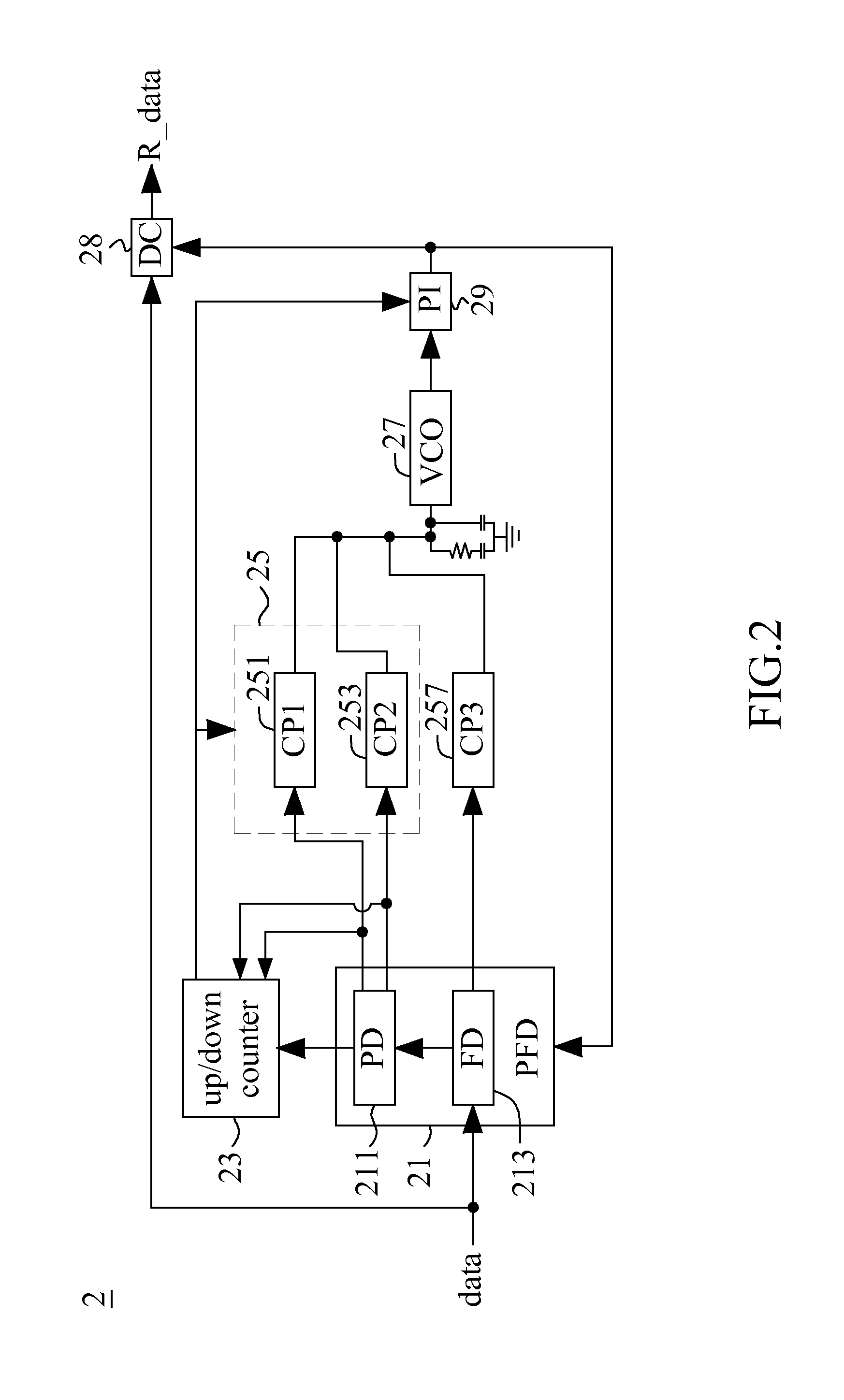

Clock and data recovery (CDR) architecture and phase detector thereof

ActiveUS20130108001A1Simplify Logic DesignSave powerPulse automatic controlAngle demodulation by phase difference detectionPhase detectorData signal

A clock and data recovery (CDR) architecture which includes a frequency detector, a phase detector, a phase charge pump circuit, a frequency charge pump circuit and a voltage controlled oscillator is provided. The phase detector is configured to only include four AND gates to receive and evaluate the intermediate signals, generated by the frequency detector, and accordingly generate a phase control signal. The voltage controlled oscillator is configured to output a plurality of clock signals with different phases according to the current signals outputted from the phase and frequency charge pump circuits, and select at least one of the plurality of clock signals with different phases for sampling a data signal.

Owner:NCKU RES & DEV FOUND +1

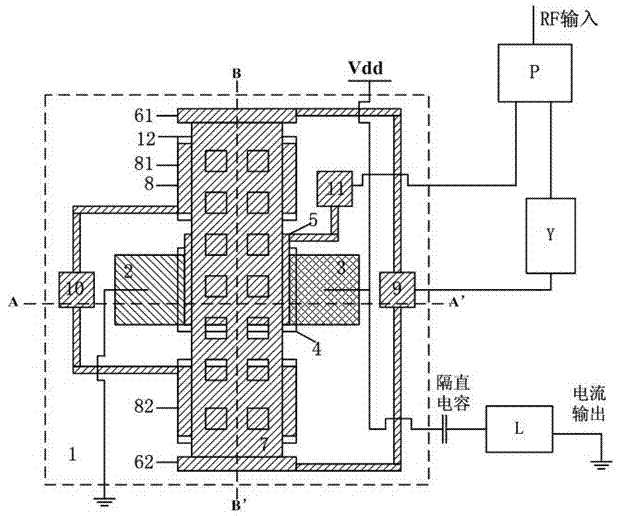

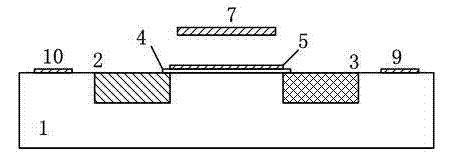

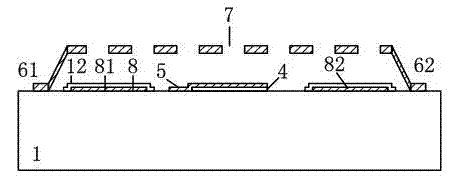

Micromechanical silicon-based clamped beam-based frequency detector and detection method

InactiveCN102735925APlay the role of frequency detectionFrequency measurement arrangementLow-pass filterEngineering

The invention discloses a micromechanical silicon-based clamped beam-based frequency detector and a detection method. The frequency detector comprises a power divider (P), a 90-degree phase shifter (Y), a low-pass filter (L) and a silicon-based metal-oxide-semiconductor field effect transistor; and the power divider is used for receiving a microwave signal to be detected and dividing the microwave signal to be detected into two branch signals with the same amplitude and phase. The detection method includes the following steps: when a direct-current offset is loaded on a first pull-down electrode (81) and a second pull-down electrode (82) and a clamped beam (7) is pulled down and is in contact with a grid (5), two channels of microwave signals are simultaneously loaded on the grid (5), the silicon-based metal-oxide-semiconductor field effect transistor is in a frequency detection state, the saturation current output between a source (2) and a drain (3) contains the current component of the frequency information of the signal to be detected, and by detecting the magnitude of saturation current, frequency detection is finally fulfilled. The structure of the frequency detector is simple, and measurement is easy.

Owner:SOUTHEAST UNIV

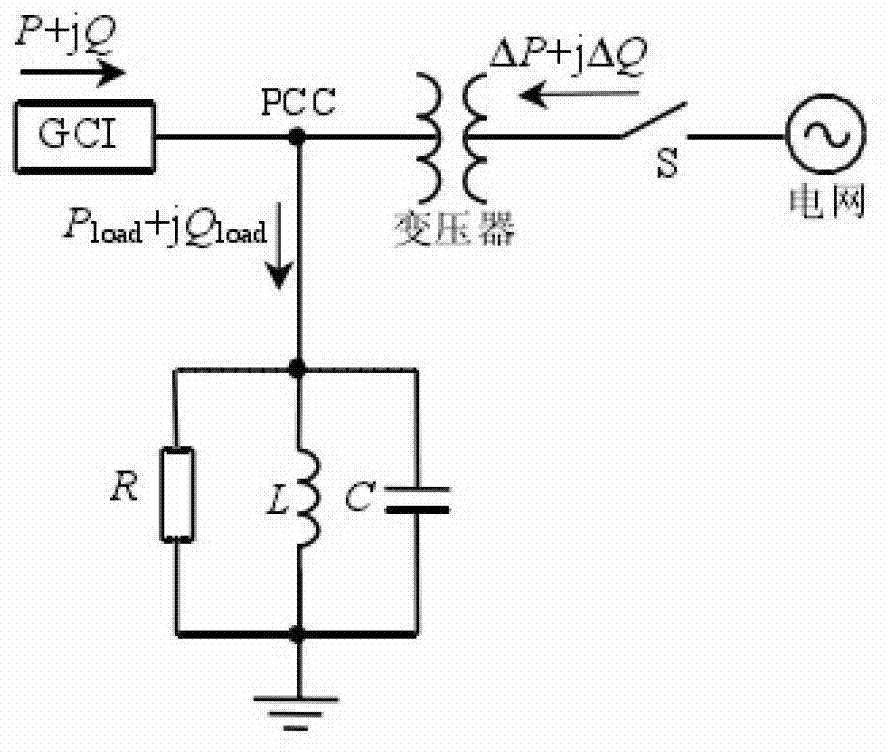

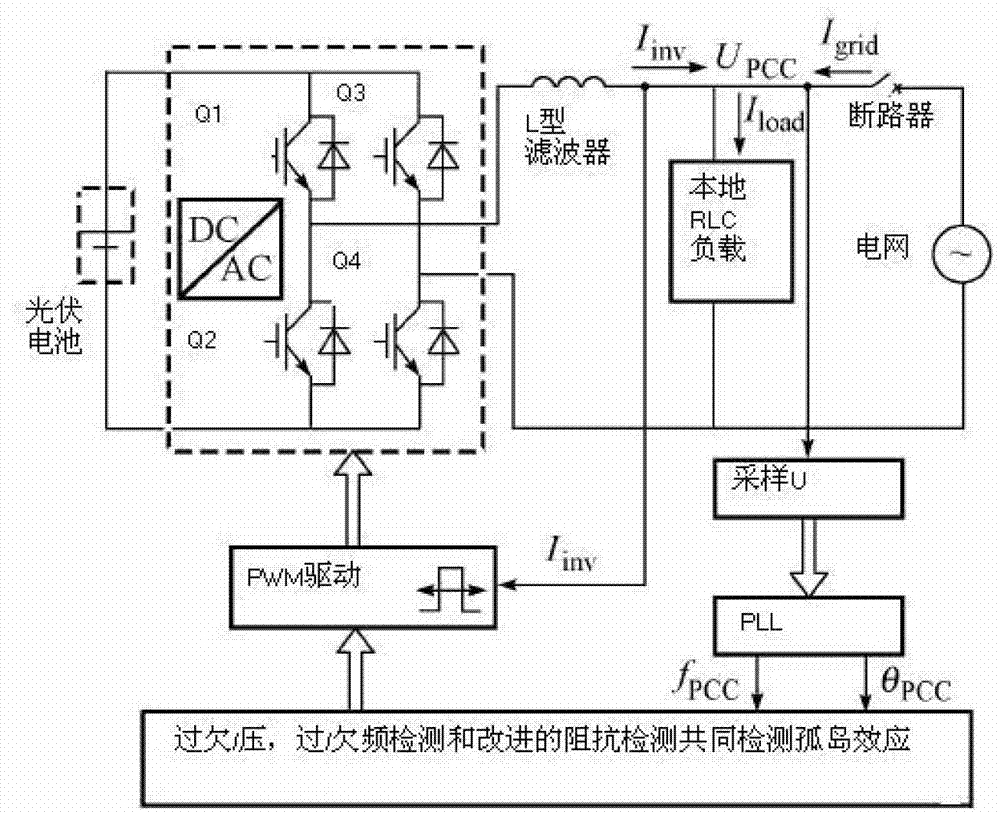

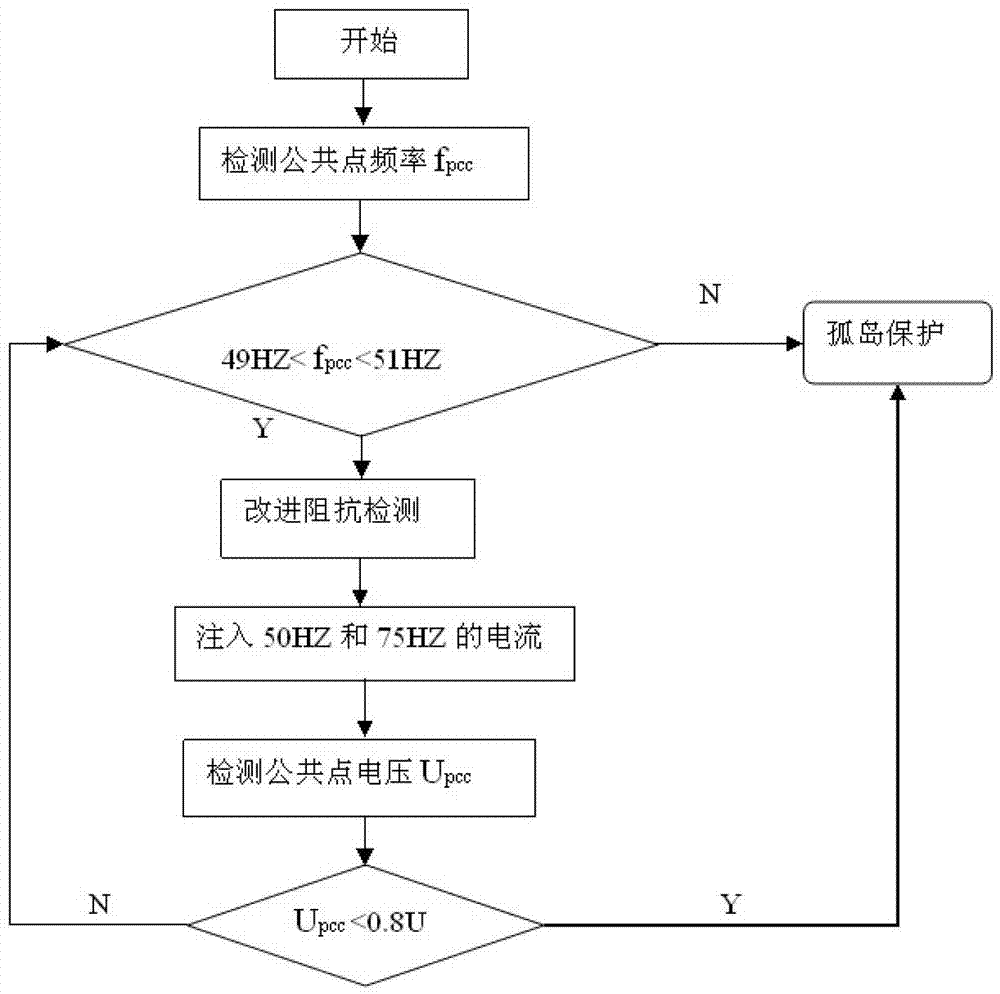

Island detection method of photovoltaic grid-connected system

InactiveCN103091578ALess detectableReduce Harmonic DistortionElectrical testingPower qualityIslanding

The invention relates to an island detection method of a photovoltaic grid-connected system. In views of the problems that independently-adopted passive detection mode is effective only when effective when mismatching degrees of source and load are large and a large non-detection zone (NDZ) can be accordingly provided; and when an active detection mode is independently-adopted, the system is disturbed, and therefore the disturbance results in instability of the system, and accordingly over-voltage / under-voltage is provided. An over-frequency / under-frequency detection method is combined with an improved impedance detection method to conduct island detection to the system, and therefore the NDZ is reduced to a minimum, quality of electric energy is improved and total harmonic distortion (THD) is reduced.

Owner:TIANJIN UNIVERSITY OF TECHNOLOGY