Patents

Literature

54results about How to "Simplify Logic Design" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

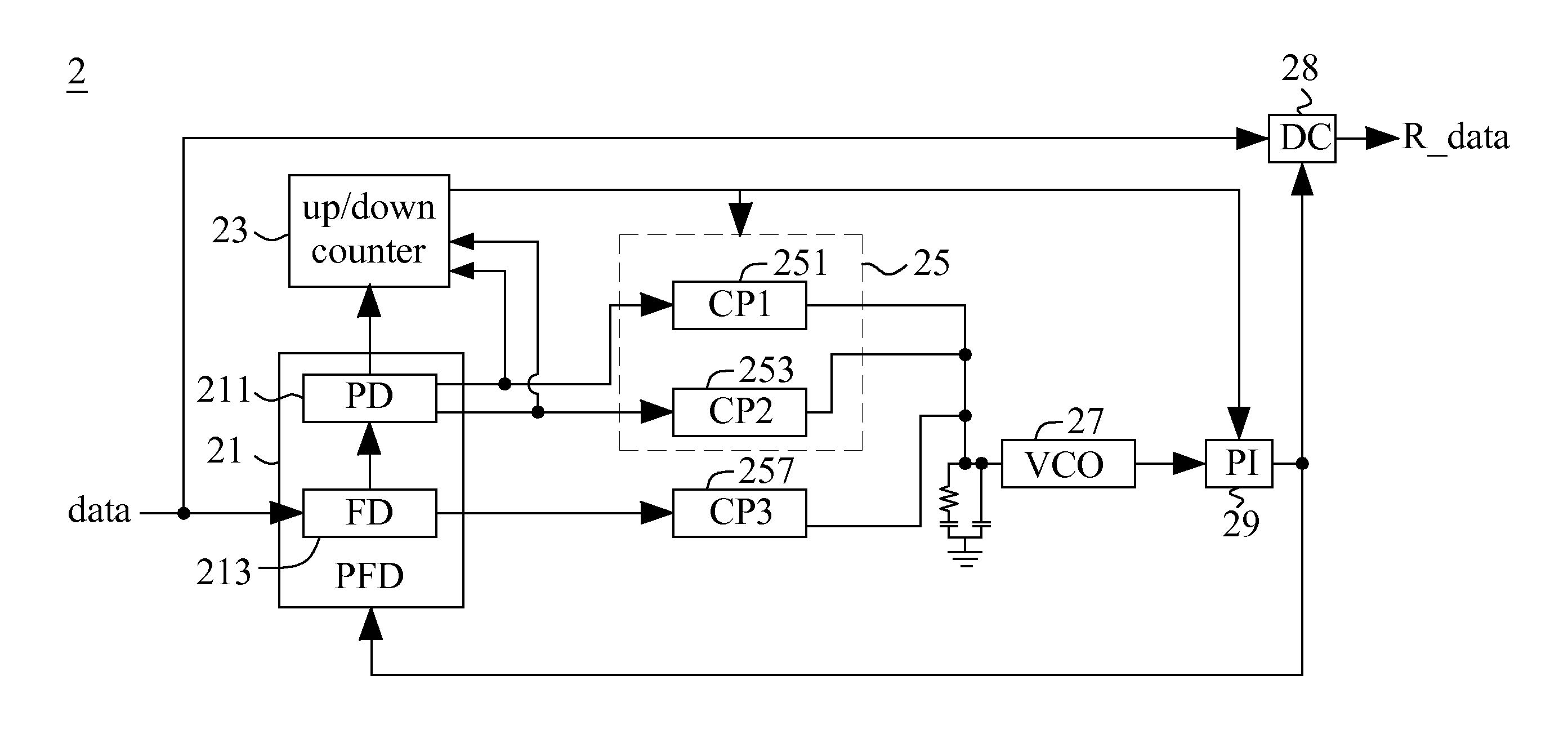

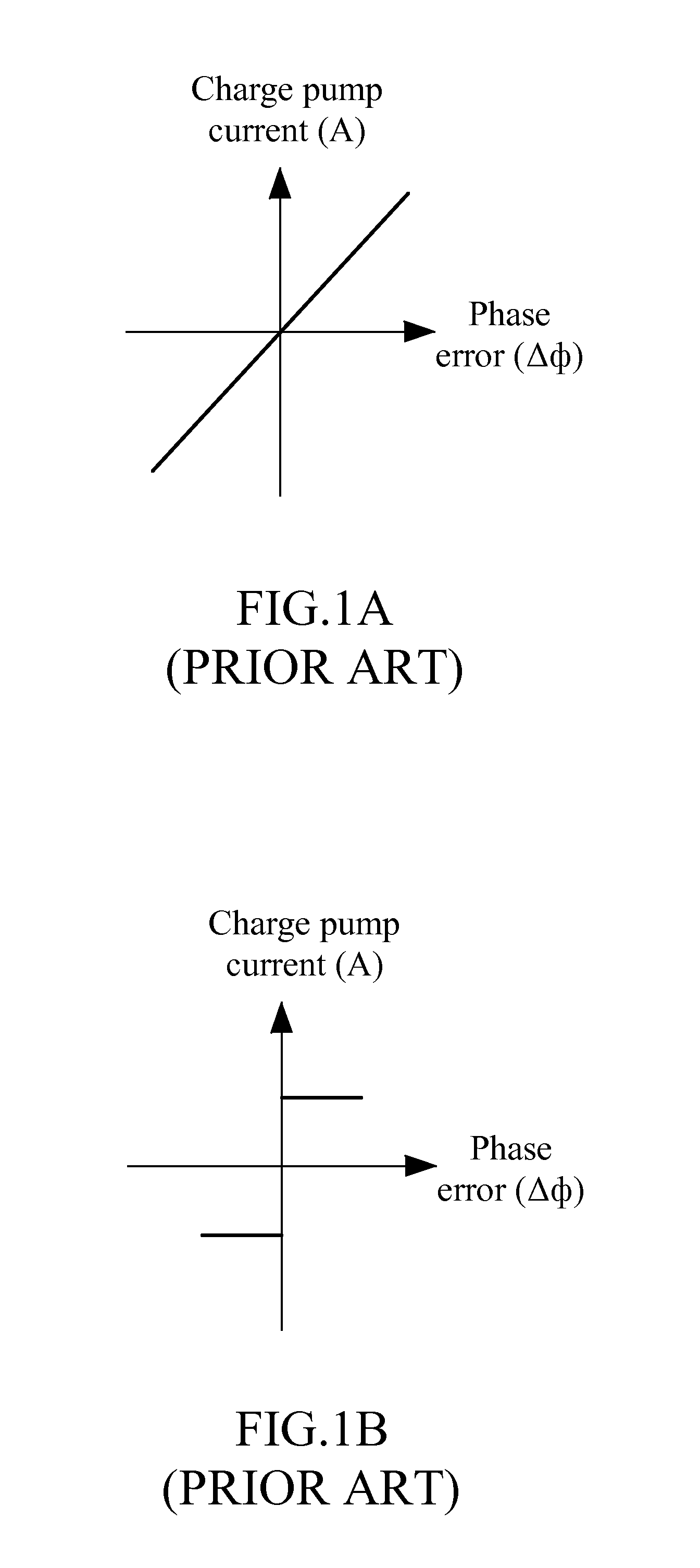

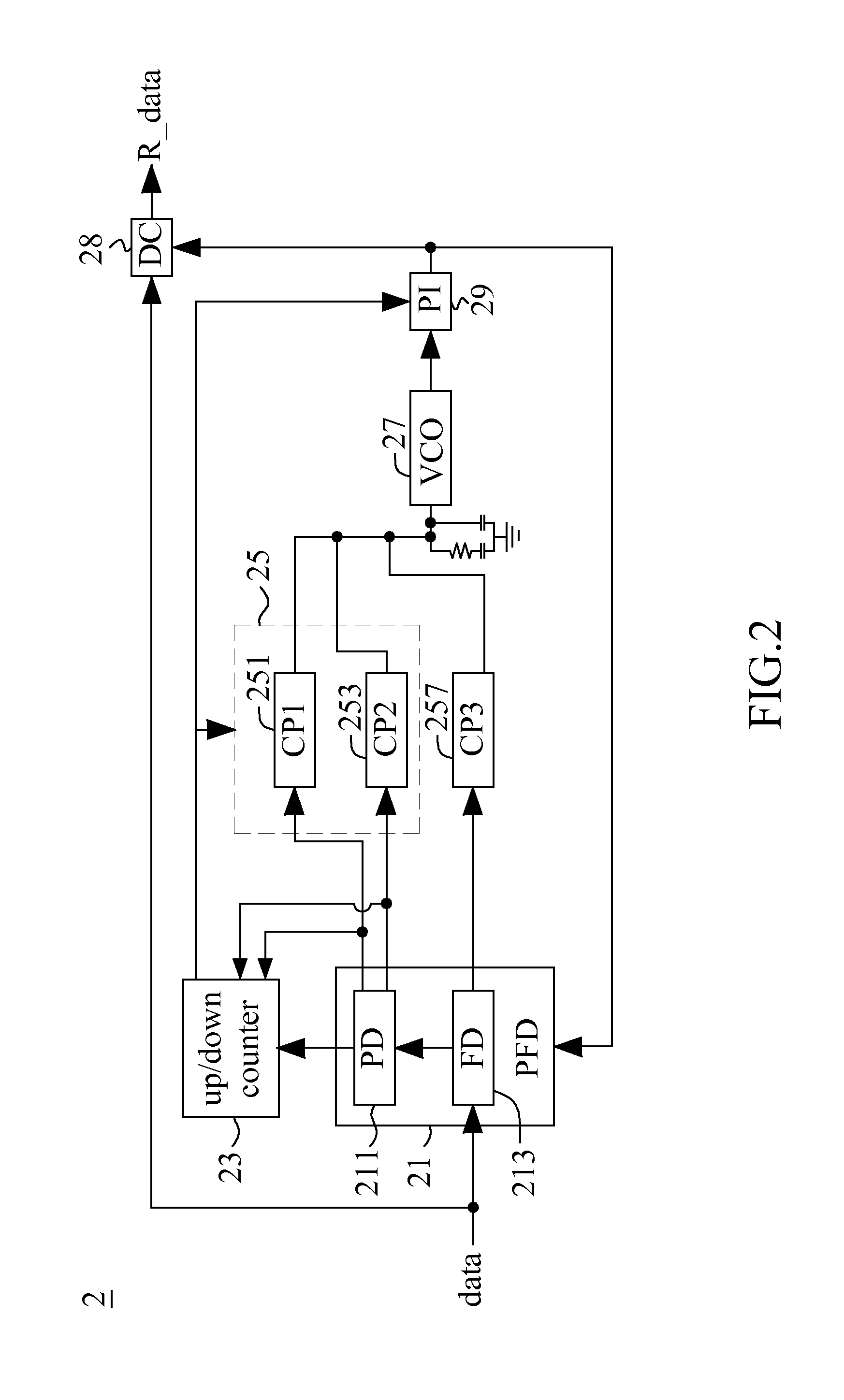

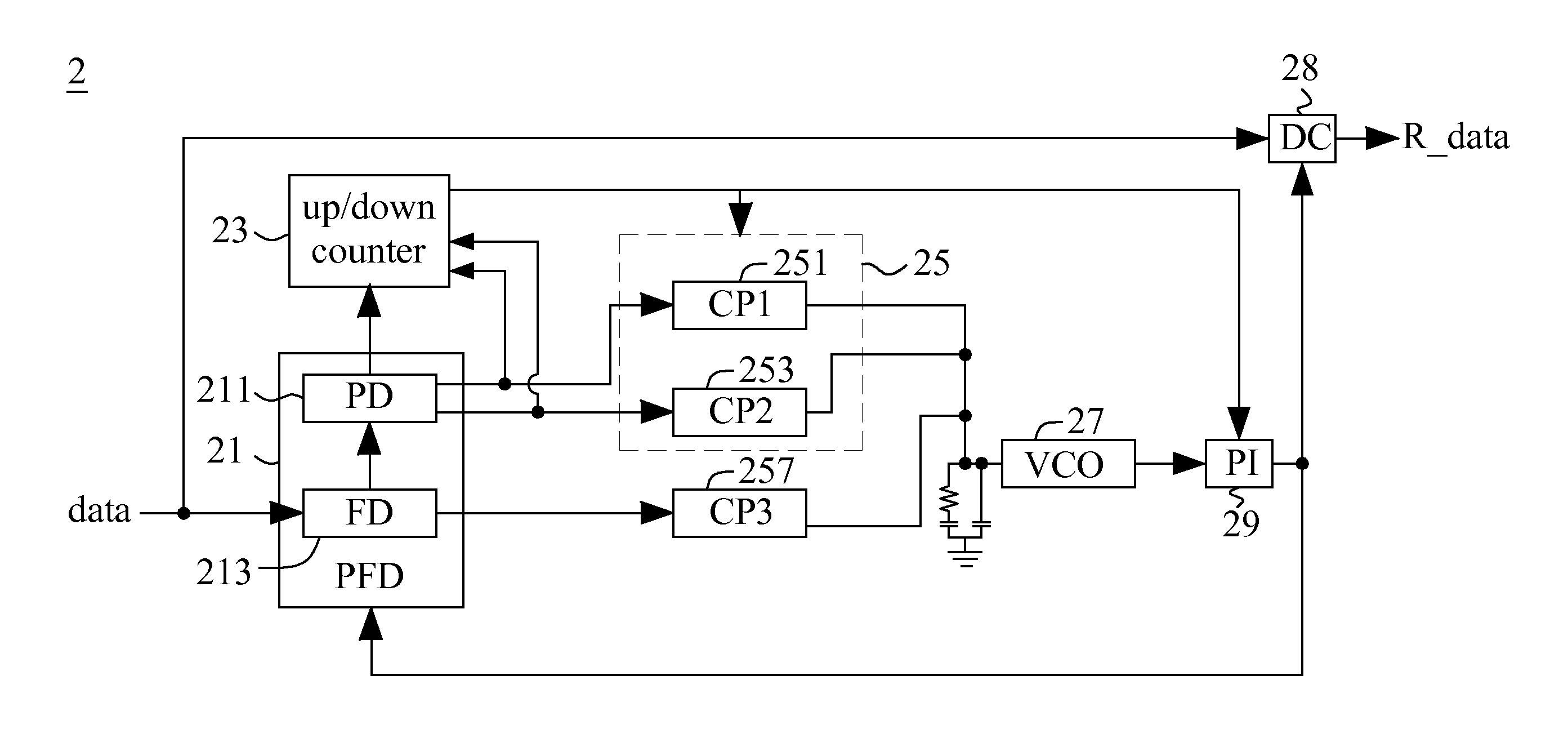

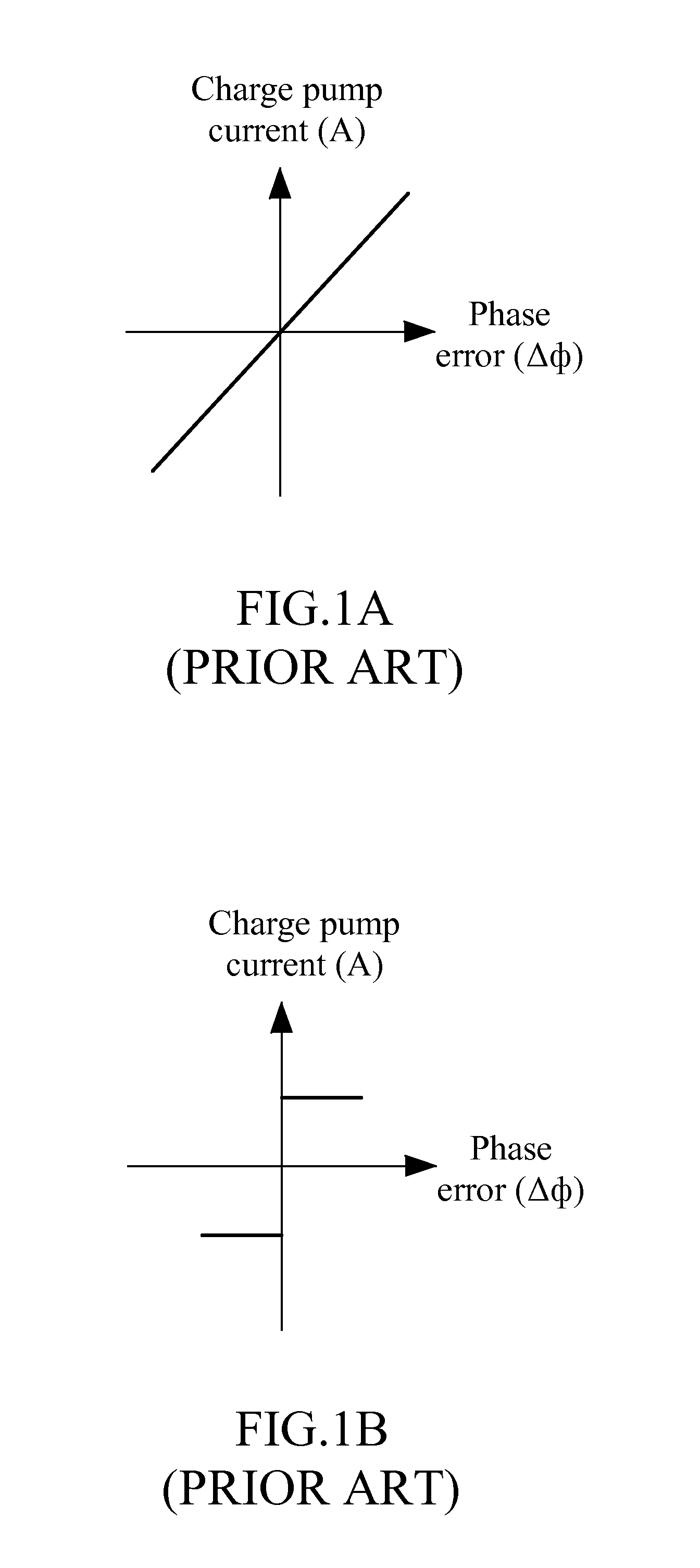

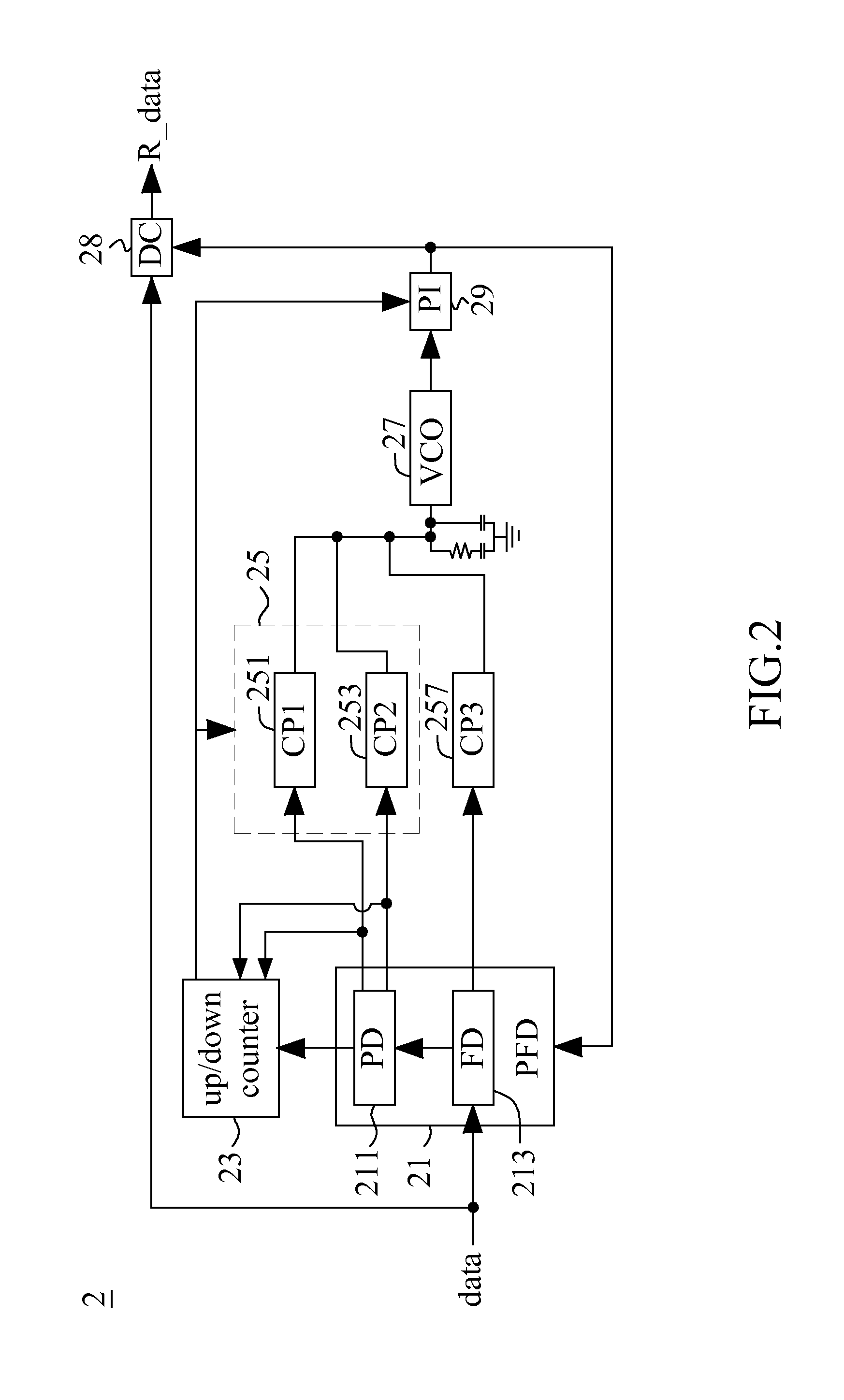

Clock and data recovery (CDR) architecture and phase detector thereof

ActiveUS20130108001A1Simplify Logic DesignSave powerPulse automatic controlAngle demodulation by phase difference detectionPhase detectorData signal

A clock and data recovery (CDR) architecture which includes a frequency detector, a phase detector, a phase charge pump circuit, a frequency charge pump circuit and a voltage controlled oscillator is provided. The phase detector is configured to only include four AND gates to receive and evaluate the intermediate signals, generated by the frequency detector, and accordingly generate a phase control signal. The voltage controlled oscillator is configured to output a plurality of clock signals with different phases according to the current signals outputted from the phase and frequency charge pump circuits, and select at least one of the plurality of clock signals with different phases for sampling a data signal.

Owner:NCKU RES & DEV FOUND +1

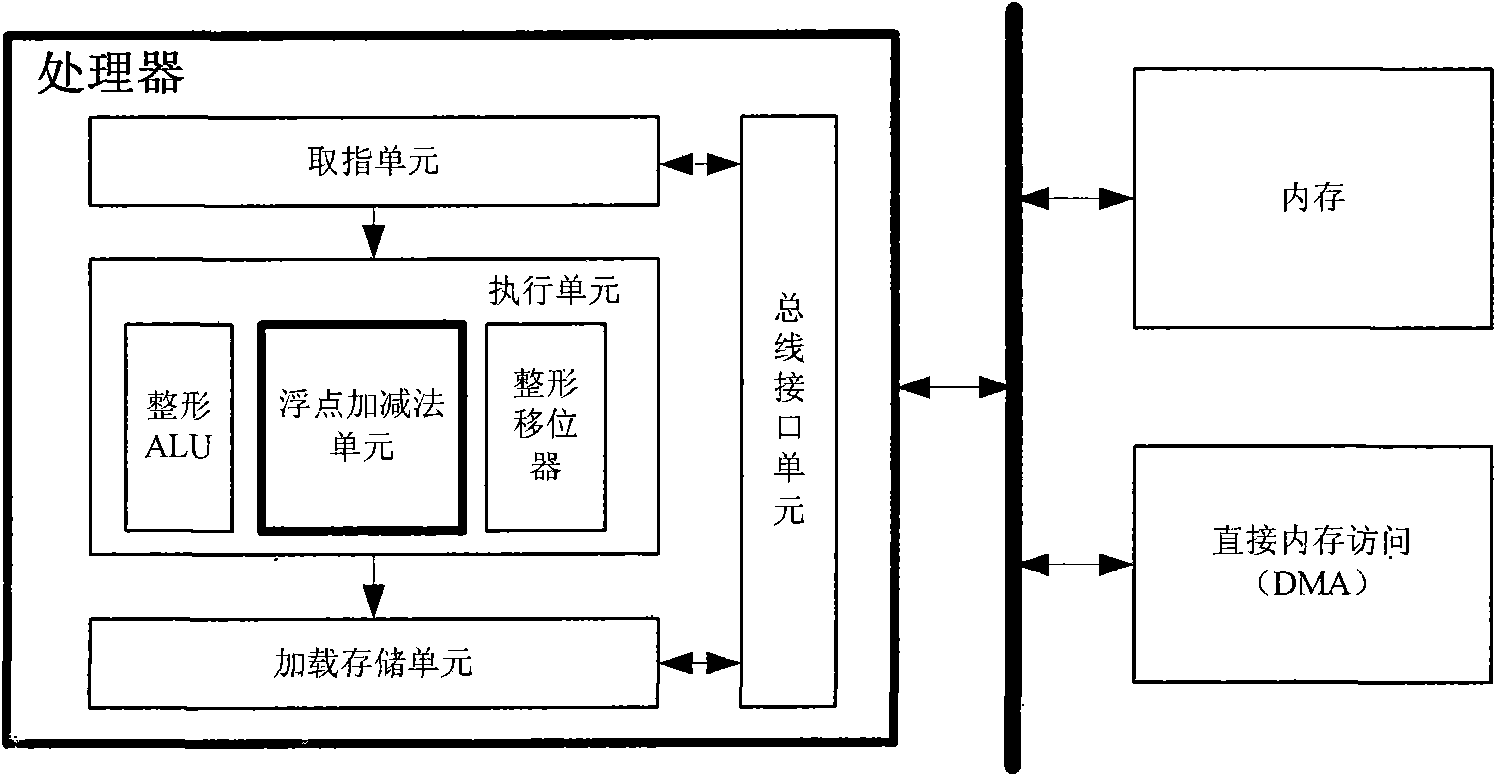

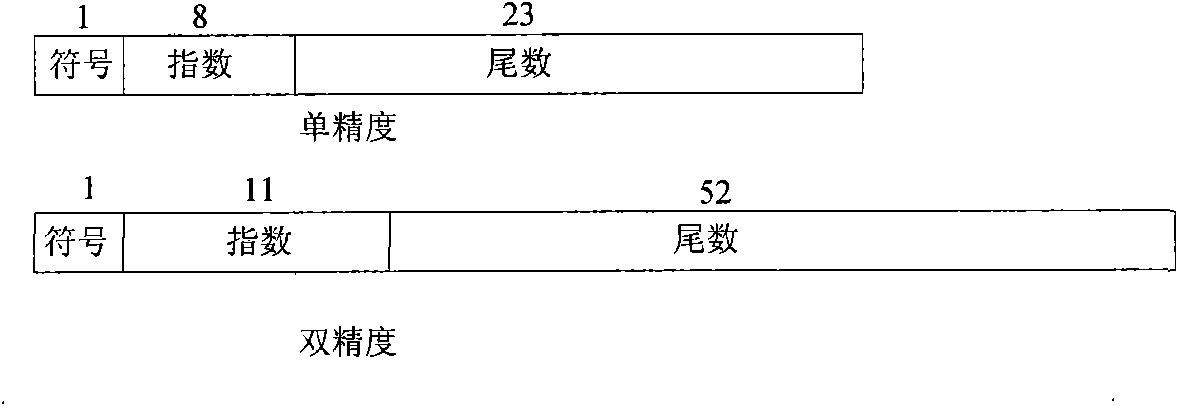

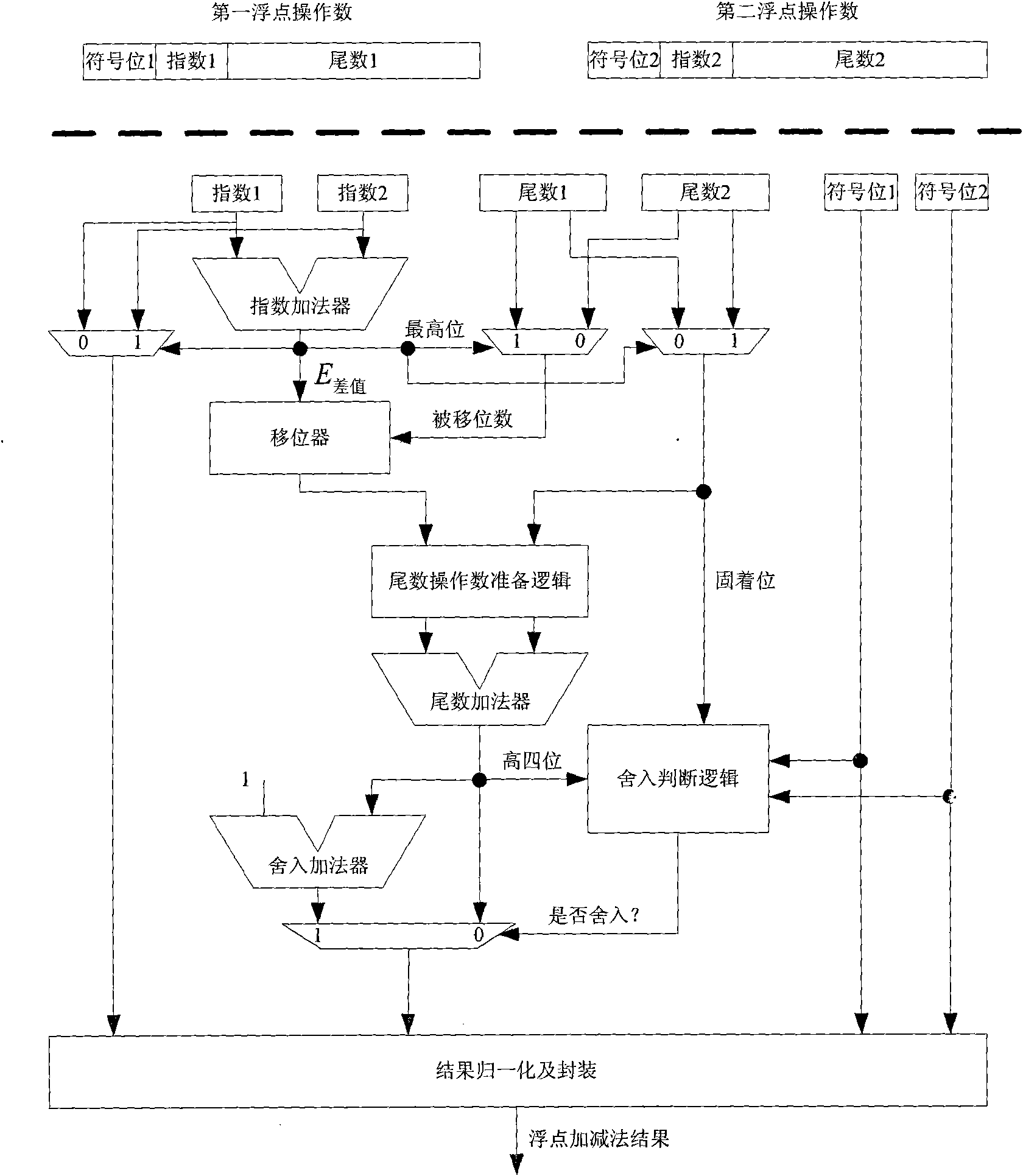

Floating point addition device based on complement rounding

InactiveCN101650642AAvoid preparationAvoid rounding judgment logicComputation using non-contact making devicesLogic complexityRounding

The invention relates to a floating point addition device based on complement rounding, which supports the floating point addition operation and the floating point subtraction operation. The floatingpoint addition device comprises an exponent adder, a mantissa shifter, a mantissa operand preparation logic unit, a mantissa adder, a rounding judgment logic unit and a rounding adder, wherein the mantissa operand preparation logic unit is used for processing the mantissa operand according to sign bits and the exponent difference of the first floating point operand and the second floating point operand, the rounding judgment logic unit is used for executing the uniform rounding judgment on a mantissa addition result, judging the positive and the negative of the mantissa sum according to the highest bit output by the mantissa adder, determining a constant bit for the rounding judgment according to the highest four bits output by the mantissa adder, and unifying original code rounding plus 1judgment logic and complement rounding plus 0 judgment logic; and the rounding adder is used for rounding the mantissa addition result of the floating point and finishing the code extraction and complement operation to the mantissa sum. The invention has the uniform mechanism, avoids the special complex mantissa operand preparation and rounding judgment logic of the floating point addition, and reduces the logic complexity.

Owner:C SKY MICROSYST CO LTD

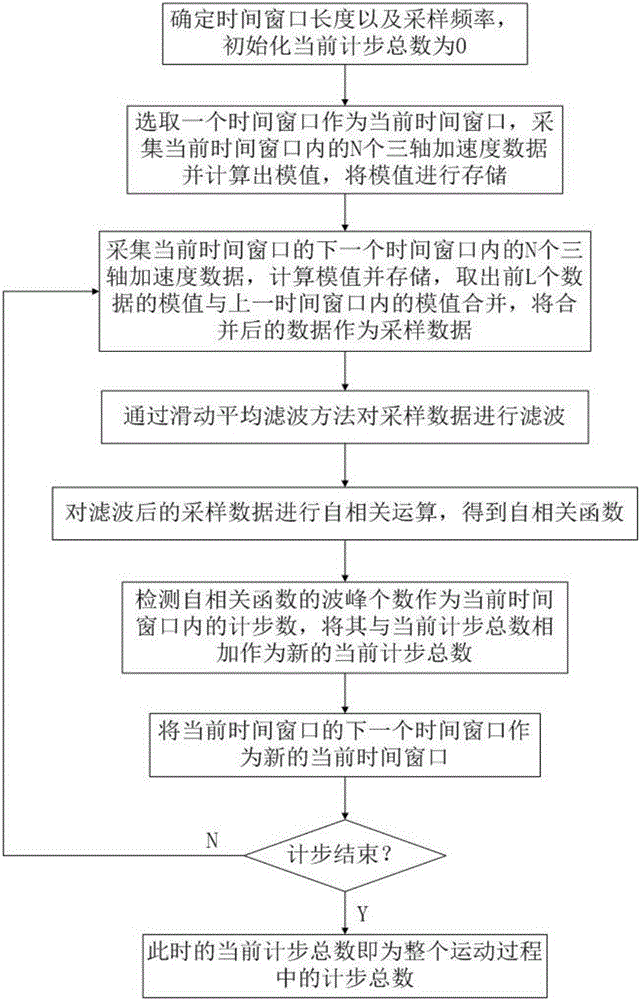

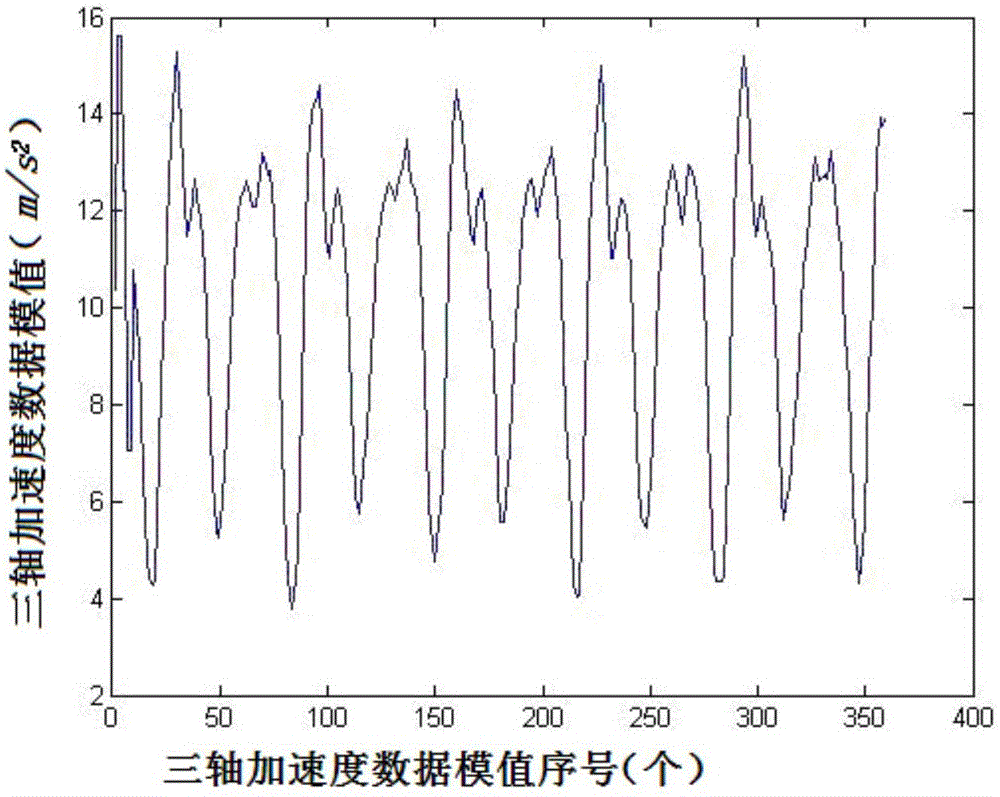

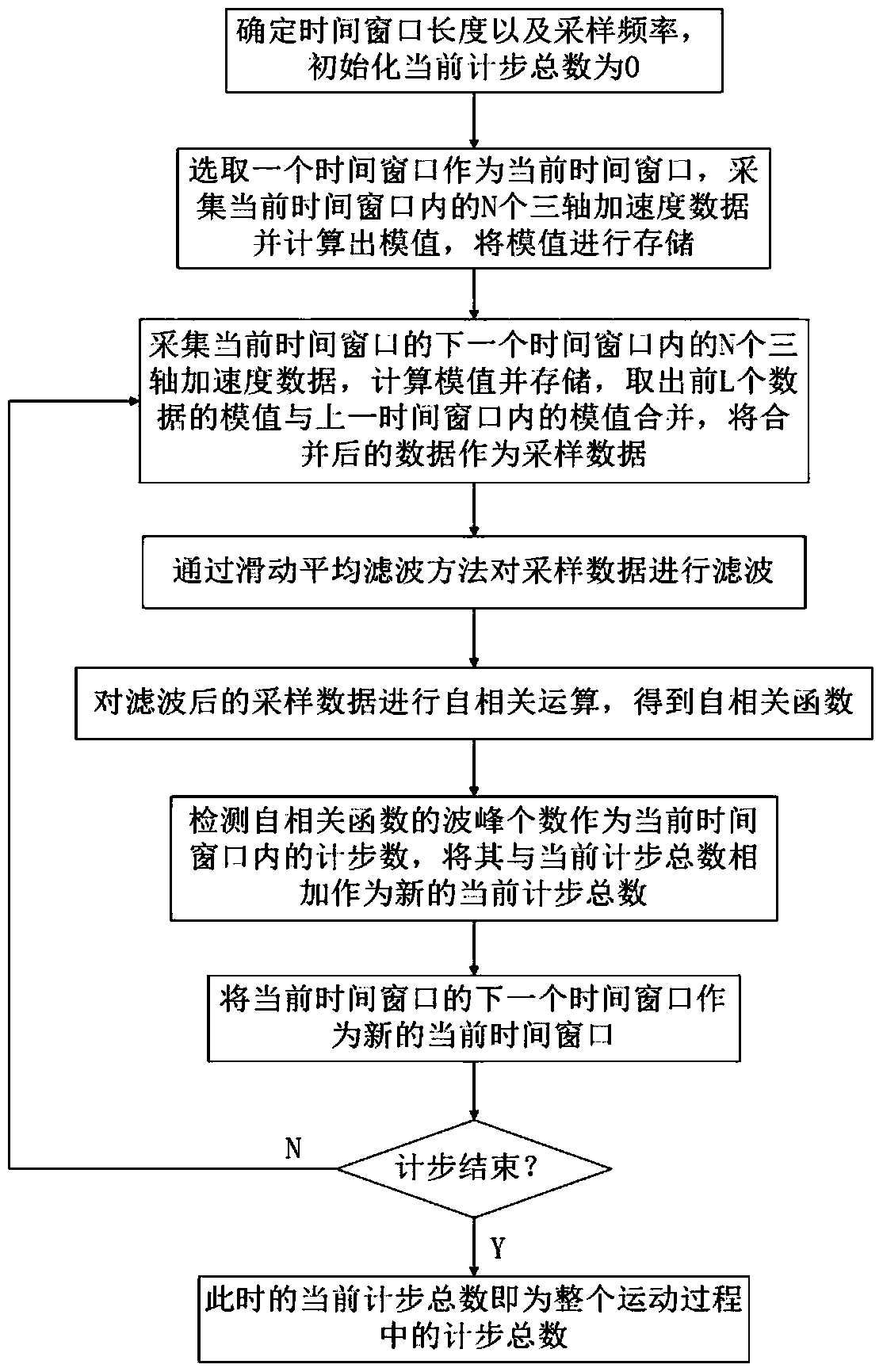

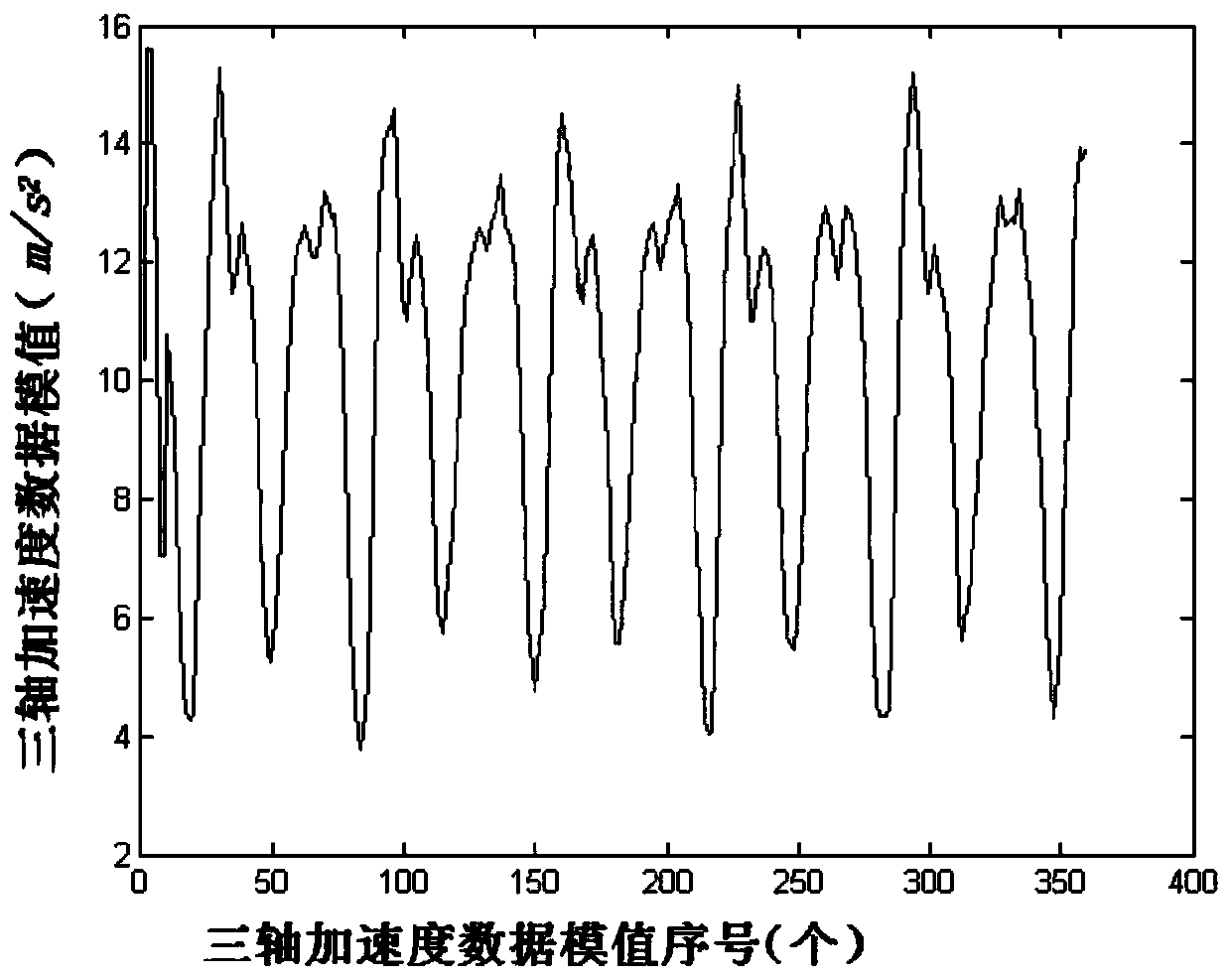

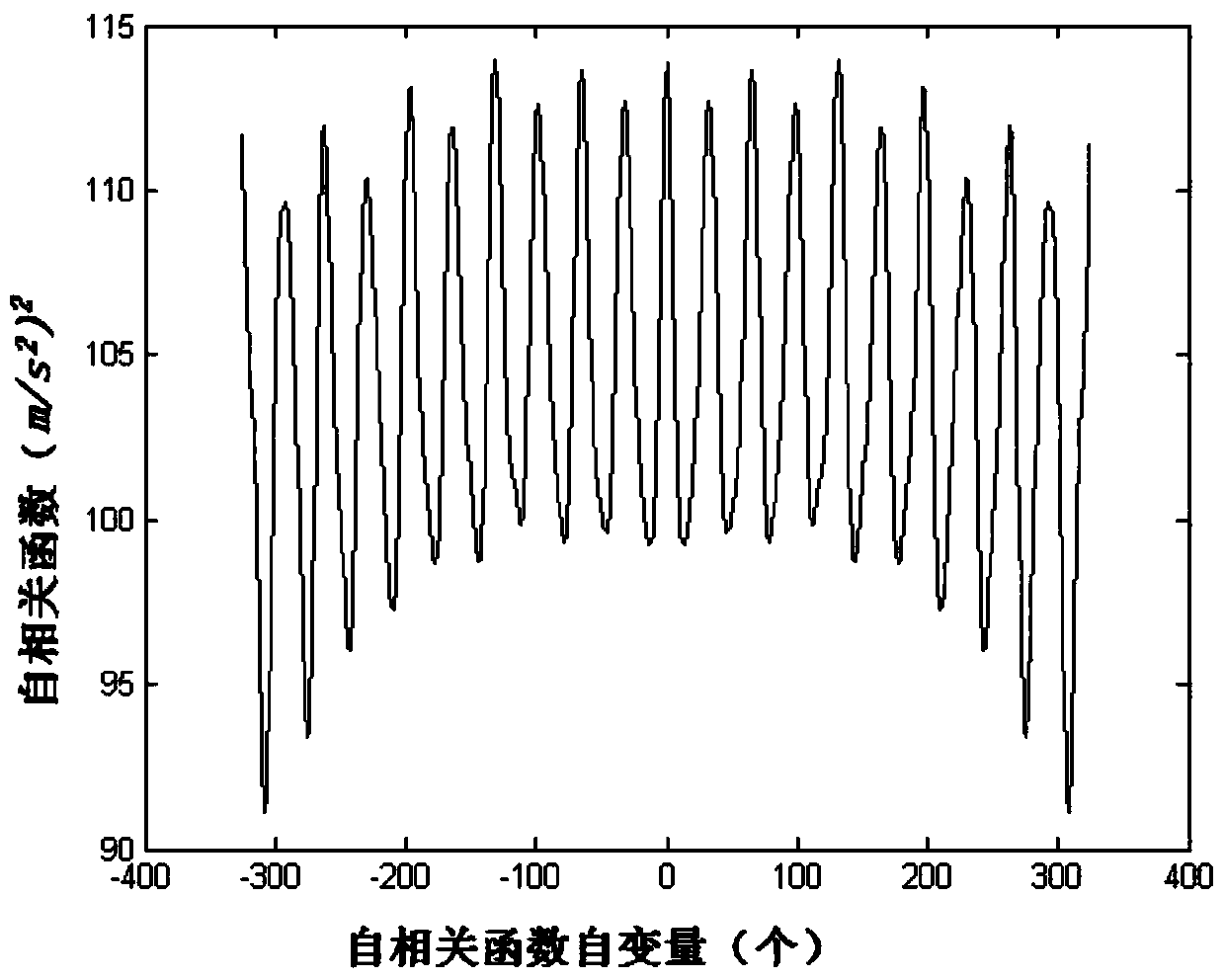

Step counting method based on autocorrecting computing

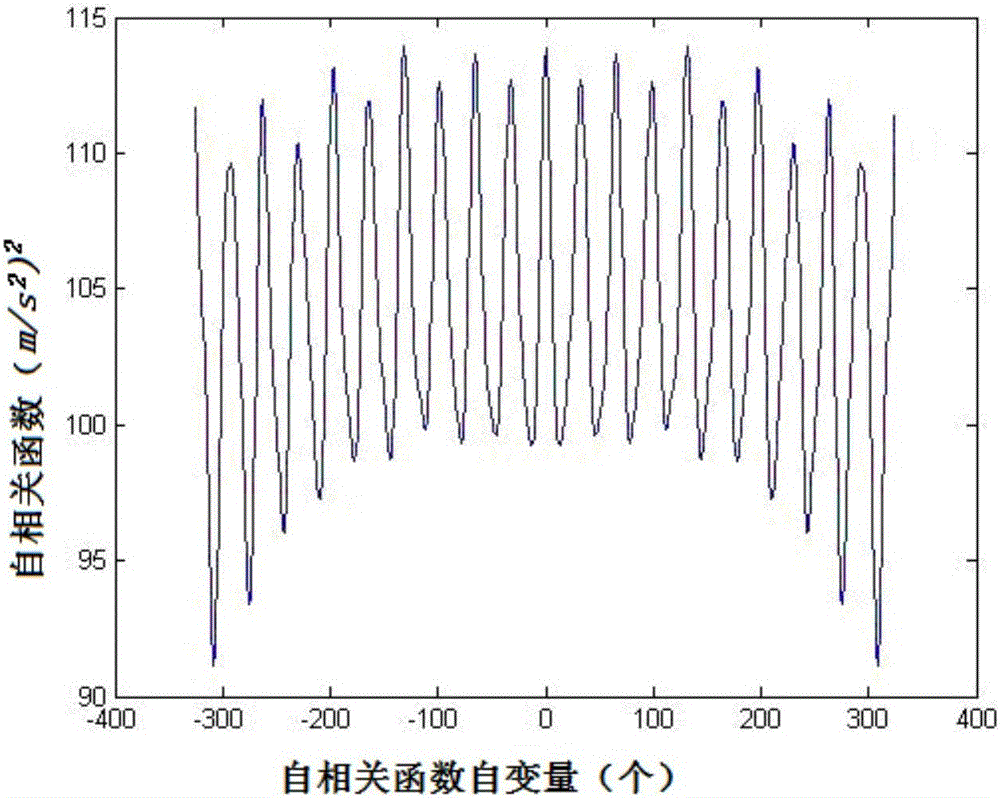

ActiveCN104990562AAvoid counting errorsSimplify Logic DesignAcceleration measurement using interia forcesComplex mathematical operationsCorrelation functionPedometer

The invention provides a step counting method based on autocorrecting computing which comprises the following steps: collecting N three-axis acceleration data in a current time window by a three-axis acceleration sensor of a pedometer, calculating the module values of the N three-axis acceleration data and storing the calculated module values; collecting and calculating the module values of N three-axis acceleration data in a next time window, and taking the first L module values to be put behind the N module values to obtain N+L merged data, denoting the N+L merged data as sample data x (n); performing filtering and autocorrecting computing on the sample data x (n) to detect the number of wave crests of the sample data x (n); taking the number of wave crests as the step number detected in the current time window, and adding the step number and the current total step number together to obtain new current total step number; taking the next time window of the current time window as a new current time window and repeating the steps until the movement course is finished. According to the step counting method based on autocorrecting computing provided by the invention, through autocorrecting computing, the periodic features of periodic signals are highlighted in signals containing a great deal of noise, and the effective step number is detected according to the counted number of crest values of autocorrelation function, and the step counting accuracy is effectively improved.

Owner:黄山市开发投资集团有限公司

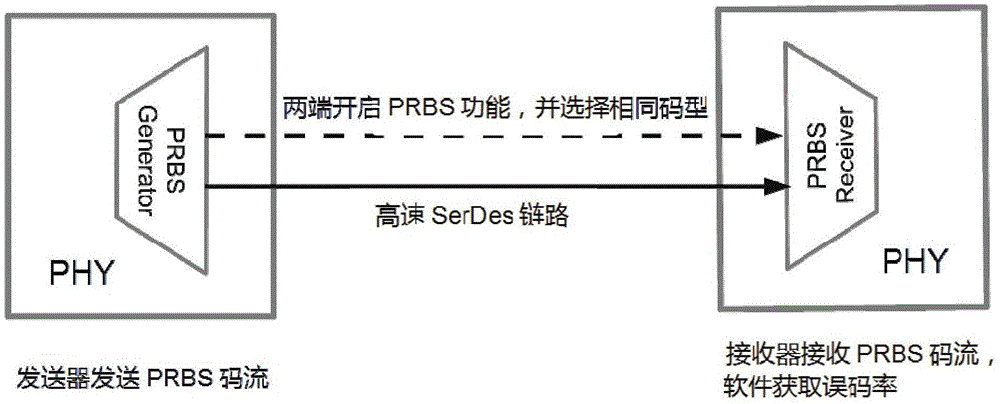

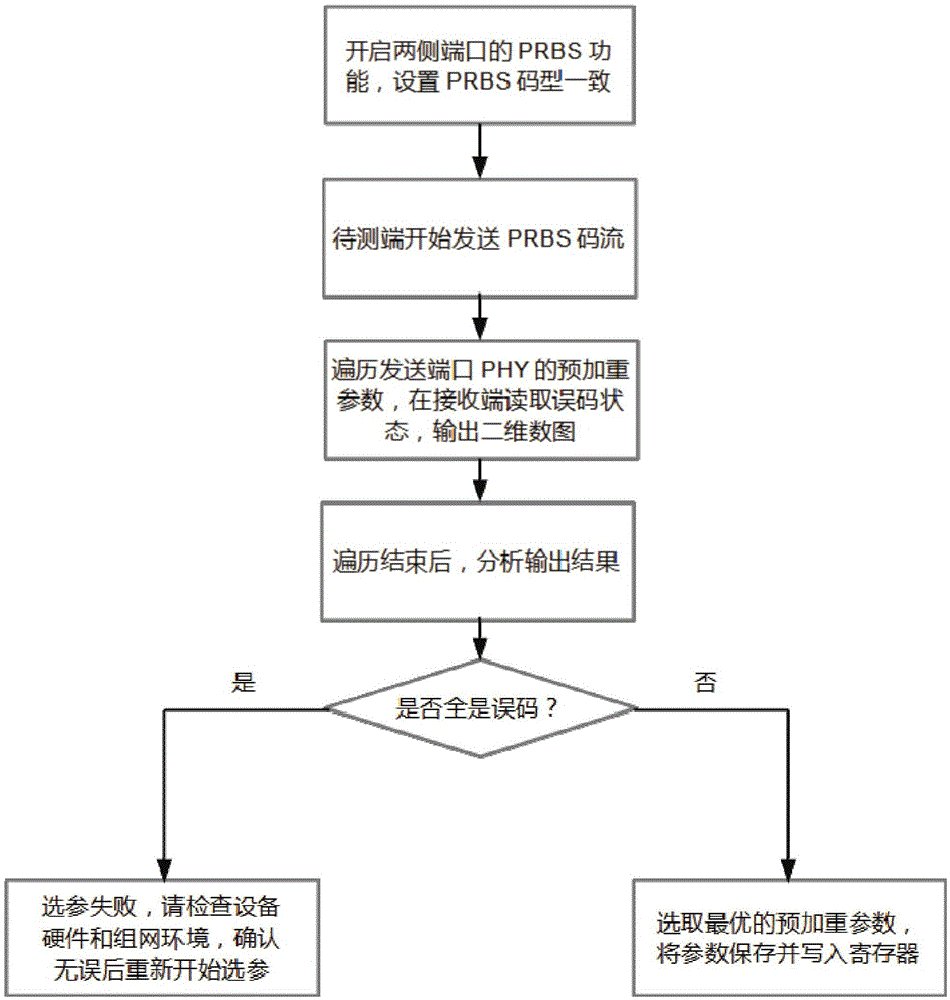

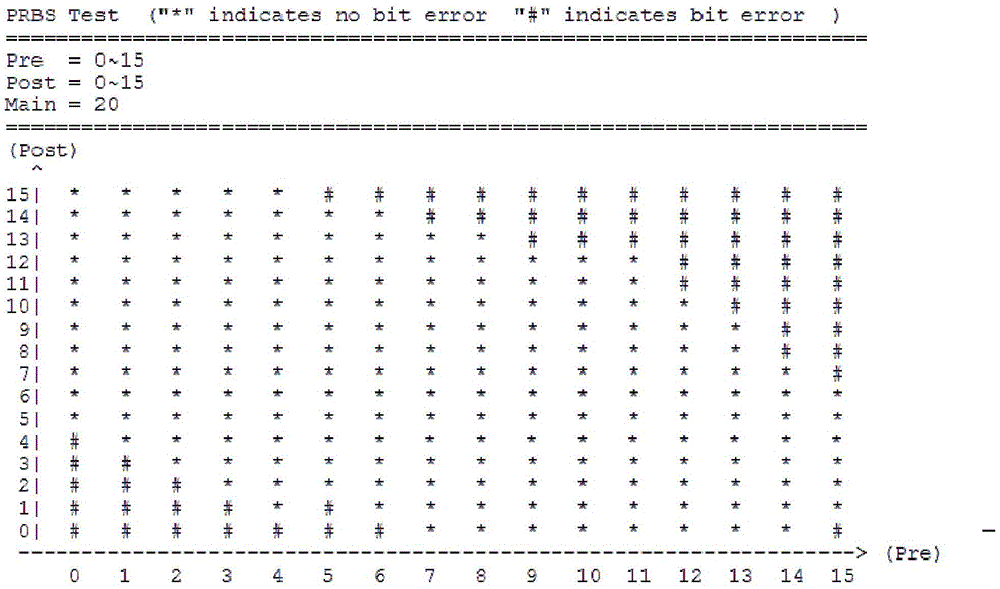

Method for achieving automatic adjustment of parameters of Ethernet based on PRBS

The invention relates to a method for achieving automatic adjustment of parameters of the Ethernet based on a PRBS, and the method comprises the steps: enabling PHY chips of a receiving end and a transmitting end to start a function of PRBS, and enabling the code patterns of the PRBS of the two PHY chips to remain the same; enabling the transmitting end to transmit a PRBS code stream to the receiving end; reading the error rate of the PRBS of the receiving end, and generating an error rate graph; analyzing the generated error rate graph, and selecting an optimal parameter; and enabling the optimal parameter to be stored and written in a register. The method can achieve the parameter adjustment of an Ethernet port in different application situations, and the function of parameter adjustment can be integrated in application layer software. Moreover, there is no need for other testing tools. The parameter selection of all ports can be achieved through the built-in PRBS transmitters and receivers in the PHY chips. In addition, the method is simple in operation, and the whole process of parameter selection can be completed through one instruction or key. Therefore, the method is flexible and convenient, is simple in software design logic, is convenient to transplant, is high in applicability, and is wider in application range.

Owner:SHANGHAI GONGJIN COMM TECH

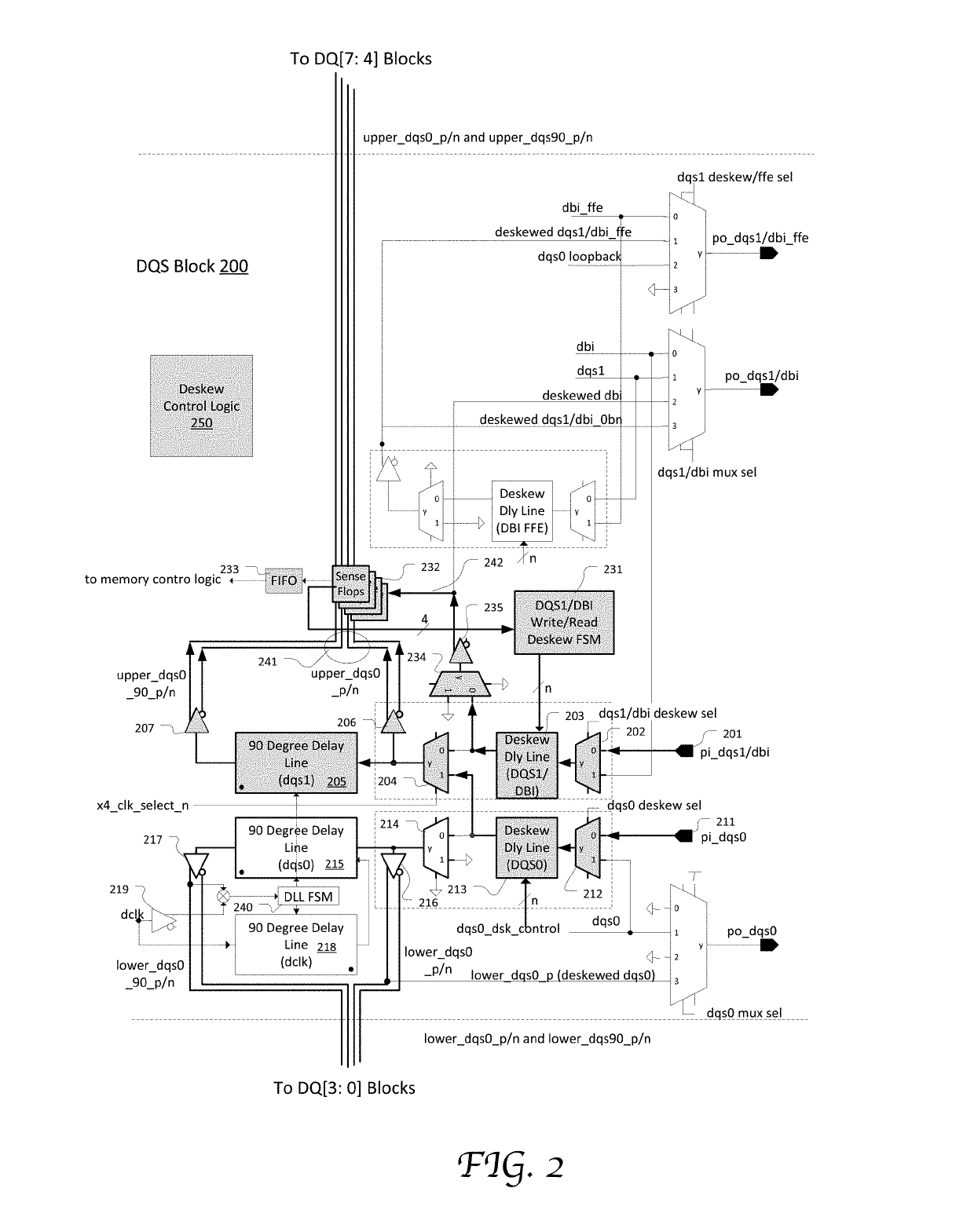

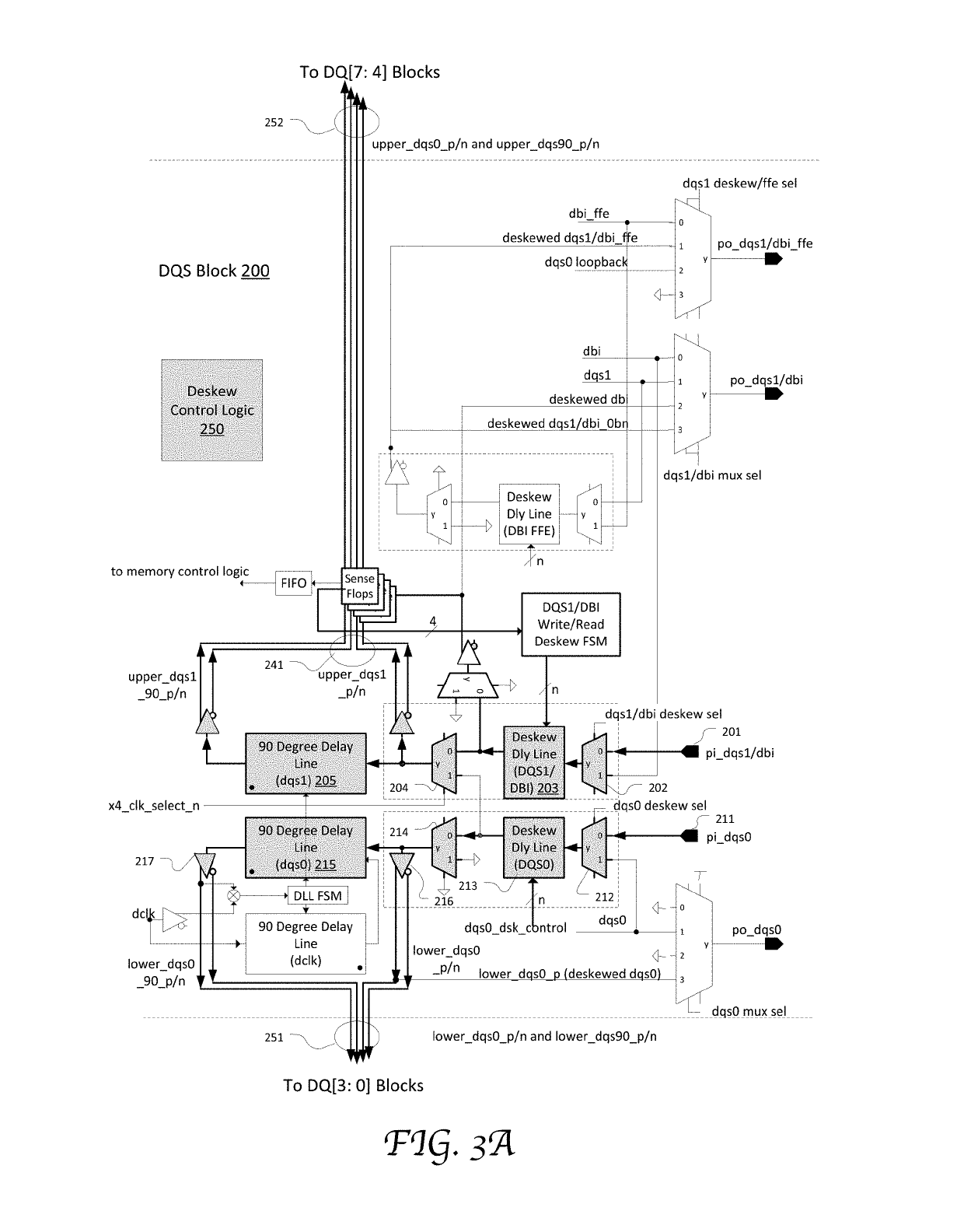

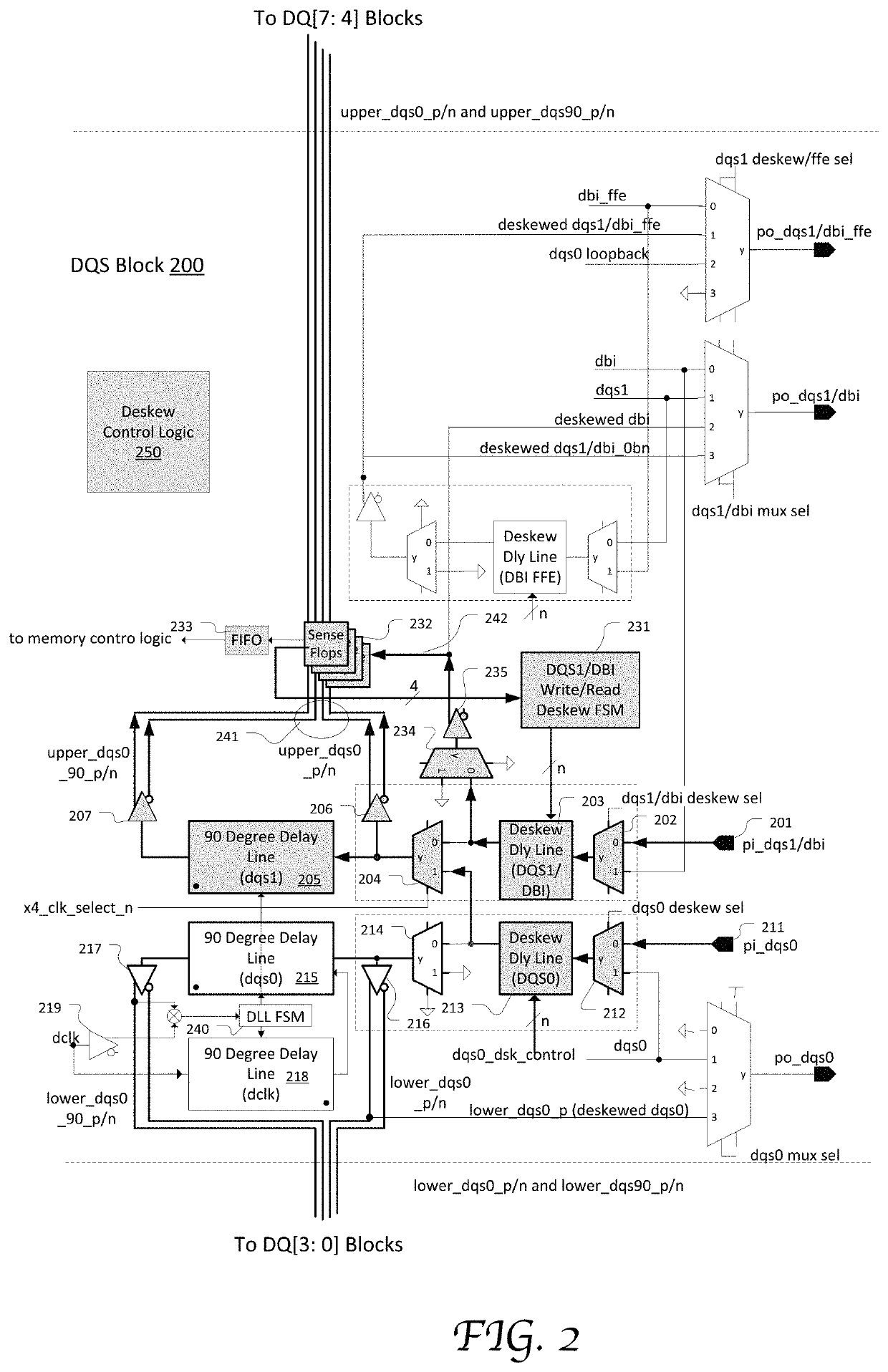

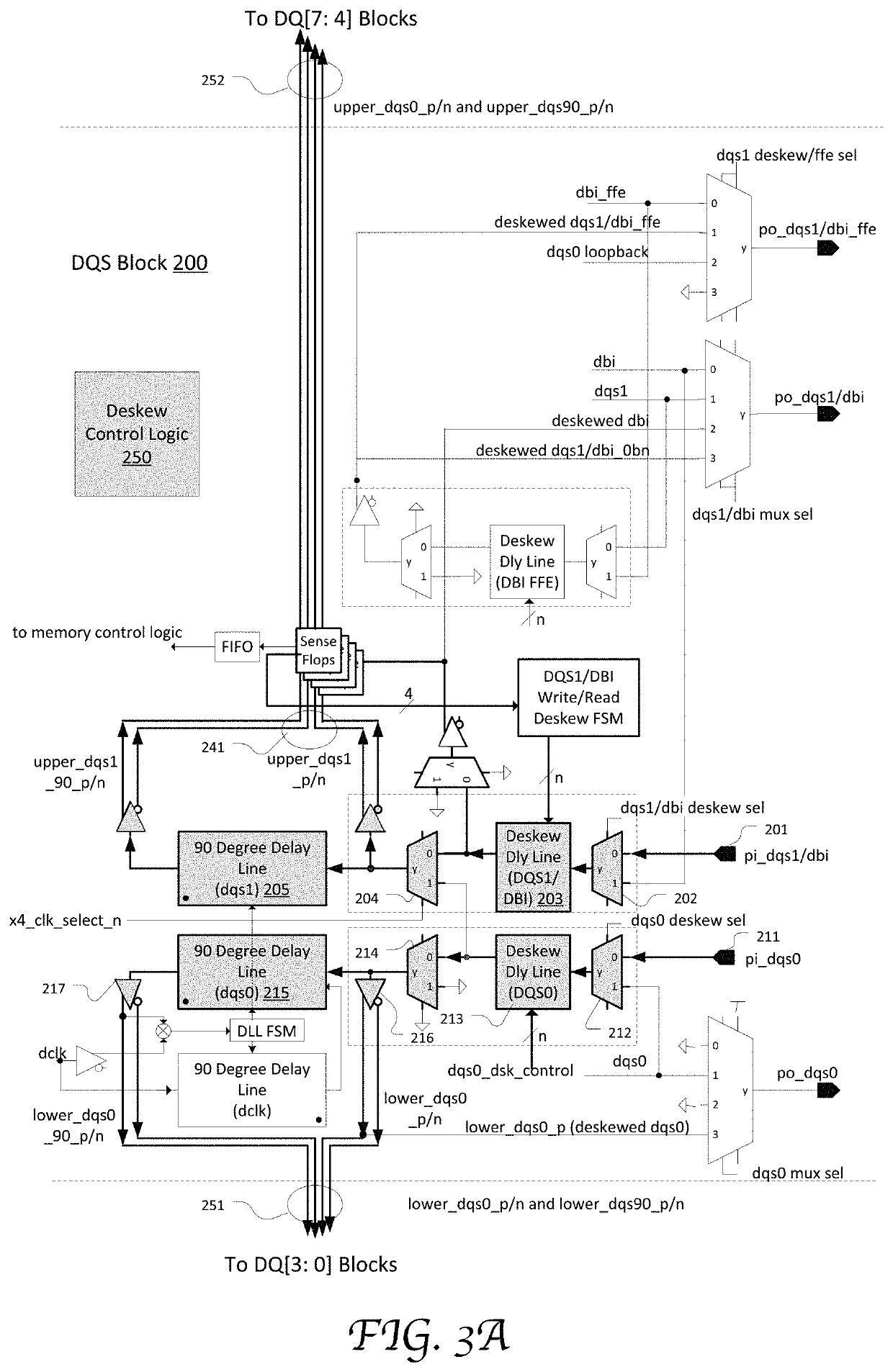

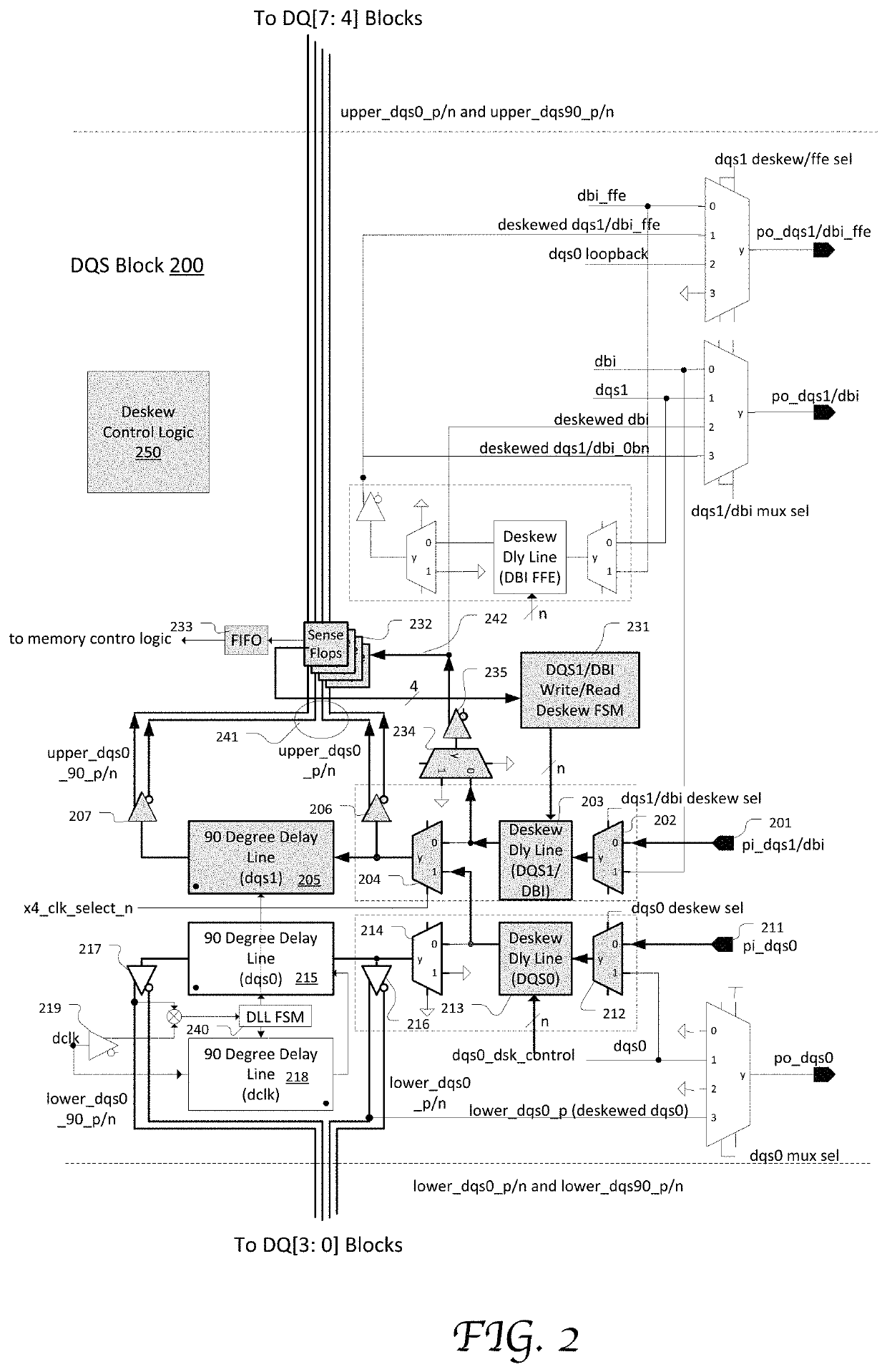

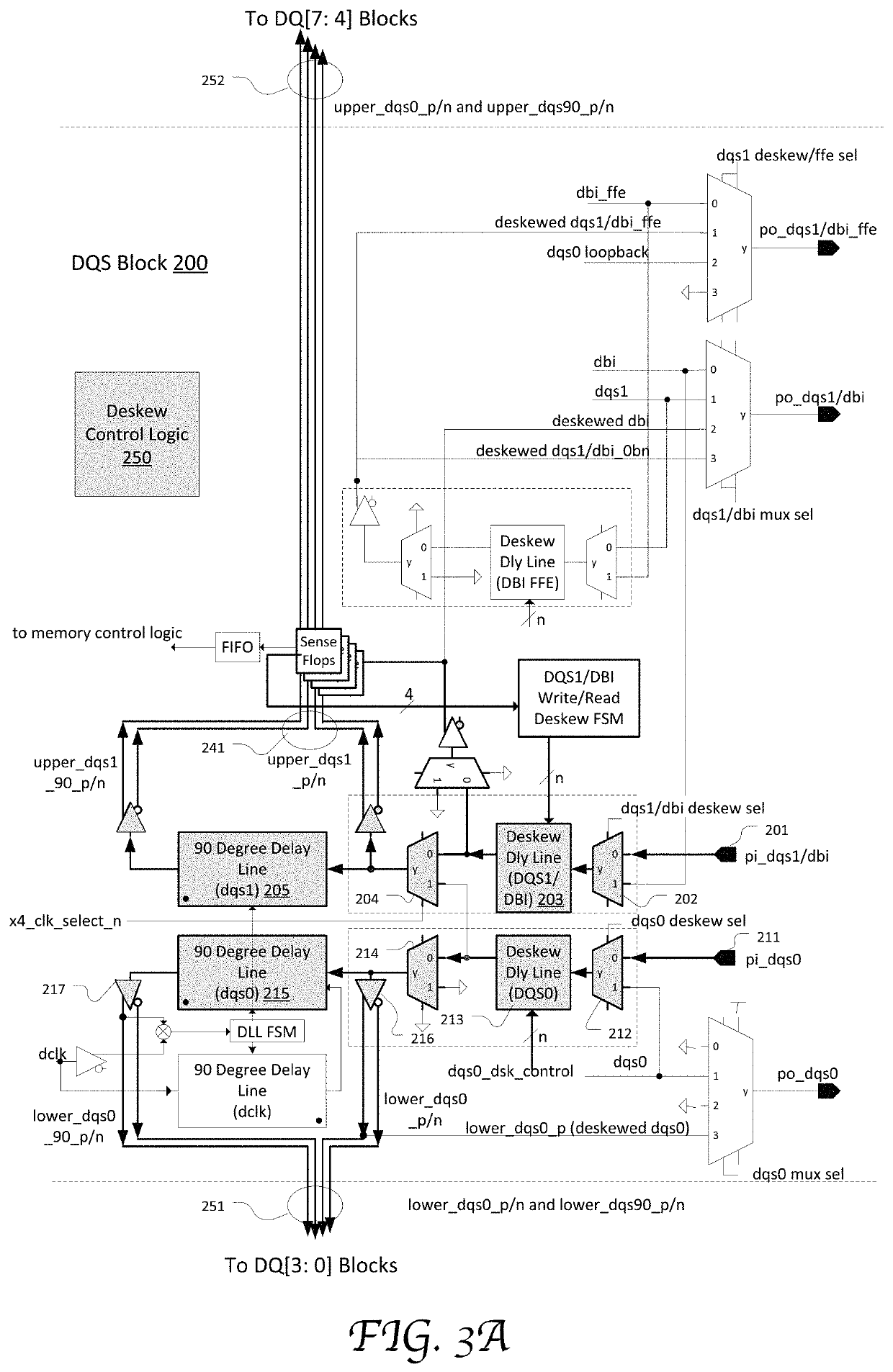

Write and read common leveling for 4-bit wide DRAMs

System and method of write deskew training for ×4 mode memory control interface configurations. Write leveling logic in the memory controller is adjusted to obtain a write leveling setting for delaying both first and second strobe signals associated with a byte. The adjustment is based on feedback of first set of bits of a byte and irrespective of the feedback of the second set of bits of the byte. The write leveling logic is then anchored at the write leveling setting, and a deskew delay line for the second strobe signal is adjusted to obtain a first deskew setting based on the feedback of the second set of bits. Thus, in write operations, the write leveling setting can be common within the byte even the two strobe signals are transmitted to or received from two different memory storage devices.

Owner:MARVELL ASIA PTE LTD

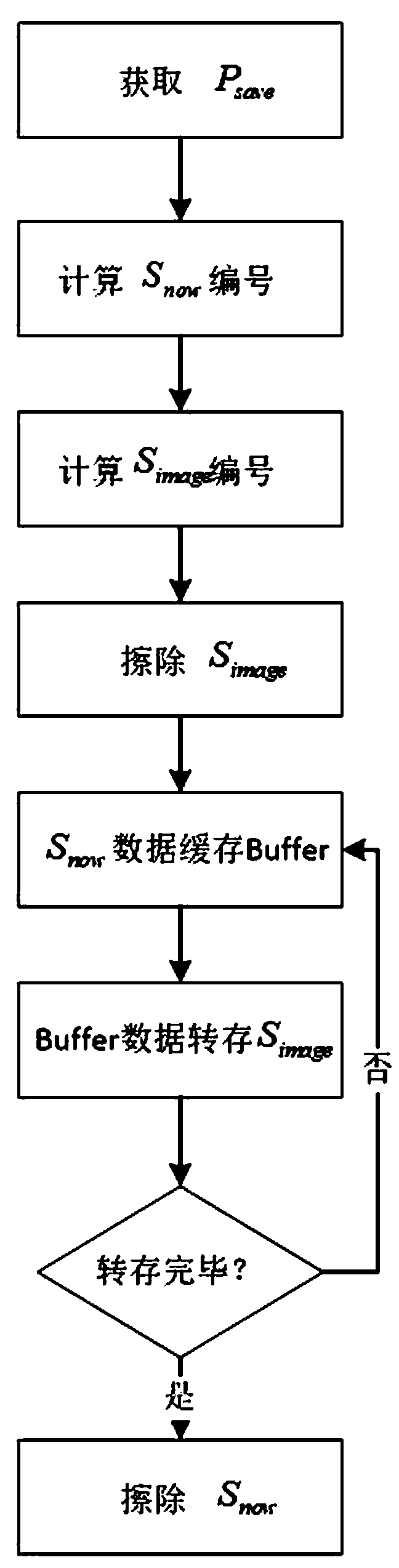

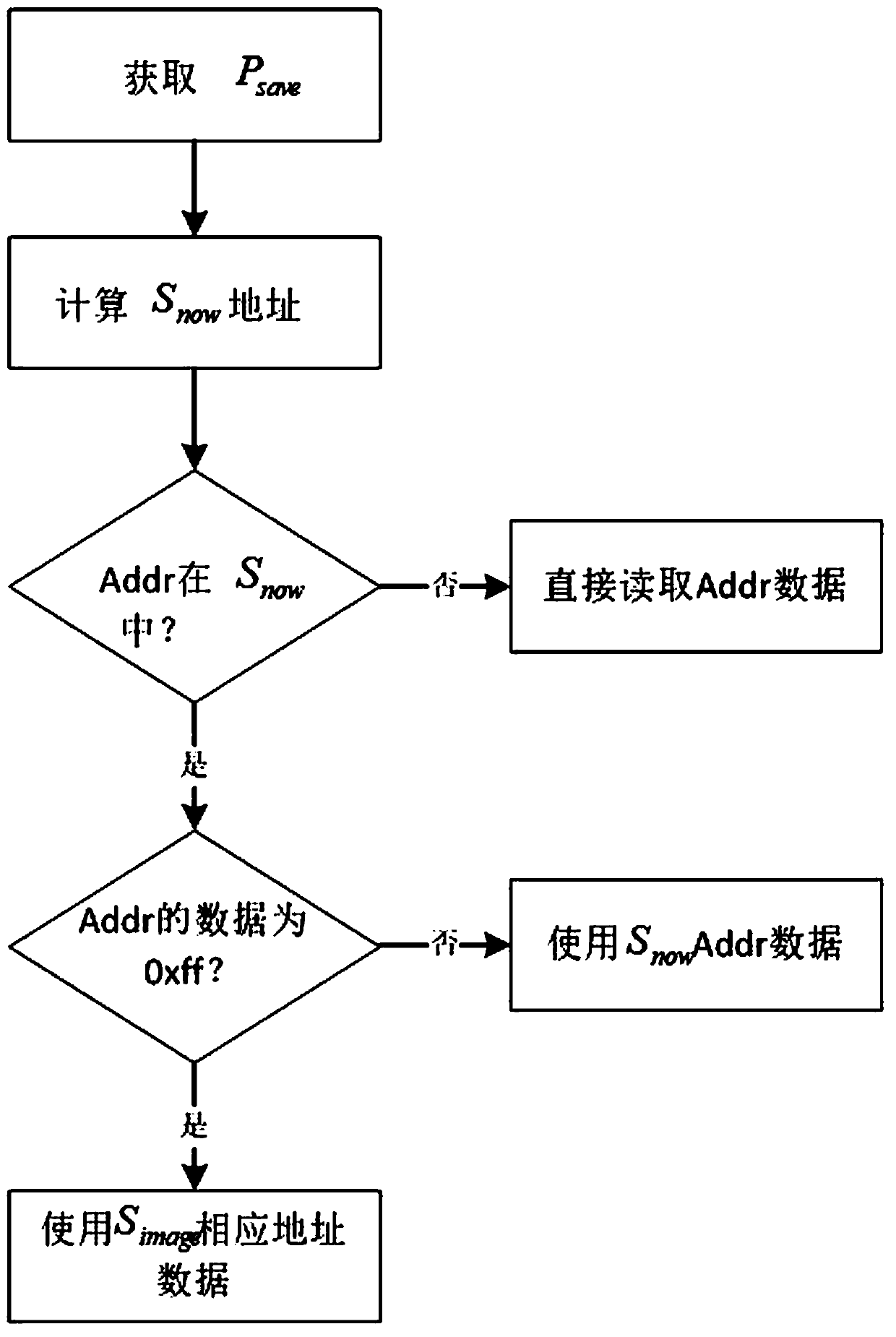

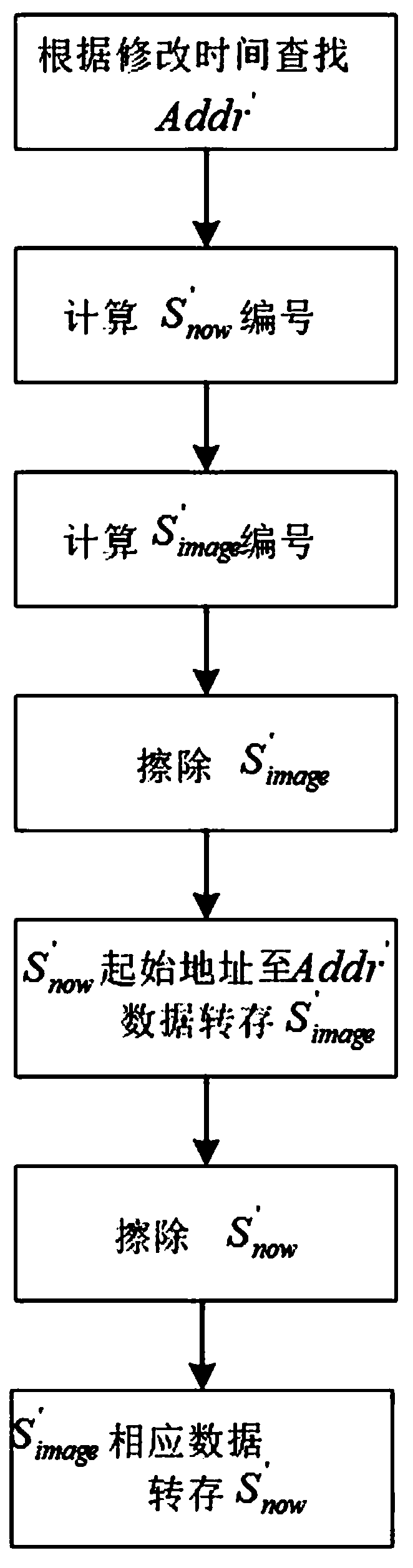

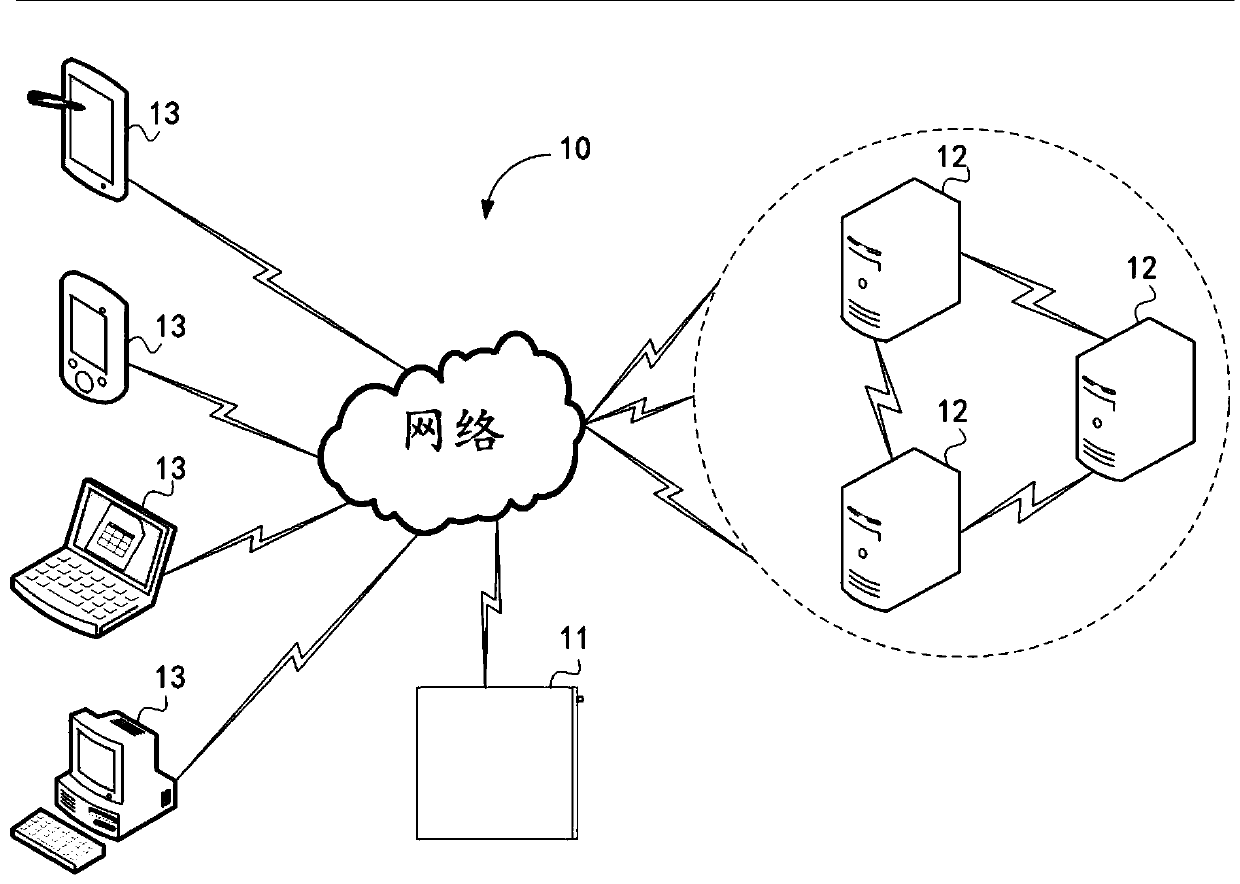

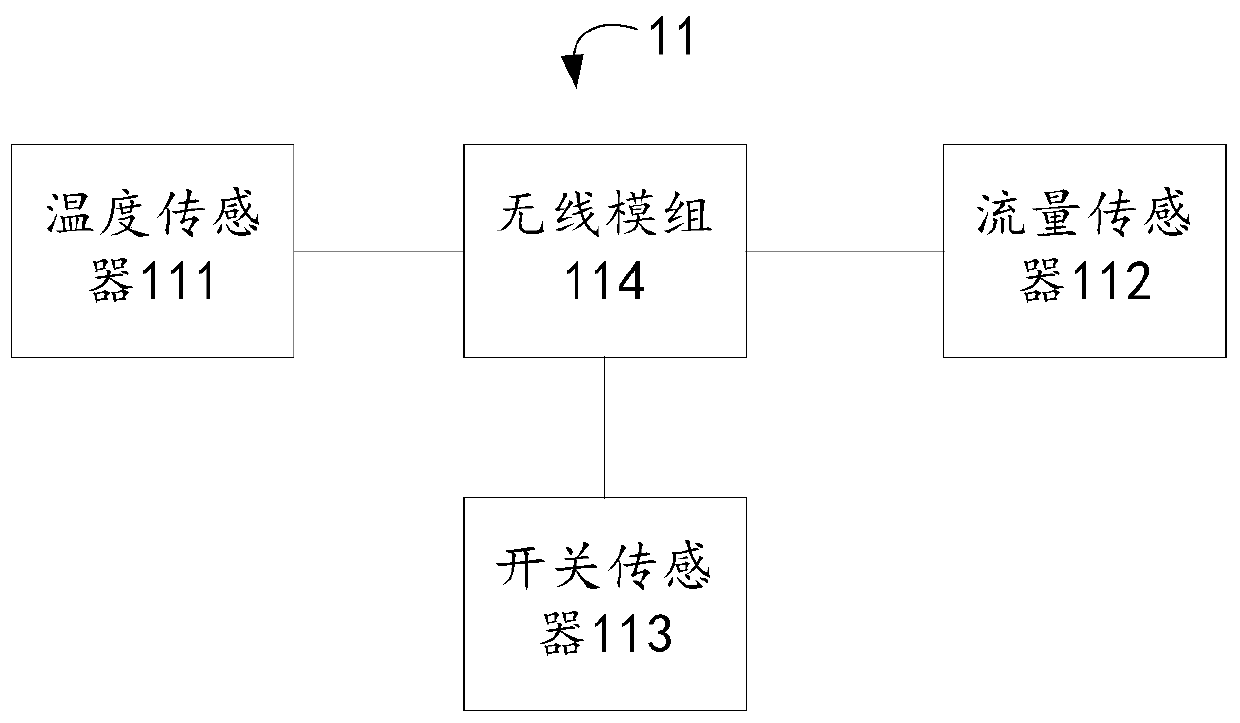

Flash operation method suitable for intelligent electric meter load curve storage

ActiveCN109597580ASimplify Logic DesignAvoid lossInput/output to record carriersMemory adressing/allocation/relocationData segmentComputer architecture

The invention discloses a flash operation method suitable for intelligent electric meter load curve storage, which realizes cyclic storage and data reading of load curve data in flash and data operation of forward time point modification by establishing a mirror image area, a data storage pointer and a data segmented cache. According to the invention, the design logic of the load curve applicationlayer is greatly simplified, the data loss caused by erasing the whole vector is avoided, the RAM overhead is reduced, the service life of the flash is prolonged, and the service life requirement iscompletely met under the extreme condition.

Owner:YANTAI DONGFANG WISDOM ELECTRIC

Hardware driving device and method, chip and non-transient computer readable storage medium

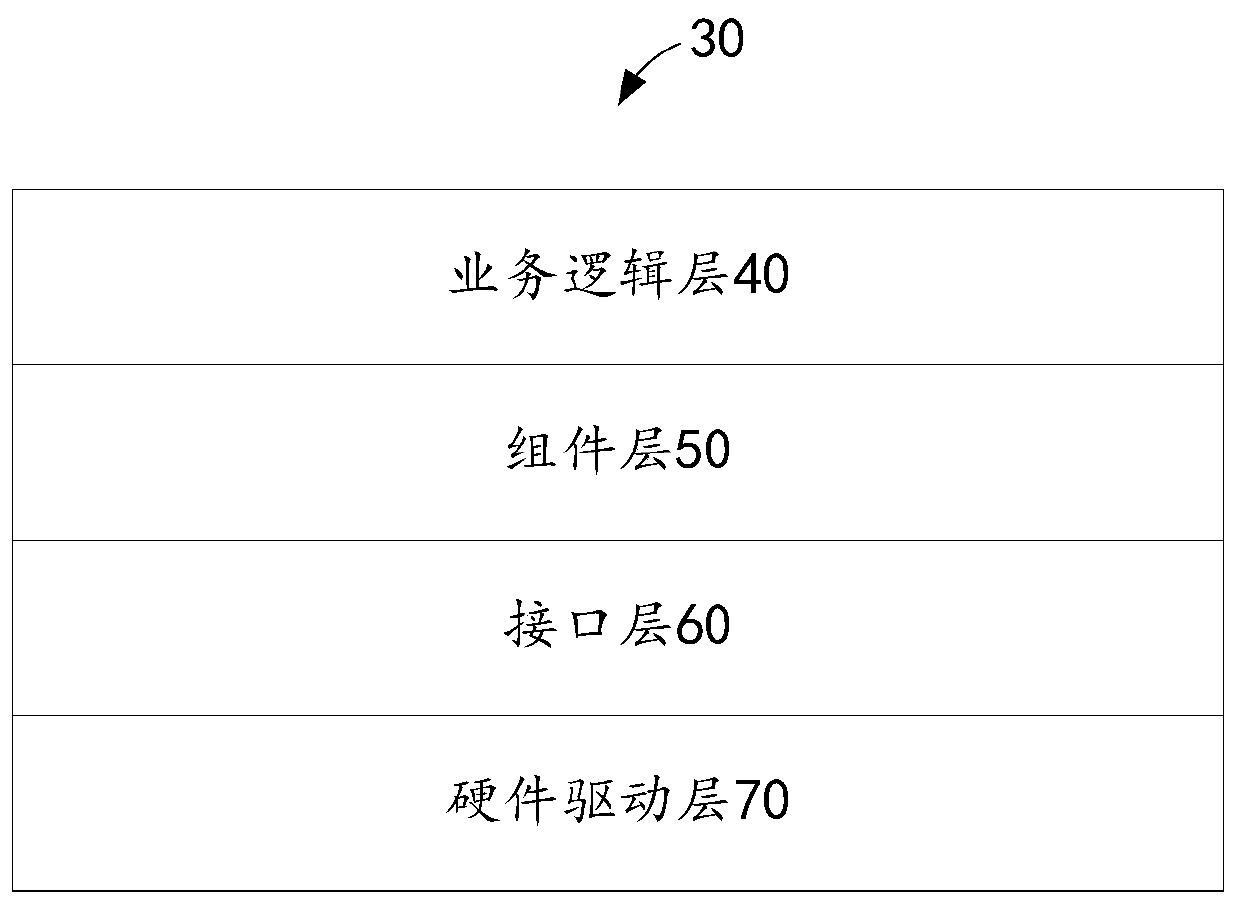

InactiveCN109871244ASimplify Logic DesignReduce couplingProgram loading/initiatingCreation/generation of source codeCouplingApplication programming interface

The invention relates to the technical field of computers, in particular to a hardware driving device and method, a chip and a non-transient computer readable storage medium. The hardware driving device comprises a service logic layer used for sending a component driving request; The component layer is used for selecting and executing a component according to the component driving request so as togenerate an interface calling instruction; The interface layer is used for calling an application programming interface corresponding to the component according to the interface calling instruction;And the hardware driving layer comprises a hardware driving program corresponding to the assembly, and the hardware driving layer is used for executing the hardware driving program according to a calling result of the application programming interface. Therefore, the logic design of the service logic layer is simplified, the service logic layer can promote the component layer to select and executethe corresponding component only by sending the component driving request according to the service requirement, so that the driving of the bottom hardware is completed, the coupling degree between different layers can be reduced, and the portability and the function clipping property of a product are improved.

Owner:SHENZHEN H&T DATA RESOURCES & CLOUD TECH LTD

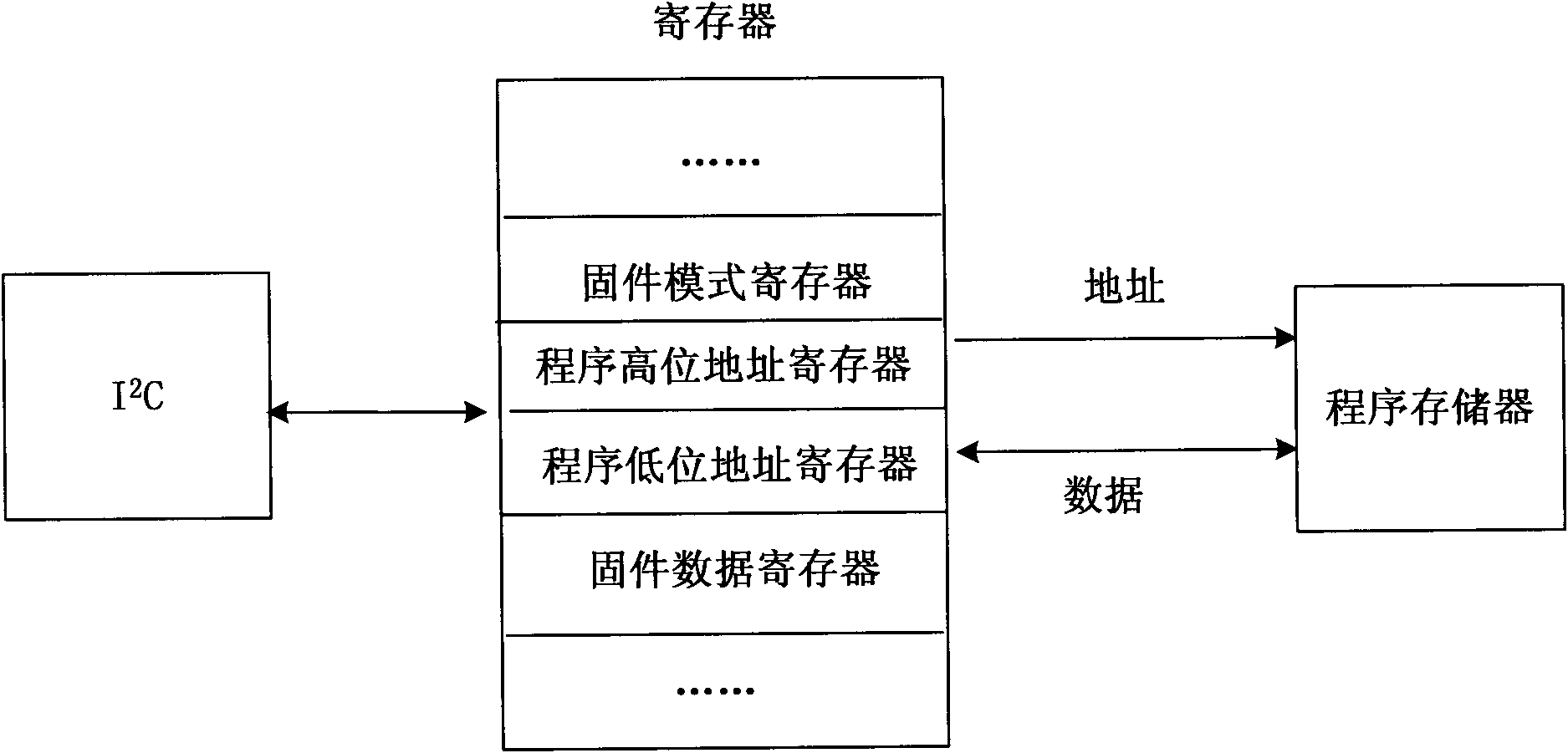

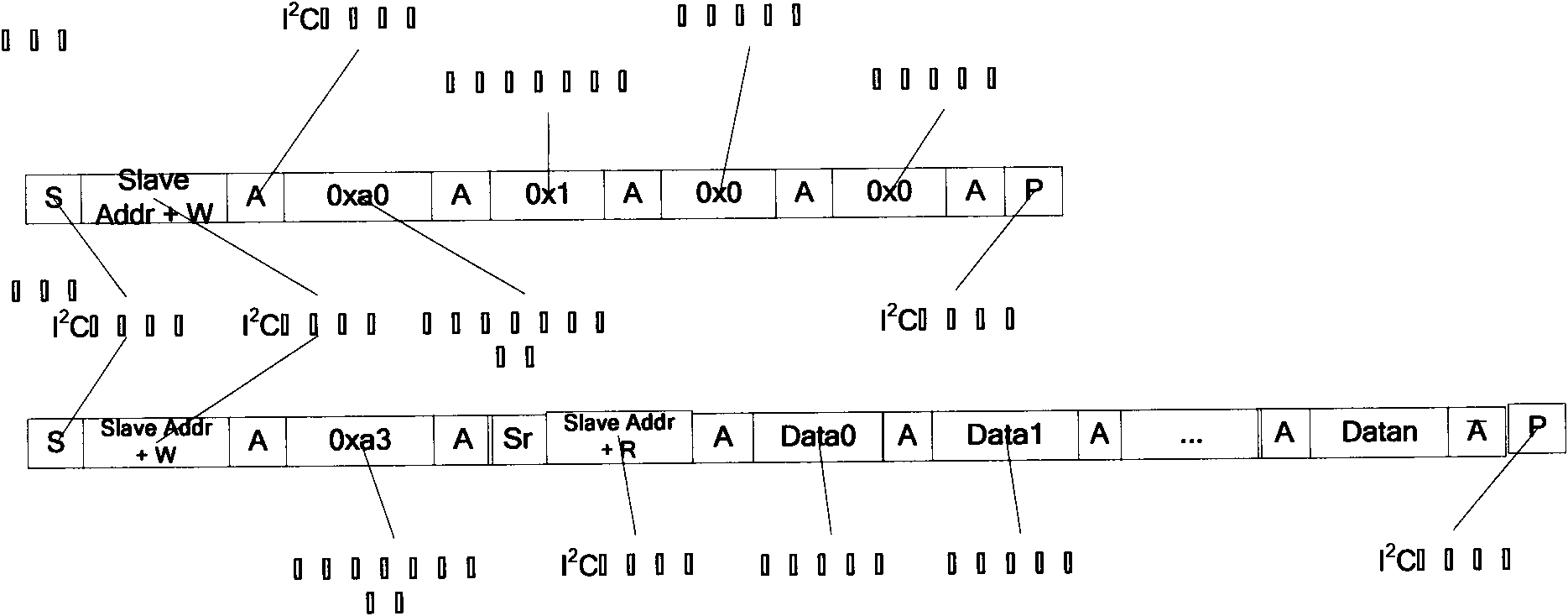

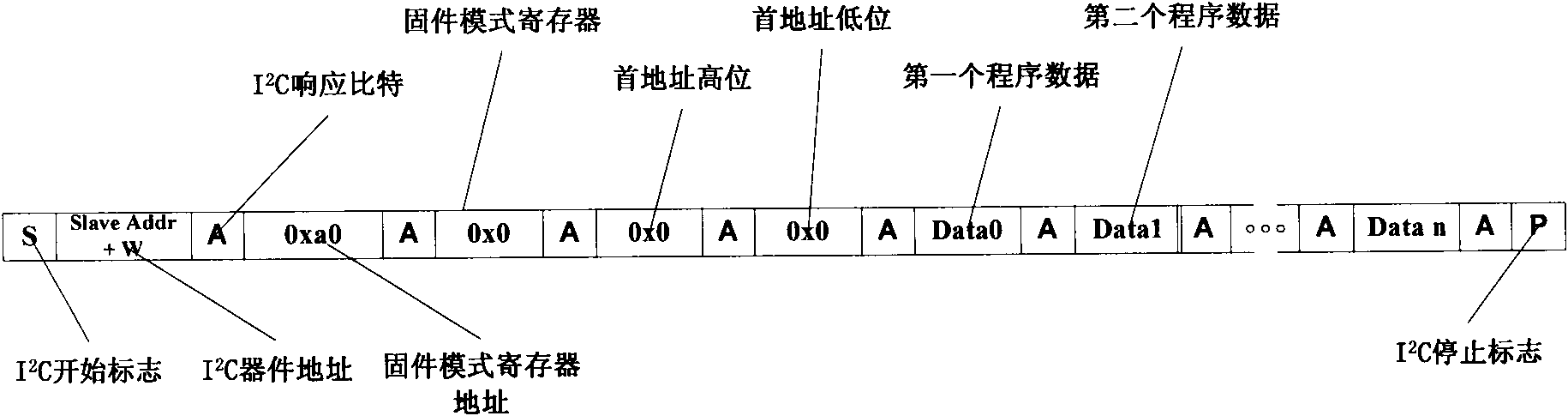

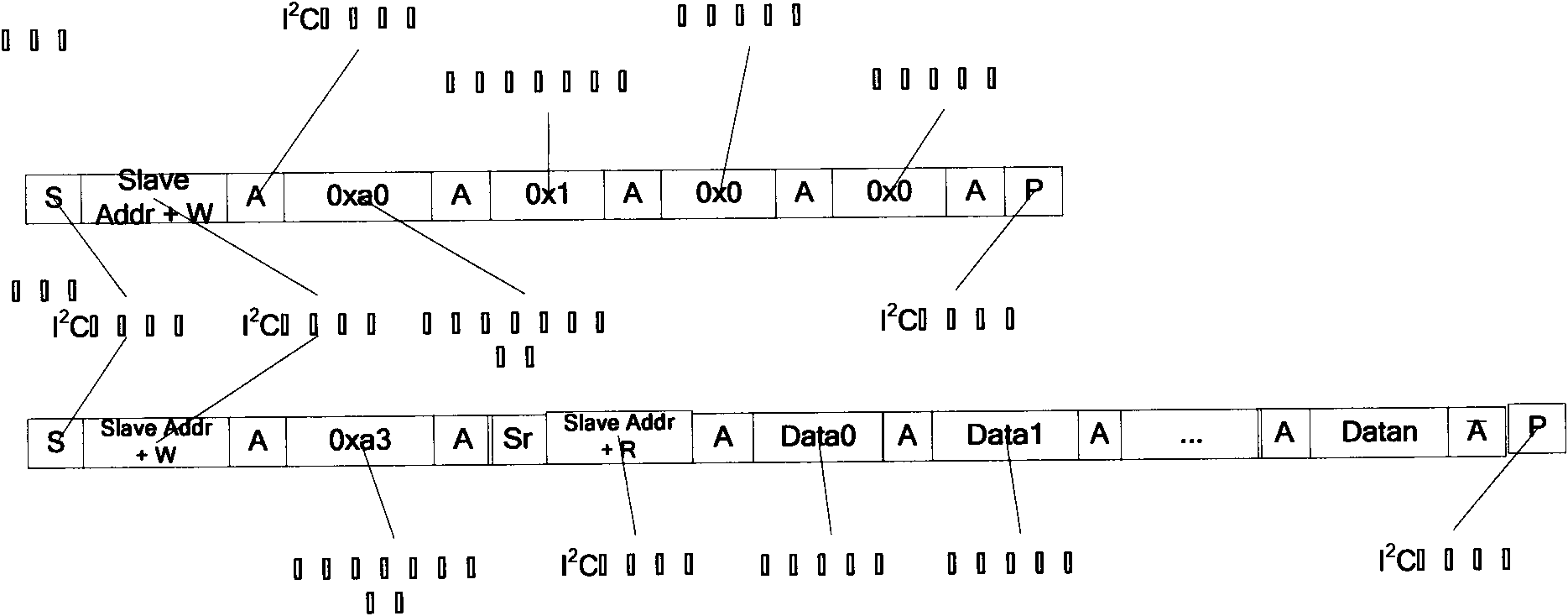

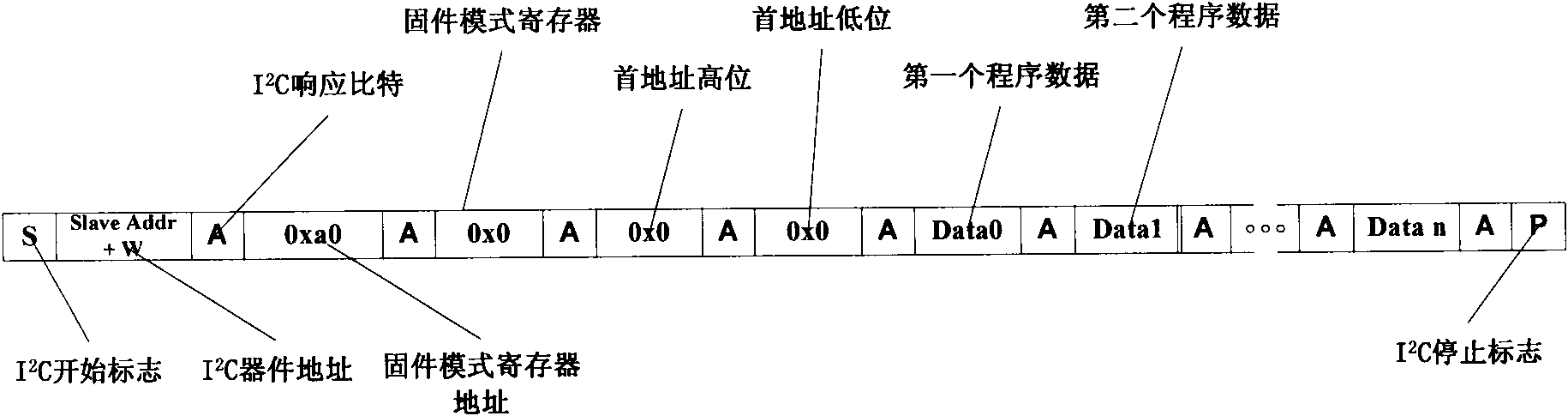

Method for quickly downloading and updating firmware by using I2C (Inter-Integrated Circuit) bus

ActiveCN102375749AReduce register spaceSimplify Design LogicProgram loading/initiatingData transmissionSoftware design

The invention provides an implementation method for updating firmware in integrated circuit design, namely a method for realizing quick downloading and updating of the firmware by using an I2C (Inter-Integrated Circuit) bus. 1 is automatically added to an address of a program memory during firmware data transmission by configuring a starting address of the I2C bus program memory before firmware data transmission without additionally transmitting address information of the program memory every time when a piece of byte data is transmitted. Space occupied by a register in design can be reduced, design logic can be simplified, single and continuous data transmission can be supported, data transmission efficiency can be effectively increased, and application requirements can be met. The method is extremely suitable for application environments of smaller software design scales or minor software modification.

Owner:SHANGHAI HUAHONG INTEGRATED CIRCUIT

Method of predicting branch transfers

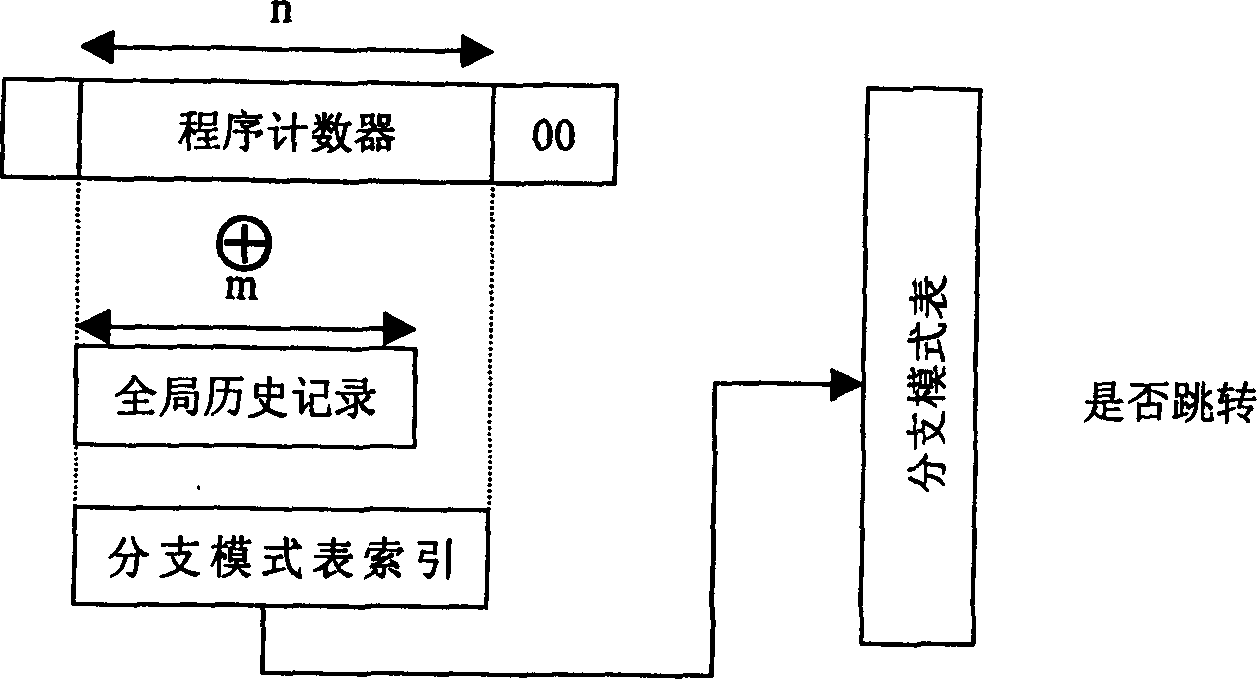

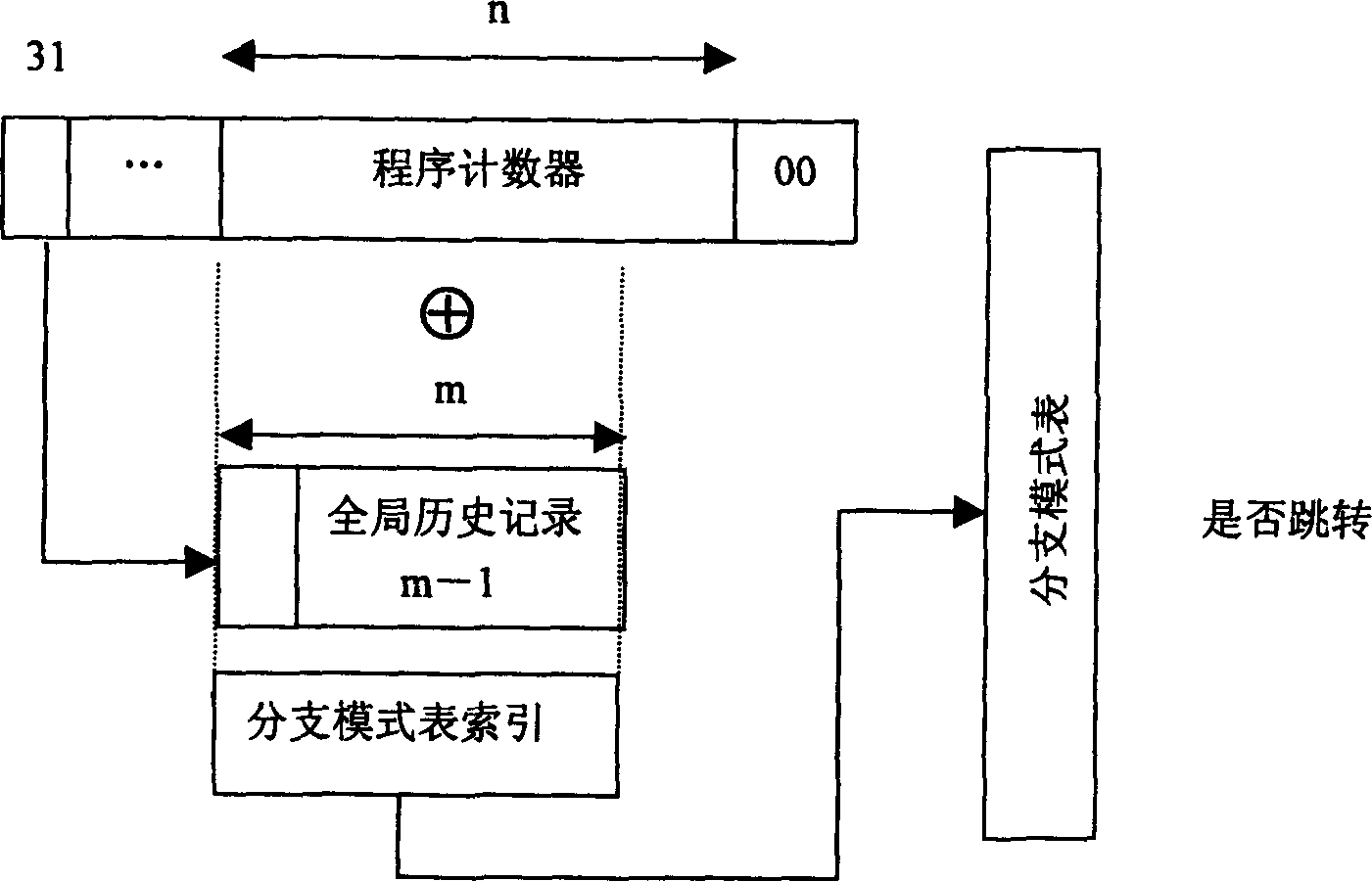

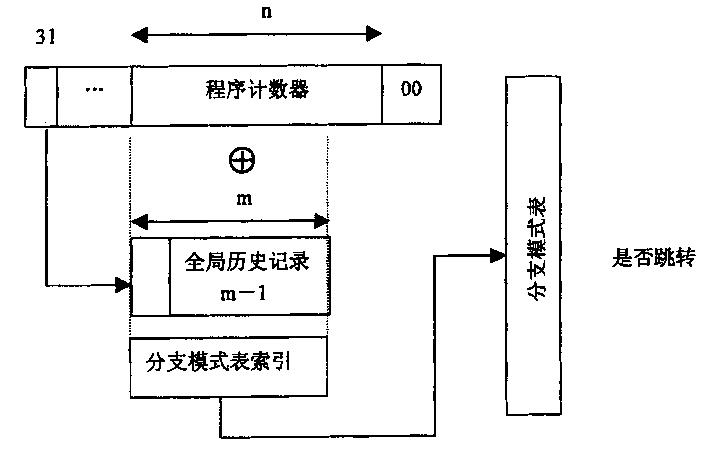

InactiveCN1447231ASimplify Logic DesignIncreased guessing hit rateProgram controlMemory systemsOperational systemPredictive methods

A branch transfer predict method includes the following steps: a) when the system meets with a branch transfer instruction, it gets the preset order computing value from PC to get historical recording from global history record b) to split join to new global record by IC and the historical record in utilizing strict control of the operation system to the system space and user space c) the new global record replaces the global historical record in traditional global historical predict method to help PC for branch prediction.

Owner:苏州中科集成电路设计中心有限公司

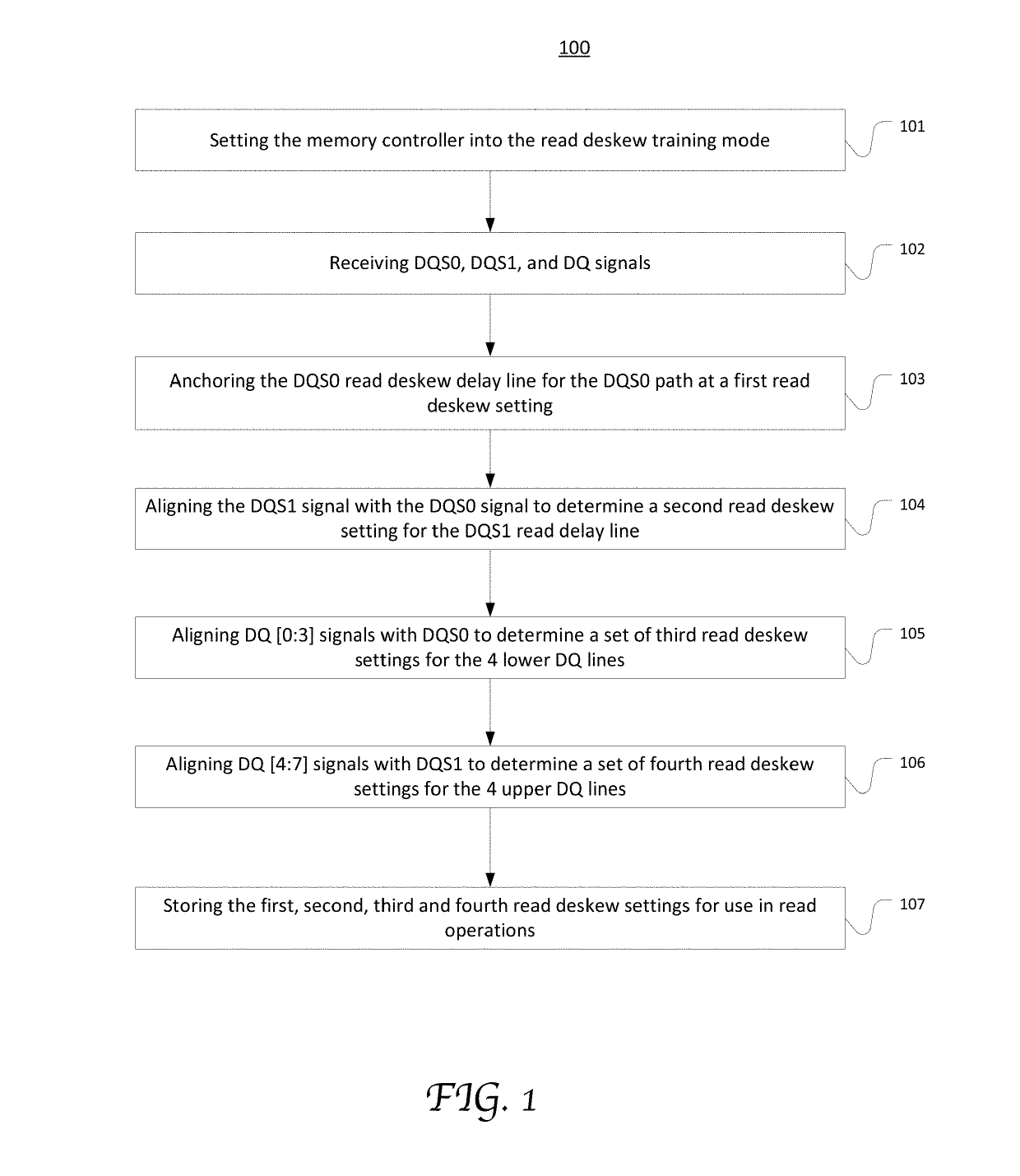

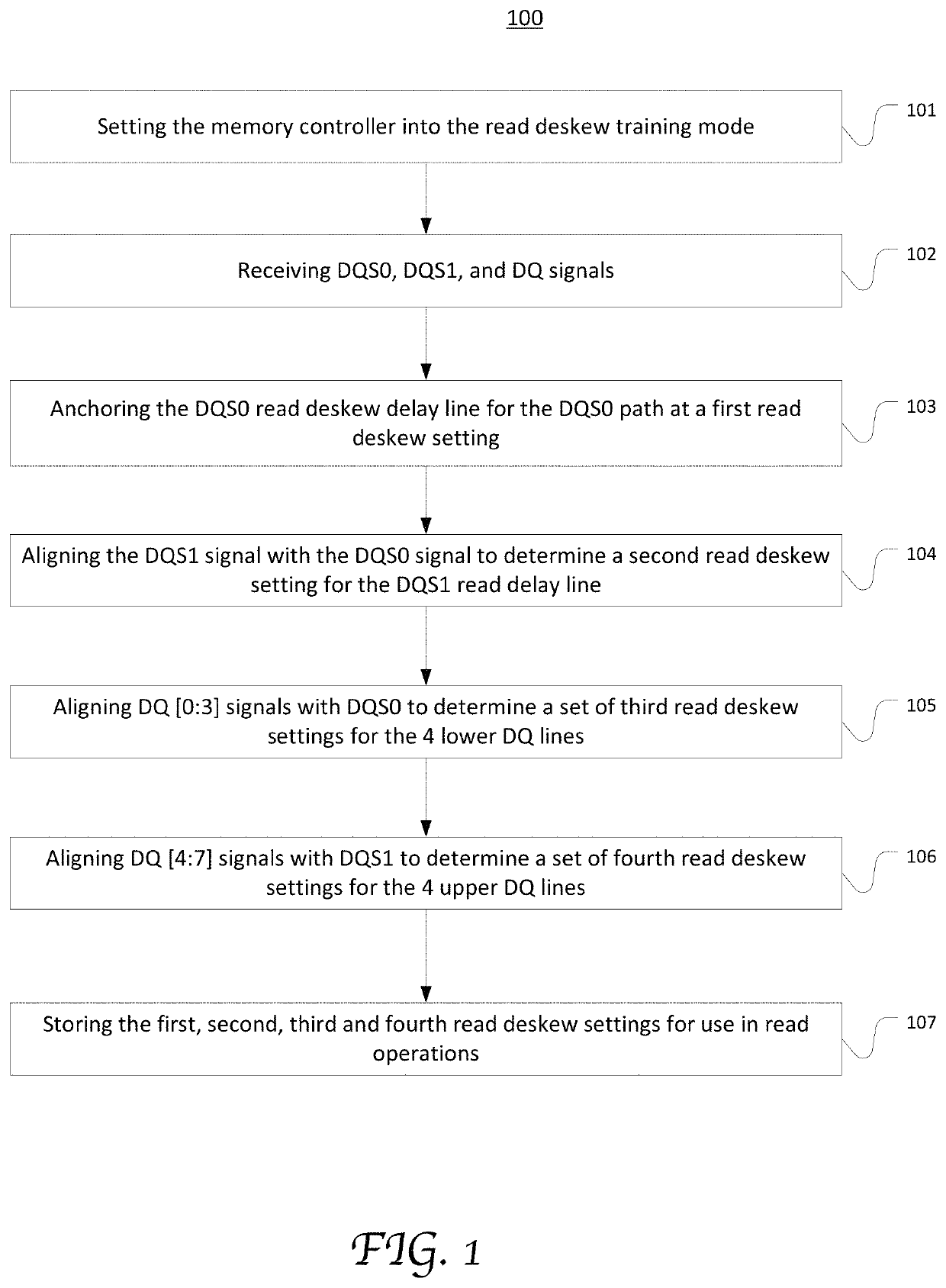

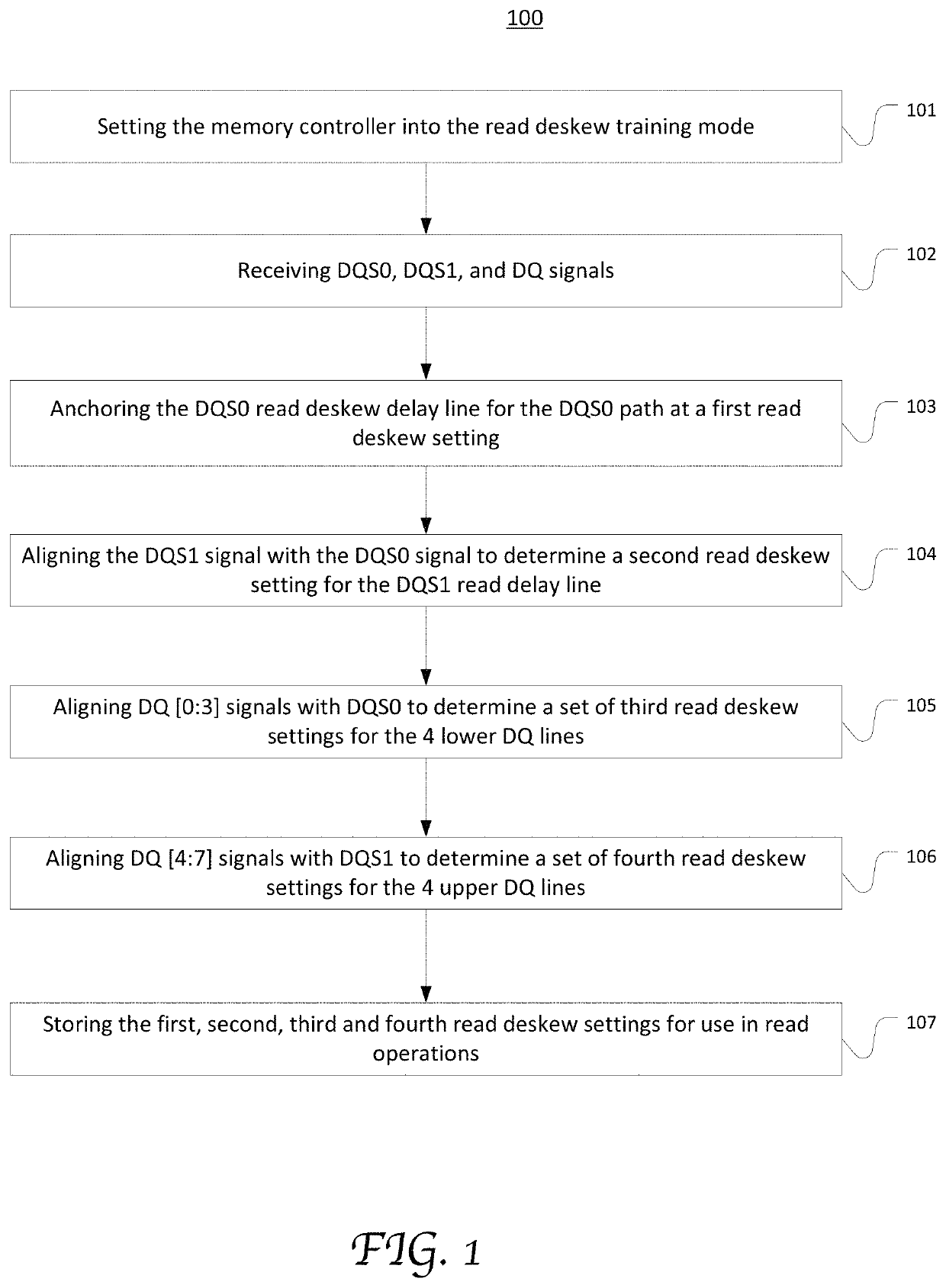

Write and read common leveling for 4-bit wide drams

System and method of read deskew training for ×4 mode memory control interface configurations. A read deskew training process includes aligning the two strobe signals serving one byte before deskewing the data bits against their corresponding strobe signals. A deskew setting of a variable delay line associated with the second strobe signal is adjusted to align the second strobe signal with reference to the first strobe signal. By aligning the two strobe signals with respect to each other, the read leveling settings can be common within the byte even the two DQS signals are transmitted to or received from two different memory storage devices.

Owner:MARVELL ASIA PTE LTD

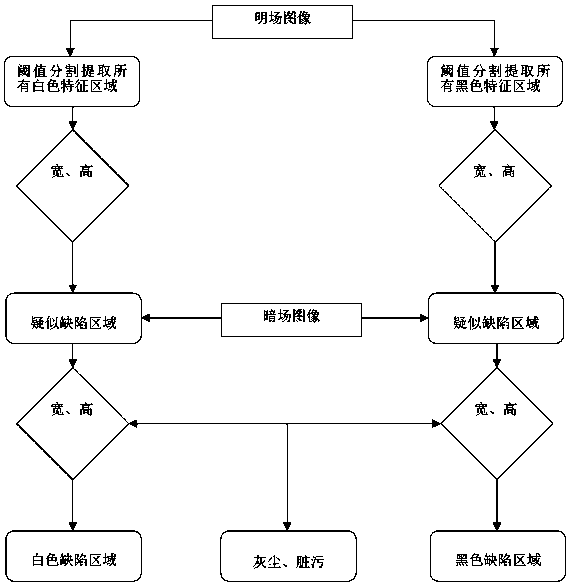

Transparent material internal defect detection method based on time-sharing exposure image synthesis

ActiveCN110441321AReduce detectionImprove operational efficiencyMaterial analysis by optical meansTime-sharingBright field image

The invention relates to a transparent material internal defect detection method based on time-sharing exposure image synthesis, and the method is characterized in that bright field irradiation and dark field irradiation are respectively carried out on a to-be-detected object made of a transparent material in transmission, and a camera acquires a bright field image and a dark field image of the surface of the to-be-detected object in a time-sharing exposure mode; after suspected defects are extracted from a bright field, the suspected defects are converted into a dark field for re-judgment, complex and time-consuming filtering processing is not required to be designed in the bright field, and the overall operation time is shortened; comprehensive processing is carried out in the bright anddark field images, and discrimination for distinguishing defects and dust is achieved through dark field assistance, so that the defect detection rate is improved; complex frequency domain processingis not needed, the development period is shortened, and the later maintenance of developers is easy; and the whole logic design is simplified, the algorithm development period is shortened, the algorithm operation efficiency is improved, and the detection problem in the actual production process of the AOI equipment is improved.

Owner:BEIJING FOCUSIGHT TECH

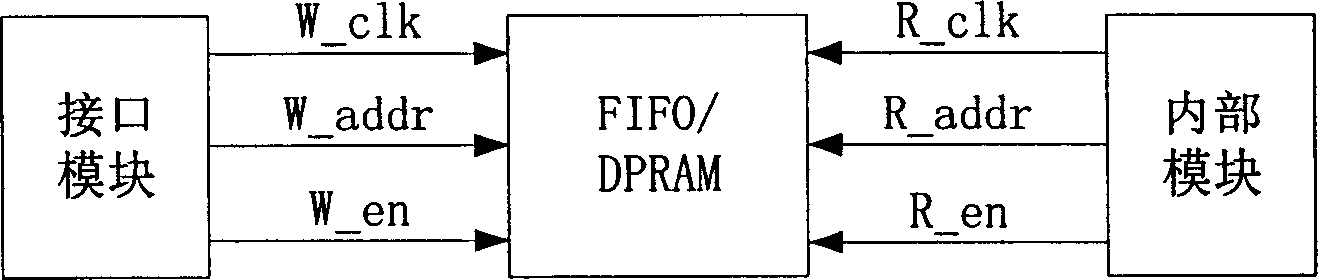

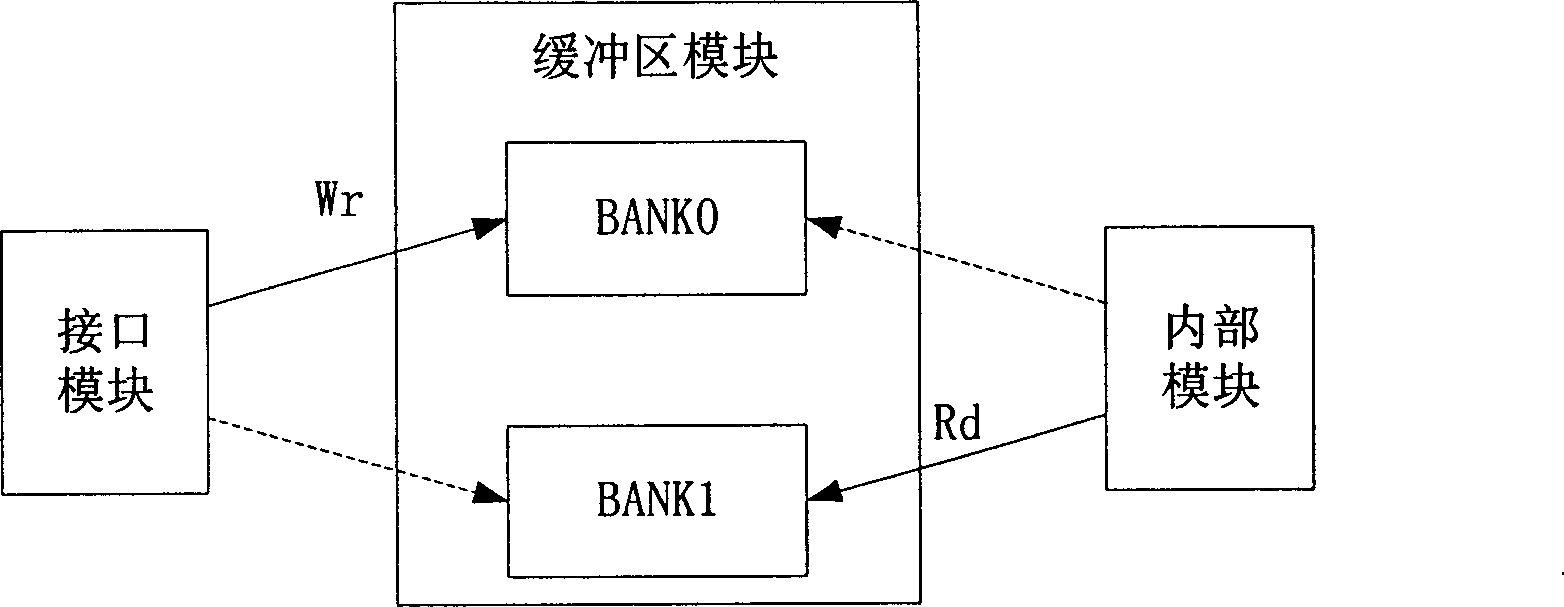

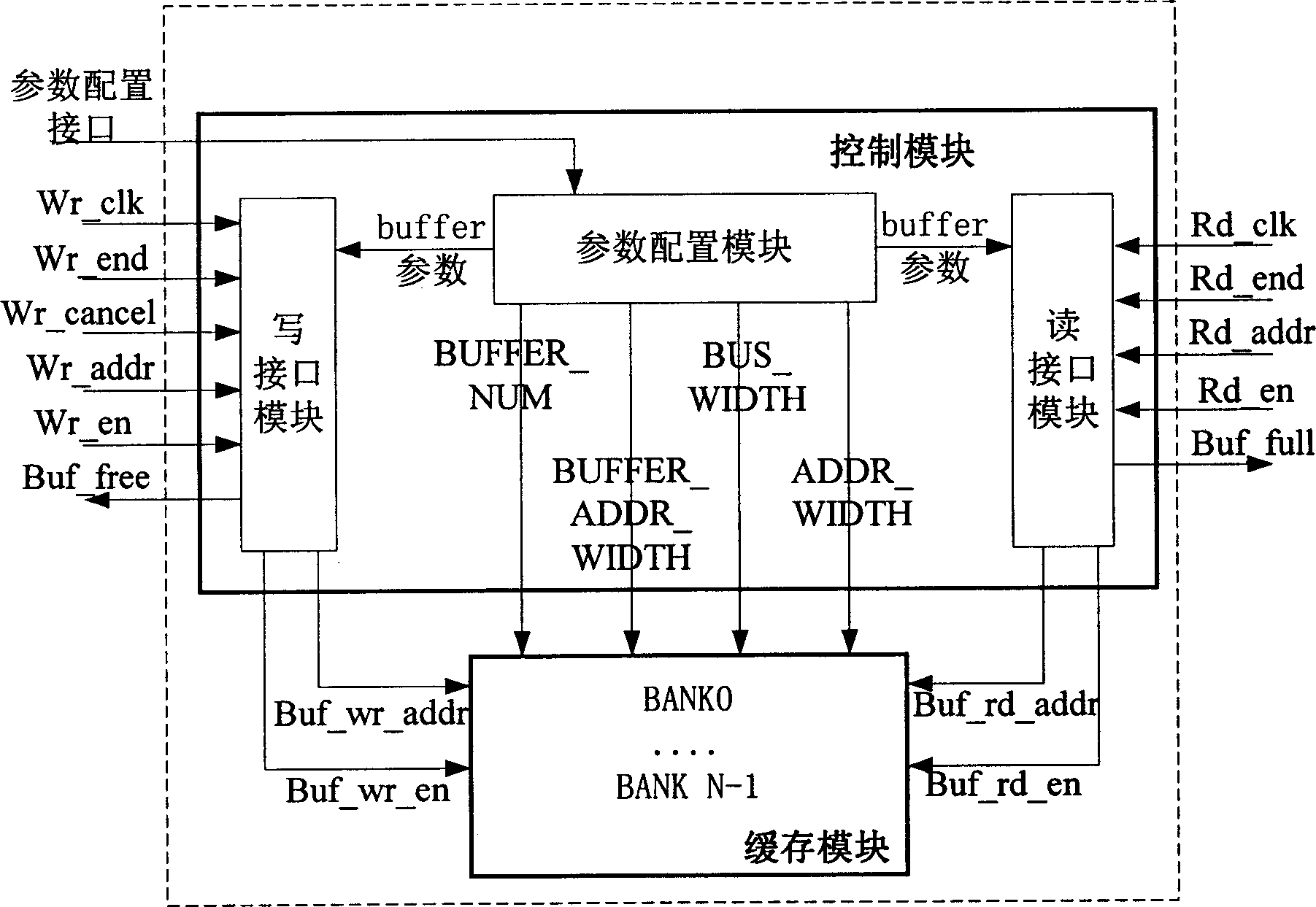

Dynamic self-management buffer zone

InactiveCN1851633AEasy to manageSimplify Logic DesignInput/output to record carriersExternal Bus InterfaceExternal interface

The present invention includes control module and cache module, wherein said cache module divided into plurality of BANK spaces; control module used for receiving outer read-write signal, controlling data writing / reading out cache module every BANK, and configuring inner BANK of cache module. Said control module also includes writing interface module, interface module, parameter configuring module, wherein writing interface module used for receiving outer write data signal and controlling data writing cache module BANK; read interface module used for receiving outer read data signal, controlling data reading out cache module BANK; parameter configuring module used for transferring configuration parameter to cache module to proceed configuring and transferring configuration parameter to writing interface module and read interface module. The present invention can simplify outside managing to buffer zone, and to make the external interface not concerning buffer zone inner BANK structure.

Owner:HUAWEI TECH CO LTD

Clock and data recovery (CDR) architecture and phase detector thereof

ActiveUS8457269B2Simplify Logic DesignSave powerPulse automatic controlAngle demodulation by phase difference detectionPhase detectorData signal

Owner:NCKU RES & DEV FOUND +1

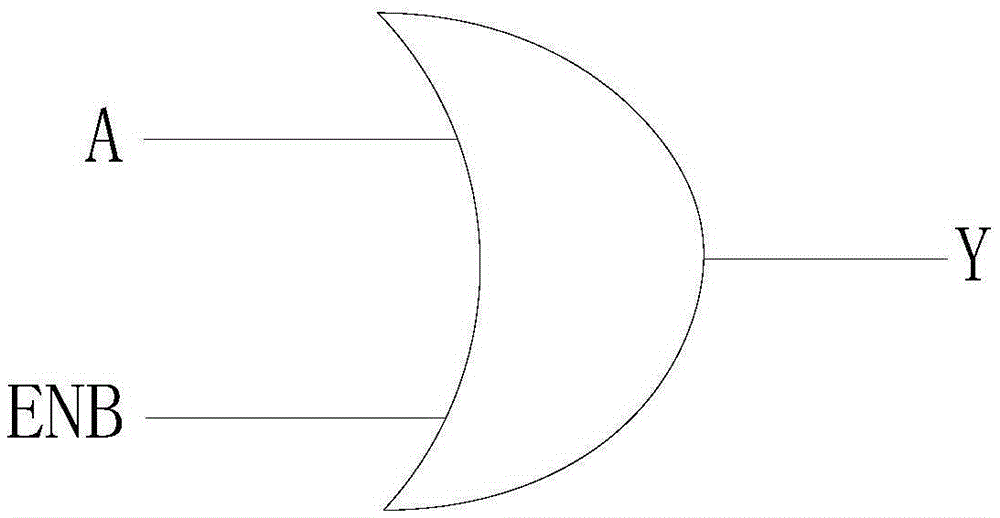

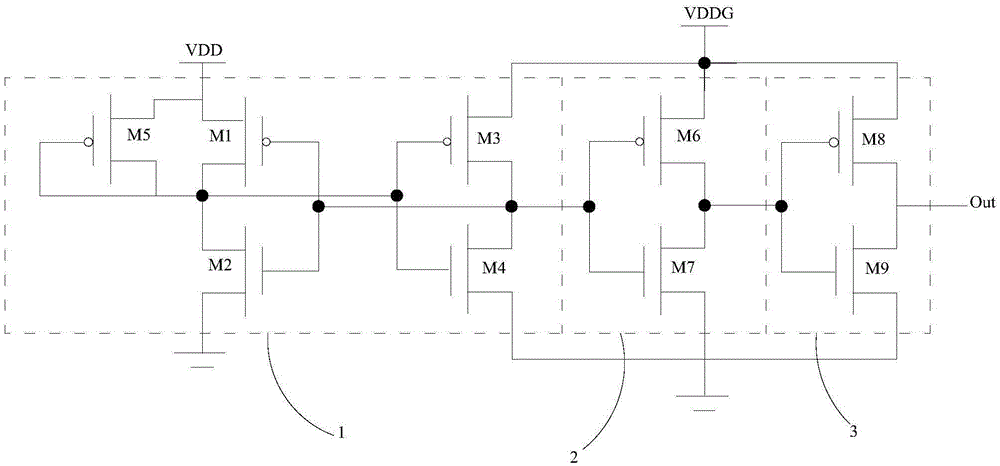

Isolation control circuit

ActiveCN105577170ASimplify Logic DesignReduce volumeLogic circuits characterised by logic functionVoltage variationControl circuit

The invention provides an isolation control circuit. The isolation control circuit, an isolation unit and a to-be-switched-off region are integrated in a same chip. The isolation control circuit is electrically connected with the isolation unit and the to-be-switched-off region; the isolation control circuit comprises a detection class connected to the to-be-switched-off region; and the detection class detects the voltage change of the to-be-switched-off power supply in the to-be-switched-off region and outputs stable switch-off or switch-on signals to the enabling end of the isolation unit according to the voltage change of the to-be-switched-off power supply.

Owner:无锡华大国奇科技有限公司

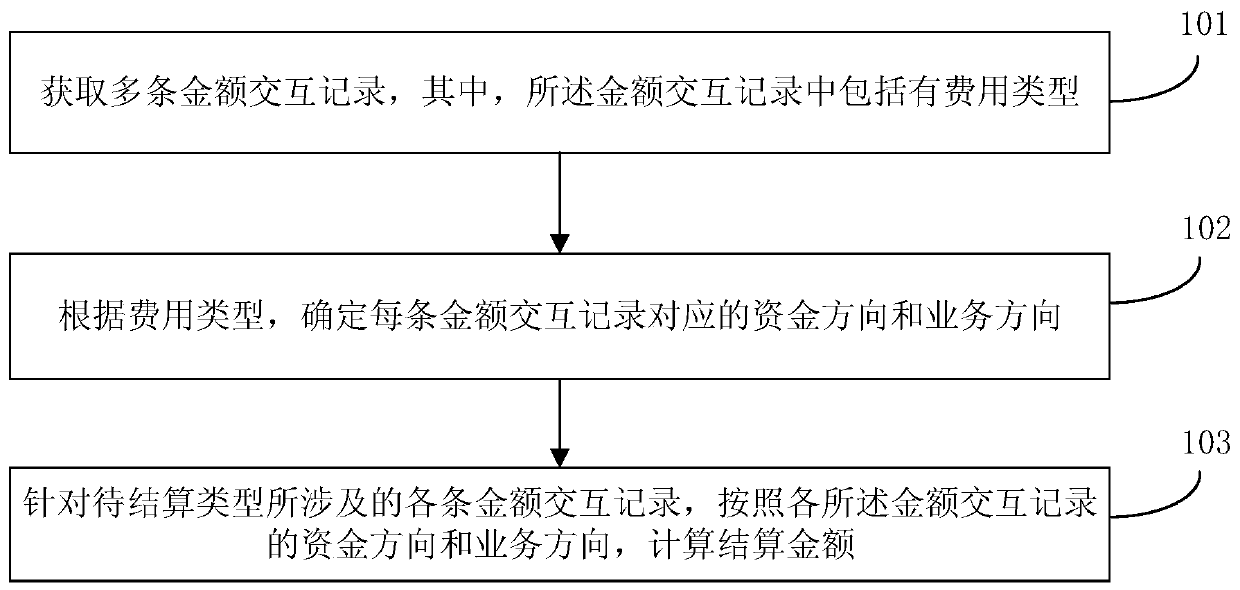

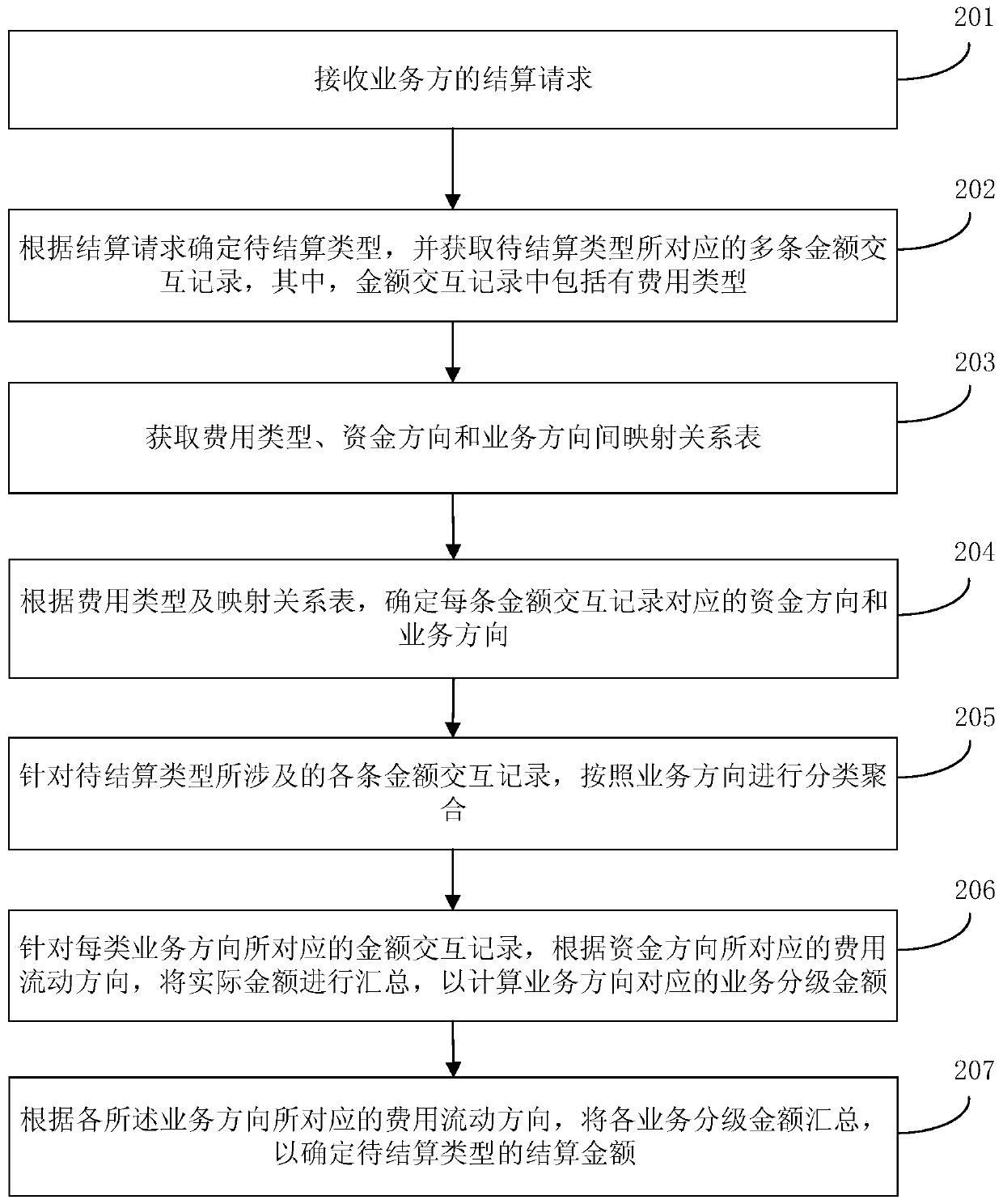

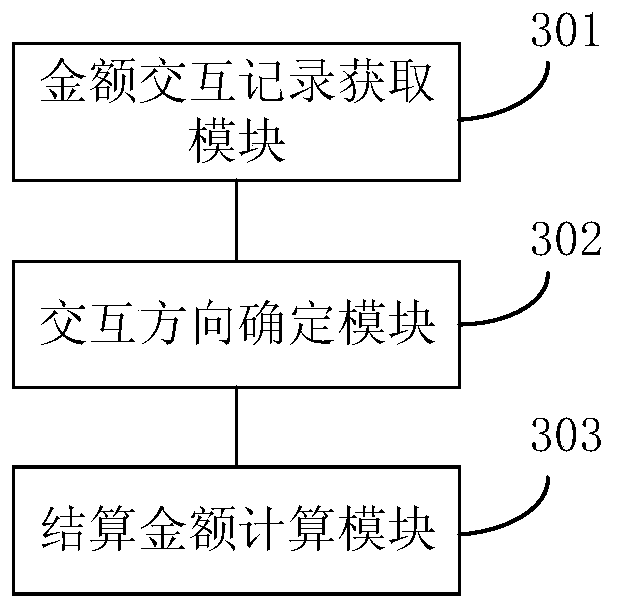

E-commerce platform settlement method and device, storage medium and settlement equipment

PendingCN111311215AOptimize settlement planSimplify Design LogicPayment architectureBuying/selling/leasing transactionsService layerProcess engineering

The embodiment of the invention discloses an e-commerce platform settlement method and device, a storage medium and settlement equipment. The method comprises the steps that multiple amount interaction records are acquired, and the amount interaction records comprise expense types; determining a fund direction and a business direction corresponding to each amount interaction record according to the expense type, the fund direction being used for representing an expense flow direction of the expense type on the e-commerce platform, and the business direction being an expense flow direction defined for the expense type according to business requirements; and for each amount interaction record involved in the to-be-settled type, calculating a settlement amount according to the fund directionand the business direction of each amount interaction record. According to the embodiment of the invention, by adopting the technical scheme, the design logic of the settlement amount is simplified, the calculation of the settlement amount can be carried out in response to various different settlement types, and the calculation of the settlement amount and the flexible decoupling of a service layer can be realized through the fund direction and the service direction of the amount interaction record.

Owner:BEIJING JINGDONG SHANGKE INFORMATION TECH CO LTD +1

Step counting method based on autocorrelation operation

ActiveCN104990562BAvoid counting errorsSimplify Logic DesignAcceleration measurement using interia forcesComplex mathematical operationsCorrelation functionPeak value

Owner:黄山市开发投资集团有限公司

Method for achieving CAM (computer-aided manufacturing) function based on FPGA (Field Programmable Gate Array)

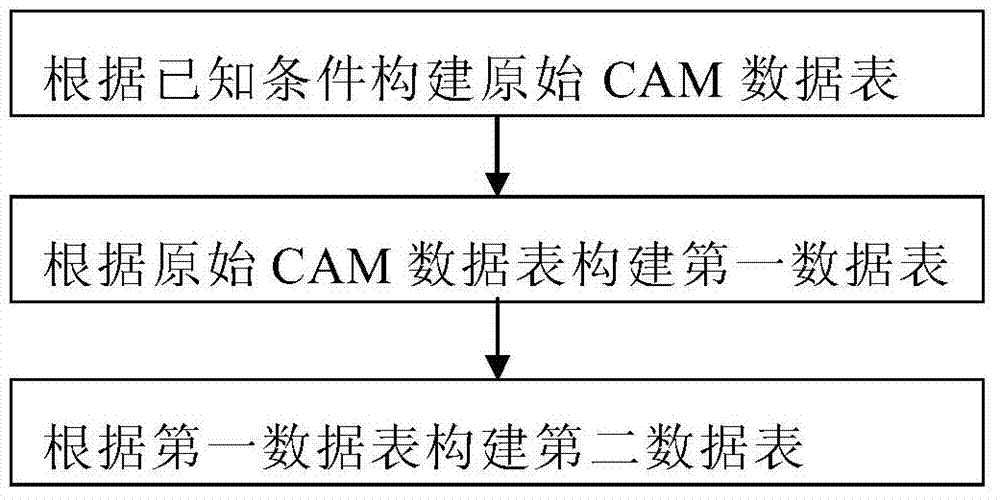

ActiveCN104751879AMeet real-time processing requirementsNo additional costDigital storageWire speedRandom access memory

The invention discloses a method for achieving the CAM (computer-aided manufacturing) function based on FPGA (Field Programmable Gate Array). The method comprises the following steps: constructing an original CAM data table according to the known conditions, wherein the CAM data table at least comprises a first address entry and a second address entry; constructing a first data table according to the first address entry in the original CAM data table and saving the first data table into an RAM (random-access memory) of the FPGA, wherein the first data table adopts the first address entry as an address index and the second address entry as corresponding data content; and constructing a second data table according to the second address entry of the first data table and saving the second data table into another RAM of the FPGA, wherein the second data table adopts the second address entry as an address index and the first address entry as corresponding data content. According to the method, the internal resource of the FPGA is utilized, all medium-small capacity CAM functions can be achieved, the logic design is simple, the linear speed real-time processing requirement can be met, the method can be flexibly customized and has strong universality, and additional cost is avoided.

Owner:BEIJING DATANG GOHIGH DATA NETWORKS TECH CO LTD

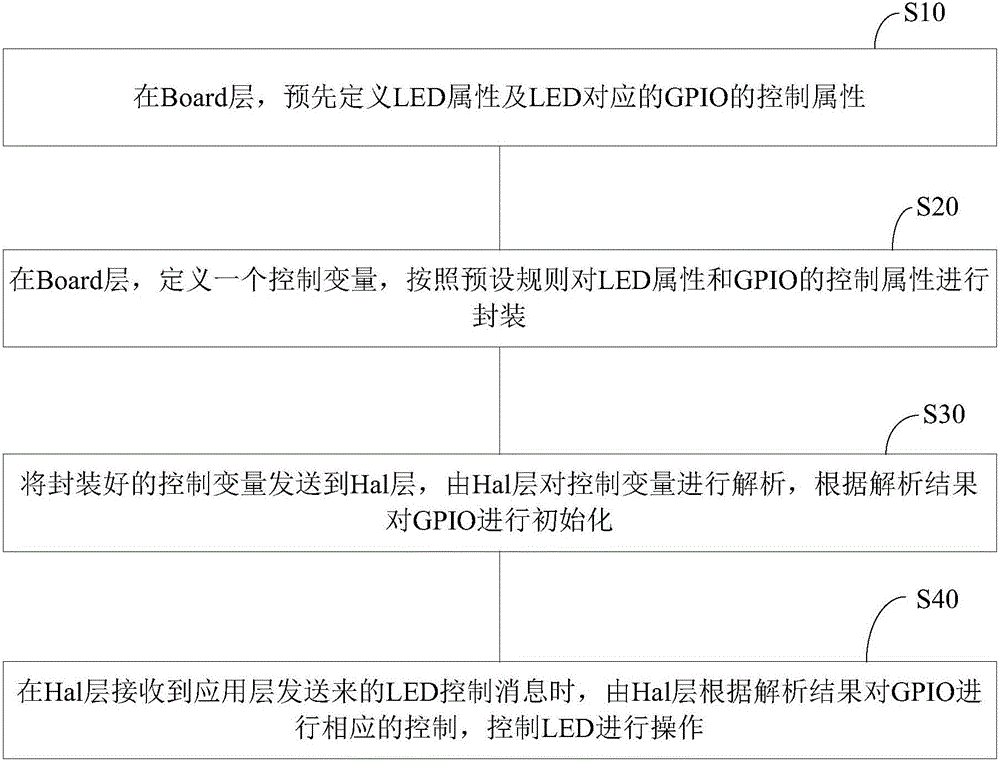

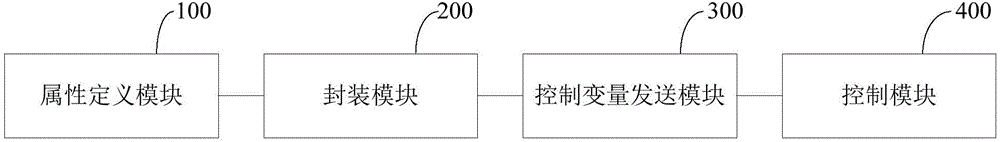

Management and control method and system for controlling GPIO of set-top box LED

ActiveCN106792052AImprove processing efficiencyAvoid Control ProblemsSelective content distributionElectric digital data processingProtocol ApplicationComputer science

The invention relates to a management and control method and system for controlling a GPIO of a set-top box LED. The method comprises the following steps: defining LED attributes and control attributes of the GPIO in advance, then packaging the defined attributes in a preset control variable, sending the packaged control variable to an Hal layer for analysis, initializing the GPIO through the defined attributes, and when an application layer operates the LED, performing management and control on the GPIO by the Hal layer by fast inquiry according to the defined attributes so as to accomplish the operation of the LED. The management and control of the GPIO are very simple and flexible. As the necessary LED attributes and control attributes of the GPIO are defined in advance, when the GPIO controlling the LED changes, only the defined attributes are modified on a Board layer and are sent to the Hal layer for analysis, the logic design is simple, the repetitive work of the Hal layer to continuously set the GPIO is relieved, the CPU processing efficiency is improved, and the control problem of the LED is avoided.

Owner:SHENZHEN JIUZHOU ELECTRIC

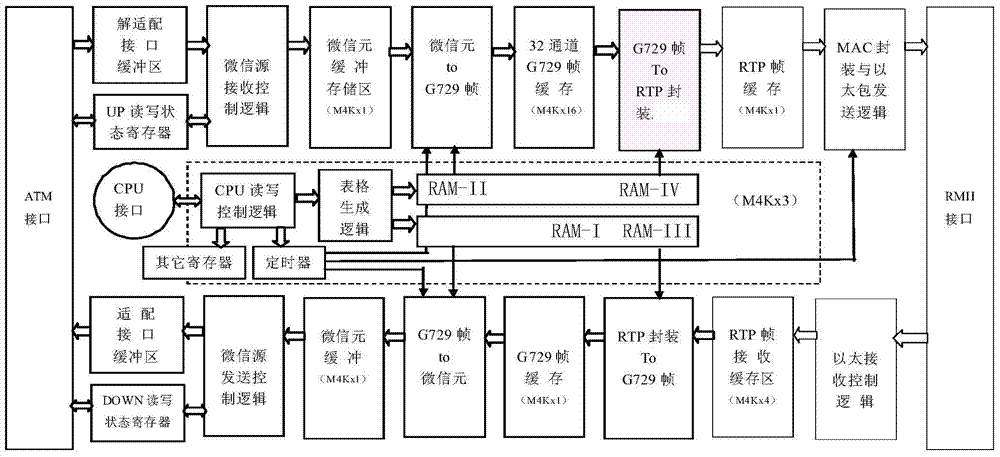

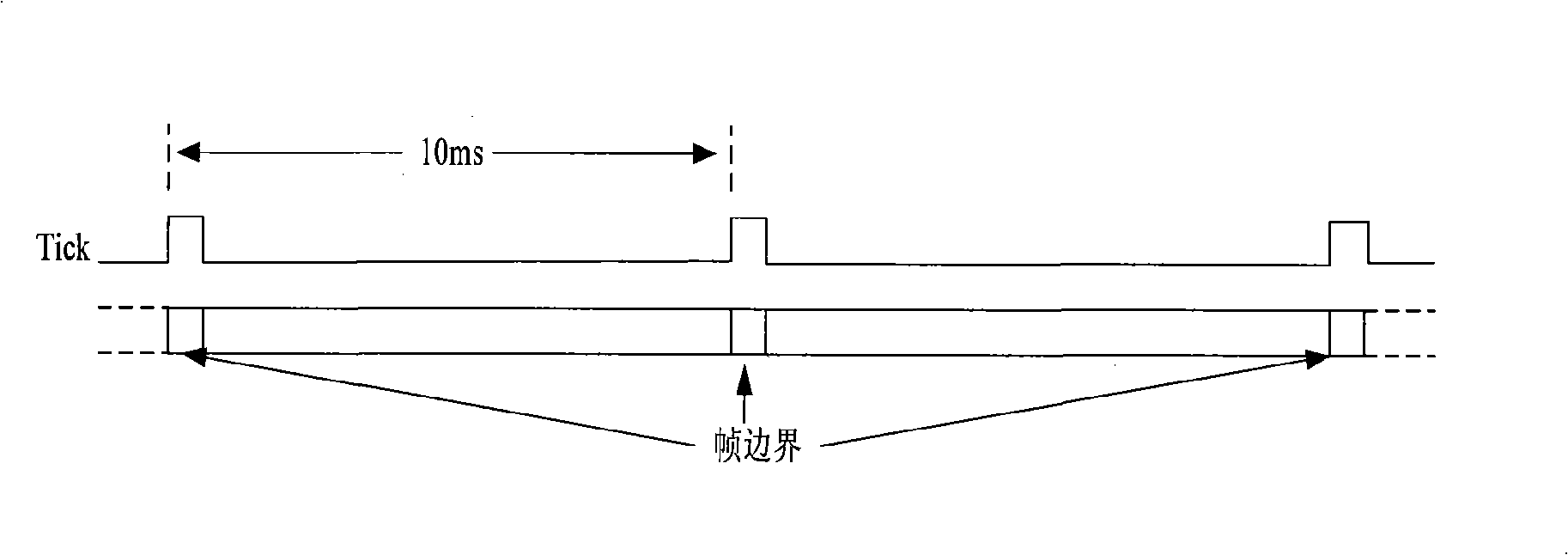

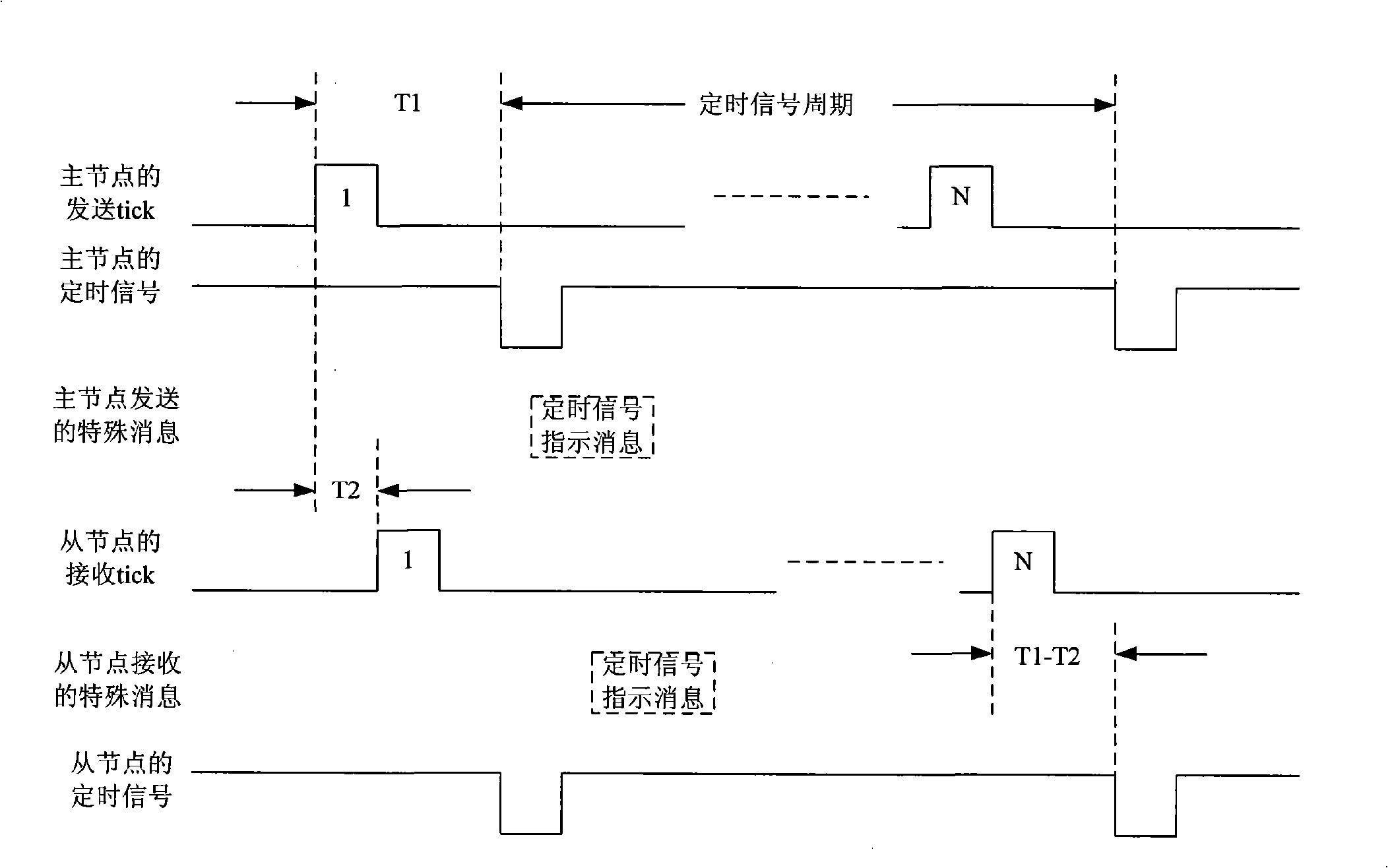

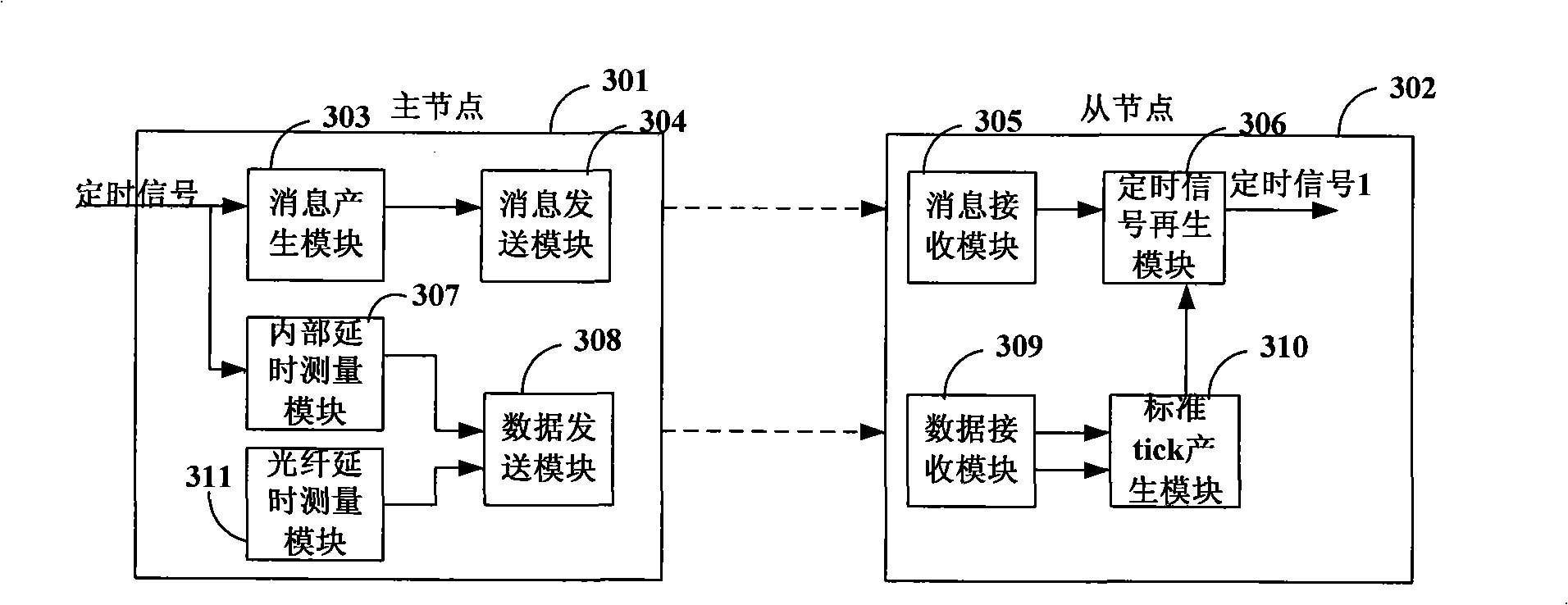

Timing signal transmitting method and system based on OBSAI protocol

InactiveCN101286797ASimplify Logic DesignReduce mistakesTransmission monitoringRadio transmission for post communicationTime signalPulse time

The invention discloses a timing signal transmission method which has high reliability and simple realization based on an OBSAI protocol, and a system thereof. The main technical proposal of the method includes that: 1. a standard tick is respectively constructed in each sub-node, wherein, the phase position of the standard pulse of the sub-node adjacent to a master node should correspond to the phase position of the standard pulse of an adjacent upstream node; 2. the advanced timing signal pulse of a master node broadcasts a timing signal indication message to each sub-node in a span; 3. after receiving the timing signal indication message, each sub-node respectively generates the timing signal of the node in the next pulse time of the standard tick. The invention can be taken as a substitute for the self-contained timing signal transmission proposal of the OBSAI protocol.

Owner:GLOBAL INNOVATION AGGREGATORS LLC

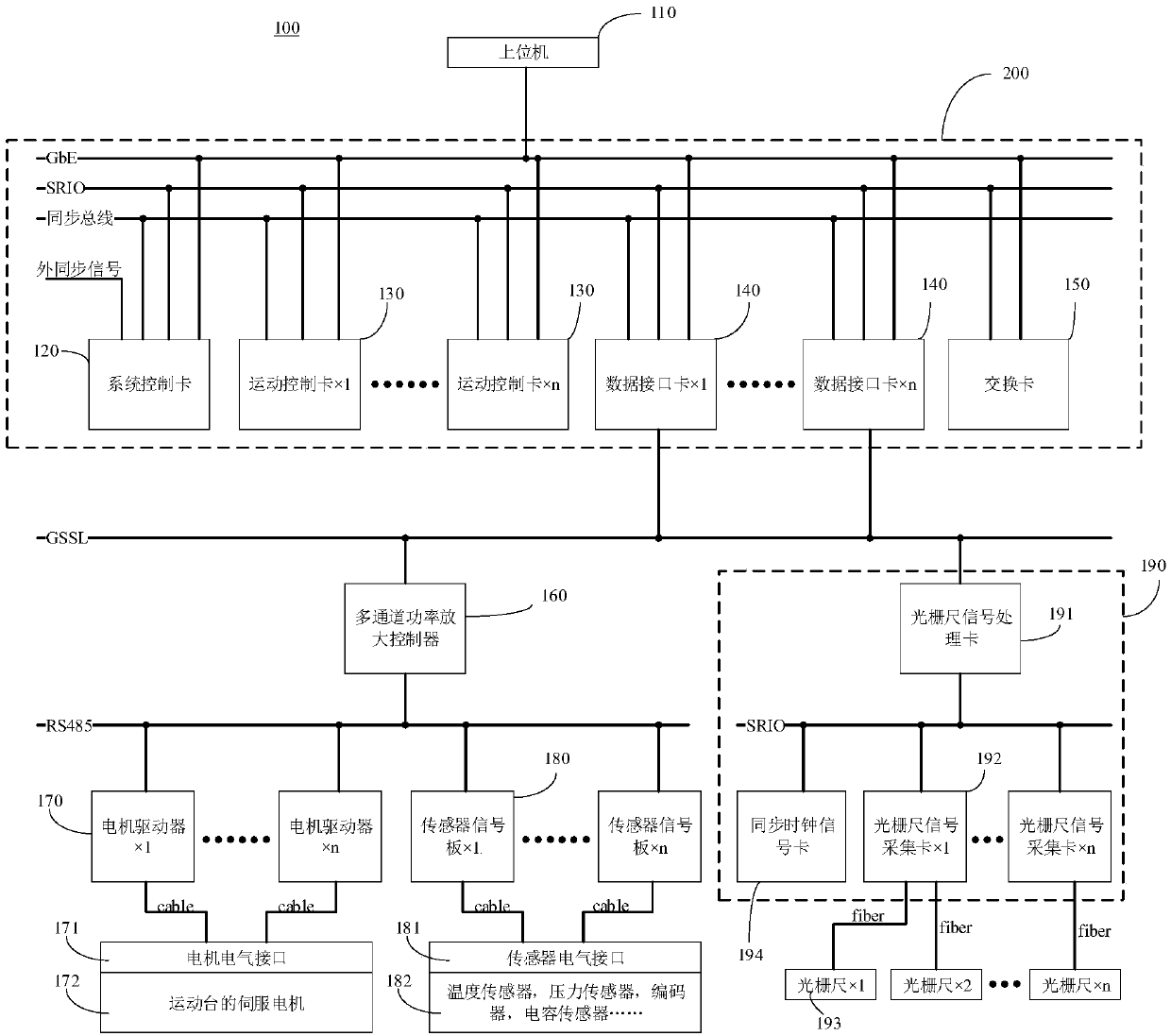

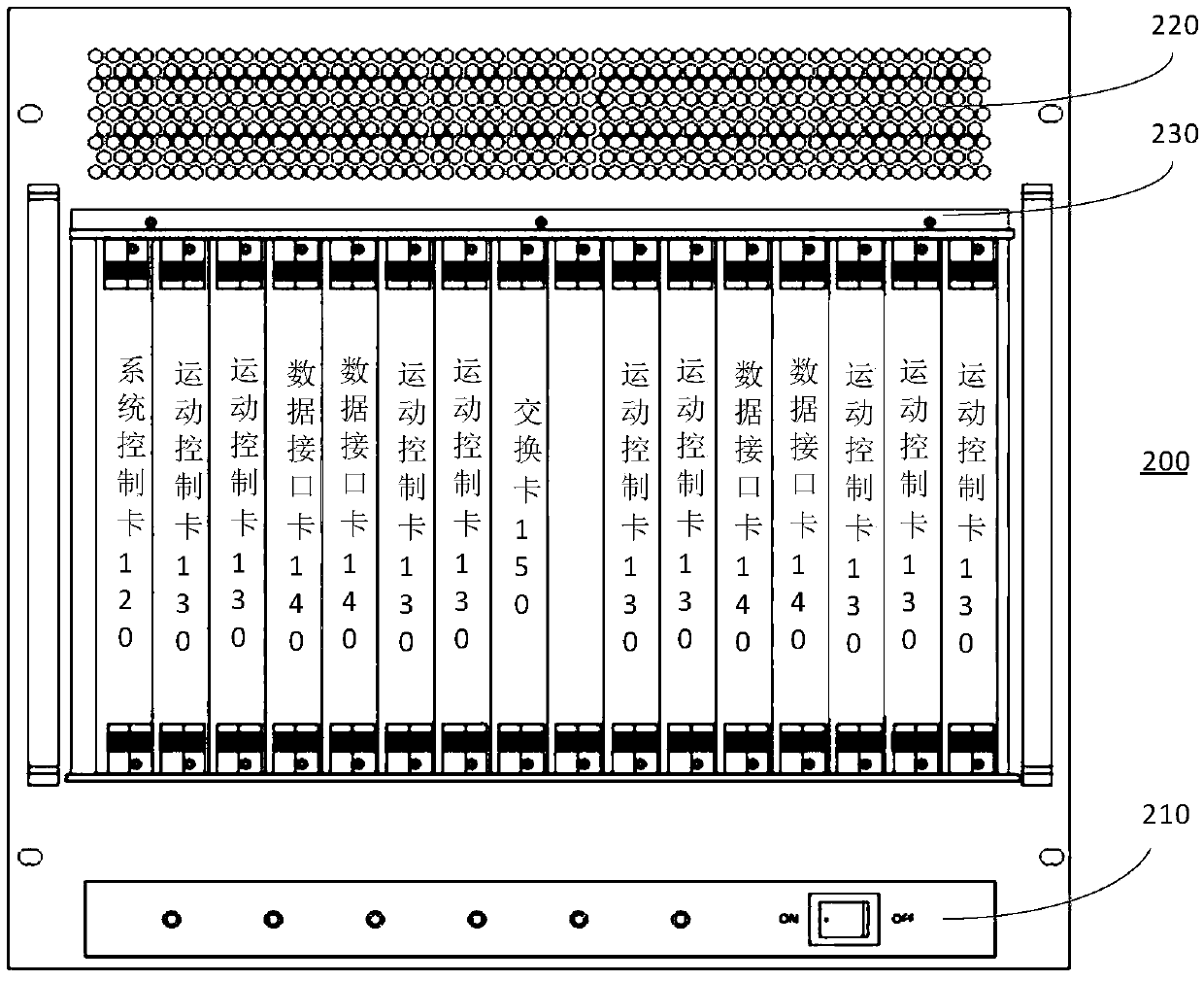

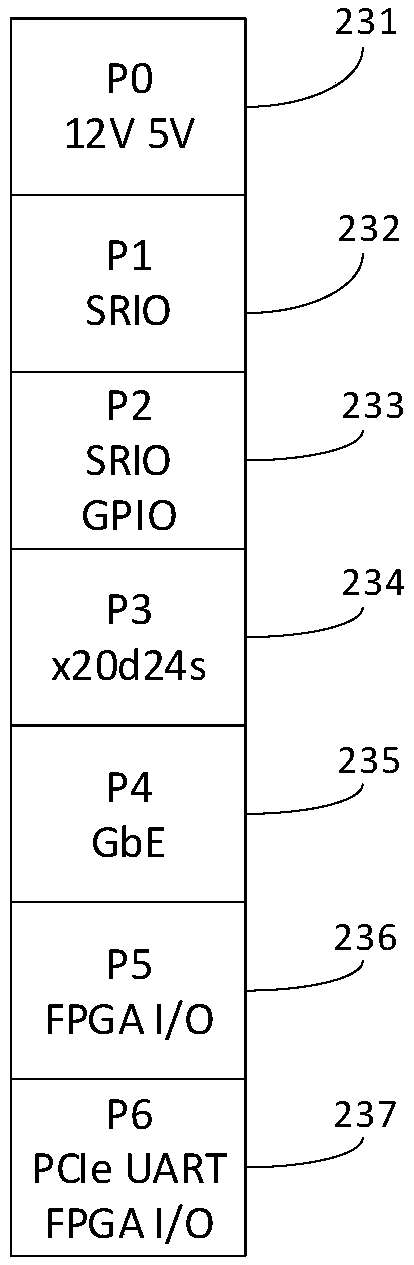

Photoetching machine control system and method

InactiveCN110874020ASimple control protocolSimplify Logic DesignPhotomechanical exposure apparatusMicrolithography exposure apparatusElectric machineryEmbedded system

The invention provides a photoetching machine control system and method. The control system comprises a system control card, a motion control card, a data interface card, an exchange card, a multi-channel power amplification controller, a motor driver, a sensor signal board, a position measurement unit and an upper computer. According to the invention, the motion precision and speed of a motion platform motor can be improved, and electromagnetic interference is reduced.

Owner:SHANGHAI MICRO ELECTRONICS EQUIP (GRP) CO LTD

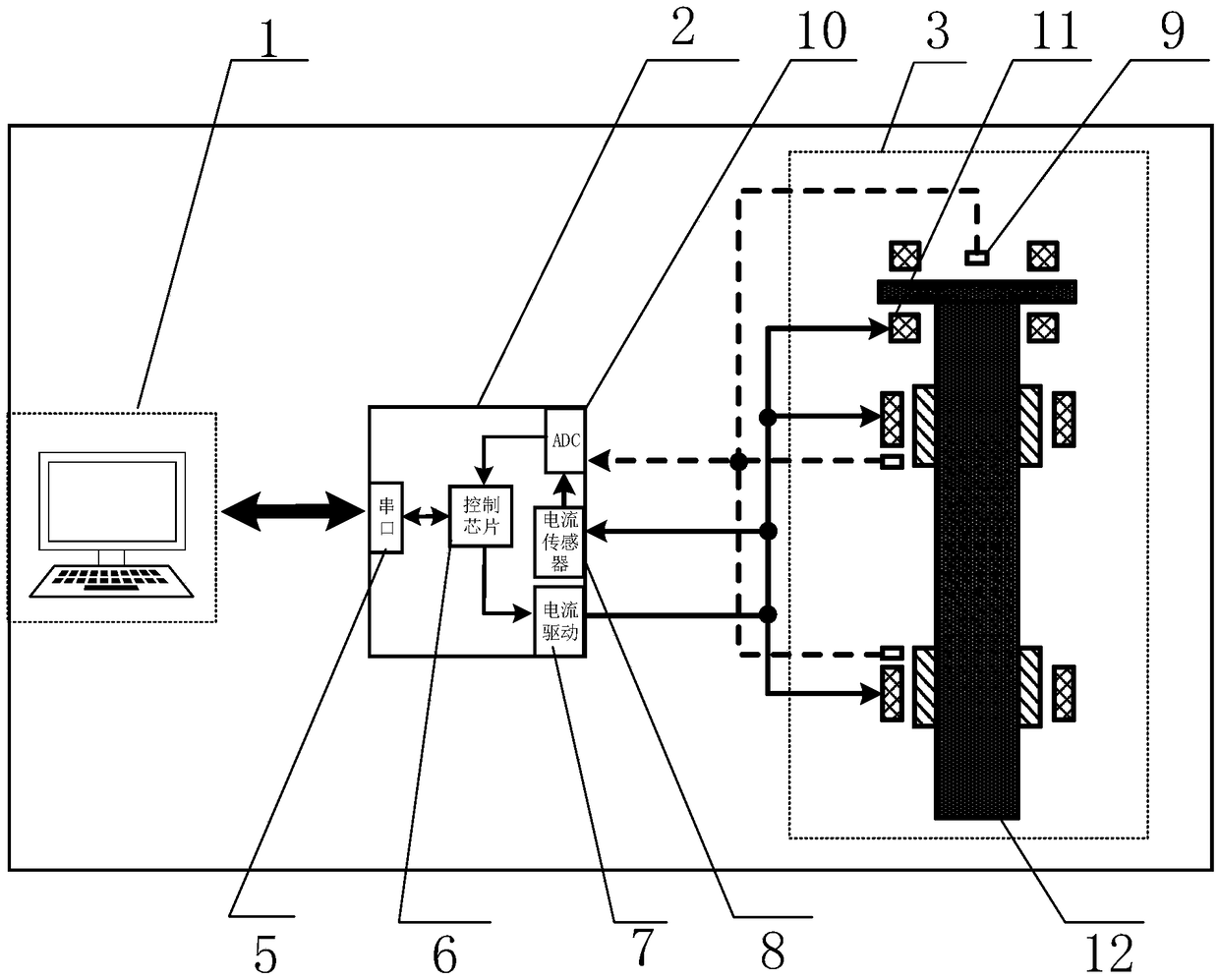

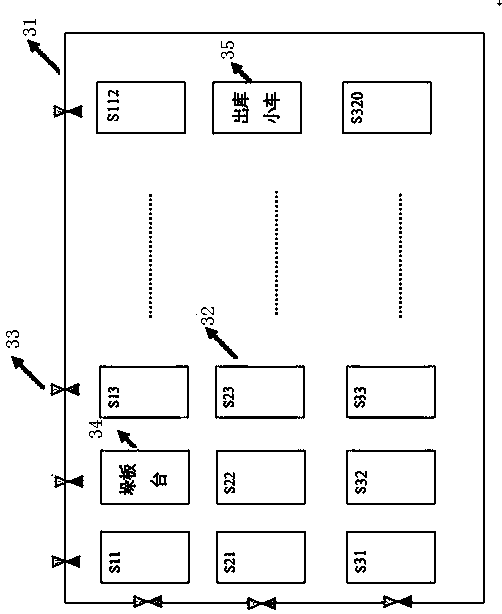

Real-time control system of magnetic suspension electric main shaft and magnetic suspension electric main shaft

The invention discloses a real-time control system of a magnetic suspension electric main shaft and the magnetic suspension electric main shaft. The system comprises an upper debugging machine and a control circuit; the control circuit comprises a controller, a current driving module, a current sensor and a sampling module; an input end of the current sensor is used for acquiring coil current of the magnetic suspension electric main shaft; a first input end of the sampling module is connected to an output end of the current sensor, and a second input end is used for acquiring position signalsof the magnetic suspension electric main shaft; an input end of the controller is connected to an output end of the sampling module, a parameter input end is connected to a parameter output end of theupper debugging machine, and a state output end is connected to a state input end of the upper debugging machine; and an input end of the current driving module is connected to an output end of the controller, and an output end is used for driving a coil of the magnetic suspension electric main shaft. The system can improve the control instantaneity and reliability, realizes online testing and adjustment of internal parameters thereof, and meanwhile, guarantees low cost.

Owner:HUAZHONG UNIV OF SCI & TECH

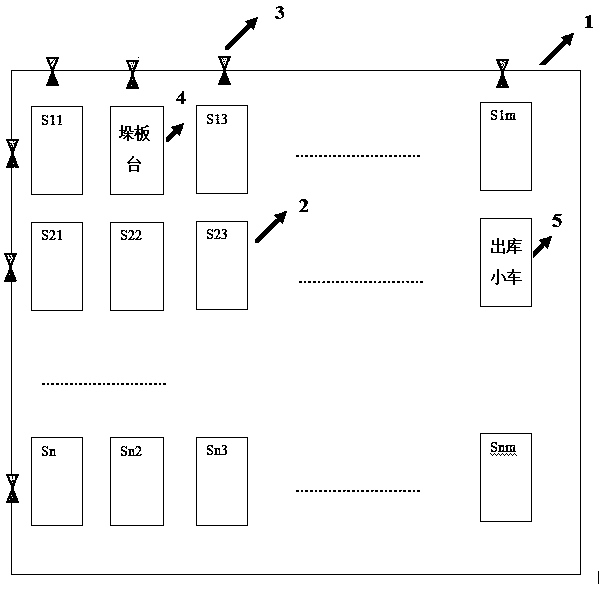

Unattended plate blank warehouse intelligent tracking management control device

The invention relates to an unattended plate blank warehouse intelligent tracking management control device. The control device comprises an operation interface module, a plate blank warehouse positioning module, an inventory information module, a plate blank warehouse-in module, a plate blank warehouse-out module, a plate blank displacement module, a plate blank information statistics module anda travelling crane control module. According to the technical scheme of the unattended plate blank warehouse intelligent tracking management control device, position-limiting switches are installed atrows and columns of a plate blank warehouse, and accurate positioning of a travelling crane is realized; and the plate blank warehouse is designed into a two-dimensional matrix type, a warehouse-in plate stacking table and a warehouse-out trolley are taken as one point of a two-dimensional matrix correspondingly, the logical design of the whole plate blank warehouse including the plate stacking table and the warehouse-out trolley is simplified, and the work efficiency is greatly improved.

Owner:SHANGHAI MEISHAN IRON & STEEL CO LTD

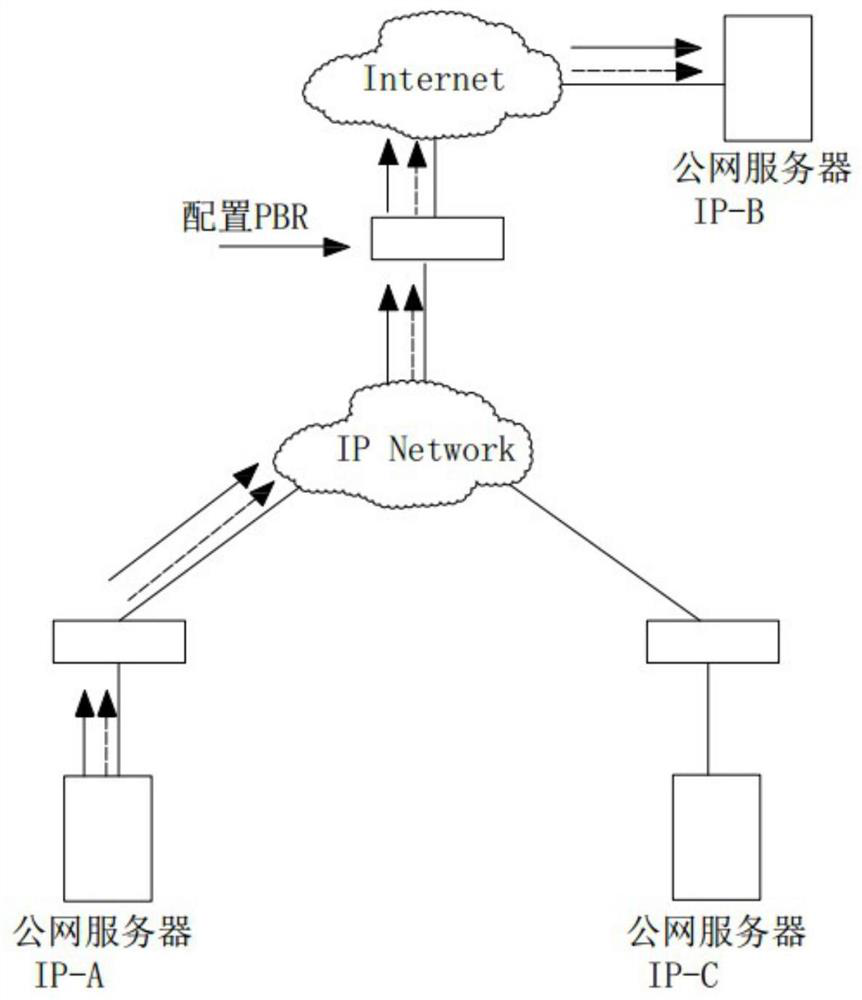

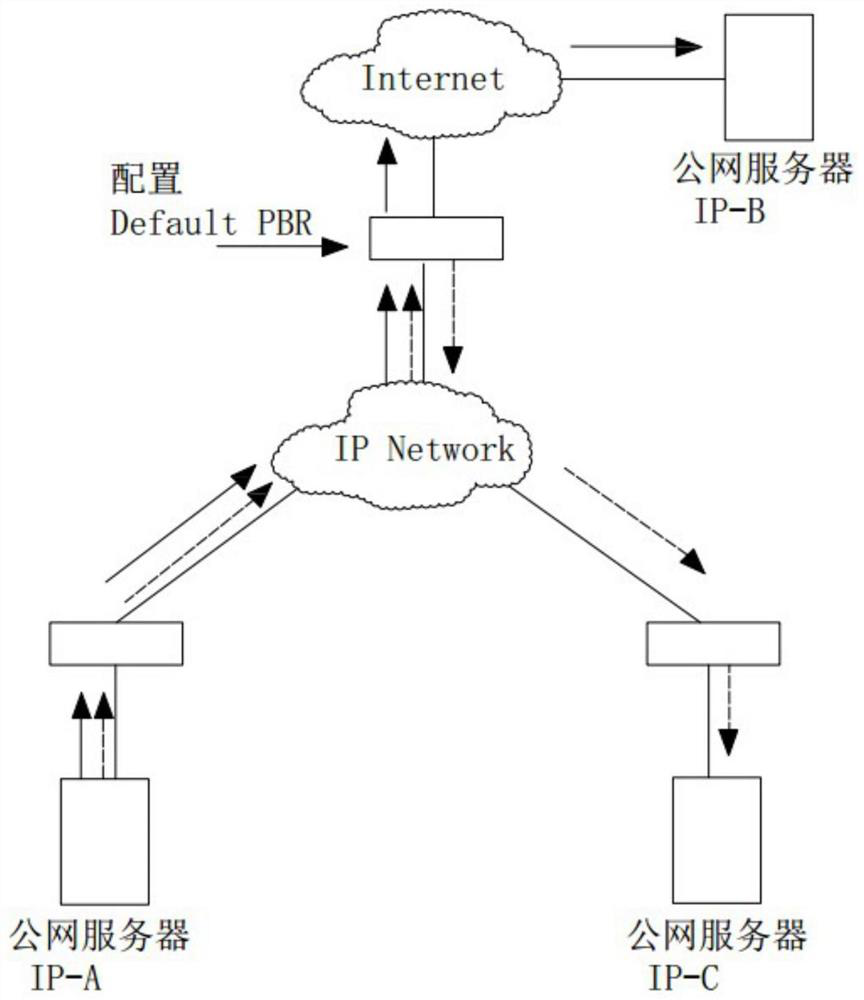

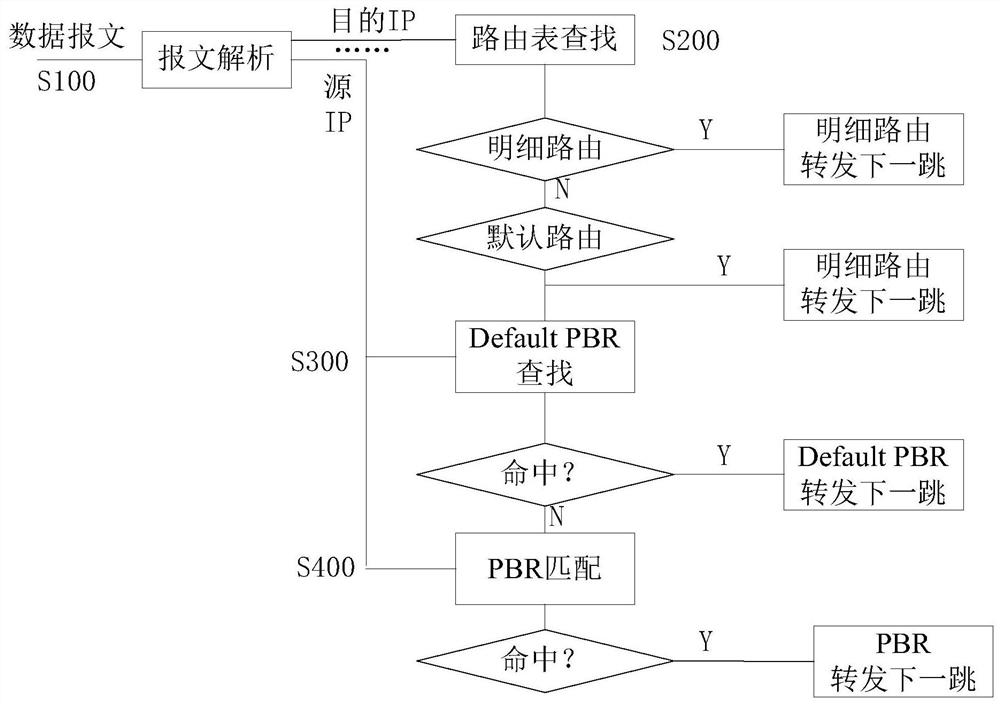

Chip implementation method of default strategy routing and chip processing method and device of data message

The invention discloses a chip implementation method of default strategy routing and a chip processing method and device of a data message. A search matching keyword of the default strategy routing isconfigured to at least comprise a source IP address and a routing matching state, and the routing matching state is obtained according to a search result after a network chip performs routing search;the matching priority of the default policy routing is less than the matching priority of the clear routing. The default strategy routing is realized by enhancing the matching capability of the ACL matching keyword, and the normal access between the private network server and the public network server can be met by deploying the Default PBR on the data center exit gateway equipment on the premiseof not influencing the chip design of the existing routing and PBR technology.

Owner:SUZHOU CENTEC COMM CO LTD

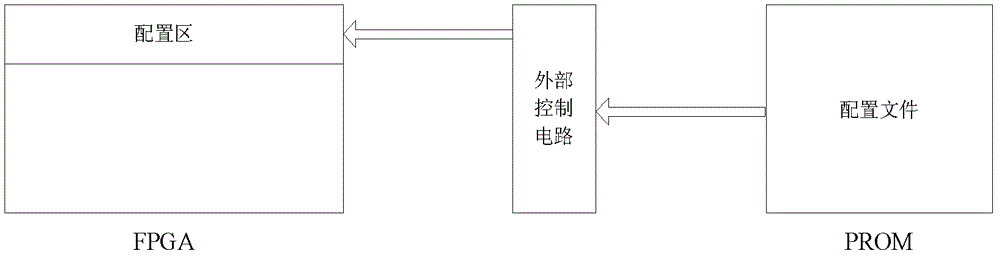

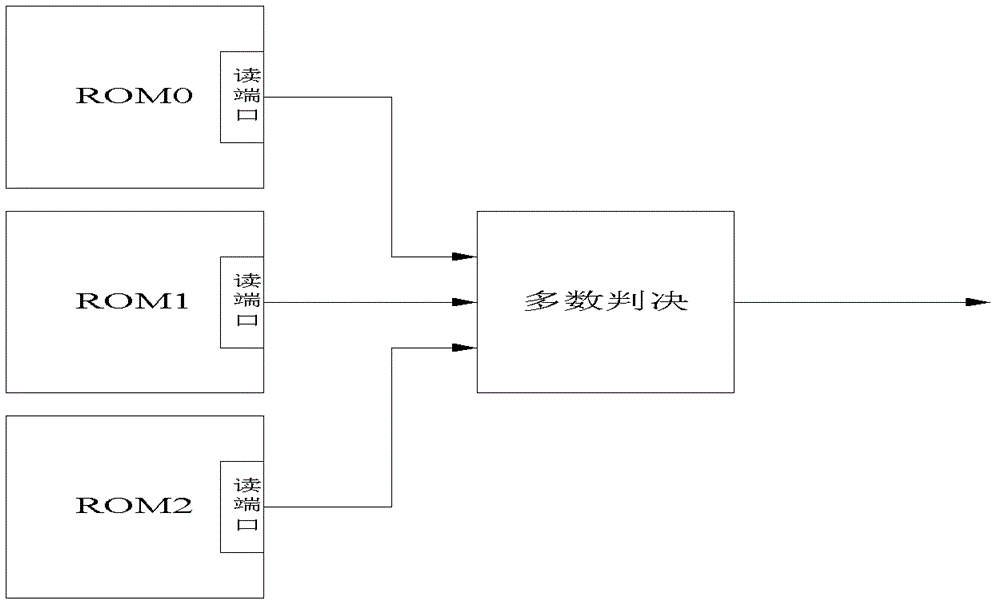

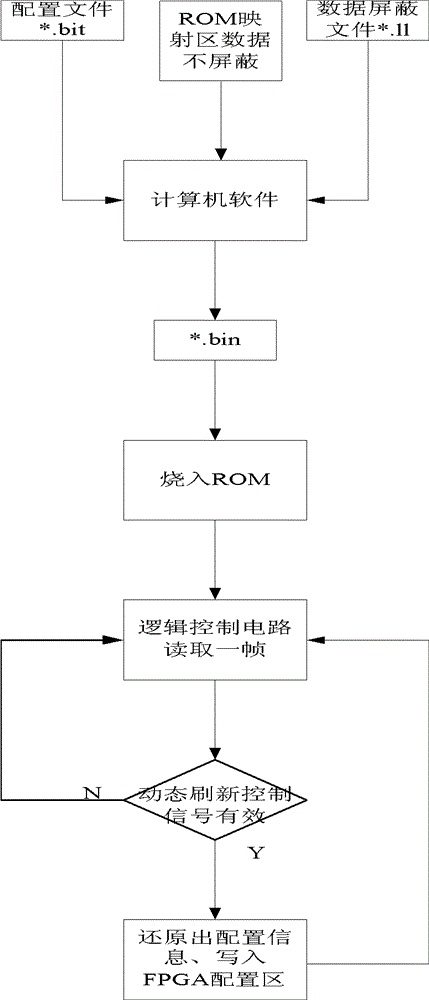

Error correction method for dynamic refreshing of ROM (read only memory) mapping zone in FRGA (field programmable gate array)

ActiveCN102508729BAccurate timingReduce usageRedundant data error correctionStatic random-access memoryDynamic data

The invention discloses an error correction method for dynamic refreshing of a ROM (read only memory) mapping zone and a configuration zone in SRAM (static random access memory) type FRGA (field programmable gate array). The method includes: firstly, reading configuration information in configuration files and shielding information in mask word files, determining dynamic refresh prohibited portions and dynamic refresh permitted portions in the configuration information, and classifying the corresponding configuration information of the ROM mapping zone in the configuration zone into dynamic refresh permitted portions; secondly, recording the configuration information into a new configuration file, and identifying whether the configuration information allows to be dynamically refreshed or not in the FPGA embedded logic operating state in the new configuration file; thirdly, using a logic control circuit to read in the configuration information and identification from the new configuration file during dynamic refreshing, and only reading the dynamic refresh permitted configuration information in the configuration zone of the FRGA. Using the method can permit dynamic data refreshing of the ROM mapping zone during repeated data refreshing of the configuration zone, so that accuracy of the data stored in the ROM can be guaranteed.

Owner:NO 513 INST THE FIFTH INST OF CHINA AEROSPACE SCI & TECH

Write and read common leveling for 4-bit wide DRAMS

ActiveUS10892032B1High resolutionSimplify Logic DesignDigital storageComputer architectureEngineering

System and method of write deskew training for ×4 mode memory control interface configurations. Write leveling logic in the memory controller is adjusted to obtain a write leveling setting for delaying both first and second strobe signals associated with a byte. The adjustment is based on feedback of first set of bits of a byte and irrespective of the feedback of the second set of bits of the byte. The write leveling logic is then anchored at the write leveling setting, and a deskew delay line for the second strobe signal is adjusted to obtain a first deskew setting based on the feedback of the second set of bits. Thus, in write operations, the write leveling setting can be common within the byte even the two strobe signals are transmitted to or received from two different memory storage devices.

Owner:MARVELL ASIA PTE LTD

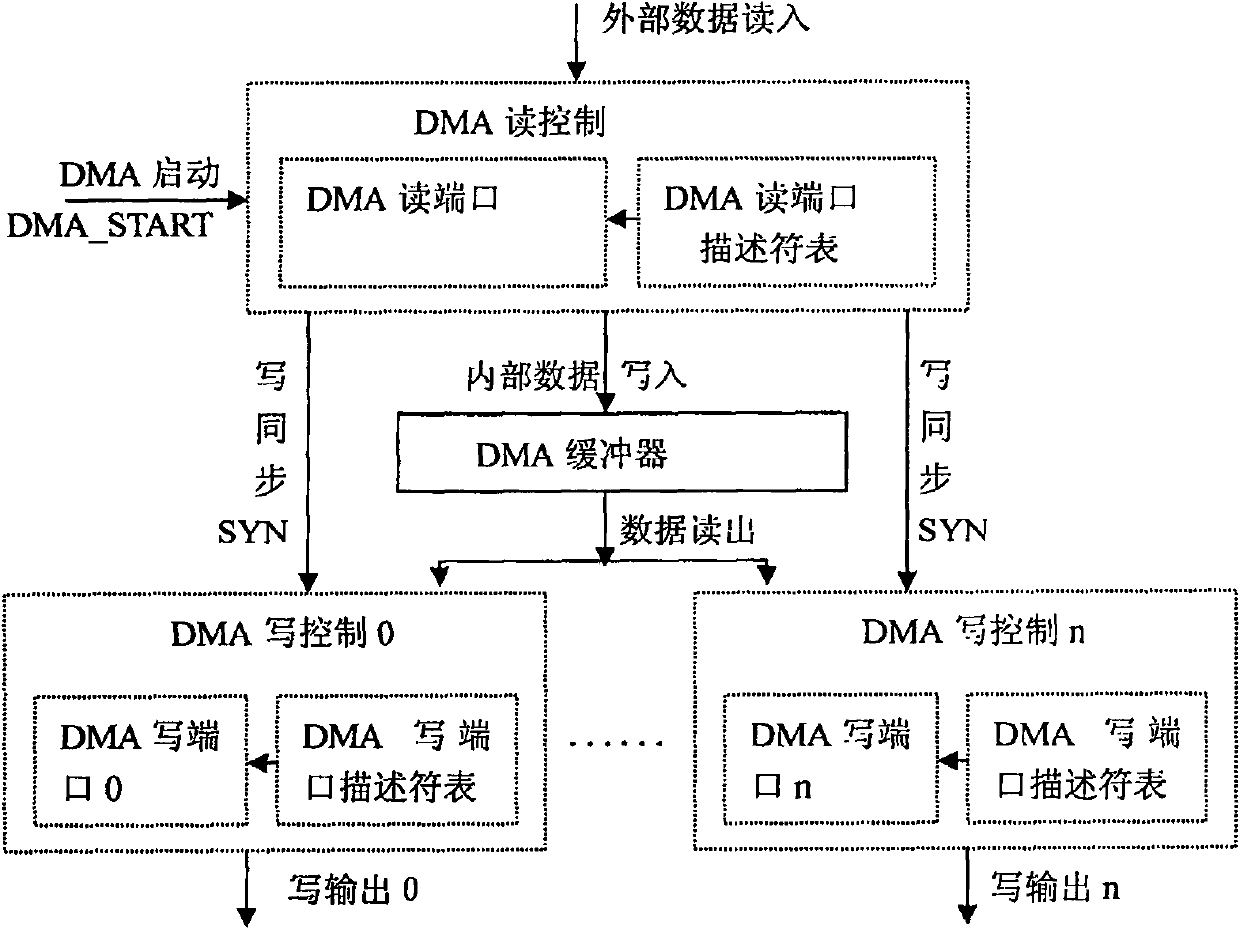

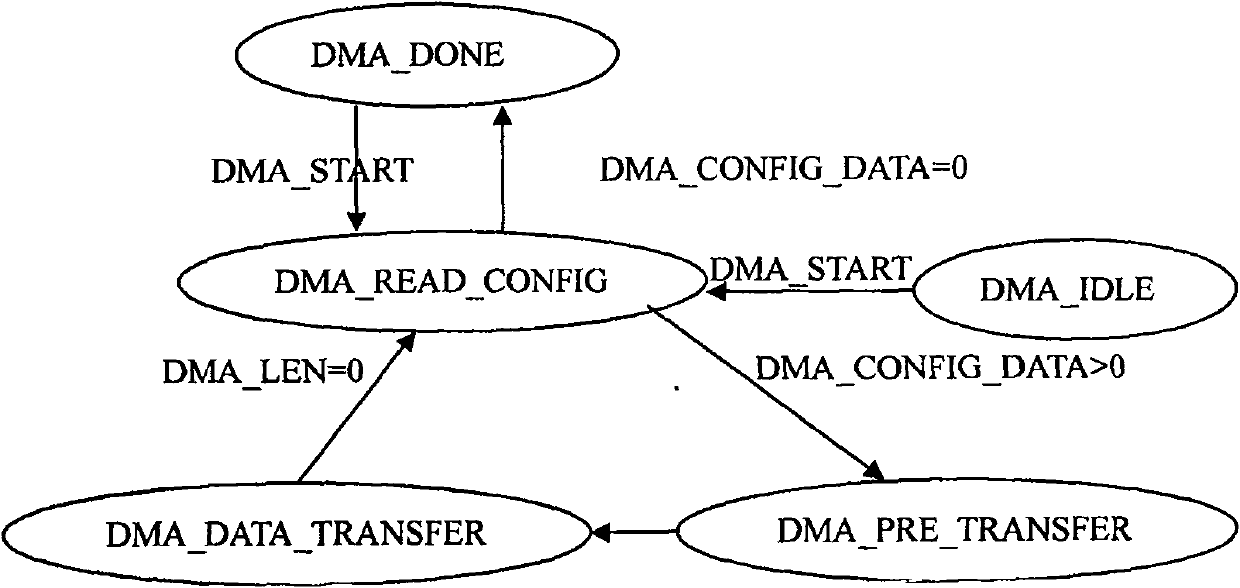

Point to multiple point data allocation DMA controller realization method

ActiveCN100593161CRealize synchronous forwardingSimplify Logic DesignElectric digital data processingData synchronizationTransfer procedure

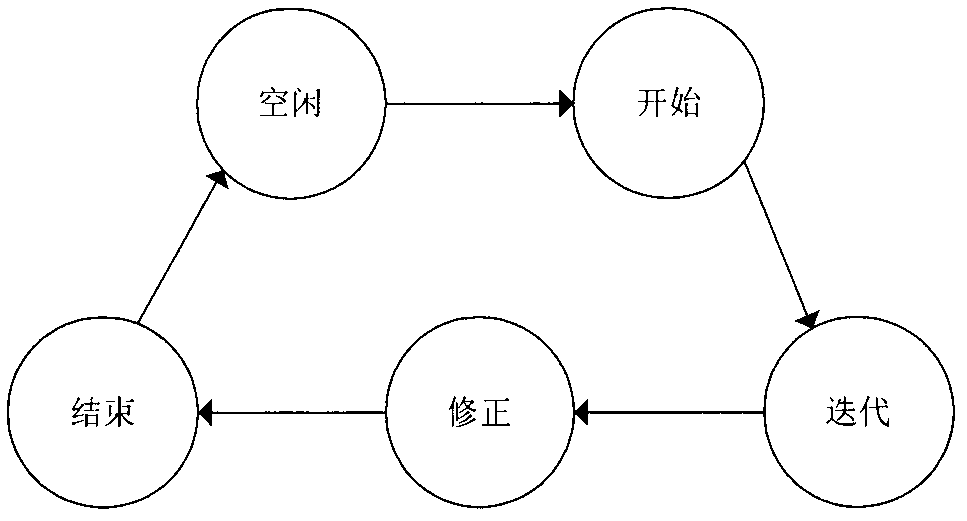

The invention discloses a point-to-multipoint data distribution DMA controller realizing method which includes the following steps: (1) a DMA reading port is established, date is read into a DMA internal buffer from the external data space, and multiple DMA reading-transmission processes can be realized by allocating the descriptors of the DMA reading port; (2) a plurality of DMA writing ports areestablished and each writing port is corresponding to an application interface thereof; (3) different descriptors are allocated for the DMA writing ports, and data customizing is realized by controlling the destination address adding means of the writing ports and shielding the writing operation to special addresses; (4) a state machine is established to realize unified control to the reading port descriptors of the DMA controller, the descriptor loading of each writing port and the start and stop of the DMA; after the reading cycle of the reading port ends, the bus writing cycles of all thewriting ports are started instantly and then an external writing sequence is generated correspondingly according to the descriptors of the writing ports so as to realize the point-to-multipoint data synchronous forwarding.

Owner:NANJING PANENG TECHNOLOGY DEVELOPMENT CO LTD

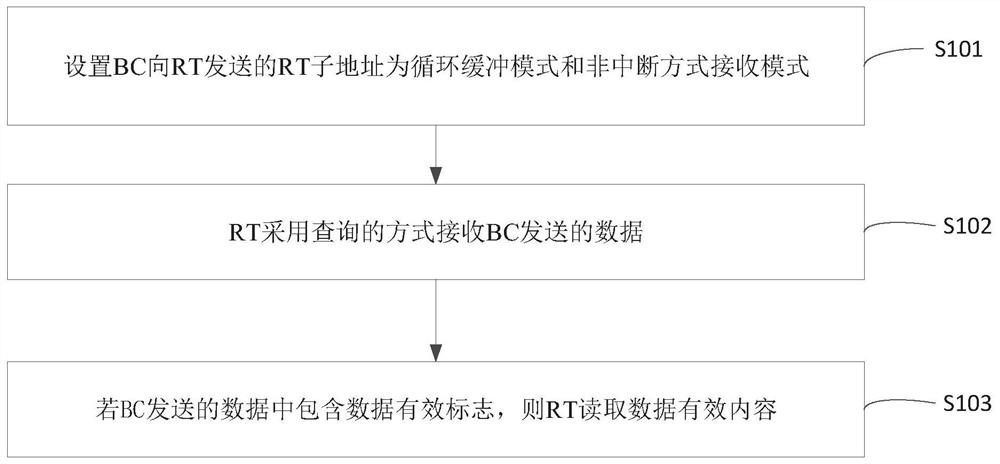

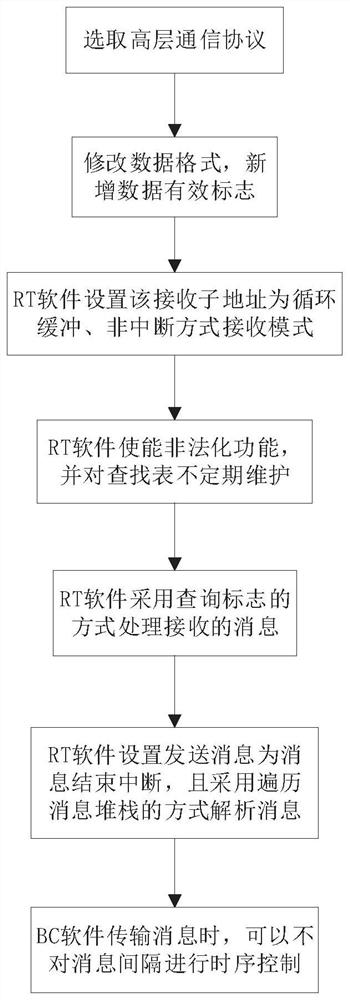

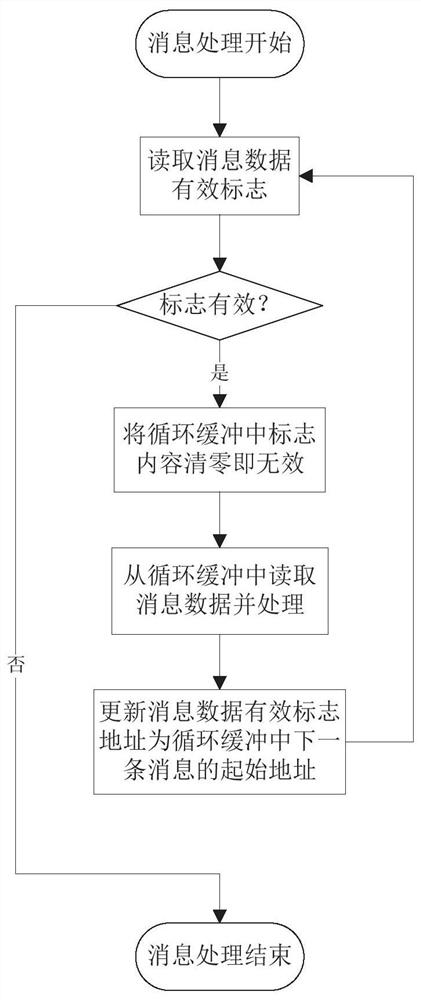

Message-interval-limitation-free 1553B bus communication method and 1553B bus communication system

ActiveCN111813734AImprove reliabilityImprove efficiencyElectric digital data processingCommunications systemBus mastering

The invention provides a message-interval-limitation-free 1553B bus communication method and 1553B bus communication system which are applied to a communication system comprising a bus controller BC and a remote terminal RT. The method is characterized by comprising the following steps that: step 1, an RT sub-address sent to an RT by a BC is set as a cyclic buffer mode and a non-interrupt mode receiving mode, the message content of the data sent by the BC to the RT comprises a data effective mark and data effective content; step 2, the RT receives data sent by the BC in a query mode; and step3, if the data sent by the BC contains a data effective mark, the RT reads the effective content of the data. According to the method provided by the invention, the bus message interval does not needto be limited, so that the reliability of 1553B bus communication is improved, the design logic of BC software is simplified, and the performance and the communication efficiency of the software are improved.

Owner:SHANGHAI AEROSPACE COMP TECH INST

Method for quickly downloading and updating firmware by using I2C (Inter-Integrated Circuit) bus

ActiveCN102375749BSave spaceImprove data transfer efficiencyProgram loading/initiatingProcessor registerSoftware design

The invention provides an implementation method for updating firmware in integrated circuit design, namely a method for realizing quick downloading and updating of the firmware by using an I2C (Inter-Integrated Circuit) bus. 1 is automatically added to an address of a program memory during firmware data transmission by configuring a starting address of the I2C bus program memory before firmware data transmission without additionally transmitting address information of the program memory every time when a piece of byte data is transmitted. Space occupied by a register in design can be reduced, design logic can be simplified, single and continuous data transmission can be supported, data transmission efficiency can be effectively increased, and application requirements can be met. The method is extremely suitable for application environments of smaller software design scales or minor software modification.

Owner:SHANGHAI HUAHONG INTEGRATED CIRCUIT

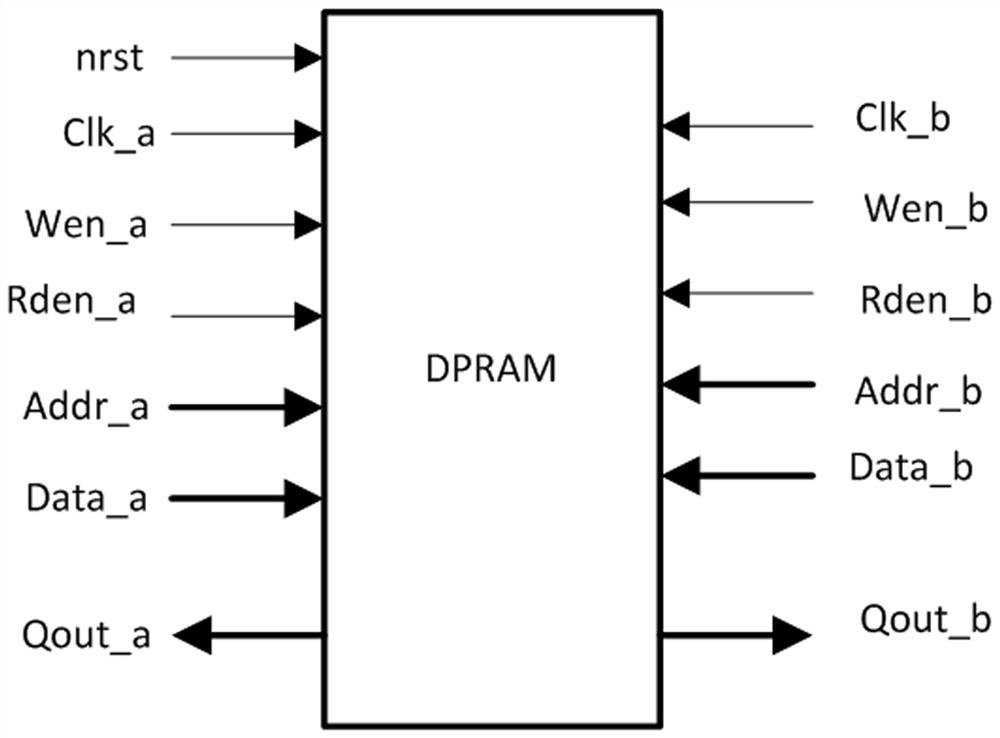

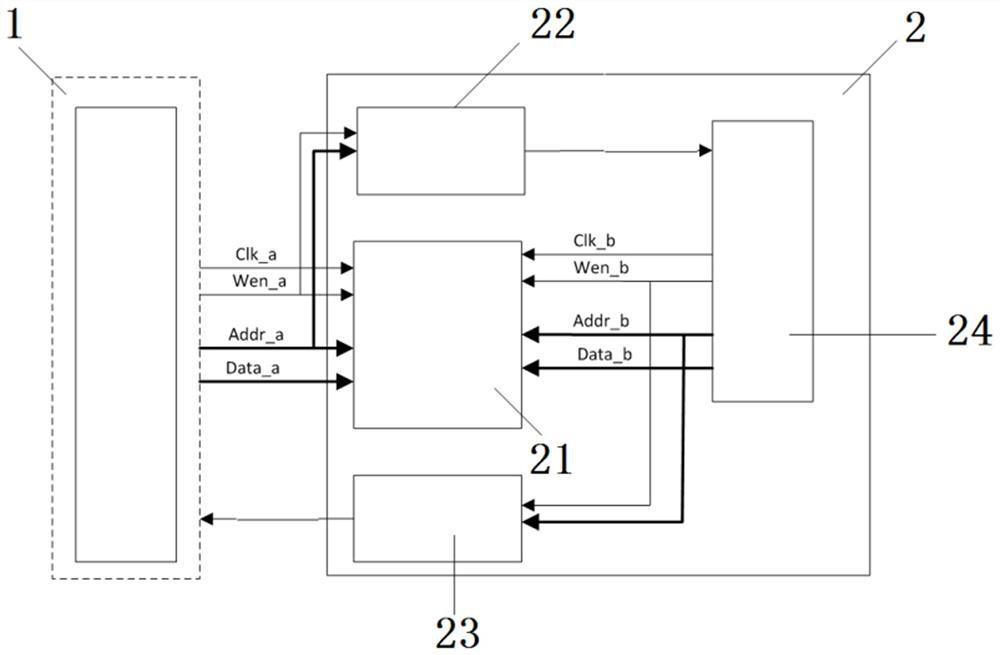

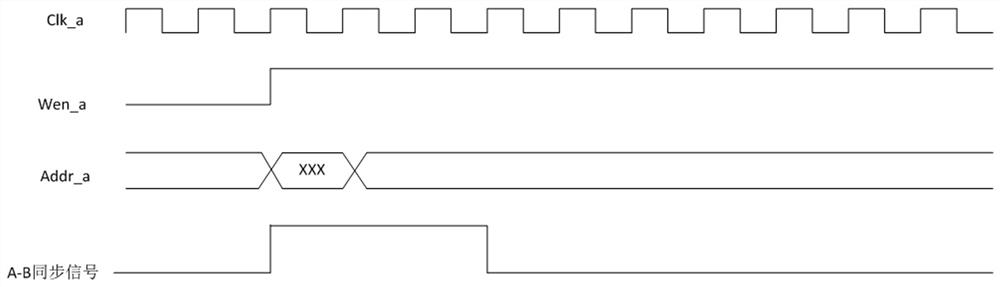

FPGA-based DPRAM two-side synchronization system and method

PendingCN114519016ASimplify Logic DesignImprove effectivenessEnergy efficient computingElectric digital data processingComputer architectureDaughterboard

The invention discloses a DPRAM two-side synchronization system and method based on an FPGA, the system comprises a mainboard and an FPGA daughter board, and the FPGA daughter board is provided with a DPRAM, an A-B synchronization module, a B-A synchronization module and a logic module. The method has the advantages that read-write synchronization of the A port and the B port is almost 100%, logic design is simple, effectiveness is high, and the method is not affected by data invariability and a 0 value.

Owner:SHANGHAI AVIATION ELECTRIC

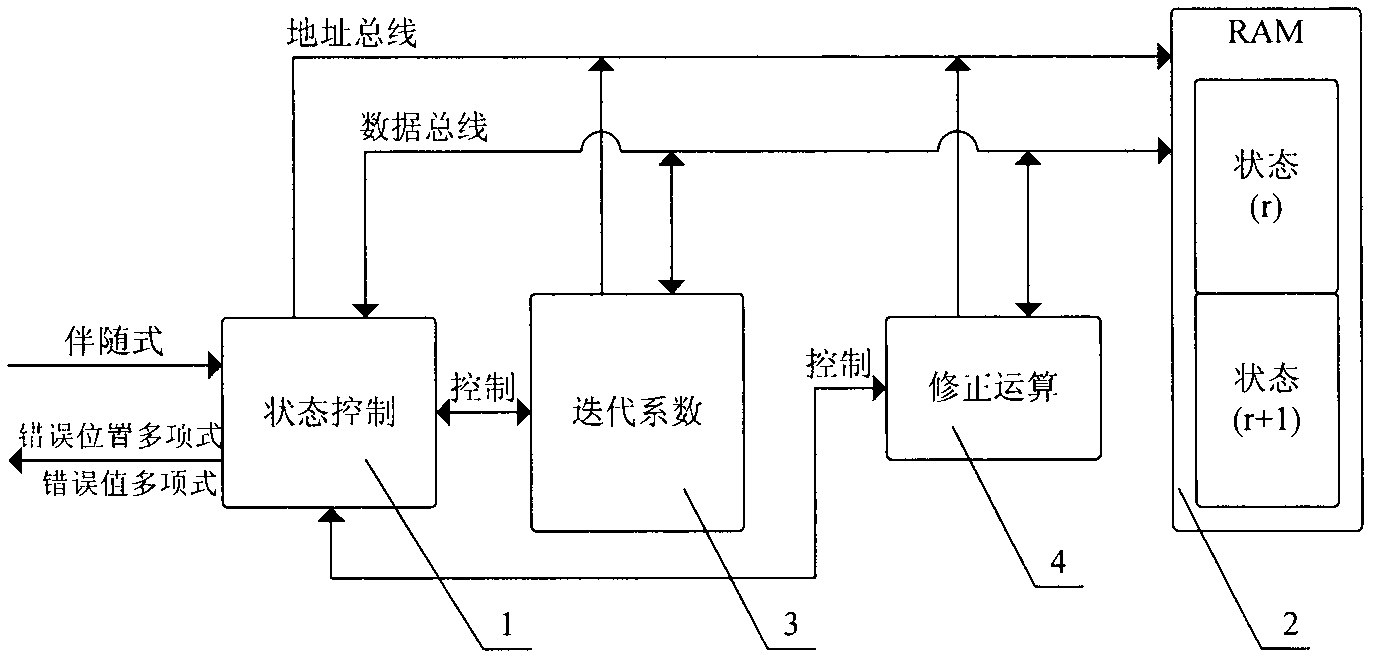

Compact high-information-rate Reed-Solomon (RS) decoding device

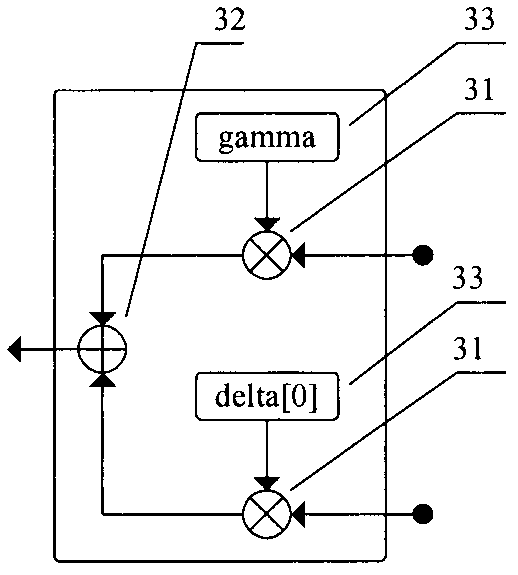

ActiveCN102075200BReduce the number of occupied FPGA logic cellsSimplify Logic Design ComplexityCyclic codesRandom access memoryComputer module

The invention discloses a compact high-information-rate Reed-Solomon (RS) decoding device, which comprises a syndrome calculation module, a key equation solving module and an error searching and error-value calculating module, wherein the key equation solving module adopts reformulated inversionless Berlekamp-Massey (riBM) or a RiBM algorithm to be used for calculating an error position polynomial and an error value polynomial. The main key equation solving module comprises a random access memory (RAM) memory module (2), an interative operation module (3) and a correction coefficient module (4).Due to the adoption of the compact high-information-rate RS decoding device, the problem that the key equation solving algorithm occupies multiple field-programmable-gate-array (FPGA) logic units during the high-information-rate RS decoding process can be solved.

Owner:BEIJING RES INST OF TELEMETRY +1