Patents

Literature

80 results about "External Bus Interface" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The External Bus Interface, usually shortened to EBI, is a computer bus for interfacing small peripheral devices like flash memory with the processor. It is used to expand the internal bus of the processor to enable connection with external memories or other peripherals. EBI can be used to share I/O pins controlling memory devices that are connected to two different memory controllers. Use of EBI reduces the total number of system pins required causing the system cost to come down. EBI manufacturers include Barco, Freescale Semiconductor,, Microchip, Atmel, and Silicon Labs.

Single-chip microcomputer

InactiveUS20120023281A1Multiple functionsPerformance multiplePower managementEnergy efficient ICTMicrocontrollerMicrocomputer

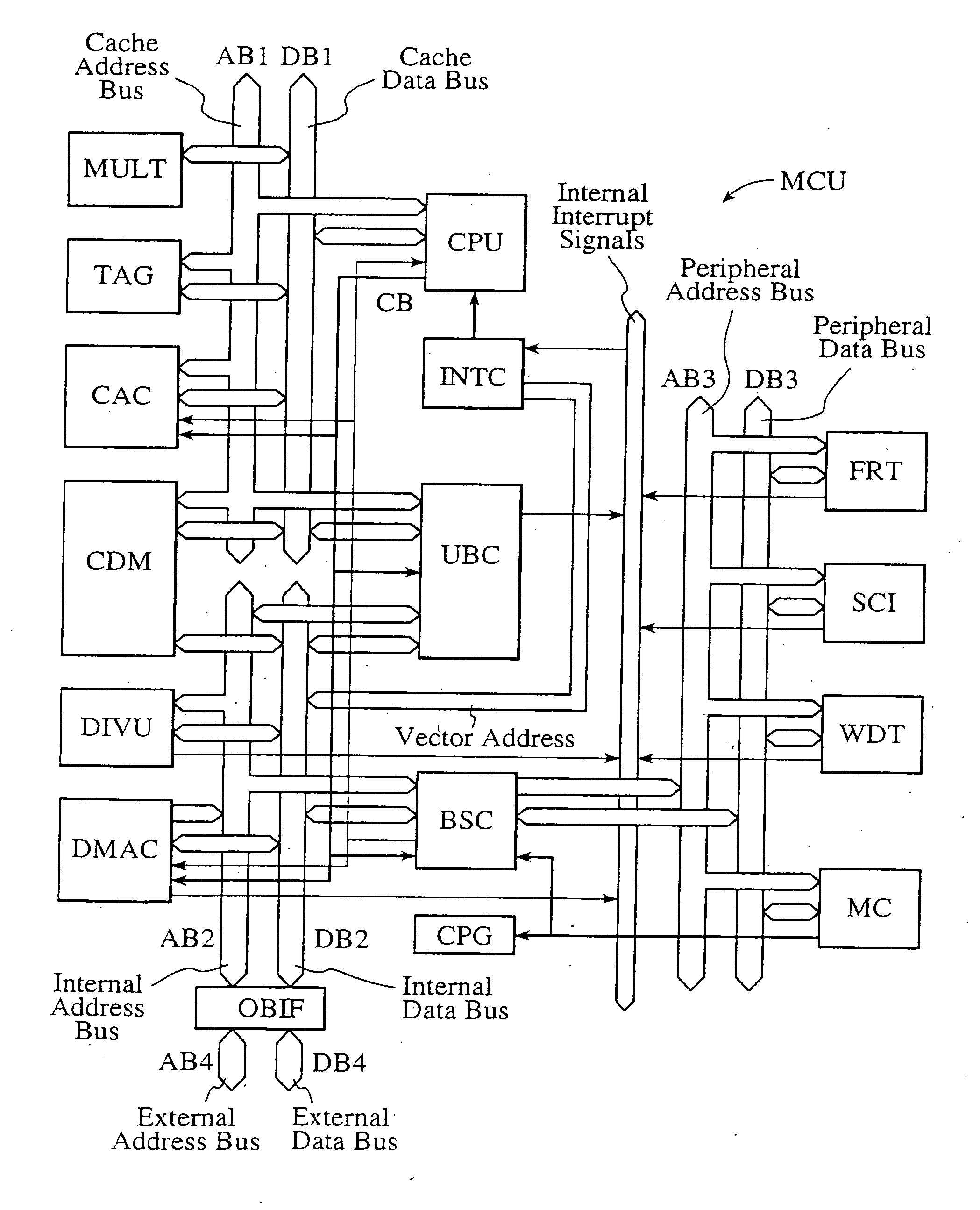

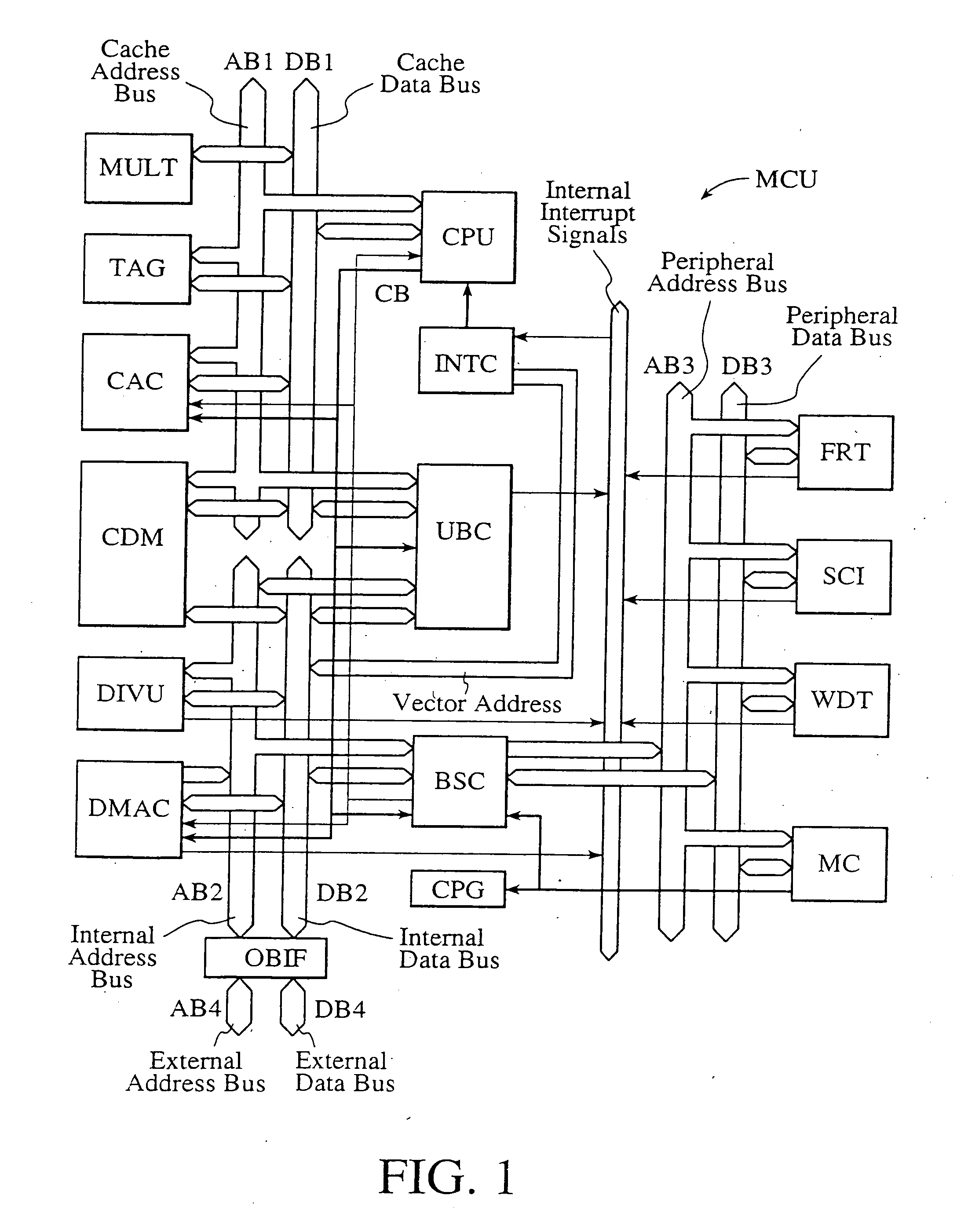

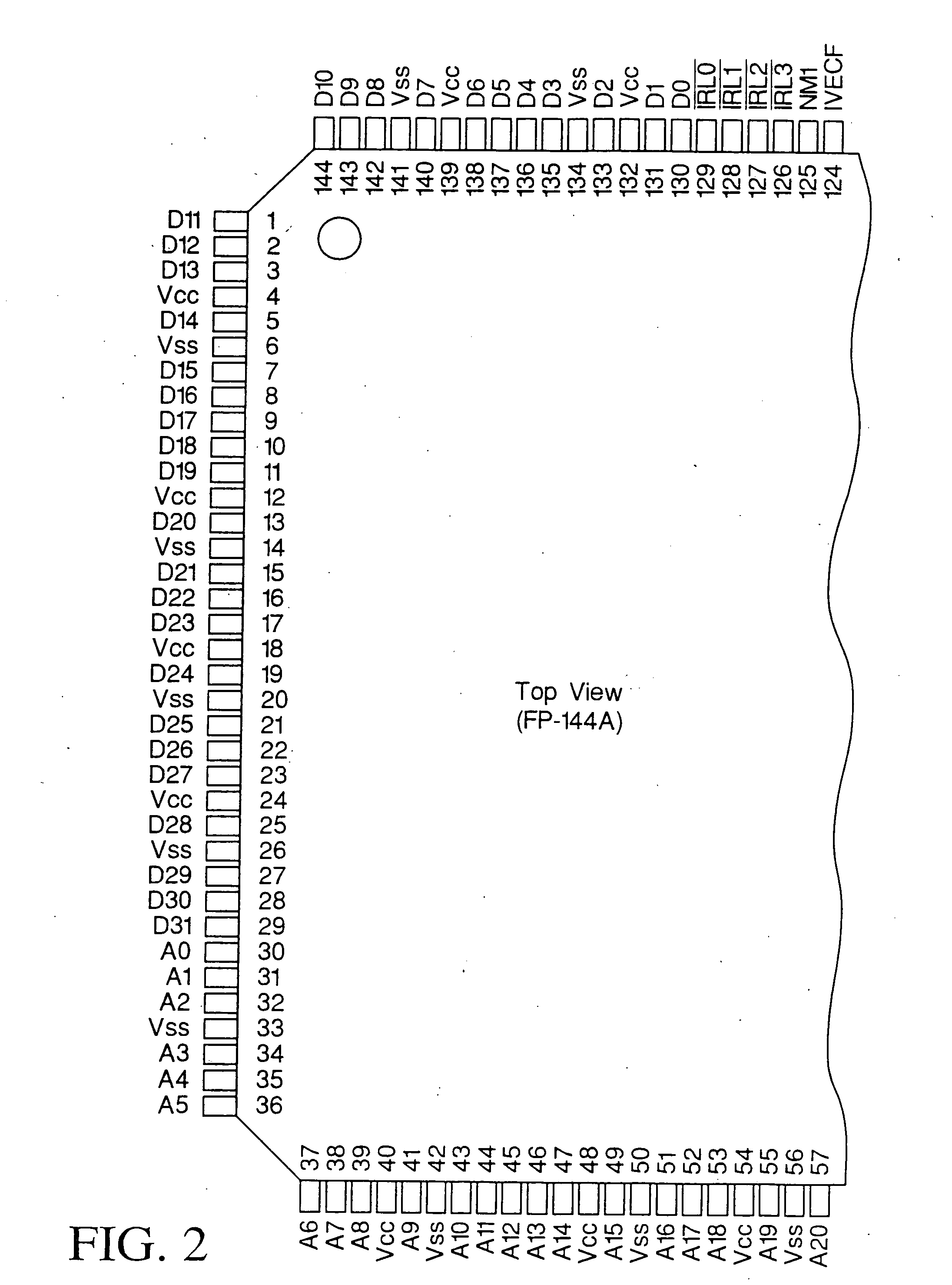

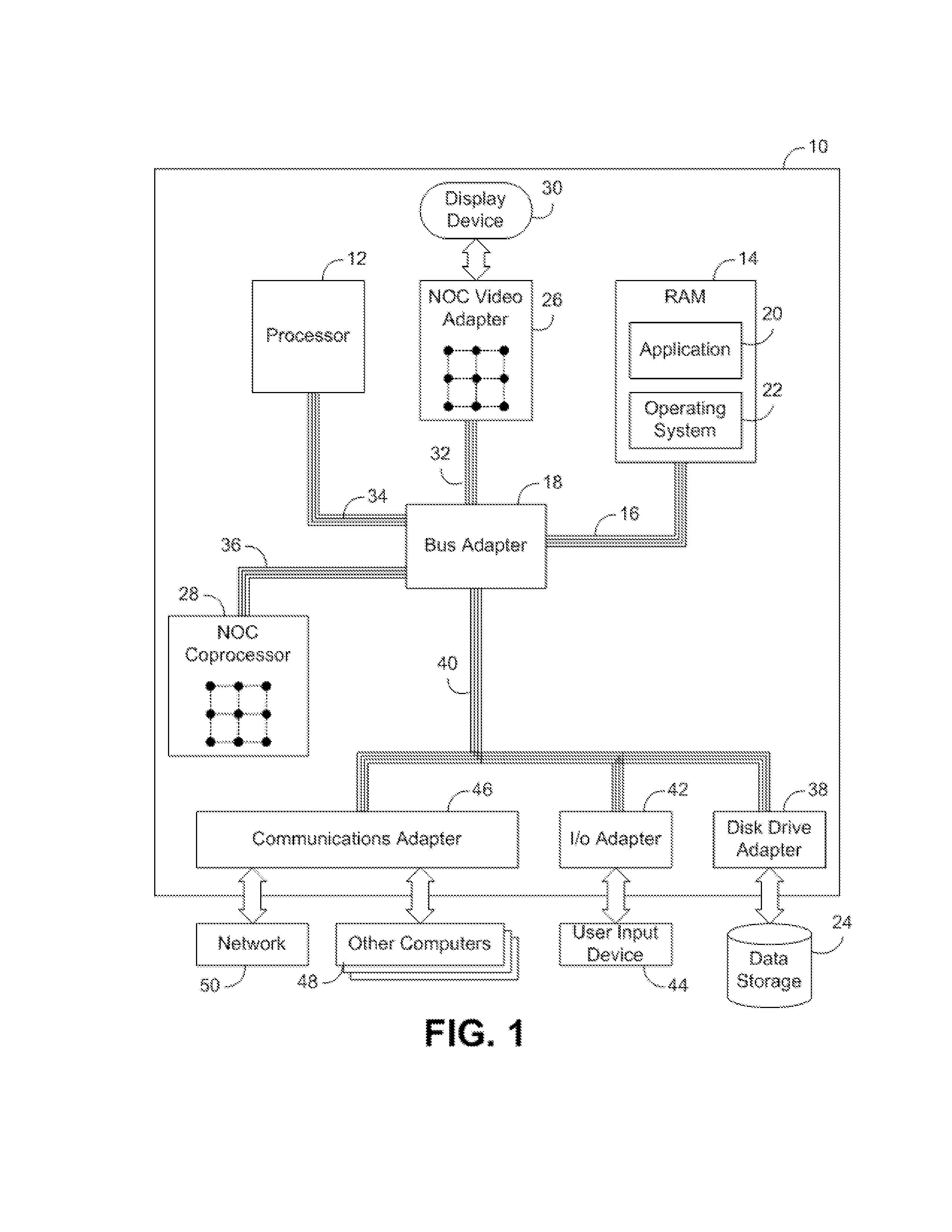

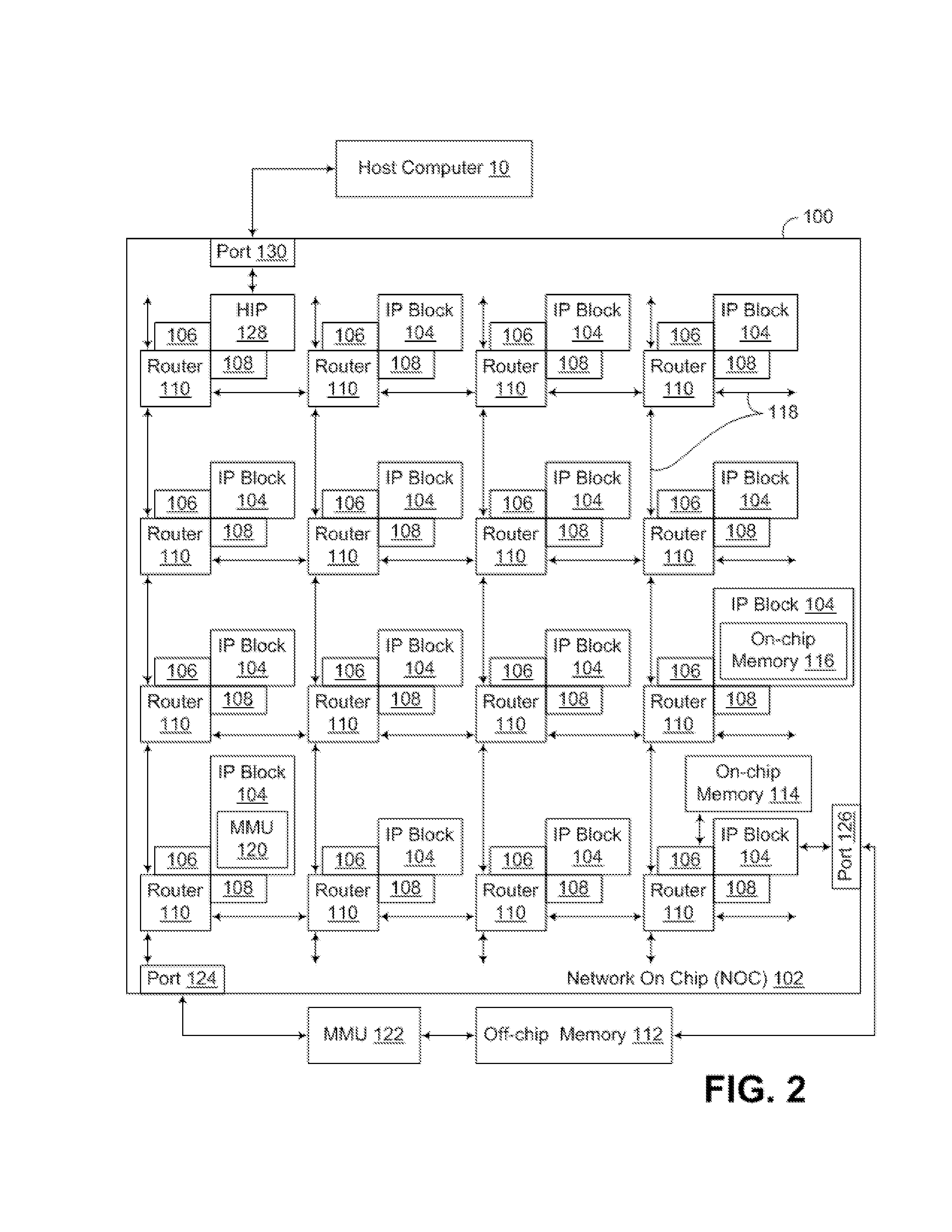

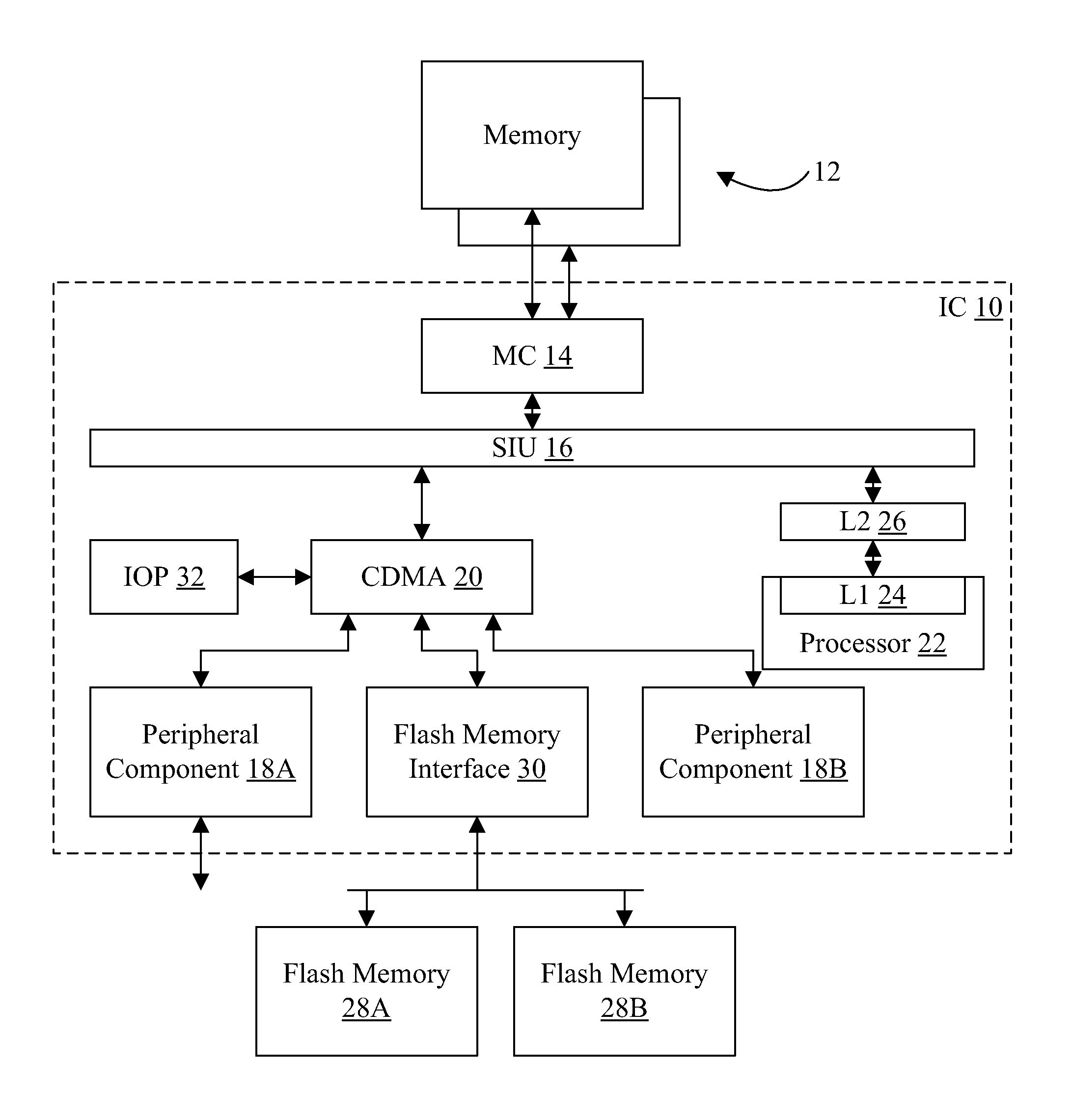

A single-chip microcomputer comprising: a first bus having a central processing unit and a cache memory connected therewith; a second bus having a dynamic memory access control circuit and an external bus interface connected therewith; a break controller for connecting the first bus and the second bus selectively; a third bus having a peripheral module connected therewith and having a lower-speed bus cycle than the bus cycles of the first and second buses; and a bus state controller for effecting a data transfer and a synchronization between the second bus and the third bus. The single-chip microcomputer has the three divided internal buses to reduce the load capacity upon the signal transmission paths so that the signal transmission can be accomplished at a high speed. Moreover, the peripheral module required to have no operation speed is isolated so that the power dissipation can be reduced.

Owner:KAWASAKI SHUMPEI +8

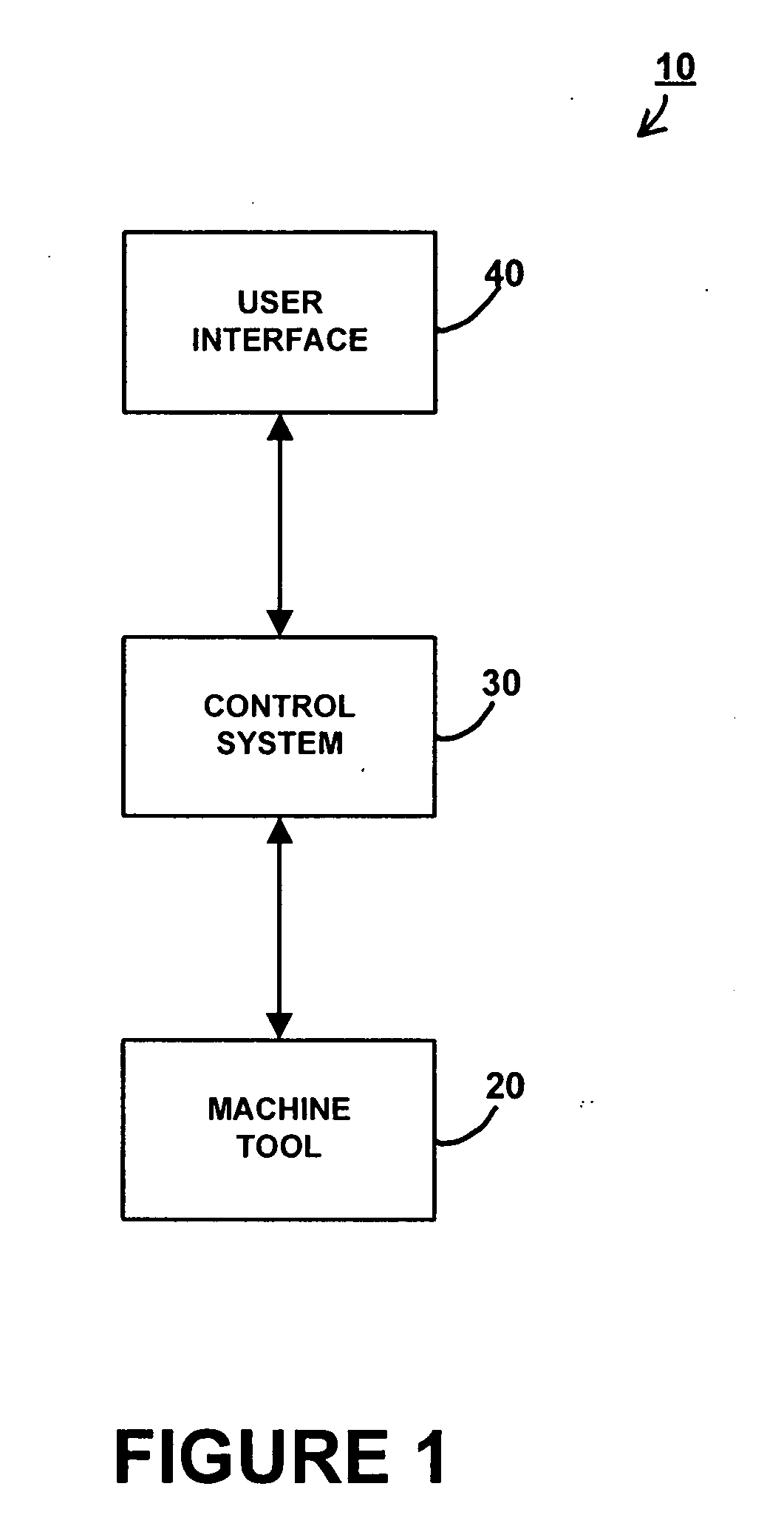

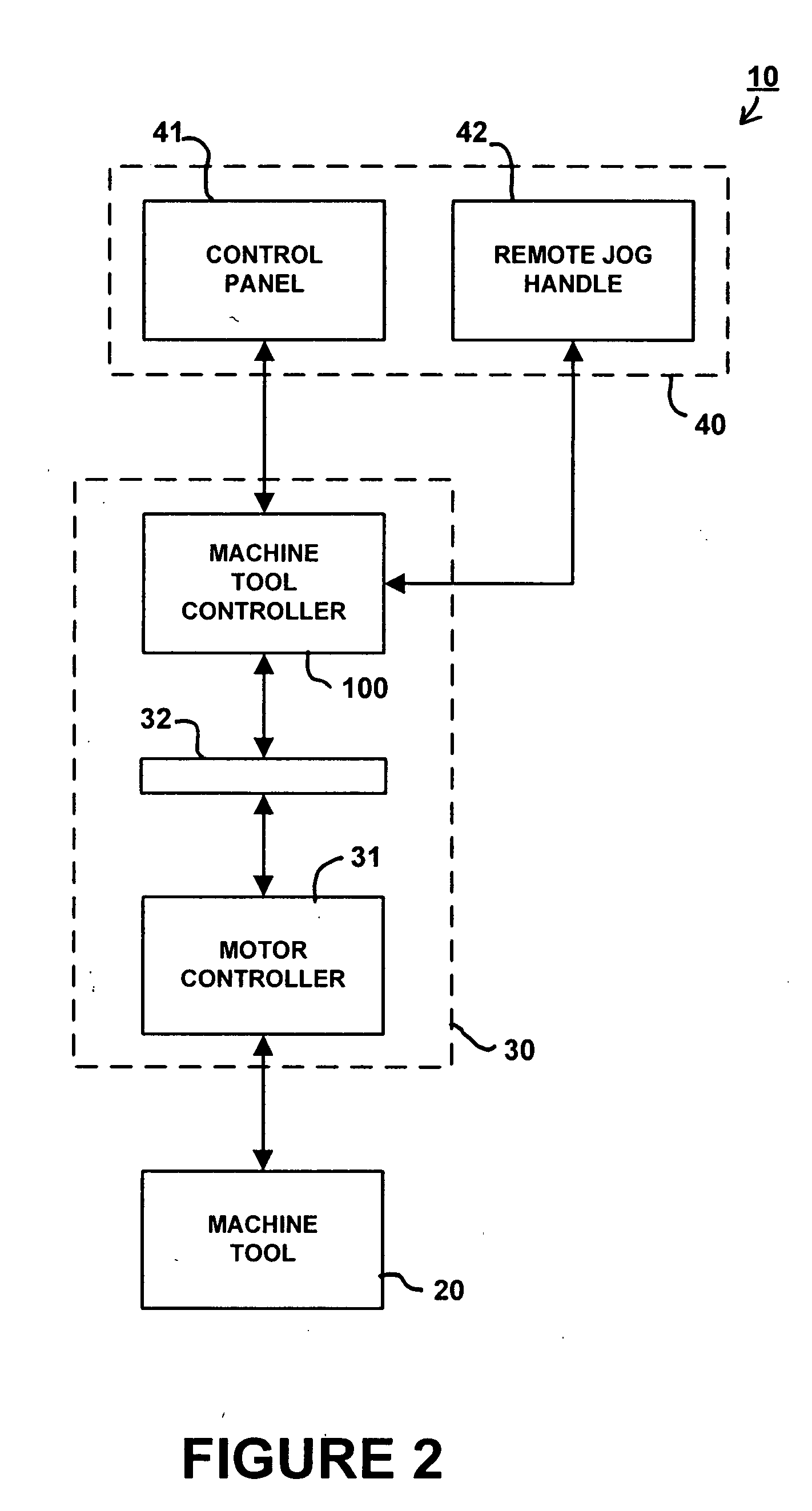

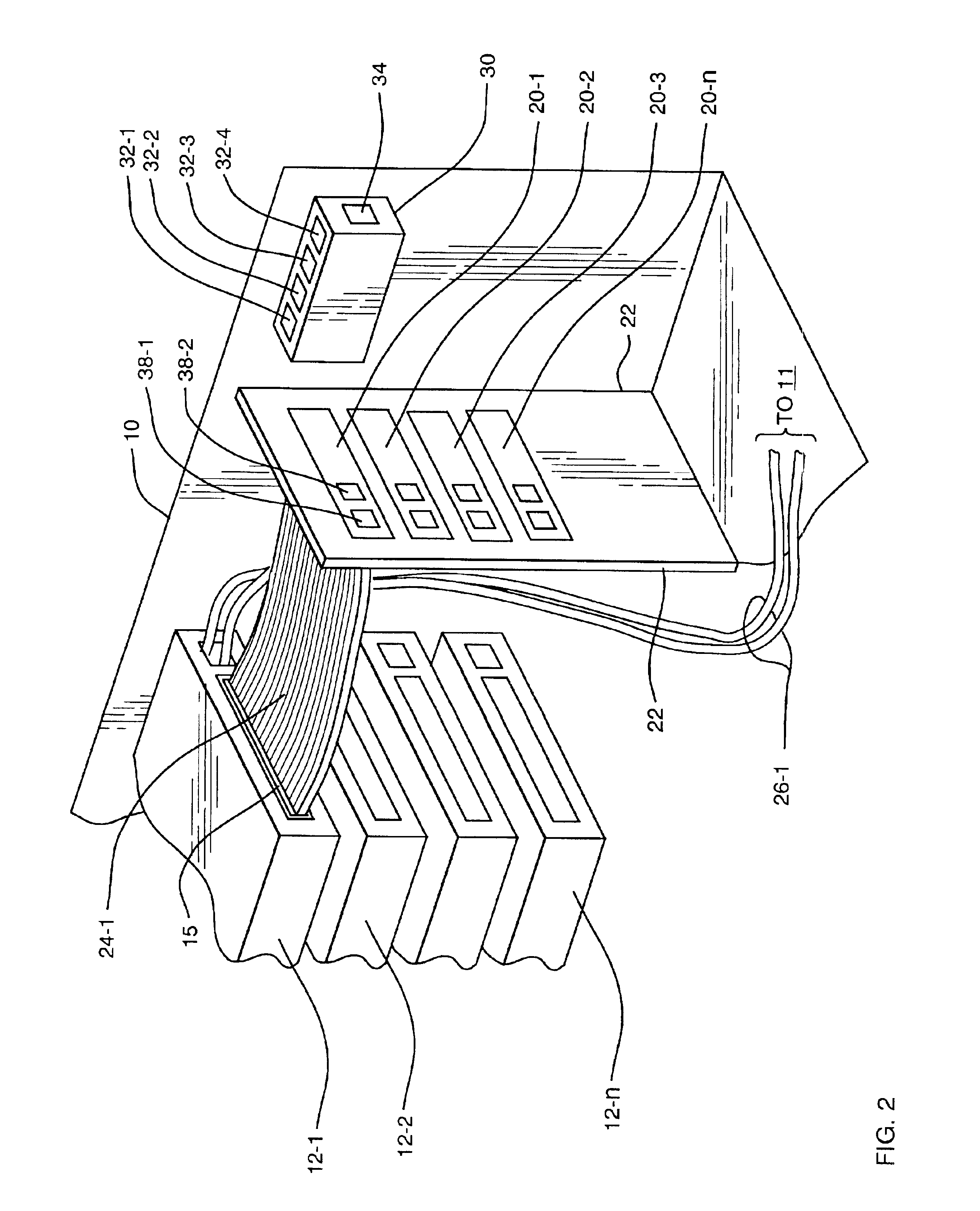

Machine tool control system

InactiveUS20080243299A1Improve performanceEasy to useSpecial data processing applicationsNumerical controlControl communicationsControl system

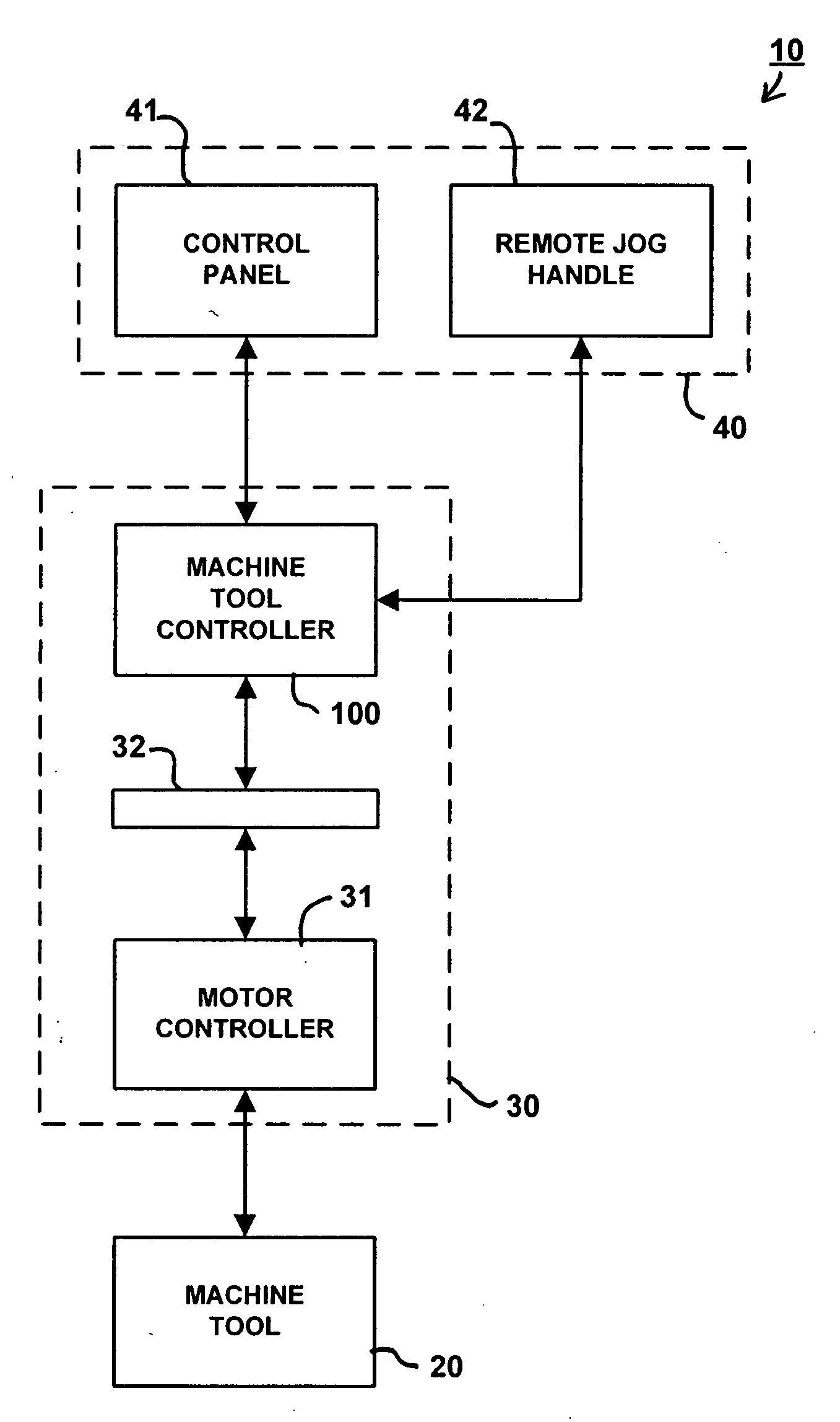

A machine tool controller is provided that includes a processor configured to execute a sequence of instructions in accordance with an operating program and a user program. A volatile memory temporarily stores instructions and data during execution of the sequence of instructions by the processor, and is coupled to the processor via a first interface. A first non-volatile memory stores the operating program and is coupled to the processor via a second interface. A second non-volatile memory stores the user program and is coupled to the processor via a third interface. A video controller is configured to control a user display in accordance with display data generated by the processor and is coupled to the processor via a fourth interface. A dual-port memory is coupled to the processor via a fifth interface and couples a serial bus controller configured to control communications with an external device via a serial bus to the processor. An external bus interface is configured to communicate control commands for controlling a machine tool generated by the processor via an external bus and is coupled to said processor via a sixth interface.

Owner:HAAS AUTOMATION

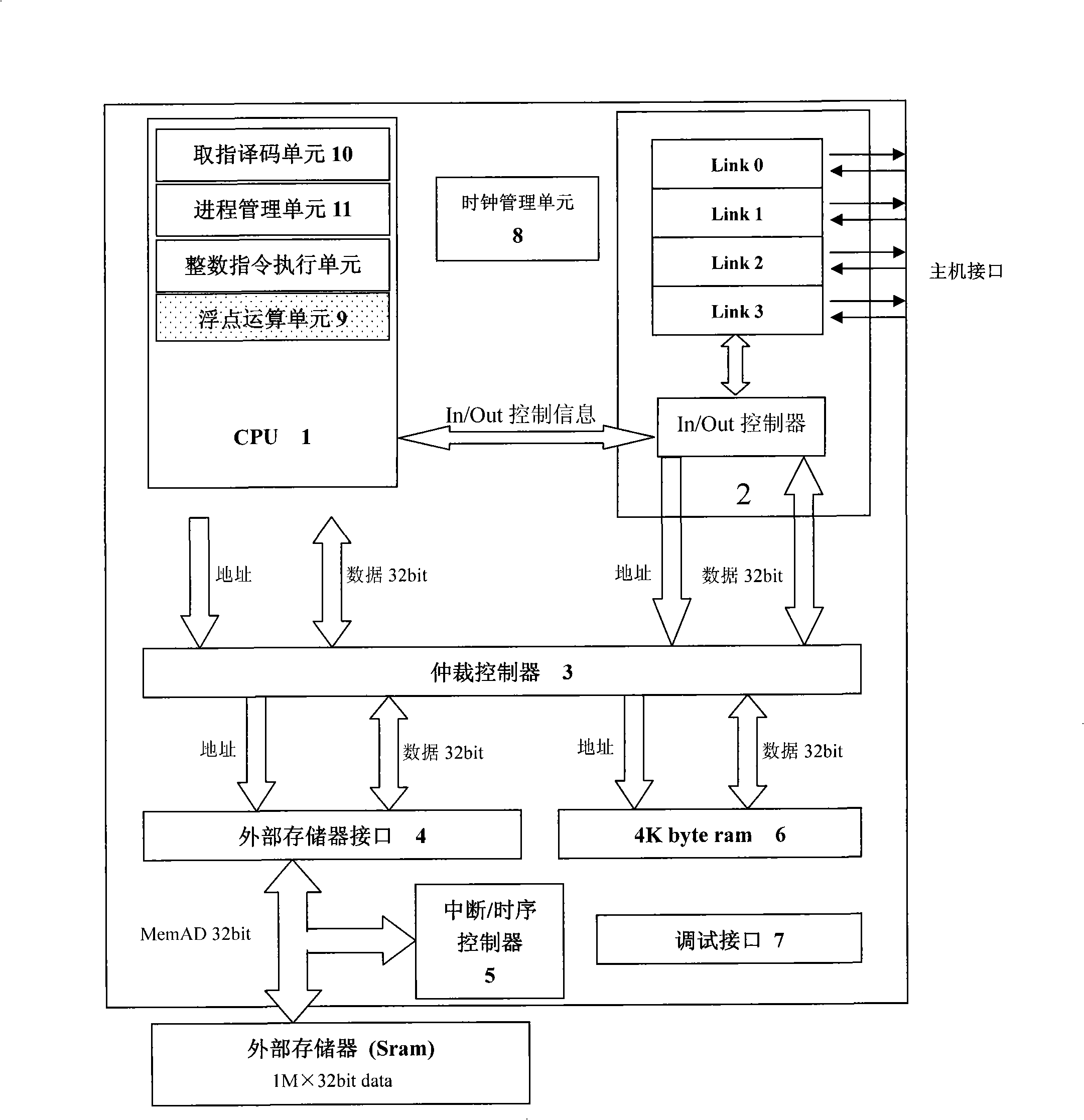

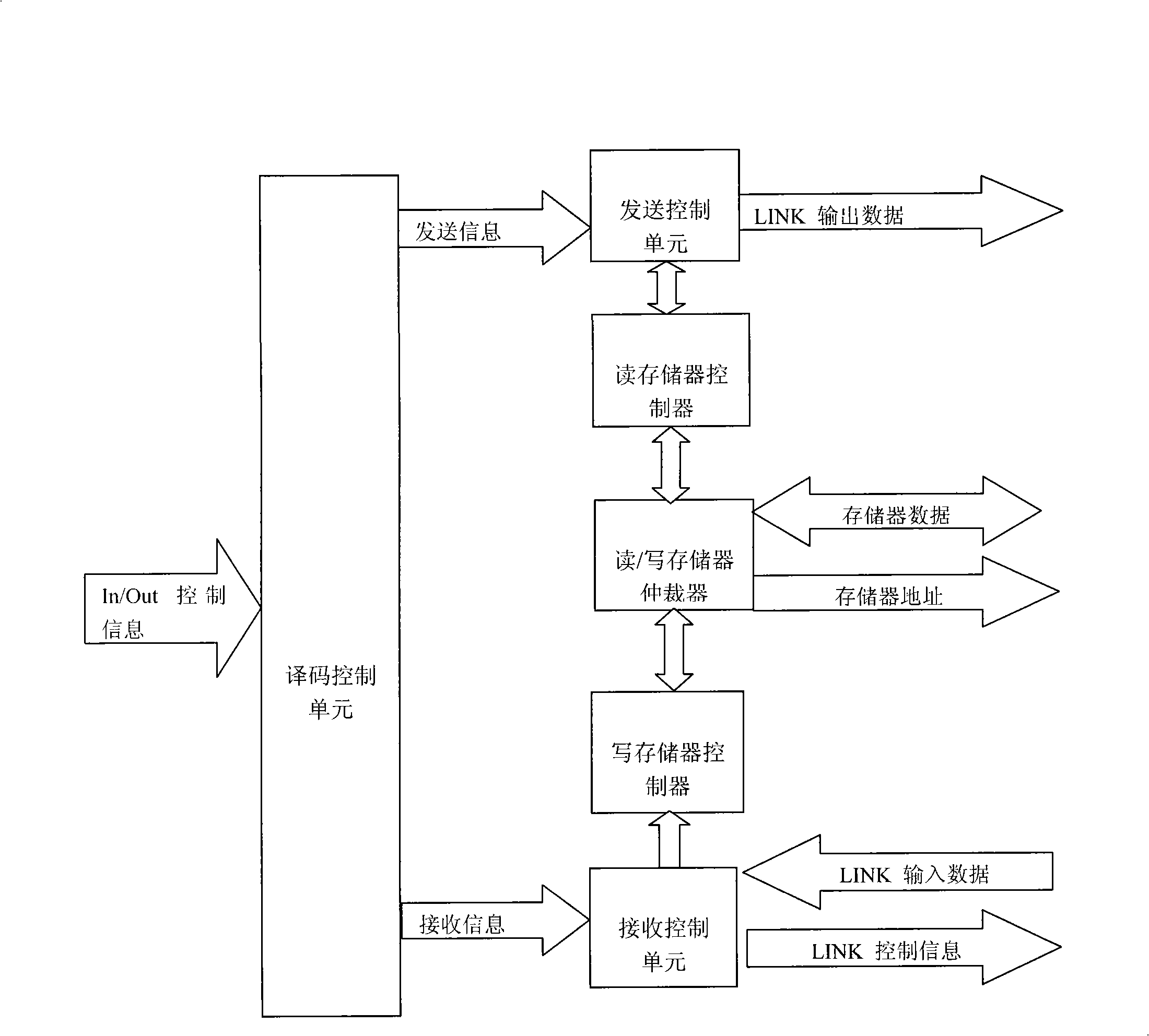

Paralleling microprocessor and its realization method

ActiveCN101334766ALow costEasy to modifyProgram initiation/switchingDigital data processing detailsInternal memoryParallel computing

The invention relates to a parallel microprocessor and a corresponding realization method which are based on FPGA development. The parallel microprocessor comprises a CPU which is a 32-bit fixed-point CPU formed by a fetch decoding unit, a process management unit and an integer instruction execution unit; a communication module formed by a plurality of units of LINK channels and In / Out controllers; an arbitration controller used for arbitrating internal and external address buses and a data bus of the CPU; an external memory interface used for providing reading / writing time-sequence logic for an external memory; an interruption / time-sequence controller used for providing timing and interruption for the CPU; an internal memory used for providing the instructions of the CPU and quickly accessing data. The CPU is also provided with a floating point unit (FPU) combining the 32-bit fixed-point CPU to form a 64-bit floating point CPU. The 32-bit fixed-point parallel microprocessor and the 64-bit floating point parallel microprocessor provided by the invention work stably, bring convenience for system modification and debugging, accelerate verification speed and provide a low-cost operation platform for programs written in OccamII language.

Owner:NEUSOFT MEDICAL SYST CO LTD

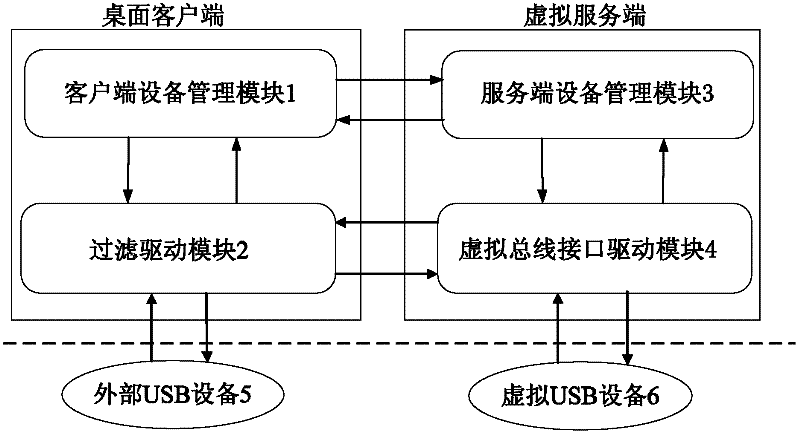

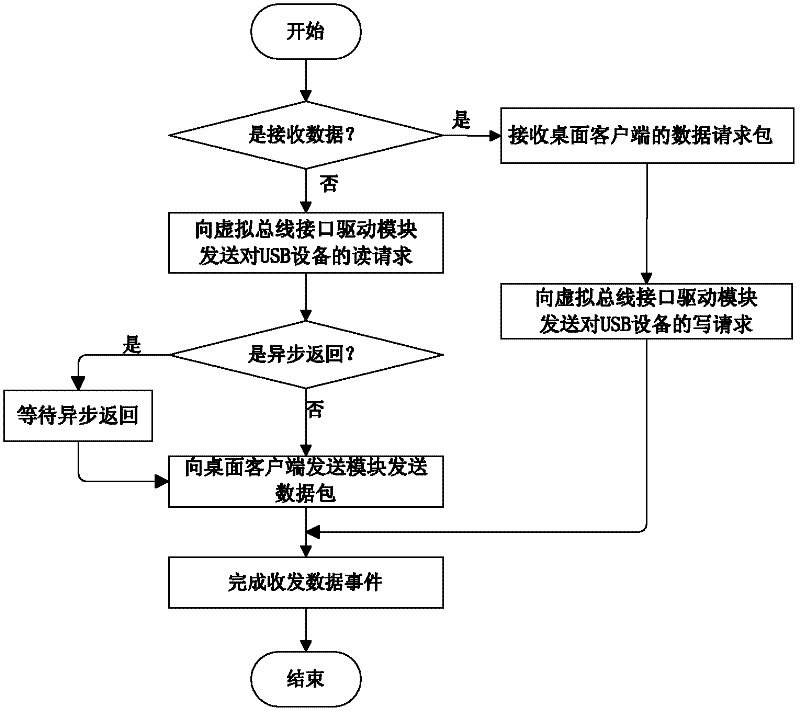

A virtual desktop external device support system

InactiveCN102270186APracticalVersatilityTransmissionElectric digital data processingSupporting systemComputer module

The invention discloses a virtual desktop external equipment support system, comprising a filter driving module, a client equipment management module, a server equipment management module and a virtual bus interface driving module. The virtual external bus interface driving module is used for setting up virtual equipment in a virtual environment according to shared real equipment, packaging a command of operating the virtual equipment into a network request packet, and forwarding the network request packet to the desktop client through a transmission interface. The filter driving module is used for receiving data forwarded by the virtual external bus interface driving module, resolving a command, and controlling physical equipment of a computer according to the command. The client equipment management module and the server equipment management module are used for establishing a connection between a desktop client and a virtual server, coordinating the data transmission and receiving between virtual equipment and real equipment, and providing a channel for data communication between the user mode and the kernel. According to the invention, the difference between the virtual equipment of the virtual desktop and the interface of the local physical equipment is completely hidden in a host control drive layer.

Owner:HUAZHONG UNIV OF SCI & TECH

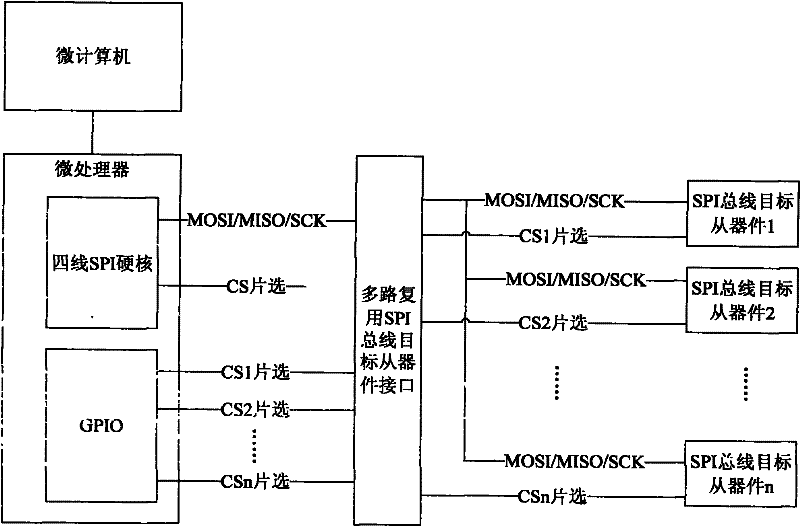

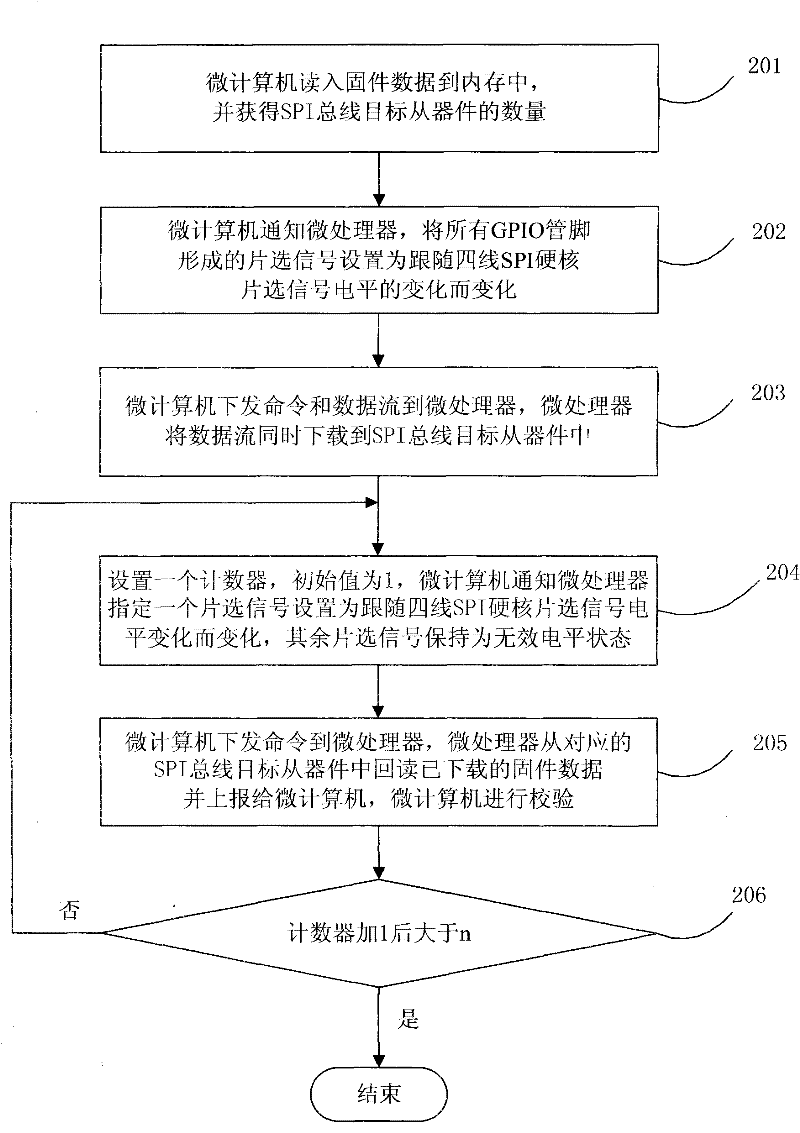

Firmware ISP writer and writing method for SPI bus interface

The invention discloses a firmware ISP writer and a writing method for an SPI bus interface. A microcomputer is connected with a microprocessor through an external interface. The microprocessor is connected with no less than one SPI bus target slave device through a multiplex SPI bus target slave device interface. The microcomputer is used to convert firmware data into SPI commands and data streams required by the SPI bus target slave device and to release the SPI commands and the data streams to the microprocessor. The microprocessor is used as a master SPI device to separately or simultaneously download the data streams into the no less than one SPI bus target slave device, and is used to read back from one designated SPI bus target slave device for verification. By adopting the technical scheme, the invention has the advantages that the working mode of simultaneous downloading and timeshare verification is realized, the cost is reduced and the efficiency is improved.

Owner:CHENGDU SUPERXON COMM TECH CO LTD

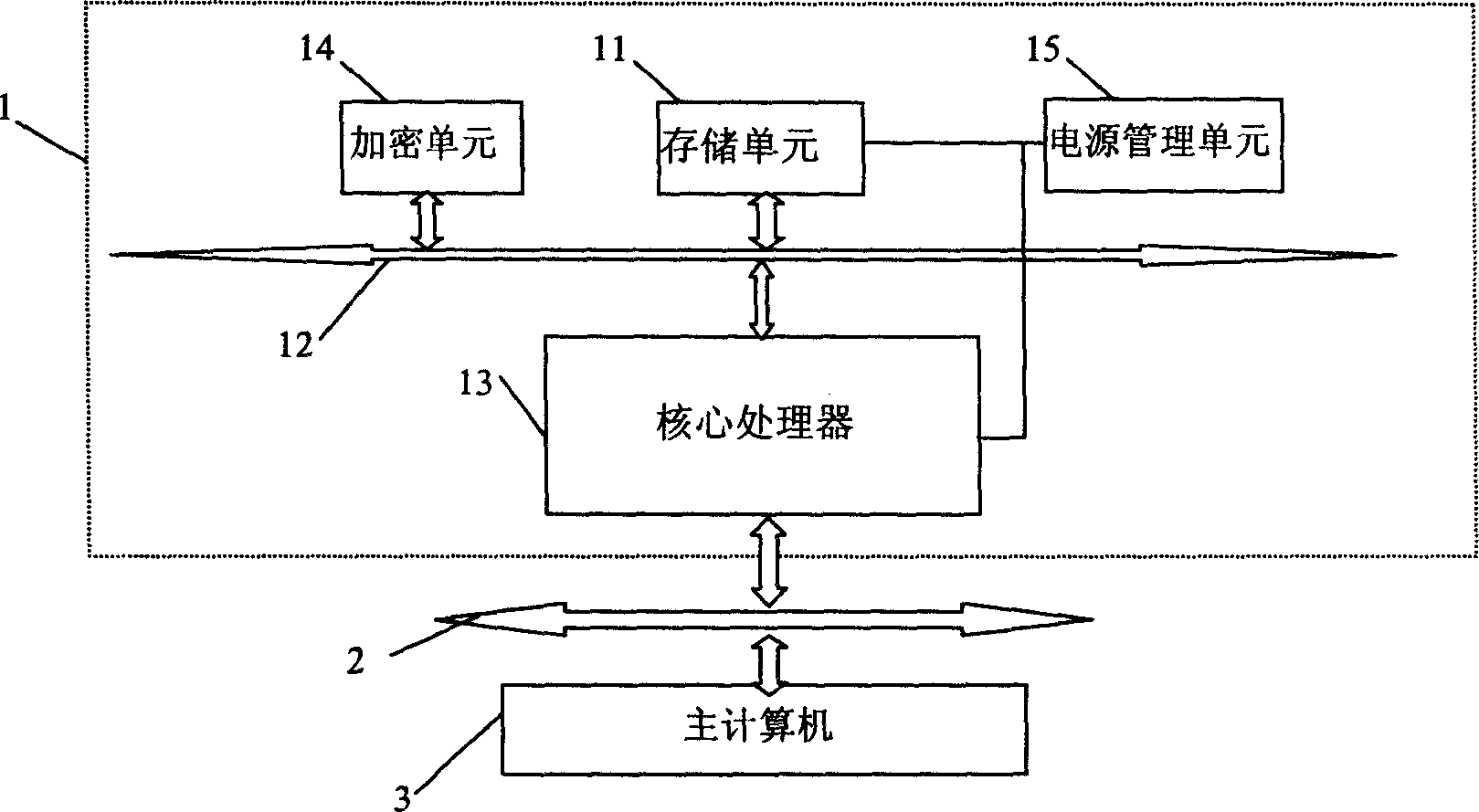

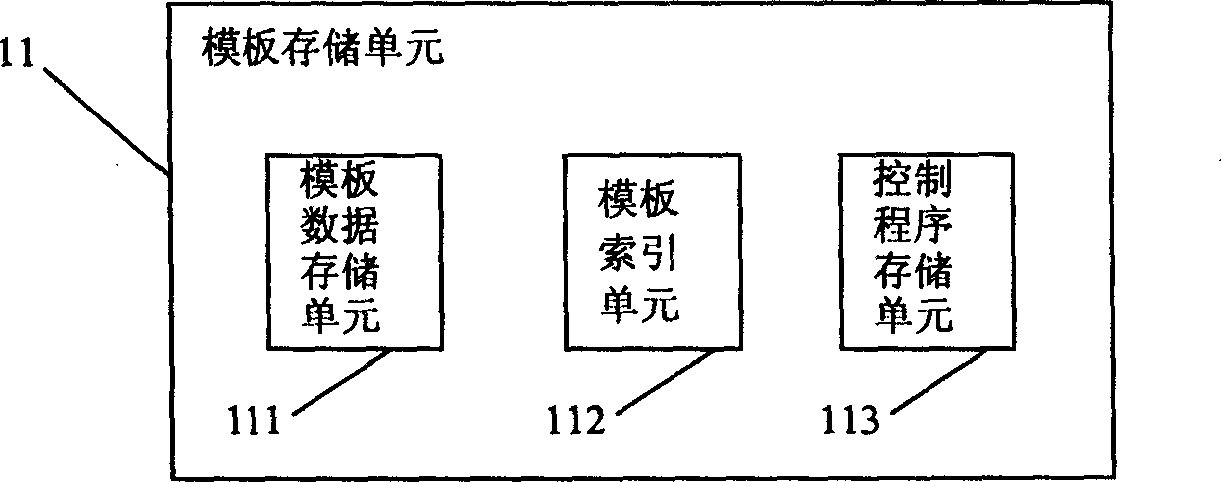

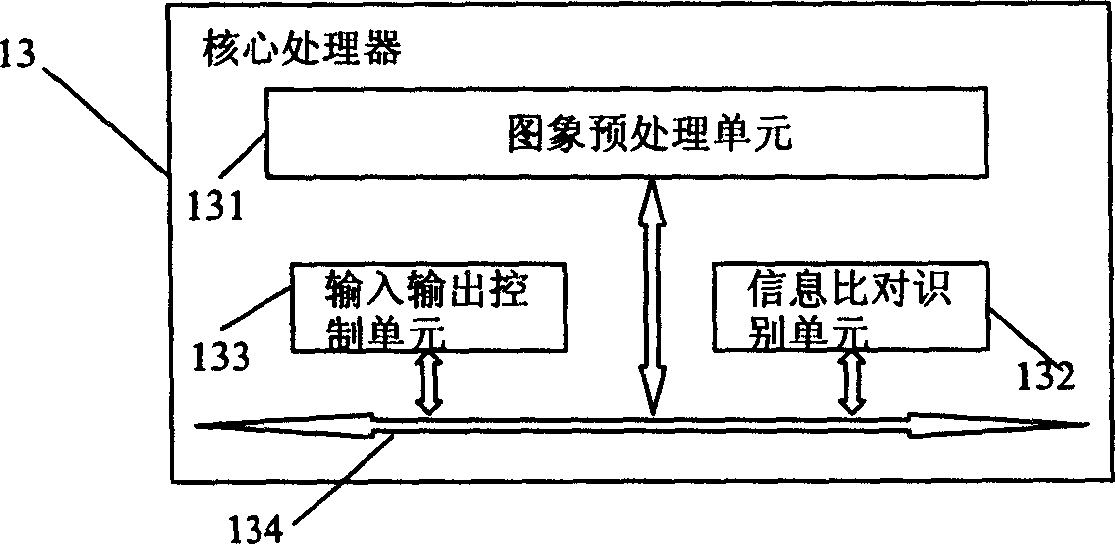

Bill image processing equipment

InactiveCN1482572AImprove processing efficiencyEasy to handleCharacter and pattern recognitionSpecial data processing applicationsImaging processingMulti-core processor

The invention discloses a bill image processing apparatus for an optical character recognition system, which comprises internal bus, memory unit and a core processor, for storing optical recognition character (OCR) font template library, page template library and bill image processing program, and external bus interface expanding unit for the bridge connection of the core processor and the host computer bus, wherein the core processor is dedicated to the use of bill image processing or recognition. The device provided by the invention can substantially increase the efficiency of system image processing. íí

Owner:SUNYARD SYST ENG CO LTD

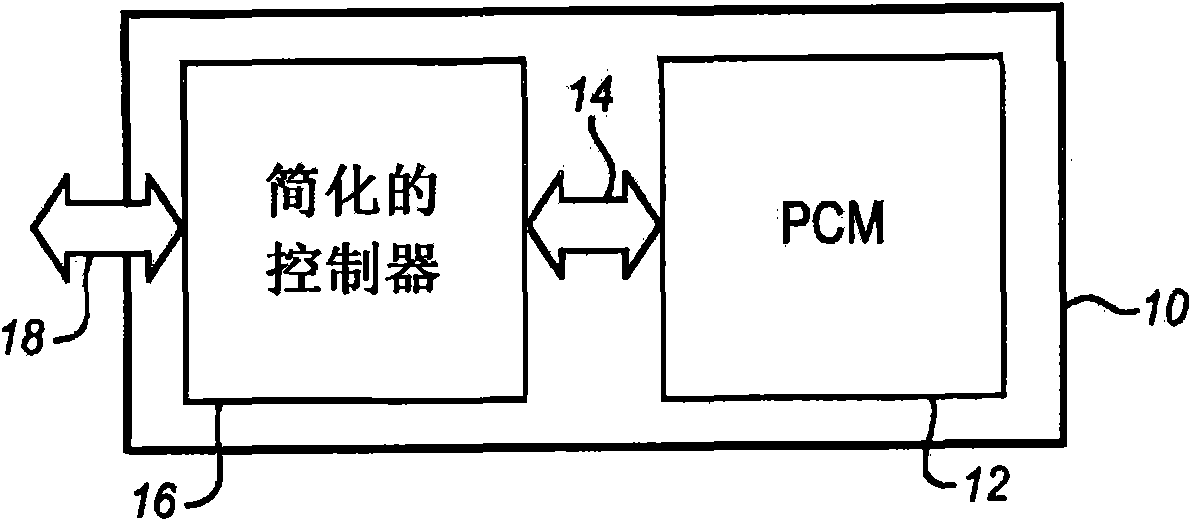

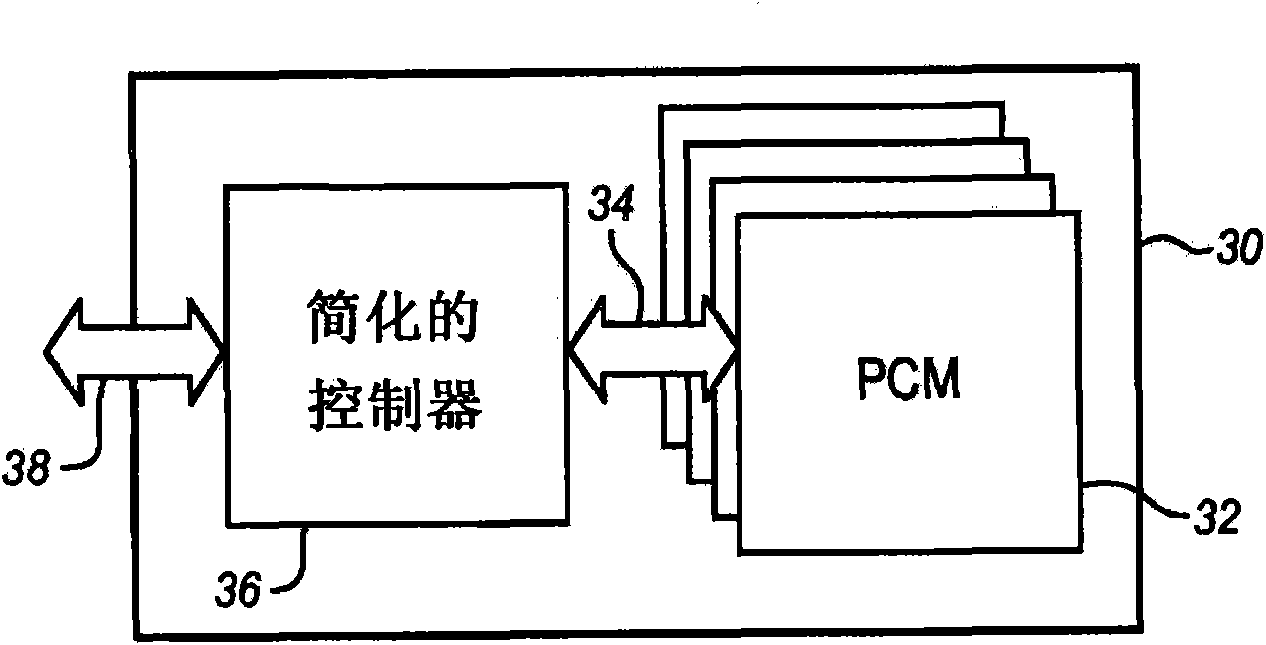

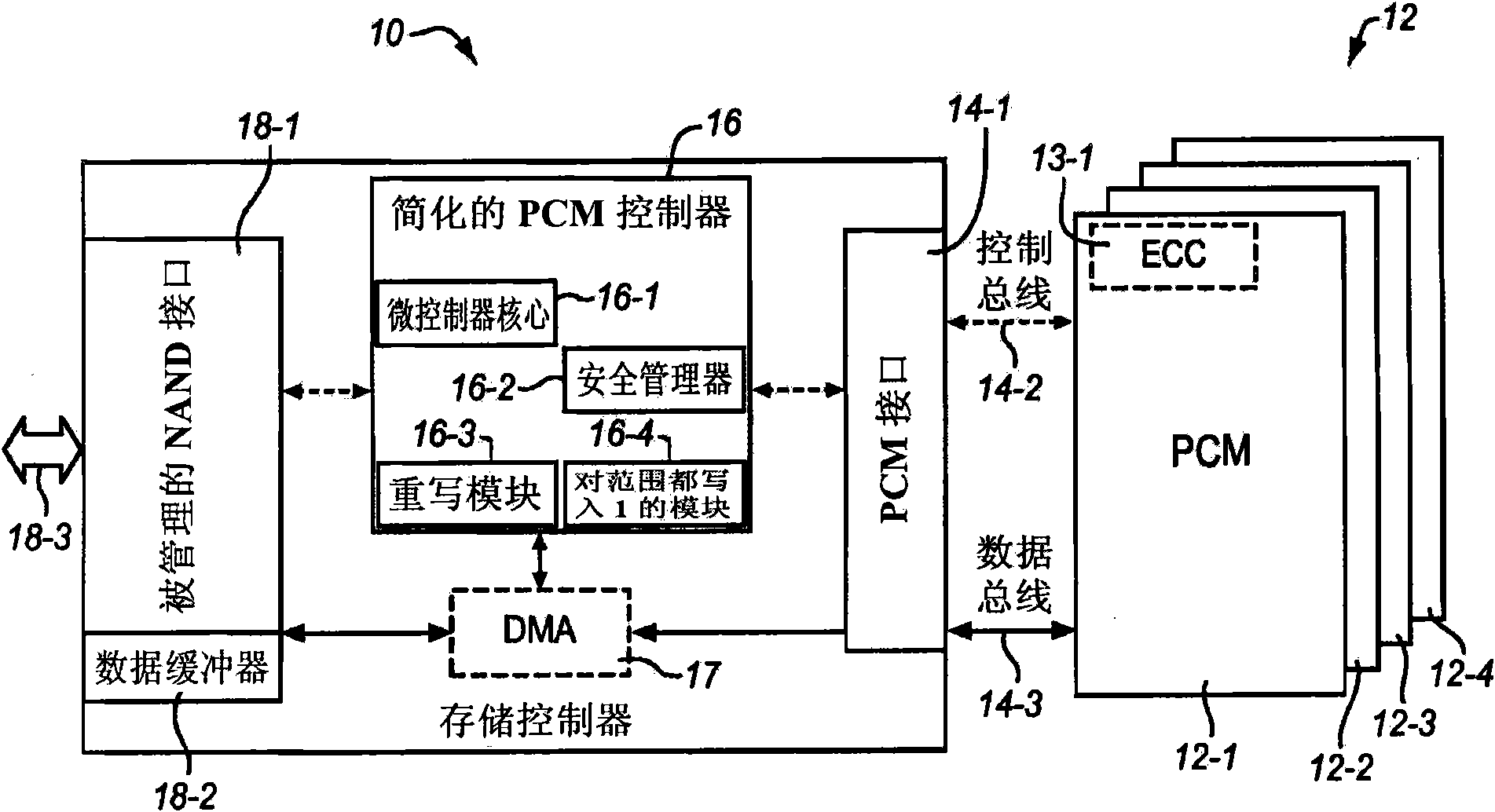

Pcm memories for storage bus interfaces

ActiveCN101887350AMemory architecture accessing/allocationInput/output to record carriersPhase-change memoryControl store

A memory controller for a phase change memory (PCM) that can be used on a storage bus interface is described. In one example, the memory controller includes an external bus interface coupled to an external bus to communicate read and write instructions with an external device, a memory array interface coupled to a memory array to perform reads and writes on a memory array, and an overwrite moduleto write a desired value to a desired address of the memory array.

Owner:E·孔法洛涅里 +2

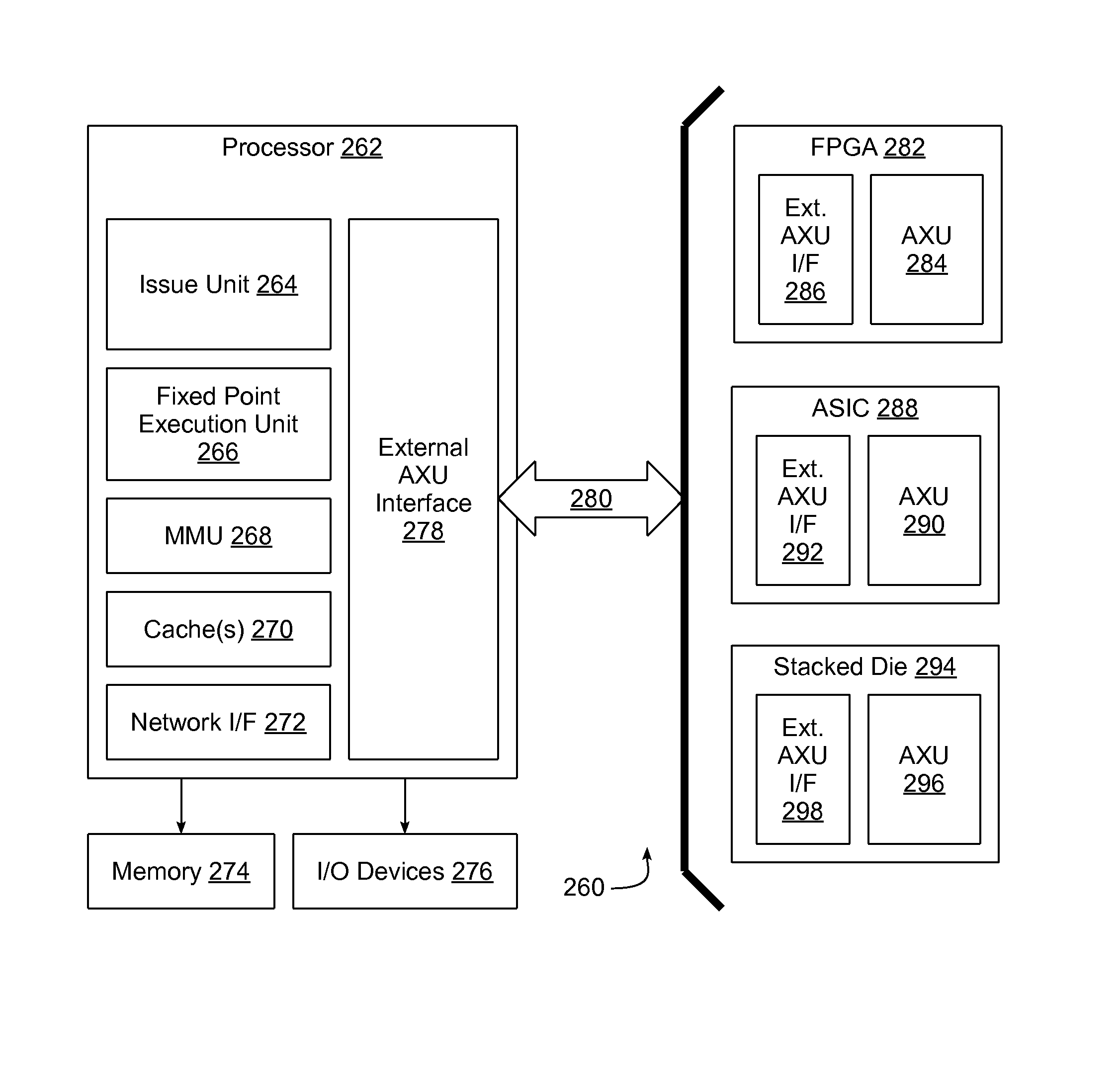

External auxiliary execution unit interface to off-chip auxiliary execution unit

An external Auxiliary Execution Unit (AXU) interface is provided between a processing core disposed in a first programmable chip and an off-chip AXU disposed in a second programmable chip to integrate the AXU with an issue unit, a fixed point execution unit, and optionally other functional units in the processing core. The external AXU interface enables the issue unit to issue instructions to the AXU in much the same manner as the issue unit would be able to issue instructions to an AXU that was disposed on the same chip. By doing so, the AXU on the second programmable chip can be designed, tested and verified independent of the processing core on the first programmable chip, thereby enabling a common processing core, which has been designed, tested, and verified, to be used in connection with multiple different AXU designs.

Owner:IBM CORP

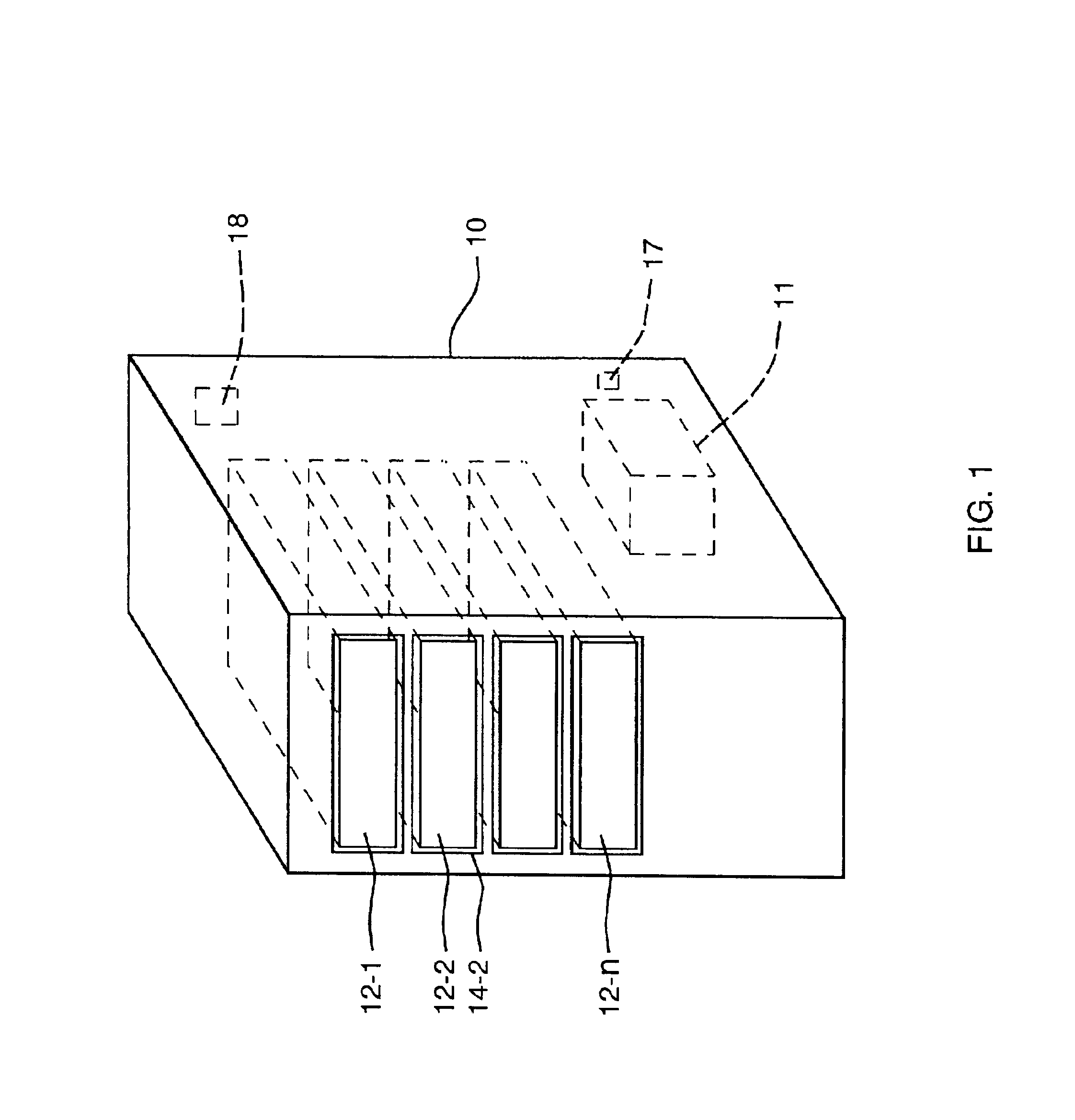

Data bank providing connectivity among multiple mass storage media devices using daisy chained universal bus interface

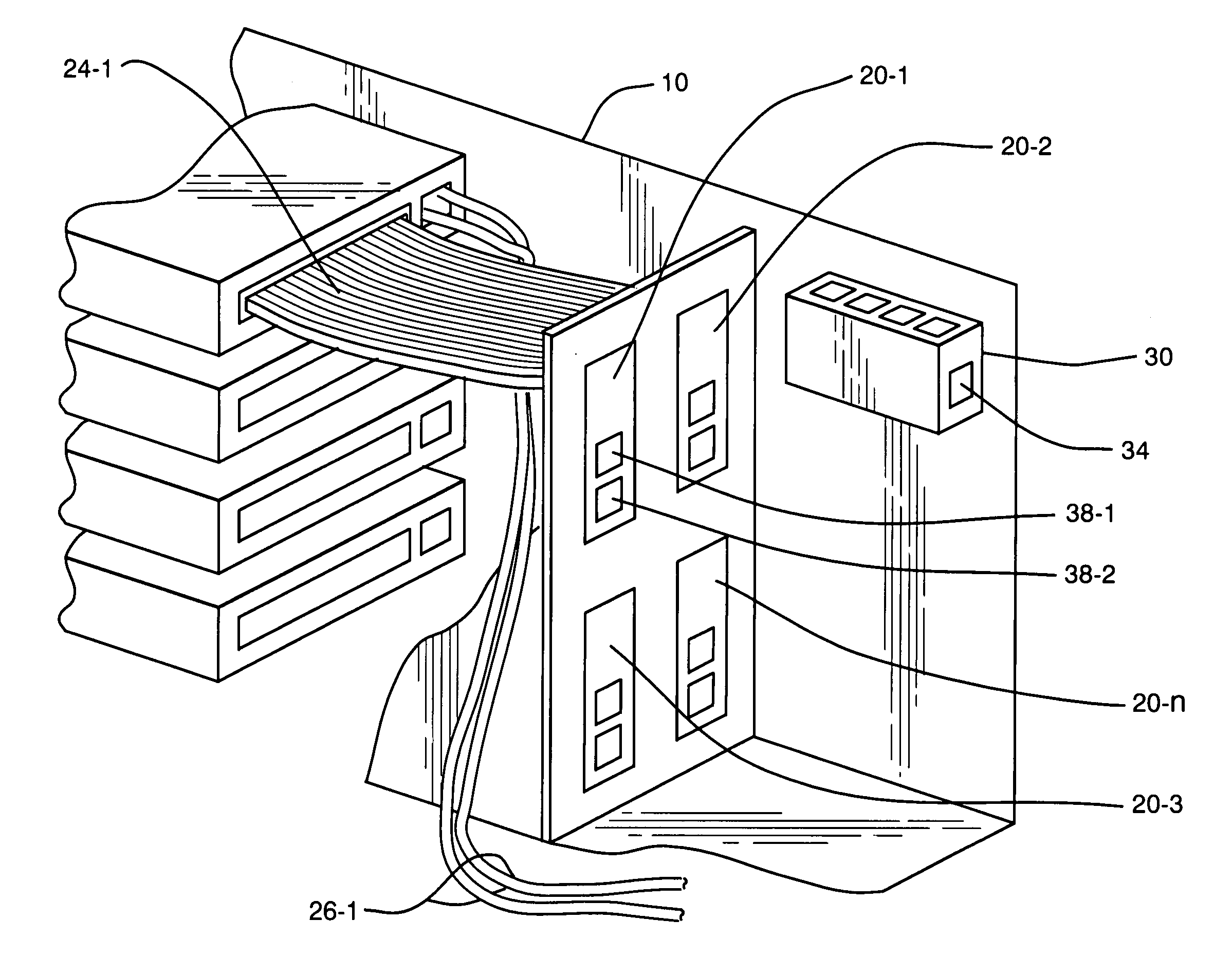

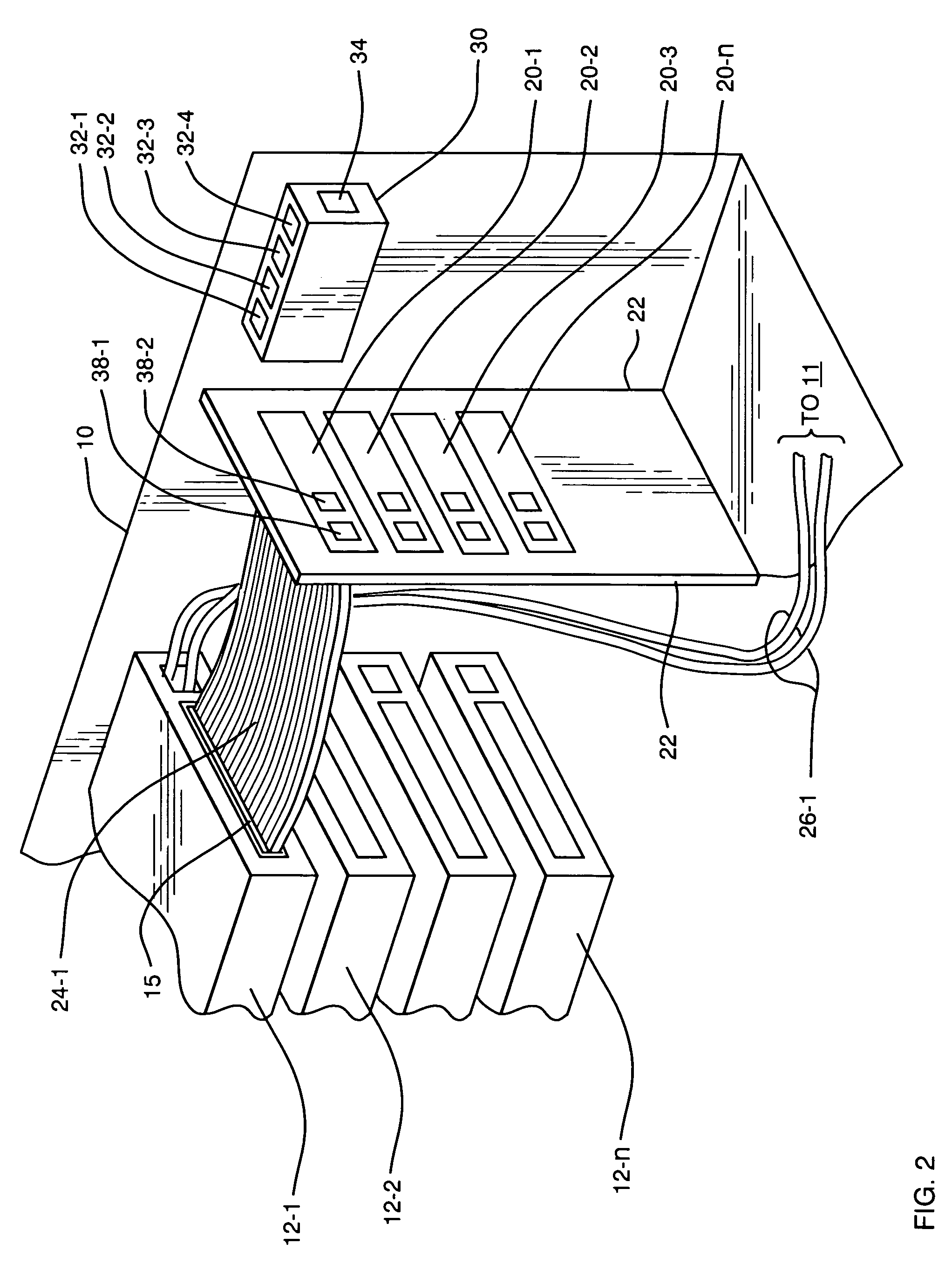

InactiveUS7008234B1Improve connectivityLow costCoupling device detailsComputer periphery connectorsMass storageBus interface

A data storage system that houses at least two mass storage devices in an enclosure, along with all interconnect cabling electronics to permit access through a shared universal-type interface. An enclosure houses multiple mass storage devices such as disk drives. A set of bridges located within the enclosure provides connectivity from the disk interface to the universal-type bus. Bridge outputs are coupled to a universal hub also located within the enclosure to provide a single port interface to the array of disks. The arrangement thus provides for connectivity to multiple mass storage devices housing in a single enclosure with a single universal bus interface.

Owner:INTERACTIVE MEDIA CORP

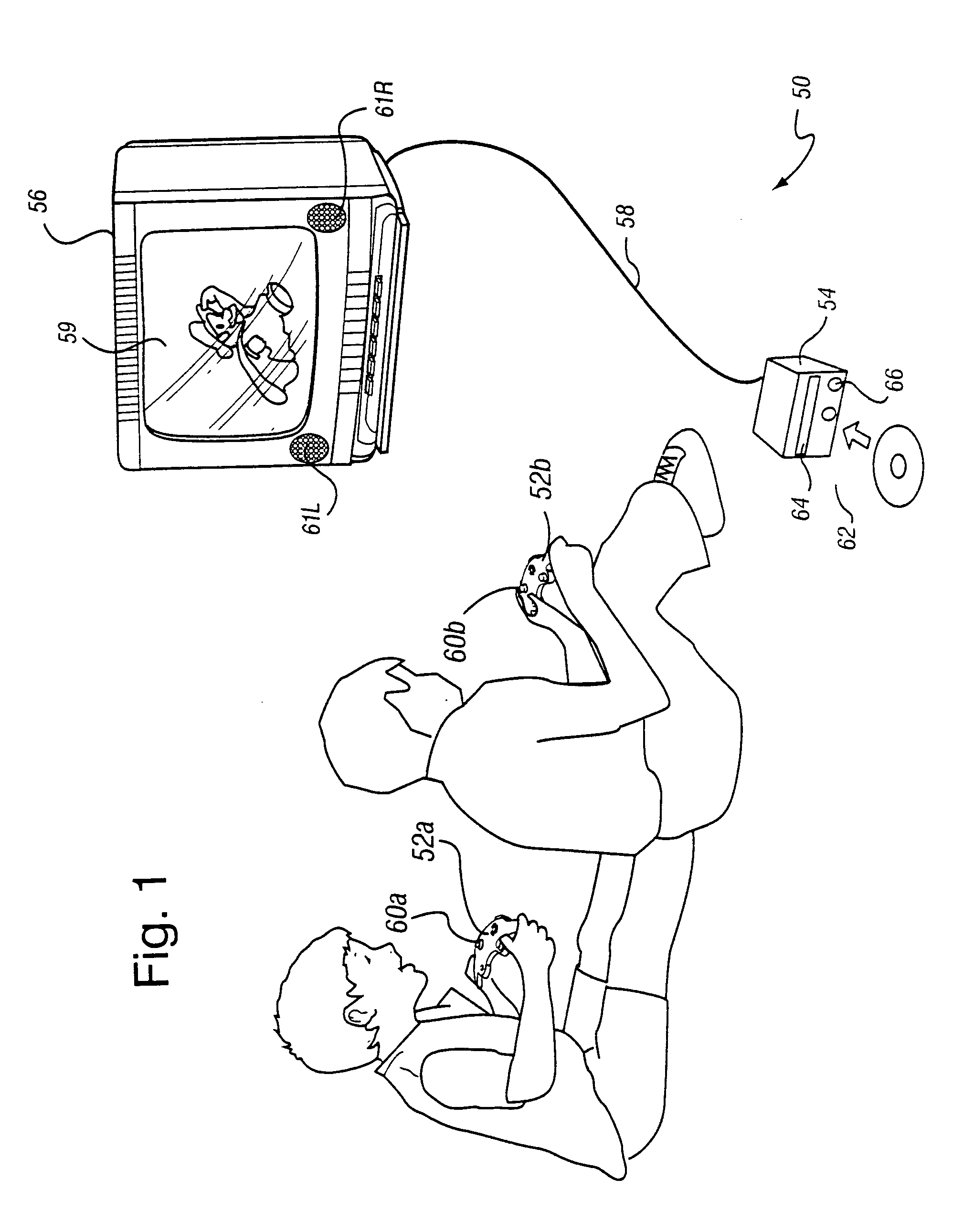

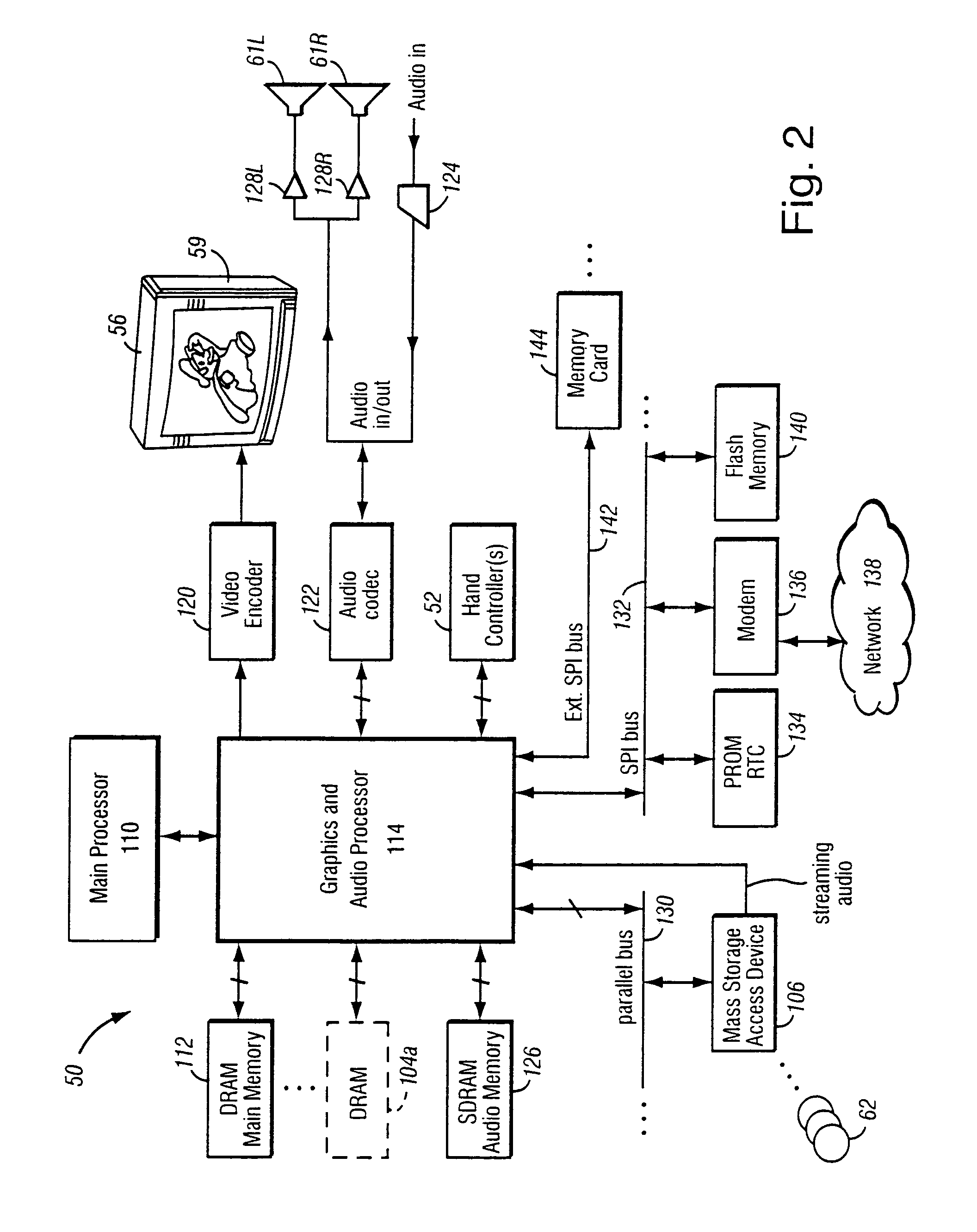

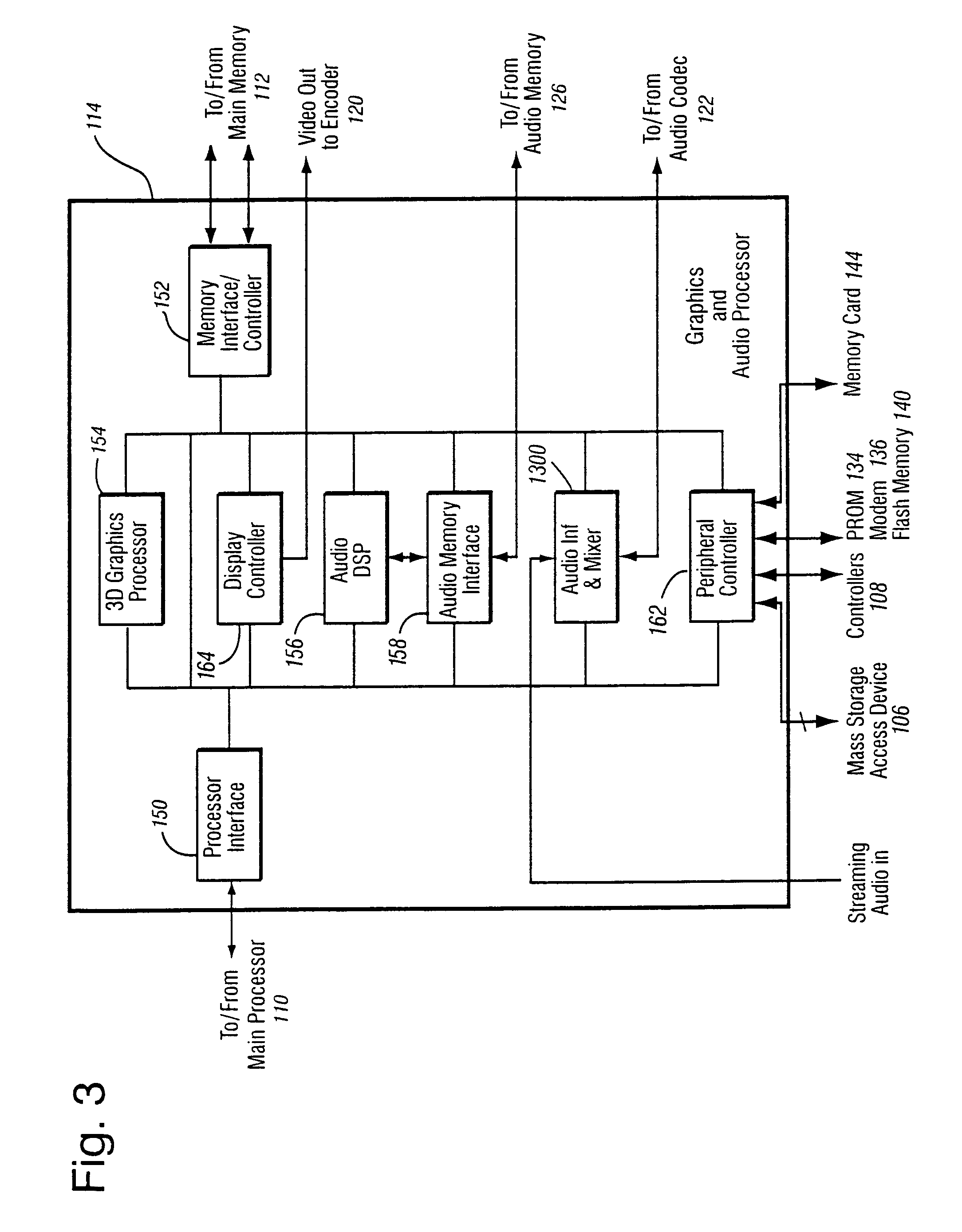

External interfaces for a 3D graphics system

InactiveUS7134960B1Reduce workloadEfficient interfaceVideo gamesSpecial data processing applicationsModem deviceOutput device

An advantageous set of external interfaces for home video game platform provide modularity and expandability while maintaining and preserving the proprietary nature of the platform. A disk drive interface provides flexible communications with an internal disk drive. Various serial bus interfaces provide expandability and interconnectability with a variety of internal and external devices including, for example, flash memory, broadband adapters, modems, and various other devices. A 4-port game controller interface provides serial interconnectability with handheld game controllers and various other input / output device. Power supply, digital and analog audio / video connections, and parallel memory expansion connections are also provided.

Owner:NINTENDO CO LTD

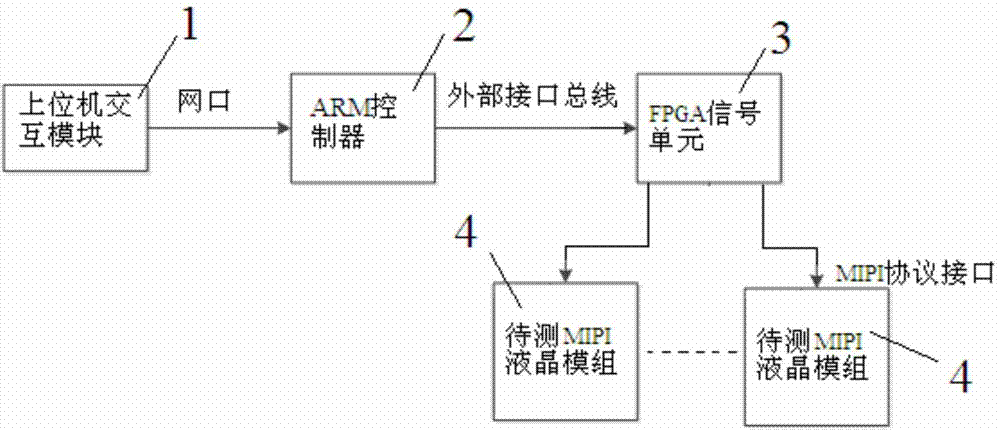

Vcom (voltage of common electrode) adjustment device and method of MIPI (mobile industry processor interface) liquid crystal module on basis of FPGA (field programmable gate array)

ActiveCN104517554AMeet the length requirementExtensive tuningStatic indicating devicesComputer moduleInternet access

The invention discloses a Vcom (voltage of common electrode) adjustment device of an MIPI (mobile industry processor interface) liquid crystal module on the basis of FPGA (field programmable gate array). The Vcom adjustment device comprises an upper computer interaction module, an ARM (advanced RISC machine) controller and an MIPI liquid crystal module to be measured. The Vcom adjustment device is characterized by comprising an FPGA signal unit, the upper computer interaction module is connected with the ARM controller through an internet access, the ARM controller is connected with the FPGA signal unit through an external bus interface, and the FPGA signal unit is connected with the MIPI liquid crystal module to be measured. The MIPI bridge chip in a multichannel testing system of the liquid crystal module can be omitted, OTP (one time password) development efficiency of the MIPI liquid crystal module is improved, various requirements of the liquid crystal module on the basis of the MIPI protocol are met, and production efficiency of the liquid crystal module is improved.

Owner:WUHAN JINGCE ELECTRONICS GRP CO LTD

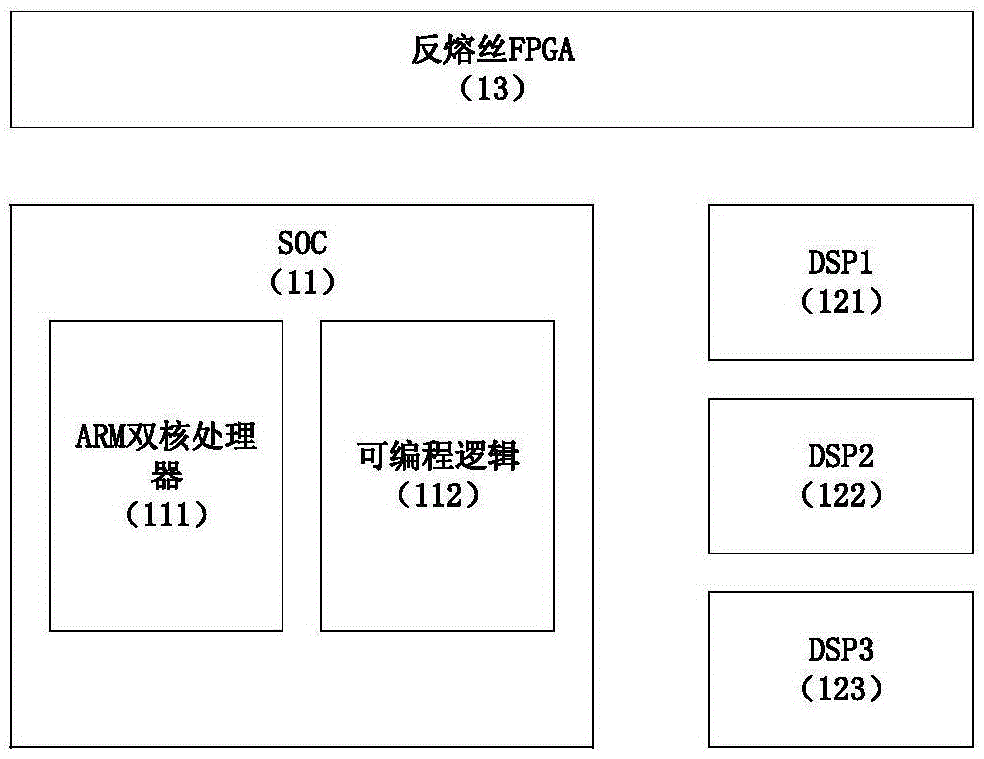

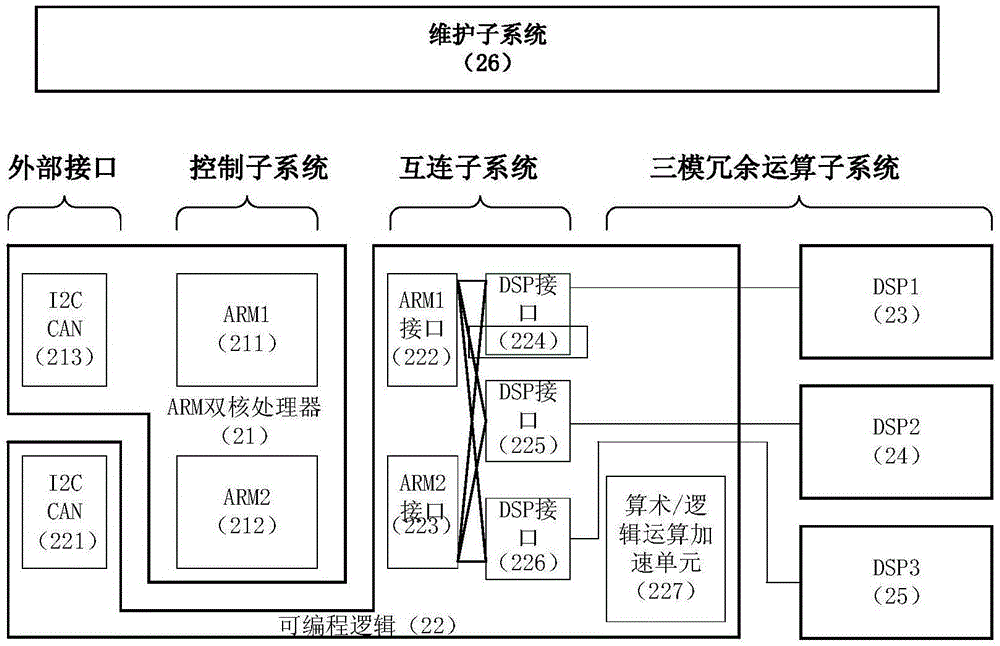

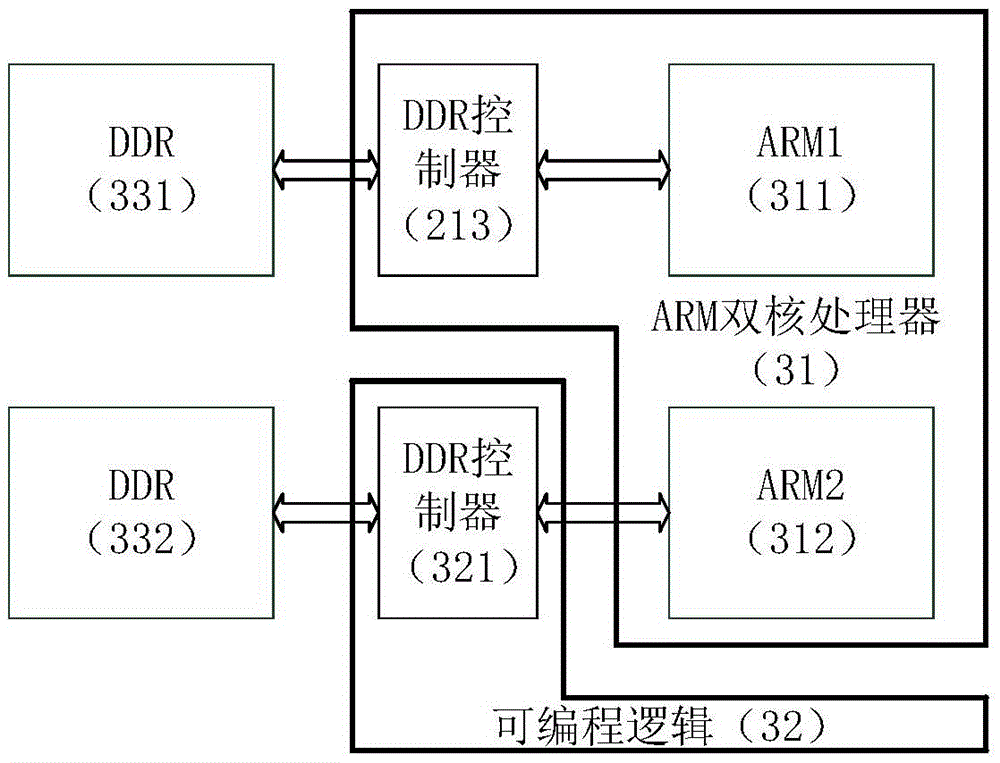

Aerospace computer

ActiveCN105550074ARealize dual machine backupImprove reliabilityRedundant hardware error correctionDual coreSystem maintenance

The invention provides an aerospace computer. The aerospace computer comprises an anti-fuse FPGA (Field Programmable Gate Array), a commercial SOC (System On Chip) and three DSPs (Digital Signal Processors), which achieve a system maintenance function. According to the aerospace computer provided by the invention, on the anti-fuse FPGA, not only is a state of each hardware unit module monitored, but also a state of each logic function operating on each hardware unit module is monitored, so that on the basis, the computer is dynamically loaded when necessary to guarantee a system to flexibly, reliably and uninterruptedly operate; the commercial SOC device adopted by the aerospace computer internally comprises an ARM dual-core processor used as a center control processor and a high-capacity programmable logic (PL) used for arithmetical logic operation acceleration, so that when a high integration level of the system is ensured, dual-computer backup of the center control processor is achieved by two cores of the ARM dual-core processor, hardware backup of a data channel and an interface is achieved by designing internal data association and an external interface on the PL, and a triple-modular redundancy voting mechanism of DSP interfaces is achieved by respectively designing the DSP interfaces; and according to the invention, the aerospace computer which is high in integration level, high in reliability and high in performance, is miniaturized and is flexible in configuration can be achieved.

Owner:CHINA JILIANG UNIV

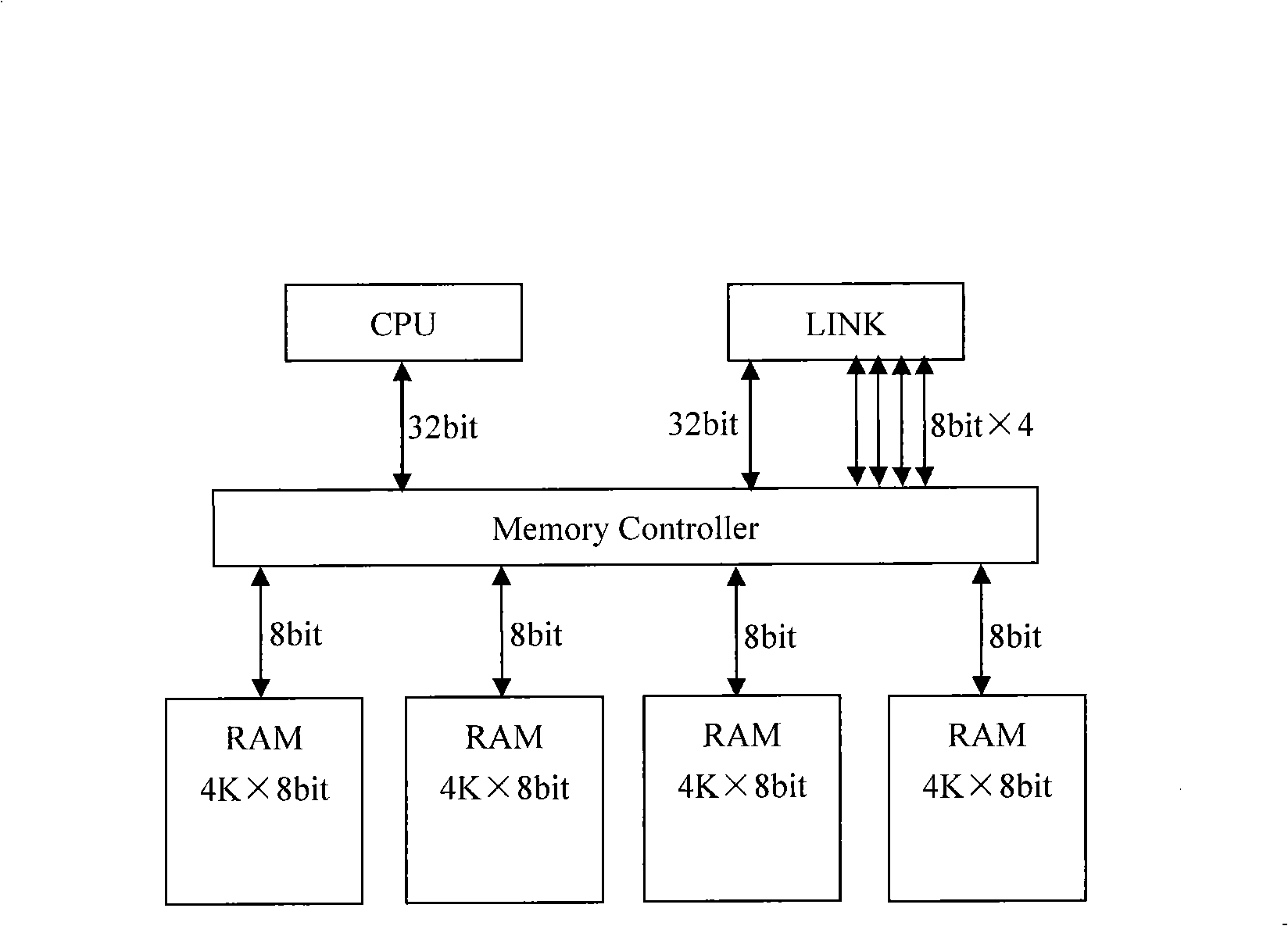

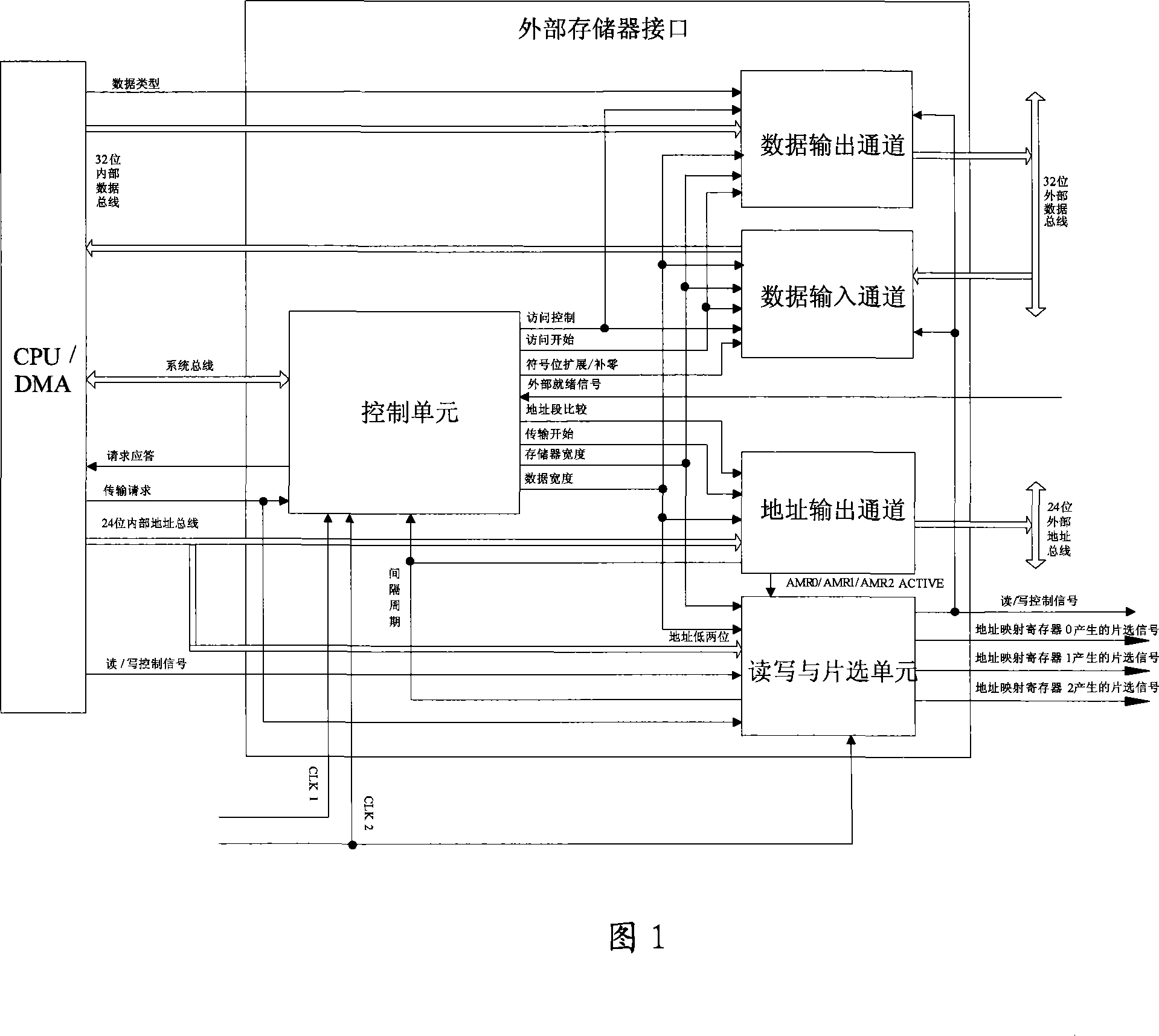

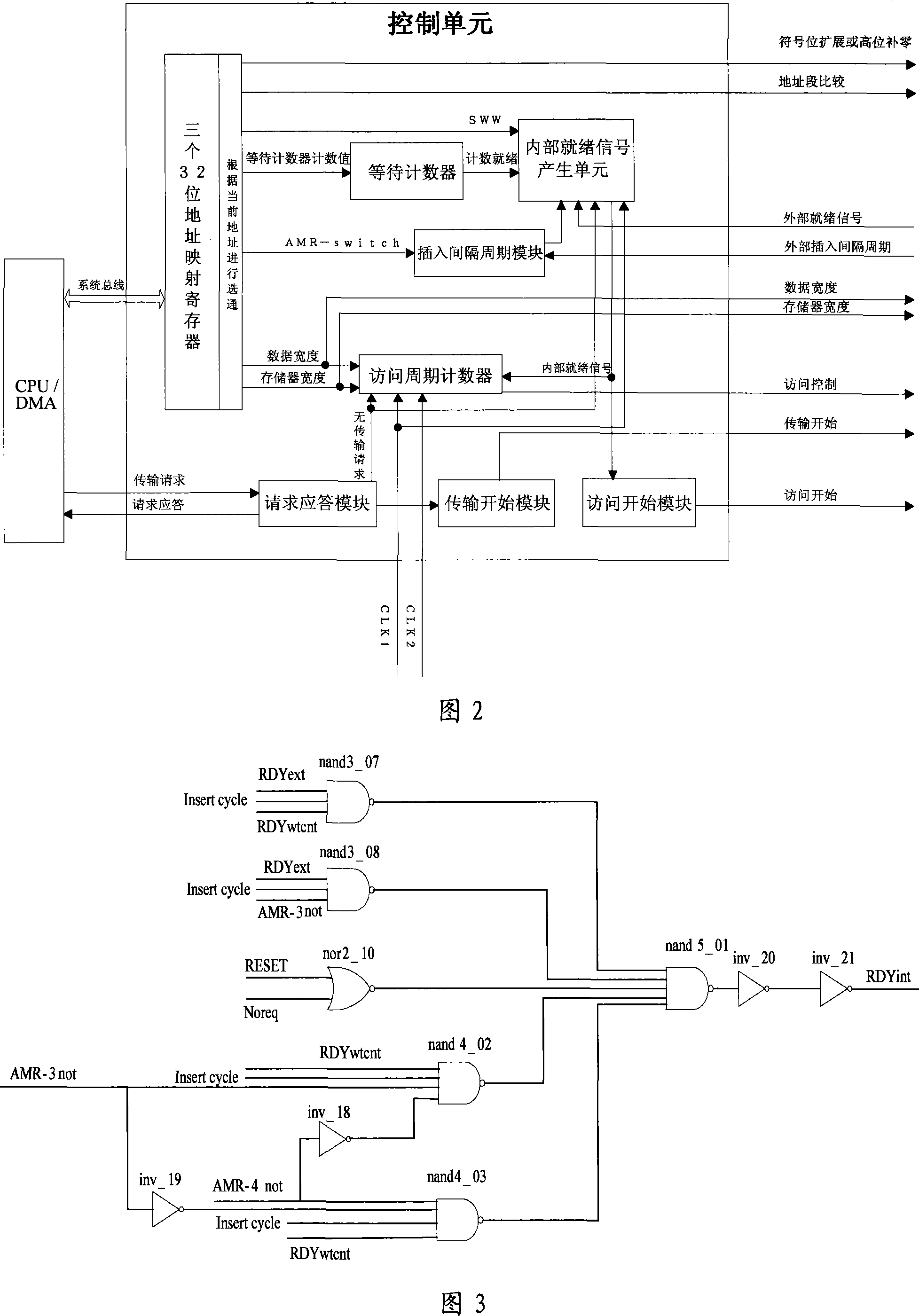

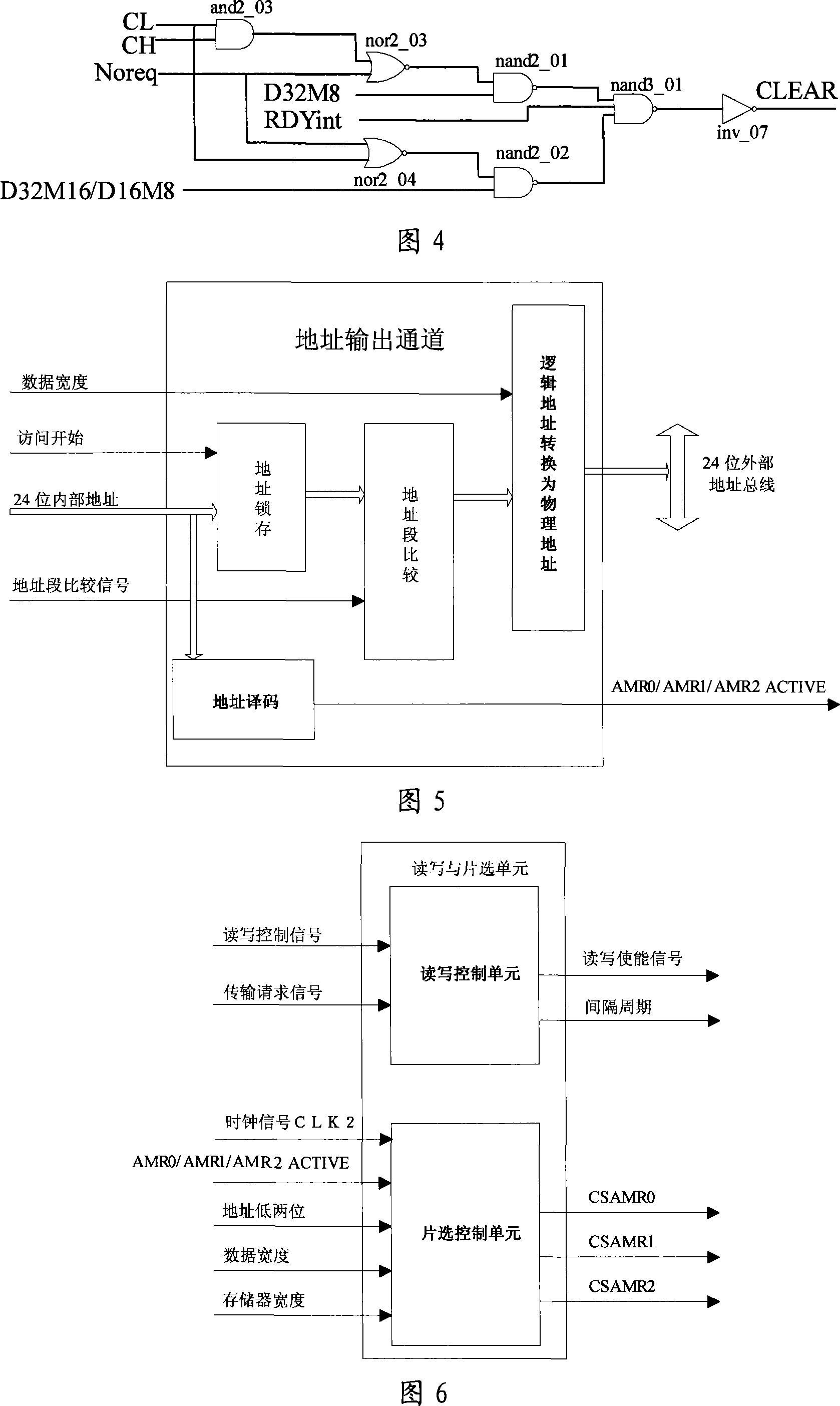

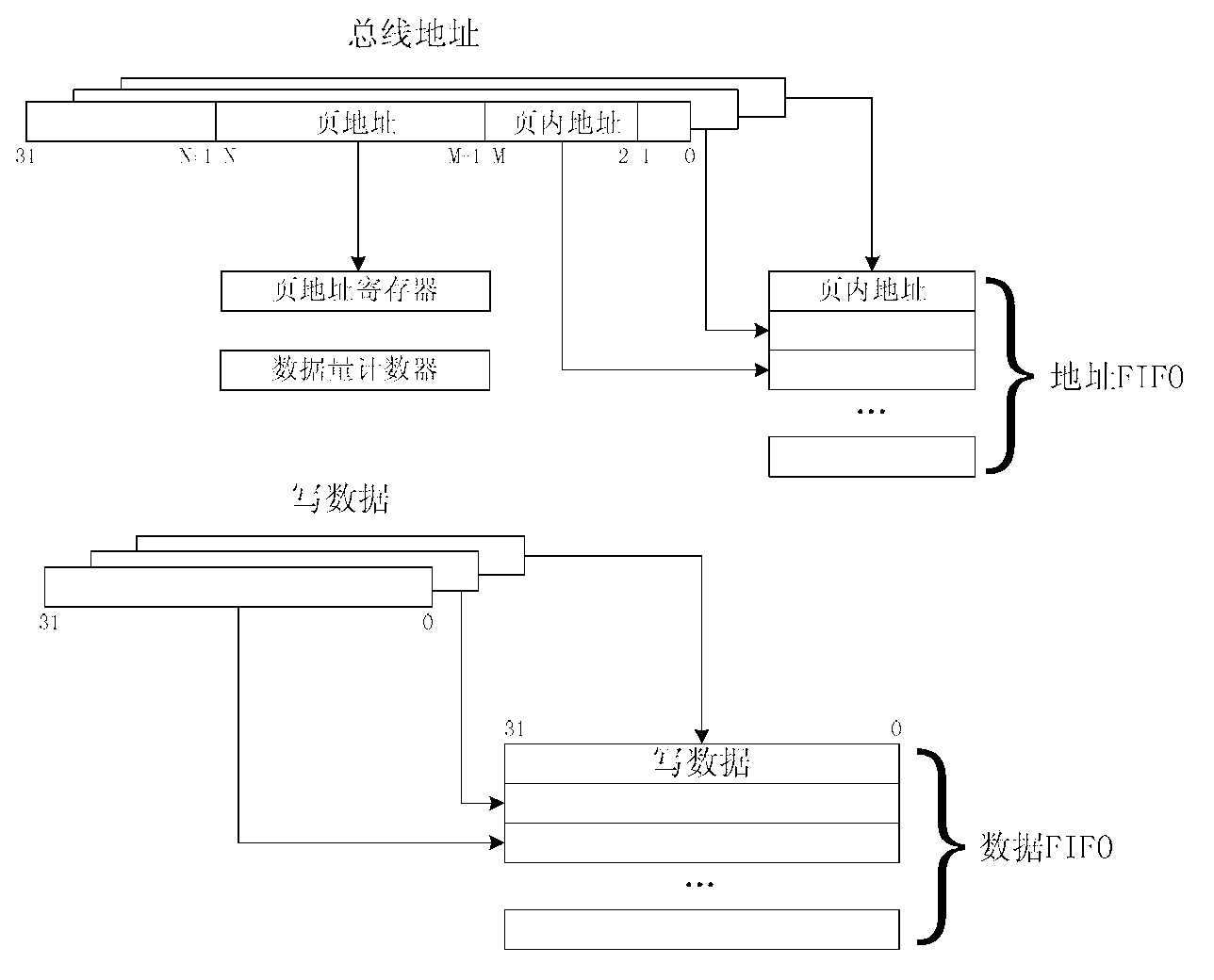

External memory storage interface

InactiveCN101221542AImprove acceleration performanceImprove work flexibilityElectric digital data processingExtensibilityExternal storage

The invention discloses an external memory interface consisting of a control unit, an address output channel, a reading-writing and chip-selection unit, a data input channel and a data output channel, wherein, the three 32-bit address mapped registers are designed in the control unit, which ensures that a 32-bit digital signal processor has the ability of interacting with a multiple bit-width external memory. The interface can synchronously make access operations to an 8-bit external memory, a 16-bit external memory and a 32-bit external memory, thereby improving the extensibility and the working flexibility of the 32-bit digital signal processor; at the same time, the interface has a simple structure, is easy to control and miniaturize, and is convenient to be realized on the chips.

Owner:BEIJING MXTRONICS CORP +1

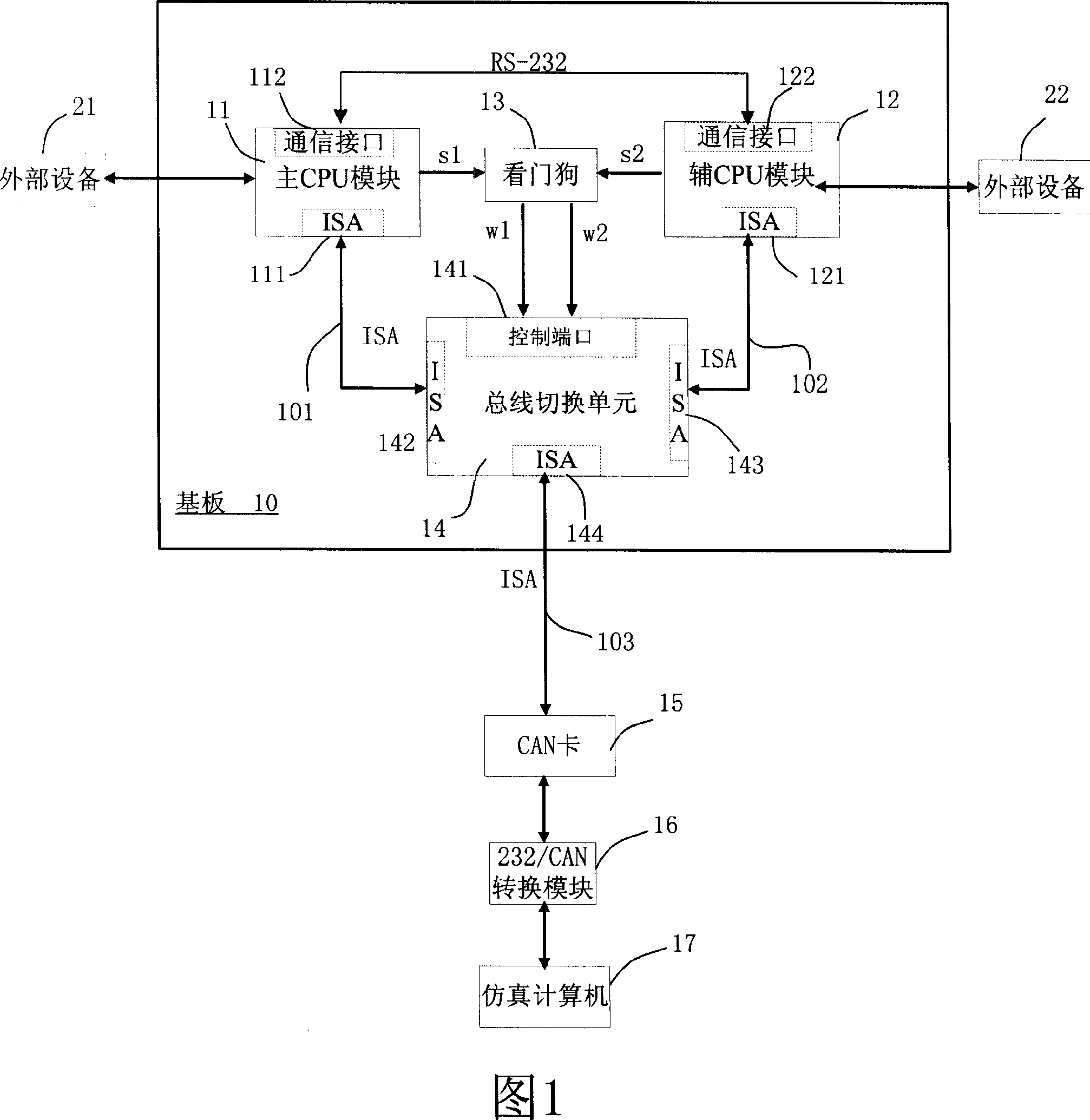

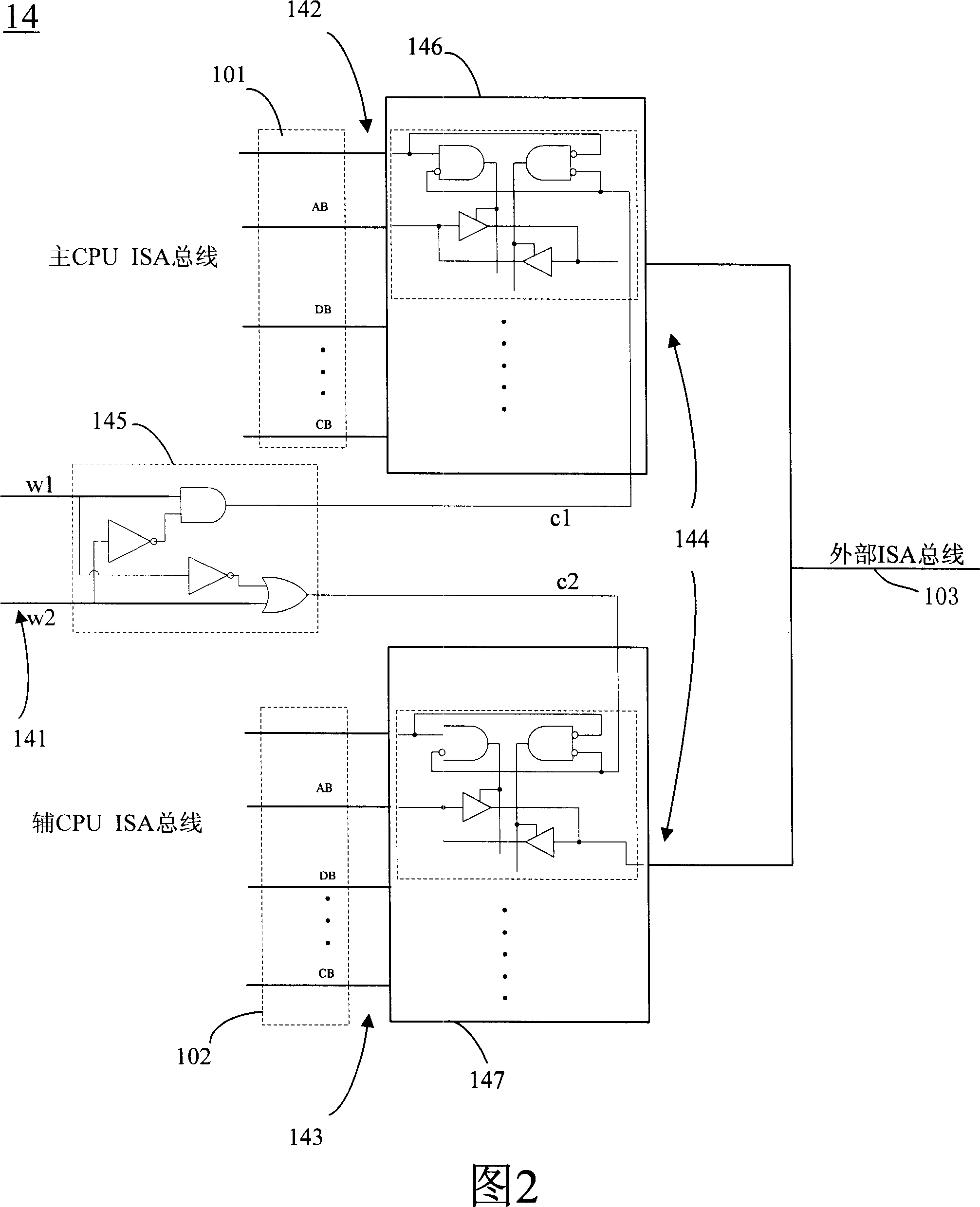

Double-machine redundancy system based on embedded CPU

InactiveCN101000591AGood value for moneyAuto switchSafety arrangmentsFault responseBus interfaceEmbedded system

A dual-machine redundant system based on embedded CPU comprises master CPU module and auxiliary CPU module both being set with a bus interface, watch dog circuit for monitoring operation states of master CPU module and auxiliary CPU module and for outputting watch dog signal presenting their operation state separately, bus switching-over unit for receiving said watch dog signal from control port and for switching over external bus read / write right between master CPU module and auxiliary CPU module according to said watch dog signal.

Owner:NO 711 RES INST CHINA SHIPPING HEAVY IND GRP

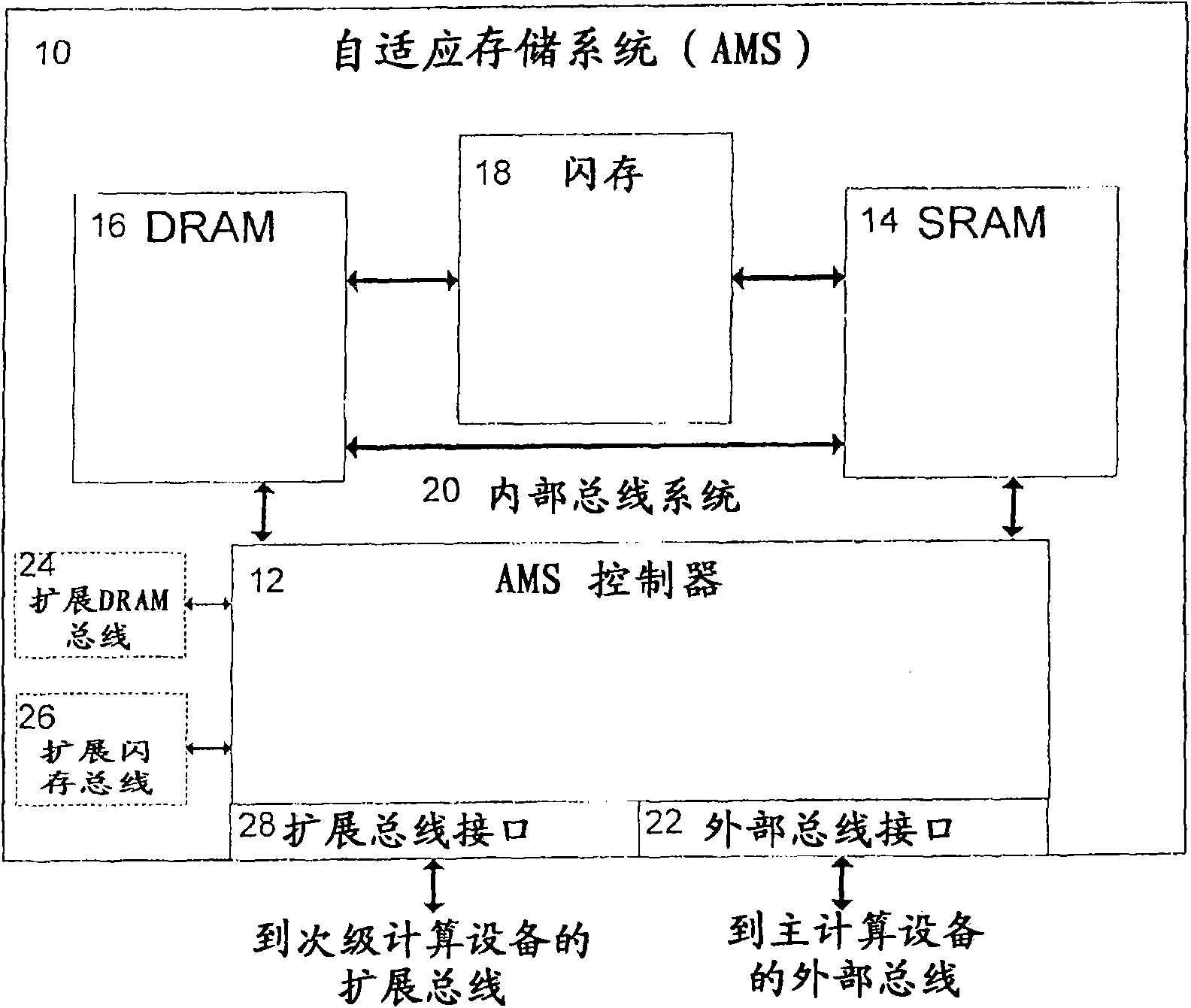

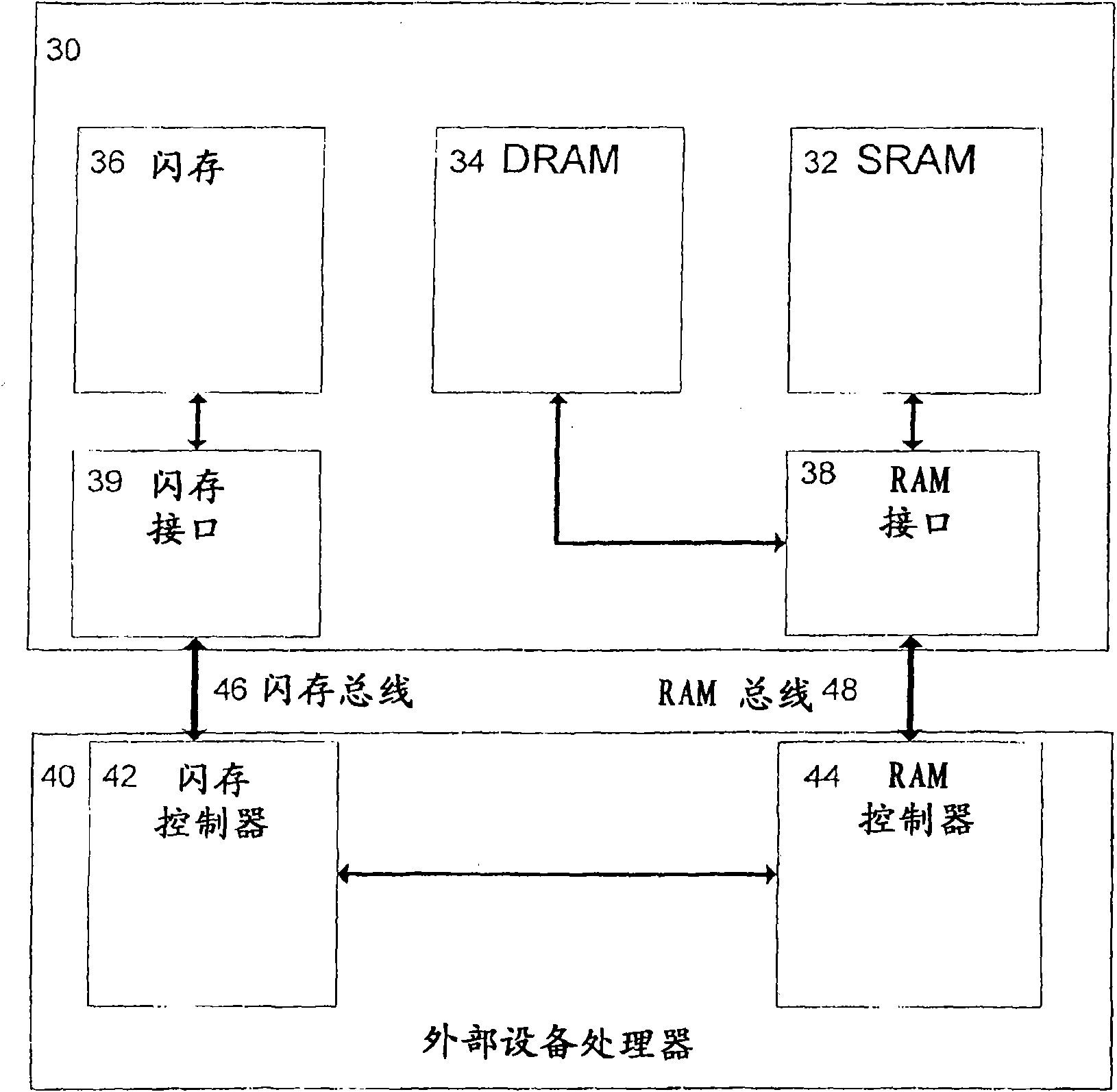

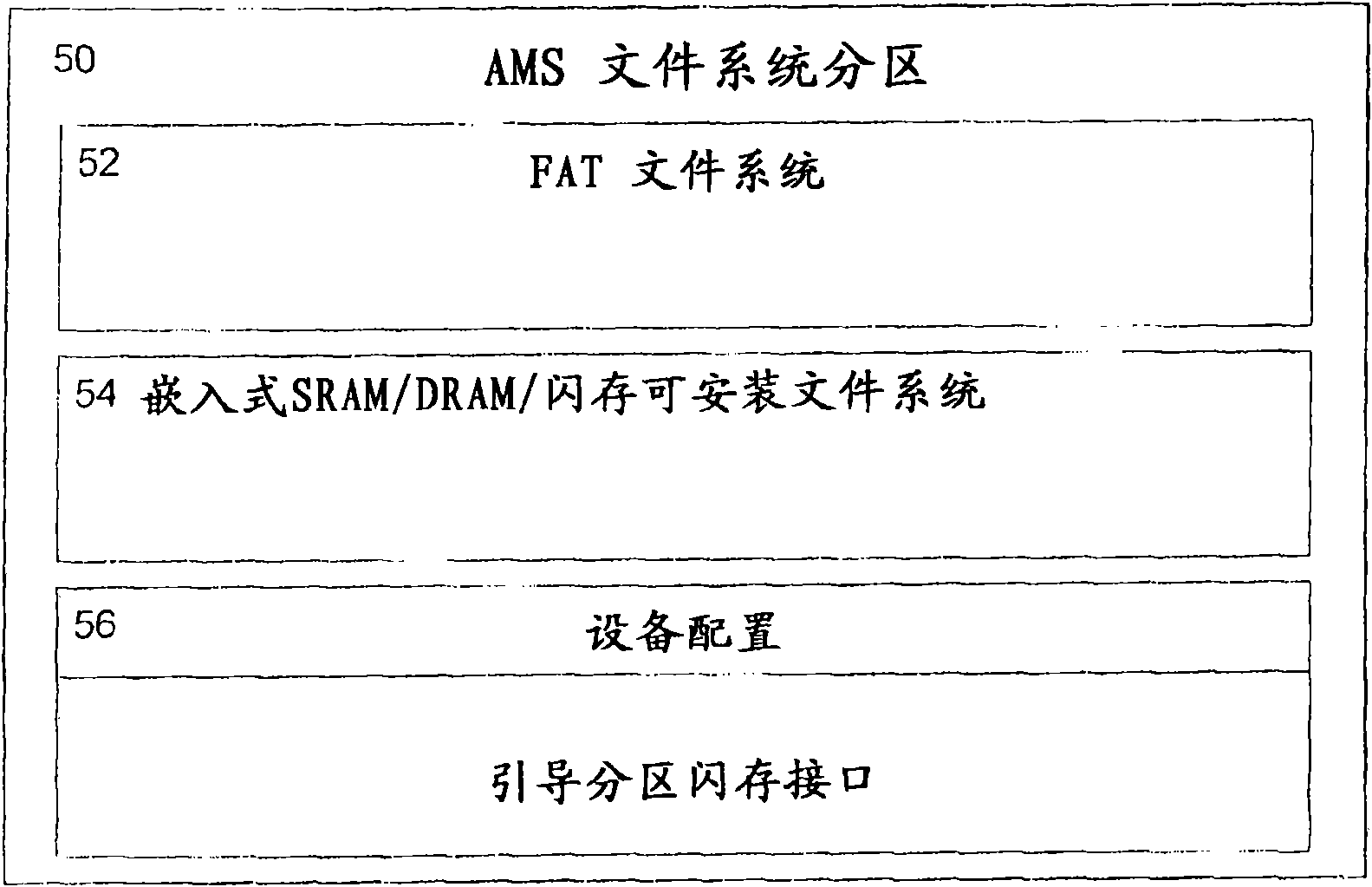

Adaptive memory system for enhancing the performance of an external computing device

InactiveCN101611387AMemory architecture accessing/allocationMemory adressing/allocation/relocationMemory typeStatic random-access memory

An adaptive memory system is provided for improving the performance of an external computing device. The adaptive memory system includes a single controller, a first memory type (e.g., Static Random Access Memory or SRAM), a second memory type (e.g., Dynamic Random Access Memory or DRAM), a third memory type (e.g., Flash), an internal bus system, and an external bus interface. The single conlrollei is configured to: (i) communicate with all three memory types using the internal bus system; (ii) communicate with the external computing device using the external bus interface; and (iii) allocatecache-data storage assignment to a storage space within the first memory type, and after the storage space within the first memory type is determined to be full, allocate cache-data storage assignment to a storage space within the second memory type.

Owner:MOBILE SEMICON CORP

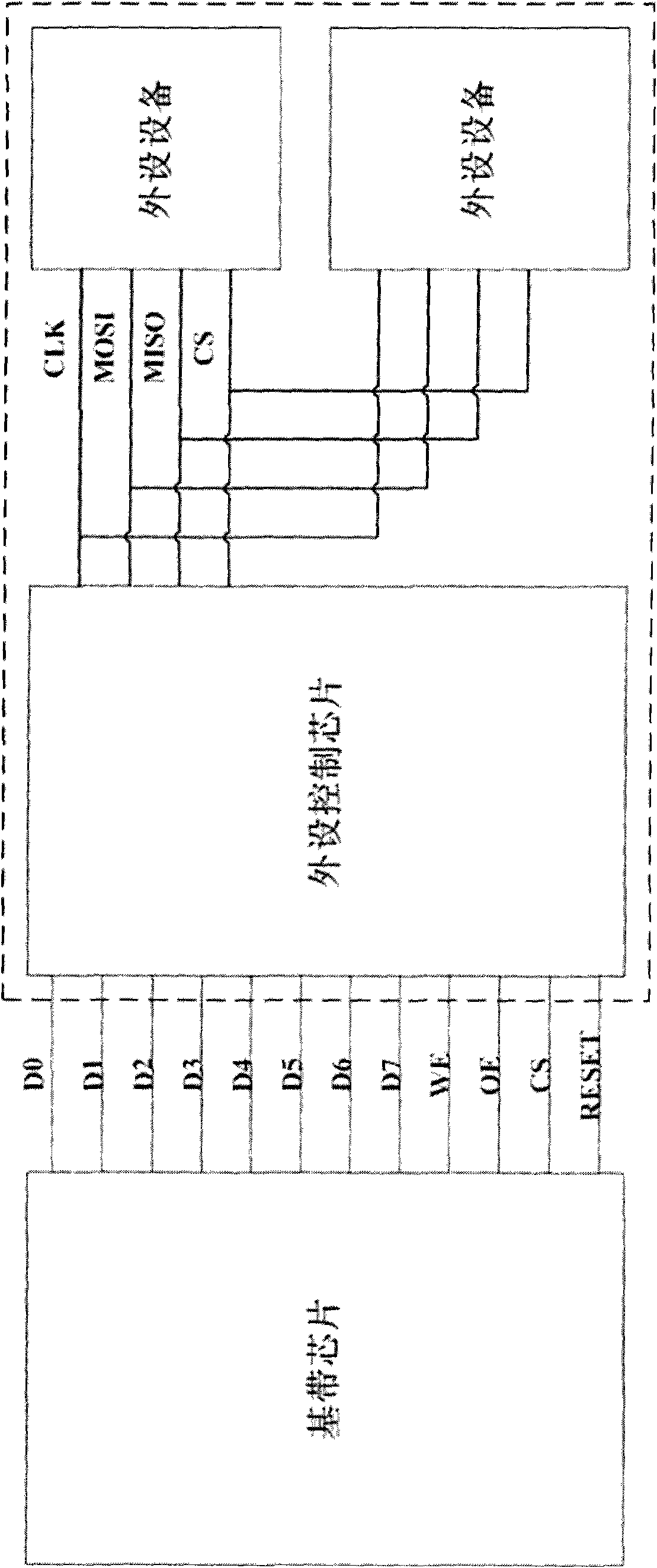

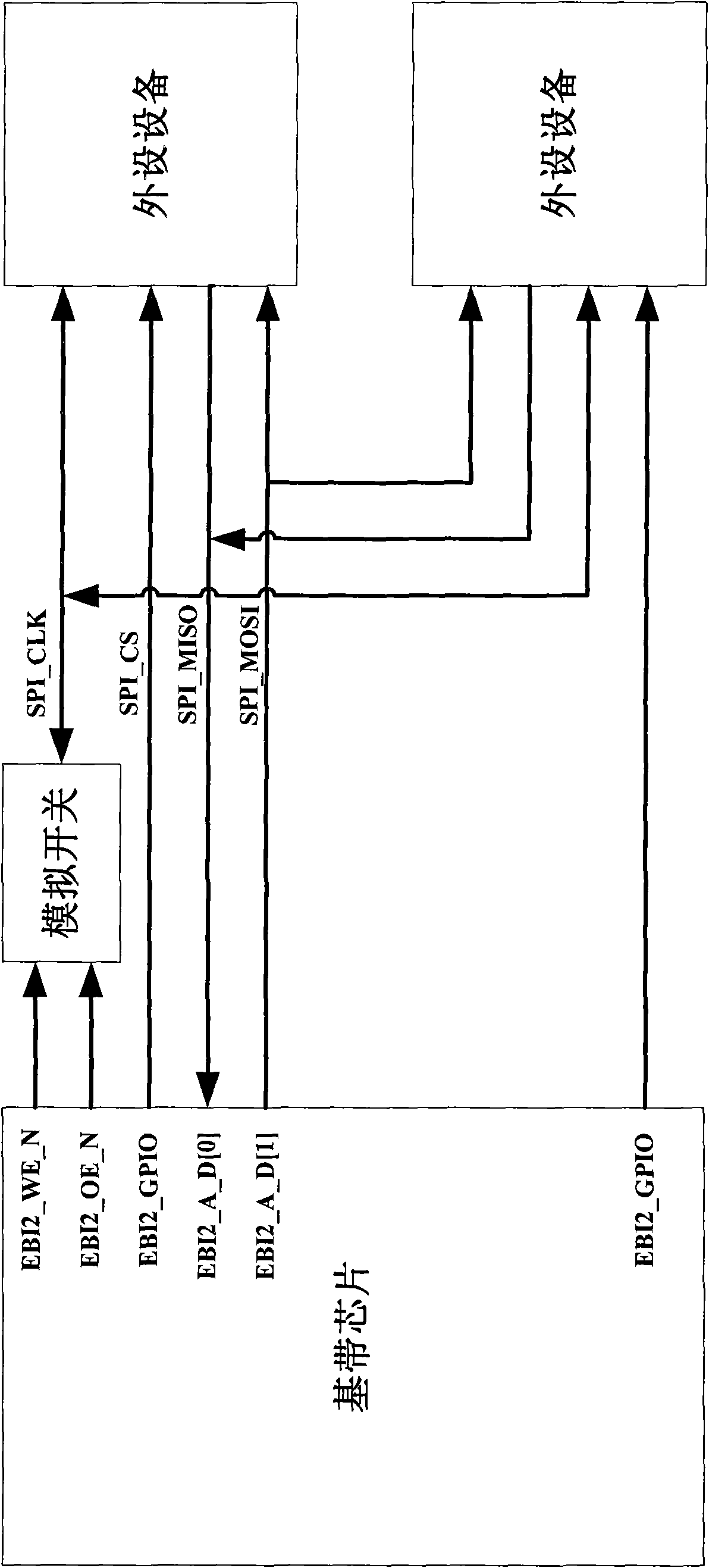

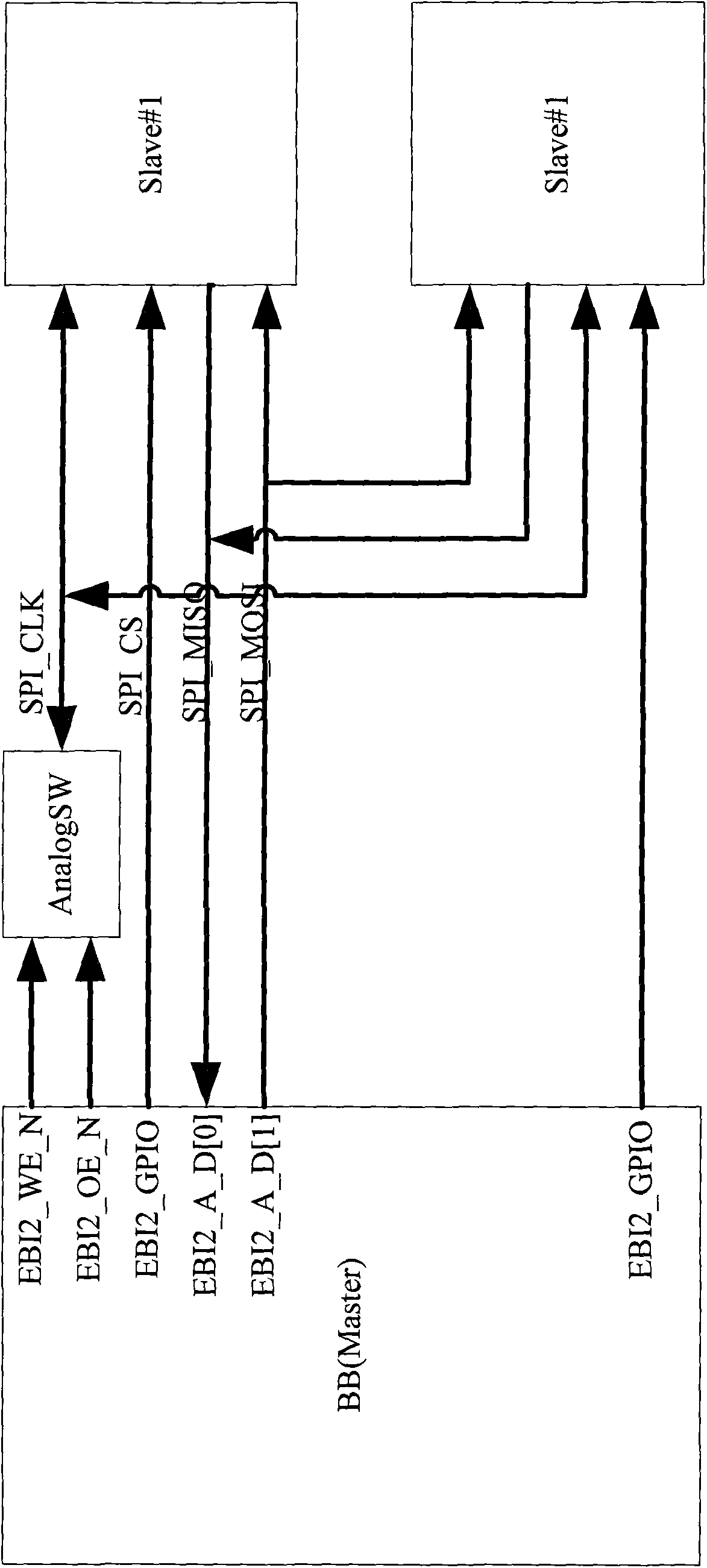

Module for realizing SPI interface

ActiveCN101820460ARich interface resourcesEasy to useTelephone set constructionsData signalUsability

The invention discloses a module for realizing an SPI interface, comprising a baseband chip, at least one peripheral and a simulation switch, wherein the external bus interface of the baseband chip simulates a white-enable pin, an output-enable pin, a universal input pin, a universal output pin, a first data signal pin and a second data signal pin; the write-enable pin and the output-enable pin are respectively connected with the input end of the simulation switch, the output end of the simulation switch serving as the clock signal pin of a serial peripheral interface (SPI) is connected with the peripheral; the universal input pin and the universal output pin which serve as chip selection signal pins are respectively connected with the peripheral; and the first data signal pin and the second data signal pin respectively serving as a master out salve in (MOSI) pin and a master in slave out (MISO) pin are connected with the peripheral. The invention can enrich interface resources for a platform, enhances platform interface usability, saves mobile phone cost and improves PCB space utilization rate to a very large extent.

Owner:HUAQIN TECH CO LTD

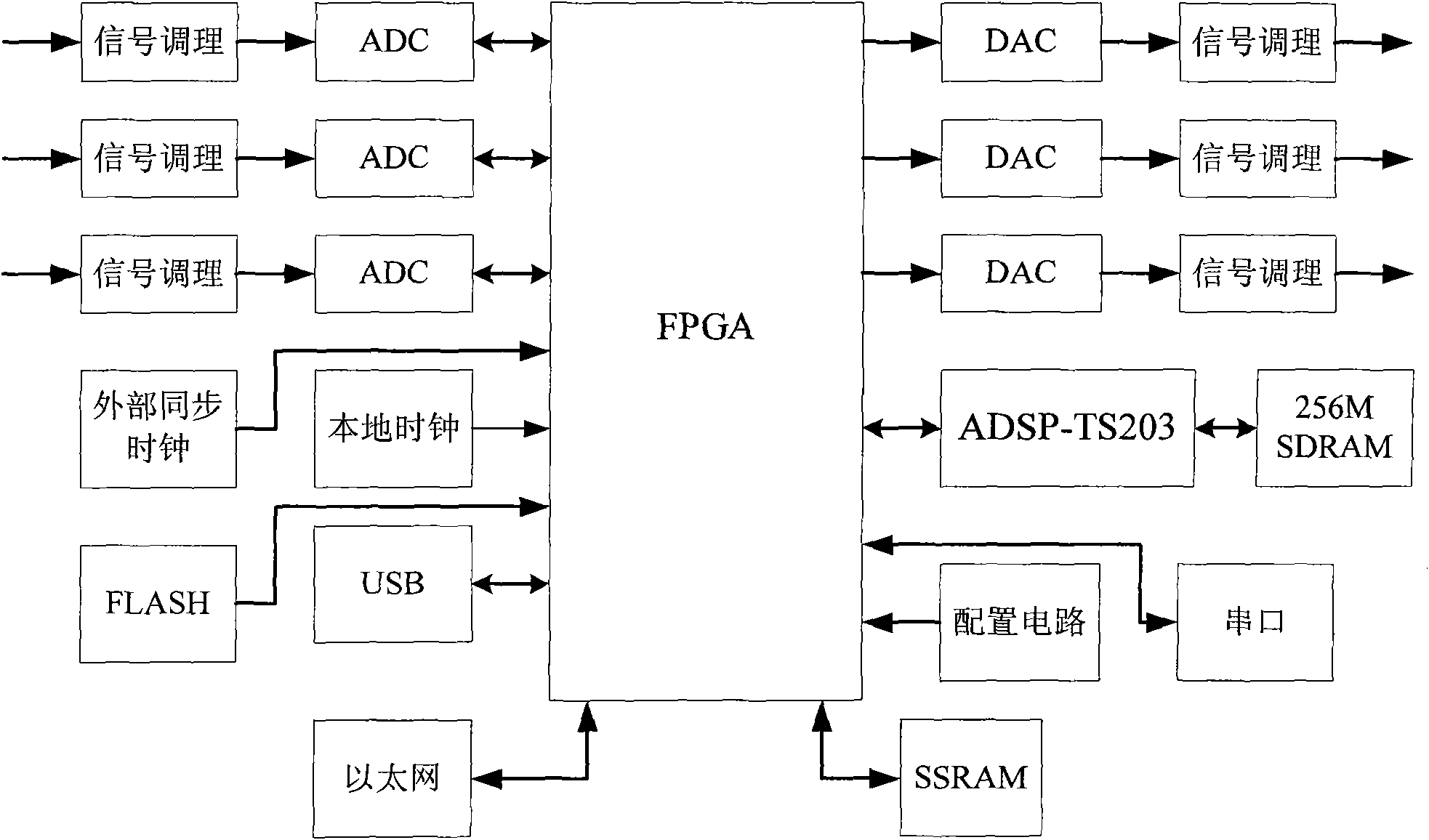

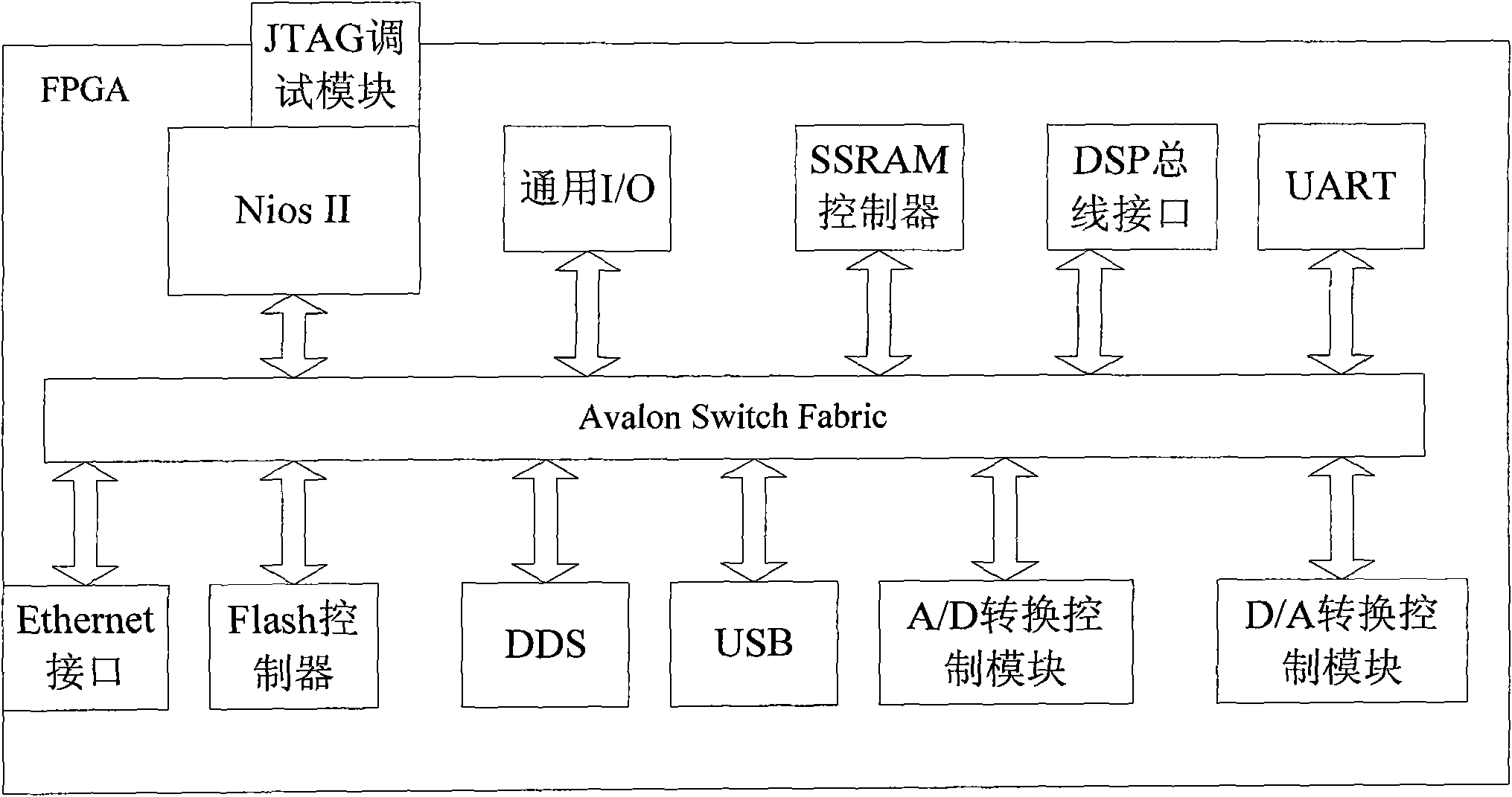

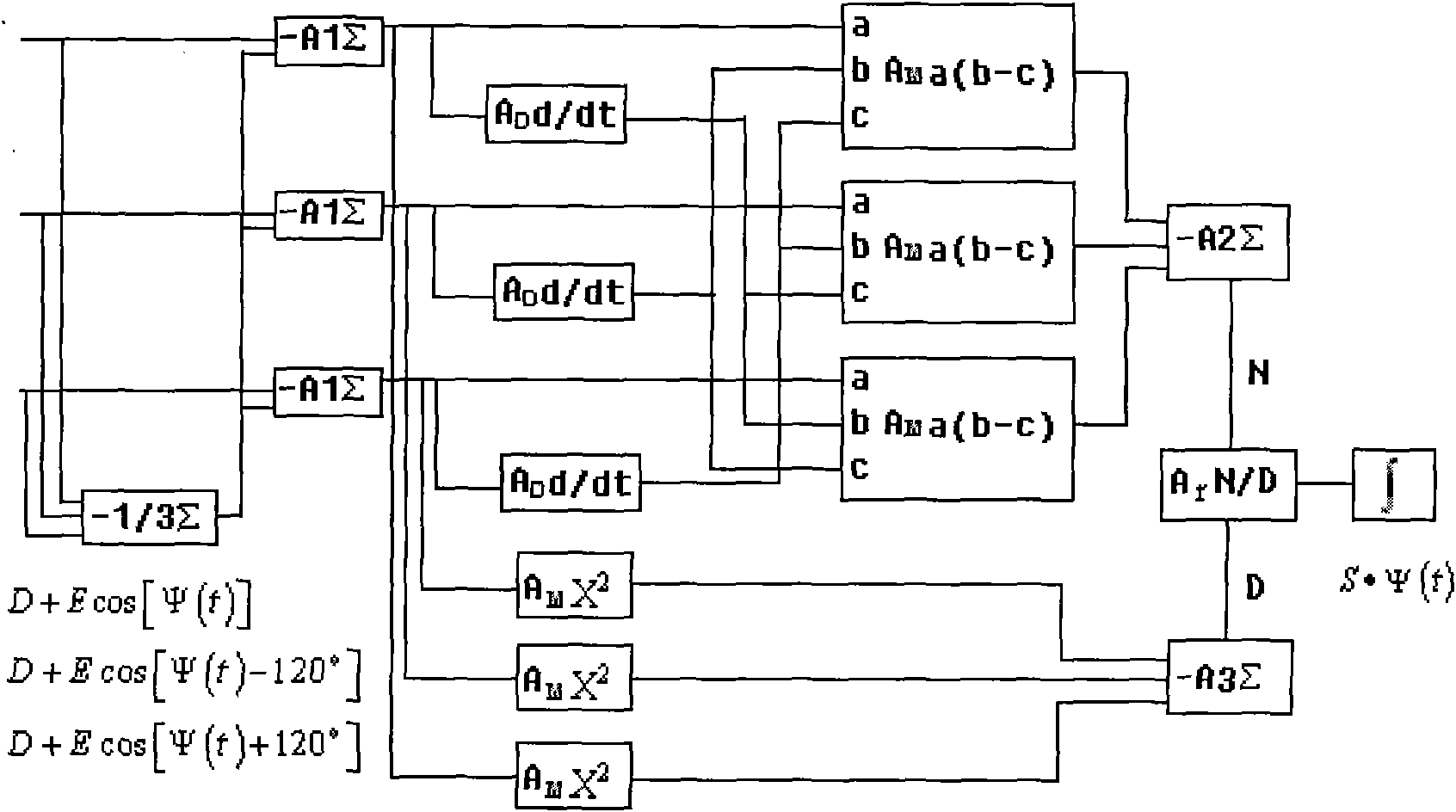

Signal demodulation method of portable multifunctional optical fiber hydrophone

InactiveCN101615888ALow costSubsonic/sonic/ultrasonic wave measurementUsing wave/particle radiation meansSignal conditioning circuitsHydrophone

The invention relates to a signal demodulation method of a portable multifunctional optical fiber hydrophone, comprising the following steps: three-path analog input is accessed into an A / D conversion module after passing through a signal conditioning circuit, the A / D conversion module is connected with an FPGA, four-path D / A conversion module is connected with the FPGA, an output end of the D / A conversion module is connected with an output analog voltage signal of the signal conditioning circuit, an FPGA chip is connected with a DSP chip by an external bus interface, and the FPGA is used for controlling the DSP to reset, start and load program; a flash memory is internally stored with 3*3 coupler digital demodulation algorithm DSP program and PGC quadrature complex demodulation algorithm DSP program which are uploaded into the DSP by the FPGA according to the selection of the user, so that one-path 3*3 coupler digital demodulation or three-path PGC digital demodulation can be realized. The signal demodulation method has the advantages of low energy consumption and cost as well as being portable and multifunctional, so as to provides a reliable, fast and convenient tool for the study of the optical fiber hydrophone and array thereof.

Owner:THE 715TH RES INST OF CHINA SHIPBUILDING IND CORP

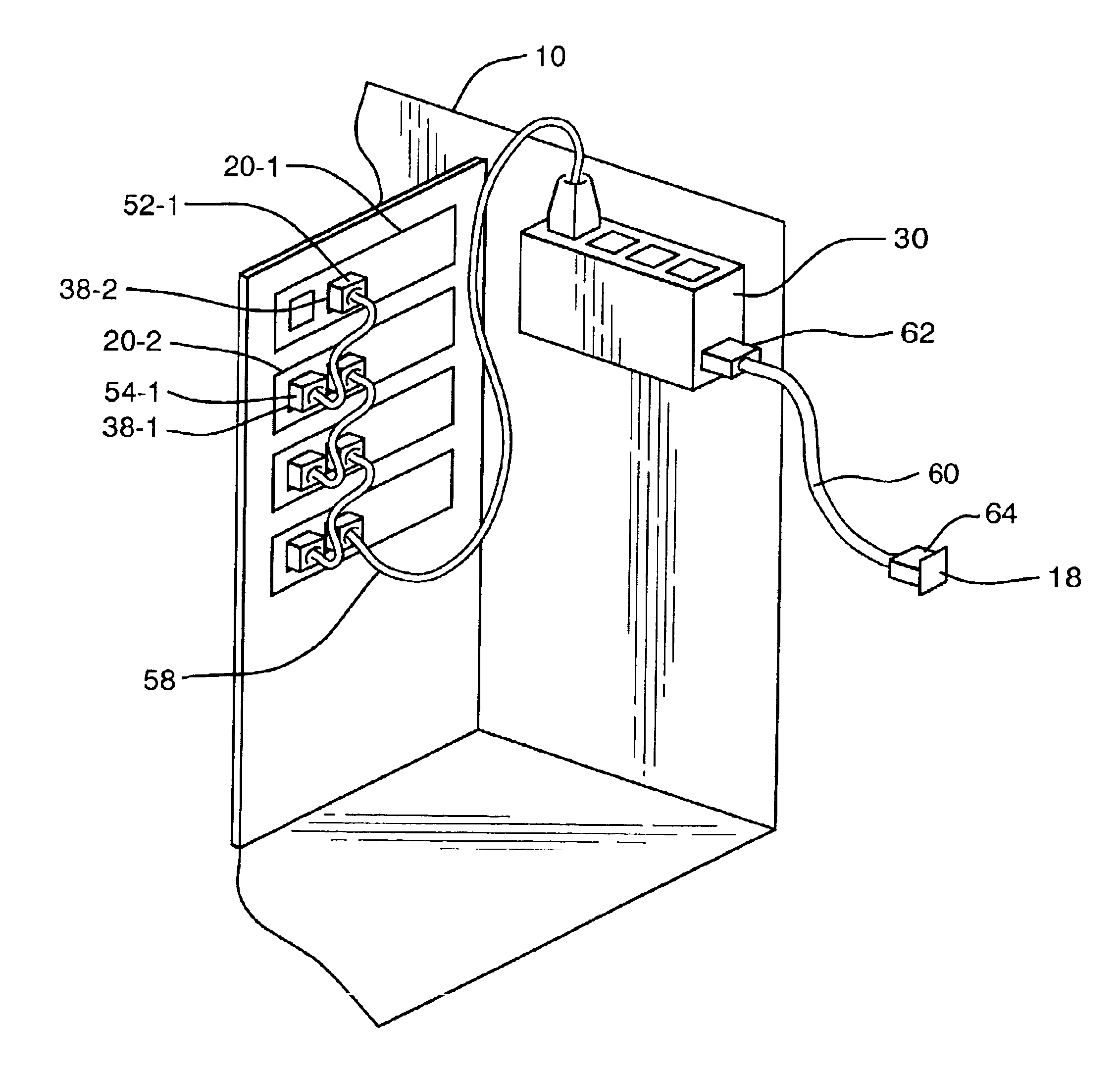

Data bank providing connectivity among multiple mass storage media devices using daisy chained universal bus interface

InactiveUS6875023B1Improve connectivityLow costElectrically conductive connectionsCoupling device detailsMass storageBus interface

A data storage system that houses at least two mass storage devices in an enclosure, along with all interconnect cabling electronics to permit access through a shared universal-type interface. An enclosure houses multiple mass storage devices such as disk drives. A set of bridges located within the enclosure provides connectivity from the disk interface to the universal-type bus. Bridge outputs are coupled to a universal hub also located within the enclosure to provide a single port interface to the array of disks. The arrangement thus provides for connectivity to multiple mass storage devices housing in a single enclosure with a single universal bus interface.

Owner:INTERACTIVE MEDIA CORP

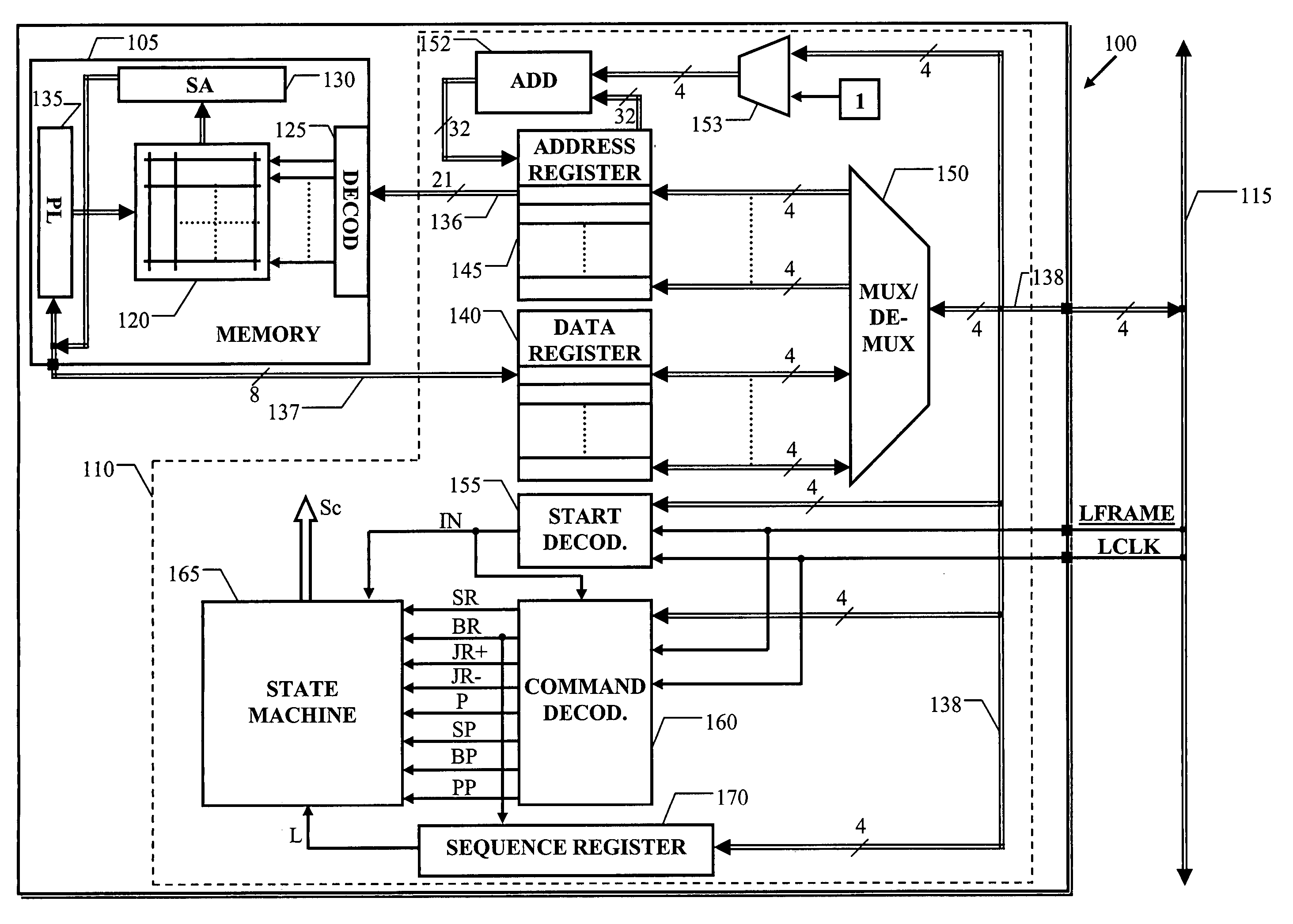

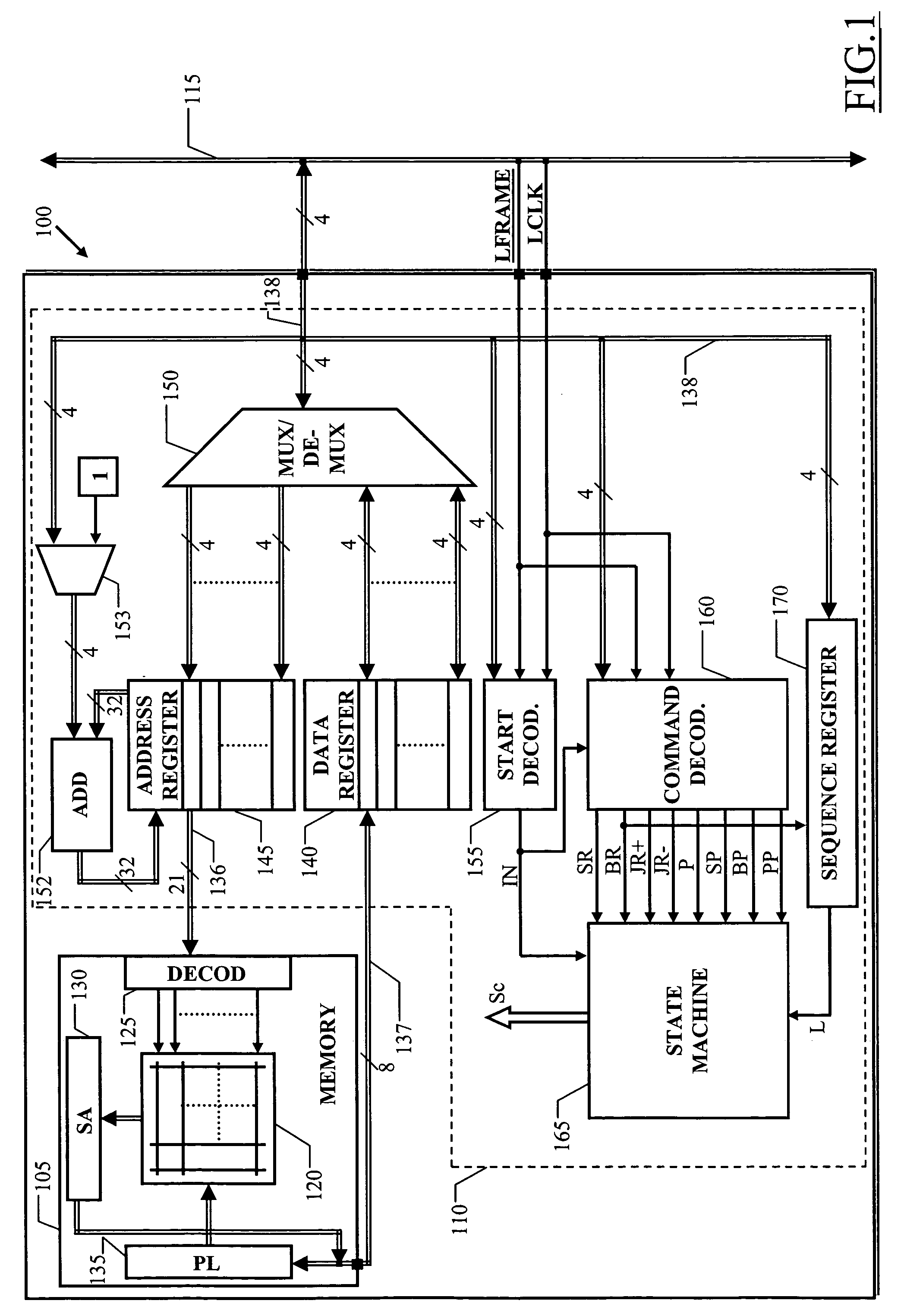

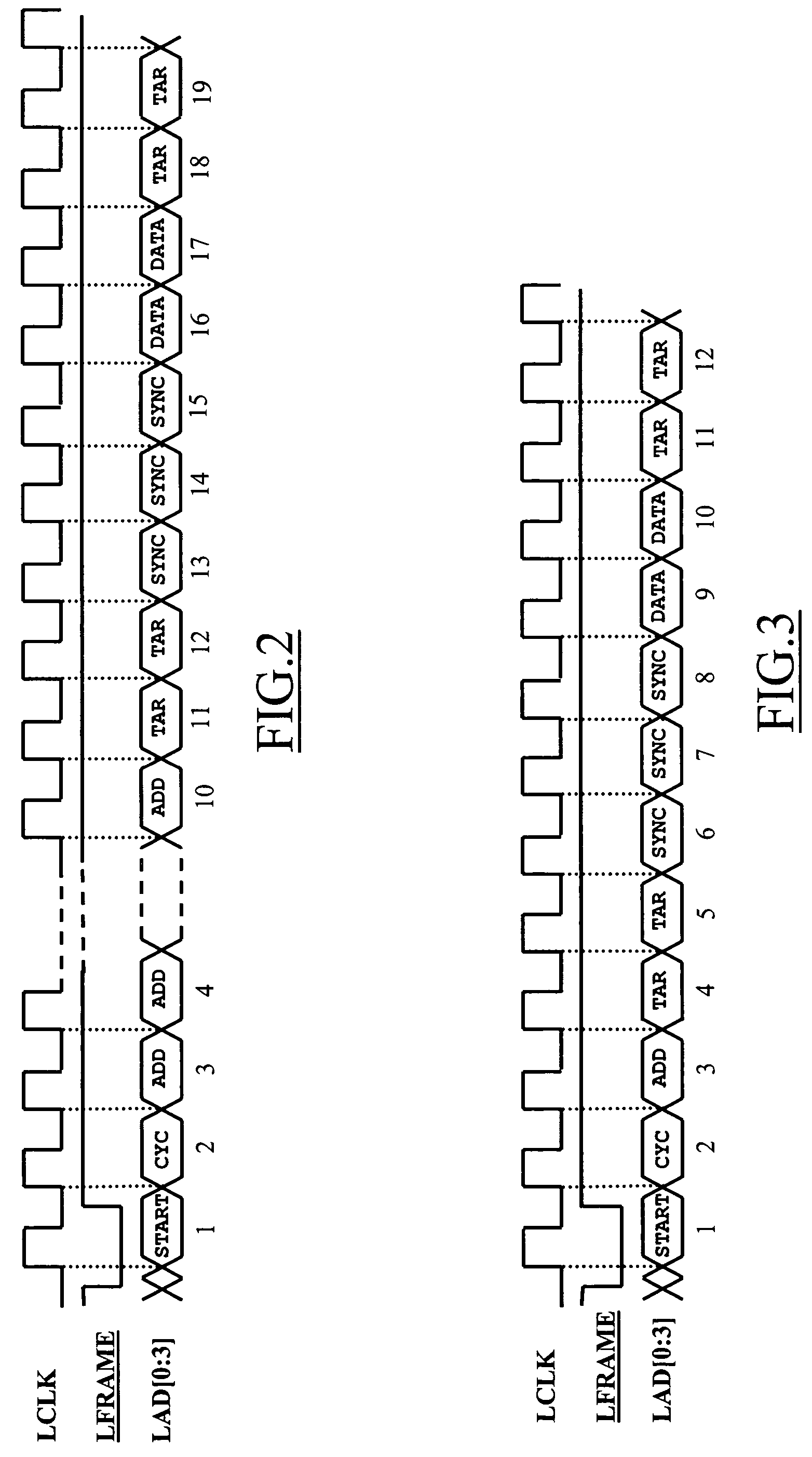

Integrated device with multiple reading and/or writing commands

ActiveUS7376810B2Memory adressing/allocation/relocationRead-only memoriesCommunication interfaceComputer science

An integrated device is provided that includes a non-volatile memory having an addressing parallelism and a data parallelism, and a communication interface for interfacing the memory with an external bus. The external bus has a transfer parallelism lower than the addressing parallelism and the data parallelism. The communication interface includes control means for executing multiple reading operations and / or multiple writing operations on the memory according to different modalities in response to corresponding command codes received from the external bus. Also provided is a method of operating such an integrated device.

Owner:STMICROELECTRONICS SRL

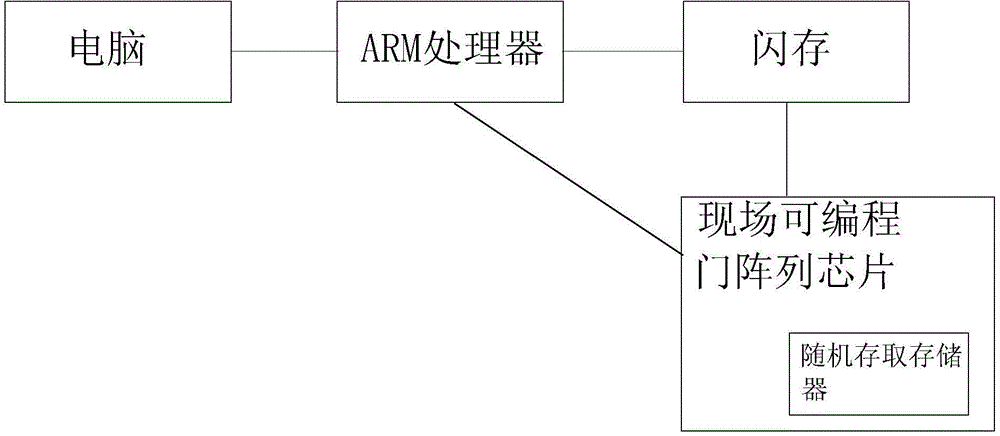

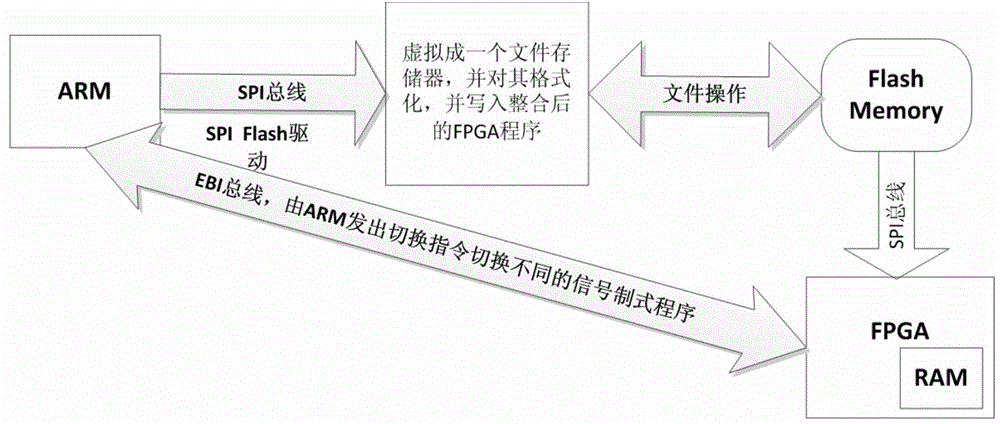

FPGA program multi-image loading method based on ARM

ActiveCN104572211AFast startup timeSatisfy R&DProgram loading/initiatingMulti-imageProcessor register

The invention relates to an FPGA (Field Programmable Gate Array) program multi-image loading method based on an ARM. The loading method comprises the following steps: 1, packing field-programmable gate array files with different signal formats in a computer through a field-programmable gate array compiler; 2, writing the packed field-programmable gate array files into a flash memory in the computer by an ARM processor via a serial peripheral interface; 3, writing external bus interface storage address information and corresponding external bus interface register addresses of the files demanded to be loaded into external bus interfaces by the ARM processor when demanding to load one of the packed field-programmable gate array files, and loading the necessary field-programmable gate array files into the random access memory of the field-programmable gate array chip from the flash memory by the field-programmable gate array chip. Fast switch and power down protection of display module test signals can be simultaneously realized by the loading method.

Owner:WUHAN JINGCE ELECTRONICS GRP CO LTD

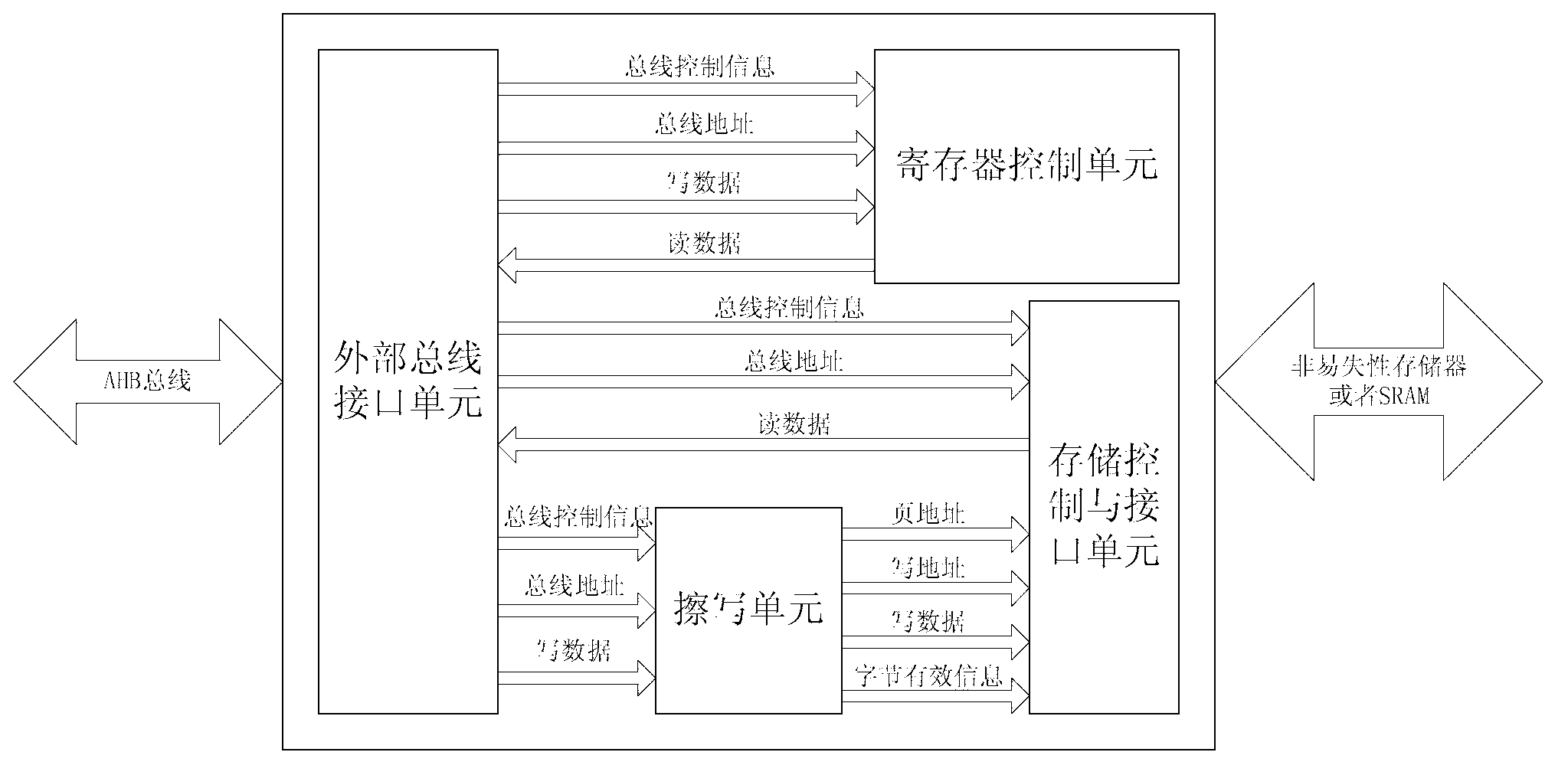

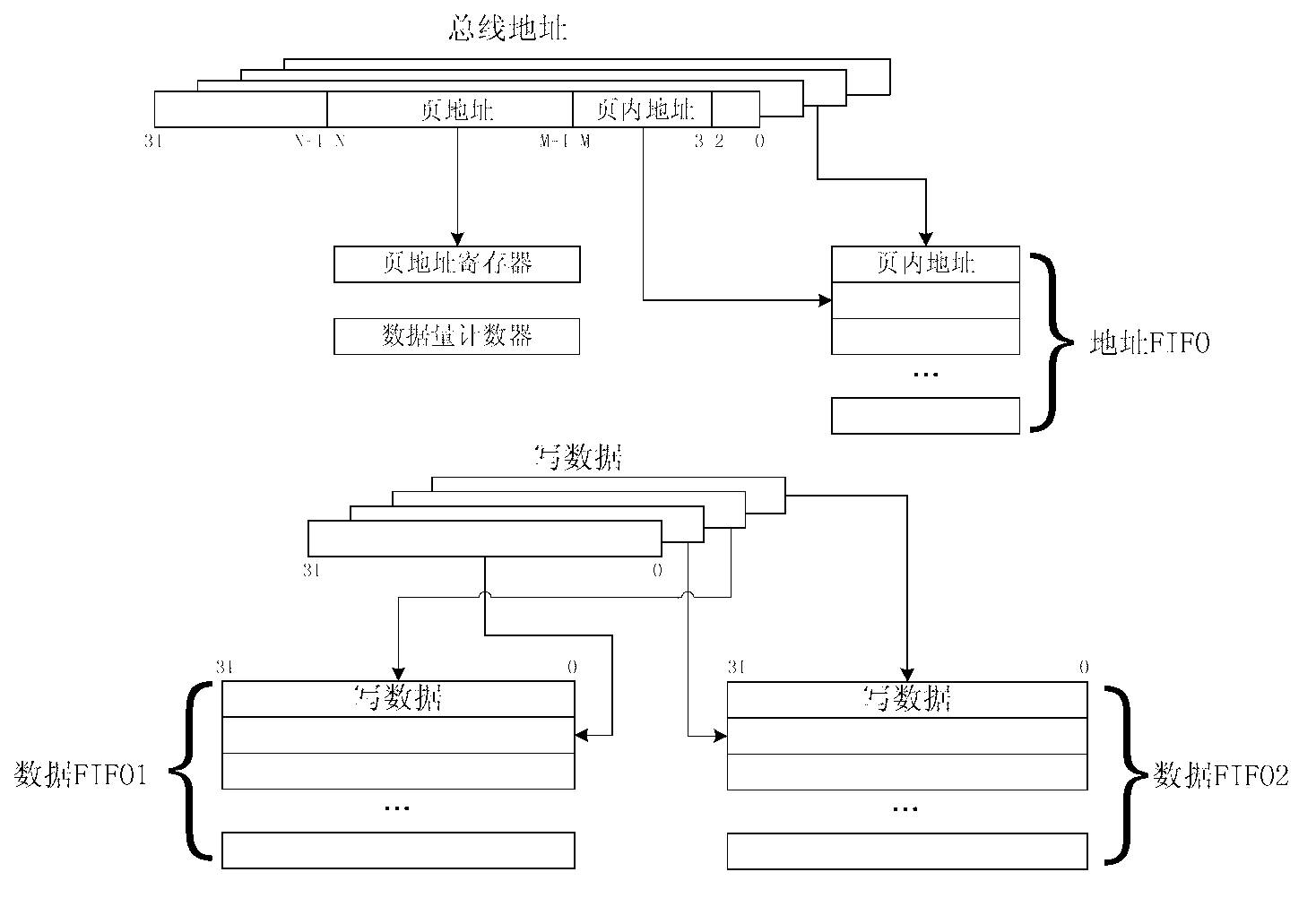

Universal nonvolatile memory control device for system on chip

ActiveCN102999453AImprove developmentUnified programmingElectric digital data processingControl signalProcessor register

The invention relates to a universal nonvolatile memory control device for a system on a chip. The control device comprises an external bus interface unit, a register control unit, an erasing unit and a storage control and interface unit. The external bus interface unit is used for collecting control signals and data of an external bus as well as analyzing the signals and data; the register control unit is used for read-write control of all registers, wherein the register data is transmitted to the storage control and interface unit for use by a finite-state machine of the storage control and interface unit; the erasing unit is used for processing bus signals transmitted by the external bus interface unit; the storage control and interface unit comprises two finite-state machines: one is a write data width conversion state machine, while the other is a master control state machine for read, write and erase control of various nonvolatile memories. The invention provides the universal nonvolatile memory control device for the system on the chip good in compatibility and simplified in design process.

Owner:C SKY MICROSYST CO LTD

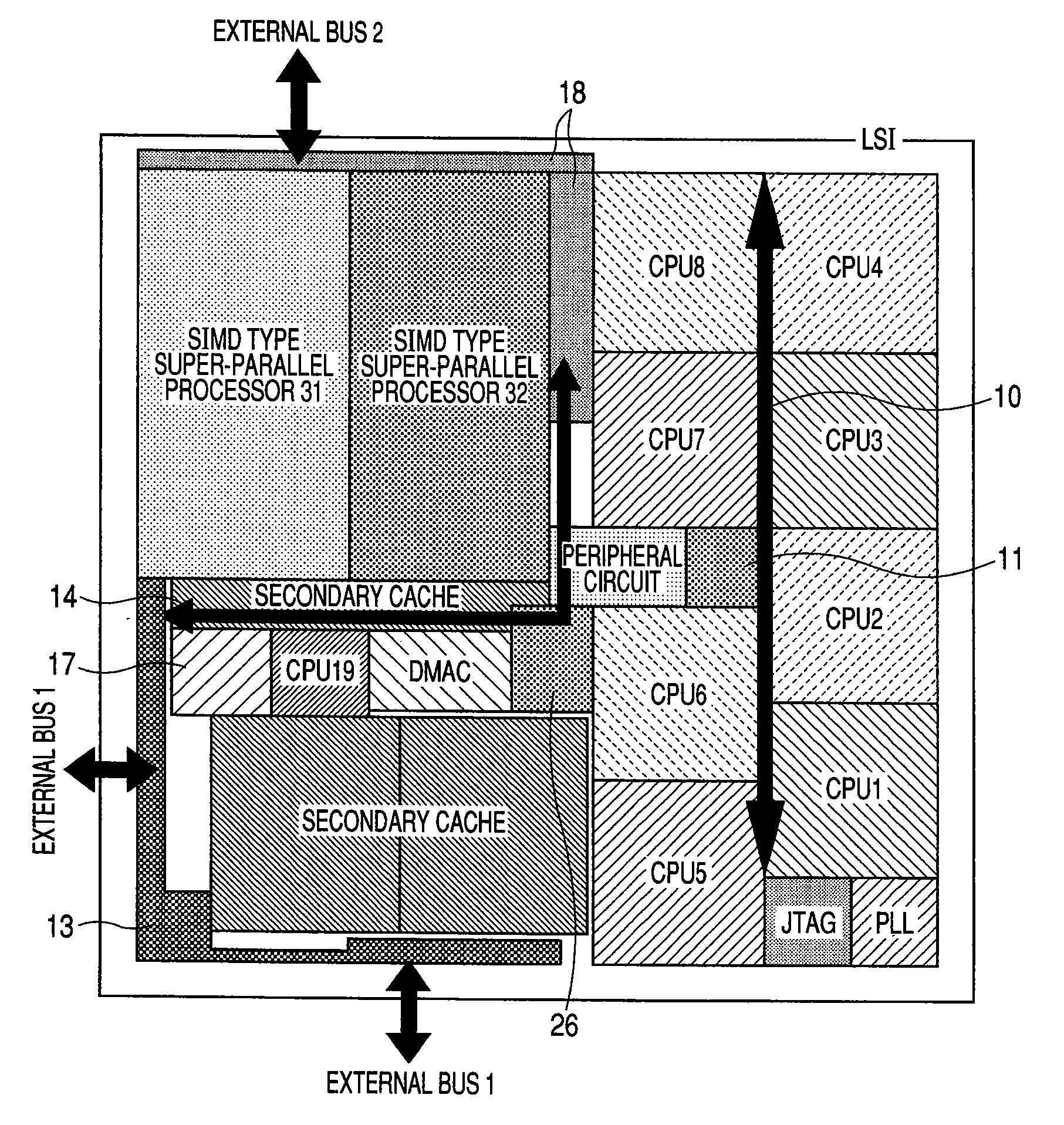

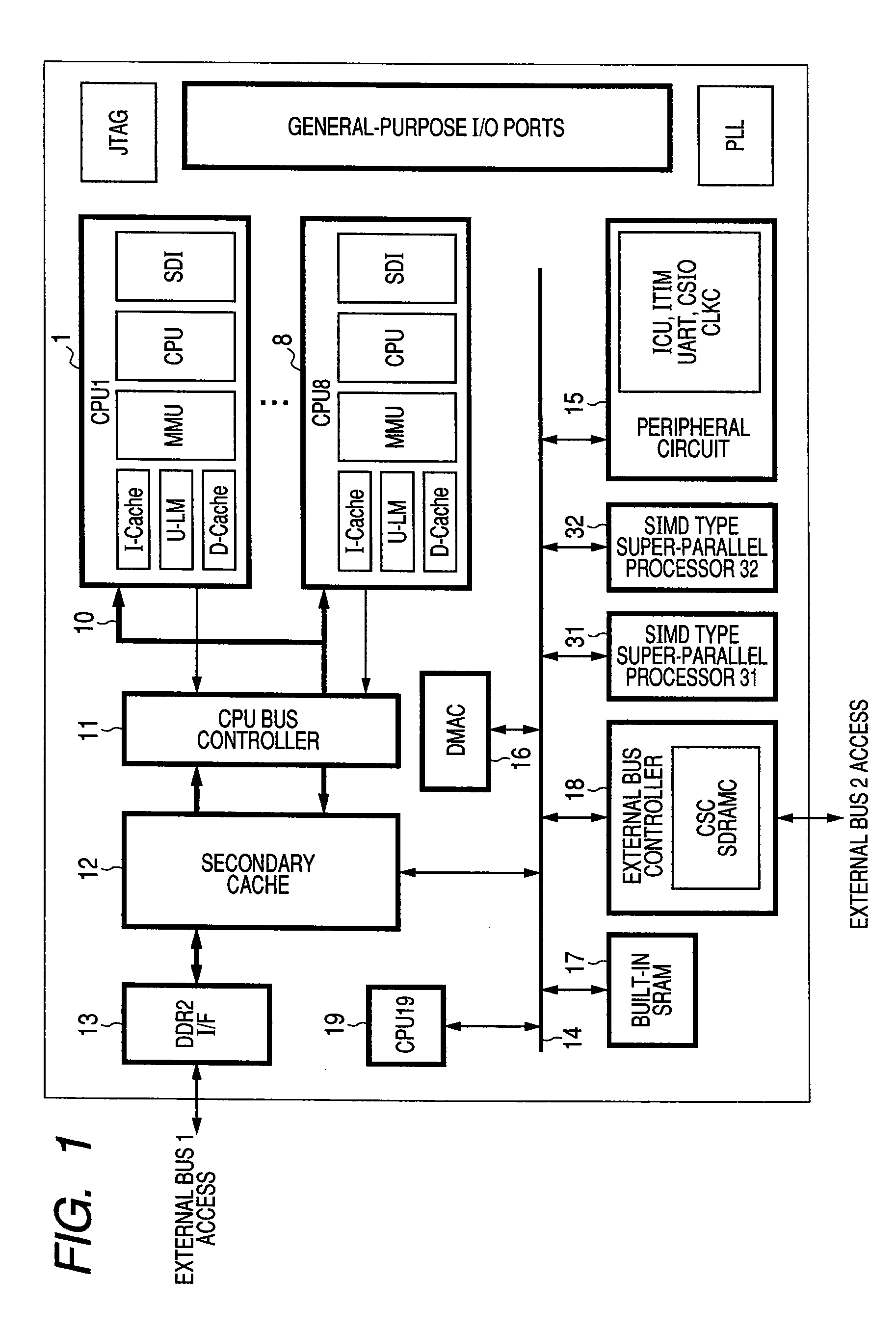

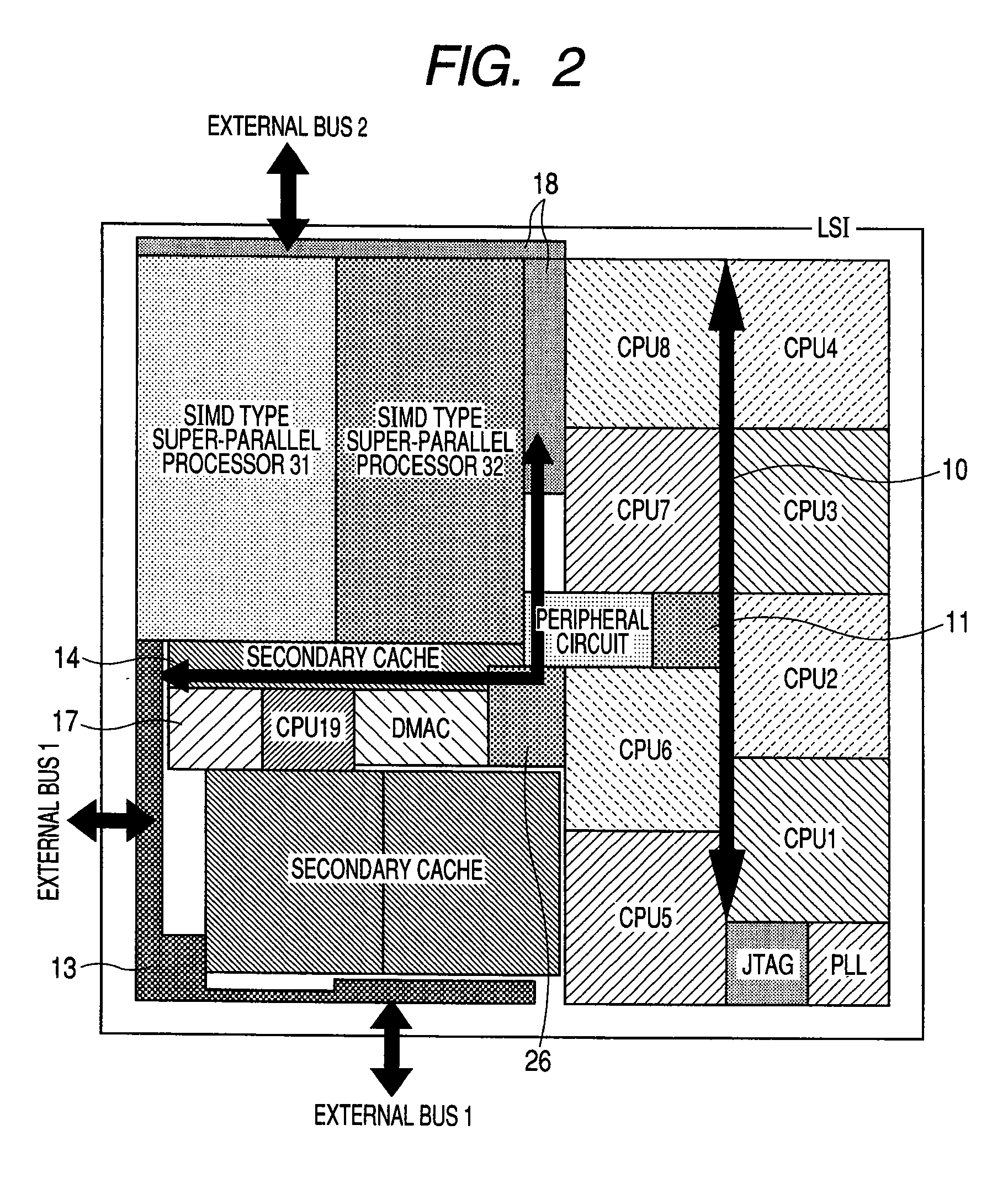

Multi-processor device

InactiveUS20080282012A1Low costCoordination and bus contentionEnergy efficient ICTSingle instruction multiple data multiprocessorsMulti processorSemiconductor chip

The present invention intends to provide a high-performance multi-processor device in which independent buses and external bus interfaces are provided for each group of processors of different architectures, if a single chip includes a plurality of multi-processor groups. A multi-processor device of the present invention comprises a plurality of processors including first and second groups of processors of different architectures such as CPUs, SIMD type super-parallel processors, and DSPs, a first bus which is a CPU bus to which the first processor group is coupled, a second bus which is an internal peripheral bus to which the second processor group is coupled, independent of the first bus, a first external bus interface to which the first bus is coupled, and a second external bus interface to which the second bus is coupled, over a single semiconductor chip.

Owner:RENESAS ELECTRONICS CORP

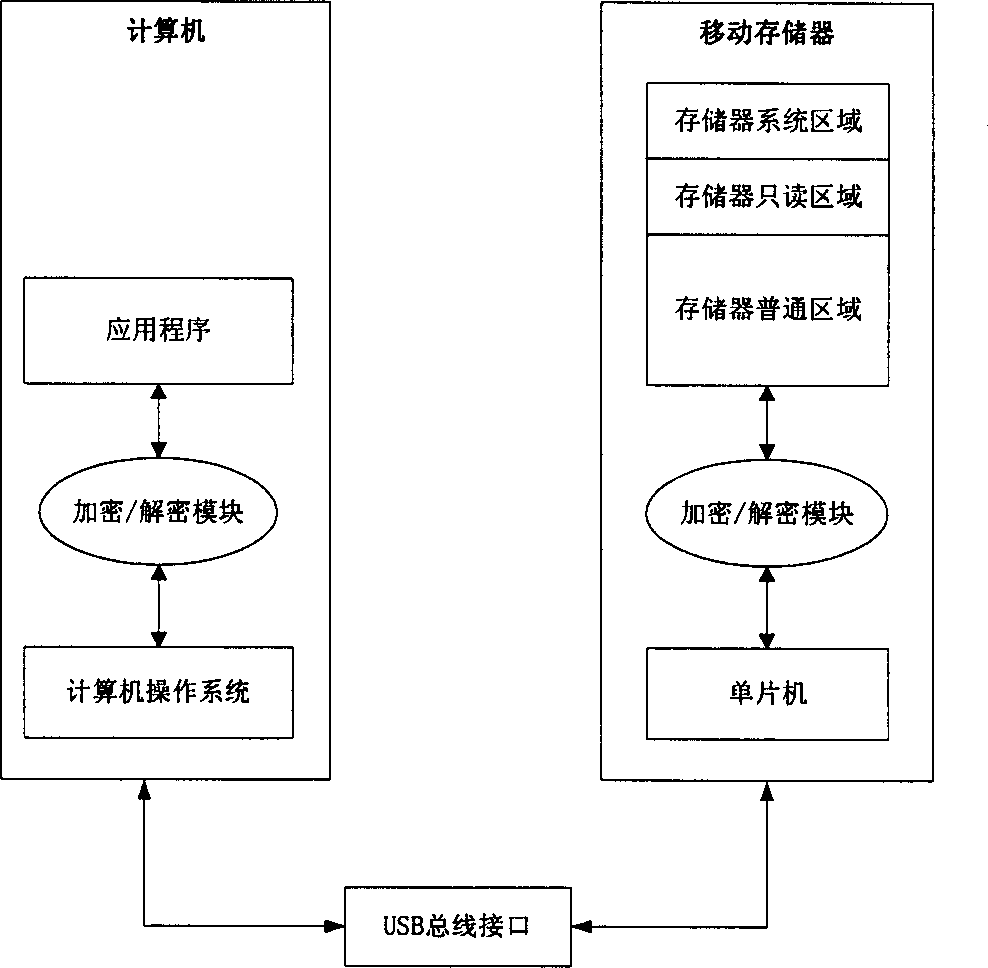

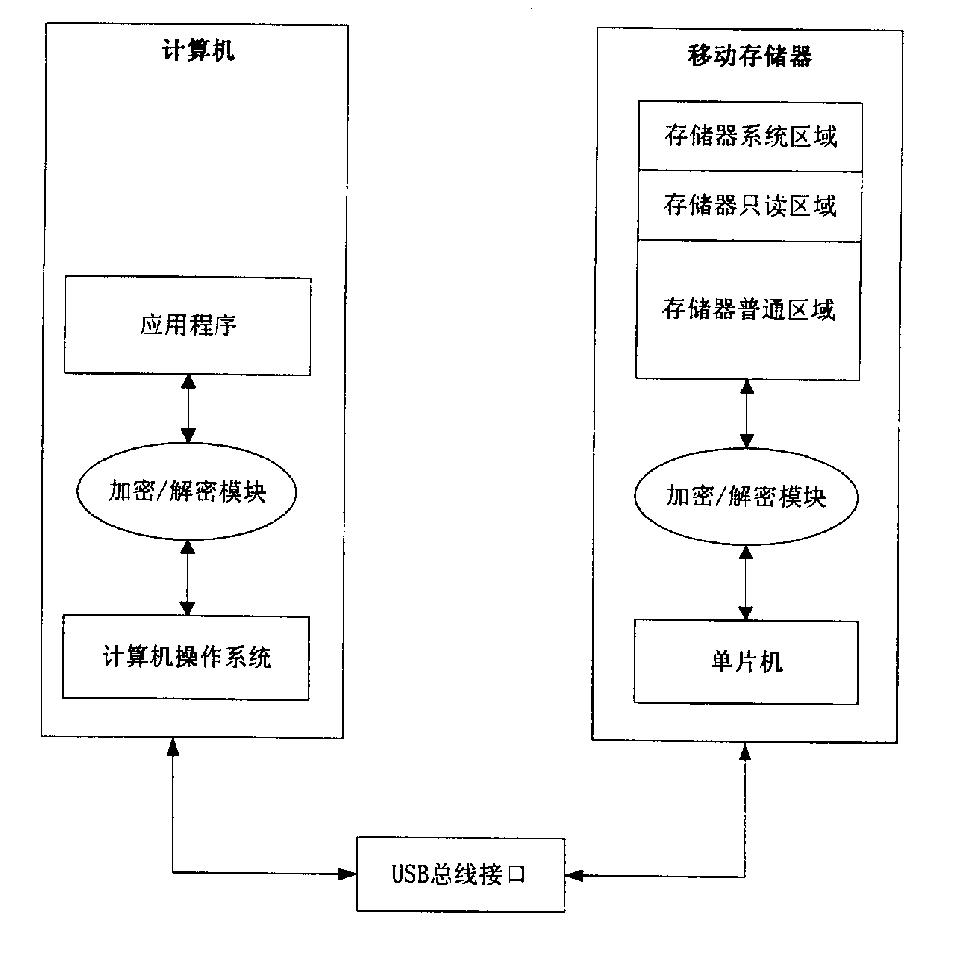

Issued software storing and enciphering method

InactiveCN1344995AImprove reliabilityImprove portabilityMemory loss protectionUnauthorized memory use protectionDECIPHERRemovable media

Owner:BEIJING BROADMAKING TECH DEV

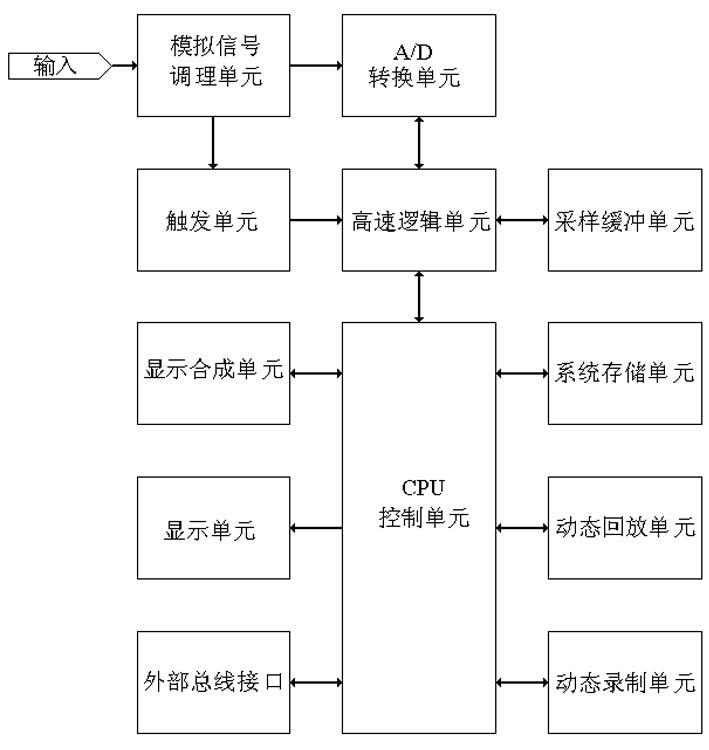

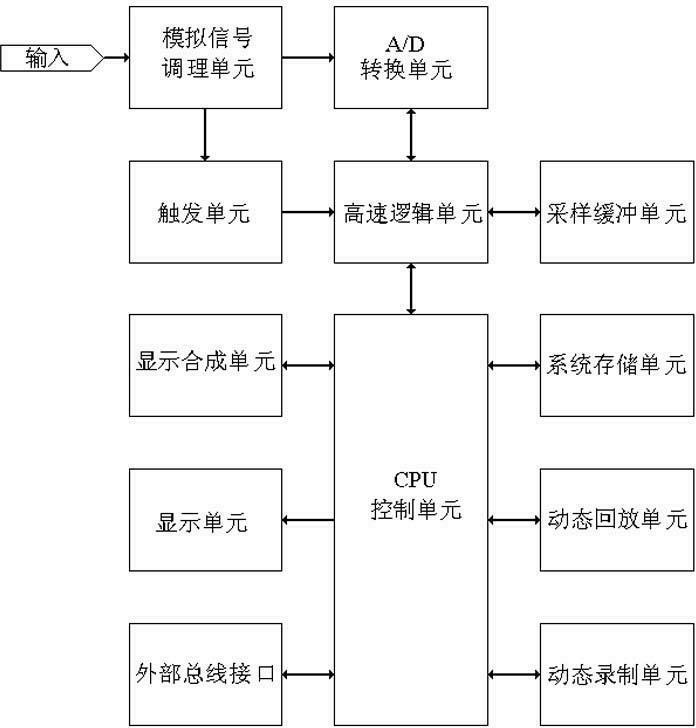

Oscilloscope with function of dynamically recording waveform image

InactiveCN102495255ADigital variable displayProduction of permanent recordsSignal conditioningImage recording

The invention discloses an oscilloscope with a function of dynamically recording a waveform image. The oscilloscope comprises an analog signal conditioning unit, an analog / digital (A / D) conversion unit, a triggering unit, a high-speed logic unit, a sampling buffering unit, a central processing unit (CPU) control unit, a system storage unit, a display unit, an external bus interface unit, a display synthesis unit, a dynamic recording unit and a dynamic playback unit, wherein a tested signal is sent into the triggering unit and the A / D conversion unit respectively after being conditioned by the signal conditioning unit; the high-speed logic unit controls the A / D conversion unit to sample under the triggering control of the triggering unit; the sampled data is transmitted to the sampling buffering unit through the high-speed logic unit; the high-speed logic unit transfers waveform data from the sampling buffering unit to the CPU control unit; and the waveform data is converted into image data corresponding to the pixel of a screen by the CPU control unit. The oscilloscope has the advantage that: an aim of recording a waveform is fulfilled by adopting an image recording method; and when recording the waveform, the oscilloscope is not restricted by the oscilloscope storage depth and the number of channels.

Owner:张兴杰

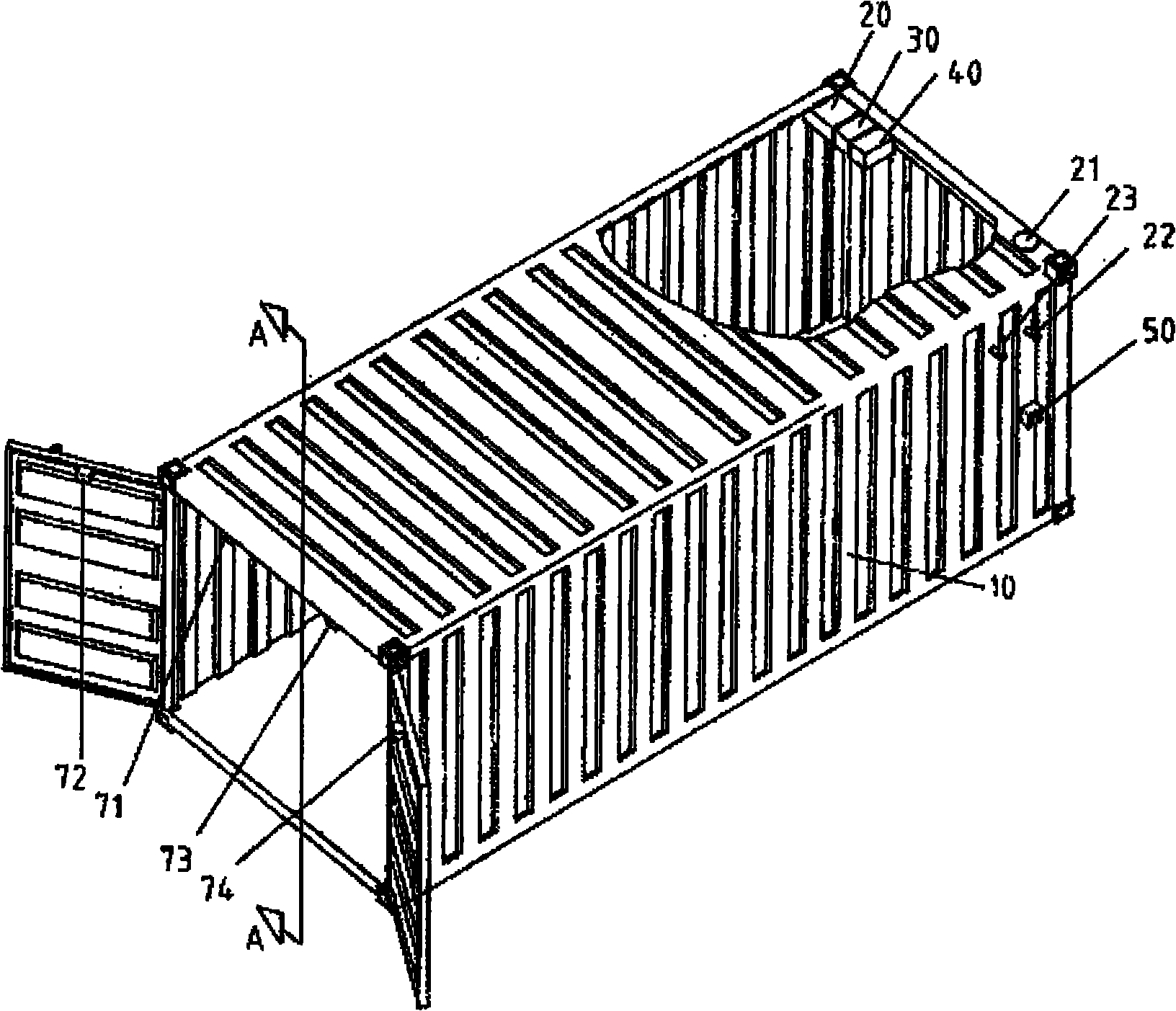

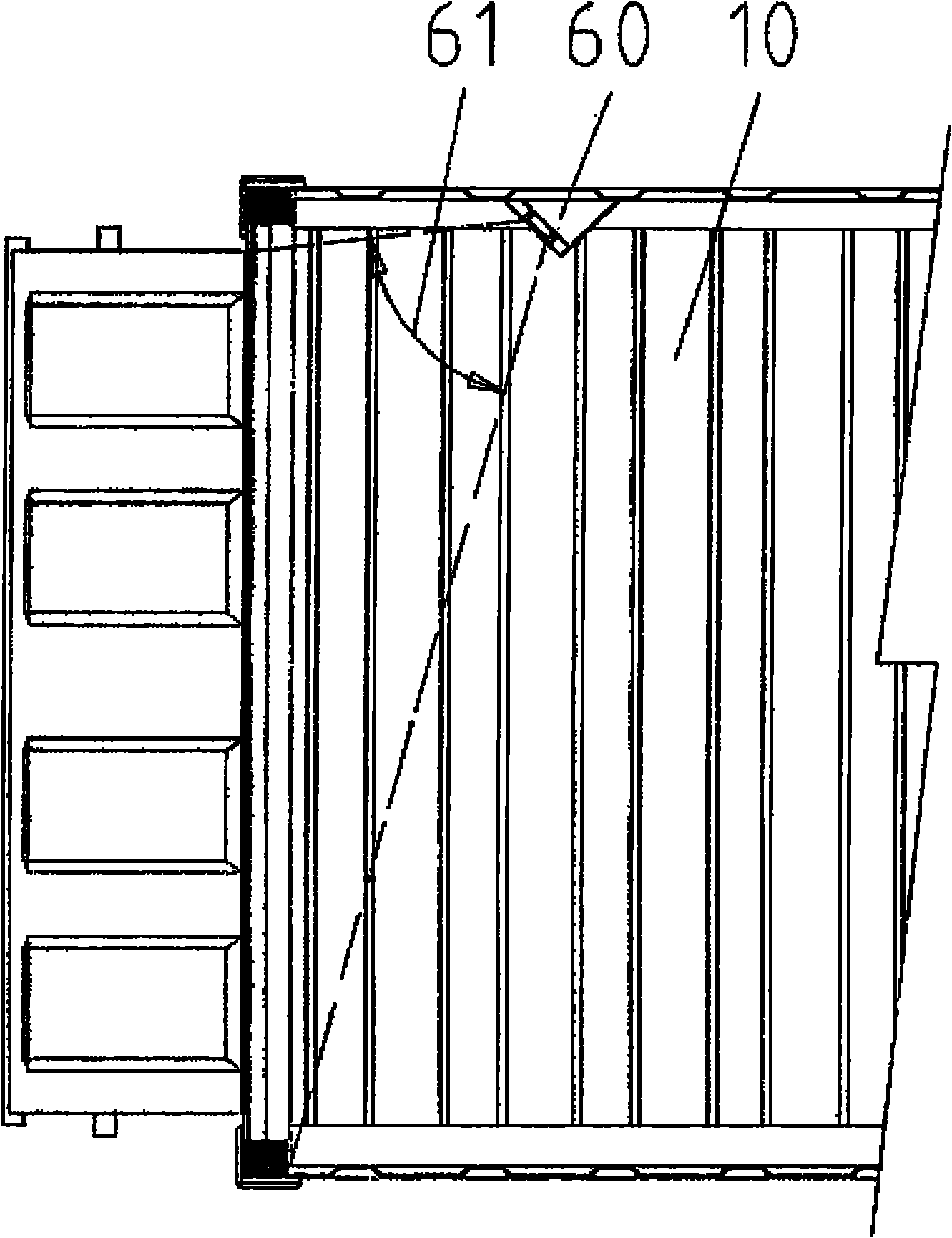

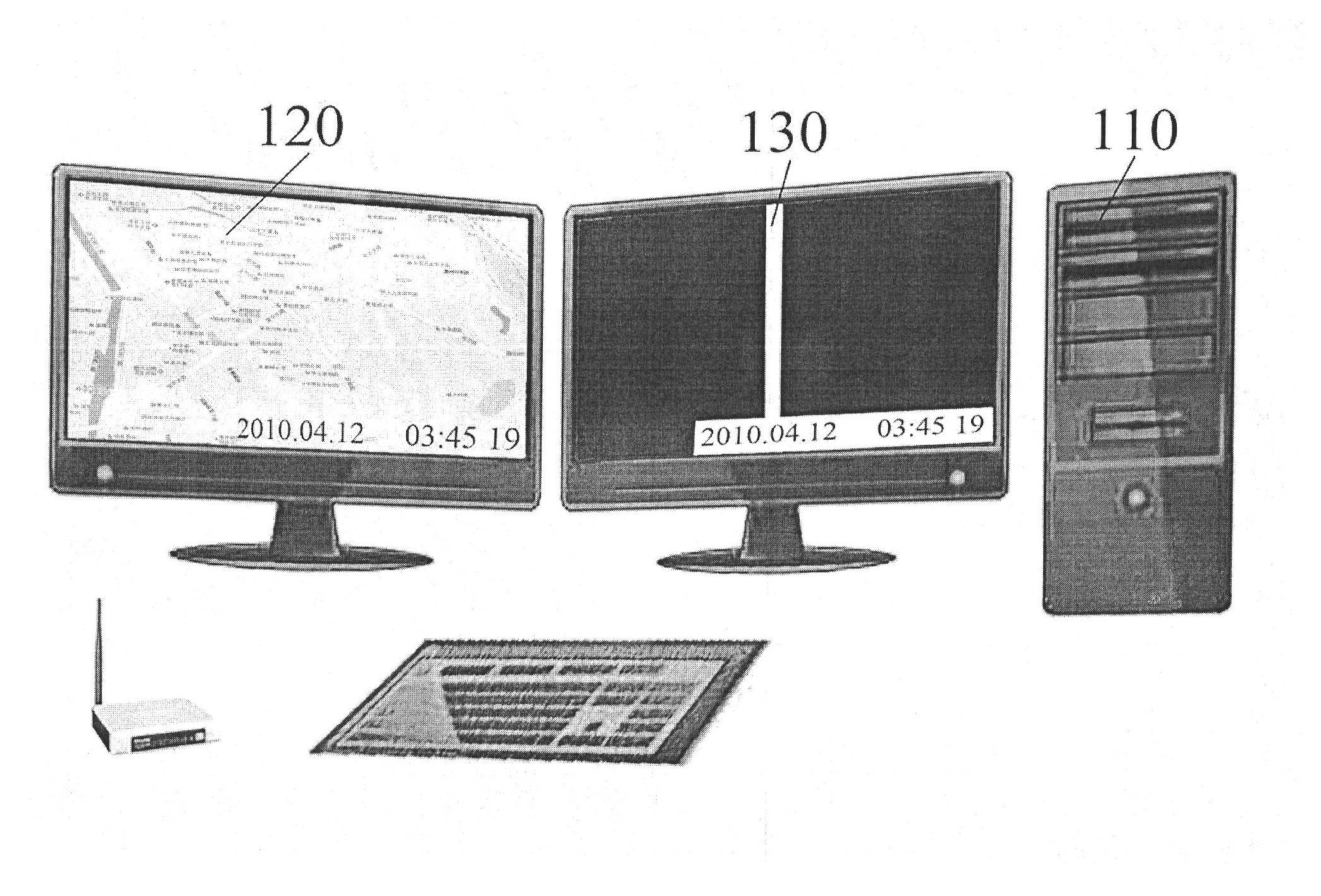

Security equipment and system of container

InactiveCN101844659AImprove customs clearance efficiencyAvoid security breachesLarge containersClosed circuit television systemsPower controllerImaging processing

The invention relates to security equipment and a system of a container, which comprise a monitoring and calculating platform and a monitoring system, wherein the monitoring and calculating platform is installed in the container, and the monitoring system is arranged at a detection unit of the container and is based on a PC. The monitoring and calculating platform comprises a mainframe box of the calculating platform, a power controller, an external battery, a camera, a visible light sensor, a box door switch sensor and a GPS antenna, wherein the mainframe box of the calculating platform is provided with an electronic circuit board and a mass memory; and the monitoring system based on the PC comprises a high-speed PC, a standard external bus interface, a character processing module and an image processing module, wherein the high-speed PC can directly drive at least two displays. In the invention, the monitoring and calculating platform is part of a container body, the cost proportion occupied by the monitoring and calculating platform is very low, the transportation cost can not be increased after the monitoring and calculating platform is distributed in a multi-time transportation process, and the monitoring system based on the PC takes the automatic operation as a main part, only can increase the clearance efficiency and does not need to increase the manpower allocation.

Owner:北京英特诺科技有限公司

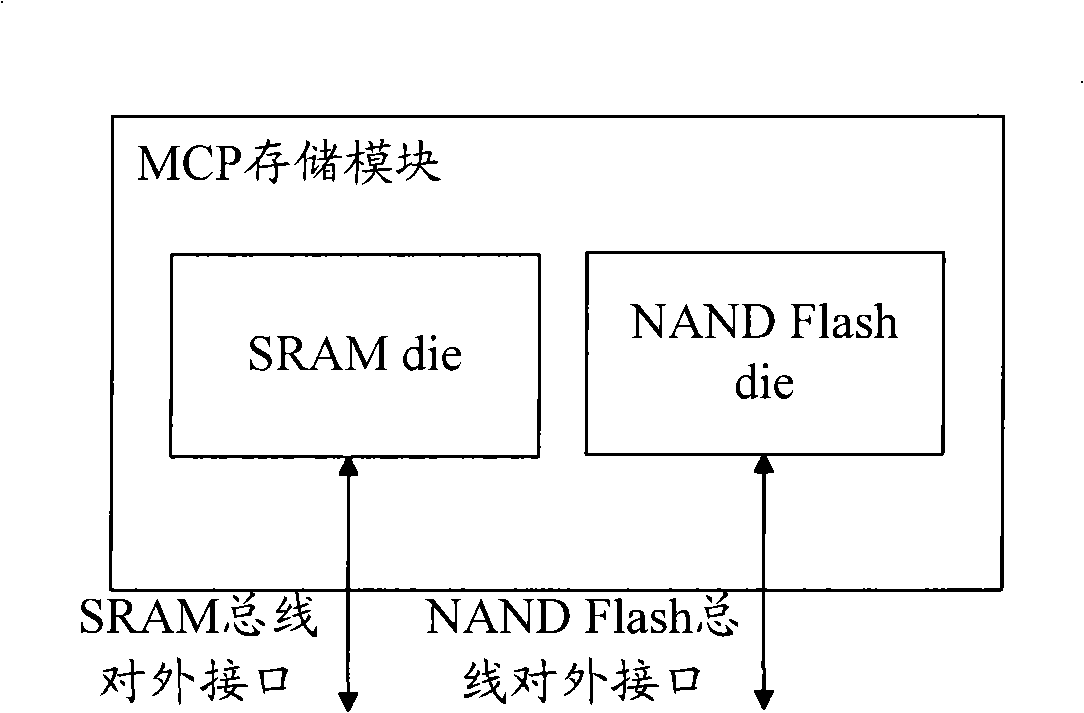

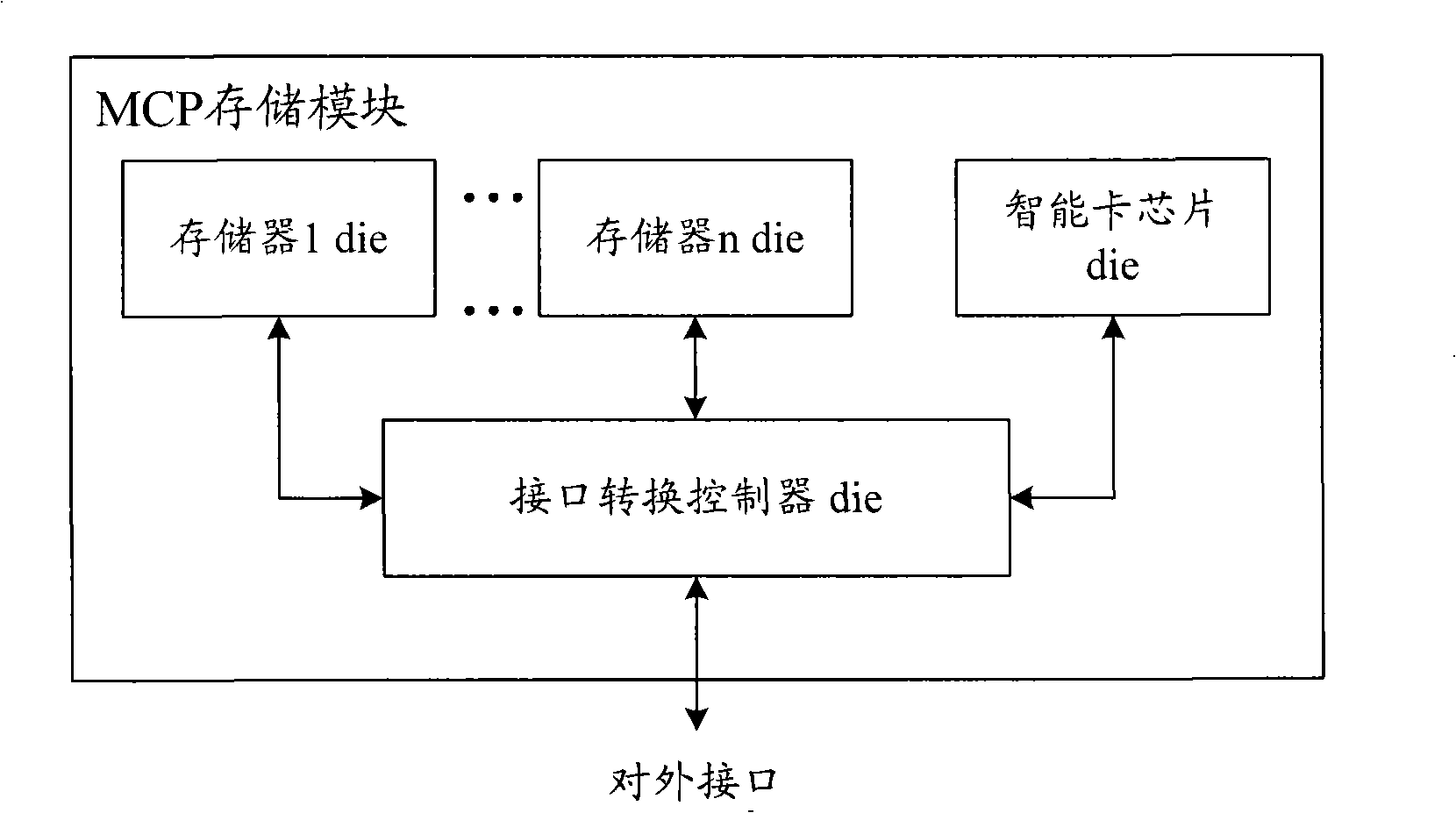

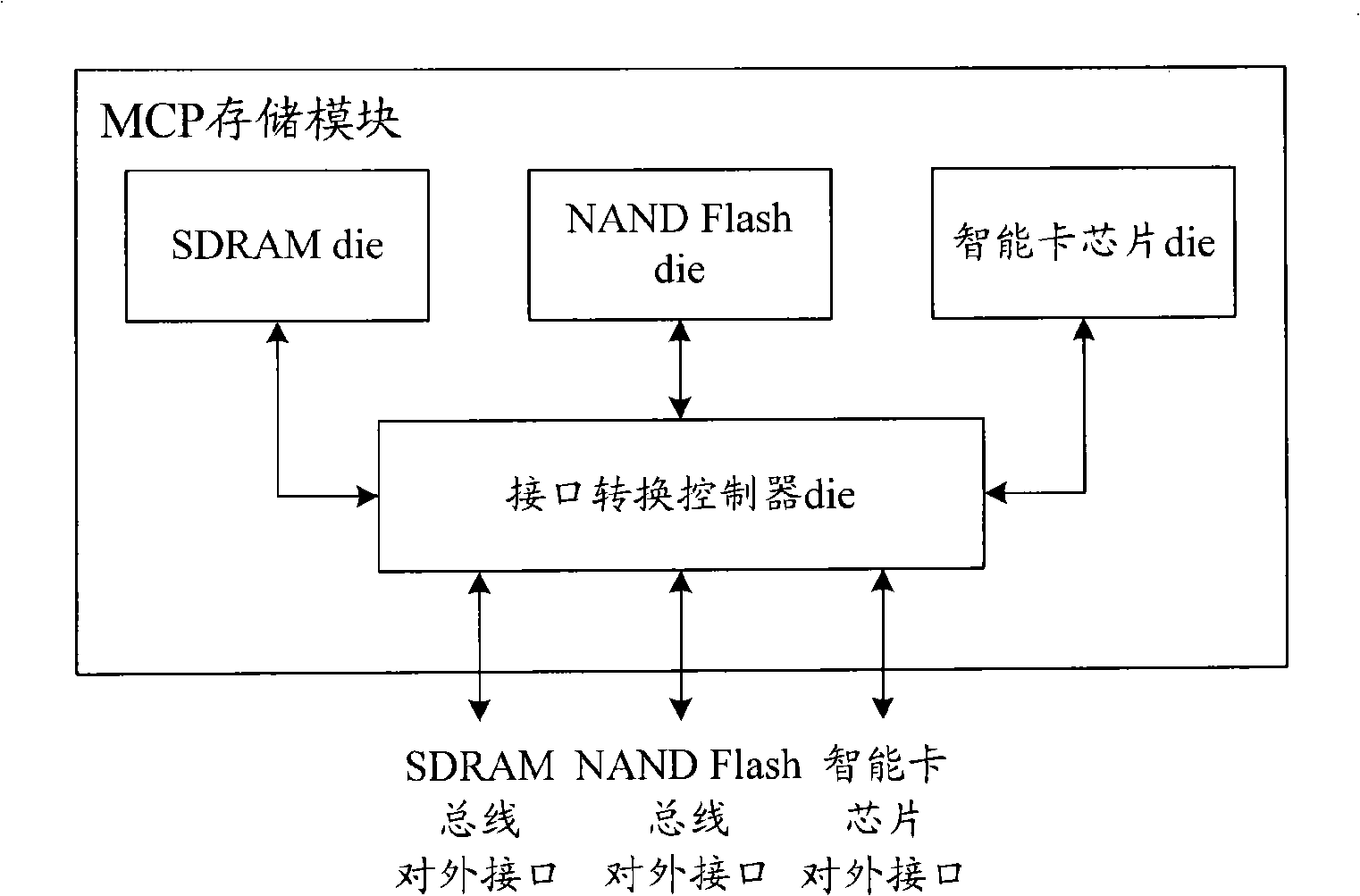

Multi-chip encapsulation storage module

InactiveCN101303885ARealize function extensionReduce in quantityDigital storageSmart card securityComputer module

The invention discloses a multi-chip packaging (MCP) memory module. The MCP memory module of the invention not only packages a plurality of types of memorizers for memory but also packages an interface conversion controller and a smart card chip; wherein, the smart card chip can realize relevant safety business of the smart card chip; the interface conversion controller can realize interface specification conversion when the outer part interacts with a plurality of types of memorizers and the smart card chip through an external interface so that the MCP memory module is not limited to the memory function but realizes functional extension. Moreover, the interface conversion controller can realize interface specification conversion, so the external interface arranged on the MCP memory module of the invention can correspond to a plurality of types of memorizers and the smart card chip one by one. Preferably, less external interfaces are needed, e.g. one or two, so that the number of external interface pins of the MCP memory module can be reduced.

Owner:POTEVIO INFORMATION TECH

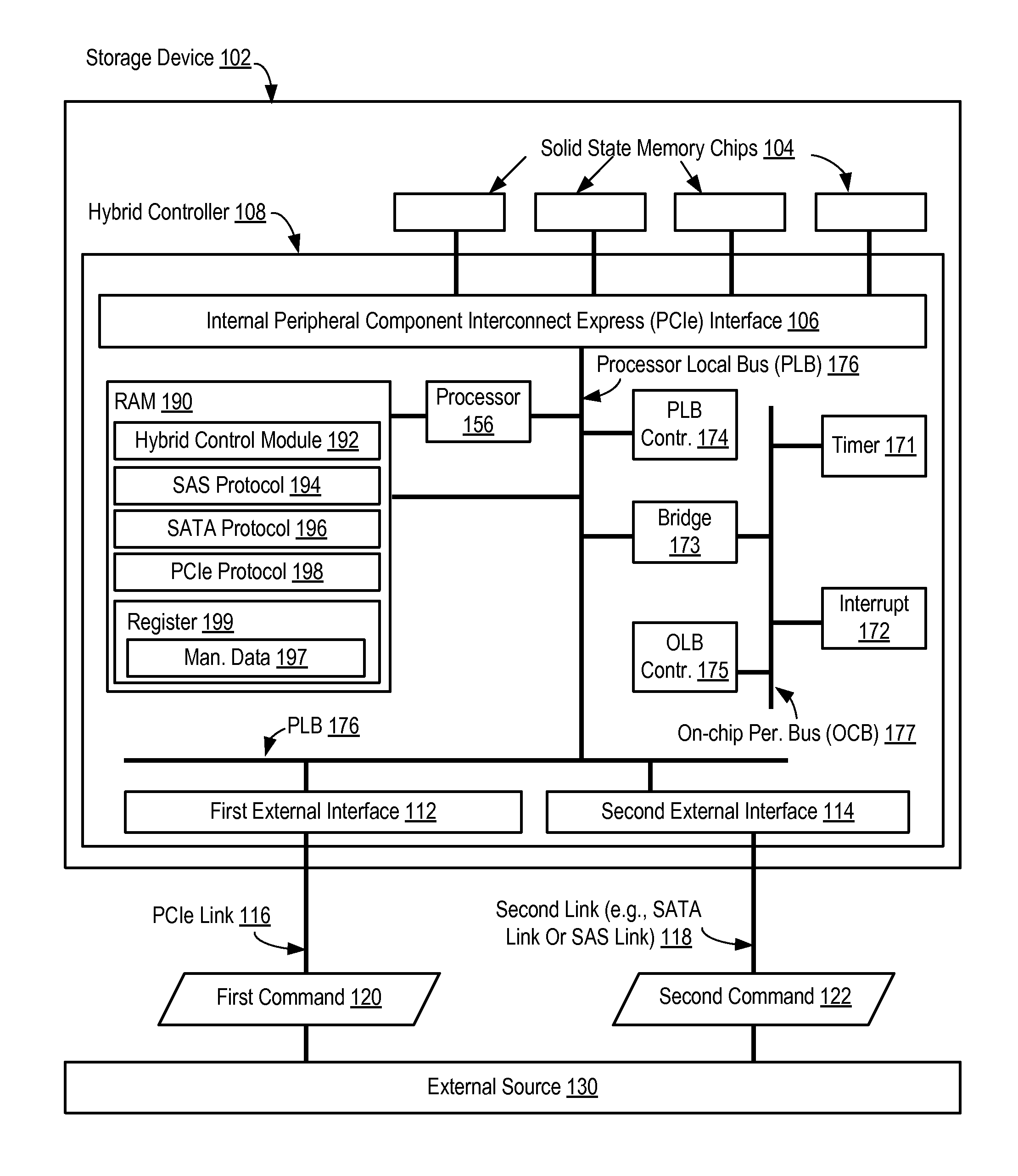

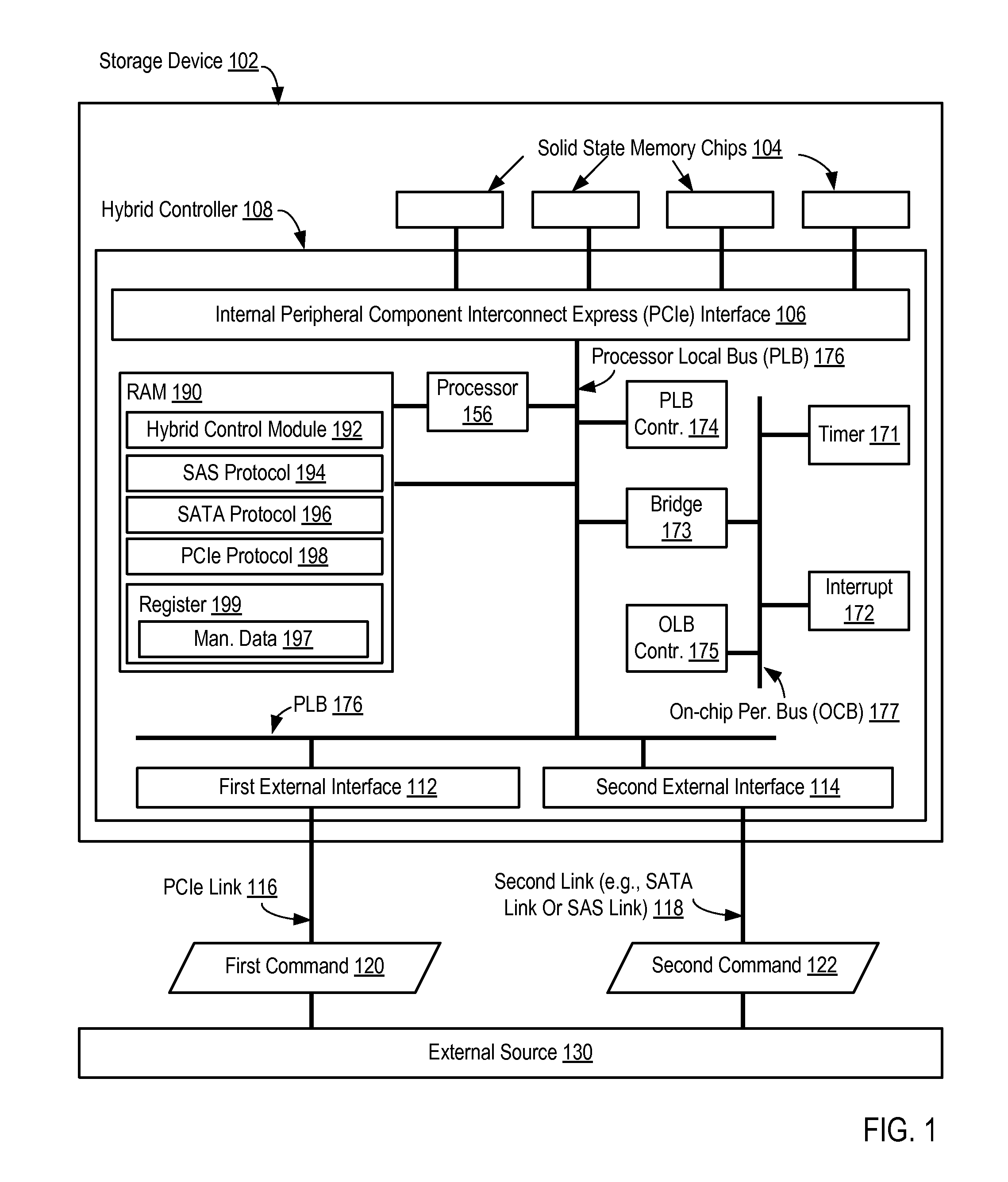

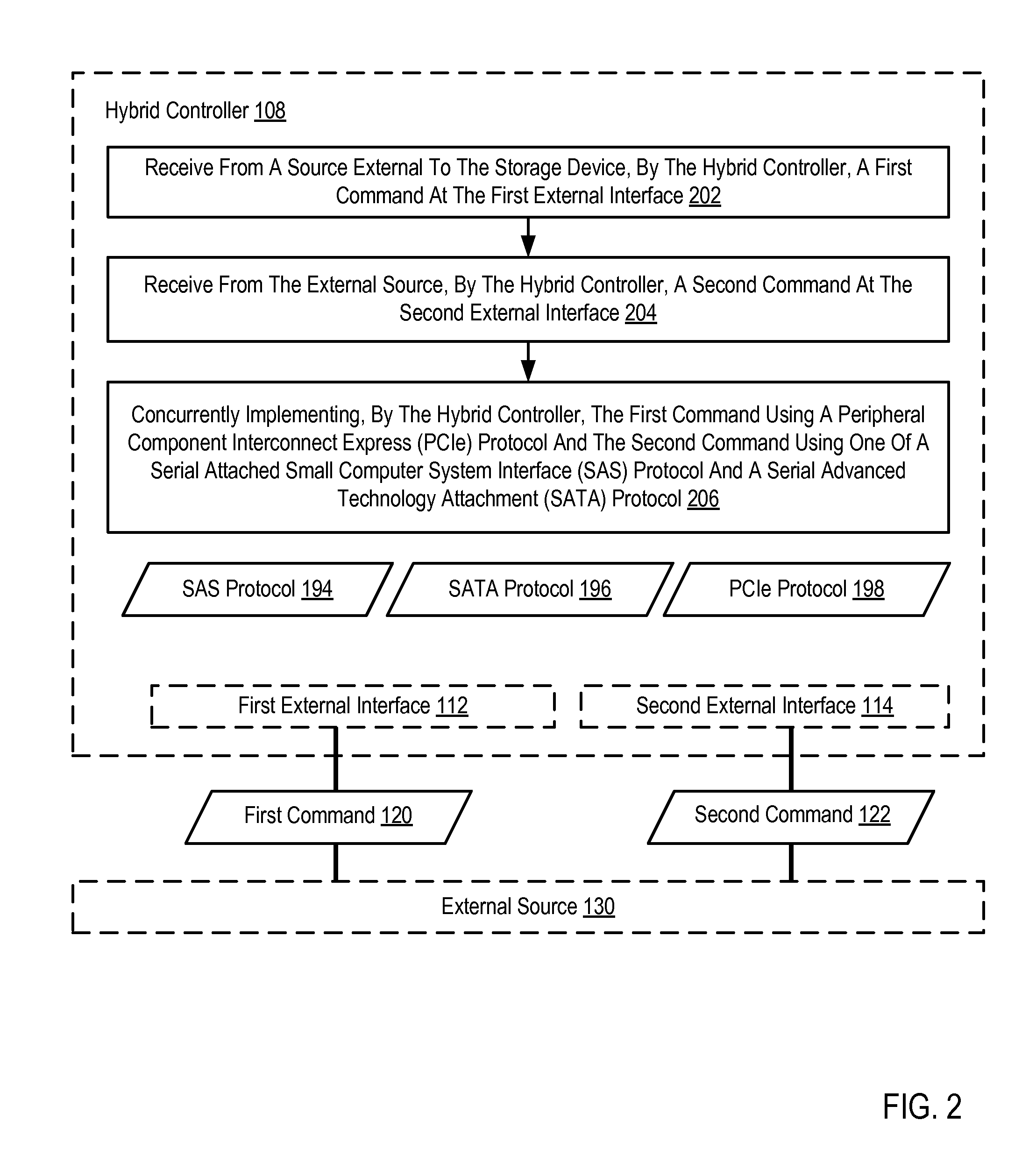

Managing A Storage Device Using A Hybrid Controller

ActiveUS20130232376A1Non-redundant fault processingRedundant hardware error correctionSCSISerial advanced technology attachment

Methods, apparatuses, and computer program products for managing a storage device using a hybrid controller are provided where the storage device comprises an internal peripheral component interconnect express (PCIe) interface to control solid state memory within the storage device. In particular embodiments, the storage device includes a first external interface configured to establish an external PCIe link and a second external interface configured to establish at least one of an external serial attached small computer system interface (SAS) link and an external serial advanced technology attachment (SATA) link. Embodiments include receiving from an external source, by the hybrid controller, a first command at the first external interface and a second command at the second external interface; and concurrently implementing, by the hybrid controller, the first command using a PCIe protocol and the second command using one of a SAS protocol and a SATA protocol.

Owner:LENOVO GLOBAL TECH INT LTD

Command queue for peripheral component

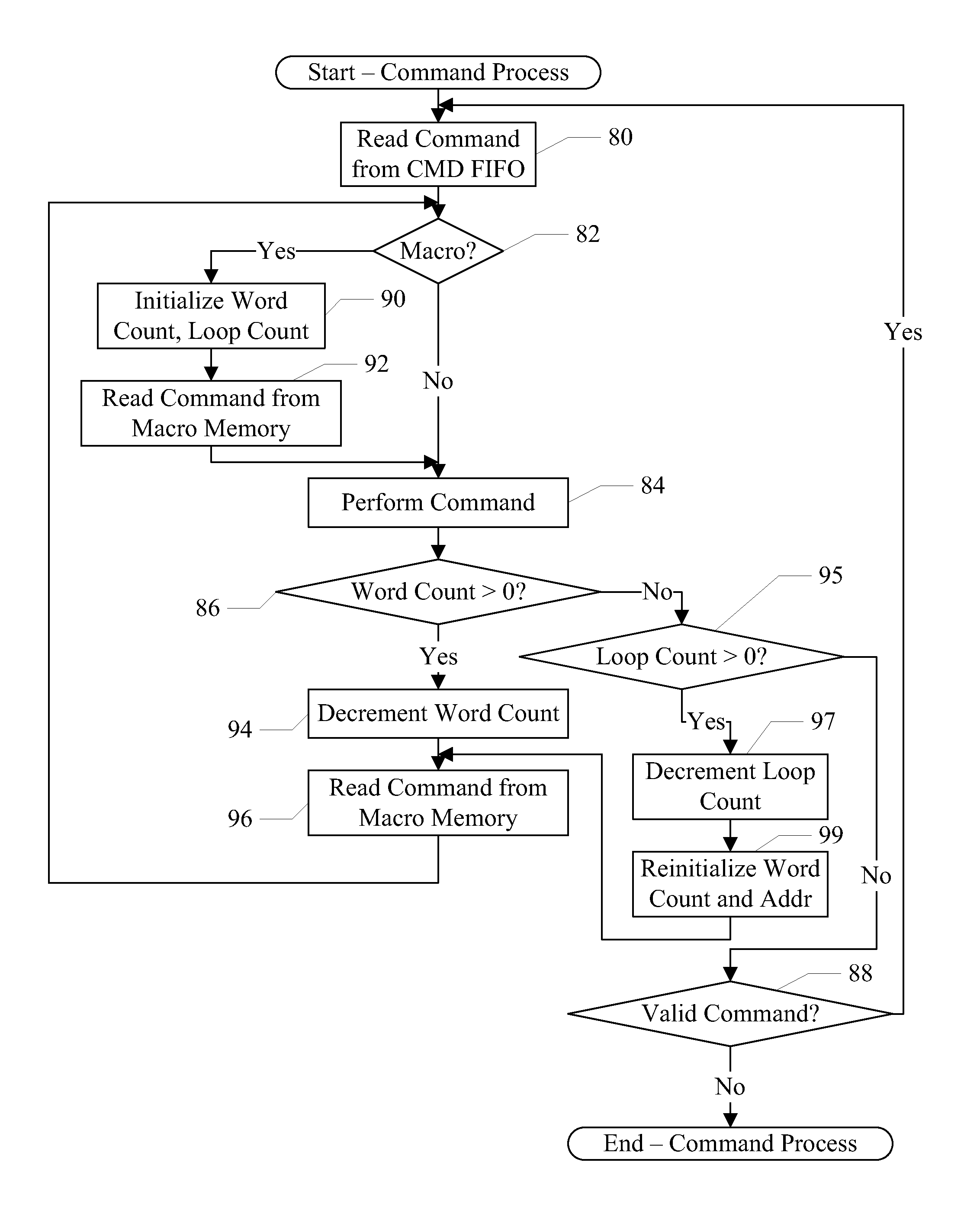

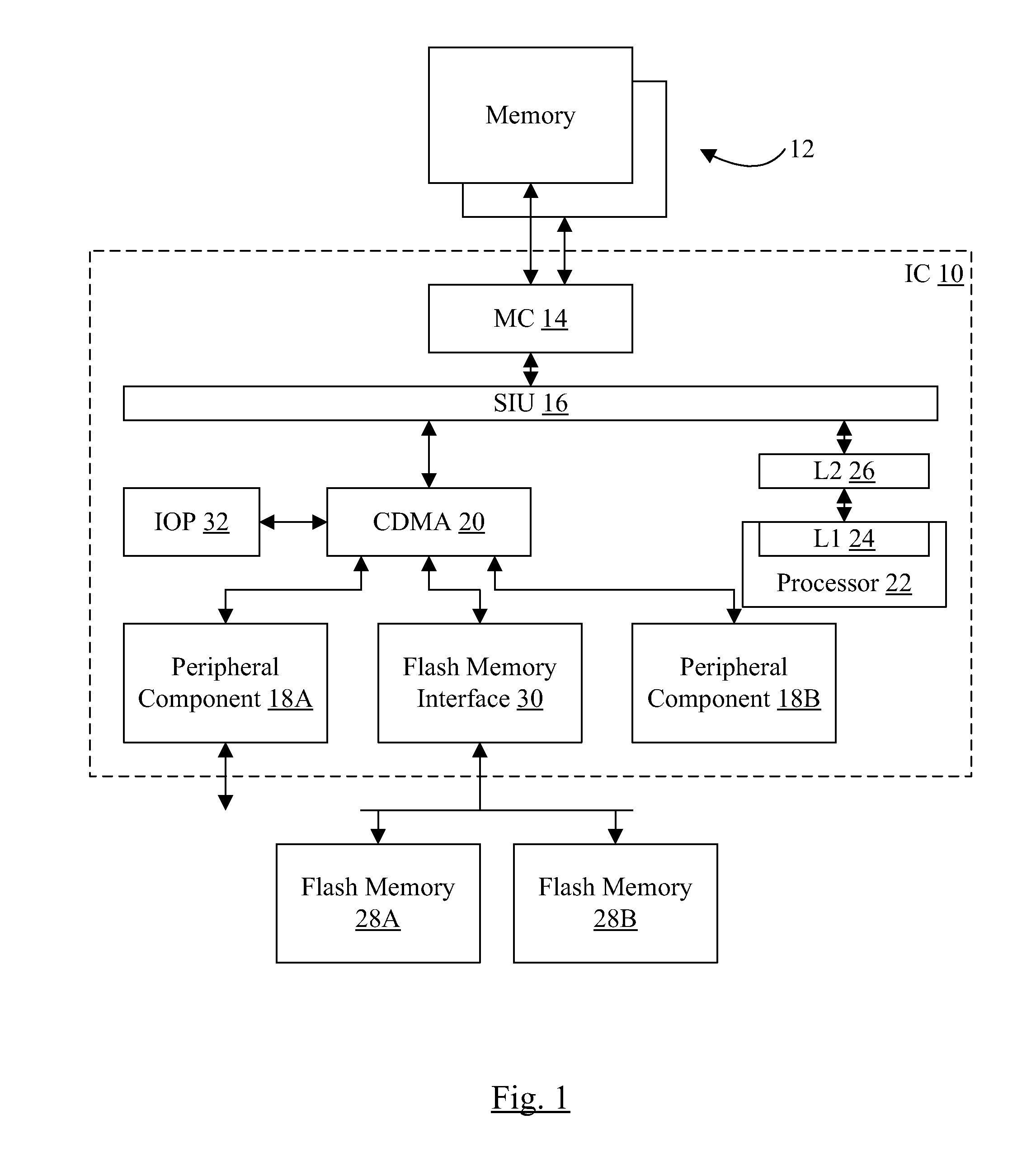

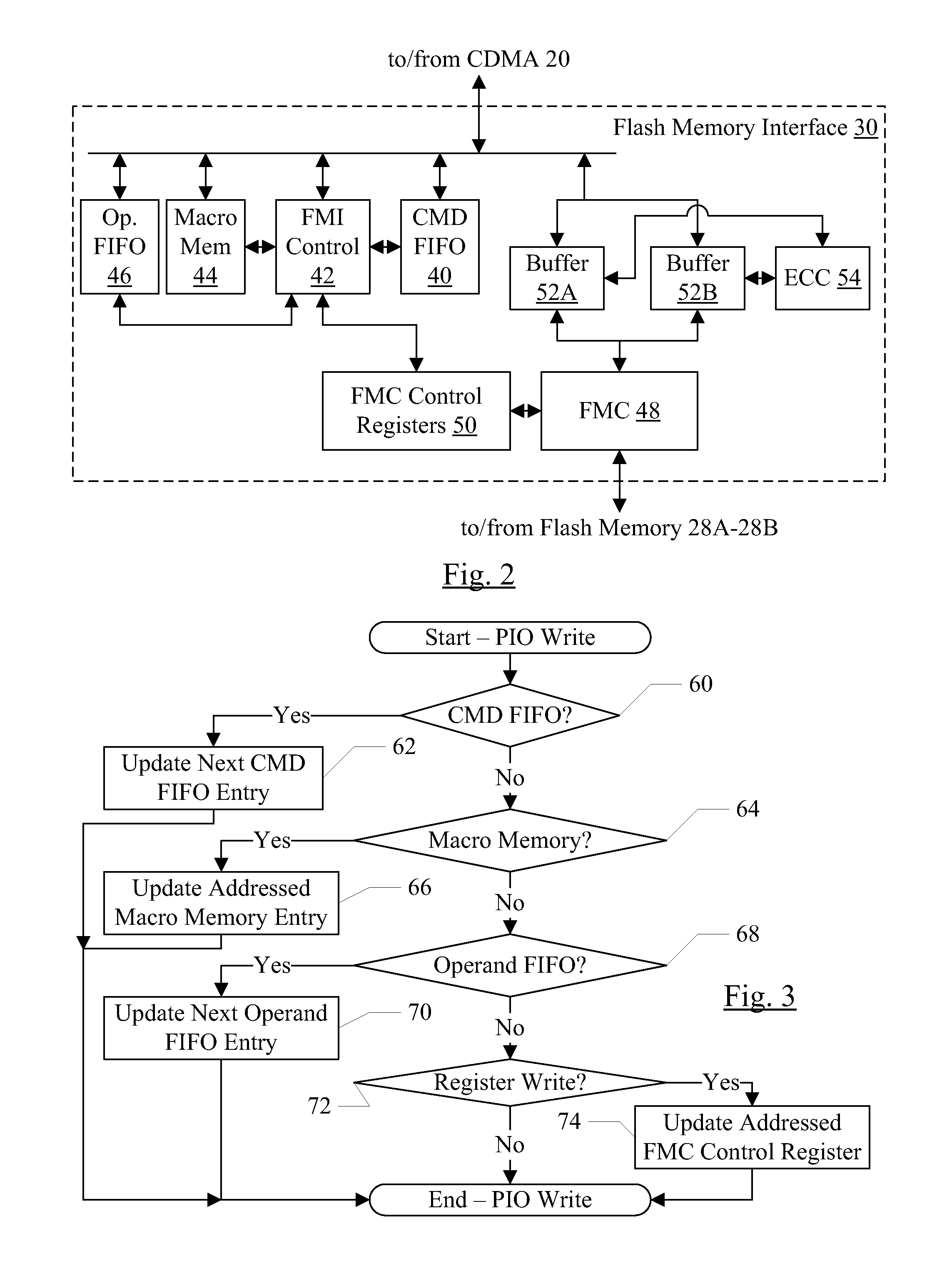

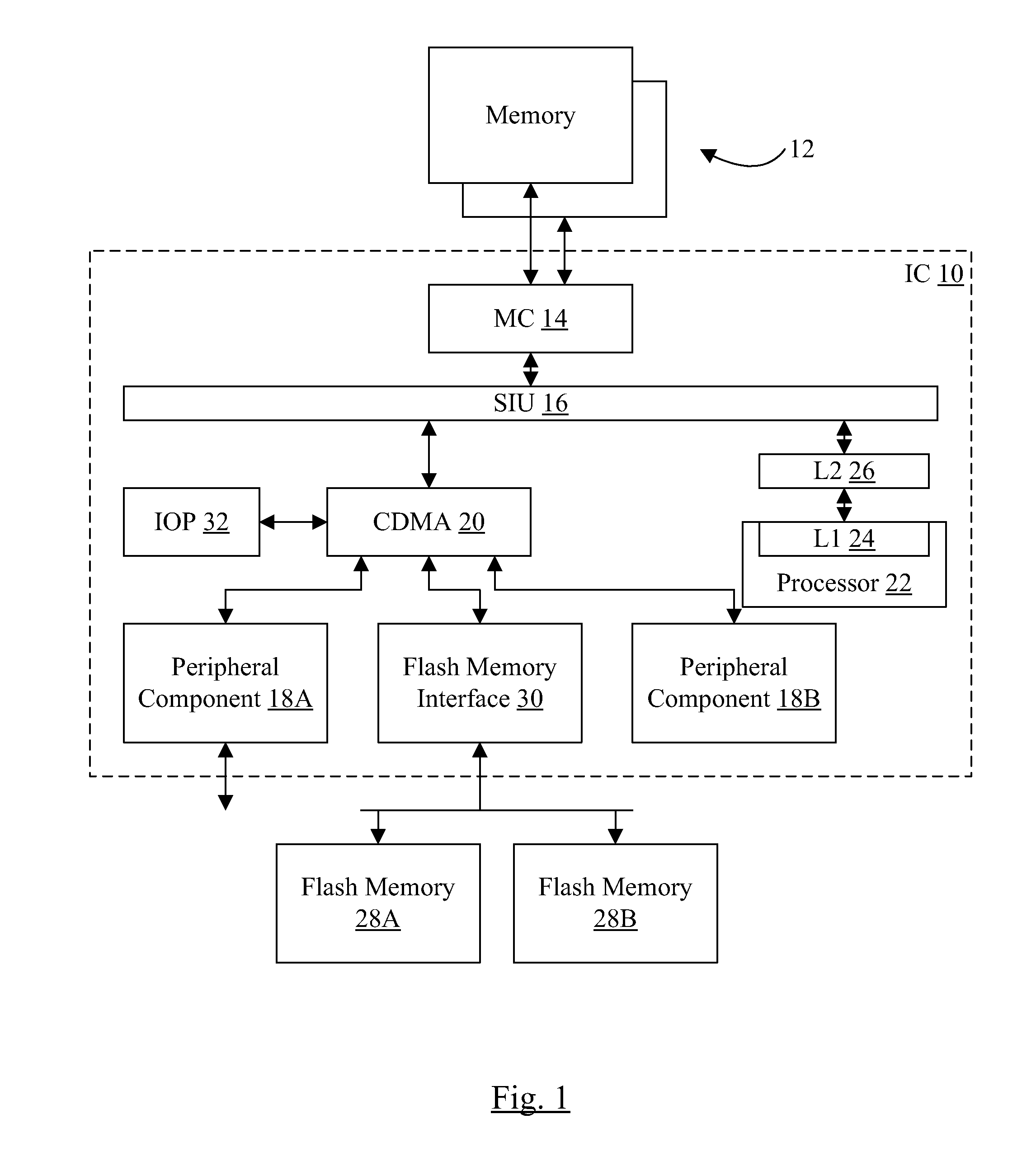

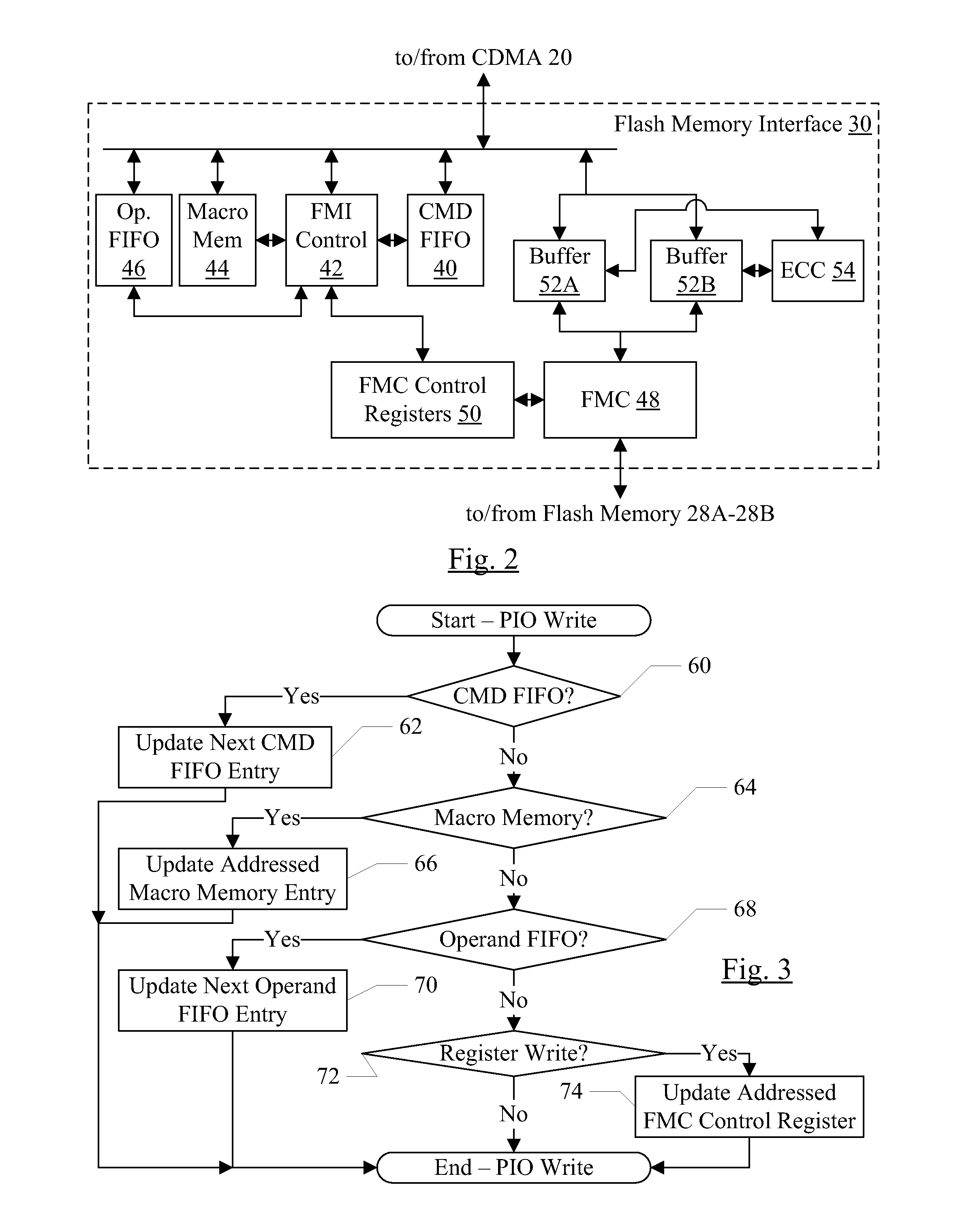

ActiveUS8131889B2Easy to useEnergy efficient ICTEnergy efficient computingMemory interfaceControl communications

In an embodiment, a peripheral component configured to control an external interface of an integrated circuit. For example, the peripheral component may be a memory interface unit such as a flash memory interface unit. The internal interface to the peripheral component may be shared between data transfers to / from the external interface and control communications to the peripheral component. The peripheral component may include a command queue configured to store a set of commands to perform a transfer on the interface. A control circuit may be coupled to the command queue and may read the commands and communicate with an interface controller to cause a transfer on the interface responsive to the commands. In an embodiment, a macro memory may store command sequences to be performed in response to a macro command in the command queue. In an embodiment, an operand queue may store operand data for use by the commands.

Owner:APPLE INC

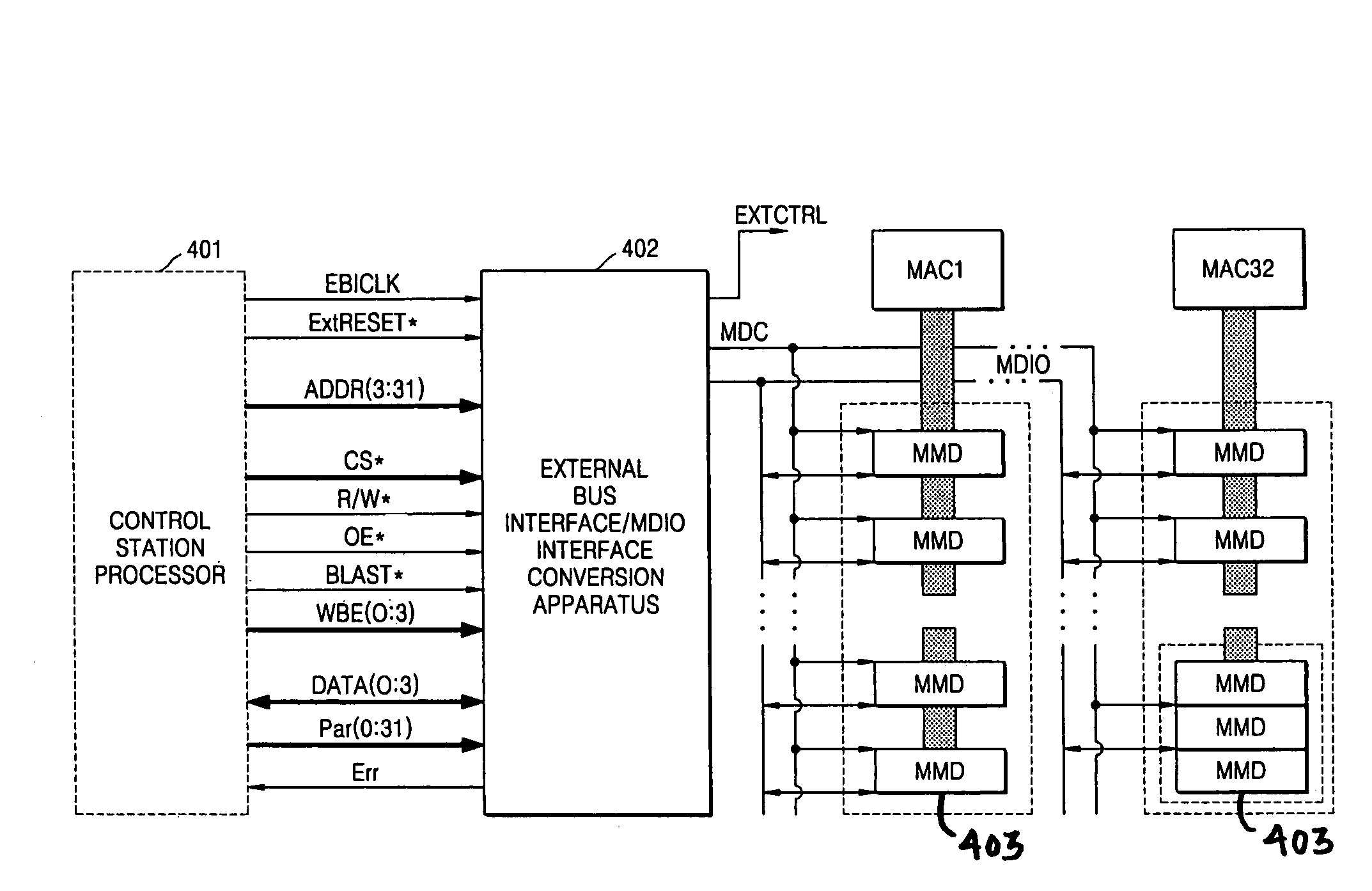

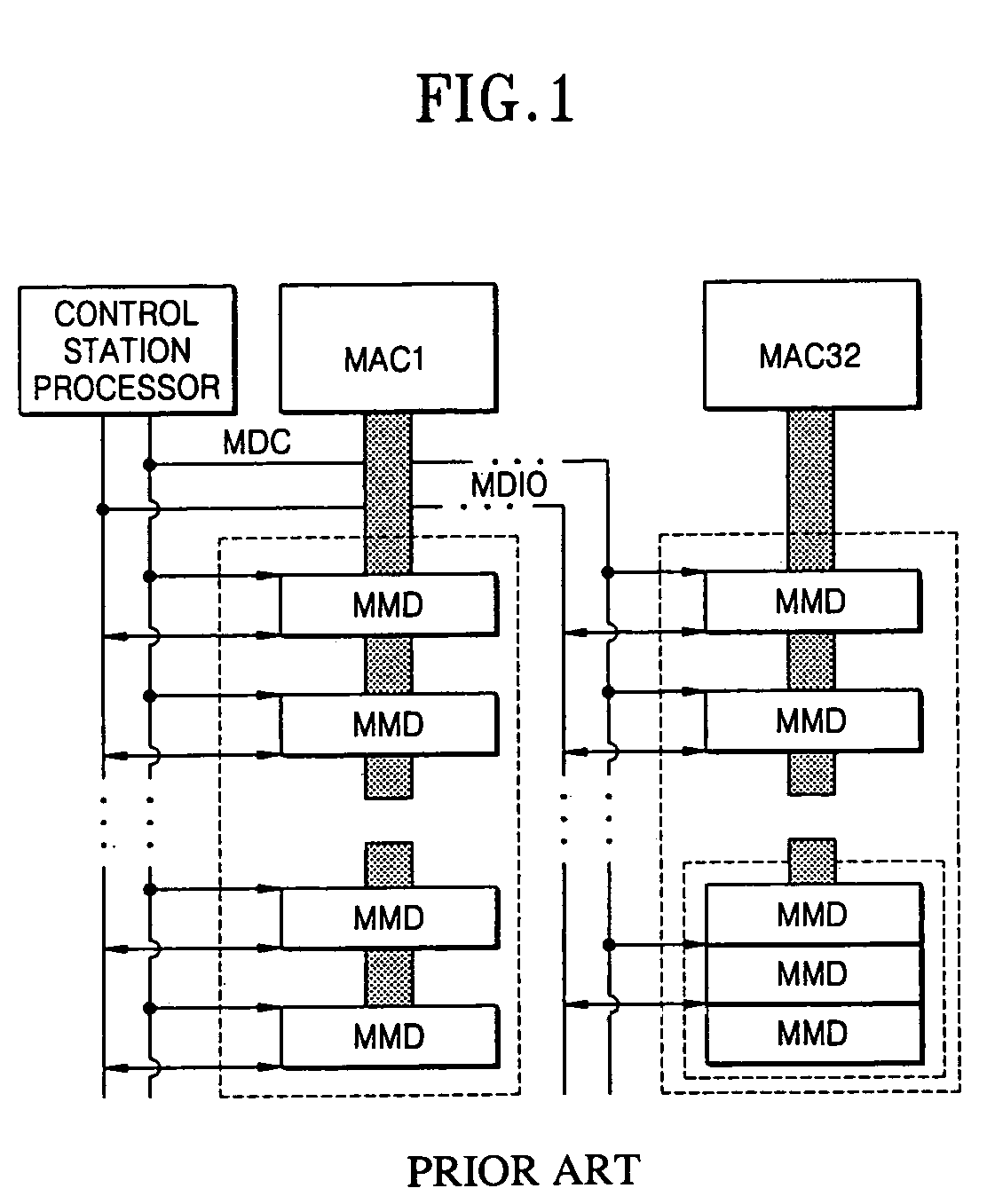

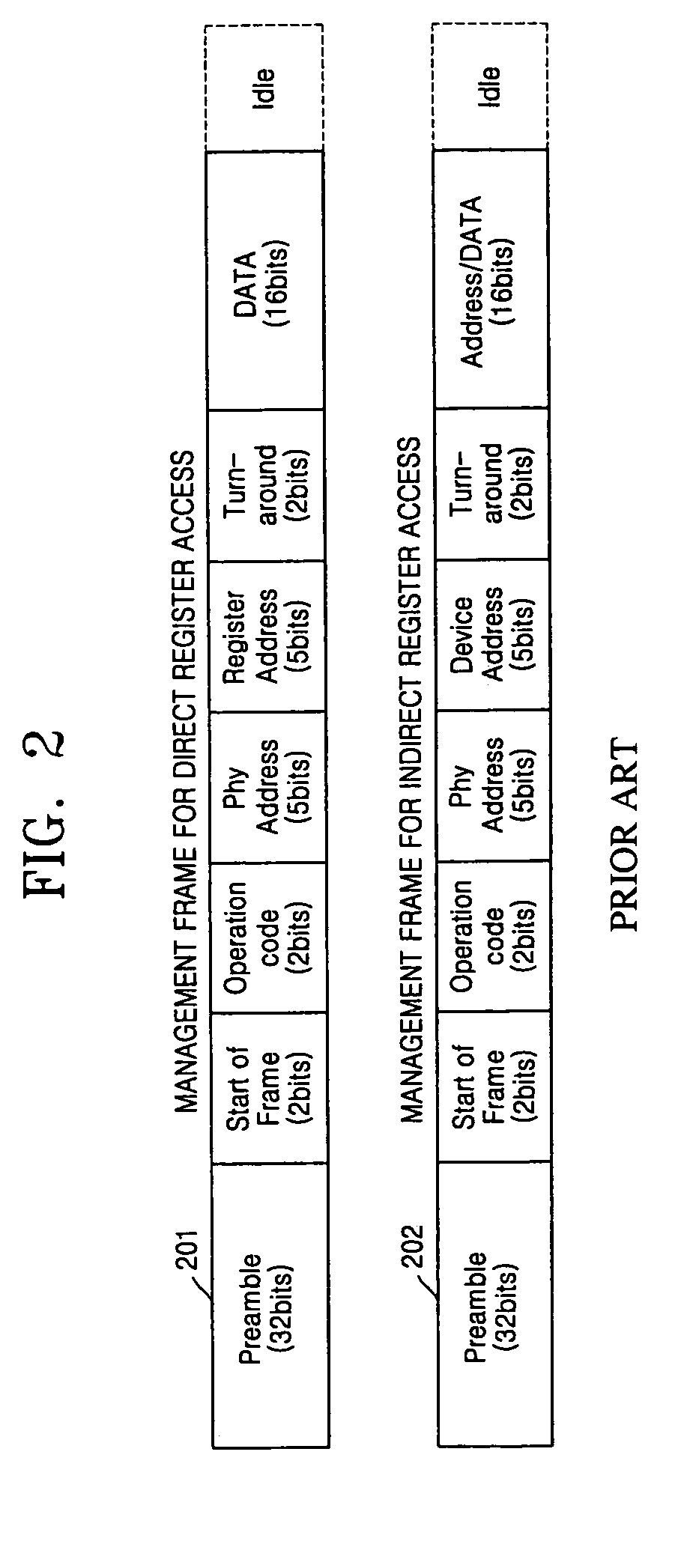

Apparatus for managing Ethernet physical layer registers using external bus interface and method thereof

InactiveUS7185134B2Multiple digital computer combinationsInput/output processes for data processingPhysical layerTransducing Unit

An apparatus for managing Ethernet physical layer registers and a method thereof are provided. The apparatus comprises a central processing unit (CPU) with an external bus interface function, and an interface conversion unit which is connected to the CPU through the external bus interface, converts the external bus interface into management data input / output (MDIO) interface and performs communications with the physical layer apparatus.

Owner:ELECTRONICS & TELECOMM RES INST

Command Queue for Peripheral Component

ActiveUS20110113167A1Easy to useEnergy efficient ICTEnergy efficient computingMemory interfaceControl communications

In an embodiment, a peripheral component configured to control an external interface of an integrated circuit. For example, the peripheral component may be a memory interface unit such as a flash memory interface unit. The internal interface to the peripheral component may be shared between data transfers to / from the external interface and control communications to the peripheral component. The peripheral component may include a command queue configured to store a set of commands to perform a transfer on the interface. A control circuit may be coupled to the command queue and may read the commands and communicate with an interface controller to cause a transfer on the interface responsive to the commands. In an embodiment, a macro memory may store command sequences to be performed in response to a macro command in the command queue. In an embodiment, an operand queue may store operand data for use by the commands.

Owner:APPLE INC