Patents

Literature

329 results about "Memory type" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

There are three basic types of memory: sensory memory (what we perceive), short-term memory (what we think about), and long-term memory (what we know). These memory types all play a role in how information is encoded, stored, and retrieved.

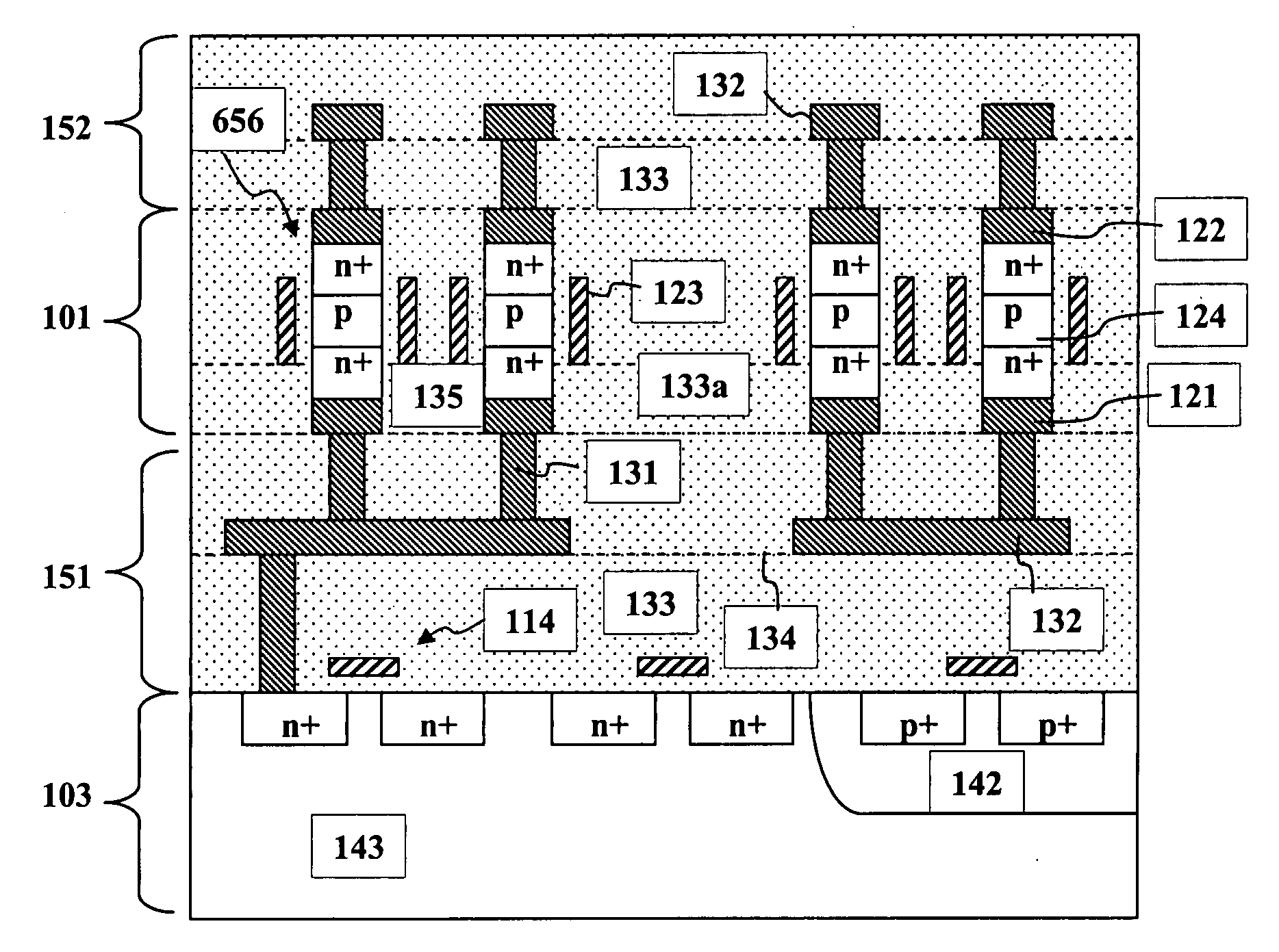

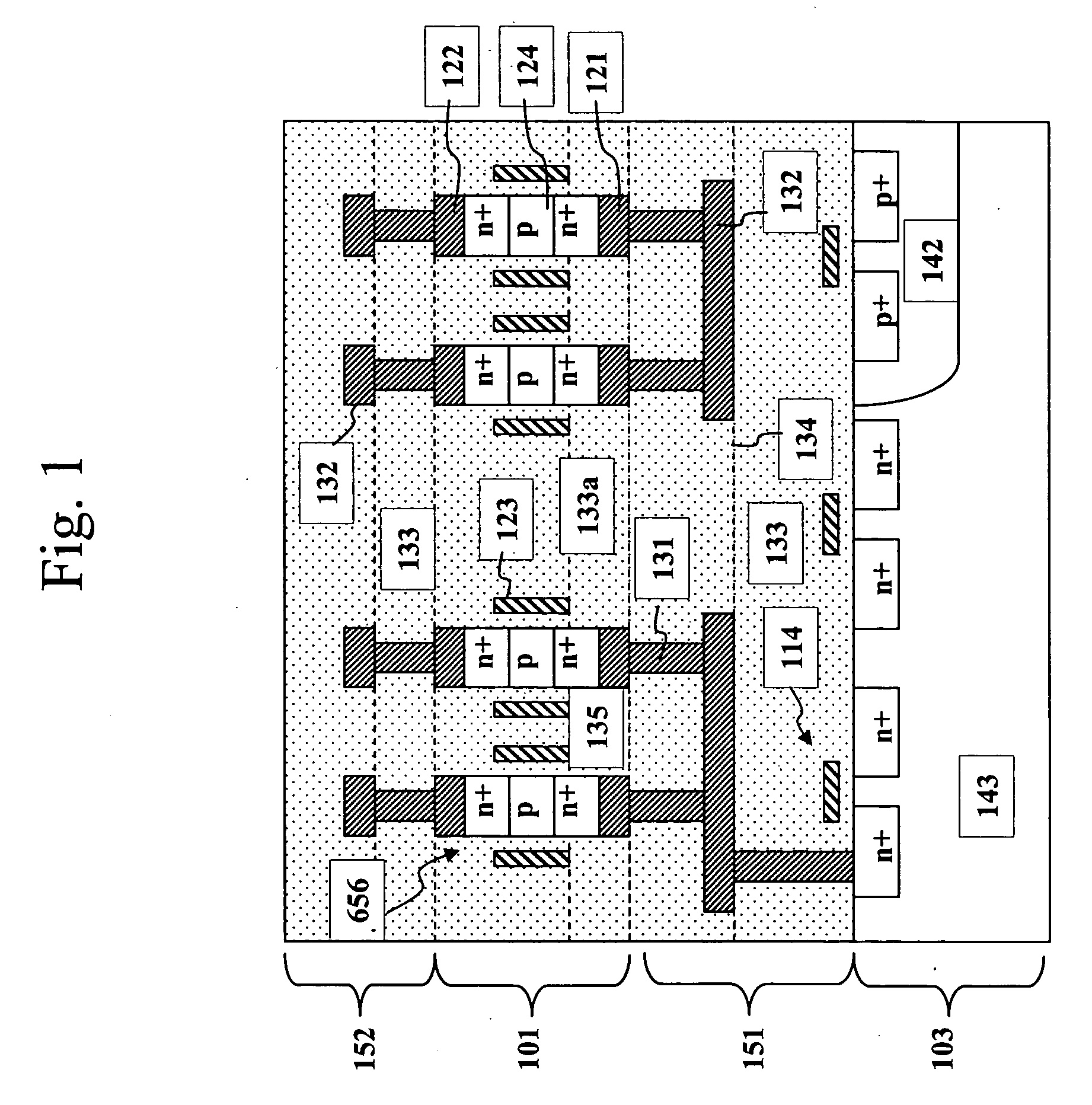

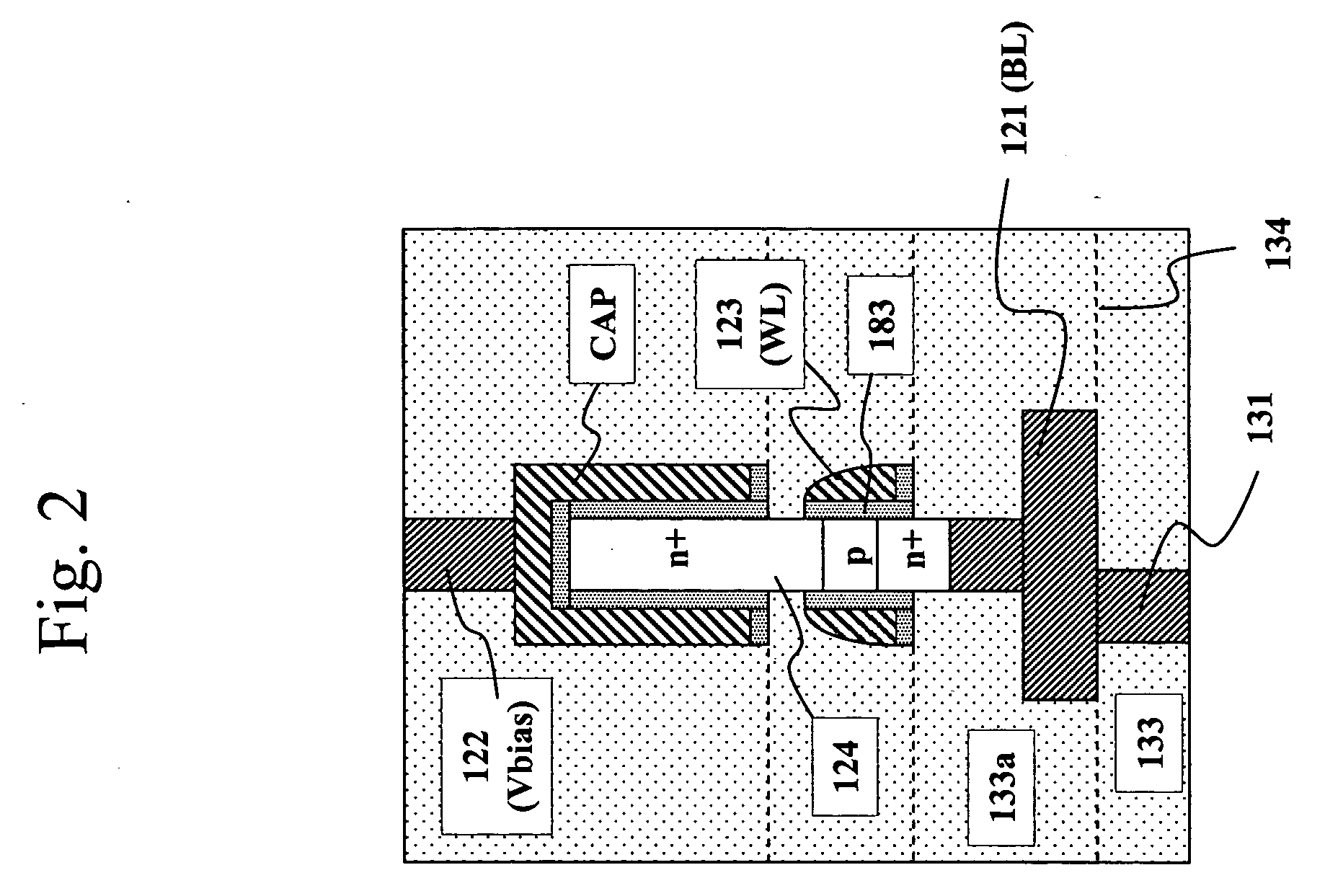

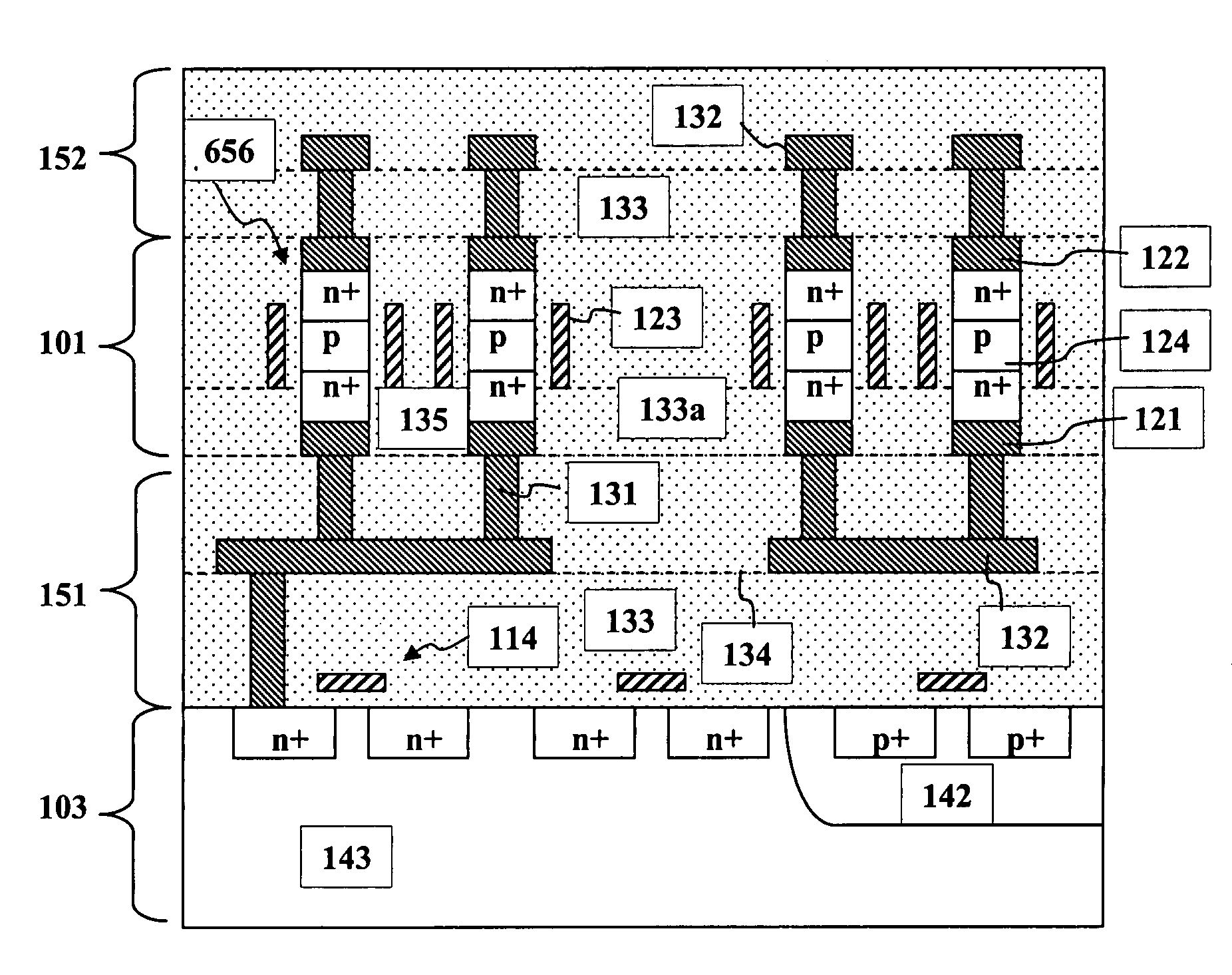

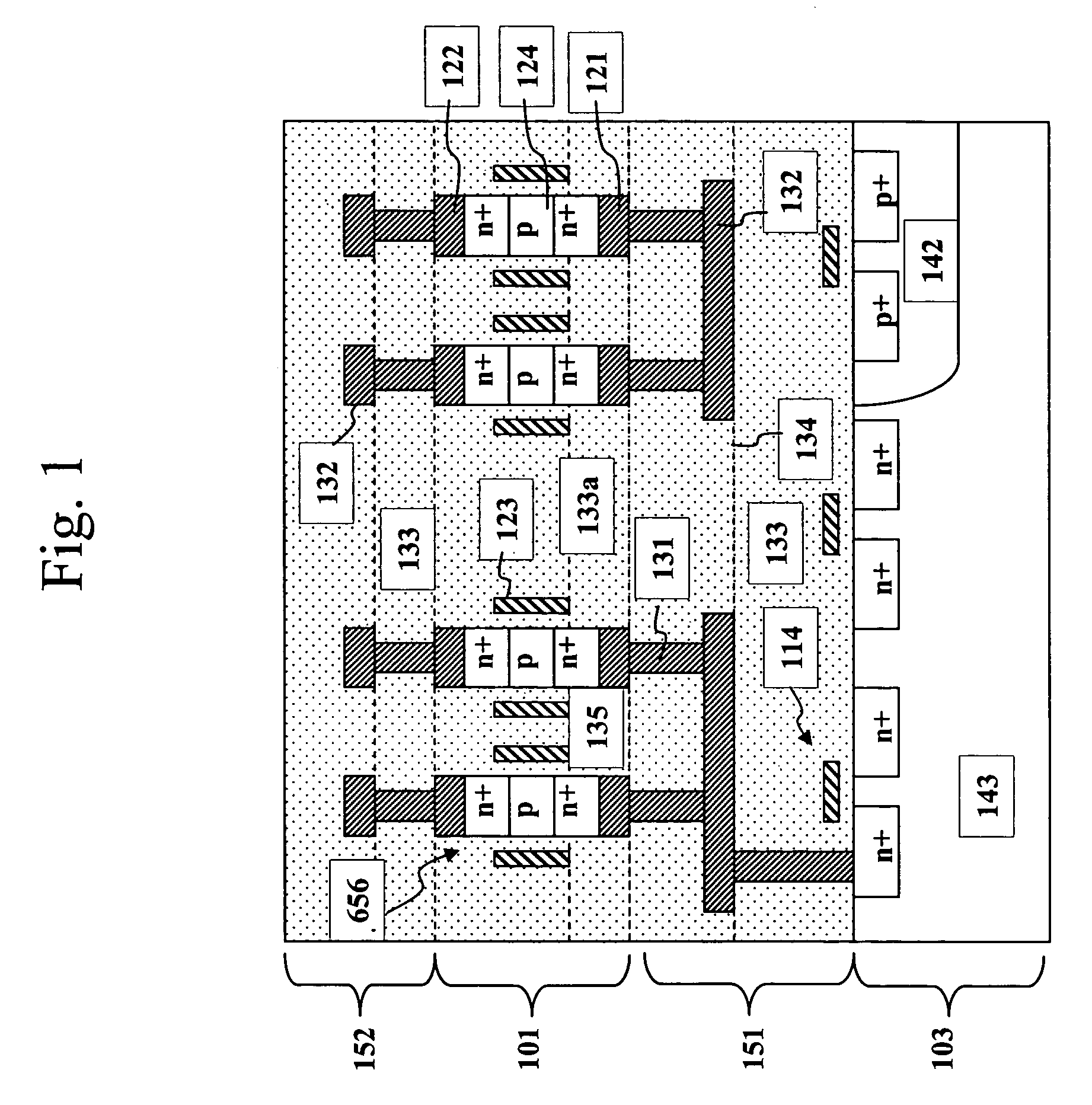

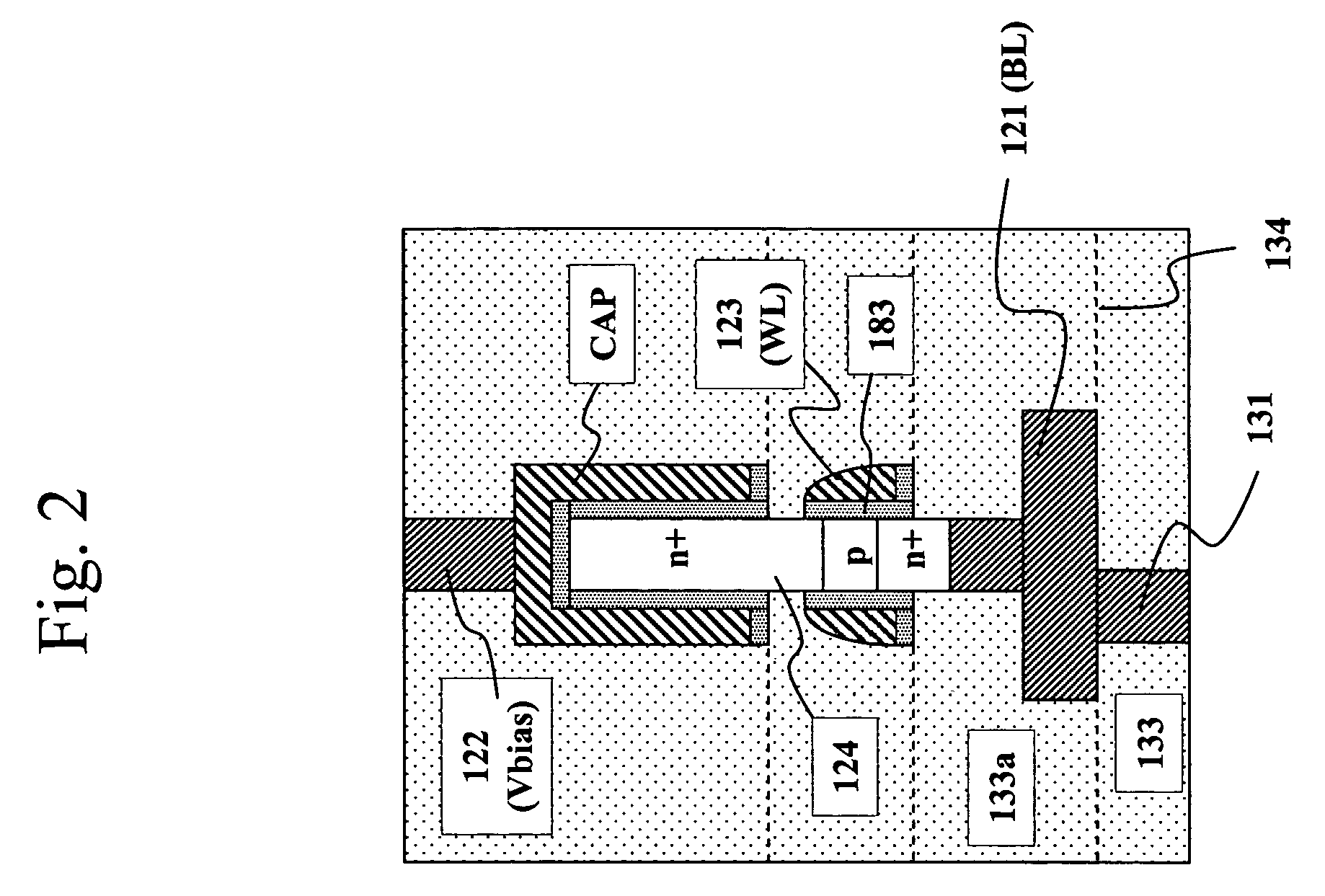

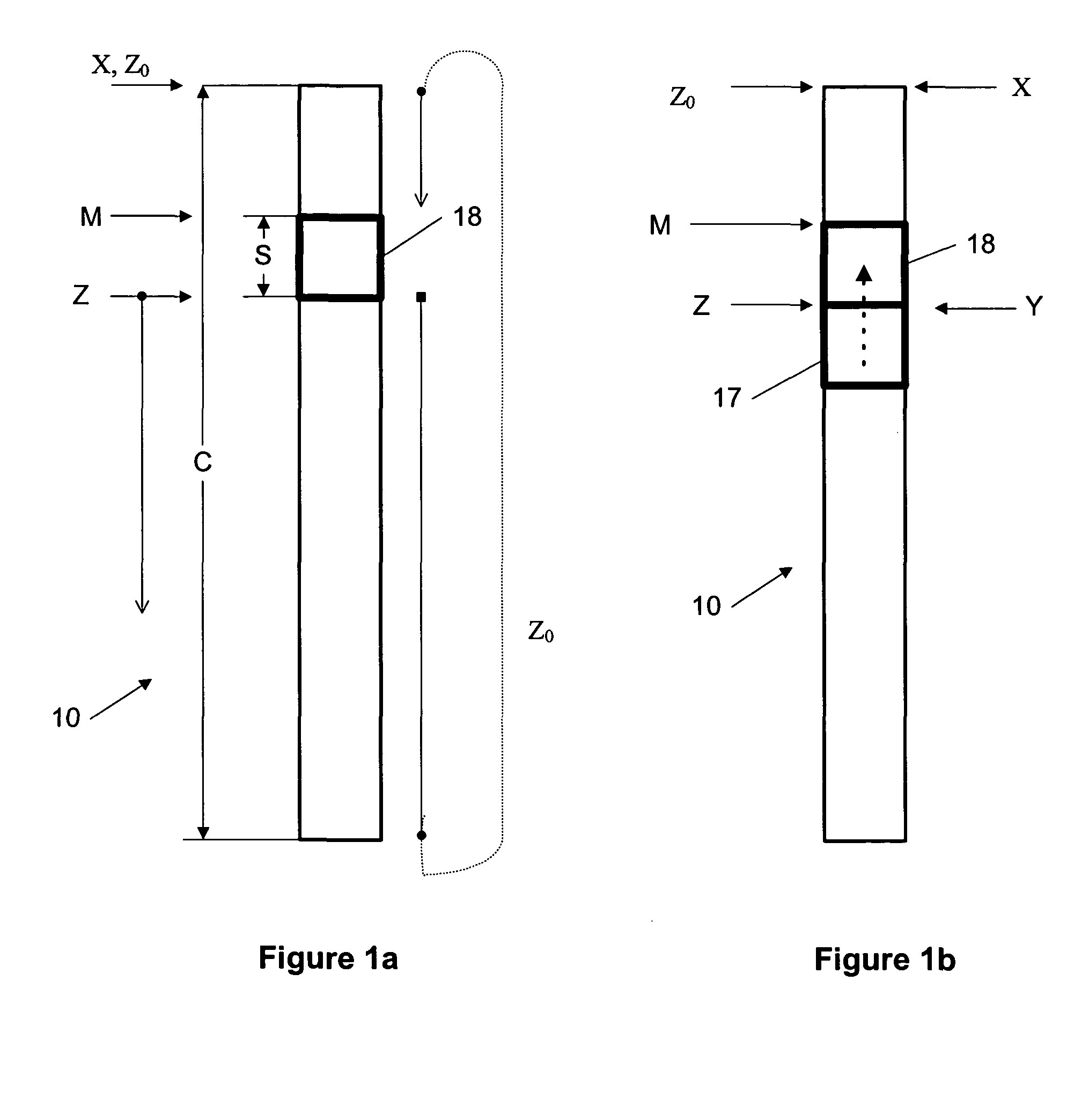

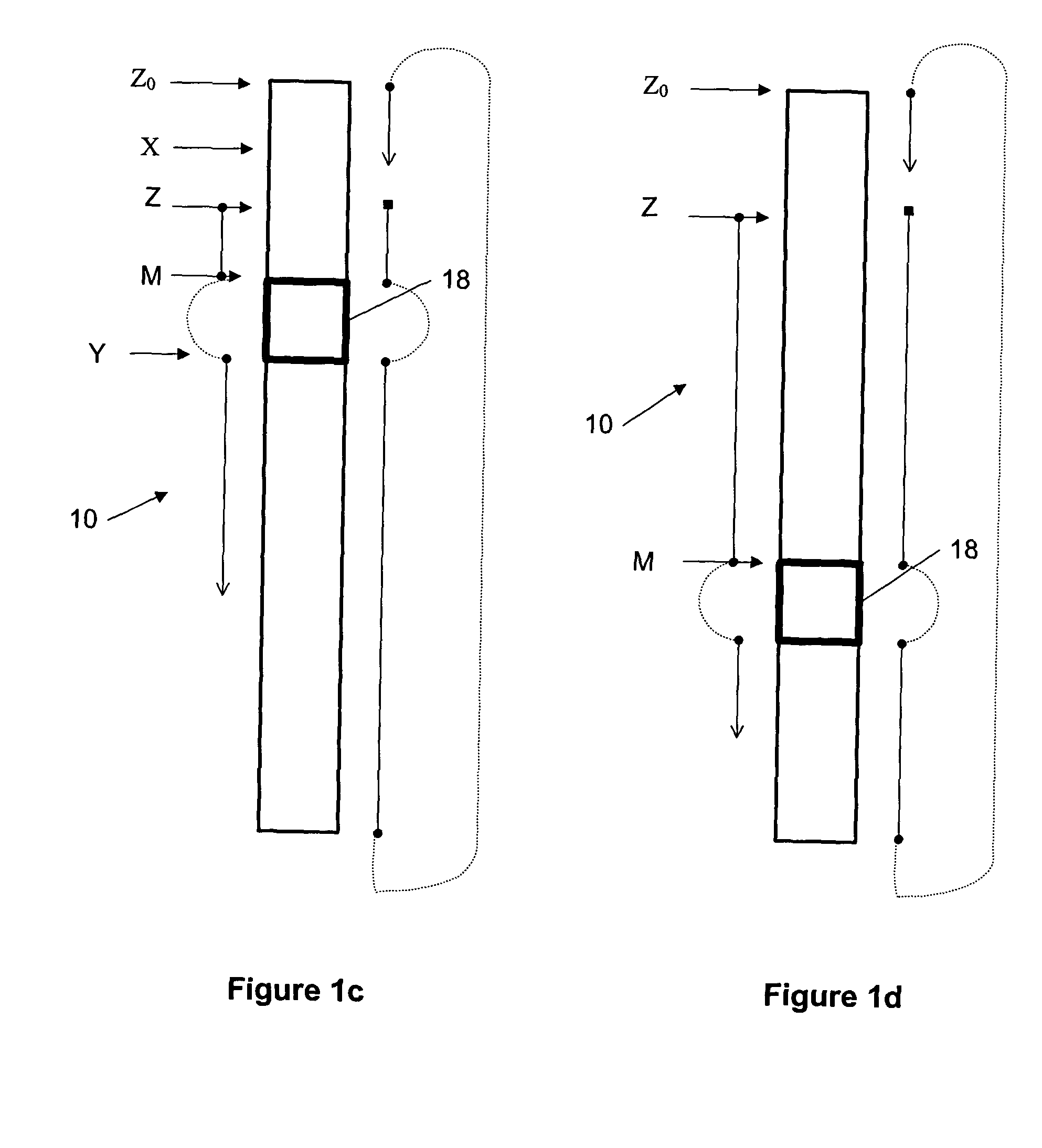

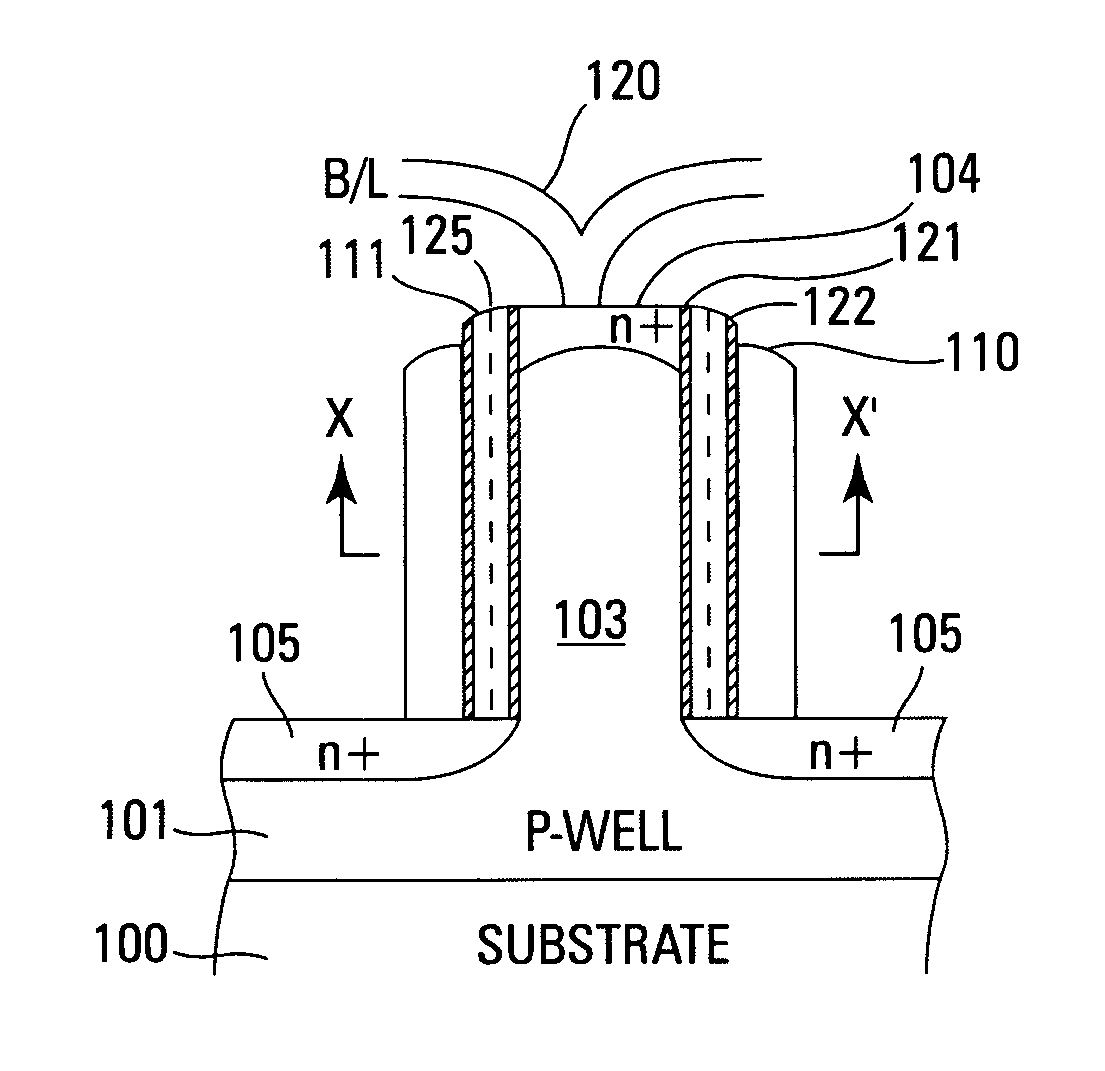

Vertical memory device structures

Vertically oriented semiconductor memory cells are added to a separately fabricated substrate that includes electrical devices and / or interconnect. The plurality of vertically oriented semiconductor memory cells are physically separated from each other, and are not disposed within the same semiconductor body. The plurality of vertically oriented semiconductor memory cells can be added to the separately fabricated substrate as a thin layer including several doped semiconductor regions which, subsequent to attachment, are etched to produce individual doped stack structures, which are then supplied with various dielectric coatings, gate electrodes, and contacts by means of further processing operations. Alternatively, the plurality of vertically oriented semiconductor memory cells may be completely fabricated prior to attachment. DRAMs, SRAMs, non-volatile memories, and combinations of memory types can be provided.

Owner:BESANG

Vertical memory device structures

Vertically oriented semiconductor memory cells are added to a separately fabricated substrate that includes electrical devices and / or interconnect. The plurality of vertically oriented semiconductor memory cells are physically separated from each other, and are not disposed within the same semiconductor body. The plurality of vertically oriented semiconductor memory cells can be added to the separately fabricated substrate as a thin layer including several doped semiconductor regions which, subsequent to attachment, are etched to produce individual doped stack structures, which are then supplied with various dielectric coatings, gate electrodes, and contacts by means of further processing operations. Alternatively, the plurality of vertically oriented semiconductor memory cells may be completely fabricated prior to attachment. DRAMs, SRAMs, non-volatile memories, and combinations of memory types can be provided.

Owner:BESANG

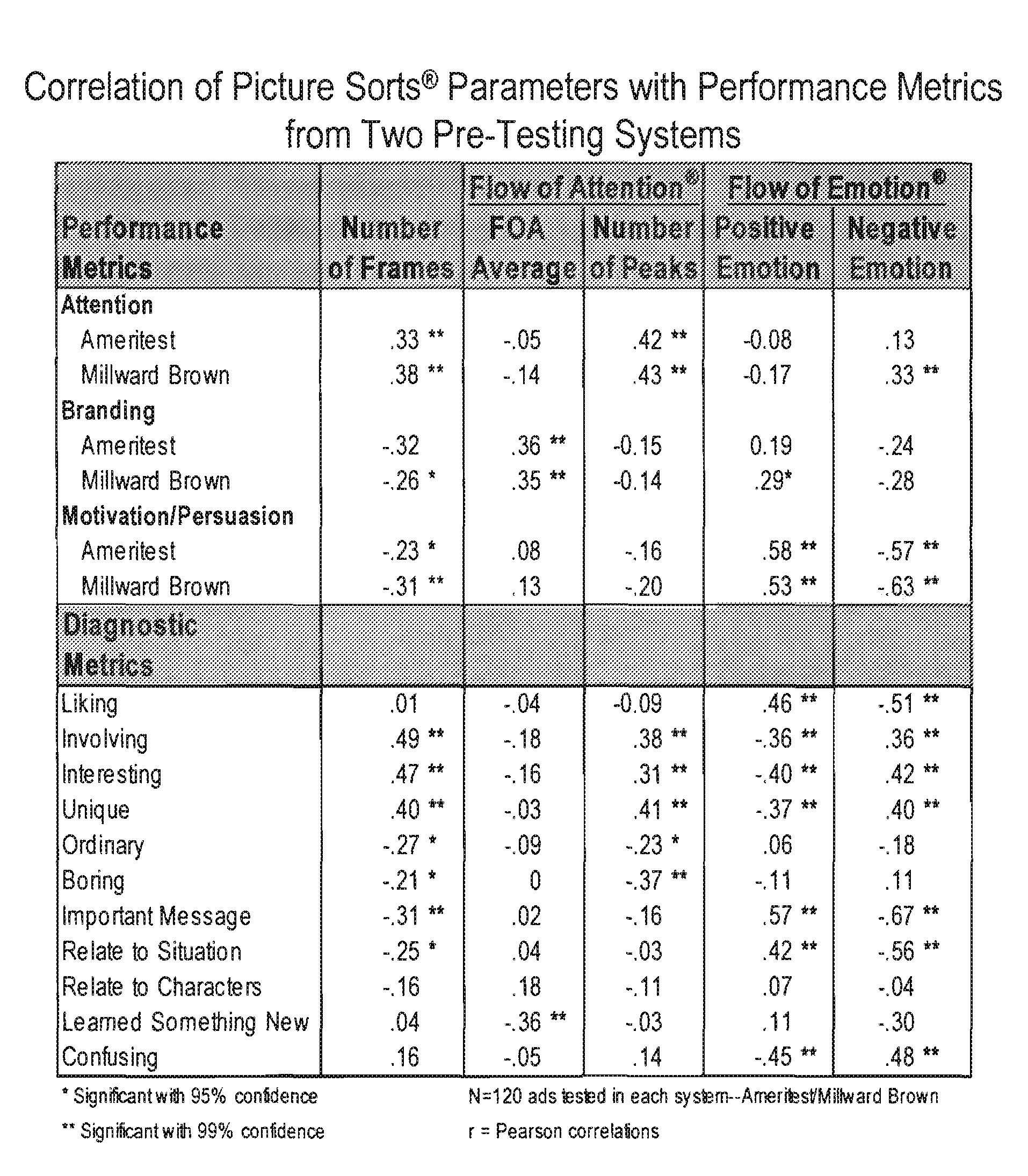

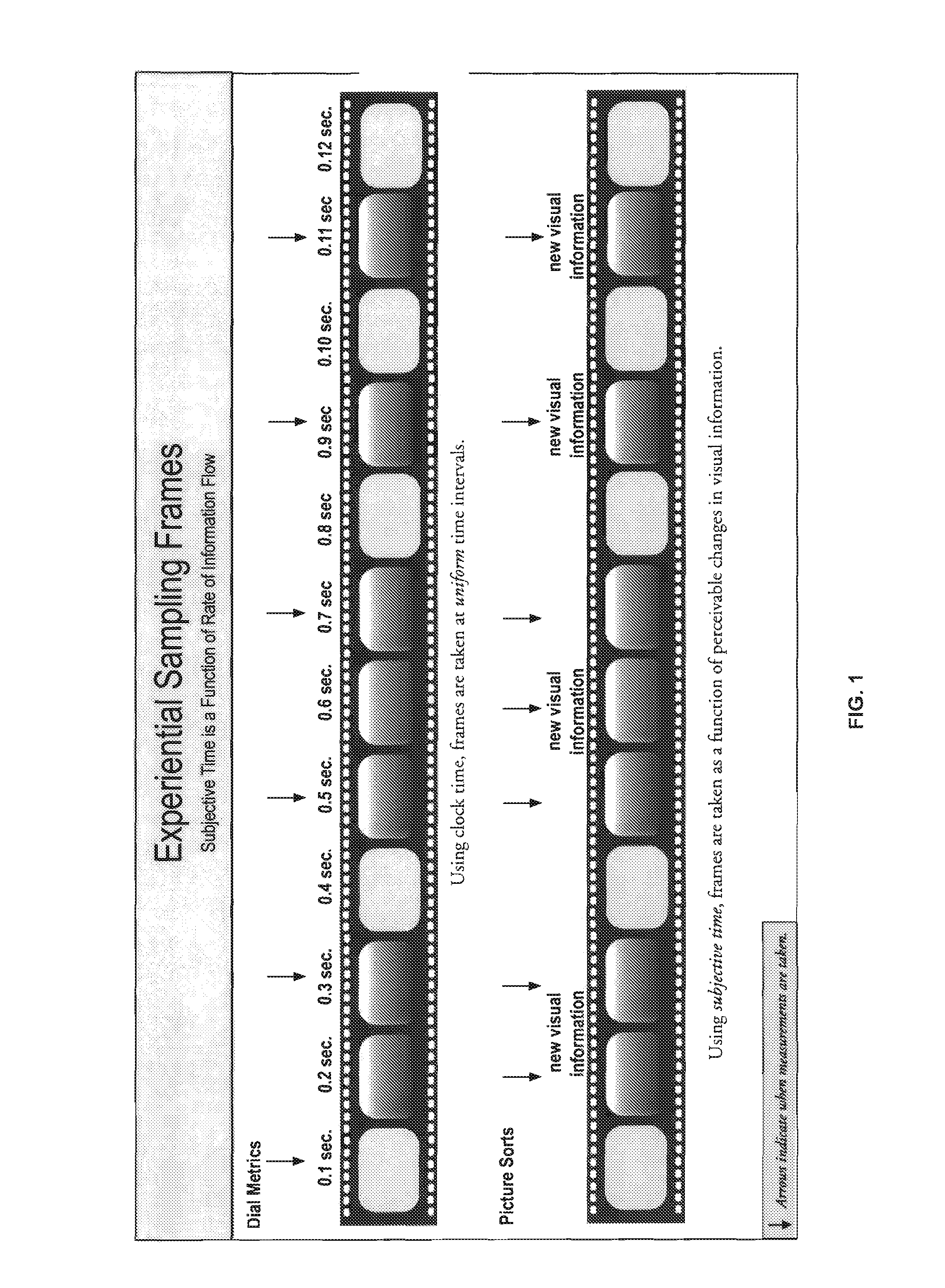

Method for Creating and Analyzing Advertisements

A method for analyzing advertisements and advertising campaigns. Important images are selected from one or more advertisements and then ranked. The most important images are then assigned to a category which preferably corresponds to a memory type, such as knowledge, emotion, or action. The relative numbers of images in each type determine the focus of the advertisement(s), and may be used to tailor the memory type(s) of subsequent advertisements.

Owner:HELLO HELLO

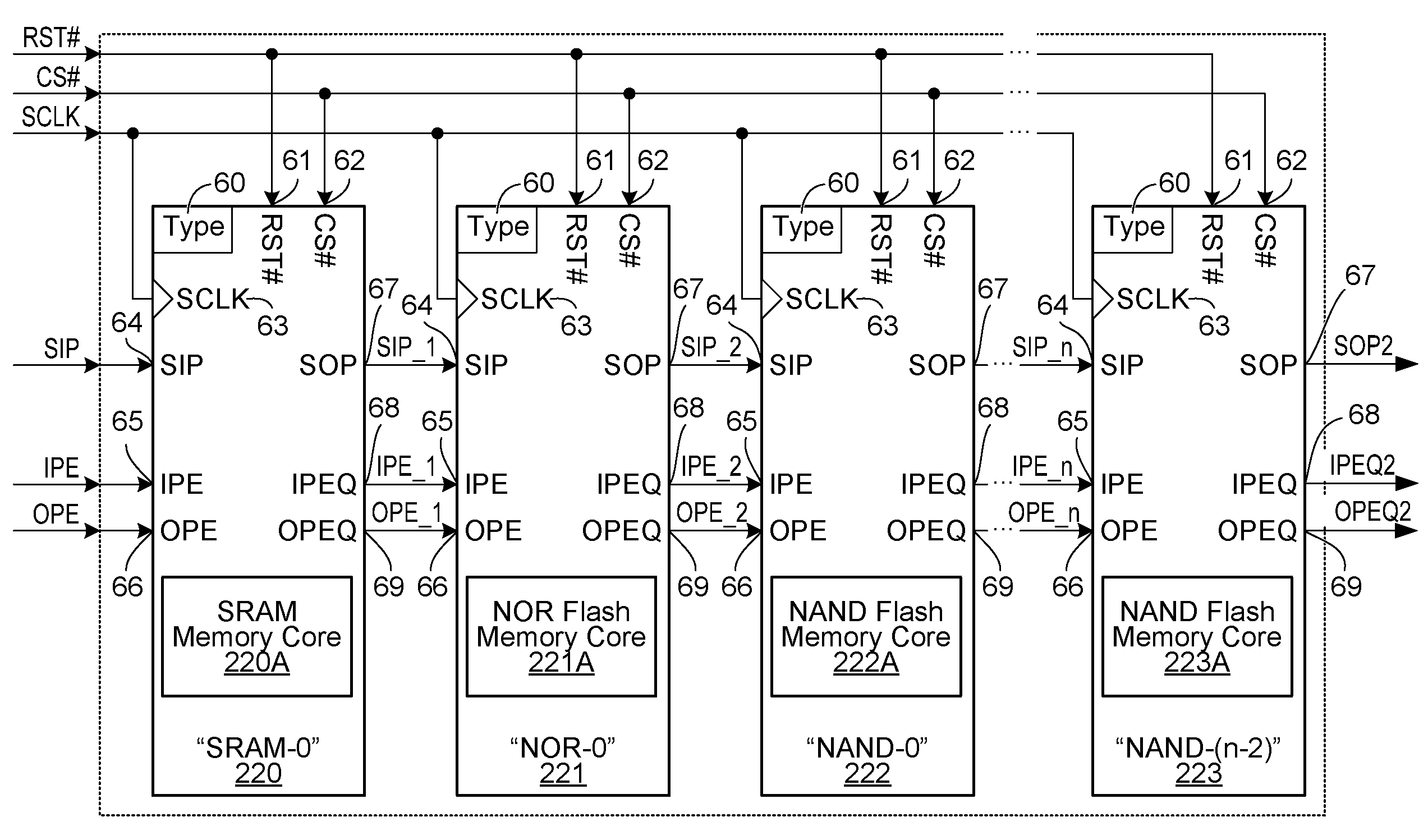

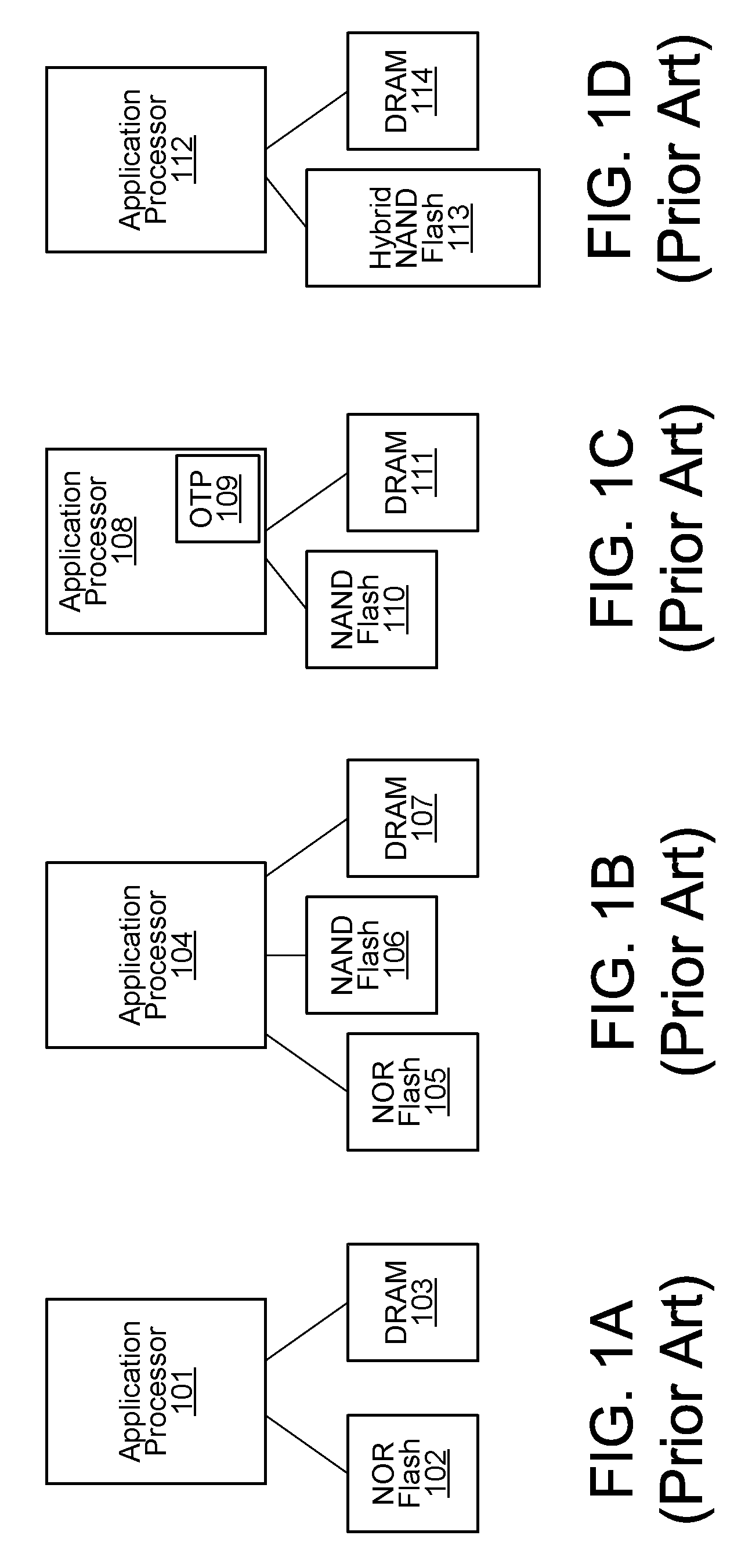

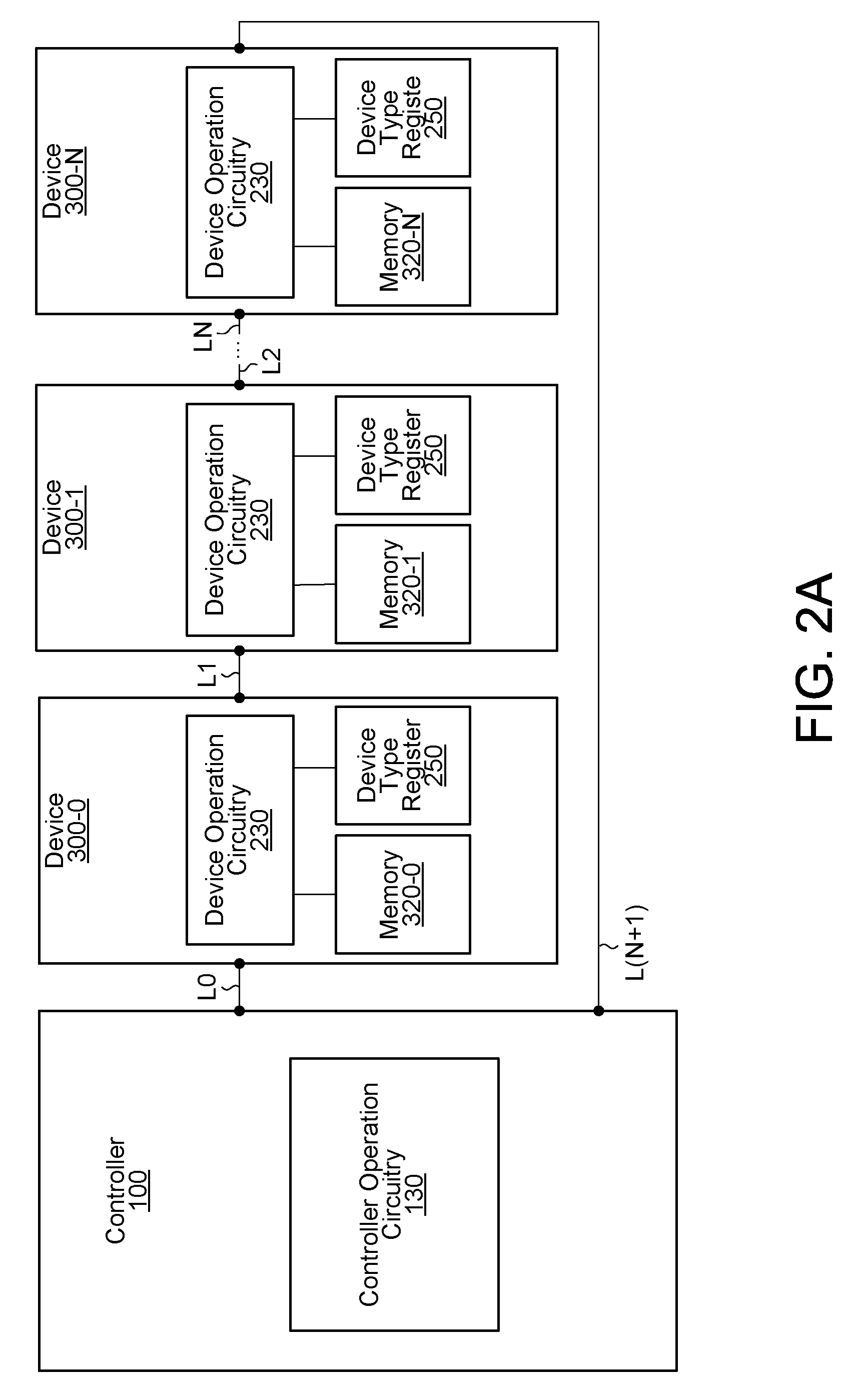

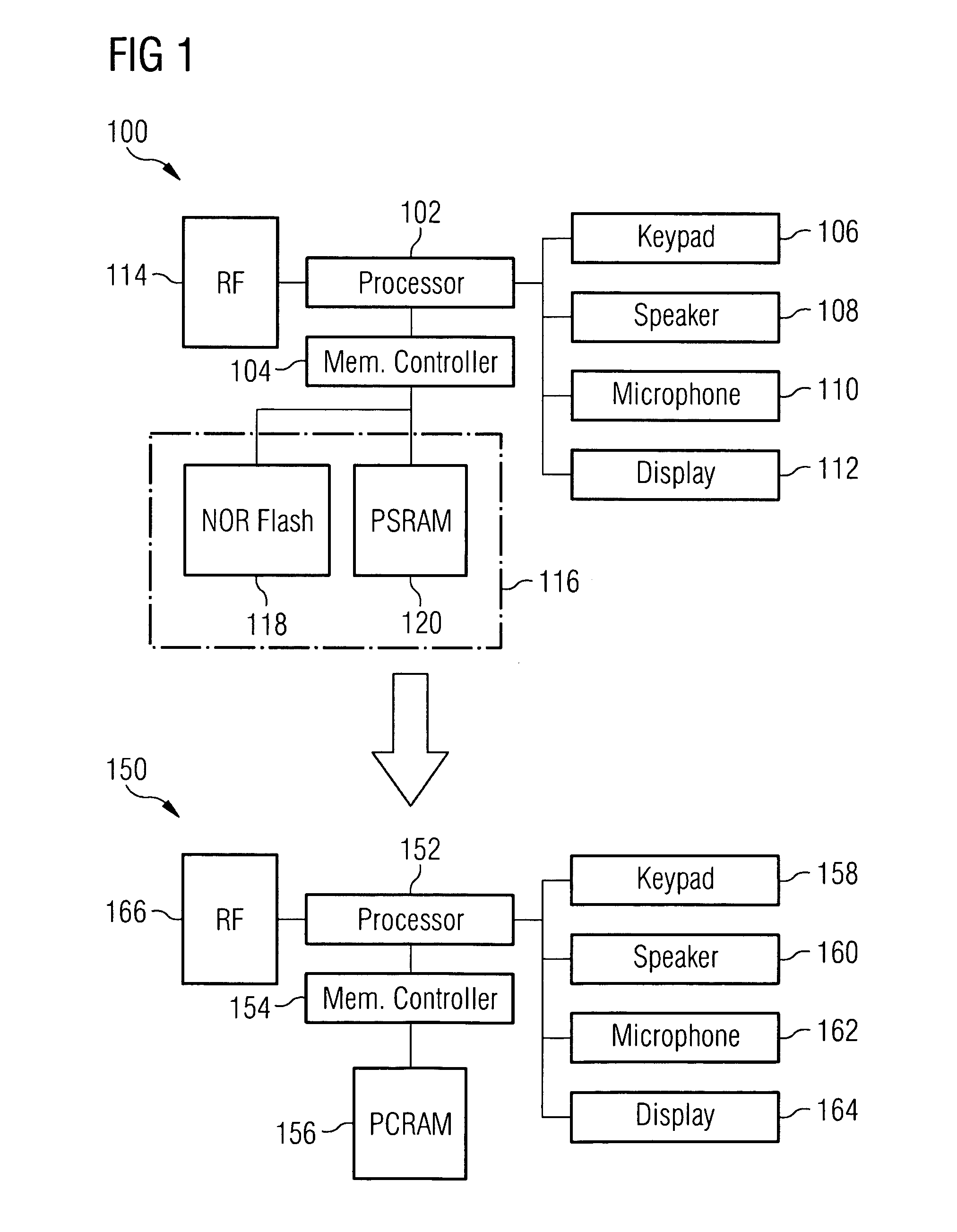

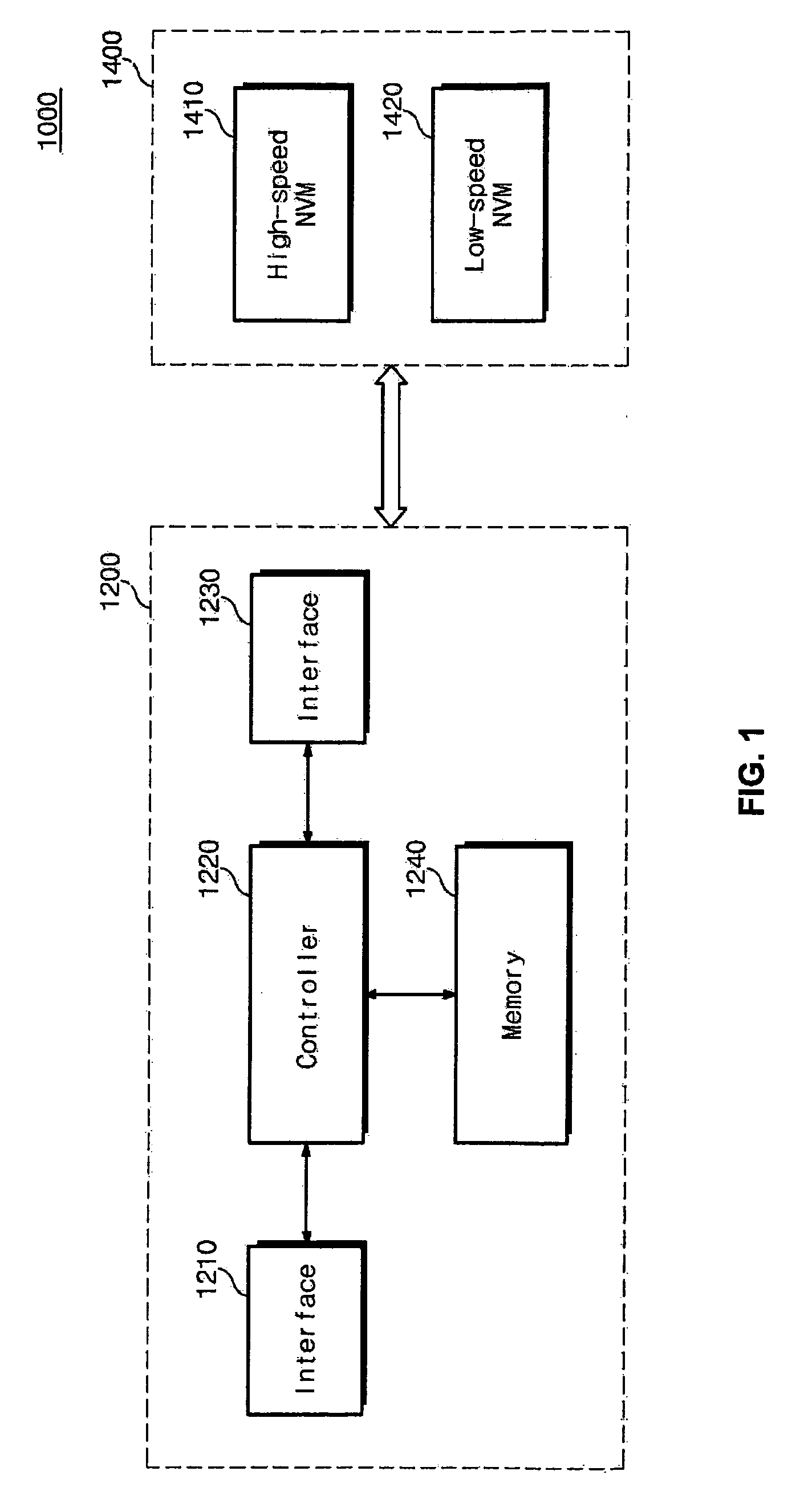

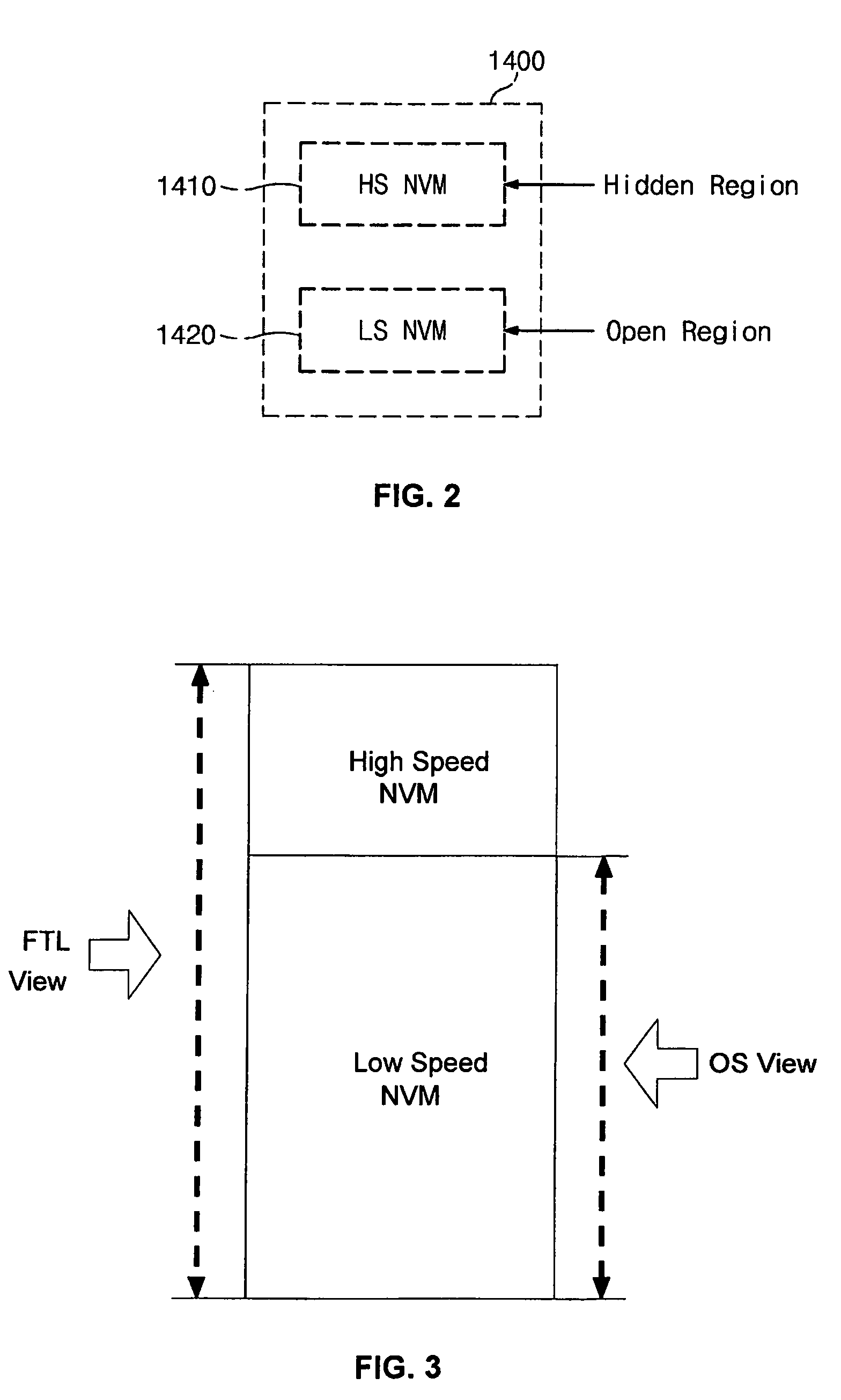

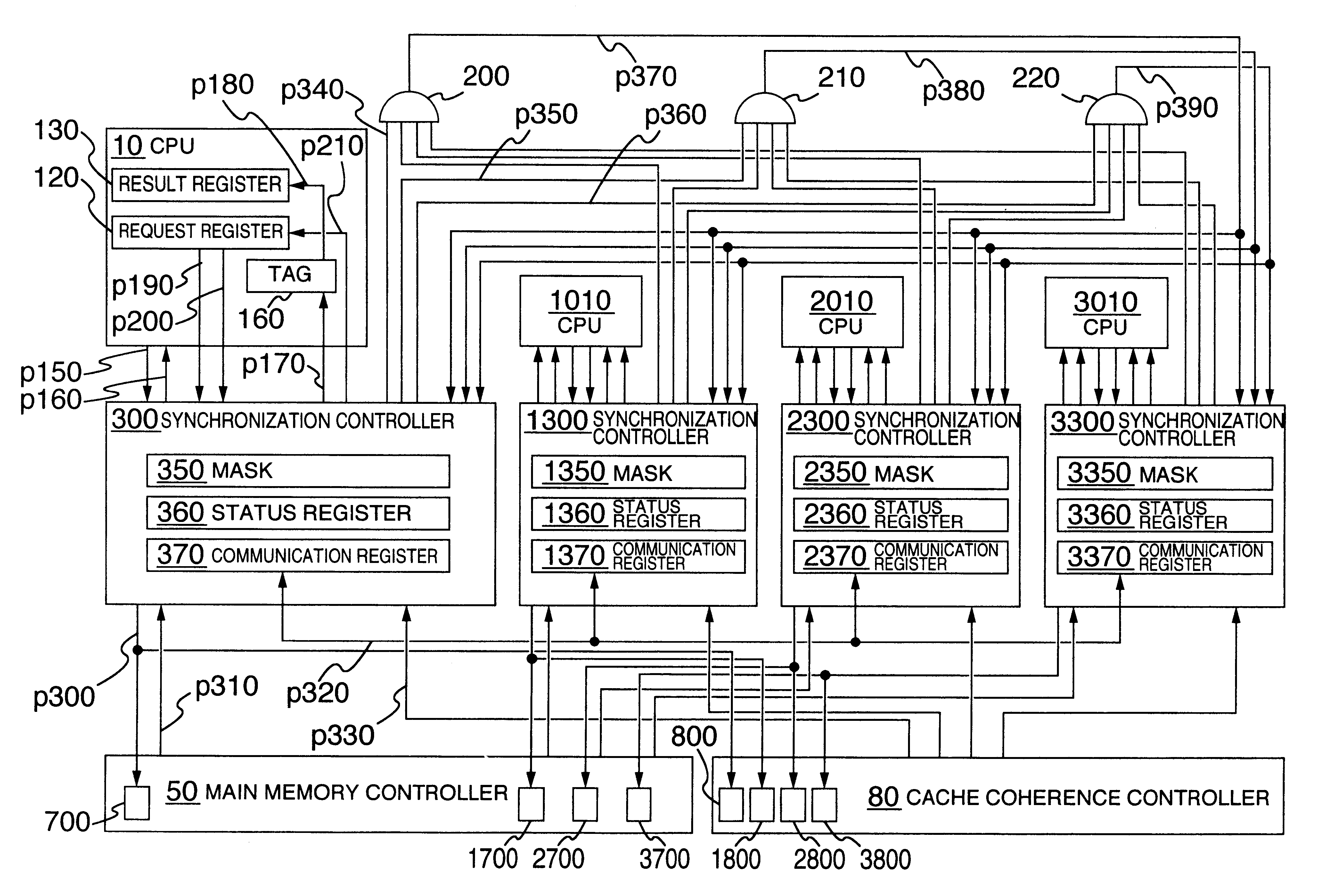

System and method of operating memory devices of mixed type

InactiveUS20080140916A1Memory adressing/allocation/relocationRead-only memoriesHybrid typeStatic random-access memory

A memory system architecture is provided in which a memory controller controls memory devices in a serial interconnection configuration. The memory controller has an output port for sending memory commands and an input port for receiving memory responses for those memory commands requisitioning such responses. Each memory device includes a memory, such as, for example, NAND-type flash memory, NOR-type flash memory, random access memory and static random access memory. Each memory command is specific to the memory type of a target memory device. A data path for the memory commands and the memory responses is provided by the interconnection. A given memory command traverses memory devices in order to reach its intended memory device of the serial interconnection configuration. Upon its receipt, the intended memory device executes the given memory command and, if appropriate, sends a memory response to a next memory device. The memory response is transferred to the memory controller.

Owner:CONVERSANT INTPROP MANAGEMENT INC

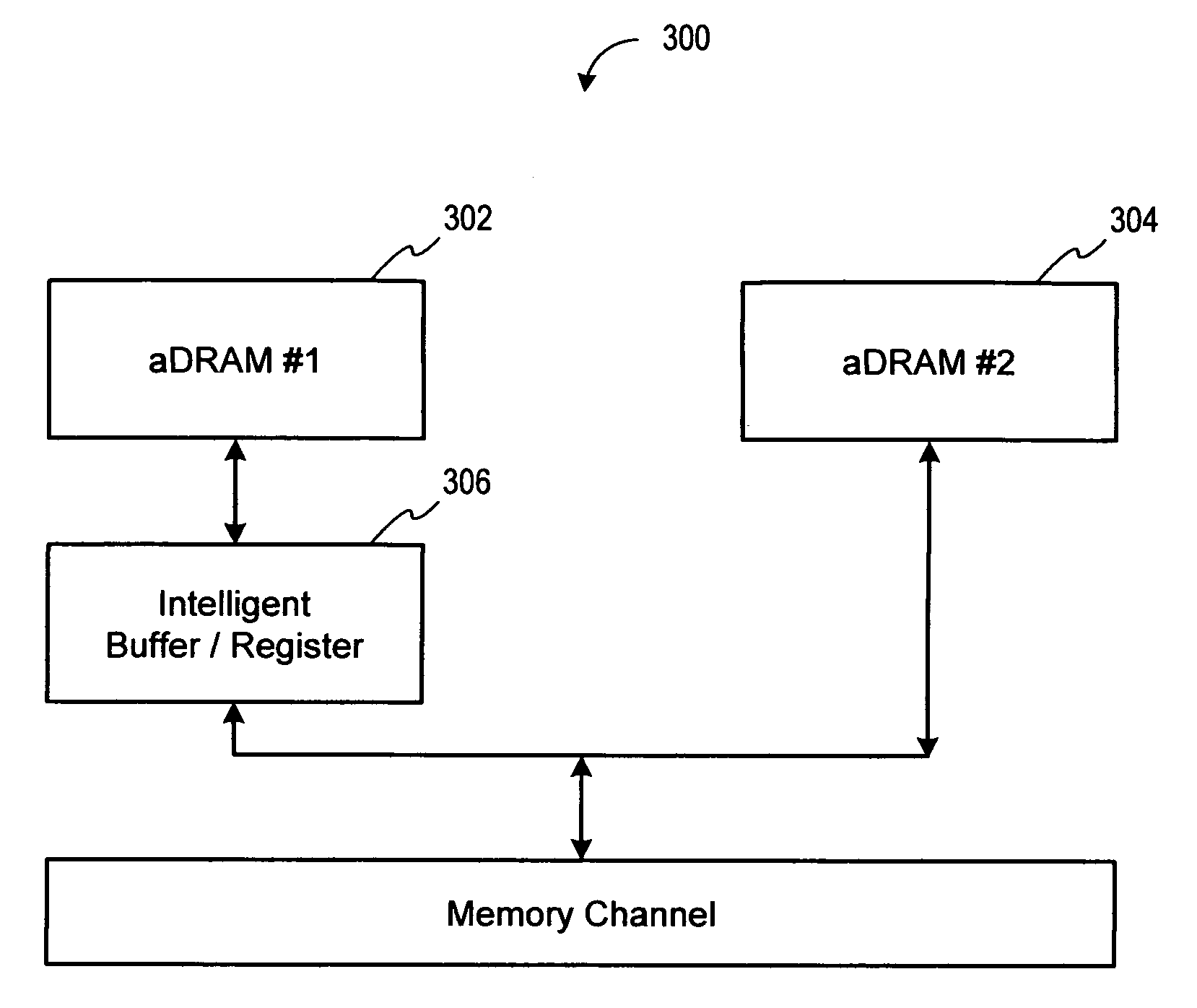

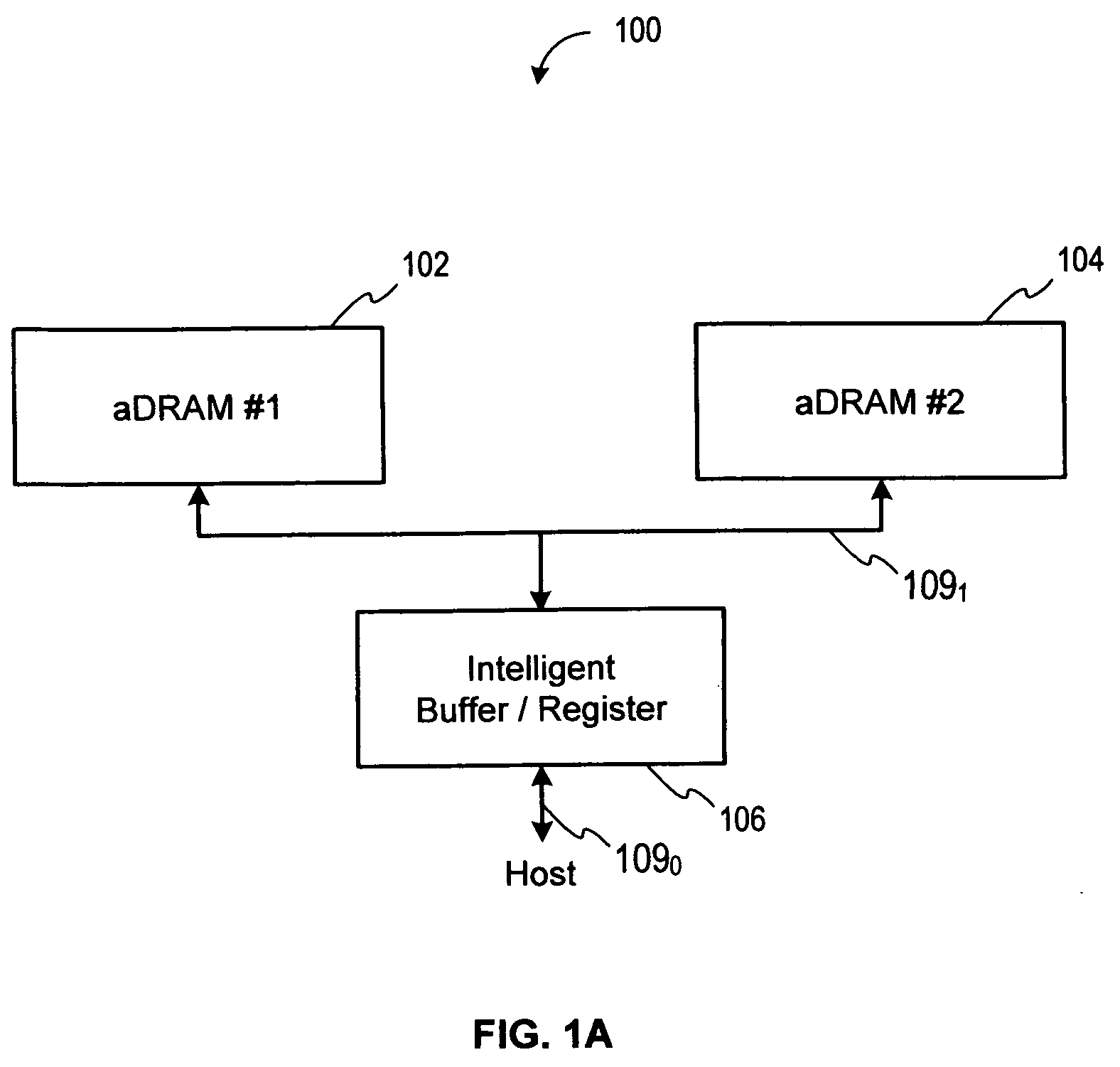

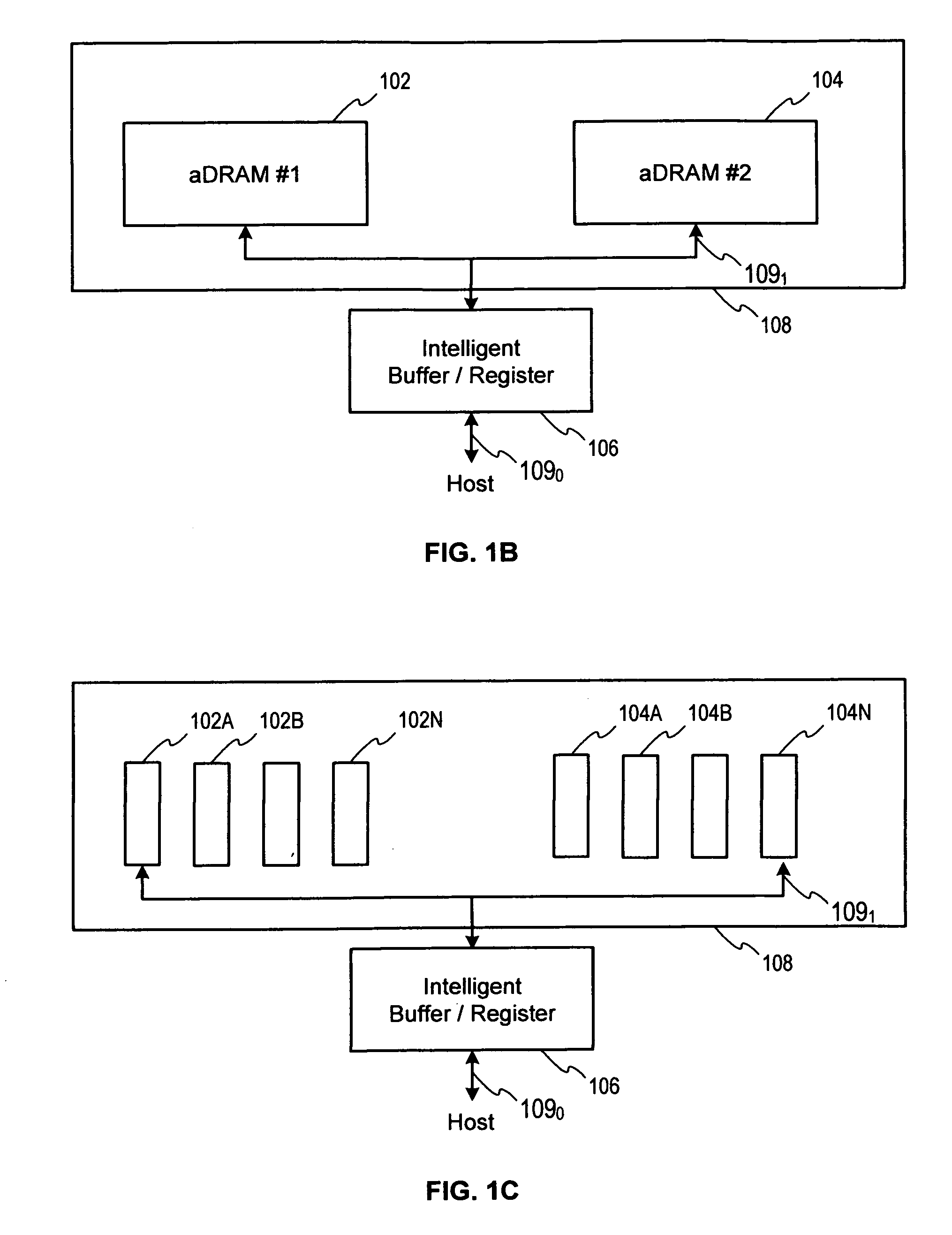

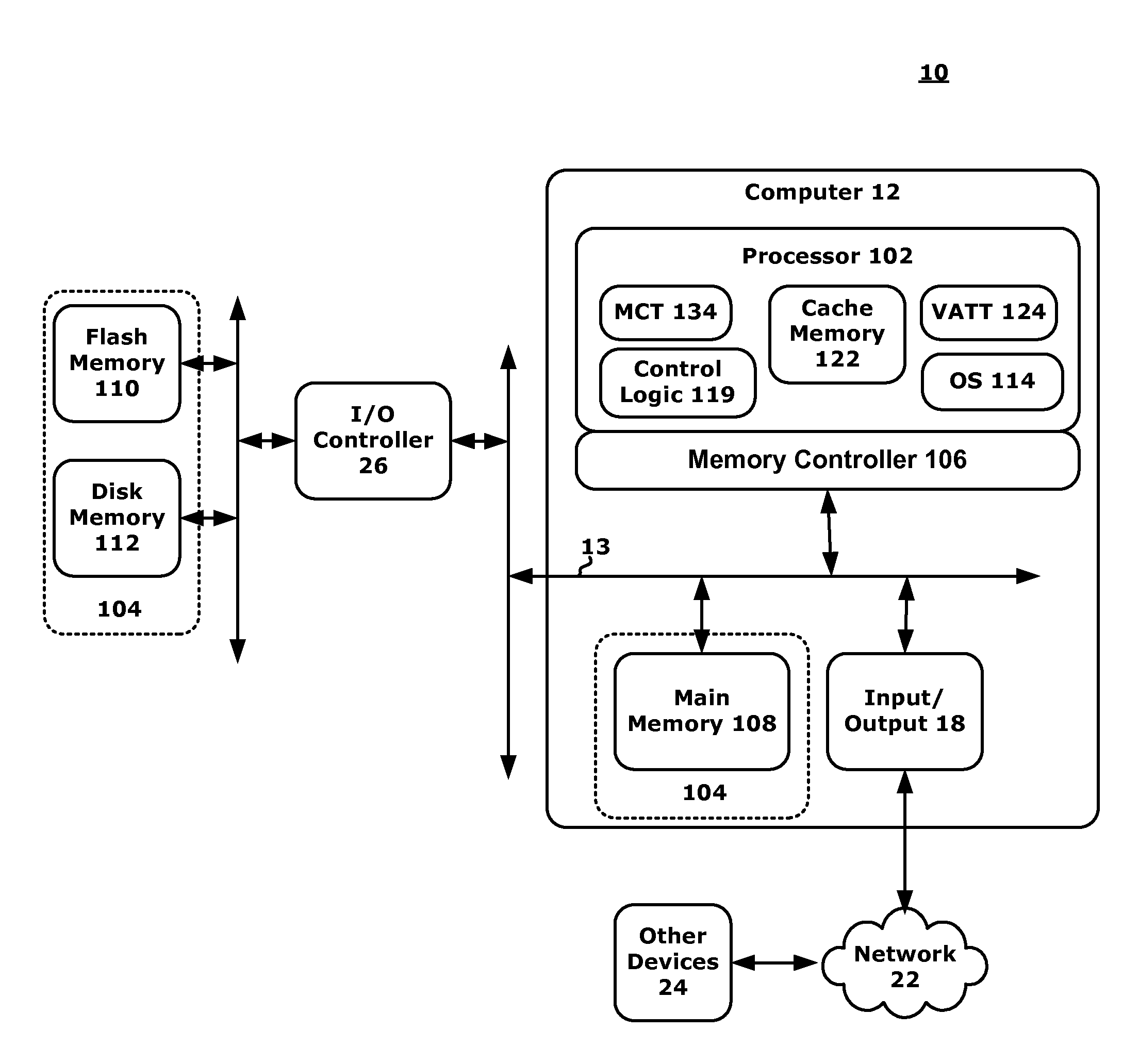

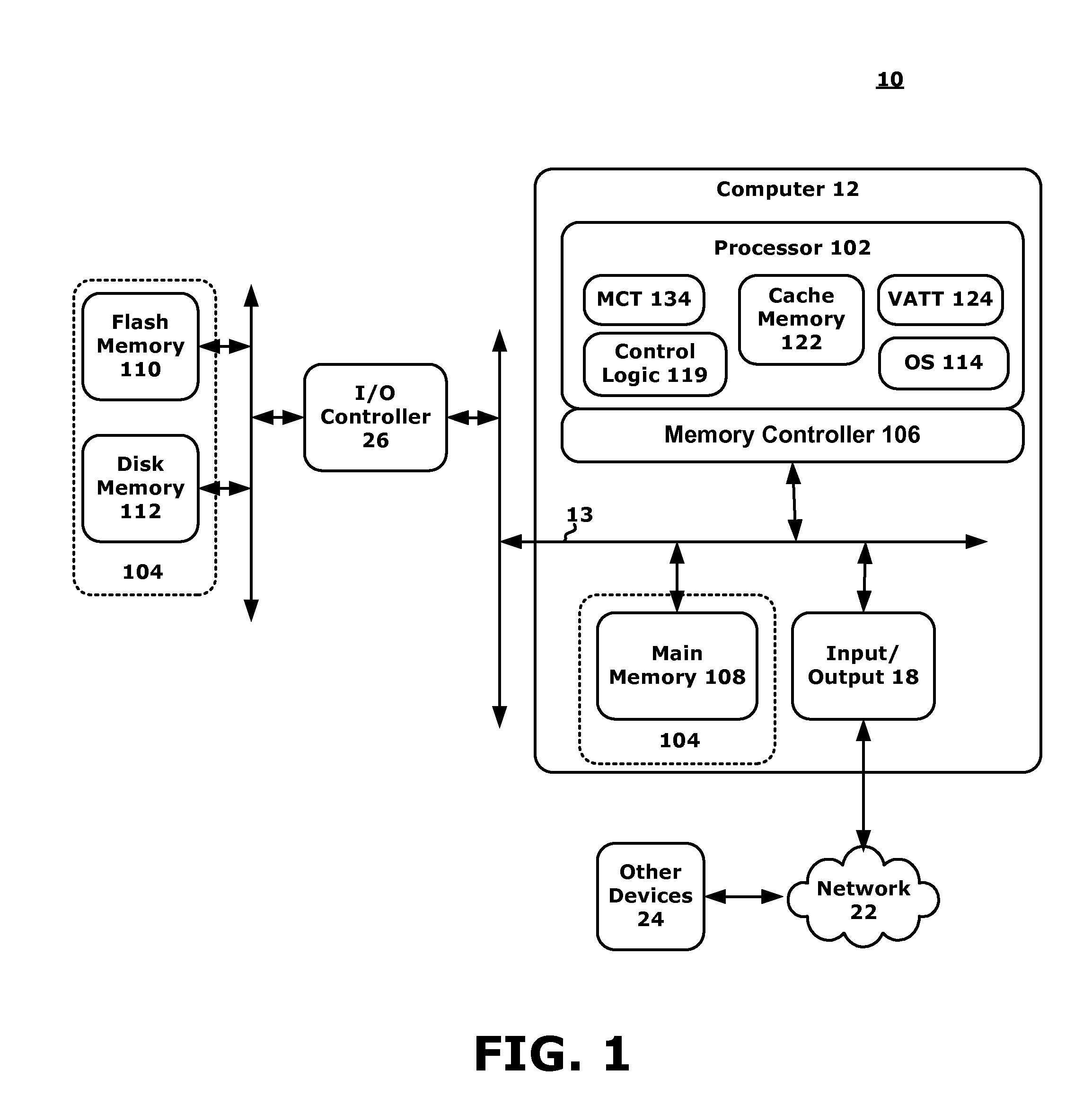

Emulation of abstracted DIMMs using abstracted DRAMs

ActiveUS20090216939A1Memory performanceEnergy efficient ICTMemory adressing/allocation/relocationMemory typeRelevant feature

One embodiment of the present invention sets forth an abstracted memory subsystem comprising abstracted memories, which each may be configured to present memory-related characteristics onto a memory system interface. The characteristics can be presented on the memory system interface via logic signals or protocol exchanges, and the characteristics may include any one or more of, an address space, a protocol, a memory type, a power management rule, a number of pipeline stages, a number of banks, a mapping to physical banks, a number of ranks, a timing characteristic, an address decoding option, a bus turnaround time parameter, an additional signal assertion, a sub-rank, a number of planes, or other memory-related characteristics. Some embodiments include an intelligent register device and / or, an intelligent buffer device. One advantage of the disclosed subsystem is that memory performance may be optimized regardless of the specific protocols used by the underlying memory hardware devices.

Owner:GOOGLE LLC

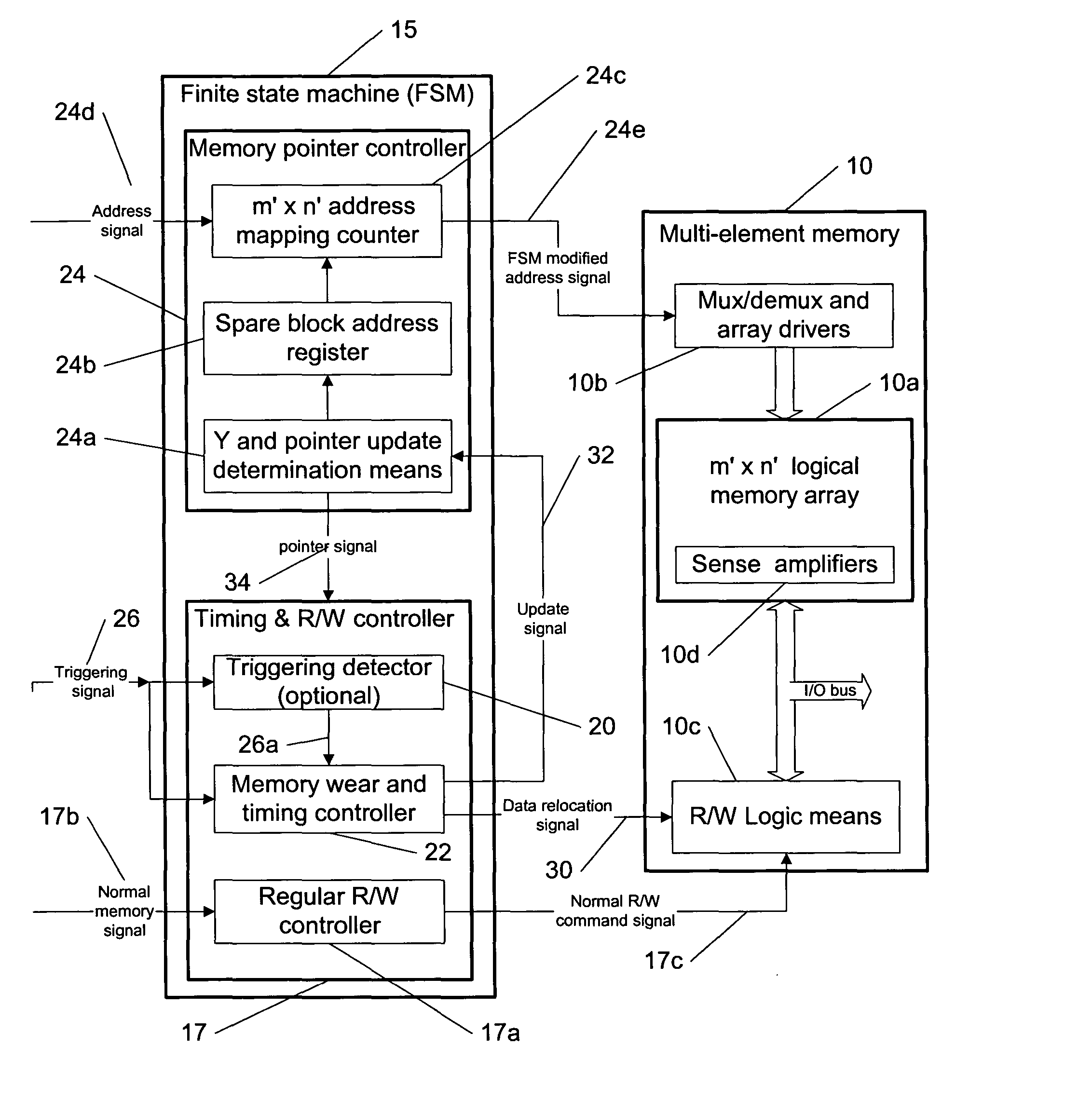

Memory wear leveling

InactiveUS20050055495A1Reduce wearMemory architecture accessing/allocationMemory loss protectionMemory typeComputer architecture

This invention describes a memory wear leveling for reducing wearing of hotspots (deteriorated memory blocks used more frequently) in all memory types by rotating the memory blocks on the physical level with the help of at least one spare memory block using predetermined criteria during both read and write operations. The invention can be implemented e.g. by using constant memory pointers at a logical level and dynamic memory pointers on the physical level. The rotation can be implemented as a combination of software and hardware functionalities or using hardware or software alone.

Owner:NOKIA SOLUTIONS & NETWORKS OY

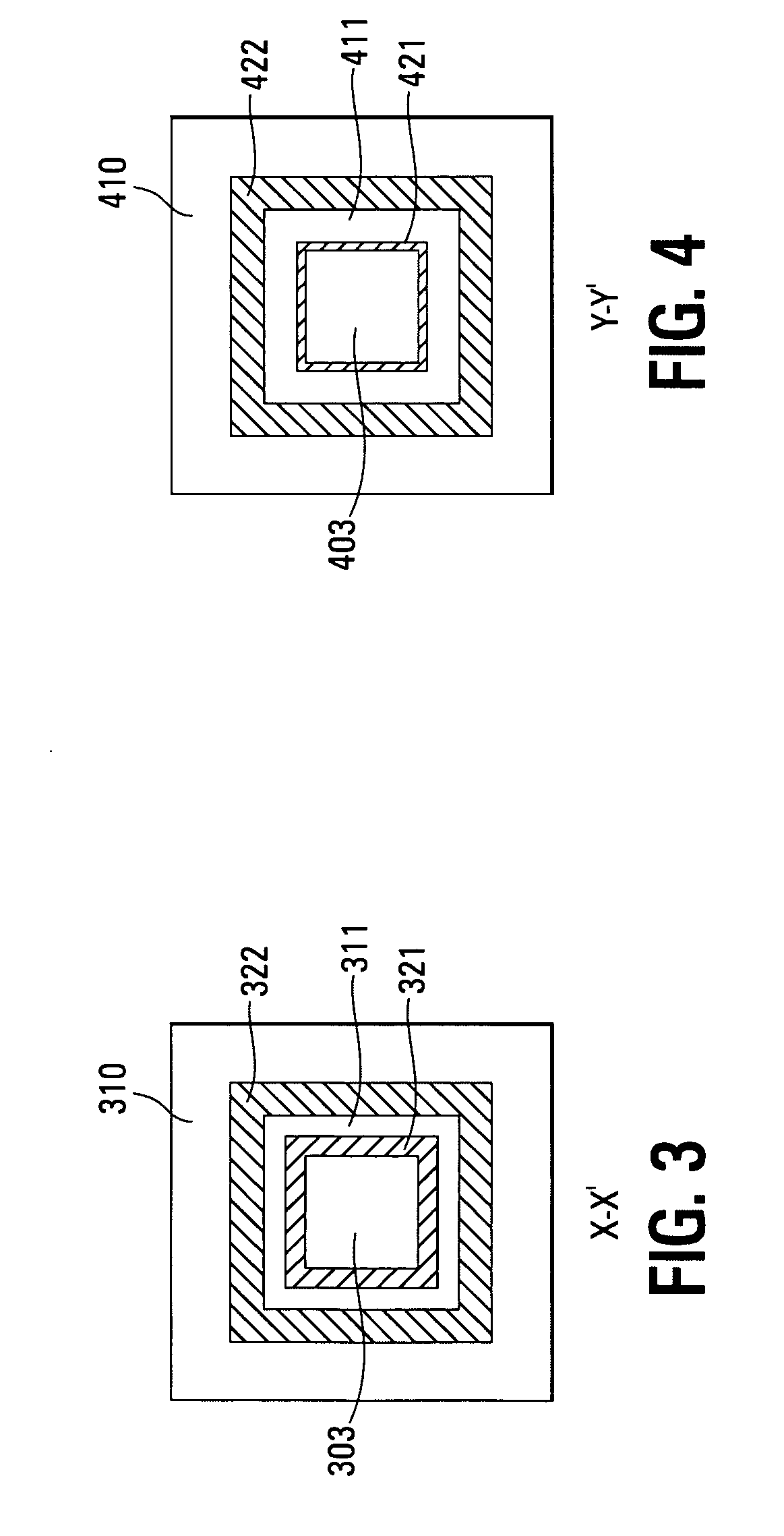

Integrated surround gate multifunctional memory device

Vertical surround gate memory cells are formed around pillars on a substrate. Each memory cell is comprised of a gate stack formed around each pillar and a gate formed around each gate stack. The substrate can have multiple integrated memory types by varying the effective oxide thickness of the tunnel insulator of each gate stack and / or customizing the materials used in the gate stack for each type of desired memory on the substrate.

Owner:MICRON TECH INC

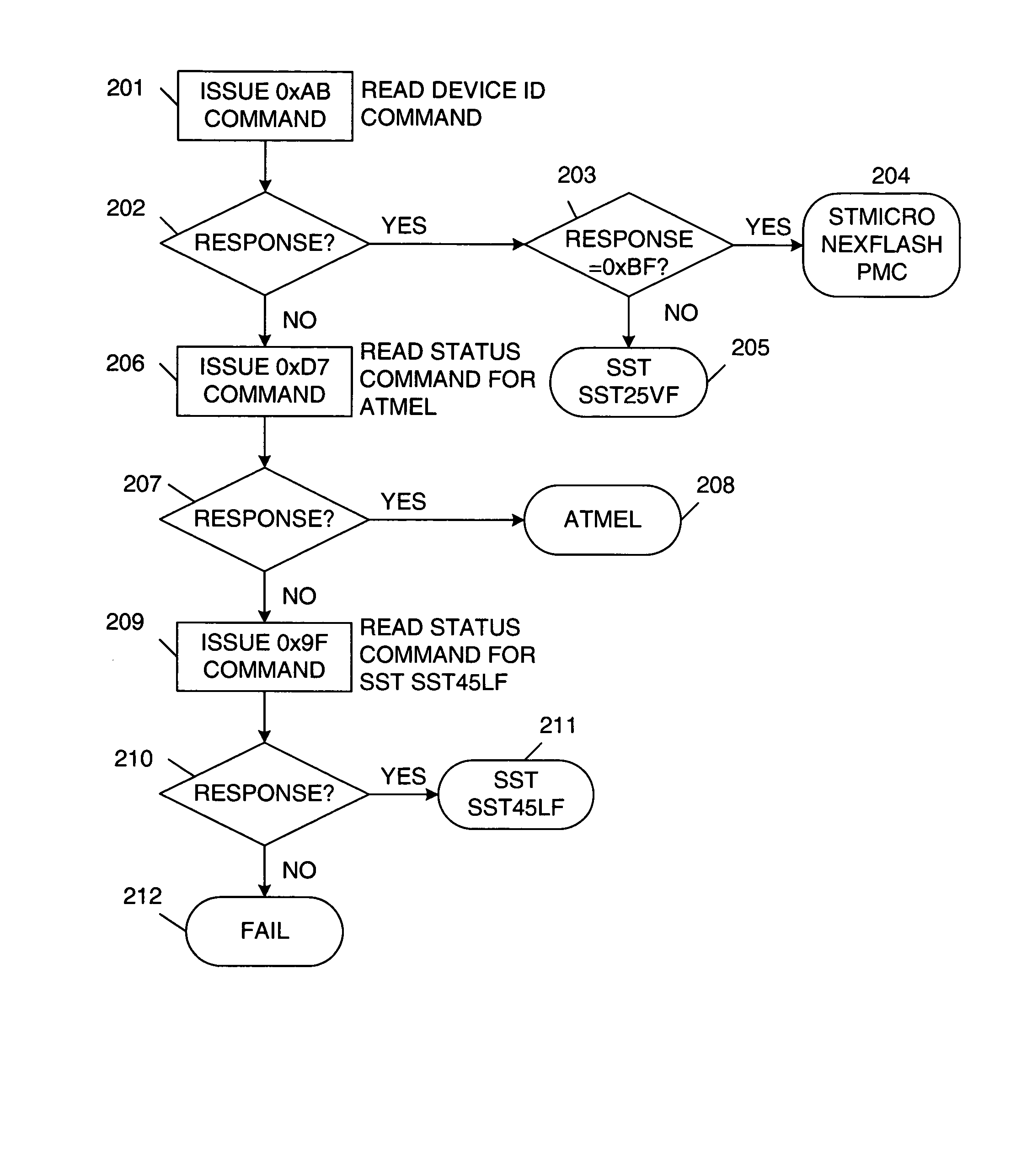

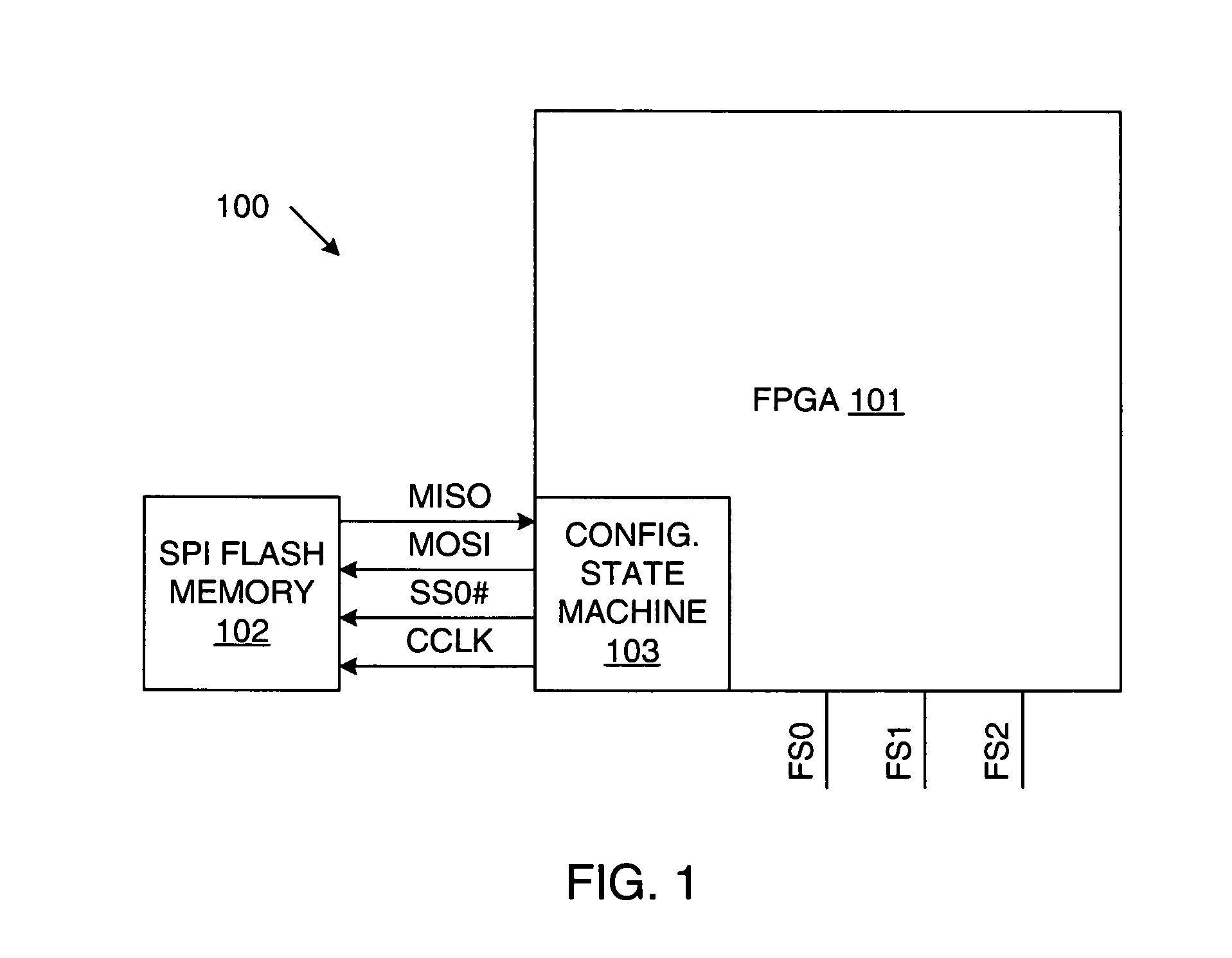

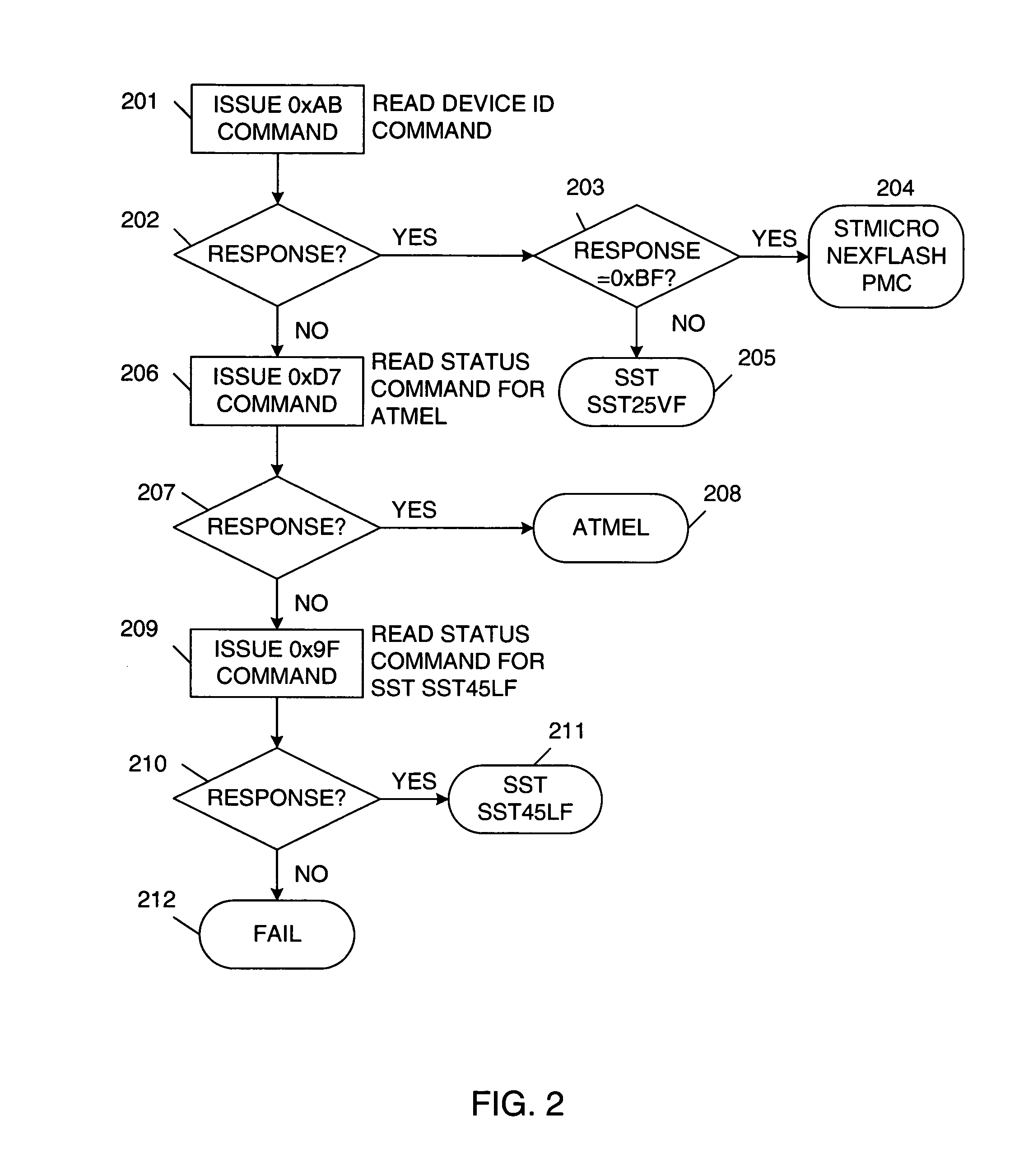

Flexible scheme for configuring programmable semiconductor devices using or loading programs from SPI-based serial flash memories that support multiple SPI flash vendors and device families

ActiveUS7281082B1Reduce configuration costsEasy to processRead-only memoriesLogic circuits using elementary logic circuit componentsMemory typeControl signal

A method and structure for configuring a programmable logic device (PLD) from a serial peripheral interface (SPI) based serial memory. The type of the SPI memory is initially identified by the PLD. The PLD then selects the appropriate read command in response to the SPI memory type. The PLD then issues the read command to the SPI memory. In response, the SPI memory continuously provides a set of configuration data to the PLD. The PLD is configured in response to the configuration data. The PLD can identify the SPI memory type in response to control signals on pins of the PLD. Alternately, the PLD can identify the SPI memory type by performing a search. The search can include issuing a plurality of known read commands to the SPI memory, and then determining which read command causes the SPI memory to respond.

Owner:XILINX INC

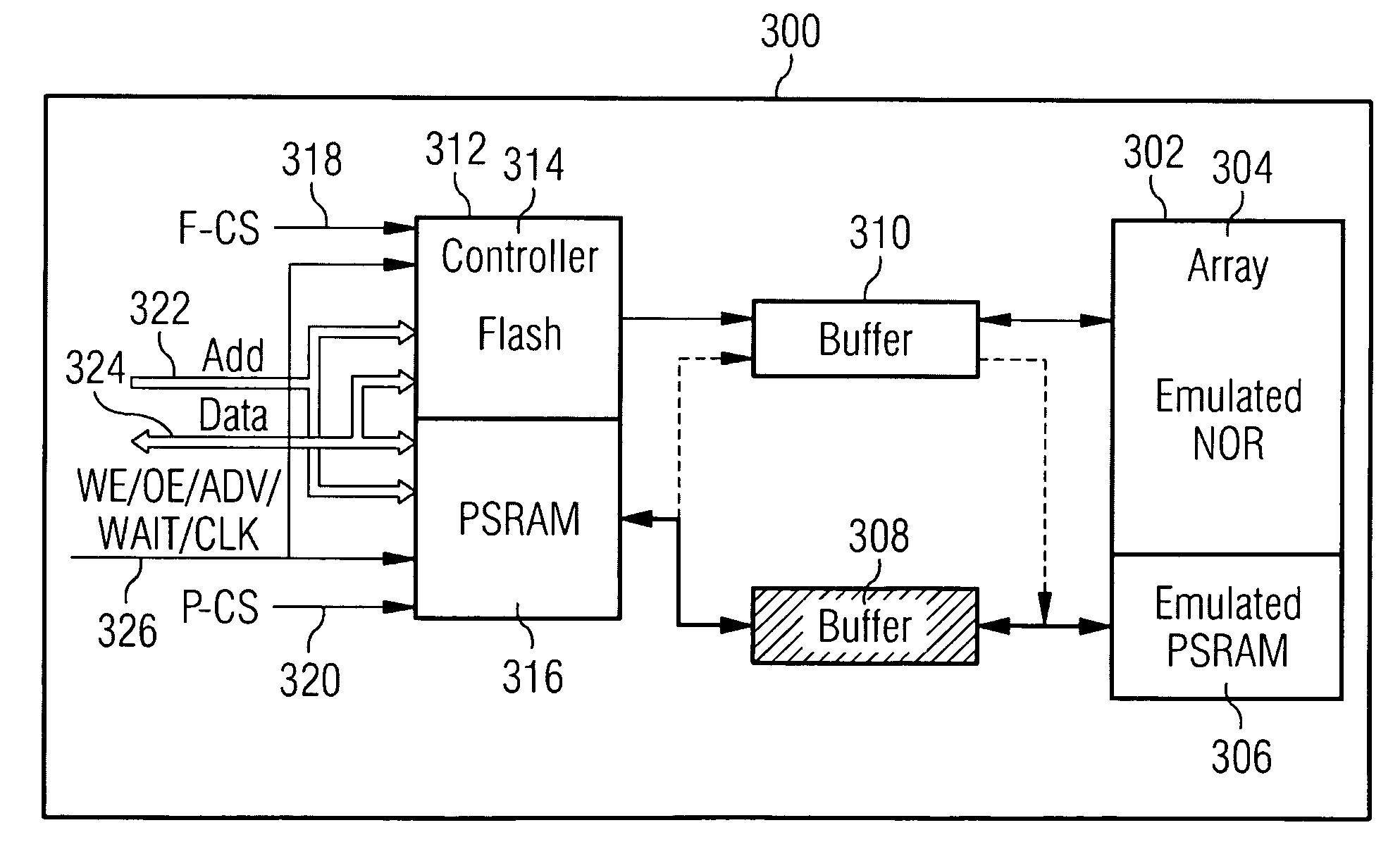

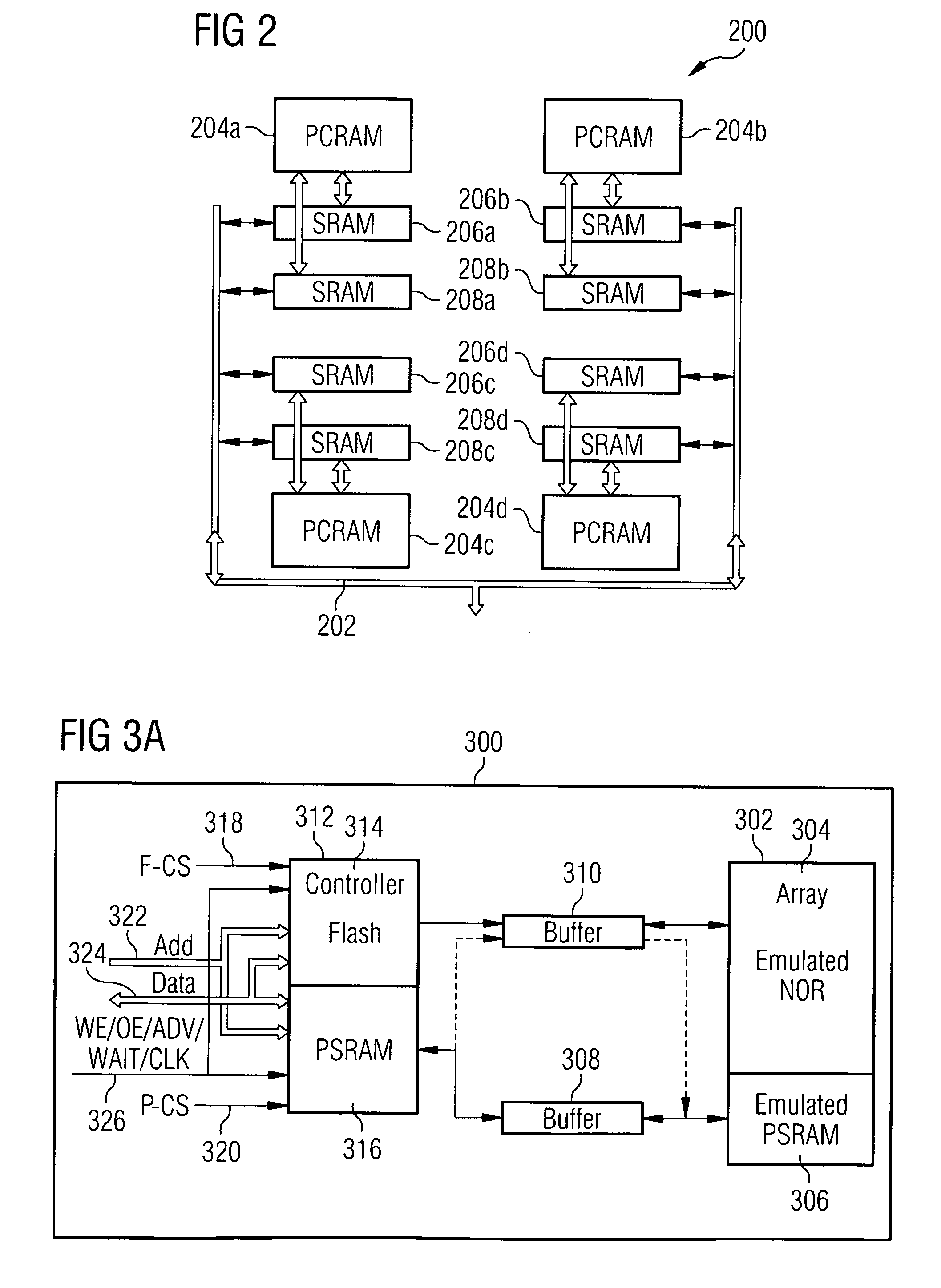

Emulated Combination Memory Device

InactiveUS20080306723A1Memory adressing/allocation/relocationDigital storageMemory typeIntegrated circuit

An integrated circuit memory device and a method of providing access to multiple memory types within a single integrated circuit memory device are described. In various embodiments, the integrated circuit memory device includes a non-volatile memory array having a first emulated memory region and a second emulated memory region, and a controller having an interface. The memory device is configured to emulate a first emulated memory type and a second emulated memory type. The memory device is further configured to store data in the first emulated memory region when the memory device emulates the first emulated memory type, and in the second emulated memory region when the memory device emulates the second emulated memory type.

Owner:QIMONDA

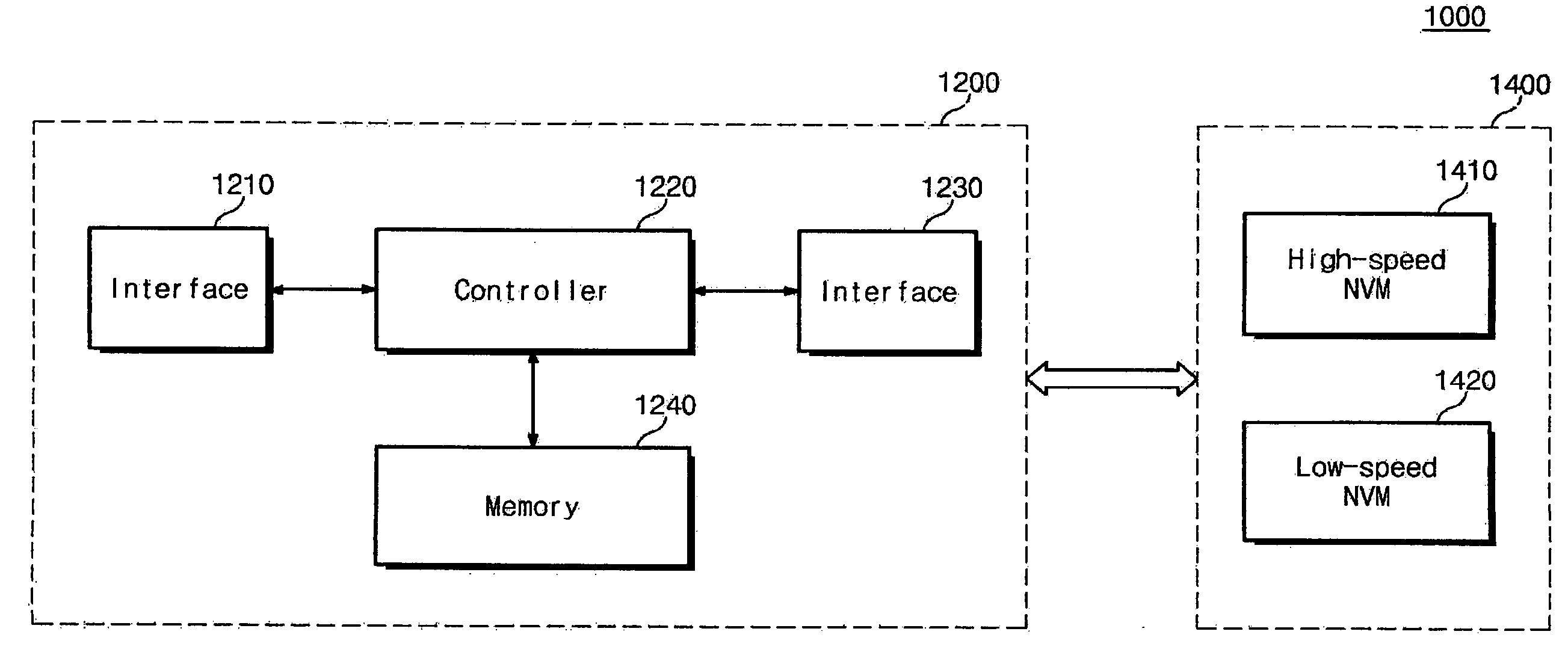

Method and data storage device for processing commands

ActiveUS20100153631A1Memory architecture accessing/allocationMemory adressing/allocation/relocationMemory typeData store

A data storage device for processing a command includes a host interface and a controller. The host interface stores program information sent within the command from a host. The controller decodes the program information that indicates a memory type to be accessed for the command. In addition, the controller determines whether the specified memory type can be accessed according to the command. The controller performs the command by accessing the memory type when the memory type specified by the program information is available for access.

Owner:SAMSUNG ELECTRONICS CO LTD

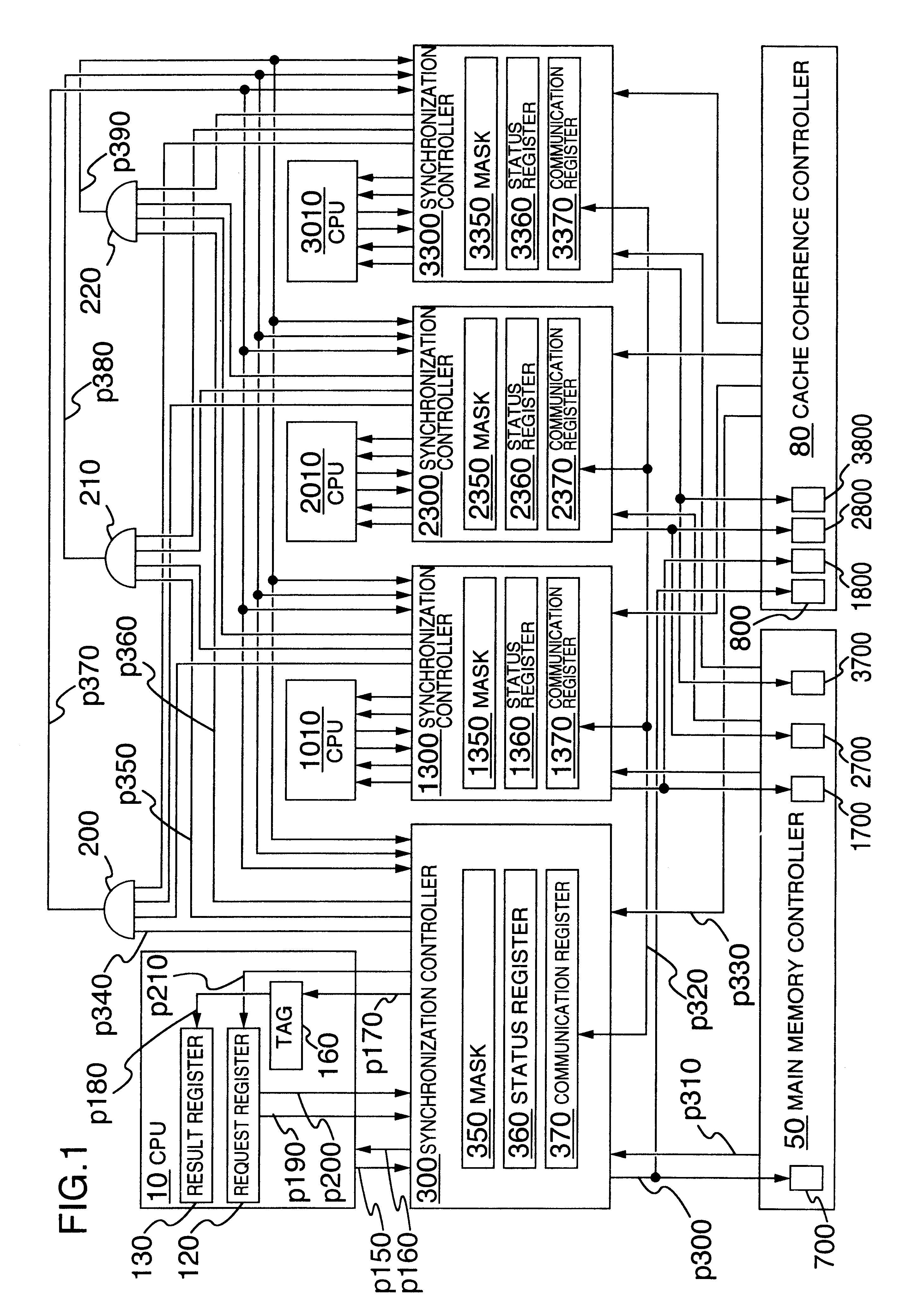

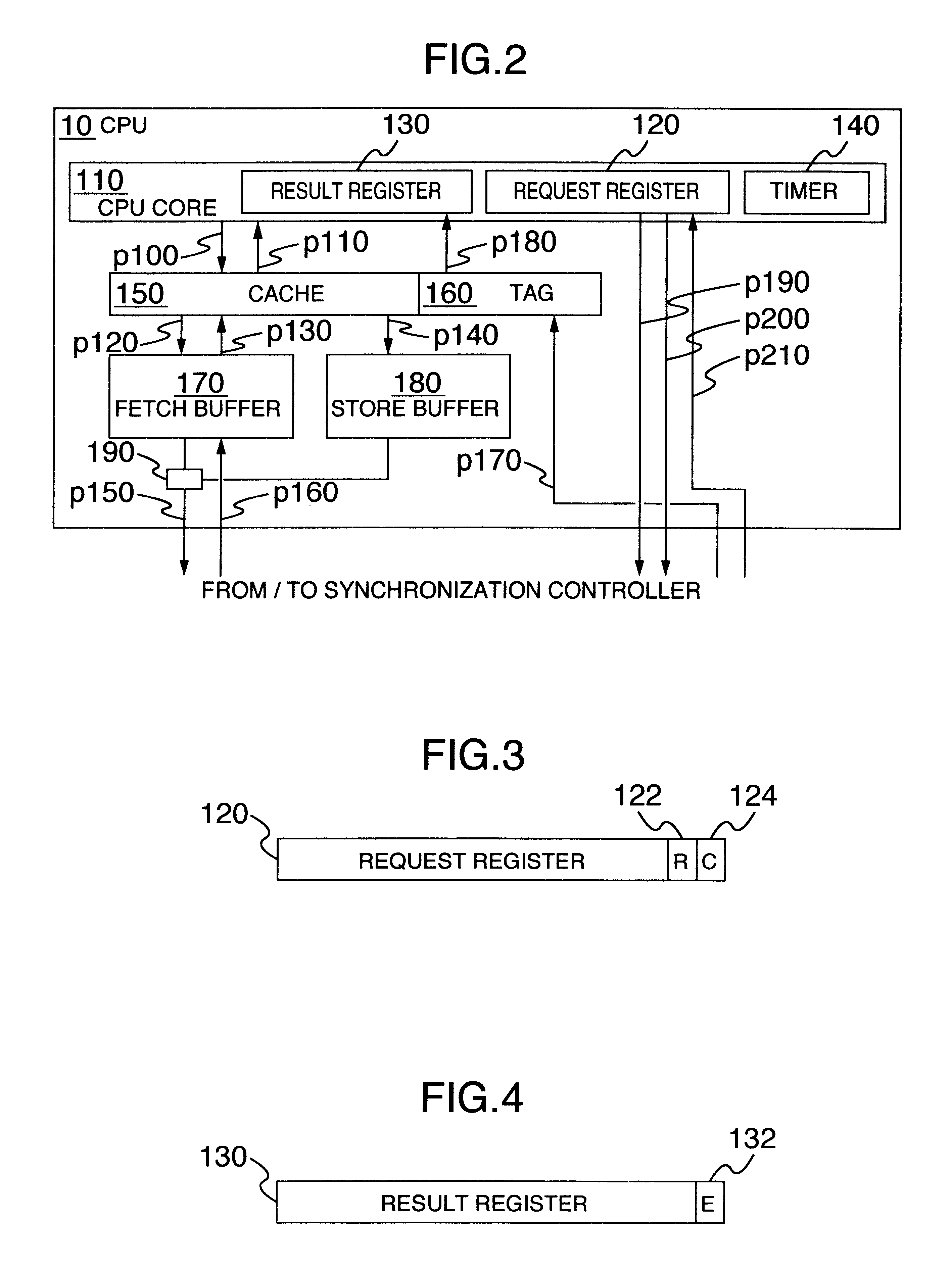

Multiprocessor synchronization and coherency control system

InactiveUS6466988B1Program synchronisationMemory adressing/allocation/relocationMemory typeConnection type

A shared main memory type multiprocessor is arranged to have a switch connection type. The multiprocessor prepares an instruction for outputting a synchronization transaction. When each CPU executes this instruction, after all the transactions of the preceding instructions are output, the synchronization transaction is output to the main memory and the coherence controller. By the synchronization transaction, the main memory serializes the memory accesses and the coherence controller guarantees the completion of the cache coherence control. This makes it possible to serialize the memory accesses and guarantee the completion of the cache coherence control at the same time.

Owner:HITACHI LTD

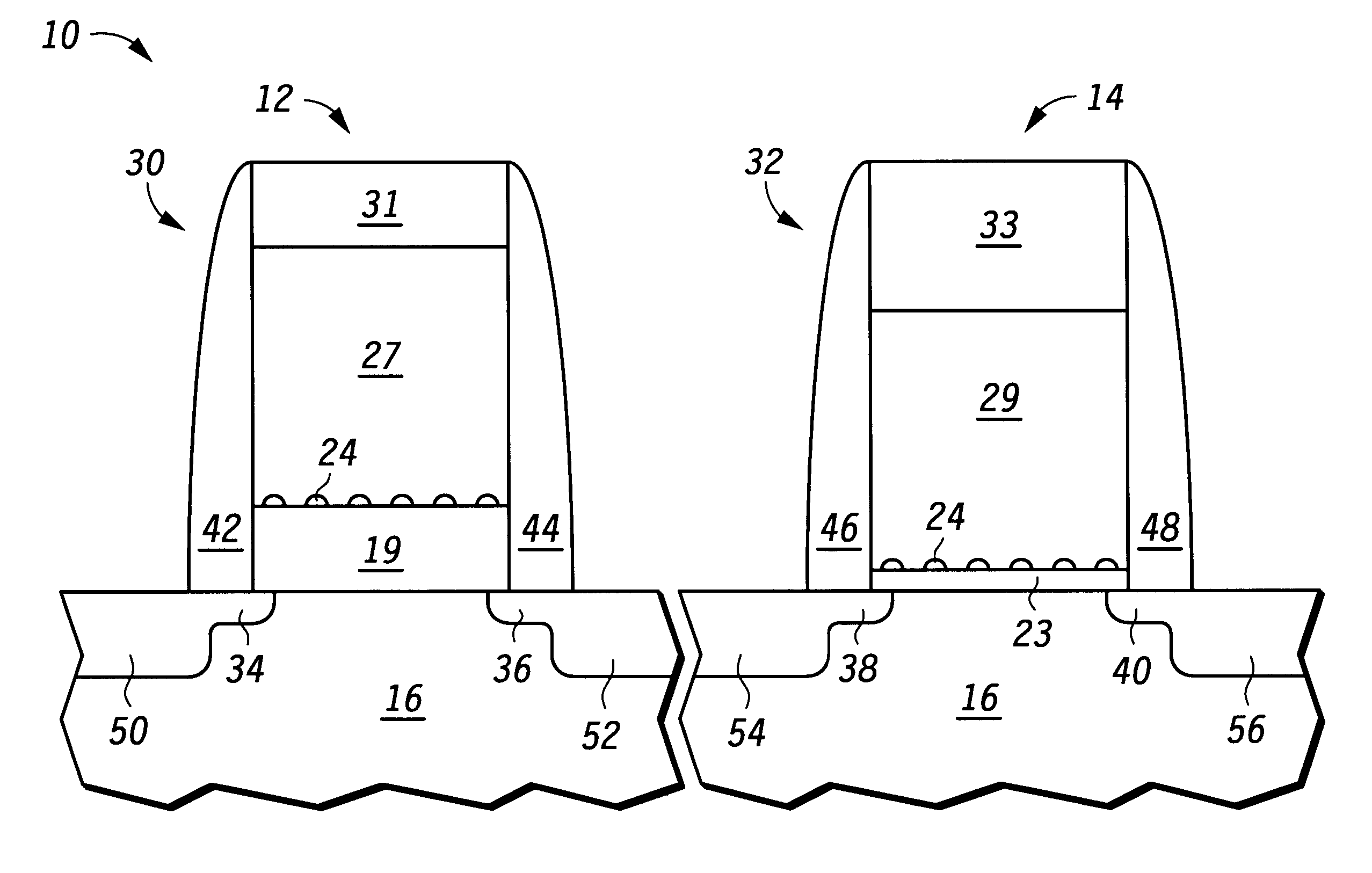

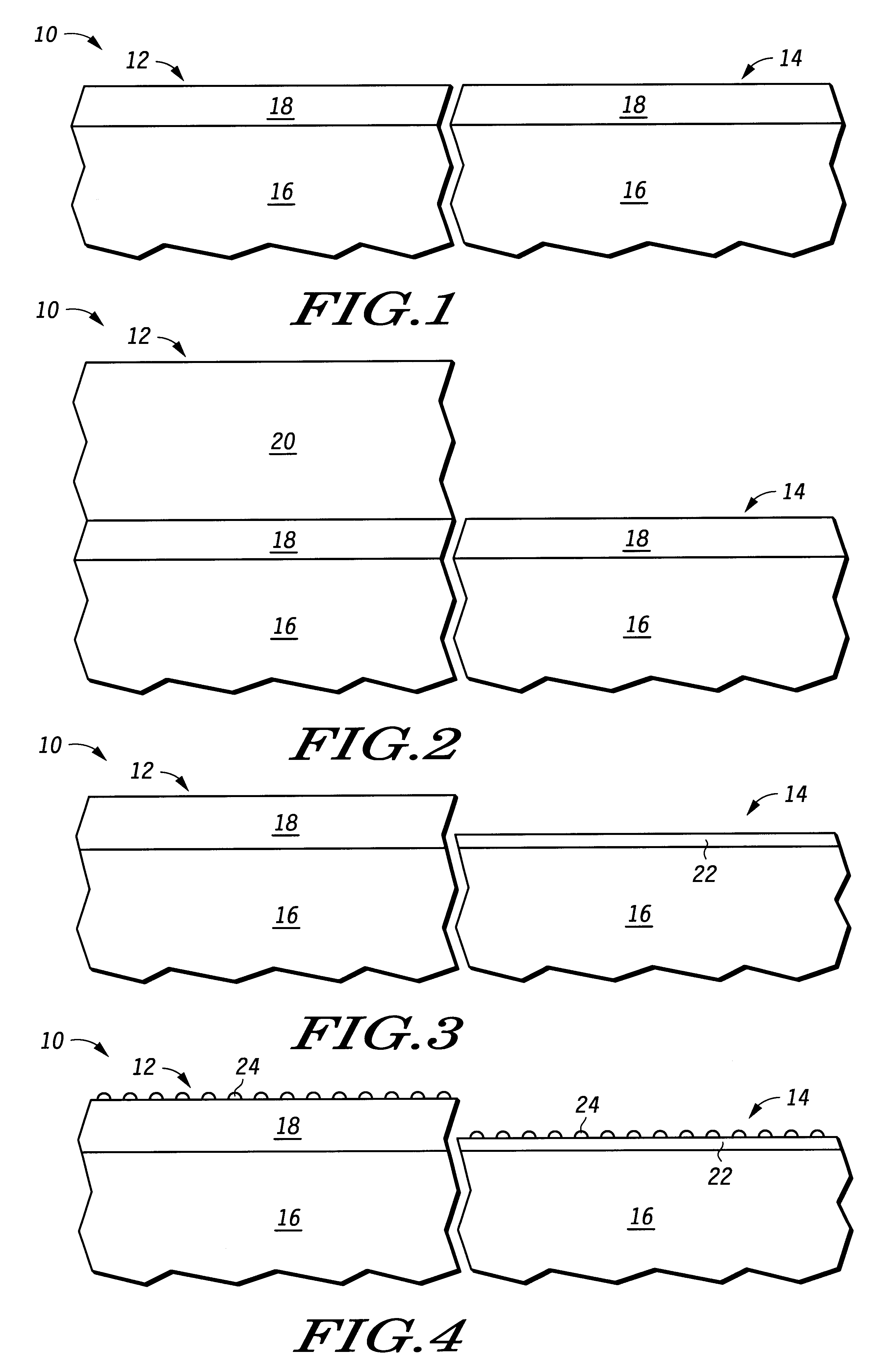

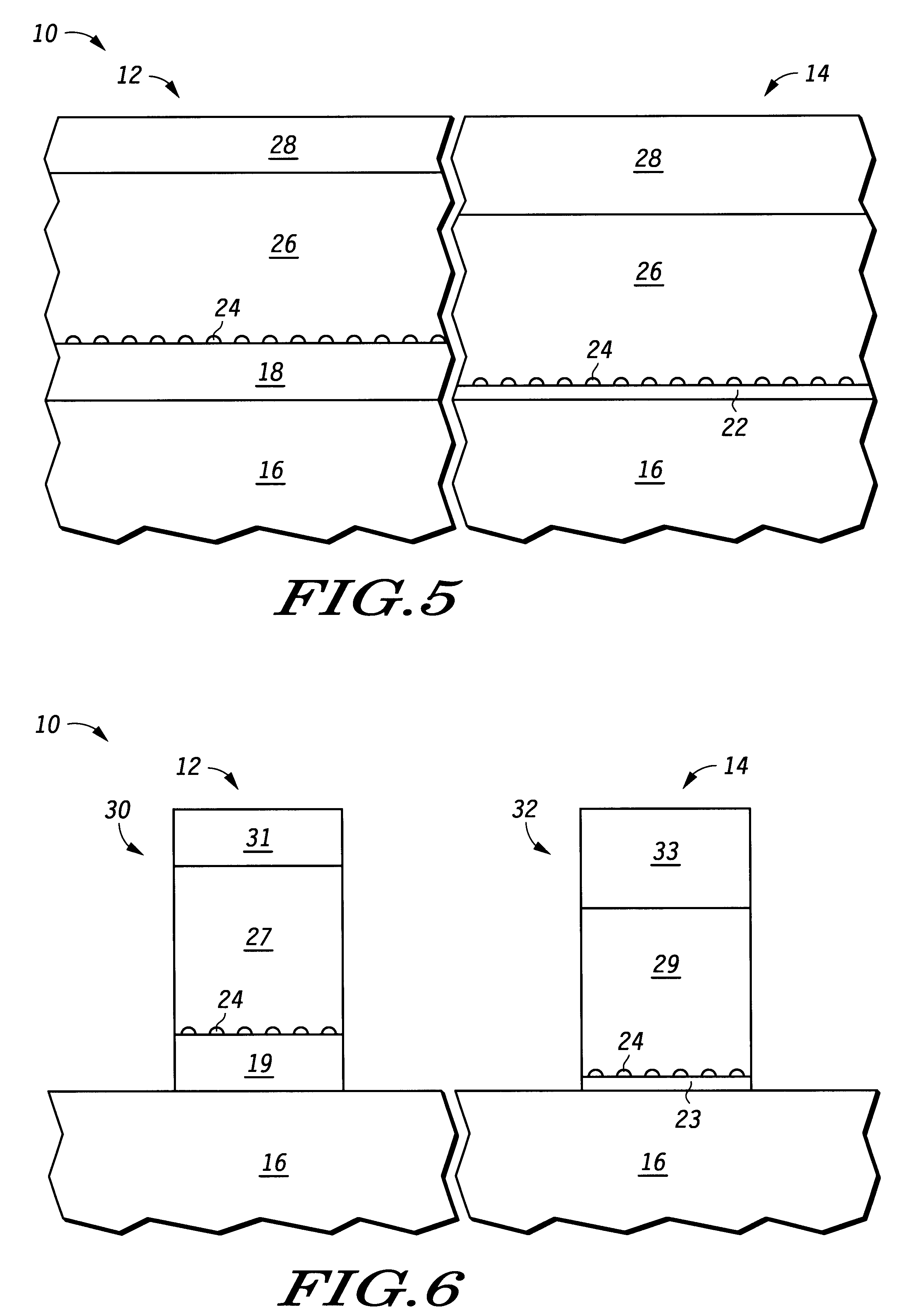

Integration of two memory types on the same integrated circuit

Both a non-volatile memory (NVM) and a dynamic nanocrystal memory (DNM) are integrated on a semiconductor substrate. Control gates and control dielectrics with embedded nanocrystals or discrete storage elements are formed over differing thicknesses of tunnel dielectrics to form the two memories. Source and drain regions are formed within the semiconductor substrate adjacent to the tunnel dielectrics. Various methods can be used to form a thin tunnel oxide and a thick tunnel oxide by adding minimum processing steps.

Owner:NXP USA INC

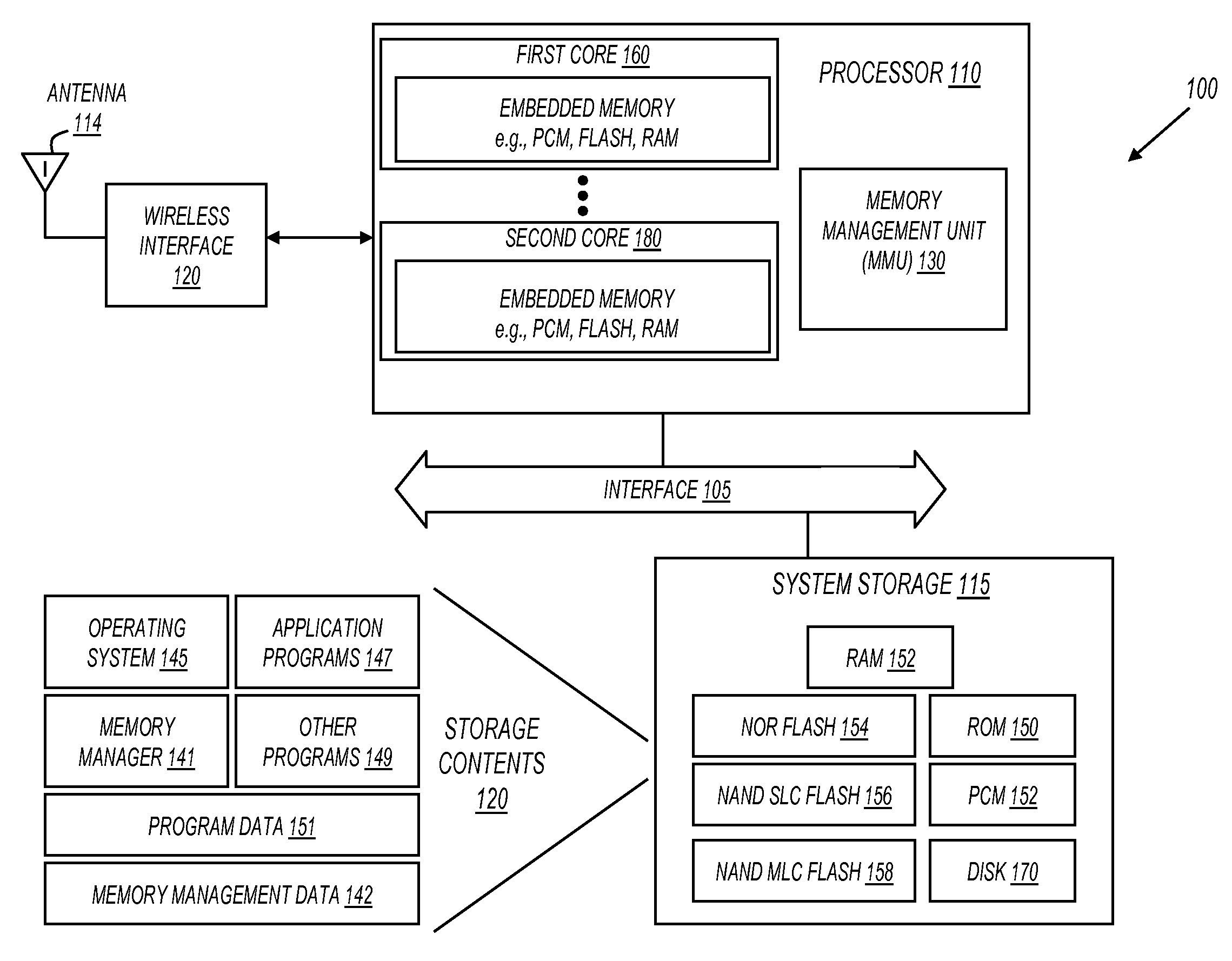

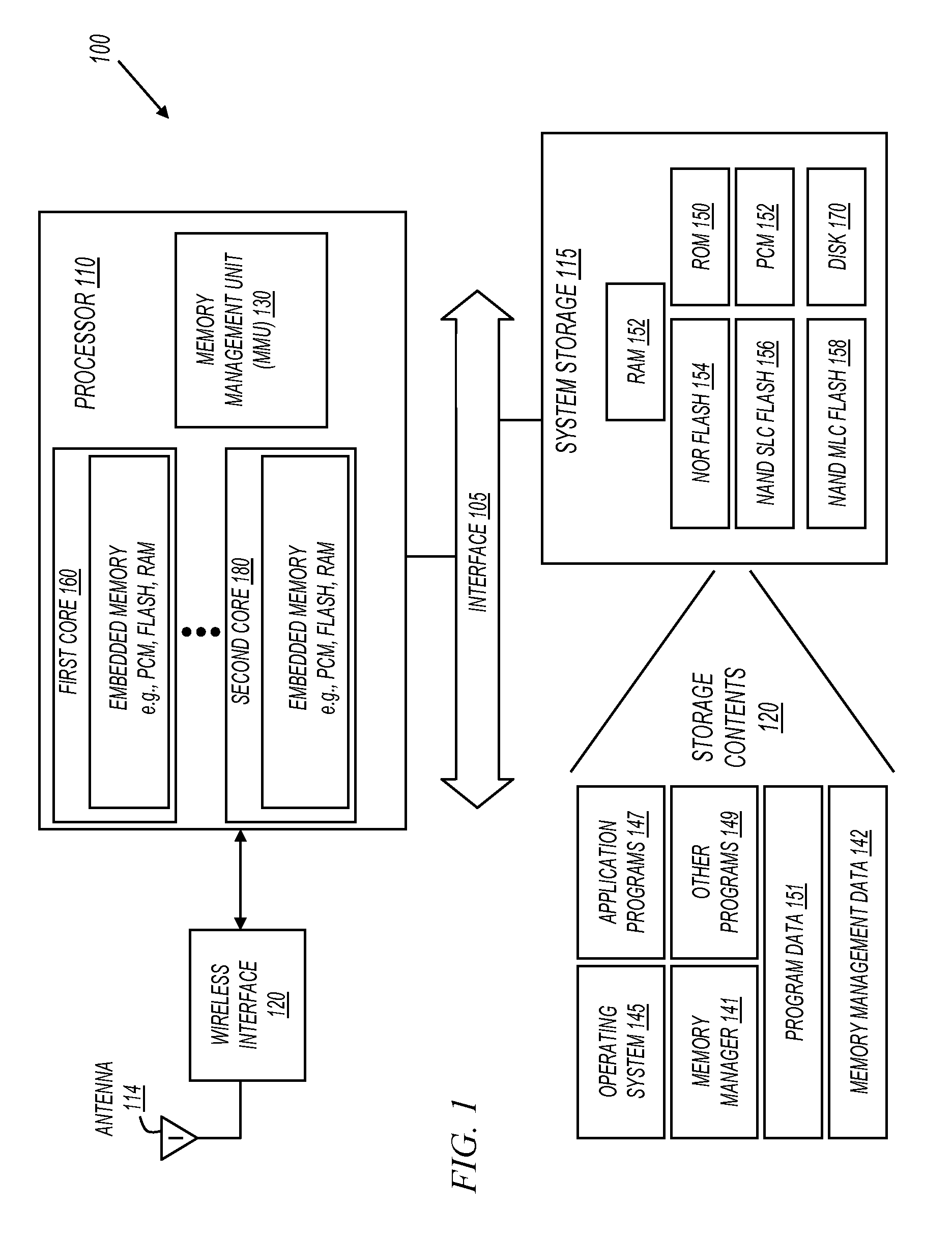

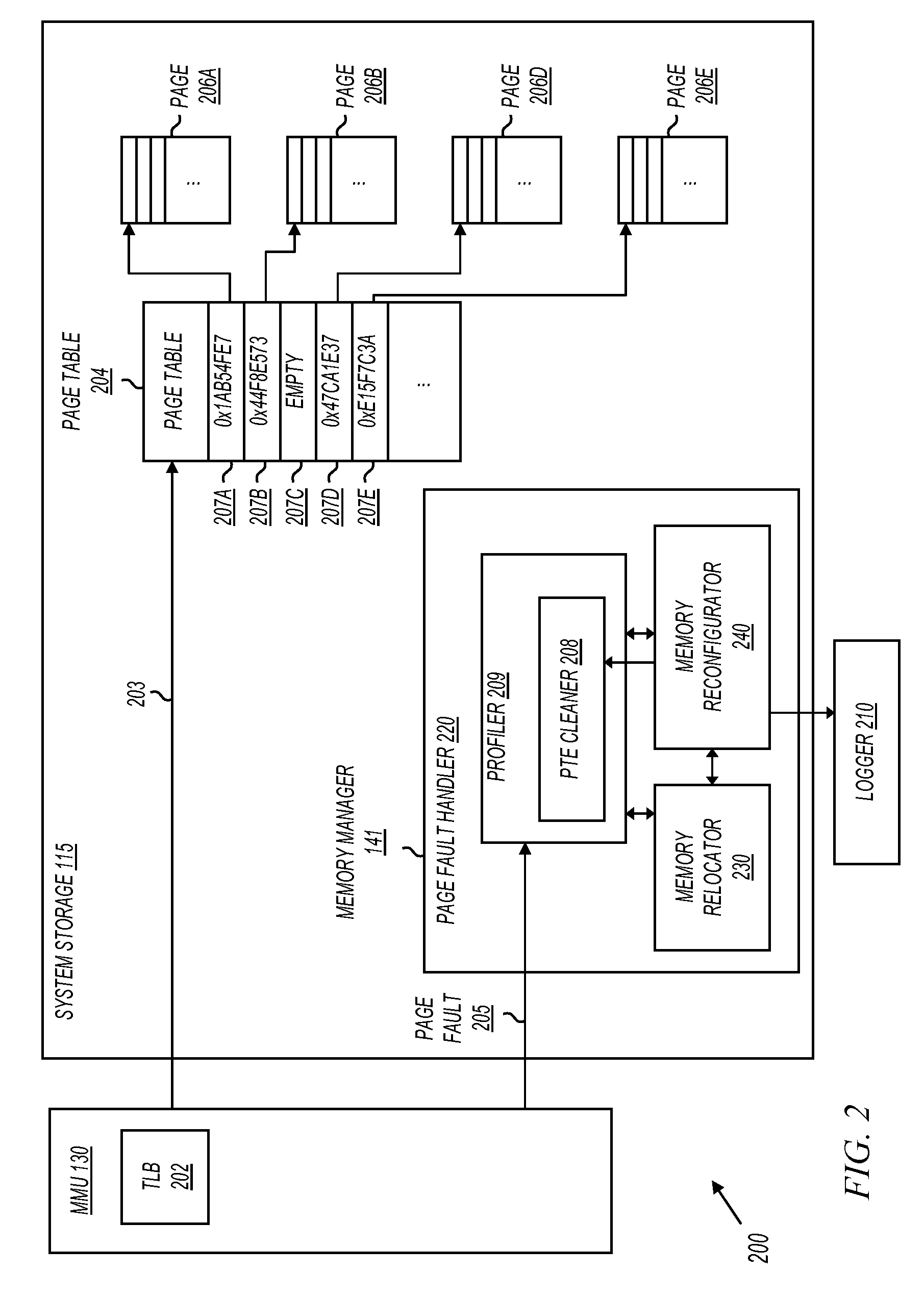

Method and Apparatus for Efficient Memory Placement

InactiveUS20100169602A1Memory architecture accessing/allocationMemory systemsMemory profilingMemory type

A memory profiling system profiles memory objects in various memory devices and identifies memory objects as candidates to be moved to a more efficient memory device. Memory object profiles include historical read frequency, write frequency, and execution frequency. The memory object profile is compared to parameters describing read and write performance of memory types to determine candidate memory types for relocating memory objects. Memory objects with high execution frequency may be given preference when relocating to higher performance memory devices.

Owner:MICRON TECH INC

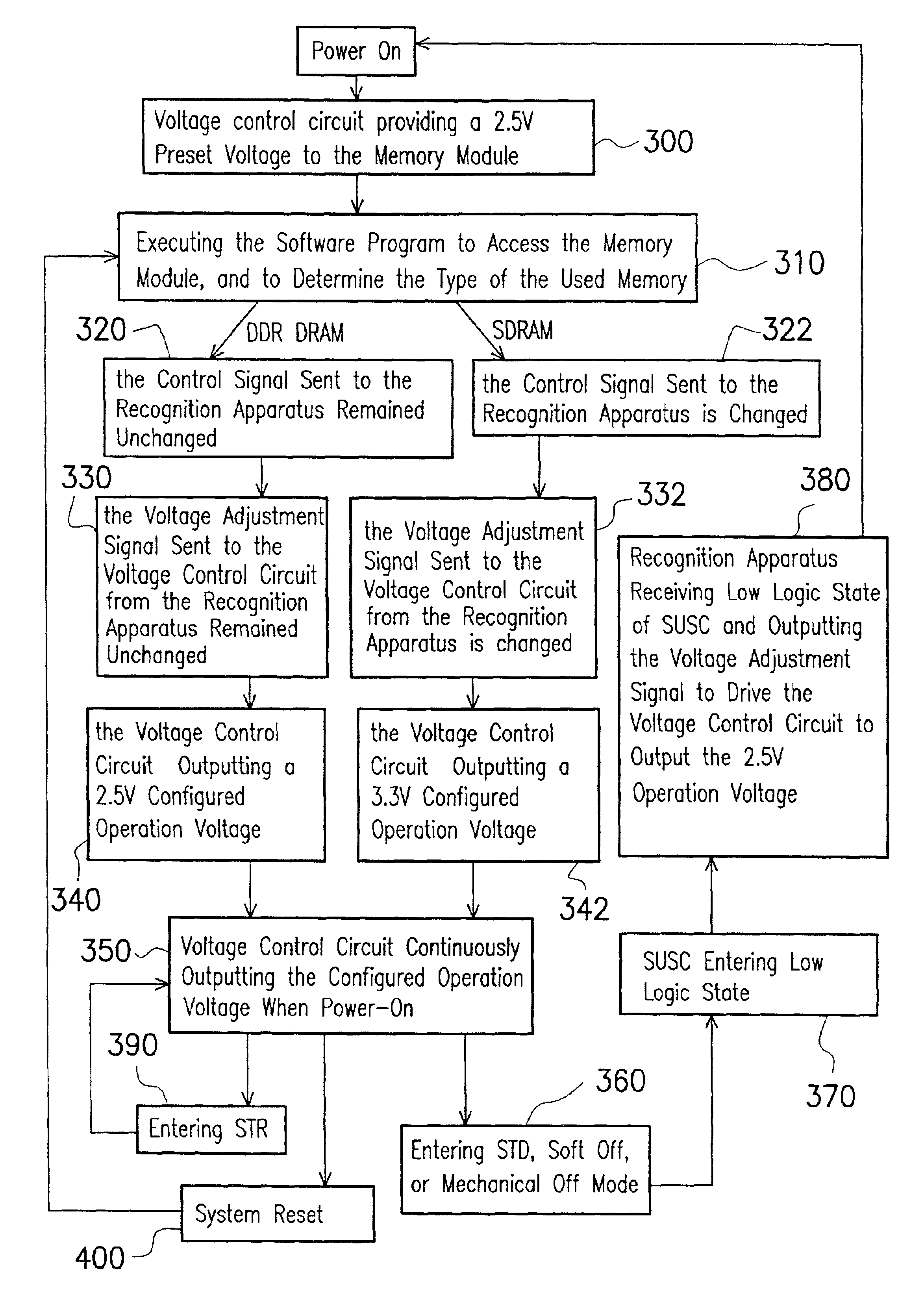

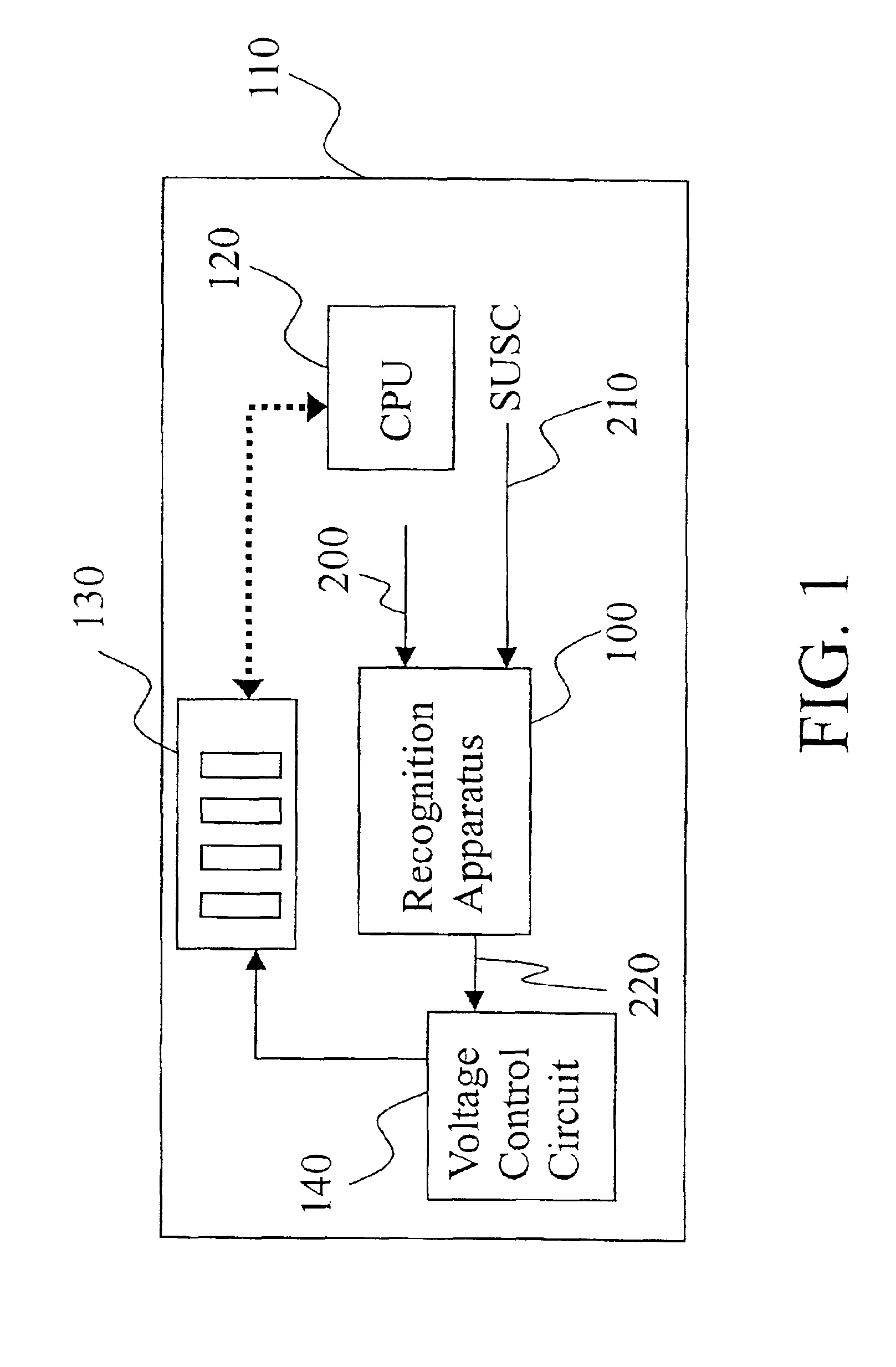

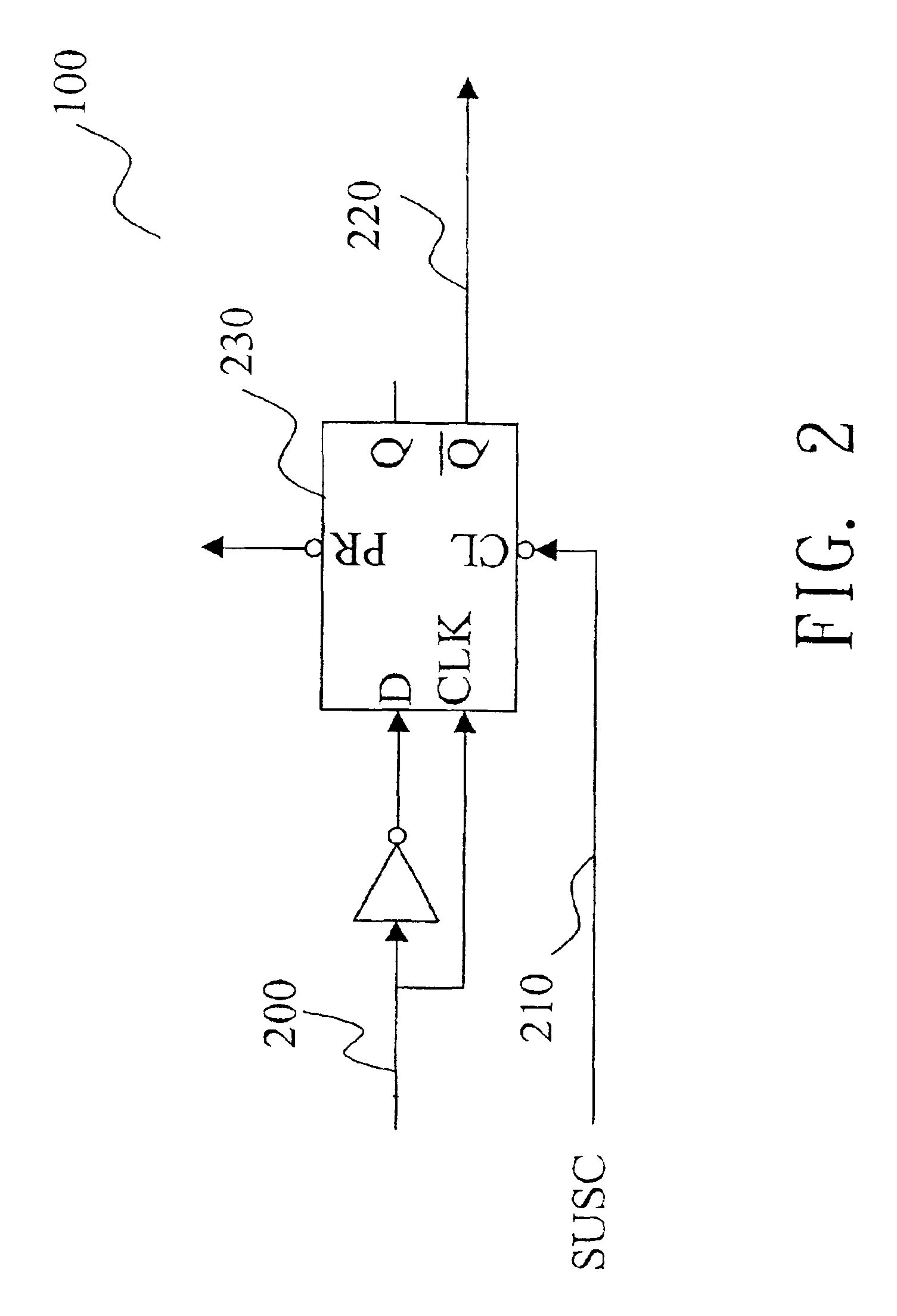

Method and motherboard for automatically determining memory type

InactiveUS6904506B2Automatically determineEnergy efficient ICTVolume/mass flow measurementPower savingMemory type

A method and a motherboard for automatically determining the memory type. By applying the characteristics of different operational voltages for various dynamic random access memory modules, a software program is used to drive a control signal and to automatically adjust the control voltage of the dynamic random access memory. An automatic detection of the types of the dynamic random access memory is obtained. The objectives of protecting the dynamic random access memory and to allow the dynamic random access memory to operate normally can thus be achieved. The invention not only provides the detection mechanism for accessing the dynamic random access memory during the initial activation of the computer system, but also determines the voltages required by the memory module for the computer system to enter various power saving modes.

Owner:VIA TECH INC

Memory Architecture with Policy Based Data Storage

InactiveUS20120066473A1Efficient storageEnergy efficient ICTMemory adressing/allocation/relocationMemory typeMemory controller

A computing system and methods for memory management are presented. A memory or an I / O controller receives a write request where the data two be written is associated with an address. Hint information may be associated with the address and may relate to memory characteristics such as an historical, O / S direction, data priority, job priority, job importance, job category, memory type, I / O sender ID, latency, power, write cost, or read cost components. The memory controller may interrogate the hint information to determine where (e.g., what memory type or class) to store the associated data. Data is therefore efficiently stored within the system. The hint information may also be used to track post-write information and may be interrogated to determine if a data migration should occur and to which new memory type or class the data should be moved.

Owner:IBM CORP

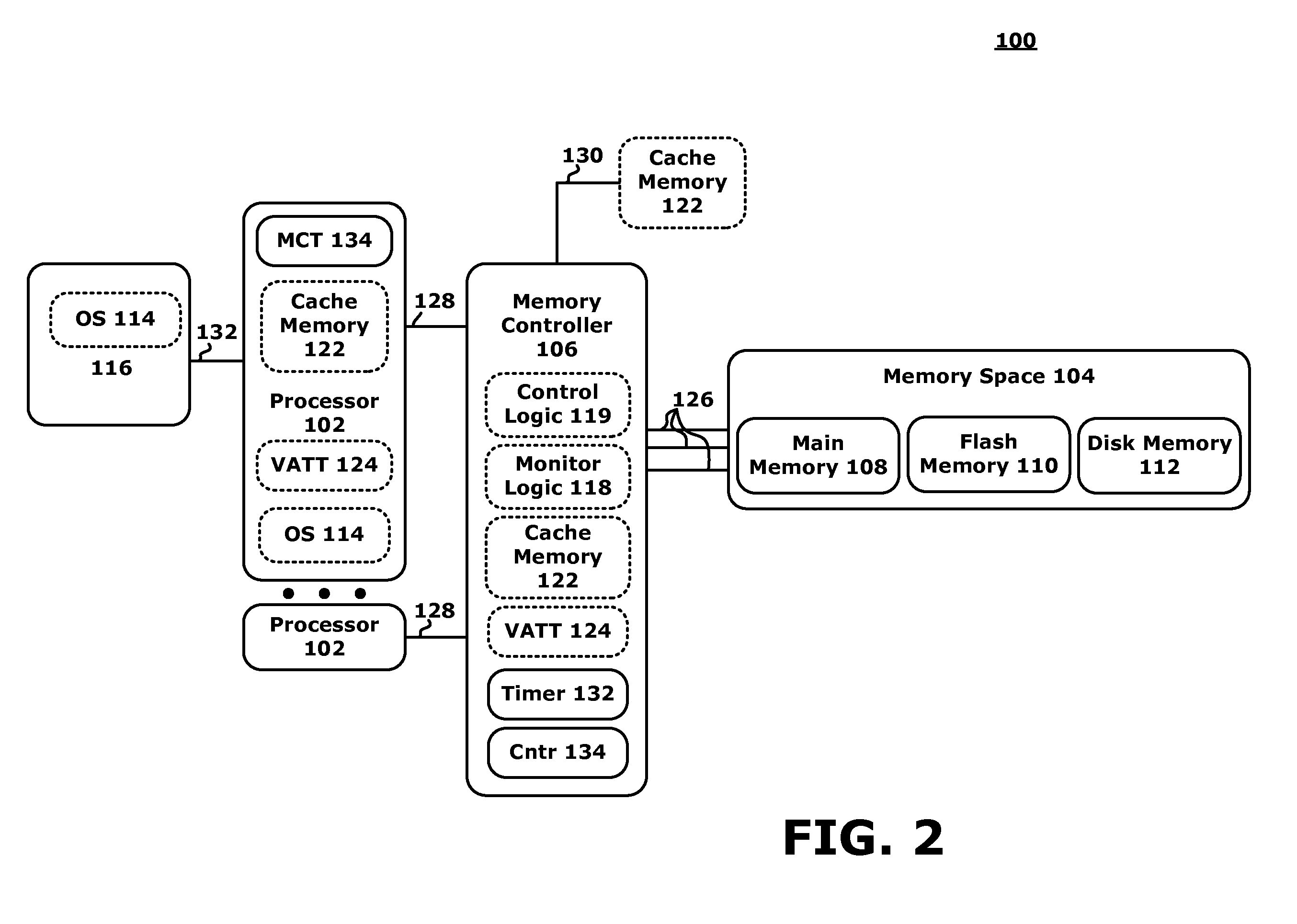

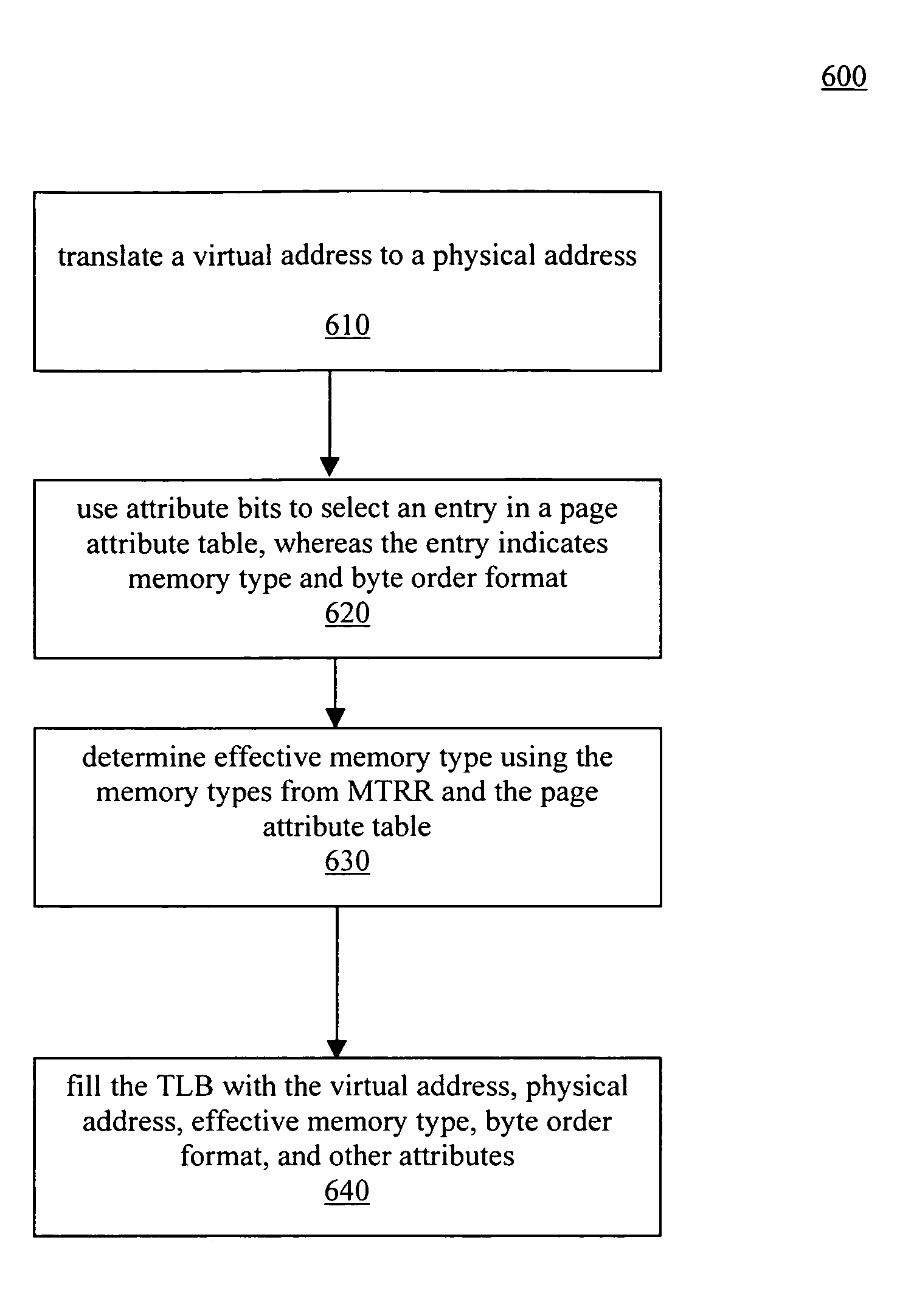

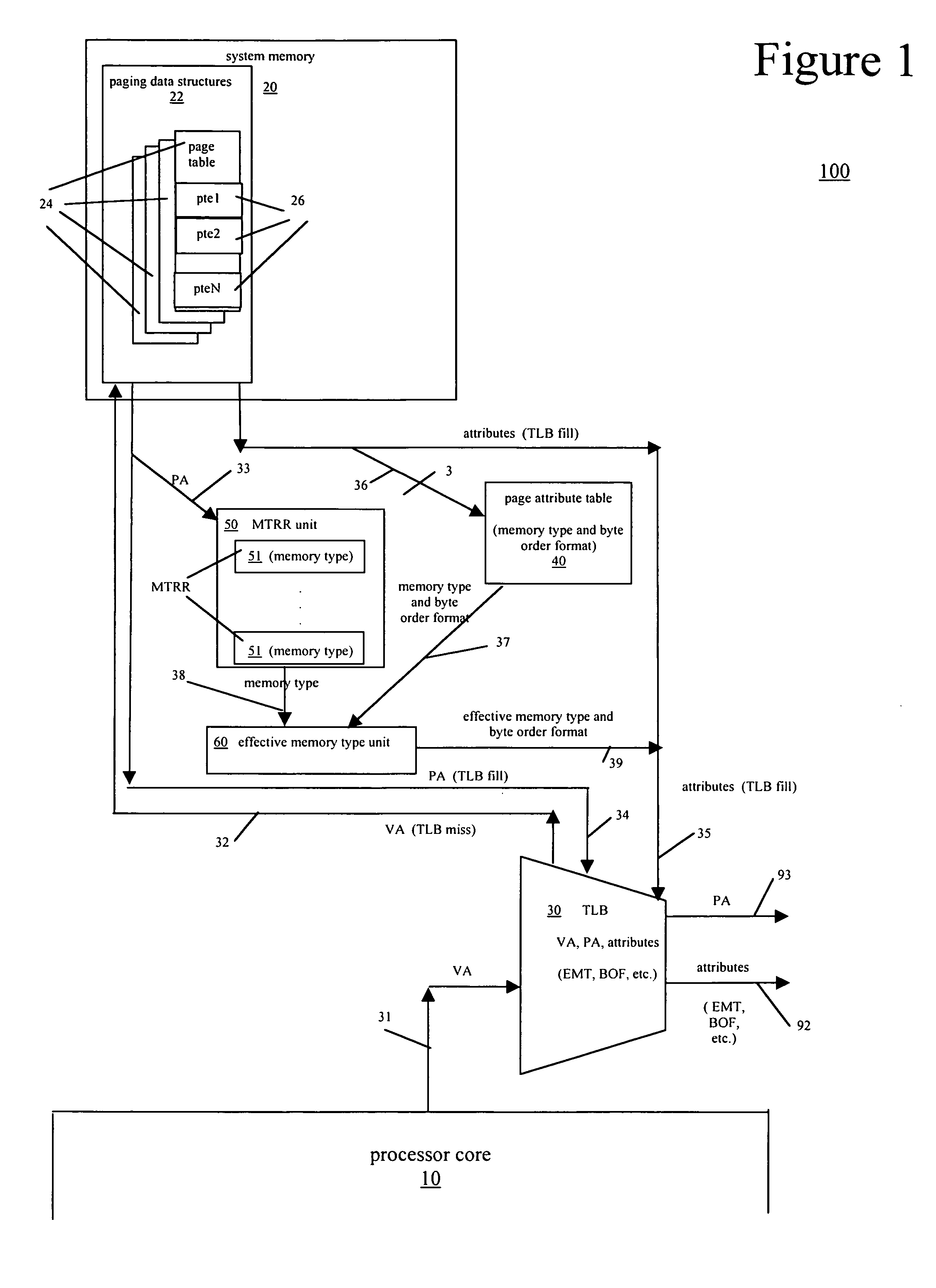

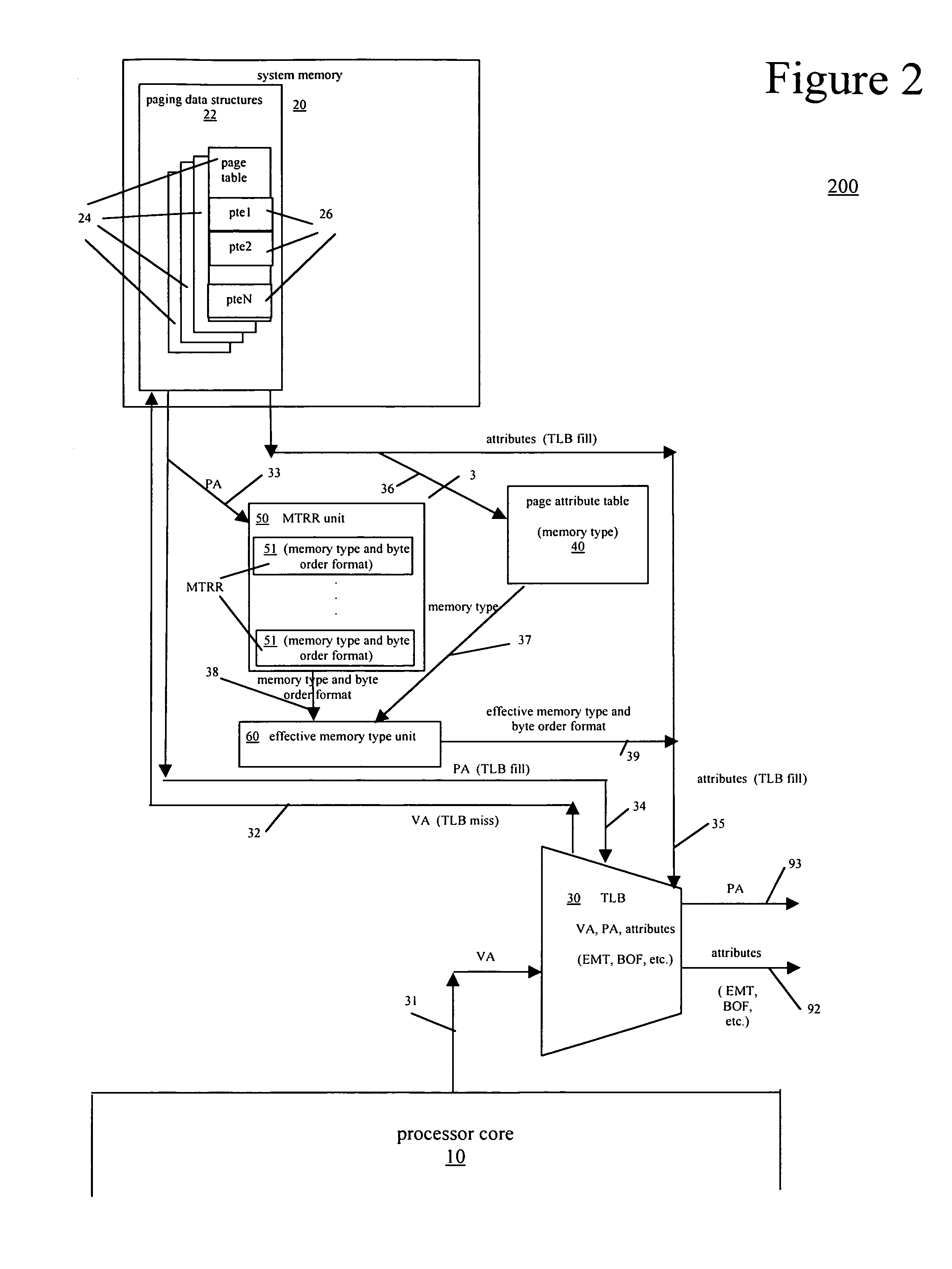

Use of MTRR and page attribute table to support multiple byte order formats in a computer system

Computer technology supports multiple byte order formats, separately or simultaneously. In one embodiment, a page attribute table (PAT), which is programmable, is utilized to indicate byte order format. The PAT has a plurality of entries. Each entry indicates a memory type and a byte order format for a physical address, wherein a plurality of attribute bits and a virtual address are associated with the physical address. A portion of the attribute bits are utilized to select one of the entries. In another embodiment, a memory type range register (MTRR), which is programmable, is utilized to indicate byte order format. The MTRR is configured to indicate a memory type and a byte order format for a range of physical addresses, wherein the memory type and range register (MTRR) receives a physical address and provides a corresponding memory type and a corresponding byte order format.

Owner:INTELLECTUAL VENTURES HOLDING 81 LLC

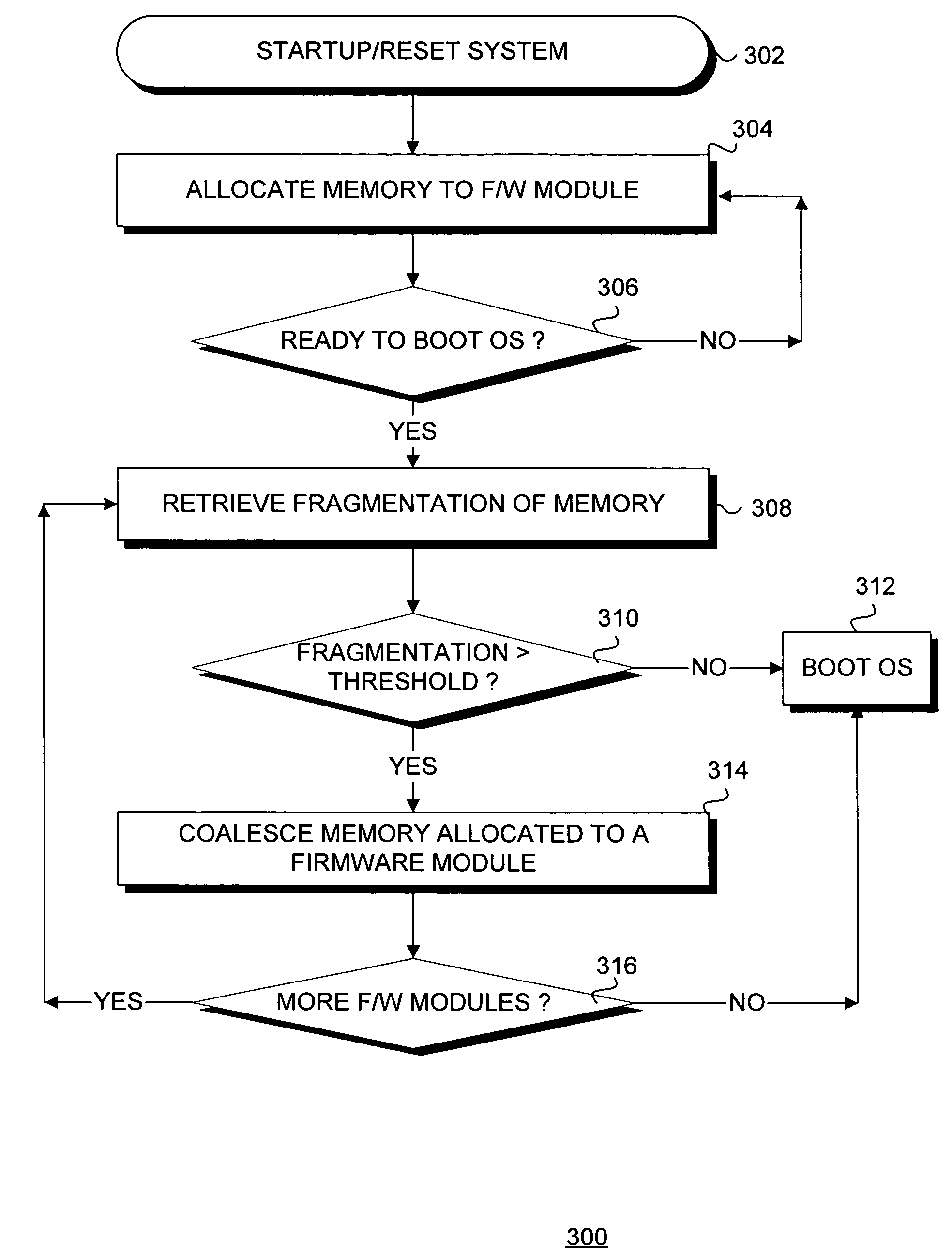

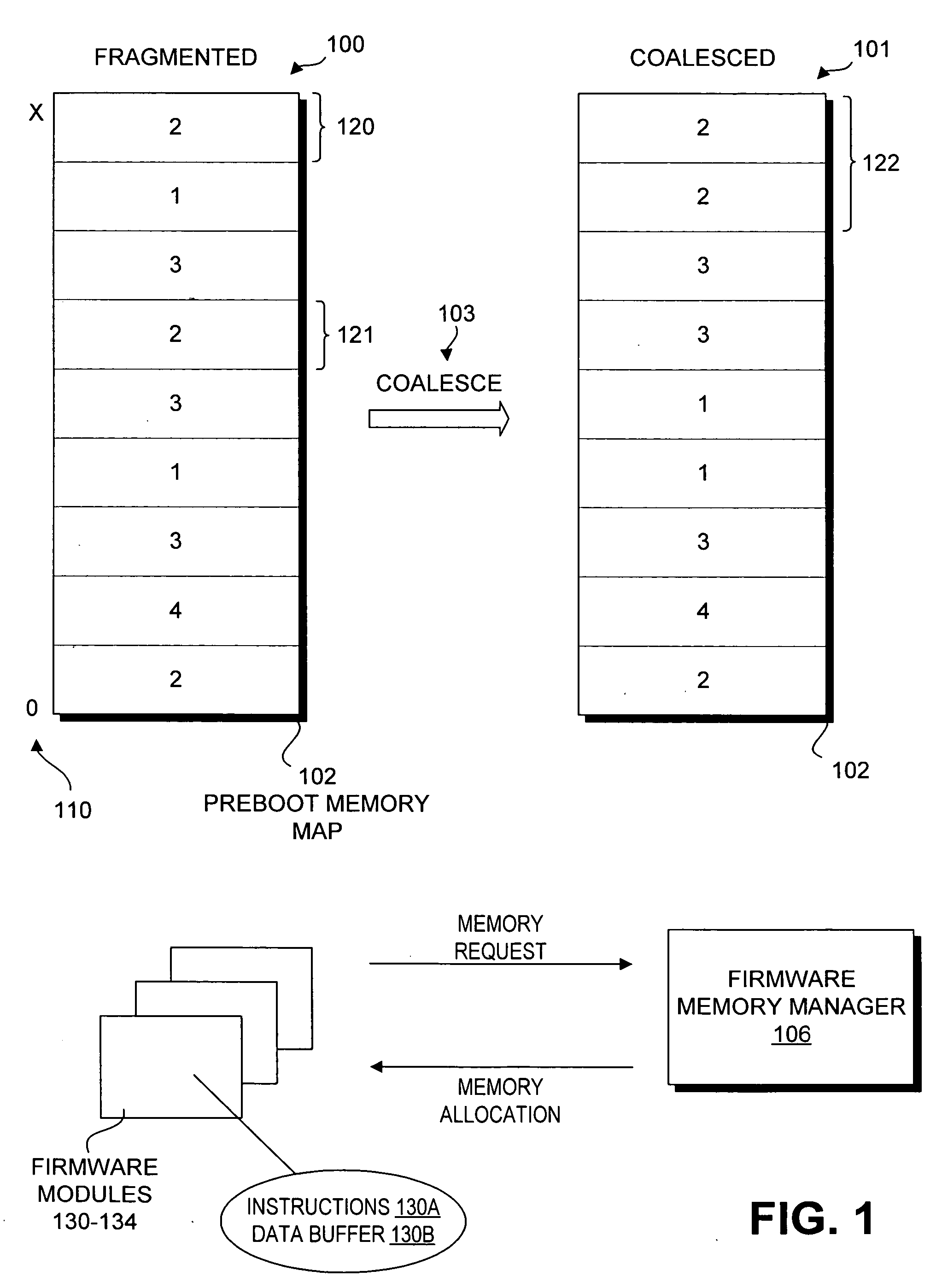

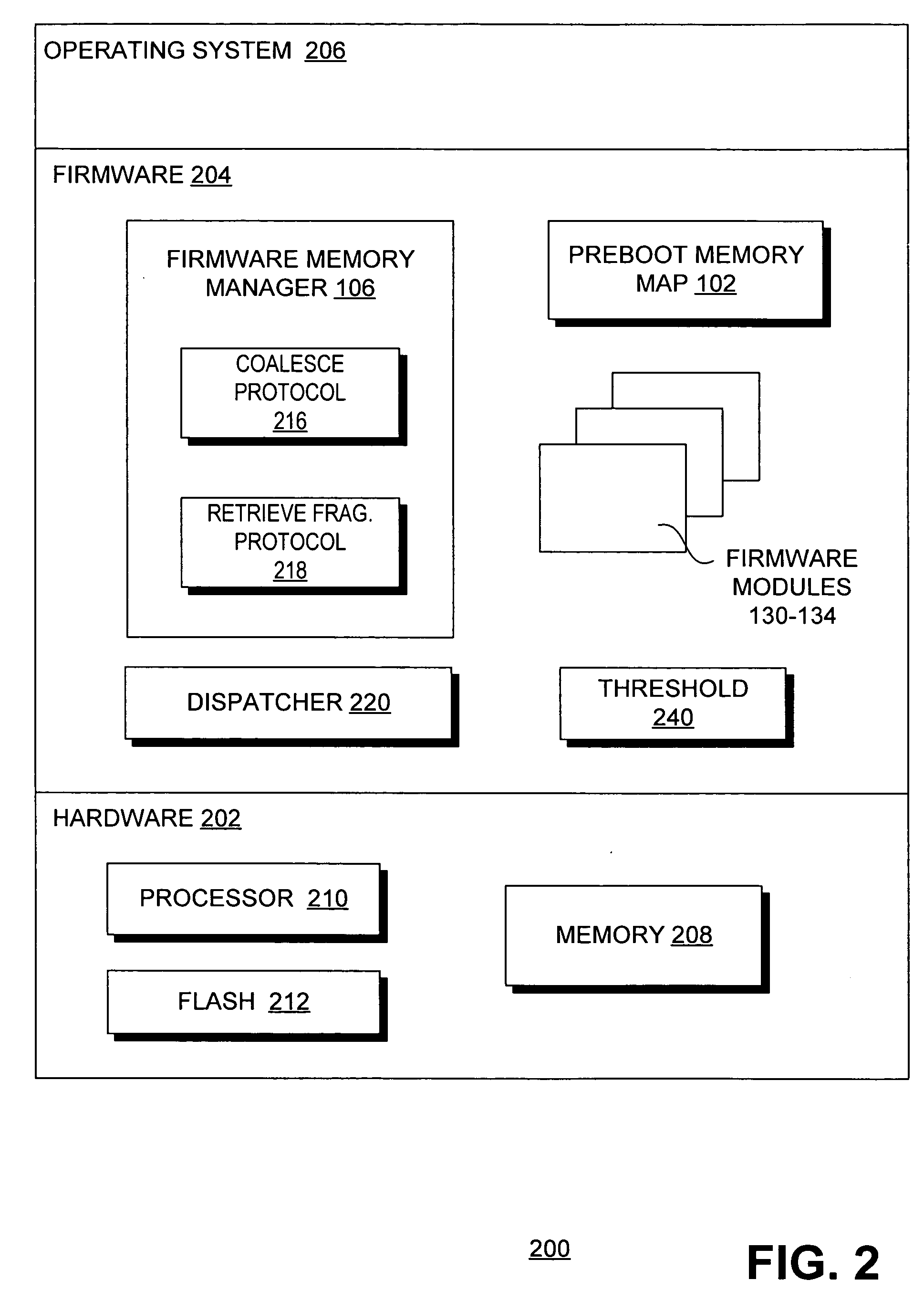

Reducing memory fragmentation

ActiveUS20060149913A1Memory architecture accessing/allocationProgram control using stored programsMemory typeOperational system

Reducing memory fragmentation. Memory is allocated during a preboot phase of a computer system, wherein the memory is allocated based on a plurality of memory types. Fragmentation of memory is determined, wherein a fragment includes a contiguous block of memory of the same type. At least a portion of memory allocated to a firmware module is coalesced based on the plurality of memory types if the fragmentation is greater than a threshold. An operating system is booted by the computer system.

Owner:INTEL CORP

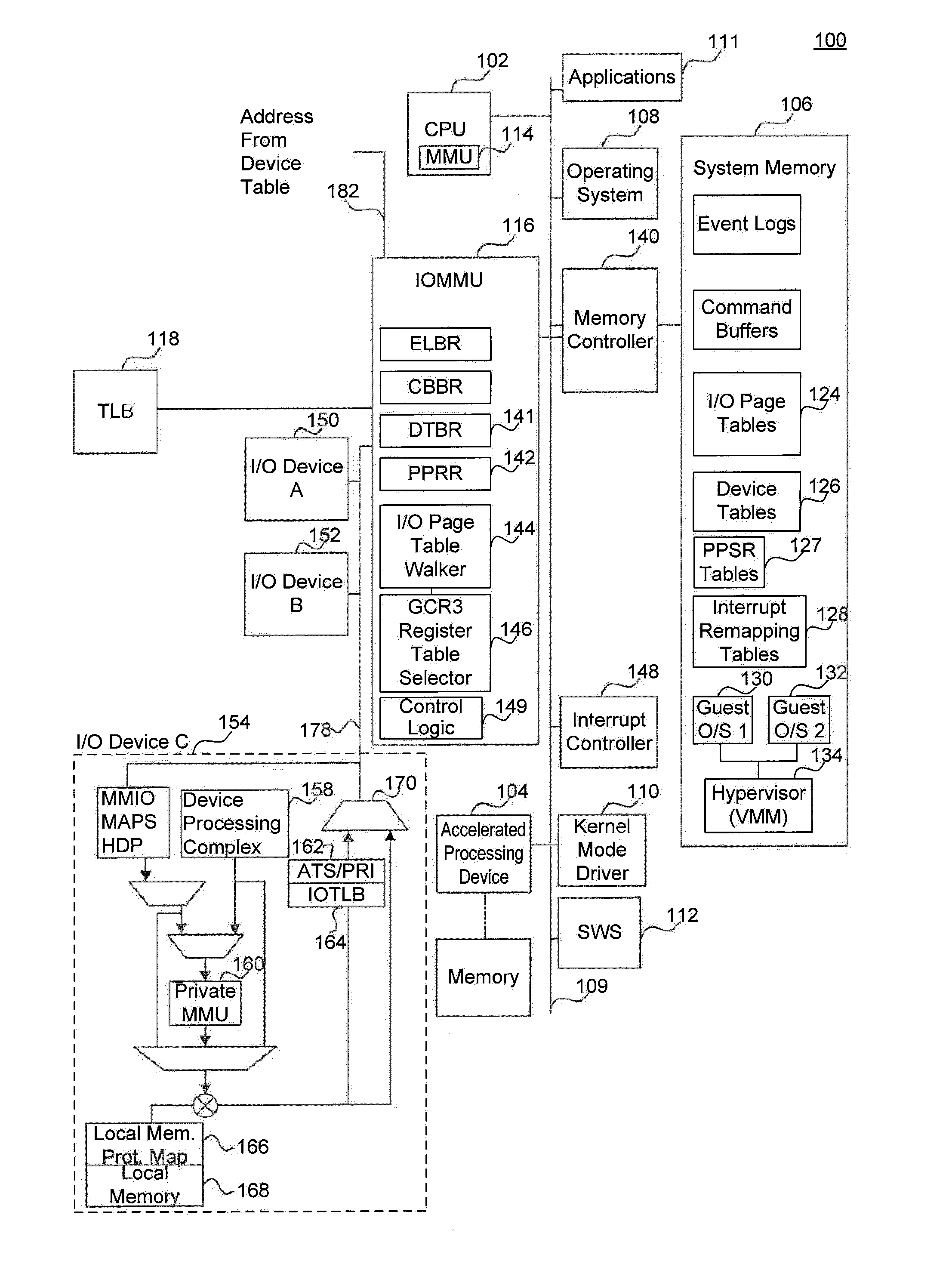

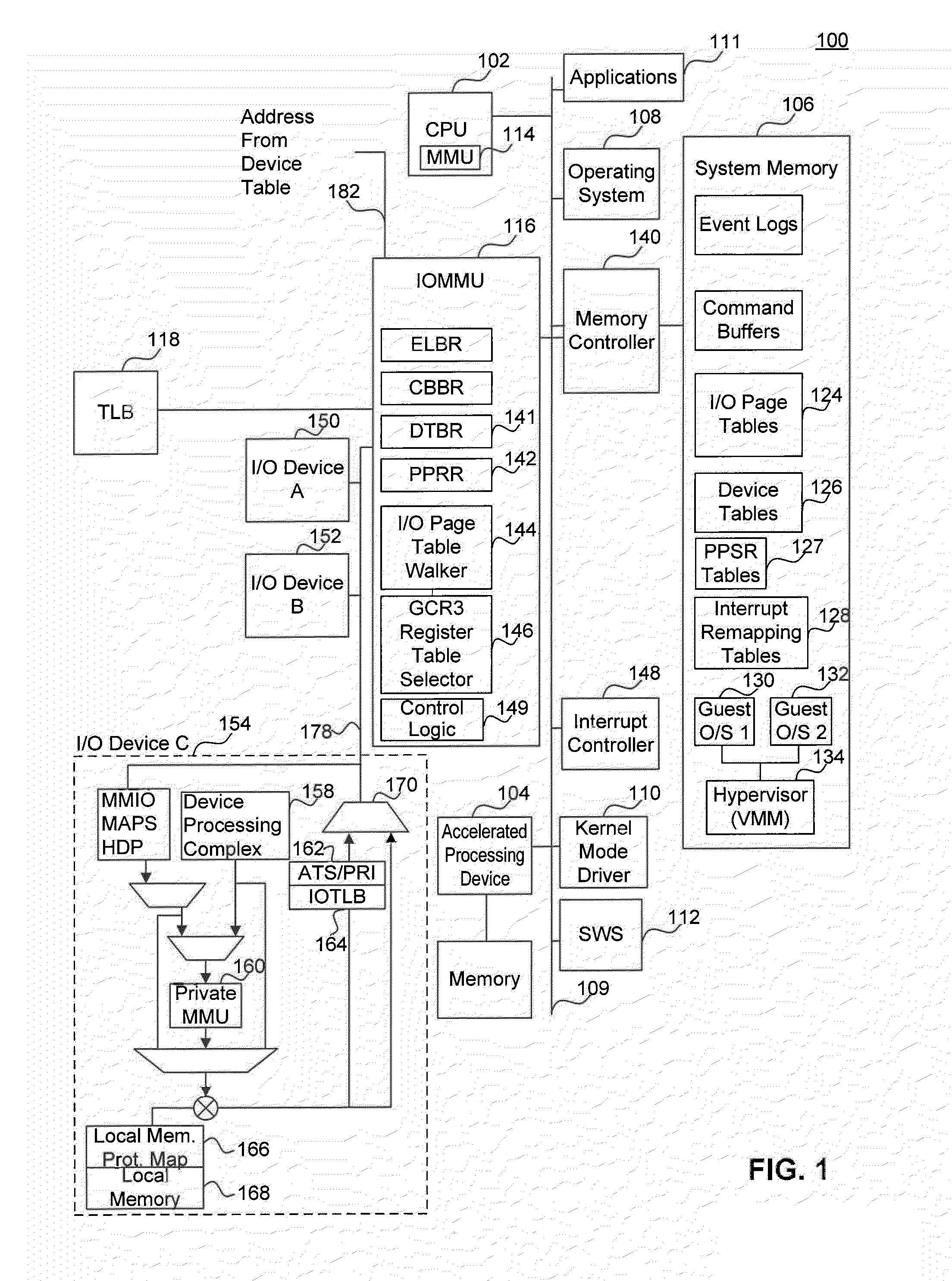

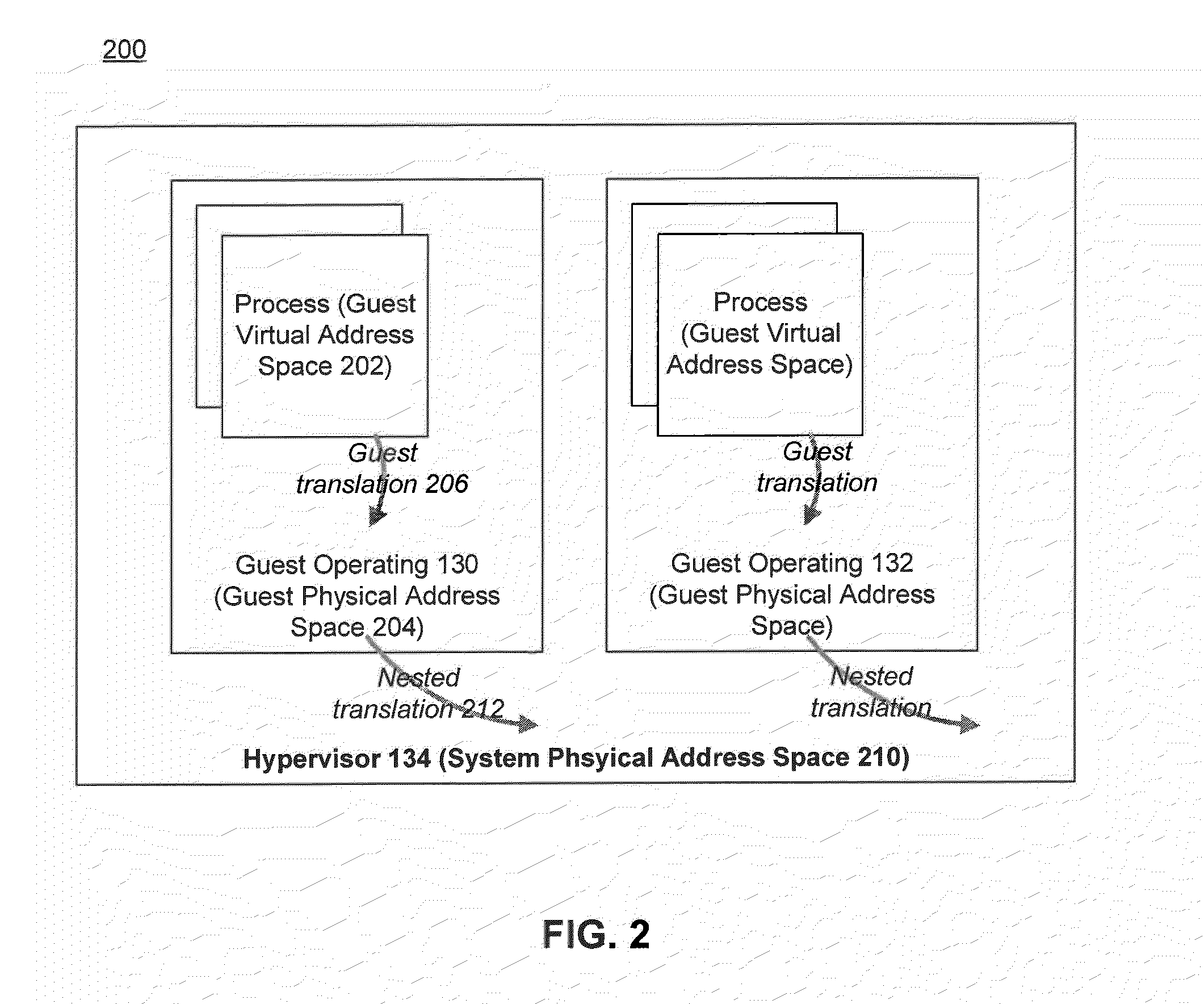

Memory types for caching policies

InactiveUS20130262736A1Optimize memory accessImprove performanceMemory adressing/allocation/relocationMemory typeOperating system

The present system enables receiving a request from an I / O device to translate a virtual address to a physical address to access the page in system memory. One or more memory attributes of the page defining a cacheability characteristic of the page is identified. A response including the physical address and the cacheability characteristic of the page is sent to the I / O device.

Owner:ATI TECH INC +1

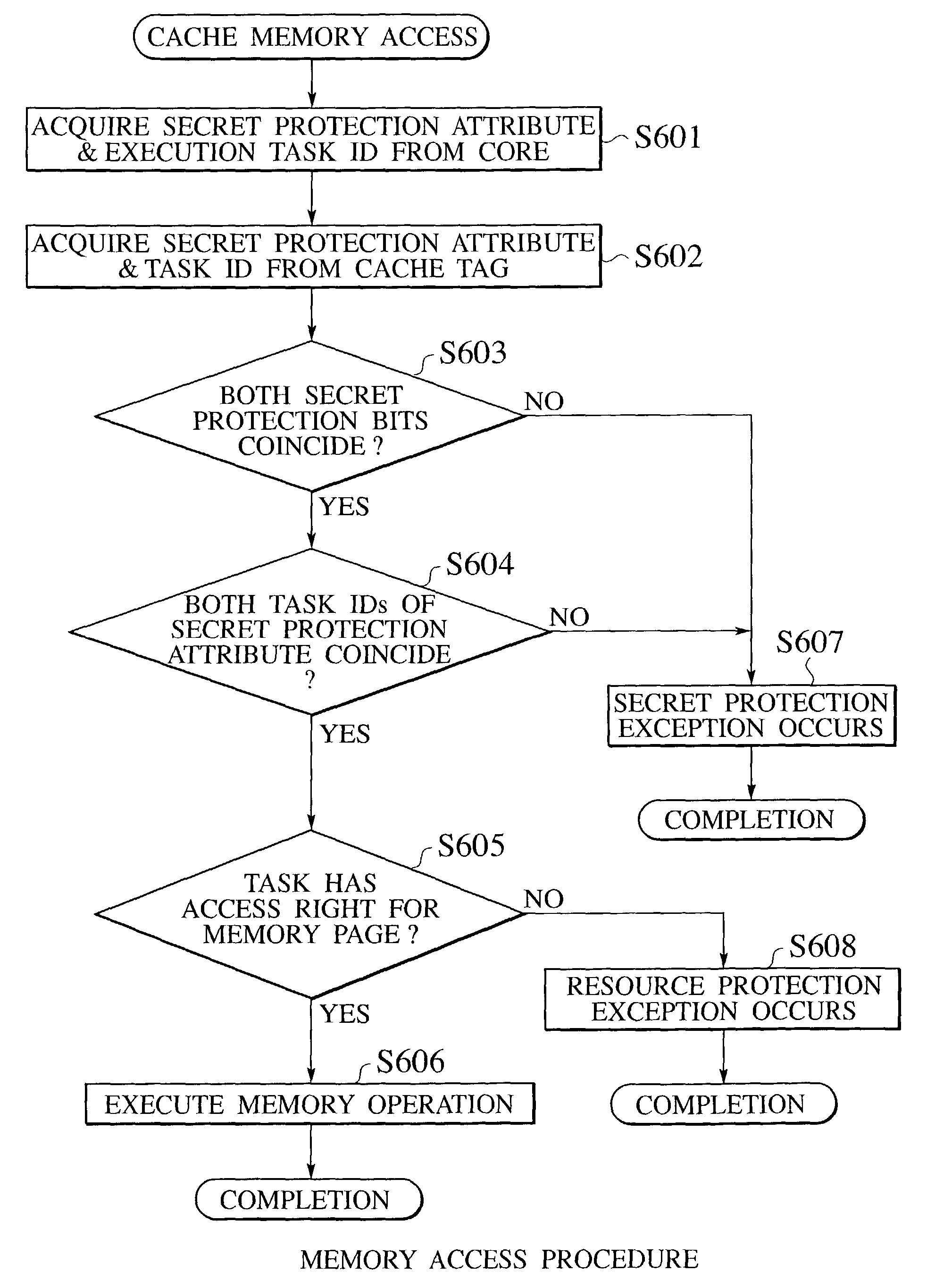

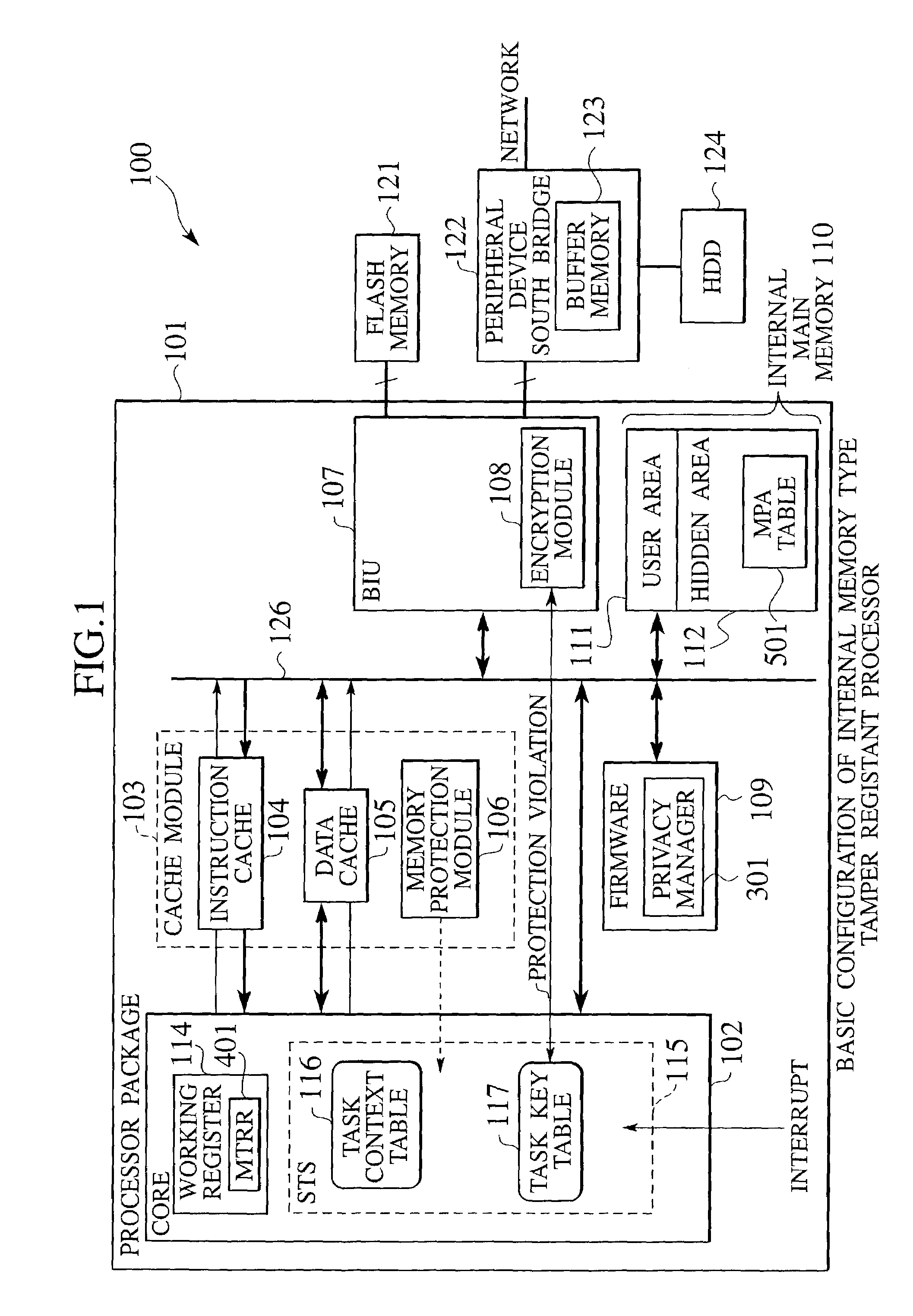

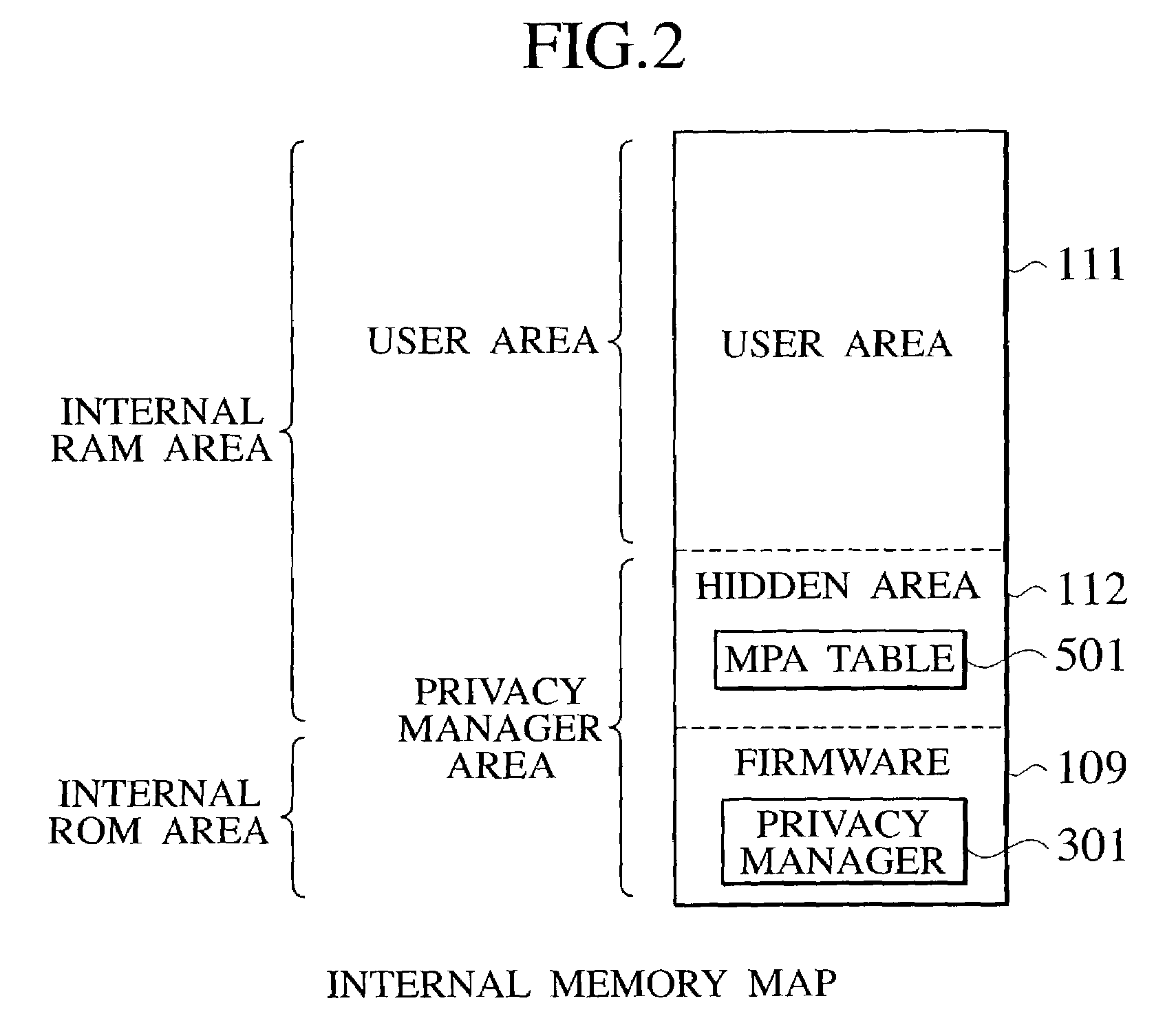

Internal memory type tamper resistant microprocessor with secret protection function

InactiveUS7219369B2Large capacityAlteration can be preventedDigital data processing detailsMultiprogramming arrangementsMemory typeInternal memory

In an inner memory type tamper resistant microprocessor, a requested secret protection attribute requested for each access target memory page by a task is set and stored exclusively from other tasks, at a time of reading a program into memory pages and executing the program as the task, and a memory secret protection attribute is set and stored for each access target memory page by the task, at a time of executing the task. Then, an access to each access target memory page is refused when the requested secret protection attribute for each access target memory page and the memory secret protection attribute for each access target memory page do not coincide.

Owner:KK TOSHIBA

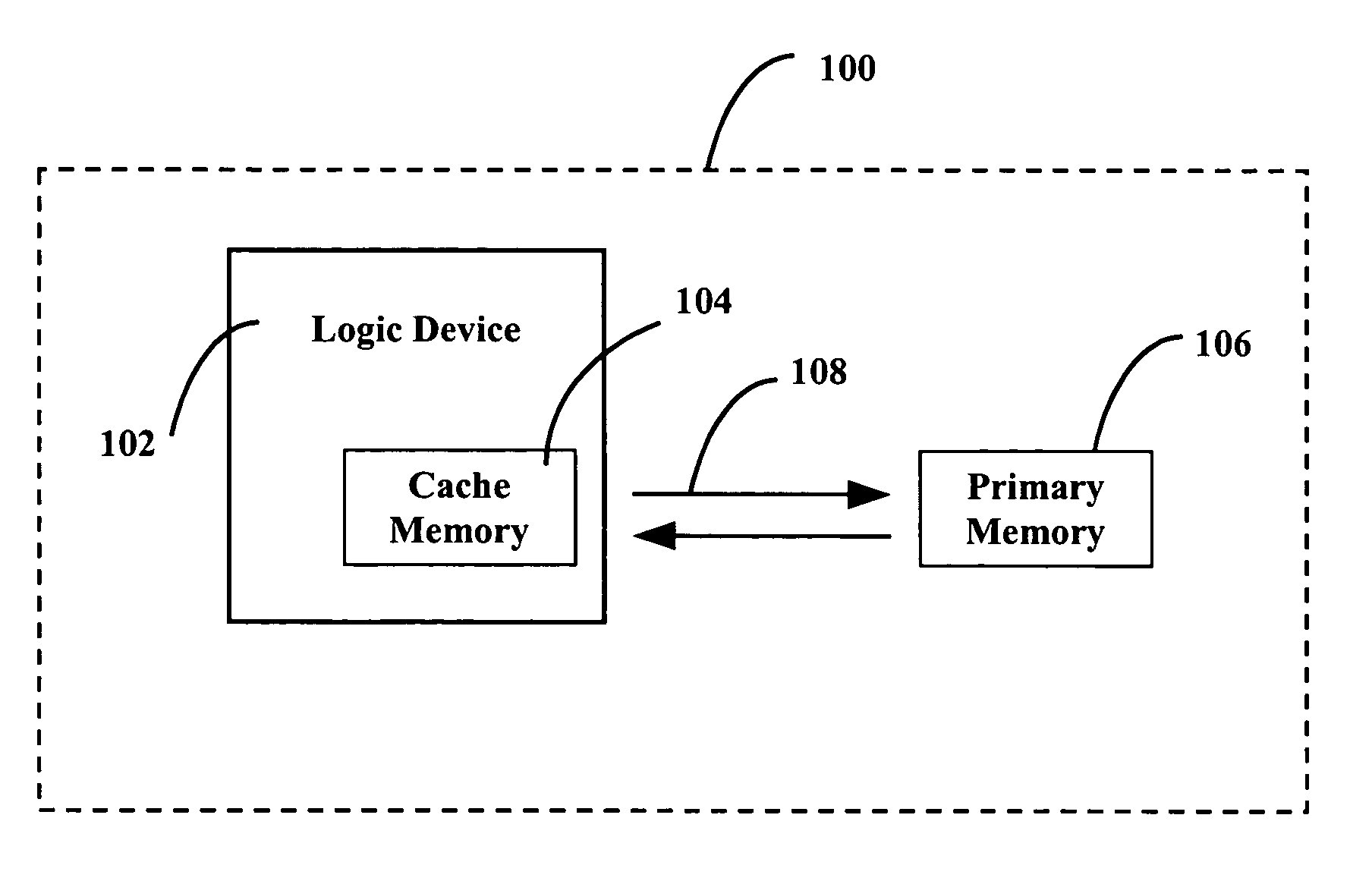

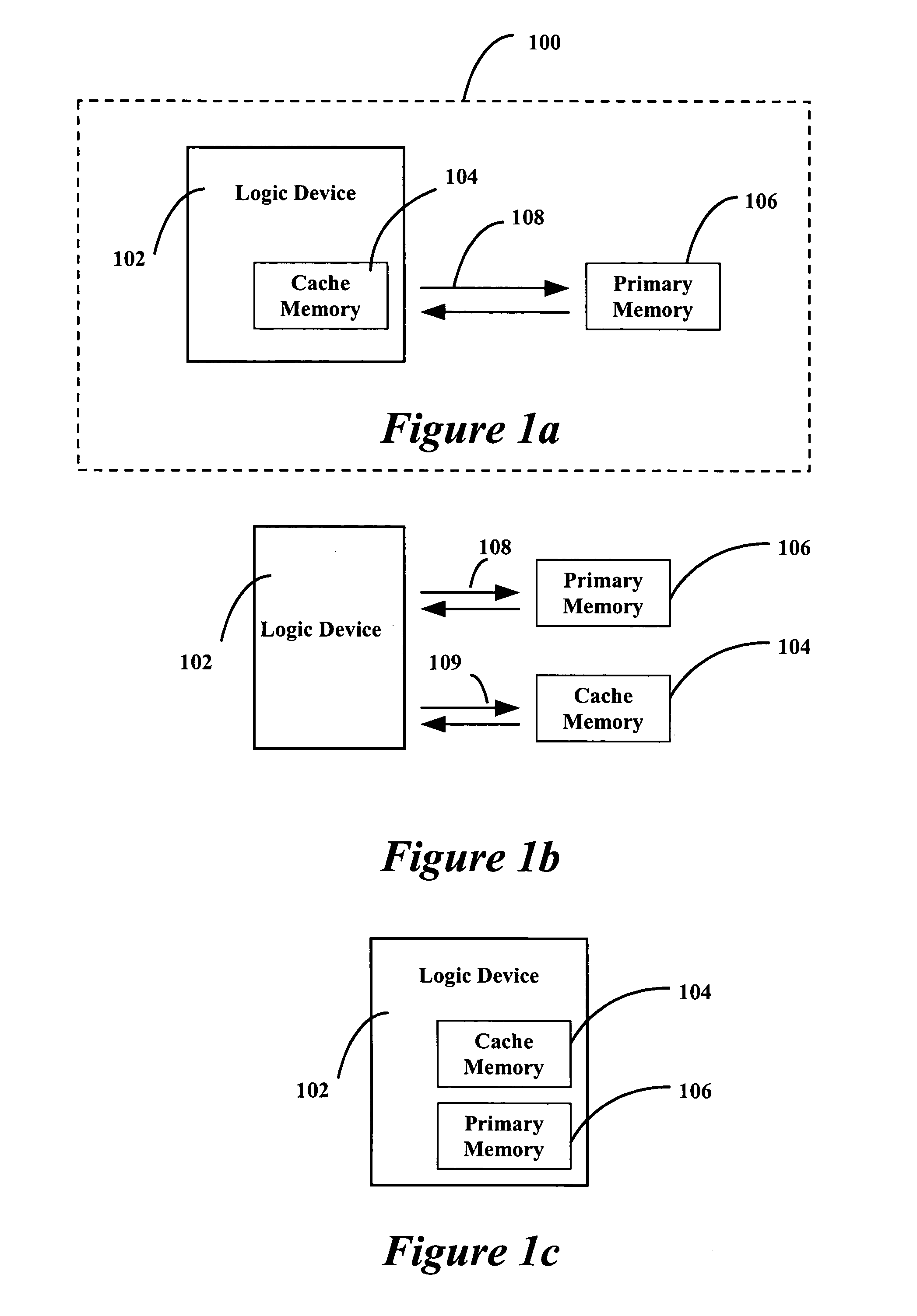

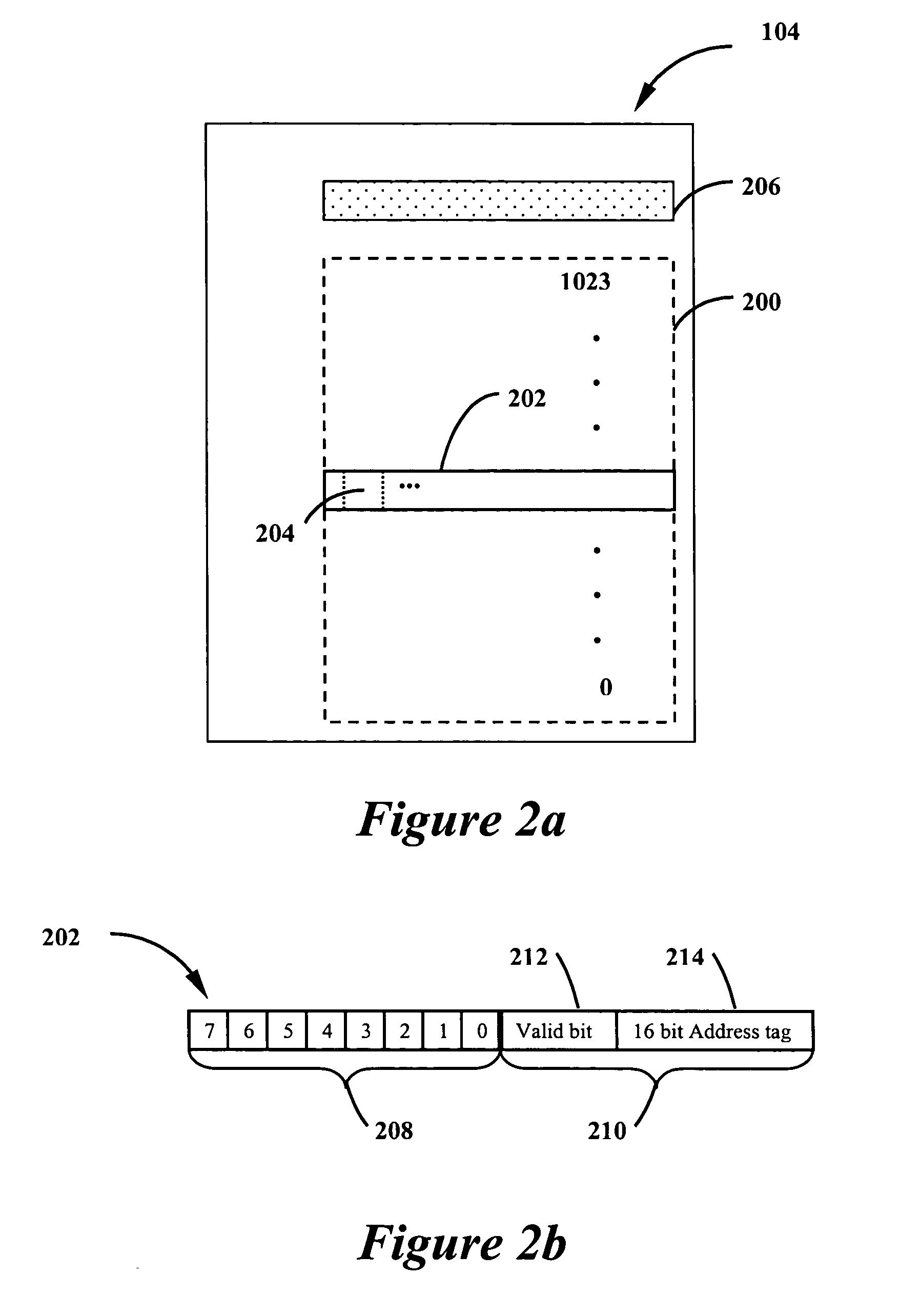

Cache operation with non-cache memory

ActiveUS7159076B2Memory architecture accessing/allocationMemory adressing/allocation/relocationMemory typeParallel computing

A system and method are provided for bypassing cache memory when reading data from system memory particularly when the primary memory could include memory types where the read operation mixes non-data with data. A system and method are provided for bypassing and invalidating cache memory when writing data to system memory particularly when the primary memory could include memory types where the write operation mixes non-data with data.

Owner:MALIKIE INNOVATIONS LTD

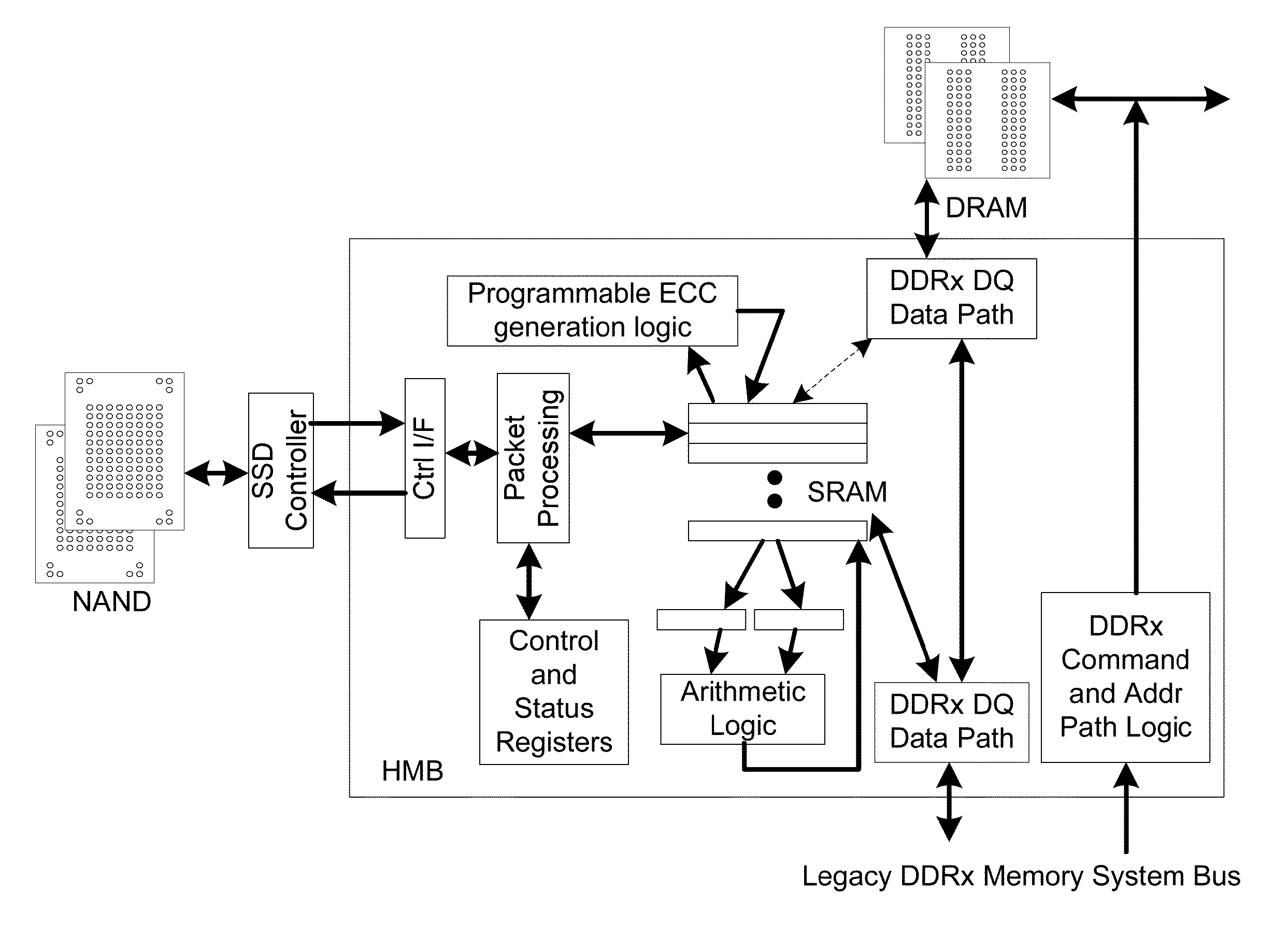

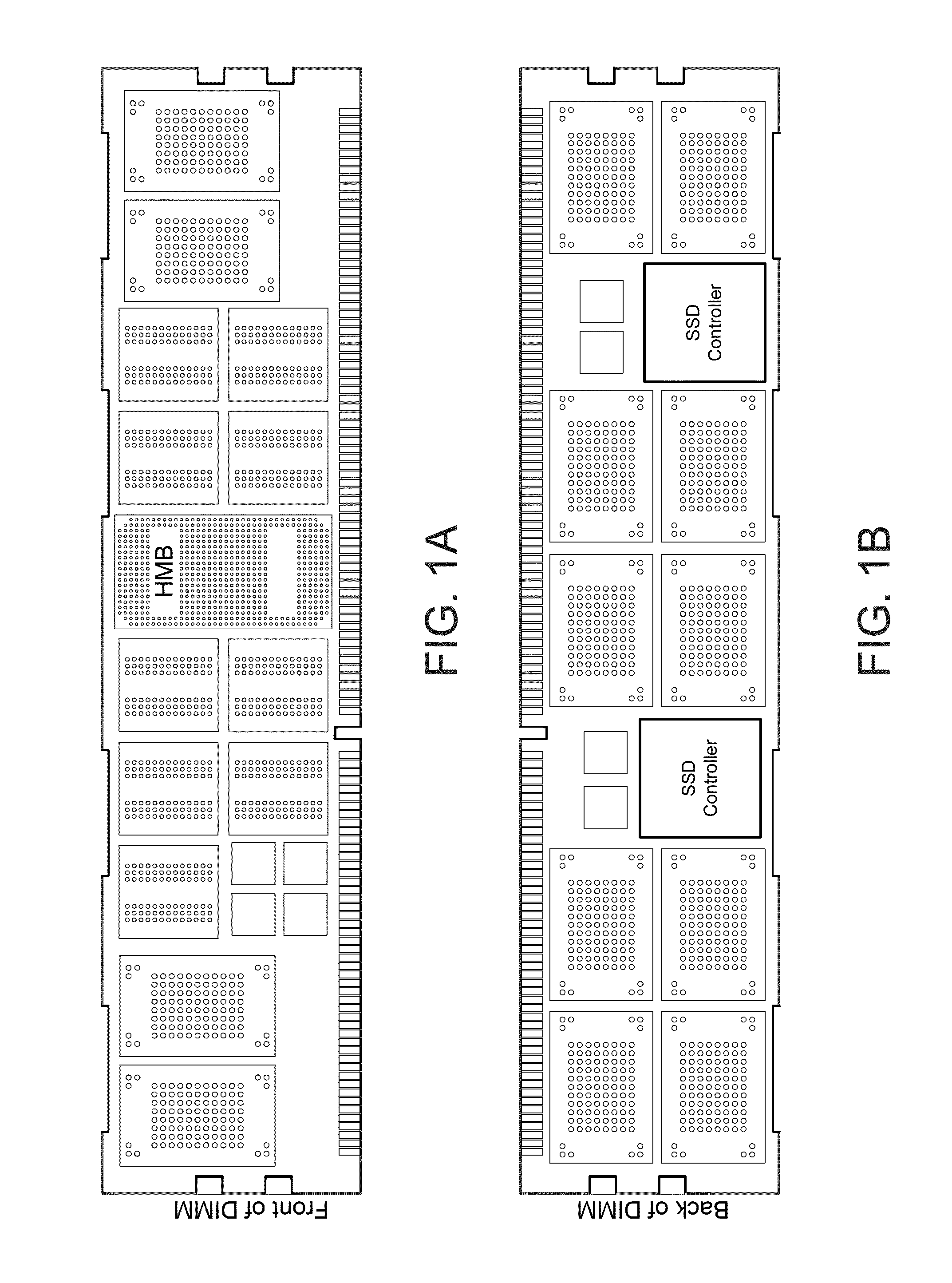

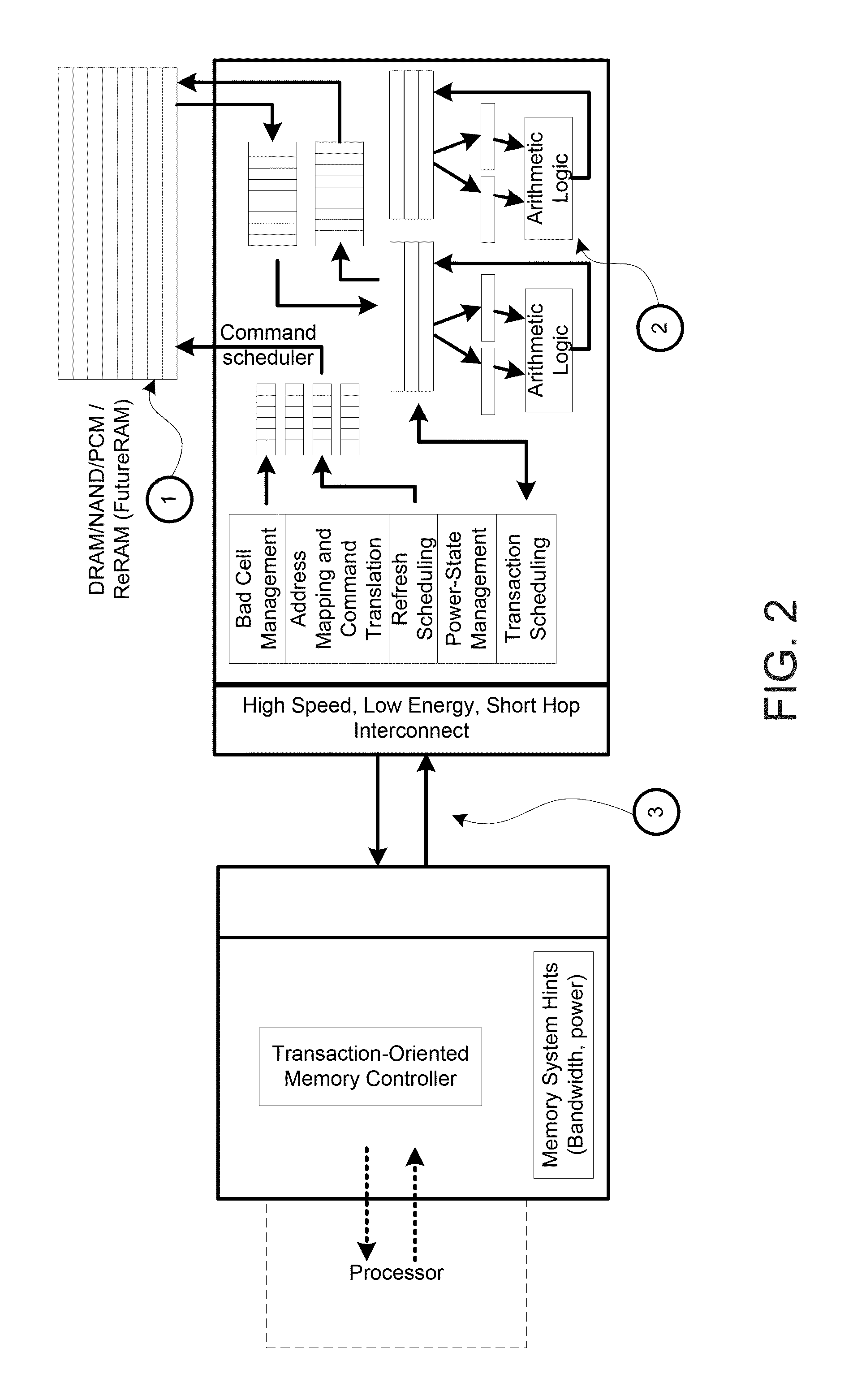

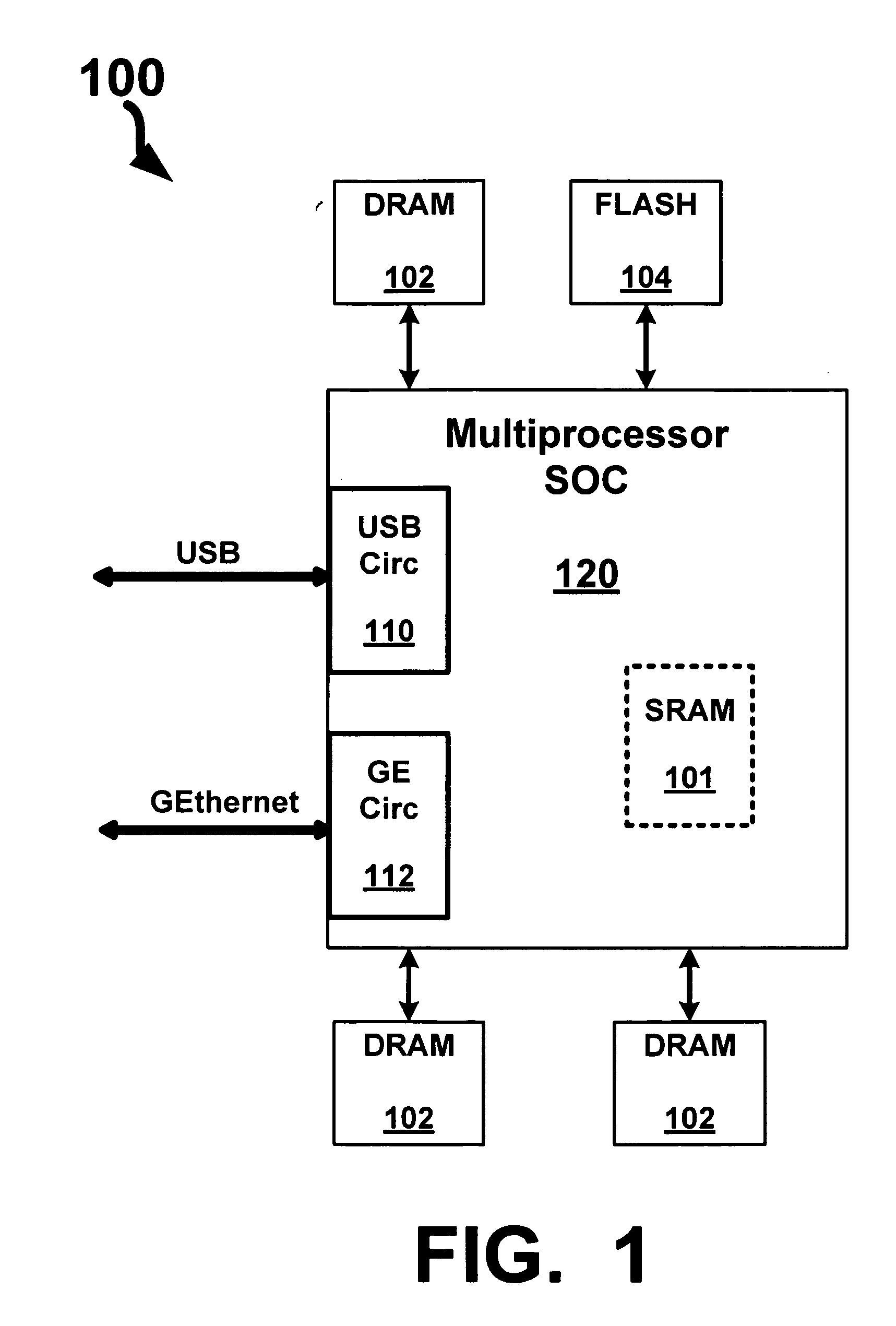

Memory centric computing

A hybrid memory system. This system can include a processor coupled to a hybrid memory buffer (HMB) that is coupled to a plurality of DRAM and a plurality of Flash memory modules. The HMB module can include a Memory Storage Controller (MSC) module and a Near-Memory-Processing (NMP) module coupled by a SerDes (Serializer / Deserializer) interface. This system can utilize a hybrid (mixed-memory type) memory system architecture suitable for supporting low-latency DRAM devices and low-cost NAND flash devices within the same memory sub-system for an industry-standard computer system.

Owner:RAMBUS INC

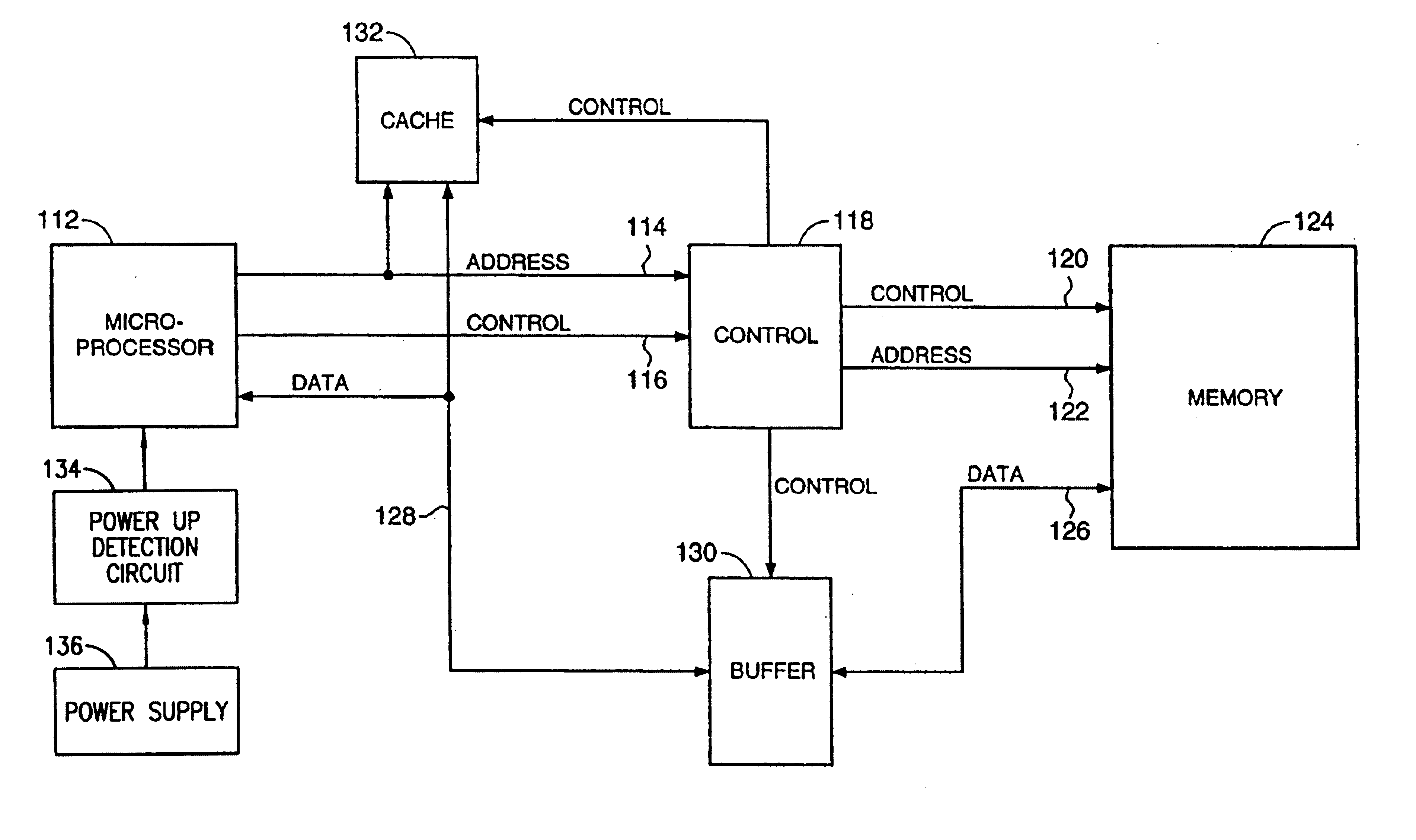

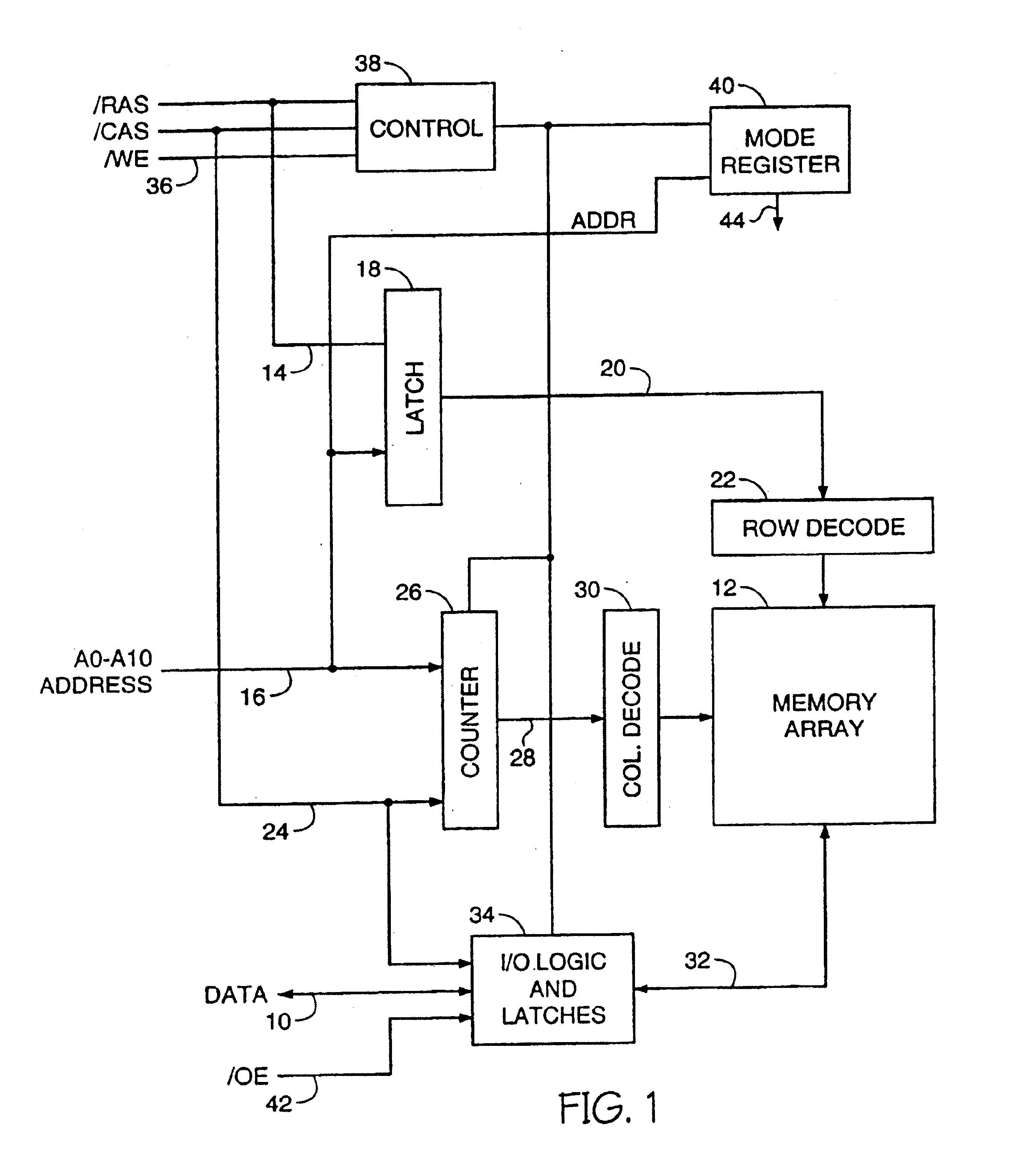

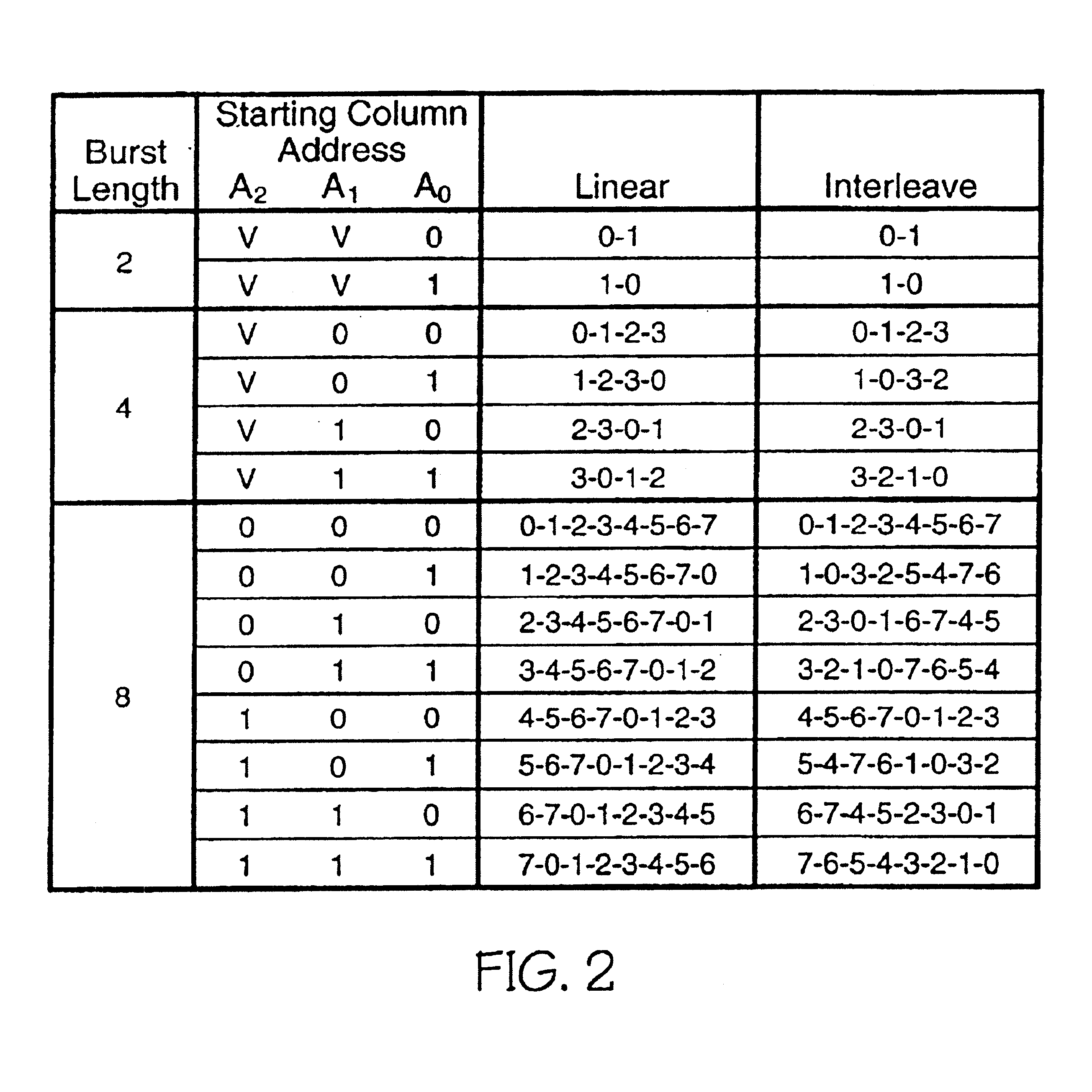

System supporting multiple memory modes including a burst extended data out mode

InactiveUS7043617B2High speed data accessFaster data access timeMemory architecture accessing/allocationMemory adressing/allocation/relocationInternal memoryMemory type

A system is capable of receiving Fast Page mode, Extended Data Out mode, Burst Extended Data Out mode, or a combination of these memory devices. A method of determining the type of memory present allows the system to adjust internal memory access signals in accordance with the type of memory installed. The system may be shipped with a first type of memory, and then upgraded to a second type of memory by the user to improve overall system performance. A first bank of memory may be of a first type, and a second bank may be of another type. The user may make cost versus performance decisions when upgrading memory types or capacities.

Owner:ROUND ROCK RES LLC

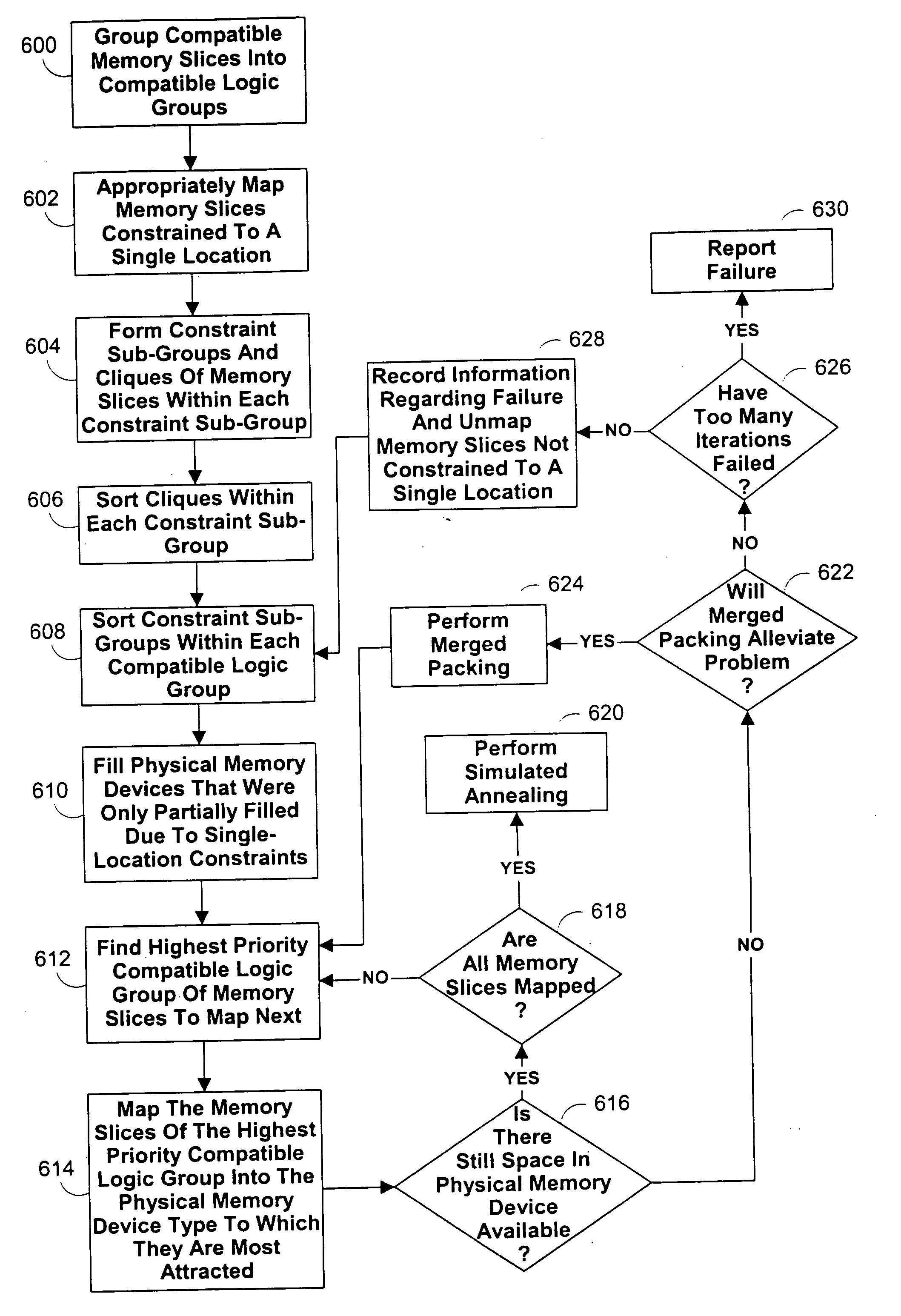

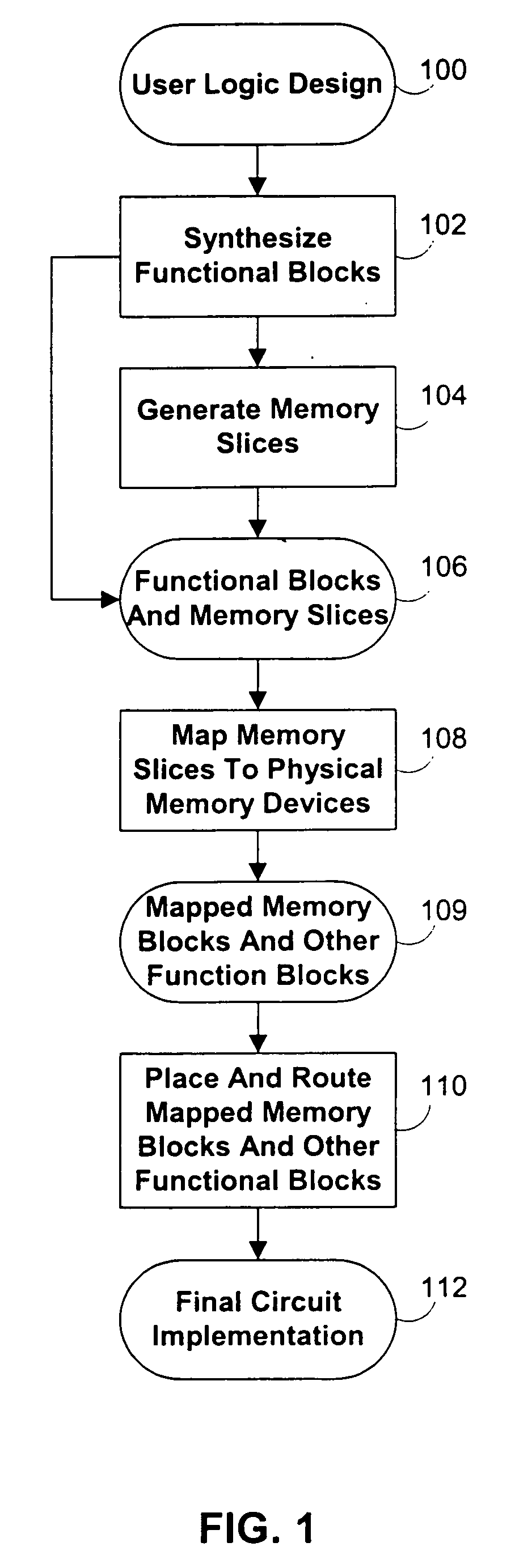

Method for mapping logic design memory into physical memory devices of a programmable logic device

InactiveUS20050204325A1CAD circuit designSpecial data processing applicationsMemory typeProgrammable logic device

A method is provided for mapping logic design memory into physical memory devices of a programmable logic device. User constraints and physical constraints may be taken into account in generating the mapping solution. Functional block layout on the programmable logic device may be taken into account when generating the mapping solution. Multiple types of physical memory types may be considered and logic design memory may be mapped to those types of physical memory devices that are determined to be the most appropriate. A mapping solution may be optimized using, for example, simulated annealing.

Owner:ALTERA CORP

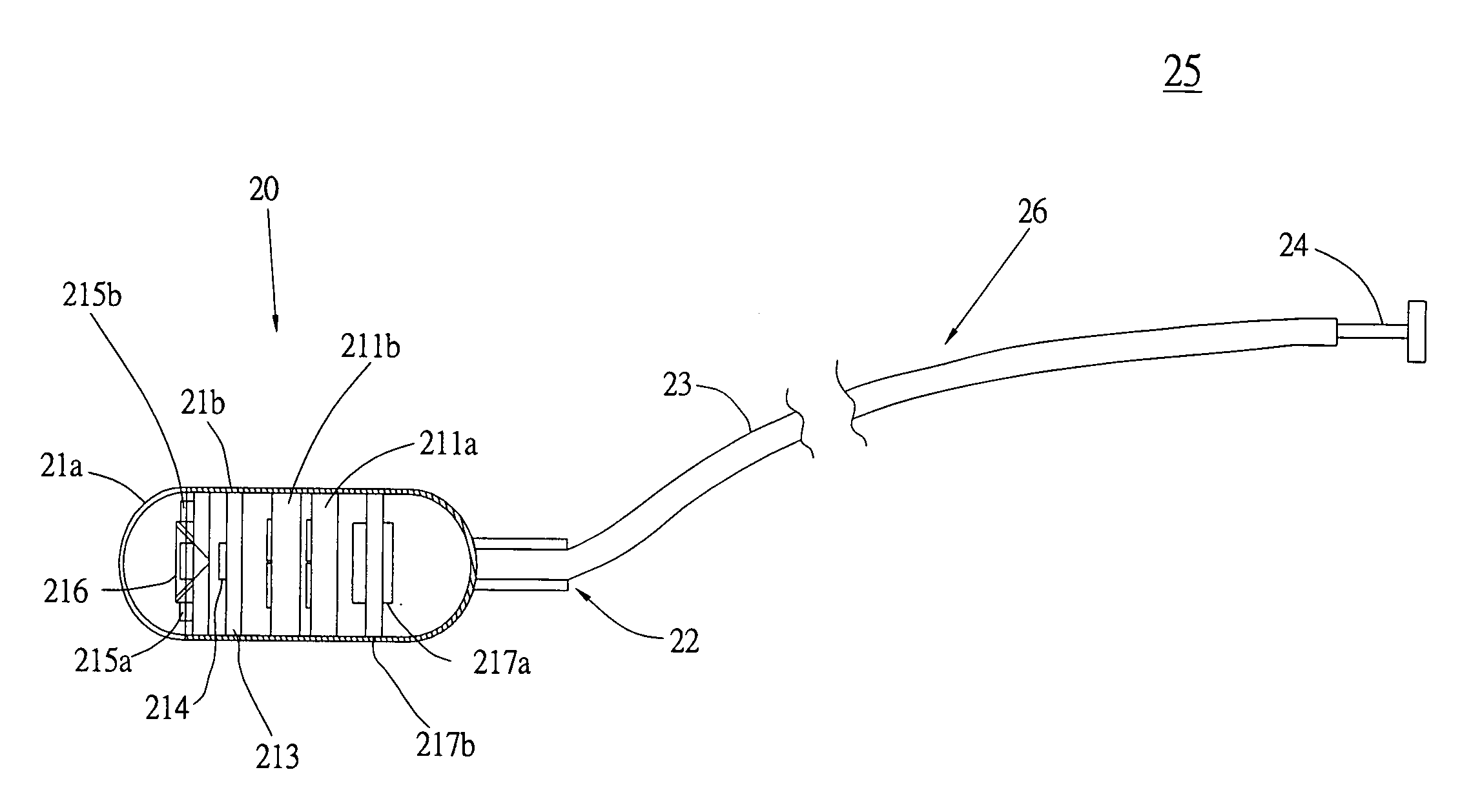

Memory-type two-section endoscopic system

The present invention provides a memory-type two-section endoscopic system, which includes an endoscope that comprises a light-emitting device, an image-capturing device, a storage module, and a transmission module adapted in a shell. A disconnectable cable connects to the shell, and can depart form the shell. When the endoscope examines the esophagus and the stomach, the disconnectable cable can be used to control the endoscope for obtaining image data of the esophagus and the stomach for the image-capturing device. Then the image data is stored in the storage module or transmitted to the transmission module. When the endoscope examines the intestines, the shell will depart from the disconnectable cable and the endoscope will continue examinations of the intestines without wire control. The image data obtained by examining the intestines is stored to the storage module. Thereby, the esophagus, the stomach, and the intestines can be examined at a time, and the efficiency of an endoscope is enhanced.

Owner:NAT CHUNG SHAN INST SCI & TECH

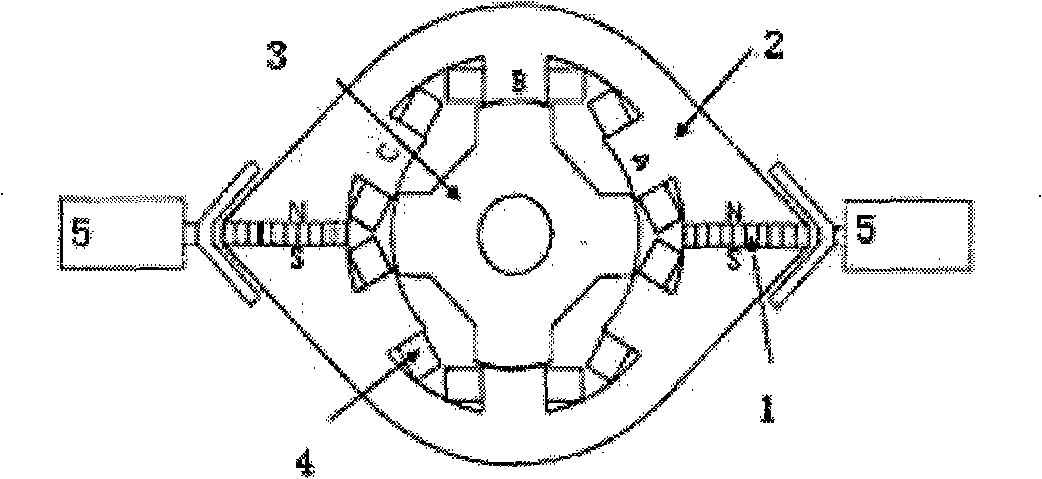

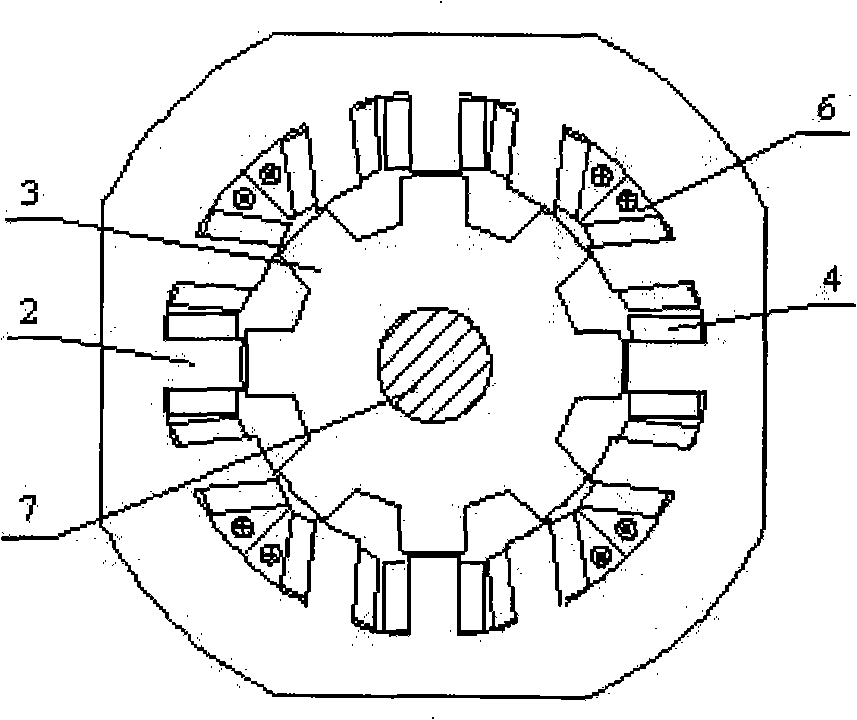

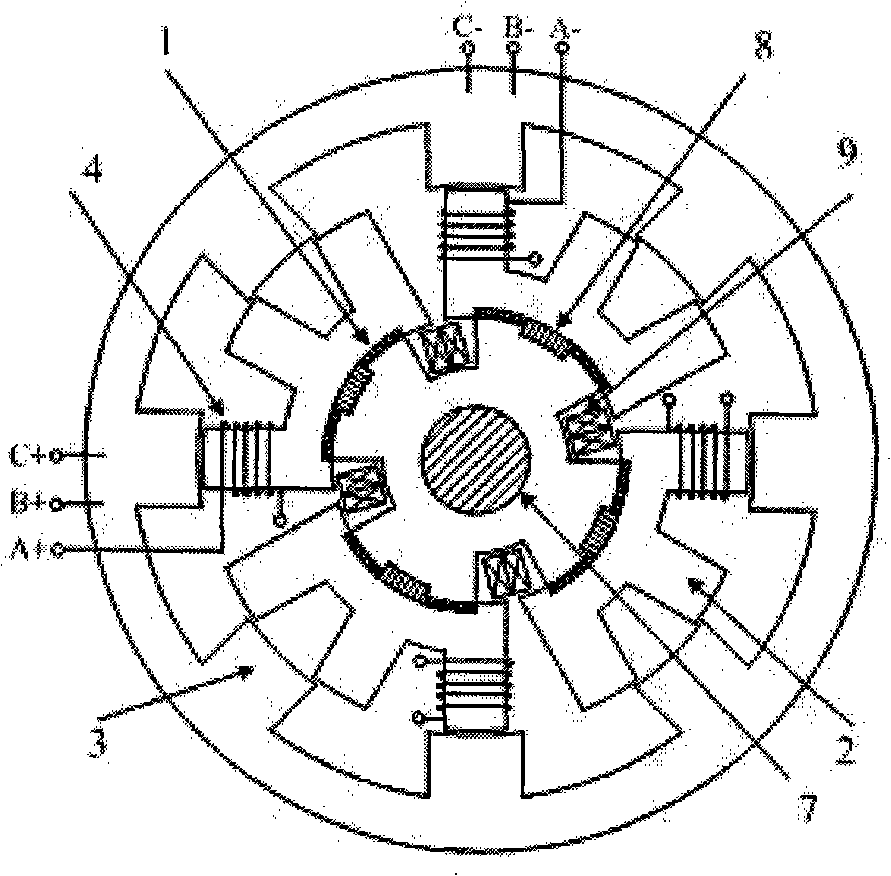

Permanent magnetism type motor of wide speed-adjusting magnetic flux memory type stator

InactiveCN101325349AHigh power densityHigh torque densityElectric machinesMagnetic circuit stationary partsMemory typeConstant power

The invention belongs to the technical field of the permanent-magnet brushless machine manufacture, particularly to a stator permanent-magnet machine adaptable to the application fields of wide speed regulation and high efficiency, such as the mixing dynamic car and the electric automobiles, composed of a stator, a rotor, an armature winding and an NdFeB permanent magnet, characterized in that, the original NdFeB permanent magnet is saved, an ALNiCo permanent magnet and a magnetizing winding for adjusting the magnetic field strength and the magnetic flux density of the ALNiCo permanent magnet are arranged on the stator. The invention has the advantage that, the ALNiCo permanent magnet and the magnetizing winding are first inducted in the stator permanent-magnet, to cause that the flux memory type stator permanent-magnet machine inherits the advantages of large power intensity and good fault tolerant performance of the stator permanent-magnet machine, meanwhile solves the defect that it is difficult to realize the weak magnetic control, the range of the constant power speed control is small and the operating efficiency of the constant power operation is low.

Owner:JIANGSU UNIV

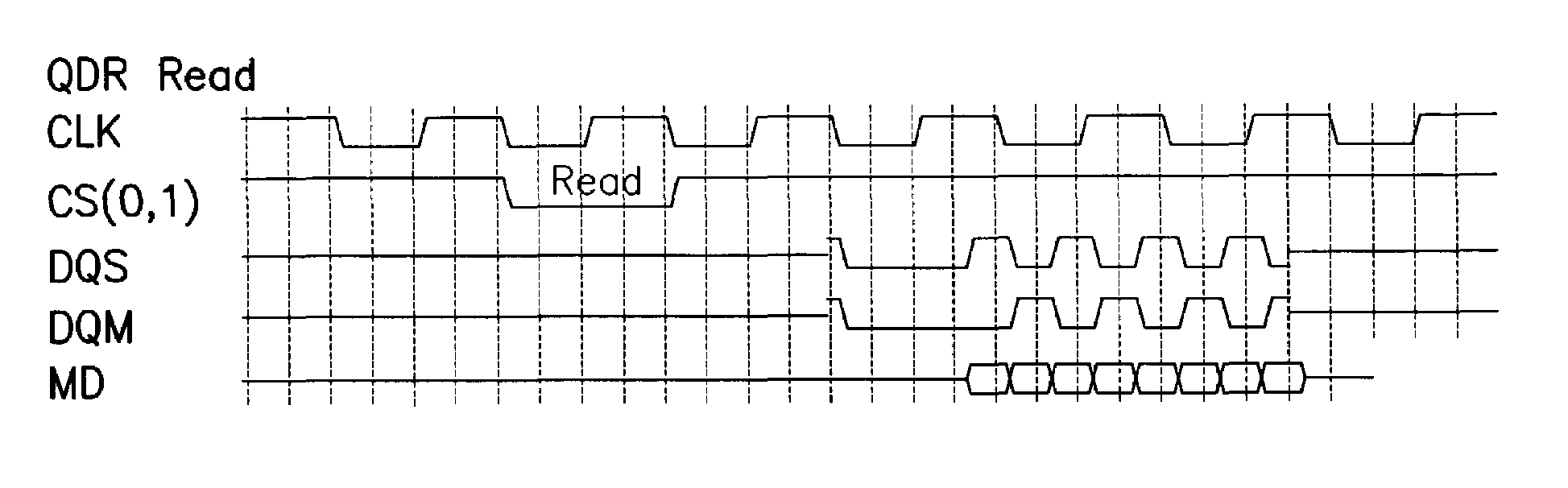

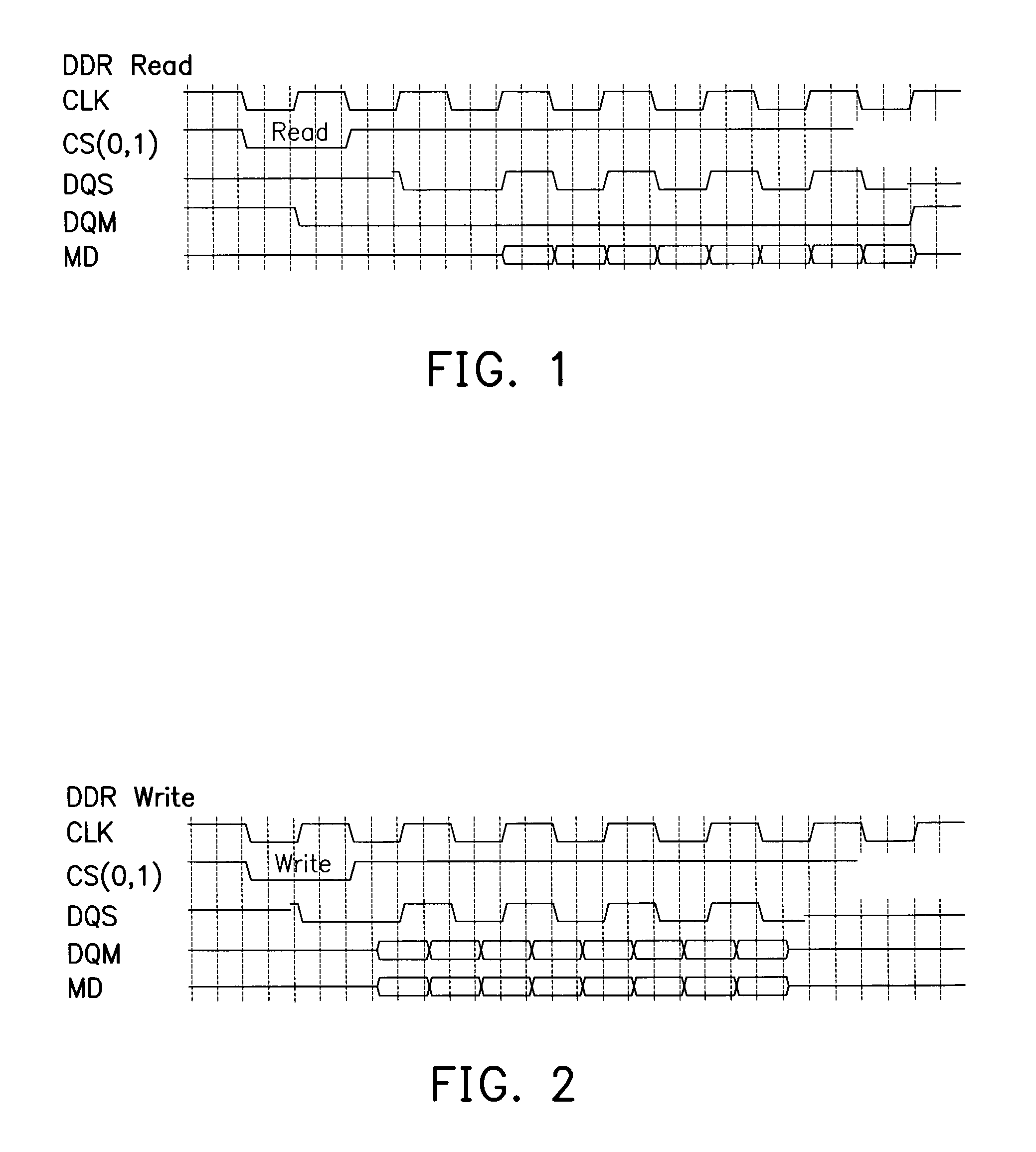

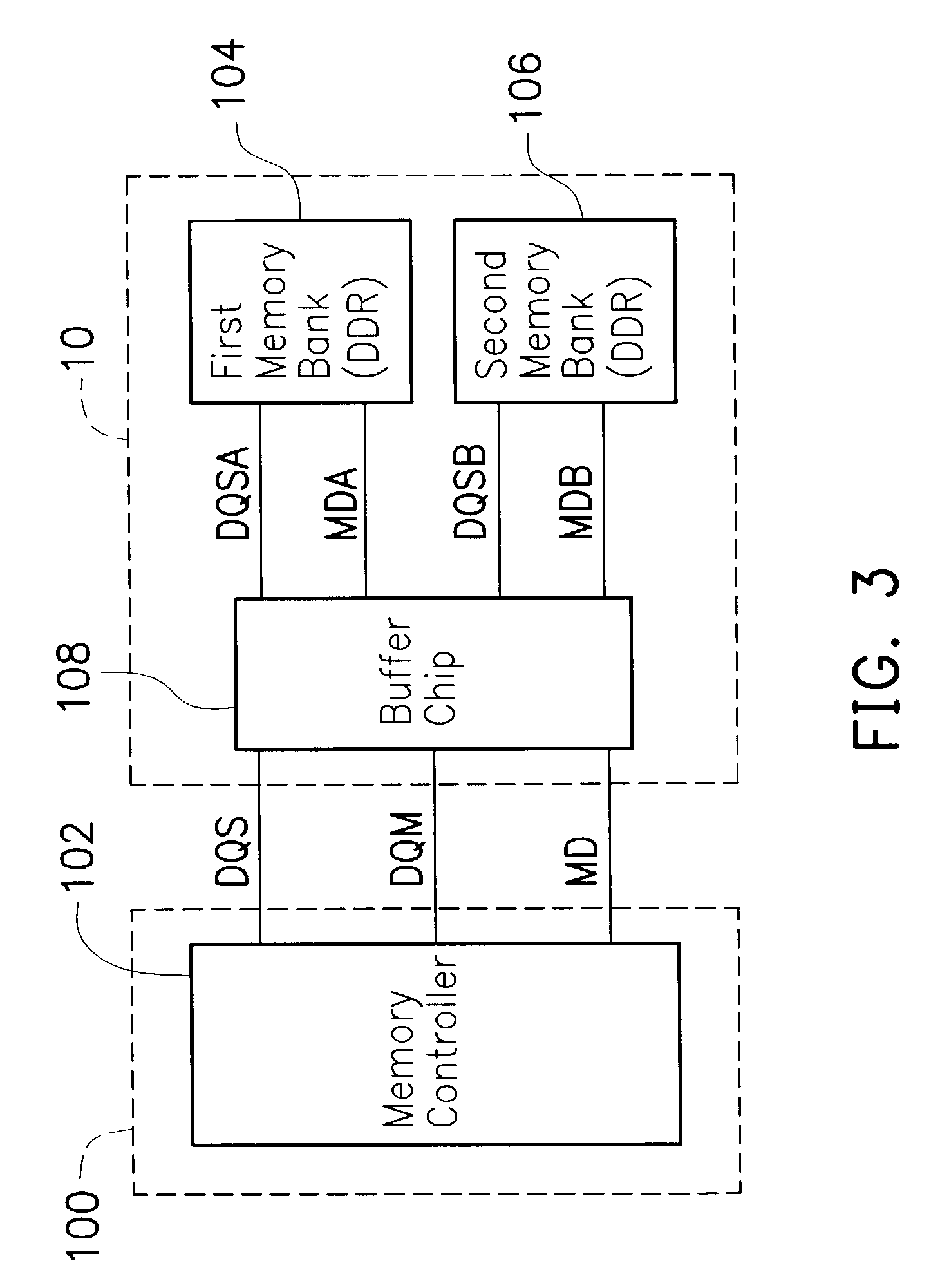

Memory controller for supporting a plurality of different memory accesse modes

A common DRAM controller is provided for supporting a plurality of memory types such as double data rate or quad data rate mode or types. The controller is adapted to use a number of clock signals to process data. The controller can further delay the data for a predetermined time period and capture the same.

Owner:VIA TECH INC

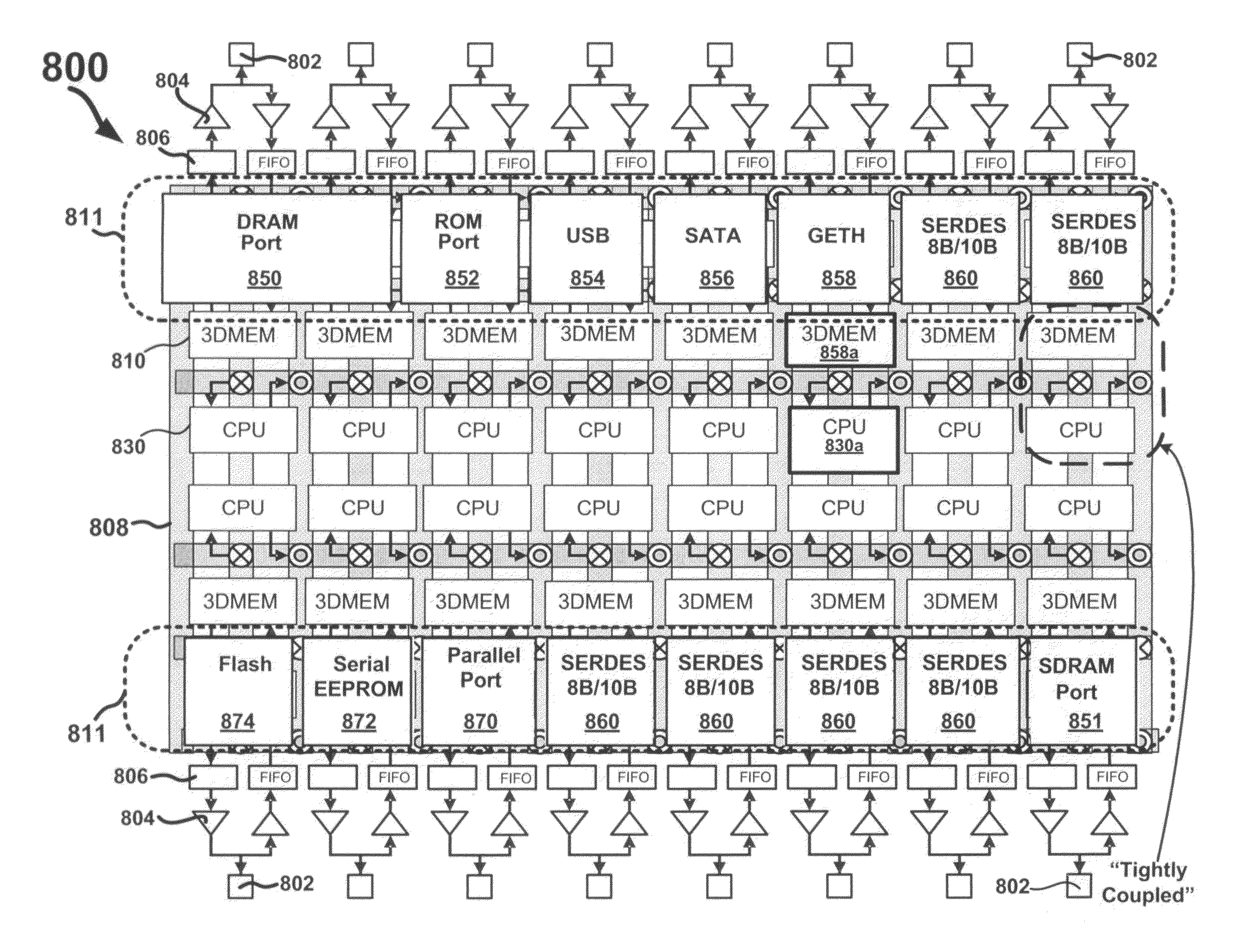

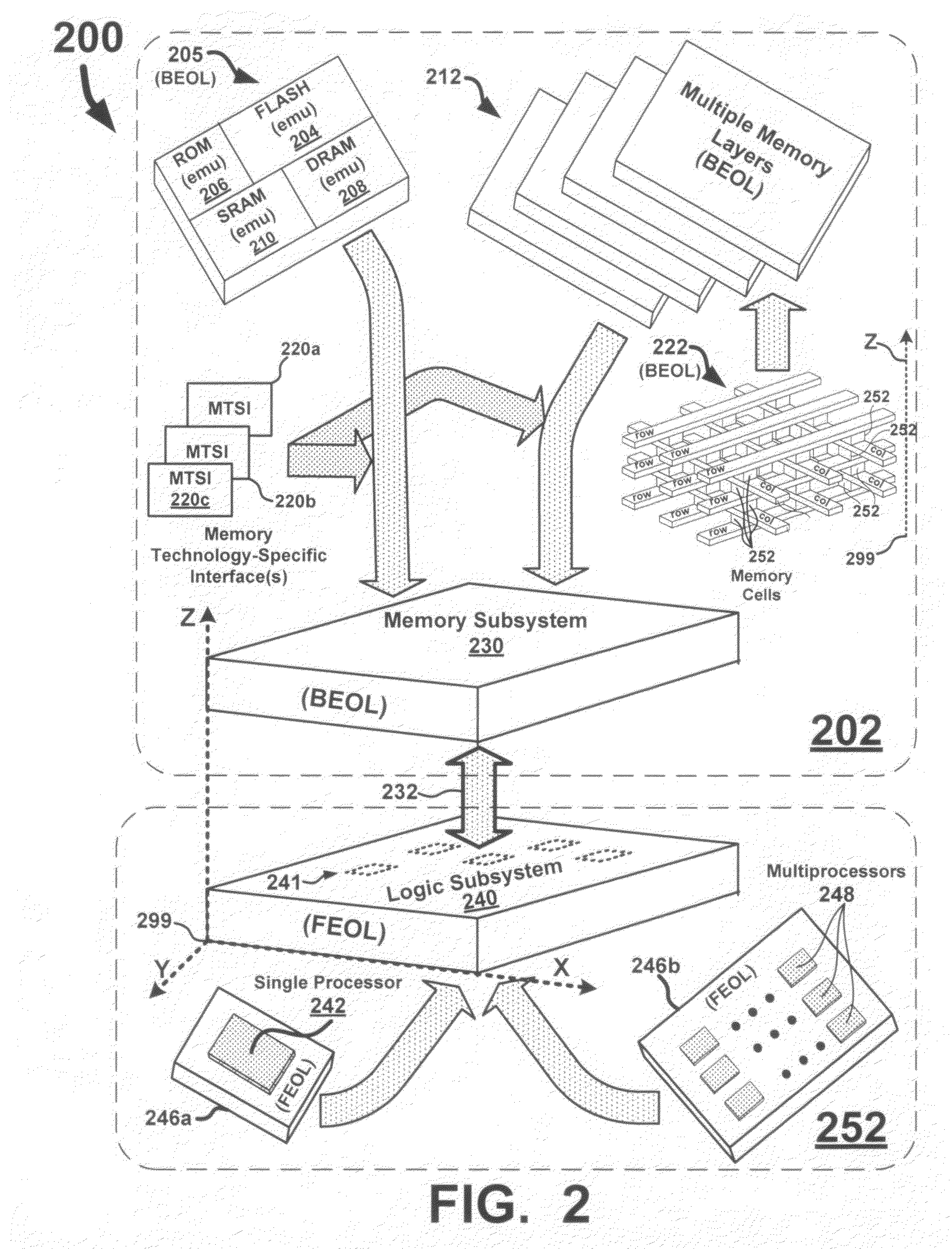

Multiple layers of memory implemented as different memory technology

InactiveUS20100195363A1Printed circuit assemblingDigital storageComputer hardwareConventional memory

Circuits and methods that use third dimension memory as a different memory technology are described. The third dimension memory can be used for application specific data storage and / or to emulate conventional memory types such as DRAM, FLASH, SRAM, and ROM or new memory types as they become available. A processor-memory system implements a memory operable as different memory technologies. The processor-memory system includes a logic subsystem and a memory subsystem, which includes third dimension memory cells. The logic subsystem implements memory technology-specific signals to interact with the third dimension memory cells as memory cells of a different memory technology. As such, the memory subsystem can emulate different memory technologies. The logic subsystem can be fabricated FEOL on a substrate and the memory subsystem can be fabricated BEOL directly on top of the substrate. An interlayer interconnect structure can electrically couple the logic subsystem with the memory subsystem.

Owner:UNITY SEMICON

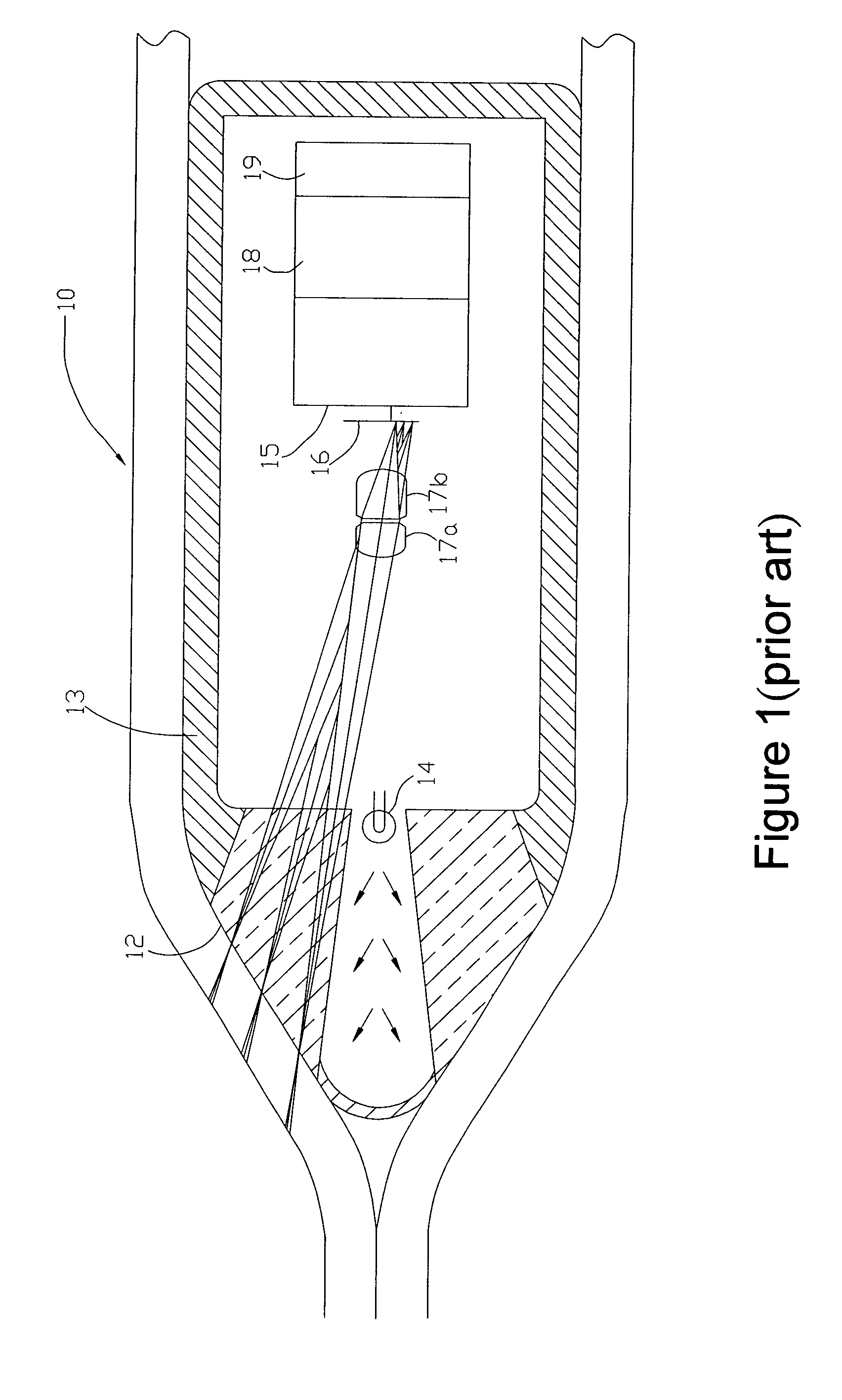

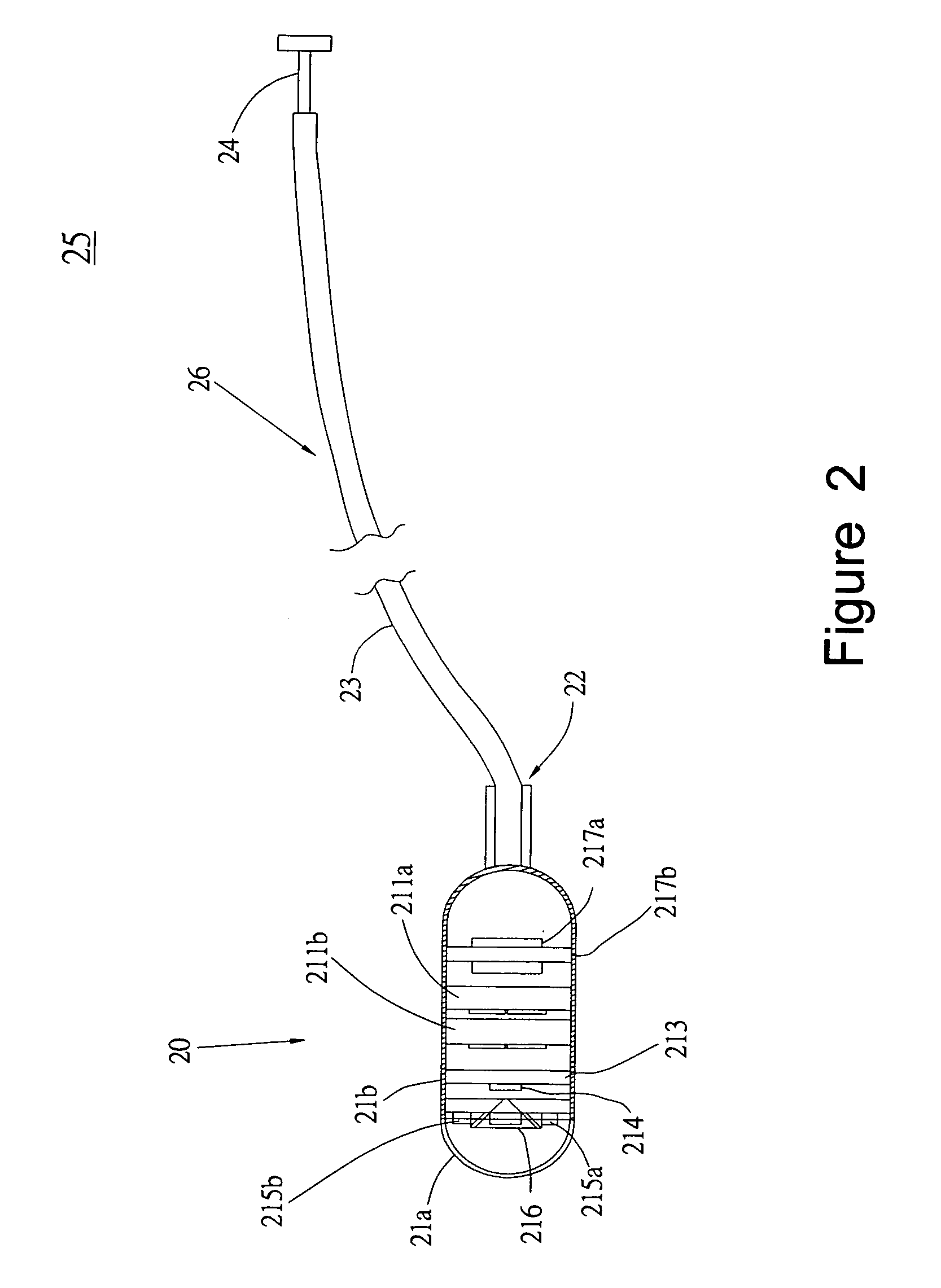

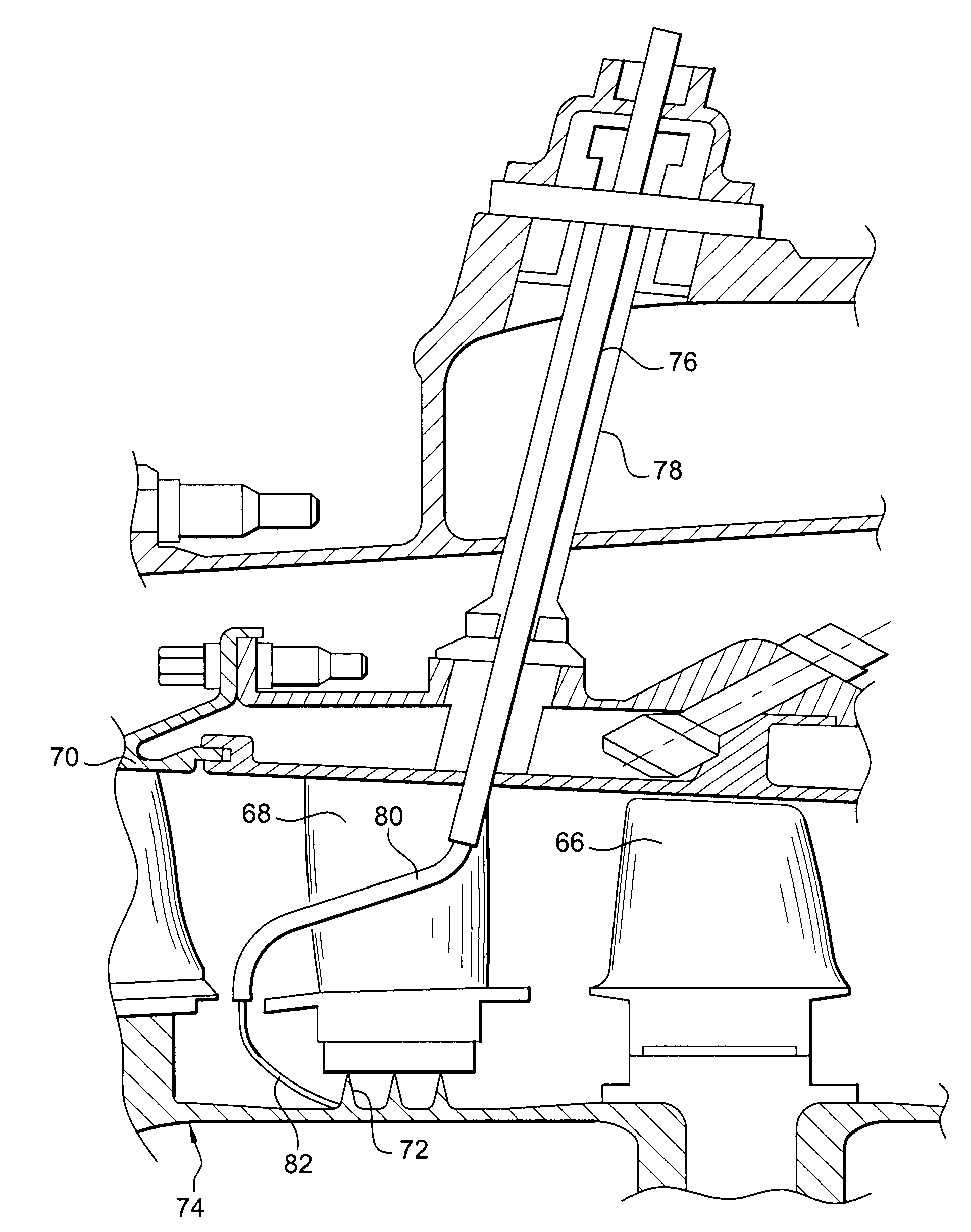

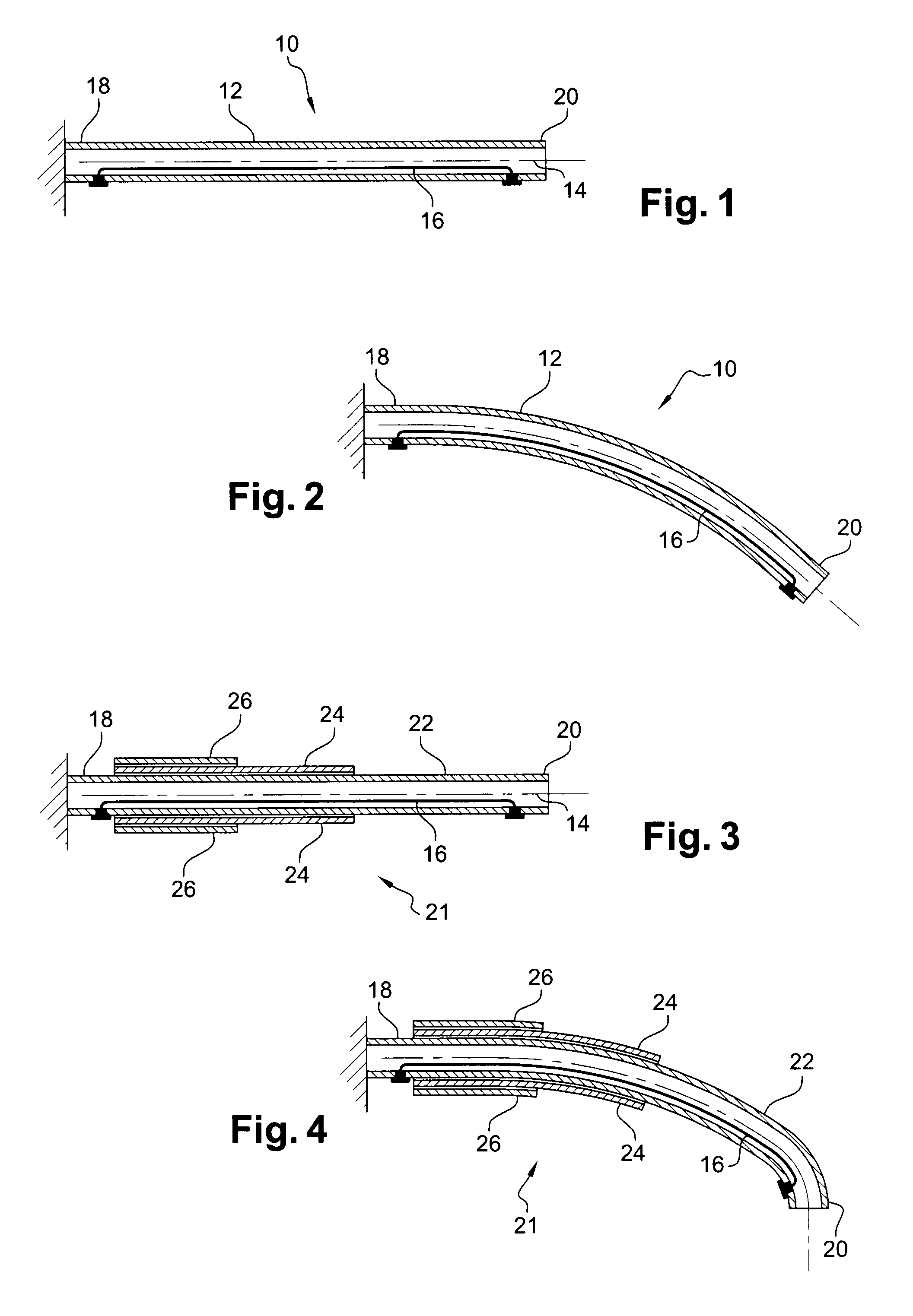

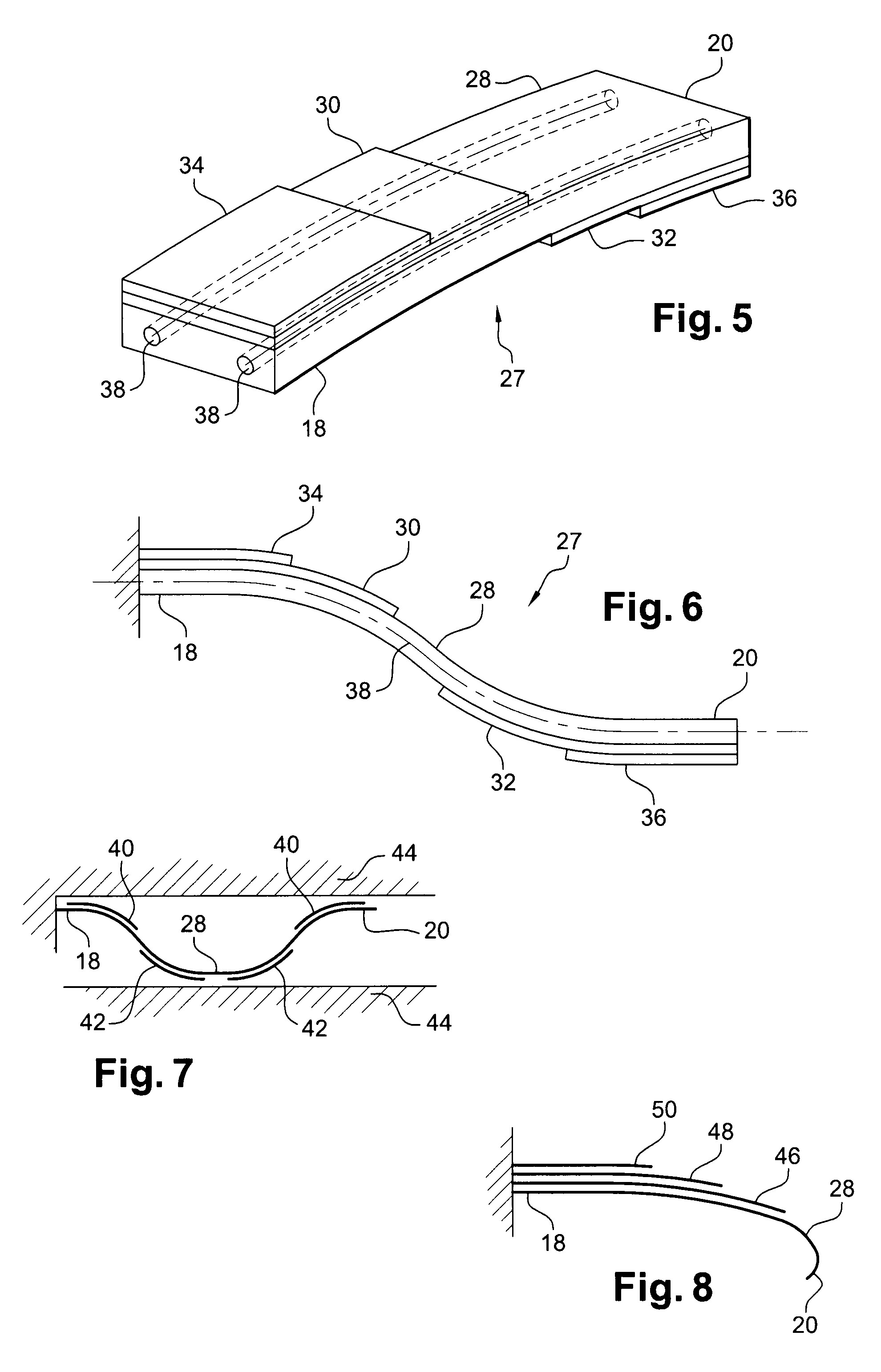

Steerable structure of catheter or endoscope type

ActiveUS20090079821A1Reduce the effect of gravityEasy to controlMachine part testingMaterial analysis using sonic/ultrasonic/infrasonic wavesMemory typeEngineering

A steerable structure (21, 27) of the catheter or endoscope type, the structure comprising an elastically or deformable longitudinal body (22, 28) including at least one actuator (16, 38) of material of the shape memory type incorporated longitudinally with the body (22, 28) together with Joule-effect heater means enabling the actuator (16, 38) to be contracted longitudinally in order to cause the longitudinal body (22, 28) to bend, wherein the actuator (16, 38) extends over at least one portion of the body (22, 28) that presents varying stiffness.

Owner:SN DETUDE & DE CONSTR DE MOTEURS DAVIATION S N E C M A +2

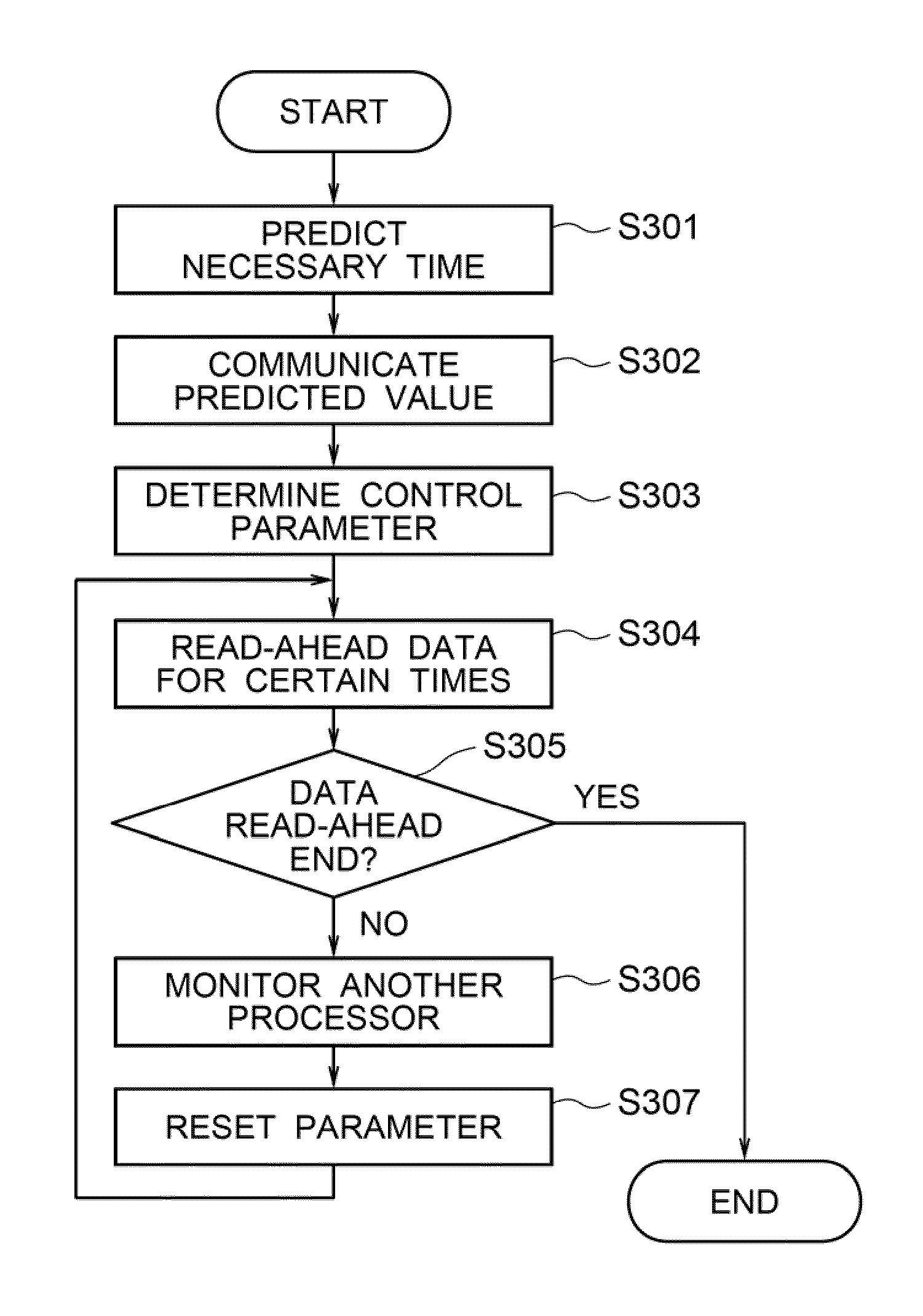

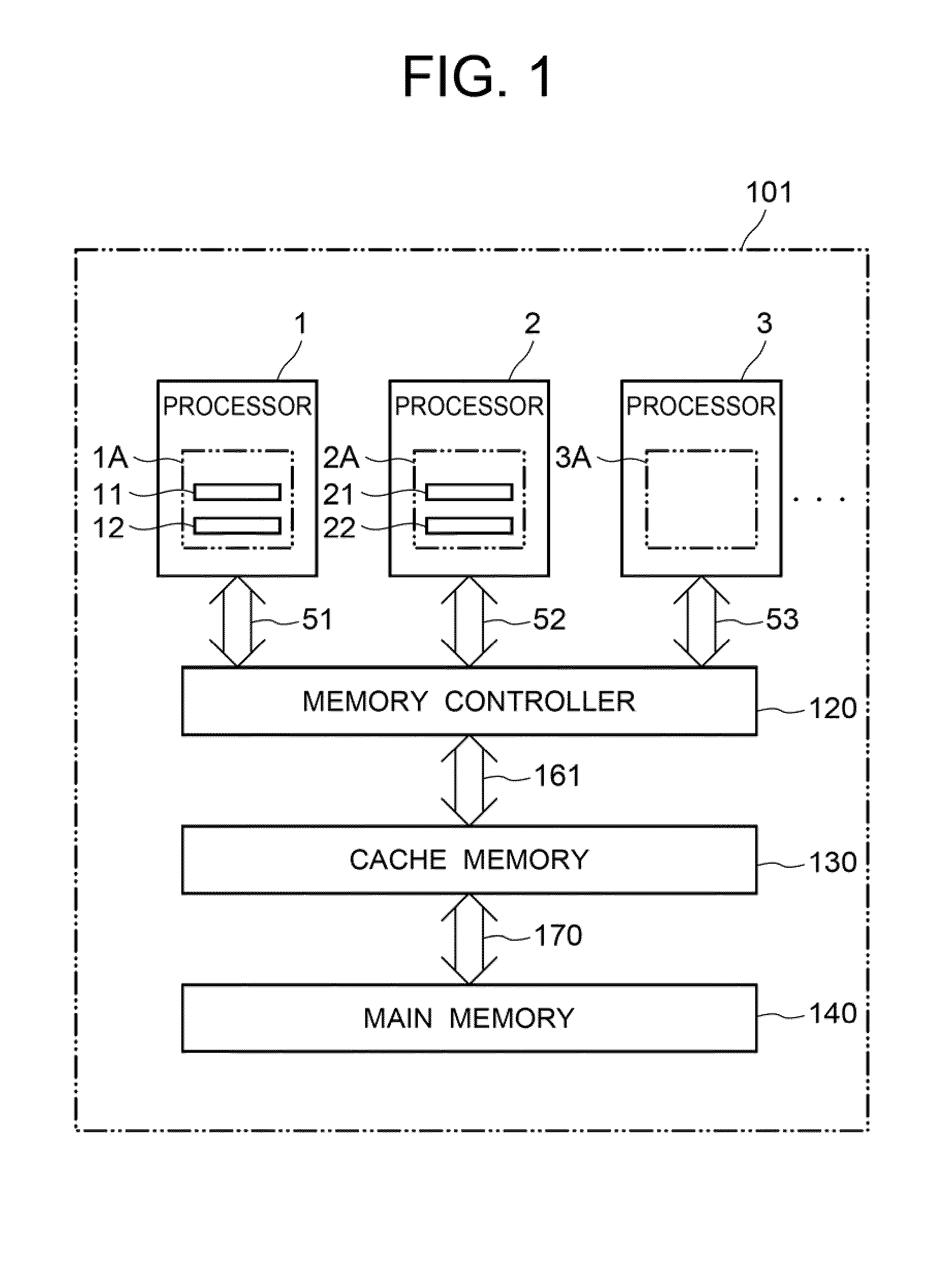

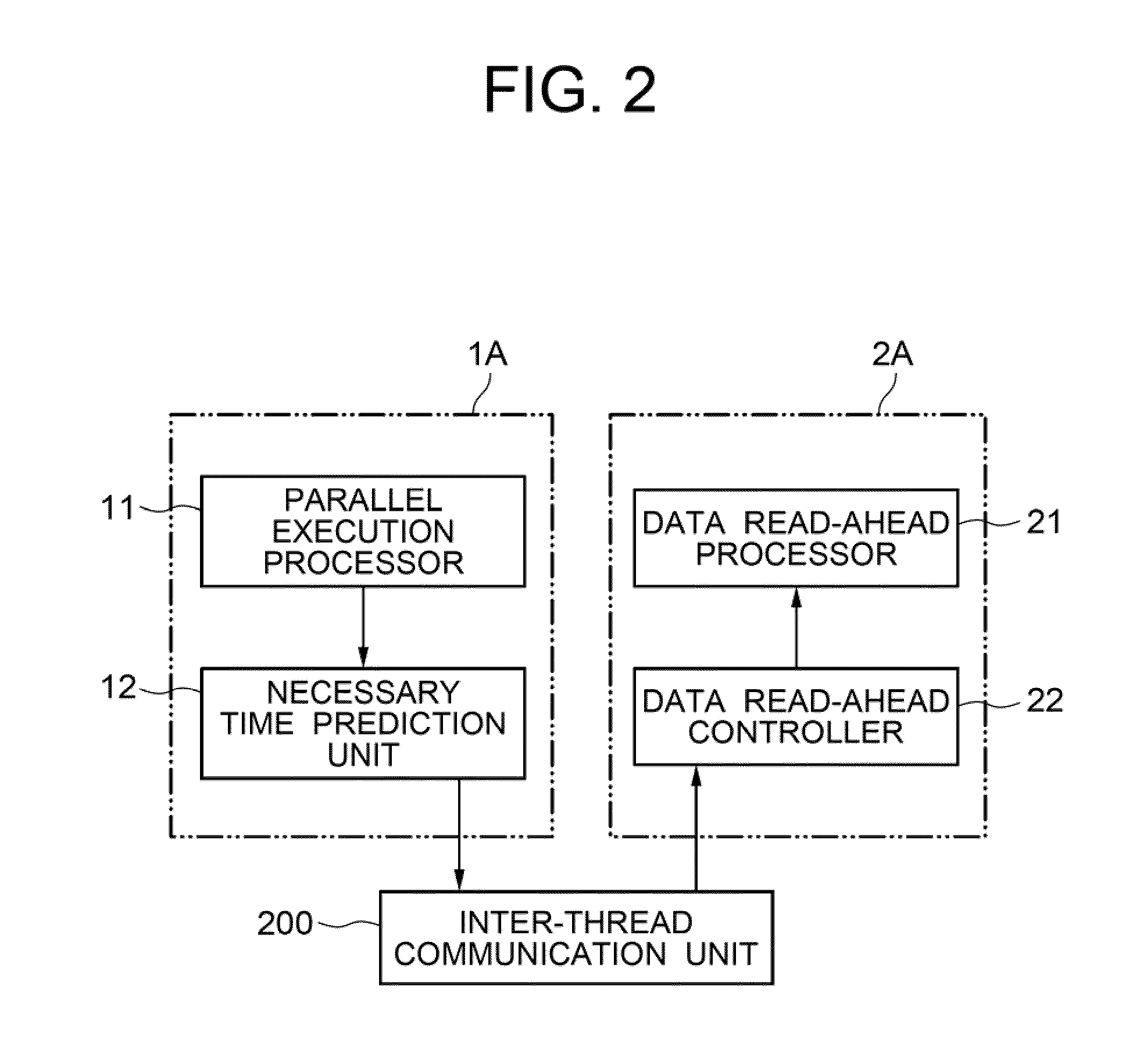

Memory access control system, memory access control method, and program thereof

ActiveUS8447933B2Efficient accessEffective maintenanceMemory adressing/allocation/relocationDigital computer detailsMemory typeControl system

In a multi-core processor of a shared-memory type, deterioration in the data processing capability caused by competitions of memory accesses from a plurality of processors is suppressed effectively. In a memory access controlling system for controlling accesses to a cache memory in a data read-ahead process when the multi-core processor of a shared-memory type performs a task including a data read-ahead thread for executing data read-ahead and a parallel execution thread for performing an execution process in parallel with the data read-ahead, the system includes a data read-ahead controller which controls an interval between data read-ahead processes in the data read-ahead thread adaptive to a data flow which varies corresponding to an input value of the parallel process in the parallel execution thread. By controlling the interval between the data read-ahead processes, competitions of memory accesses in the multi-core processor are suppressed.

Owner:NEC CORP

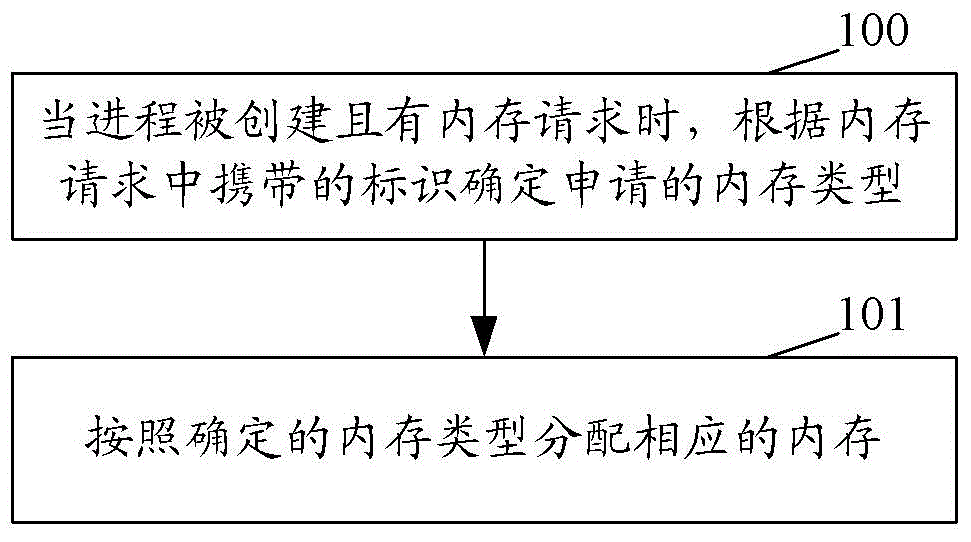

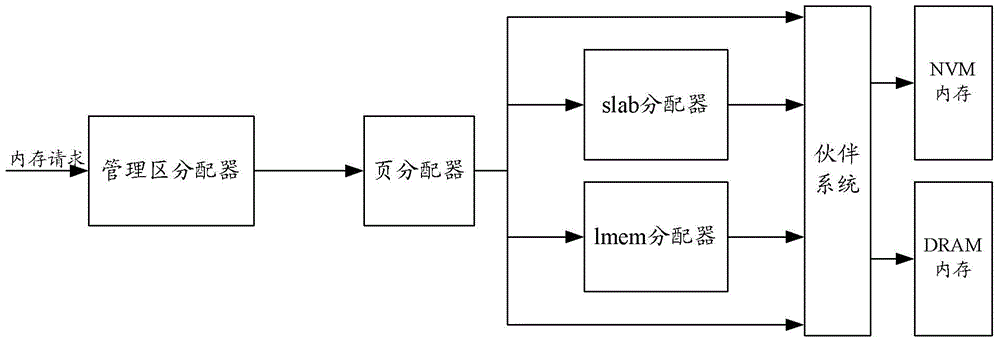

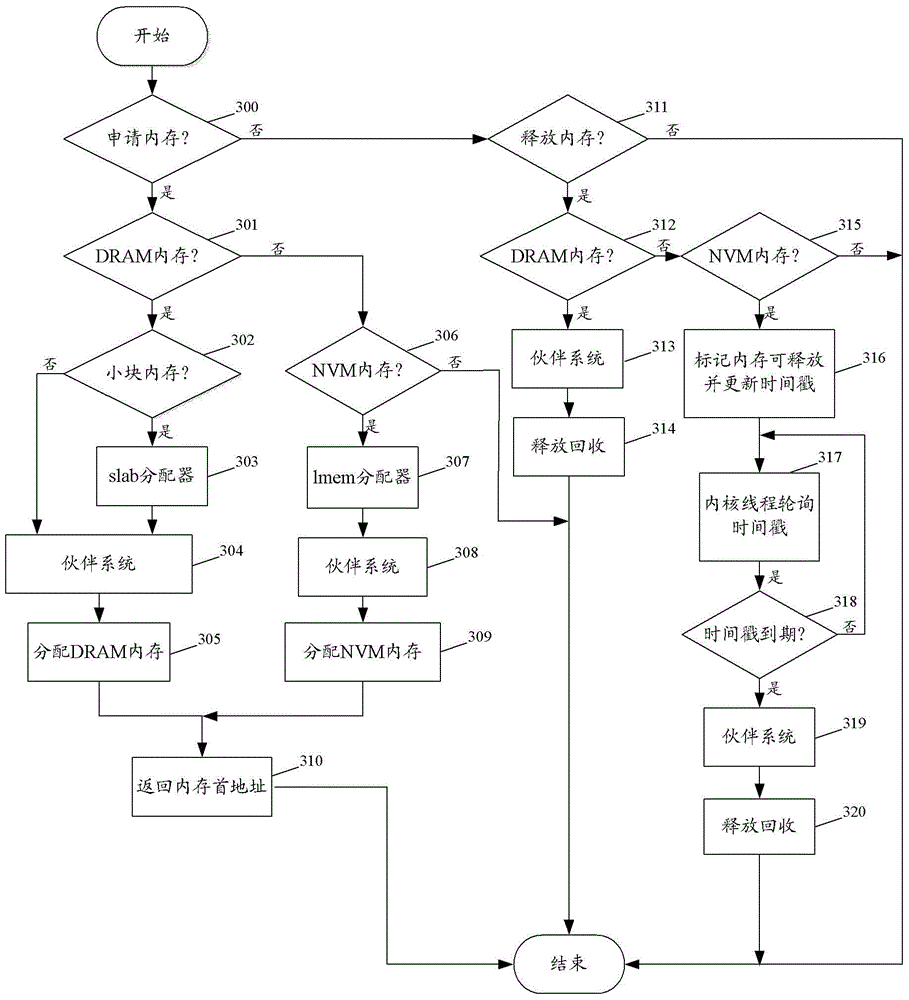

Heterogeneous memory management method and device

InactiveCN104102590AEfficient managementImprove throughputMemory adressing/allocation/relocationMemory typeDram memory

The invention discloses a heterogeneous memory management method and device. The method includes: when a process is created and a memory request is received, determining an applied memory type according to an identifier carried in the memory request; allocating a corresponding memory according to the determined memory type. By the method and device, a system-level process is ensured to be allocated to a fast DRAM (dynamic random access memory) for data processing, and a process for big data processing is reasonably put in an NVM (non-volatile memory) to run. By the method and device, the different types of memories perform data processing of specific types, so that influence on data processing due to access speed difference of the DRAM and the NVM is reduced greatly. On the other hand, when the allocated NVM is recycled, a recycling delay mechanism is adopted, and waiting time for big data processing process access is prolonged, so that the problem of deadlocking possibly caused by access to the DRAM and the NVM is avoided.

Owner:INSPUR BEIJING ELECTRONICS INFORMATION IND