Patents

Literature

3700results about "Logic circuits using elementary logic circuit components" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

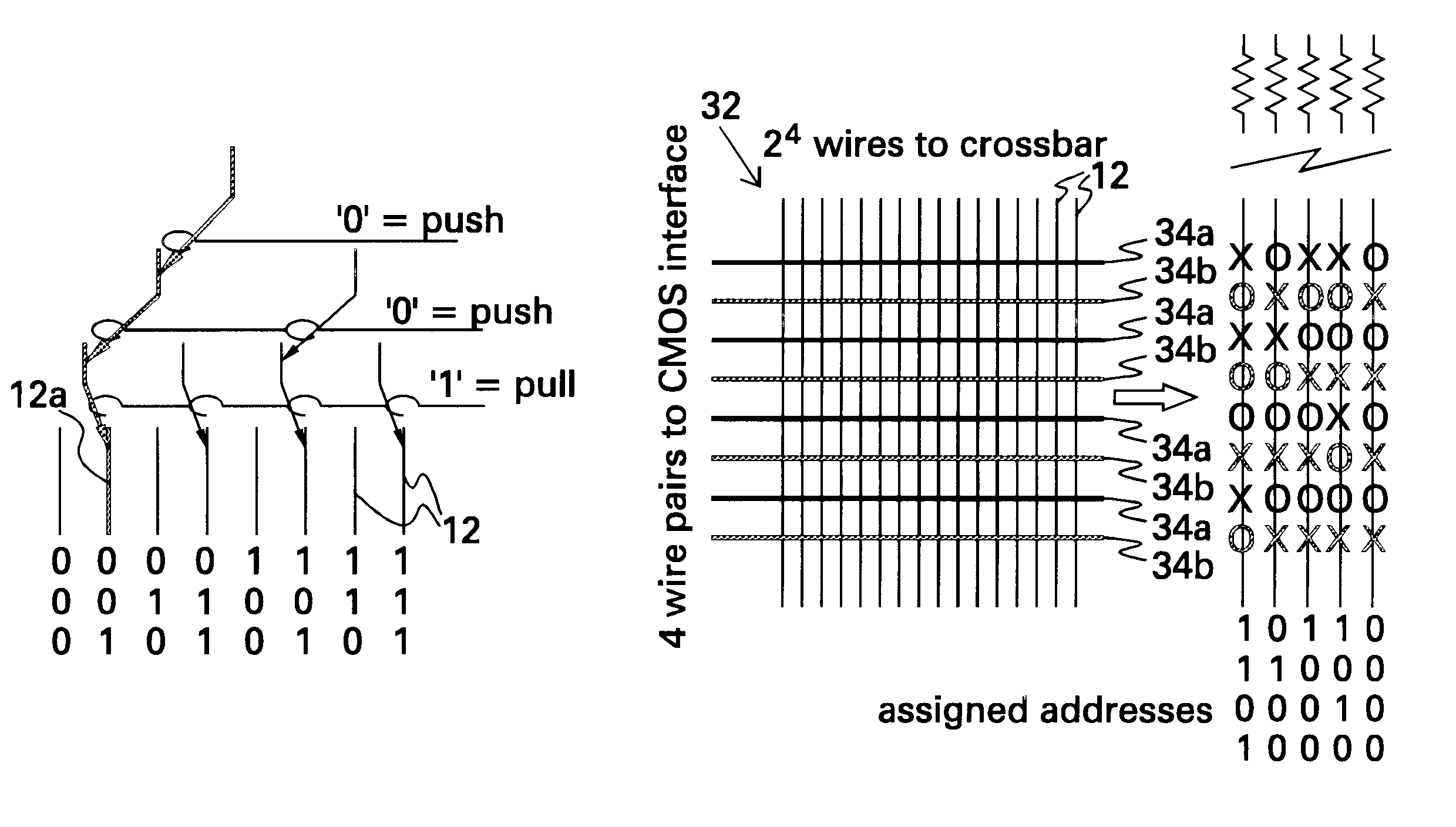

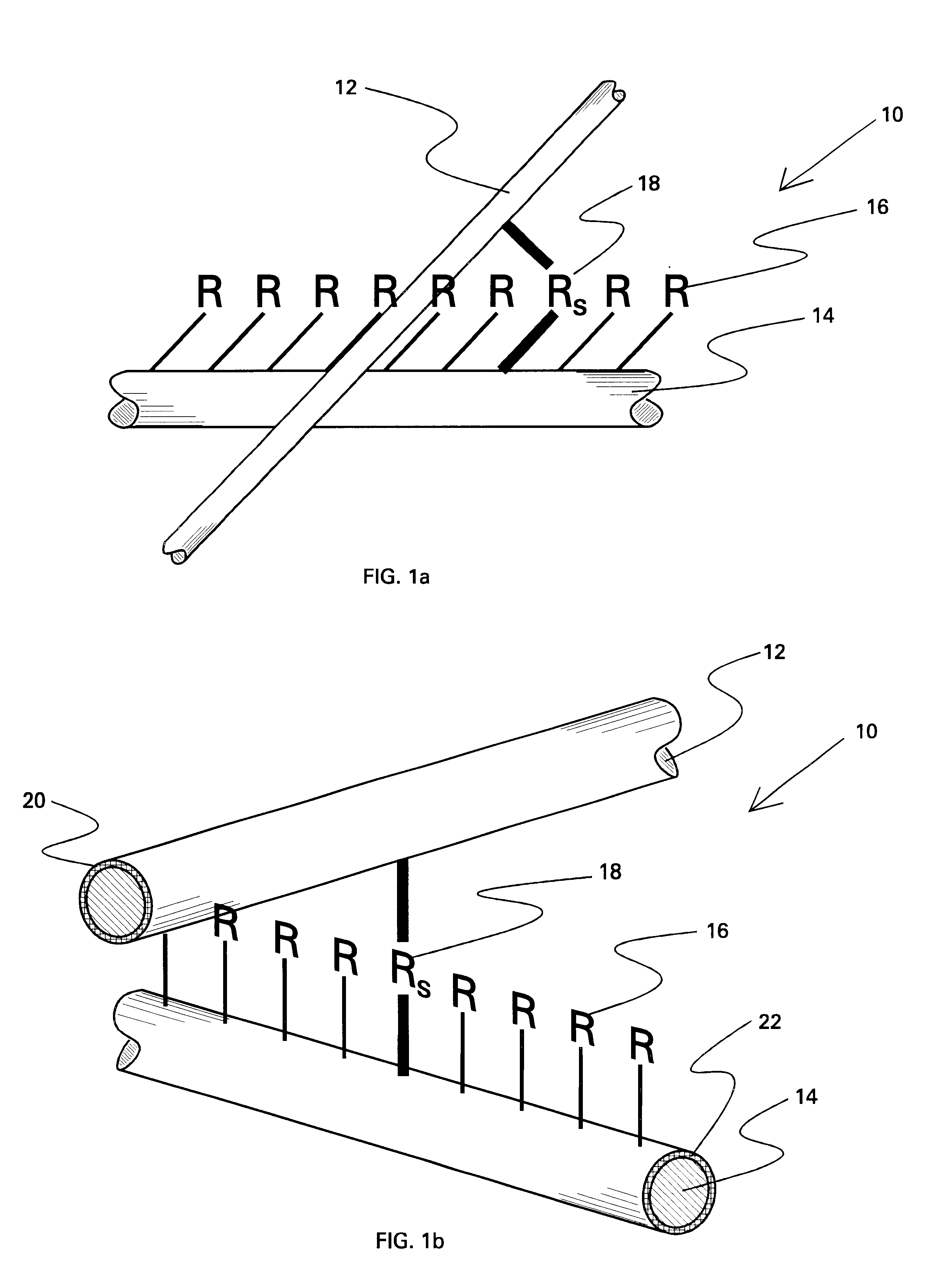

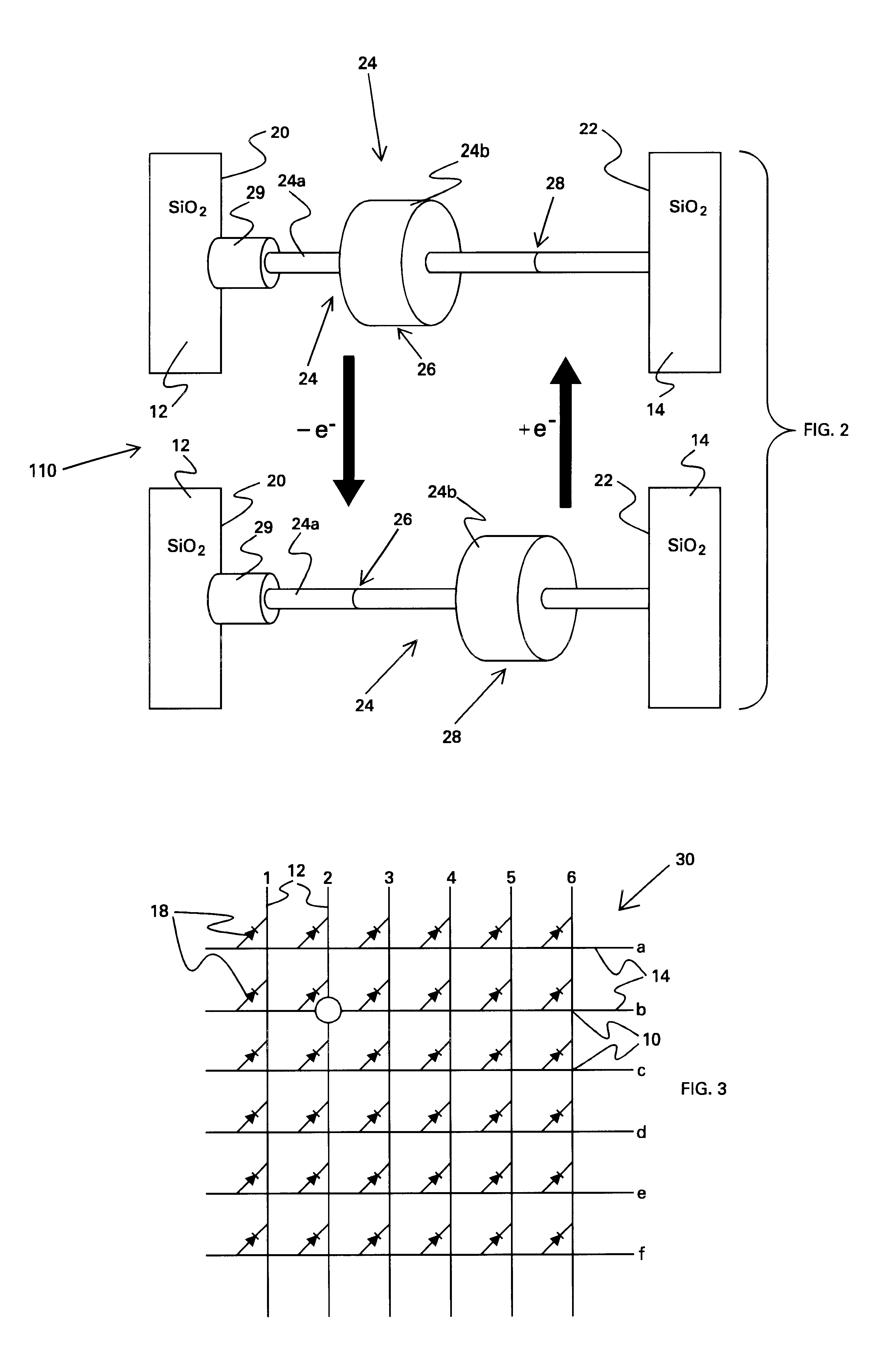

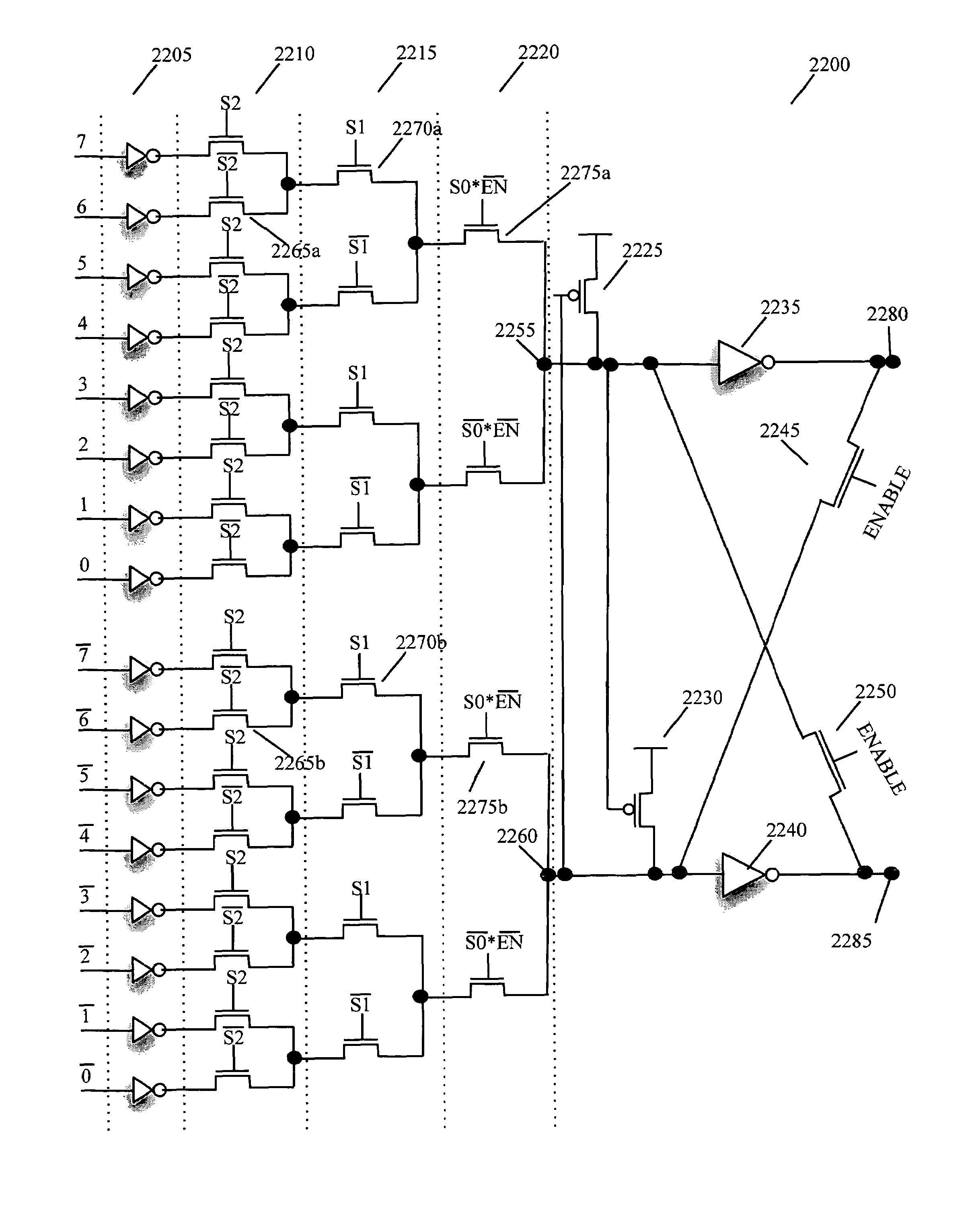

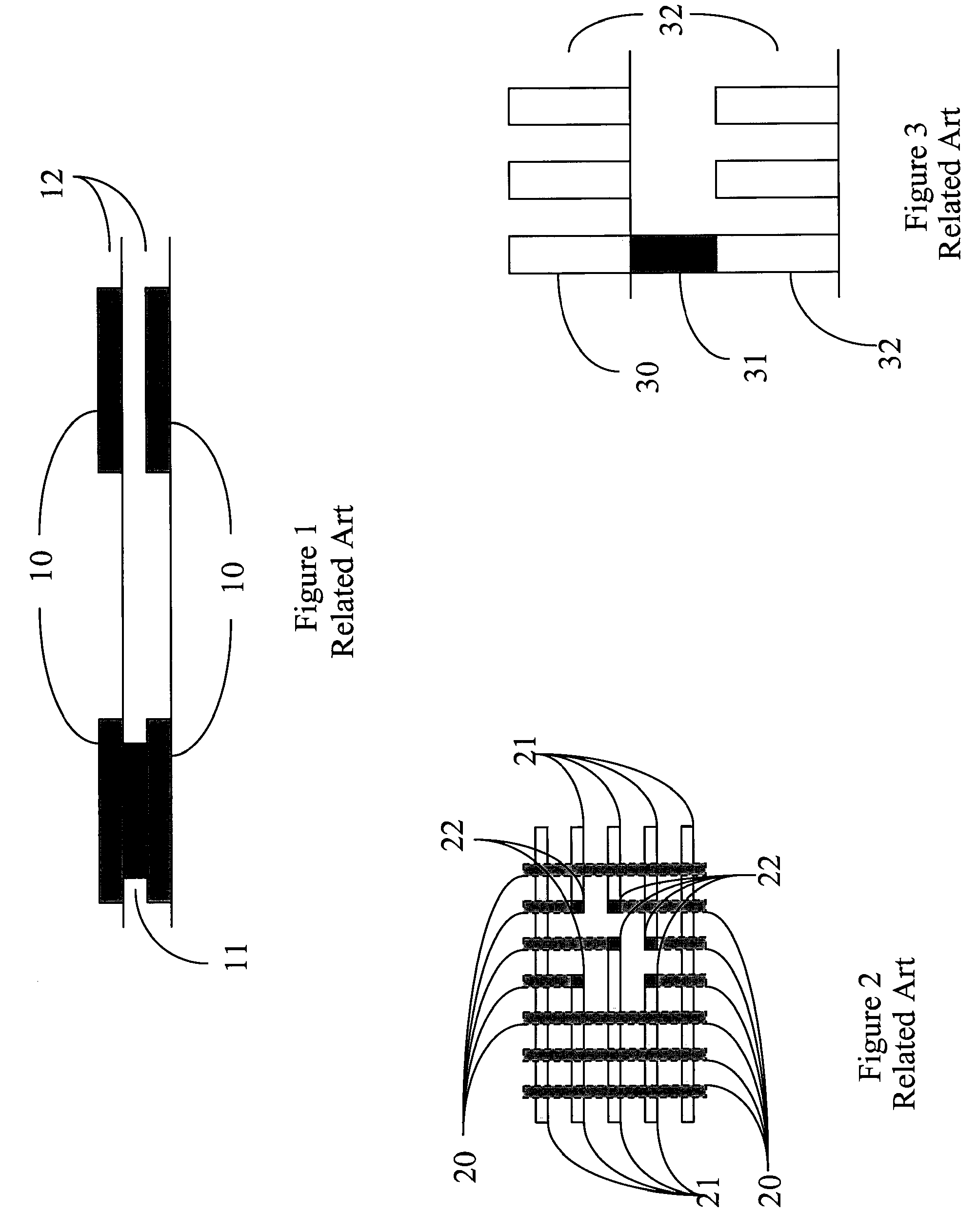

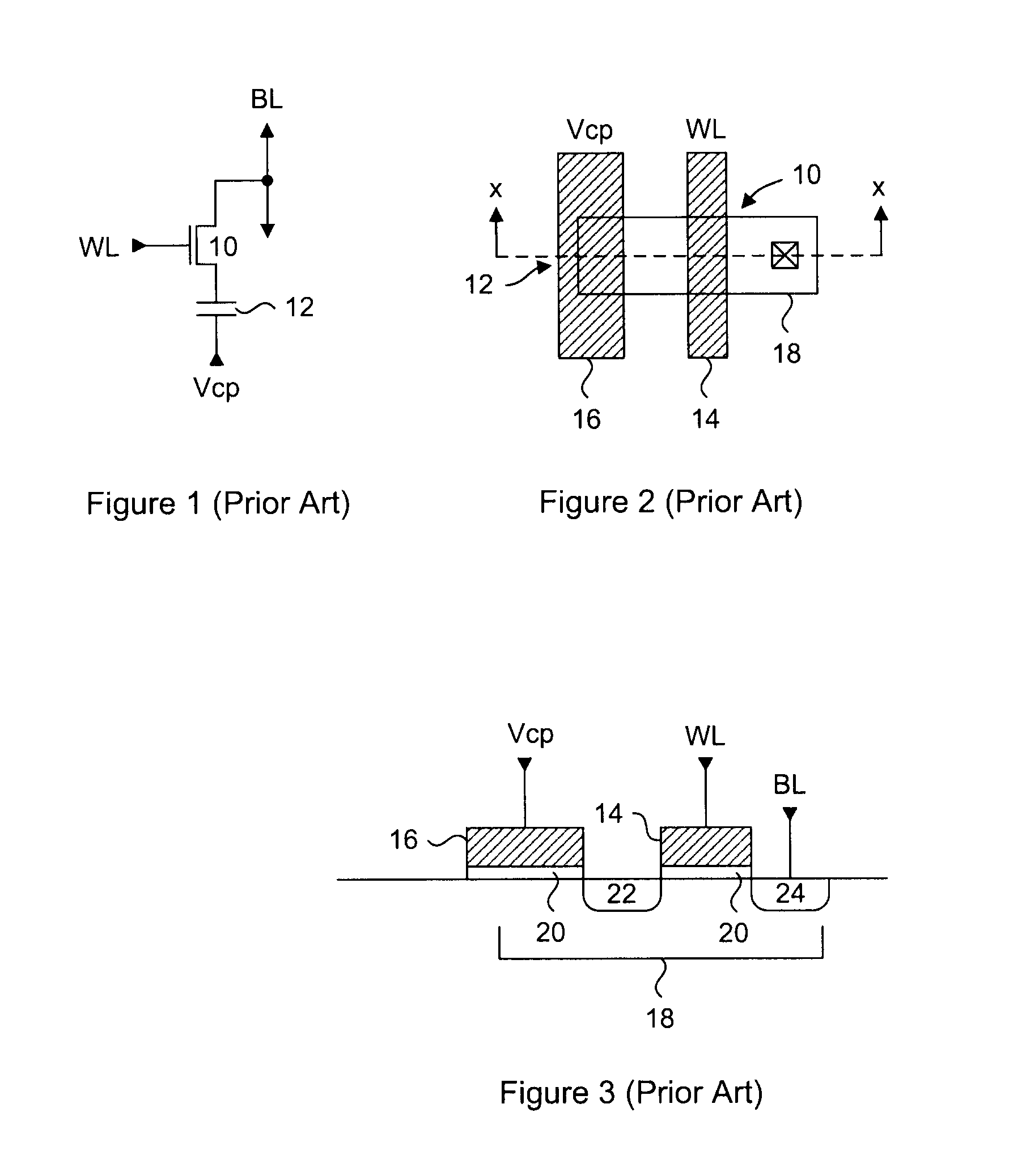

Demultiplexer for a molecular wire crossbar network (MWCN DEMUX)

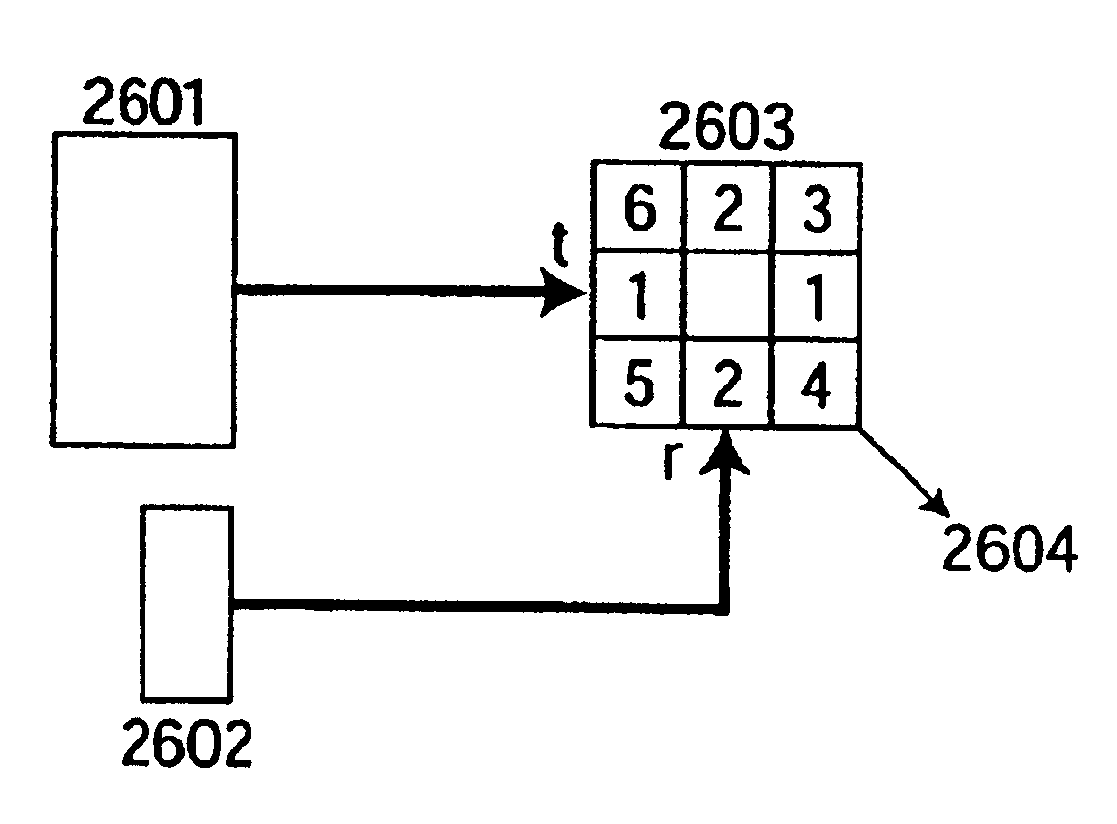

A demultiplexer for a two-dimensional array of a plurality of nanometer-scale switches (molecular wire crossbar network) is disclosed. Each switch comprises a pair of crossed wires which form a junction where one wire crosses another and at least one connector species connecting said pair of crossed wires in said junction. The connector species comprises a bi-stable molecule. The demultiplexer comprises a plurality of address lines accessed by a first set of wires in the two-dimensional array by randomly forming contacts between each wire in the first set of wires to at least one of the address lines. The first set of wires crosses a second set of wires to form the junctions. The demultiplexer solves both the problems of data input and output to a molecular electronic system and also bridges the size gap between CMOS and molecules with an architecture that can scale up to extraordinarily large numbers of molecular devices. Further, the demultiplexer is very defect tolerant, and can work despite a large number of defects in the system.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

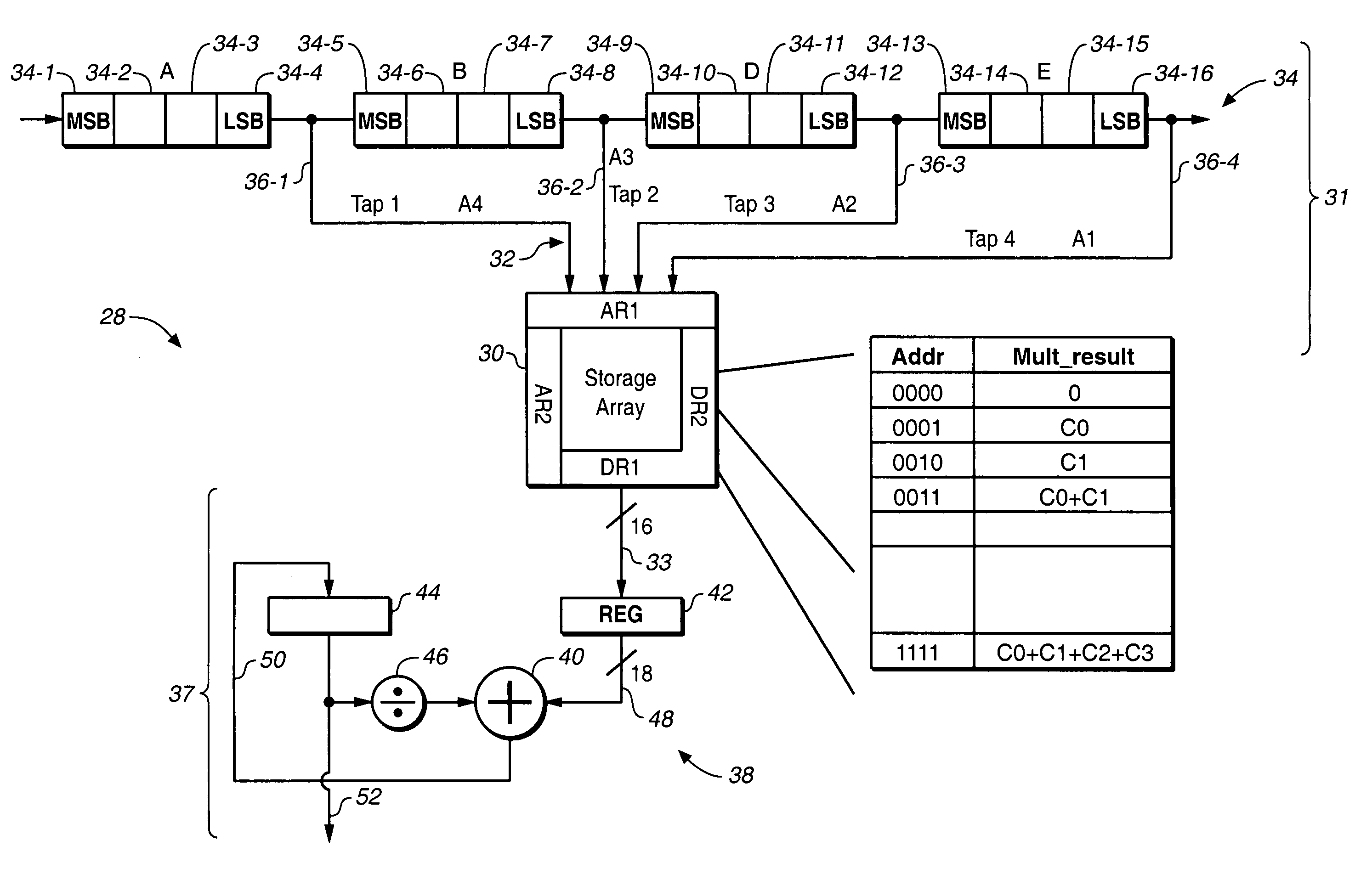

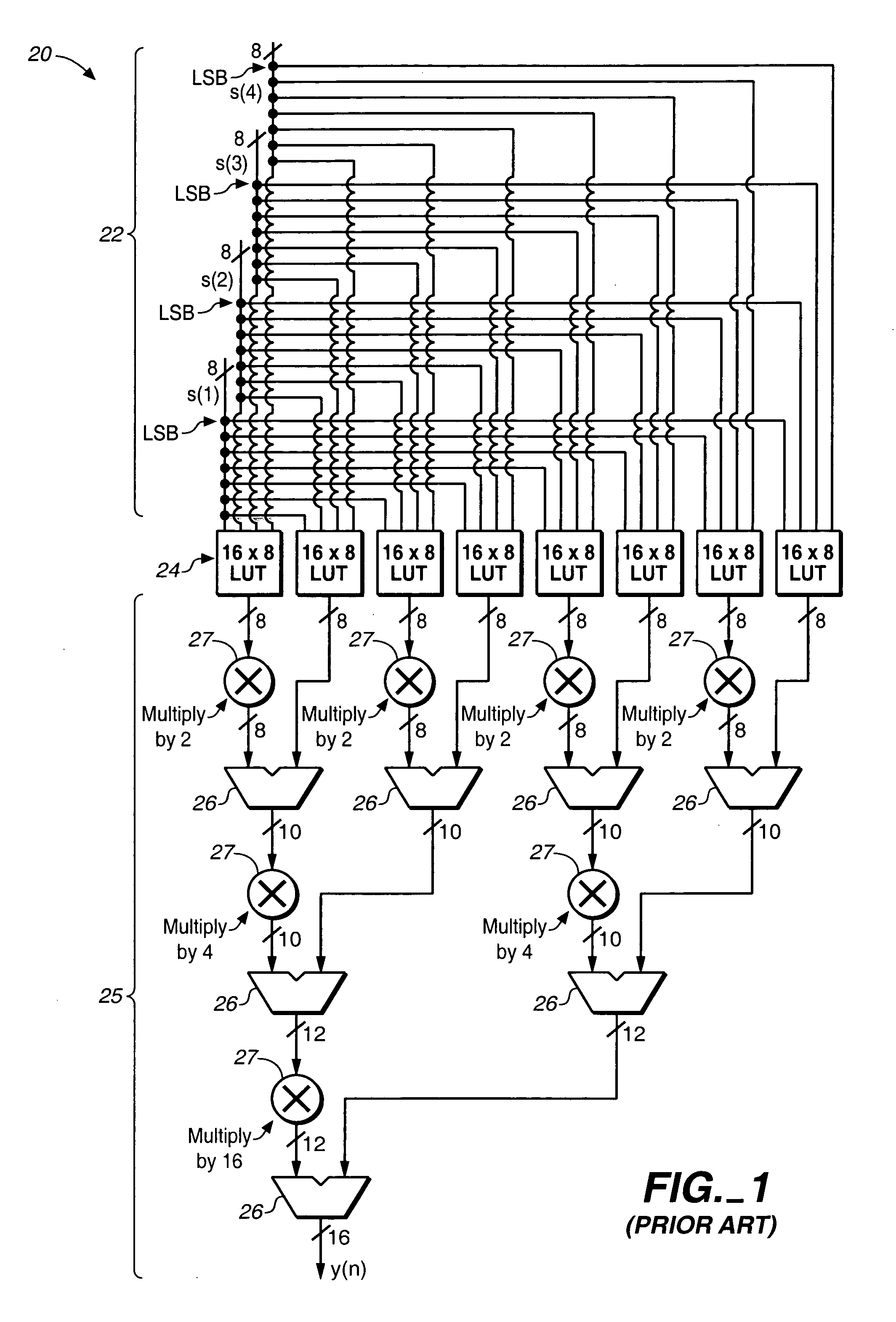

Variable fixed multipliers using memory blocks

InactiveUS6943579B1Computations using contact-making devicesComputation using non-contact making devicesProgrammable logic deviceOperand

A programmable logic device includes at least one RAM block generating a first multi-bit calculation result which may, but does not necessarily, involve a multiplication of two operands. A shift operation is driven by a second multi-bit calculation result shifts the second multi-bit calculation result by at least one bit to generate a shifted second multi-bit calculation result. A multi-bit adder coupled to the at least one RAM block adds the shifted second multi-bit calculation result to the first multi-bit calculation result.

Owner:ALTERA CORP

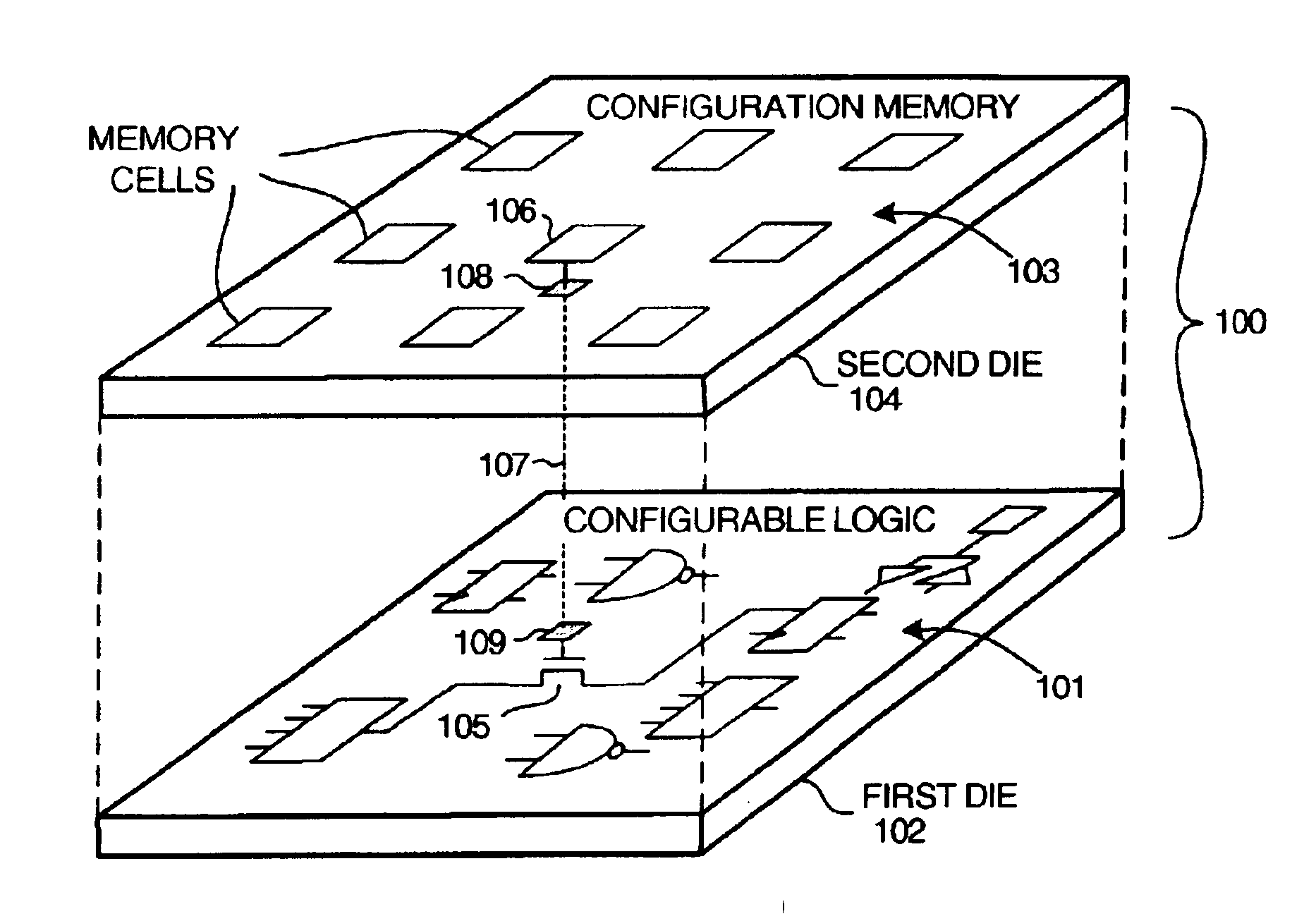

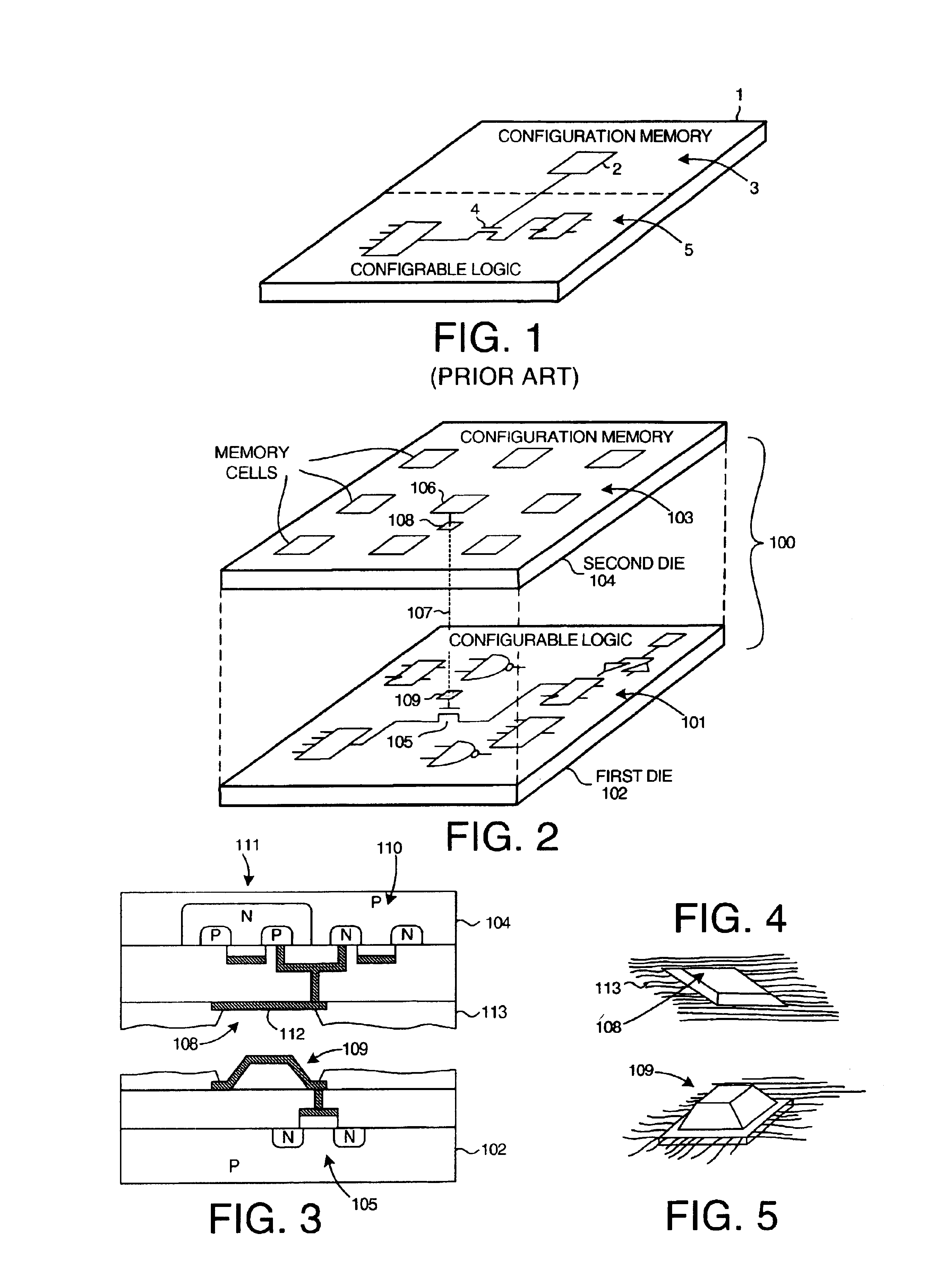

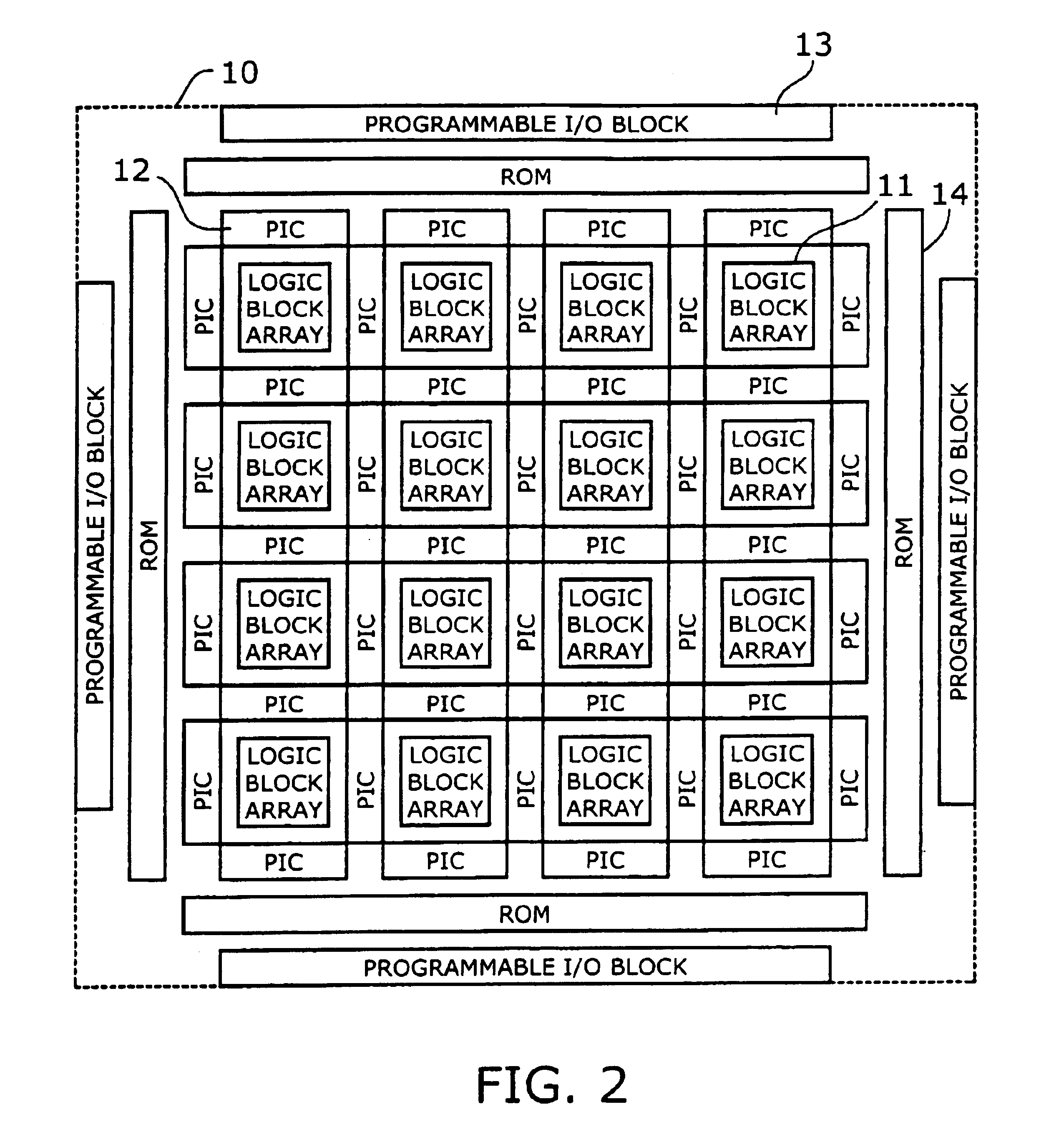

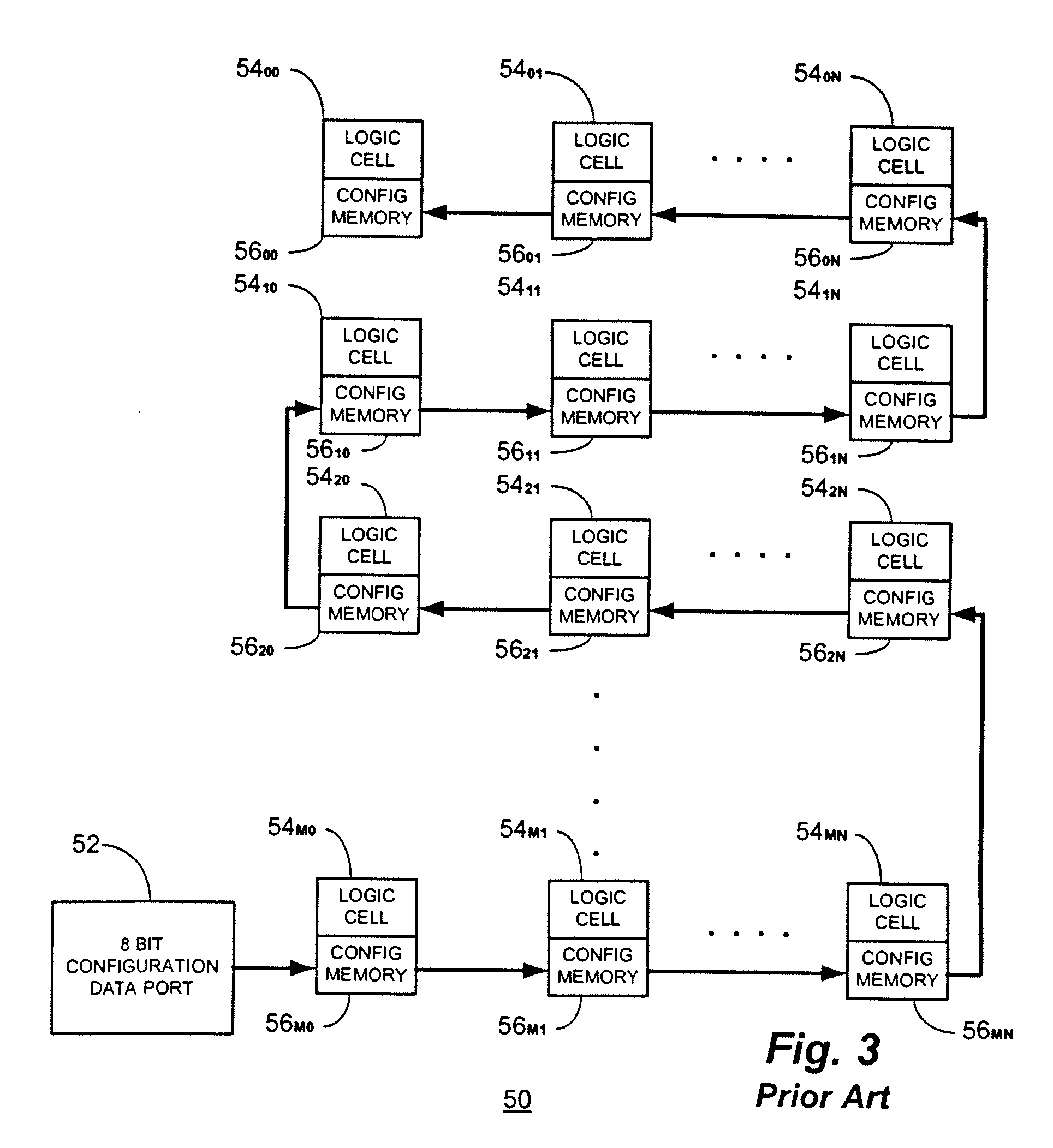

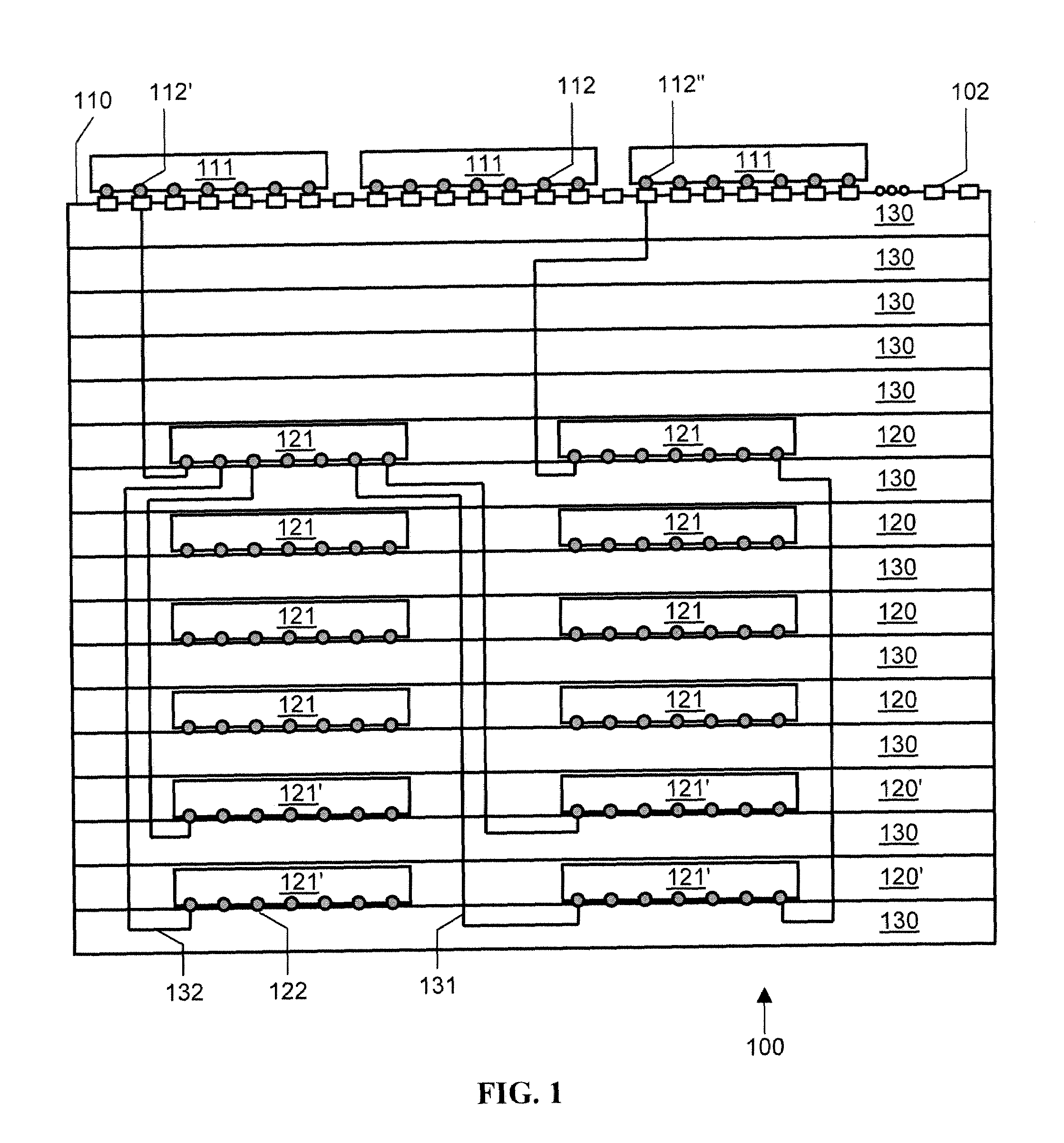

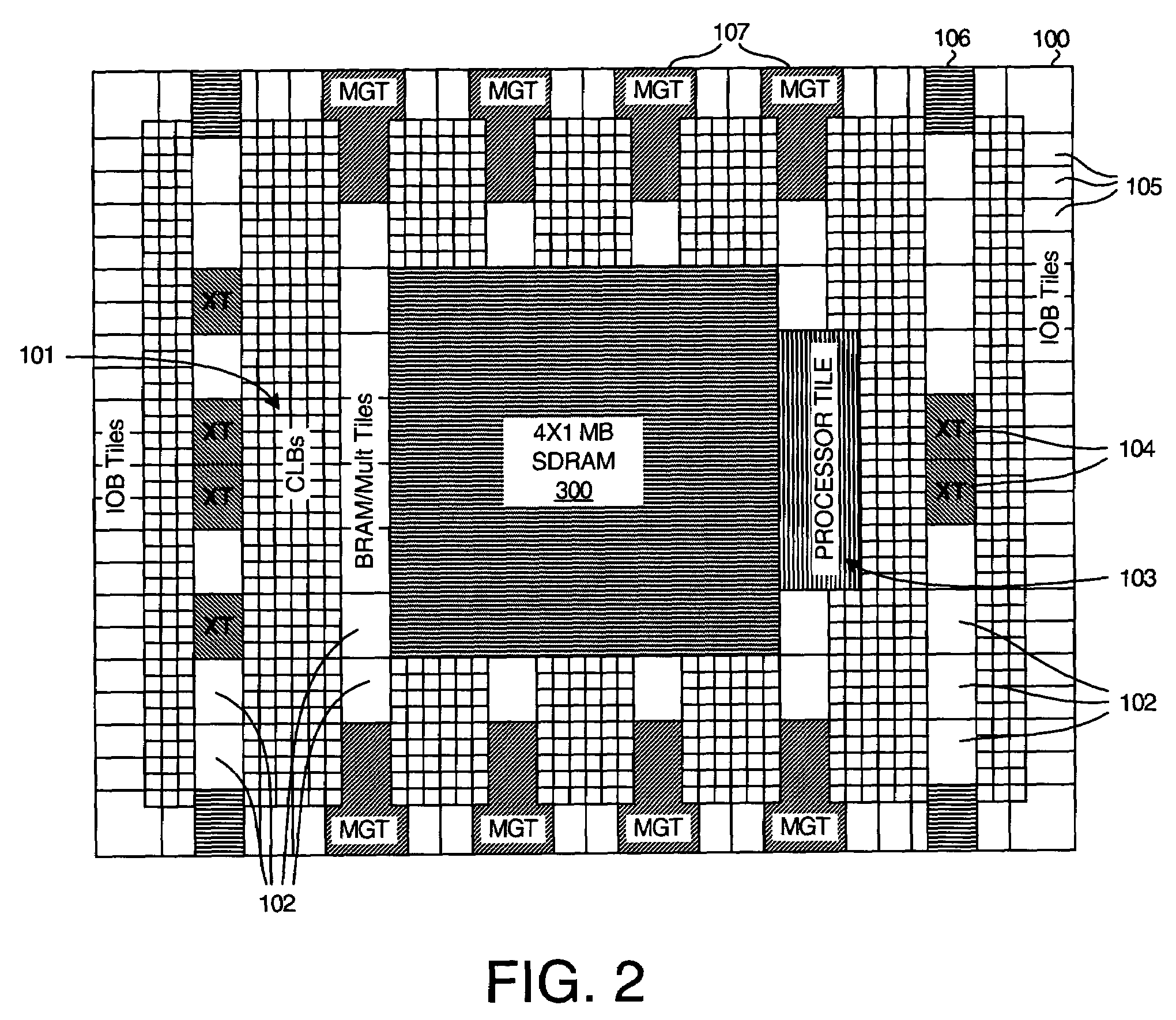

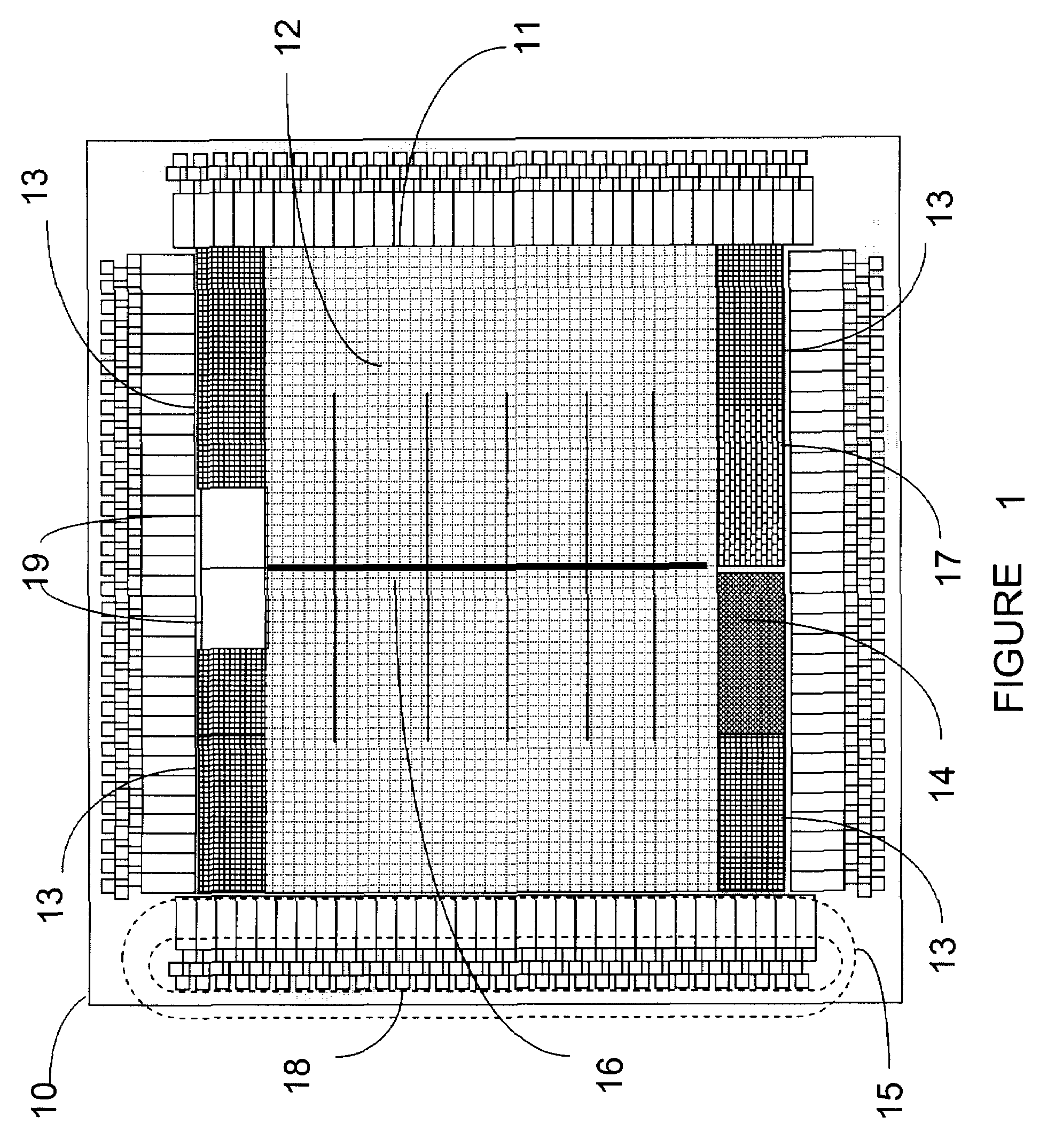

Multi-chip programmable logic device having configurable logic circuitry and configuration data storage on different dice

InactiveUS6917219B2Increase volumeIncrease productionSemiconductor/solid-state device detailsSolid-state devicesProgrammable logic deviceLogical part

The circuitry of a programmable logic device (for example, an FPGA) includes a configurable logic portion and a configuration memory. The configuration memory stores configuration data that configures the configurable logic portion to realize a user-defined circuit. The configurable logic portion is disposed on a first die whereas the configuration memory is disposed on a second die. The second die is bonded to the first die in stacked relation. Each bit of configuration data passes from the second die to the first die through a pair of micropads. One micropad of the pair is disposed on the first die and the other micropad of the pair is disposed on the second die. When the first die and second die are brought together in face-to-face relation, the two micropads form an electrical connection through which the configuration data bit passes from the second die to the first die.

Owner:XILINX INC

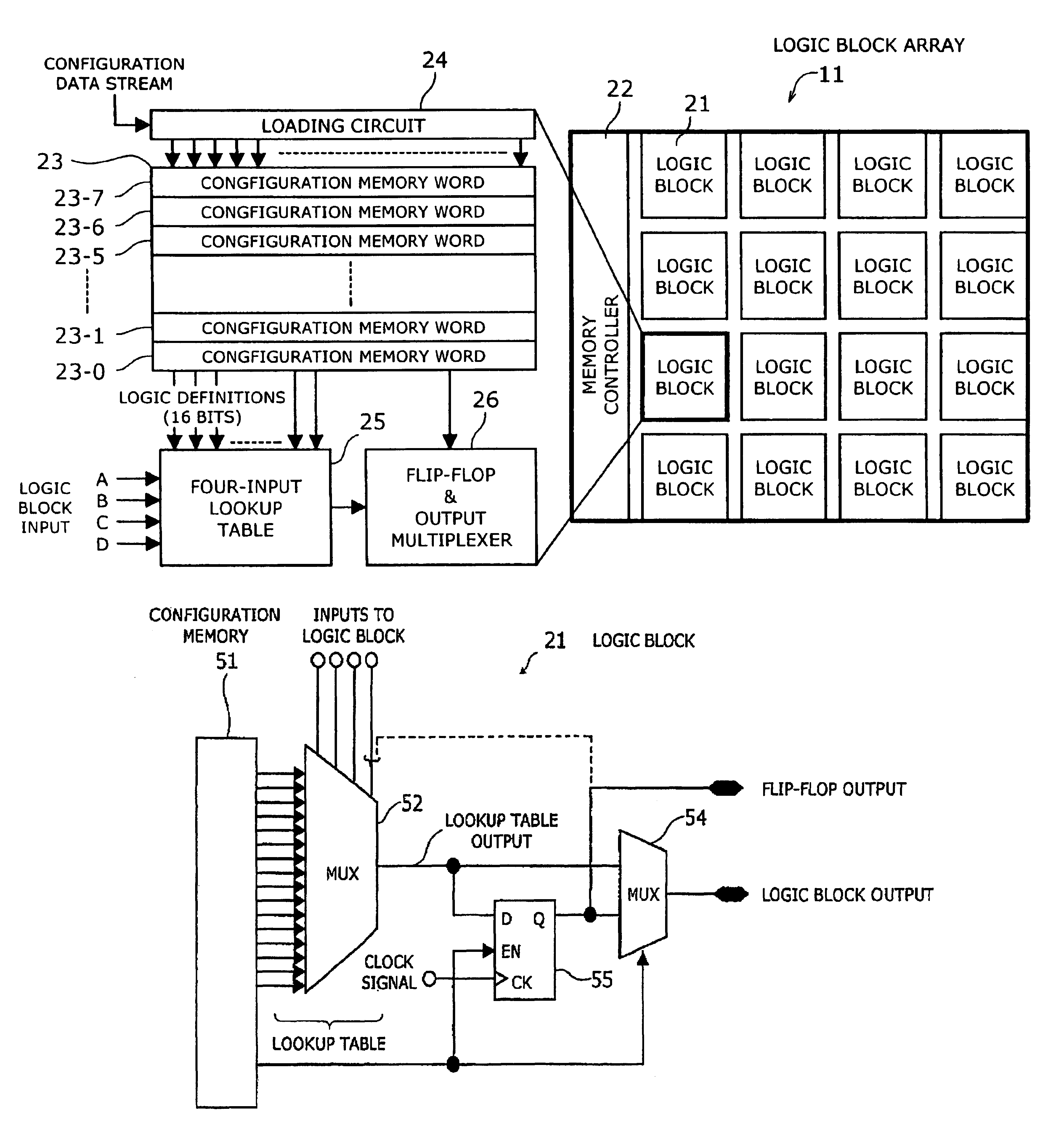

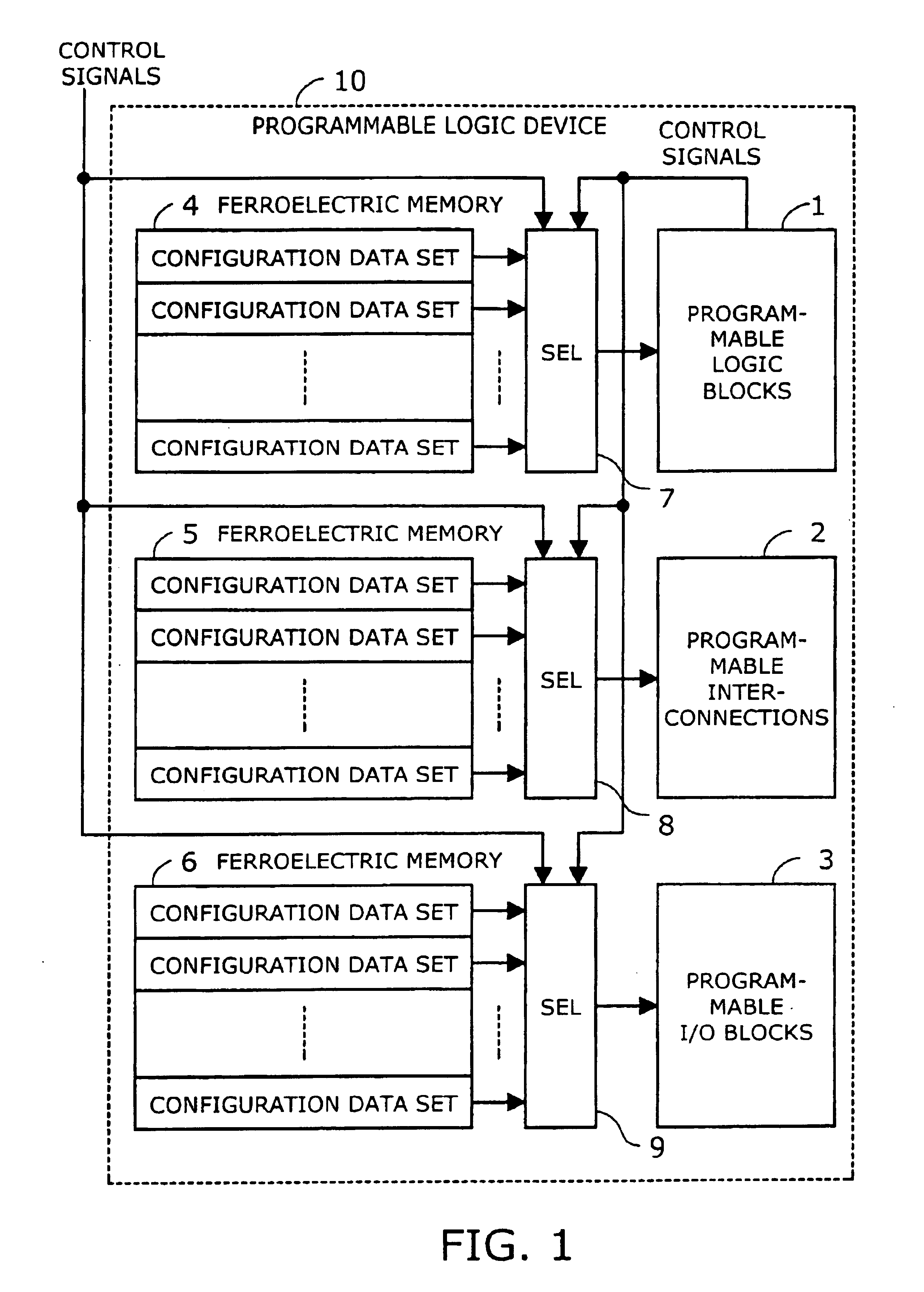

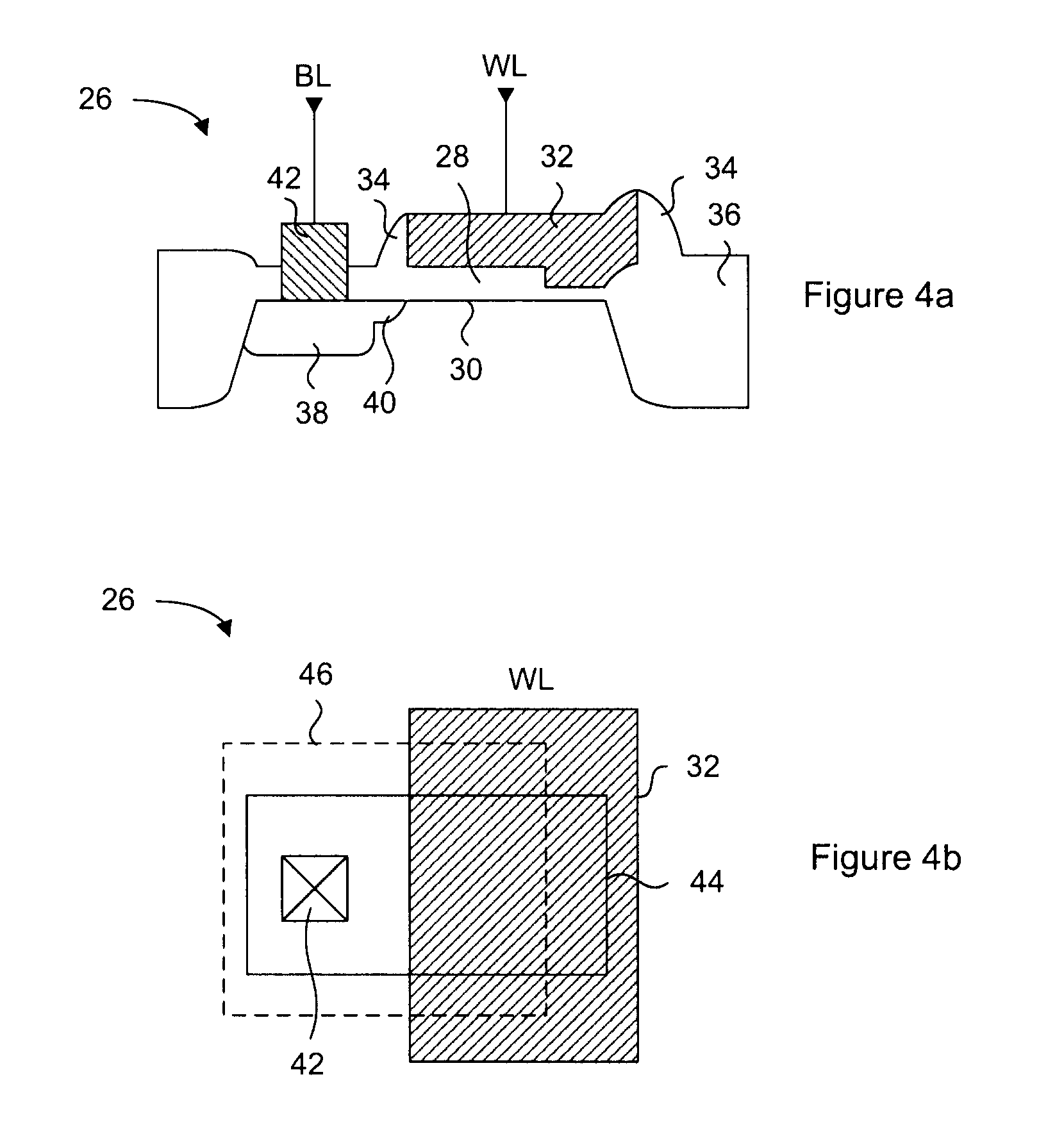

Programmable logic device with ferroelectric configuration memories

InactiveUS6924663B2Increase the effective amountEfficient architectureDigital storageInternal/peripheral component protectionElectricityData stream

A programmable logic device with ferroelectric configuration memories storing multiple configuration data sets. The device has programmable logic blocks, interconnections, and I / O blocks to provide desired logic functions. Those building blocks can be dynamically reconfigured by changing the selection of configuration data stored in the device's integral configuration memories. The configuration memories are divided into groups, so that they can be loaded concurrently with multiple configuration data streams. To protect the content of configuration memories from unauthorized access, the device employs an authentication mechanism that uses security IDs stored in the configuration memories. The device has a memory controller to provide an appropriate power supply sequence for ferroelectric memory cells to ensure the reliable data retention when the device is powered up or shut down.

Owner:FUJITSU SEMICON LTD

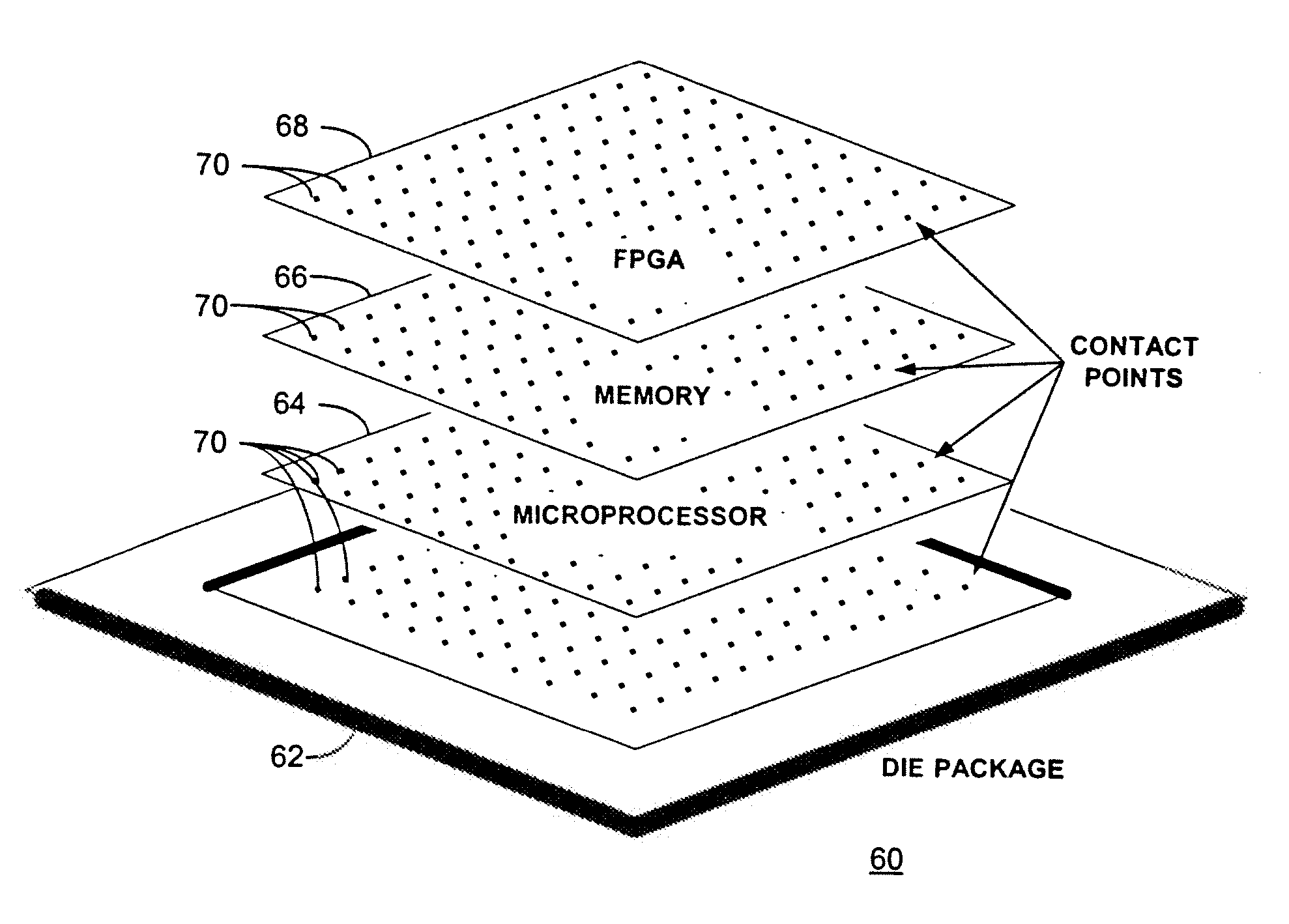

Reconfigurable processor module comprising hybrid stacked integrated circuit die elements

InactiveUS20060195729A1Energy efficient ICTError detection/correctionEngineeringField-programmable gate array

A reconfigurable processor module comprising hybrid stacked integrated circuit (“IC”) die elements. In a particular embodiment disclosed herein, a processor module with reconfigurable capability may be constructed by stacking one or more thinned microprocessor, memory and / or field programmable gate array (“FPGA”) die elements and interconnecting the same utilizing contacts that traverse the thickness of the die. The processor module disclosed allows for a significant acceleration in the sharing of data between the microprocessor and the FPGA element while advantageously increasing final assembly yield and concomitantly reducing final assembly cost.

Owner:ARBOR GLOBAL STRATEGIES LLC

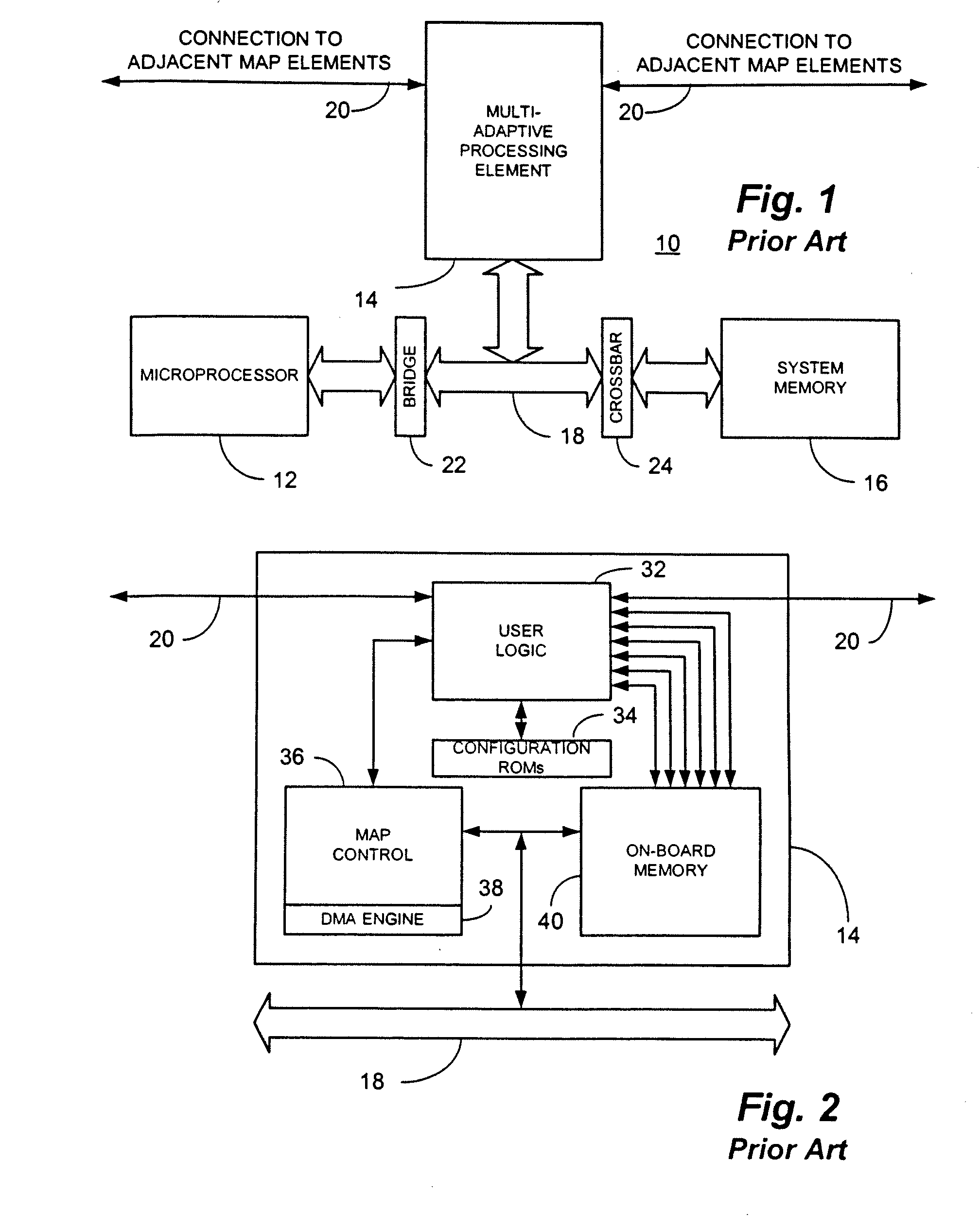

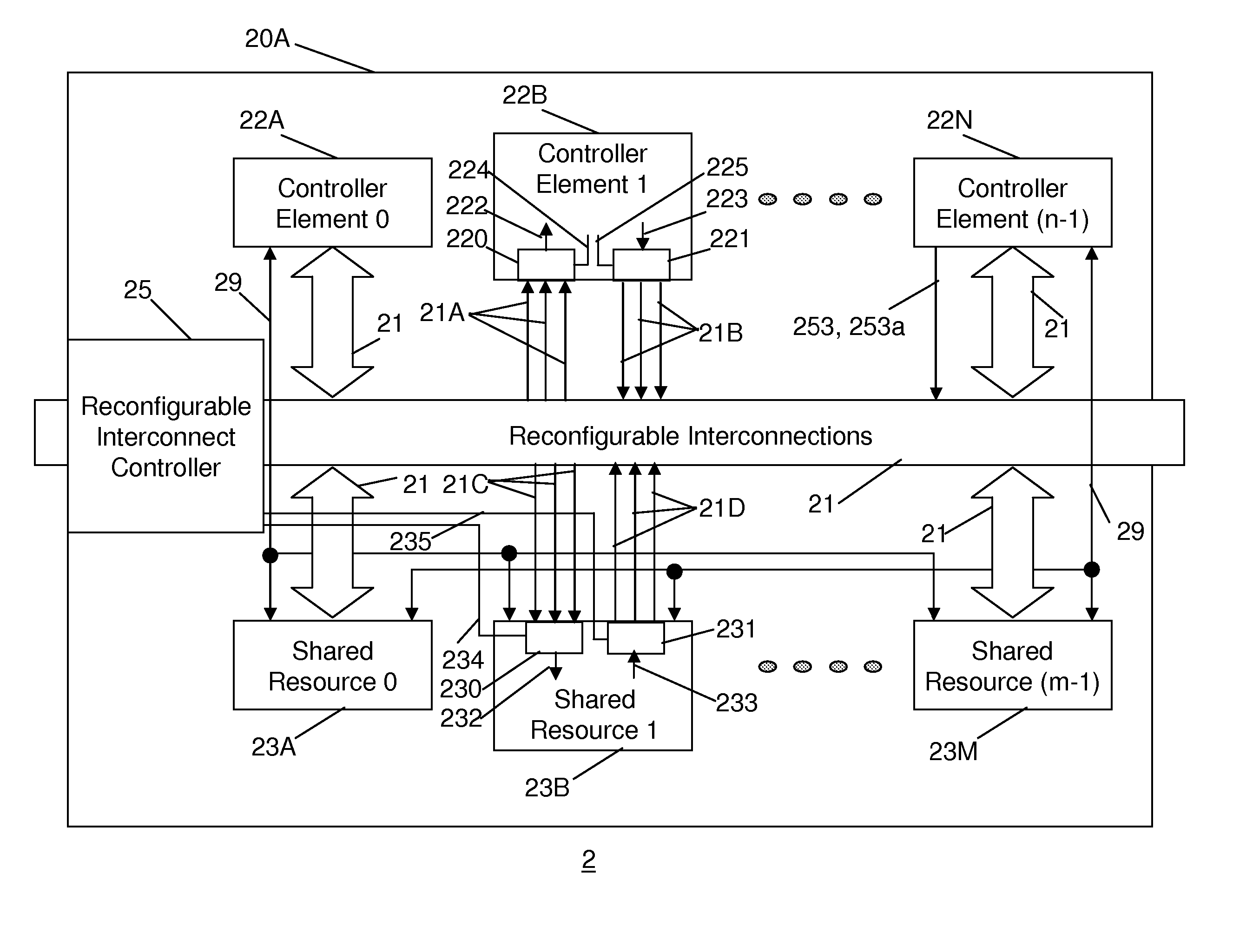

Reconfigurable integrated circuit

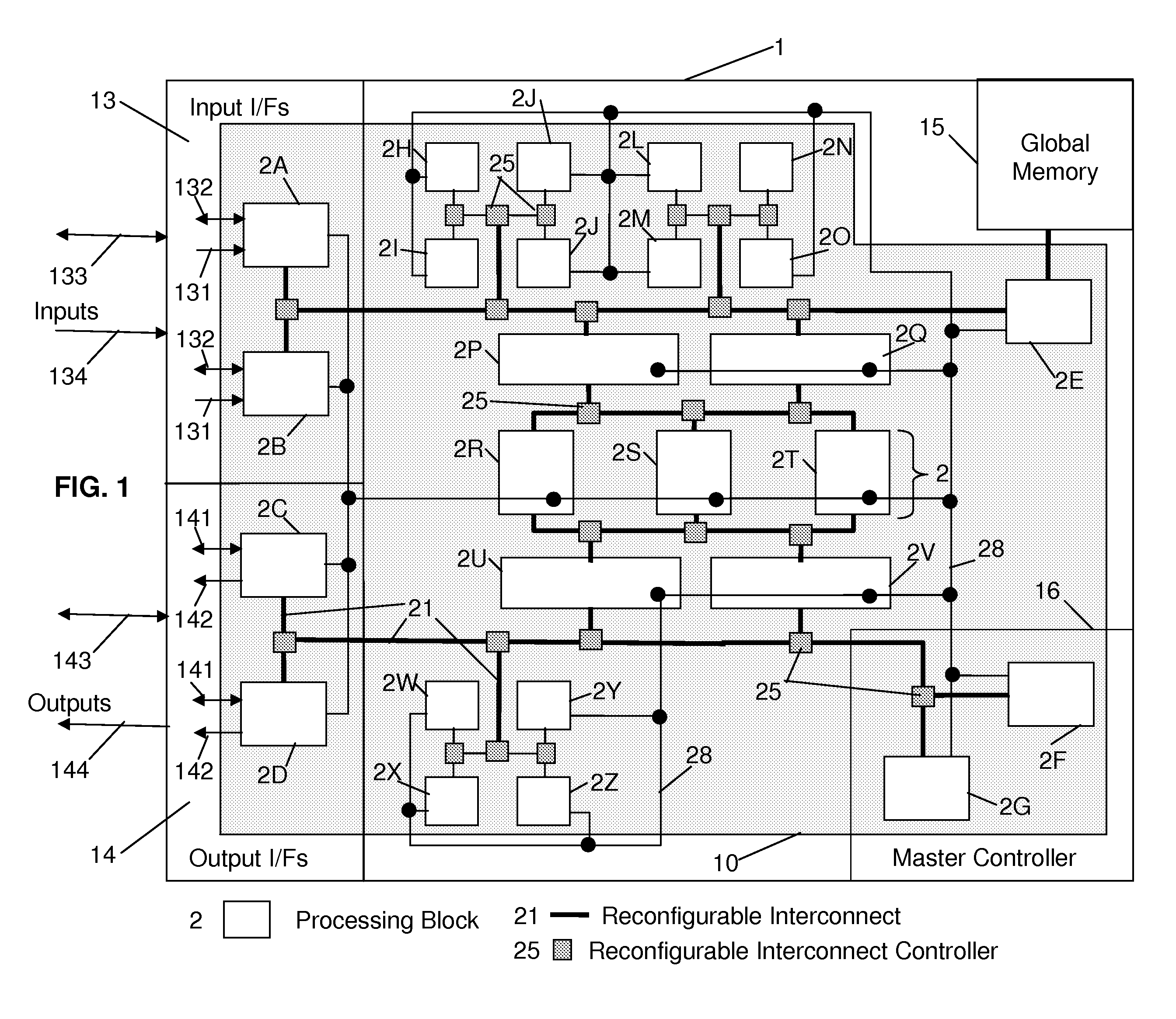

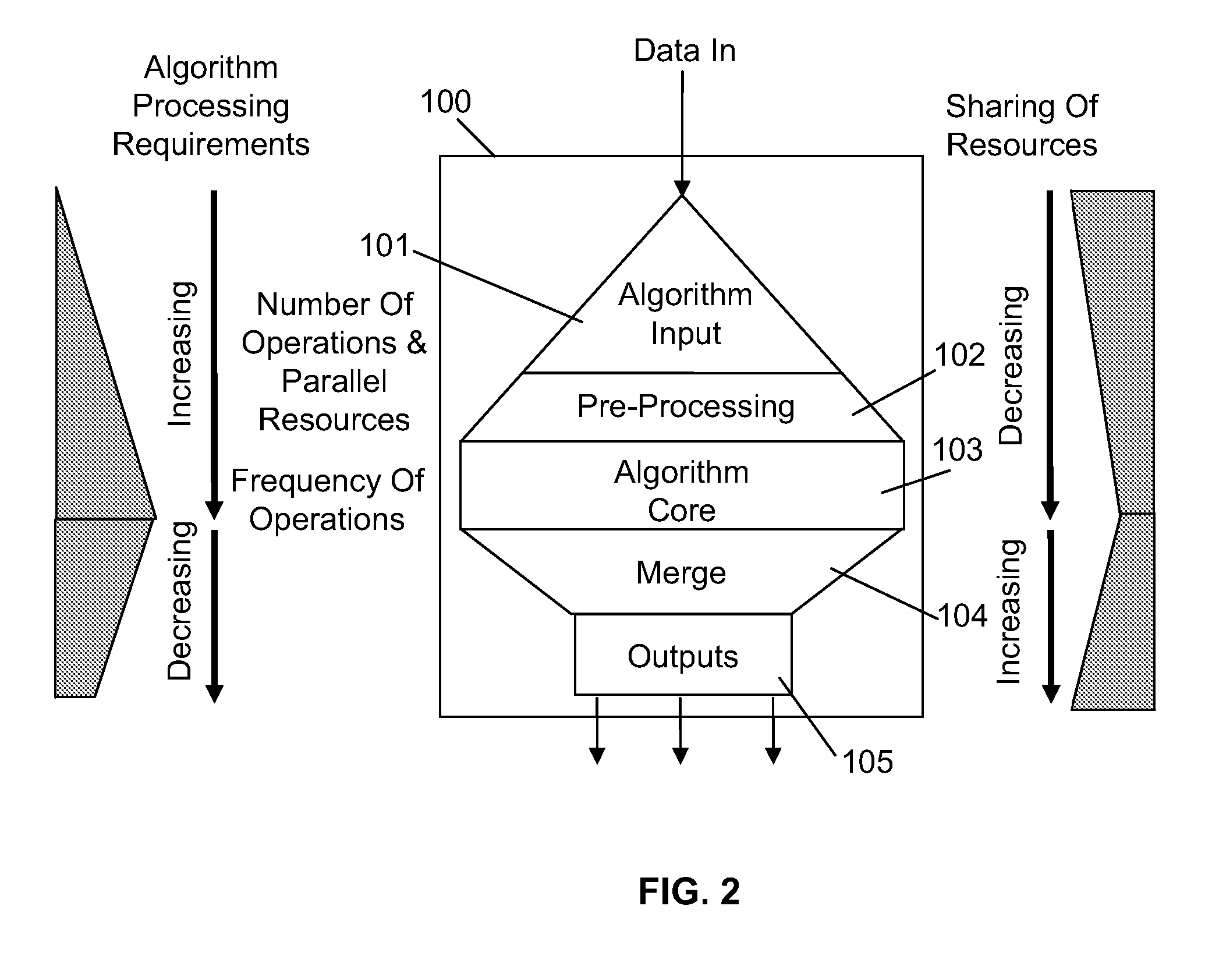

InactiveUS20070143577A1Energy efficient ICTArchitecture with single central processing unitNon real timeResource block

A reconfigurable integrated circuit is provided wherein the available hardware resources can be optimised for a particular application. Dynamically reconfiguring (in both real-time and non real-time) the available resources and sharing a plurality of processing elements with a plurality of controller elements achieve this. In a preferred embodiment the integrated circuit includes a plurality of processing blocks, which interface to a reconfigurable interconnection means. A processing block has two forms, namely a shared resource block and a dedicated resource block. Each processing block consists of one or a plurality of controller elements and a plurality of processing elements. The controller element and processing element generally comprise diverse rigid coarse and fine grained circuits and are interconnected through dedicated and reconfigurable interconnect. The processing blocks can be configured as a hierarchy of blocks and or fractal architecture.

Owner:AKYA HLDG

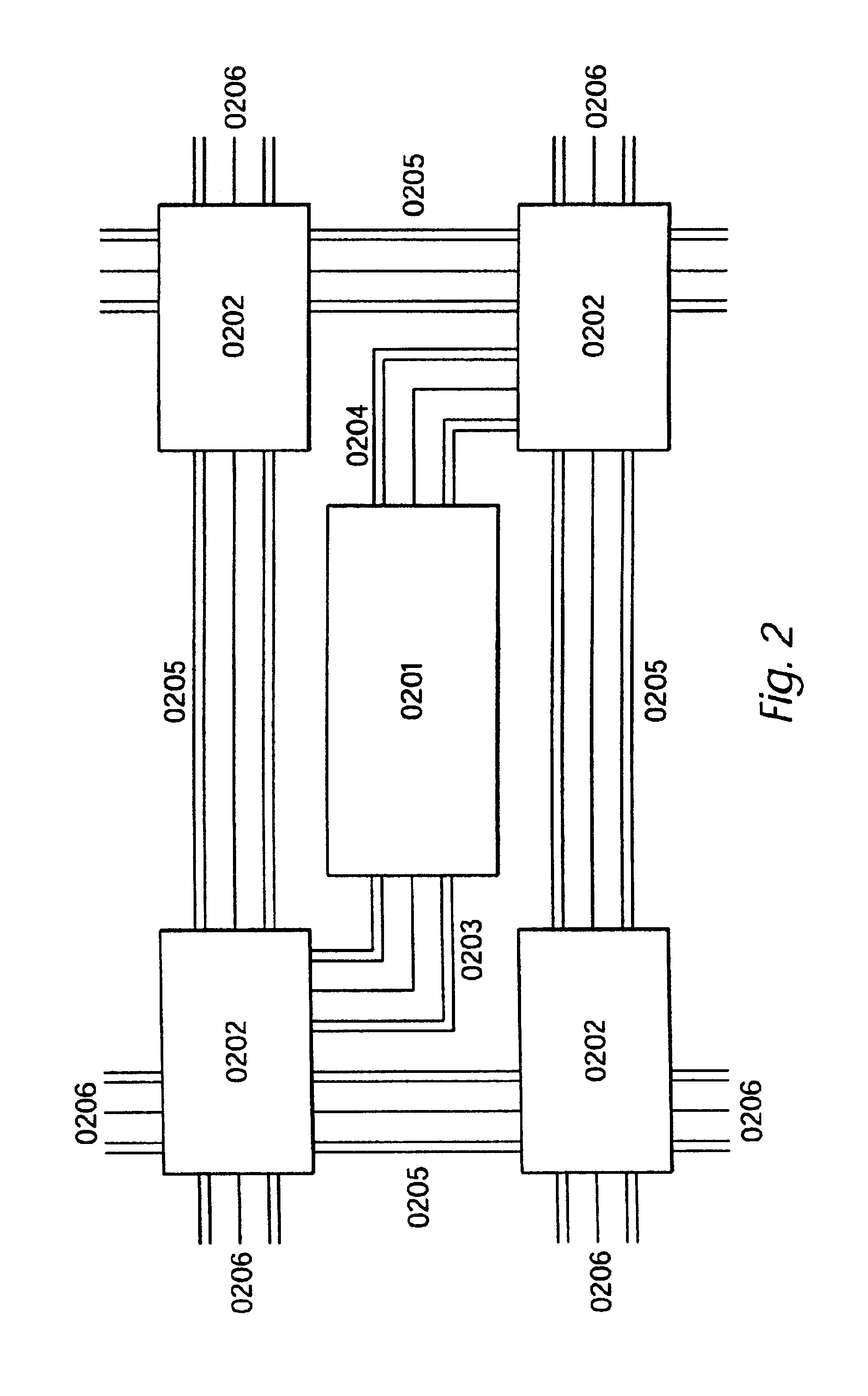

Internal bus system for DFPS and units with two- or multi-dimensional programmable cell architectures, for managing large volumes of data with a high interconnection complexity

InactiveUS7010667B2Multiple digital computer combinationsArchitecture with single central processing unitNetwork packetInterconnection

An internal bus system for DFPs and units with two- or multi-dimensional programmable cell architectures, for managing large volumes of data with a high interconnection complexity. The bus system can transmit data between a plurality of function blocks, where multiple data packets can be on the bus at the same time. The bus system automatically recognizes the correct connection for various types of data or data transmitters and sets it up.

Owner:PACT XPP TECH

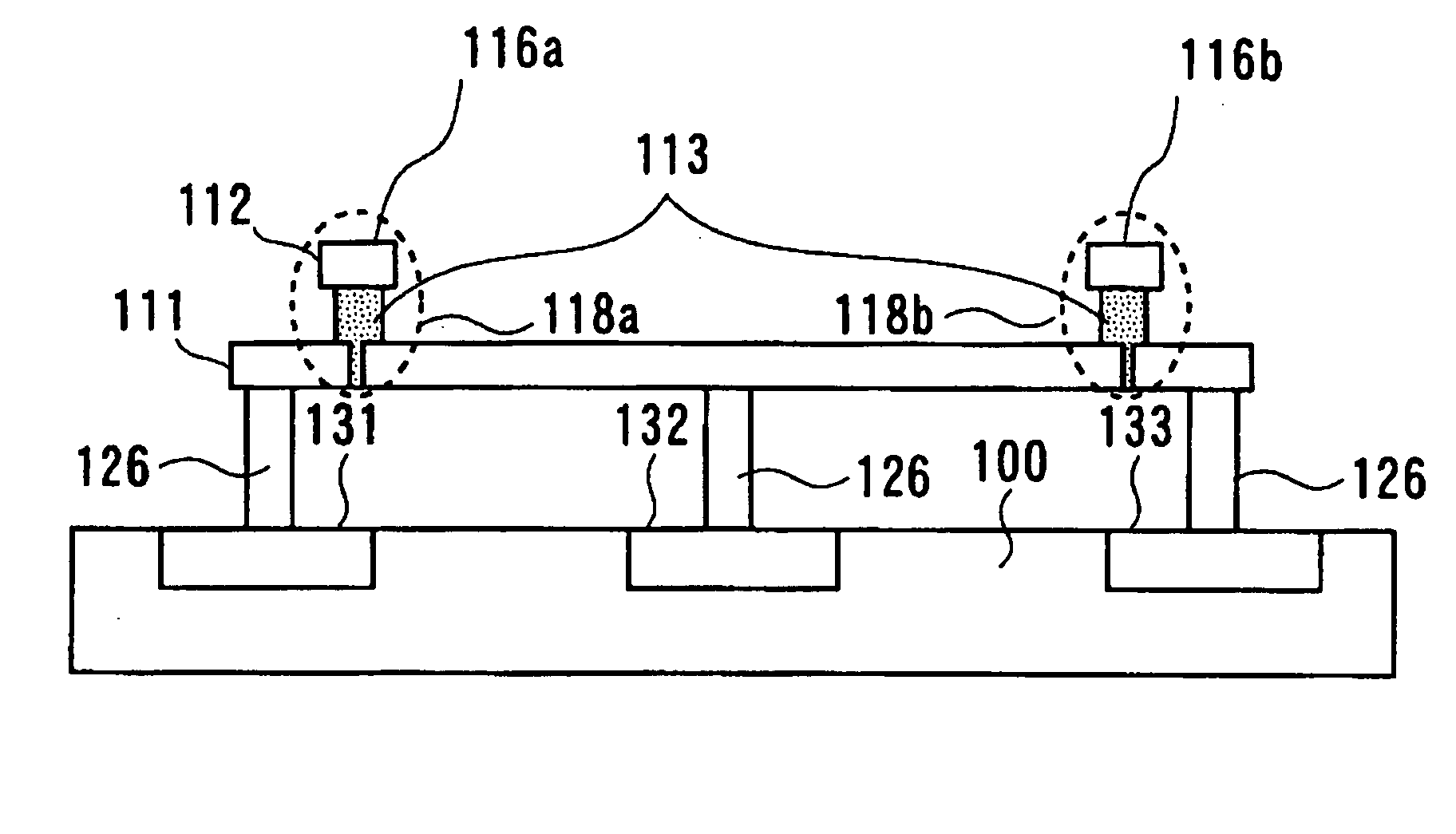

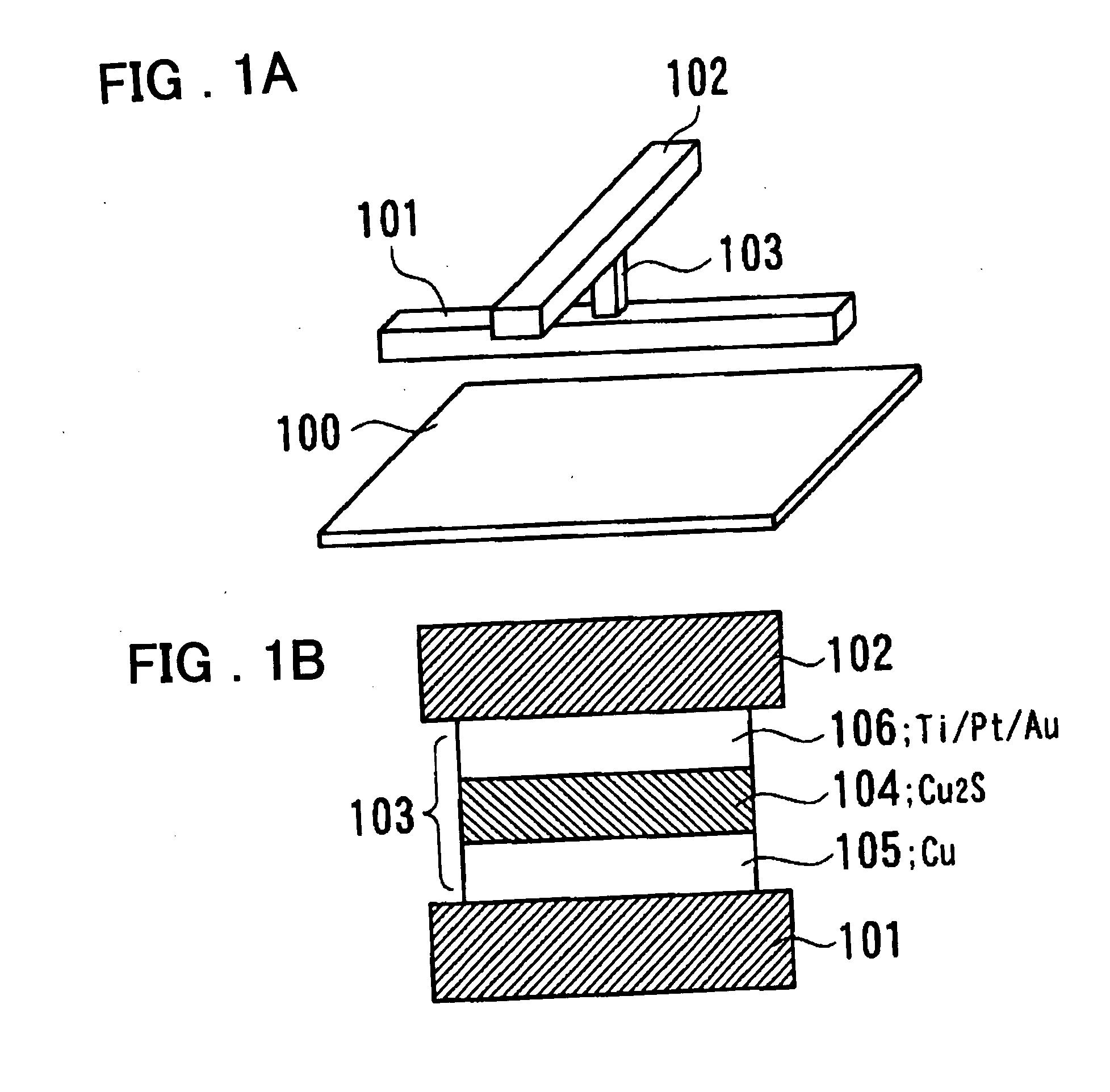

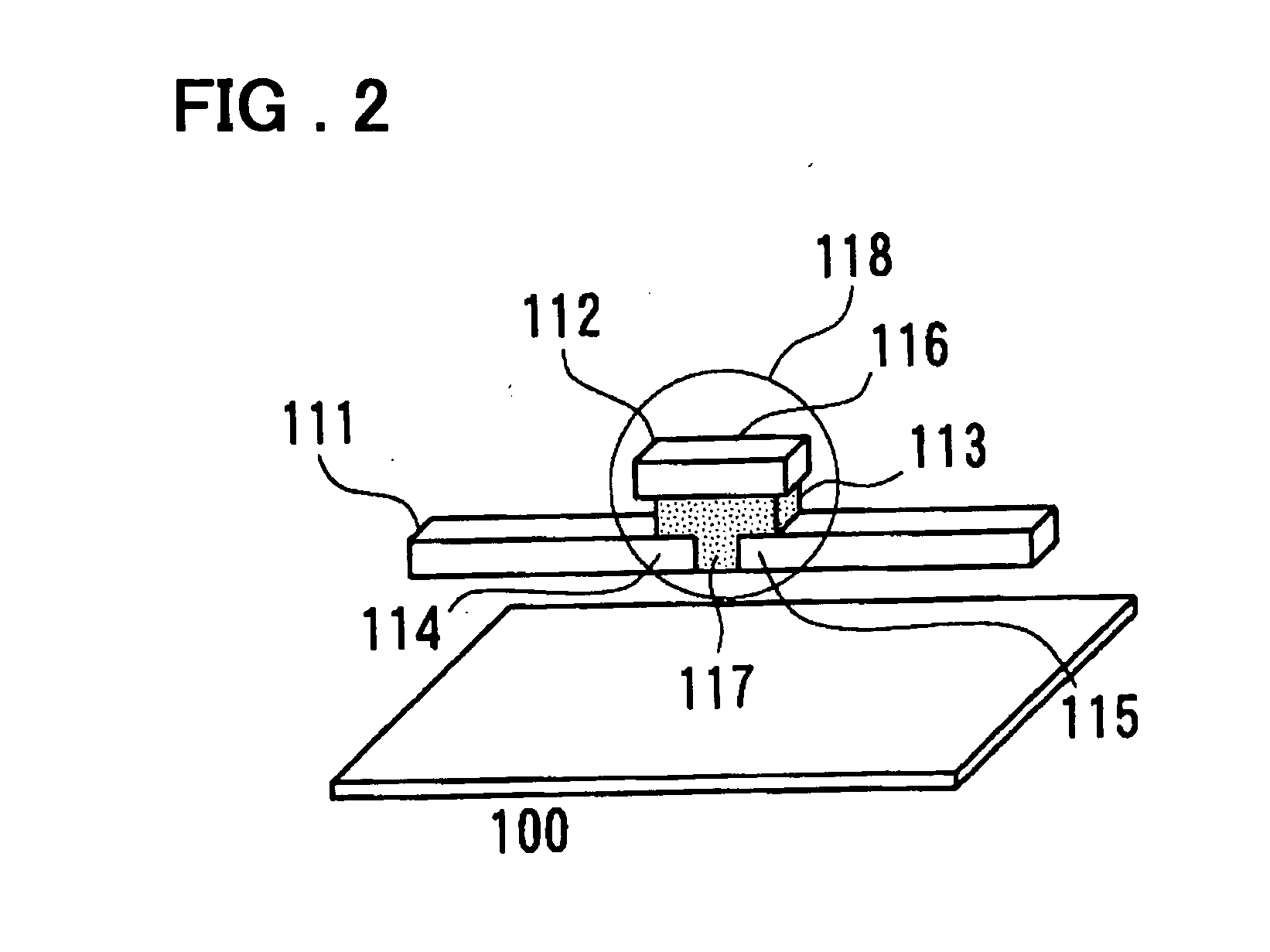

Semiconductor device

InactiveUS20050045919A1Increase the areaFine granularitySemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

A programmable semiconductor device has a switch element in an interconnection layer, wherein in at least one of the inside of a via, interconnecting a wire of a first interconnection layer and a wire of a second interconnection layer, a contact part of the via with the wire of the first interconnection layer and a contact part of the via with the wire of the second interconnection layer, there is provided a variable electrical conductivity member, such as a member of an electrolyte material. The via is used as a variable electrical conductivity type switch element or as a variable resistance device having a contact part with the wire of the first interconnection layer as a first terminal and having a contact part with the wire of the second interconnection layer as a second terminal. By varying the electrical conductivity of the switch element, the state of connection of the via with the wire of the first interconnection layer and the state of connection of the via with the wire of the second interconnection layer may be variably set to a shorted state, an open-circuited state or to an intermediate state A two-state switch element includes an ion conductor for conducting metal ions interposed between the first and second electrodes. The second electrode is formed of a material lower in reactivity than the first electrode. The electrical conductivity across the first and second electrodes is changed by the oxidation-reduction reaction of the metal ions. There are provided first and second transistors of opposite polarities, connected to the first electrode, and third and fourth transistors of opposite polarities, connected to the second electrode.

Owner:NEC CORP

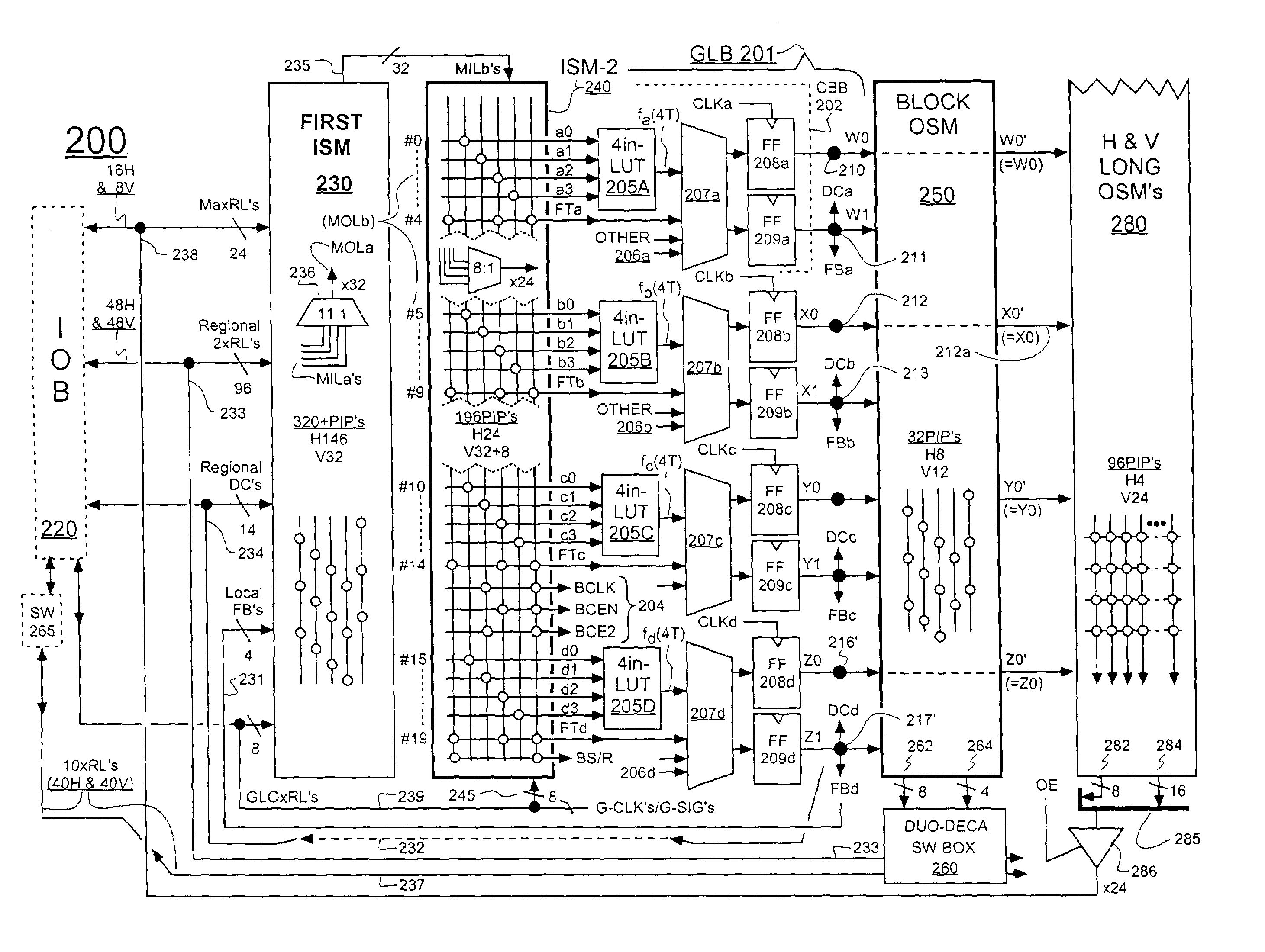

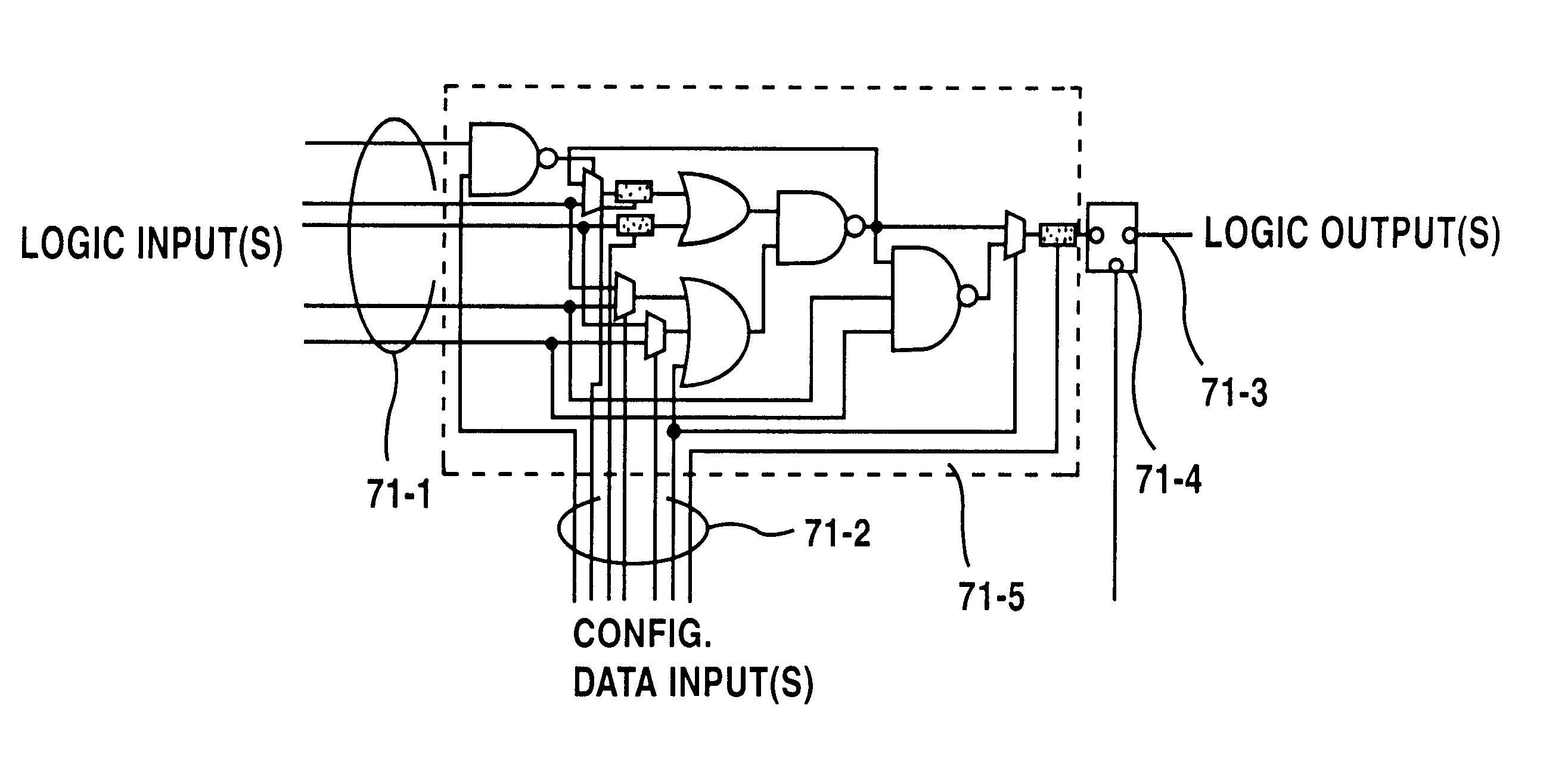

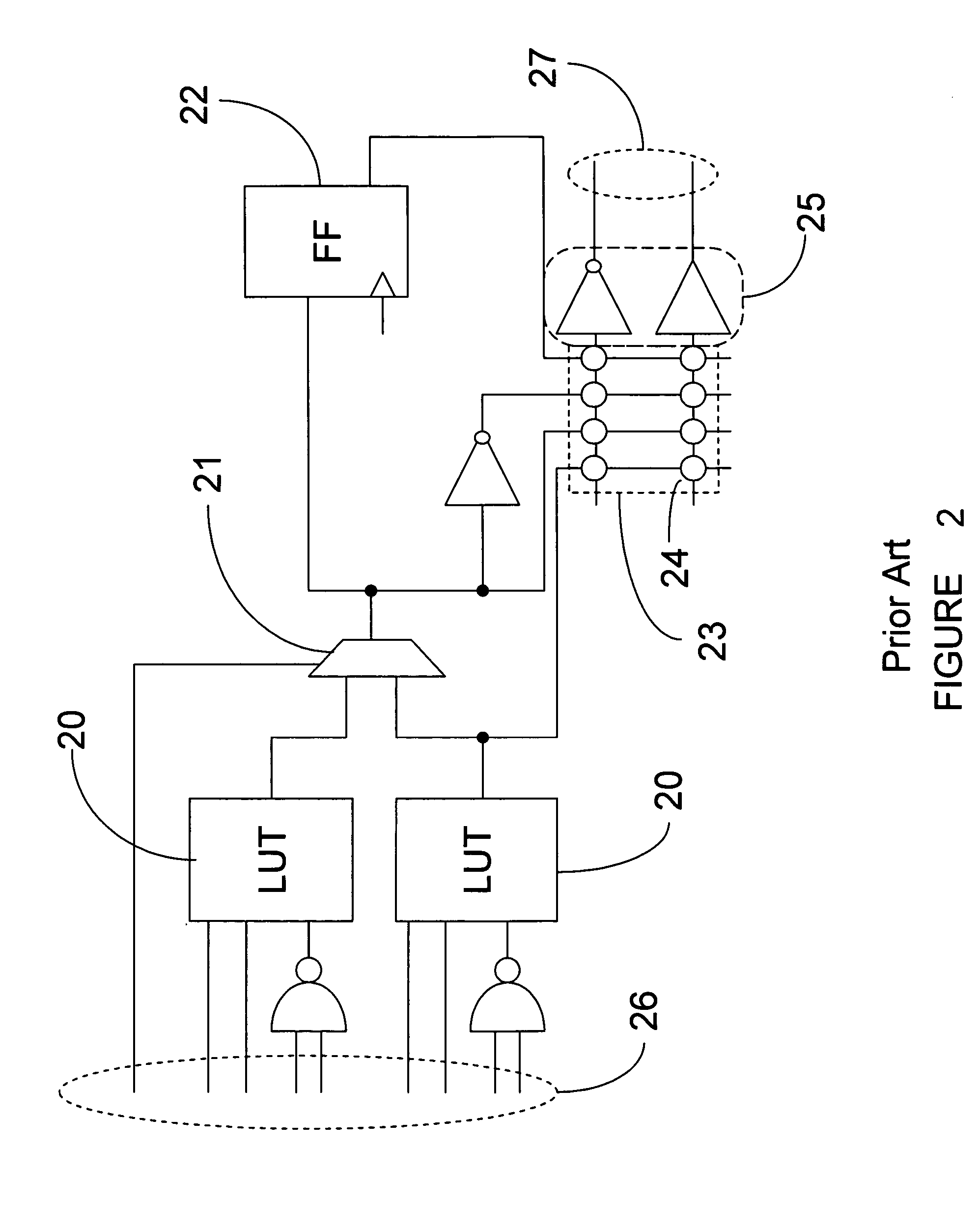

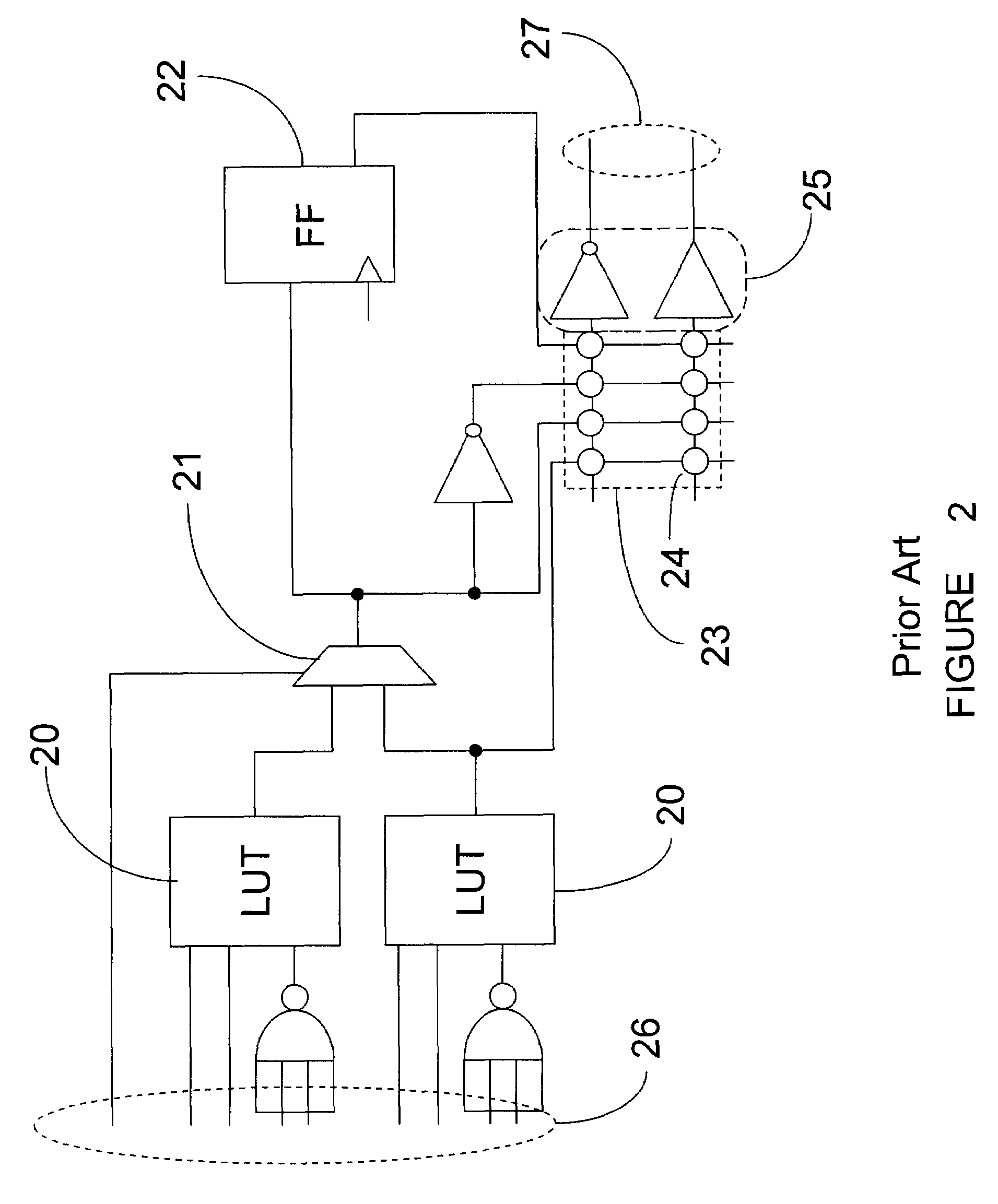

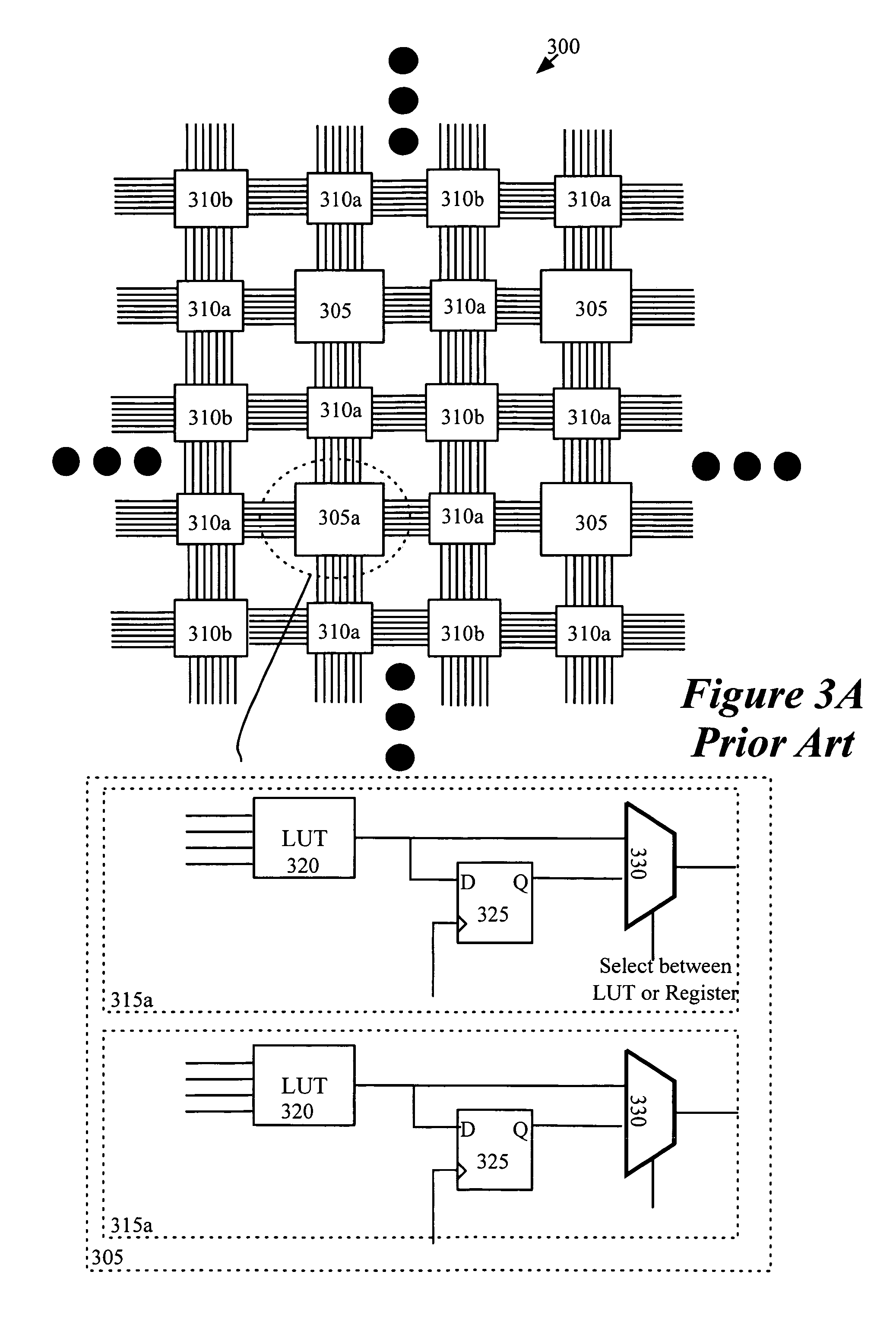

FPGA with register-intensive architecture

ActiveUS7028281B1Minimize resourceReduce consumptionSolid-state devicesCAD circuit designProcessor registerMultiplexer

Field programmable gate arrays (FPGA's) may be structured in accordance with the disclosure to have a register-intensive architecture that provides, for each of plural function-spawning LookUp Tables (e.g. a 4-input, base LUT's) within a logic block, a plurality of in-block accessible registers. A register-feeding multiplexer means may be provided for allowing each of the plural registers to equivalently capture and store a result signal output by the corresponding, base LUT of the plural registers. Registerable, primary and secondary feedthroughs may be provided for each base LUT so that locally-acquired input signals of the LUT may be fed-through to the corresponding, in-block registers for register-recovery purposes without fully consuming (wasting) the lookup resources of the associated, base LUT. A multi-stage, input switch matrix (ISM) may be further provided for acquiring and routing input signals from adjacent, block-interconnect lines (AIL's) and / or block-intra-connect lines (e.g., FB's) to the base LUT's and / or their respective, registerable feedthroughs. Techniques are disclosed for utilizing the many in-block registers and / or the registerable feedthroughs and / or the multi-stage ISM's for efficiently implementing various circuit designs by appropriately configuring such register-intensive FPGA's.

Owner:LATTICE SEMICON CORP

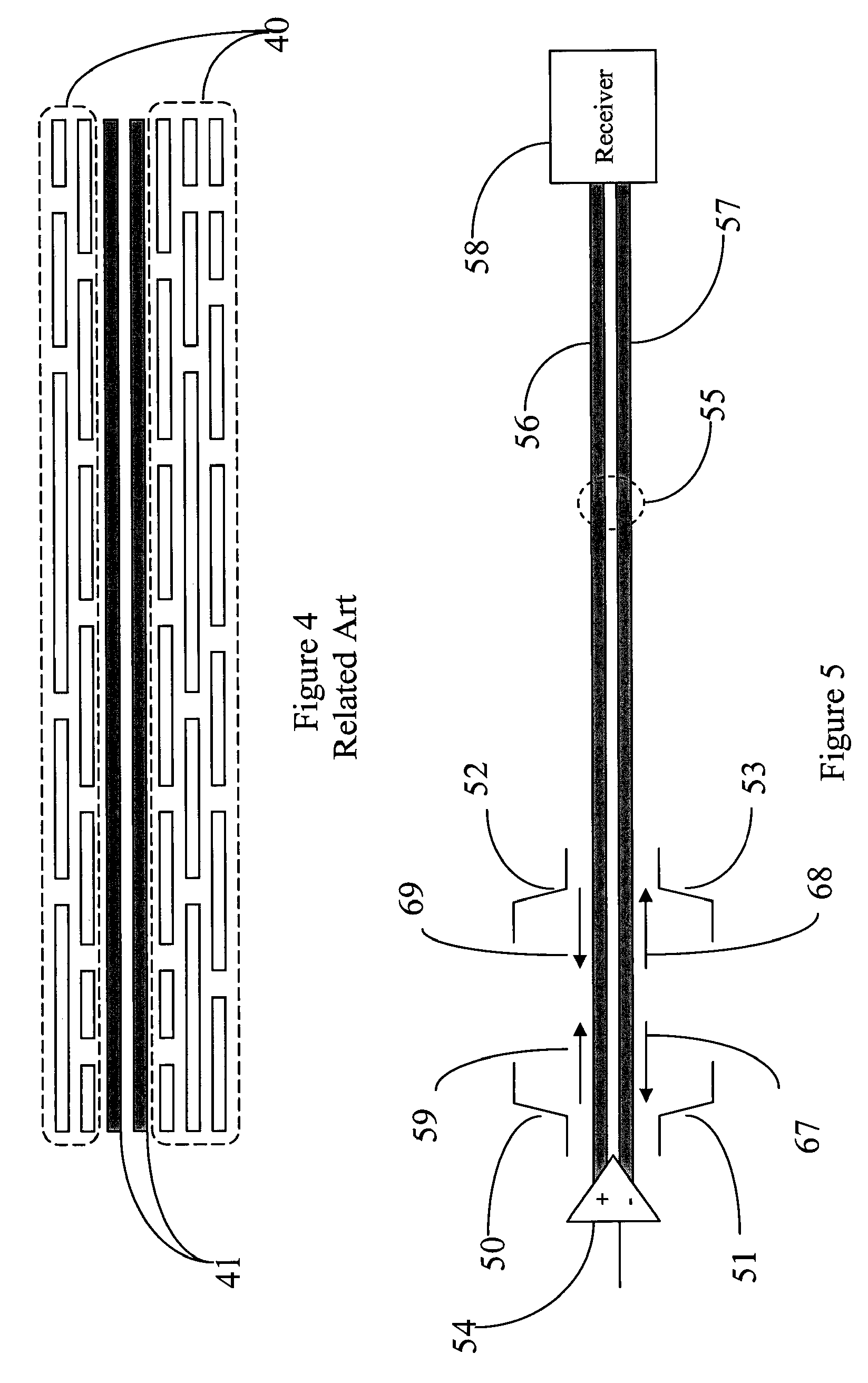

Reprogrammable circuit board with alignment-insensitive support for multiple component contact types

InactiveUS20080143379A1Semiconductor/solid-state device testing/measurementWave amplification devicesSignal conditioningContact type

The present invention is directed to a system that programmably interconnects integrated circuit chips and other components at near-intra-chip density. The system's contact structure allows it to adapt to components with a wide variety of contact spacings and interconnection requirements, the use of releasable attachment means allows component placement to be modified as needed, the system identifies the contacts and the components to facilitate specifying the inter-component connections, and the system provides signal conditioning and retiming to minimize issues with signal integrity and signal skew.

Owner:NORMAN RICHARD

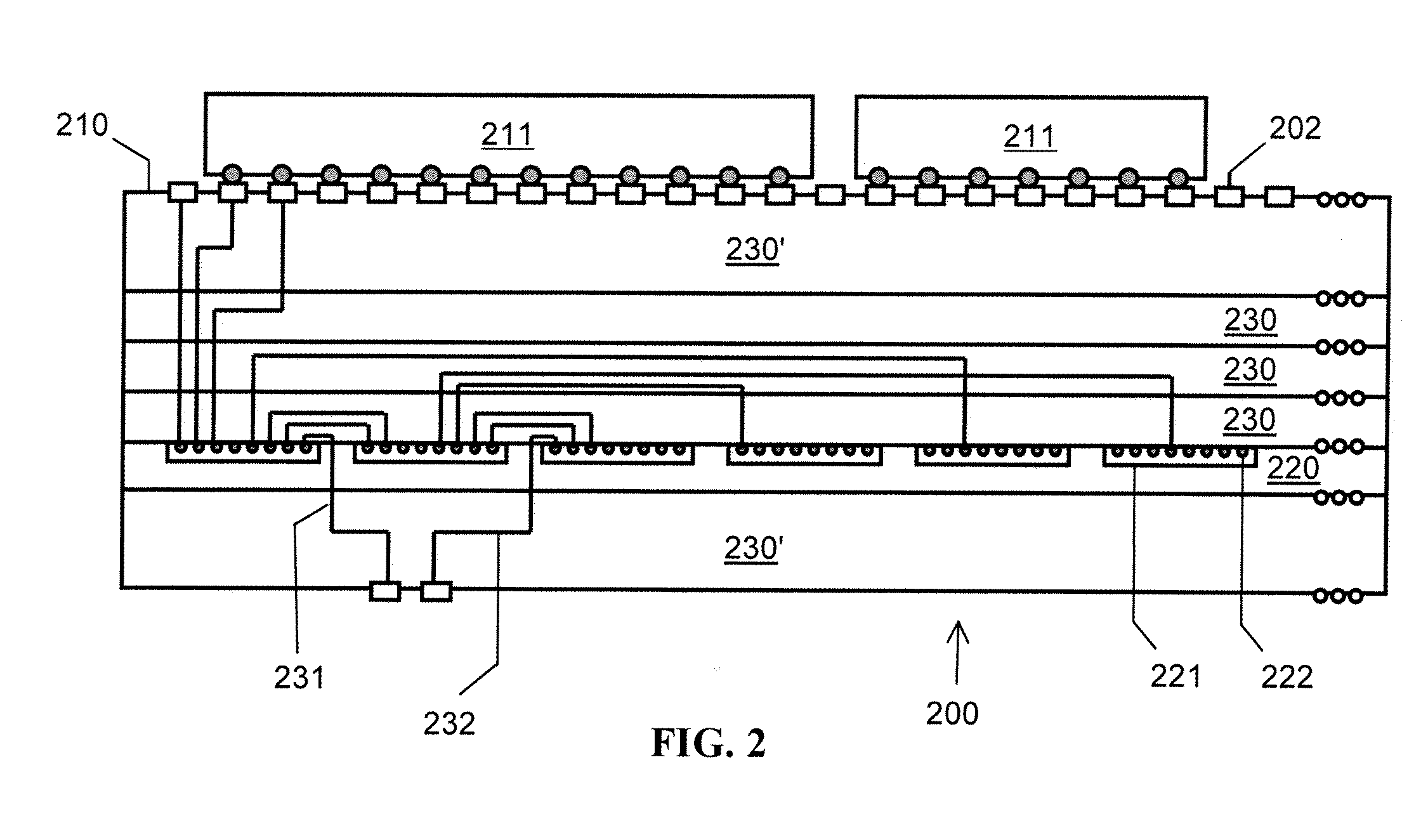

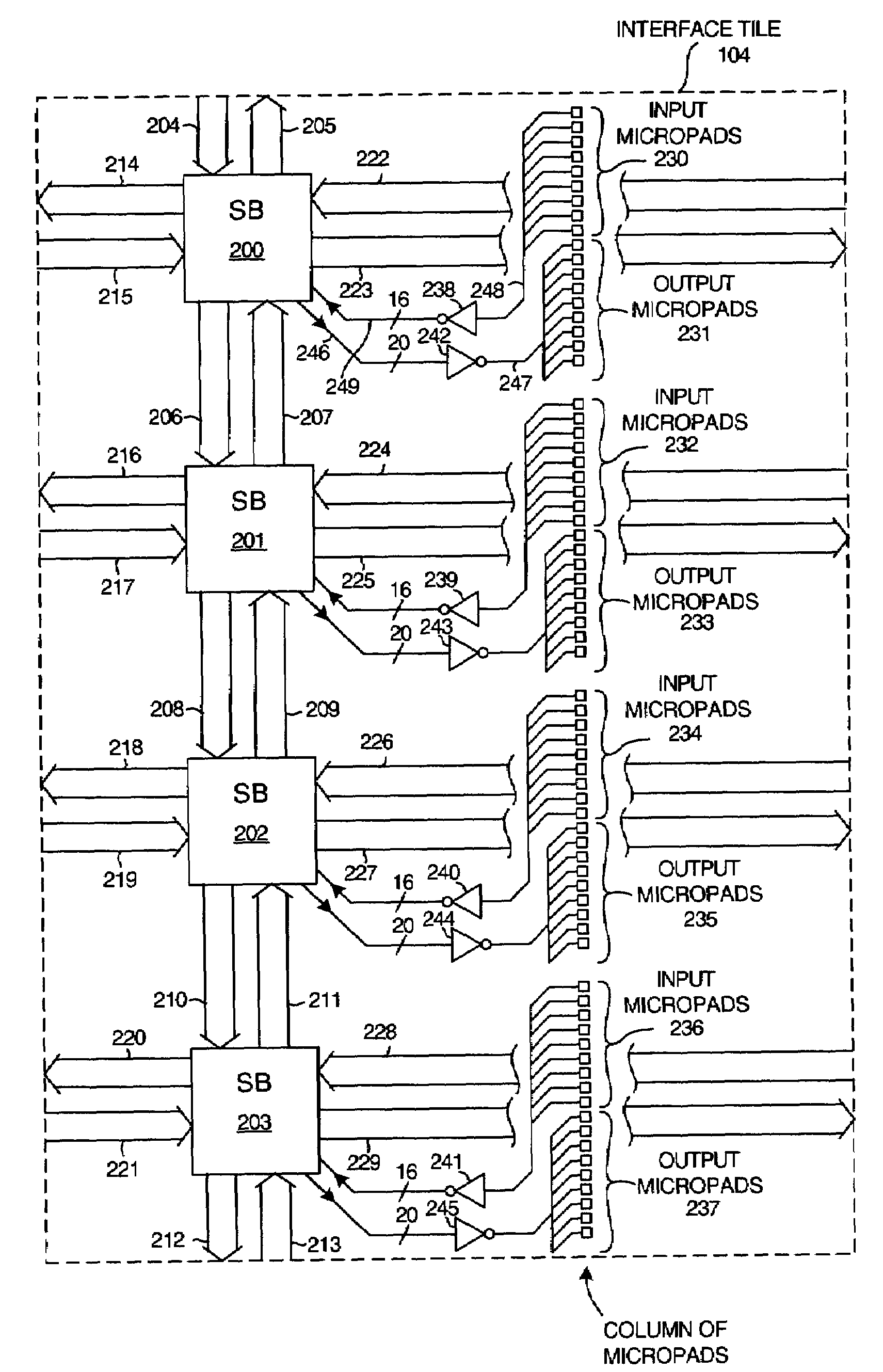

Integrated circuit with interface tile for coupling to a stacked-die second integrated circuit

ActiveUS7068072B2Designing can be facilitatedPromote formationSemiconductor/solid-state device detailsSolid-state devicesGeneral purposeProgrammable logic device

A general purpose interface tile of a first integrated circuit includes a plurality of micropads. A second integrated circuit may be stacked on the first integrated circuit such that signals from the second integrated circuit are communicated through the micropads and the interface tile to other circuitry on the first integrated circuit. Similarly, signals from the first integrated circuit are communicated through the interface tile and the micropads to the second integrated circuit. In the event that the first integrated circuit is a programmable logic device having a programmable interconnect structure, the interface tile is part of and hooks into the programmable interconnect structure and provides a general purpose mechanism for coupling signals from the second integrated circuit to the programmable interconnect structure and / or for coupling signals from the programmable interconnect structure to the second integrated circuit.

Owner:XILINX INC

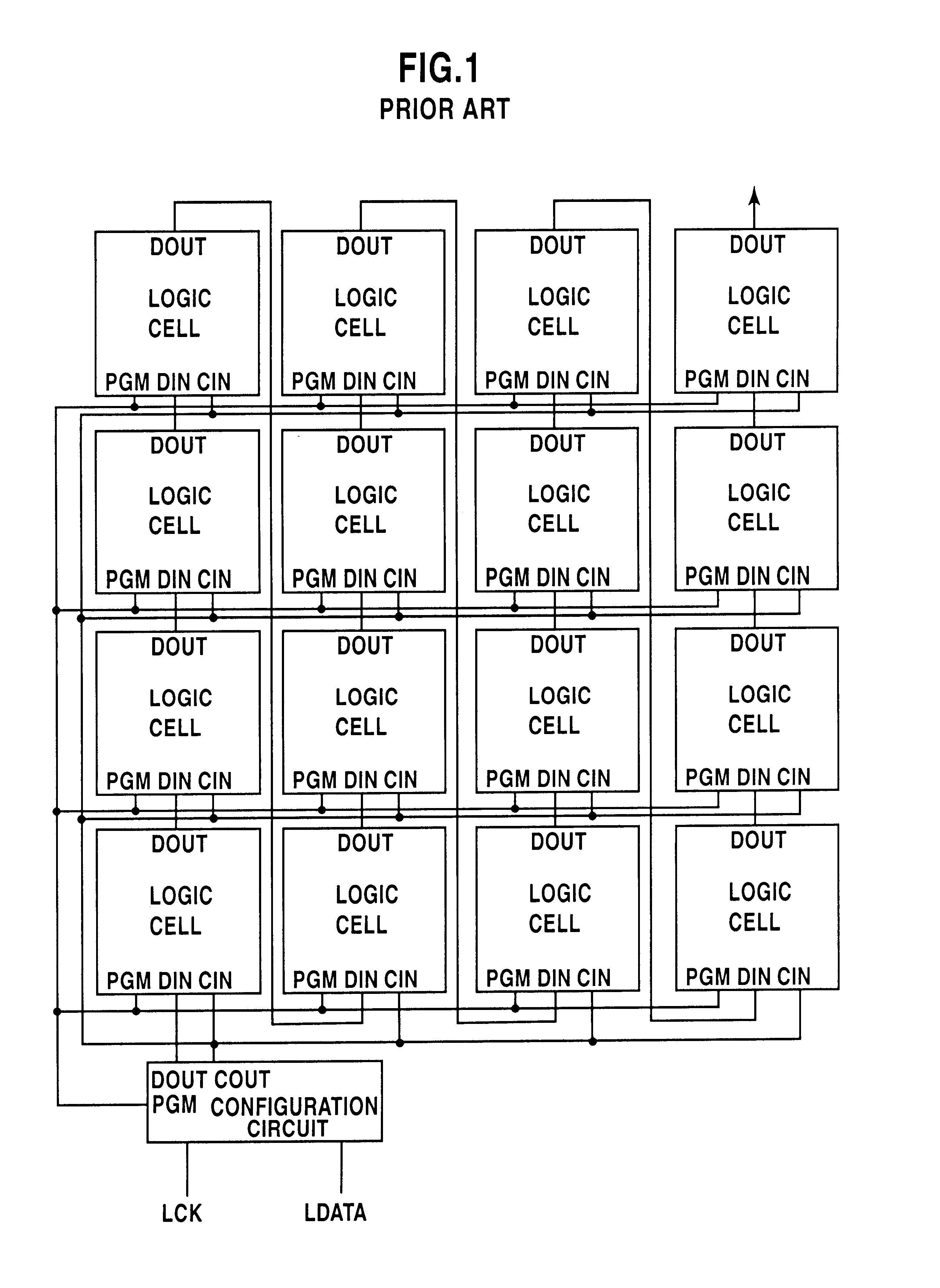

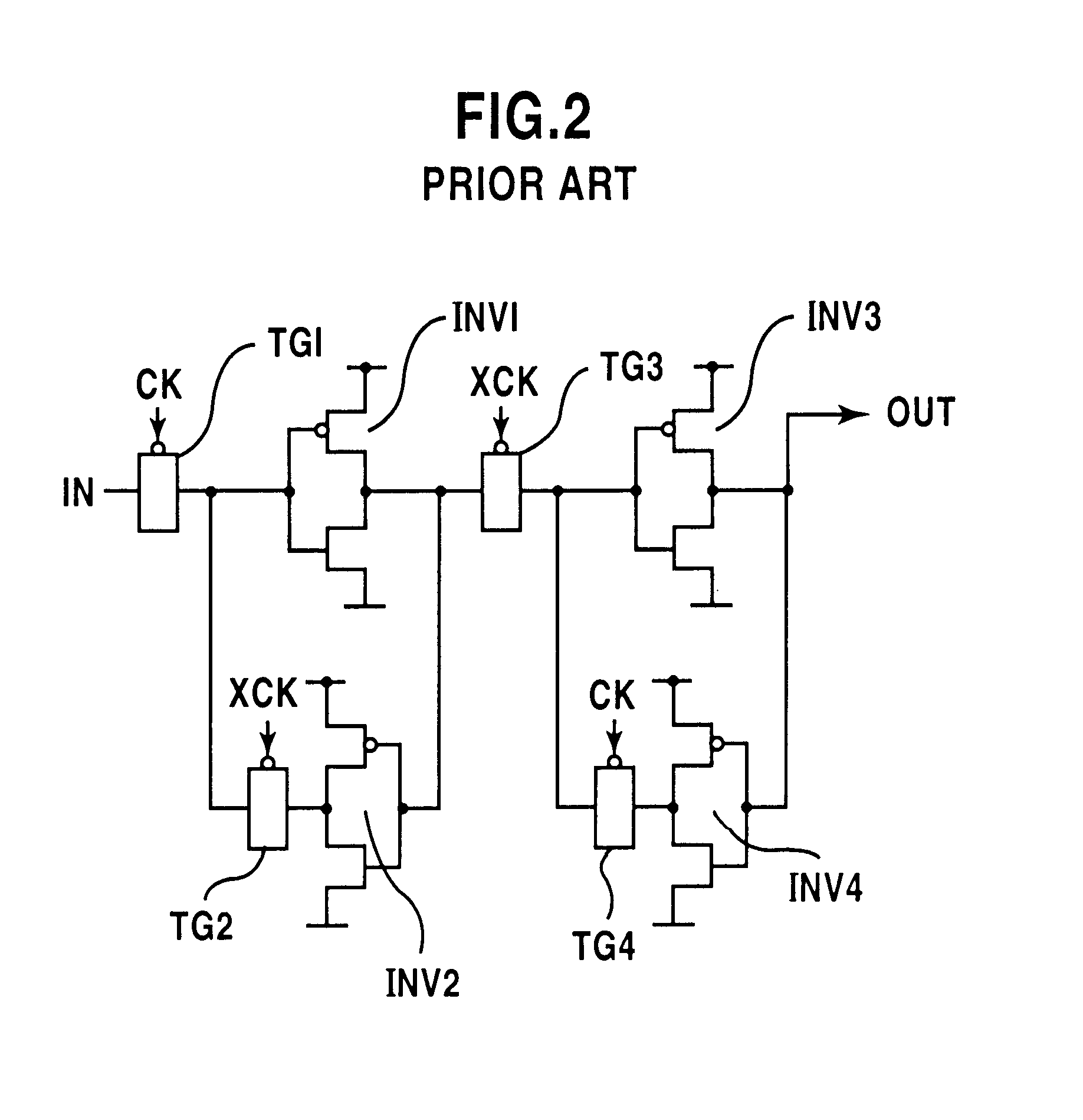

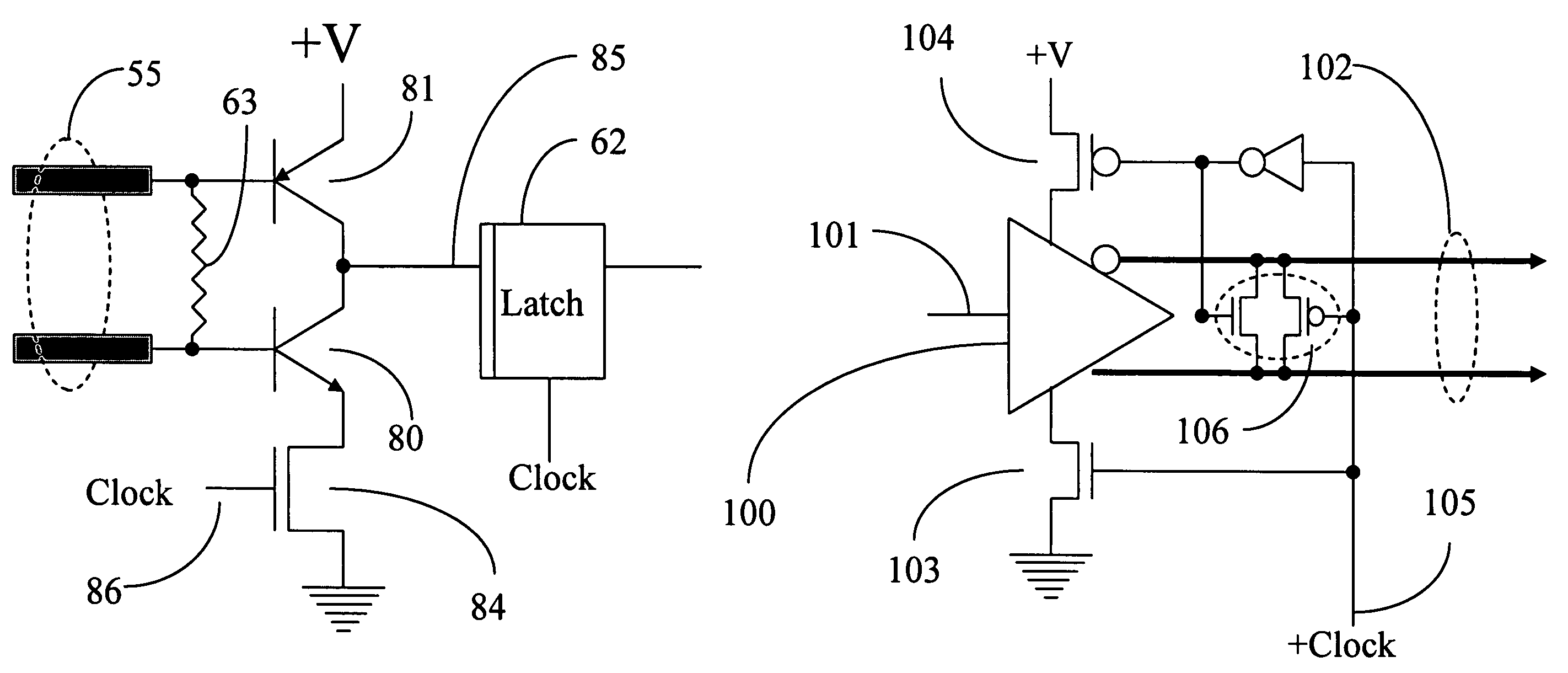

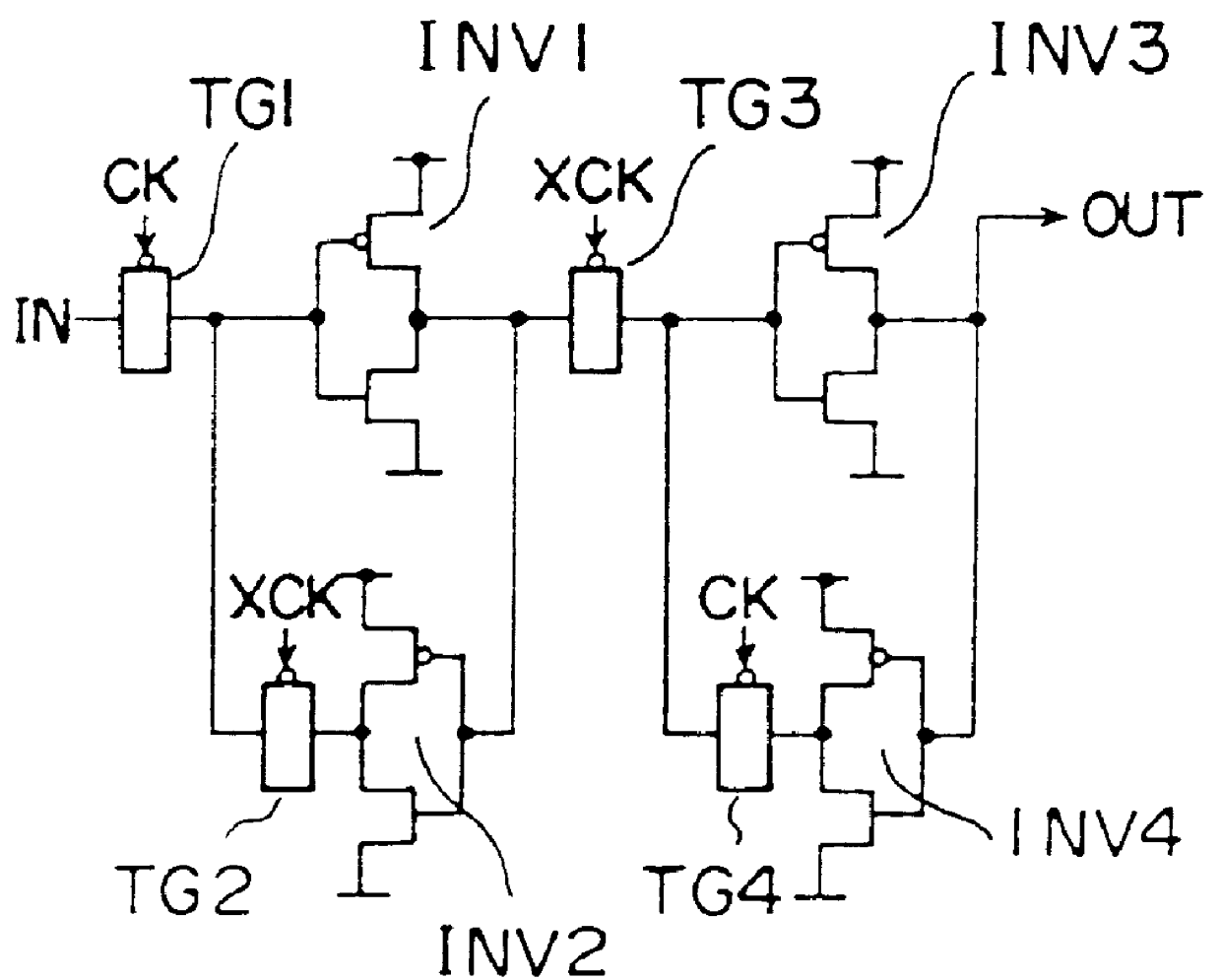

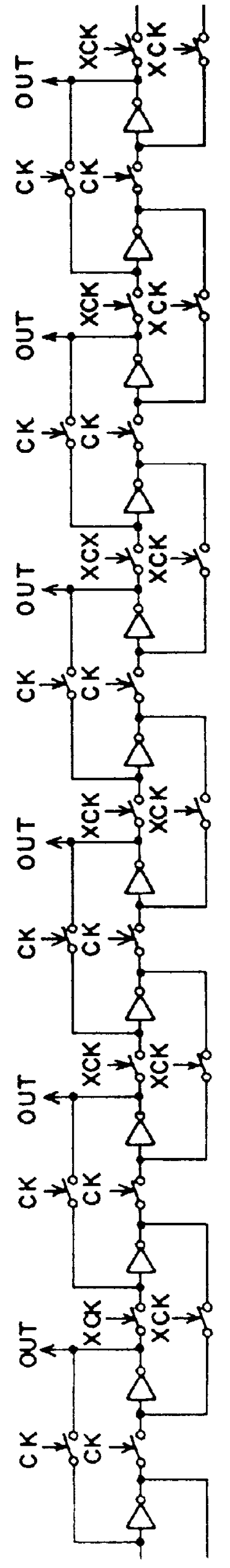

Chain-connected shift register and programmable logic circuit whose logic function is changeable in real time

A shift register having a plurality of circuit cells successively connected in a chain formation is proposed. Each of the circuit cells includes a first inversion gate, a first transmission gate, connected to an output of the first inversion gate, being switched by a clock, and a second inversion gate connected to an output of the first transmission gate. The circuit cell further includes a first P-channel transistor, connected between an output of the second inversion gate and an input of the first inversion gate, being switched by the clock, a second transmission gate, connected to the output of the second inversion gate, being switched by an inversion clock, and a second P-channel transistor, connected to the output of the first transmission gate, being switched by the inversion clock. In the shift register, the plurality of circuit cells are successively connected such that the input of the first inversion gate of the circuit cell is connected to an output of a second transmission gate of a former-stage circuit cell, and the output of the first inversion gate of the circuit cell is connected to an output of a second P-channel transistor of the former-stage circuit cell.

Owner:FUJITSU LTD

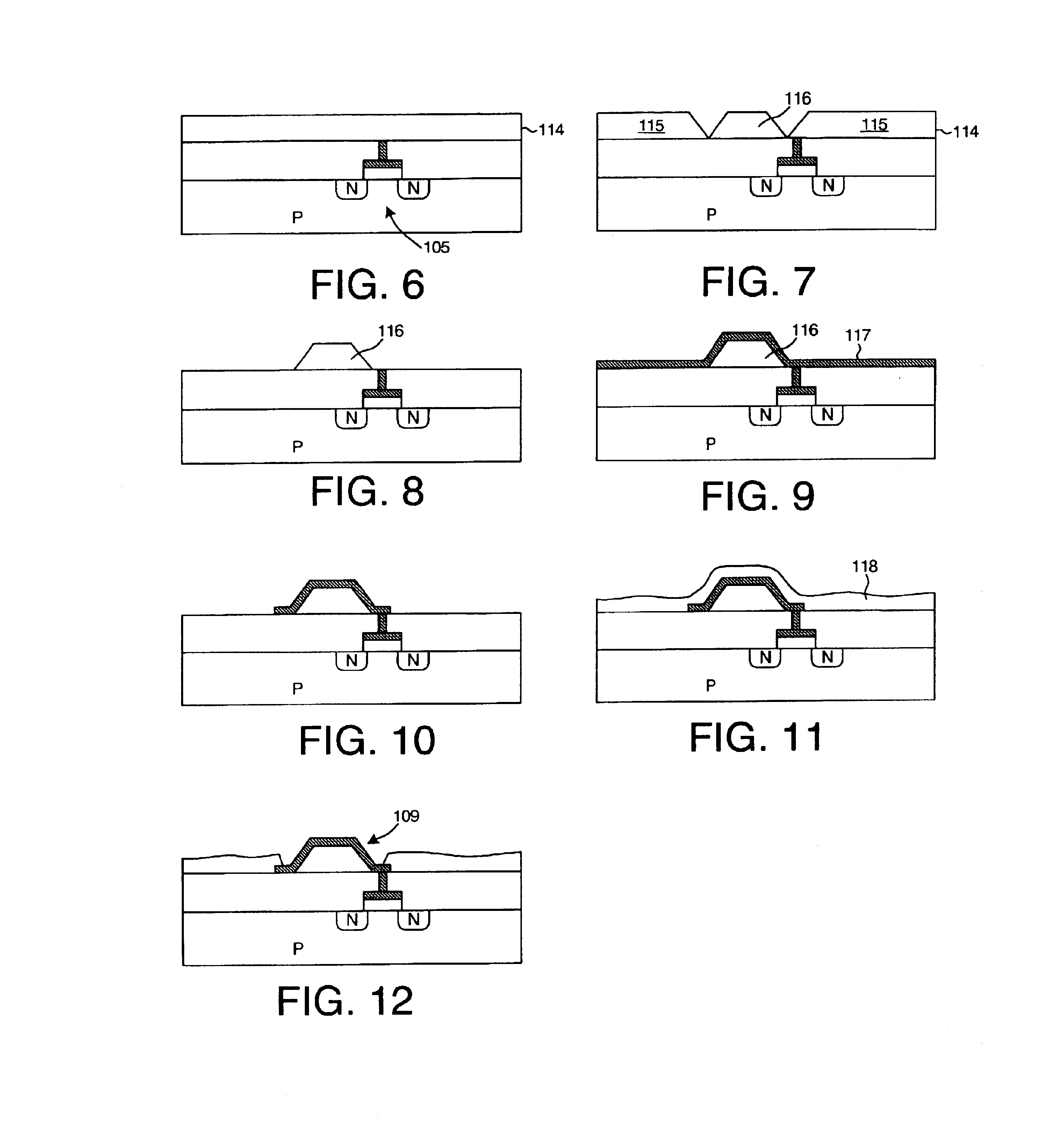

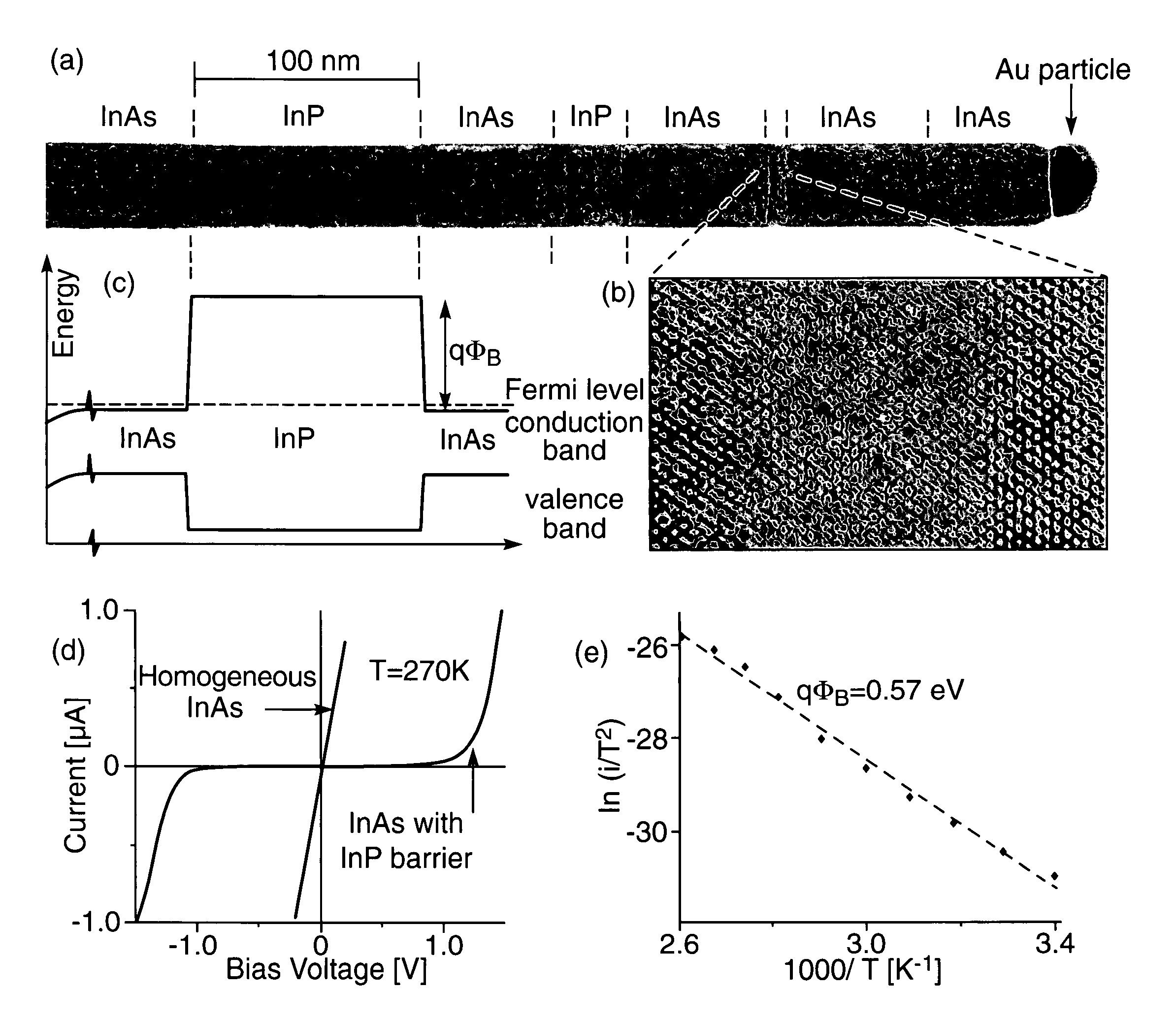

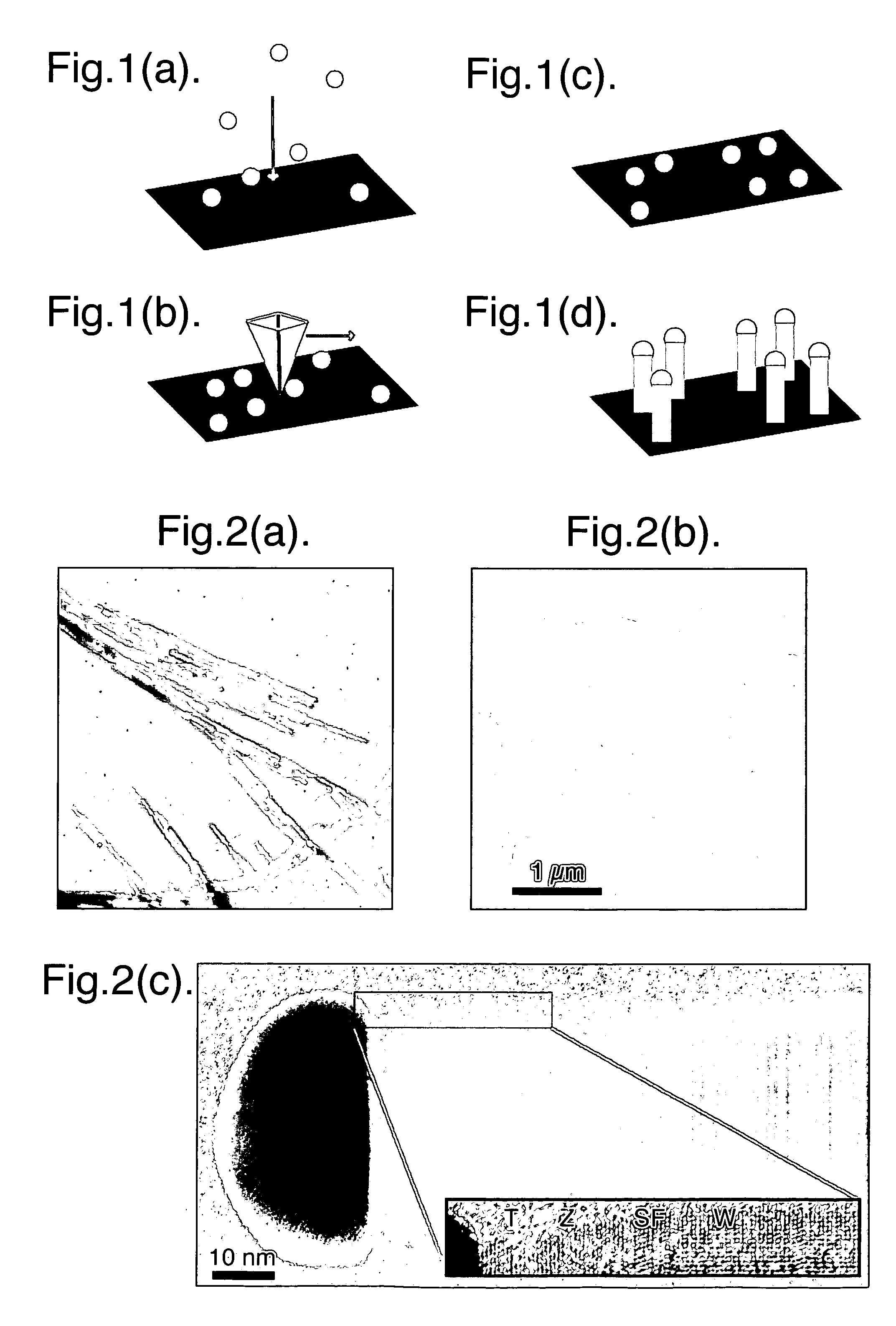

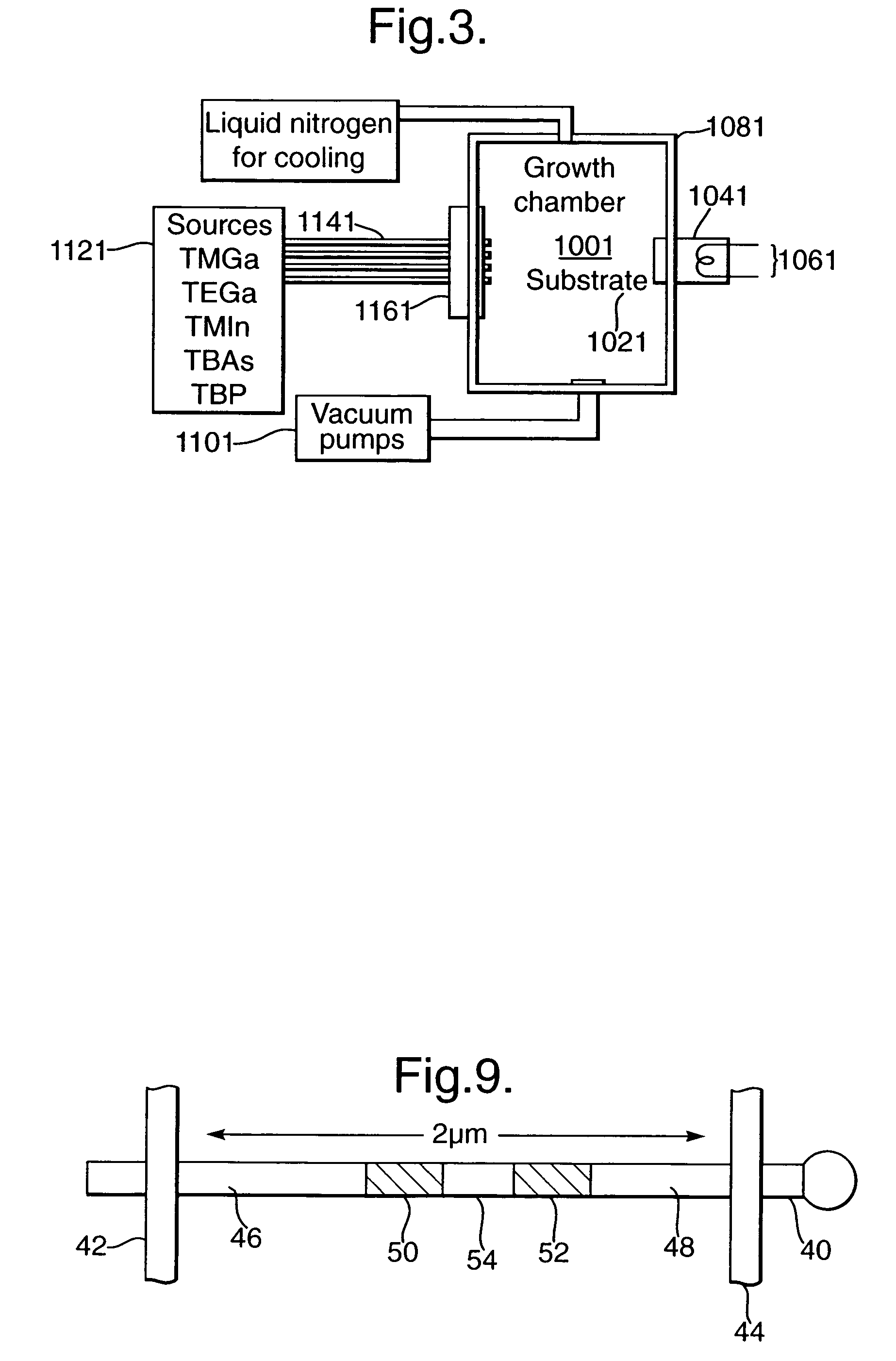

Nanostructures and methods for manufacturing the same

InactiveUS7335908B2Accurate weighingEnhances width controlPolycrystalline material growthIndividual molecule manipulationPhotonicsWhiskers

A resonant tunneling diode, and other one dimensional electronic, photonic structures, and electromechanical MEMS devices, are formed as a heterostructure in a nanowhisker by forming length segments of the whisker with different materials having different band gaps.

Owner:QUNANO

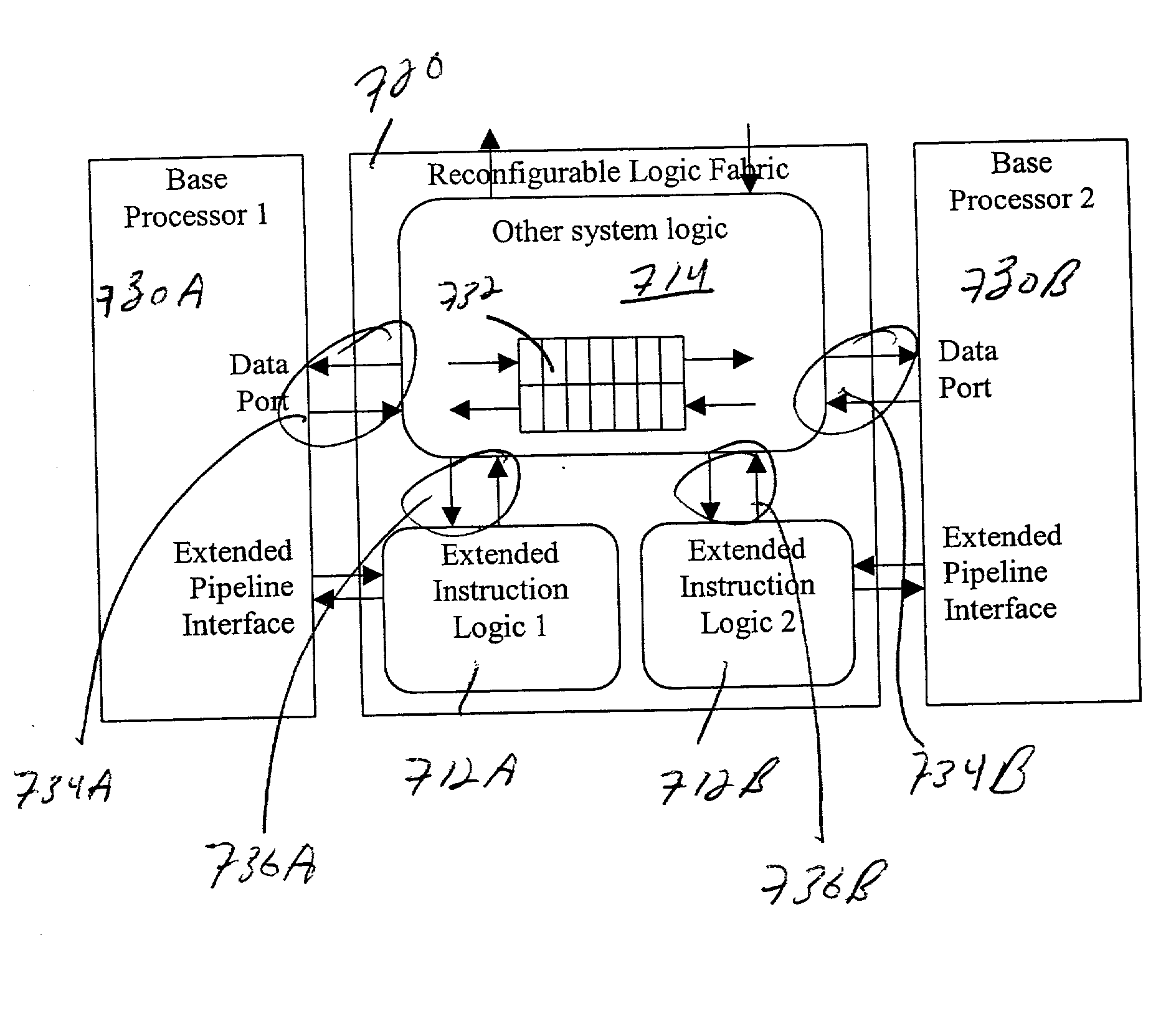

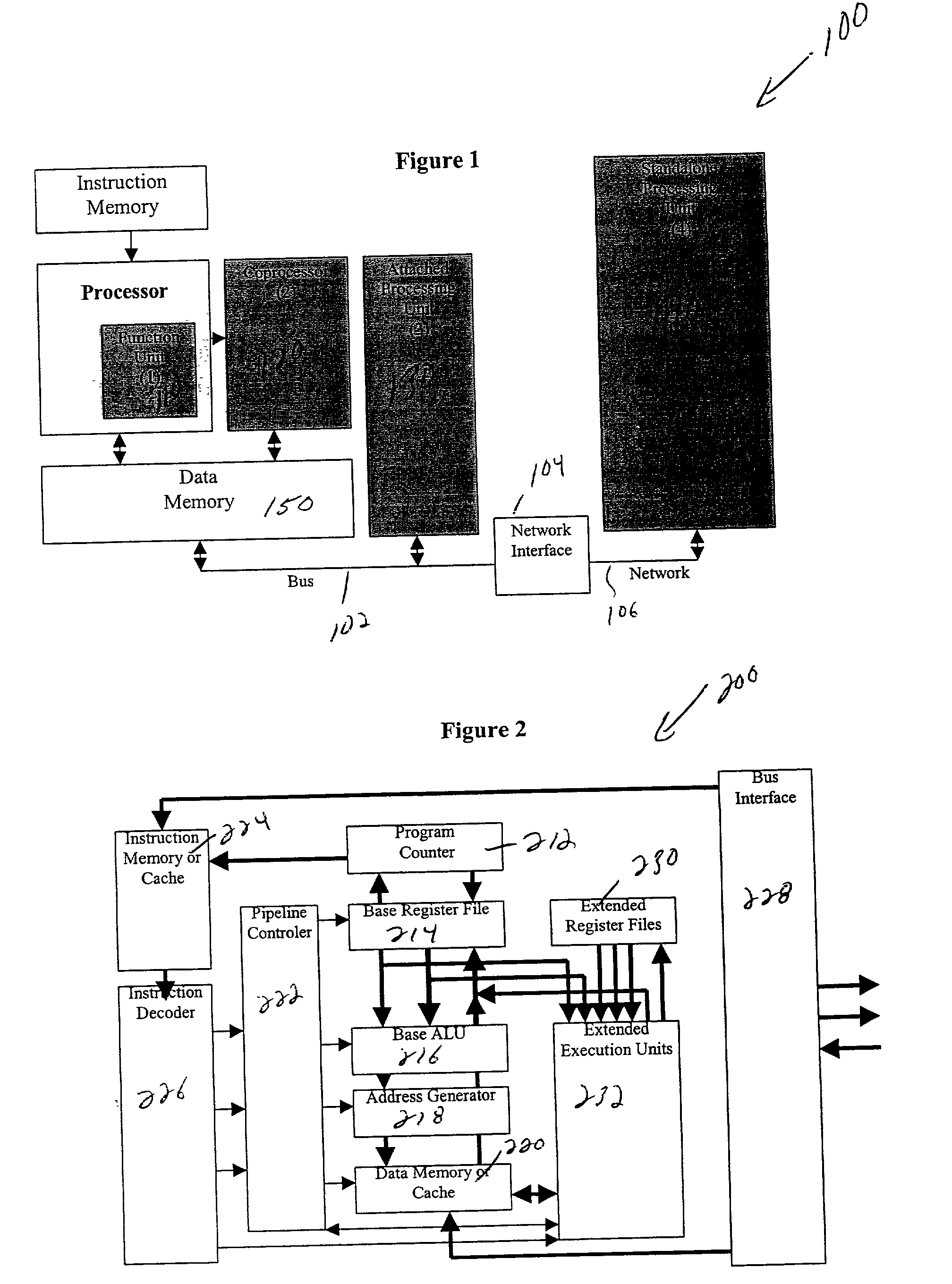

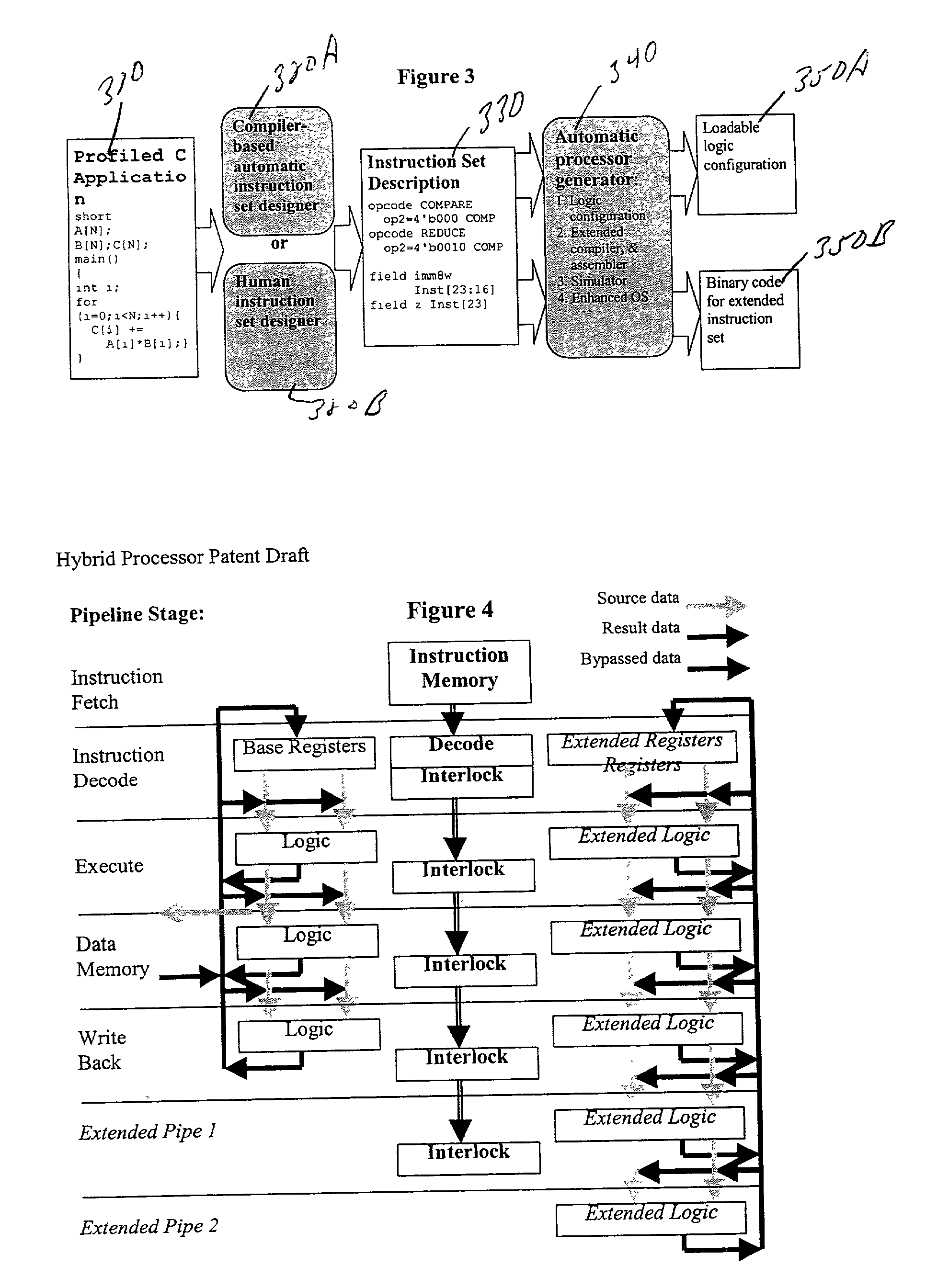

High-performance hybrid processor with configurable execution units

InactiveUS20050166038A1High bandwidthFlexibilityInstruction analysisConcurrent instruction executionHigh bandwidthLatency (engineering)

A new general method for building hybrid processors achieves higher performance in applications by allowing more powerful, tightly-coupled instruction set extensions to be implemented in reconfigurable logic. New instructions set configurations can be discovered and designed by automatic and semi-automatic methods. Improved reconfigurable execution units support deep pipelining, addition of additional registers and register files, compound instructions with many source and destination registers and wide data paths. New interface methods allow lower latency, higher bandwidth connections between hybrid processors and other logic.

Owner:TENSILICA

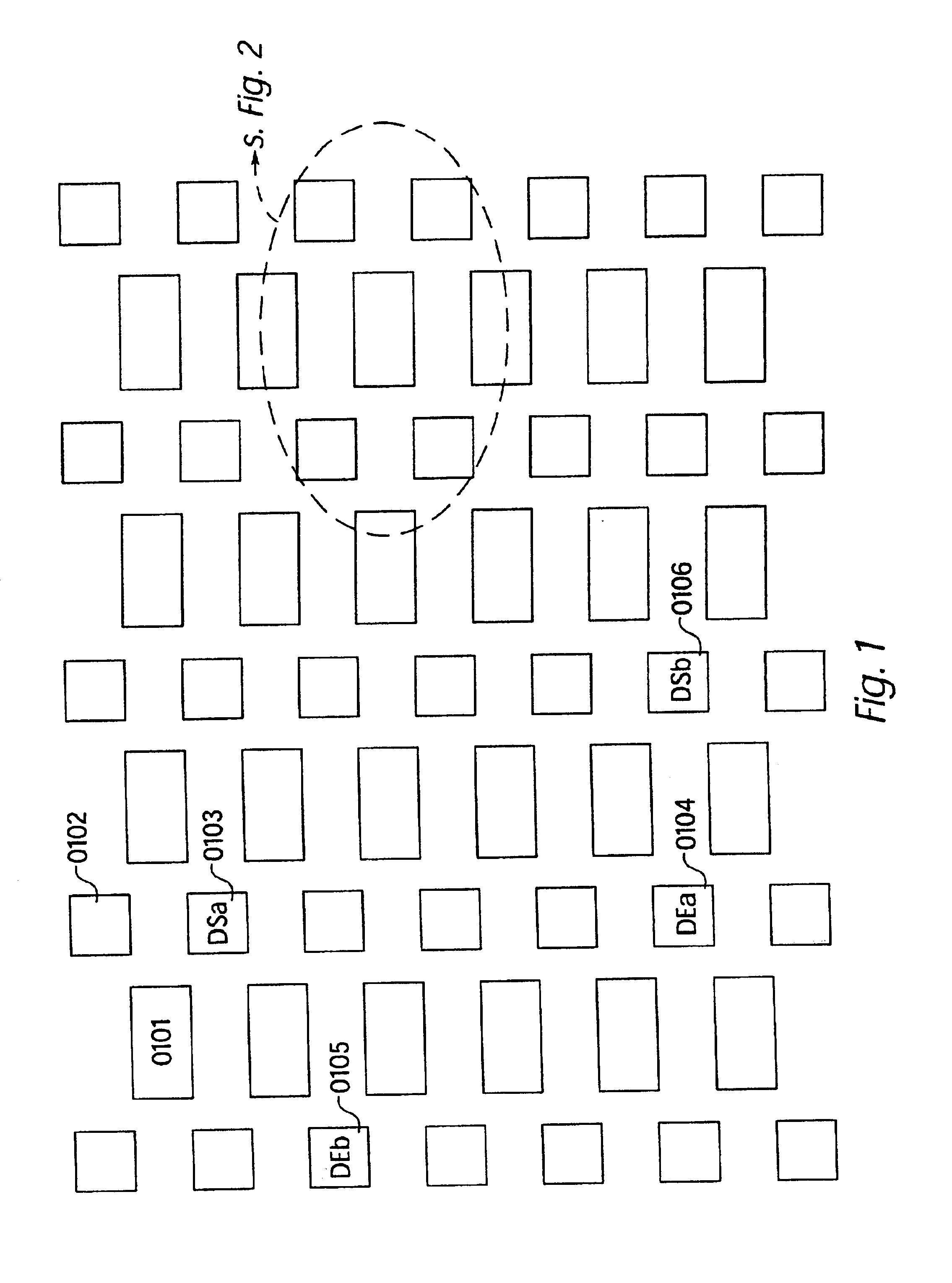

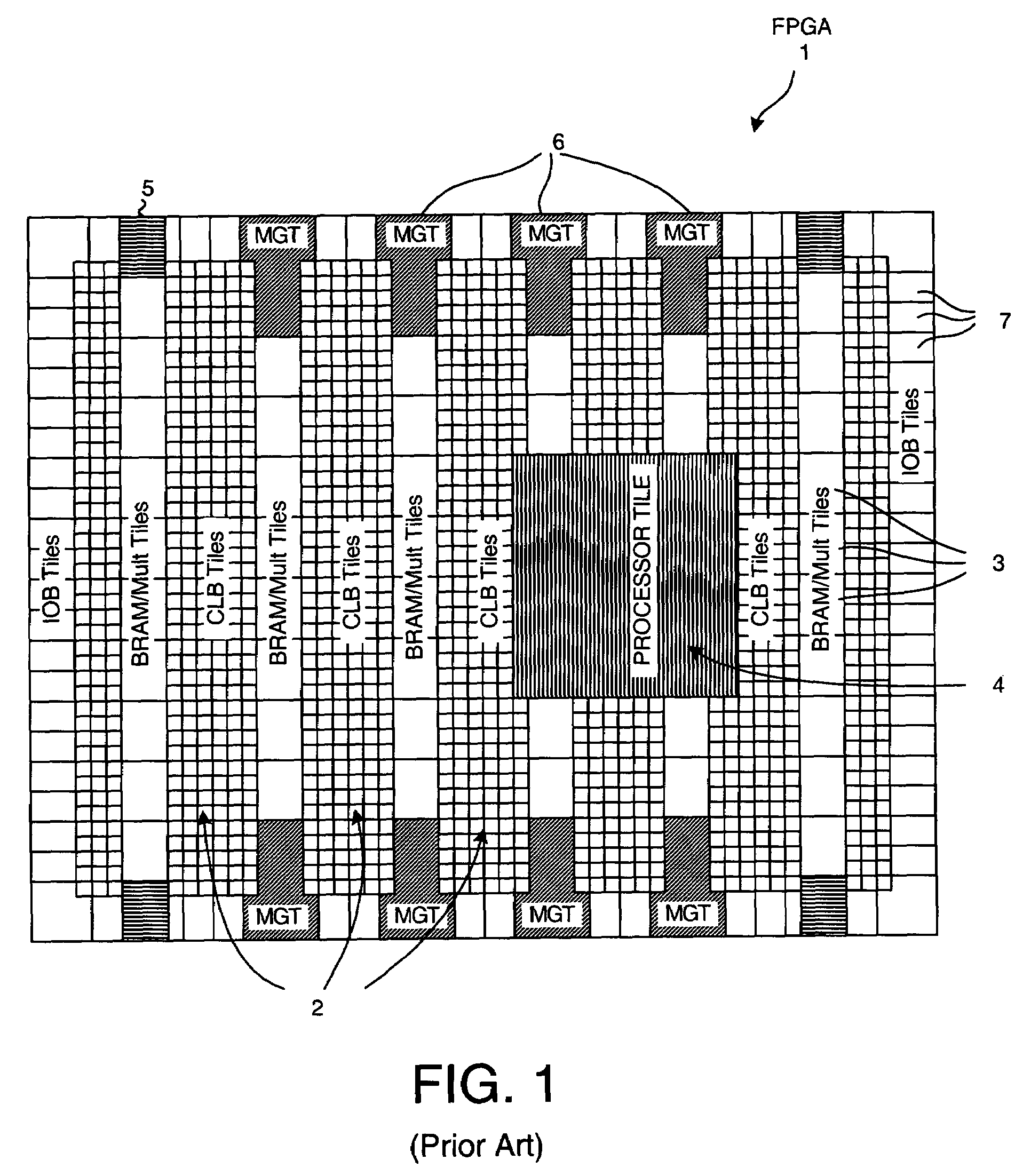

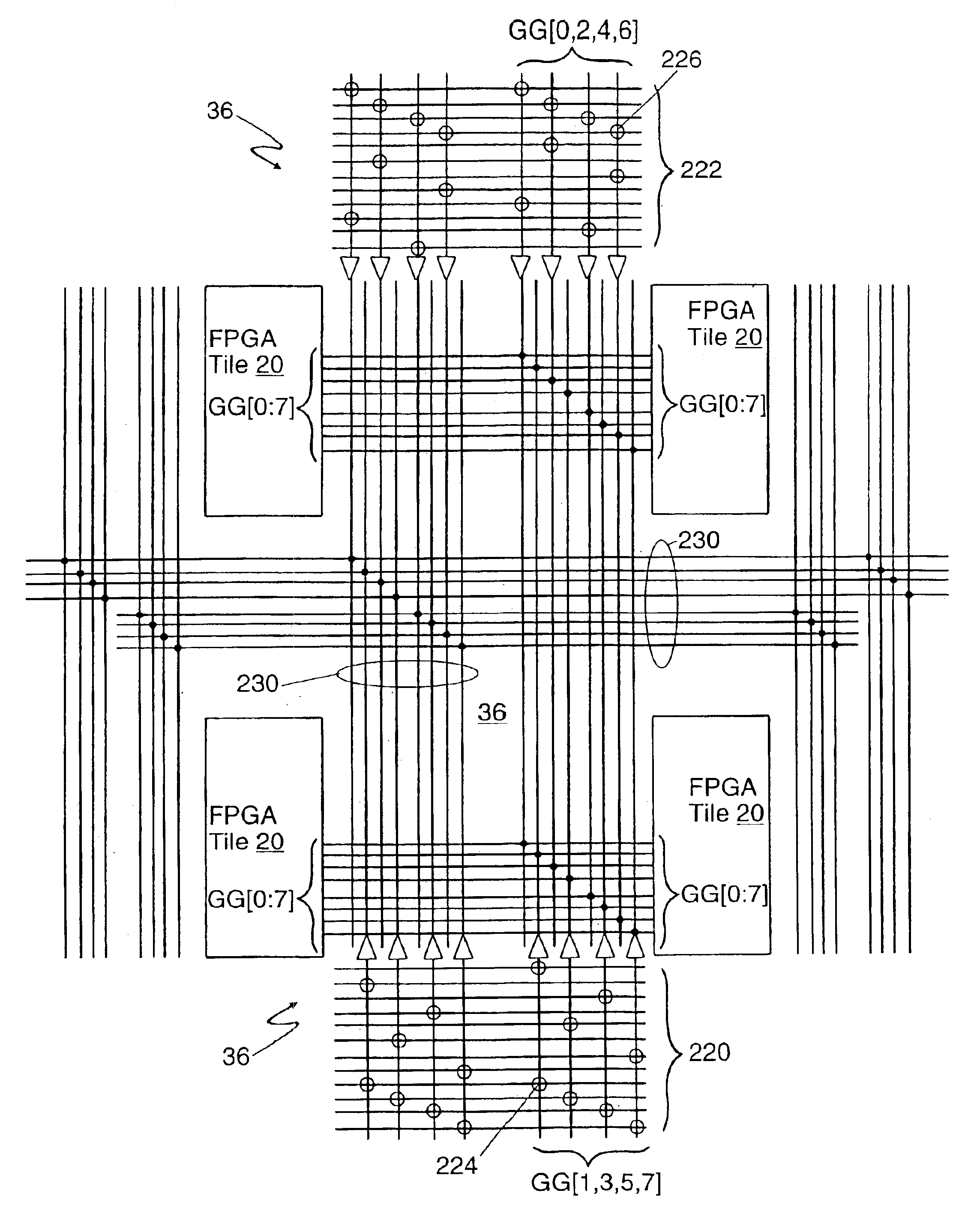

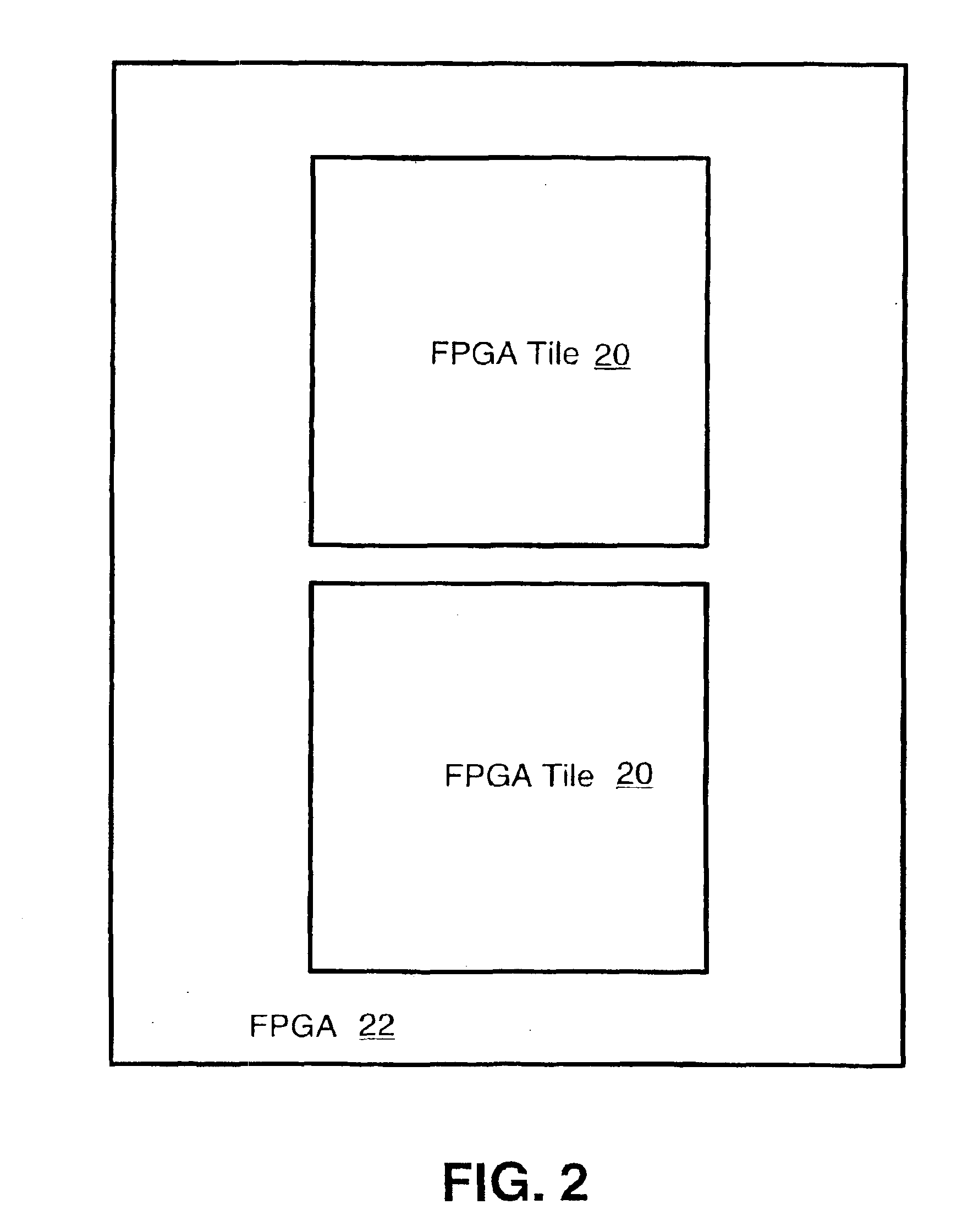

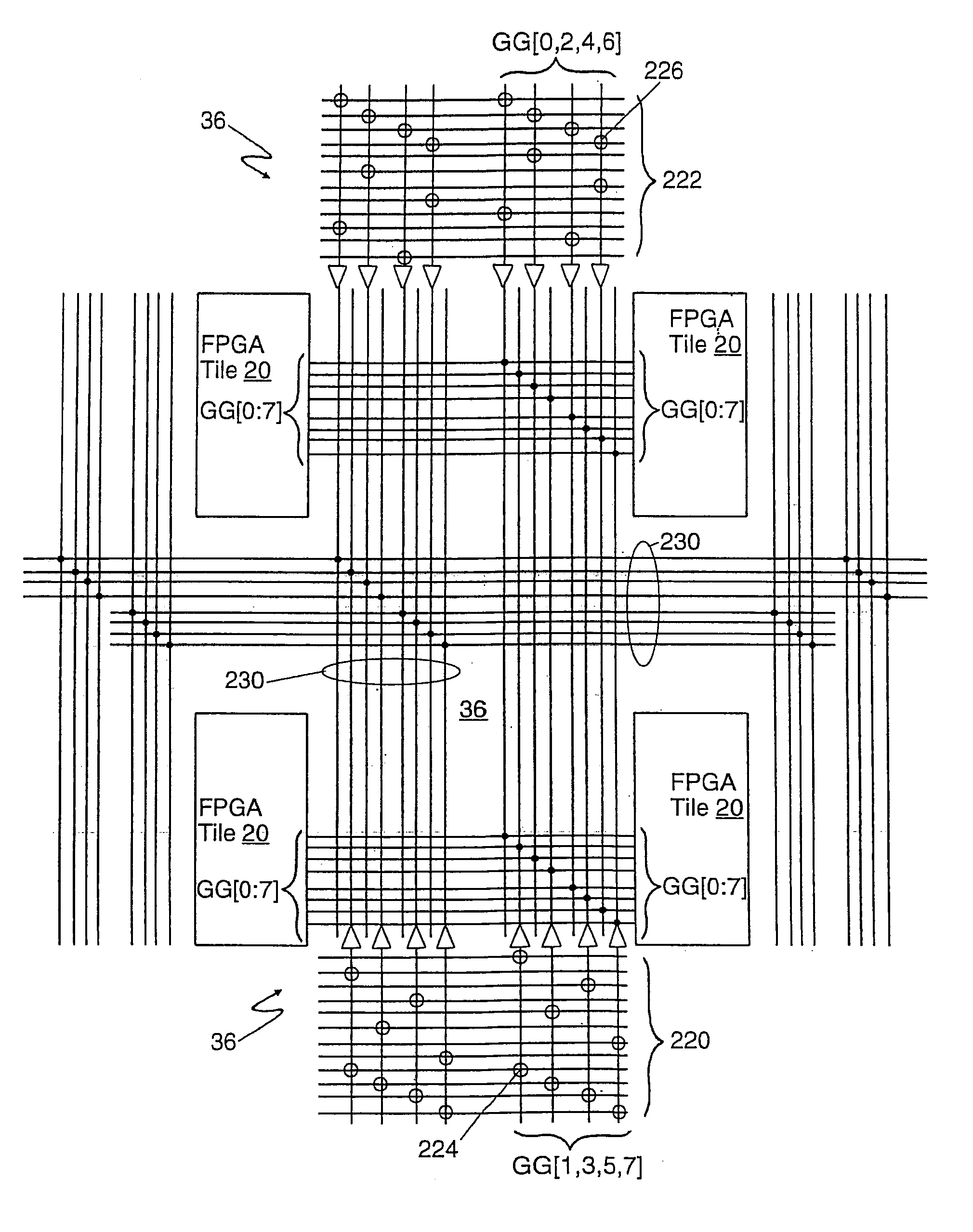

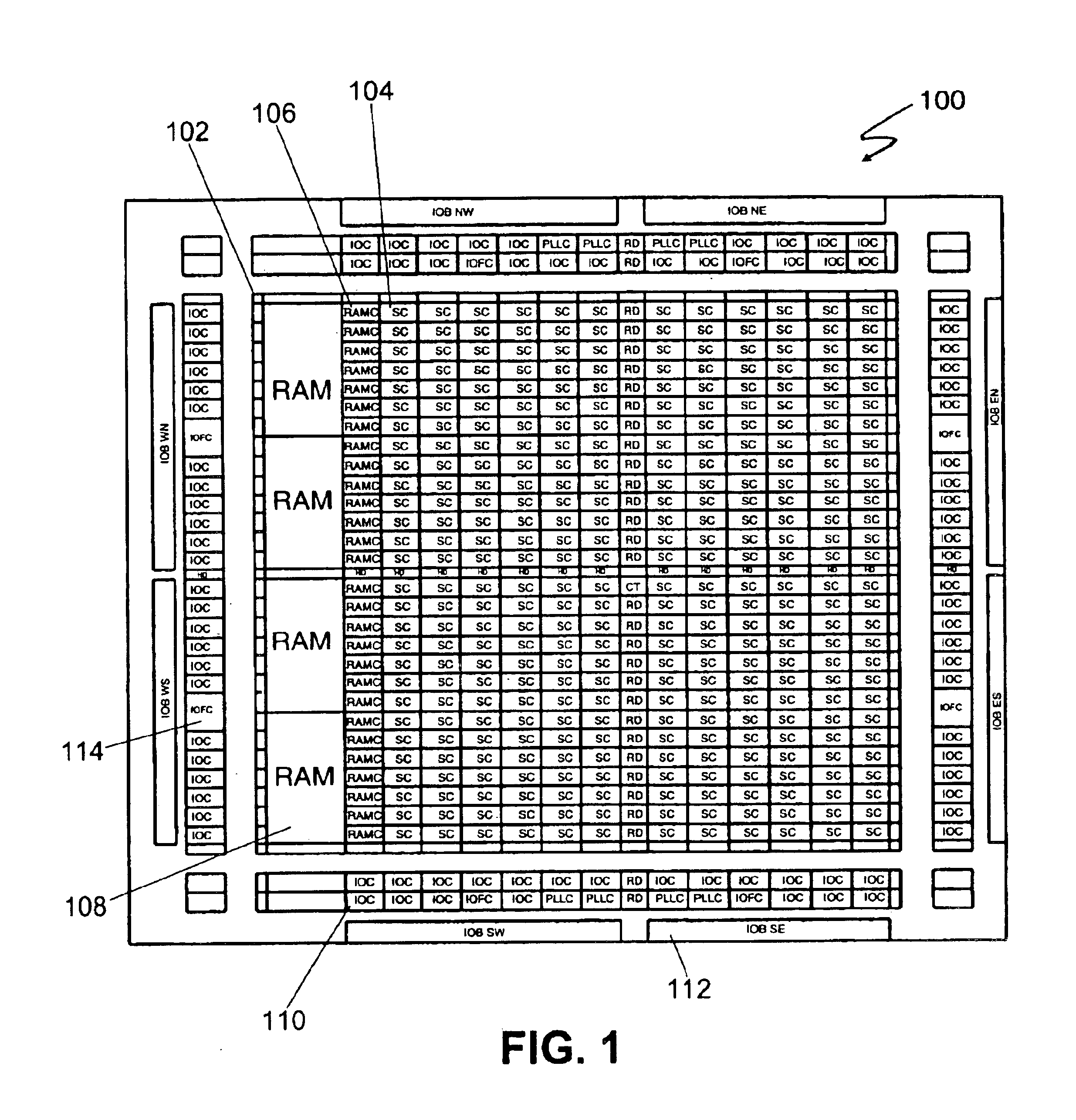

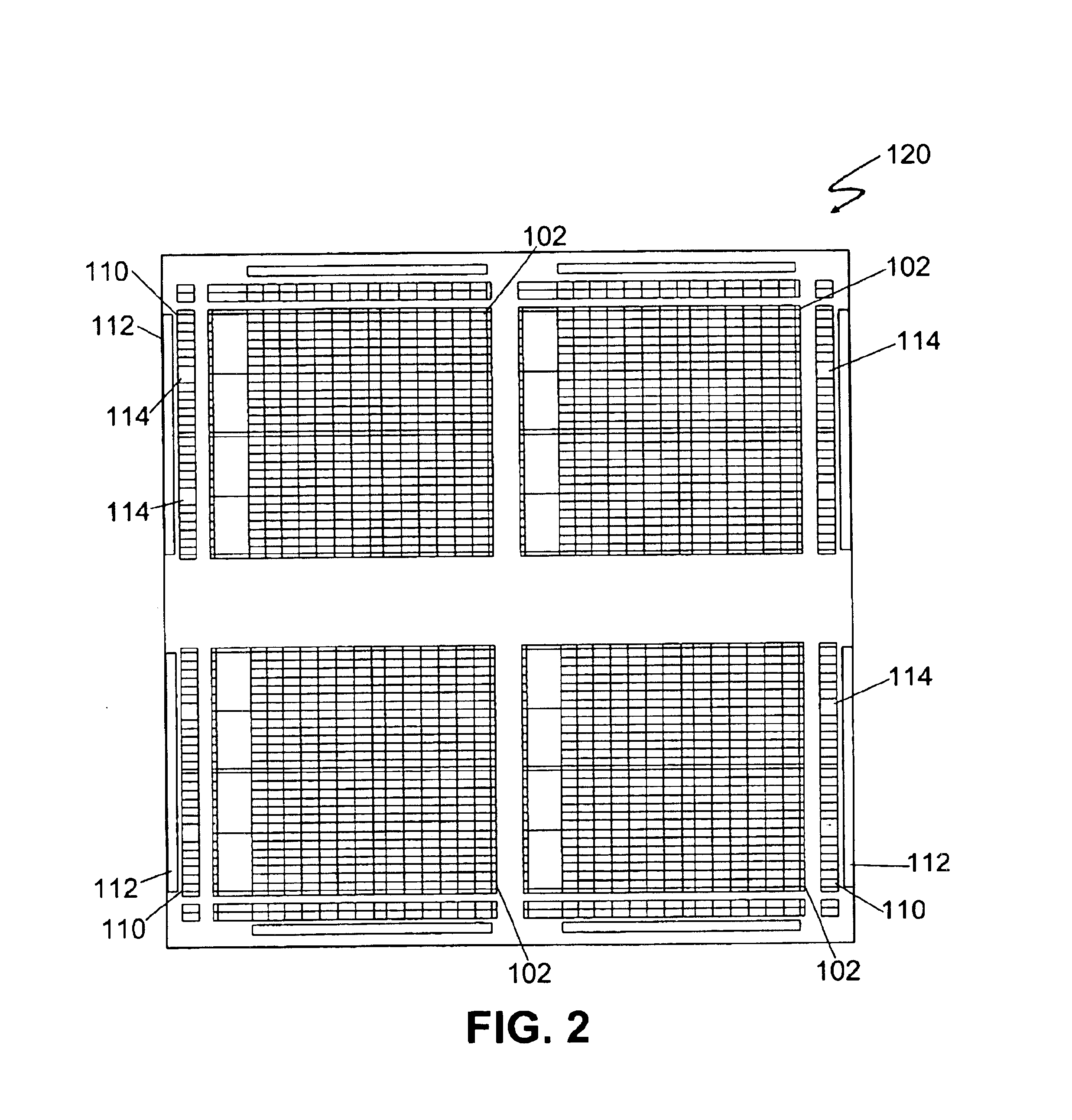

Tileable field-programmable gate array architecture

InactiveUS6888375B2Solid-state devicesCAD circuit designElectrical conductorField-programmable gate array

An apparatus includes a field-programmable gate array (FPGA). The FPGA includes a first FPGA tile, and the first FPGA tile includes a plurality of functional groups (FGs), a third set of routing conductors, in addition to a first set of routing conductors and a second set of routing conductors and a plurality of interface groups (IGs). The plurality of FGs are arranged in rows and columns with each of the FGs being configured to receive tertiary input signals as well as regular input signals, perform a logic operation, and generate regular output signals. The third set of routing conductors is coupled to the first set of output ports of the FGs and configured to receive signals, route signals within the first FPGA tile, and provide input signals to the third set of input ports of the FGs. The plurality of IGs surround the plurality of FGs such that one IG is positioned at each end of each row and column. Each of the IGs is coupled to the third set of routing conductors and configured to transfer signals from the third set of routing conductors to outside of the first FPGA tile.

Owner:MICROSEMI SOC

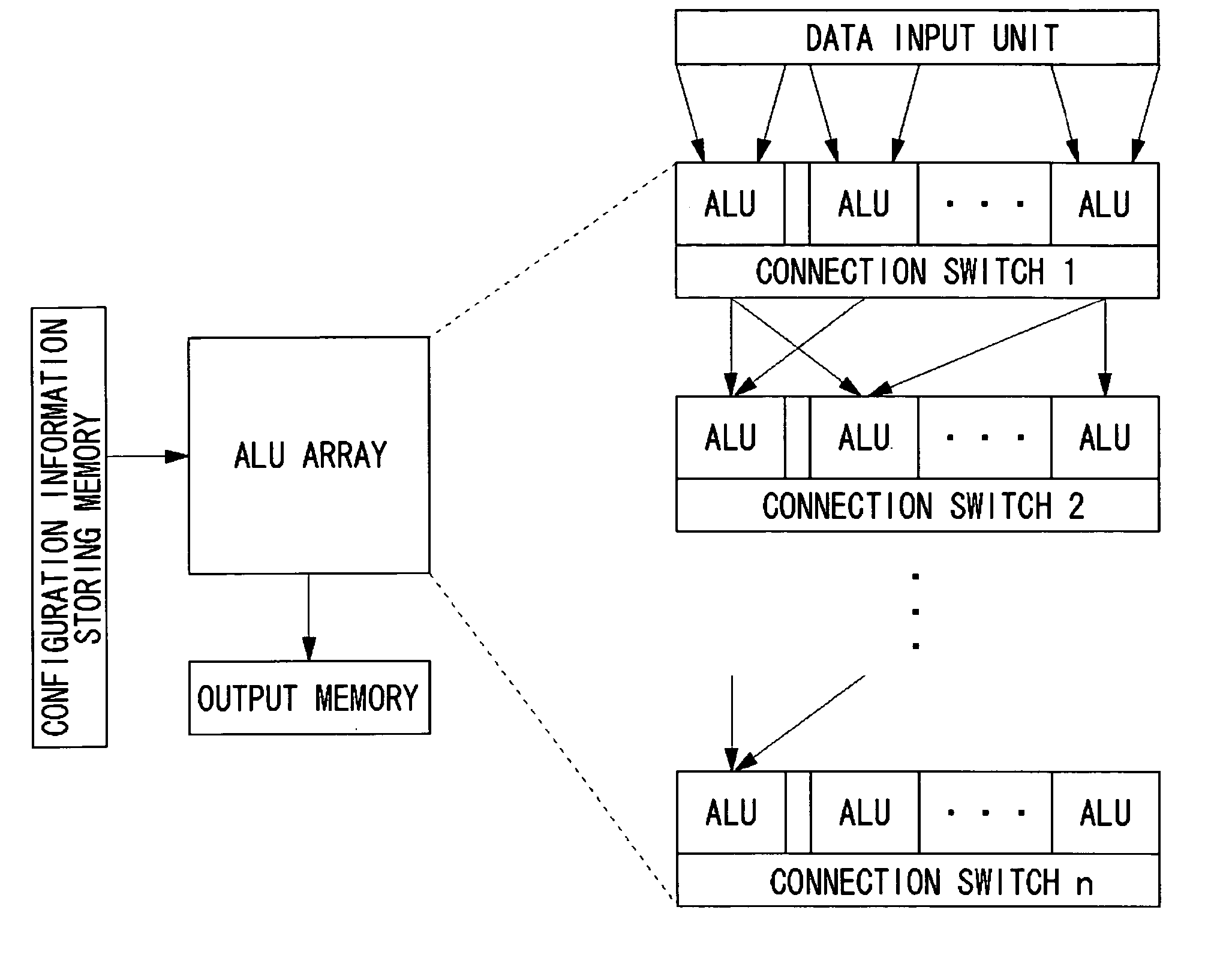

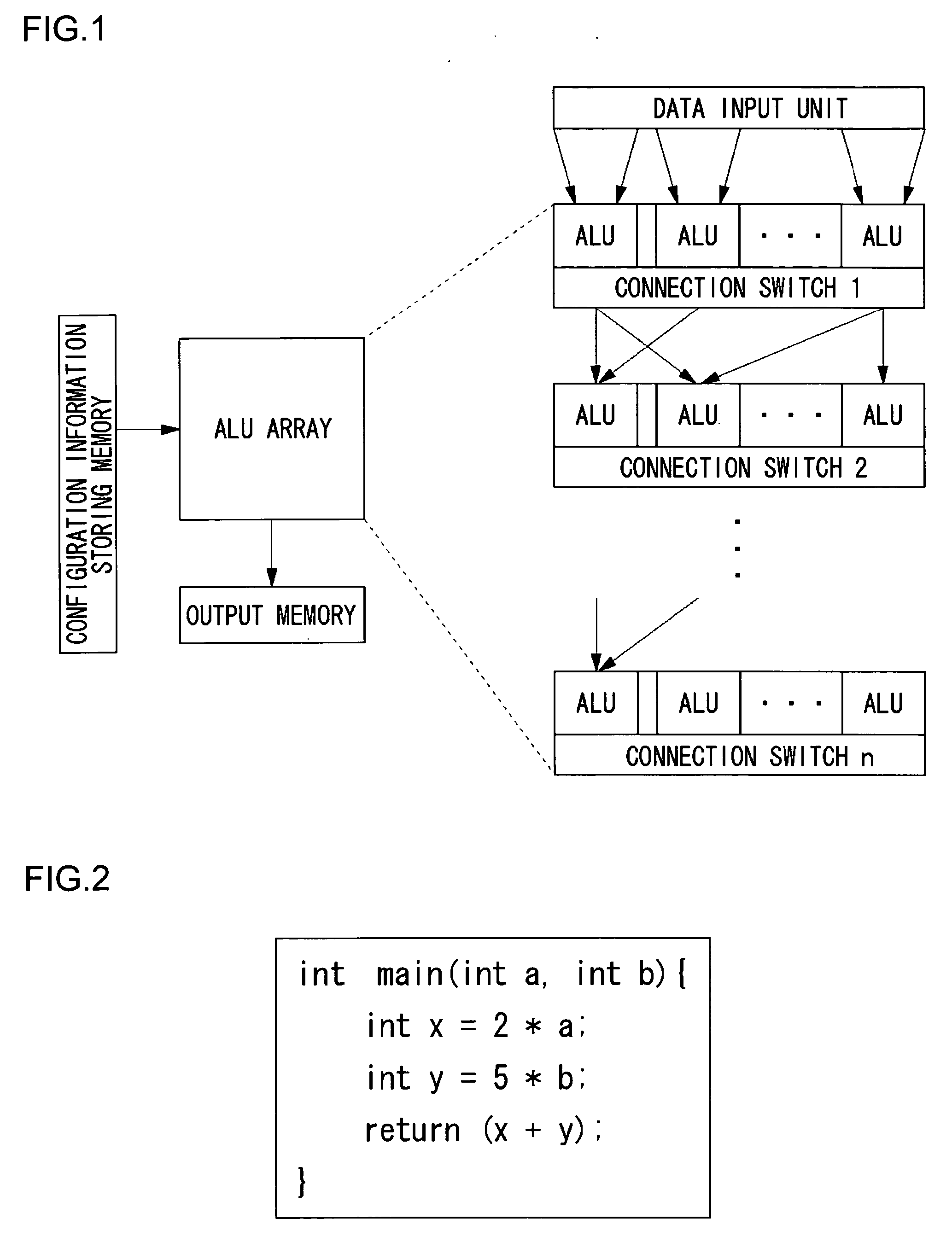

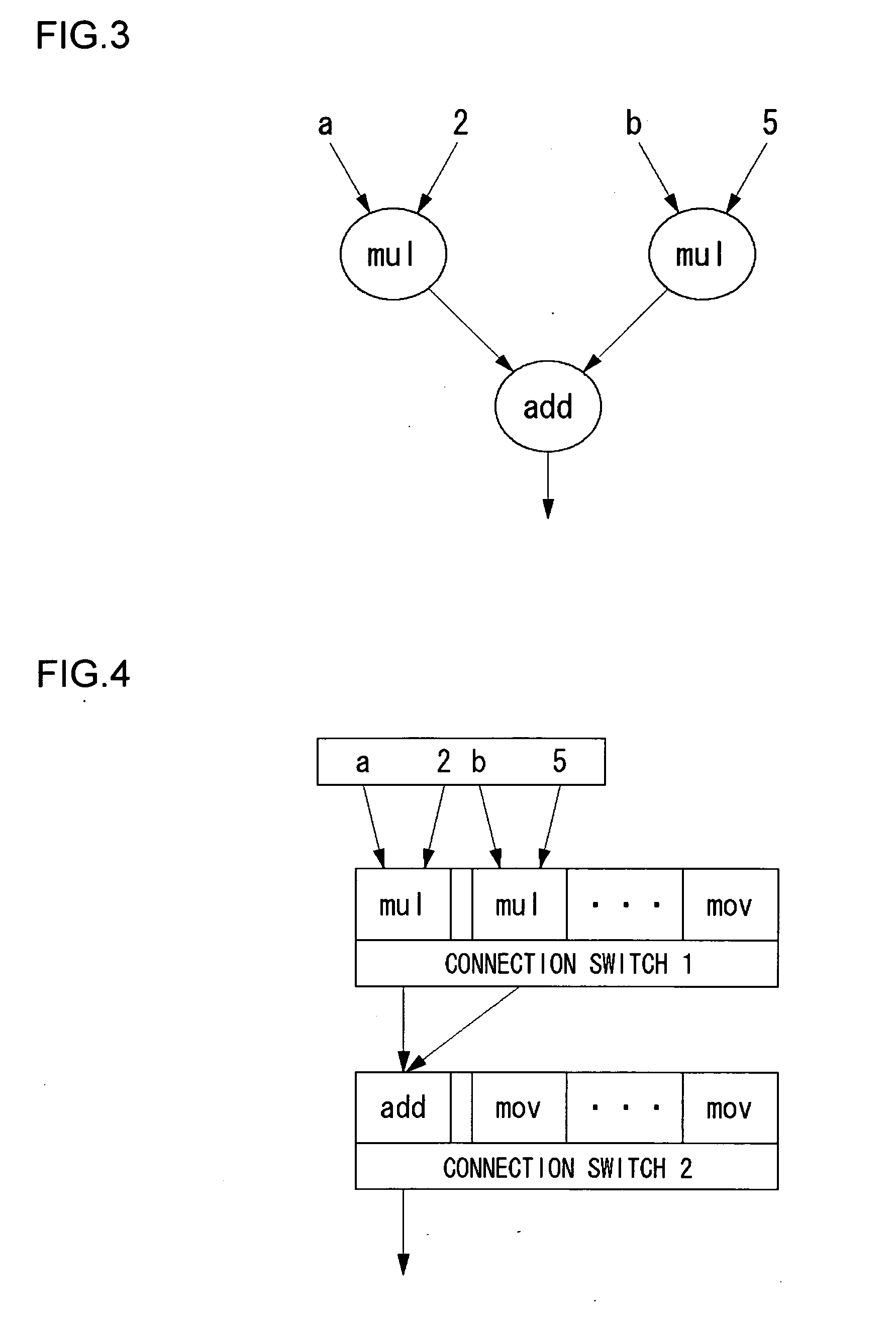

Reconfigurable circuit, processor having reconfigurable circuit, method of determining functions of logic circuits in reconfigurable circuit, method of generating circuit, and circuit

InactiveUS20050134308A1Reduce in quantityReduce switchingEnergy efficient ICTSemiconductor/solid-state device manufacturingLogical circuit

Owner:SANYO ELECTRIC CO LTD

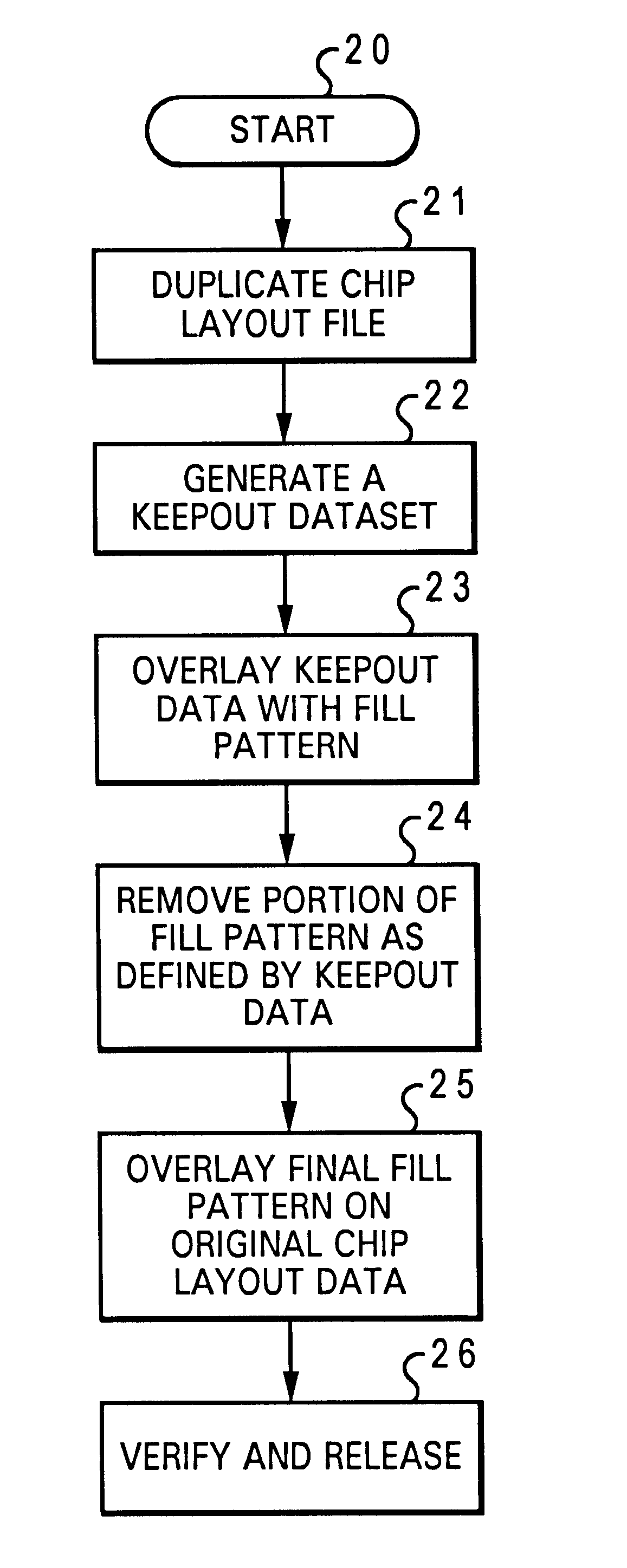

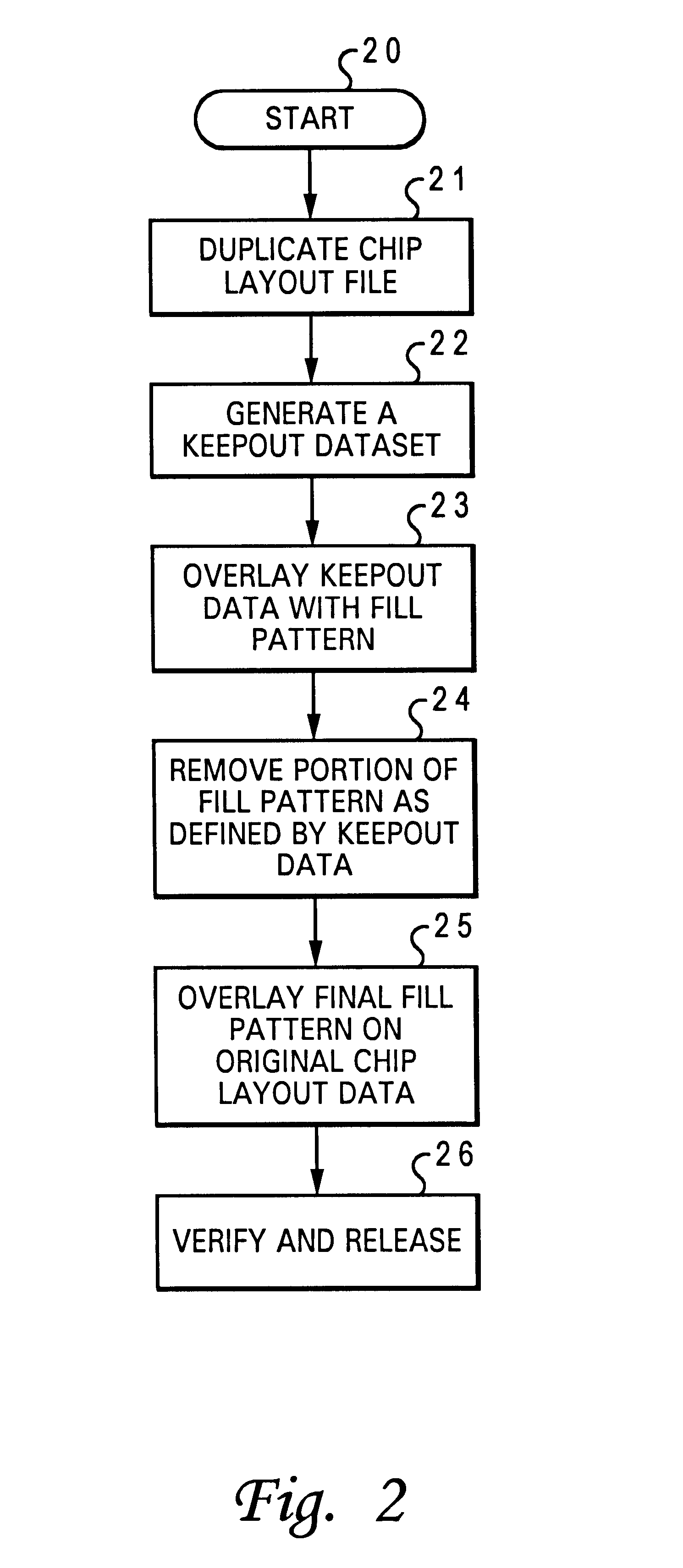

Method for providing a fill pattern for an integrated circuit design

InactiveUS6609235B2Solid-state devicesSemiconductor/solid-state device manufacturingComputer architectureIntegrated circuit design

A method for providing a fill pattern for integrated circuit designs is disclosed. A keepout file having keepout data is generated from a chip design layout file having chip design layout data. The keepout file includes a map of areas of an integrated circuit design where fill patterns cannot be placed. The map of areas from the keepout file is then overlaid with a fill pattern to yield a fill-pattern file. Fill patterns from the fill-pattern file is removed from locations that coincide with locations as defined by the keepout data to yield a final-fill file with crucial fill pattern data. The crucial fill pattern data from the final-fill file is overlaid on the design layout data in the chip design layout file to yield a complete design layout file. Finally, the design rule integrity and logical to physical correspondence of the complete design layout file is verified.

Owner:MIND FUSION LLC

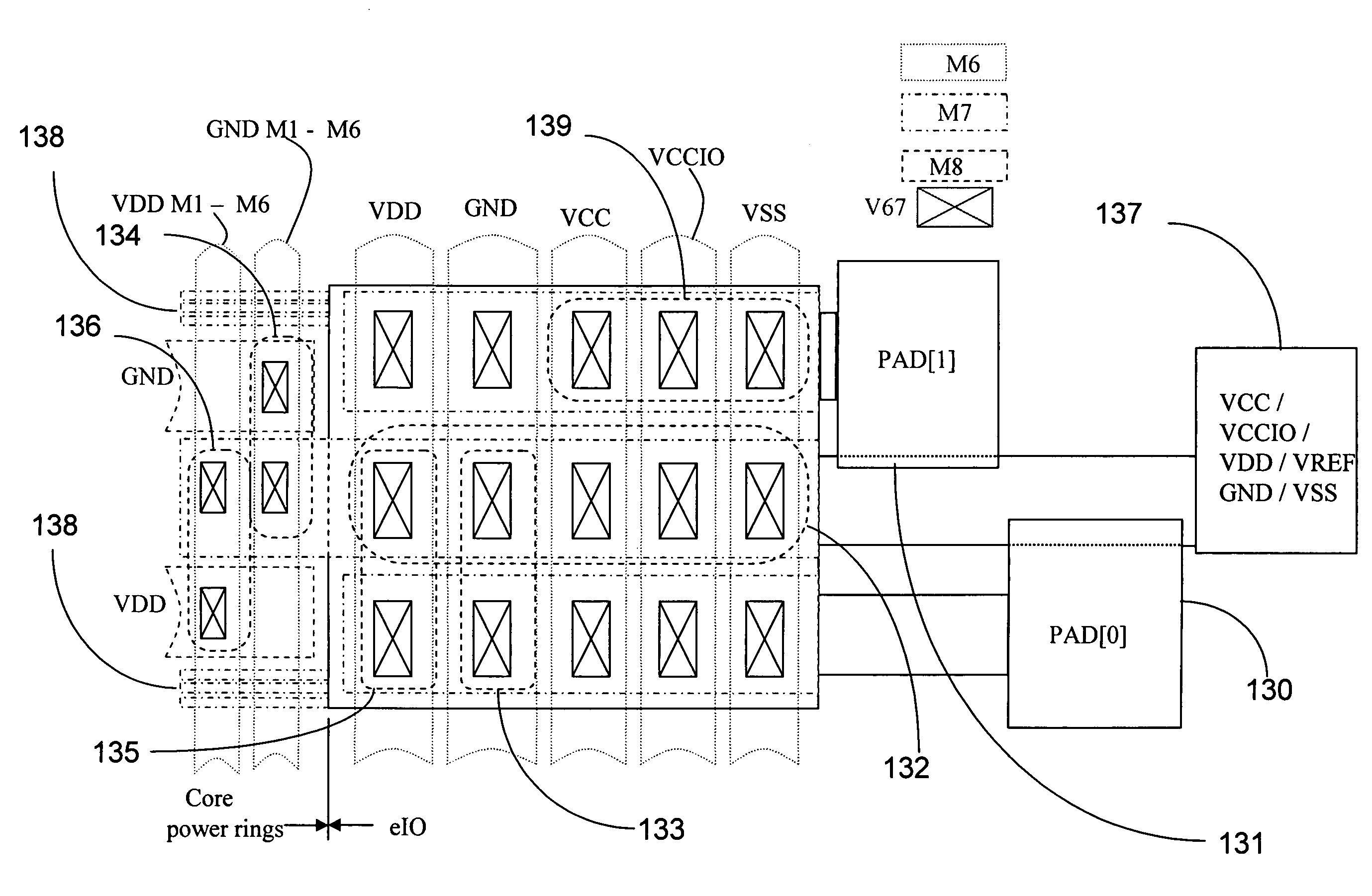

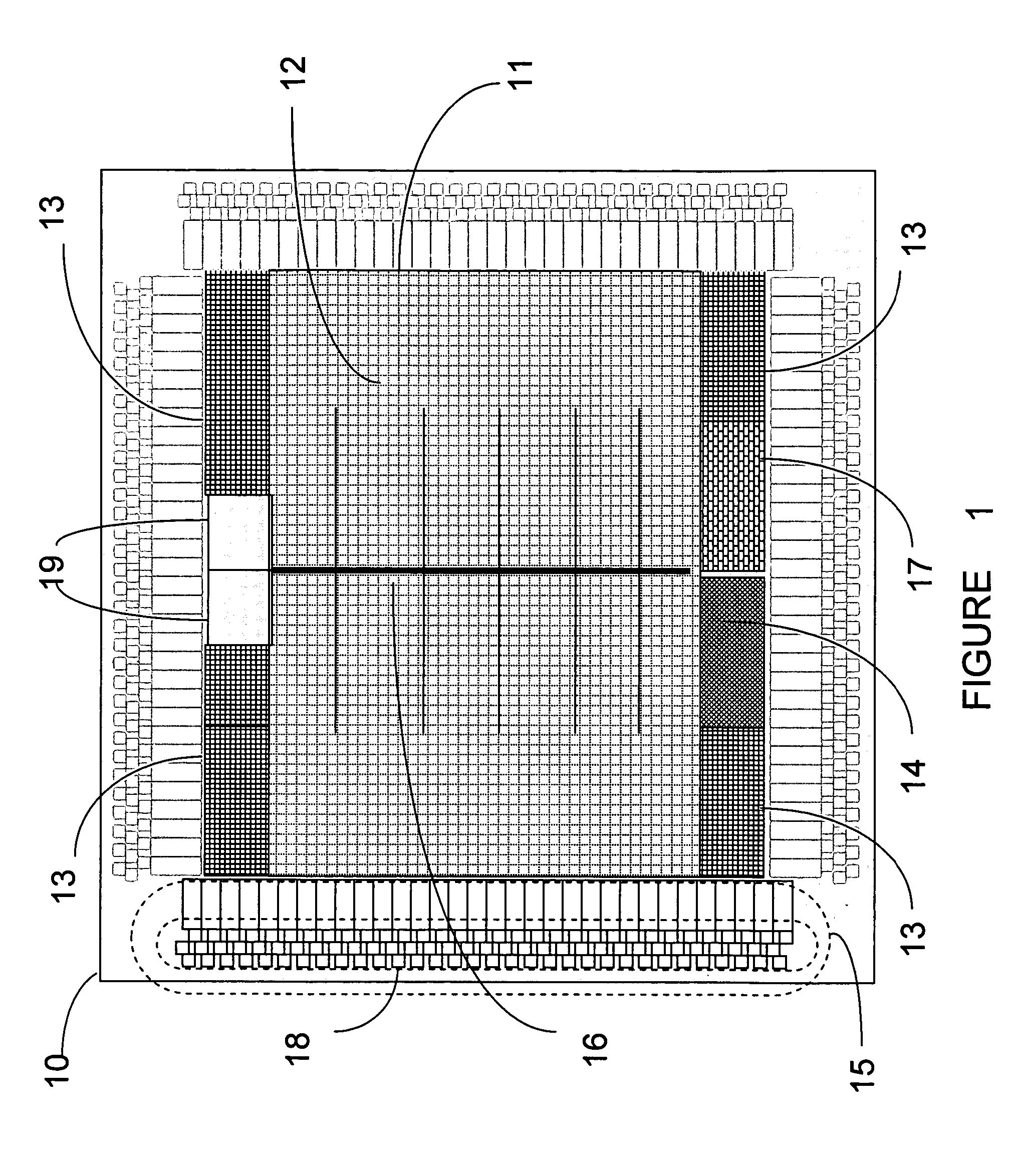

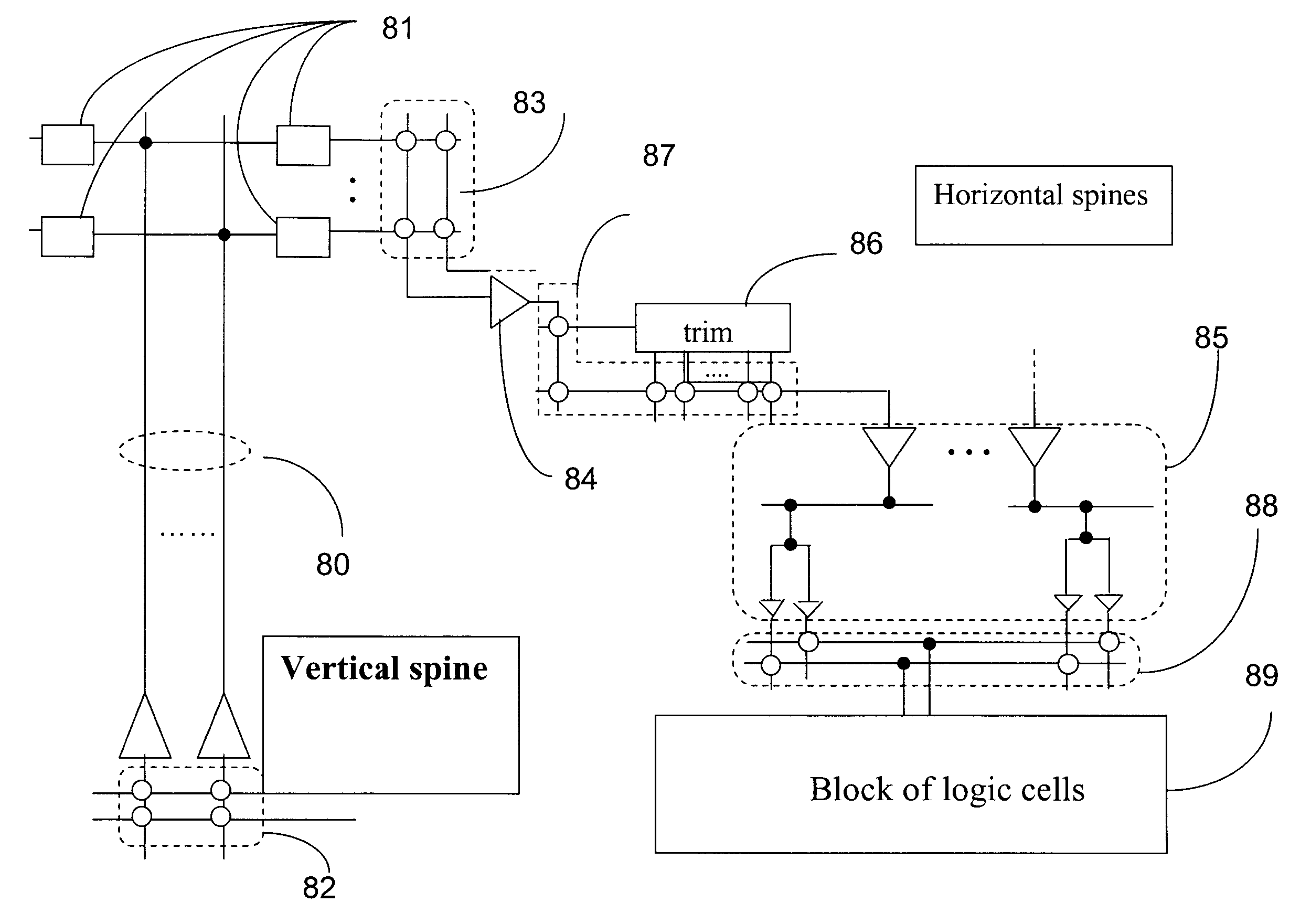

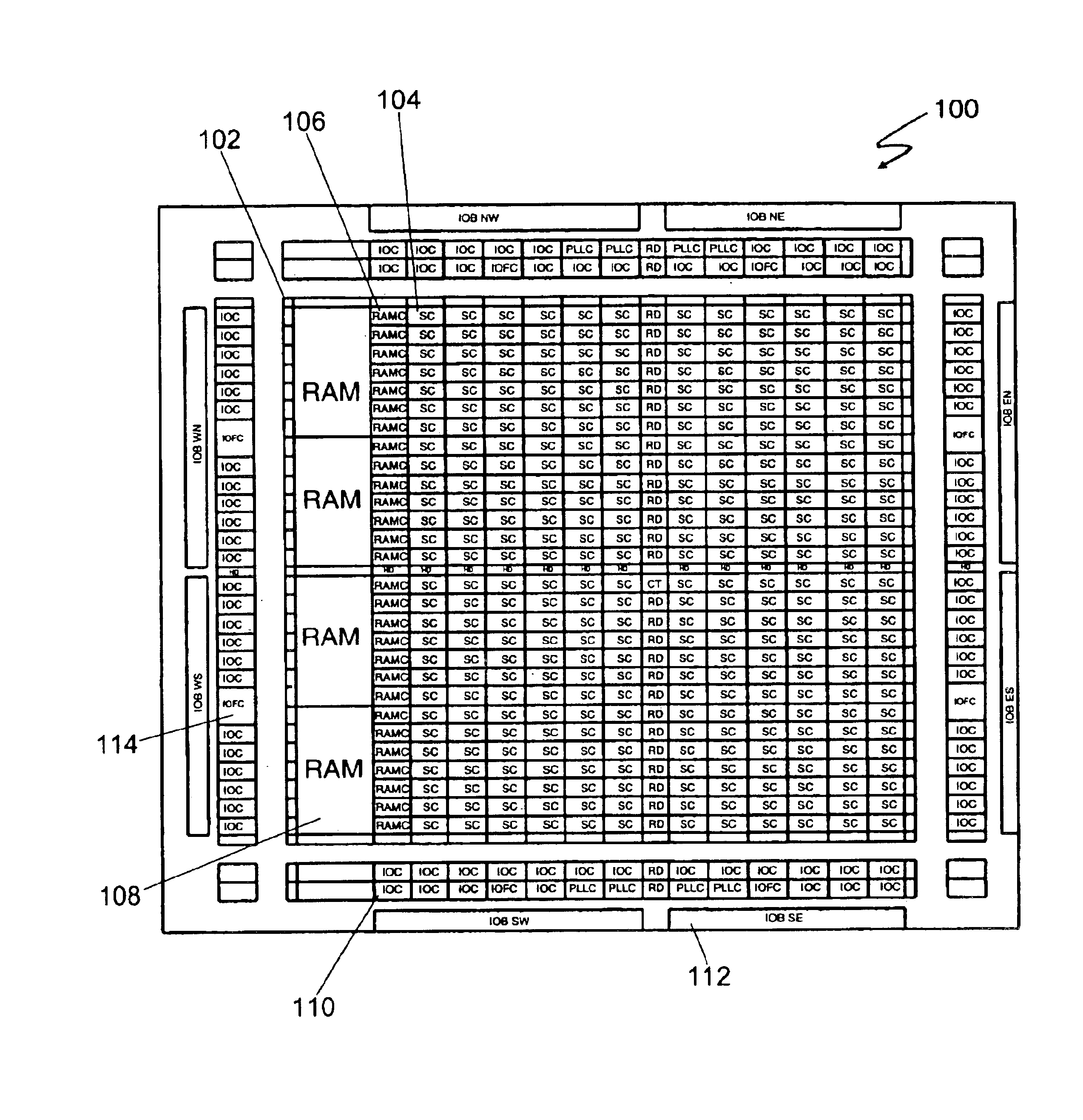

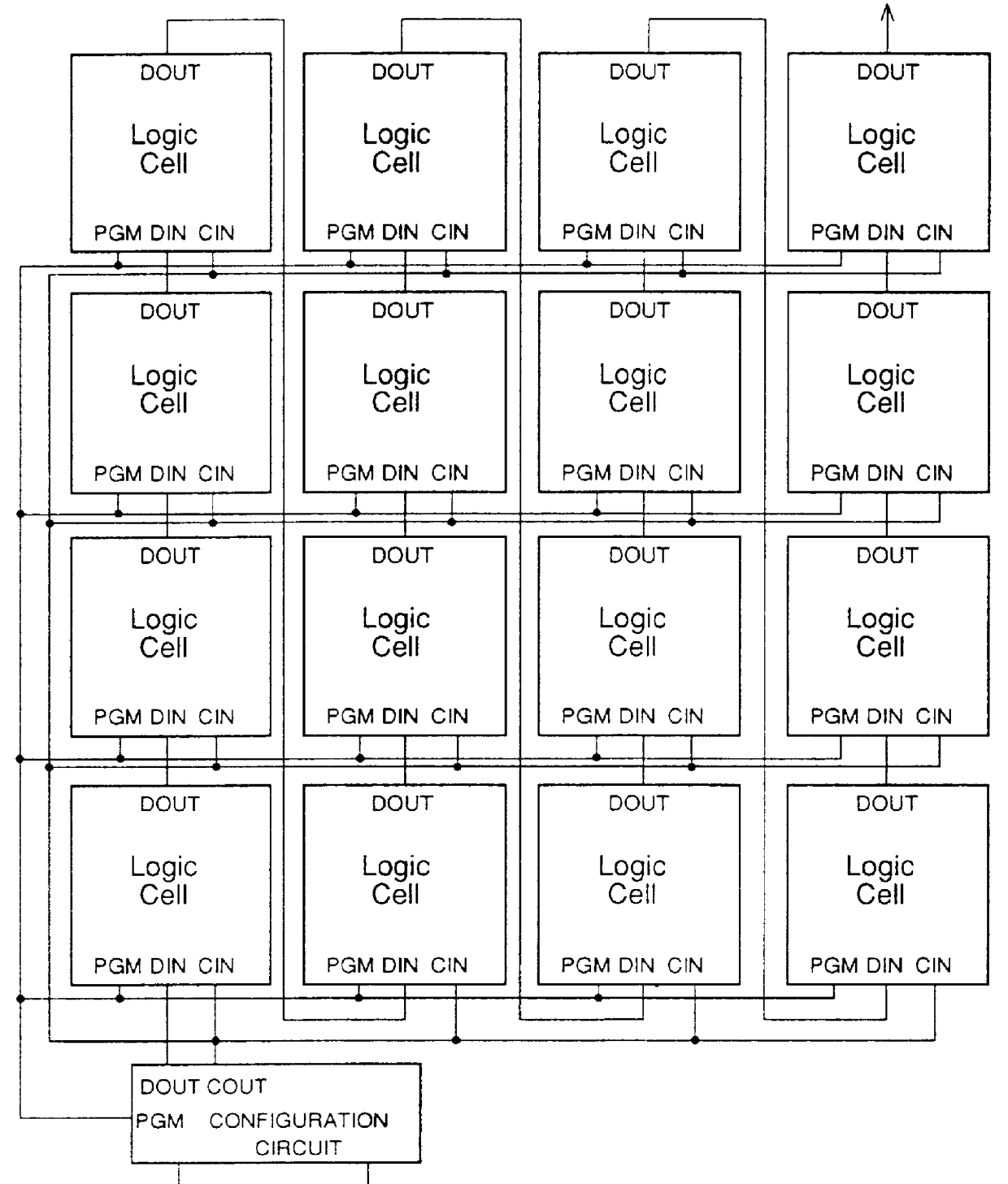

Structured integrated circuit device

InactiveUS7514959B2Solid-state devicesLogic circuits using elementary logic circuit componentsLogic cellMetal

A configurable logic array may include: a multiplicity of logic cells, containing look-up tables; customizable metal and via connection layers overlying the multiplicity of logic cells; a multiplicity of device customizable I / O cells; a multiplicity of configuration customizable RAM blocks; a ROM block with customizable contents; and a microprocessor with customizable I / O for configuring and testing the array, where the customizations are all done on a single via layer.

Owner:TAHOE RES LTD

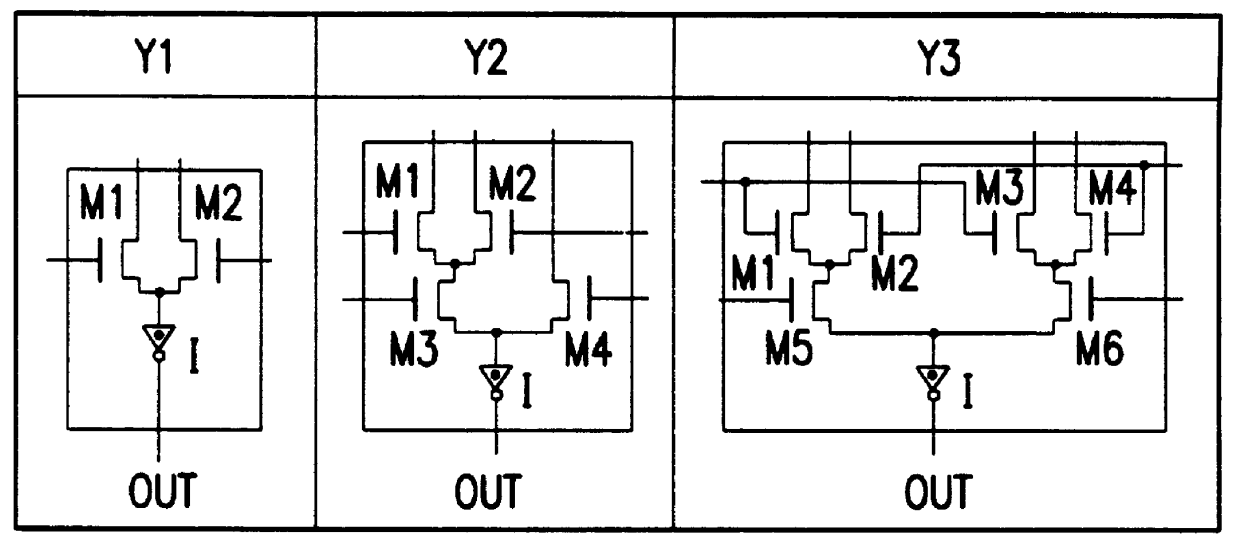

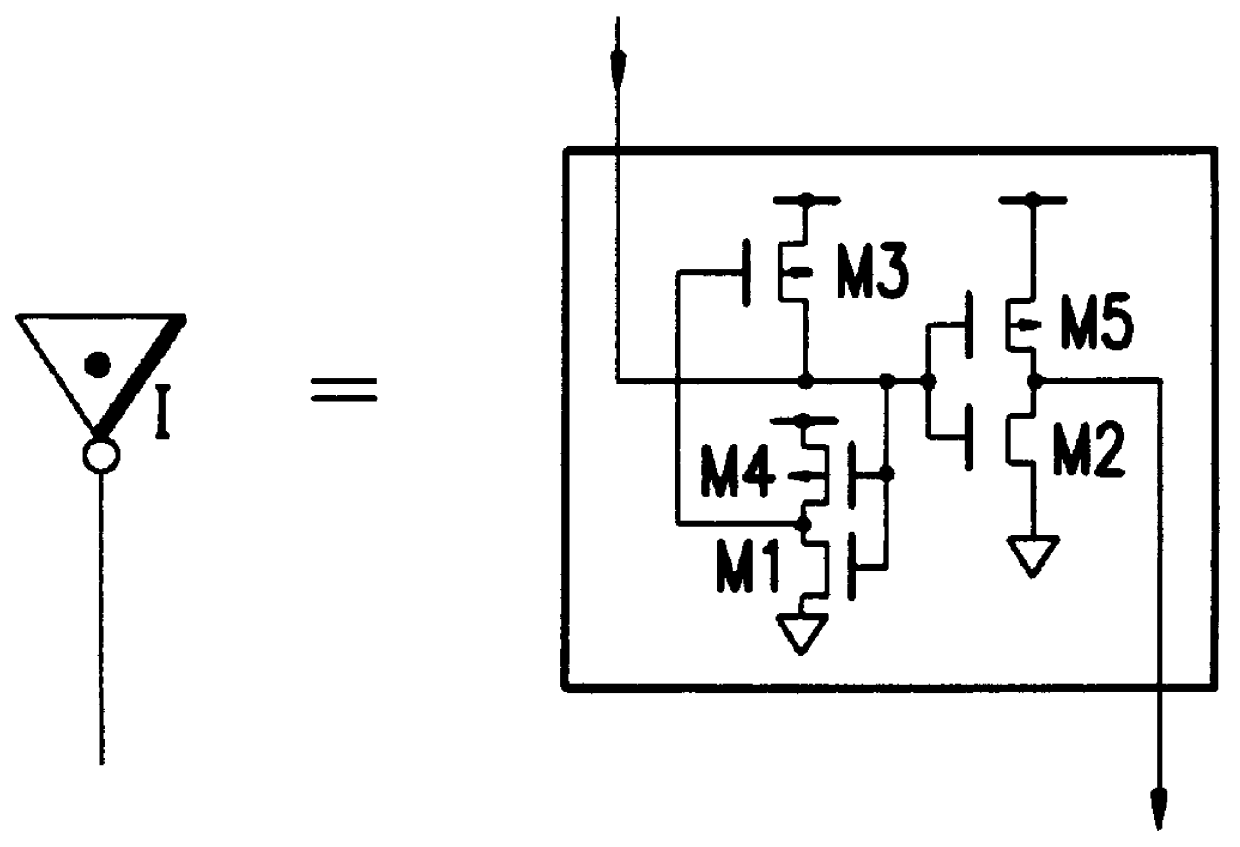

Logic circuit utilizing pass transistors and logic gate

InactiveUS6084437ATransistorReliability increasing modificationsCmos logic circuitsLogical operations

A logic circuit combines a plurality of pass-transistor logic trees and a multiple-input logic gate for receiving intermediate logic signals from the respective pass-transistor logic trees, and can express a complex logical operation while decreasing the number of stages in pass-transistor logic trees and improving operation speed. Even a logical operation that cannot be expressed efficiently by a known or conventional pass-transistor logic circuit can be expressed efficiently with performance higher than that of a known CMOS logic circuit. Furthermore, when a static feedthrough current of the multiple-input logic gate is suppressed, power consumption can be reduced. In some embodiments, since circuitry for suppressing a static feedthrough current of the multiple-input logic gate is arranged so that a probability of occurrence of logical collision with a preceding stage will decrease or will be nil, power consumption can further be reduced.

Owner:KAWASAKI MICROELECTRONICS

Structured integrated circuit device

ActiveUS7463062B2Solid-state devicesLogic circuits using elementary logic circuit componentsLogic cellComputer science

A configurable logic array may include: a multiplicity of logic cells, containing look-up tables; customizable metal and via connection layers overlying the multiplicity of logic cells; a multiplicity of device customizable I / O cells; a multiplicity of configuration customizable RAM blocks; a ROM block with customizable contents; and a microprocessor with customizable I / O for configuring and testing the array, where the customizations may all be done on a single via layer.

Owner:TAHOE RES LTD

Configurable IC with interconnect circuits that also perform storage operations

InactiveUS7342415B2Logic circuits characterised by logic functionSolid-state devicesComputer scienceLogic circuitry

Owner:ALTERA CORP

Integrated circuit communication techniques

ActiveUS7439773B2Reduce the required powerReduce power consumptionReliability increasing modificationsPower reduction by control/clock signalEngineeringSemiconductor

Owner:TAHOE RES LTD

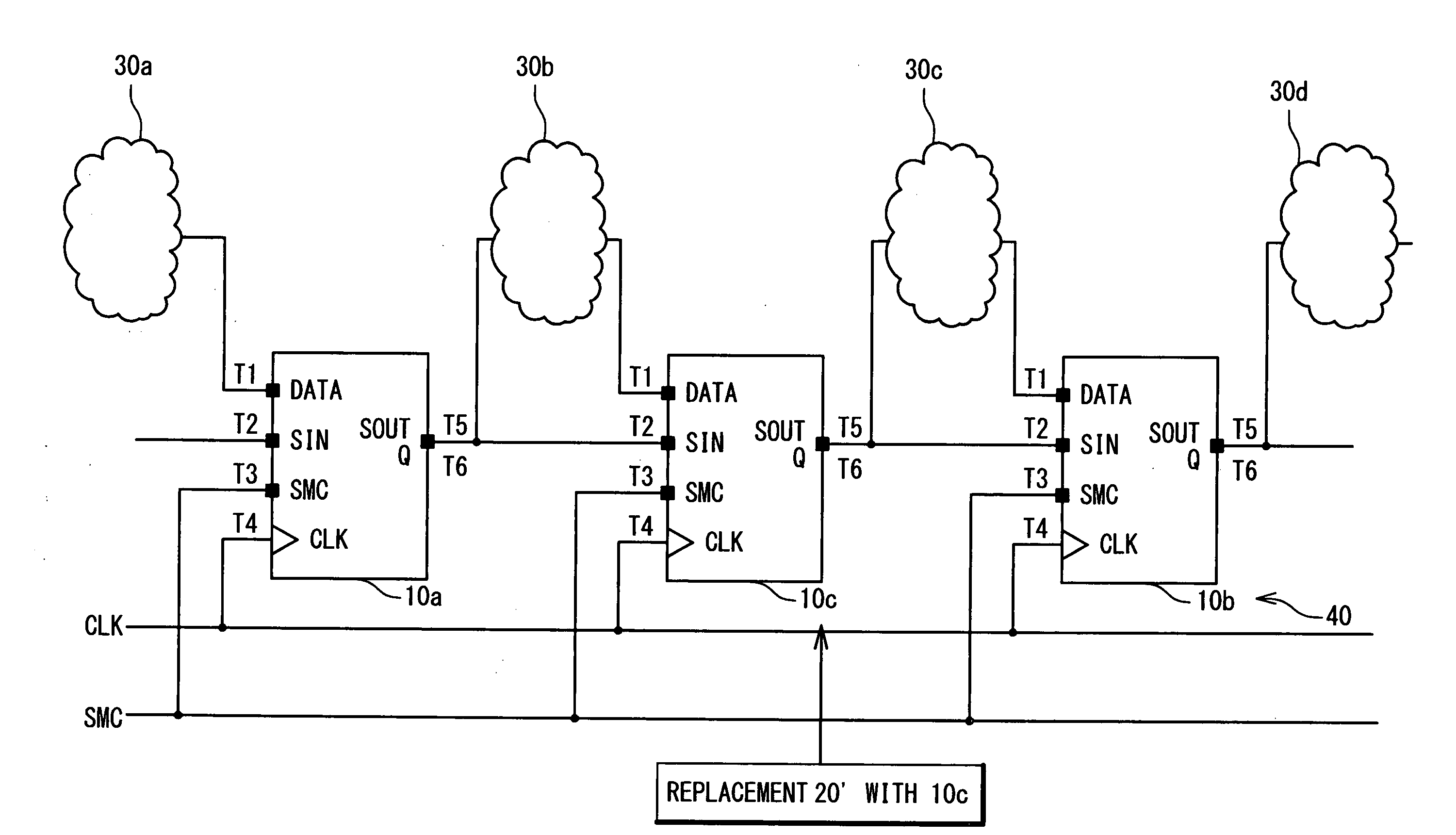

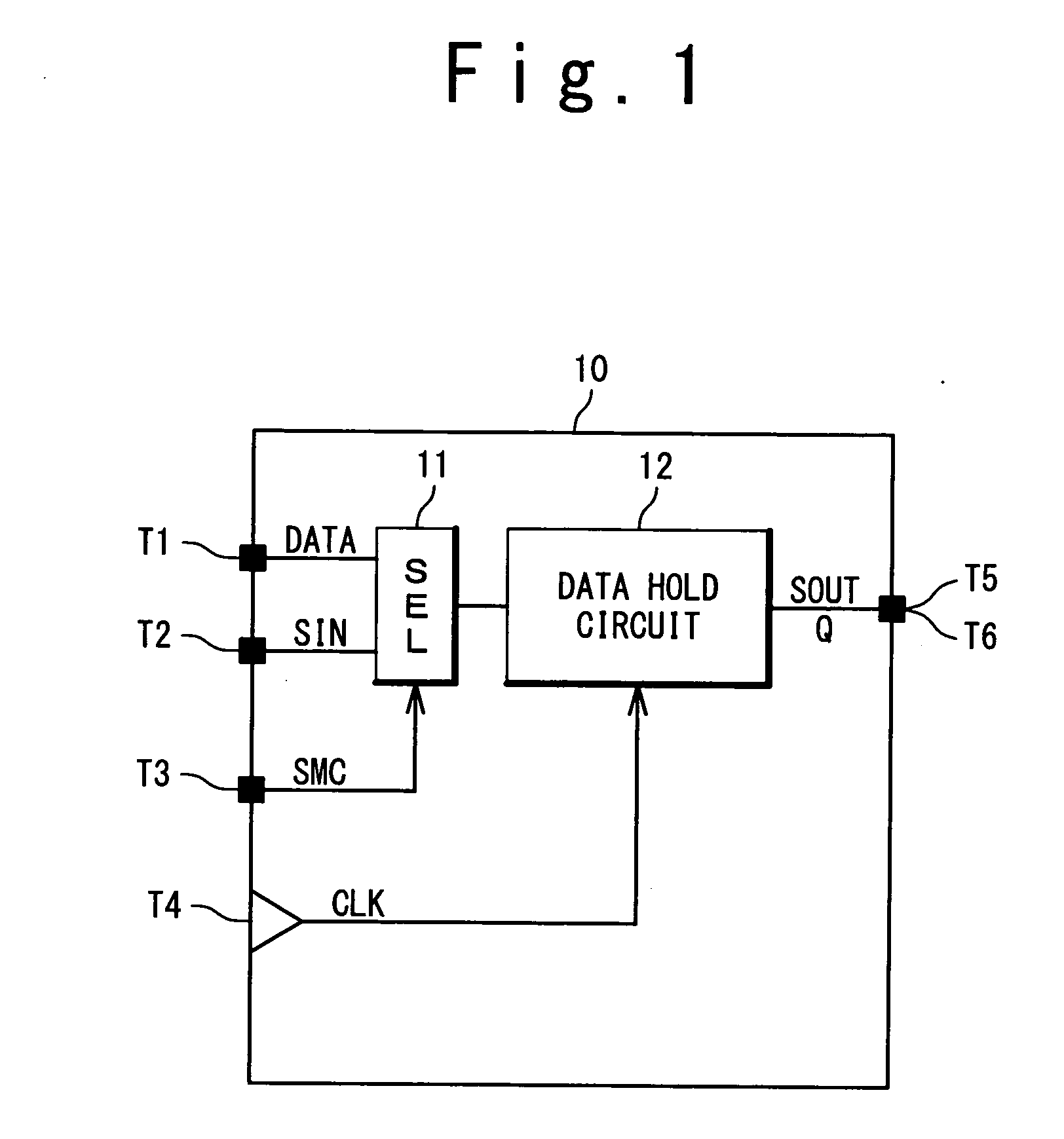

Integrated circuit design based on scan design technology

InactiveUS20090032899A1Effect of power consumption reduction is enhancedReduce power consumptionElectronic circuit testingSolid-state devicesEngineeringCircuit design

An integrated circuit is provided with a scan chain including a scan flip-flop and a dummy block. The dummy block has a clock terminal receiving a clock signal, a scan input terminal connected to a scan data line within the scan chain, and a scan output terminal connected to another scan data line within the scan chain. The dummy block is configured to output data on the scan output terminal in response to input data fed to the scan input terminal, not responsively to the clock signal.

Owner:RENESAS ELECTRONICS CORP

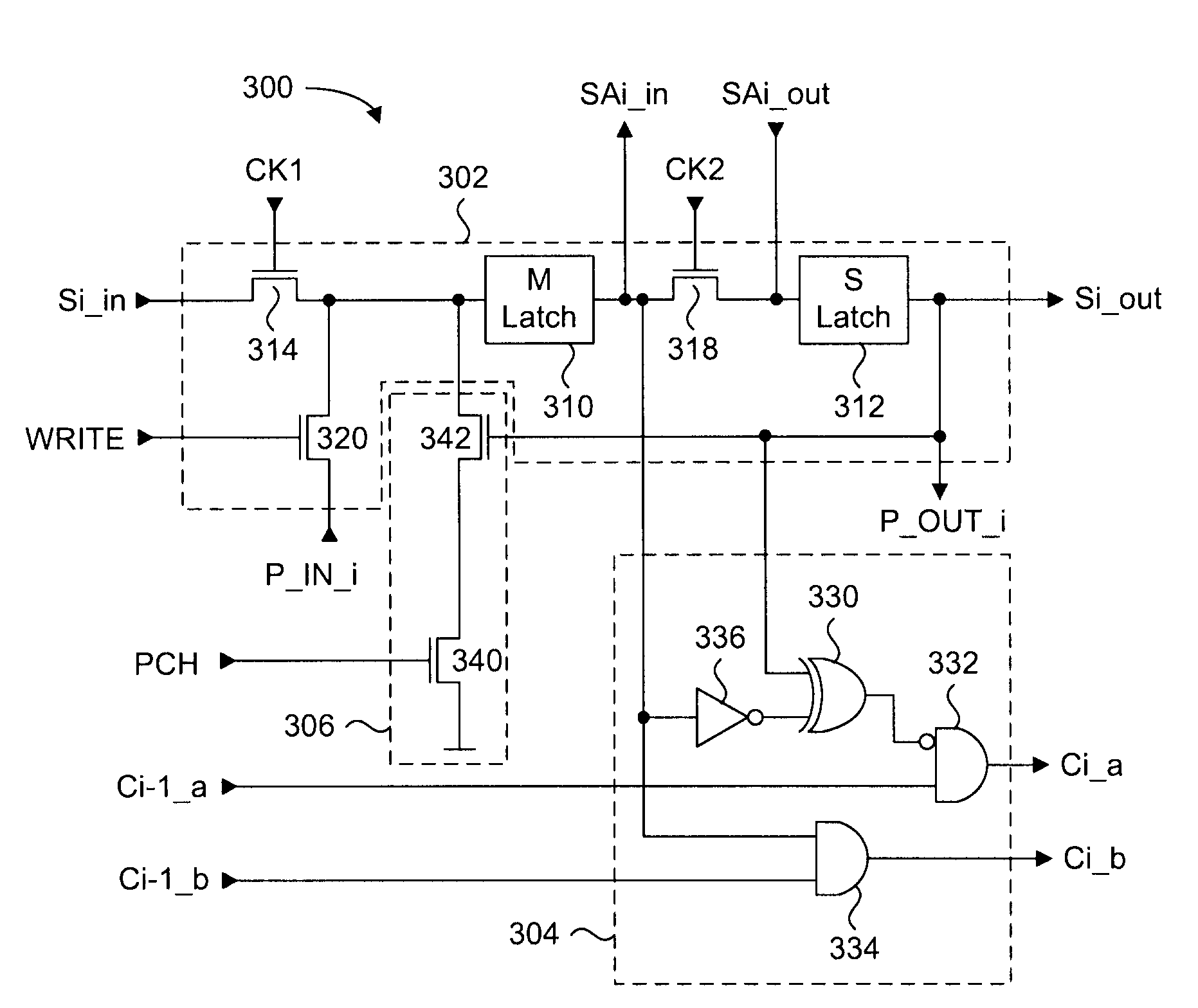

Dual function data register

ActiveUS20090290434A1Reduce disadvantagesRead-only memoriesDigital storageProcessor registerTheoretical computer science

A dual function serial and parallel data register with integrated program verify functionality. The master and slave latching circuits of the dual function data register can concurrently store two different words of data. In a program verify operation, the master latch stores program data and the slave latch will receive and store read data. Comparison logic in each register stage will compare the data of both latches, and integrate the comparison result to that of the previous register stage. The final single bit result will indicate the presence of at least one bit that has not been programmed. Automatic program inhibit logic in each stage will prevent successfully programmed bits from being re-programmed in each subsequent reprogram cycle. Either data word can be serially clocked out by selectively starting the shift operations on either the low or high active logic level of a clock signal.

Owner:SYNOPSYS INC

Tileable field-programmable gate array architecture

InactiveUS7015719B1Solid-state devicesLogic circuits using elementary logic circuit componentsElectrical conductorEngineering

An apparatus includes an FPGA, which includes a first FPGA tile including a plurality of FGs, a first, second, and third set of routing conductors, and a plurality of IGs. The FGs are arranged in rows and columns with each FG being configured to receive tertiary and regular input signals, perform a logic operation, and generate regular output signals. The third set of routing conductors is coupled to the first set of output ports of the FGs and configured to receive signals, route signals within the FPGA tile, and provide input signals to the third set of input ports of the FGs. The IGs surround the FGs such that one IG is positioned at each end of each row and column. Each IG is coupled to the third set of routing conductors and configured to transfer signals from the third set of routing conductors to outside the first FPGA tile.

Owner:MICROSEMI SOC

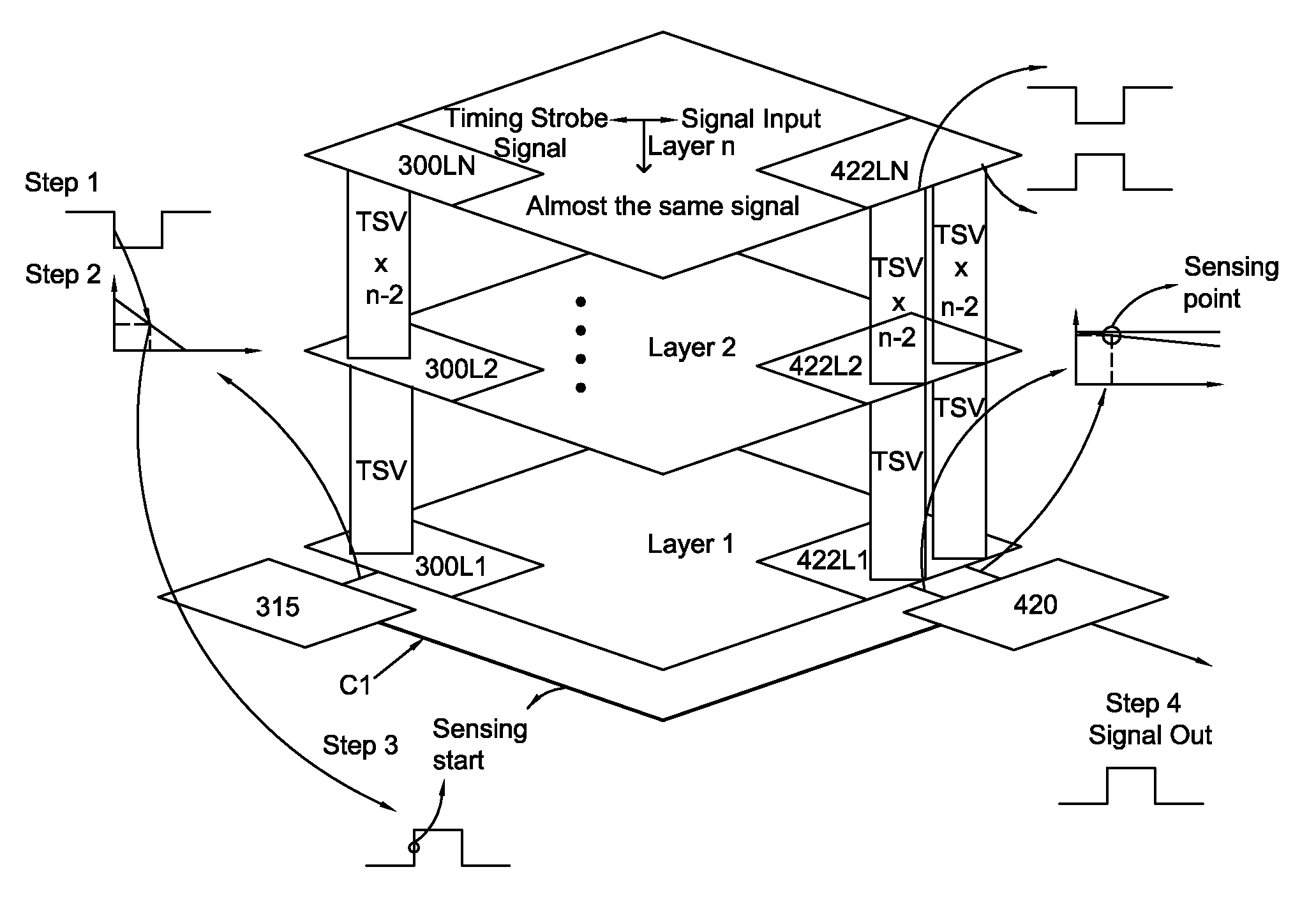

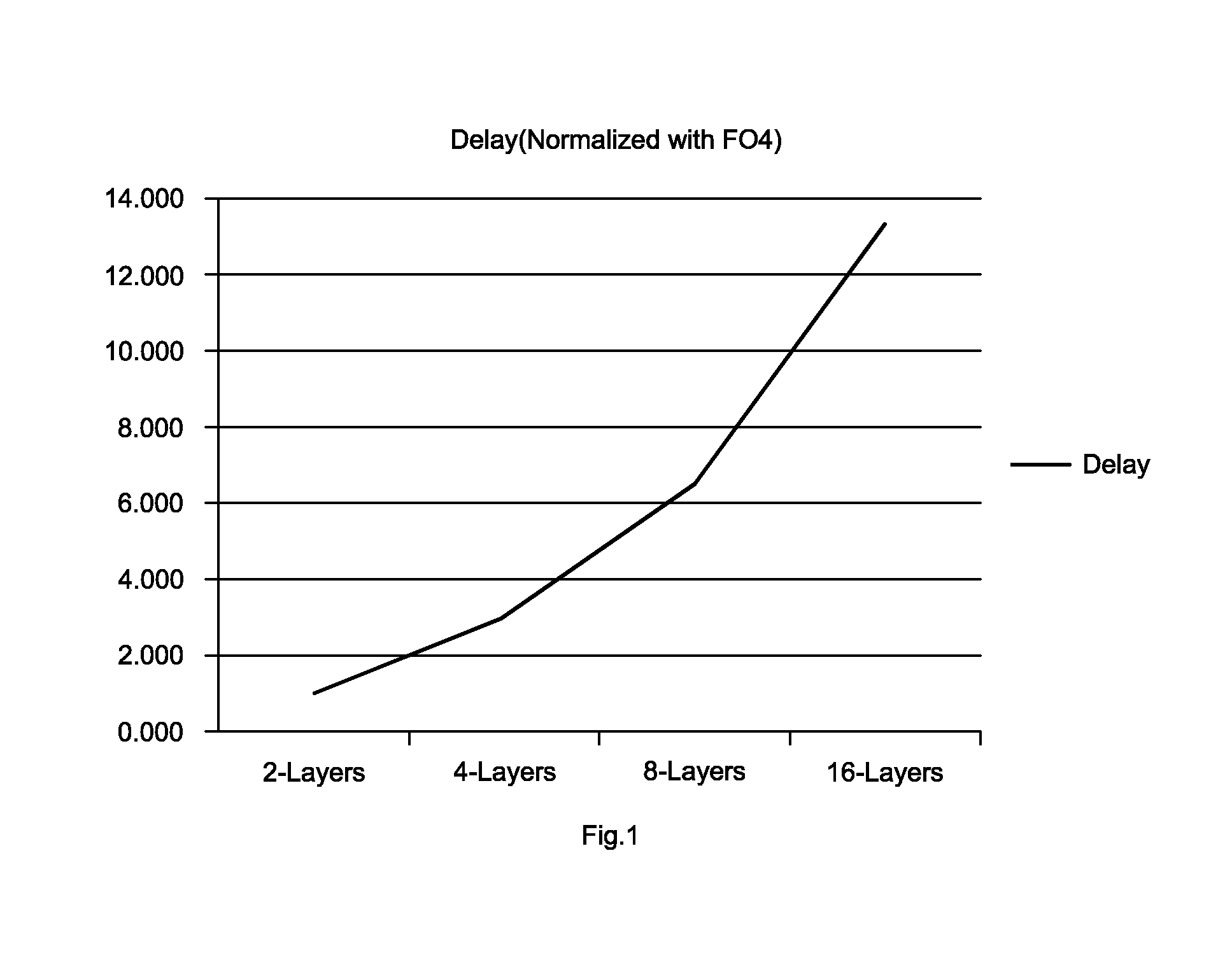

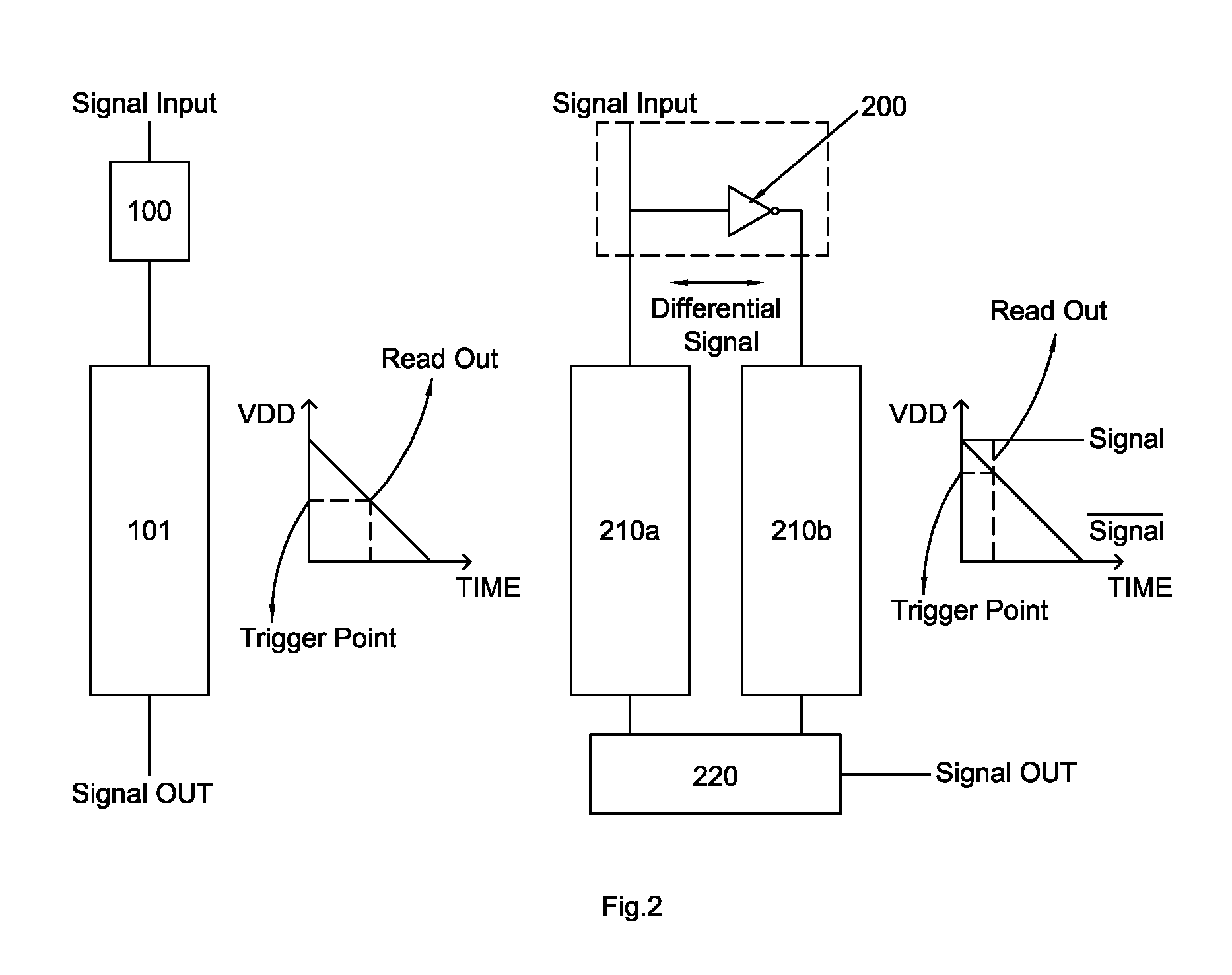

Differential sensing and TSV timing control scheme for 3D-IC

ActiveUS7969193B1Improve signal transmission speedSemiconductor/solid-state device detailsSolid-state devicesDummy loadHigh ability

This disclosure uses a differential sensing and TSV timing control scheme for 3D-IC, which includes a first chip layer of the stacked device having a detecting circuits and a relative high ability driver horizontally coupled to the detecting circuits. A sensing circuit is coupled to the detecting circuits by a horizontal line, a first differential signal driver is coupled to the sensing circuit, horizontally. The Nth chip layer of the stacked device includes a Nth relative high ability driver and a Nth differential signal driver formed on the Nth chip layer. The Nth relative high ability driver is vertically coupled to the first relative high ability driver through one relative low loading TSV and (N−2) TSVs to act as dummy loadings. The TSV and (N−2) TSVs penetrate the stacked device from Nth chip layer to first chip layer. The TSV shares same configuration with the (N−2) TSVs. The Nth differential signal driver is vertically coupled to the first differential signal driver through a pair of TSVs and (N−2) pairs of TSVs, vertically. The pair of TSVs and the (N−2) TSVs penetrate the stacked device from the Nth chip layer to the first chip layer. Each of TSV is formed between a first and a second chip layers. Each of TSV is formed between any adjacent two chip layers of the stacked device.

Owner:NATIONAL TSING HUA UNIVERSITY

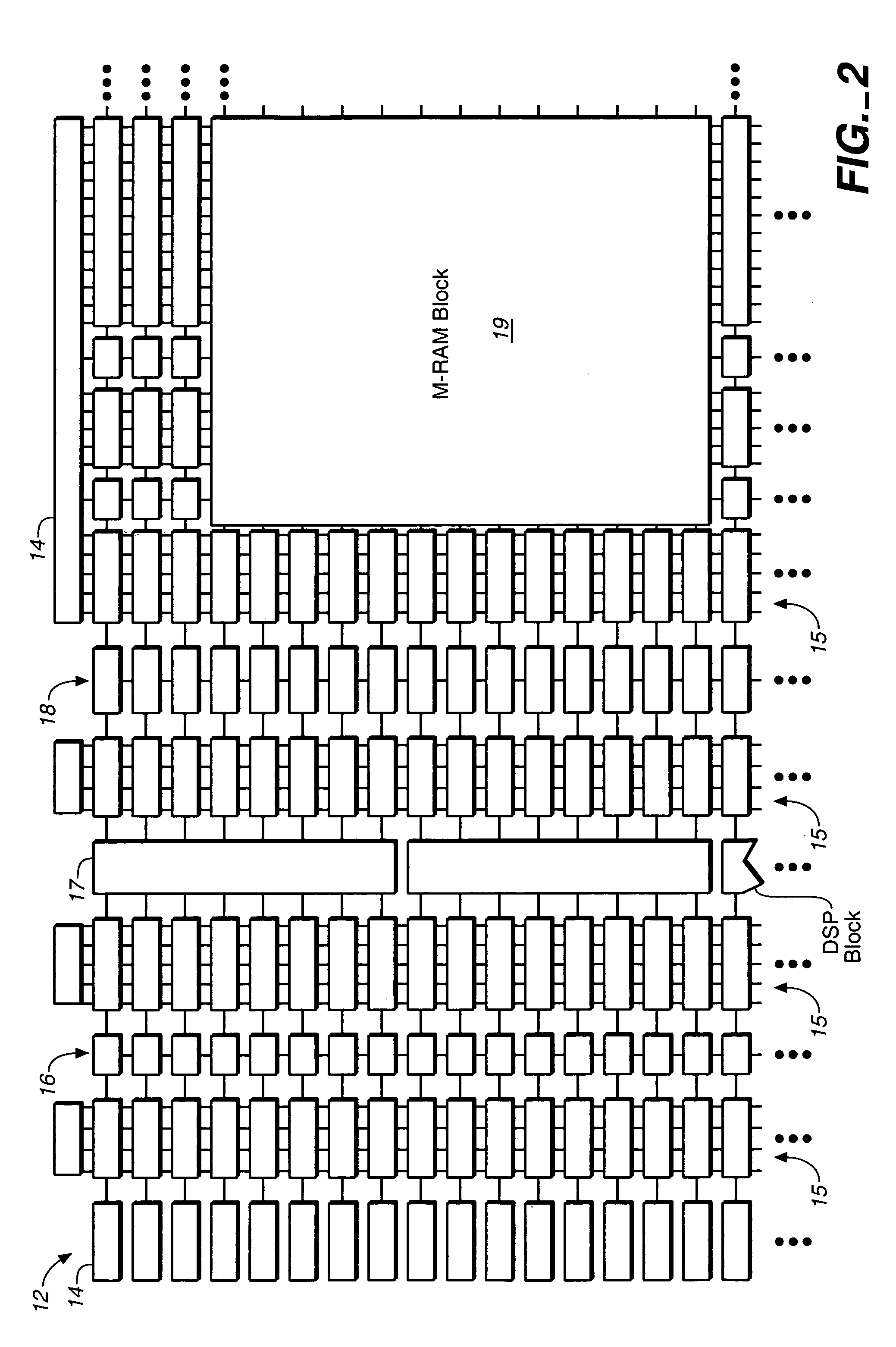

Synchronous first-in/first-out block memory for a field programmable gate array

The present invention comprises a field programmable gate array that has a plurality of dedicated first-in / first-out memory logic components. The field programmable gate array includes a plurality of synchronous random access memory blocks that are coupled to a plurality of dedicated first-in / first-out memory logic components and a plurality of random access memory clusters that are programmably coupled to the plurality of dedicated first-in / first-out memory logic components and to the plurality of synchronous random access memory blocks.

Owner:MICROSEMI SOC

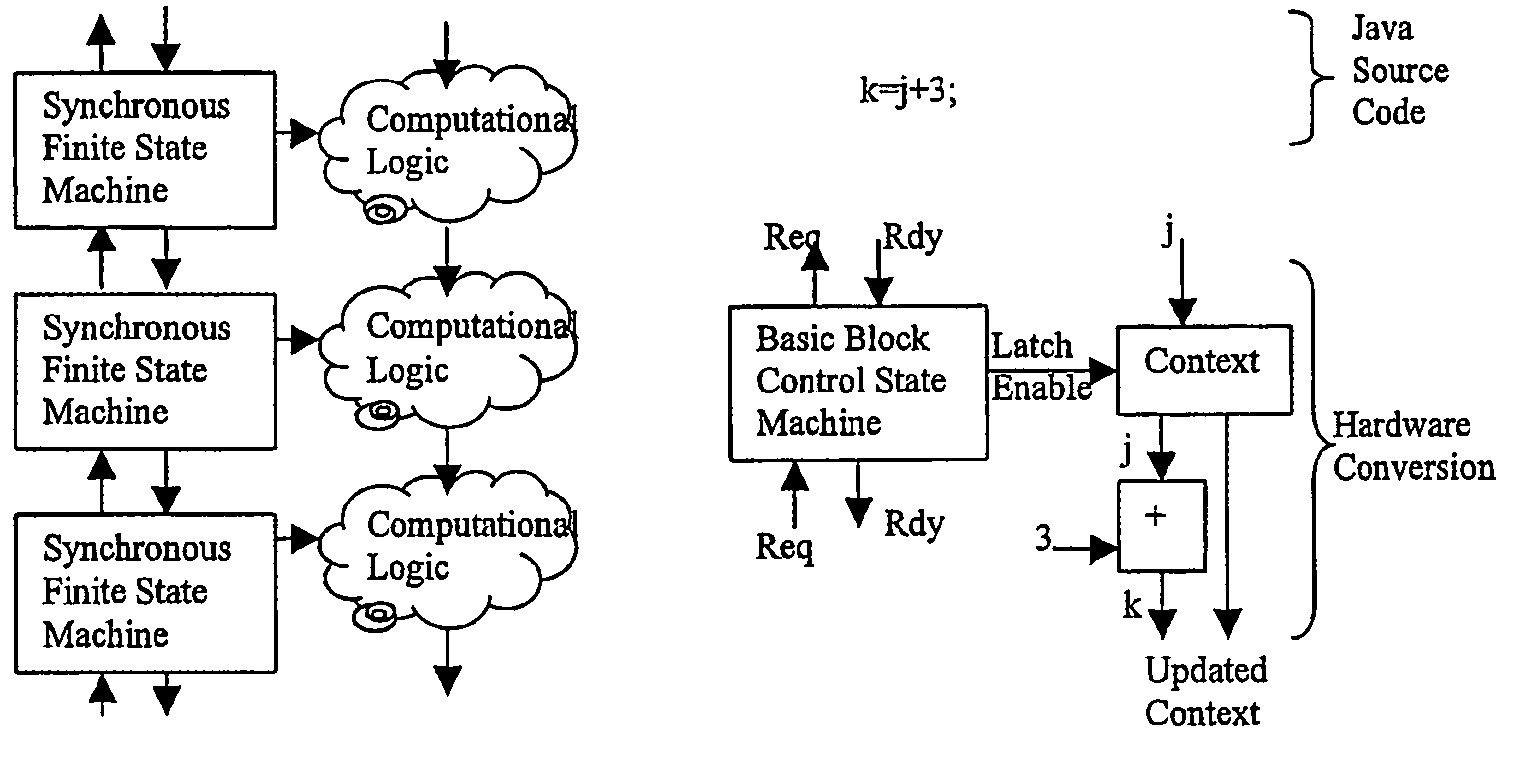

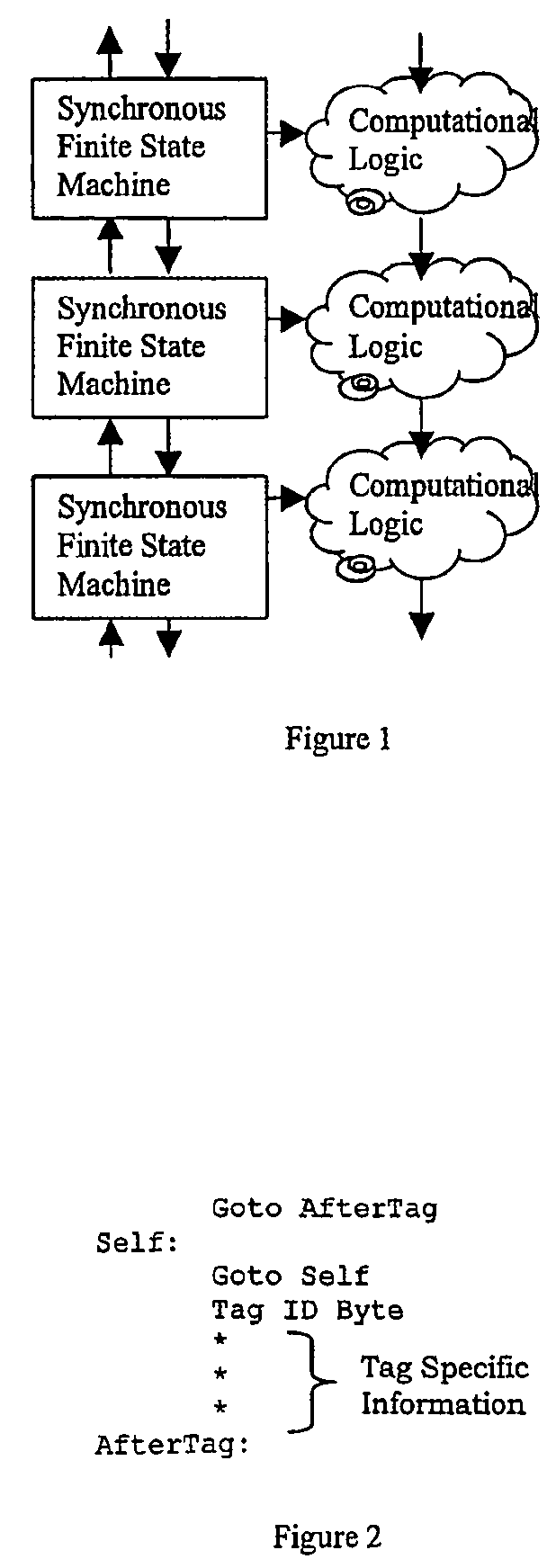

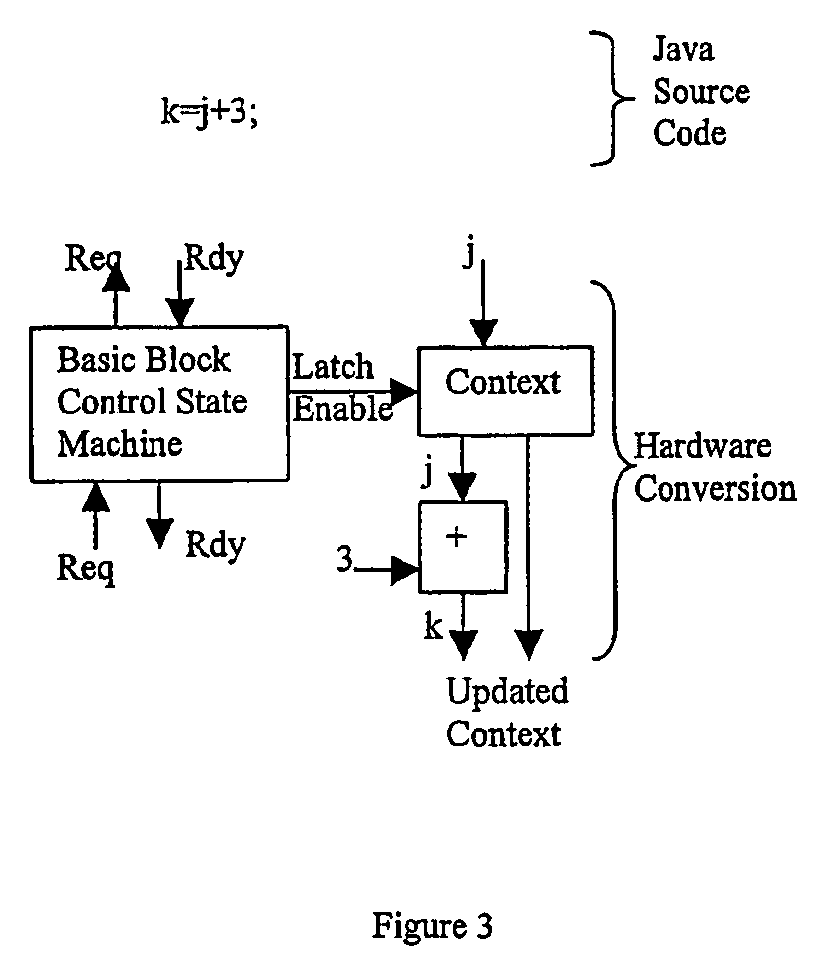

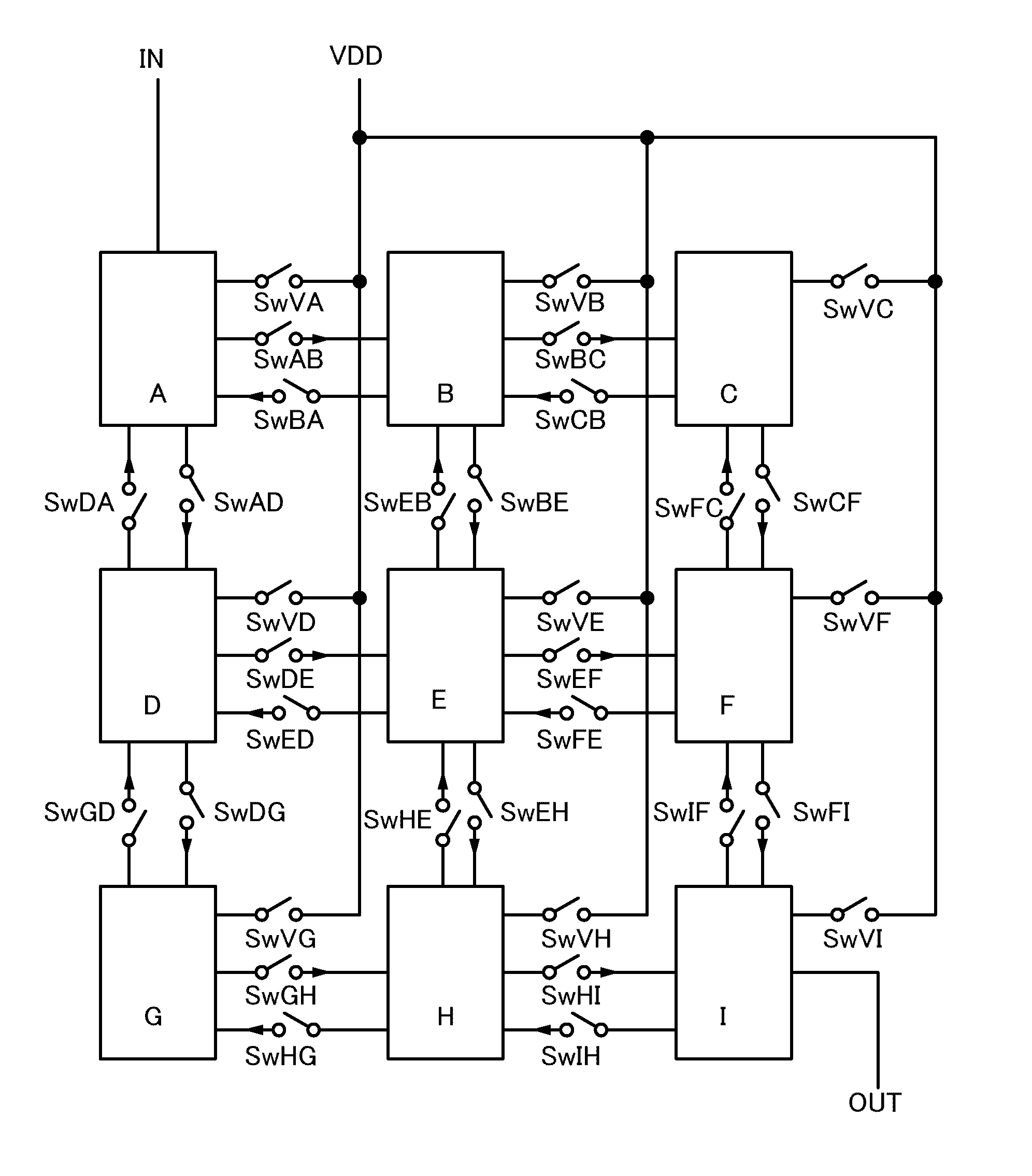

System of finite state machines

InactiveUS7224185B2Enough timeConcurrent instruction executionMultiple digital computer combinationsSufficient timeComputational logic

A system of finite state machines built with asynchronous or synchronous logic for controlling the flow of data through computational logic circuits programmed to accomplish a task specified by a user, having one finite state machine associated with each computational logic circuit, having each finite state machine accept data from either one or more predecessor finite state machines or from one or more sources outside the system and furnish data to one or more successor finite state machines or a recipient outside the system, excluding from consideration in determining a clock period for the system logic paths performing the task specified by the user, and providing a means for ensuring that each finite state machine allows sufficient time to elapse for the computational logic circuit associated with that finite state to perform its task.

Owner:CAMPBELL JOHN +1

Chain-connected shift register and programmable logic circuit whose logic function is changeable in real time

InactiveUS6018559ADigital storageLogic circuits using elementary logic circuit componentsShift registerTransmission gate

A shift register having a plurality of circuit cells successively connected in a chain formation is proposed. Each of the circuit cells includes a first inversion gate, a first transmission gate, connected to an output of the first inversion gate, being switched by a clock, and a second inversion gate connected to an output of the first transmission gate. The circuit cell further includes a first P-channel transistor, connected between an output of the second inversion gate and an input of the first inversion gate, being switched by the clock, a second transmission gate, connected to the output of the second inversion gate, being switched by an inversion clock, and a second P-channel transistor, connected to the output of the first transmission gate, being switched by the inversion clock. In the shift register, the plurality of circuit cells are successively connected such that the input of the first inversion gate of the circuit cell is connected to an output of a second transmission gate of a former-stage circuit cell, and the output of the first inversion gate of the circuit cell is connected to an output of a second P-channel transistor of the former-stage circuit cell.

Owner:FUJITSU LTD

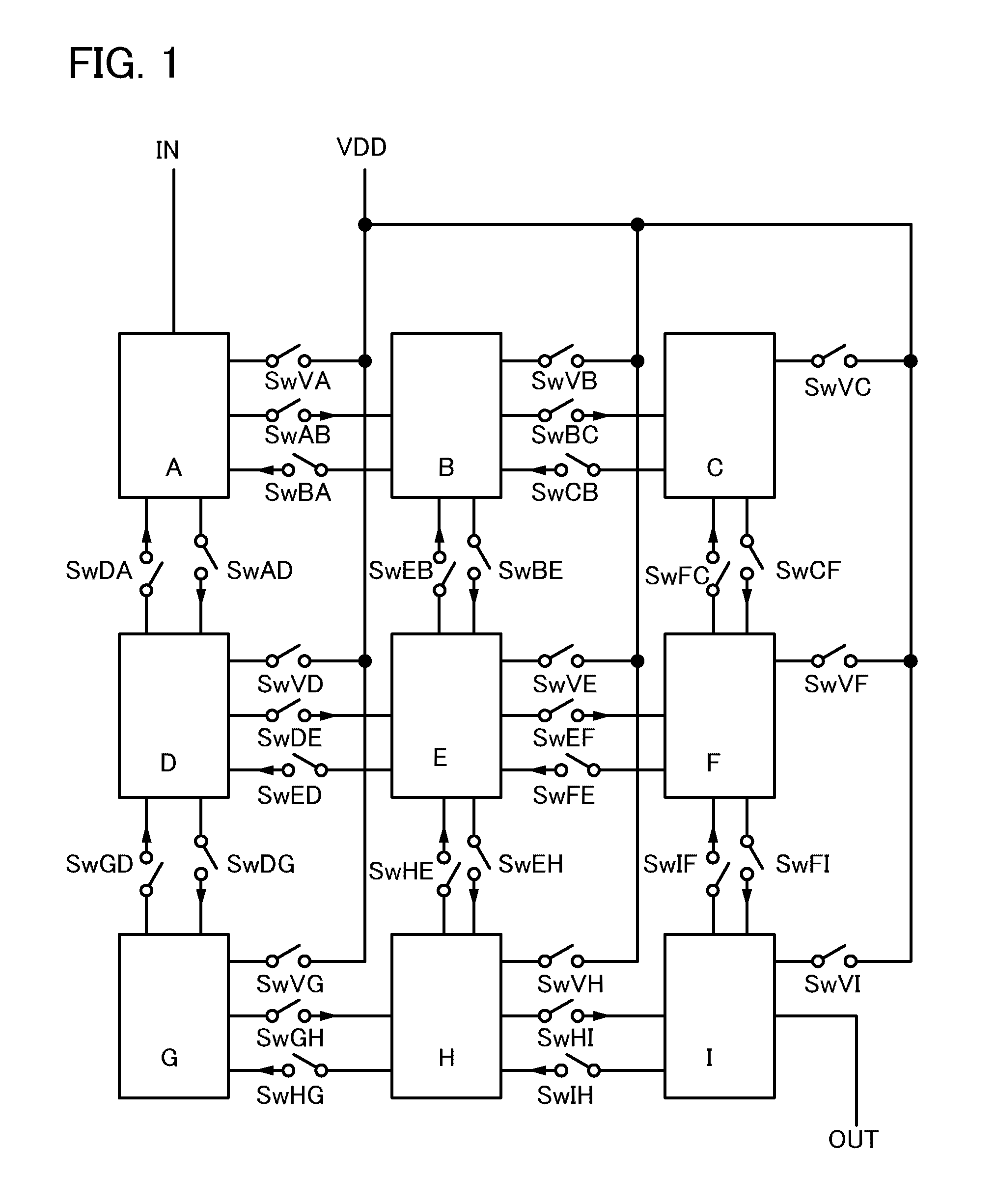

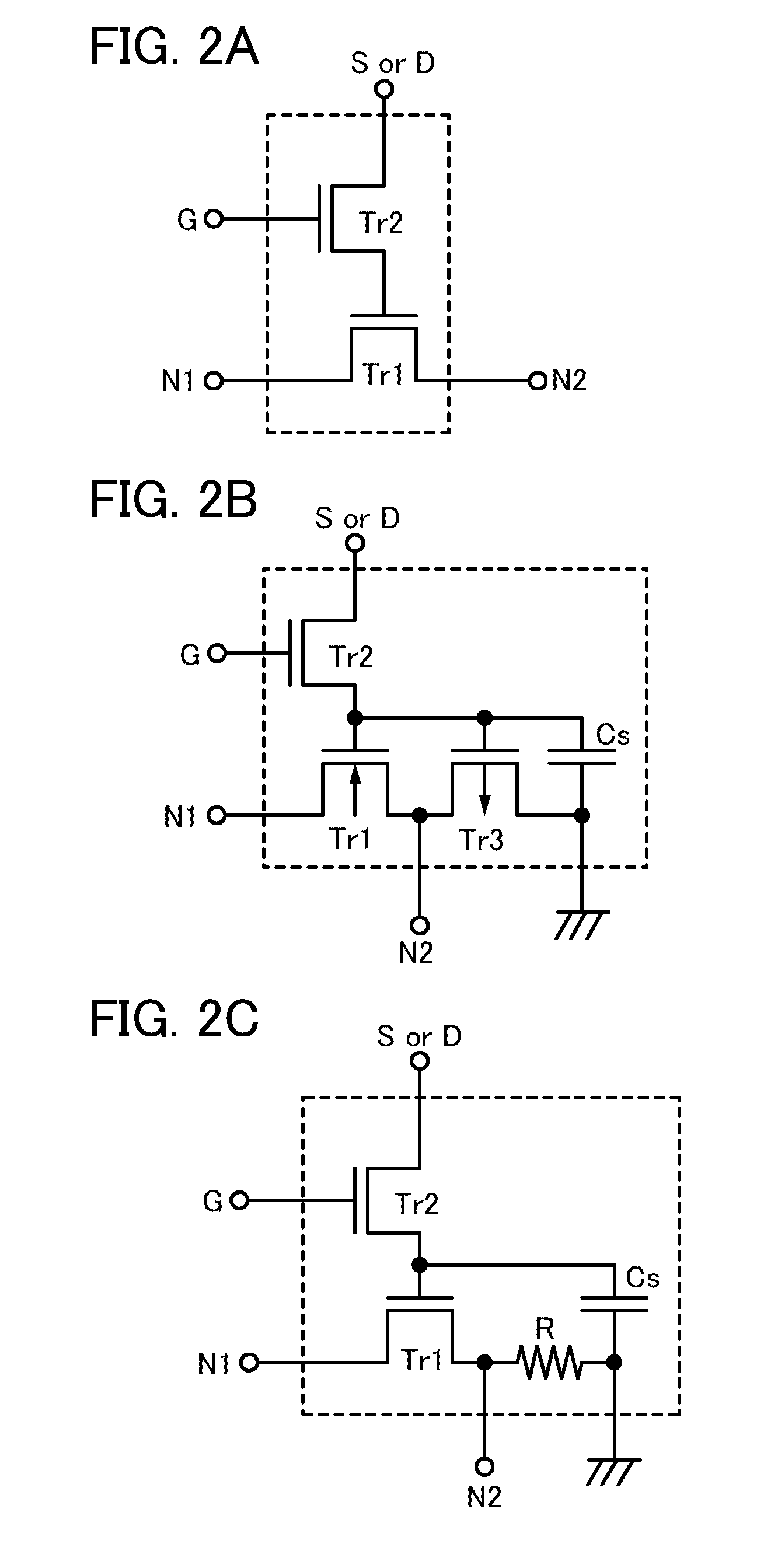

Semiconductor device

ActiveUS20110175646A1Suppress power consumptionPrevent degradationTransistorPower reduction in field effect transistorsProgrammable logic deviceLow leakage

It is an object to provide a semiconductor device in which power consumption can be reduced. It is another object to provide a highly reliable semiconductor device using a programming cell, such as a programmable logic device (PLD). In accordance with a change in a configuration of connections between basic blocks, power supply voltage furnishing to the basic blocks is changed. That is, when the structure of connections between the basic blocks is such that a basic block does not contribute to a circuit, the supply of the power supply voltage to this basic block is stopped. Further, the supply of the power supply voltage to the basic blocks is controlled using a programming cell formed using a field effect transistor whose channel formation region is formed using an oxide semiconductor, the field effect transistor having extremely low off-state current or extremely low leakage current.

Owner:SEMICON ENERGY LAB CO LTD

Popular searches

Special data processing applications Semiconductor devices Computation using denominational number representation Energy efficient computing Specific program execution arrangements Memory systems Electric digital data processing Software simulation/interpretation/emulation Architecture with multiple processing units Individual semiconductor device testing