Patents

Literature

66 results about "Cmos logic circuits" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

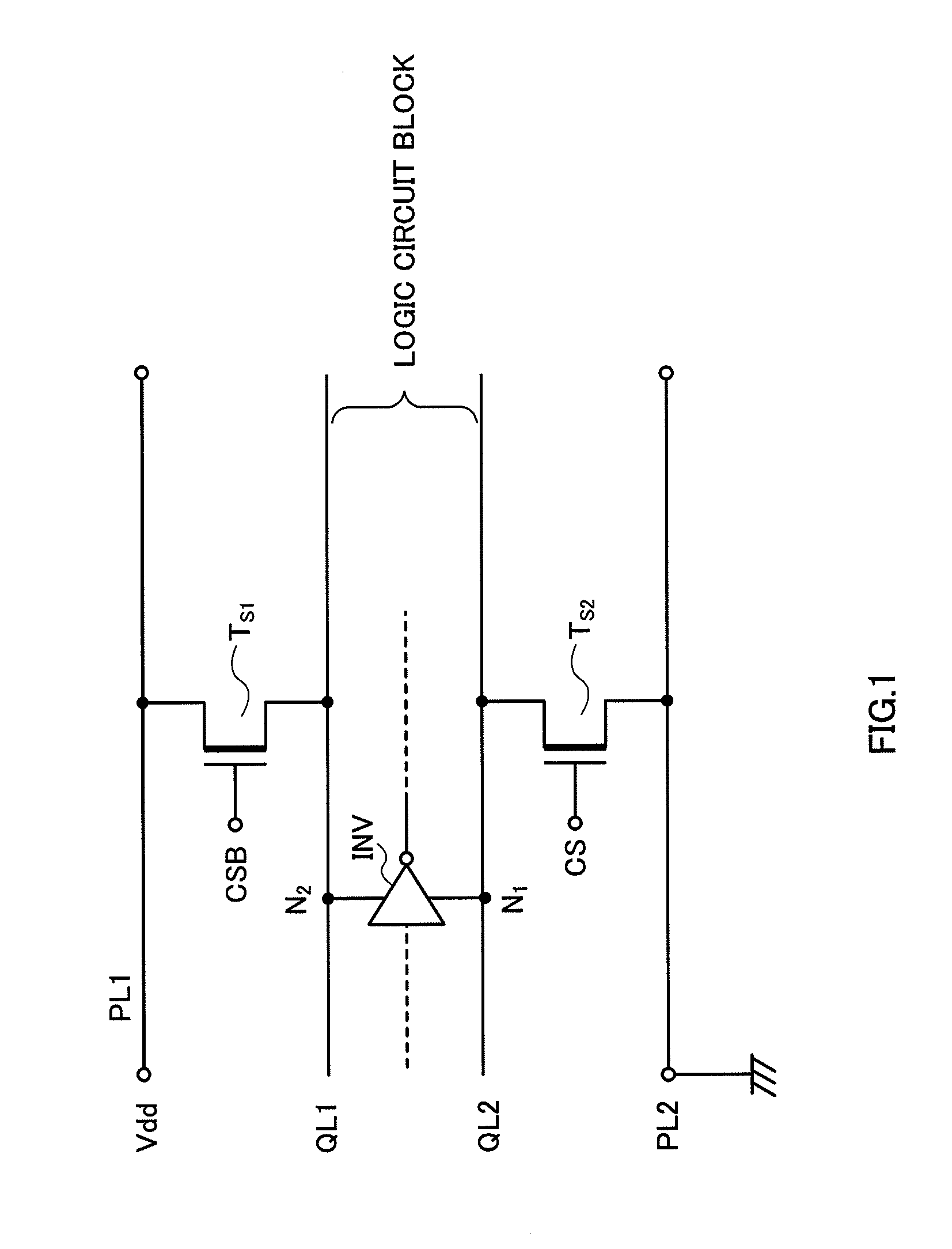

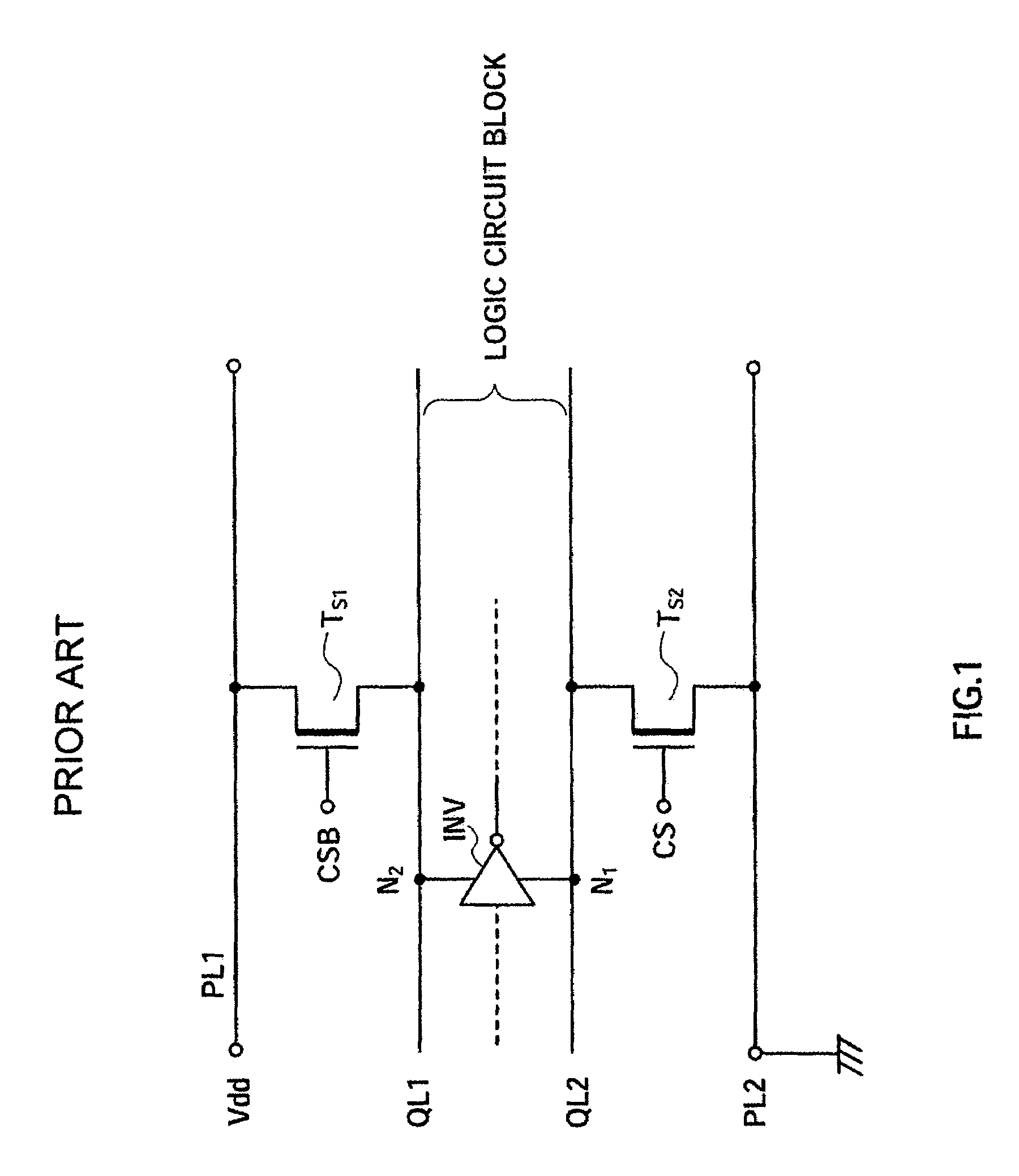

Logic circuit utilizing pass transistors and logic gate

InactiveUS6084437ATransistorReliability increasing modificationsCmos logic circuitsLogical operations

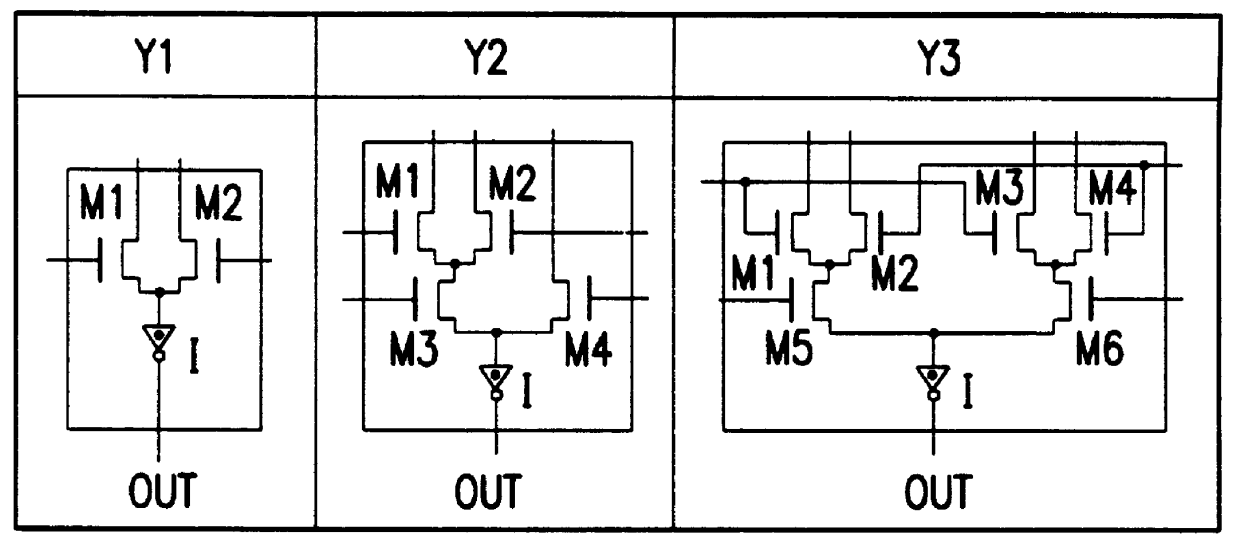

A logic circuit combines a plurality of pass-transistor logic trees and a multiple-input logic gate for receiving intermediate logic signals from the respective pass-transistor logic trees, and can express a complex logical operation while decreasing the number of stages in pass-transistor logic trees and improving operation speed. Even a logical operation that cannot be expressed efficiently by a known or conventional pass-transistor logic circuit can be expressed efficiently with performance higher than that of a known CMOS logic circuit. Furthermore, when a static feedthrough current of the multiple-input logic gate is suppressed, power consumption can be reduced. In some embodiments, since circuitry for suppressing a static feedthrough current of the multiple-input logic gate is arranged so that a probability of occurrence of logical collision with a preceding stage will decrease or will be nil, power consumption can further be reduced.

Owner:KAWASAKI MICROELECTRONICS

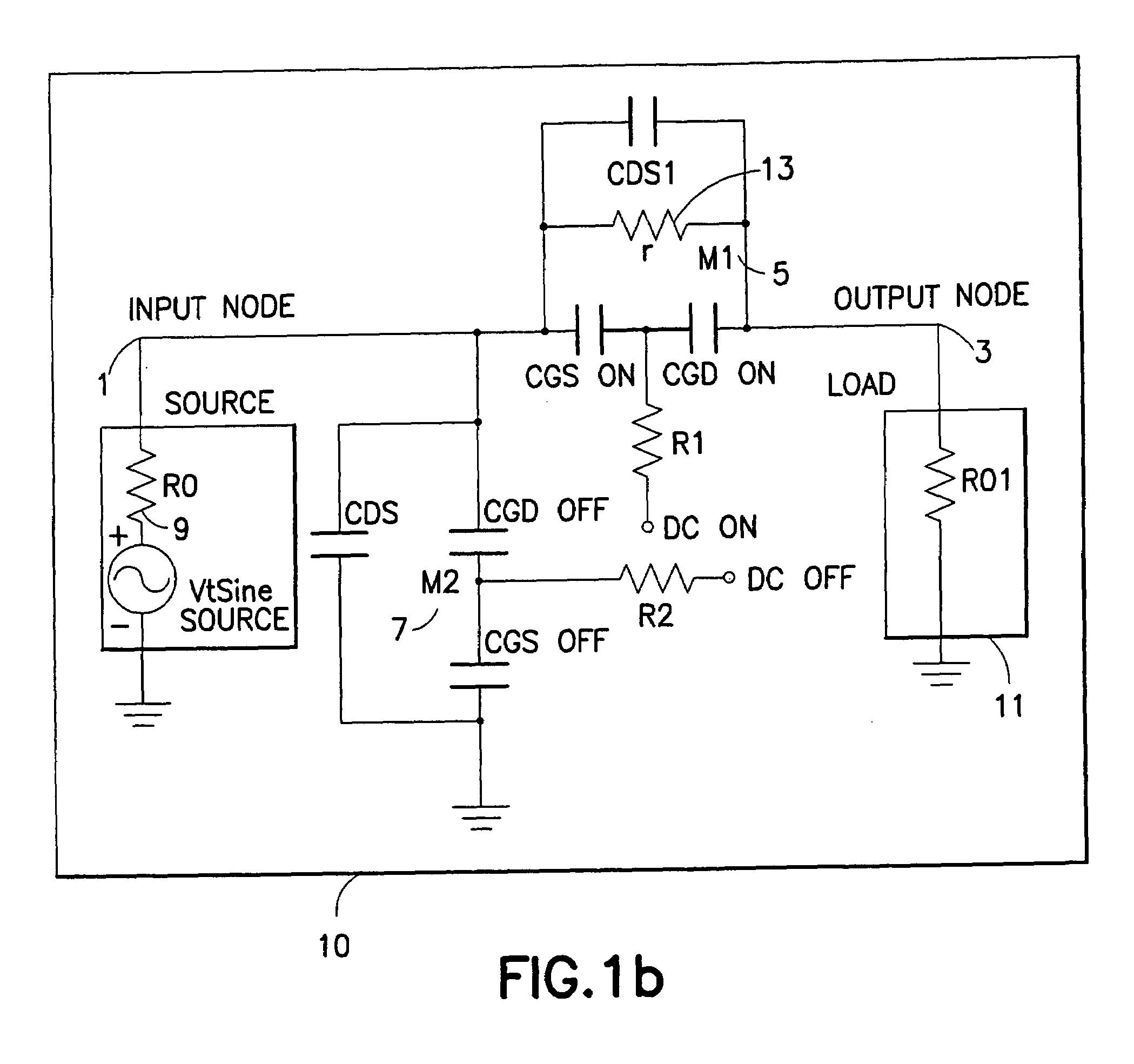

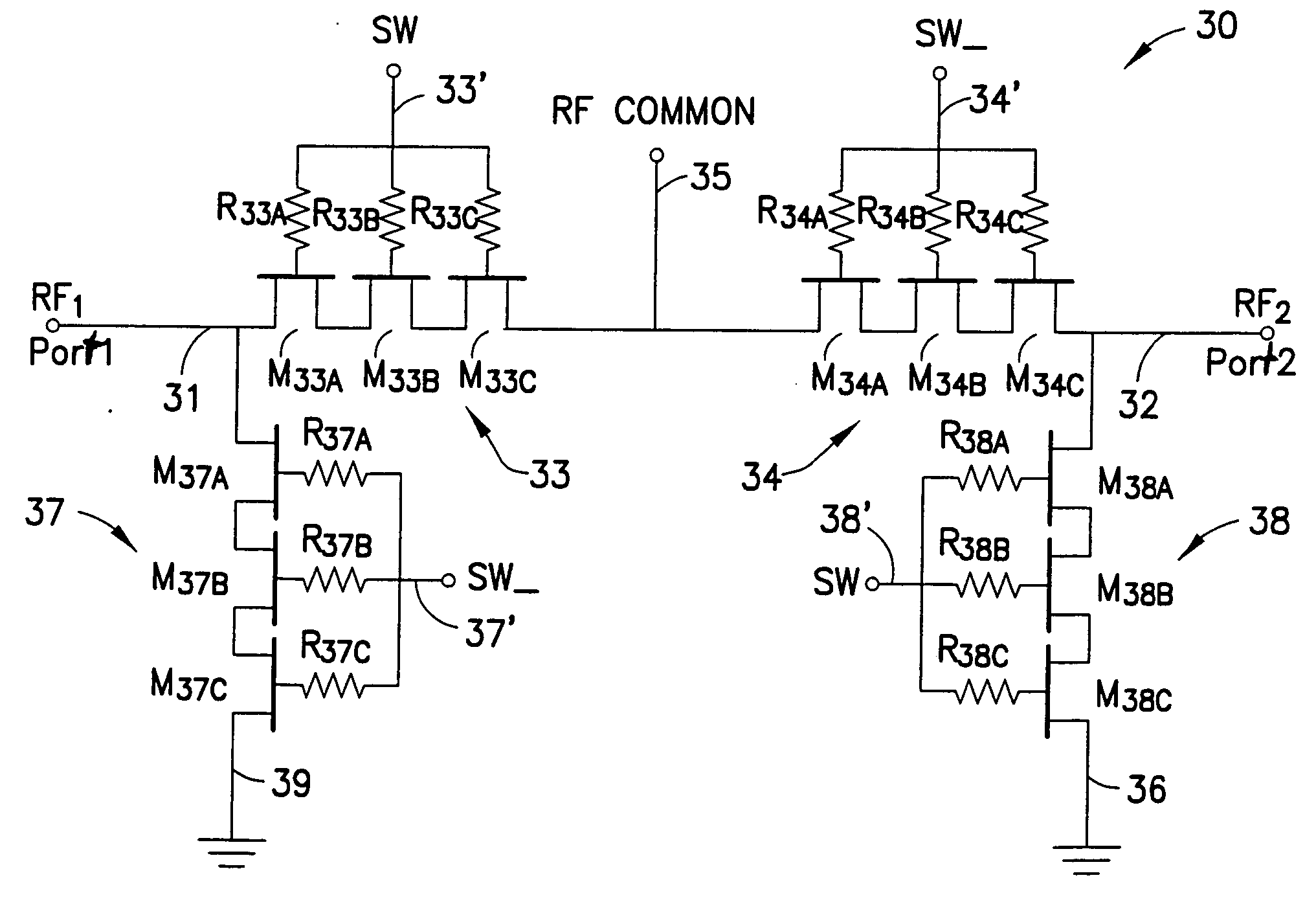

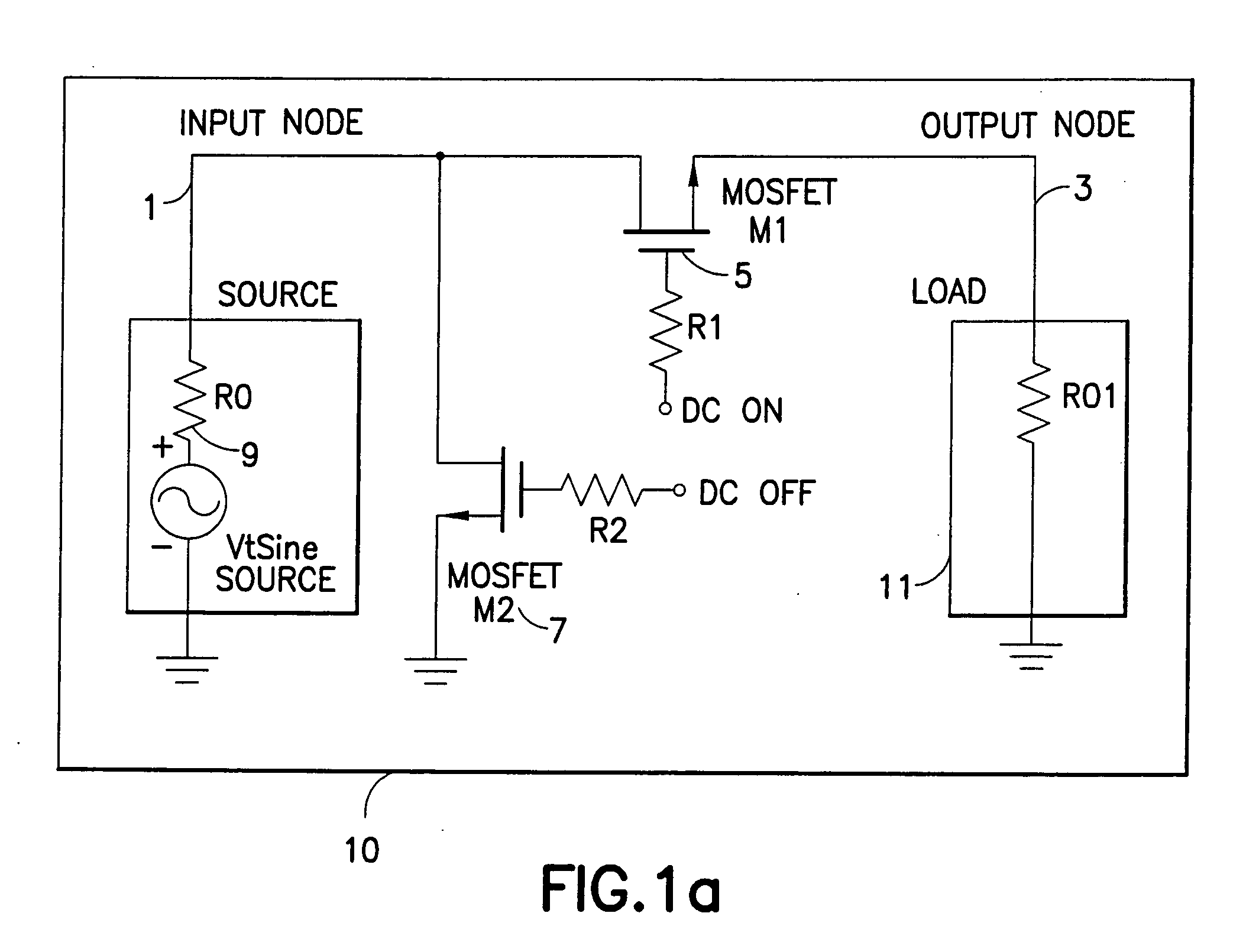

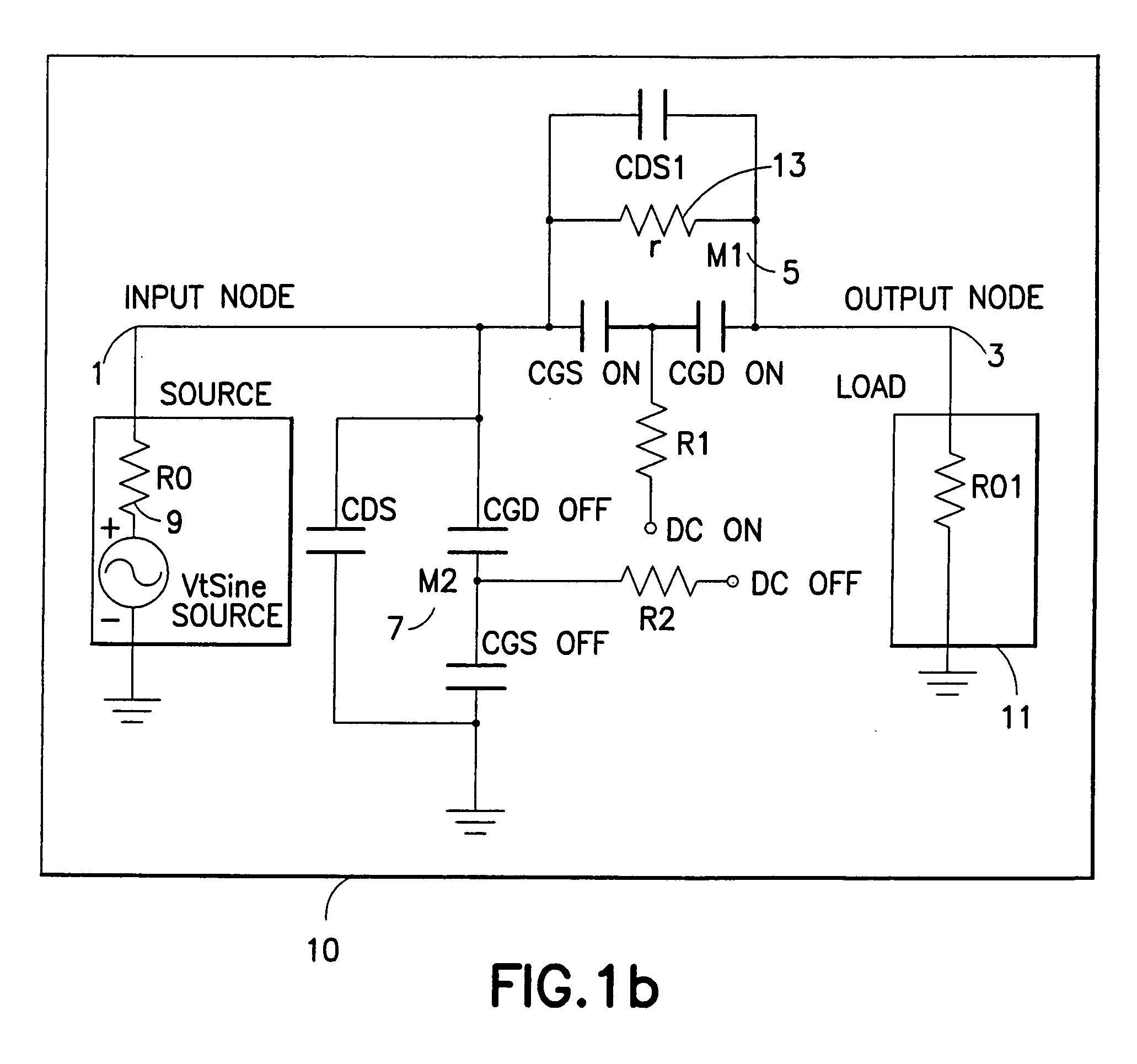

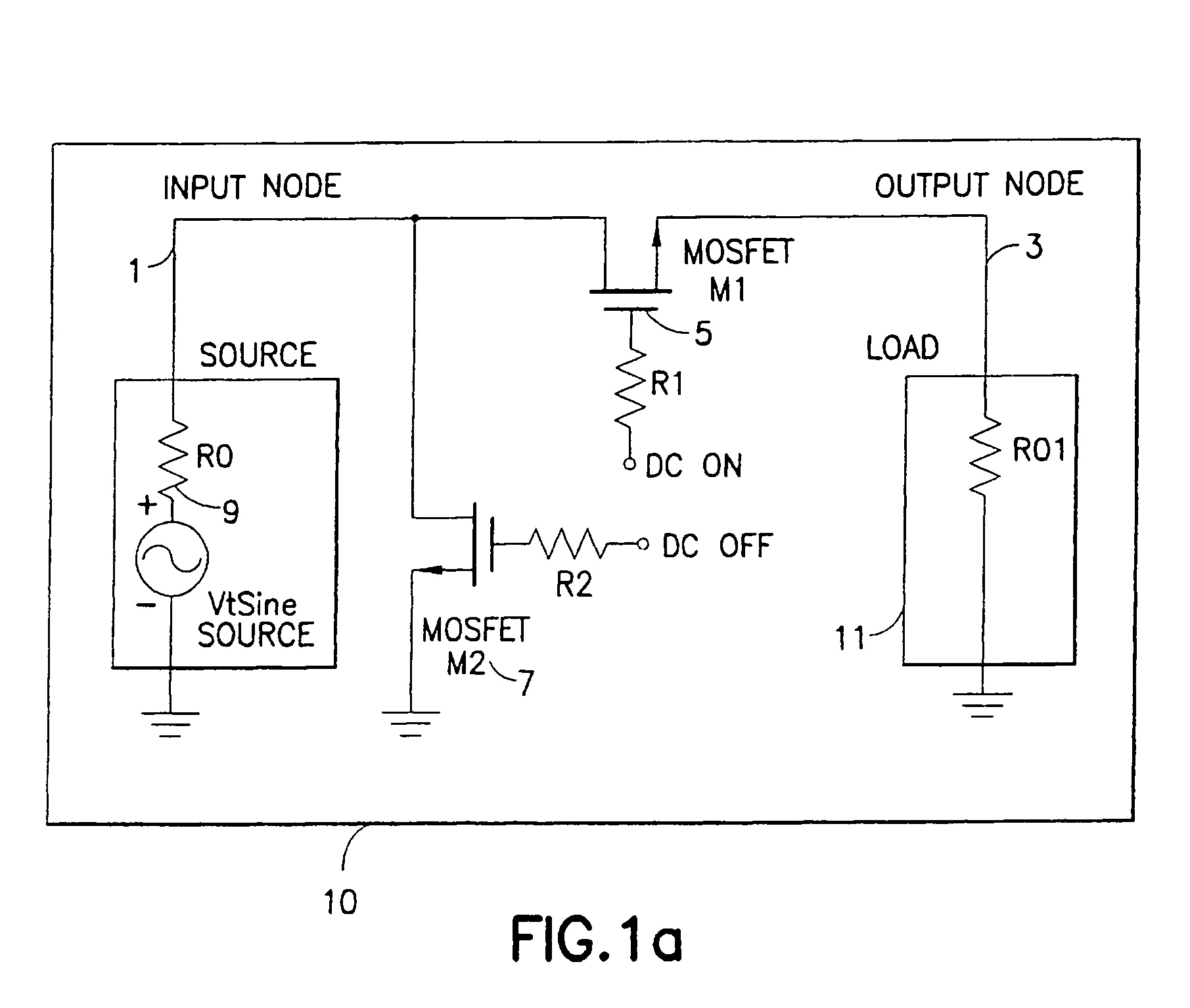

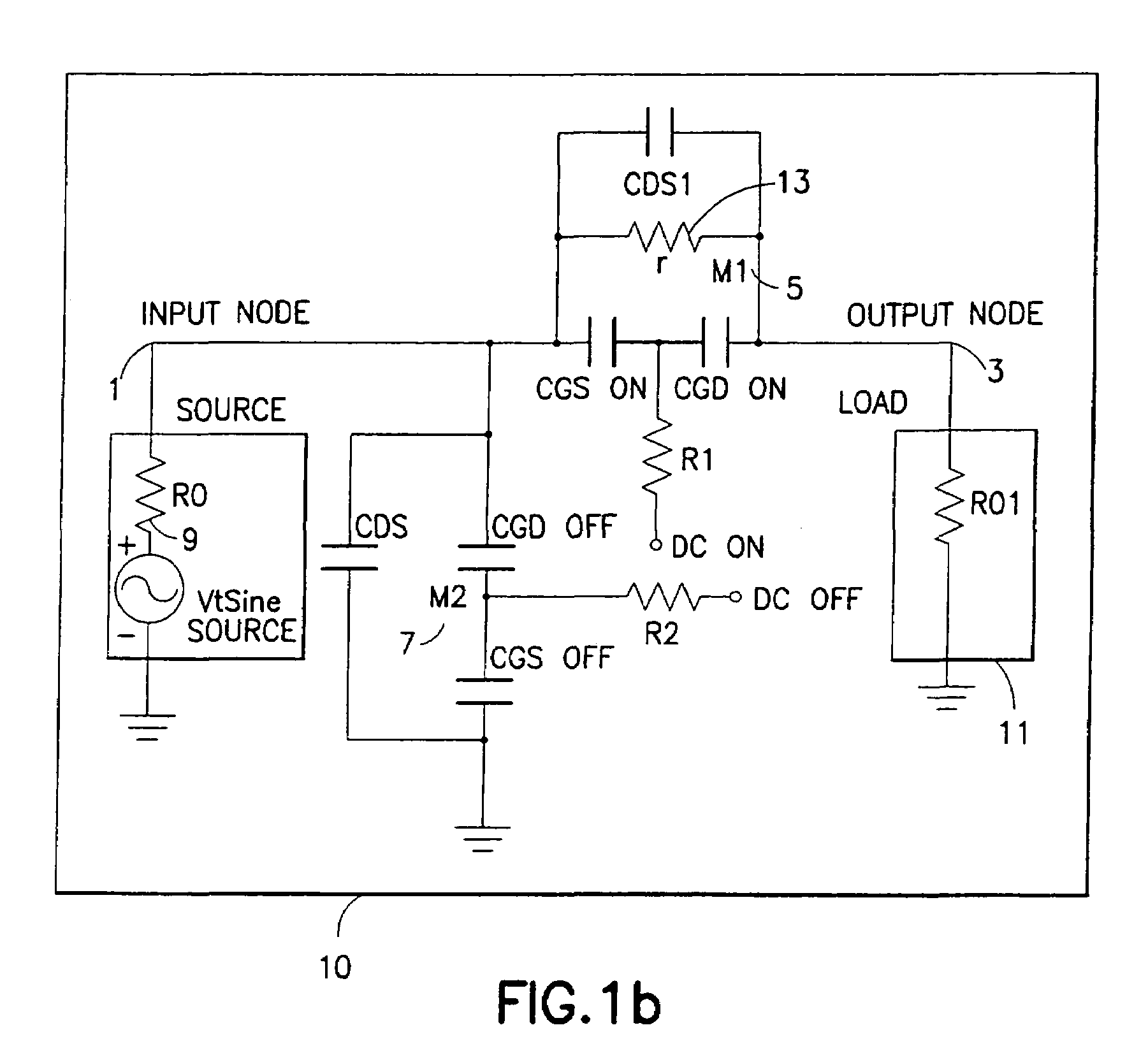

Switch circuit and method of switching radio frequency signals

InactiveUS7123898B2Easy to switchImprove reliabilityTransistorSolid-state devicesMOSFETDigital control

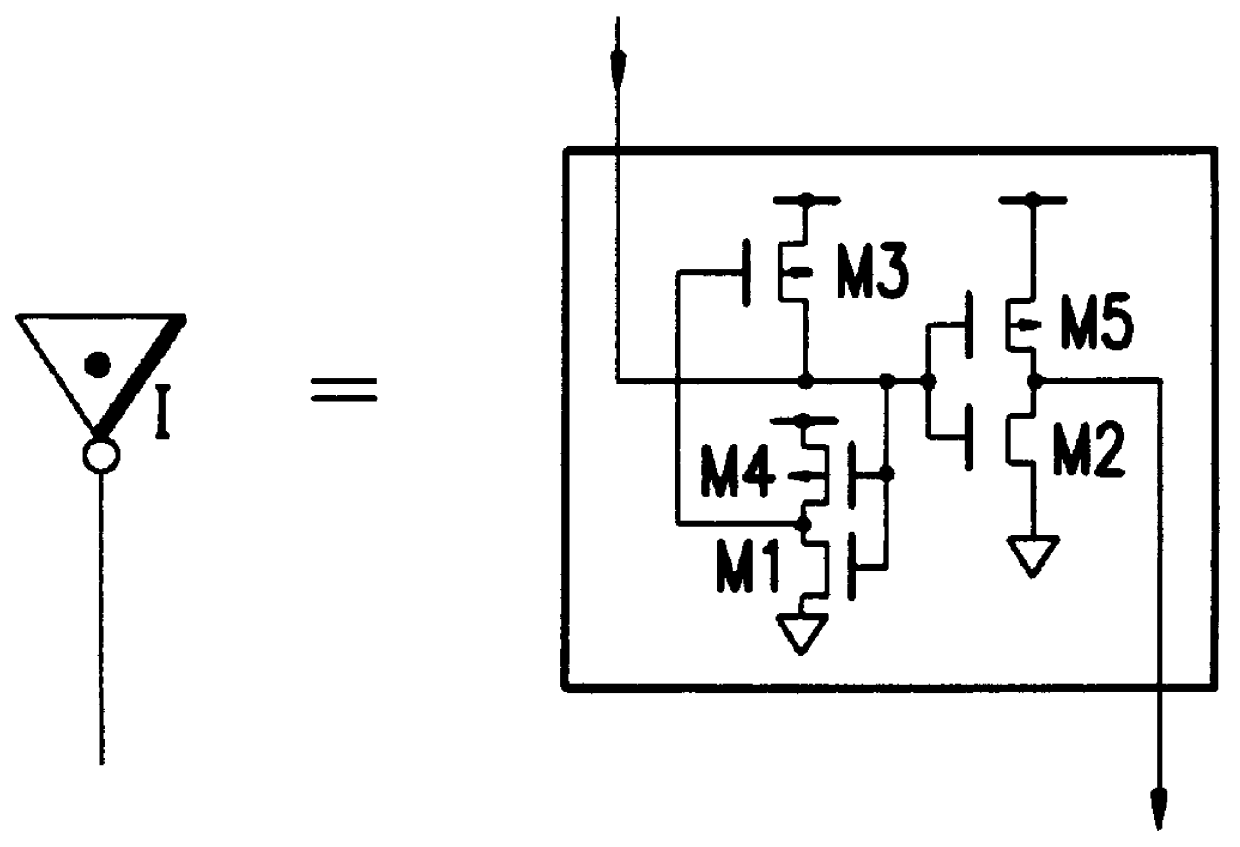

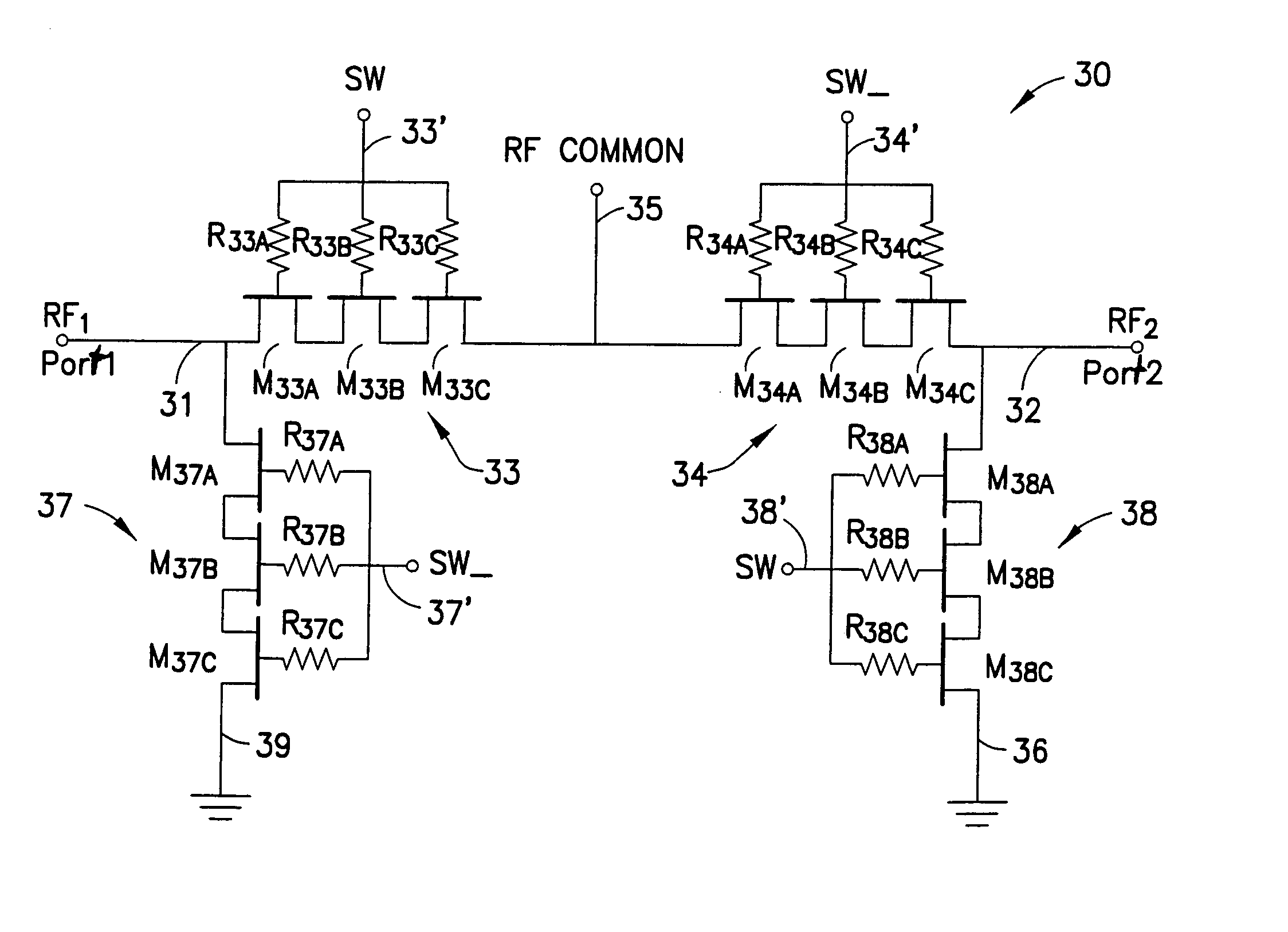

A novel RF buffer circuit adapted for use with an RF switch circuit and method for switching RF signals is described. The RF switch circuit is fabricated in a silicon-on-insulator (SOI) technology. The RF switch includes pairs of switching and shunting transistor groupings used to alternatively couple RF input signals to a common RF node. The switching and shunting transistor grouping pairs are controlled by a switching control voltage (SW) and its inverse (SW_). The switching and shunting transistor groupings comprise one or more MOSFET transistors connected together in a “stacked” or serial configuration. The stacking of transistor grouping devices, and associated gate resistors, increase the breakdown voltage across the series connected switch transistors and operate to improve RF switch compression. A fully integrated RF switch is described including digital control logic and a negative voltage generator integrated together with the RF switch elements. In one embodiment, the fully integrated RF switch includes a built-in oscillator, a charge pump circuit, CMOS logic circuitry, level-shifting and voltage divider circuits, and an RF buffer circuit. Several embodiments of the charge pump, level shifting, voltage divider, and RF buffer circuits are described. The inventive RF switch provides improvements in insertion loss, switch isolation, and switch compression.

Owner:PSEMI CORP

Switch circuit and method of switching radio frequency signals

InactiveUS20050017789A1Improving RF switch isolationRaise the compression pointTransistorSolid-state devicesMOSFETEngineering

A novel RF buffer circuit adapted for use with an RF switch circuit and method for switching RF signals is described. The RF switch circuit is fabricated in a silicon-on-insulator (SOI) technology. The RF switch includes pairs of switching and shunting transistor groupings used to alternatively couple RF input signals to a common RF node. The switching and shunting transistor grouping pairs are controlled by a switching control voltage (SW) and its inverse (SW_). The switching and shunting transistor groupings comprise one or more MOSFET transistors connected together in a “stacked” or serial configuration. The stacking of transistor grouping devices, and associated gate resistors, increase the breakdown voltage across the series connected switch transistors and operate to improve RF switch compression. A fully integrated RF switch is described including digital control logic and a negative voltage generator integrated together with the RF switch elements. In one embodiment, the fully integrated RF switch includes a built-in oscillator, a charge pump circuit, CMOS logic circuitry, level-shifting and voltage divider circuits, and an RF buffer circuit. Several embodiments of the charge pump, level shifting, voltage divider, and RF buffer circuits are described. The inventive RF switch provides improvements in insertion loss, switch isolation, and switch compression.

Owner:PSEMI CORP

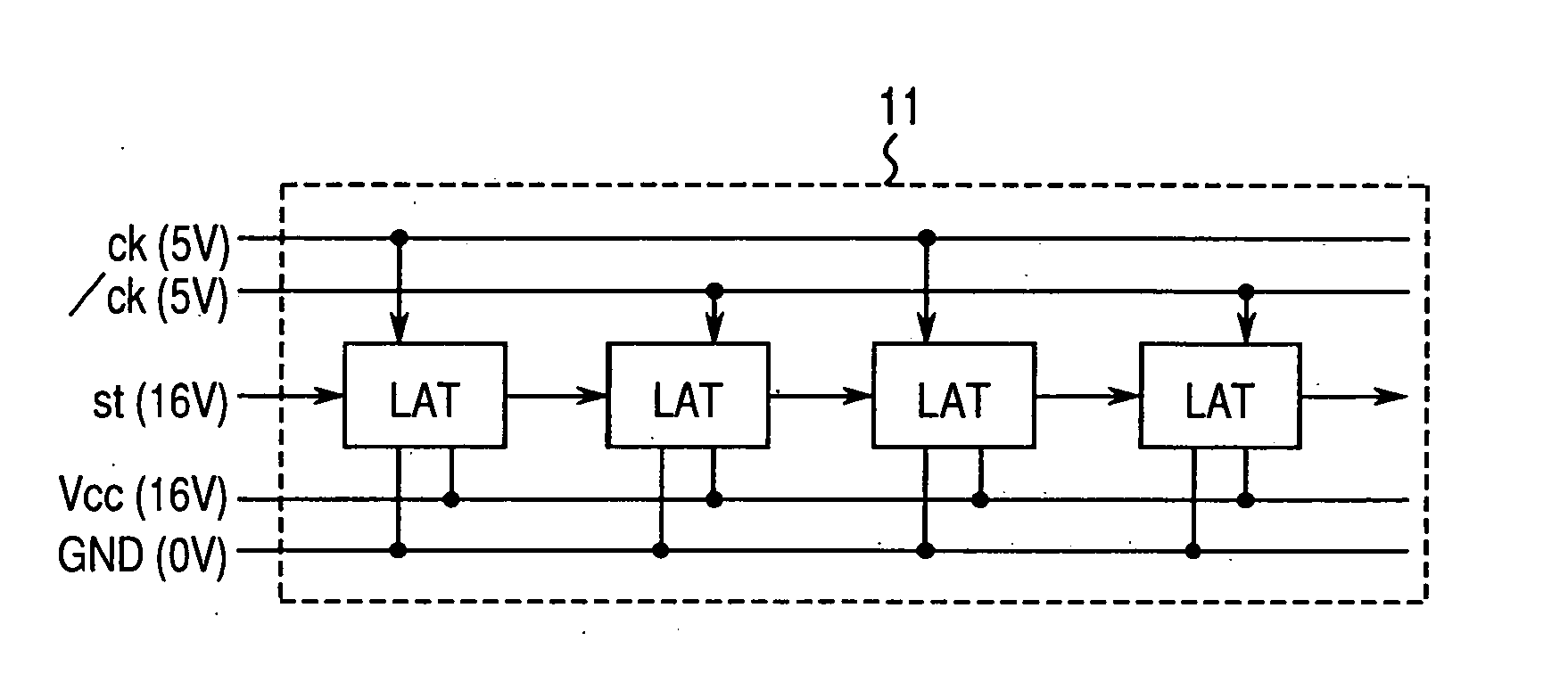

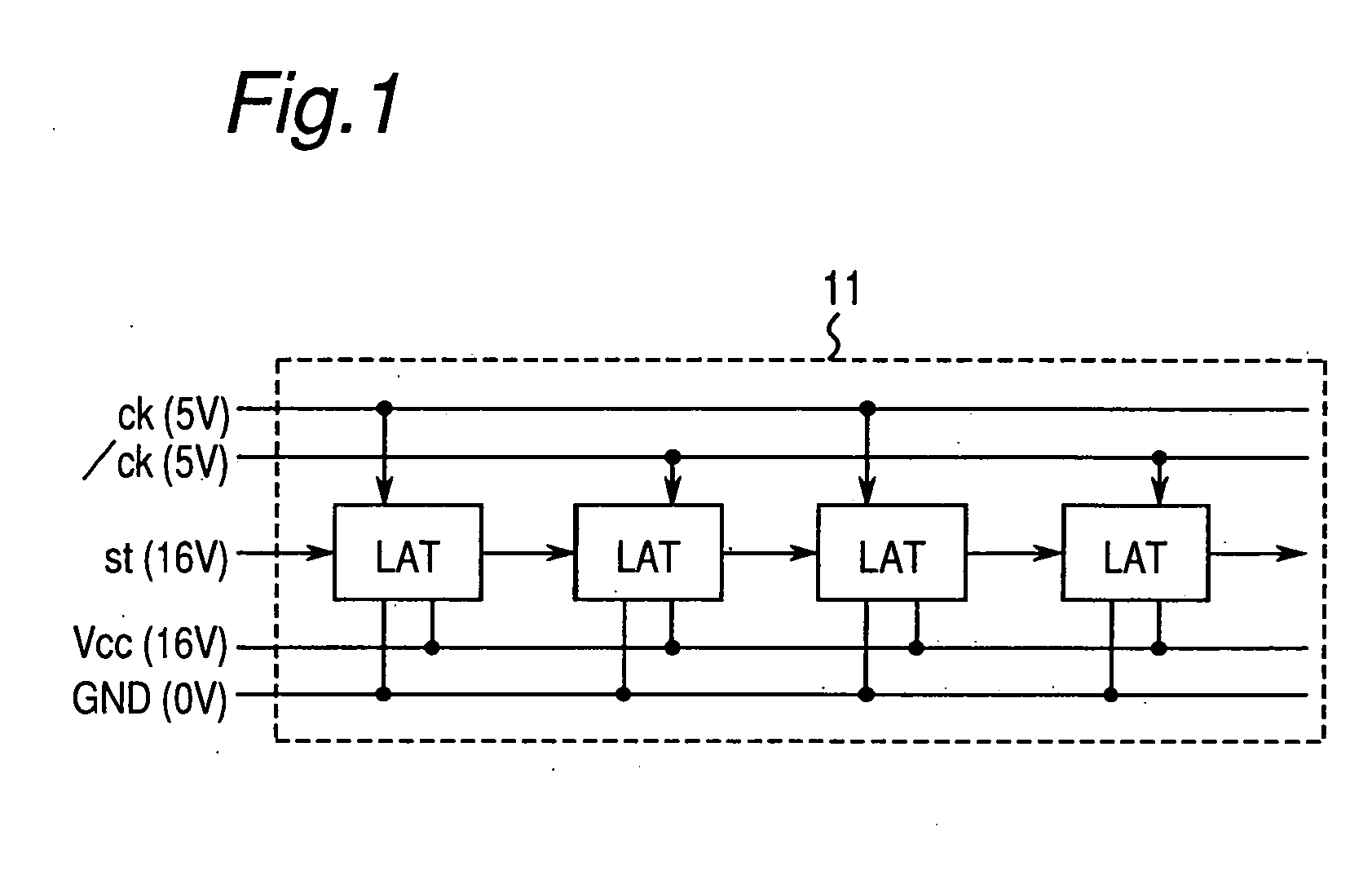

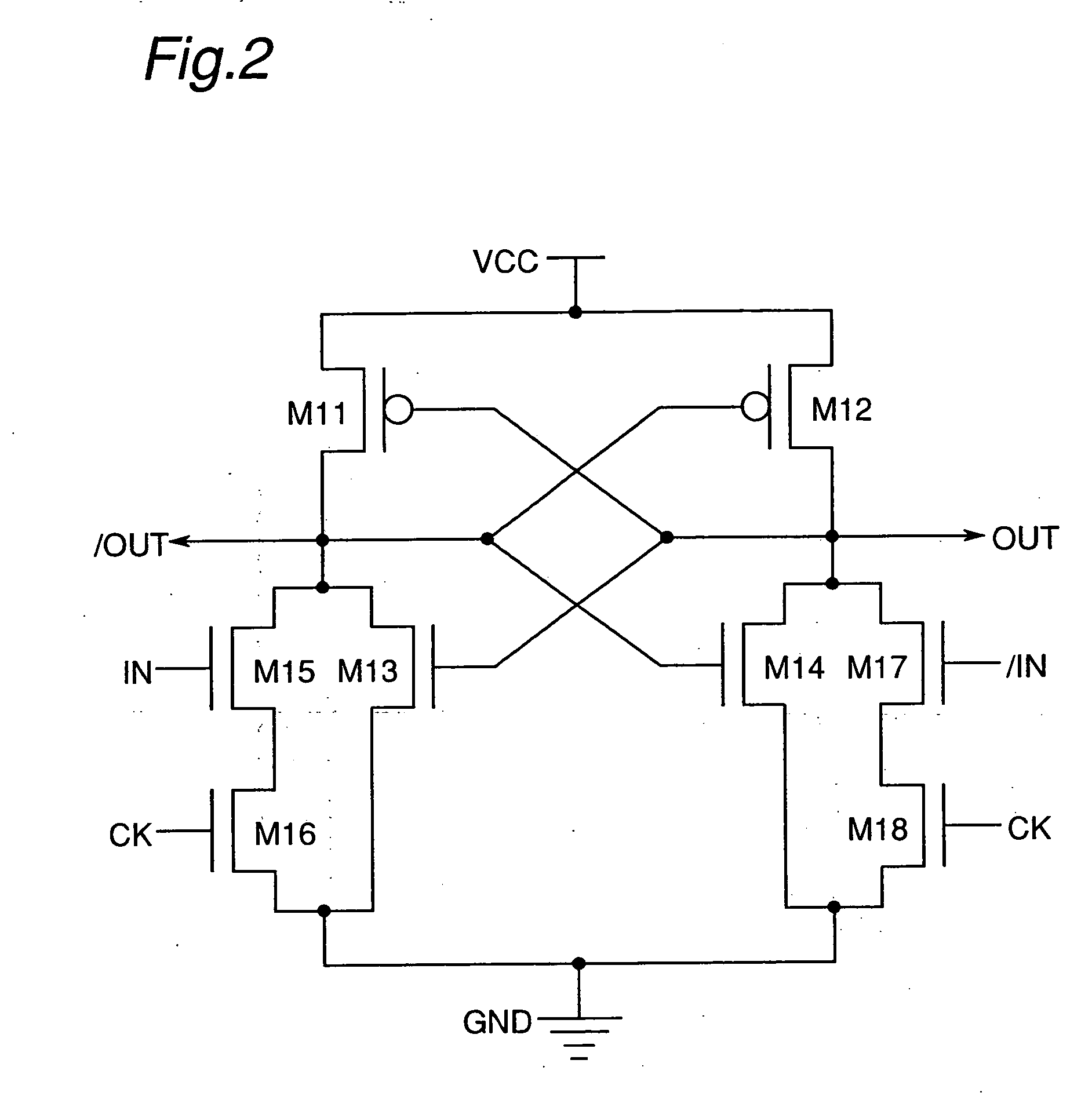

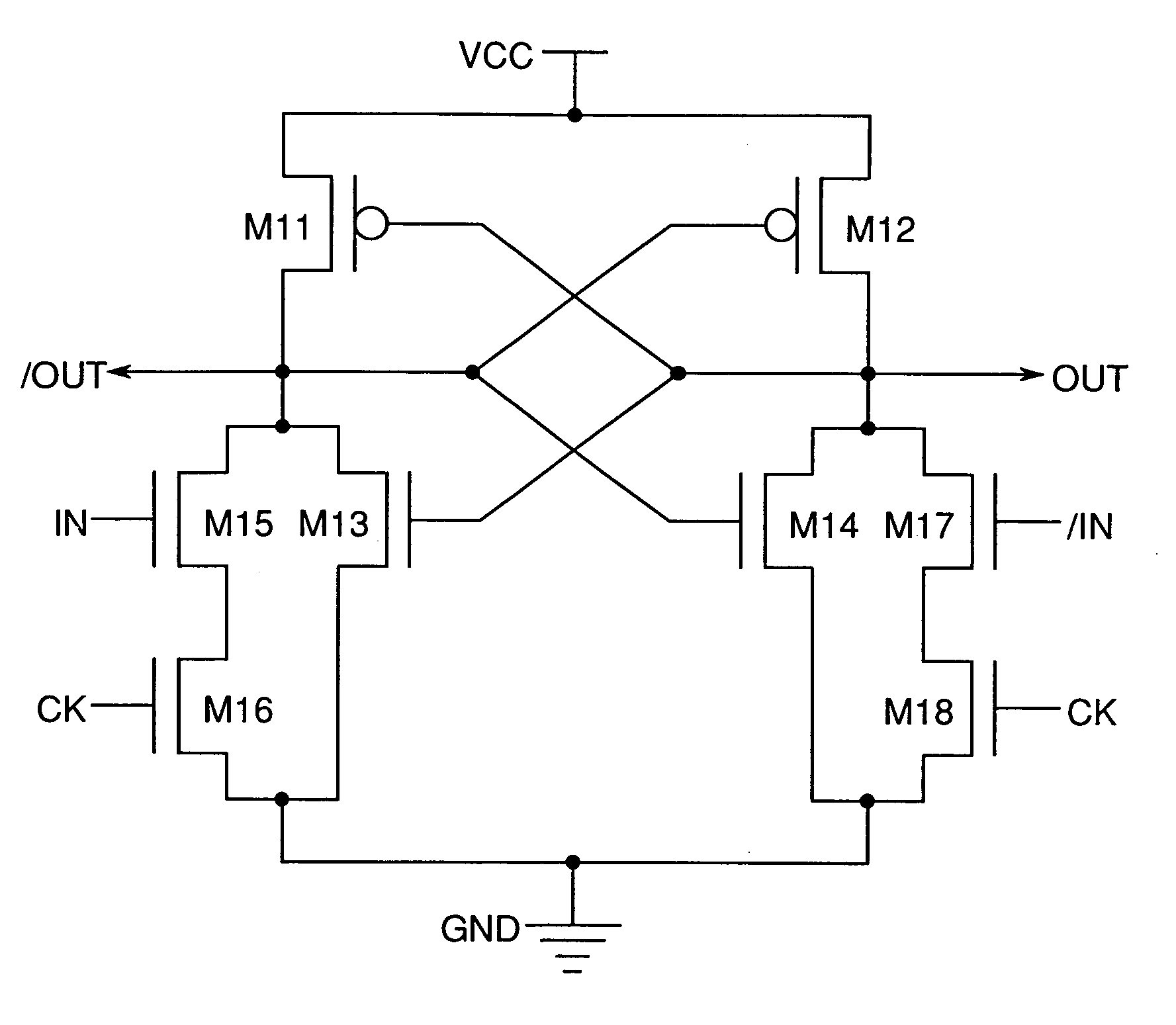

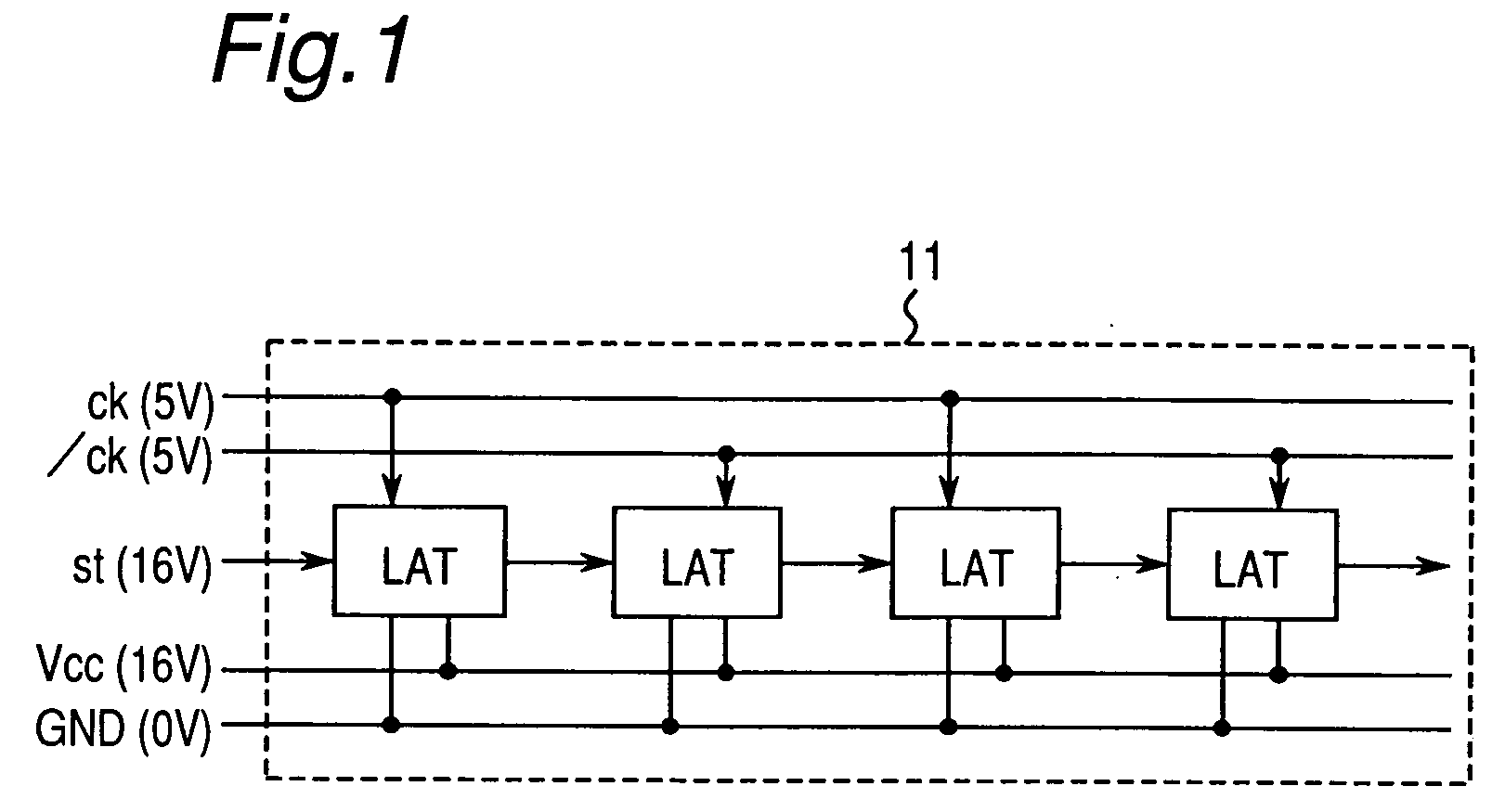

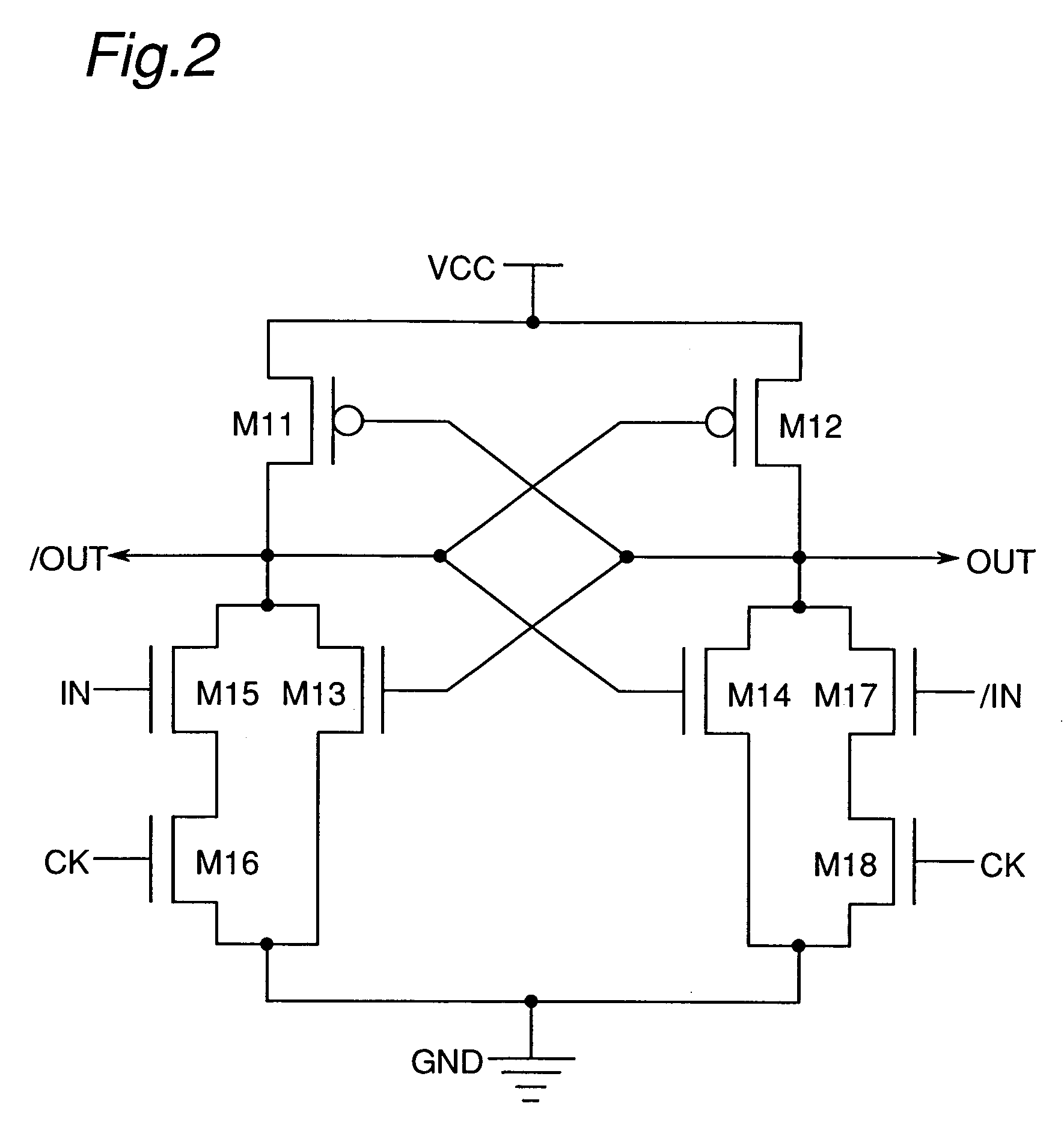

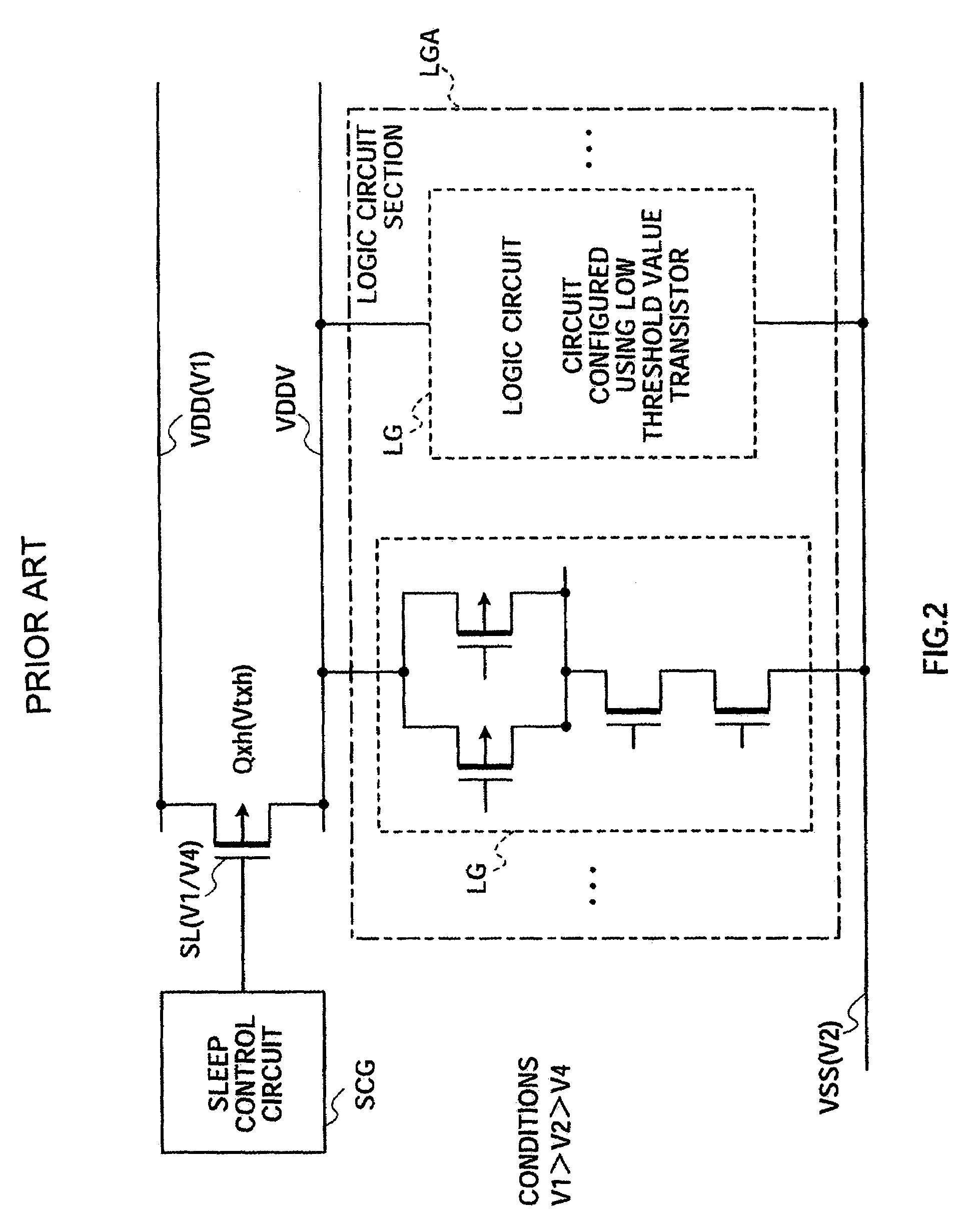

Latch circuit, shift register circuit, logical circuit and image display device operated with a low consumption of power

InactiveUS20050057556A1Easy to operateControl flowCathode-ray tube indicatorsDigital storageShift registerCMOS

A CMOS logical circuit comprises two electric current paths each of which has circuits consisting of n-type and p-type transistors. In a circuit consisting of n-type or p-type transistors, one electric current path is provided with a circuit having the same construction as that of a circuit having an n-type transistor of a CMOS logical circuit outputting a logical operation result similar to that of this logical circuit, and the other electric current path is provided with a circuit having the same construction as that of a circuit having a p-type transistor of the CMOS logical circuit outputting a logical operation result similar to that of this logical circuit. In another circuit consisting of the other channel type, a gate electrode of the transistor provided on the one electric current path and that of the transistor provided on the other electric current path are connected to drain electrodes of the counterparts. According to the construction, the amplitude of an input signal can be made smaller than a supply voltage of the logical circuit.

Owner:SHARP KK

Latch circuit, shift register circuit, logical circuit and image display device operated with a low consumption of power

InactiveUS7196699B1Improve display qualityReduce power consumptionInstant pulse delivery arrangementsCathode-ray tube indicatorsShift registerDisplay device

A CMOS logical circuit comprises two electric current paths each of which has circuits consisting of n-type and p-type transistors. In a circuit consisting of n-type or p-type transistors, one electric current path is provided with a circuit having the same construction as that of a circuit having an n-type transistor of a CMOS logical circuit outputting a logical operation result similar to that of this logical circuit, and the other electric current path is provided with a circuit having the same construction as that of a circuit having a p-type transistor of the CMOS logical circuit outputting a logical operation result similar to that of this logical circuit. In another circuit consisting of the other channel type, a gate electrode of the transistor provided on the one electric current path and that of the transistor provided on the other electric current path are connected to drain electrodes of the counterparts. According to the construction, the amplitude of an input signal can be made smaller than a supply voltage of the logical circuit.

Owner:SHARP KK

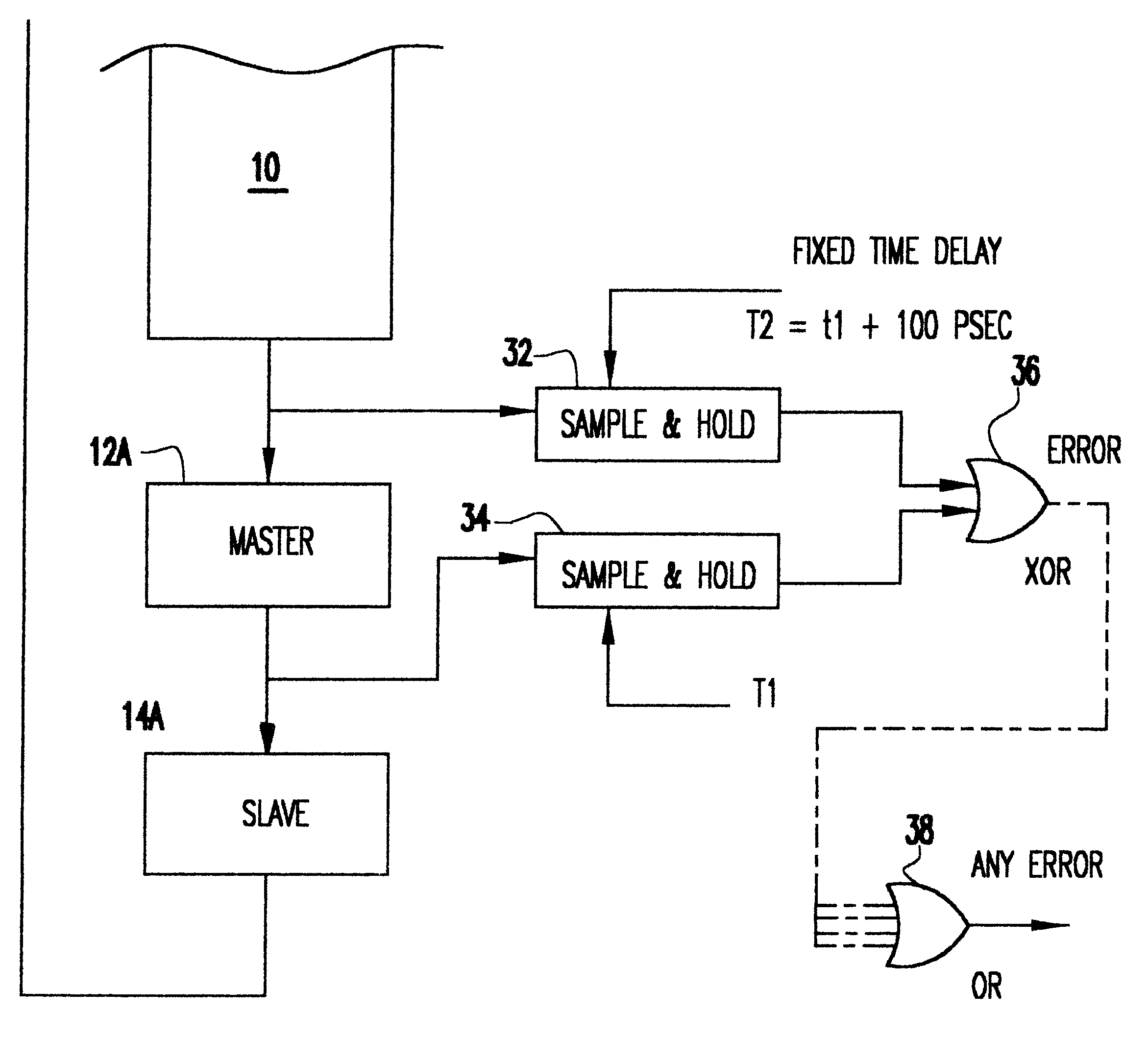

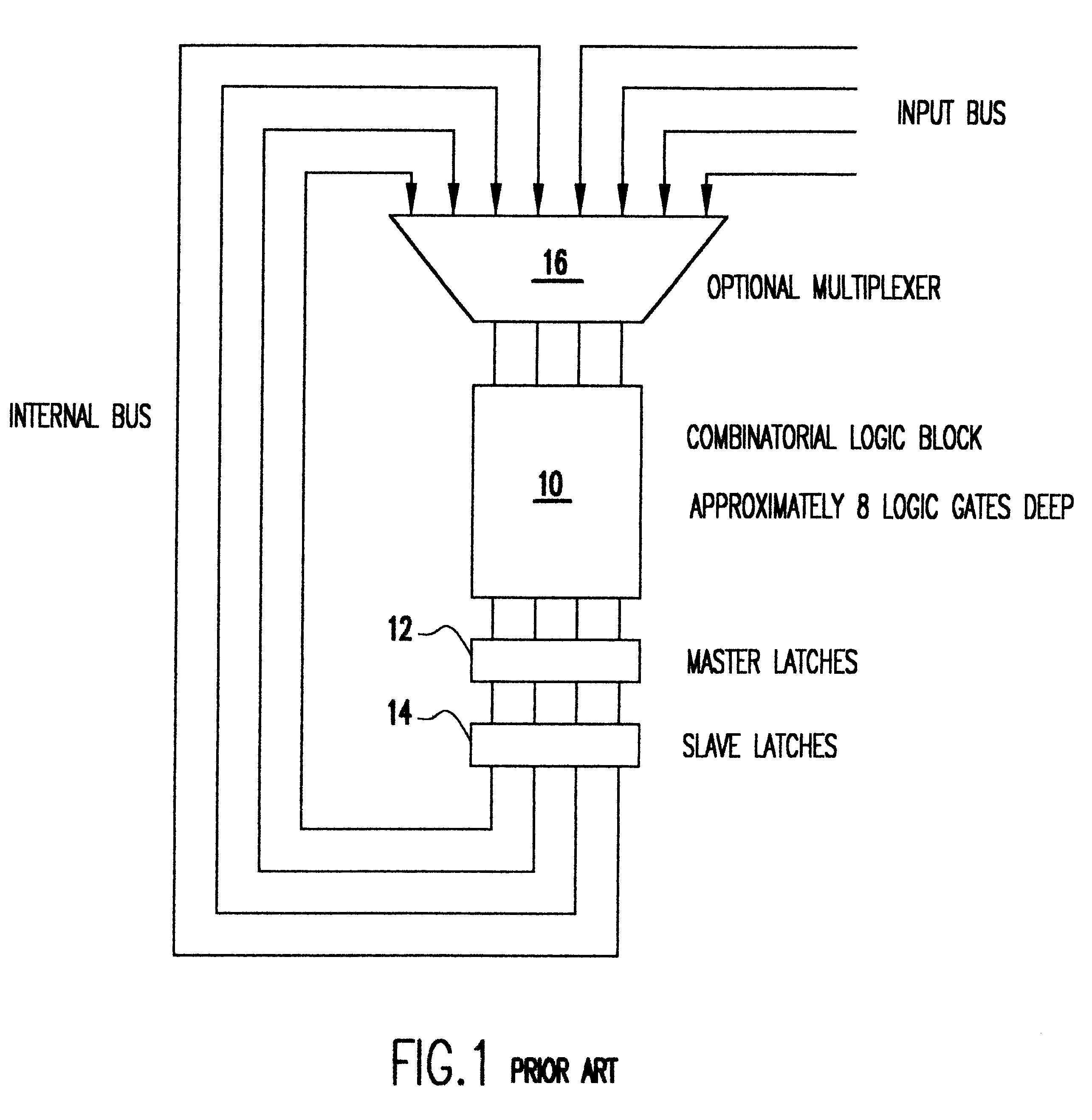

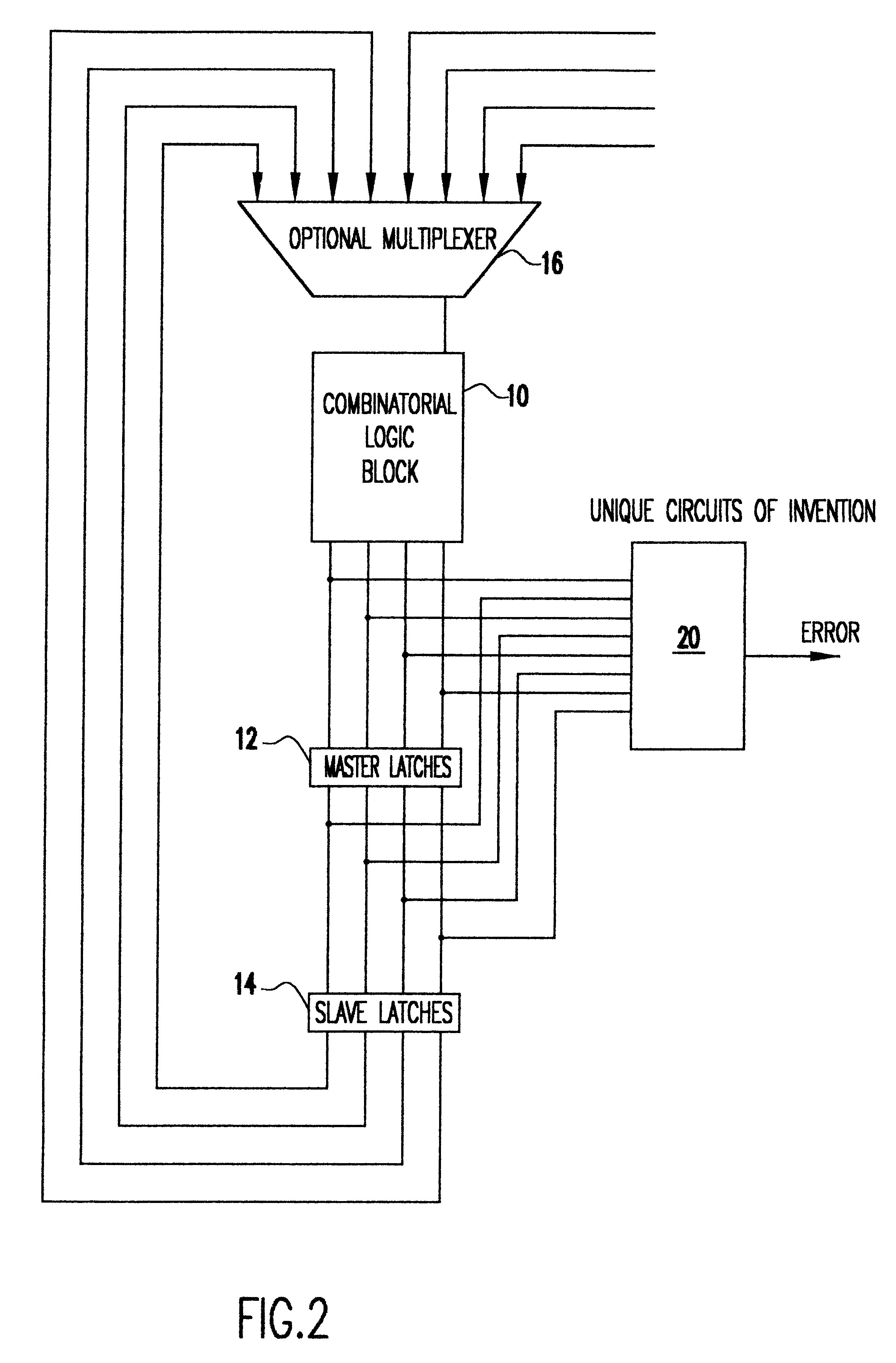

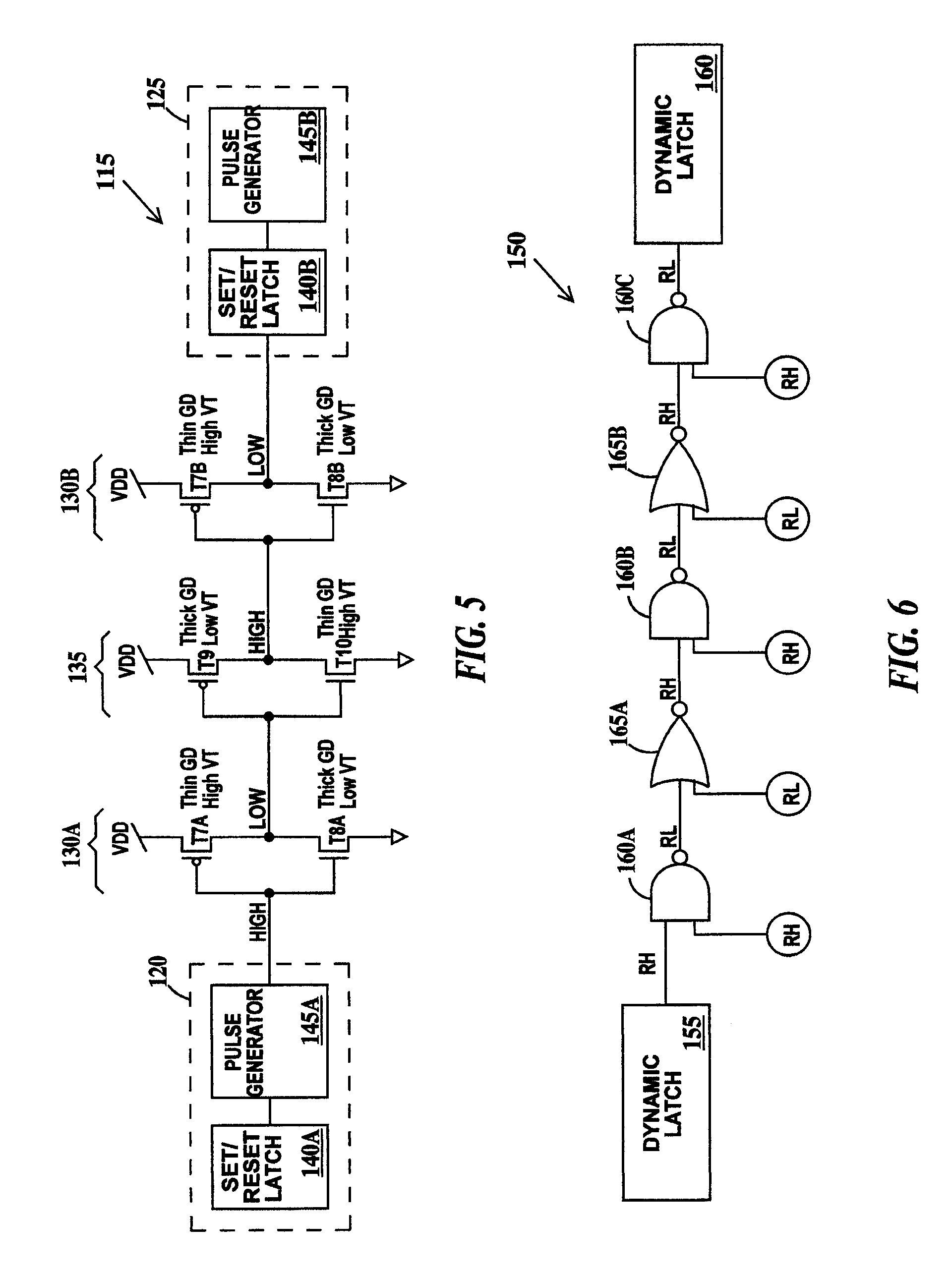

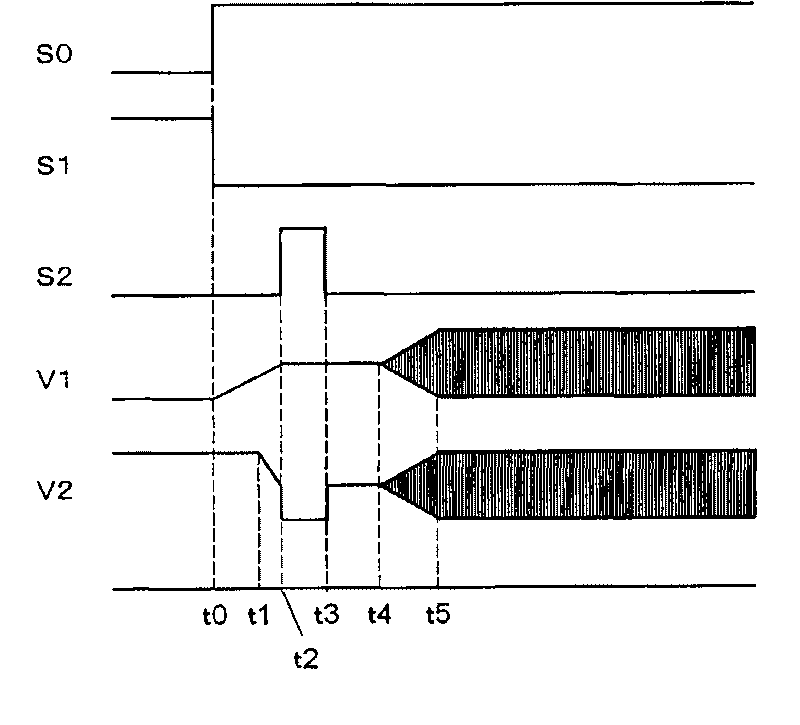

System technique for detecting soft errors in statically coupled CMOS logic

Circuit for detecting error transients in logic circuits due to atomic events or other non-recurring noise sources includes a first circuit coupled to a data line for sensing a first signal on the data line at a first point in time (T1) and a second circuit coupled to the data line for sensing the first signal on the data line at a second point in time (T2) such that a time difference between T1 and T2 is small enough so that the first signal is still present on the data line in the absence of a perturbation event and such that the time difference between T1 and T2 is large enough so that any such perturbation event is resolved. A compare circuit coupled to the first and second circuits compares the sensing of the first signal by the first and second circuits, and generates an error signal in response to a non-compare.

Owner:IBM CORP

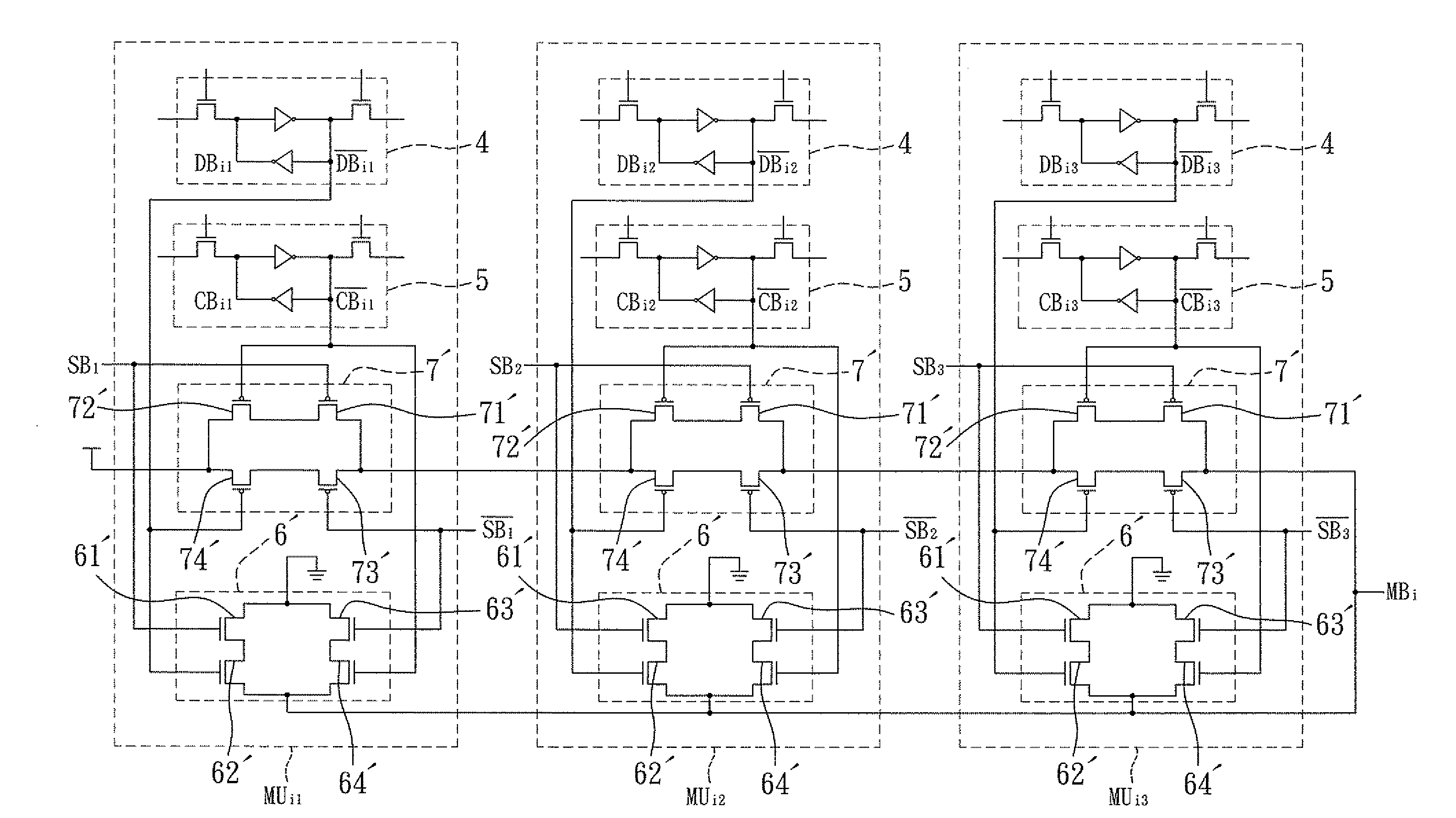

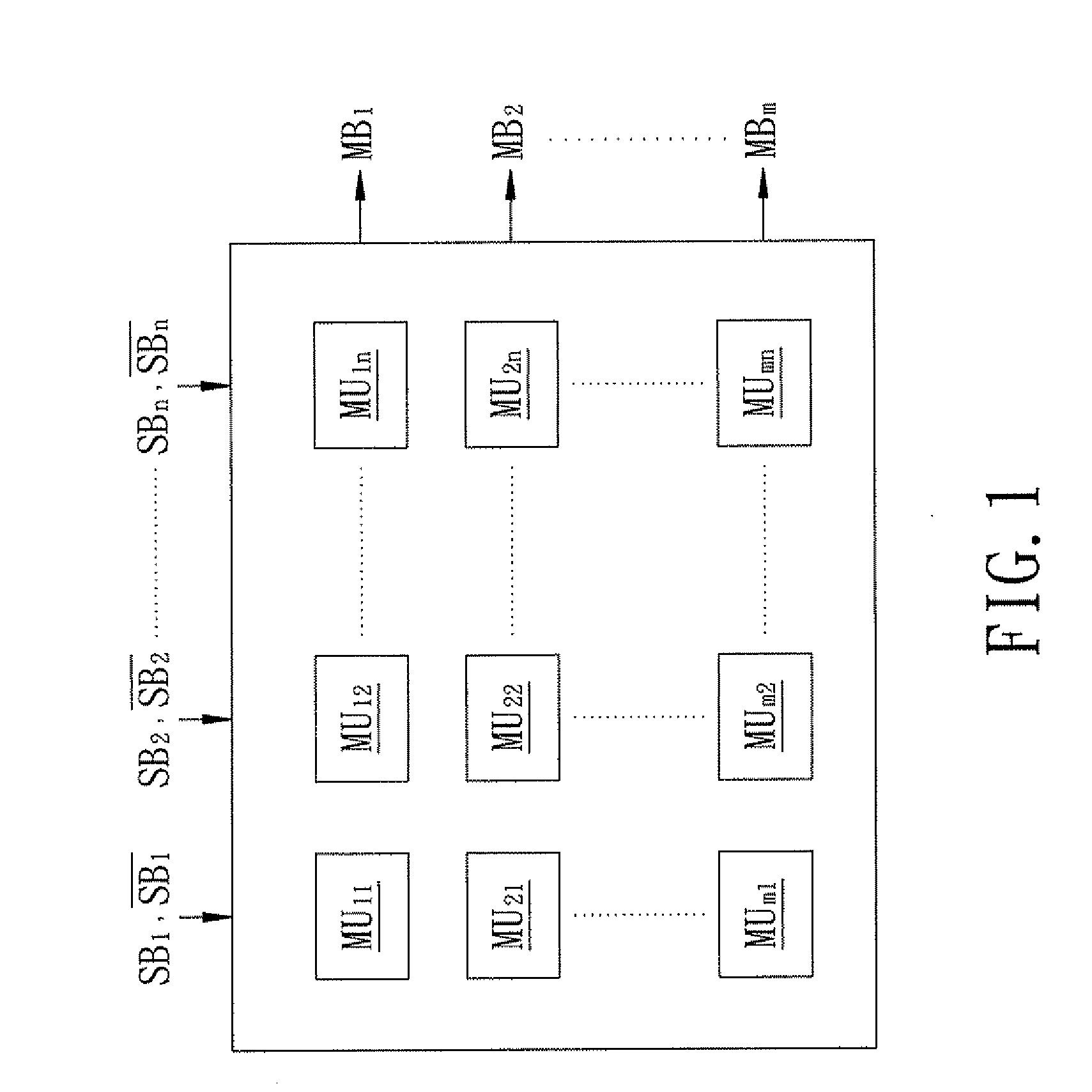

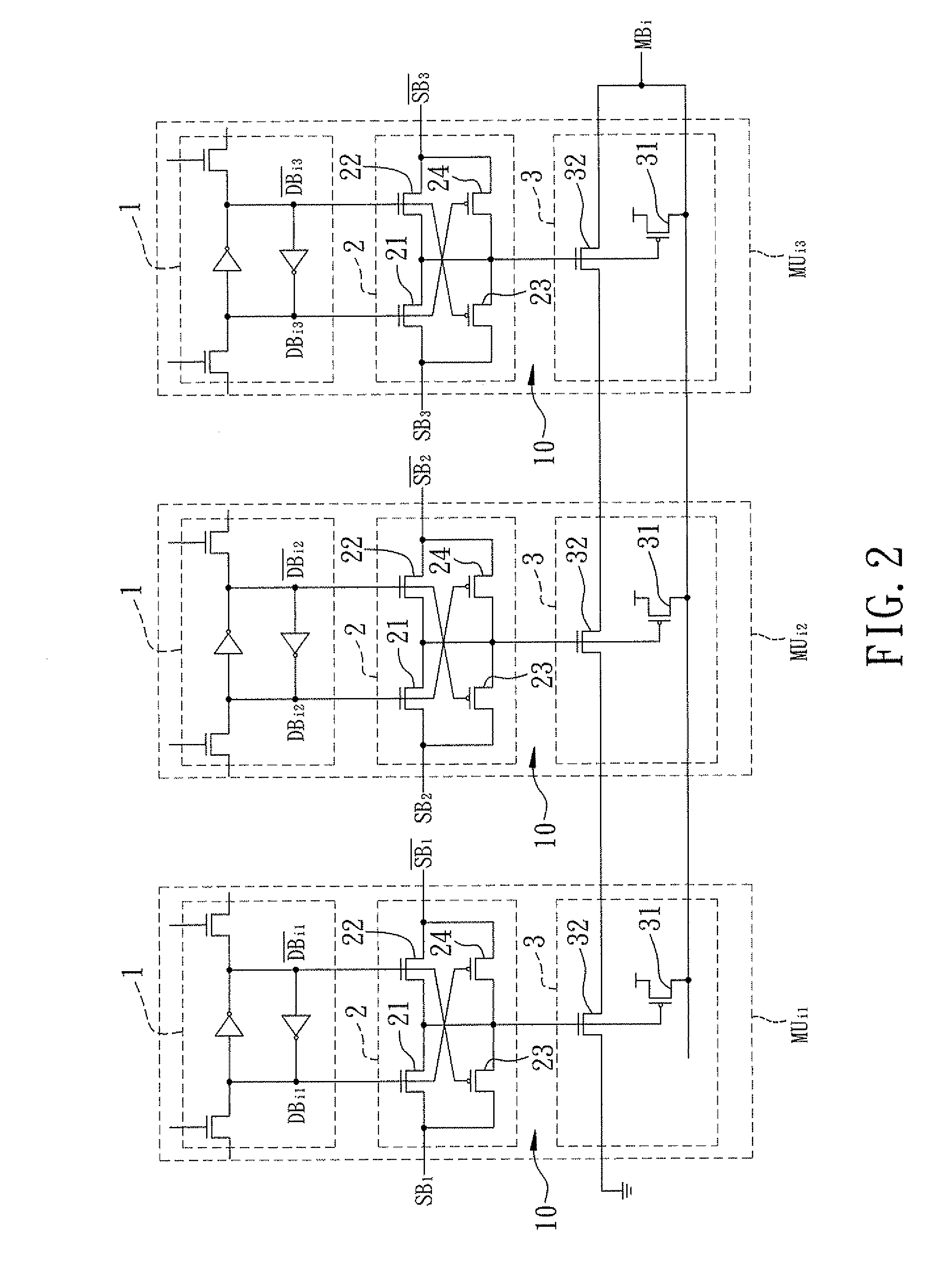

Content-Addressable Memory

ActiveUS20090310395A1Increase computing speedReduce power consumptionDigital storageCmos logic circuitsTheoretical computer science

A content-addressable memory (CAM) comprises a first CAM cell and a second CAM cell. The first CAM cell stores a first data bit, and compares the first data bit with a first search bit to determine if they are matched. The second CAM cell stores a second data bit, and compares the second data bit with a second search bit to determine if they are matched. The first CAM cell comprises a first logic circuit, the second CAM cell comprises a second logic circuit, and the first logic circuit and the second logic circuit form a static CMOS logic circuit.

Owner:REALTEK SEMICON CORP

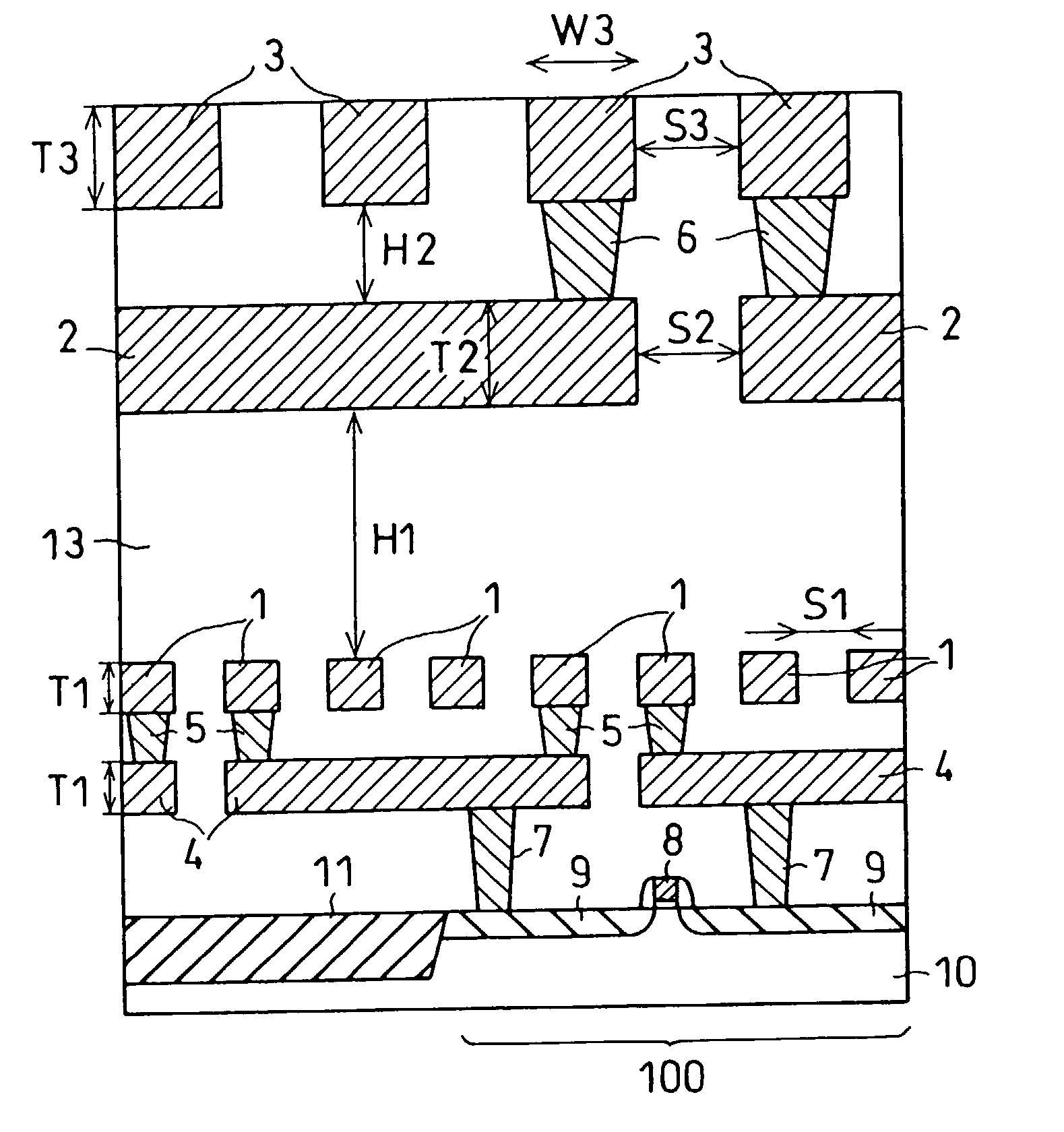

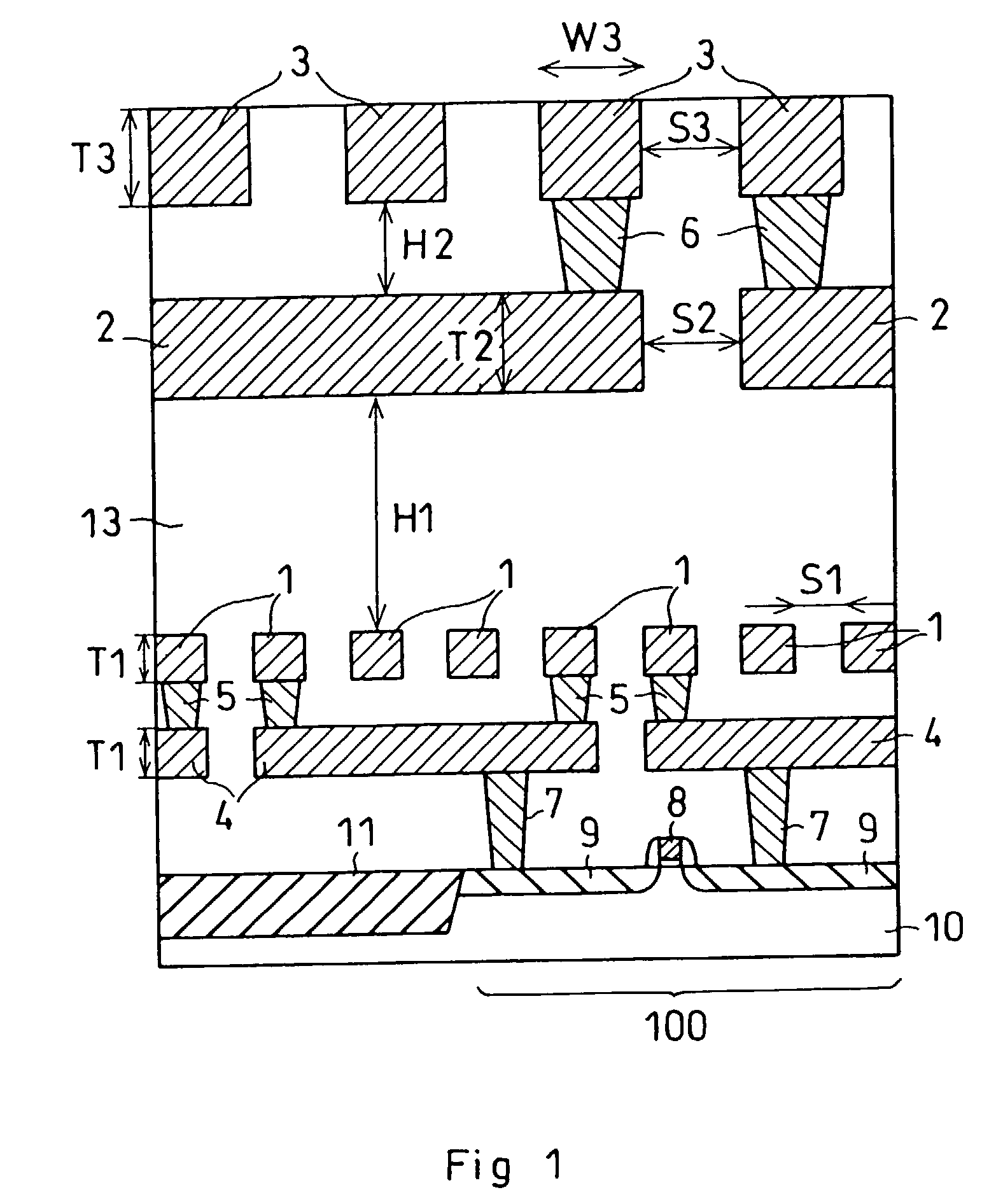

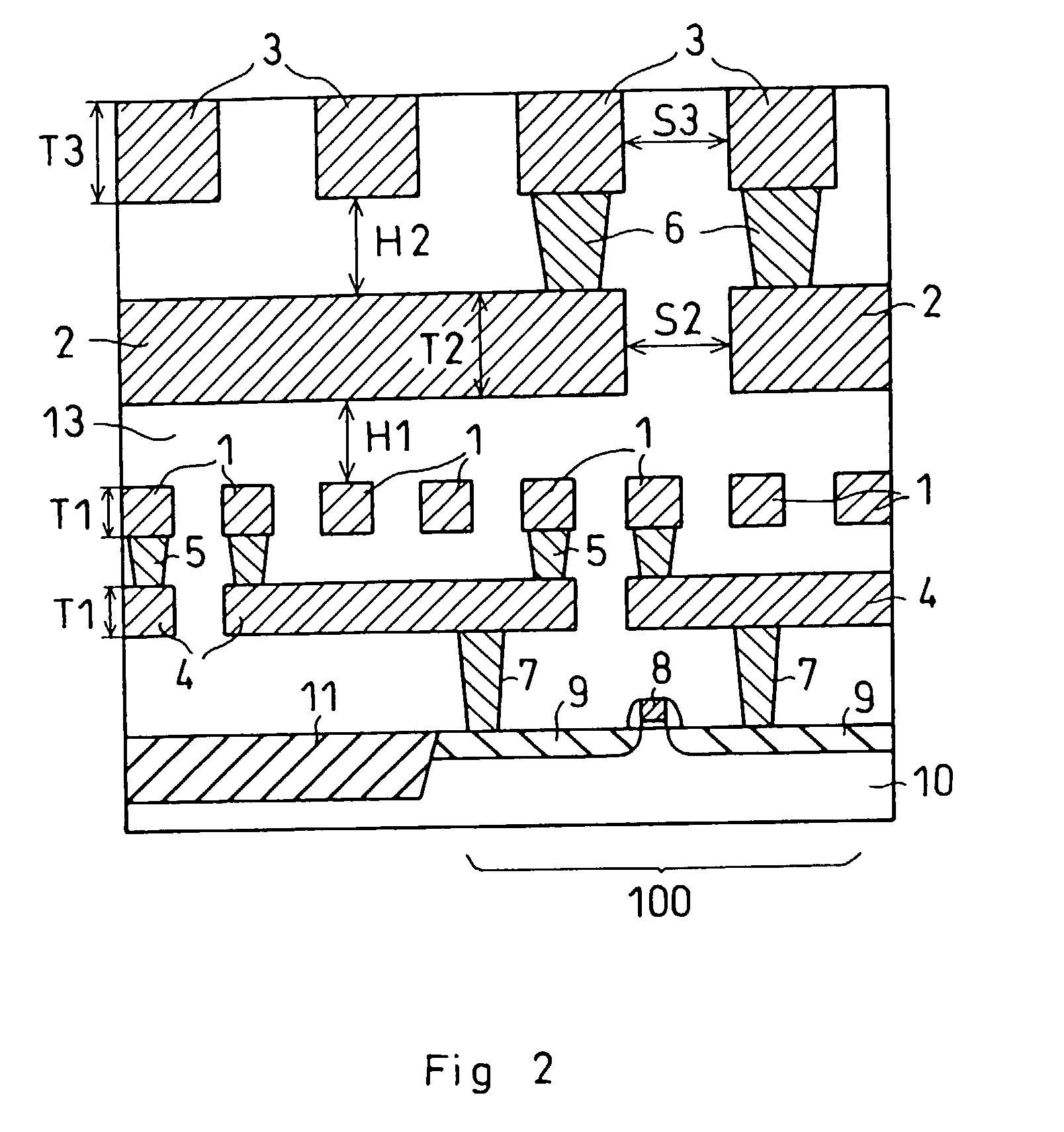

Semiconductor device

InactiveUS20020163063A1Reduce stepsEasy dischargeTransistorSemiconductor/solid-state device detailsCMOSCmos logic circuits

An electrical wiring structure capable of improving a wiring delay to thereby achieve both low power consumption and high-speed performances without accompanying any significant changes in circuit layout and wiring structure of prior known CMOS logic circuitry and also alterations of the multilayer configuration of wiring layers is provided. A local wiring 1 and global wirings 2, 3 are stacked over a semiconductor substrate 10 in this order of sequence when looked at from lower part in a lamination direction, with dielectric layers sandwiched between adjacent ones of these layers. A distance between the local wiring 1 and the global wiring 2 is so formed as to be greater than a distance between the global wiring layer 2 and the global wiring, 3. Thus provided is a semiconductor device featured in that a drive voltage used to drive the global wirings 2, 3 is potentially lower than a drive voltage for driving inside of the local wiring 1.

Owner:KK TOSHIBA

Switch circuit and method of switching radio frequency signals

ActiveUS7613442B1Improving RF switch isolationEasy to switchTransistorElectronic switchingCmos logic circuitsCMOS

A novel RF switch circuit and method for switching RF signals is described. The RF switch circuit is fabricated in a silicon-on-insulator (SOI) technology. The RF switch includes pairs of switching and shunting transistor groupings used to alternatively couple RF input signals to a common RF node. A fully integrated RF switch is described including digital control logic and a negative voltage generator integrated together with the RF switch elements. In one embodiment, the fully integrated RF switch includes a built-in oscillator, a charge pump circuit, CMOS logic circuitry, level-shifting and voltage divider circuits, and an RF buffer circuit. Several embodiments of the charge pump, level shifting, voltage divider, and RF buffer circuits are described. The RF switch provides improvements in insertion loss, switch isolation, and switch compression. An improved voltage reducing circuit is described. The improved voltage reducing circuit limits voltages applied to selected nodes within the integrated circuit.

Owner:PSEMI CORP

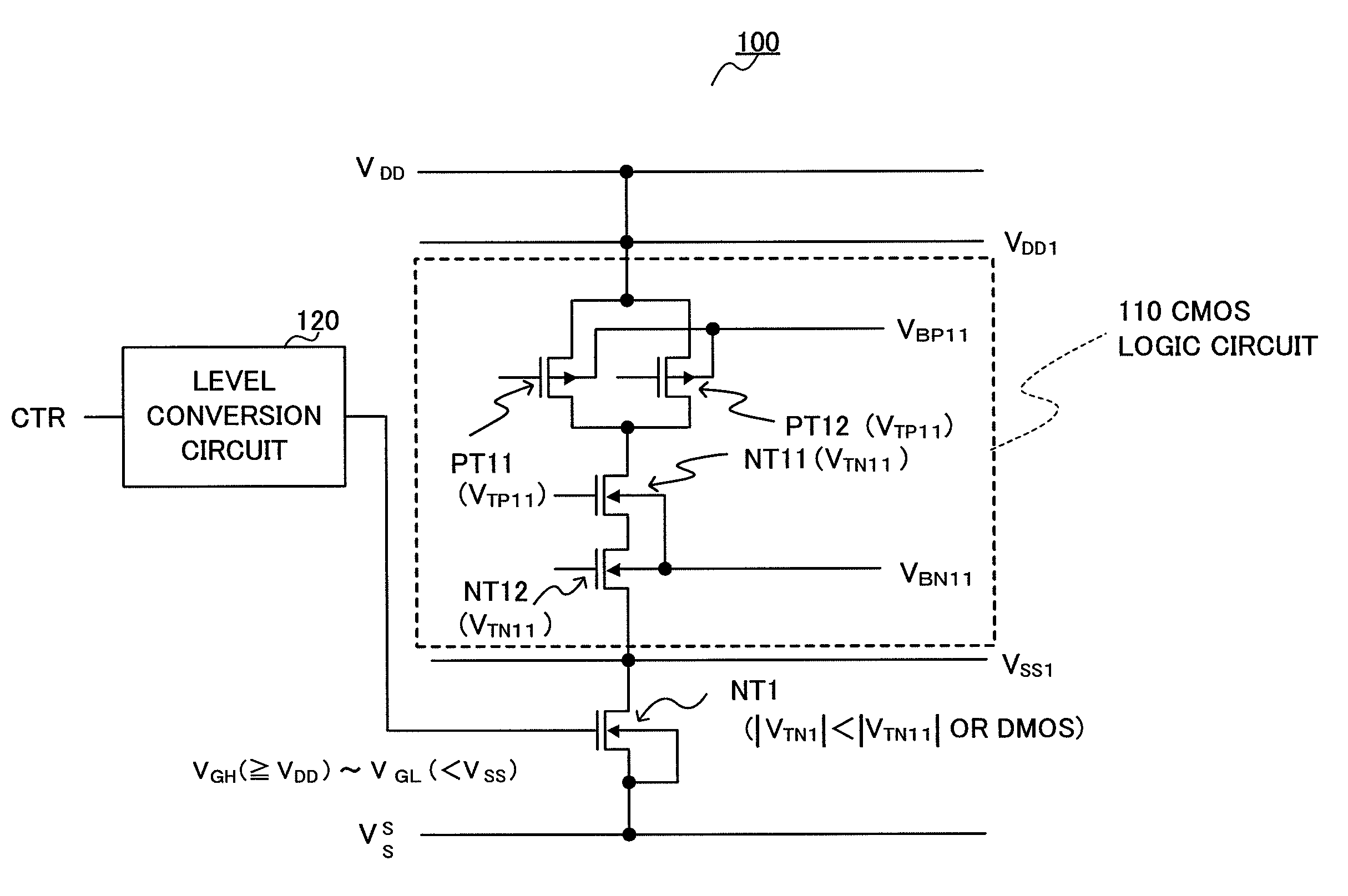

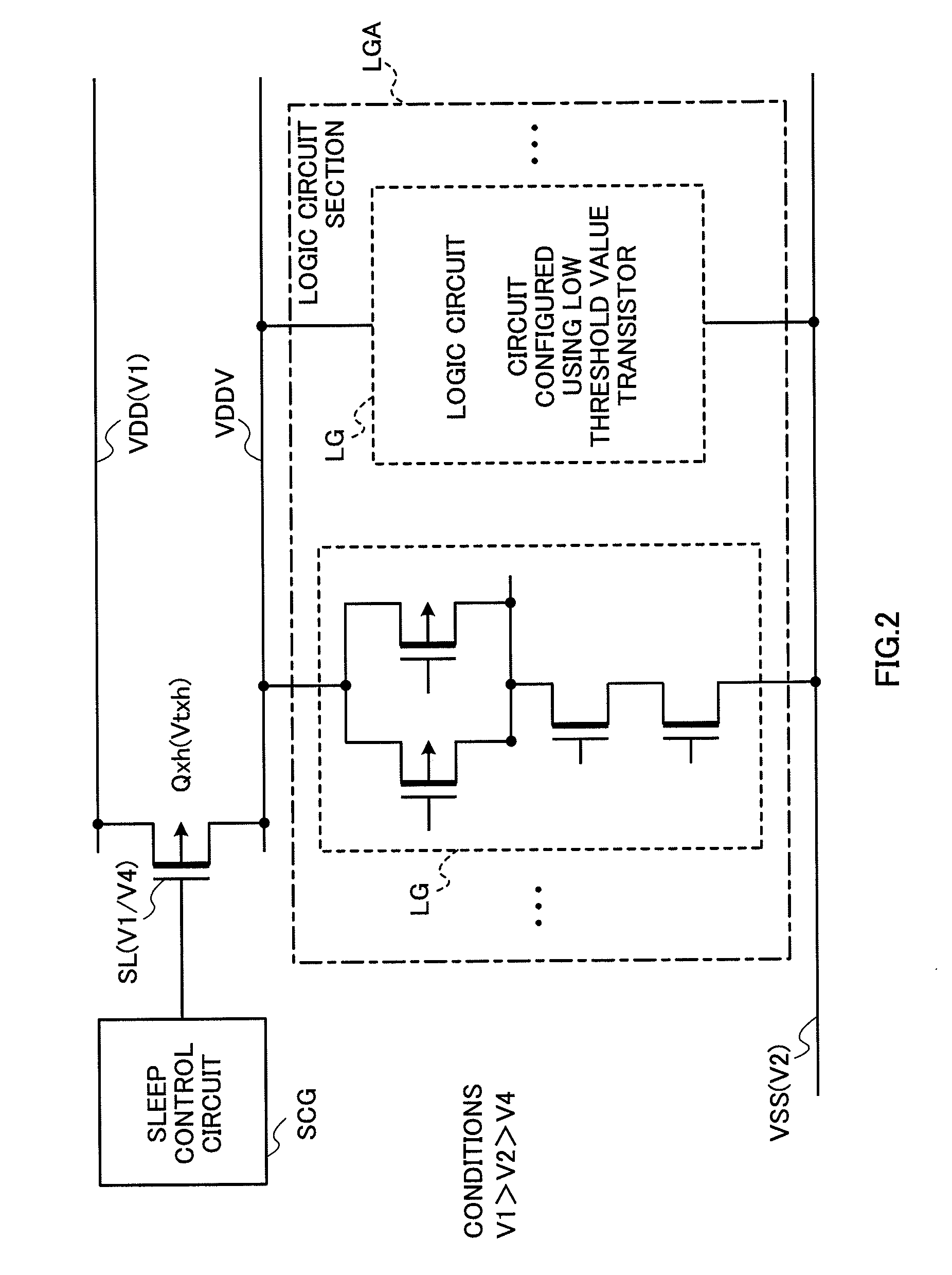

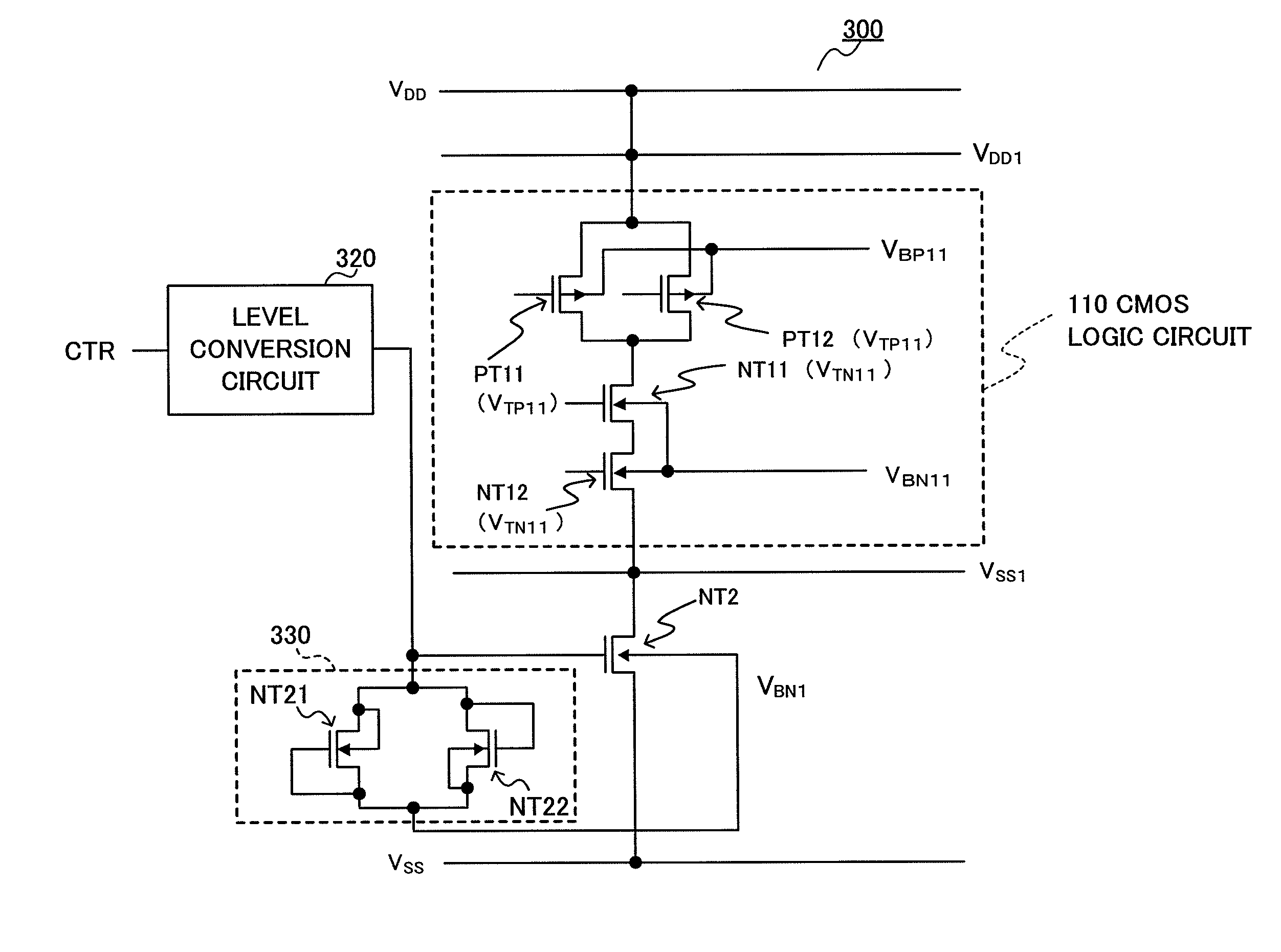

Semiconductor integrated circuit apparatus and electronic apparatus

InactiveUS20070176673A1Power reduction by control/clock signalLogic circuits characterised by logic functionElectricityCmos logic circuits

A semiconductor integrated circuit apparatus and an electronic apparatus having a power control function configured from power control MOS transistors in such a manner that leakage current and on resistance at the time of cut-off is sufficiently small in actual use. Semiconductor integrated circuit apparatus is comprised of a CMOS logic circuit, a second pseudo power supply line connected to a low potential side power supply terminal of the CMOS logic circuit, and a power control NchMOS transistor connected across a second pseudo power supply line and a low potential side power supply line, with the substrate and gate of power control NchMOS transistor being electrically connected. The gate and the substrate may also, for example, be connected via a current limiter utilizing, for example, a source follower of a depletion type NchMOS transistor.

Owner:COLLABO INNOVATIONS INC

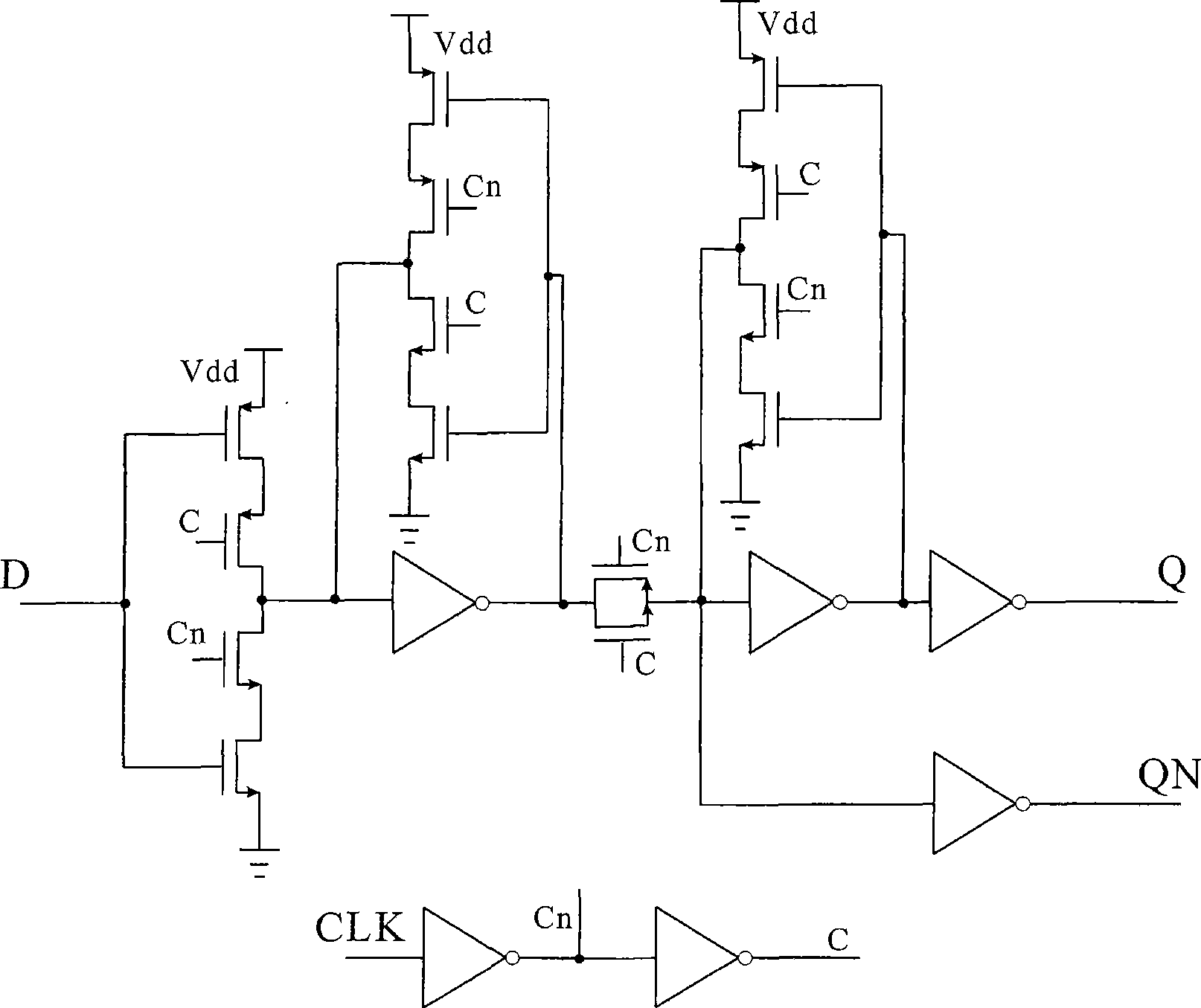

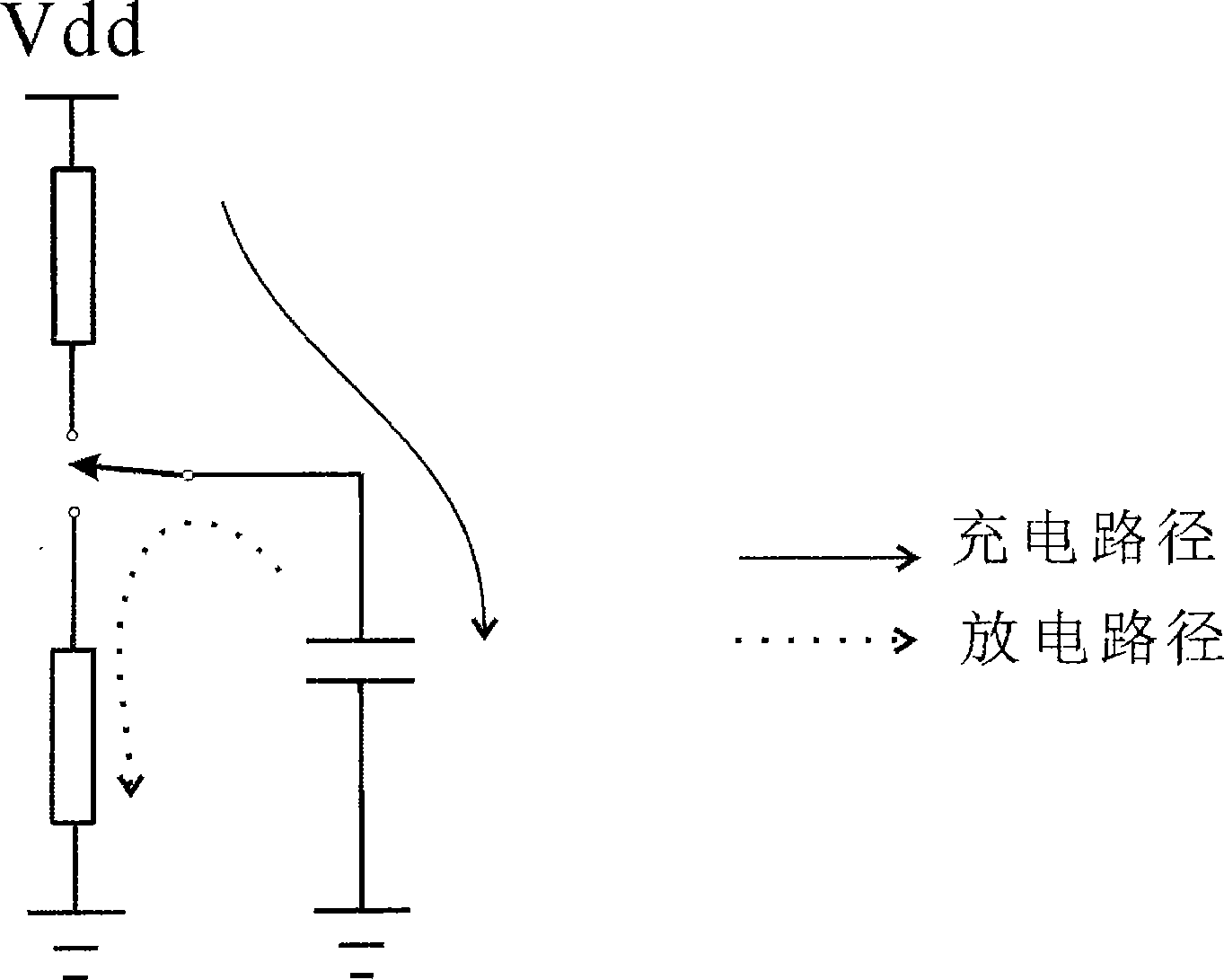

Single-phase power clock trigger based on electric charge resumption

InactiveCN101471642AReduce power consumptionLogic circuits characterised by logic functionElectric pulse generatorSquare waveformCoupling

The invention relates to a single-phase power clock trigger based on charge recovering. The trigger comprises an input inverter used for generating two inverse signals and sending the two signals to a charge recovery unit, a cross-coupling charge recovery unit used for reducing the power consumption of a circuit, and a RS trigger used for latching the output of a charge recycling unit, wherein, the input and the output of the inverter are connected with two input terminals of the cross-coupling charge recovery unit respectively; and two output terminals of the cross-coupling charge recovery unit are connected with two input terminals of the RS trigger. The trigger adopts the single phase power clock (similar to a sine wave power) Pclk to complete the function of the trigger D, input and output signals adopt the square wave and can be directly cascaded with a traditional CMOS logic circuit to complete the logic. Compared with a traditional trigger, the trigger of the invention has the advantages that the power consumption is low, and the extremely low power consumption can be realized particularly when the data change rate is low; the number of transistors is small; and the single-phase clock is adopted.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

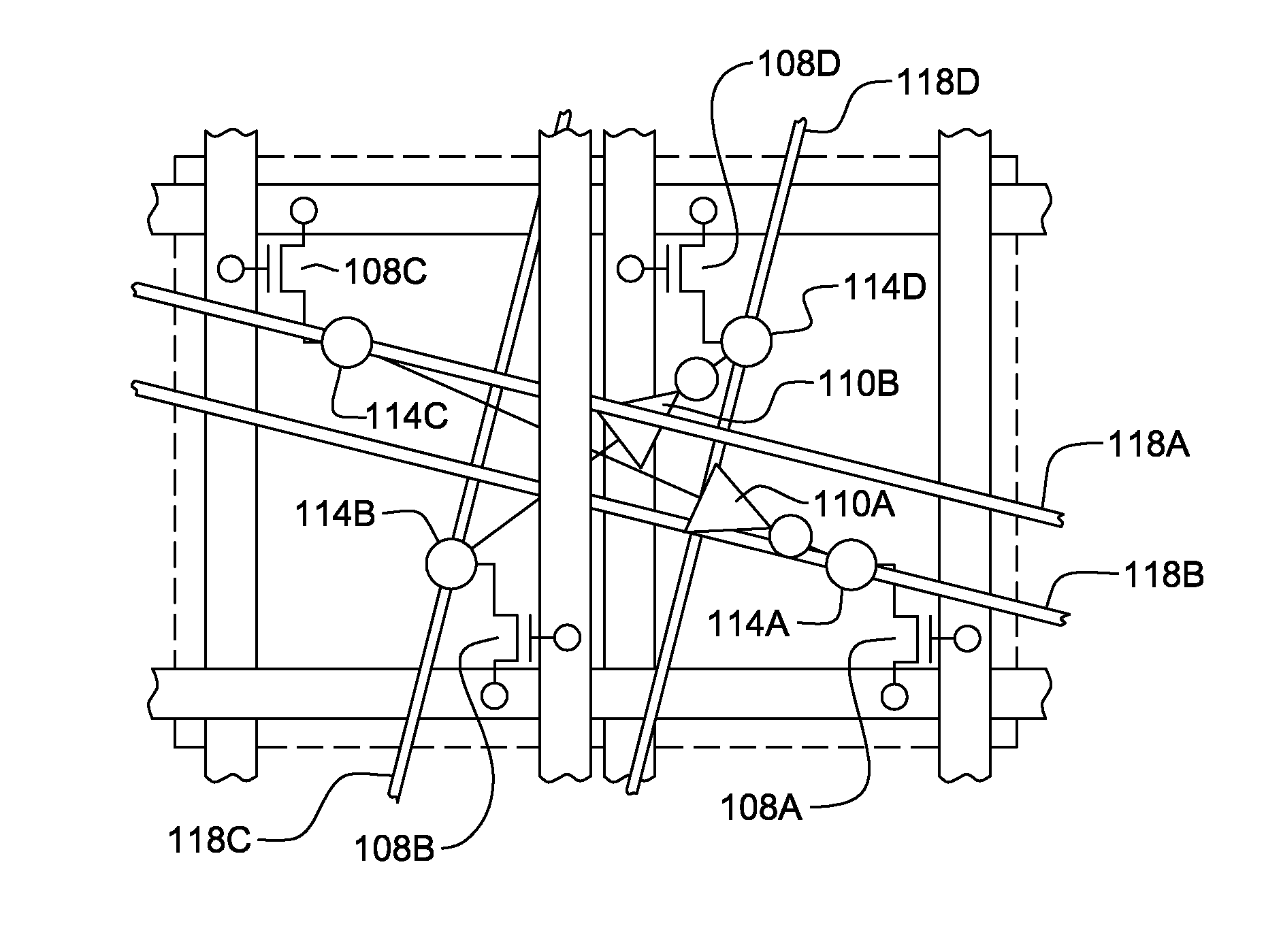

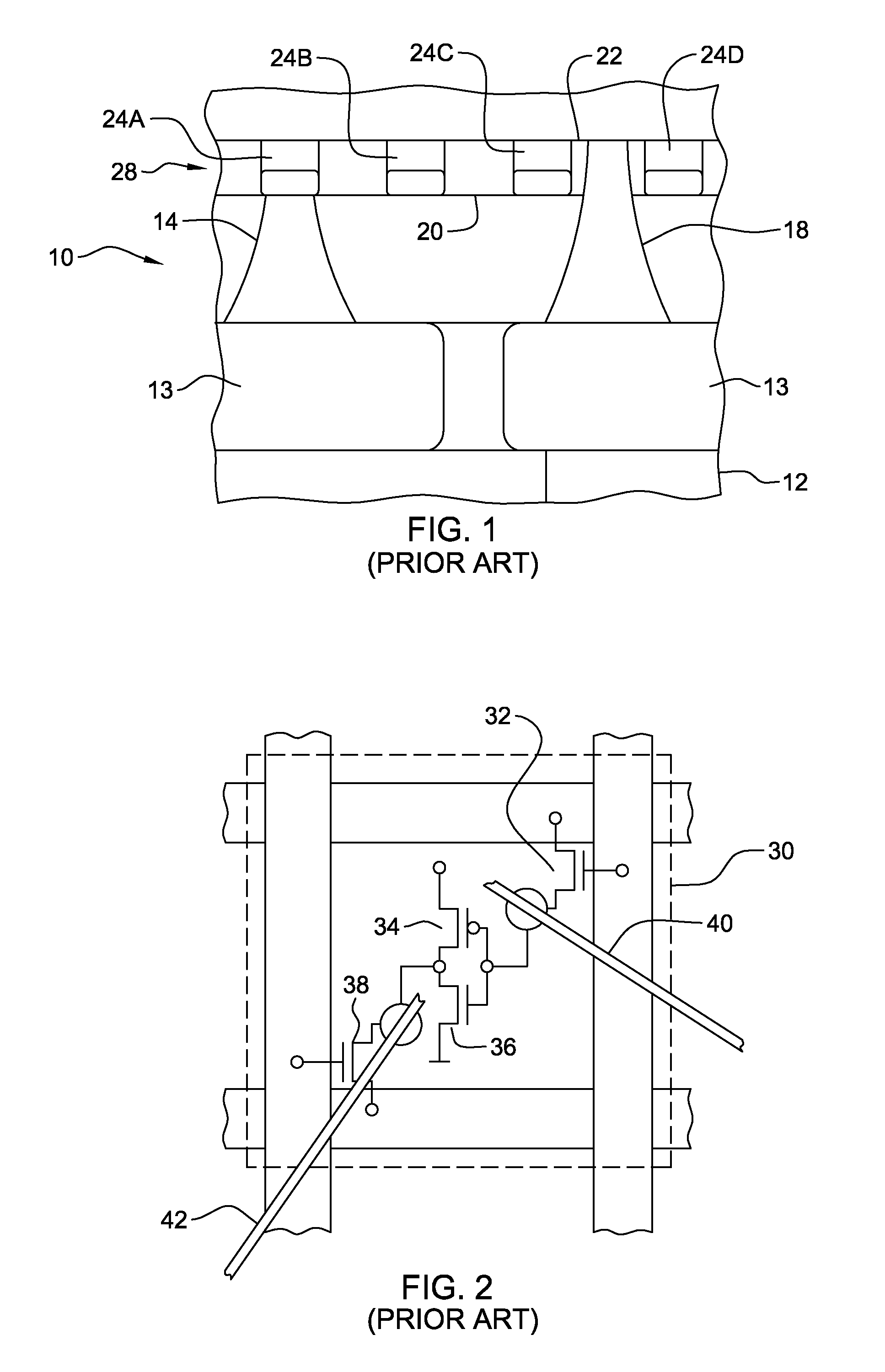

Three-dimensional architecture for integration of CMOS circuits and nano-material in hybrid digital circuits

InactiveUS20100133587A1Efficient use ofIncrease contactTransistorNanoinformaticsCMOSCmos logic circuits

A hybrid CMOL stack enables more efficient design of CMOS logical circuits. The hybrid CMOL structure includes a first substrate having a CMOS device layer on the substrate, a first interconnect layer with interface pins over the CMOS device layer of the first substrate, a first array of nanowires connected to the interface pins of the first interconnect layer, a layer of nanowire junction material over the first array of nanowires, a second array of nanowires over the nanowire junction material, a second interconnect layer having interface pins disposed over the second array of nanowires, the interface pins being connected to the second array of nanowires, and a second substrate, the second substrate including a second CMOS device layer disposed over the second interconnect layer.

Owner:THE RES FOUND OF STATE UNIV OF NEW YORK

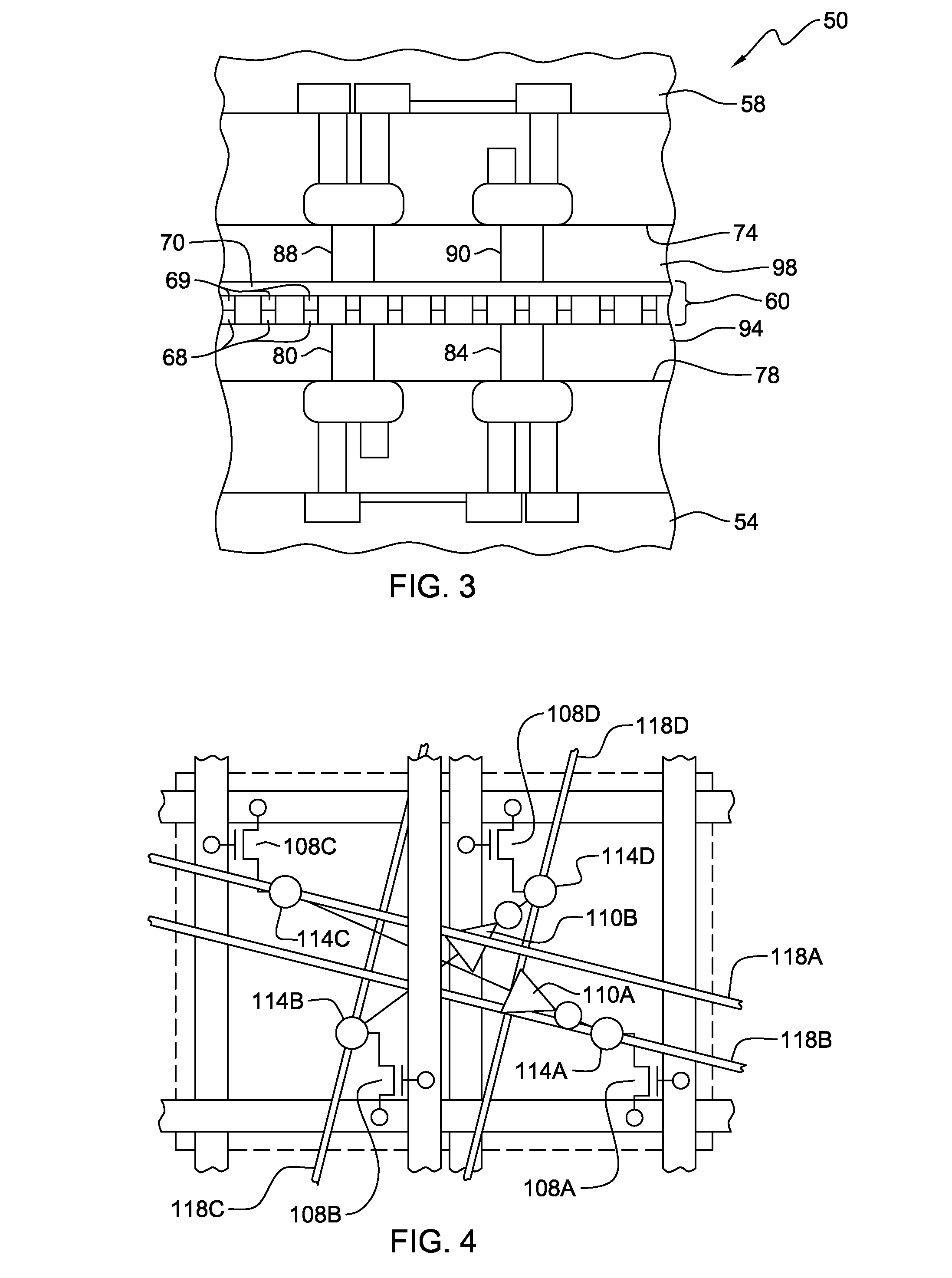

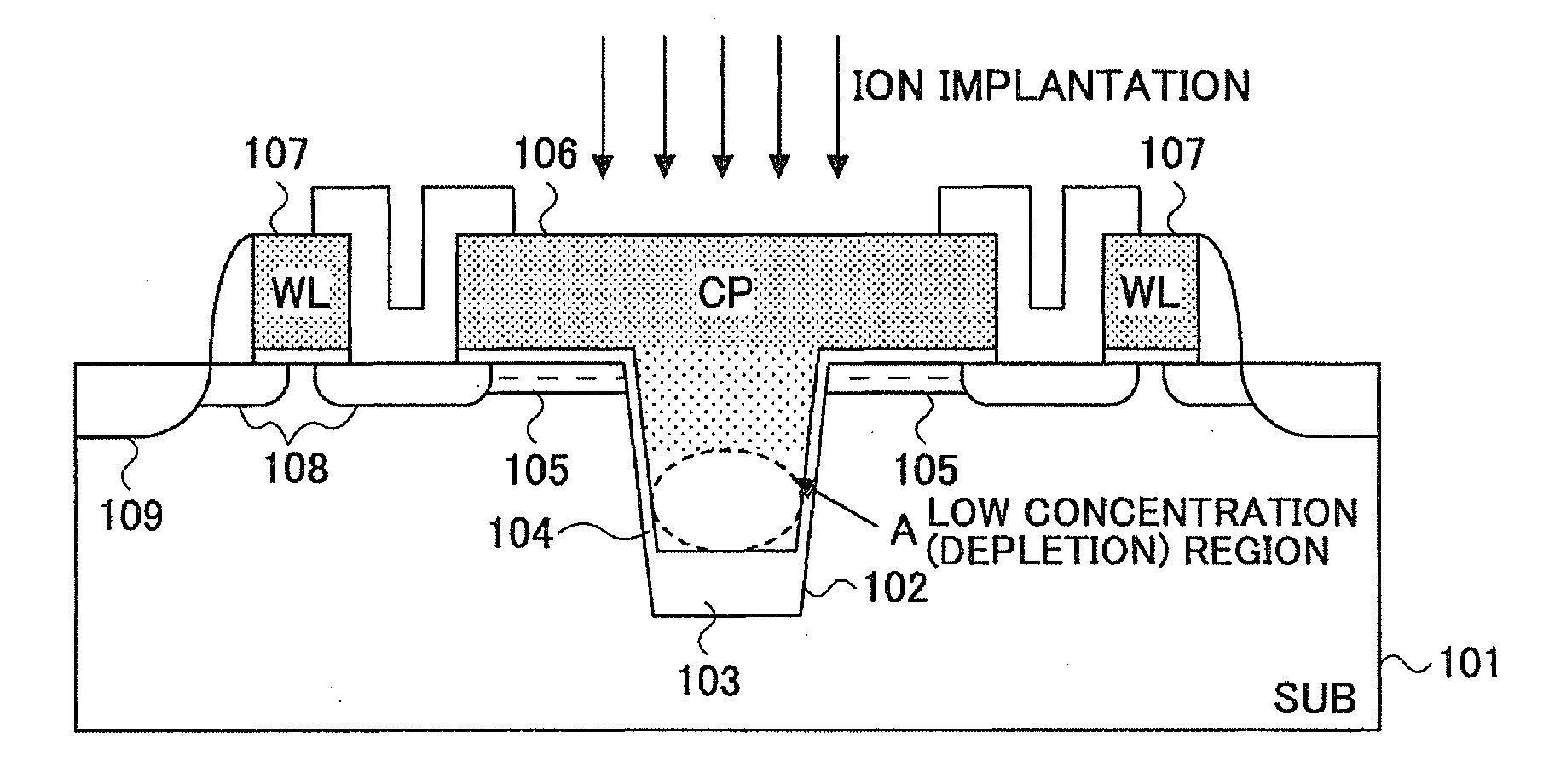

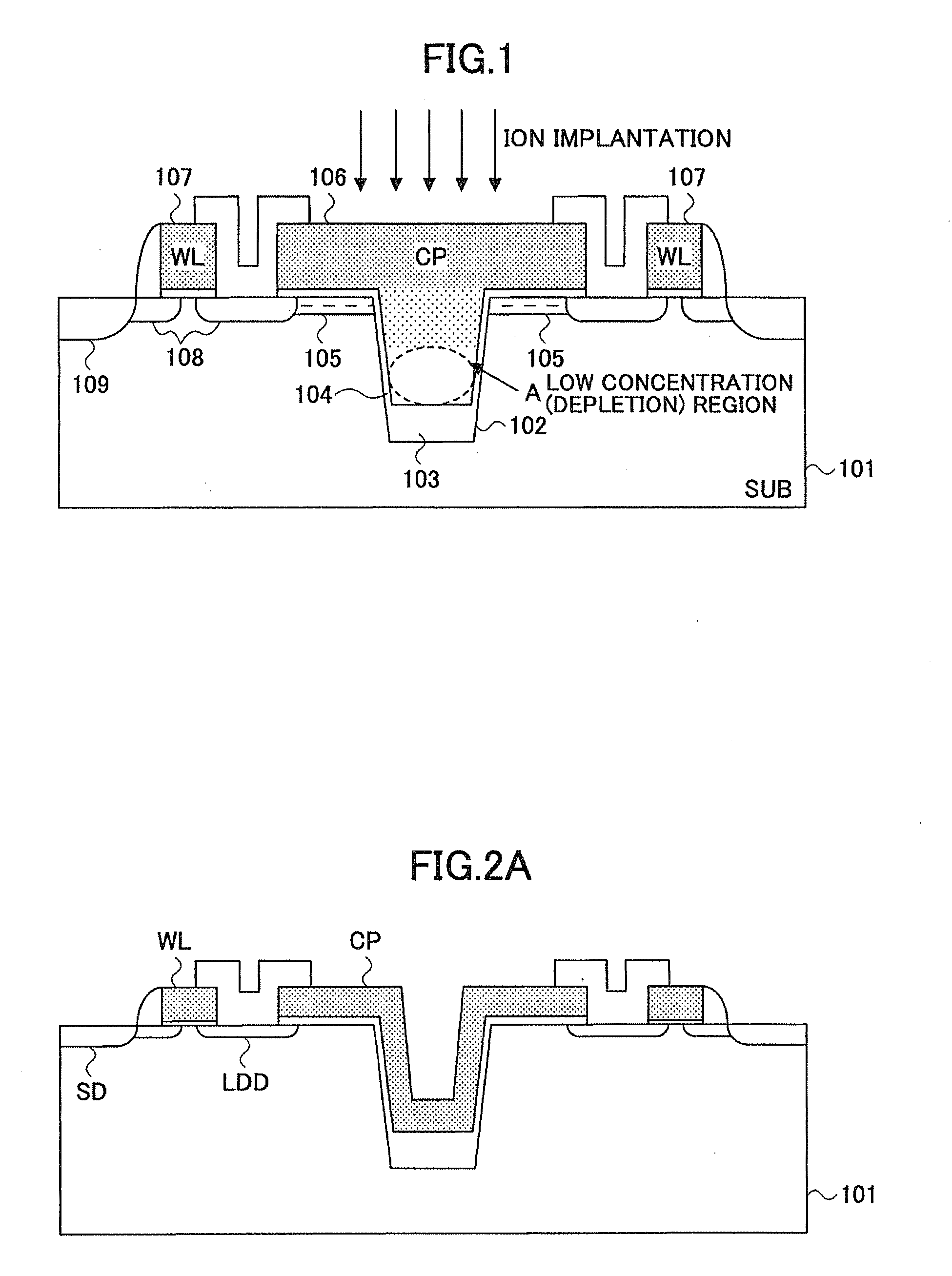

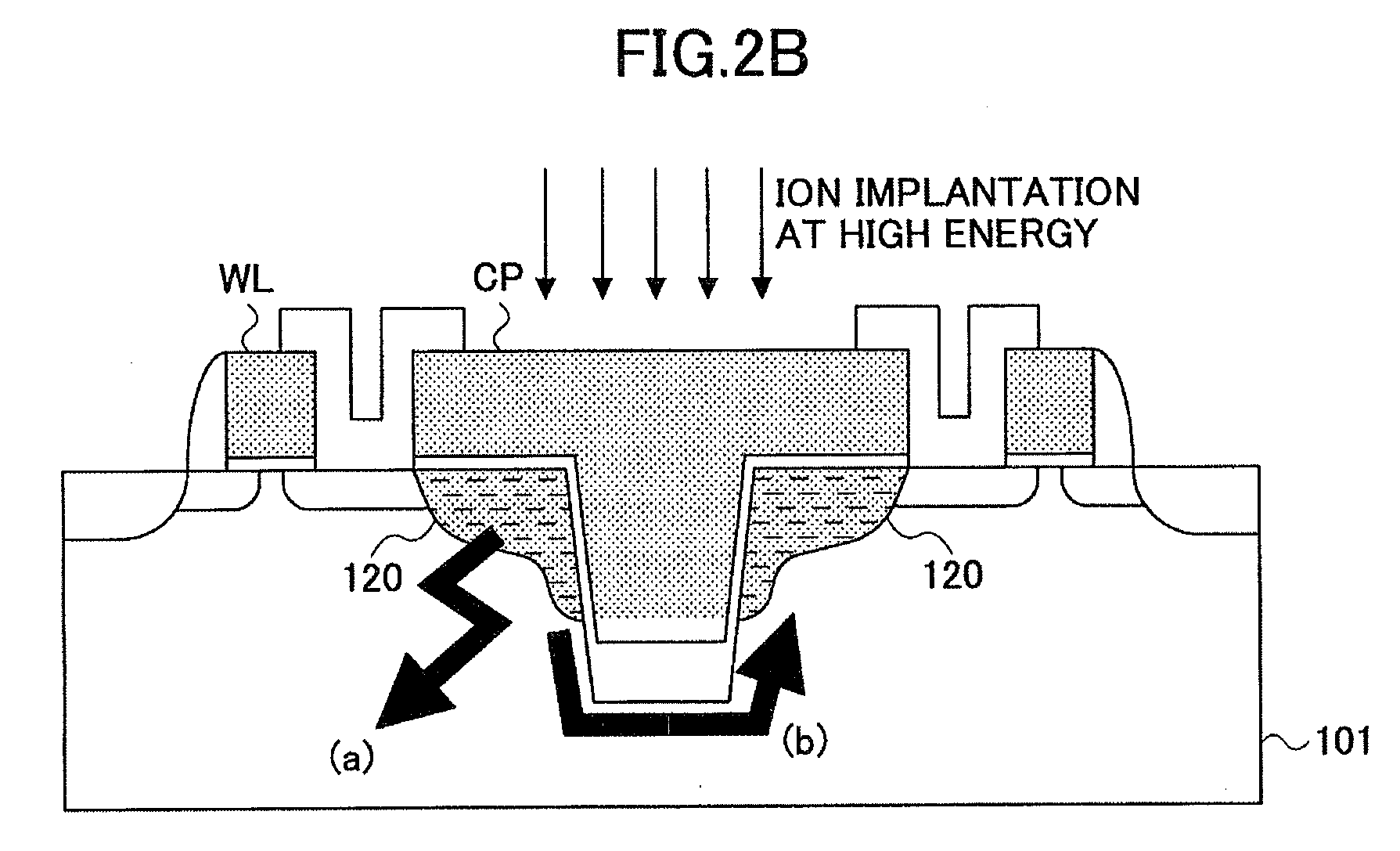

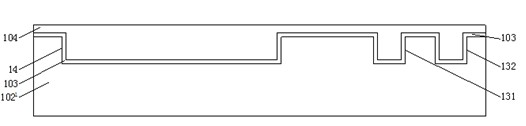

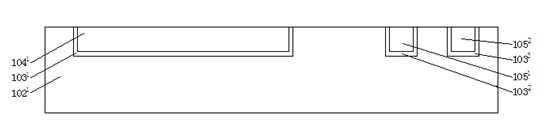

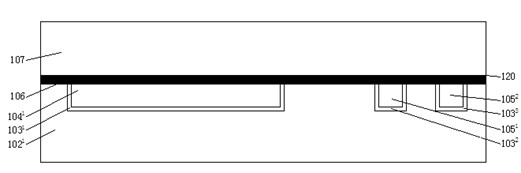

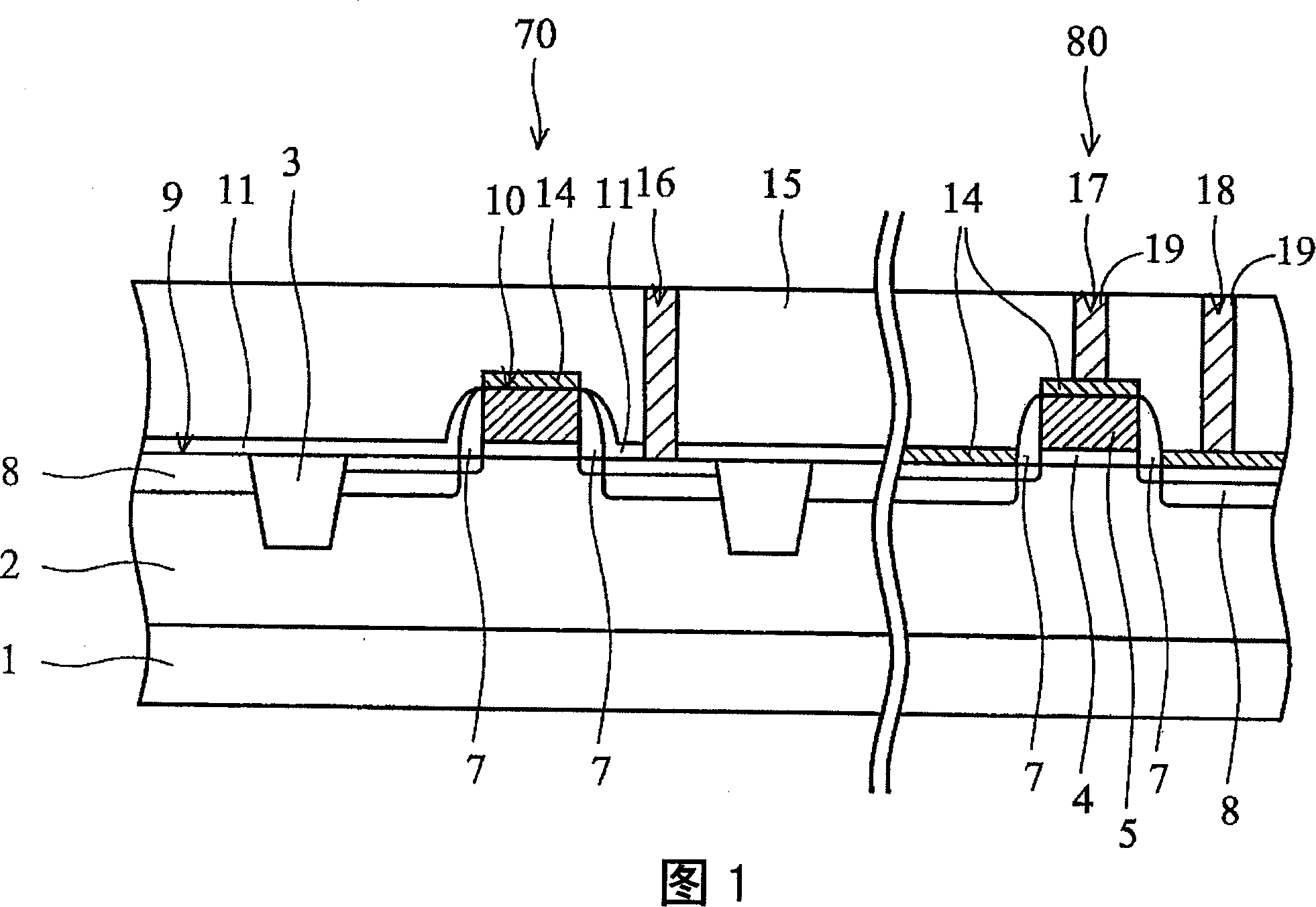

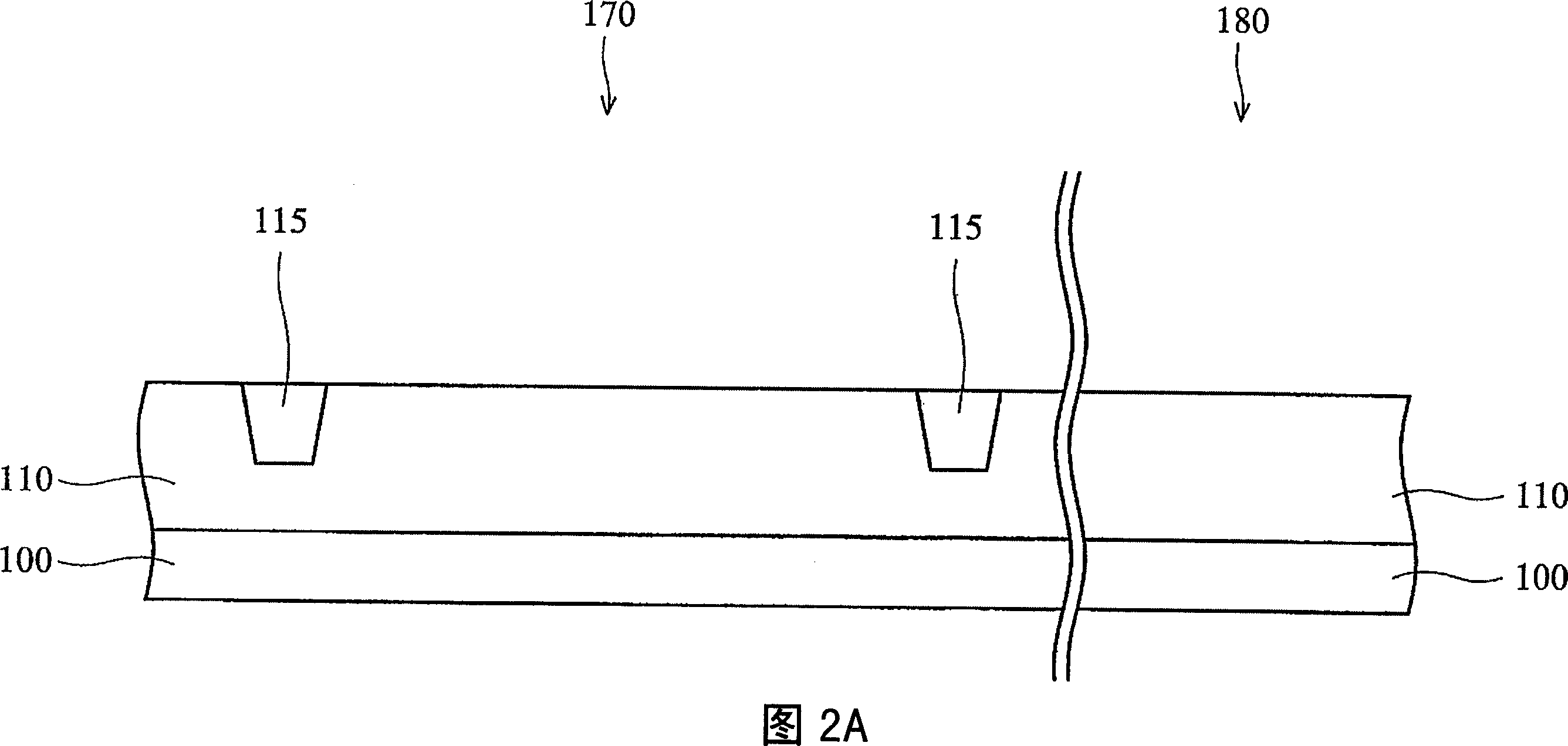

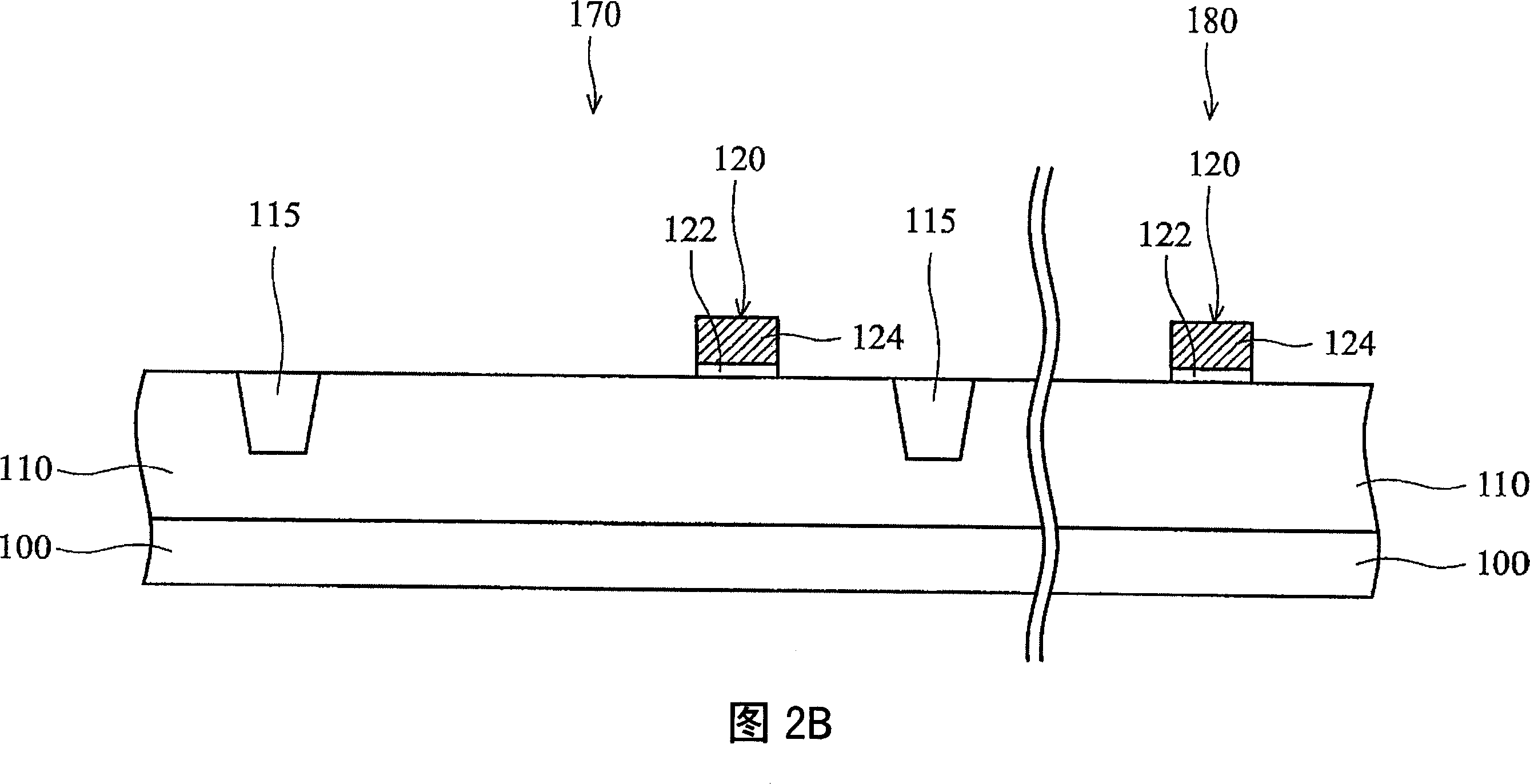

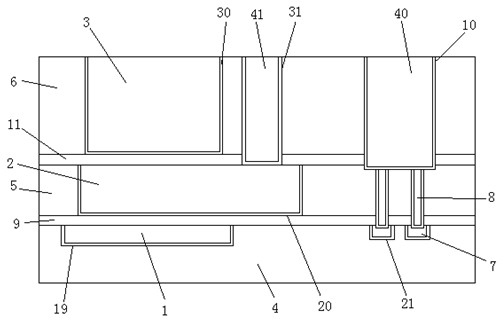

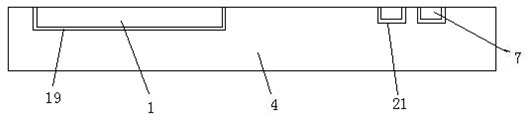

Semiconductor device and manufacturing method of the semiconductor device

ActiveUS20080315319A1Increase the number ofReduced characteristicsTransistorSolid-state devicesDevice materialCmos logic circuits

A semiconductor device includes a dual gate CMOS logic circuit having gate electrodes with different conducting types and a trench capacitor type memory on a same substrate includes a trench of the substrate for the trench capacitor, a dielectric film formed in the trench, a first poly silicon film formed inside of the trench, and a cell plate electrode located above the dielectric film. The cell plate electrode includes a first poly silicon film formed on the dielectric film partially filling the trench, and a second poly silicon film formed on the first poly silicon film to completely fill the trench. The second poly silicon film includes a sufficient film thickness for forming gate electrodes, wherein the impurity concentration of the first poly silicon film is higher than the impurity concentration of the second poly silicon film.

Owner:FUJITSU LTD

Copper Damascus process MIM (metal-insulator-metal) capacitor manufacturing process and structure

ActiveCN102420107AHigh densitySemiconductor/solid-state device detailsSolid-state devicesMetal-insulator-metalCapacitance

The invention relates to a copper Damascus process and a structure, and particularly relates to a copper Damascus process MIM (metal-insulator-metal) capacitor manufacturing process and structure. According to the copper Damascus process MIM capacitor structure and the manufacturing process thereof provided by the invention, a single Damascus process is utilized to manufacture MIM double-layer capacitor and an inductor simultaneously, and an dielectric barrier layer is removed in the manufacturing processes of a second electrode and a third electrode; and a dielectric layer made of a high-dielectric material is deposited again so as to serve as a metal insulating layer. According to the technical scheme of the invention, the manufactured MIM double-layer capacitor structure can be completely compatible with a CMOS (complementary metal-oxide-semiconductor transistor) logic circuit and an inductive copper Damascus process, and the density of the MIN capacitor is increased.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

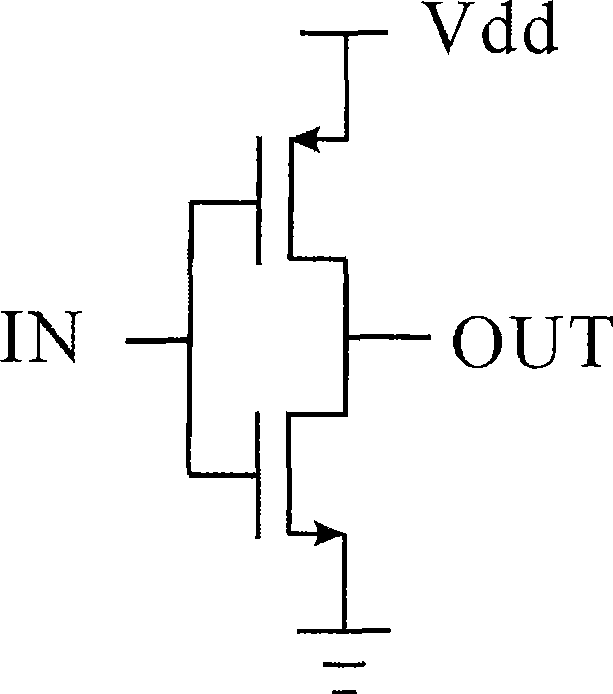

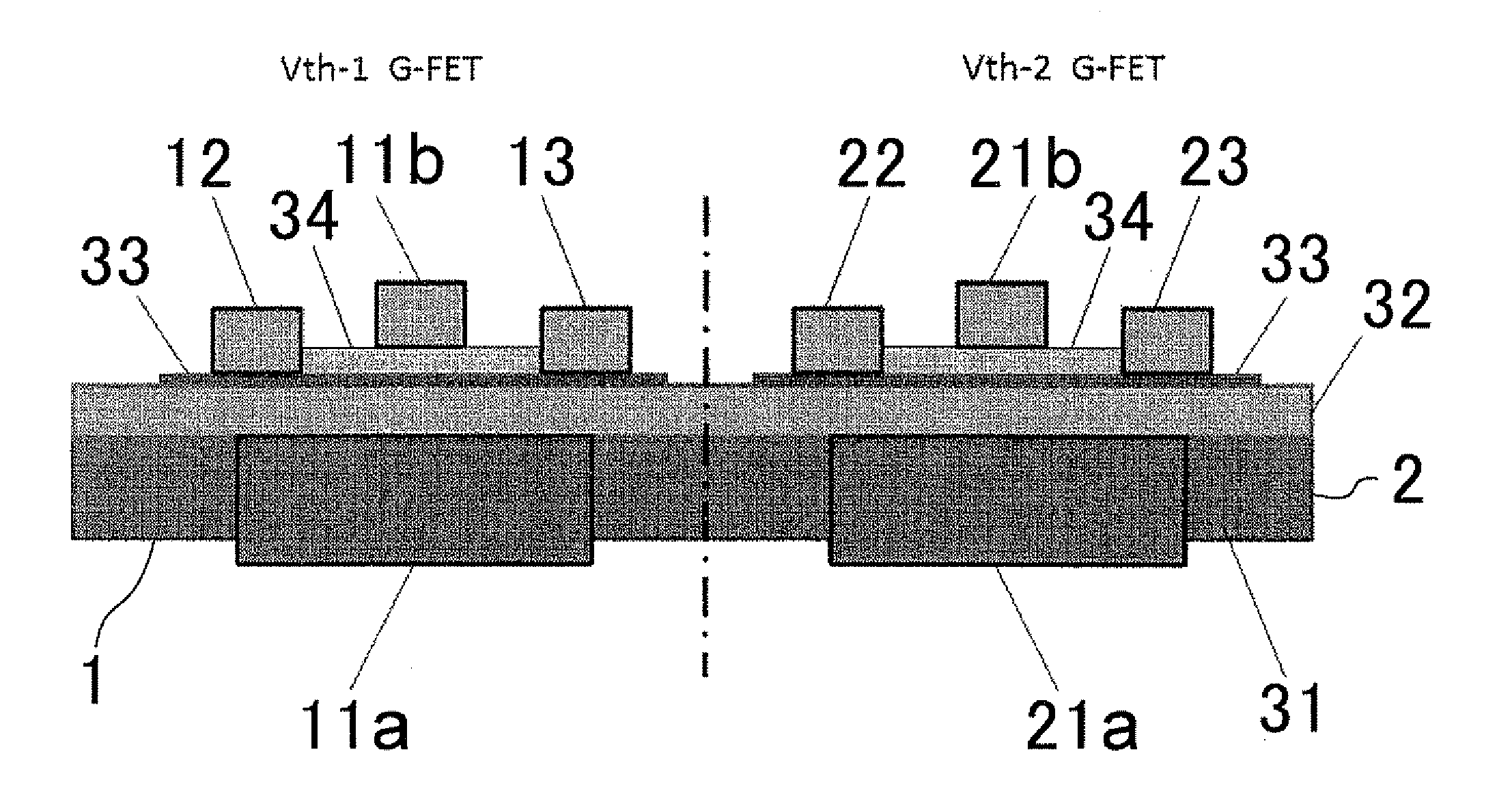

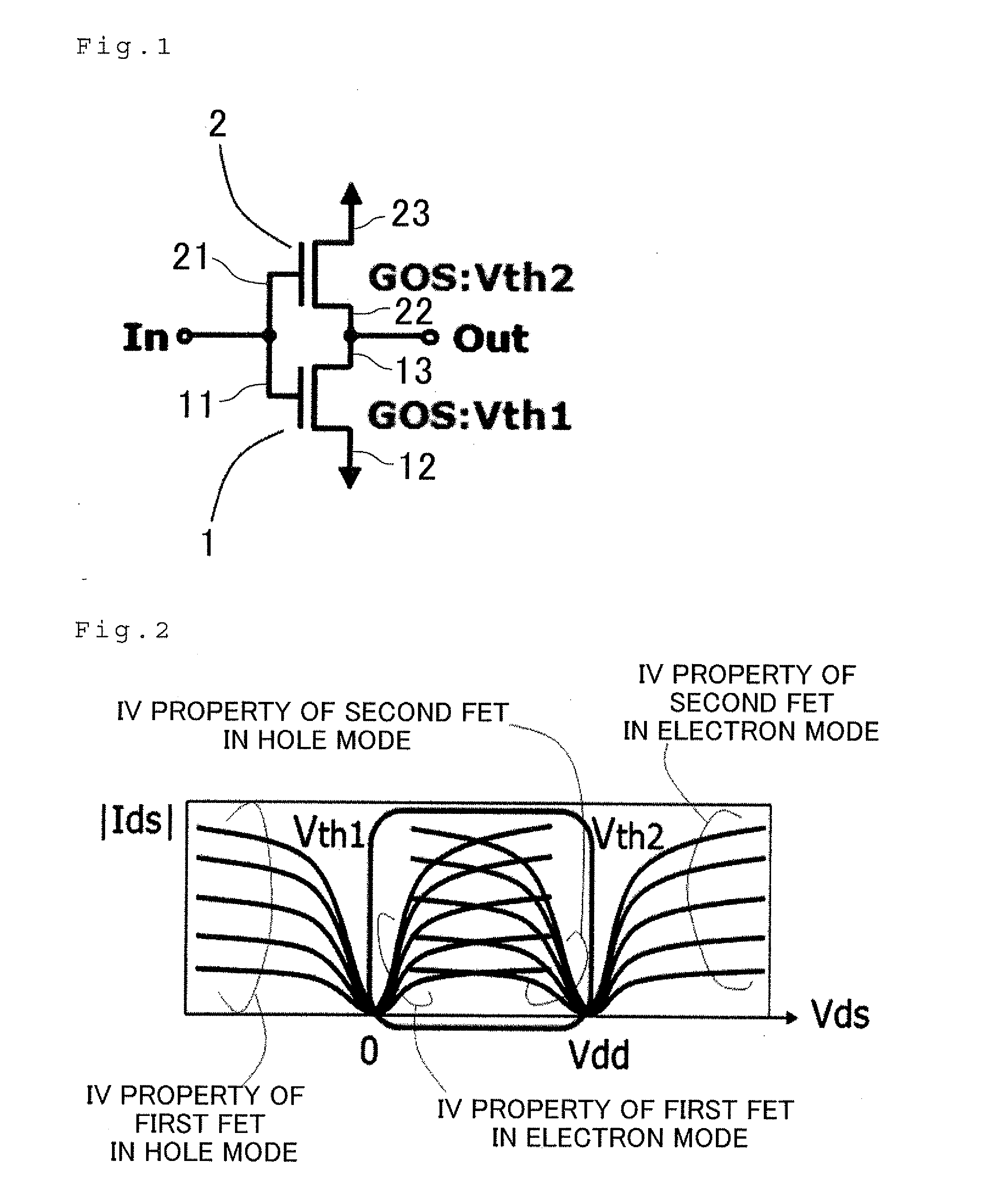

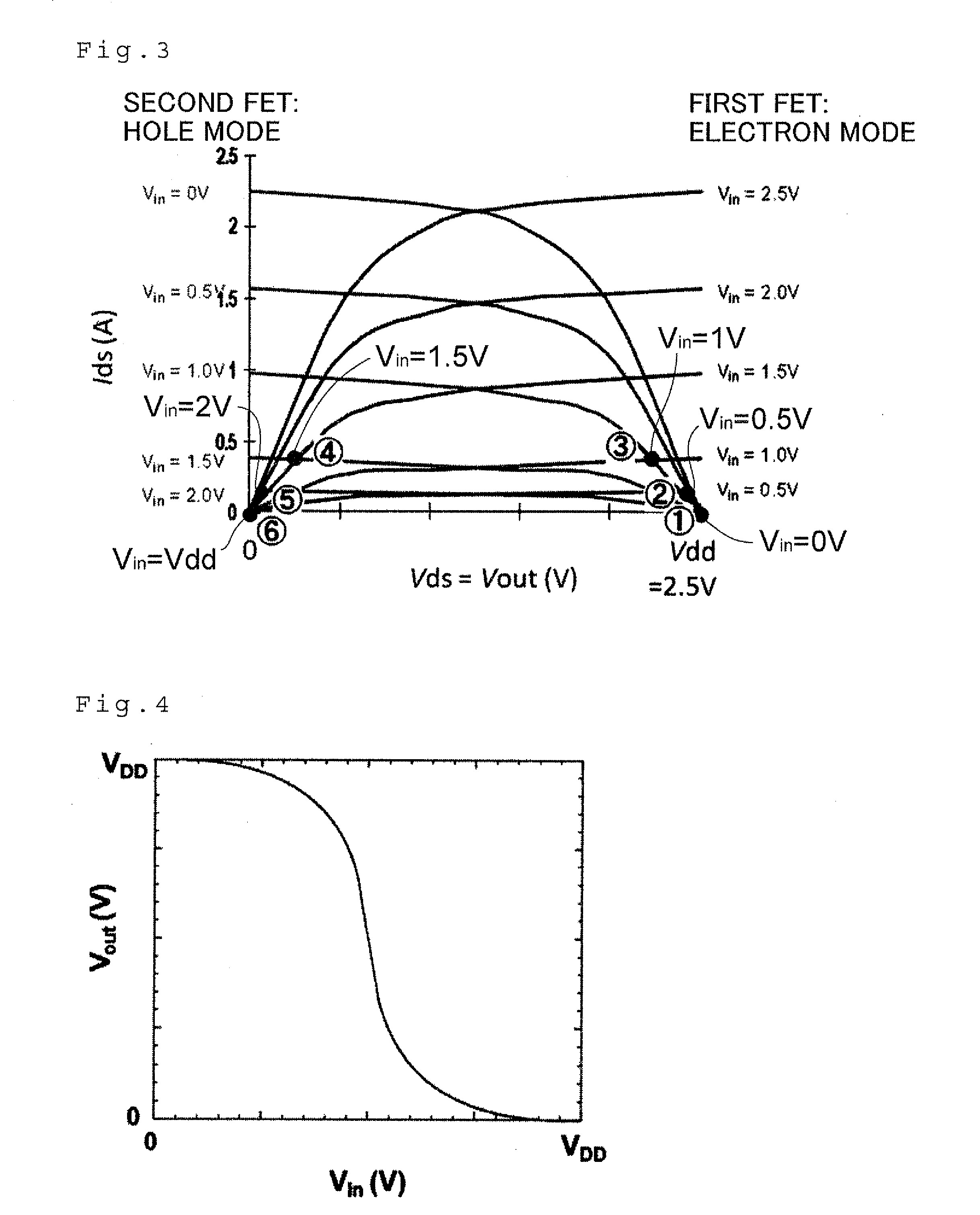

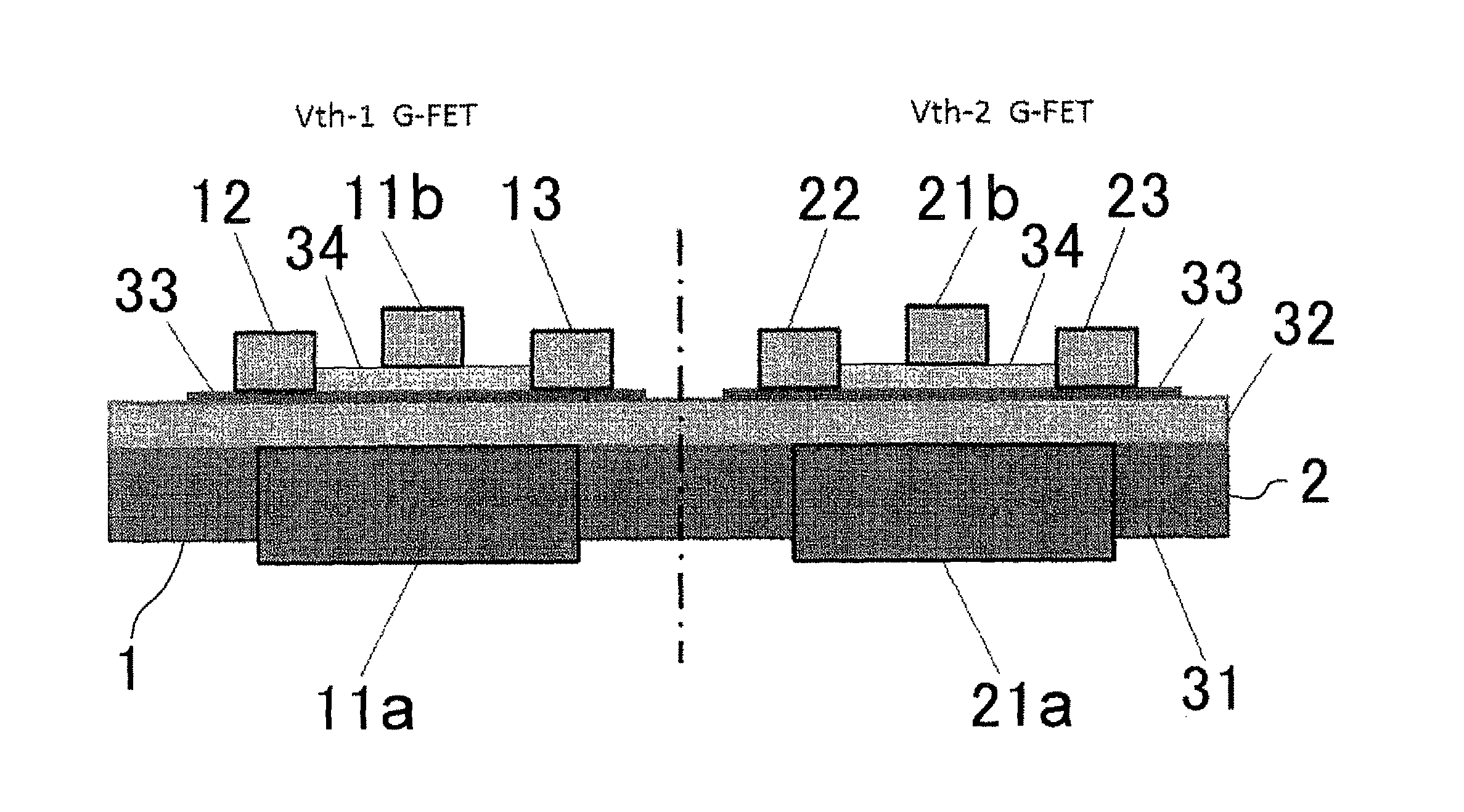

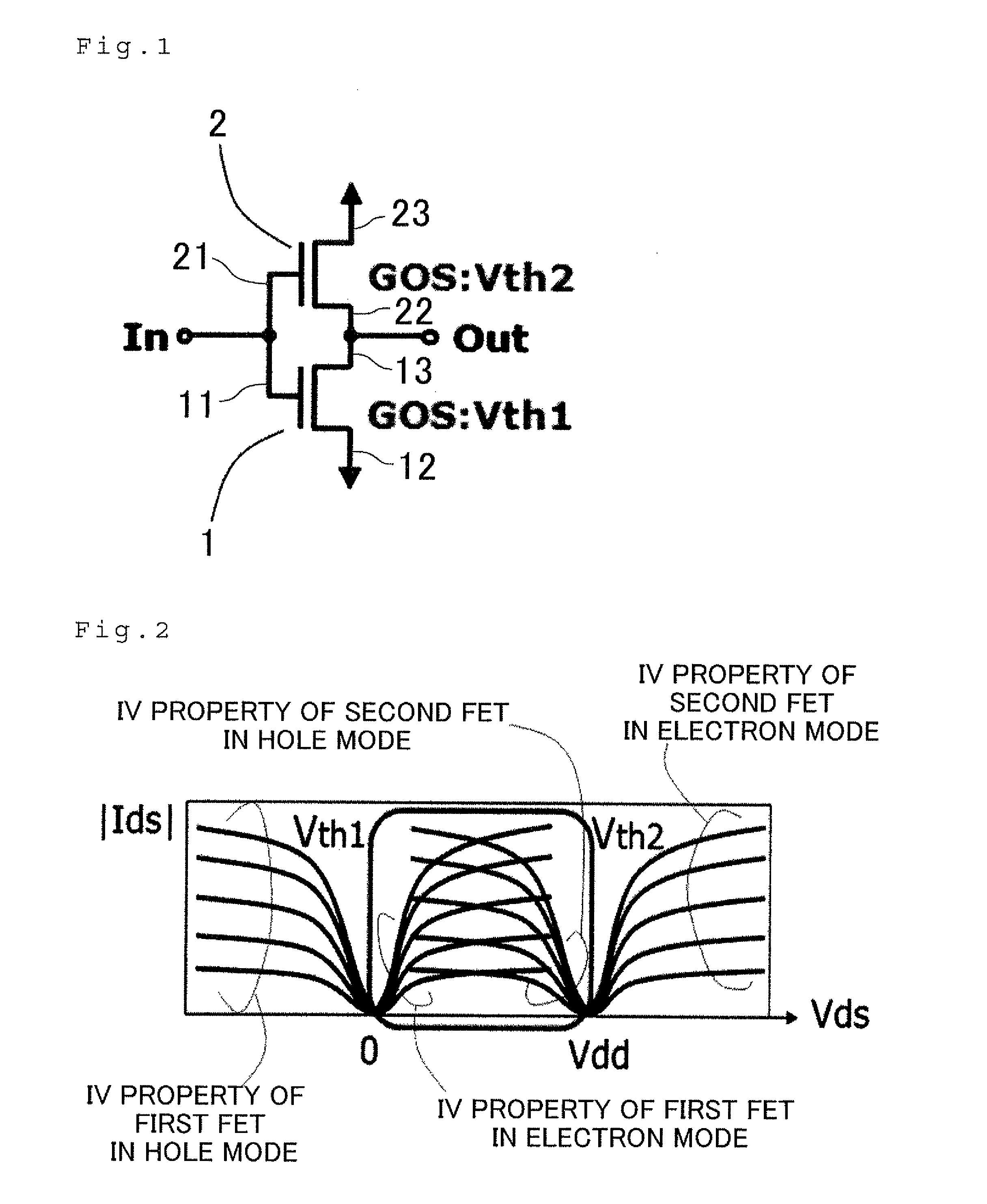

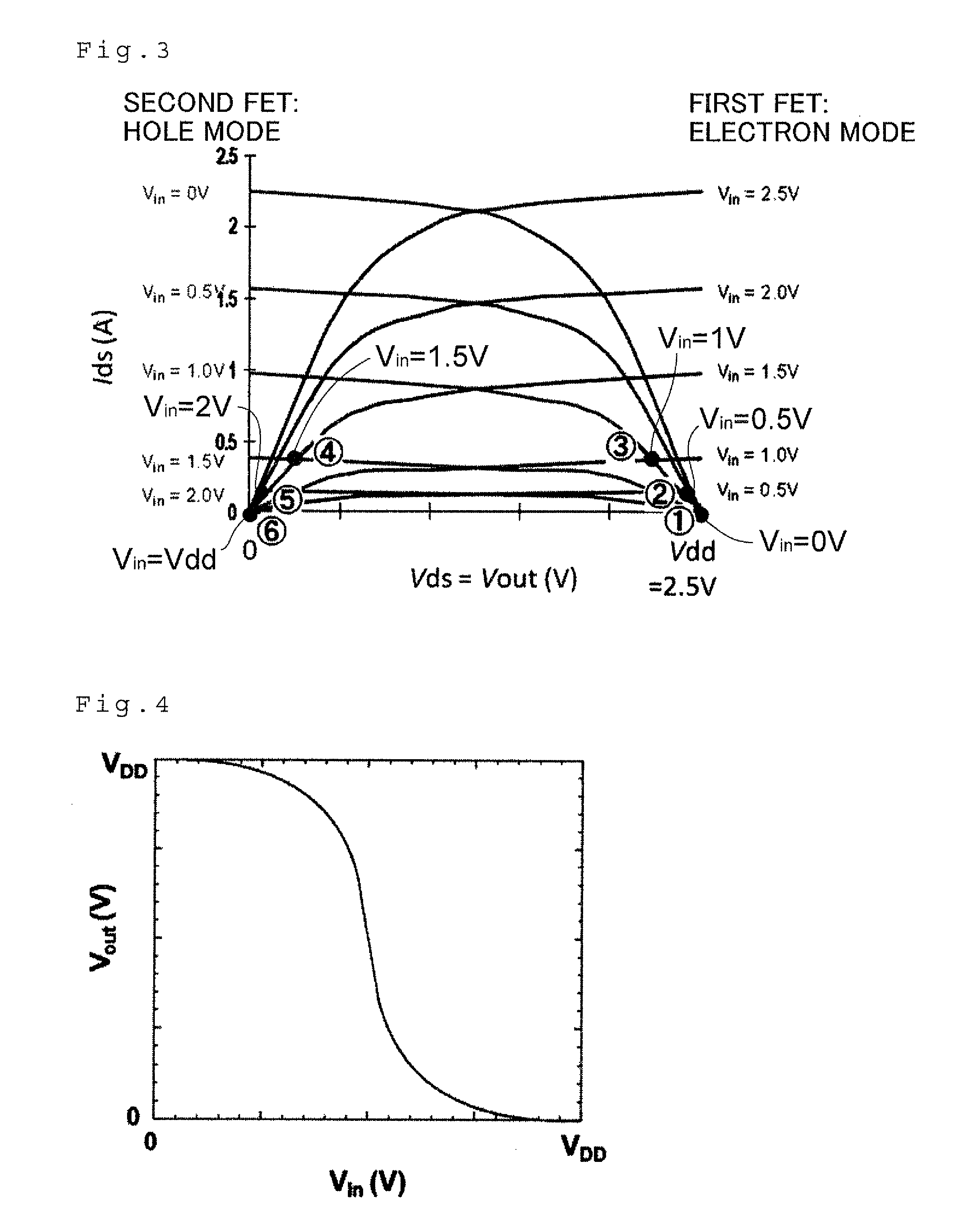

Complementary logic gate device

Provided is a complementary logical gate device represented by a silicon CMOS logical circuit among semiconductor integrated logical circuits which can effectively solve the problem of the speed performance limit of an ultra-large scale integration and an ultra-low power consumption type logical circuit. The complementary logical gate includes an electron running layer formed by grapheme without using an n-channel FET or a p-channel FET, has the ambipolar characteristic, and uses only two FET having different threshold values, i.e., a first FET and a second FET. The first FET has a gate electrode short-circuited to a gate electrode of the second FET so as to constitute an input terminal. The first FET has a source electrode set to a low potential. The first FET has a drain electrode connected to a source electrode of the second FET so as to constitute an output terminal. The second FET has a drain electrode set to a high potential.

Owner:OTSUJI TAIICHI +1

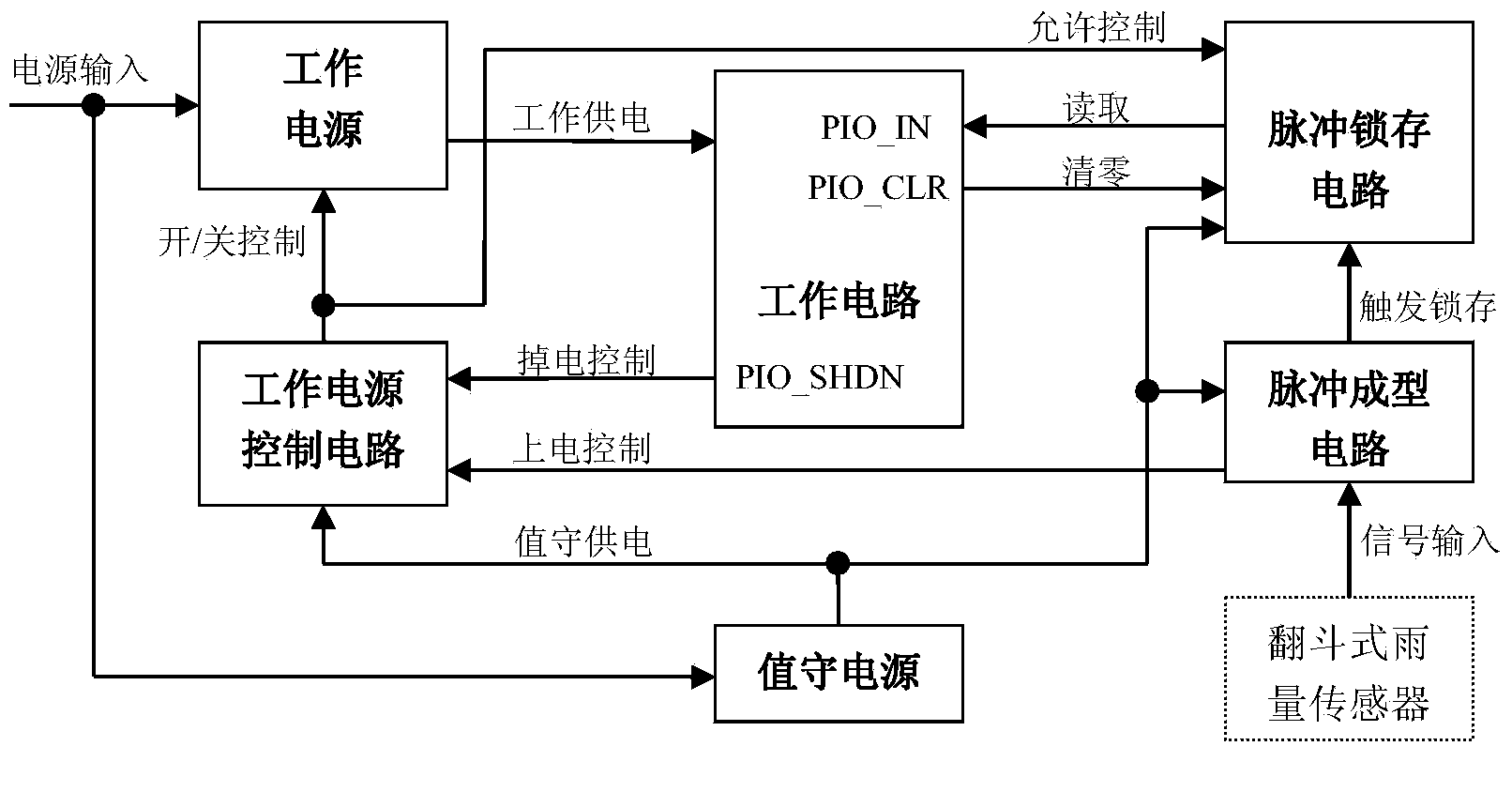

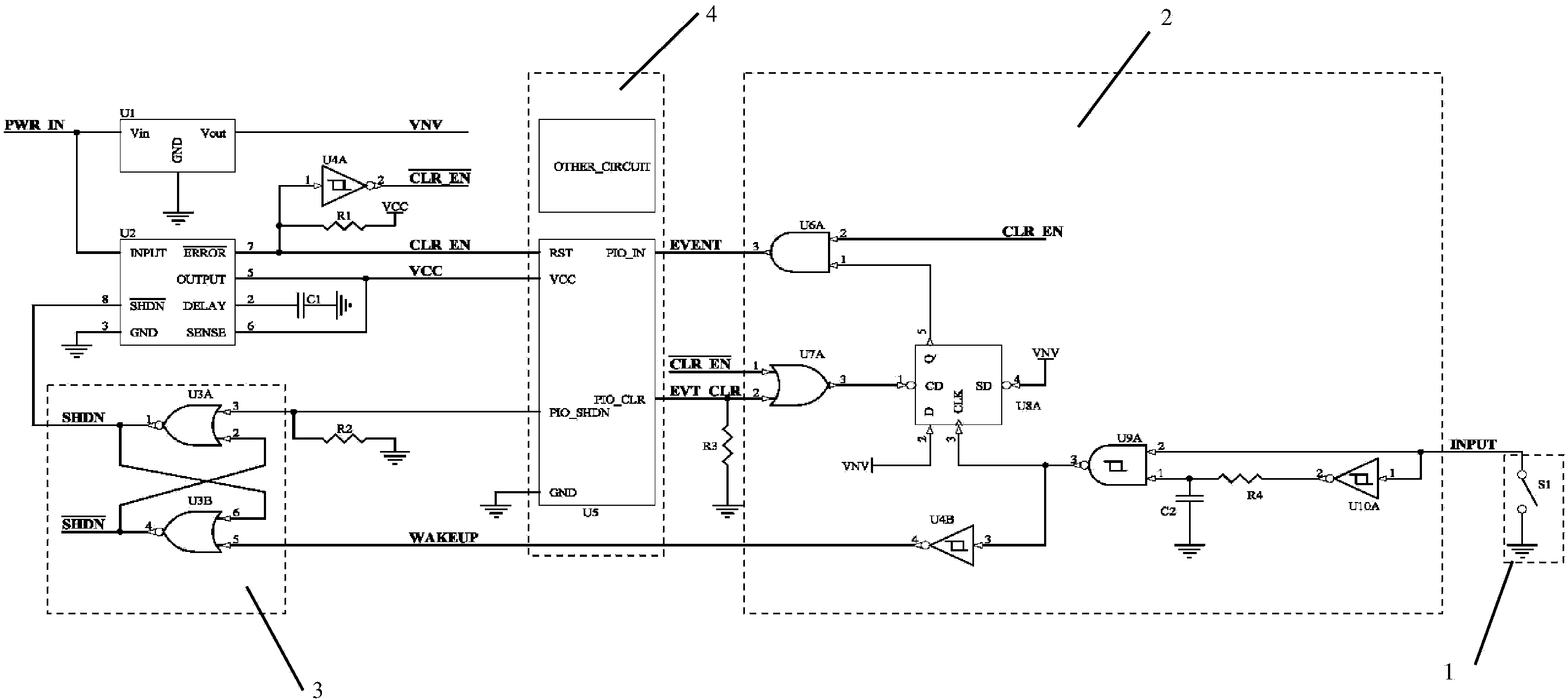

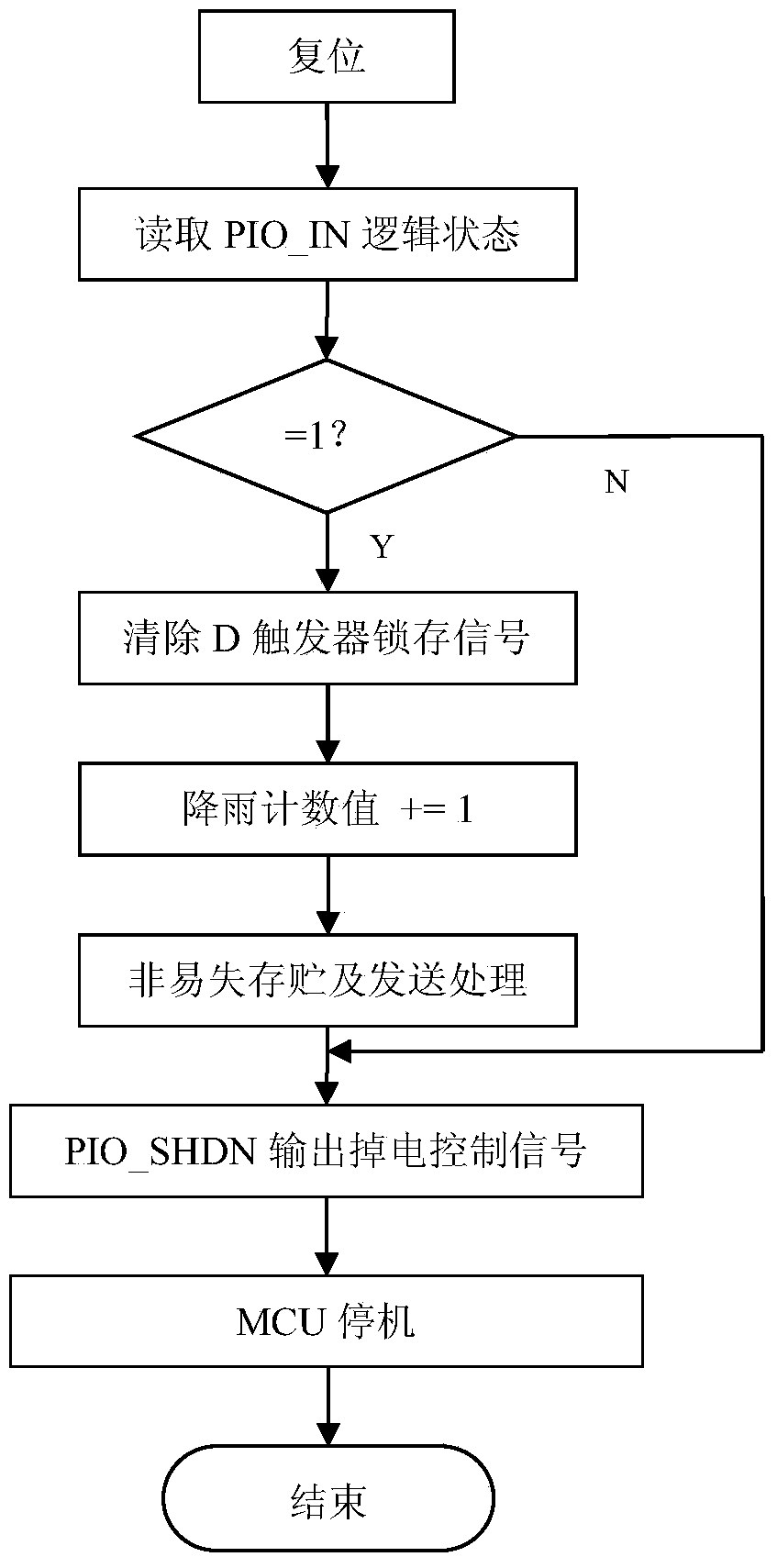

Micro-power-consumption tipping bucket type rainfall pulse signal collecting device and method

ActiveCN103869384AReduce power consumptionNo power consumptionProgramme controlRainfall/precipitation gaugesCmos logic circuitsElectrical battery

The invention relates to a micro-power-consumption tipping bucket type rainfall pulse signal collecting device and method. The device comprises a first attendant circuit, a second attendant circuit, a working circuit, an attendant power source and a working power source. The first attendant circuit and the second attendant circuit are CMOS logic circuits of the micro-power-consumption design, the working current of each attendant circuit is in microampere level, and the working power source has the switch-on state and the switch-off state, and is in the switch-off state when it does not rain. The first attendant circuit locks and stores a pulse signal of a dipping bucket type rainfall sensor when it rains and generates an awakening signal. The second attendant circuit receives the awakening signal and controls the working power source to be switched on so as to supply power to the working circuit. The working circuit reads the pulse signal locked and stored by the first attendant circuit and controls the second attendant circuit to switch off the working power source after data processing is carried out on the pulse signal. The micro-power-consumption tipping bucket type rainfall pulse signal collecting device has the advantages of working in the microampere power consumption state when it does not rain, being capable of saving energy, and prolonging the service life of a one-shot battery.

Owner:CHINA GEOKON INSTR

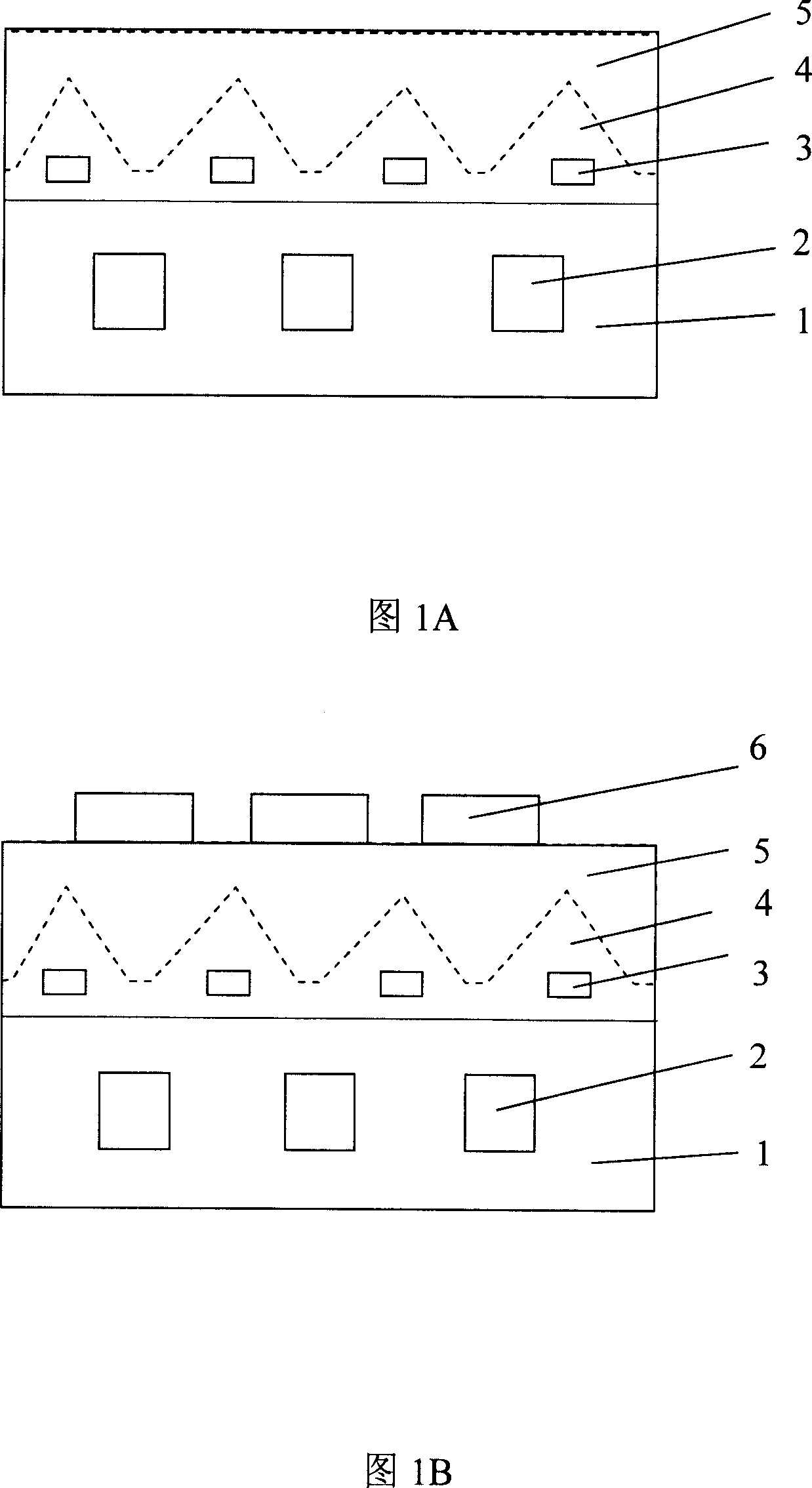

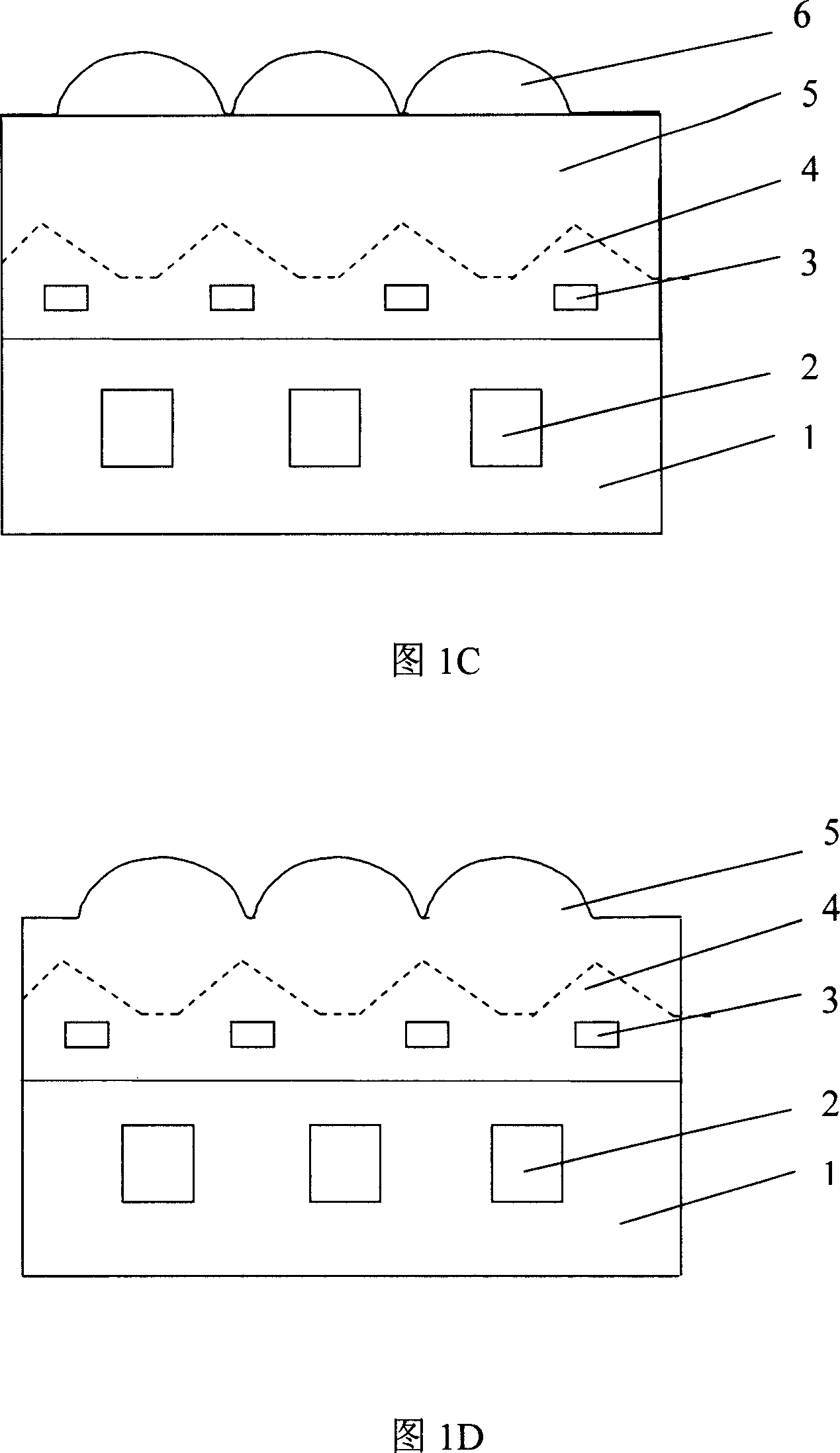

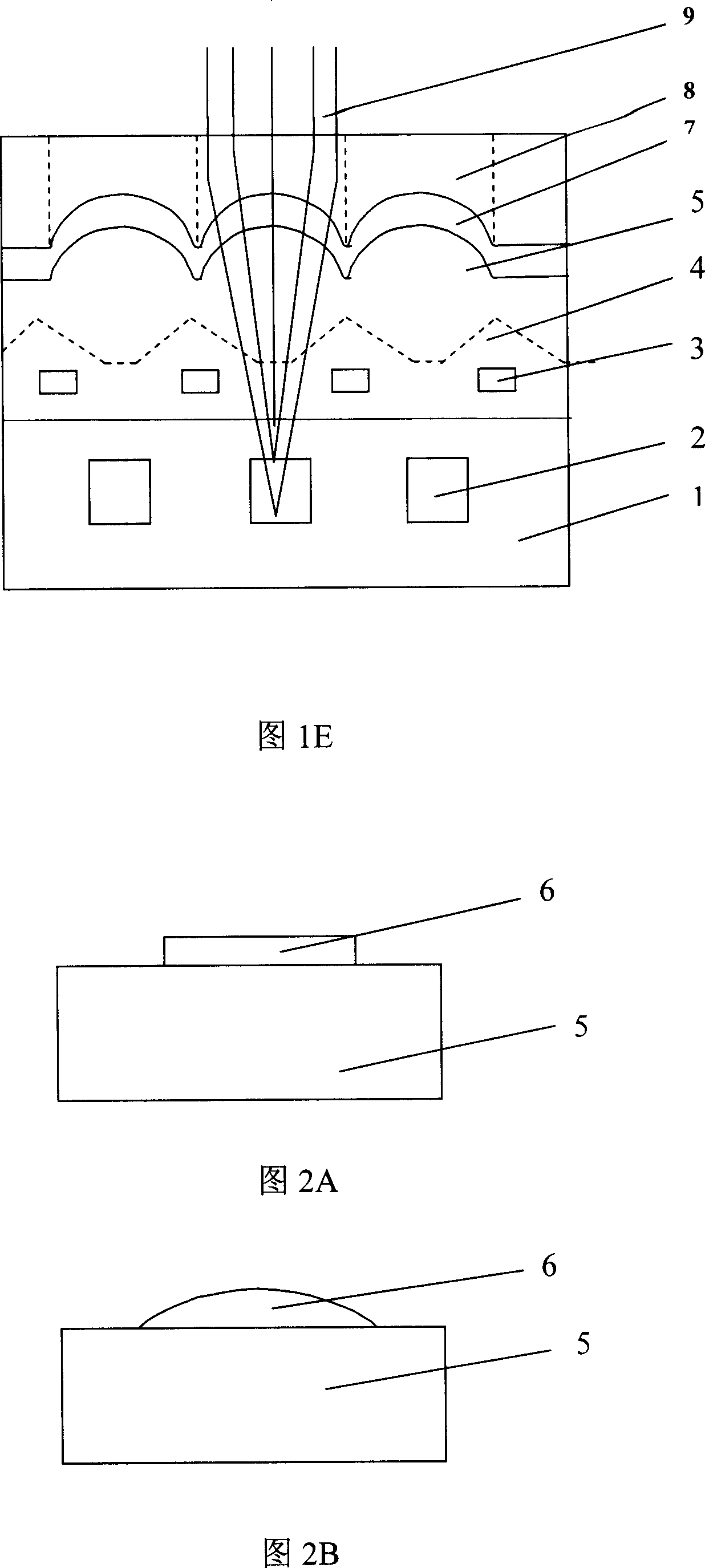

Single chip integrated CMOS imaging sensor with dual-focus microlens array

InactiveCN101114662AImprove collection efficiencyImprove quantum efficiencySemiconductor/solid-state device manufacturingRadiation controlled devicesRefractive indexDual focus

A monolithically integrated CMOS image sensor with double focal micro-lens array comprises a standard CMOS logic circuit integrating a photodiode of silicon pin, a micro-lens array integrated on an optical absorption surface corresponding to an active region of the CMOS circuit, a silicon nitride layer covering the micro-lens array, a color filter arranged on the silicon nitride layer. The invention is characterized in that the micro-lens array, which is a double focal micro-lens array, is monolithically integrated with the CMOS circuit, and with a 1.44-2.0 refractive index, the micro-lens array is applied on a good optical focusing double focal micro-lens array to improve light collection efficiency and quantum efficiency.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

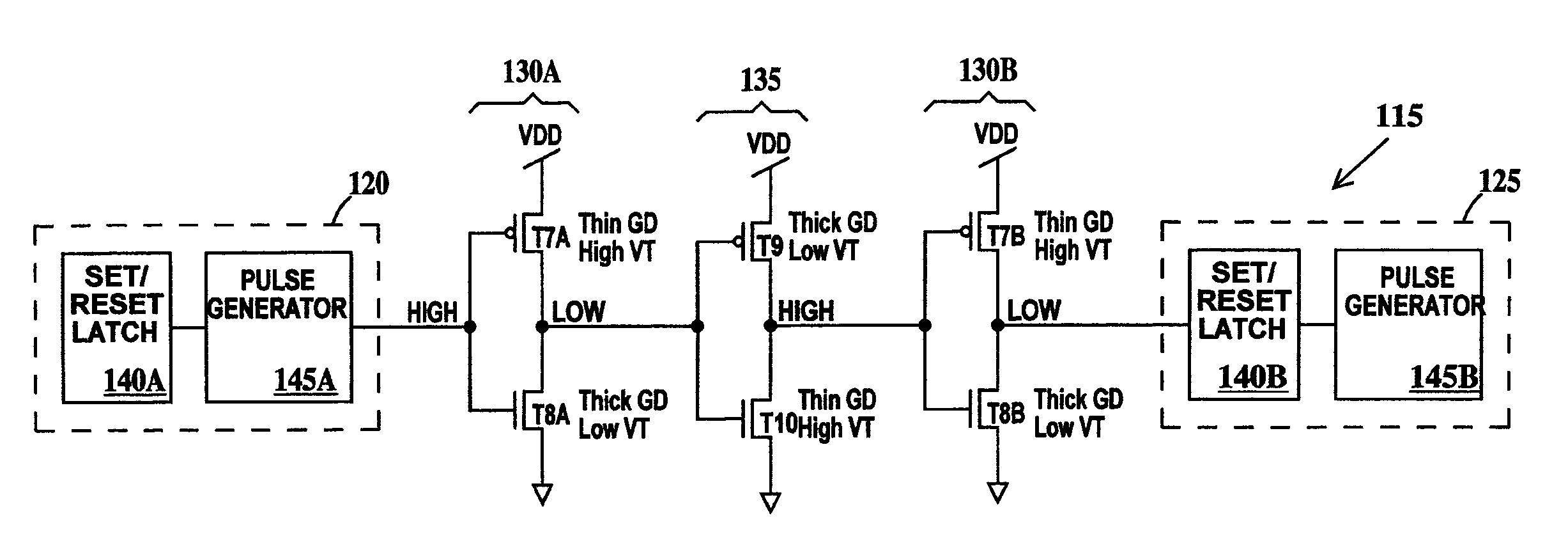

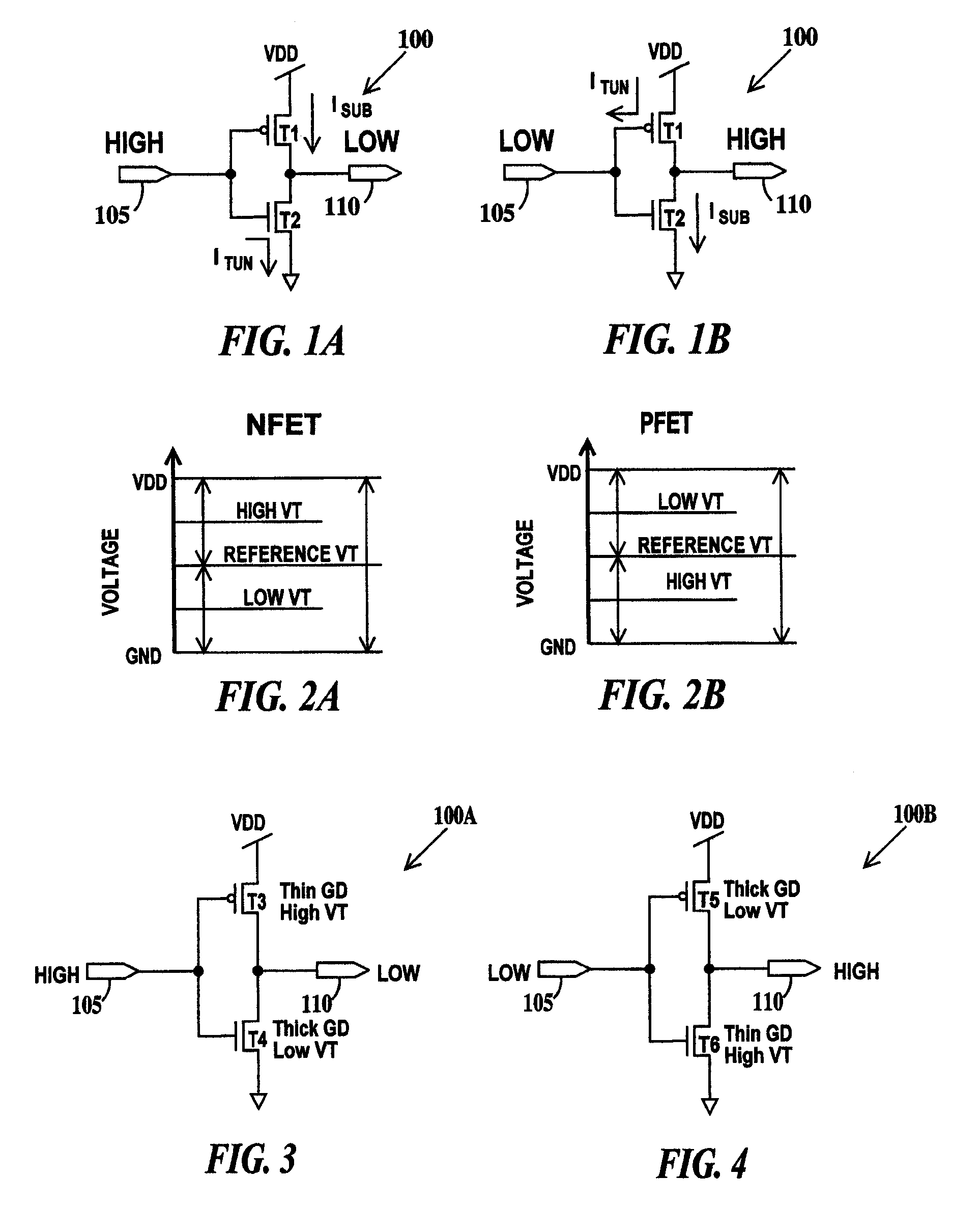

Low leakage monotonic CMOS logic

ActiveUS7084667B2Reduce leakage currentPower reduction by control/clock signalComputer aided designCMOSGate dielectric

A low leakage monotonic CMOS logic circuit and a method, a method of design and a system for designing such circuits. The circuit, including: one or more logic stages, at least one of the logic stages having a predominantly high input state or having a predominantly low input state; wherein the logic stages having the predominantly high input state, comprise one or more thin gate dielectric and high threshold voltage PFETs with respect to a reference PFET and one or more thick gate dielectric and low threshold voltage NFETs with respect to a reference NFET; and wherein the logic stages having the predominantly low input state, comprise one or more thick gate dielectric and low threshold voltage PFETs with respect to the reference PFET and one or more thin gate dielectric and high threshold voltage NFETs with respect to the reference NFET.

Owner:MARVELL ASIA PTE LTD

Process for manufacturing metal-insulator-metal capacitor by adopting copper damascene process, and structure

ActiveCN102420108AHigh densitySemiconductor/solid-state device manufacturingSemiconductor devicesMetal-insulator-metalCapacitance

The invention relates to a copper damascene process and a structure, in particular to a process for manufacturing a metal-insulator-metal capacitor by adopting a copper damascene process, and a structure. According to the structure of the metal-insulator-metal capacitor structure and the process for manufacturing the metal-insulator-metal capacitor structure by adopting the copper damascene process, the metal-insulator-metal capacitor and an inductor are simultaneously manufactured by adopting the copper damascene process; a third electrode and other structures are simultaneously manufactured; a dielectric barrier layer is removed in the manufacturing process of a second electrode and the third electrode; and a dielectric layer made of a high-dielectric-constant material is re-deposited as an intermetallic insulating layer, so that the structure of the metal-insulator-metal double-layer capacitor produced by adopting the technical scheme provided by the invention can be completely compatible with the copper damascene process of a CMOS (Complementary Metal-Oxide-Semiconductor Transistor) logic circuit and the inductor; and the density of the metal-insulator-metal capacitor is increased.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Image sensor devices and photoelectric element

ActiveCN1983609AHigh signal-to-noise ratioImprove computing speedTelevision system detailsSolid-state devicesSalicideCMOS

The present invention provides an image sensor device and photoelectric element. The image sensor device includes a first area with image sensing pixel array disposed on the underlay, and a second area with a logic circuit disposed on the underlay, wherein the logic circuit includes CMOS transistor. Each image sensing pixel includes transistor without self-aligned silicide and pinning photodiode. The CMOS transistor of the second area has self-aligned silicide, but the transistor of the first area has no self-aligned silicide. The present invention forms no metal silicide on the surface of the image sensing pixel area, thereby reduce the dark current effectively and further get an image sensor device with high signal-noise ratio. On the other hand, only forming the metal silicide on the top of the gate structure of the CMOS logic circuit area and the surface of the source / drain area, so the computing rate for the CMOS logic circuit is improved remarkably.

Owner:TAIWAN SEMICON MFG CO LTD

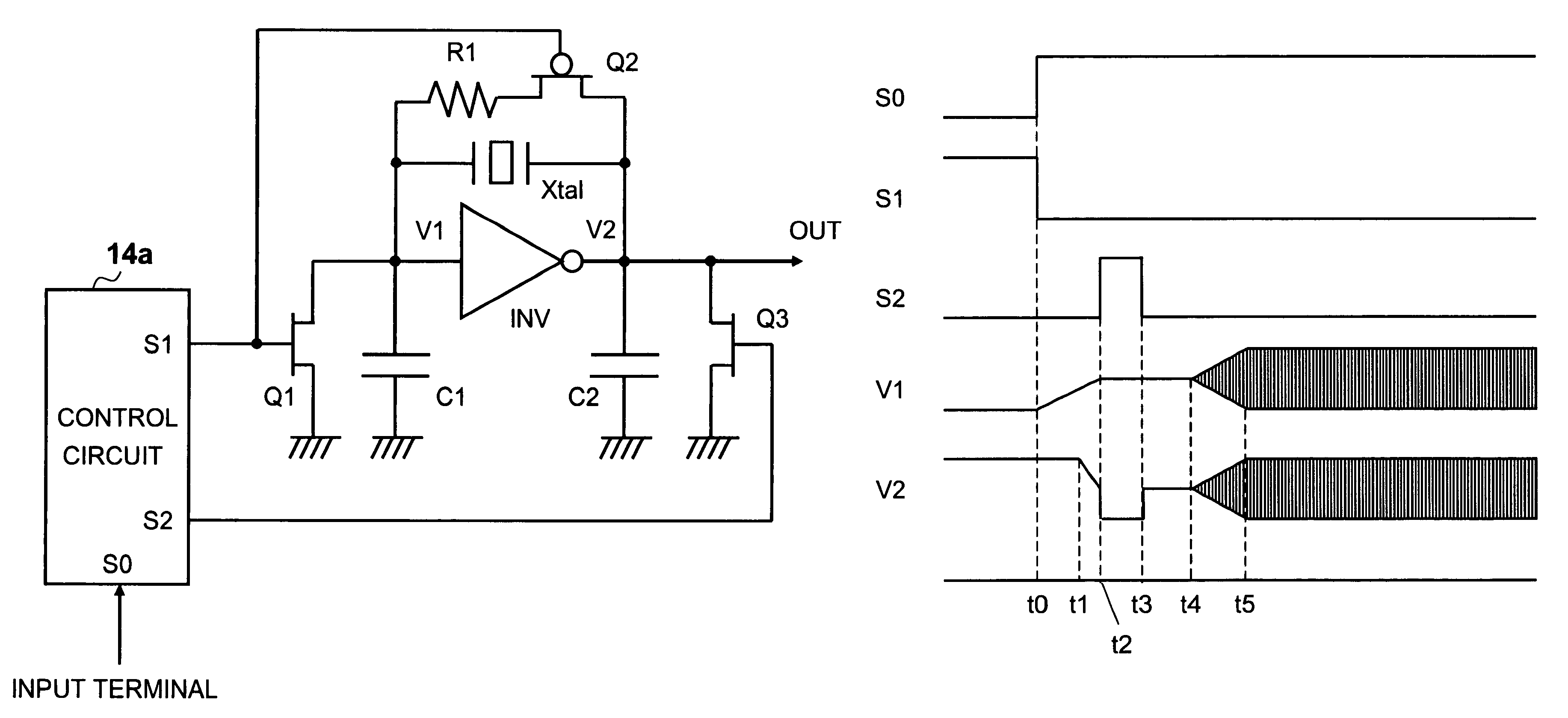

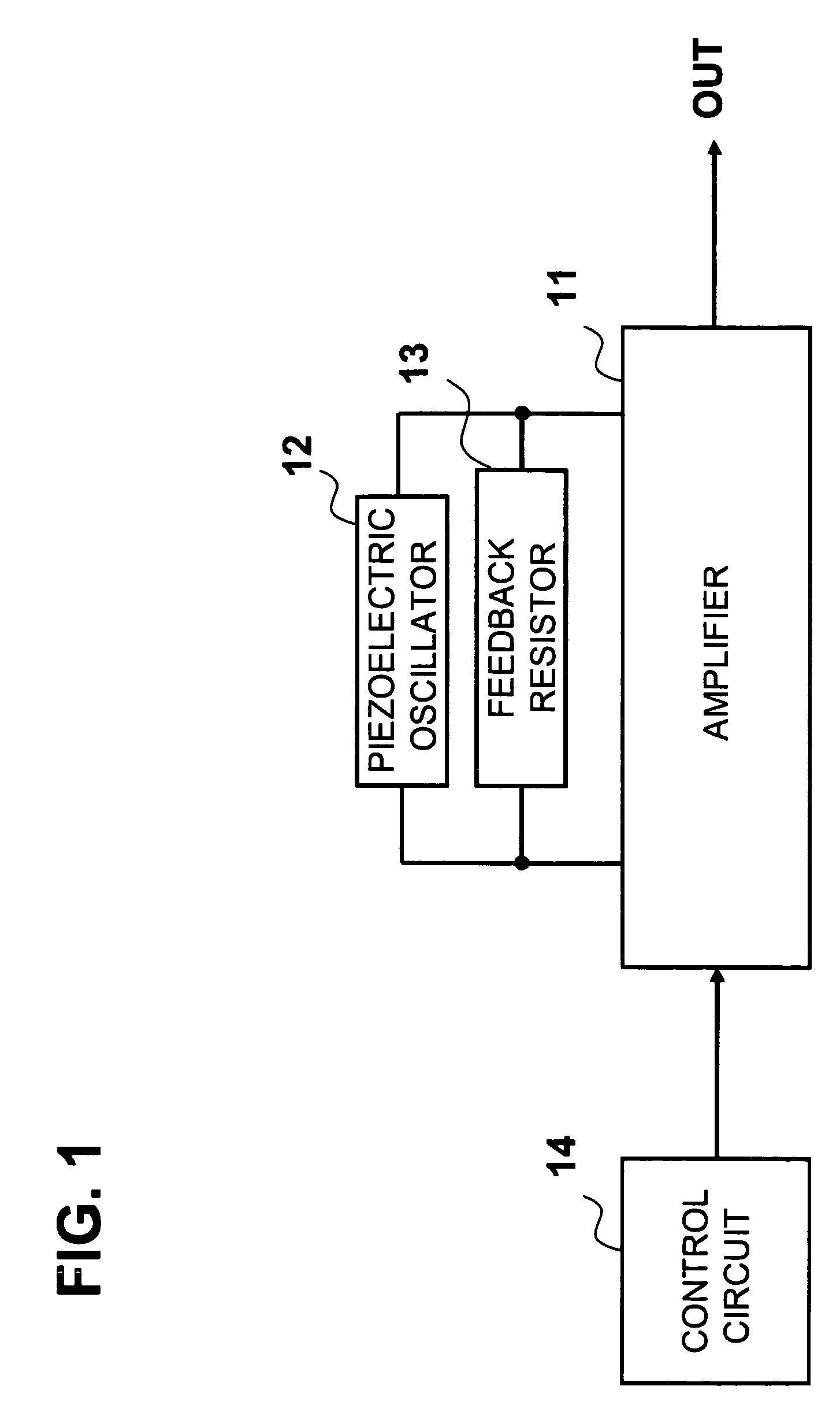

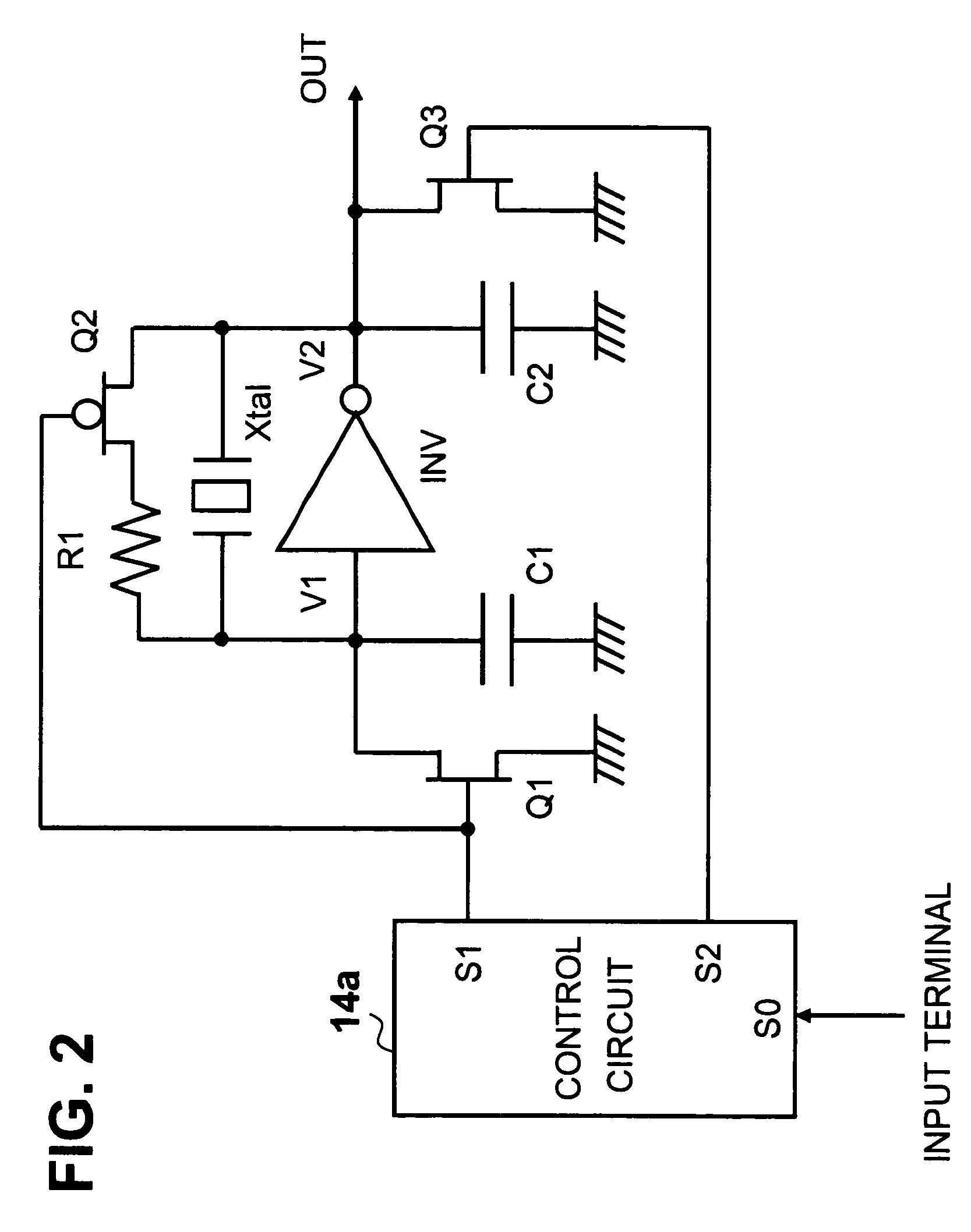

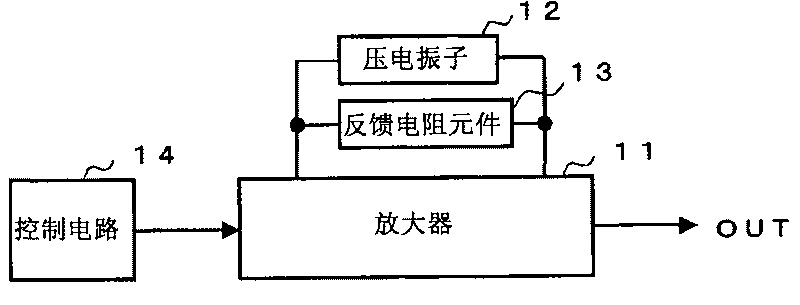

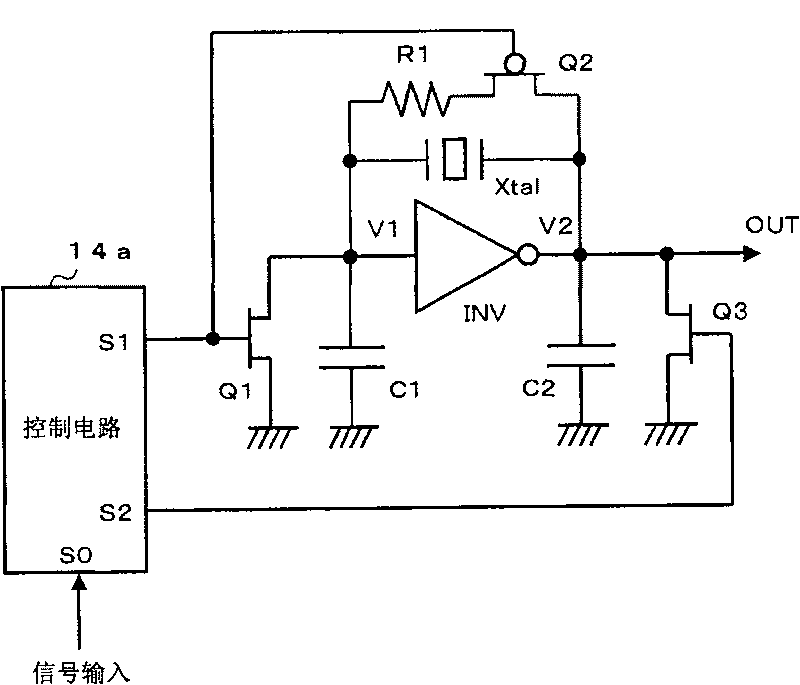

Oscillation circuit and method of controlling same

ActiveUS8115562B2Current consumptionSuppresses wasteful currentElectric pulse generatorApparatus using electrochemical resonatorsCMOSPower flow

Disclosed is an oscillator in which current consumption relating to oscillation is reduced. The oscillator comprises: an amplifier to an input and output of which a piezoelectric oscillator and a feedback resistor are connected in parallel, and which is constituted by a CMOS logic inverter circuit; and a control circuit, which is constituted by a CMOS logic circuit, for clamping input / output levels of the amplifier and halting oscillation before oscillation start-up, unclamping the input / output levels at beginning of oscillation start-up and supplying a pulse signal to an output terminal of the amplifier a prescribed period of time after the beginning of oscillation start-up.

Owner:RENESAS ELECTRONICS CORP

Oscillation circuit and method of controlling same

InactiveCN101714863ACurb consumptionShorten start timeElectric pulse generatorOscillations generatorsCMOSAudio power amplifier

Disclosed is an oscillator in which current consumption relating to oscillation is reduced. The oscillator comprises: an amplifier to an input and output of which a piezoelectric oscillator and a feedback resistor are connected in parallel, and which is constituted by a CMOS logic inverter circuit; and a control circuit, which is constituted by a CMOS logic circuit, for clamping input / output levels of the amplifier and halting oscillation before oscillation start-up, unclamping the input / output levels at beginning of oscillation start-up and supplying a pulse signal to an output terminal of the amplifier a prescribed period of time after the beginning of oscillation start-up.

Owner:NEC ELECTRONICS CORP

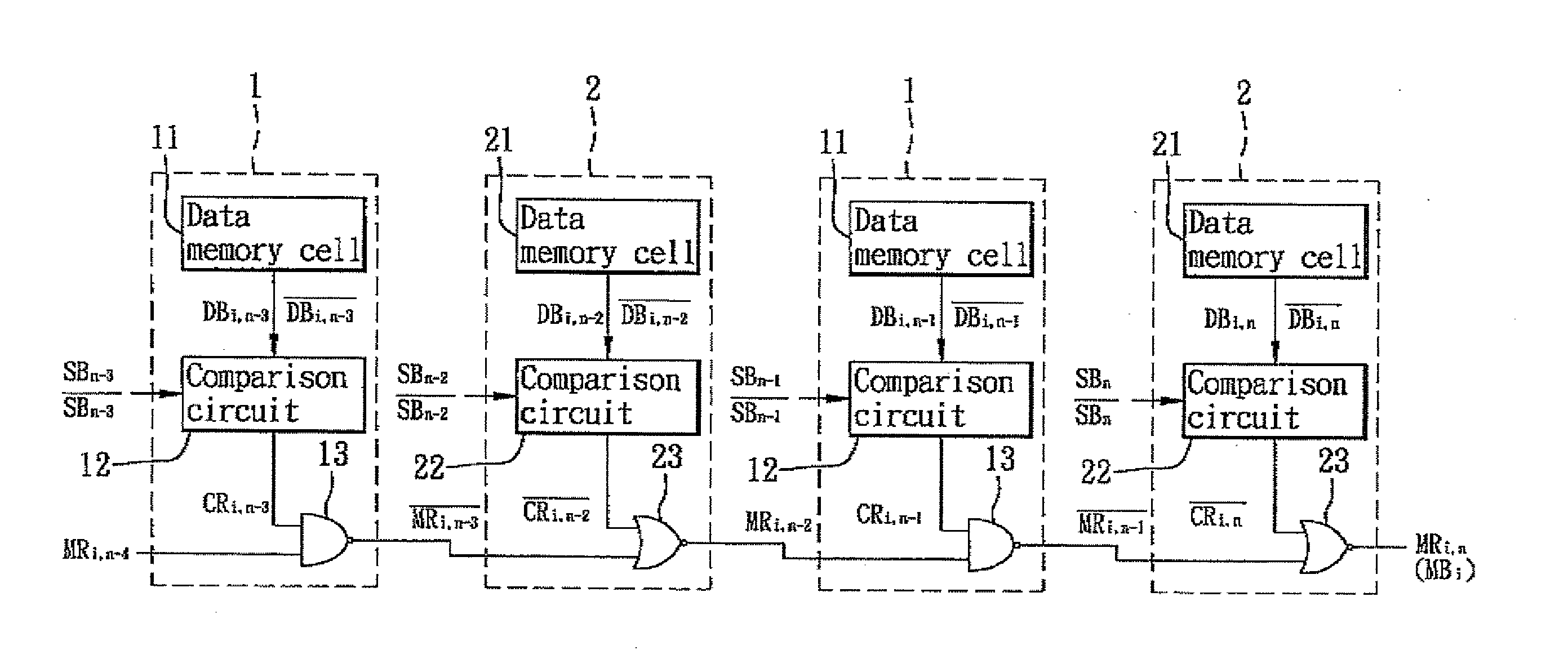

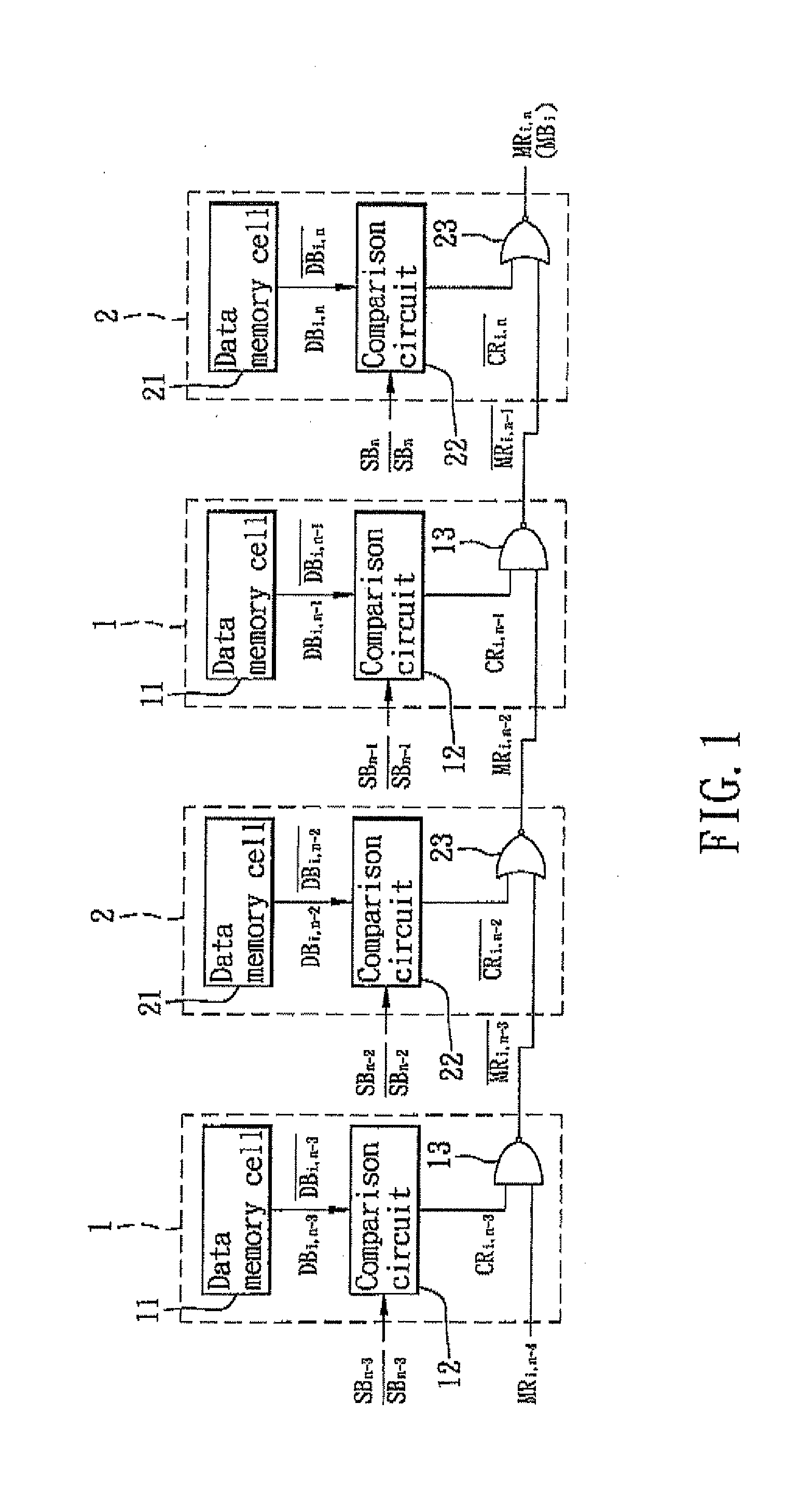

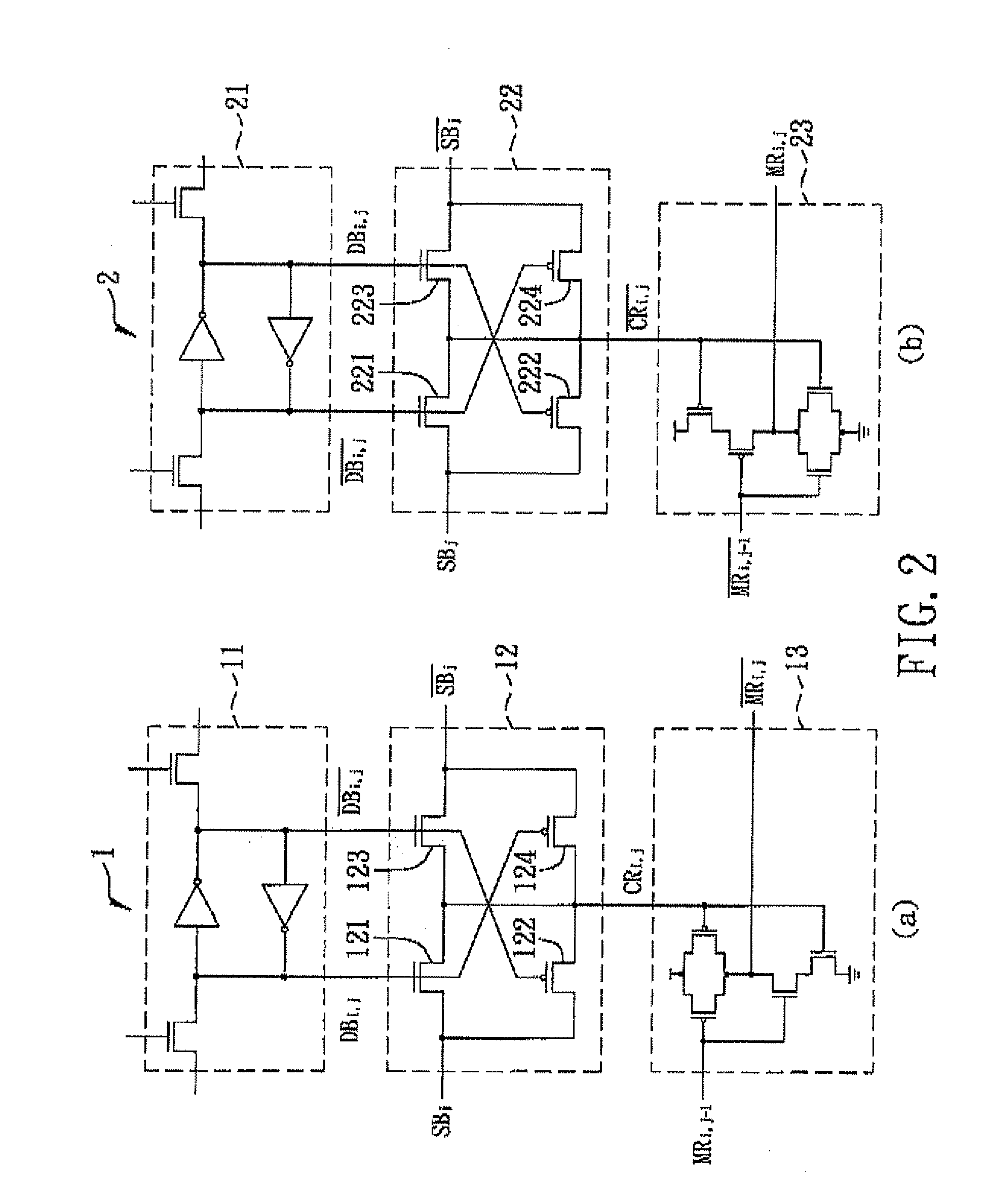

Content-Addressable Memory

ActiveUS20100067277A1Increase computing speedReduce power consumptionDigital storageCmos logic circuitsParallel computing

A CAM includes first and second memory units. The first memory unit includes: a first data memory cell for storing a first data bit; a first comparison circuit for comparing a first search bit with the first data bit to determine if there is a match, and outputting a first comparison result; and a first CMOS logic circuit for performing a logic operation on the first comparison result and outputting a first matching result. The second memory unit includes: a second data memory cell for storing a second data bit; a second comparison circuit for comparing a second search bit with the second data bit to determine if there is a match, and outputting a second comparison result; and a second static CMOS logic circuit for performing a logic operation on the first matching result and the second comparison result, and outputting an output matching result.

Owner:REALTEK SEMICON CORP

Semiconductor integrated circuit apparatus and electronic apparatus

InactiveUS7598802B2Power reduction by control/clock signalLogic circuits characterised by logic functionEngineeringElectron

A semiconductor integrated circuit apparatus and an electronic apparatus having a power control function configured from power control MOS transistors such that leakage current and on-resistance at the time of cut-off is sufficiently small in actual use. The semiconductor integrated circuit apparatus includes a CMOS logic circuit, a first pseudo power supply line connected to a high potential side power supply terminal of the CMOS logic circuit, a second pseudo power supply line connected to a low potential side power supply terminal of the CMOS logic circuit, and a power control NchMOS transistor connected across the second pseudo power supply line and a low potential side power supply line, with the substrate and gate of the power control NchMOS transistor being electrically connected. The gate and the substrate may also be connected via a current limiter utilizing a source follower of a depletion type NchMOS transistor.

Owner:COLLABO INNOVATIONS INC

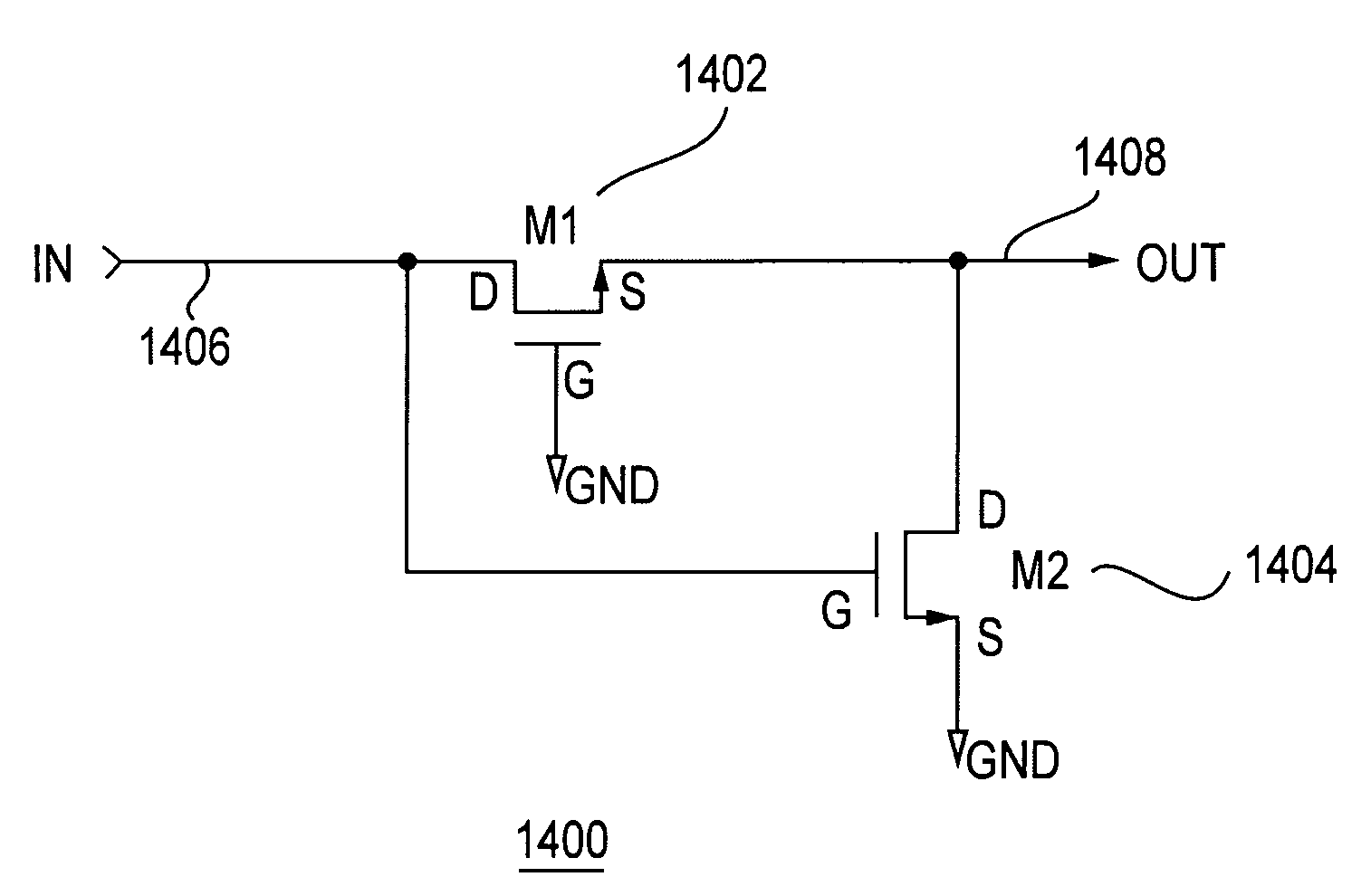

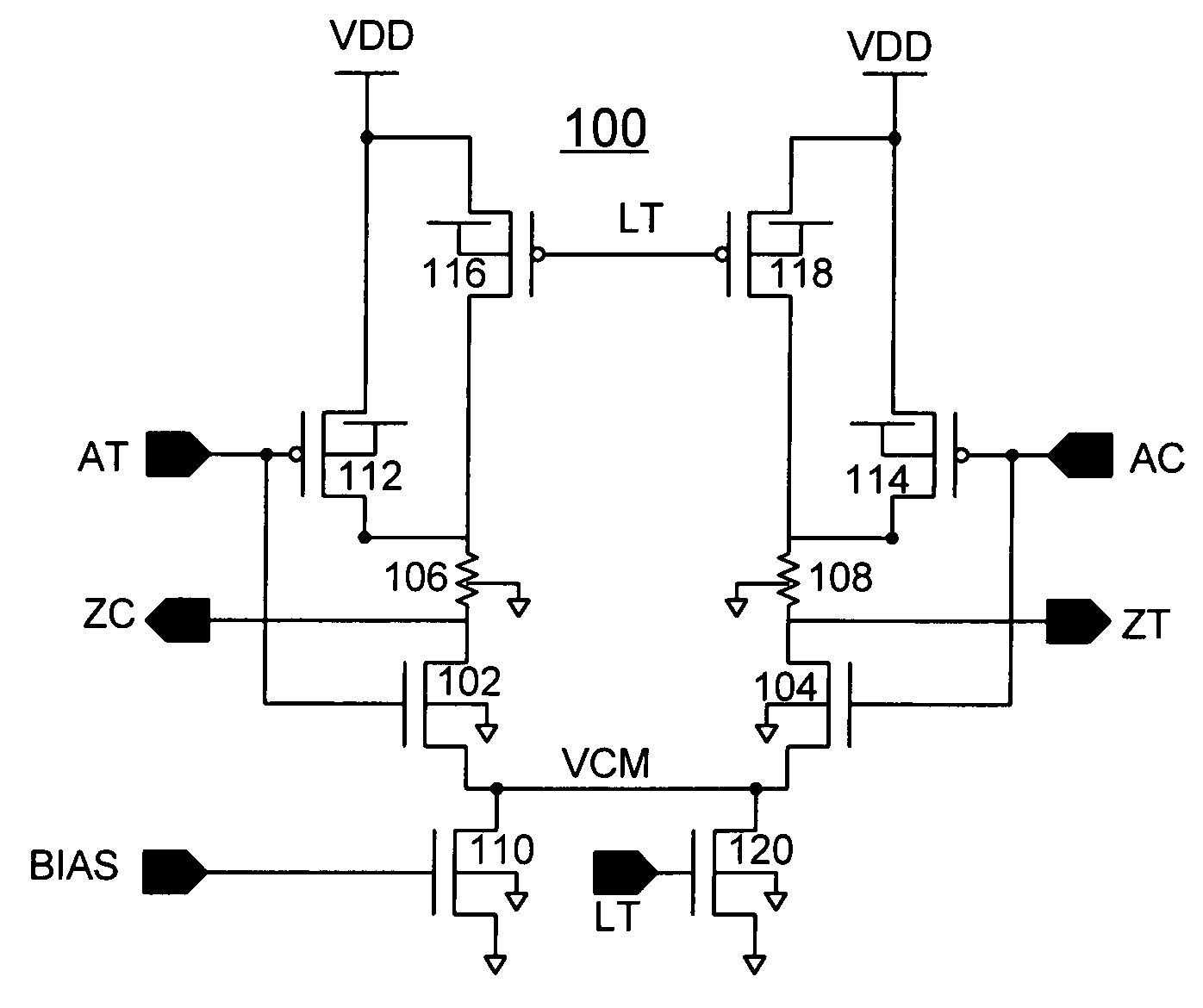

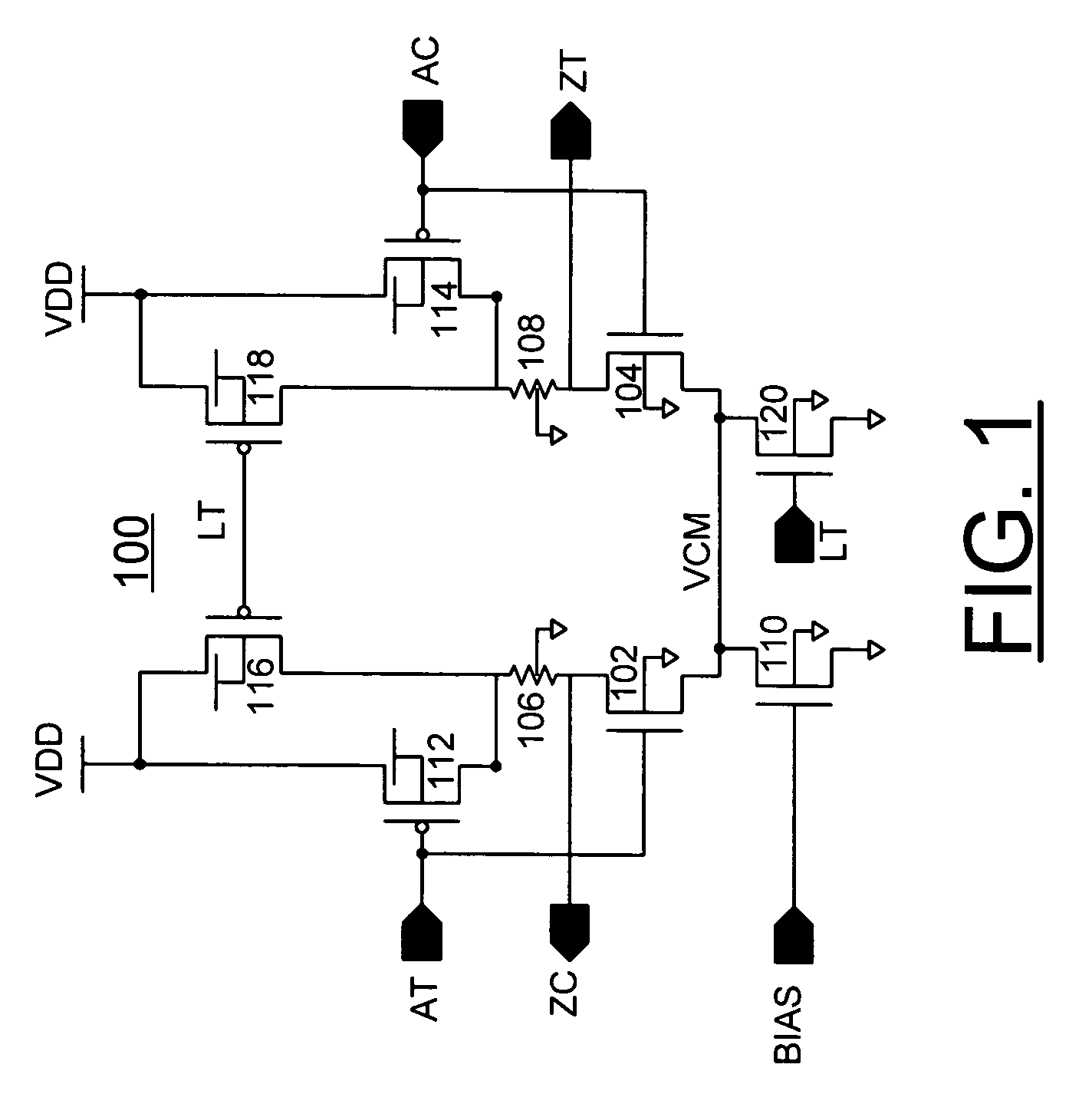

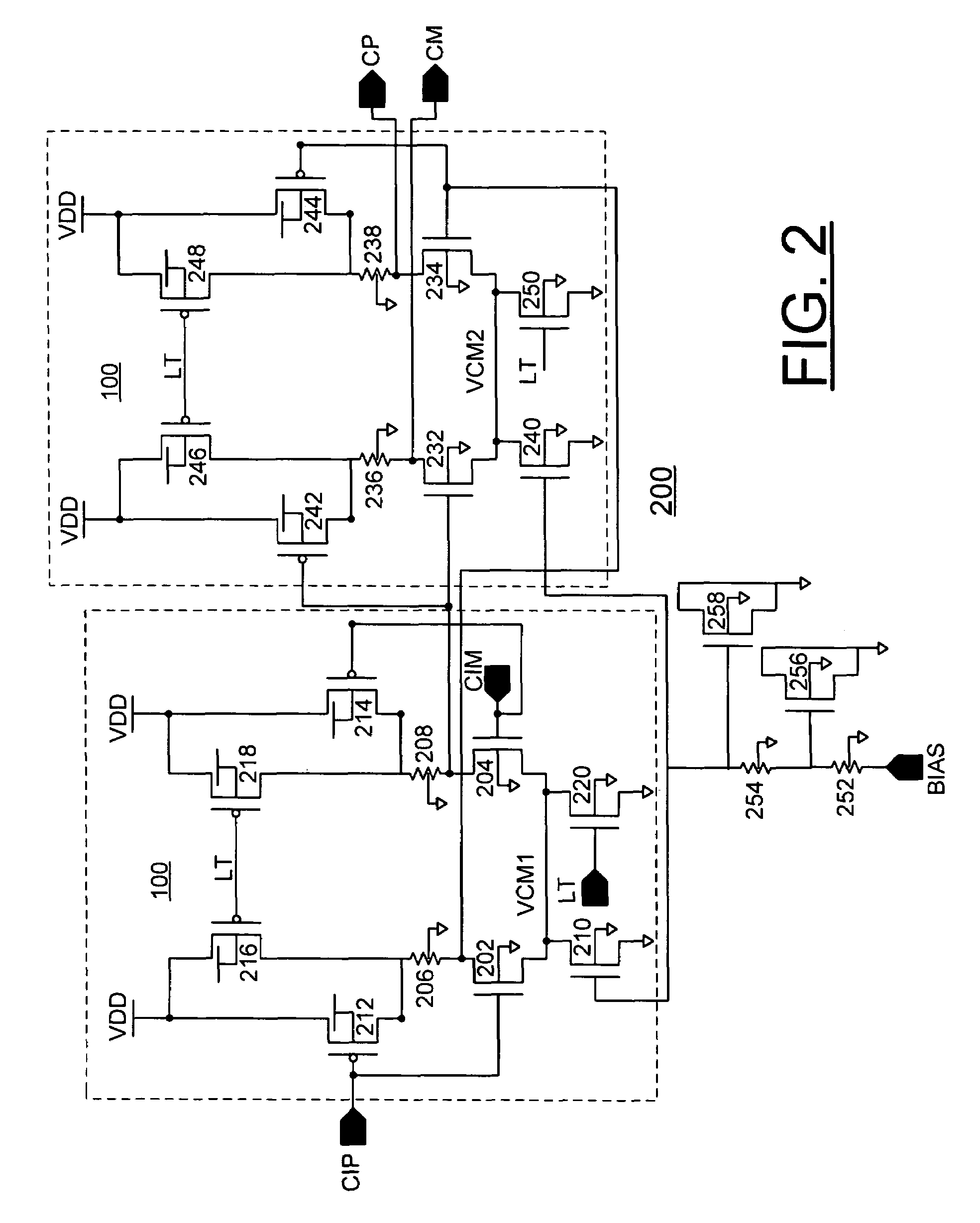

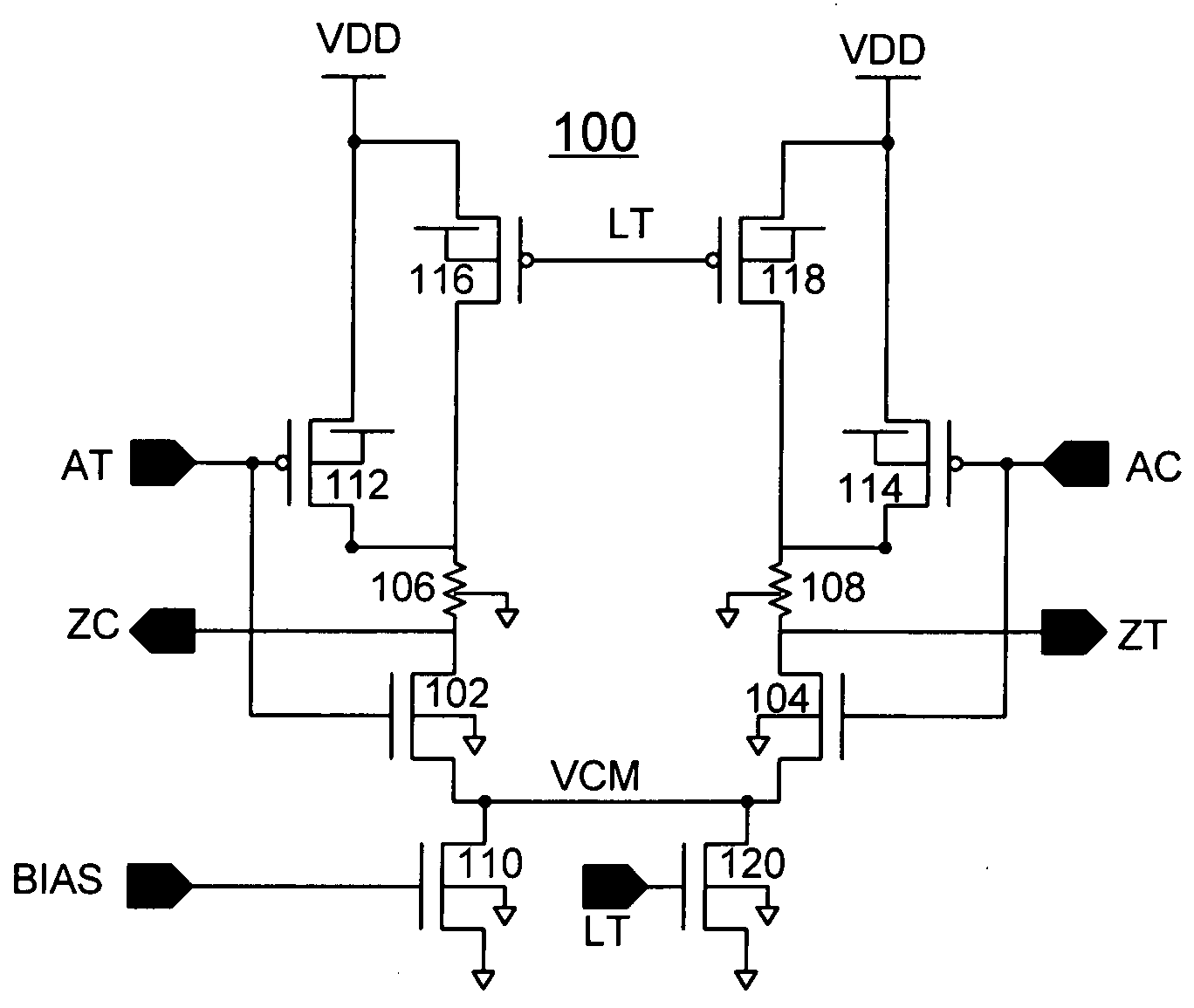

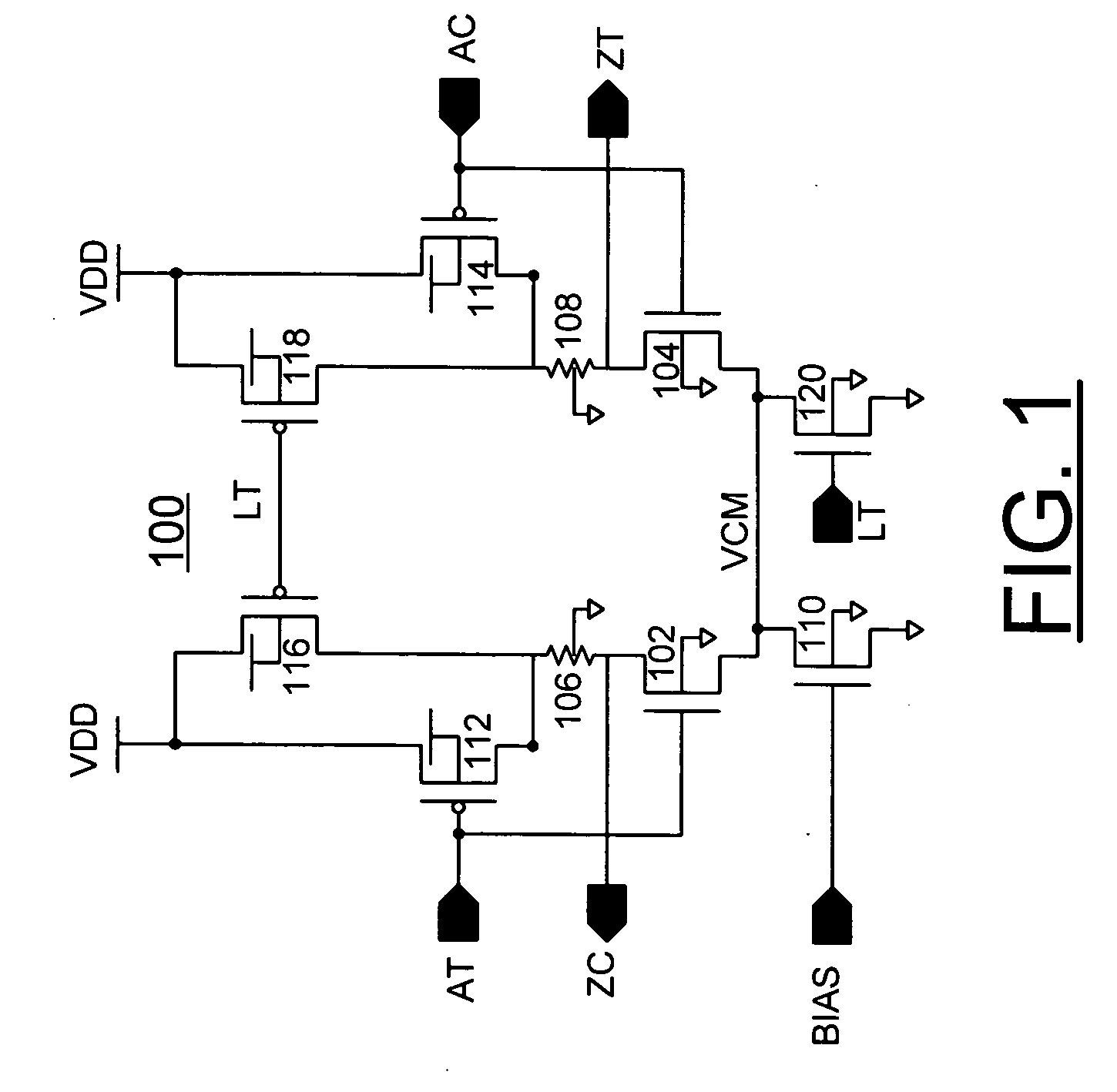

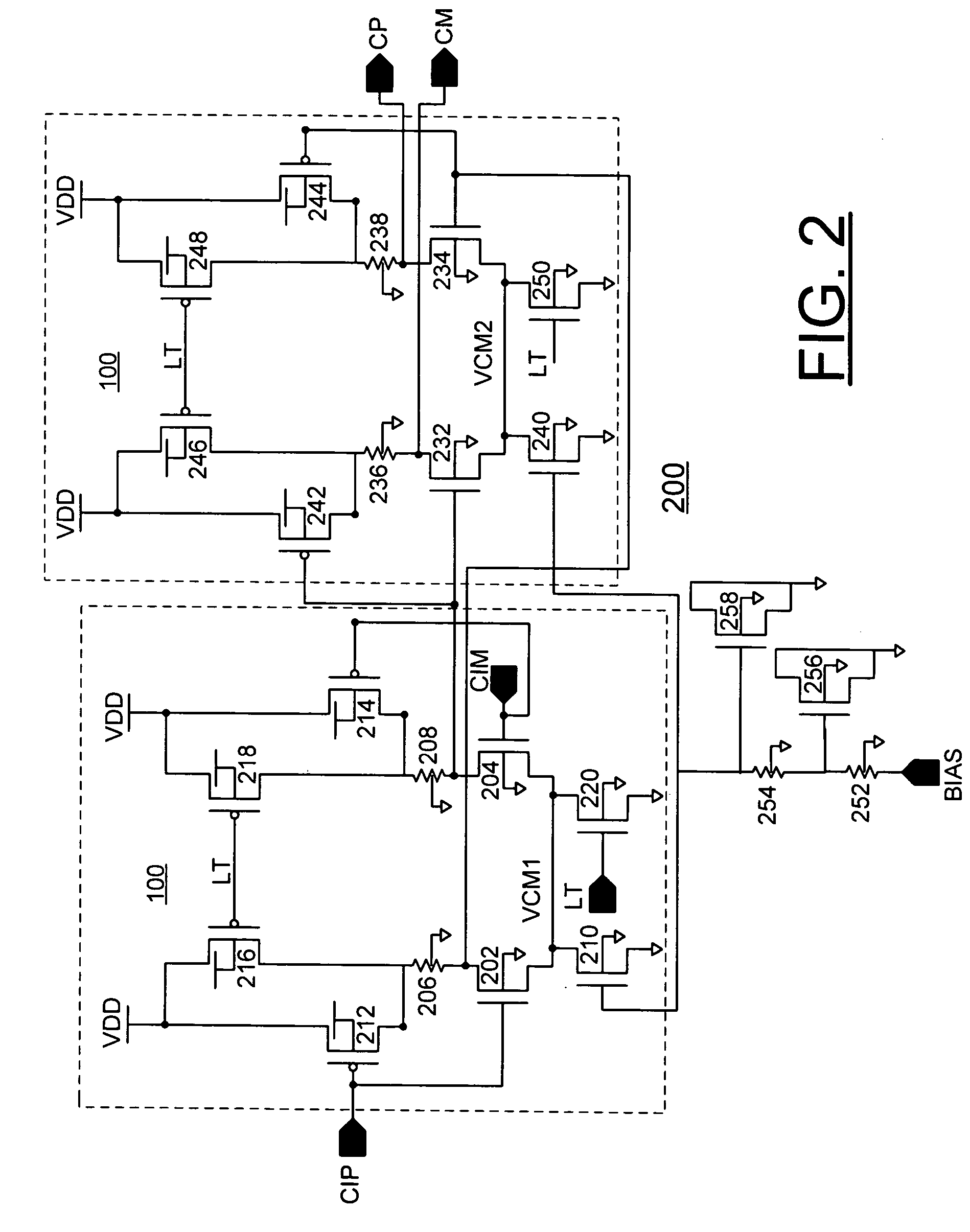

Dual mode analog differential and CMOS logic circuit

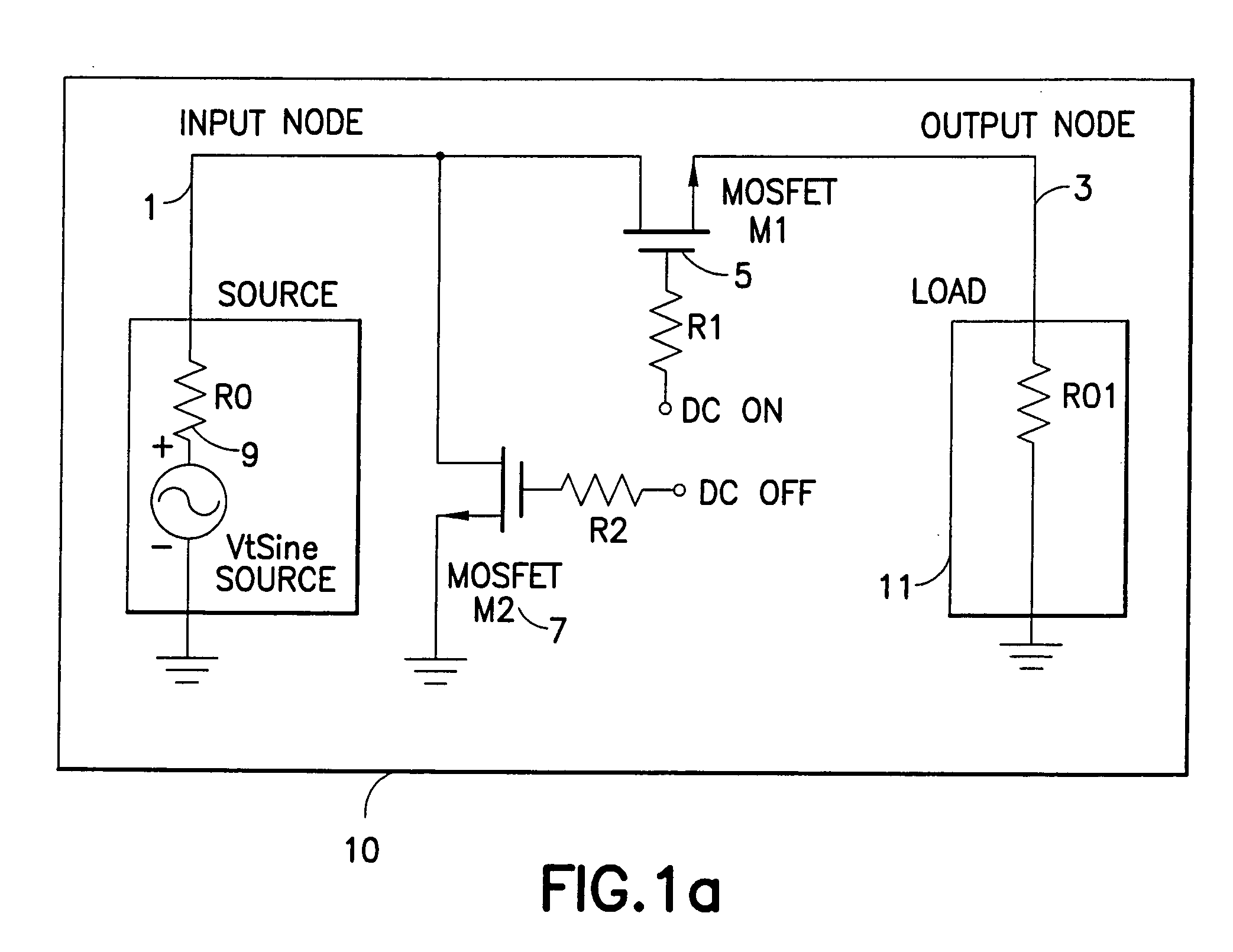

ActiveUS6933743B2Digital circuit testingLogic circuit coupling/interface arrangementsCMOSControl signal

A dual mode, analog differential and complementary metal oxide semiconductor (CMOS) logic circuit is provided. The circuit includes a differential input for receiving a differential input signal. A switch pair is coupled to the differential input. A pair of load resistors coupled to the switch pair defines a differential output for providing a differential output signal. A current source is coupled to the switch pair. A control input receives a control signal and control circuitry coupled to the control input disable the current source to select a CMOS testing mode responsive to the control signal being activated.

Owner:INTELLECTUAL DISCOVERY INC

Method for manufacturing double-layer metal-insulator-metal capacitor by using copper damascene process

ActiveCN102420101AHigh densityExcellent capacitance performanceSemiconductor/solid-state device manufacturingMetal-insulator-metalCapacitance

The invention discloses a method for manufacturing a double-layer metal-insulator-metal capacitor by using a copper damascene process. In the method, a double-layer MIM (Metal-Insulator-Metal) capacitor structure and the copper damascene manufacturing process are used, and the method can be completely compatible with the copper damascene process of a CMOS (Complementary Metal-Oxide-Semiconductor Transistor) logic circuit and an inductor, and can be used for increasing the capacitance density of an MIM. According to the double-layer metal-insulator-metal capacitor manufactured by using the copper damascene process, disclosed by the invention, the method is completely compatible with the copper damascene process of the CMOS logic circuit and the inductor while the density of the MIM capacitor is increased.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

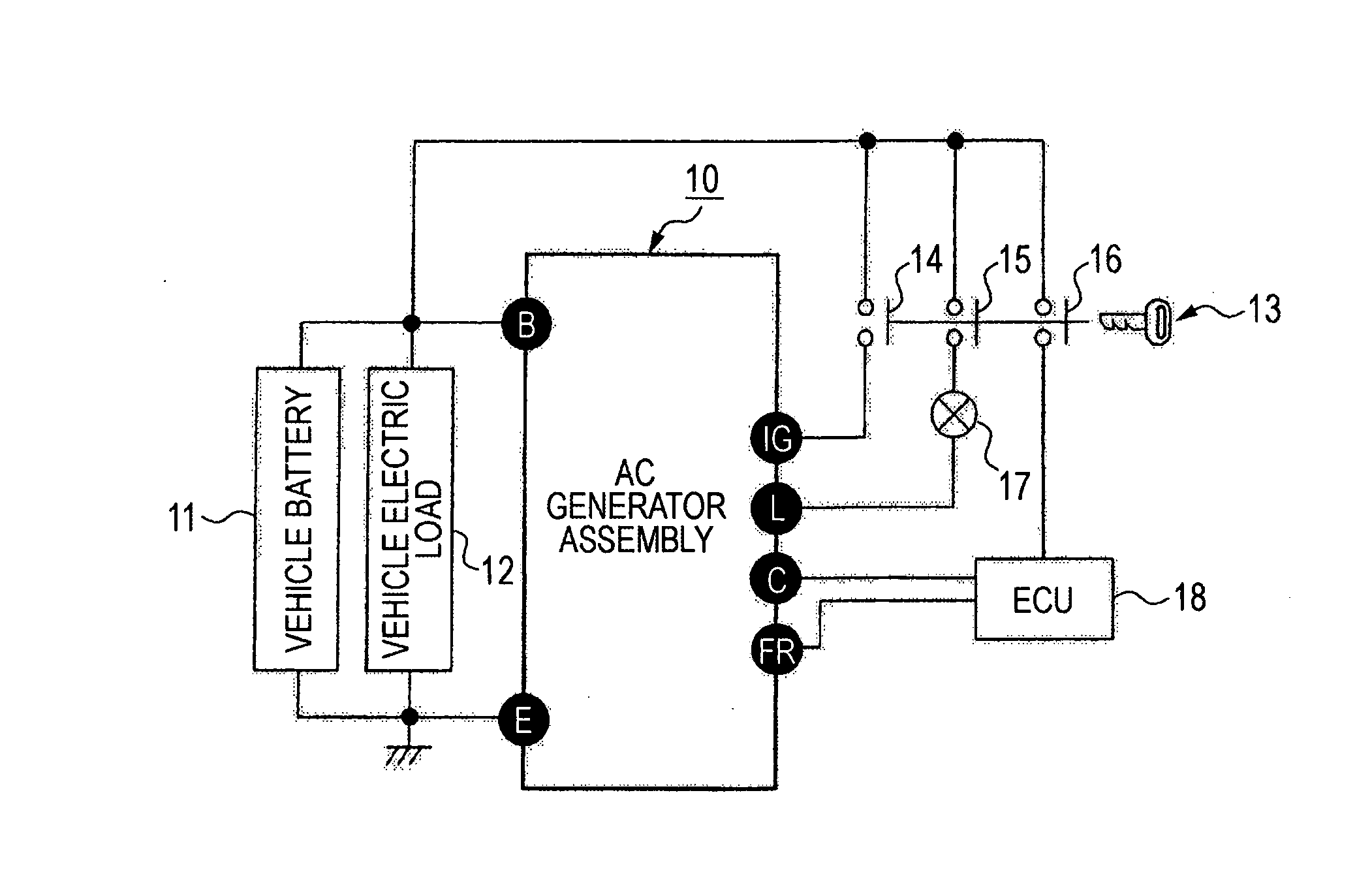

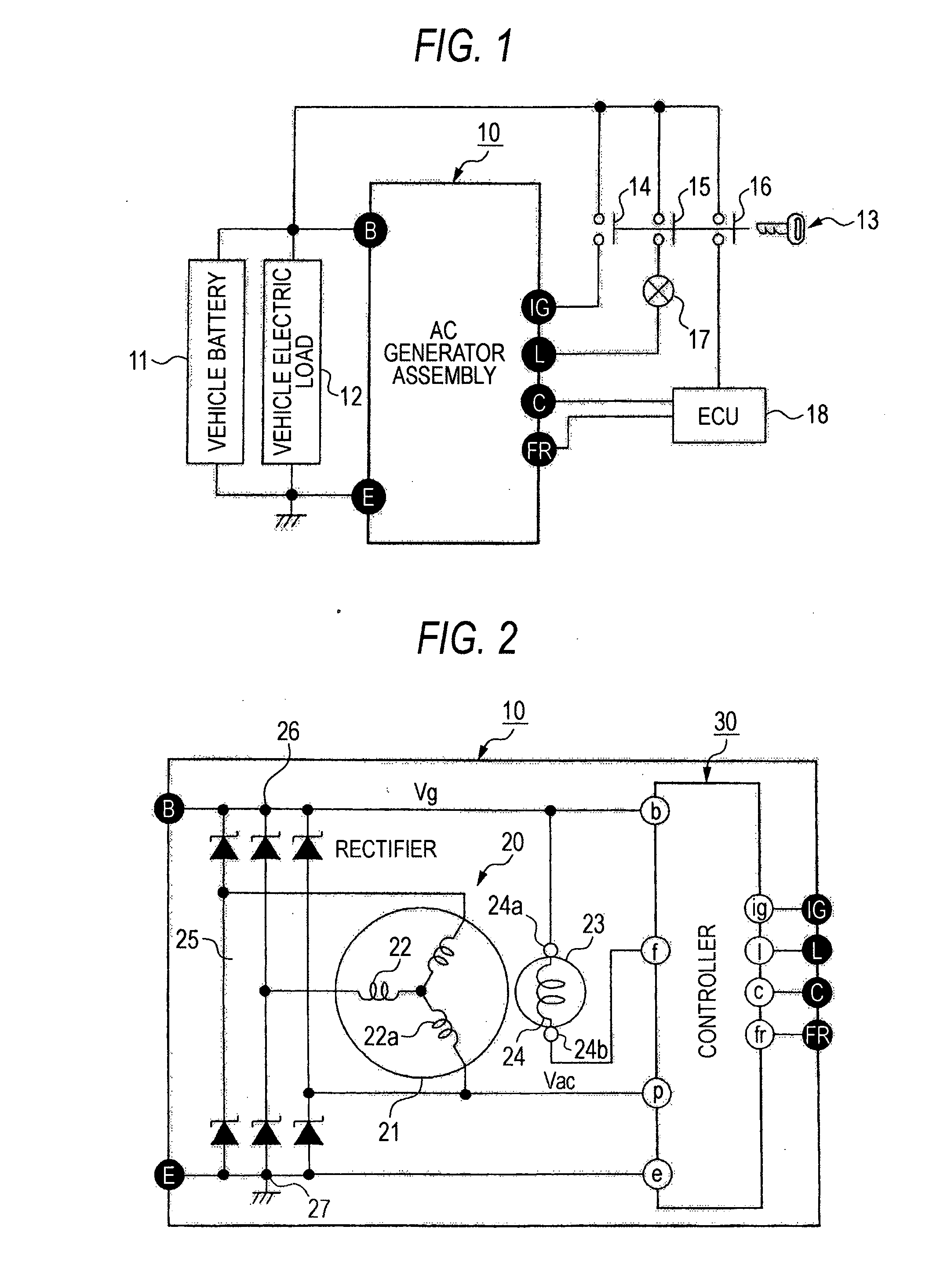

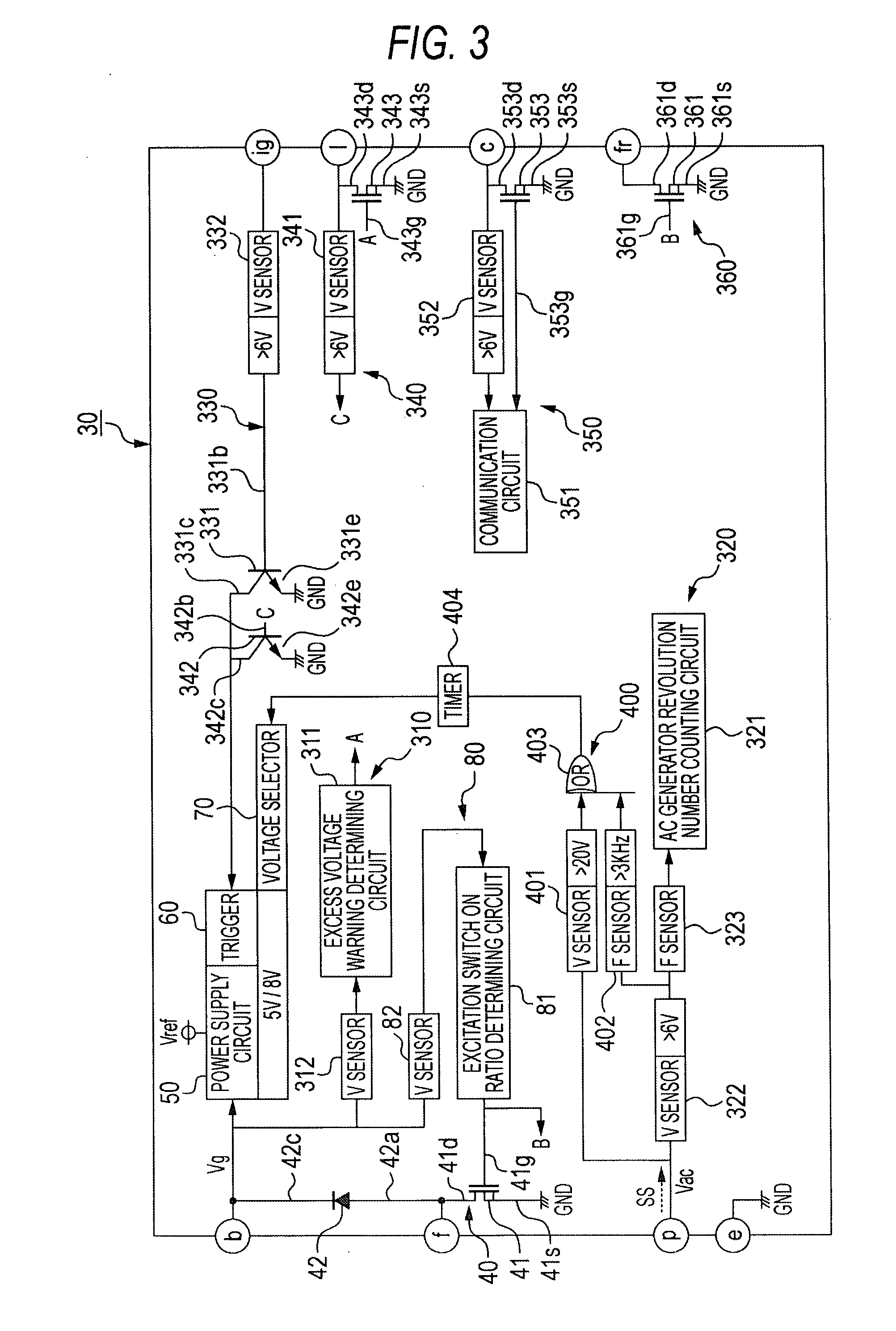

Controller for vehicle AC generator

InactiveUS20080106240A1Shorten the timeShorten aging timeBatteries circuit arrangementsEmergency protective circuit arrangementsCmos logic circuitsEngineering

A controller for a vehicle AC generator that allows the aging test time of a CMOS logic circuit to be reduced is provided. The controller includes a specified signal detecting circuit connected to a third external terminal to detect a specified signal, a voltage selector circuit that generates a voltage selector signal in response to the detection output of the specified signal detecting circuit, and a power supply circuit connected to the first external terminal to output, as internal power supply voltage, first power supply voltage in a first state in which the specified signal is not input to the third external terminal and second power supply voltage higher than the first power supply voltage in a second state in which the specified signal is input to the third external terminal.

Owner:MITSUBISHI ELECTRIC CORP

Complementary logic gate device

Provided is a complementary logical gate device represented by a silicon CMOS logical circuit among semiconductor integrated logical circuits which can effectively solve the problem of the speed performance limit of an ultra-large scale integration and an ultra-low power consumption type logical circuit. The complementary logical gate includes an electron running layer formed by grapheme without using an n-channel FET or a p-channel FET, has the ambipolar characteristic, and uses only two FET having different threshold values, i.e., a first FET and a second FET. The first FET has a gate electrode short-circuited to a gate electrode of the second FET so as to constitute an input terminal. The first FET has a source electrode set to a low potential. The first FET has a drain electrode connected to a source electrode of the second FET so as to constitute an output terminal. The second FET has a drain electrode set to a high potential.

Owner:OTSUJI TAIICHI +1

Copper Damascus process MIM (metal-insulator-metal) capacitor structure and manufacturing process

ActiveCN102420103AHigh densitySemiconductor/solid-state device manufacturingSemiconductor devicesMetal-insulator-metalCapacitance

The invention relates to a copper Damascus process MIM (metal-insulator-metal) capacitor structure and a manufacturing process thereof. The structure is characterized that through adding two maskplates, a single Damascus process is used so as to manufacture an MIM capacitor and an inductor simultaneously. According to the technical scheme of the invention, the manufactured MIM double-layer capacitor structure can be completely compatible with a CMOS (complementary metal-oxide-semiconductor transistor) logic circuit and an inductive copper Damascus process, and the density of the MIN capacitor is increased.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Dual mode analog differential and CMOS logic circuit

ActiveUS20050110521A1Overcome disadvantagesDigital circuit testingLogic circuit coupling/interface arrangementsCMOSControl signal

A dual mode, analog differential and complementary metal oxide semiconductor (CMOS) logic circuit is provided. The circuit includes a differential input for receiving a differential input signal. A switch pair is coupled to the differential input. A pair of load resistors coupled to the switch pair defines a differential output for providing a differential output signal. A current source is coupled to the switch pair. A control input receives a control signal and control circuitry coupled to the control input disable the current source to select a CMOS testing mode responsive to the control signal being activated.

Owner:INTELLECTUAL DISCOVERY INC