Patents

Literature

127 results about "Charge recovery" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

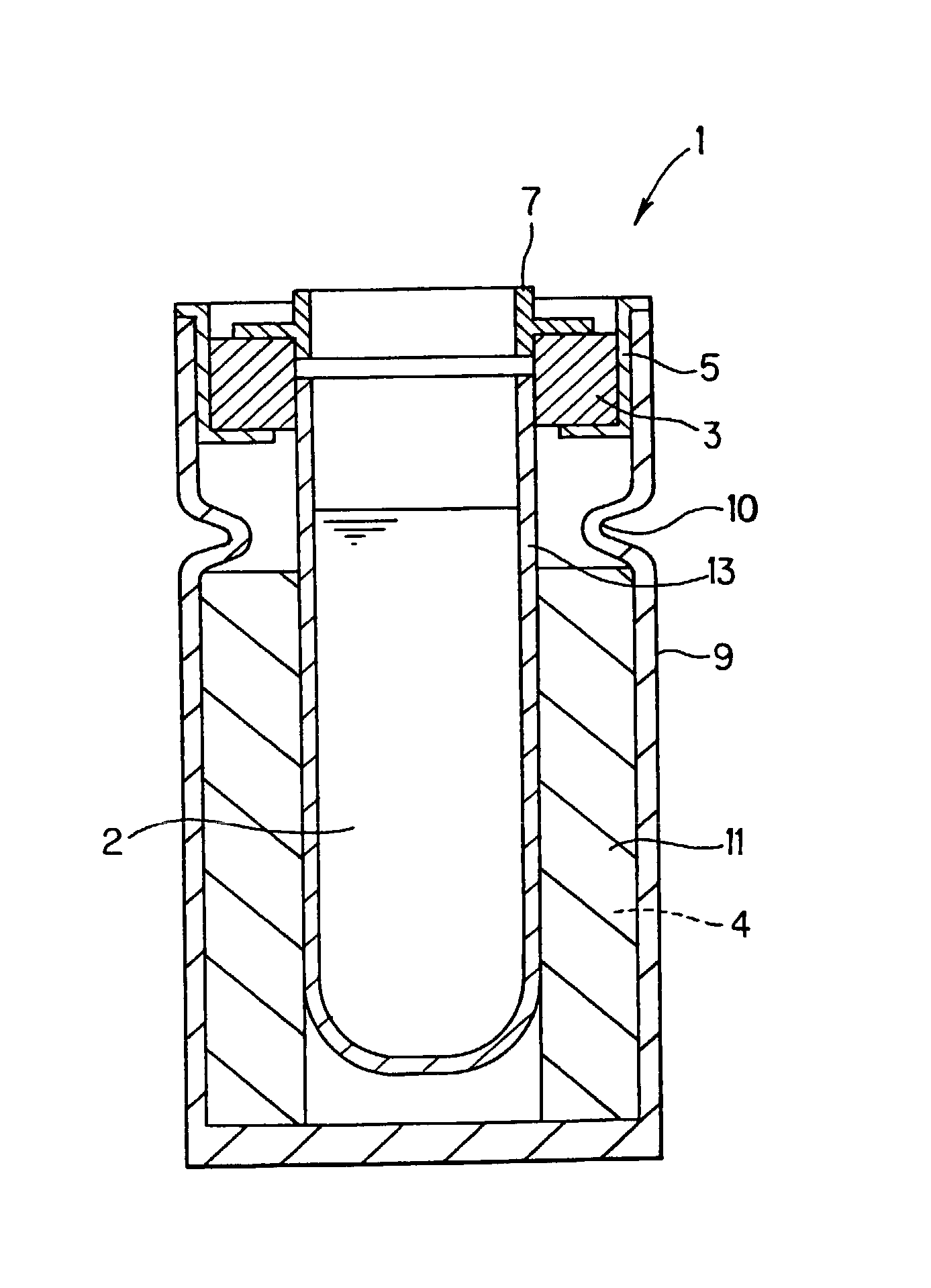

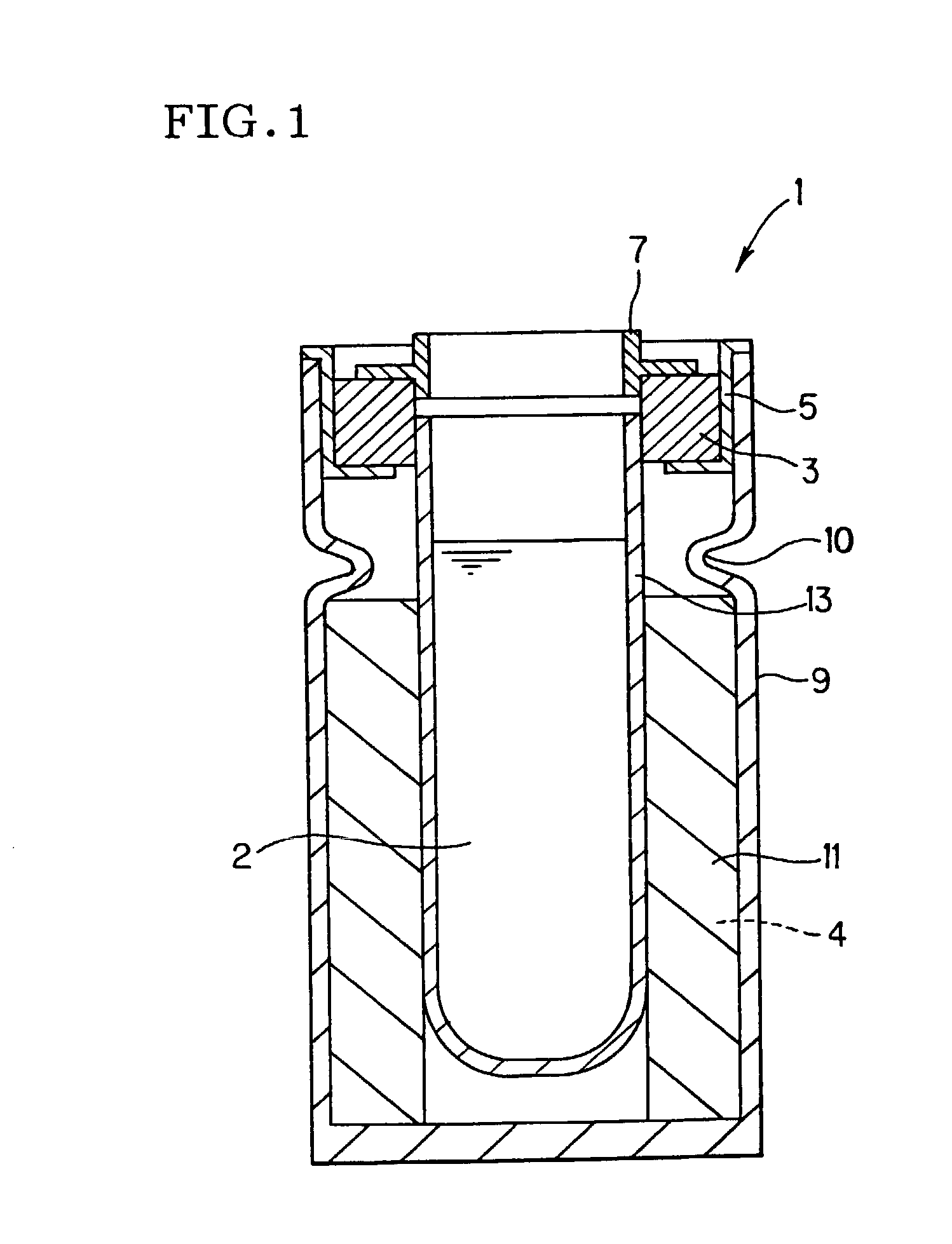

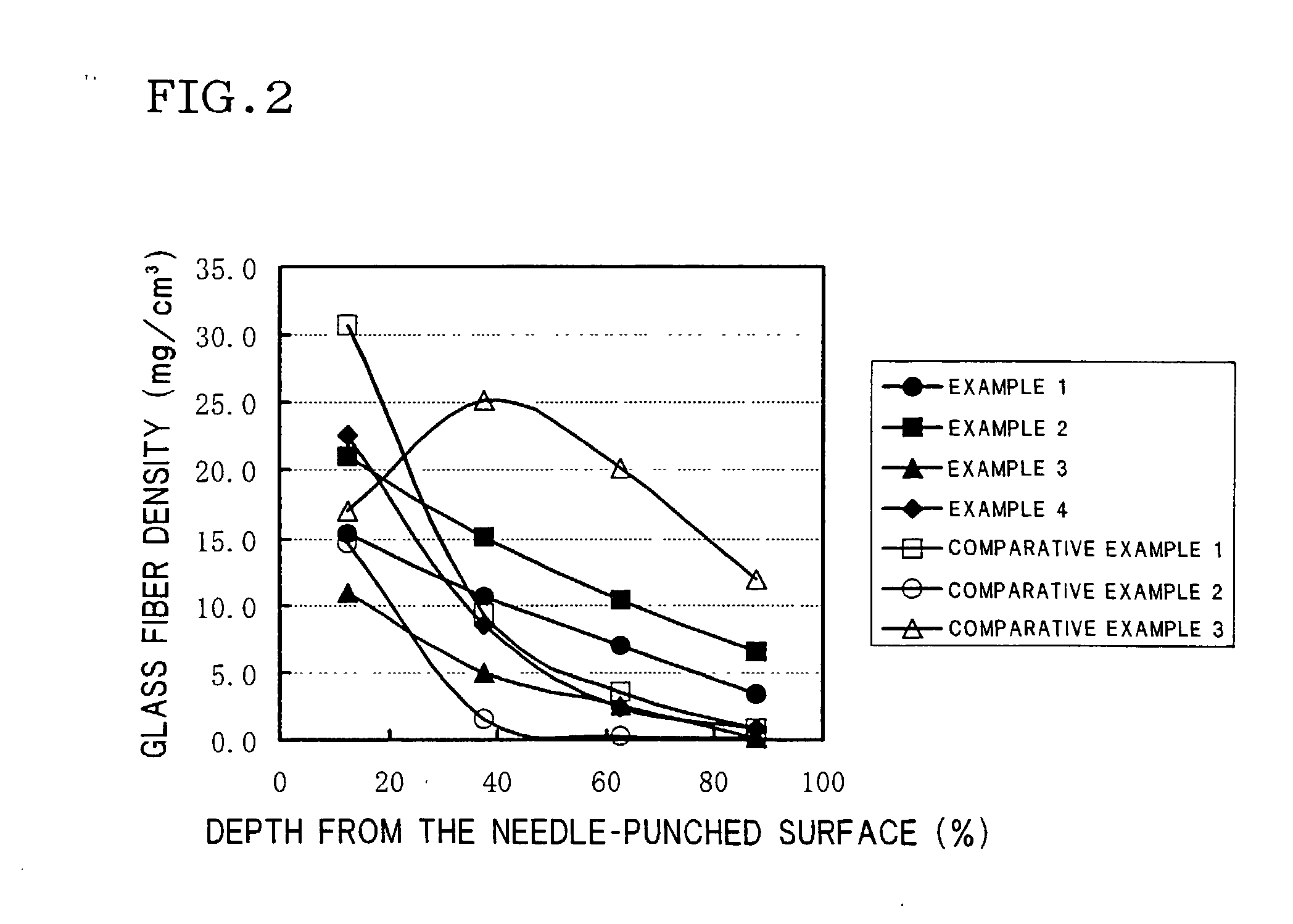

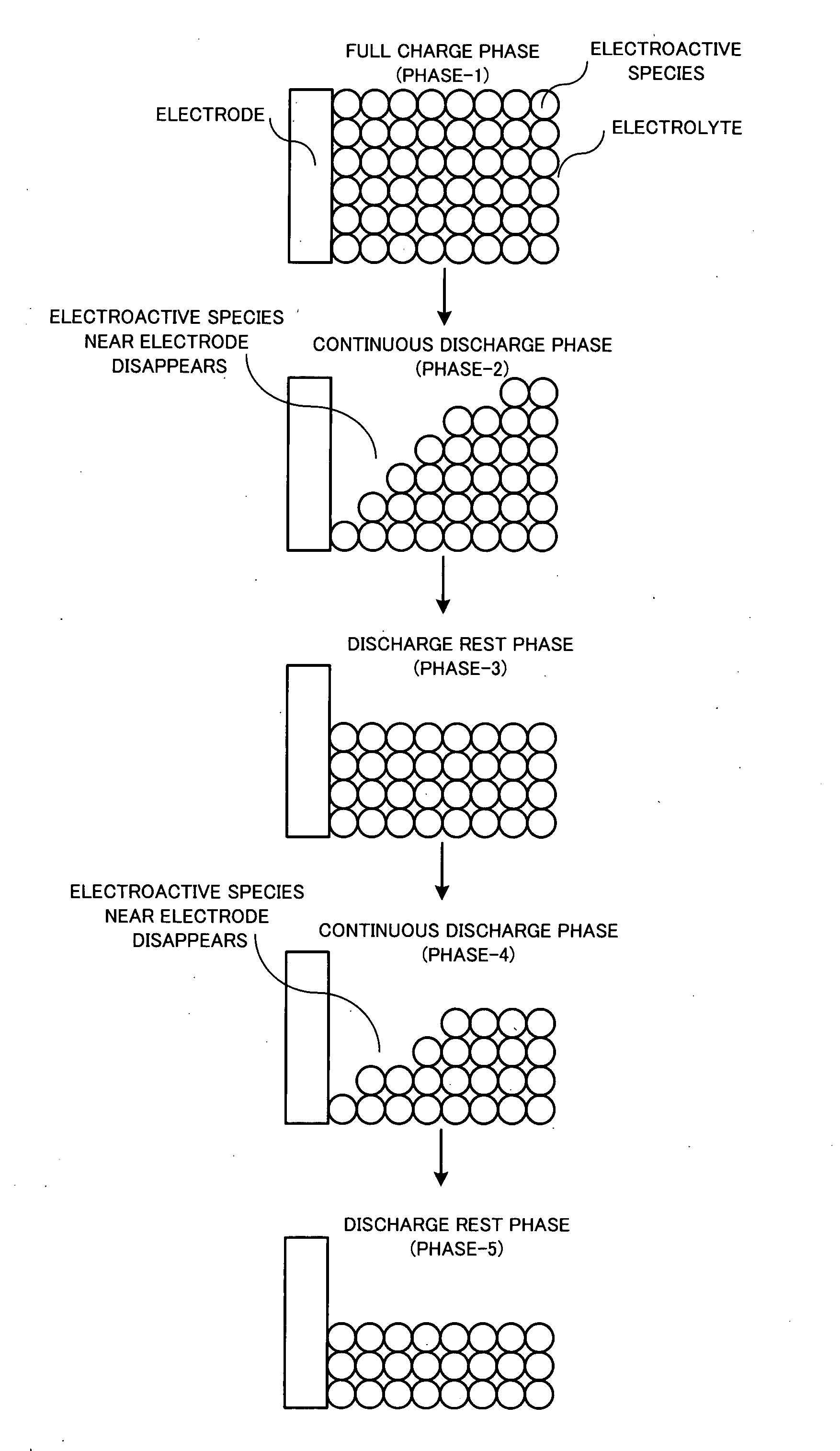

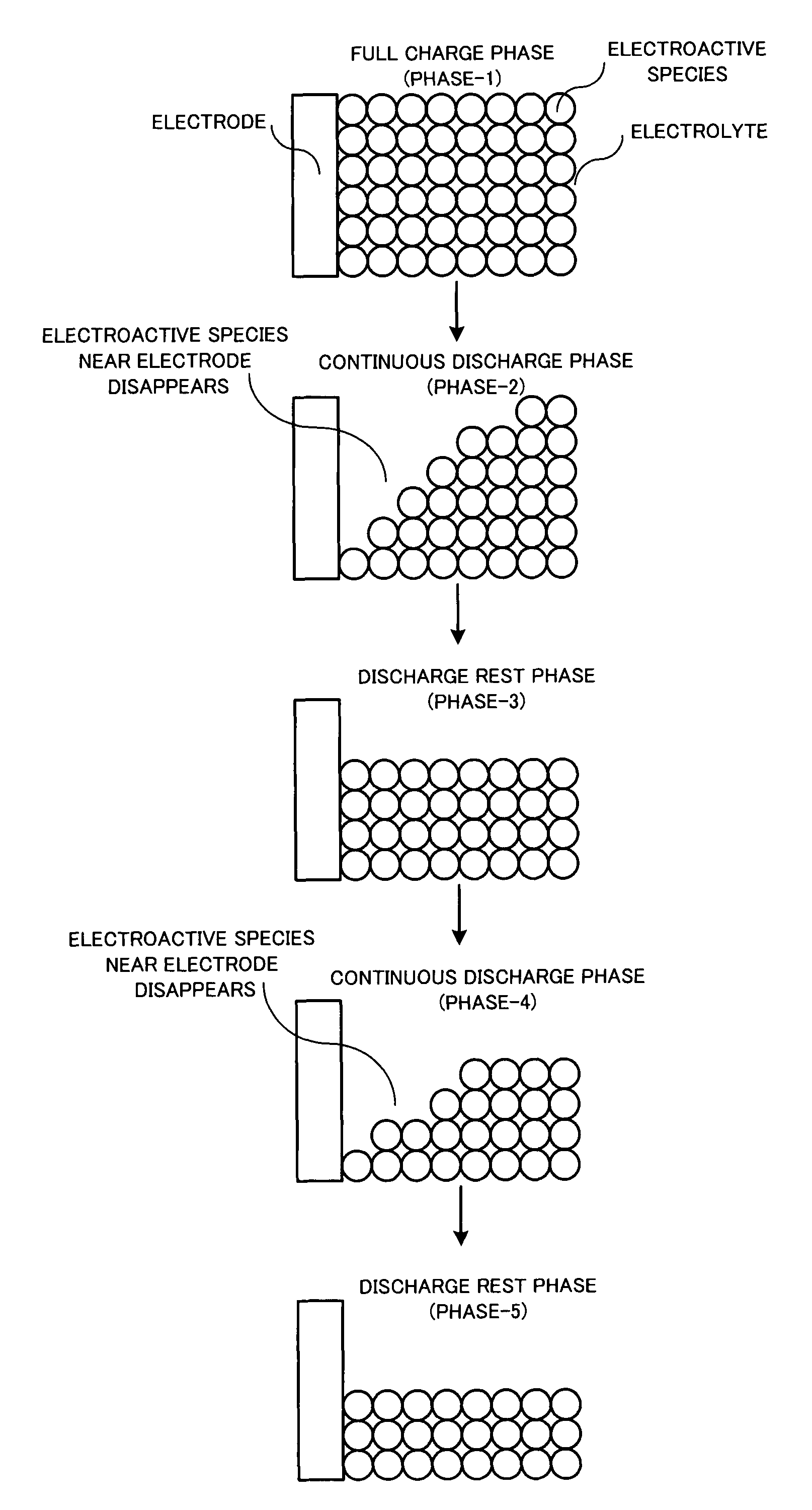

Current collector of positive electrode and sodium-sulfur battery using the same

InactiveUS20030054255A1Electrode carriers/collectorsSolid electrolyte cellsHigh resistanceGlass fiber

A current collector of positive electrode enabling a NaS battery to be excellent in the charge recovery characteristic and low in internal resistance is provided, which collector has a high resistance layer formed by needle-punching glass fibers with 5 to 15 mum fiber diameters into a felt substrate made of carbon fibers or graphite fibers by needle-punching from the one surface of the substrate. The density of the glass fibers needle-punched into the substrate is gradually decreased in the direction from the above mentioned surface to the other surface of the substrate, and the deepest portions of the needle-punched glass fibers reach the depths of 85 to 100% of the substrate thickness.

Owner:NGK INSULATORS LTD

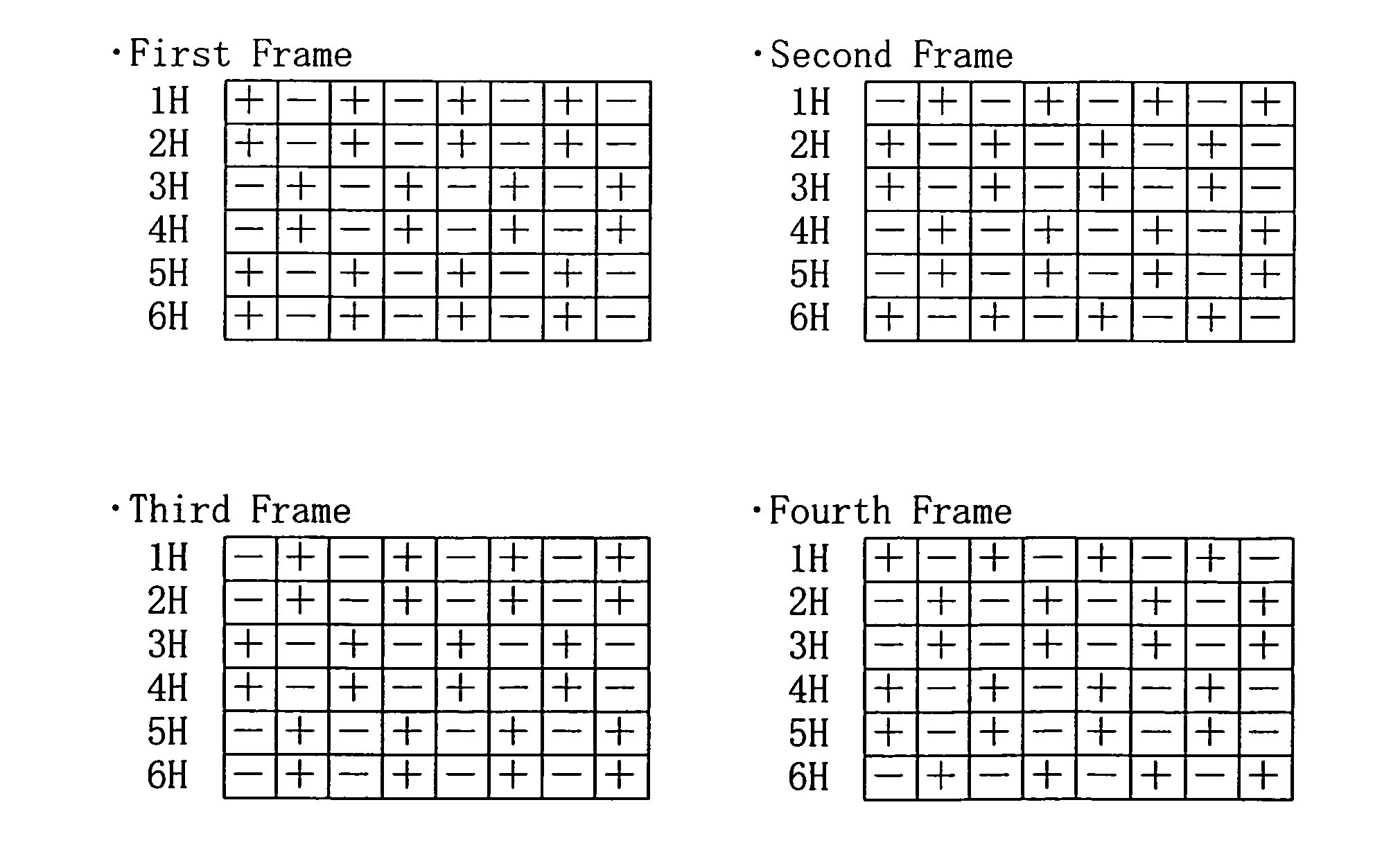

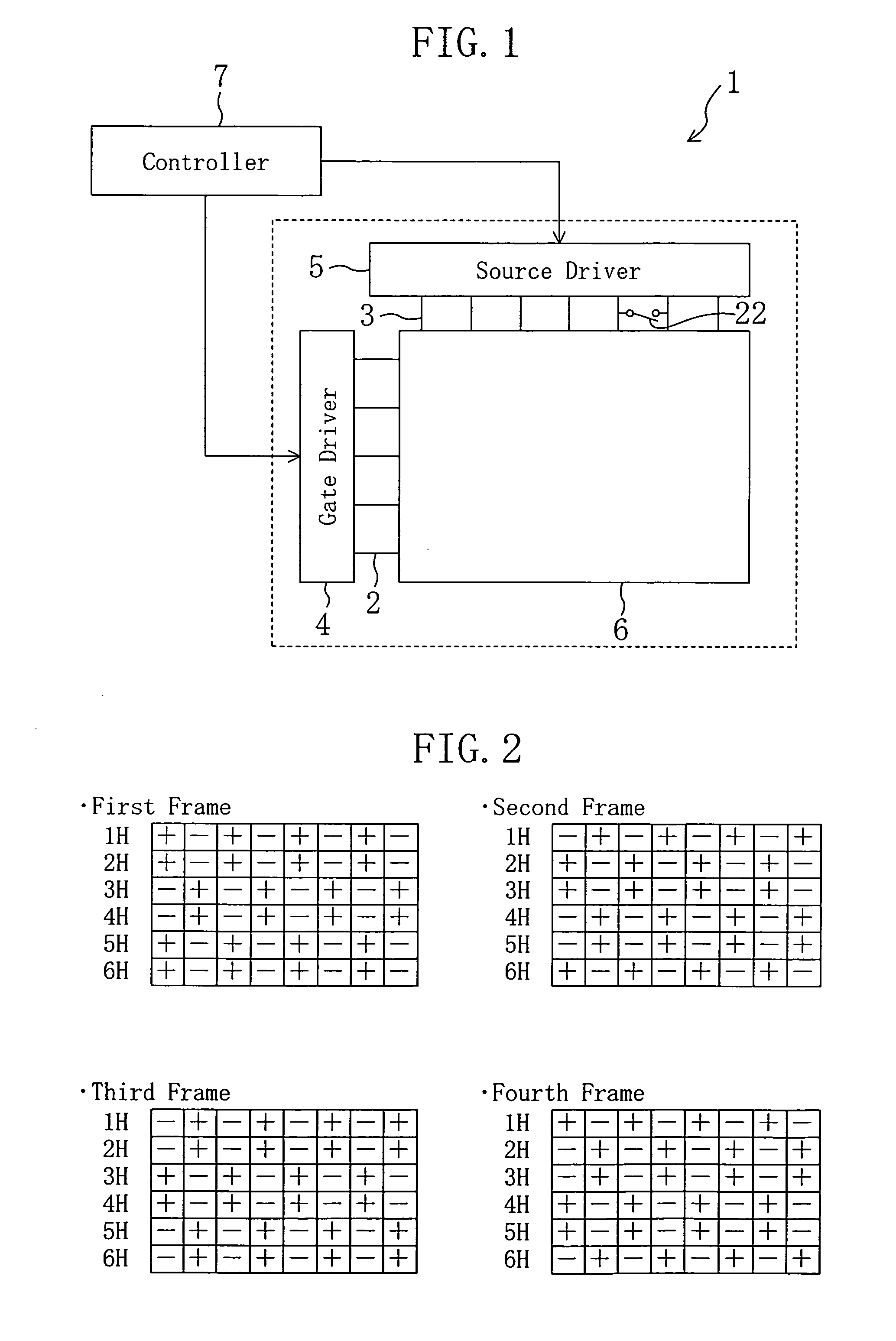

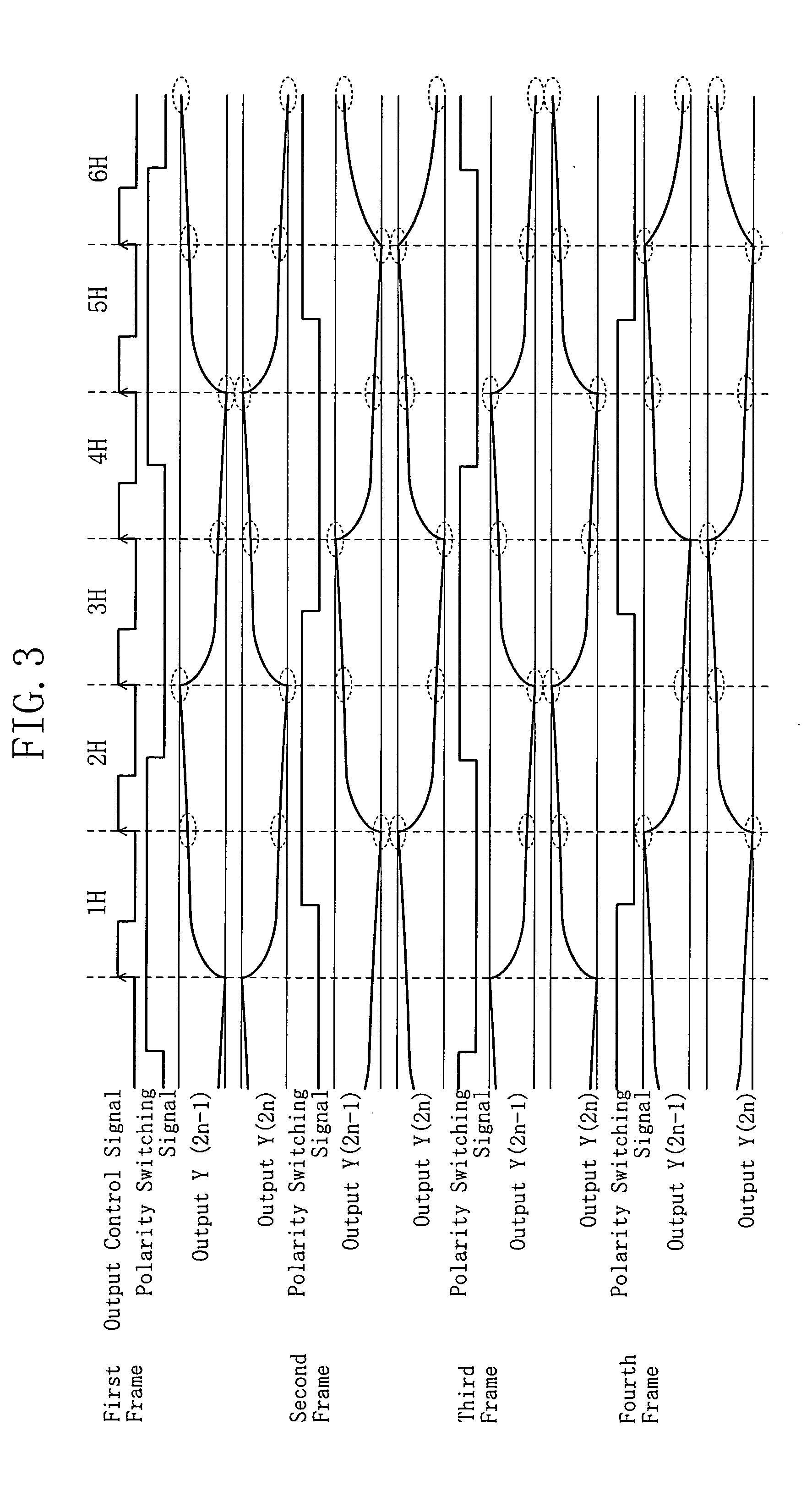

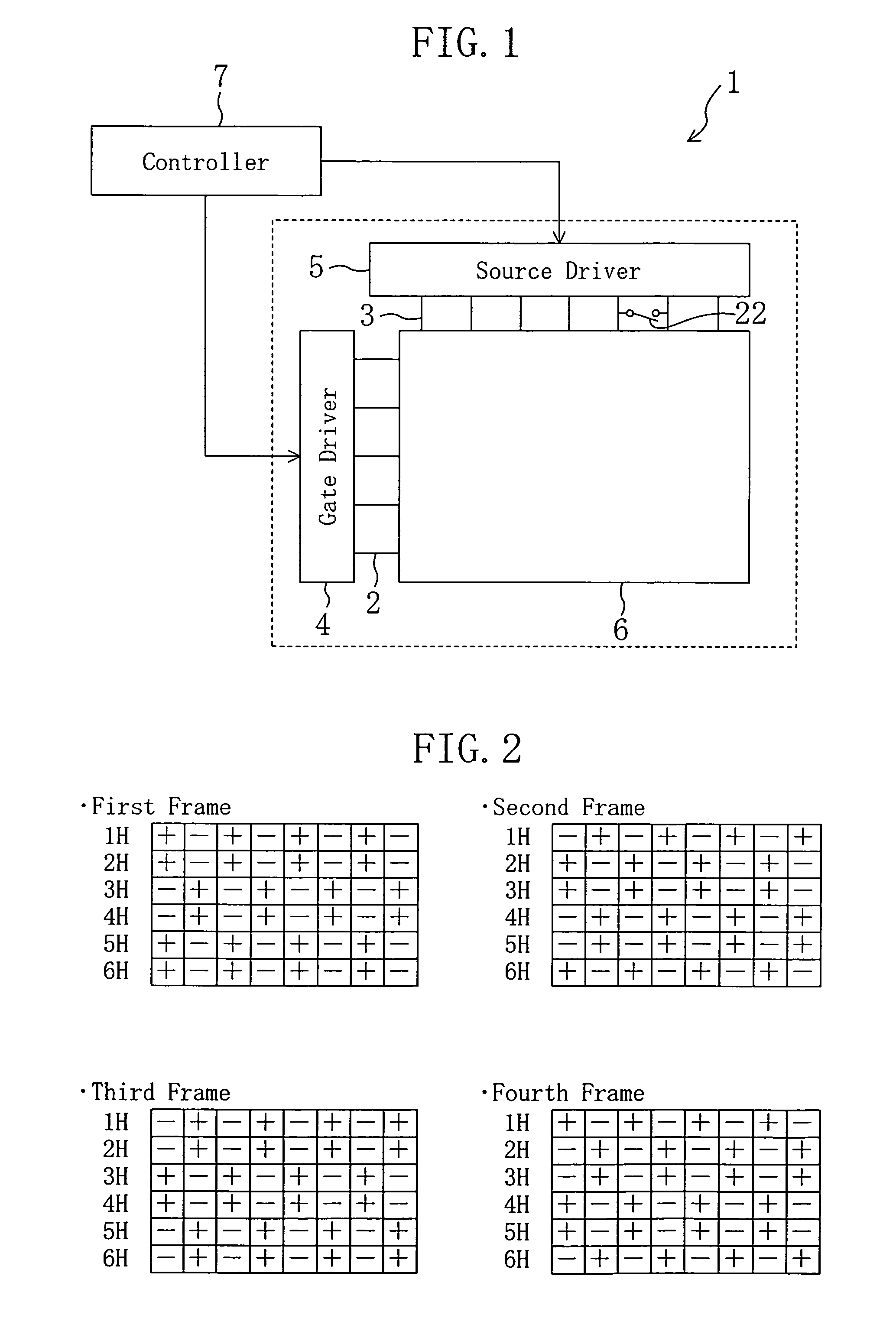

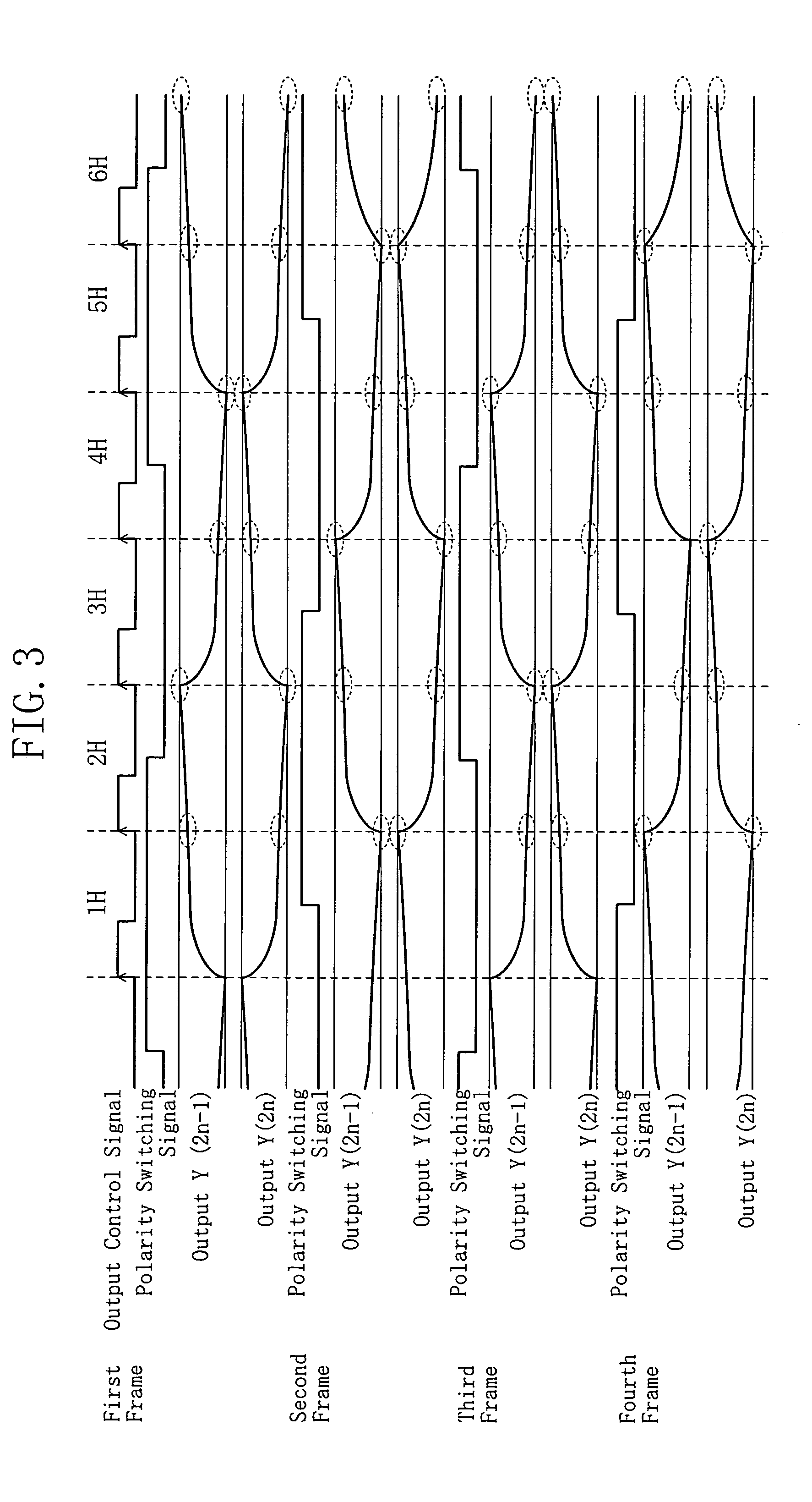

Display and method for driving the same

If a display is subjected to n line dot inversion drive control, the polarity pattern of sub-pixels is shifted line by line in a cycle of n frames. Furthermore, in every n horizontal scanning periods in which the polarities of output terminals of a source driver are switched, at least two of the output terminals are short-circuited to carry out electrical charge recovery. By using these methods, it is possible to achieve a reduction in power consumption while improving image quality.

Owner:COLLABO INNOVATIONS INC

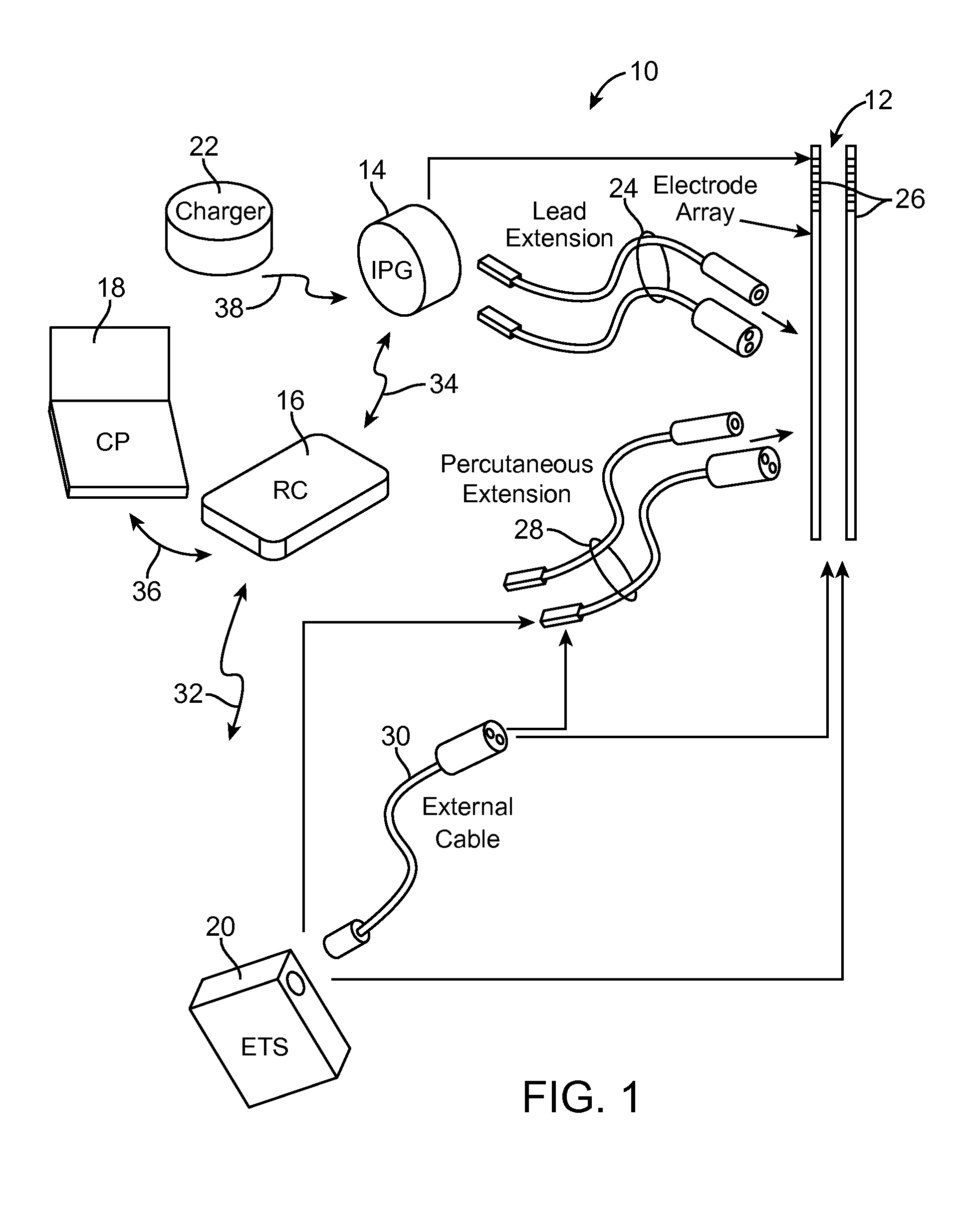

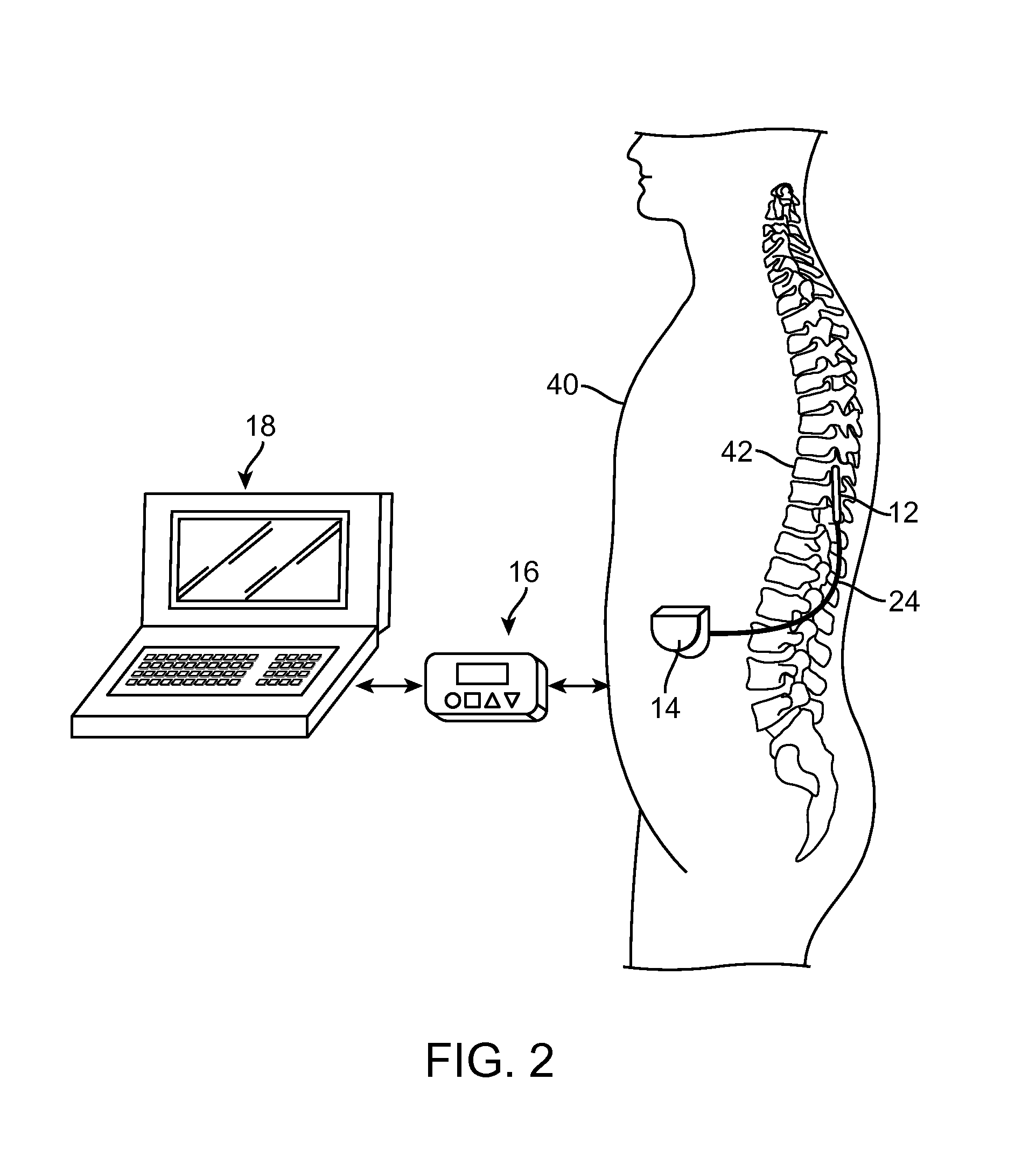

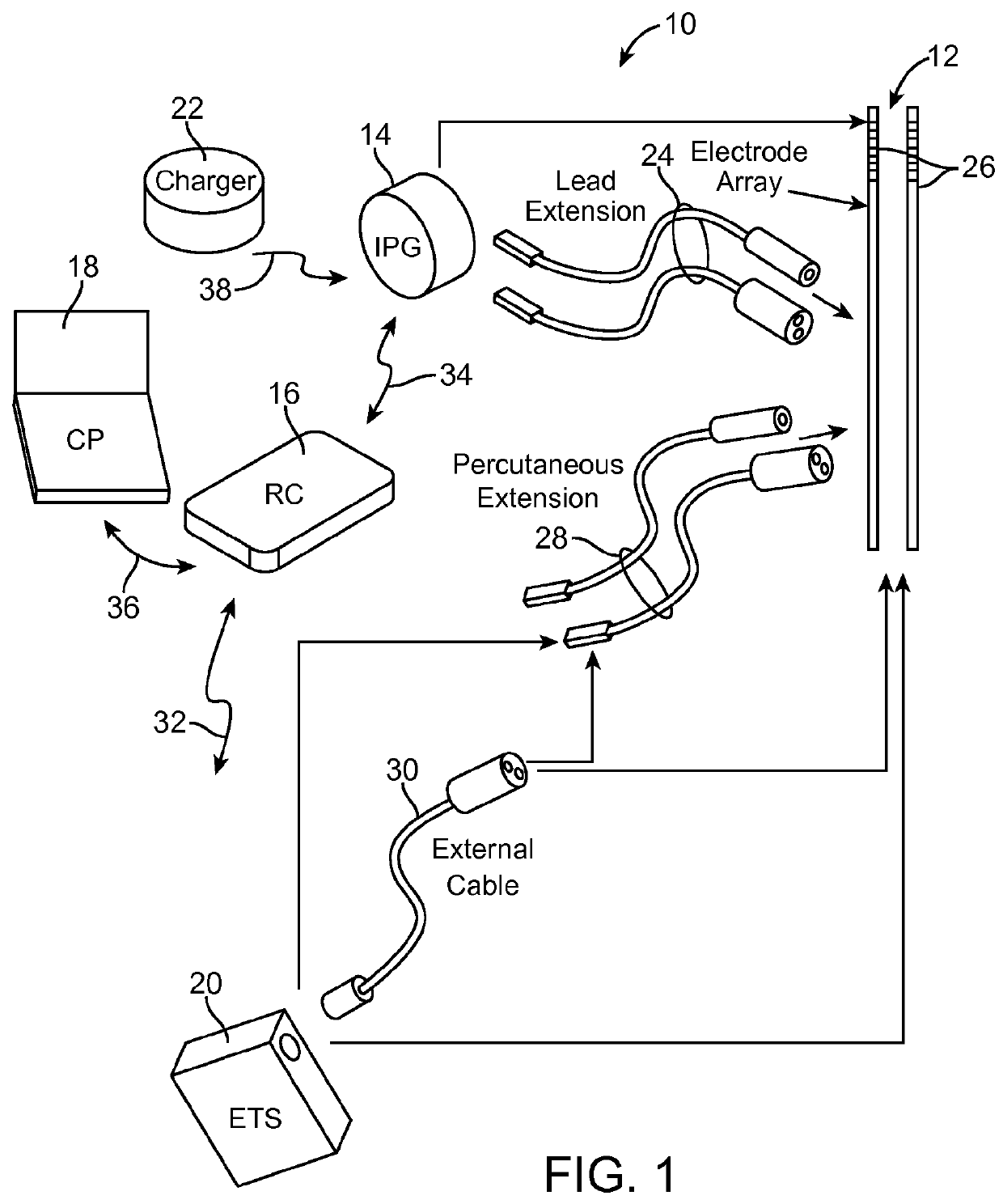

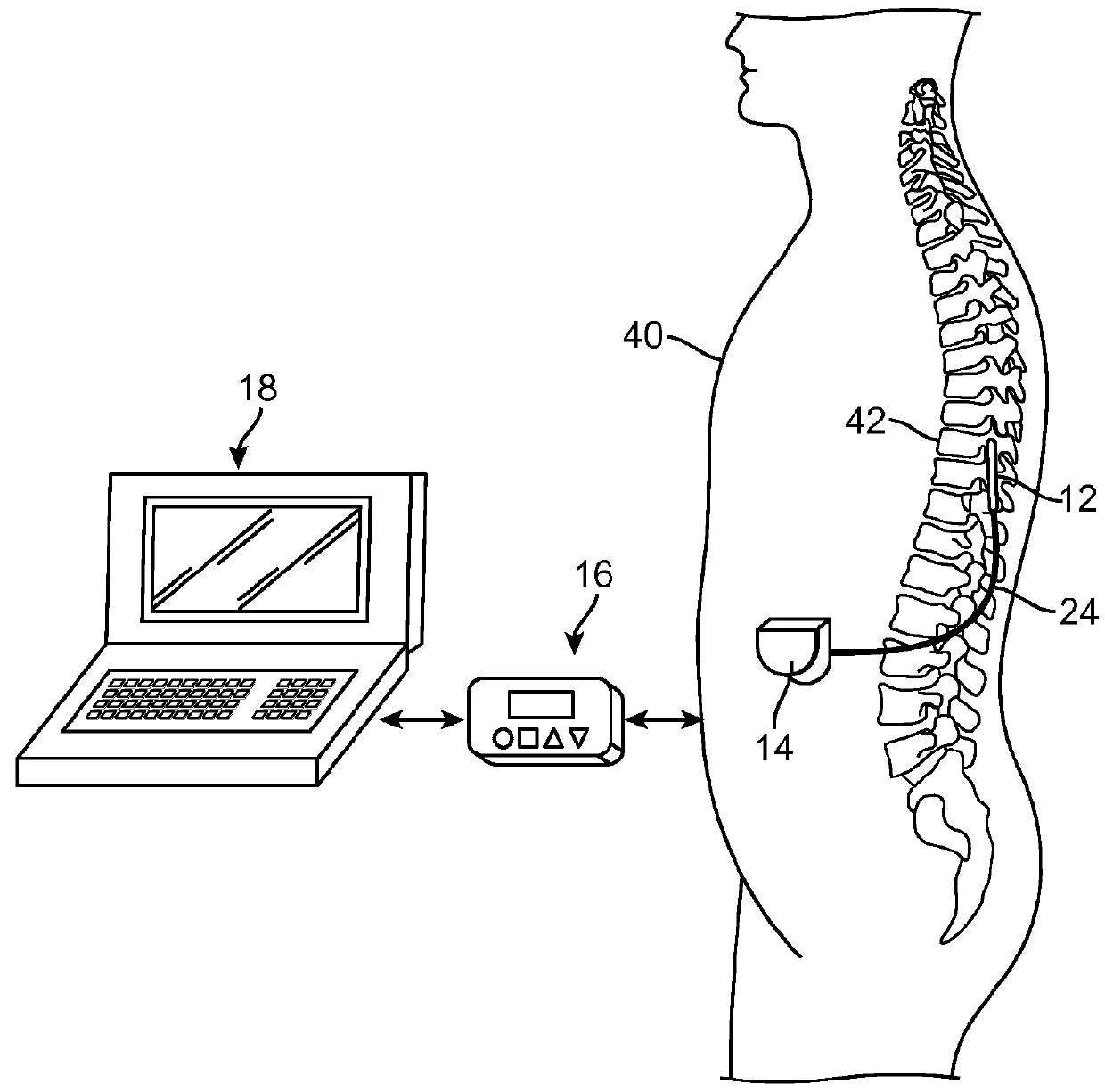

Neurostimulation system having increased flexibility for creating complex pulse trains

ActiveUS20140243924A1Facilitate temporal integrationElectrotherapyArtificial respirationPhysical medicine and rehabilitationMedicine

Owner:BOSTON SCI NEUROMODULATION CORP

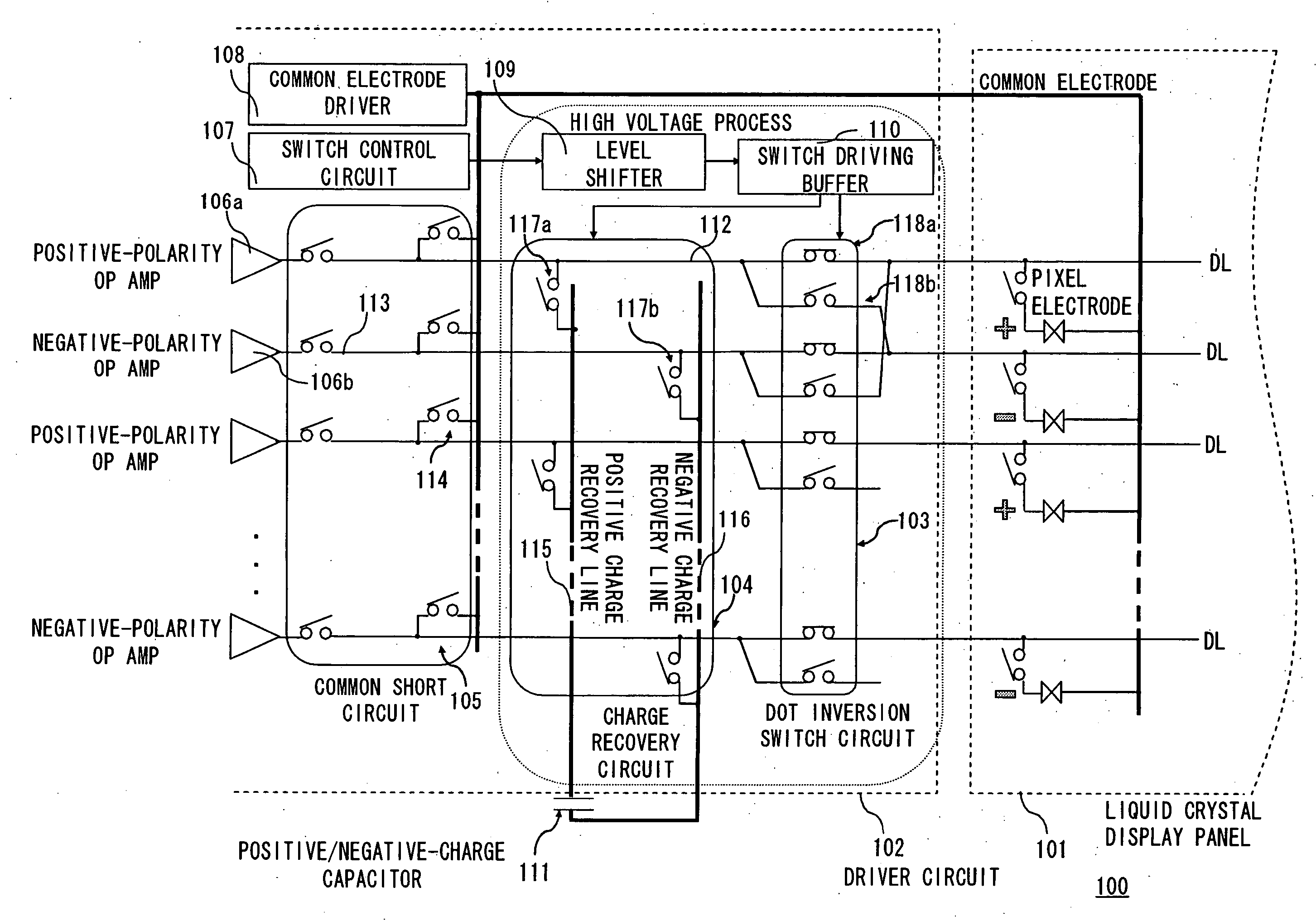

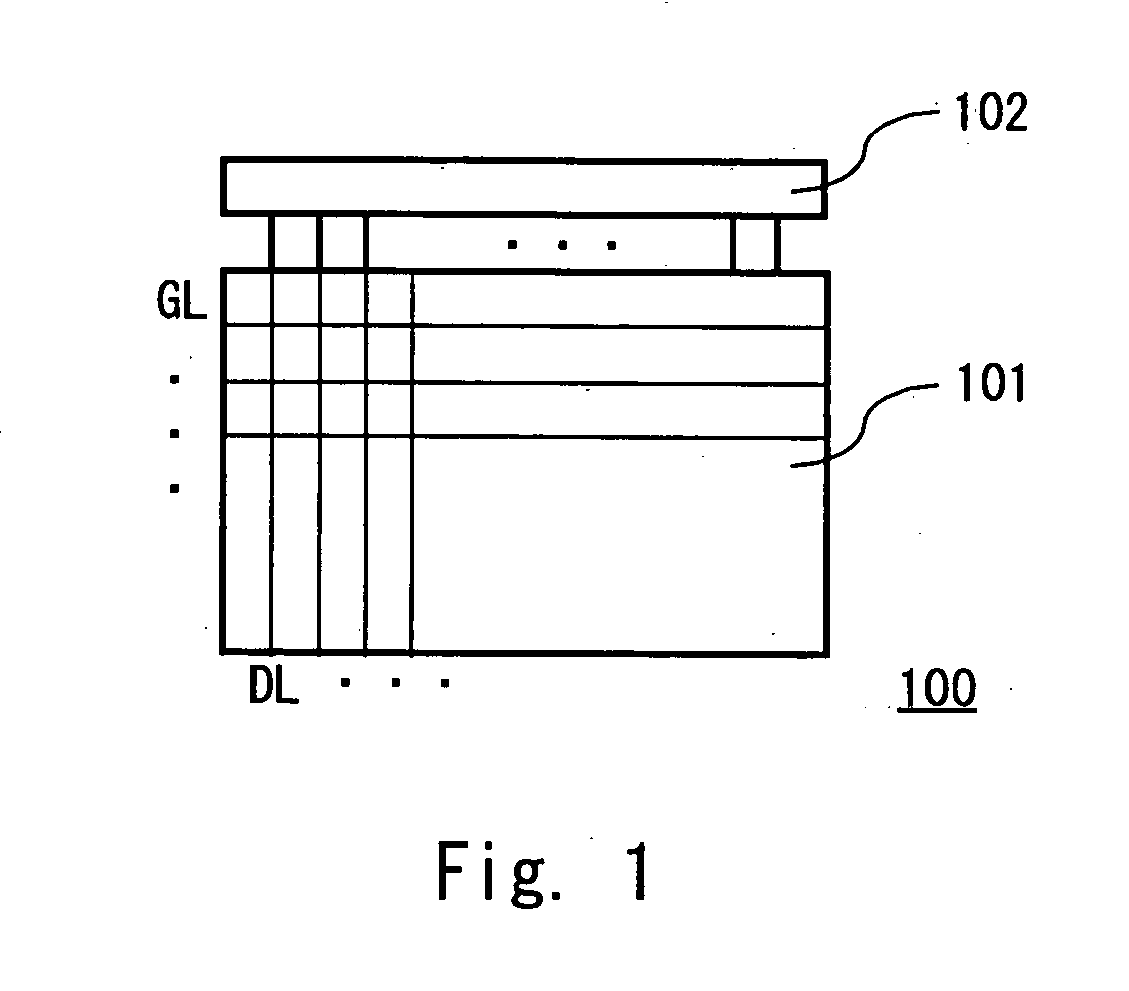

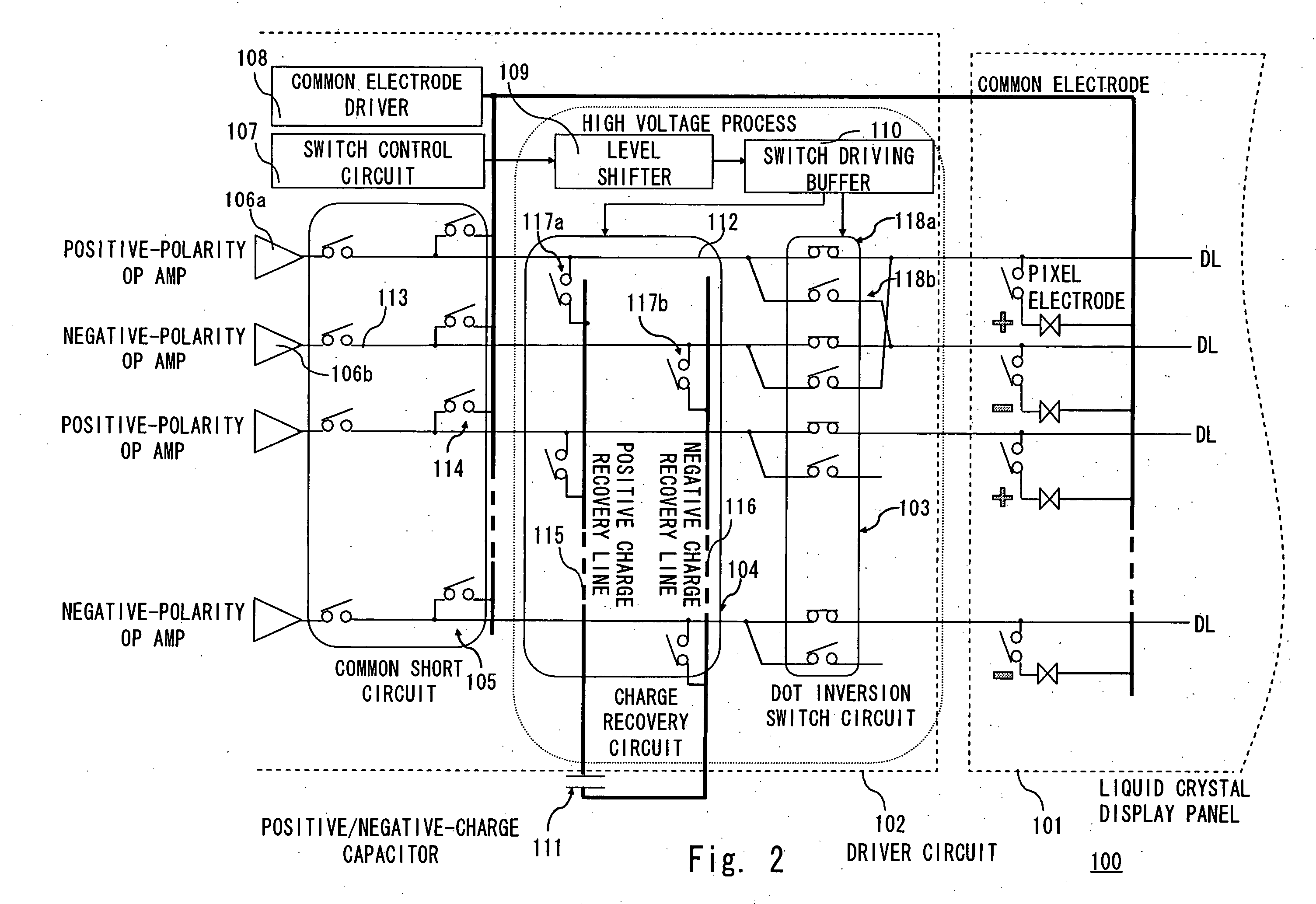

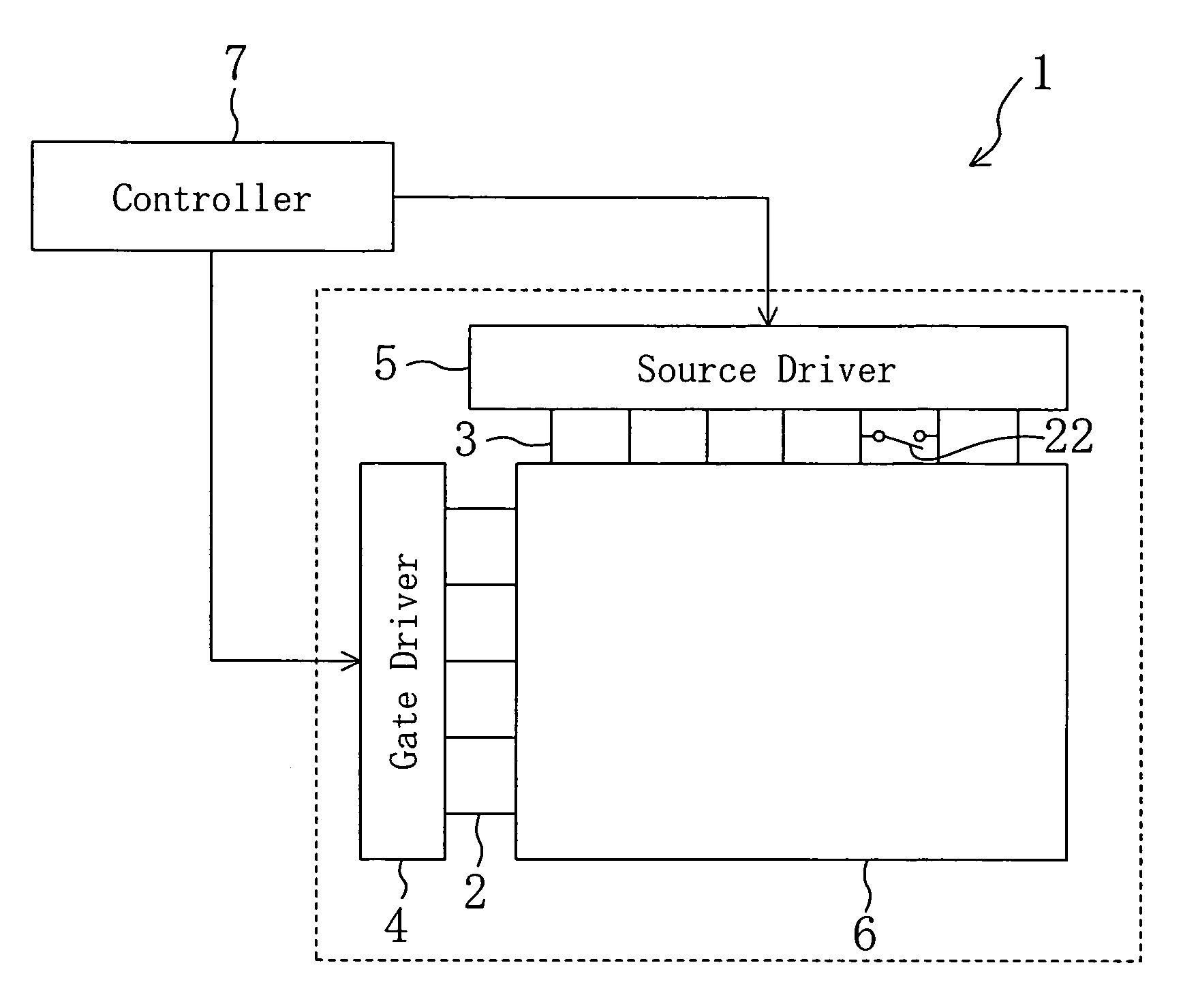

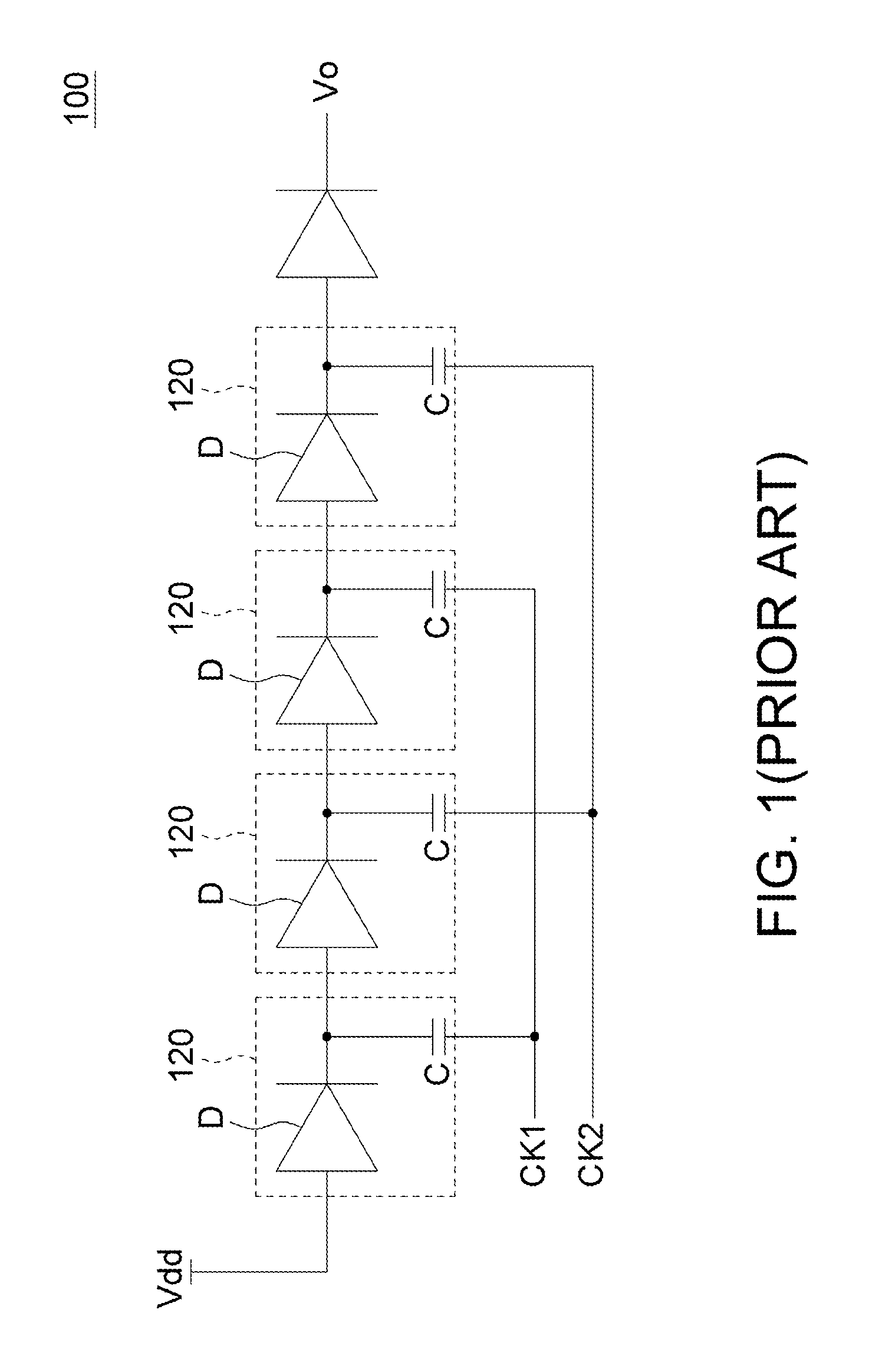

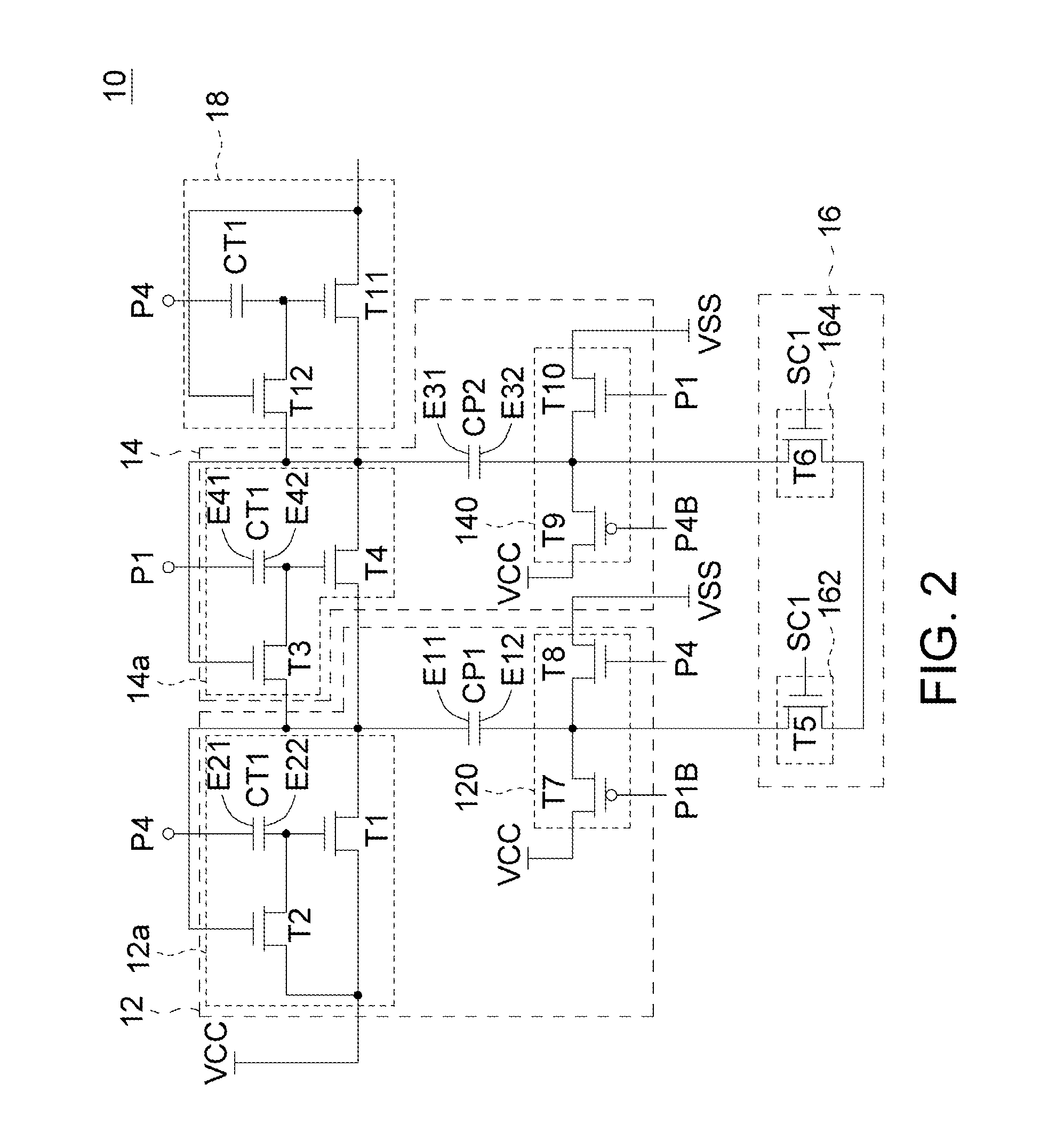

Driver circuit and display device

InactiveUS20060103618A1Reduce power consumptionCathode-ray tube indicatorsInput/output processes for data processingCharge recoveryDisplay device

To provide a driver circuit that enables reduction in the number of elements formed through a high-voltage process and in chip size. An embodiment of the present invention relates to a driver circuit for inversion-driving a liquid crystal display panel, including: a positive-polarity line transmitting a positive display signal relative to a common electrode signal; a negative-polarity line transmitting a negative display signal relative to the common electrode signal; a dot inversion switch circuit switching the positive-polarity line and the negative-polarity line from each other to be connected with a source line; a charge recovery circuit connected with the positive-polarity line through a positive charge recovery switch and connected with the negative-polarity line through a negative charge recovery switch; and a common short circuit connecting the positive-polarity line and the negative-polarity line with a common electrode.

Owner:RENESAS ELECTRONICS CORP

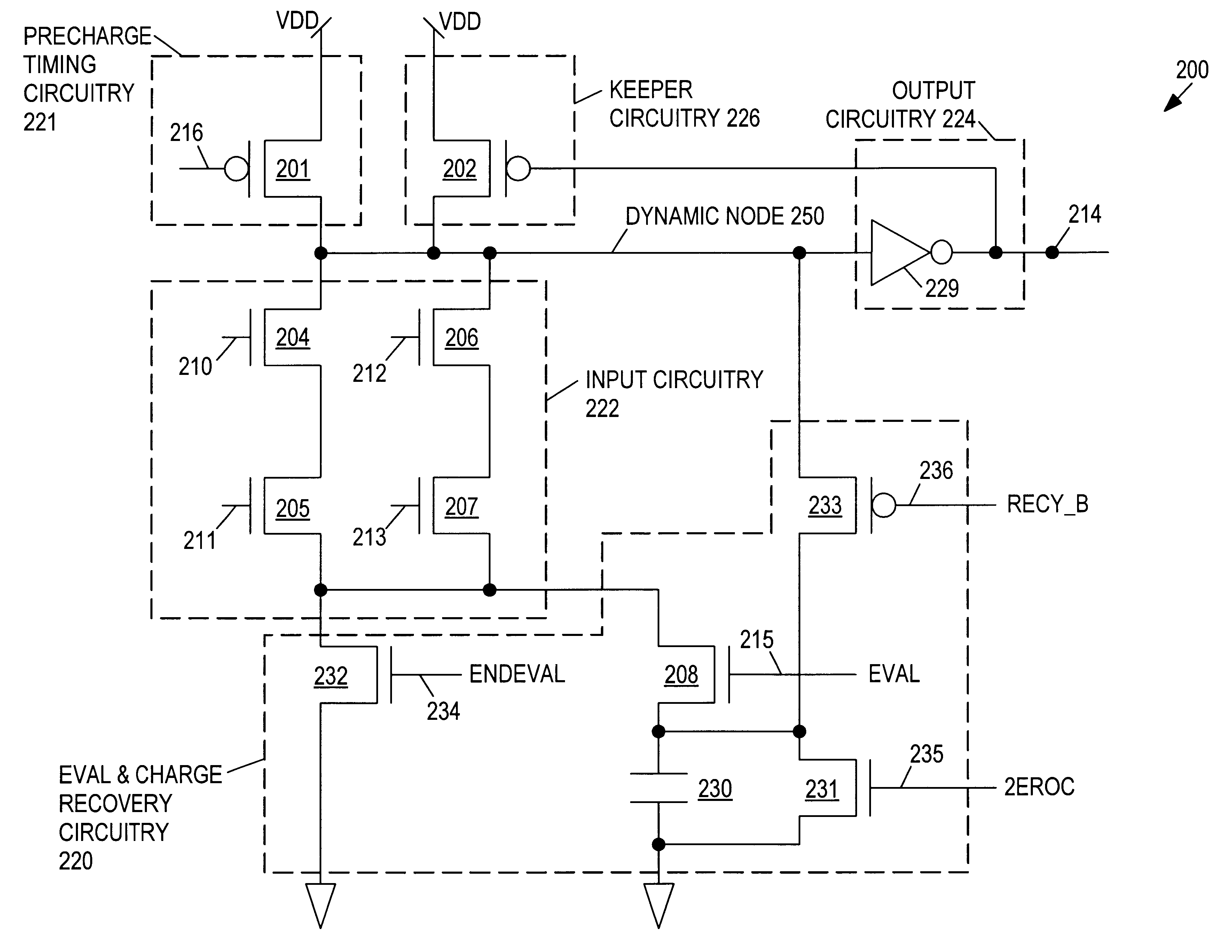

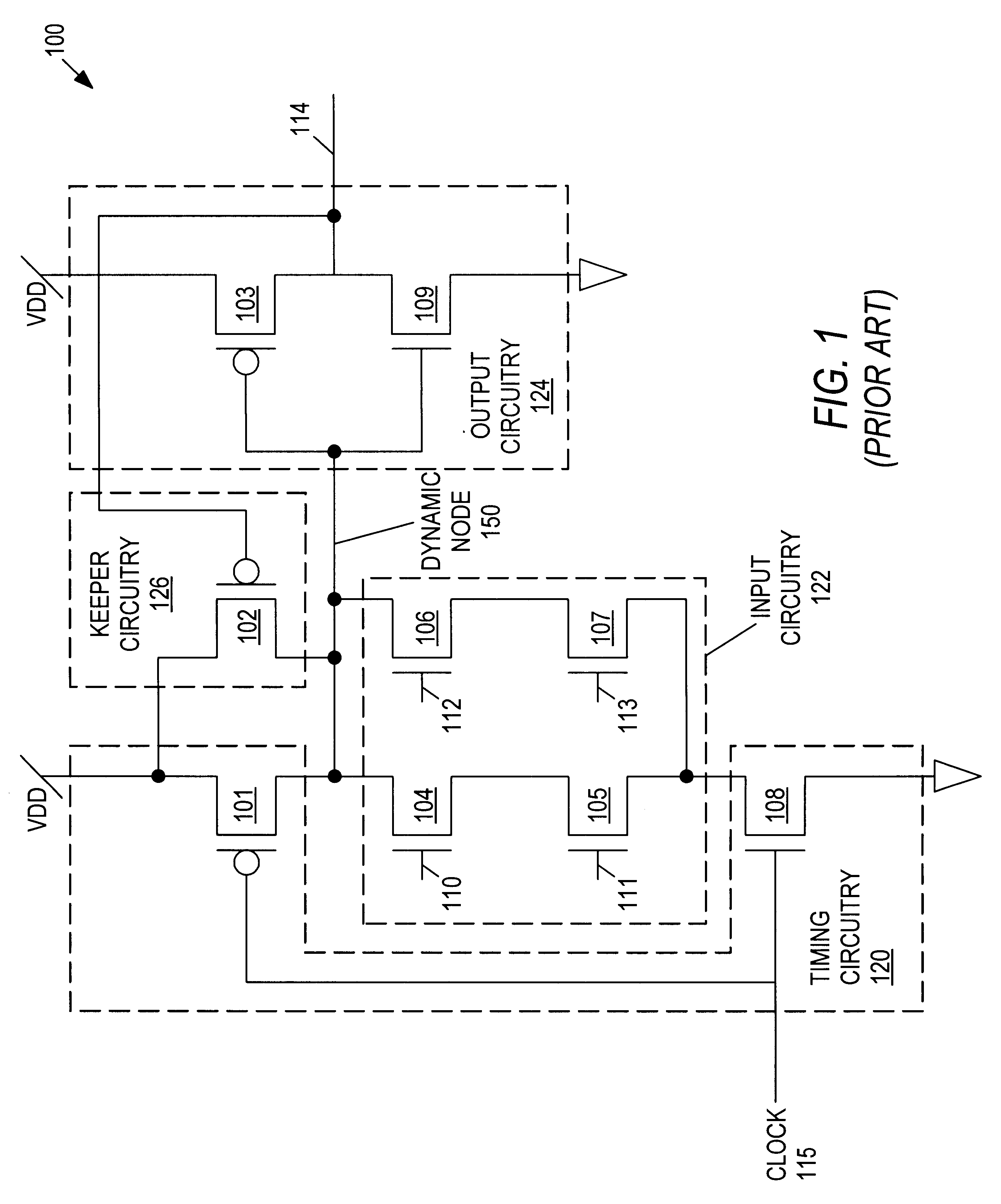

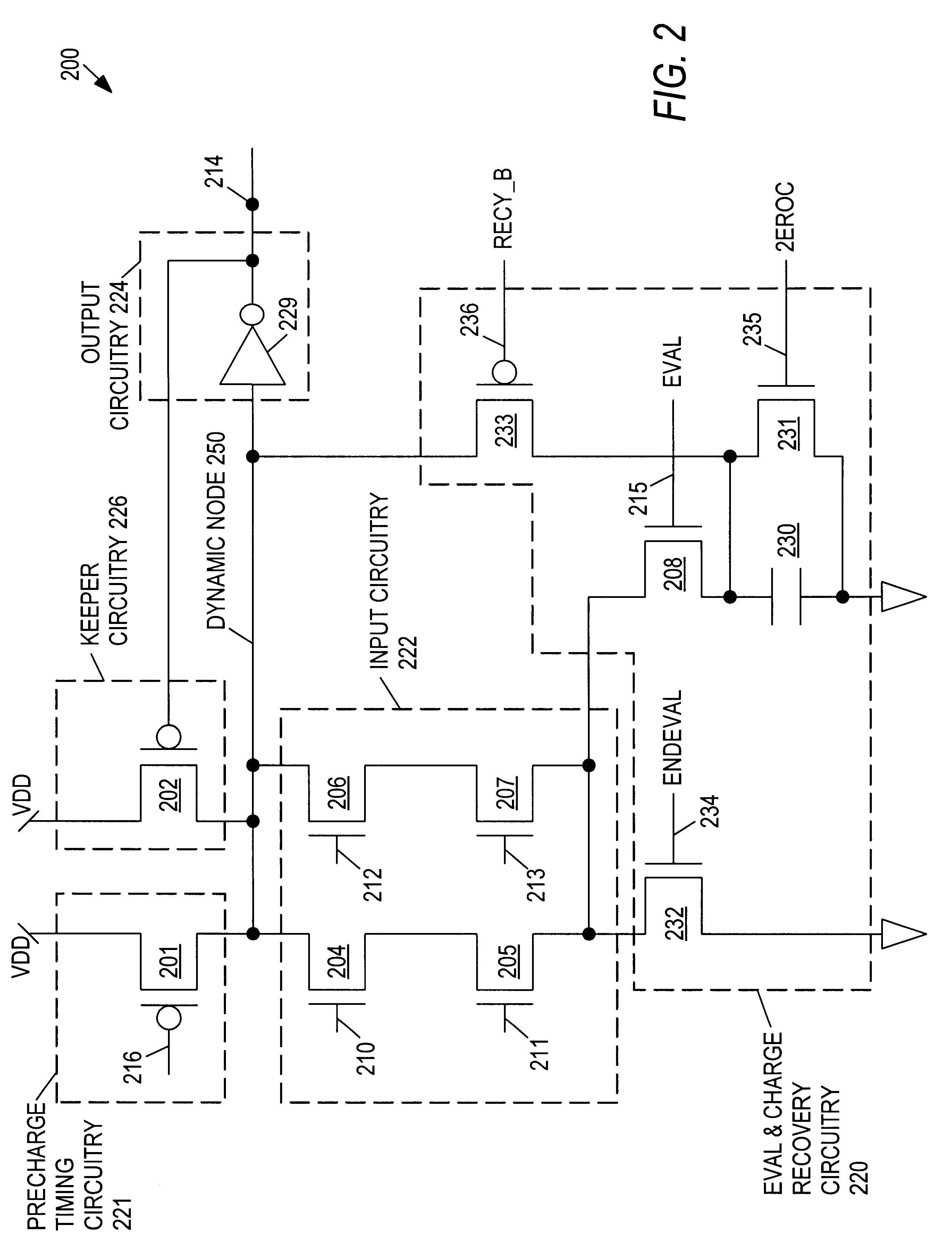

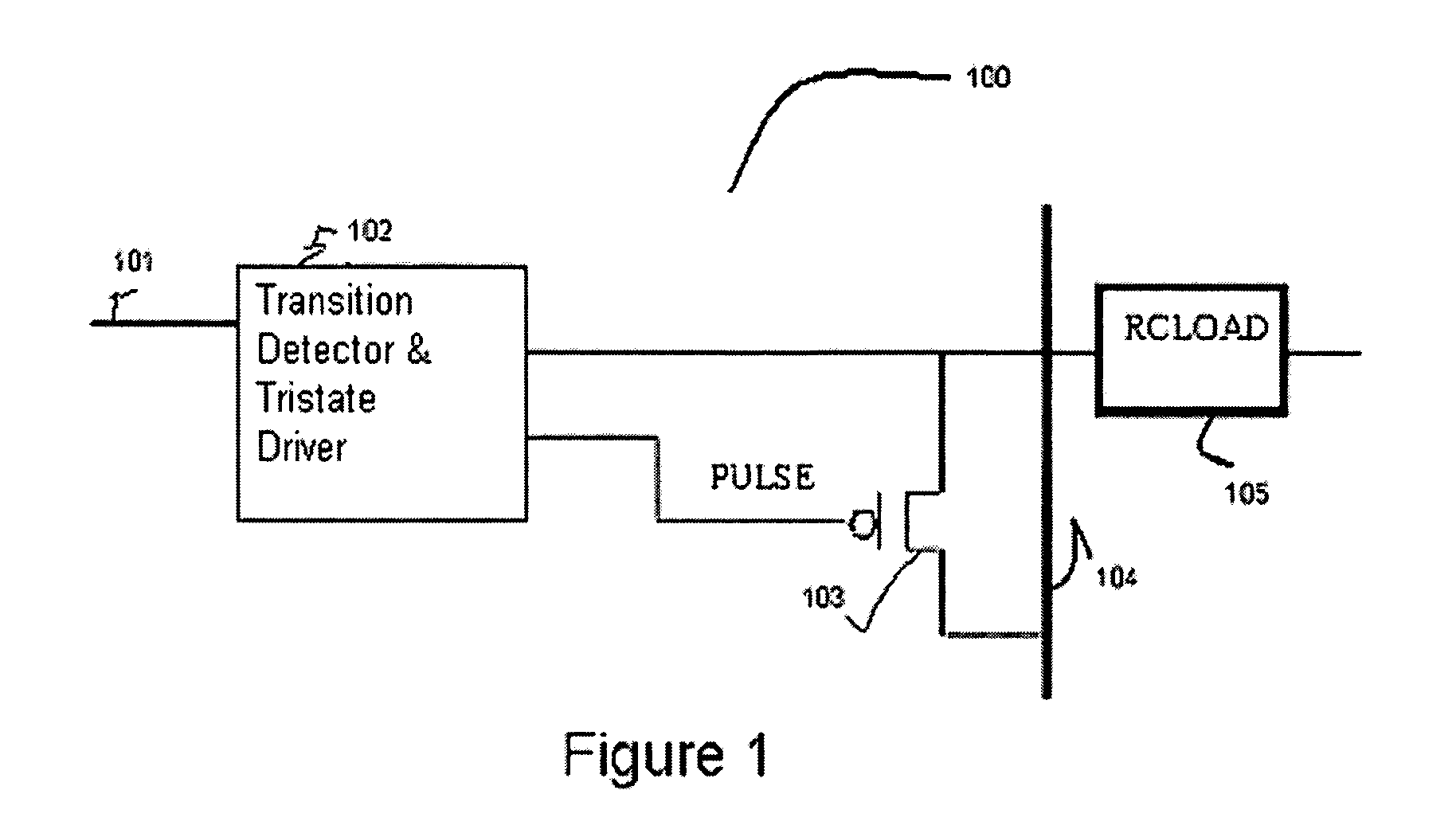

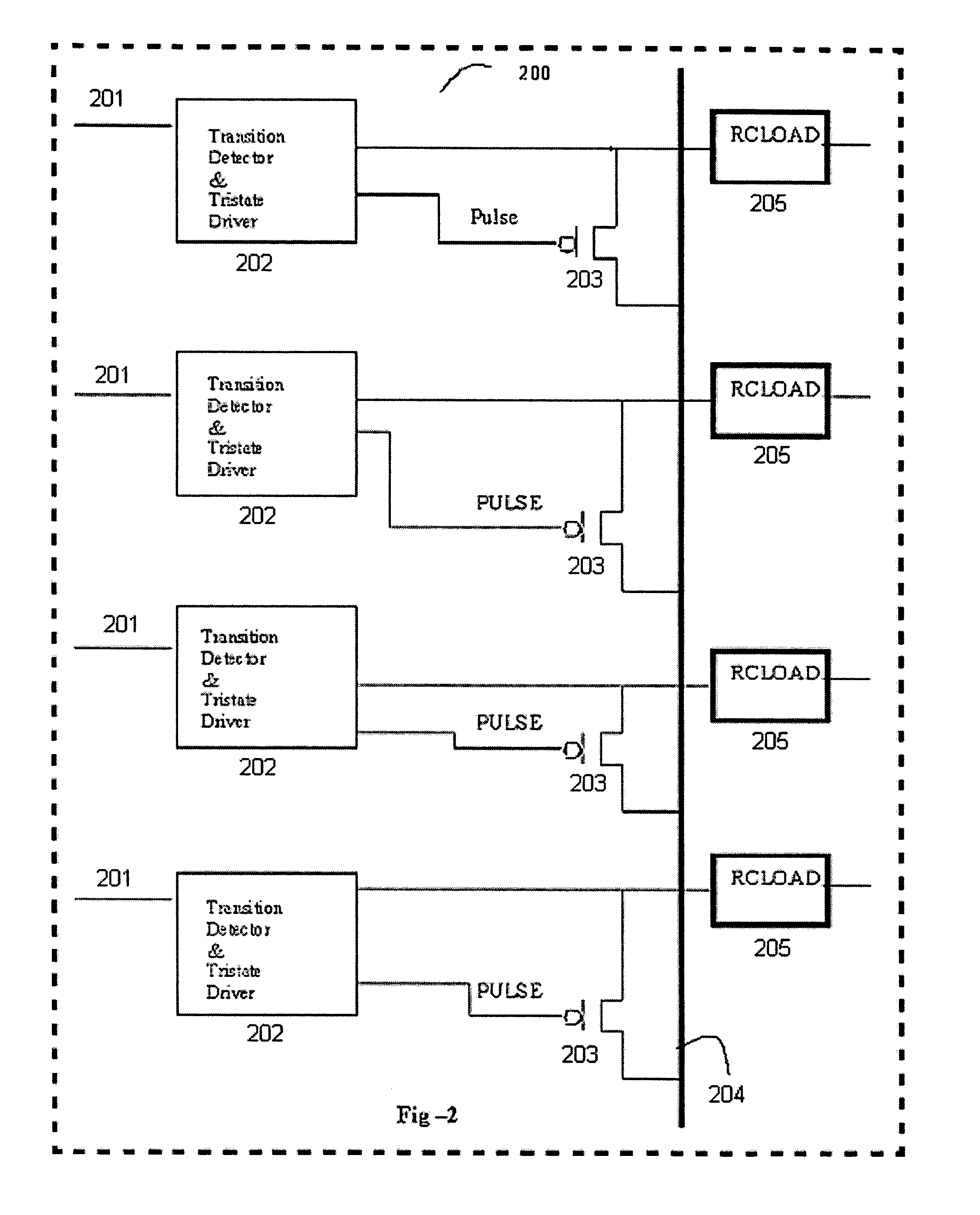

Charge recovery for dynamic circuits

InactiveUS6570408B2Power reduction by energy recoveryPower reduction by adiabatic operationEvaluation IntervalCharge recovery

In one aspect, a method for charge recovery in dynamic circuitry includes discharging a dynamic node during an evaluation interval by input circuitry coupled to the dynamic node responsive to one or more input signals. The discharging includes transferring the charge from the dynamic node to a capacitor during the evaluation time interval. The dynamic node is charged during a precharge interval by a voltage source and precharge timing circuitry coupled to the dynamic node responsive to a precharge signal. The charging includes transferring the charge from the capacitor back to the dynamic node.

Owner:GOOGLE LLC

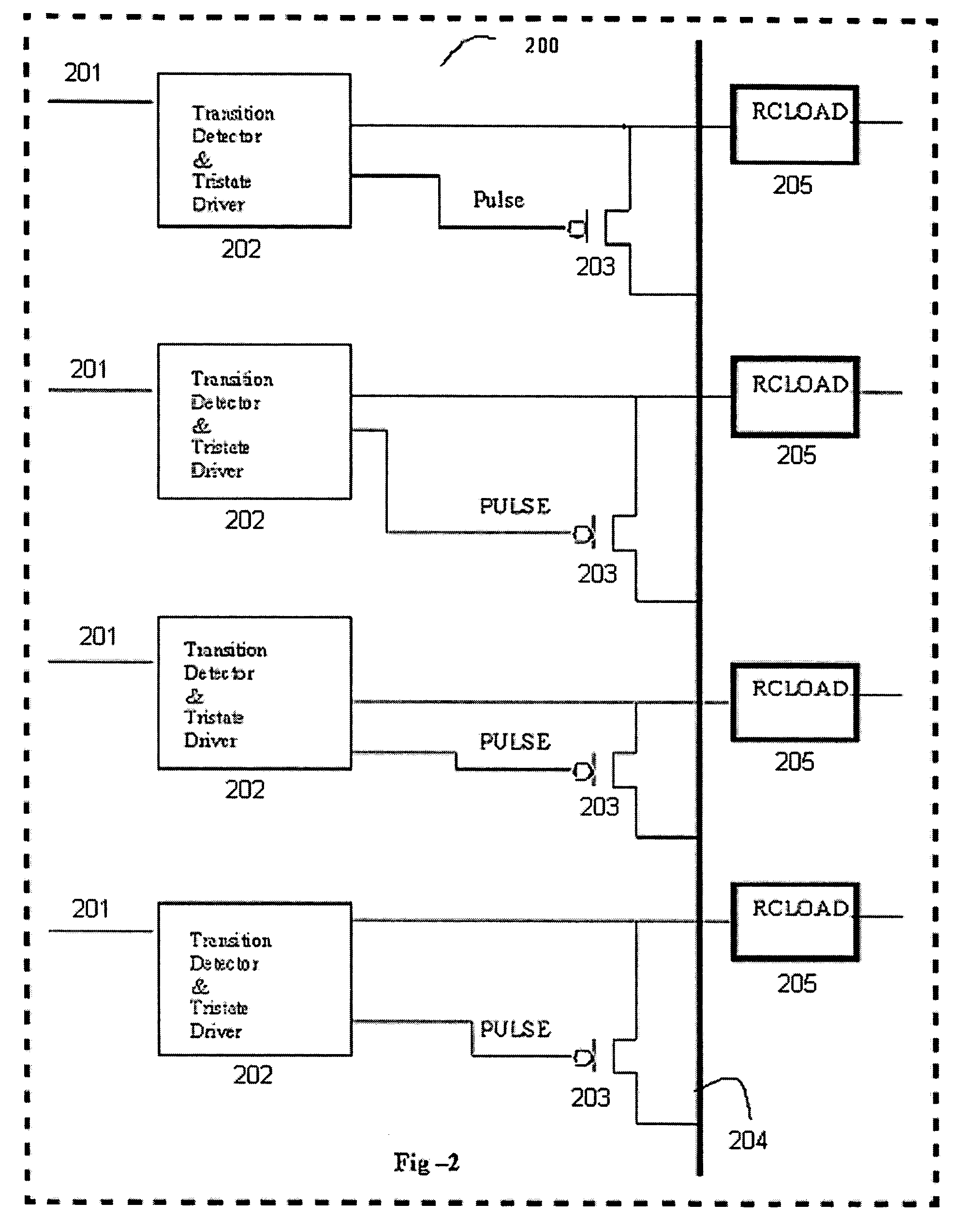

Method and system for reducing power consumption in digital circuitry using charge redistribution circuits

ActiveUS7116137B2Reduce power consumptionPower reduction by energy recoveryPower reduction by adiabatic operationCharge recoveryEngineering

A method and system for reducing power consumption in digital circuits using charge redistribution include a plurality of signal lines, an intermediate floating virtual source / sink, and a charge redistribution circuit connected to each signal line that isolates the signal line from its source and connects it to the intermediate floating virtual source / sink during an idle period prior to a change of state.This charge redistribution provides steady state statistical independent advantage due to charge recycling without inserting extra complimentary lines.

Owner:STMICROELECTRONICS PVT LTD

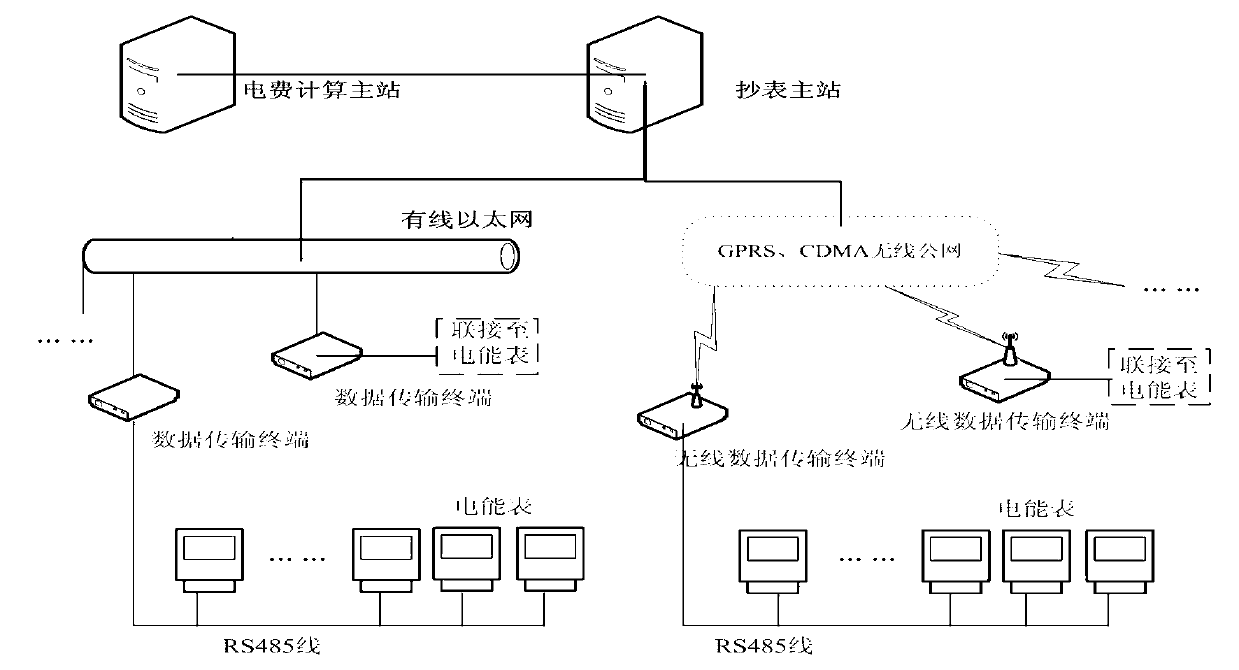

Real-time concentrated long-distance charge-control power system

InactiveCN103106743AEasy maintenanceReduce maintenance workloadApparatus for hiring articlesPrimary stationControl power

A real-time concentrated long-distance charge-control power system comprises an electricity charge calculation main station, a communication network, a data transparent transmission terminal and a watt-hour meter with long-distance brake-opening and brake-closing multiple functions. The system is characterized in that the electricity charge calculation main station is connected with a meter reading main station through a port, and a meter connection main station is linked with a wired or wireless communication network and is linked with the watt-hour meter through the data transparent transmission terminal. The system has the advantages that the electricity charge calculation main station carries out data processing in a concentrated mode, and efficiency and safety are high; functions of the watt-hour meter are simplified; investment is saved; and the effects of an electricity charge recovery rate of a power supply company can be effectively improved.

Owner:XISHUANGBANNA POWER SUPPLY BUREAU OF YUNNAN POWER GRID CO LTD

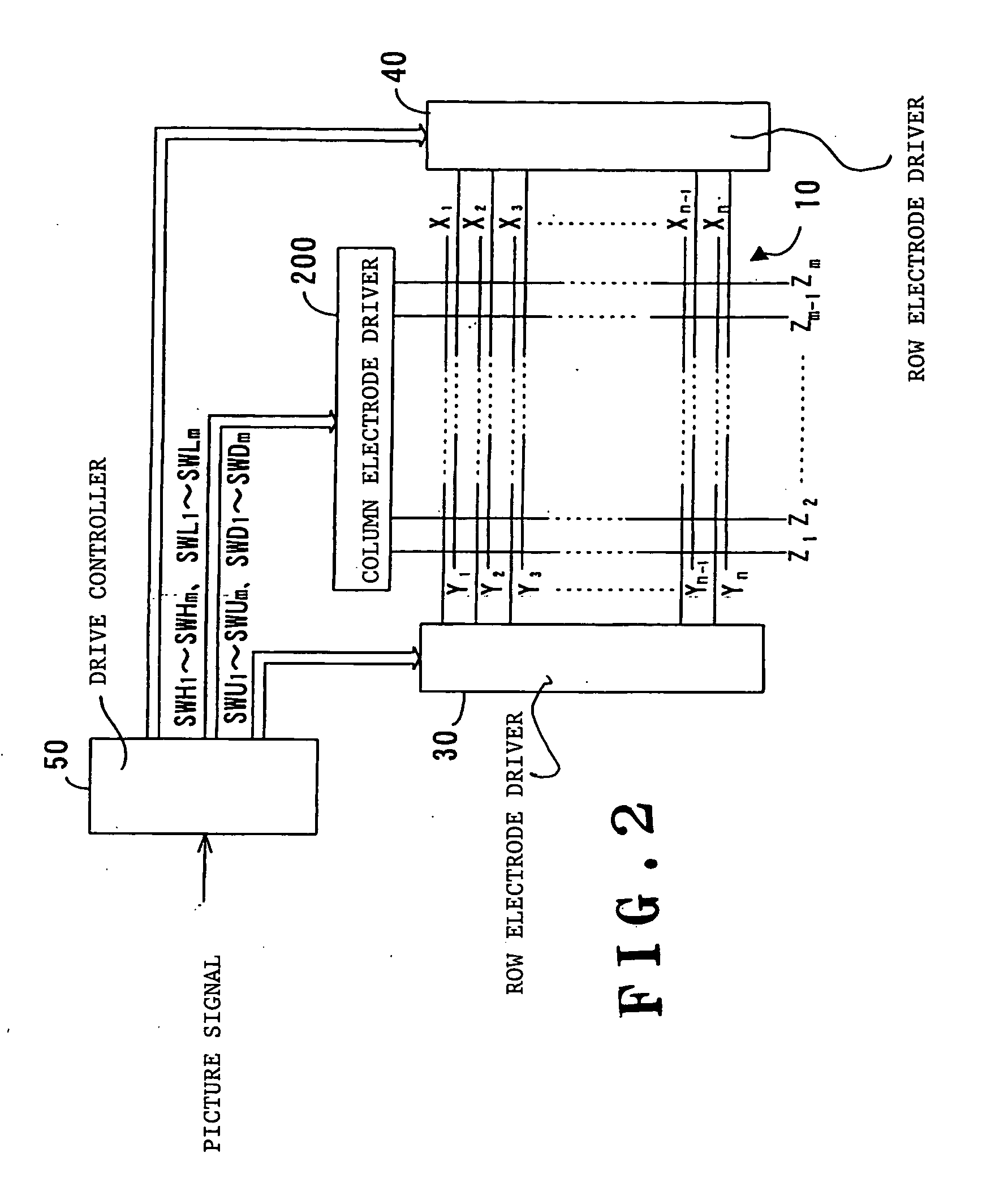

Display and method for driving the same

InactiveUS7327344B2Suppressing screen flickerReduce power consumptionCathode-ray tube indicatorsNon-linear opticsImaging qualityCharge recovery

If a display is subjected to n line dot inversion drive control, the polarity pattern of sub-pixels is shifted line by line in a cycle of n frames. Furthermore, in every n horizontal scanning periods in which the polarities of output terminals of a source driver are switched, at least two of the output terminals are short-circuited to carry out electrical charge recovery. By using these methods, it is possible to achieve a reduction in power consumption while improving image quality.

Owner:COLLABO INNOVATIONS INC

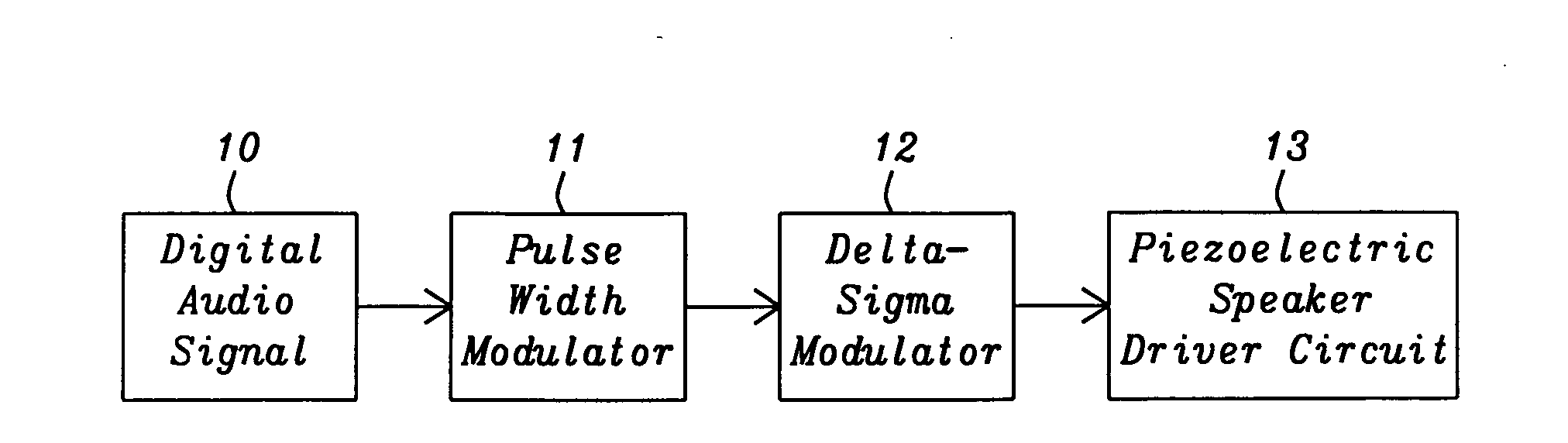

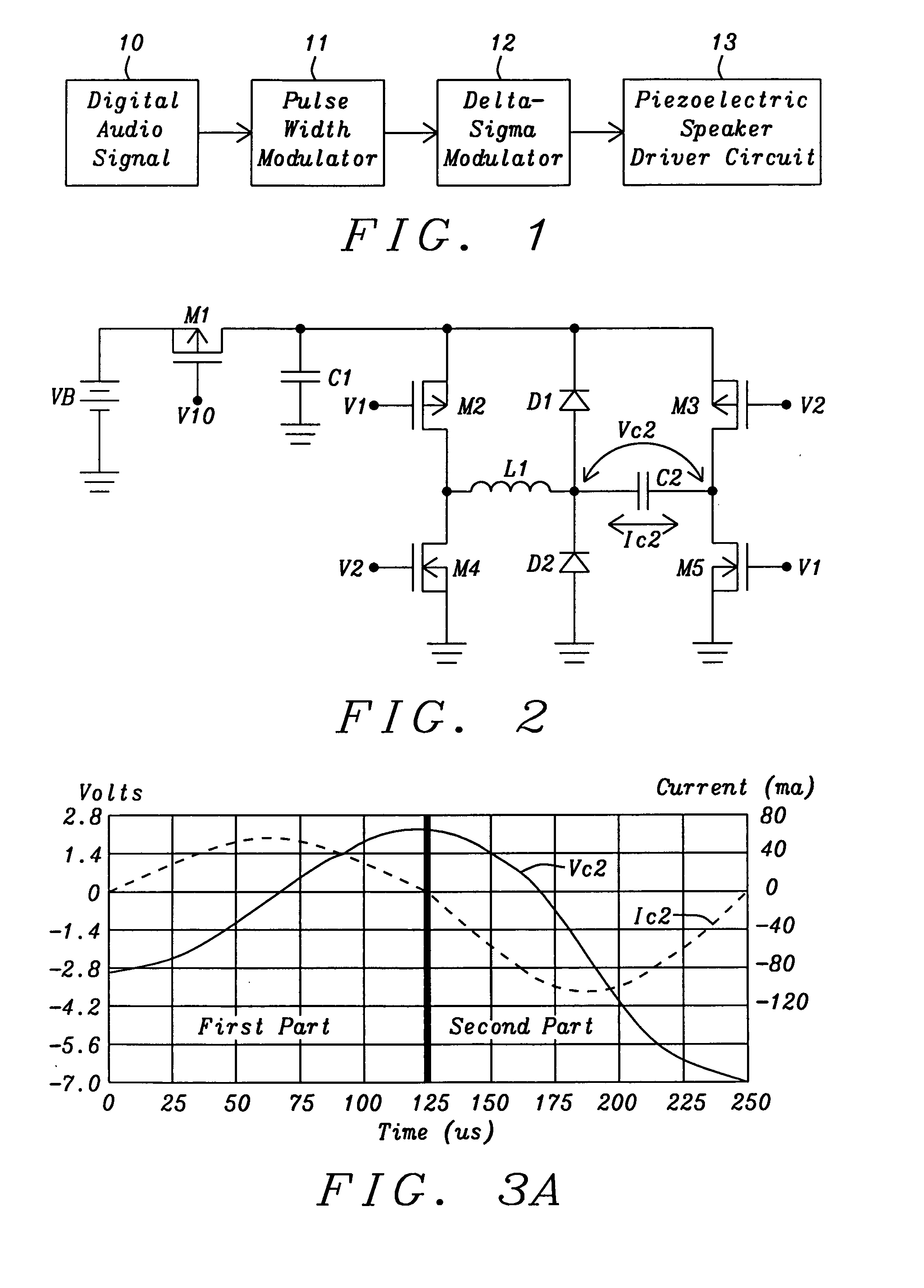

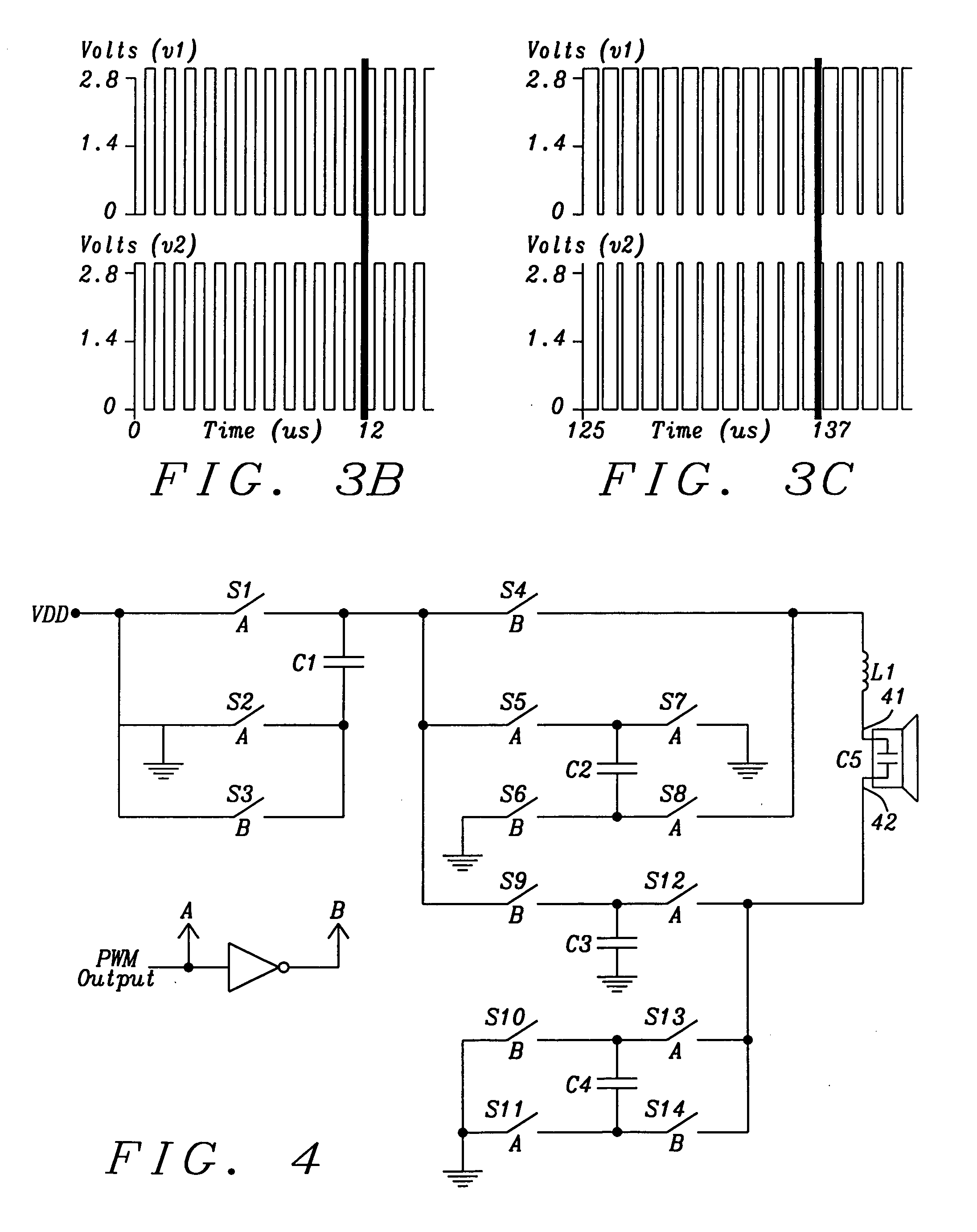

Audio output drivers for piezo speakers

ActiveUS20110305356A1Improve low frequency responseImprove efficiencyPiezoelectric/electrostrictive transducersFrequency response correctionCharge recoveryPush pull

A driver circuit for a piezoelectric speaker is described, wherein charge is transferred from a charge reservoir to the speaker. In a first embodiment a delta sigma circuit uses a pulse width modulated digital audio signal to control a push-pull circuit to drive the piezoelectric speaker. High frequency harmonics are introduced to the delta sigma drive signals to enhance the low frequency response of the speaker. A charge recovery mechanism recovers charge from the speaker to reduce the frequency of replenishing the charge reservoir and to provide additional drive current for the speaker. In a second embodiment the pulse width modulated signal is used to drive a voltage quadrupling circuit that drives the piezoelectric speaker, wherein the reservoir capacitor is integrated with the capacitors of quadrupling circuit, which provides charge recovery.

Owner:WISILICA INC

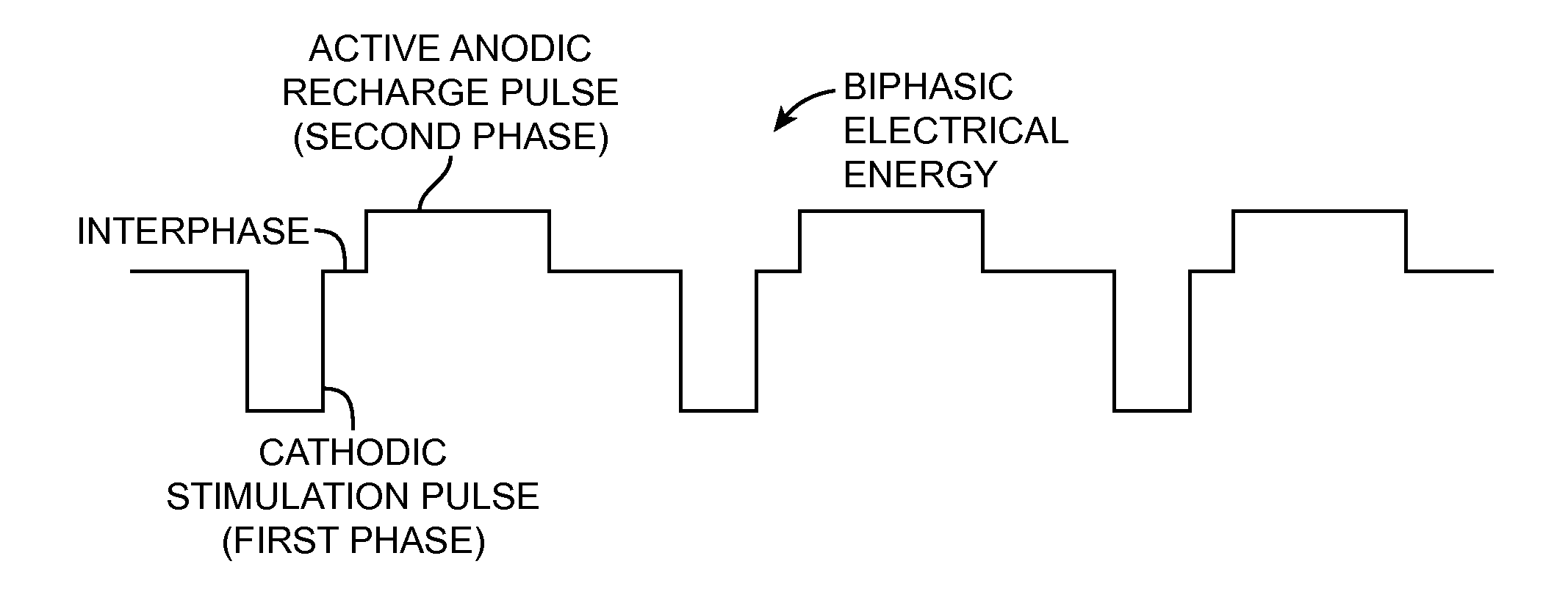

Neurostimulation system having increased flexibility for creating complex pulse trains

A neuromodulation system comprises electrical terminals configured for being respectively coupled to electrodes. The system further comprises modulation output circuitry configured for respectively outputting individual electrical pulse trains in timing channels to the electrical terminals, wherein each of the pulse trains has a modulation pulse, and at least one of the pulse trains has a charge recovery pulse associated with the modulation pulse of the respective pulse train. The neuromodulation system further comprises control circuitry configured for controlling the modulation output circuitry in a manner that sequentially outputs the modulation pulses of the respective pulse trains to a common set of the electrical terminals without an intervening charge recovery pulse, and outputting the charge recovery pulse(s) to the common set of the electrical terminals subsequent to the sequential modulation pulses, thereby creating a combined electrical pulse train at the common set of electrical terminals.

Owner:BOSTON SCI NEUROMODULATION CORP

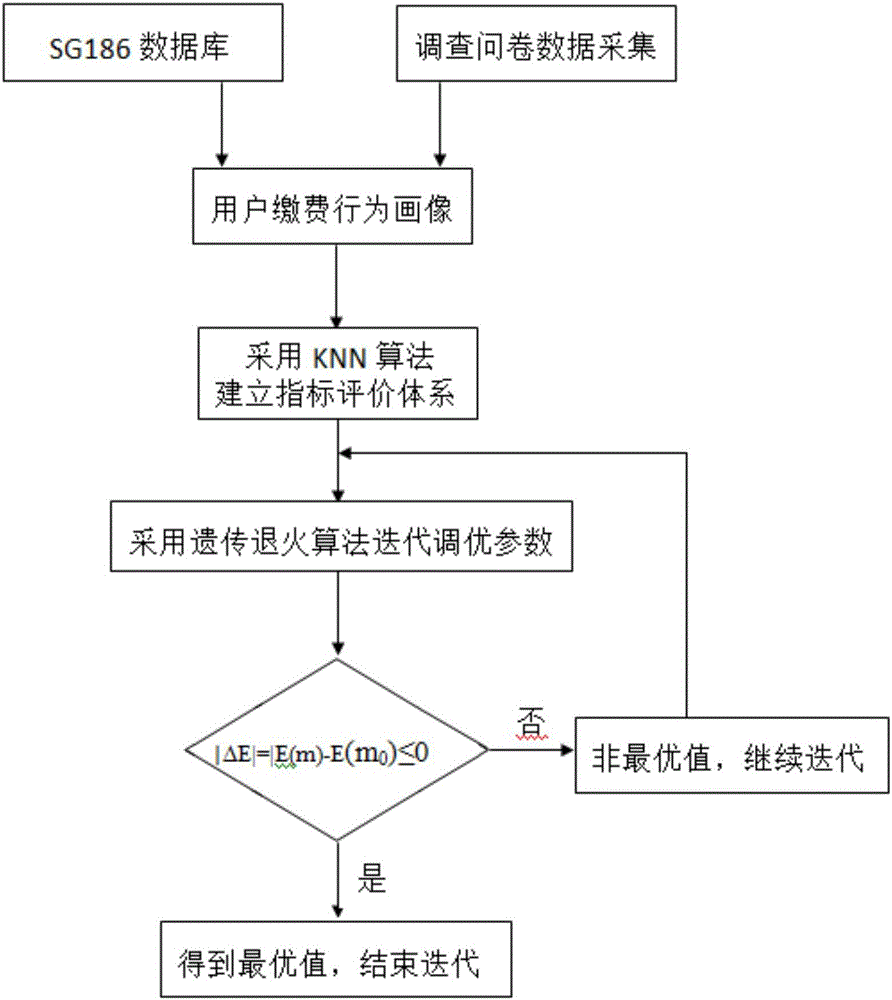

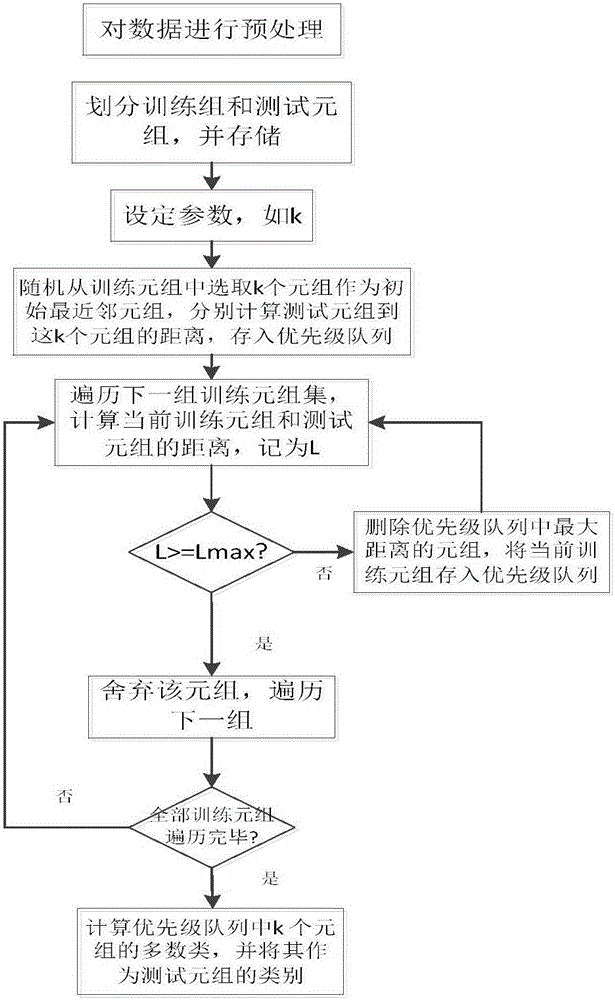

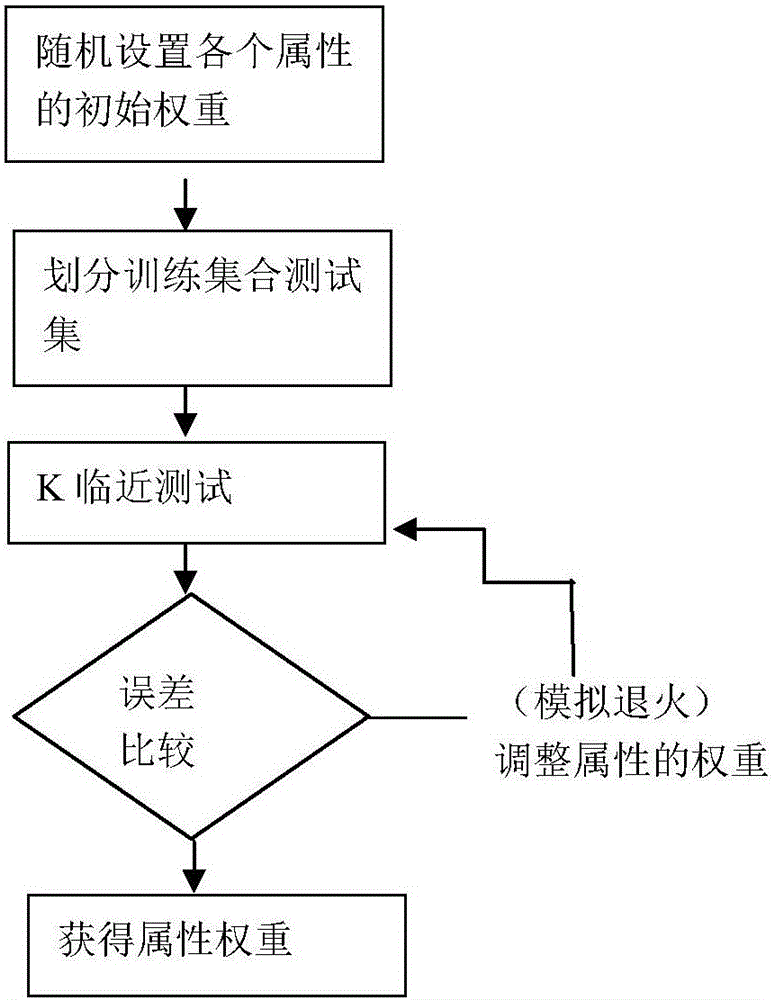

Calculating method of index selection, weight optimization and channel planning of electric power payment channel analysis

InactiveCN106650763AConvenient paymentImprove the level of lean managementCharacter and pattern recognitionCharge recoveryNear neighbor

A calculating method of index selection, weight optimization and channel planning of electric power payment channel analysis is disclosed. The method comprises the following steps of step1, through a SG186 system or a questionnaire, acquiring data of basic attribute information and payment habit attribute information of a user who pays; step2, using a characteristic weight optimization method to optimize each weight in an individual user figure, acquiring an optimal individual user figure, and through a clustering algorithm, establishing a group user payment behavior figure; step3, using a K-nearest neighbor classification algorithm to establish an index evaluation system; step4, using a genetic annealing algorithm to calculate a weight value of each attribute index; and step5, determining whether the value is an optimal value and determining an optimal payment channel. In the invention, based on user payment large data, a lean management level of marketing electricity charge recovery work is increased and finally a payment service channel through which the user can pay conveniently and which is satisfied by the user is realized.

Owner:ELECTRIC POWER RES INST OF EAST INNER MONGOLIA ELECTRIC POWER +2

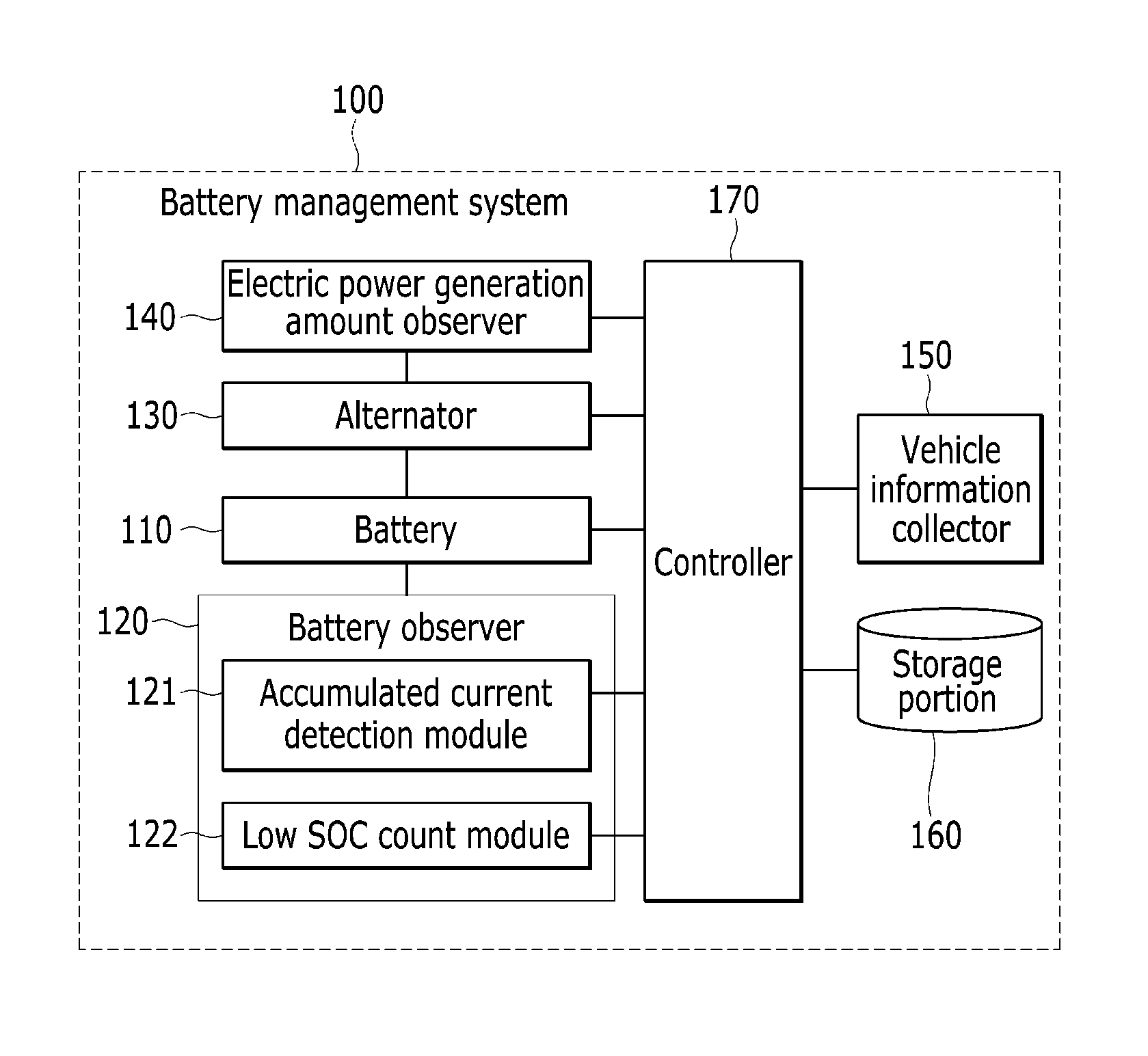

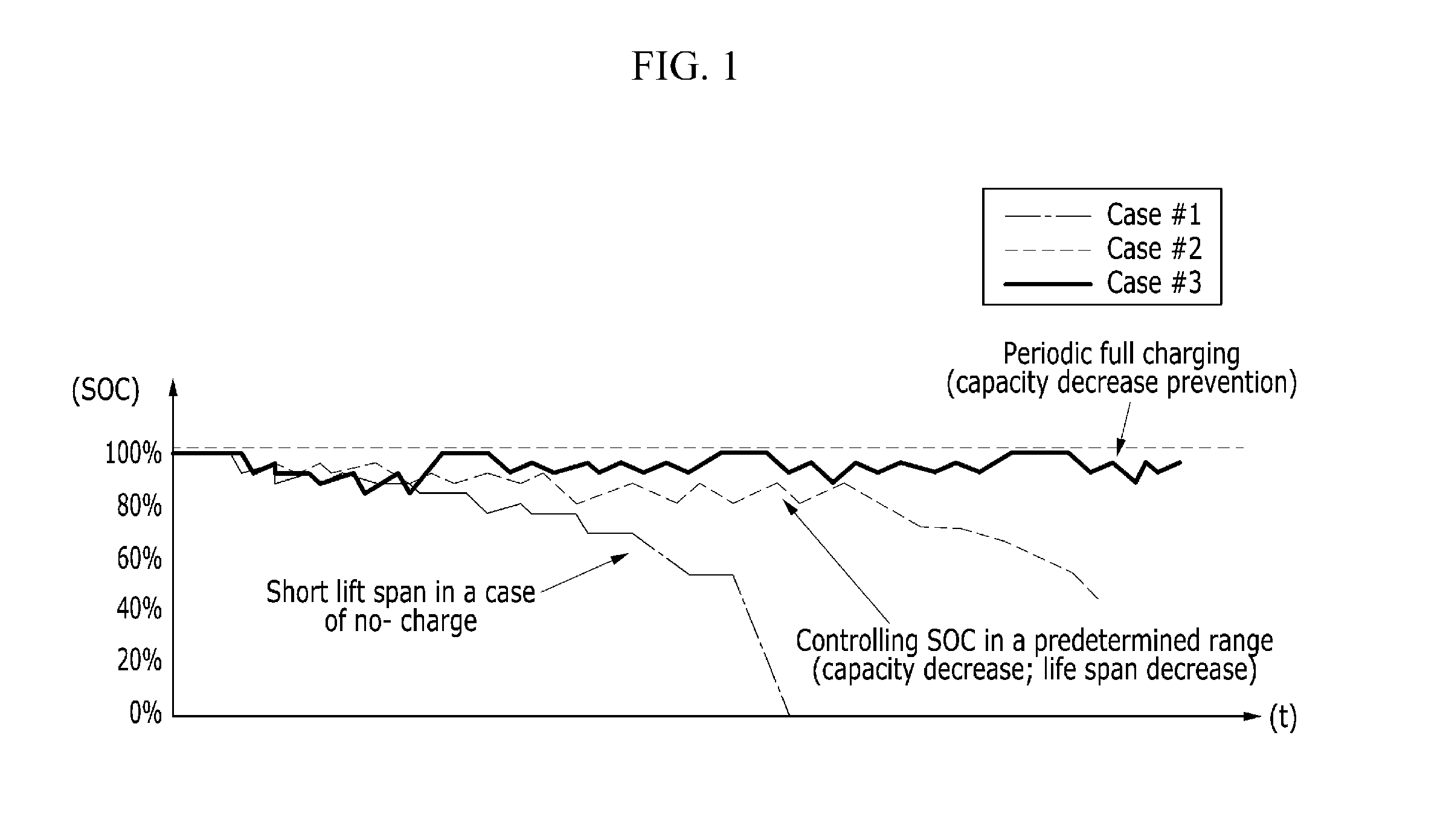

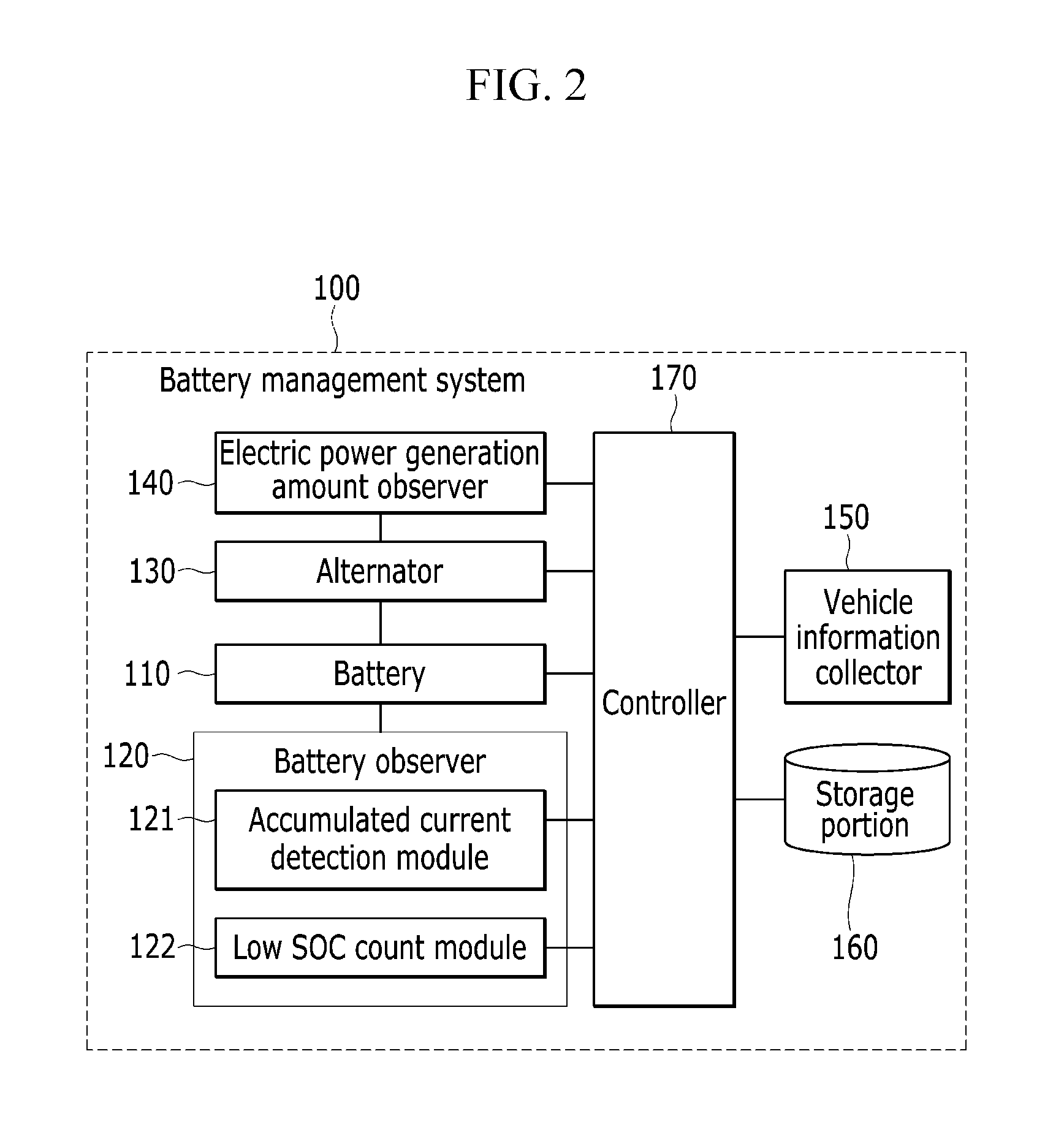

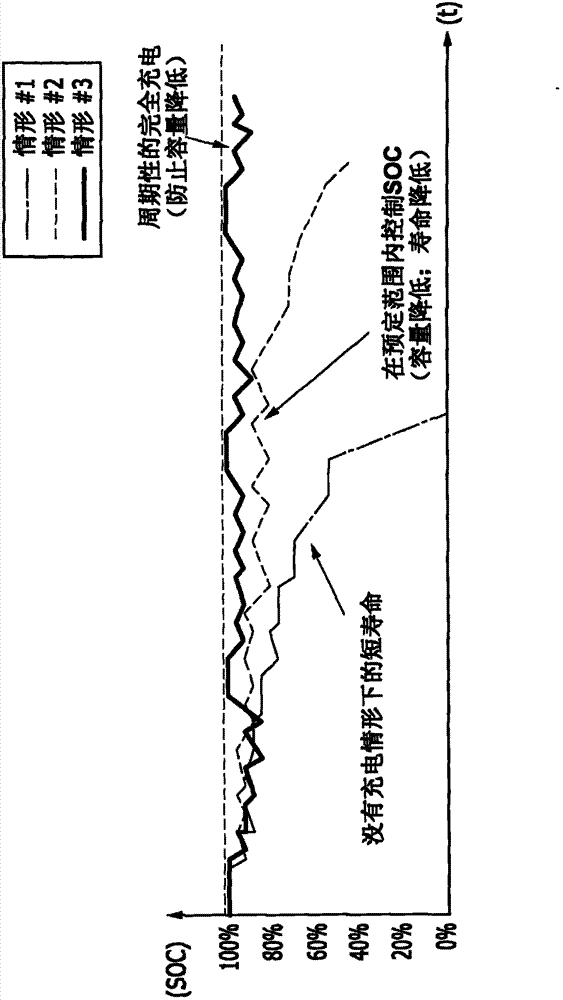

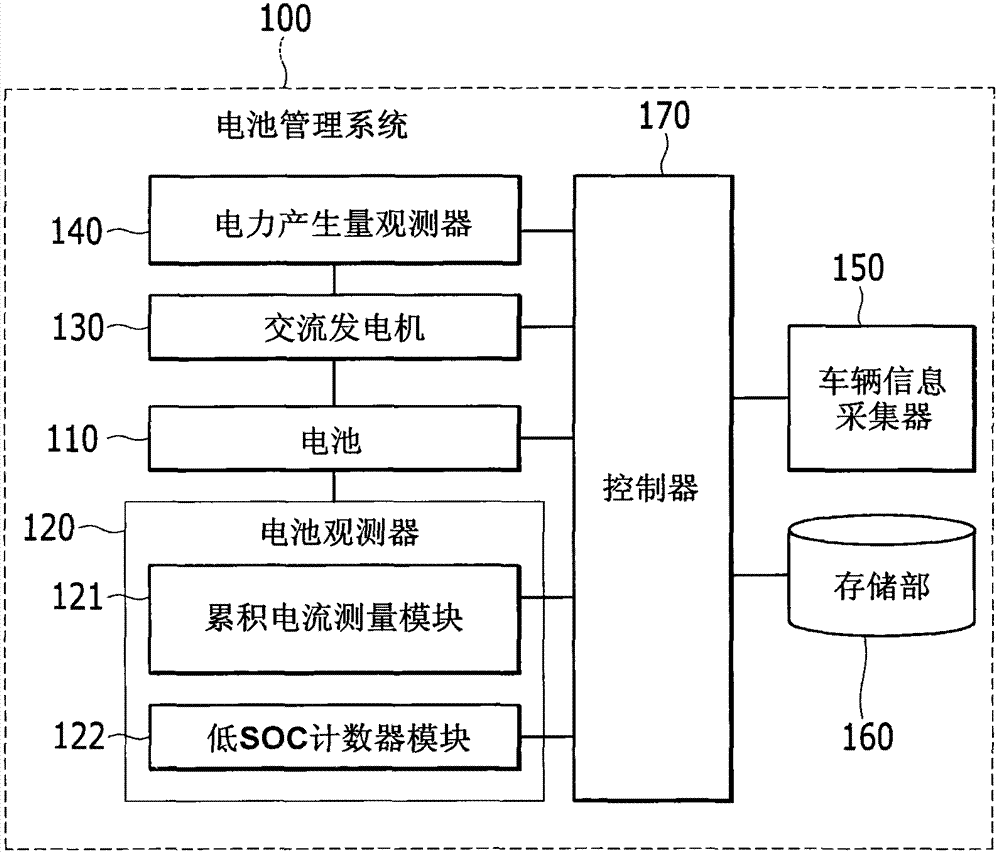

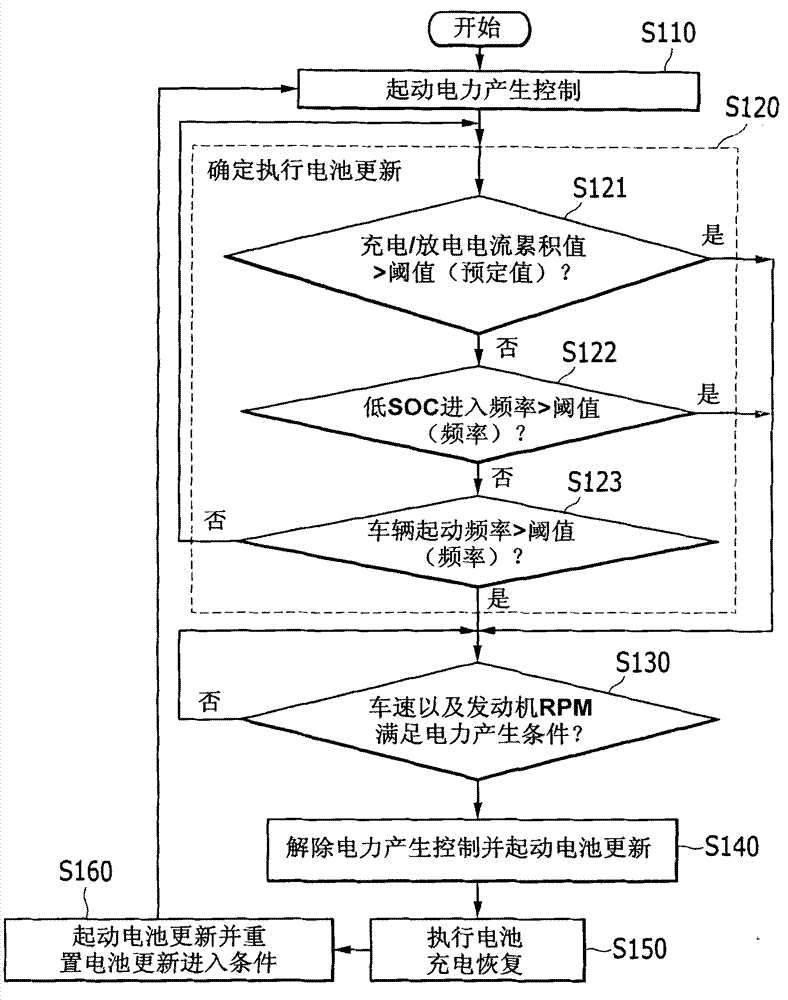

Battery management system and method of vehicle

InactiveUS20130113277A1Inhibition of capacity fadingIncreased durabilityBatteries circuit arrangementsElectric devicesElectricityAlternator

Disclosed is a battery management system. More specifically, the battery management system includes an alternator that supplies a battery and electronic equipment of a vehicle with electricity that is generated by a driving torque of the vehicle, a battery that supplies the electronic equipment with power that is charged by the alternator, a battery observer that observes a condition of the battery, a vehicle information collection portion that collects vehicle condition information according to driving of the vehicle, and a control portion that performs charging recovery of the battery by activating a battery refresh operation when at least one condition of a current accumulation value of the battery, a low SCO entry frequency, and a vehicle starting frequency satisfies a predetermined battery refresh condition.

Owner:HYUNDAI MOTOR CO LTD +1

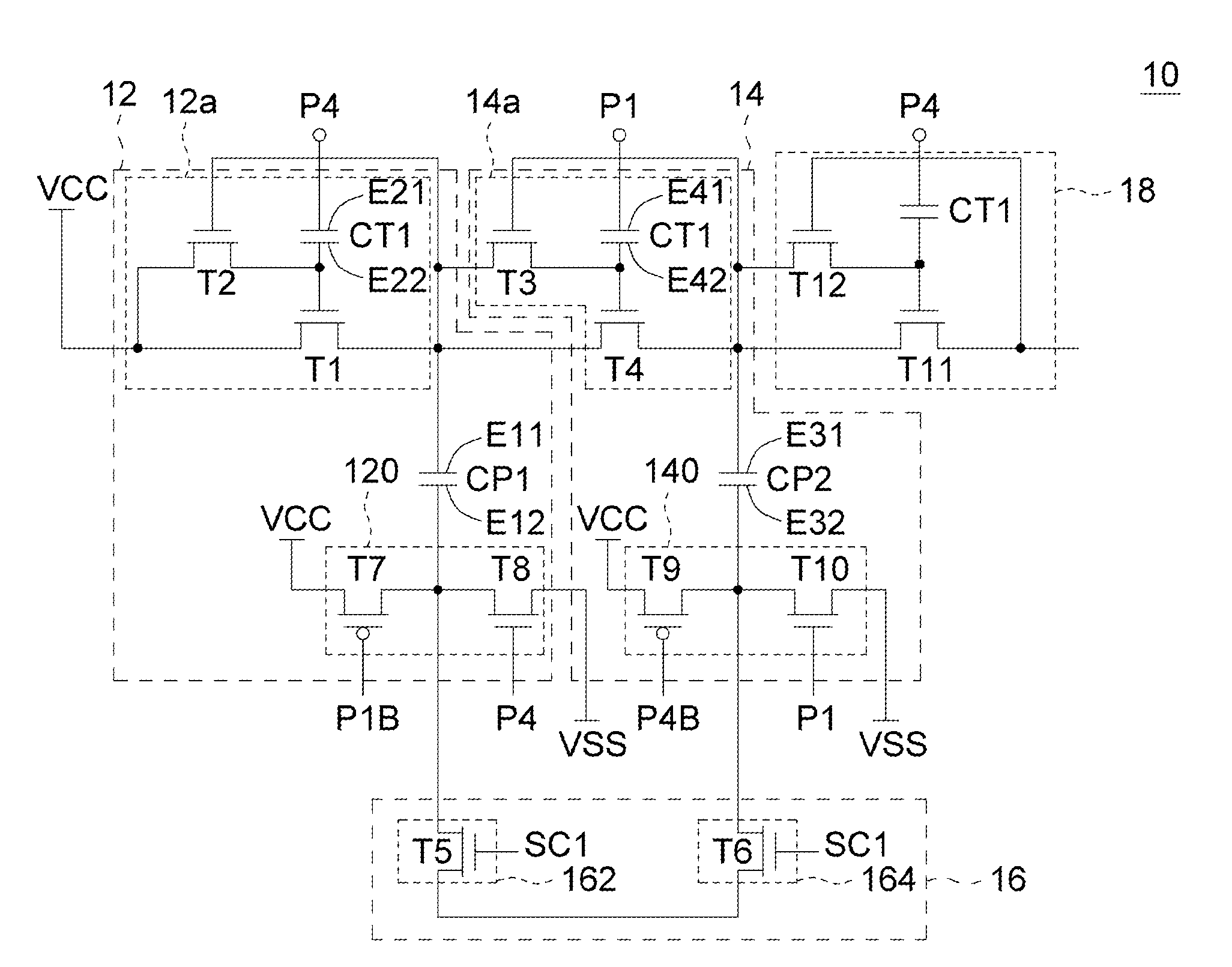

Multiple-Stage Charge Pump with Charge Recycle Circuit

InactiveUS20100219881A1Reduce power consumptionImprove power efficiencyDc-dc conversionElectric variable regulationCharge recoveryCapacitor

A multiple-stage charge pump circuit comprises first and second pump capacitors, first and second transfer circuits, first and second driving circuits, and a charge recycle circuit. The first pump capacitor, the first transfer circuit, and the first driving circuit form a first stage circuit, and the second pump capacitor, the second transfer circuit and the second driving circuit form a second stage circuit. The first and the second stage circuits operate 180 degree out of phase with each other. The charge recycle circuit transfers the charge at the second end of the first pump capacitor to the second end of the second pump capacitor in a first time interval, and transferring the charge at the second end of the second pump capacitor to the second end of the first pump capacitor in a second time interval.

Owner:MACRONIX INT CO LTD

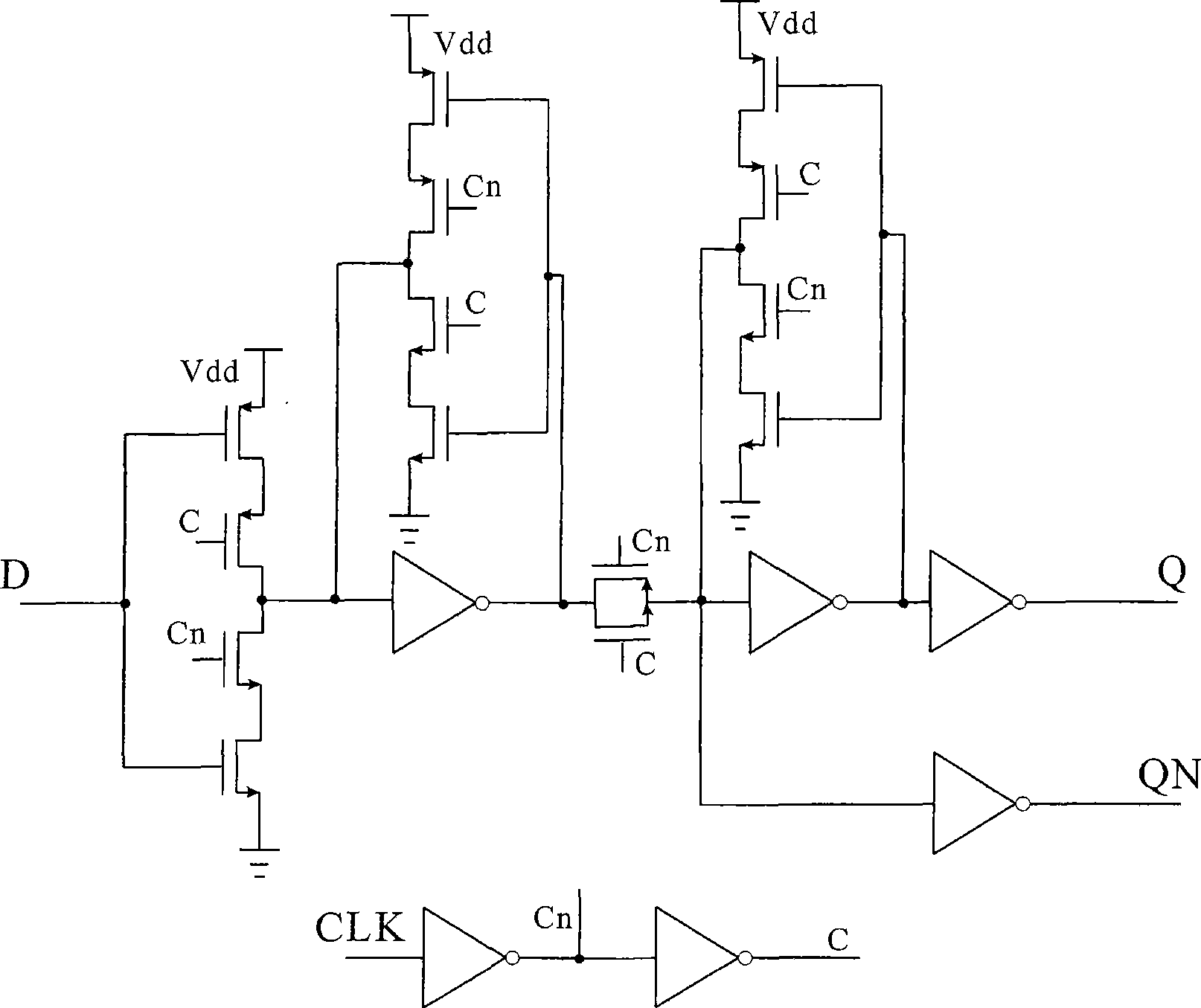

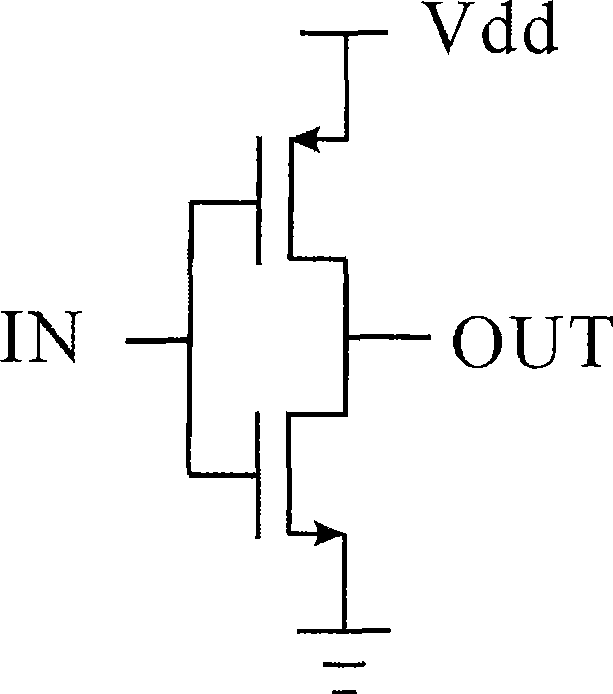

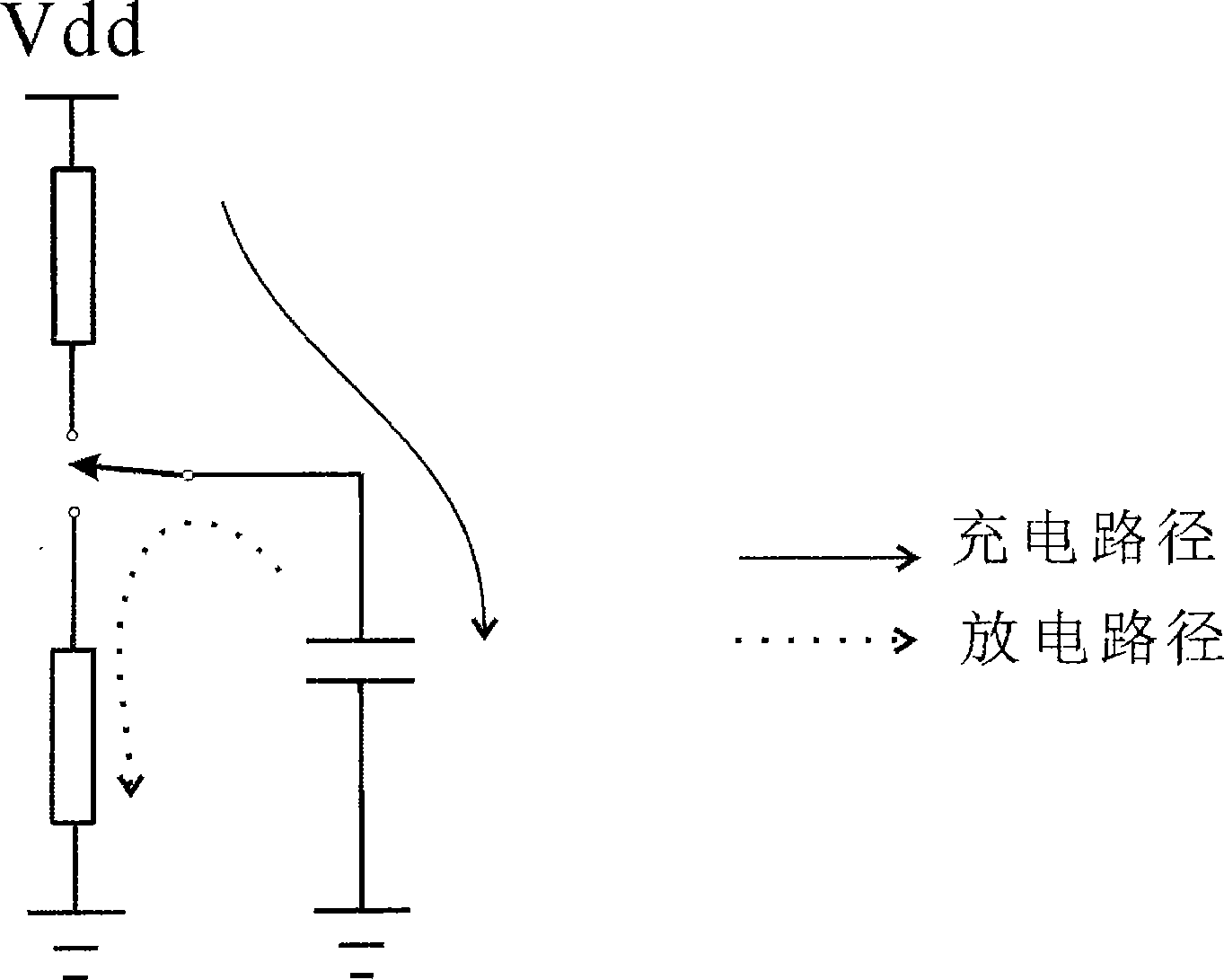

Single-phase power clock trigger based on electric charge resumption

InactiveCN101471642AReduce power consumptionLogic circuits characterised by logic functionElectric pulse generatorSquare waveformCoupling

The invention relates to a single-phase power clock trigger based on charge recovering. The trigger comprises an input inverter used for generating two inverse signals and sending the two signals to a charge recovery unit, a cross-coupling charge recovery unit used for reducing the power consumption of a circuit, and a RS trigger used for latching the output of a charge recycling unit, wherein, the input and the output of the inverter are connected with two input terminals of the cross-coupling charge recovery unit respectively; and two output terminals of the cross-coupling charge recovery unit are connected with two input terminals of the RS trigger. The trigger adopts the single phase power clock (similar to a sine wave power) Pclk to complete the function of the trigger D, input and output signals adopt the square wave and can be directly cascaded with a traditional CMOS logic circuit to complete the logic. Compared with a traditional trigger, the trigger of the invention has the advantages that the power consumption is low, and the extremely low power consumption can be realized particularly when the data change rate is low; the number of transistors is small; and the single-phase clock is adopted.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

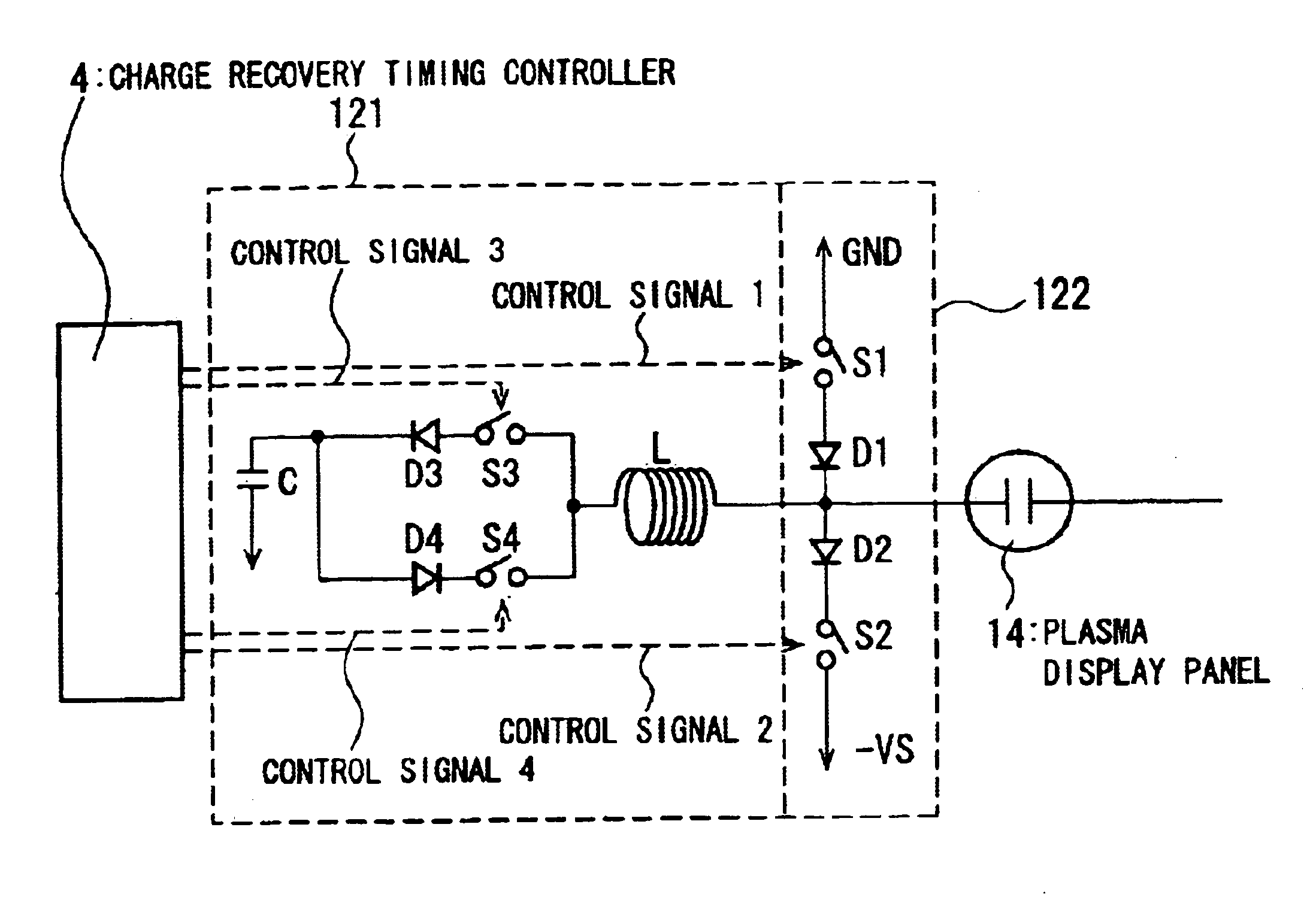

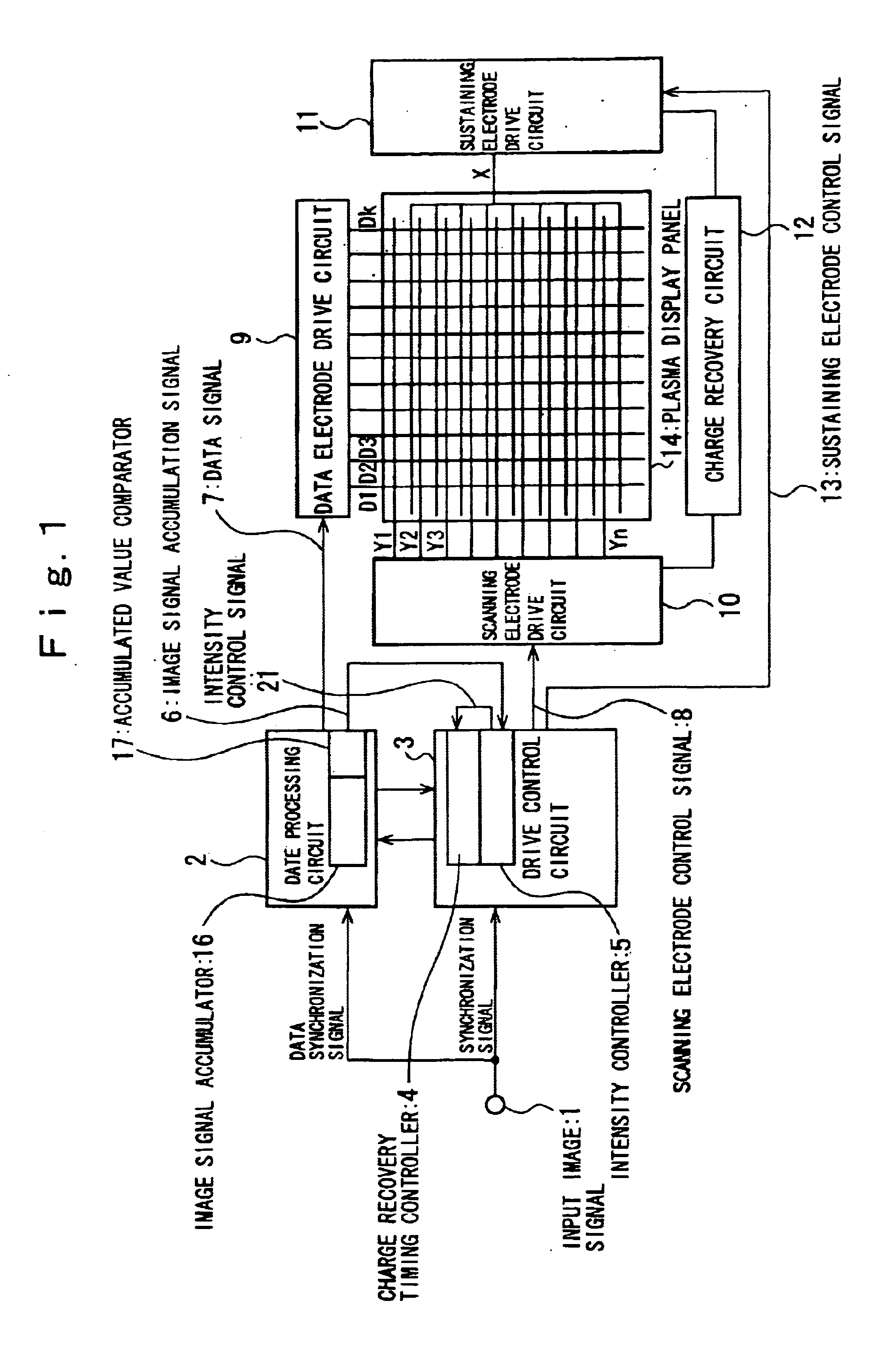

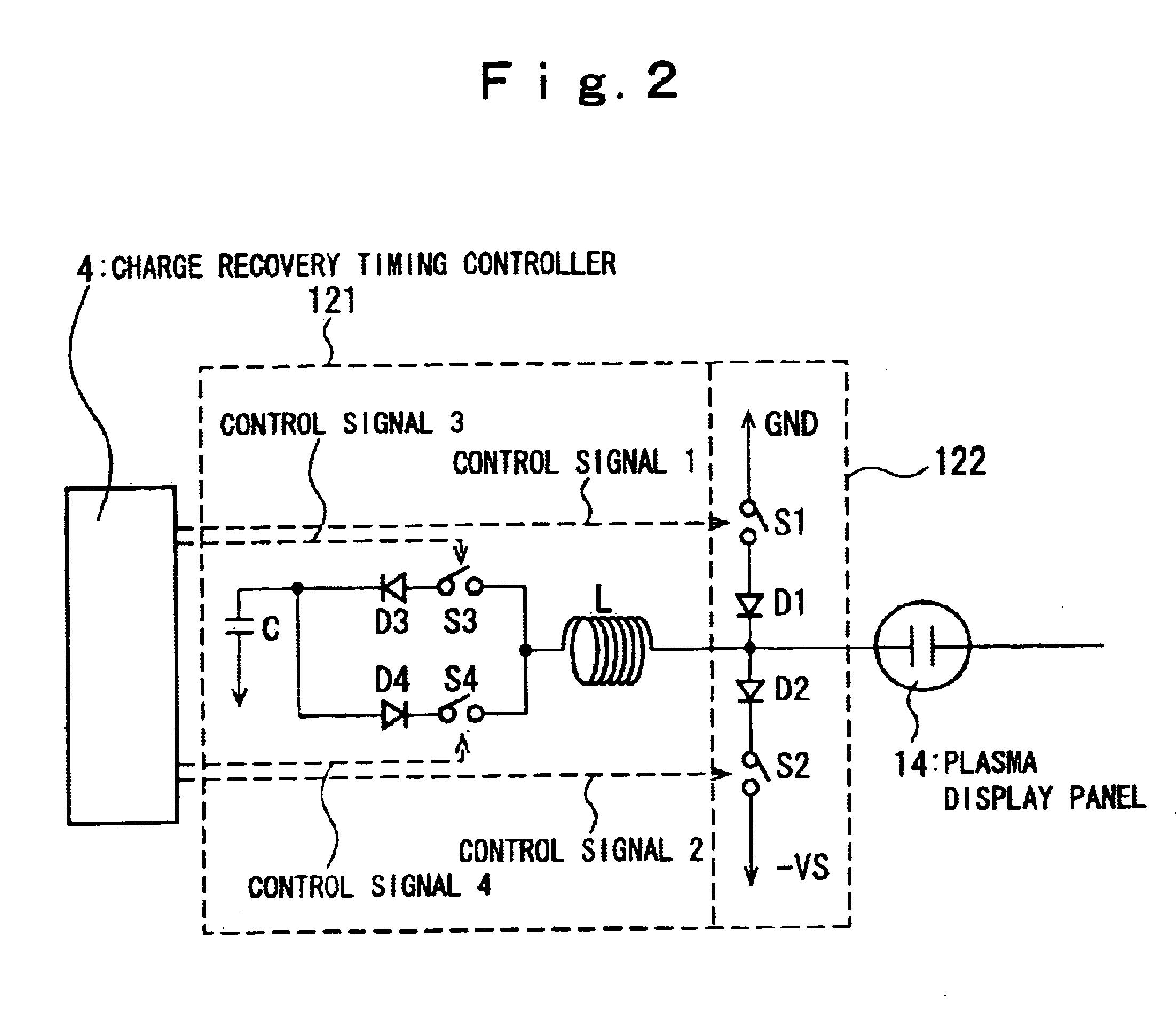

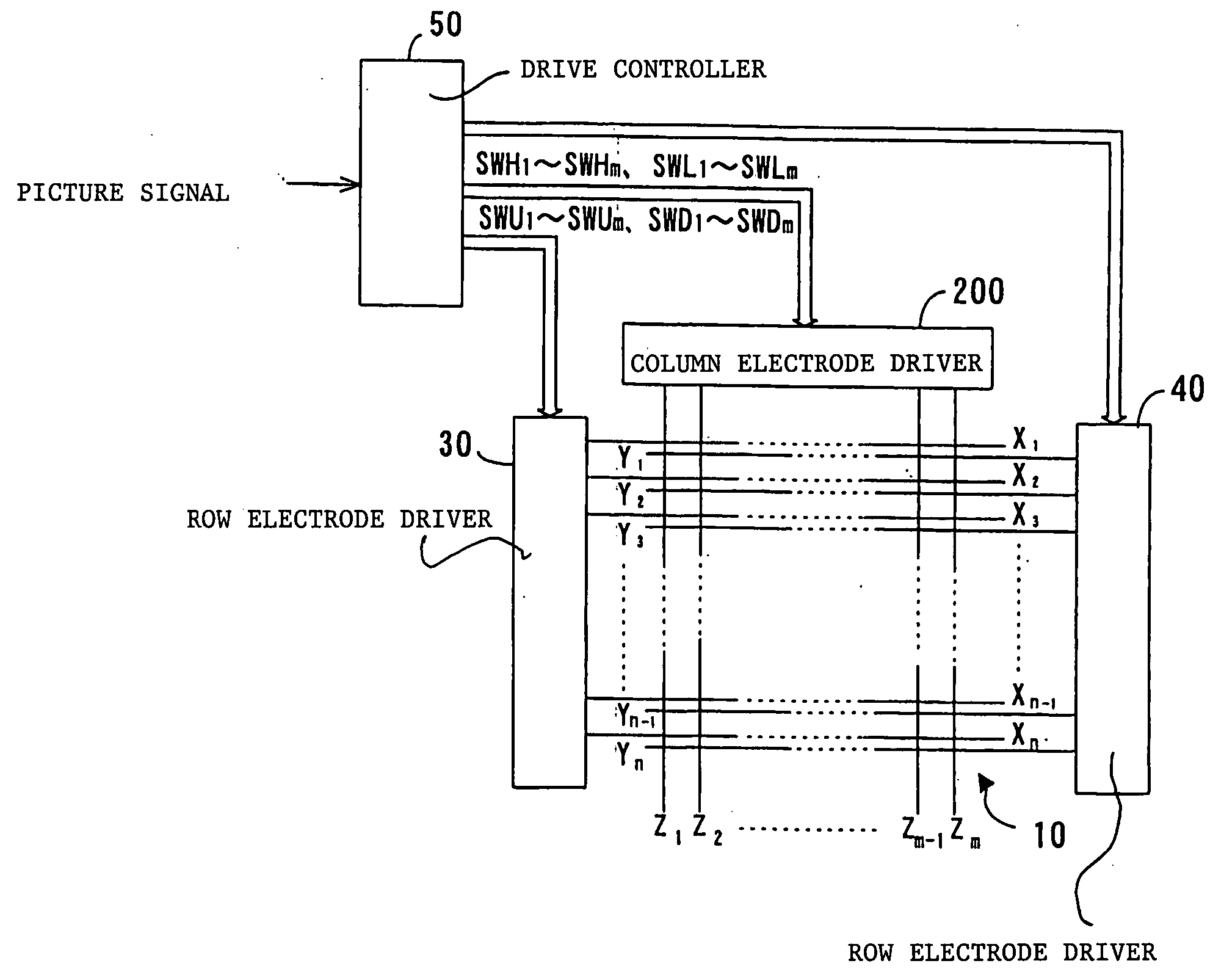

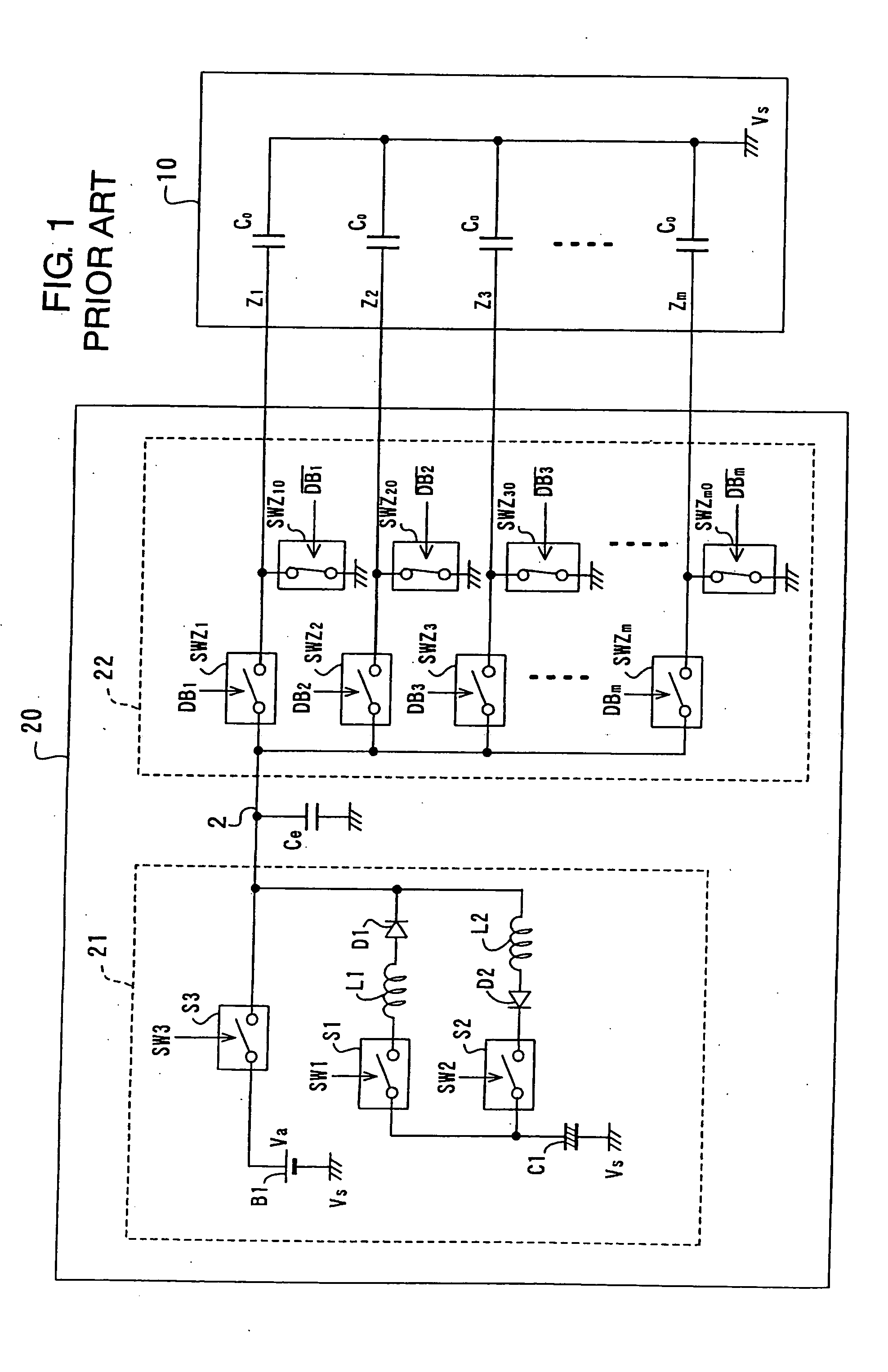

Plasma display panel drive apparatus and drive method

InactiveUS6922191B2Great variationImprove power efficiencyCathode-ray tube indicatorsInput/output processes for data processingCharge recoveryEngineering

A drive apparatus for a plasma display panel useing a charge recovery circuit 12 that re-uses a recovered electrical charge, the drive apparatus comprising: a brightness detection means 16, 17 for detecting a brightness so as to obtain screen brightness information; and a charge recovery timing control means 4 for controlling a charge recovery period T from a time at which a charge recovery operation of the charge recovery circuit 12 starts to a time of fixing to a sustaining potential or a ground potential, wherein the charge recovery timing control means 4 controls the charge recovery period of the charge recovery circuit 4 in response to the brightness information obtained by the brightness detection means 16, 17.

Owner:PANASONIC CORP

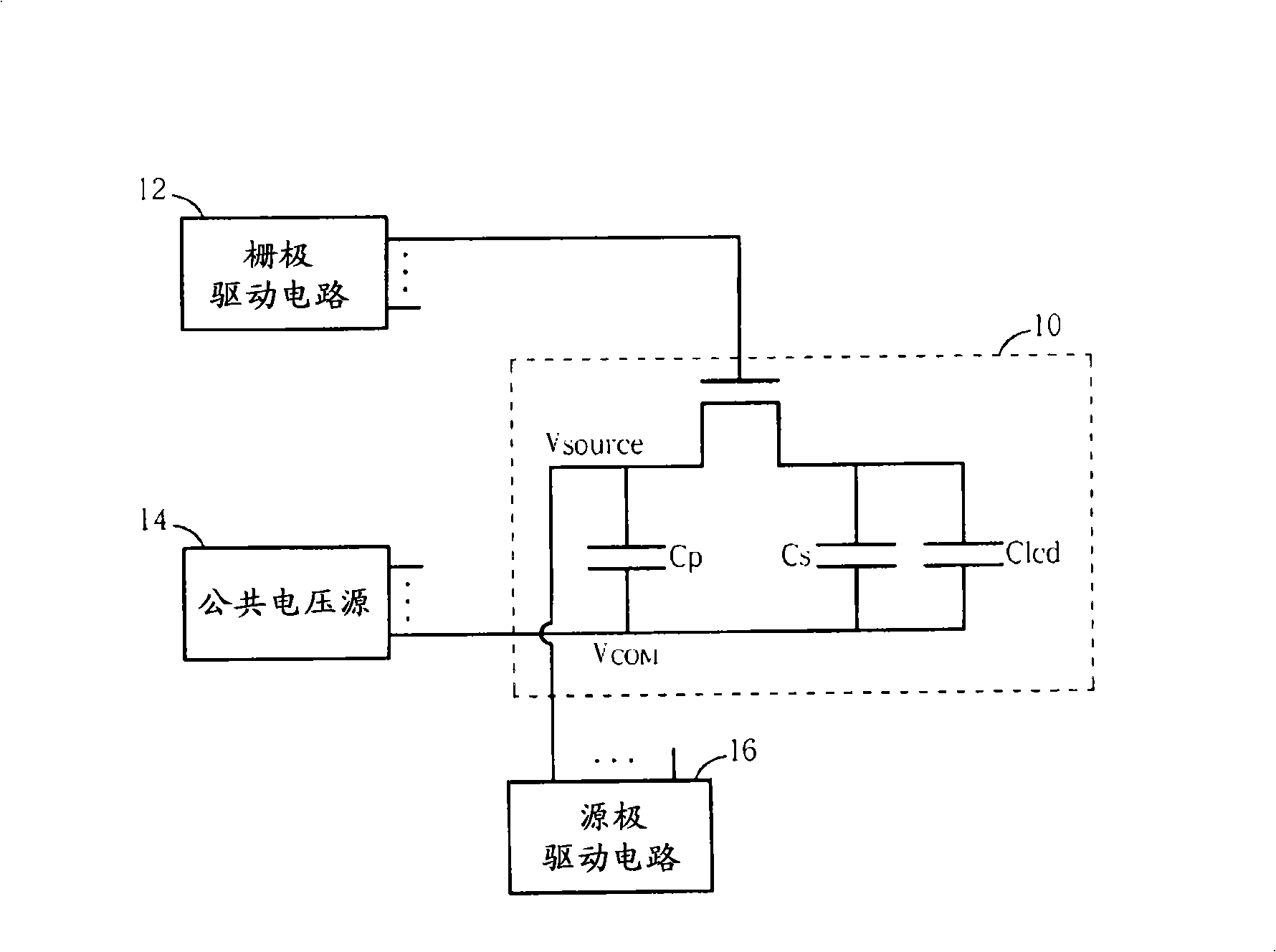

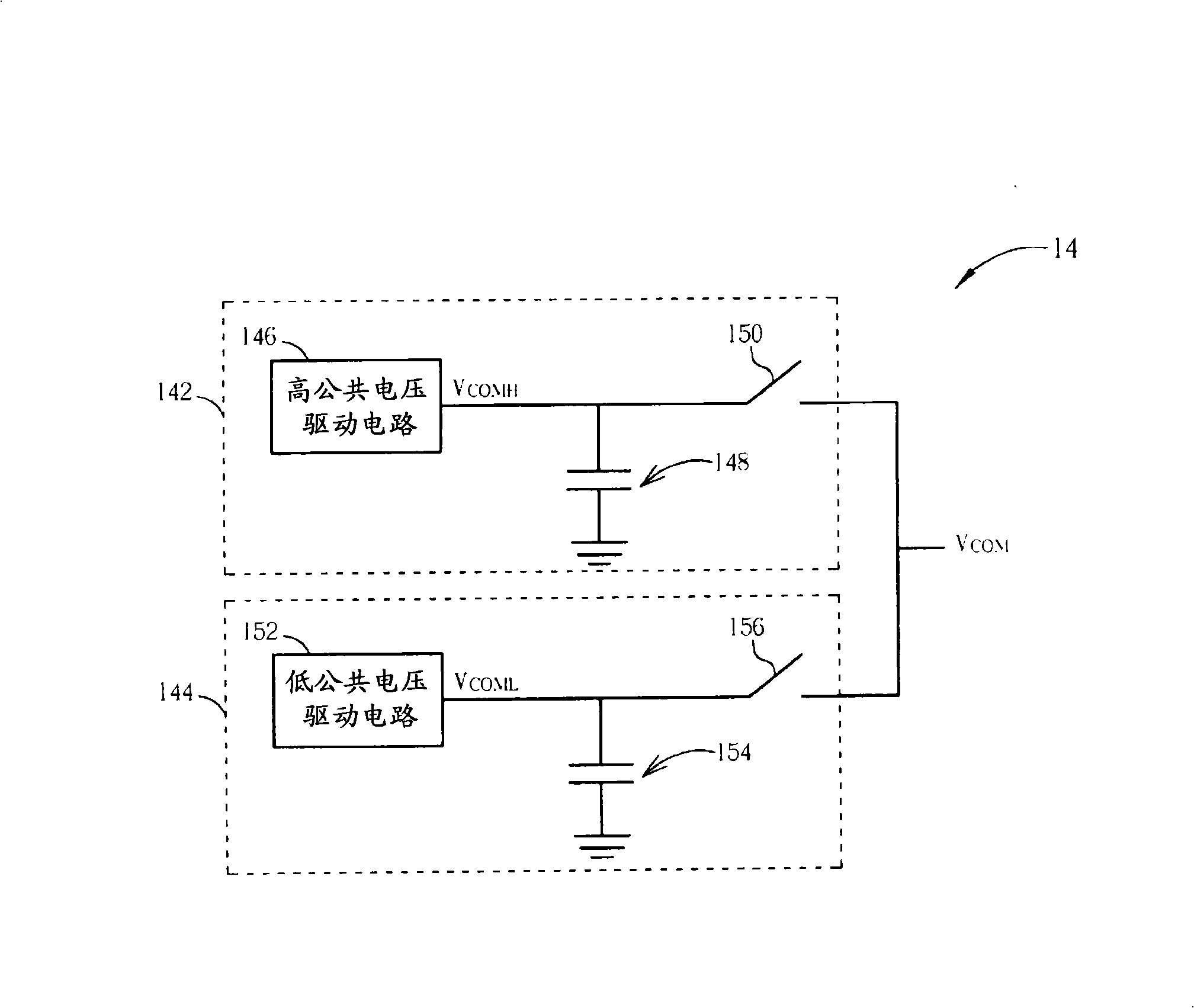

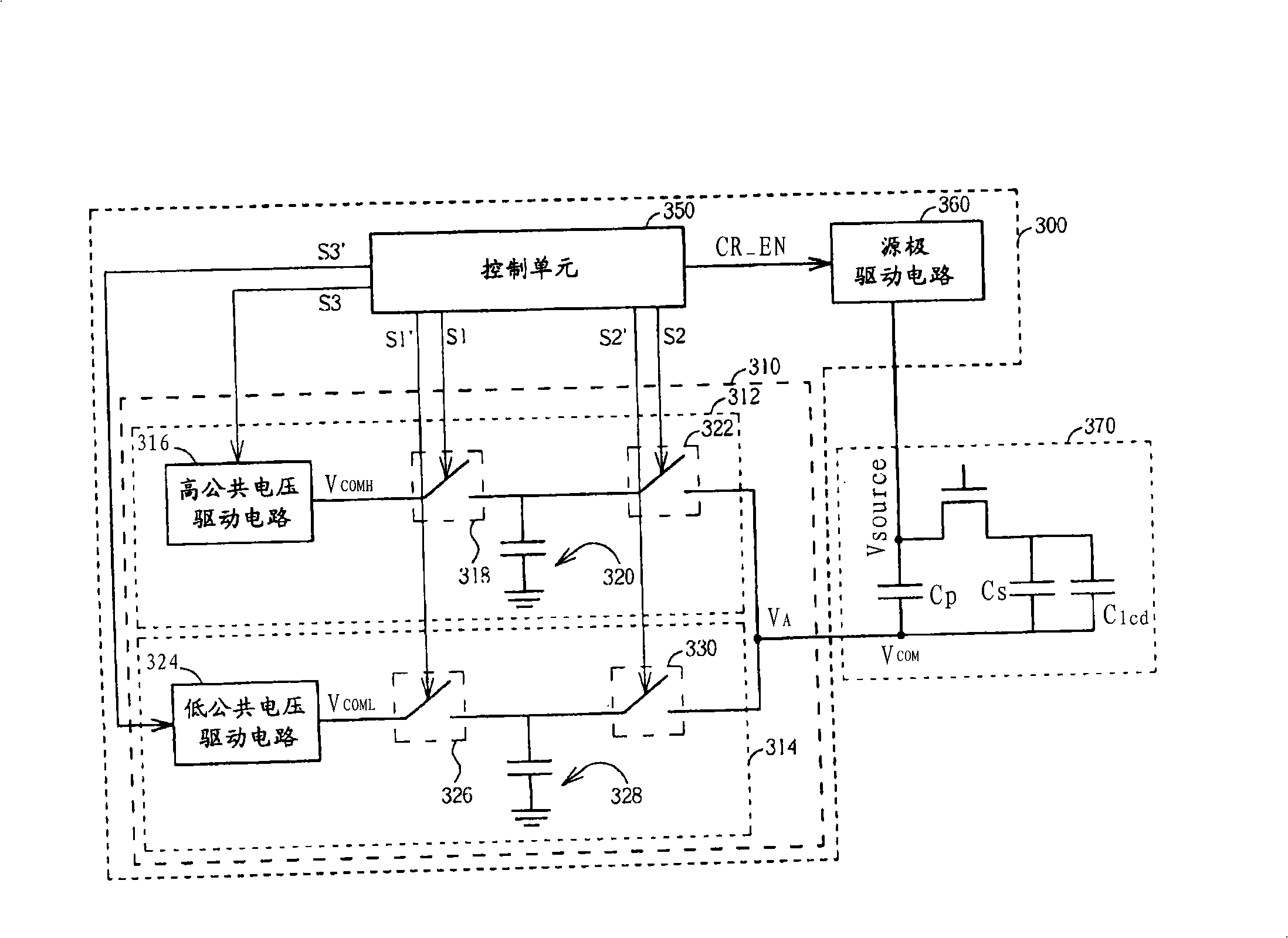

LCD device public voltage source and its electric charge recovery system

The invention provides a public voltage source applied to a liquid crystal display and a charge recovery system. The charge recovery system comprises the public voltage source, a control unit and a source cathode driving circuit, wherein, before the public voltage source switches the output level of the public voltage source, the control unit controls the public voltage source so as to lead a voltage driving circuit in the public voltage source to be broken with an output end, a charge recovery start signal is output to the source cathode driving circuit so as to adjust the level of source cathode voltage output by the source cathode driving circuit, by increasing or decreasing the level of the source cathode voltage, the charge stored in the liquid crystal cell of the liquid crystal display is recycled to the public voltage source, thus achieving the aim of increasing the charge use efficiency of the liquid crystal display and reducing consumed power.

Owner:ILI TECHNOLOGY CORPORATION

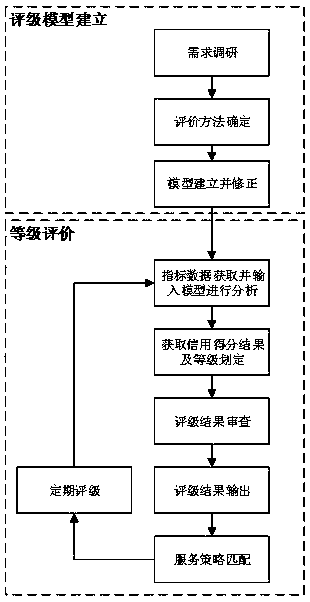

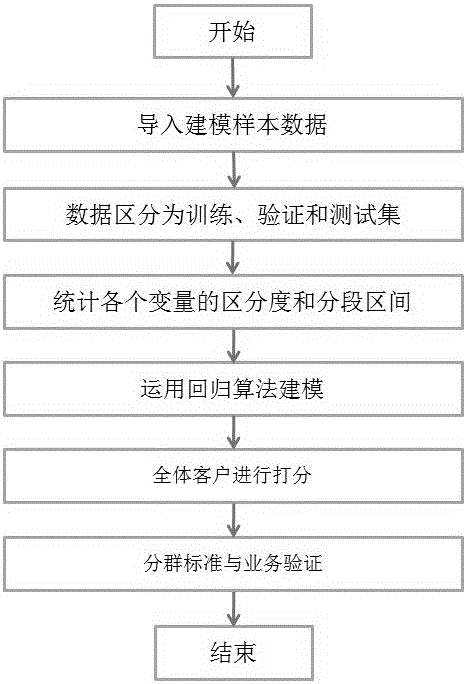

Multidimensional data-based method for evaluating credit rating of electricity customers

InactiveCN108596443APrevention and Avoidance of Recycling RisksResourcesSpecial data processing applicationsElectricityCharge recovery

The invention relates to the technical field of interactive communication, and in particular to a multidimensional data-based method for evaluating the credit rating of electricity consumers. The method comprises the steps of establishing a model, calculating a credit evaluating score, delimiting the credit rating and matching a service strategy. According to the method disclosed by the invention,a credit evaluating model is established; the corresponding relationship between the credit evaluating score and a credit assessing index is determined; the credit evaluating score is calculated according to the input credit assessing index; the corresponding credit rating is delimited according to the evaluating score; different service principles and service strategies are adopted according tothe credit rating; and therefore, the risk of electricity charge recovery is effectively prevented and avoided while faithful behaviors of users are encouraged at the same time.

Owner:GUANGDONG POWER GRID CO LTD +1

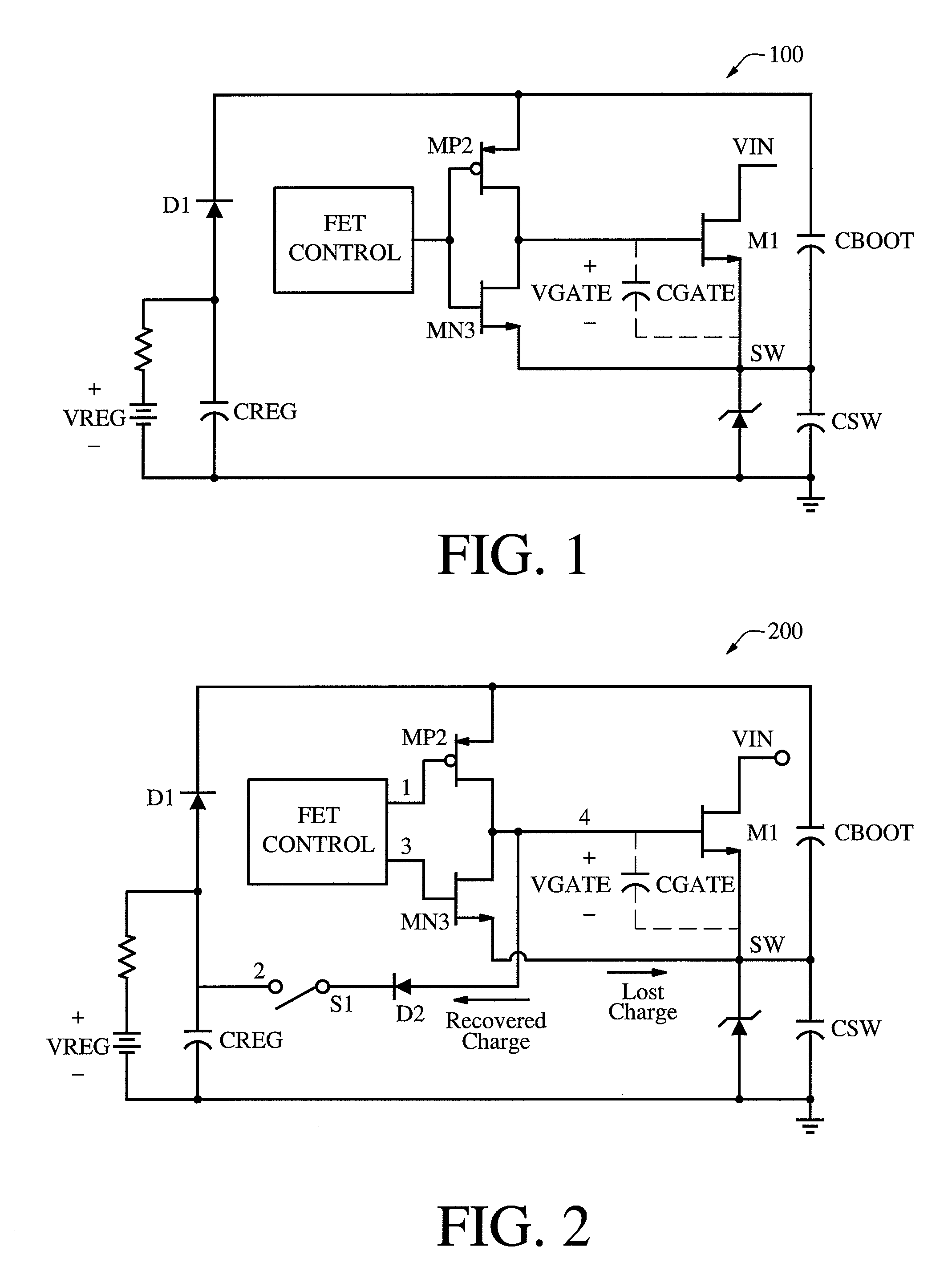

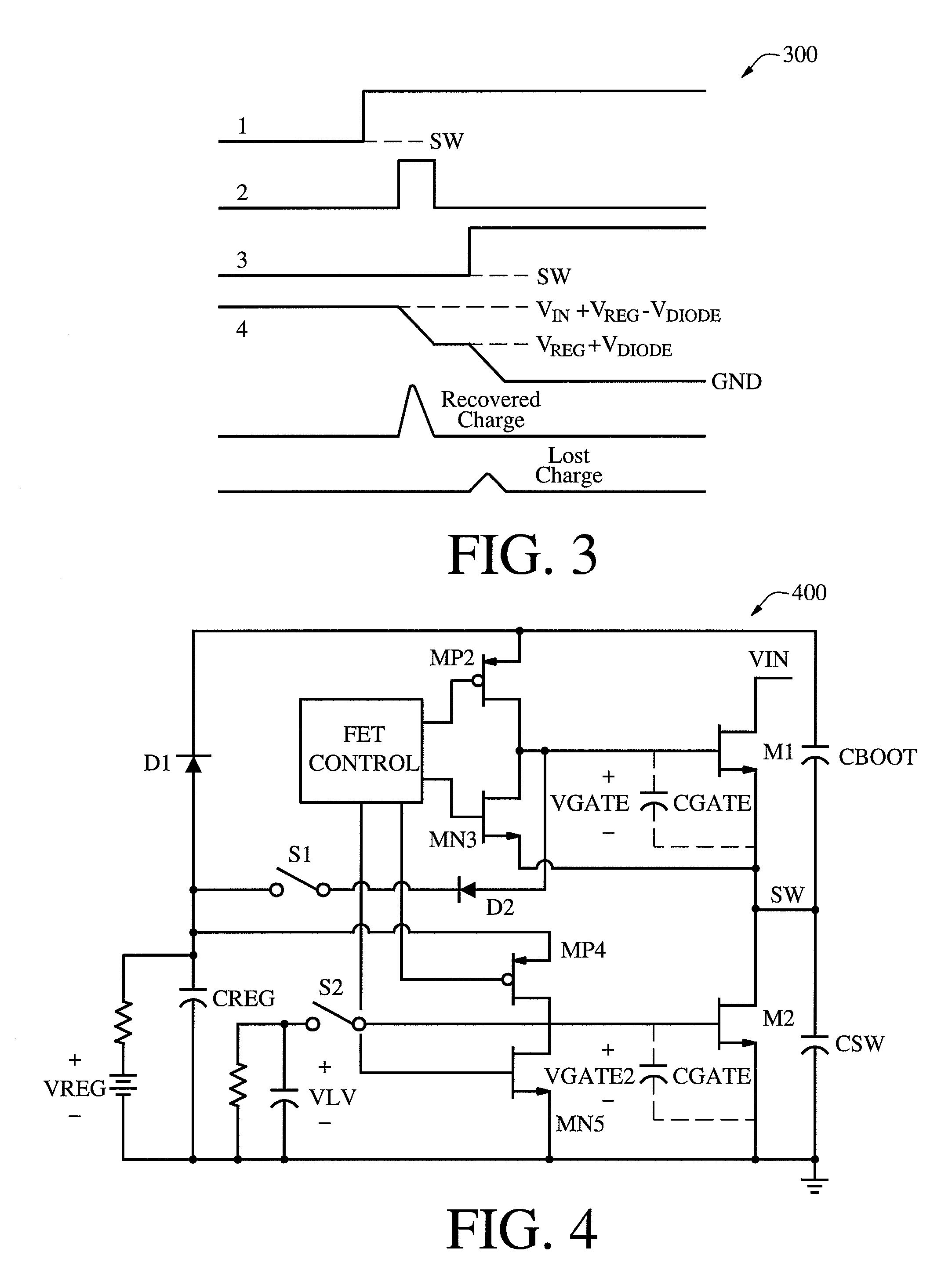

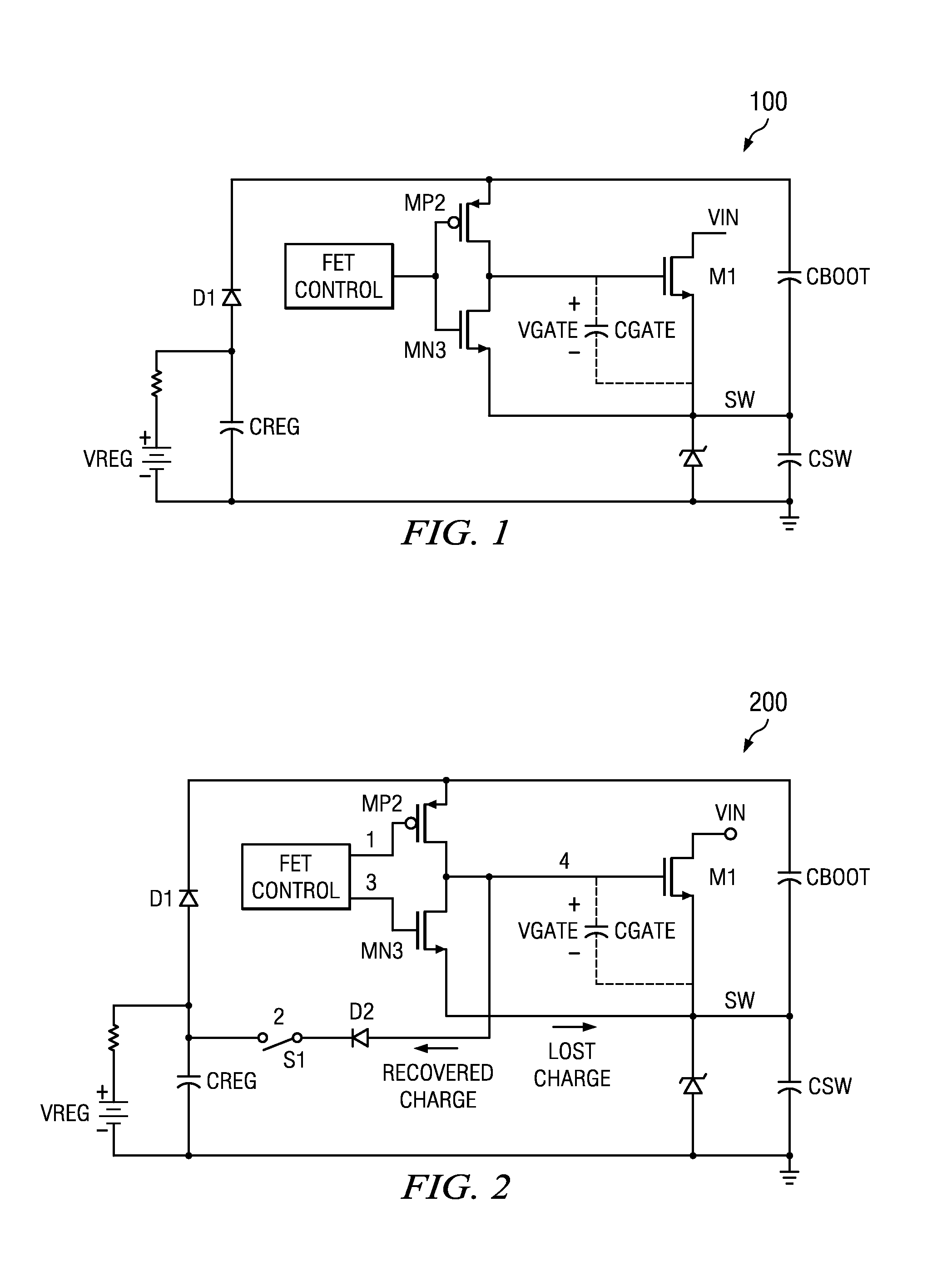

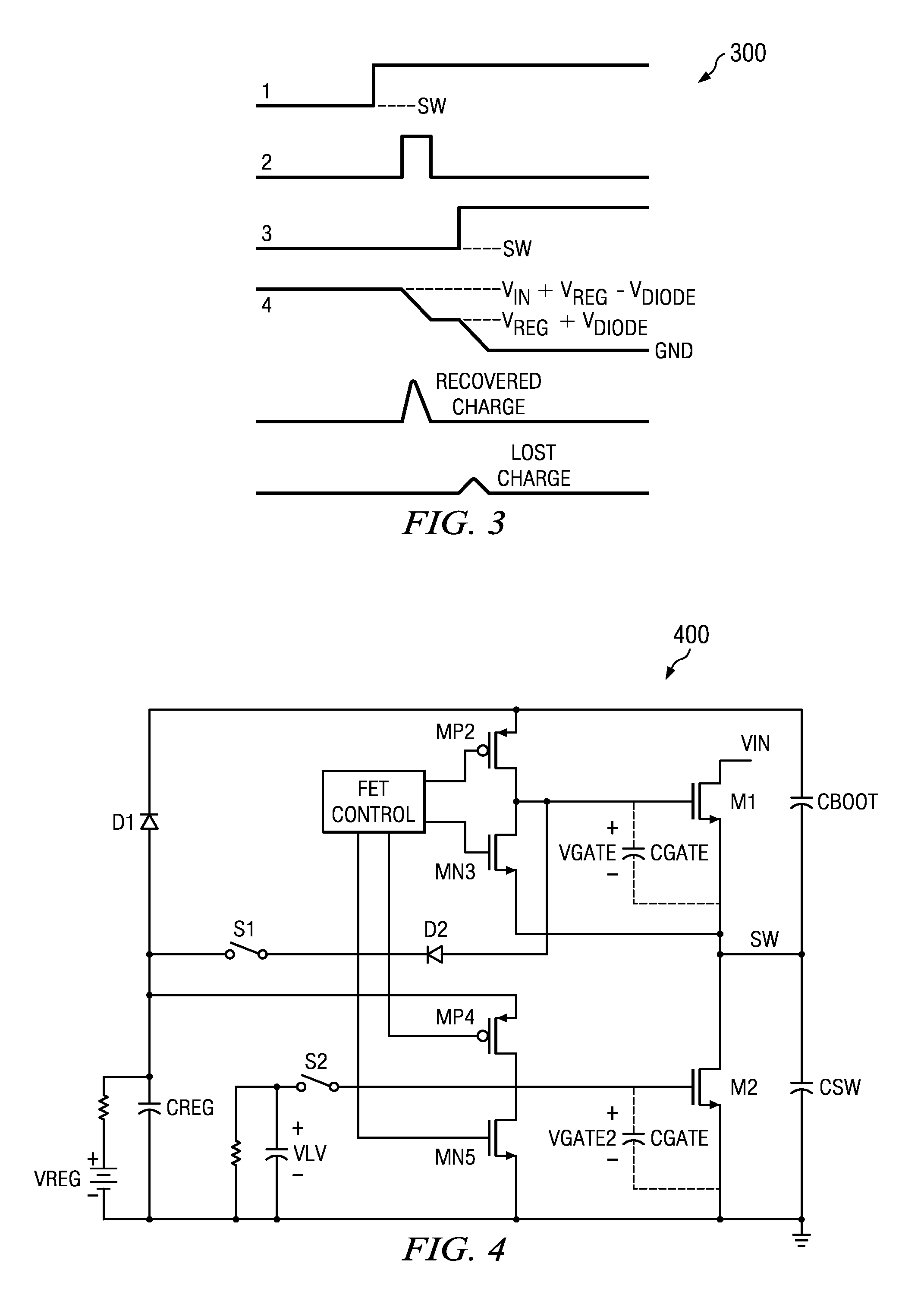

Power FET gate charge recovery

ActiveUS7746153B1Electronic switchingApparatus without intermediate ac conversionCharge recoverySwitching cycle

A circuit for recovering charge at the gate of an output transistor arranged to drive the output of a switching circuit such as a switching regulator or controller. A substantial portion of the charge for each switching cycle is recovered under a wide range of load conditions for the switching circuit, e.g., no load, partial load, or full load. Also, charge recovery operates effectively with a switching circuit that is arranged to switch in a synchronous or asynchronous manner. Additionally, if the output voltage of a switching circuit is 12 or more volts, the amount of charge that can be saved can be relatively substantial.

Owner:NAT SEMICON CORP

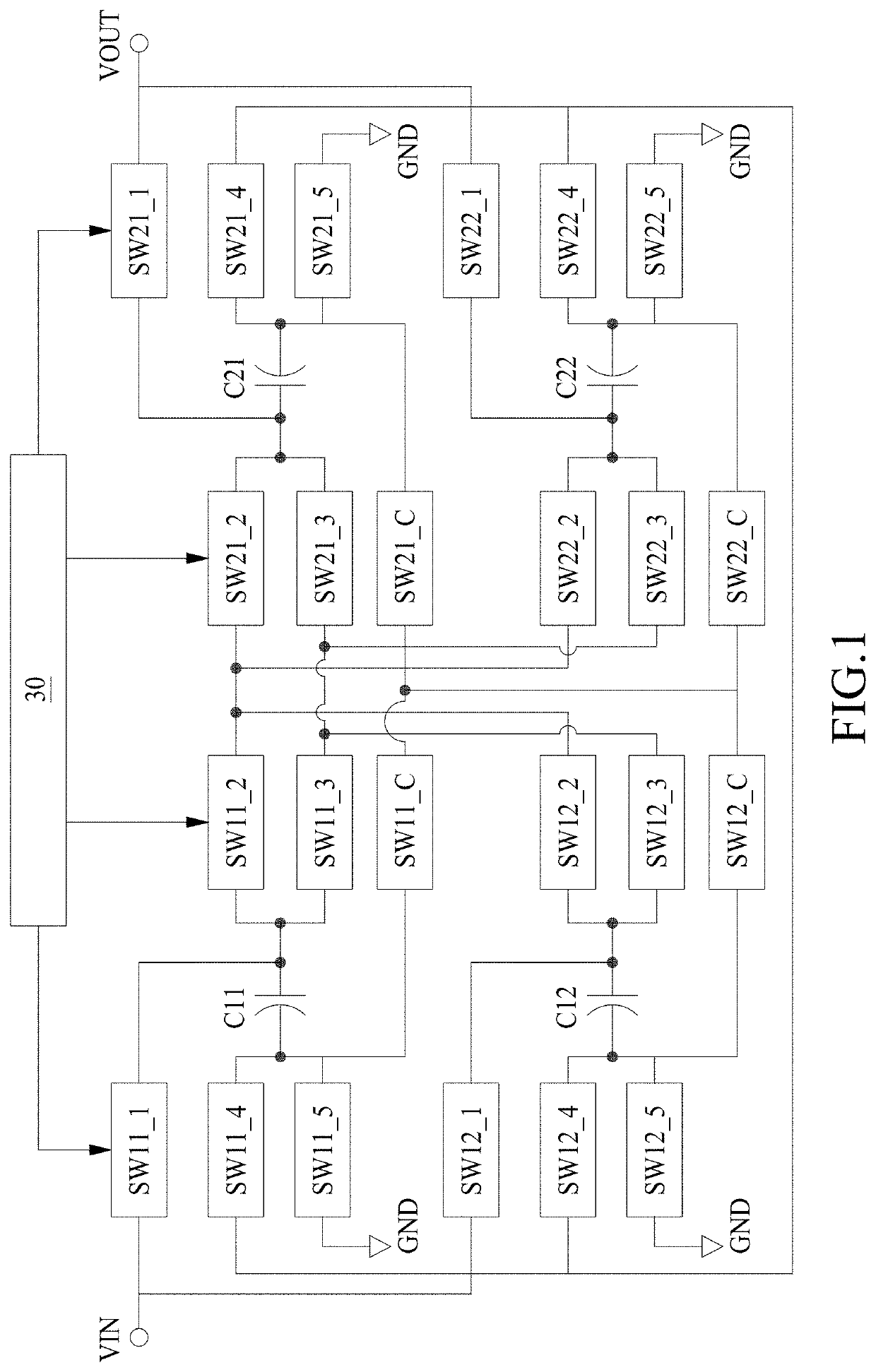

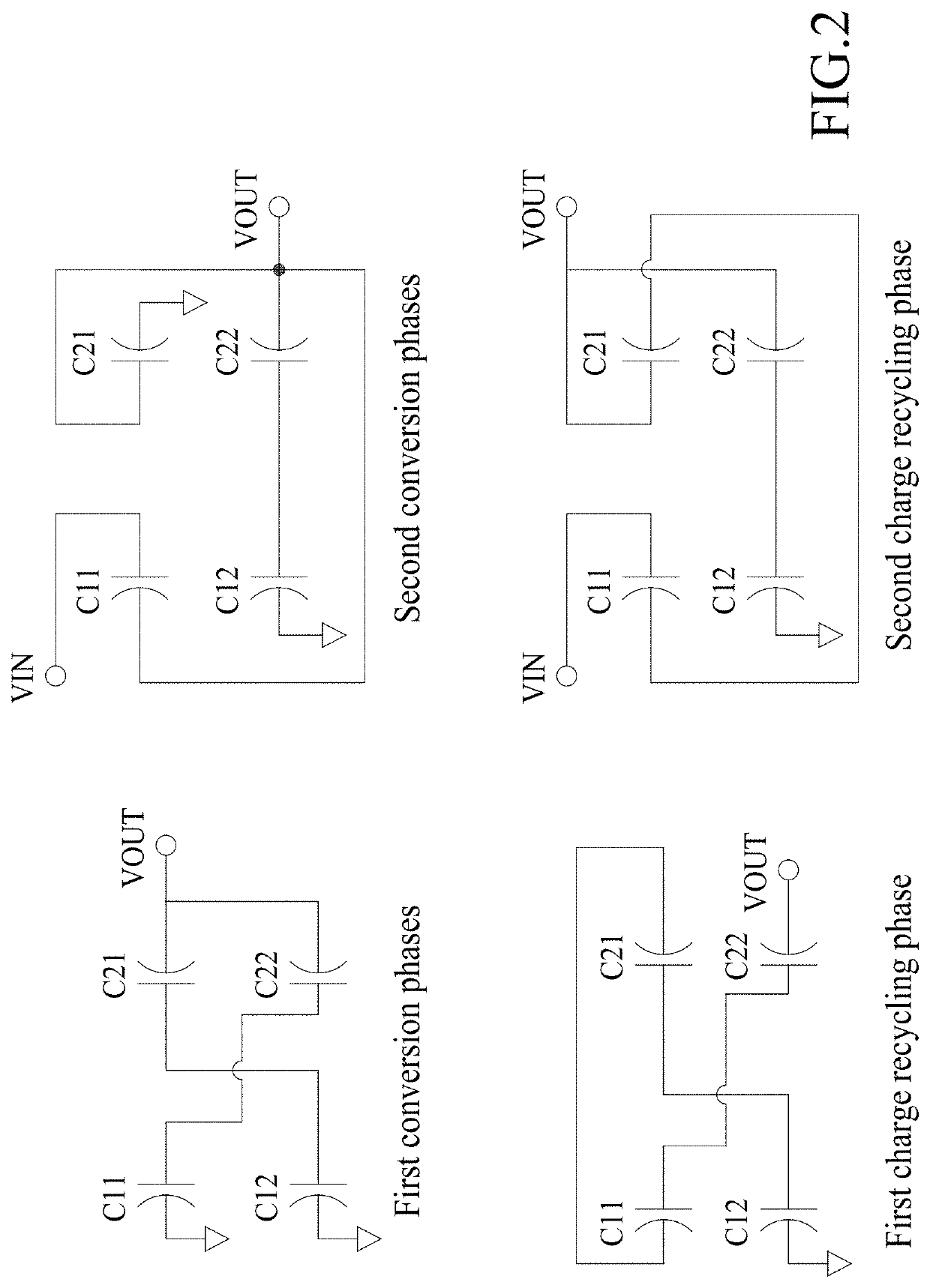

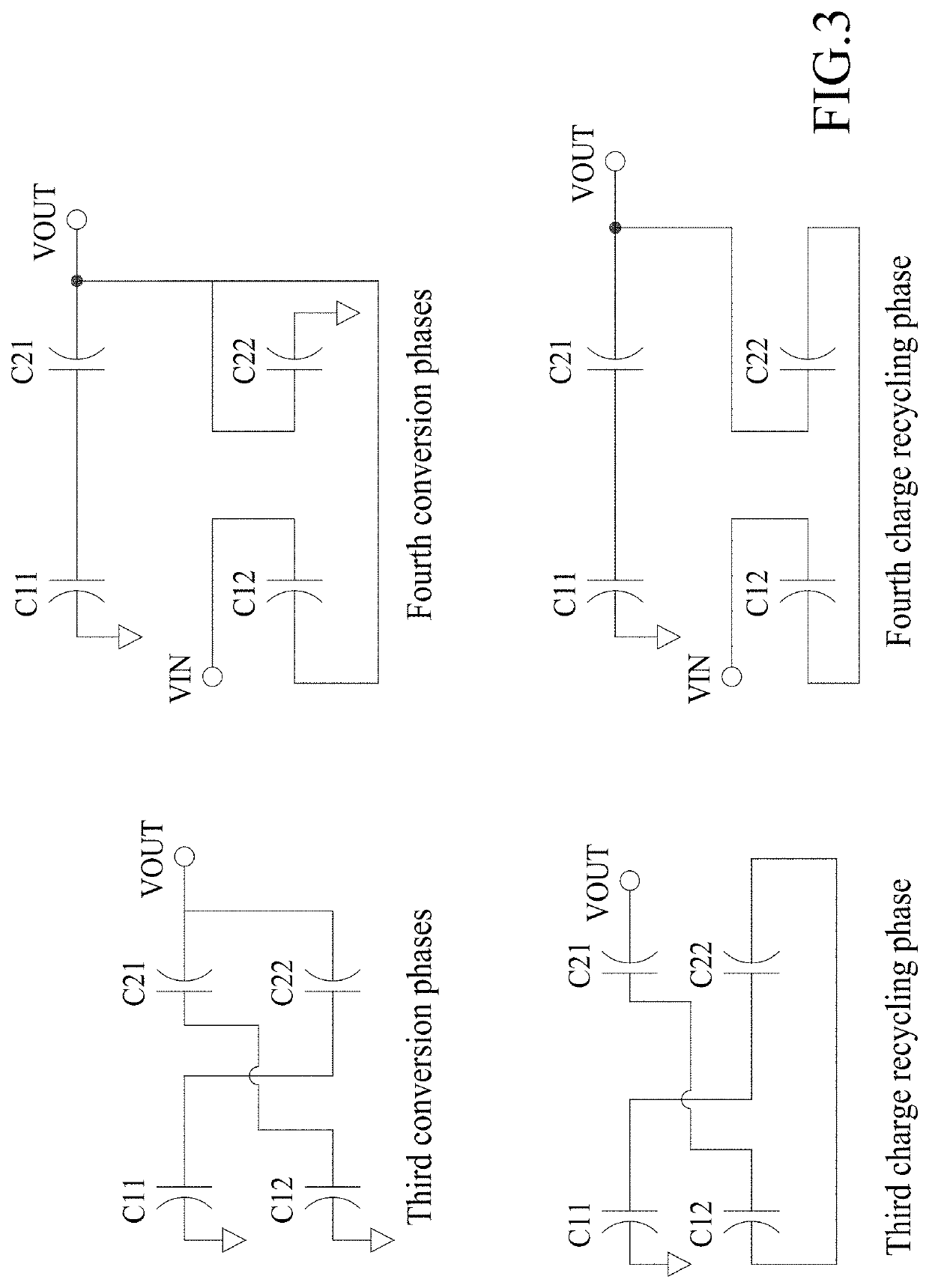

Movable touch device and electronic device thereof

ActiveUS20200195136A1Reduce energy consumptionEfficient power electronics conversionApparatus without intermediate ac conversionCapacitanceConverters

A switched-capacitor DC-DC power converter circuit is provided. The switched-capacitor DC-DC power converter circuit includes N input-side switched capacitor units and N output-side switched capacitor units. There is a charge recycling phase located between two adjacent conversion phases. In the 2N conversion phases, a bottom end of a capacitor of at least one of the input-side switched capacitor units and a bottom end of a capacitor of at least one of N output-side switched capacitor units is selectively electrically connected to an output terminal of the switched-capacitor DC-DC power converter circuit. In each charge recycling phase, bottom ends of two capacitors of N input-side switched capacitor units and N output-side switched capacitor units are electrically connected to each other through two of the input-side charge recycle switches and output-side charge recycle switches.

Owner:NUVOTON

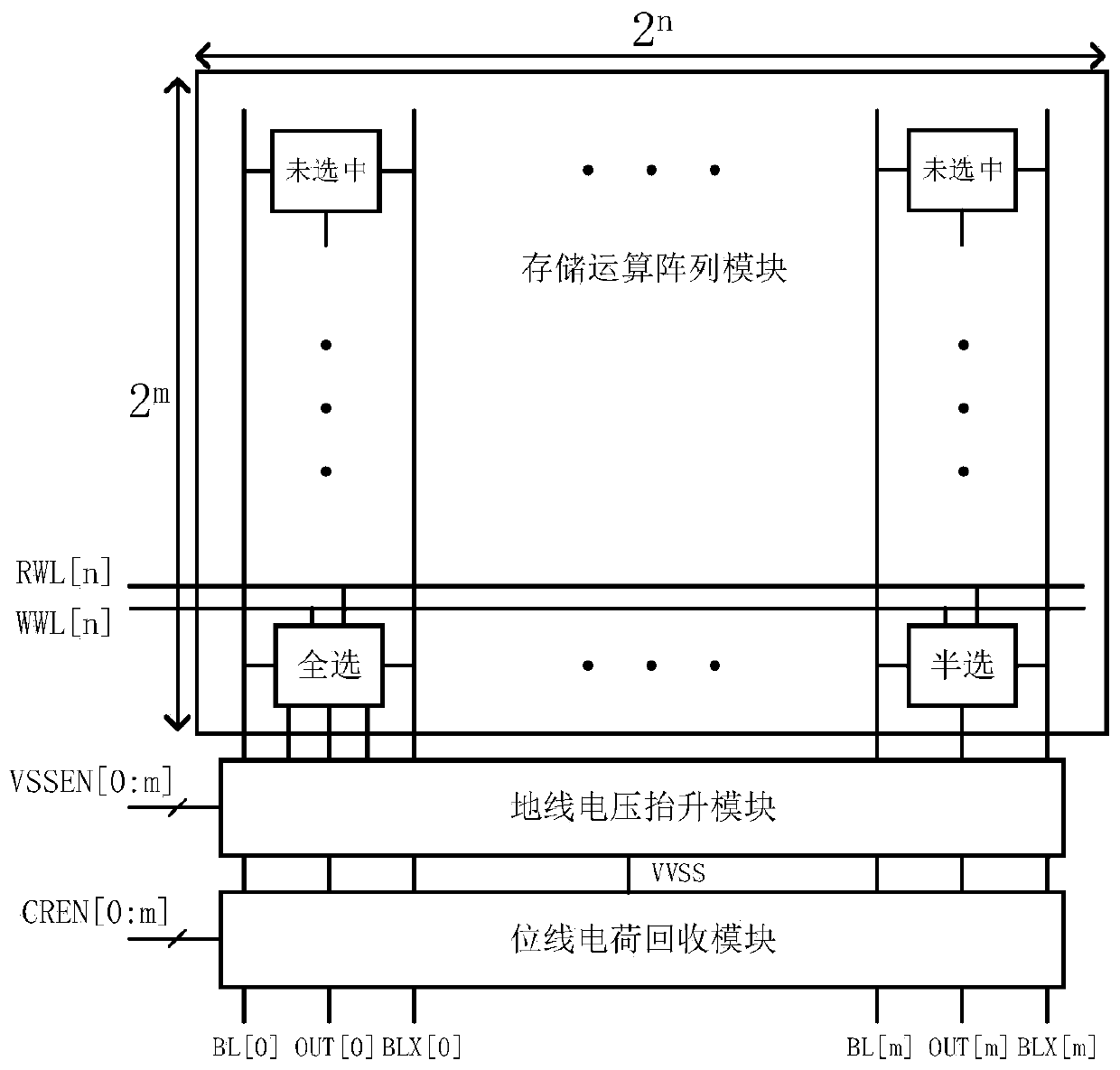

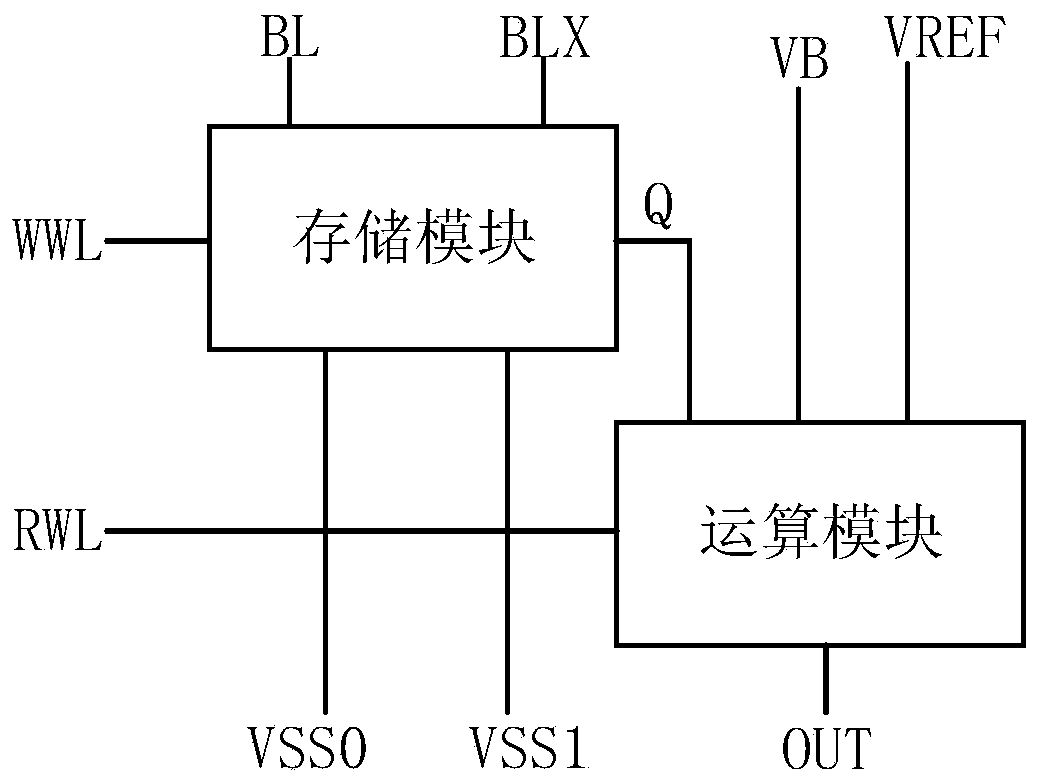

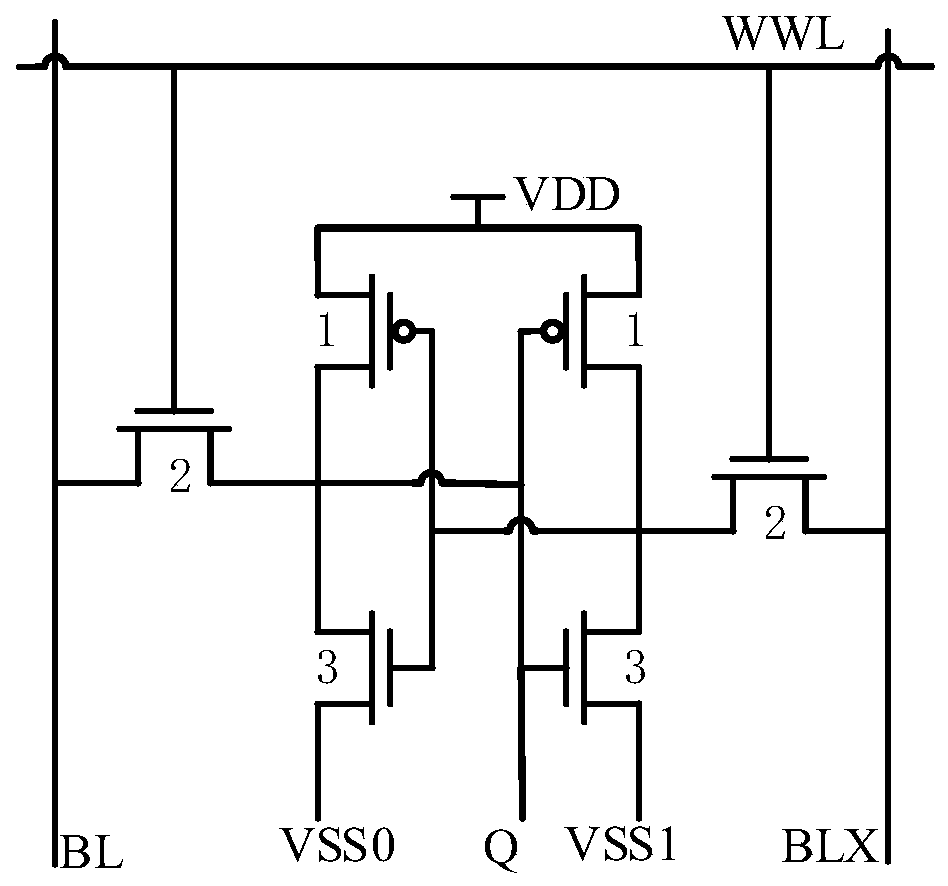

Low-power-consumption and low-leakage SRAM applied to storage and calculation integrated chip

ActiveCN110942792AReduce the minimum operating voltageImprove static noise marginDigital storageEnergy efficient computingArithmetic logic unitBit line

The invention discloses a low-power-consumption and low-leakage SRAM applied to a storage and calculation integrated chip. The low-power-consumption and low-leakage SRAM comprises: an SRAM storage operation unit array which comprises N rows and M columns of storage operation units, wherein each storage operation unit comprises a storage module and an operation module and is used for realizing voltage signal input, storing input data in the storage module and calculating and outputting the data by the operation module; a ground wire voltage raising module which is used for raising the voltage of the power supply ground wire of the selected column in the SRAM storage operation unit array so as to improve the writing threshold value of the full-selection unit when the SRAM writes data; and abit line charge recovery module which is used for recovering the leakage charge of the bit line of the half-selection unit when the SRAM writes data so as to drive the ground line voltage lifting module, reducing the voltage of the bit line of the half-selection unit and improving the static noise margin of the half-selection unit. According to the invention, the arithmetic logic unit is integrated into the SRAM, so that the design of the storage and calculation integrated chip is realized.

Owner:TIANJIN UNIV

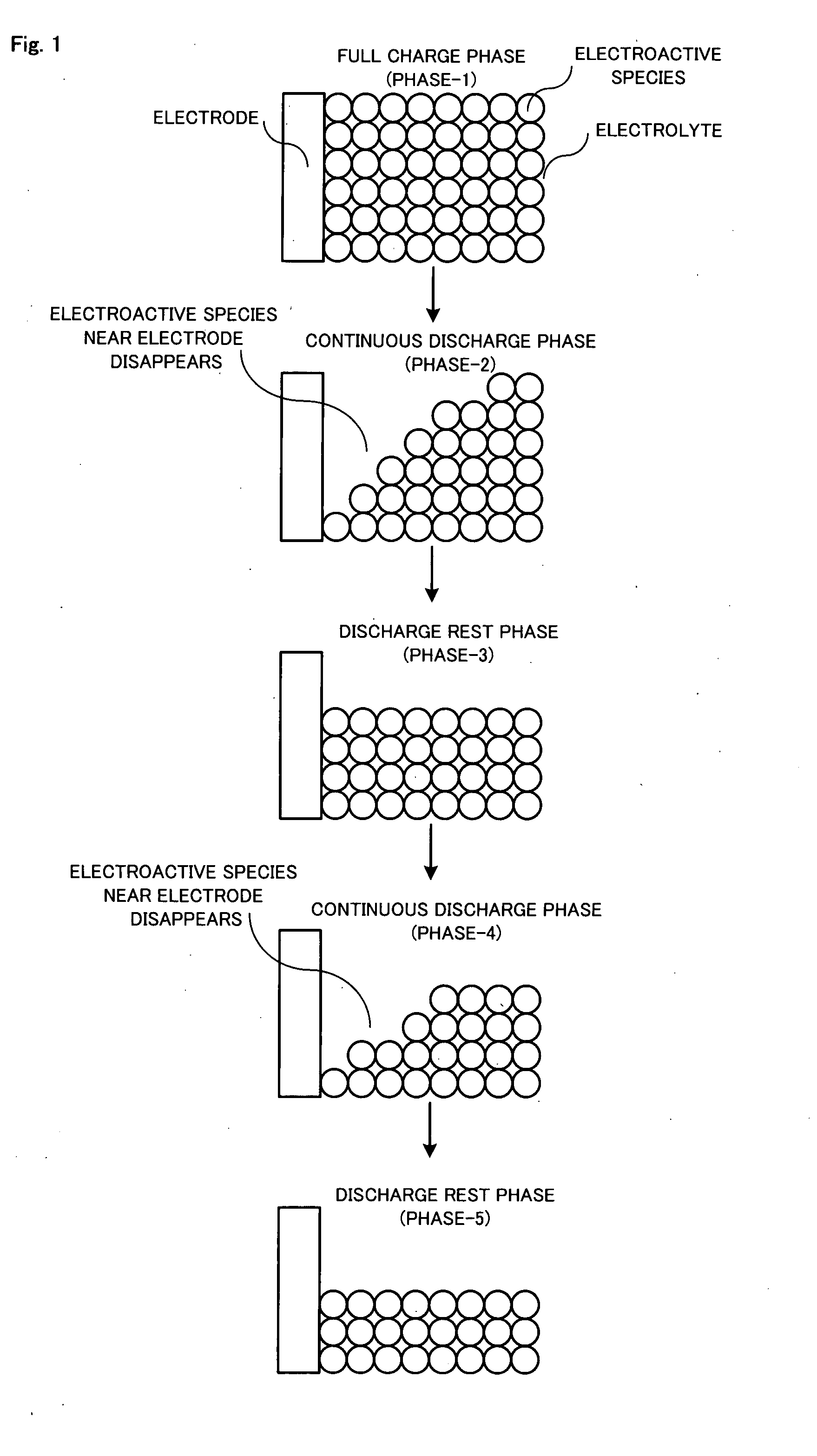

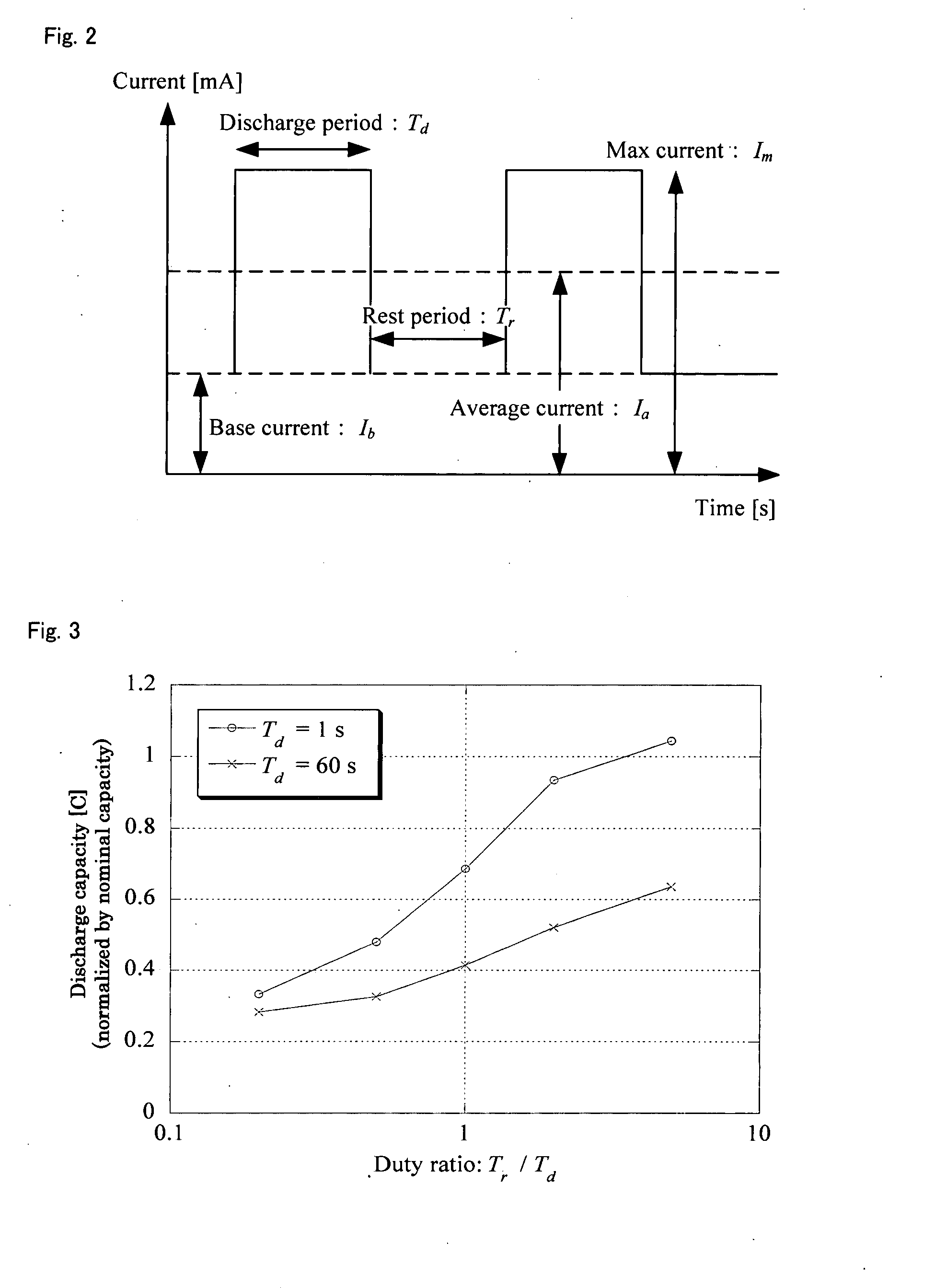

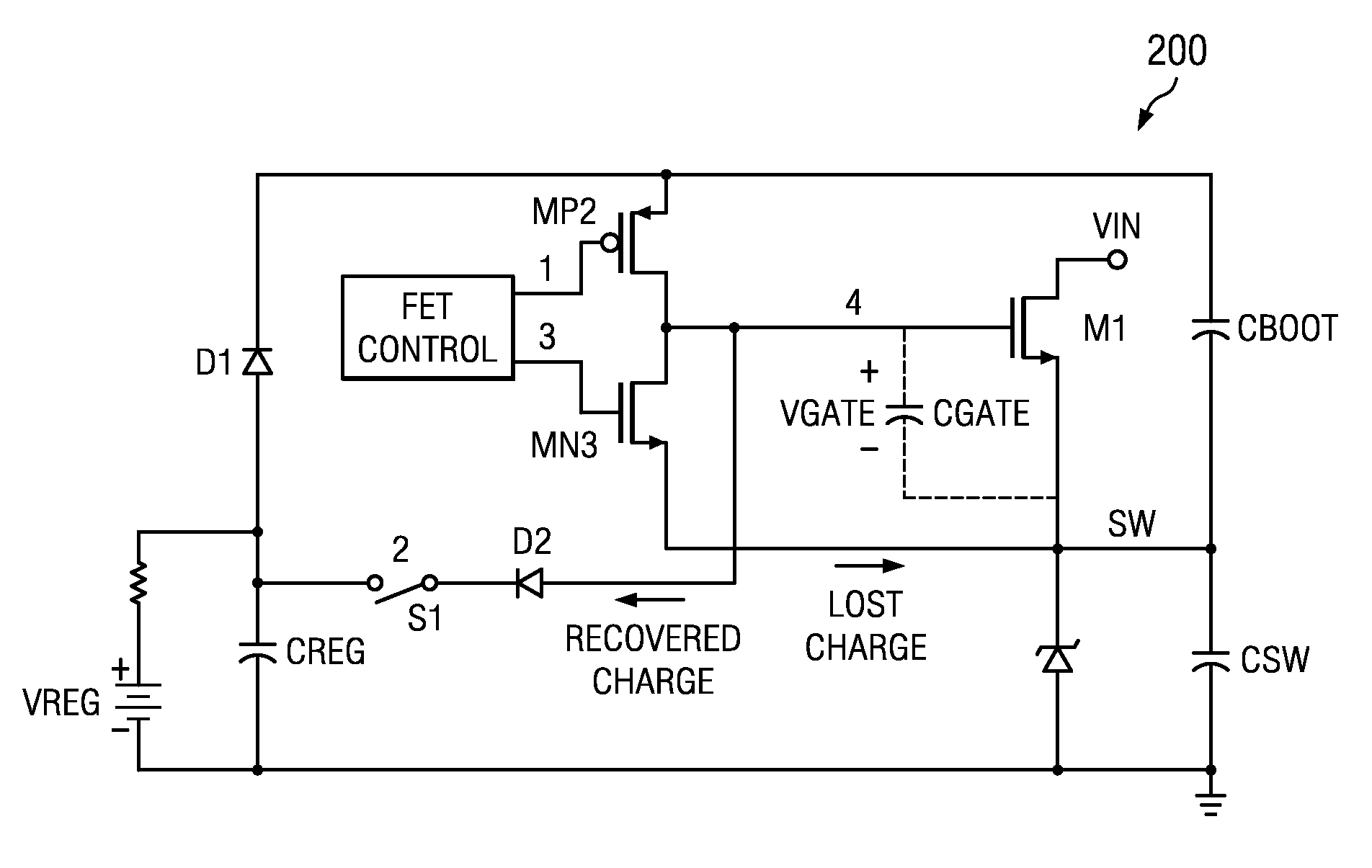

Radio communication apparatus and traffic control method for extending drive-time of battery

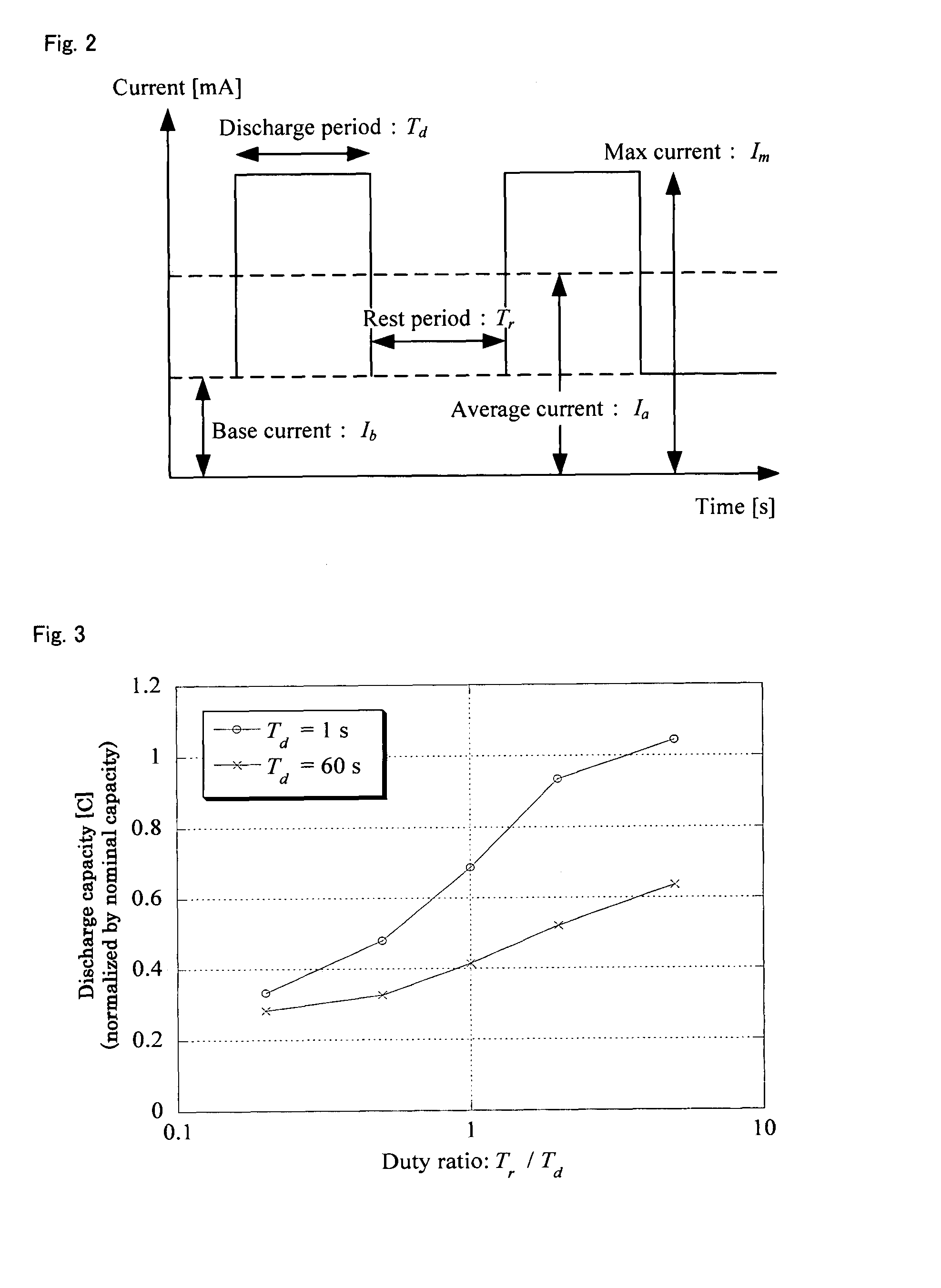

InactiveUS20070248031A1Extend drive timeLower average currentPower managementEnergy efficient ICTCharge recoveryEngineering

A radio communication apparatus has a battery, a transmit buffer for temporarily accumulating packets to be sent, a battery state monitoring unit for monitoring a battery state of the battery, and a traffic control unit. The traffic control unit determines a packet burst length and an interval time between the packet bursts in order to obtain charge recovery effect based on the battery state, and controls so as to take out data packets of the packet burst length from the transmit buffer for every interval time between the packet bursts of the packet burst.

Owner:KDDI CORP

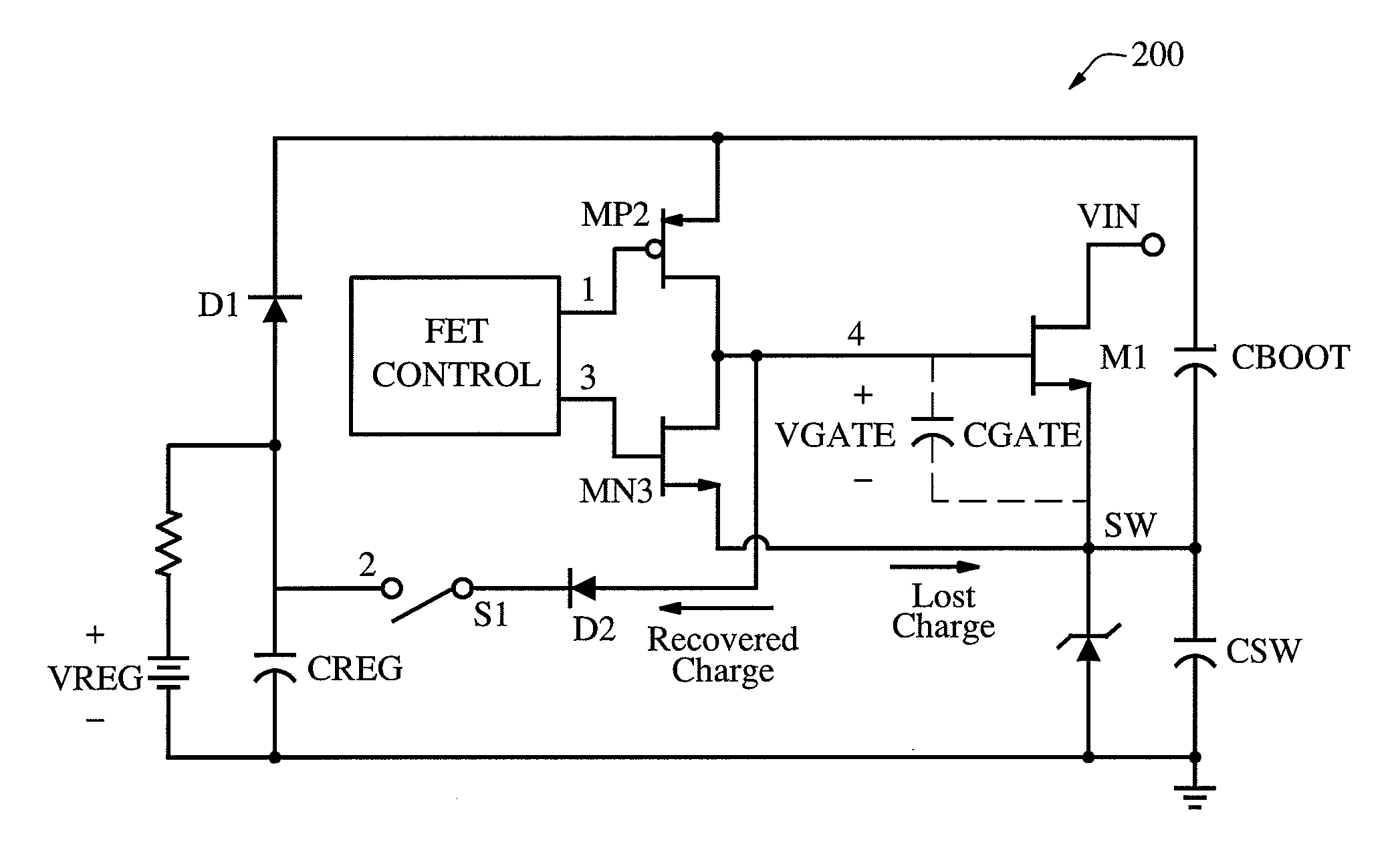

Power FET gate charge recovery

ActiveUS8278886B2Electronic switchingApparatus without intermediate ac conversionSwitching cycleCharge recovery

A circuit for recovering charge at the gate of an output transistor arranged to drive the output of a switching circuit such as a switching regulator or controller. A substantial portion of the charge for each switching cycle is recovered under a wide range of load conditions for the switching circuit, e.g., no load, partial load, or full load. Also, charge recovery operates effectively with a switching circuit that is arranged to switch in a synchronous or asynchronous manner. Additionally, if the output voltage of a switching circuit is 12 or more volts, the amount of charge that can be saved can be relatively substantial.

Owner:NAT SEMICON CORP

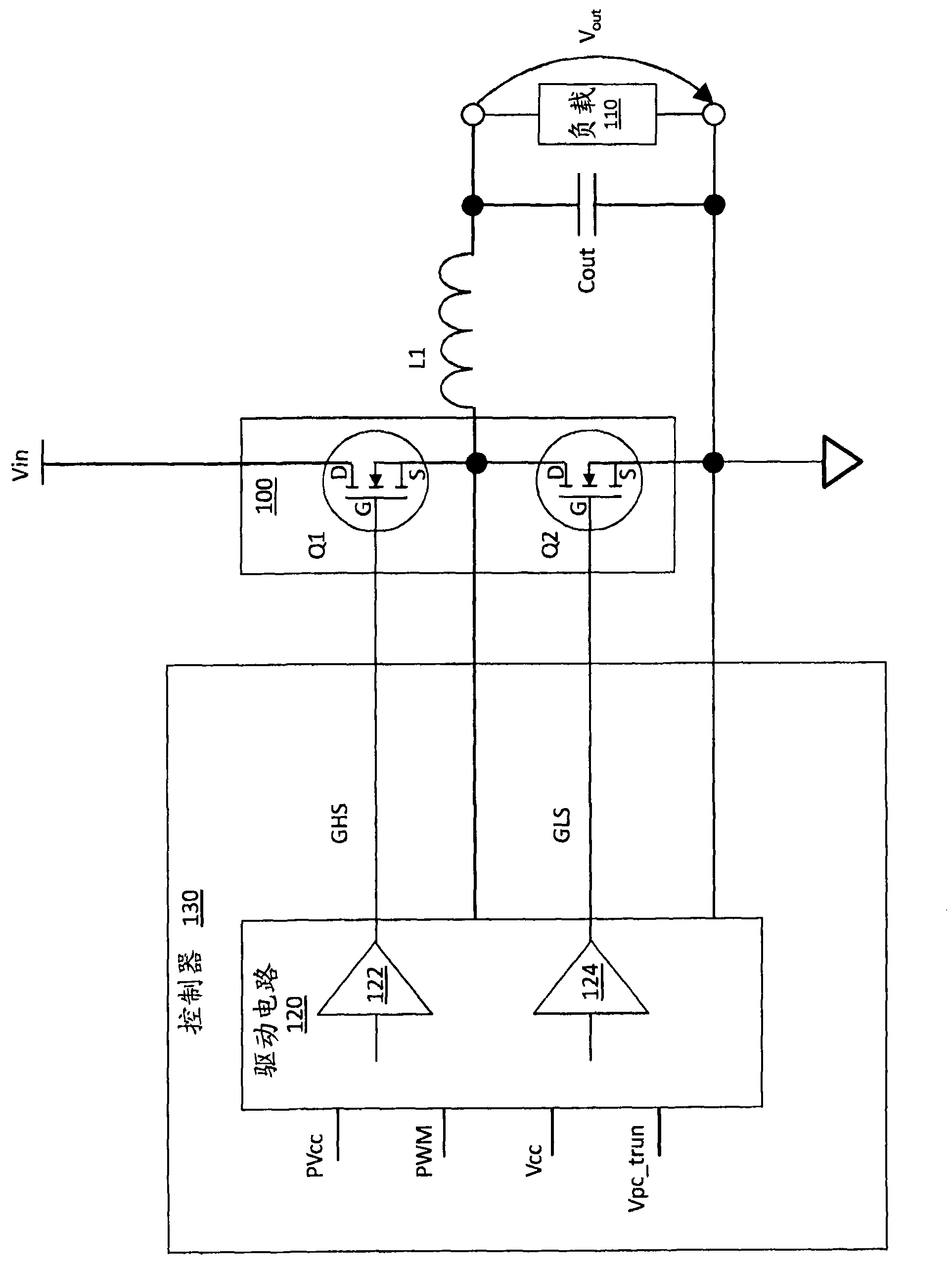

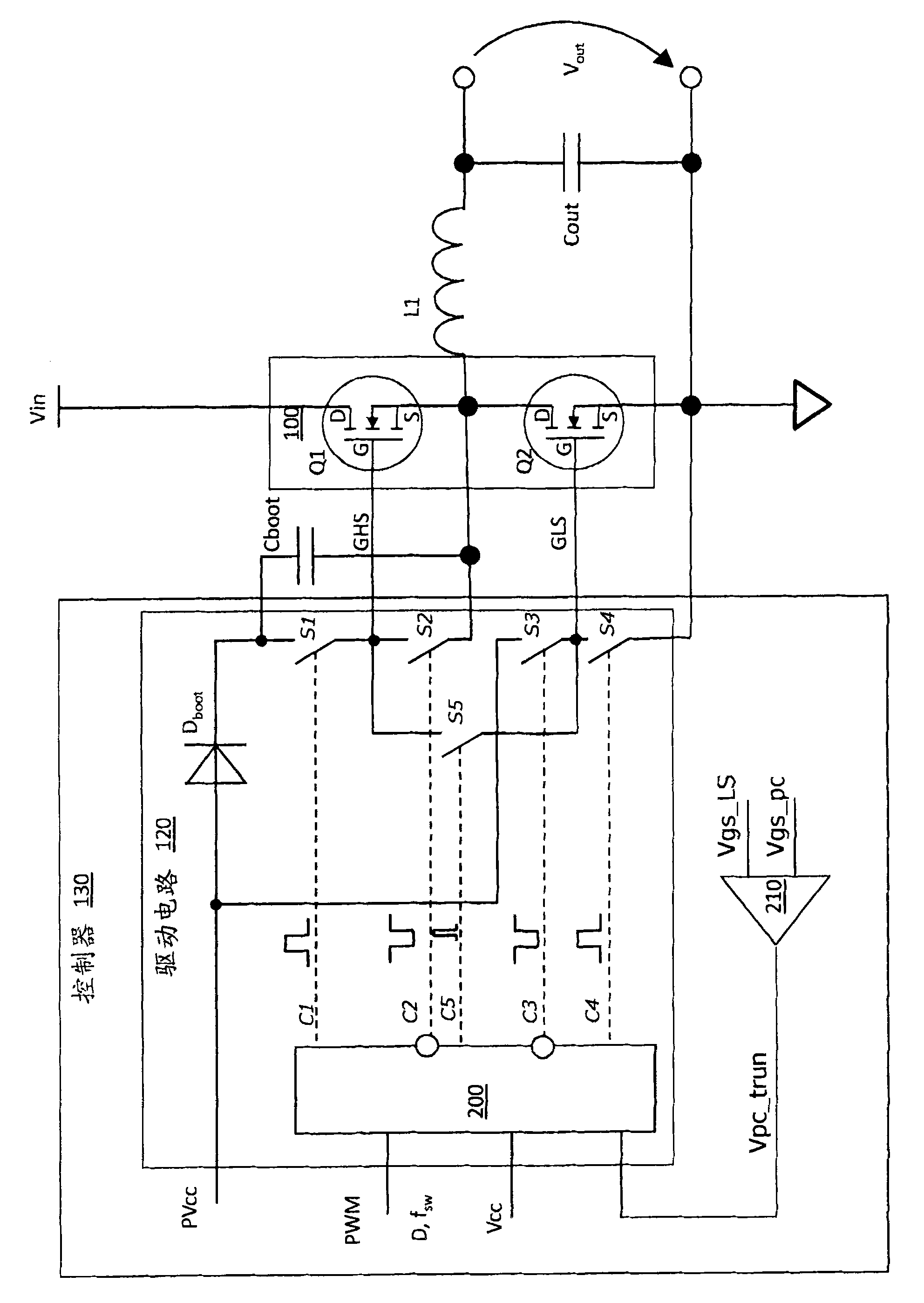

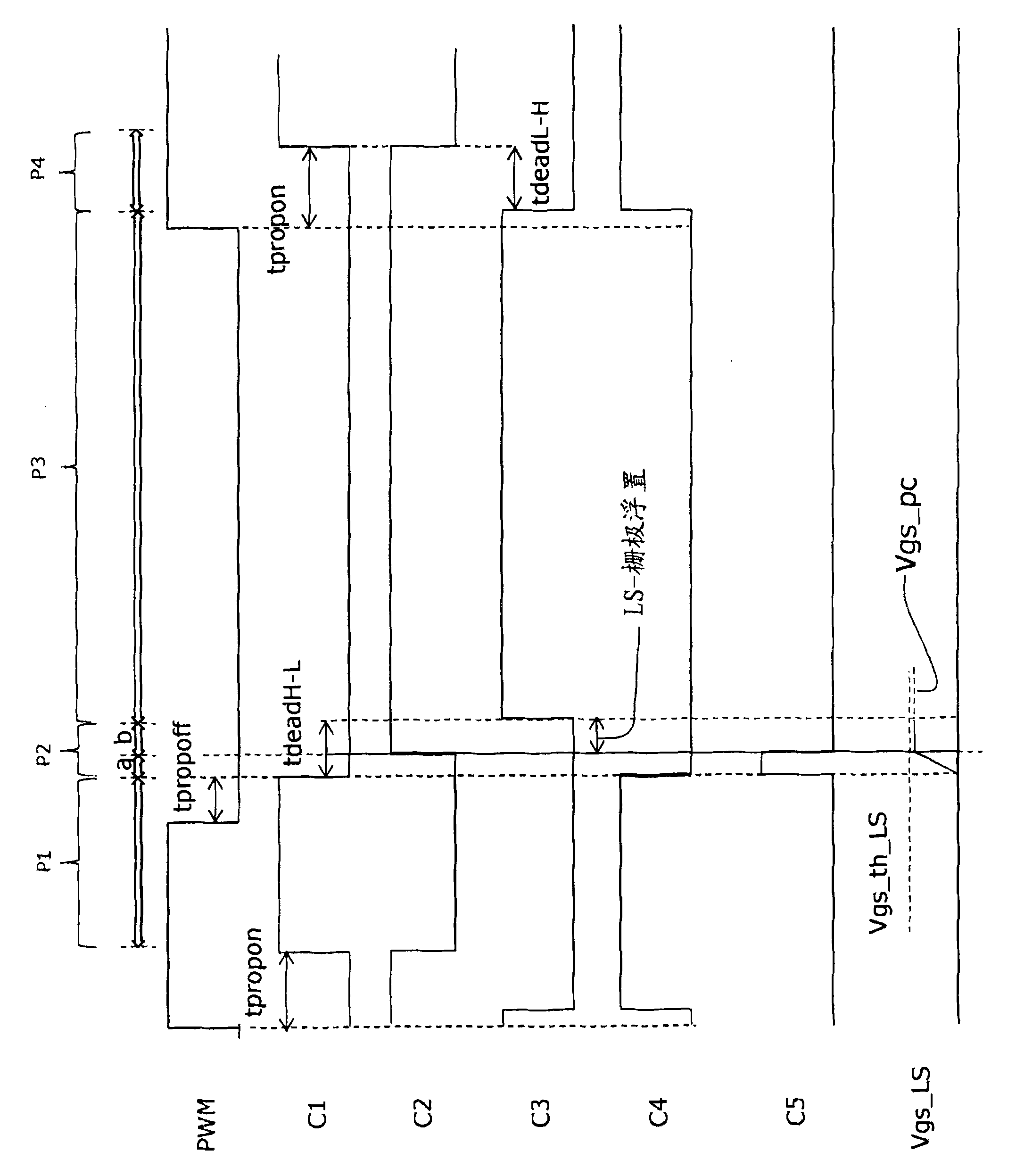

Charge recovery in power converter driver stages

ActiveCN103580475AEfficient power electronics conversionDc-dc conversionDriver circuitCharge recovery

A power converter includes a first transistor operable to source current to a load when switched on, a second transistor operable to freewheel inductor current or sink current from the load when switched on, and a driver circuit. The driver circuit is operable to switch the first transistor on and the second transistor off during a first period, switch the first transistor off and the second transistor on during a third period after the first period, and connect a gate of the first transistor to a gate of the second transistor during a second period between the first and third periods when the gates of both transistors are floating.

Owner:INFINEON TECH AUSTRIA AG

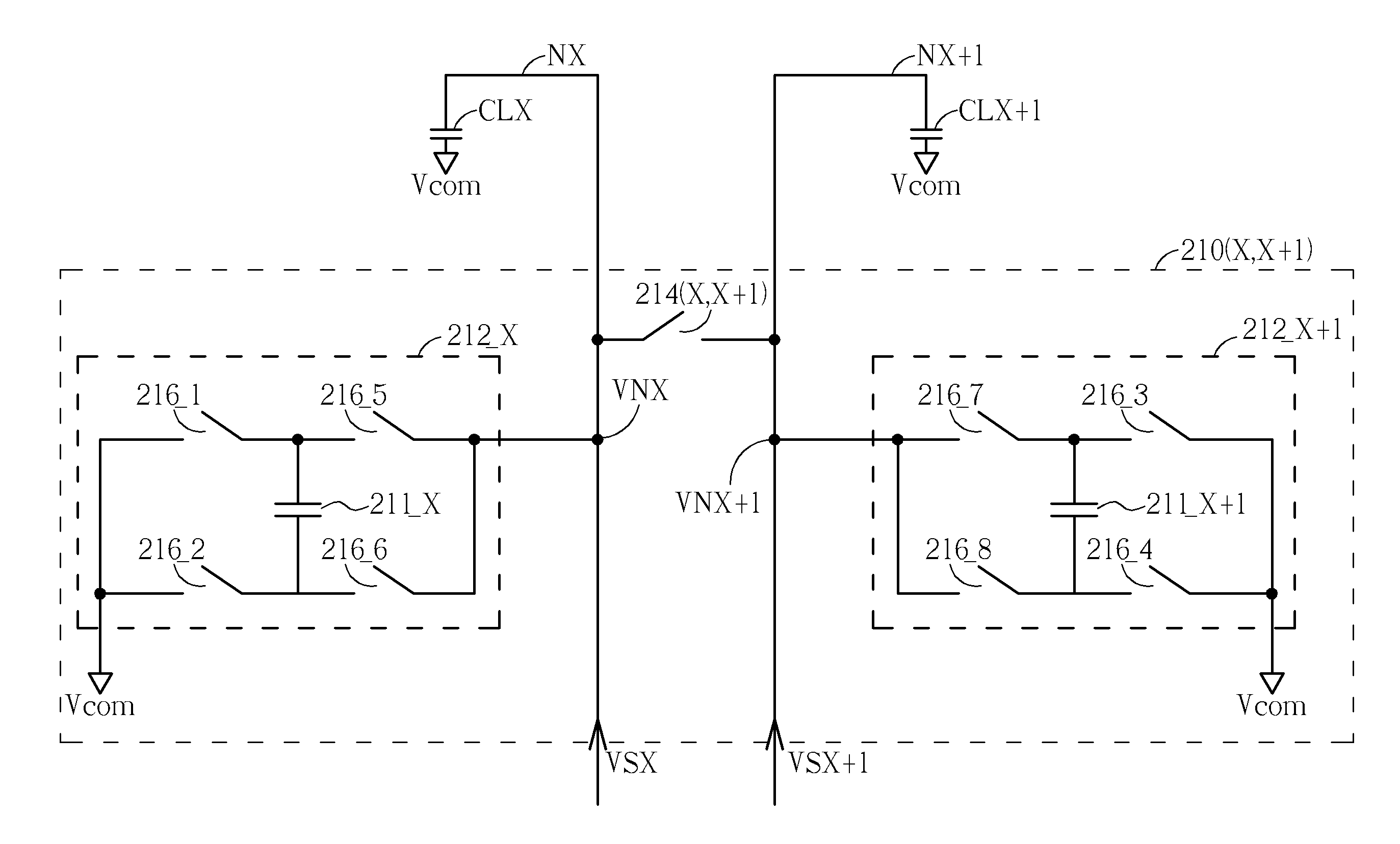

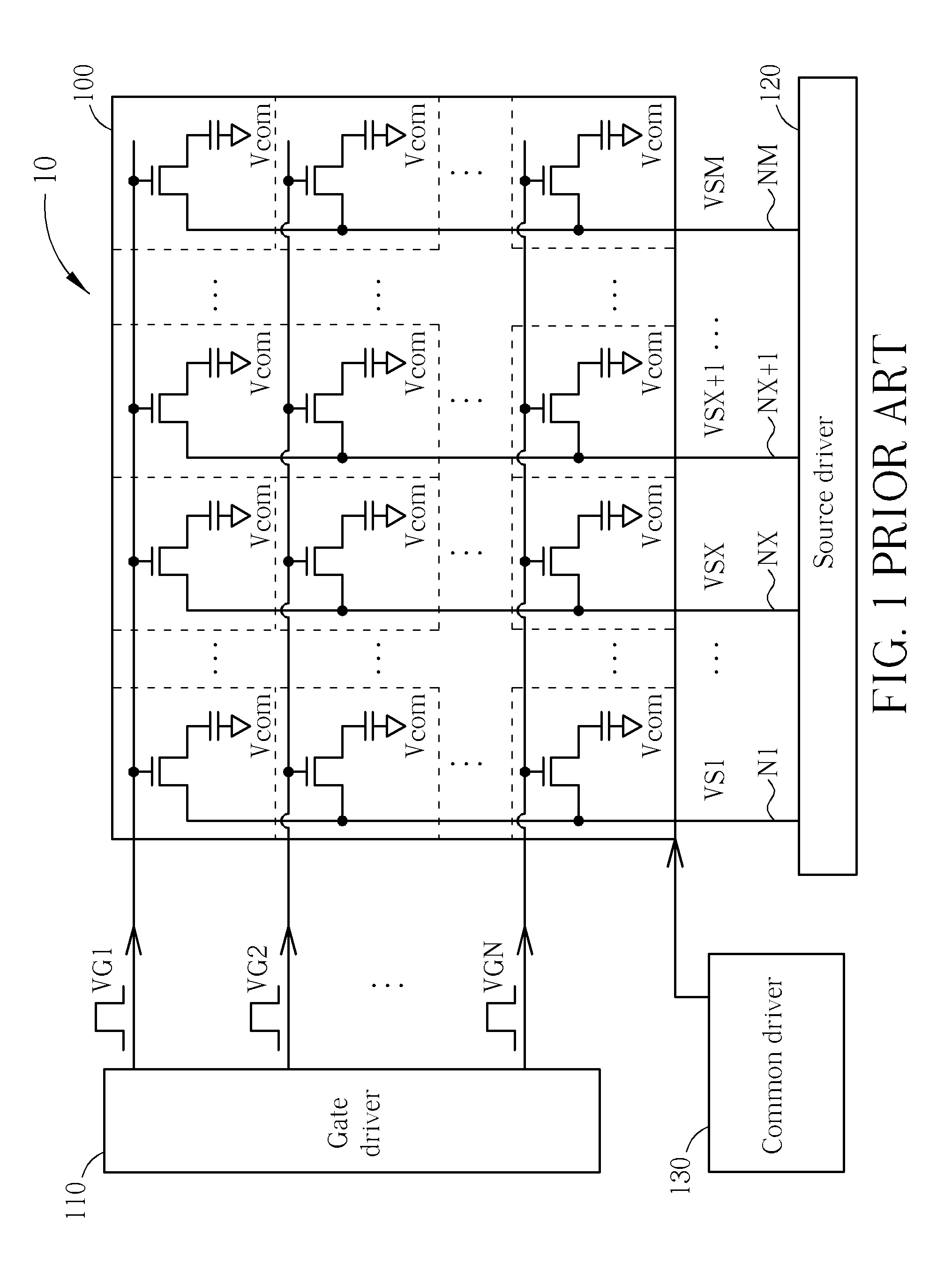

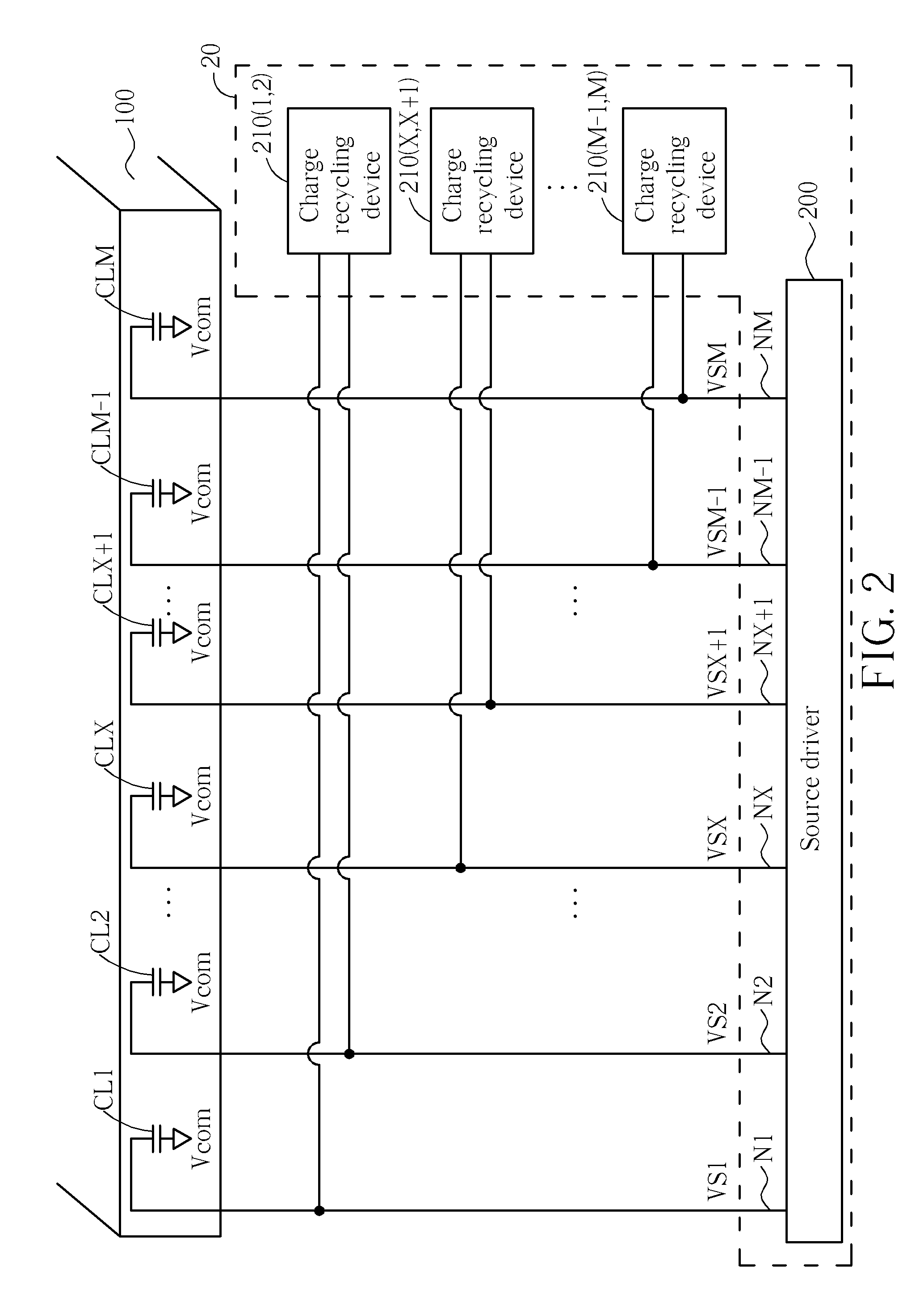

Charge recycling device and panel driving apparatus and driving method using the same

Owner:NOVATEK MICROELECTRONICS CORP

Electrolyte preparation method of three-dimensional nanometer silicon liquid storage battery

ActiveCN101867066ASolution to short lifeLarge capacityFinal product manufactureLead-acid accumulators constructionCharge recoveryInternal resistance

The invention relates to an electrolyte preparation method of three-dimensional nanometer silicon liquid storage batteries. The electrolyte consists of double ingredients: an ingredient A and an ingredient B, and contains silicon, sulphuric acid, phosphoric acid, lithium, potassium, aluminum, polyethylene glycol and purified water. The invention can realize the effects of high power, small internal resistance, long service life, at least five years of the colloid stability period, little self discharge and two years of storage period after sufficient charging of a colloid storage battery. The power maintains 90 percent, the self charging recovery reaches 90 percent, the invention is applicable to military combat readiness and automobile manufacture and storage, and the environment protection and energy saving effect reaches 30 percent. The maintenance is avoided, and the use is safe and reliable.

Owner:东莞市德东科技有限公司

Driver device for driving capacitive light emitting elements

InactiveUS20050083257A1Improve reliabilityReduce power consumptionElectroluminescent light sourcesSolid-state devicesCapacitanceCharge recovery

A device for driving capacitive light emitting elements includes a plurality of electrical charge recovery switches that send a current corresponding with an electrical charge, which has accumulated in a capacitor, individually to a plurality of drive electrodes connected to the respective capacitive light emitting elements. The electrical charge recovery switches also supply a current corresponding with the electrical charge that has accumulated in each of the capacitive light emitting elements to the capacitor individually via each of the drive electrodes. The driver device also includes a plurality of output buffers that apply a pixel-data-dependent voltage to the drive electrodes. It is determined, for each drive electrode, whether the voltage of the drive electrode has shifted from a high voltage to a low voltage or from a low voltage to a high voltage on the basis of the pixel data. If the voltage shift has occurred on the drive electrode concerned, the associated electric charge recovery switch is set to the ON state over a predetermined period. If no voltage shift has occurred, the electrical charge recovery switch is set to the OFF state.

Owner:PANASONIC CORP

Power grid user electricity charge recovery model construction method based on big data

InactiveCN105760937AGuaranteed electricity incomeControl business riskSustainable waste treatmentResourcesElectricity marketCharge recovery

The invention discloses a power grid user electricity charge recovery model construction method based on big data, which analyzes electricity charge paying behaviors and client basic attribute characteristics of different clients, and performs client electricity charge recovery risk prediction, thereby being favorable for taking different electricity charge recovery strategies and prevention measures for different clients in advance, guaranteeing enterprise electricity charge income and effectively controlling enterprise operation risks.

Owner:广州铭诚计算机科技有限公司

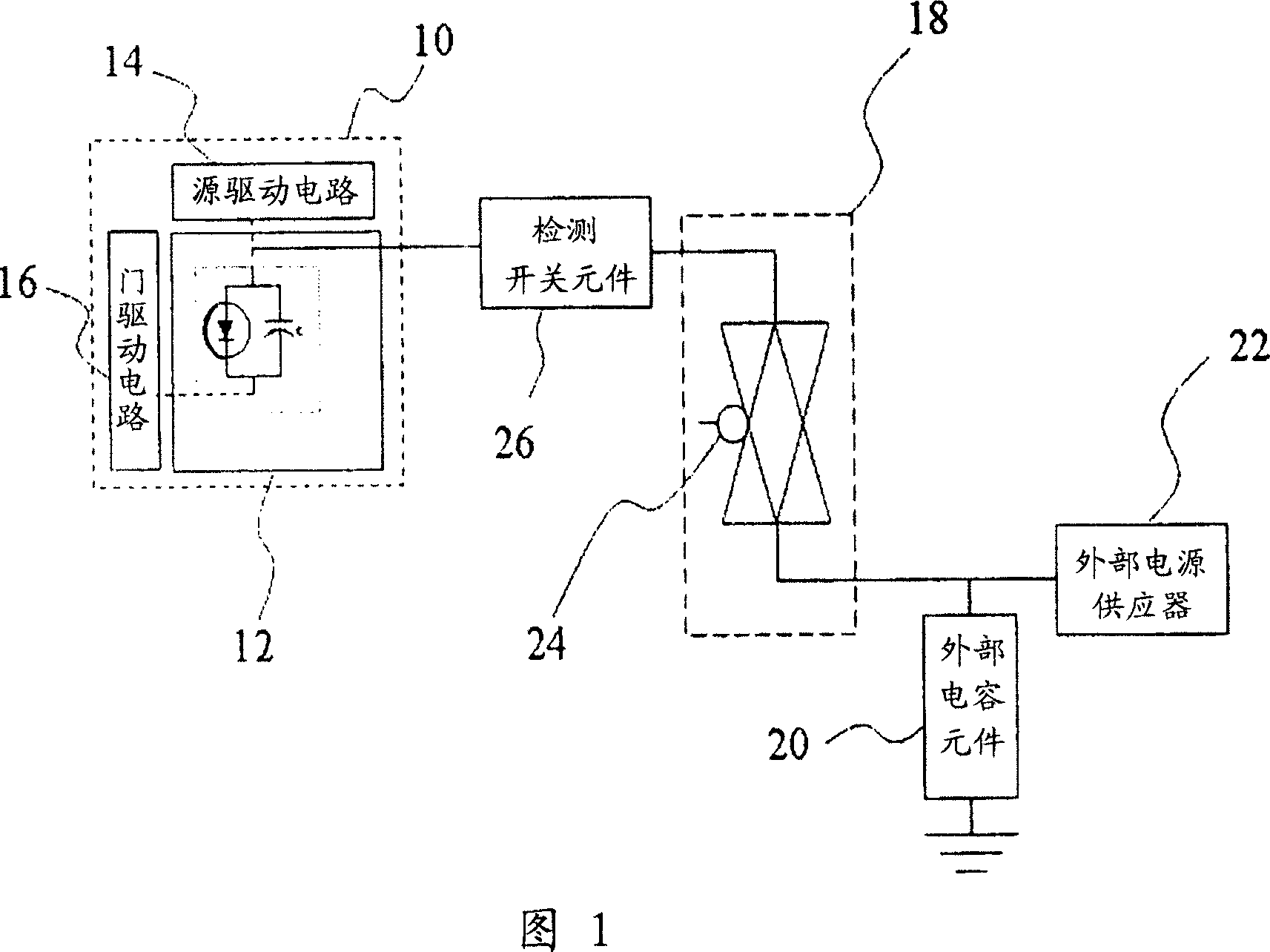

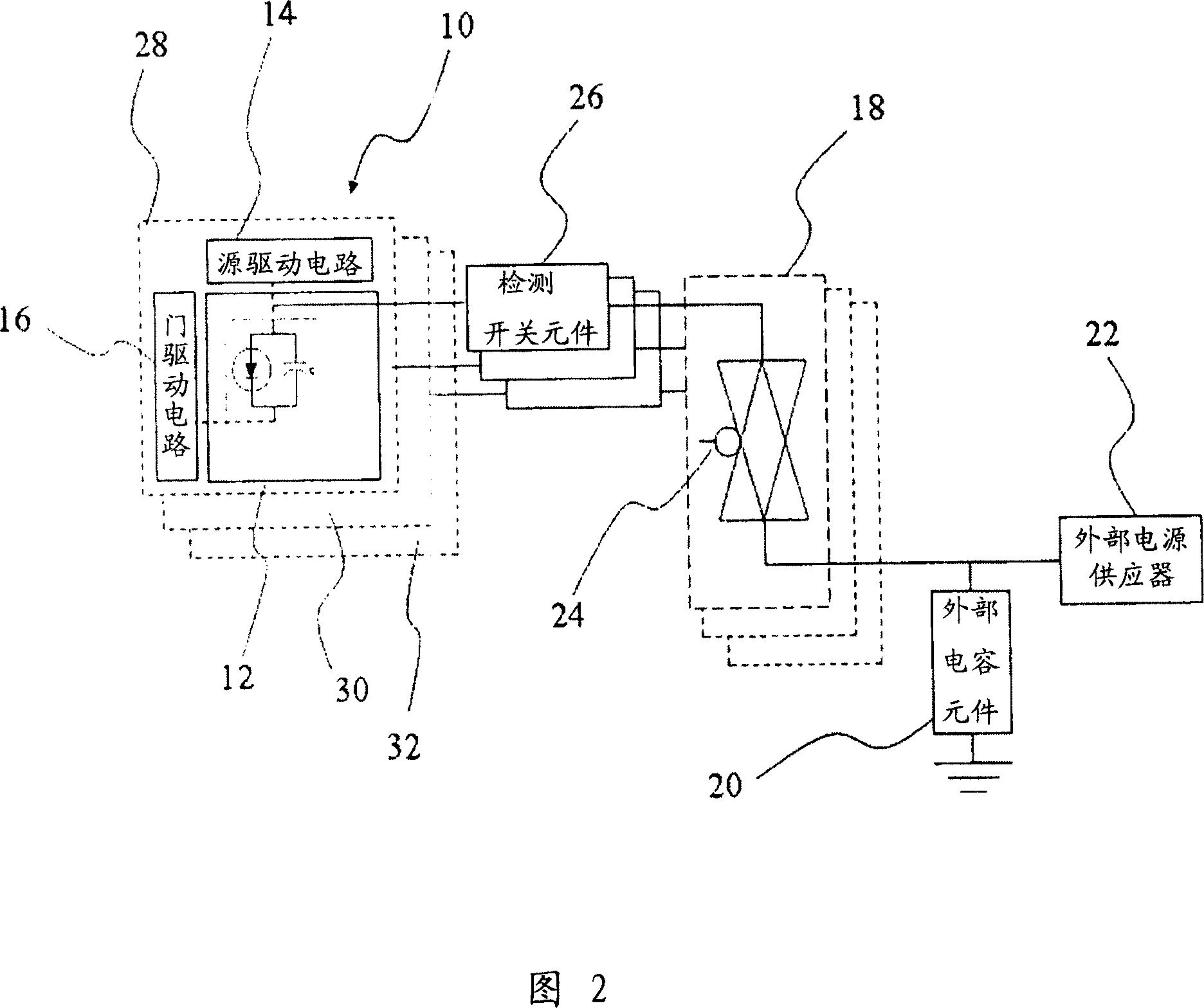

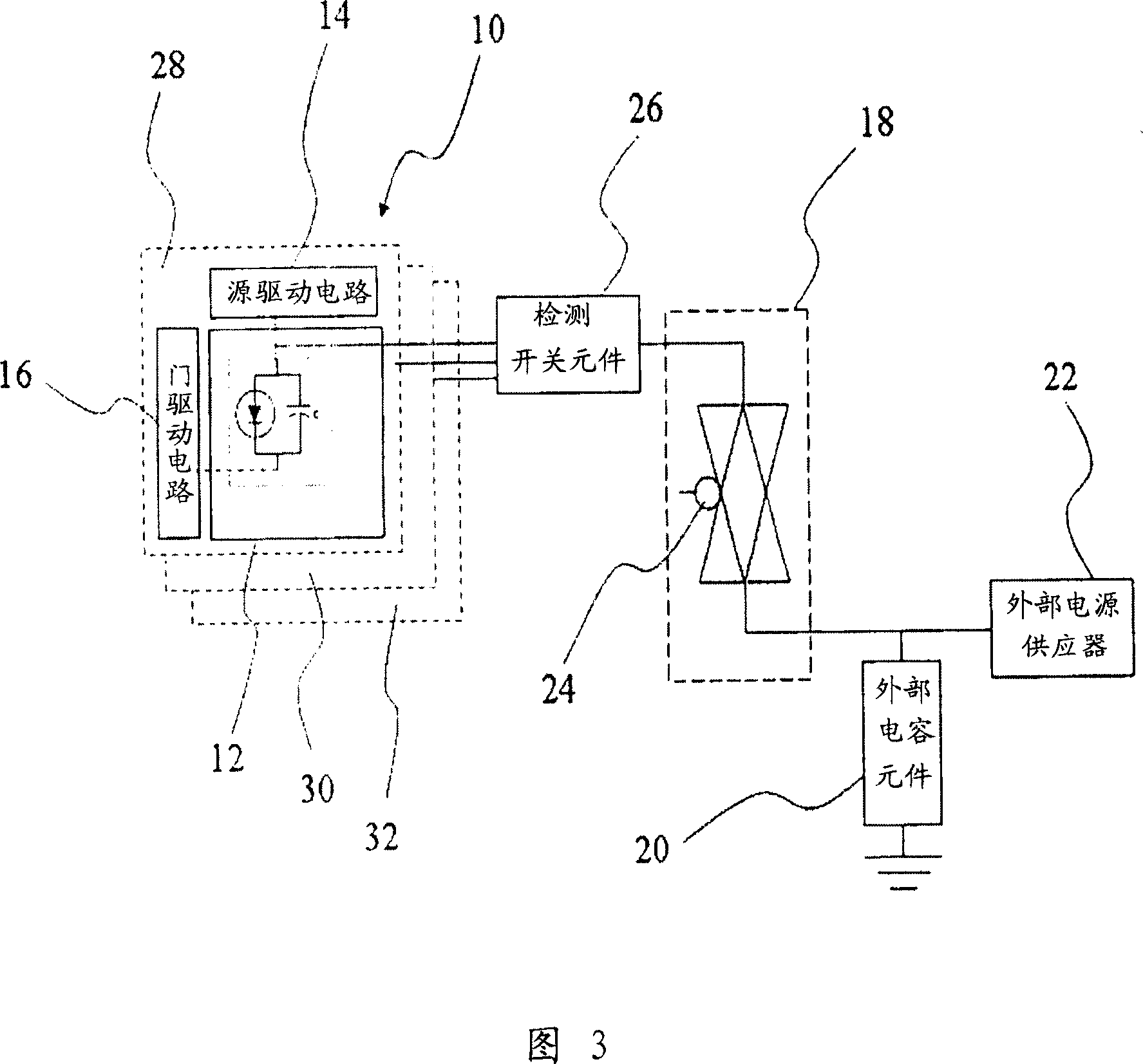

Electric charge recovery circulating circuit of display equipment

The invention discloses an electric charge recycle circuit of a display unit used to connect between a display panel and a source drive circuit which are both of a display module, wherein, the display module is provided with the source drive circuit and a gate drive circuit; when the source drive circuit closes, the electric charge recycle circuit transfers the electric charge to a system external capacity. The invention comprises an electric charge transfer circuit and a sense switching element, wherein, the electric charge transfer circuit can transfer the electric charge stored of a parasitic capacitor of the display panel to a system external capacity element to be stored; the sense switching element can sense voltage level between the display panel and the source drive circuit, and the on-state between the electric charge transfer circuit and the source drive circuit is determined according to a luminous critical pressure of the display panel of different color layers. The invention can effectively save electricity of a power supply and improve service efficiency of a battery.

Owner:ILI TECHNOLOGY CORPORATION

Radio communication apparatus and traffic control method for extending drive-time of battery

InactiveUS7889688B2Extend drive timeLower average currentEnergy efficient ICTPower managementElectrical batteryCharge recovery

A radio communication apparatus has a battery, a transmit buffer for temporarily accumulating packets to be sent, a battery state monitoring unit for monitoring a battery state of the battery, and a traffic control unit. The traffic control unit determines a packet burst length and an interval time between the packet bursts in order to obtain charge recovery effect based on the battery state, and controls so as to take out data packets of the packet burst length from the transmit buffer for every interval time between the packet bursts of the packet burst.

Owner:KDDI CORP

Battery management system and method of vehicle

InactiveCN103085678AReduce capacityIncreased durabilityBatteries circuit arrangementsElectrical testingElectricityAlternator

Disclosed is a battery management system and method of a vehicle. More specifically, the battery management system includes an alternator that supplies a battery and electronic equipment of a vehicle with electricity that is generated by a driving torque of the vehicle, a battery that supplies the electronic equipment with power that is charged by the alternator, a battery observer that observes a condition of the battery, a vehicle information collection portion that collects vehicle condition information according to driving of the vehicle, and a control portion that performs charging recovery of the battery by activating a battery refresh operation when at least one condition of a current accumulation value of the battery, a low SOC entry frequency, and a vehicle starting frequency satisfies a predetermined battery refresh condition.

Owner:HYUNDAI MOTOR CO LTD +1