Patents

Literature

13969results about "Electric pulse generator" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

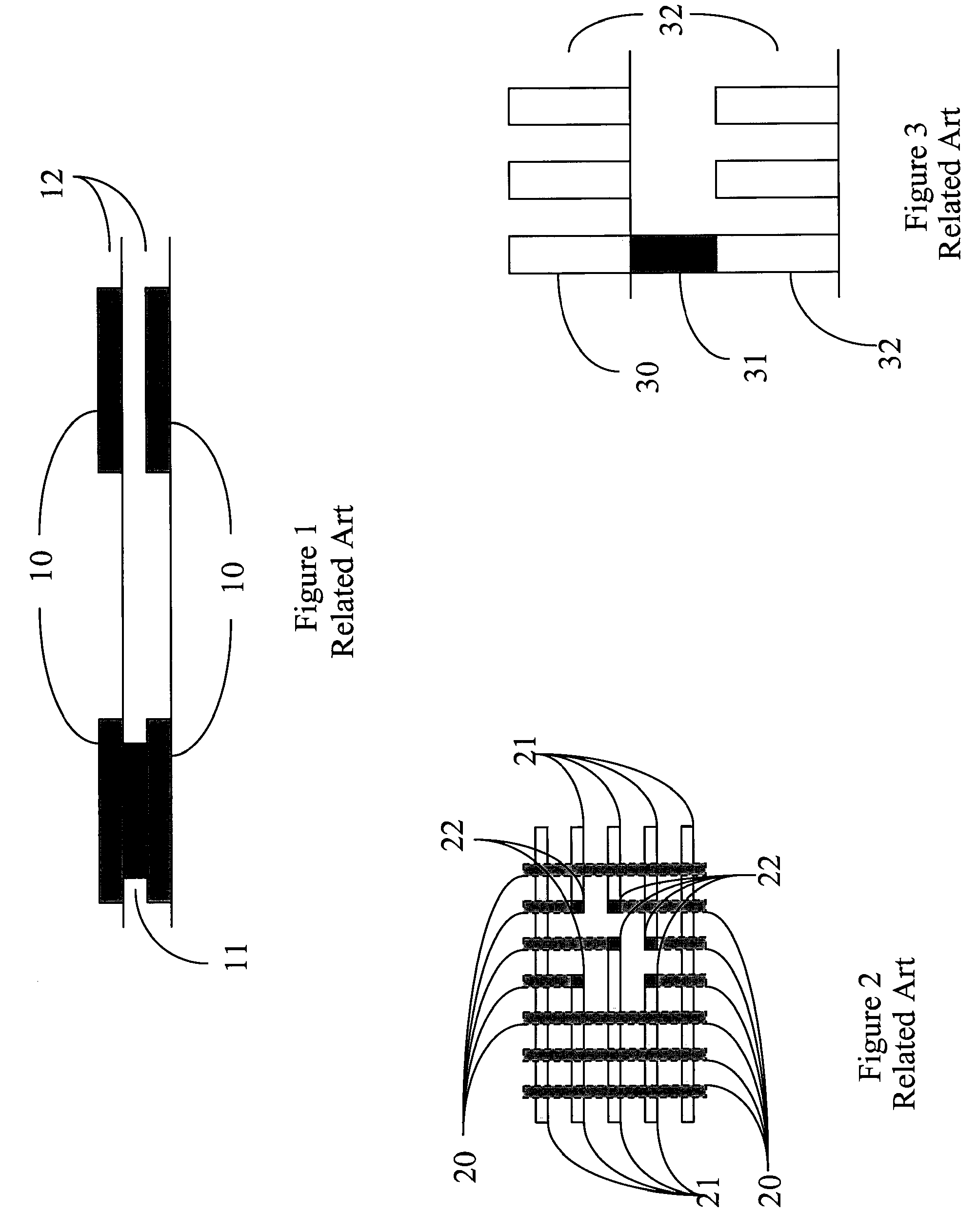

Barcode reader with edge detection enhancement

ActiveUS8950678B2Character and pattern recognitionElectric pulse generatorPropagation delayTelecommunications

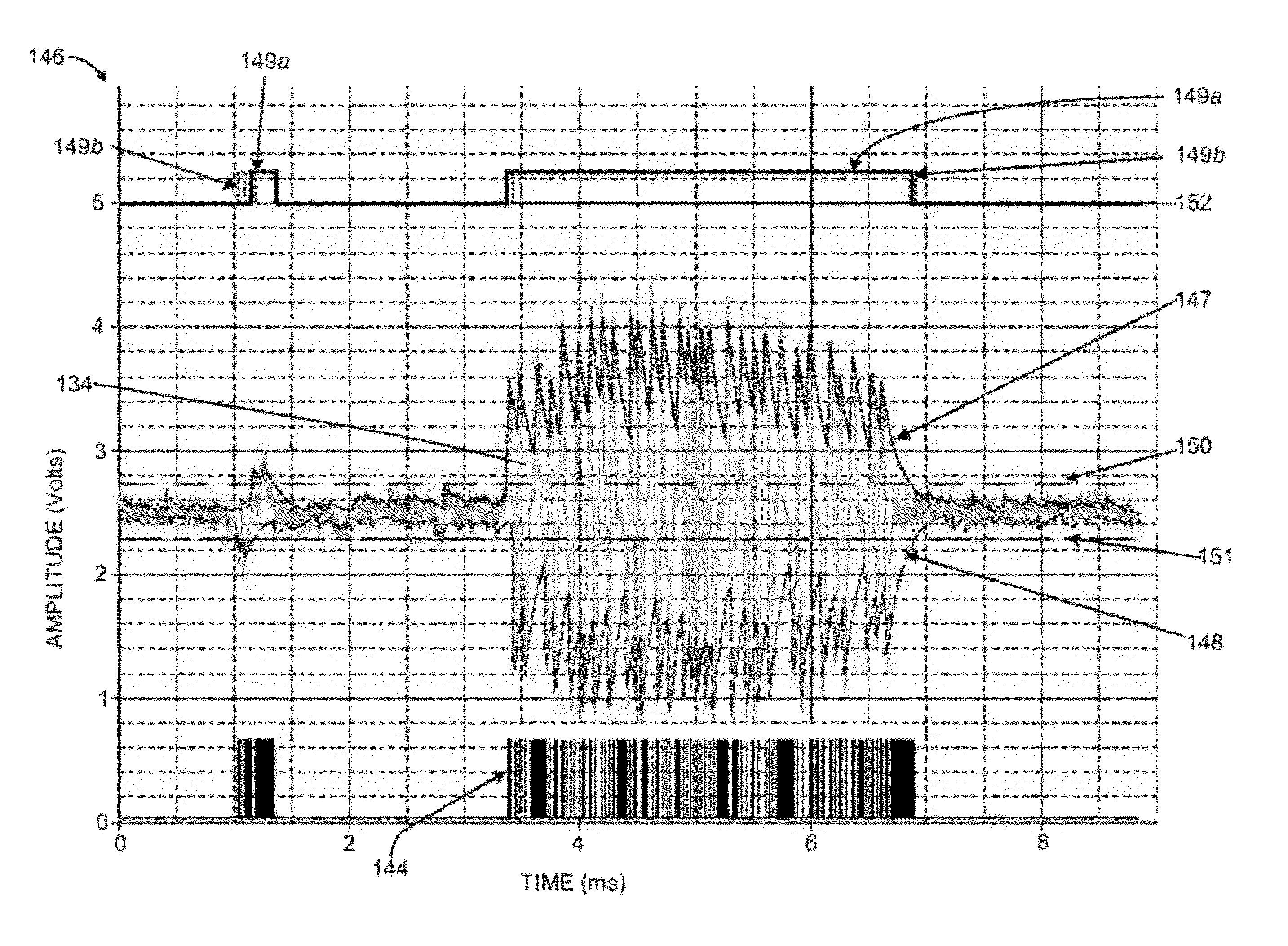

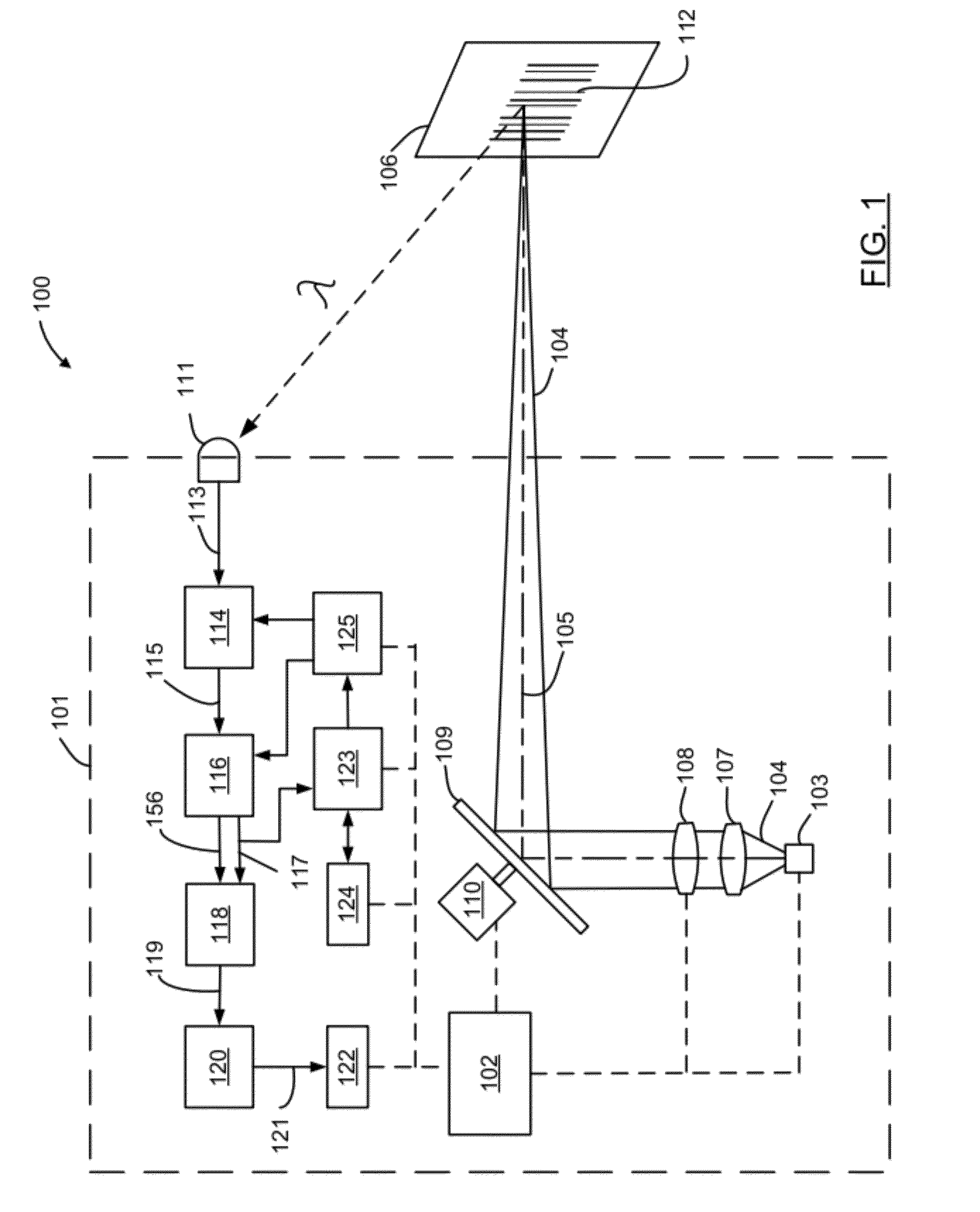

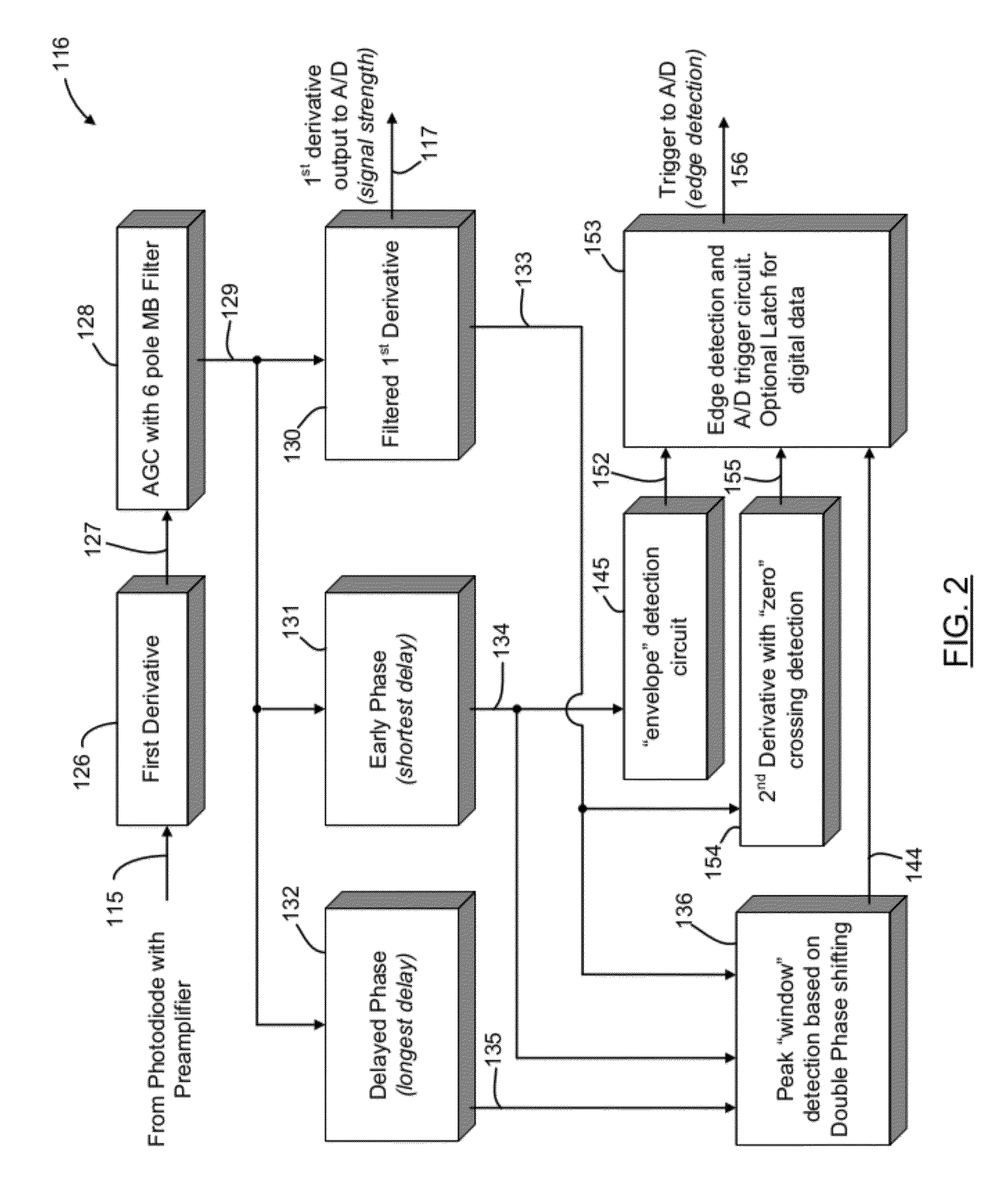

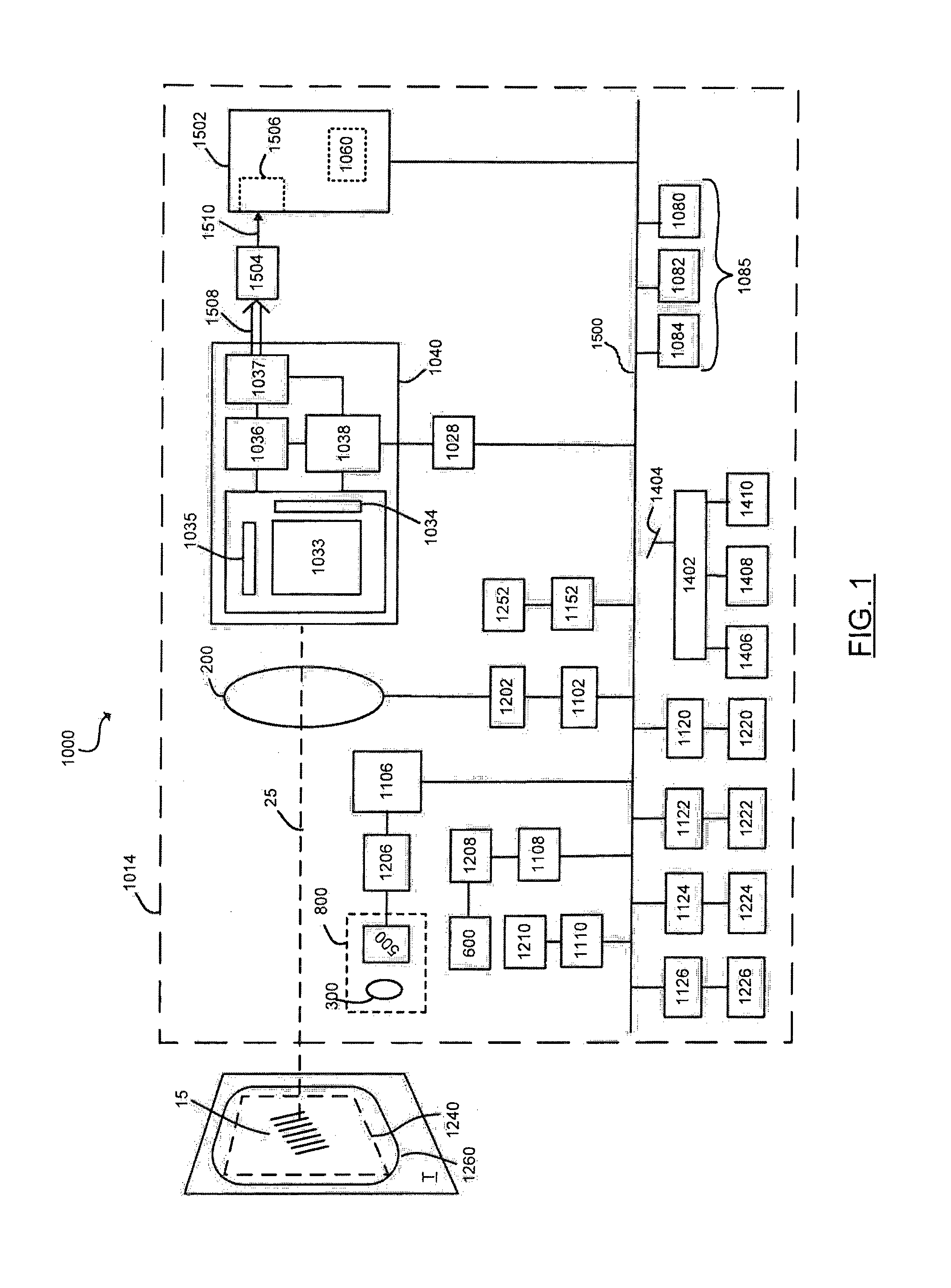

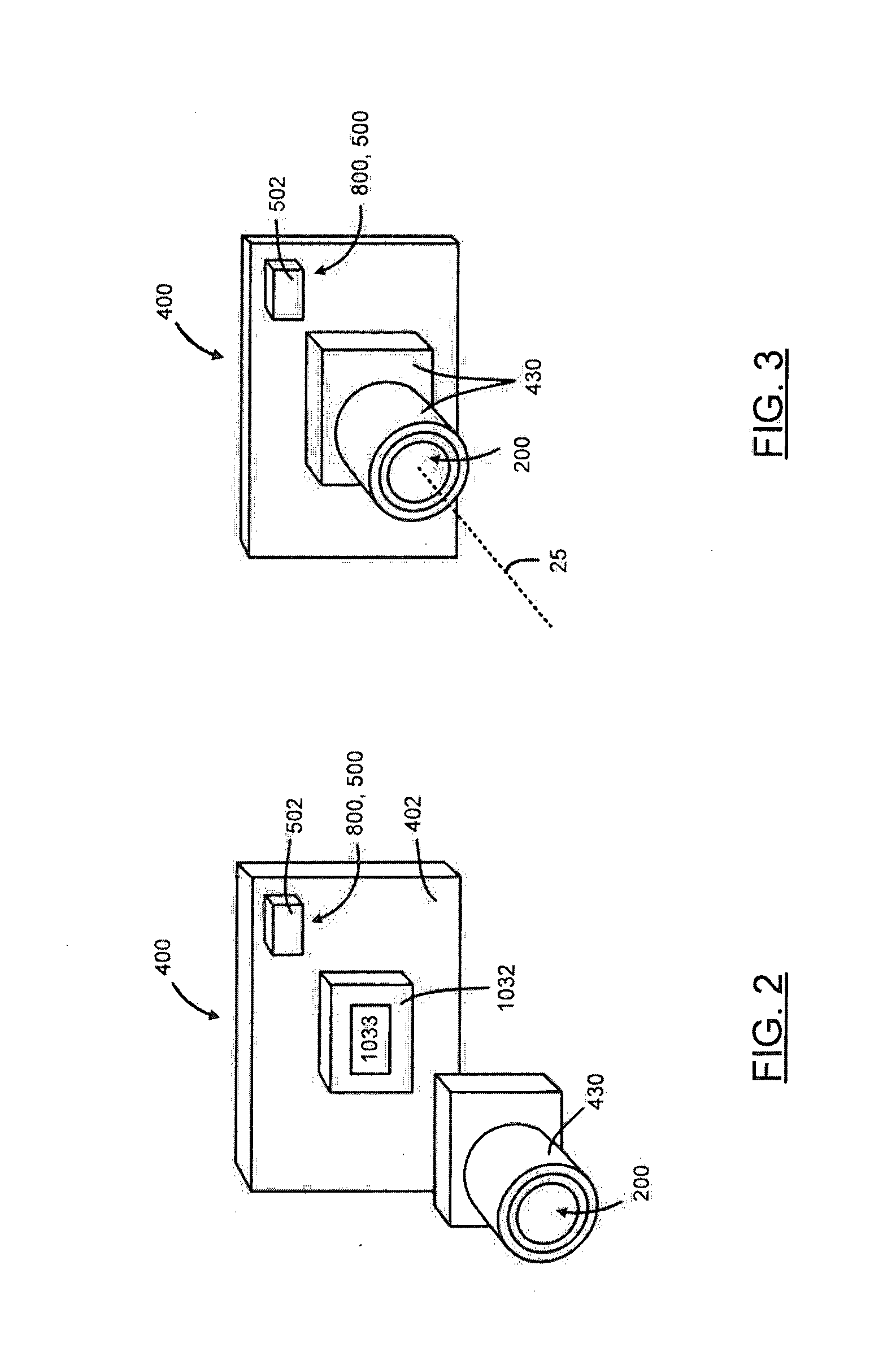

An optical reader for decoding an encoded symbol character of a symbology includes a scan data signal processor having as an input a scan data signal encoding information representative of the encoded symbol character. The scan data signal processor includes a first time delay stage adapted to provide a primary phase waveform from the scan data signal, a second time delay stage adapted to provide an early phase waveform from the scan data signal, and a third time delay stage adapted to provide a delayed phase waveform from the scan data signal. The early phase waveform has a propagation delay less than the primary phase waveform, and the delayed phase waveform has a propagation delay greater than the primary phase waveform. The scan data signal processor further includes a peak window detection stage for generating a peak window timeframe when an amplitude of the primary phase waveform is greater than, less than, or equal to both an amplitude of the early phase waveform and the delayed phase waveform. The optical reader further includes a digitizer circuit adapted to accept, within the peak window timeframe, the scan data signal processor output.

Owner:HAND HELD PRODS +1

Terminal having image data format conversion

InactiveUS20140197238A1Character and pattern recognitionElectric pulse generatorEngineeringData shipping

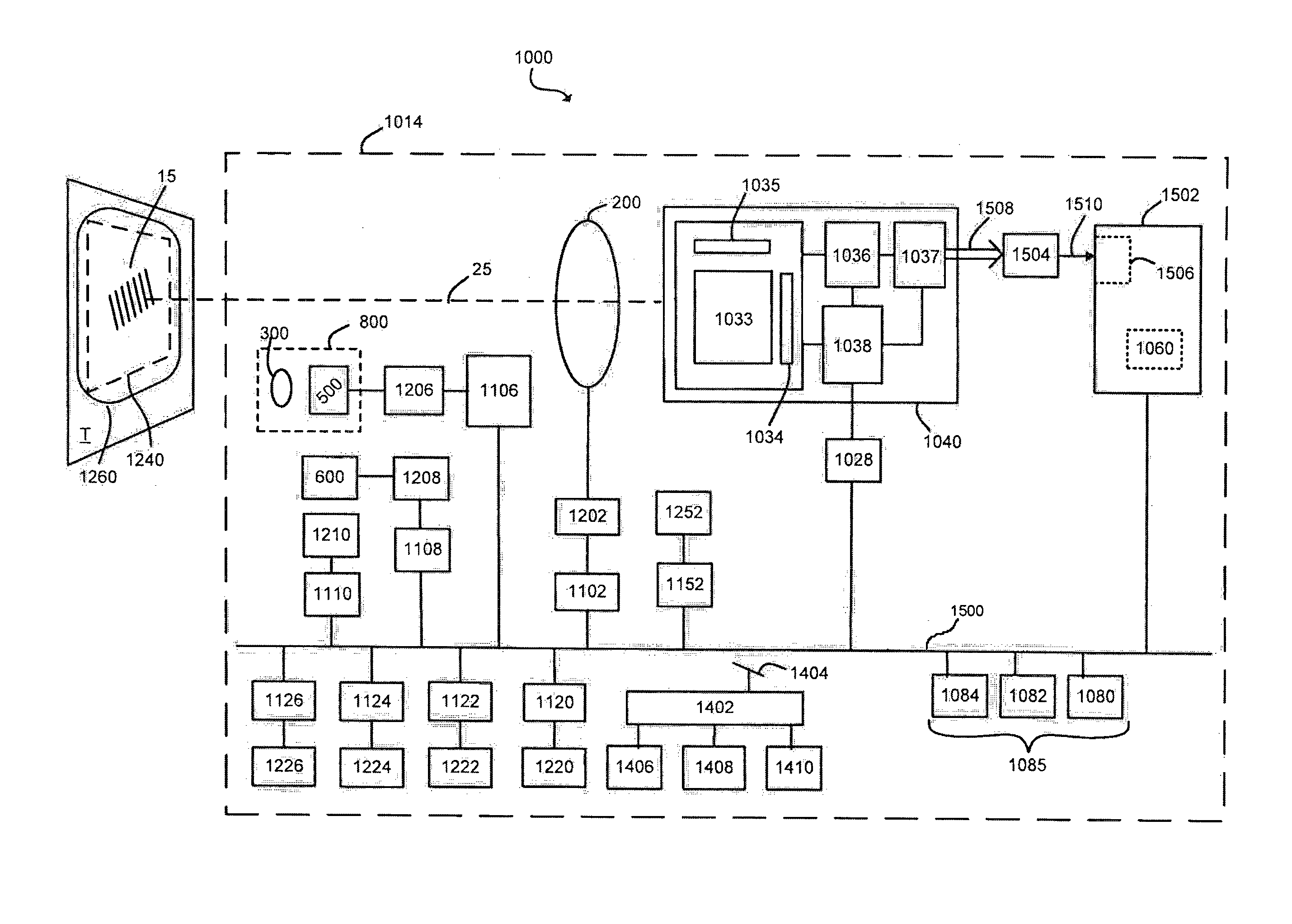

There is set forth herein an indicia reading terminal having data format conversion capabilities. The indicia reading terminal includes an image sensor integrated circuit with an image sensor array comprising a plurality of pixels. The image sensor integrated circuit is configured to output image data in a first data format to a data formatting circuit for conversion to image data in a second data format. The data formatting circuit is configured to provide the image data in the second data format to the at least one data interface of a microprocessor integrated circuit, which is operative to transfer image data received by the at least one data interface into memory of the indicia reading terminal. A CPU of the microprocessor integrated circuit is operative for executing a decoding algorithm for processing image data in the memory for attempting to decode at least one symbol represented in the memory.

Owner:METROLOGIC INSTR

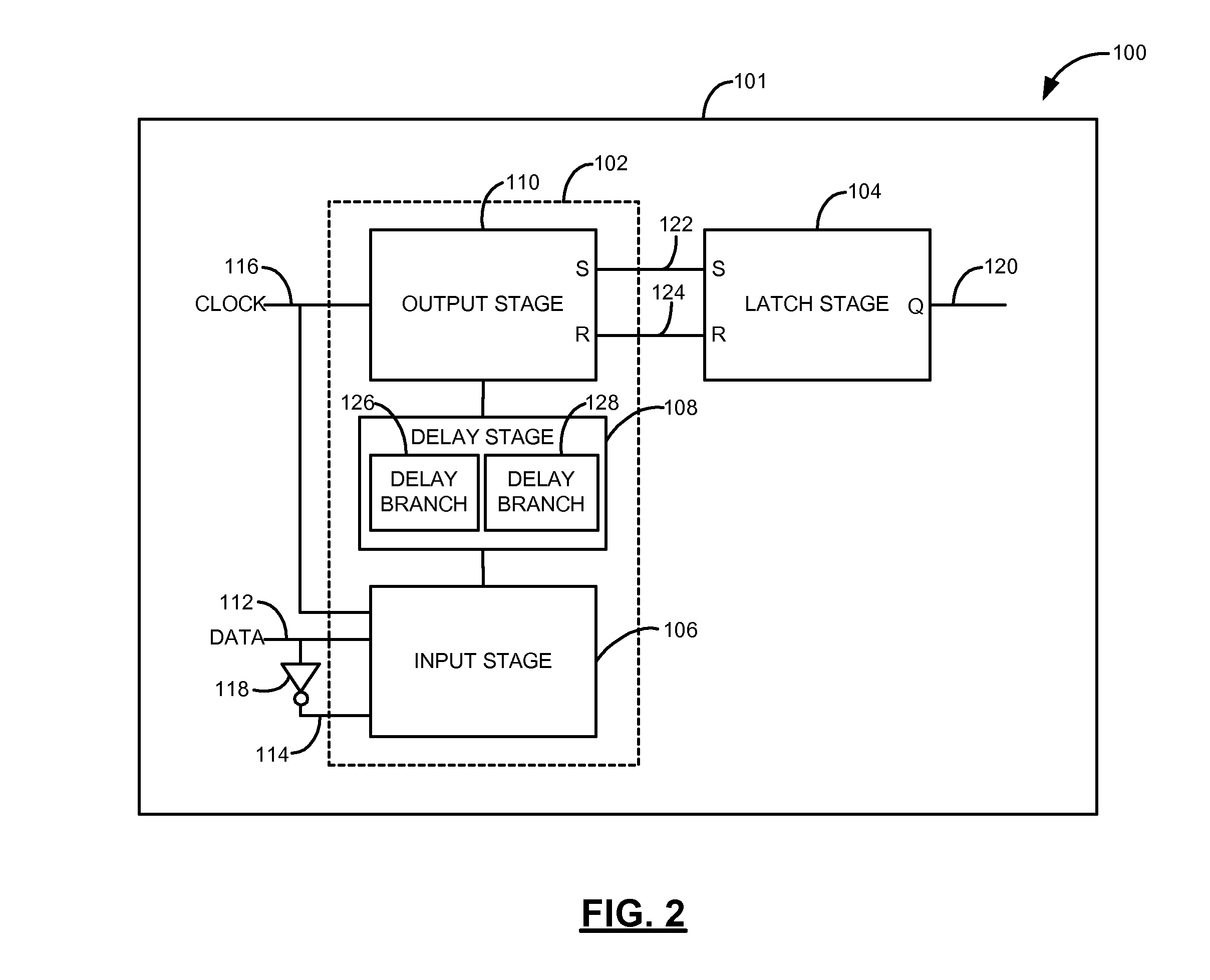

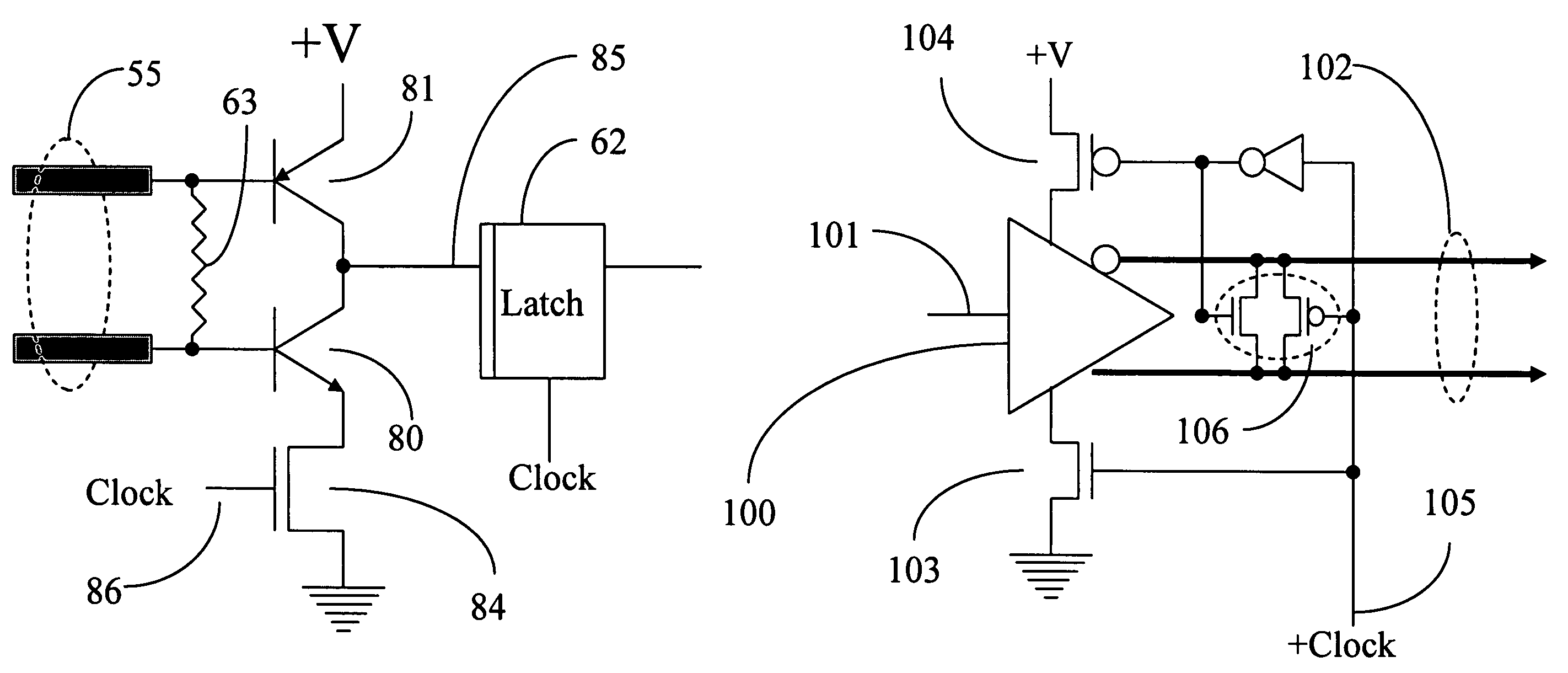

Sense amplifier based flip-flop

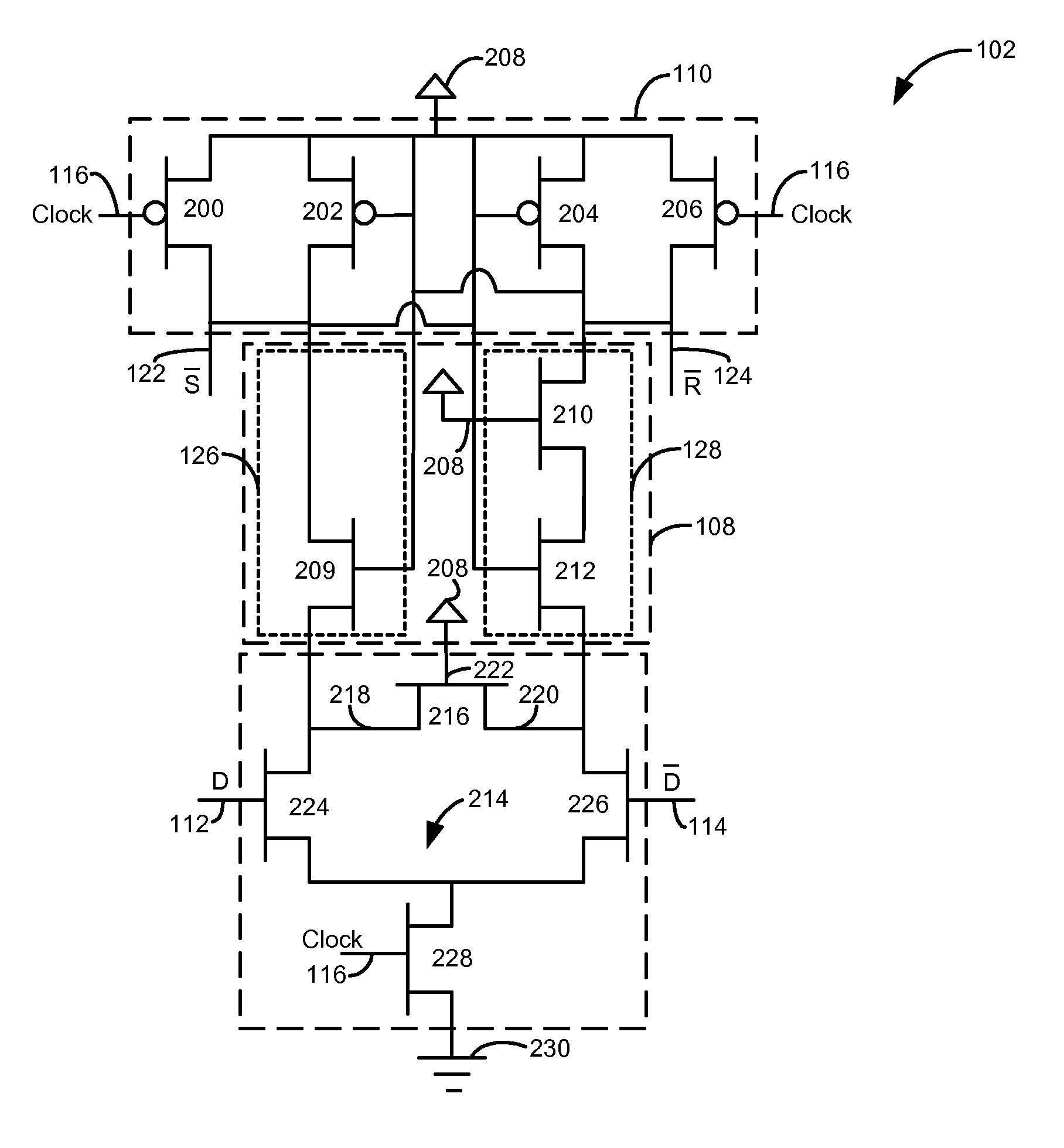

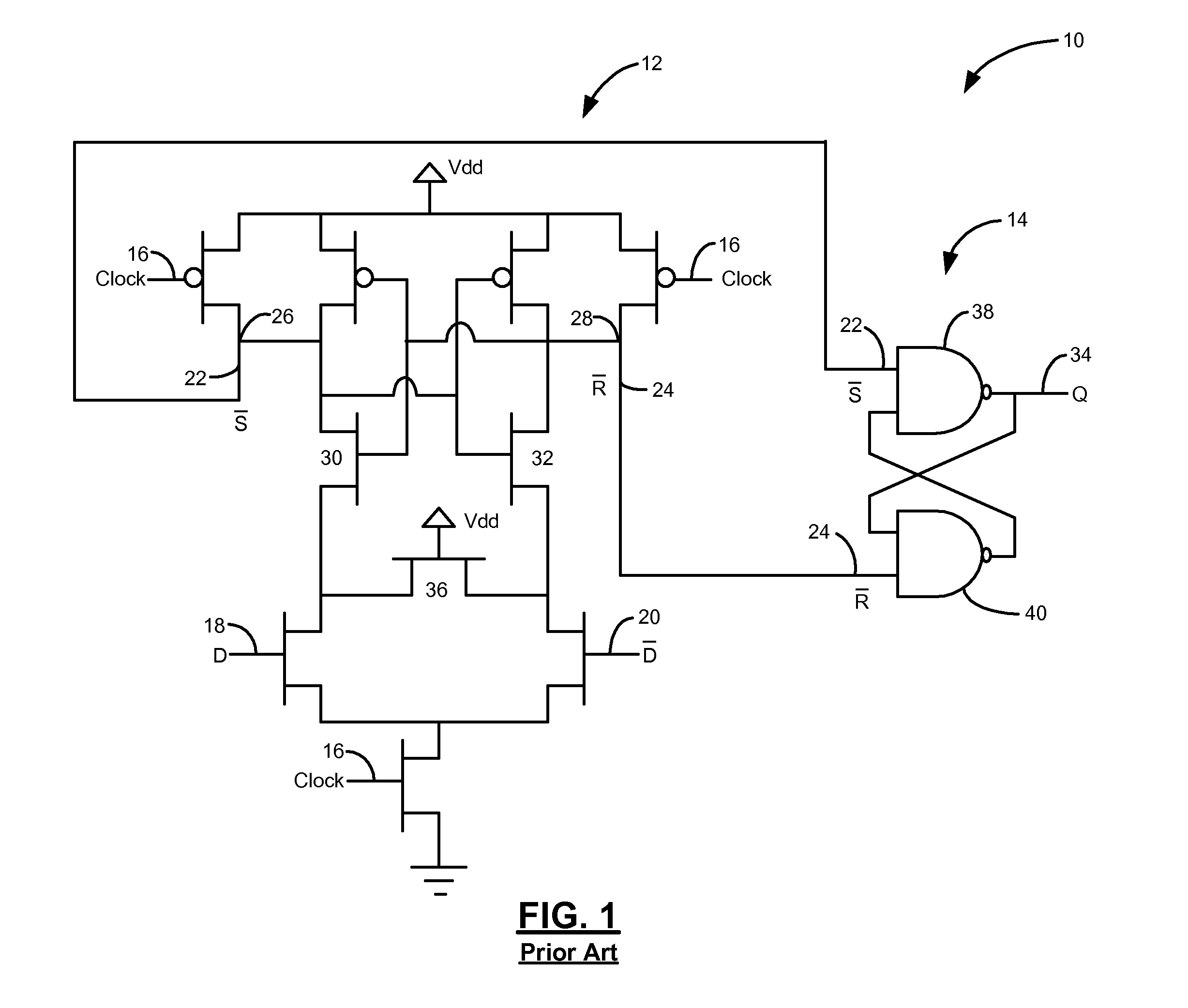

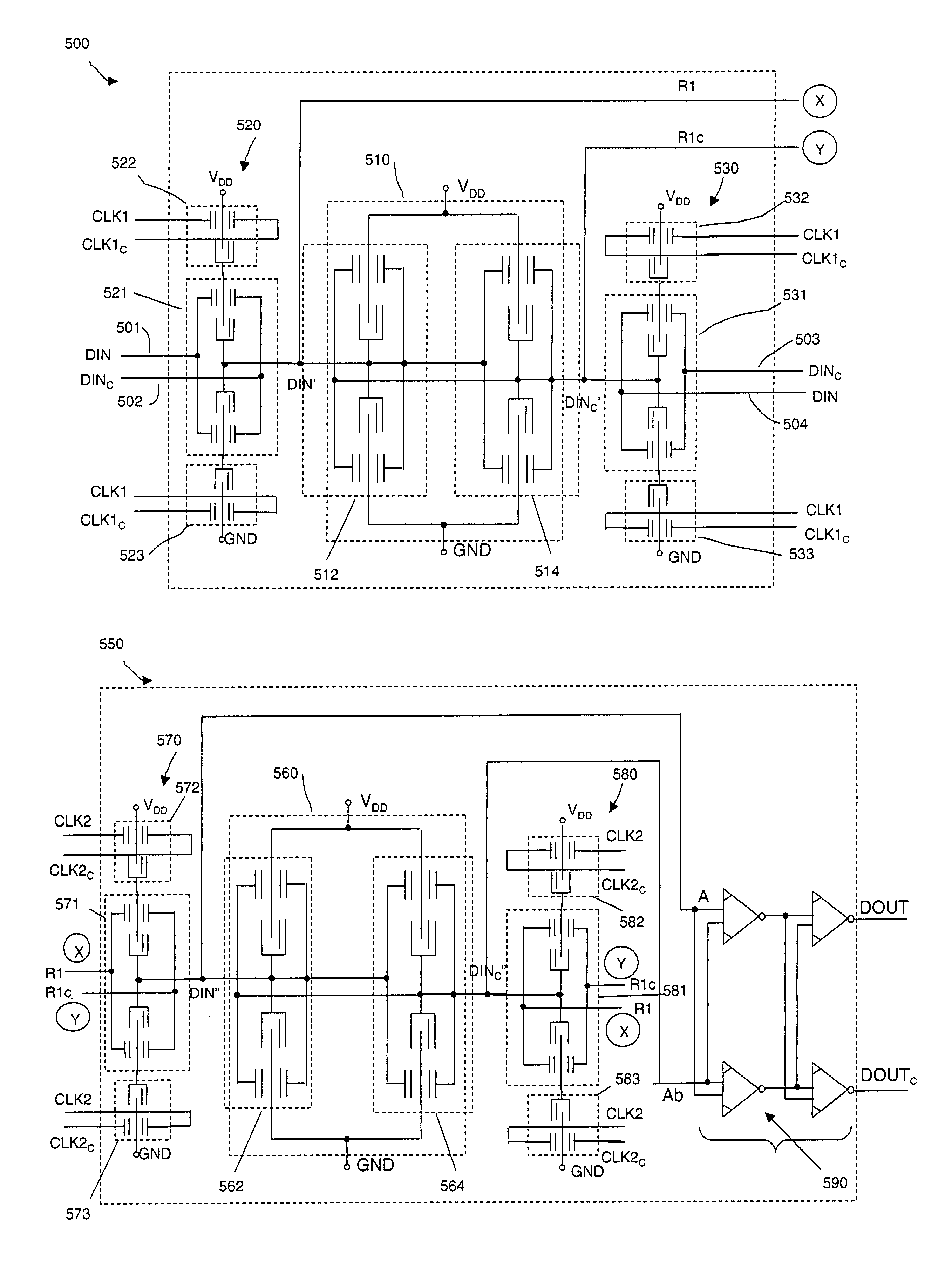

A circuit includes an input stage, an output stage, and a delay stage. The input stage is operative to receive a clock signal and a first and second input signal. The output stage is operative to receive the clock signal. The output stage is also operative to generate a first and second output signal based on the clock signal and the first and second input signals. The delay stage is operatively coupled to the input and output stages. The delay stage includes a first and second branch. The second branch includes at least one more delay element than the first branch.

Owner:ATI TECH INC

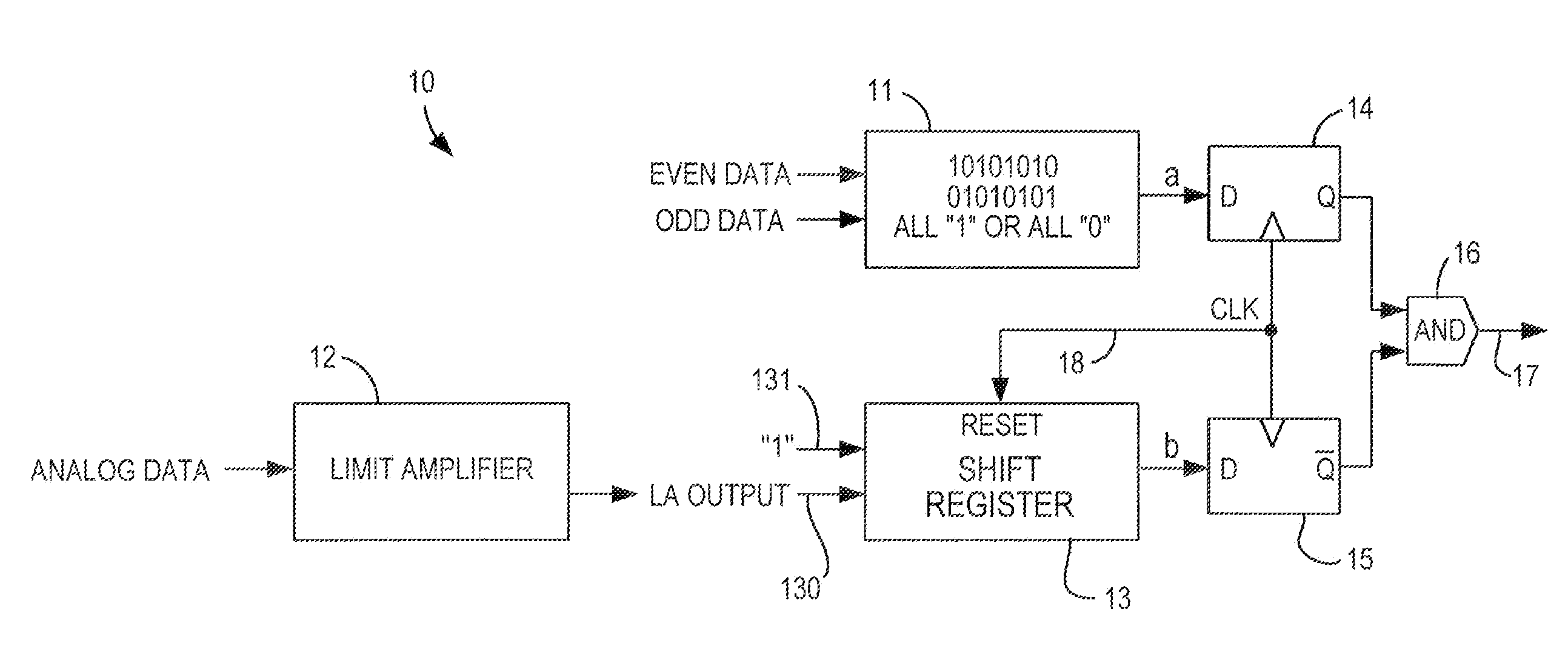

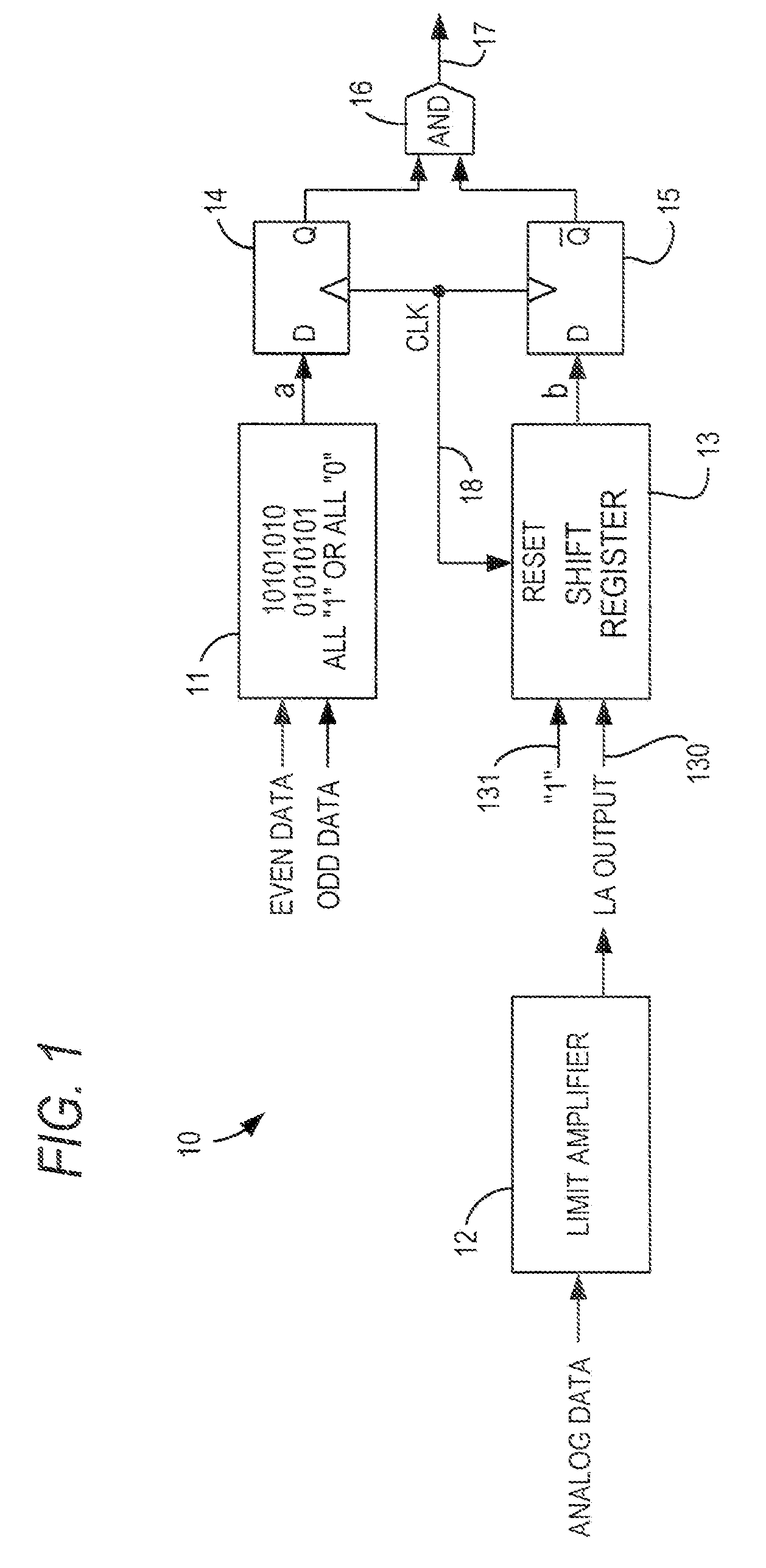

Signal loss detector for high-speed serial interface of a programmable logic device

InactiveUS7996749B2Multiple-port networksData representation error detection/correctionPattern matchingProgrammable logic device

Owner:ALTERA CORP

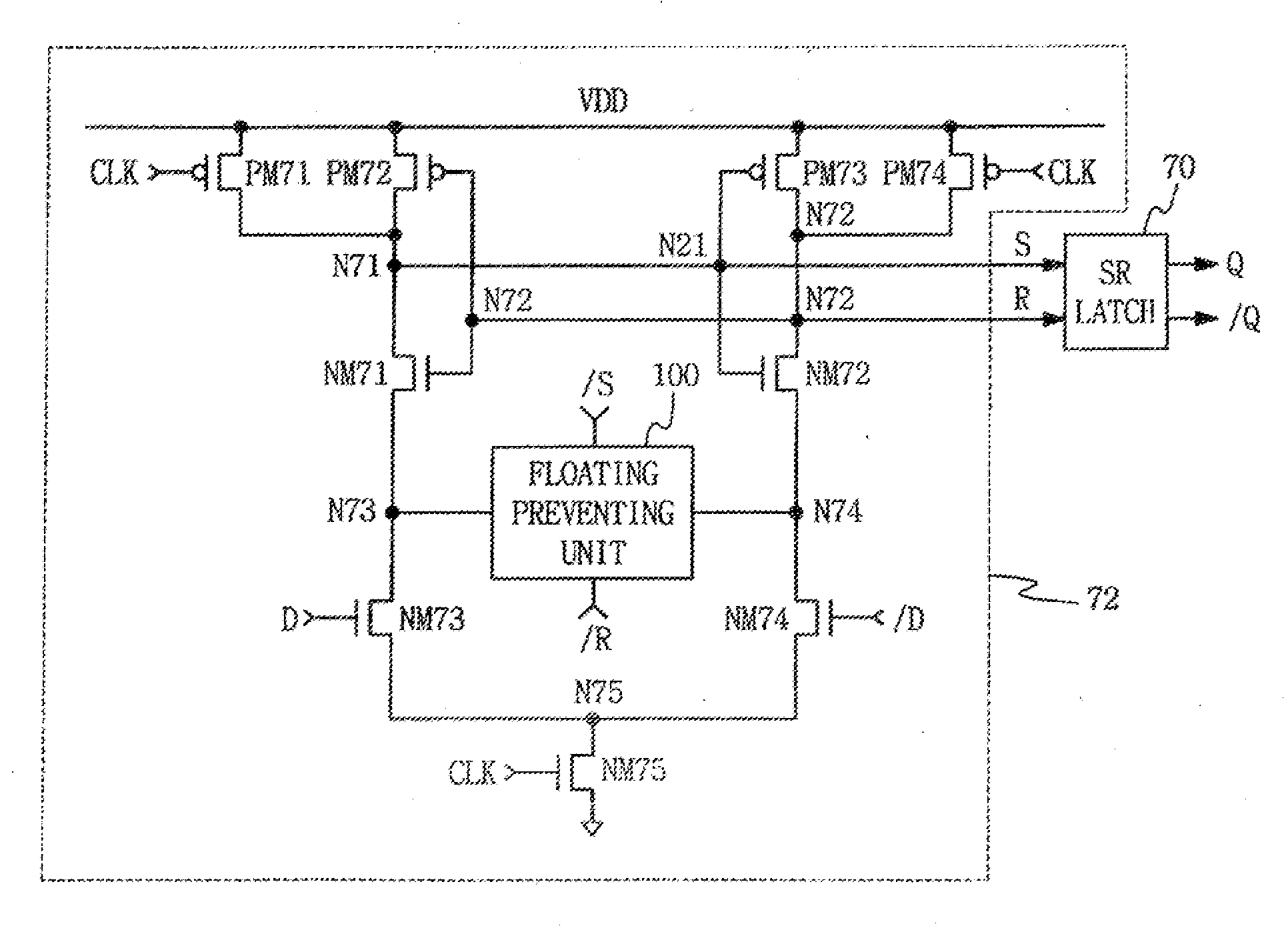

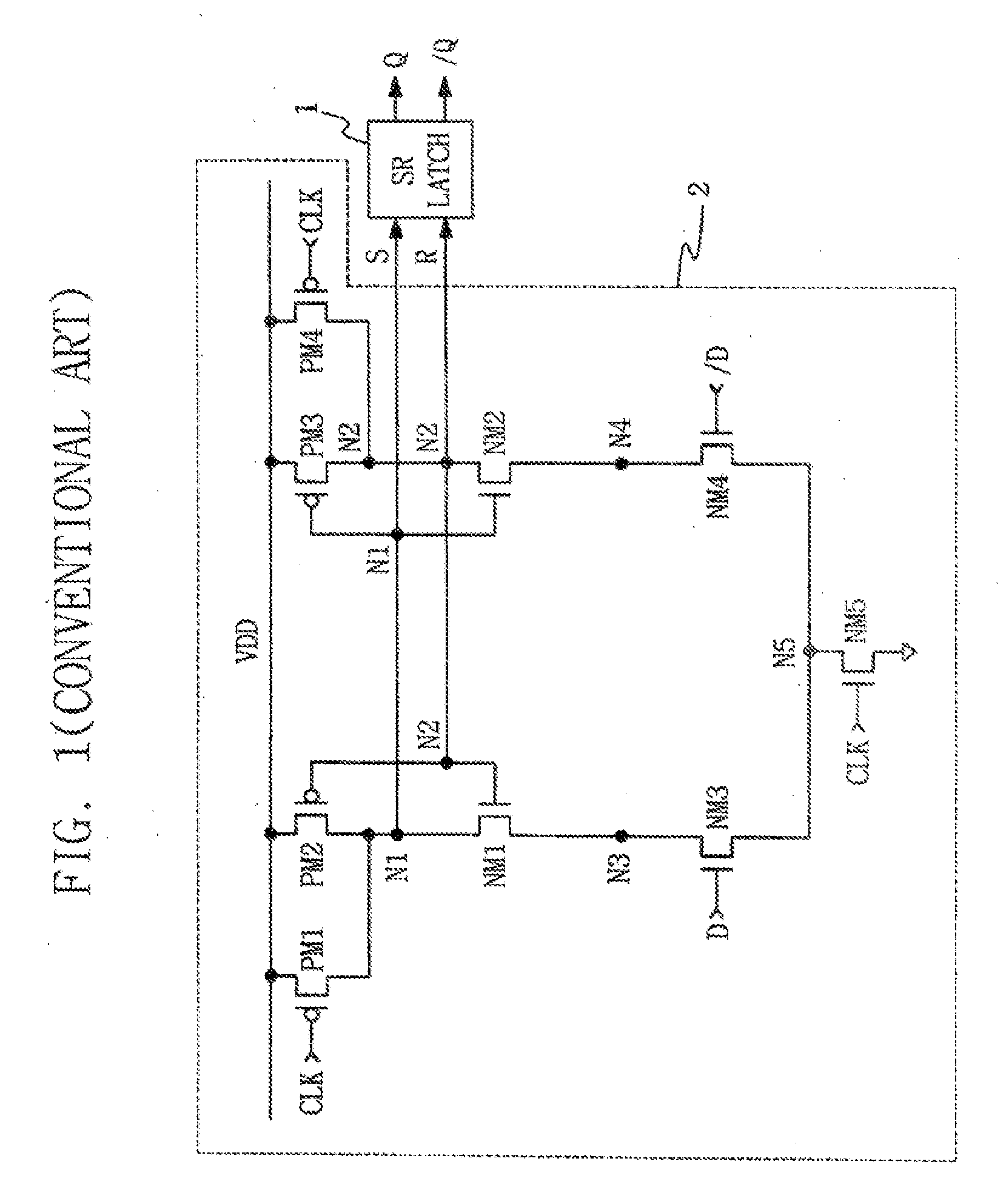

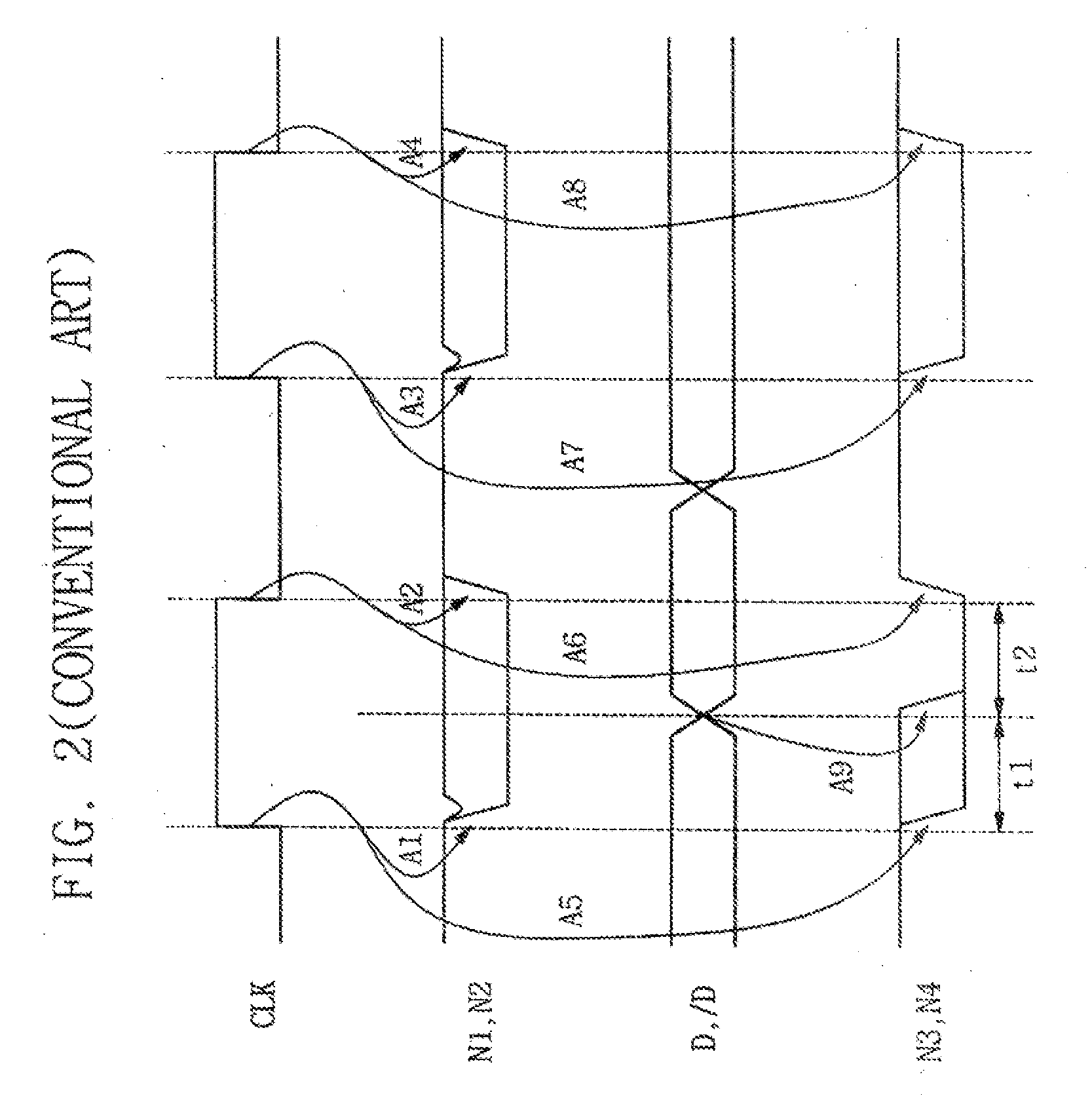

Sense amplifier circuit and sense amplifier-based flip-flop having the same

ActiveUS20070285131A1Reducing signal delay timePrevent degradation of outputCurrent/voltage measurementDigital storageAudio power amplifierControl delay

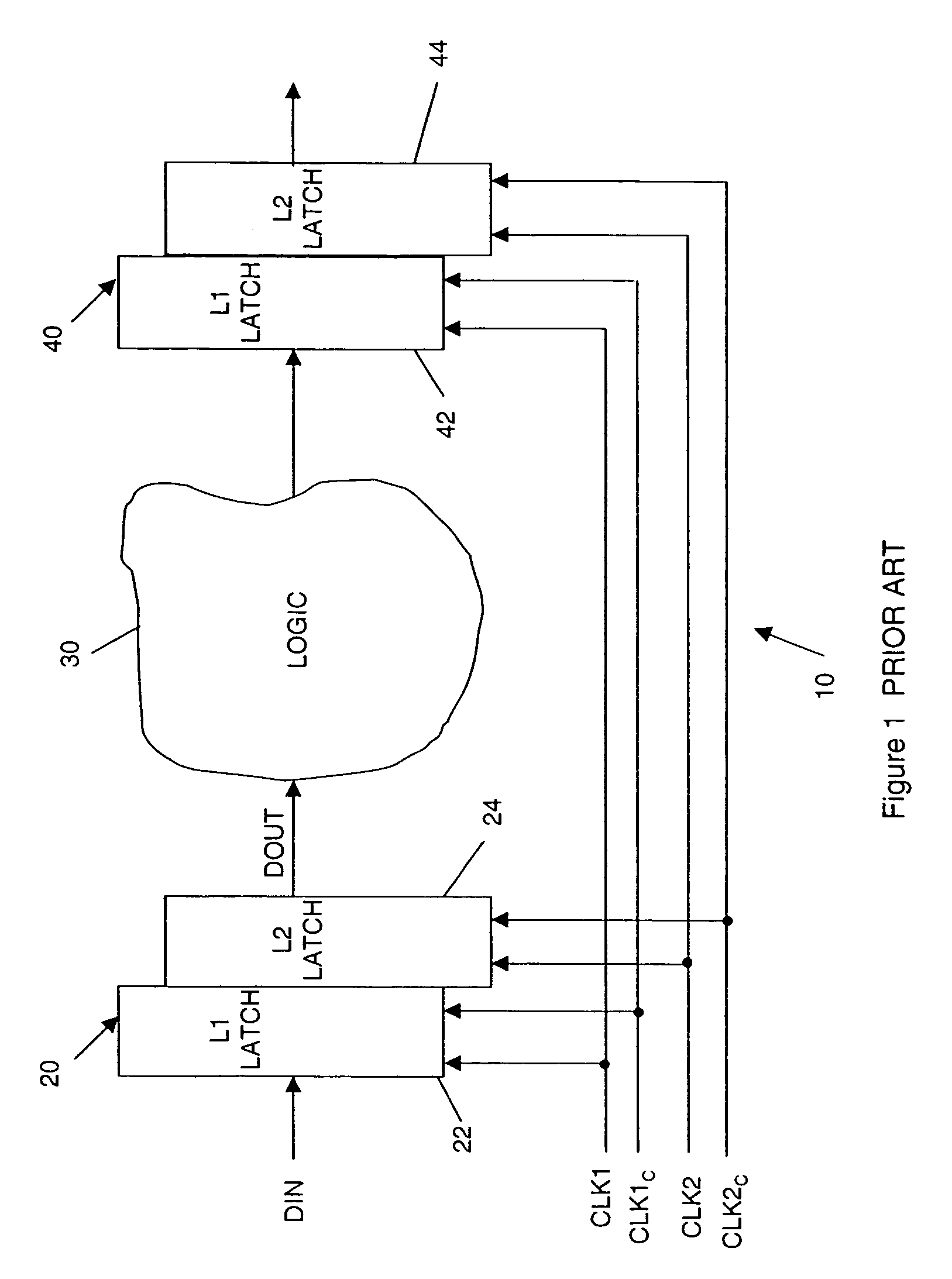

A sense amplifier-based flip-flop includes a first latch, a second latch, a floating reduction unit, an input signal applying unit, a ground switch and a delay reduction unit. The first latch outputs a signal to a first output terminal pair, and outputs an evaluation signal pair corresponding to an input single pair to the first output terminal pair. The second latch latches the evaluation signal pair and outputs the evaluation signal pair to a second output terminal pair. The floating reduction unit is controlled by signals of the first output terminal pair and is operationally connected between current passing nodes of the first latch to prevent the first output terminal pair from floating. The input signal applying unit is disposed between the current passing nodes and a ground terminal, and receives the input signal pair. The ground switch is disposed between the input signal applying unit and the ground terminal, and is controlled by the clock signal. The delay reduction unit is disposed between the input signal applying unit and the ground switch, and reduces a signal delay from when the clock signal to when the evaluation signal pair is output from the second output terminal pair.

Owner:SAMSUNG ELECTRONICS CO LTD

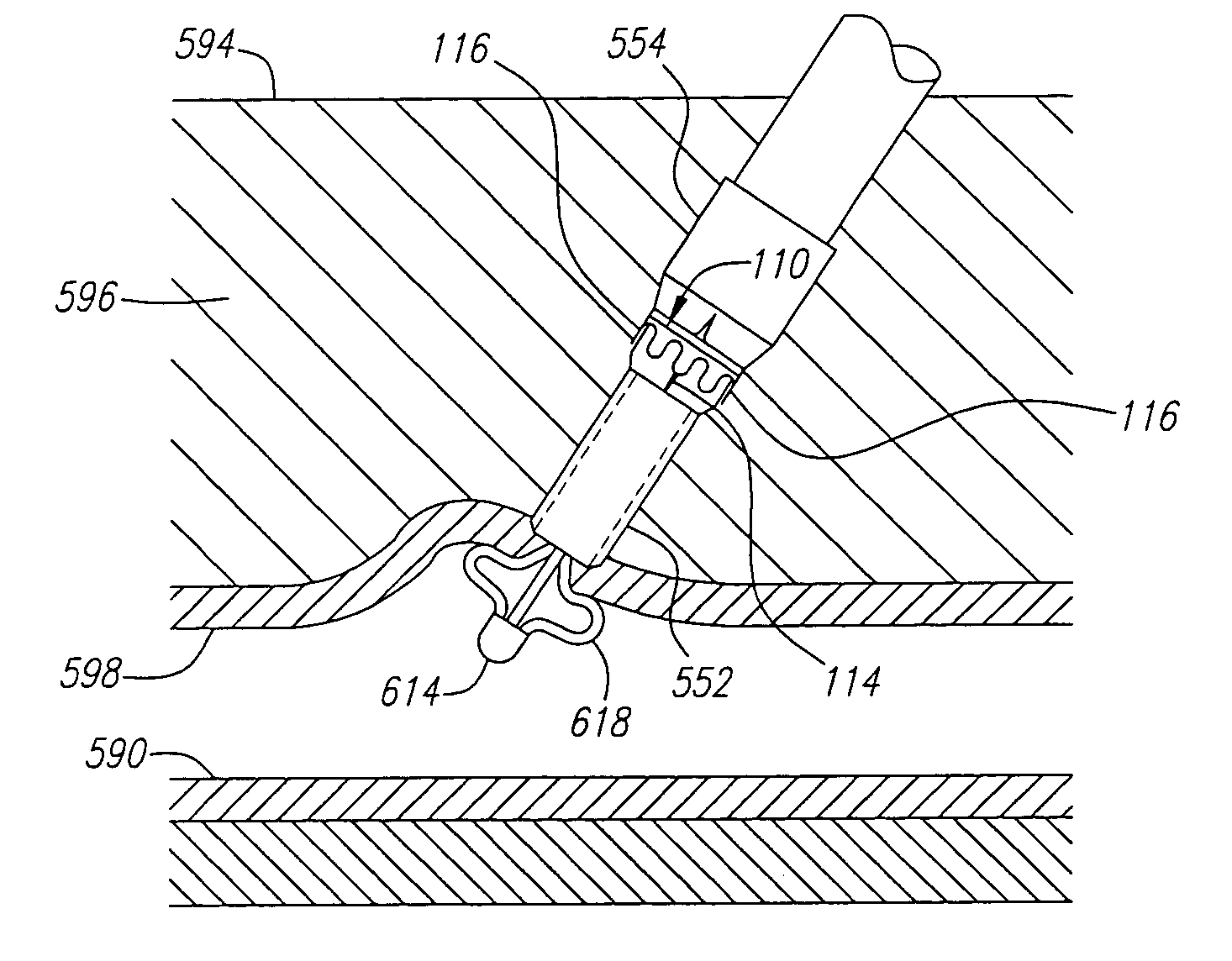

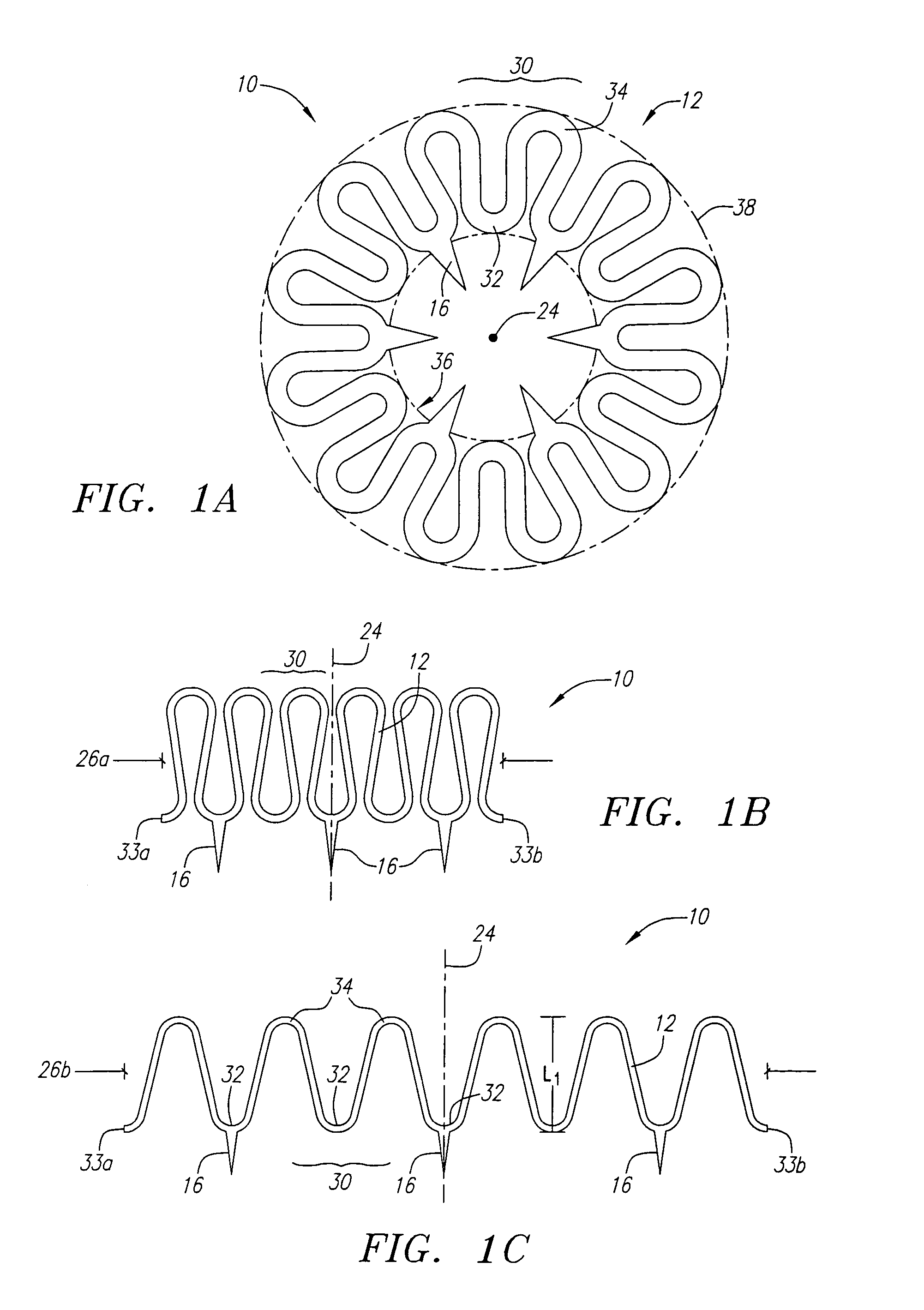

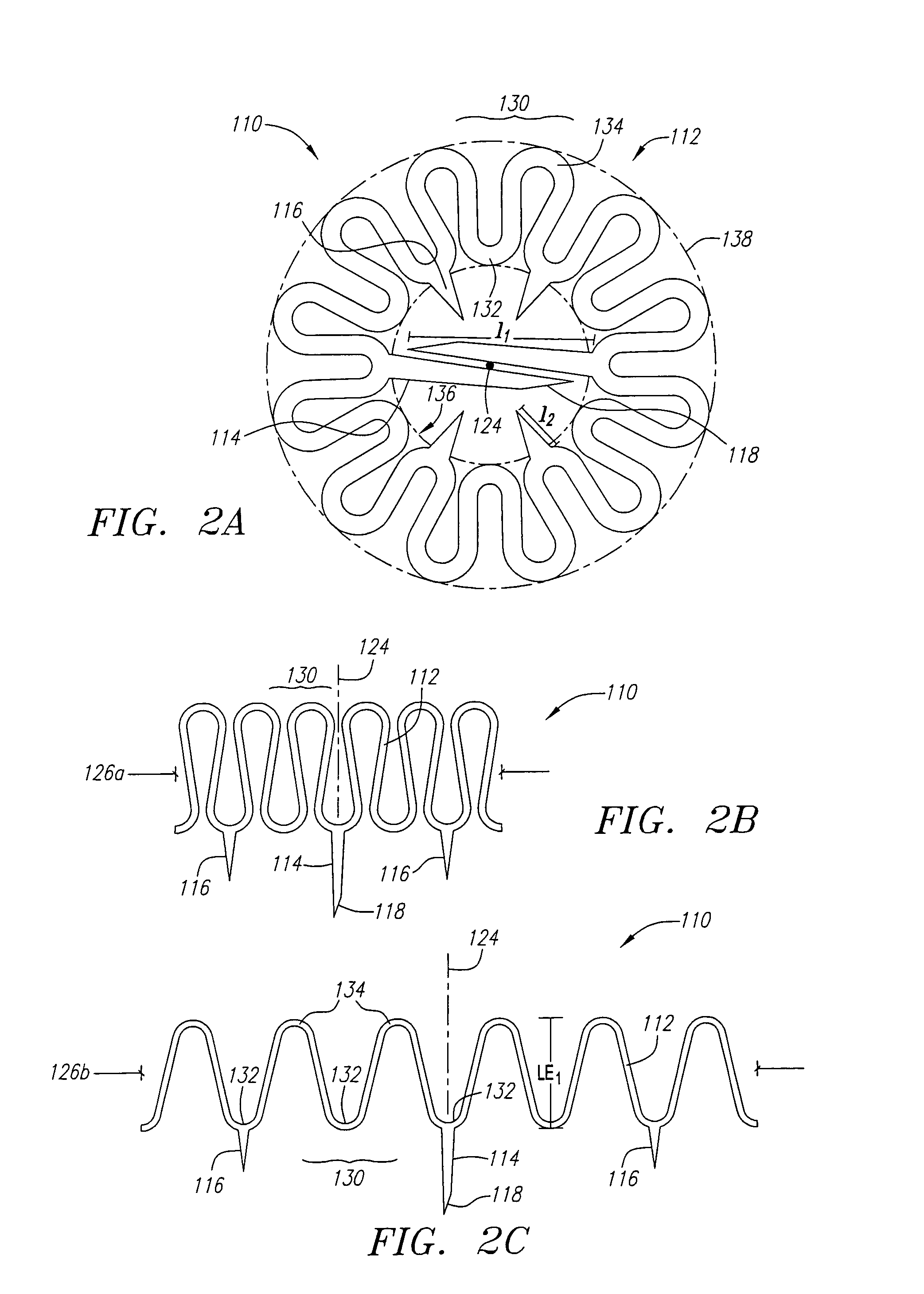

Closure device and methods for making and using them

InactiveUS7001398B2Improve deformationStress minimizationStaplesDiagnostic markersDistal portionSurgery

Owner:INTEGRATED VASCULAR SYST

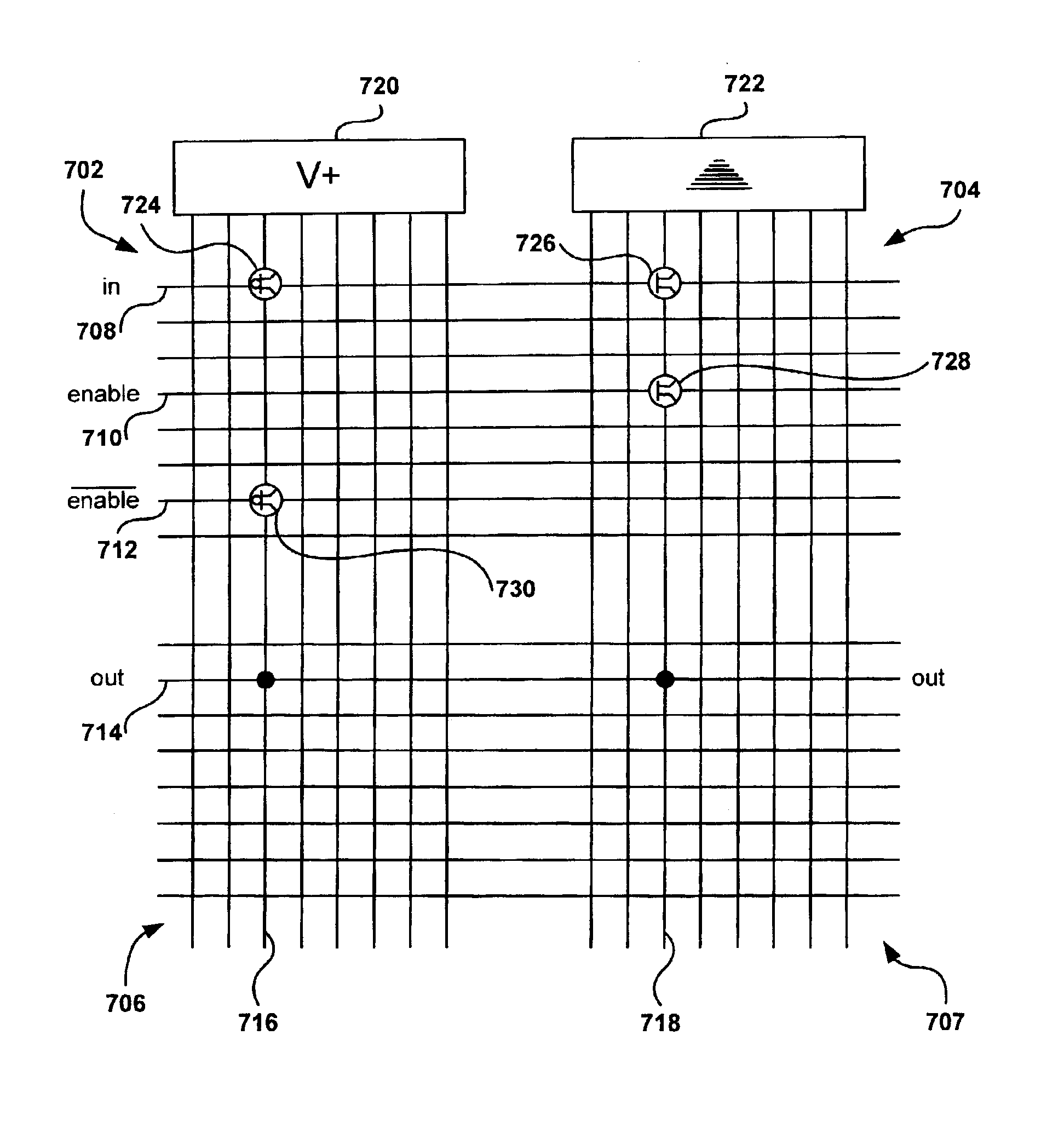

Molecular-junction-nanowire-crossbar-based inverter, latch, and flip-flop circuits, and more complex circuits composed, in part, from molecular-junction-nanowire-crossbar-based inverter, latch, and flip-flop circuits

InactiveUS6919740B2High densityLittle powerLogic circuits characterised by logic functionNanoinformaticsCrossbar switchNanowire

Methods for implementing familiar electronic circuits at nanoscale sizes using molecular-junction-nanowire crossbars, and nanoscale electronic circuits produced by the methods. In one embodiment of the present invention, a 3-state inverter is implemented. In a second embodiment of the present invention, two 3-state inverter circuits are combined to produce a transparent latch. The 3-state inverter circuit and transparent-latch circuit can then be used as a basis for constructing additional circuitry, including master / slave flip-flops, a transparent latch with asynchronous preset, a transparent latch with asynchronous clear, and a master / slave flip-flop with asynchronous preset. 3-state inverters can thus be used to compose latches and flip-flops, and latches and flip-flops can be used, along with additional Boolean circuitry, to compose a wide variety of useful, state-maintaining circuits, all implementable within molecular-junction-nanowire crossbars by selectively configuring junctions within the molecular-junction-nanowire crossbars.

Owner:HEWLETT PACKARD DEV CO LP

Contactless battery charging apparel

InactiveUS7863859B2Reduced Power RequirementsReduce chargeDc network circuit arrangementsBatteries circuit arrangementsBattery chargeEngineering

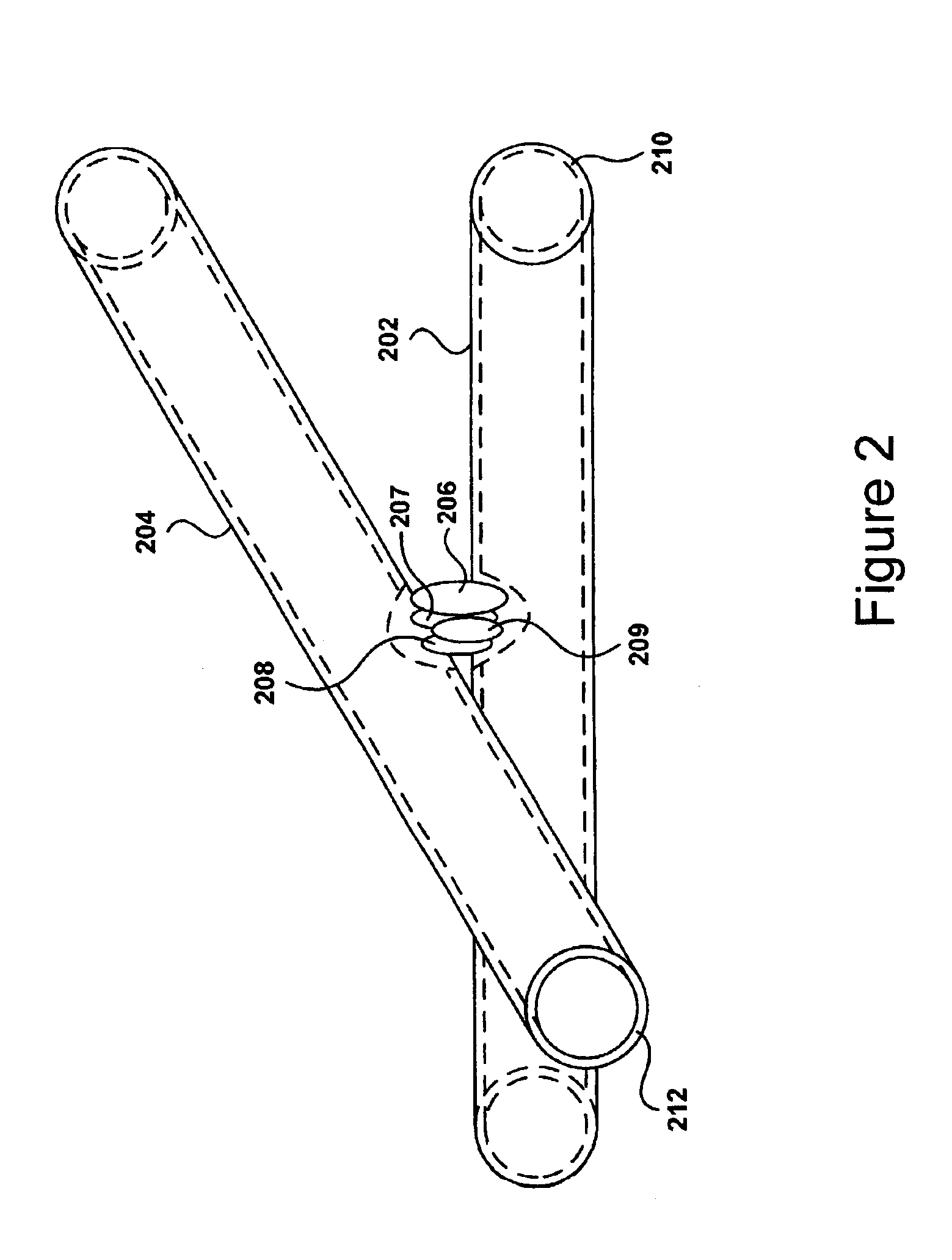

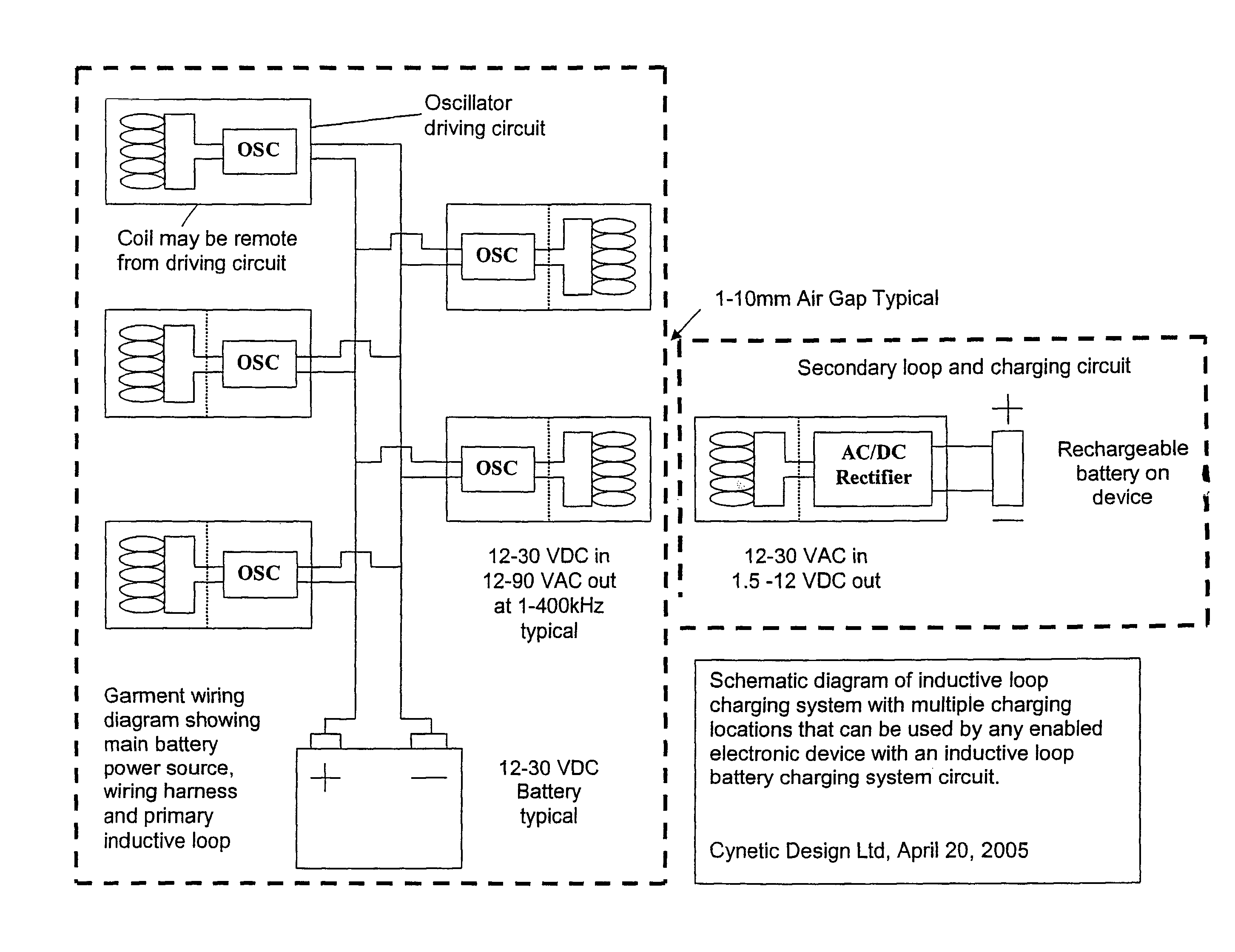

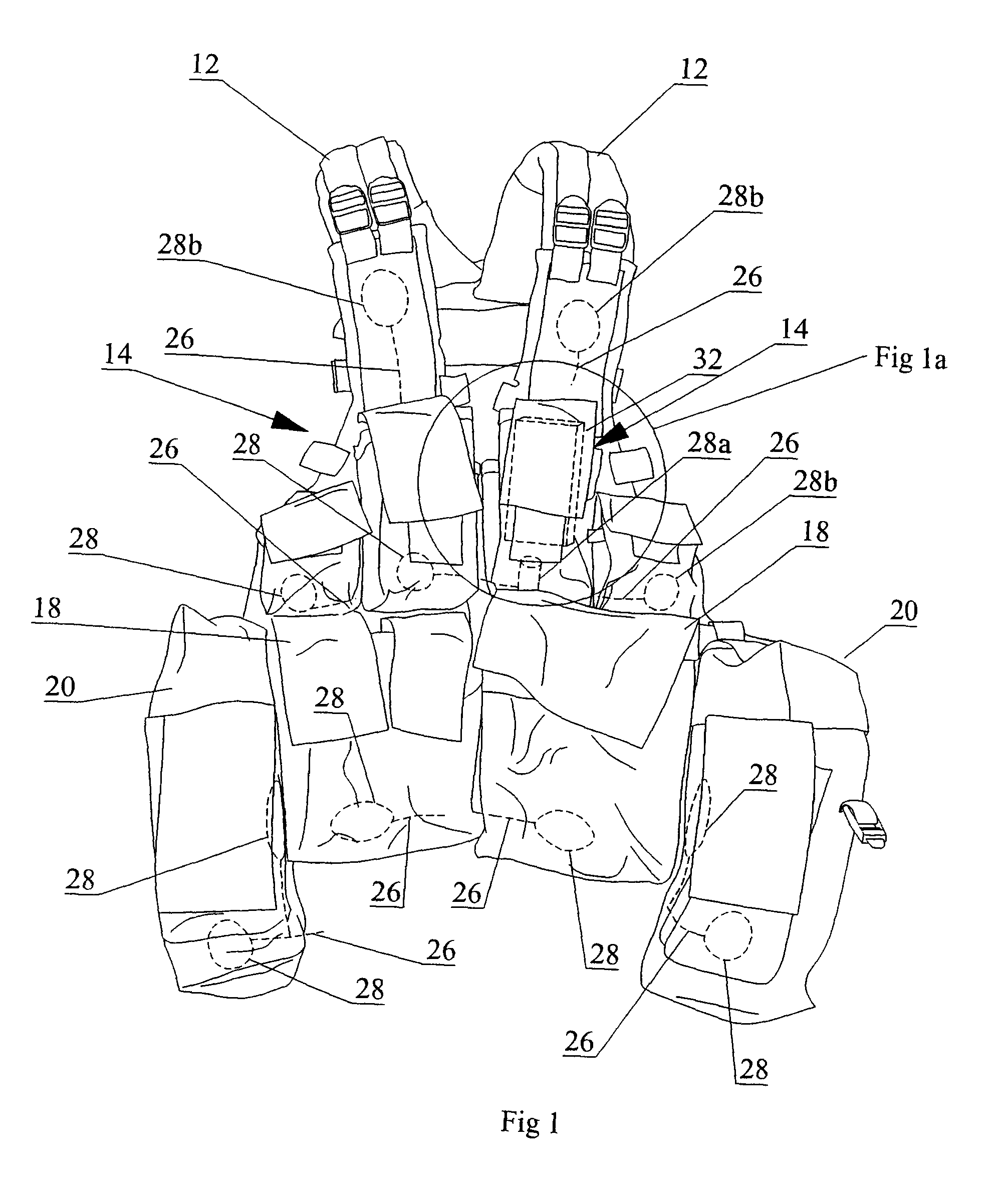

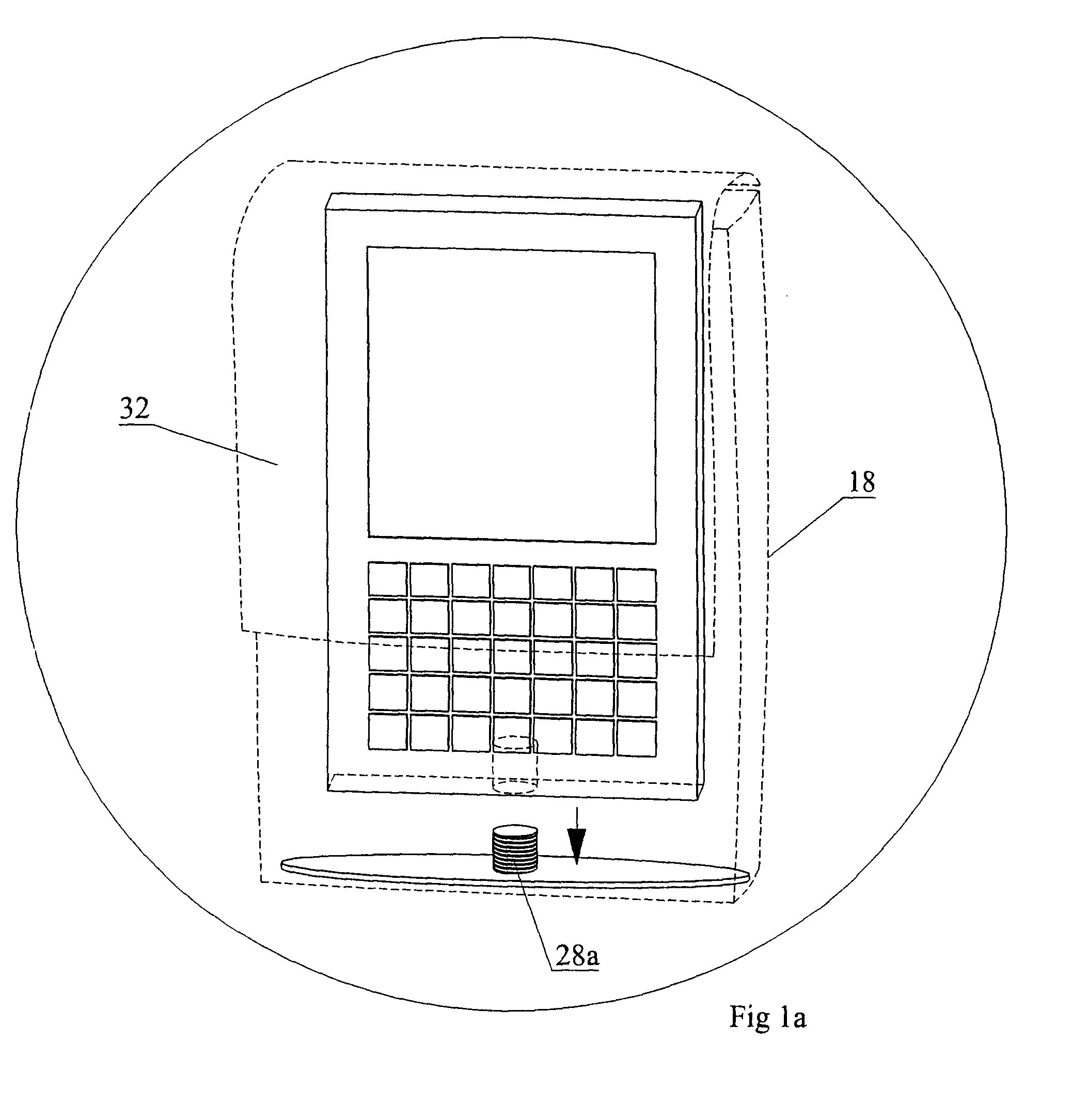

A sequential power transmission between a portable user-carried battery and first and second independent accessories. At least one primary inductive coupling coil is mounted on an article of apparel worn by the user, so as to place a primary coil adjacent a first intermediary inductive coupling coil on the first independent accessory. The energizing of the first intermediary coil energizes a second intermediary coil on the first independent accessory. The second intermediary coil, when energized, energizes a secondary coil on the second independent accessory for powering the use, including the charging of the batteries of that accessory.

Owner:CYNETIC DESIGNS

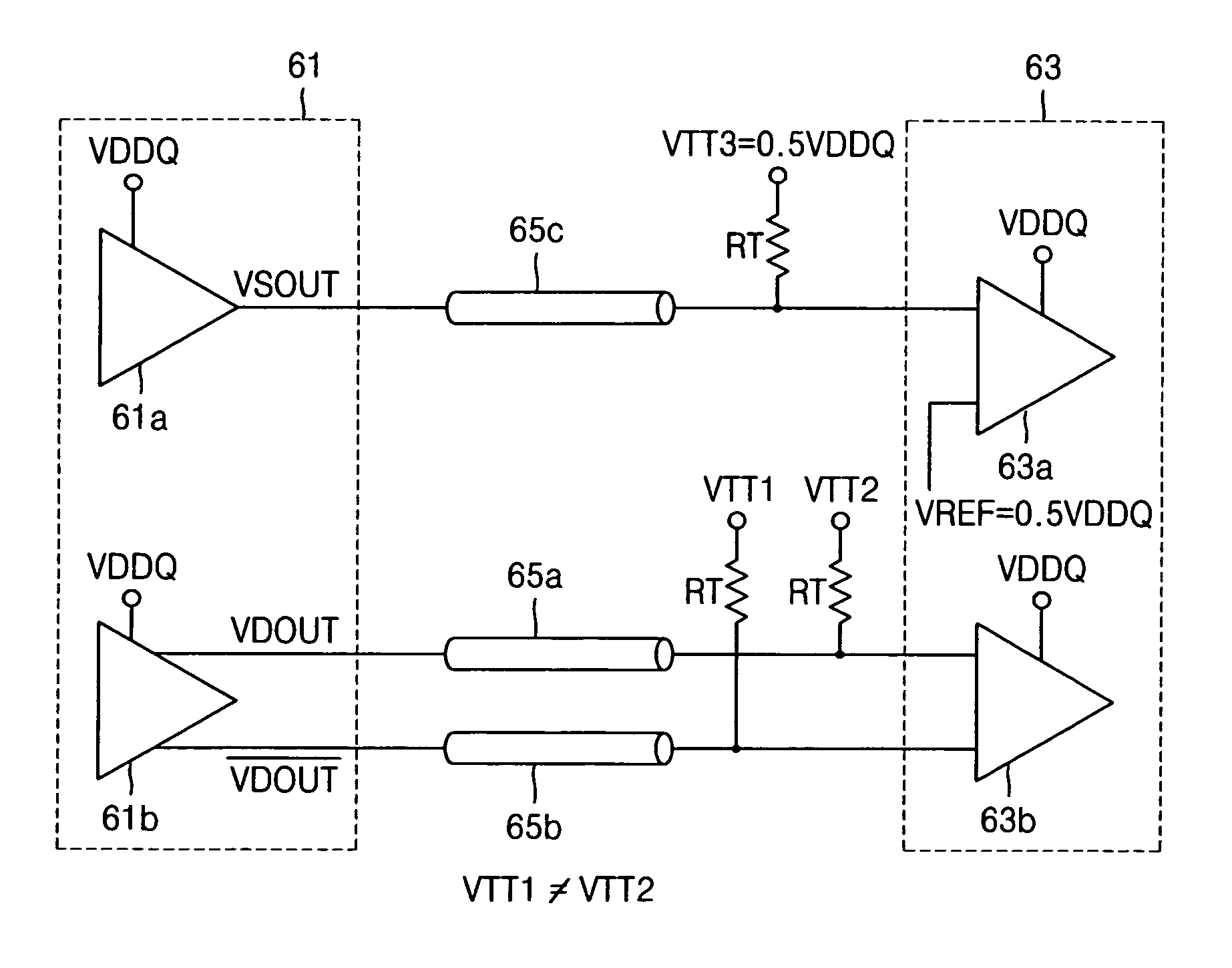

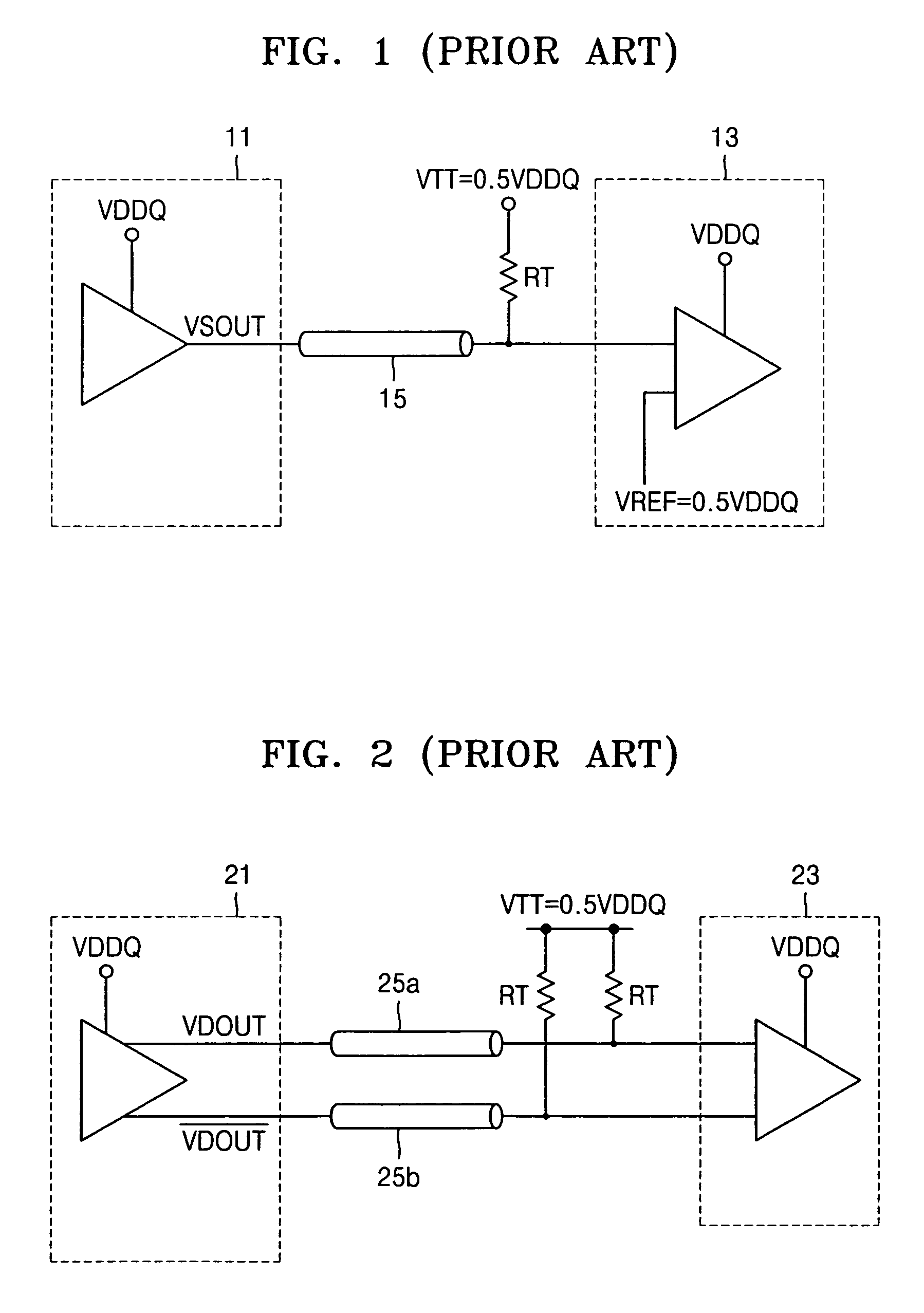

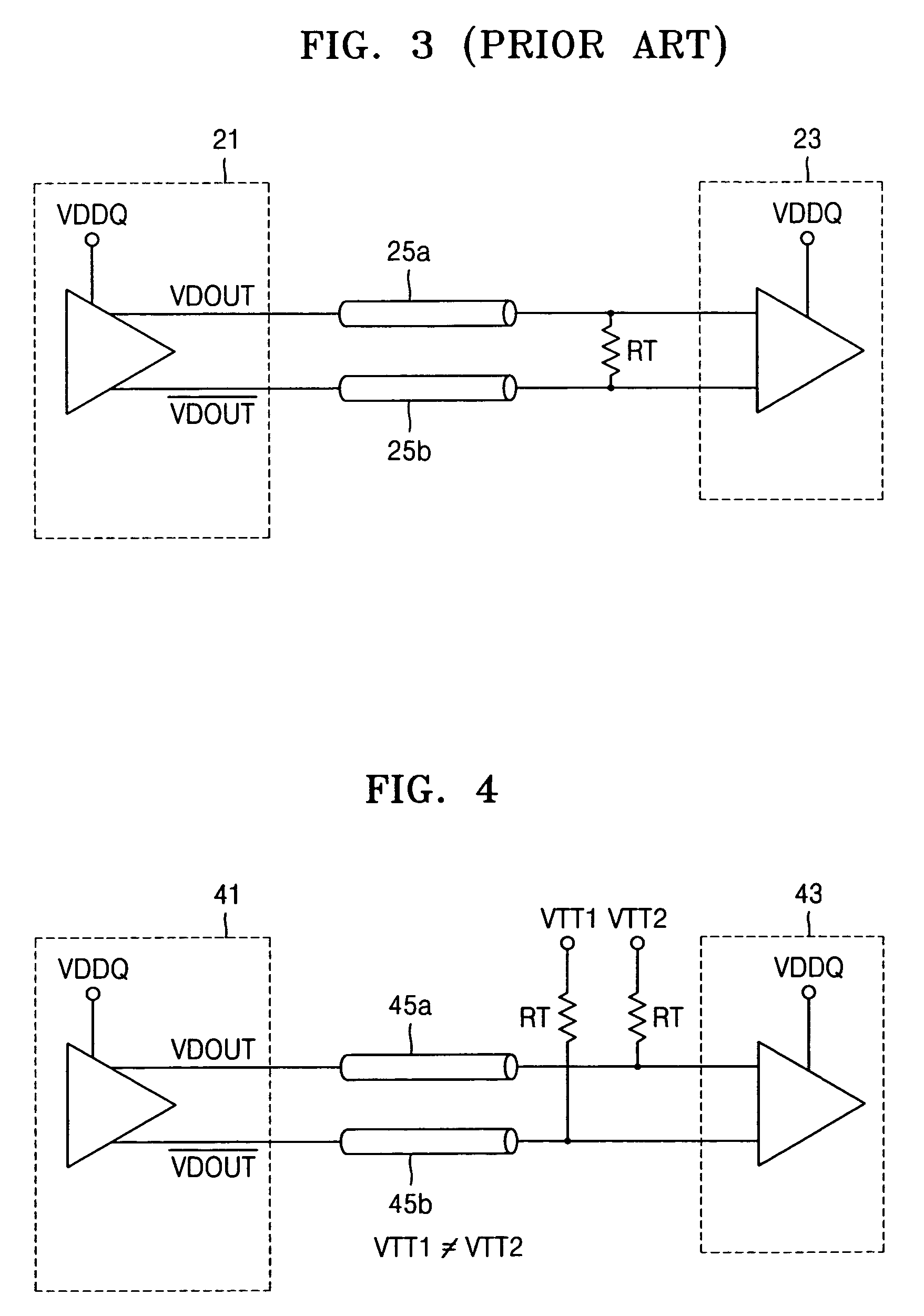

Memory system with stable termination of a pair of differential signals transmitted via a pair of transmission lines

InactiveUS7456650B2Avoid instabilityReliability increasing modificationsBaseband system detailsEngineeringTransmitter

Provided is a memory system in which a pair of differential signals transmitted via a pair of transmission lines are prevented from being terminated at the same voltage during a standby mode, thereby preventing a receiver from entering an unstable state. The memory system includes a pair of transmission lines, a transmitter that outputs a pair of differential signals to the pair of transmission lines, and a receiver that receives the pair of differential signals via the pair of transmission lines. A first termination voltage is applied to one of the pair of transmission lines, and a second termination voltage is applied to the other transmission line. The first termination voltage is determined to be different from the second termination voltage.

Owner:SAMSUNG ELECTRONICS CO LTD

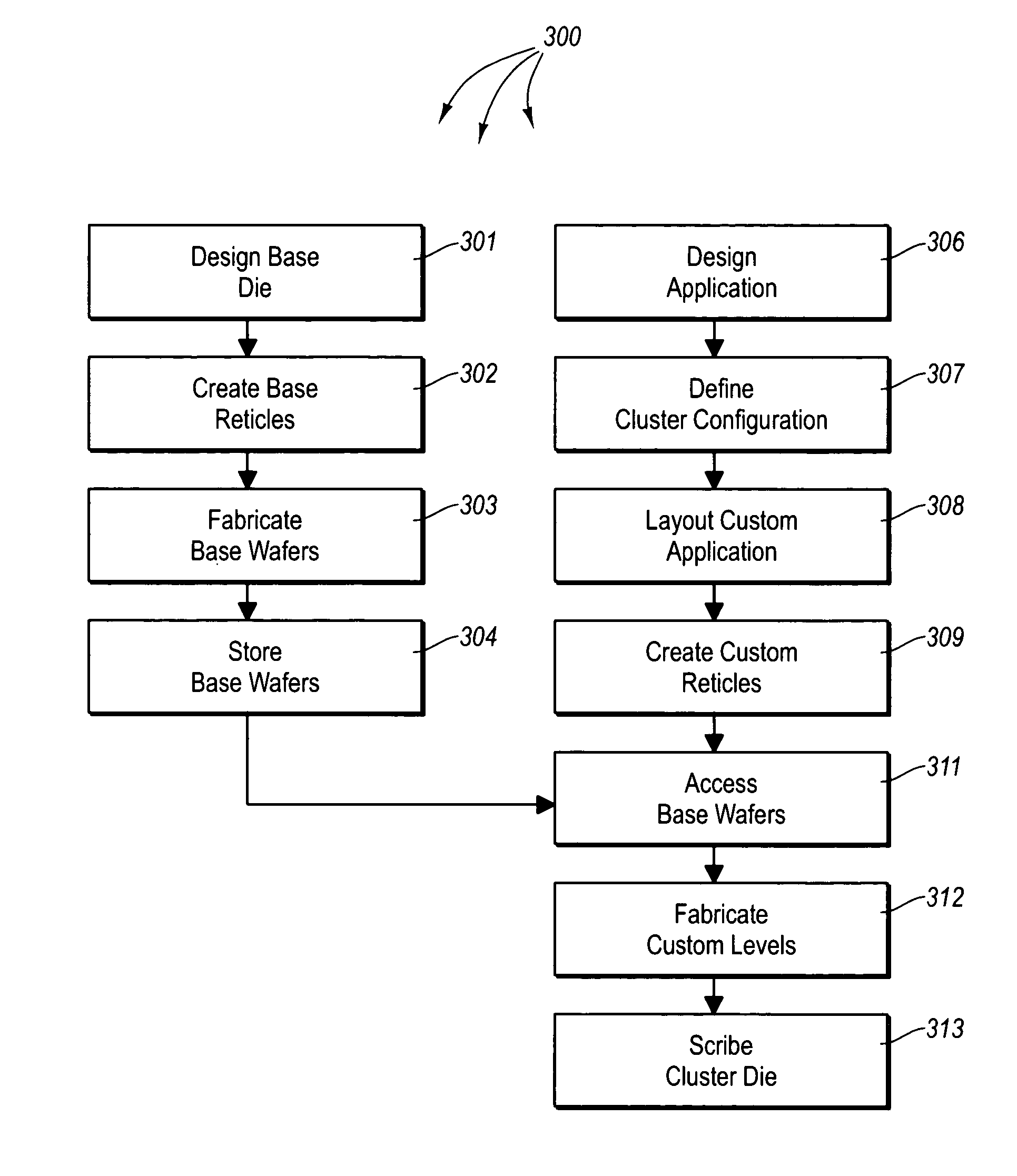

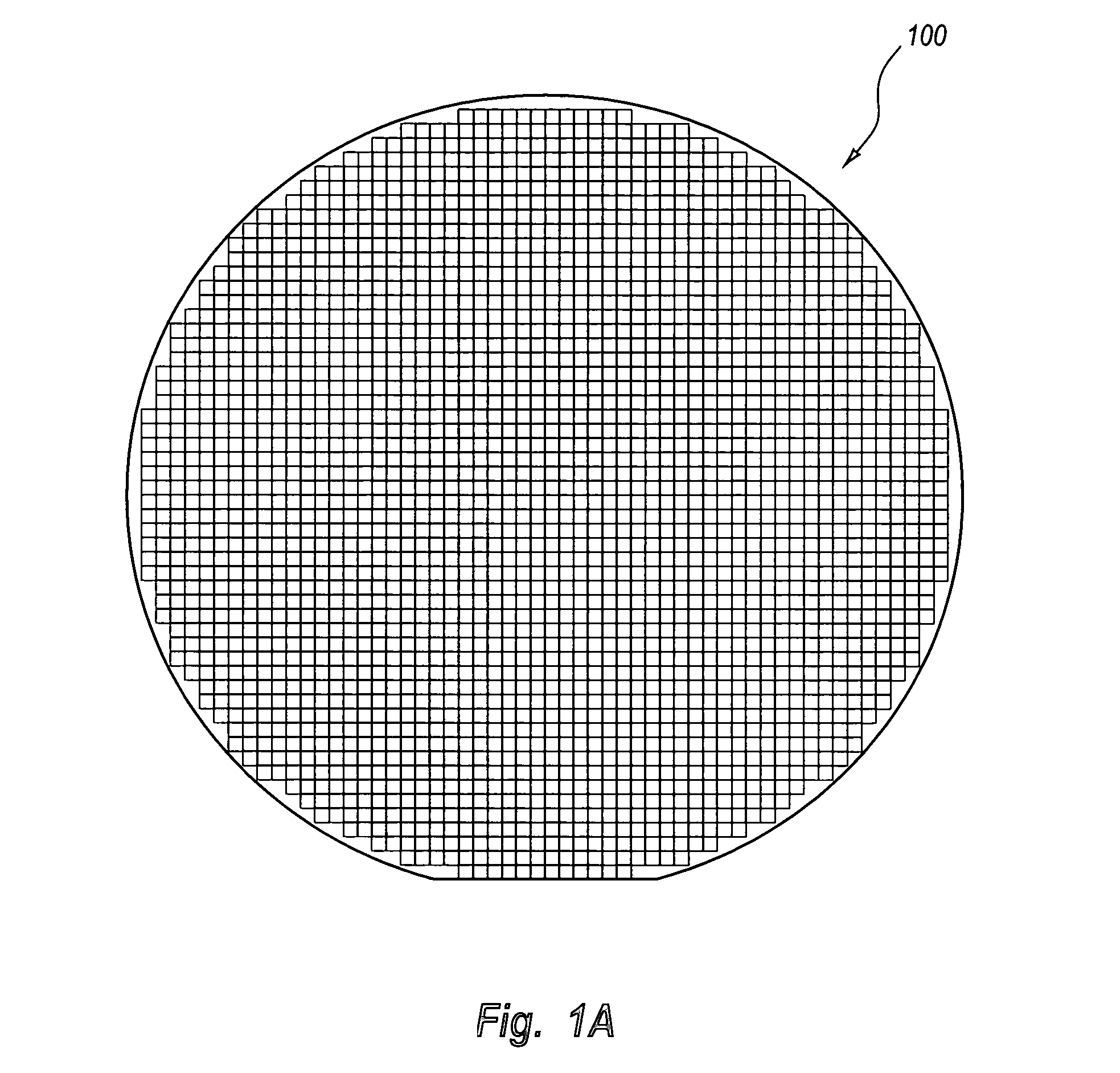

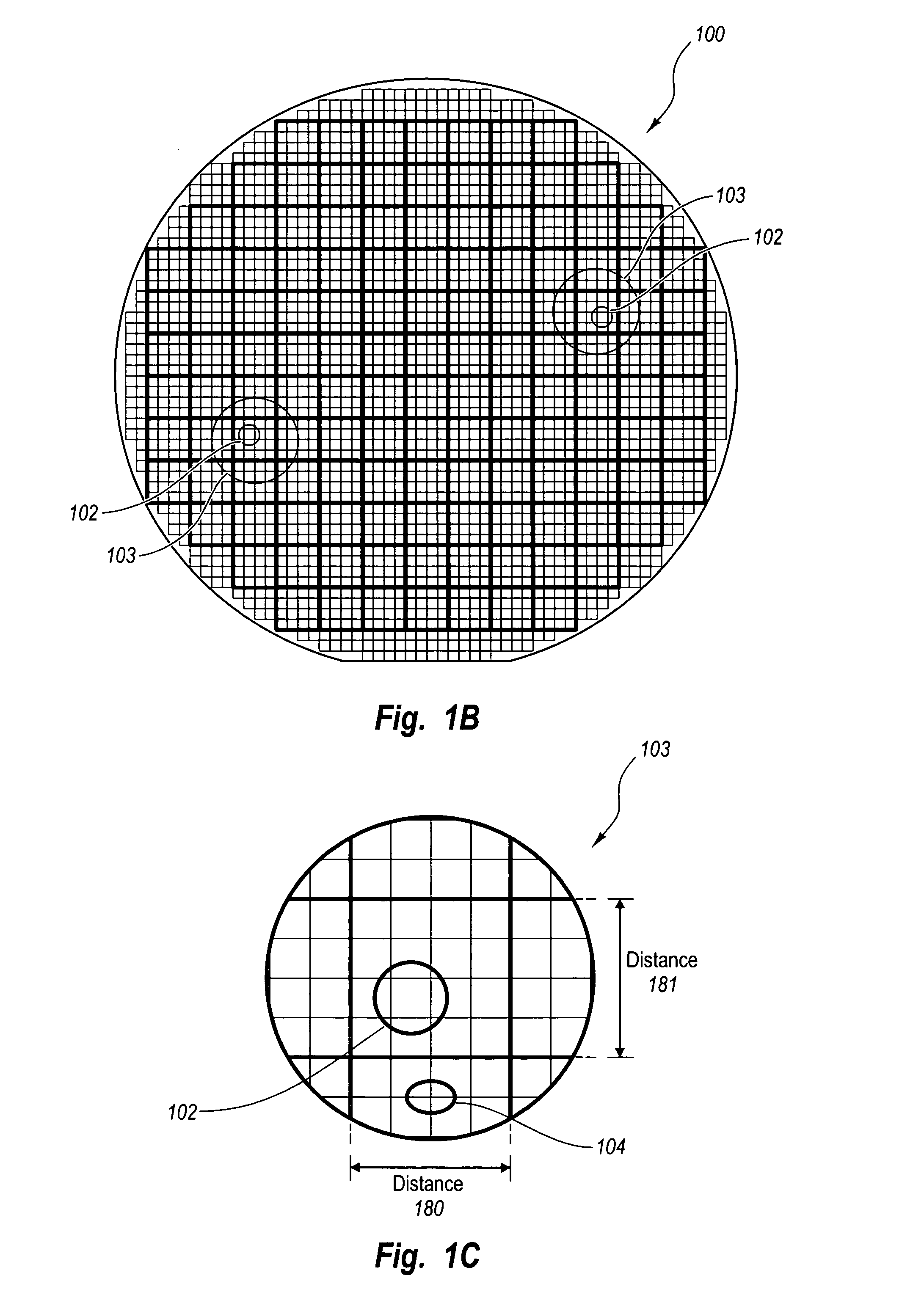

Structured ASIC device with configurable die size and selectable embedded functions

ActiveUS7337425B2Reduce the numberReduce tooling costsSemiconductor/solid-state device detailsSolid-state devicesGeneral purposeChip size

One embodiment of the present invention provides for a master or universal base and base tooling which addresses the general purpose Structured ASIC requirements. Another embodiment of the present invention provides for a common set of base tooling from which the master / universal base is created as well as additional custom bases with customized selection and quantity of embedded Platform ASIC functions. Embodiments can utilize conventional Structured ASIC architecture and processing and are compatible with traditional probing and packaging.

Owner:SEMICON COMPONENTS IND LLC

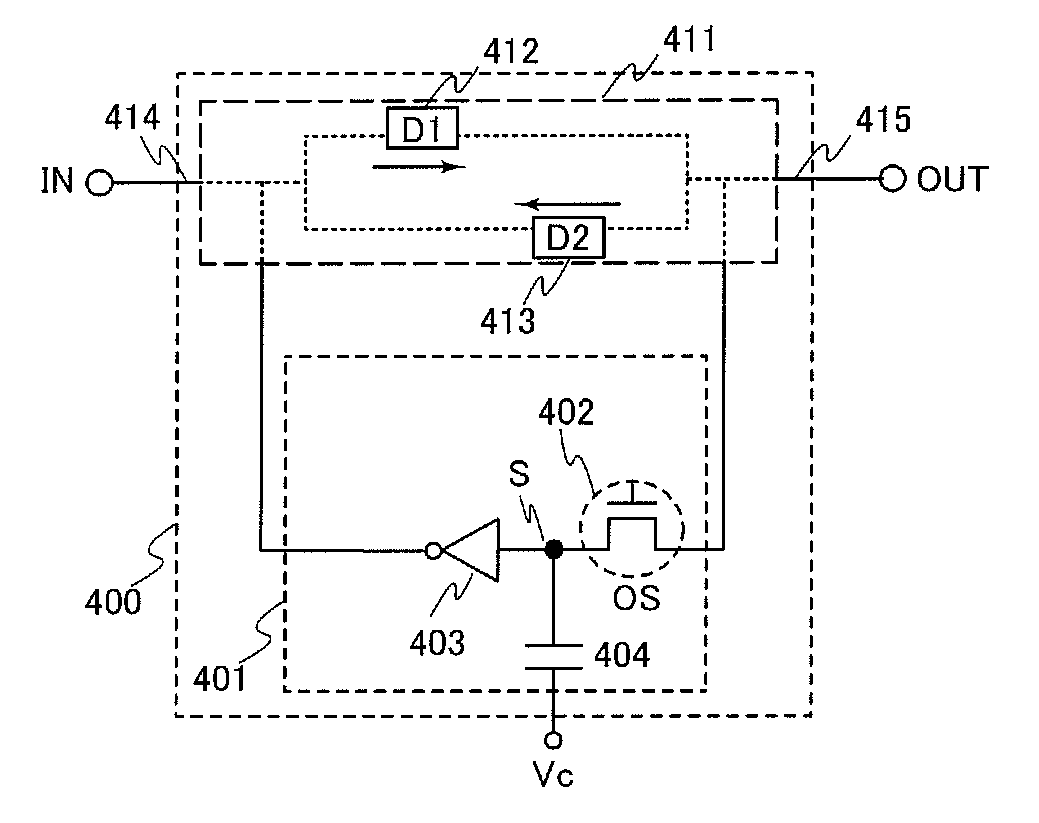

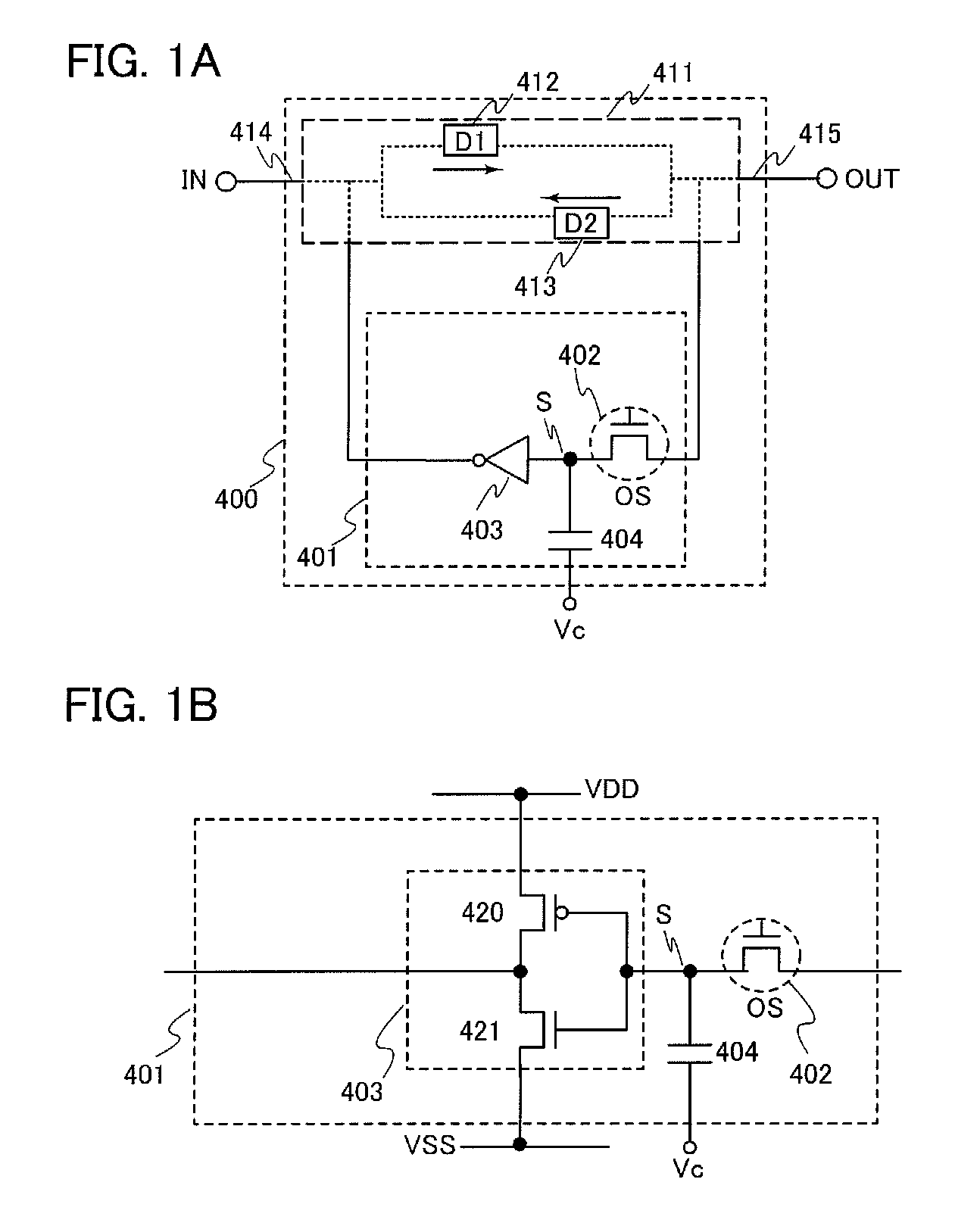

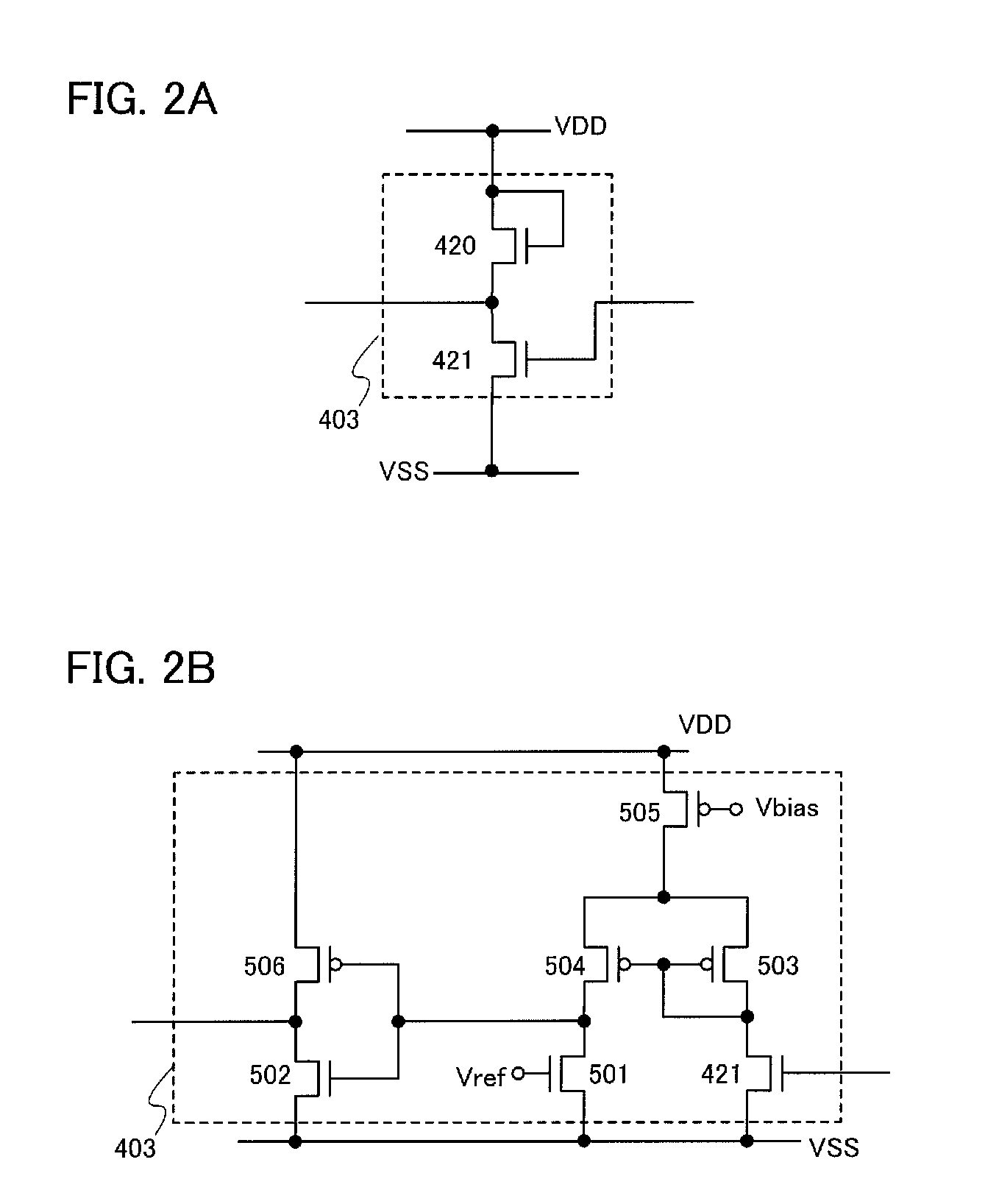

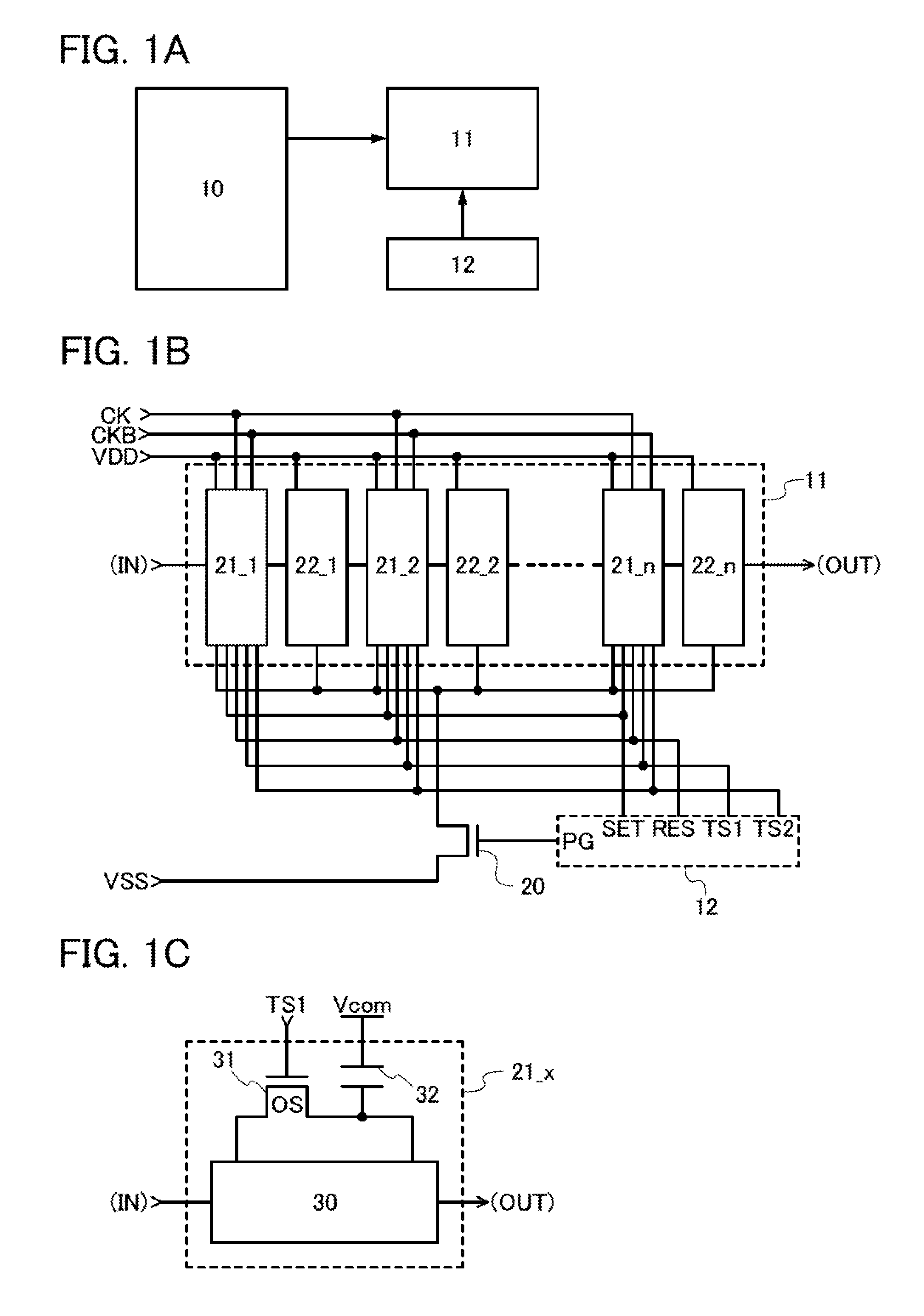

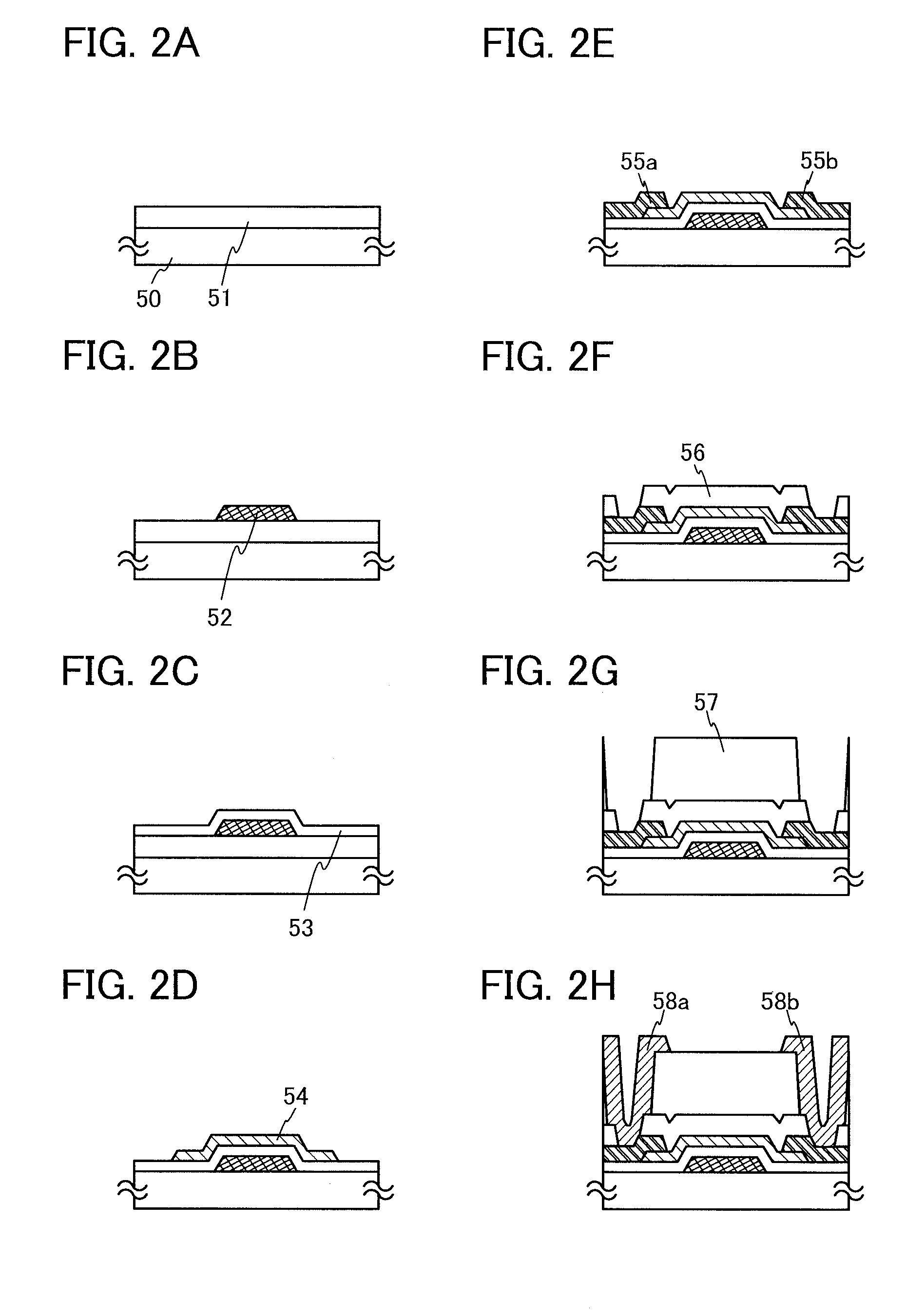

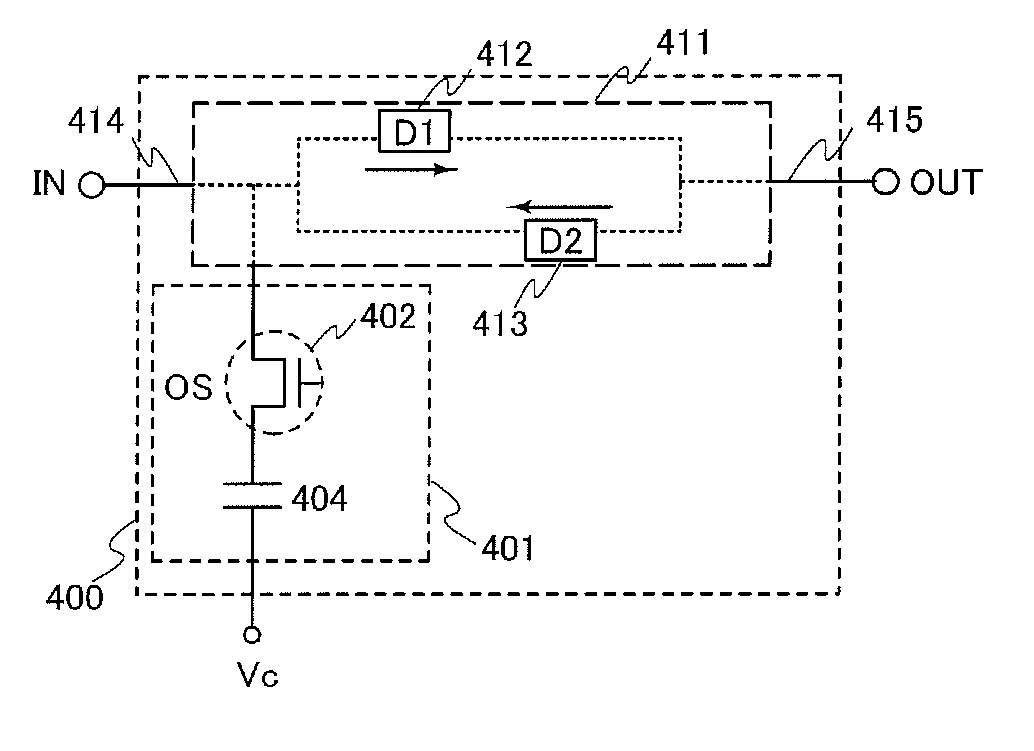

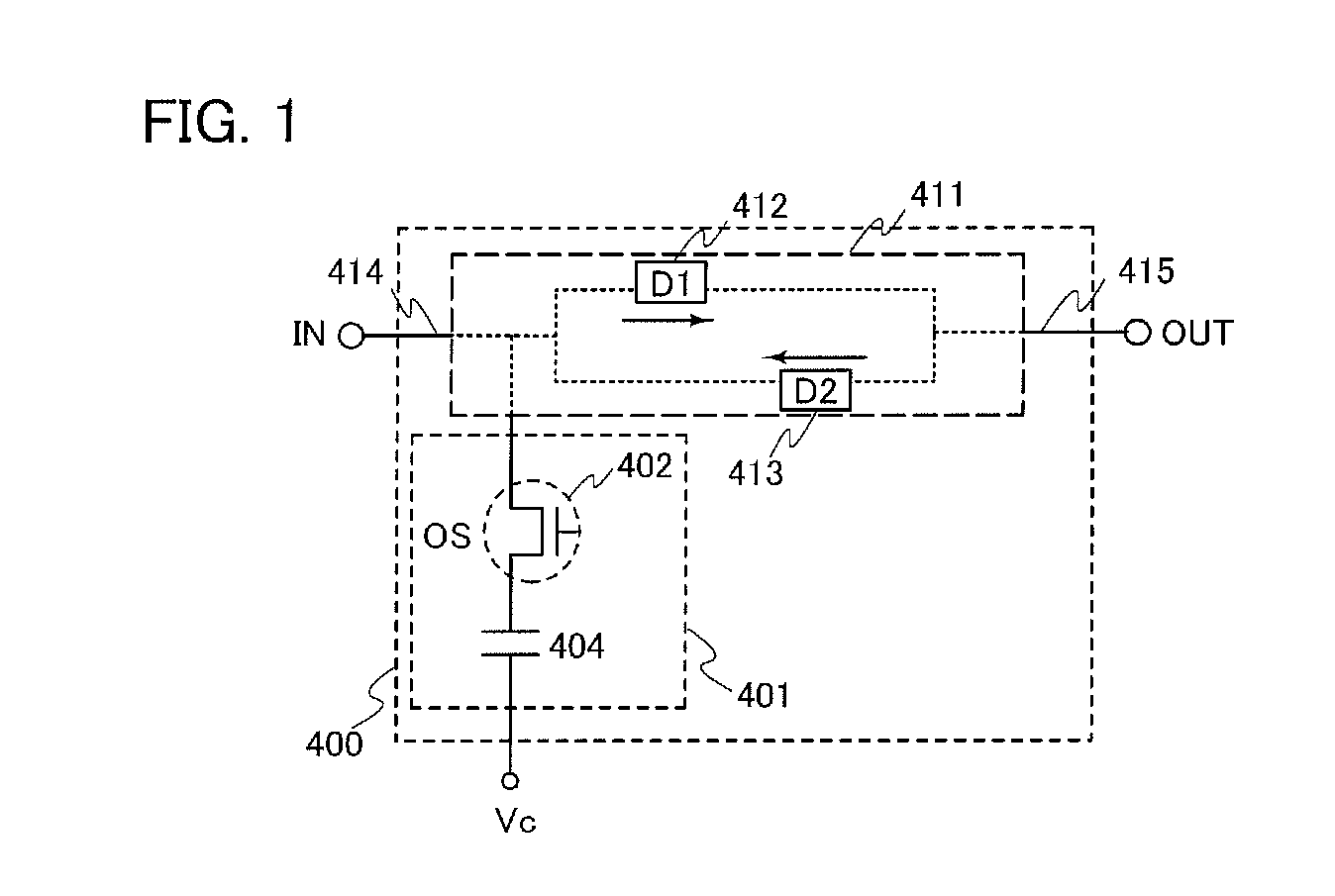

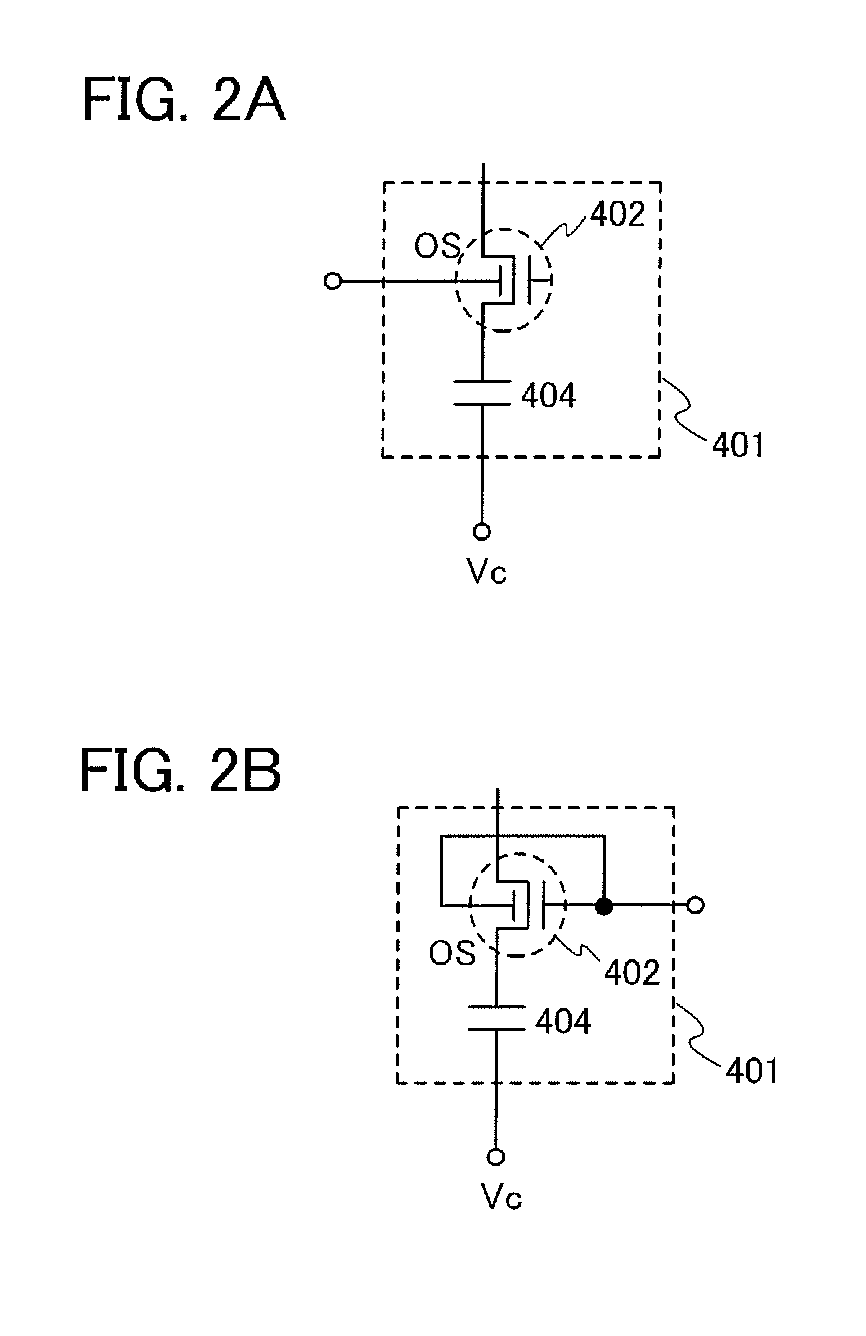

Nonvolatile latch circuit and logic circuit, and semiconductor device using the same

ActiveUS20110121878A1Wide operating temperature rangeGuaranteed uptimeTransistorSolid-state devicesPower semiconductor deviceSemiconductor materials

To provide a novel nonvolatile latch circuit and a semiconductor device using the nonvolatile latch circuit, a nonvolatile latch circuit includes a latch portion having a loop structure where an output of a first element is electrically connected to an input of a second element, and an output of the second element is electrically connected to an input of the first element; and a data holding portion for holding data of the latch portion. In the data holding portion, a transistor using an oxide semiconductor as a semiconductor material for forming a channel formation region is used as a switching element. In addition, an inverter electrically connected to a source electrode or a drain electrode of the transistor is included. With the transistor, data held in the latch portion can be written into a gate capacitor of the inverter or a capacitor which is separately provided.

Owner:SEMICON ENERGY LAB CO LTD

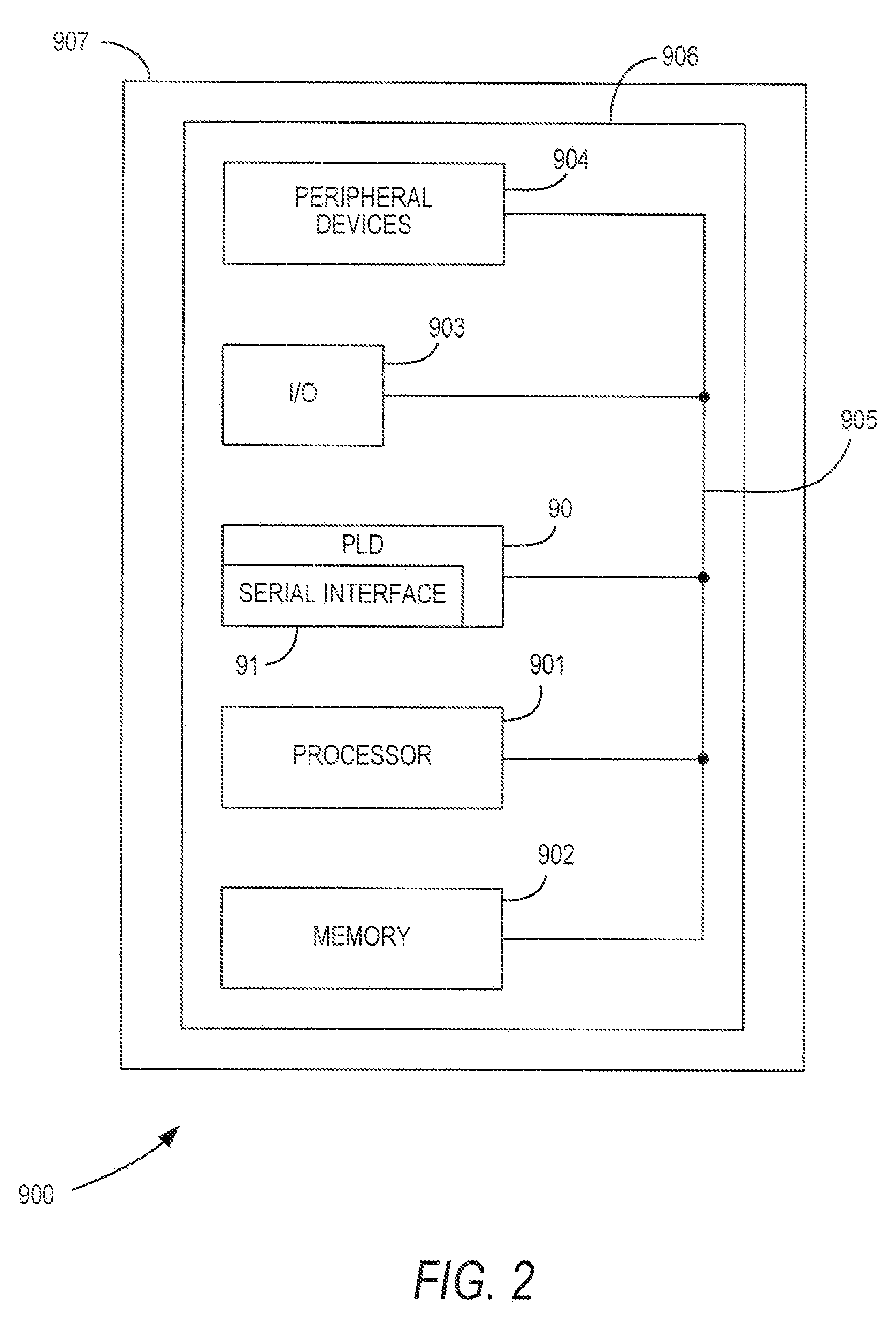

Integrated circuit communication techniques

ActiveUS7439773B2Reduce the required powerReduce power consumptionReliability increasing modificationsPower reduction by control/clock signalEngineeringSemiconductor

Owner:TAHOE RES LTD

Semiconductor integrated circuit

InactiveUS8547771B2Reduce power consumptionReduce delaysTransistorPower consumption reductionElectricityHemt circuits

To reduce power consumption of a semiconductor integrated circuit and to reduce delay of the operation in the semiconductor integrated circuit, a plurality of sequential circuits included in a storage circuit each include a transistor whose channel formation region is formed with an oxide semiconductor, and a capacitor whose one electrode is electrically connected to a node that is brought into a floating state when the transistor is turned off. By using an oxide semiconductor for the channel formation region of the transistor, the transistor with an extremely low off-state current (leakage current) can be realized. Thus, by turning off the transistor in a period during which power supply voltage is not supplied to the storage circuit, the potential in that period of the node to which one electrode of the capacitor is electrically connected can be kept constant or almost constant. Consequently, the above objects can be achieved.

Owner:SEMICON ENERGY LAB CO LTD

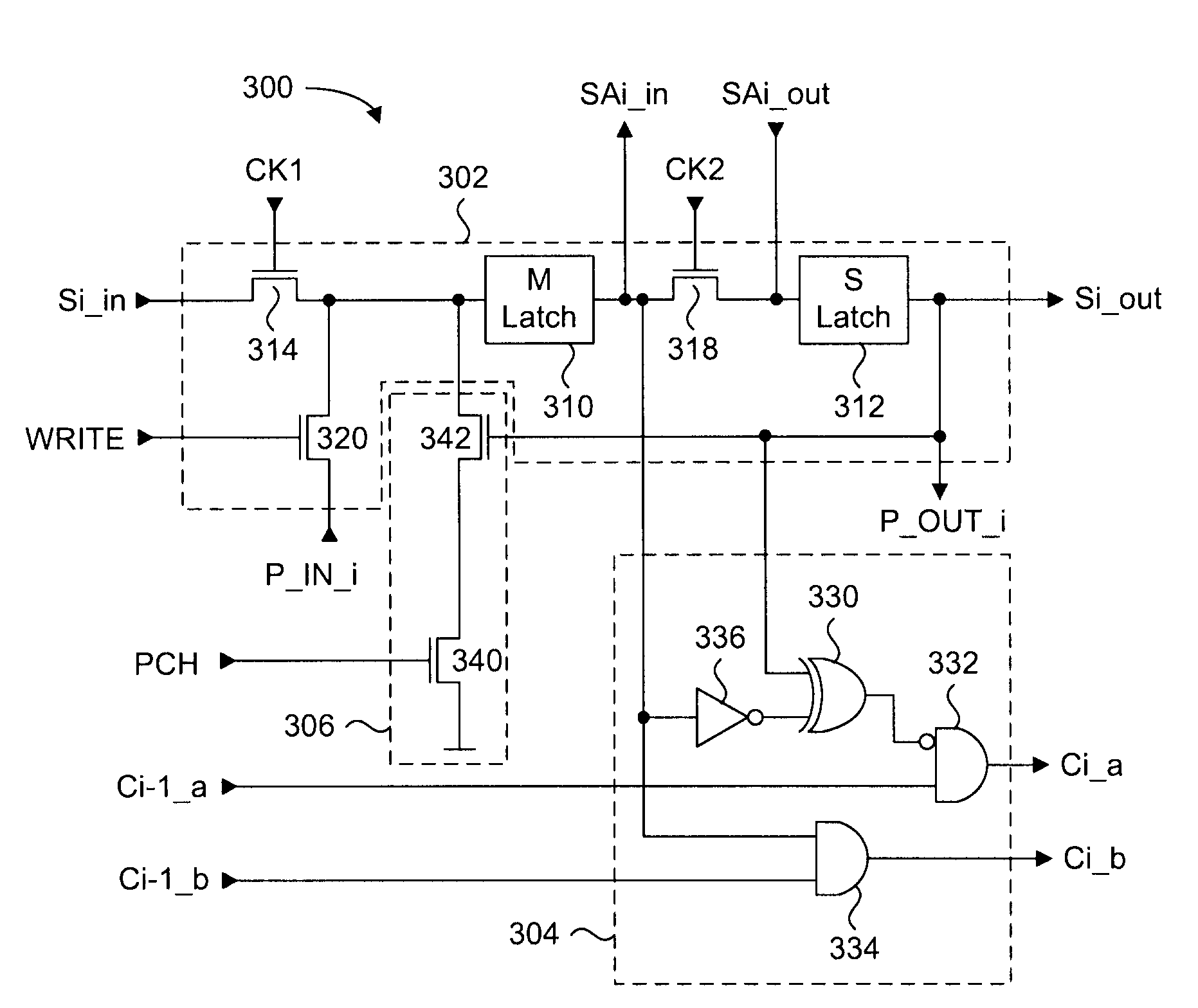

Dual function data register

ActiveUS20090290434A1Reduce disadvantagesRead-only memoriesDigital storageProcessor registerTheoretical computer science

A dual function serial and parallel data register with integrated program verify functionality. The master and slave latching circuits of the dual function data register can concurrently store two different words of data. In a program verify operation, the master latch stores program data and the slave latch will receive and store read data. Comparison logic in each register stage will compare the data of both latches, and integrate the comparison result to that of the previous register stage. The final single bit result will indicate the presence of at least one bit that has not been programmed. Automatic program inhibit logic in each stage will prevent successfully programmed bits from being re-programmed in each subsequent reprogram cycle. Either data word can be serially clocked out by selectively starting the shift operations on either the low or high active logic level of a clock signal.

Owner:SYNOPSYS INC

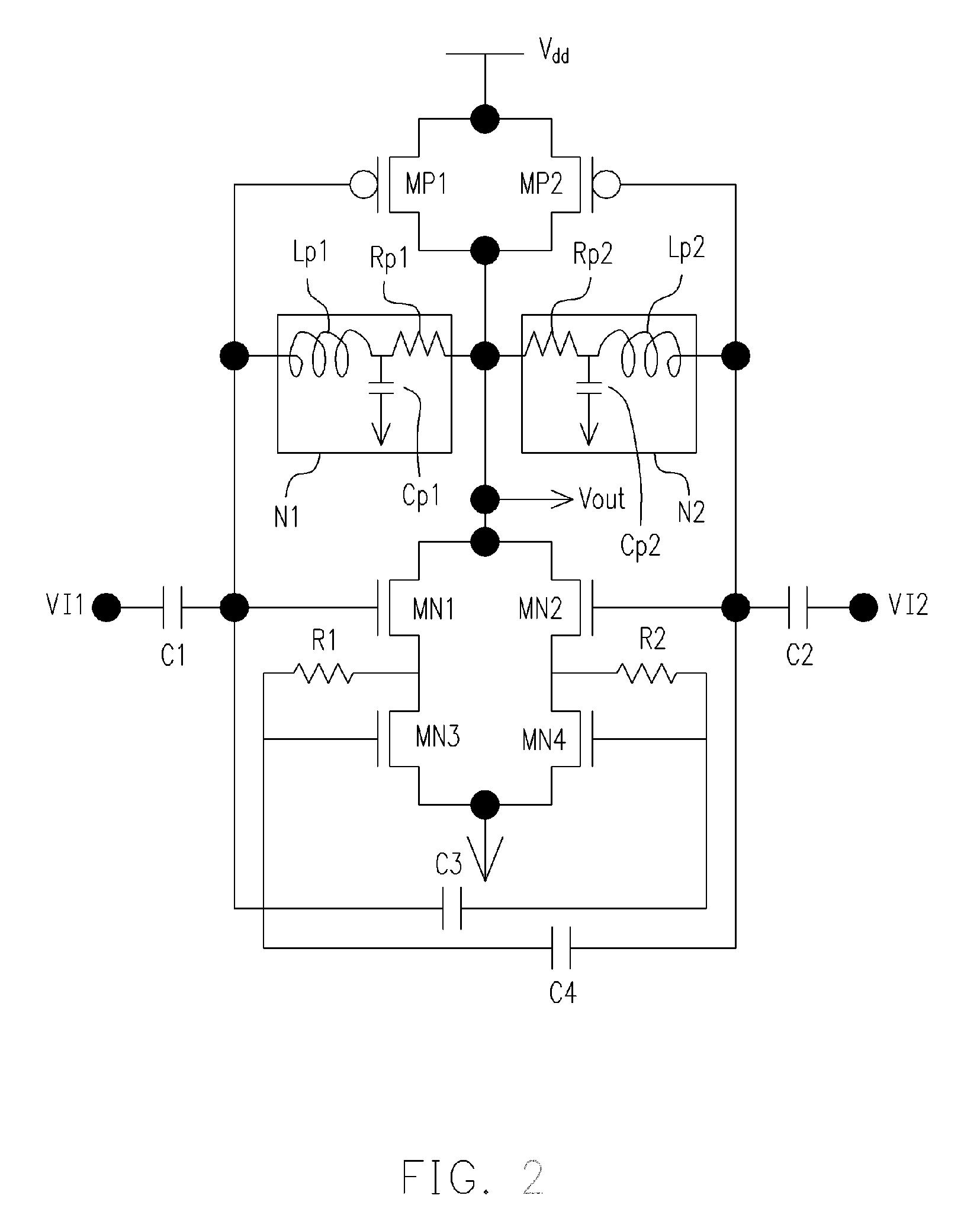

Self dc-bias high frequency logic gate, high frequency NAND gate and high frequency nor gate

InactiveUS20060197557A1Electric power will not be wastedNot to wasteReliability increasing modificationsMultiple input and output pulse circuitsNOR gateNAND gate

A self DC-bias high frequency logic gate is disclosed. The logic gate comprises at least one input terminal and one output terminal for performing Boolean operation on the high frequency input signals. The logic gate is characterized in that each transistor is coupled to an impedance matching network. The impedance matching network comprises a first terminal and a second terminal. Wherein, the first terminal is coupled to a gate of the transistor, and the second terminal is coupled to a drain of the transistor for providing an operation voltage to the transistor. When a gate of an N-type transistor and a gate of a P-type transistor are coupled with each other, and a drain of the N-type transistor and a drain of the P-type transistor are also coupled with each other, a common impedance matching network is shared with both the N-type transistor and the P-type transistor.

Owner:SUNPLUS TECH CO LTD

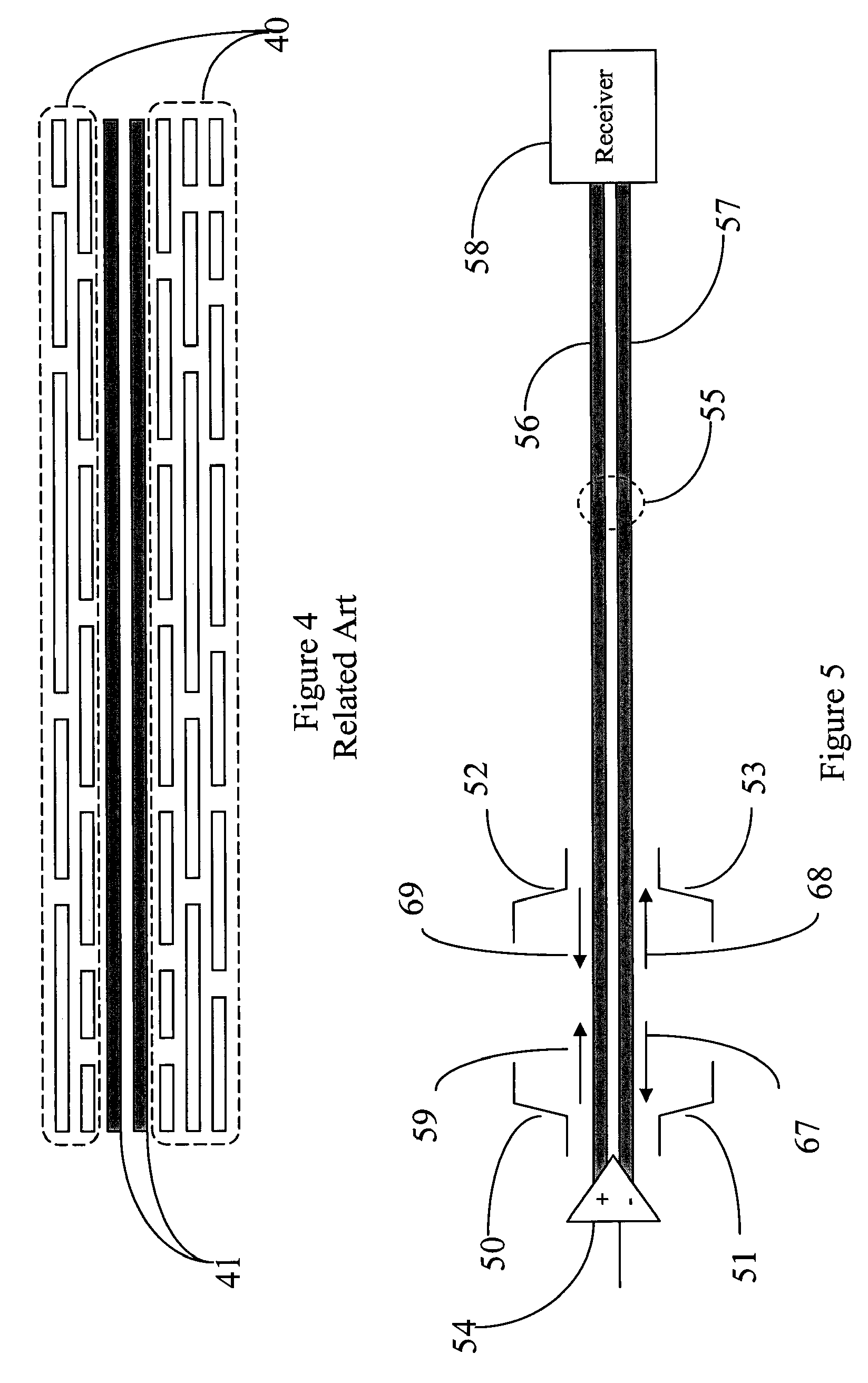

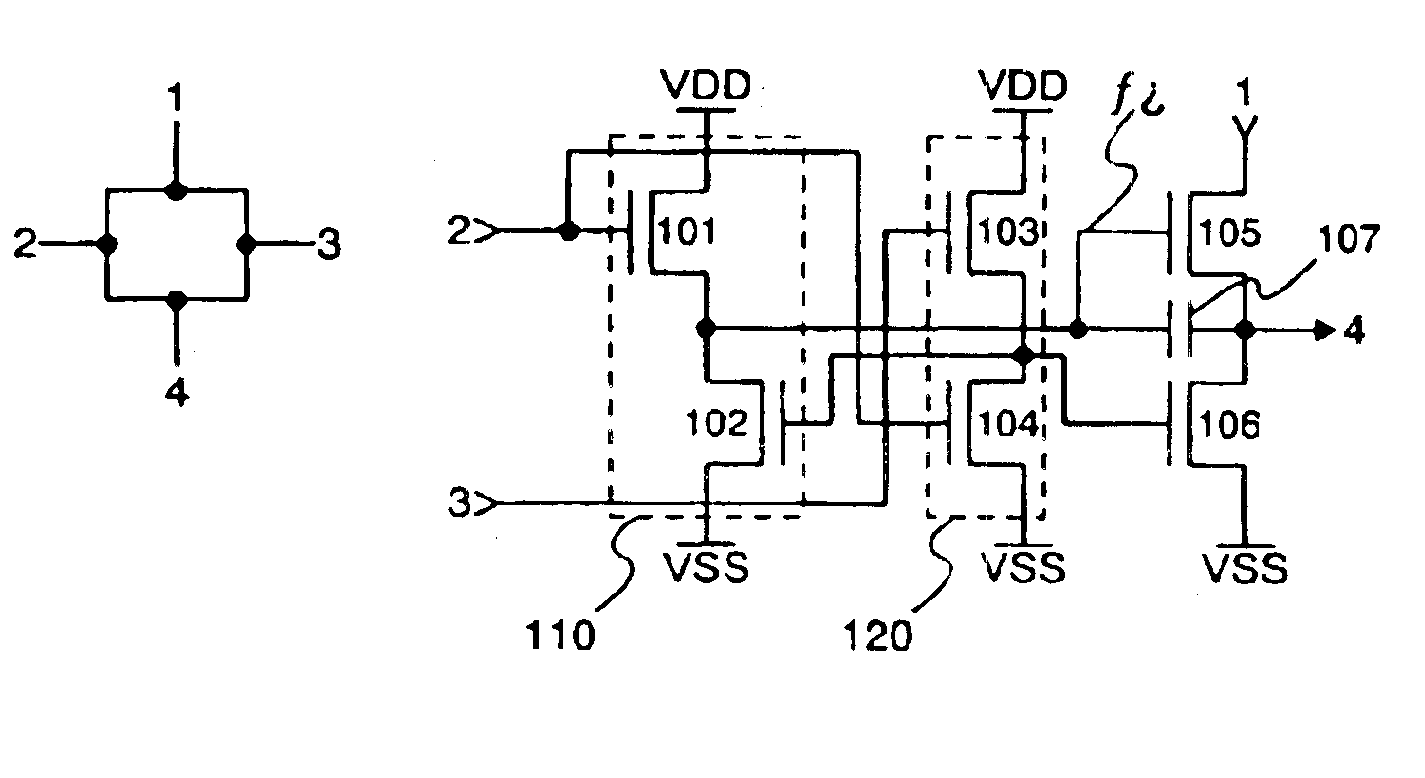

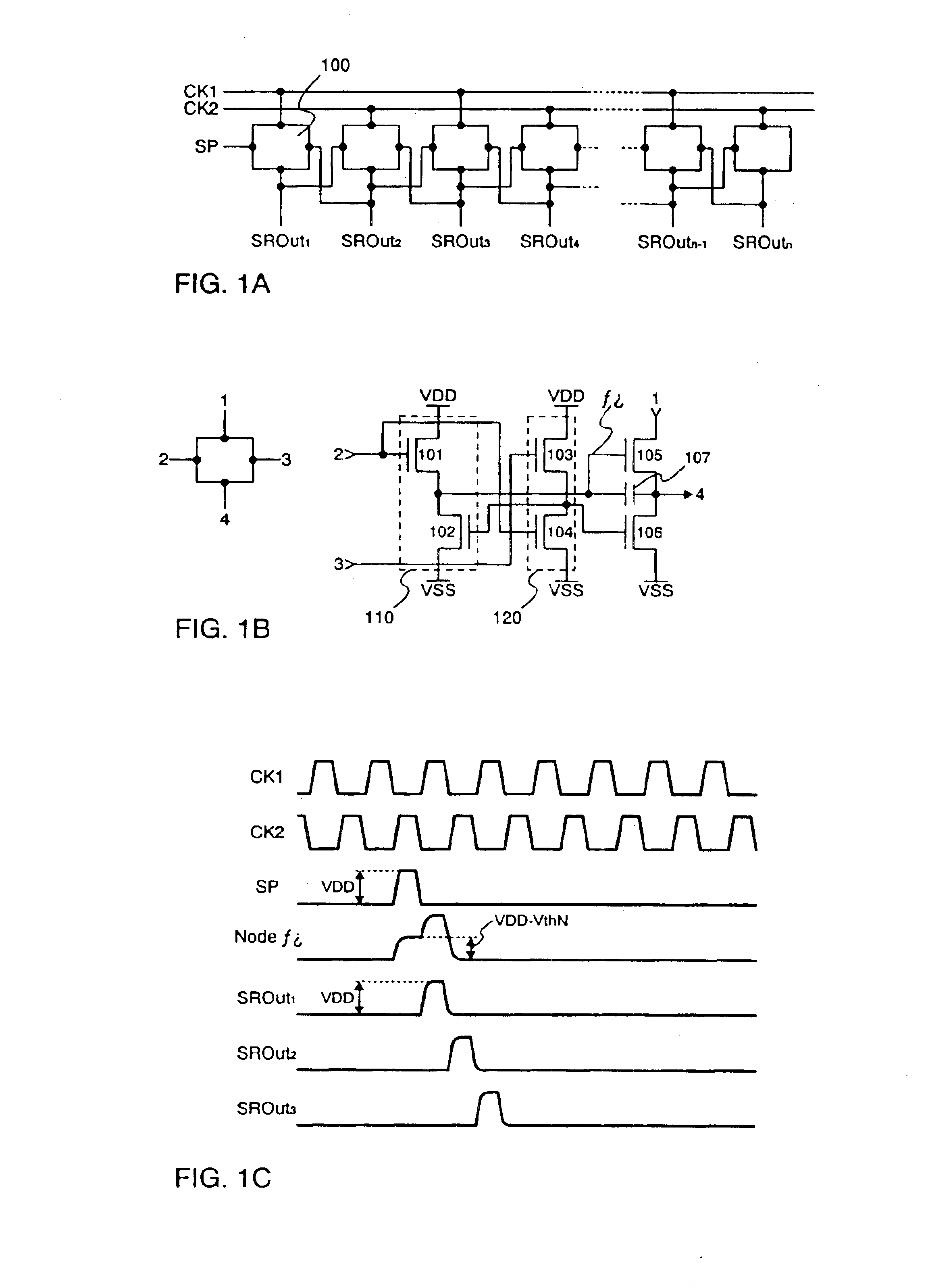

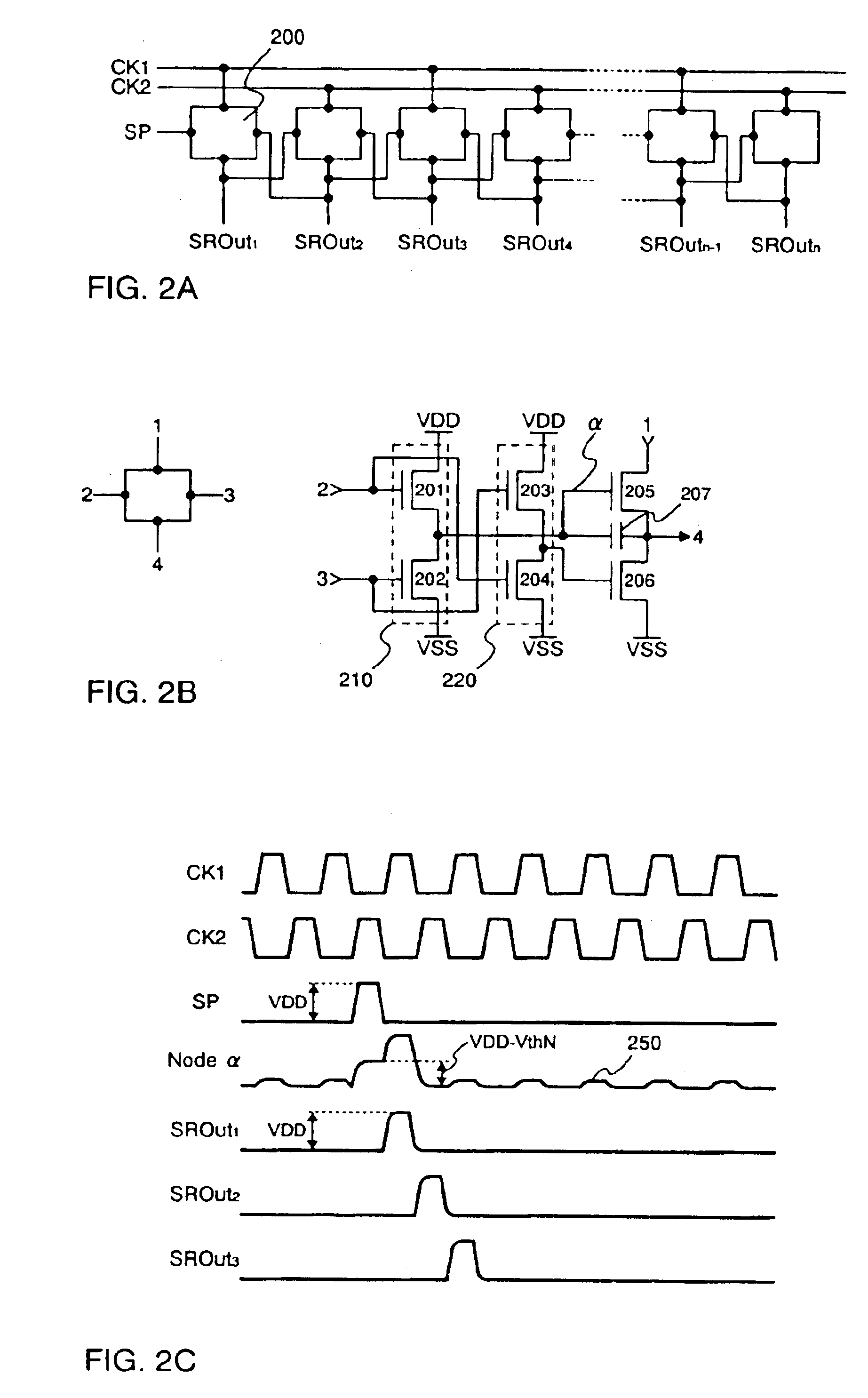

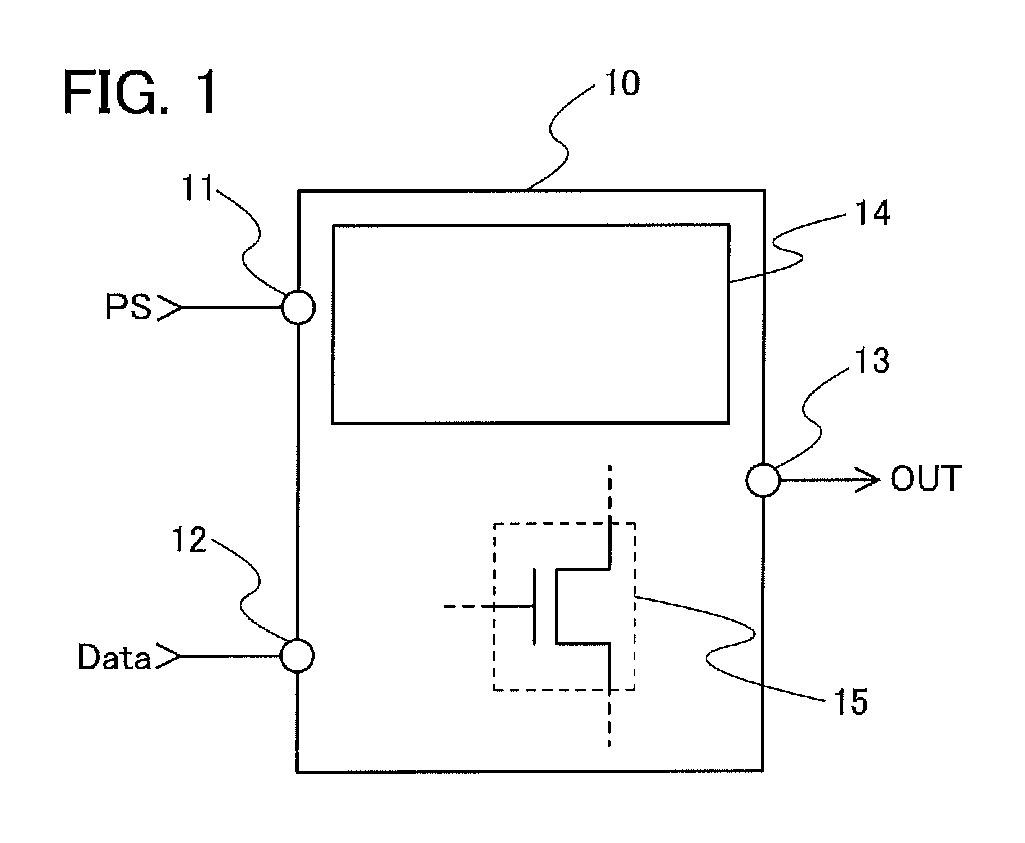

Pulse output circuit, shift register and electronic equipment

A driver circuit of a display device, which includes TFTs of a single conductivity type and outputs an output signal with normal amplitude. A pulse is inputted to TFTs 101 and 104 to turn ON the TFTs and a potential of a node alpha is raised. When the potential of the node alpha reaches (VDD-VthN), the node alpha becomes in a floating state. Accordingly, a TFT 105 is turned ON and a potential of an output node is raised as a clock signal becomes High level. On the other hand, a potential of a gate electrode of the TFT 105 is further raised due to an operation of a capacitance means 107 as the potential of the output node is raised, so that the potential of the gate electrode of the TFT 105 becomes higher than (VDD+VthN). Thus, the potential of the output node is raised to VDD without causing a voltage drop due to a threshold voltage of the TFT 105. An output at the subsequent stage is then inputted to a TFT 103 to turn the TFT 103 On, while the potential of the node alpha of TFTs 102 and 106 is dropped to turn the TFT 105 OFF. As a result, the potential of the output node becomes Low level.

Owner:SEMICON ENERGY LAB CO LTD

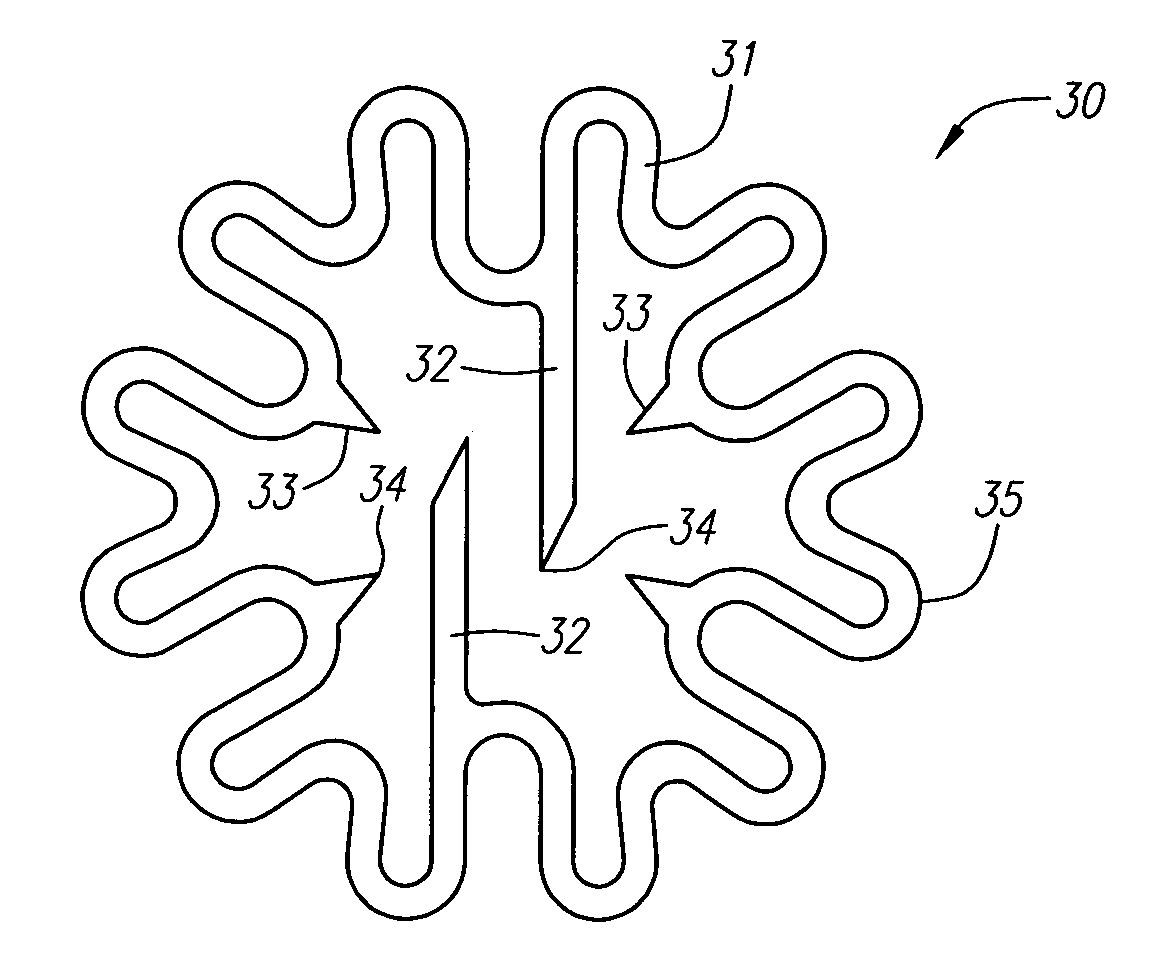

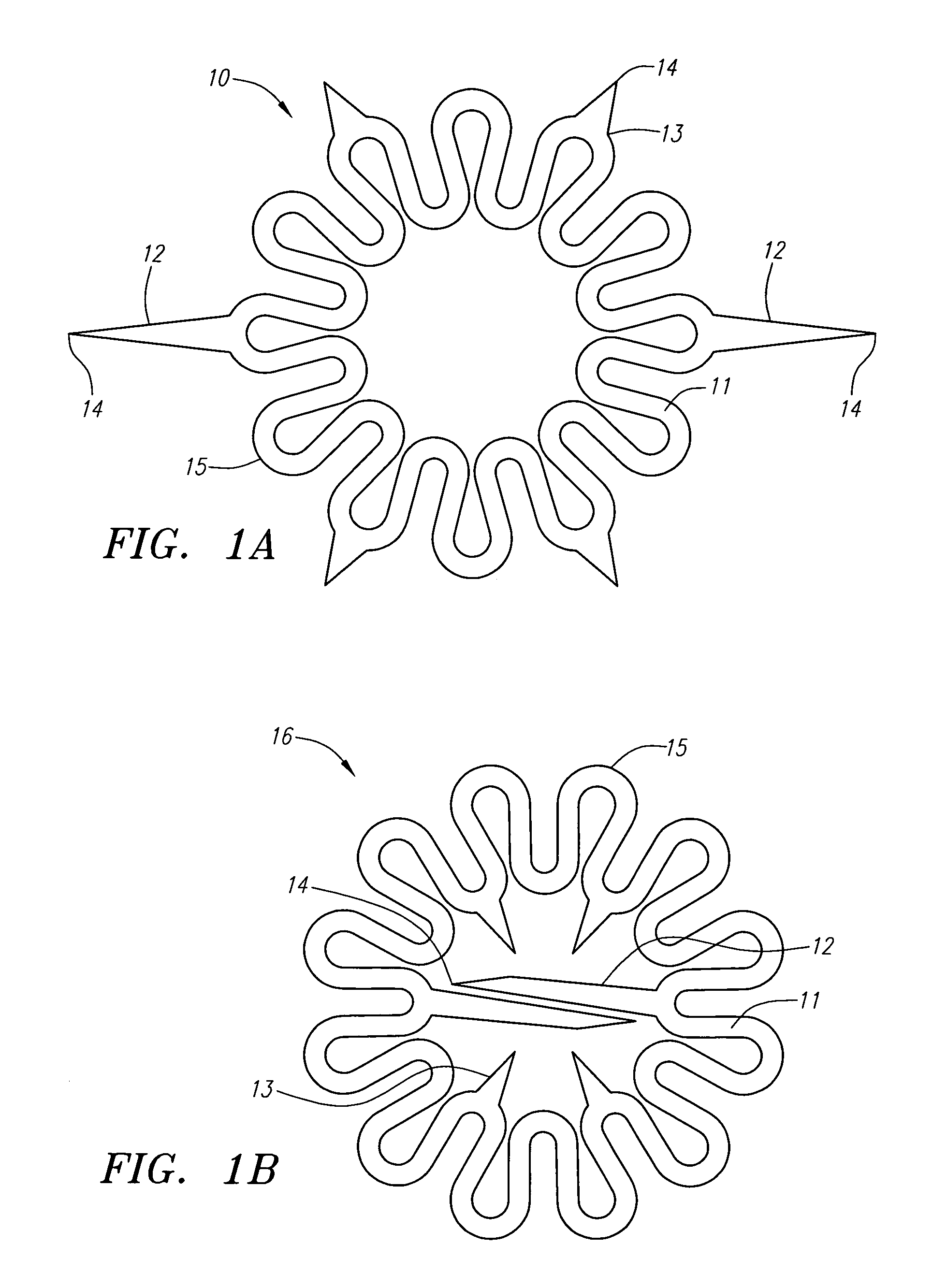

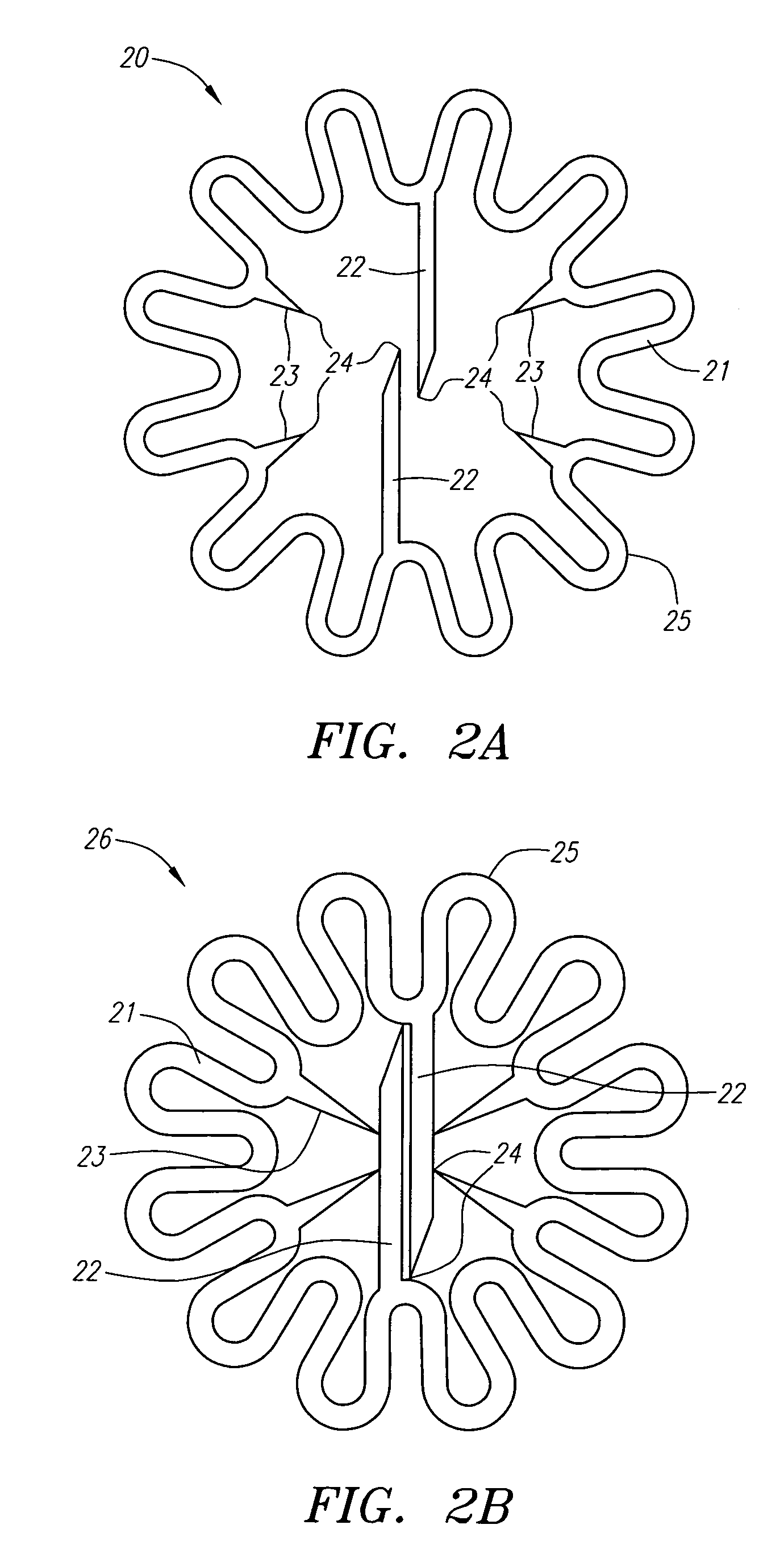

Methods for manufacturing a clip and clip

The present invention relates to a method of making clips which can be used to engage body tissue for the purpose of closing wounds. Such clips are generally annular in shape and have radially inwardly extending tines. It is often desirable for such clips to have a small lateral dimension, but manufacturing difficulty has been encountered in making small clips because of the difficulty in cutting materials accurately when attempting to produce a clip with closely packed elements. The present invention avoids these difficulties by first forming a precursor which, in one embodiment, has the tines extending radially outwardly from the annular body and then forms the clip by inverting the precursor such that the tines extend radially inwardly. In an alternate embodiment, the precursor is formed with an over-sized lateral dimension and then compressed inwardly to bring the tines closer together and to reduce the lateral dimension of the precursor. It is preferred to manufacture such clips from a superelastic alloy such as nickel-titanium, in which case the inverted or compressed precursor must be heated and quenched to heat set the clip in its final shape.

Owner:INTEGRATED VASCULAR SYST

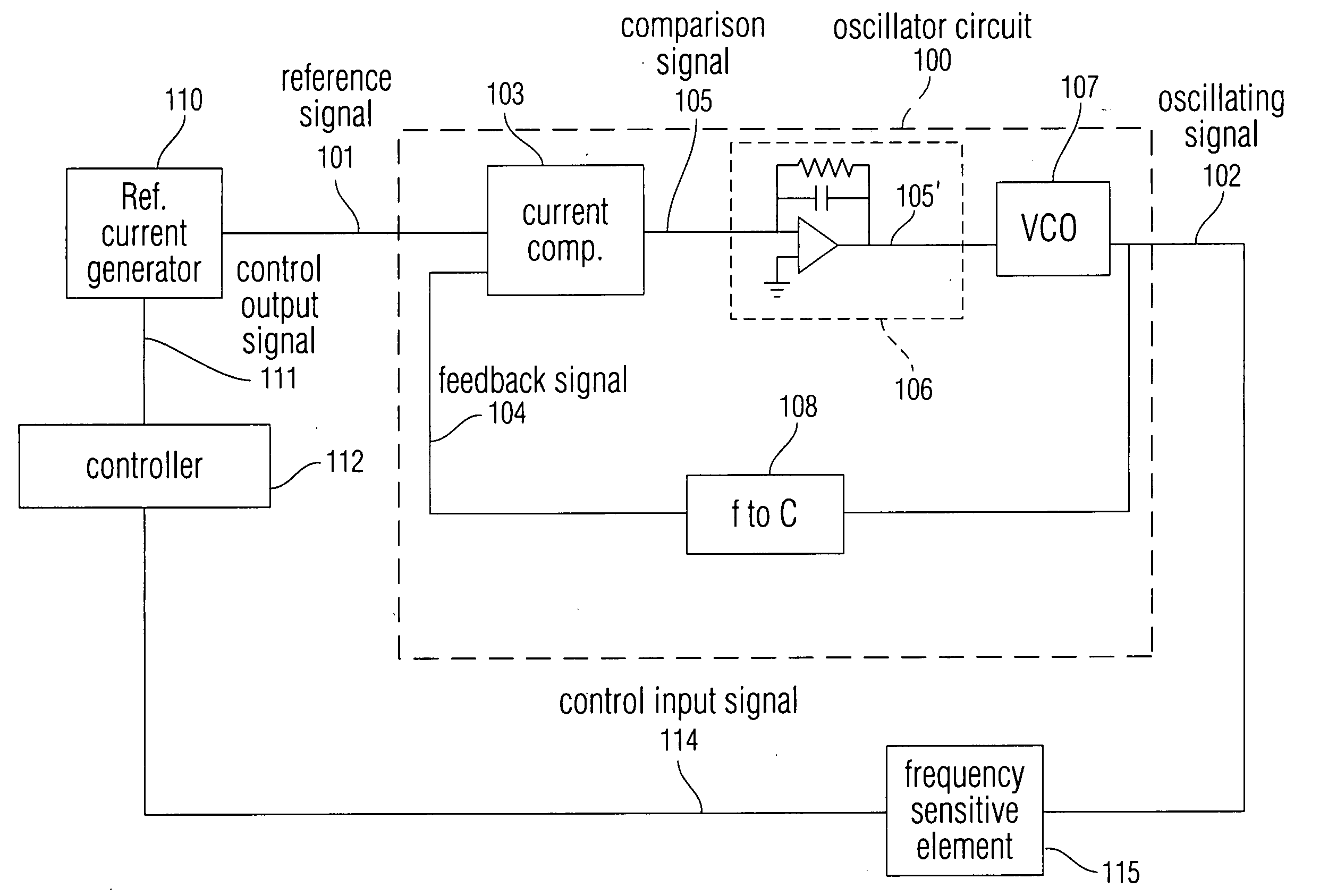

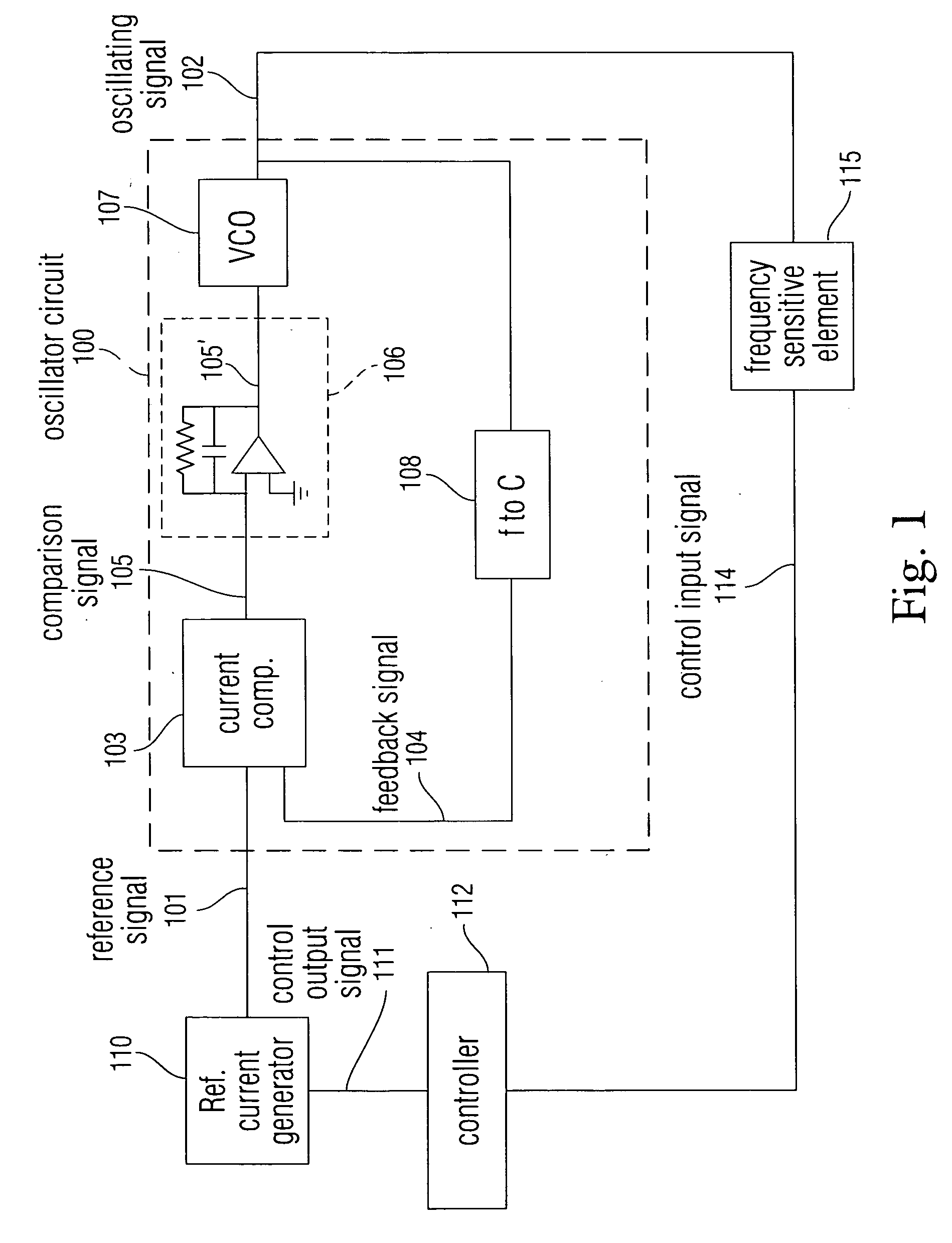

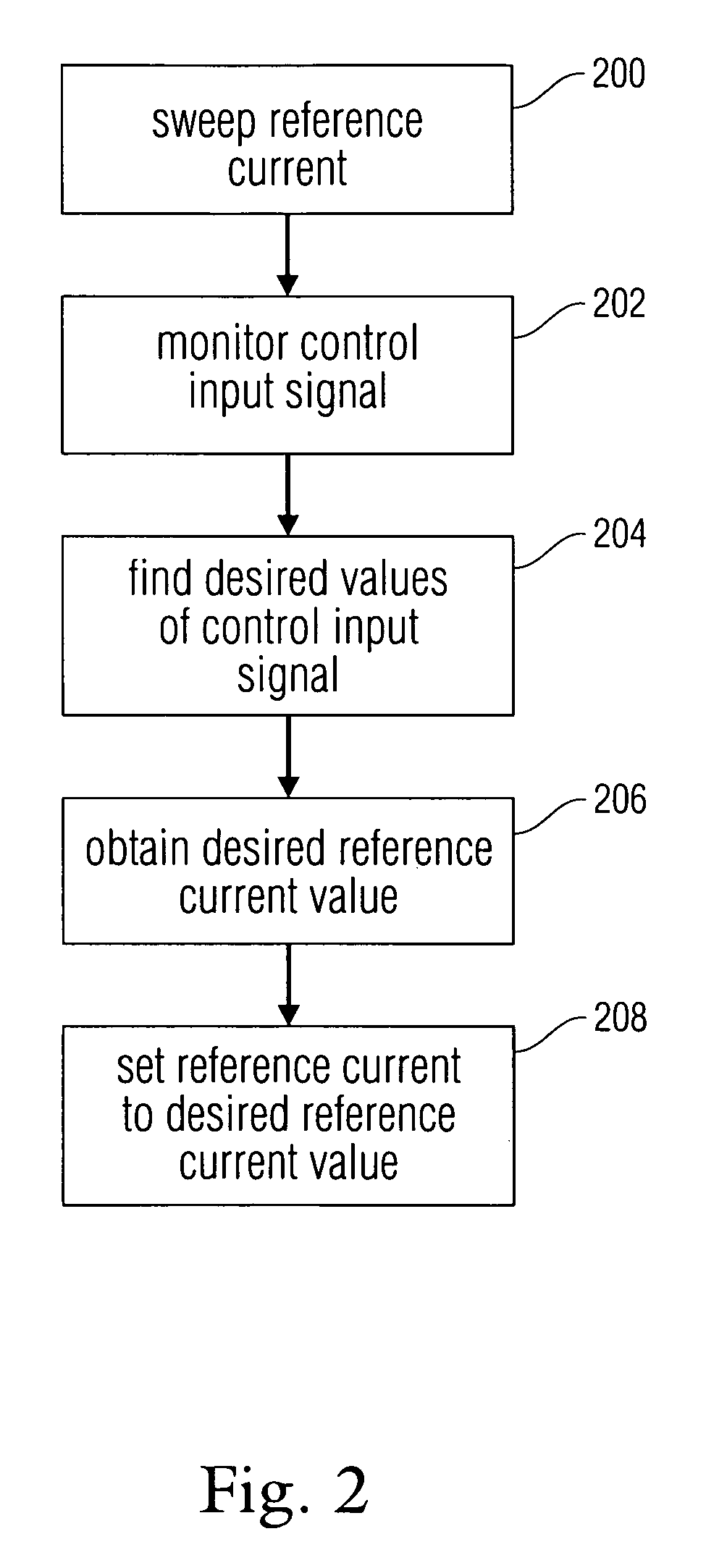

Noise reduction within an electronic device using automatic frequency modulation

ActiveUS20080157893A1High frequencyLimitation to input signalPulse automatic controlFrequency analysisEngineeringNoise reduction

Disclosed is a system and method for providing an oscillating signal of relatively precise frequency without using a signal provided by a crystal as a reference. Disclosed is a feedback oscillator circuit configured to output an oscillating signal having a frequency defined by a reference signal. The oscillating signal can be sent to one or more circuits including at least one frequency sensitive element. The frequency sensitive element produces an output signal which depends on the frequency of the oscillating signal. A controller controls the reference signal in order to cause an attribute of the output signal to have a value within a desired range.

Owner:APPLE INC

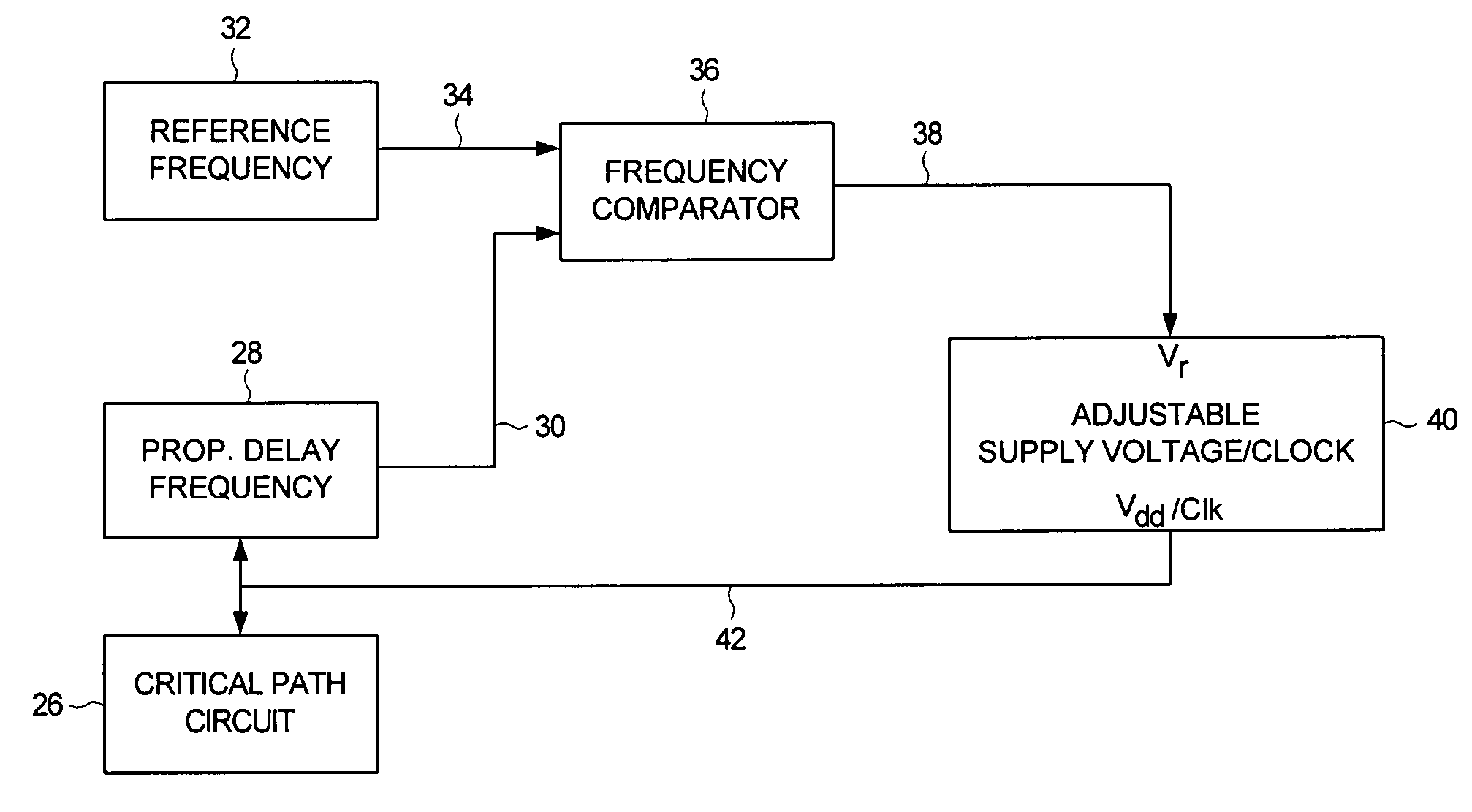

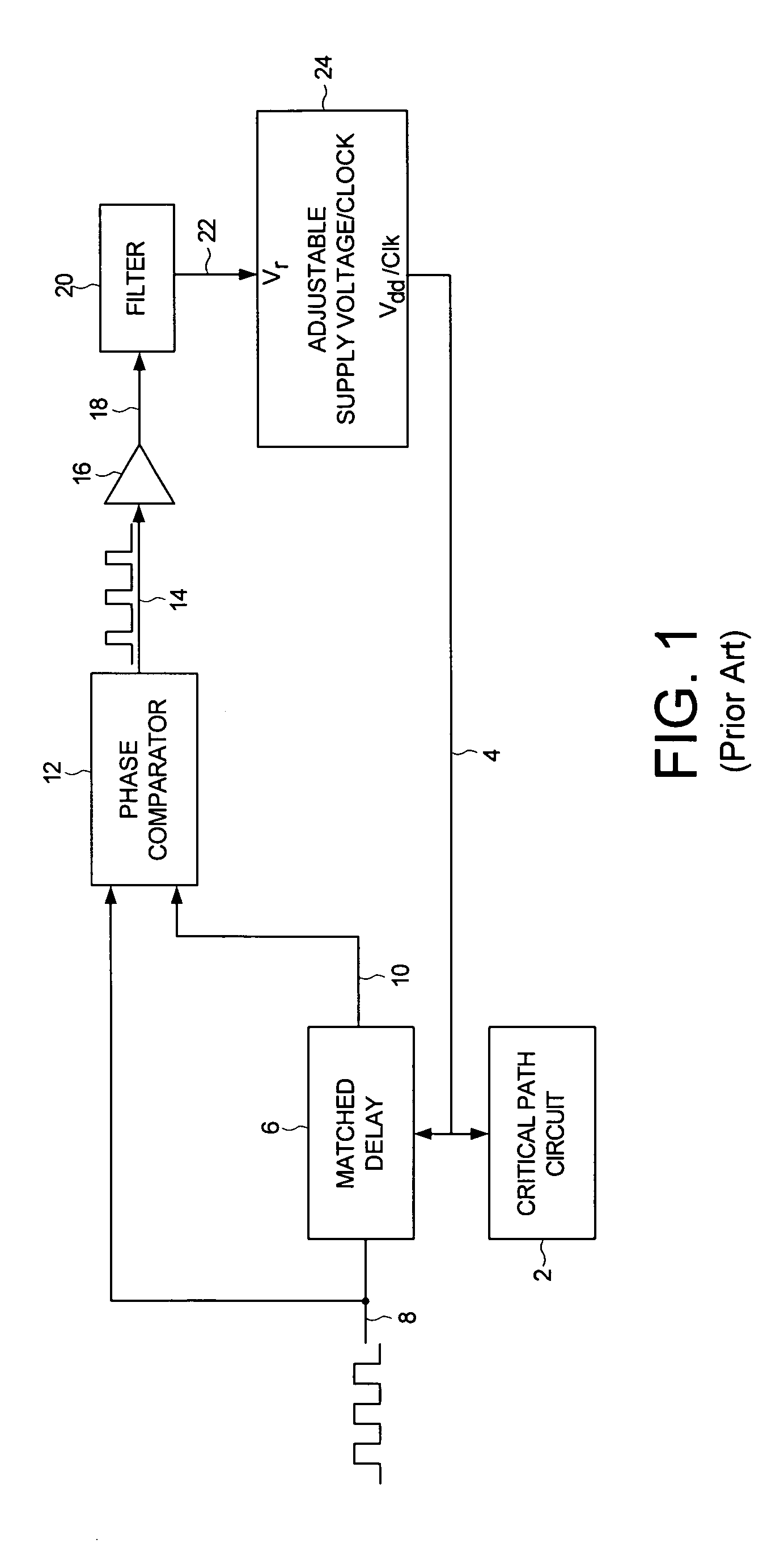

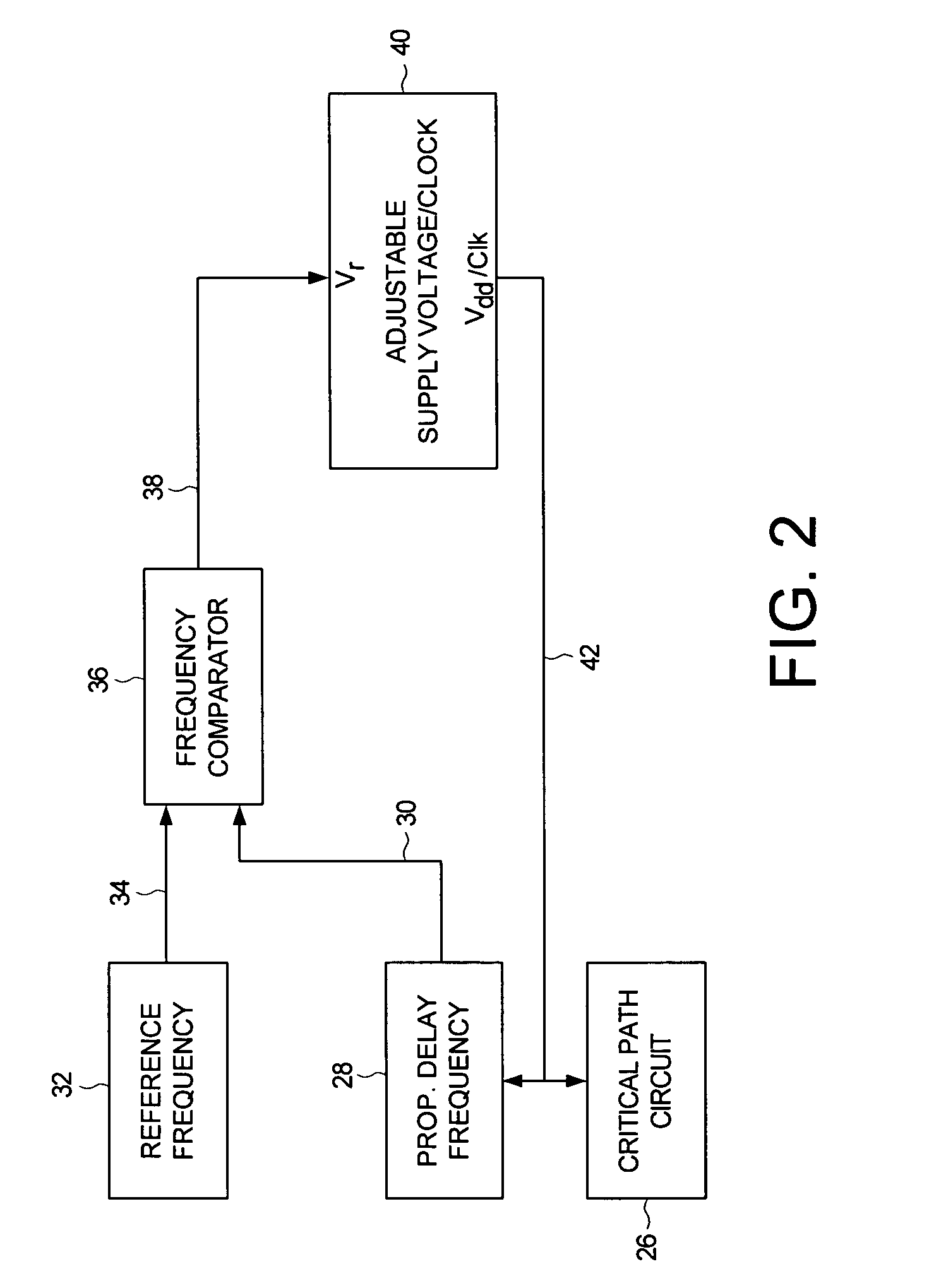

Adjusting power consumption of digital circuitry by generating frequency error representing error in propagation delay

A method and apparatus is disclosed for adjusting at least one of a supply voltage and a clocking frequency applied to digital circuitry of a computing device, wherein the digital circuitry comprises a critical path circuit. A propagation delay frequency representing a propagation delay of the critical path circuit is generated, and a frequency error signal is generated representing a difference between a reference frequency and the propagation delay frequency. At least one of the supply voltage and the clocking frequency is adjusted in response to the frequency error signal.

Owner:WESTERN DIGITAL TECH INC

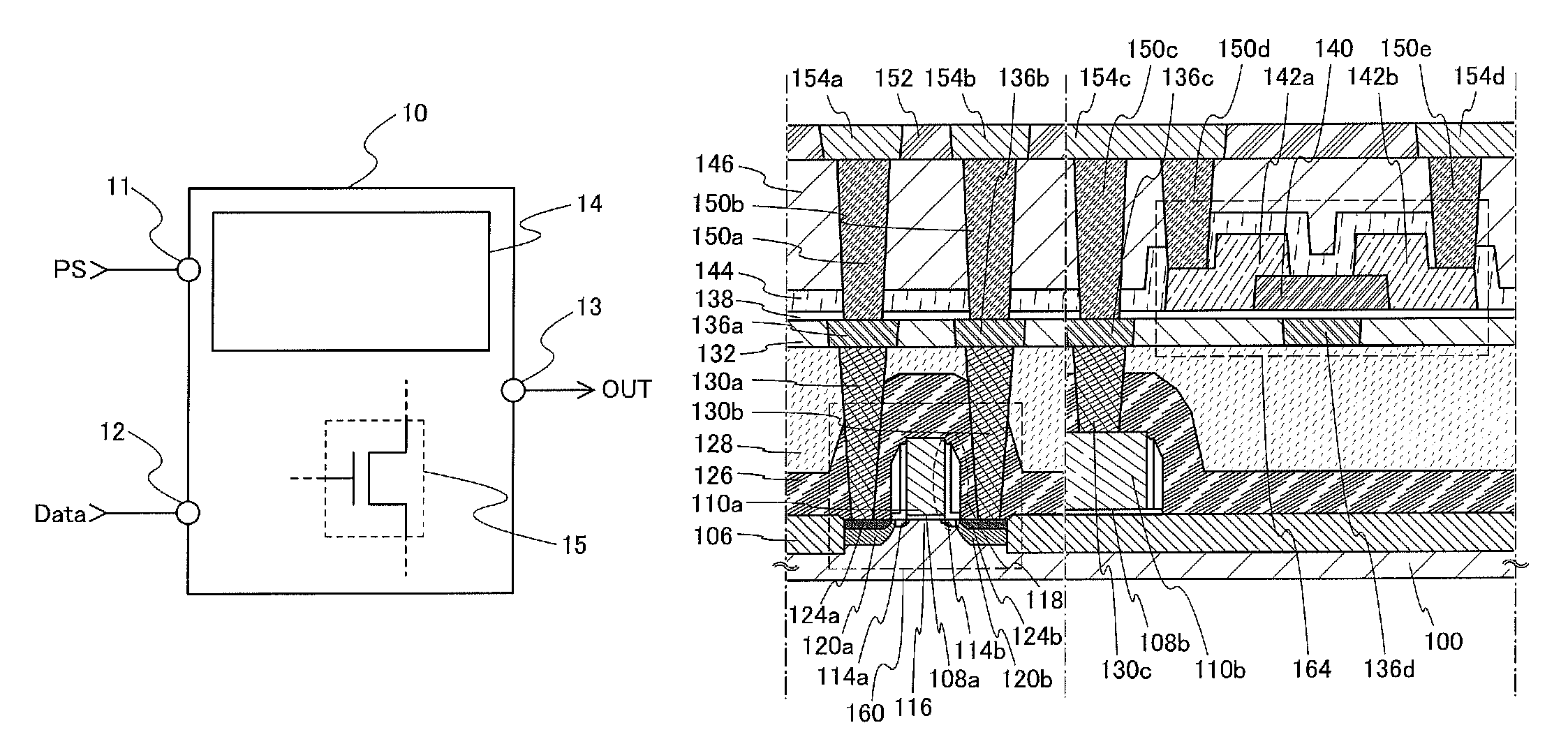

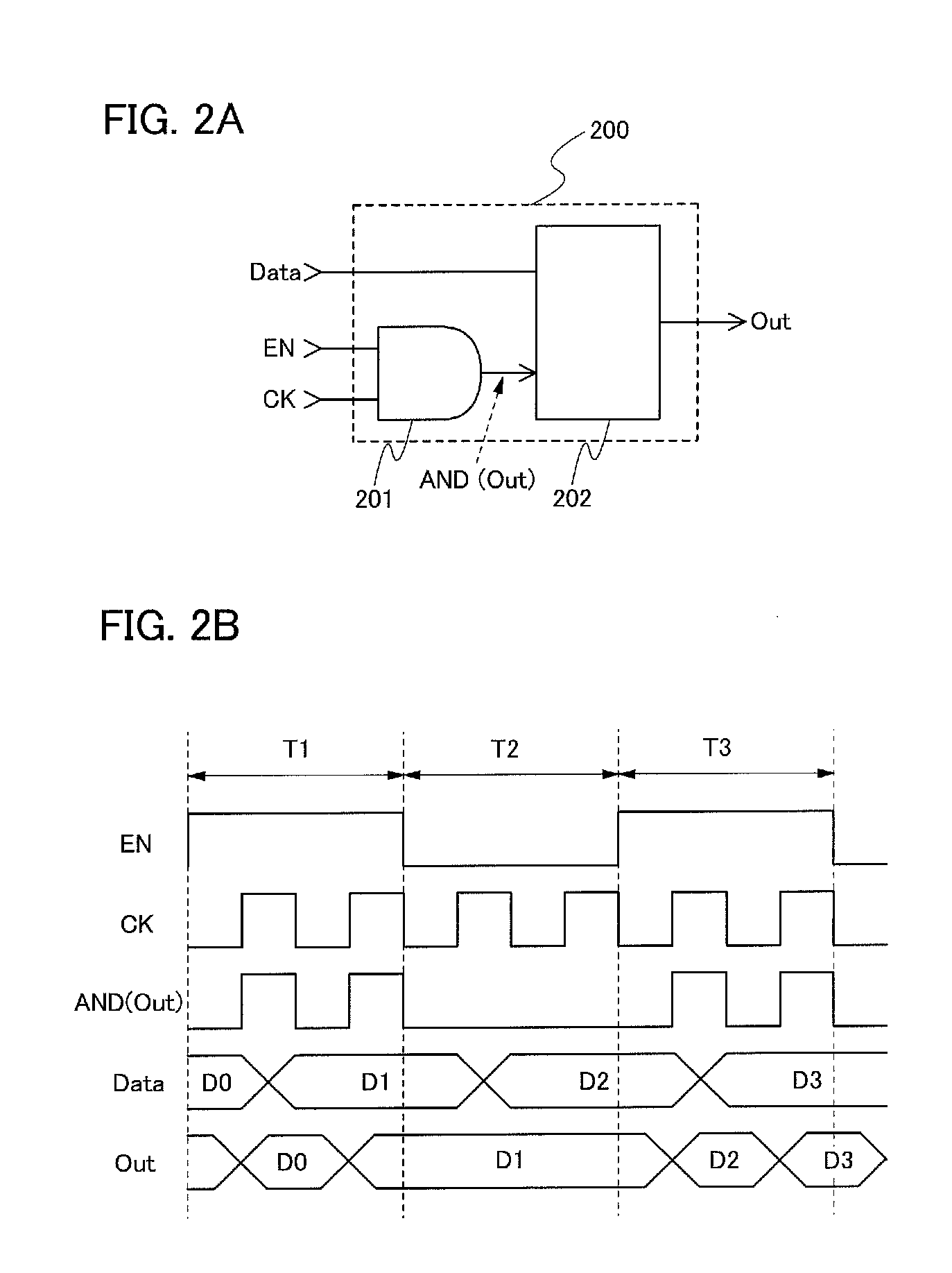

Logic circuit and semiconductor device

ActiveUS8207756B2Reduce dynamic power consumptionLeakage of highTransistorPower reduction by control/clock signalHydrogen concentrationPower semiconductor device

In a logic circuit where clock gating is performed, the standby power is reduced or malfunction is suppressed. The logic circuit includes a transistor which is in an off state where a potential difference exists between a source terminal and a drain terminal over a period during which a clock signal is not supplied. A channel formation region of the transistor is formed using an oxide semiconductor in which the hydrogen concentration is reduced. Specifically, the hydrogen concentration of the oxide semiconductor is 5×1019 (atoms / cm3) or lower. Thus, leakage current of the transistor can be reduced. As a result, in the logic circuit, reduction in standby power and suppression of malfunction can be achieved.

Owner:SEMICON ENERGY LAB CO LTD

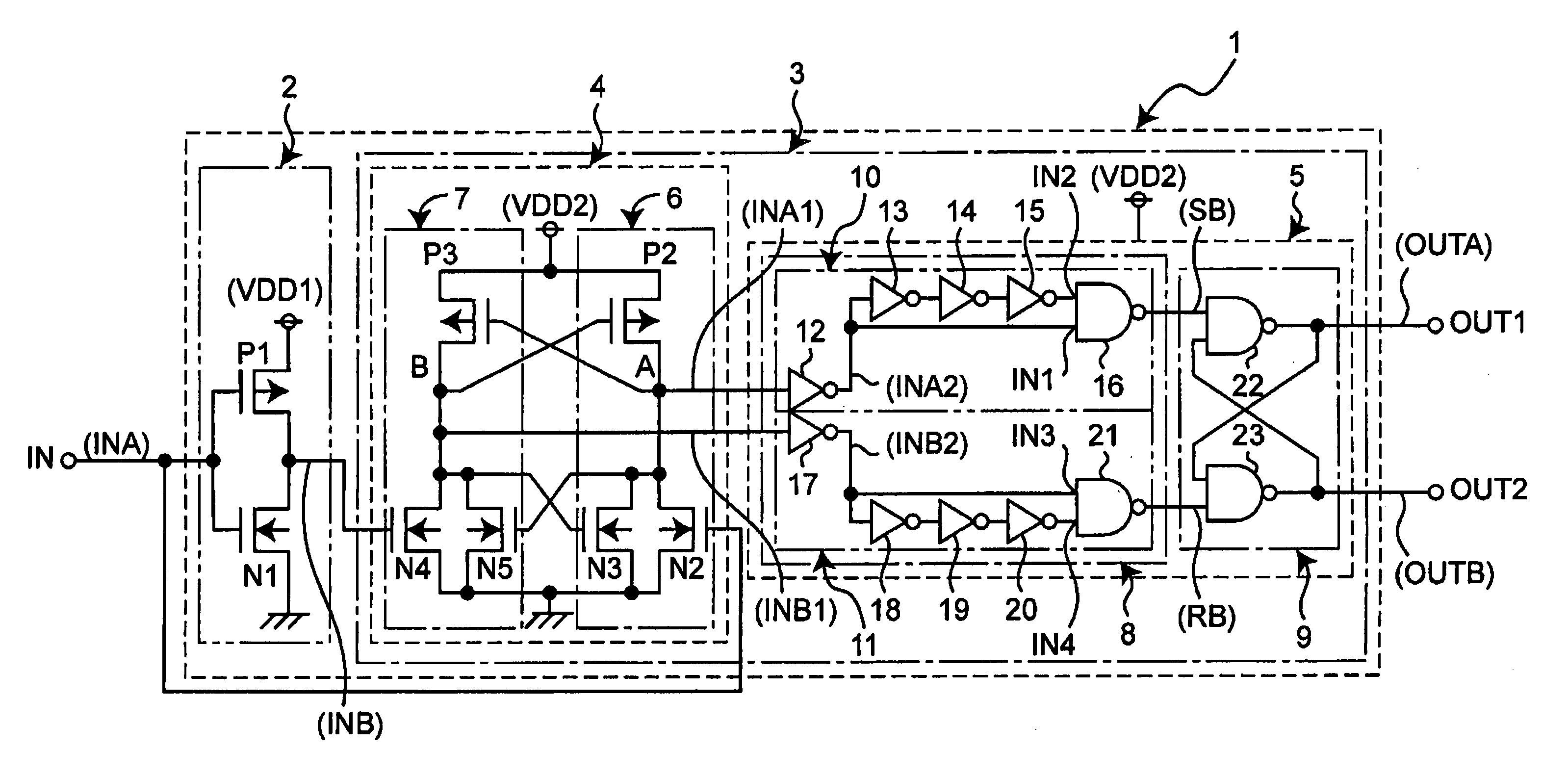

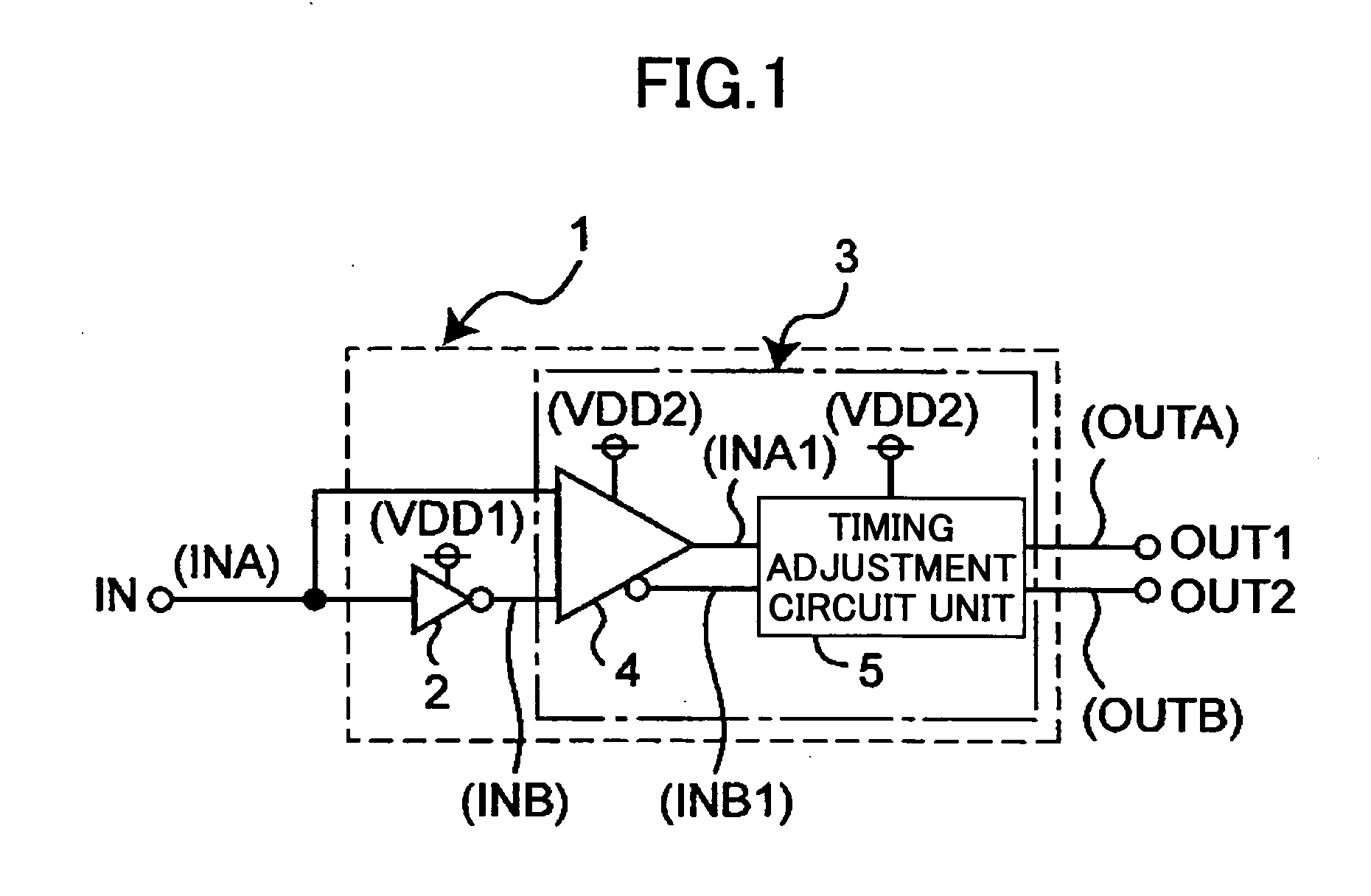

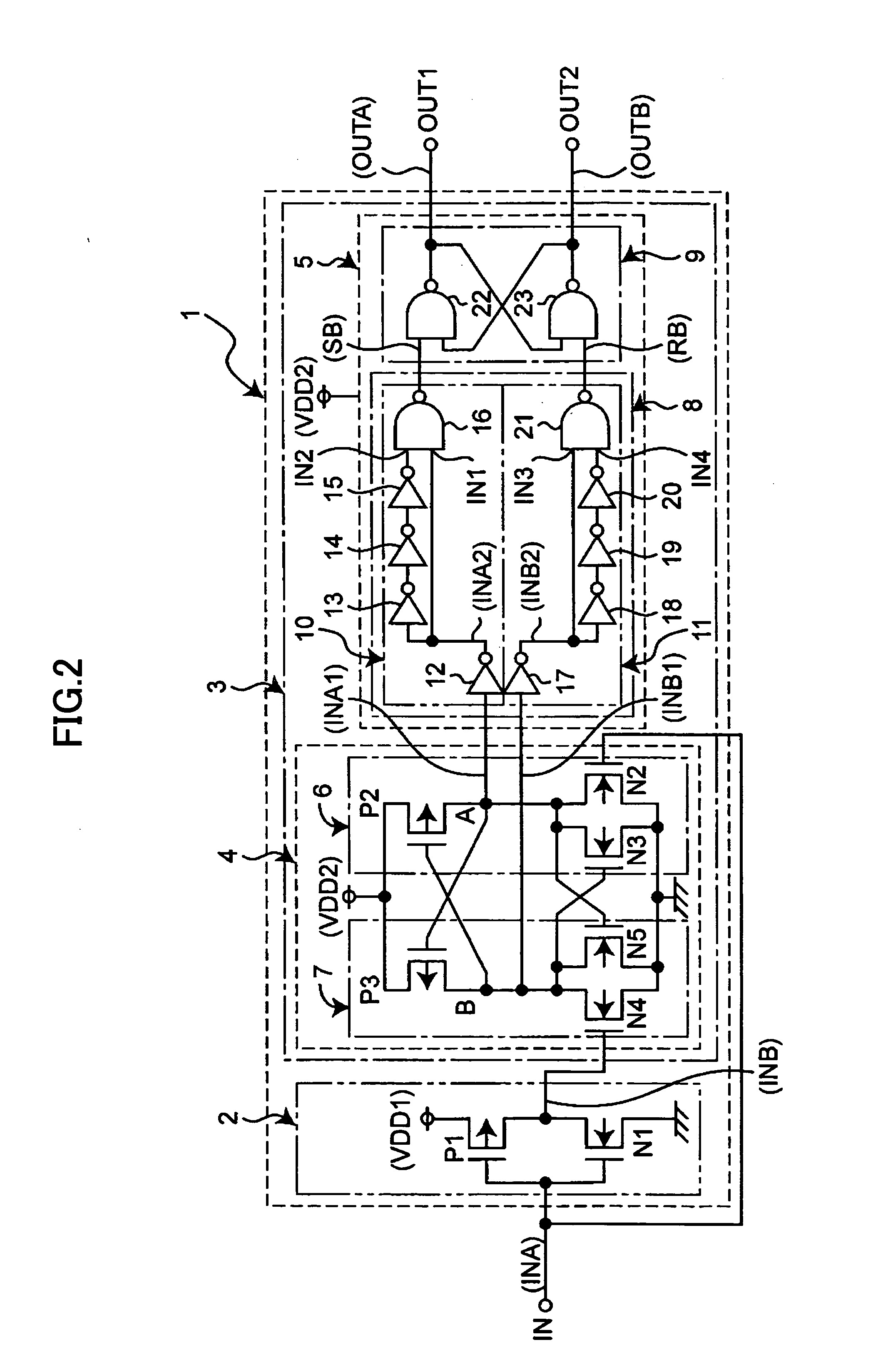

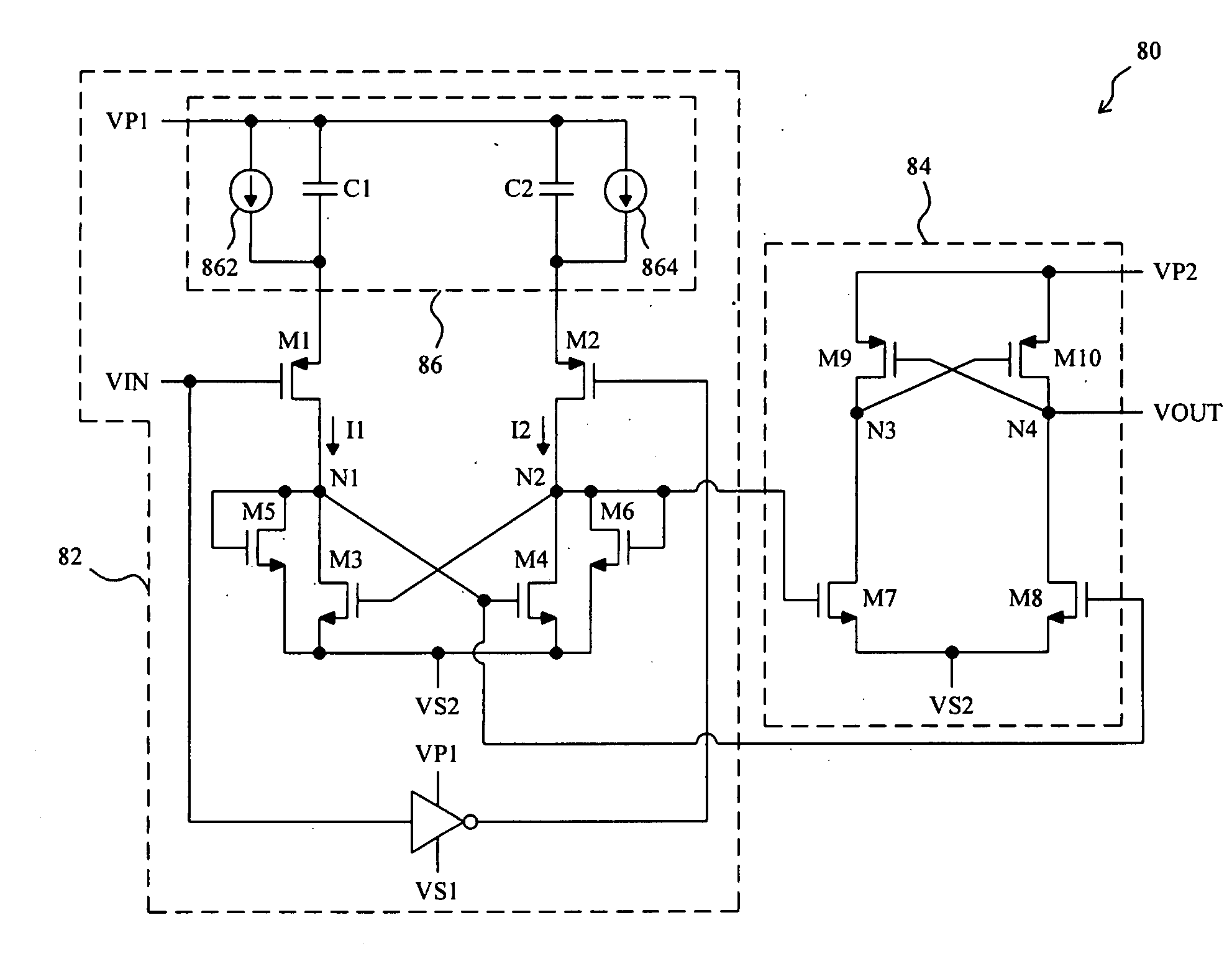

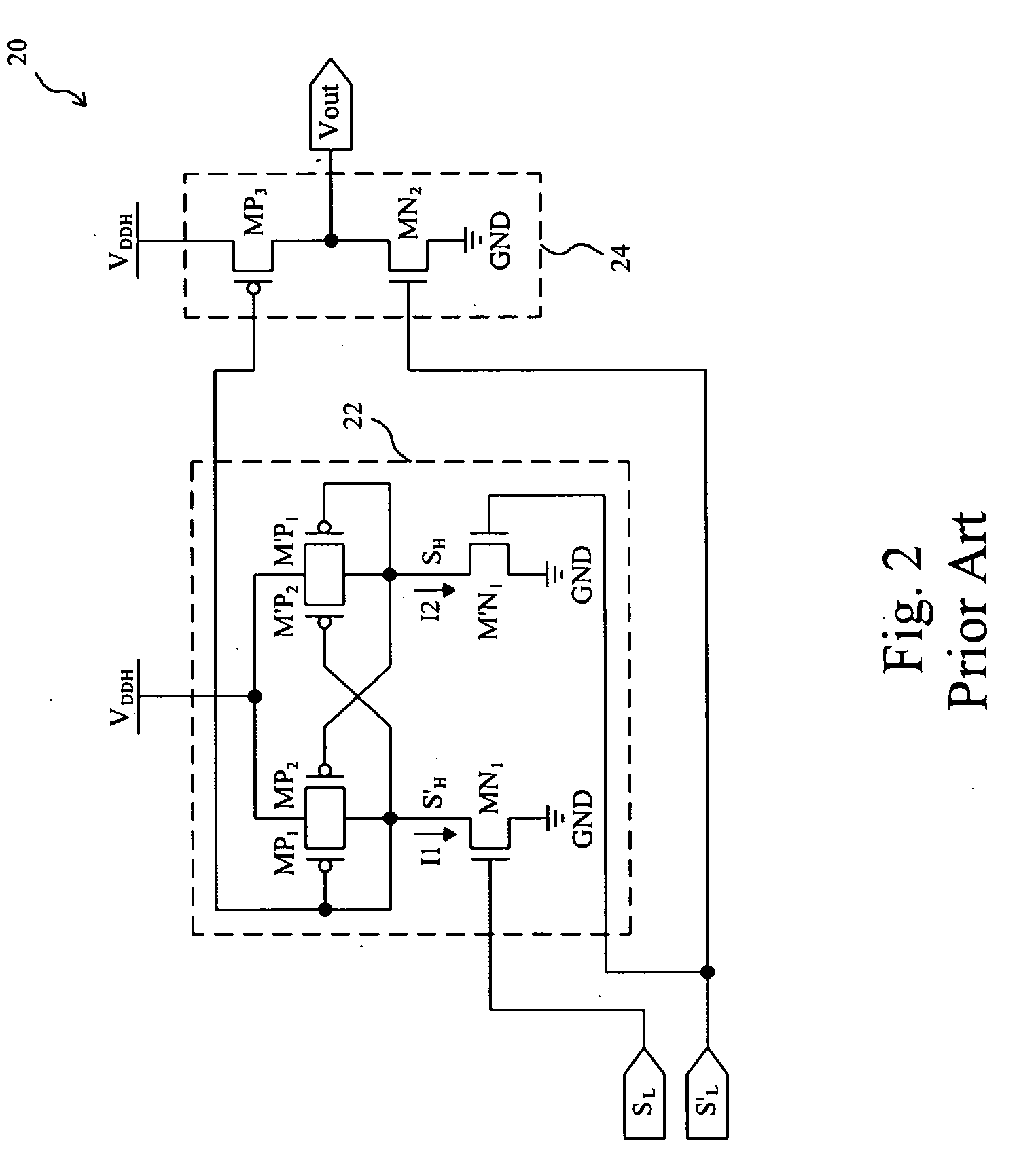

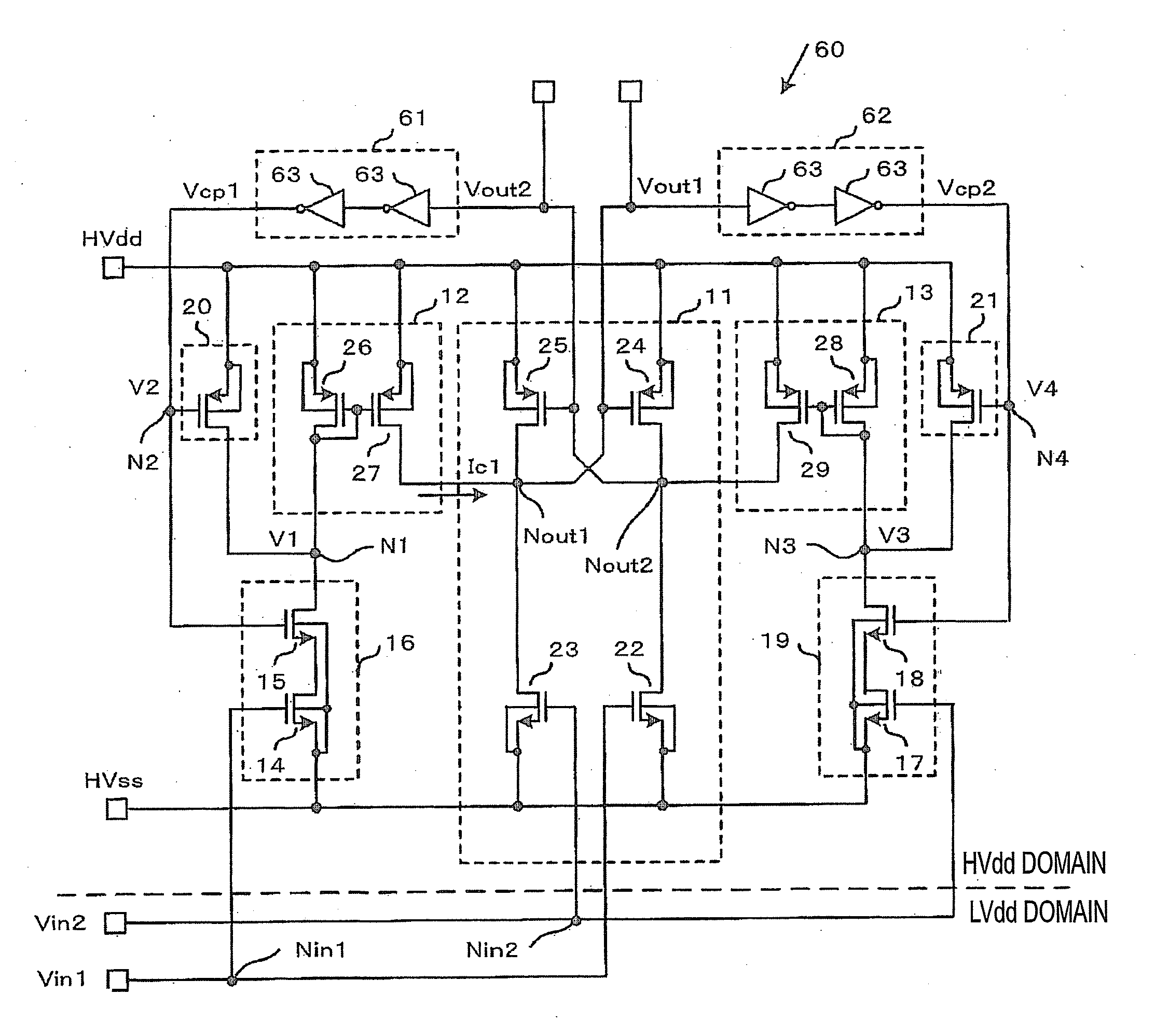

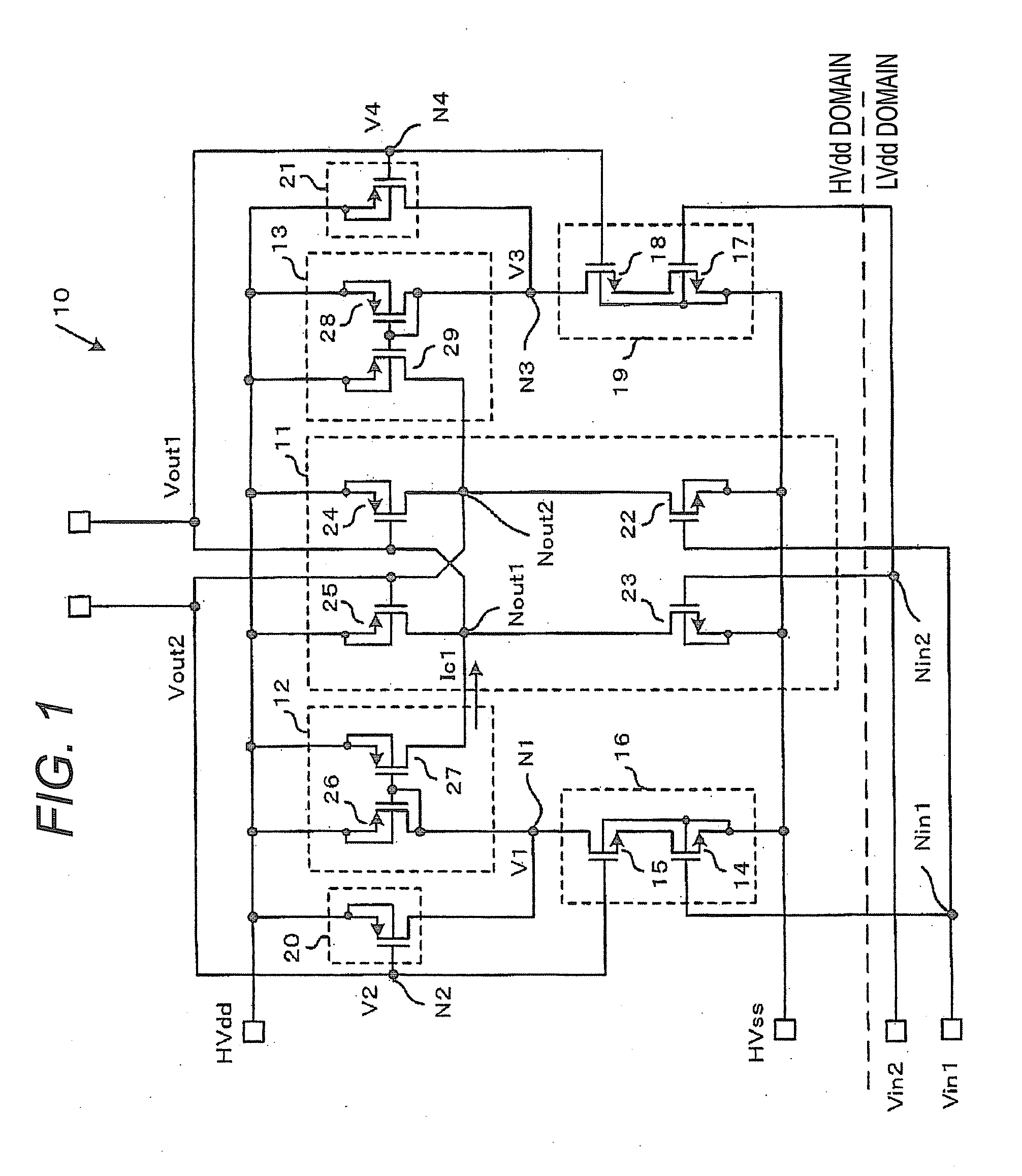

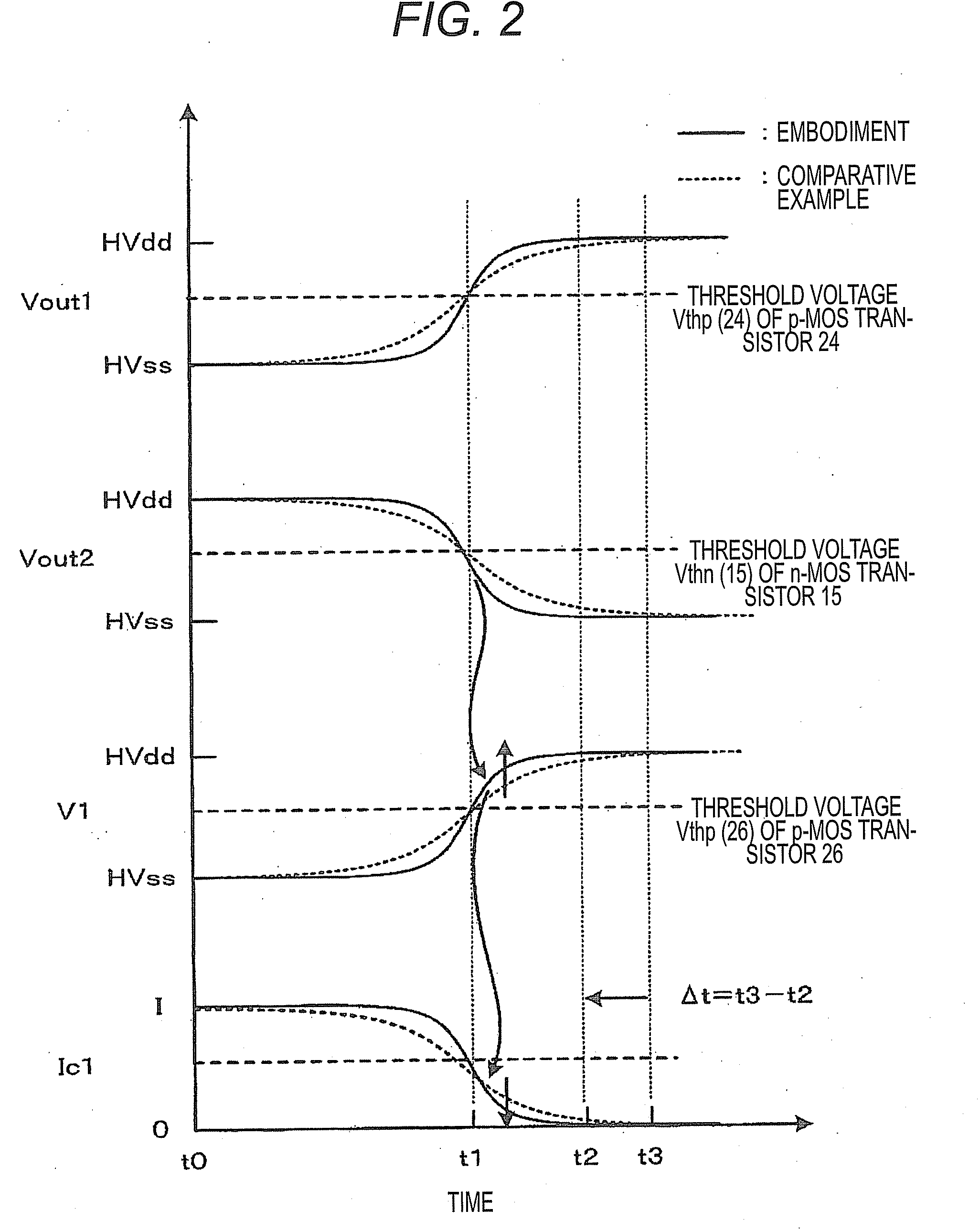

Level shift circuit having timing adjustment circuit for maintaining duty ratio

InactiveUS20060066349A1Accurate operationReliability increasing modificationsElectronic switchingEngineeringVoltage range

A level shift circuit for shifting levels of a pair of binary input signals having a first voltage range to produce a pair of binary output signals having a second voltage range includes a first circuit to shift a level of a first one of the binary input signals thereby to produce a first signal having the second voltage range, a second circuit to shift a level of a second one of the binary input signals thereby to produce a second signal having the second voltage range, and a timing adjustment circuit to produce the binary output signals by adjusting a pulse width thereof in response to the first and second signals such that the pulse width is equal to a time interval from when one of the first and second circuits stops level shift operation to when another one of the first and second circuits stops level shift operation.

Owner:RICOH ELECTRONIC DEVICES CO LTD

Nonvolatile latch circuit and logic circuit, and semiconductor device using the same

ActiveUS20110187410A1Wider range of operating temperatureGuaranteed uptimeSolid-state devicesDigital storageSemiconductor materialsCapacitor

To provide a novel nonvolatile latch circuit and a semiconductor device using the nonvolatile latch circuit, a nonvolatile latch circuit includes a latch portion having a loop structure where an output of a first element is electrically connected to an input of a second element, and an output of the second element is electrically connected to an input of the first element; and a data holding portion configured to hold data of the latch portion. In the data holding portion, a transistor using an oxide semiconductor as a semiconductor material for forming a channel formation region is used as a switching element. In addition, a capacitor electrically connected to a source electrode or a drain electrode of the transistor is included.

Owner:SEMICON ENERGY LAB CO LTD

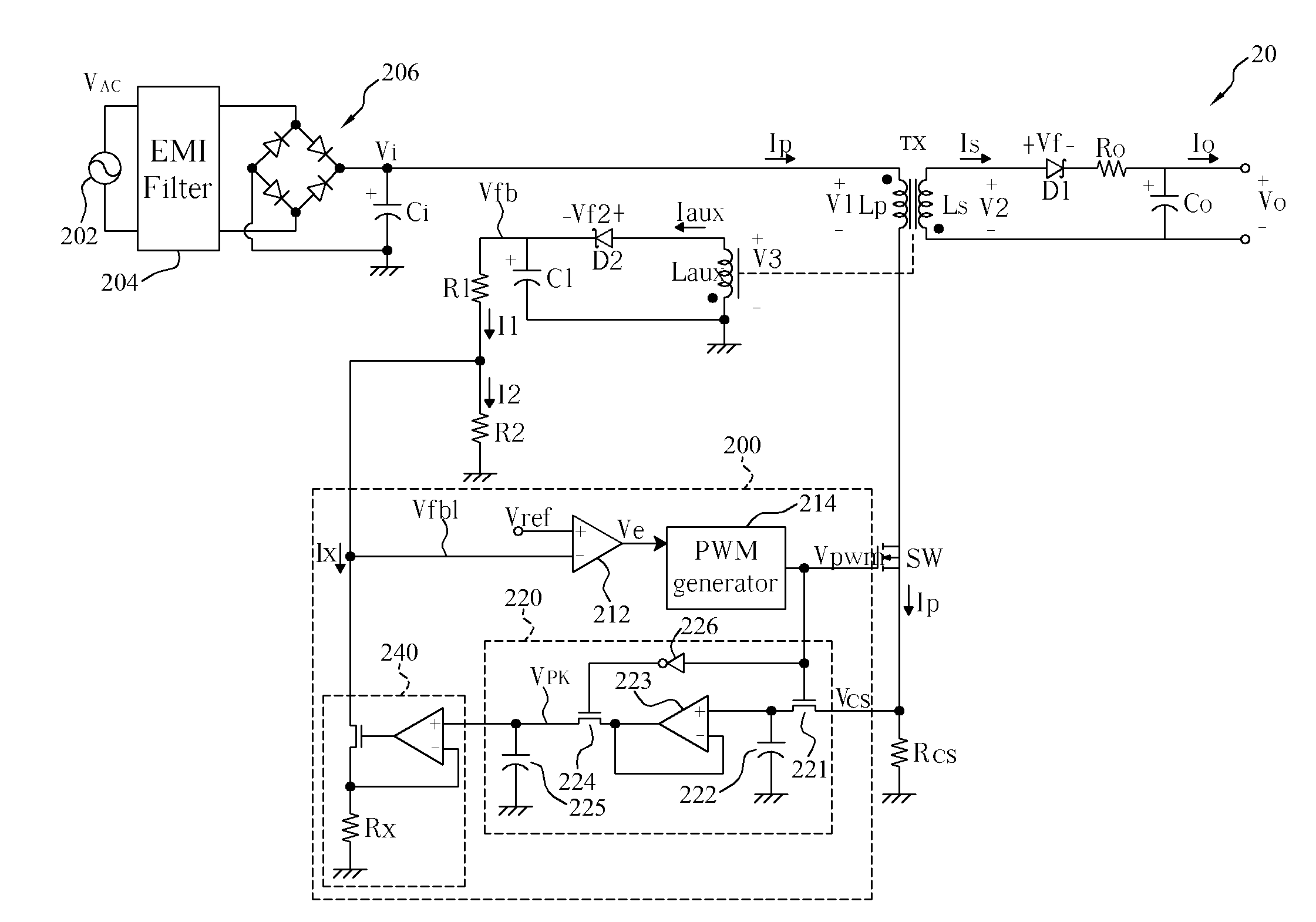

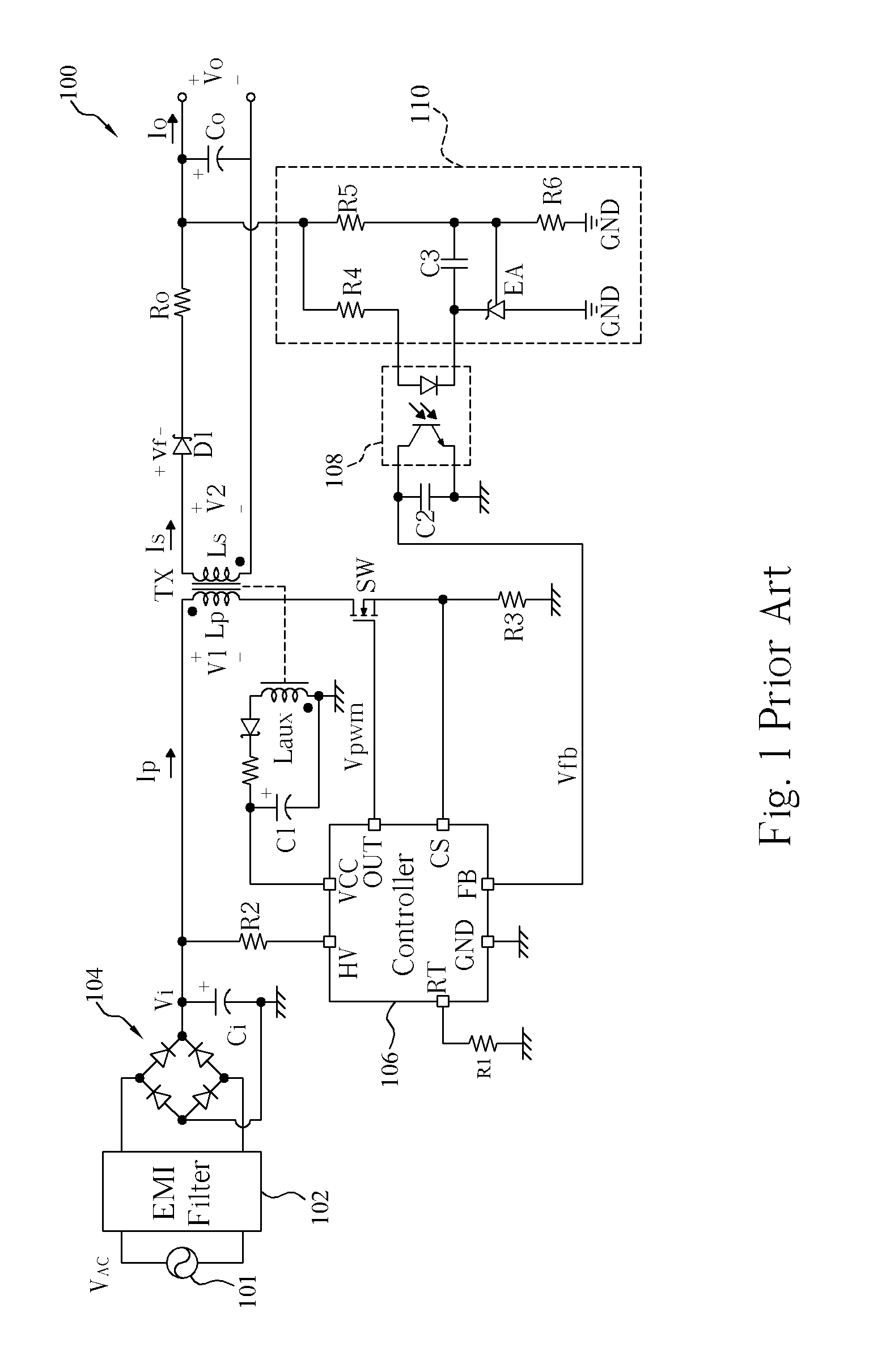

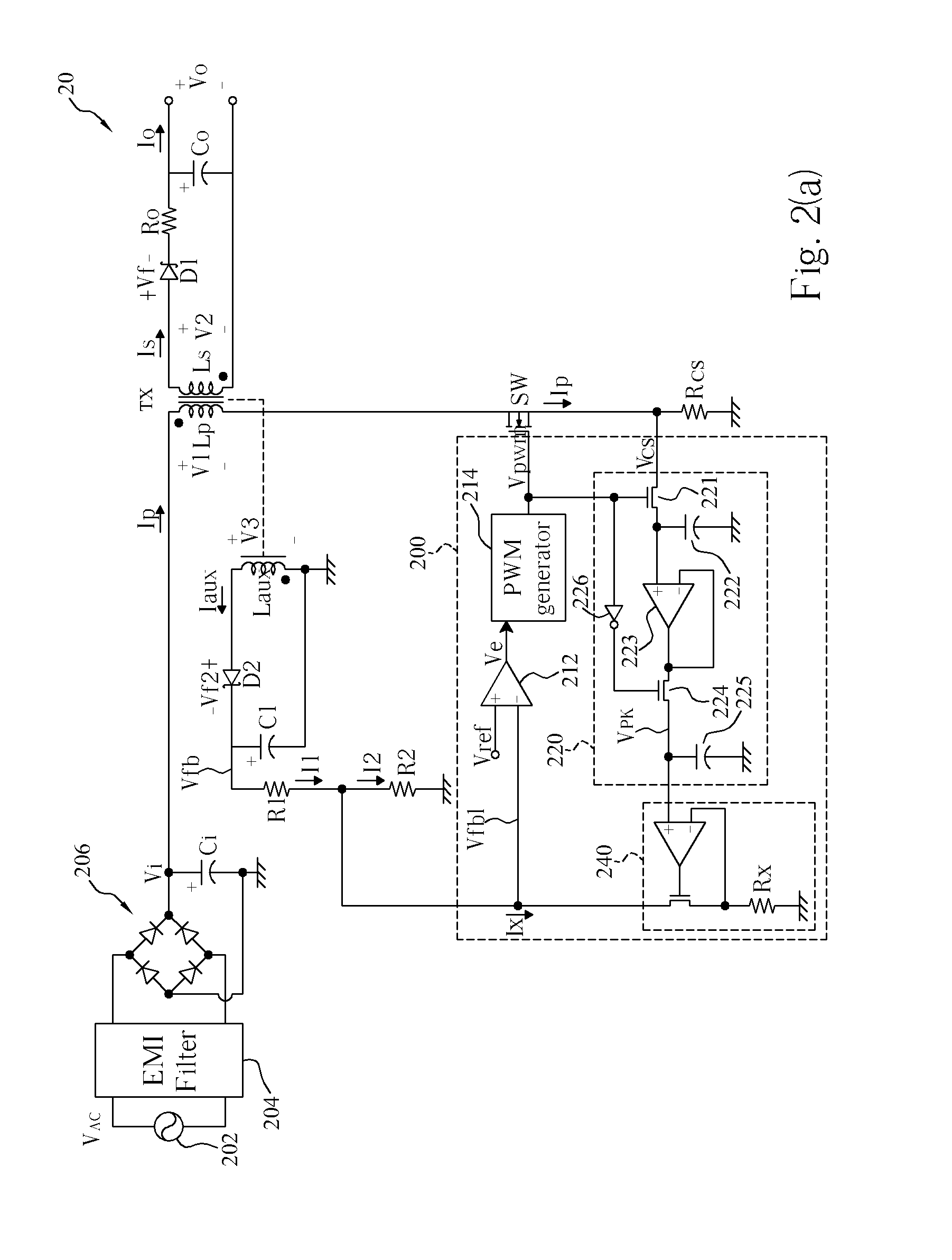

Switching-mode power converter and pulse-width-modulation control circuit with primary-side feedback control

A pulse-width-modulation control circuit of a switching-mode power converter with a primary-side feedback control is disclosed. The switching-mode power converter includes a transformer, a power switch, a current sensing resistor and the pulse-width-modulation control circuit. The transformer includes a primary-side winding, a secondary-side winding and an auxiliary winding. The pulse-width-modulation control circuit includes a sample and hold circuit, a transconductor circuit, an error amplifier and a pulse-width-modulation generator.

Owner:LEADTREND TECH

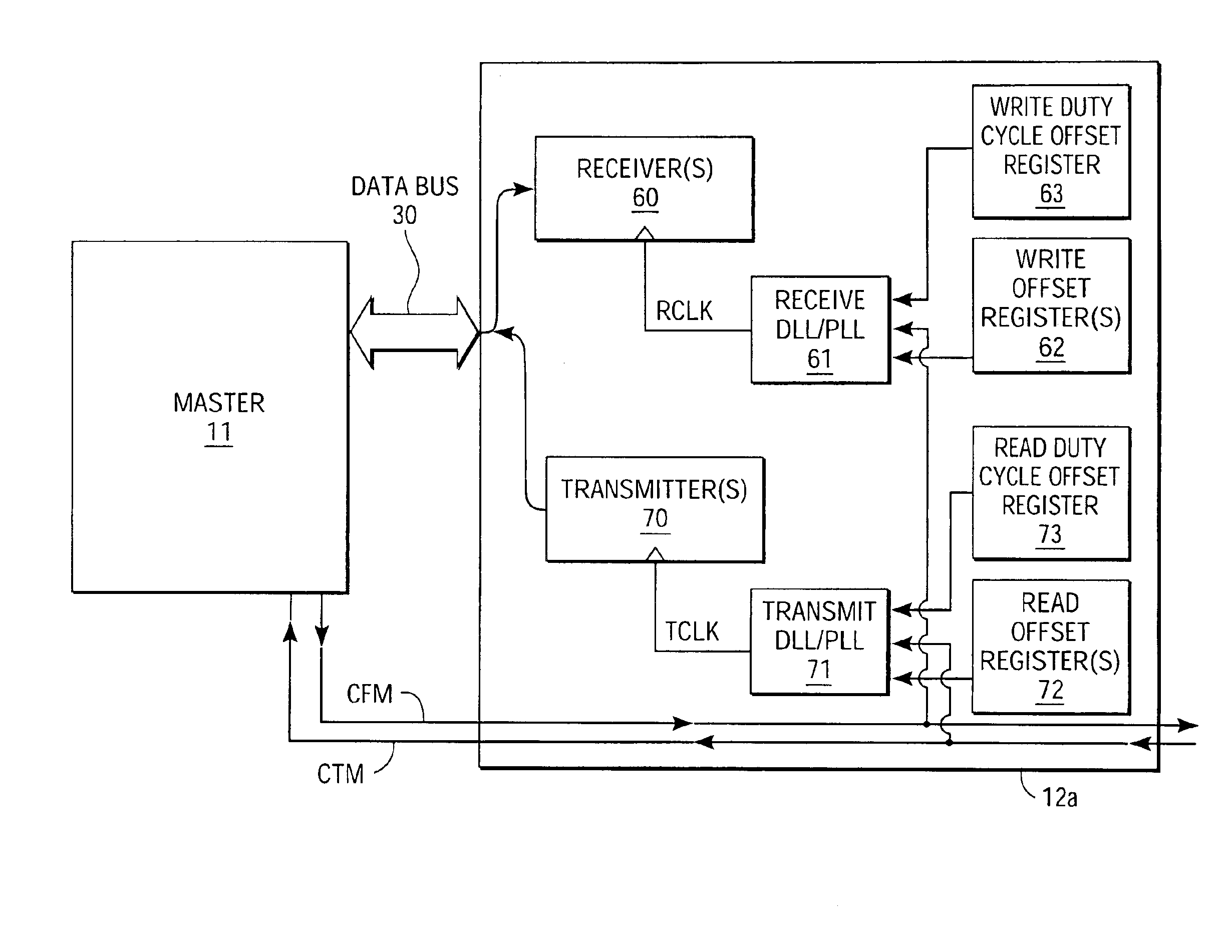

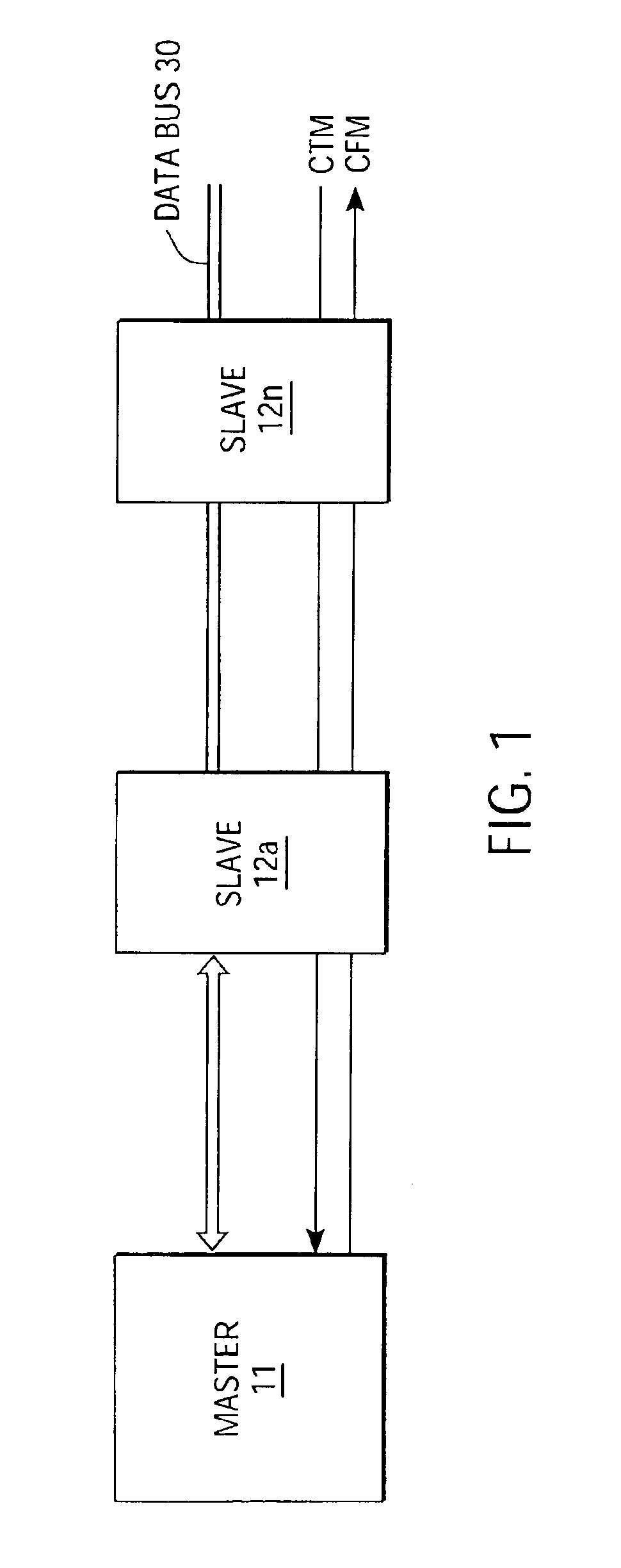

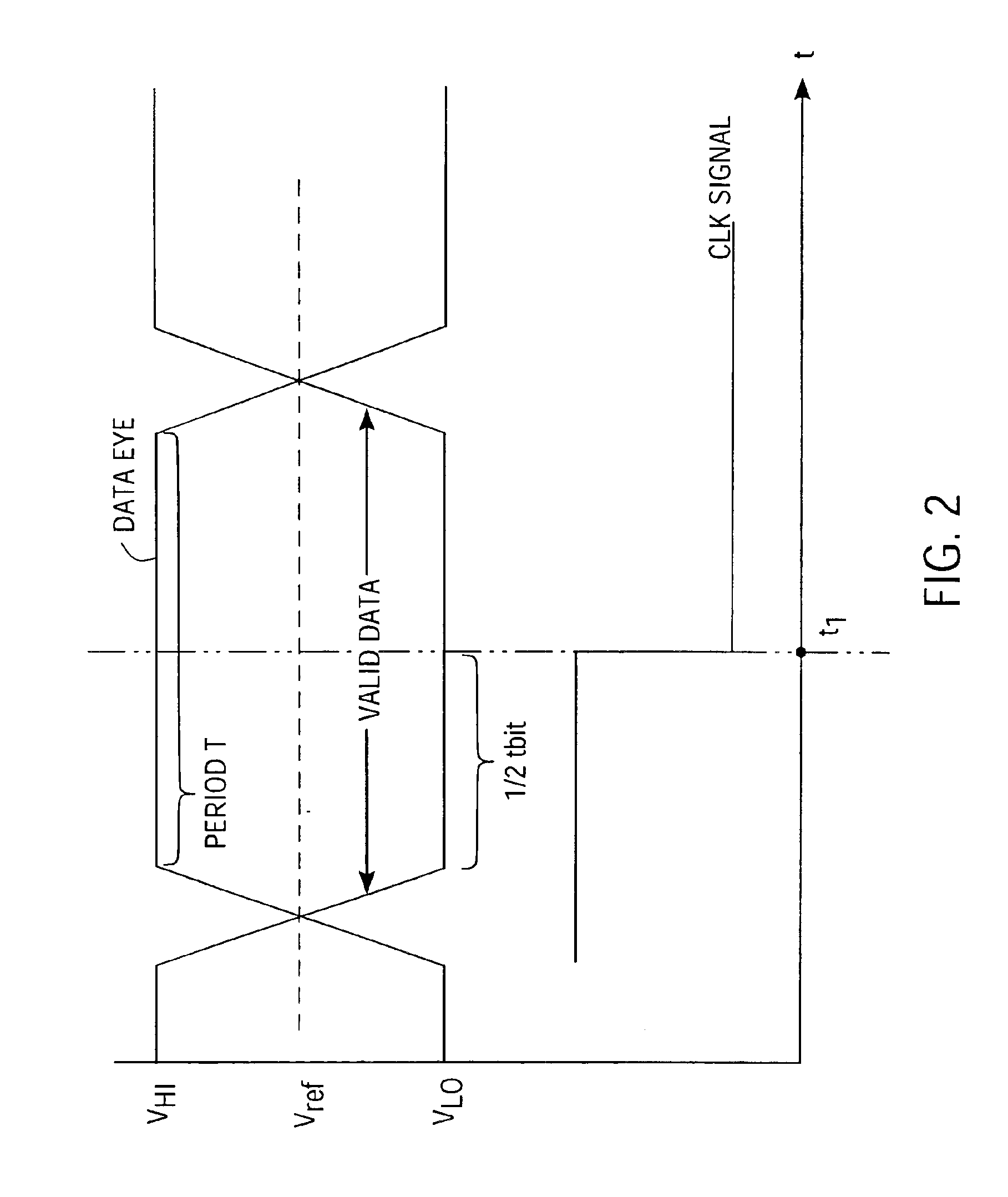

Integrated circuit with timing adjustment mechanism and method

InactiveUS6950956B2Multiple-port active networksModulated-carrier systemsComputer scienceIntegrated circuit

An integrated circuit device includes a receiver, a register and a clock circuit. The receiver samples data from an external signal line in response to an internal clock signal. The register stores a value that represents a timing offset to adjust the time at which the data is sampled. The clock circuit generates the internal clock signal such that the internal clock signal maintains a controlled timing relationship with respect to an external clock signal. The clock circuit includes an interpolator that phase mixes a set of reference clock signals such that the internal clock signal is phase offset in accordance with the value.

Owner:RAMBUS INC

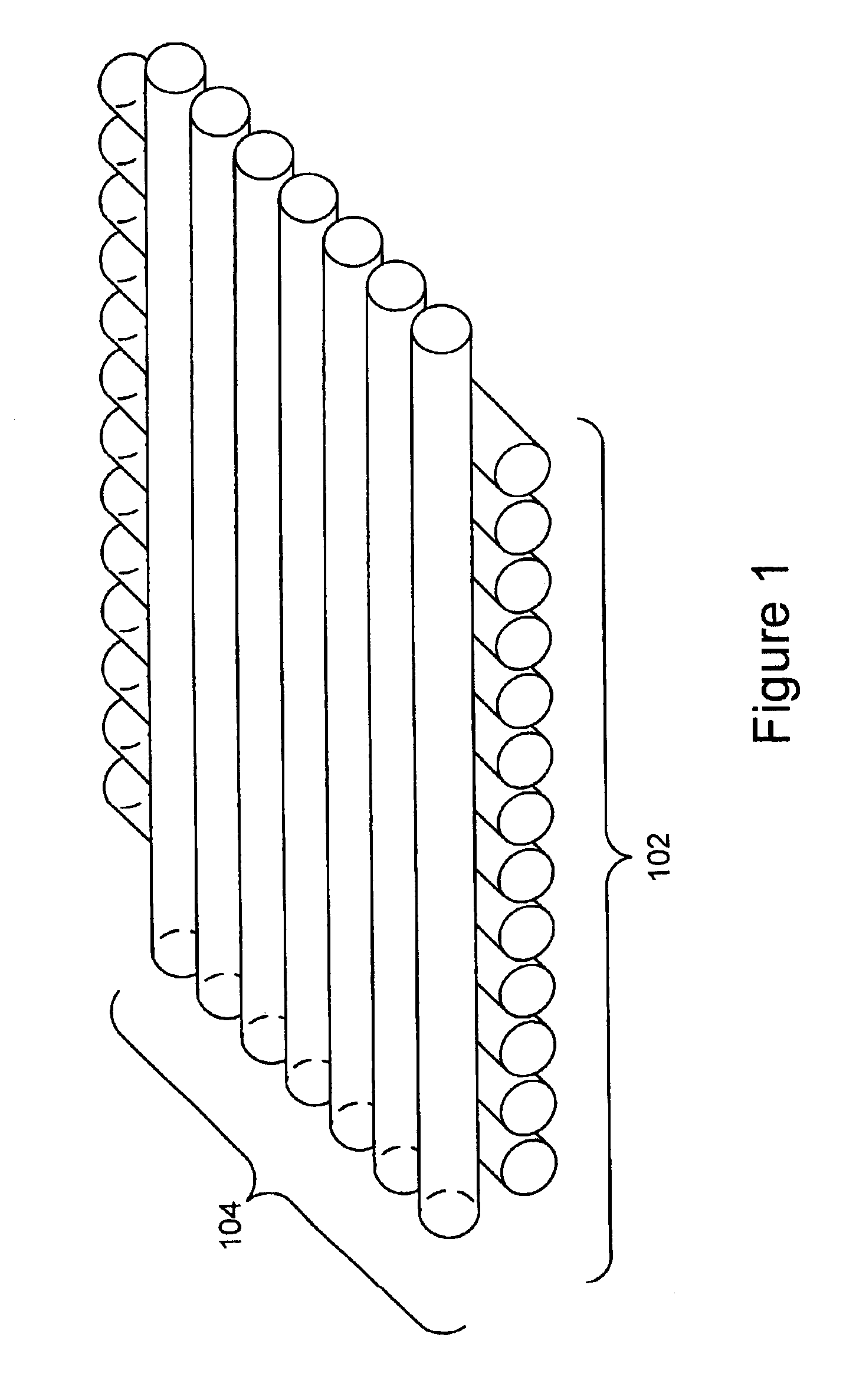

Storage elements using nanotube switching elements

Owner:NANTERO

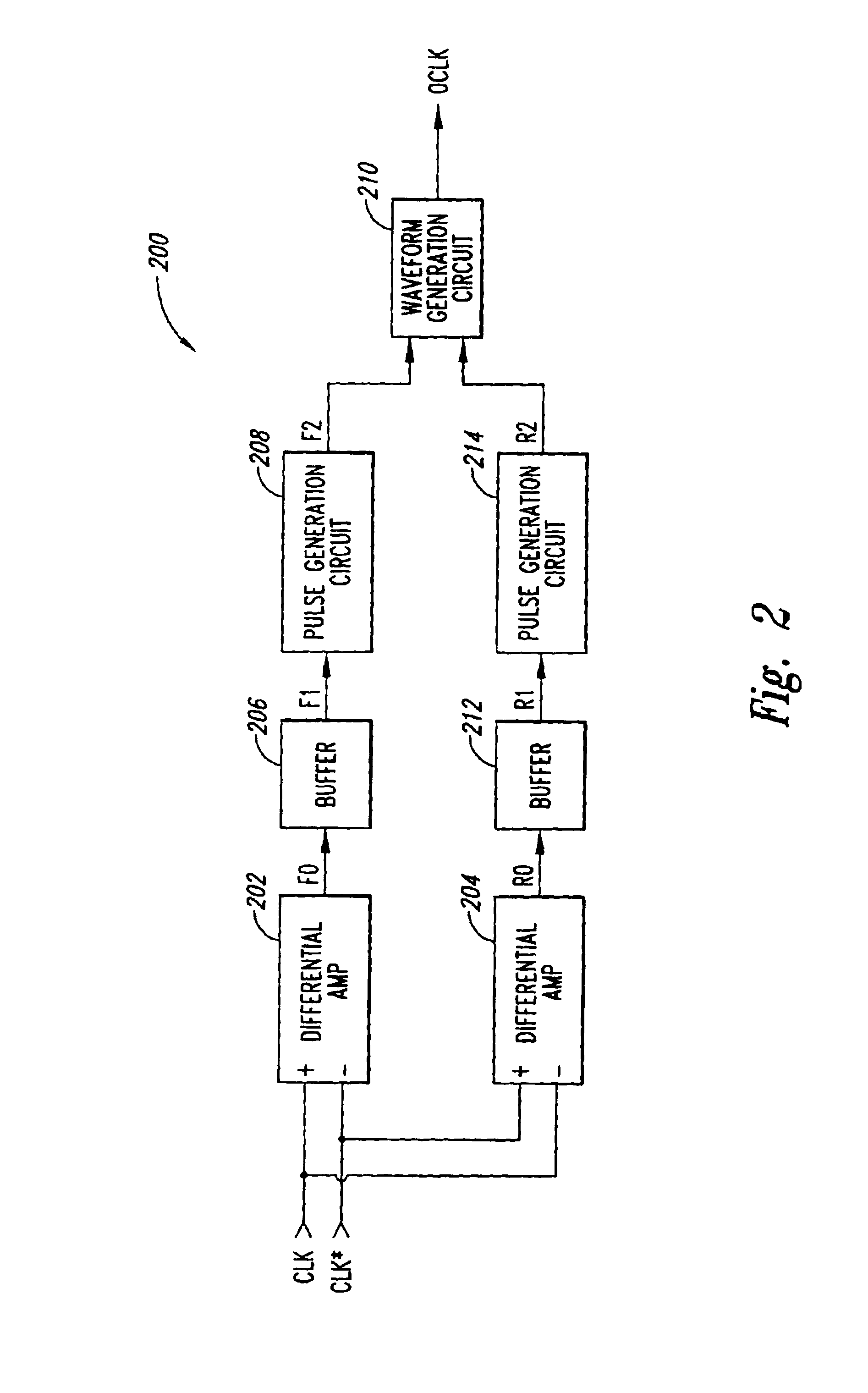

Low skew clock input buffer and method

InactiveUS6847582B2Reliability increasing modificationsDigital storageAudio power amplifierLogic state

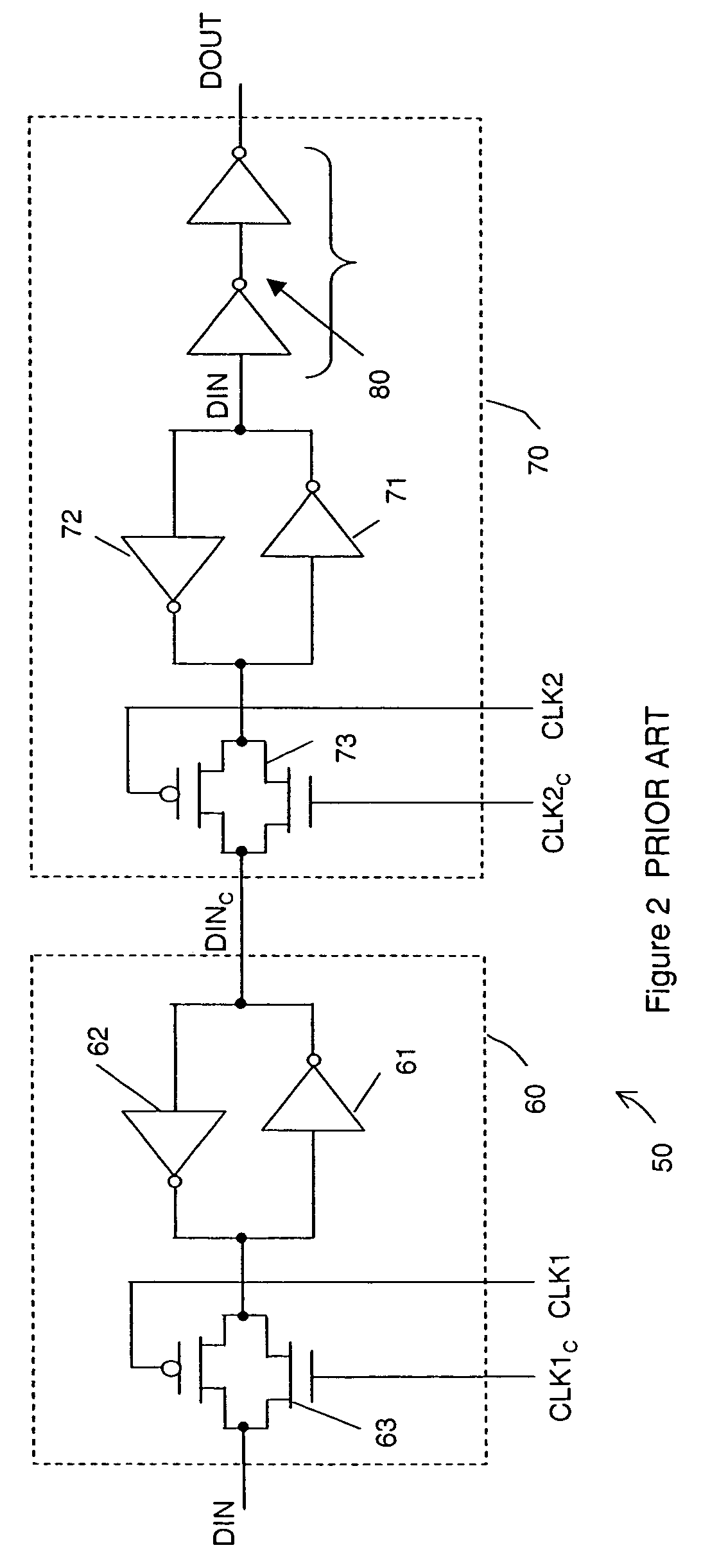

An input buffer includes first and second cross-coupled differential amplifiers. Each amplifier drives a buffer signal from a first logic state to a second logic state at a first slew rate when input signal transitions from a first logic state to a second logic state and a complementary input signal transitions from the second logic state to the first logic state, and drives the buffer signal from the second logic state to the first logic state at a second slew rate when the signal transitions are the complement of these previous transitions. An output circuit generates a first edge of an output signal when the buffer signal from the first amplifier transitions from the first logic state to the second logic state and generates a second edged of the output signal when the buffer signal from the second amplifier transitions from the first to the second logic state.

Owner:MICRON TECH INC

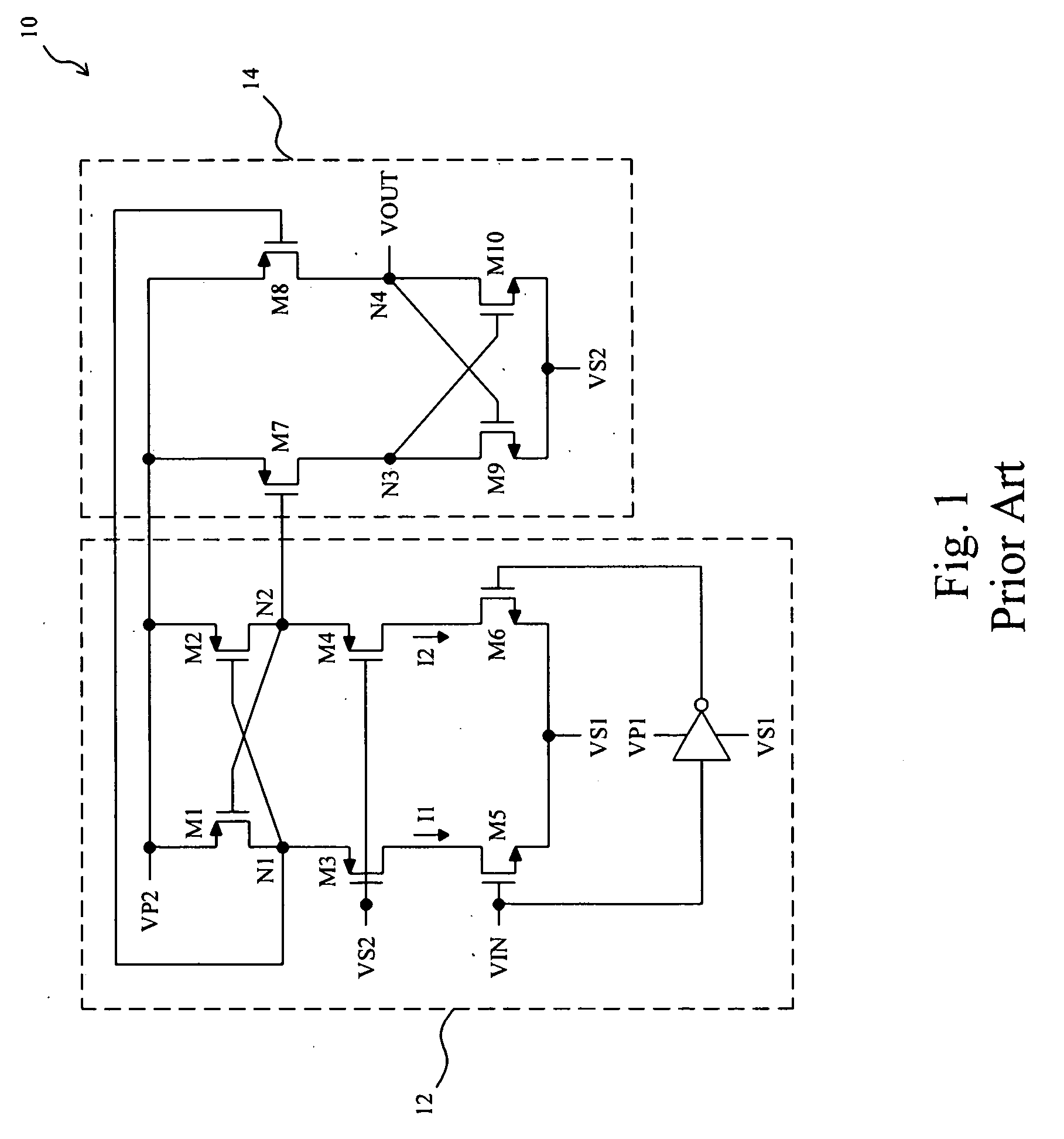

Level shift circuit

ActiveUS20090066399A1Fast processReduce layoutPulse automatic controlElectric pulse generatorLevel shiftingStable status

A level shift circuit includes an input stage and an output stage coupled to each other by two nodes. The input stage changes the voltages on the nodes according to an input signal, and the output stage determines an output signal according to the voltages on the two nodes. In a transition state, the input stage provides a large current to charge or discharge the first node or the second node so as to quickly change the voltage thereon. In a steady state, the input stage lowers the current so as to reduce power consumption.

Owner:RICHTEK TECH

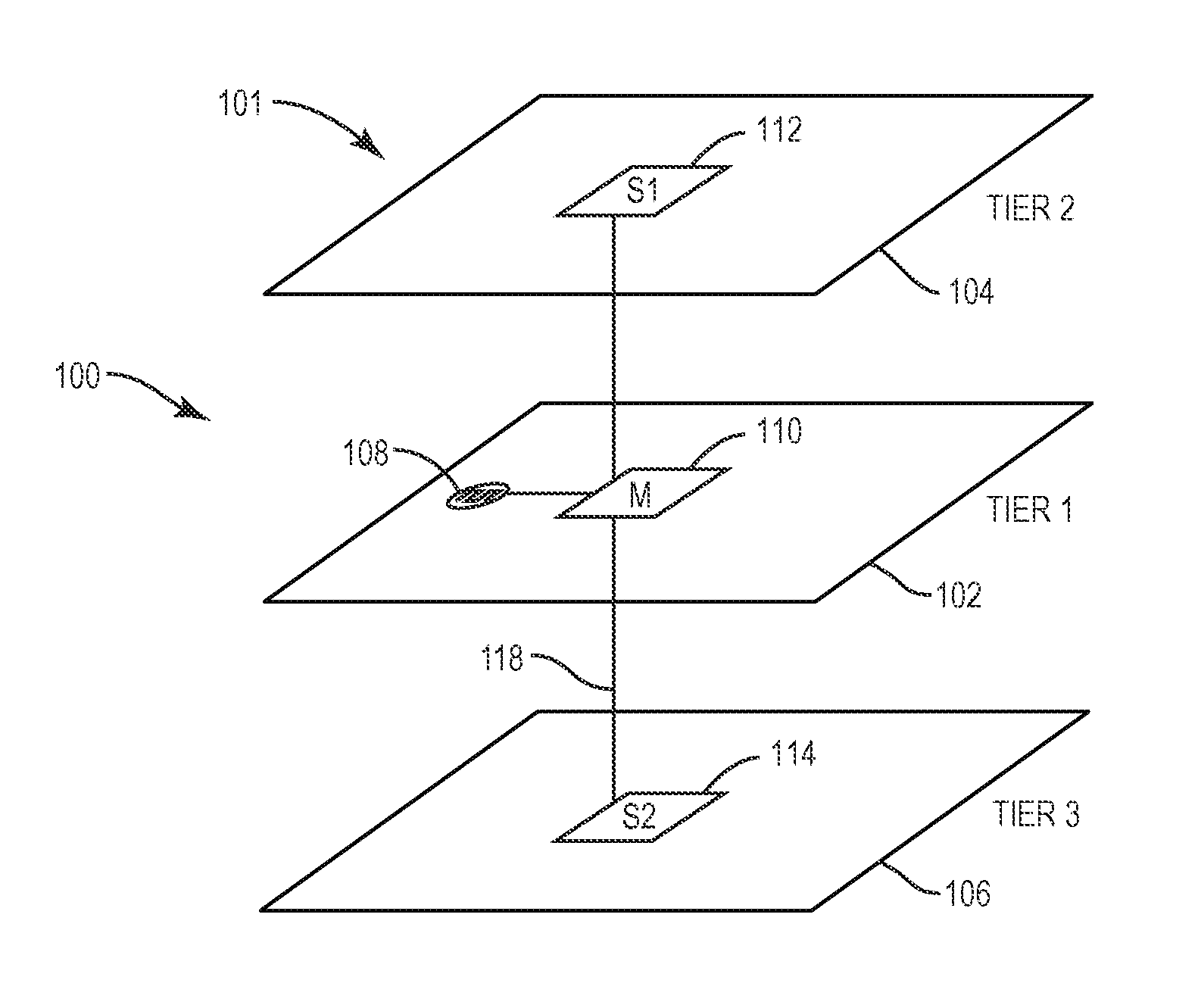

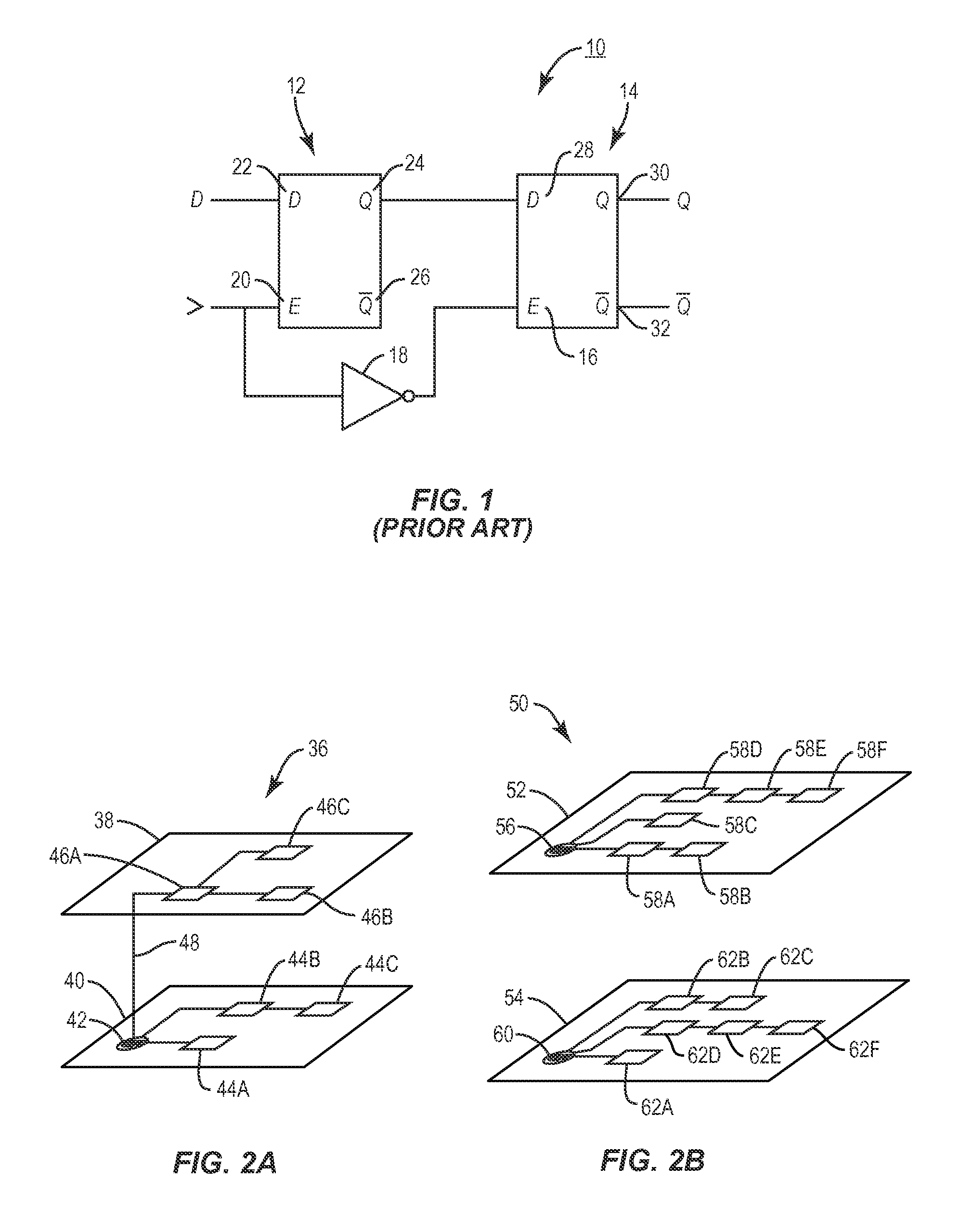

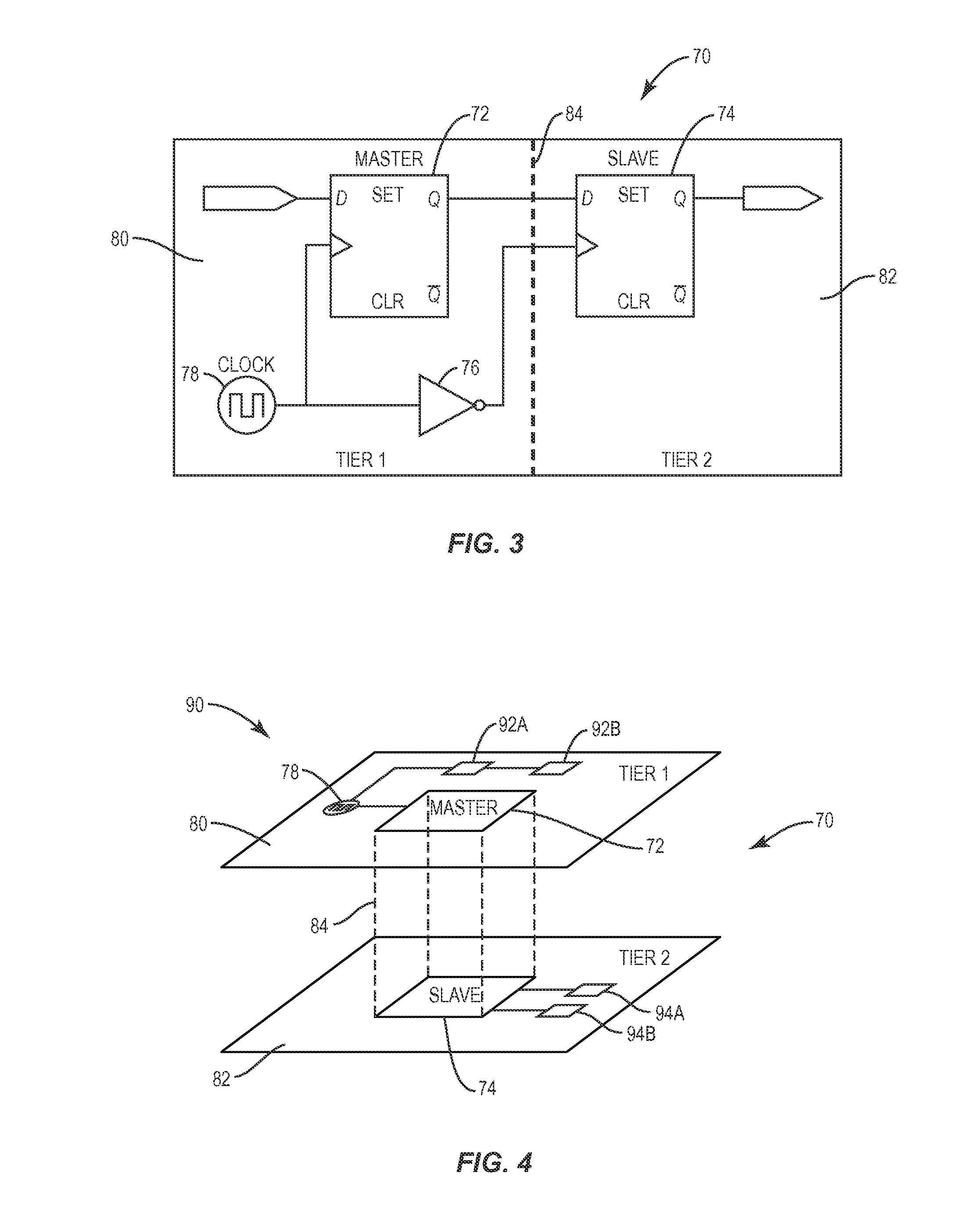

Flip-flops in a monolithic three-dimensional (3D) integrated circuit (IC) (3DIC) and related methods

ActiveUS20140253196A1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringIntegrated circuit

Owner:QUALCOMM INC

Semiconductor integrated device

InactiveUS20090224817A1Pulse automatic controlElectric pulse generatorSemiconductorIntegrated devices

According to an aspect of the present invention, there is provided a semiconductor integrated device including: a level-shifting circuit including: a first and a second input nodes; and a first and a second output nodes; a first current mirror circuit connected with the first output node; a second current mirror circuit connected with the second output node; a first switch circuit series-connected with an input-side of first current mirror circuit; a second switch circuit series-connected with an input-side of the second current mirror circuit; a fifth switching element parallel-connected with the input-side of the first current mirror circuit; and a sixths switching element parallel-connected with the input-side of the second current mirror circuit.

Owner:KK TOSHIBA

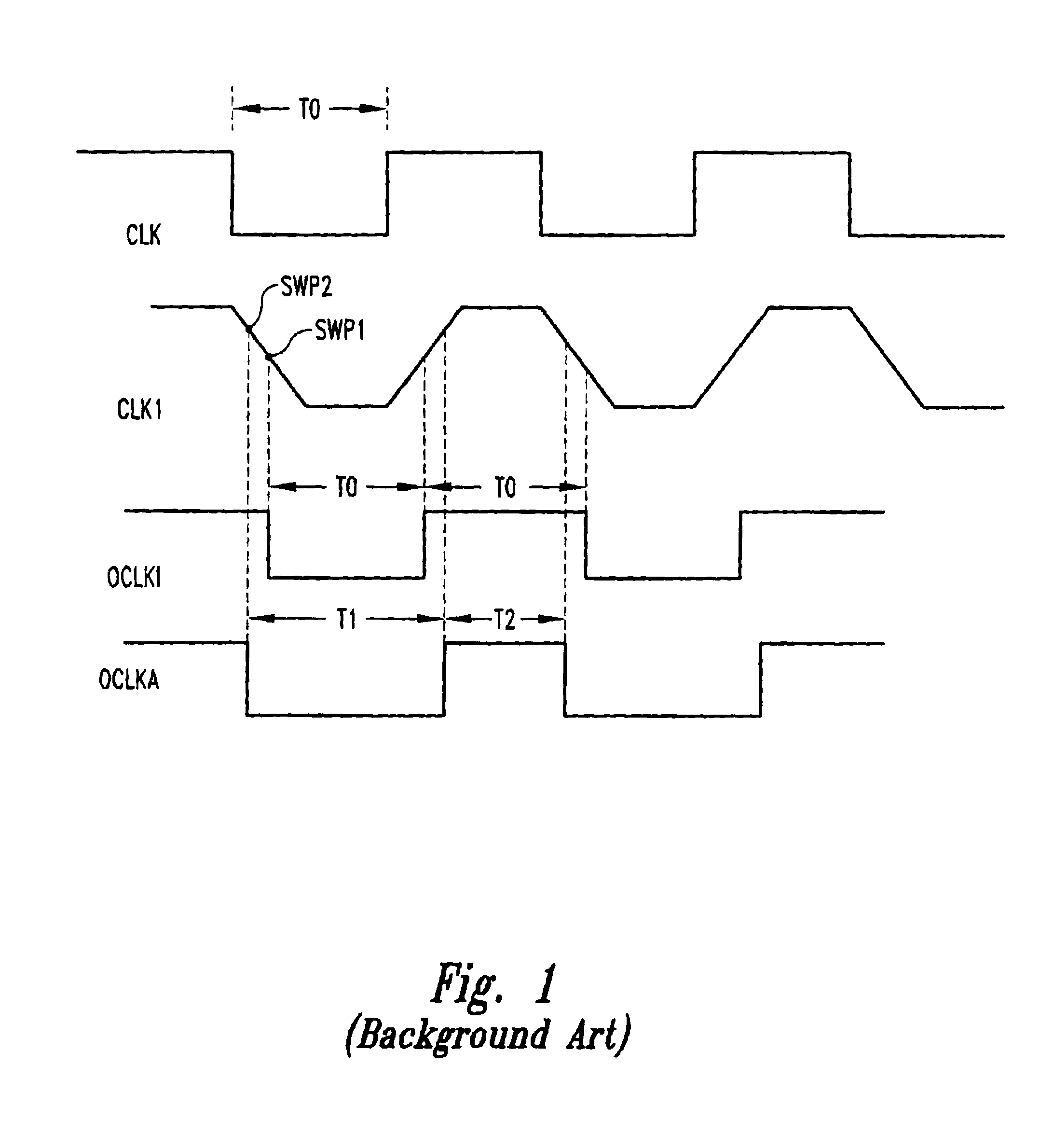

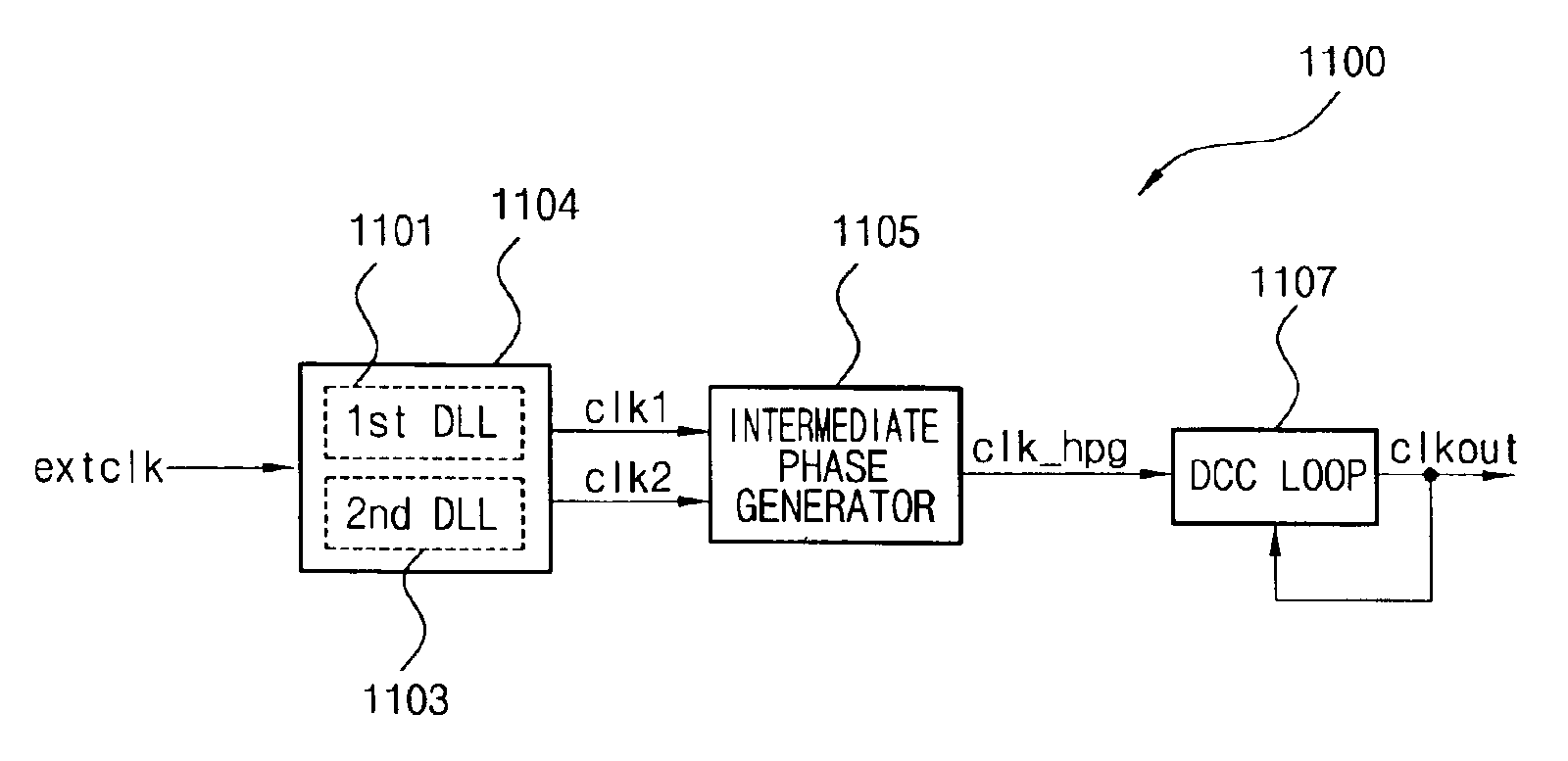

Delay locked loop circuit with duty cycle correction function

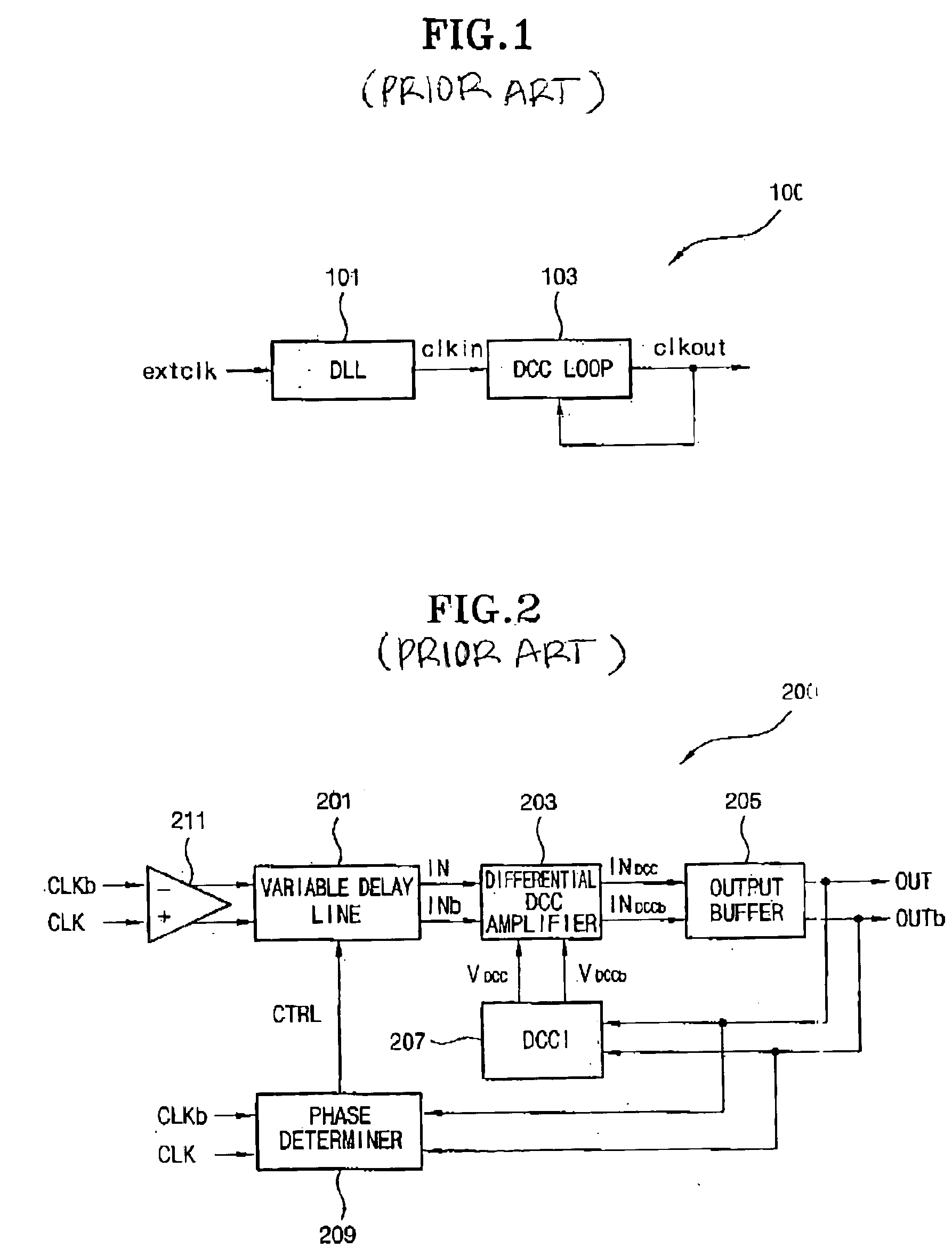

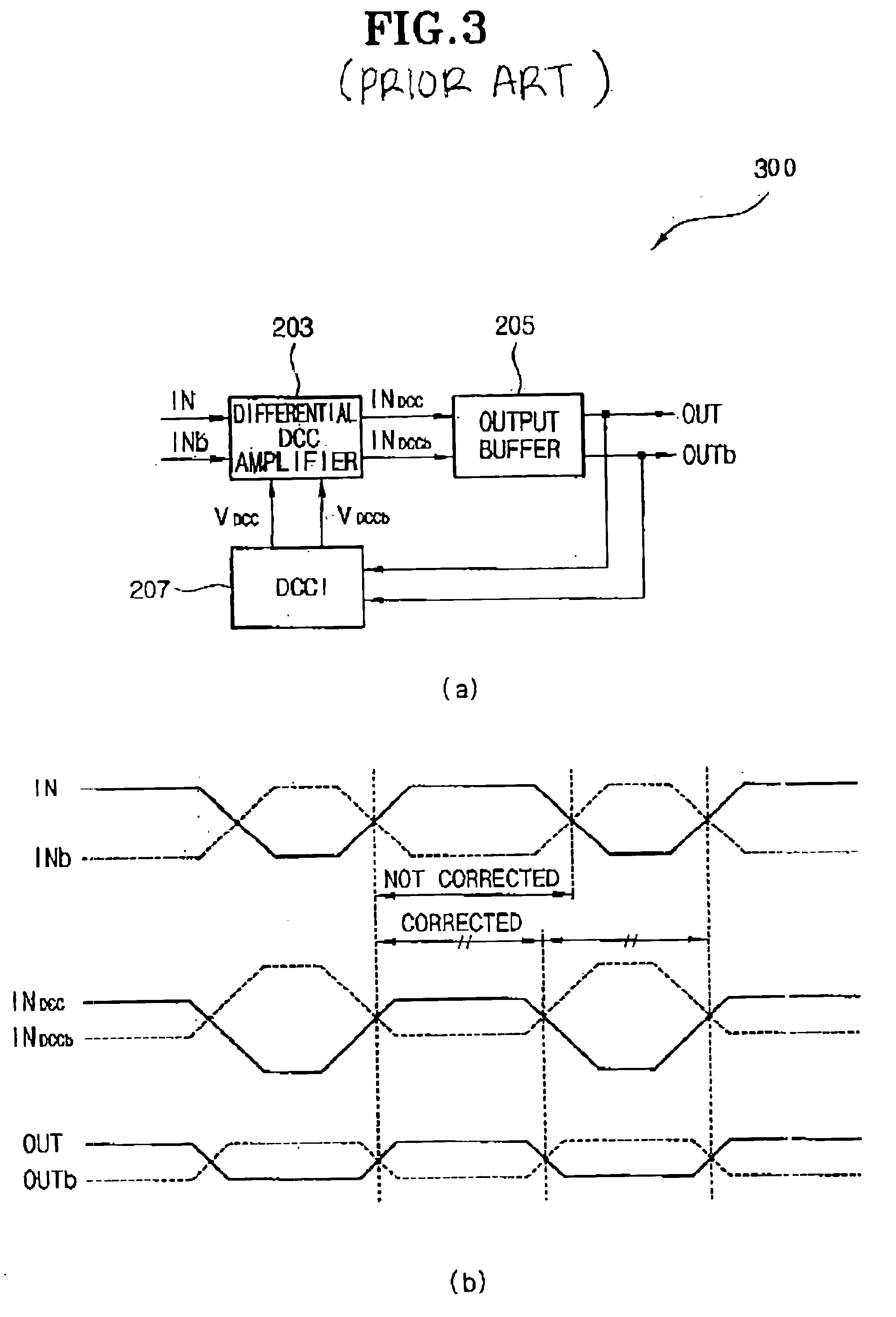

InactiveUS6853225B2Improve accuracyShort lock timePulse automatic controlContinuous to patterned pulse manipulationNegative feedbackDelay-locked loop

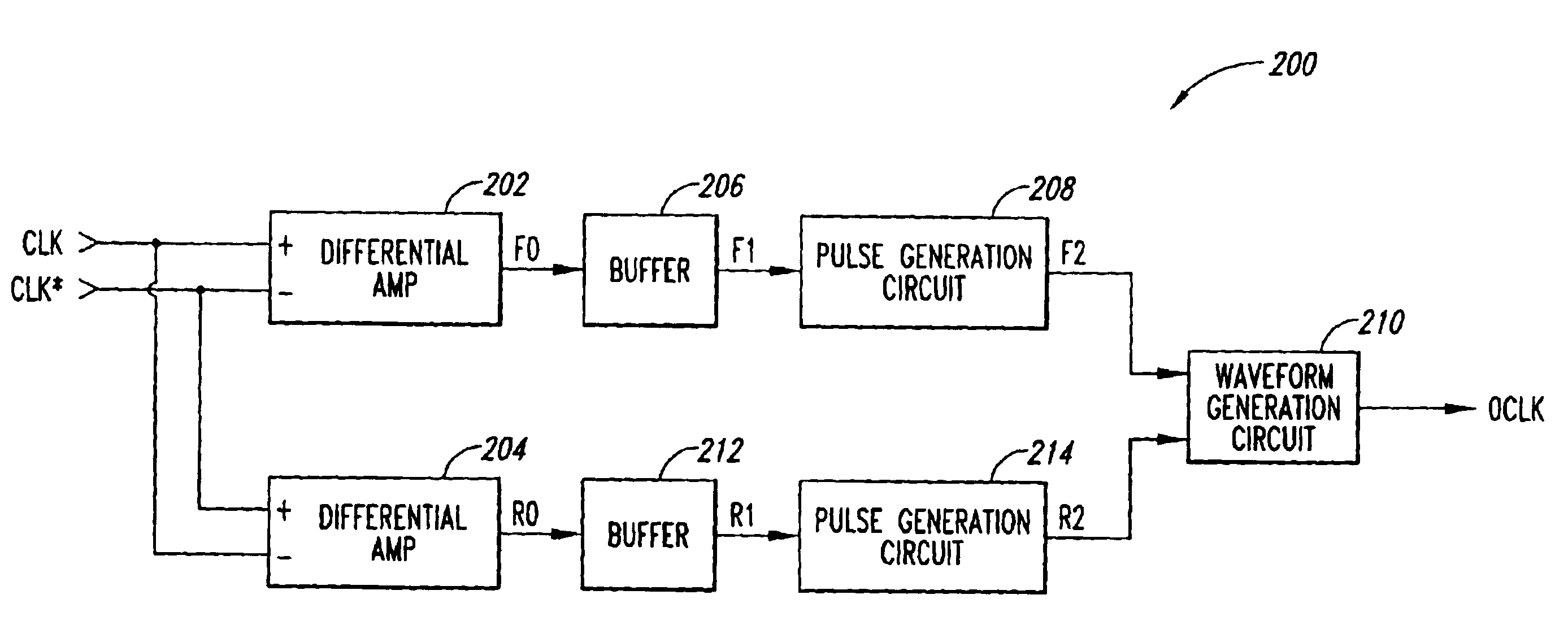

A delay locked loop (DLL) circuit having a structure in which a method of performing duty cycle correction (DCC) using two DLLs and an intermediate phase composer and a method of performing DCC by forming a closed loop using a negative feedback are combined with each other is provided. The DLL circuit includes a first DLL for receiving an external clock signal and generating a first clock signal and a second DLL for receiving an external clock signal and generating a second clock signal. The first clock signal and the second clock signal are synchronized with an external clock signal. The DLL circuit further includes an intermediate phase generation circuit for receiving the first and second clock signals and generating an intermediate phase clock signal and a DCC loop for receiving the intermediate phase clock signal and generating an output clock signal. The intermediate phase clock signal has an intermediate phase between the phases of the first and second clock signals. The output clock signal is generated through correction of the duty cycle of the intermediate phase clock signal using a value obtained by integrating the output clock signal.

Owner:SK HYNIX INC