Patents

Literature

258 results about "Early phase" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Lithium ion battery thermal runaway early warning system and early warning method

ActiveCN109786872AImprove timelinessEasy to implementSecondary cells servicing/maintenanceUltrasonic sensorThermal safety

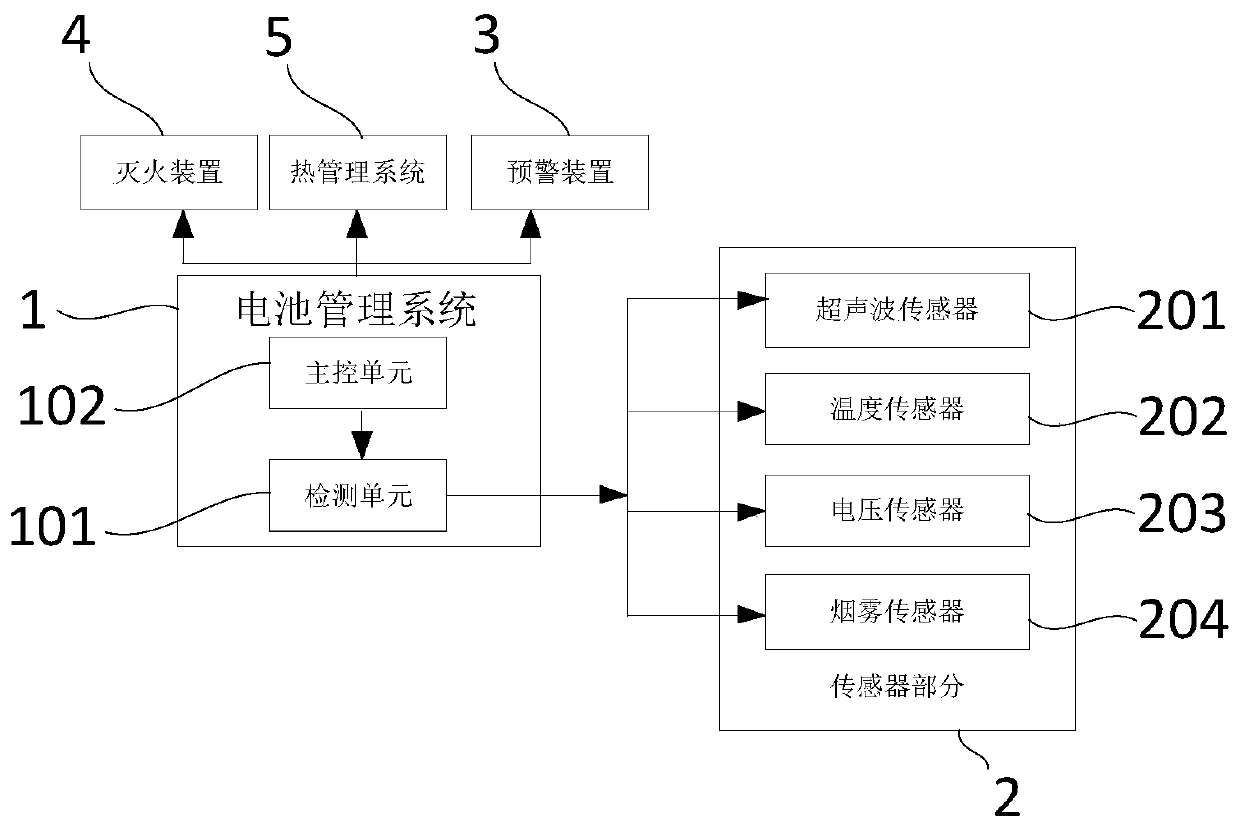

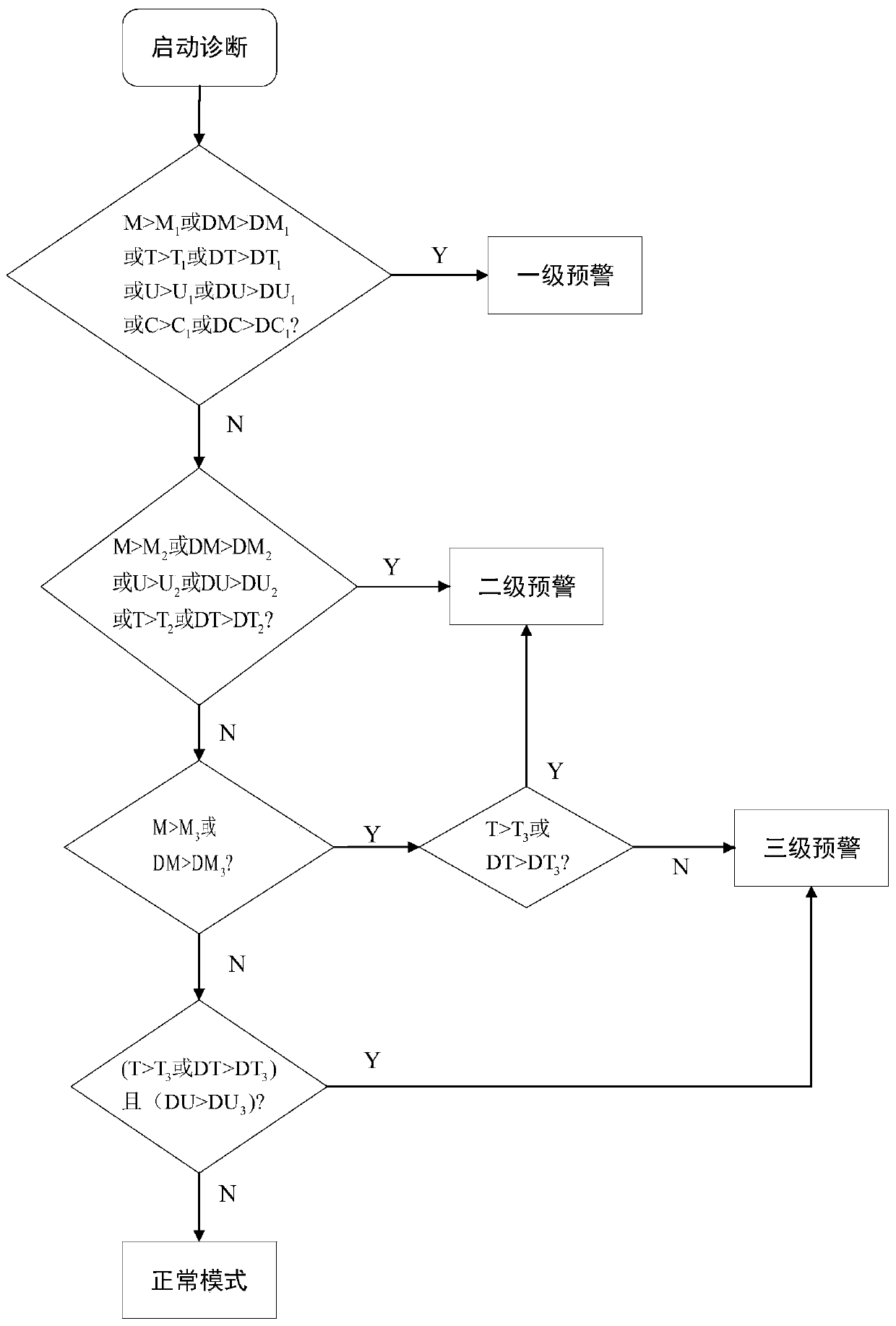

The invention designs a lithium ion battery thermal runaway early warning system and an early warning method. The early warning system comprises various sensors, a battery management system, a warningdevice and an automatic emergency fire extinguishing device. The sensors comprise an ultrasonic sensor, a temperature sensor, a voltage sensor and a smoke sensor. The ultrasonic sensor can reflect abattery internal gas state characteristic, so prejudgment and diagnosis are carried out on battery thermal safety in a thermal runaway risk emerging early phase timely and early warning is rapid and efficient. The battery management system carries out data analysis based on various sensor combined detection, compares a plurality of parameters with set thresholds, sends out different levels of early warning signals and takes different control policies. A safety accident risk resulting from thermal runaway is reduced, and personnel injury is reduced.

Owner:BEIHANG UNIV

Intelligent tunnel safety monitoring apparatus based on omnibearing computer vision

InactiveCN1852428ACarry out the function of monitoringLow maintenanceImage analysisClosed circuit television systemsDisplay deviceVision sensor

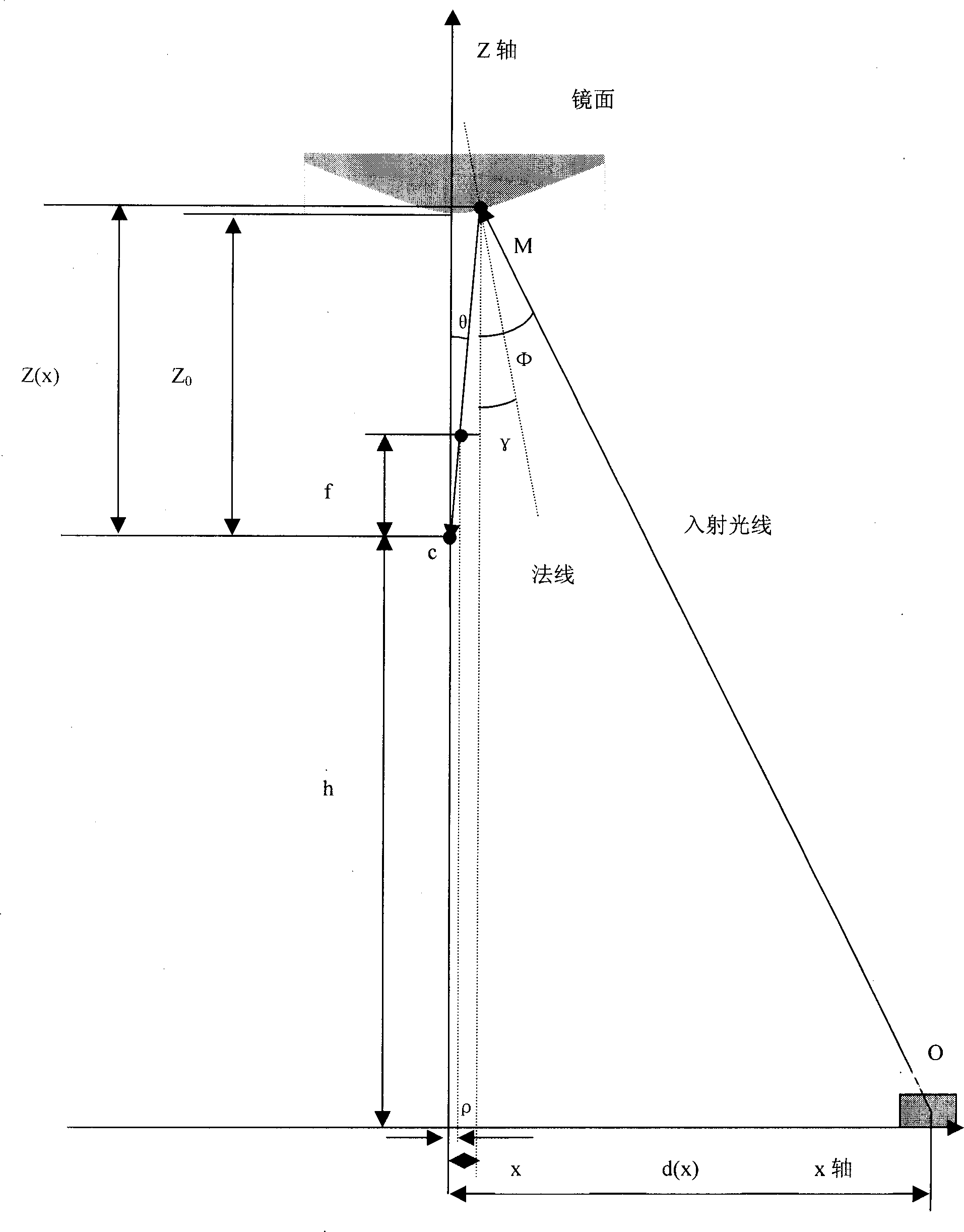

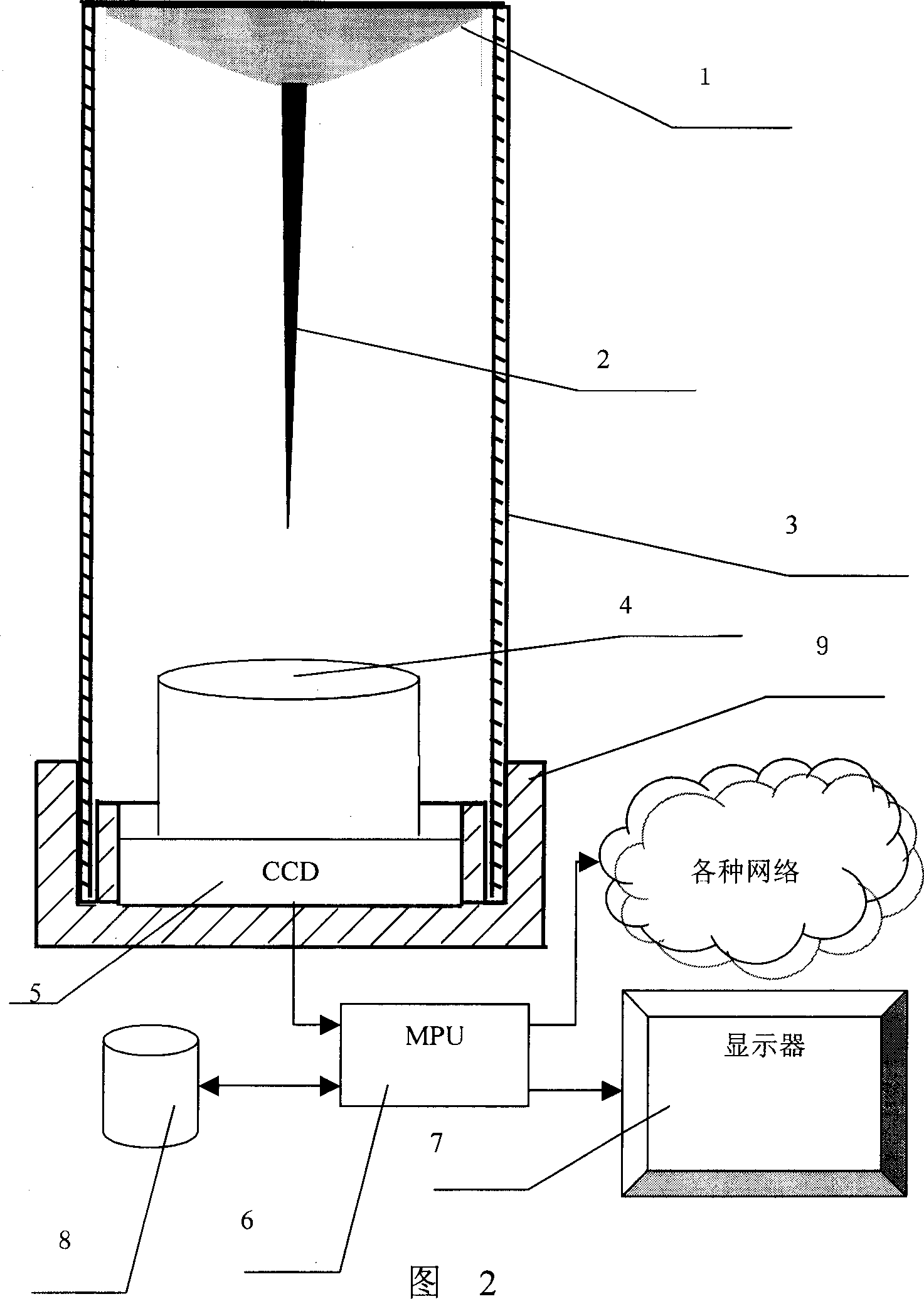

The monitoring equipment includes microprocessor, video sensor in use for monitoring site of tunnel, and communication module for communication outside. Microproceesor includes following modules: reading module for image dada in use for reading information of video image transferred from video sensor; file storage module in use for storing data collected by video sensor to storage device; real time playing module on site connected to external display device is in use for playing monitored image on site in real time. Output of the video sensor is connected to microprocessor through communication. Using all directional computer vision sensor monitors tunnel site, processes and analyzes images. Using detected variation character for fire flame in early phase, the invention finds early fire in tunnel as well as obtains traffic data including vehicle flowrate, and occupancy ratio, speed, and traffic accident etc.

Owner:ZHEJIANG UNIV OF TECH

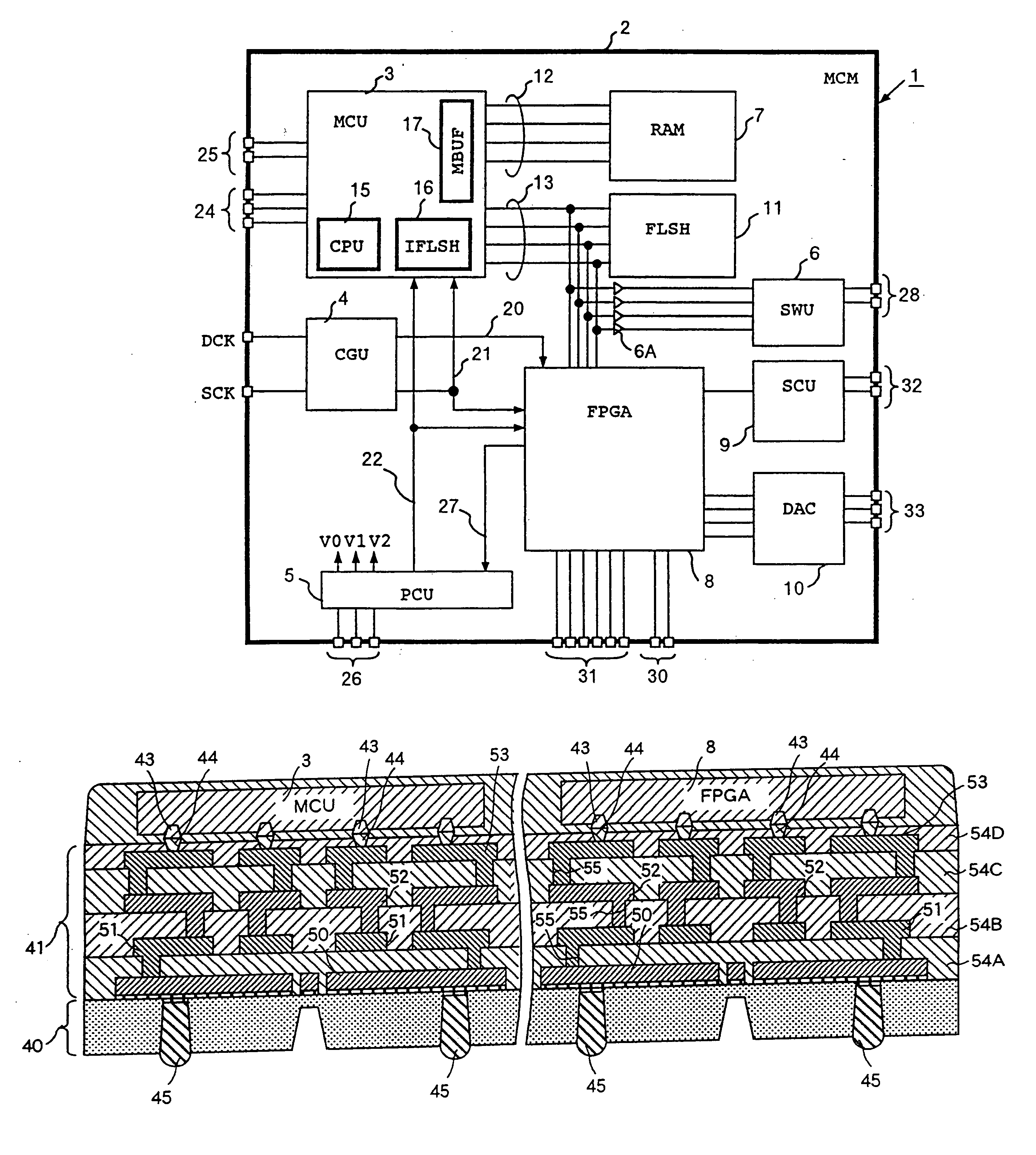

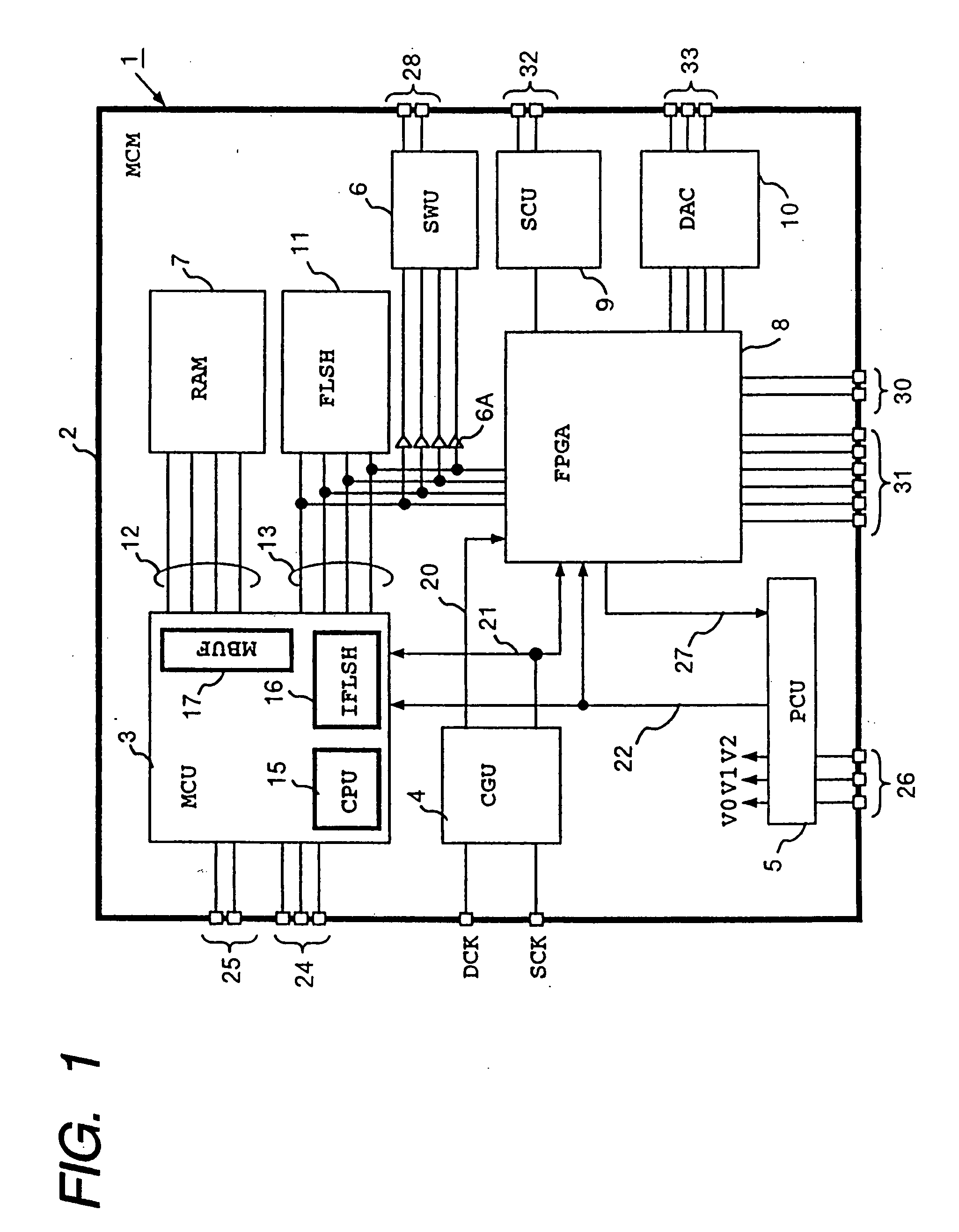

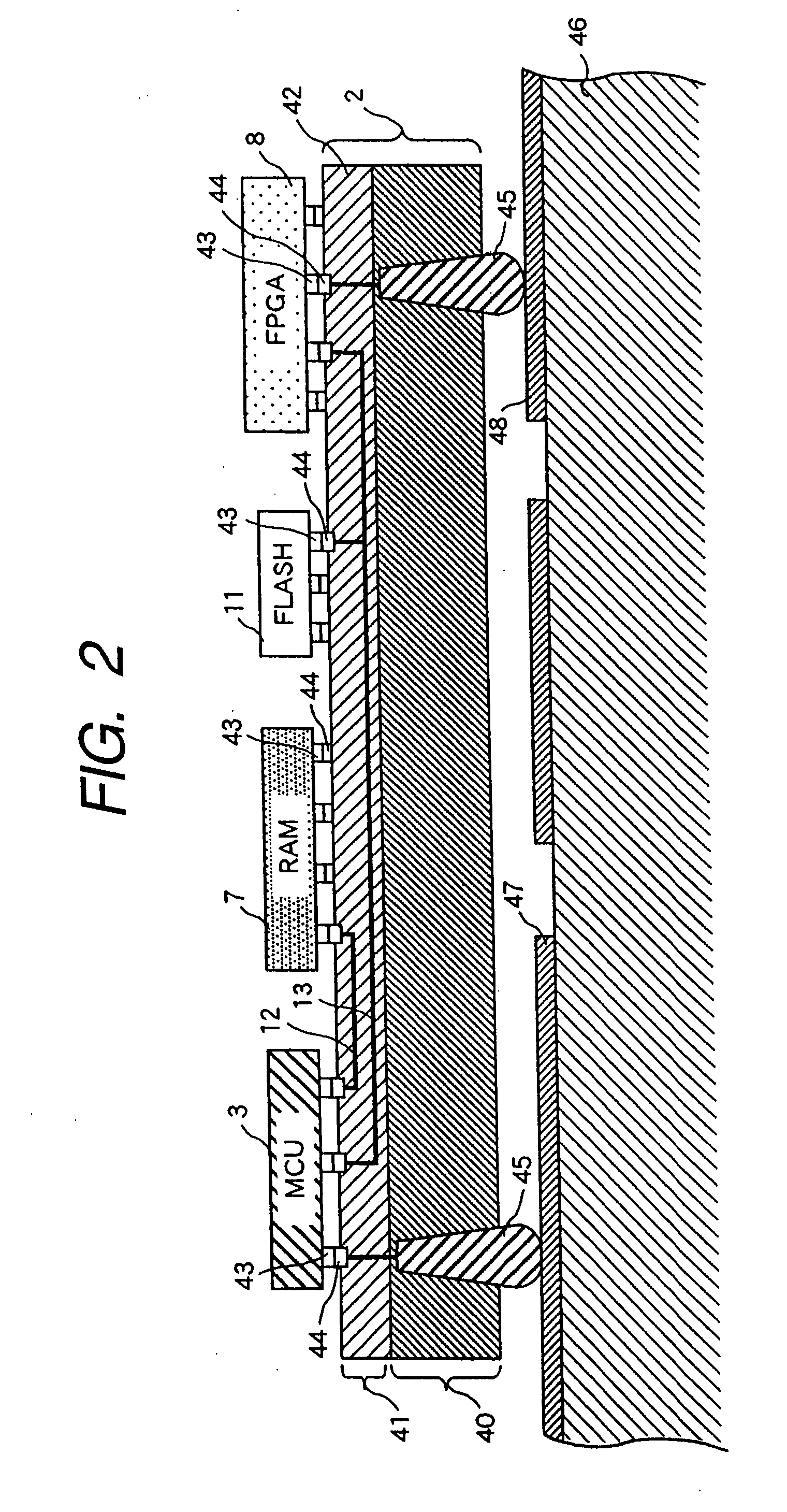

Electronic circuit device

InactiveUS7091598B2Easy to debugLow costError detection/correctionSemiconductor/solid-state device detailsStatic random-access memoryBase function

An electronic circuit device has a high-density mount board, on which are disposed a microcomputer, a random access memory, a programmable device which is a variable logic circuit represented by FPGA, and an electrically-rewritable nonvolatile memory which can store the operation program of the microcomputer. The high-density mount board has external mounting pins on the bottom surface so as to be mounted on a mother board in the same manner as a system on-chip multi-chip module. With an intended logic function being set on the programmable device, a hardware-based function to be realized by the electronic circuit device is simulated. With an operation program being written to the nonvolatile memory, a software-based function to be realized is simulated. Consequently, the device facilitates the debugging at early stages of system development, configures a prototype system, and contributes to the time reduction throughout the system development, prototype fabrication and large-scale production.

Owner:RENESAS TECH CORP

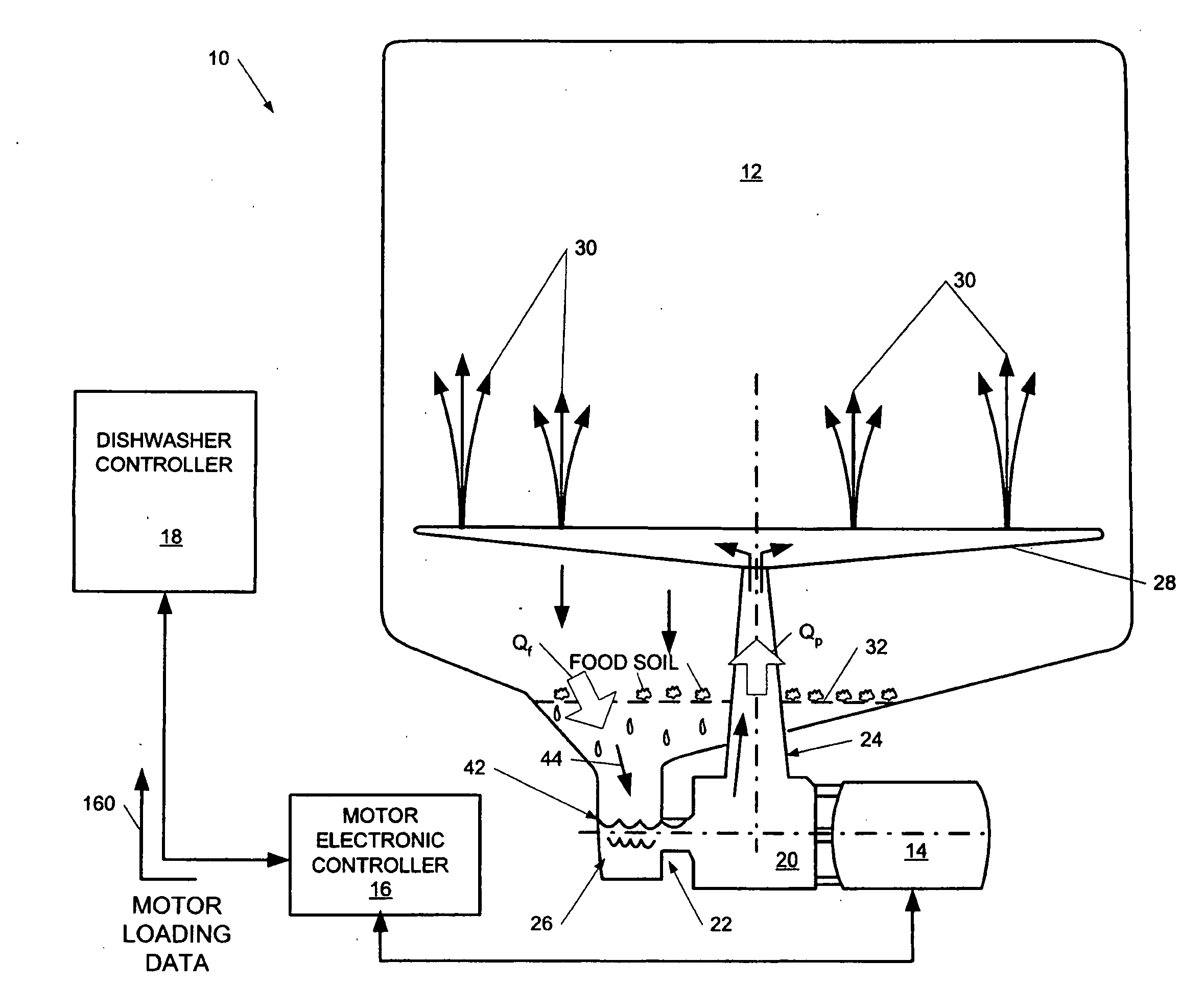

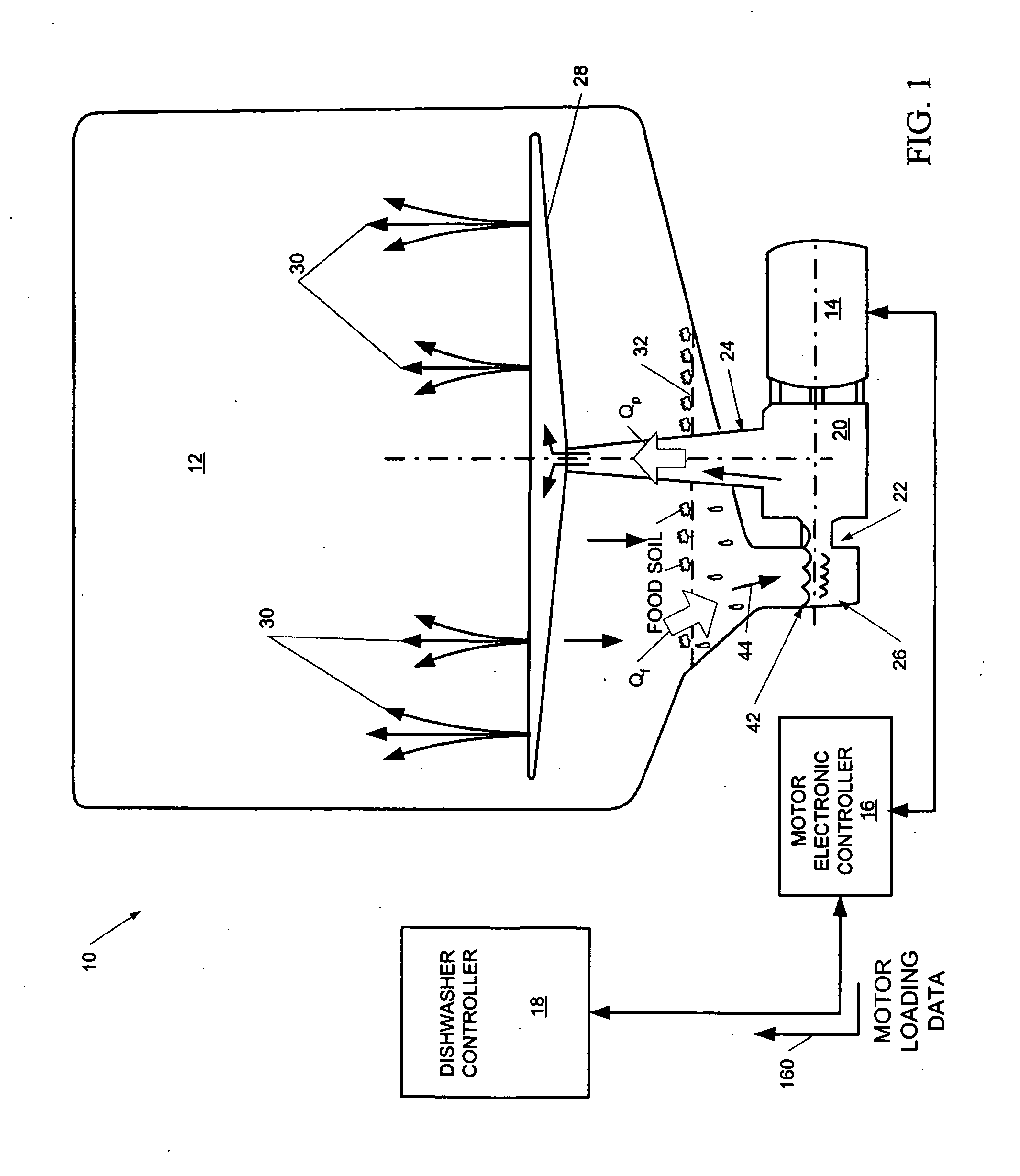

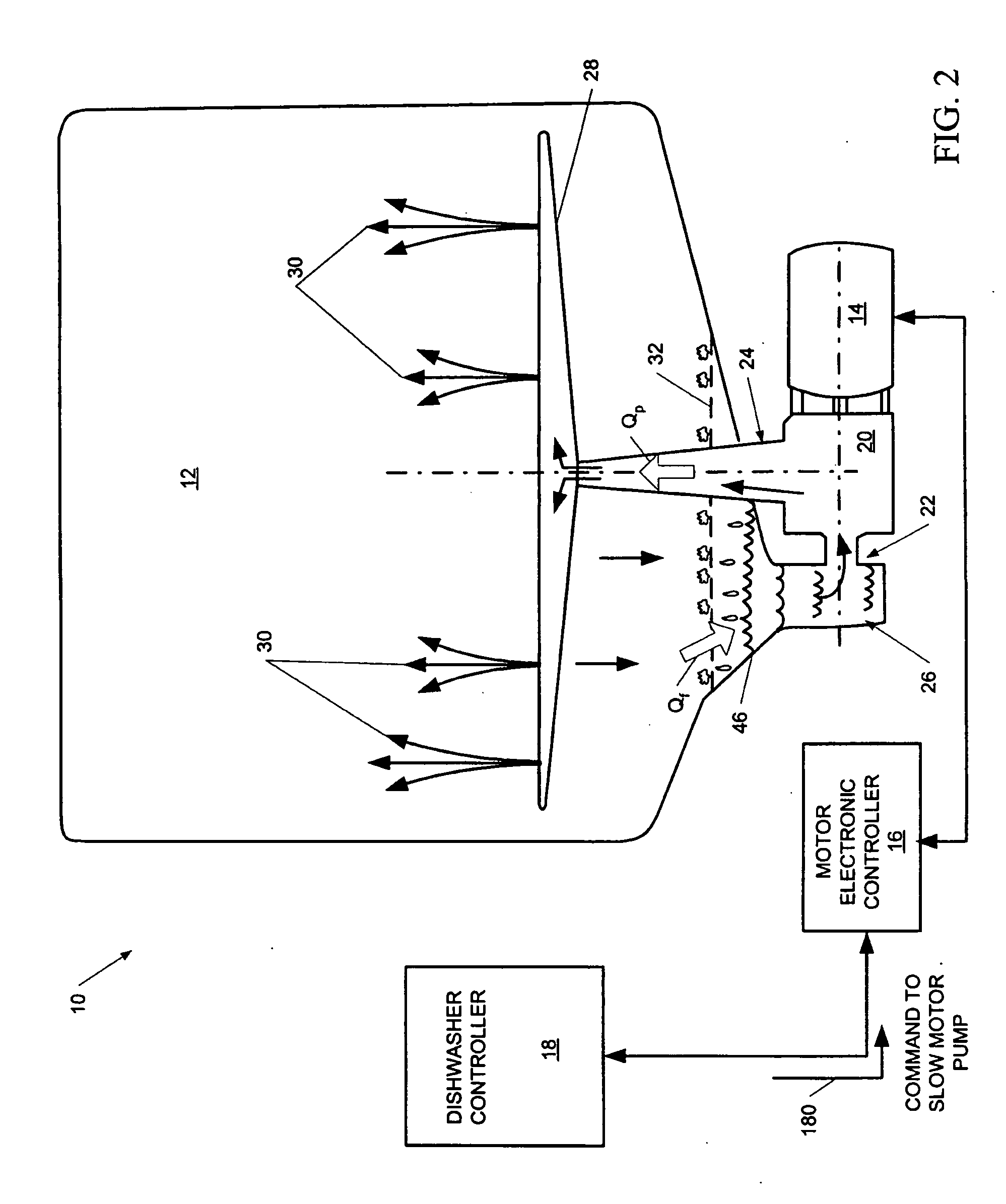

Dishwasher with controlled induction motor/pump

InactiveUS20060237044A1Easy to coverEasy to cleanAC motor controlAutomatic washing/rinsing machine detectionMotor speedMotor controller

A dishwasher having a speed-controlled induction motor coupled to a pump to drive the pump during dishwasher operation. A motor controller is connected to the induction motor to control the speed of operation of the induction motor. A dishwasher controller is connected to the motor controller for sending signals to, and receiving signals from, the motor controller during operation to control the motor speed. The flow rate of water through the pump discharge to a spray arm is controlled based on the phase of the wash cycle and the condition of the filter that blocks food debris from entering the sump. The motor speed is decreased to decrease the pump flow rate when the flow rate through the filter decreases in an early phase of the wash cycle. The motor speed is increased to increase the pump flow rate during later phases of the wash cycle. In steady state operation, the flow rate through the filter is matched to the flow rate through the pump discharge.

Owner:VIKING RANGE

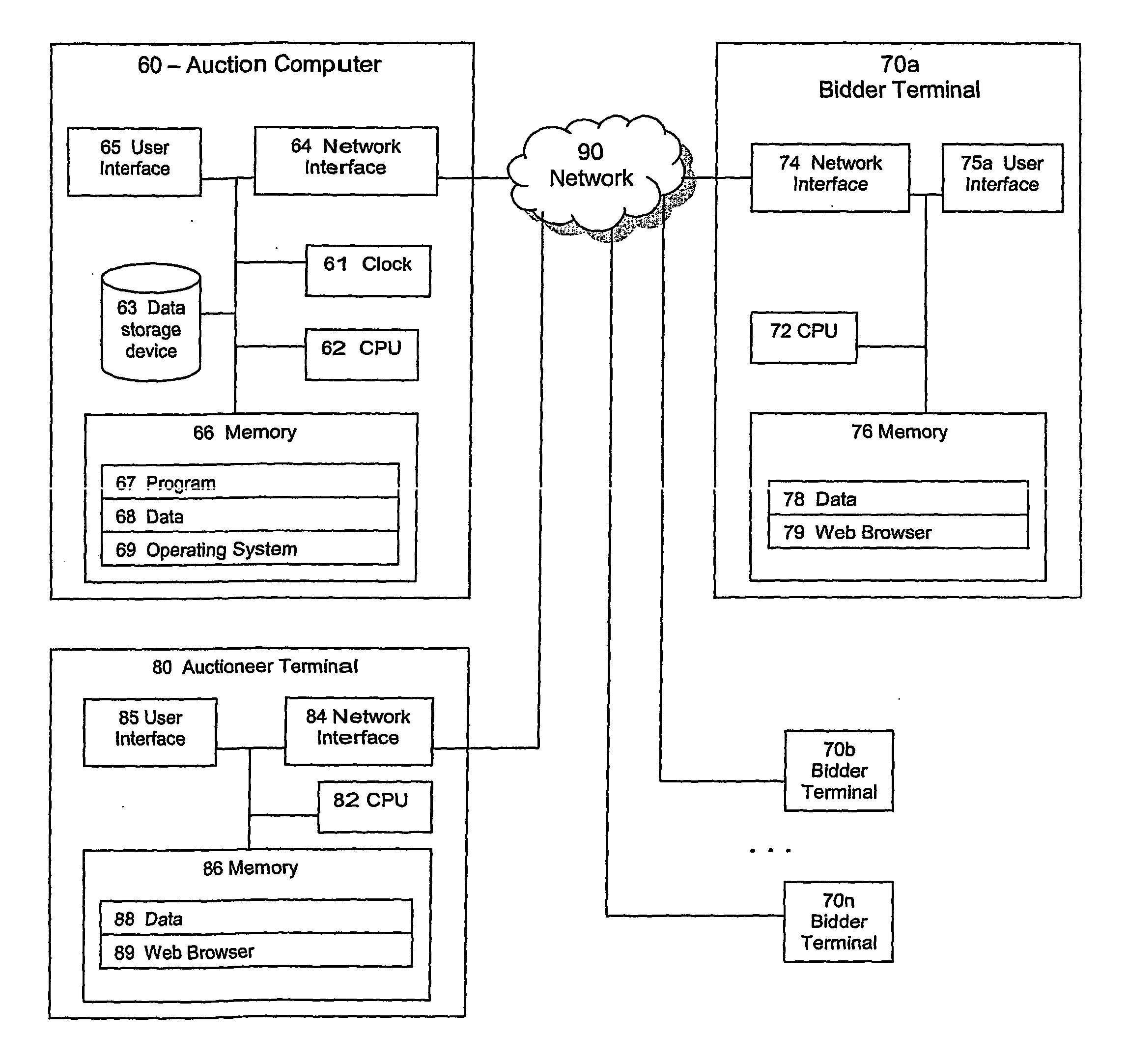

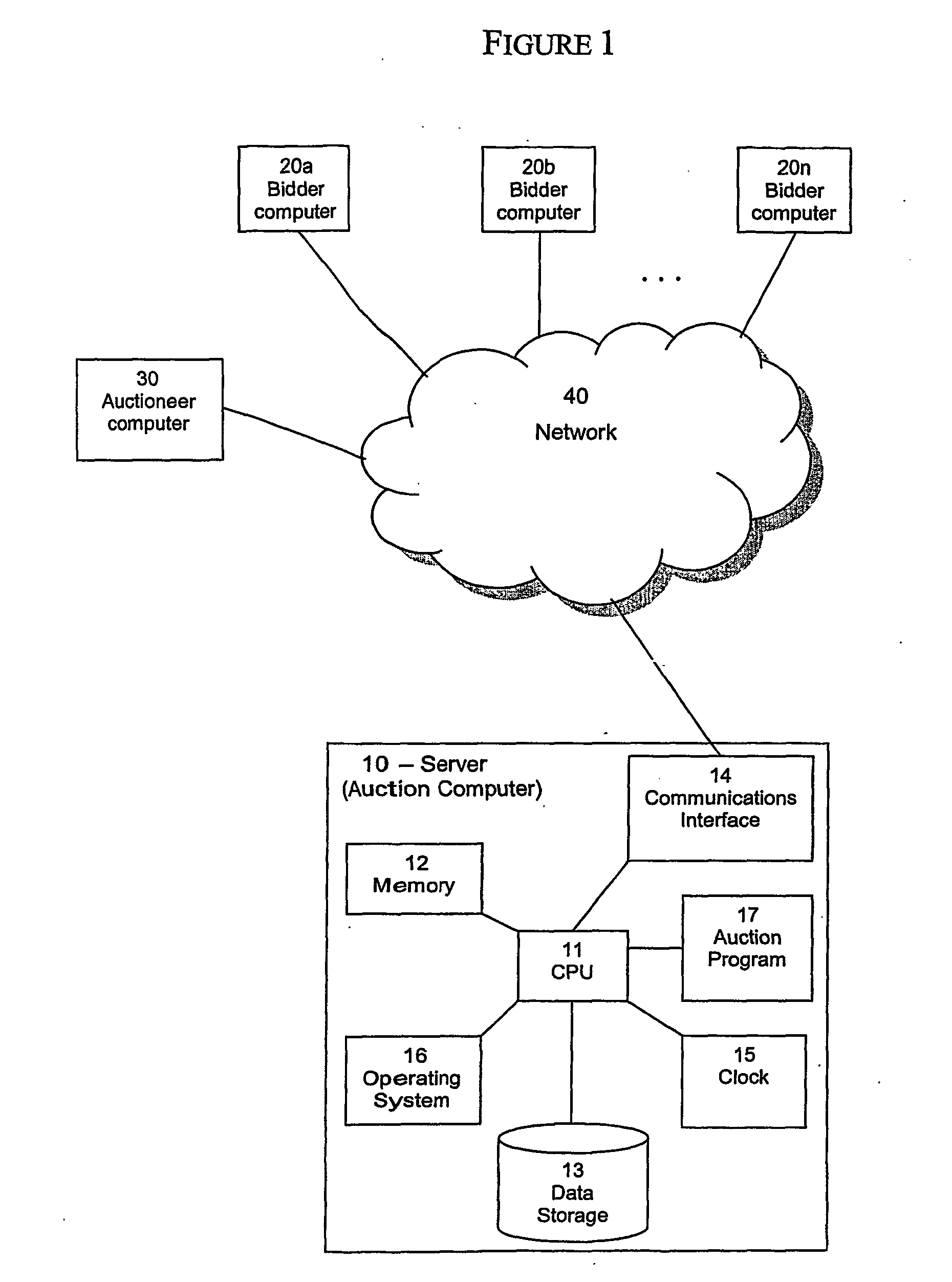

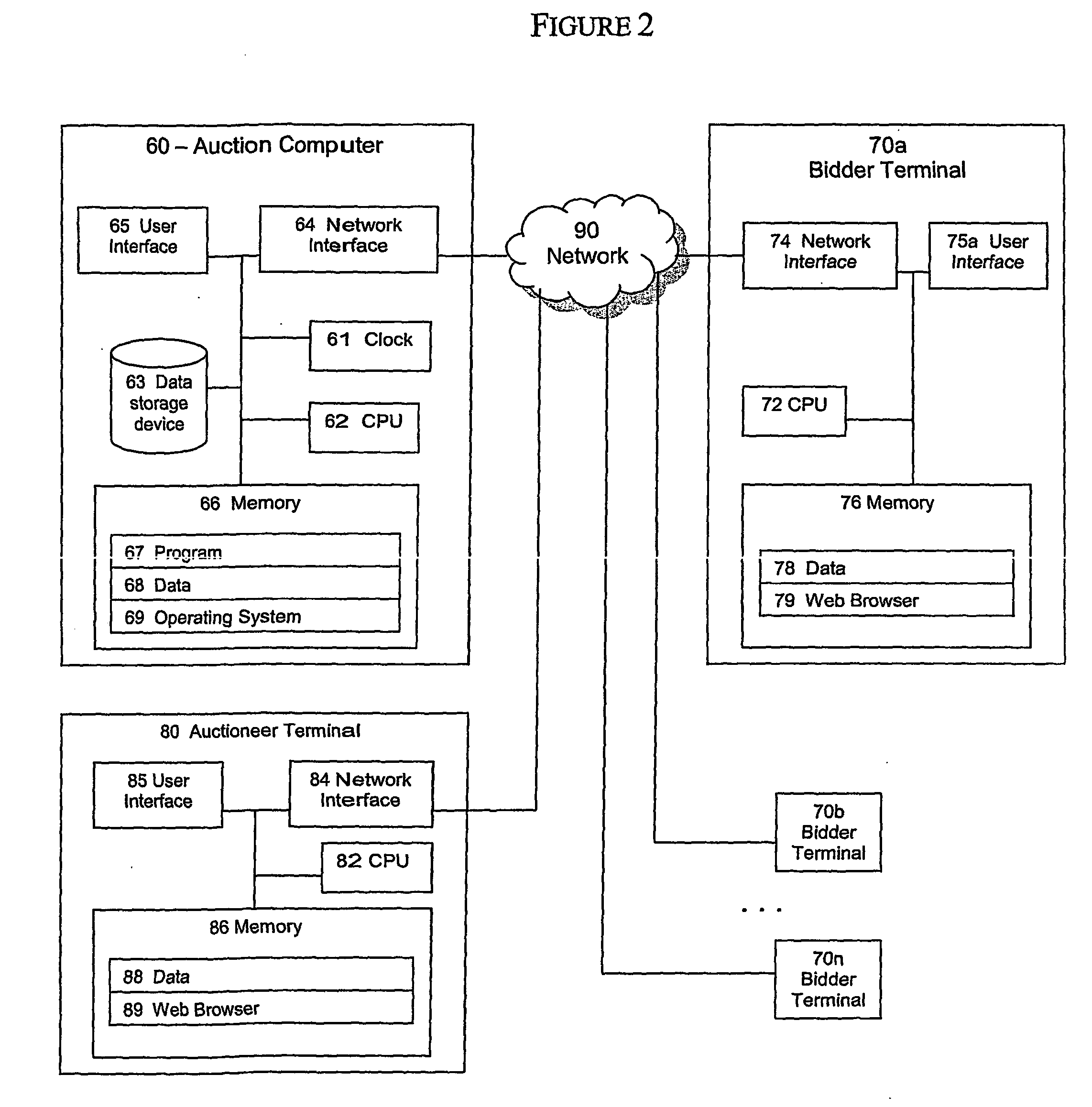

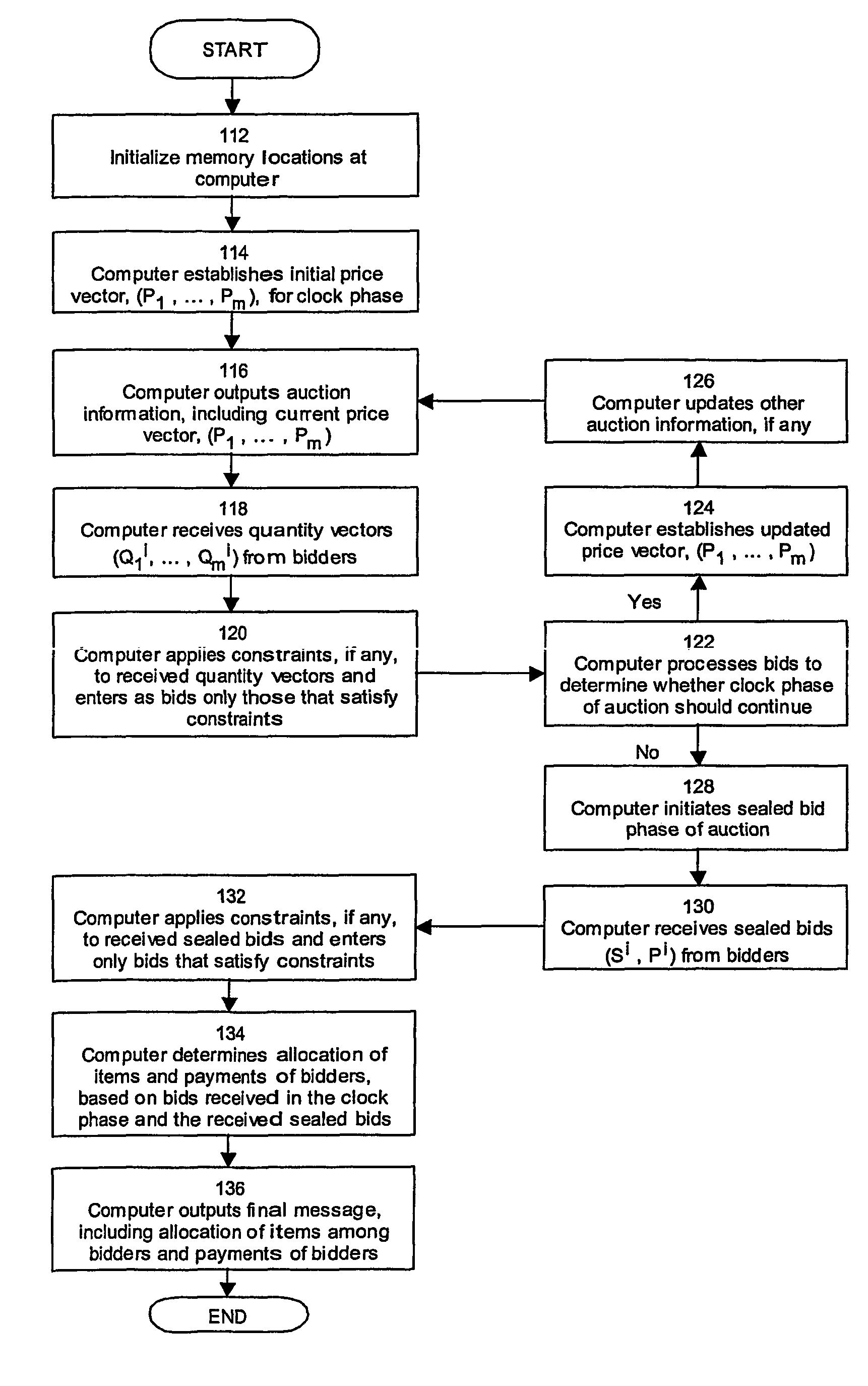

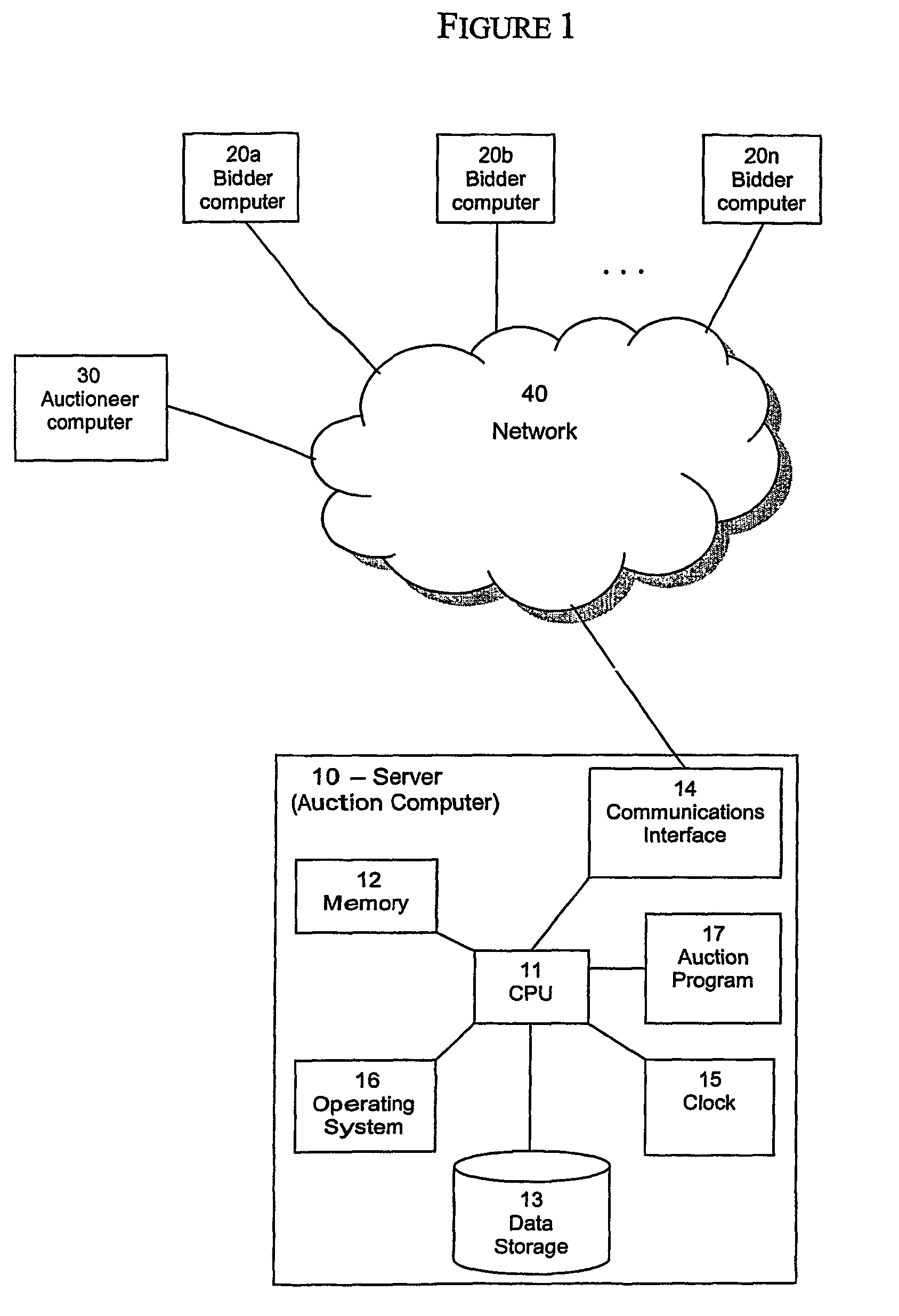

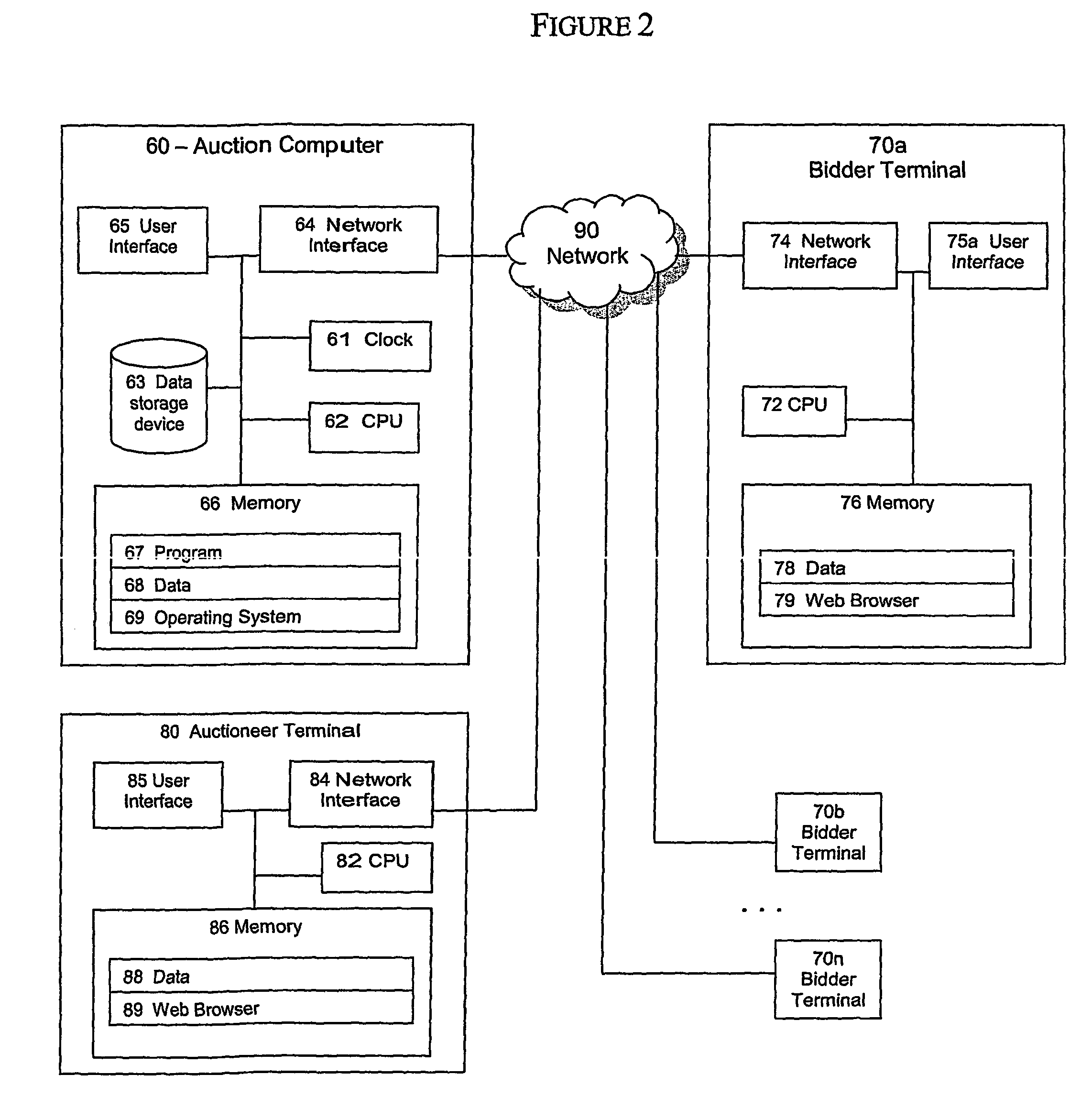

System and method for a hybrid clock and proxy auction

The present invention is a system and method for a computer-implemented auction wherein a hybrid auction combining elements of a clock auction and a proxy auction. In particular, if the earlier phase (104) is a clock auction and the later phase (108) is a proxy auction, then the resulting hybrid auction will combine the transparency and the simplicity of the clock auction with the efficiency outcome and competitive revenues of the proxy auction. The system includes receiving bids (118), determining an outcome (134) and outputting the results (136).

Owner:EFFICIENT AUCTIONS

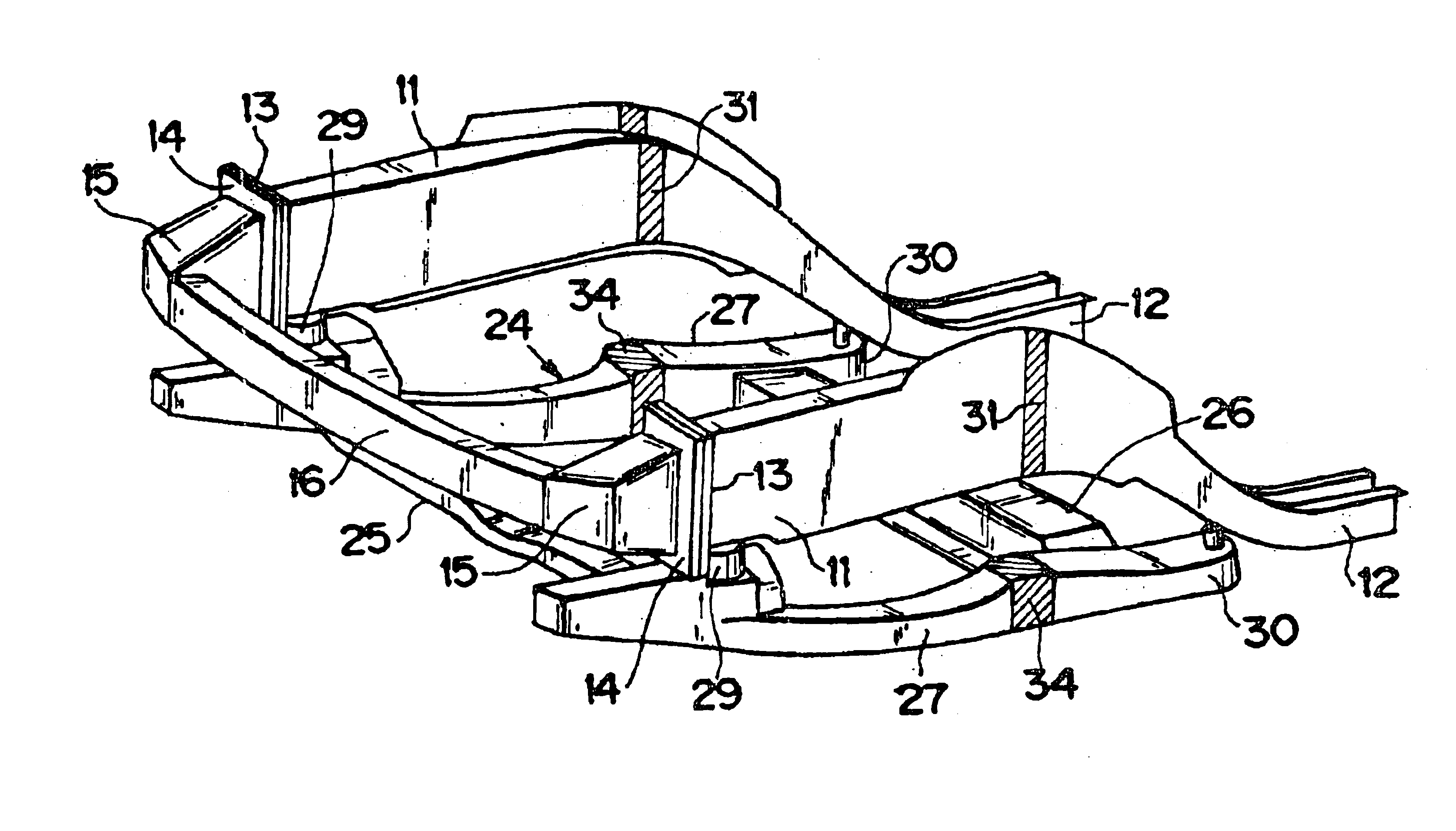

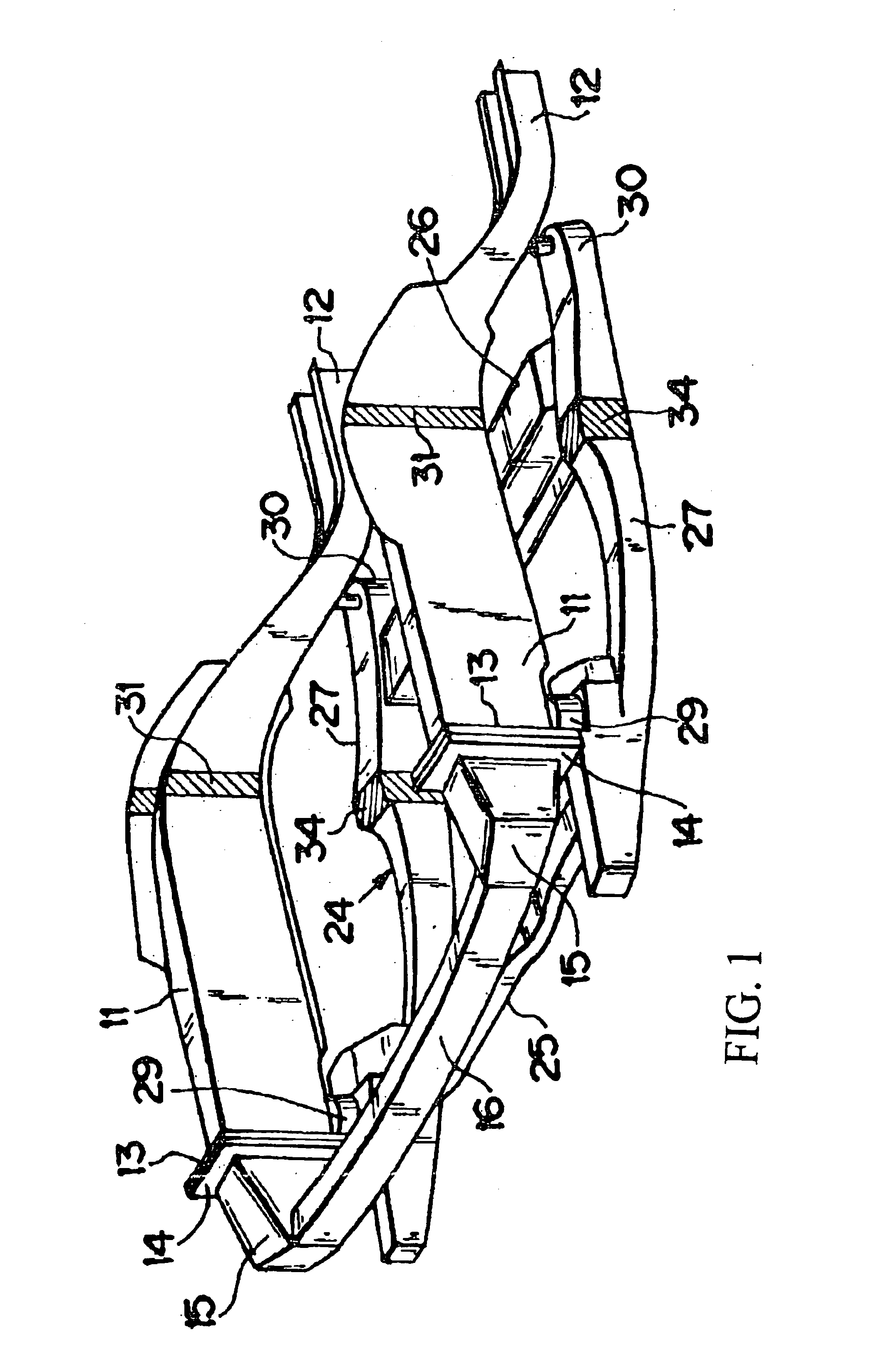

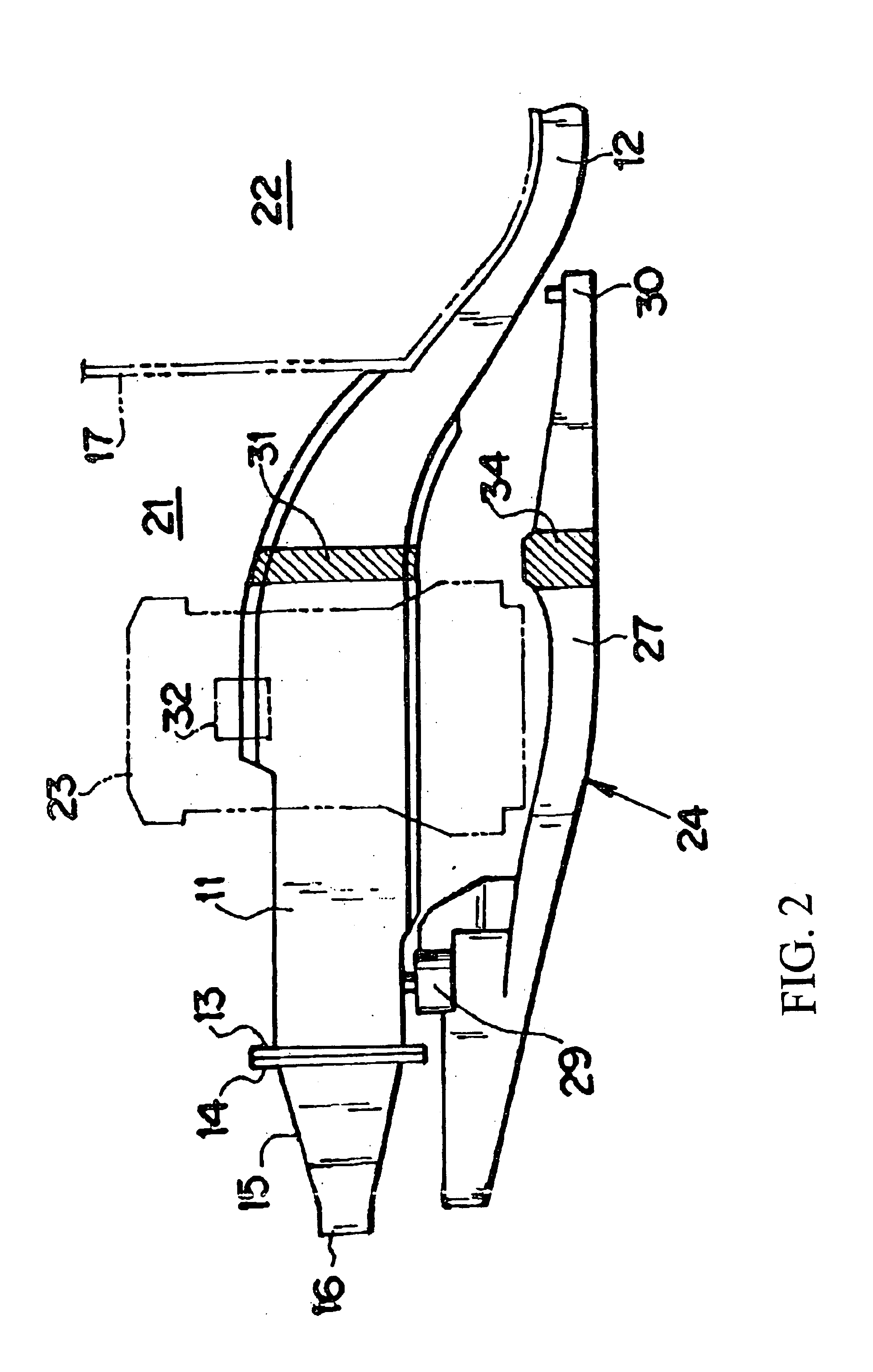

Body frame structure for a vehicle and method for manufacturing thereof

InactiveUS6736448B2Effectively absorb collision energySimple structureVehicle seatsUnderstructuresEngineeringCompressive strength

A pair of left and right front frames are formed with brittle sections on proximal portions of the frames, by the provision of the smaller cross-sectional area than other sections of the frame. The brittle sections and their peripheral sections are processed so as to become approximately equal to the other sections of the front frames in axial compressive strength by way of a hardening treatment like quenching. In an early-phase of a collision, the hardened brittle sections will not buckle so as to induce larger initial load. Thereafter, the brittle sections will buckle because of their lower ductility, so that the front frames begin bending deformation to effectively absorb the collision energy.

Owner:MAZDA MOTOR CORP

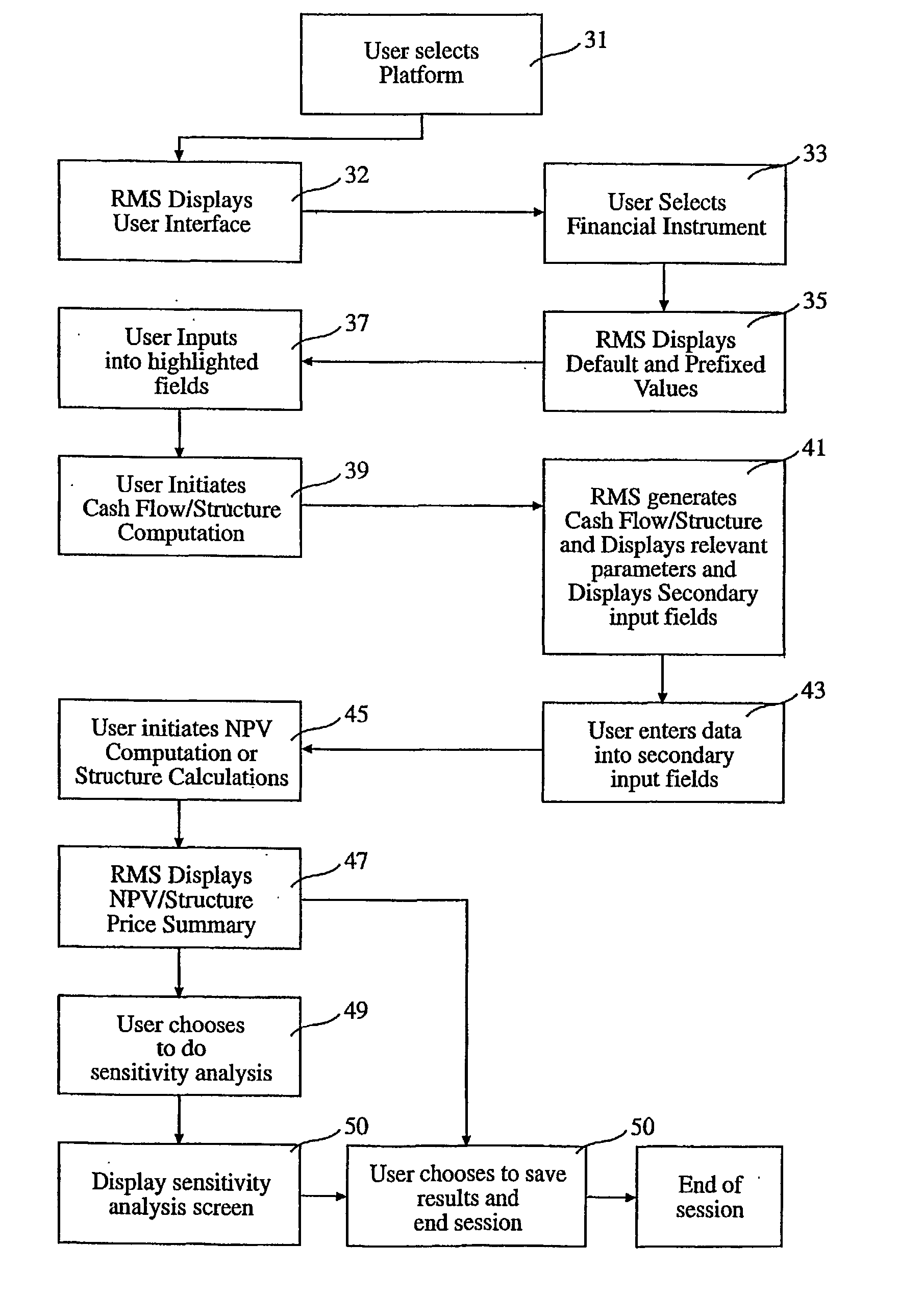

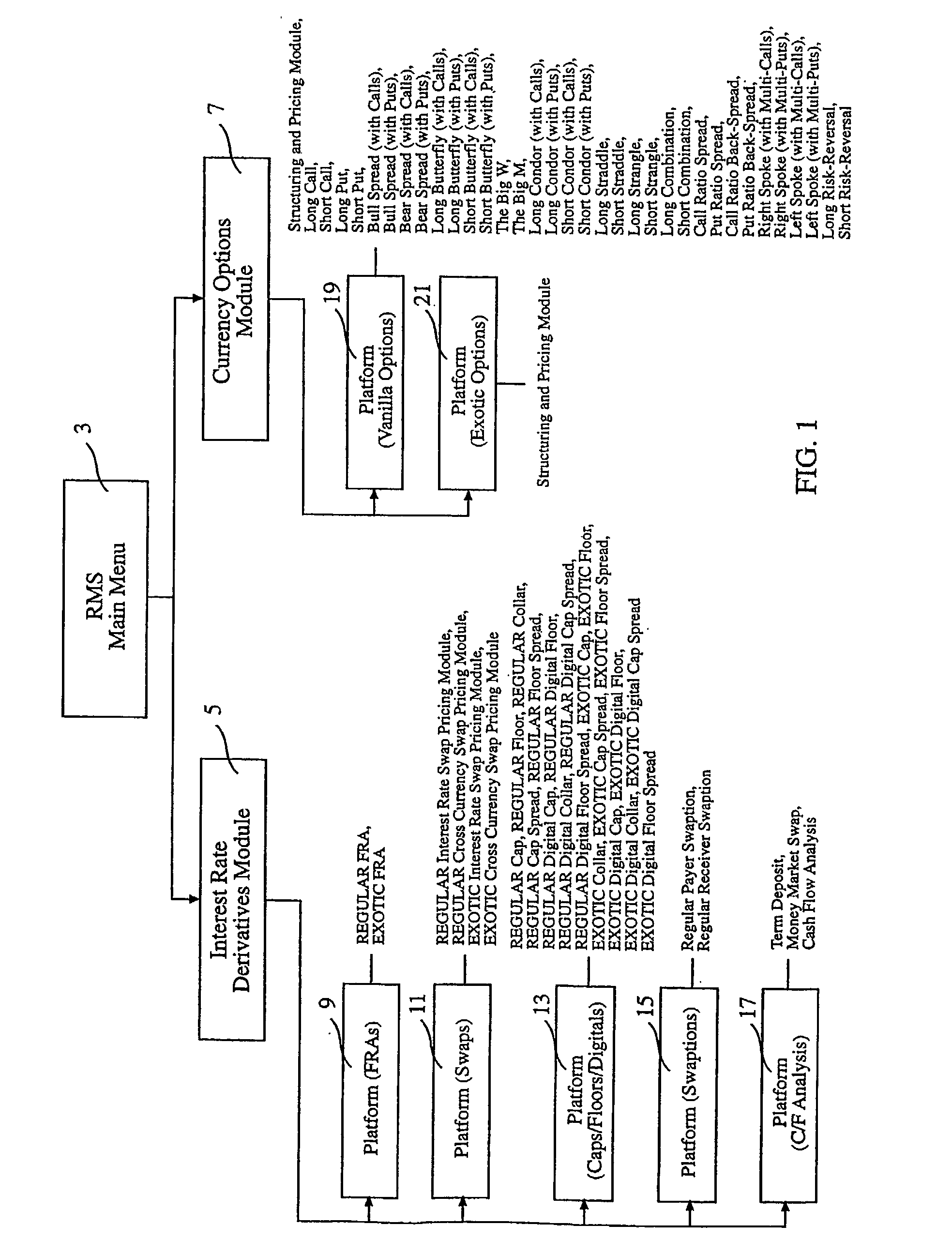

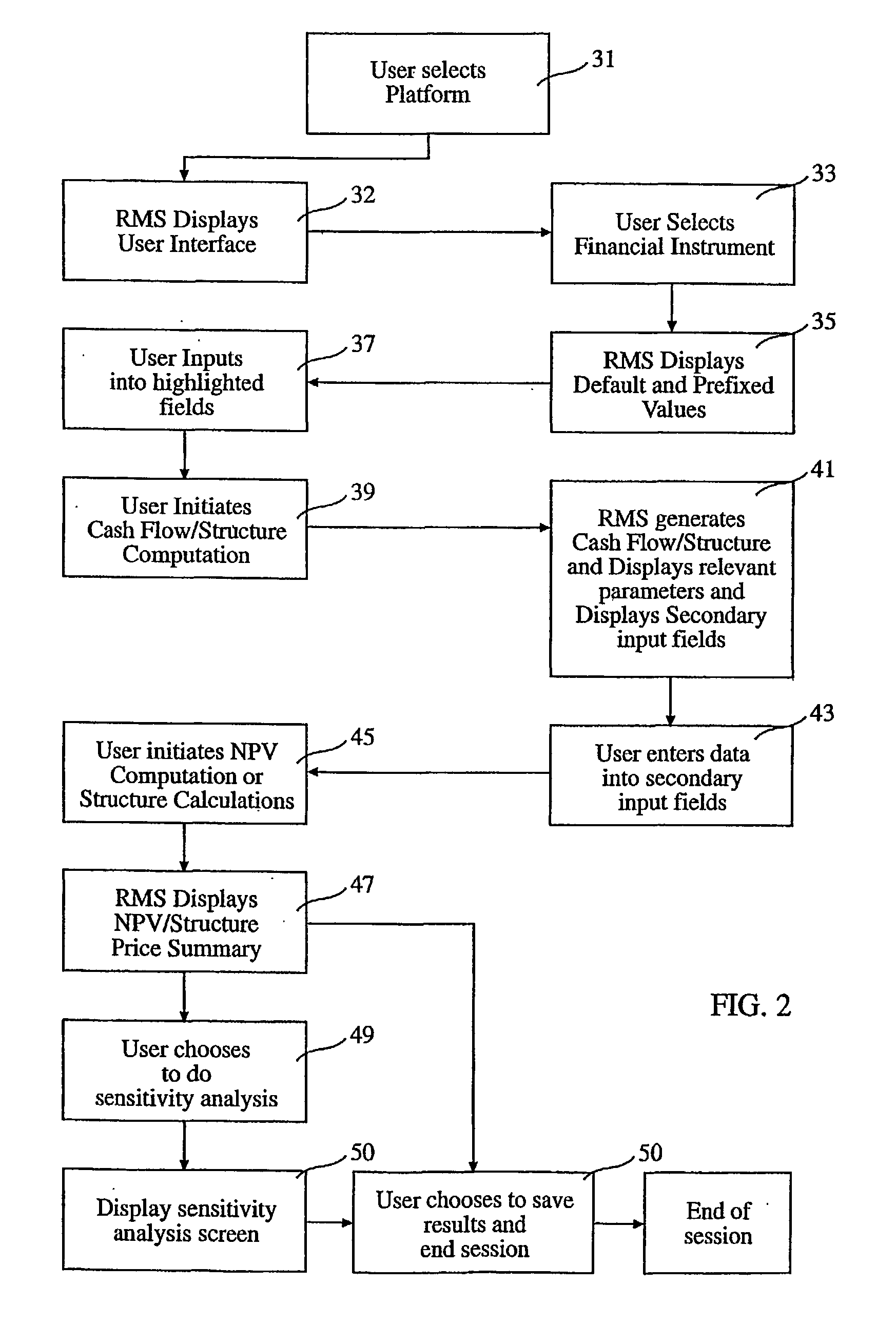

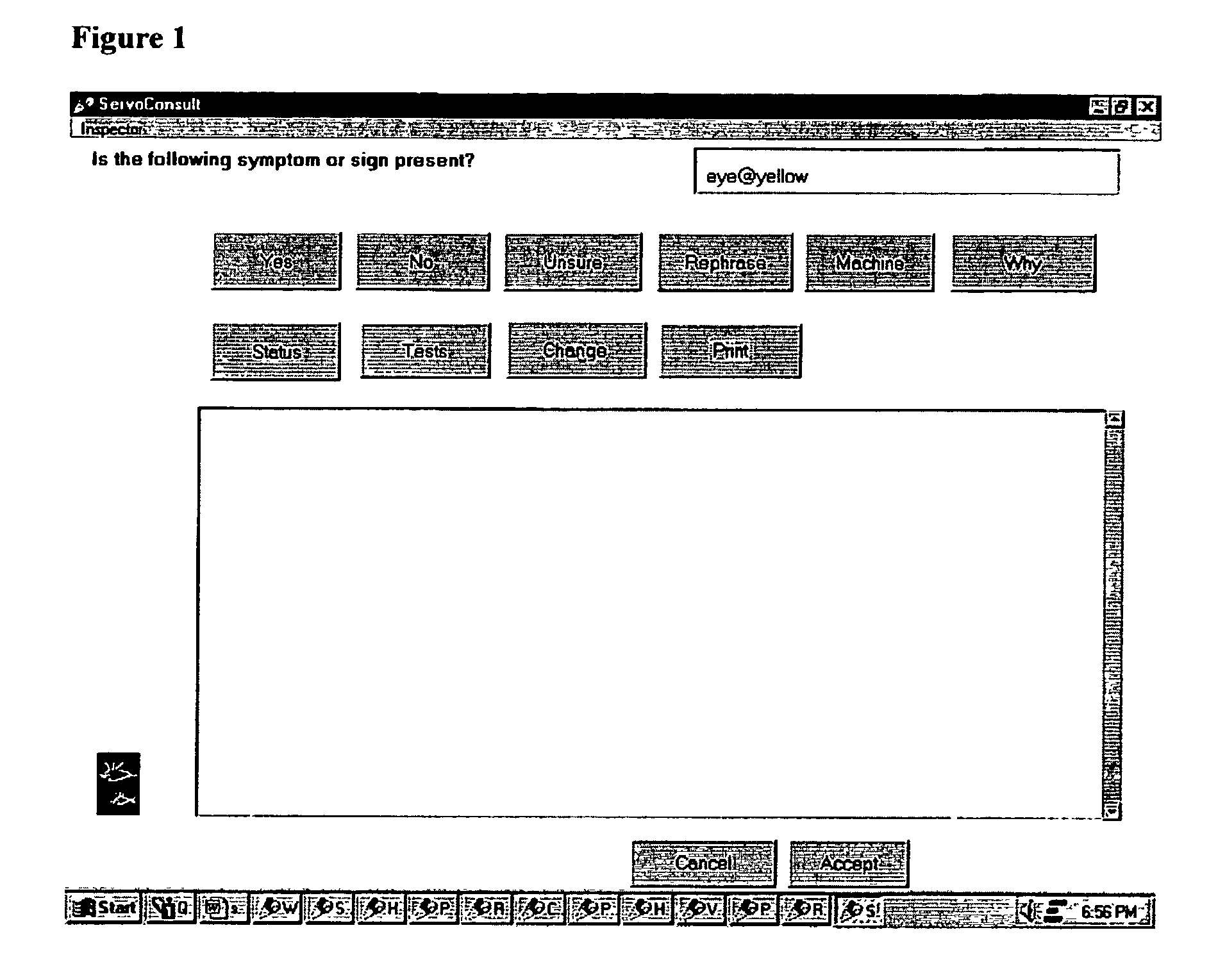

Fully flexible financial instrument pricing system with intelligent user interfaces

InactiveUS20030014345A1Overcomes shortcomingMinimizes user inputFinanceSpecial data processing applicationsGuidance systemSoftware

The present risk management system with intelligent user interfaces divides all processes within the system into different "flowchart" phases. Decisions or inputs that can have knock-on effects on other decisions or inputs will be required at an earlier phase or level. If say, a particular decision or input has a knock-on effect on another decision or input, the system will require this decision or input to be entered at an earlier phase. This ensures a systematic and logical input of data as opposed to having all decisions or inputs appearing at the same time or in one phase, as in the case of other financial option and derivative pricing and structuring software programs. The system uses this "flowchart" process to provide an on-line guidance system for the users to input only the required decisions or inputs as they go along. As such, in adopting the intelligent user interface processing methodology, the user need not be an "expert" in knowing which inputs are required and which are not This system also minimizes user input errors.

Owner:PI & CONSULTING PTE

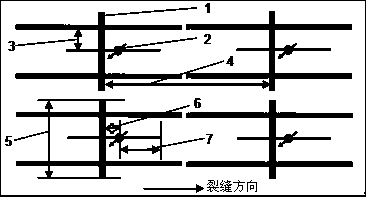

Placing method of self-simulating lateral-displacement horizontal well of super-low permeability tight reservoir

ActiveCN105239990AAvoid re-openingReduce water injection pressureFluid removalOffset distanceWater flooding

The invention provides a placing method of a self-simulating lateral-displacement horizontal well of a super-low permeability tight reservoir. The placing method comprises the following specific steps: determining a main force construction layer section; determining the positions of horizontal wells, water injection wells and artificial fractures; determining a well row direction of the horizontal wells; determining a well spacing between the horizontal wells; determining a distance between the rows of the horizontal wells; determining the length of each horizontal well; determining an offset distance of each water injection well; determining a length of each artificial fracture of each water injection well; and injecting water; scattered water injection in the past is changed into linear water injection, and in case of the same water injection amount, a water injection pressure is reduced so that secondary opening of a natural fracture generated in the water injection process can be avoided and a risk of fractured water flooding can be reduced; elastic solution gas drive in a region between the artificial fractures is converted to water drive and a fracture dominant direction of a local region is kept consistent so that early-phase water breakthrough can be avoided and an energy supplementing level can be increased. Row water injection displacement is formed through appropriate fracturing of the directional water injection wells, leading to the advantages that layered water injection can be realized and maximum draw-on in a longitudinal direction can be realized, compared with taking the horizontal wells as the water injection wells.

Owner:PETROCHINA CO LTD

Electronic circuit device

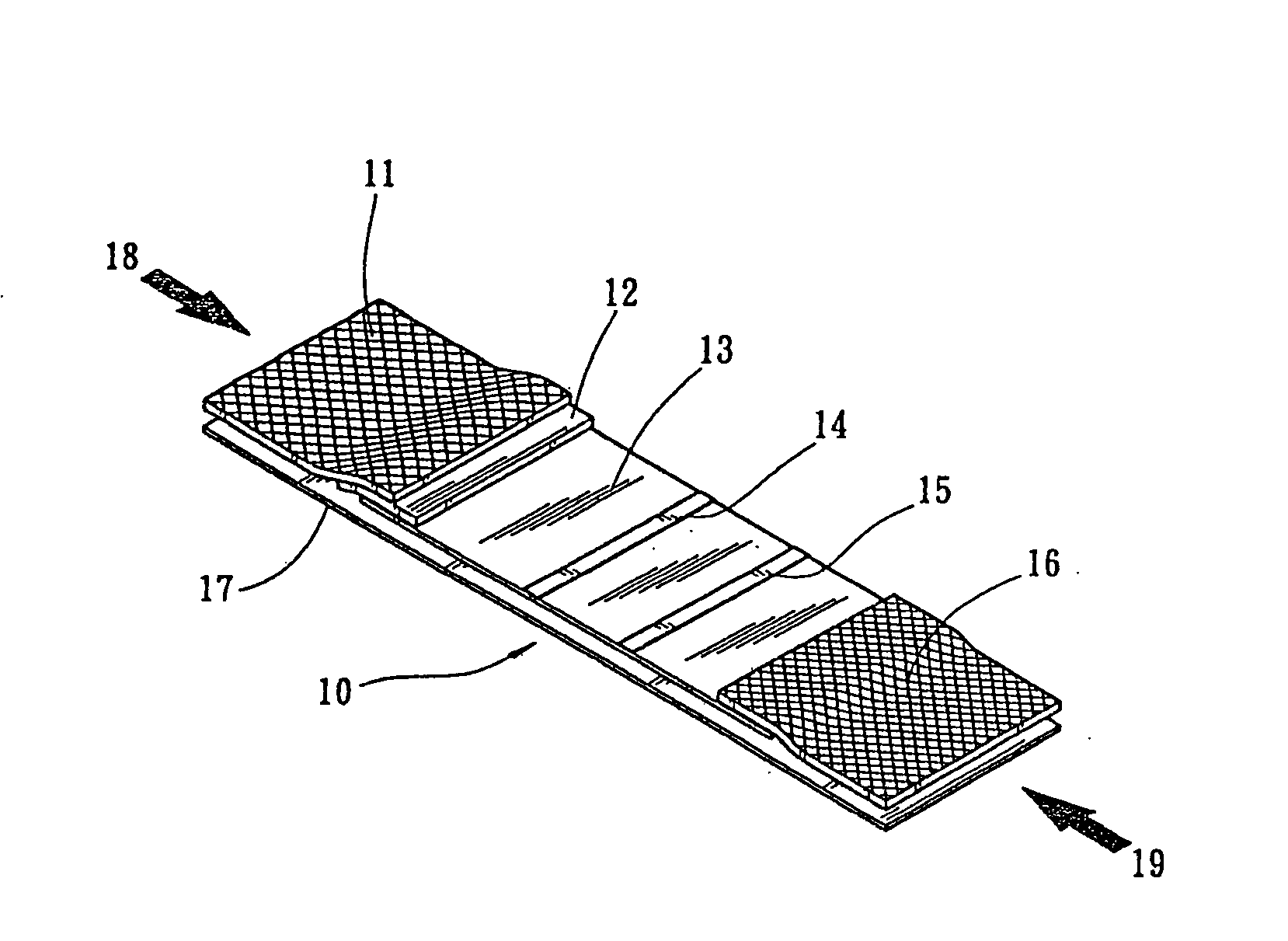

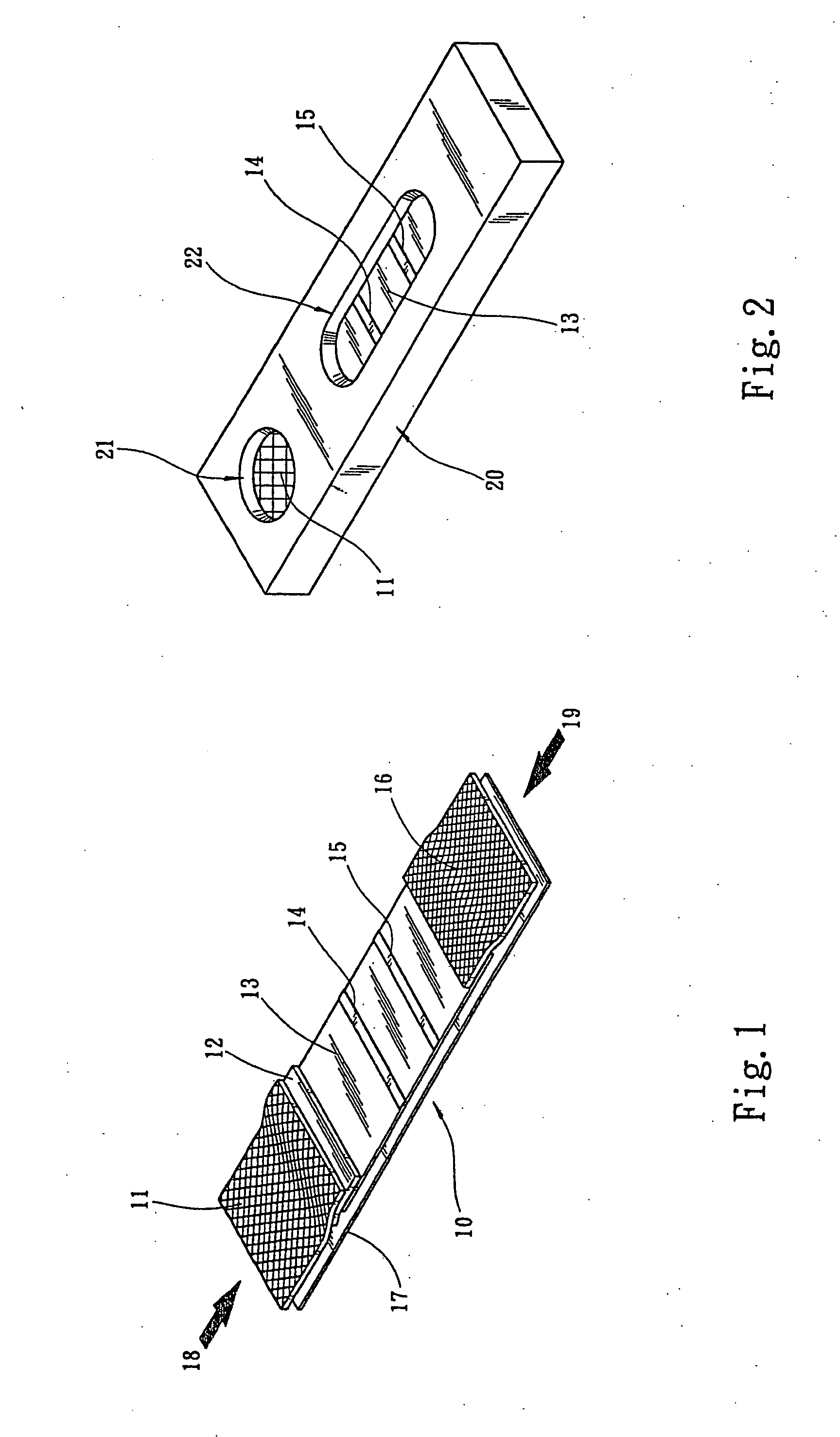

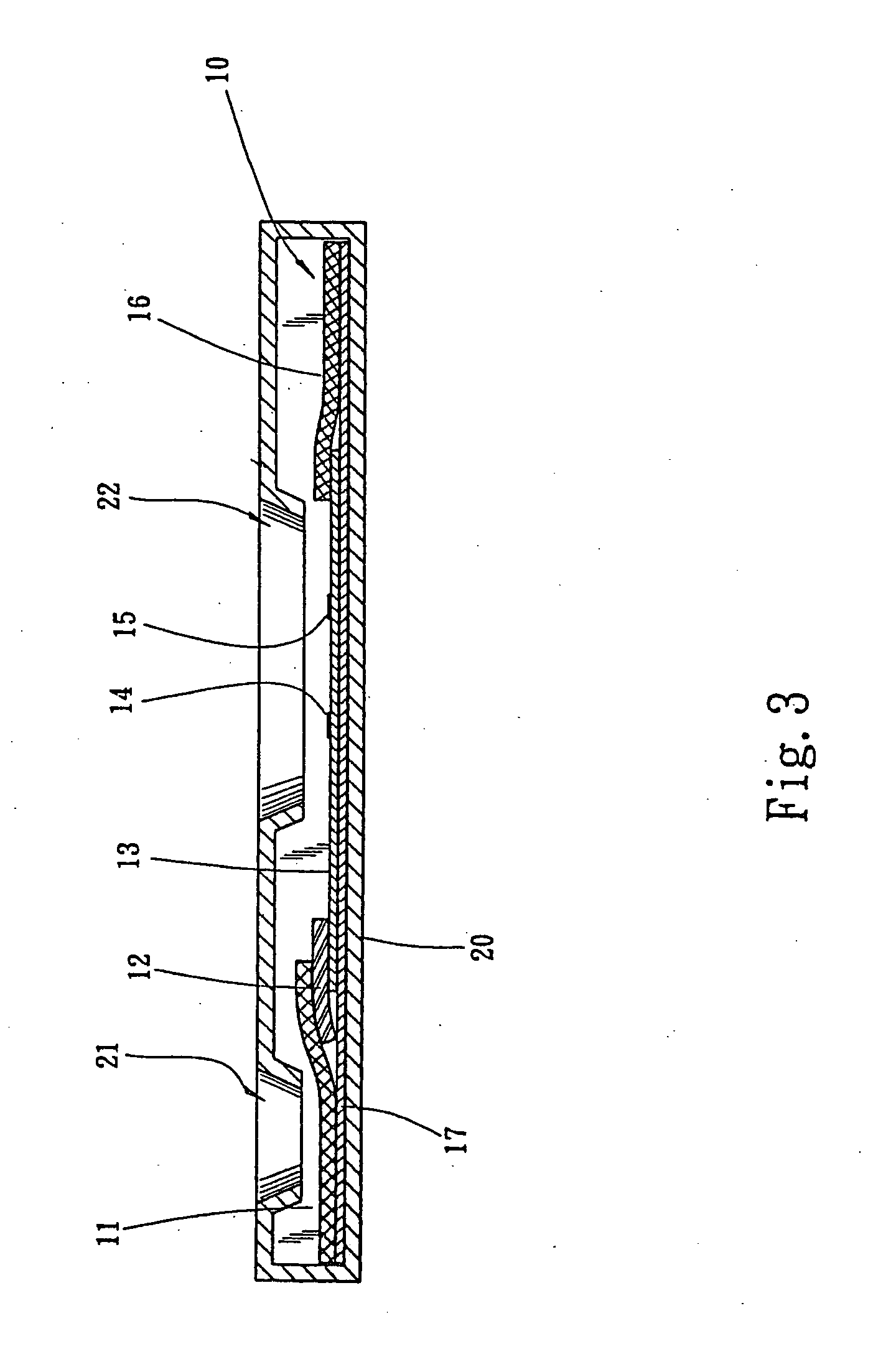

InactiveUS20060237835A1Easy to debugLow costError detection/correctionSemiconductor/solid-state device detailsStatic random-access memoryProgrammable logic device

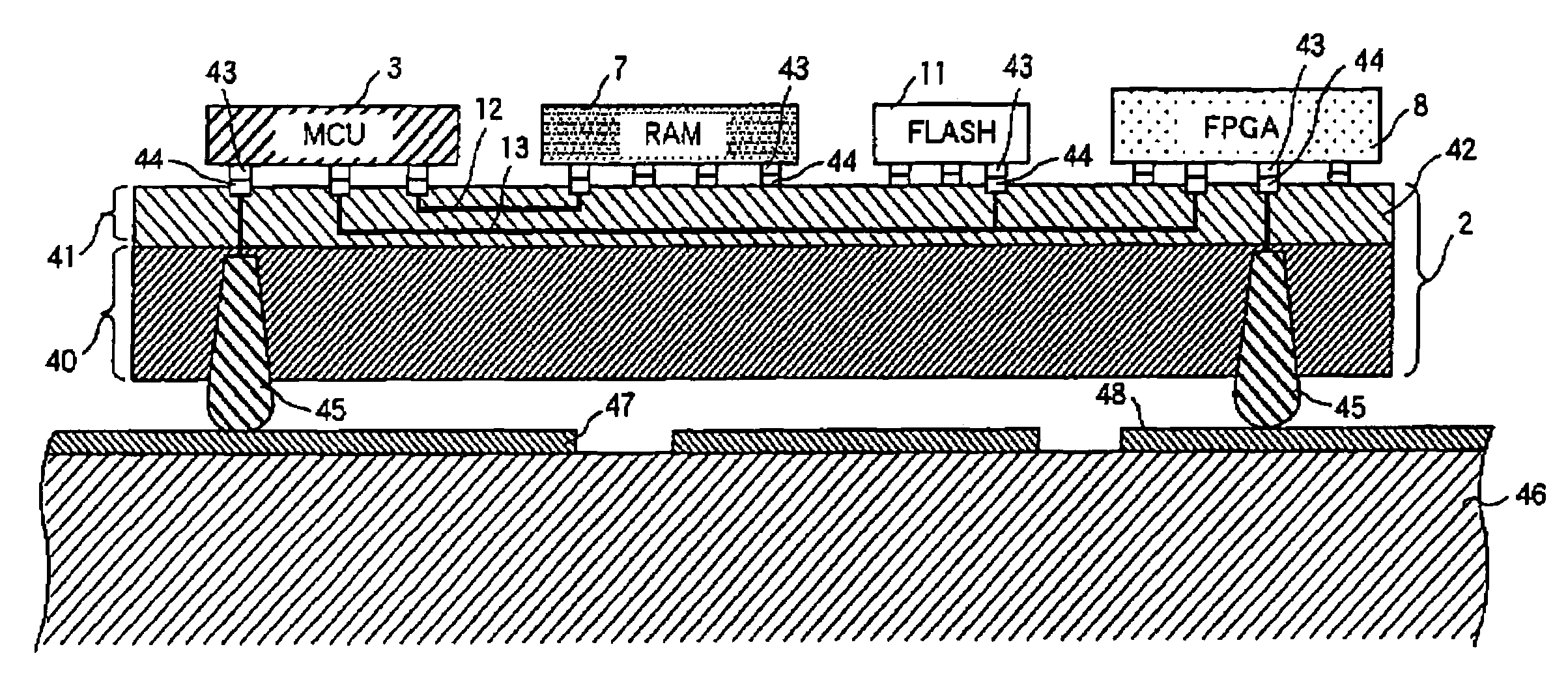

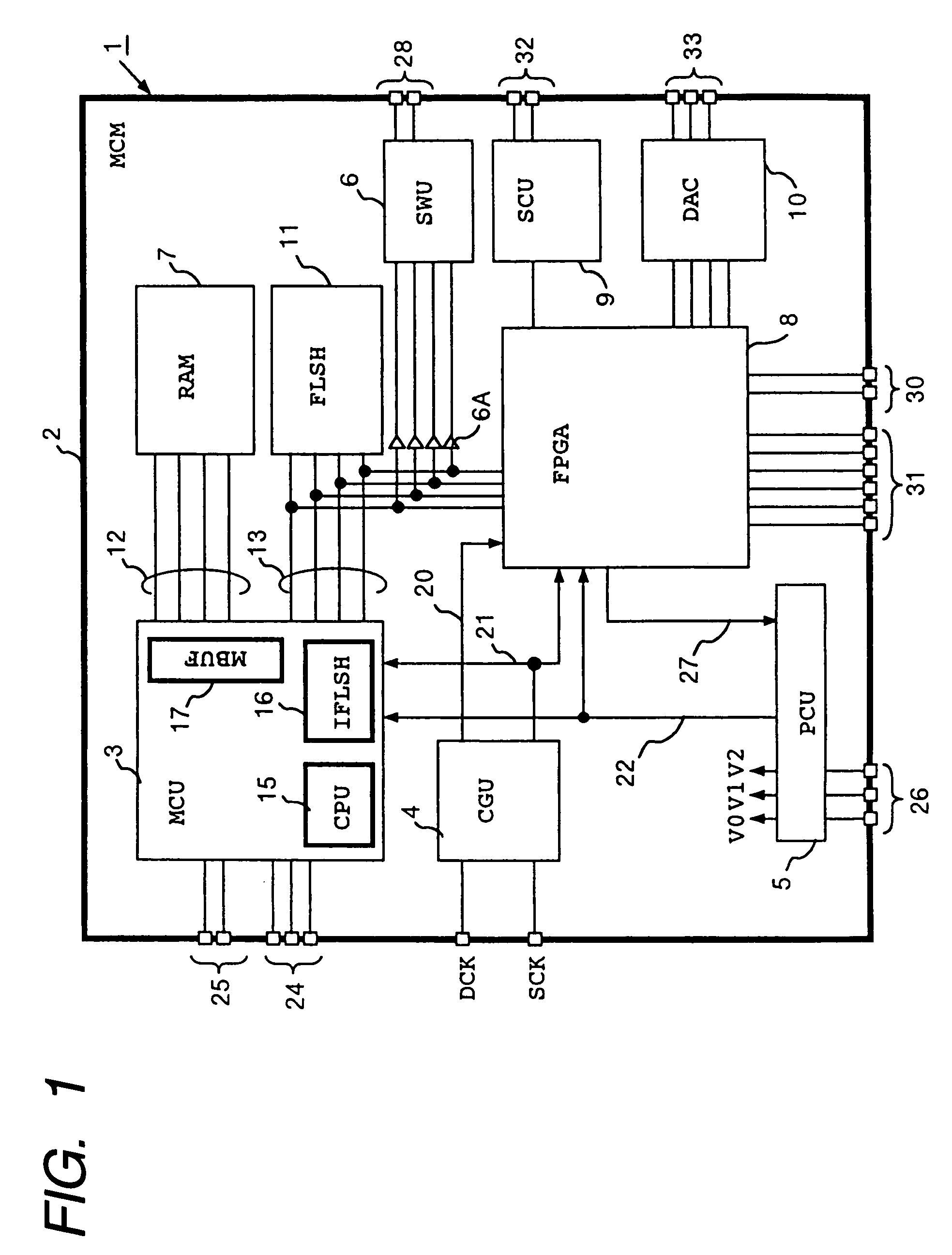

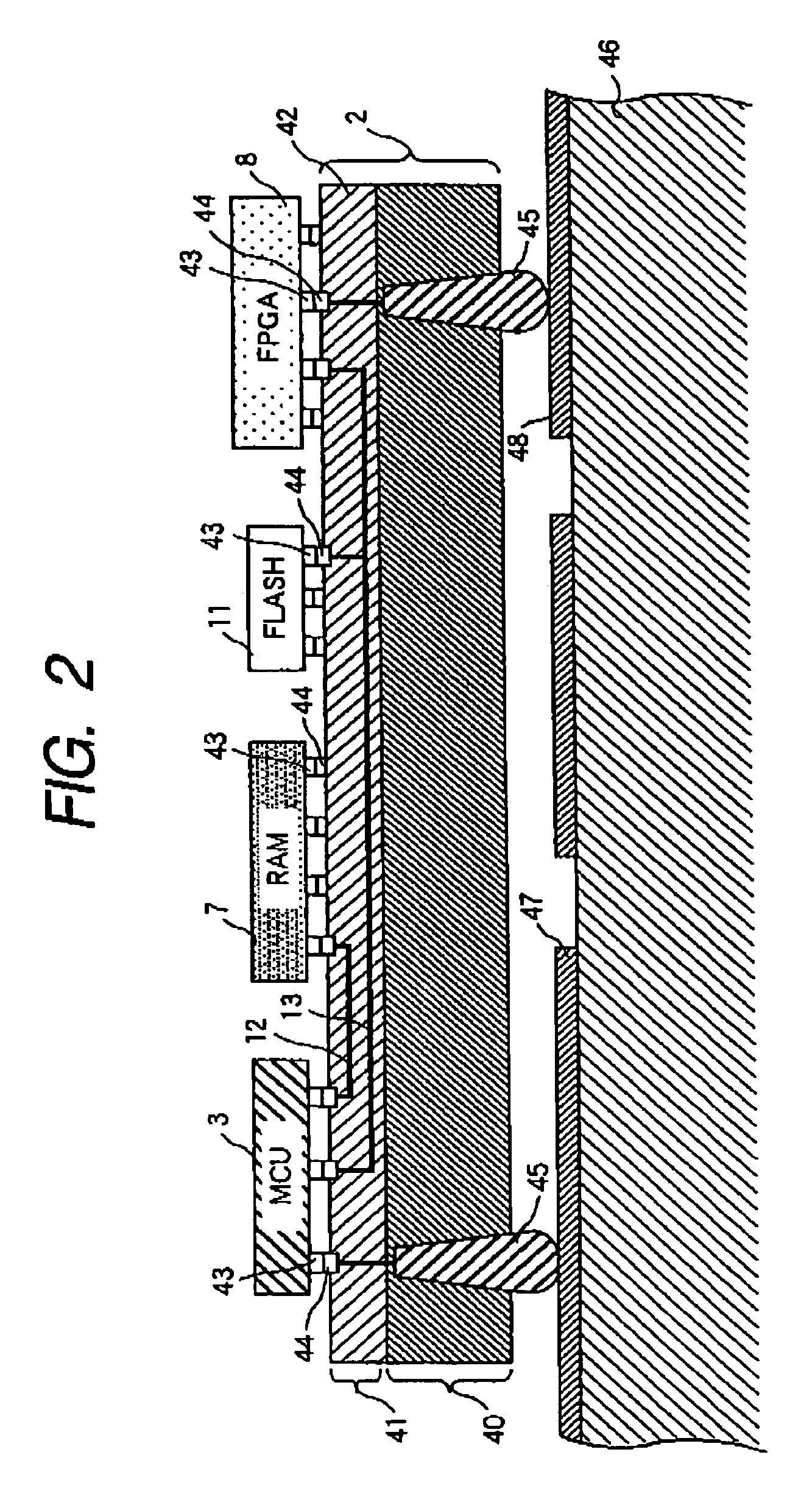

An electronic circuit device has a high-density mount board (2), on which are disposed a microcomputer (3) and random access memory (7) which are connected to each other through an exclusive memory bus (12) for high-speed data transfer, a programmable device (8) which is a variable logic circuit represented by FPGA, and an electrically-rewritable nonvolatile memory (16) which can store the operation program of the microcomputer. The high-density mount board has external mounting pins on the bottom surface so that it can be mounted on a mother board in the same manner as a system on-chip multi-chip module. With an intended logic function being set on the programmable device, a hardware-based function to be realized by the electronic circuit device can be simulated. With an operation program being written to the nonvolatile memory, a software-based function to be realized can be simulated. Consequently, the device facilitates the debugging at early stages of system development, configures a prototype system, and contributes to the time reduction throughout the system development, prototype fabrication and large-scale production.

Owner:RENESAS ELECTRONICS CORP

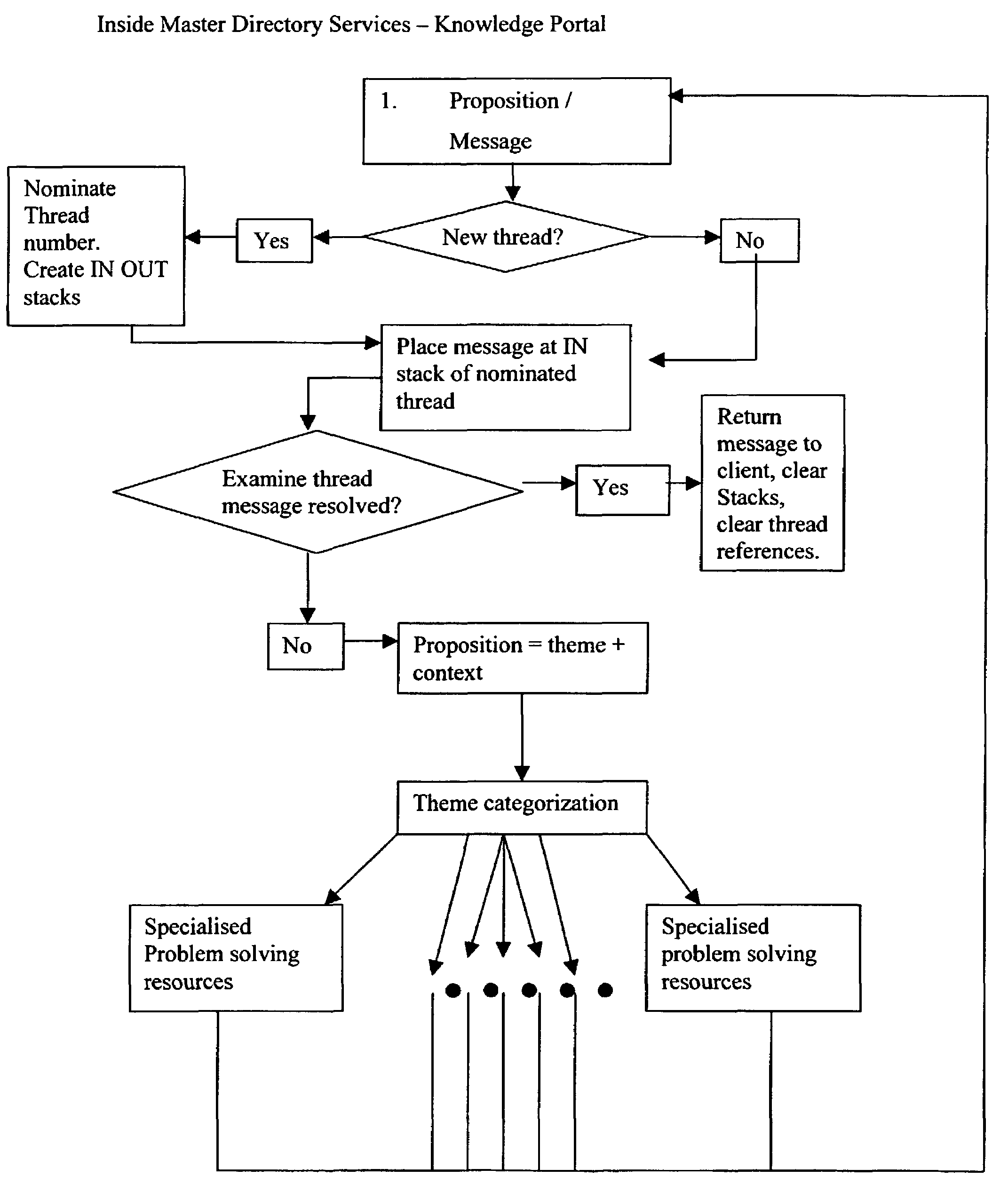

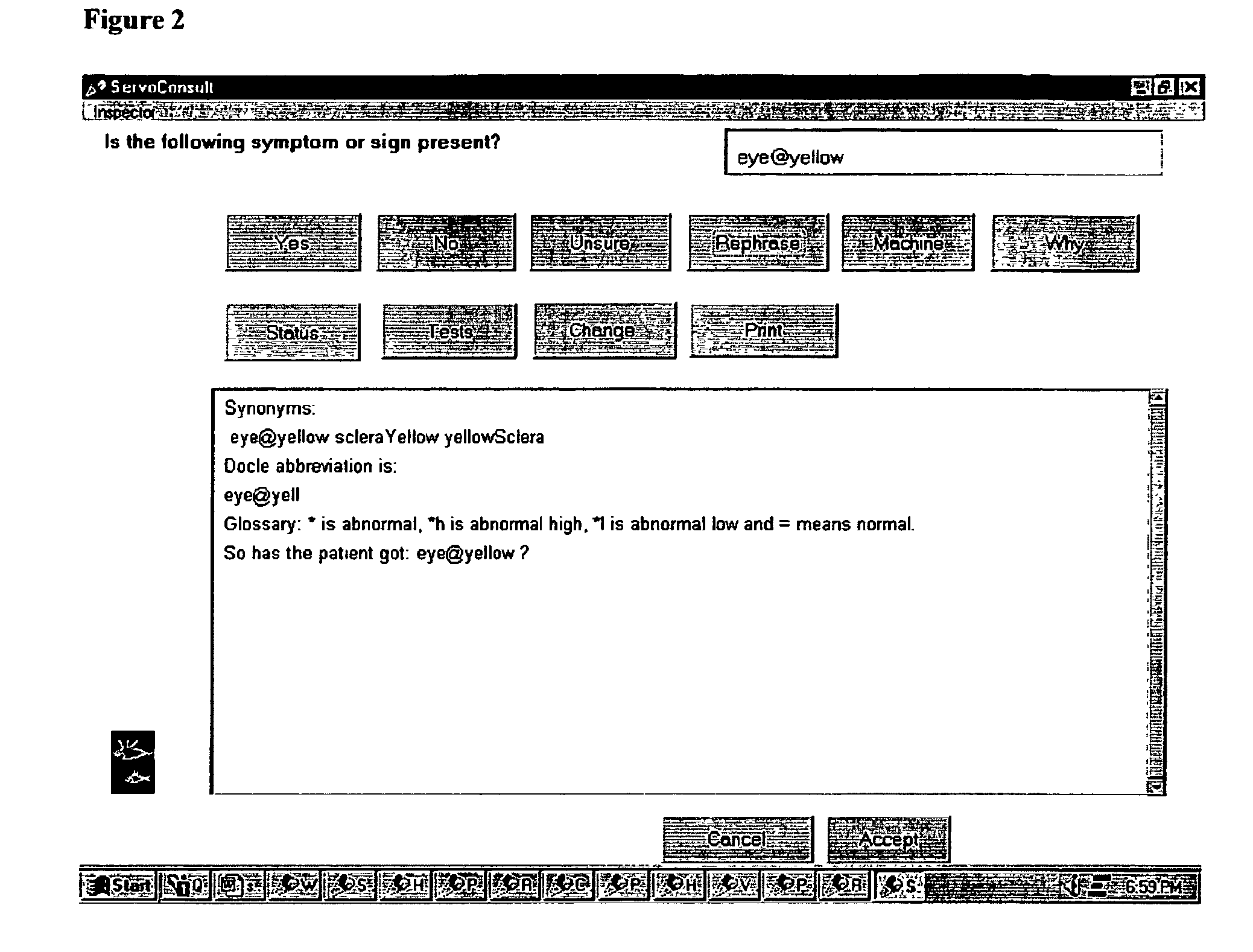

Unitary language for problem solving resources for knowledge based services

ActiveUS7222066B1Improve expressivenessMinimal compromiseSpecial data processing applicationsTeaching apparatusEarly phaseProblem solve

A unitary machine parsable language for use in data representation and problem solving in knowledge based services having a vocabulary of terms which derive from a natural human language to facilitate ease of comprehension by humans based upon a definition of the context of an item of information. A method of increasing the effectiveness of a knowledge based service consultation comprising splitting the consultation into at least a pre-consultation phase, a consultation phase and a post-consultation phase wherein information collected during earlier phases is electronically checked during the post-consultation phase.

Owner:OON YEONG KUANG

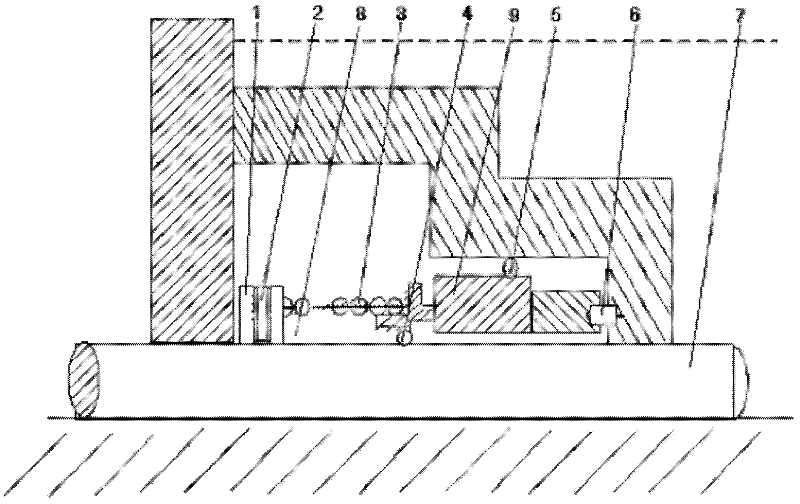

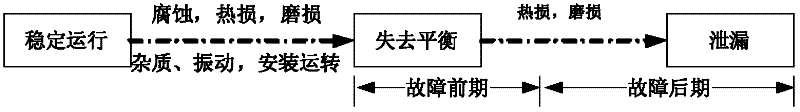

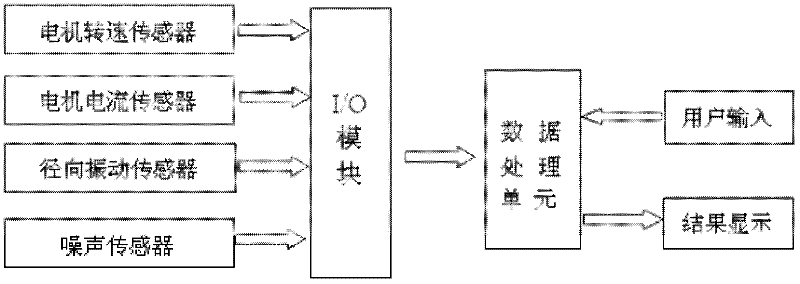

Mechanical seal online monitoring system

InactiveCN102313578AReduce lossesIncrease productivityEngine sealsMeasurement devicesCurrent sensorRadial vibration

The invention relates to a mechanical seal online monitoring system which comprises a data processing unit, a detection unit and a user terminal, wherein the detection unit is connected with the data processing unit; and the detection unit comprises an I / O (Input / Output) module, and a motor rotating speed sensor, a current sensor, a radial vibration sensor and a noise sensor which are connected with the I / O module. In the system, acquired data is subjected to the multivariable statistics process monitoring by the data processing unit, so that the indirect monitoring for the mechanical seal operation condition is realized and an early warning signal can be given in the fault early phase of the mechanical seal, and thus, a production accident is avoided, the loss of raw materials, equipment and other aspects of an enterprise is reduced and the possibility is provided for detection of the mechanical seal state and failure prediction. Meanwhile, the equipment is checked by the monitoring system without shutting down, so that compared with the prior art, a great amount of time and human resources are saved and the production efficiency of the enterprise is improved.

Owner:GUANGZHOU HKUST FOK YING TUNG RES INST

Biomarkers for neurological conditions

InactiveUS20100159486A1Microbiological testing/measurementImmunoglobulins against animals/humansNervous systemCognitive diseases

Low molecular weight (LMW) peptides have been discovered that are indicative of neurological conditions, such as Alzheimer's Disease (AD), cognitive impairment and brain microhemmorhages. Evaluating patient samples for the presence of such LMW peptides is an effective means of detecting neurological conditions and monitoring the progression of the disease. The LMW peptides are particularly useful in detecting neurological conditions during the early stages without invasive procedures.

Owner:GEORGE MASON INTPROP INC +1

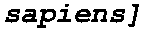

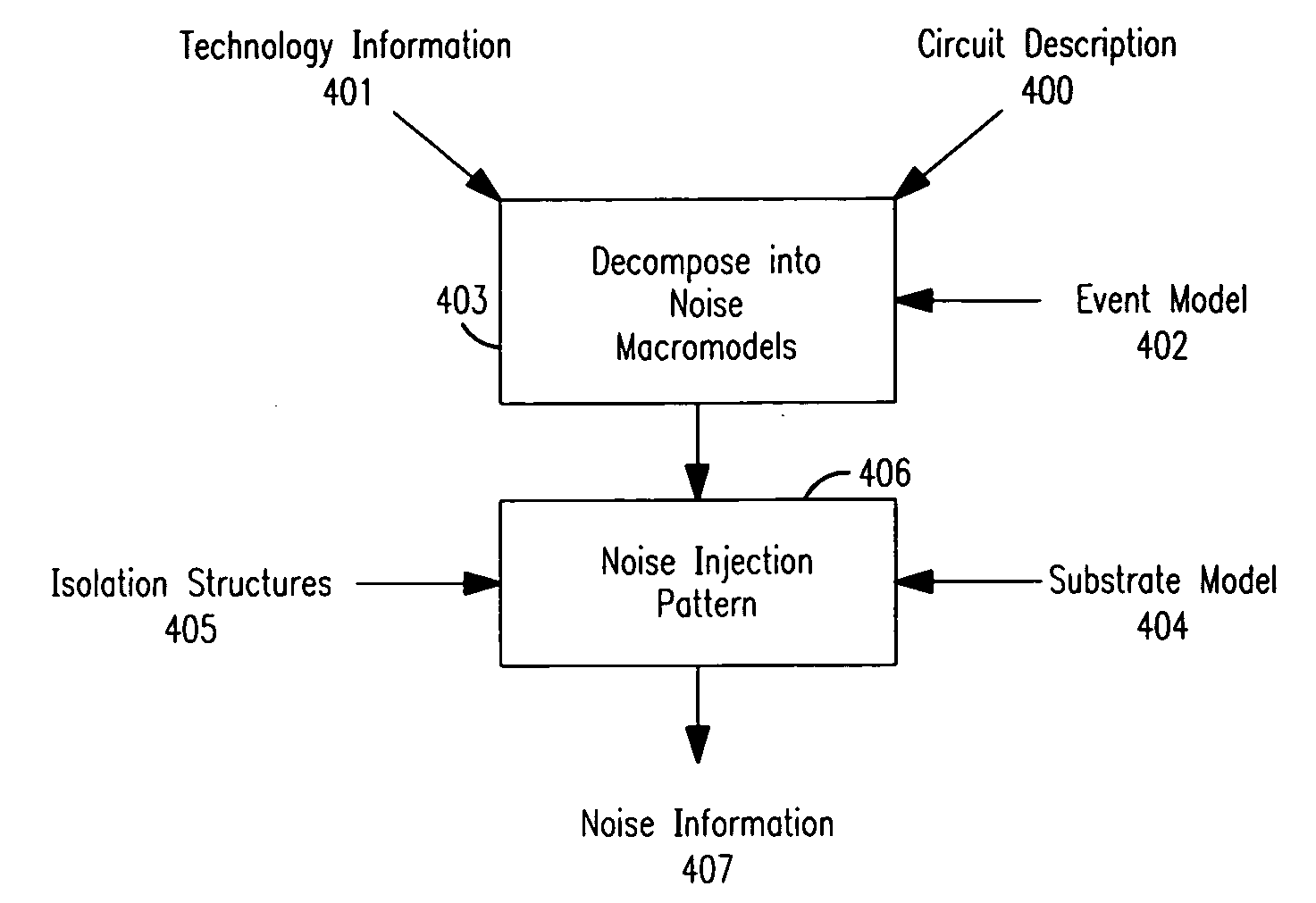

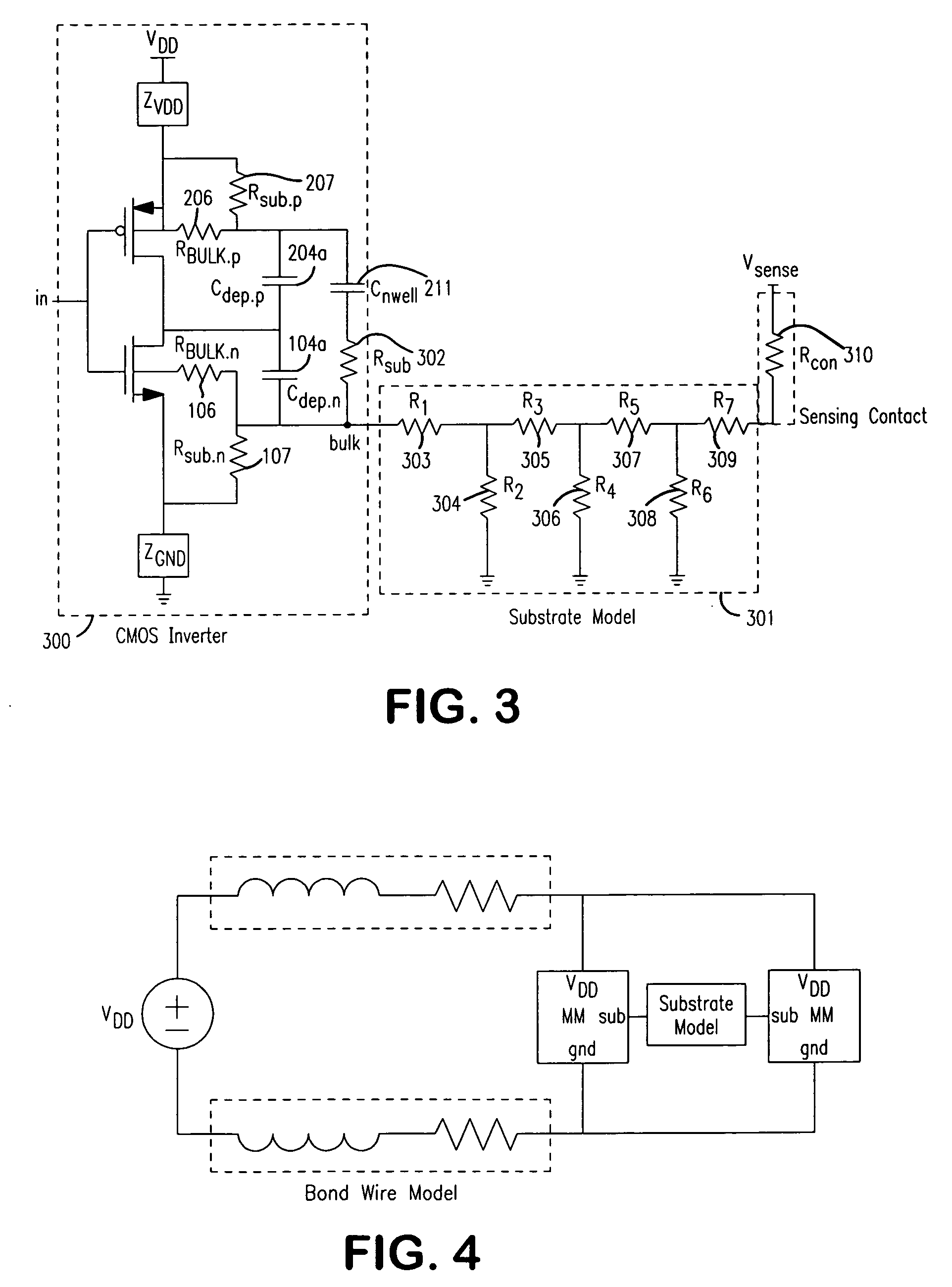

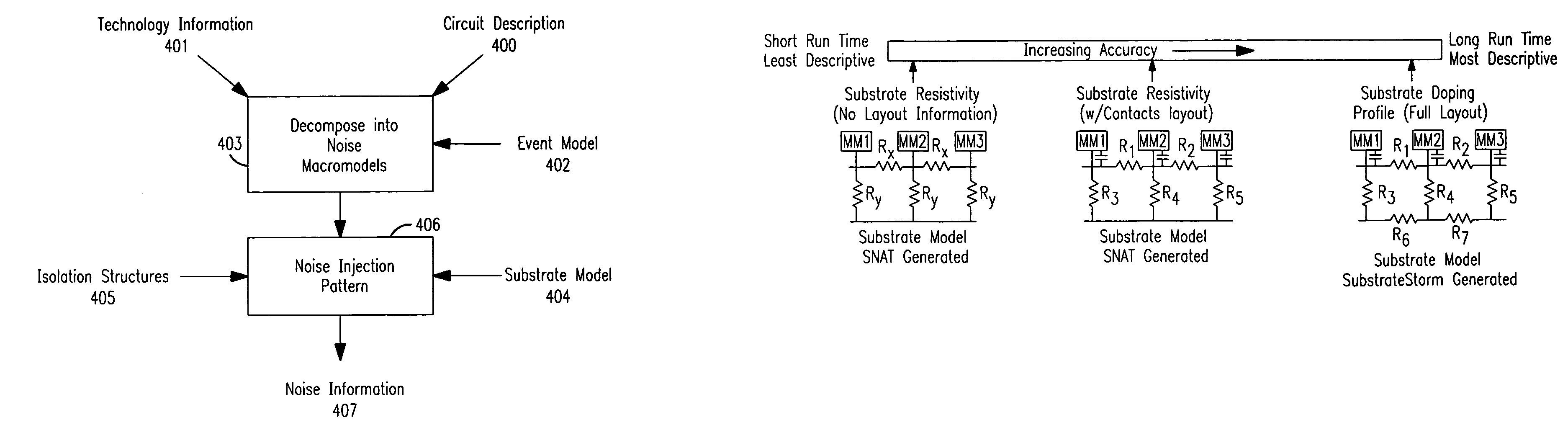

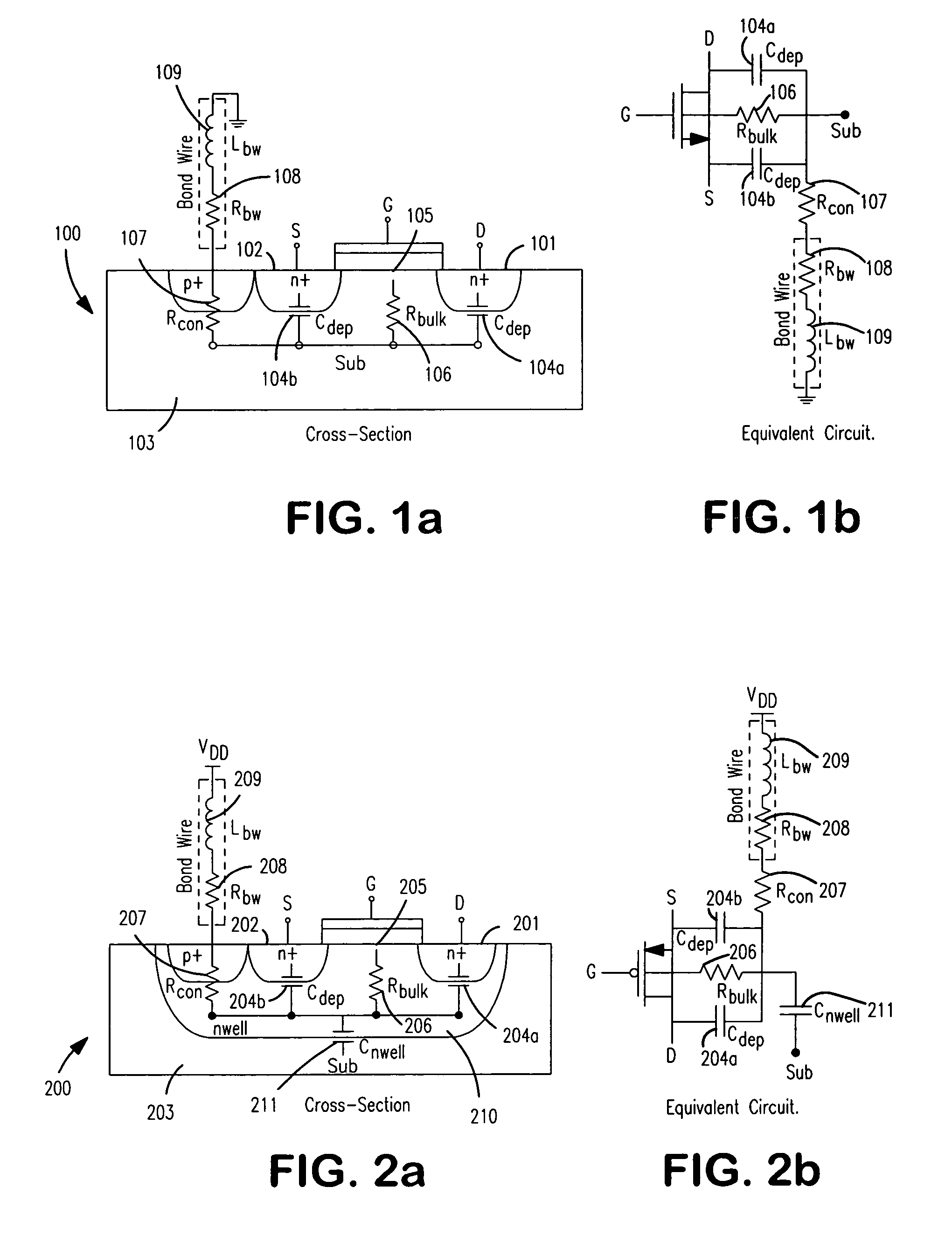

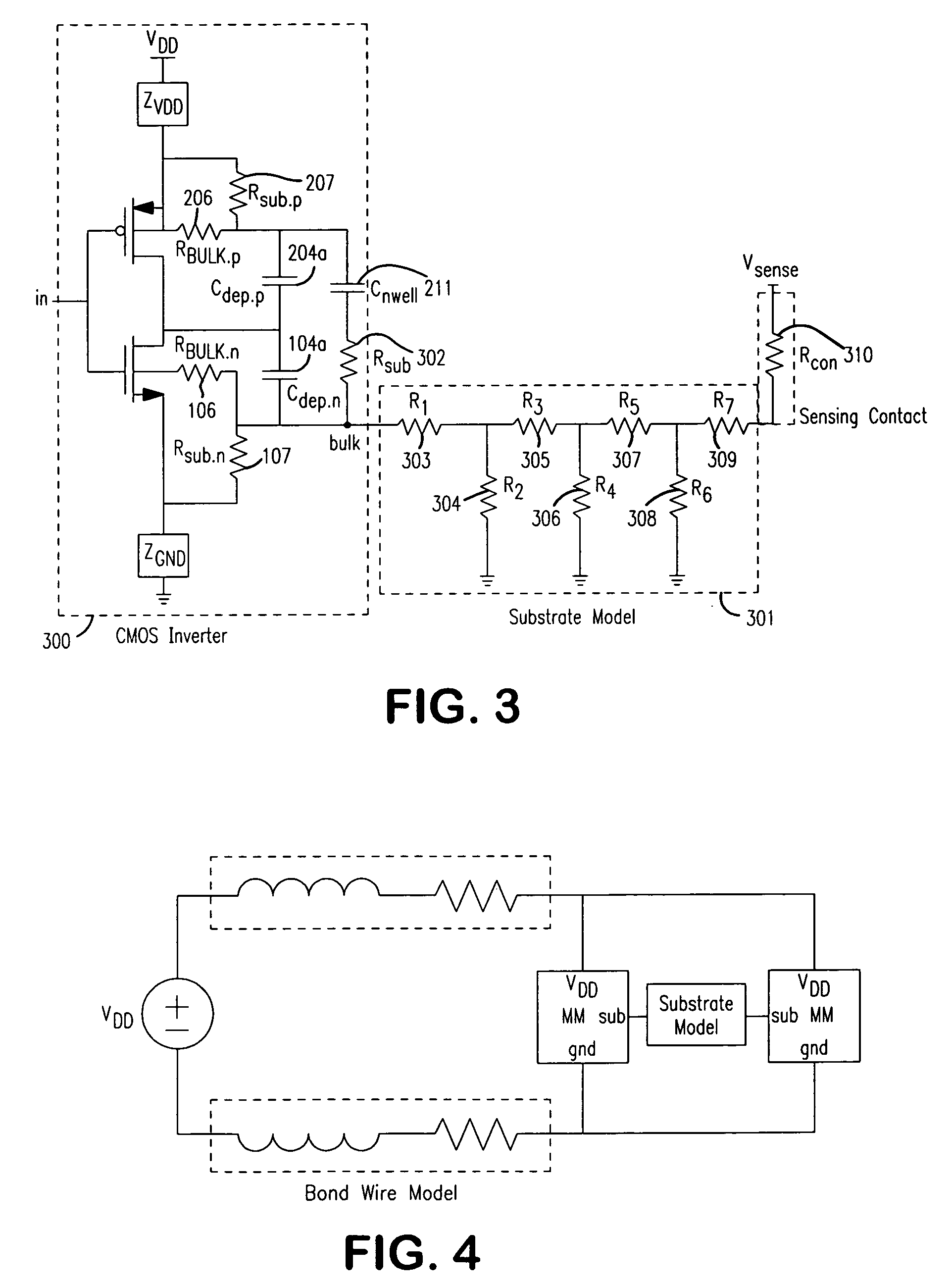

Substrate noise tool

InactiveUS20070067747A1Reduce noise couplingHigh level of abstractionDetecting faulty computer hardwareComputer aided designGranularityParasitic capacitance

Owner:MASSACHUSETTS INST OF TECH

System and method for a hybrid clock and proxy auction

The present invention primarily concerns hybrid auctions that may, for example, combine a clock auction with a proxy auction. Hybrid auctions include multi-item auctions that comprise at least two phases of package auctions: an earlier phase in which bidders participate in a clock auction (or other dynamic auction); and a later phase in which bidders participate in a proxy auction (or some other package auction). By combining the earlier phase and the later phase as in some of the embodiments described herein, it is possible to combine the advantages of the dynamic auction and the advantages of the sealed-bid package auction. In particular, if the earlier phase is a clock auction and the later phase is a proxy auction, then the resulting hybrid auction will combine the transparency and simplicity of the clock auction with the efficient outcome and competitive revenues of the proxy auction.

Owner:EFFICIENT AUCTIONS

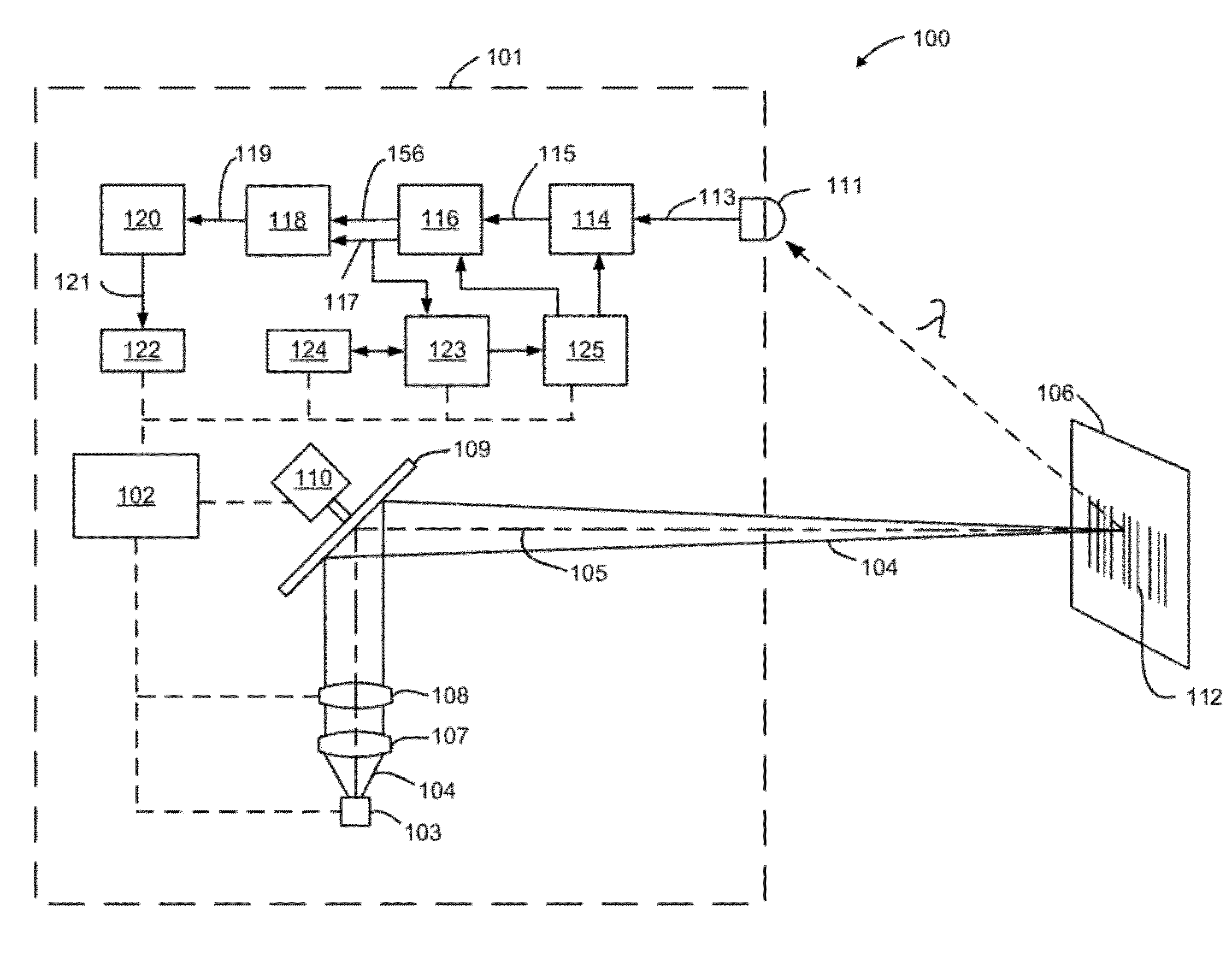

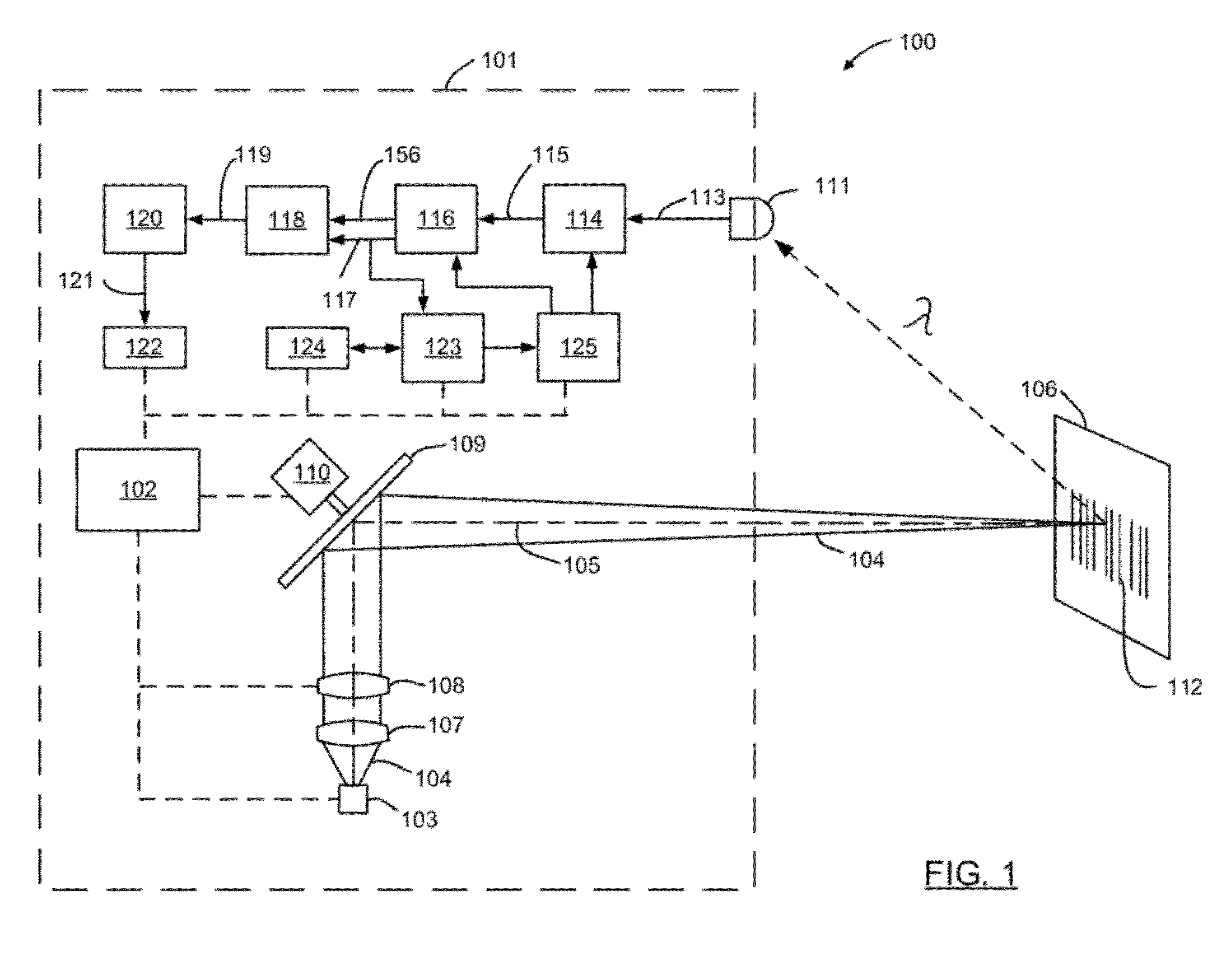

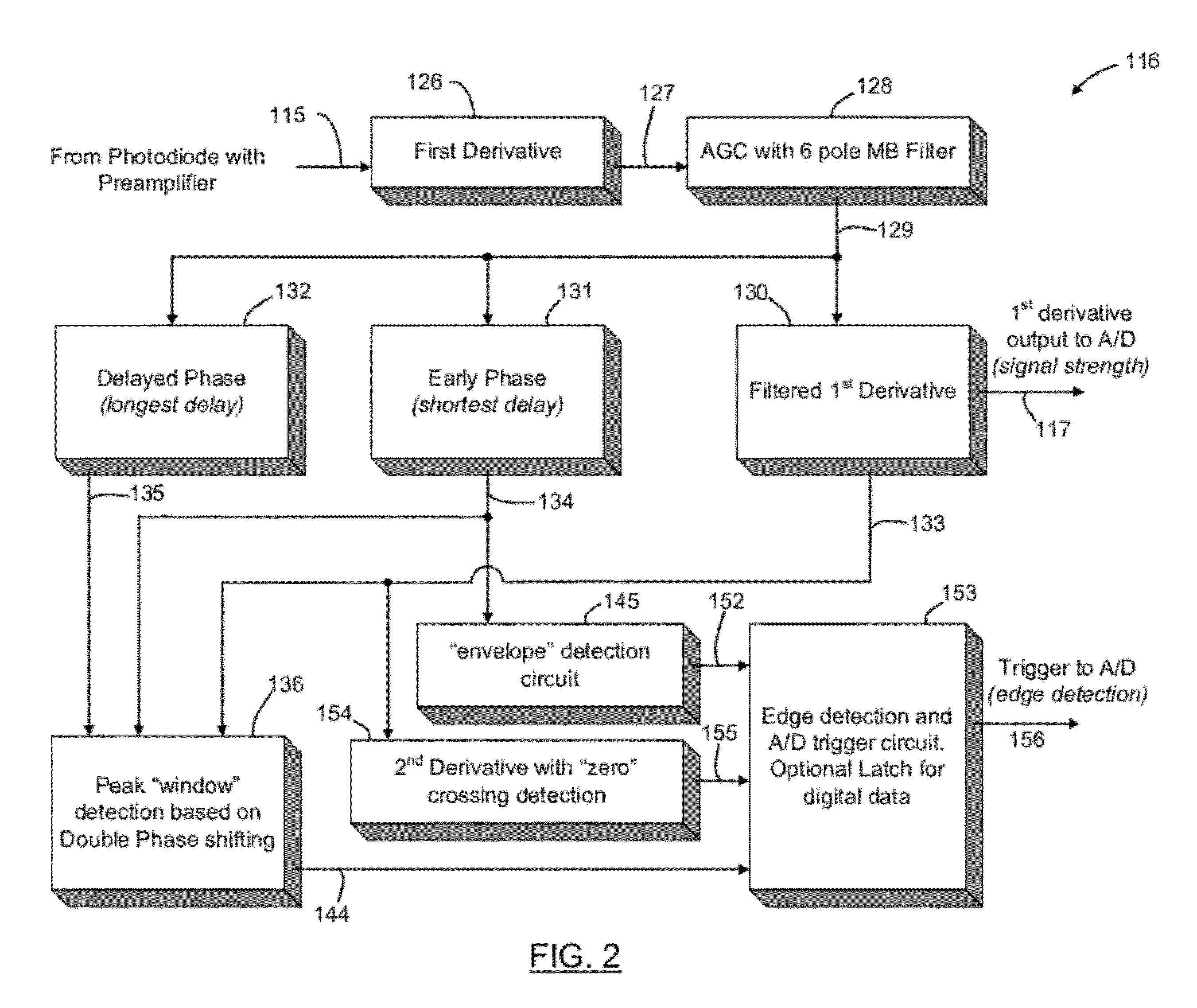

Barcode reader with edge detection enhancement

ActiveUS20120118974A1Character and pattern recognitionElectric pulse generatorWindow detectionBarcode reader

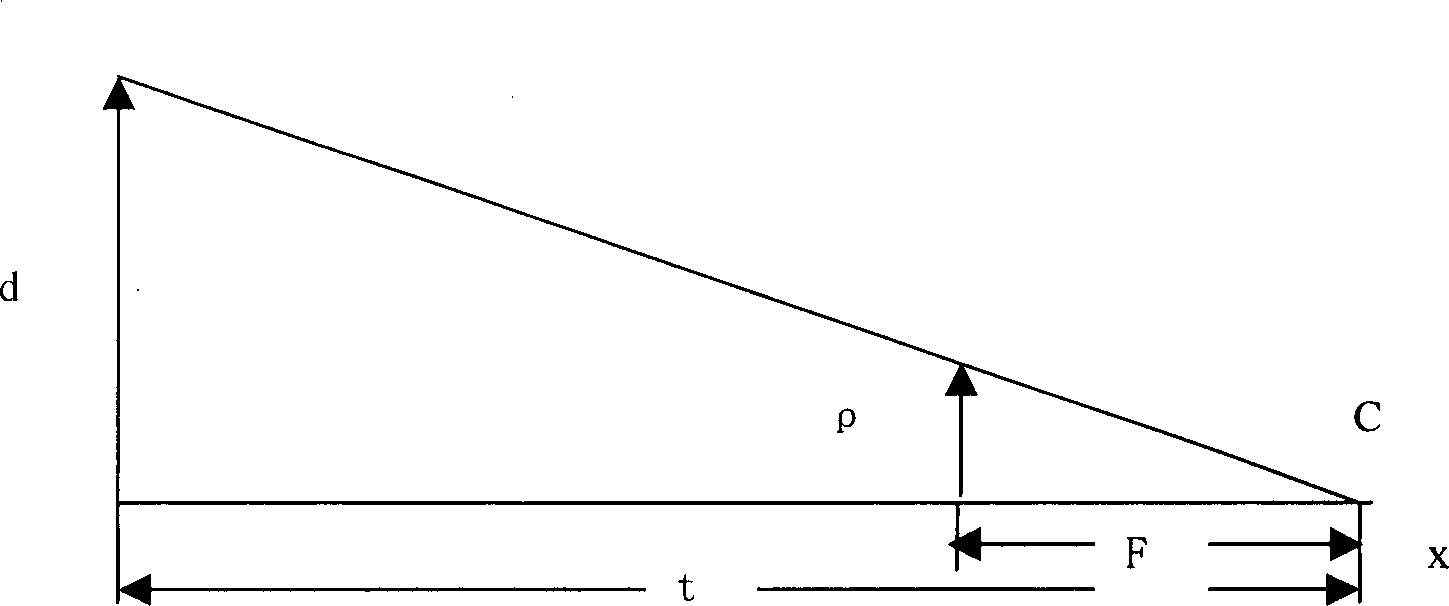

An optical reader for decoding an encoded symbol character of a symbology includes a scan data signal processor having as an input a scan data signal encoding information representative of the encoded symbol character. The scan data signal processor includes a first time delay stage adapted to provide a primary phase waveform from the scan data signal, a second time delay stage adapted to provide an early phase waveform from the scan data signal, and a third time delay stage adapted to provide a delayed phase waveform from the scan data signal. The early phase waveform has a propagation delay less than the primary phase waveform, and the delayed phase waveform has a propagation delay greater than the primary phase waveform. The scan data signal processor further includes a peak window detection stage for generating a peak window timeframe when an amplitude of the primary phase waveform is greater than, less than, or equal to both an amplitude of the early phase waveform and the delayed phase waveform. The optical reader further includes a digitizer circuit adapted to accept, within the peak window timeframe, the scan data signal processor output.

Owner:HAND HELD PRODS +1

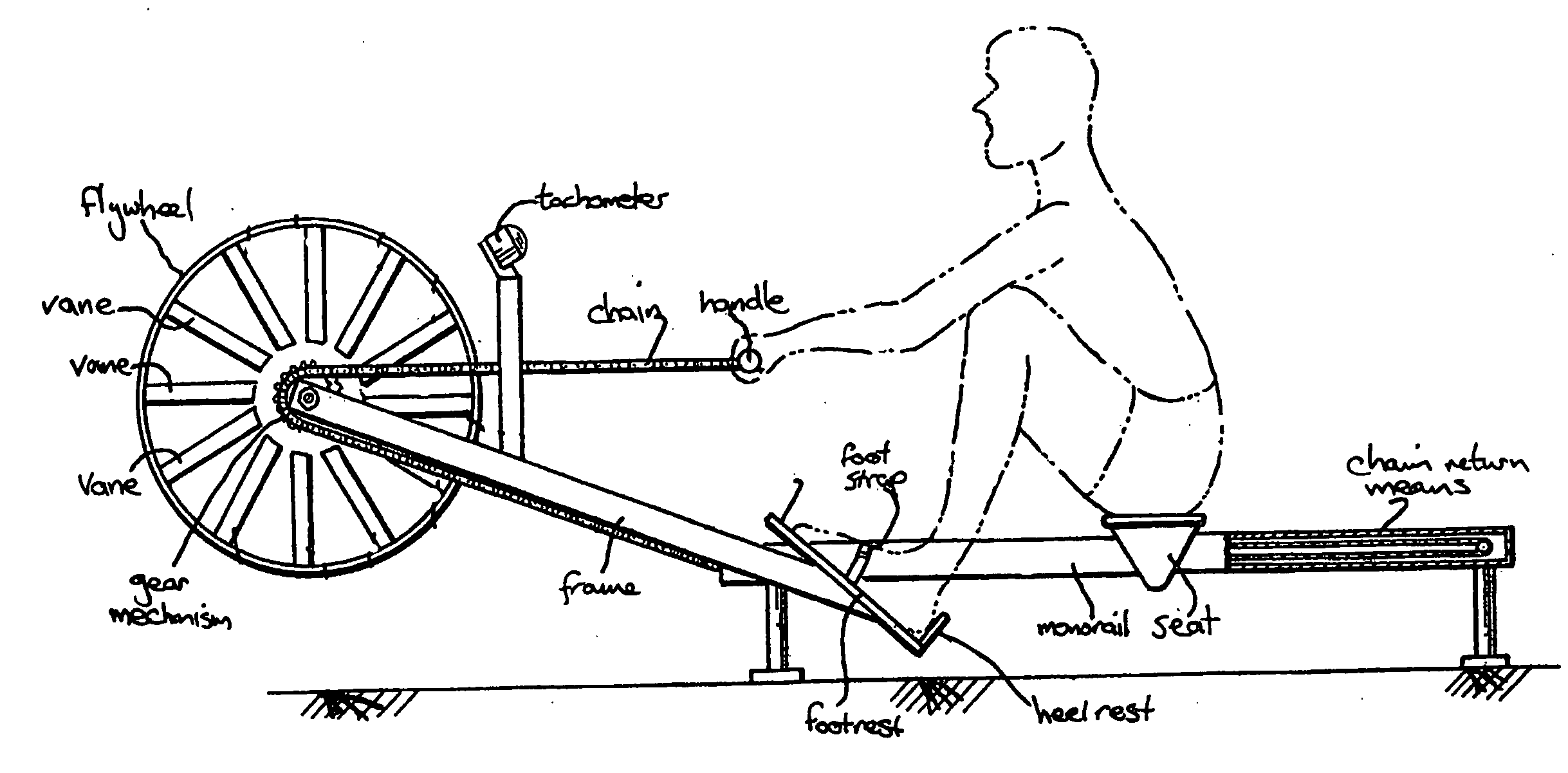

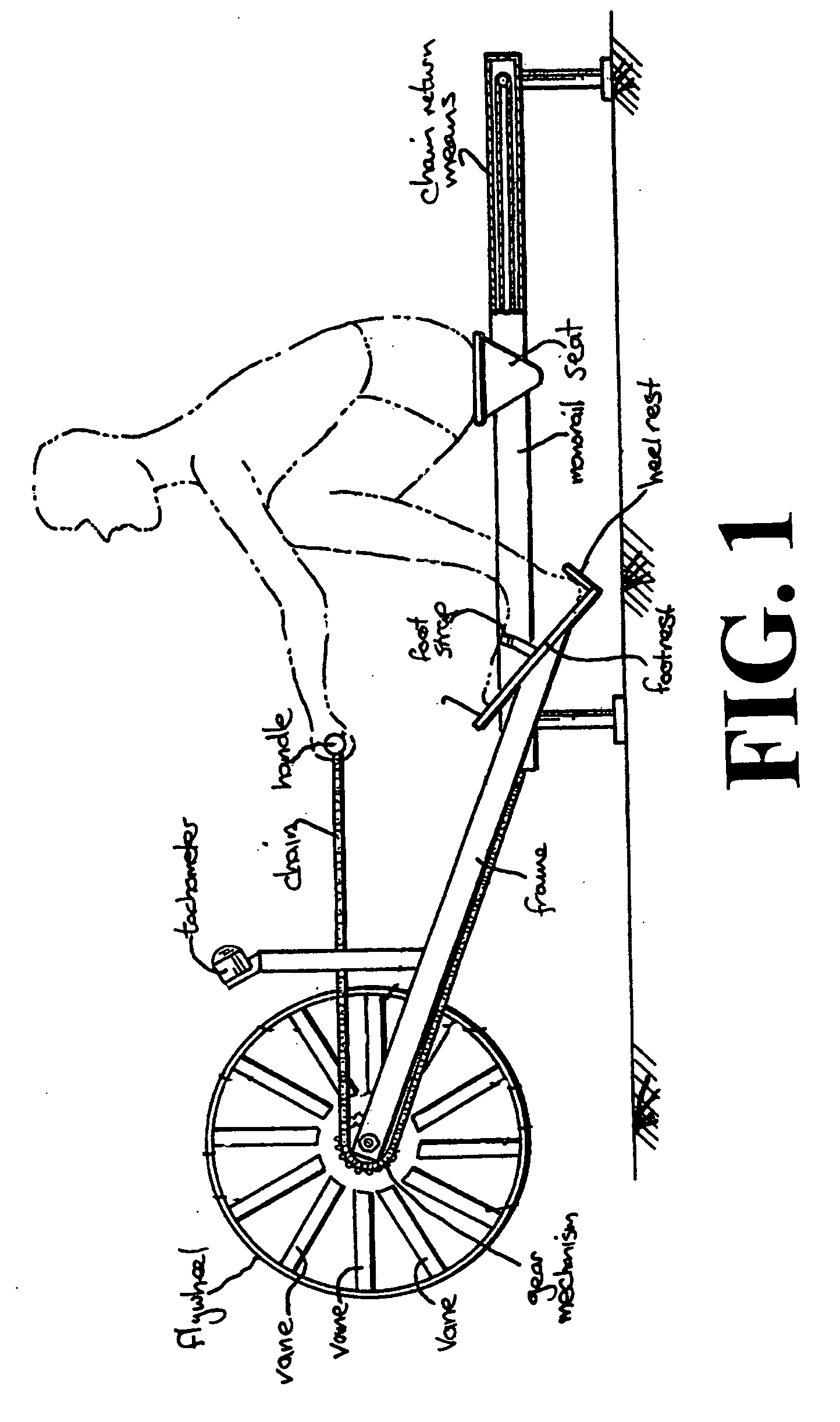

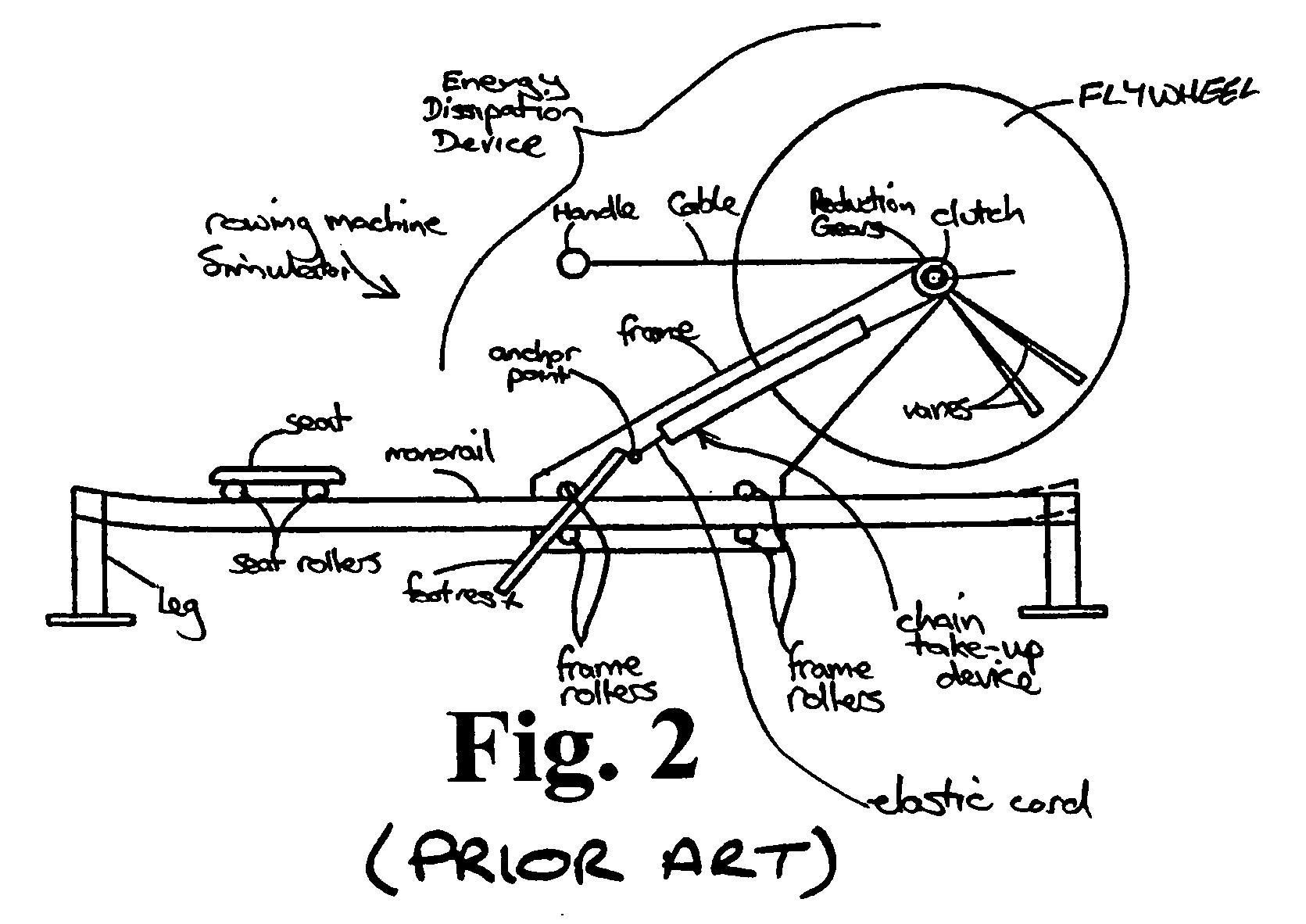

Rowing Machine Simulators

InactiveUS20080261782A1Stable simulatorMovement coordination devicesCardiovascular exercising devicesAbsorbed energyEarly phase

One aspect is an energy storage device for a rowing machine simulator having a rowing handle connected to an energy dissipation device. The energy storage device is configured to be disposed intermediate the rowing handle and the energy dissipation device and configured to elastically absorb a predetermined proportion of the force applied to the rowing handle by an oarsman during the early phase of a stroke. The elastically absorbed energy is released during later phases of said stroke.

Owner:ROWPERFECT

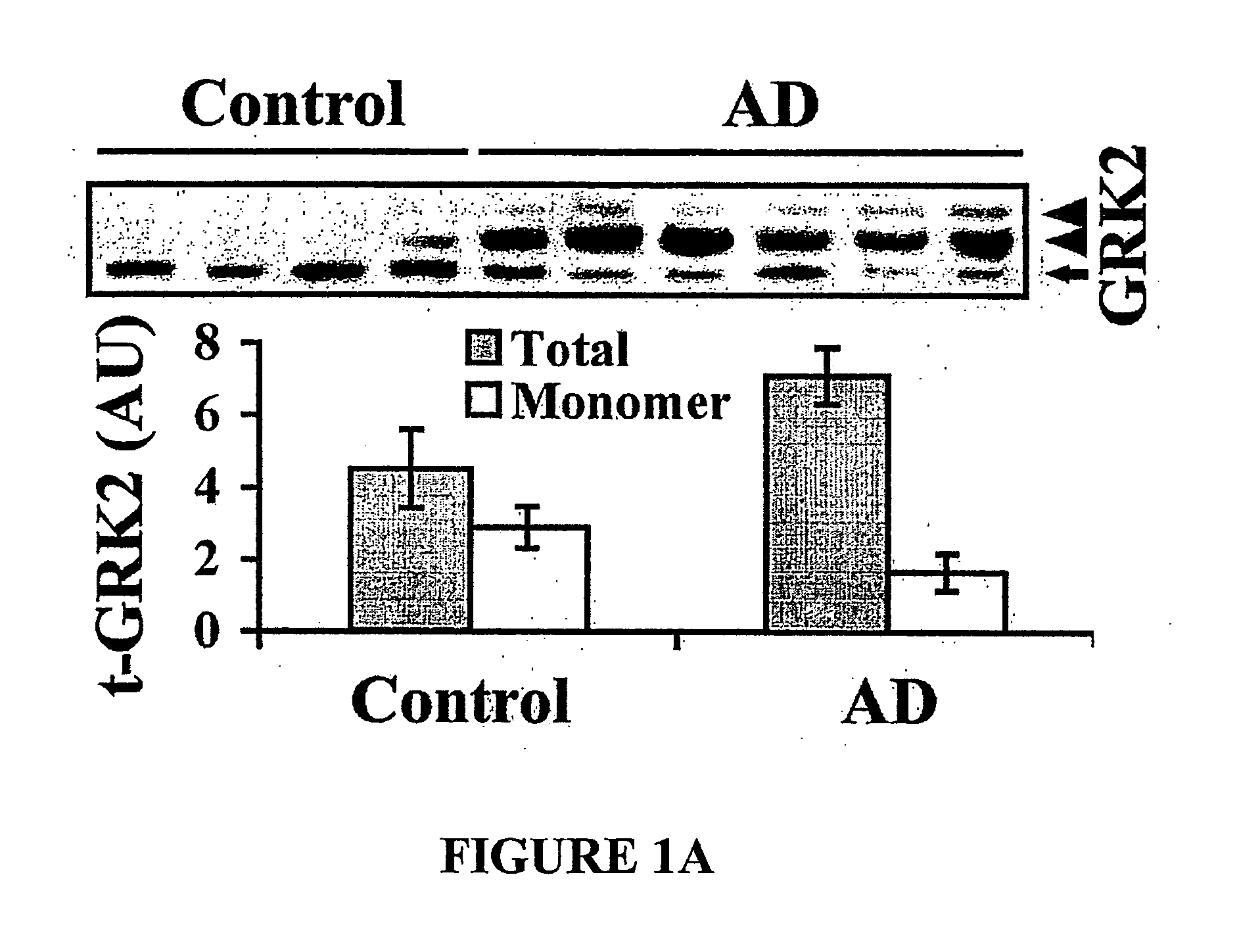

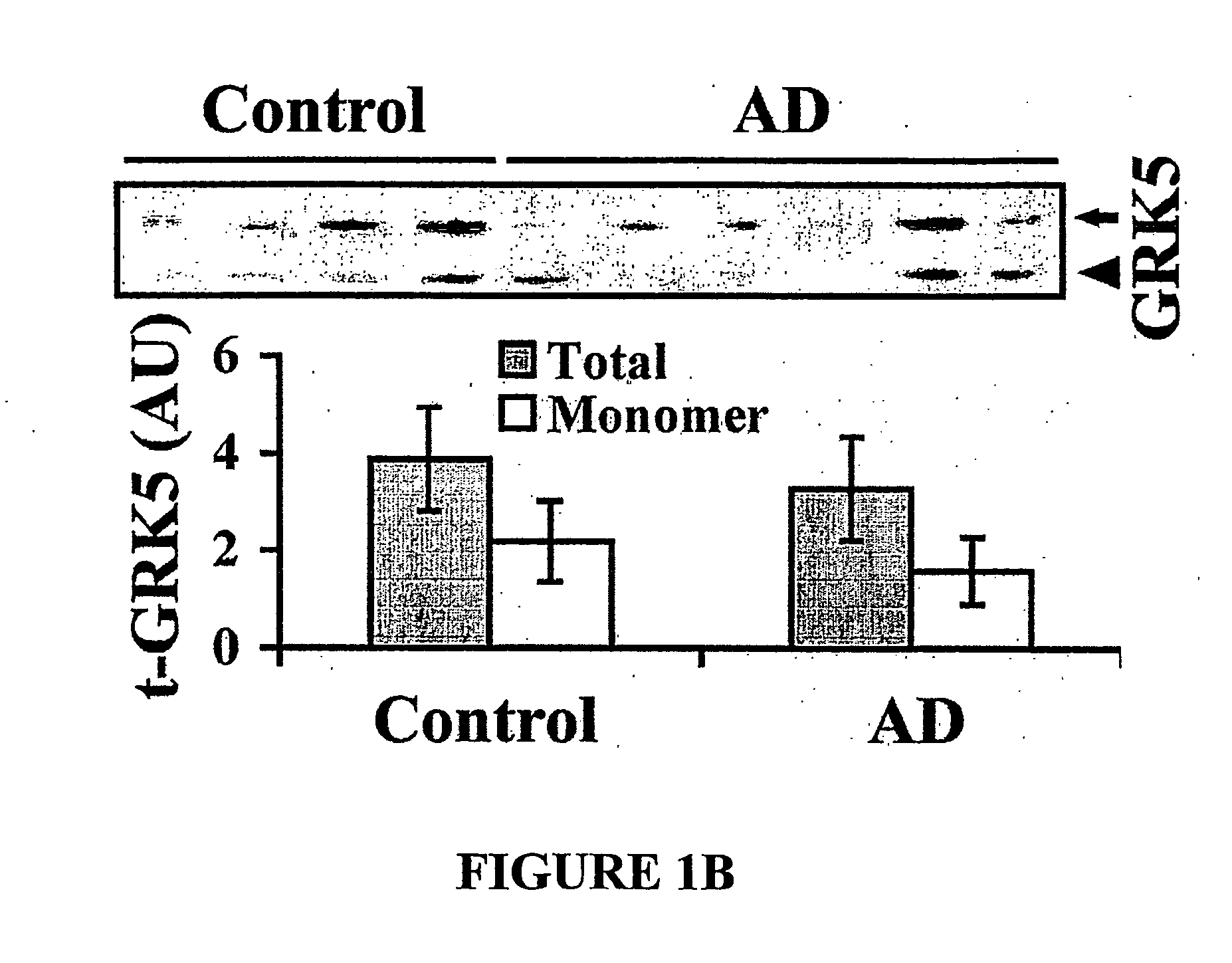

Method of detecting and preventing alzheimer's disease, particularly at prodromal and early stages

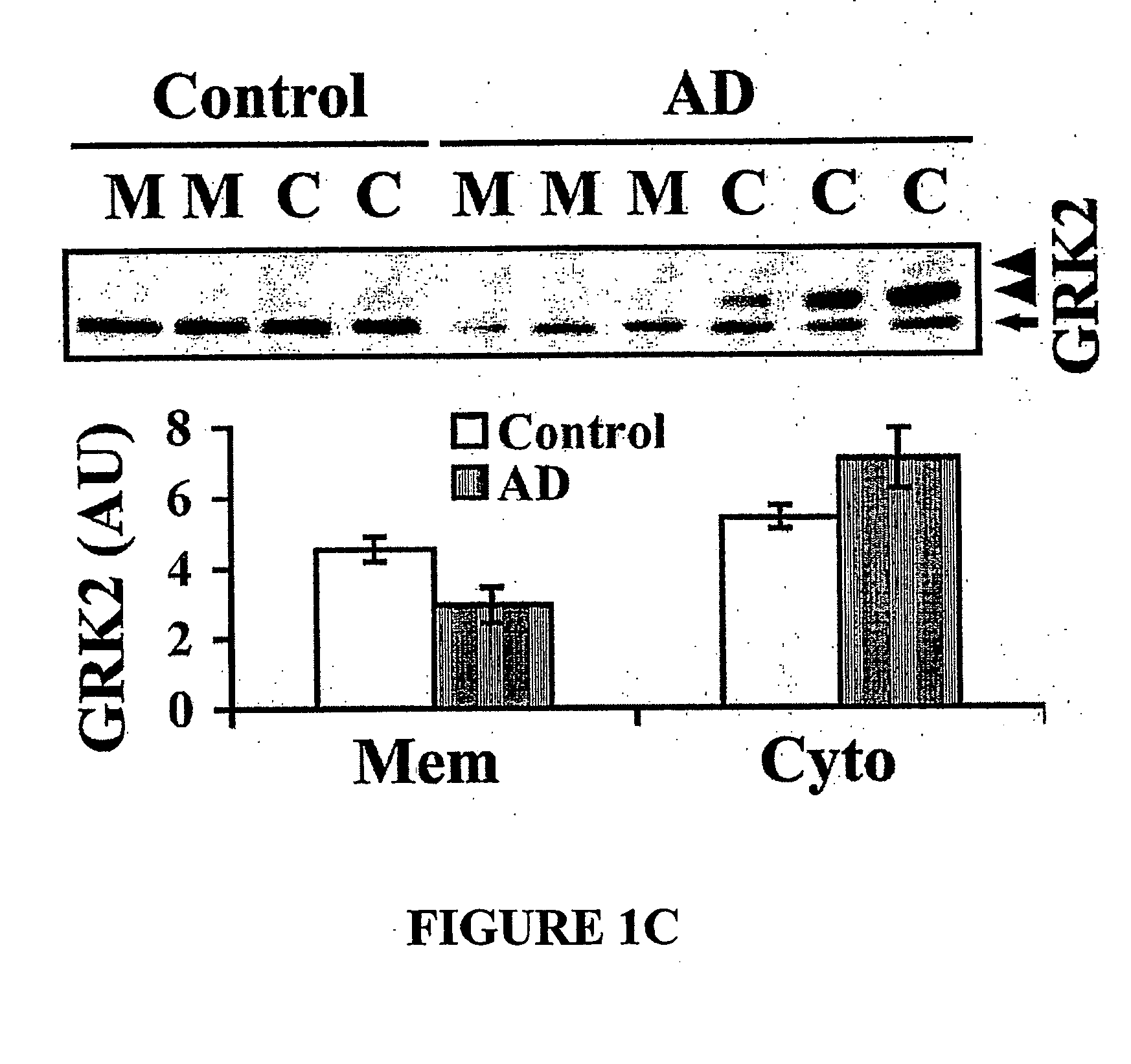

InactiveUS20050272025A1Preventing or suppressing Alzheimer's disease progressionCompound screeningNervous disorderSubcellular distributionAmyloid beta

A method of detecting Alzheimer's disease includes detecting a disruption or alteration in normal sub-cellular distribution of G-protein receptor kinases (GRKs), particularly GRK2 and GRK5. The disruption is caused by abnormal accumulation of soluble β-amyloid. The prevention or suppression of the disease progression at prodromal or early stages includes correction of GRK dysfunction.

Owner:U S GOVERNMENT REPRESENTED BY THE DEPT OF VETERANS AFFAIRS

Immunological analytical method and device for the determination of advanced glycosylation end products (AGEs)

The invention provides an immunological analytical method and devices for determination of the advanced glycosylation end products (AGEs), comprising a reagents for determining the AGEs, which comprises a displaying carrier suspension and the antigen or antibody immobilized on the surface of the said displaying carrier; and a test strip, comprising of: a base plate, and constitutive parts provided on the said base plate. After infusing the said reagent into the said test strip, the immunological reaction of the AGEs antigen or antibody can be determined based on the agglutination phenomenon or accompanied changes of absorbance or color and the presence or raised level of the AGEs in the diabetic patient can be known accordingly such that the practitioner can prevent the occurrence of the complications, or block further the progression of the complications at the earlier stage.

Owner:LIU YUNG HSIANG +1

Gene chip for gynecologic malignant tumor early screening and detection method thereof

InactiveCN101230390AClear functionEasy to sampleMicrobiological testing/measurementMortality rateOvarian cancer

The invention provides a method of manufacturing an oligonucleotide gene chip for screening and diagnosing the normally gynecological malignant tumor in early phase and the method of detecting the same. The method uses the related genes of normally gynecological malignant tumor (breast cancer, ovarian cancer and uterine cancer) as control, and determines whether the patient has the malignant tumor by manufacturing the oligonucleotide and chip hybridizing and detecting. The invention provides a detecting method of screening and diagnosing the normally gynecological malignant tumor in early phase based on gene chip, which makes the characteristic gene of the normally gynecological malignant tumor into a gene chip so as to keep the consistence of the clinic detecting condition. The method can screen and diagnose the normally malignant tumor ASAP. With convenience in sampling and good consistence, the method of the invention is prone to popularize; by proper application, the cancer mortality can be reduced by 1 / 3.

Owner:HUBEI UNIV

Method for isolating stem cells and stem cells derived from a pad-like tissue of teeth

InactiveUS20090162326A1Easy to doReadily availableBiocideDigestive systemDevelopmental stageDeveloping tooth

The invention relates to a method for isolating non-embryonic stem cells from a tissue that is located in immediate vicinity of immature, developing teeth or wisdom teeth. The invention further relates to non-embryonic stem cells derived from said tissue. The method according to the invention utilises a living soft tissue residing underneath the dental papilla 12 in immediate vicinity of the apical side of a developing tooth, which is clearly distinguished from other tooth tissue, such as dental papilla 12 or follicle. The pad-like tissue 16 can only be detected in a defined, specific developmental stage in an early phase of root formation. That is, identifying and separating the pad-like tissue 16 is only possible from the appearance of the bony alveolar fundus to the end of the formation of the root of the tooth.

Owner:STIFTUNG CAESAR +1

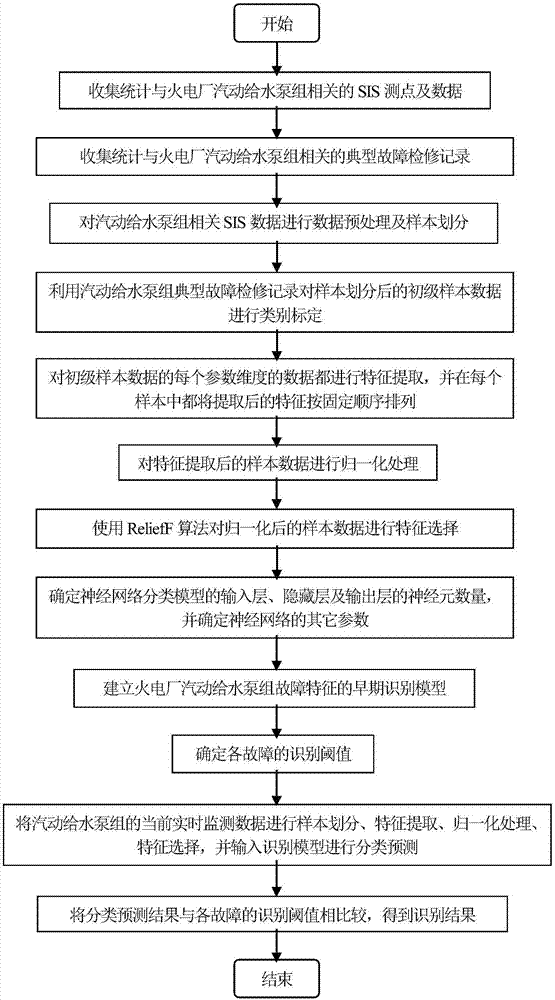

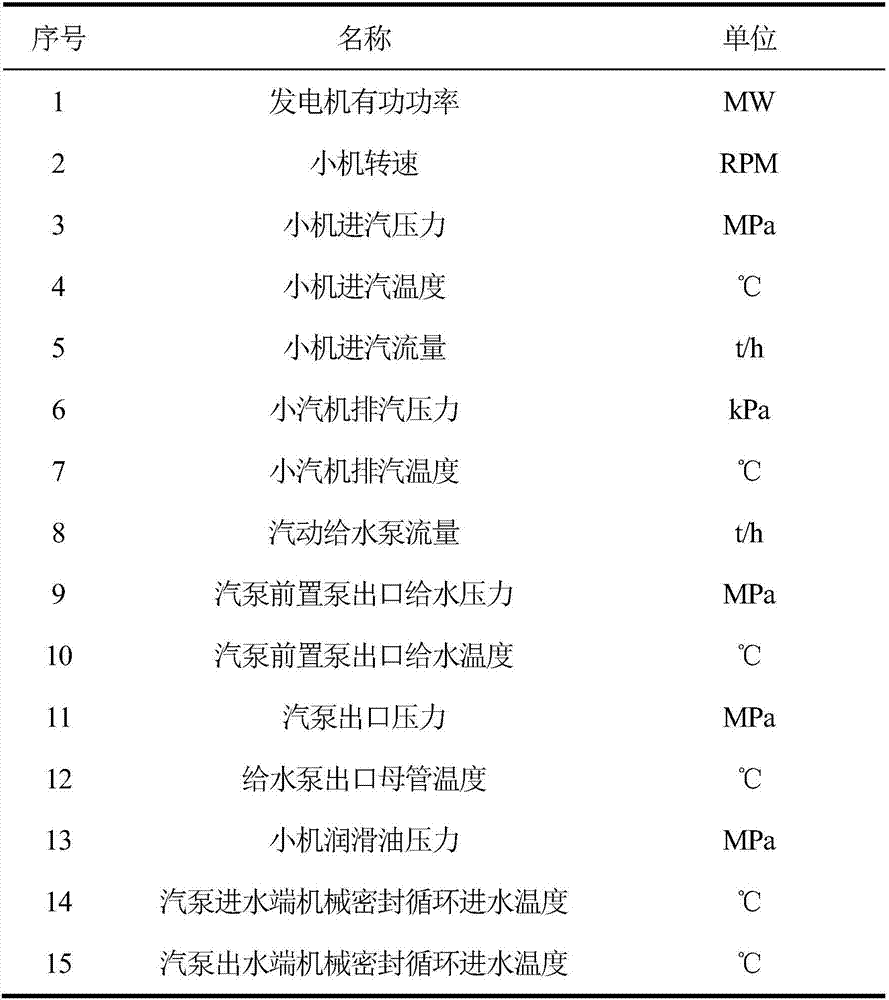

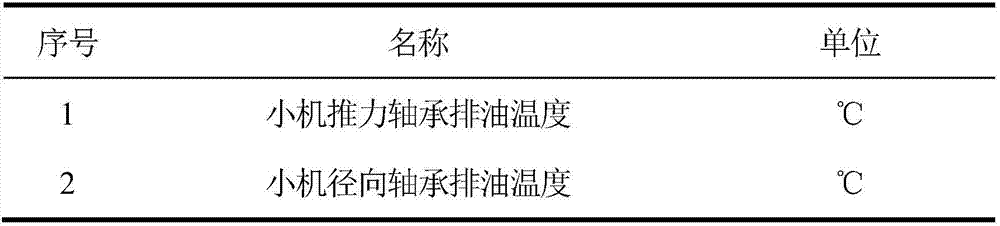

Early recognition method of thermal power plant steam feed pump fault features

InactiveCN107480731AExtended availabilityReduce failure ratePump testingCharacter and pattern recognitionMeasurement pointEngineering

An early recognition method of thermal power plant steam feed pump fault features depend on the supervision information system (SIS) of a thermal power plant configured by a lot of thermal power plants, and through joining and processing of historical data of related measurement points of a steam feed pump set and the typical fault maintenance record of the steam feed pump set in an SIS database, the neural network classification method in the data mining algorithm is employed to realize the classification of the data features prior to the generation of the typical faults of the steam feed pump set so as to realize that a classification model can perform identification of fault features and perform timely alarm at the early phase when the fault features are represented in the data to select time to perform maintenance and avoid generation of accidents or unsafe events caused by device faults. The early recognition method of the thermal power plant steam feed pump fault features depends on the SIS, is convenient to use and high in practicality, finds new values for massive historical data stored by the SIS of the thermal power plant and explores new direction for the state maintenance of the steam feed pump set even the thermal power plant or more devices or systems.

Owner:西安西热电站信息技术有限公司

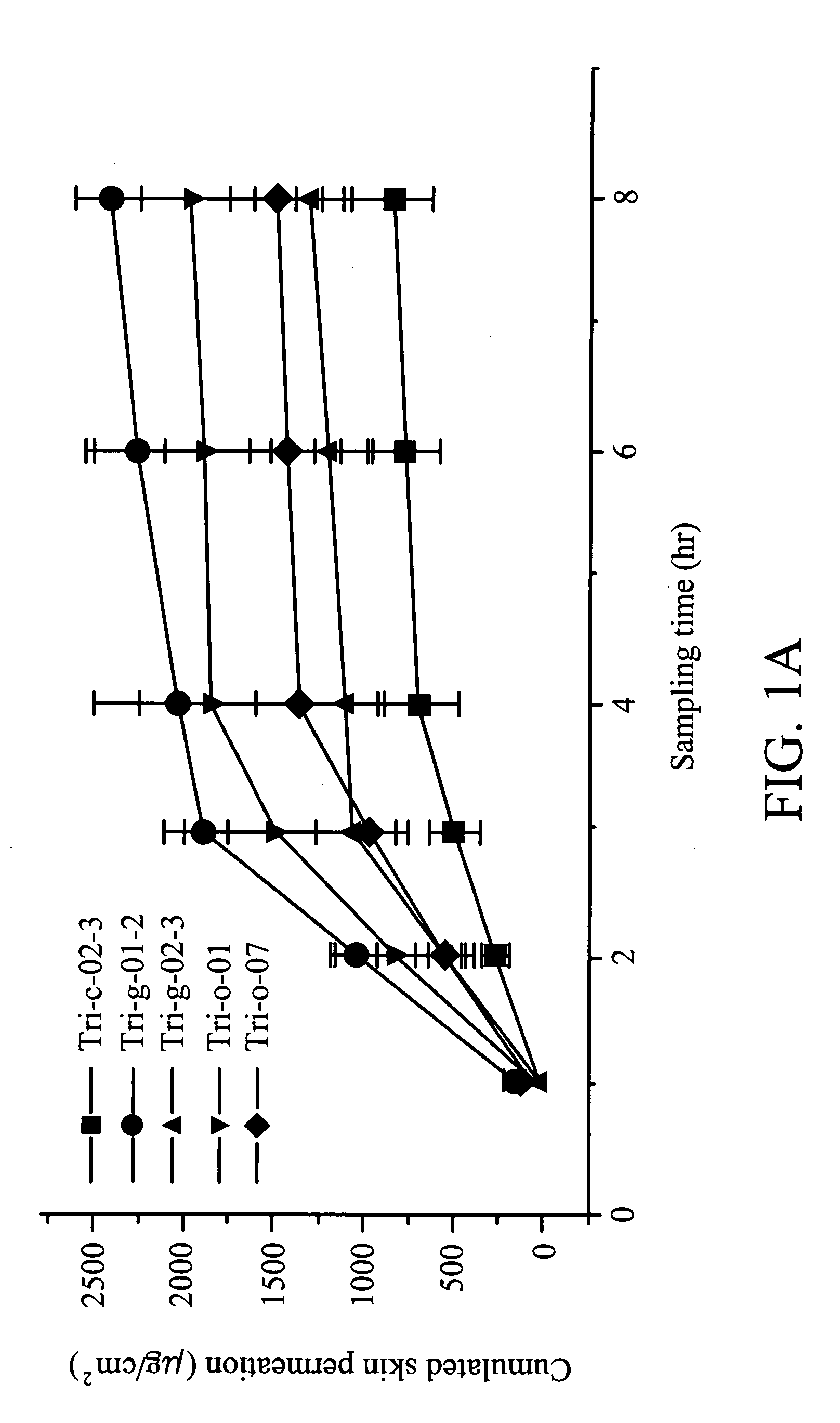

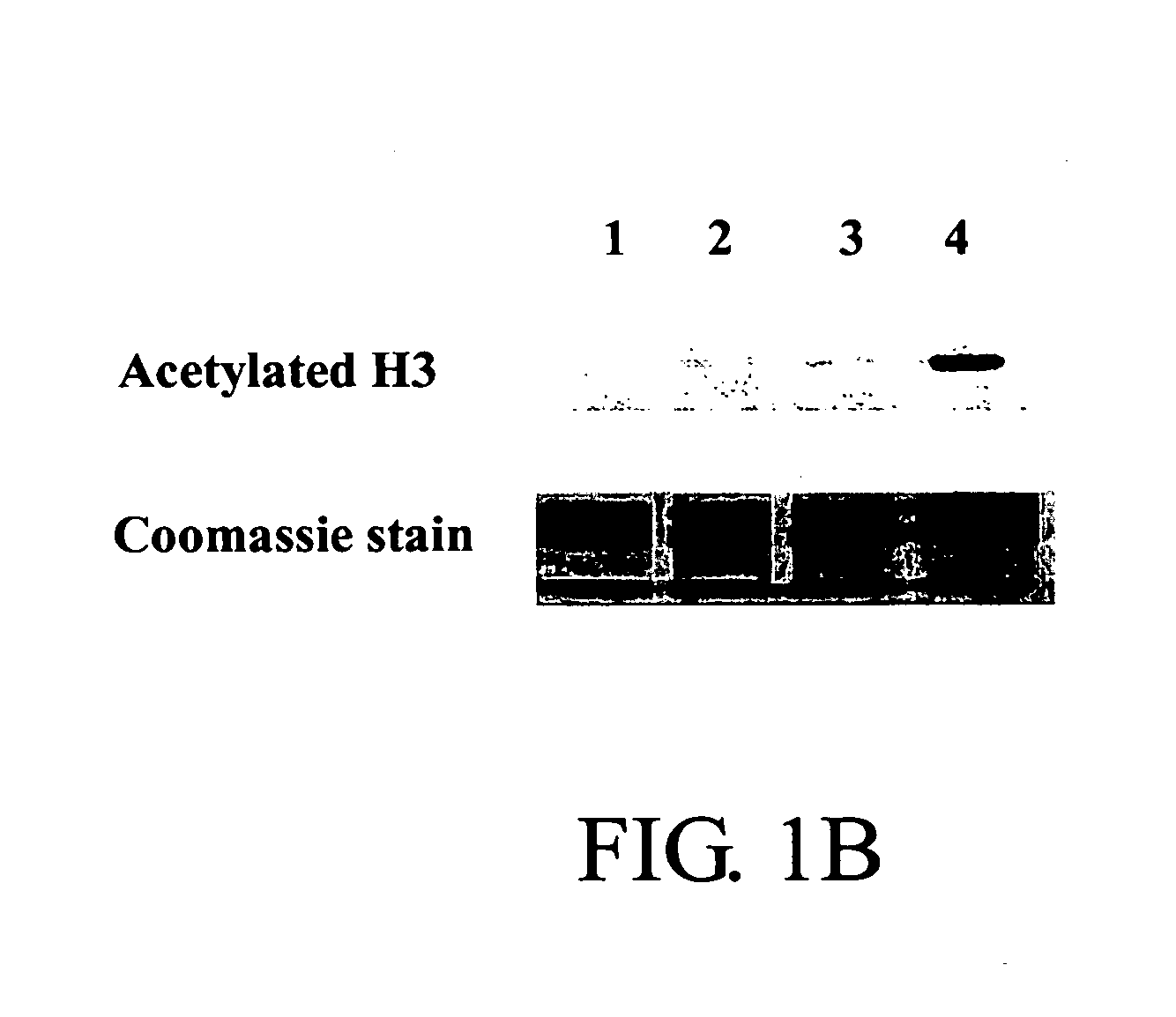

Histone hyperacetylating agents for promoting wound healing and preventing scar formation

InactiveUS20070072793A1Preventing fibroproliferative disorderInhibits the formation of scarsBiocideCyclic peptide ingredientsTissue remodelingLate phase

A method for promoting wound healing and preventing scar formation in a variety of wounds in skin, mucosa, and cornea. The method comprises administering a therapeutically effective amount of a histone deacetylase inhibitor or a hyperacetylating agent. The histone deacetylase inhibitor or hyperacetylating agent is capable of stimulating multiple cytokines / growth factors in the early phase of wound healing, and suppressing fibrogenic cytokines / growth factors in the late phase of tissue remodeling in the wound site, and is useful in promoting epithelial cell re-growth and reducing excessive collagen accumulation, which results in rapid wound closure with reduced scaring.

Owner:SUNNY PHARMTECH

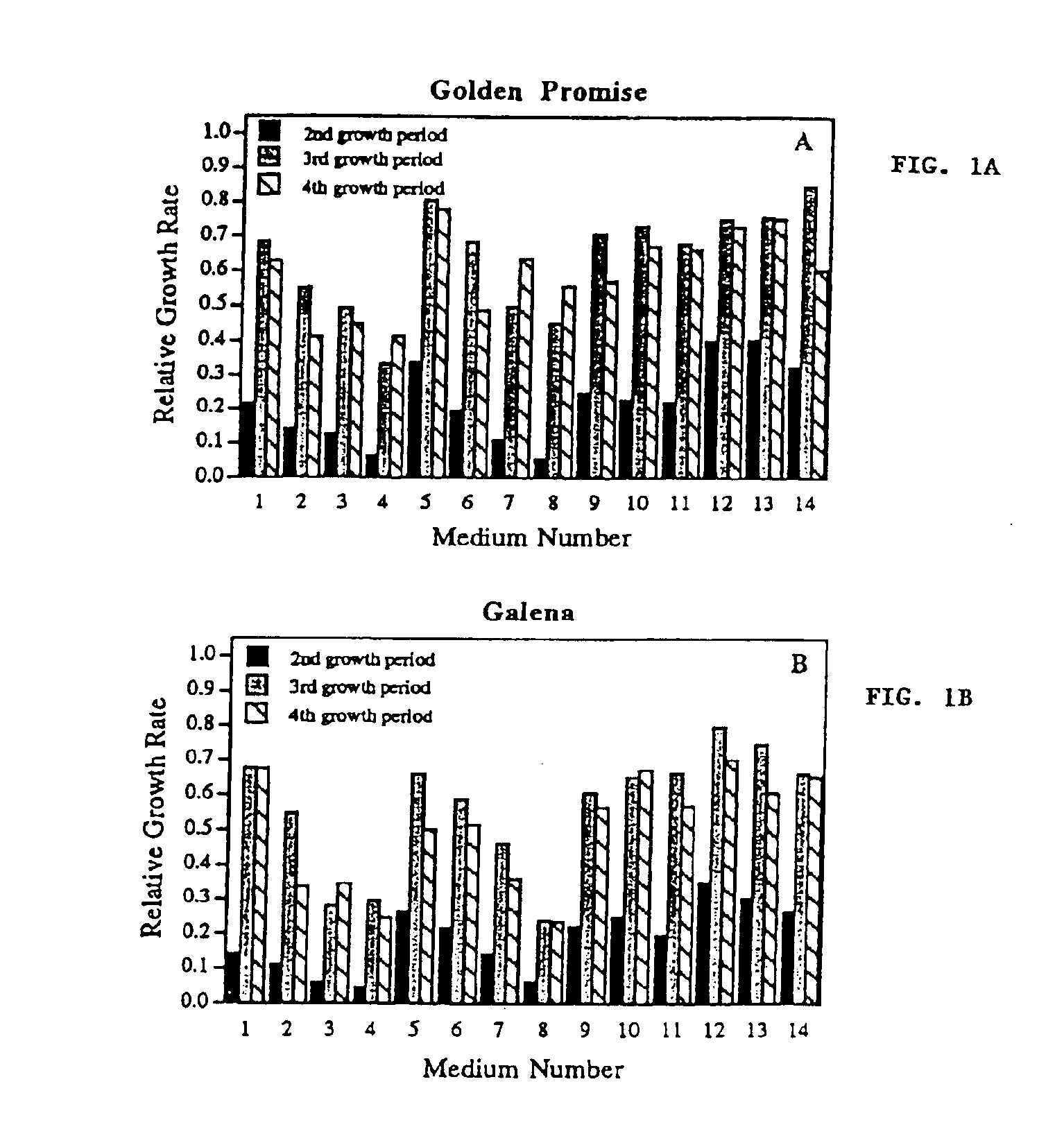

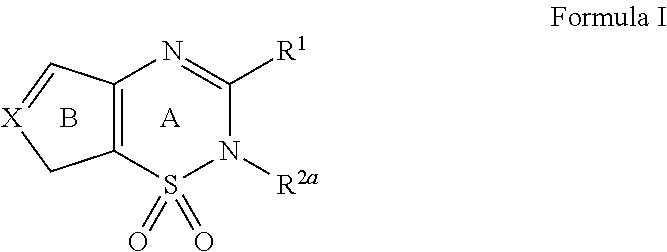

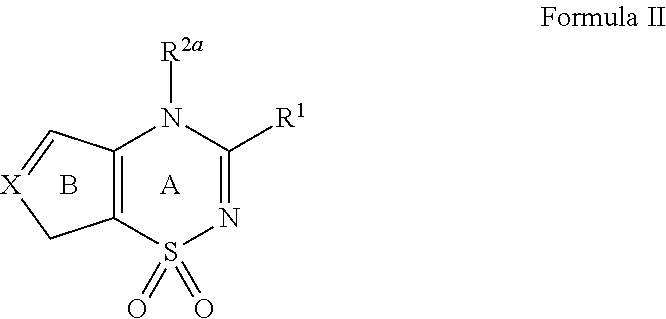

Compositions and methods for plant transformation and regeneration

InactiveUS7102056B1High regeneration frequencyReduce variationSugar derivativesOther foreign material introduction processesMicroparticleCopper

Improved compositions and methods for transformation and regeneration of plants from embryogenic callus are disclosed that include, for example: use of an intermediate-incubation medium after callus induction to increase the competence of the transformed cells for regeneration; dim light conditions during early phases of selection; use of green callus tissue as a target for microprojectile bombardment; and media with optimized levels of phytohormones and copper concentrations.

Owner:RGT UNIV OF CALIFORNIA

Repair of defects or lesions in cartilage and bone using a chondro-regulative matrix

InactiveUS20110184381A1Promote healingInduce the repair of lesions in cartilage and boneBiocidePowder deliveryProgenitorMatrix method

Methods and compositions are provided for the treatment and repair of defect in the cartilage in partial- or full-thickness defects in joints of animals, in particular humans. To induce cartilage formation, a defect in cartilage is filled with layers of thin flaps of synovium or of peritendineum, which contains chondro- and osteo-progenitor cells, with interposed layers of a matrix. The matrix contains a chondrogenic factor, which induces chondrogenesis of chondroprogenitor cells in the flaps, and an anti-hypertrophic agent, which arrest differentiation of chondrocytes in an early phase, in an appropriate delivery system. The matrix filling the bone area of a full-thickness defect may contain an osteogenic factor, which induces osteogenesis of osteoprogenitor cells. The layer of a flap between cartilage and bone areas may work as a barrier, which prevents blood vessels and associated cells from penetrating from the bone area into the cartilage area. To promote the induction of chondro- and osteo-genesis of the progenitor cells in the flaps of synovium or peritendineum effectively, the flaps may be treated with enzymes, e.g., matrix metalloproteinases or be punched by a needle before filling a defect.

Owner:UNIVERSITY OF BERN

Methods of treating prader willi syndrome and conditions associated with low basal metabolic rate or hyperphagia using a katp channel opener

InactiveUS20140364367A1Inhibit progressPeptide/protein ingredientsAnhydride/acid/halide active ingredientsDiseaseEugeroic

This invention relates to treating Prader-Willi Syndrome (PWS) using a KATP channel opener. The channel opener may be coadministered with other therapies used to treat PWS, such as human growth hormone, a wakefulness promoting agent, or a psychiatric or mood stabilizing drug, thereby allowing the baseline dosages of these other therapies to be decreased or making these other therapies unnecessary. The invention also relates to treating PWS based on the PWS nutritional phase of a patient, to prevent the patient's PWS nutritional phase from progressing or shift the patient's PWS nutritional phase back to an earlier phase. The invention further relates to treating PWS, and conditions associated with low basal metabolic rate or hyperphagia, with the KATP channel opener based on a patient's blood ketone levels.

Owner:SEDOGEN

Substrate noise tool

InactiveUS7480879B2Accurate representationFast simulationDetecting faulty computer hardwareComputer aided designGranularityParasitic capacitance

Owner:MASSACHUSETTS INST OF TECH

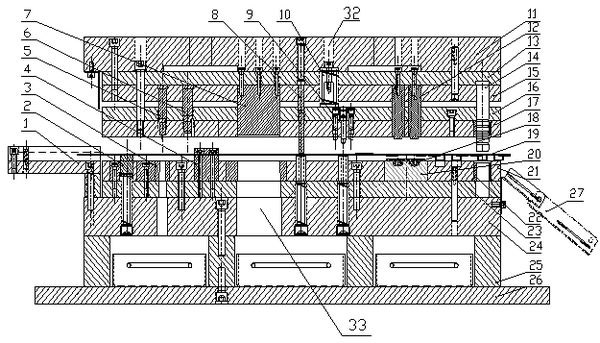

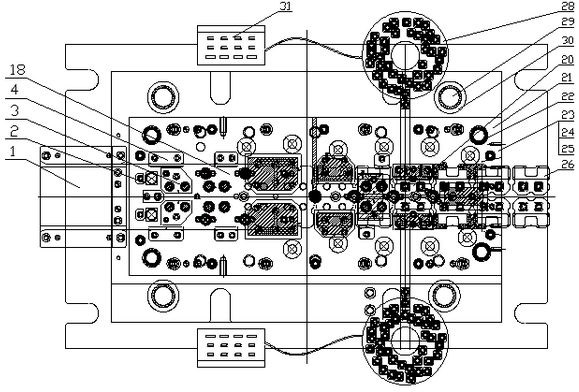

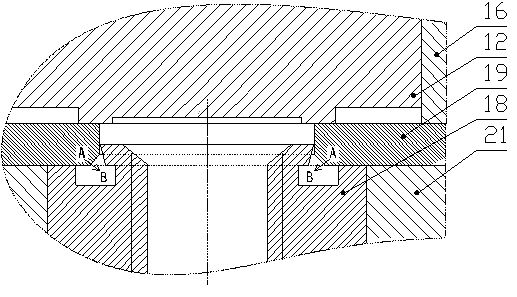

Continuous punching and nut riveting device for automobile door lock catch

The invention discloses a continuous punching and nut riveting device for an automobile door lock catch, which is used for continuously punching and riveting nuts on a material tape in the process of manufacturing the door lock catch. A die body consists of upper and lower die assemblies; an automatic nut conveyor connected with an automatic nut conveying electric control cabinet is arranged on front and rear sides of a lower die holder; when the material tape is subjected to early-phase blanking, chamfering and molding for riveting, the die is opened, the material tape is floated, the nut conveyor automatically feeds nuts of which the riveting surfaces face upwards, and puts the nuts into a riveting female die positioning groove below the material tape; an upper slide block descends, a riveting male die extrudes the material tape, and a lock catch plate material flows to a nut riveting taper available part so as to realize riveting. By adopting a mode of combining the automatic nut conveyor with a continuous nut riveting die, the production efficiency is greatly improved; the actions of automatically feeding and automatically conveying nuts are accurate; the material tape is accurately guided and positioned; and the produced workpieces are attractive in appearance, high in accuracy, high in riveting strength without disordered wires, stable in quality and environmentally-friendly; the labor intensity of a worker is greatly reduced; and the device can be used for riveting other products in different specifications and types.

Owner:XIANGYANG SUNRISE MACHINERY

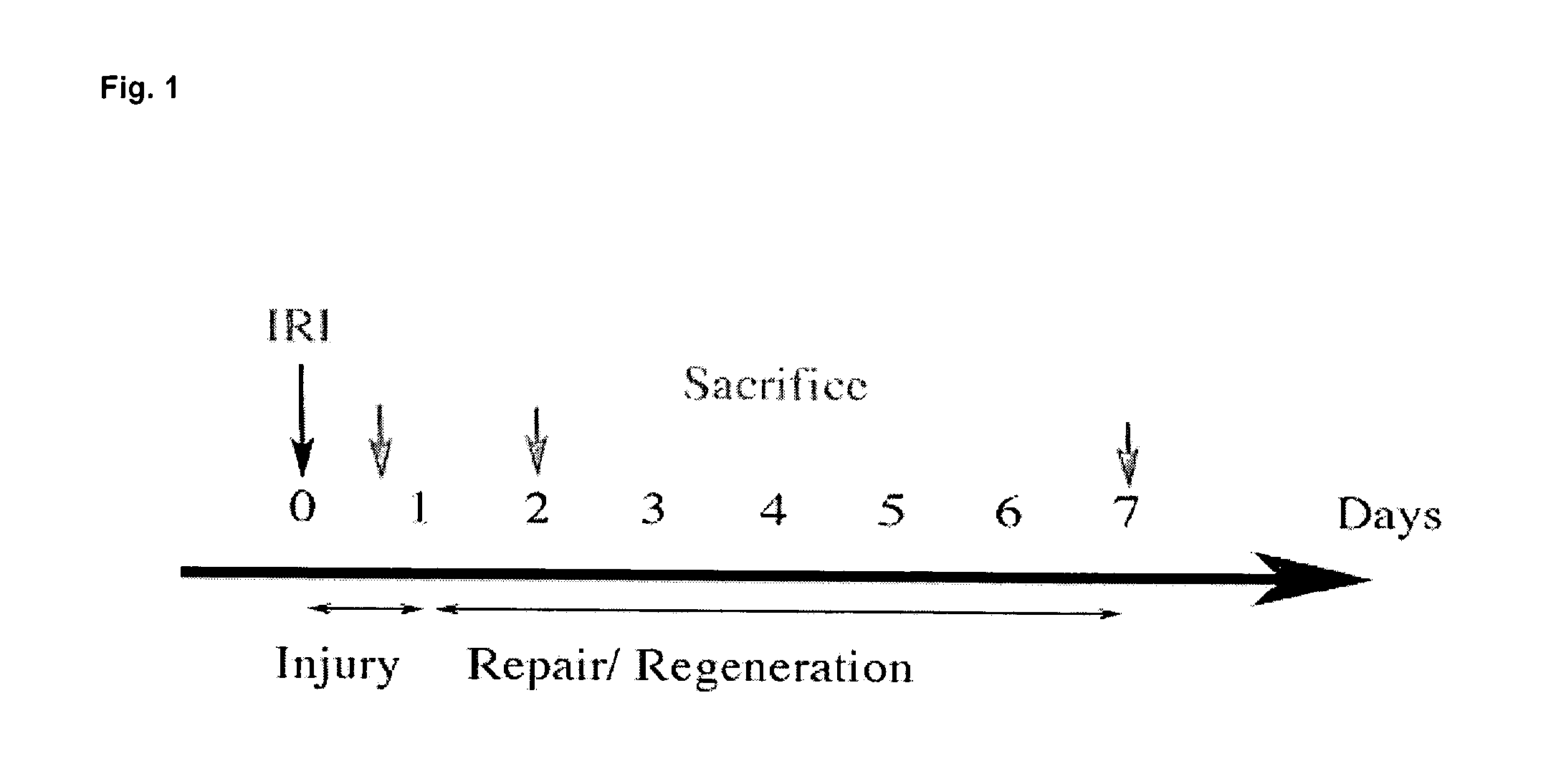

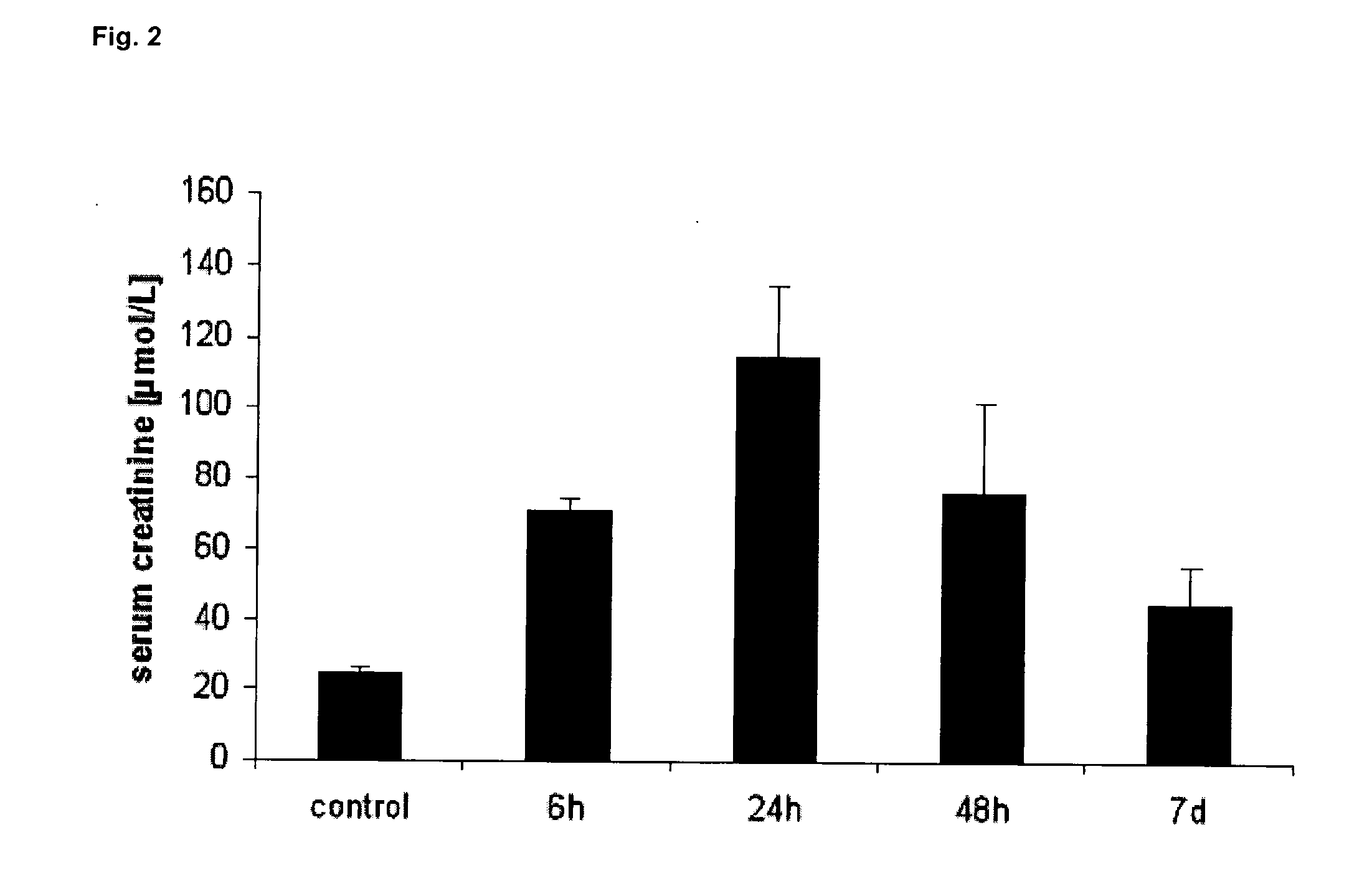

Biomarkers for determination of temporal phase of acute kidney injury

ActiveUS20130165338A1Shorten the timeAccurately and quickly carry-outMicrobiological testing/measurementLibrary screeningTest sampleBiomarker (petroleum)

The invention relates to a method for determining the temporal phase of acute kidney injury, comprising obtaining a test sample from a subject and measuring the expression level of at least one biomarker selected from the group comprising Chac1, Birc5 and Angpt17. The invention also relates to a method for determining the early early phase, the late early phase, the severity and / or timing of acute kidney injury via analysis of the biomarkers Chac1, Birc5 and / or Angptl7, in addition to a test kit for carrying out said methods and antibodies directed against Chac1, Birc5 or Angptl7.

Owner:MAX DELBRUECK CENT FUER MOLEKULARE MEDIZIN

Optimized technique of fertilization of lagging nitrogen fertilizer for paddy rice in cold farmland

InactiveCN1759651AImprove group qualityImprove root vitalityFertilising methodsAgricultural scienceEarly phase

An optimized fertilizer application technique for paddy rice in cold region features that the N fertilizer applied in early phase is decreased and the N fertilizer applied in later phase is increased for increasing yield and improving quality. The percentages of the N fertilizer applied in different stages are 45% for base fertilizer, 20% in early tiller stage, 15% for young ear differentiating stage and 20% for reduction division stage.

Owner:NORTHEAST AGRICULTURAL UNIVERSITY

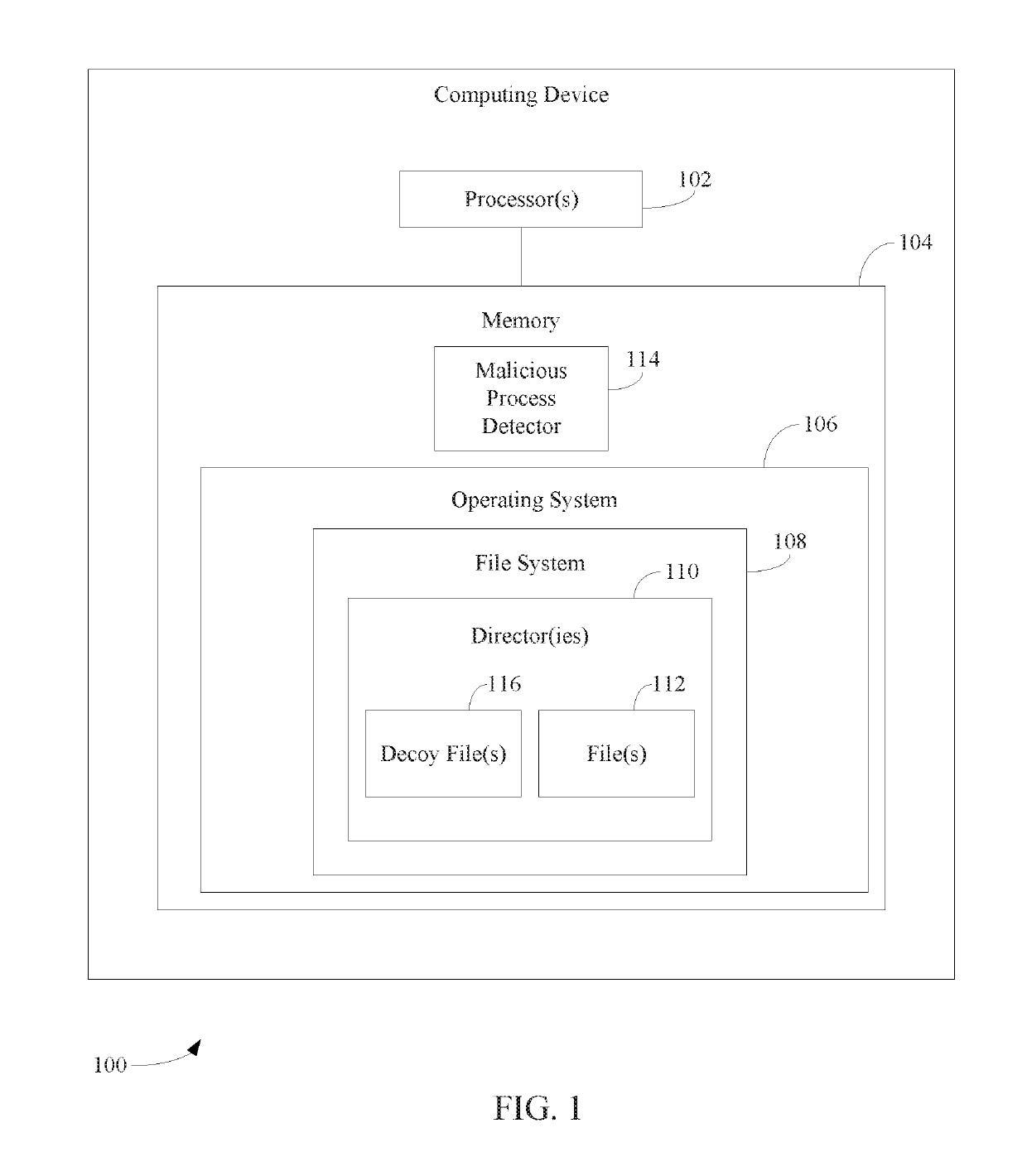

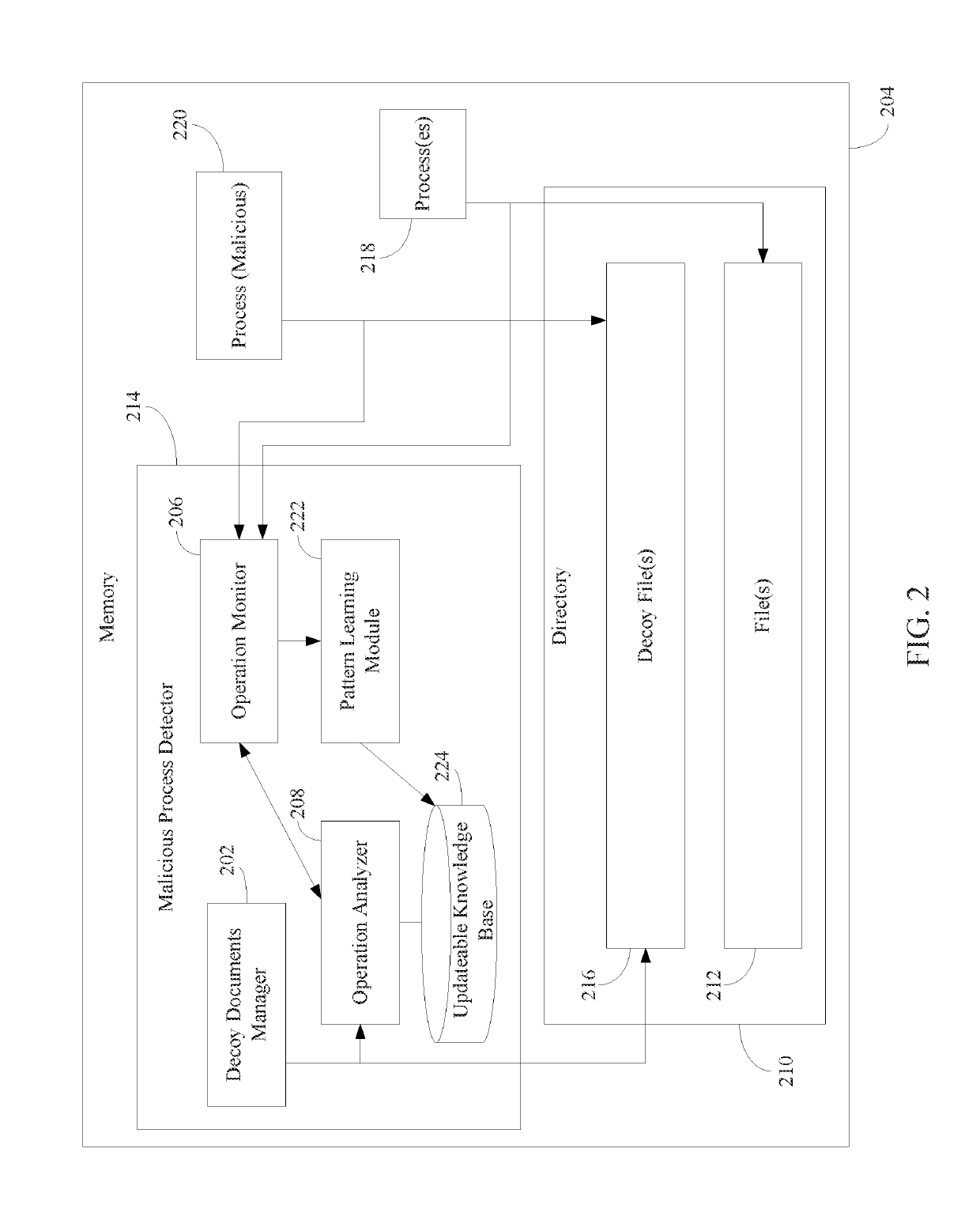

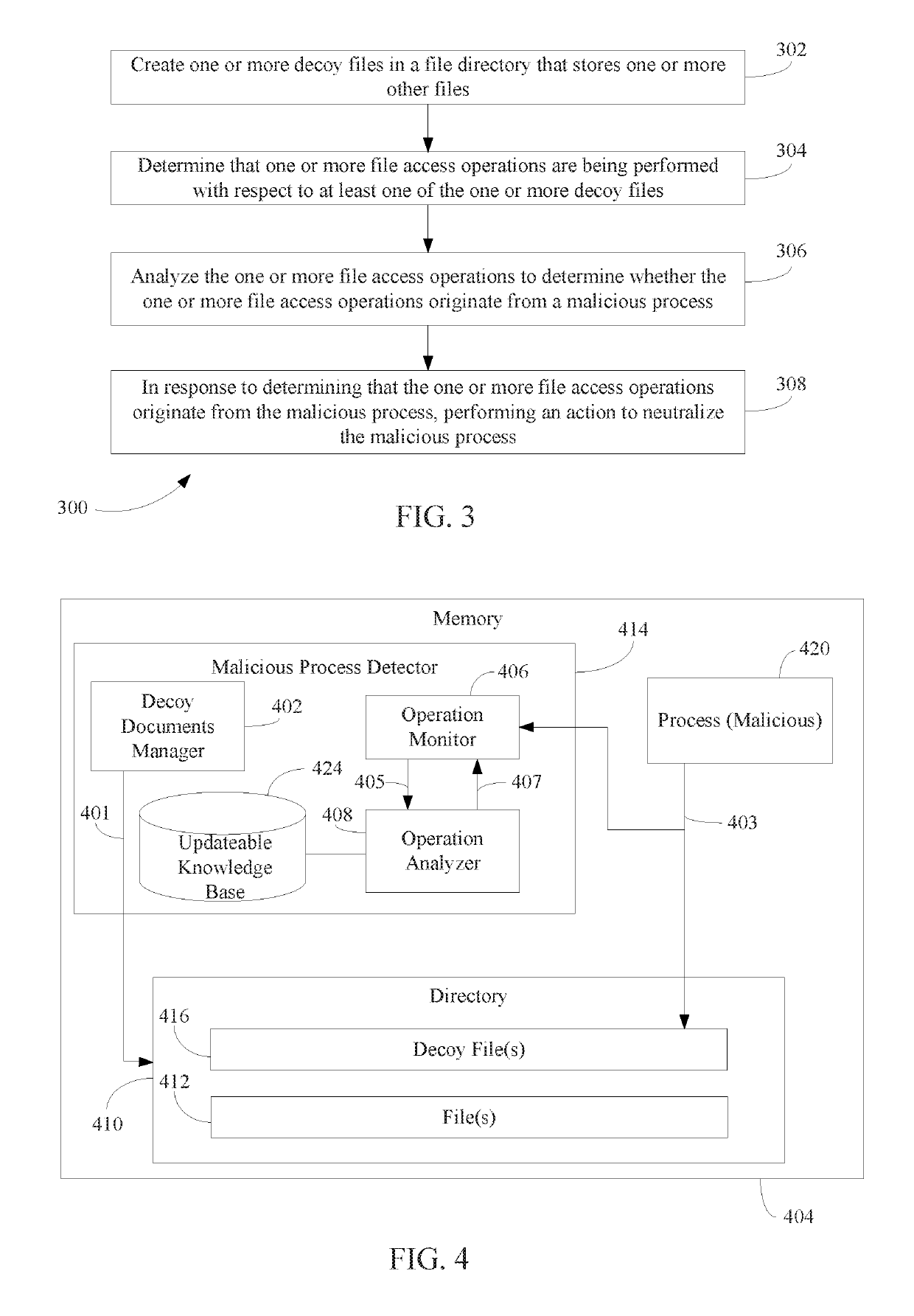

Early runtime detection and prevention of ransomware

Various automated techniques are described herein for the runtime detection / neutralization of malware executing on a computing device. The foregoing is achievable during a relatively early phase, for example, before the malware manages to encrypt any of the user's files. For instance, a malicious process detector may create decoy file(s) in a directory. The decoy file(s) may have attributes that cause such file(s) to reside at the beginning and / or end of a file list. By doing so, a malicious process targeting files in the directory will attempt to encrypt the decoy file(s) before any other file. The detector monitors operations to the decoy file(s) to determine whether a malicious process is active on the user's computing device. In response to determining that a malicious process is active, the malicious process detector takes protective measure(s) to neutralize the malicious process.

Owner:MORPHISEC INFORMATION SECURITY 2014