Patents

Literature

57 results about "Delayed phase" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Delayed sleep phase syndrome (DSPS) is a type of circadian rhythm sleep disorder. It’s also known as delayed sleep phase disorder or delayed sleep-wake phase disorder. DSPS is a problem with your internal body clock. If you have DSPS, you can’t fall asleep at a socially acceptable bedtime. Instead, your sleep is delayed by at least two hours.

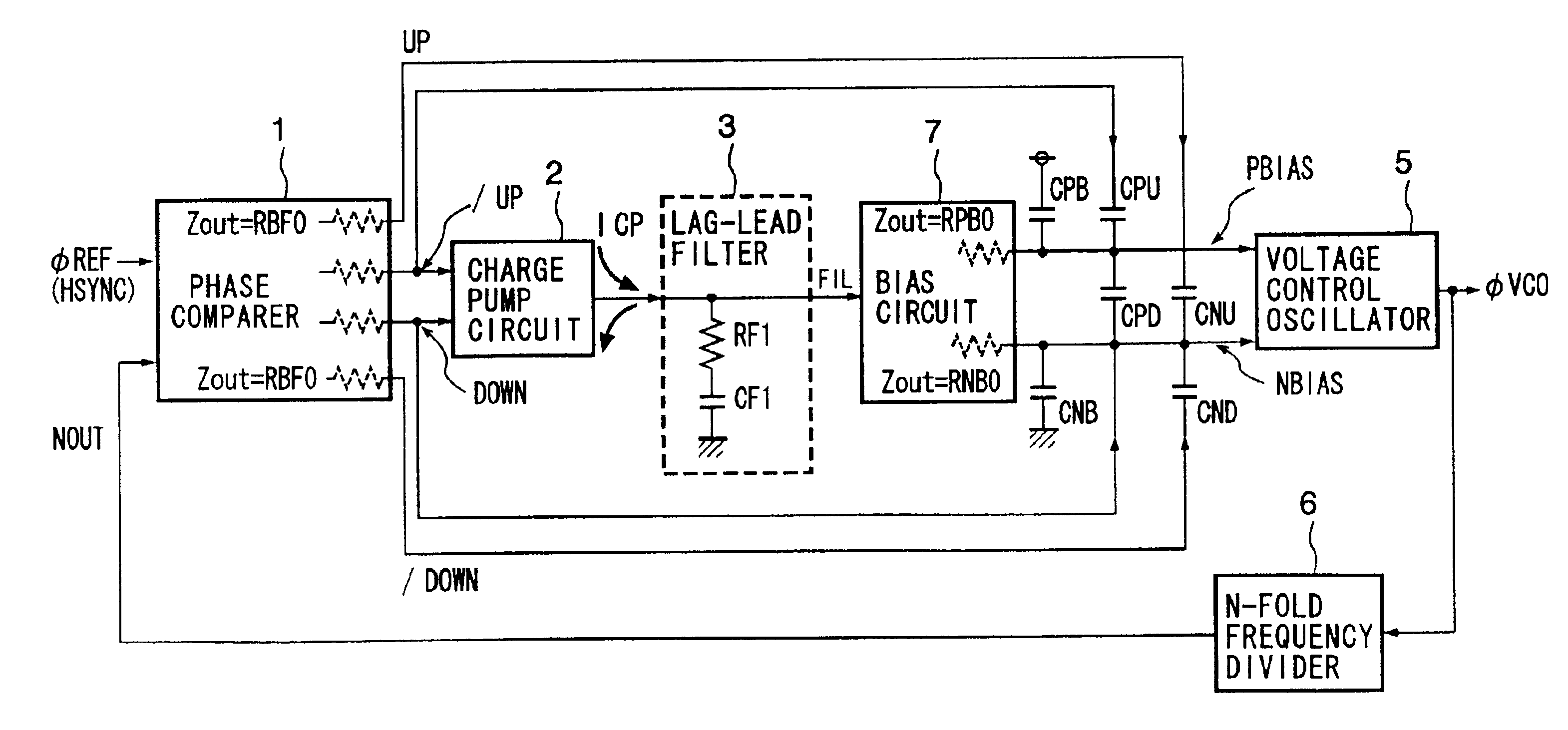

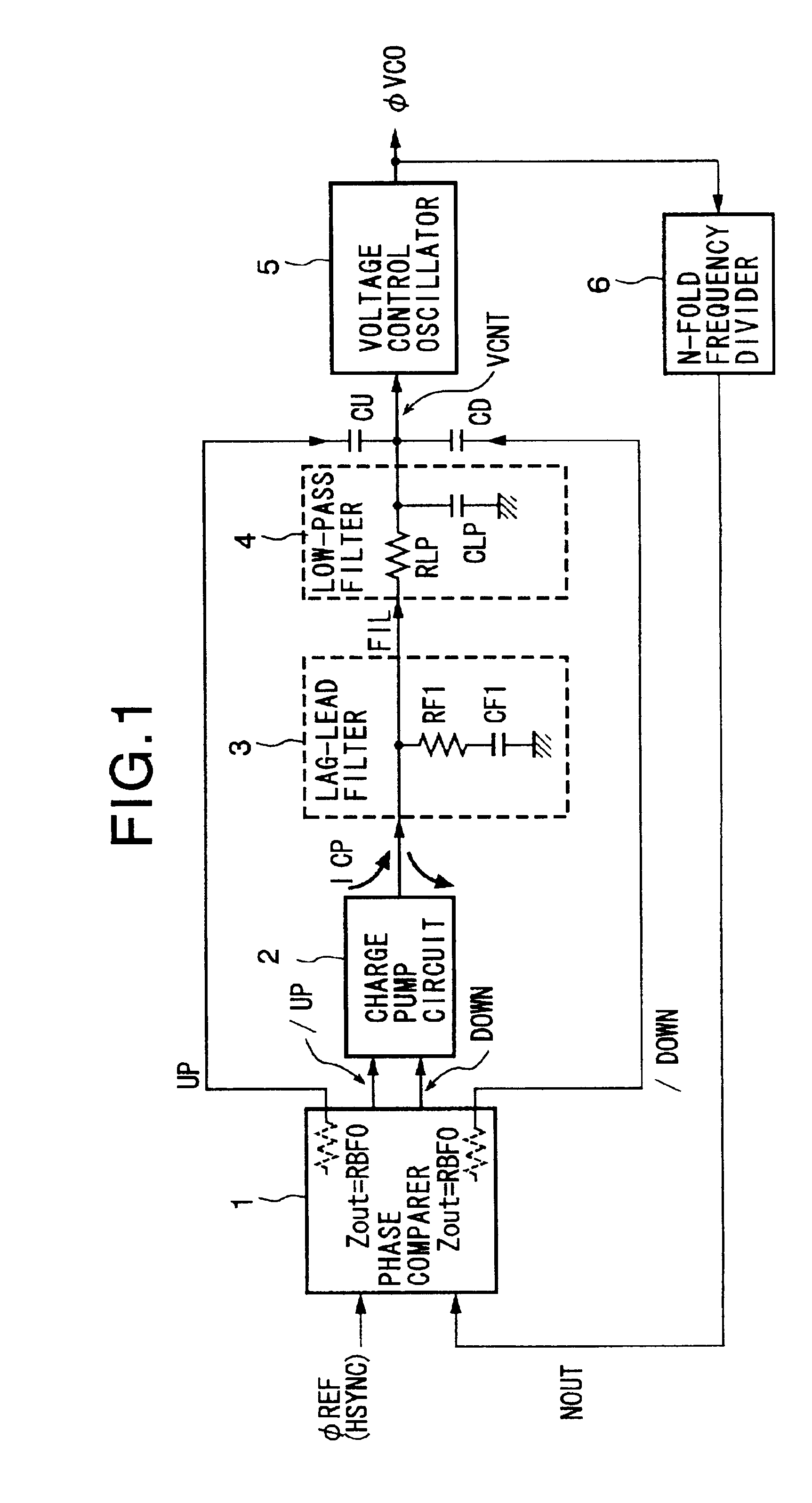

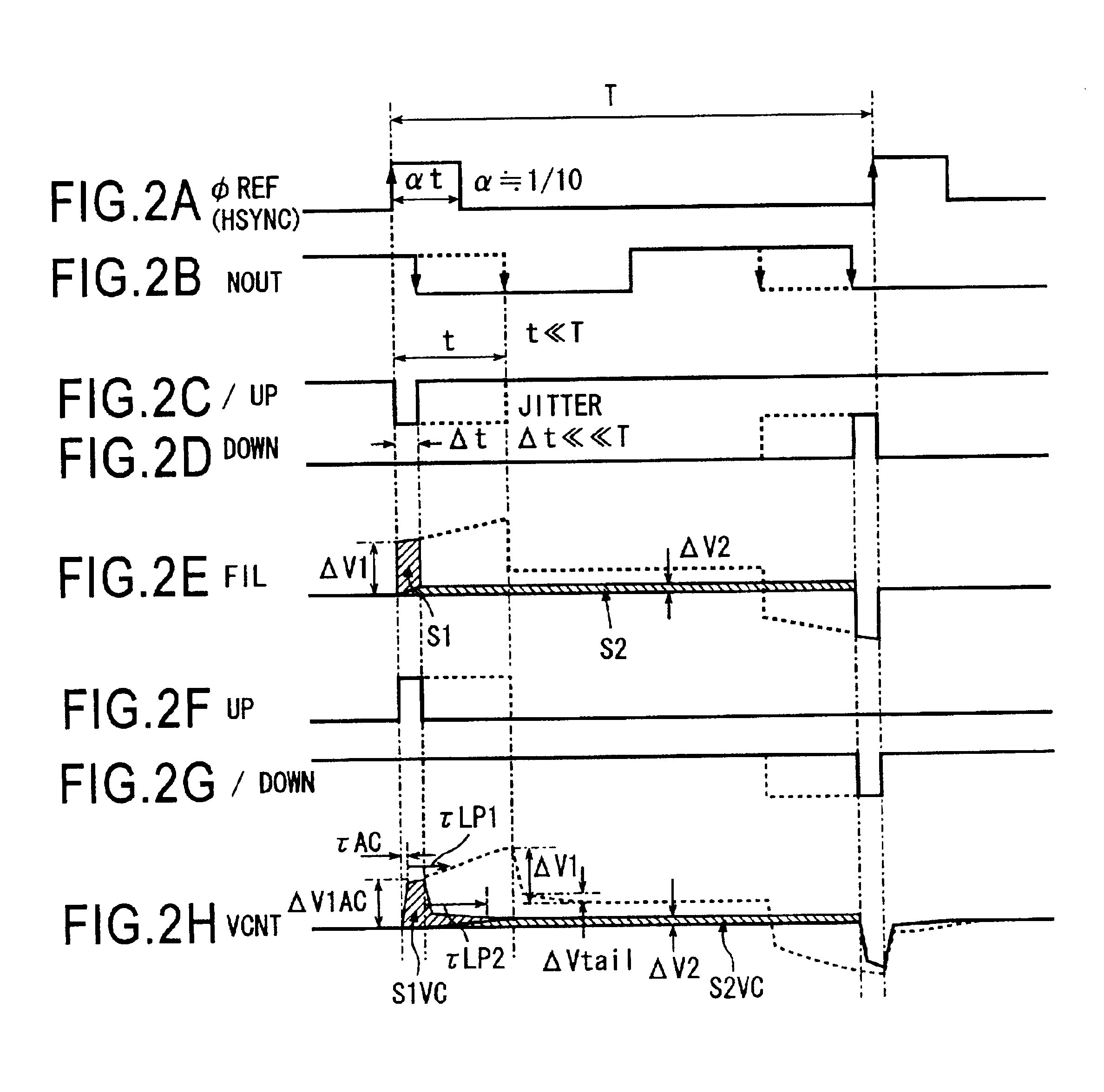

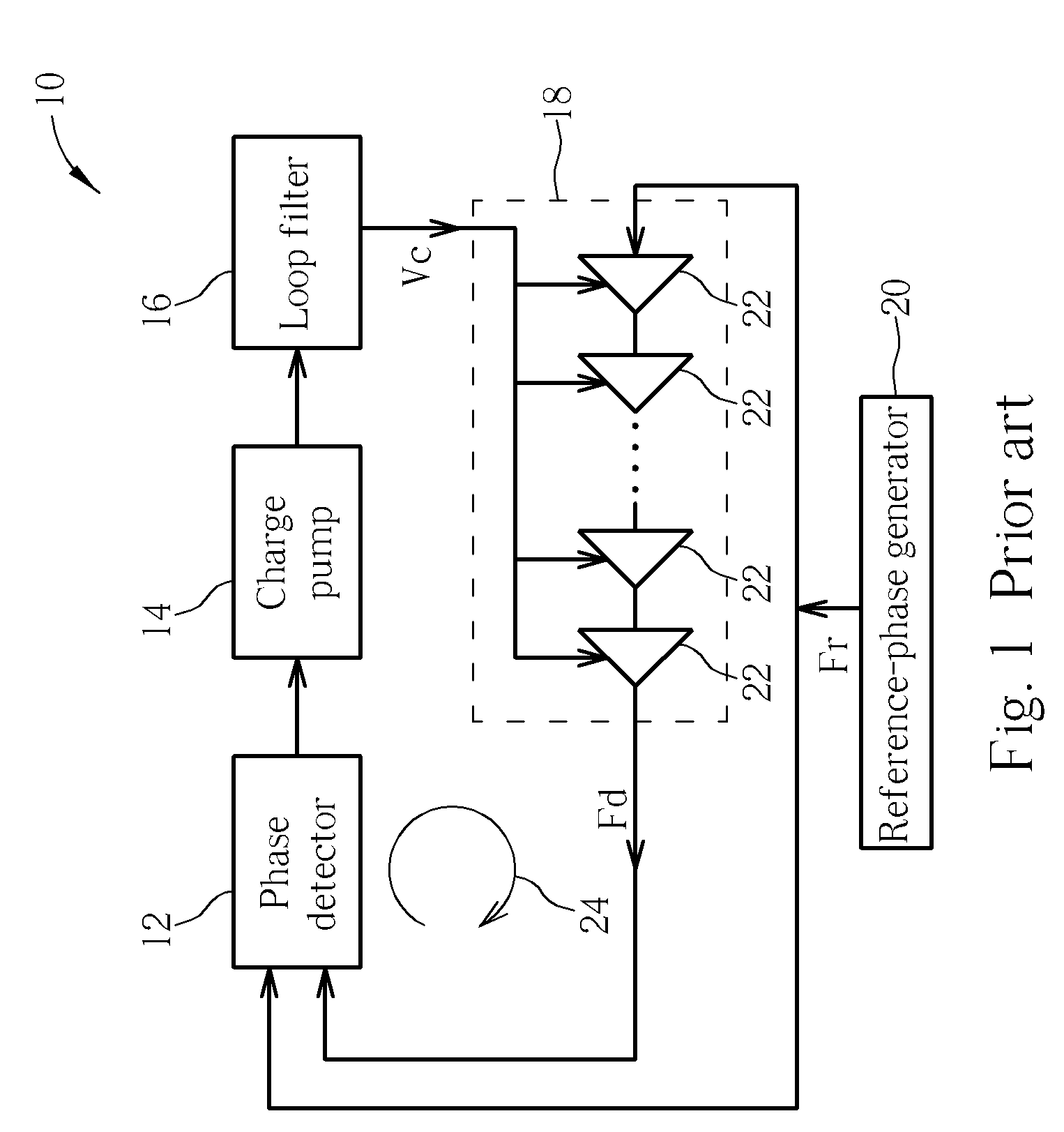

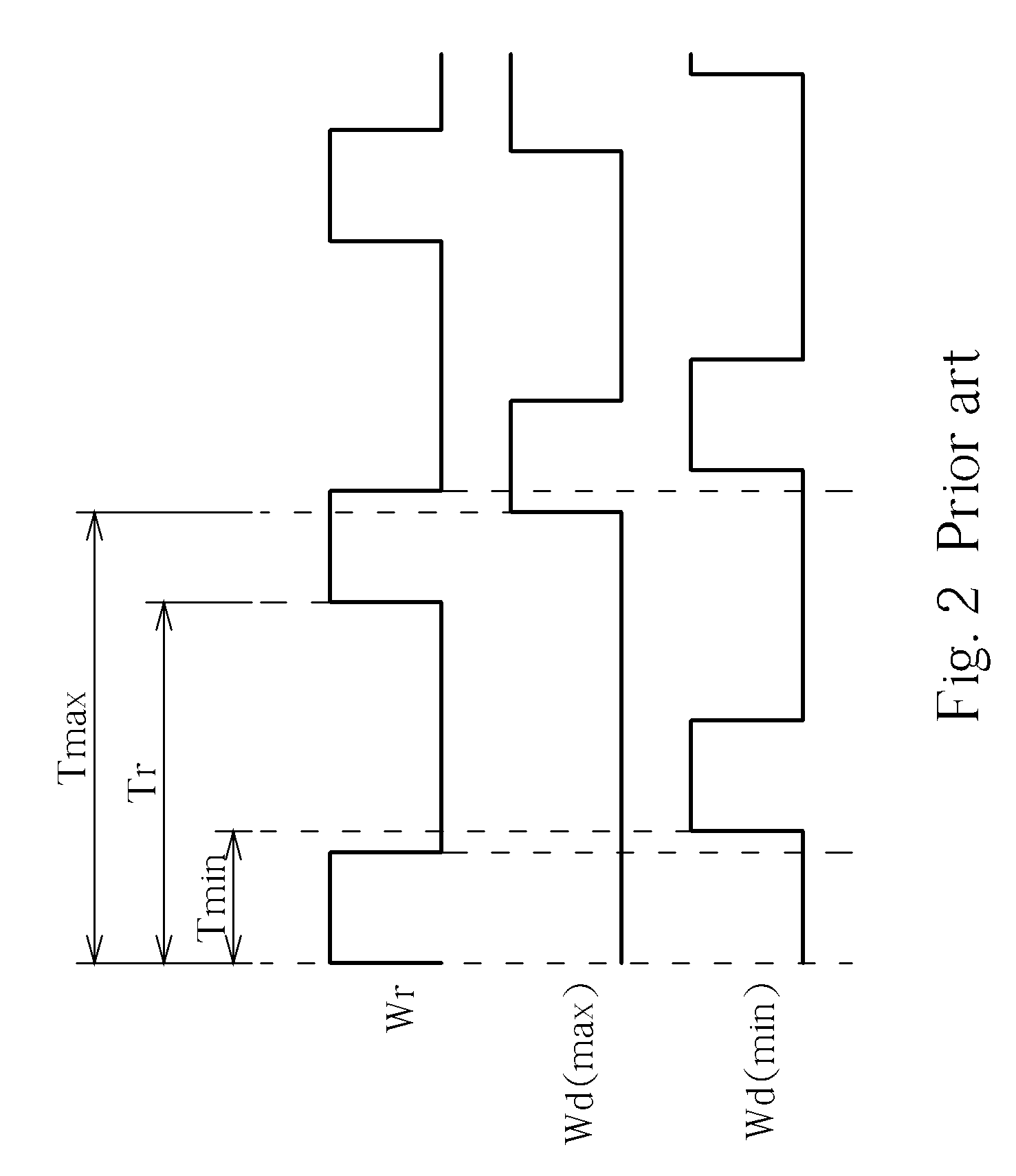

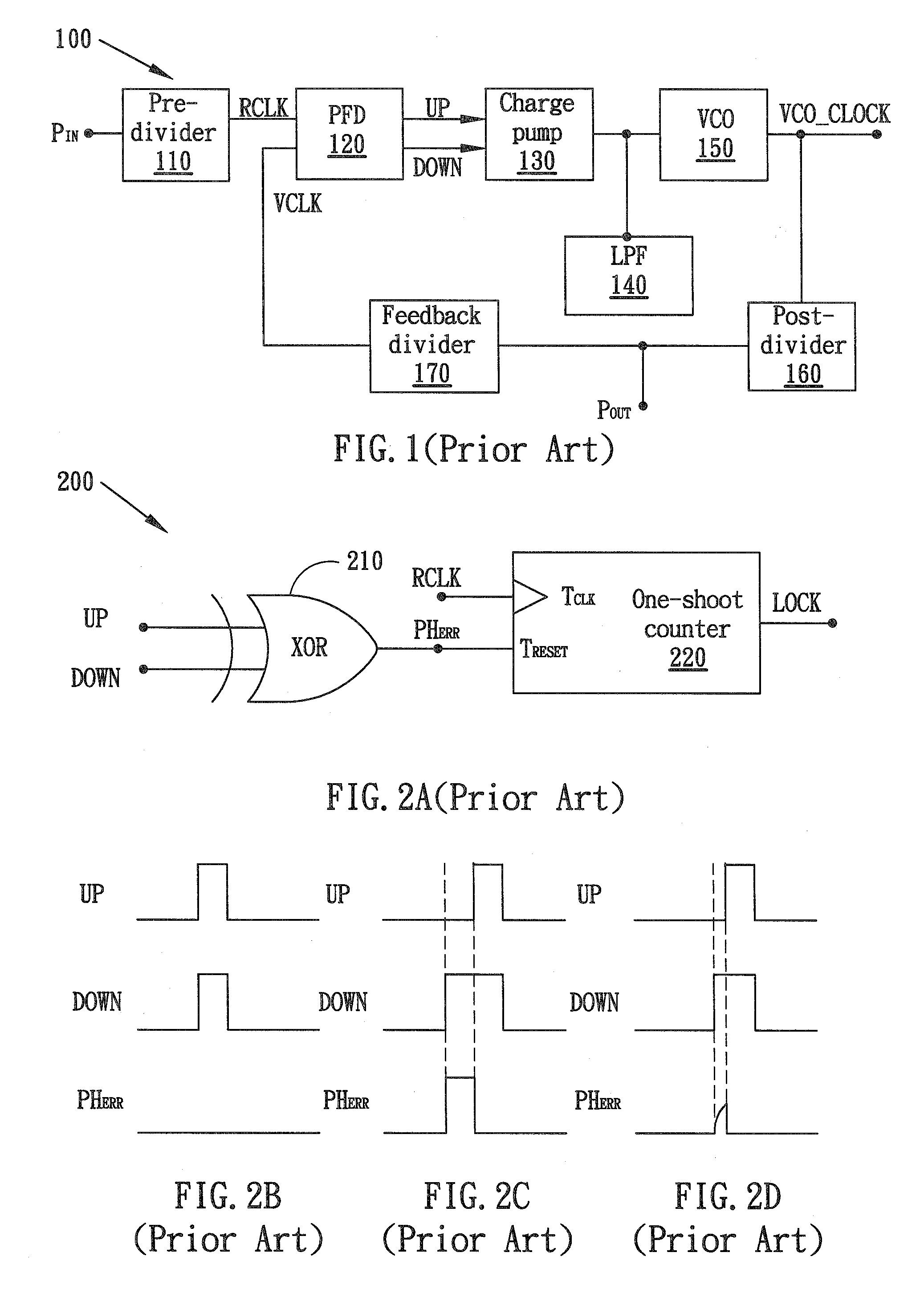

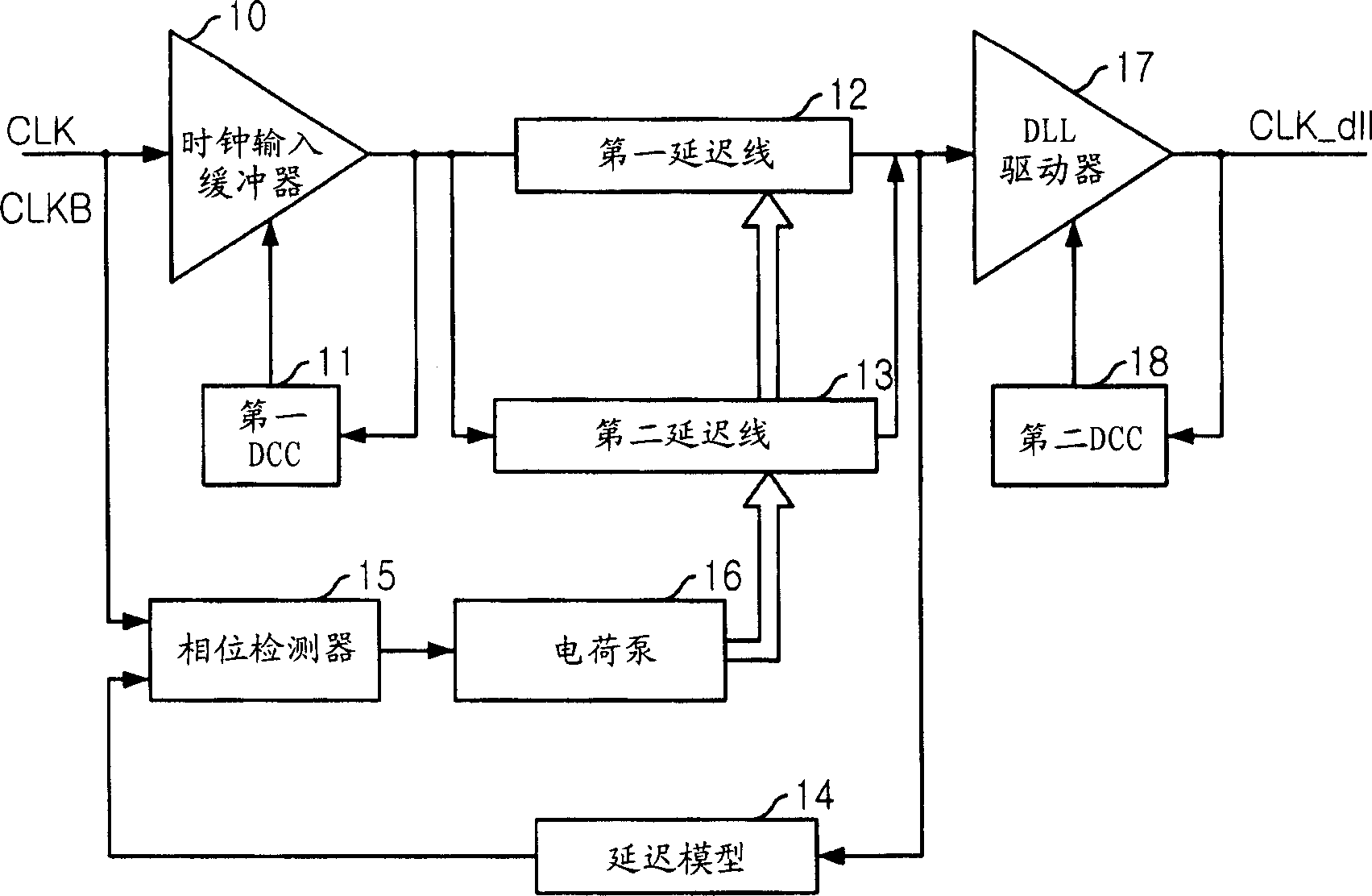

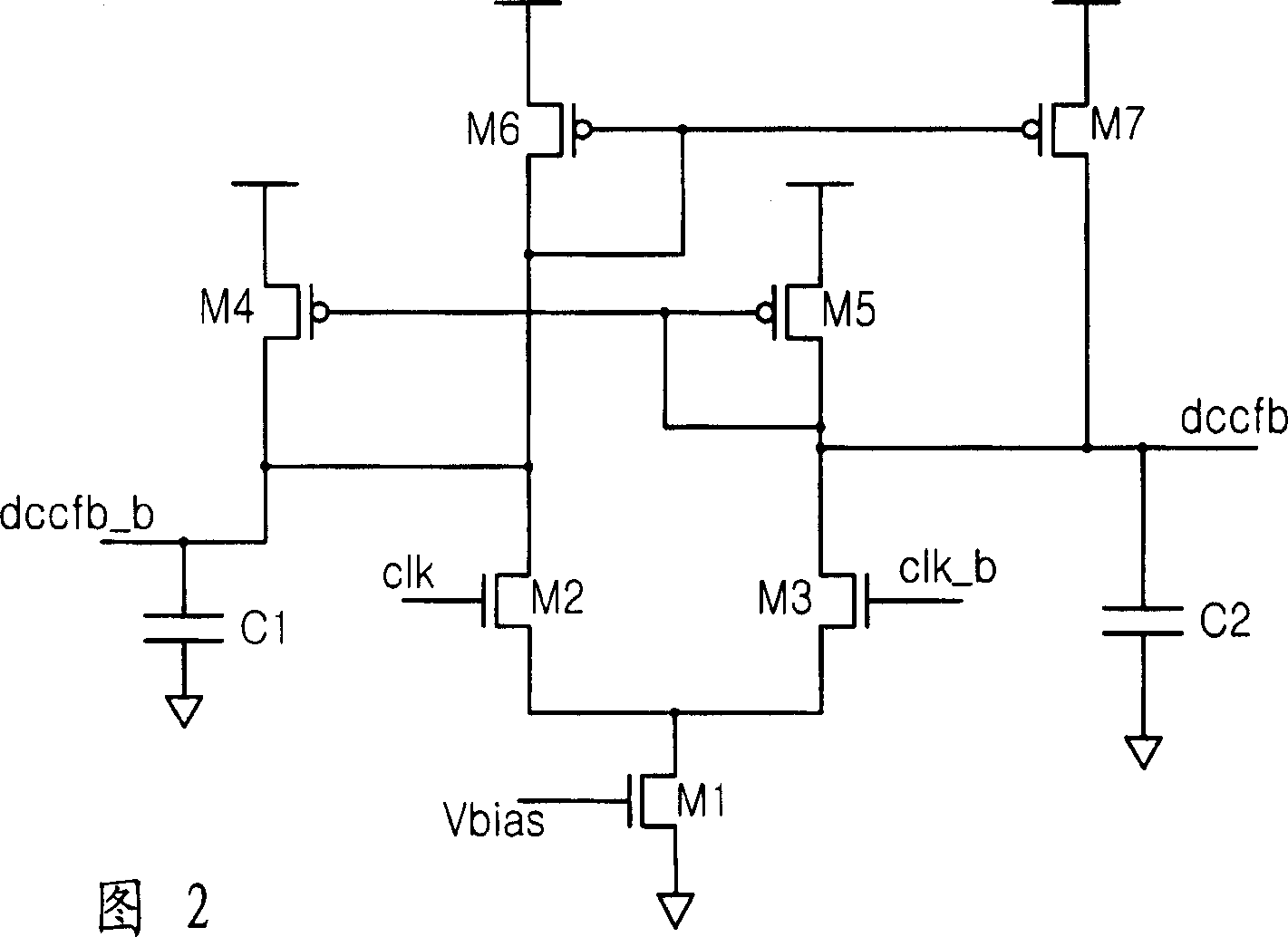

Phase-locked loop circuit and delay-locked loop circuit

InactiveUS6954511B2Reduce changesPulse automatic controlTransmissionPhase locked loop circuitLow-pass filter

A PLL circuit and a DLL circuit able to stabilize a control voltage within a short time after a phase pull-in operation in each cycle of a reference clock. In a phase comparator, the size of a leading phase or a delayed phase of a feedback signal is detected with respect to a reference clock signa, and pulse signals having pulse widths corresponding to the size are output. A current corresponding to the signals is output from a charge pump circuit to a lag-lead filter, and a control voltage obtained by removing noise of the above output is output from a low-pass filter to a voltage-controlled oscillator. Furthermore, through capacitors, pulse signals are superposed on the control voltage, and a sharp waveform is obtained by correcting blunting of the waveform by the low-pass filter. Due to this, the control voltage is stabilized within a short time after a phase pull-in operation in each cycle of the reference clock signal.

Owner:SONY CORP

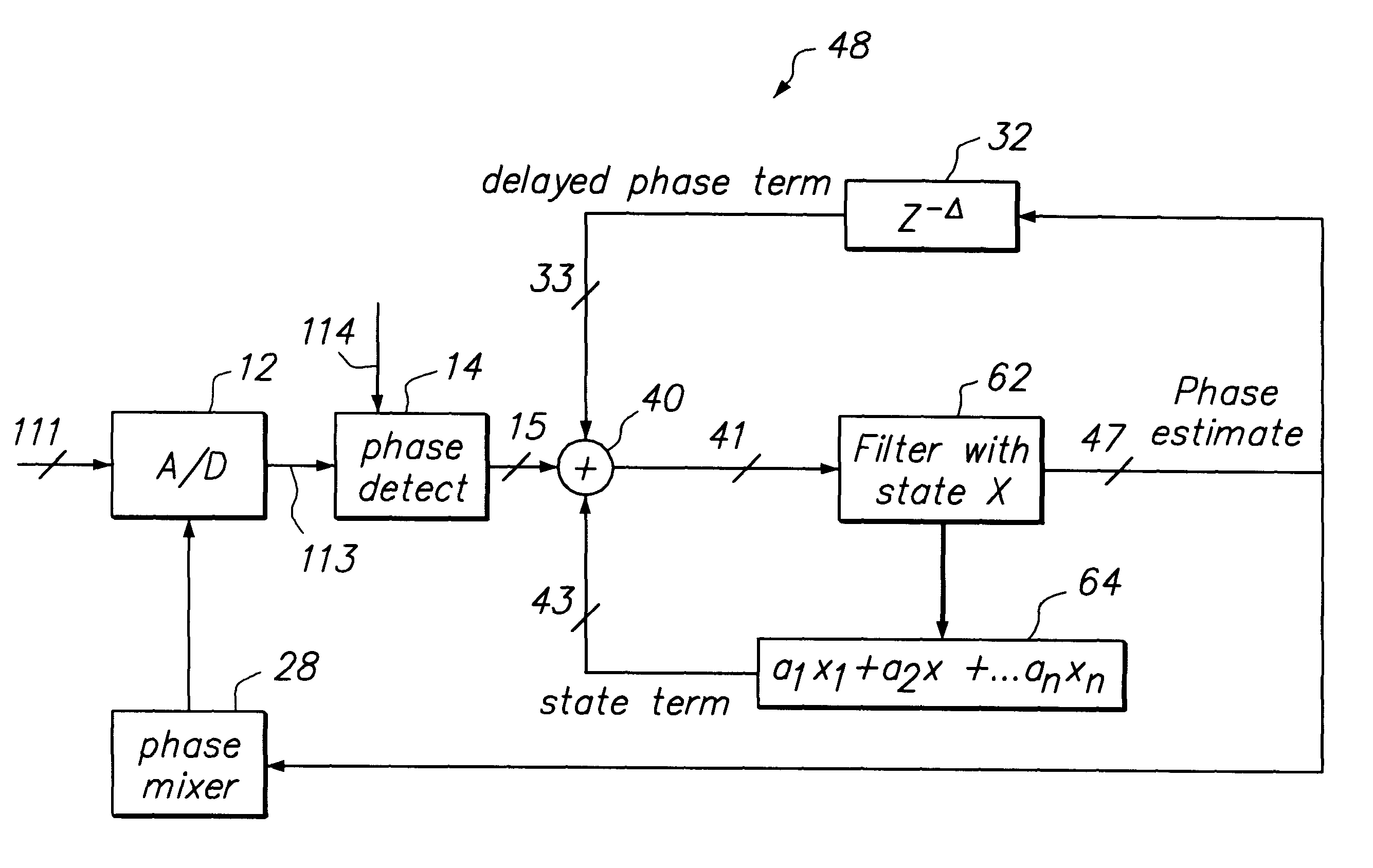

Loop latency compensated PLL filter

InactiveUS6236343B1Minimize jitterReduce sensitivityAnalogue/digital conversionElectric signal transmission systemsPhase detectorSquare waveform

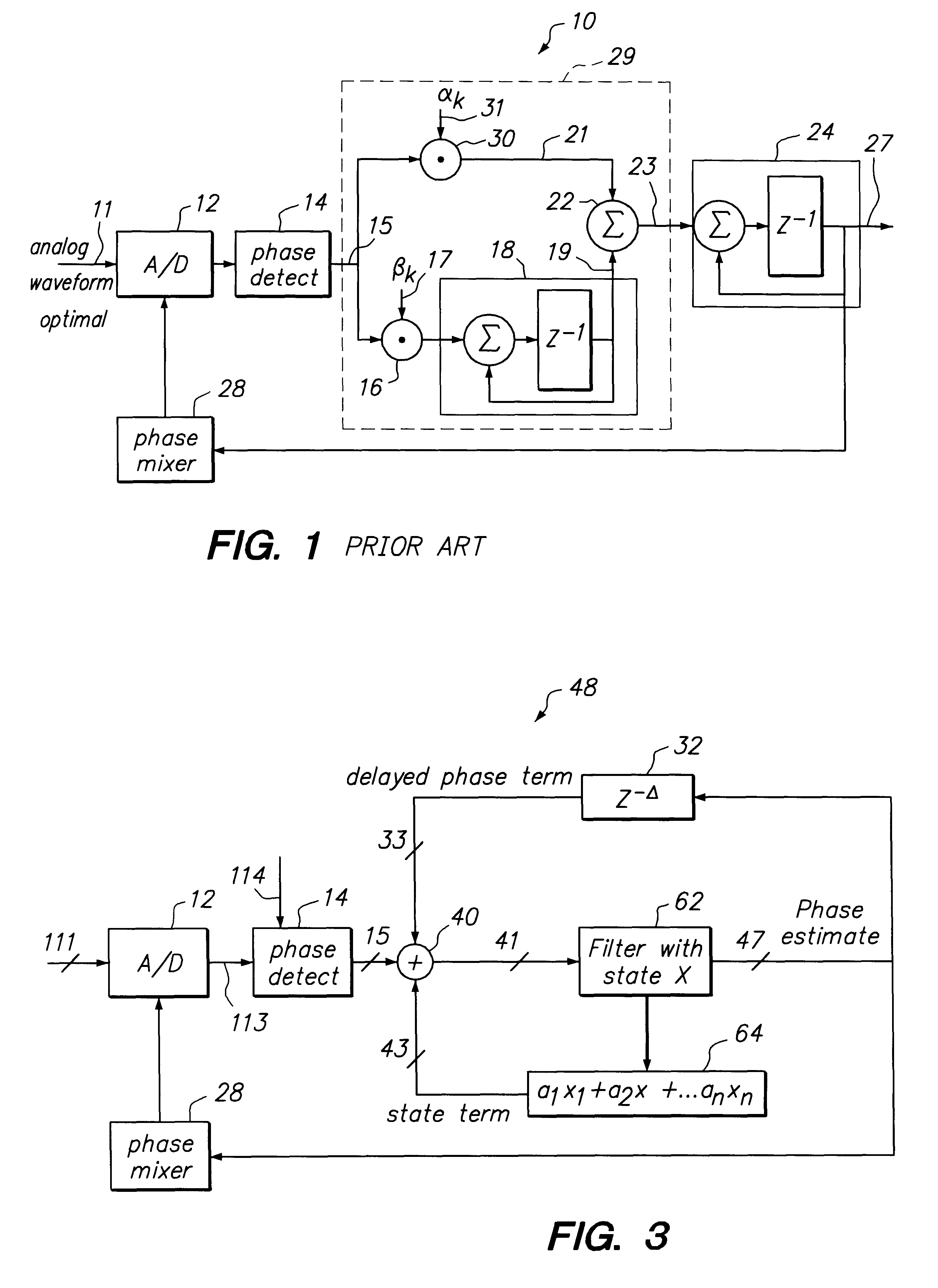

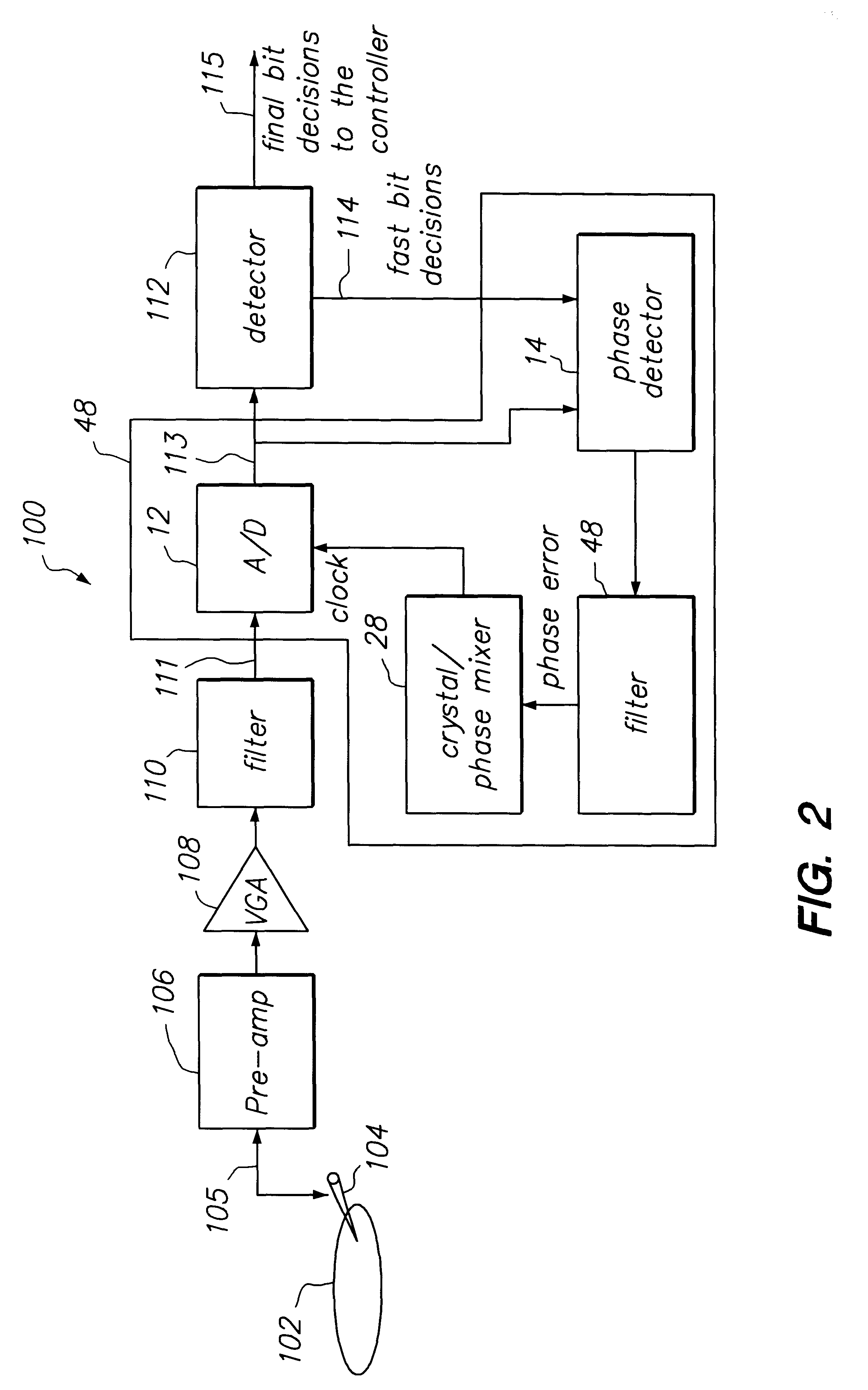

The loop latency compensated PLL filter comprising two additional feedback terms, a delayed phase compensation signal and a state compensation signal, that are provided as input of a PLL filter. Accordingly, the PLL filter input comprises two additional compensation input signals: the delayed phase compensation signal and the state compensation signal in addition to a phase estimated error output from a phase detector that is also coupled to the input of the PLL filter. Consequently, PLL filter thus is able to provide a latency compensated phase error control output that is fedback to control a phase mixer to generate a square waveform used to drive an A / D of the PLL in accordance with the principles of this invention. The loop latency compensated PLL of this invention thus minimizes the jitter of the PLL circuit, provides higher format efficiency, and also has reduced sensitivity to large bursty noises.

Owner:MAXTOR

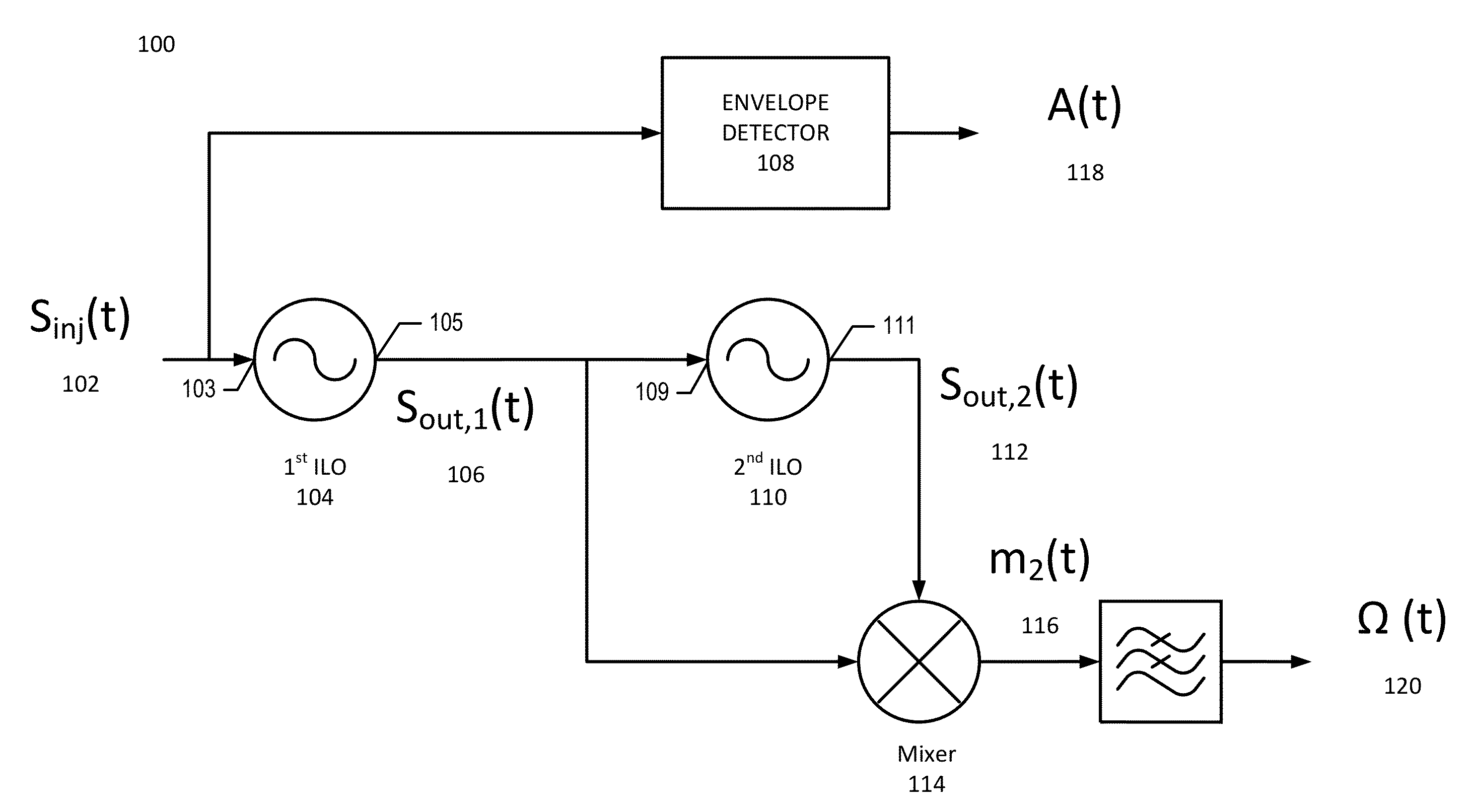

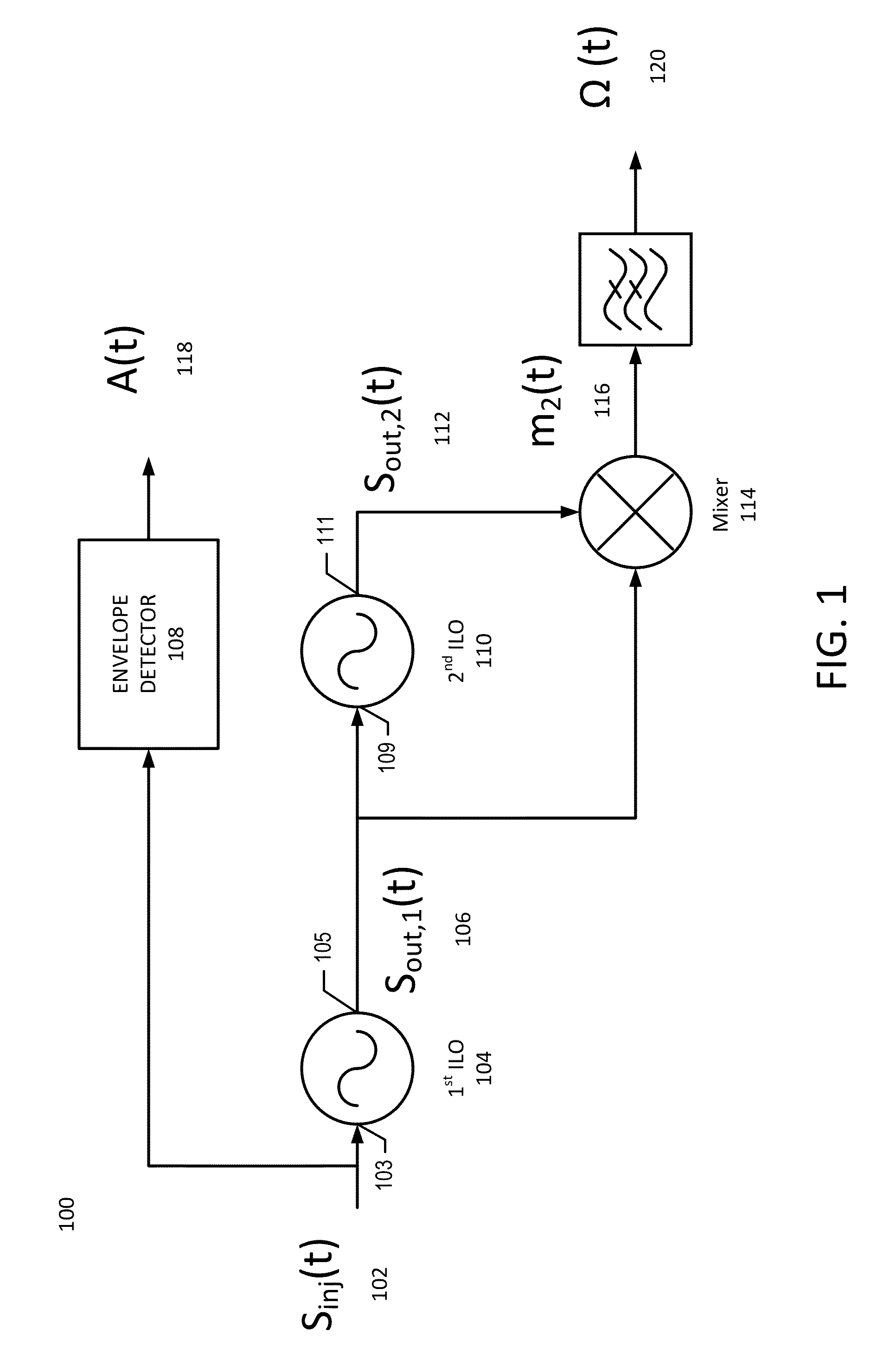

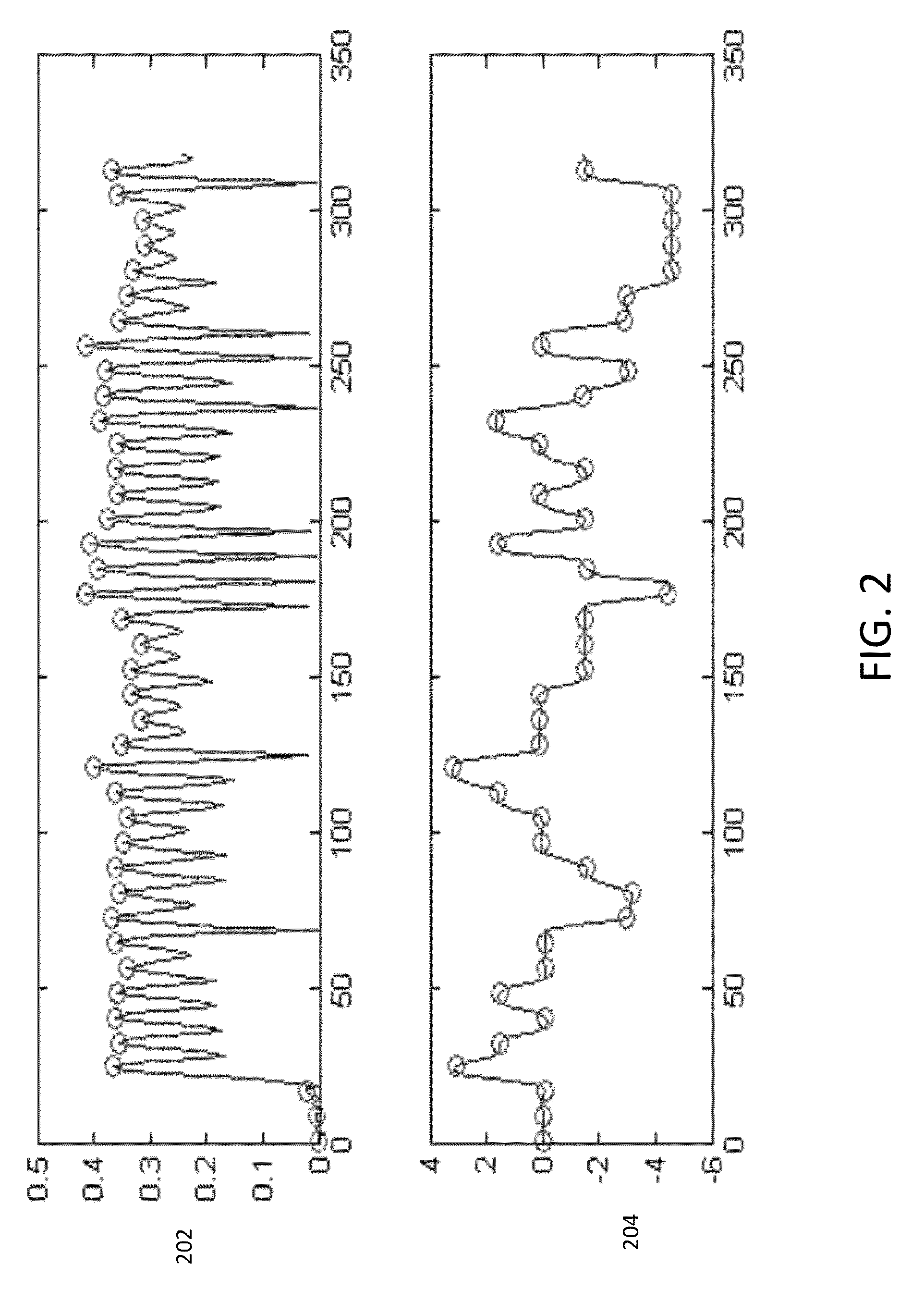

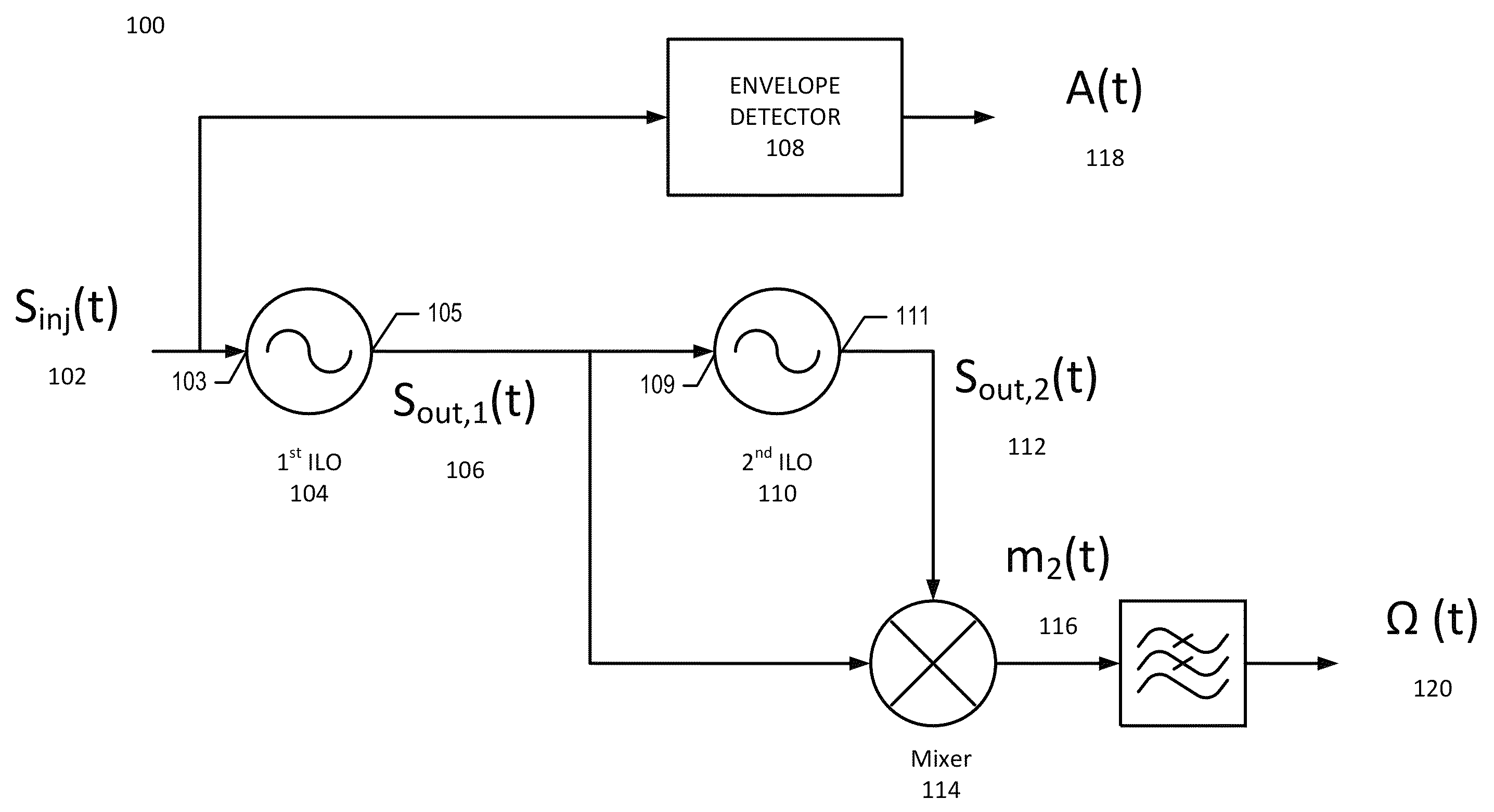

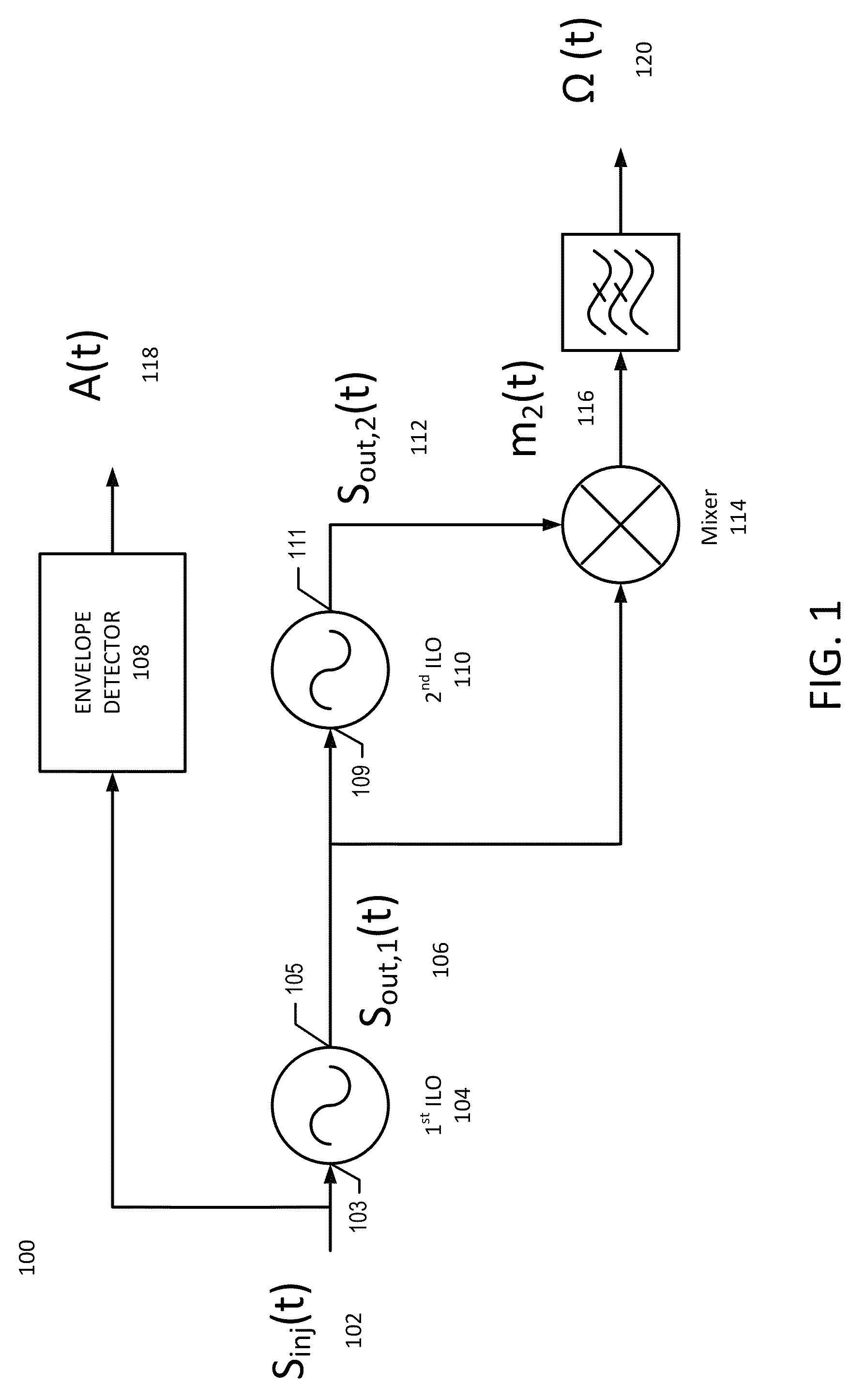

Polar receiver architecture and signal processing methods

ActiveUS8804875B1Simultaneous amplitude and angle demodulationAmplitude demodulation by homodyne/synchrodyne circuitsInjection lockedHarmonic

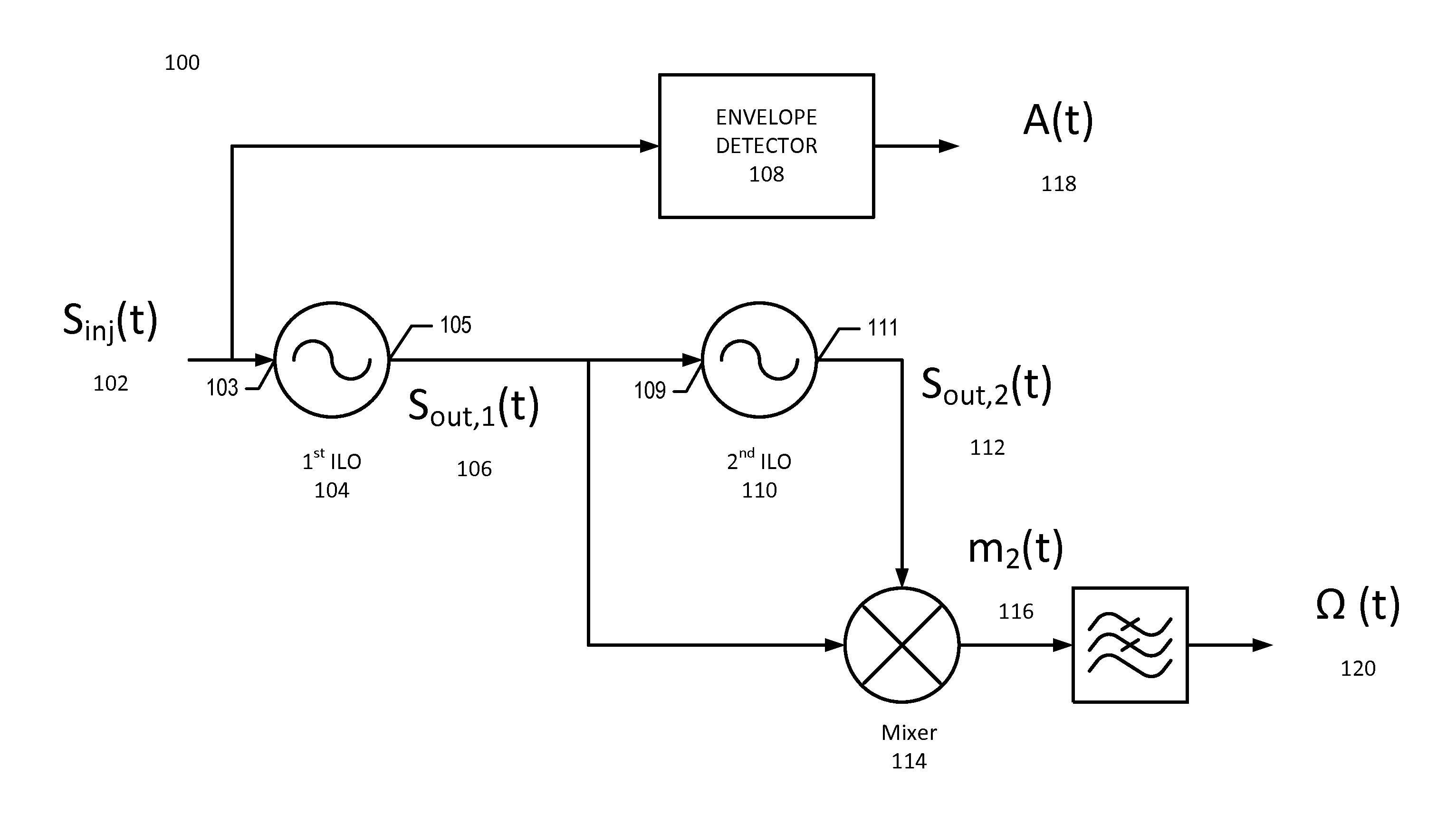

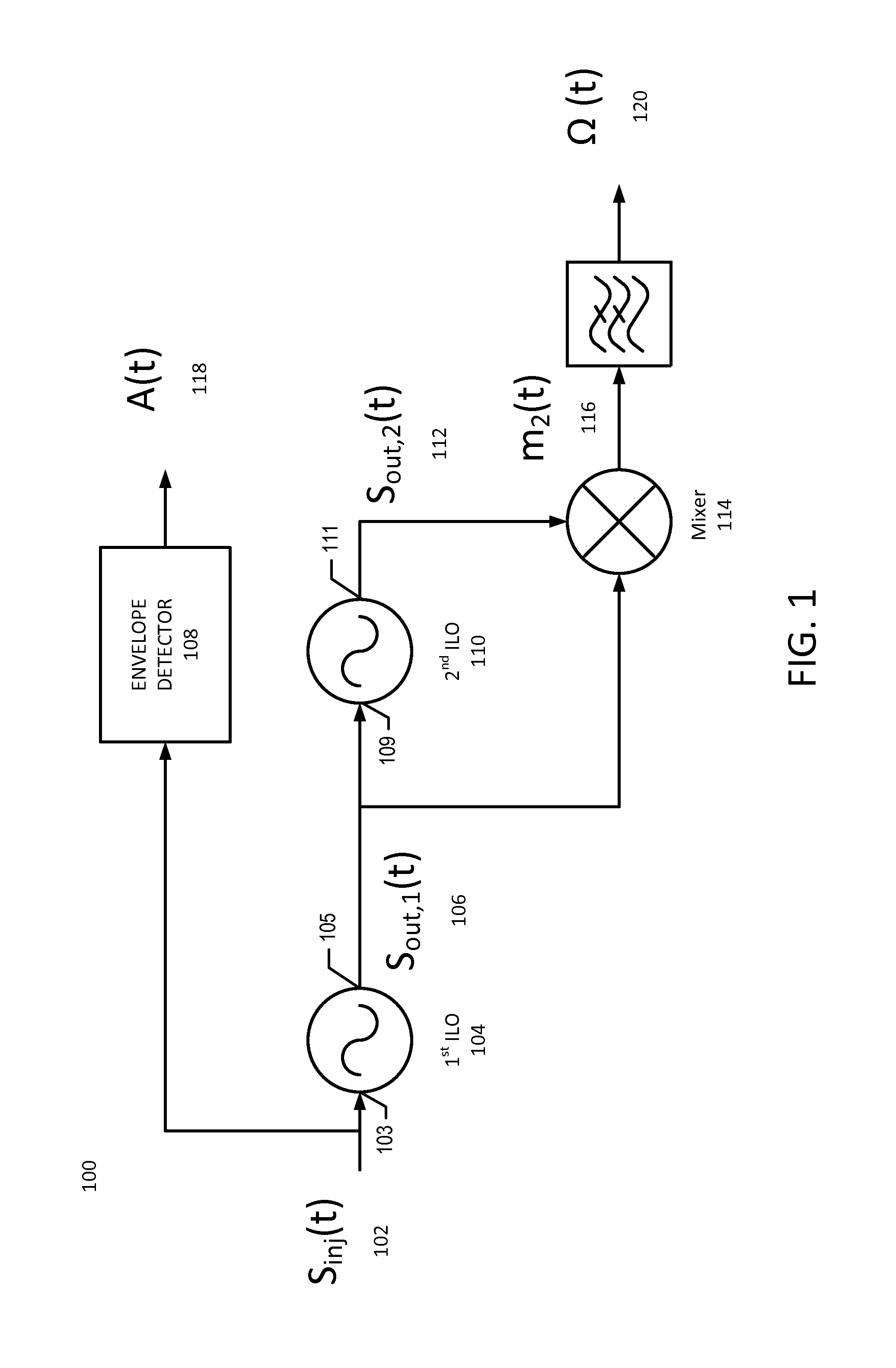

Compressing a variable phase component of a received modulated signal with a second harmonic injection locking oscillator, and generating a delayed phase-compressed signal with a fundamental injection locking oscillator, and combining the phase-compressed signal and the delayed phase-compressed signal to obtain an estimated derivative of the variable phase component, and further processing the estimated derivative to recover data contained within the received modulated signal.

Owner:INNOPHASE

Barcode reader with edge detection enhancement

ActiveUS20120118974A1Character and pattern recognitionElectric pulse generatorWindow detectionBarcode reader

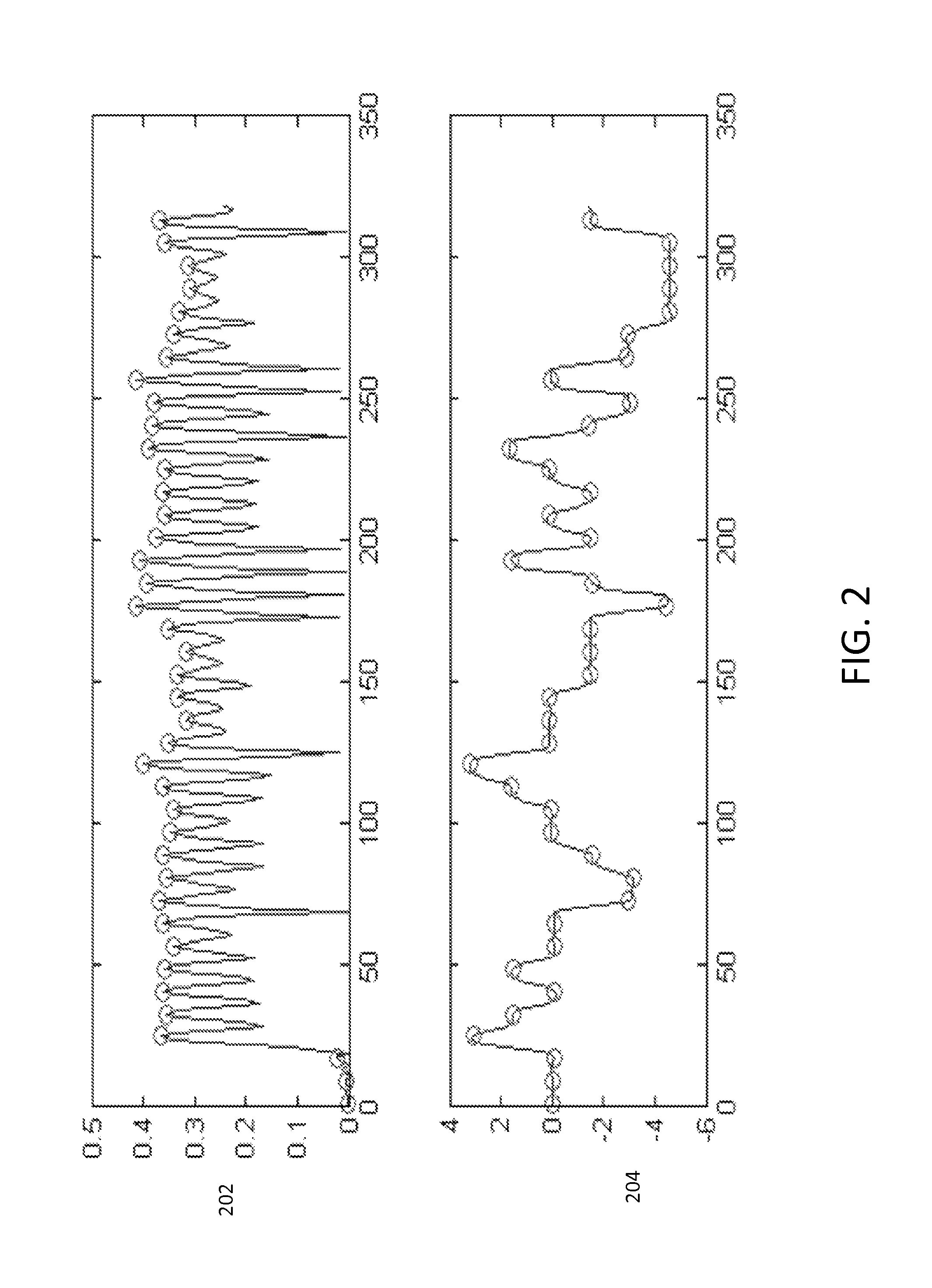

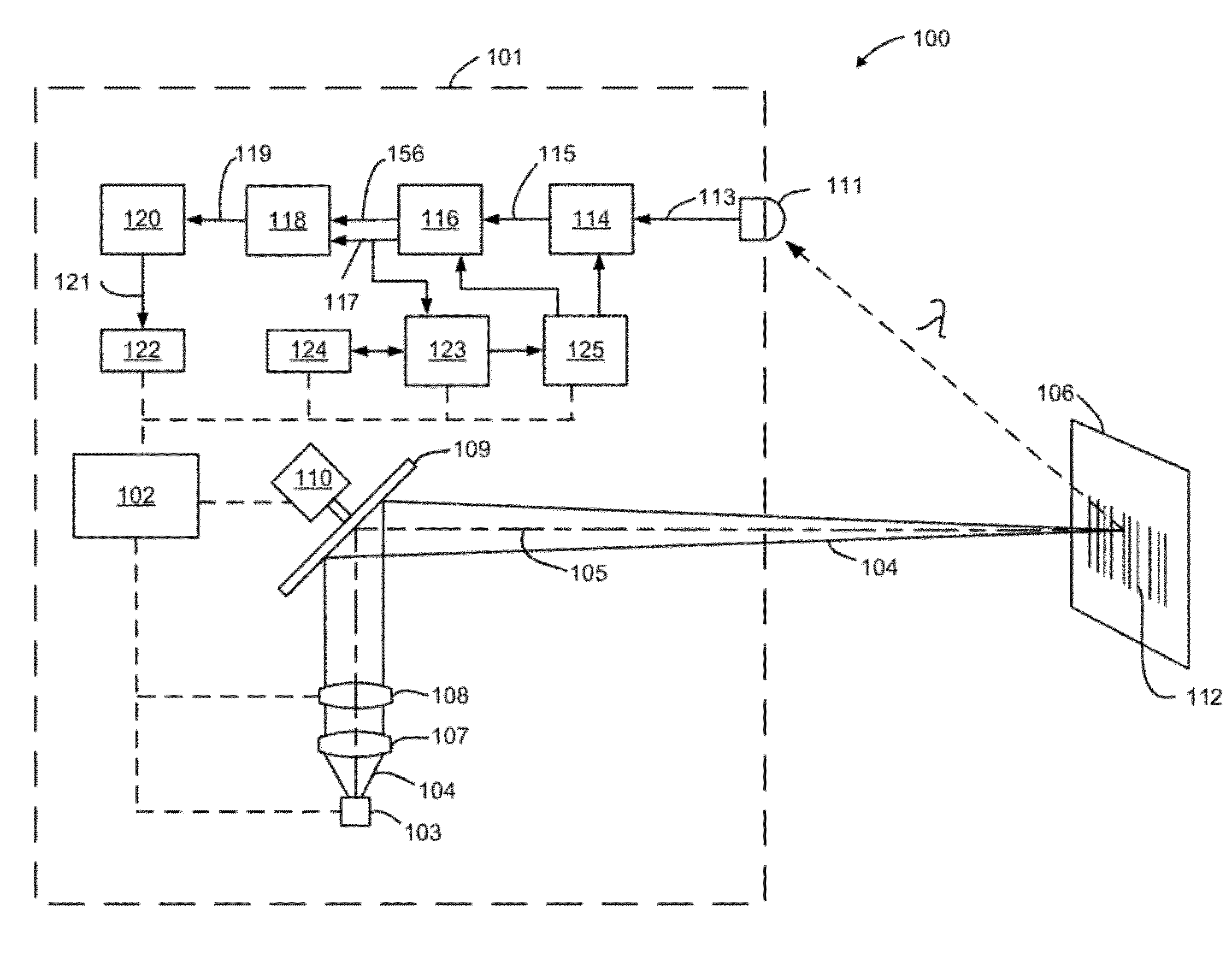

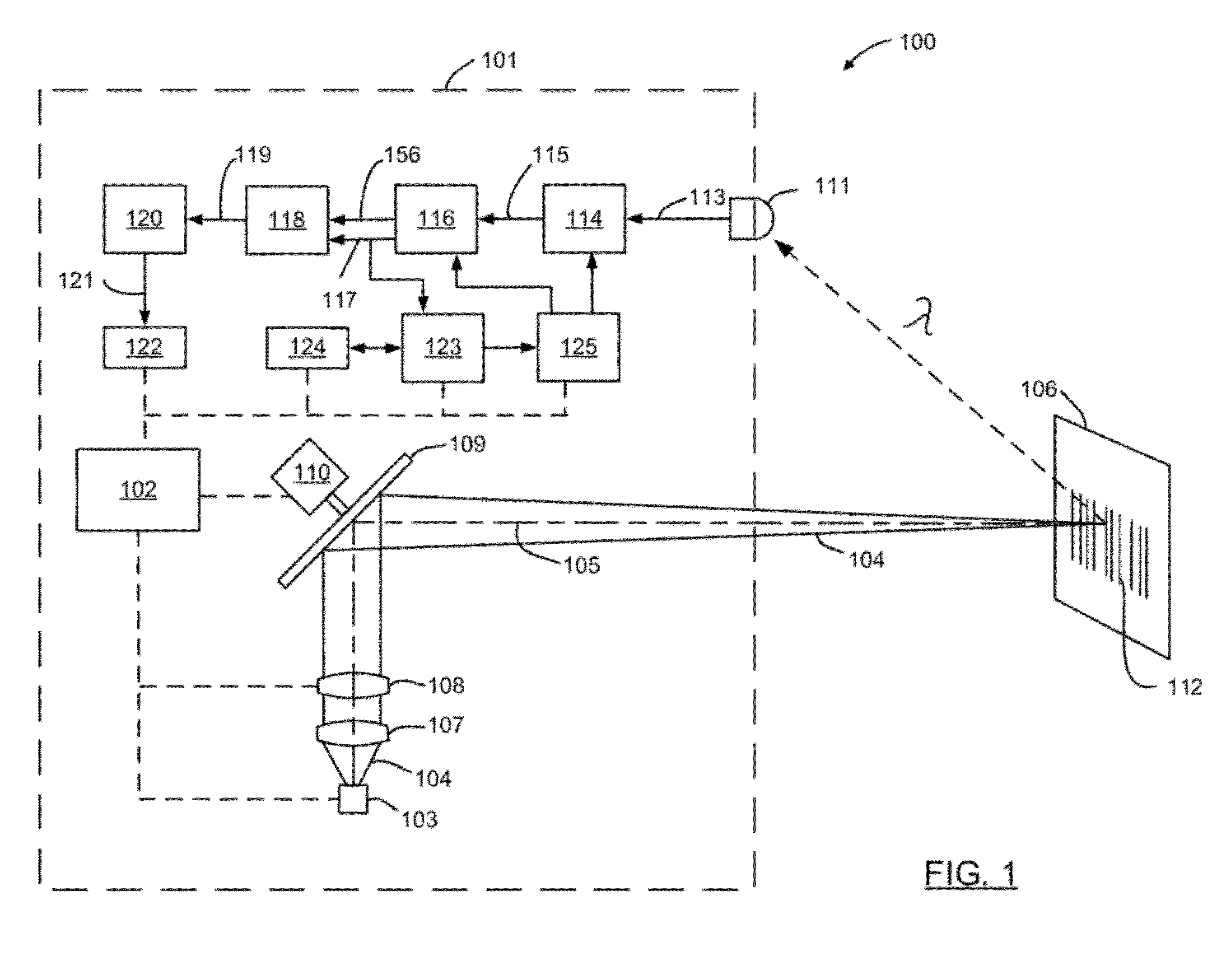

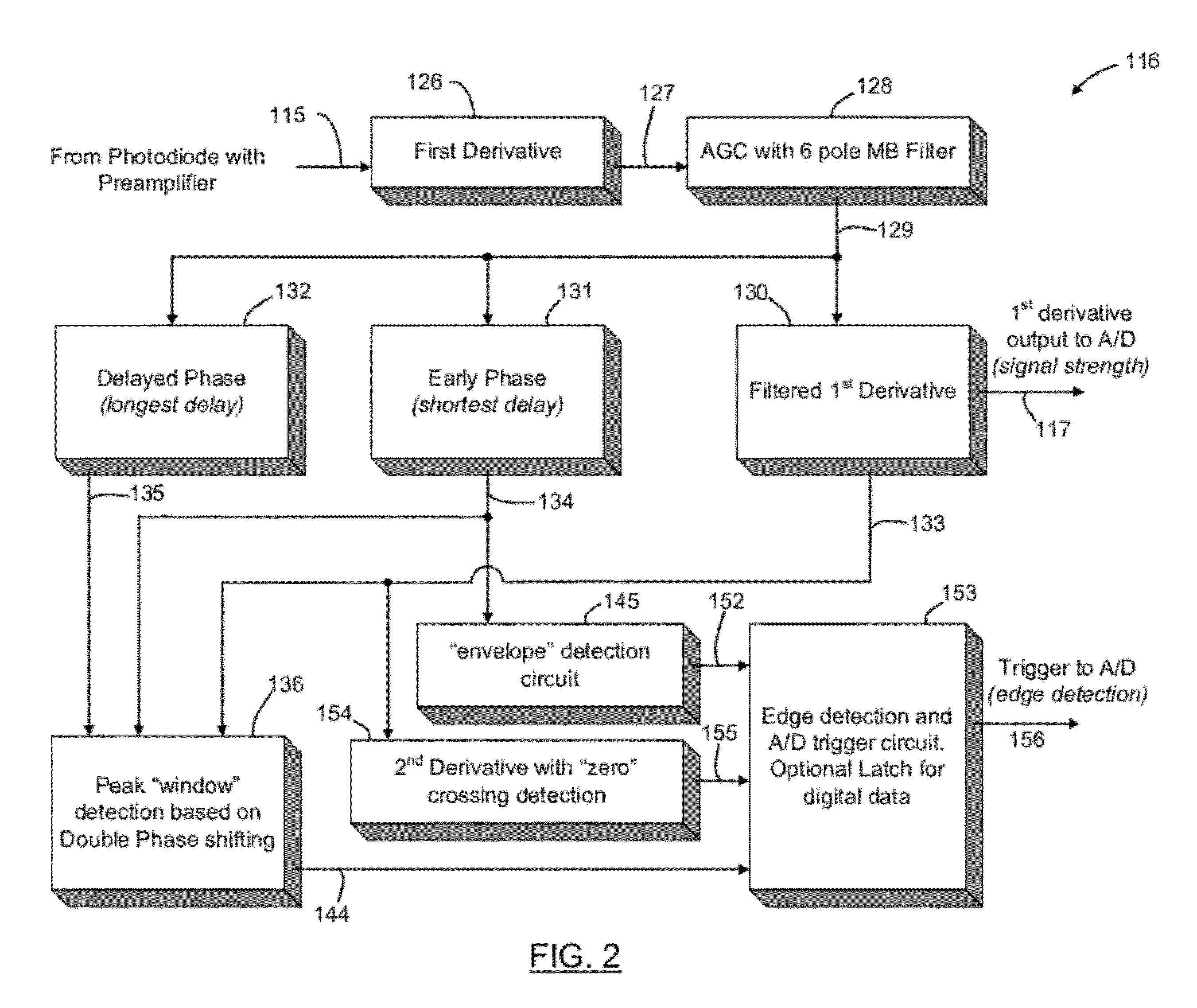

An optical reader for decoding an encoded symbol character of a symbology includes a scan data signal processor having as an input a scan data signal encoding information representative of the encoded symbol character. The scan data signal processor includes a first time delay stage adapted to provide a primary phase waveform from the scan data signal, a second time delay stage adapted to provide an early phase waveform from the scan data signal, and a third time delay stage adapted to provide a delayed phase waveform from the scan data signal. The early phase waveform has a propagation delay less than the primary phase waveform, and the delayed phase waveform has a propagation delay greater than the primary phase waveform. The scan data signal processor further includes a peak window detection stage for generating a peak window timeframe when an amplitude of the primary phase waveform is greater than, less than, or equal to both an amplitude of the early phase waveform and the delayed phase waveform. The optical reader further includes a digitizer circuit adapted to accept, within the peak window timeframe, the scan data signal processor output.

Owner:HAND HELD PRODS +1

Polar Receiver Architecture and Signal Processing Methods

ActiveUS20140270003A1Amplitude demodulation by homodyne/synchrodyne circuitsModulated-carrier systemsInjection lockedHarmonic

Compressing a variable phase component of a received modulated signal with a second harmonic injection locking oscillator, and generating a delayed phase-compressed signal with a fundamental injection locking oscillator, and combining the phase-compressed signal and the delayed phase-compressed signal to obtain an estimated derivative of the variable phase component, and further processing the estimated derivative to recover data contained within the received modulated signal.

Owner:INNOPHASE

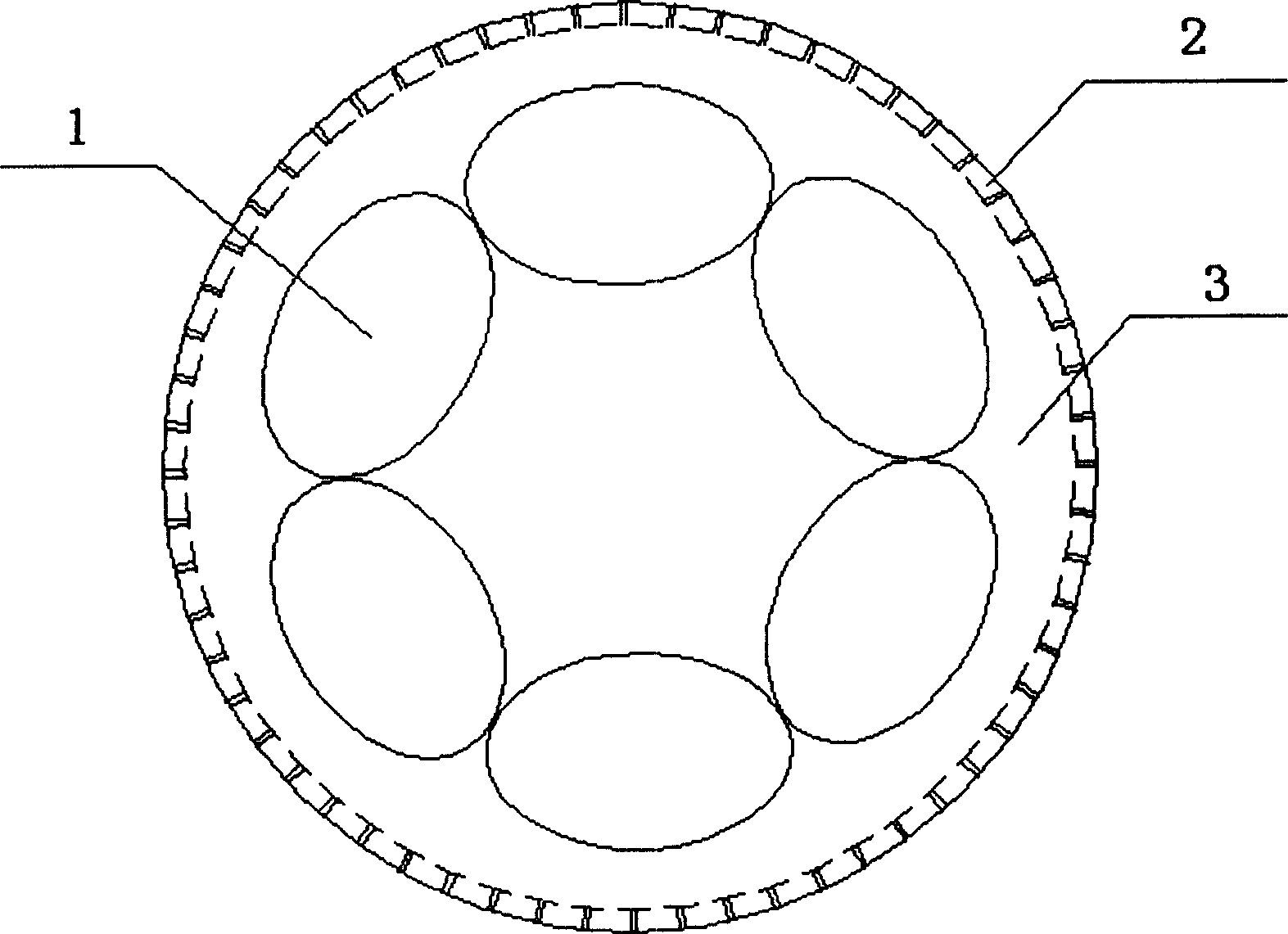

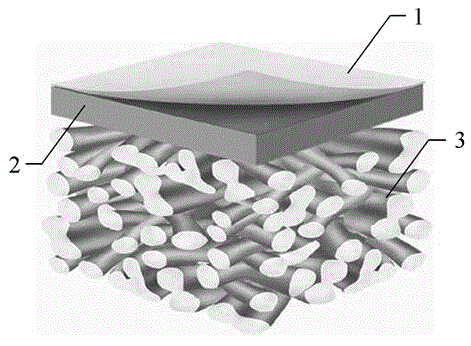

Reinforced hollow fiber super filter film and its preparing method

InactiveCN1683059AGood chemical stabilityImprove aging resistanceSemi-permeable membranesFiberHollow fibre

The present invention discloses a kind of reinforced hollow fiber superfiltering film and its preparation process. Polyvinylidene fluoride resin is first dissolved in organic solvent and additive is added to compound filming liquid. The filming liquid is then painted onto hollow support material and made to pass through solidifying bath, so that the filming material producing delayed phase separation inside the solvent owing to the action of the additive and great amount of micelle diffuse to the contact interface between the filming liquid and the solidifying bath to form one compact layer, which is finally solidified to form the hollow superfiltering film with surface control layer. The hollow superfiltering film has the advantages of both the polyvinylidene fluoride material and the high strength support material, including excellent filtering performance, low resistance, high mechanical strength and high chemical stability.

Owner:上海一鸣过滤技术有限公司

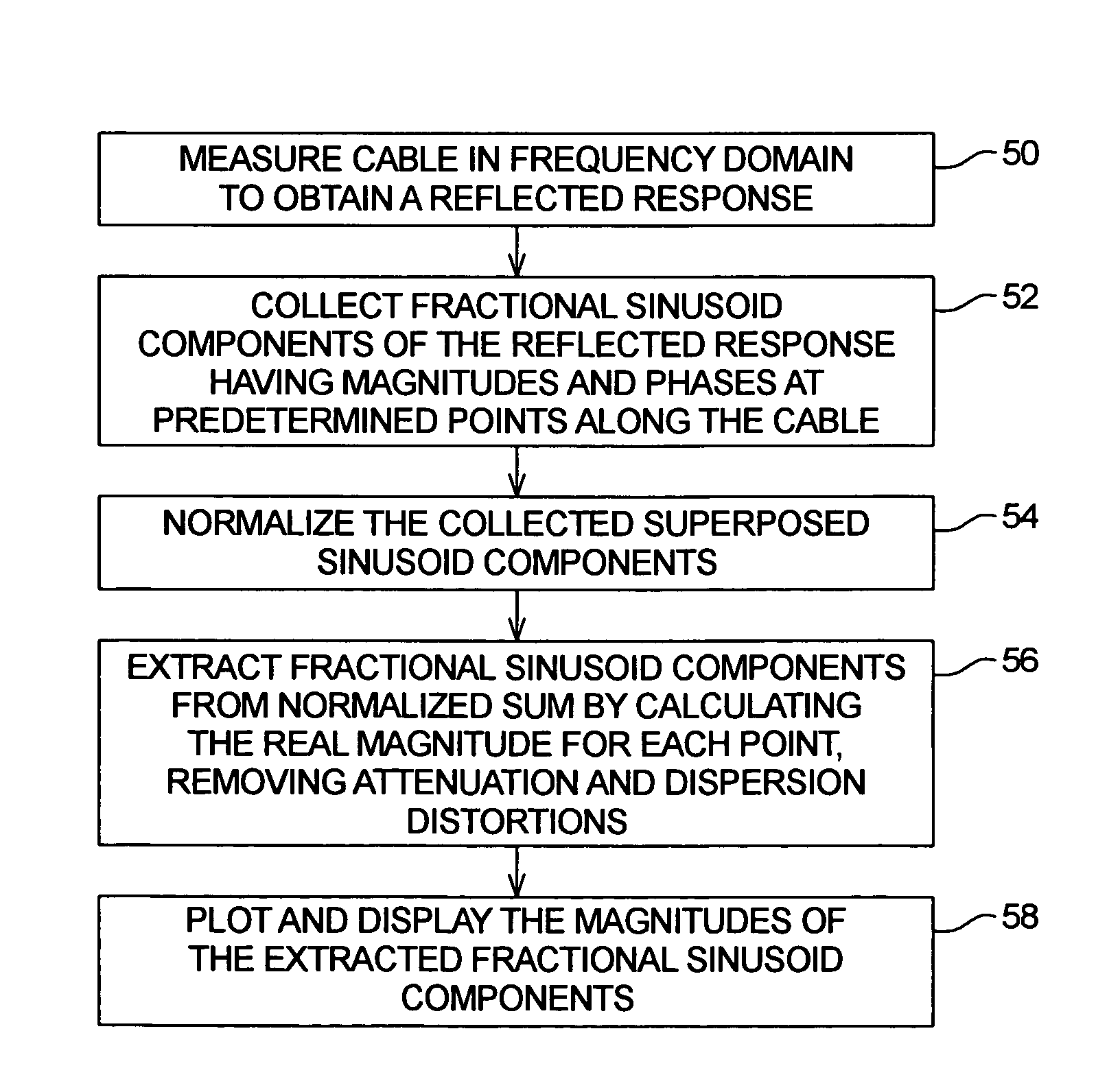

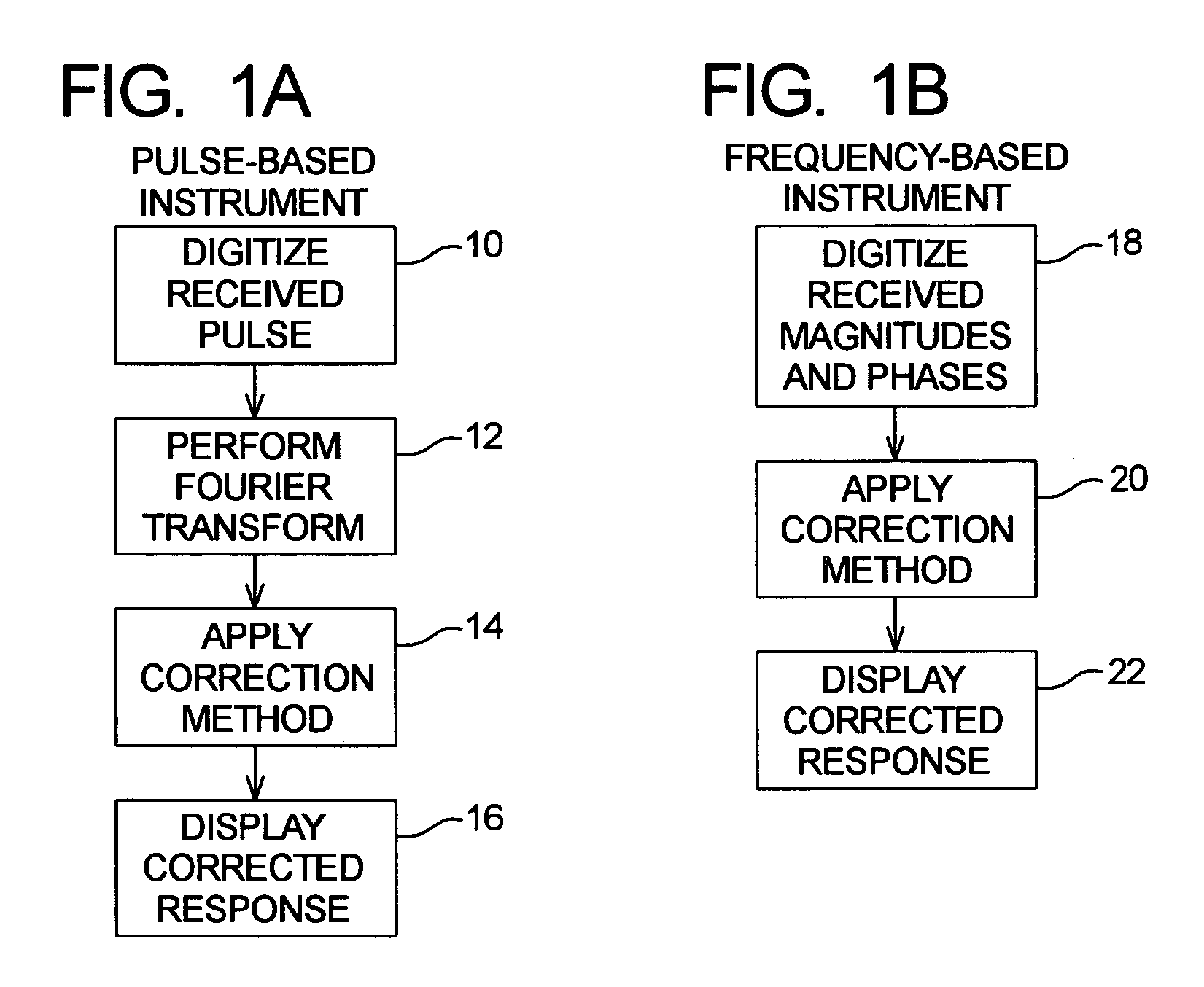

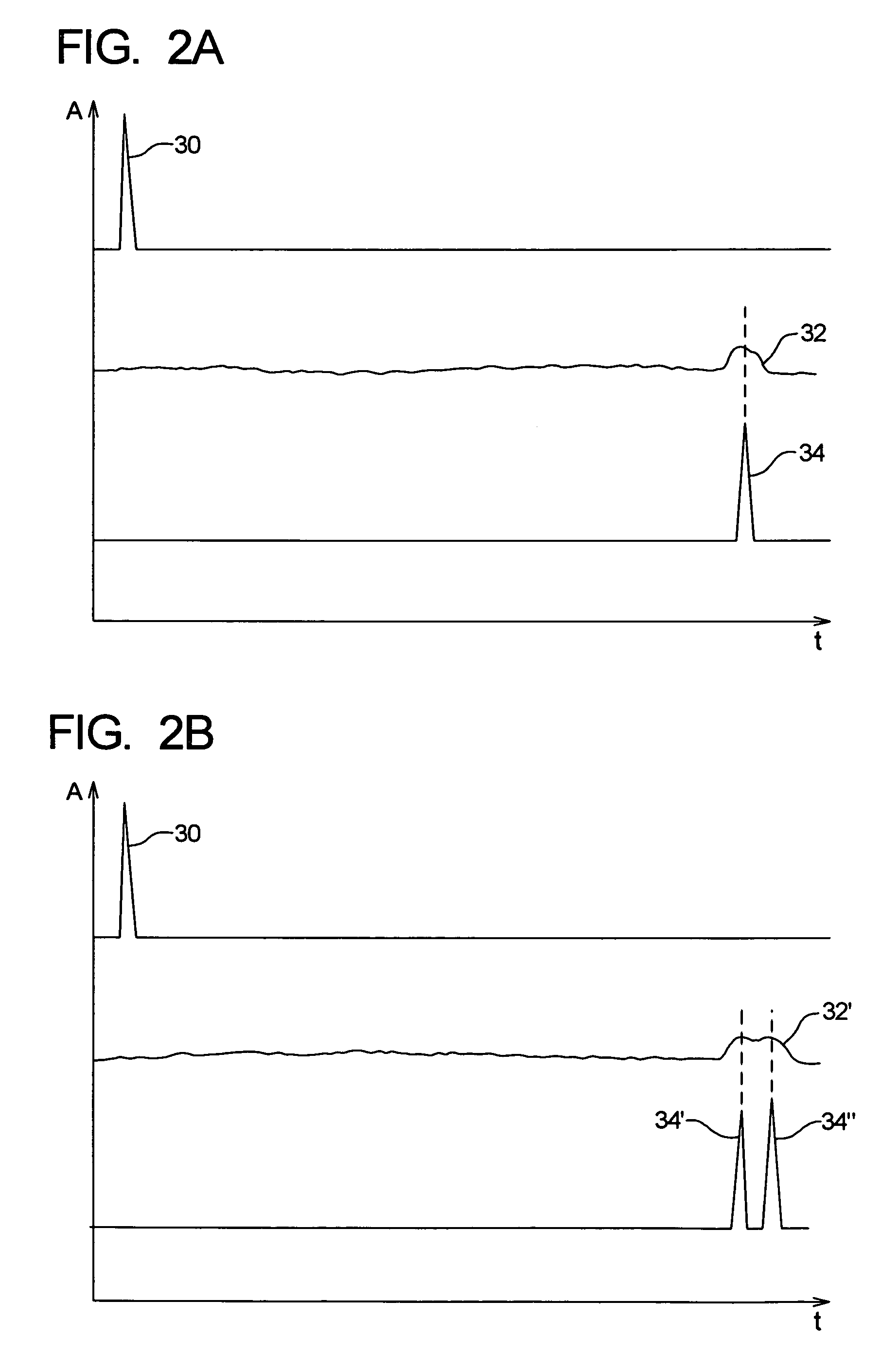

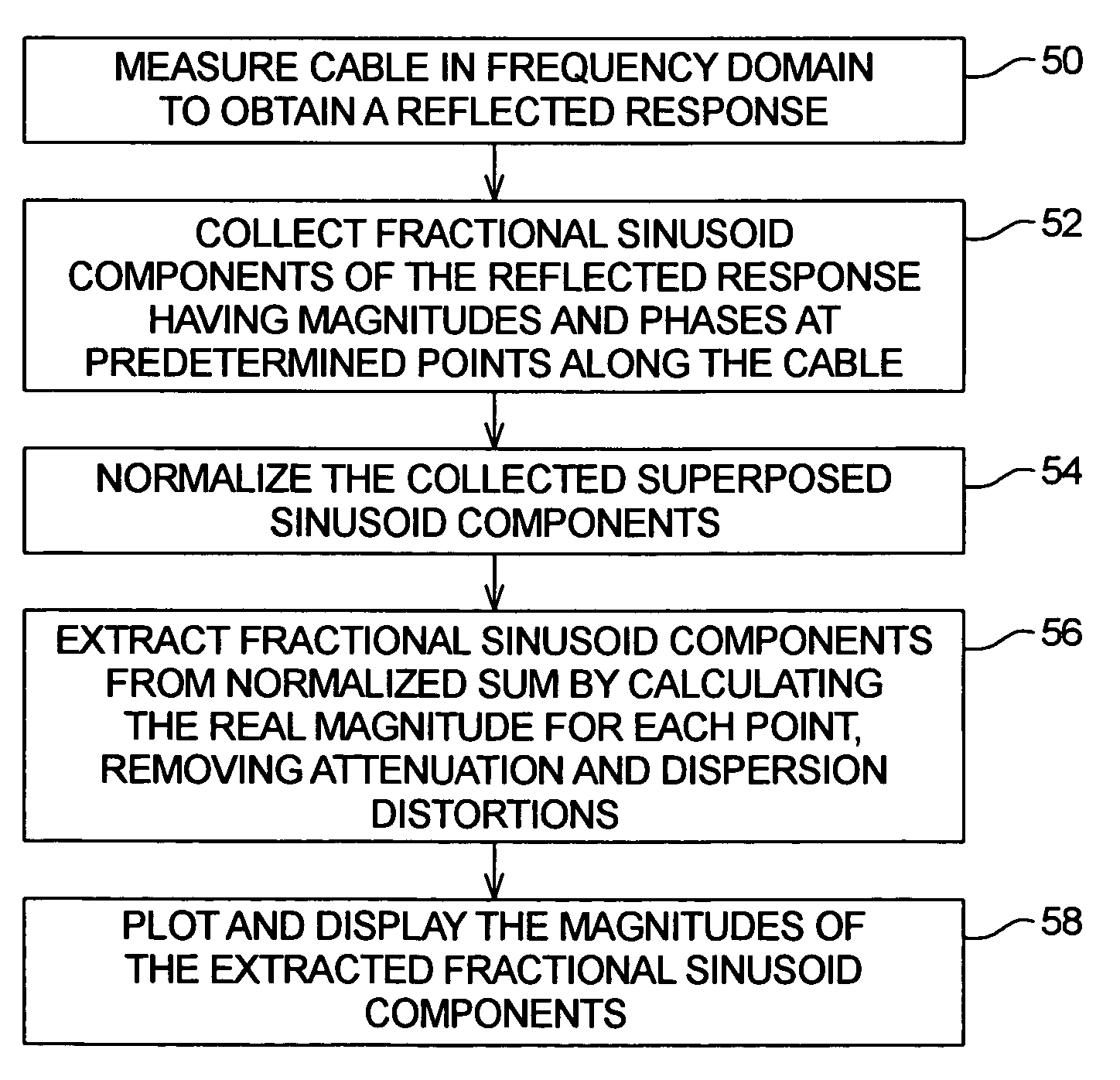

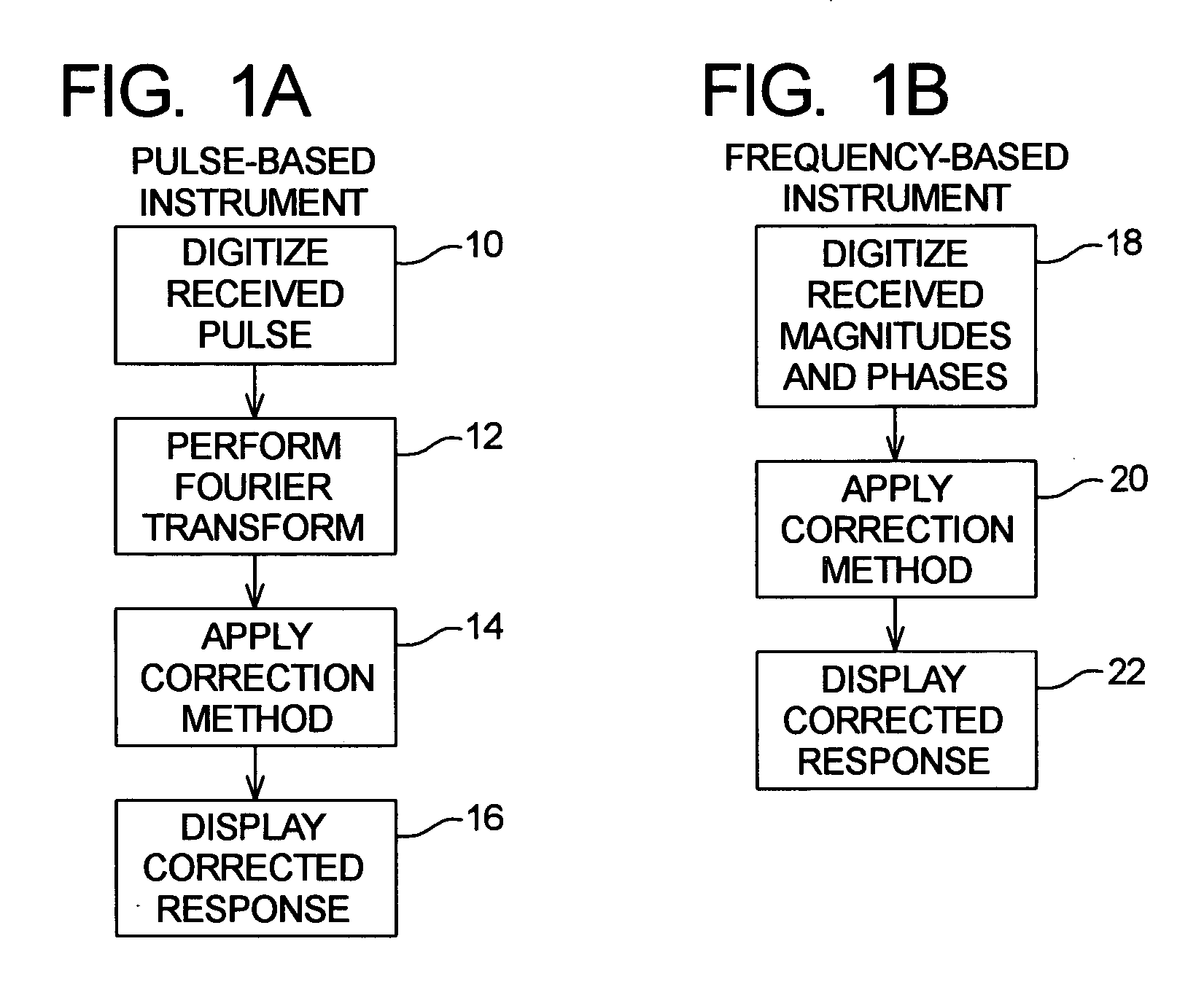

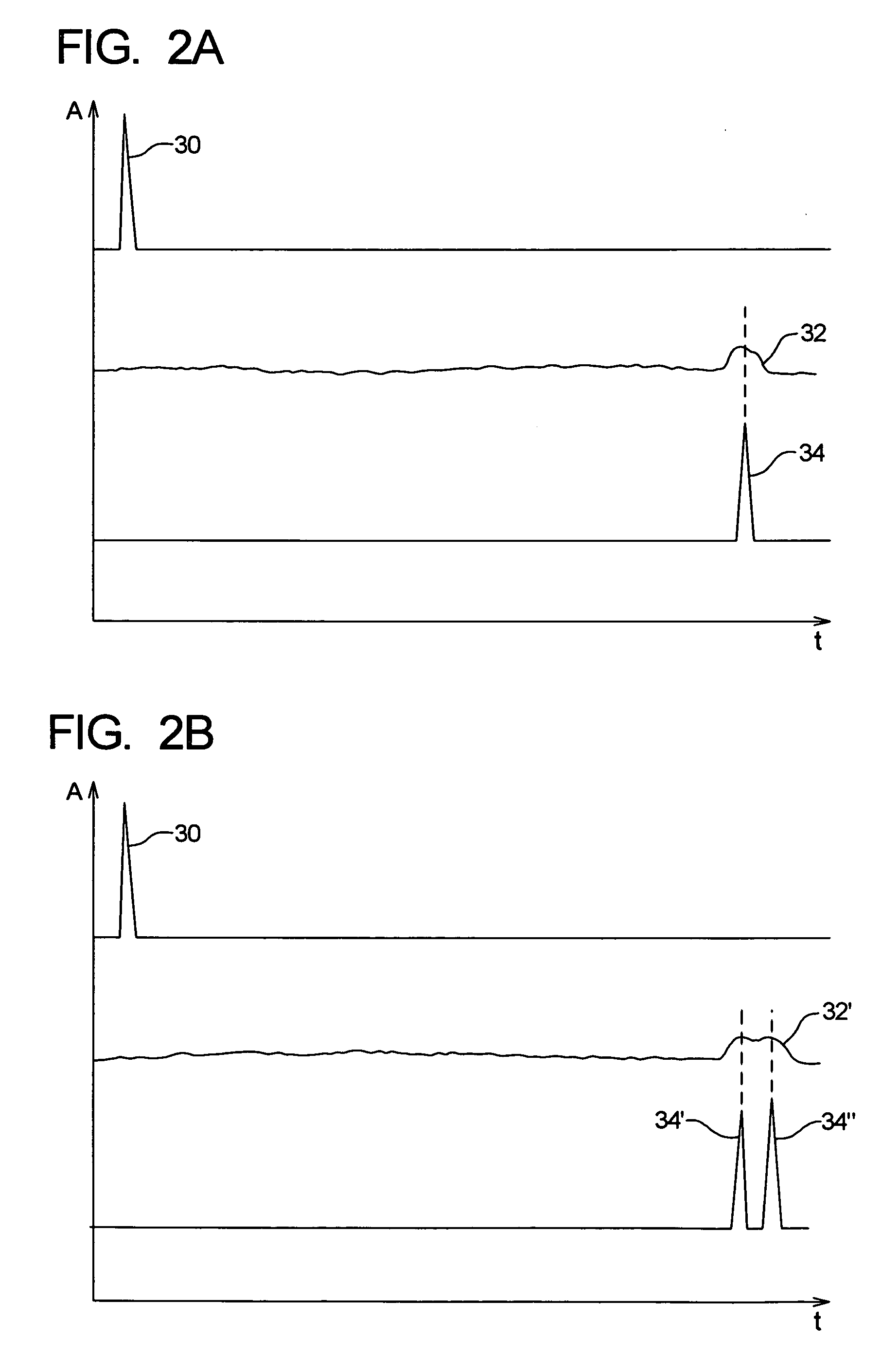

Correction of loss and dispersion in cable fault measurements

ActiveUS7295018B2Resistance/reactance/impedenceFault location by pulse reflection methodsEngineeringDistortion

A method of correcting distortions resulting from loss and dispersion in cable fault measurements. A cable is measured in the frequency domain to obtain a reflected response. Fractional sinusoidal components of the reflected response having attenuated amplitude and delayed phase values at points defining the junctures of adjacent equal predetermined lengths are collected and normalized. Then the fractional sinusoidal components of the reflected response are extracted from normalized sum by mathematically calculating the real value at each point, thereby removing all loss and dispersion distortion components.

Owner:JOHN FLUKE MFG CO INC

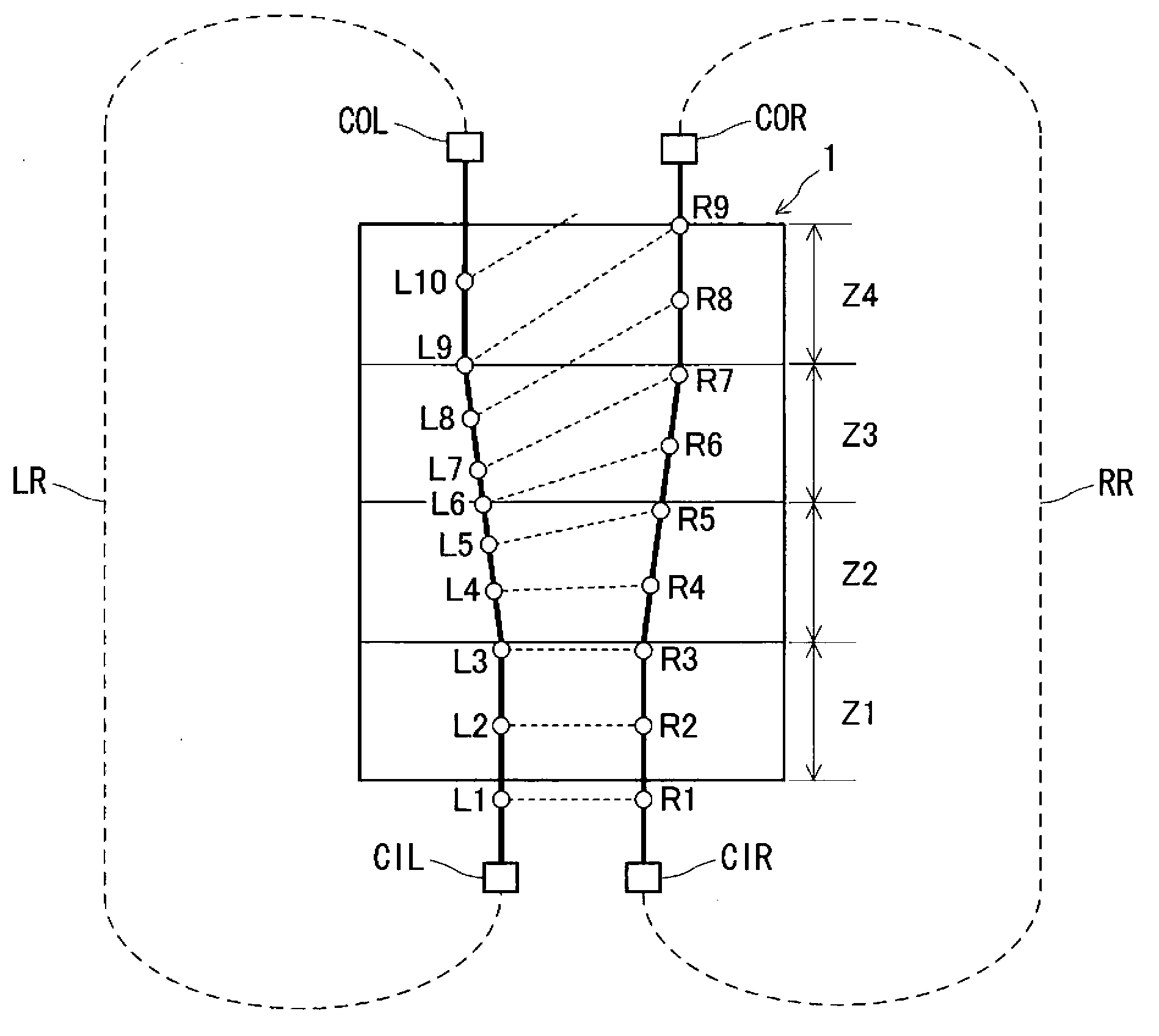

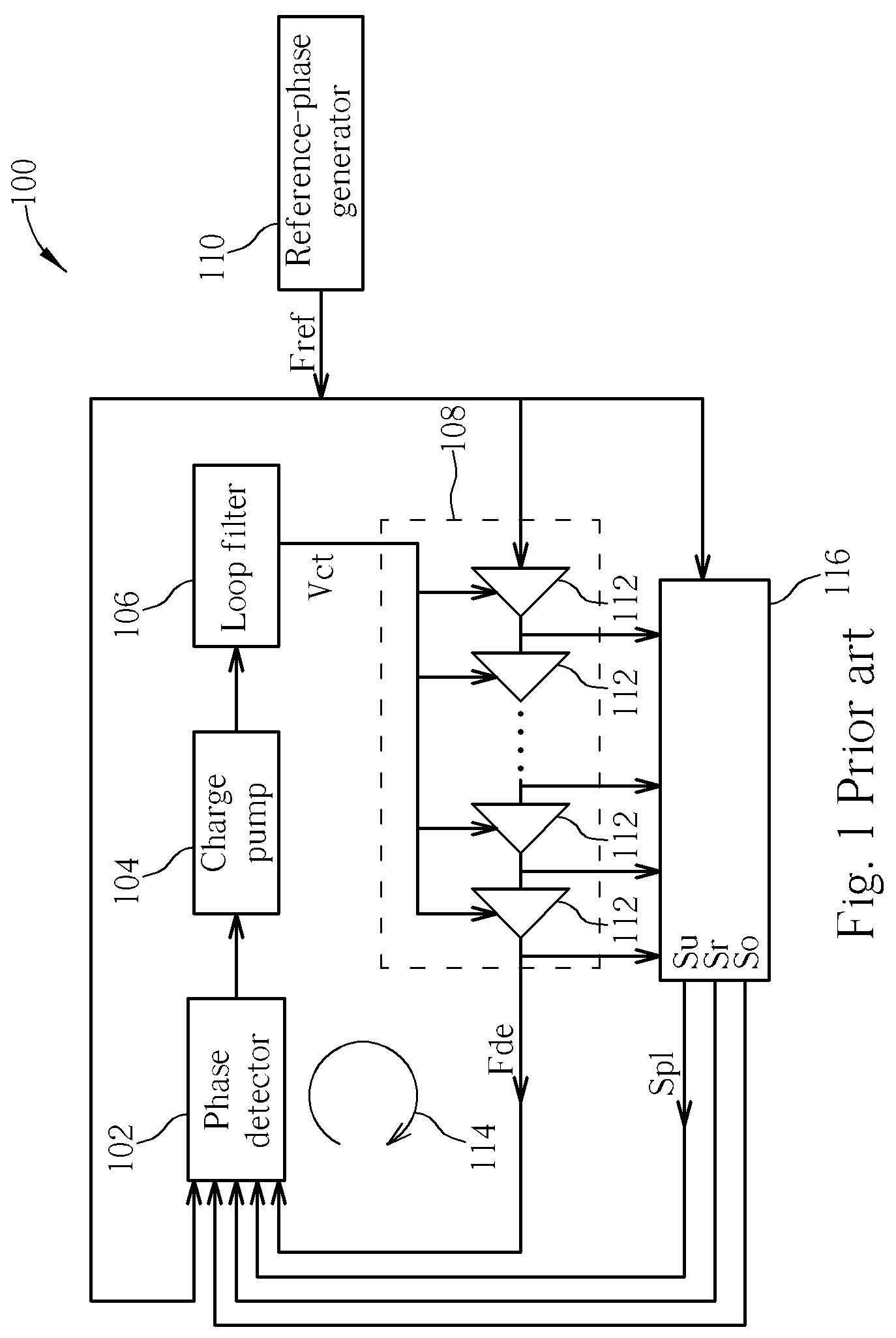

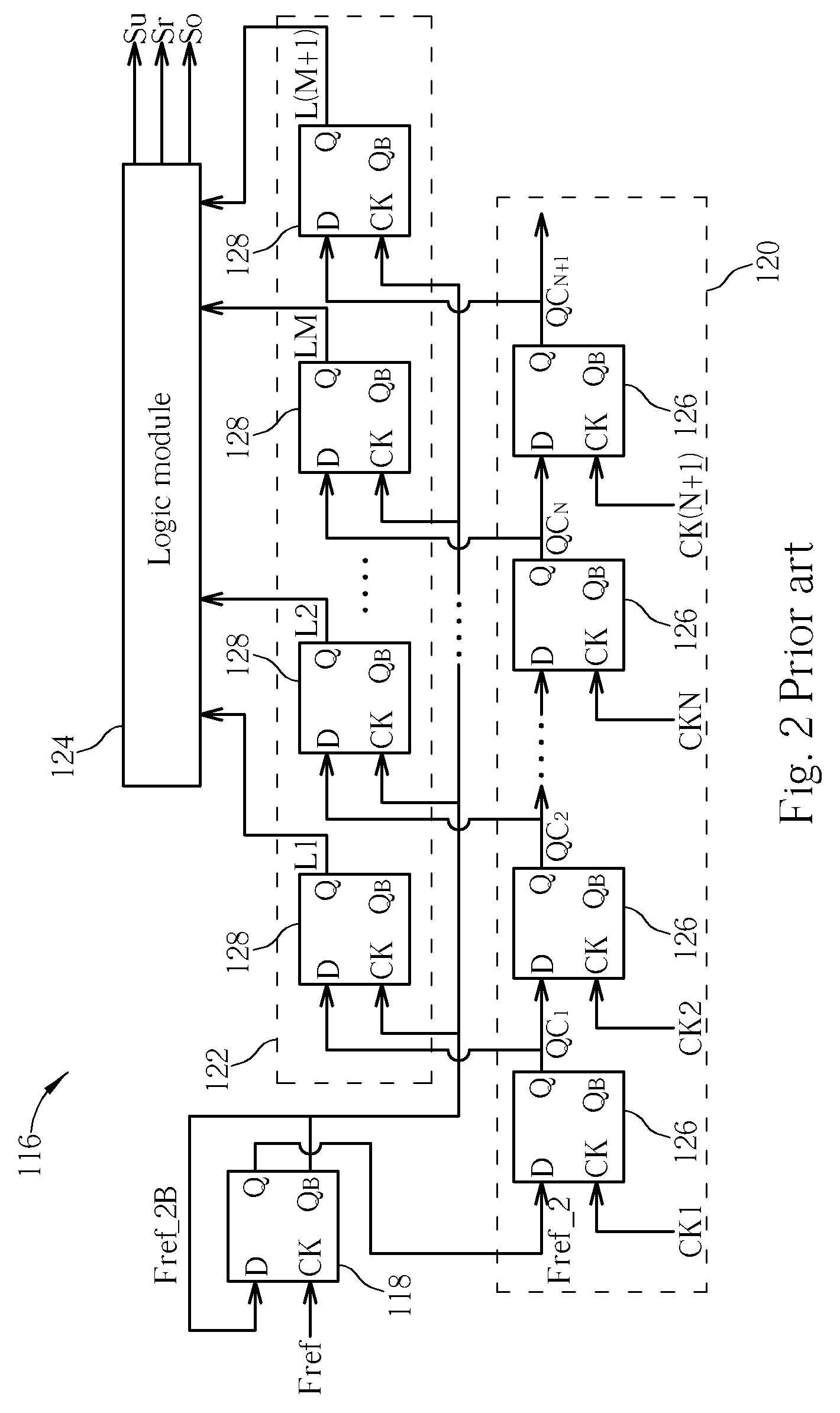

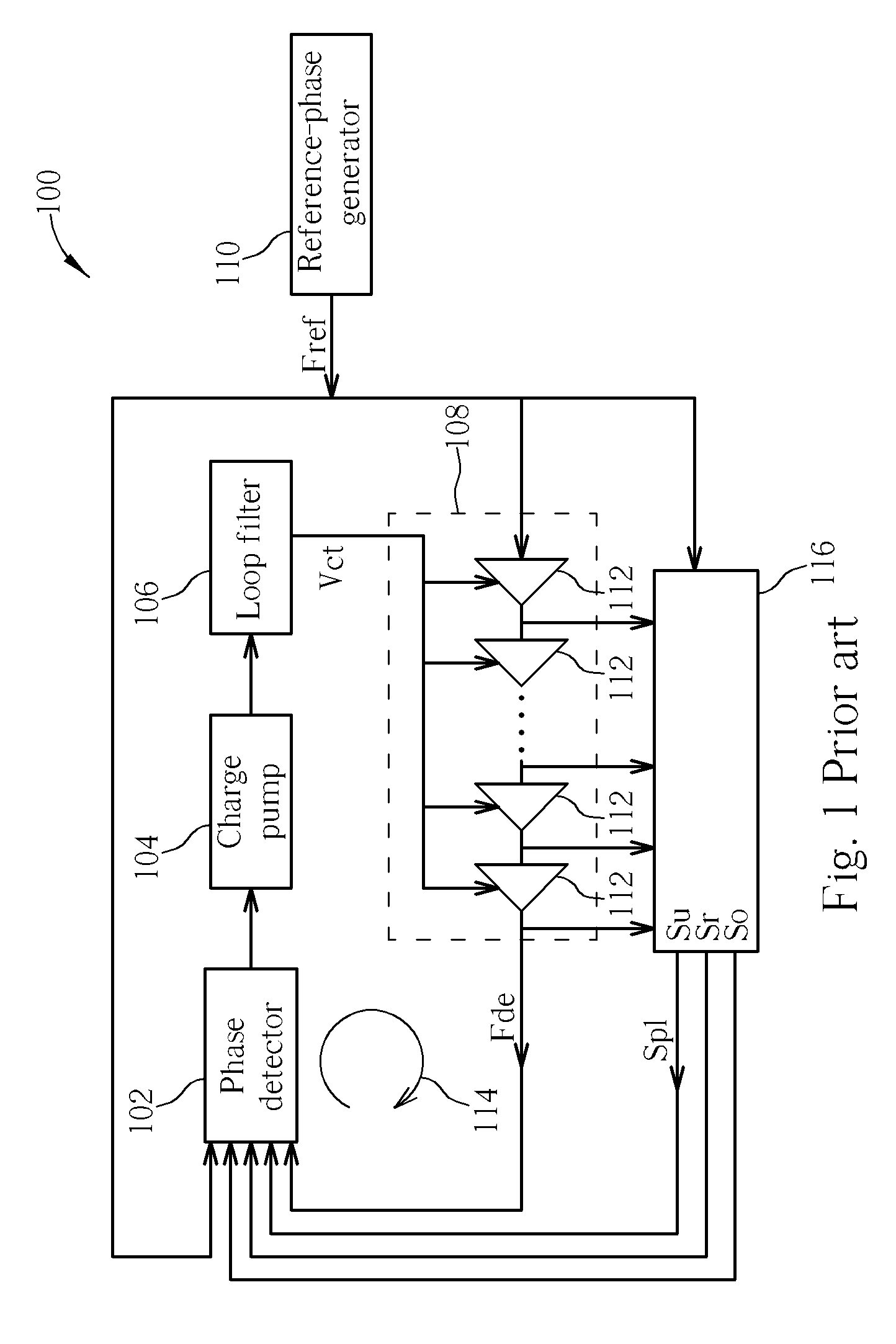

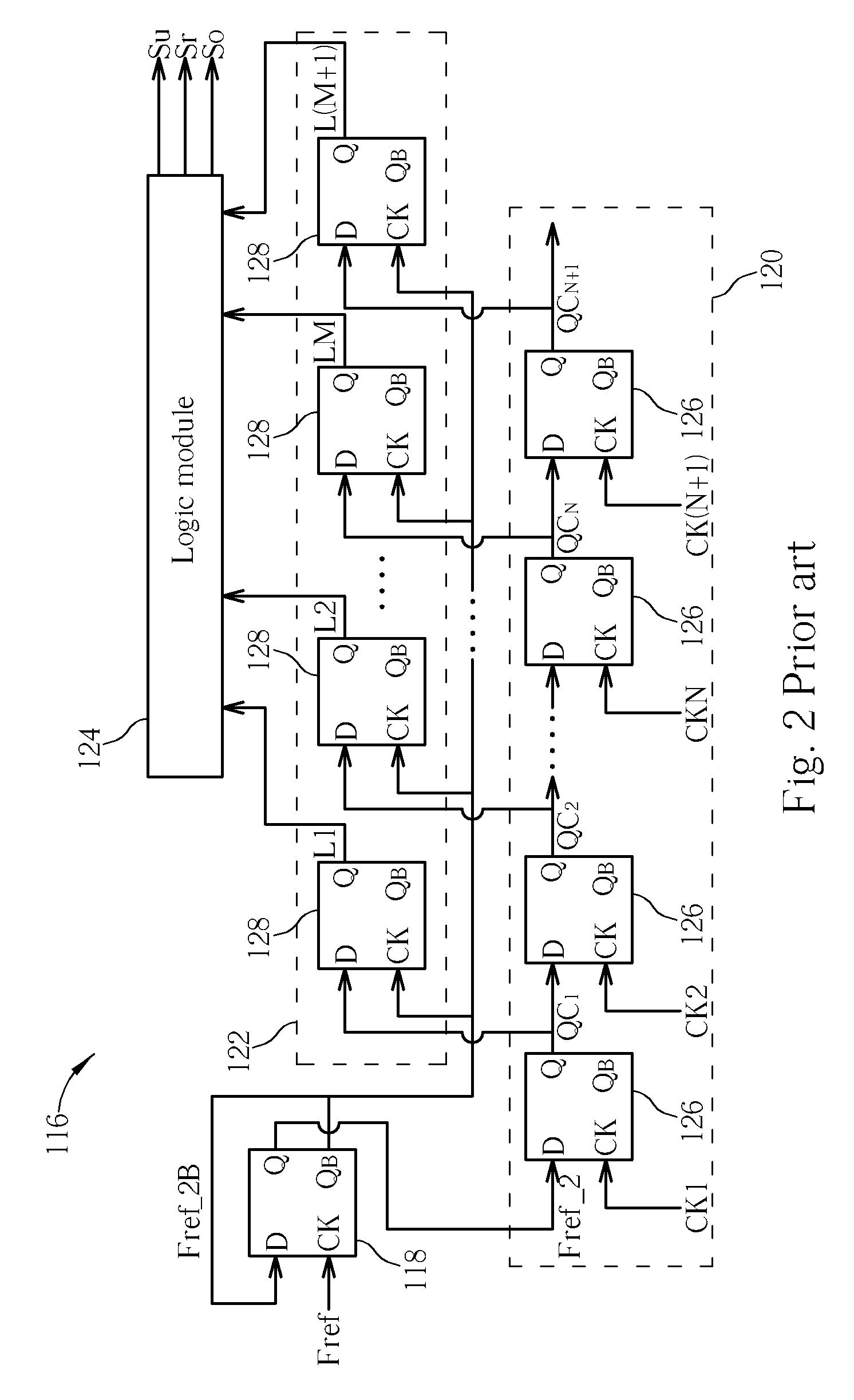

Delay-locked loop device capable of anti-false-locking

A delay-locked loop device capable of anti-false-locking includes a voltage control delay circuit including a plurality of delay units in a series for generating a delayed phase according to a reference phase and a control voltage; a phase detector coupling to the voltage control delay circuit for generating a control signal according to a lock indication signal, the reference phase, and the delayed phase; a charge pump coupling to the phase detector for generating the control voltage to the voltage control delay circuit according to the control signal; and a lock detector coupling to the voltage control delay circuit for generating the lock indication signal for the phase detector according to output phases of each delay unit of the voltage control delay circuit.

Owner:FARADAY TECH CORP

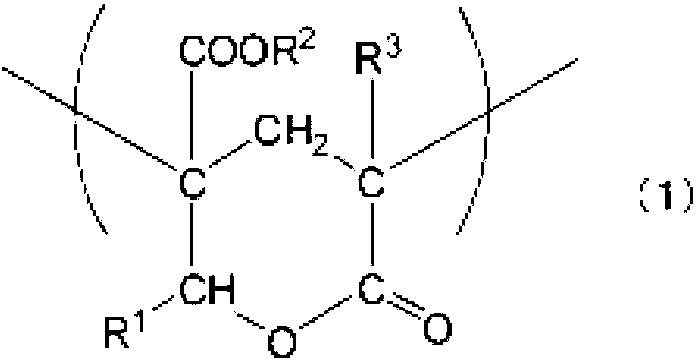

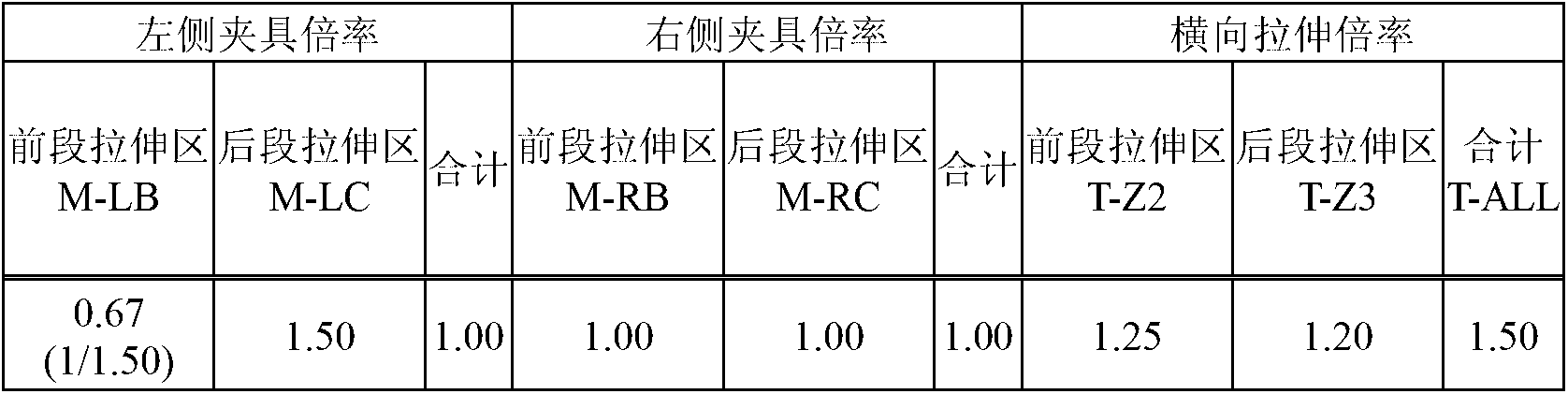

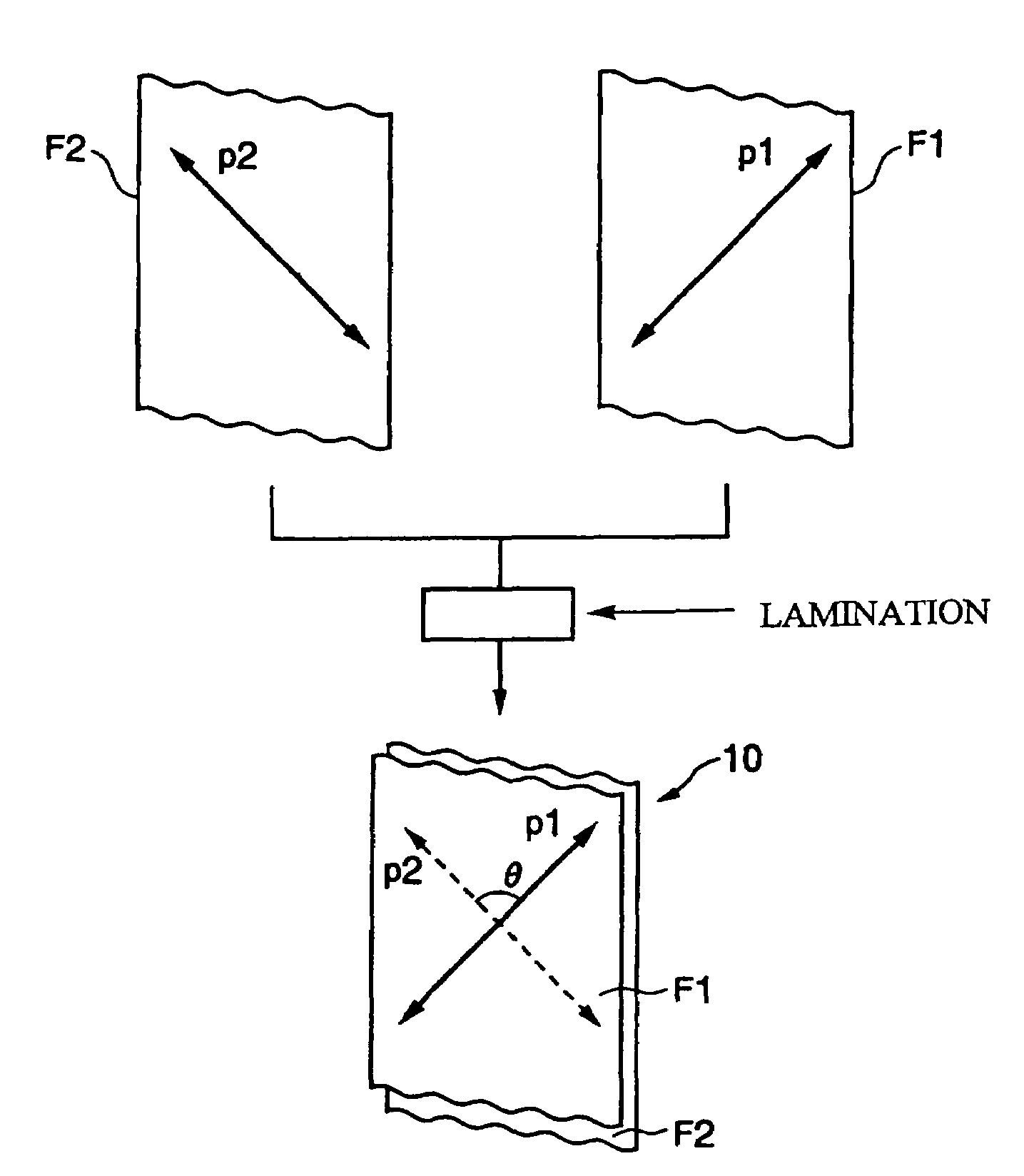

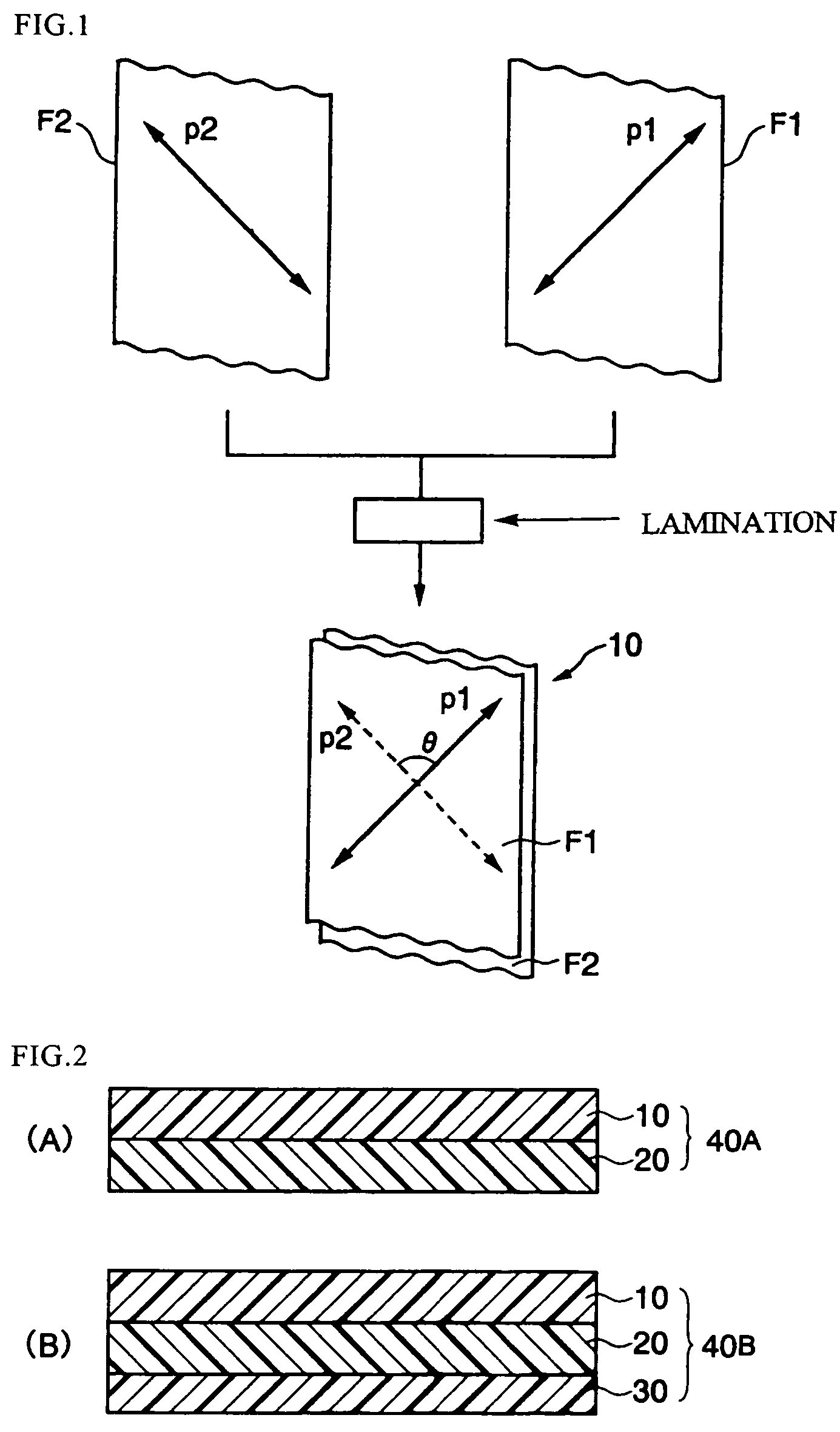

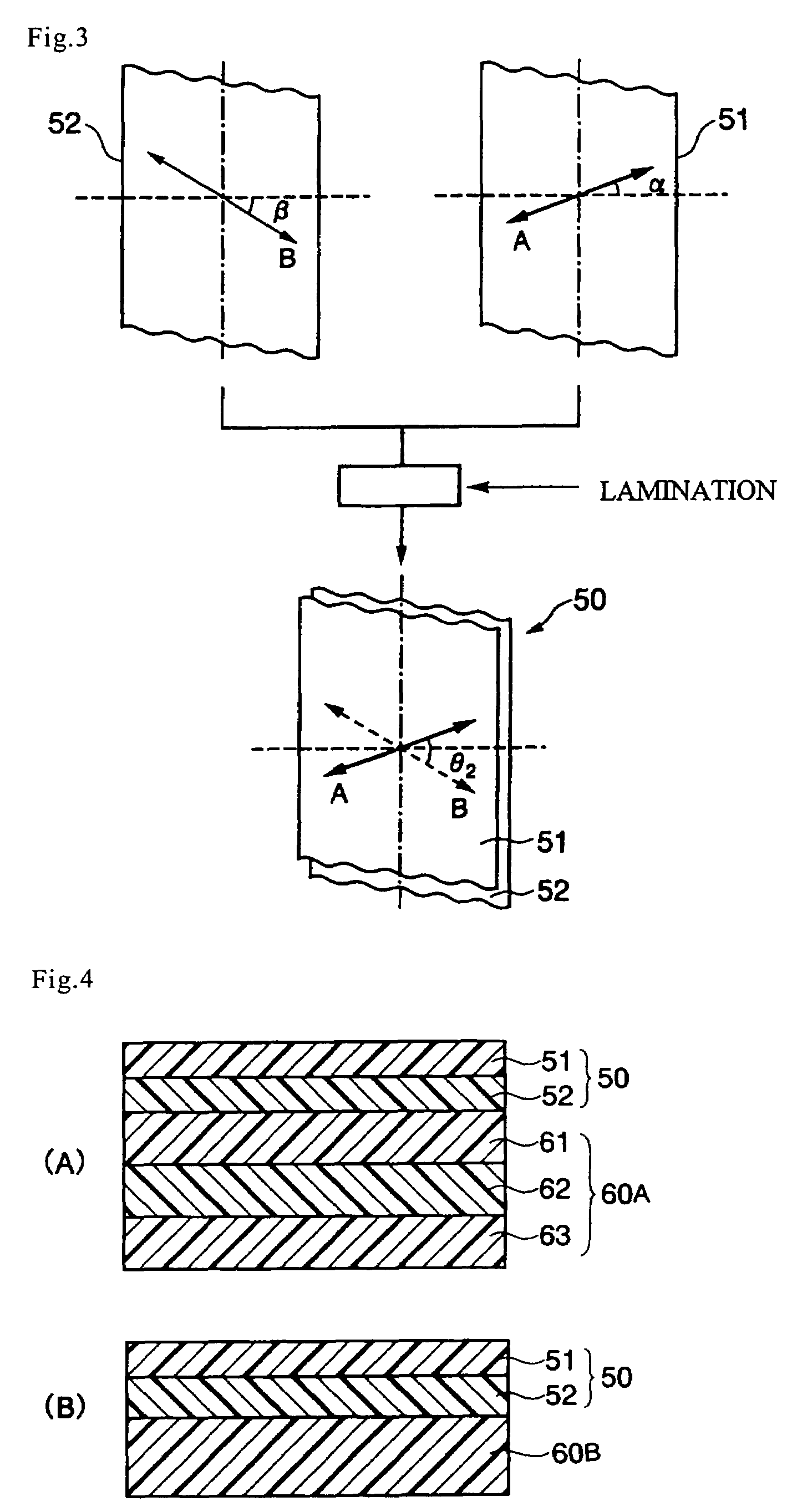

Method of manufacturing phase difference film and phase difference film roll

ActiveCN103052489AWeak two-way stretchImprove area utilization efficiencyOptical articlesPolarising elementsPhase differenceEngineering

One of the methods of manufacturing a phase difference film of the present invention provides a strip-shaped phase difference film which has a delayed phase axis that is inclined with respect to the longitudinal direction, an NZ coefficient closer to 1 than conventional values, and a weak biaxial stretchability (has strong uniaxial stretchability). In the manufacturing method is used a pair of clip sets that grip both peripheral edge parts of the strip-shaped raw film, and a heating and stretching apparatus having a stretching zone. At the time the clip sets grip the raw film, the traveling speed of the pair of clip sets is the same. The stretching zone has a first segment in which the traveling speed of one of the clip sets that have traveled into the zone is successively reduced, and after the first segment, a second segment in which the traveling speed of the above one of the clip sets that have traveled via the first segment is successively restored.

Owner:NIPPON SHOKUBAI CO LTD

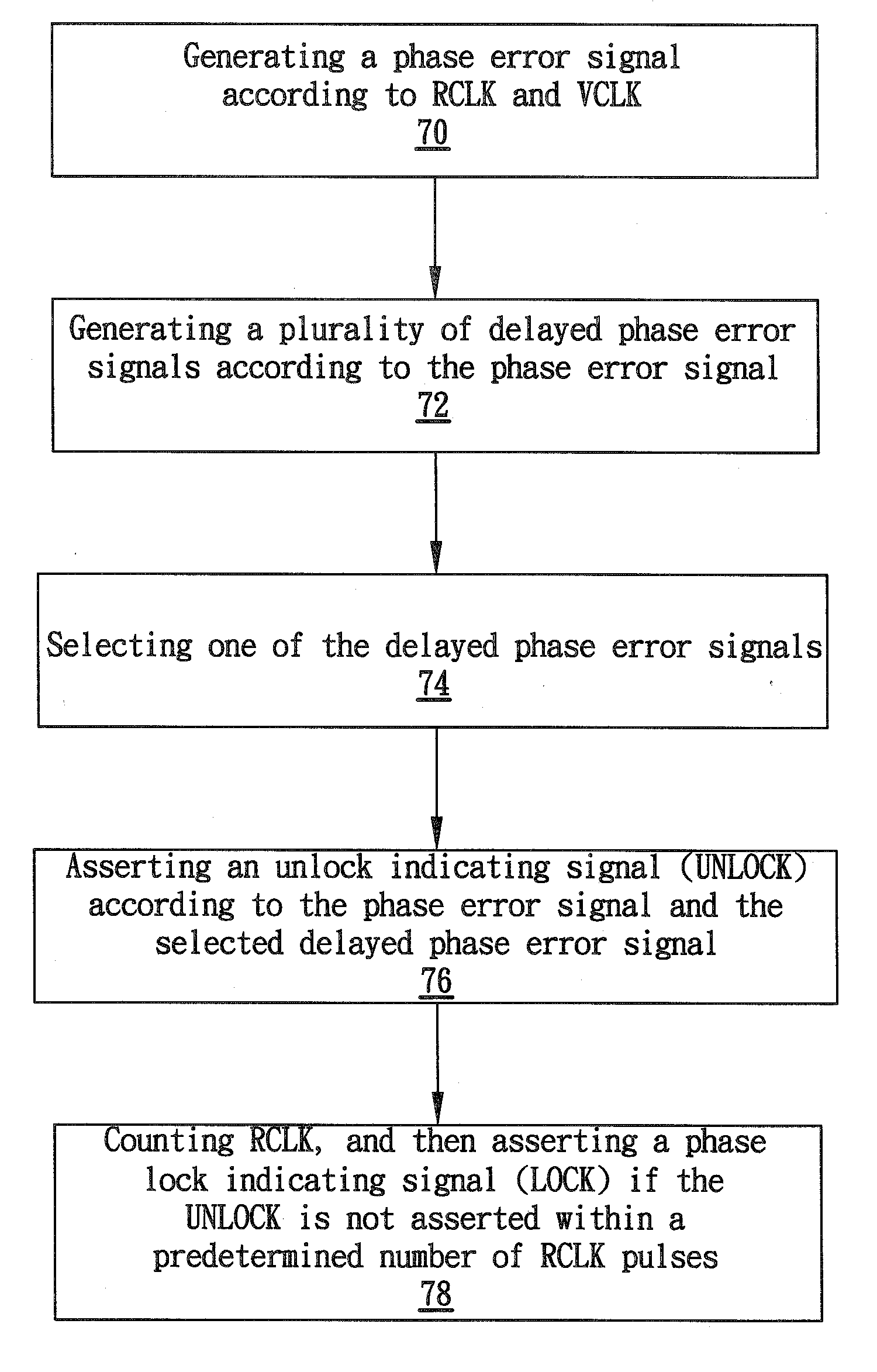

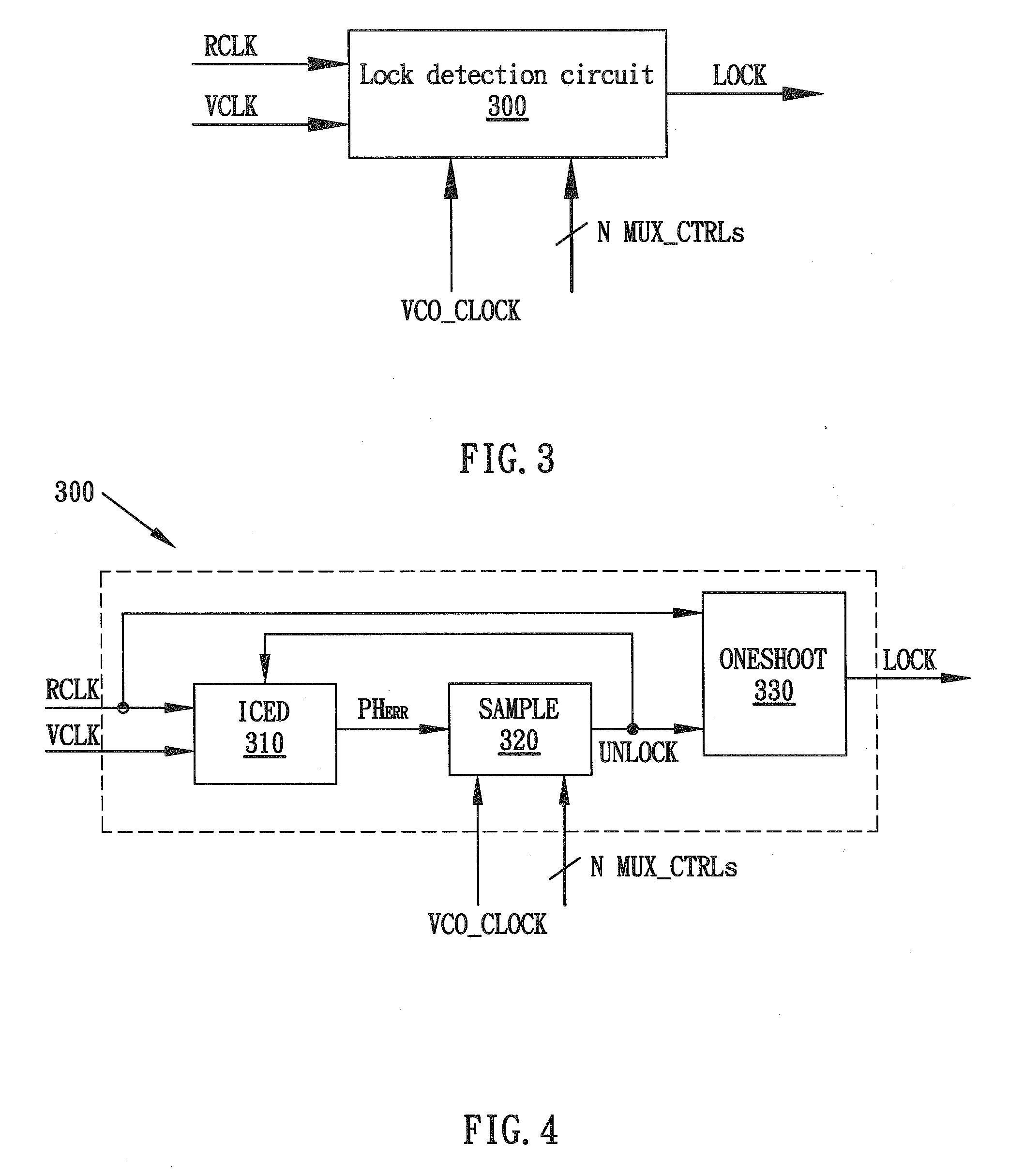

Lock detection circuit and method for phase locked loop system

A lock detection circuit and method are disclosed for phase locked loop (PLL) systems. The lock detection circuit primarily includes a delay unit and an asserting logic unit. The delay unit receives the phase error signal of the PLL and produces a present phase error signal, and then accordingly generates at least one delayed phase error signal. The asserting logic unit generates an unlock indicating signal (UNLOCK) according to the present phase error signal and the delayed phase error signal. A phase lock indicating signal will be asserted if the unlock indicating signal is not asserted within a predetermined number of counting pulses.

Owner:VIA TECH INC

Polyvinylidene fluoride-hexafluoropropylene super-hydrophobic composite film and preparation method thereof

ActiveCN104307387AImprove performanceHigh mechanical strengthSemi-permeable membranesComposite filmDistillation

The invention discloses a method for preparing a polyvinylidene fluoride-hexafluoropropylene super-hydrophobic composite film. According to the method, the surface of a non-woven fabric is respectively coated with a porous supporting layer and a super-hydrophobic layer in a blade coating manner by adopting an immersion-precipitation phase transformation method, and the size of the pore diameter of a composite film is controlled by virtue of the porous supporting layer. According to the polyvinylidene fluoride-hexafluoropropylene super-hydrophobic composite film, six fluorine atoms in the structure unit show high hydrophobic performance, and the super-hydrophobic layer is formed on the surface of the porous supporting layer by delayed phase transformation. The method is simple to operate, low in manufacture cost and easy to industrialize; the super-hydrophobic composite film has a water contact angle of 153+ / -3 degrees, a rolling angle of 3+ / -1 degrees and pore diameter of 0.05-2 microns, is stable in performance and high in mechanical strength, shows excellent super-hydrophobic performance and self-cleaning function, and can be used in liquid degassing, defoaming, film distillation and other industries.

Owner:JIANGSU JIUMO HIGH TECH CO LTD

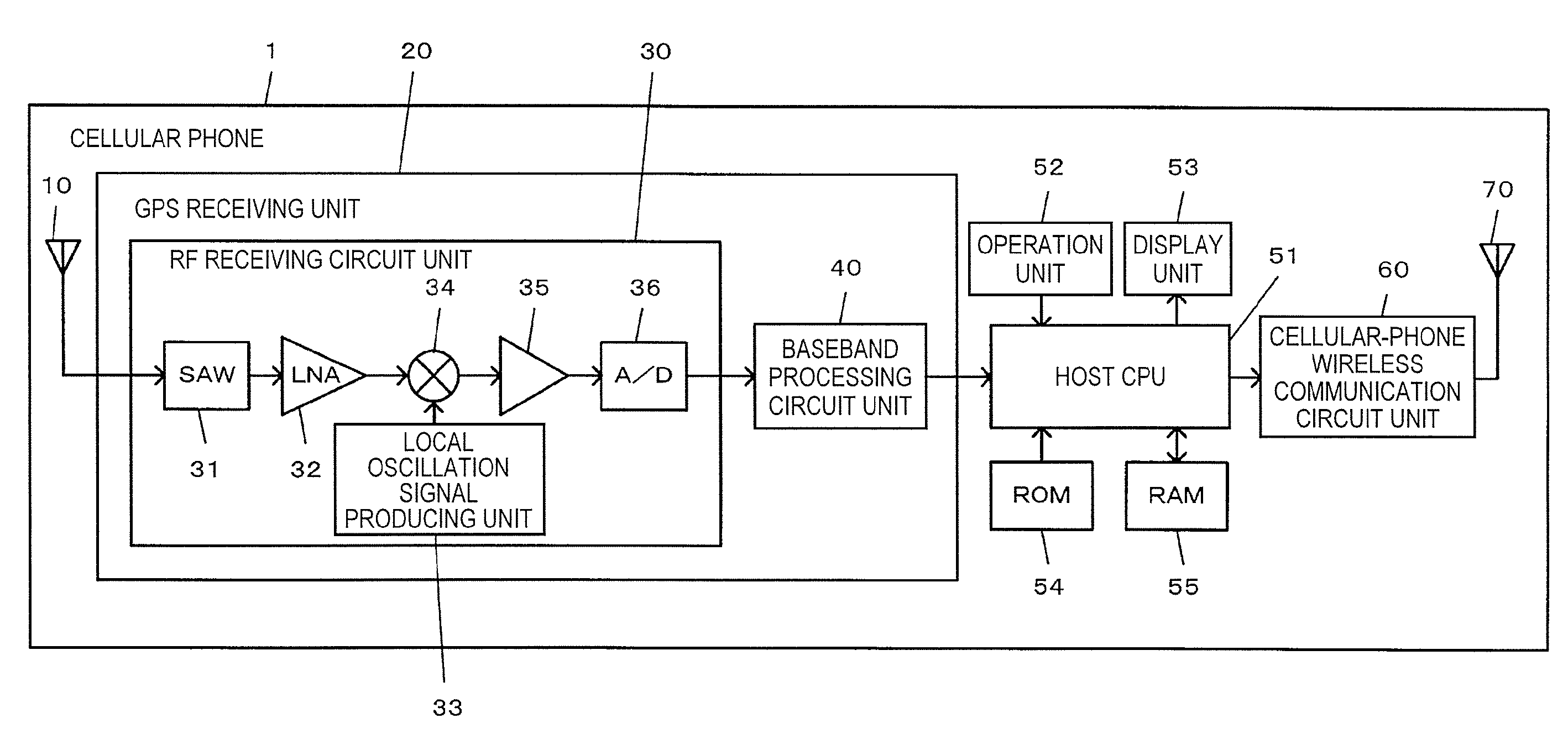

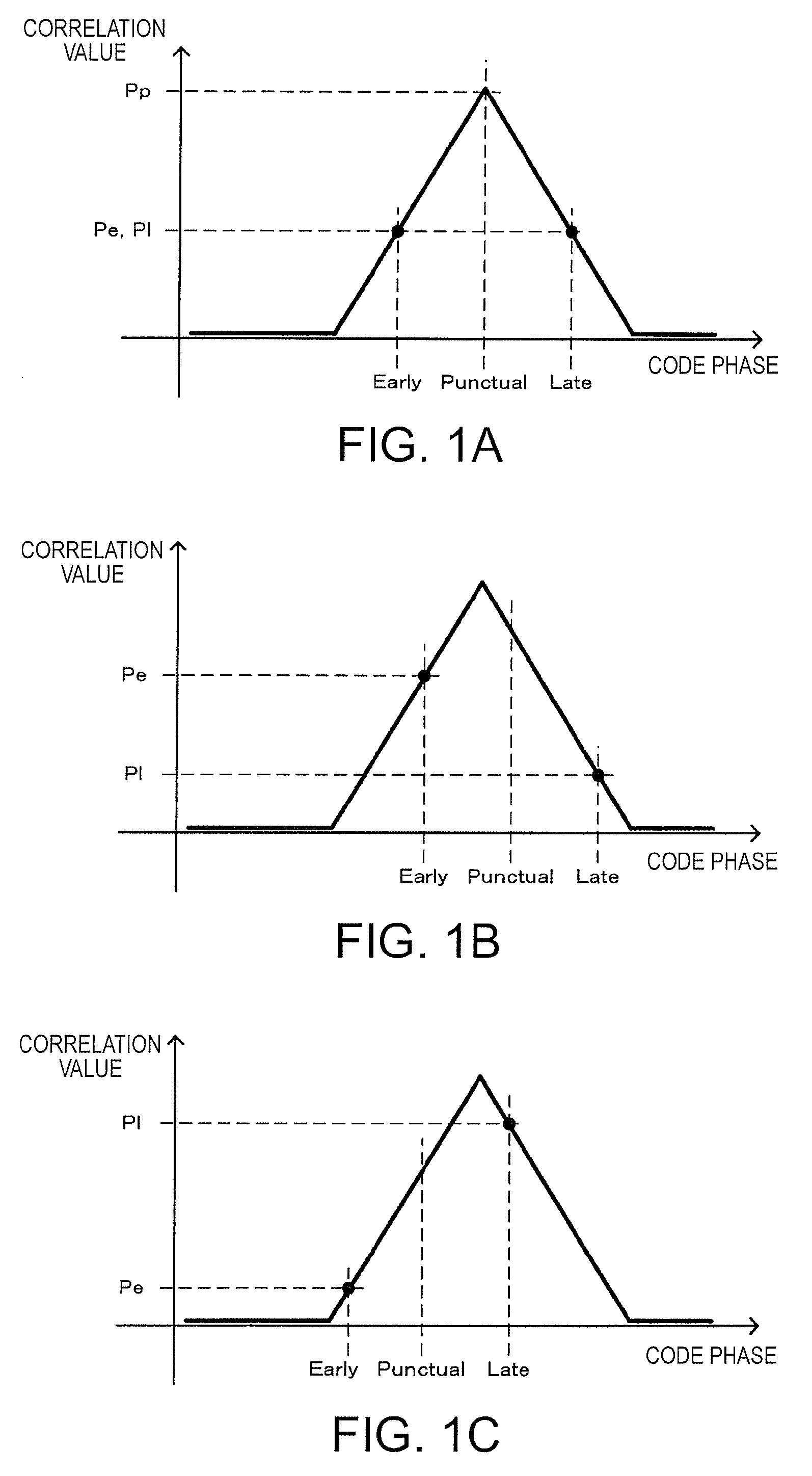

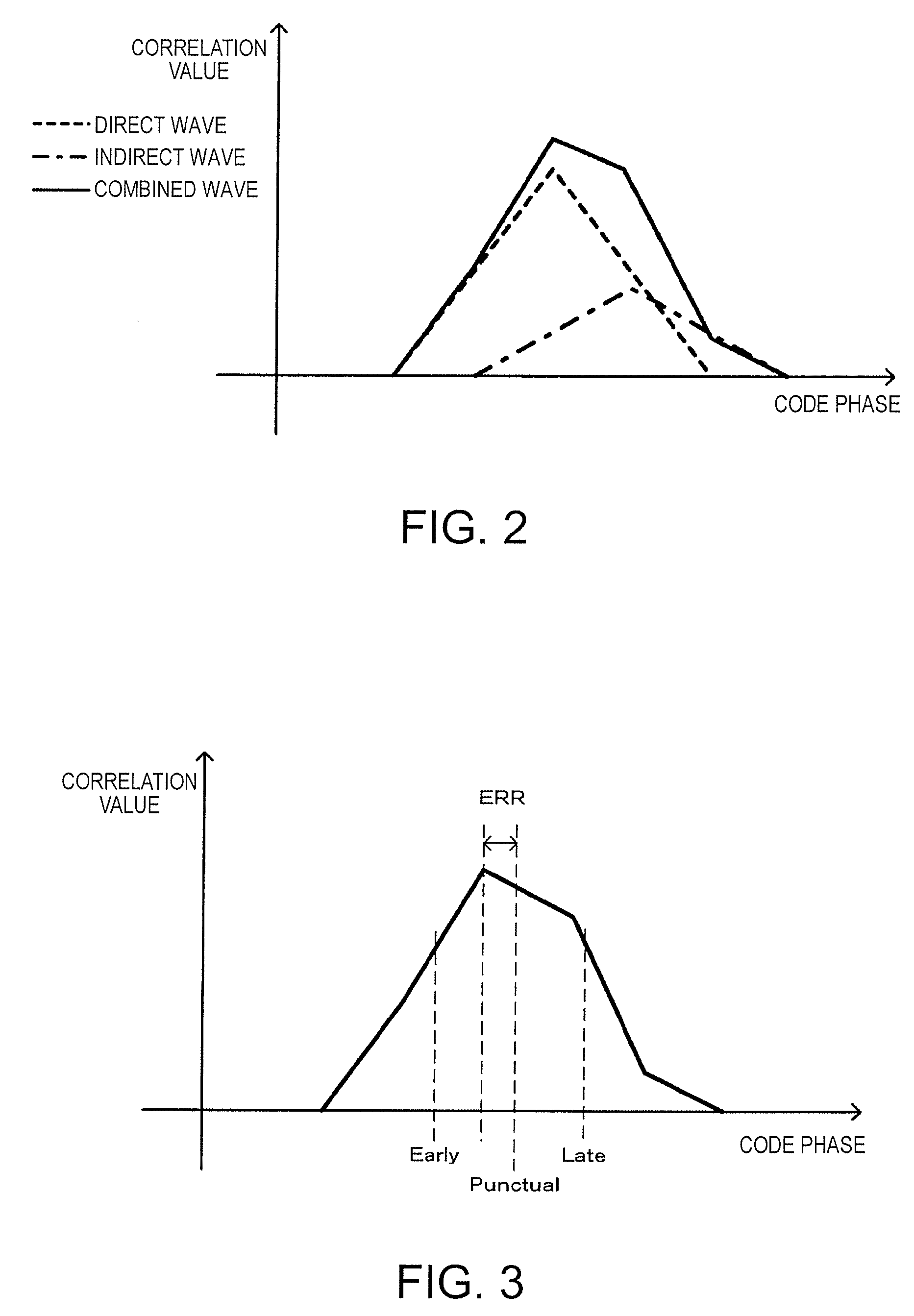

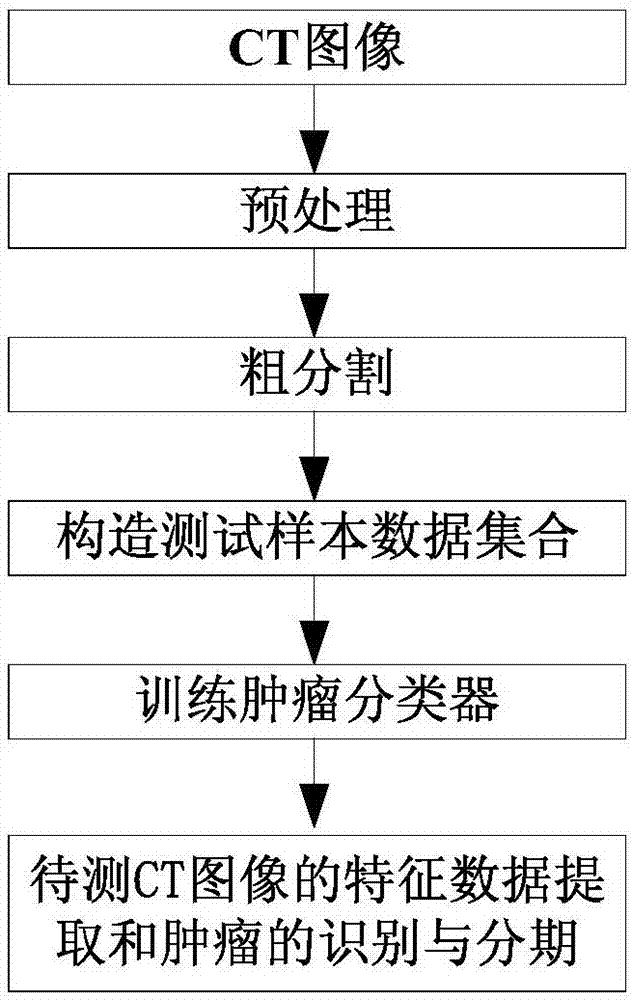

Multipath signal judging method, program, and multipath signal judging device

ActiveUS20090168925A1Position fixationAmplitude-modulated carrier systemsComputer scienceAdvanced phase

Owner:SEIKO EPSON CORP

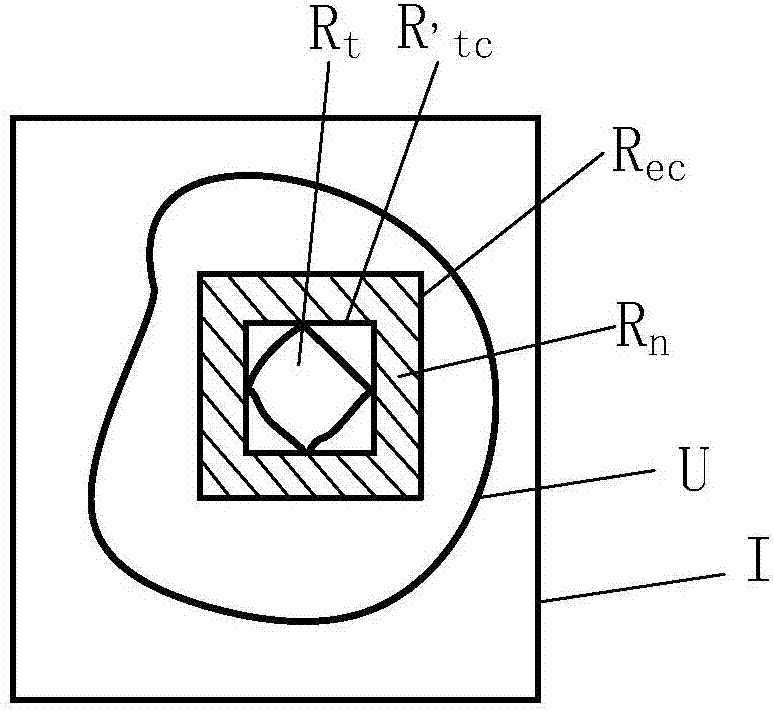

Tumor identification method

ActiveCN107292312AThe identification method is objectiveQuantitative identification methodCharacter and pattern recognitionData setBlood vessel

The invention discloses a tumor identification method, which comprises the following steps: rough segmentation: sequentially performing organ segmentation and blood vessel segmentation on a CT image to obtain a CT image of an organ with blood vessel being removed; constructing a test sample data set: based on an the CT image of the organ, sequentially constructing the tumor area sub-graph sets for an arterial phase, a venous phase and a delayed phase to form a test positive sample data set and the organ normal area subgraph set constitutes the test negative sample data set. The training tumor classifier: extracts the characteristic data of the test sample data set, Good / bad identification and staging of the tumor classifier; feature extraction of CT images and tumor identification and staging: the arterial phase, venous phase and the delay of the CT images to be extracted feature data extraction to form the characteristic data to be measured Set, will feature data to be tested input tumor classification for benign / malign tumor classification and staging. The present invention can accurately distinguish between benign and malignant staging and staging of the segmented tumor.

Owner:SUZHOU INST OF BIOMEDICAL ENG & TECH CHINESE ACADEMY OF SCI

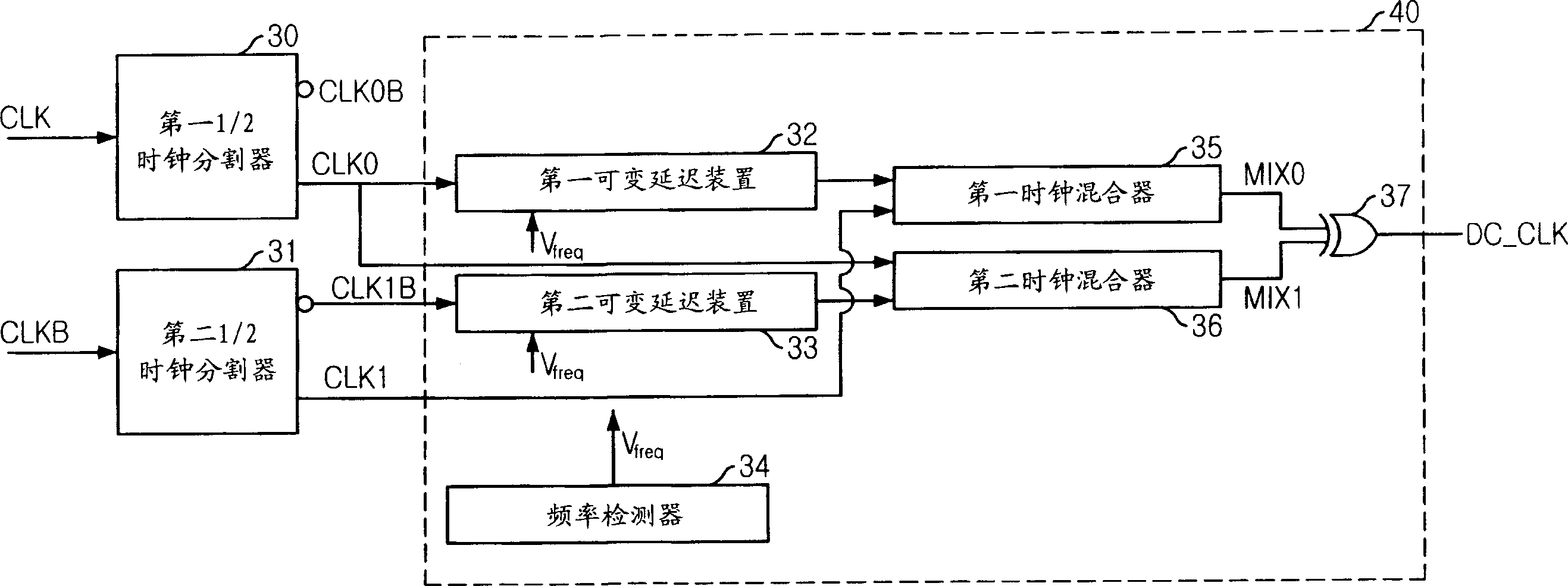

Duty degree correction circuit and delayed phase-lock loop having same

InactiveCN1499726AReduce power consumptionPulse automatic controlContinuous to patterned pulse manipulationDelay-locked loopEngineering

Owner:CONVERSANT IP N B 868

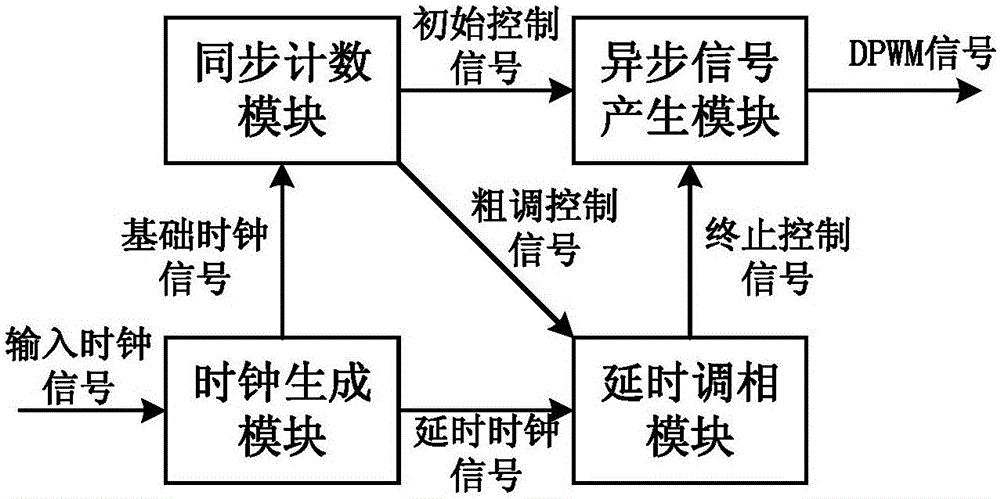

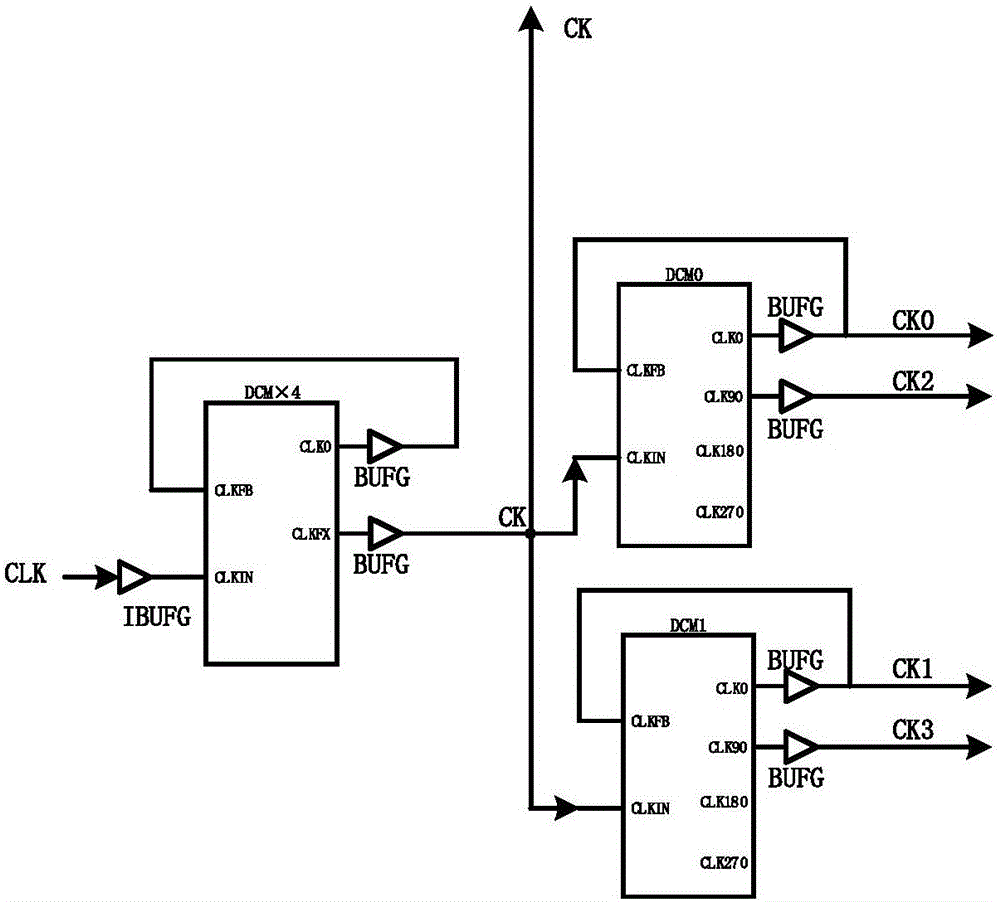

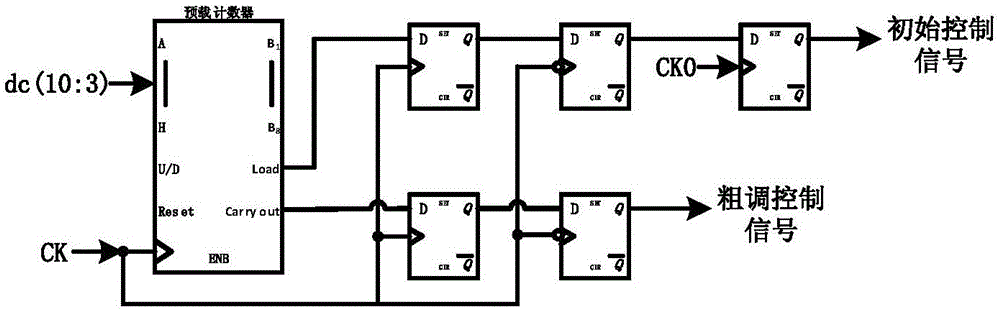

Digital pulse width modulator based on delayed phase modulation

InactiveCN106301301ASimple designEasy to implementPulse duration/width modulationControl signalComputer science

The invention discloses a digital pulse width modulator based on delayed phase modulation. The digital pulse width modulator is composed of a clock generating module, a synchronous counting module, a delayed phase modulation module and an asynchronous signal generating module. The clock generating module performs frequency multiplication on an input clock signal and outputs a fundamental clock signal to the synchronous counting module, simultaneously delays the fundamental clock signal and outputs the delayed clock signal to the delayed phase modulation module. The synchronous counting module finishes coarse adjustment of the pulse width and respectively outputs an initial control signal and a coarse-adjusted control signal to the asynchronous signal generating module and the delayed phase modulation module. The delayed phase modulation module delays the coarse-adjusted control signal for generating eight paths of termination control signals and selects one path of termination control signal for outputting to the asynchronous signal generating module. The initial control signal and the termination control signal are input into an RS trigger in the asynchronous signal generating module and a final DPWM signal is output. The digital pulse width modulator improves modulation precision on the condition of no fundamental clock signal change and furthermore has advantages of relatively high accuracy, high versatility and high applicability.

Owner:NANJING UNIV OF SCI & TECH +1

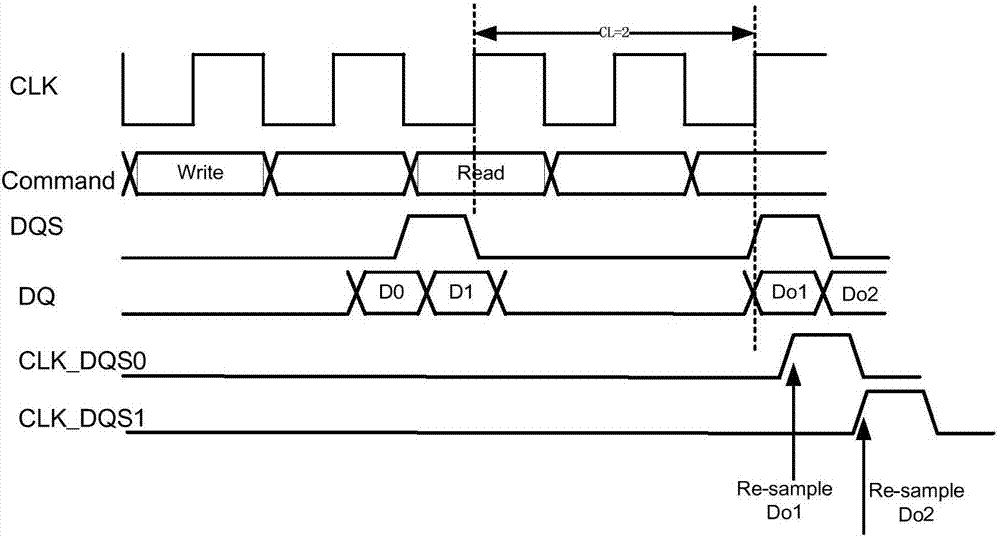

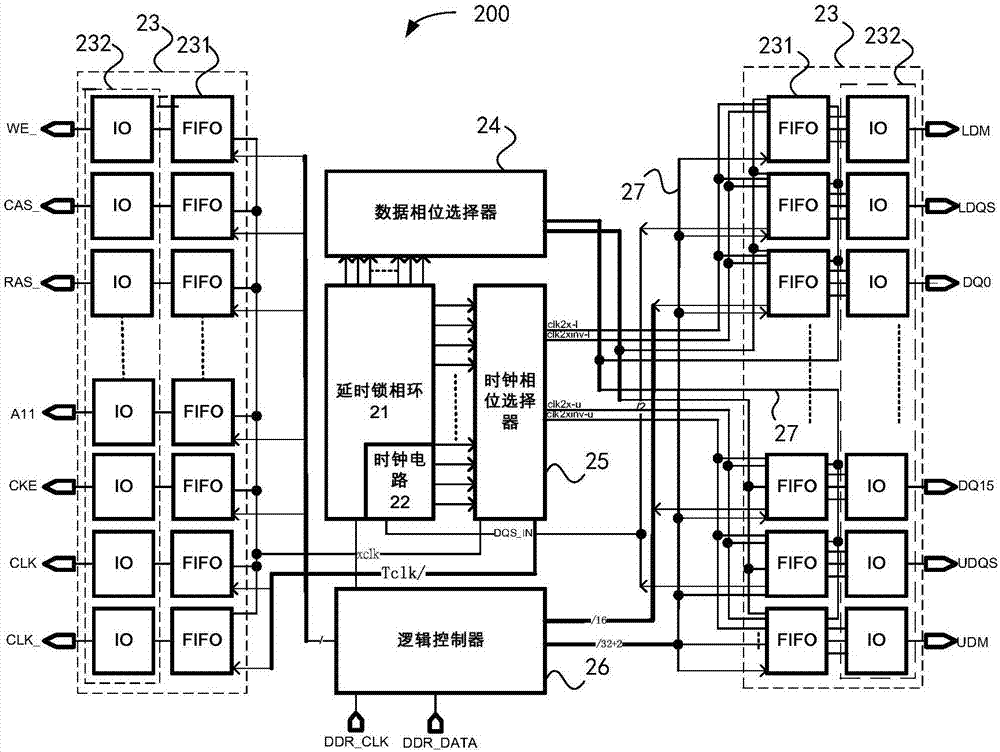

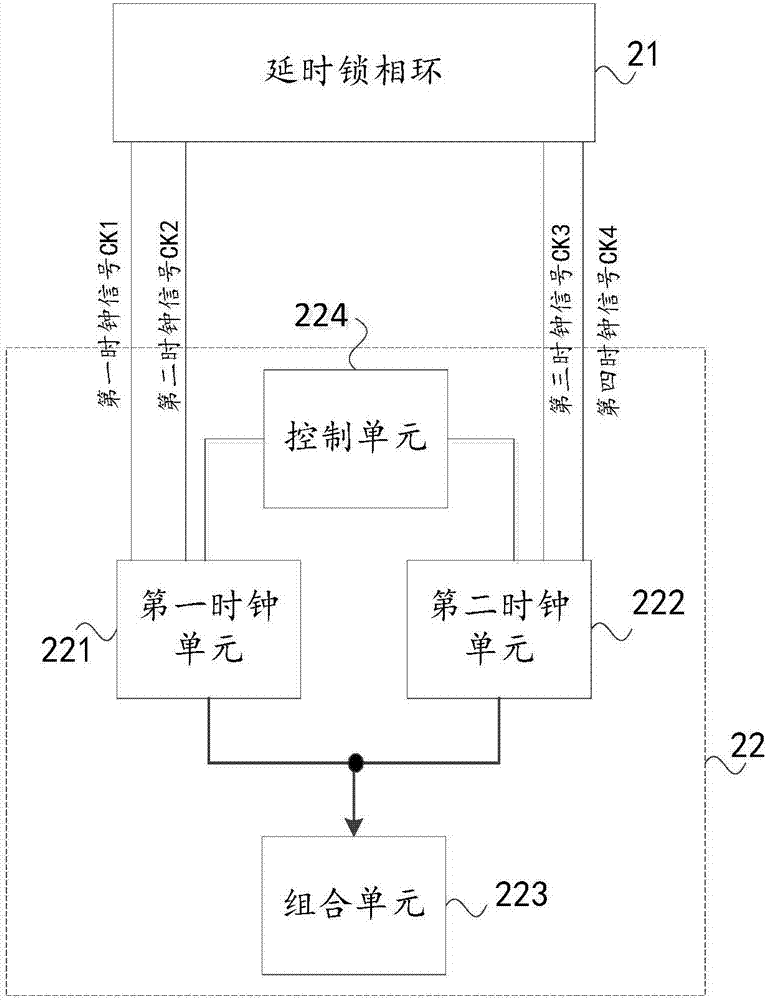

DDR SDRAM control circuit, DDR SDRAM chip, PCB and electronic equipment

The invention relates to the technical field of integrated circuits, in particular to a DDR SDRAM control circuit, a DDR SDRAM chip, a PCB and electronic equipment. The DDR SDRAM control circuit comprises a delayed phase-locked loop, a clock circuit, a clock phase selector and a logic controller, wherein the delayed phase-locked loop is used for generating a preset clock signal; the clock circuit is used for generating a reference clock signal, the frequency of which is at least doubled; and the logic controller d for controlling a data strobe pulse DQS to be centrally aligned with a data pulse DQ according to the reference clock signal when a writing operation is carried out. Compared with the clock signal of the existing DDR SDRAM control circuit, the reference clock signal is a clock signal, the frequency of which is at least doubled, so that the low-frequency clock signals are replaced by high-frequency clock signals, the designers can decrease or shorten the length of high-speed clock wires connected to interface modules, and then benefit is brought to the balance the delayed control.

Owner:APPOTECH

Polar receiver architecture and signal processing methods

ActiveUS8929486B2Amplitude demodulation by homodyne/synchrodyne circuitsSimultaneous amplitude and angle demodulationInjection lockedHarmonic

Compressing a variable phase component of a received modulated signal with a second harmonic injection locking oscillator, and generating a delayed phase-compressed signal with a fundamental injection locking oscillator, and combining the phase-compressed signal and the delayed phase-compressed signal to obtain an estimated derivative of the variable phase component, and further processing the estimated derivative to recover data contained within the received modulated signal.

Owner:INNOPHASE

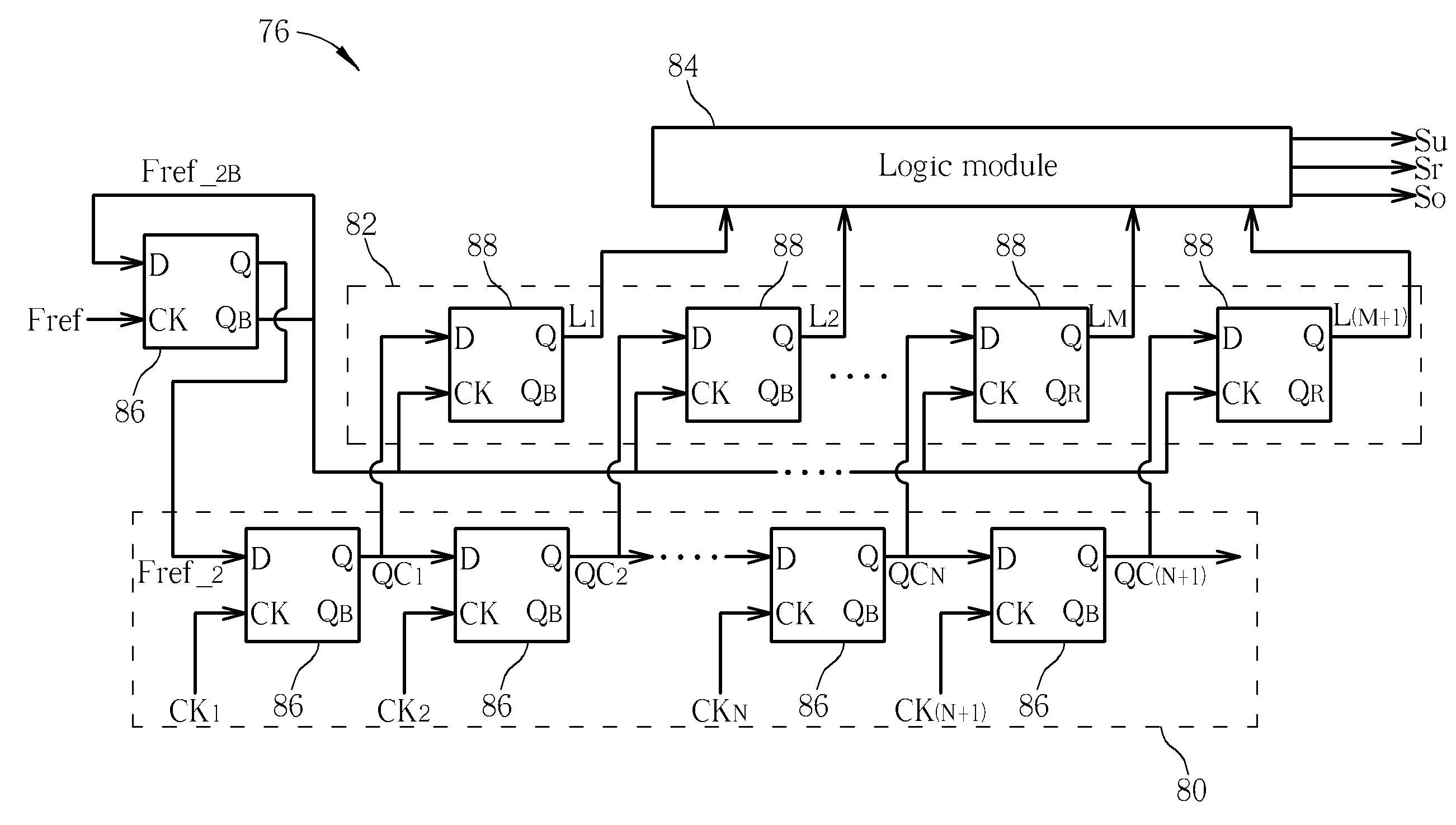

A high-precision pulse width comparison device based on time-to-digital conversion

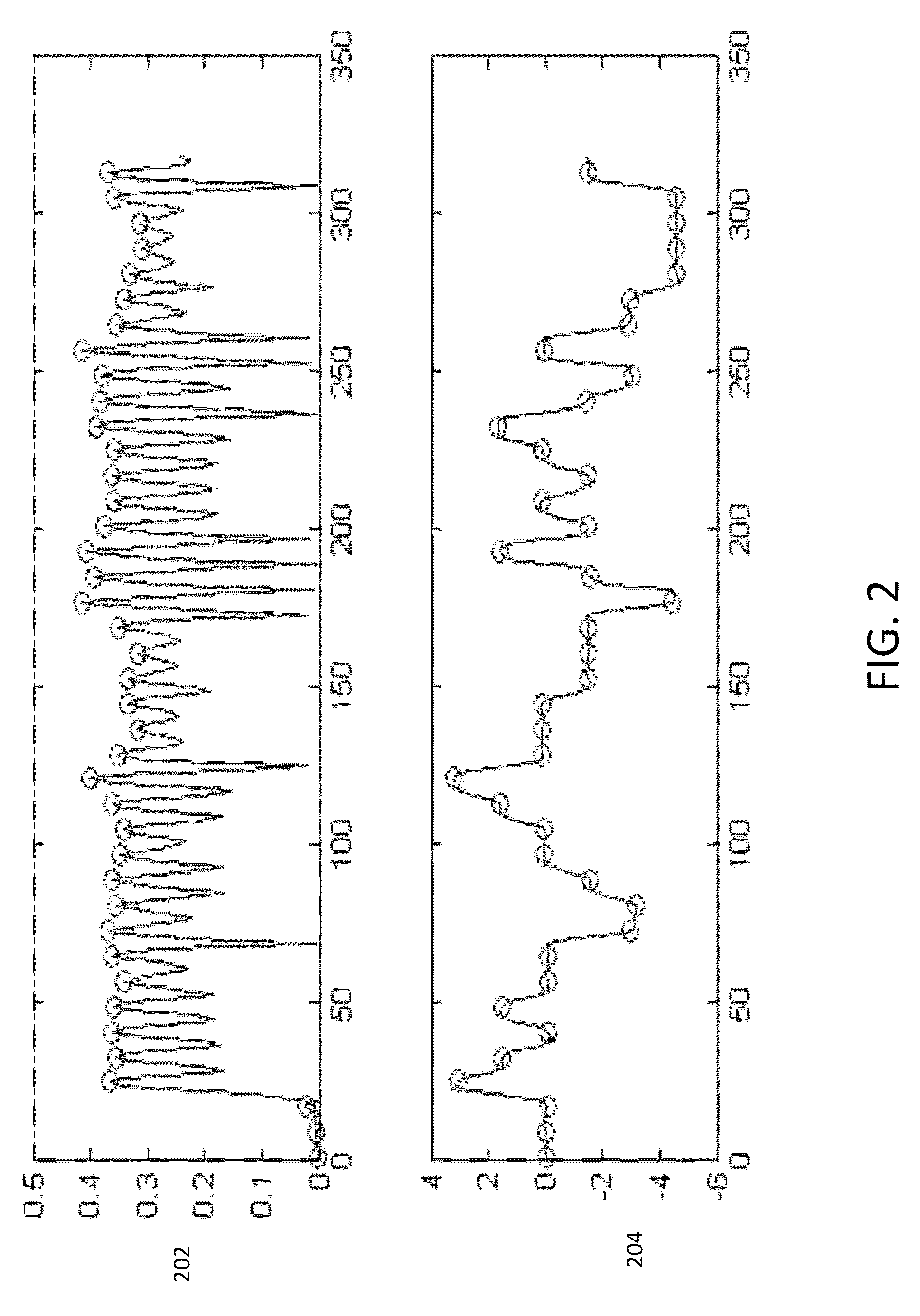

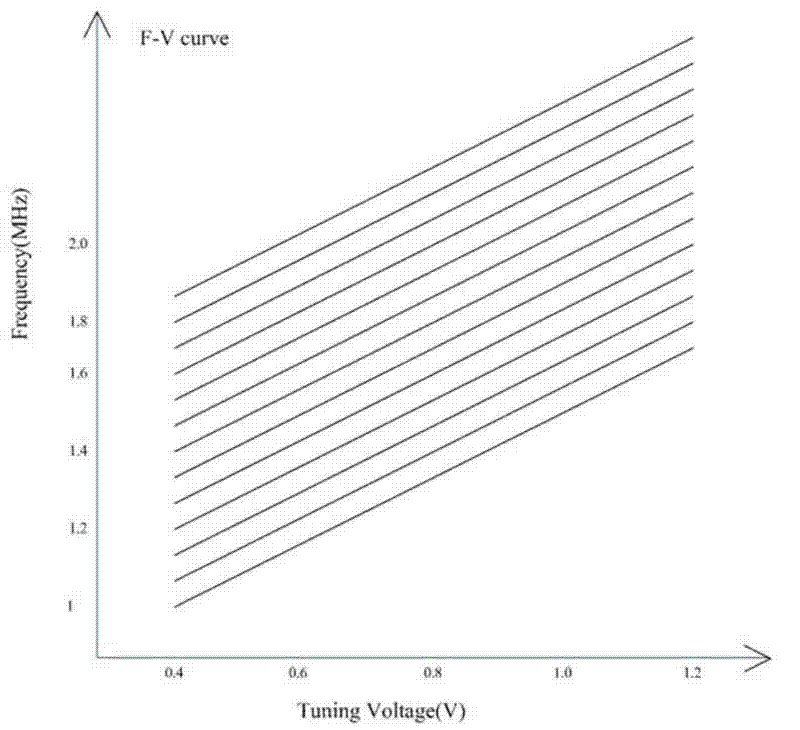

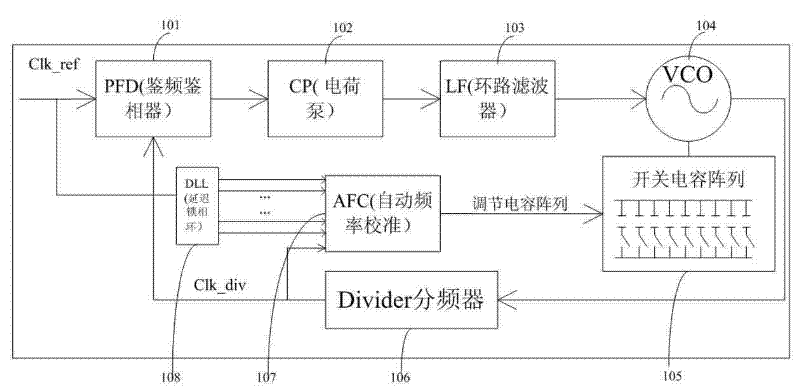

InactiveCN102299709AShorten lock timeReduce count cyclePulse automatic controlCapacitanceCommunications system

The invention discloses an automatic frequency comparison circuit using a high-precision pulse width comparison device based on time-to-digital conversion. On the basis of the automatic frequency calibration device of the original phase-locked loop of the present invention, a DLL module is added to generate a plurality of delayed phase clocks with the same frequency and phase difference as the reference clock, and simultaneously count the reference clock and its delayed clock and accumulate all counter results, At the same time, the feedback clock is counted, and the capacitor array is adjusted by comparing the accumulated value of the reference clock and its delayed clock counter with the value of the feedback counter. Only need to add a DLL delay phase-locked loop circuit on the circuit, the frequency resolution can be greatly improved, the frequency difference between the reference clock and the feedback clock can be distinguished with higher precision, the automatic calibration time is greatly reduced, and the phase-locked loop lock is shortened. Time, so it can meet the needs of modern communication systems for fast switching of phase-locked loop frequencies.

Owner:广州润芯信息技术有限公司

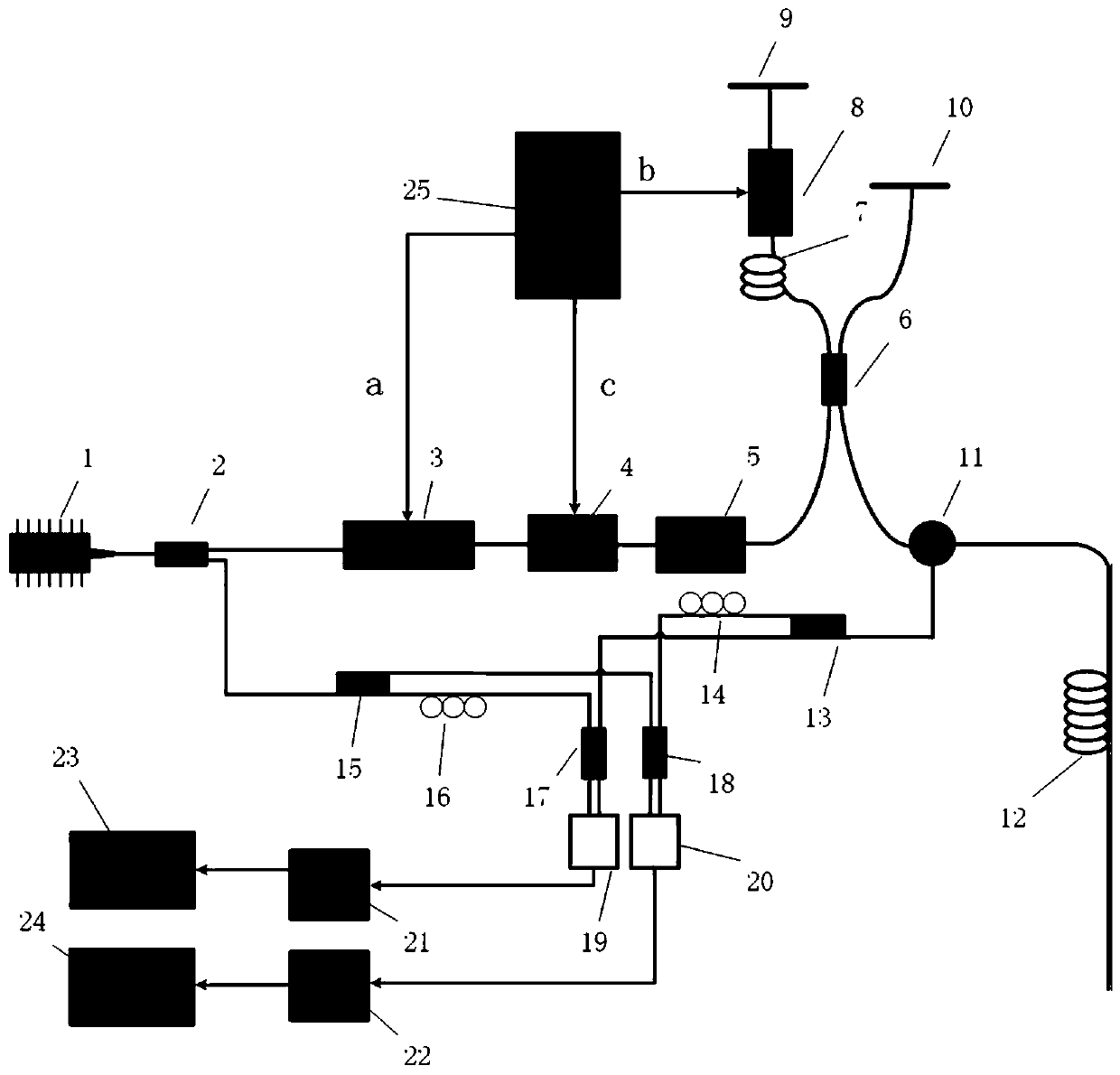

Optical fiber vibration sensor based on delayed phase-modulated chirped pulse pairs

ActiveCN110108346AEliminate the effect of signal-to-noise ratioExpand sweep rangeSubsonic/sonic/ultrasonic wave measurementUsing wave/particle radiation meansTime-domain reflectometerDigital signal processing

The invention relates to an optical fiber vibration sensor based on delay phase-modulated chirped pulse pairs. The sensor comprises a narrow linewidth laser, a first optical fiber coupler, an electro-optical modulator, an acousto-optic modulator, an optical amplifier, a second optical fiber coupler, a delay optical fiber, an optical fiber expansion device, a first Faraday rotator mirror, a secondFaraday rotator mirror, an annular device, a to-be-measured optical fiber, a third optical fiber coupler, a first polarization controller, a fourth optical fiber coupler, a second polarization controller, a fifth optical fiber coupler, a sixth optical fiber coupler, a first double-balance detector, a second double-balance detector, a first analog-to-digital converter, a second analog-to-digital converter, a first digital signal processing unit, a second digital signal processing unit and an arbitrary waveform generator. With the optical fiber vibration sensor adopted, the contradiction betweenspatial resolution and sensing distances in a traditional sensing system based on a time-domain reflectometer can be eradicated; the problem of interference attenuation in an interference sensing system can be solved; and indexes such as a long sensing distance, high spatial resolution and a high signal-to-noise ratio can be achieved simultaneously.

Owner:SHANGHAI INST OF OPTICS & FINE MECHANICS CHINESE ACAD OF SCI

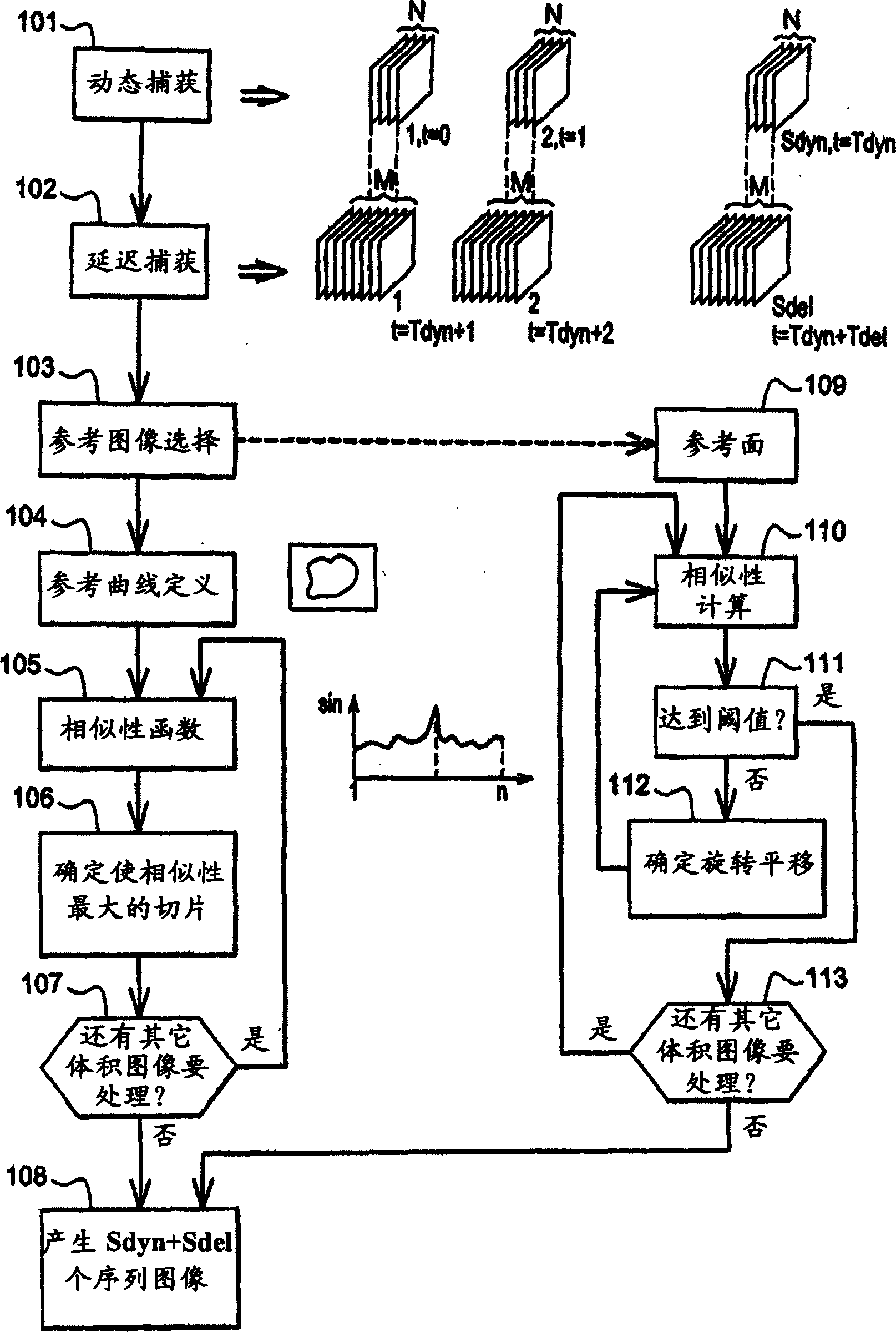

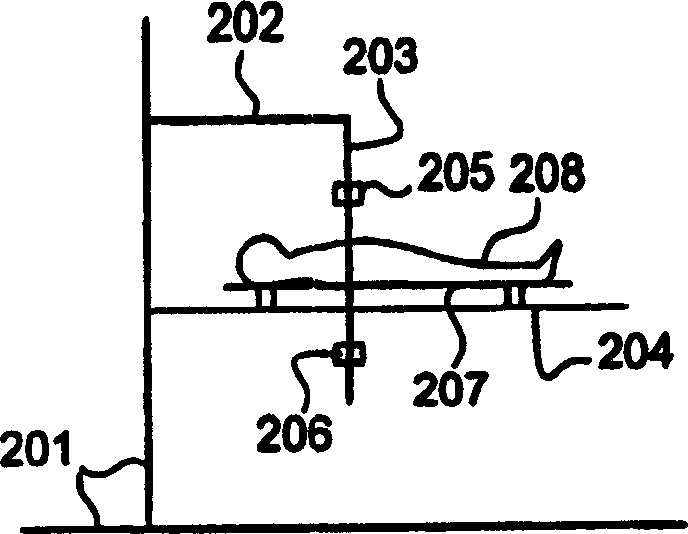

Method and apparatus for motion correction in 3-D medical image sequence

In order to prolong the duration of an examination by a scanner the examination is carried out in two phases. A first dynamic phase (101) during which the patient holds his breath and the scanner explores a region Rdyn, and a second delayed phase (102) during which the patient breathes freely and the scanner explores the region Rdel. The latter comprises the region Rdyn. The images acquired during the delayed phase are registered (103-107, 109-113) with relation to at least one dynamic phase image. This registration allows an image sequence covering a long time period for region Rdyn to be obtained. This registration permits being free from the effects of the respiratory and cardiac cycles. <IMAGE>

Owner:GE MEDICAL SYST GLOBAL TECH CO LLC

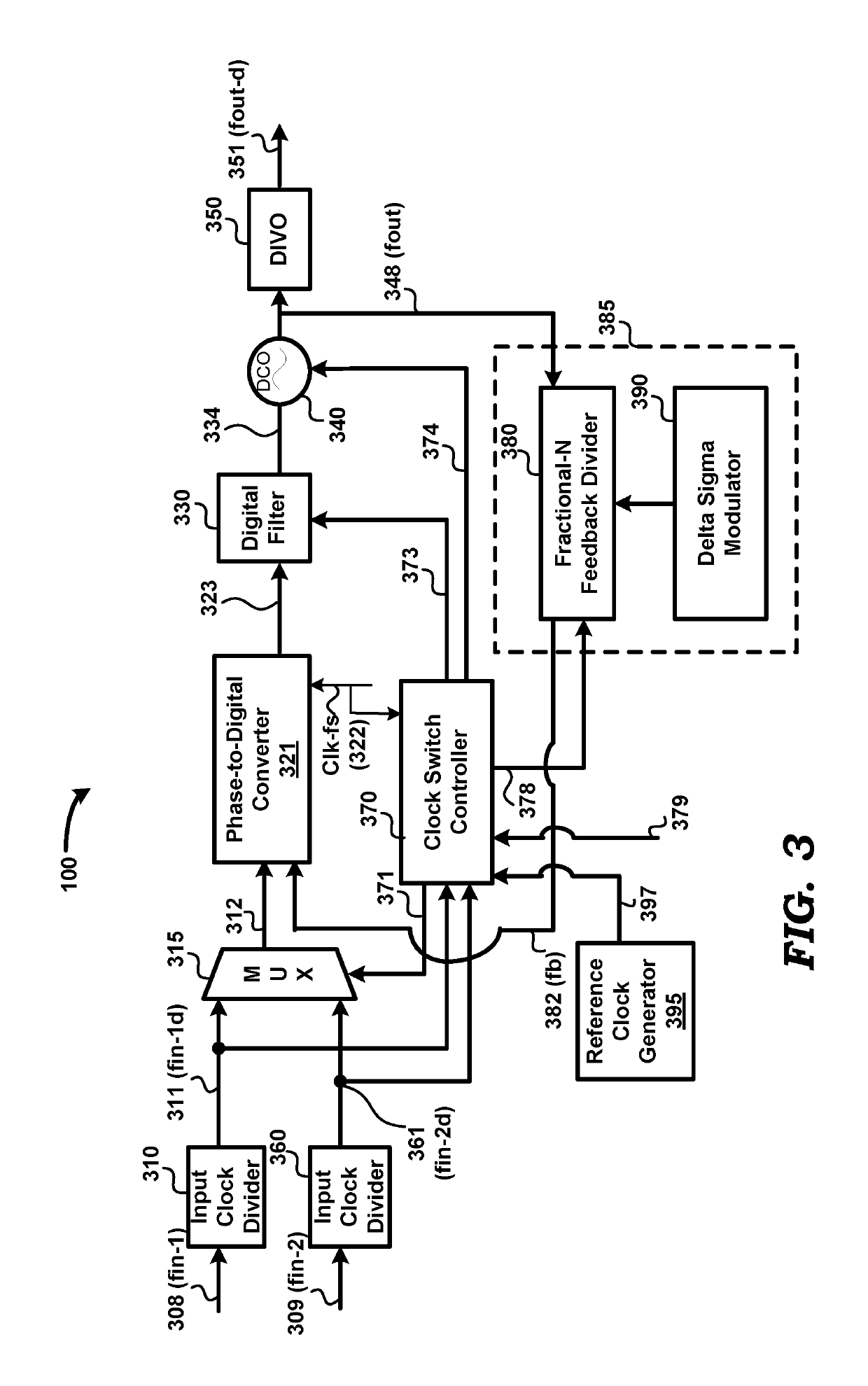

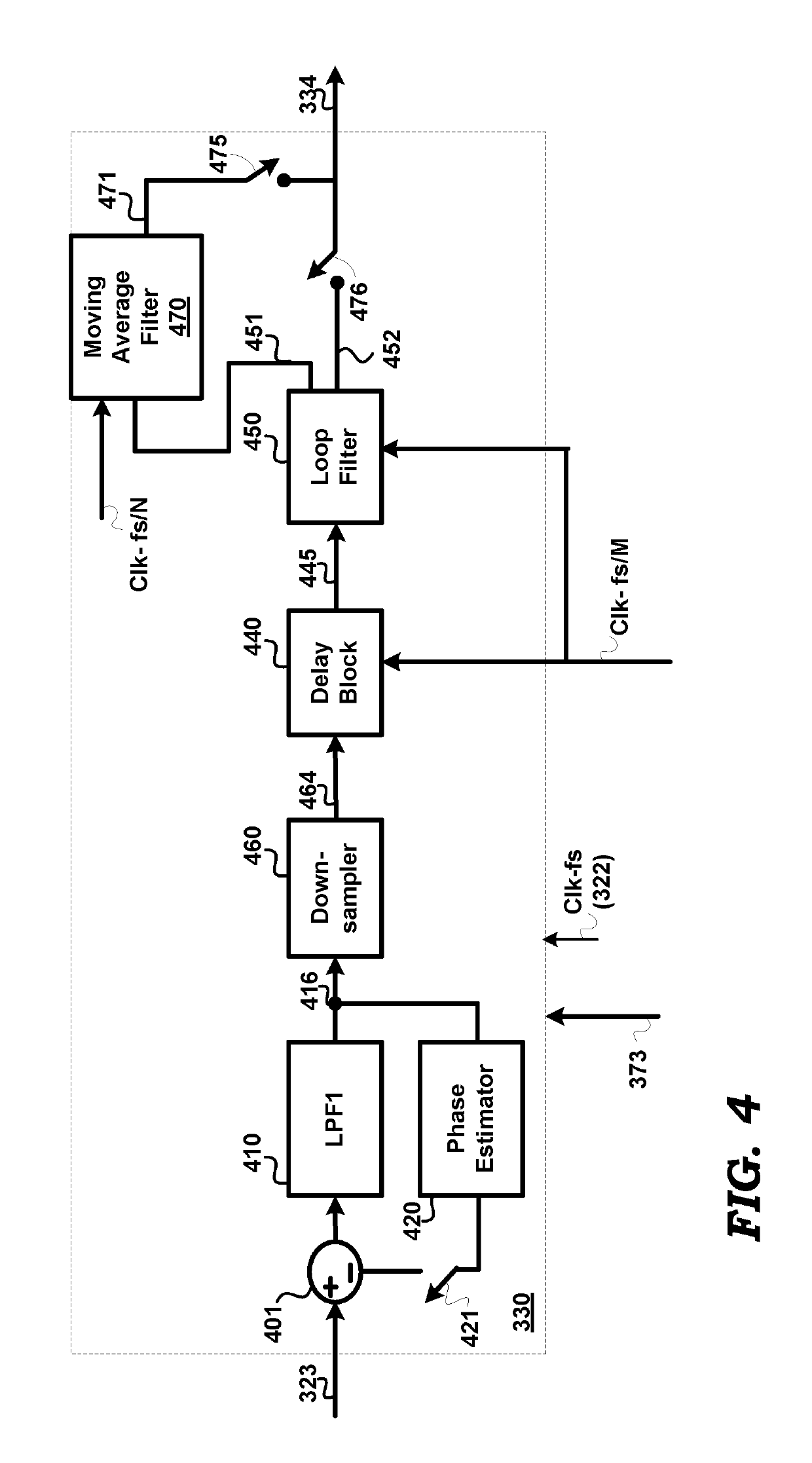

Hitless switching when generating an output clock derived from multiple redundant input clocks

ActiveUS20190384351A1Pulse automatic controlGenerating/distributing signalsPhase detectorMultiplexer

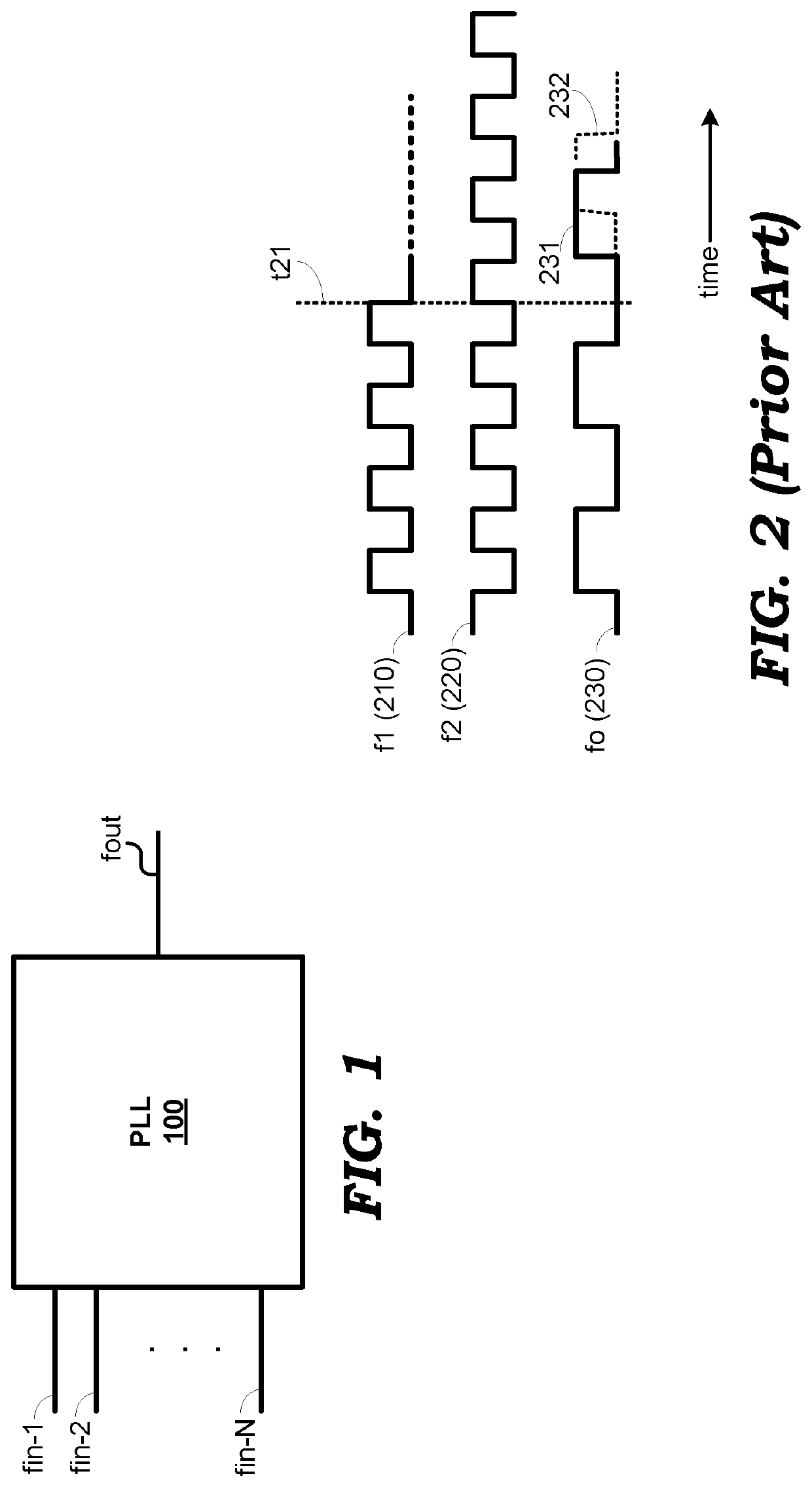

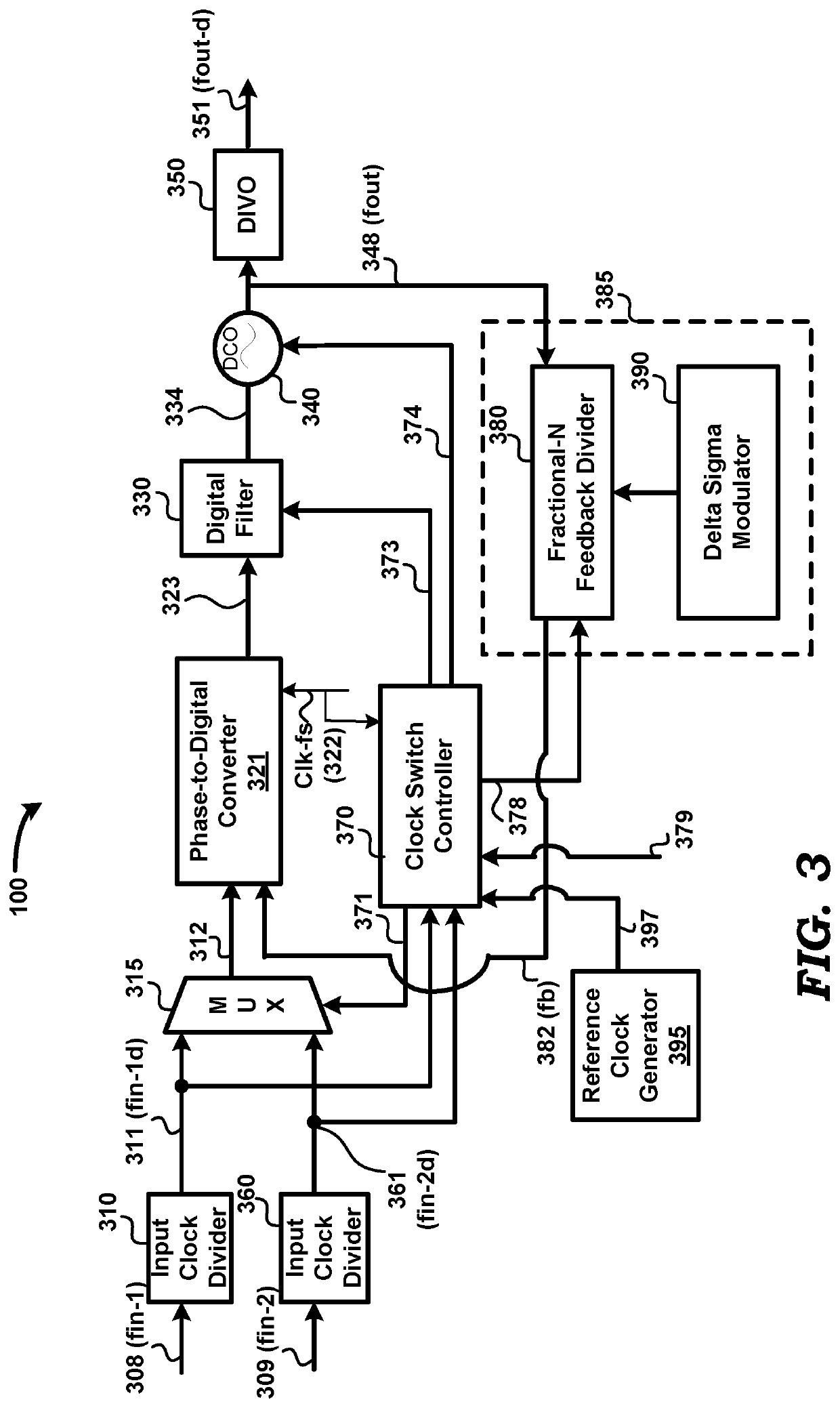

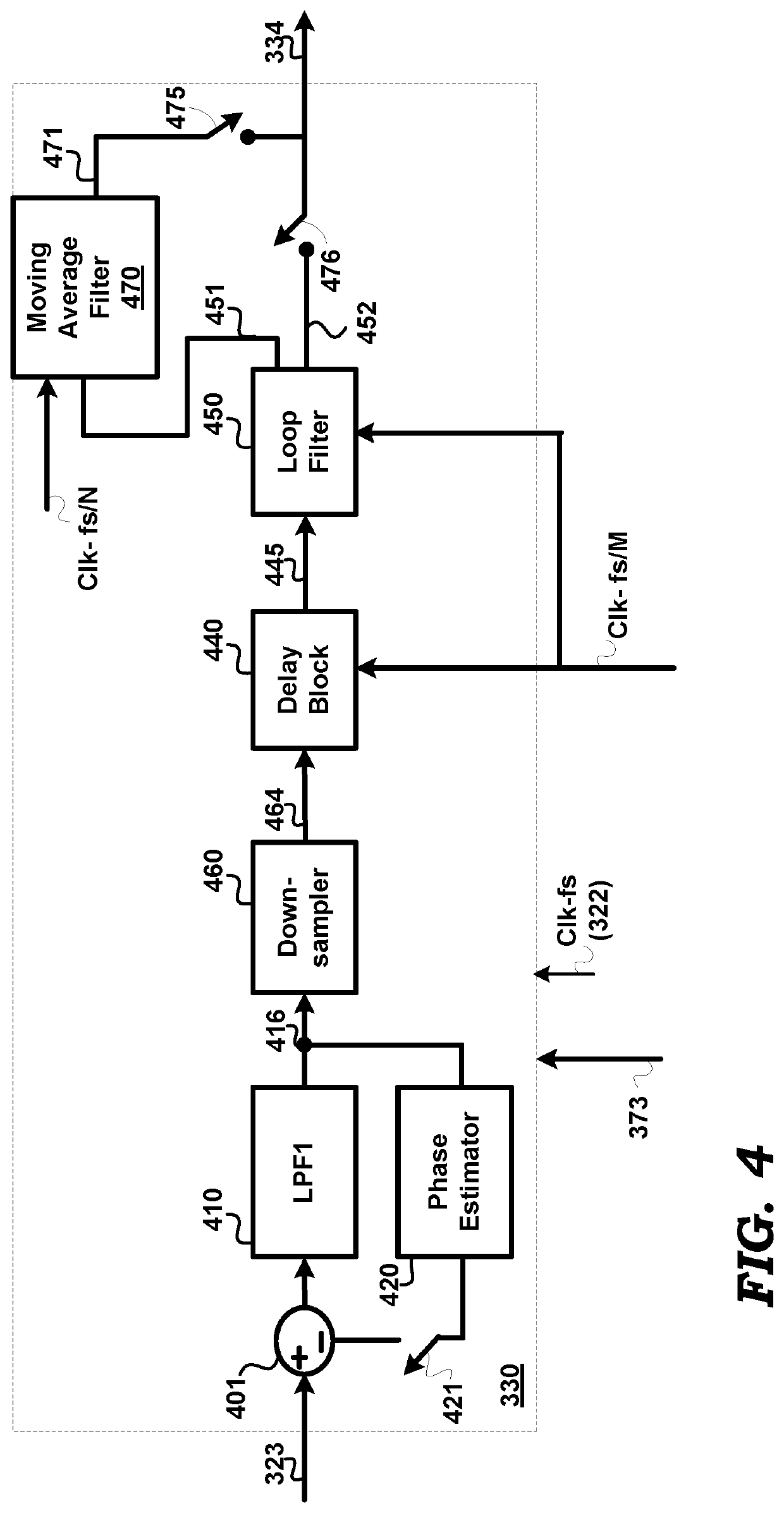

A phase locked loop (PLL) includes a multiplexer (MUX), a phase detector, a filter block, an oscillator, a frequency divider, and a clock switch controller, and achieves hitless switching between a primary clock and a redundant clock. The clock switch controller, upon detecting a condition requiring switching from the primary clock to the redundant clock, is operable to restart the feedback divider synchronously with respect to the redundant clock, and derive the output of the PLL from the redundant clock. The PLL further includes a delay block to process delayed phase error signals generated by the phase detector. The PLL performs hitless clock switching in the event of input clock loss or in response to a command to switch input clocks. The PLL further includes circuitry for estimating and cancelling residual phase errors.

Owner:AURA SEMICON PVT +1

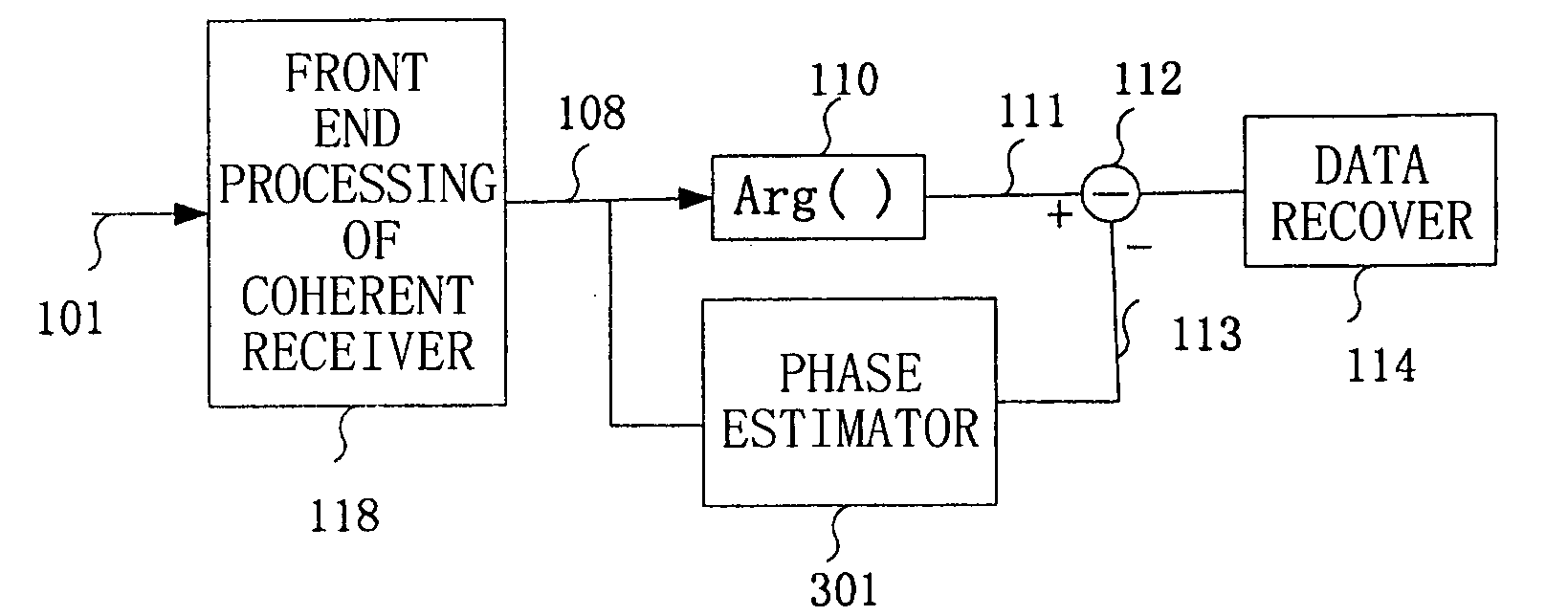

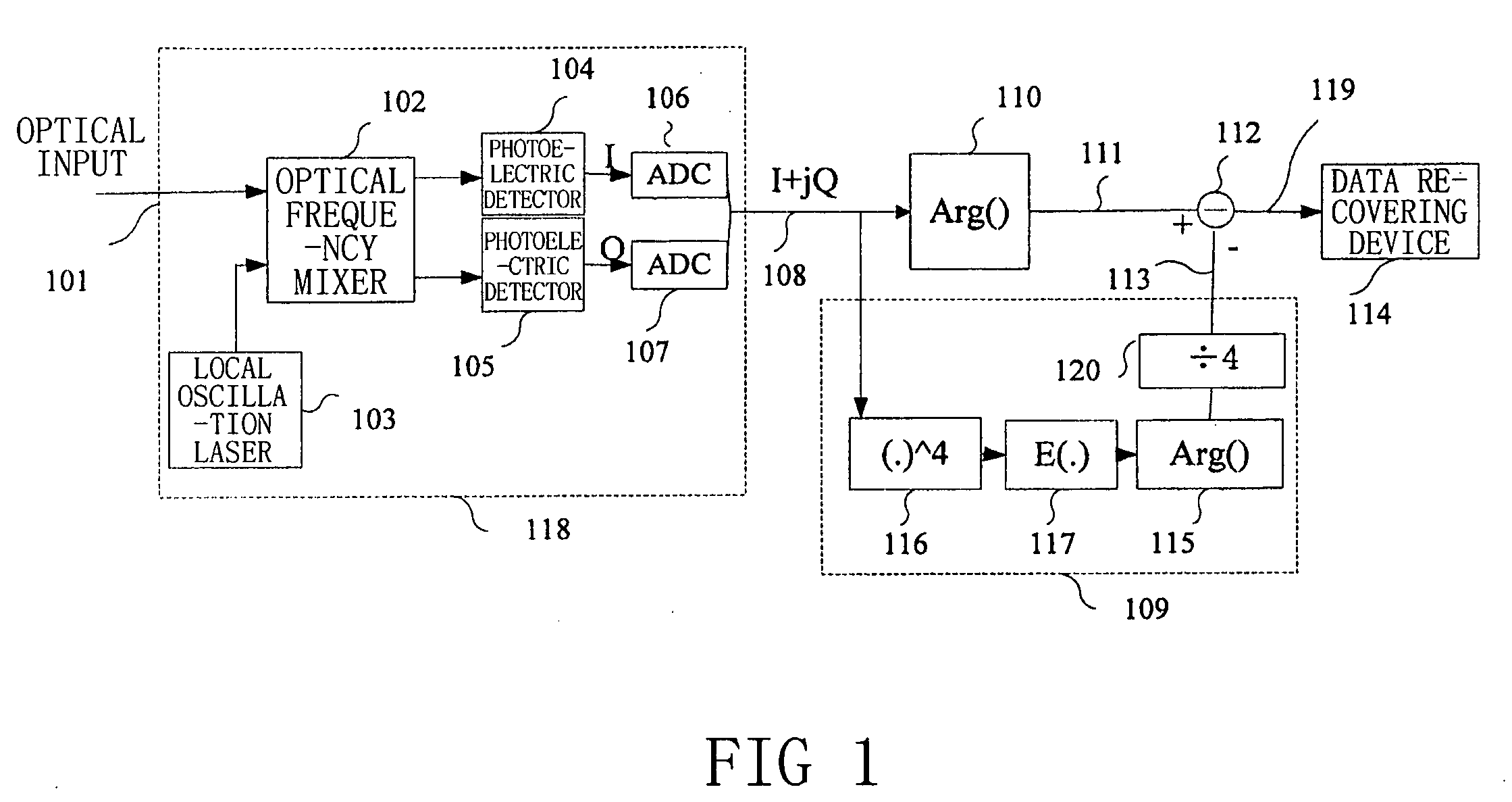

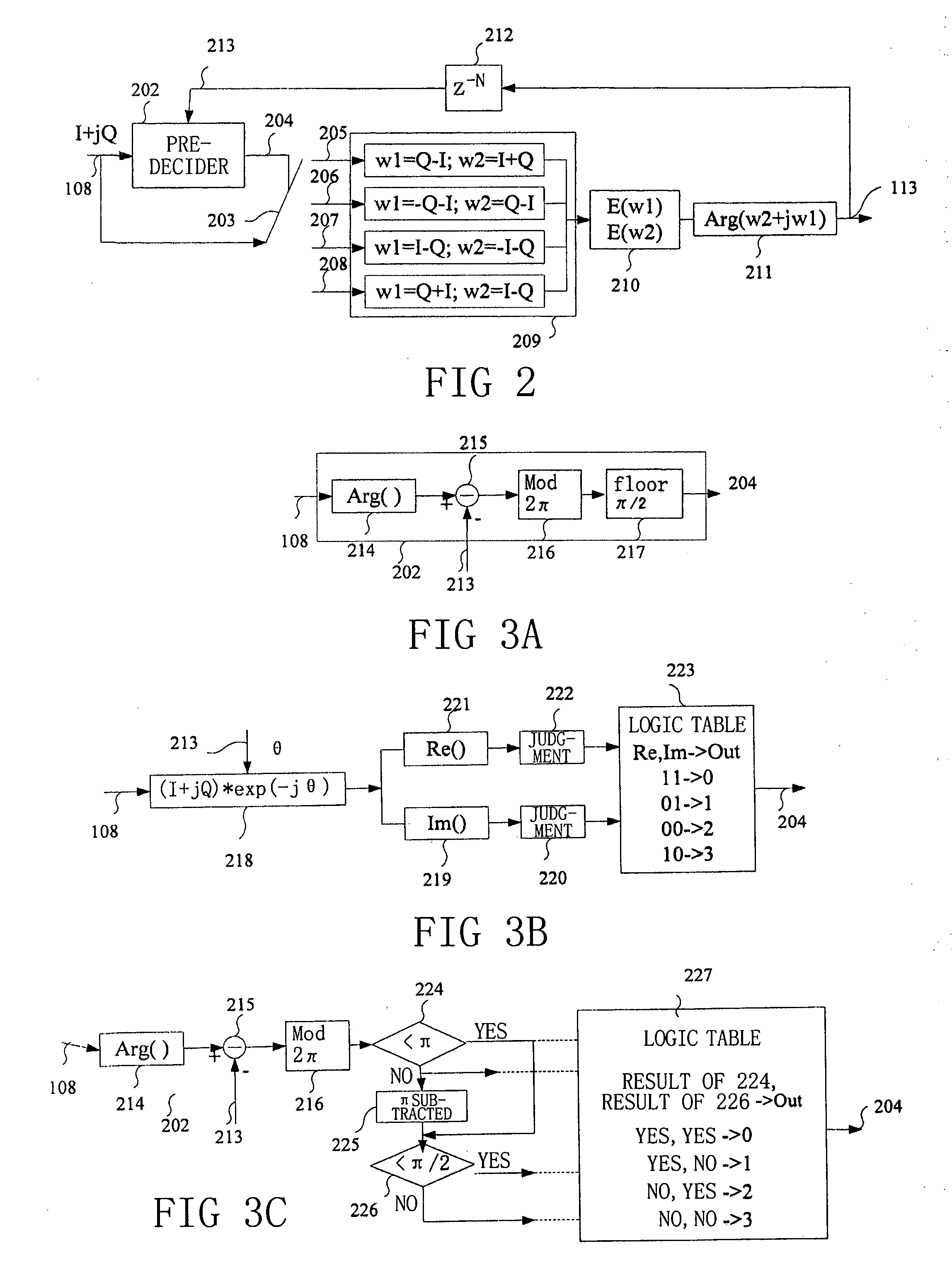

Phase error estimator, coherent receiver and phase error estimating method

The present invention relates to a phase error estimator, a coherent receiver and a phase error estimating method. The phase error estimator estimates a phase error in an inputted base band electric signal and feeds back said phase error; said phase error estimator comprises: a pre-decider, for judging a phase of data in said base band electric signal in accordance with said feedback phase error; a phase error complex value extracting section, for extracting a real part and an imaginary part of the phase error in accordance with the judgment result of said pre-decider; a phase error determining section, for determining said phase error in accordance with the real part and the imaginary part of the phase error extracted by the phase error complex value extracting section; and a time delay feeding back section, for delaying said phase error by N number of symbols and feeding back the delayed phase error to said pre-decider, wherein N is an integer greater than 1.

Owner:FUJITSU LTD

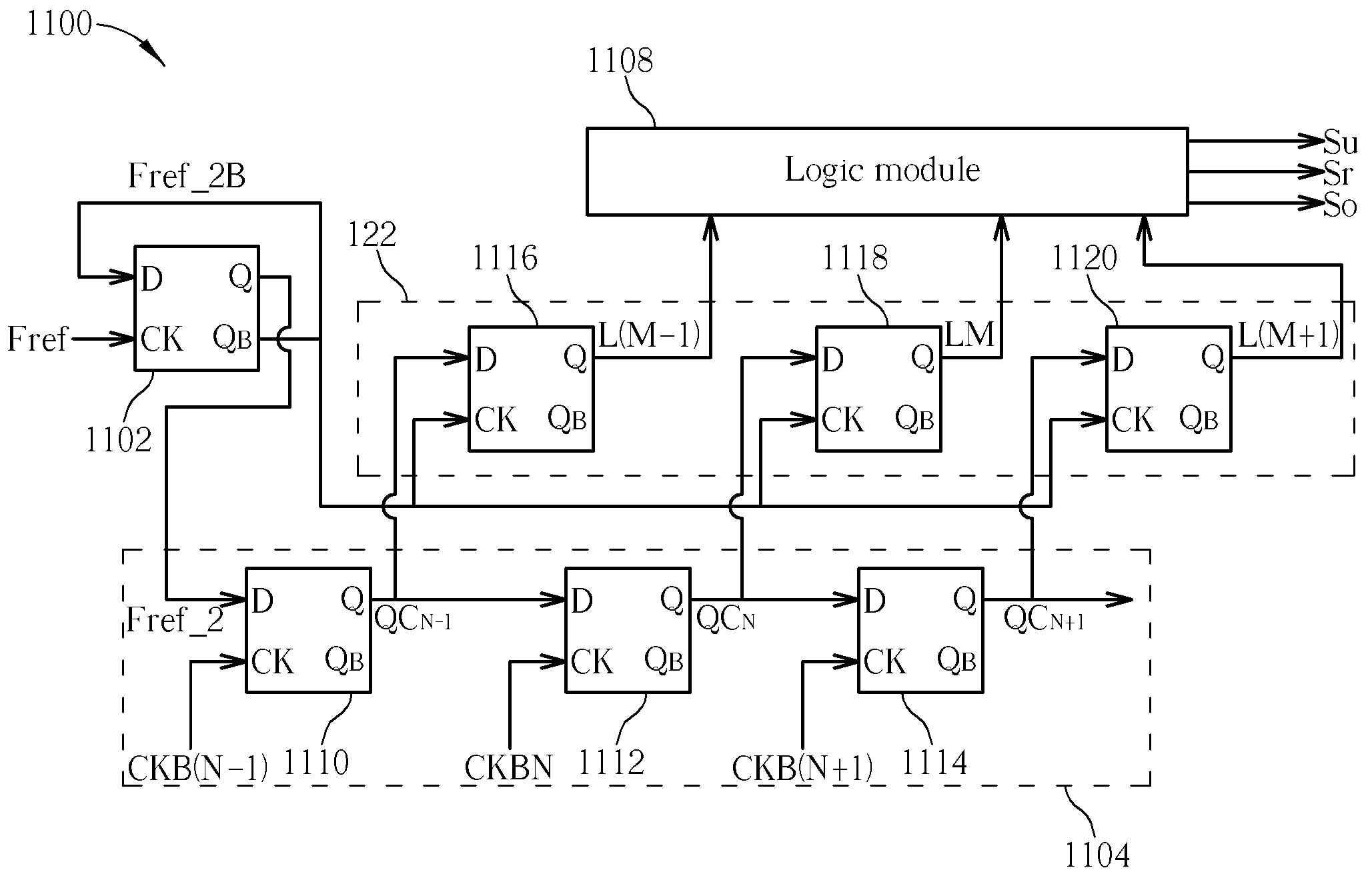

Delay-locked loop device capable of anti-false-locking and related methods

The present invention discloses a delay-locked loop device capable of anti-false-locking, which comprises: a voltage control delay circuit comprising a plurality of delay units in a series for generating a delayed phase according to a reference phase and a control voltage; a phase detector coupled to the voltage control delay circuit for generating a control signal according to a lock indication signal, the reference phase, and the delayed phase; a charge pump coupled to the phase detector for transmitting the control voltage to the voltage control delay circuit according to the control signal; and a lock detector coupled to the voltage control delay circuit for generating the lock indication signal for the phase detector according to output phases of at least one delay unit of the voltage control delay circuit.

Owner:FARADAY TECH CORP

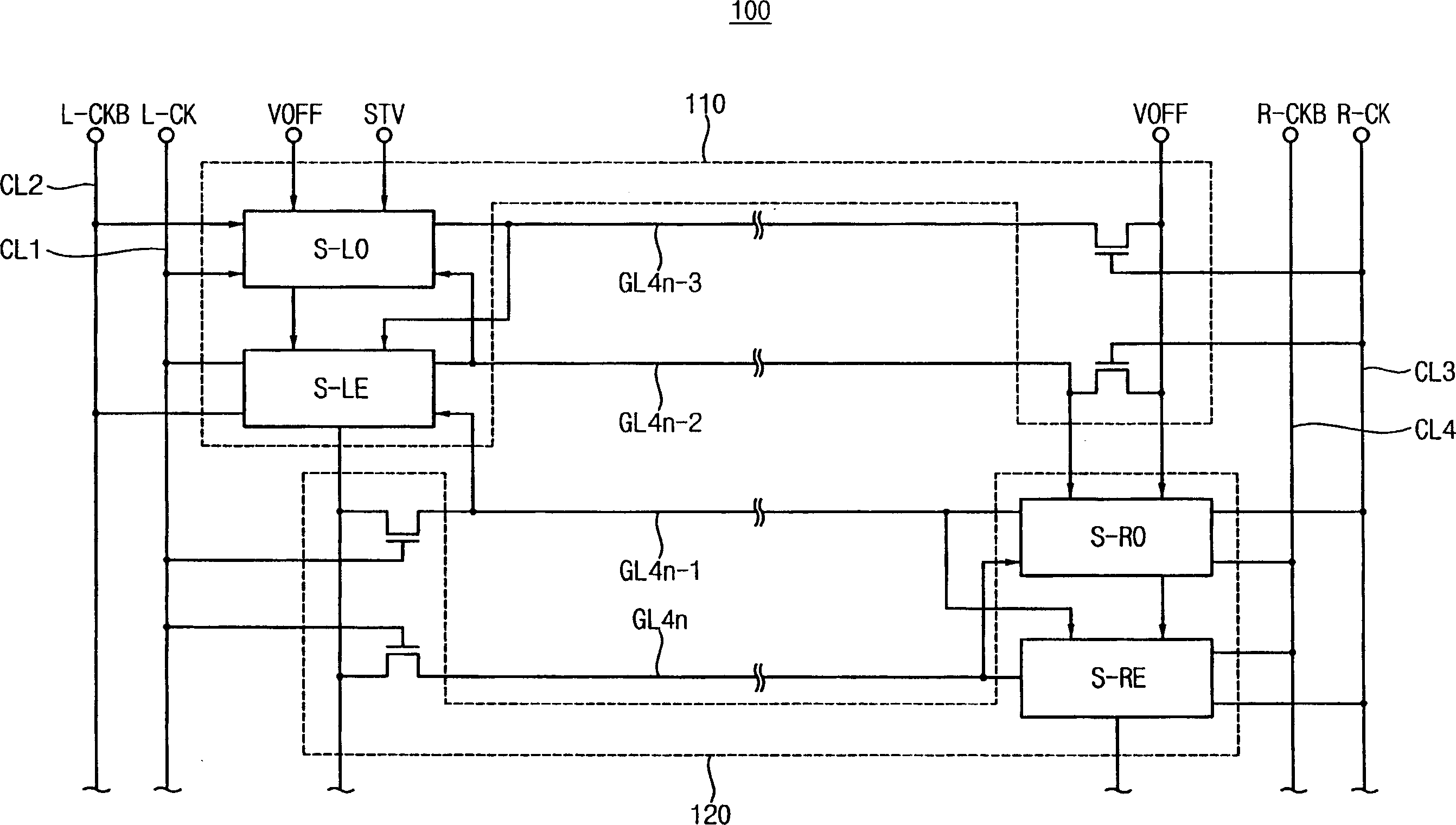

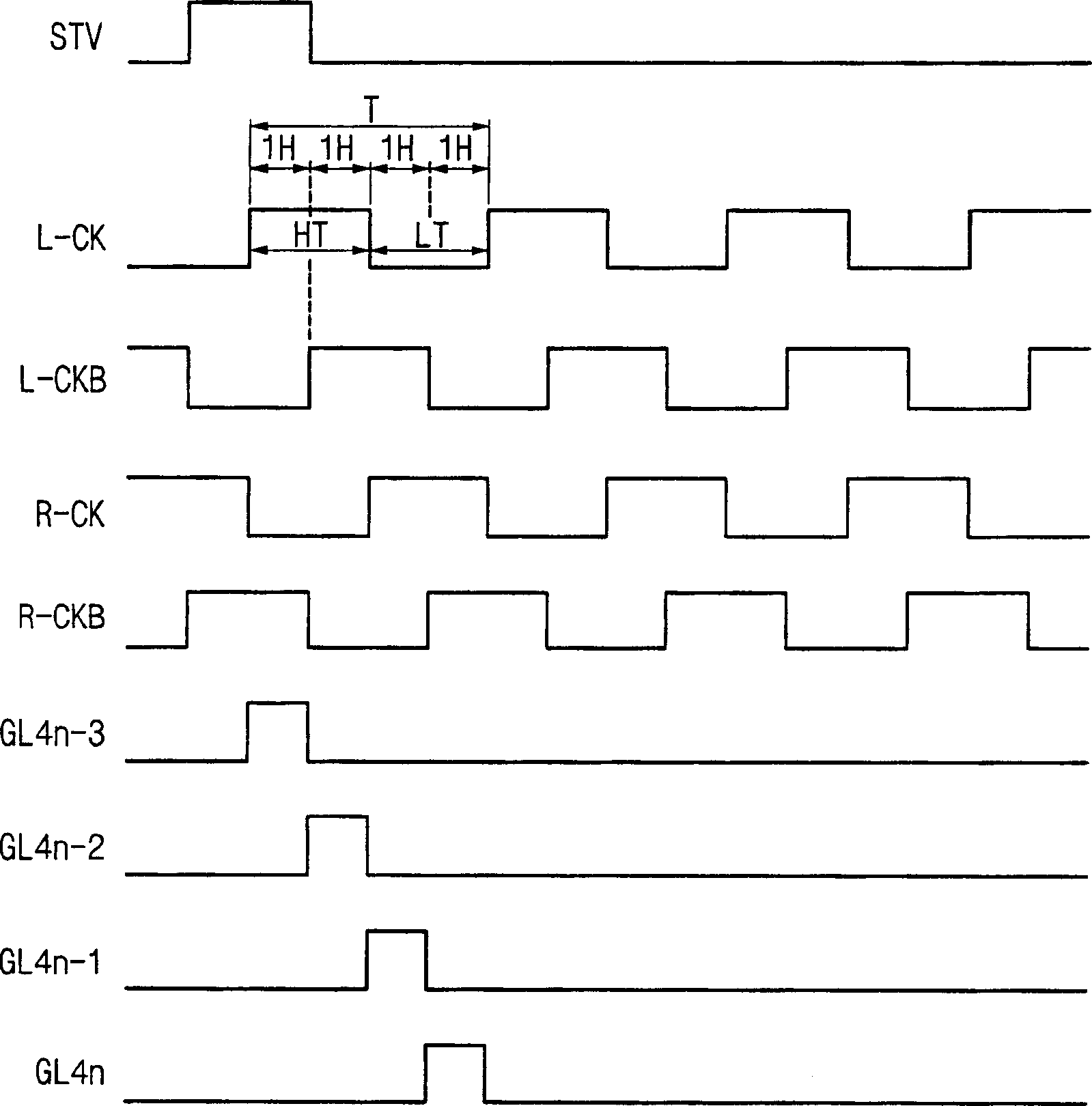

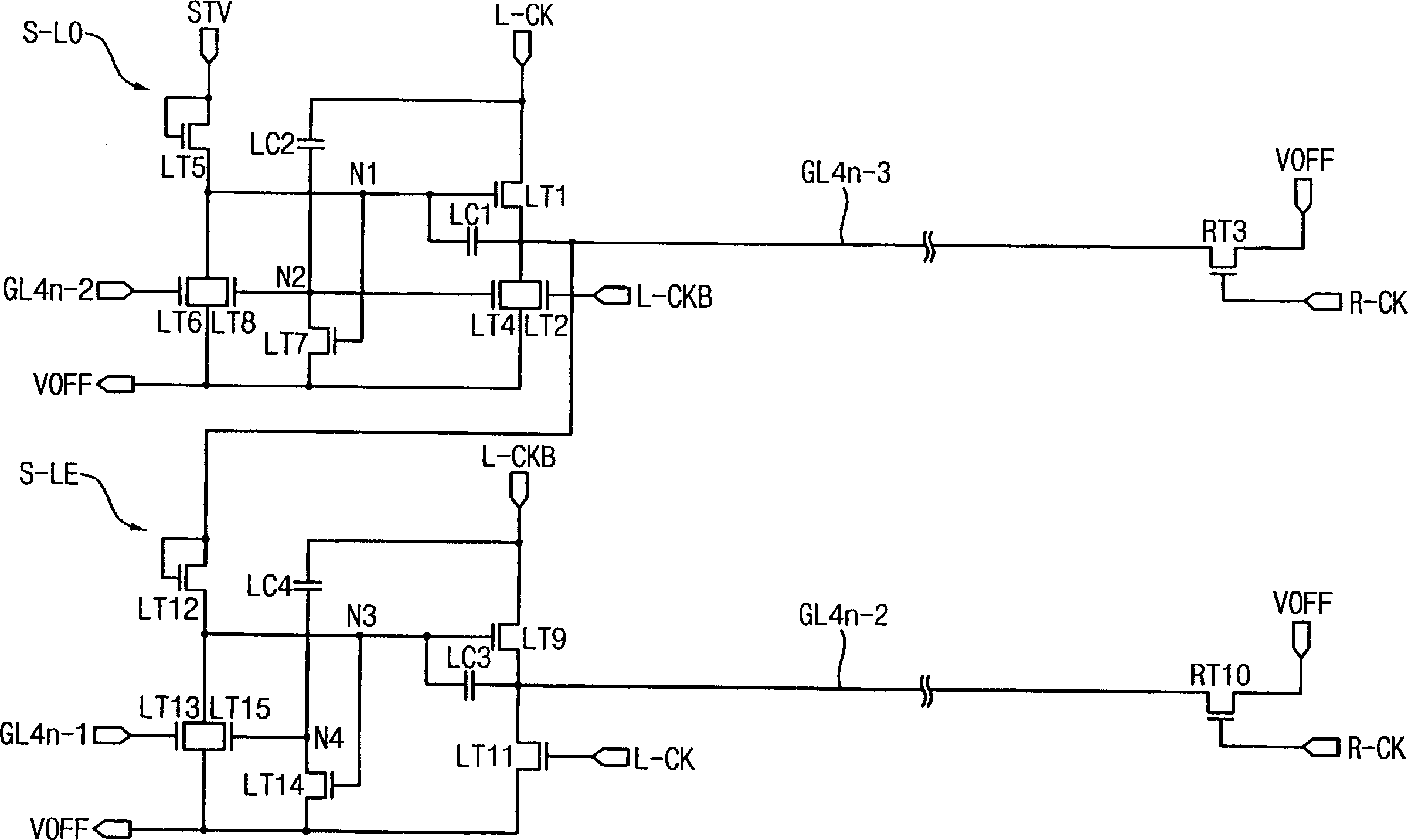

Gate driver circuit and display device having the same

InactiveCN1841484AReduce the numberSmall sizeStatic indicating devicesDigital storageShift registerDisplay device

A gate driver circuit includes a first shift register and a second shift register. The first shift register applies (4n-3)-th and (4n-2)-th gate signals to (4n-3)-th and (4n-2)-th gate lines, respectively, in response to a first clock signal, a second clock signal having a delayed phase by 1H time with respect to the first clock signal, and a third clock signal having opposite phase to the first clock signal. The second shift register applies (4n-1)-th and 4n-th gate signals to (4n-1)-th and 4n-th gate lines, respectively, in response to the first clock signal, the third clock signal, and a fourth clock signal having opposite phase to the second clock signal. Therefore, a number of transistors in the first and second shift registers may be reduced.

Owner:SAMSUNG ELECTRONICS CO LTD

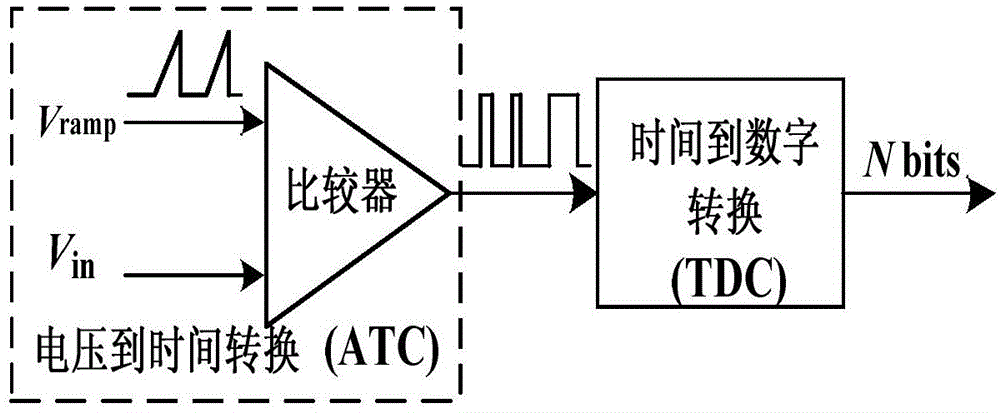

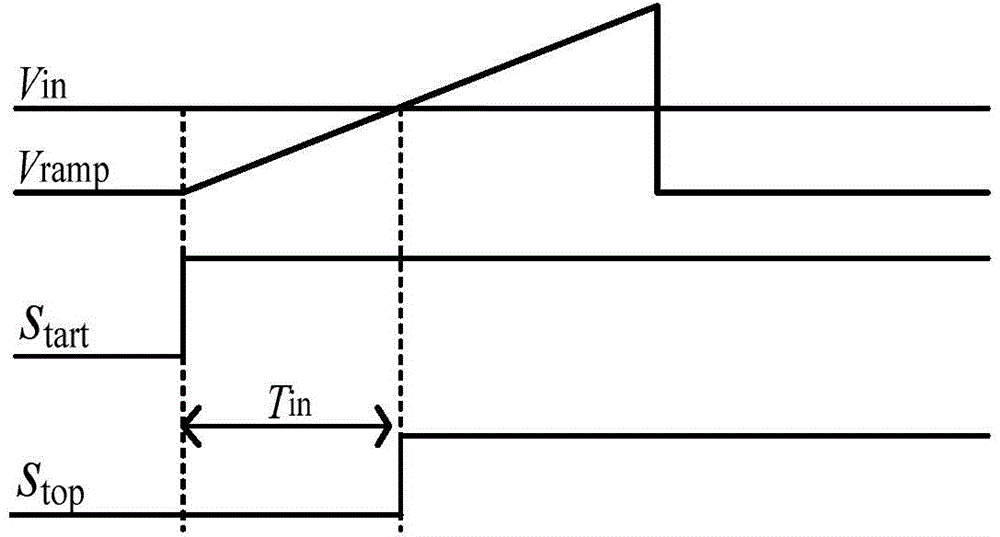

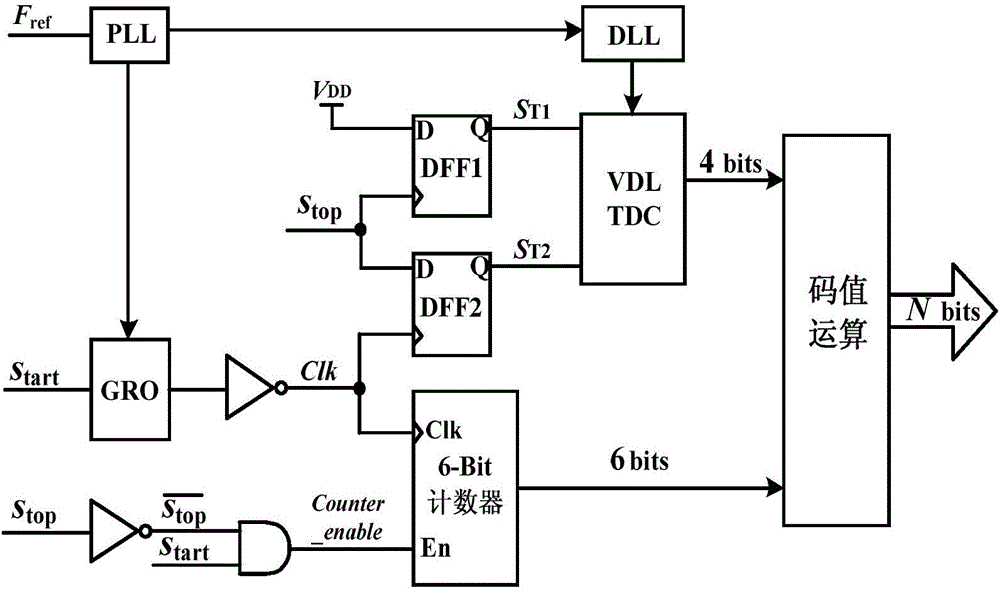

TDC-based high-speed column level ADC for imaging sensor

InactiveCN104539856AFast conversionTelevision system detailsColor television detailsPhase locked loop circuitPixel array

The invention belongs to the field of analog-digital conversion circuits. For the CIS with a large pixel array or high scanning speed, in order to reducing conversion time of a column level single-slope ADC under the condition that the area and power consumption are not greatly increased, the adopted technical scheme is that a TDC-based high-speed column level ADC for an imaging sensor is provided. The TDC-based high-speed column level ADC is composed of a phase-locked loop circuit PLL, a gating ring oscillator GRO, two phase inverters, an AND gate circuit, two D triggers, a counter, a delayed phase-locked loop circuit DLL, a vernier delay line VDL and a code value arithmetic unit. The TDC-based high-speed column level ADC for the imaging sensor is mainly applied to analog-digital conversion devices.

Owner:TIANJIN UNIV

Delay-Locked Loop Device Capable Of Anti-False-Locking And Related Methods

The present invention discloses a delay-locked loop device capable of anti-false-locking, which comprises: a voltage control delay circuit comprising a plurality of delay units in a series for generating a delayed phase according to a reference phase and a control voltage; a phase detector coupled to the voltage control delay circuit for generating a control signal according to a lock indication signal, the reference phase, and the delayed phase; a charge pump coupled to the phase detector for transmitting the control voltage to the voltage control delay circuit according to the control signal; and a lock detector coupled to the voltage control delay circuit for generating the lock indication signal for the phase detector according to output phases of at least one delay unit of the voltage control delay circuit.

Owner:FARADAY TECH CORP

Correction of loss and dispersion in cable fault measurements

ActiveUS20050225329A1Removing all loss and dispersion distortionResistance/reactance/impedenceFault location by pulse reflection methodsEngineeringDistortion

A method of correcting distortions resulting from loss and dispersion in cable fault measurements. A cable is measured in the frequency domain to obtain a reflected response. Fractional sinusoidal components of the reflected response having attenuated amplitude and delayed phase values at points defining the junctures of adjacent equal predetermined lengths are collected and normalized. Then the fractional sinusoidal components of the reflected response are extracted from normalized sum by mathematically calculating the real value at each point, thereby removing all loss and dispersion distortion components.

Owner:JOHN FLUKE MFG CO INC

Optical laminate

ActiveUS7354632B2Improve featuresImprove production efficiencyLiquid crystal compositionsSynthetic resin layered productsOptical propertyPhase difference

Owner:ZEON CORP

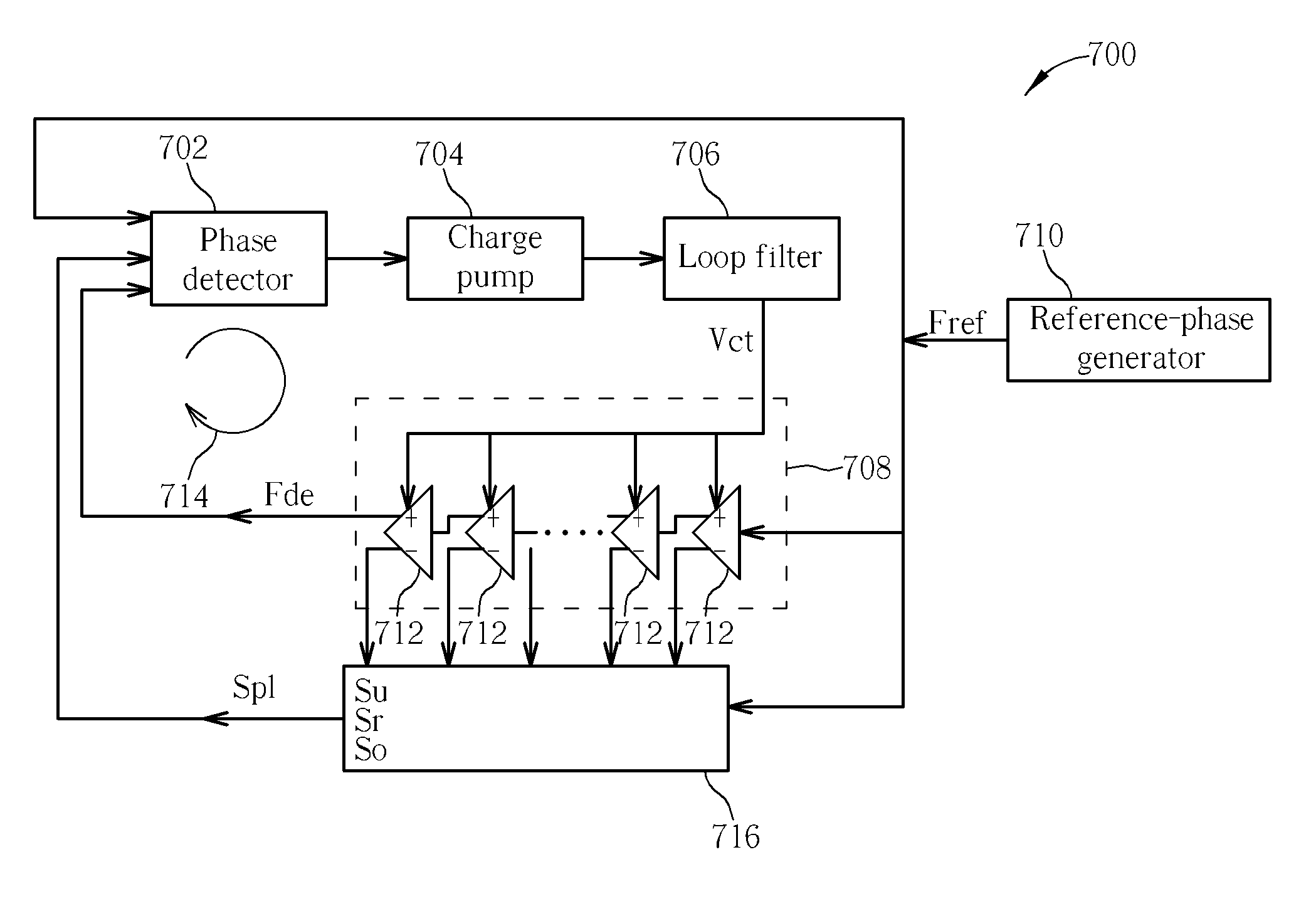

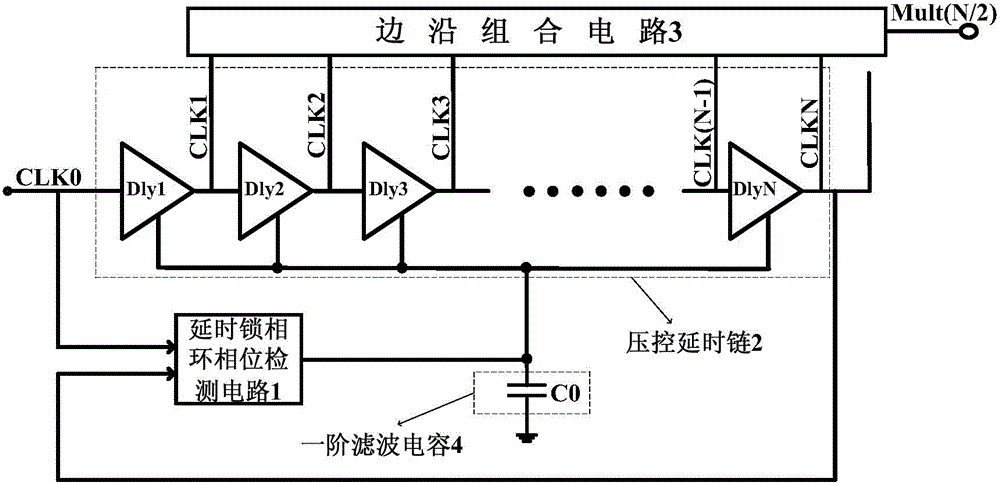

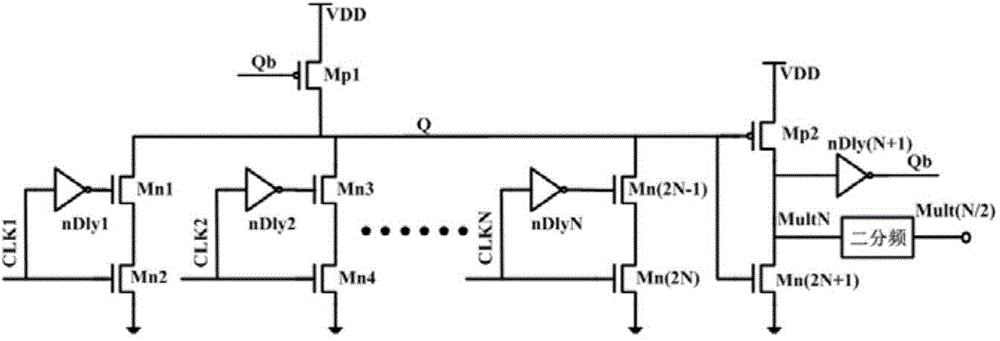

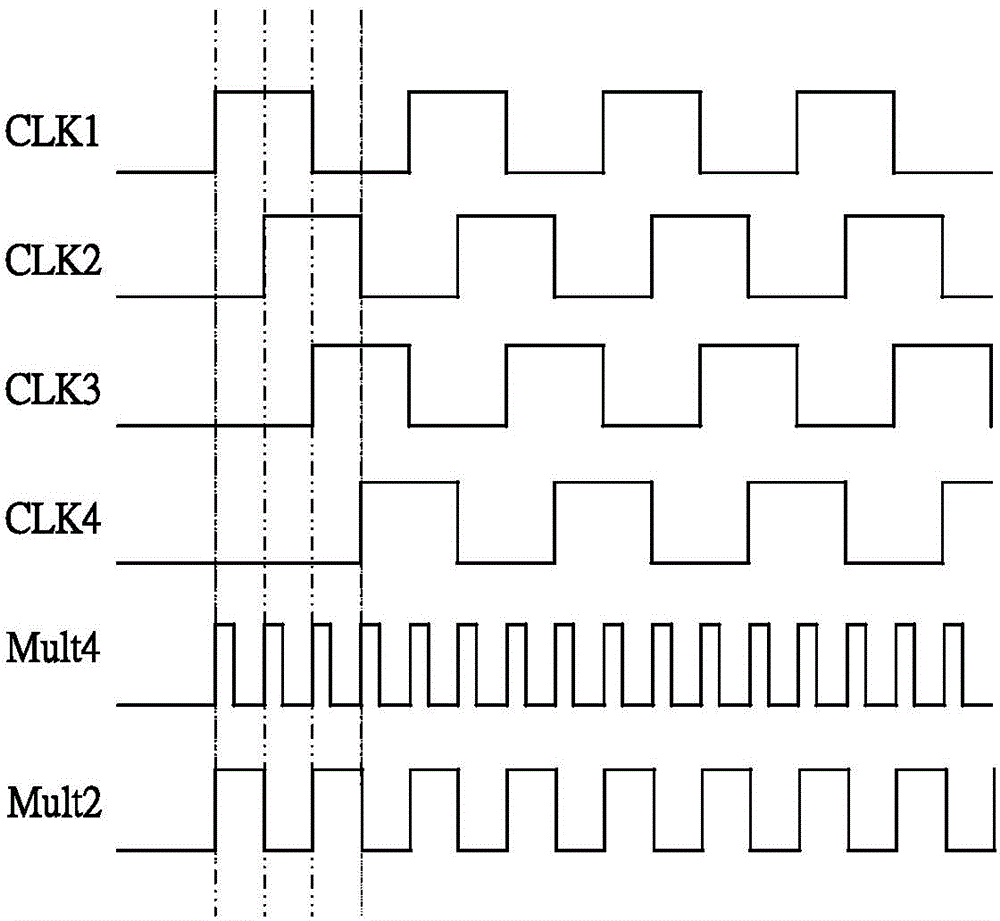

Frequency multiplier based on delayed phase-locked loop structure

ActiveCN104601116ACutting costsNormal multiplier operationPulse automatic controlOscillations generatorsPhase differenceFrequency multiplier

The invention discloses a frequency multiplier based on a delayed phase-locked loop structure. The frequency multiplier based on the delayed phase-locked loop structure can solve the problem that the implementation cost of the existing frequency multiplication technical hardware based on the delayed phase-locked loop structure is too large. The frequency multiplier comprises a delayed phase-locked phase detection circuit, a voltage-controlled delay chain and an edge combination circuit, wherein the delayed phase-locked phase detection circuit is used for detecting the phase relationship between the input reference lock signal CLK0 and the output feedback clock signal CLKN of the voltage-controlled delay chain and generating the control voltage Vc which adjusts the delay of the voltage-controlled delay chain. The voltage-controlled delay chain comprises multiple delay units which are used for generating multiple multi-phase clock signals with equal phase differences. The edge combination circuit is composed of multiple frequency multiplier circuits and a two frequency-dividing circuit, wherein the multiple frequency multiplier circuits are used of conducting edge combination on multiple clock signals with equal phases so as to obtain a multiple frequency multiplication output signals, the two frequency-dividing circuit is used for conducting frequency-dividing operation on the multiple frequency multiplication output signals to obtain frequency multiplication out signals whose duty ratio is 50% (N / 2).

Owner:PEKING UNIV

Hitless switching when generating an output clock derived from multiple redundant input clocks

Owner:AURA SEMICON PVT +1