Patents

Literature

4330 results about "Frequency divider" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

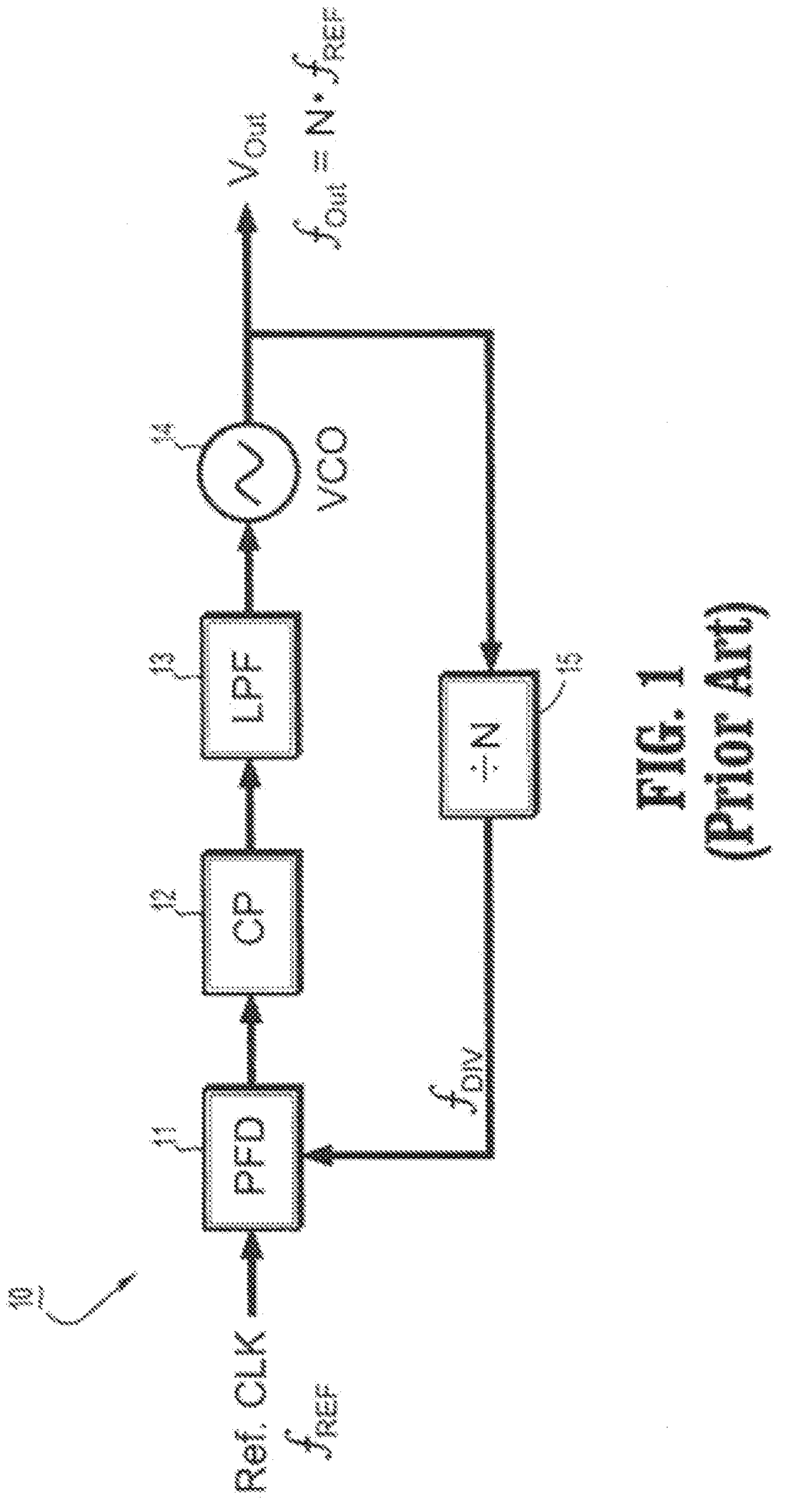

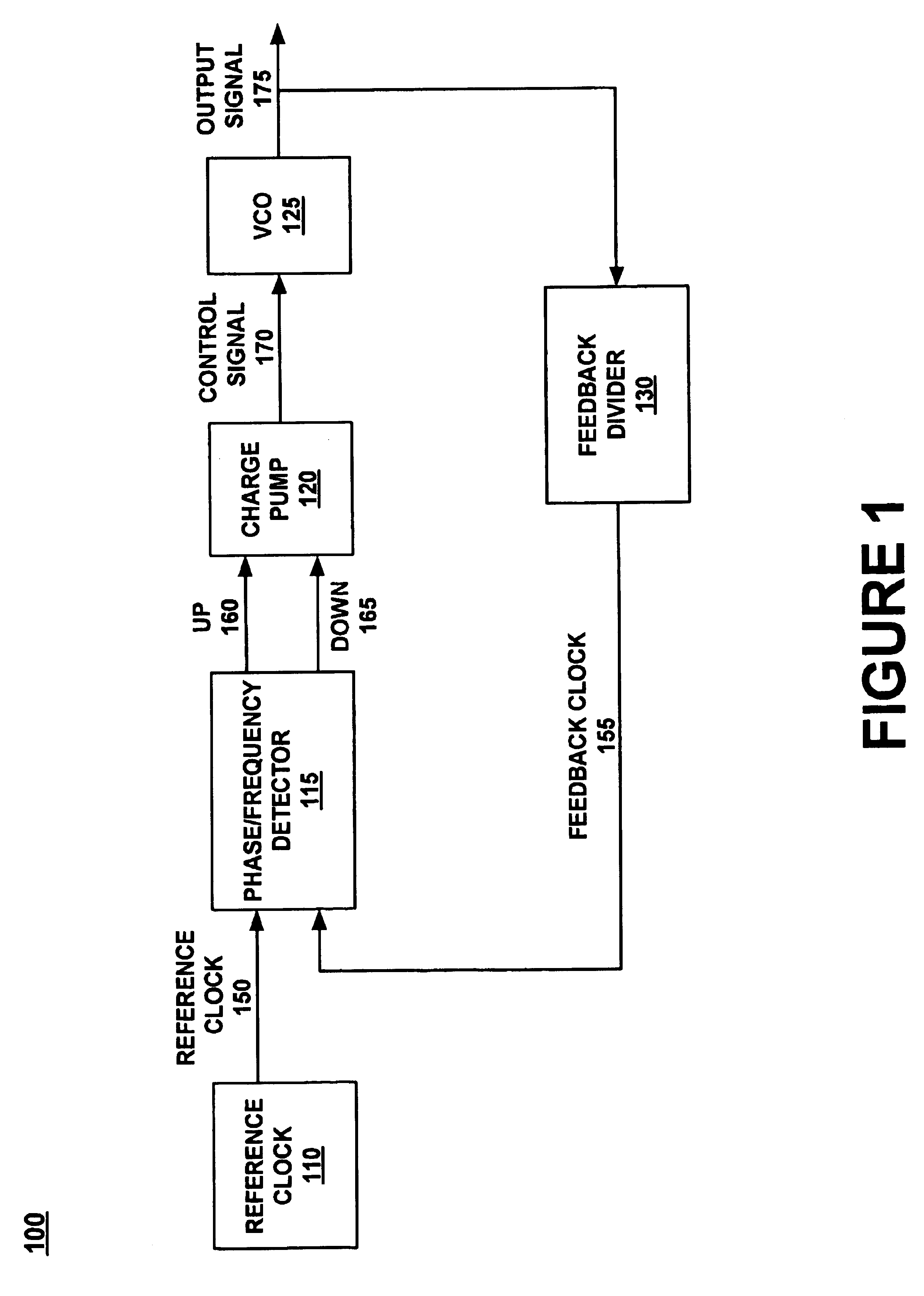

A frequency divider, also called a clock divider or scaler or prescaler, is a circuit that takes an input signal of a frequency, fᵢₙ, and generates an output signal of a frequency: fₒᵤₜ=fᵢₙ/n where n is an integer. Phase-locked loop frequency synthesizers make use of frequency dividers to generate a frequency that is a multiple of a reference frequency. Frequency dividers can be implemented for both analog and digital applications.

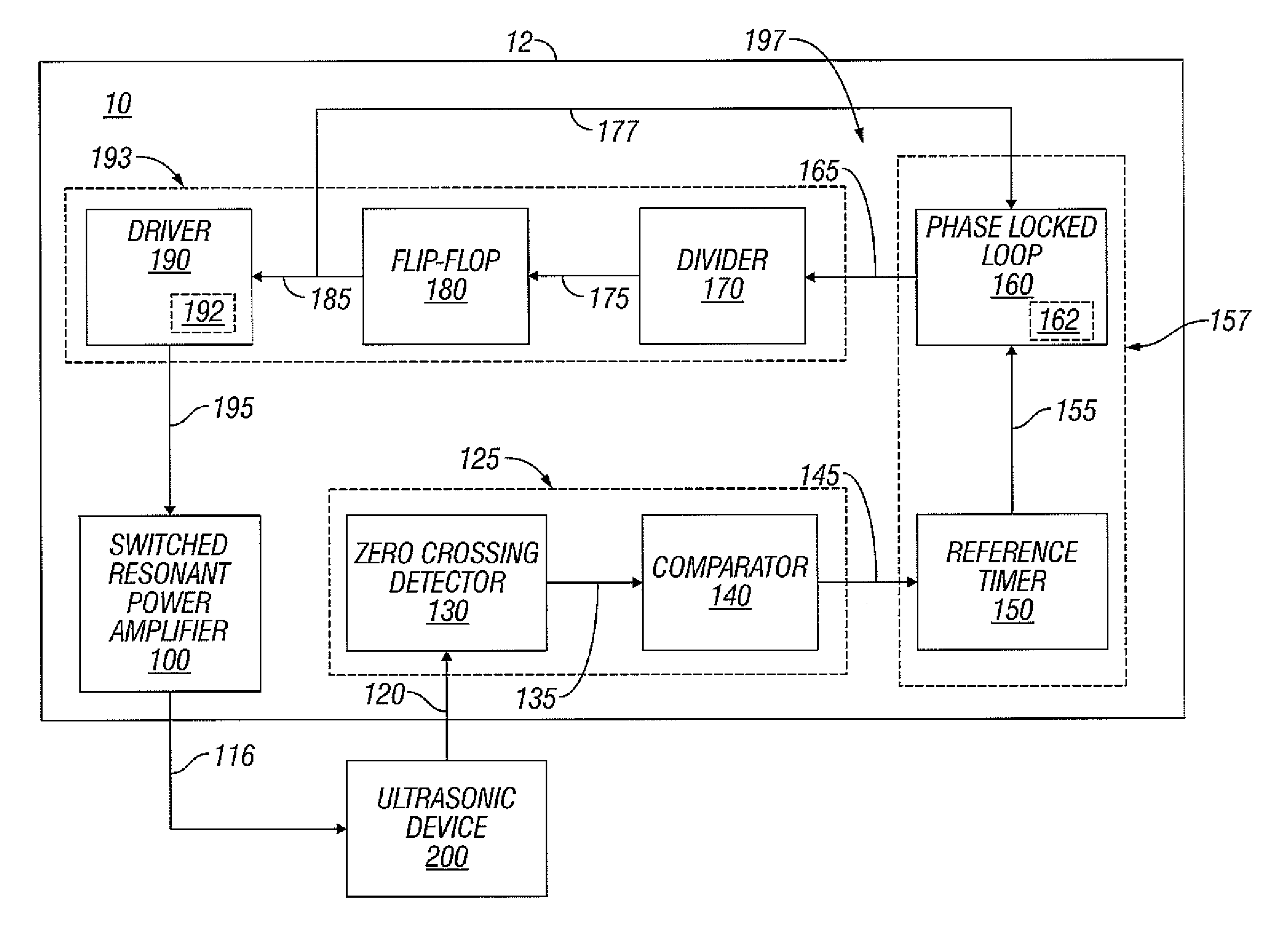

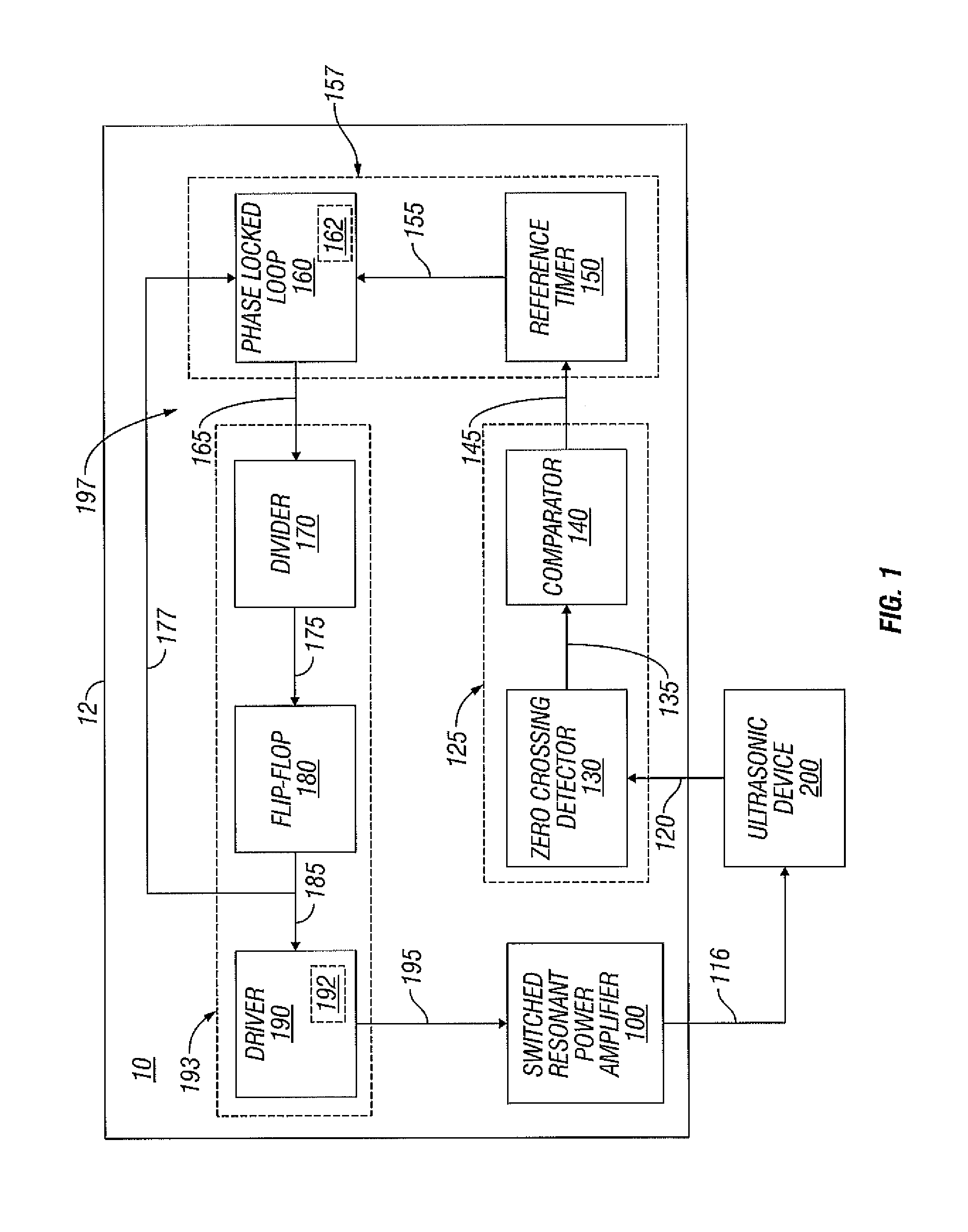

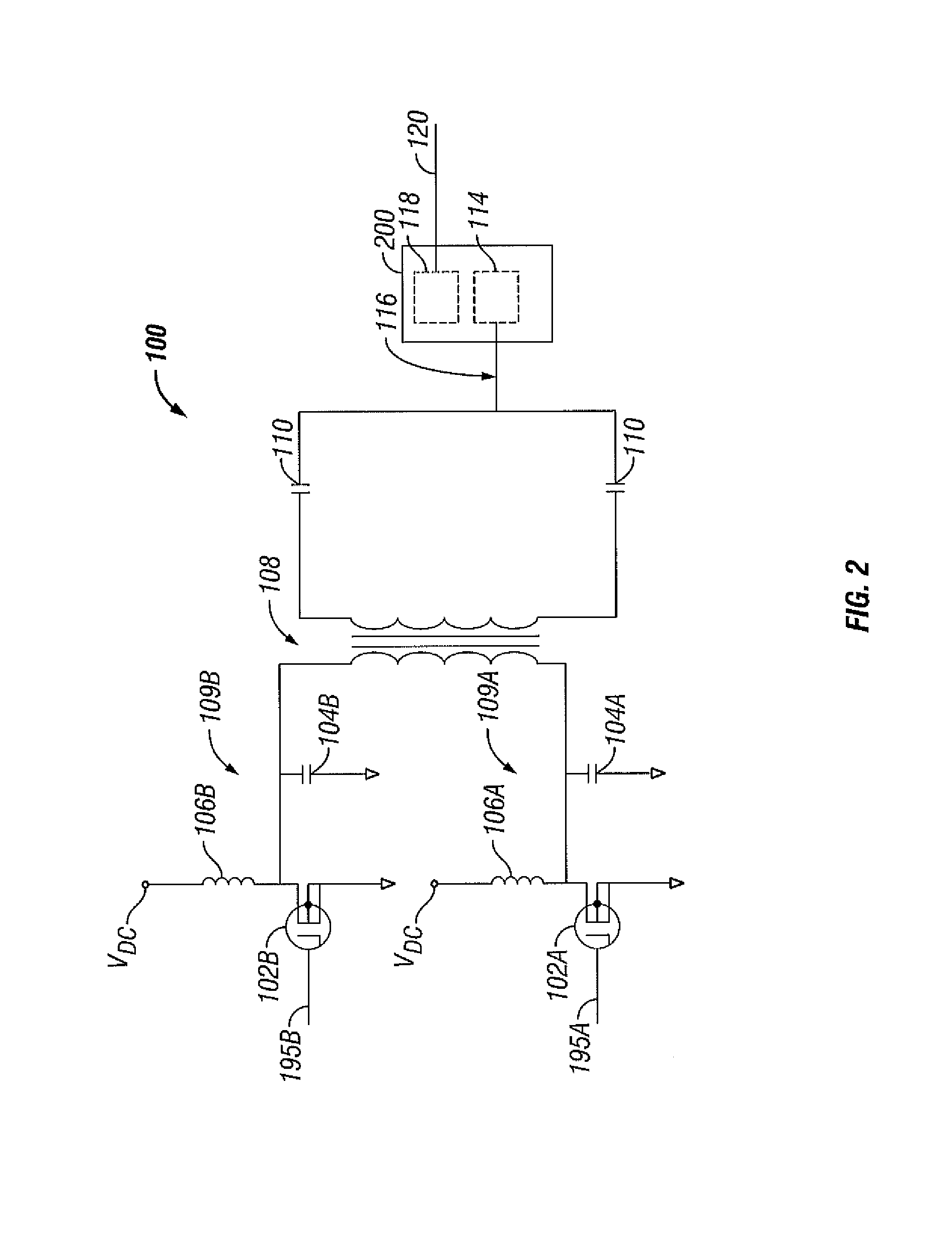

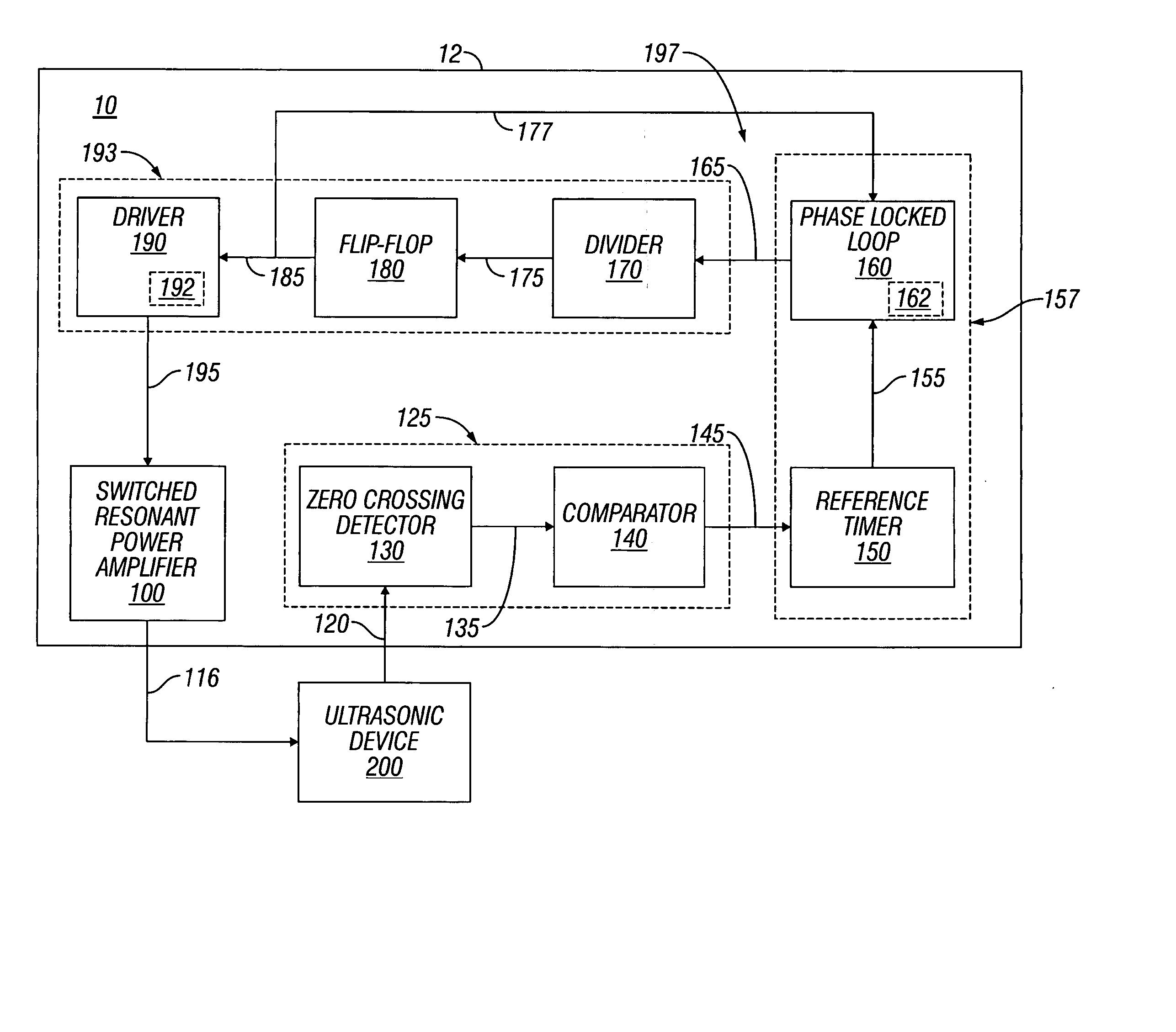

Switched resonant ultrasonic power amplifier system

ActiveUS7396336B2Operation efficiency can be improvedSmall footprintUltrasound therapyAmplifier modifications to raise efficiencyHemt circuitsControl ultrasound

Owner:COVIDIEN AG

Switched resonant ultrasonic power amplifier system

ActiveUS20050149151A1Reduce frequencyControl outputUltrasound therapyAmplifier modifications to raise efficiencySonificationAudio power amplifier

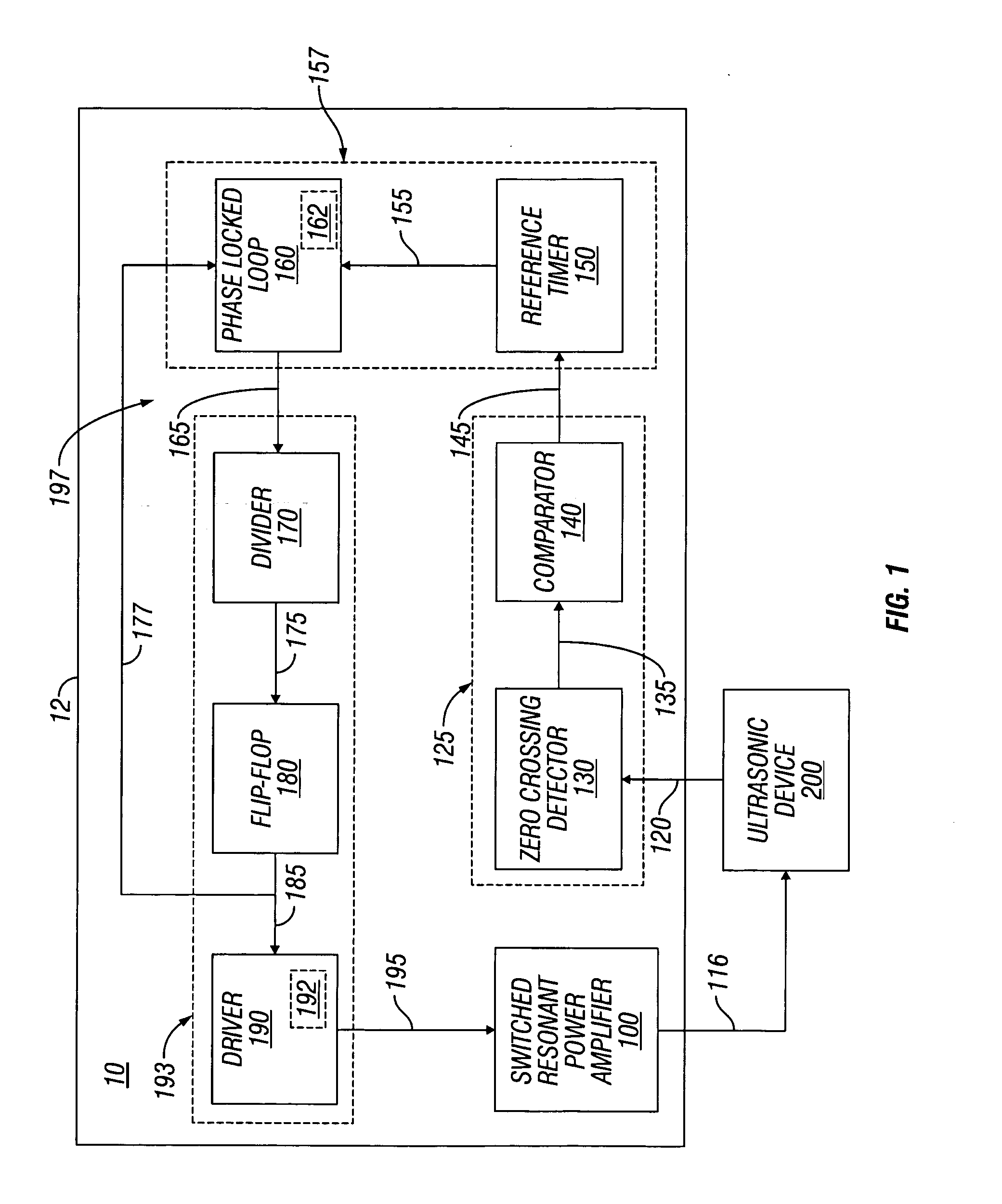

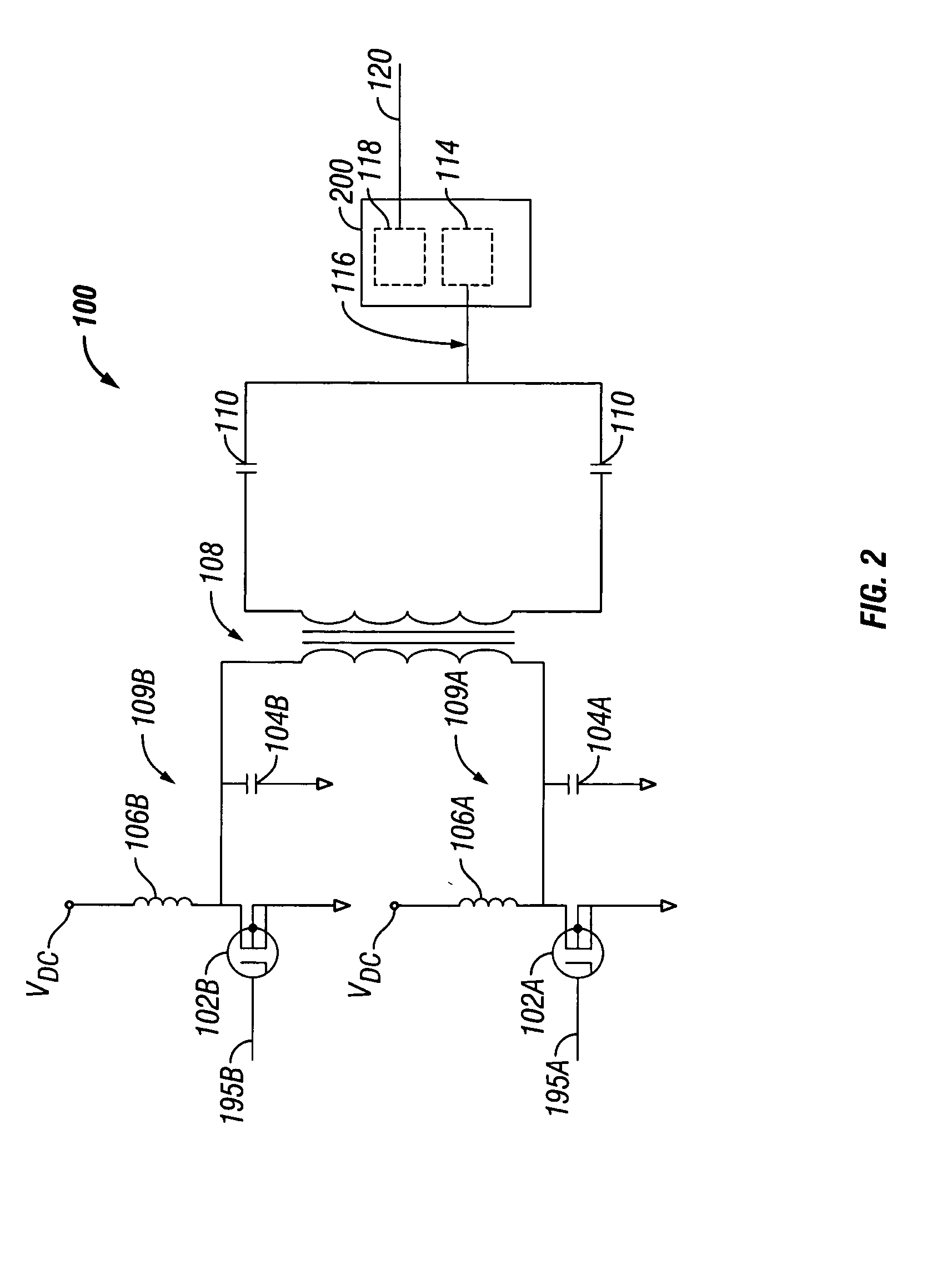

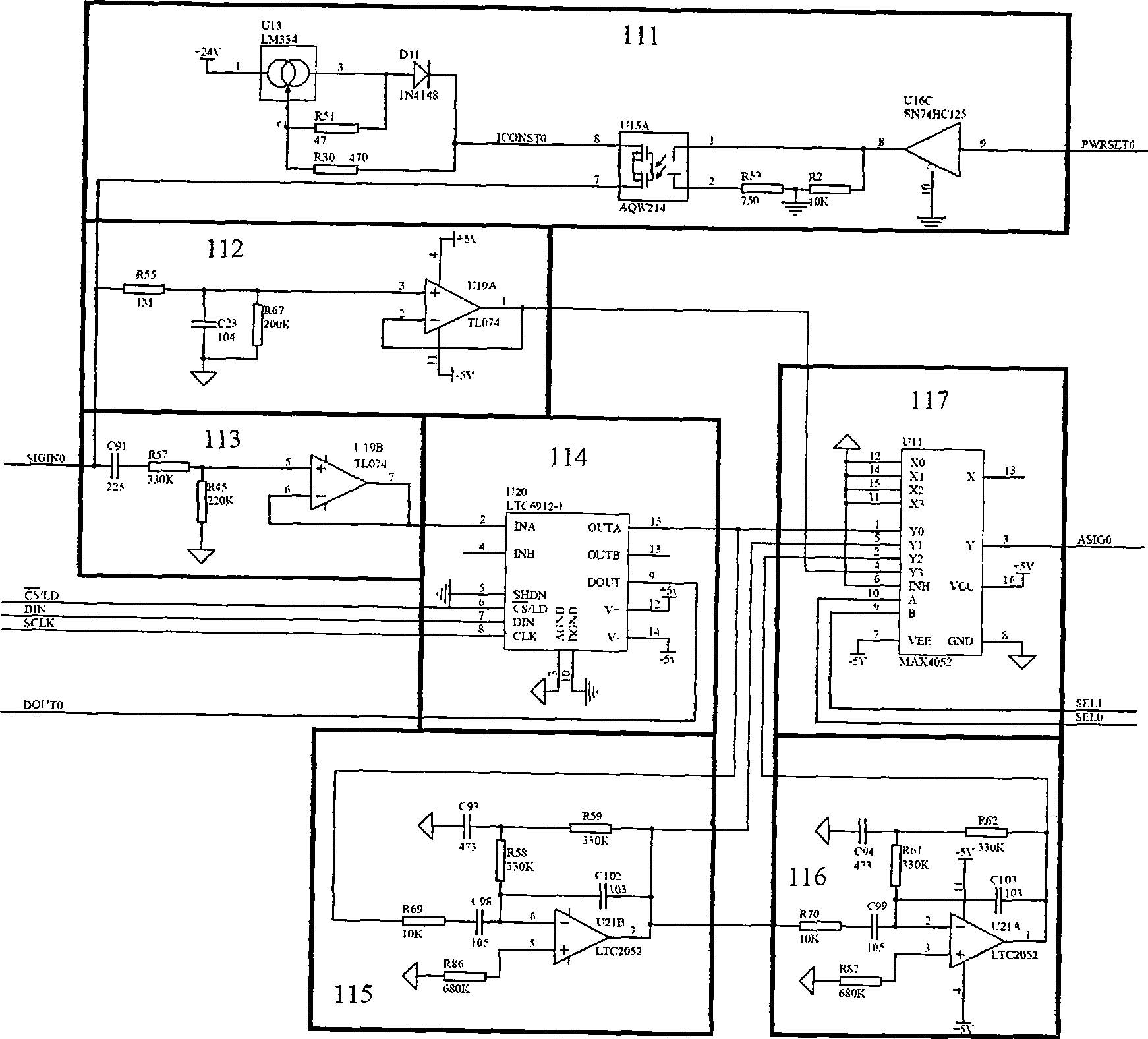

A switched resonant power amplifier system for ultrasonic transducers is disclosed. The system includes an amplifier that receives and processes a driver output signal for generating a drive signal that is provided to an ultrasonic device for controlling output of the ultrasonic device. An output control circuit receives and processes a signal related to a feedback signal generated by the ultrasonic device and a divider reference signal, and generates a compensated clock signal that is adjusted for at least one of phase and frequency differences between the received feedback signal and the divider reference signal. A compensated drive circuit receives and processes the compensated clock signal for generating the divider reference signal, and for generating the driver output signal.

Owner:COVIDIEN AG

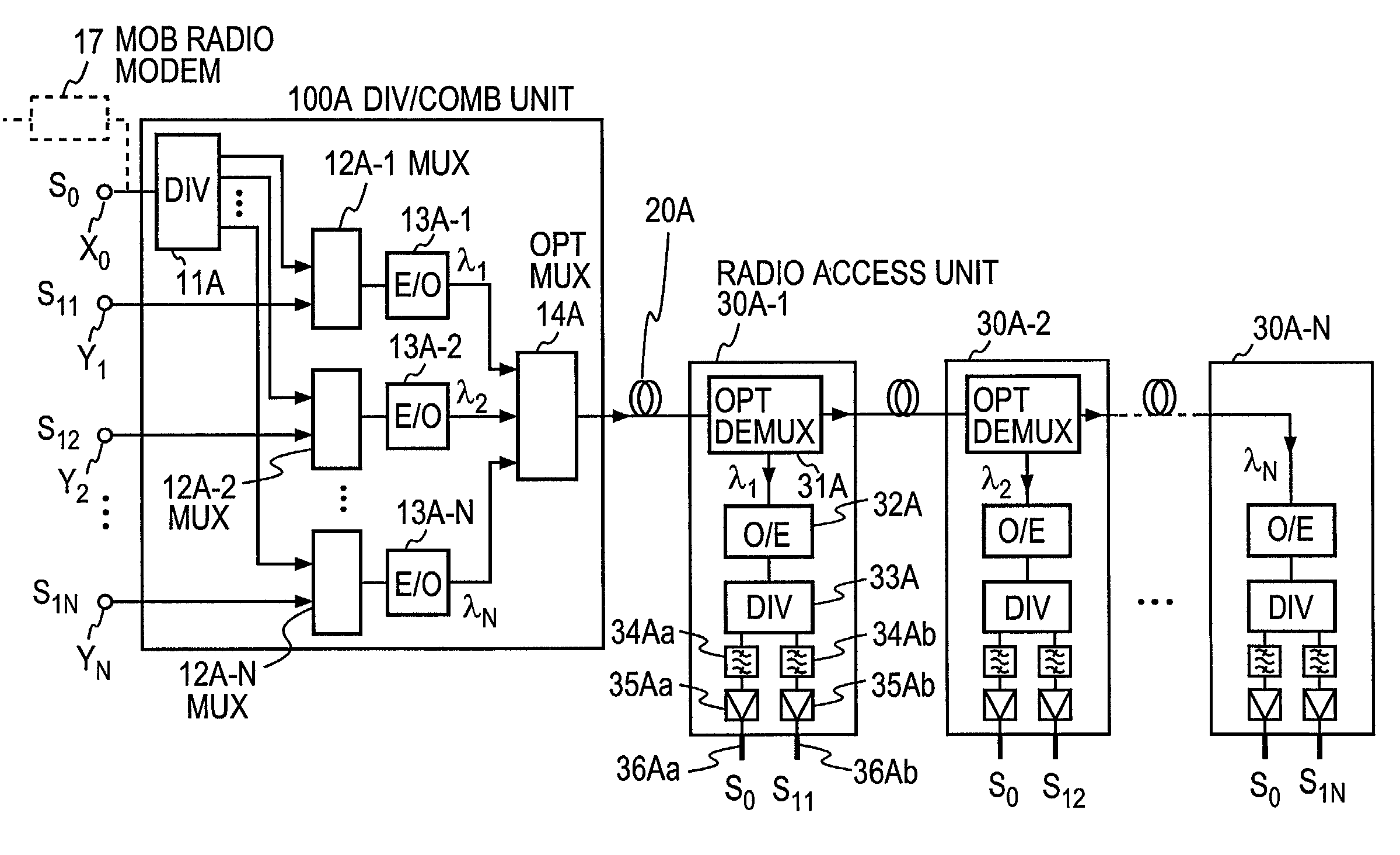

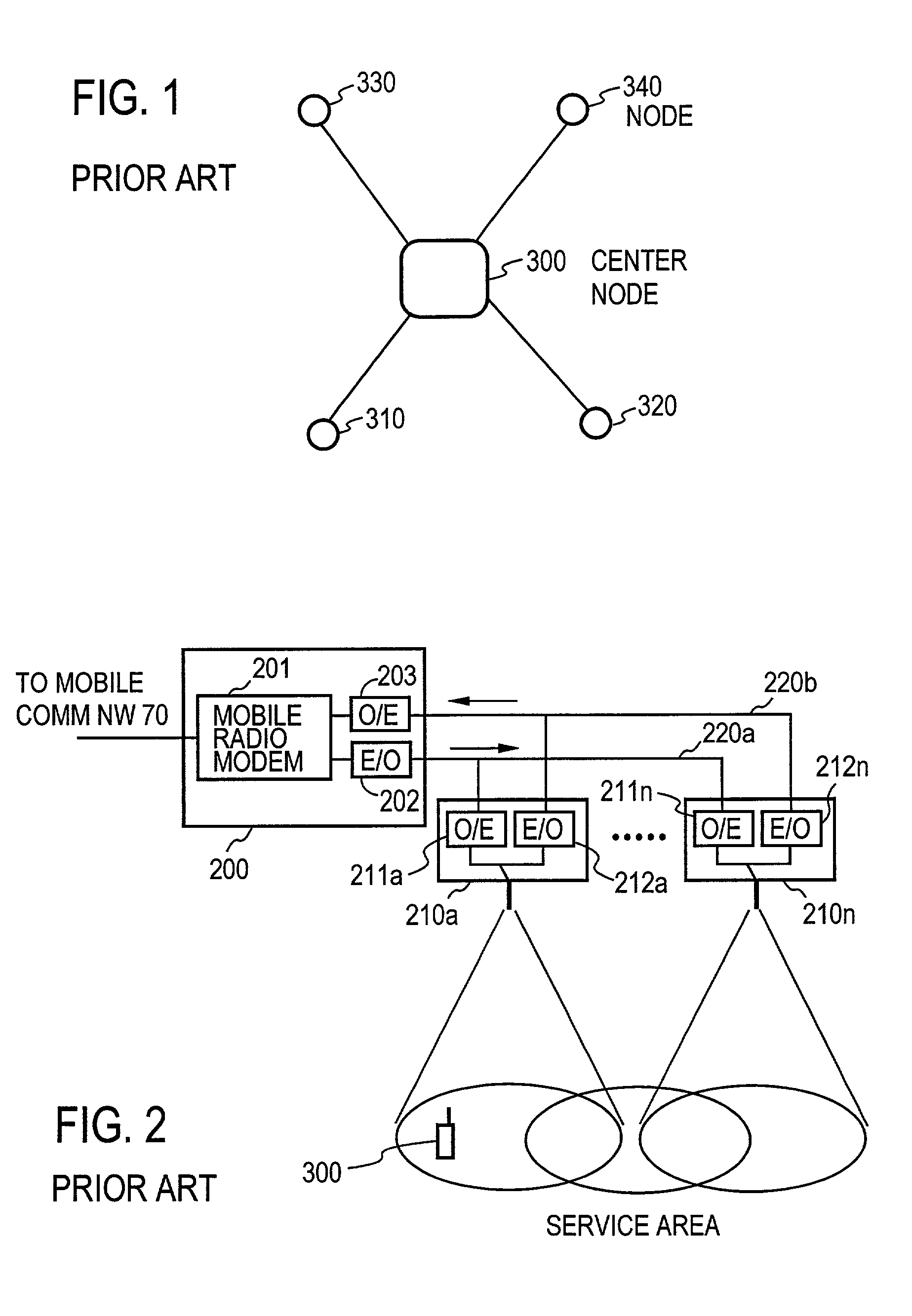

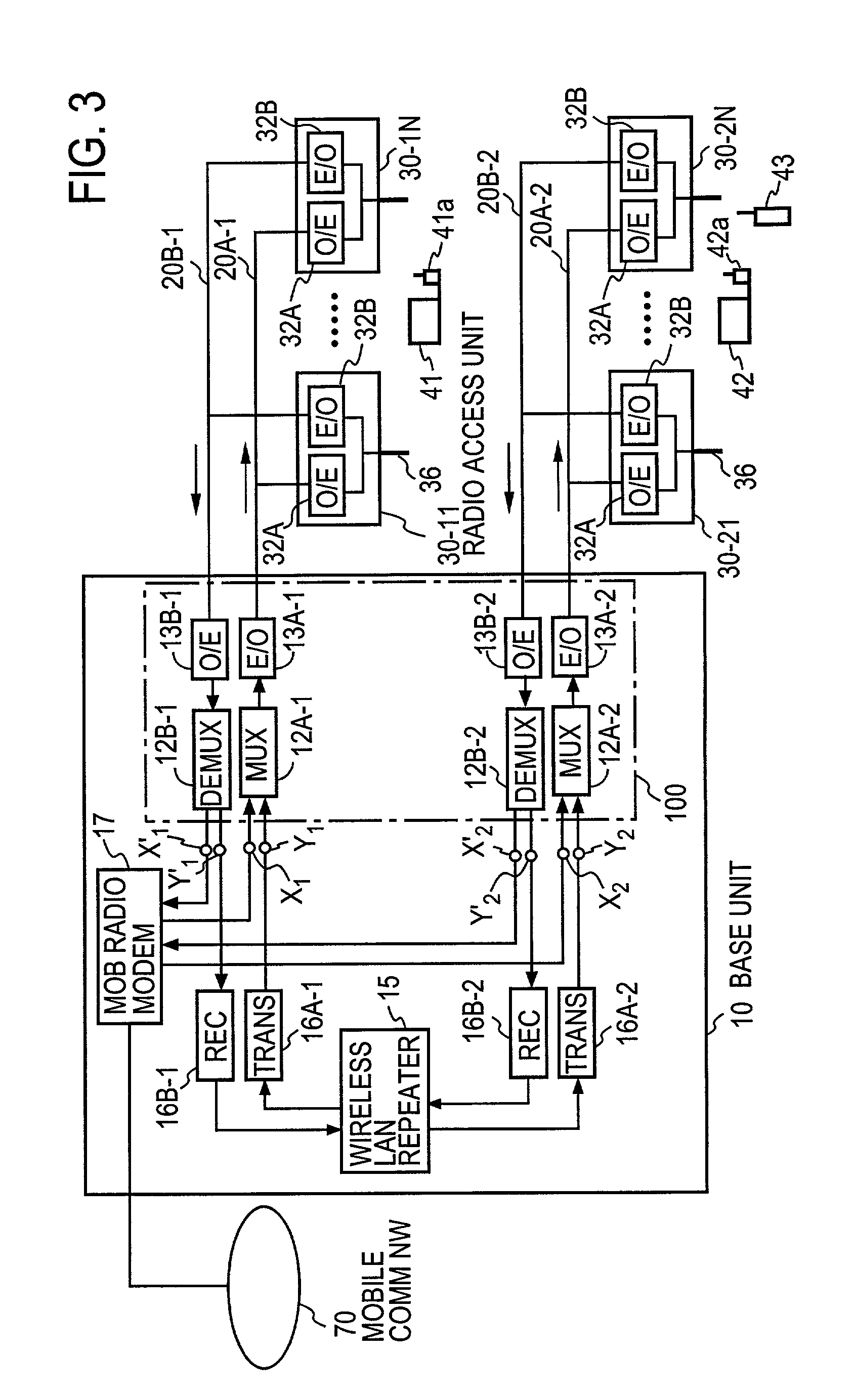

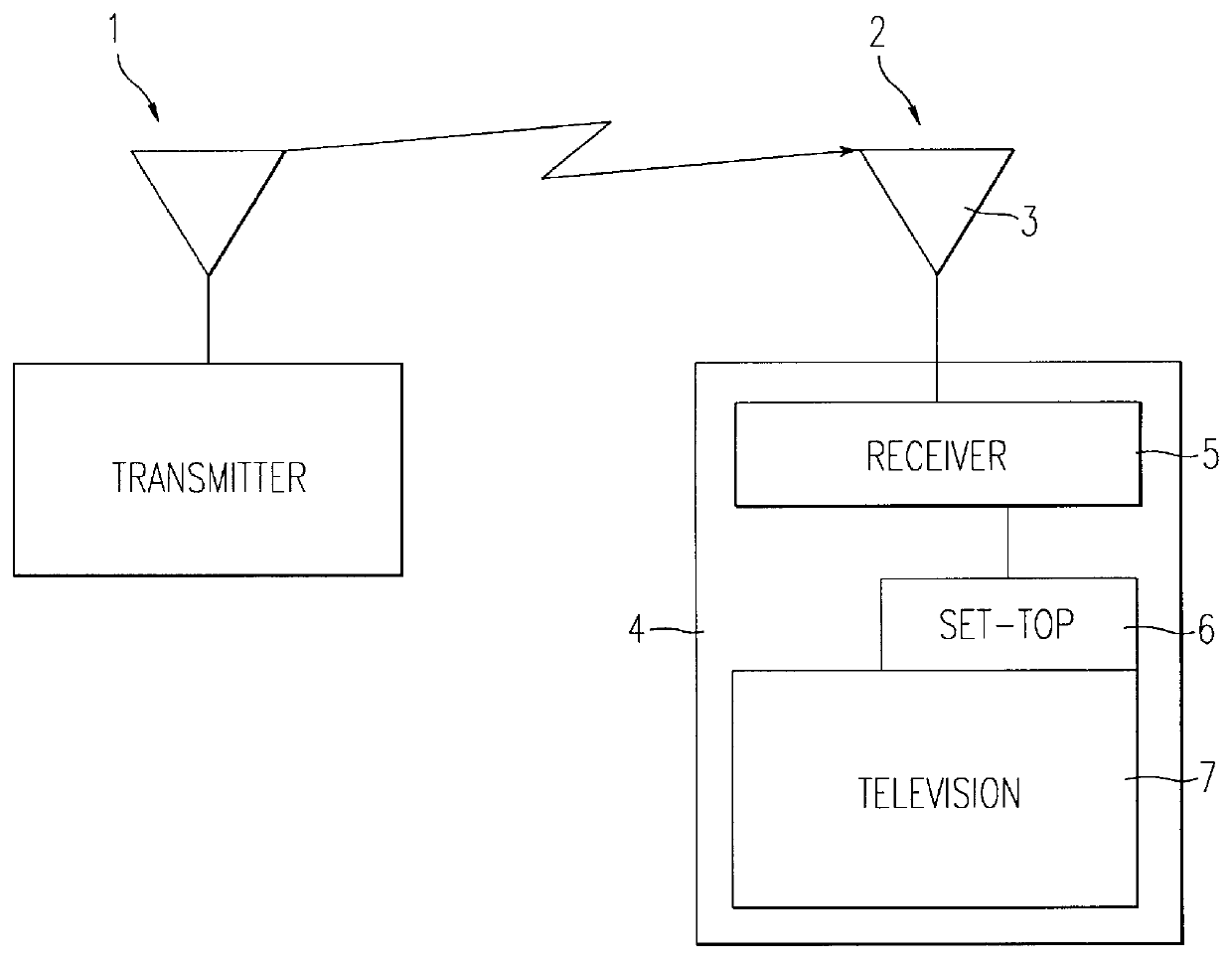

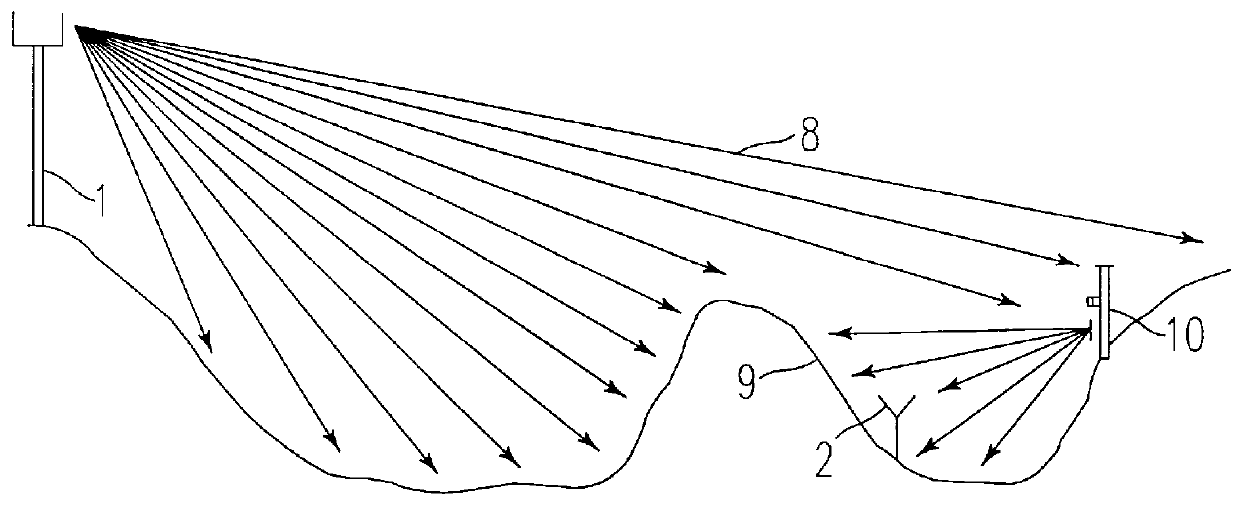

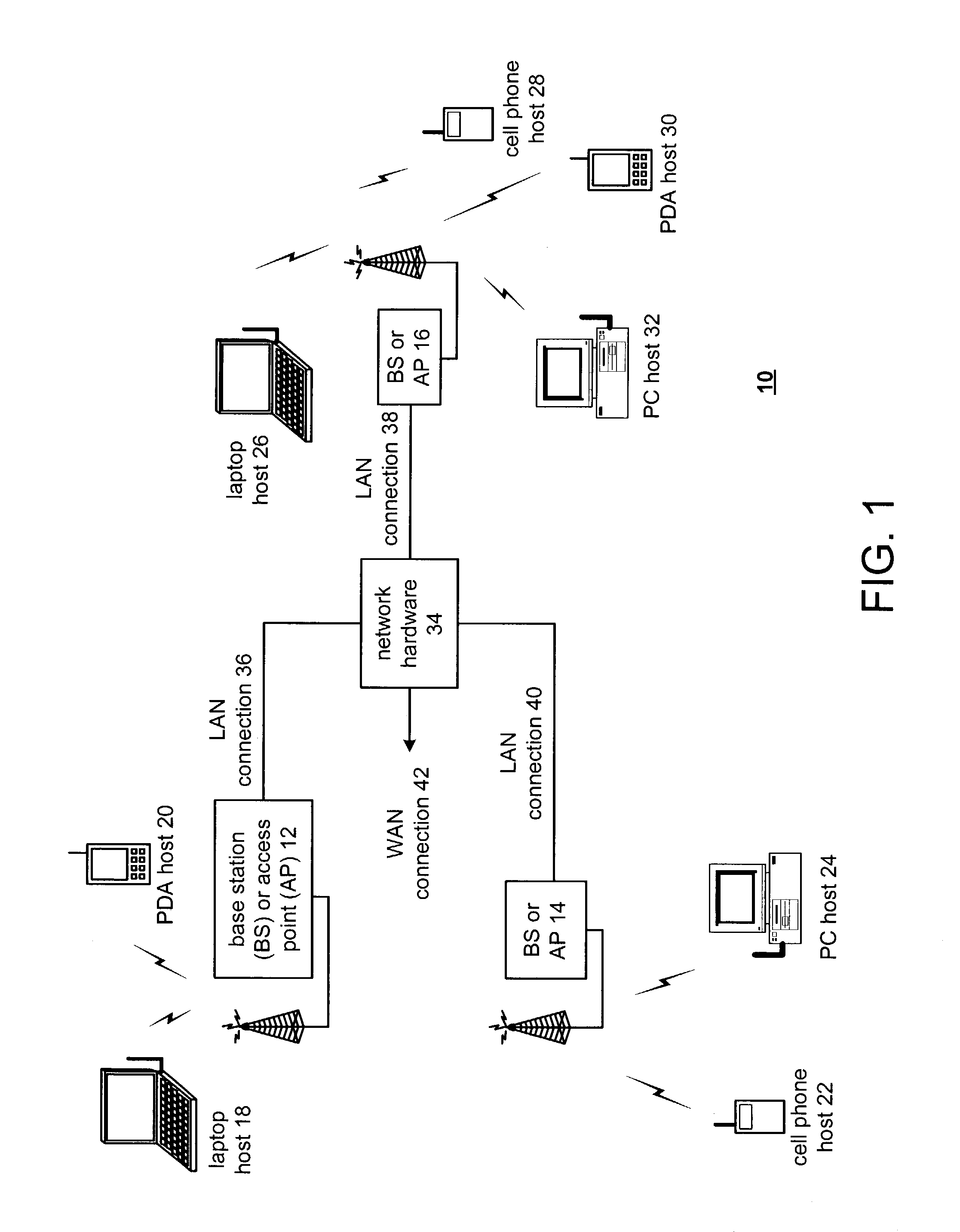

Communication system using optical fibers

ActiveUS7013087B2Increase user capacityRadio transmissionOptical multiplexCommunications systemSignal transition

A divider / combiner unit combines RF signals, then converts the combined signal into an optical signal and sends it over an optical fiber. N radio access units each convert the optical signal received from the optical fiber into an RF signal and transmits it from an antenna, and each radio access unit converts an RF signal received by the antenna into an optical signal and sends it over an optical fiber to the divider / combiner unit. The divider / combiner unit converts the received optical signal into RF signals and outputs them. This system is operated as plurality of communication systems in common to them in correspondence to a plurality of input / output terminals of the divider / combiner unit.

Owner:NTT DOCOMO INC

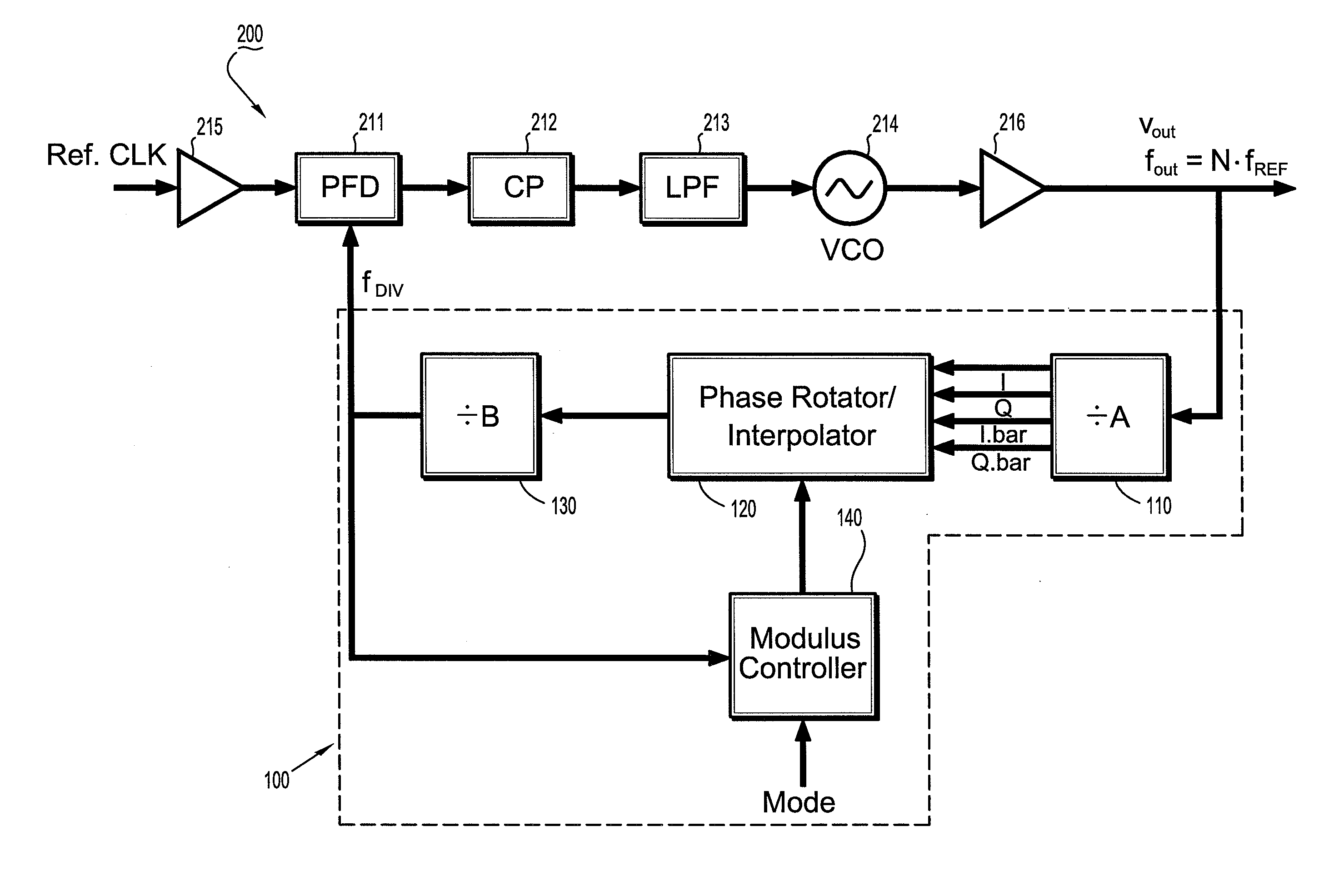

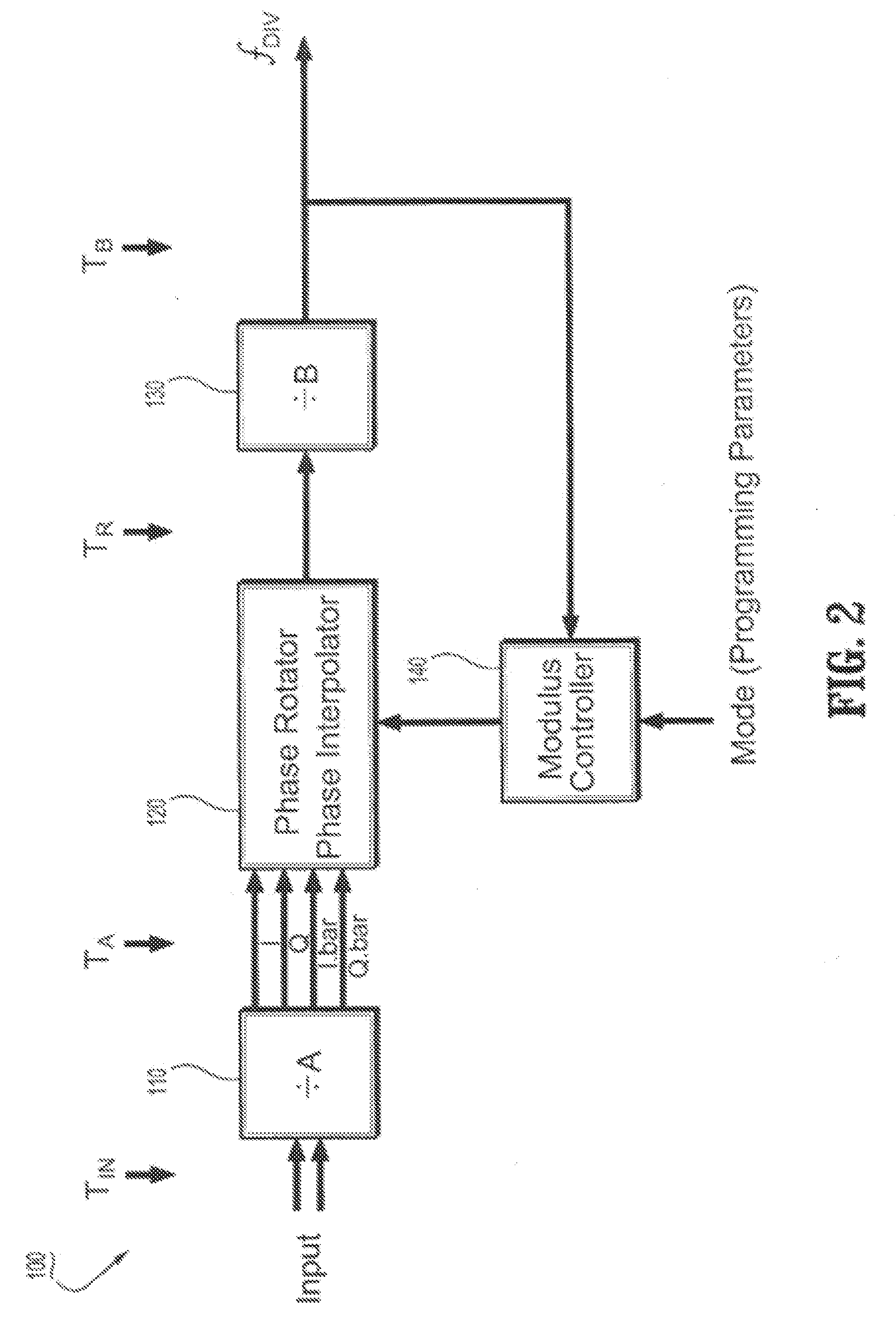

Circuits and methods for implementing sub-integer-n frequency dividers using phase rotators

ActiveUS20080164917A1Reduce and eliminate glitch in output signalPulse automatic controlCounting chain pulse countersFrequency synthesizerFrequency divider

Circuits and methods are provided for implementing programmable sub-integer N frequency dividers for use in, e.g., frequency synthesizer applications, providing glitch free outputs signals with minimal fractional spurs. Phase-rotating sub-integer N frequency dividers are programmable to provide multi-modulus division with a wide range of arbitrary sub-integer division ratios.

Owner:IBM CORP

Battery capacity measuring and remaining capacity calculating system

InactiveUS6621250B1Quick calculationEnhanced advantageCircuit monitoring/indicationInternal combustion piston enginesBattery state of chargeIntegrator

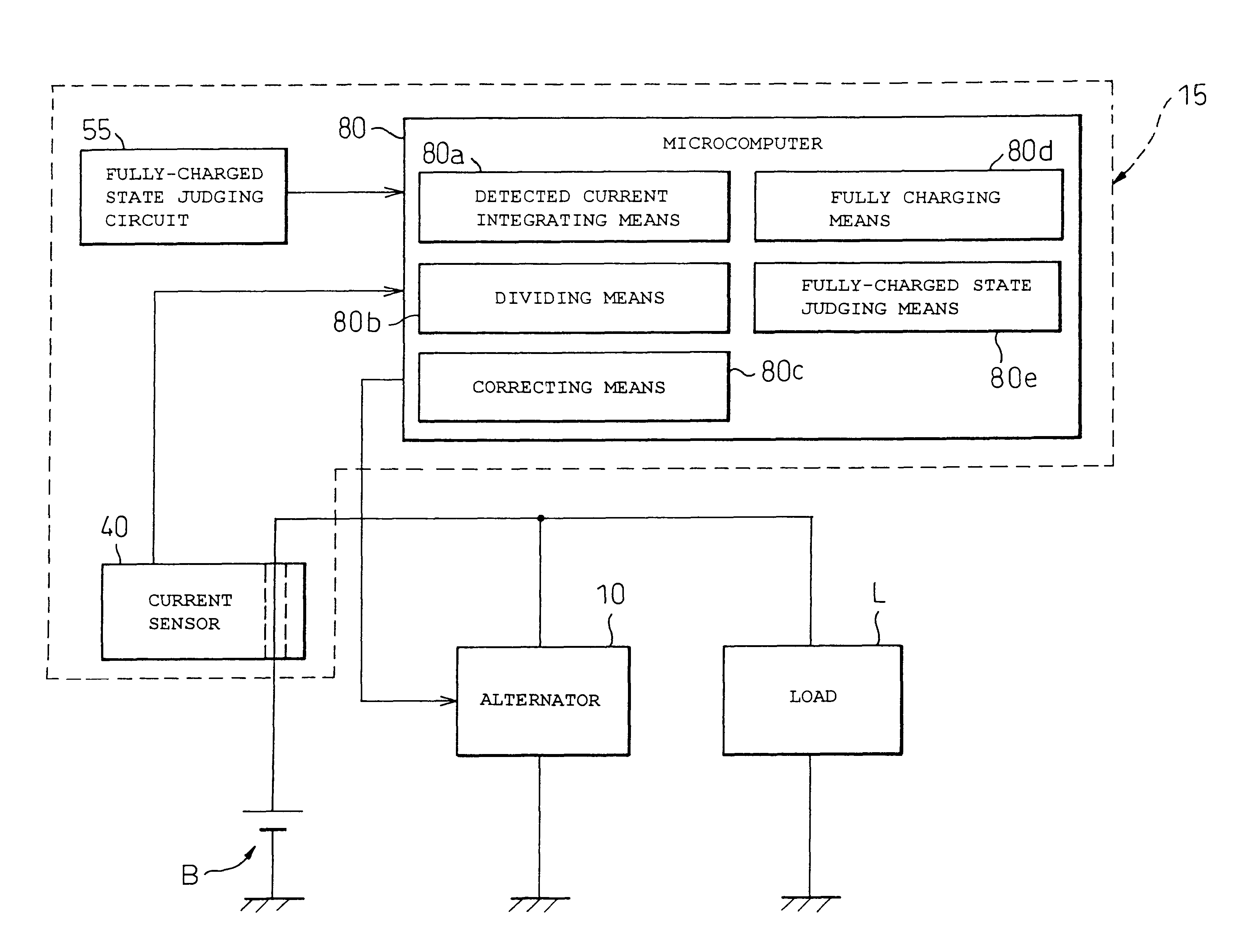

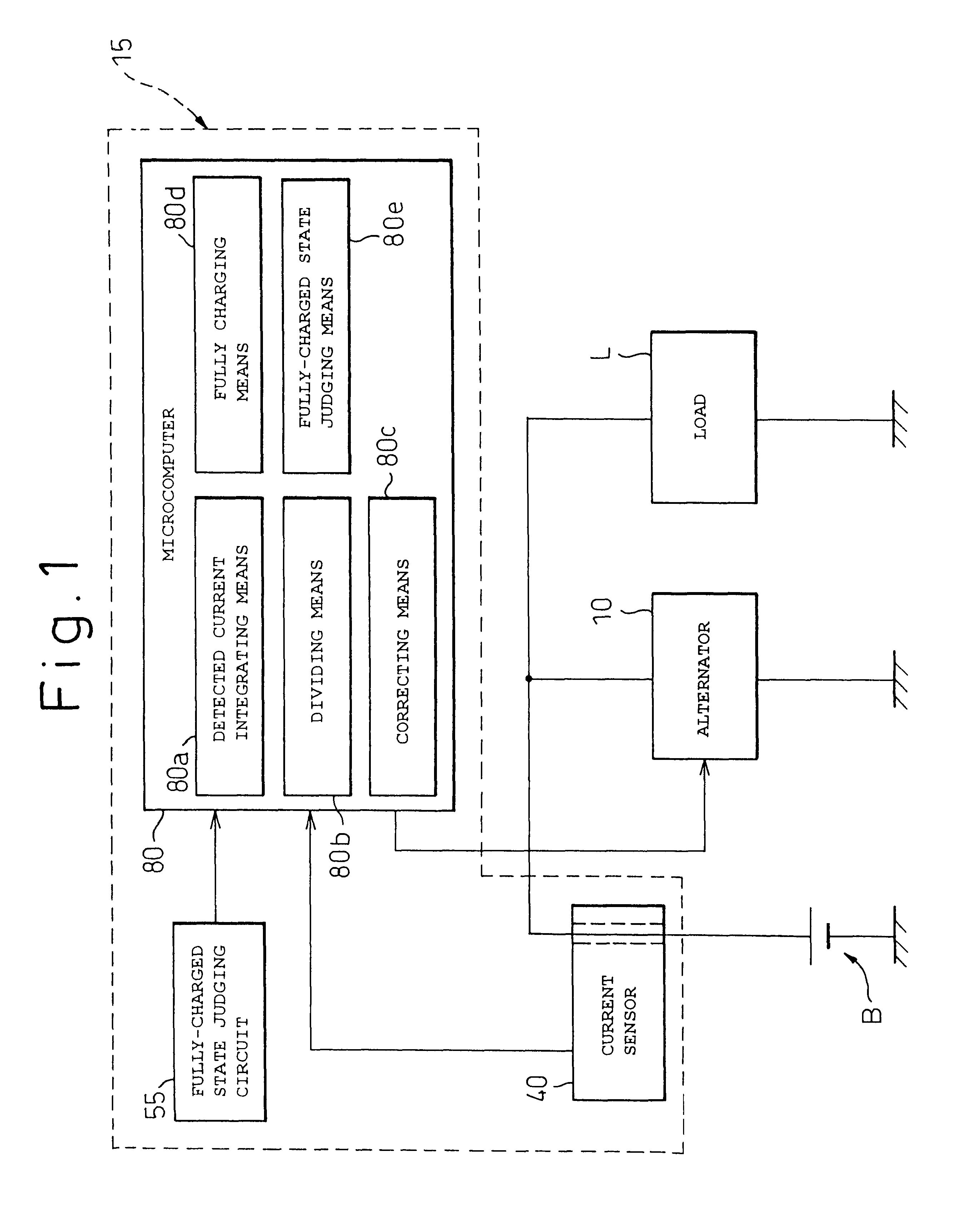

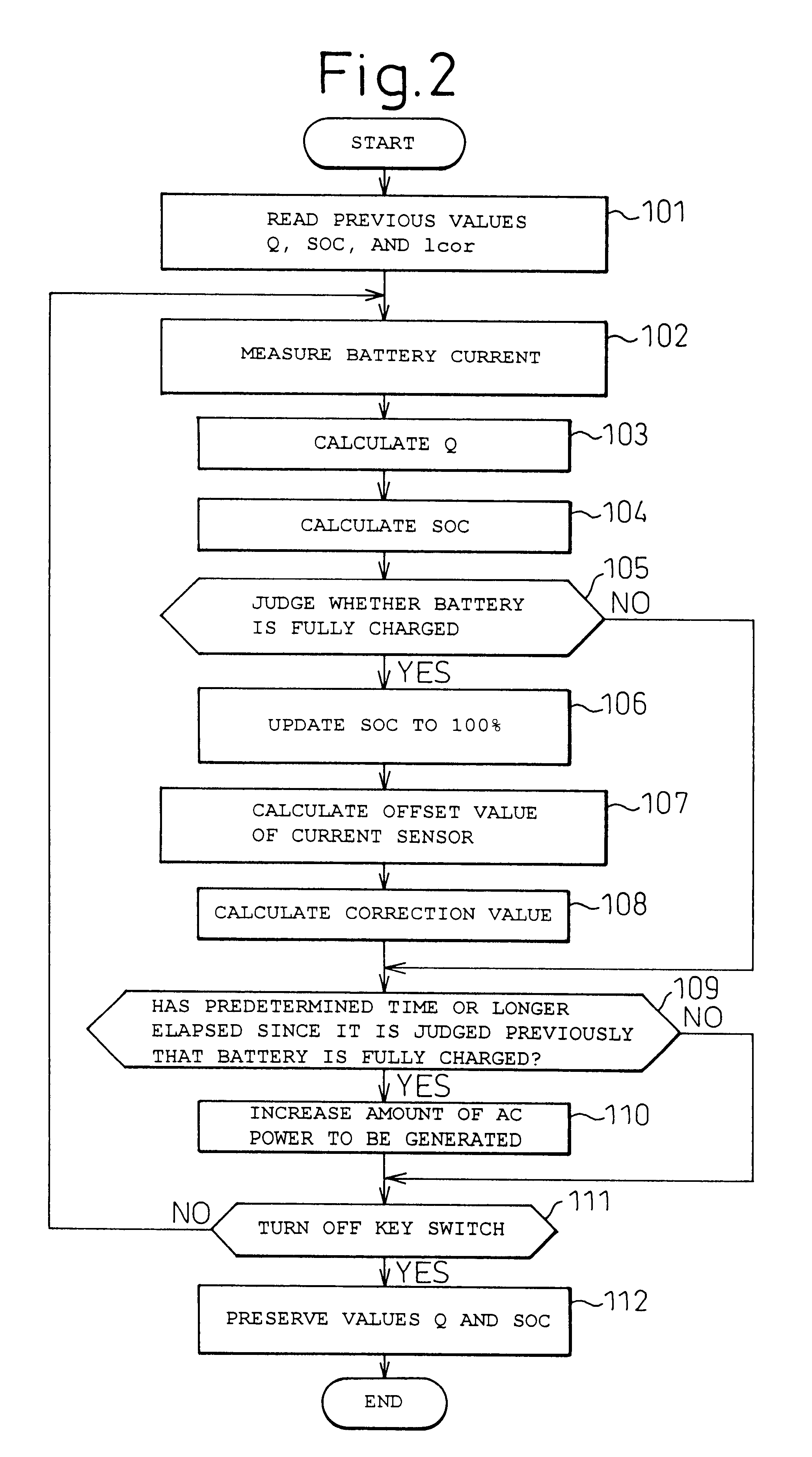

A battery capacity measuring device in accordance with the present invention has a fully-charged state detector (80e), a detected current integrator (80a), a divider (80b), and a corrector (80c) incorporated in a microcomputer (80). The fully-charged state detector detects that a battery is fully charged. The detected current integrator integrates current values that are detected by a current sensor during a period from the instant the battery is fully charged to the instant it is fully charged next. The divider divides the integrated value of detected current values by the length of the period. The corrector corrects a detected current using the quotient provided by the divider as an offset. Furthermore, a remaining battery capacity calculating system comprises a voltage detecting unit (50), a current detecting unit (40), an index calculating unit, a control unit, and a calculating unit. The voltage detecting unit detects the voltage at the terminals of a battery. The current detecting unit detects a current flowing through the battery. The index calculating unit calculates the index of polarization in the battery according to the detected current. The control unit controls the output voltage of an alternator so that the index of polarization will remain within a predetermined range which permits limitation of the effect of polarization on the charged state of the battery. When the index of polarization remains within the predetermined range, the calculating unit calculates the remaining capacity of the battery according to the terminal voltage of the battery, that is, the open-circuit voltage of the battery.

Owner:TOYOTA JIDOSHA KK +1

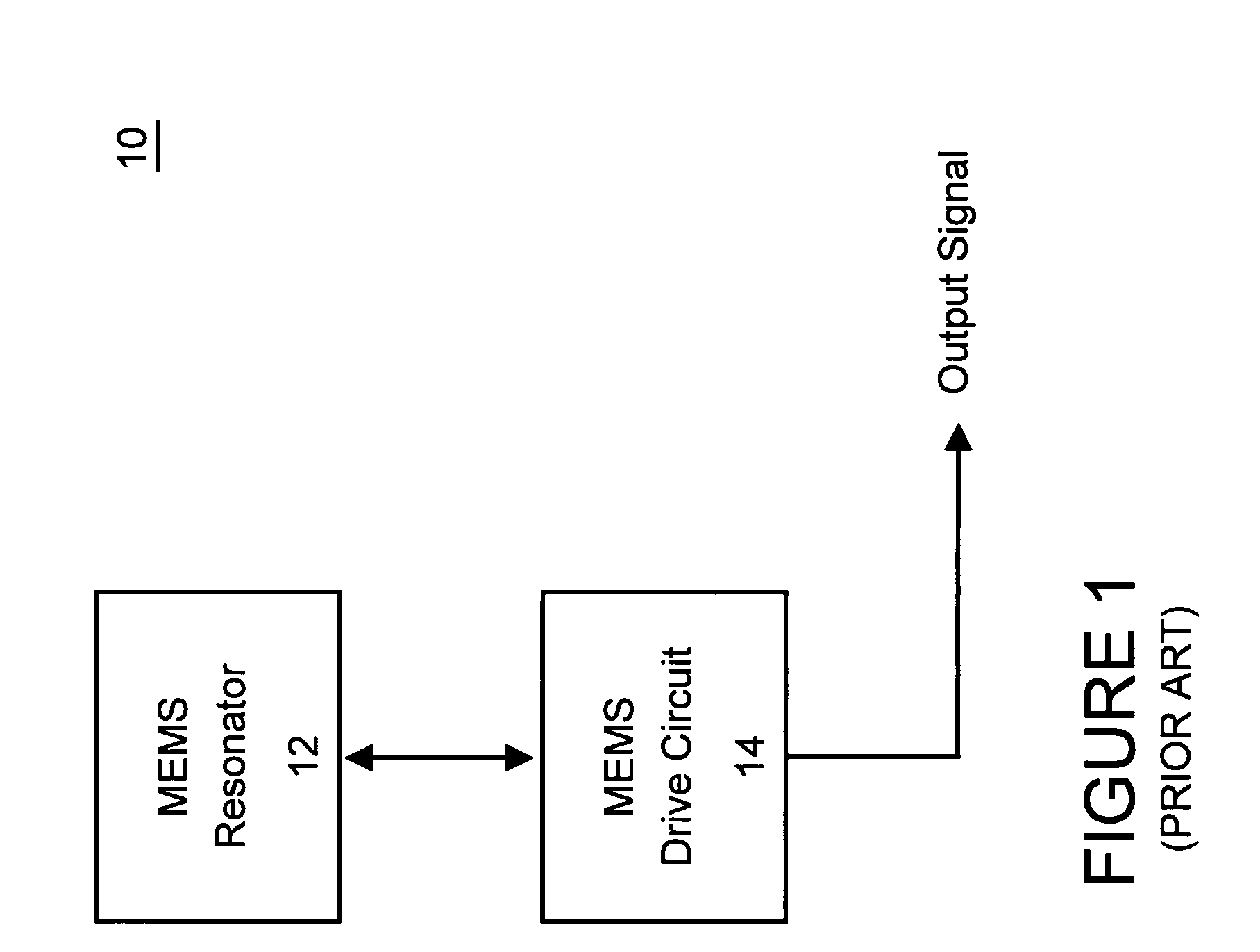

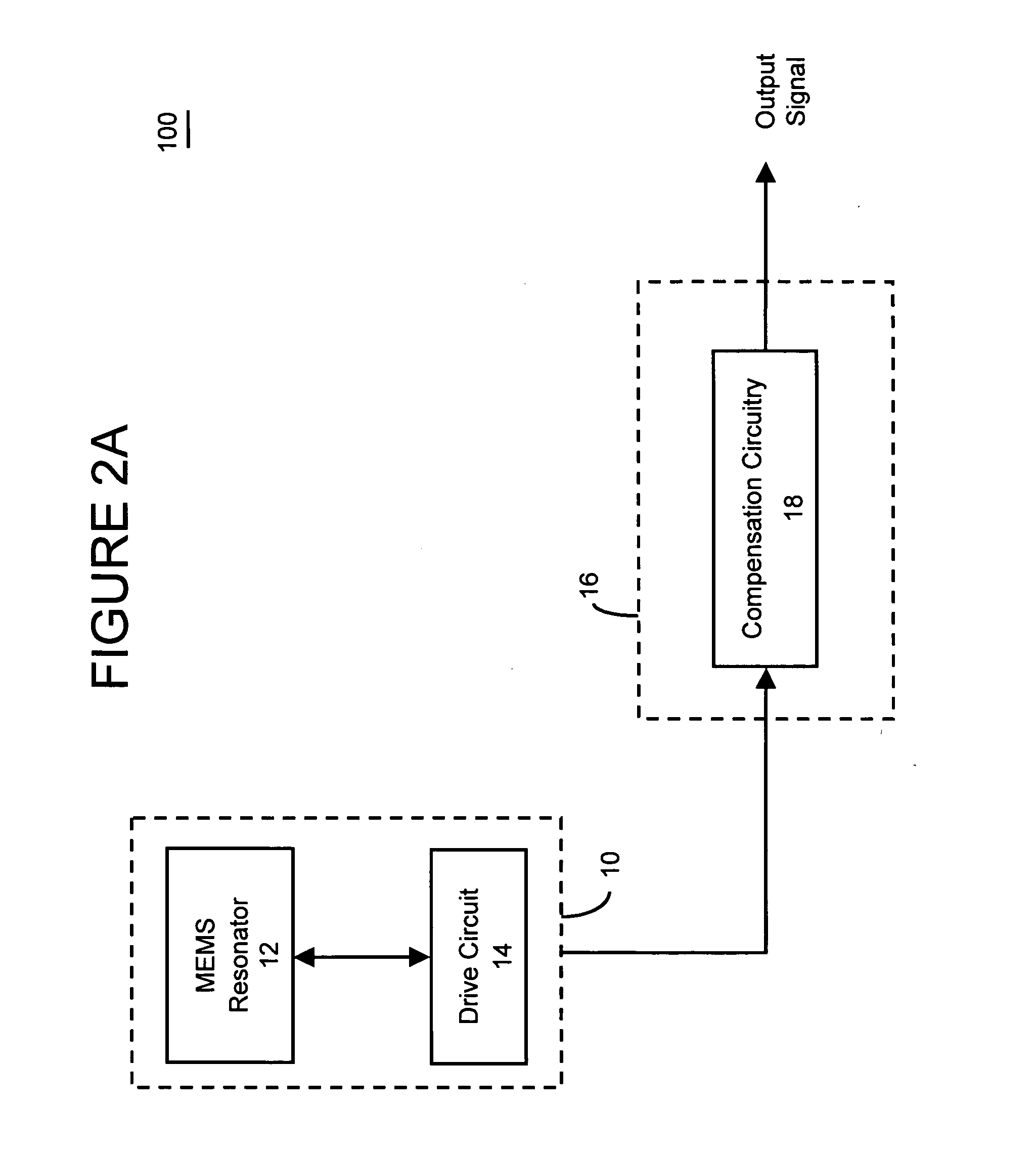

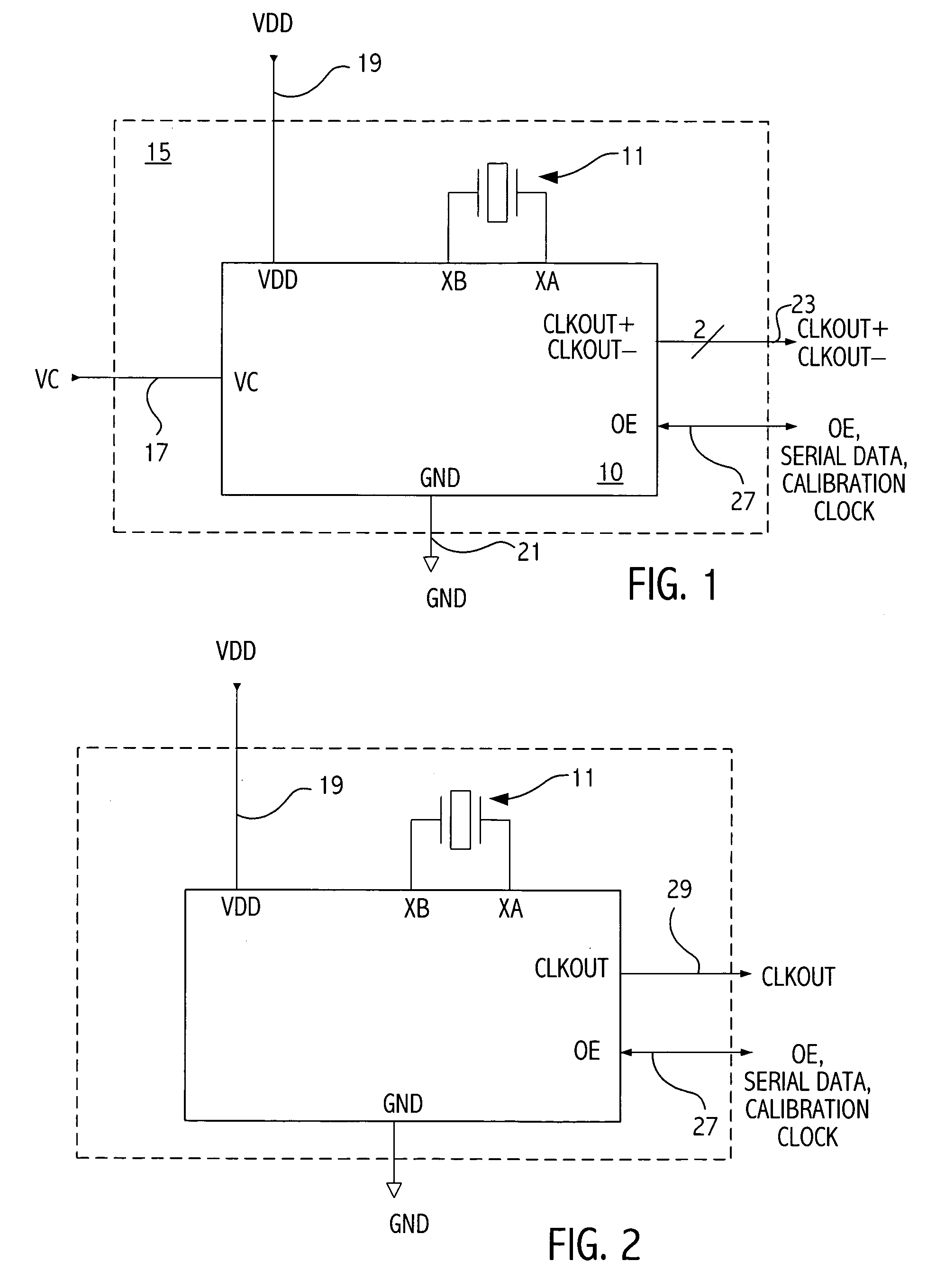

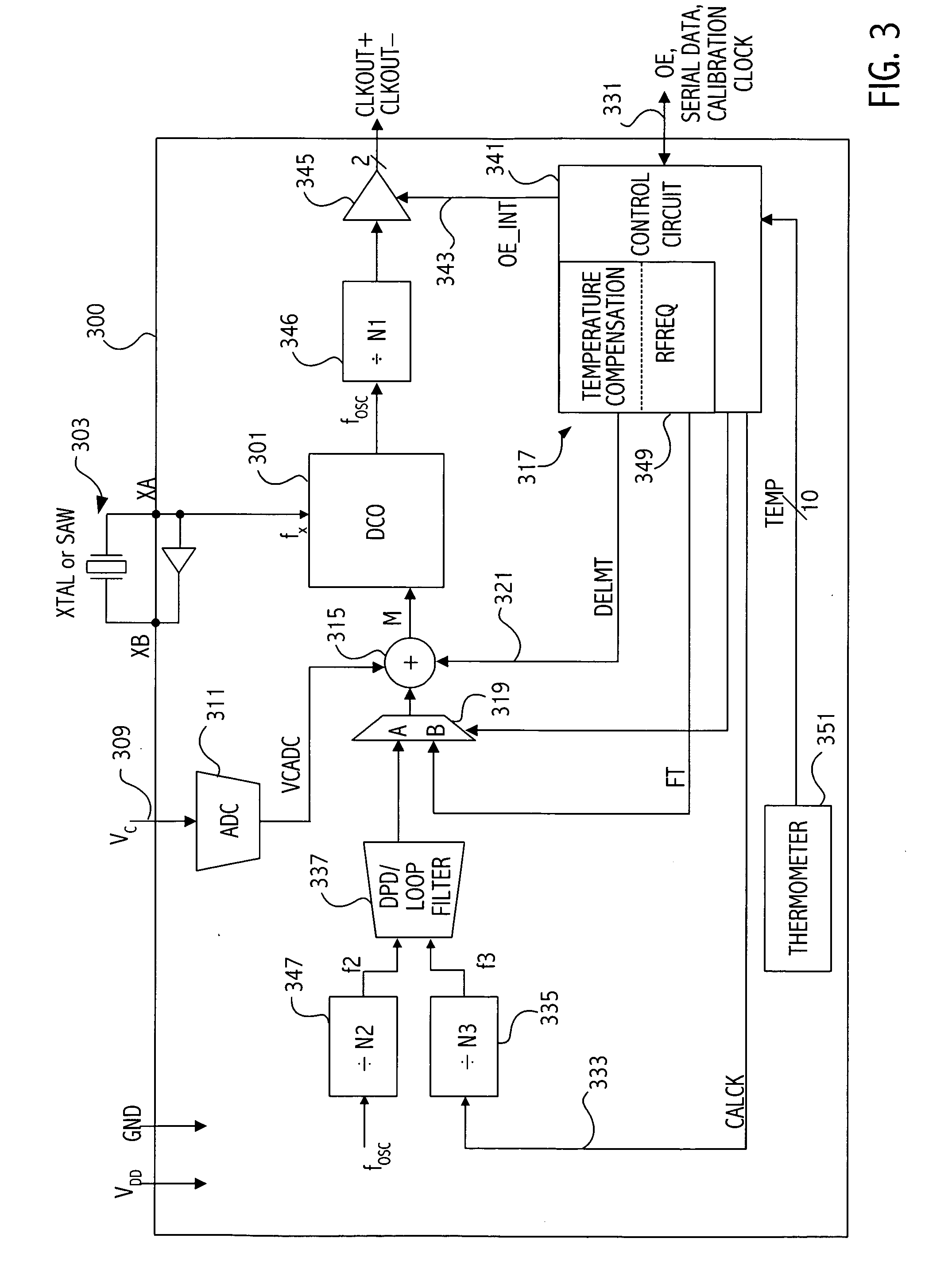

Frequency and/or phase compensated microelectromechanical oscillator

ActiveUS20050151592A1Reduce the gap widthIncreasing available voltage to applyRadiation pyrometryPulse automatic controlFrequency synthesizerFrequency multiplier

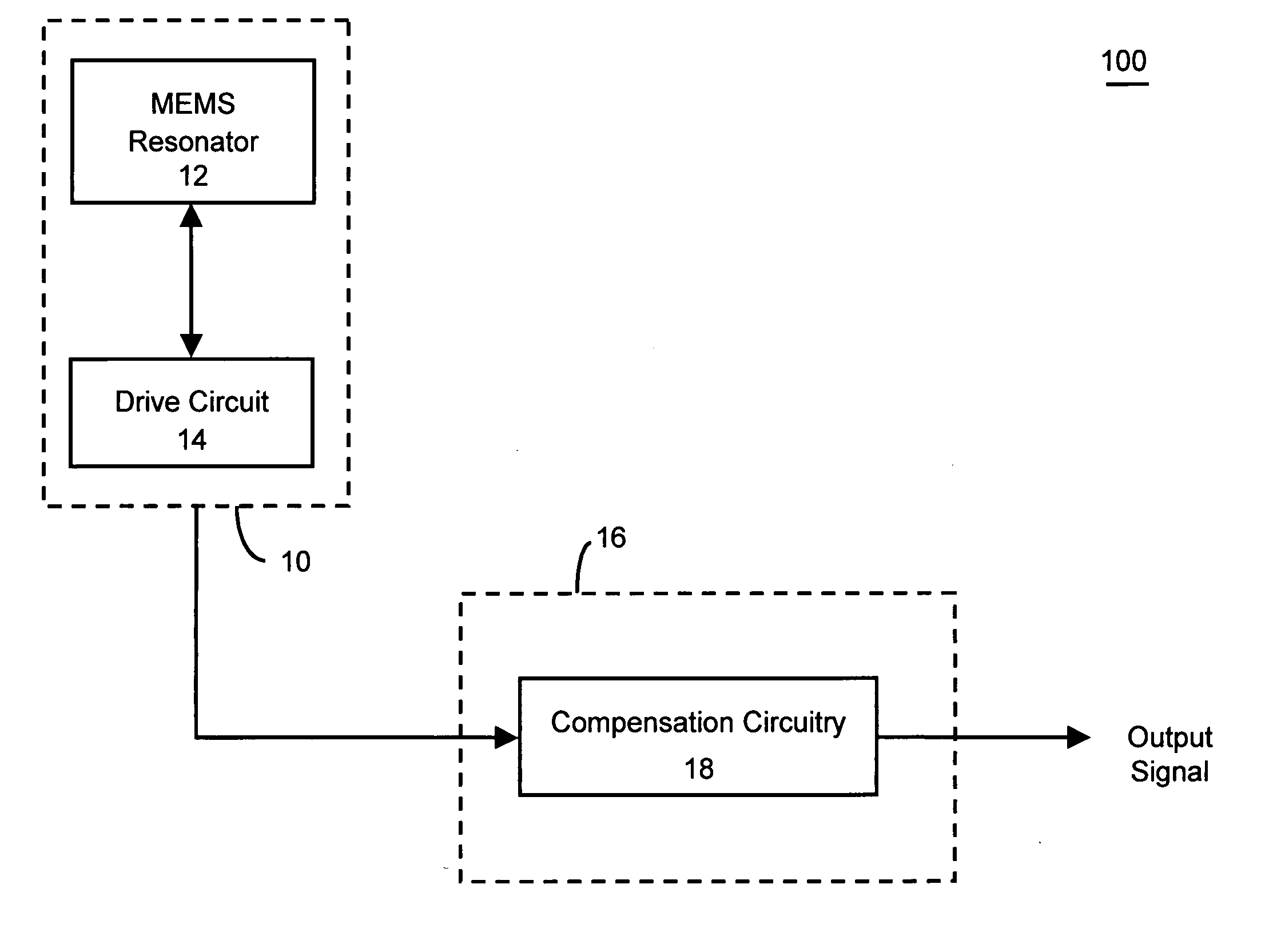

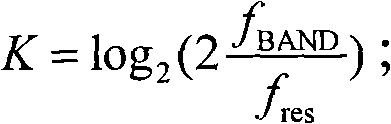

There are many inventions described and illustrated herein. In one aspect, the present invention is directed to a compensated microelectromechanical oscillator, having a microelectromechanical resonator that generates an output signal and frequency adjustment circuitry, coupled to the microelectromechanical resonator to receive the output signal of the microelectromechanical resonator and, in response to a set of values, to generate an output signal having second frequency. In one embodiment, the values may be determined using the frequency of the output signal of the microelectromechanical resonator, which depends on the operating temperature of the microelectromechanical resonator and / or manufacturing variations of the microelectromechanical resonator. In one embodiment, the frequency adjustment circuitry may include frequency multiplier circuitry, for example, PLLs, DLLs, digital / frequency synthesizers and / or FLLs, as well as any combinations and permutations thereof. The frequency adjustment circuitry, in addition or in lieu thereof, may include frequency divider circuitry, for example, DLLS, digital / frequency synthesizers (for example, DDS) and / or FLLs, as well as any combinations and permutations thereof.

Owner:ROBERT BOSCH GMBH

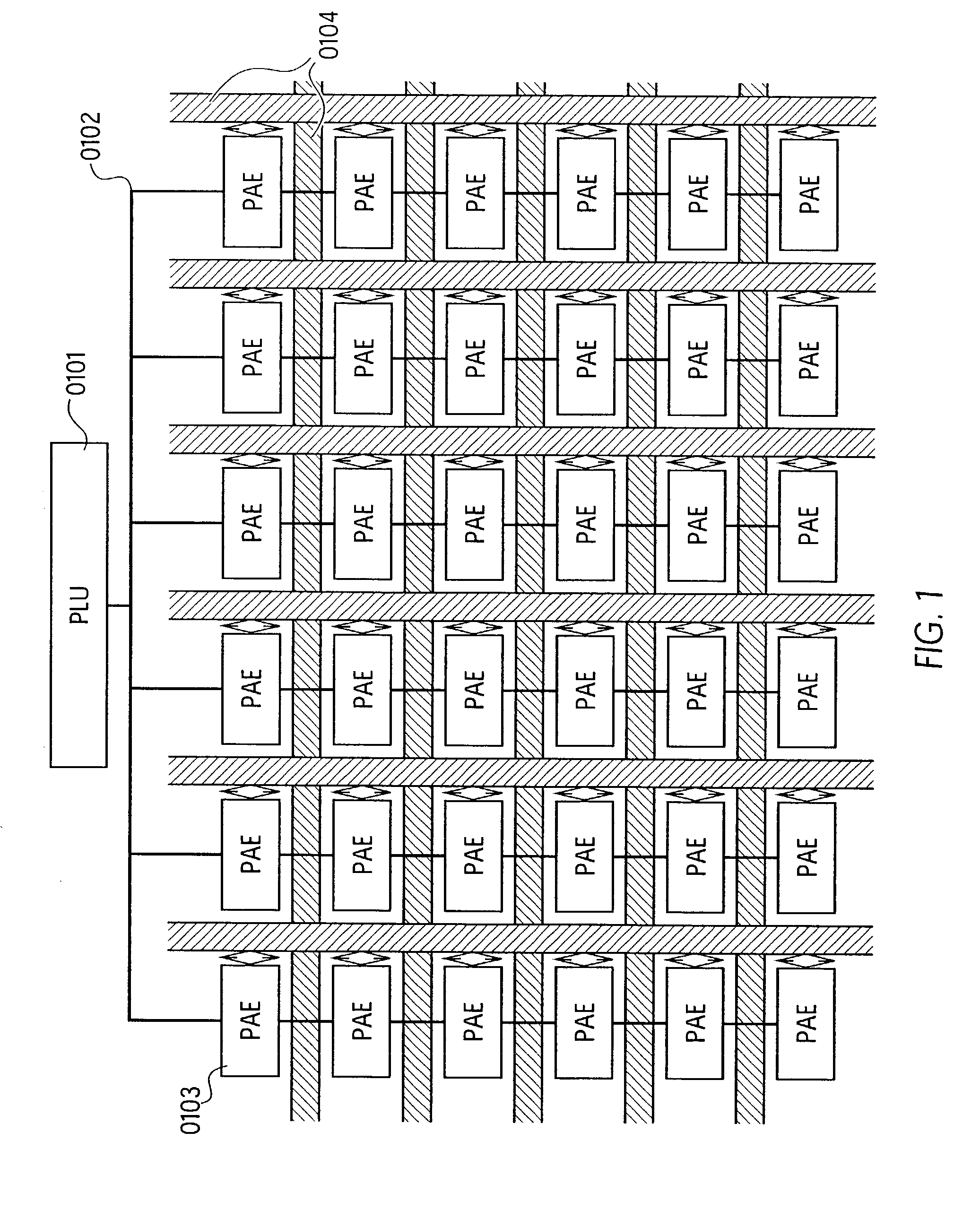

Computer program product configured to control modular transmission system components

A computer program product is configured to control a modular transmission system having a control processor and at least N power amplifier modules, each having a controller submodule, wherein the system receives an input signal which may be a single carrier or multiple carriers. The signal is passed to a one-by-N divider which divides the signal N ways. Each of the N divided signals are independently amplified by the power amplifier (PA) modules "slices" (i.e., PA modules) that includes an RF amplifier module, a microcontroller module, and a power supply module, all of which are tightly coupled via a plurality of signal, power, control, and status connections. Each the PA slices amplifies its respective input signal and outputs a respective radio frequency output signal at a predetermined power level as controlled by the microcontrol module, the driver, and the system controller, or a network manager via a system input / output interface. The output coupler provides power coupling and status monitoring via feedback lines to support control at a module-level, a system-level, and a network-level.

Owner:THALES BROADCAST & MULTIMEDIA

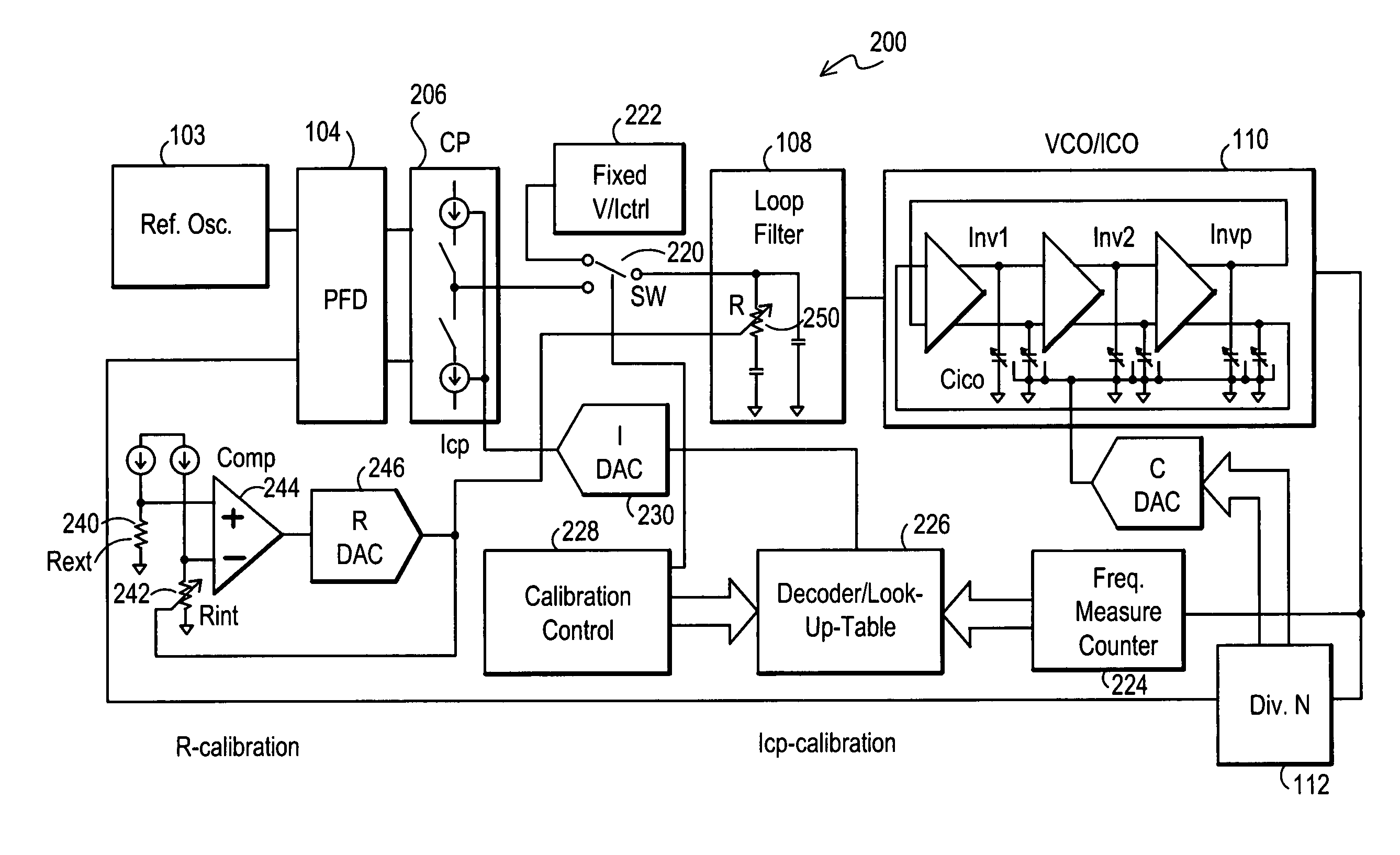

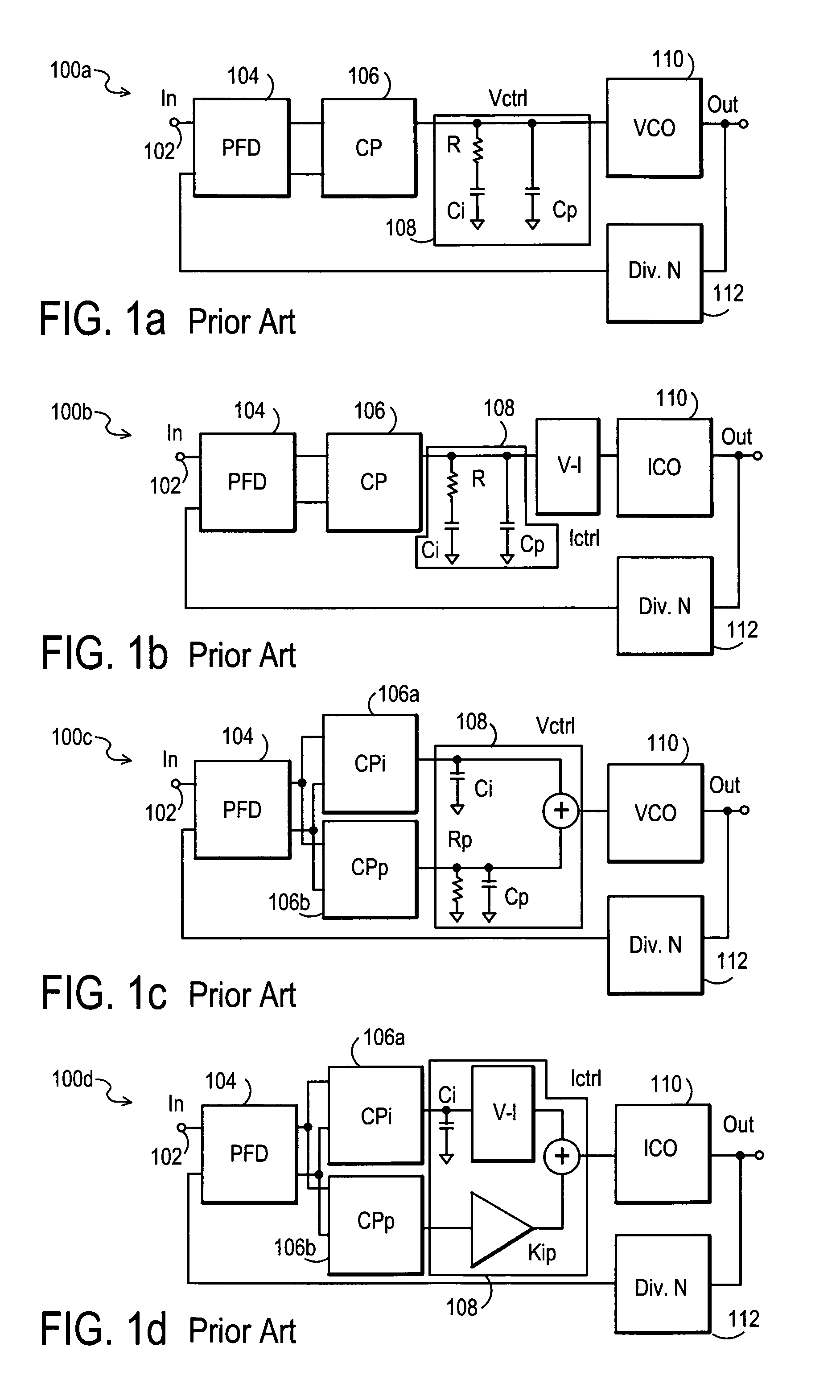

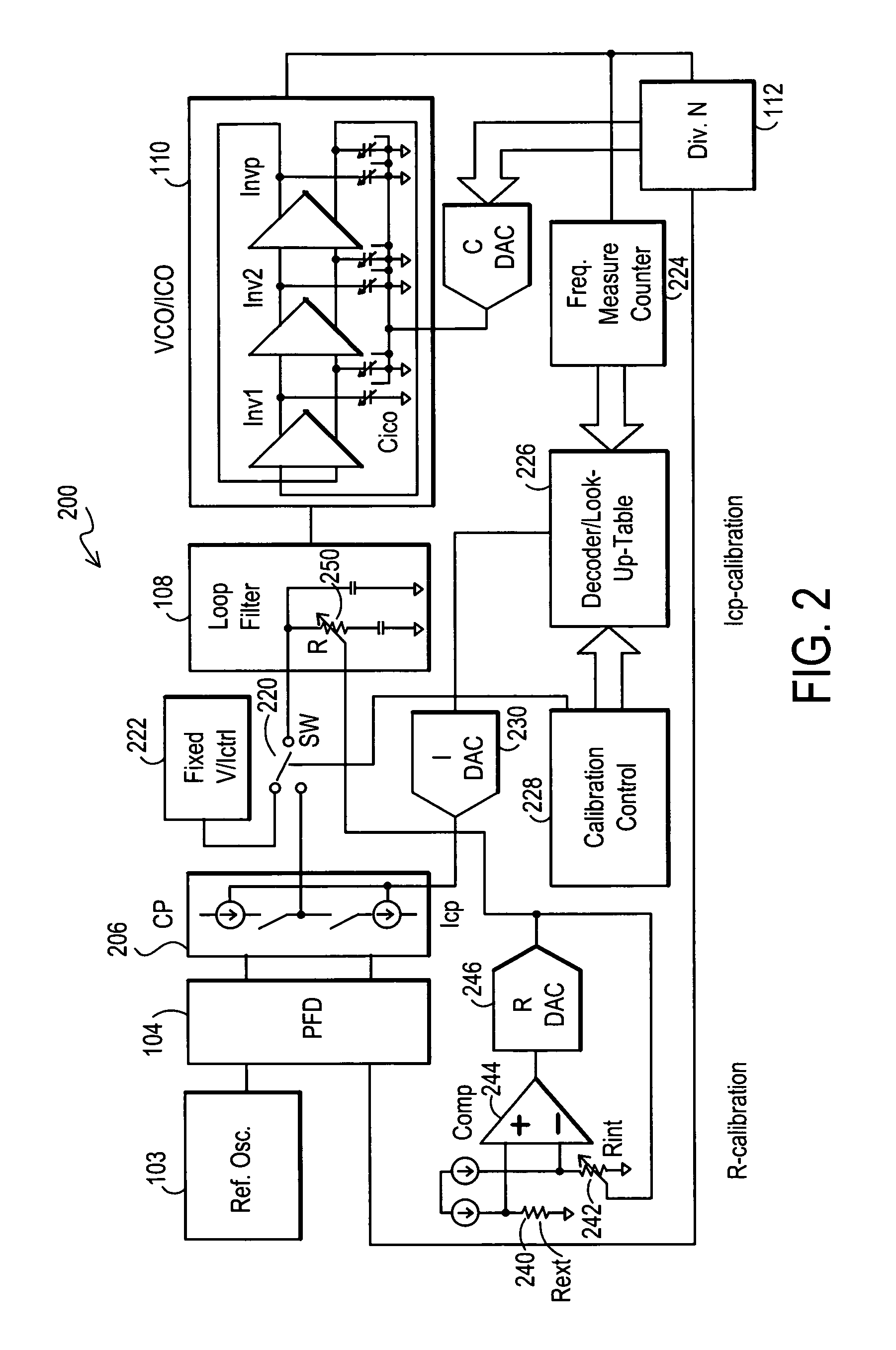

Method and apparatus to achieve a process, temperature and divider modulus independent PLL loop bandwidth and damping factor using open-loop calibration techniques

InactiveUS7095287B2Reduce complexityImprove accuracyPulse automatic controlFrequency analysisDamping factorProportional control

Several open-loop calibration techniques for phase-locked-loop circuits (PLL) that provide a process, temperature and divider modulus independence for the loop bandwidth and damping factor are disclosed. Two categories of open-loop techniques are presented. The first method uses only a single measurement of the output frequency from the oscillator and adjusts a single PLL loop element that performs a simultaneous calibration of both the loop bandwidth and damping factor. The output frequency is measured for a given value of the oscillator control signal and the charge-pump current is adjusted such that it cancels the process variation of the oscillator gain. The second method uses two separate and orthogonal calibration steps, both of them based on the measurement of the output frequency from the oscillator when a known excitation is applied to the open loop signal path. In the first step the loop bandwidth is calibrated by adjusting the charge-pump current based on the measurement of the forward path gain when applying a constant phase shift between the two clocks that go to the phase frequency detector, while the integral path is hold to a constant value. During the second step the damping factor is calibrated by adjusting the value of the integral loop filter capacitor based on the measurement of the oscillator output frequency when excited with a voltage proportional with the integral capacitor value, while the proportional control component is zeroed-out.

Owner:SILICON LAB INC

Dual loop architecture useful for a programmable clock source and clock multiplier applications

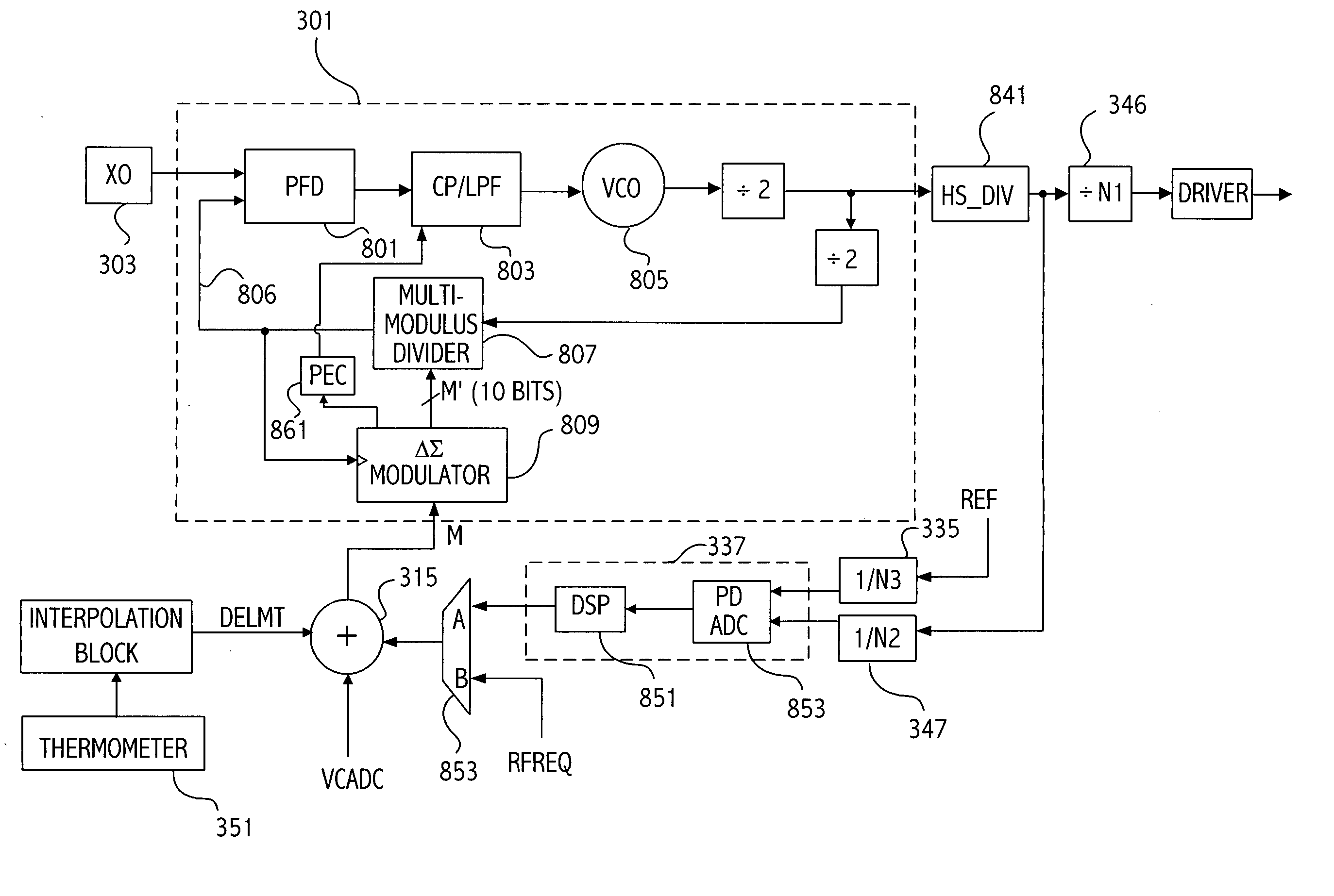

InactiveUS20040232995A1Pulse automatic controlGenerator stabilizationFrequency multiplierDigital control

A first phase-locked loop (PLL) circuit includes an input for receiving a timing reference signal from an oscillator, a controllable oscillator circuit supplying an oscillator output signal, and a multi-modulus feedback divider circuit. A second control loop circuit is selectably coupled through a select circuit to supply a digital control value (M) to the multi-modulus feedback divider circuit of the first loop circuit to thereby control the oscillator output signal. While the second control loop is coupled to supply the control value to the feedback divider circuit, the control value is determined according to a detected difference between the oscillator output signal and a reference signal coupled to the second control loop circuit at a divider circuit. While the second control loop circuit is not coupled to control the first PLL circuit, the first PLL circuit receives a digital control value to control a divide ratio of the feedback divider, the digital control value is determined at least in part according to a stored control value stored in nonvolatile storage, the stored control value corresponding to a desired frequency of the oscillator output signal.

Owner:SKYWORKS SOLUTIONS INC

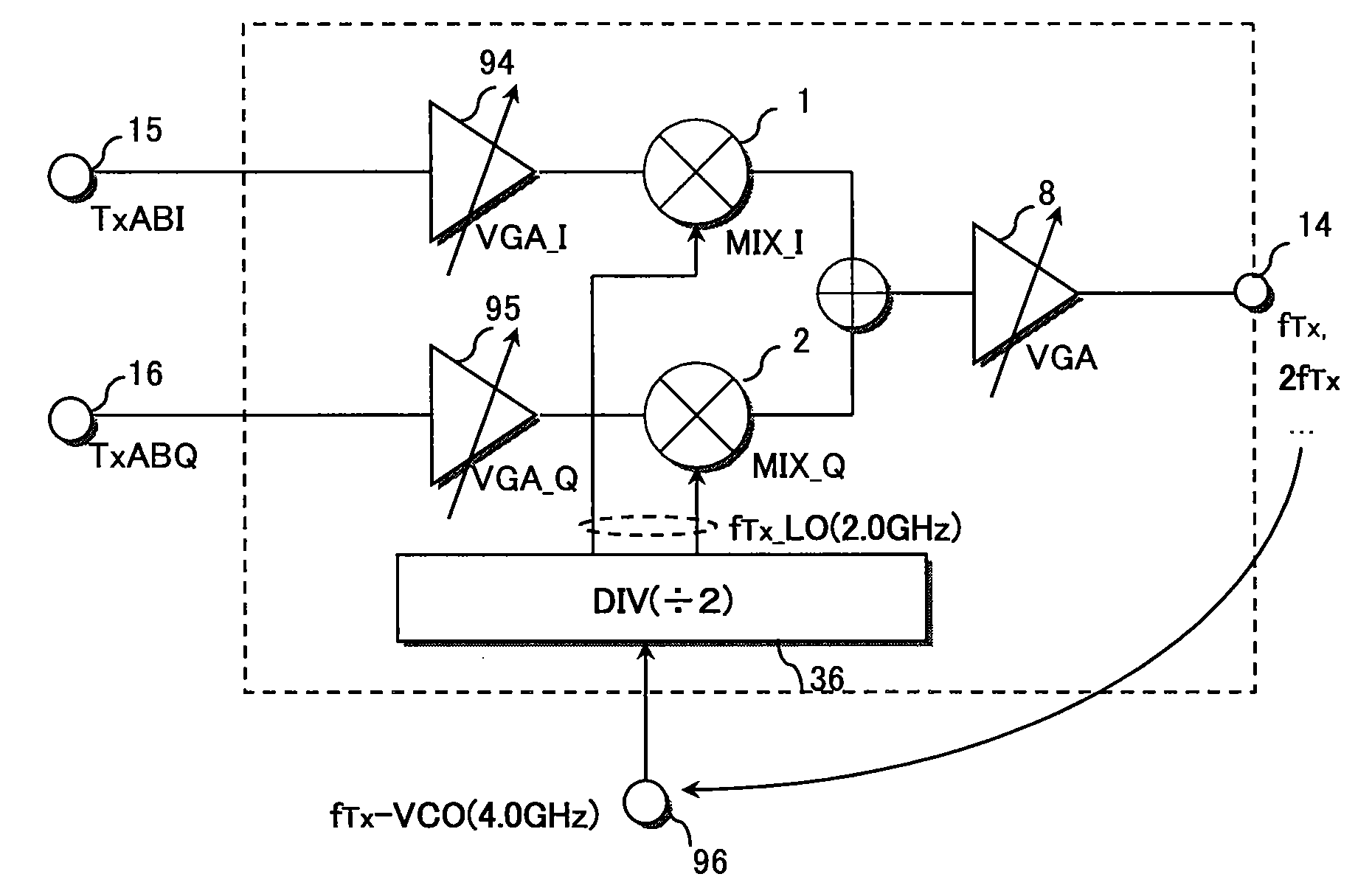

Transceiver

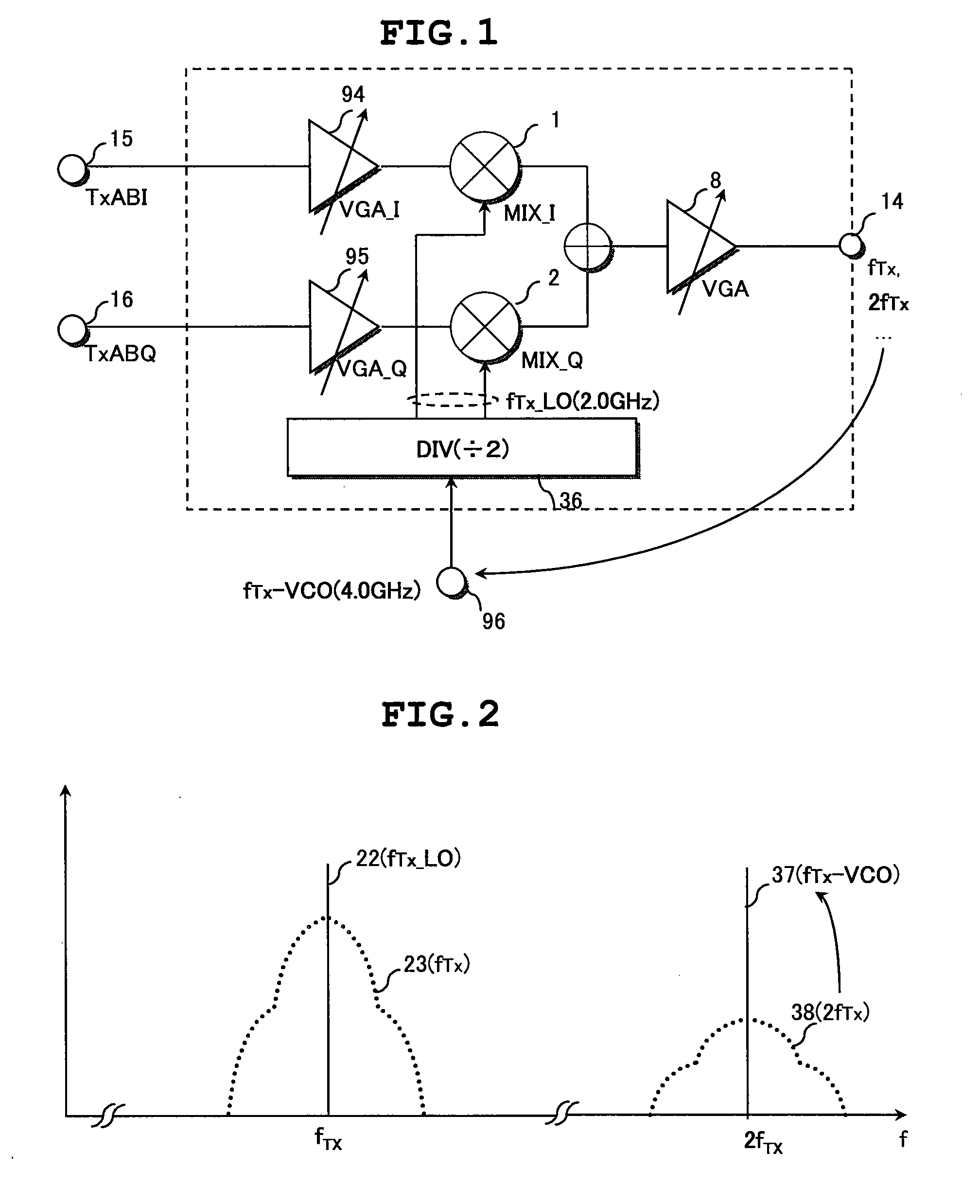

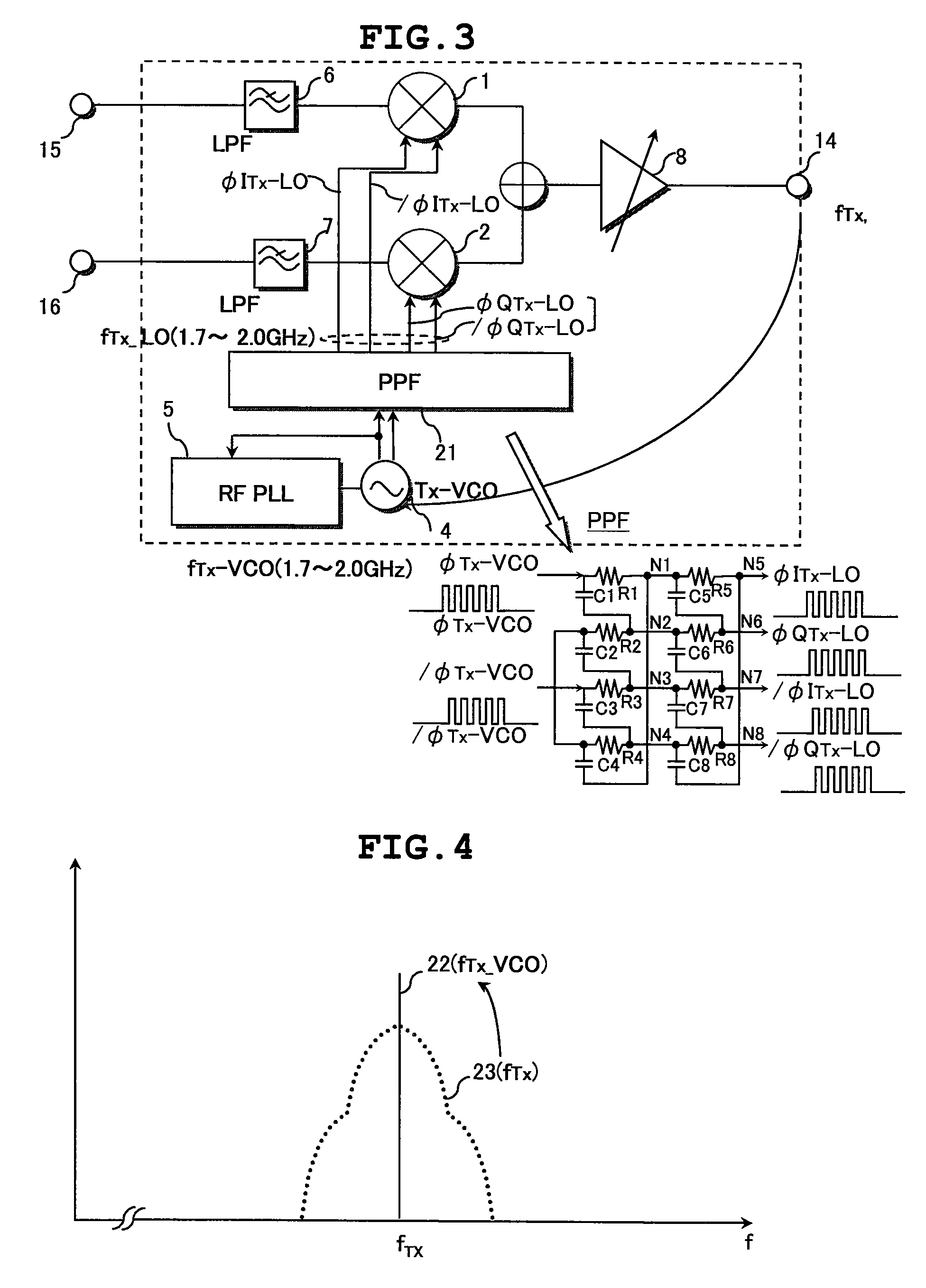

ActiveUS20080311860A1Reduce distractionsResonant long antennasTransmissionQuadrature modulationPhase shifted

Owner:RENESAS ELECTRONICS CORP

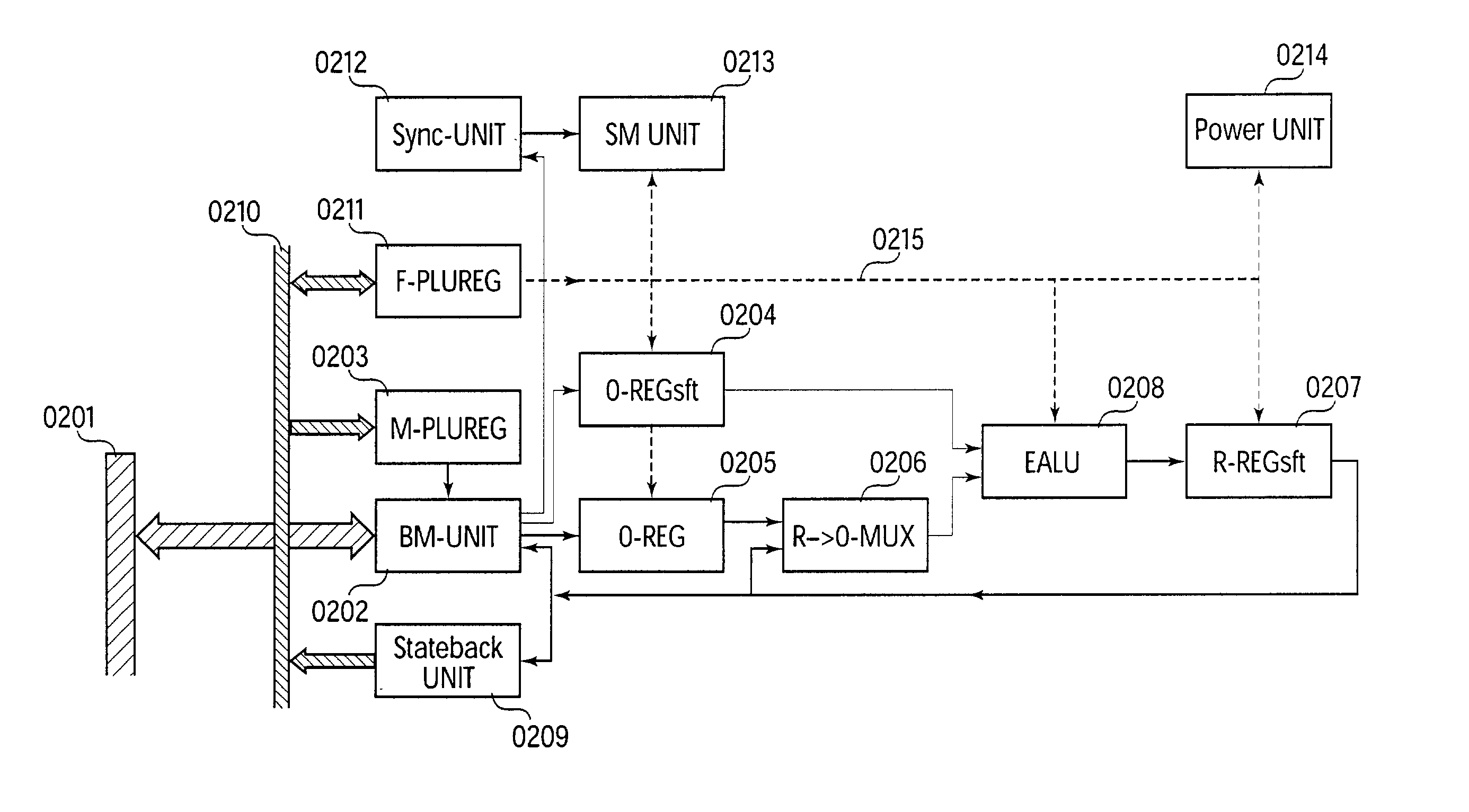

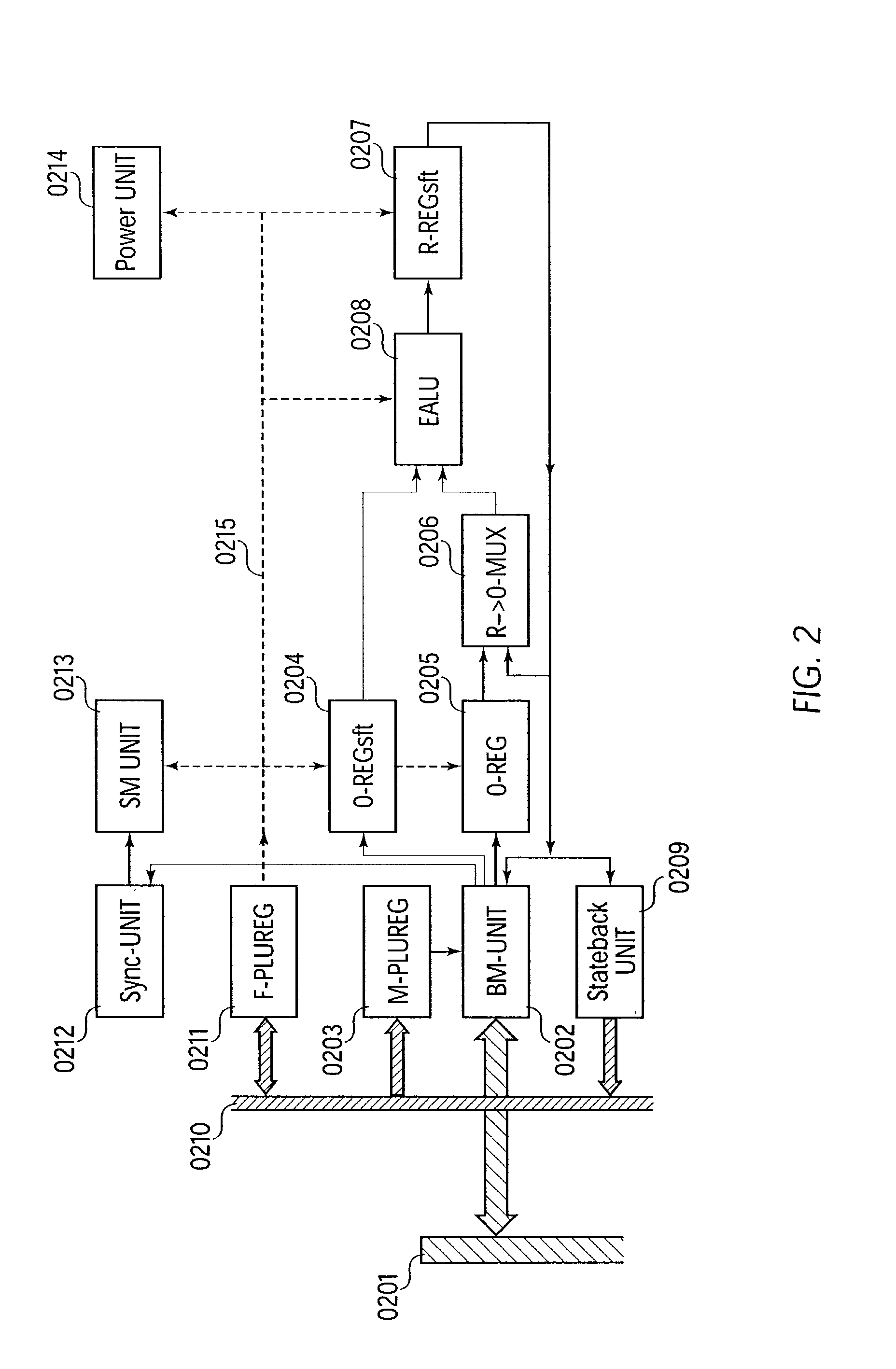

Unit for processing numeric and logic operations for use in central processing units (CPUS), multiprocessor systems, data-flow processors (DSPS), systolic processors and field programmable gate arrays (FPGAS)

InactiveUS20030056085A1The process is convenient and fastSimplifies (re)configurationEnergy efficient ICTMultiple digital computer combinationsBus masteringBroadcasting

An expanded arithmetic and logic unit (EALU) with special extra functions is integrated into a configurable unit for performing data processing operations. The EALU is configured by a function register, which greatly reduces the volume of data required for configuration. The cell can be cascaded freely over a bus system, the EALU being decoupled from the bus system over input and output registers. The output registers are connected to the input of the EALU to permit serial operations. A bus control unit is responsible for the connection to the bus, which it connects according to the bus register. The unit is designed so that distribution of data to multiple receivers (broadcasting) is possible. A synchronization circuit controls the data exchange between multiple cells over the bus system. The EALU, the synchronization circuit, the bus control unit, and registers are designed so that a cell can be reconfigured on site independently of the cells surrounding it. A power-saving mode which shuts down the cell can be configured through the function register; clock rate dividers which reduce the working frequency can also be set.

Owner:PACT +1

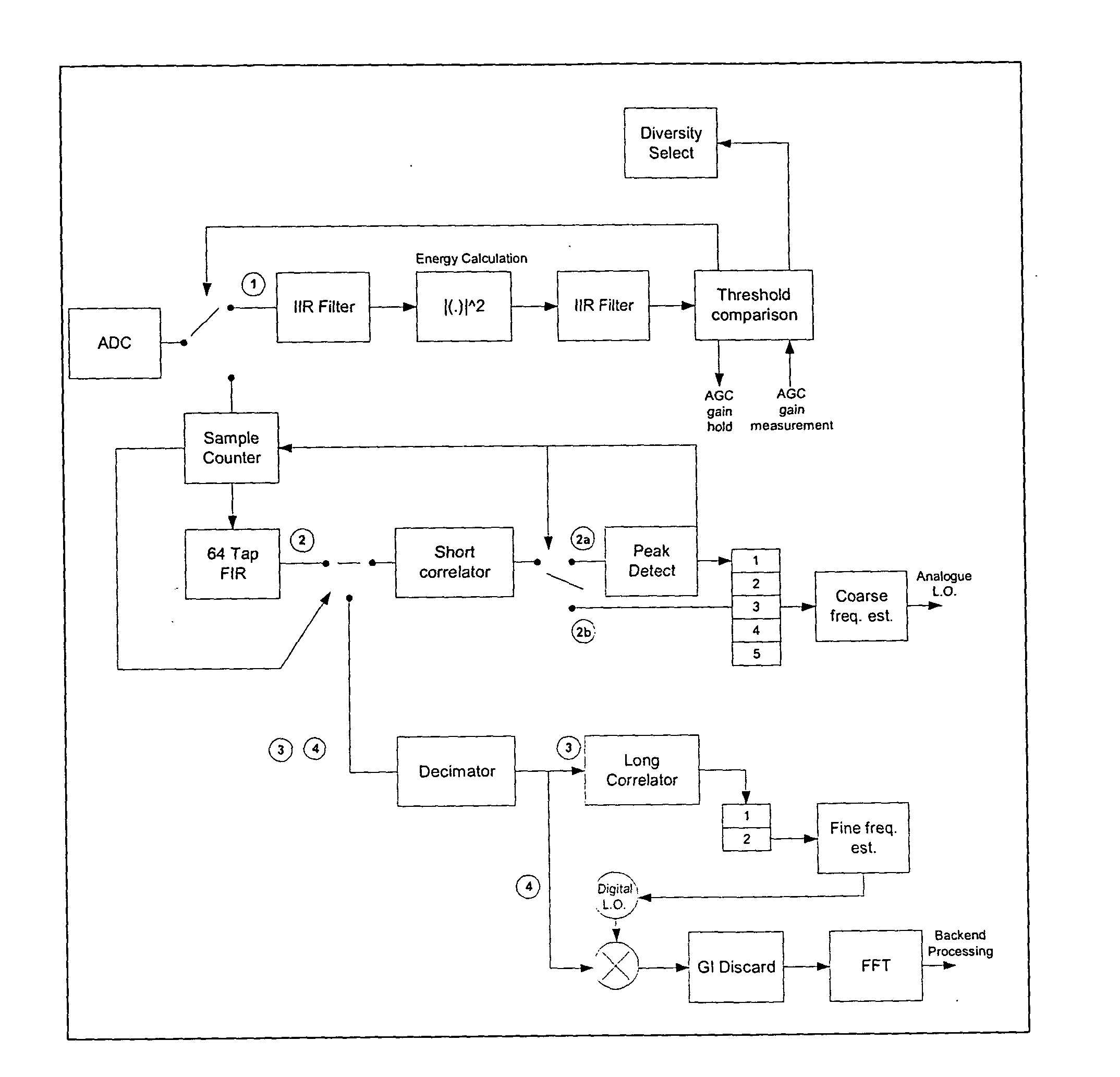

Method for amplitude insensitive packet detection

ActiveUS20050058227A1High outputEasy to detectAmplitude-modulated carrier systemsSynchronisation signal speed/phase controlPhase correlationComputer science

The invention relates generally to the field of wireless communications and more particularly to a method of and device for detecting the presence of a received data packet in a digital receiver. The present invention proposes a simplified method of correlation by removing dependency on the amplitude fluctuations while at the same time maintaining phase relevancy. The key advancement involves mapping the complex quadrature amplitude modulation (QAM) preamble to a quantized phase shift keying (PSK) constellation before application to a matched complex correlator. The proposed process essentially “amplitude normalizes” the input signal without the use or complexity associated with a divider. This simplified normalization scheme makes the packet detection algorithm robust against amplitude variations in the input signal, while still allowing for good correlation output. In applications where interference is superimposed on the I / Q input signals, the invention improves the detection capability over automatic gain control (AGC) normalization methods.

Owner:ZARBANA DIGITAL FUND

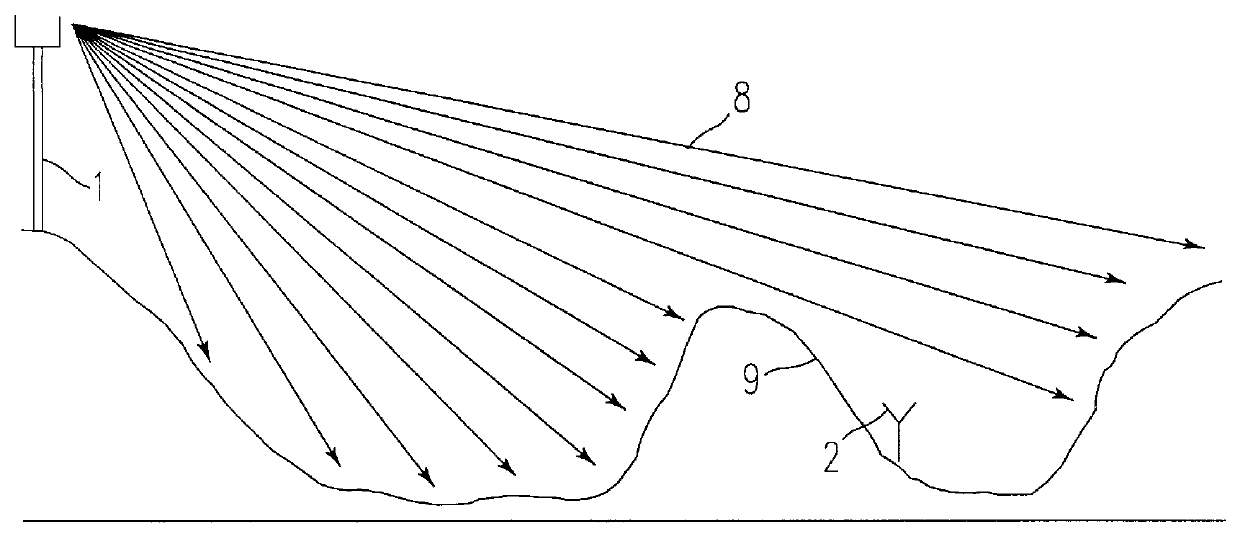

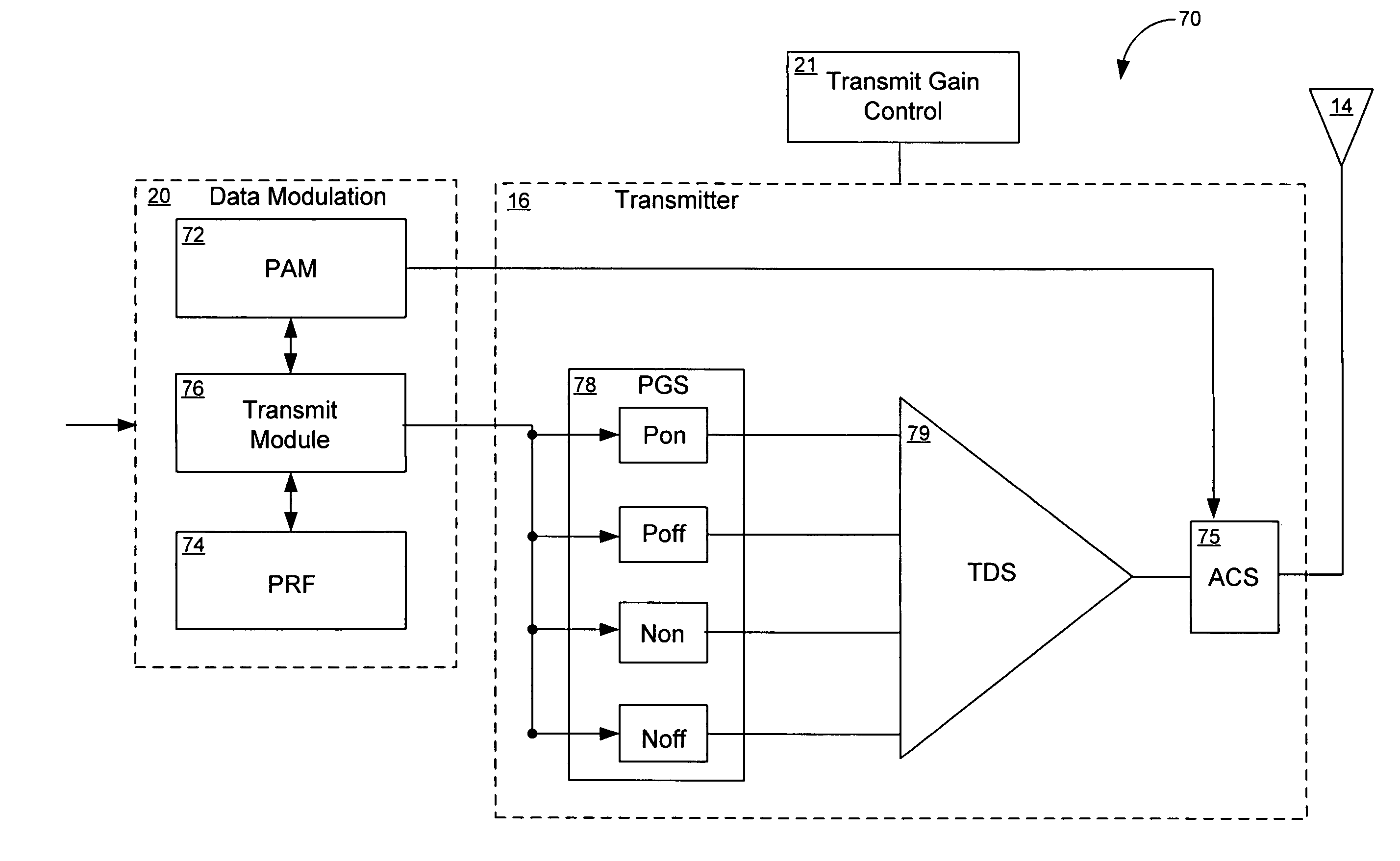

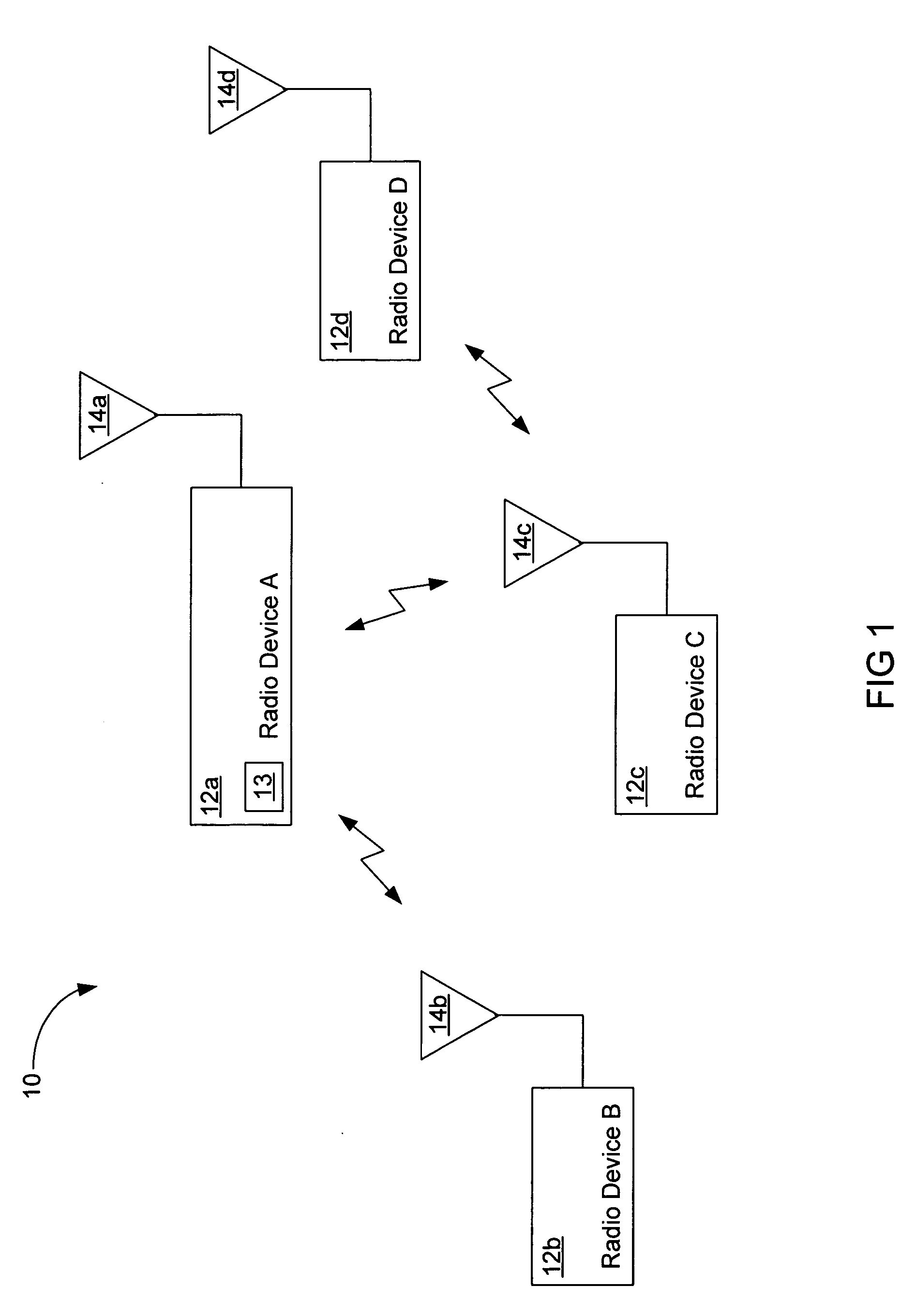

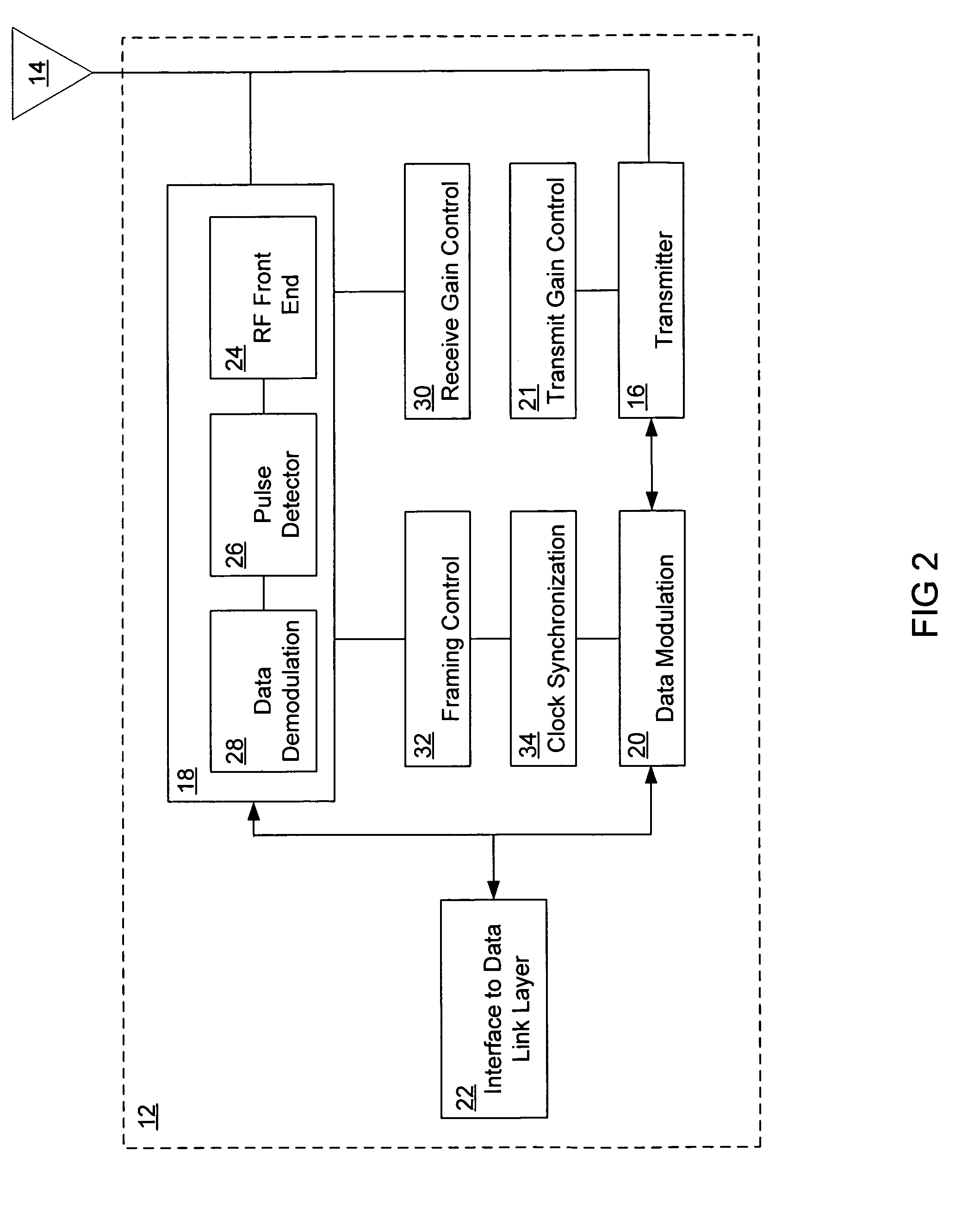

Ultra wide band transmitter

InactiveUS6952456B1Reduced clock speedMultiple modulation transmitter/receiver arrangementsAngle to amplitude modulation conversionMultiplexerSubject matter

A transmitter system is provided. In one embodiment, the transmitter system includes a data modulation unit, which generates a stream of data that is synchronized with a master clock. The transmitter system additionally includes a transmitter that transmits the stream of synchronized data by way of an attached antenna. In another embodiment the transmitter system includes a Medium Access Control (MAC) layer that includes a clock synchronization device, a frequency divider, a slot allocation unit, and a multiplexer / demultiplexer. This Abstract is provided for the sole purpose of complying with the Abstract requirement rules that allow a reader to quickly ascertain the subject matter of the disclosure contained herein. This Abstract is submitted with the explicit understanding that it will not be used to interpret or to limit the scope or the meaning of the claims.

Owner:INTELLECTUAL VENTURES HLDG 73

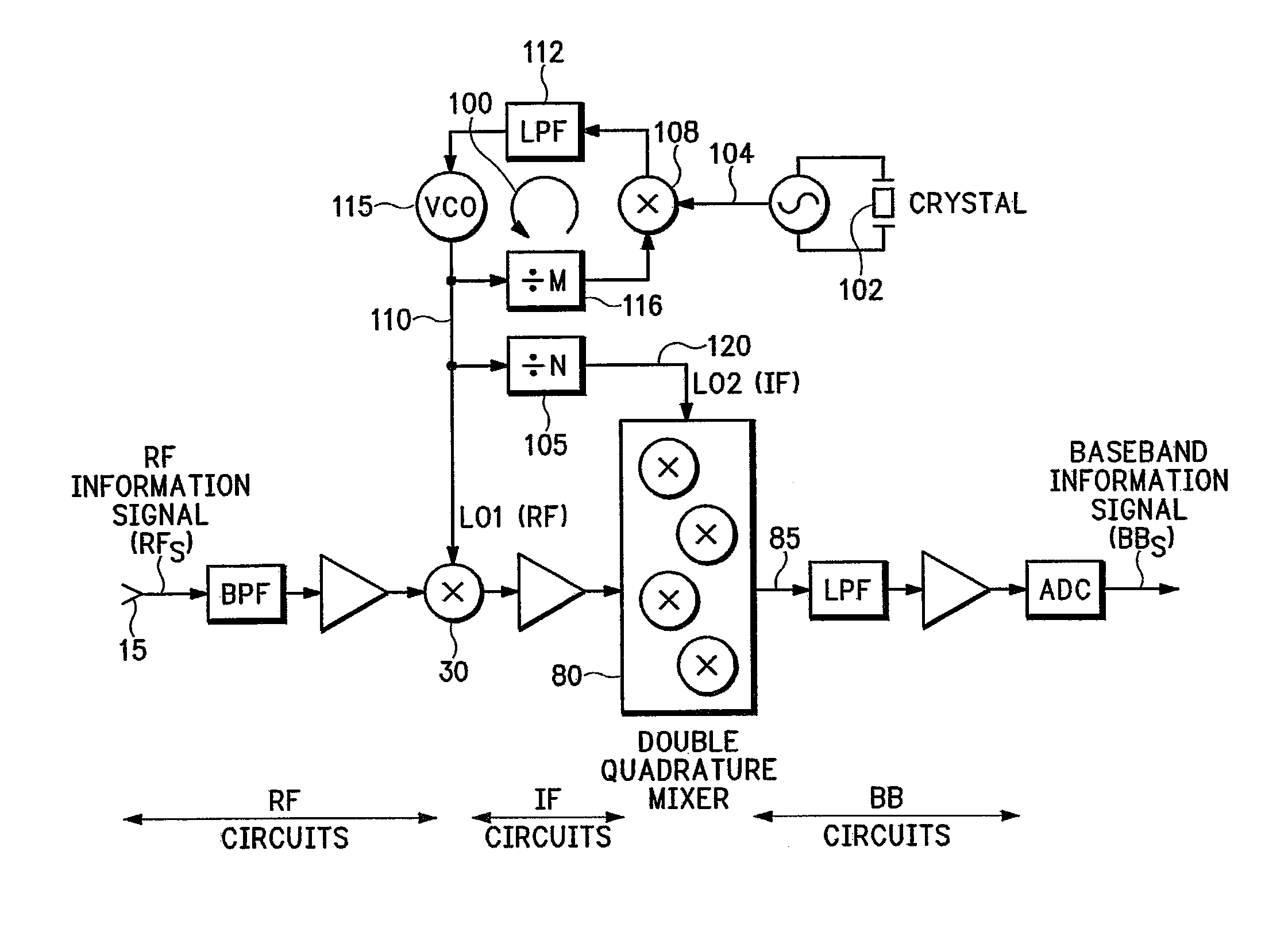

Up/down conversion circuitry for radio transceiver

ActiveUS7194044B2Resonant long antennasAmplitude-modulated carrier systemsEngineeringQuadrature mixer

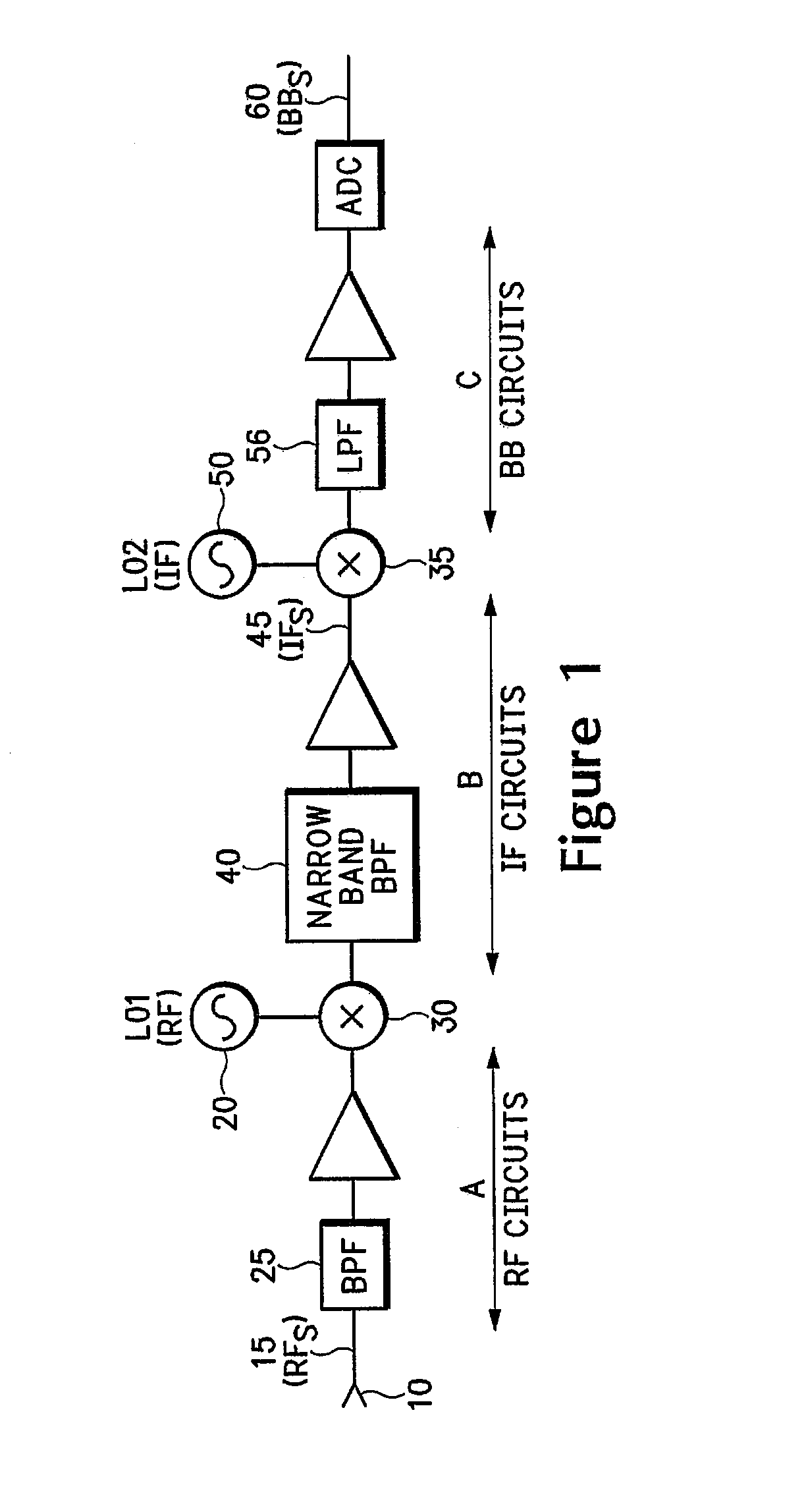

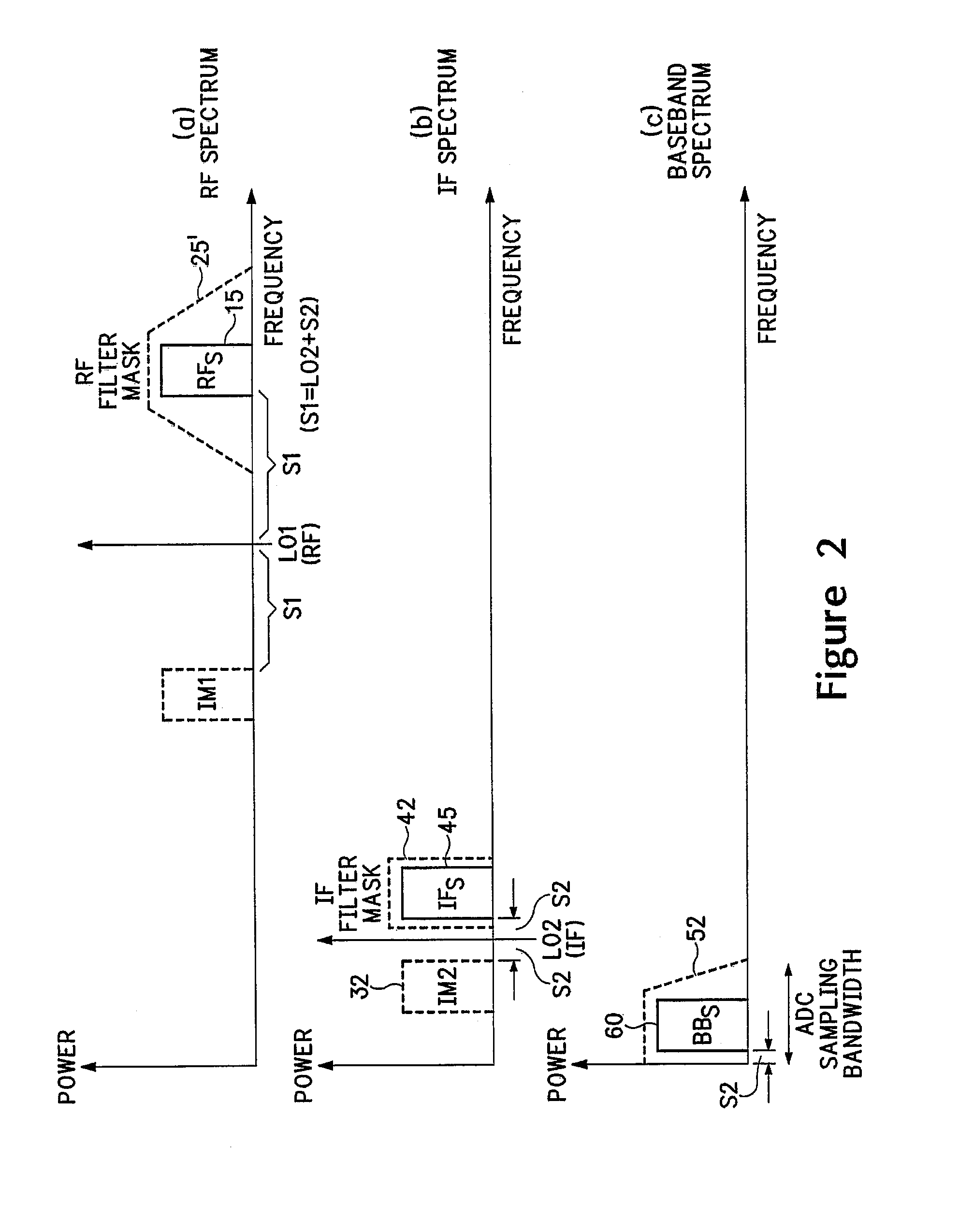

A multi-channel RF receiver uses an image rejection mixer (e.g. double quadrature mixer) in the IF down conversion stage for image side band rejection (whereby use of an IF narrow band filter for image rejection may be omitted if desired) and comprises a simplified frequency synthesizer which generates both a “wandering” IF oscillator frequency and an RF oscillator frequency for the up / down conversion stages (being, for down conversion, from RF to IF and from IF to base band. The IF used for a particular RF carrier (channel) is selected so as to be both an integer (N) sub-harmonic of that RF carrier and within the operating frequency band of the image rejection mixer. Advantageously, the synthesizer comprises only one loop and one VCO, wherein the IF oscillator signal is produced from the RF oscillator signal by means of a frequency divider.

Owner:ZARBANA DIGITAL FUND

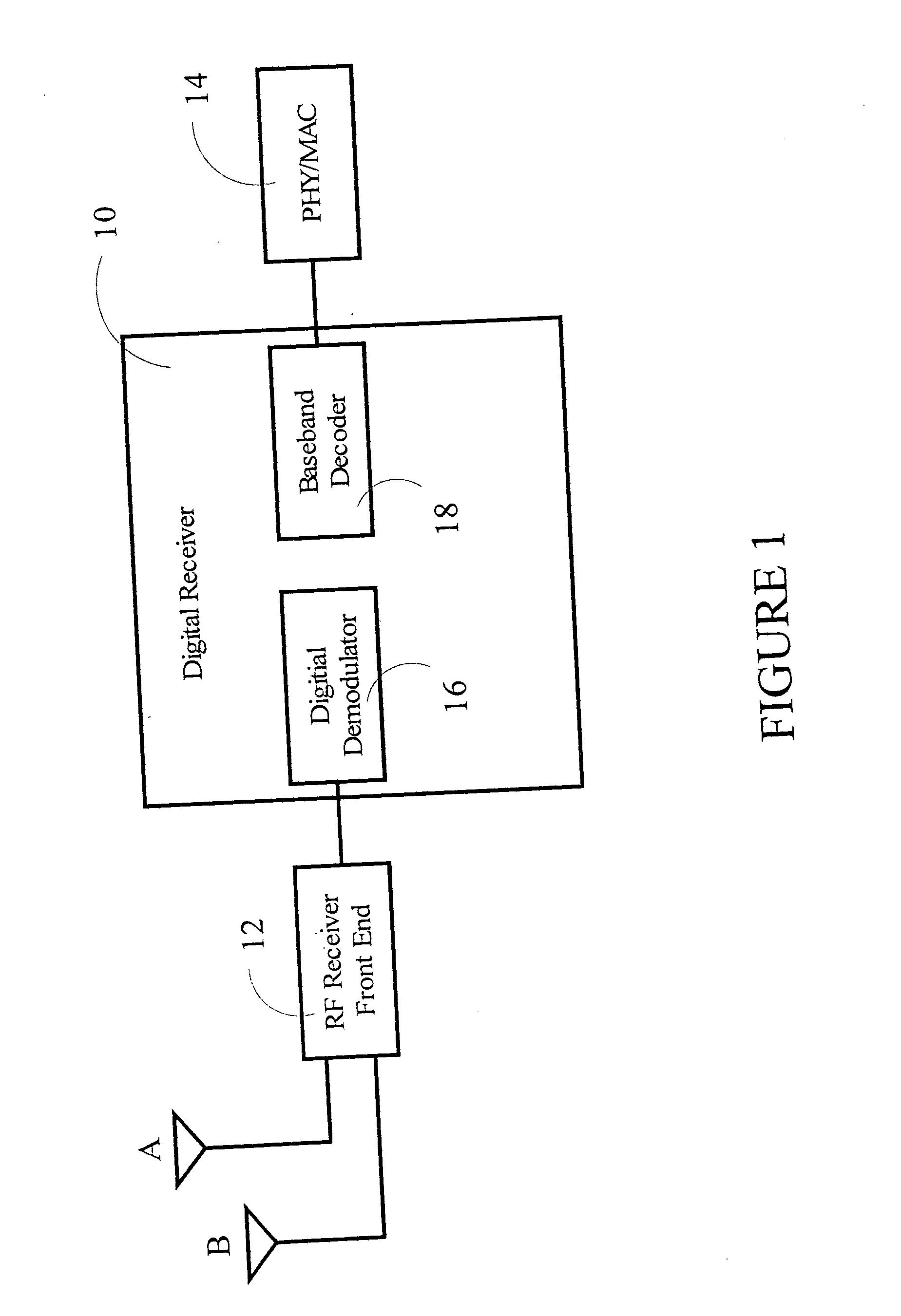

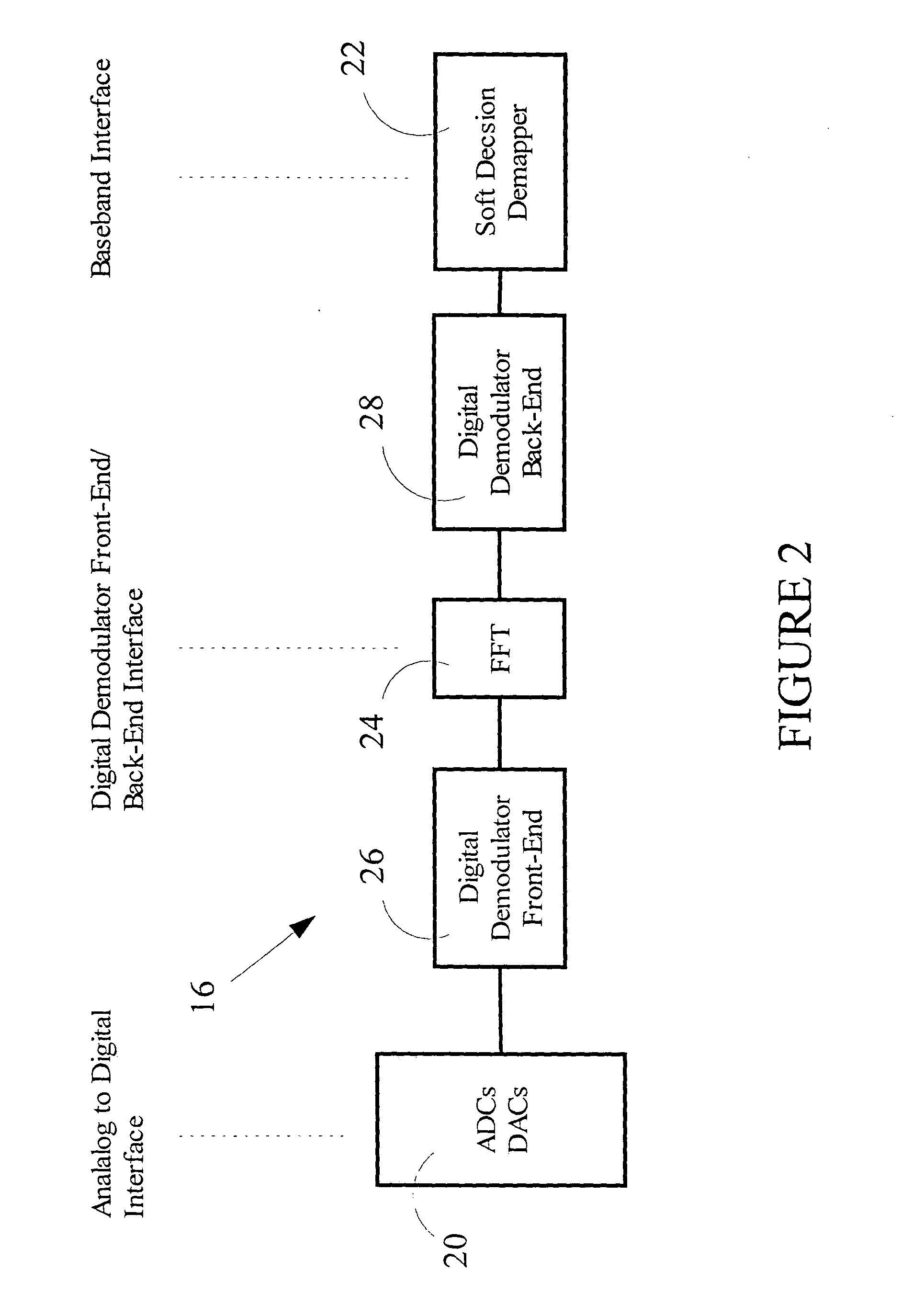

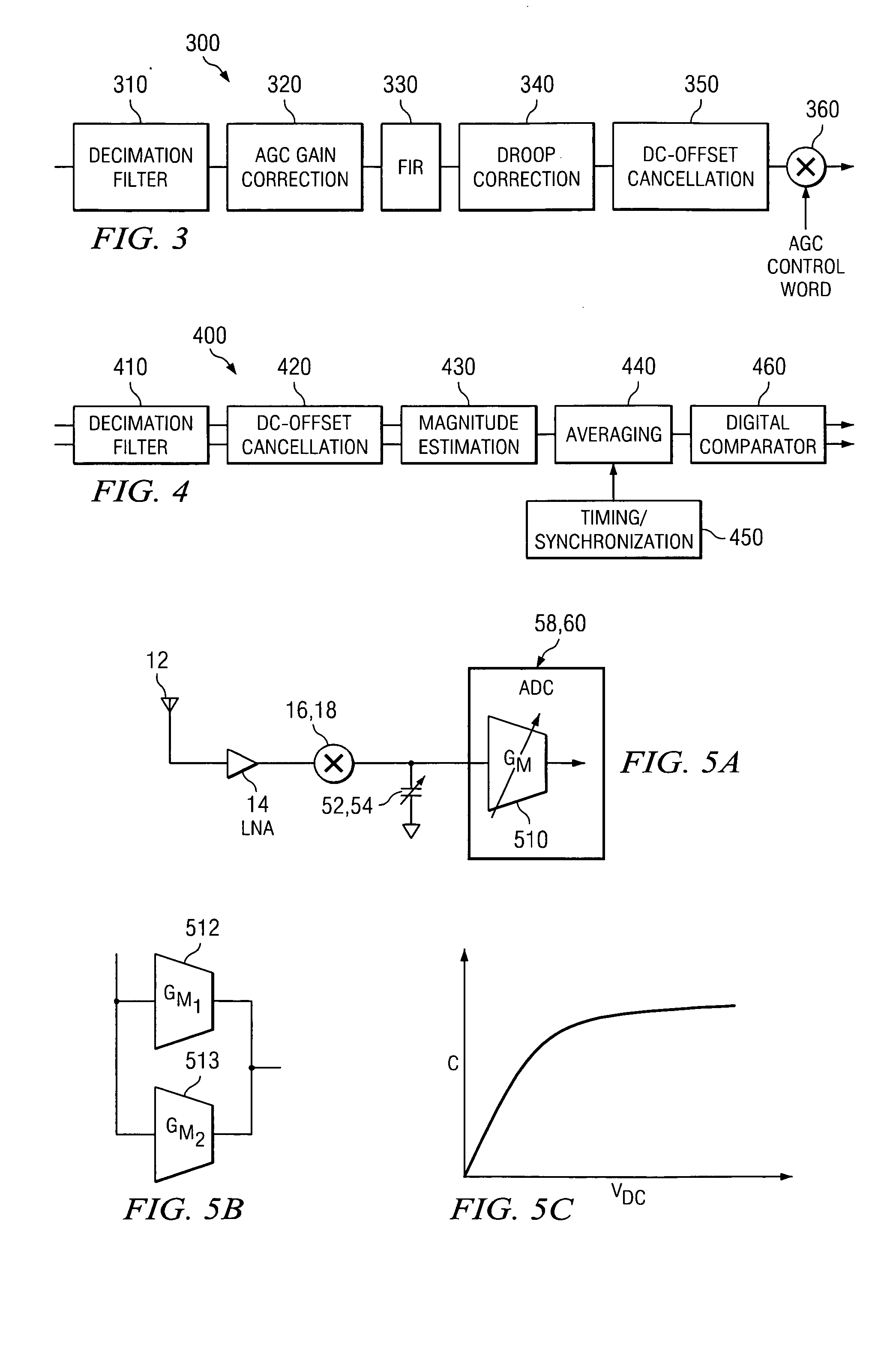

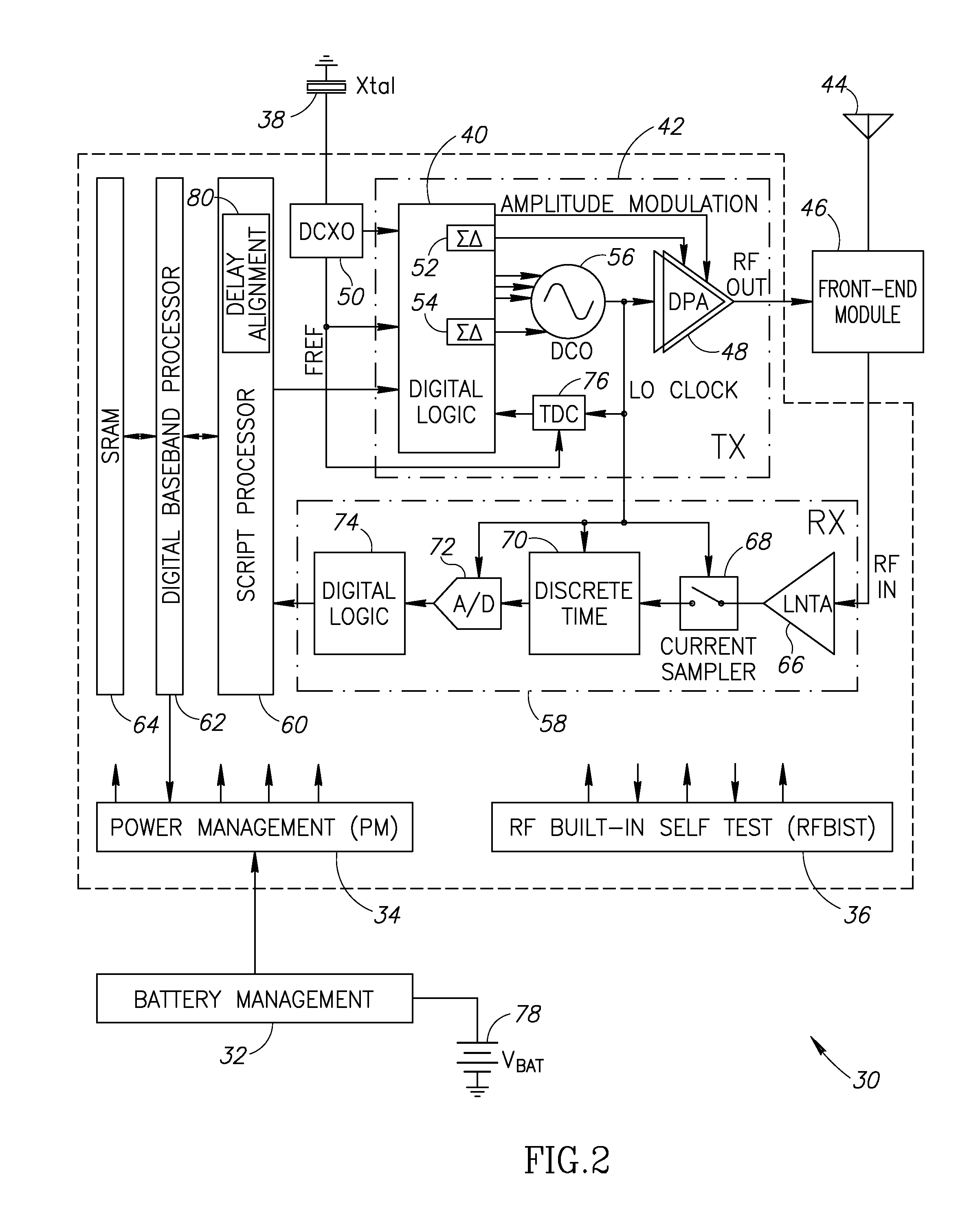

System and method for digital radio receiver

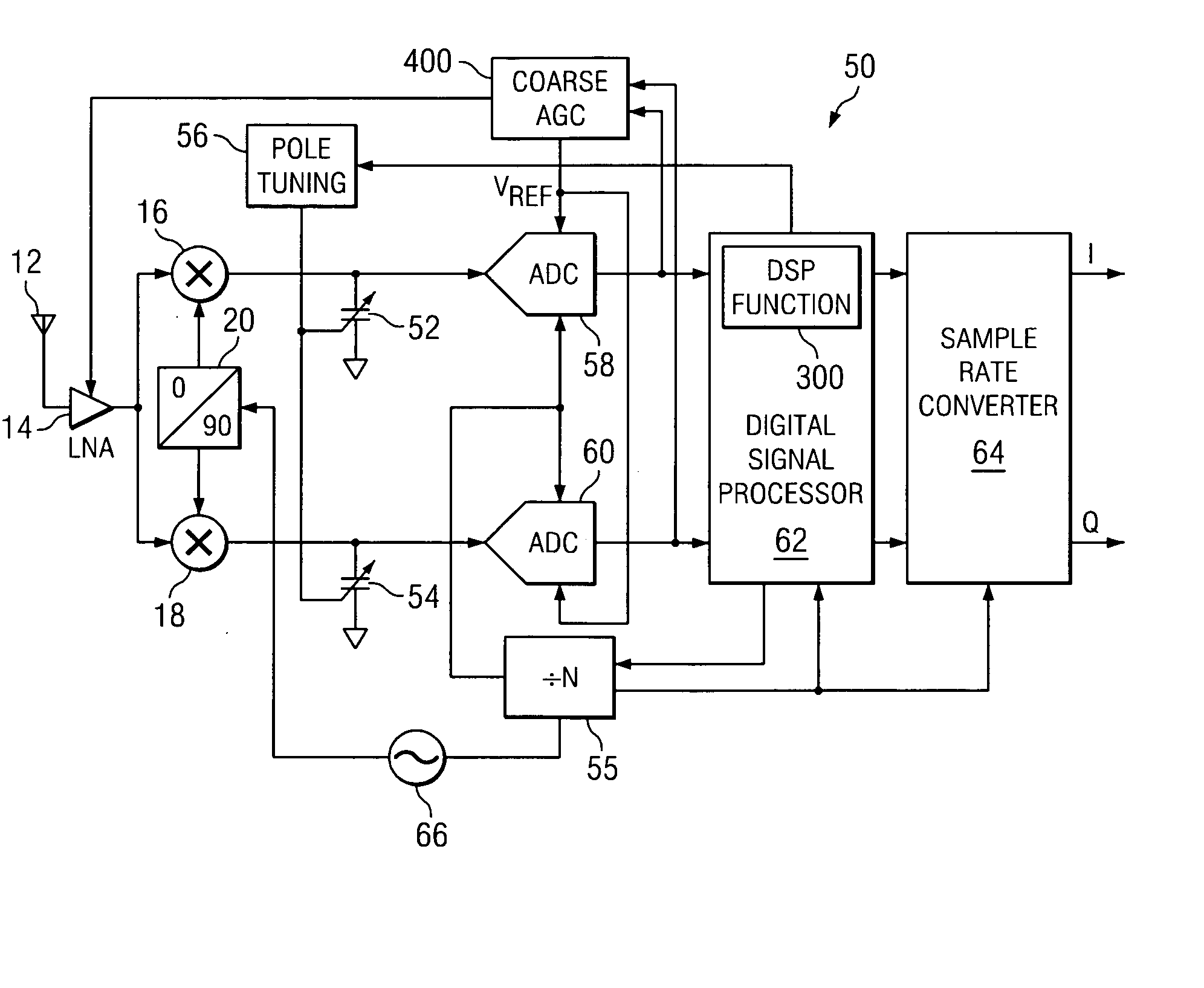

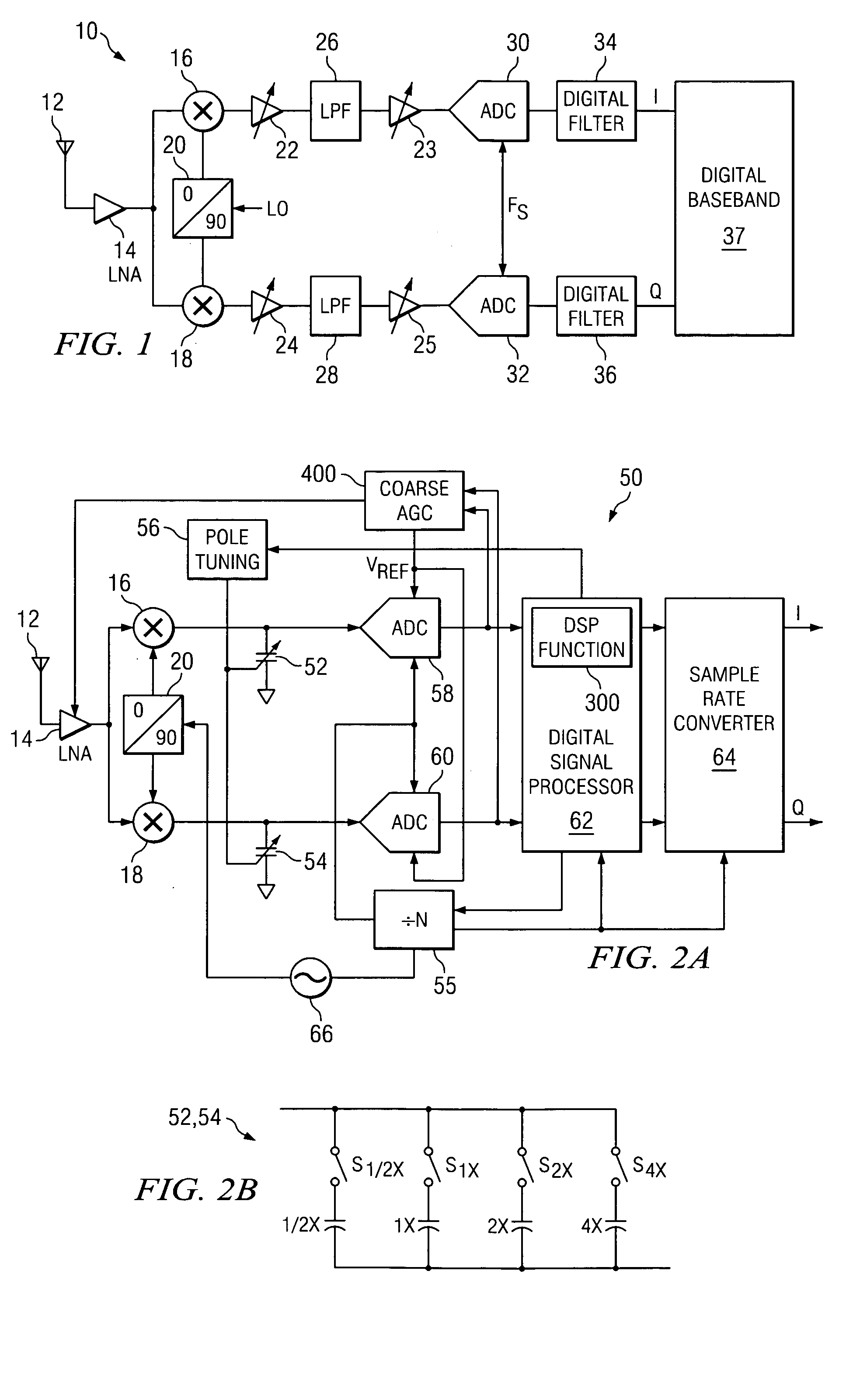

ActiveUS20050070325A1Reduce the sampling frequencySubstation equipmentRadio transmissionCommunications systemDigital radio

A communications system comprising a processor, a variable oscillator, a radio frequency (RF) quadrature demodulator, a variable capacitor, a continuous-time, sigma-delta analog-to-digital converter (ADC), and a frequency divider, all integrated on a single semiconductor chip. The ADC samples the RF quadrature demodulator output. The processor sets the communications system frequency by controlling the oscillator, the frequency divider and the variable capacitor.

Owner:TEXAS INSTR INC

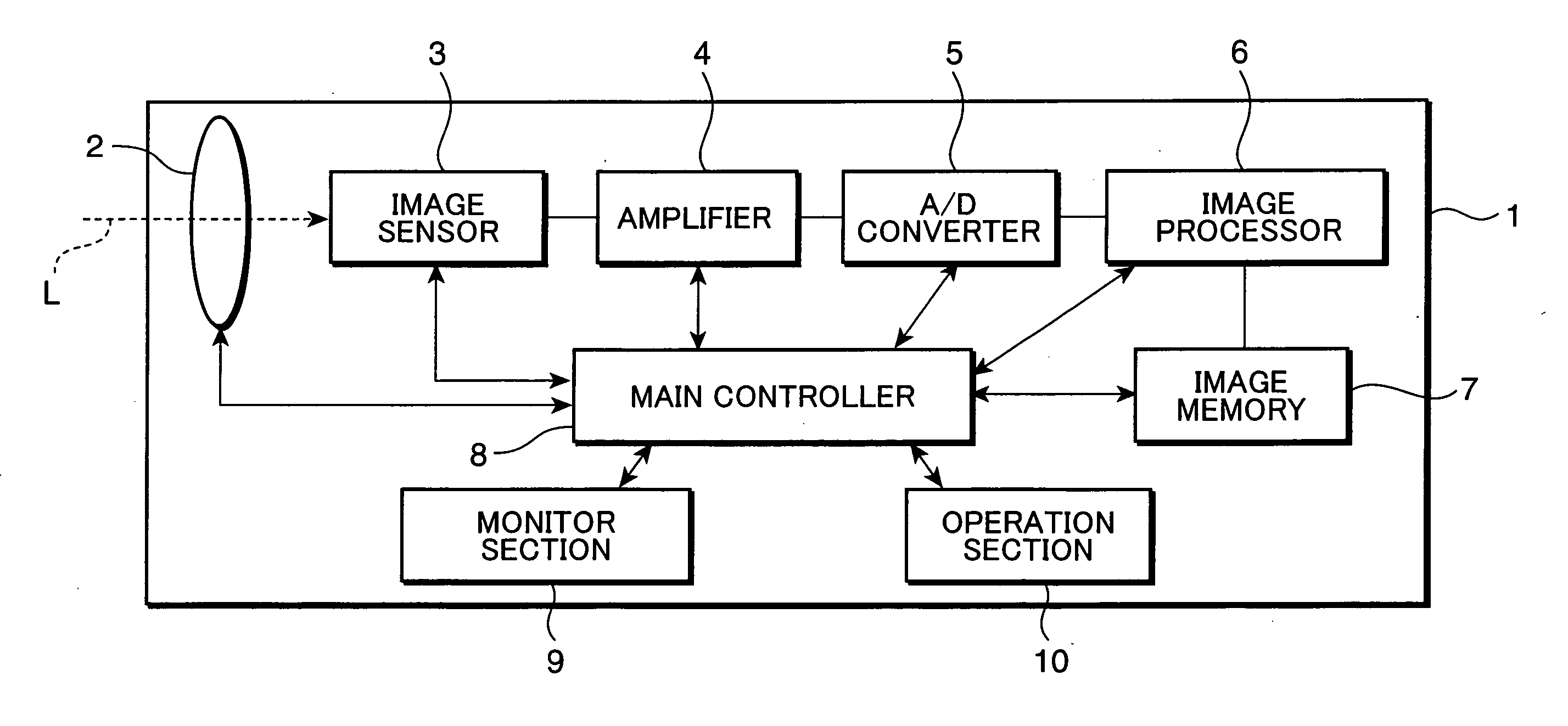

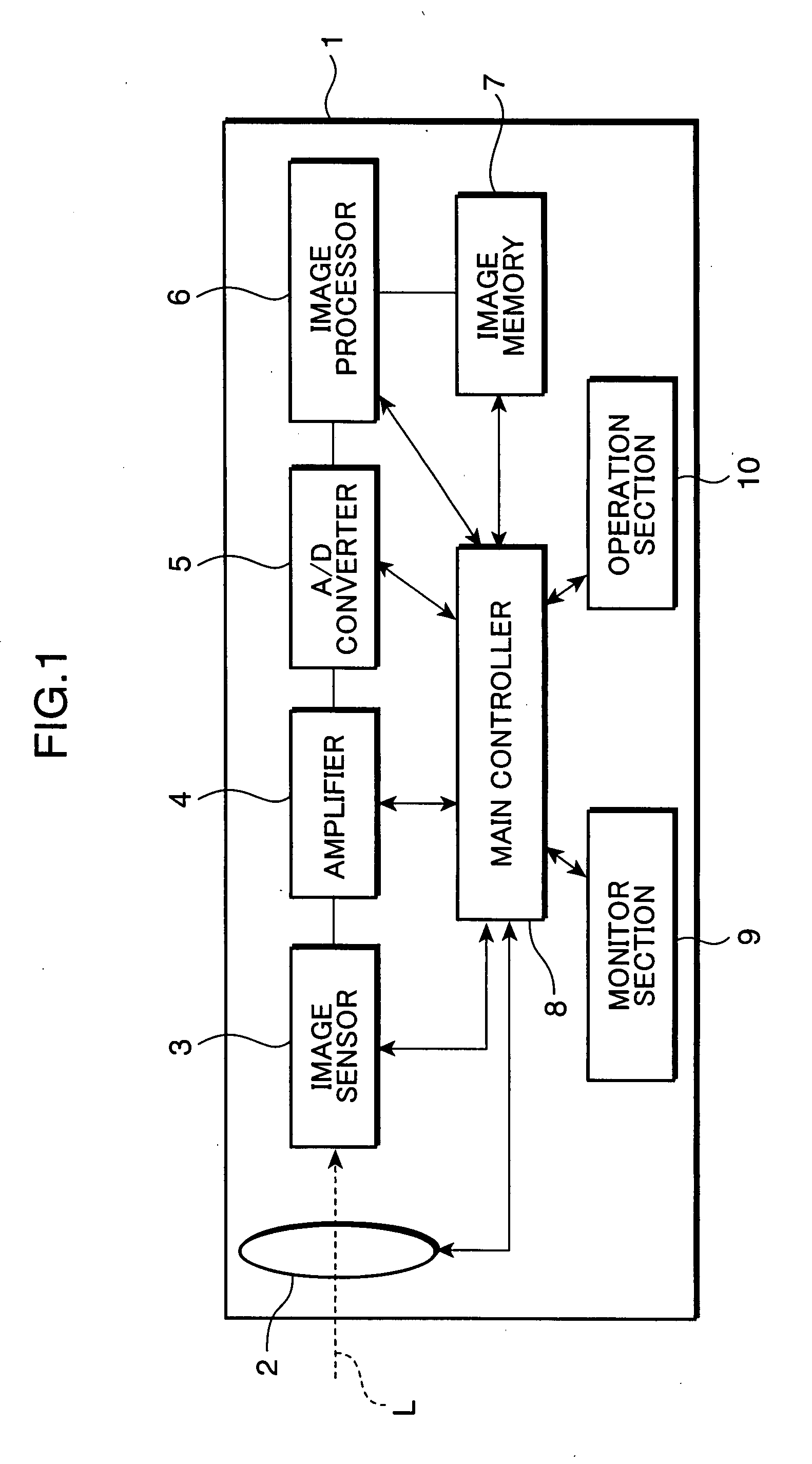

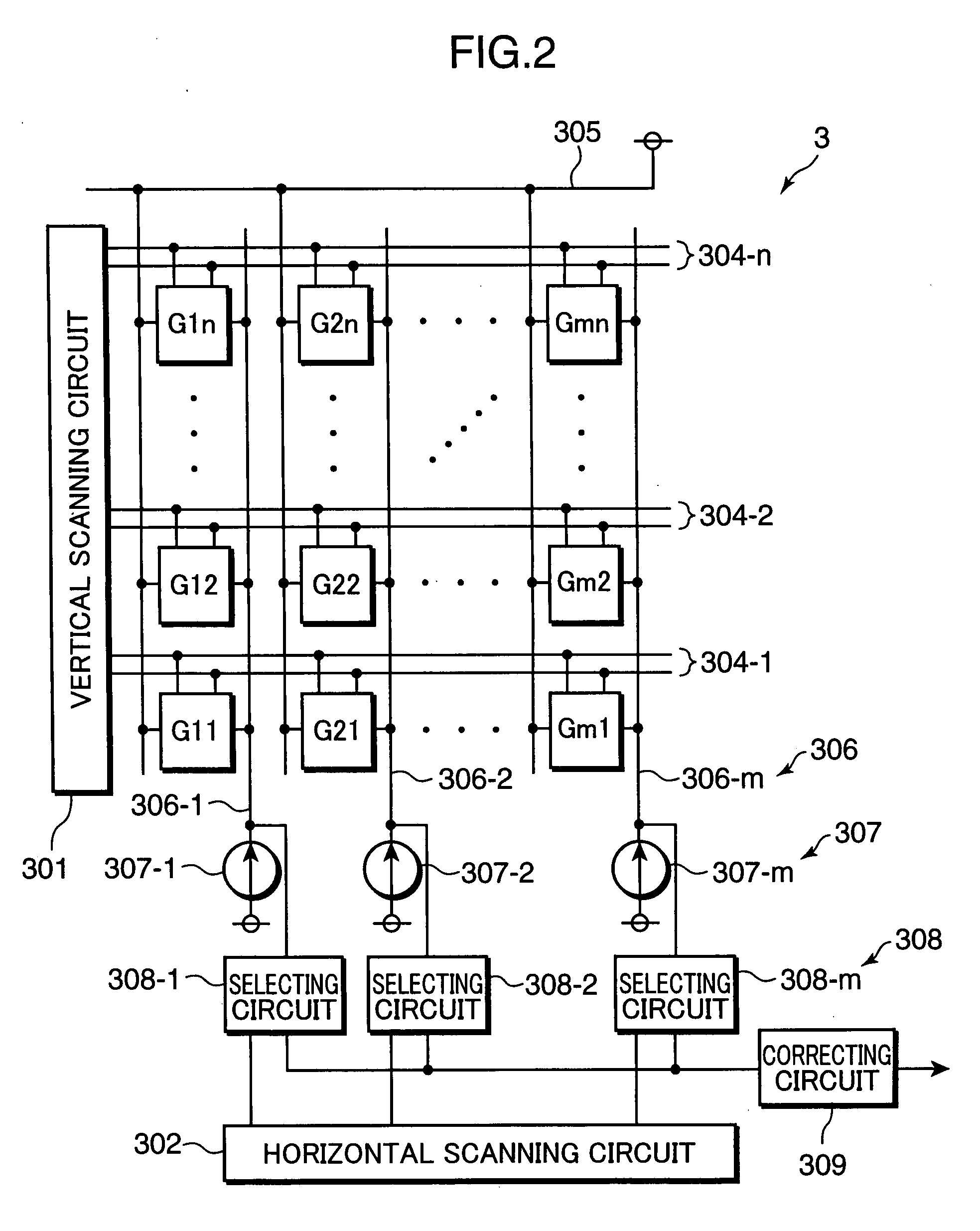

Image processing device, image processing method, and image sensing apparatus

ActiveUS20080122953A1Good removal effectLess and influenceImage enhancementTelevision system detailsImaging processingFrequency synthesizer

An image processing device includes: a frequency divider for performing a frequency division processing of dividing an input image into a plurality of frequency components each having a frequency band; a noise remover for performing a noise component removal processing of removing a noise component from a high frequency component in the frequency components each having the frequency band obtained by the frequency division processing by the frequency divider; an edge preservation information calculator for detecting an edge intensity based on a low frequency component in the frequency components each having the frequency band obtained by the frequency division processing by the frequency divider, and calculating edge preservation information relating to a degree of preserving an edge component based on the detected edge intensity; an edge preserving section for preserving the edge component in the high frequency component, based on the edge preservation information calculated by the edge preservation information calculator; and a frequency synthesizer for synthesizing the high frequency component whose noise component is removed by the noise remover and whose edge component is preserved by the edge preserving section, and the low frequency component, in each of the frequency bands.

Owner:KONICA MINOLTA INC

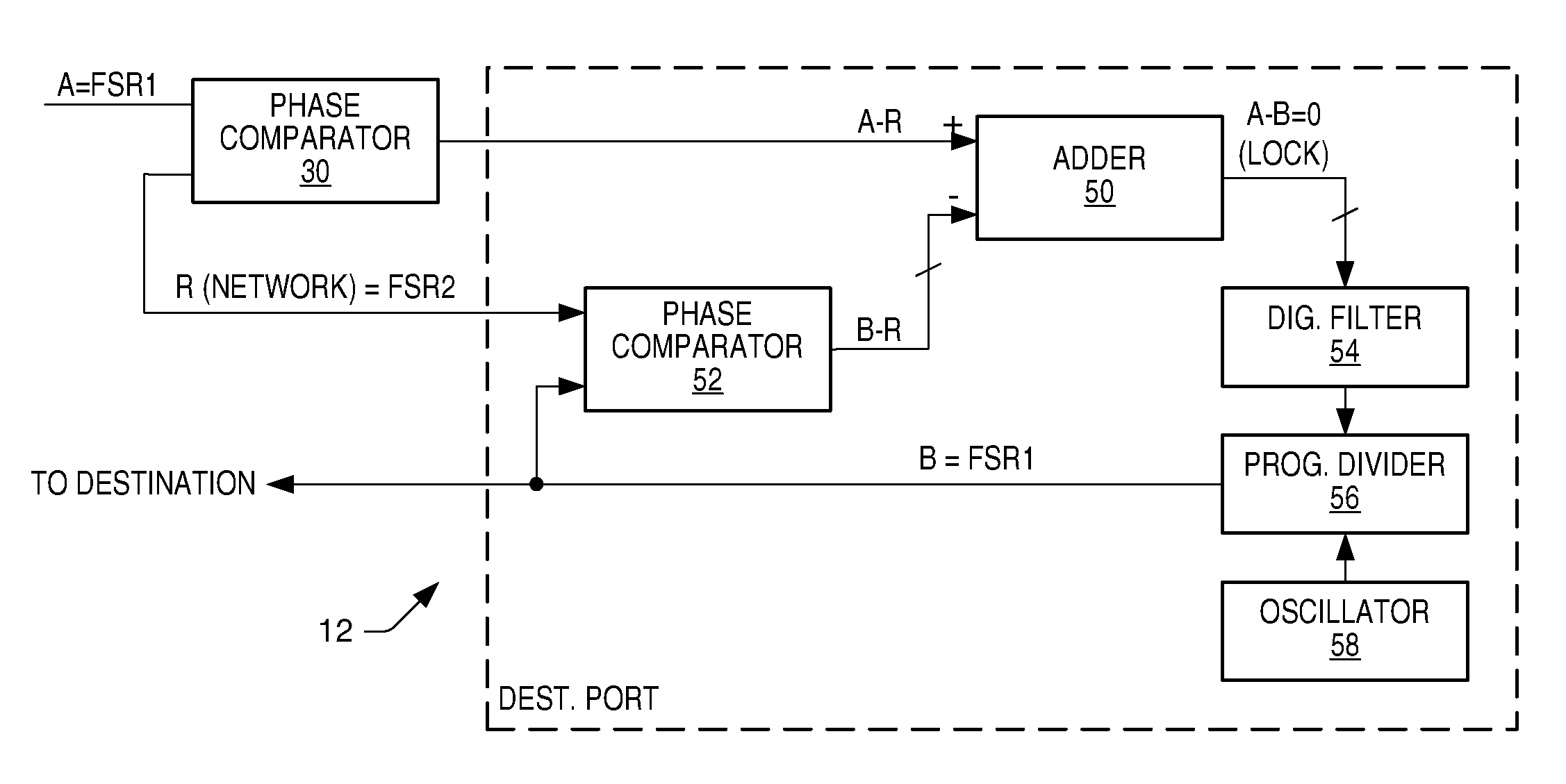

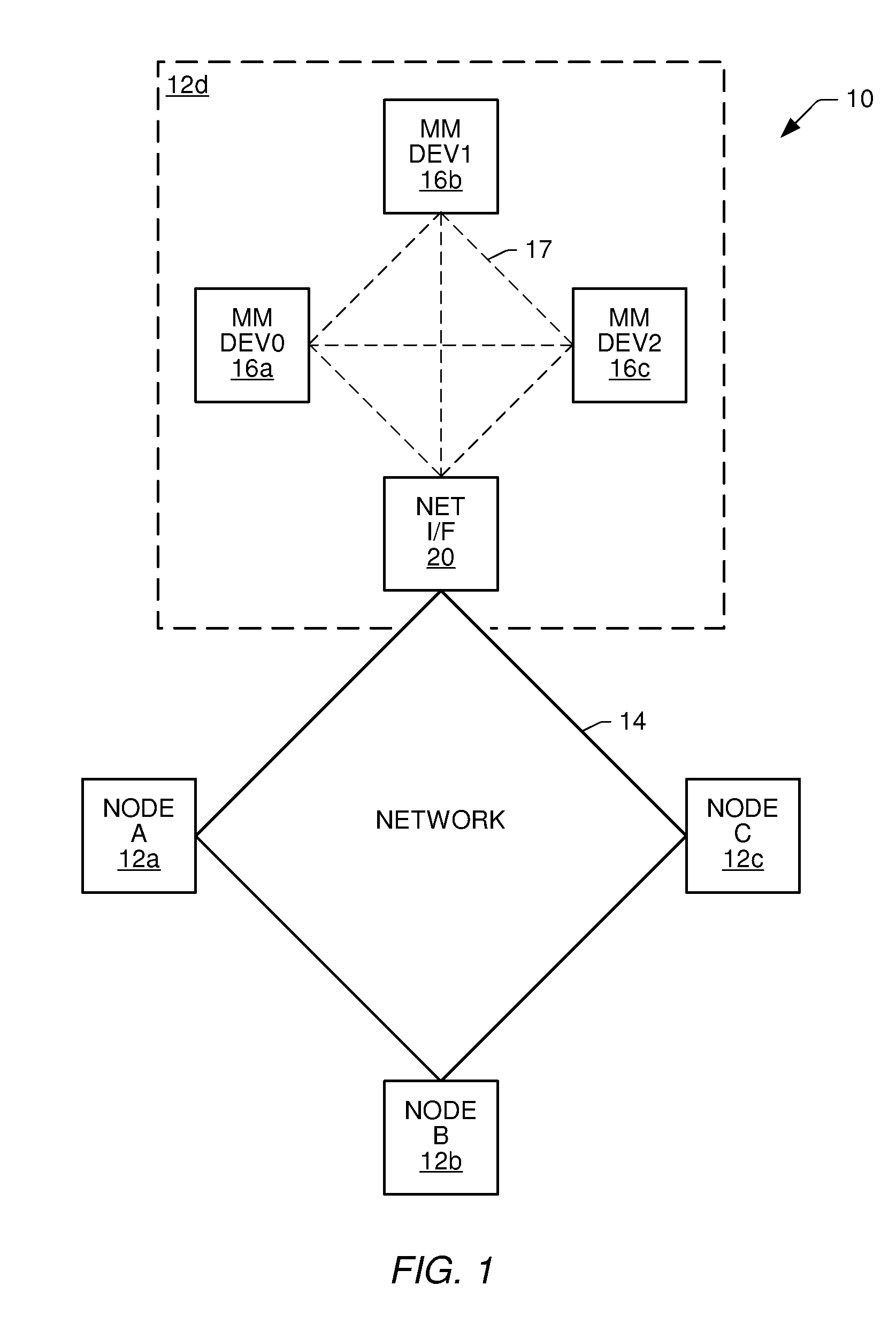

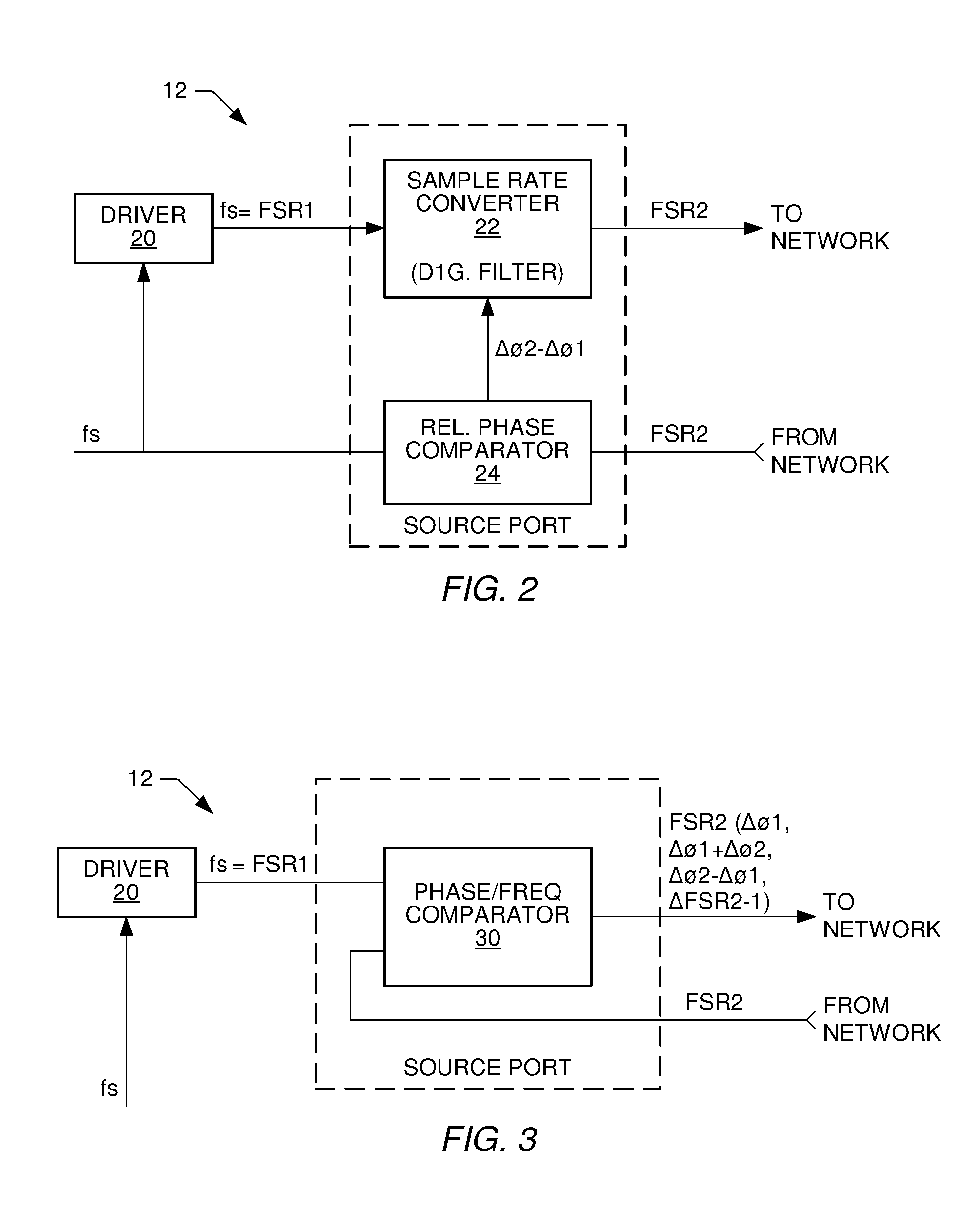

Communication system and method for sample rate converting data onto or from a network using a high speed frequency comparison technique

ActiveUS7106224B2High resolutionImprove accuracyTime-division multiplexIndividual digits conversionSample rate conversionPhase difference

A communication system, source and destination ports of the communication system, and methodology is provided for transporting data in one of possibly three different ways. Data is transported across the network at a frame sample rate that can be the same as or different from the sample rate or master clock within the source port or the destination port. If the sample rate of the source port is known, the sample rate of the destination port can be created using a PLL within the destination port and simply employing a phase comparator in the source port. The phase comparator forwards the phase or frequency difference of the network transfer rate and the source sample rate to the destination port, which then generates a local clock equivalent to the source which then compiles audio data being played at the same rate in which it was sampled at the source. Where economically feasible, sample rate conversion can be used at the source. However, sample rate conversion at the destination is preferred if the source sample rate is forwarded across the network relative to the frame transfer rate of the synchronous network. The sample rate converter simply produces a play rate from the transmitted information at the destination. Again, however, sample rate conversion compares relative phase difference changes similar to the phase difference compared in the digital PLL mode. As a further alternative, sample rates within the source and destination ports can be derived from the network frame rate using fractional dividers in the source and destination ports.

Owner:STANDRD MICROSYSTEMS CORPORATION

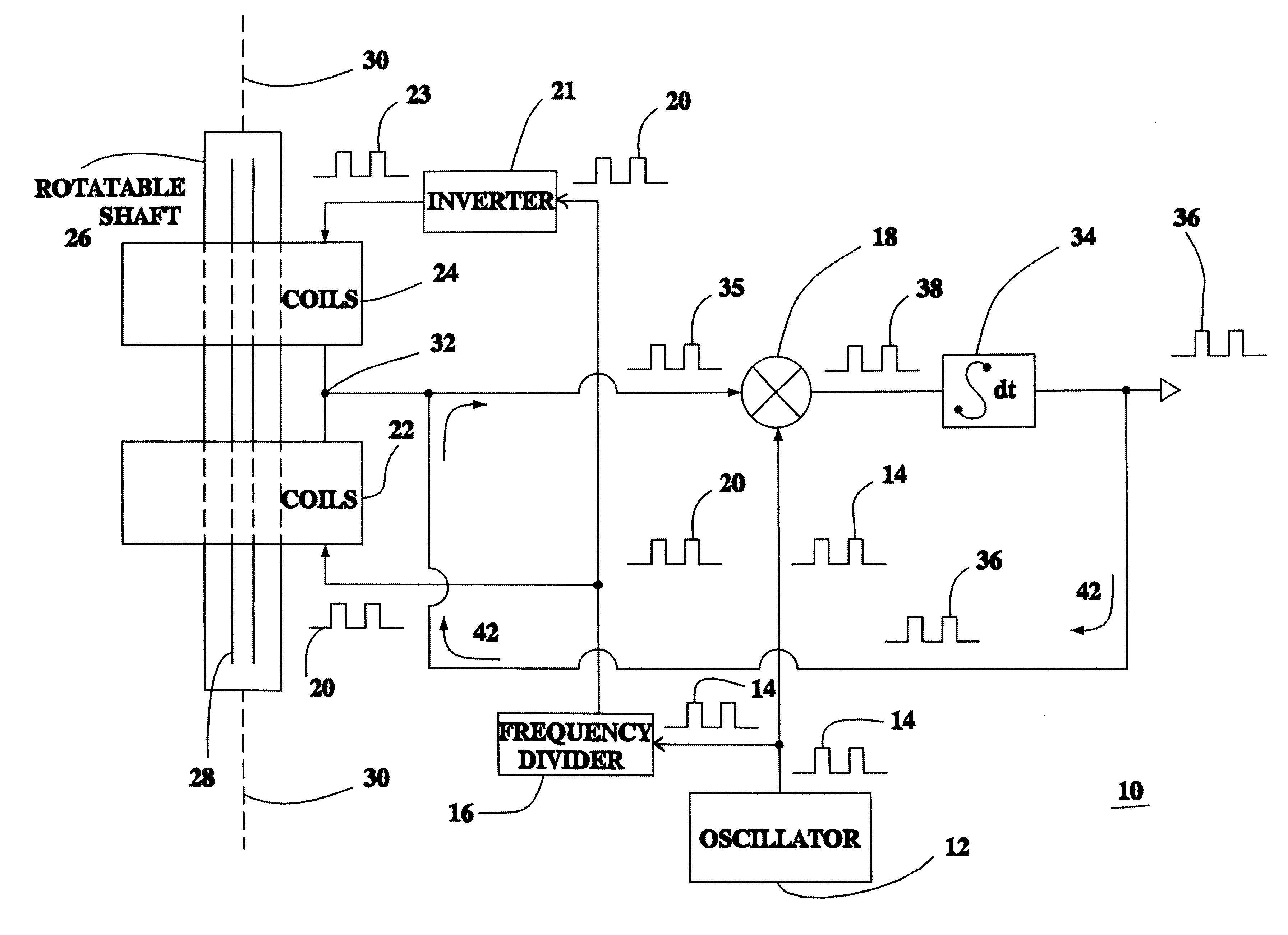

Magnetoelastic torque sensor

InactiveUS6698299B2Improve accuracyLow costOptical rangefindersWork measurementIntegratorMagnetic wires

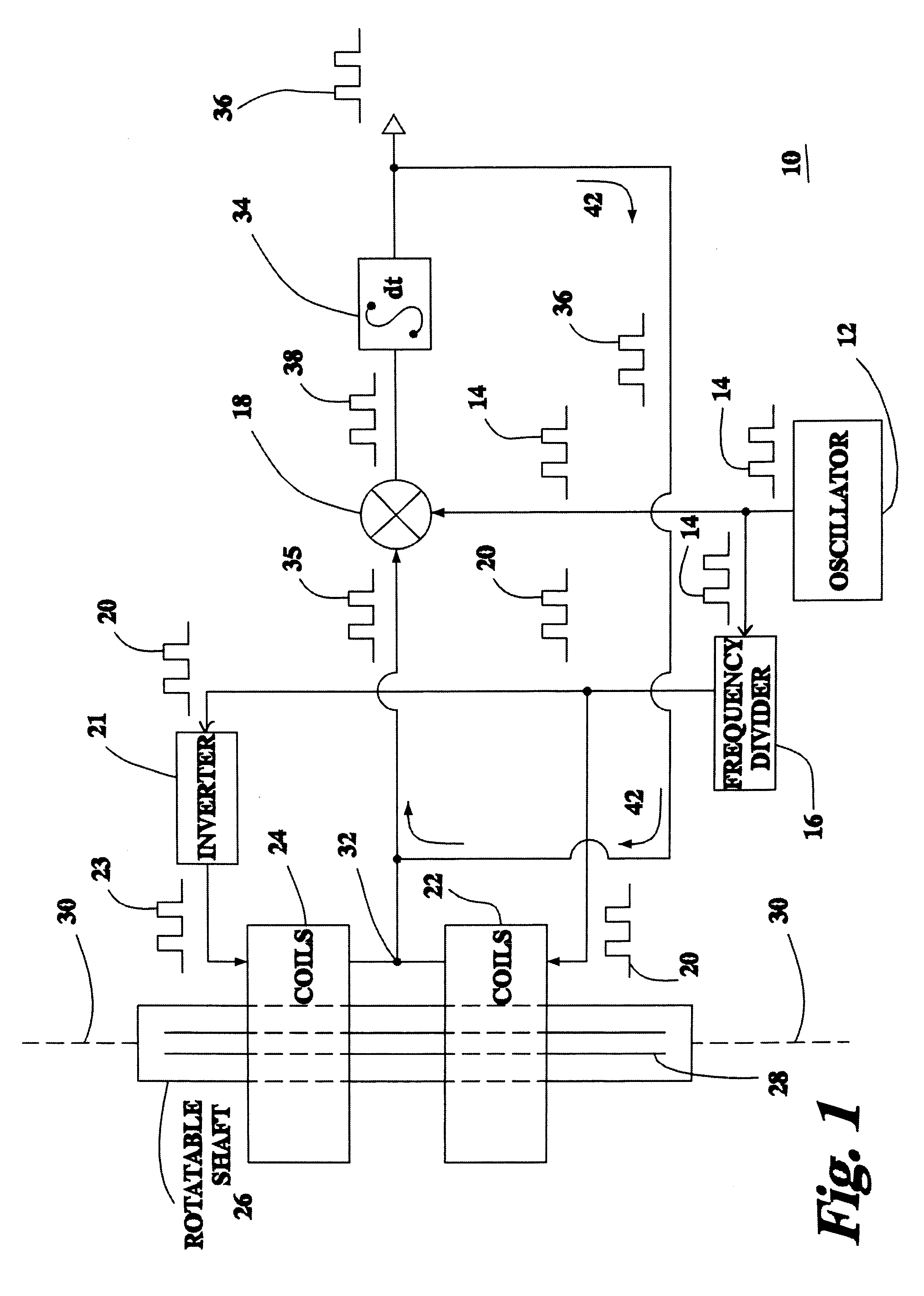

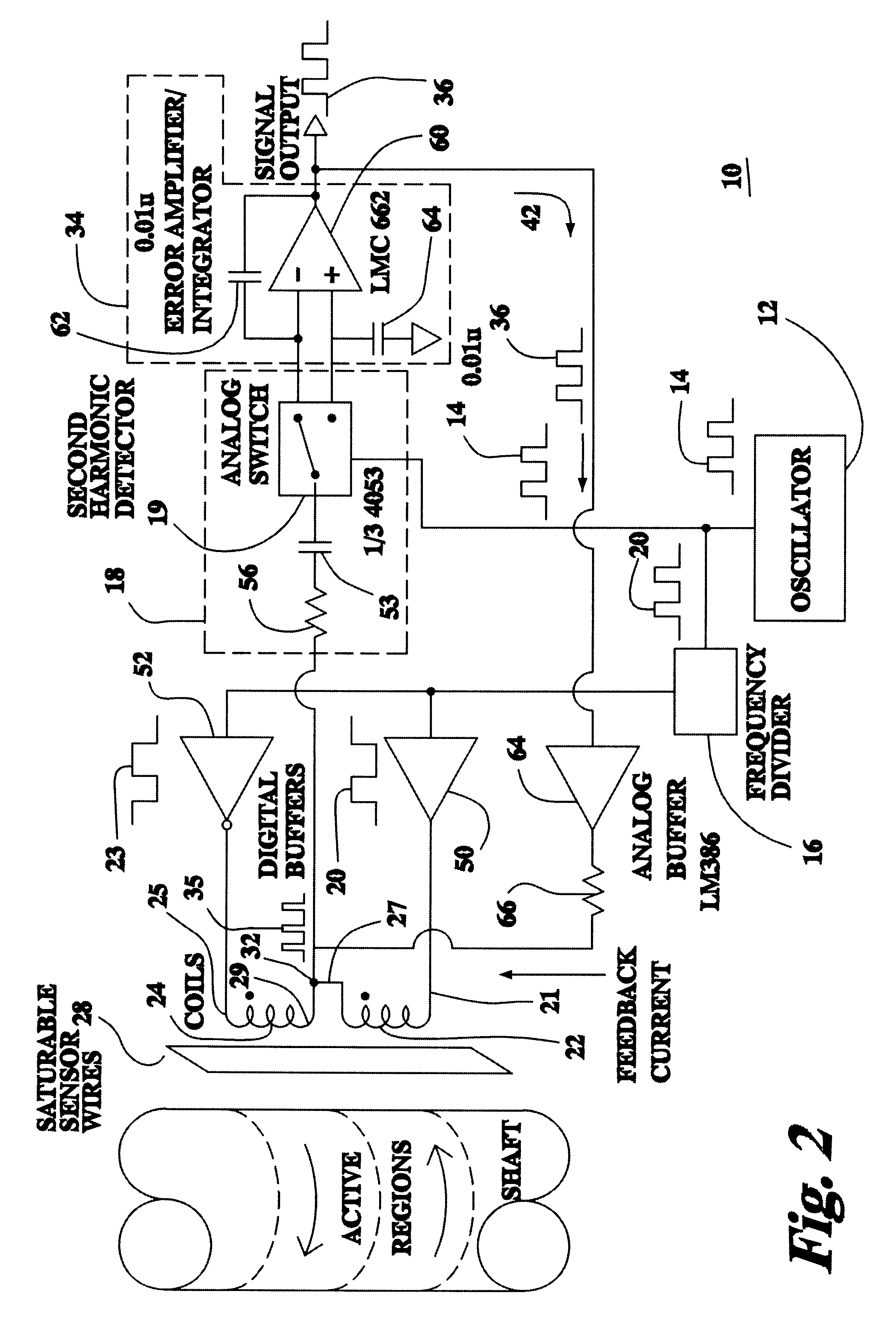

A flux-gate magnetometer torque sensor is provided having a rotatable shaft to which a torque force is to be applied, a sleeve of conductive foil affixed to the surface of the shaft over the magnetically active regions, a plurality of saturable magnetic wires or strips mounted to the rotatable shaft and parallel to an axis of rotation, sensor circuitry containing an oscillator for generating a signal, a divider coupled to the oscillator for dividing the frequency of the signal by two, a first and second coil each surrounding a different section of the rotatable shaft and having an input coupled to the divider output, a multiplier having inputs coupled to outputs of the first coil, the second coil, and the oscillator, and an integrator having an input coupled to the multiplier output and an output coupled to both outputs of the first and second coils, wherein the output voltage of the integrator corresponds to the torque being applied to the rotatable shaft.

Owner:METHODE ELETRONICS INC

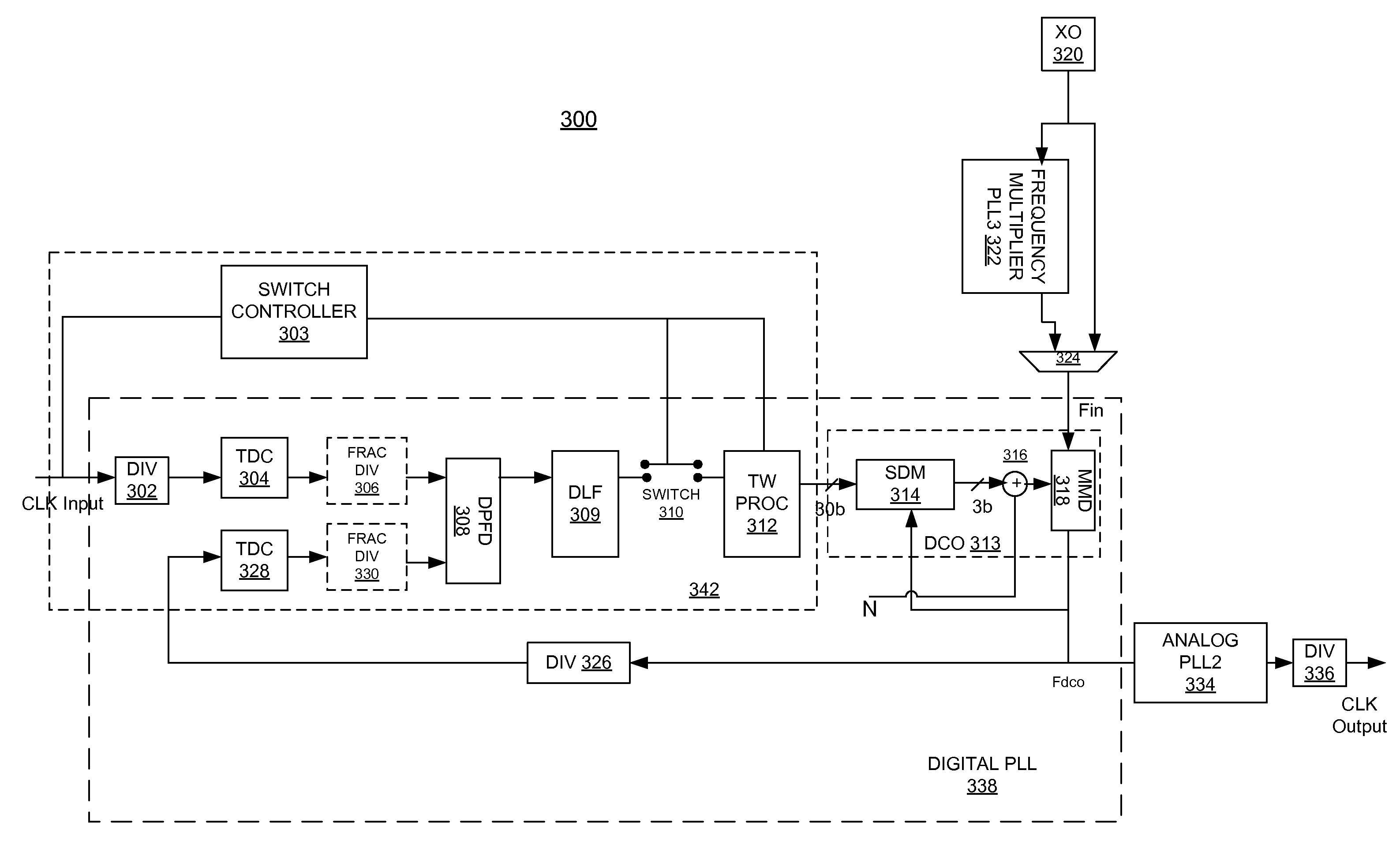

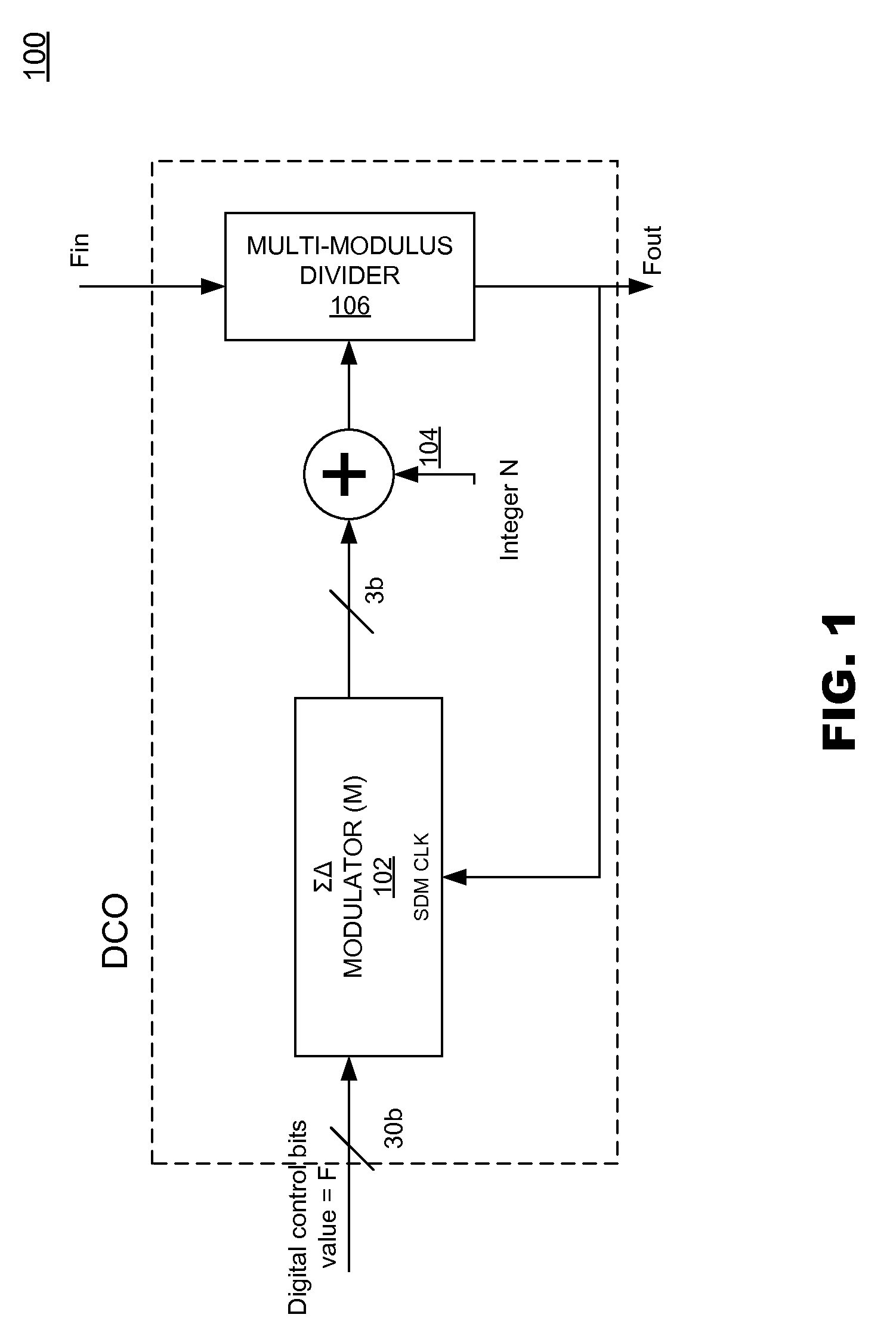

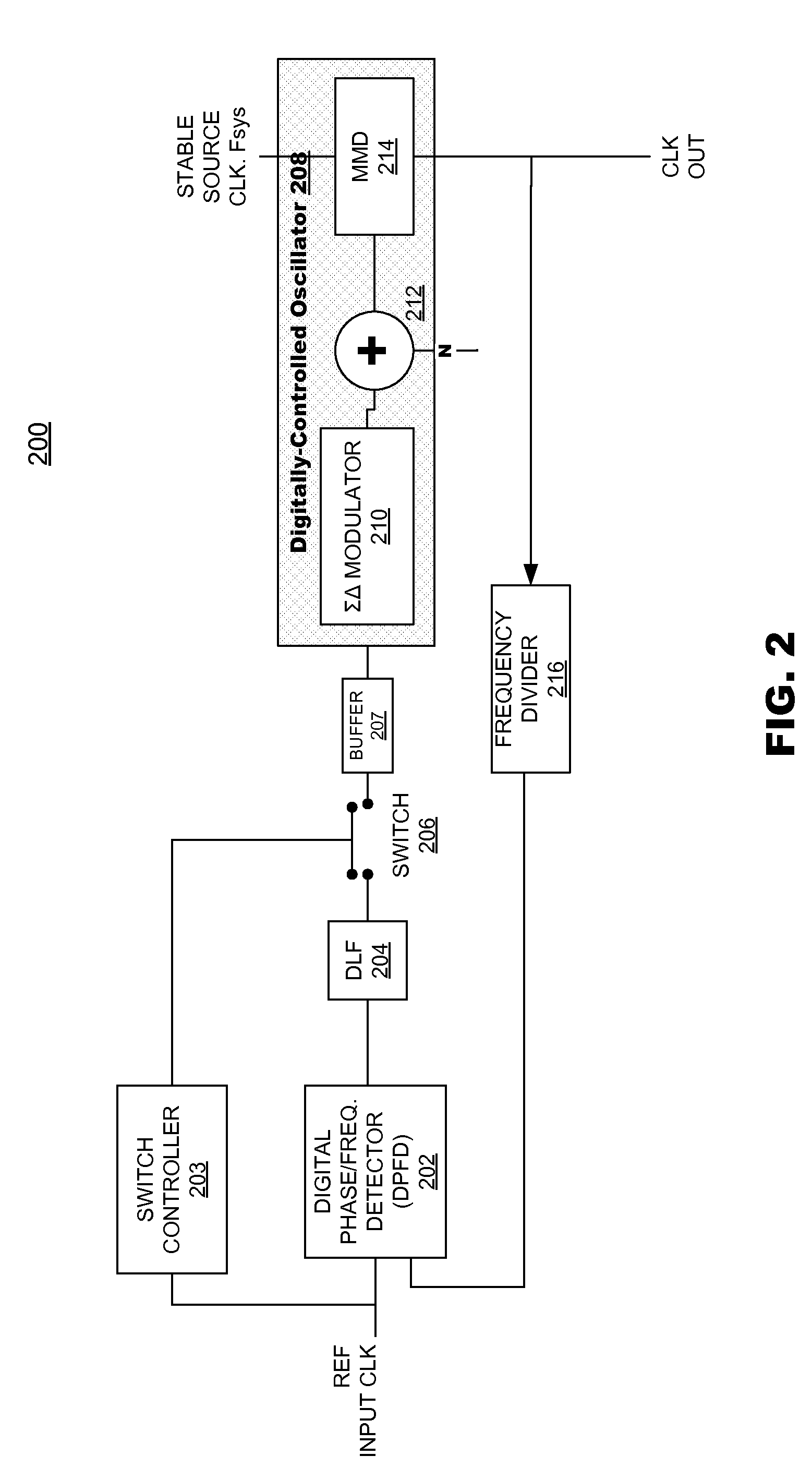

Digital Phase-Locked Loop Clock System

A clock system includes a digital phase / frequency detector (DPFD), a buffer, a digitally-controlled oscillator (DCO) including a sigma-delta modulator (SDM), an adder, a first frequency divider. The DPFD may have a first input for a reference input clock and a second input for a feedback signal, and outputting a difference signal representing a phase and / or frequency difference between the reference input clock and the feedback signal. The buffer may be coupled to the DPFD for accumulating the difference signal over time. The sigma-delta modulator (SDM) may have a control input coupled to the buffer. The adder may have inputs coupled to the (SDM) and a source of an integer control word. The first frequency divider may have an input for a clock signal and a control input coupled to the adder, the DCO generating an output clock signal having an average frequency representing a frequency of the input clock signal divided by (N+F / M), wherein N is determined by the integer control word and F / M is determined by an output of the SDM. The system clock also may include a phase-locked loop (PLL) including a phase / frequency detector that has a first input coupled to the output of the DCO and a second input that is phase-locked to the first input, and a second frequency divider coupled from the second input of the PLL to the second input of the DPFD.

Owner:ANALOG DEVICES INC

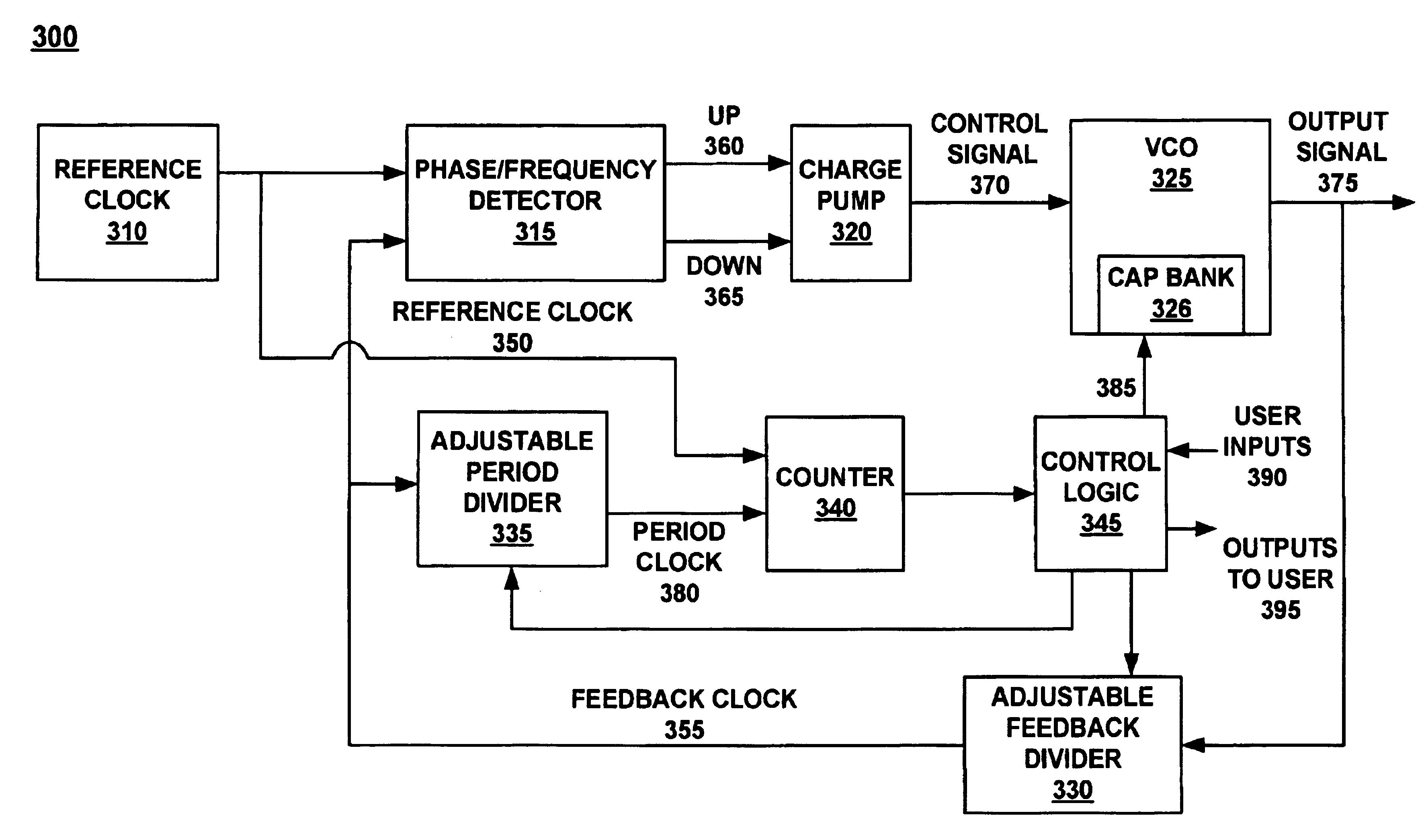

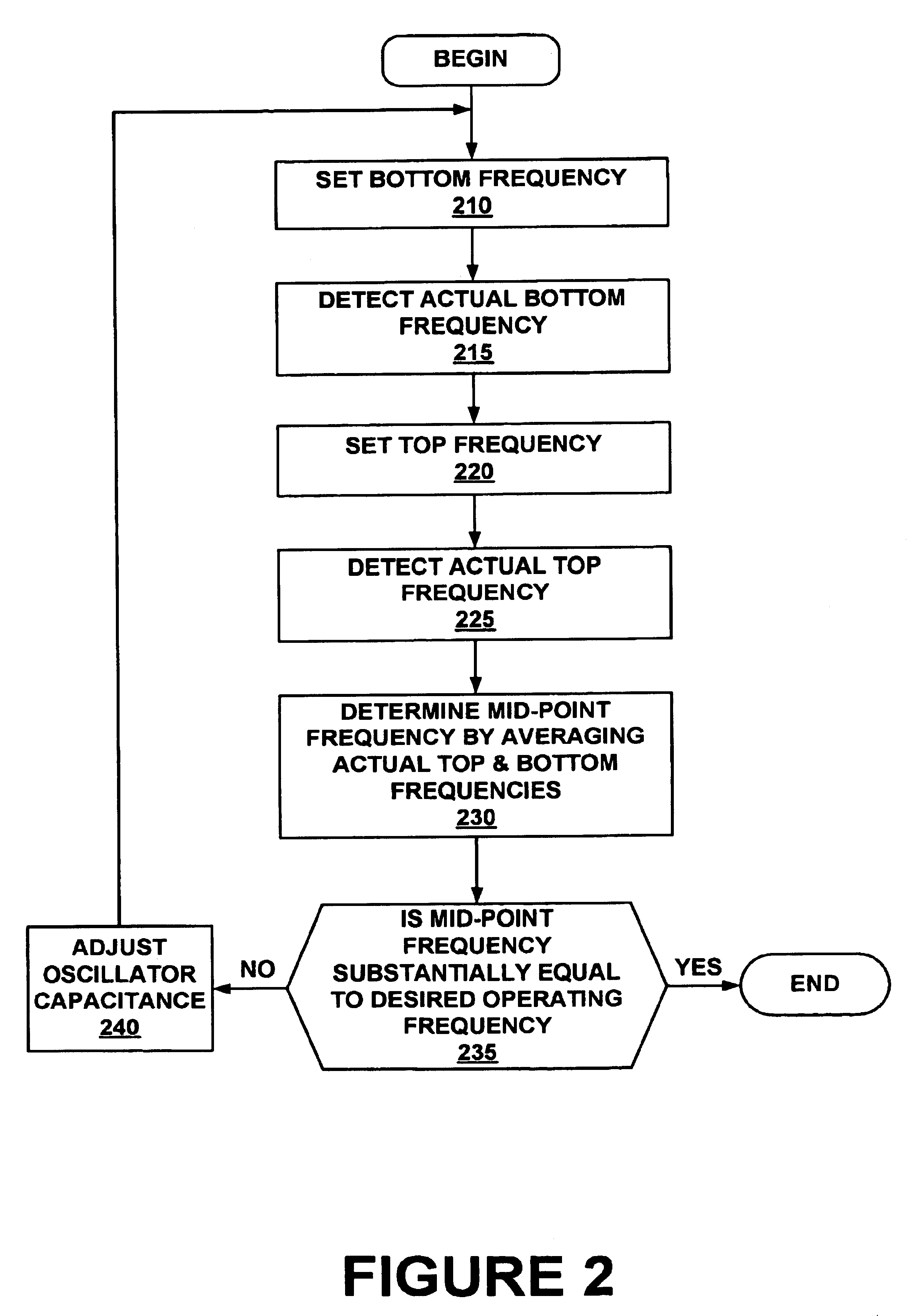

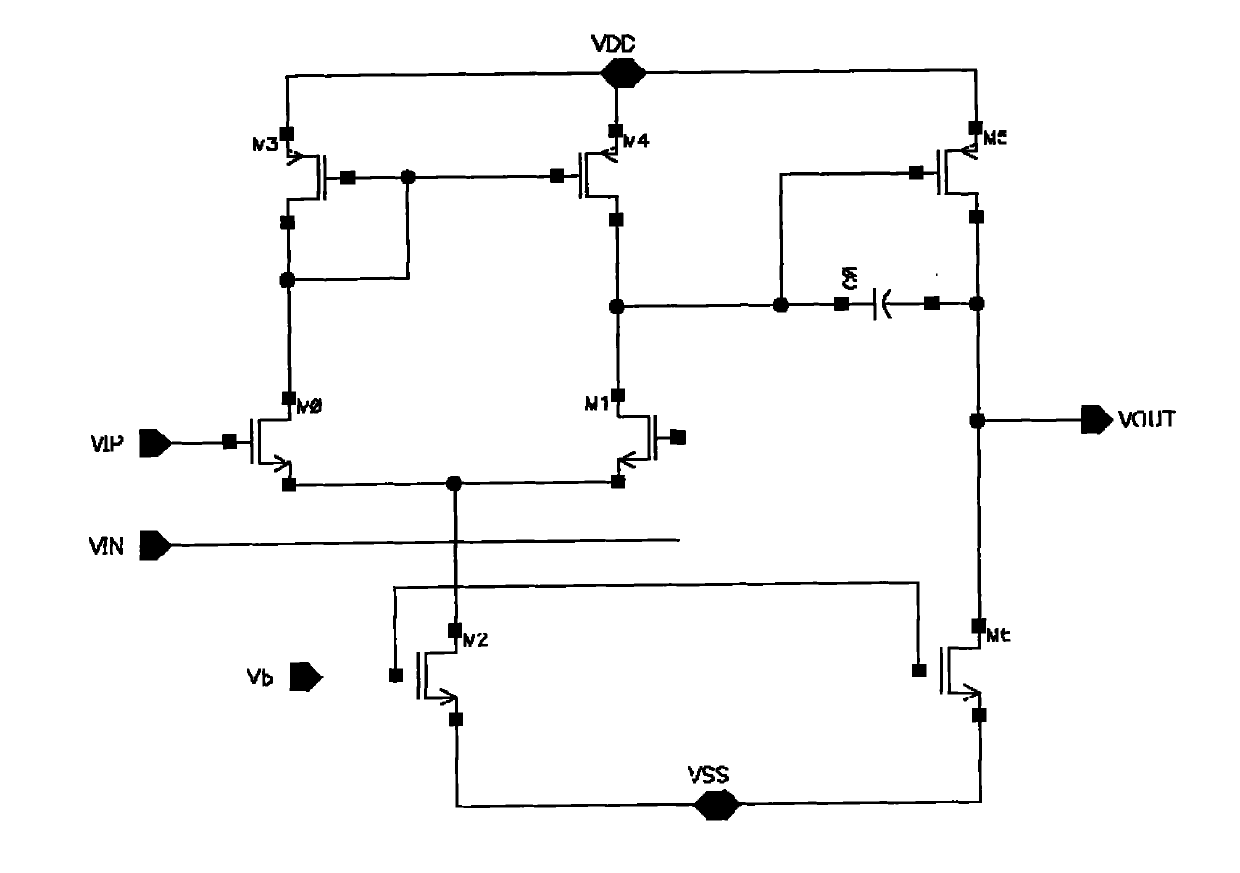

Voltage controlled oscillator

InactiveUS6903613B1Easy to centerEasy to adjustPulse automatic controlFrequency analysisCapacitanceEngineering

Embodiments of the present invention provide a method of centering an operating band of a voltage controlled oscillator around a desired operating frequency. In one embodiment, an adjustable feedback divider provides for driving an output signal to the top and bottom of the operating band. An adjustable period divider and counter provide a plurality of count values for use in determining a mid-point of the operating band. A capacitance bank provides for selectively adjusting a capacitance of the voltage controlled oscillator, thereby adjusting the operating band.

Owner:TAMIRAS PER PTE LTD LLC

Direct digital interpolative synthesis

ActiveUS7417510B2Reduce noisePulse automatic controlGenerator stabilizationEngineeringFrequency divider

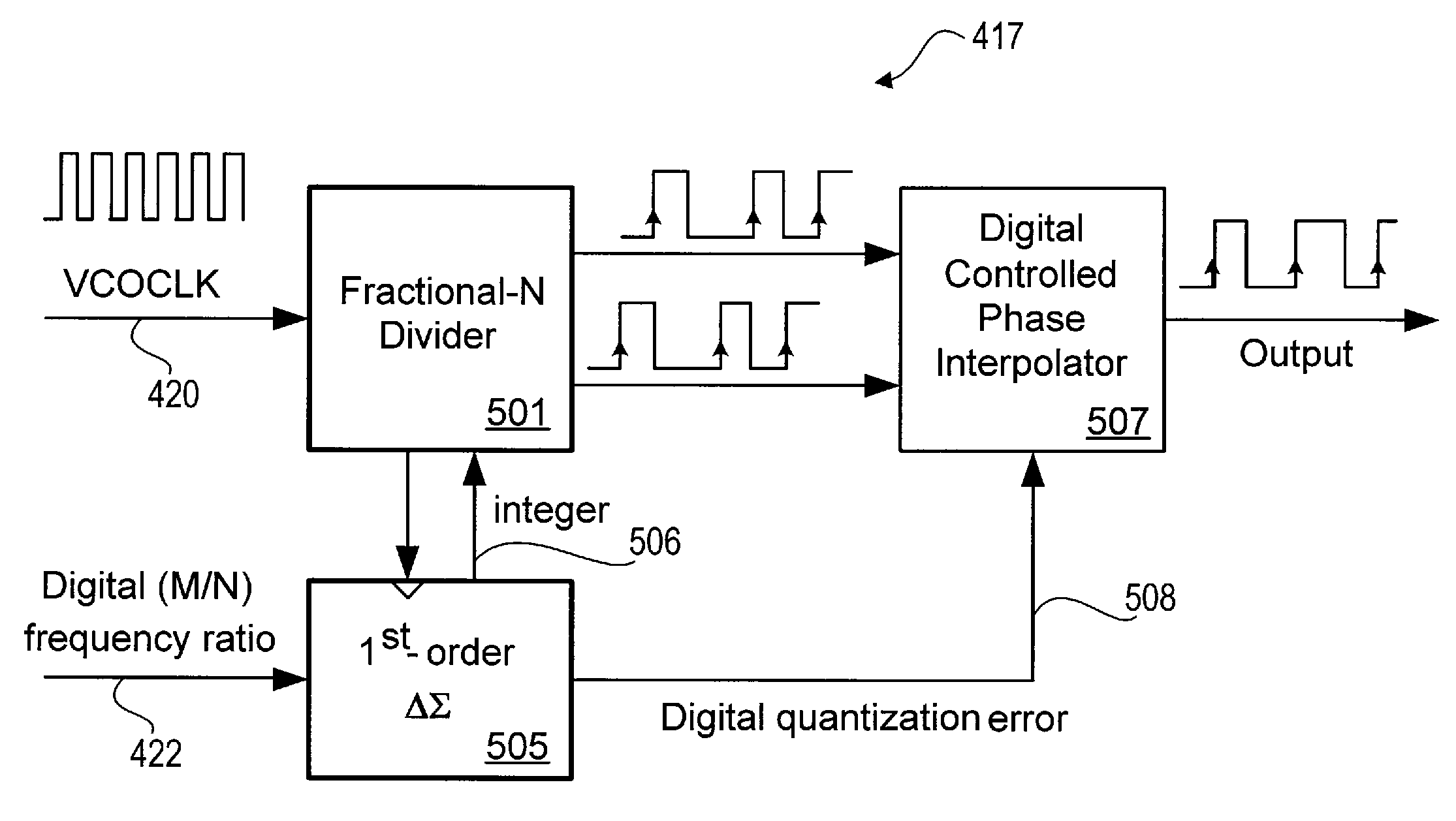

A clock synthesis circuit includes a delta sigma modulator that receives a divide ratio and generates an integer portion and a digital quantization error (a fractional portion). A fractional-N divider divides a received signal according to a divide control value corresponding to the integer portion and generates a divided signal. A phase interpolator adjusts a phase of the divided signal according to the digital quantization error to thereby reduce noise associated with the fractional-N divider.

Owner:SKYWORKS SOLUTIONS INC

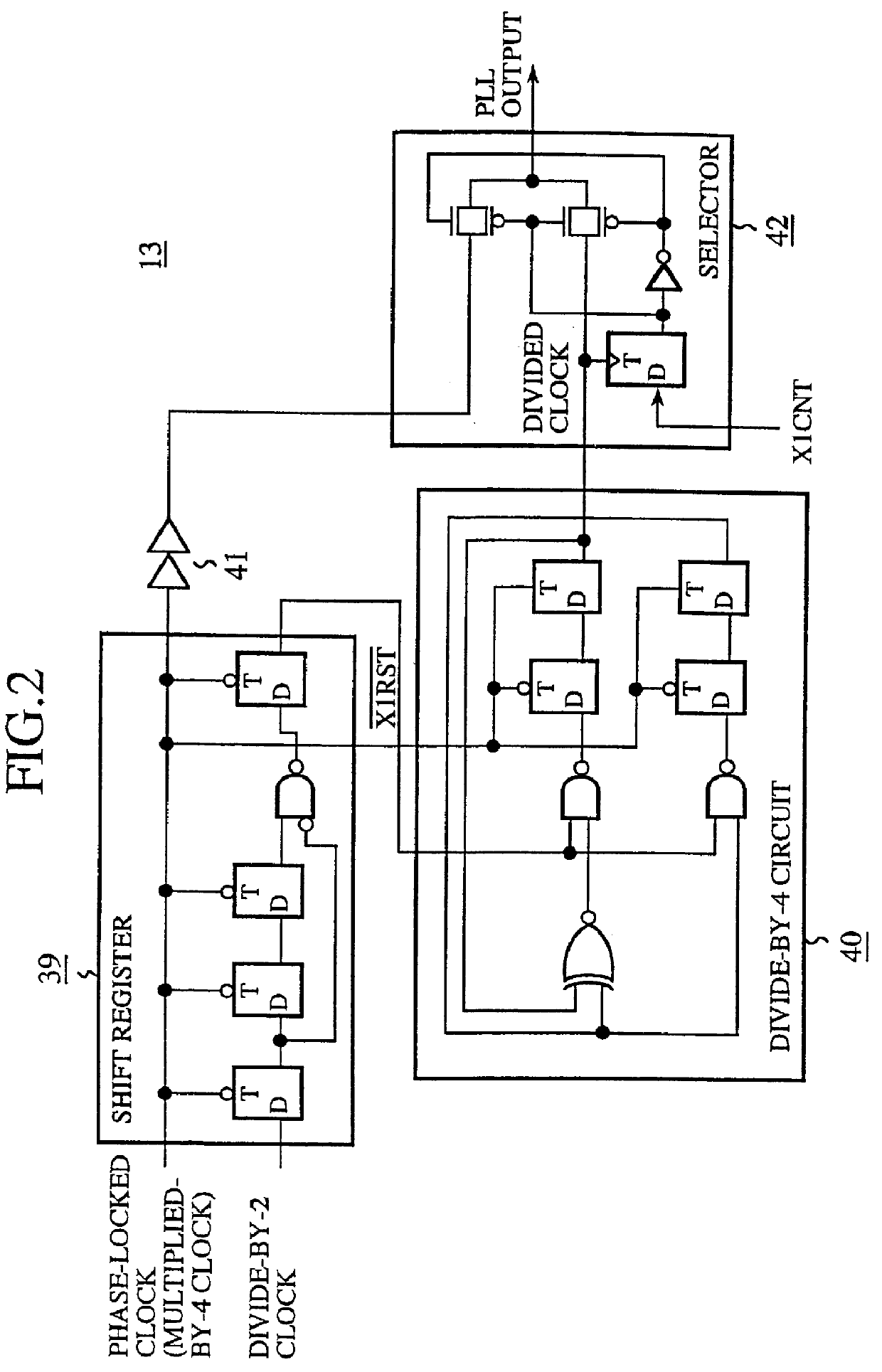

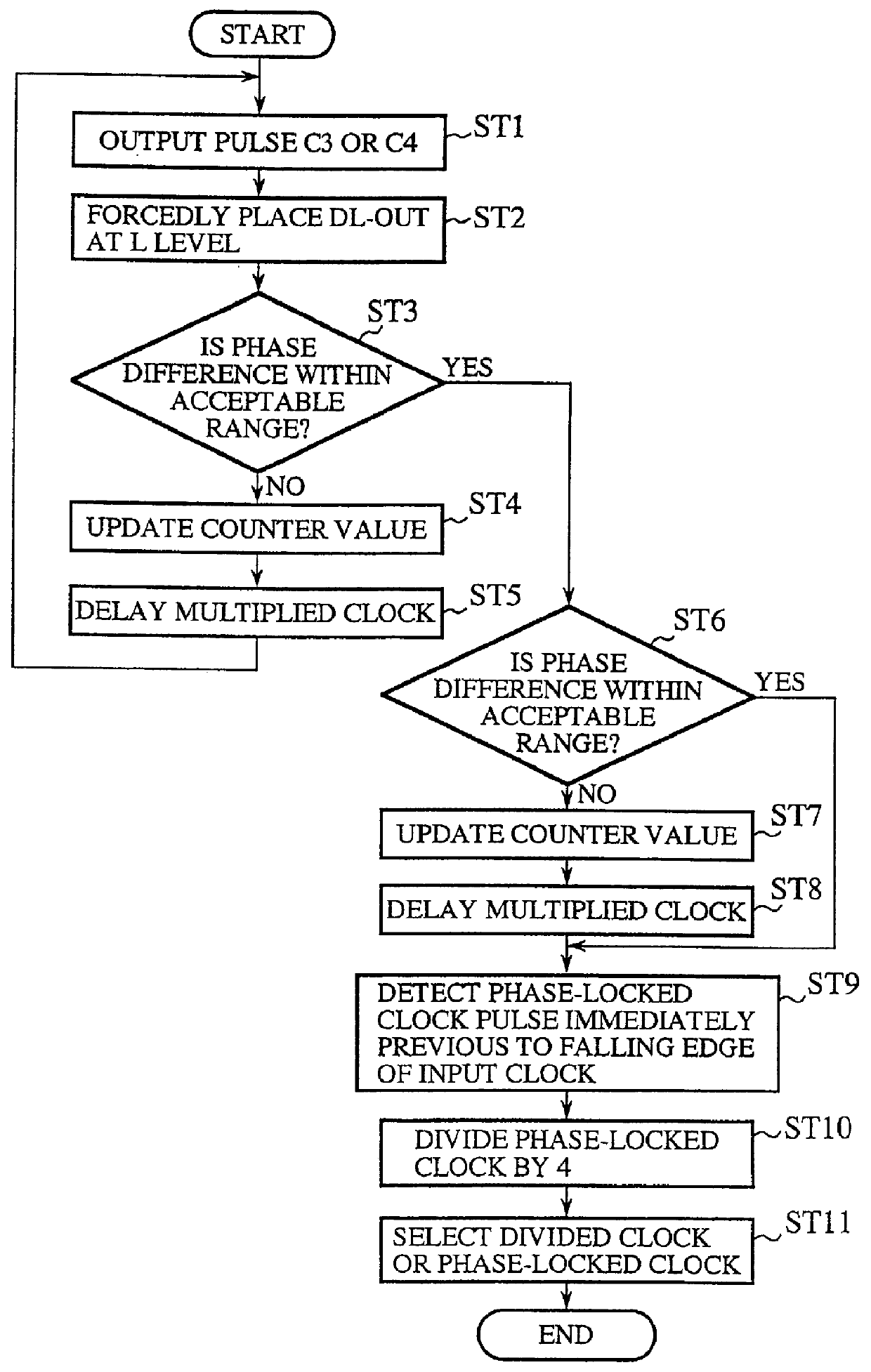

Clock generator and clock generating method capable of varying clock frequency without increasing the number of delay elements

InactiveUS6049238AReduce frequencyDelay lines pulse generationPulse automatic controlPhase differenceDelayed time

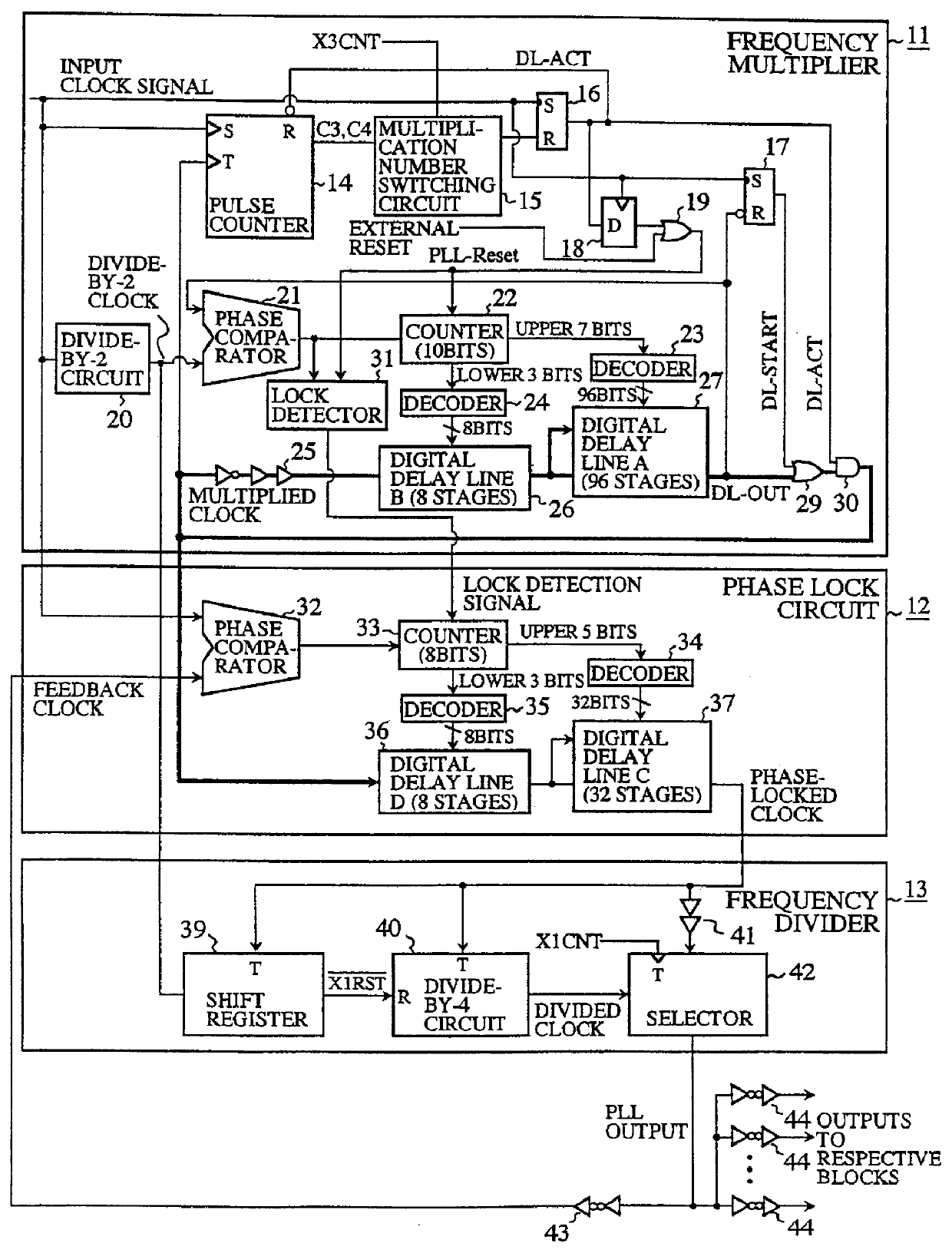

A clock generator including a frequency multiplier, a phase lock circuit and a frequency divider. The frequency multiplier generates a frequency multiplied clock by multiplying the frequency of an input clock. The phase lock circuit detects a phase difference between the input clock and a frequency divided clock, and generates, by delaying the frequency multiplied clock by an amount corresponding to the phase difference, a phase-locked clock with its phase locked with the input clock. The frequency divider detects in every fixed cycle a particular pulse of the phase-locked clock, and generates the frequency divided clock by dividing the phase-locked clock with reference to the particular pulse of the phase-locked clock. In particular, the frequency divider detects the particular pulse immediately previous to a falling edge of the input clock. This can reduce the phase difference between the input clock and the phase-locked clock, and hence to solve a problem of a conventional clock generator in that a delay time of a digital delay line in a phase lock circuit must be lengthened with a reduction in the multiplication number of the frequency multiplied clock, which requires a greater number of delay elements because of a large occupying area of the delay elements and a decoder, thereby increasing the circuit scale and cost of a chip to reduce the multiplication number of the frequency multiplied clock.

Owner:RENESAS ELECTRONICS CORP

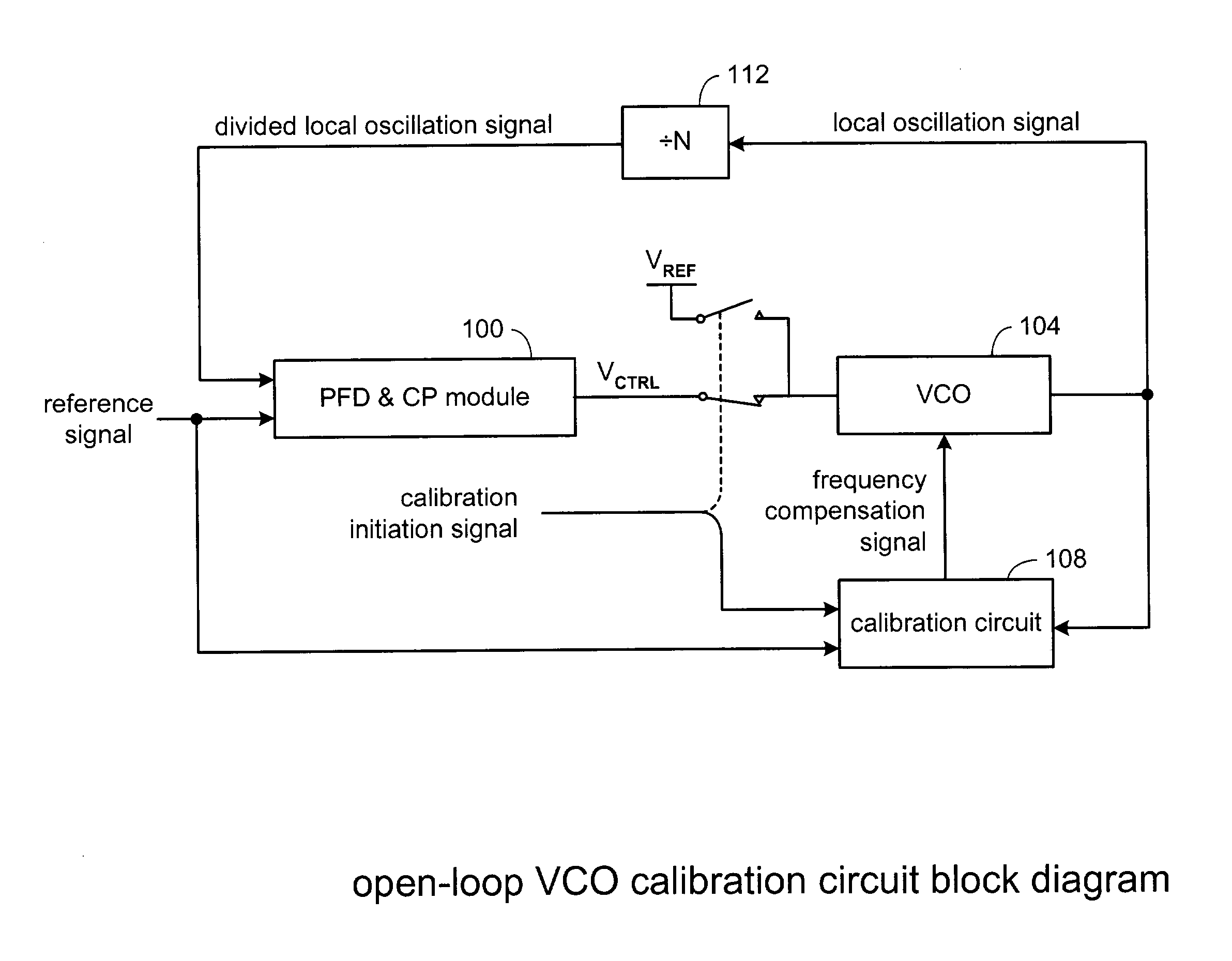

Analog open-loop VCO calibration method

InactiveUS7099643B2Quick calibrationQuick correctionAutomatic scanning with simultaneous frequency displayPulse automatic controlFrequency compensationEngineering

An analog open-loop voltage controlled oscillator (VCO) calibration circuit and method for selecting the frequency of the VCO for a phase locked loop (PLL).A frequency divider module produces a 50% duty cycle divided local oscillation and a 50% duty cycle divided reference signal, wherein the divided signals are substantially equal. A period-to-voltage conversion module converts the divided local oscillation signal and the divided reference signal to voltages proportional to the divided signals. A comparator module produces a frequency adjustment signal based on a comparison of the proportional voltages and couples the frequency adjustment signal to a logic module which produces a frequency compensation signal based on the frequency adjustment signal. The frequency compensation signal functions to adjust the configuration of switched capacitors in a capacitor bank, coupled to the VCO tuned circuit, until the divided local oscillation signal is substantially equal to the divided reference signal.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

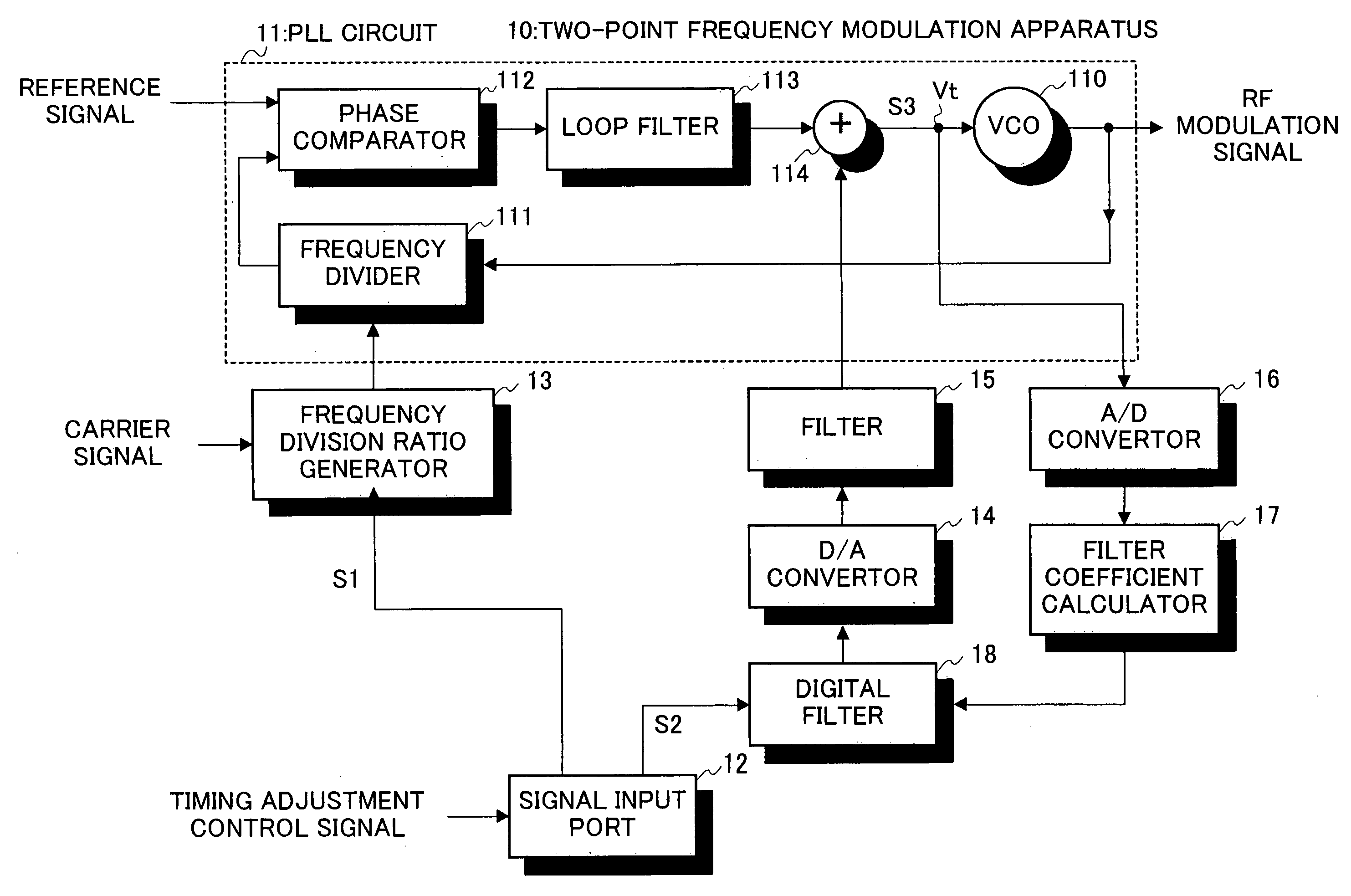

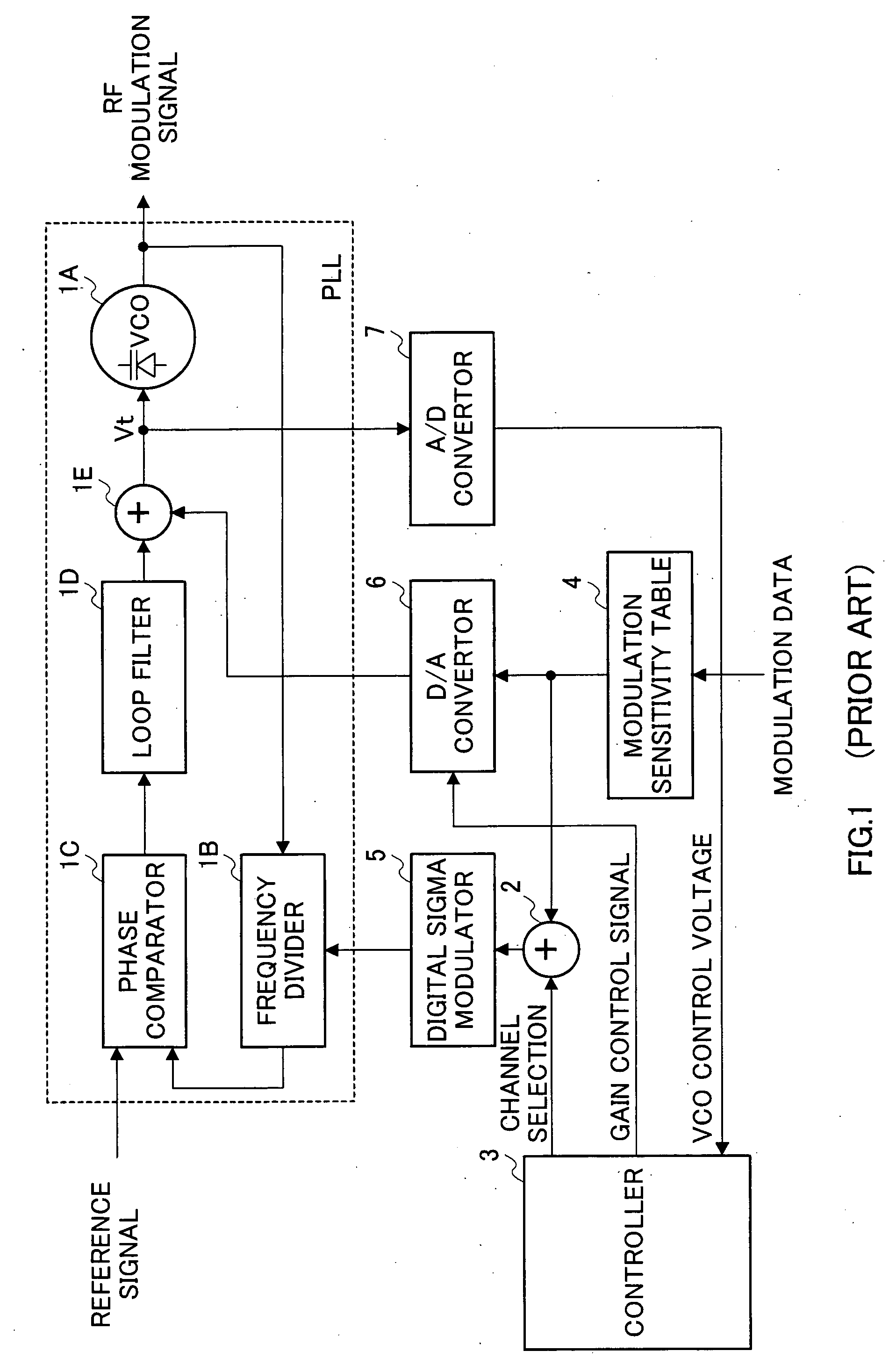

Two-point frequency modulation apparatus, wireless transmitting apparatus, and wireless receiving apparatus

InactiveUS20050232385A1Reduces input timing differenceHigh modulation accuracyPulse automatic controlAngle modulation detailsLoop filterPhase difference

A two-point frequency modulation apparatus is provided that reduces input timing difference and improves modulation accuracy. Two-point frequency modulation apparatus 10 has: PLL circuit 11; frequency division ratio generator 13 that generates the frequency division ratio in frequency divider 111 based on first digital baseband signal S1 and carrier signal; adder 114 that adds second digital baseband signal S2 to the output signal of loop filter 113; a delay index calculator (filter coefficient calculator 17) that calculates the delay index based on the magnitude of change in the amplitude of the output signal of adder 114; and a delay adjuster (digital filter 18) that shifts the phase of one of first digital baseband signal S1 and second digital baseband signal S2 according to the delay index so as to reduce the phase difference.

Owner:PANASONIC CORP

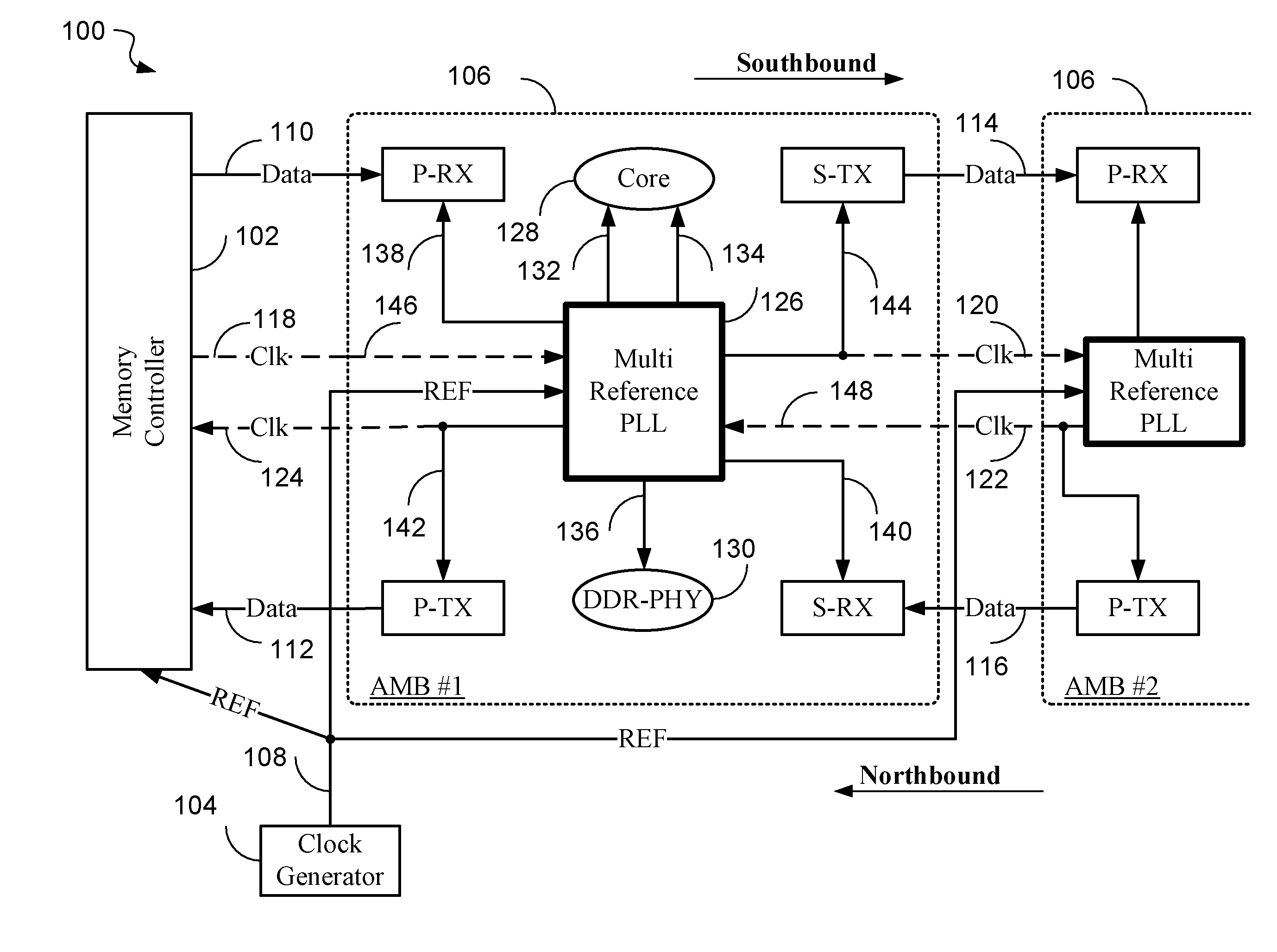

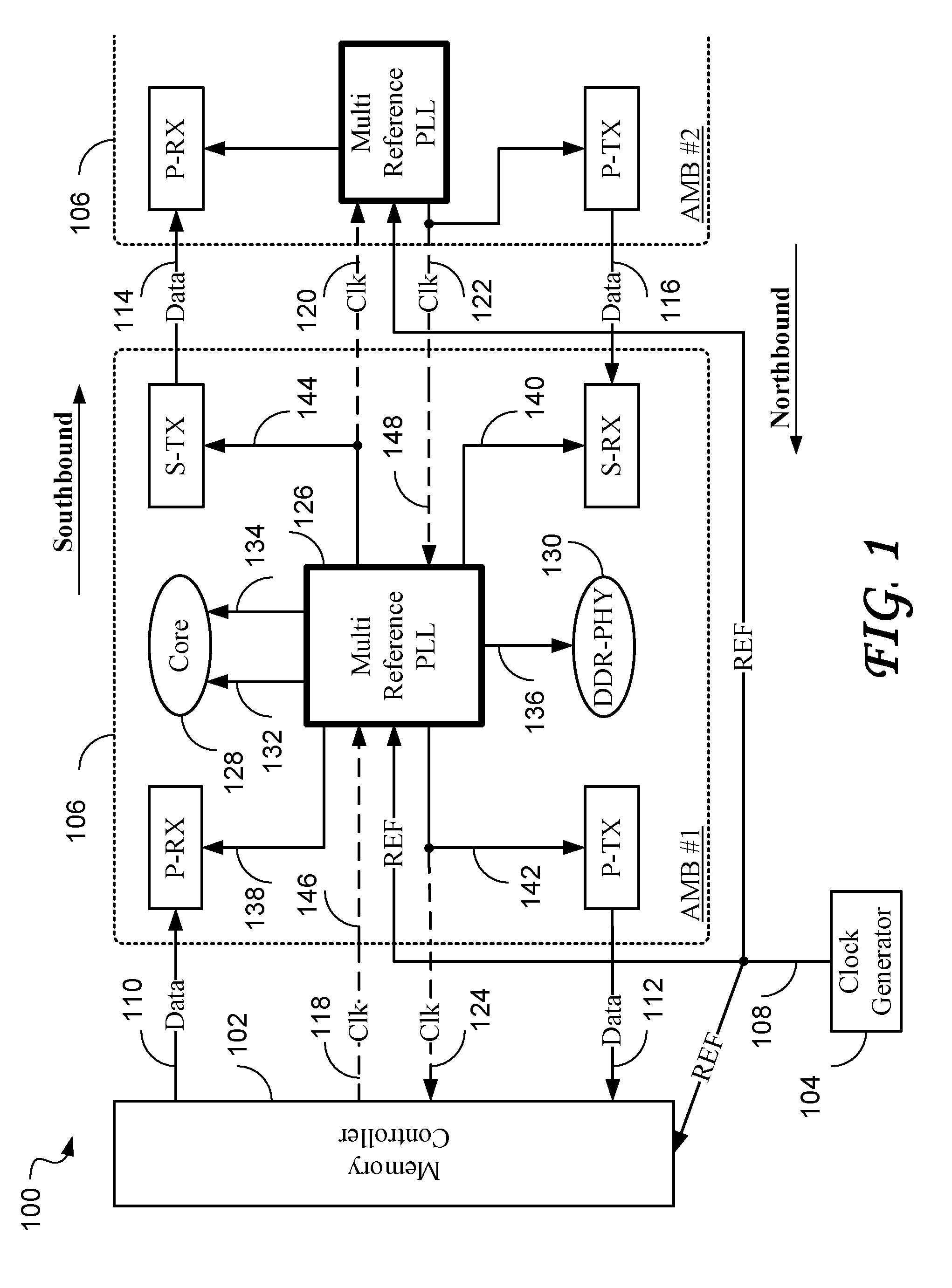

Multiple reference phase locked loop

A multi reference phase locked loop (MPLL) generates a high speed clock frequency and phase locks it to a lowest common reference frequency derived from a selected one of at least two reference clocks. One of the reference clocks is a system reference clock in a FBDIMM system, another may be a forwarded clock in an AMB2. A prescaler reduces the frequency of at least the forwarded clock to the lowest common reference frequency which is the frequency of the system reference clock. A PLL at the core of the MPLL may be locked to the forwarded clock or the system reference clock for generating a high speed clock. A feedback divider generates the feedback clock for the PLL as well as other clocks required in the system. Furthermore, the MPLL provides a number of clocking modes, including modes to facilitate testing and powering down of sections of the circuitry for conserving power.

Owner:RAMBUS INC

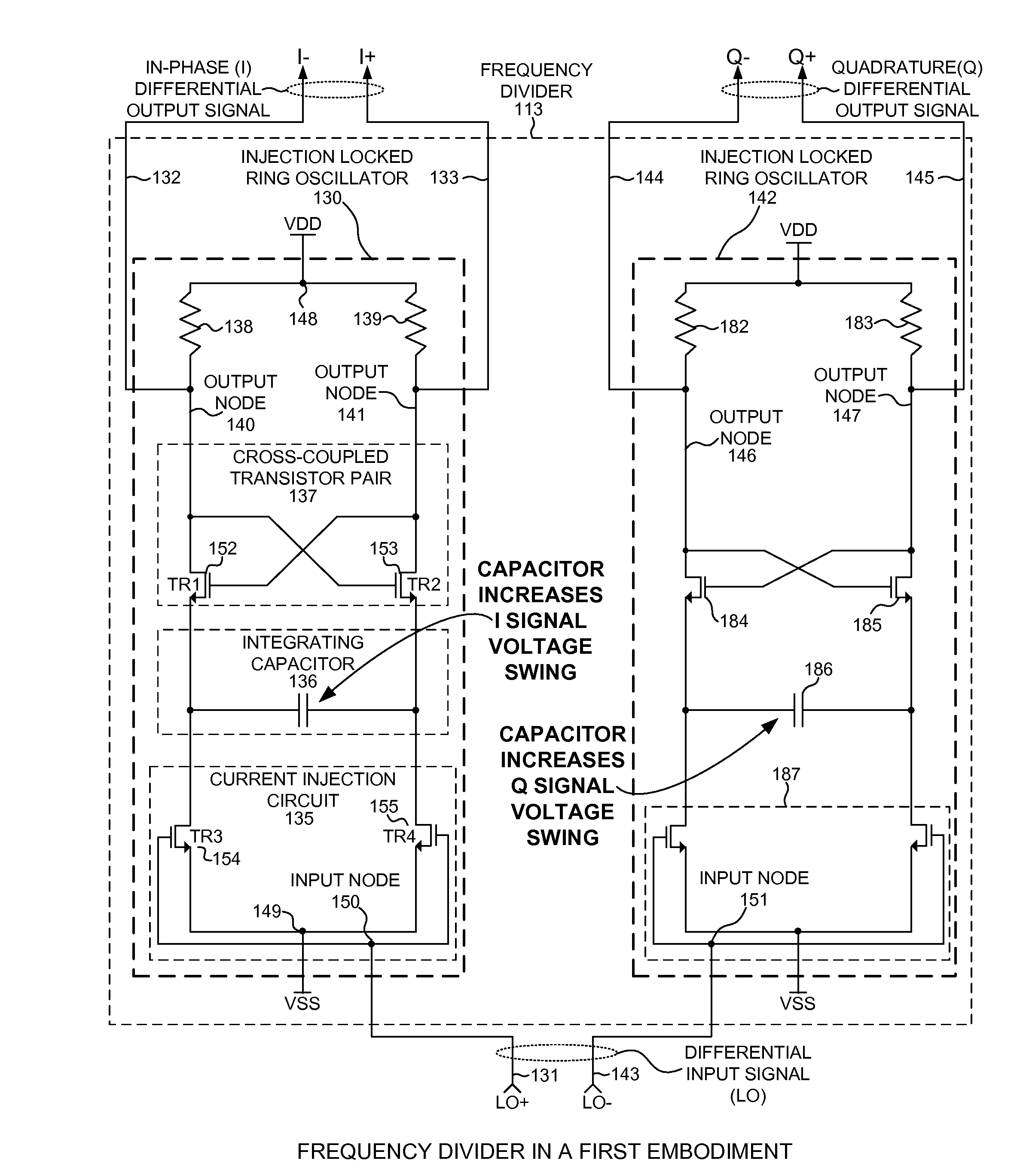

Divide-by-two injection-locked ring oscillator circuit

InactiveUS20110050296A1Improved output signal slew rateIncrease productivityPulse generation by logic circuitsOscillations generatorsInjection lockedLoad resistance

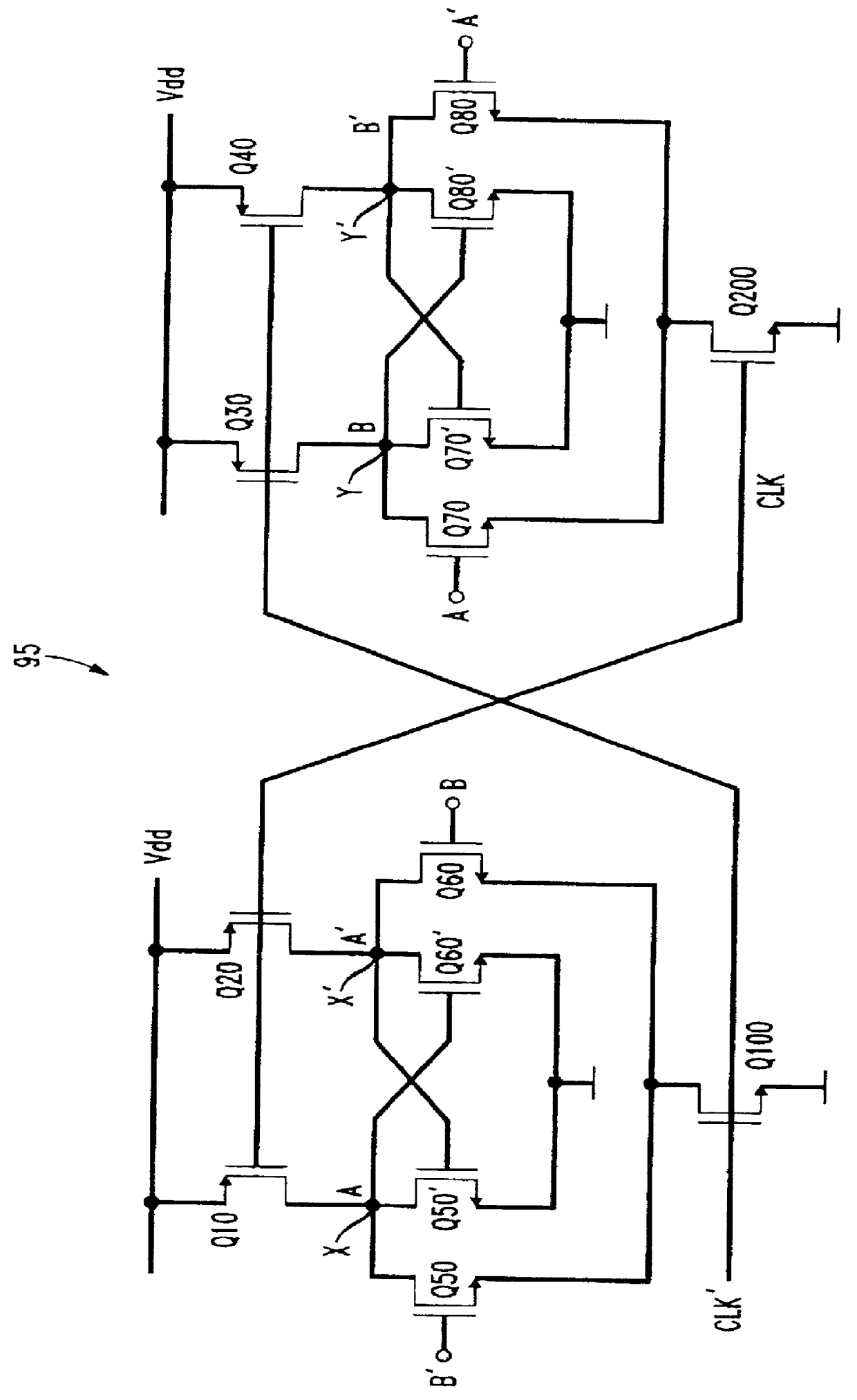

A frequency divider involves a plurality of Injection-locked Ring Oscillators (ILRO). A first ILRO includes a pair of cross-coupled N-channel transistors, a pair of load resistors, an integrating capacitor, and a current injection circuit. The drain of each transistor is coupled to the gate of the other transistor. Each load resistor couples the drain of each transistor to a circuit voltage source. The integrating capacitor couples the sources of each transistor. The current injection circuit alternately opens and closes a path from the source of each transistor to circuit ground in response to an oscillatory input signal of a first frequency. In response, the voltage state at the drain of each transistor is alternately latched and toggled, generating a differential pair of oscillating signals frequency divided by two. A first and second ILRO driven in antiphase generate two differential output signals in phase quadrature.

Owner:QUALCOMM INC

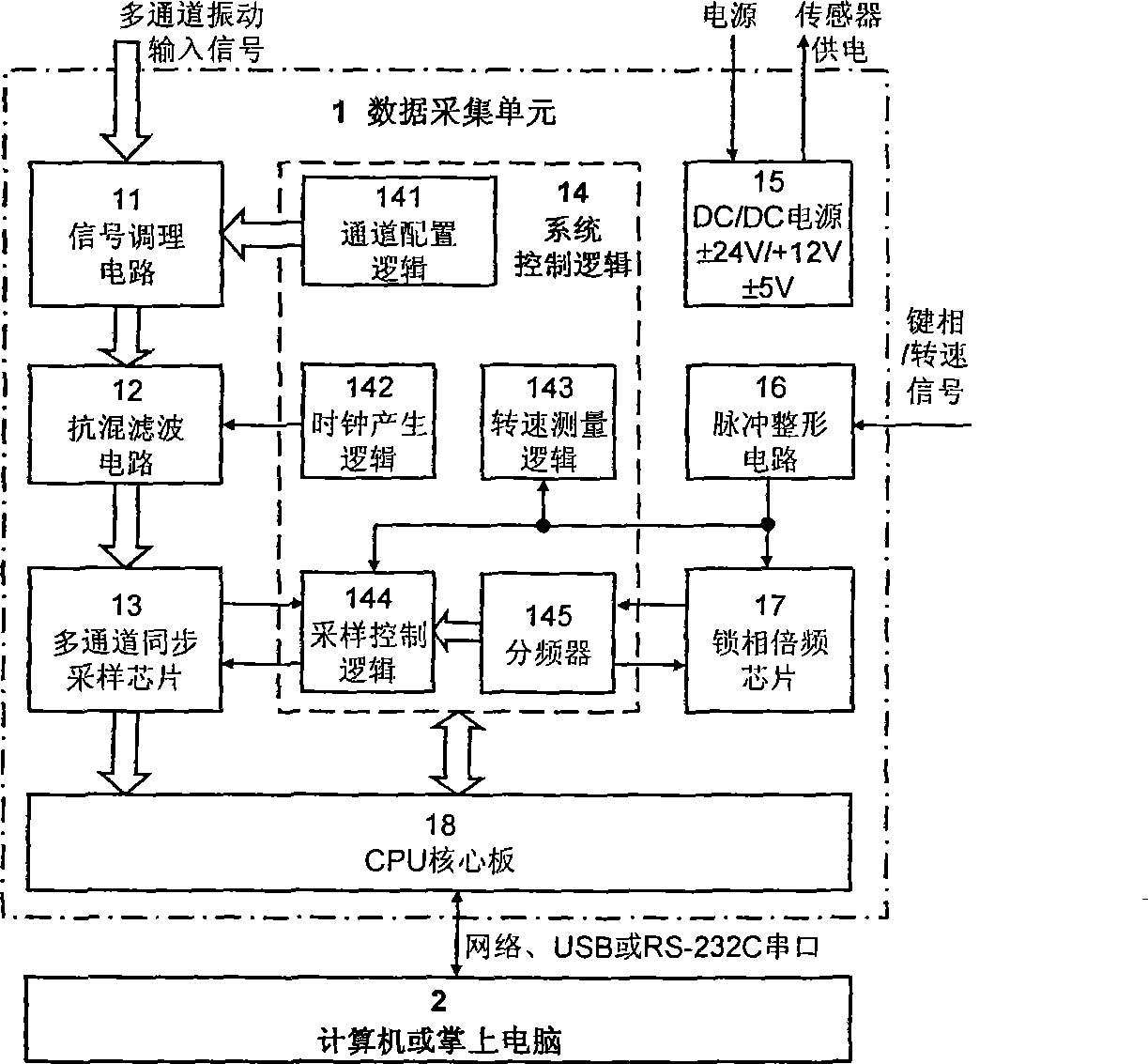

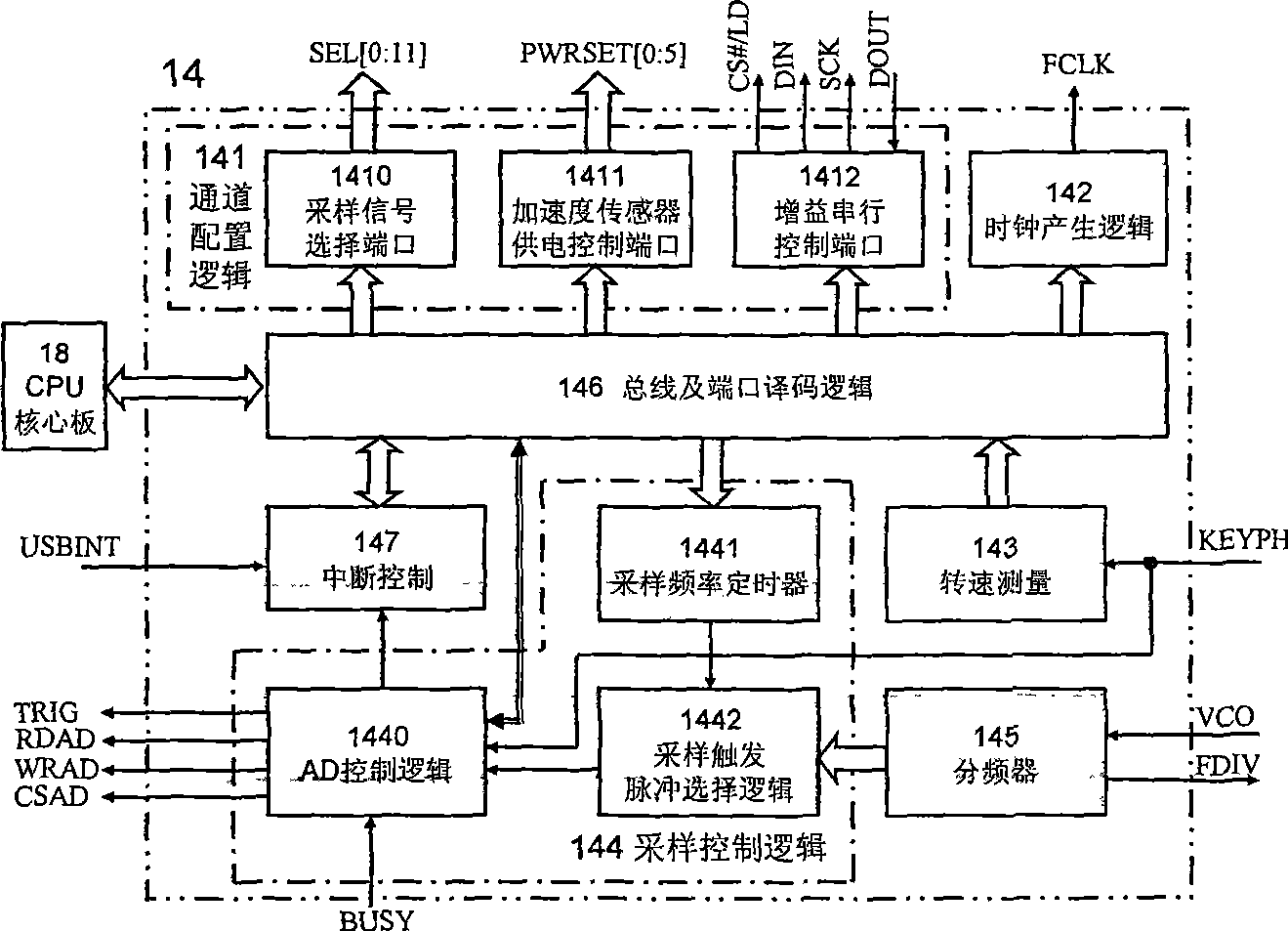

Integrated multichannel synchronous oscillation data acquiring and monitoring and analysis diagnostic device

InactiveCN101436046AMiniaturizationSimple structureProgramme controlComputer controlAnti-aliasingVibration acceleration

The invention discloses an integrated multi-channel synchronous vibration data acquisition, monitoring and analysis diagnosis device. The data acquisition unit comprises a signal conditioning circuit, an anti-aliasing filtering circuit, a multi-channel synchronous sampling chip, a system control logic unit, a pulse-shaping circuit (16), a phaselocking frequency multiplication chip and a microprocessor CPU, wherein the system control logic unit comprises a channel configuration logic unit, a clock generation logic unit, a rotating speed measurement logic unit, a sampling control logic unit and a frequency divider, and the data acquisition unit (1) is directly connected with a plurality of eddy current vibration displacement sensors, ICP type piezoelectric vibration acceleration sensors or magnetoelectric vibration speed sensors, and has an interface of a single-channel direct-connected eddy-current, photoelectric or magnetoelectric key phase / revolution speed sensor and so on. The CPU core board is connected with a computer or a palm computer through a network and a USB or a serial interface and finishes the data acquisition for monitoring and analysis diagnosis.

Owner:SOUTHEAST UNIV +1

High speed frequency divider circuit

InactiveUS6166571ACounting chain synchronous pulse countersPulse counters with static storageRC time constantEngineering

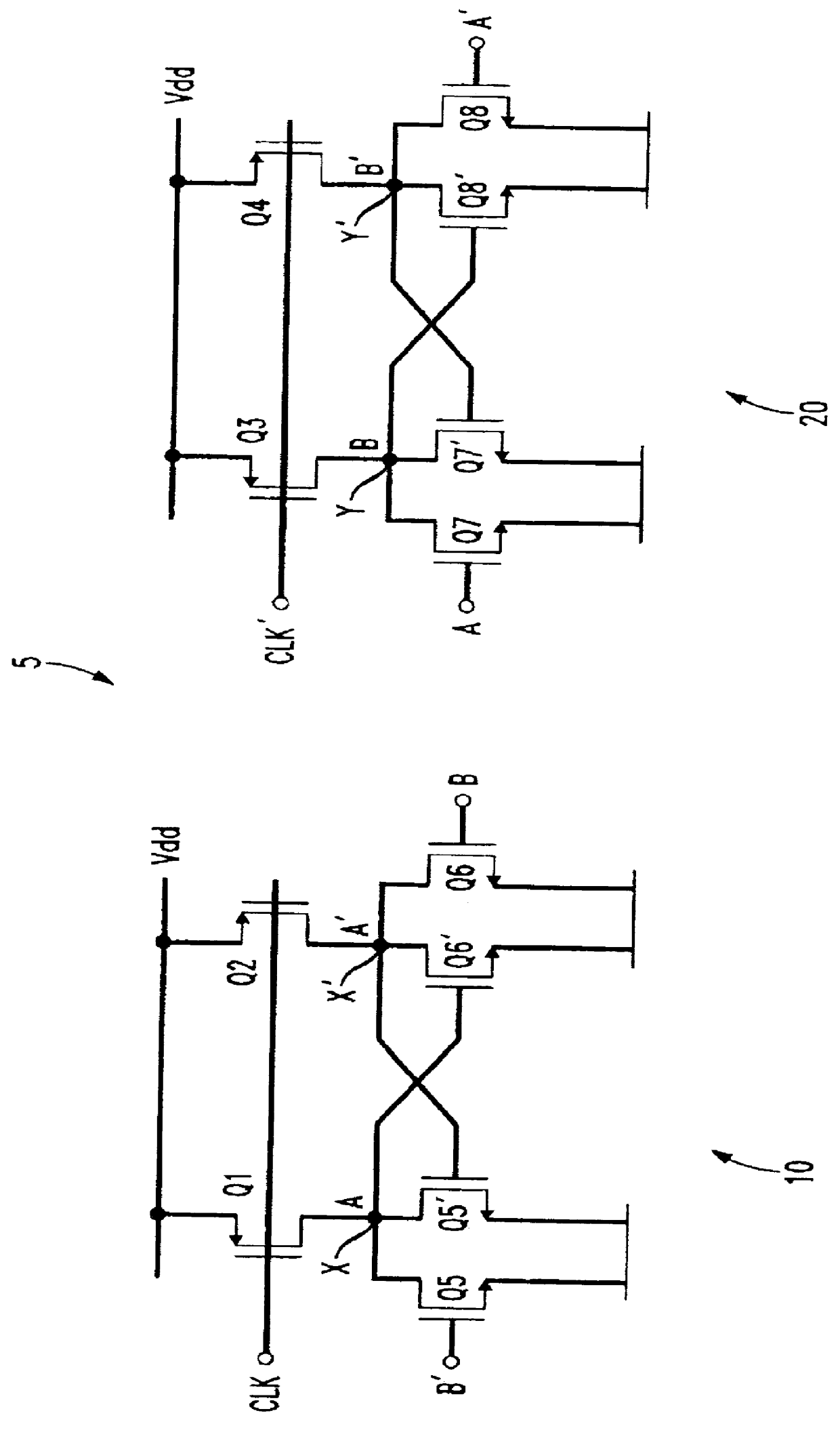

A high frequency divider circuit for producing output signals of half the frequency of an input clock signal includes two identical circuit sections, each producing an output signal and its complement. The circuit sections are connected to each other so that the output signals of one circuit section serve as input signals to the other circuit section. Each circuit section contains a load transistor which is controlled by one of the clock signal and the clock signal complement, and a switch transistor which is controlled by the other of the clock signal and the clock signal complement. The inventive circuit exhibits a reduced RC time constant for each circuit section and an increased output signal swing between the output signals and their respective complements, as contrasted with prior art frequency dividers, thereby increasing the overall circuit response time and its ability to operate at high frequencies.

Owner:LUCENT TECH INC

Phase-locked loop and automatic frequency calibration circuit thereof and phase-locked loop self-tuning locking method

InactiveCN101951259ASpeed up lock timeGuaranteed robustnessPulse automatic controlSelf-tuningLock time

The invention discloses a phase-locked loop and an automatic frequency calibration circuit thereof. The phase-locked loop comprises a phase / frequency detector, a charge pump, a filter, a voltage-controlled oscillator (VCO) and a first frequency divider which are connected in sequence, wherein the phase-locked loop further comprises the automatic frequency calibration circuit; the automatic frequency calibration circuit reduces the oscillation frequency CKV of the VCO when the oscillation frequency CKV of the VCO after undergoing frequency division by the first frequency divider is higher than the reference frequency CKR, and increases the oscillation frequency CKV of the VCO when the oscillation frequency CKV of the VCO is lower than the reference frequency CKR; and a precharging circuit A0 is connected at the input end of the filter and carries out precharging when AFC carries out searching. The phase-locked loop has the rapid self-tuning locking function and ensures the VCO to carry out coarse tuning automatically to approach the final tuning coil, thus reducing the locking time of the phase-locked loop.

Owner:SHANGHAI NATLINEAR ELECTRONICS CO LTD

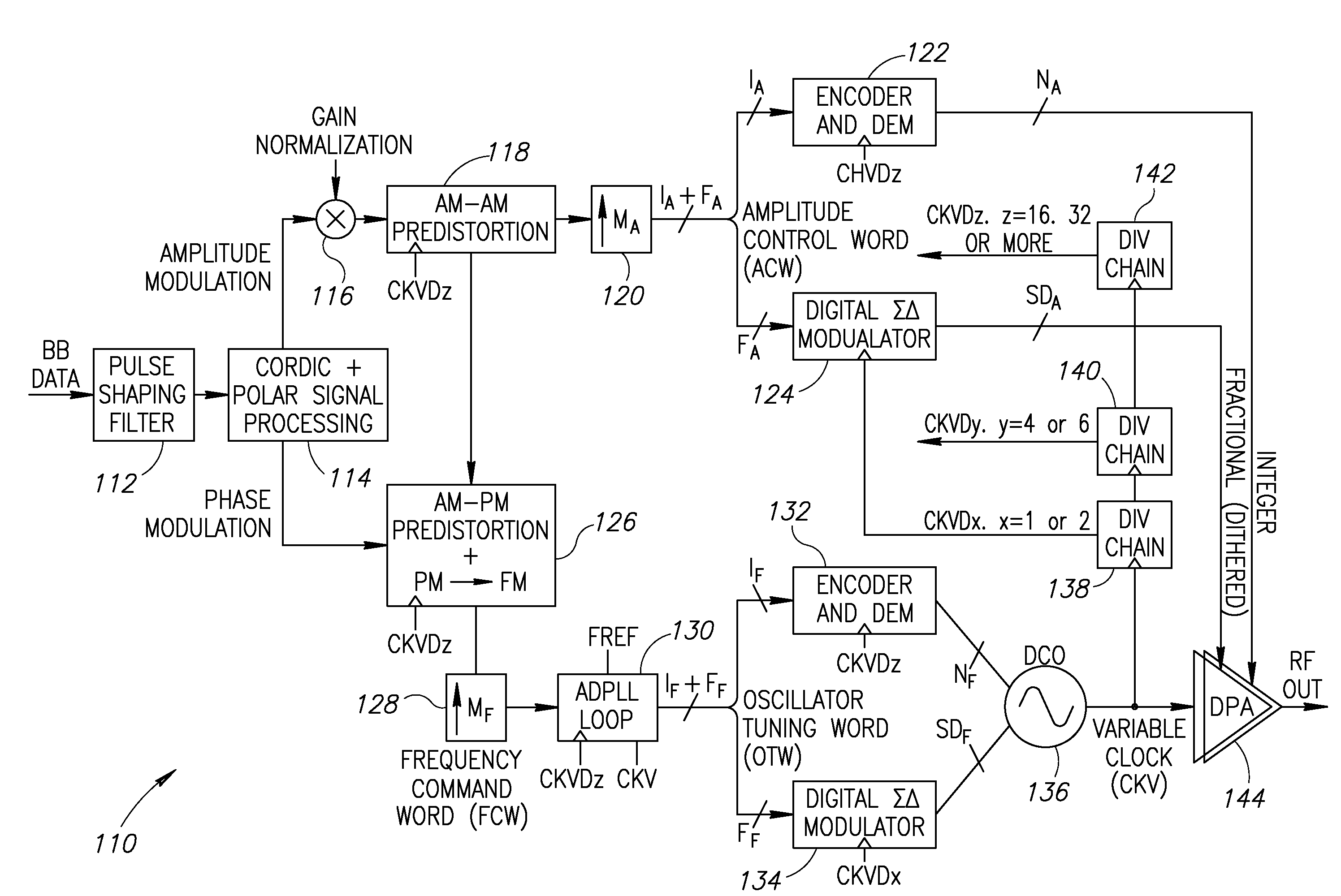

Precise delay alignment between amplitude and phase/frequency modulation paths in a digital polar transmitter

ActiveUS20070189417A1Achieve alignmentHigh phase modulation accuracy requirementSimultaneous amplitude and angle modulationModulation with suppressed carrierAudio power amplifierNanosecond

A novel apparatus for and method of delay alignment between amplitude and phase / frequency modulation paths in a digital polar transmitter. The invention provides a fully digital delay alignment mechanism where better than nanosecond alignment is achieved by accounting for processing delays in the digital circuit modules of the transmitter and by the use of programmable delay elements spread across several clock domains. Tapped delay lines compensate for propagation and settling delays in analog elements such as the DCO, dividers, quad switch, buffers, level shifters and digital pre-power amplifier (DPA). A signal correlative mechanism is provided whereby data from the amplitude and phase / frequency modulation paths to be matched is first interpolated and then cross-correlated to achieve accuracy better than the clock domain of comparison. Within the ADPLL portion of the transmitter, precise alignment of reference and direct point injection points in the ADPLL is provded using multiple clock domains, tapped delay lines and clock adjustment circuits.

Owner:TEXAS INSTR INC