Patents

Literature

131results about "Automatic scanning with simultaneous frequency display" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

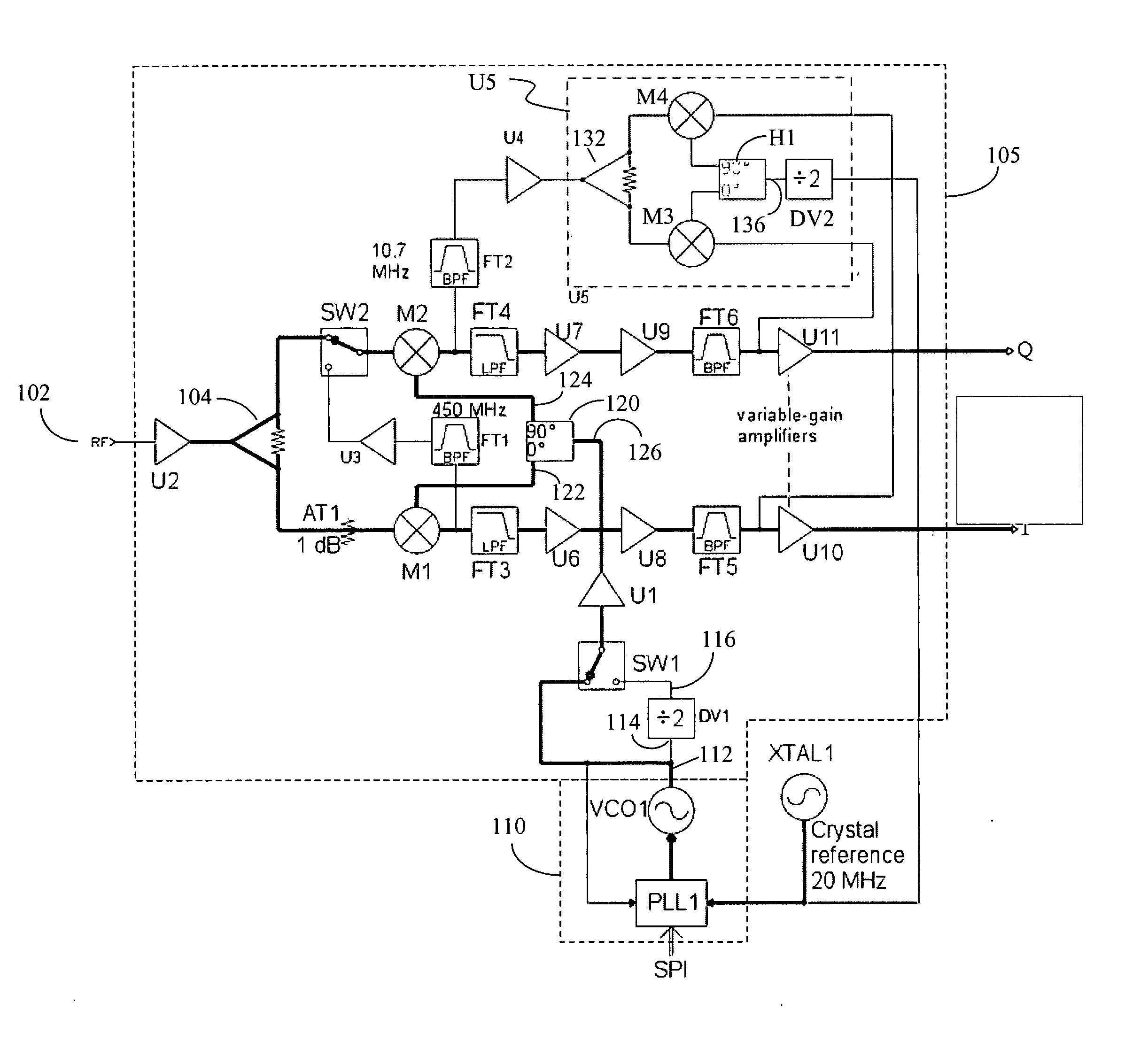

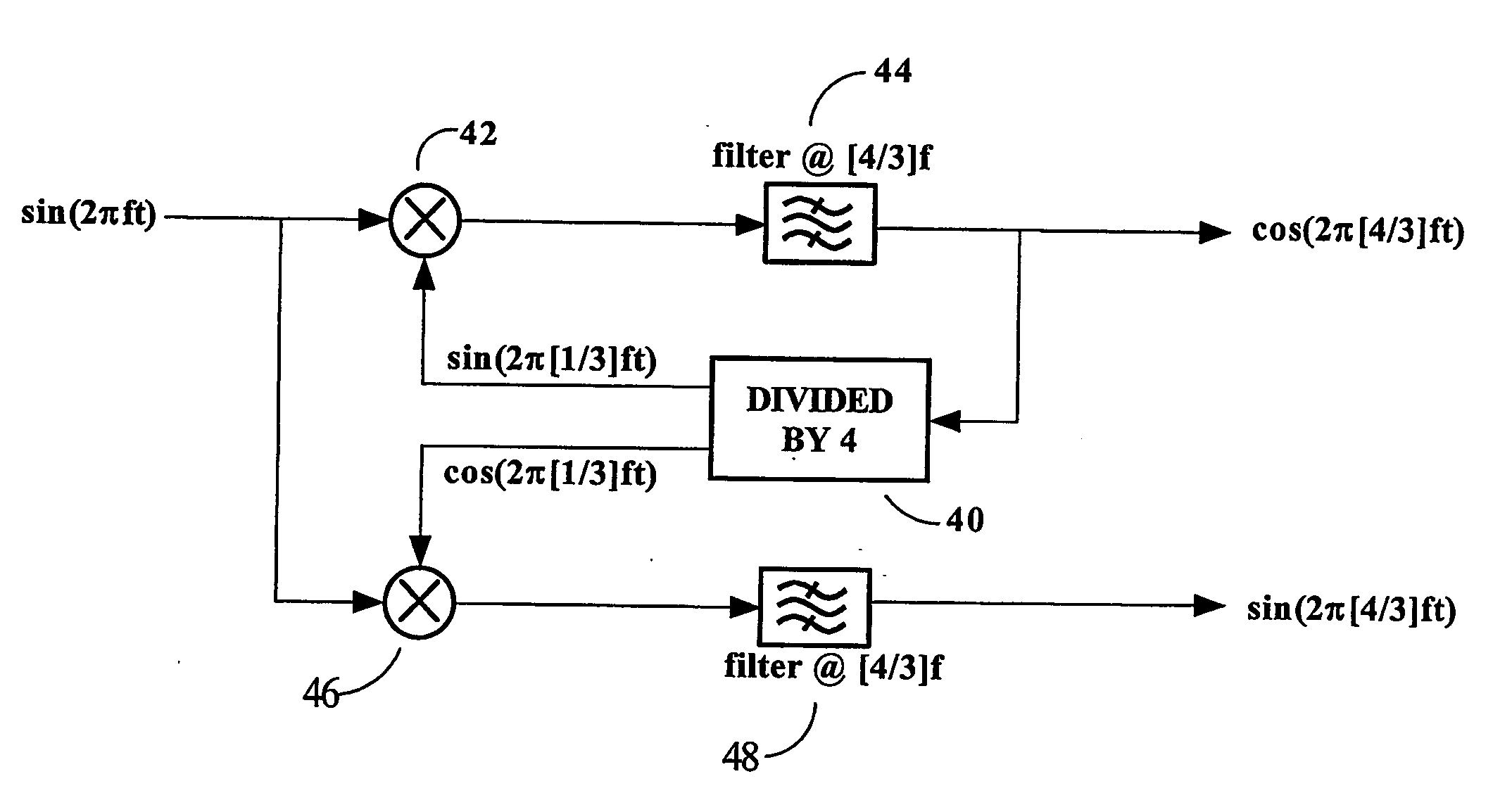

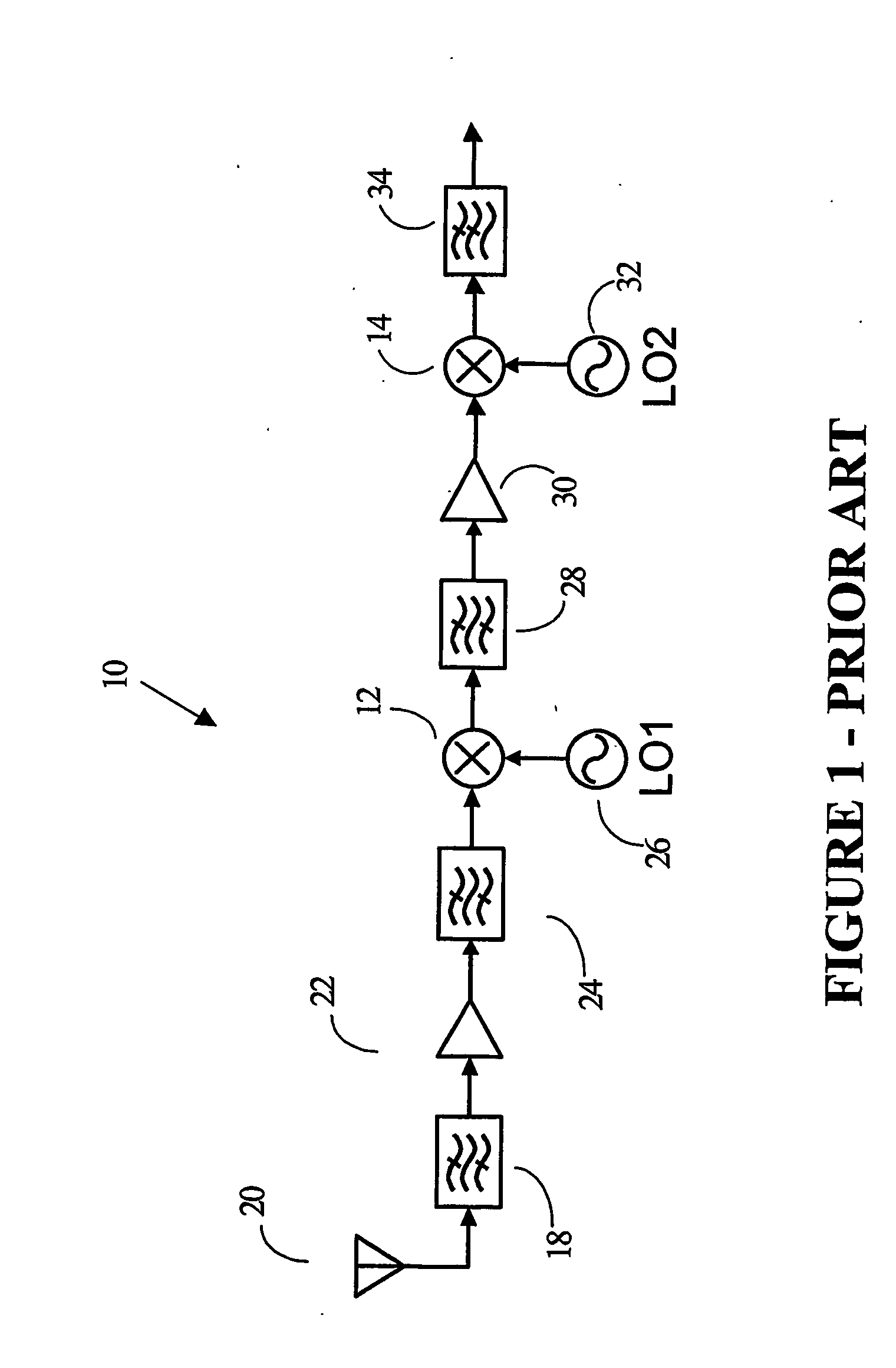

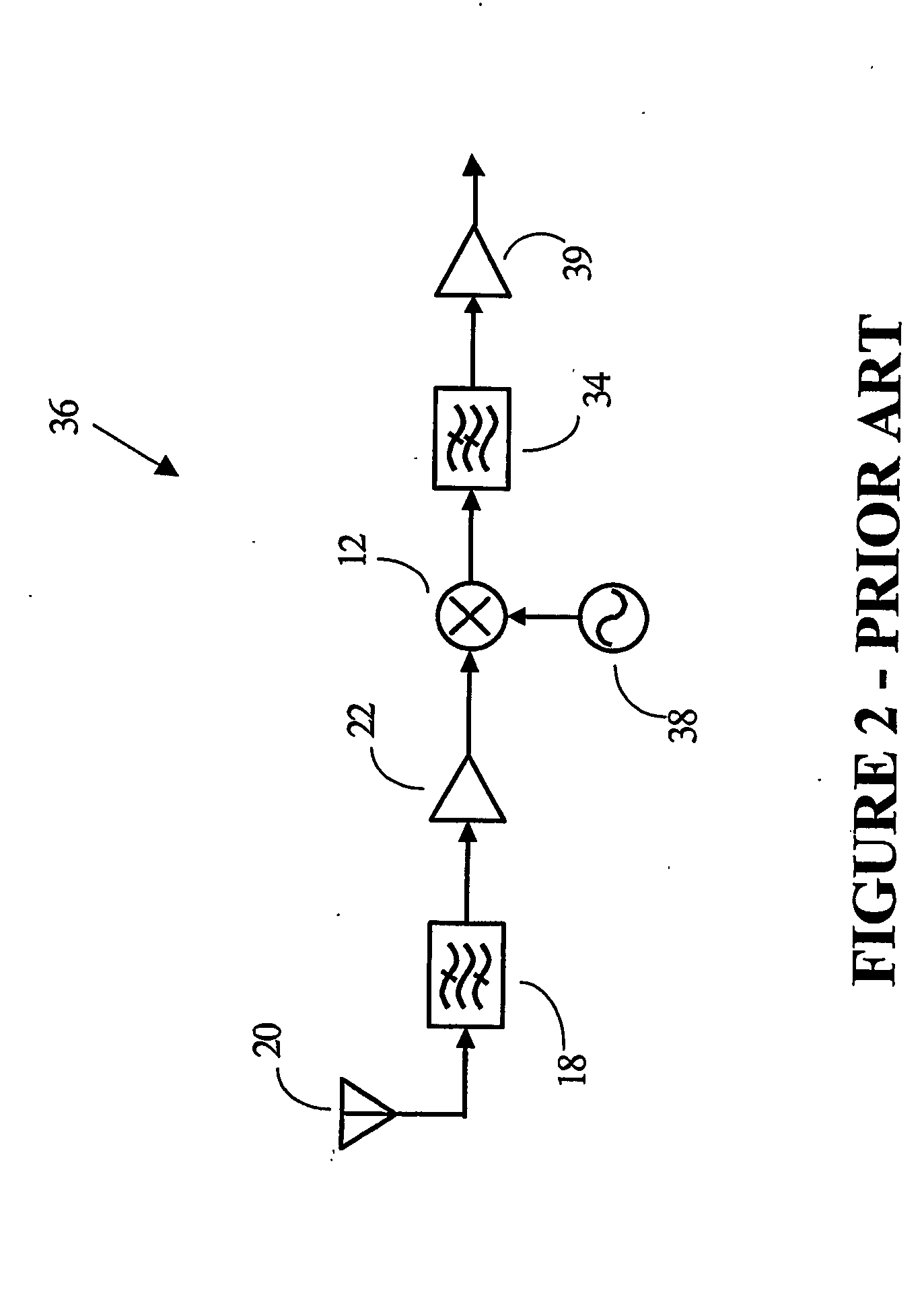

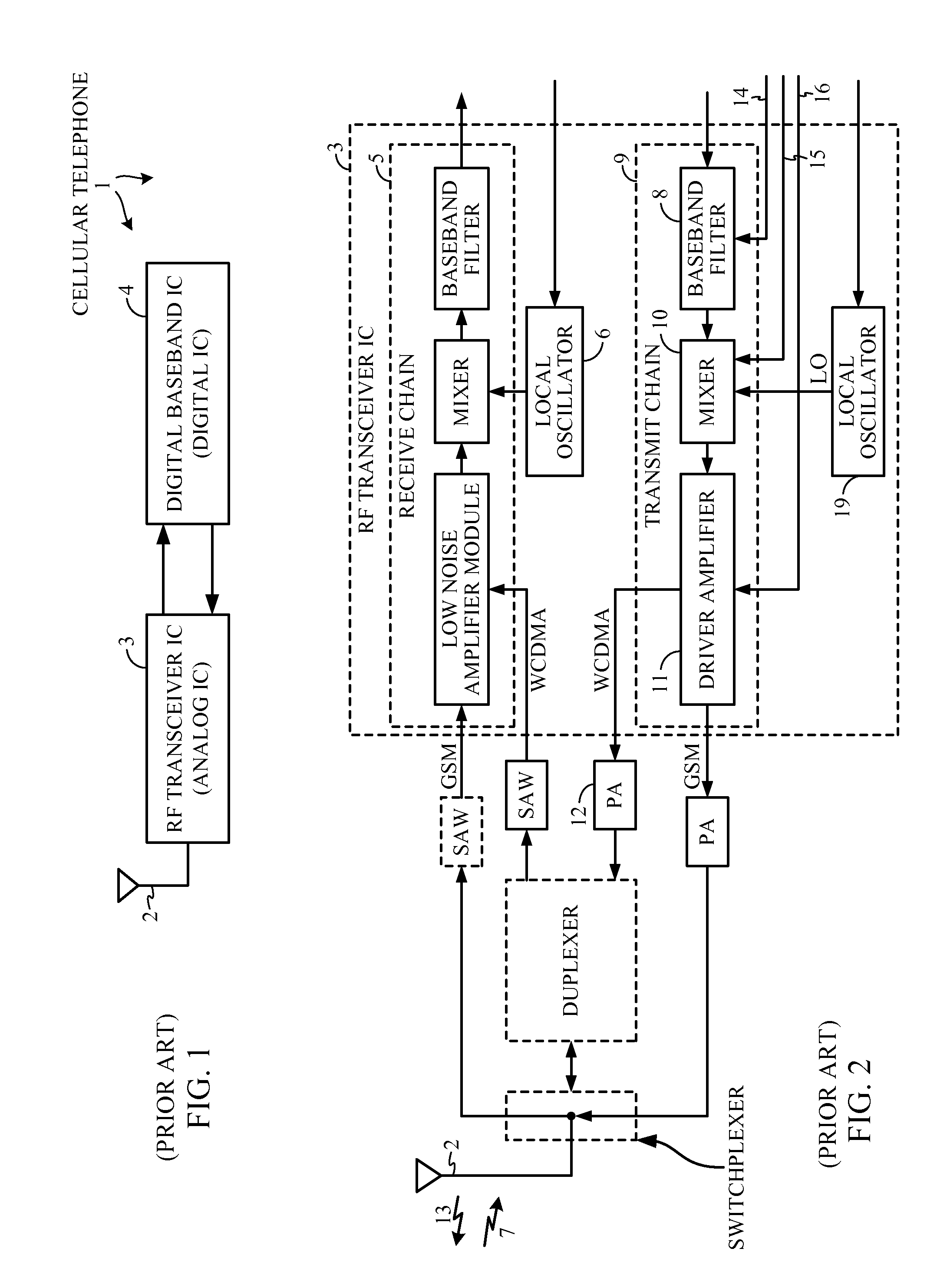

Local oscillator leakage control in direct conversion processes

InactiveUS6960962B2Automatic scanning with simultaneous frequency displaySpatial transmit diversityIntermediate frequencyLocal oscillator

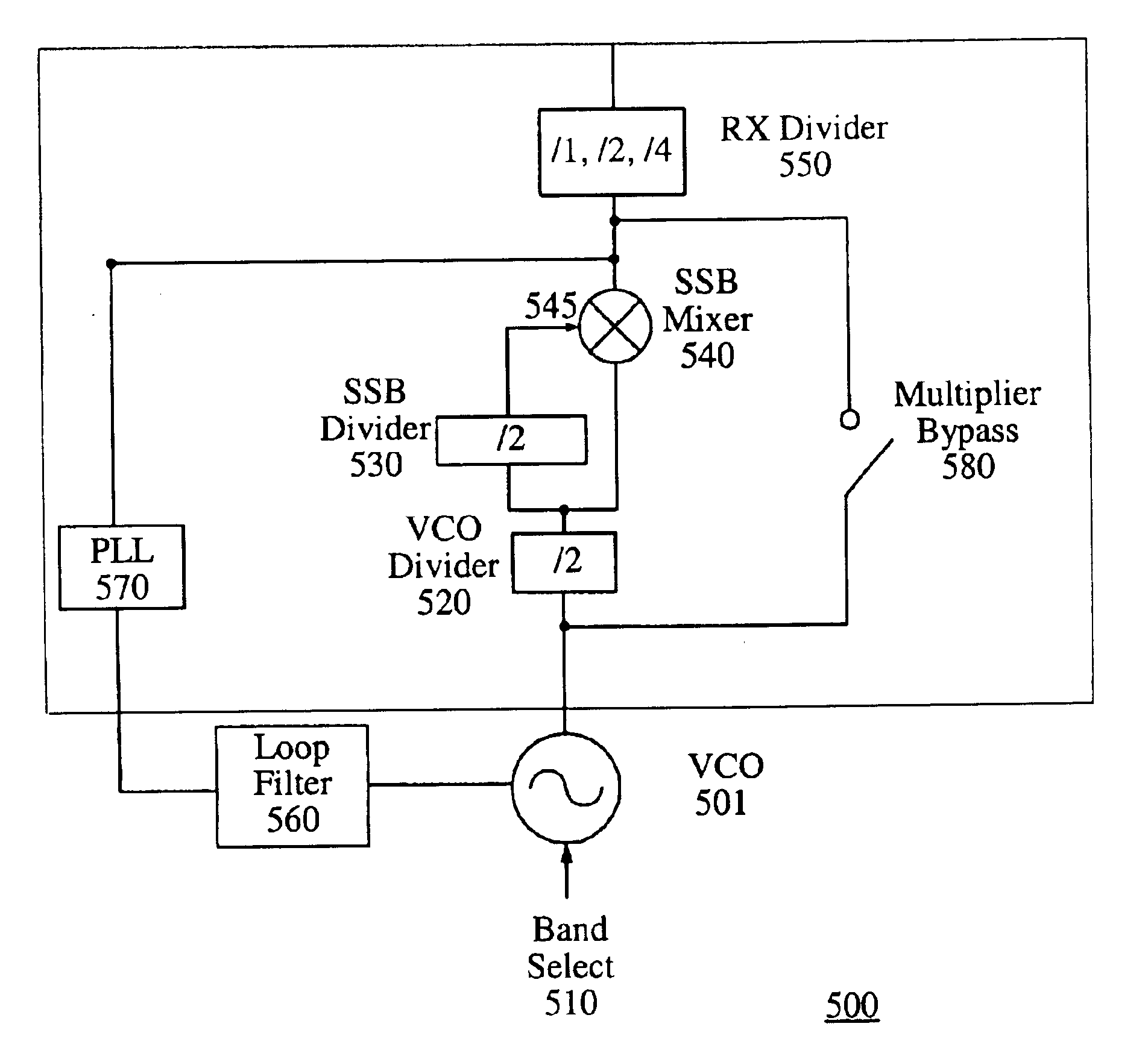

A system and method for generating a local oscillator (LO) frequency in a zero intermediate frequency (IF) receiver or transmitter is presented. A signal is received from a voltage controlled oscillator (VCO). The signal has a VCO frequency. The VCO frequency is divided by a number N to produce a signal having a divided-down frequency. The signal having the VCO frequency is then mixed with the signal having the divided-down frequency to produce an output signal having an output frequency. Local oscillator leakage is reduced. Thus, the receiver or transmitter may operate in multiple wireless communication bands and modes and meet the associated specifications.

Owner:QUALCOMM INC

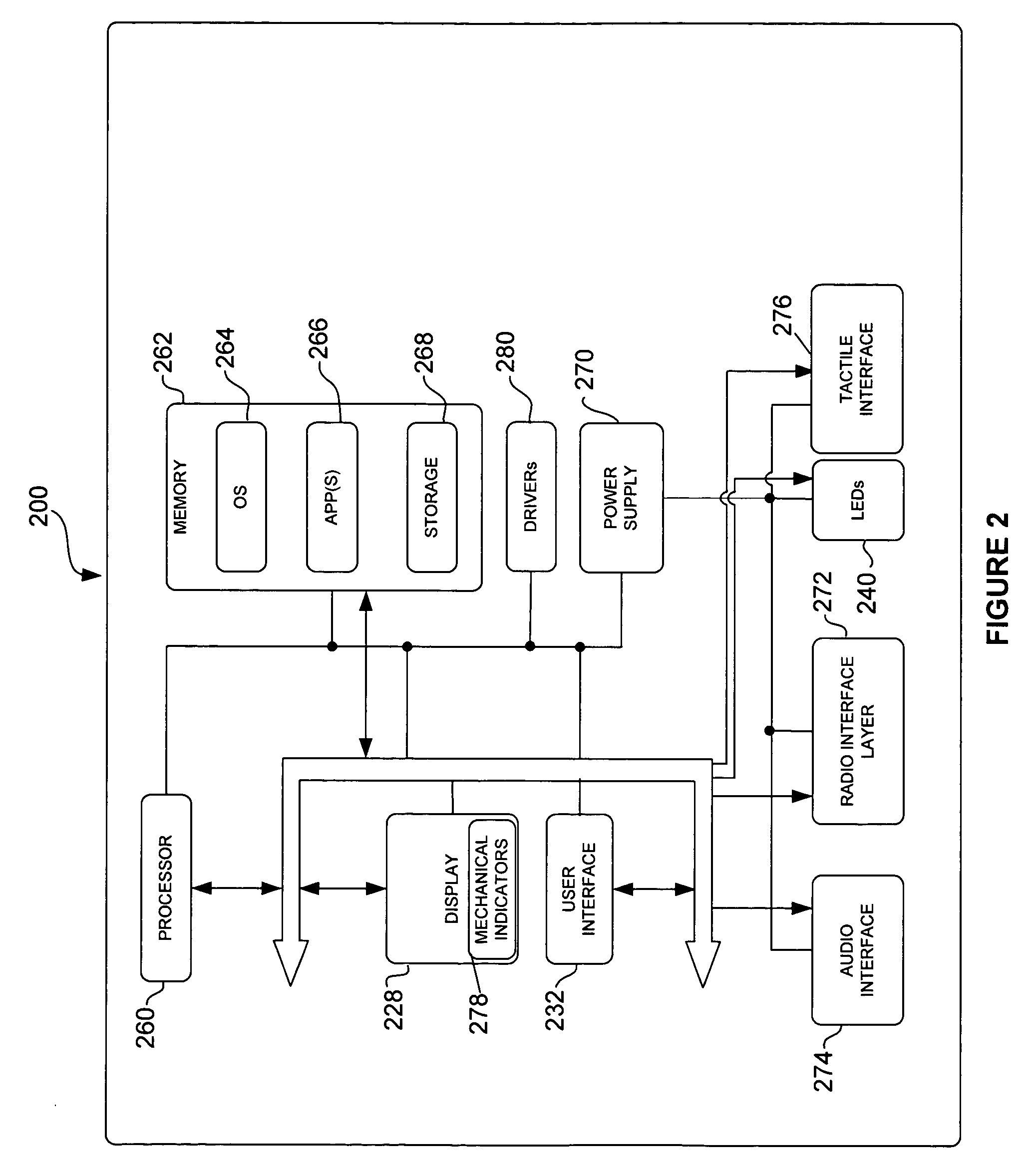

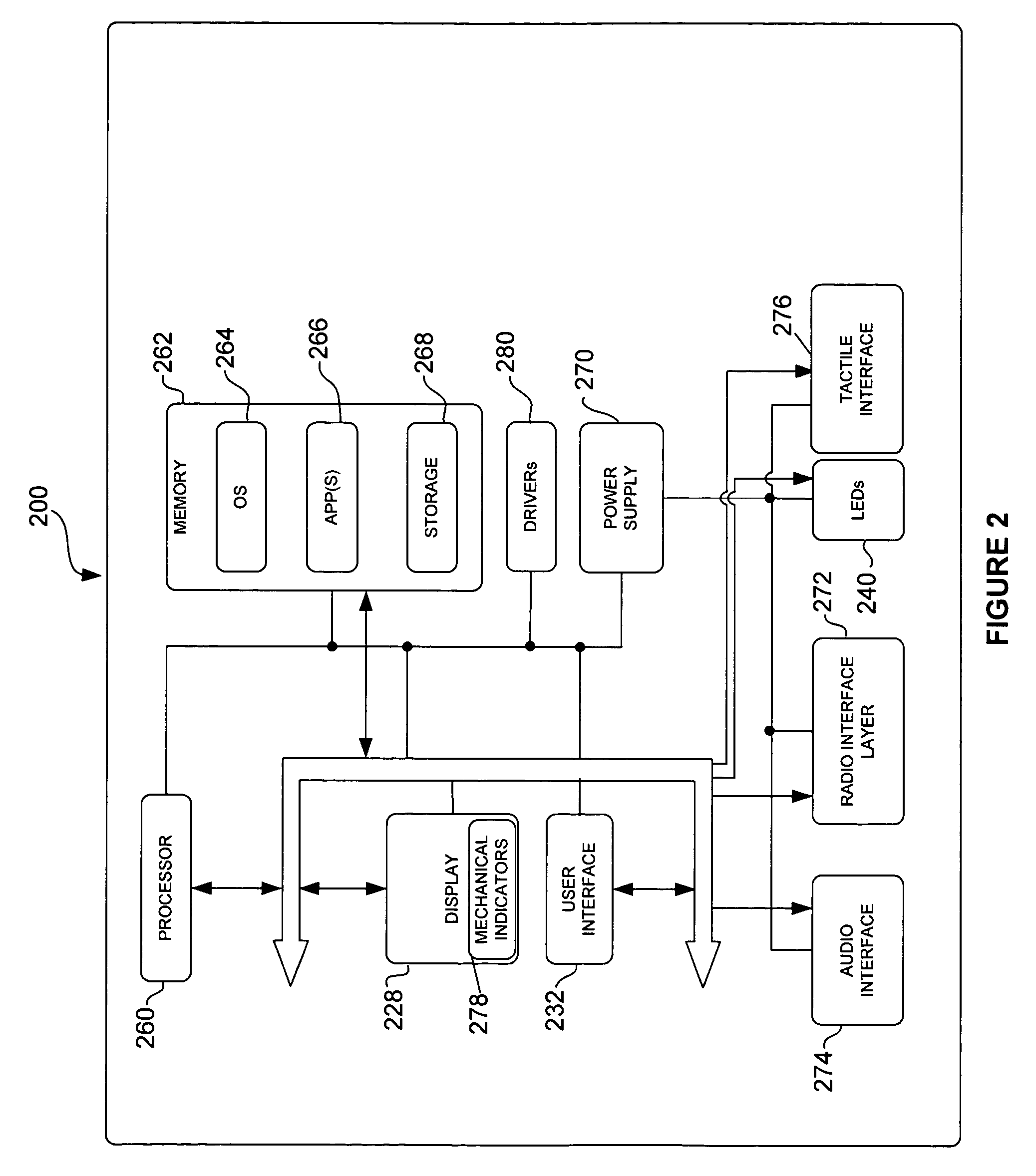

Display of wireless data

InactiveUS20060073851A1Improve customizationBroadcast with distributionAutomatic scanning with simultaneous frequency displayWireless transmissionWireless data

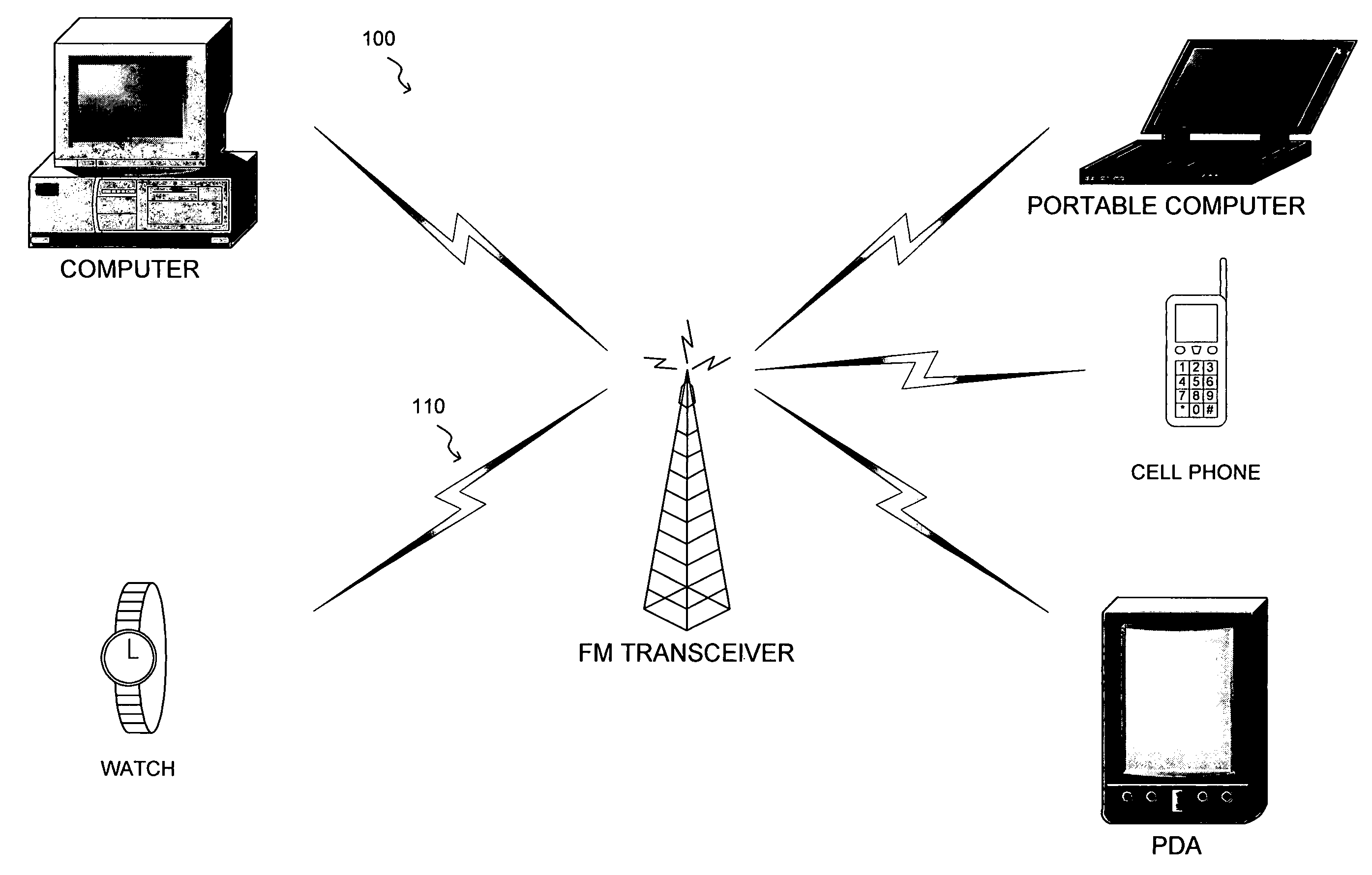

A mobile electronic device for receiving and displaying information from a wireless signal transmission is provided. The device utilizes one or more mechanical and / or digital indicators for displaying the information. One embodiment of the invention provides a smart personal object, such as a watch device, for receiving and displaying wireless transmission information, wherein the object has a traditional style and look. The device is operable to convey received information using hands, sliders, dials, rings, disks, etc. and can be constructed in traditional high fidelity / quality.

Owner:MICROSOFT TECH LICENSING LLC

Display of wireless data

InactiveUS7593755B2Improve customizationBroadcast with distributionAutomatic scanning with simultaneous frequency displayWireless transmissionWireless data

A mobile electronic device for receiving and displaying information from a wireless signal transmission is provided. The device utilizes one or more mechanical and / or digital indicators for displaying the information. One embodiment of the invention provides a smart personal object, such as a watch device, for receiving and displaying wireless transmission information, wherein the object has a traditional style and look. The device is operable to convey received information using hands, sliders, dials, rings, disks, etc. and can be constructed in traditional high fidelity / quality.

Owner:MICROSOFT TECH LICENSING LLC

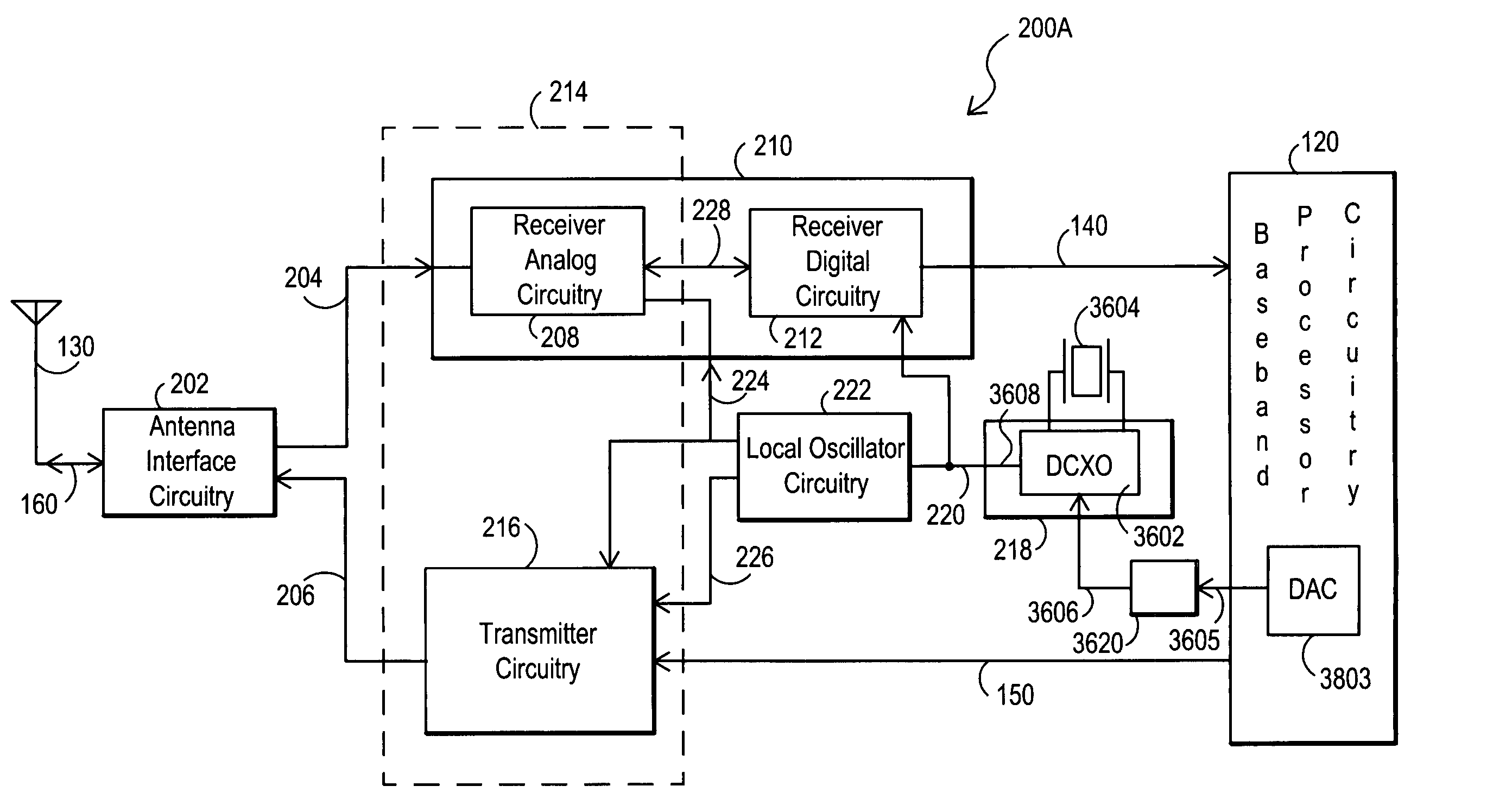

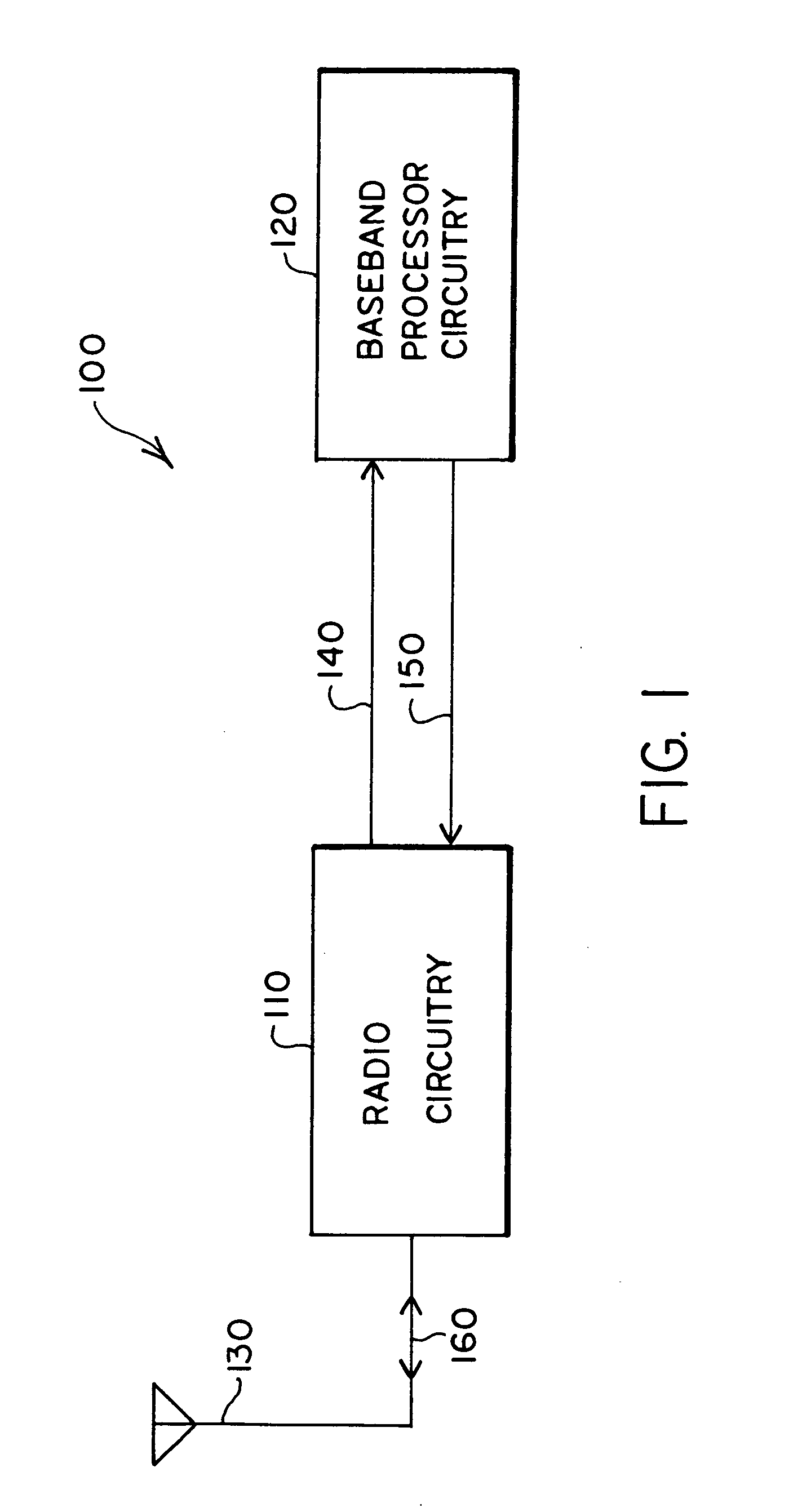

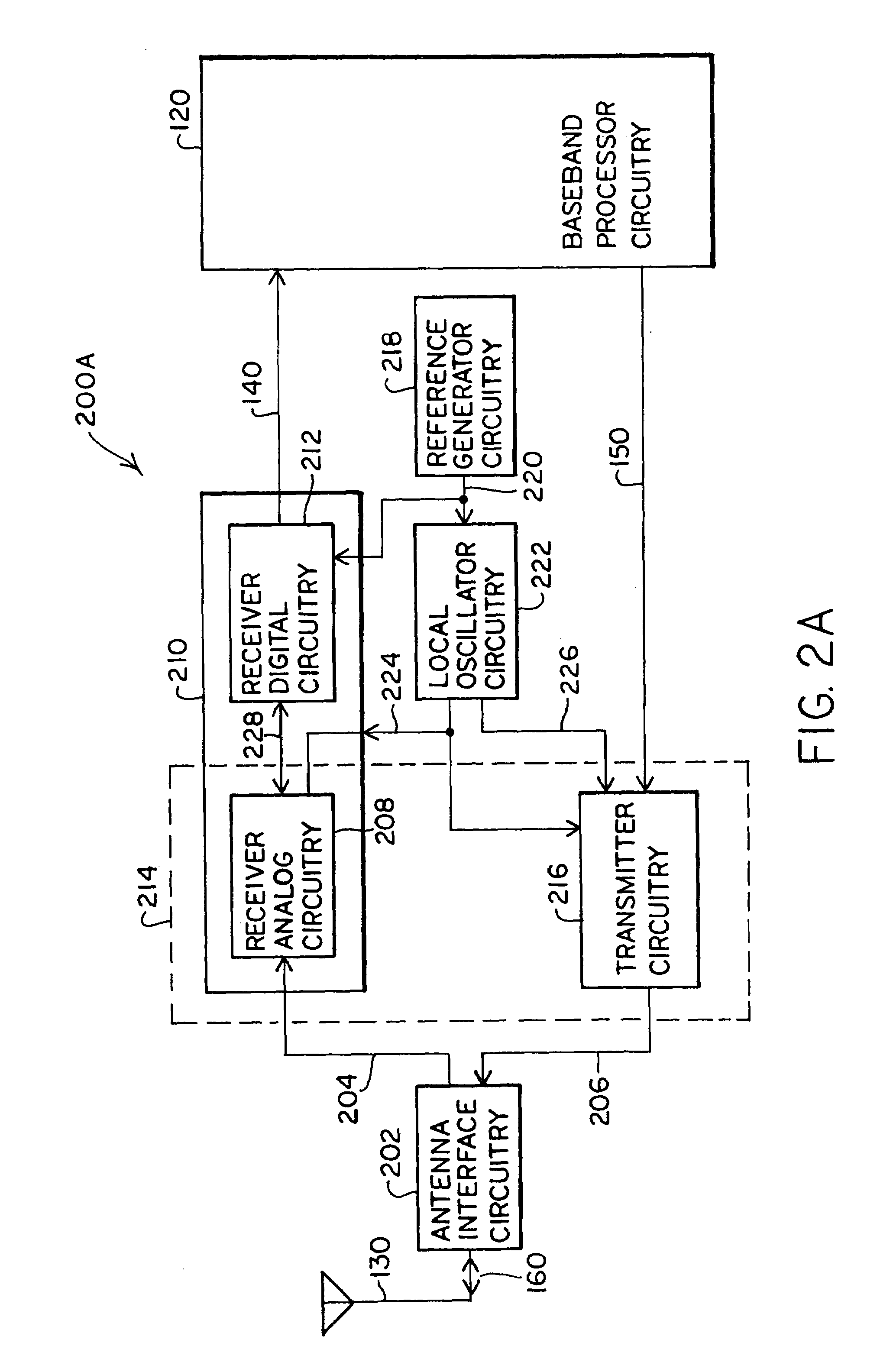

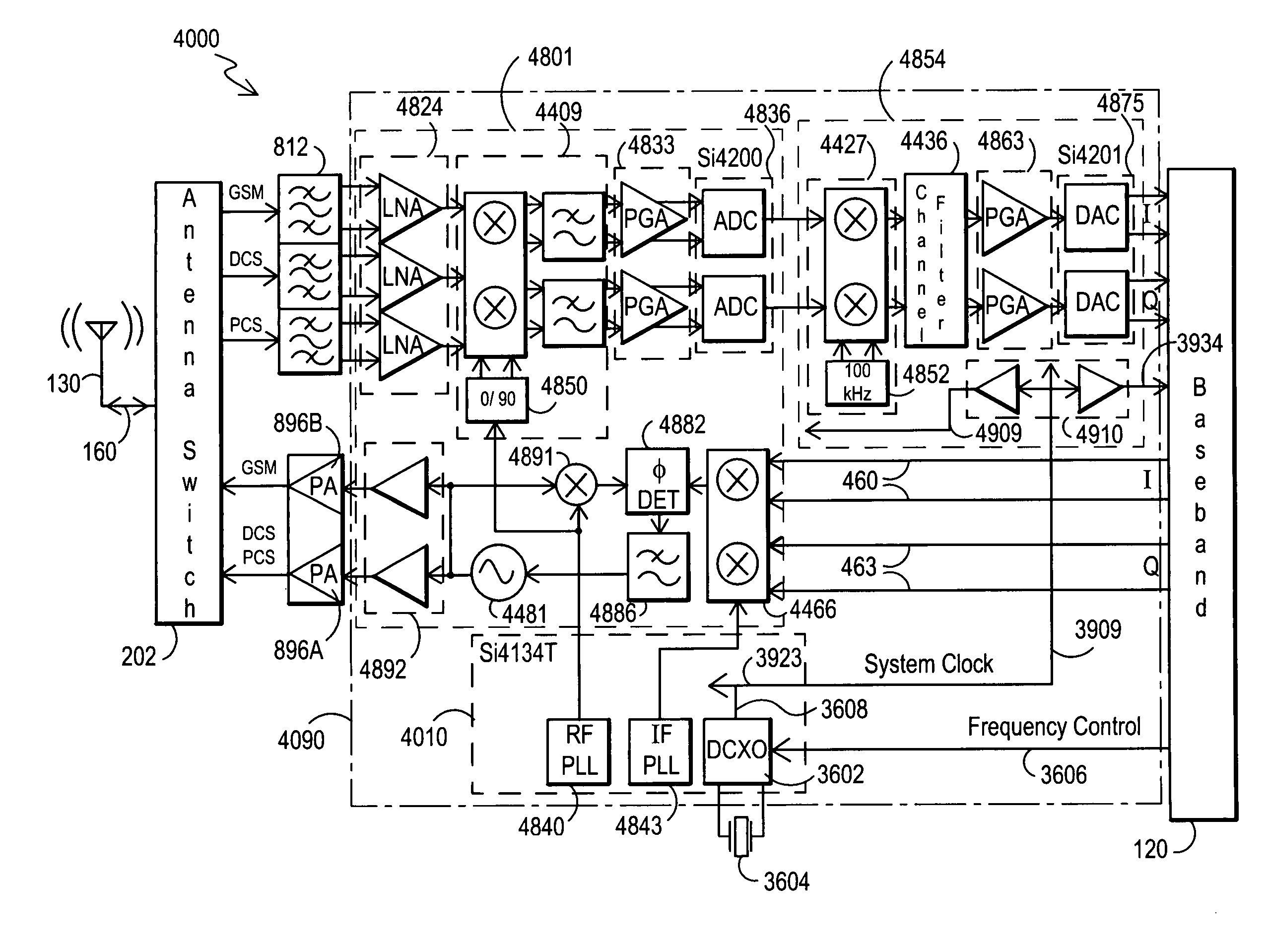

Systems and methods for providing an adjustable reference signal to RF circuitry

InactiveUS7035607B2Guaranteed interference effectReduce the impact of interferenceAutomatic scanning with simultaneous frequency displayPulse automatic controlControl signalEngineering

Frequency modification circuitry may be employed as part of a crystal oscillator circuit to generate a reference signal with adjustable frequency. The frequency modification circuitry may be implemented as part of a crystal oscillator circuit that includes digitally controlled crystal oscillator (“DCXO”) circuitry and a crystal. The frequency modification circuitry may adjust the frequency of the reference signal in response to one or more frequency control signals. In one example, the frequency modification circuitry may include variable capacitors such as one or more continuously variable and / or discretely variable capacitors for providing coarse and / or fine adjustment of the reference signal frequency.

Owner:SILICON LAB INC

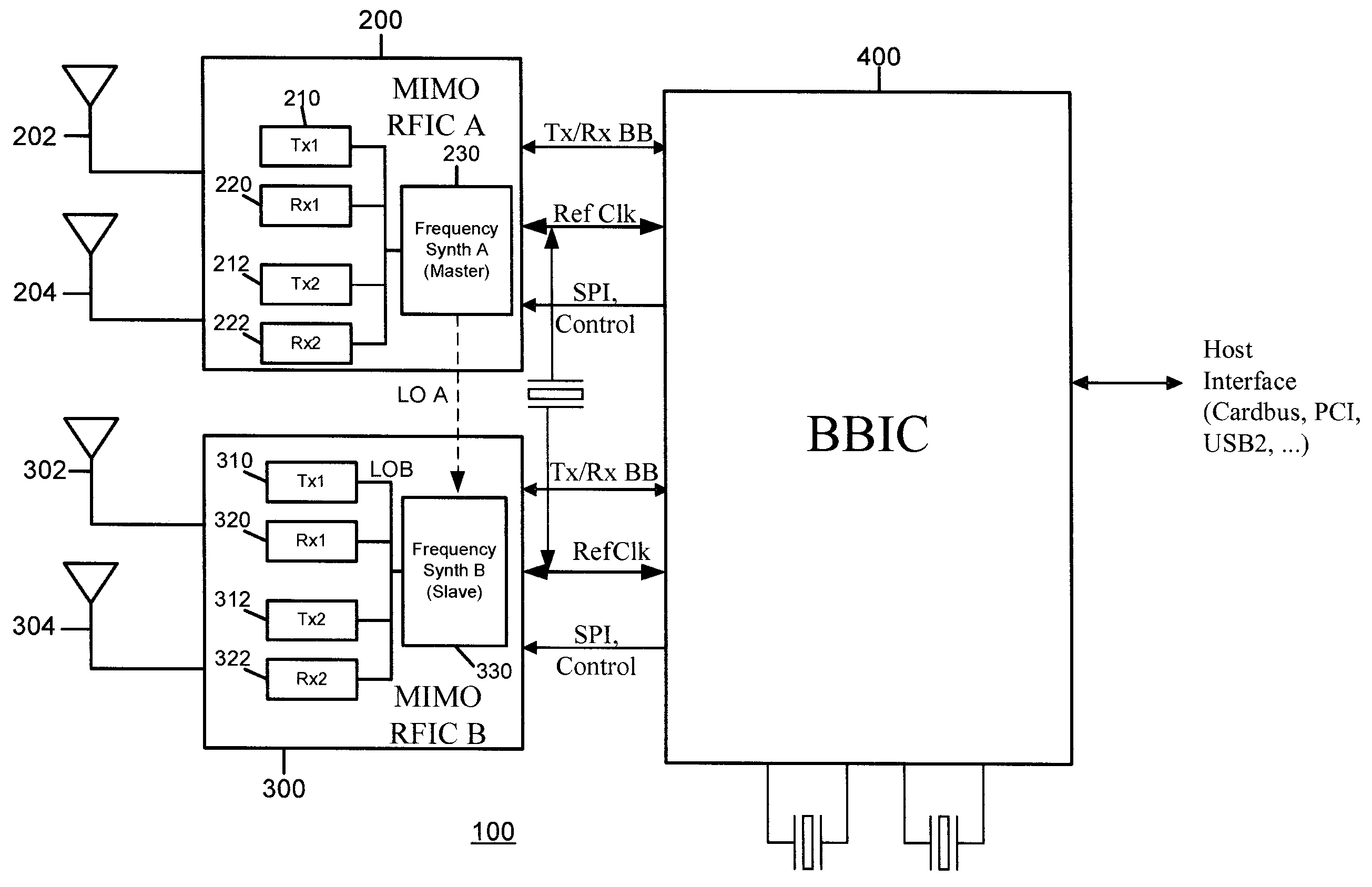

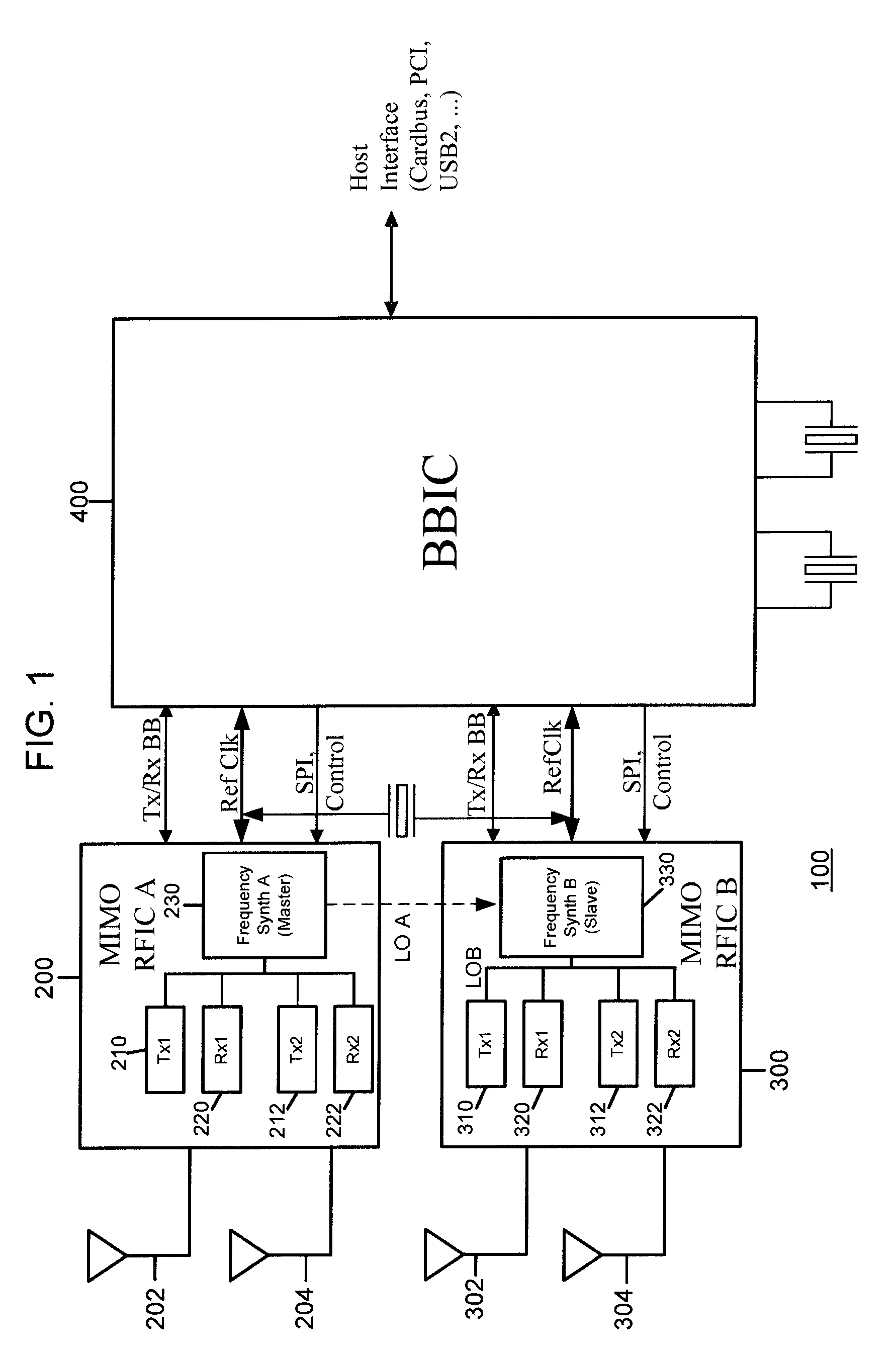

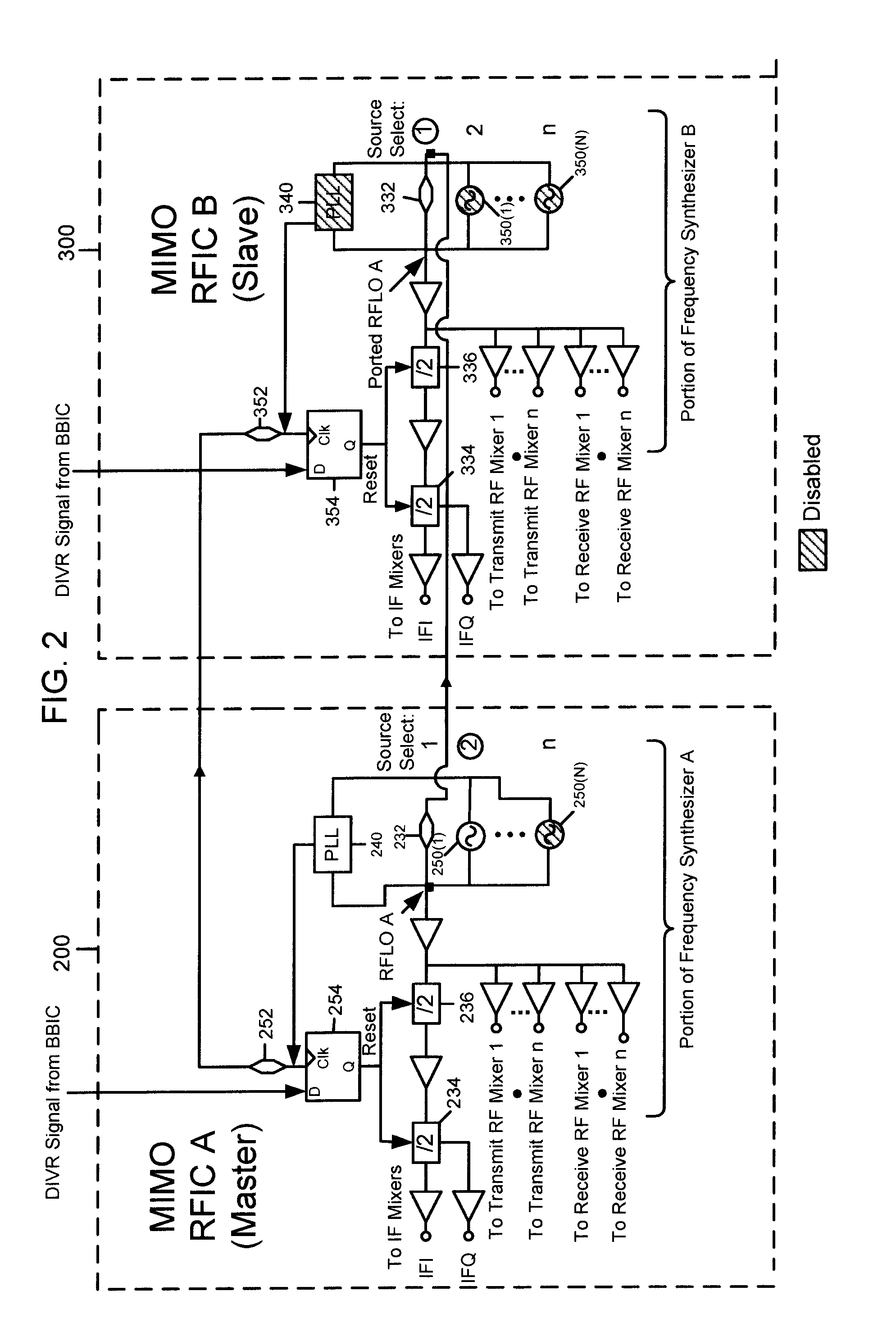

Master-Slave Local Oscillator Porting Between Radio Integrated Circuits

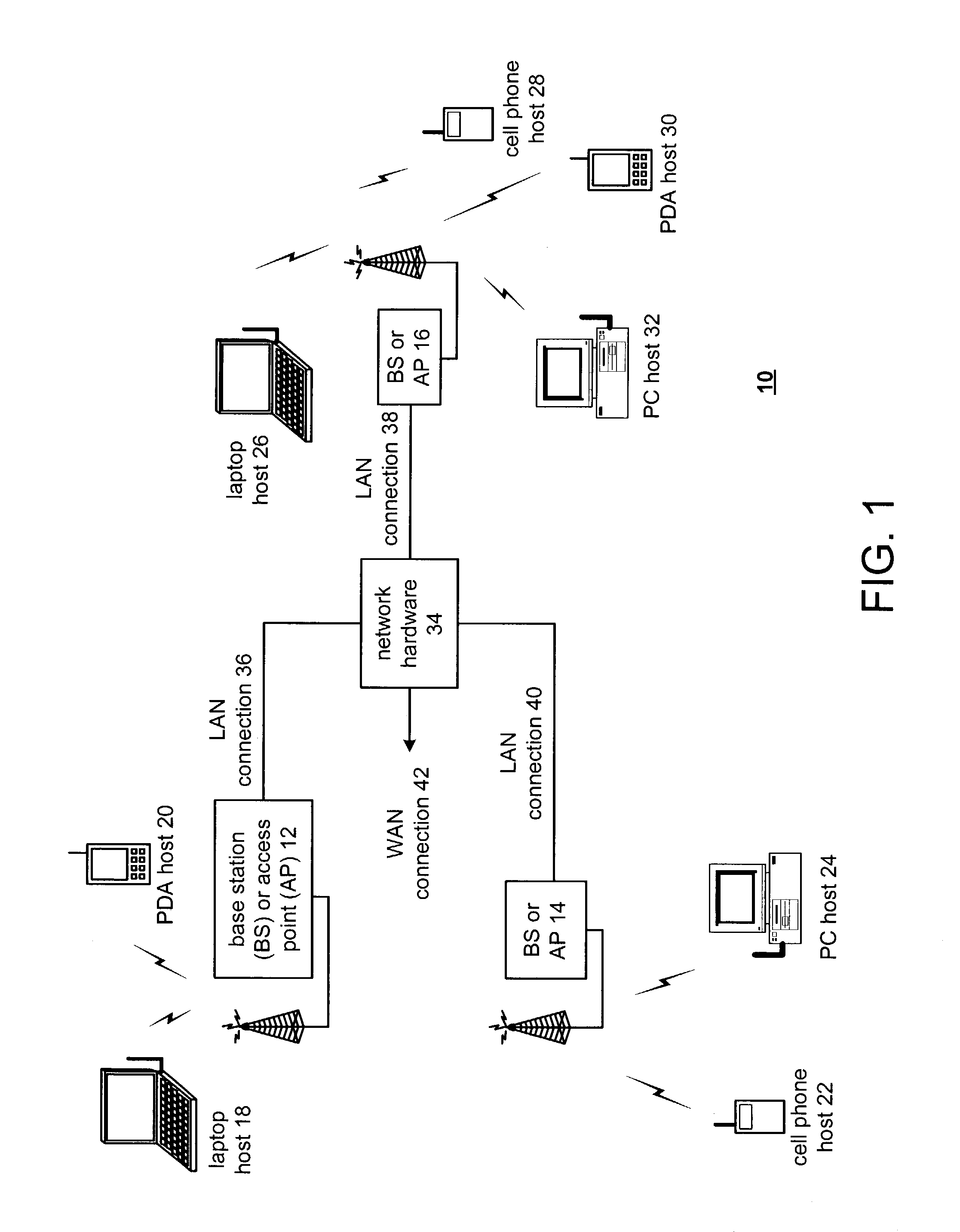

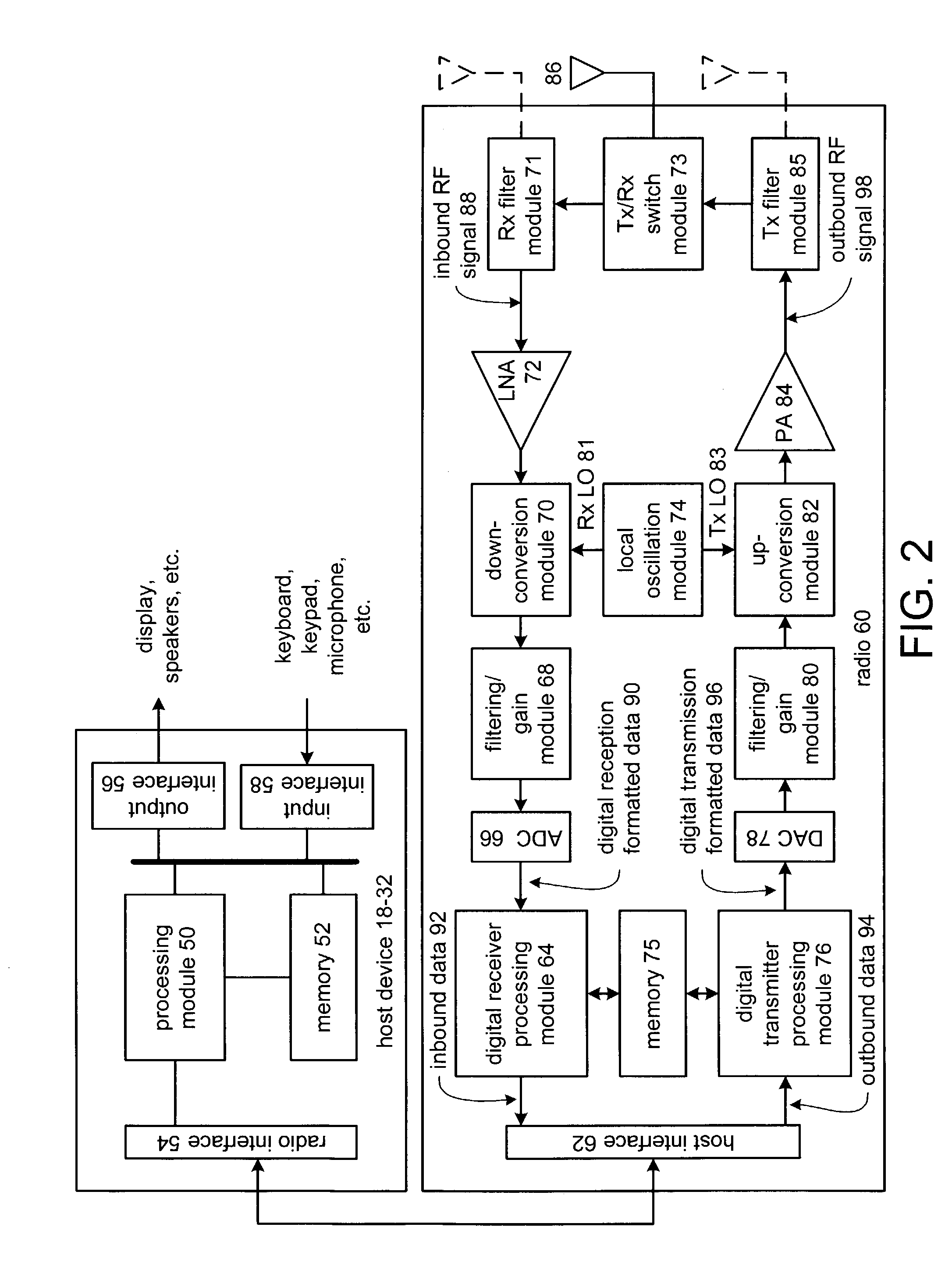

ActiveUS20050064892A1Improve performanceAutomatic scanning with simultaneous frequency displayPulse automatic controlLocal oscillator signalRFIC

A technique to share a local oscillator signal between two radio frequency integrated circuits (RFICs). The local oscillator signal generated internally by one RFIC is ported to the other RFIC for use in transmit and / or receive operation. The local oscillator signal that is ported may be an RF local oscillator signal. Each RFIC may include a bi-directional port circuit that can be operated to make the RFIC a master, slave or may be totally disabled to disable the porting feature. This is particularly useful in RFICs that are used to communicate using MIMO radio algorithms which rely for optimum performance on phase and frequency coherency among a plurality of transmitters and a plurality of receivers.

Owner:IPR LICENSING INC

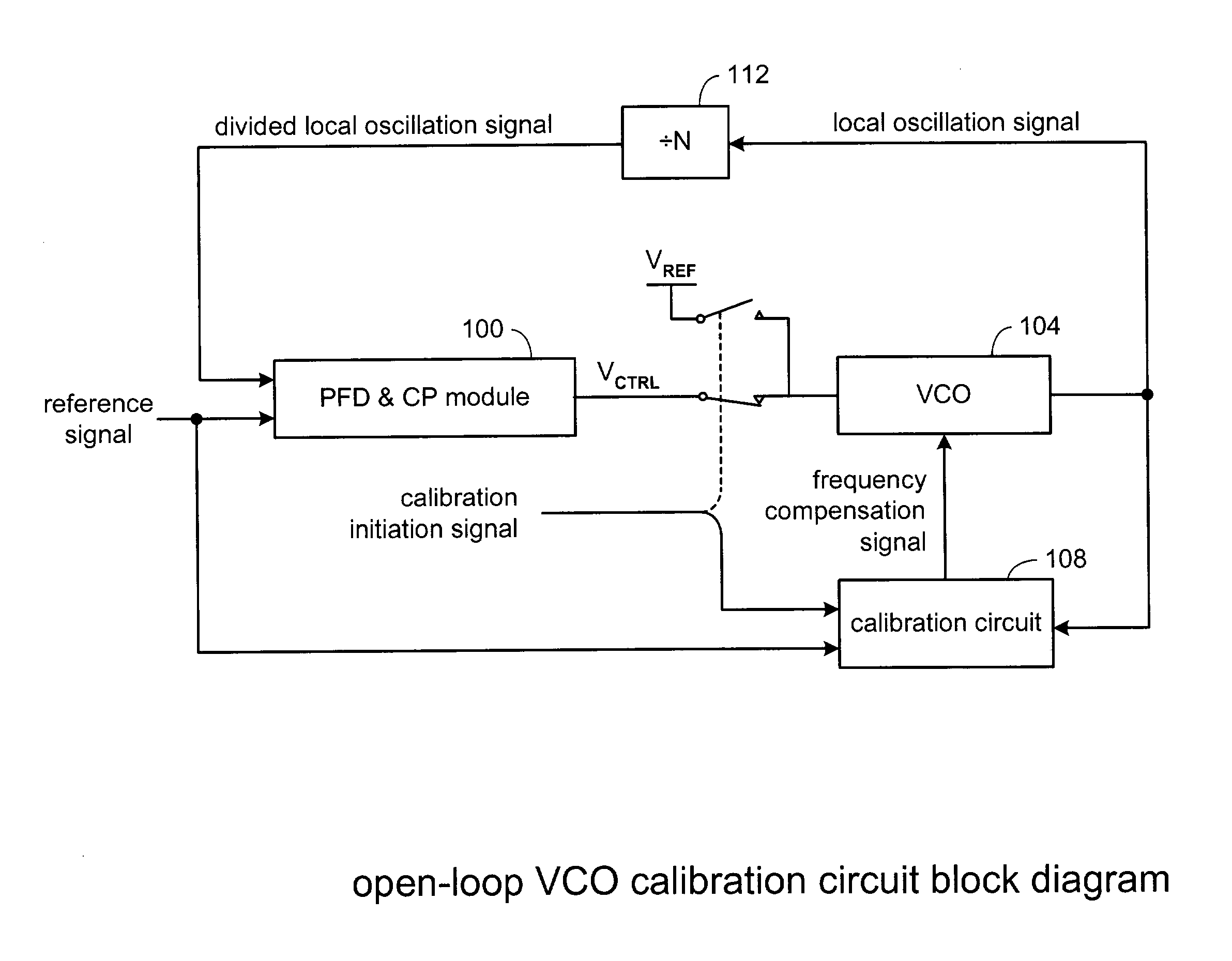

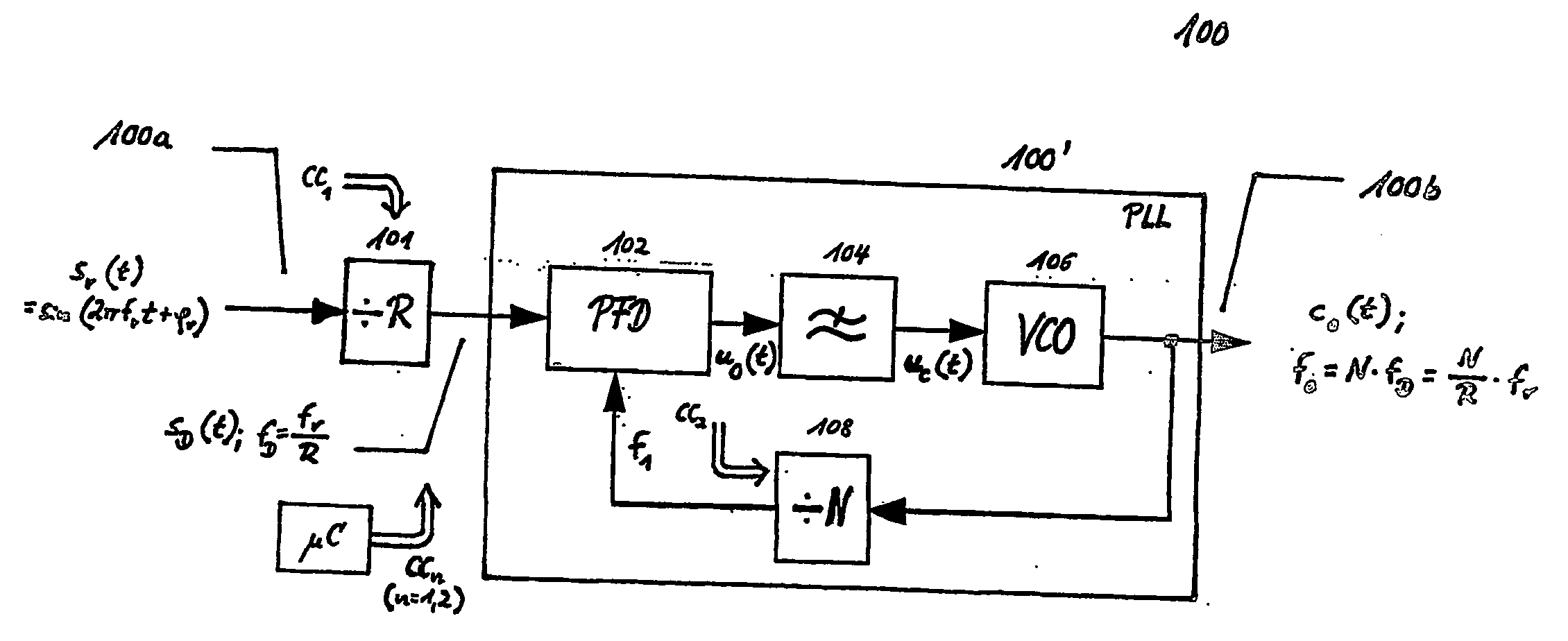

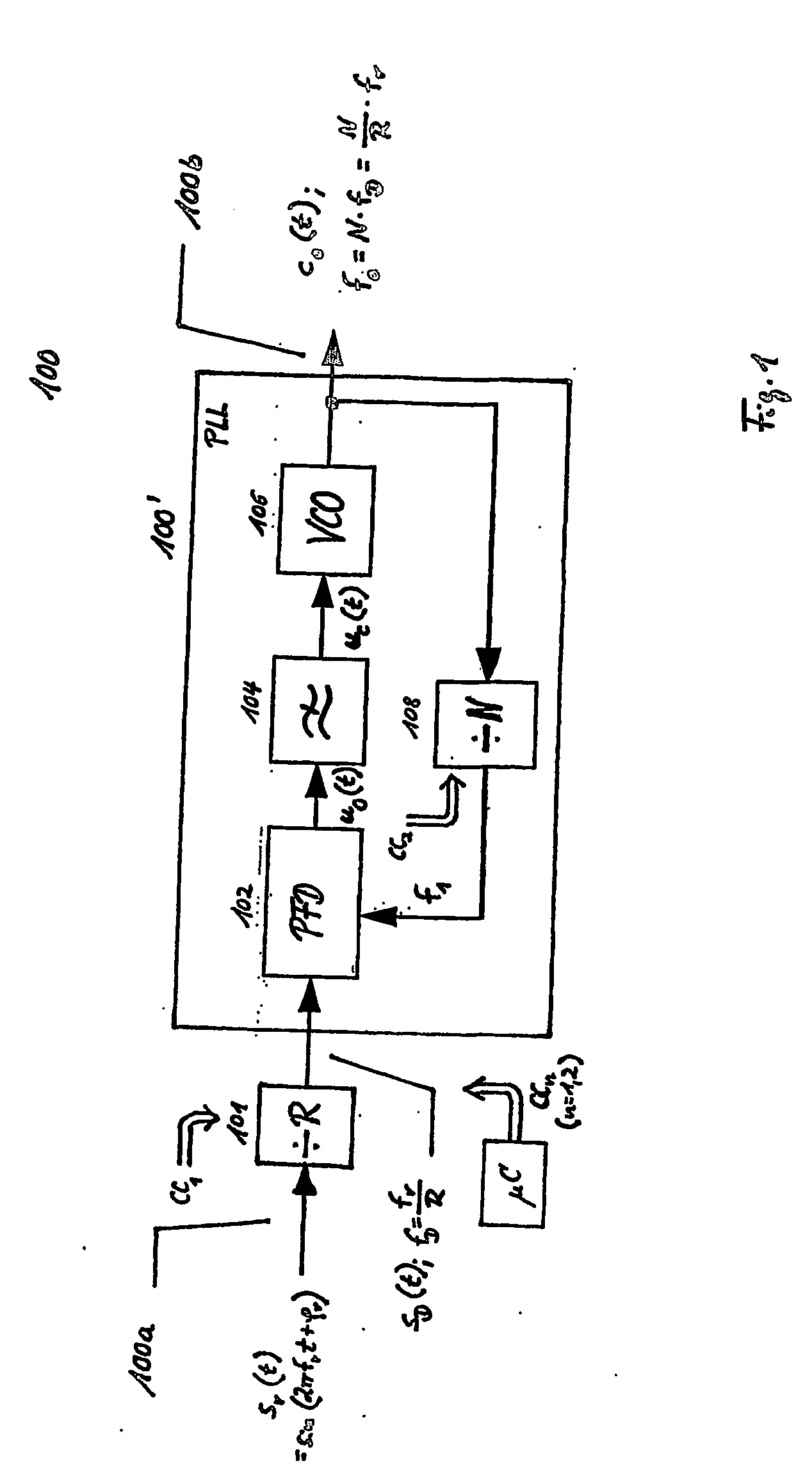

Analog open-loop VCO calibration method

InactiveUS7099643B2Quick calibrationQuick correctionAutomatic scanning with simultaneous frequency displayPulse automatic controlFrequency compensationEngineering

An analog open-loop voltage controlled oscillator (VCO) calibration circuit and method for selecting the frequency of the VCO for a phase locked loop (PLL).A frequency divider module produces a 50% duty cycle divided local oscillation and a 50% duty cycle divided reference signal, wherein the divided signals are substantially equal. A period-to-voltage conversion module converts the divided local oscillation signal and the divided reference signal to voltages proportional to the divided signals. A comparator module produces a frequency adjustment signal based on a comparison of the proportional voltages and couples the frequency adjustment signal to a logic module which produces a frequency compensation signal based on the frequency adjustment signal. The frequency compensation signal functions to adjust the configuration of switched capacitors in a capacitor bank, coupled to the VCO tuned circuit, until the divided local oscillation signal is substantially equal to the divided reference signal.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

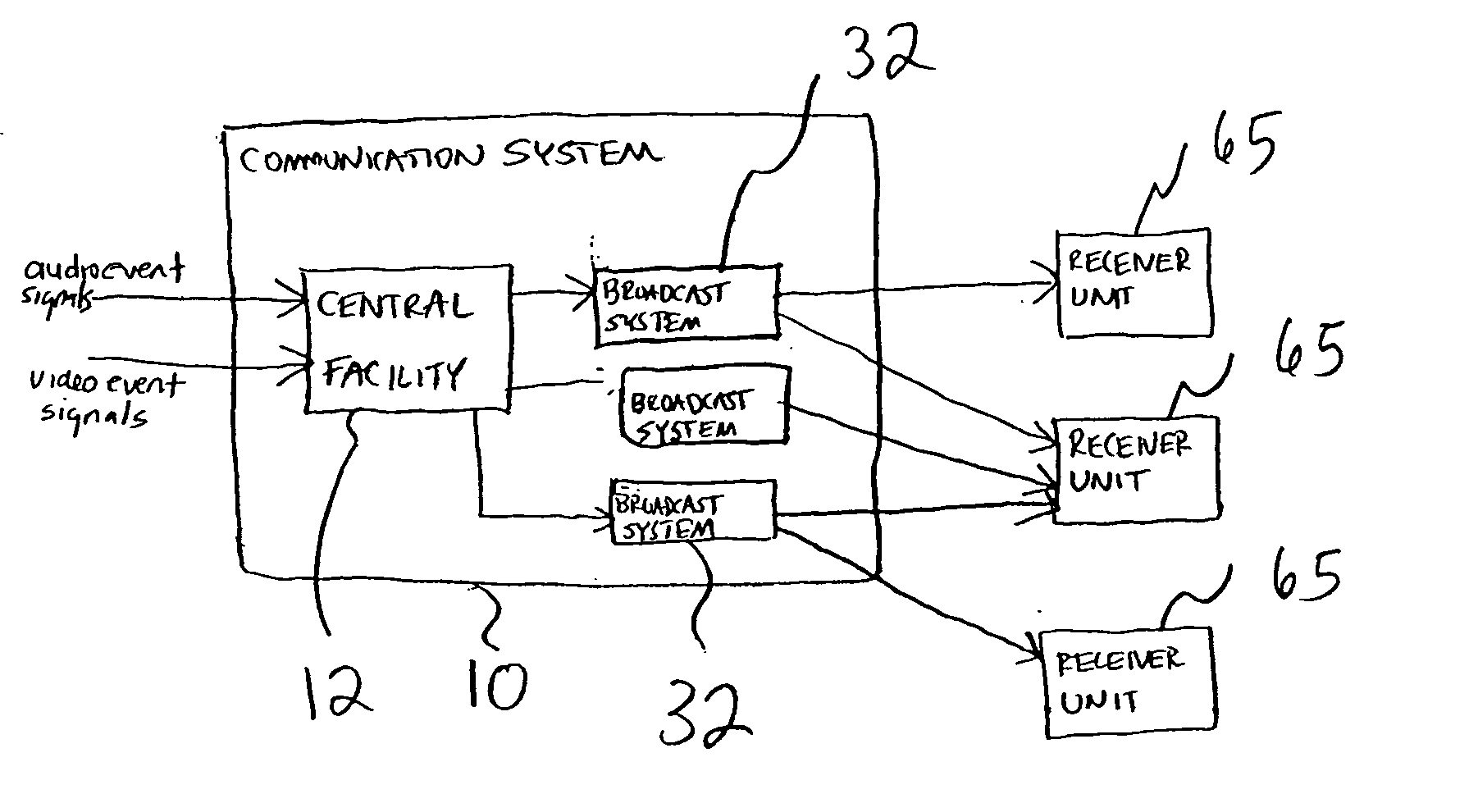

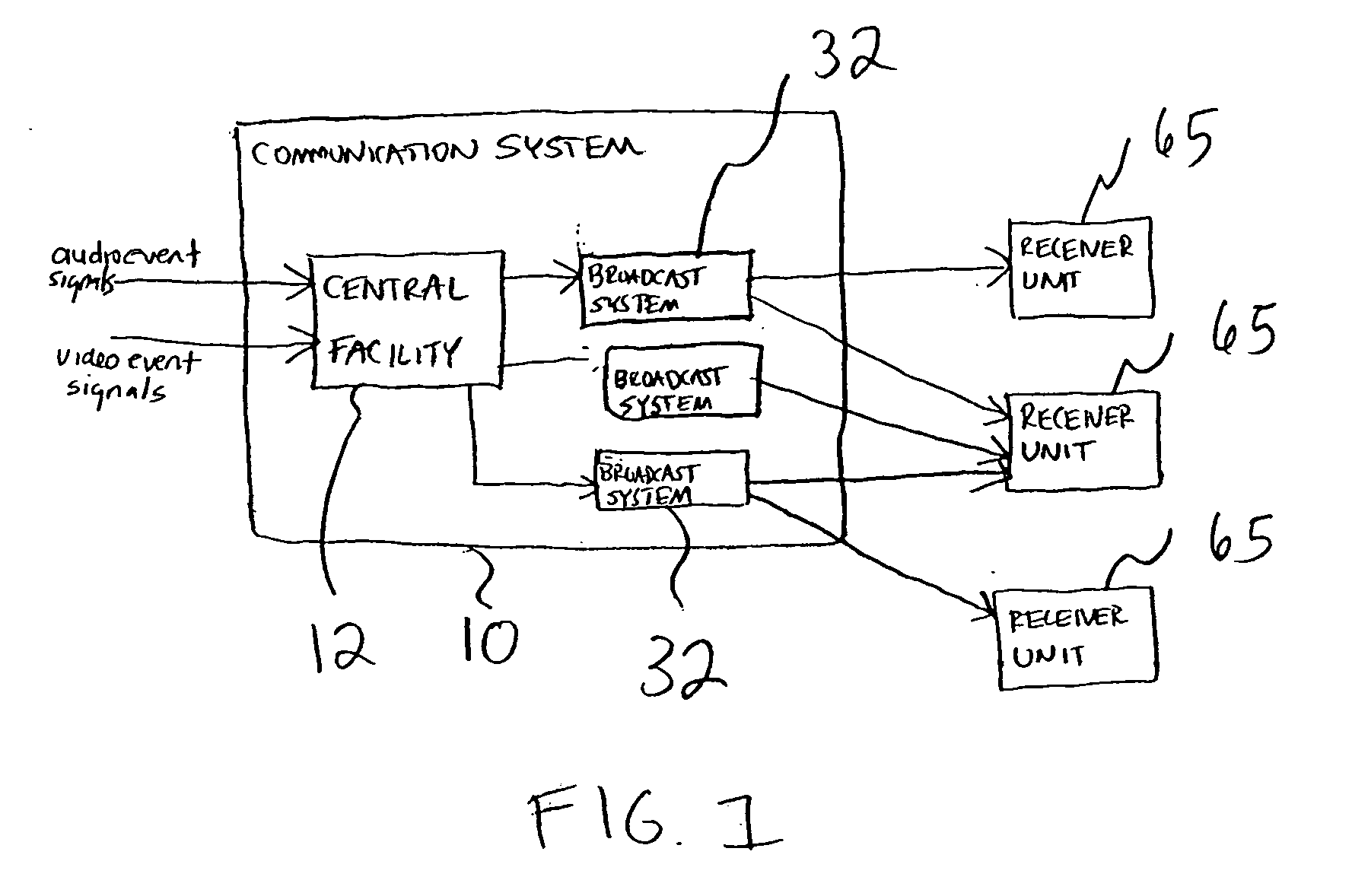

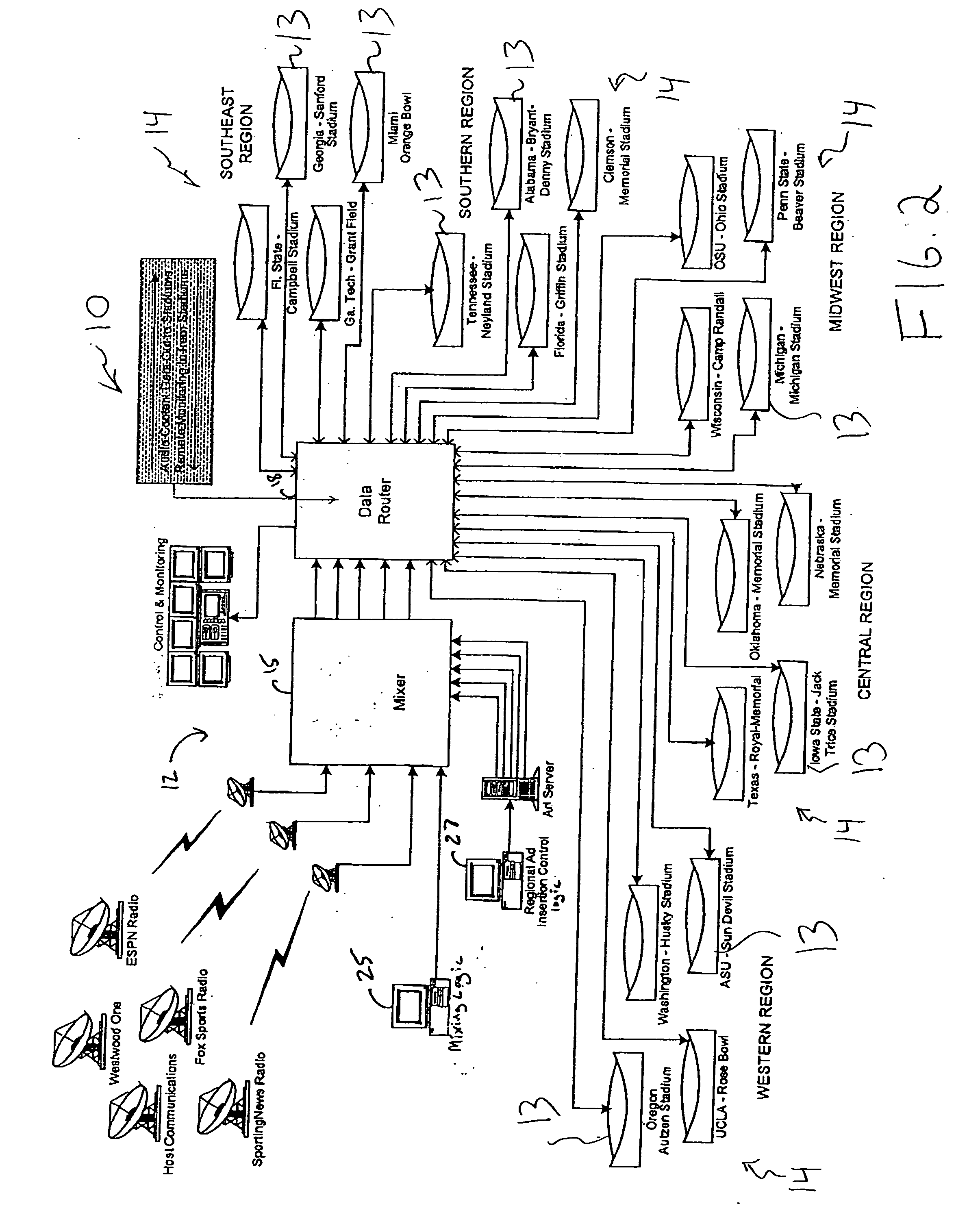

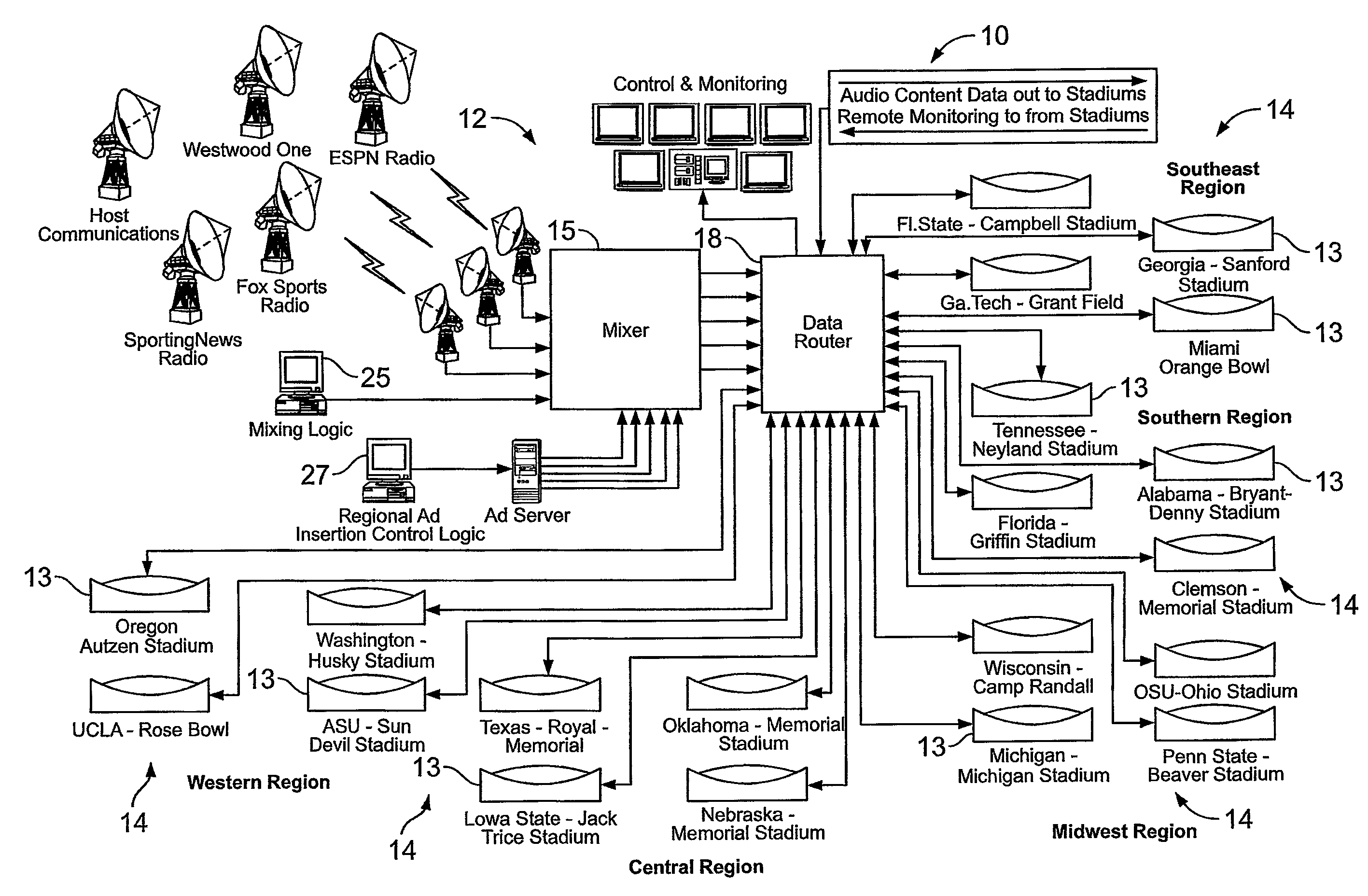

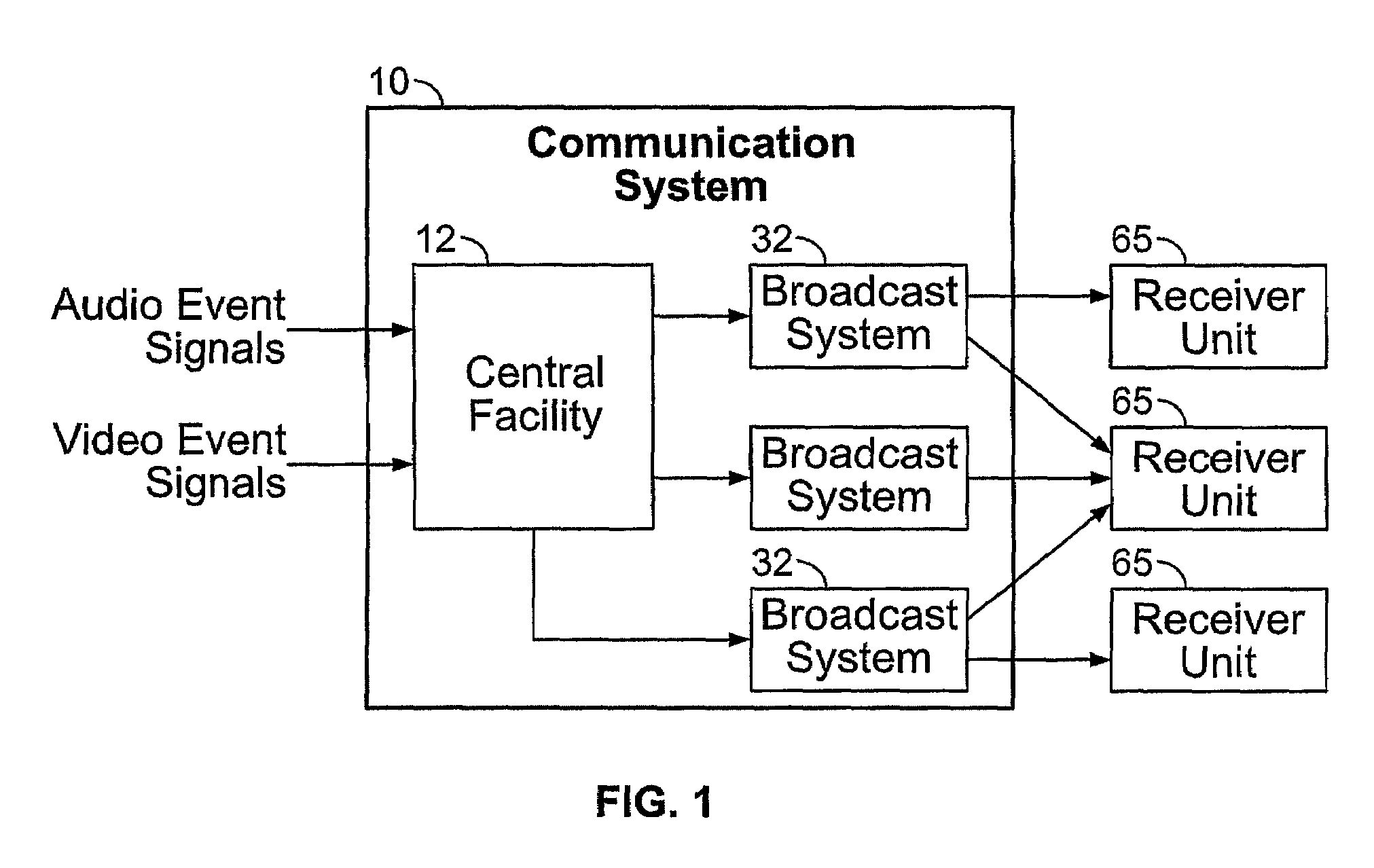

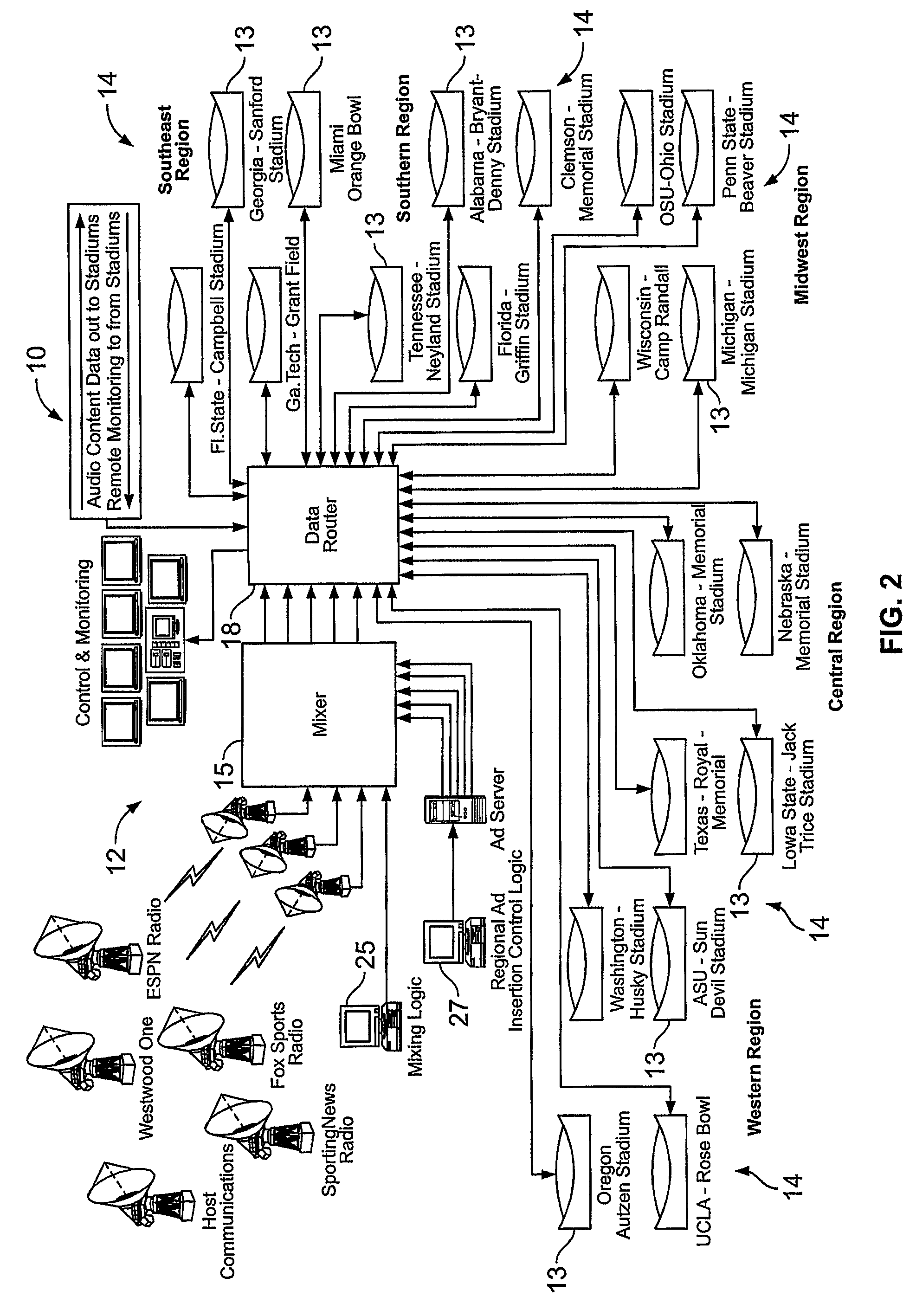

System and method for providing event spectators with audio/video signals pertaining to remote events

InactiveUS20050210512A1Automatic scanning with simultaneous frequency displayBroadcast specific applicationsComputer scienceAudio frequency

A system and method for providing content for access by a portable device at an event are provided. The system includes an interface to receive signals from a plurality of sources. The plurality of sources are located at an event and remote from the event. The signals define event content and non-event content. The system further includes a processor for processing the received signals to generate combined signals based upon the received signals from the plurality of sources. The system also includes a transmitter for transmitting to a plurality of portable devices at the event the combined signals. The combined signals are configured to allow a user to select content using the portable device receiving the combined signals.

Owner:IMMERSION ENTERTAINMENT L L C

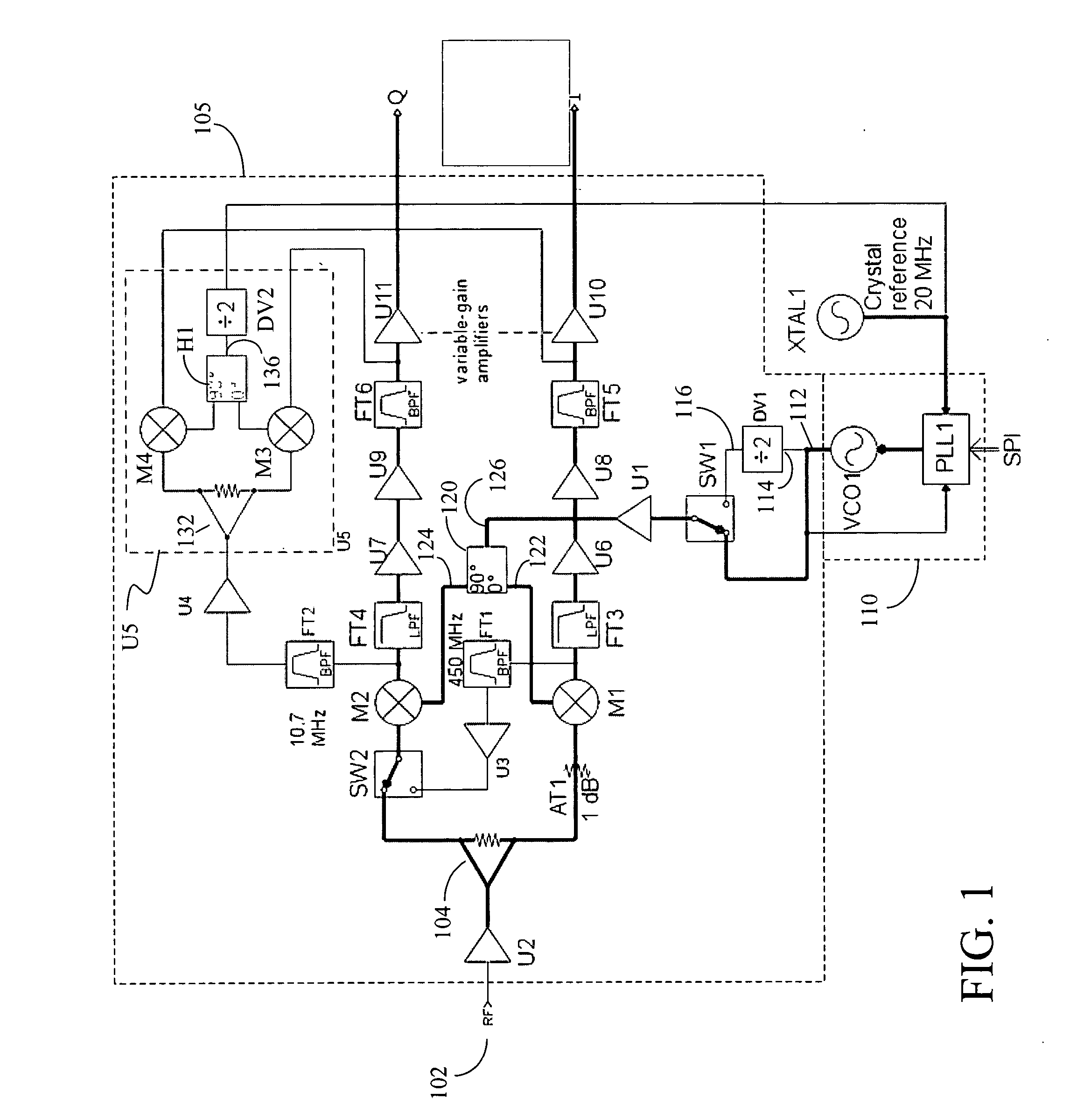

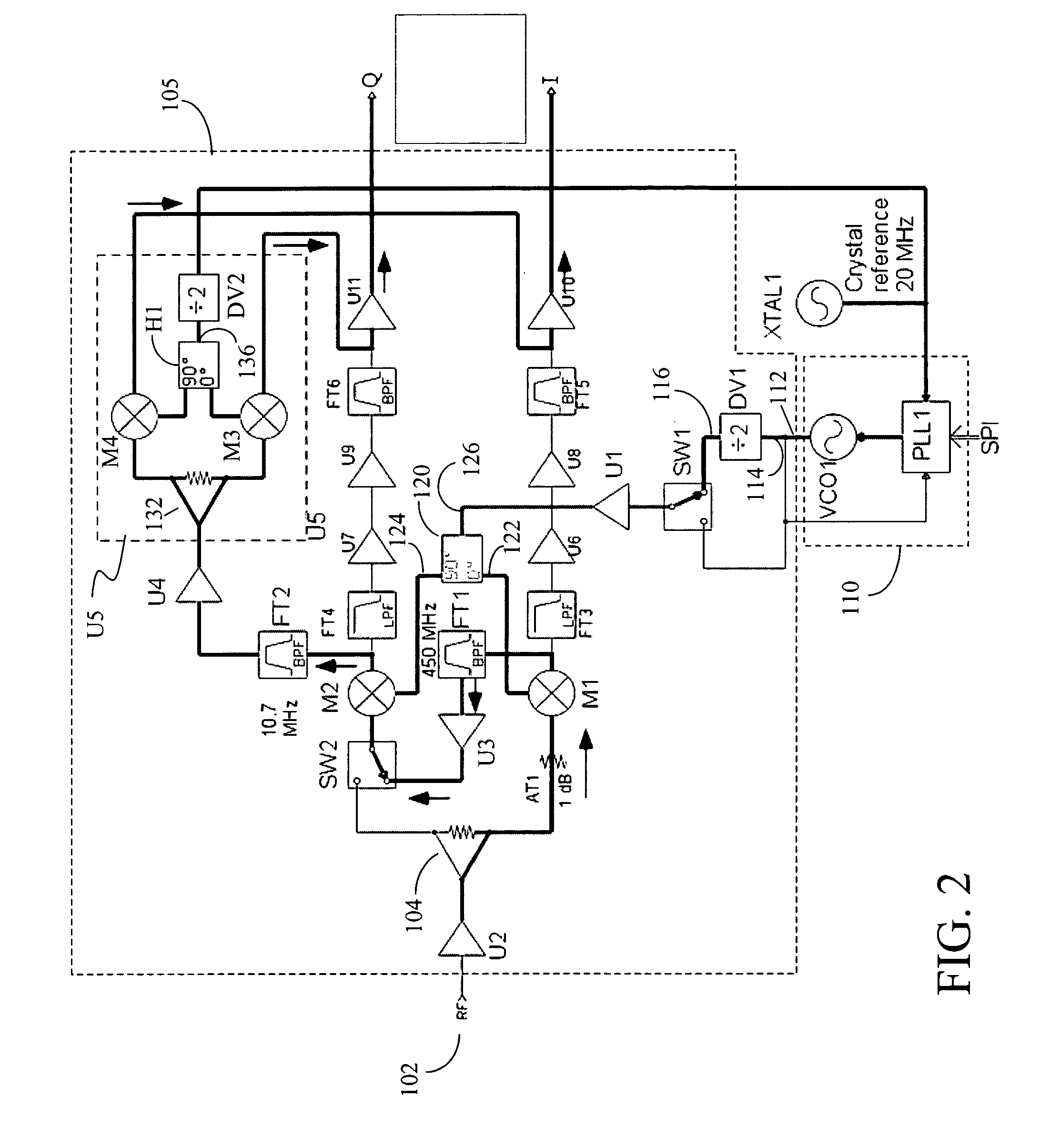

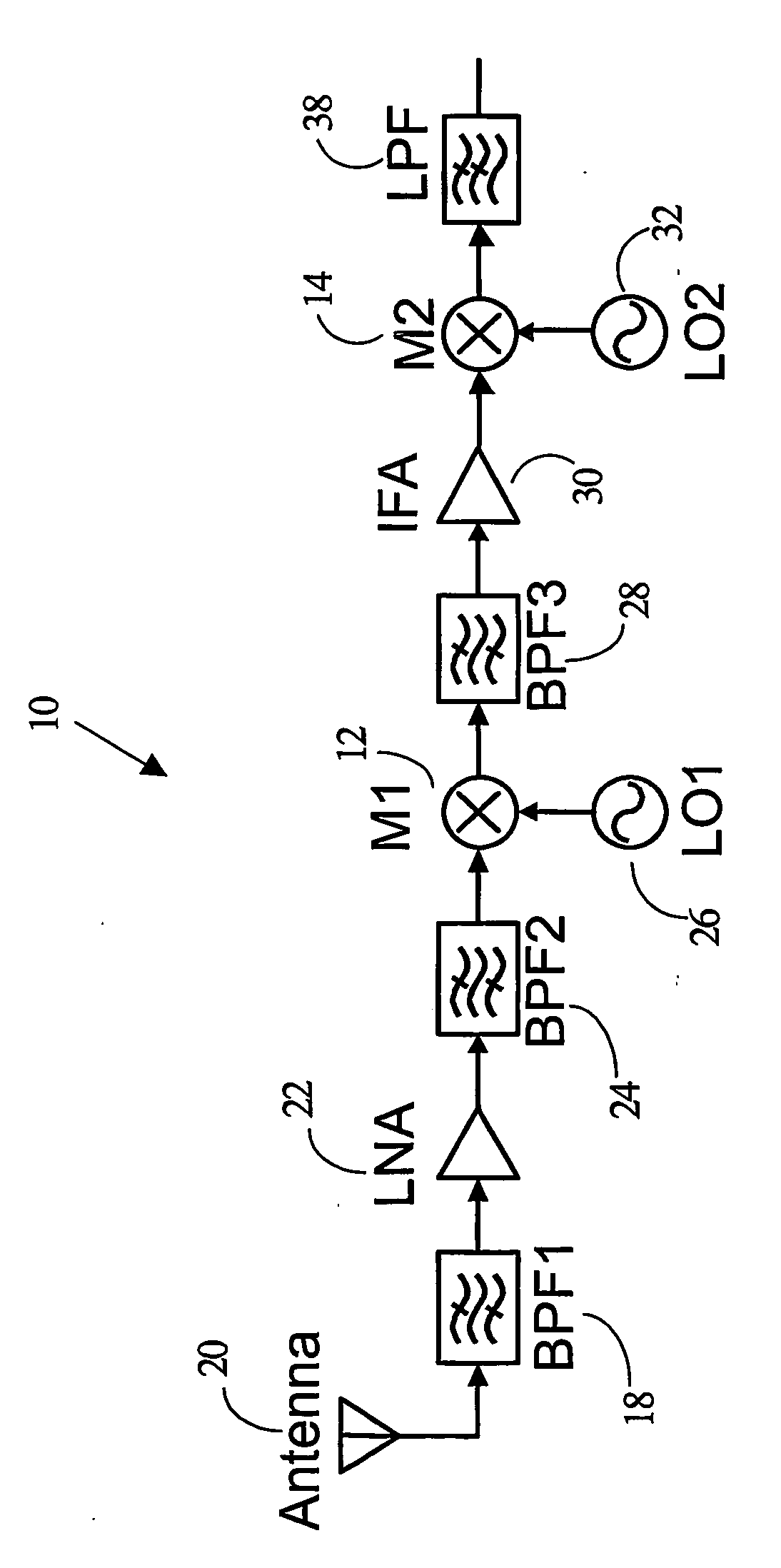

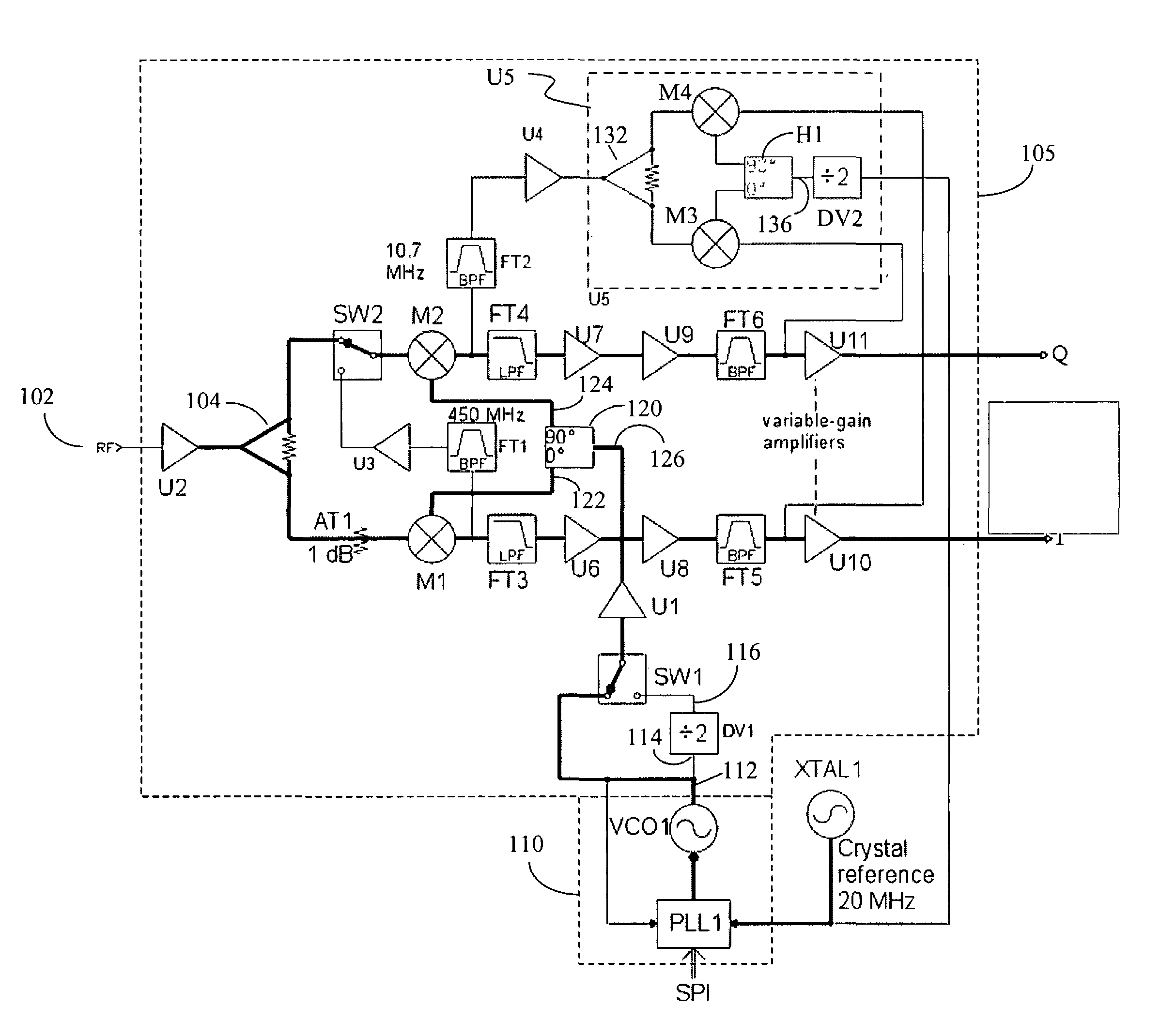

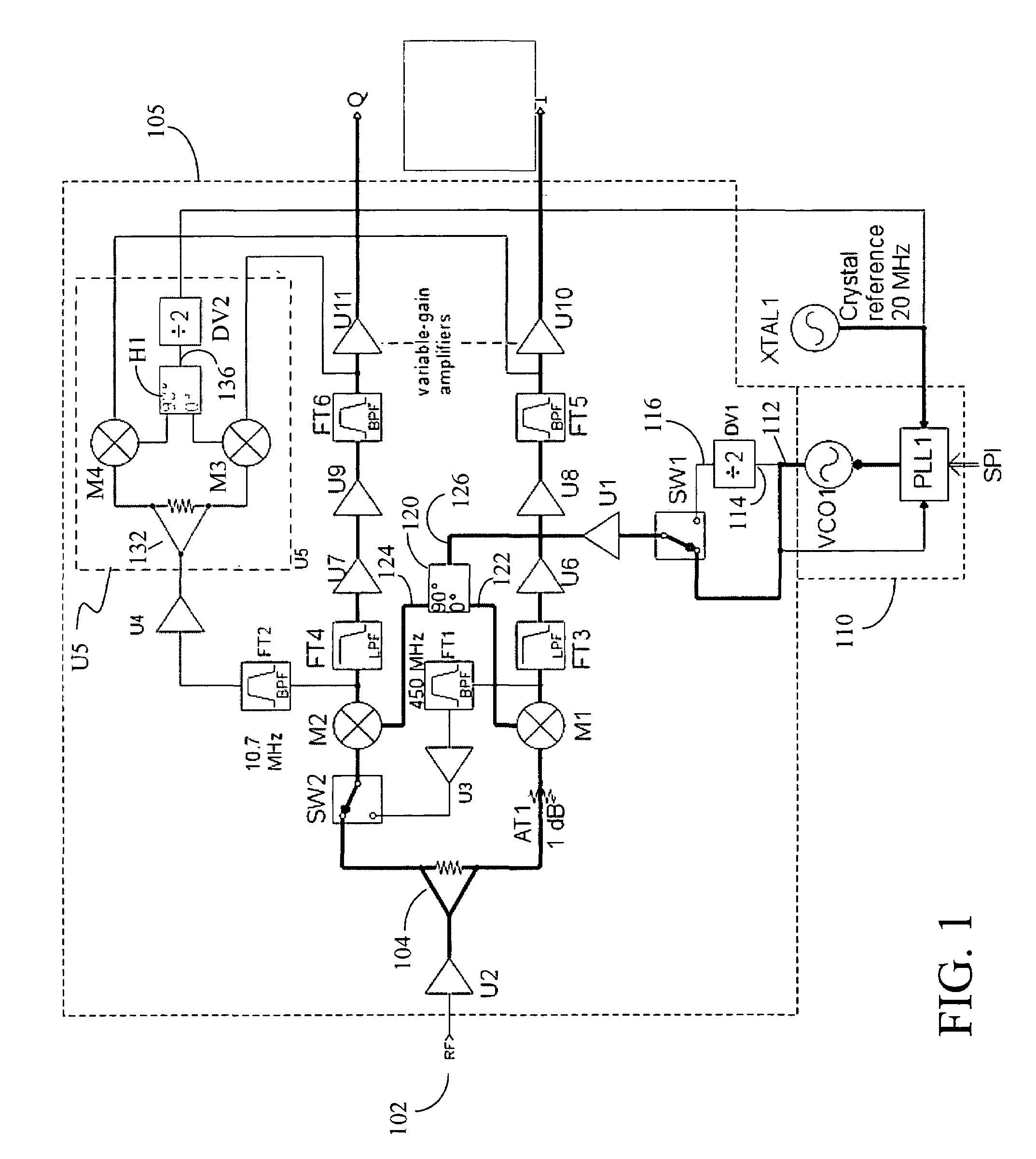

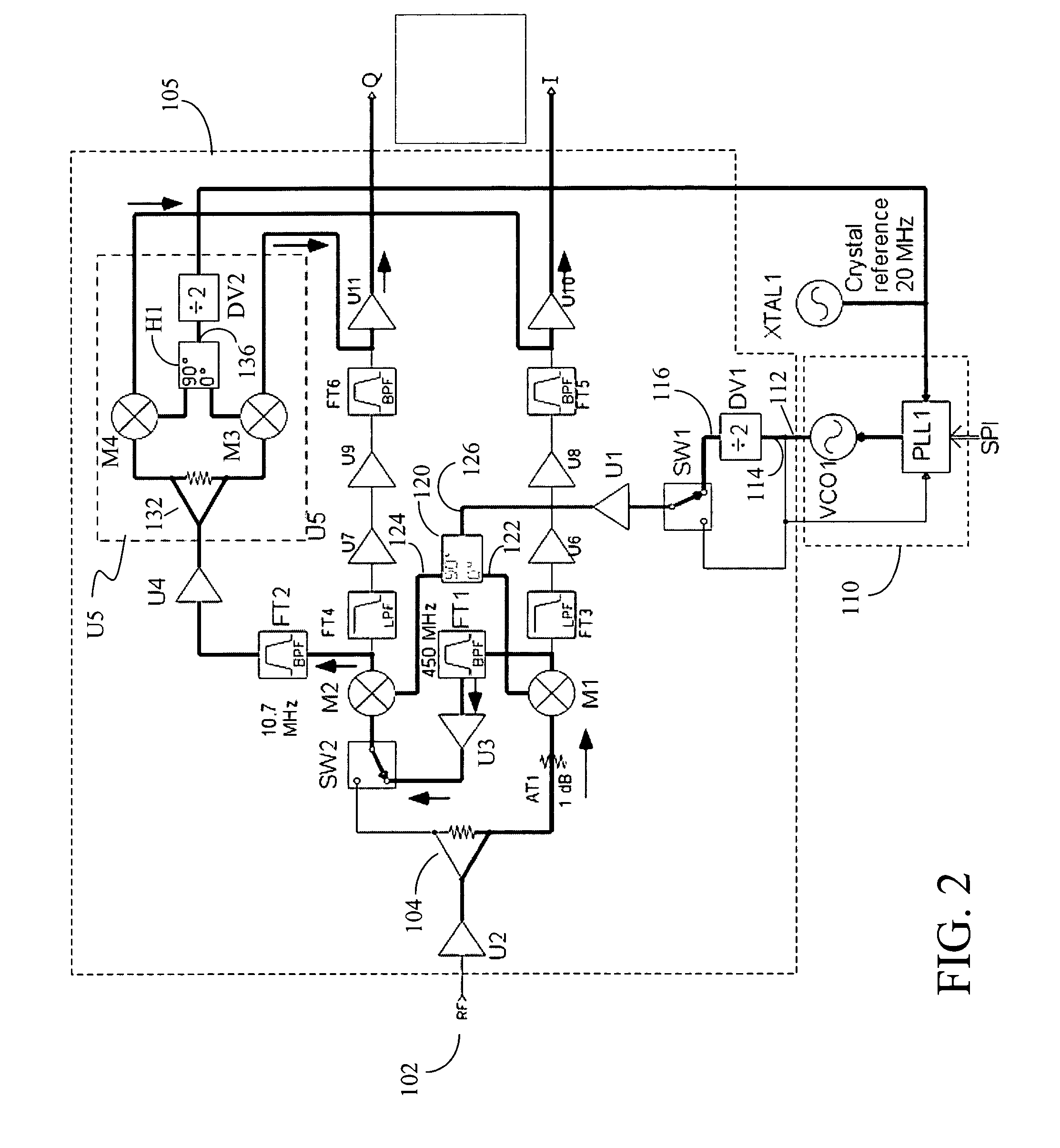

Configurable homodyne/heterodyne radio receiver and RFID reader employing same

InactiveUS20070111697A1Facilitate listen-before-talk functionHigh sensitivityNear-field transmissionAutomatic scanning with simultaneous frequency displayRadio receiverReceiver function

The embodiments of the present invention provide a configurable homodyne / heterodyne RF receiver including first and second mixers. The configurable homodyne / heterodyne RF receiver functions as a homodyne receiver when the first and second mixers are configured to operate in parallel, and as a heterodyne receiver when the first and second mixers are configured to operate in series. The embodiments of the present invention further provides an RFID reader employing the configurable homodyne / heterodyne RF receiver to facilitate a listen-before-talk function.

Owner:TRIQUINT SEMICONDUCTOR

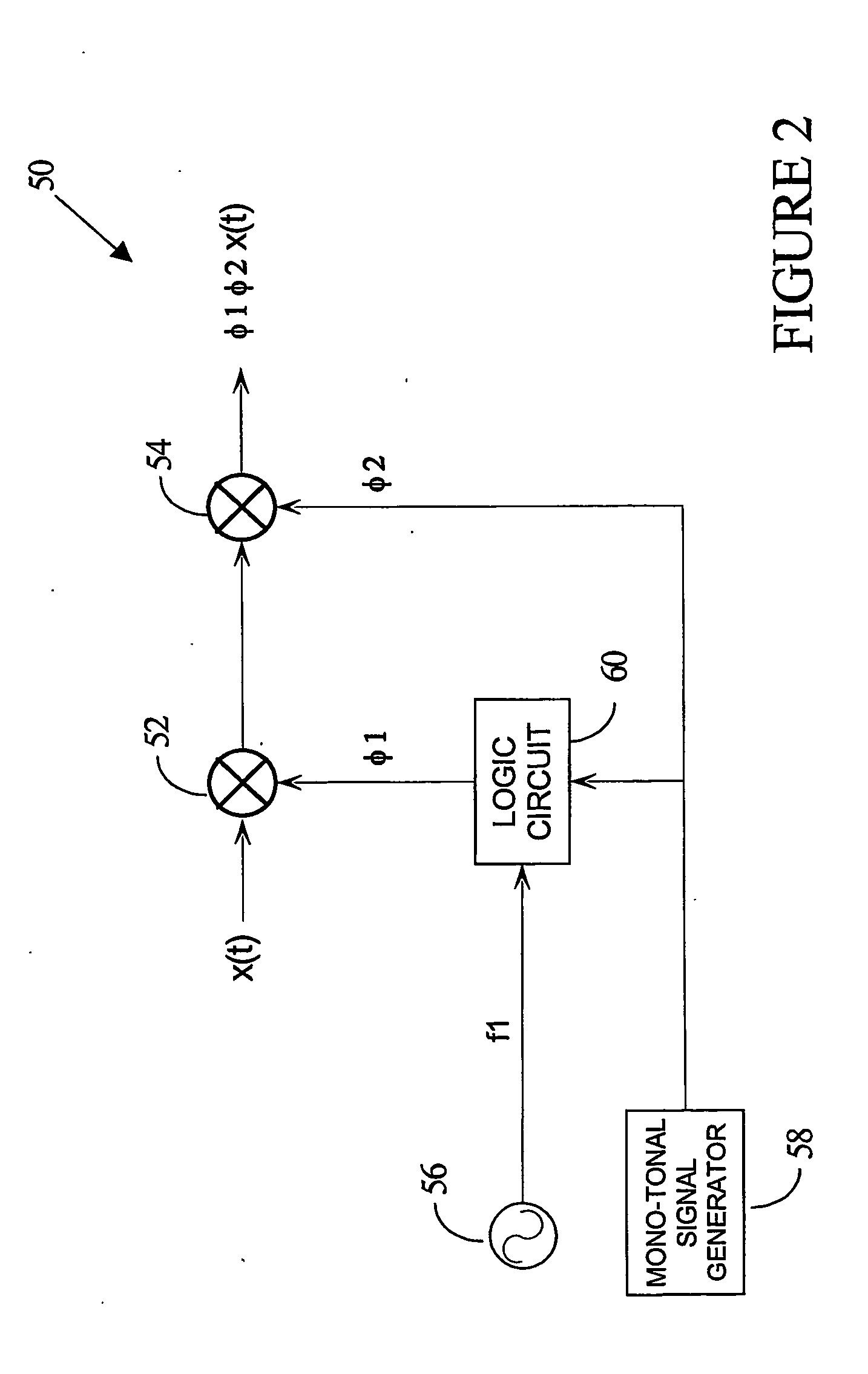

Regenerative divider for up and down conversion of radio frequency (rf) signals

ActiveUS20060246861A1Multiple-port networksAutomatic scanning with simultaneous frequency displayLocal oscillator signalHarmonic

The present invention relates generally to communications, and more specifically to a method and apparatus for generating local oscillator signals used for up- and down-conversion of RF (radio frequency) signals. A major problem in the design of modulators and demodulators, if the leakage of local oscillator (LO) signals into the received signal path. The invention presents a number of highly integratable circuits which resolve the LO leakage problem, using regenerative divider circuits acting on oscillator signals which are running at a multiple or fraction of the frequency of the desired LO signal, to generate in-phase (I) and quadrature (Q) mixing signals. Embodiments of these circuits also use harmonic subtraction and polyphase mixers, as well as virtual local oscillator TM (VLO) mixing signals. VLO mixing signals are signal pairs which emulate local oscillator signals by means of complementary mono-tonal and multi-tonal mixing signals.

Owner:ICERA CANADA ULC

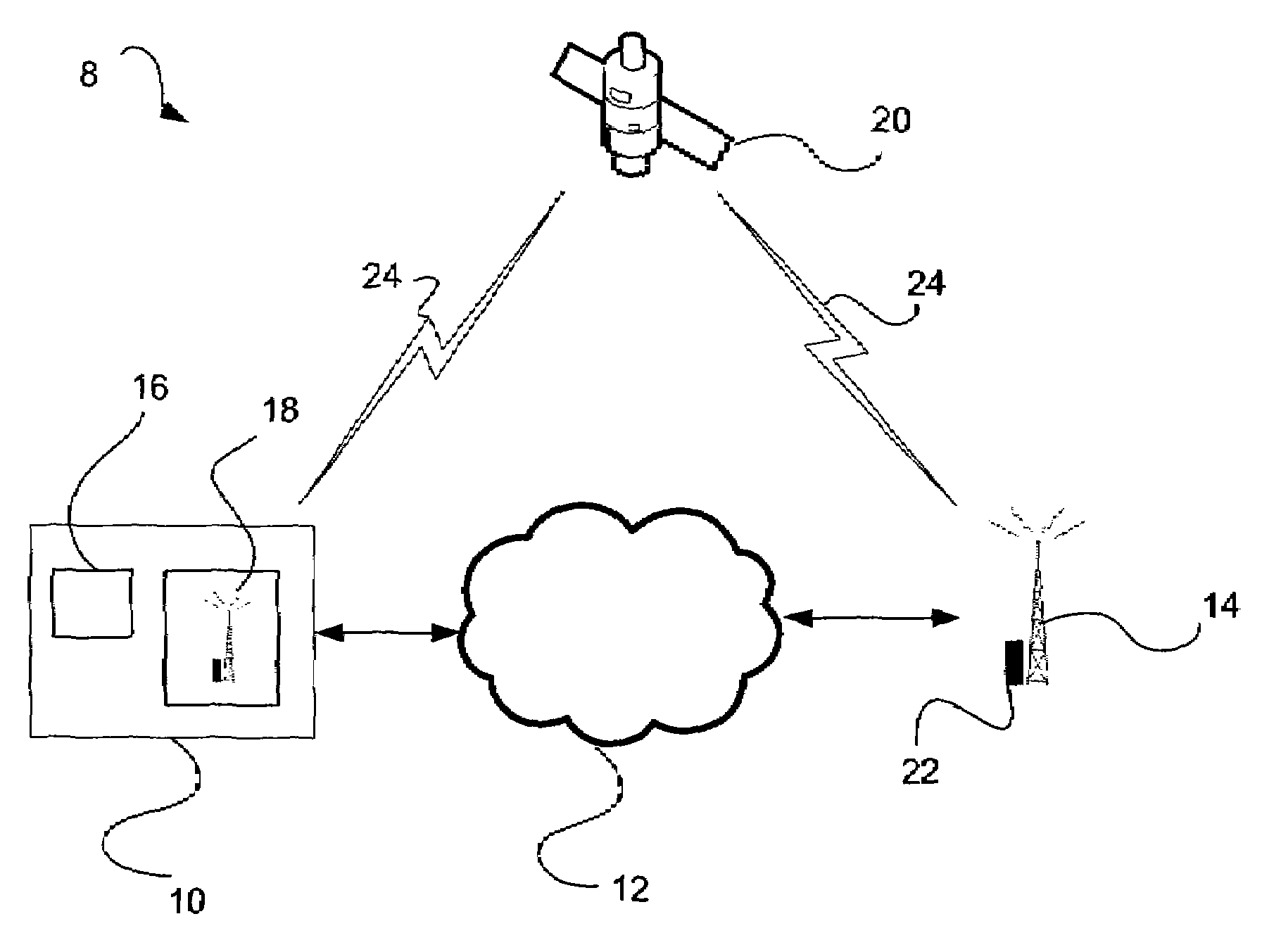

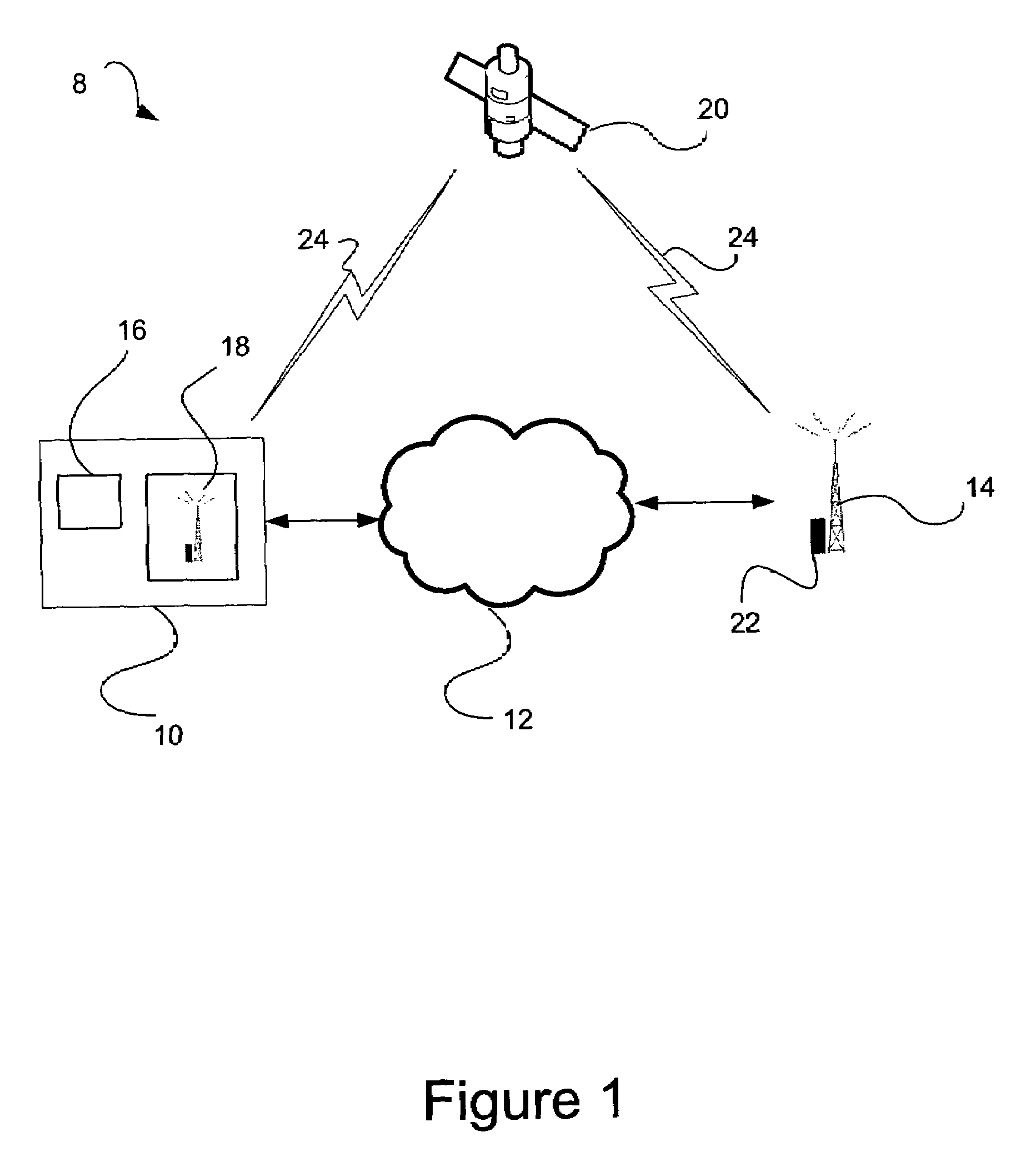

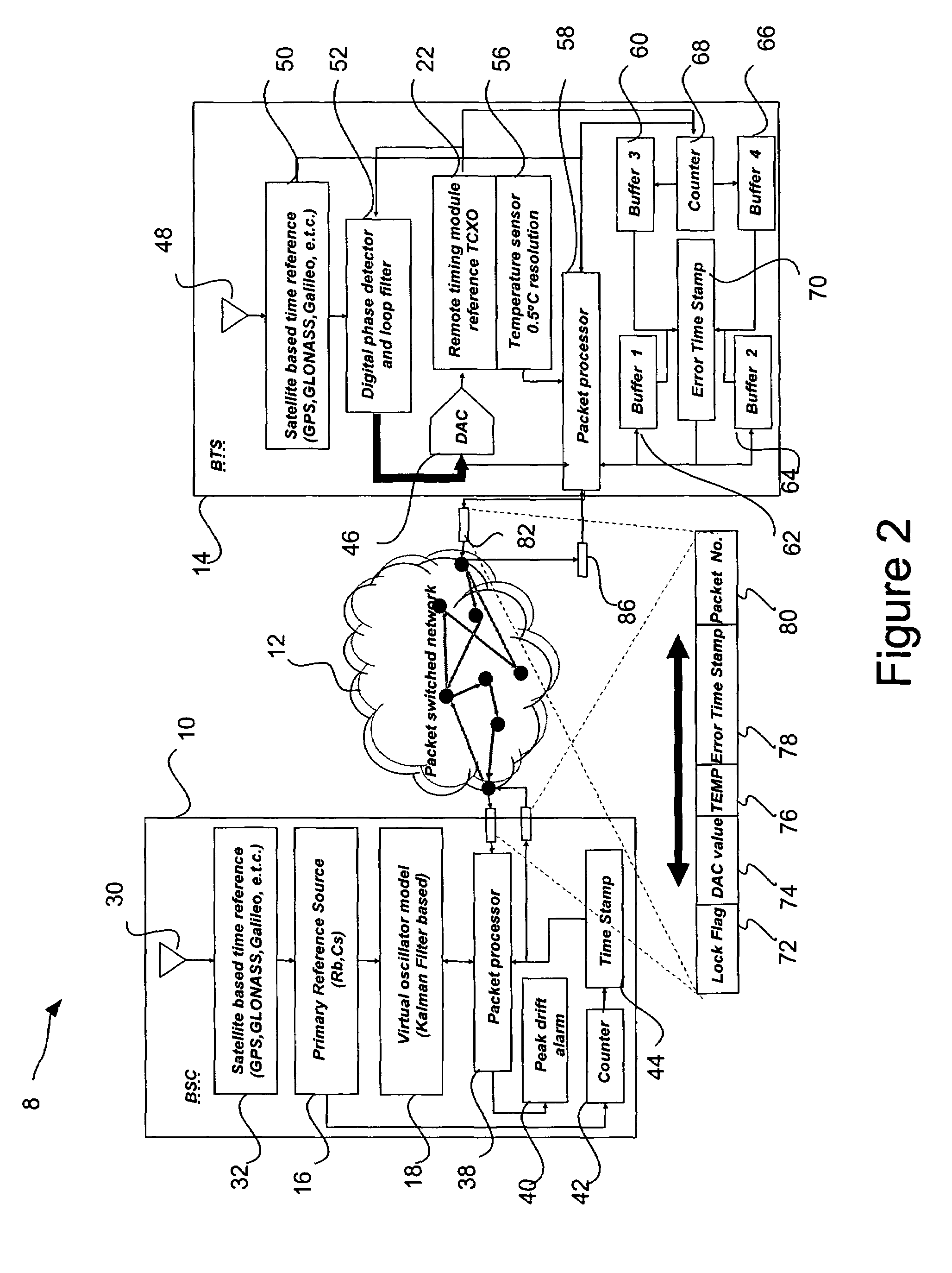

Enhanced holdover for synchronous networks employing packet switched network backhaul

ActiveUS7606541B1Automatic scanning with simultaneous frequency displayTime-division multiplexCommunication unitSynchronous network

Systems and methods are disclosed to maintain synchronous communications that uses a global positioning system satellite, a primary communication unit, and a secondary communication unit. The satellite based time reference broadcasts a reference signal to the primary communication unit and the secondary communication unit. The primary communication unit contains a high quality oscillator, and operates a virtual model of a secondary oscillator which is located in the secondary communication unit. The primary and secondary units have synchronous communications with each other by using a global positioning system satellite broadcast as a reference signal. If the secondary unit loses its signal from the global positioning system, the secondary oscillator enters a holdover state and transmits a notification of the holdover state to the primary communications unit. The primary communication unit then transmits time insensitive synchronization data based upon the virtual model through the packet switched network to the secondary communications unit to maintain synchronization.

Owner:MALIKIE INNOVATIONS LTD

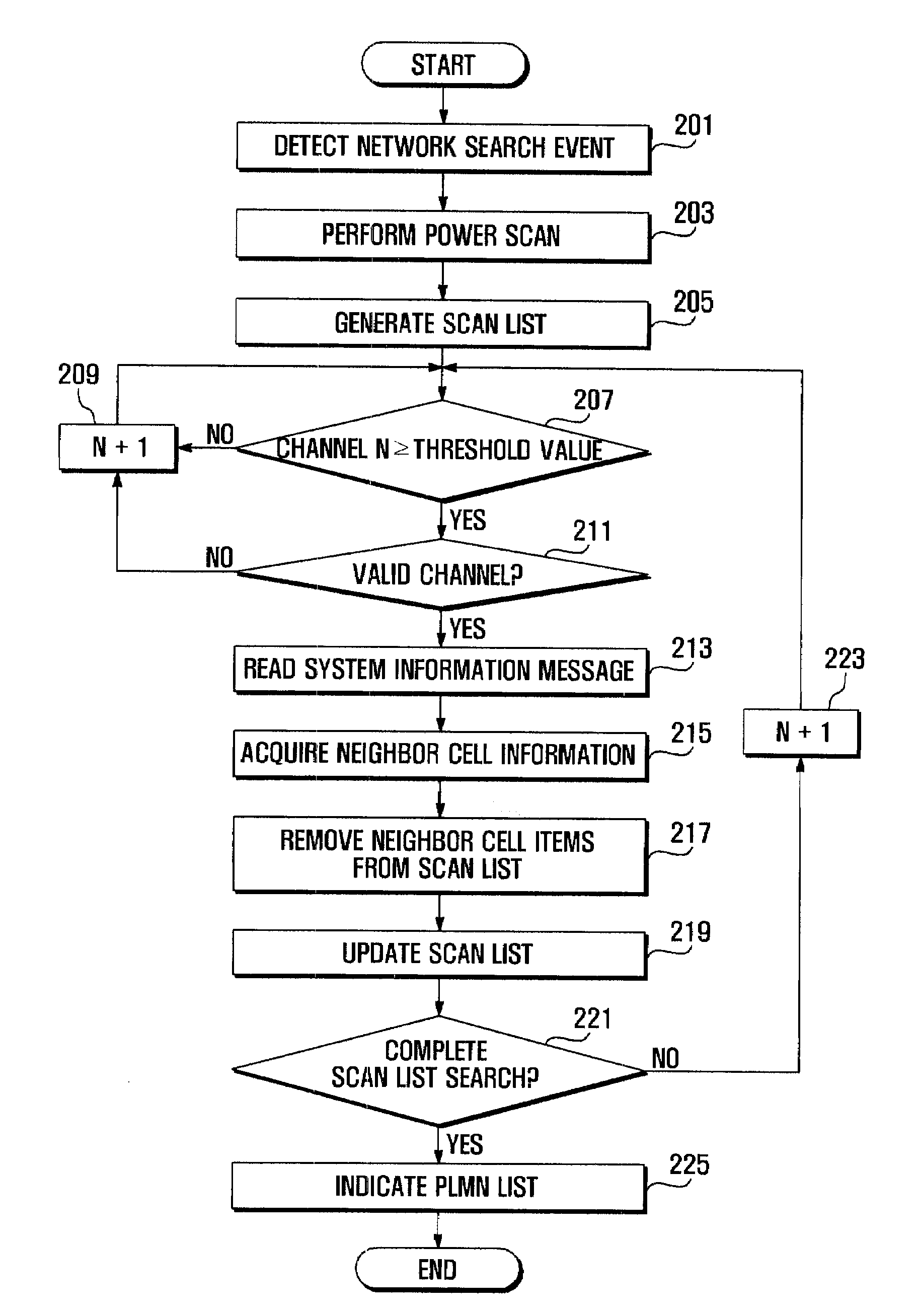

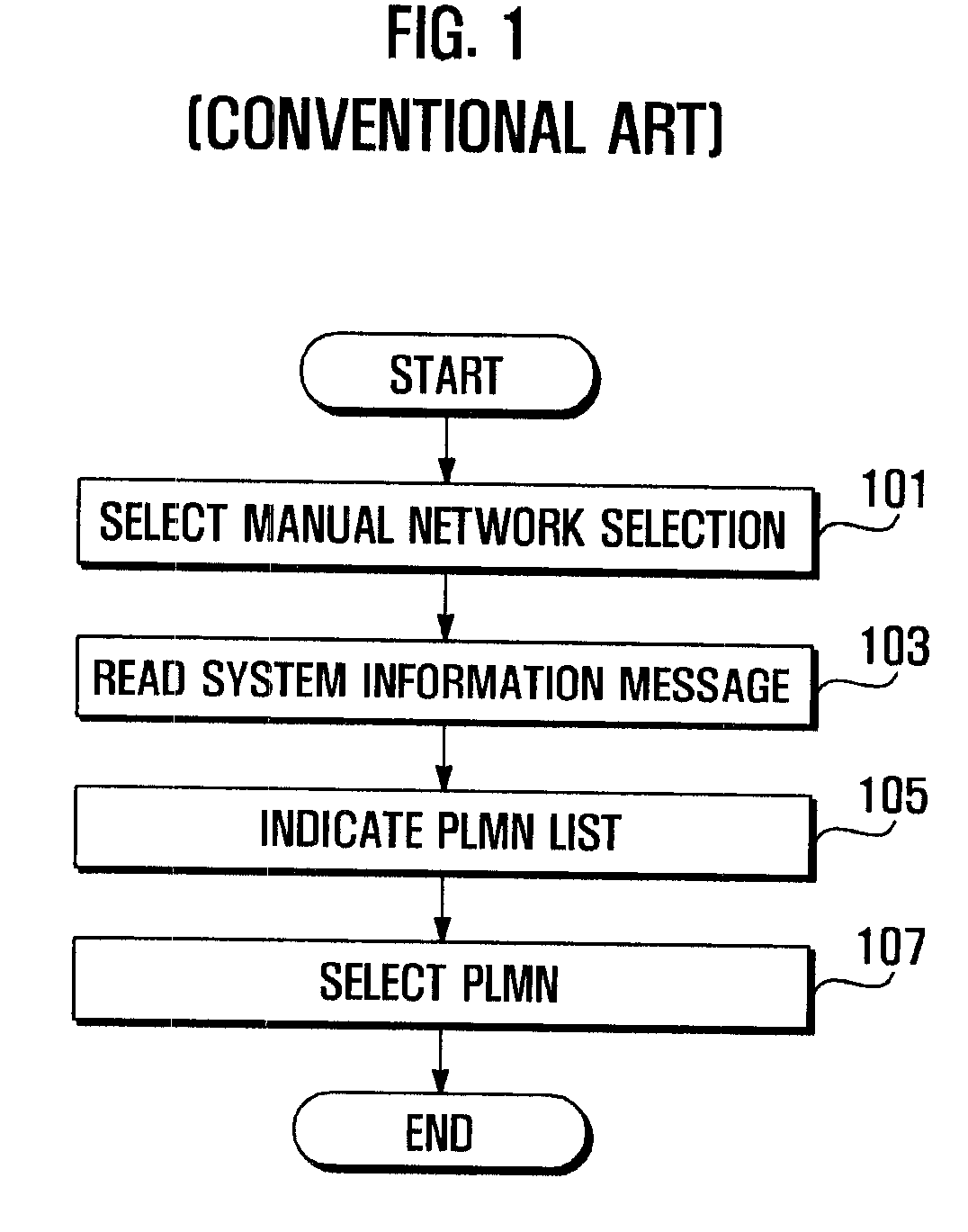

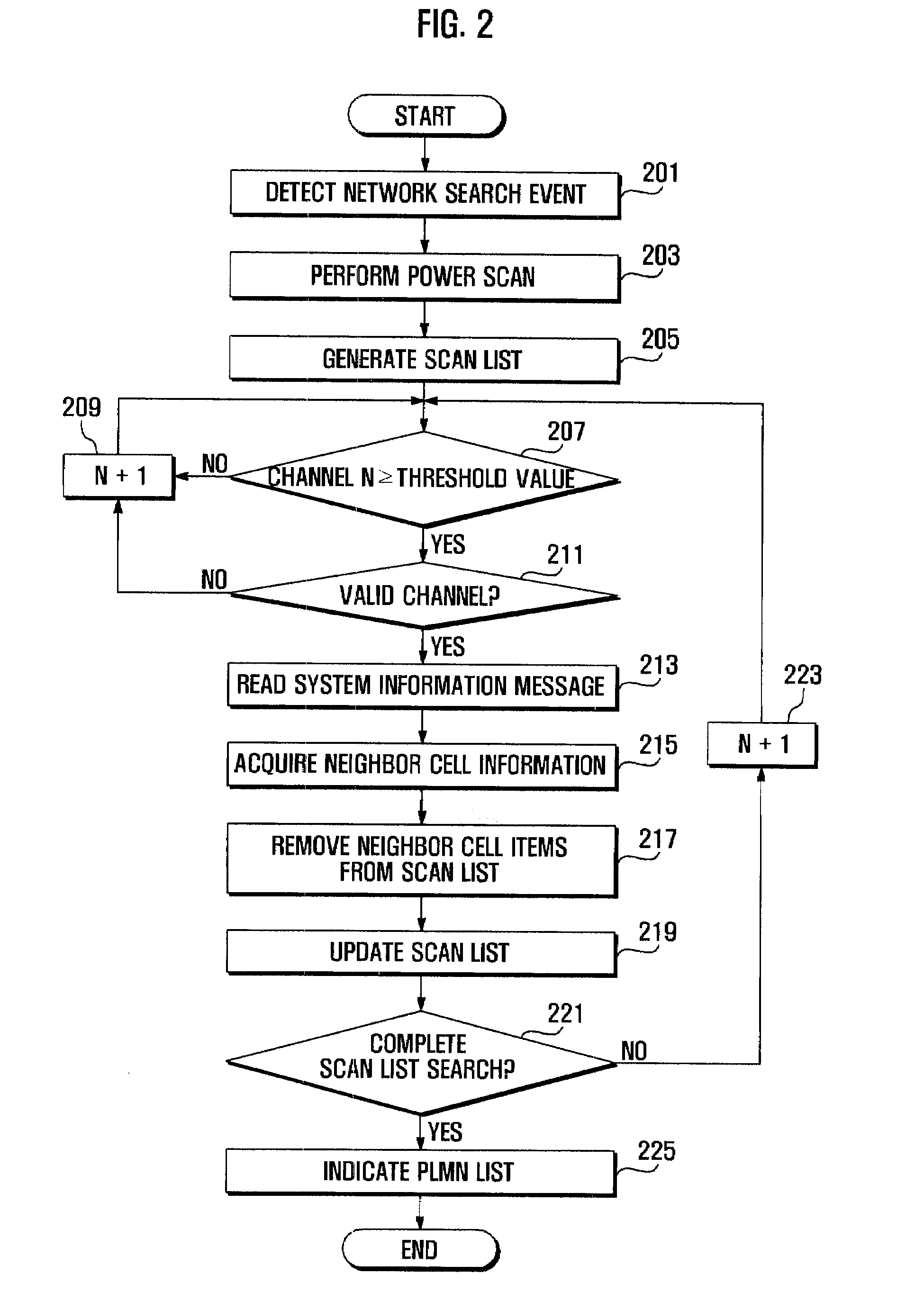

Network search method of user equipment for wireless communication system

InactiveUS20100081433A1Reduce PLMN list indication delayImproving network search speedAutomatic scanning with simultaneous frequency displayAssess restrictionCommunications systemPublic land mobile network

A network search method of a user equipment (UE) for a wireless communication system that improves network search speed for acquiring Public Land Mobile Network (PLMN) available list available where the user equipment is located. A network search method measures powers of all the frequency bands supported by a UE in response to a network search request, generates a scan list as a result of measurement of the powers, searches networks listed in the scan list for available channels; acquires neighbor cell information from a system information message of one of the available channels. In addition, the method skips the networks indicated by the neighbor cell information in search of networks by removing the networks from the scan list.

Owner:SAMSUNG ELECTRONICS CO LTD

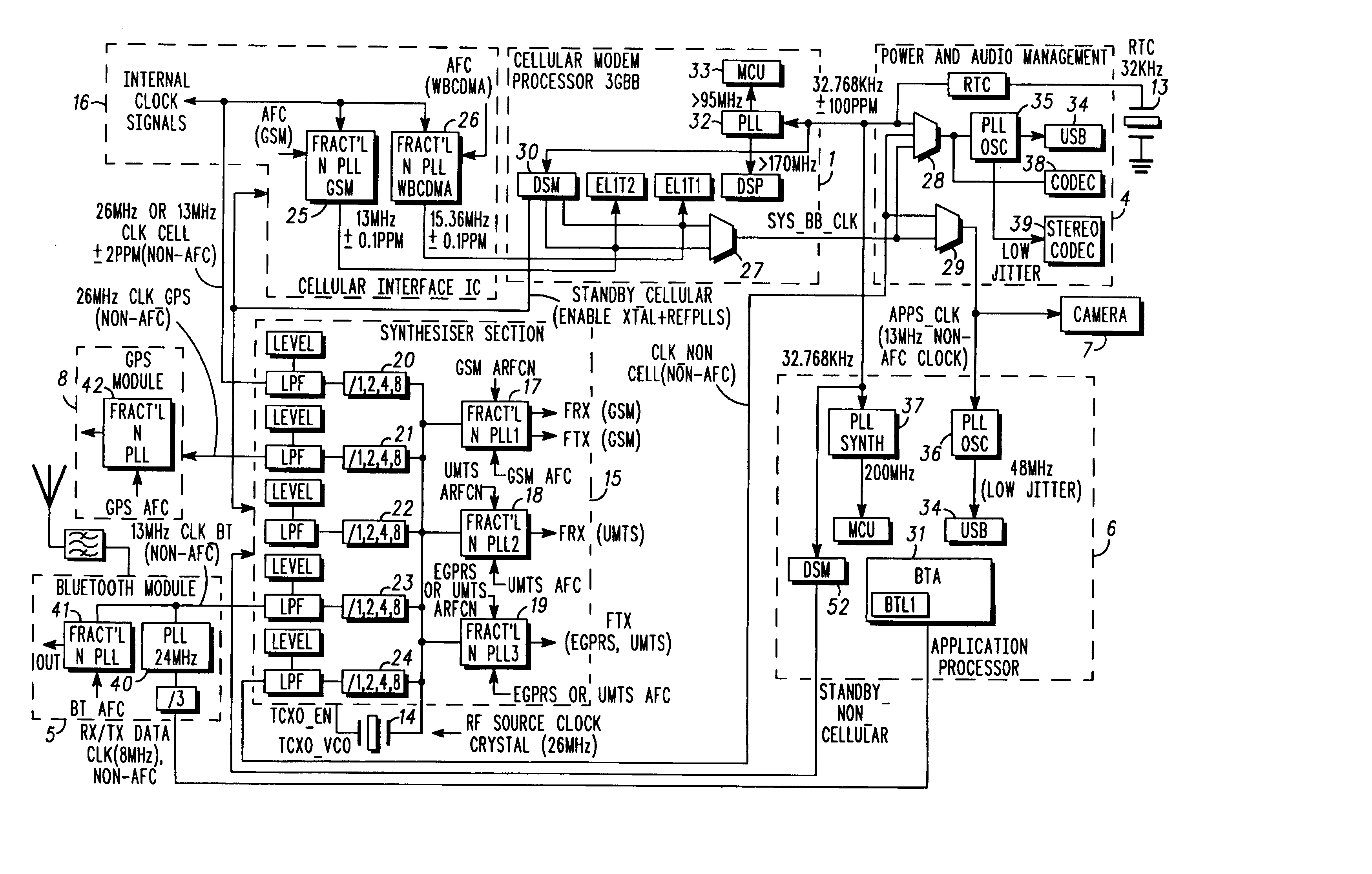

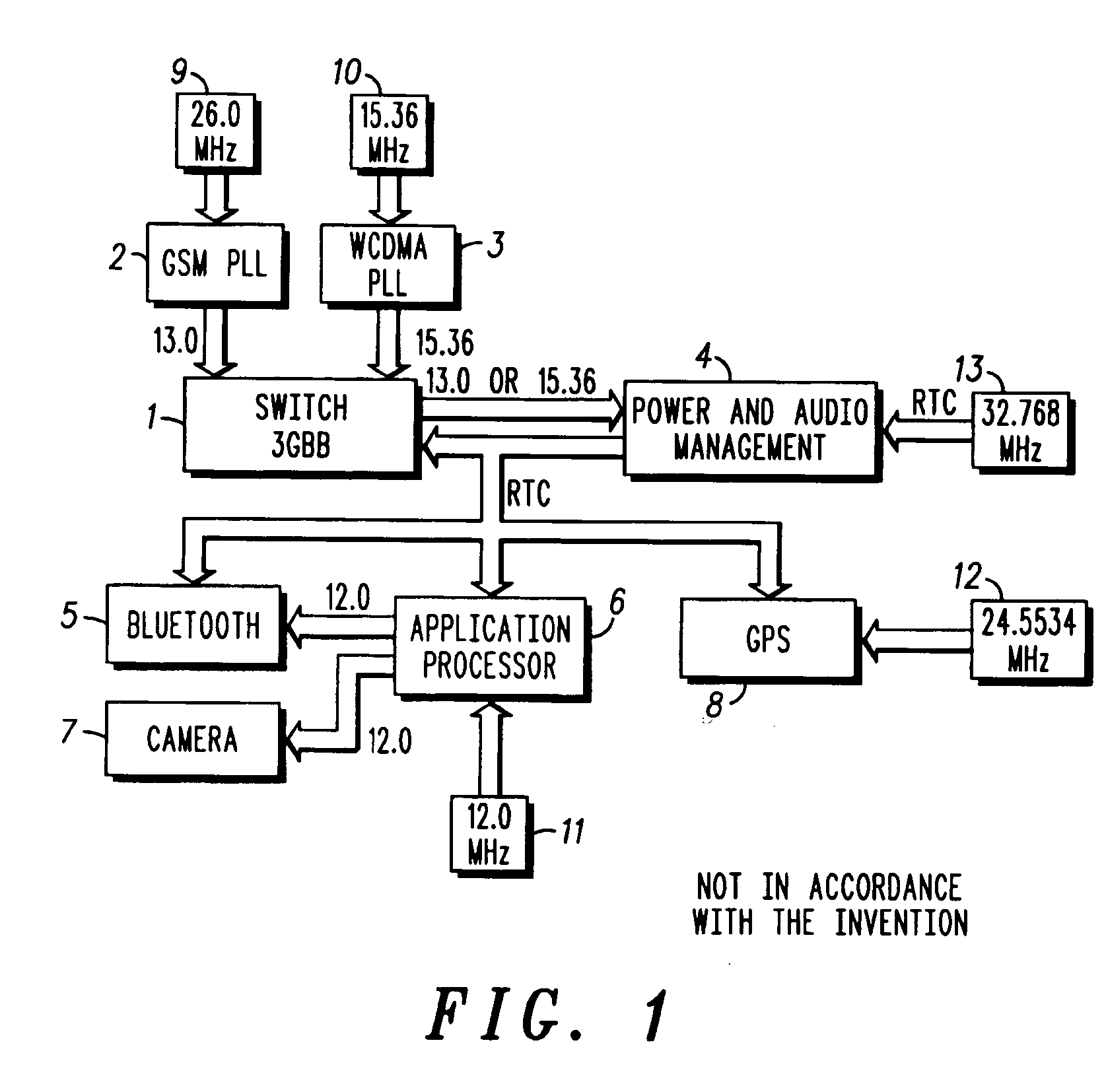

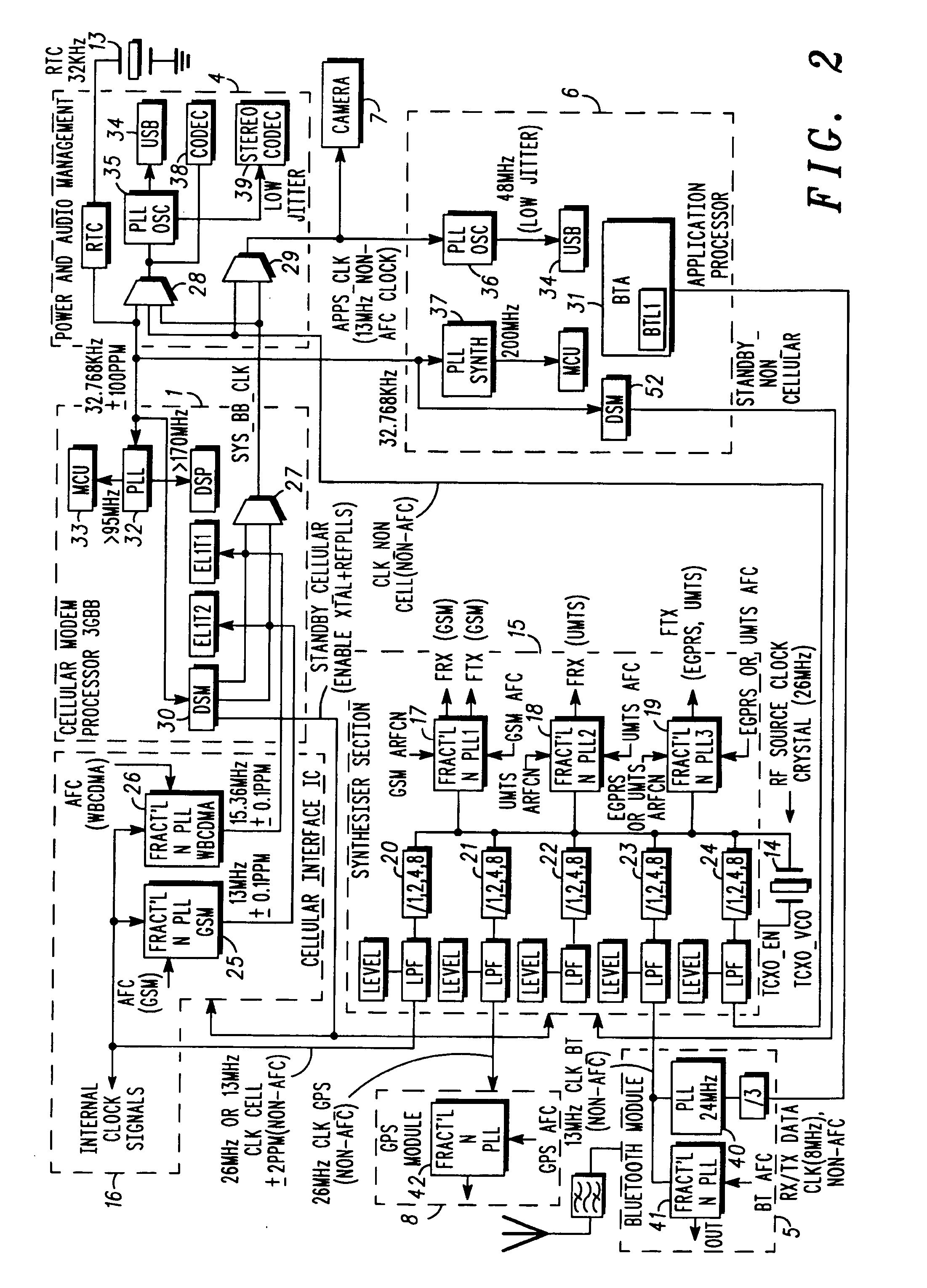

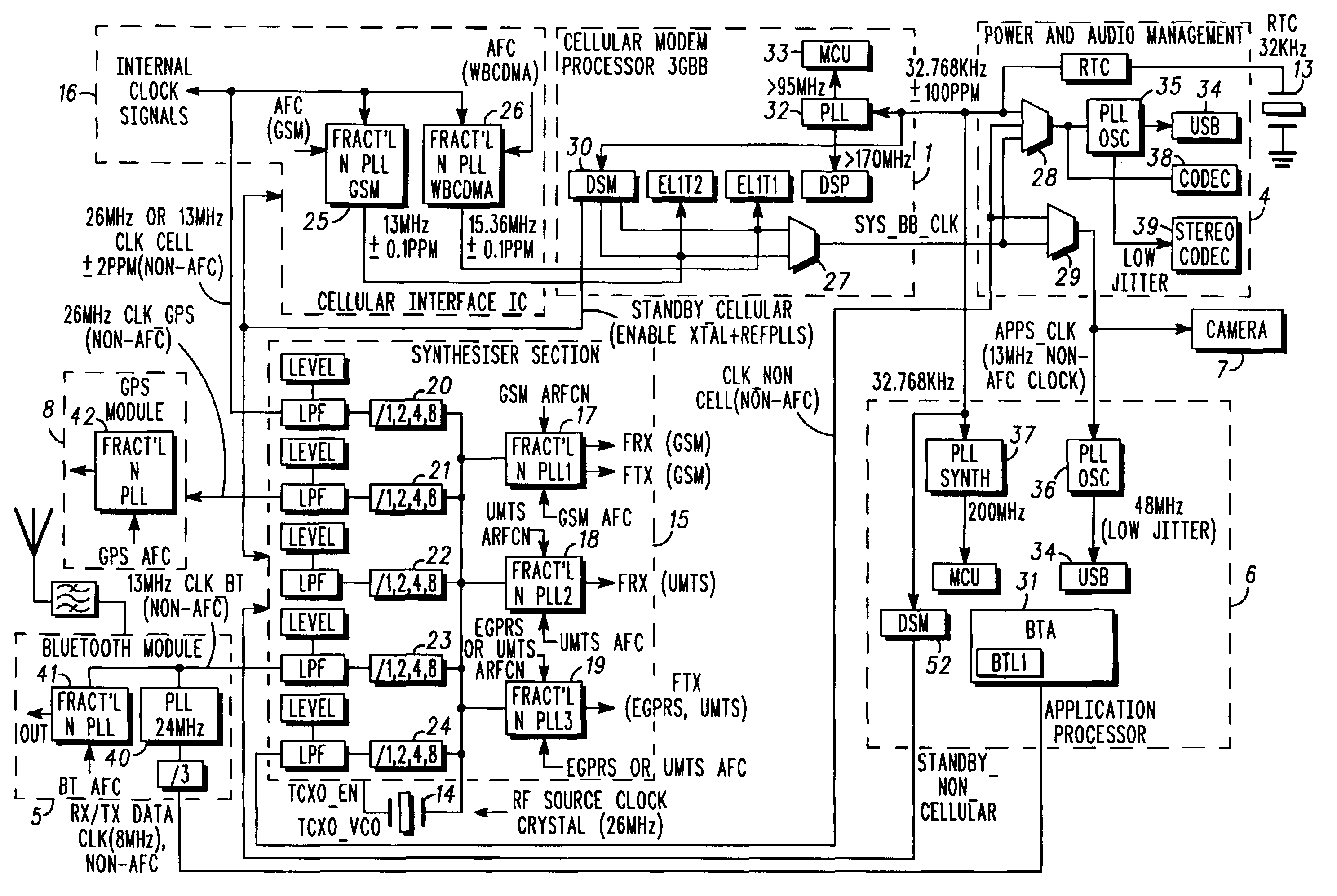

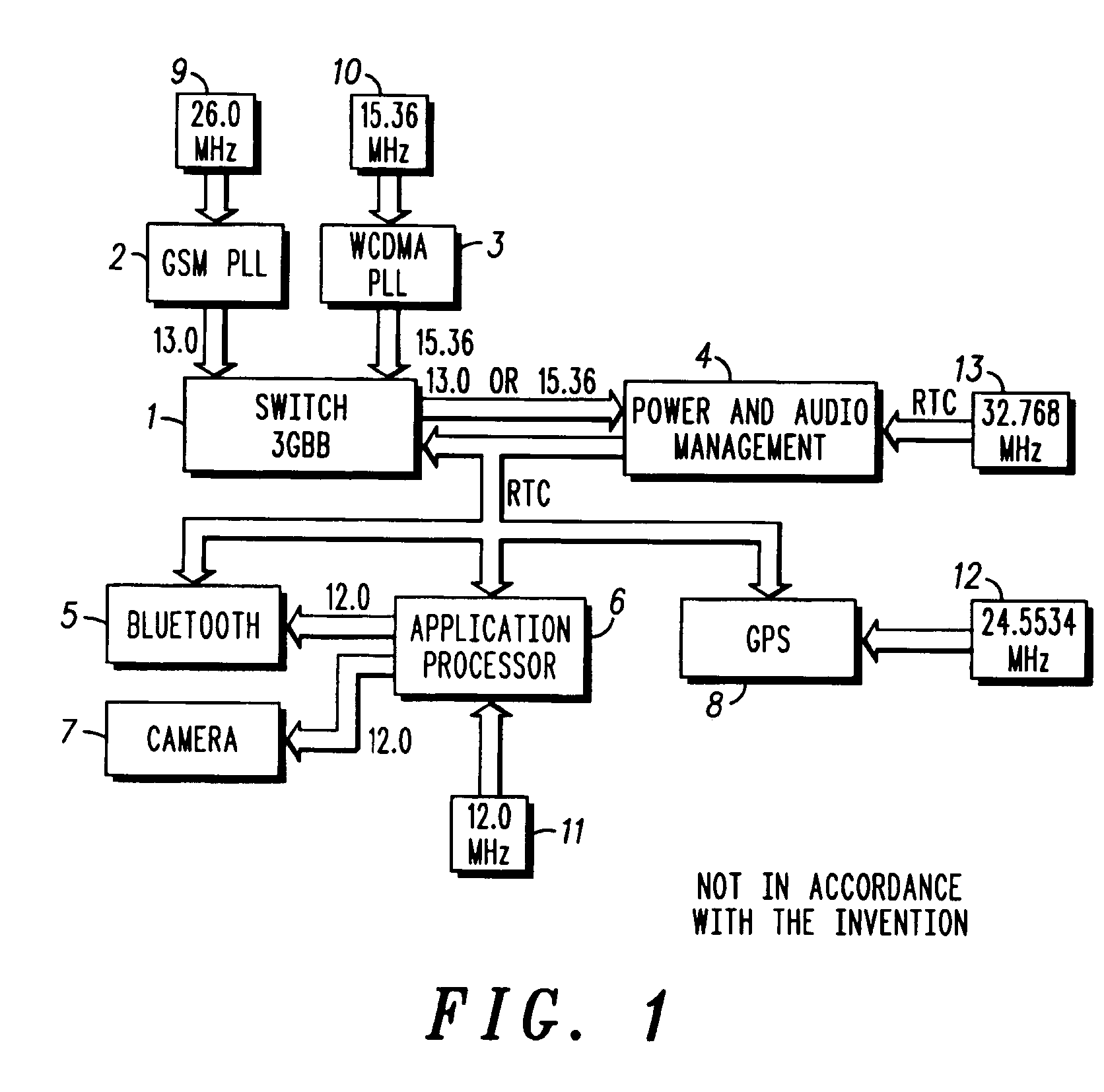

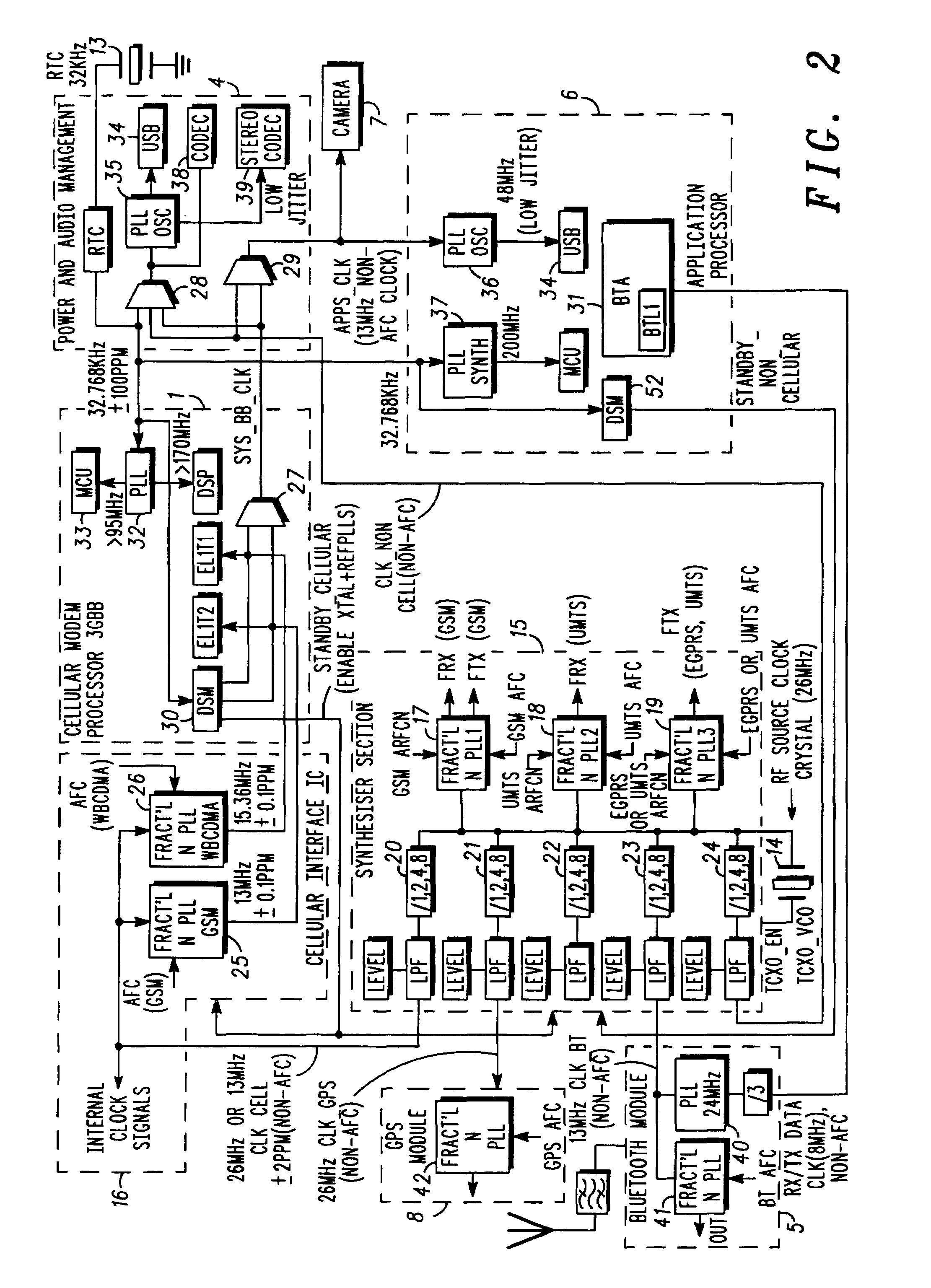

Apparatus for generating multiple clock signals of different frequency characteristics

InactiveUS20050042996A1Automatic scanning with simultaneous frequency displayPulse transformerClock rateComputer module

A terminal includes at least one wireless communication application module (1) and a plurality of further application modules (4, 5, 6, 8). Multiple radio frequency clock signals are generated for the different modules having respective clock frequency characteristics and including at least first and second clock frequencies that are not integral multiples nor sub-multiples of each other nor of a third frequency. The clock generation comprises reference frequency means (14), fractional-N phase-locked loop frequency synthesizer means (15) responsive to the reference frequency means, and different automatic frequency control means for adjusting clock frequencies relative to received signals. The reference frequency means (14) is arranged to supply a common reference frequency signal to a plurality of the fractional-N phase-locked loop frequency synthesizer means (17, 18, 19, 25, 26, 41,42) that supply the first and second clock frequencies respectively for the application modules. Selective activation means (30,52) selectively activates and de-activates the phase lock loop means as required by the corresponding application module or modules.

Owner:APPLE INC +1

System and method for providing event spectators with audio/video signals pertaining to remote events

InactiveUS7593687B2Automatic scanning with simultaneous frequency displayBroadcast specific applicationsAudio frequencyComputer science

A system and method for providing content for access by a portable device at an event are provided. The system includes an interface to receive signals from a plurality of sources. The plurality of sources are located at an event and remote from the event. The signals define event content and non-event content. The system further includes a processor for processing the received signals to generate combined signals based upon the received signals from the plurality of sources. The system also includes a transmitter for transmitting to a plurality of portable devices at the event the combined signals. The combined signals are configured to allow a user to select content using the portable device receiving the combined signals.

Owner:IMMERSION ENTERTAINMENT L L C

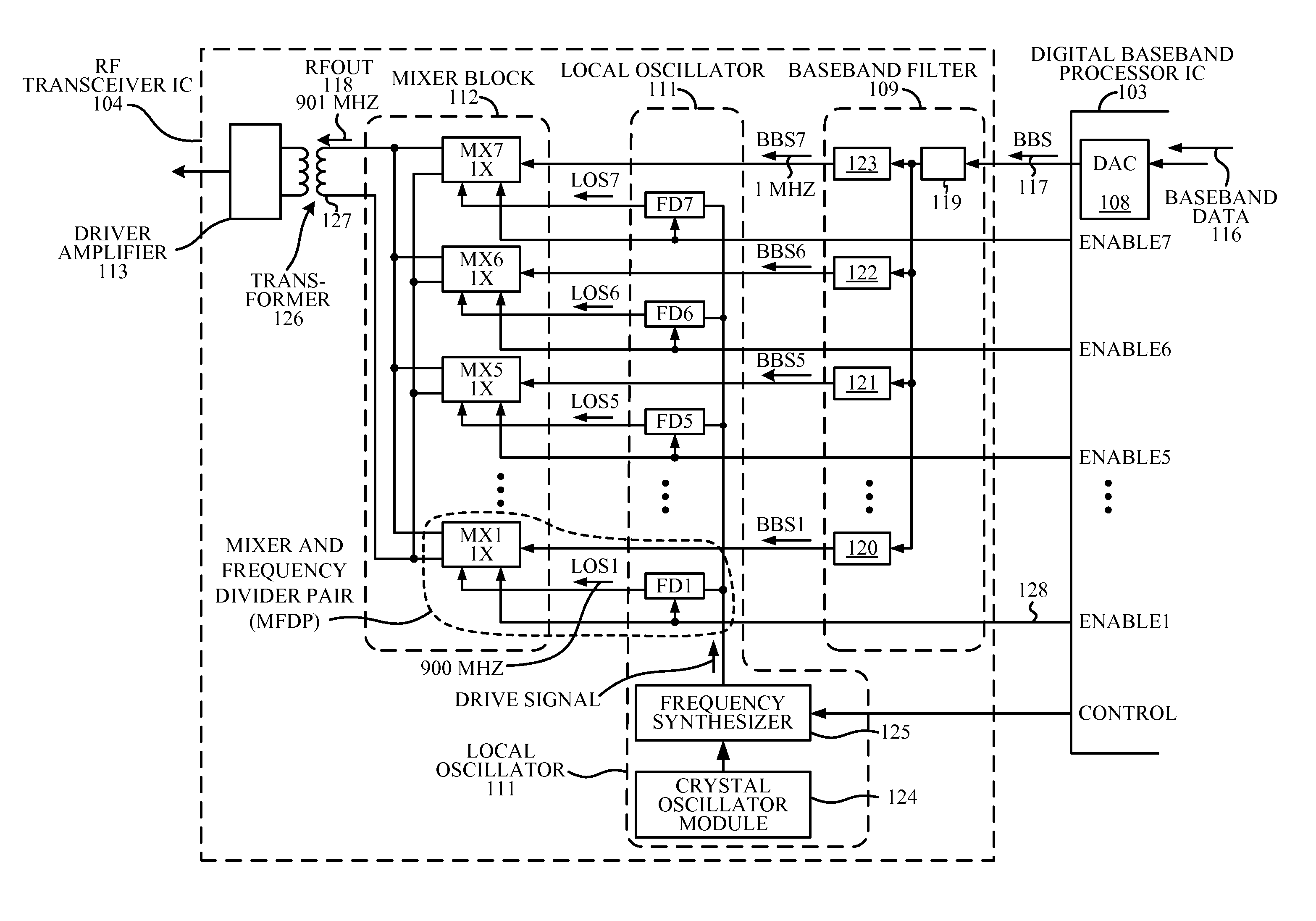

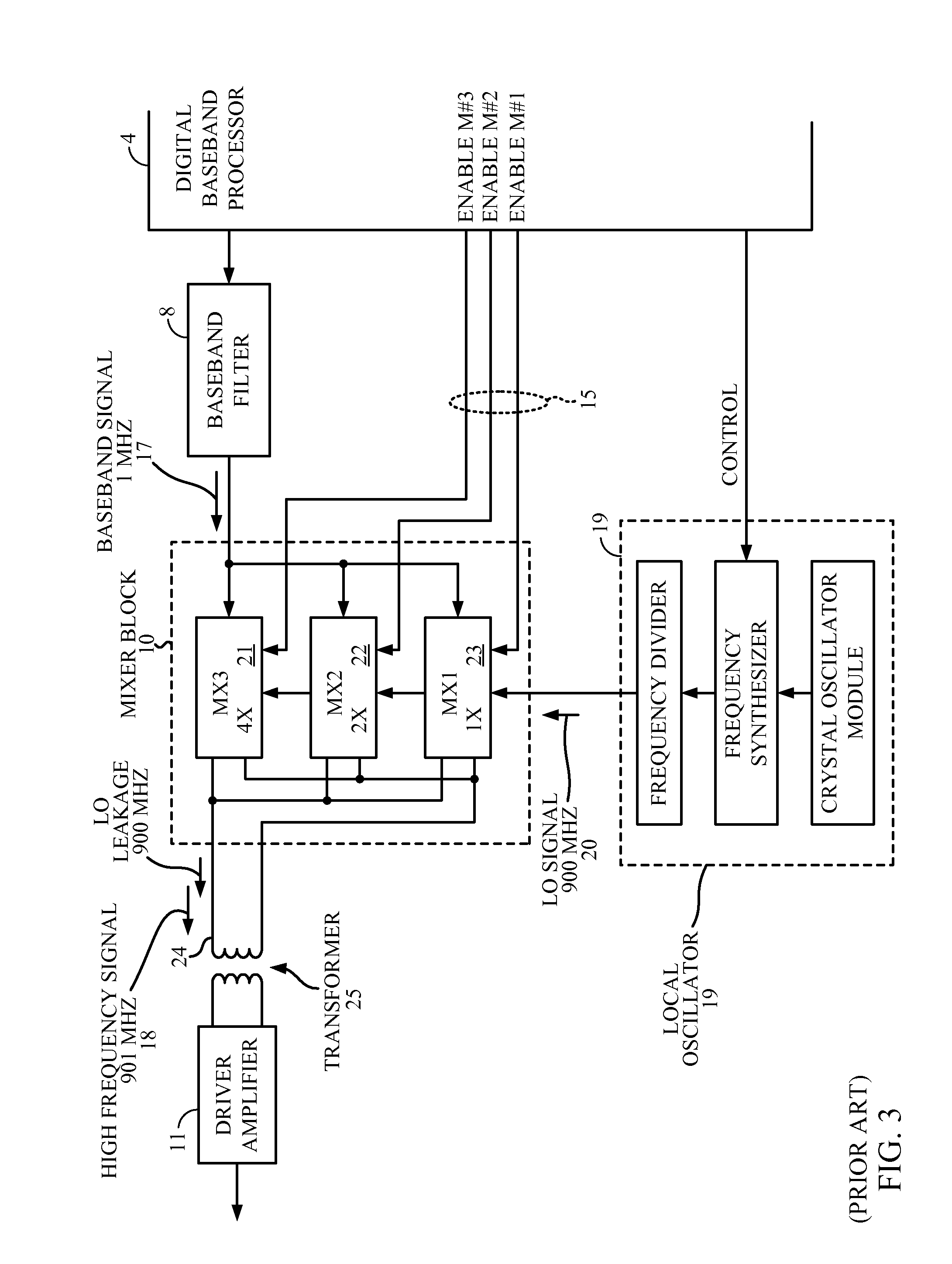

Mixer with high output power accuracy and low local oscillator leakage

ActiveUS7941115B2Identical layoutImprove accuracyAutomatic scanning with simultaneous frequency displayModulation transferenceFrequency mixerLocal oscillator

A circuit receives a first signal (for example, a baseband signal) and mixes it with a local oscillator (LO) signal, and outputs a second signal (for example, an RFOUT signal). The circuit includes multiple identical Mixer and Frequency Divider Pair (MFDP) circuits. Each MFDP can be enabled separately. Each MFDP includes a mixer and a frequency divider that provides the mixer with a local version of the LO signal. The MFDP outputs are coupled together so that the output power of the second signal (RFOUT) is the combined output powers of the various MFDPs. By controlling the number of enabled MFDPs, the output power of the second signal is controlled. Because the MFDPs all have identical layouts, accuracy of output power step size is improved. Because LO signal power within the circuit automatically changes in proportion to the number of enabled MFDPs, local oscillator leakage problems are avoided.

Owner:QUALCOMM INC

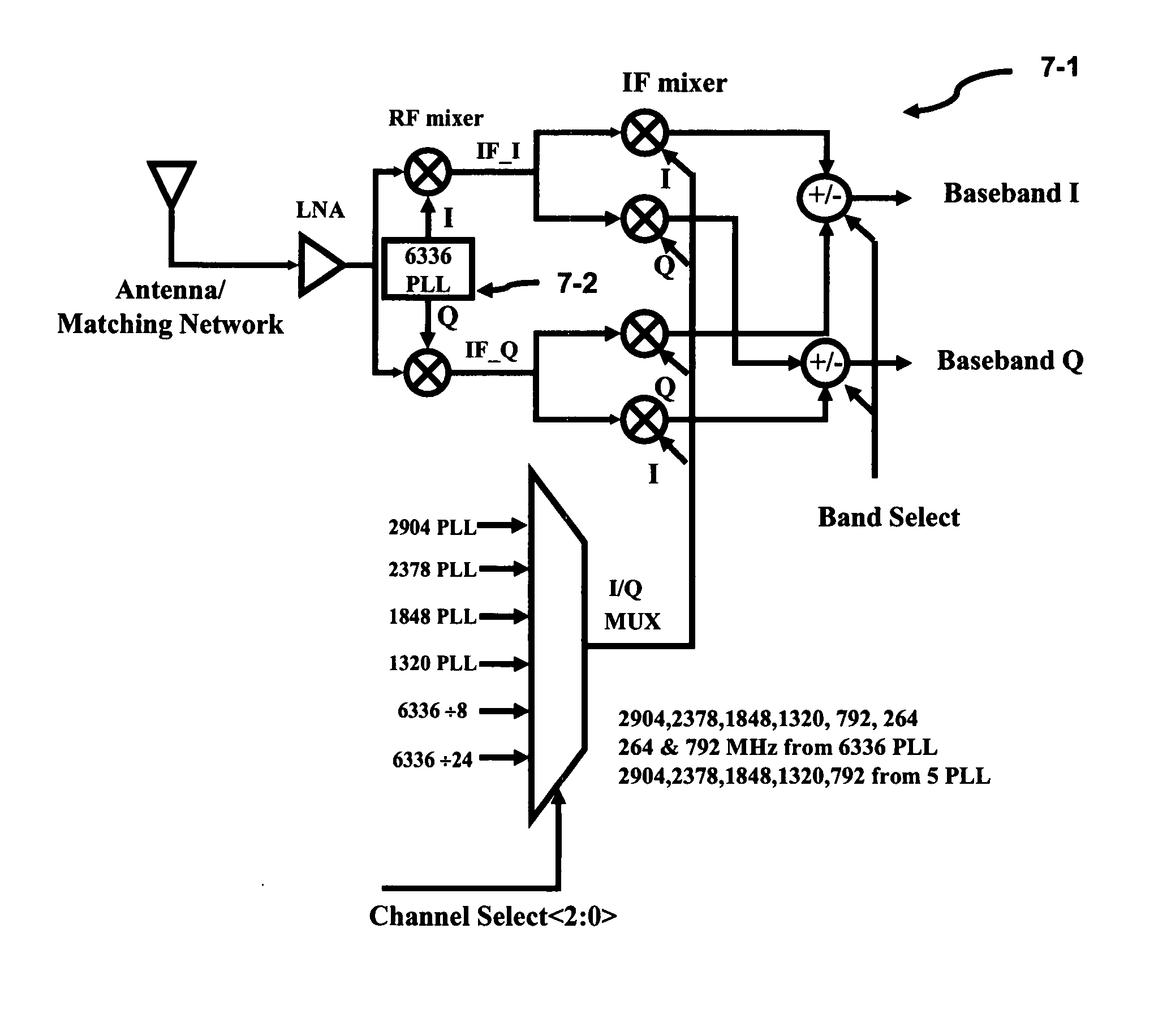

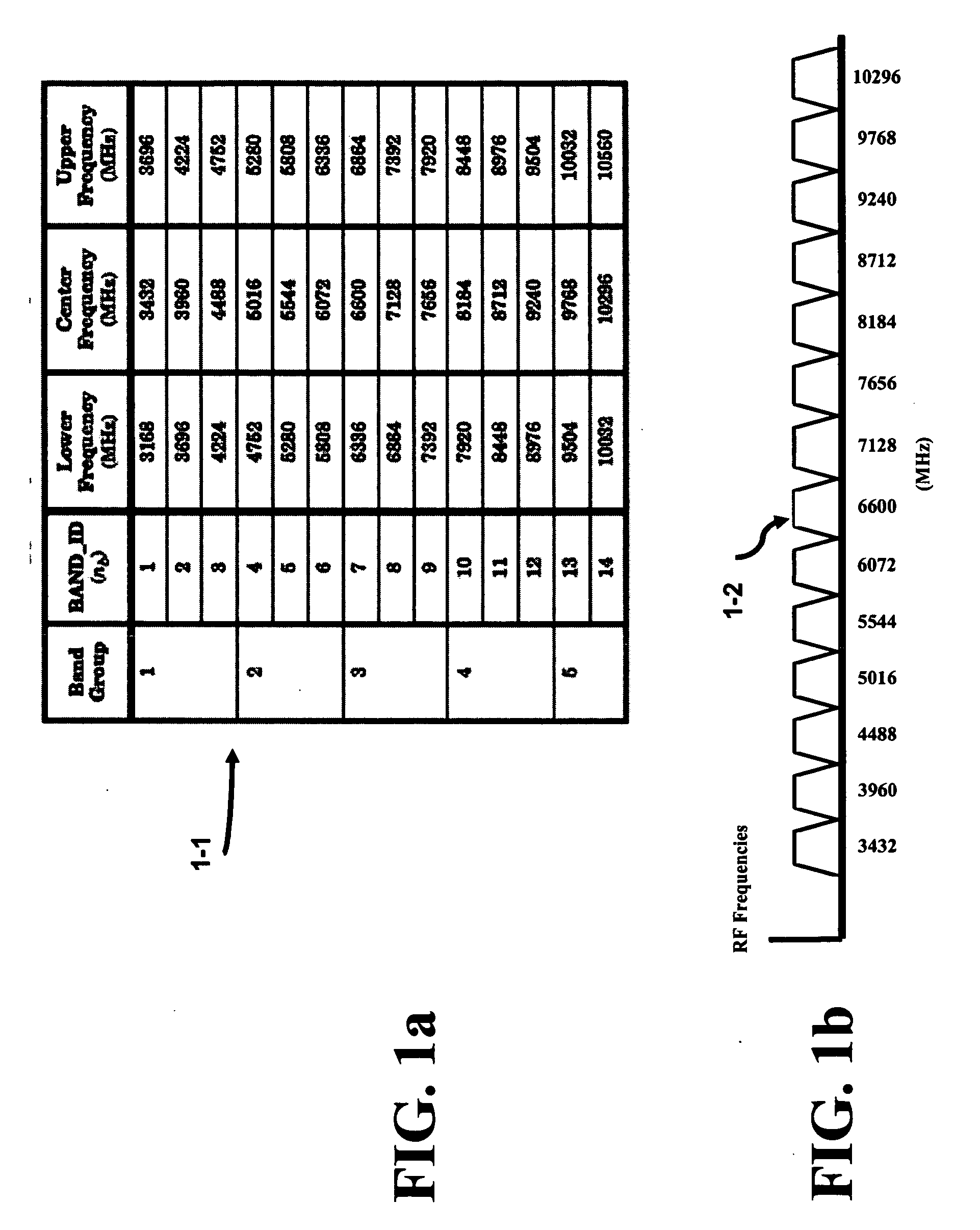

Method of frequency planning in an ultra wide band system

InactiveUS20070155350A1Simple technologyReduce in quantityAutomatic scanning with simultaneous frequency displayModulation transferenceOperational systemOperating frequency

The present invention provides reduces the number of required synthesizers thereby reducing the area and power concerns to extract / insert a signal from / to a multi-channel communication system and is also known as frequency planning. The highest frequency of operation required for the synthesizers or oscillators is approximately the midpoint of the entire signal frequency range. Two superimposed Weaver architectures are used to form the architecture. The receiver extracts the baseband I and Q signals from the multi-channel communication system, while the transmitter upconverts the baseband I and Q signals to the multi-channel communication system. The Weaver architecture, depending on the select bit, can enhance the image signal and reduce the desired signal or the image signal can be reduced while the desired signal is enhanced. Because the image and signal components are symmetrically displaced from the RF LO, less IF LO frequencies or synthesizers are required to operate the system.

Owner:WINONICS RES

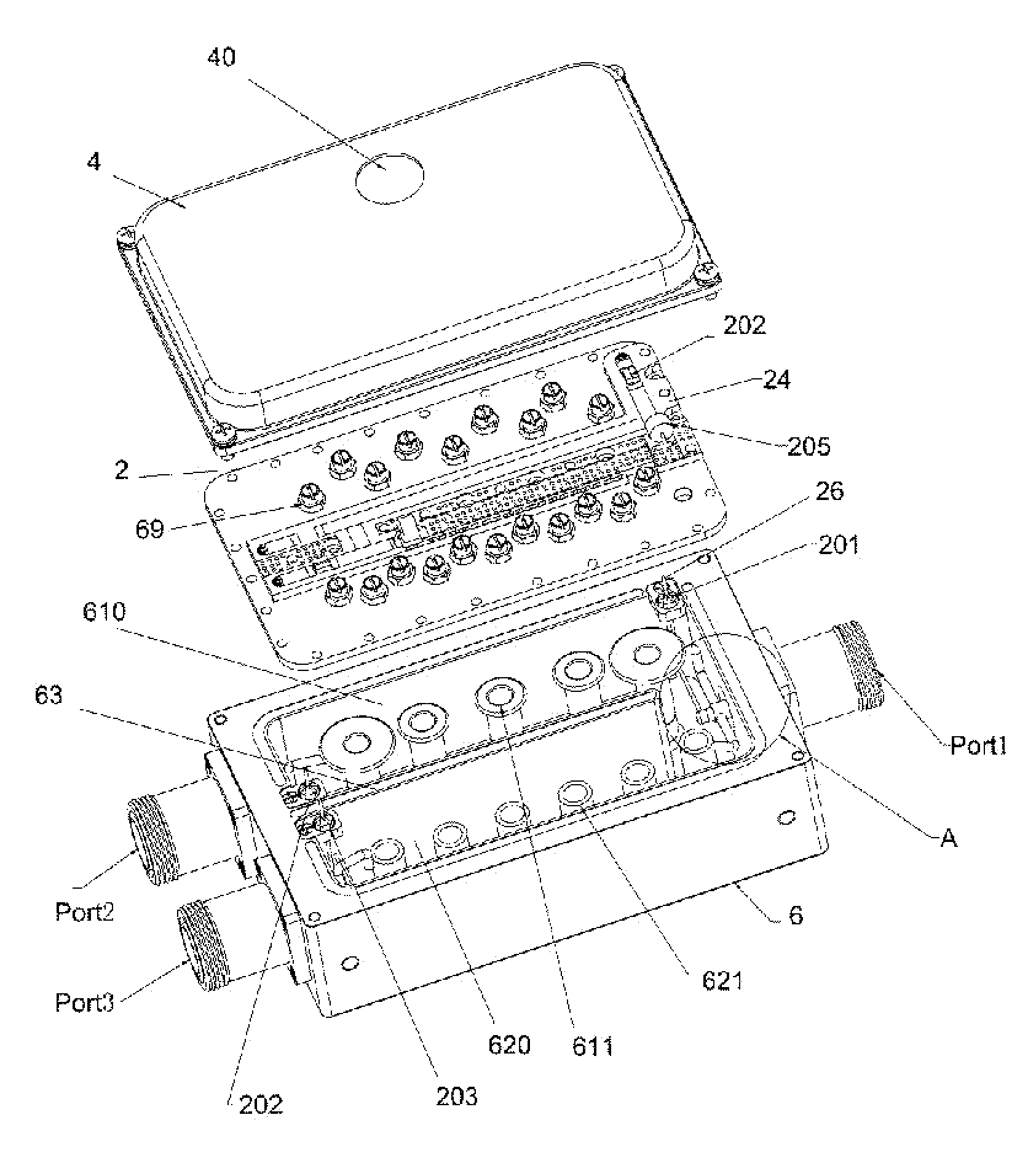

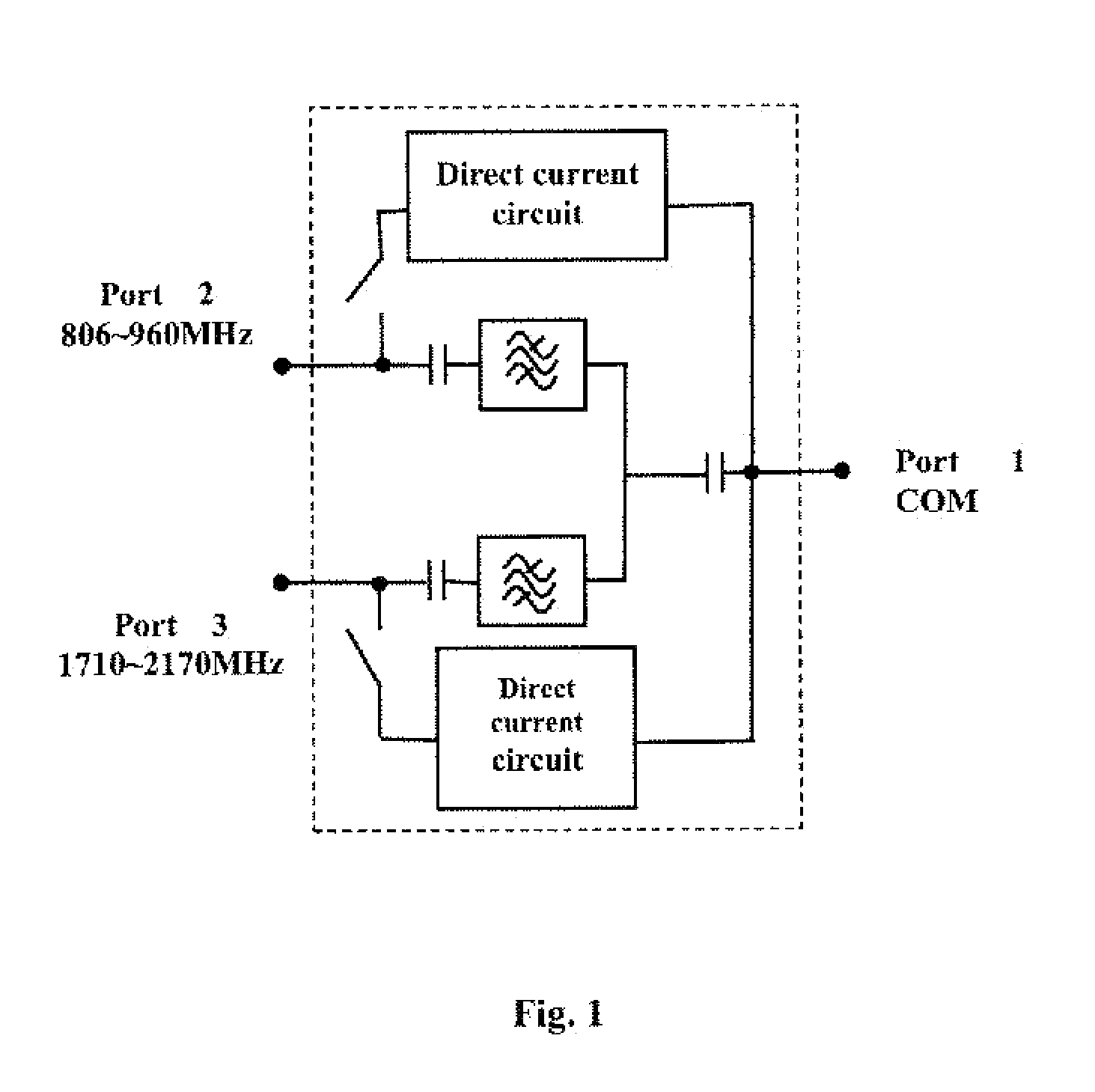

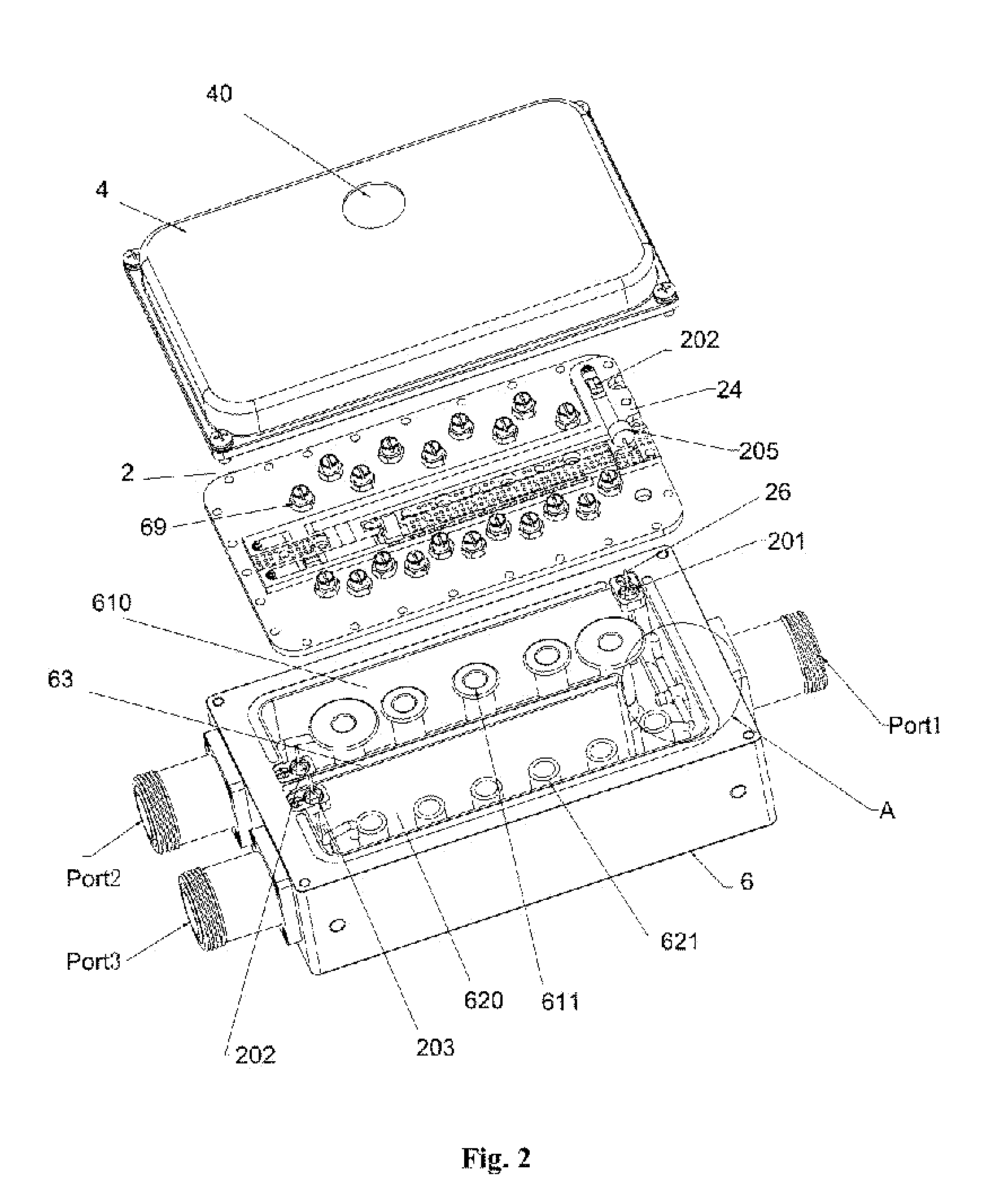

Double frequency combiner

ActiveUS20100278197A1Less differential lossLarge power capacityAutomatic scanning with simultaneous frequency displayPulse automatic controlLow-pass filterBand-pass filter

The invention discloses a dual frequency multiplexer by which a first and second coaxial harmonic oscillator type band pass filters are disposed in a box. The box includes a base body, a cover plate and a cover body. The two coaxial harmonic oscillator type hand pass filters are located on the base body and spaced each other by a metal plate; the multiplexer port, first and second ports are positioned on lateral side of the base body. The blocking capacitors are contained in the coaxial chamber of the two coaxial harmonic oscillator type band pass filters. The cover plate is secured on the base body; the first and second direct current circuits are placed on the cover plate; the low pass filters of the first and second direct current circuits are fixed on an edge of a top surface of the coaxial chamber by means of a support member; the cover body and the base body are fastened with each other. The blocking capacitors each are of distributed parameter capacitor. Utilization of distributed blocking capacitors makes the product of the invention small. Moreover, improvement of the structure of the invention brings effect such as less differential loss, large power capacity, as well as high isolation degree between circuits.

Owner:COMBA TELECOM TECH (GUANGZHOU) CO LTD

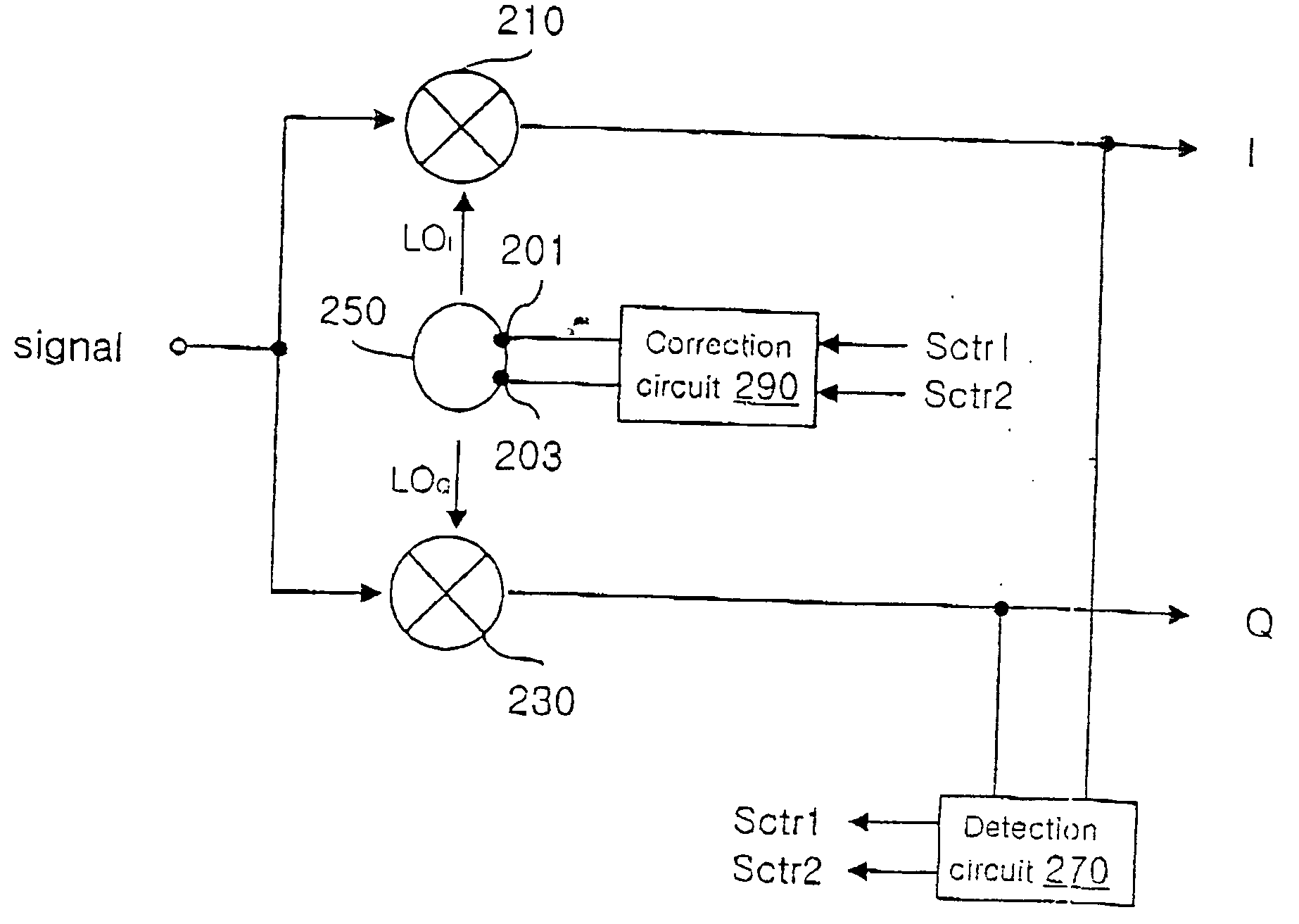

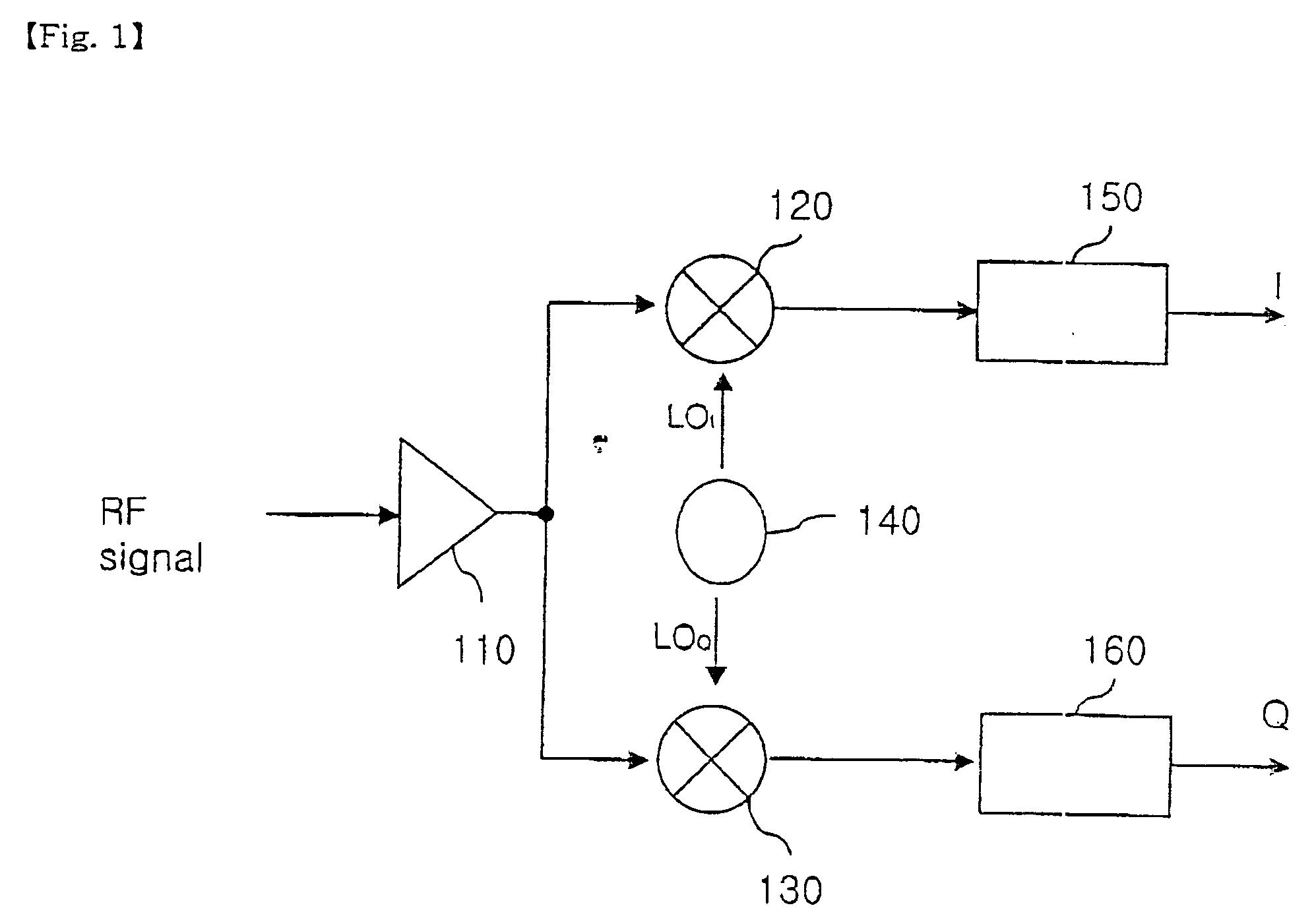

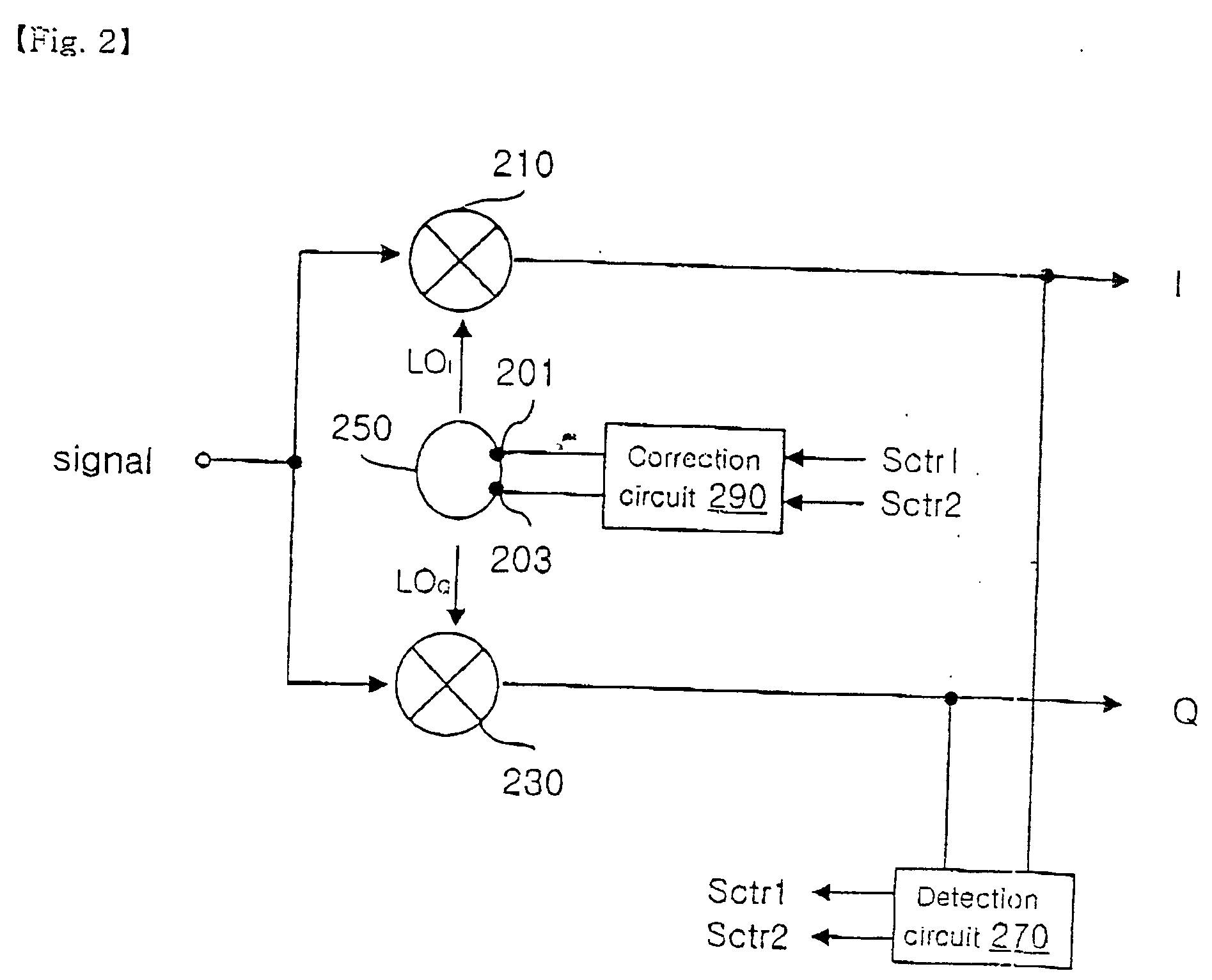

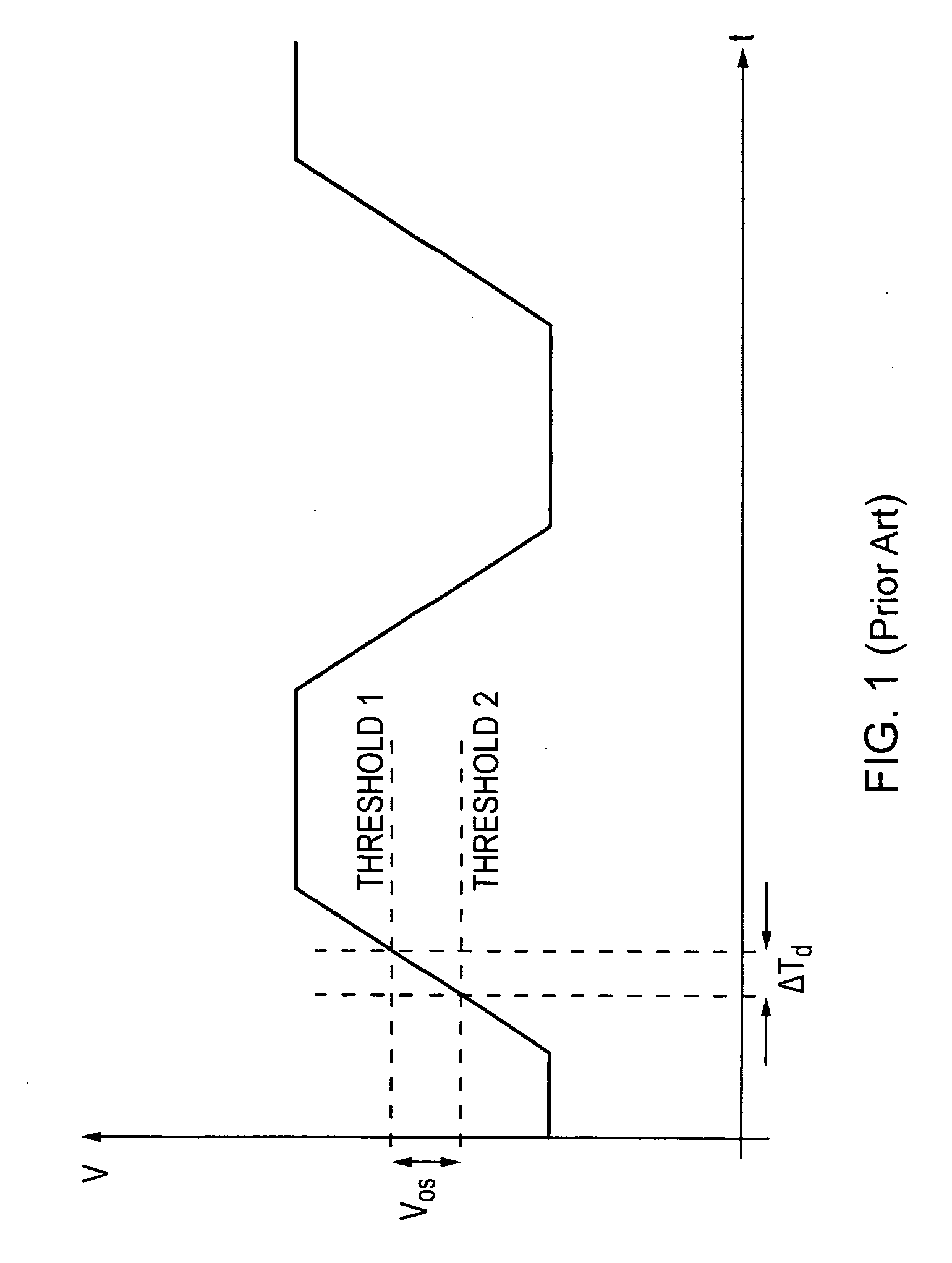

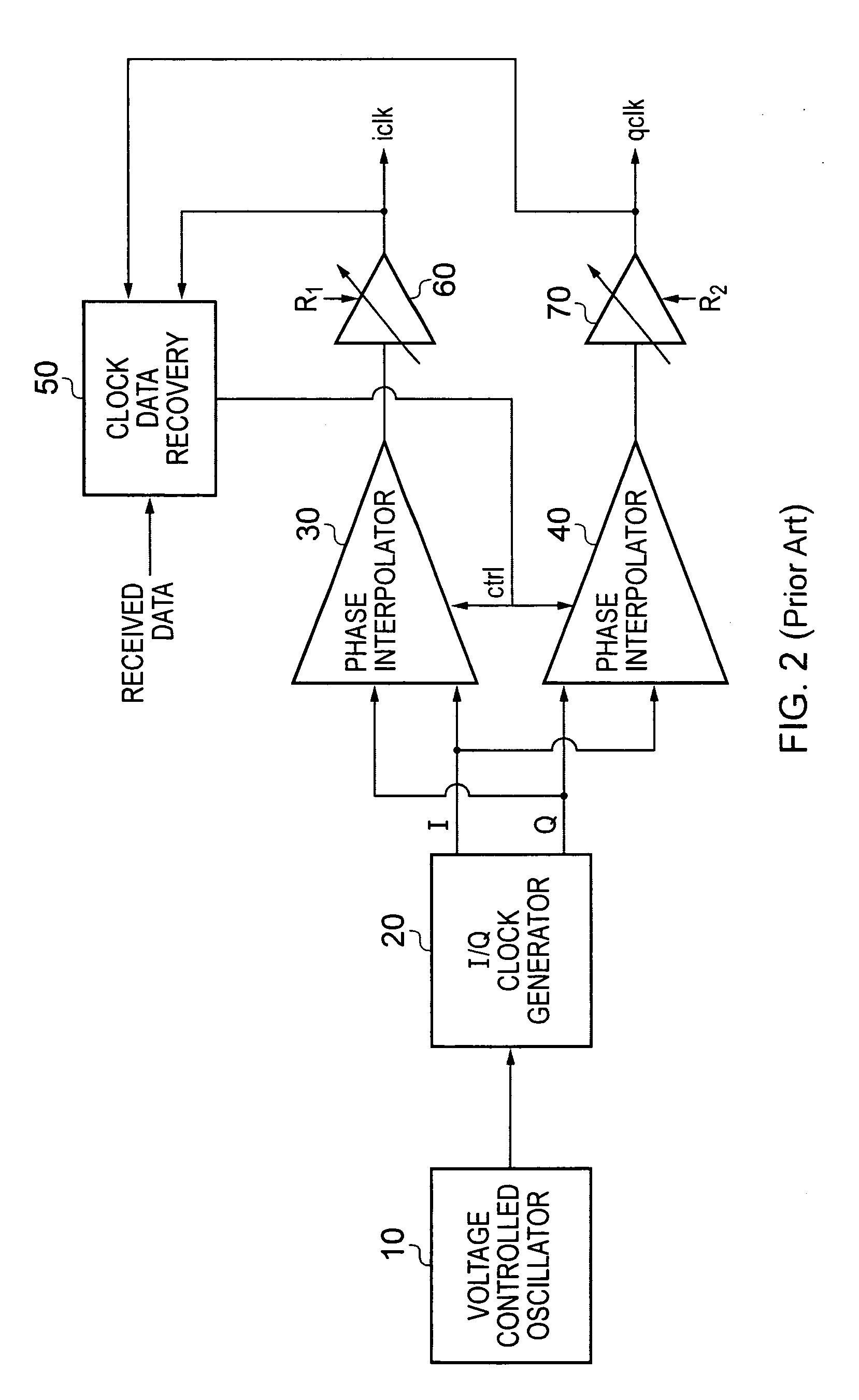

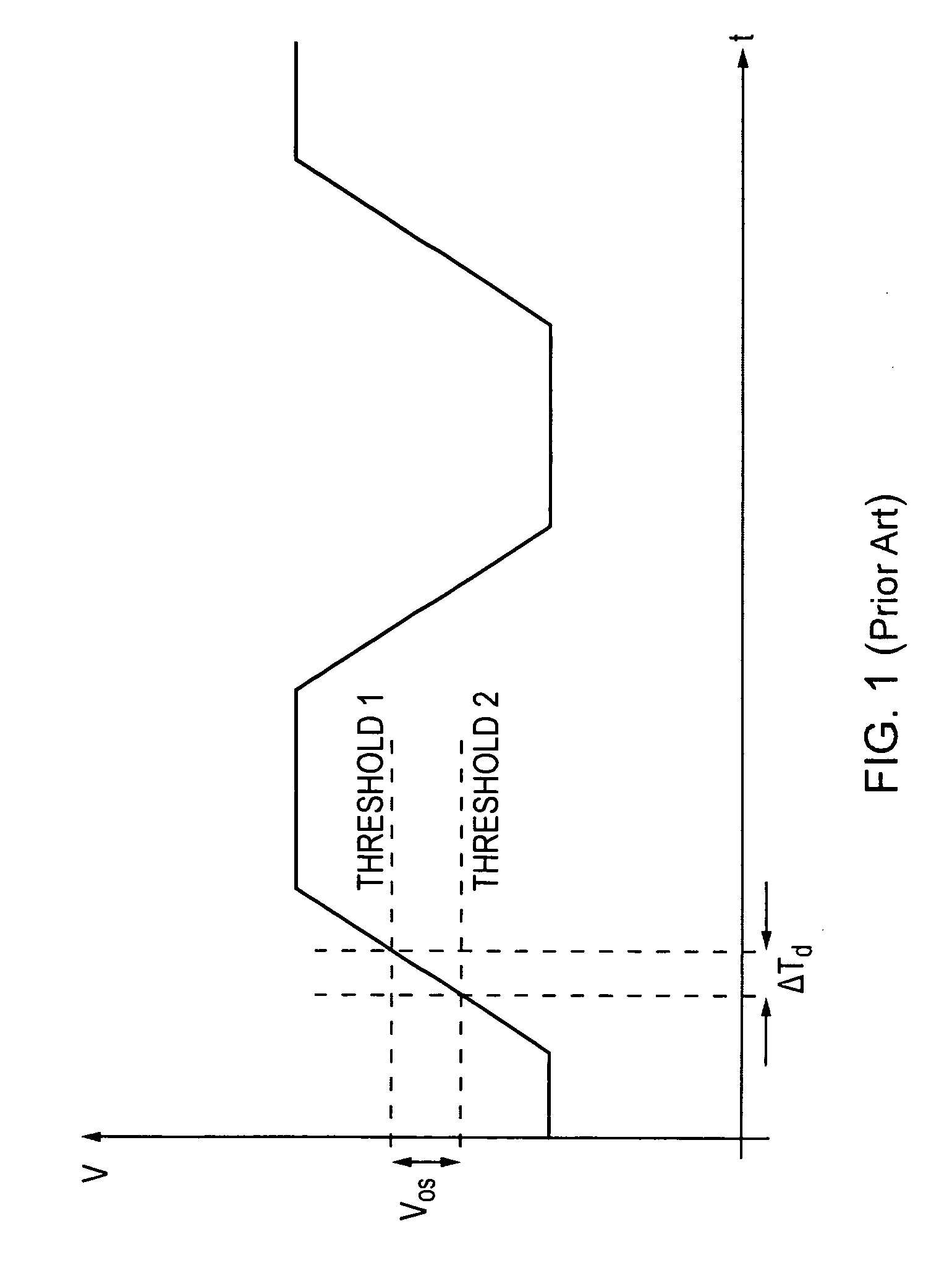

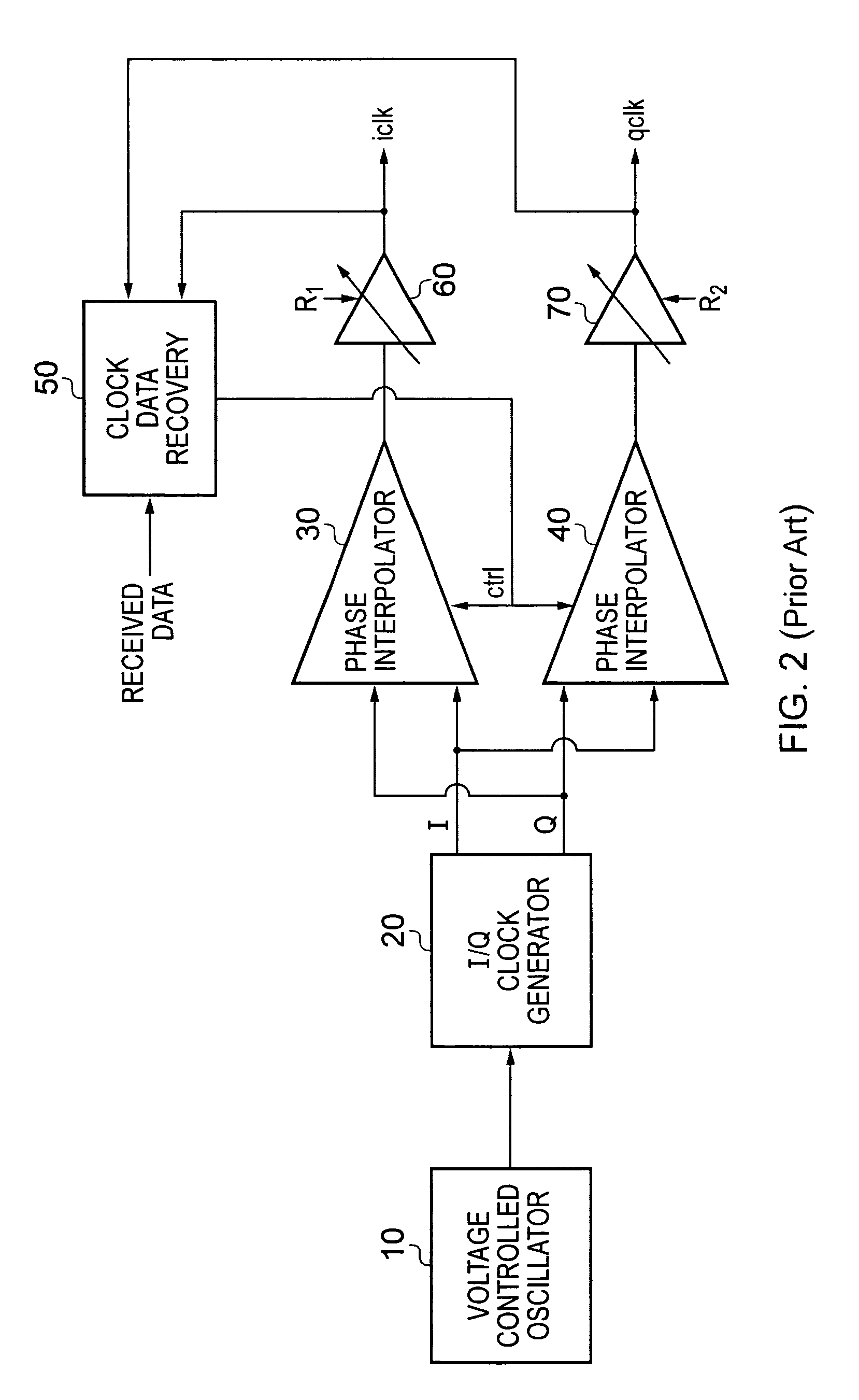

Local oscillator using I/Q mismatch compensating circuit through LO path receiver using thereof

InactiveUS20040092241A1Efficient use ofAutomatic scanning with simultaneous frequency displayModulated-carrier systemsFrequency mixerLocal oscillator

This invention relates to a local oscillator using a correction circuit for correcting I / Q mismatch through LO path and a receiver using the same. The local oscillator provides in-phase local oscillating signal and quadrature-phase signal to first and second mixers outputting input signal with mixing in-phase local oscillating signal and quadrature-phase local oscillating signal, respectively. The oscillator comprises a local oscillator having first and second delay cells and outputting said in-phase local oscillating signal and said quadrature-phase local oscillating signal; and a correction circuit for controlling phase matching characteristic between said in-phase local oscillating signal and said quadrature-phase local oscillating signal outputted from said local oscillator, said correction circuit setting bias current flowing in said first and second delay cells of said local oscillator as being different. In another embodiments, the phase matching characteristic is controlled by setting bias voltage applied to the first and second delay cells as being different, by setting width of active device included in the first and second delay dells as being different, or by setting impedance of passive device as being different.

Owner:INTEGRANT TECH

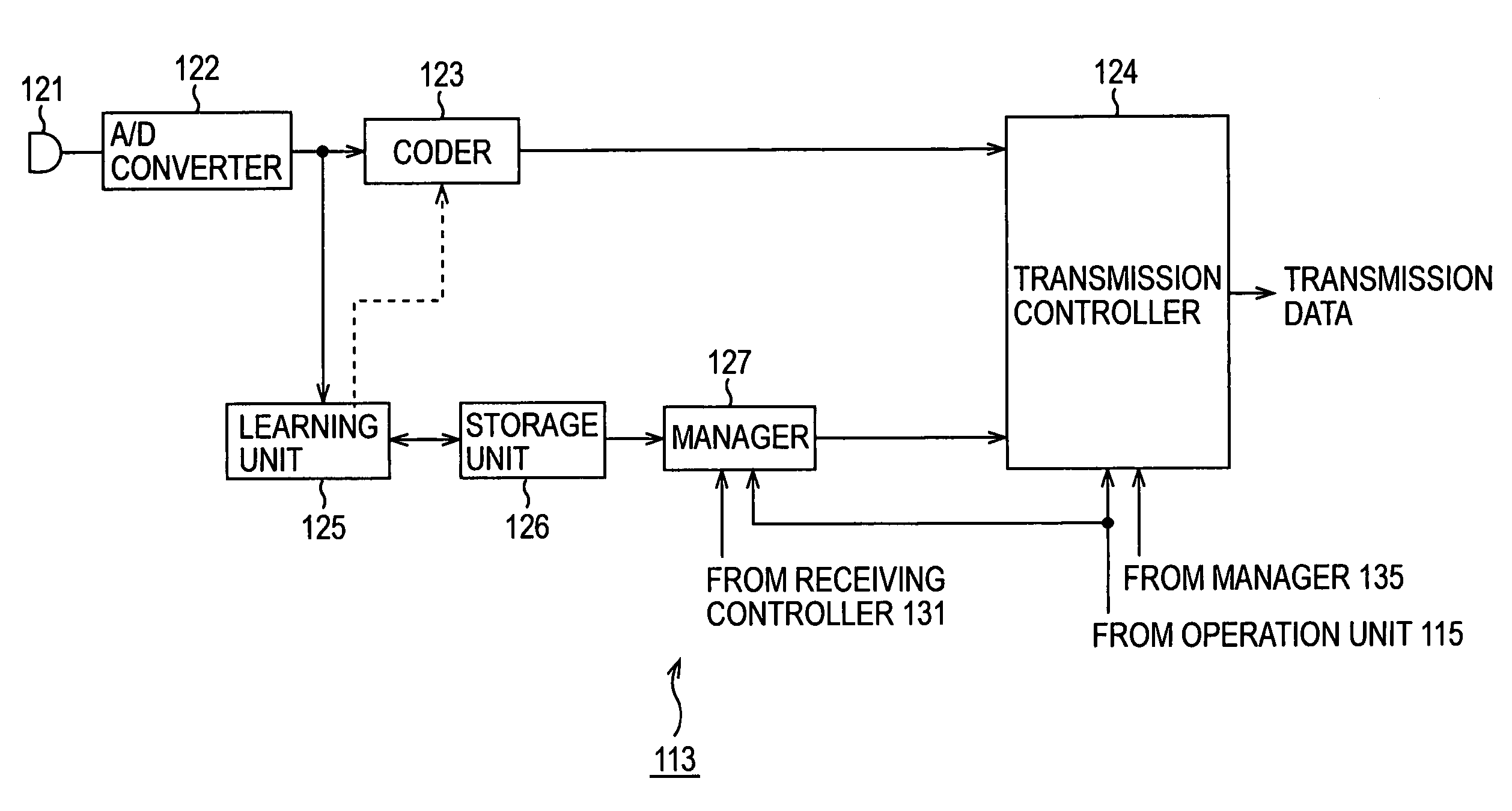

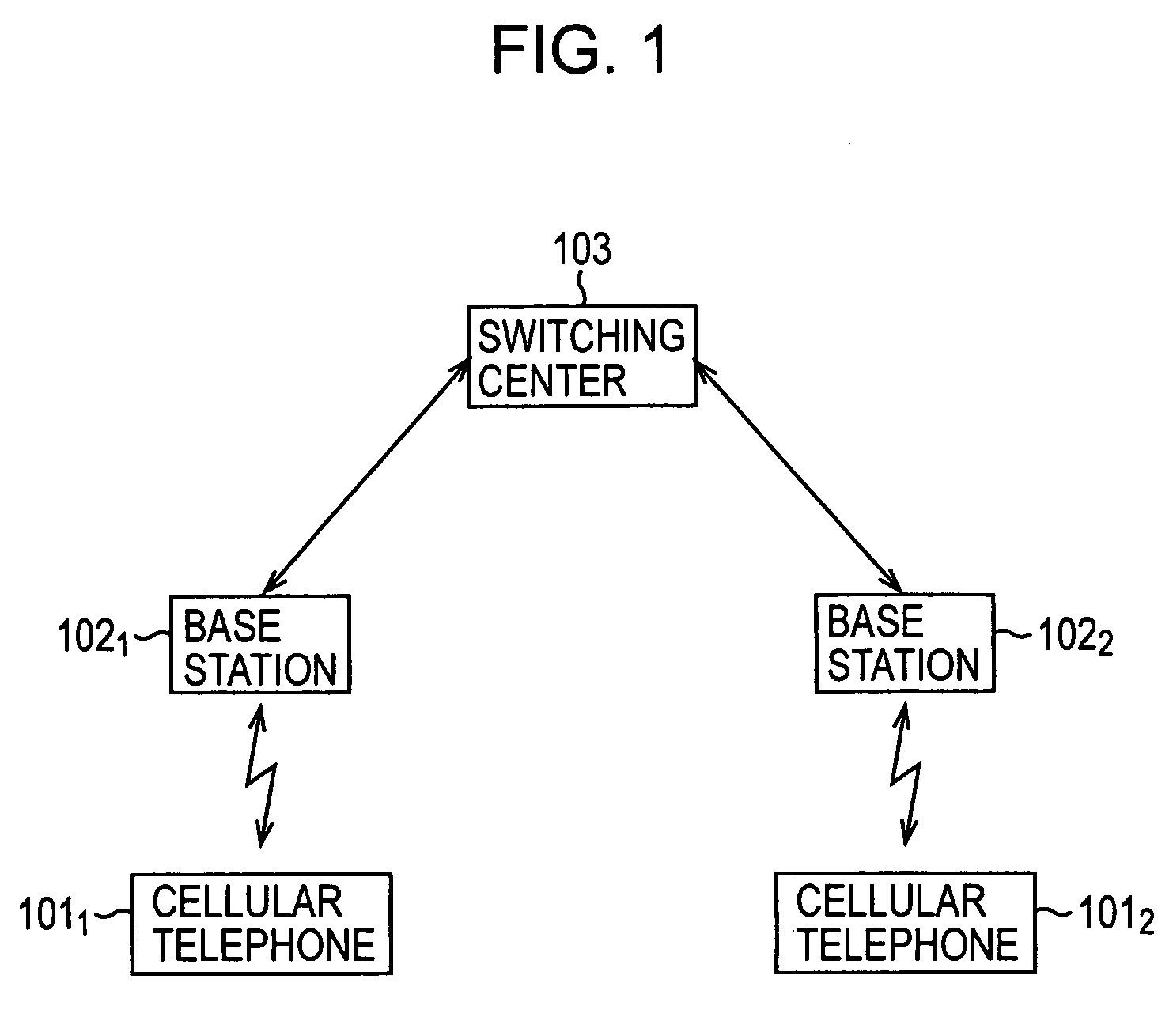

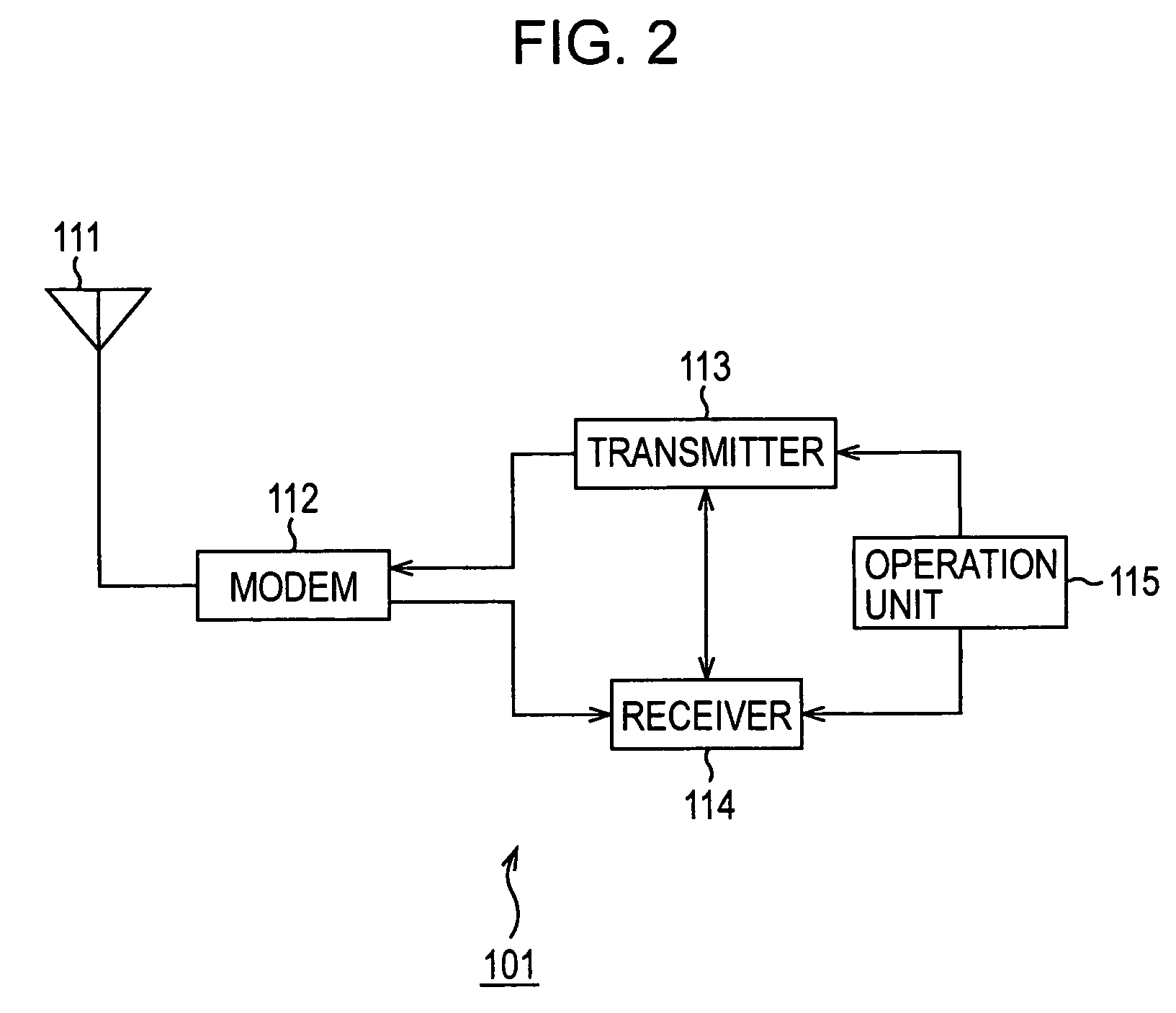

Transmission device, transmission method, reception device, reception method, transmission/reception device, communication method, recording medium, and program

InactiveUS20060046671A1Quality improvementError preventionLine-faulsts/interference reductionTransceiverCellular telephone

The present invention relates to a transmitting apparatus, a transmitting method, a receiving apparatus, a receiving method, a transceiver, a communication apparatus and method, a recording medium, and a program in which high quality voice can be decoded. A cellular telephone 421-1 outputs coded voice data and also supplies uncoded voice sample data to a switching center 423 while a telephone call is not made. Based on voice data used for the previous calculation processing and newly input voice data, the switching center 423 performs calculation processing for quality-improving data for improving the quality of voice to be output from a cellular telephone 421-2 that receives the coded voice data. The switching center 423 stores the optimal quality-improving data as a user information database in association with the cellular telephone 421-1. The cellular telephone 421-2 decodes the coded voice data based on the optimal quality-improving data supplied from the switching center 423. The present invention can be applied to cellular telephones.

Owner:SONY CORP

Apparatus for generating multiple clock signals of different frequency characteristics

InactiveUS7046977B2Automatic scanning with simultaneous frequency displayPulse transformerClock rateFrequency synthesizer

Owner:APPLE INC +1

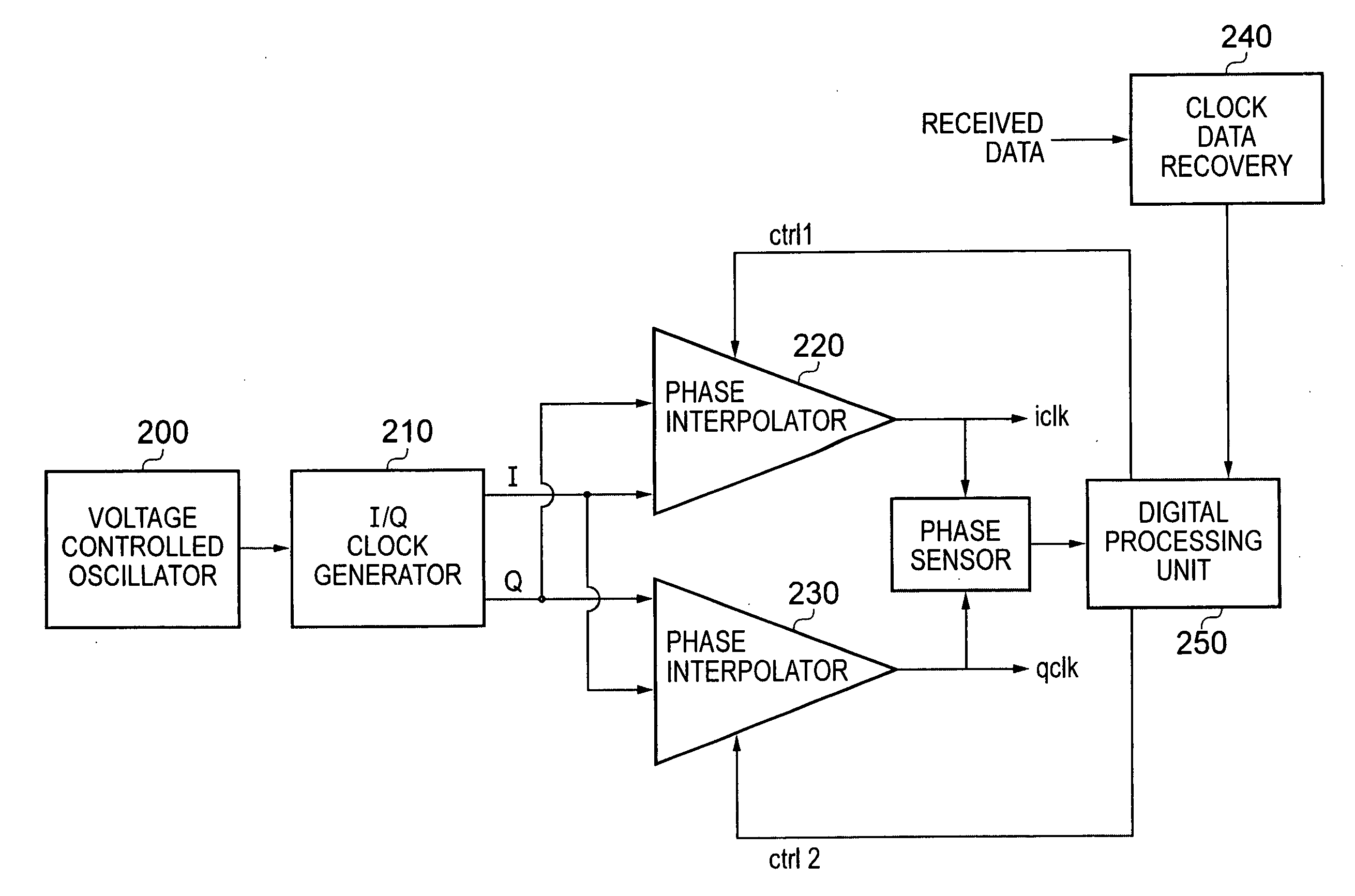

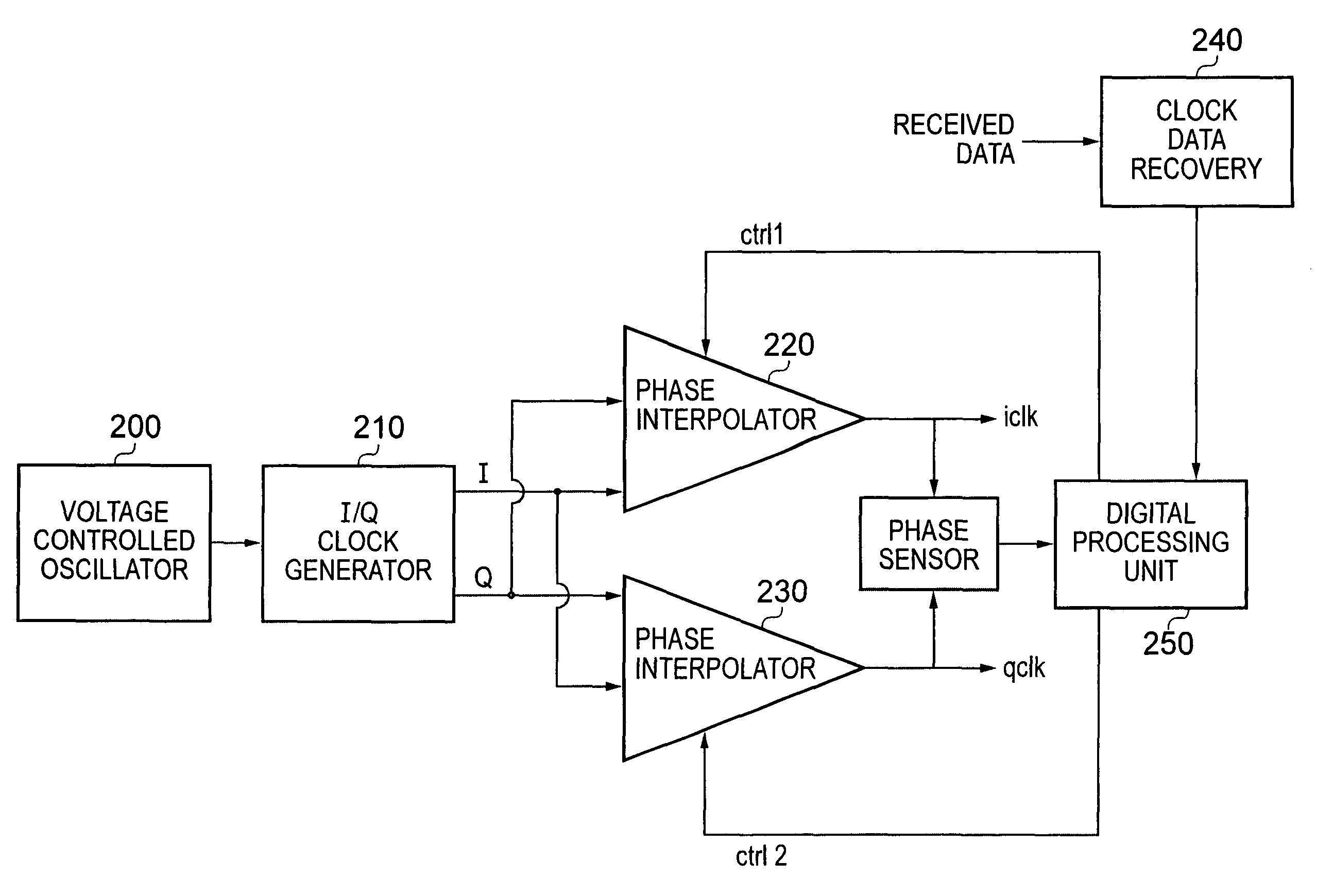

Method of processing signal data with corrected clock phase offset

ActiveUS20090289672A1Data processing is accurateAutomatic scanning with simultaneous frequency displayPulse automatic controlPhase differenceClock phase

The present invention provides a method of processing signal data comprising generating a first clock signal and a second clock signal and processing the signal data using the first clock signal and the second clock signal. While processing the signal data, the phase difference between the first clock signal and the second clock signal is measured and corrected for so that a target phase difference between the first clock signal and the second clock signal is maintained.

Owner:INTEGRATED DEVICE TECH INC

Method of processing signal data with corrected clock phase offset

ActiveUS8259888B2Data processing is accurateAutomatic scanning with simultaneous frequency displayPulse automatic controlPhase differenceClock phase

The present invention provides a method of processing signal data comprising generating a first clock signal and a second clock signal and processing the signal data using the first clock signal and the second clock signal. While processing the signal data, the phase difference between the first clock signal and the second clock signal is measured and corrected for so that a target phase difference between the first clock signal and the second clock signal is maintained.

Owner:INTEGRATED DEVICE TECH INC

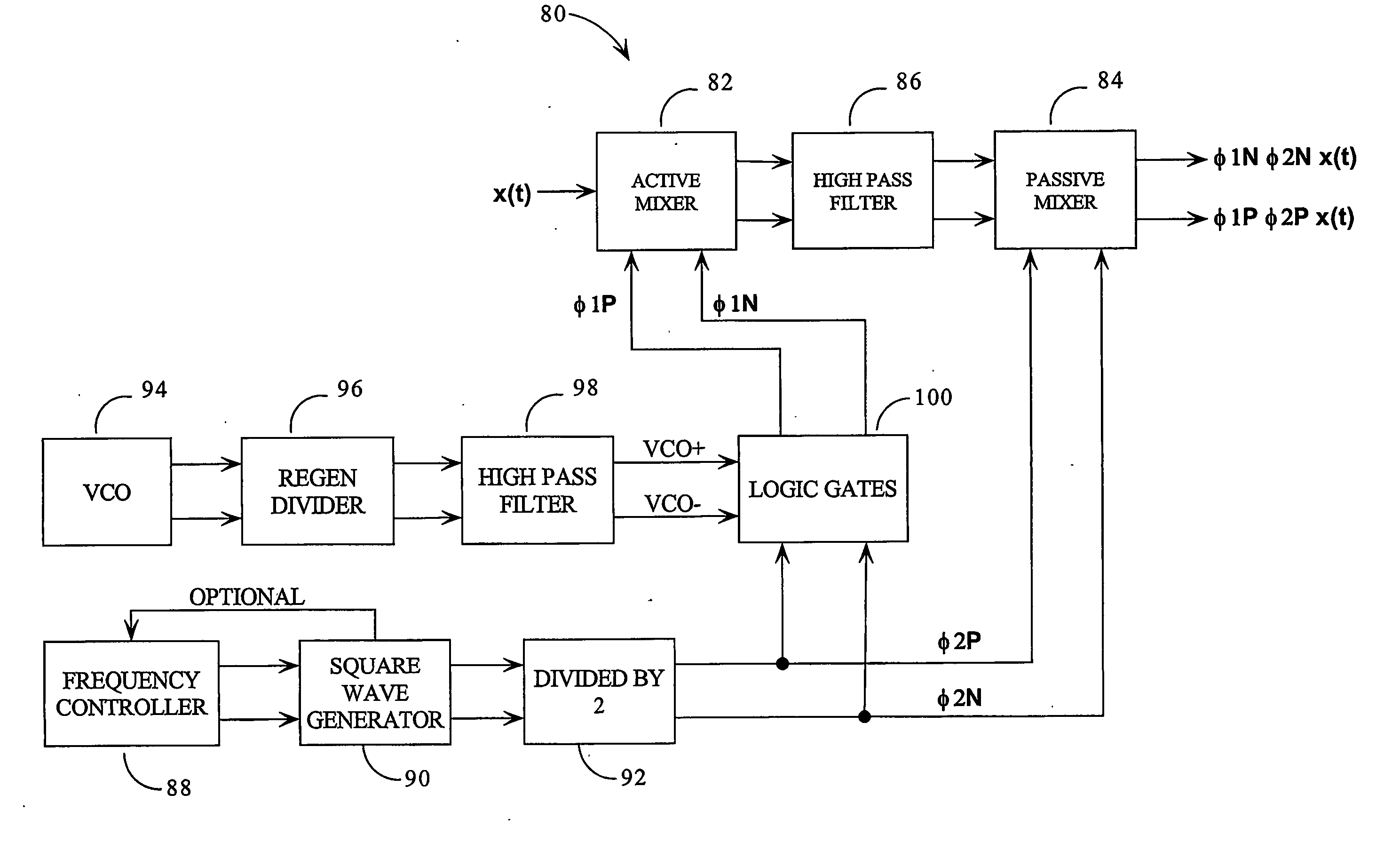

Method and apparatus for down conversion of radio frequency (rf) signals

ActiveUS20050180528A1Automatic scanning with simultaneous frequency displayAmplitude-modulated carrier systemsTransceiverLocal oscillator signal

There is a need for an inexpensive, high-performance, fully-integrable, multi-standard transceiver, which suppresses spurious noise signals. The invention provides a topology that satisfies this need, using a first signal generator which produces an oscillator signal f1 and a second signal generator which produces a mono-tonal mixing signal φ2, where f1 is a multiple of the frequency of φ2; and a logic circuit for generating a multi-tonal mixing signal φ1, where φ1*φ2 has significant powerat the frequency of said local oscillator signal being emulated, neither of said cp1 nor said φ2 having significant power at the carrier frequency of said input signal x(t) or said LO signal being emulated.

Owner:ICERA CANADA ULC

Frequency modification circuitry for use in radio-frequency communication apparatus and associated methods

InactiveUS7200364B2Automatic scanning with simultaneous frequency displayPulse automatic controlControl signalEngineering

Frequency modification circuitry may be employed as part of a crystal oscillator circuit to generate a reference signal with adjustable frequency. The frequency modification circuitry may be implemented as part of a crystal oscillator circuit that includes digitally controlled crystal oscillator (“DCXO”) circuitry and a crystal. The frequency modification circuitry may adjust the frequency of the reference signal in response to one or more frequency control signals. In one example, the frequency modification circuitry may include variable capacitors such as one or more continuously variable and / or discretely variable capacitors for providing coarse and / or fine adjustment of the reference signal frequency.

Owner:SILICON LAB INC

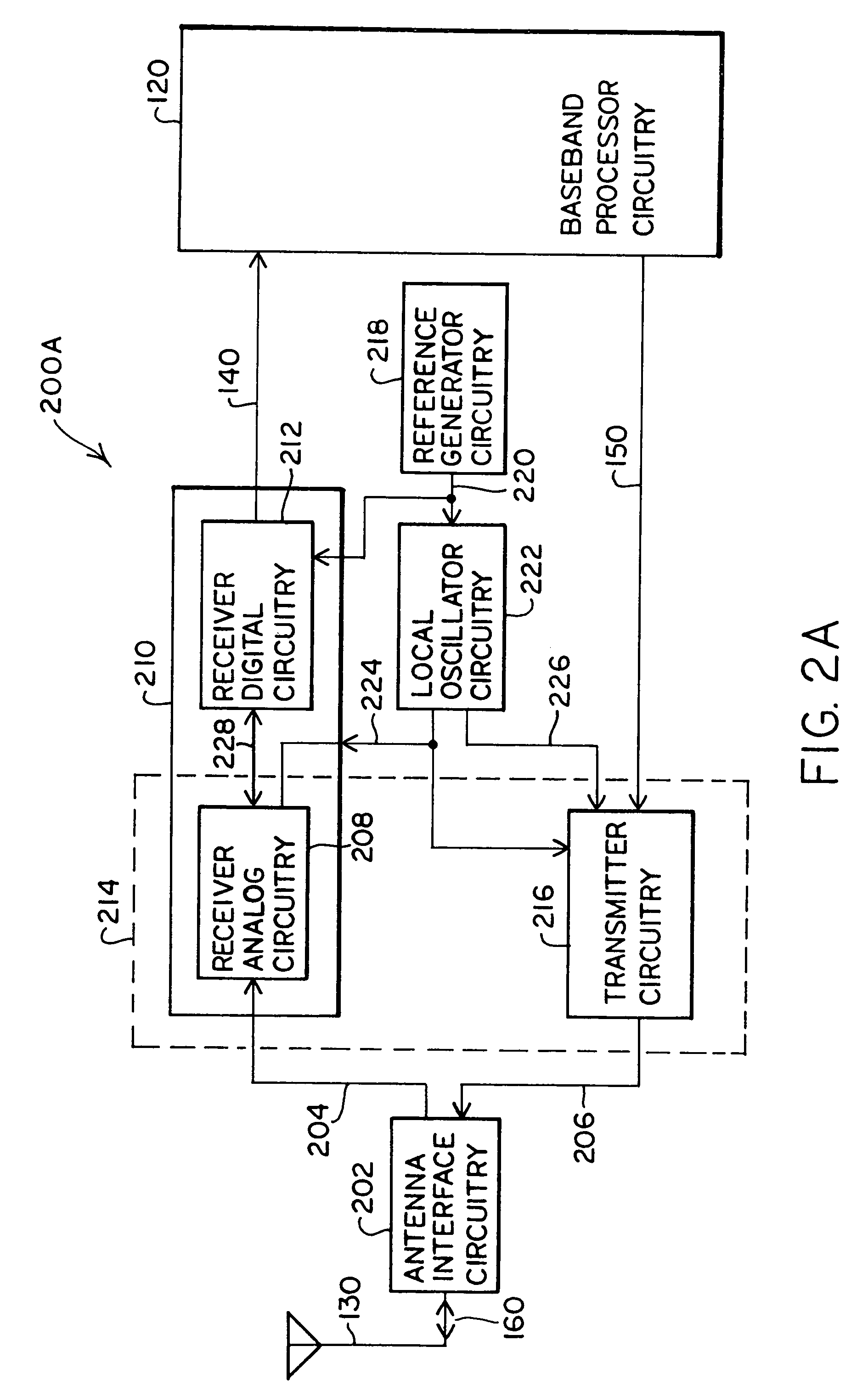

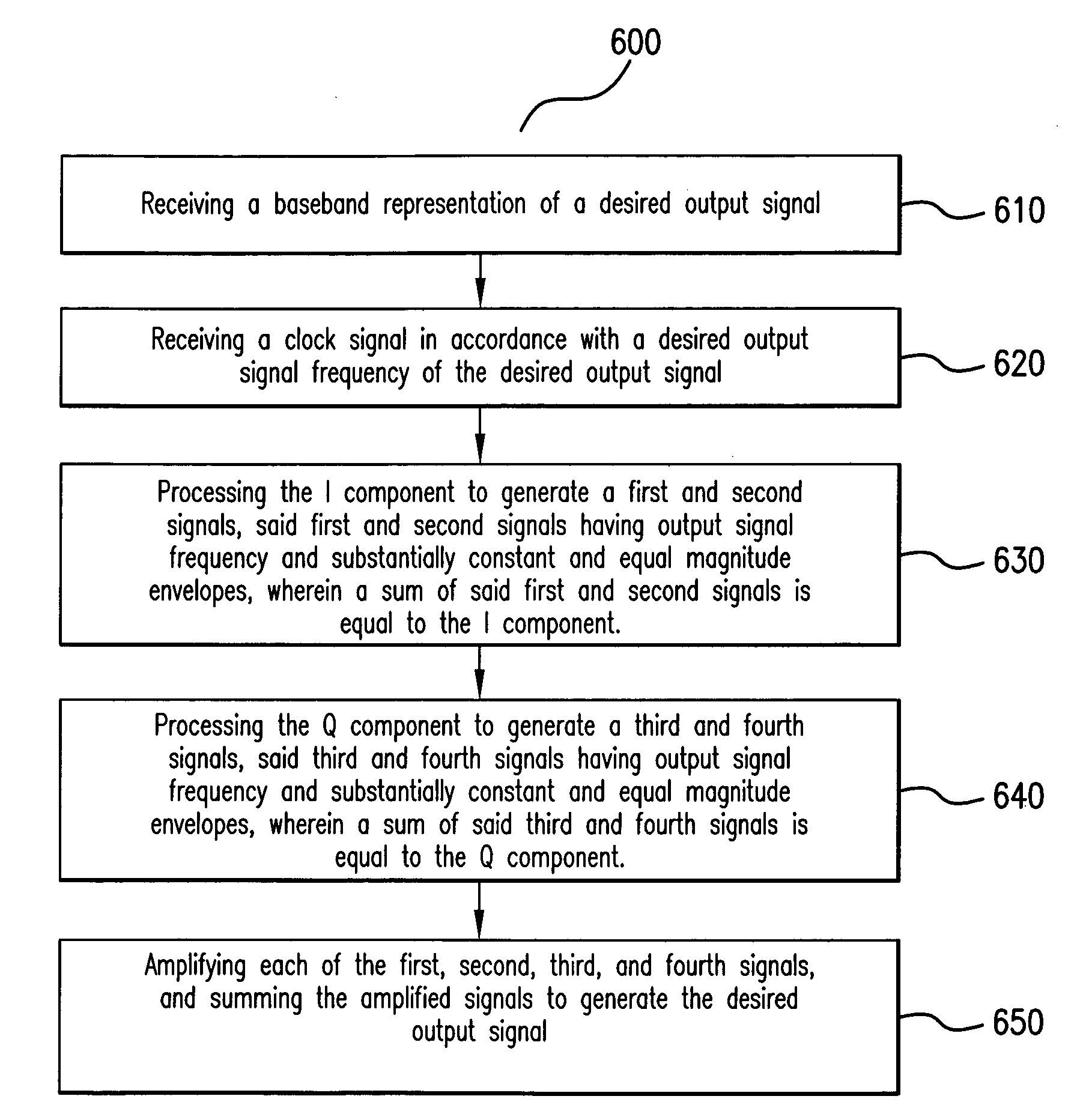

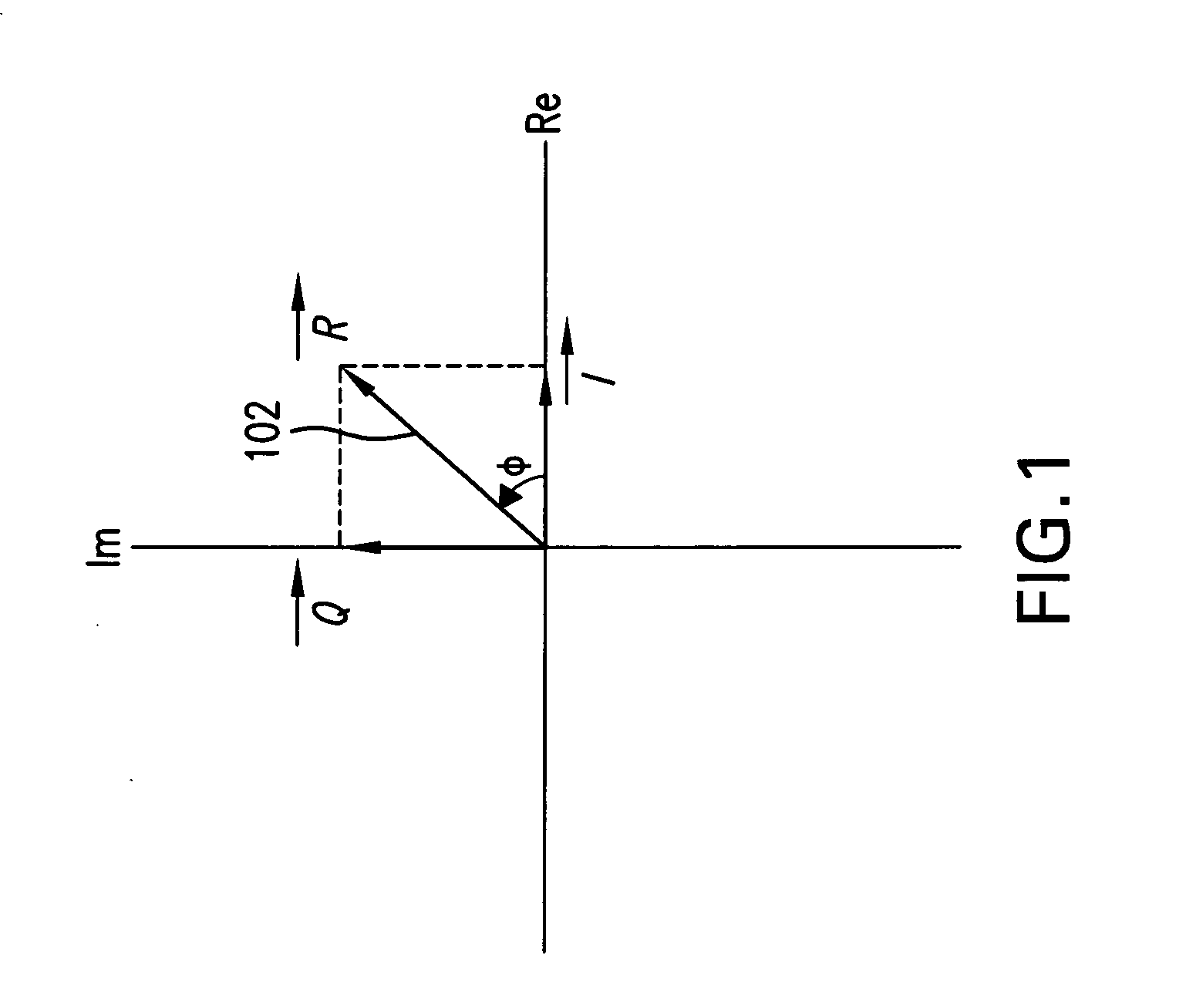

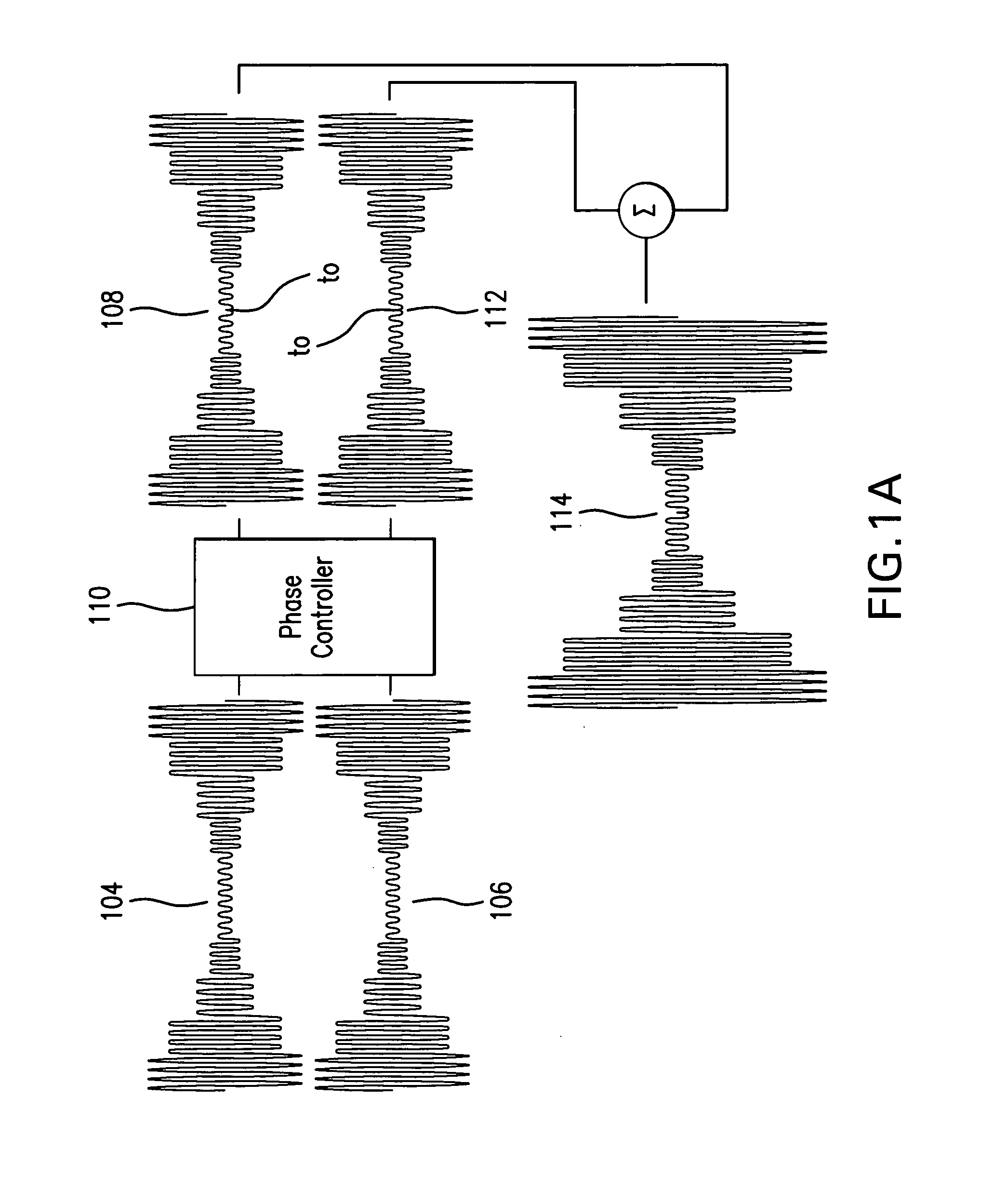

Systems and methods of RF power transmission, modulation, and amplification, including architectural embodiments of same

InactiveUS20070249388A1Increase costLow costMultiple-port networksAutomatic scanning with simultaneous frequency displayElectric power transmissionEngineering

Methods and systems for vector combining power amplification are disclosed herein. In one embodiment, a plurality of signals are individually amplified, then summed to form a desired time-varying complex envelope signal. Phase and / or frequency characteristics of one or more of the signals are controlled to provide the desired phase, frequency, and / or amplitude characteristics of the desired time-varying complex envelope signal. In another embodiment, a time-varying complex envelope signal is decomposed into a plurality of constant envelope constituent signals. The constituent signals are amplified equally or substantially equally, and then summed to construct an amplified version of the original time-varying envelope signal. Embodiments also perform frequency up-conversion.

Owner:PARKER VISION INC

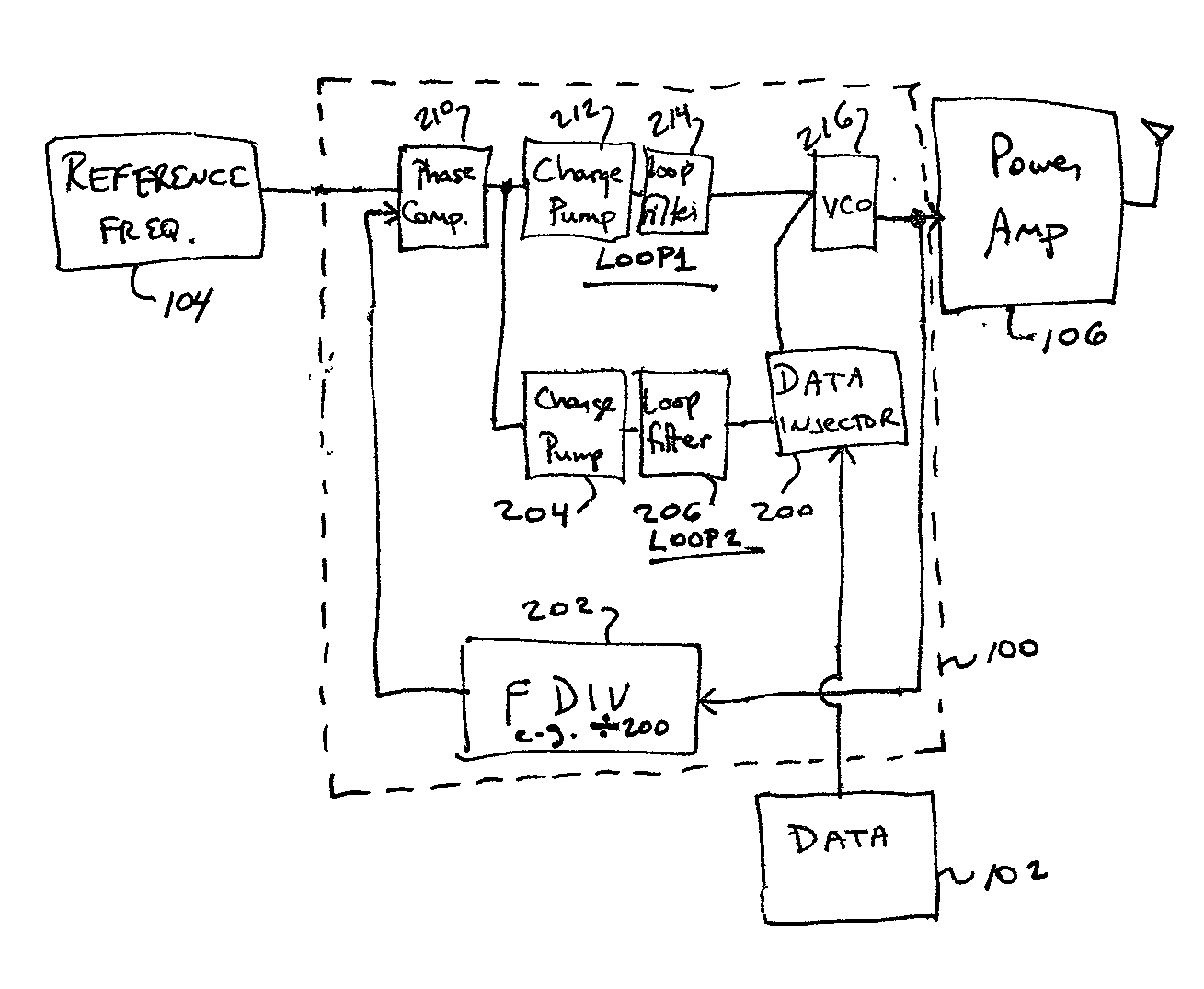

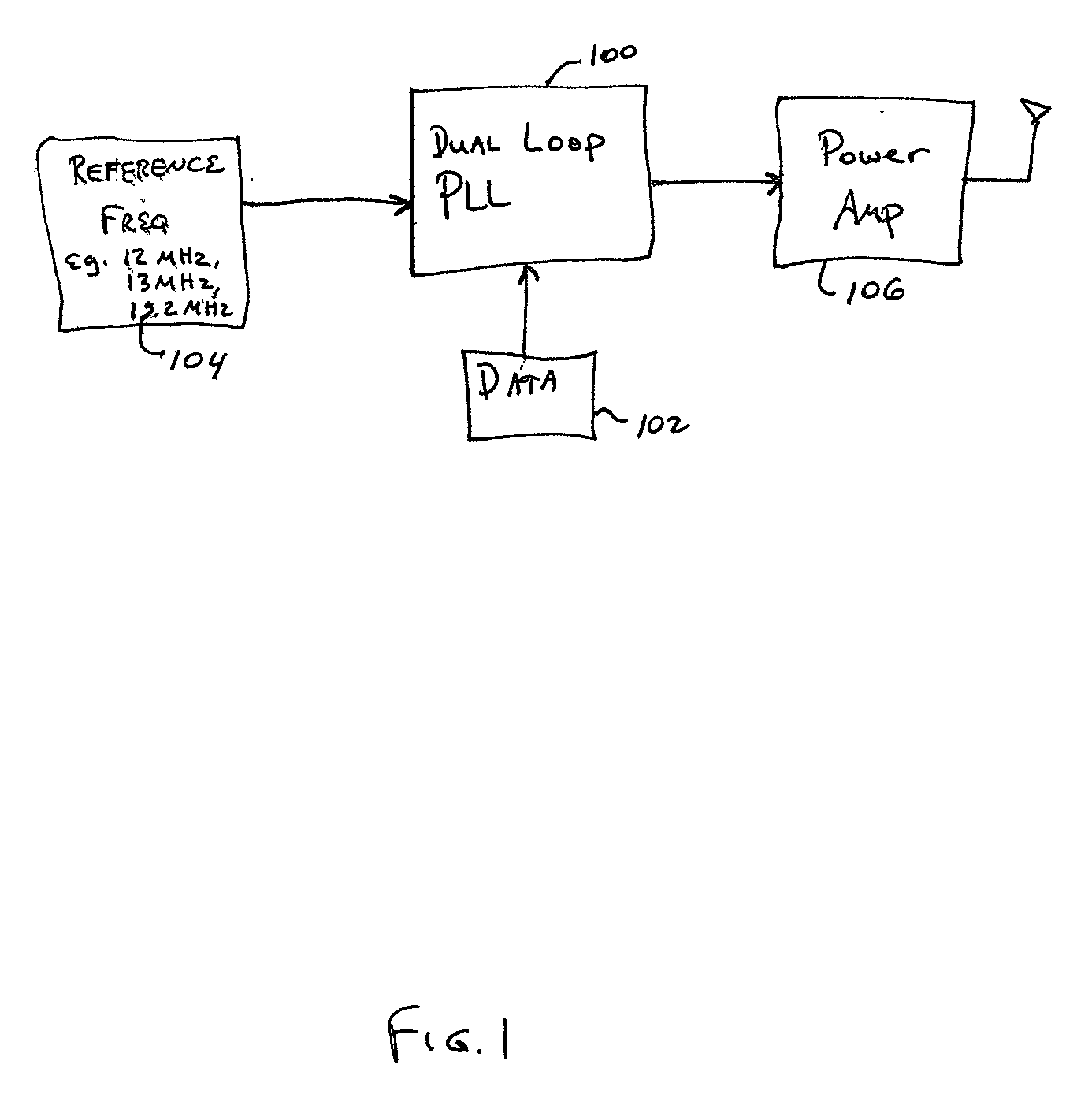

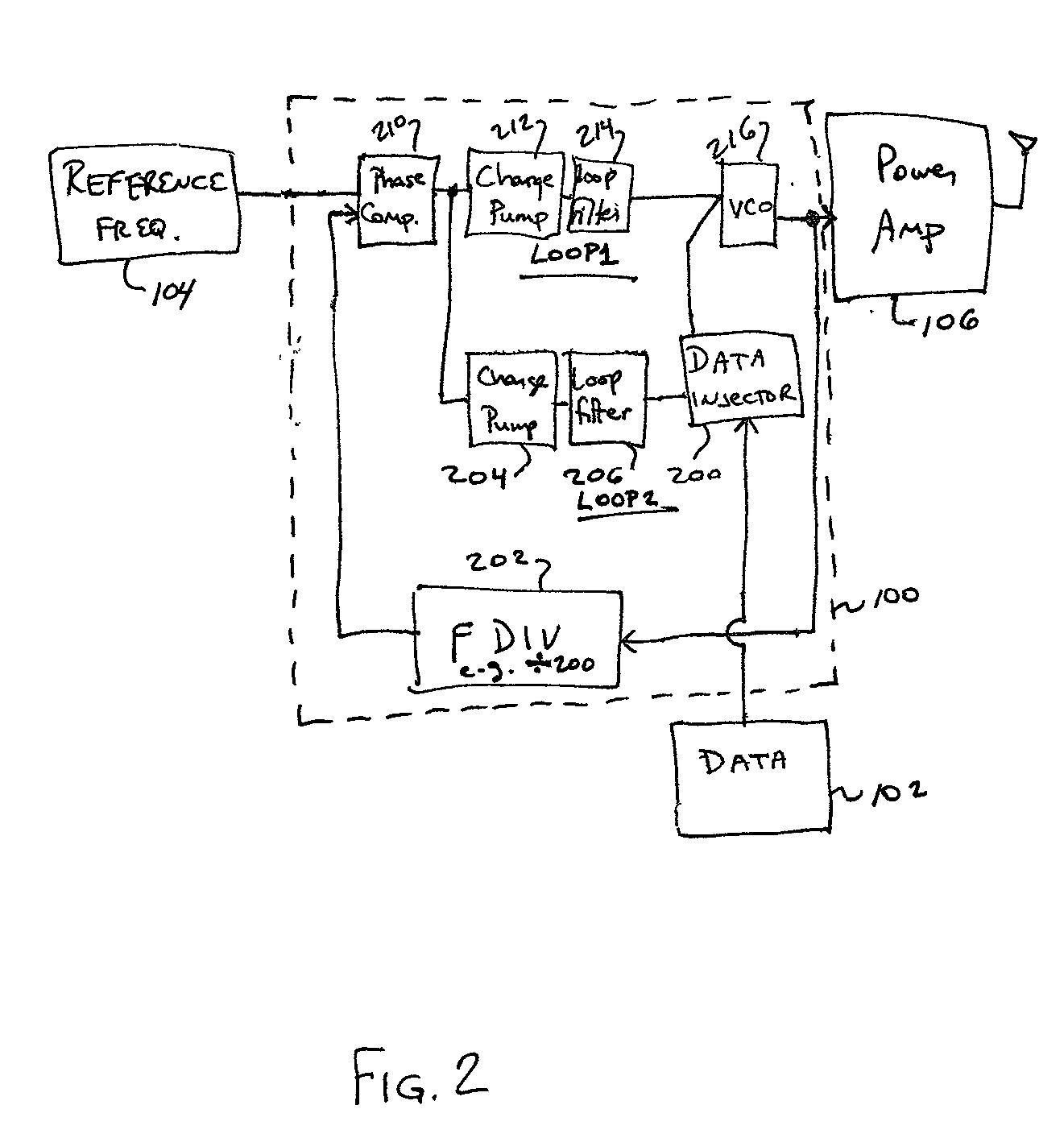

Accurate gain direct modulation (KMOD) using a dual-loop PLL

InactiveUS20030203724A1Automatic scanning with simultaneous frequency displayPulse automatic controlBluetooth piconetsFrequency synthesizer

The present invention provides a baseband RF clock synthesizer having particular use in a BLUETOOTH piconet device, which has the capability of providing simple and accurate calibration of modulation path gain (KMOD) by introducing a dual-loop phase locked loop (PLL) in the RF clock signal synthesizer. The disclosed technique and apparatus controls the maximum frequency deviation by the difference of two locked frequencies, one frequency in each path of the dual-path PLL. Once the PLL is locked within some frequency error, the present technique and apparatus calibrates for the deviation of amplitude of the modulation due to the modulation path. Accordingly, modulation gain (KMOD) calibration is provided by adding an auxiliary loop to a PLL in an RF frequency synthesizer.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Configurable homodyne/heterodyne radio receiver and RFID reader employing same

InactiveUS7529533B2Facilitate listen-before-talk functionEnhance the imageNear-field transmissionAutomatic scanning with simultaneous frequency displayReceiver functionRadio receiver

Owner:TRIQUINT SEMICONDUCTOR

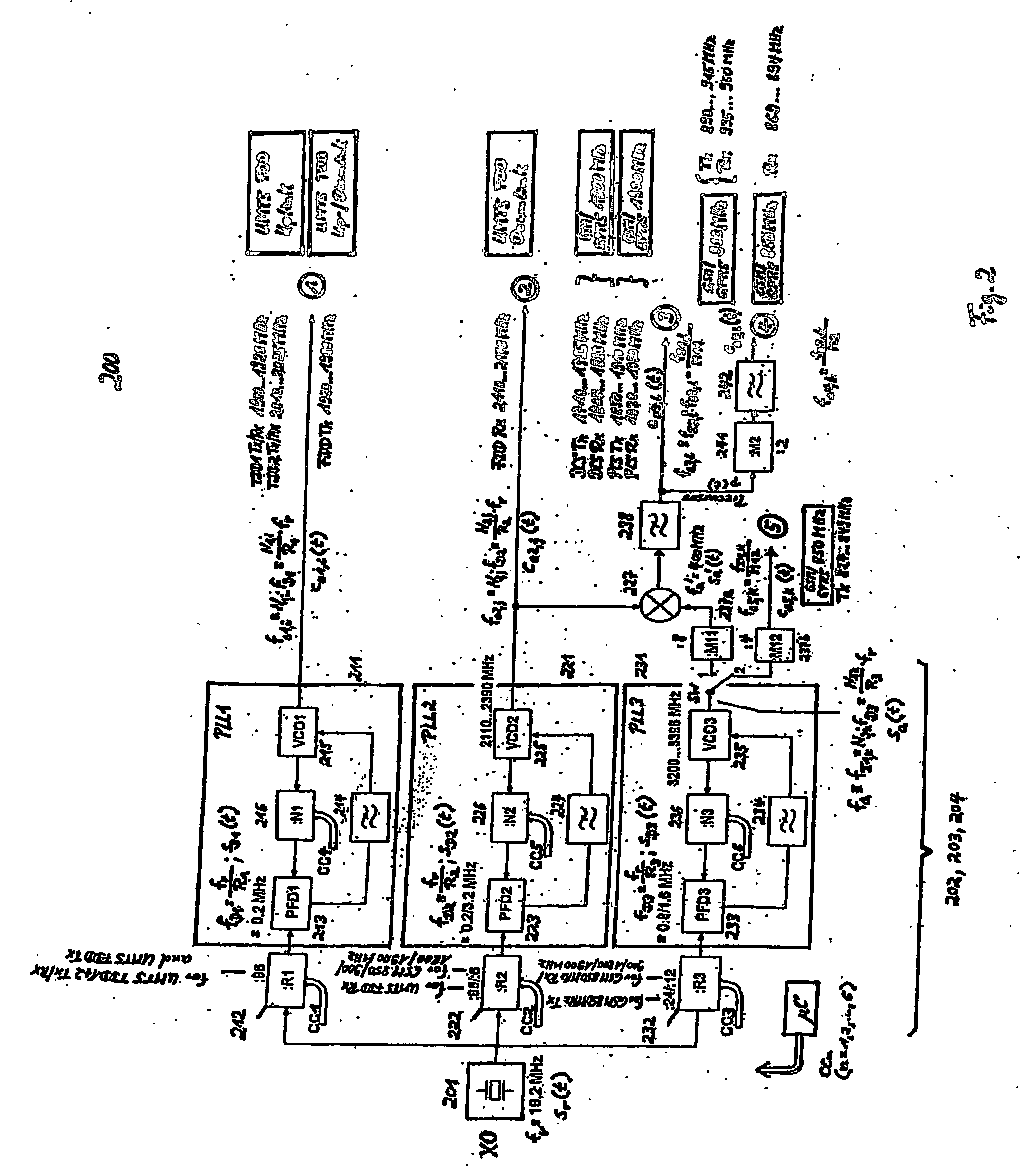

Multi-band frequency synthesizer

InactiveUS20060258311A1Interference be notReduced chip-space requirementDigital storageAngle modulationMulti bandTransceiver

A multi-mode PLL frequency synthesizer of a wireless multi-mode transceiver is provided which includes a reference frequency source providing an oscillator signal with a constant reference frequency, a first frequency synthesizer subunit for converting the signal into carrier signals with frequencies in the range of a first frequency band, a second frequency synthesizer subunit for transforming the oscillator signal into carrier signals having frequencies in the range of a second frequency band, and a third frequency synthesizer subunit for converting the oscillator signal into an auxiliary signal with a fixed frequency. The auxiliary signal is used together with the carrier signals of the second frequency band to generate carrier signals with frequencies in the range of a third and fourth frequency band. A frequency divider derives a signal in the range of a fifth frequency band from further intermediate frequency signals supplied by the third frequency synthesizer subunit by dividing the frequency of the auxiliary signal by an integer value.

Owner:SONY ERICSSON MOBILE COMM AB

Frequency modification circuitry for use in radio-frequency communication apparatus and associated methods

InactiveUS20060160512A1Automatic scanning with simultaneous frequency displayPulse automatic controlControl signalEngineering

Frequency modification circuitry may be employed as part of a crystal oscillator circuit to generate a reference signal with adjustable frequency. The frequency modification circuitry may be implemented as part of a crystal oscillator circuit that includes digitally controlled crystal oscillator (“DCXO”) circuitry and a crystal. The frequency modification circuitry may adjust the frequency of the reference signal in response to one or more frequency control signals. In one example, the frequency modification circuitry may include variable capacitors such as one or more continuously variable and / or discretely variable capacitors for providing coarse and / or fine adjustment of the reference signal frequency.

Owner:SILICON LAB INC

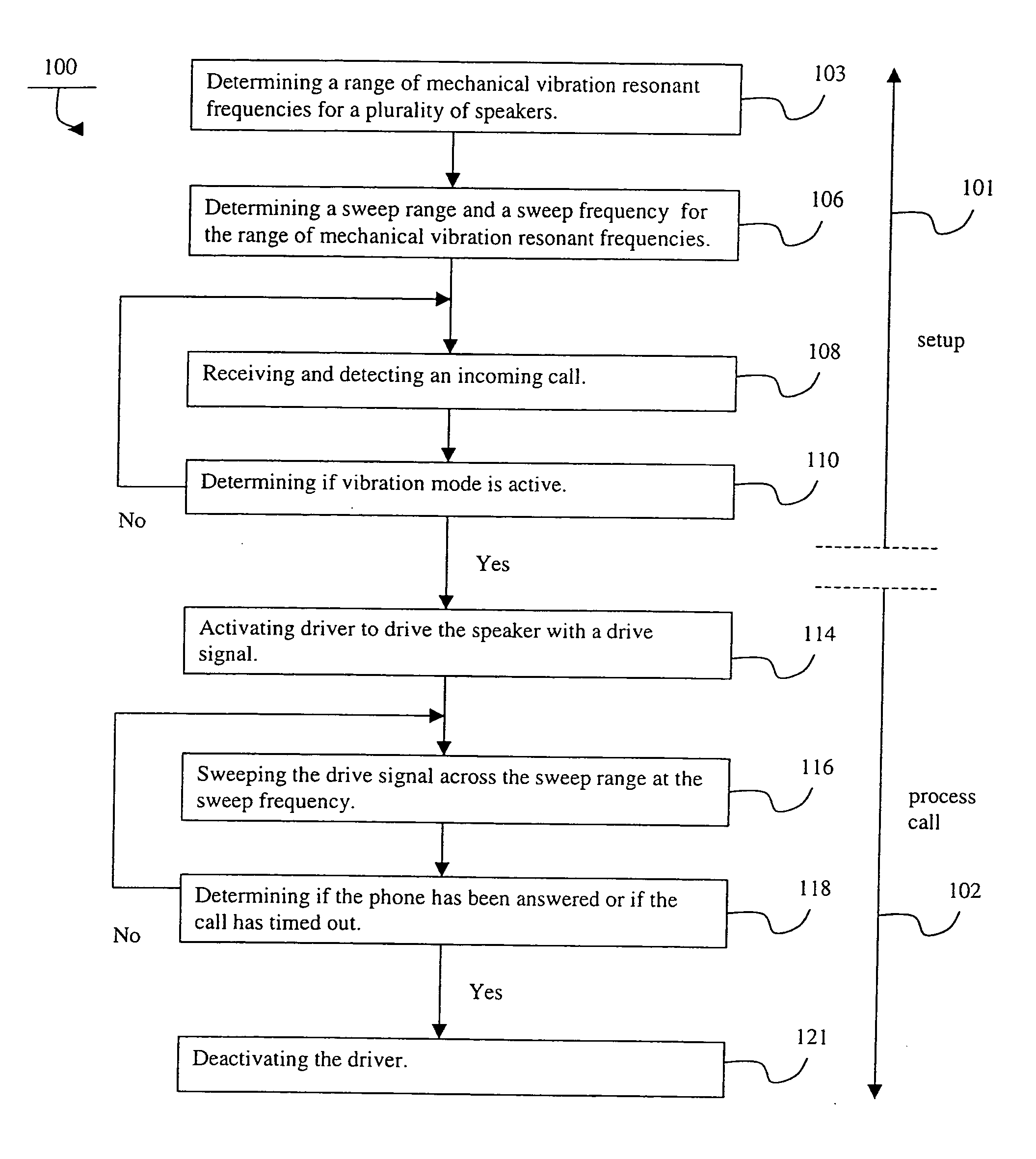

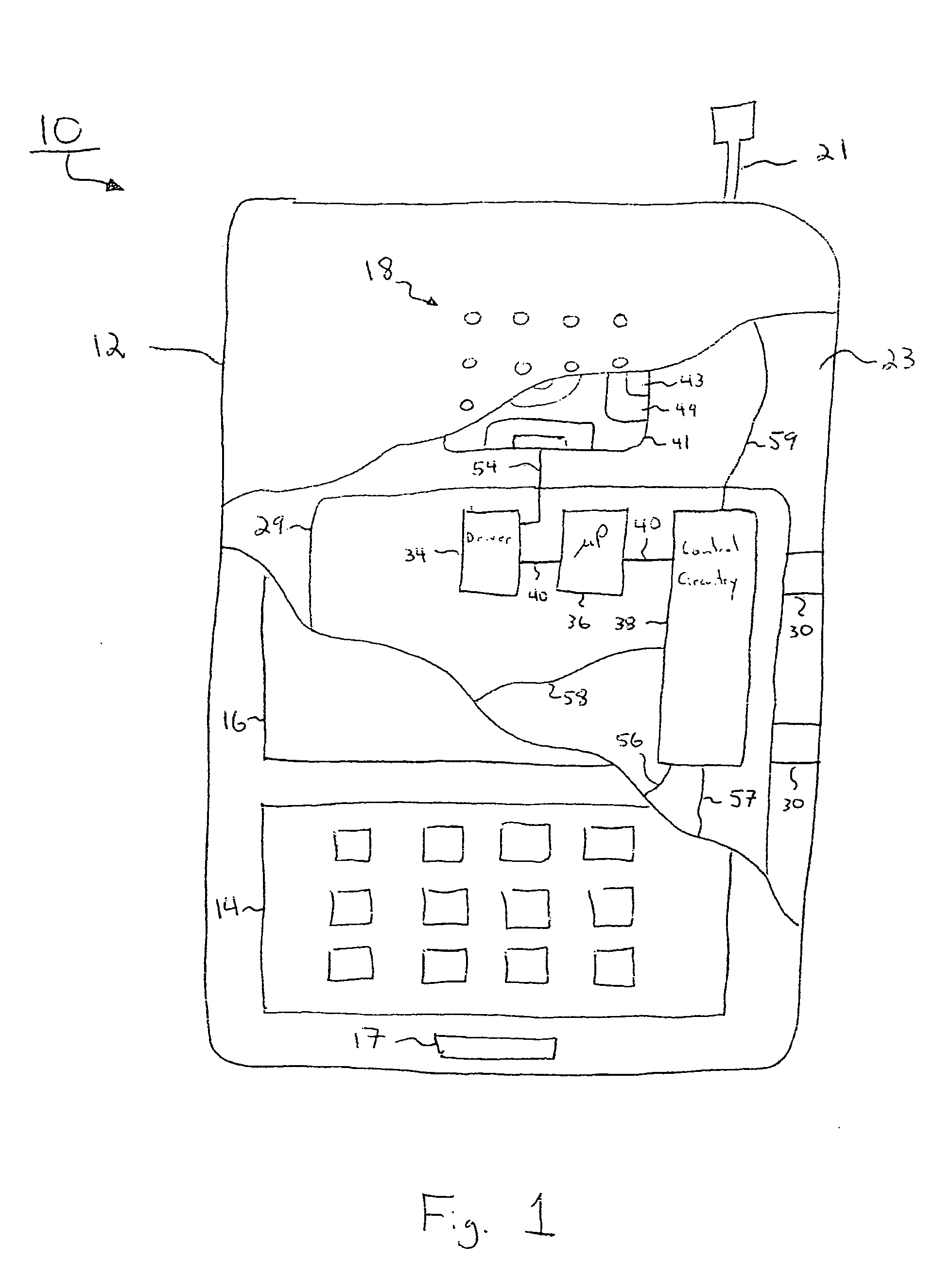

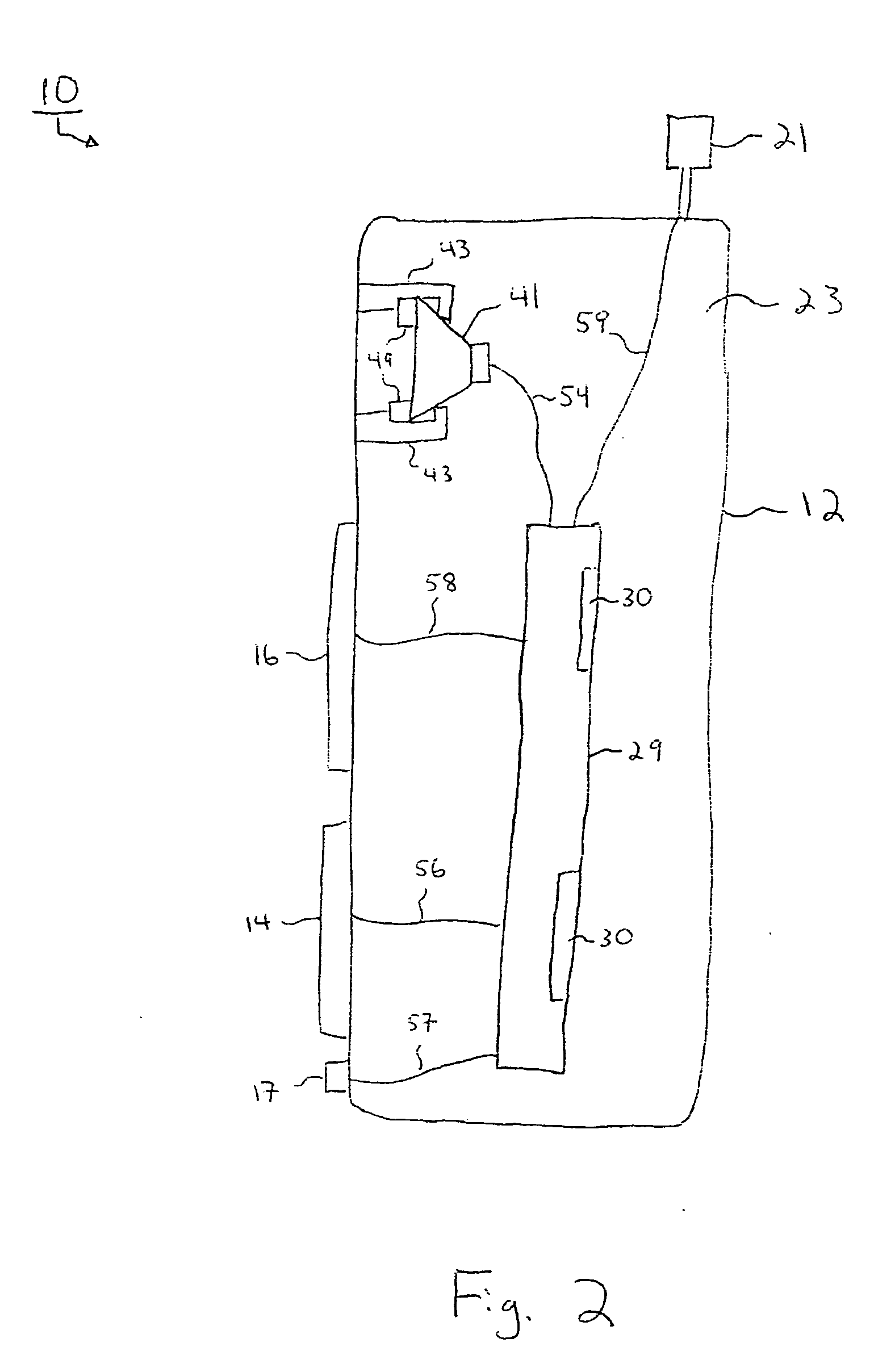

Wireless mobile communication device having a speaker vibration alert and method of using same

InactiveUS20050085275A1Improve efficiencyEliminate needAutomatic scanning with simultaneous frequency displayCurrent supply arrangementsEngineeringOutput device

A mobile wireless communication device has a speaker that functions as a vibration alert in addition to an audio output device. The speaker is selected from a group of speakers having variation in mechanical vibration resonant frequency. A drive signal sweeps back and forth across a sweep frequency range including the varient speaker mechanical vibration resonant frequencies. The drive signal drives the speaker causing it to vibrate at the mechanical vibration resonant frequency and in turn causing the mobile wireless communication device to vibrate, thereby alerting the user. In this manner, the same drive signal can be used to vibrate each speaker at the speaker's mechanical vibration resonant frequency despite the variation in mechanical vibration resonant frequencies among the group of speakers.

Owner:KYOCERA CORP

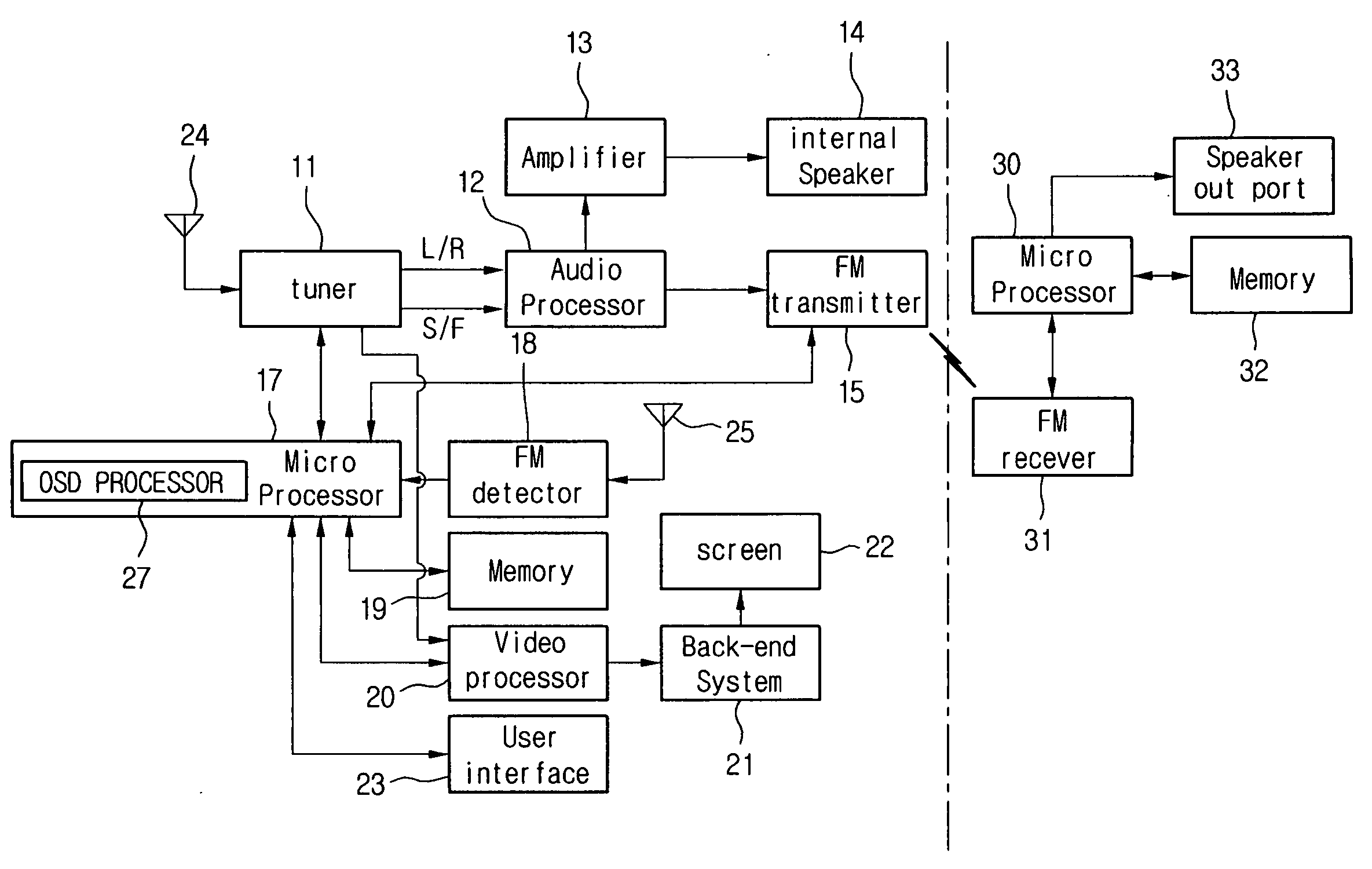

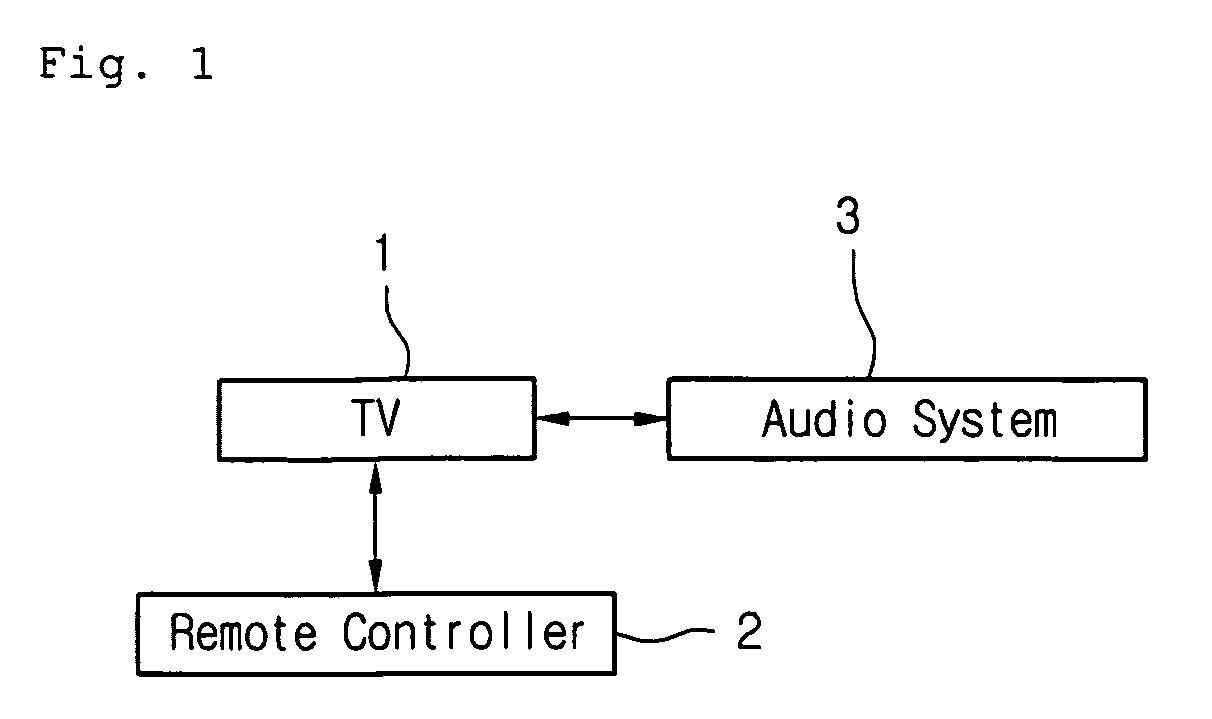

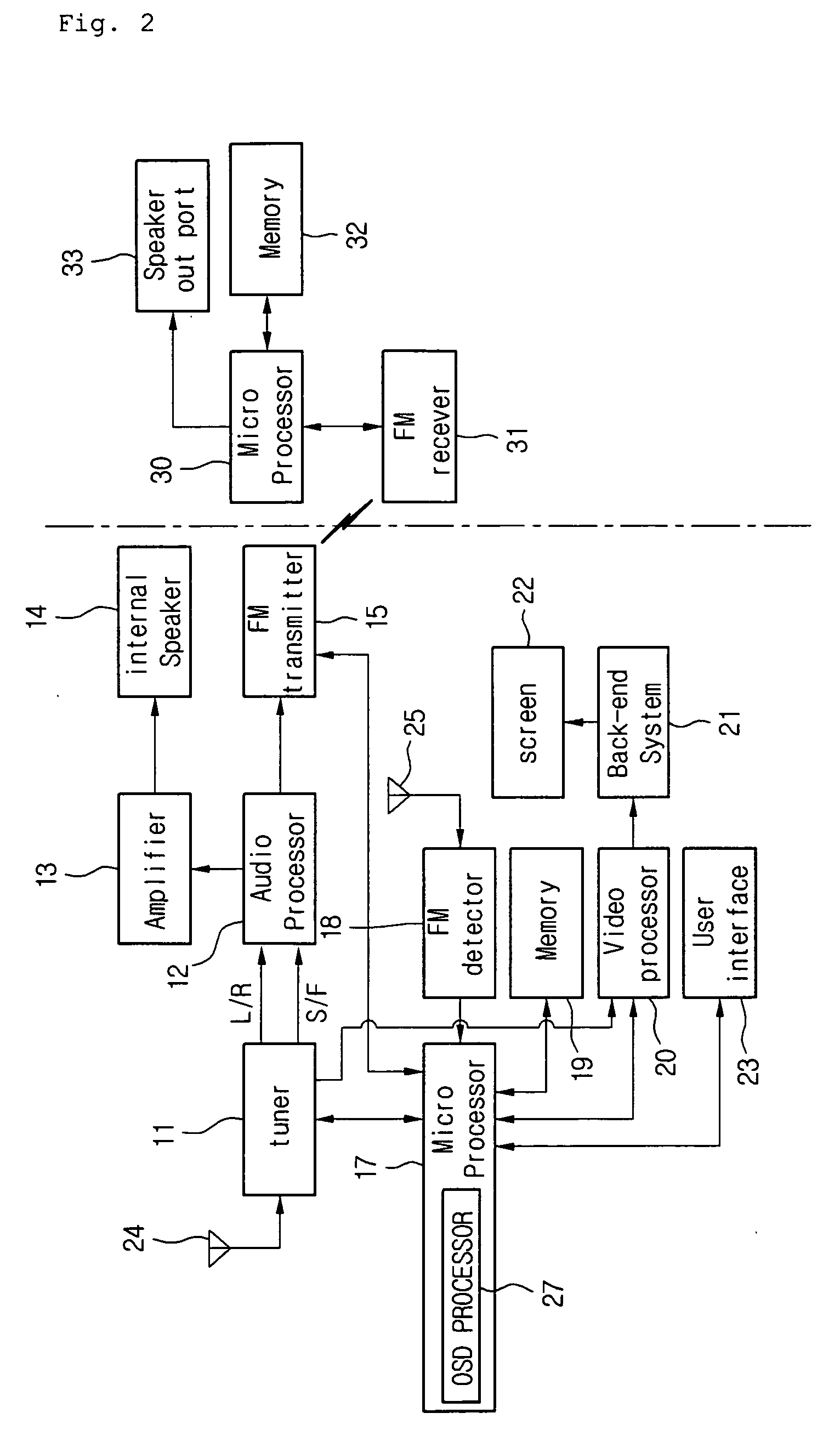

Display system and FM signal transferring method thereof

InactiveUS20060293007A1Convenient setEasy to useTelevision system detailsAutomatic scanning with simultaneous frequency displayEngineeringAudio frequency

Provided is a display system for transmitting FM signals to an external audio system having an FM reception function. The display system includes: a tuner for receiving an RF signal and dividing the RF signal into a video signal and an audio signal; an audio processor for receiving the audio signal from the tuner; an FM detector for searching usable channels or unused channels among FM frequency bands of a reception area and transmitting information on the unused channels; a microprocessor for setting at least one of the unused channels as an available channel, the unused channels being provided from the FM detector; a memory for storing the available channel under control of the microprocessor; and an FM transmitter for receiving the audio signal from the audio processor and transmitting the audio signal over at least one channel selected among the channels stored in the memory under control of the microprocessor.

Owner:LG ELECTRONICS INC