Patents

Literature

222results about "Pulse transformer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

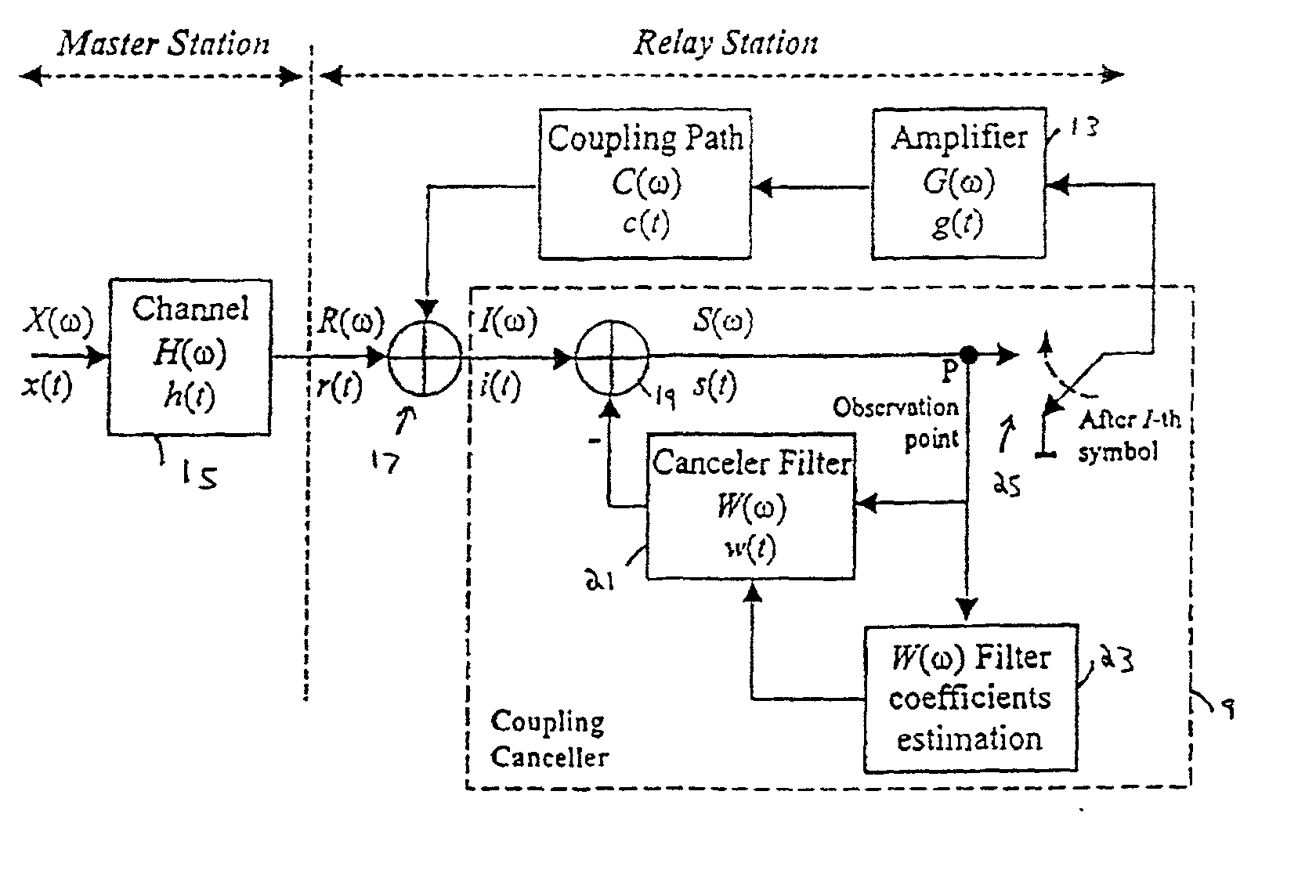

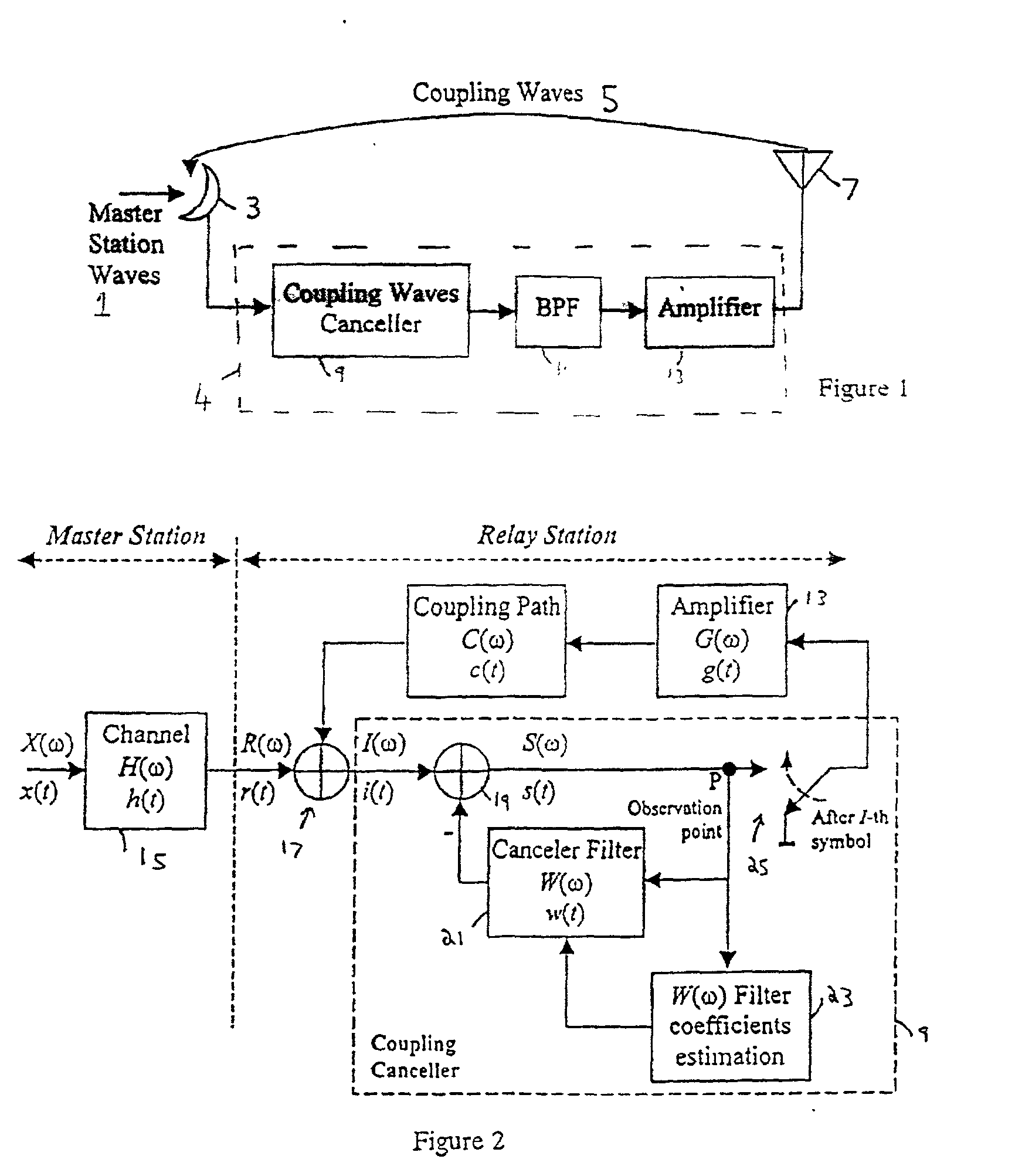

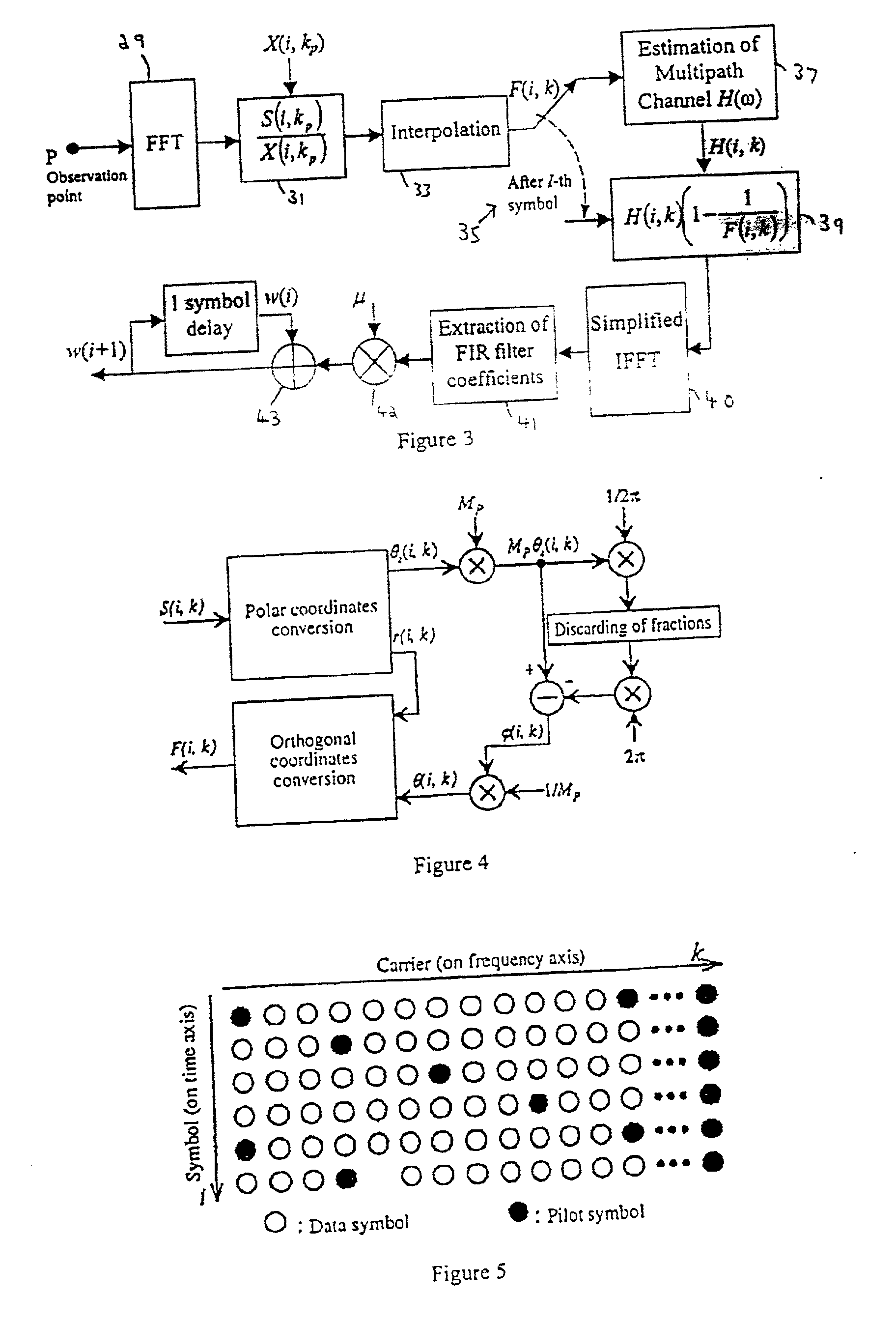

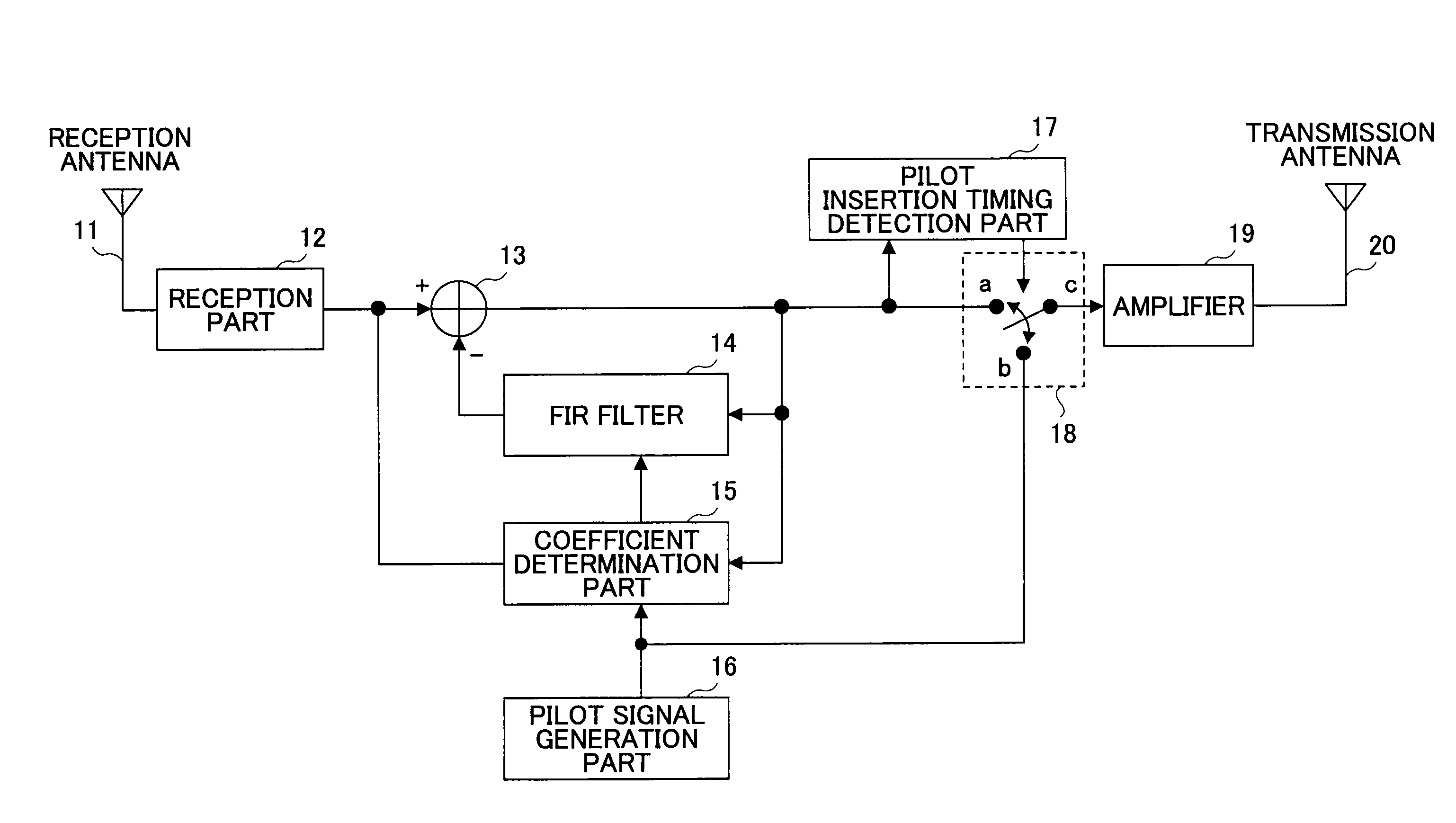

Methods and apparatus for reducing signal degradation

ActiveUS20020039383A1Error minimizationReduce the differencePulse transformerAdaptive networkFast Fourier transformMultipath interference

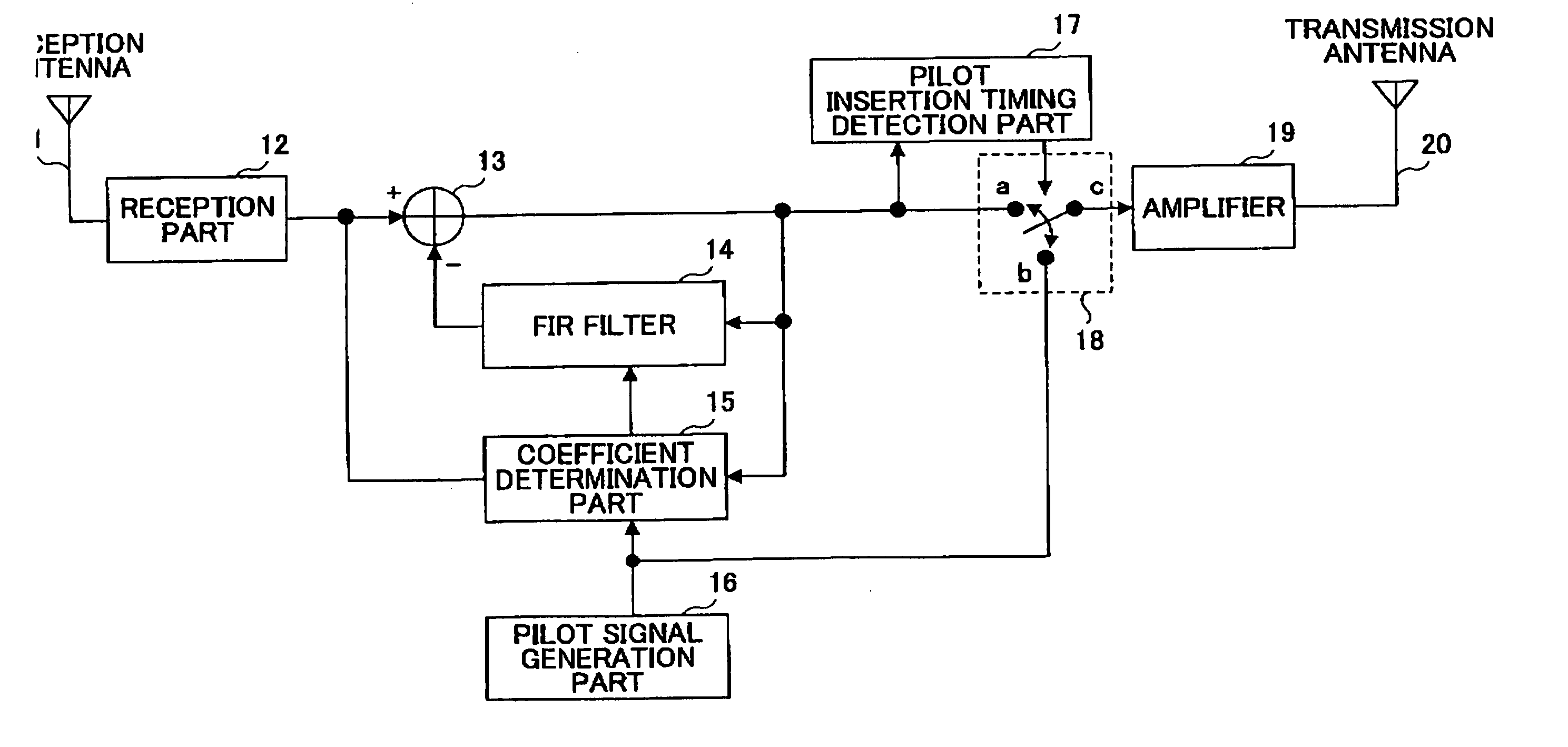

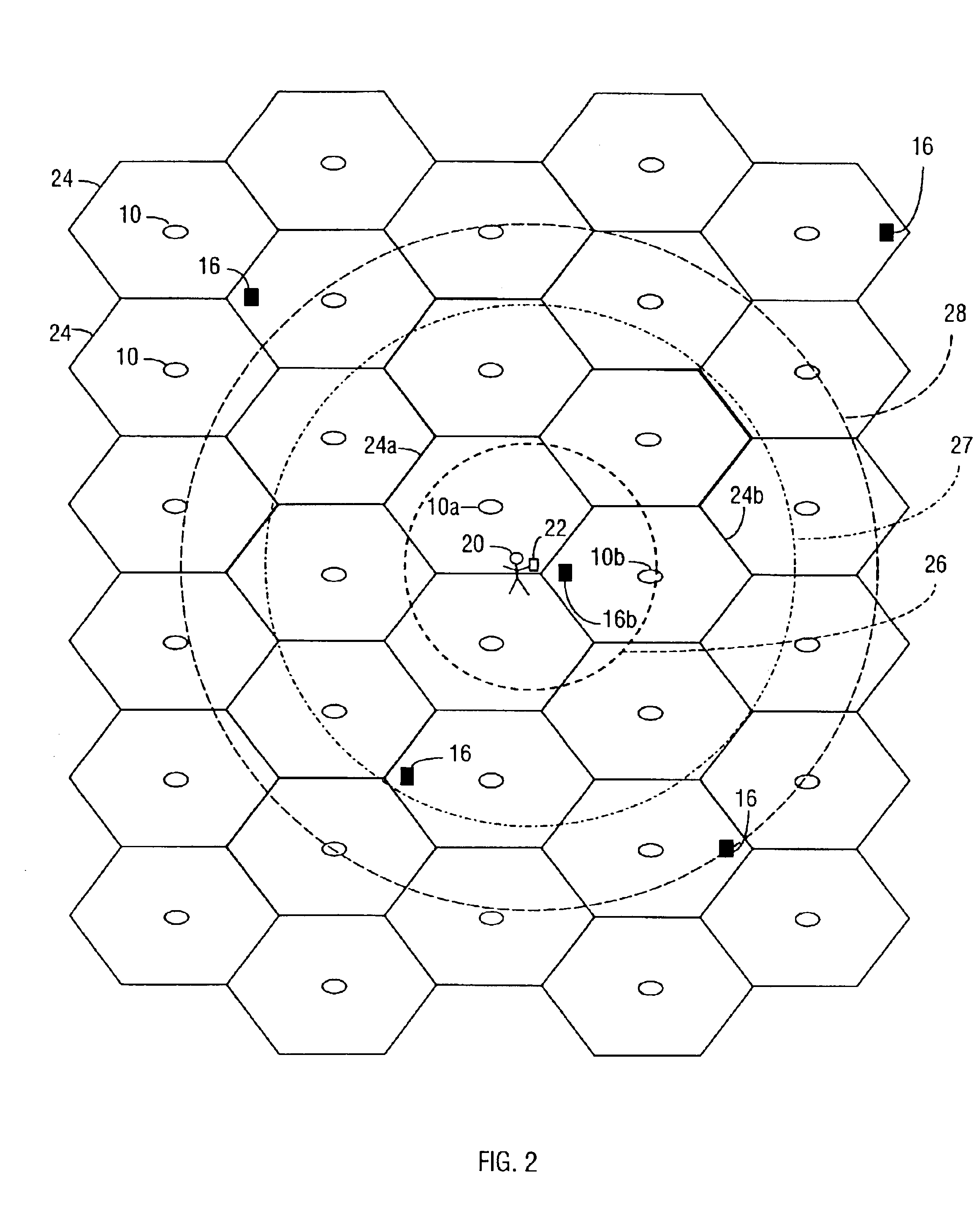

A single frequency relay station receives a signal from a master station, and retransmits it. Before retransmitting the signal, the relay station uses a digital filter to subtract from the signal components which arise from multipath interference and coupling interference. The coefficients used by the digital filter are derived from characteristics of the multipath interference and the overall transfer function of the relay station. These are derived by turning off the retransmission, so that the multipath interference can be estimated from the received signal, and commencing the retransmission again, to determine the transfer function. A simplified inverse fast Fourier transform is used to simplify the calculations.

Owner:WIPRO LTD

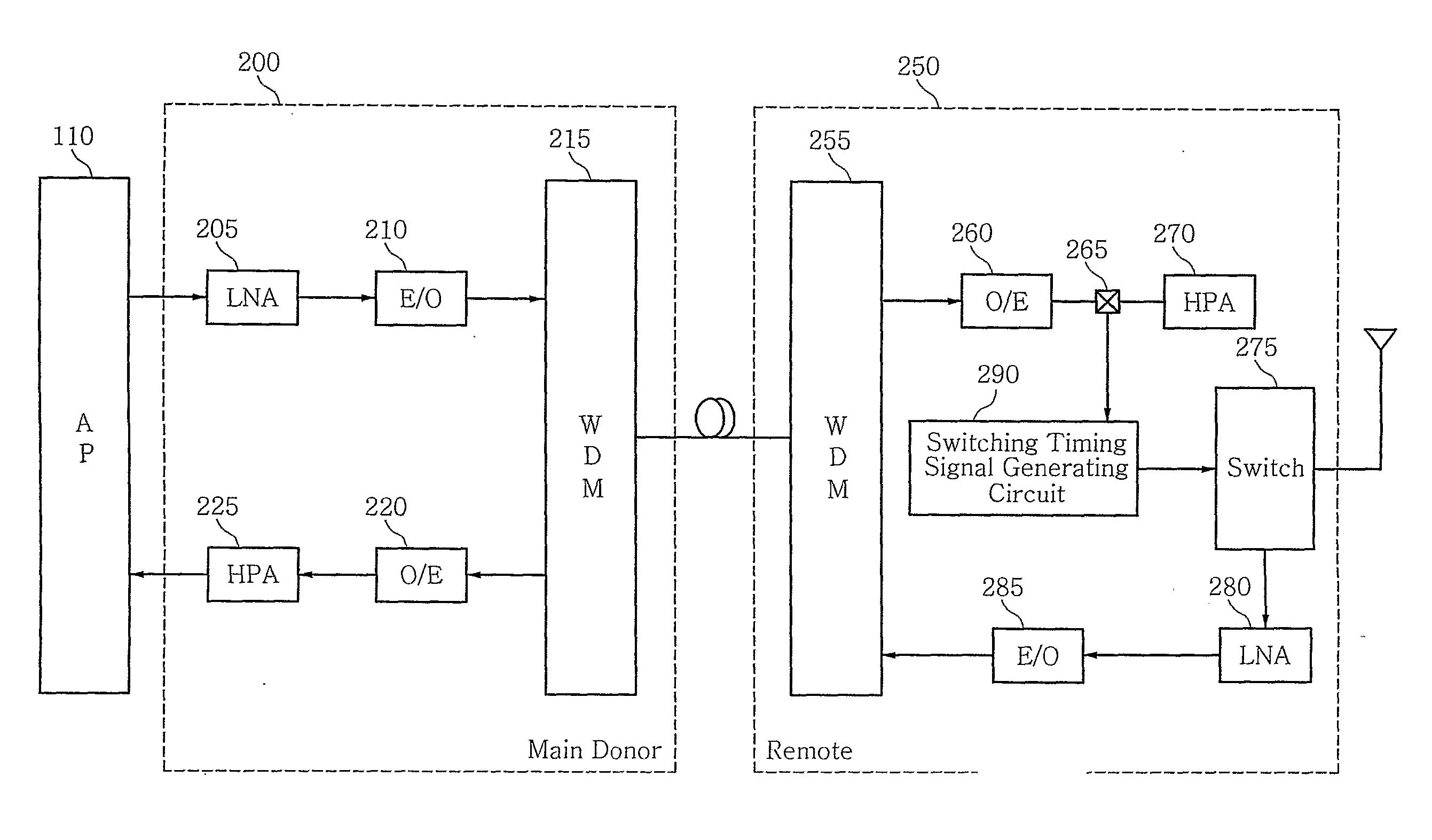

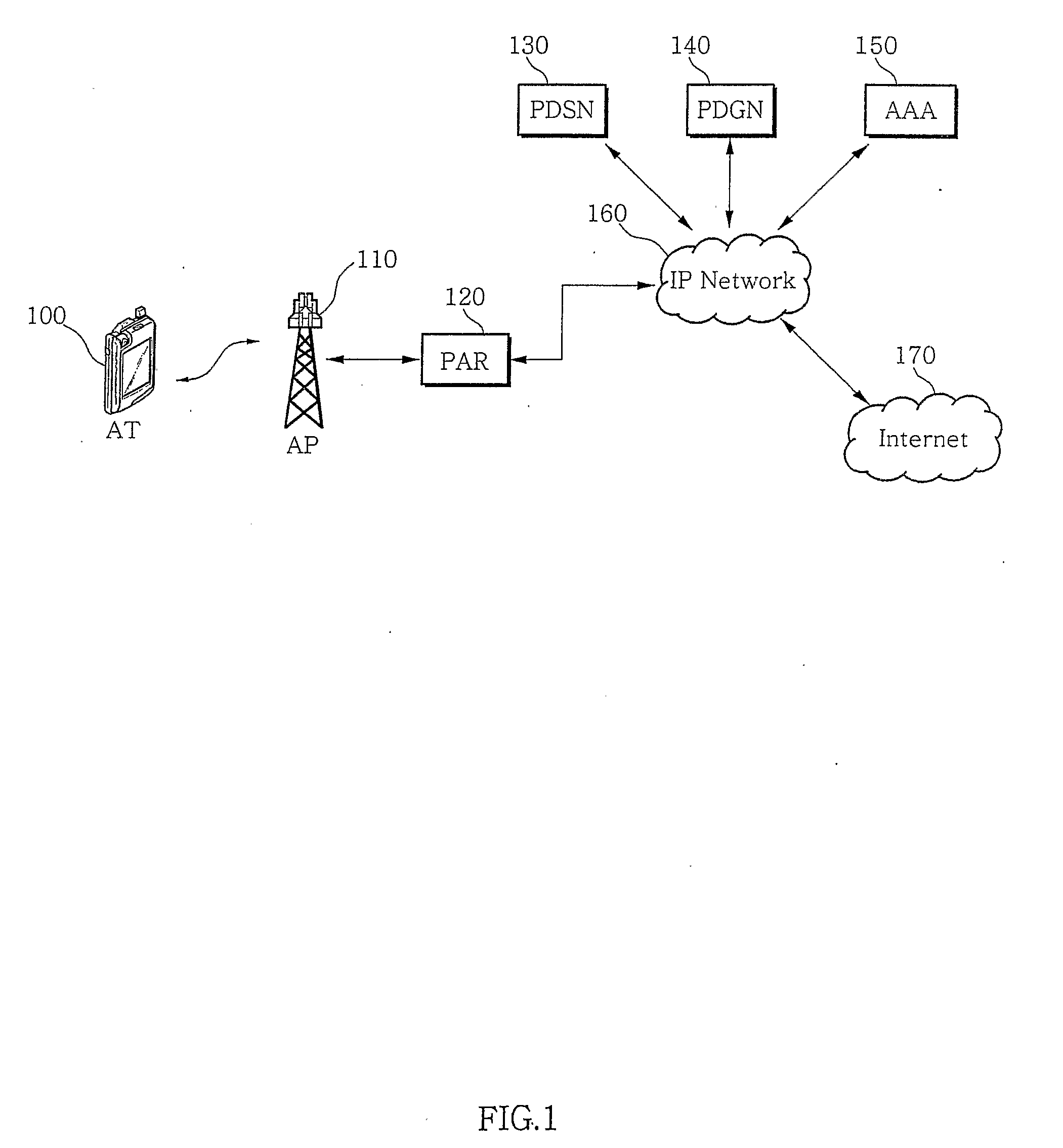

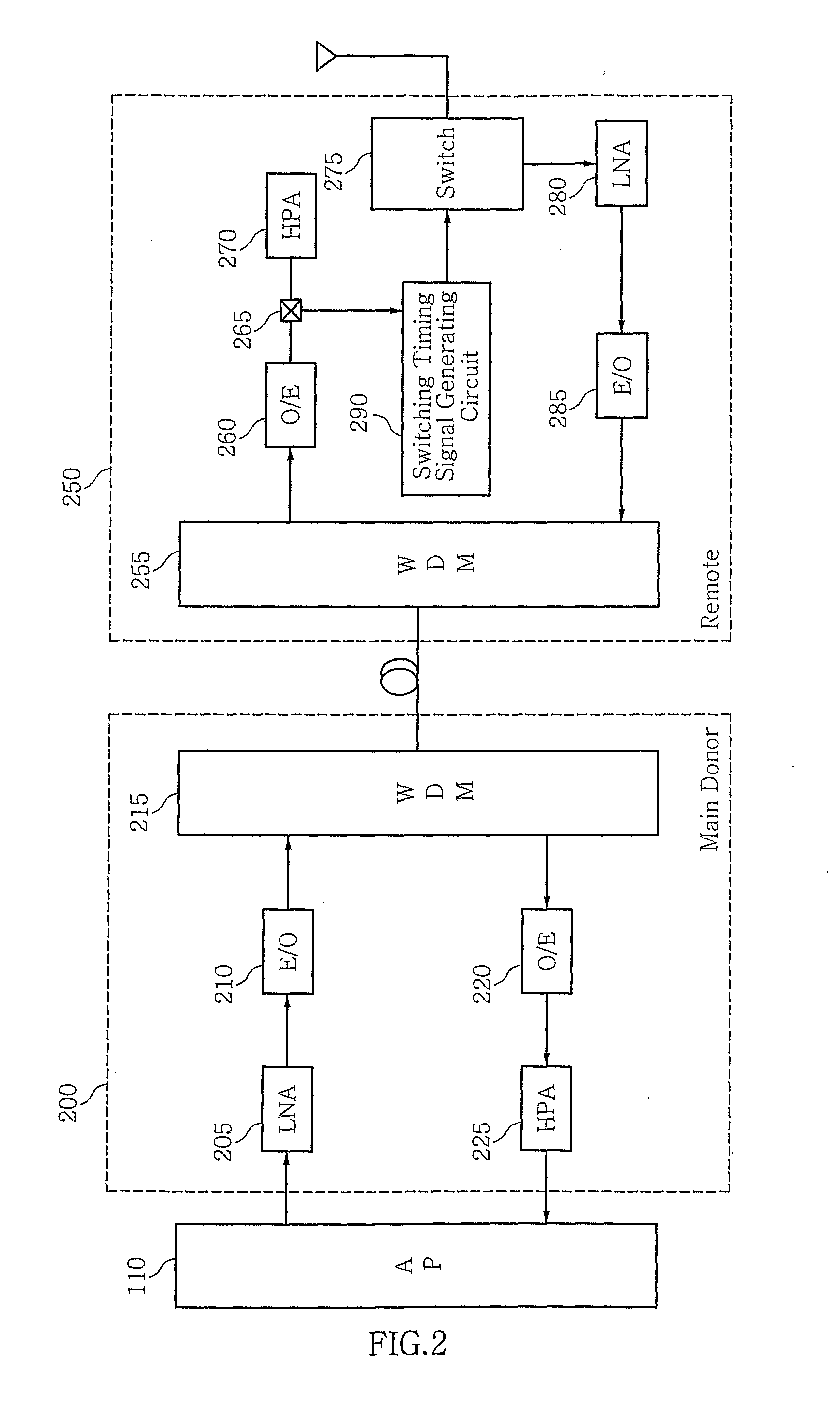

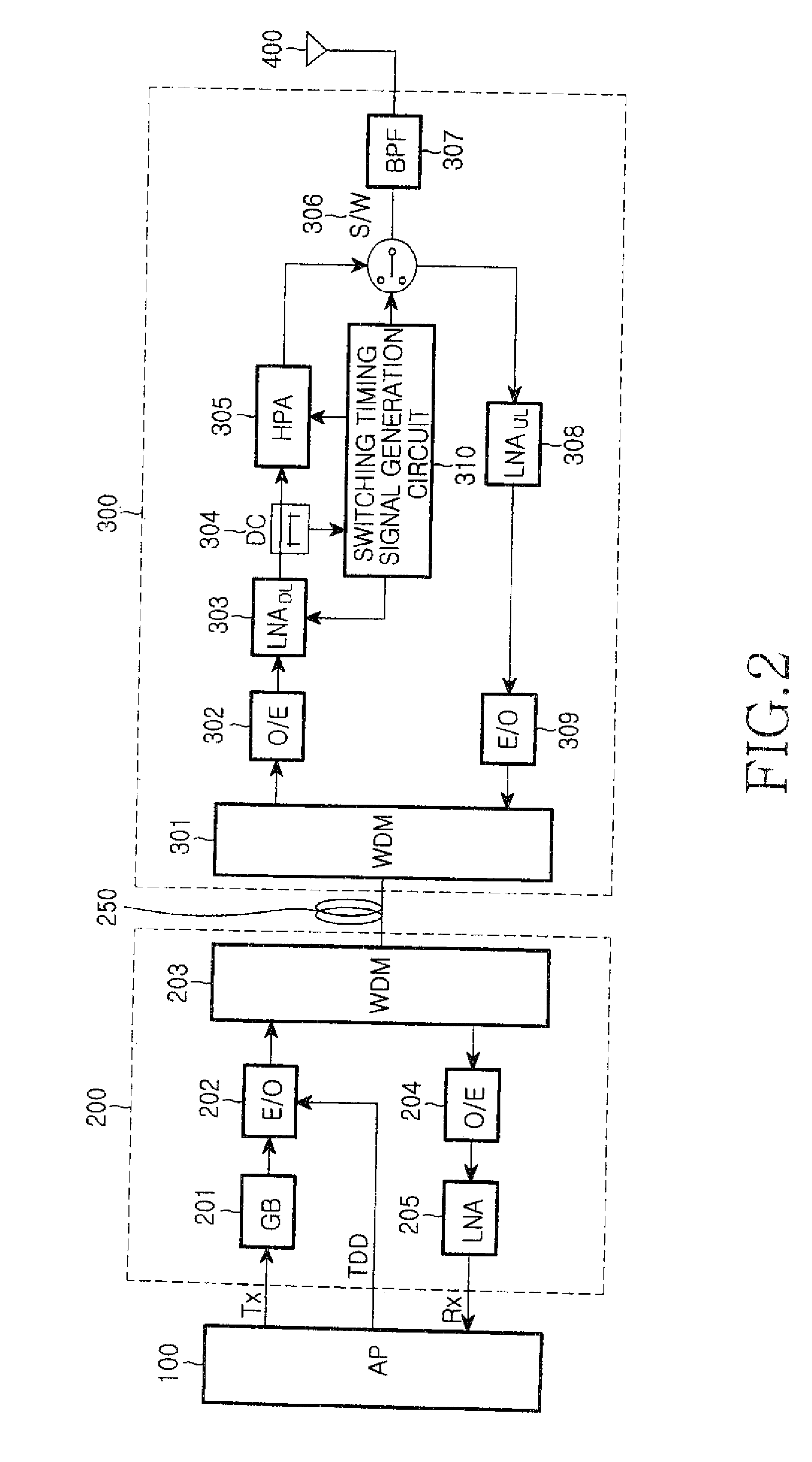

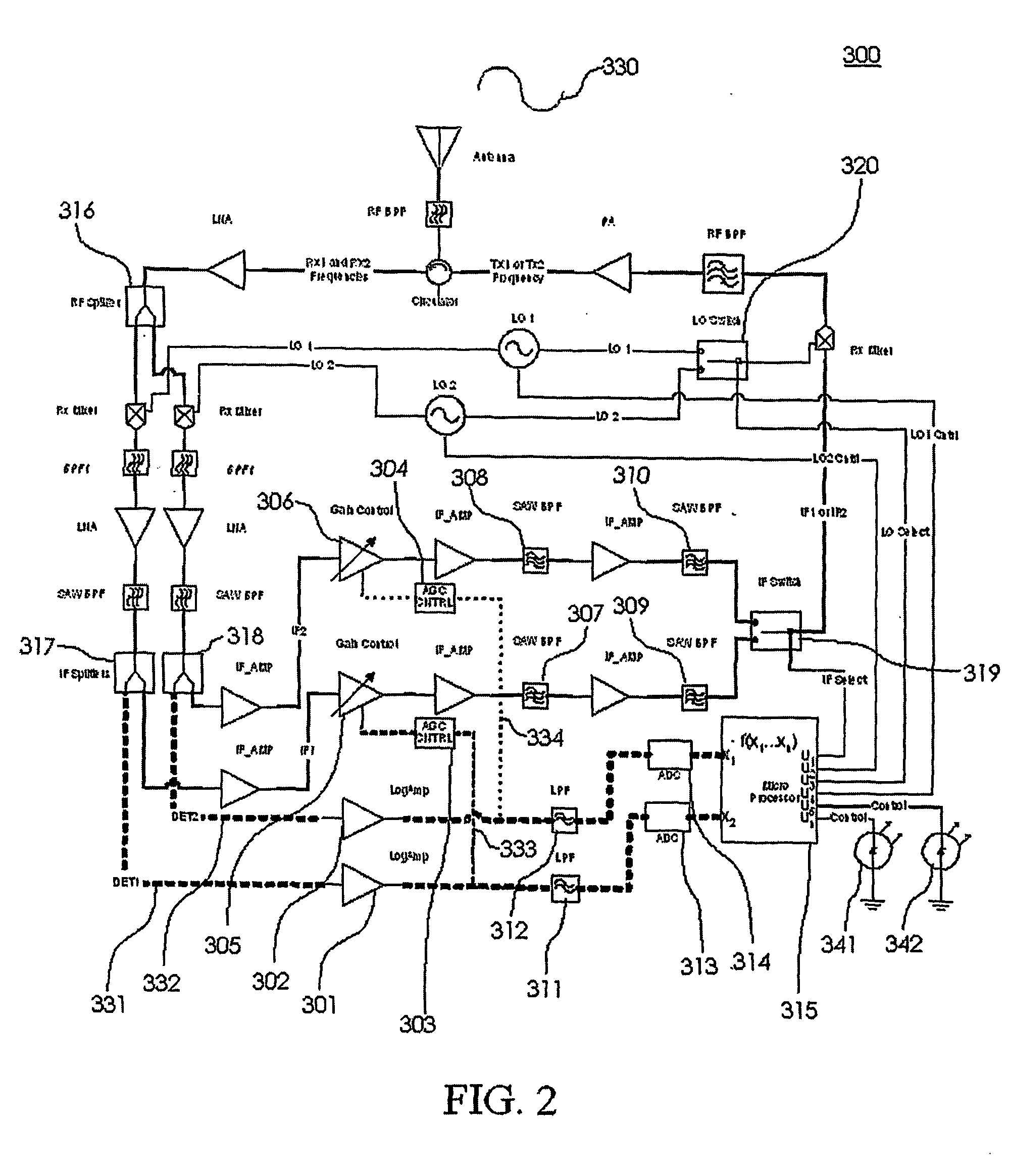

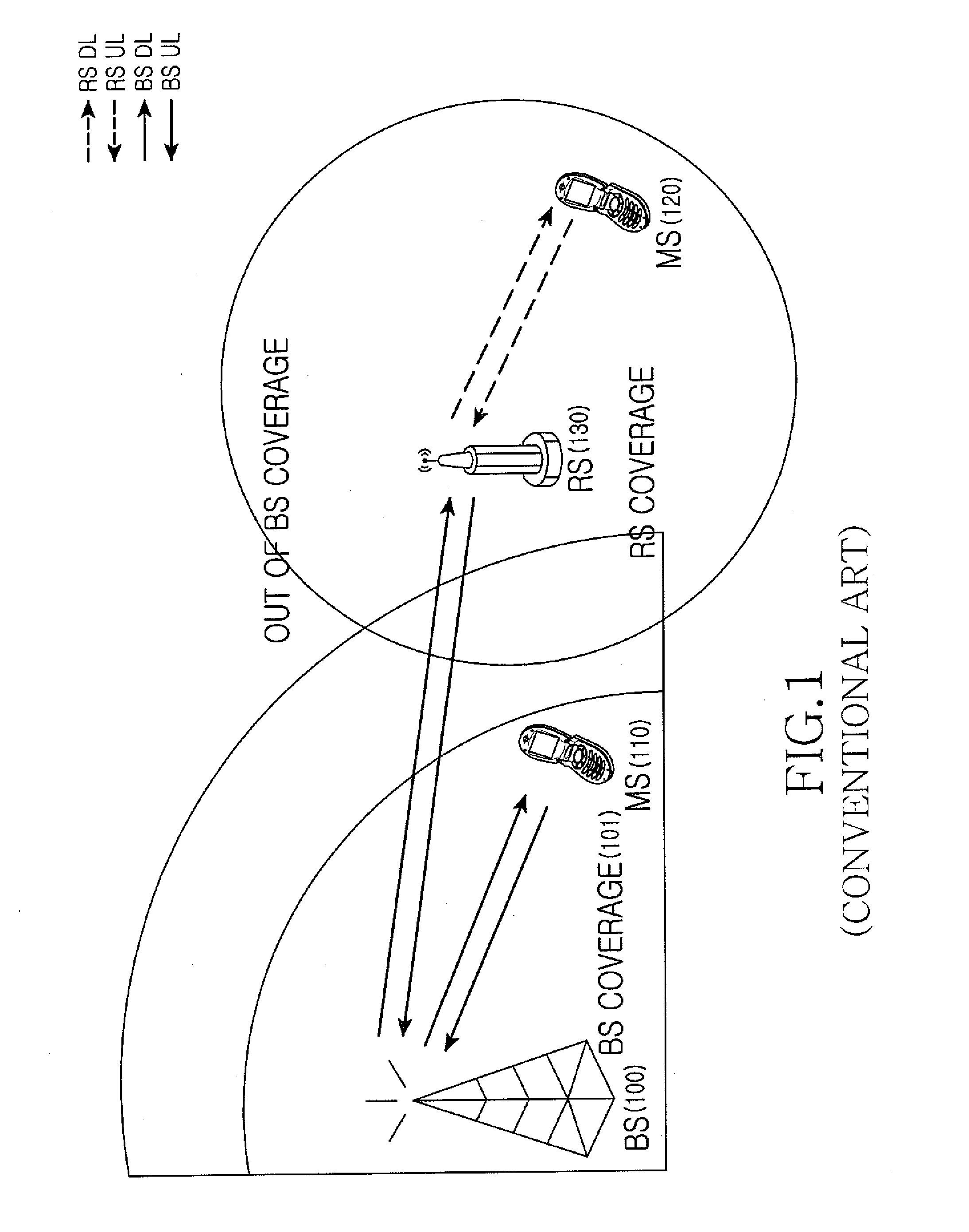

Method and System for Generating Switching Timing Signal for Separating Transmitting and Receiving Signal in Optical Repeater of Mobile Telecommunication Network Using Tdd and Ofdm Modulation

InactiveUS20070237181A1Pulse transformerWavelength-division multiplex systemsTelecommunications networkSignal on

Disclosed are a method and system for generating switching a timing signal for separating a transmitting and receiving signal in an optical repeater of a mobile telecommunication network by using a Time Division Duplex (hereinafter, referred to as “TDD”) scheme and an Orthogonal Frequency Division Multiplexing (hereinafter, referred to as “OFDM”) modulation scheme, which transmits a part of a RF signal extracted from a coupler included in a remote of an optical repeater to a switching timing signal generating circuit, locates a frame start position of a RF signal by correlating a reference signal generated in a switching timing signal generating circuit with a RF signal extracted from a coupler, and is capable of transmitting a RF signal by distinguishing between a downlink signal and a uplink signal by using a switching timing signal in a switch when calculating a starting point of a downlink signal and a uplink signal included in an RF signal on the basis of a frame starting location, generating a switching timing signal by using it, and transmitting to a remote's switch.

Owner:SK TELECOM CO LTD

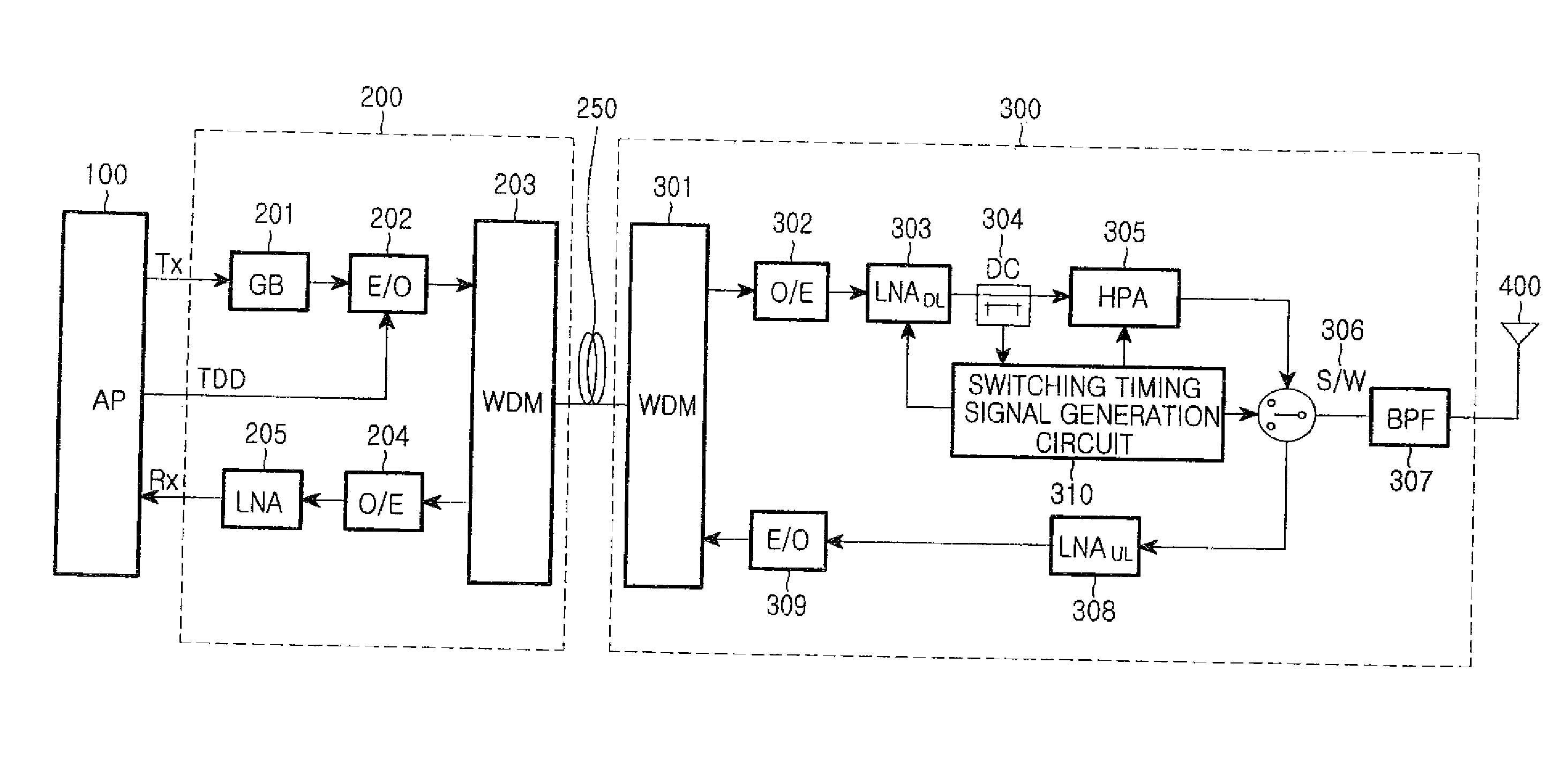

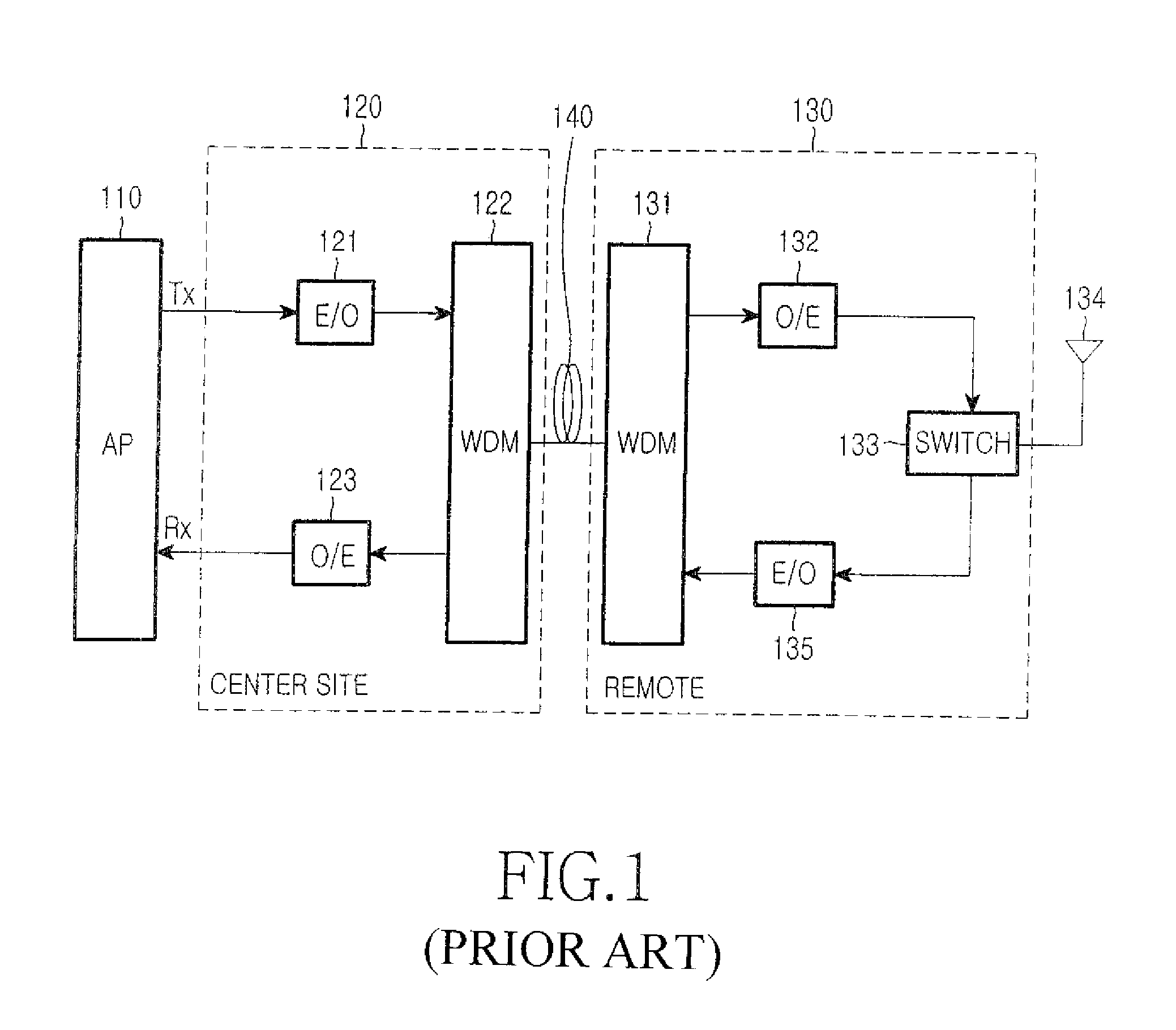

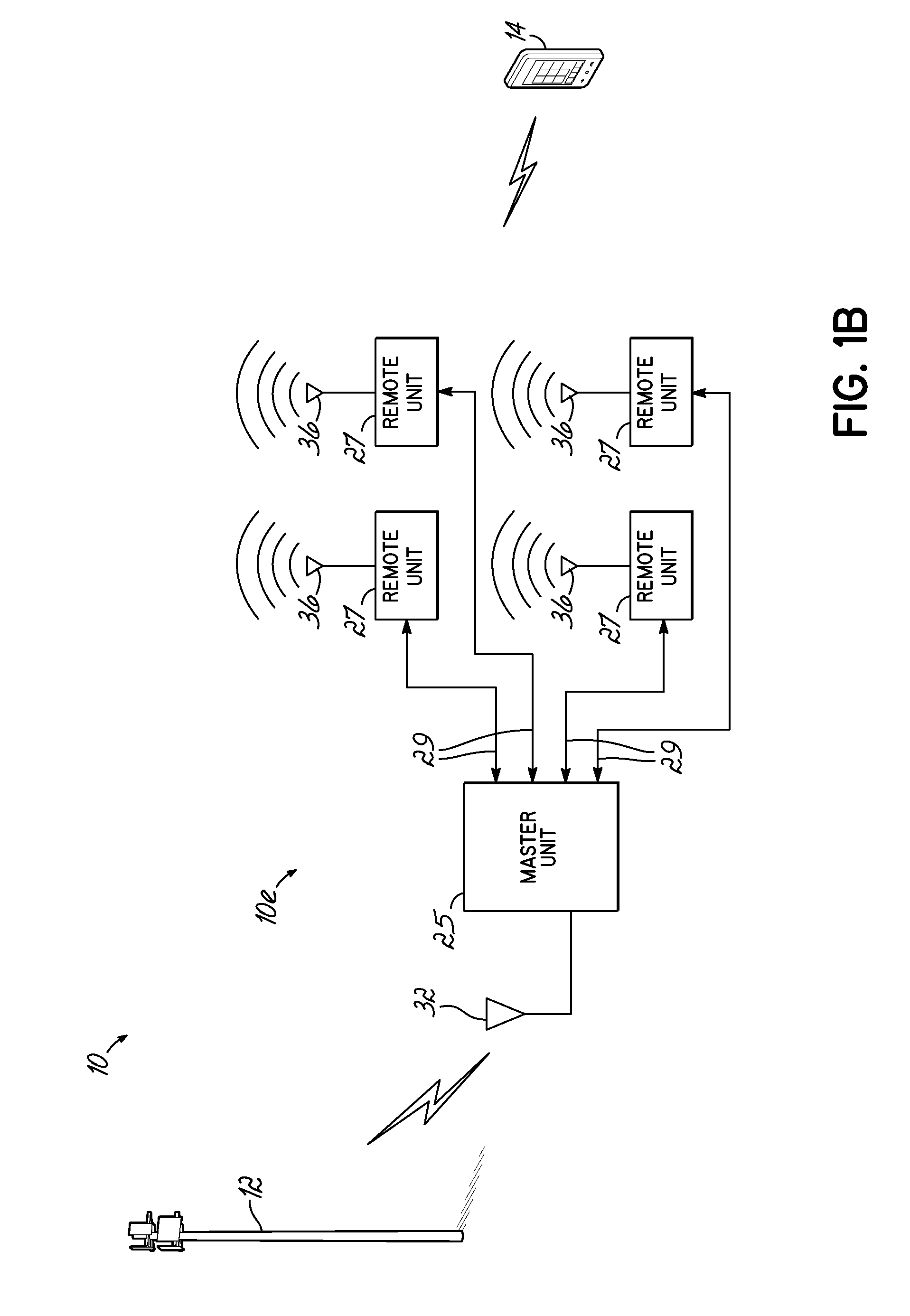

Radio over fiber link apparatus of time division duplex scheme

InactiveUS20080145061A1Minimizing deteriorationPulse transformerWavelength-division multiplex systemsRadio over fiberRadio equipment

A radio over fiber link apparatus for transmitting / receiving radio frequency up / downlink signals in a TDD mobile communication system. The radio over fiber link apparatus includes a center site for receiving radio frequency signals from an access point of the mobile communication system. The center site has a first electro-optic converter for converting the radio frequency signals into optical signals, bias control of the first electro-optic converter being performed based on the switching of TDD signals; and a remote for transmitting the radio frequency signals to a mobile communication terminal through an antenna. The remote site has a first photoelectric converter for converting the optical signals transmitted through an optical fiber from the center site into radio frequency signals.

Owner:SAMSUNG ELECTRONICS CO LTD

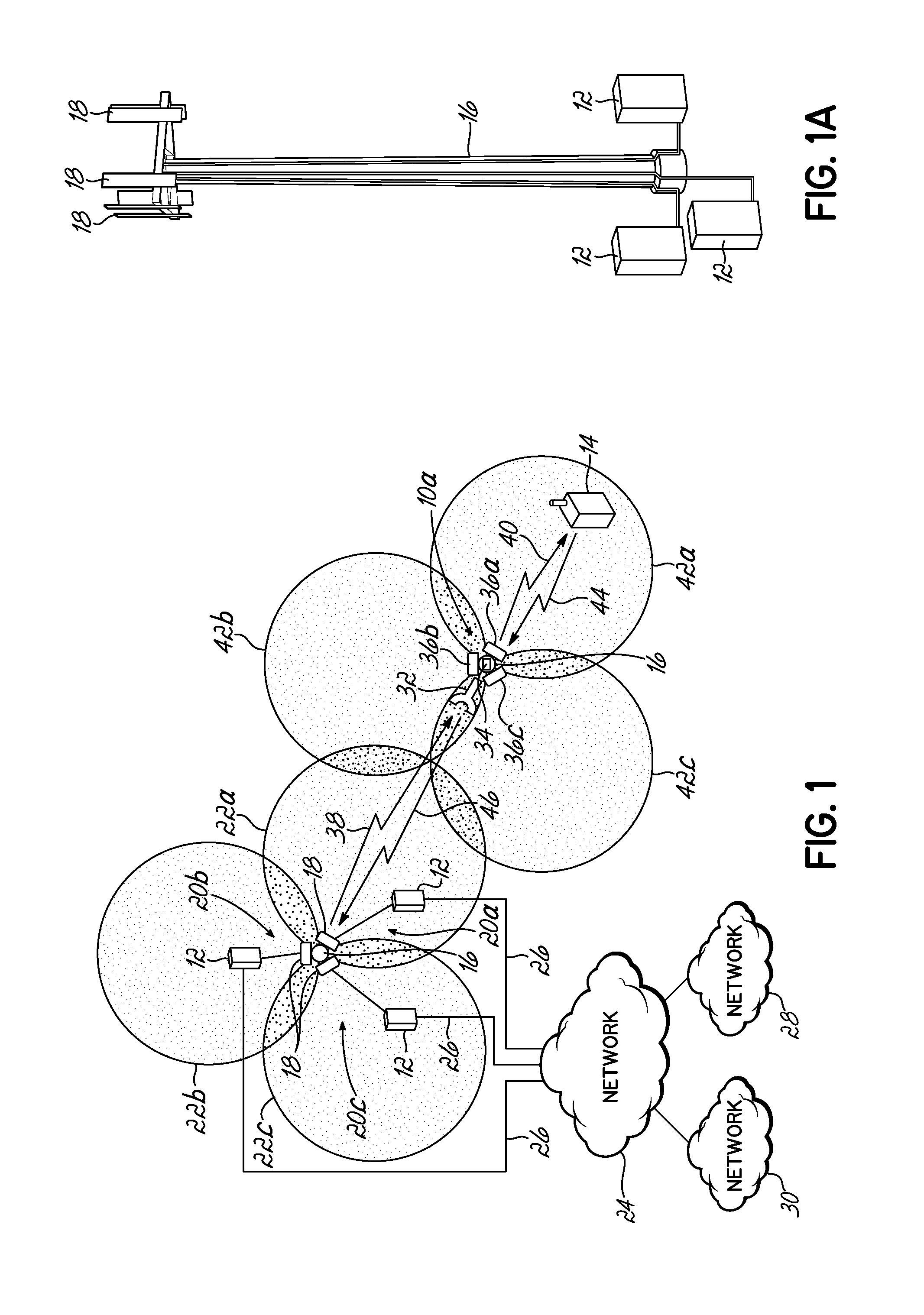

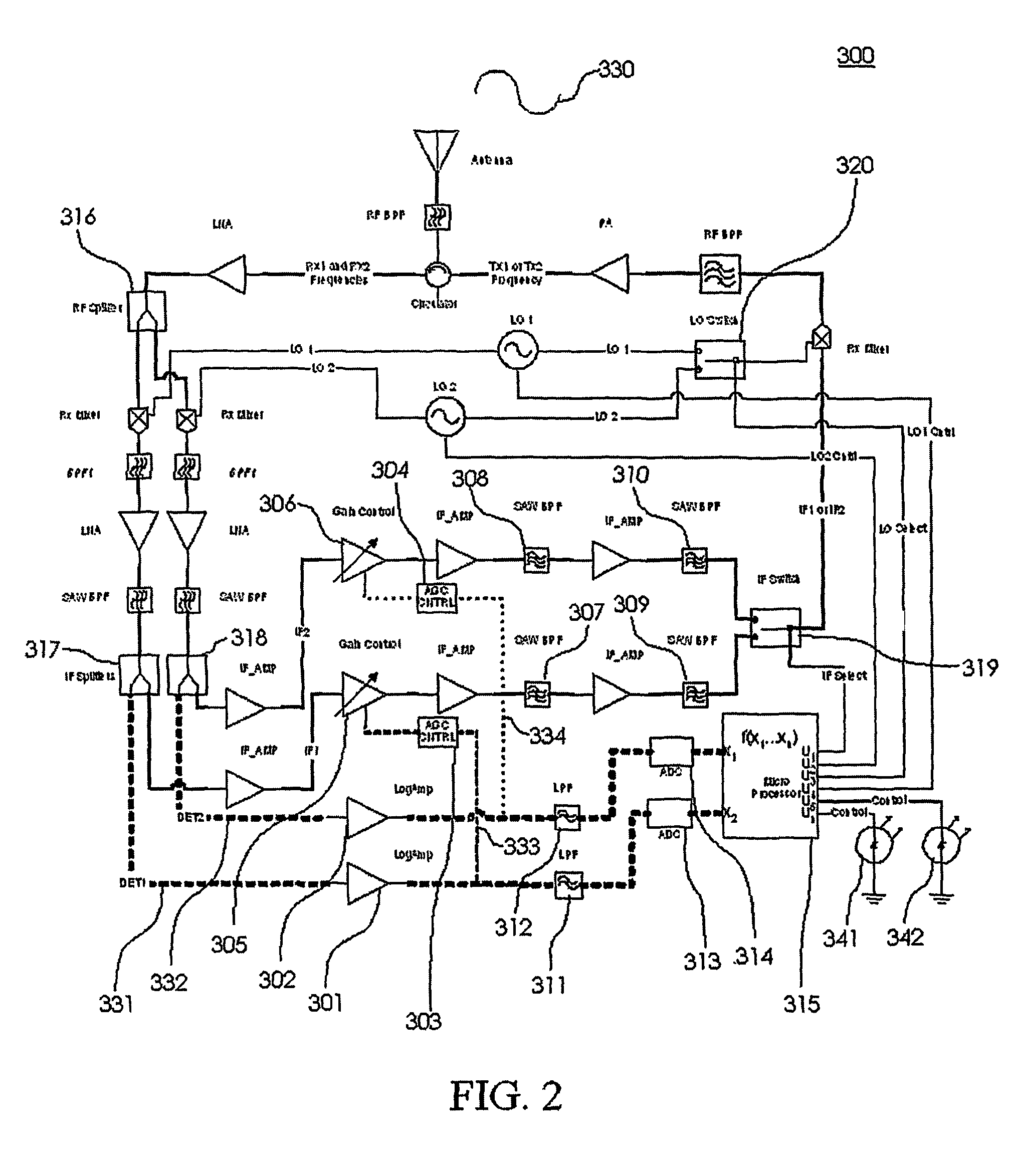

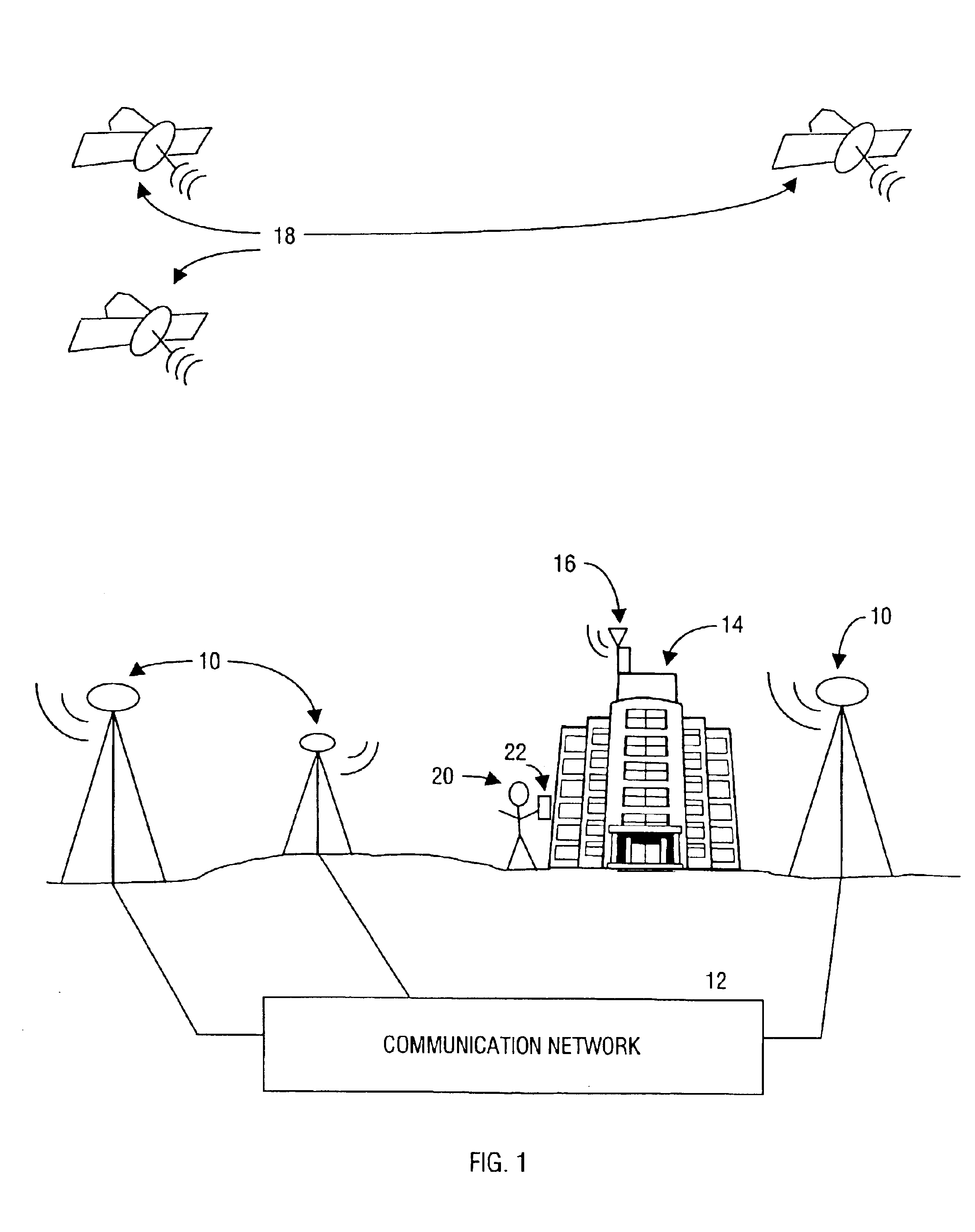

Communication system with channel compensating equalizer

A communication system and method for extending coverage of a base transceiver station. The communication system includes processing circuitry that receives a communication signal over a wireless channel. The received communication signal is processed through an adaptable equalizer to reduce noise, distortion, interference, and frequency errors. In another aspect of the invention, a frequency of a reference signal in the communication system is adjusted to compensate for frequency errors between the communication system and the source of the communication signal. The equalized and frequency adjusted communication signal is then retransmitted into an extended coverage area. Wireless coverage is thereby provided between a base transceiver station and a mobile device in the extended coverage area.

Owner:COMMSCOPE TECH LLC

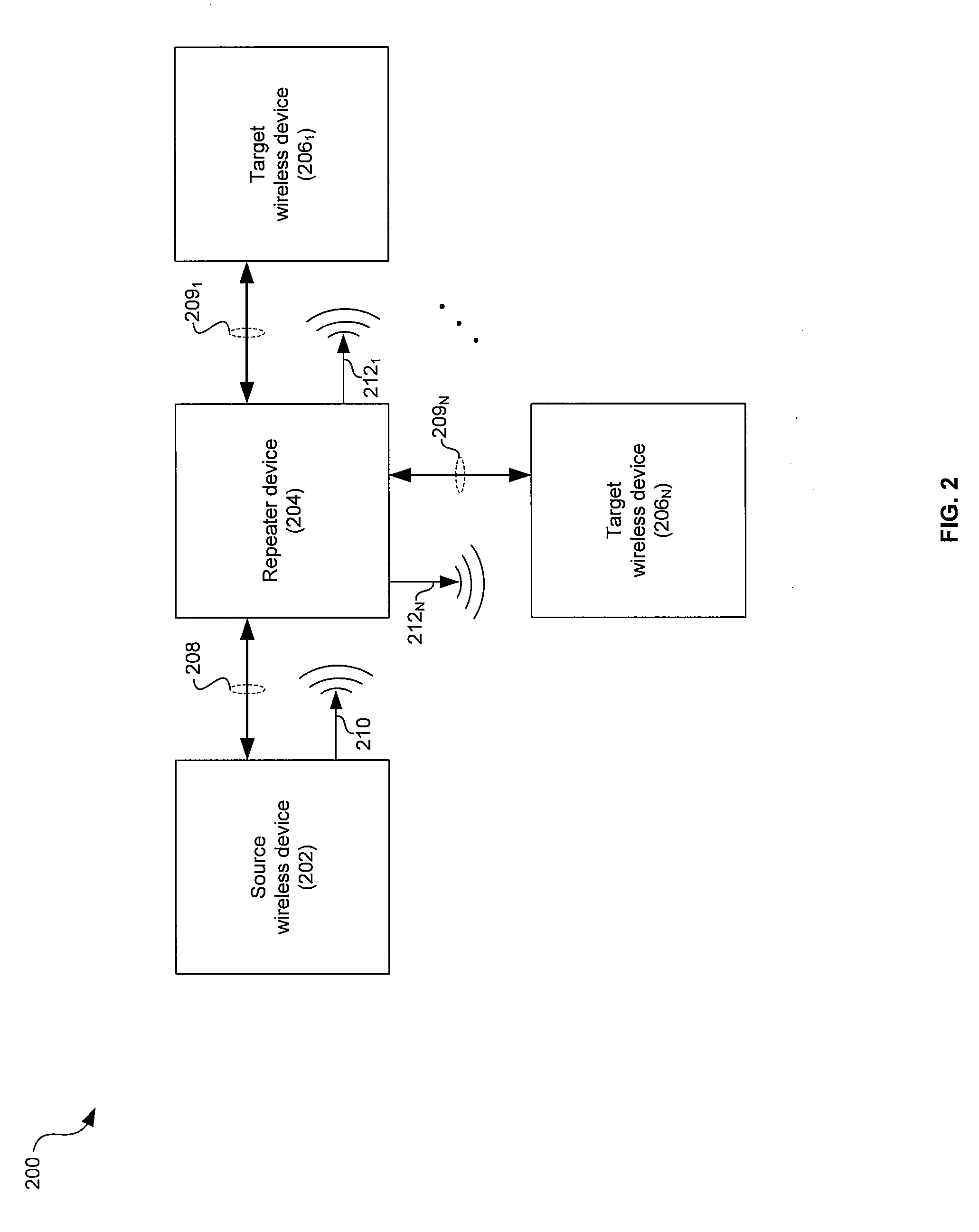

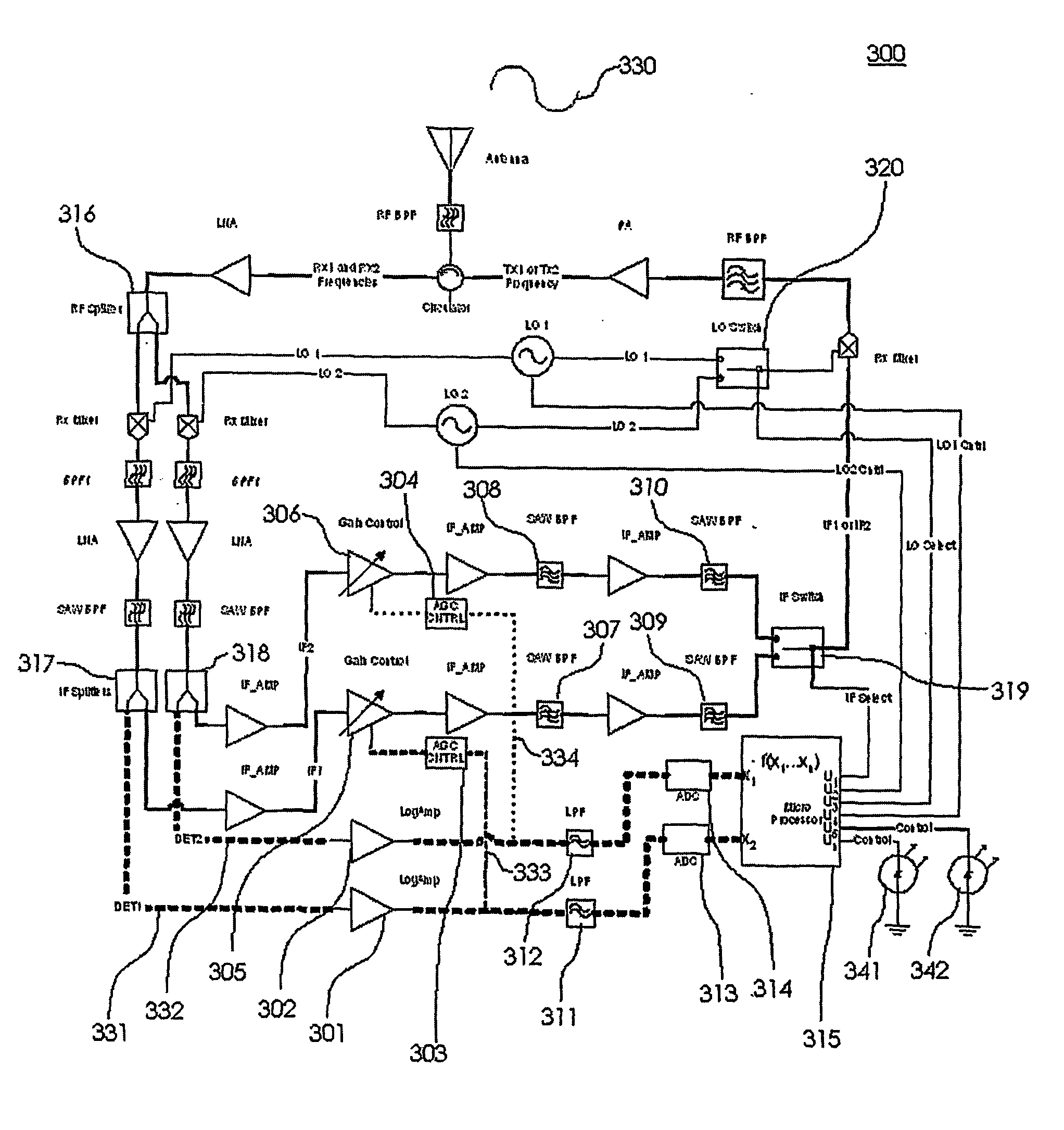

Method And System For Communicating Via A Spatial Multilink Repeater

Aspects of a method and system for communicating via a spatial multilink repeater are provided. In this regard, a received signal may be frequency shifted to generate a plurality of repeated signals, wherein each repeated signal may be shifted by a different frequency with respect to the received signal. Each repeated signal may comprise one or more signal components and a phase and / or amplitude of each of the components may be controlled to control a directivity of the repeated signals. Each of the repeated signals may be generated by quadrature down-converting said received signal by mixing the received signal with a first LO signal pair, up-converting the down-converted signal by mixing it with a second LO signal pair, and adding or subtracting an in-phase portion and a quadrature-phase portion of the up-converted signal.

Owner:AVAGO TECH INT SALES PTE LTD

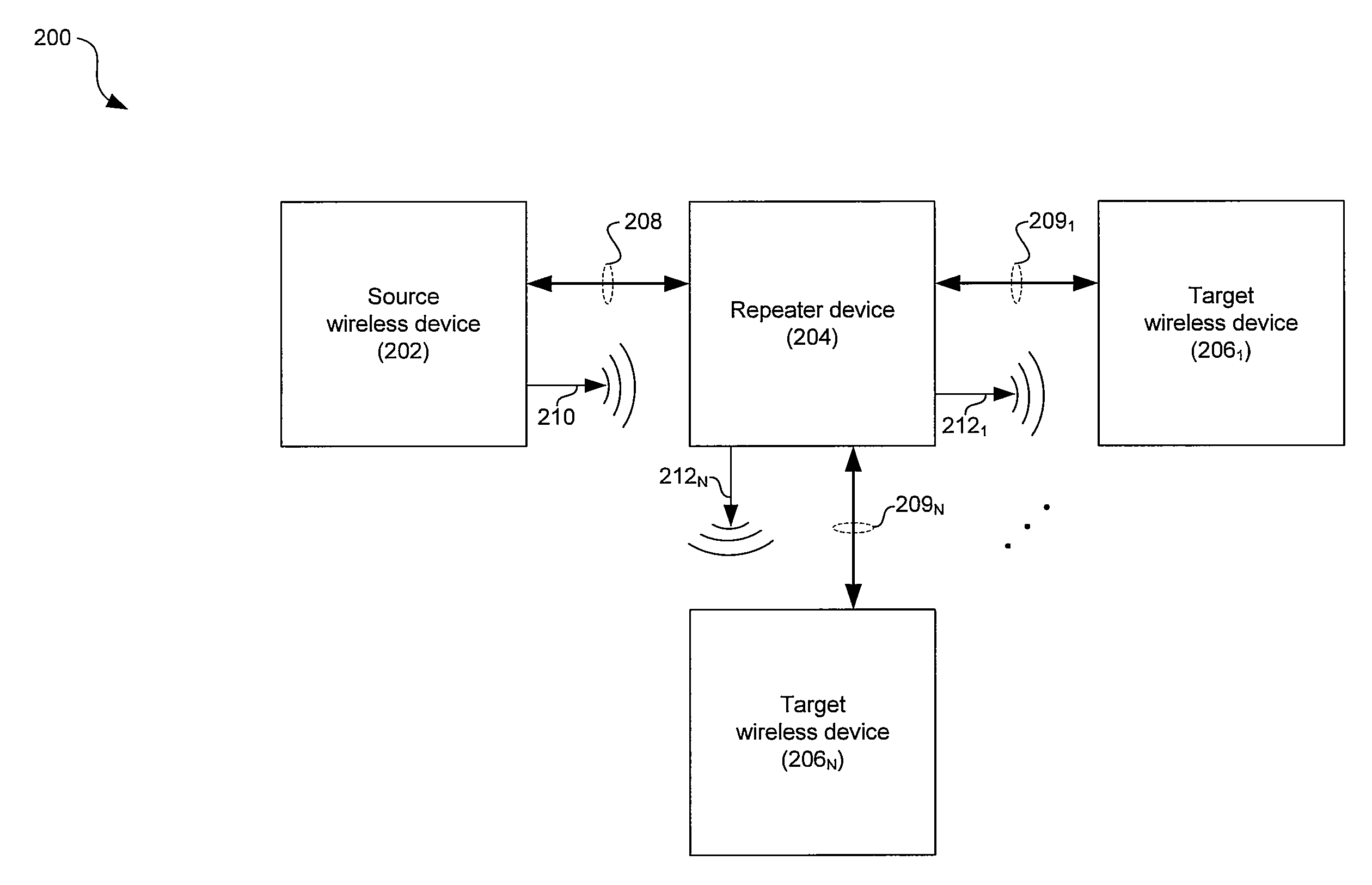

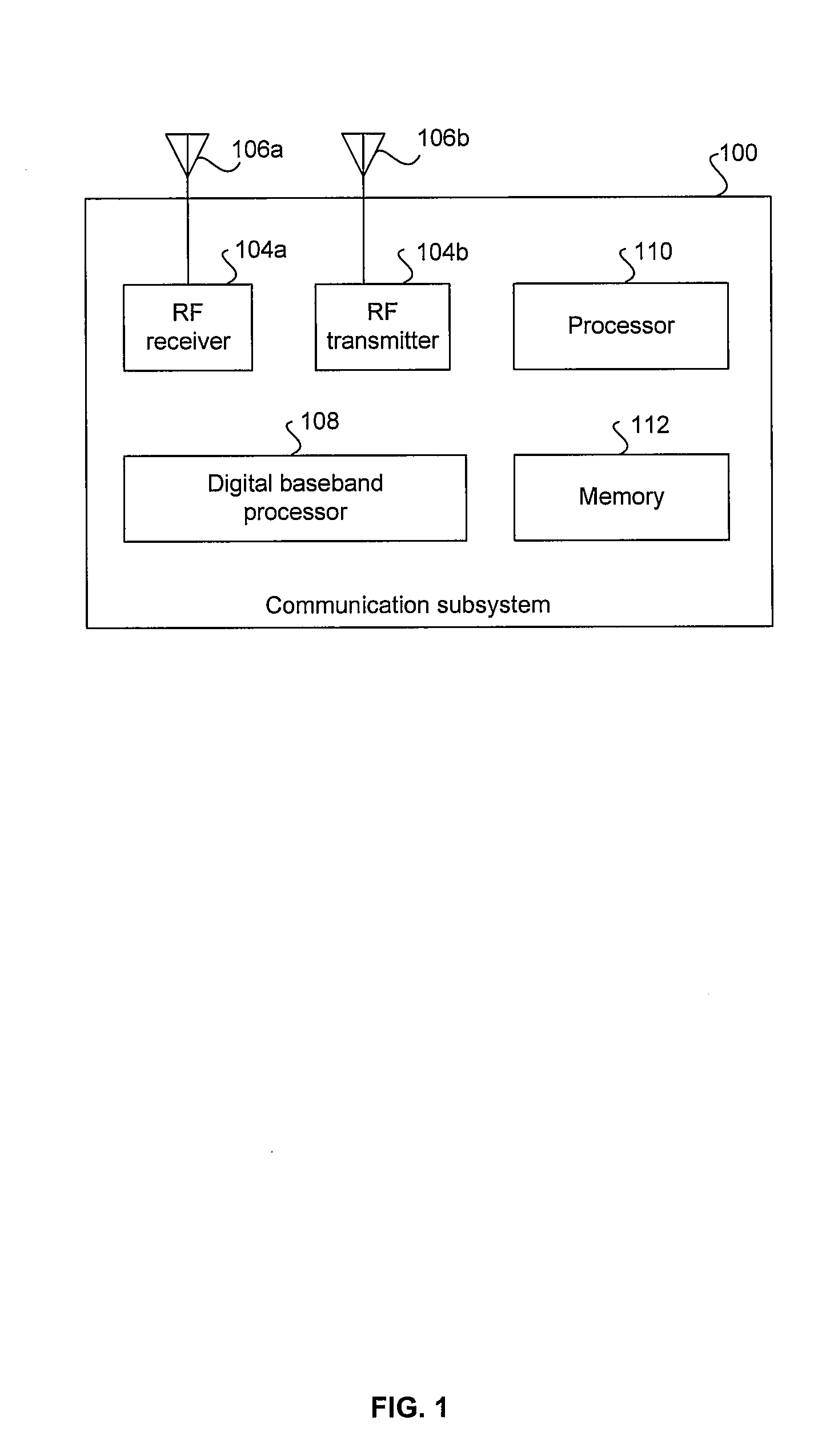

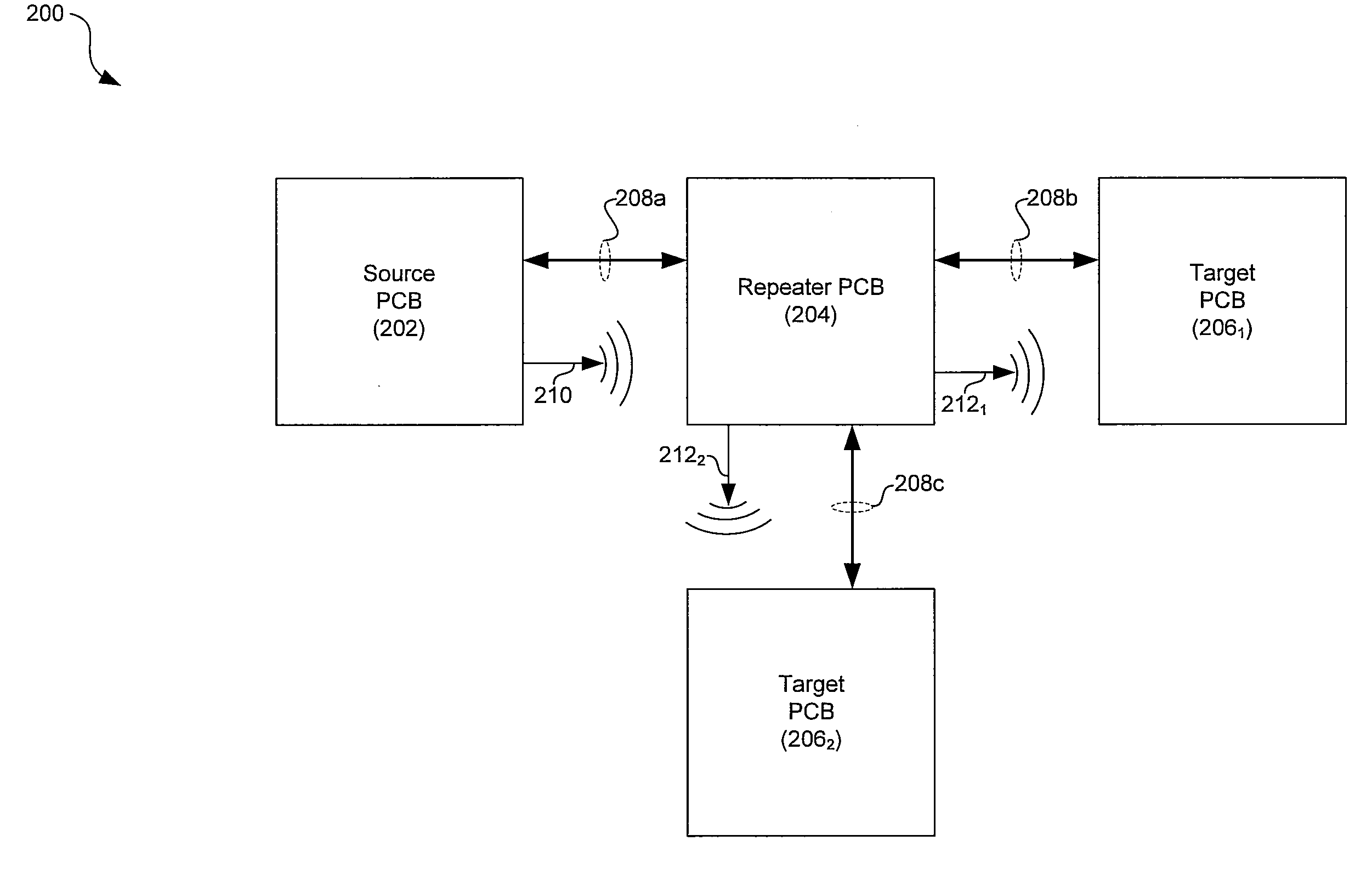

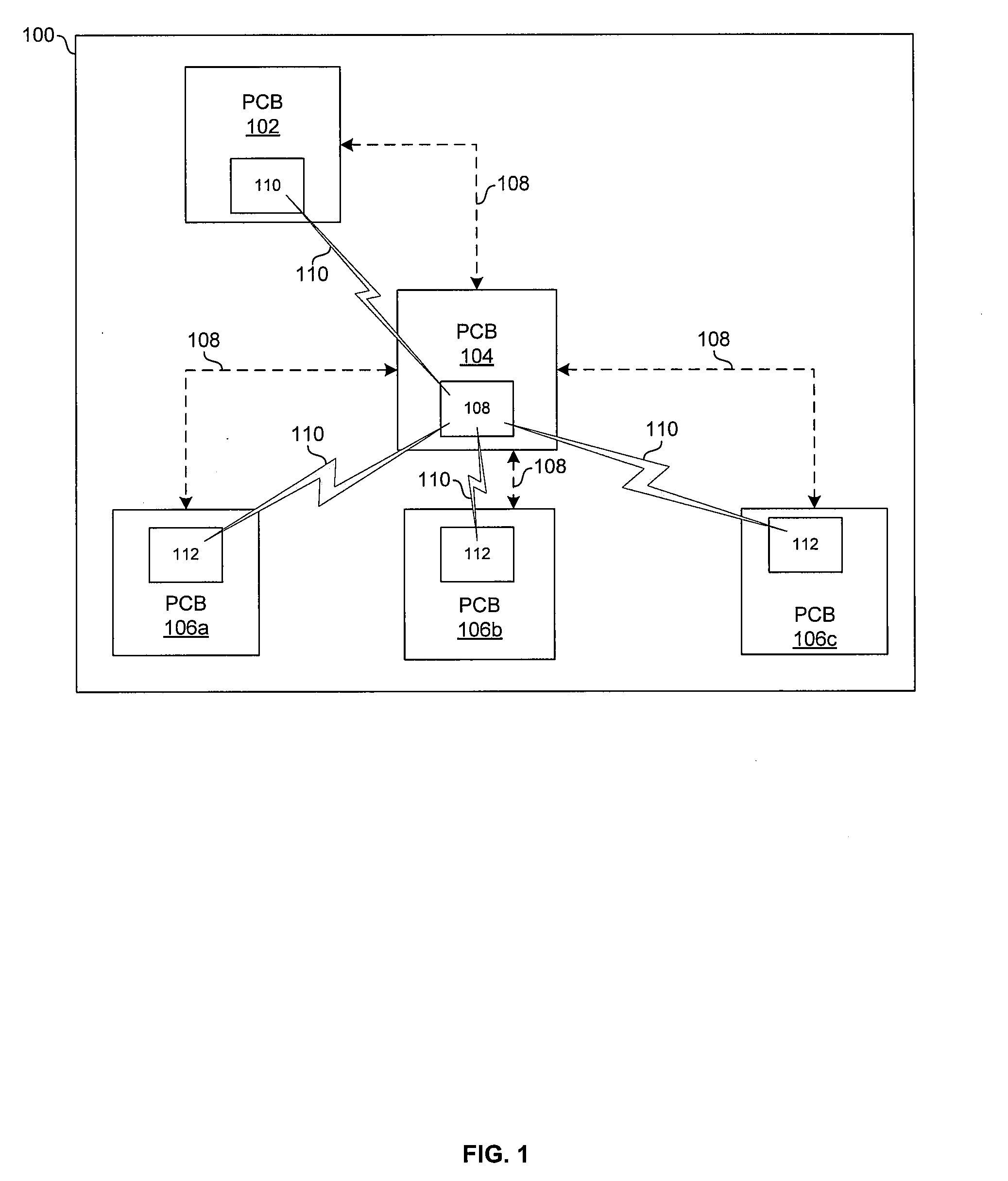

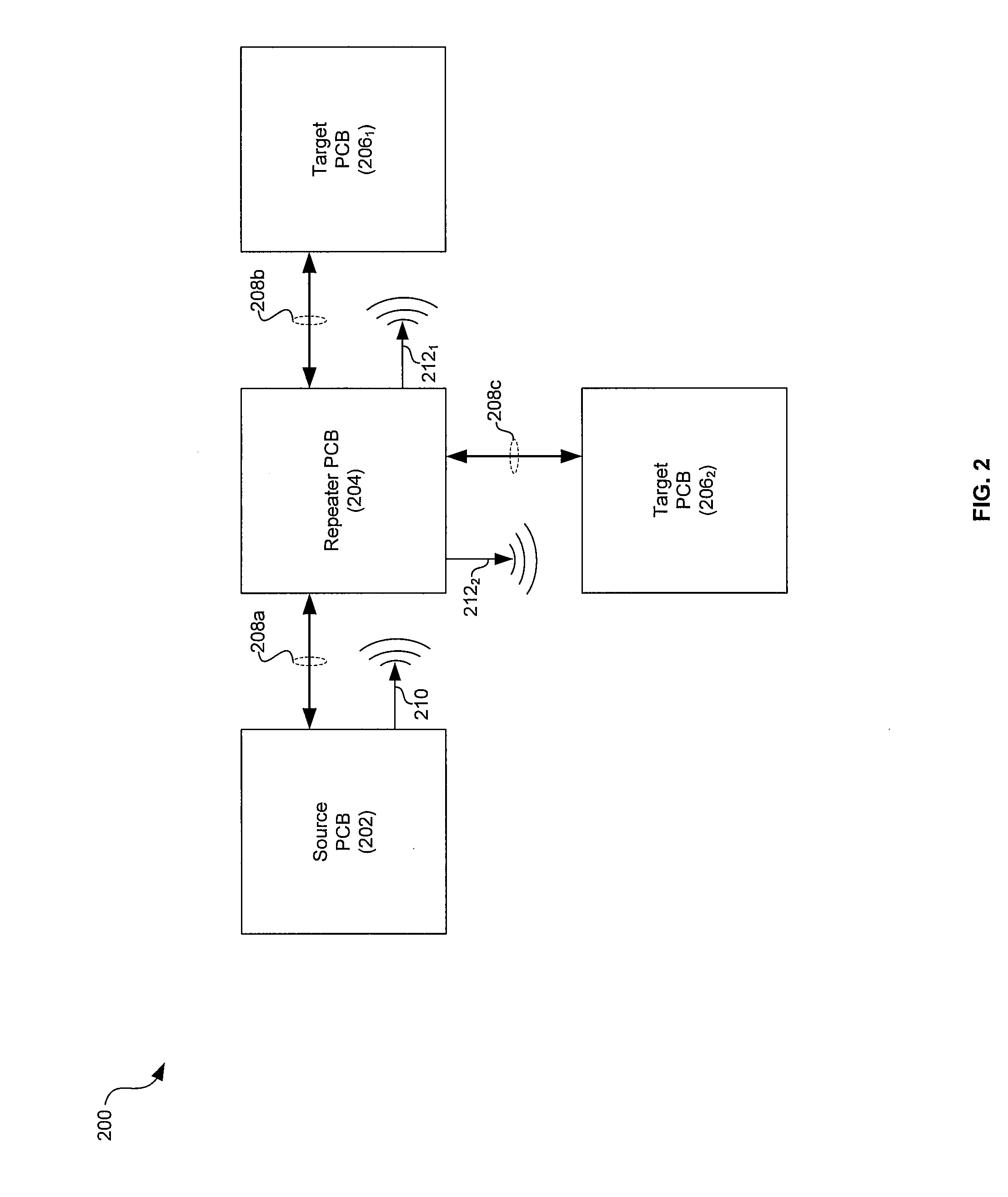

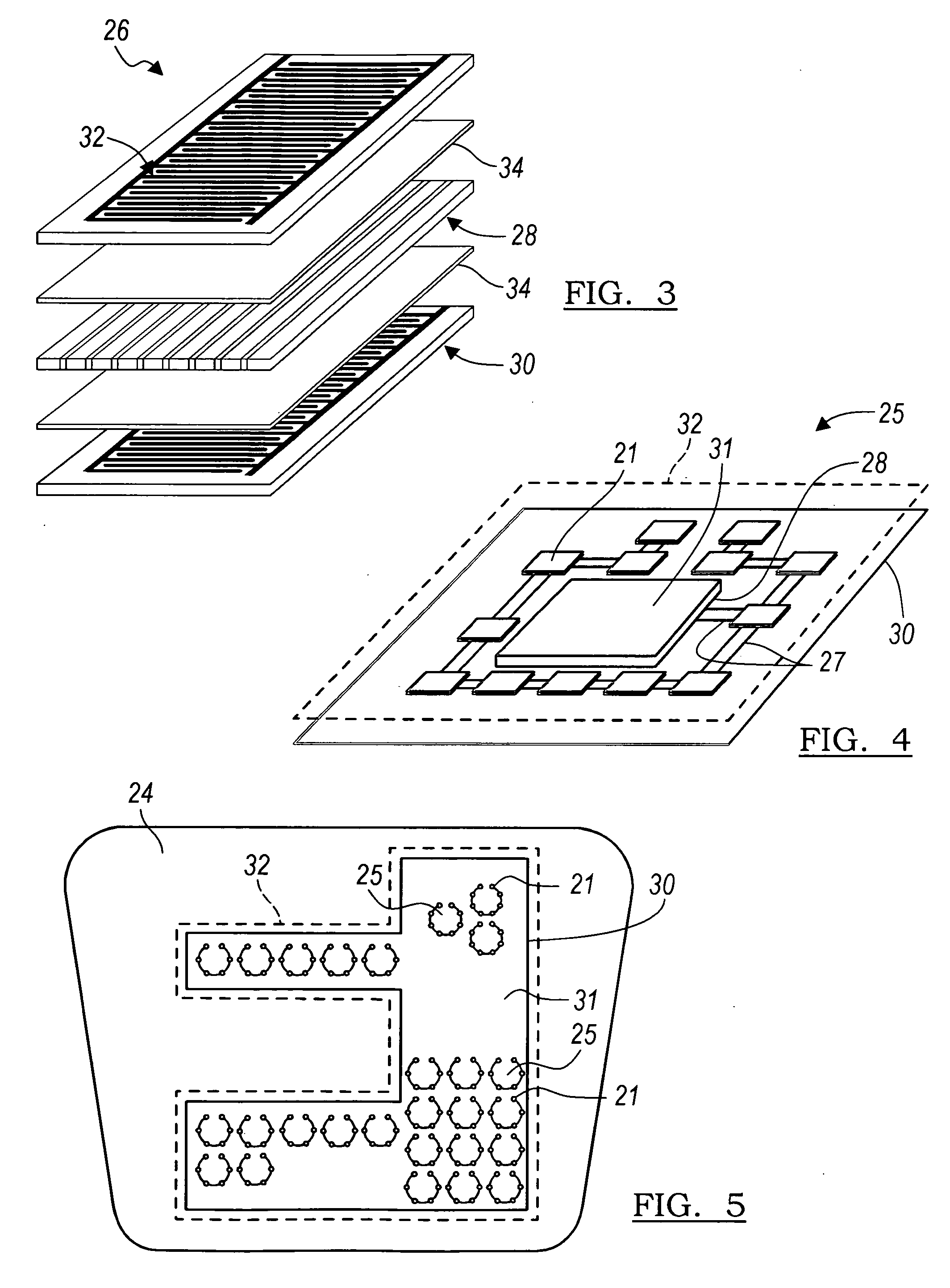

Method And System For Inter-PCB Communication Utilizing A Spatial Multi-Link Repeater

Aspects of a method and system for inter-PCB communication utilizing a spatial multi-link repeater are provided. In this regard, a signal may be transmitted between printed circuit boards via one or more repeaters, wherein the repeaters may frequency shift received signals to generate repeated signals. Each of the repeated signals may be generated by quadrature down-converting said received signal by mixing the received signal with a first LO signal pair, up-converting the down-converted signal by mixing it with a second LO signal pair, and adding or subtracting an in-phase portion and a quadrature-phase portion of the up-converted signal. Each repeated signal may comprise one or more signal components and a phase and / or amplitude of each of the components may be controlled to control a directivity of the repeated signals. The repeater may reside on one of the plurality of printed circuit boards.

Owner:AVAGO TECH INT SALES PTE LTD

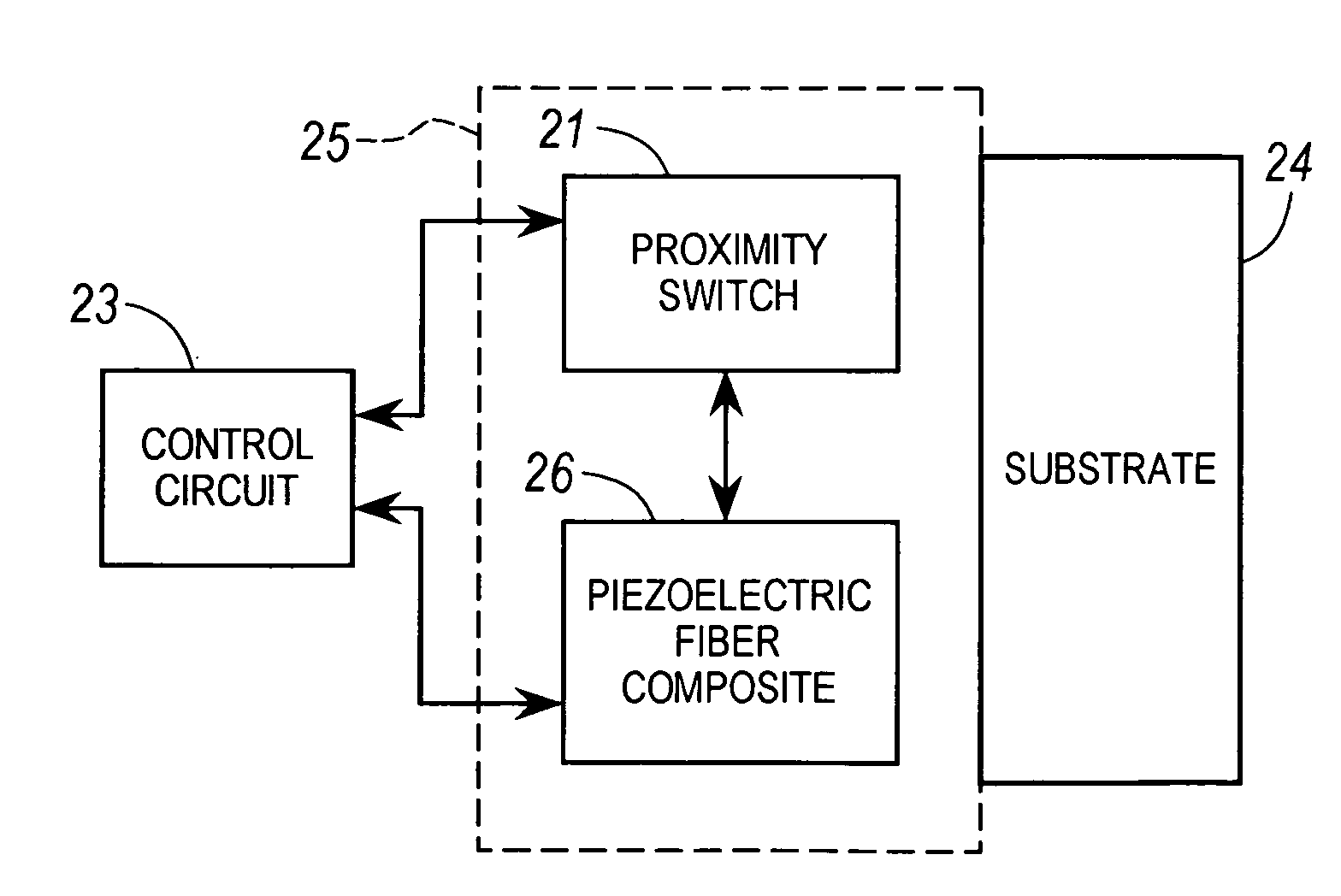

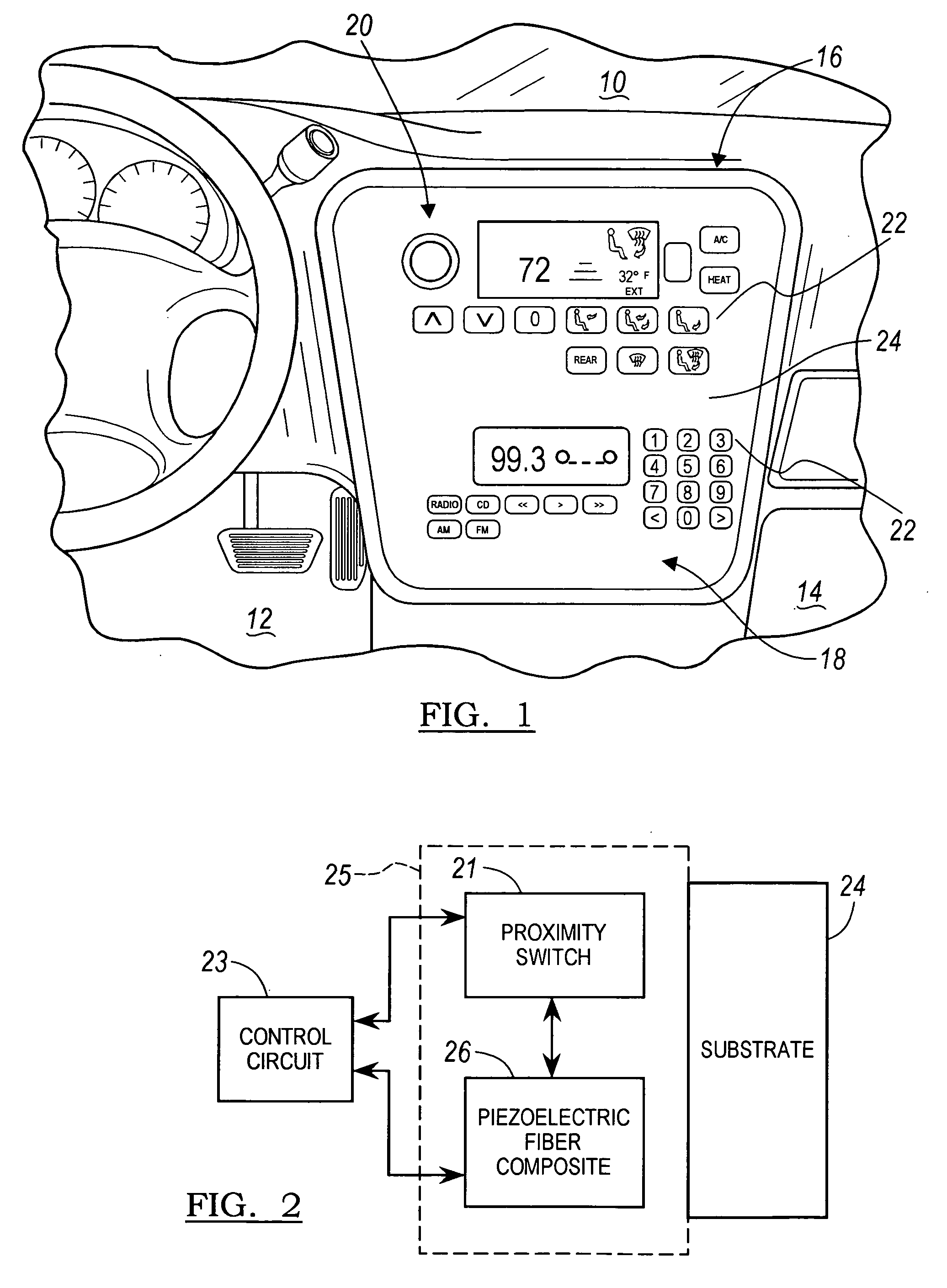

Flexible touch-sense switch

A flexible touch-sense switch includes a force sensitive composite and an at least one proximity sensor. The force sensitive composite includes a plurality of force sensors disposed between a first layer and a second layer of polymide film defining a displacement region. The at least one proximity sensor generates an electromagnetic field that defines a detection region. The force sensitive composite and the at least one proximity sensor are mounted to the first layer of the polymide film for forming a flexible printed circuit board. A control circuit is electrically connected to the force sensitive composite and the at least one proximity sensor for selectively controlling the touch-sense switch activation in response to coincident actuation thereof.

Owner:LEAR CORP

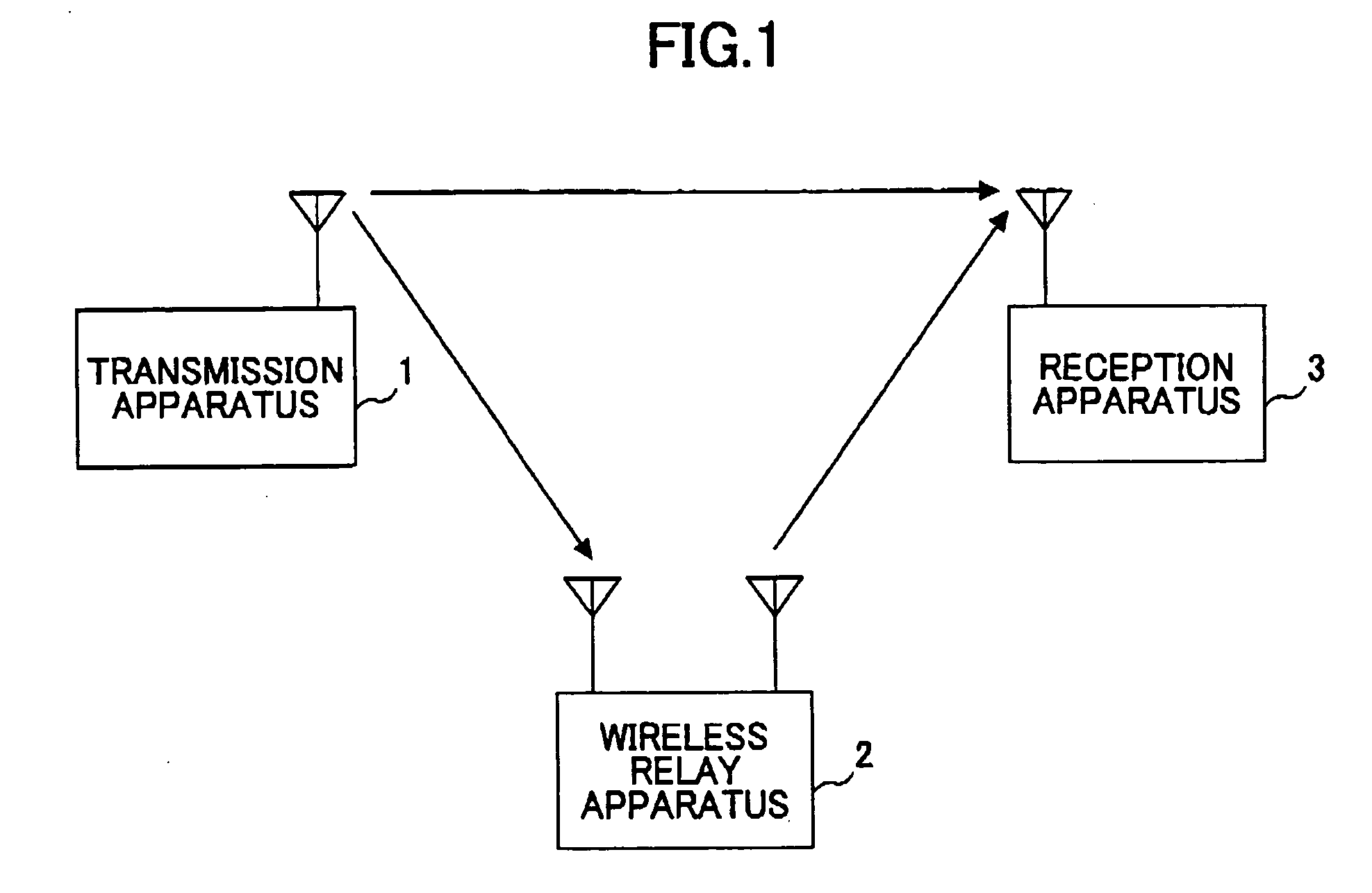

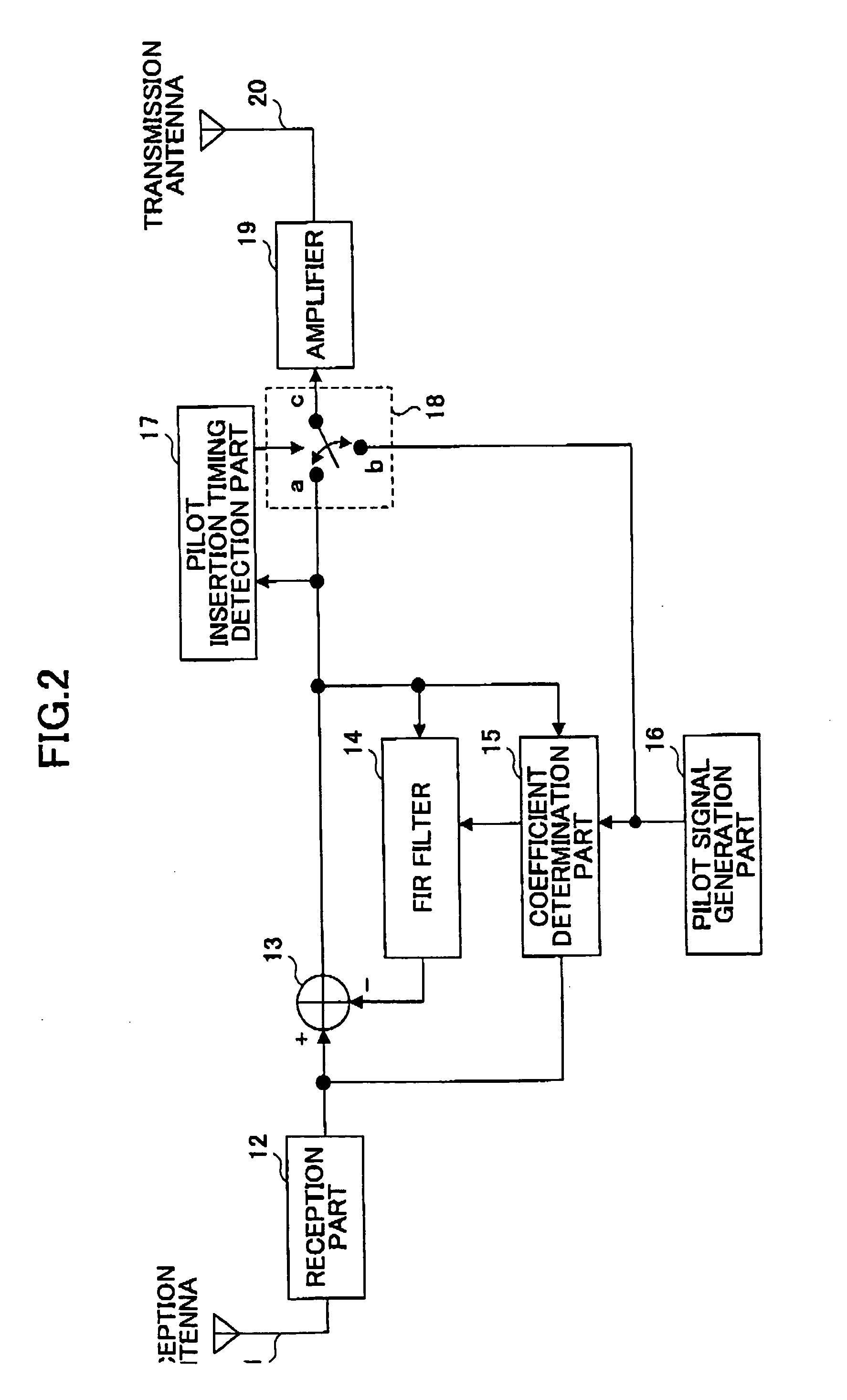

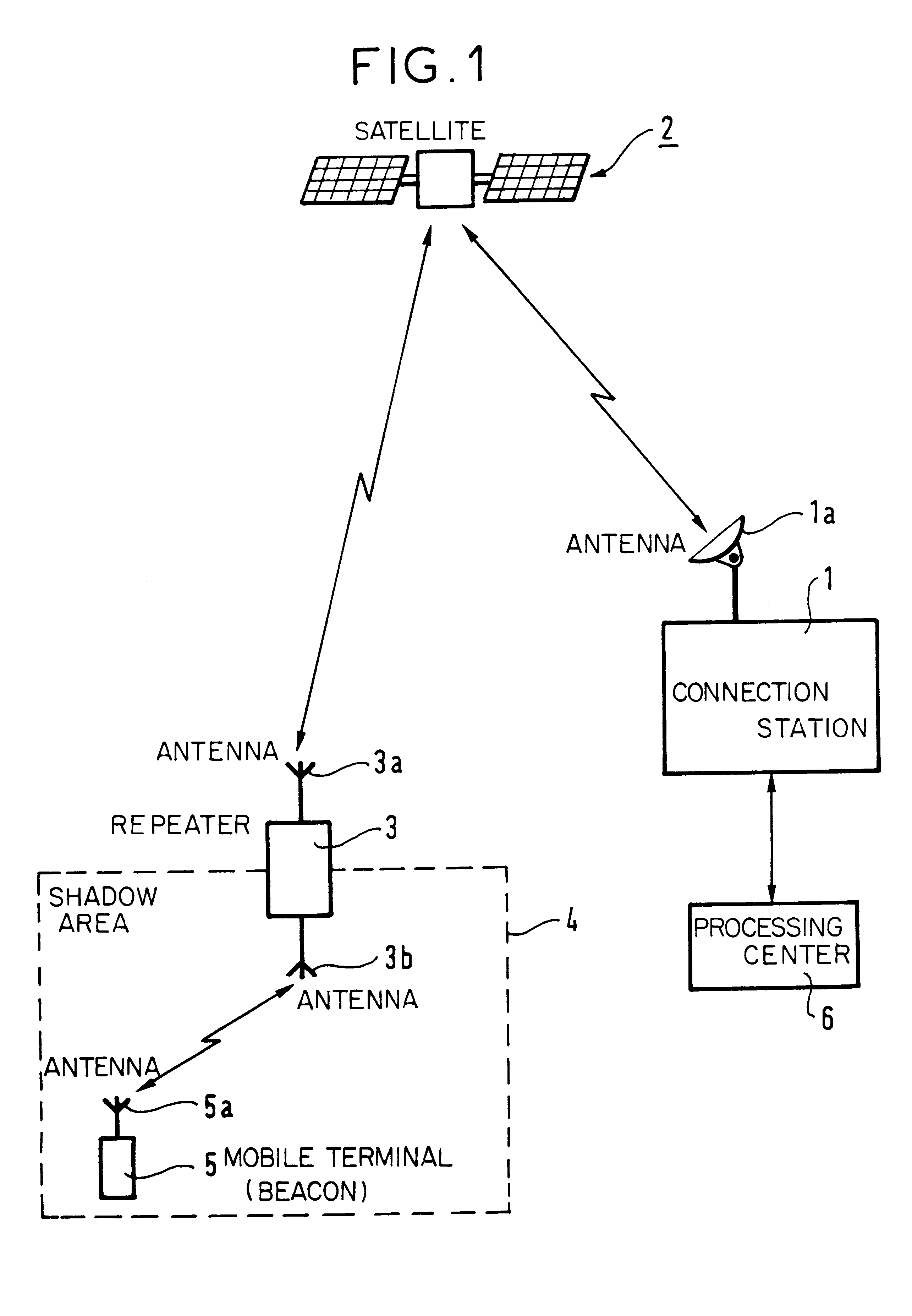

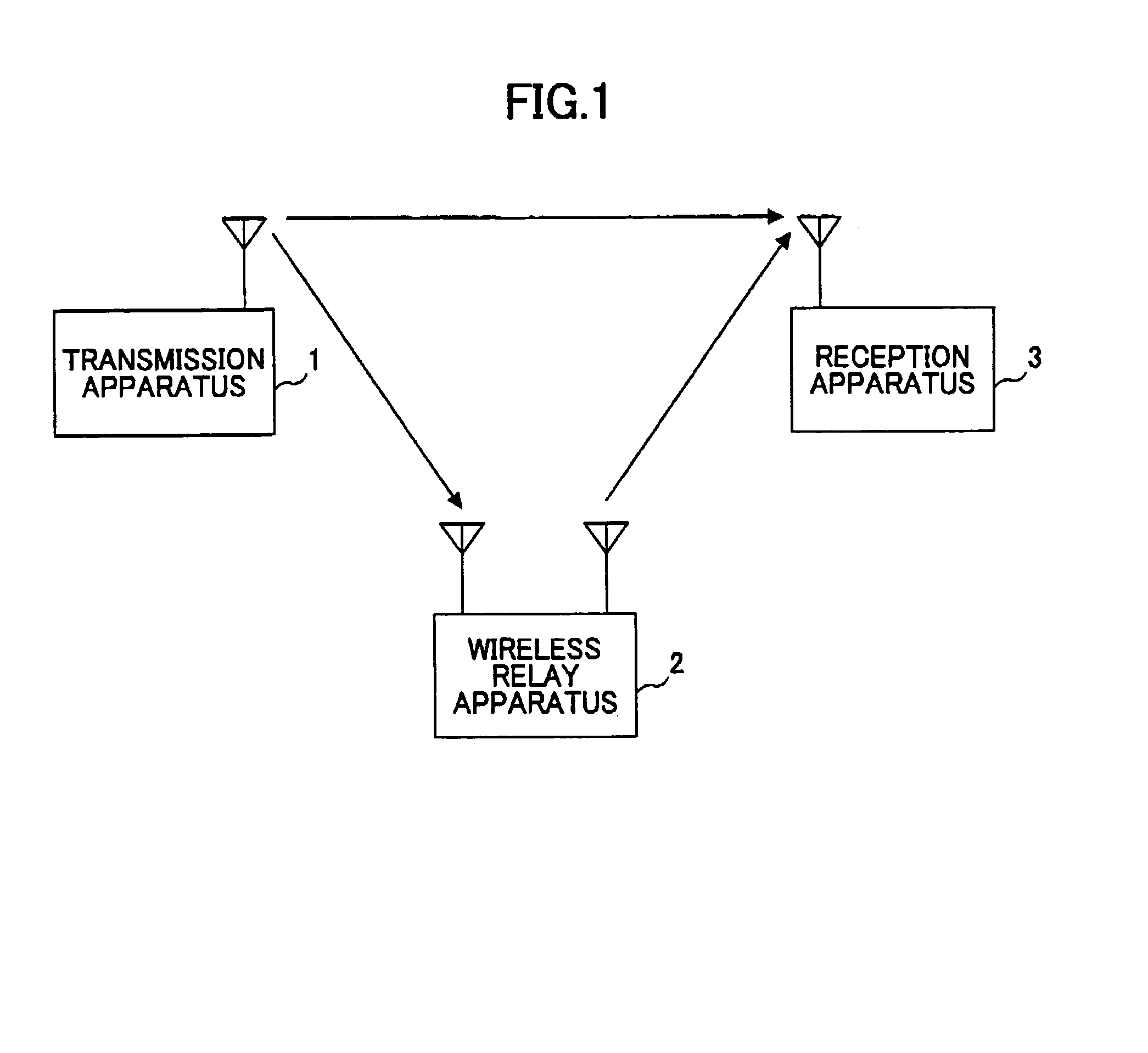

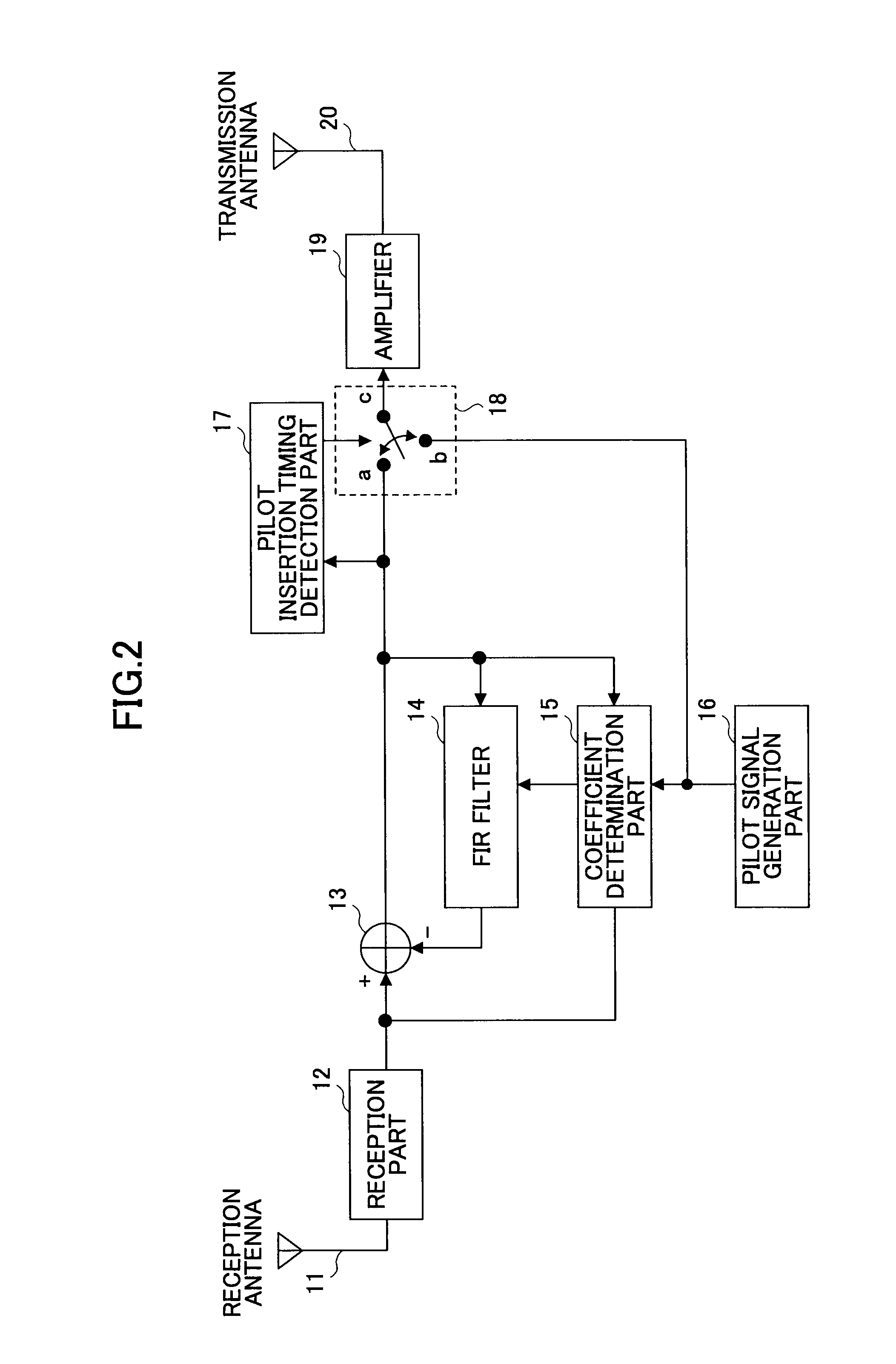

Wireless relay system, wireless relay apparatus, and wireless relay method

A wireless relay system for relaying a radio signal transmitted from a first wireless station to a second wireless station via a wireless relay apparatus is disclosed. The wireless relay system includes a relay control part for receiving transmission symbols transmitted from the first wireless station and refraining from relaying a portion of the symbols, a pilot signal transmission part for transmitting a pilot signal that is inserted into a section of the portion of the transmission symbols, a coupling loop interference wave estimation part for receiving the pilot signal and estimating a coupling loop interference wave based on the pilot signal, and a coupling loop interference wave cancellation part for subtracting the estimated coupling loop interference wave from a reception signal.

Owner:NTT DOCOMO INC

Transmission canceller for wireless local area network

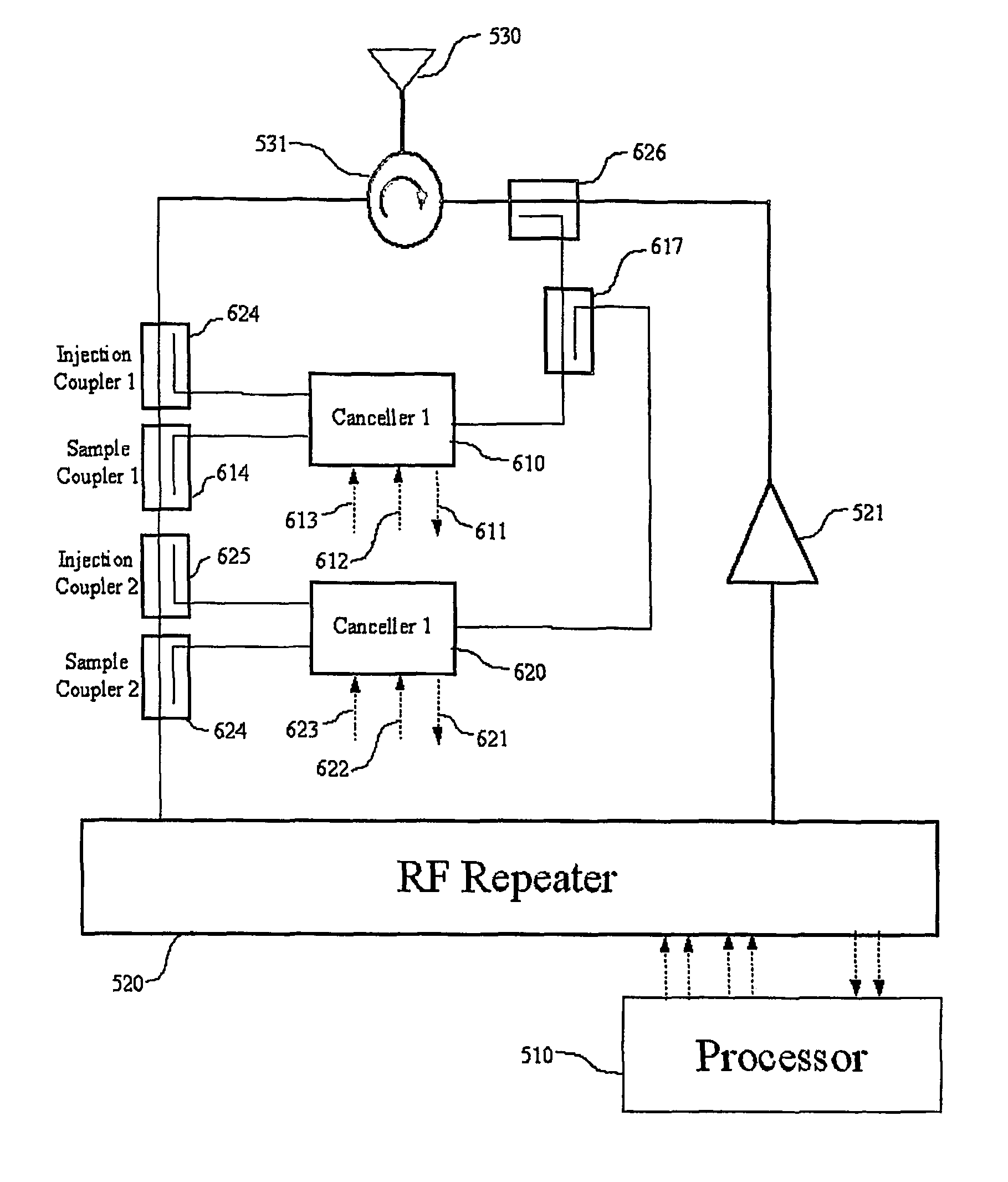

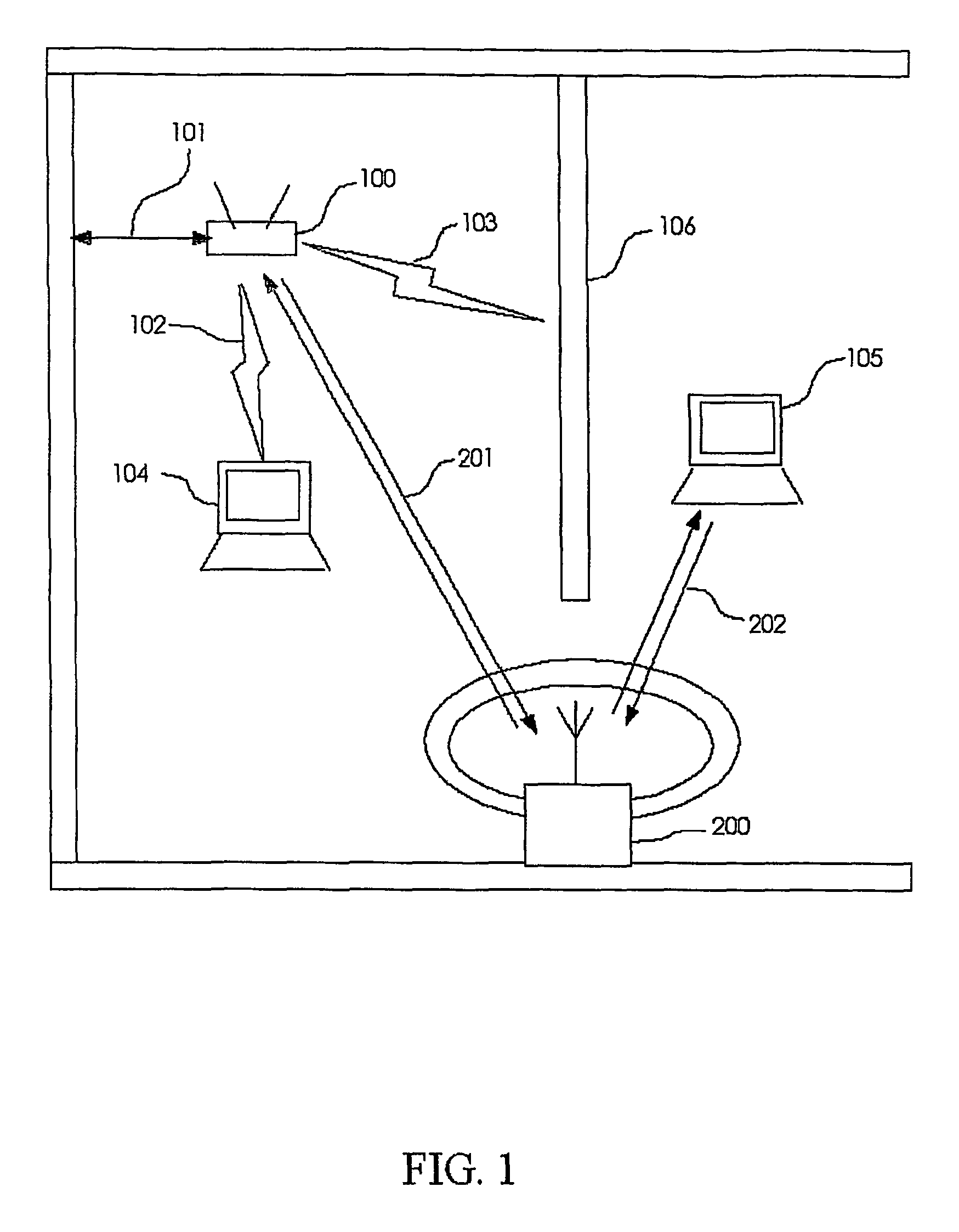

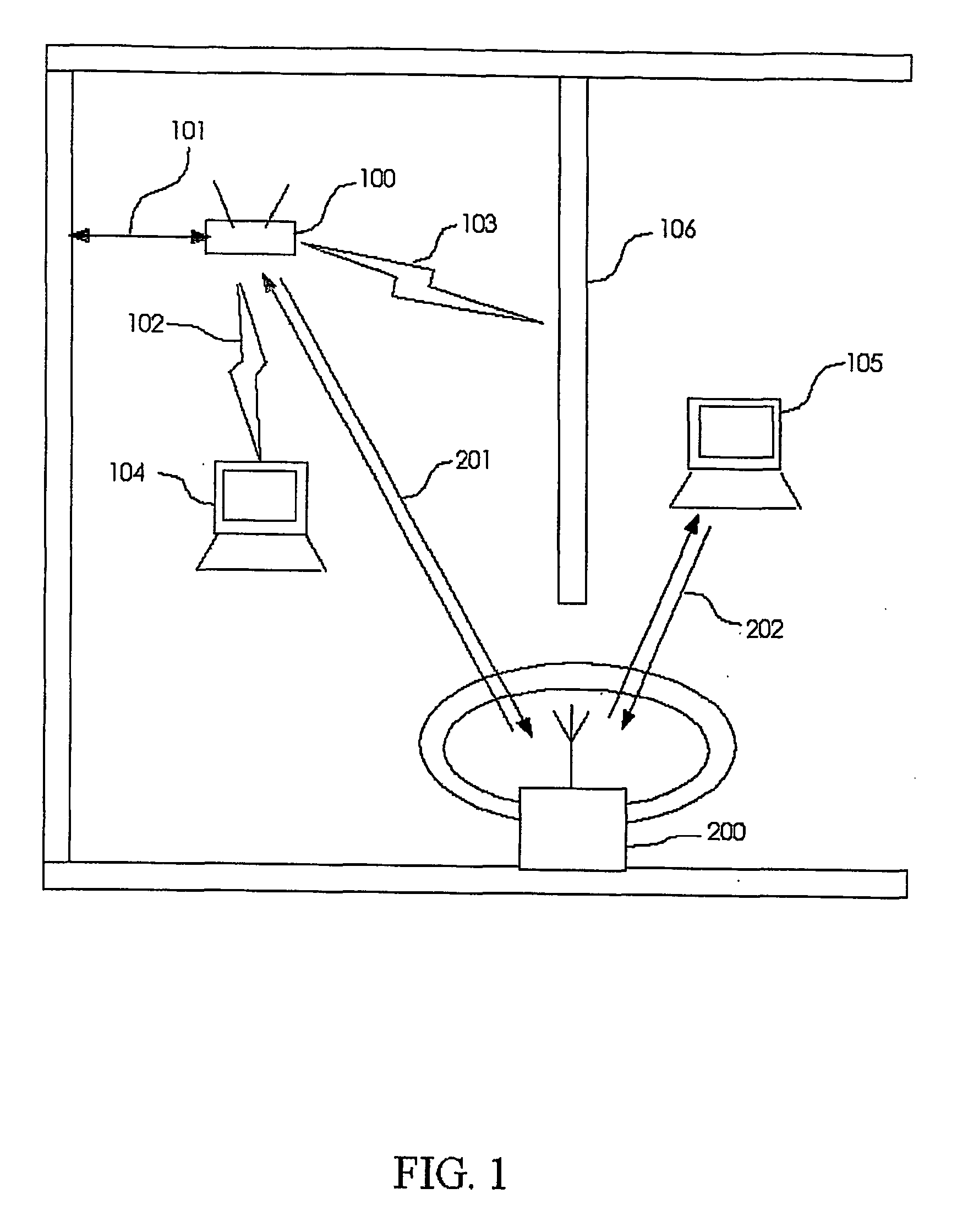

InactiveUS8027642B2Improve performanceIncrease the areaPulse transformerFrequency-division multiplex detailsTransceiverEngineering

A frequency translating repeater (200) for use in a wireless local area network includes a cancellation unit. Canceller (402) is controlled by control (401) to provide an injection signal for canceling leakage in a receive signal path. Reference coupler (403) provides a reference signal from the transmit signal, injection coupler (404) injects a correction signal, and sample coupler (405) provides a sample for feedback. A processor (510) receives the sample signal through a detector (415). Although the present invention is intended for a frequency translating repeater, it has broad applications in radio transceivers in general. One specific application is with frequency division duplex (FDD) handsets or base stations utilizing CDMA technologies such as W-CDMA and IS-2000 or 1XEV-DV / DO.

Owner:QUALCOMM INC

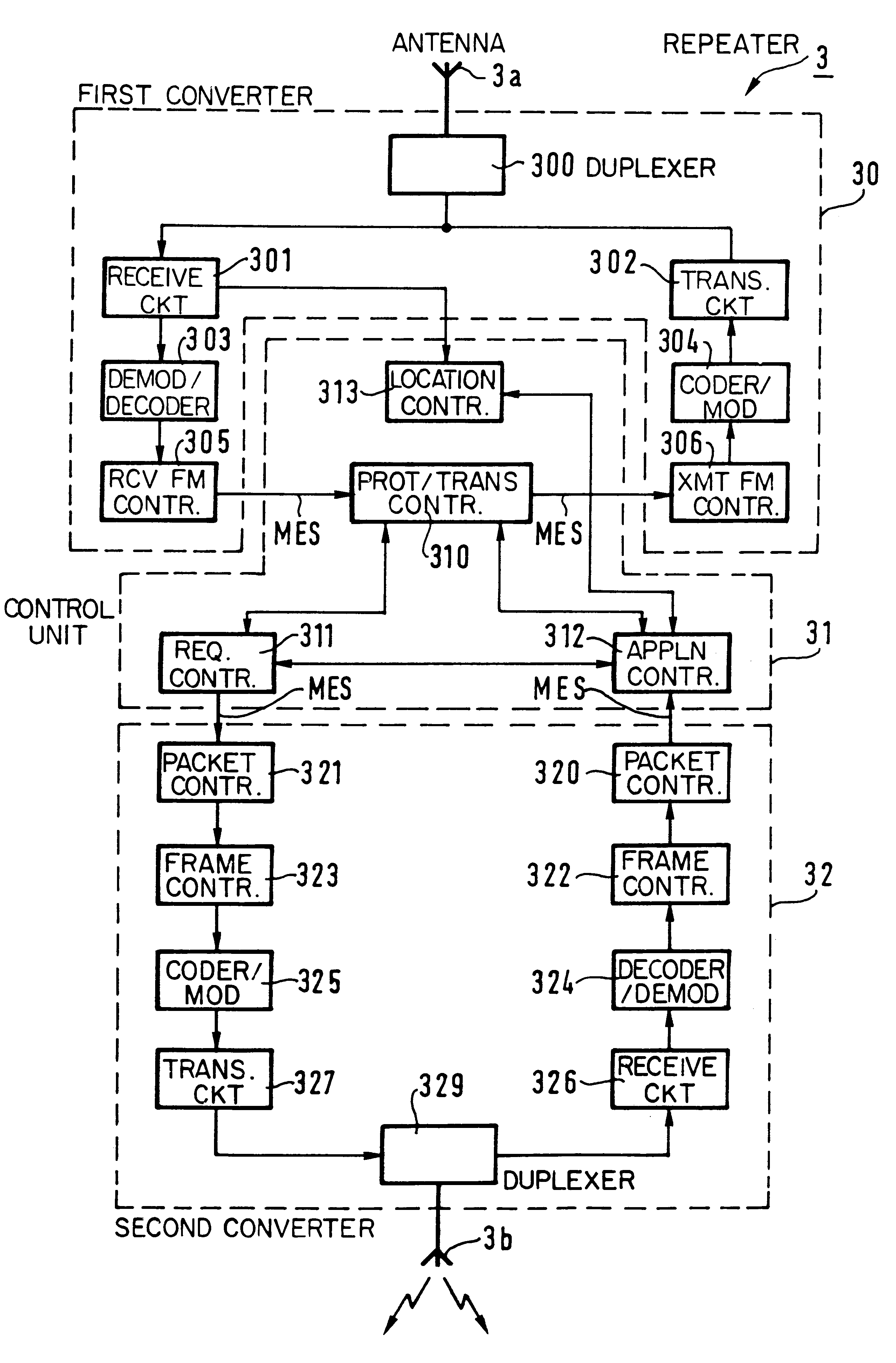

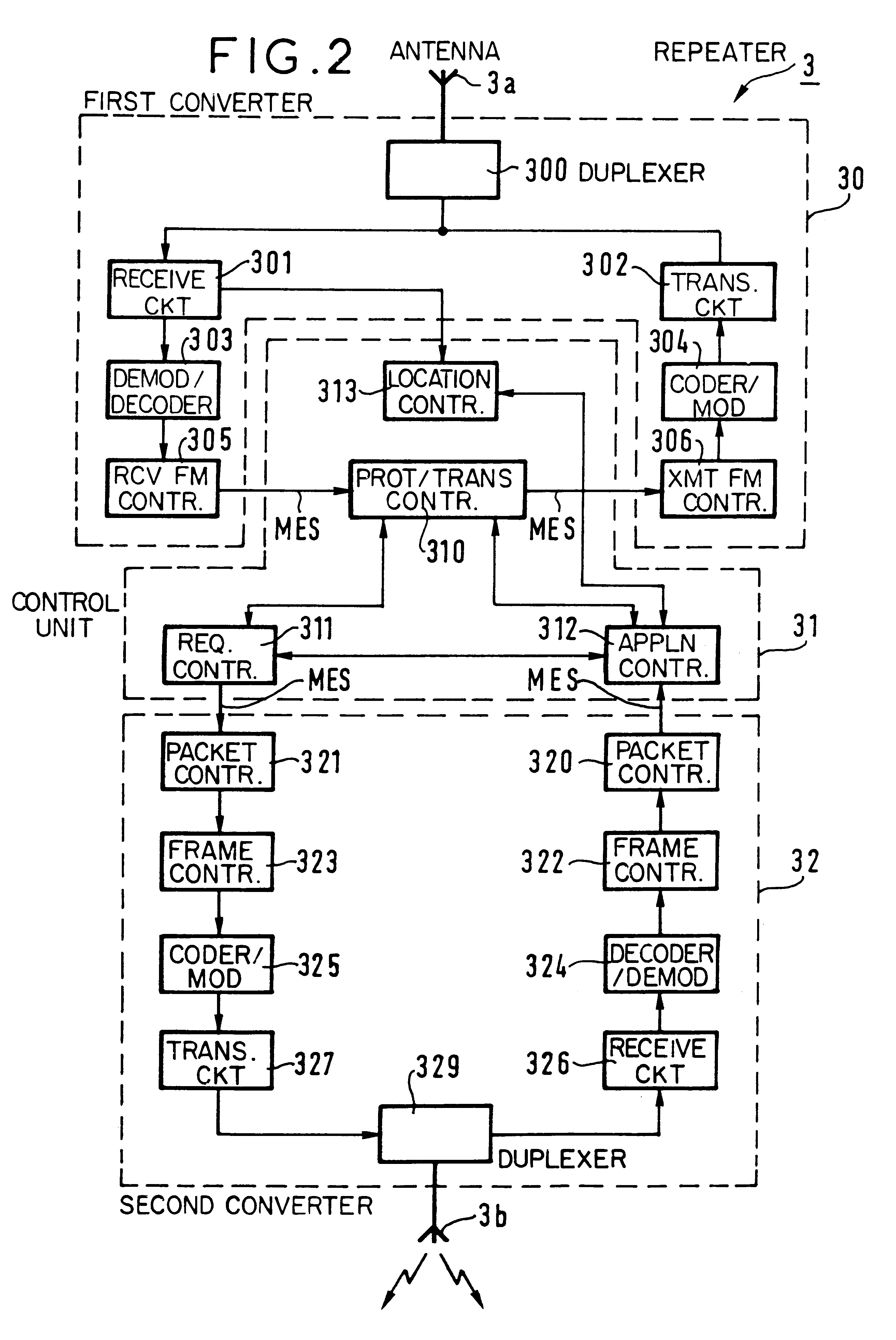

Radiocommunication system repeater

A repeater for use in a radiocommunication network for relaying data communications between first and second stations between which data communication via the radiocommunication network alone is impossible includes a first converter for converting a first radio signal received from the first station into the form of first receive messages and converting first transmit messages into the form of a first radio signal transmitted to a first station. A second converter converts a second radio signal received from said second station into the form of second receive messages and second transmit messages into the form of a second radio signal transmitted to the second station. An application controller manages the first receive messages and the first transmit messages and the second receive messages and the second transmit messages.

Owner:ALCATEL ESPACE

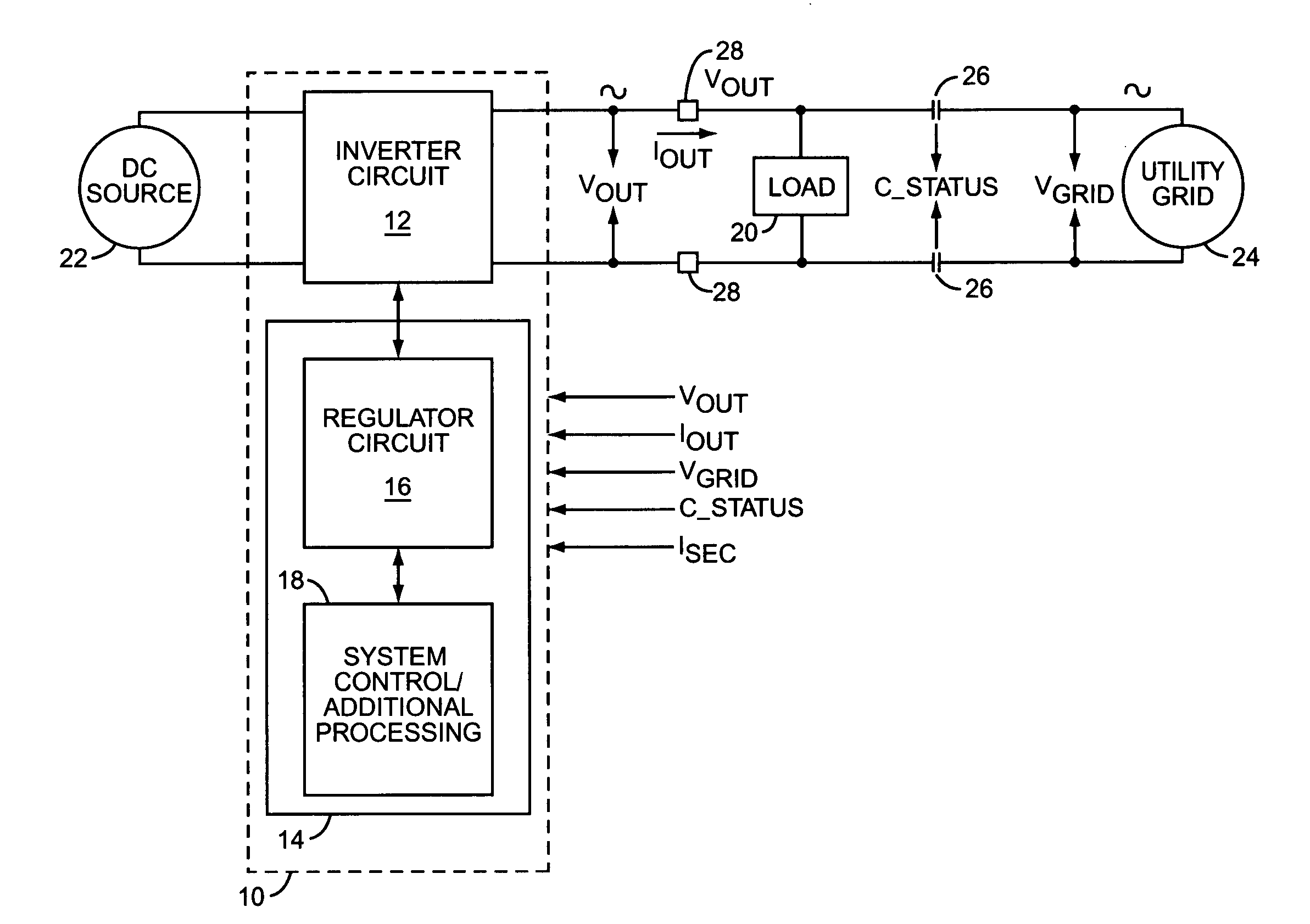

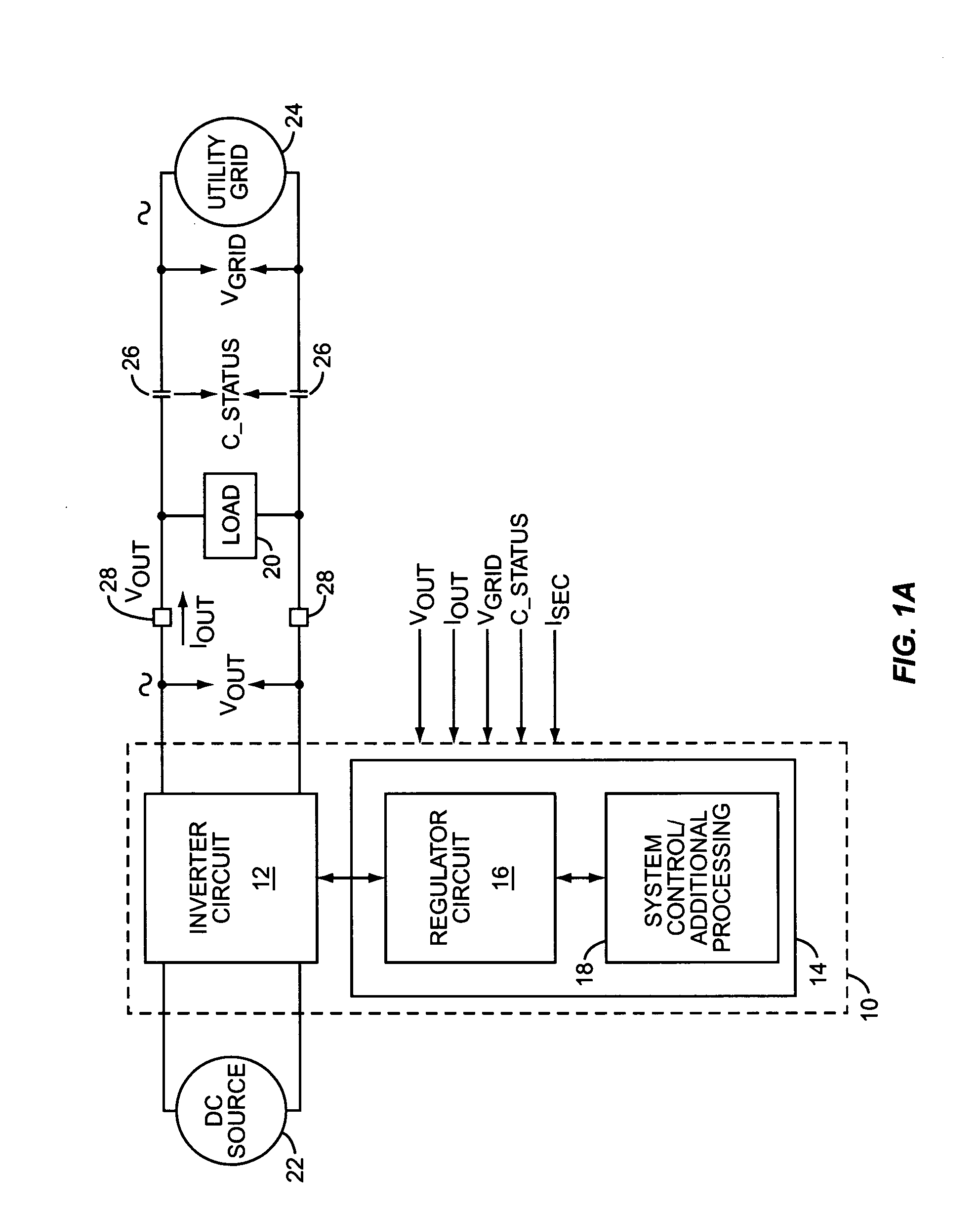

Method and apparatus for signal phase locking

A phase locked loop (PLL) circuit provides ac devices, such as power inverters and power measurement devices, with a reliable means for synchronizing to ac electrical systems. In an exemplary embodiment, the PLL circuit is configured for operation with single-phase electrical systems and offers substantial noise immunity by basing its locking operations on measured fundamental components, i.e., measured x-y phasors, of the electrical system voltage. Further, with its phasor-based locking operations and with its timer / counter-based operation, the PLL circuit can be implemented partly or wholly in digital processing logic.

Owner:SQUARE D CO

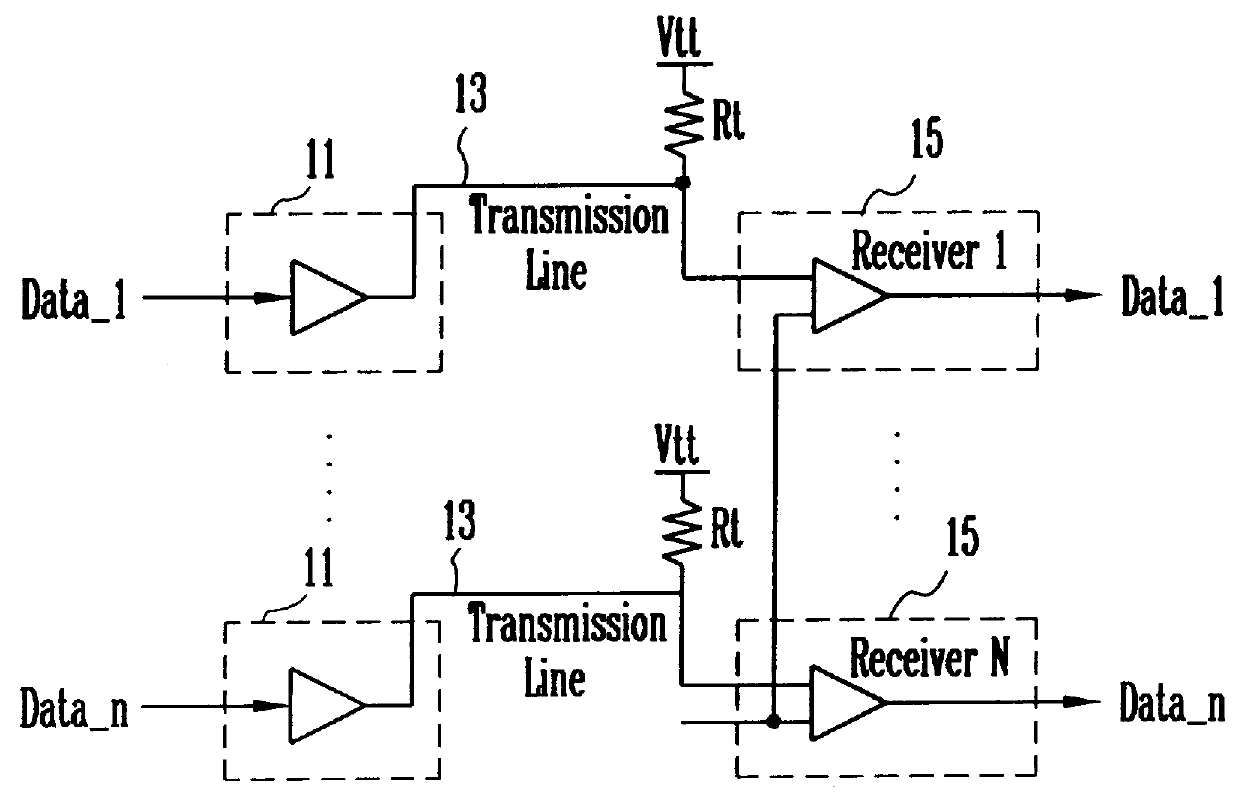

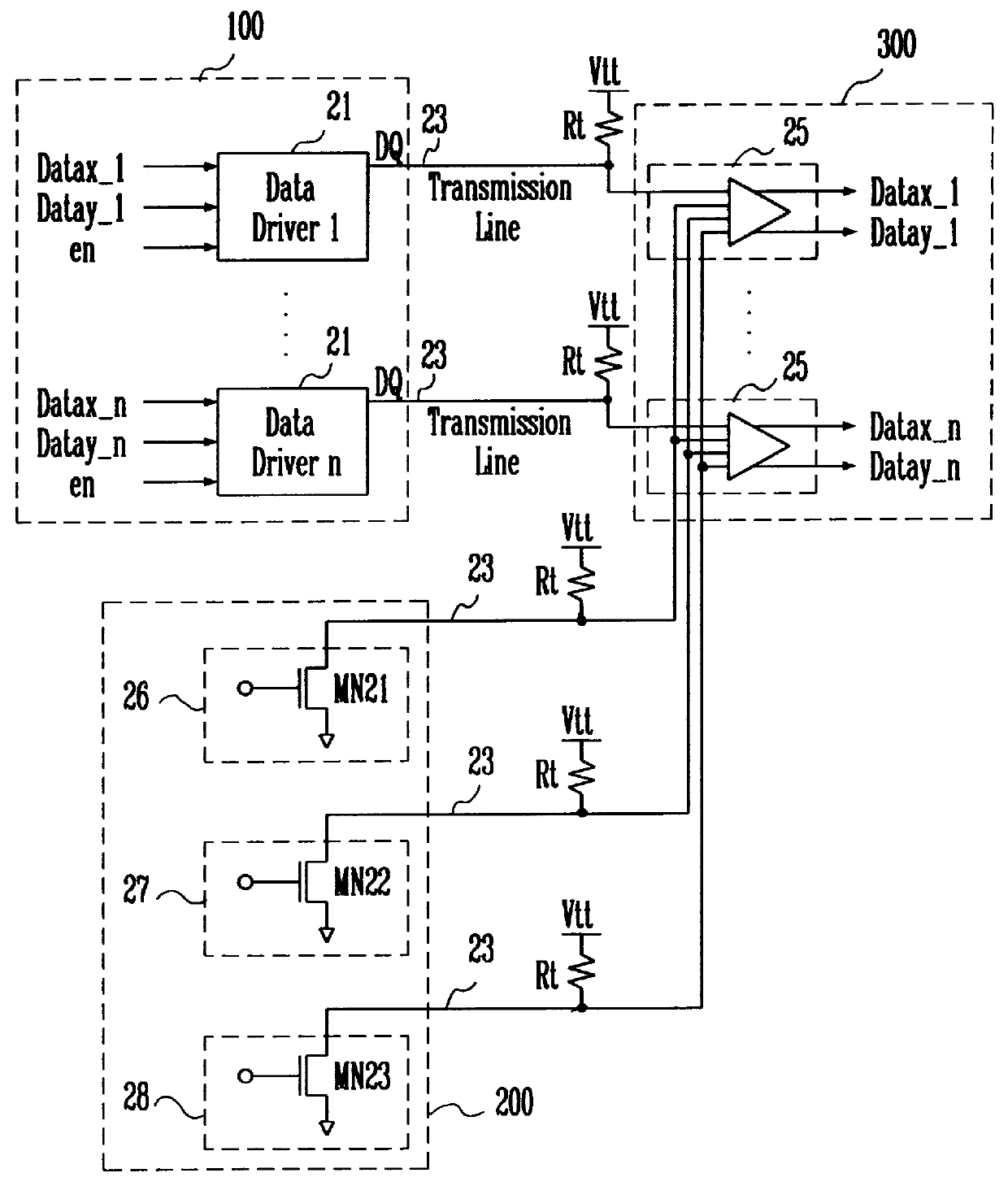

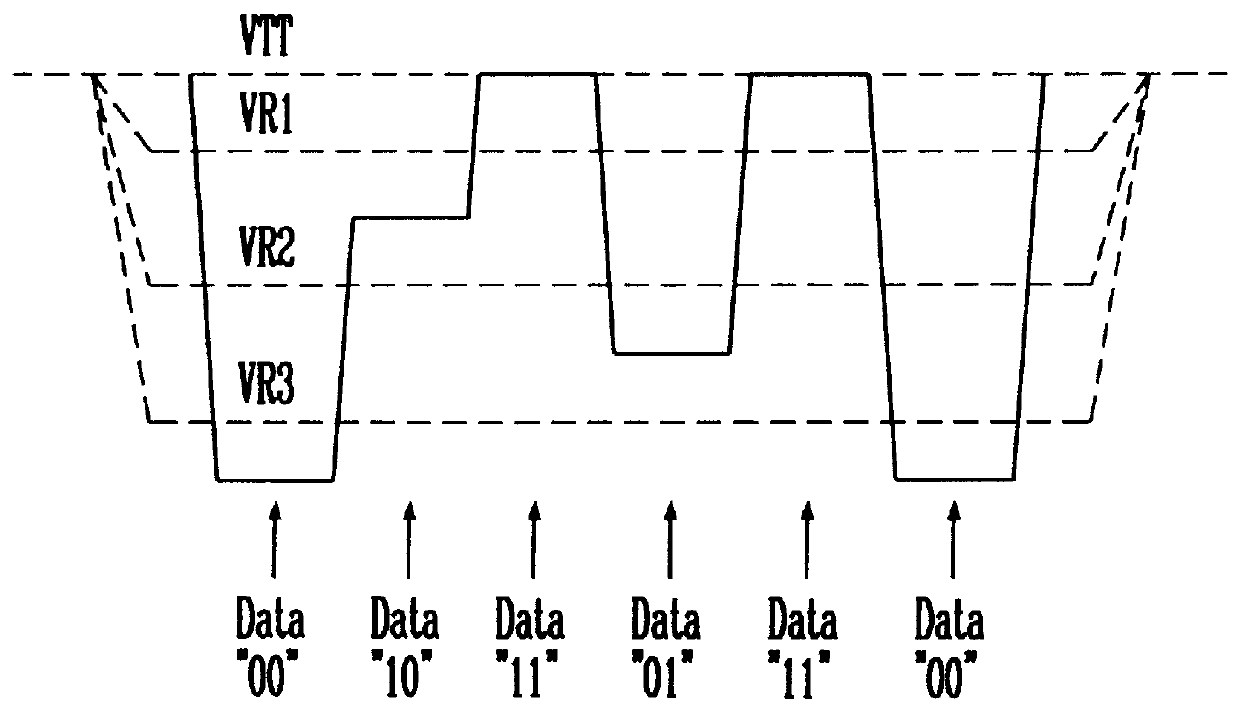

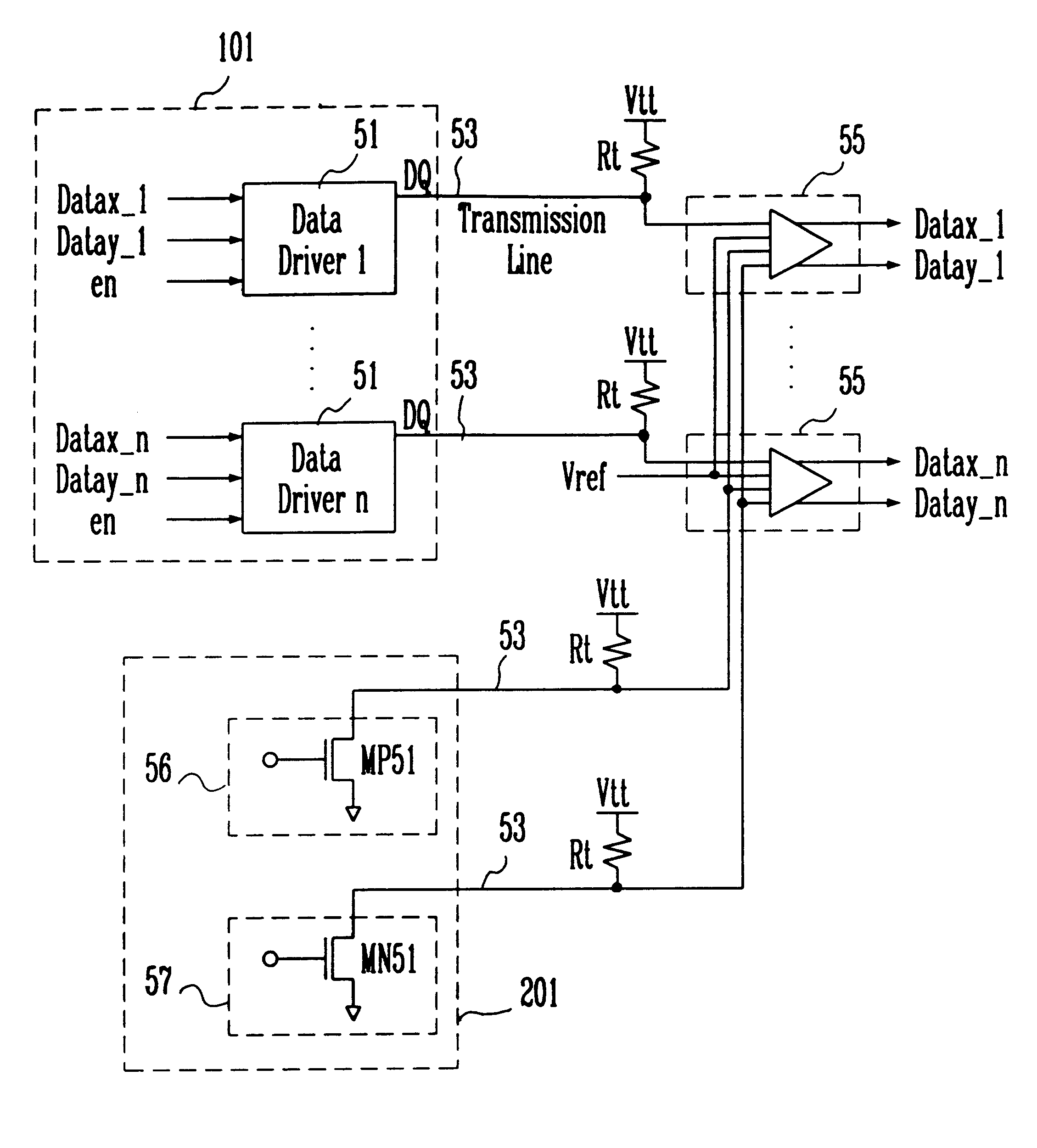

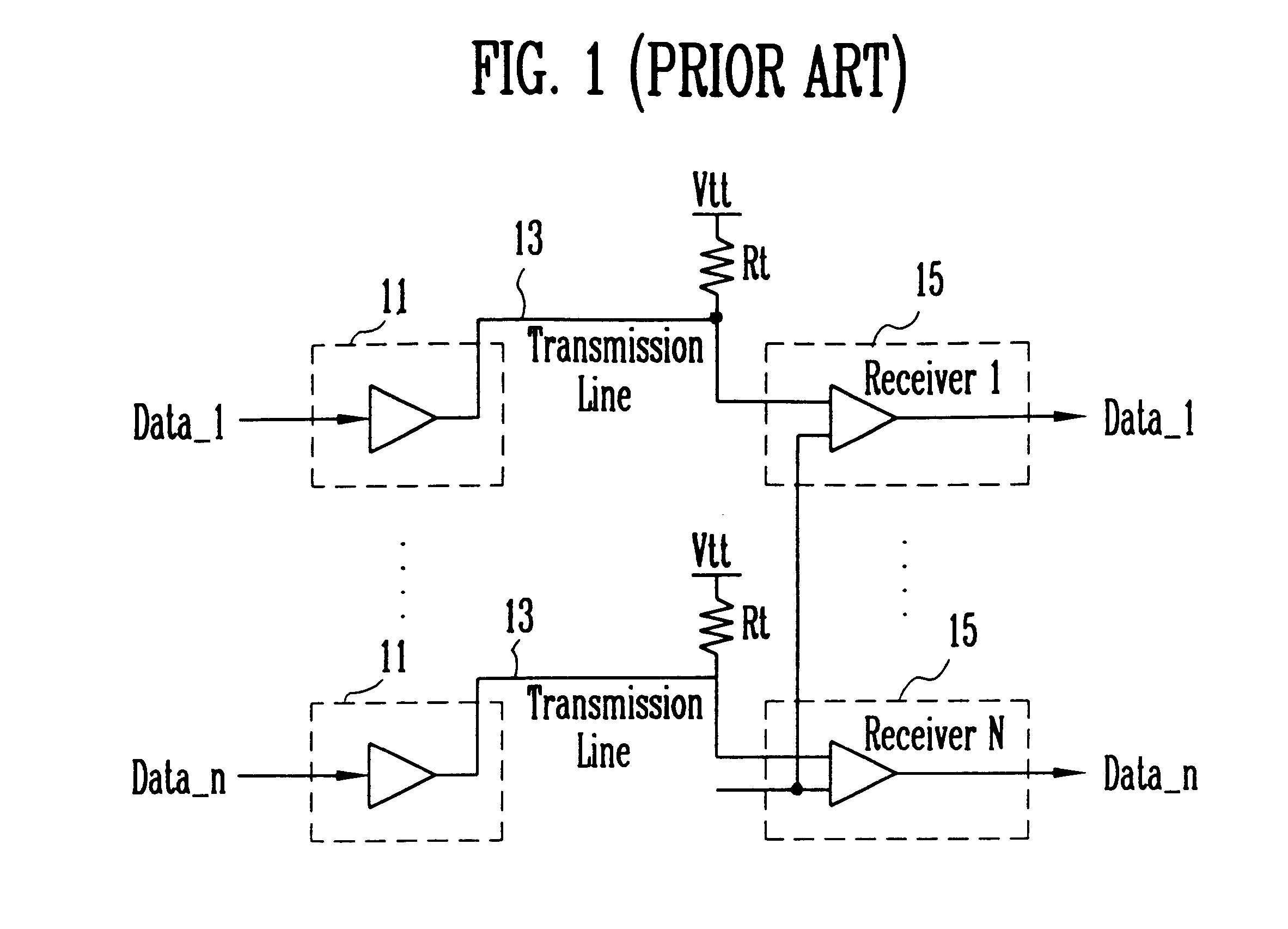

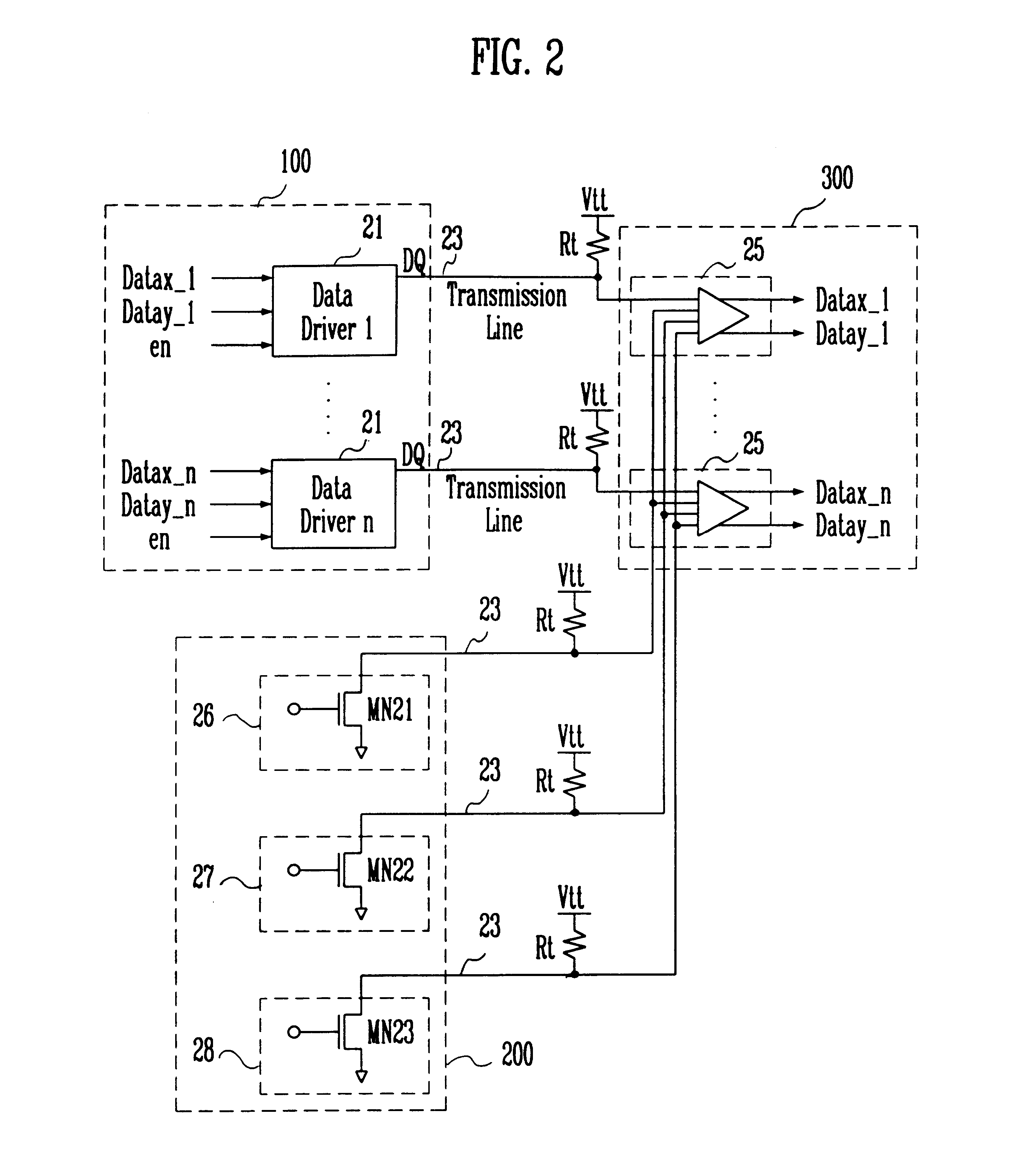

High speed interface apparatus

InactiveUS6140841AElectric signal transmission systemsElectric analogue storesThree levelData signal

The present invention discloses a much higher speed interface apparatus which comprises a data driving means for decoding two-bit data signals using them as inputs to output four-level data signals; a reference voltage generating means for generating three-level reference voltages to discriminate the voltage levels of the four-level data signals; and a receiver means for comparing the four-level data signals and the three-level reference voltage signals using them as inputs and for encoding the resulting signals to output two data signals.

Owner:HYUNDAI ELECTRONICS IND CO LTD

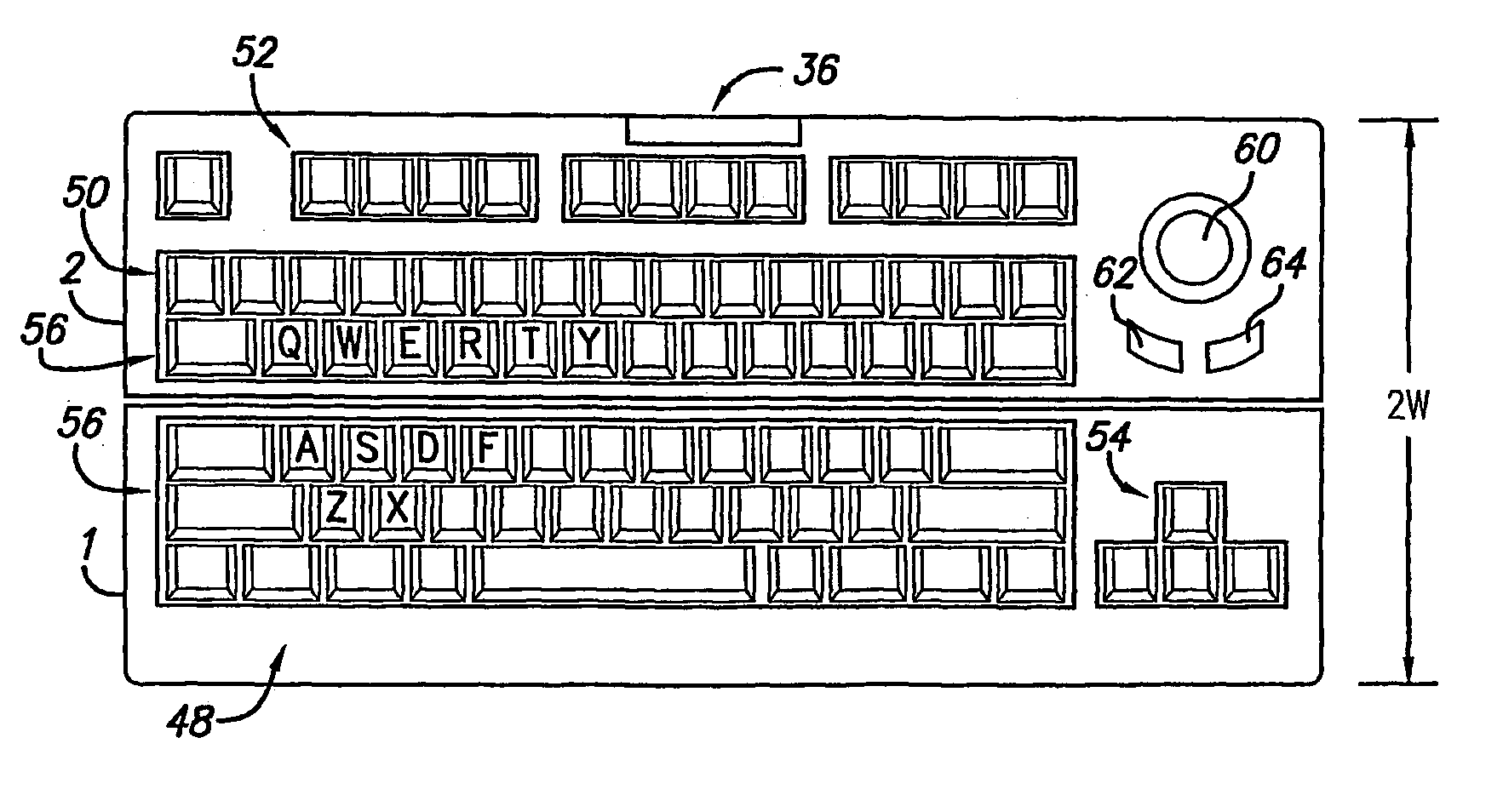

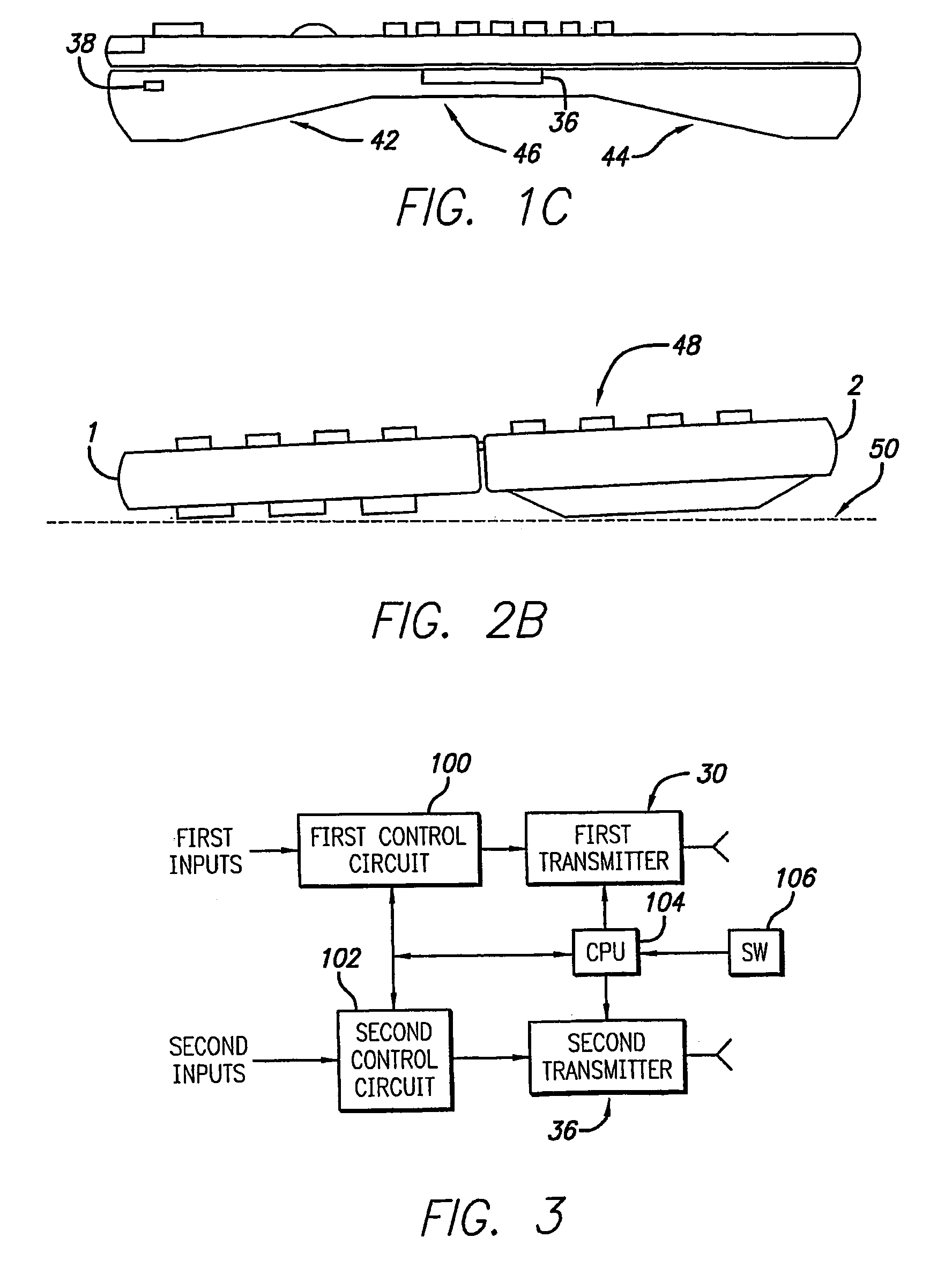

Remote control method using remote control device with keyboard

InactiveUS7123242B1Convenient to accommodateInput/output for user-computer interactionTelevision system detailsRemote controlDisplay device

A remote control method and system employ remote controller (10) which is adapted for use with an entertainment system of a type including a display (222) as well as providing functions such as Internet access or other functions requiring a keyboard and / or a mouse. The remote controller includes a folding housing and may be operated in a closed or opened configuration. A first set of control inputs (12) are provided on the outer surface of the housing. The housing may be opened, thereby doubling the surface area of the remote controller, to expose a keyboard (56). One or more wireless transmitters are operable with the housing in either of two configurations oriented at 90 degrees to each other and controlled by the first set of control inputs and the keyboard. The remote controller may be conveniently held in one hand of a user when in the folded or closed position and conveniently rested on the lap of the user or a support surface when in the opened position and used as a keyboard.

Owner:I INTERACTIVE LLC

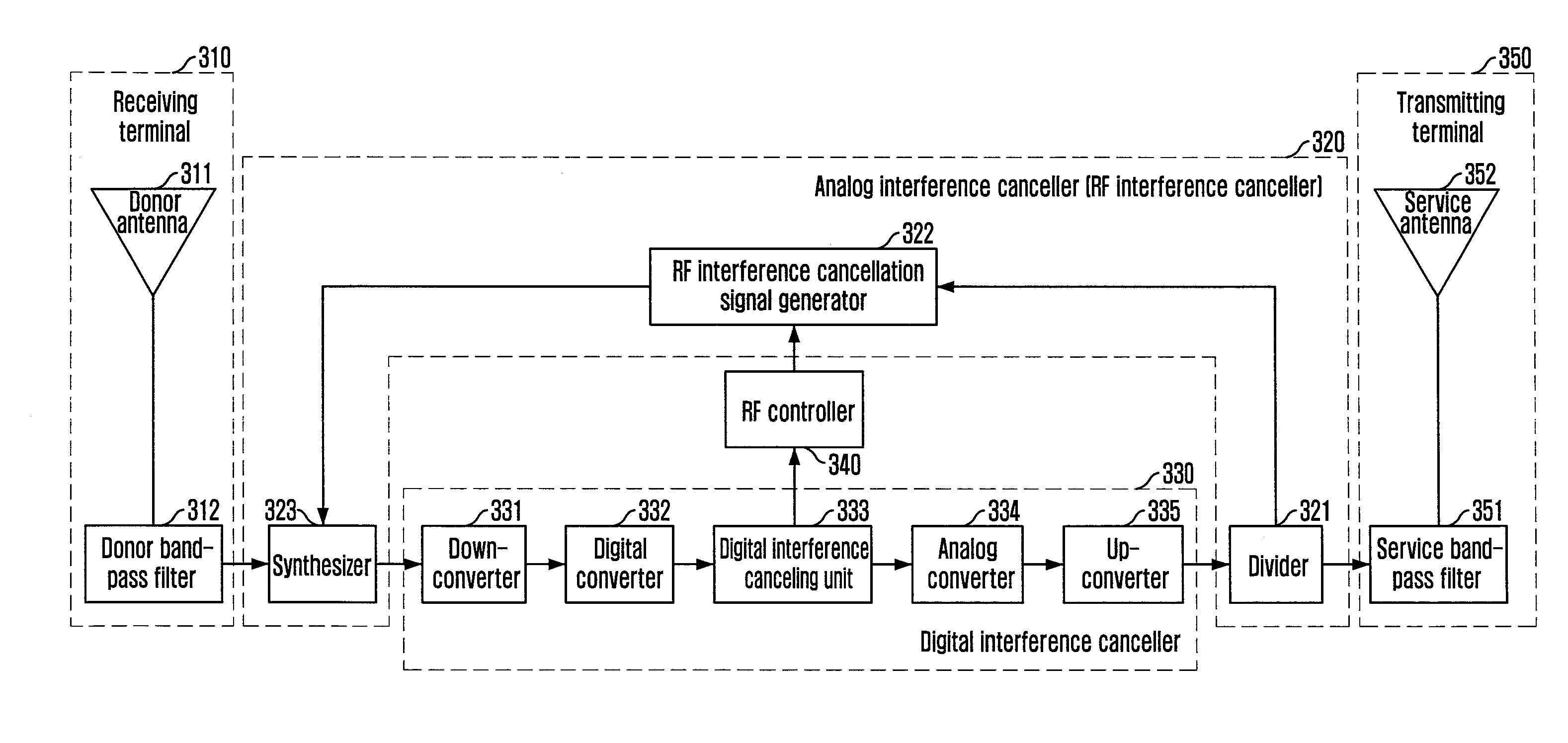

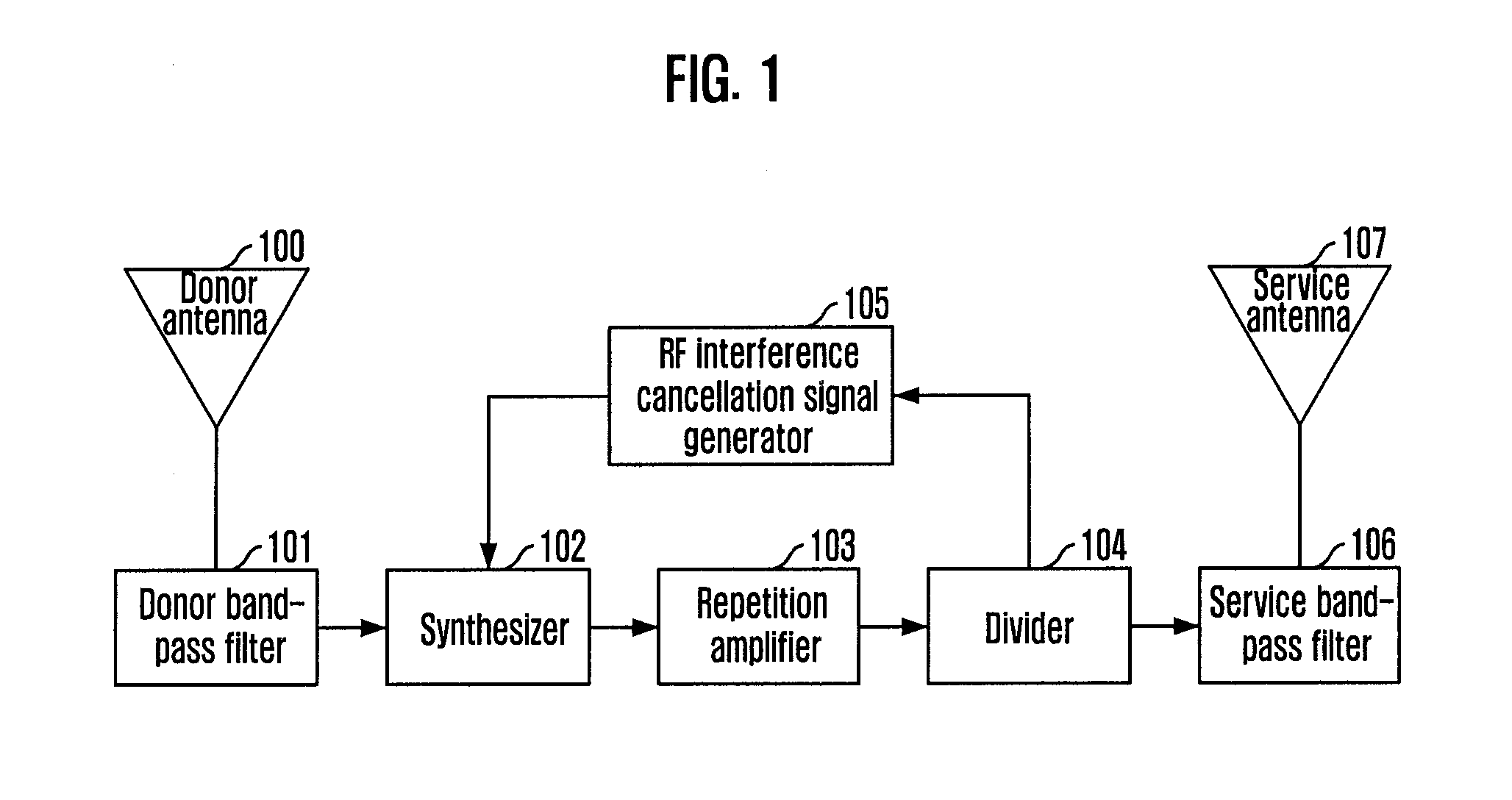

Wireless repeater apparatus for canceling interference signal

InactiveUS20100118922A1Improve stabilityImprove signal qualityPulse transformerTransmission noise suppressionInterference cancelationControl signal

There is provided a micro integrated wireless repeater apparatus for canceling an interference signal, including: a receiving means for receiving a repetition signal; an analog interference cancellation means for generating an interference cancellation signal according to a control signal and removing an interference signal from the repetition signal received from the receiving means; a digital interference cancellation means for canceling a residual interference signal remaining in a repetition signal obtained by canceling an interference signal component by the analog interference cancellation means; a control means for controlling the analog interference cancellation means by transmitting the control signal to the analog interference cancellation means according to control information received from the digital interference cancellation means; and a transmitting means for transmitting a repetition signal obtained by canceling a residual interference signal component by the digital interference cancellation means.

Owner:AHN BYUNG YANG

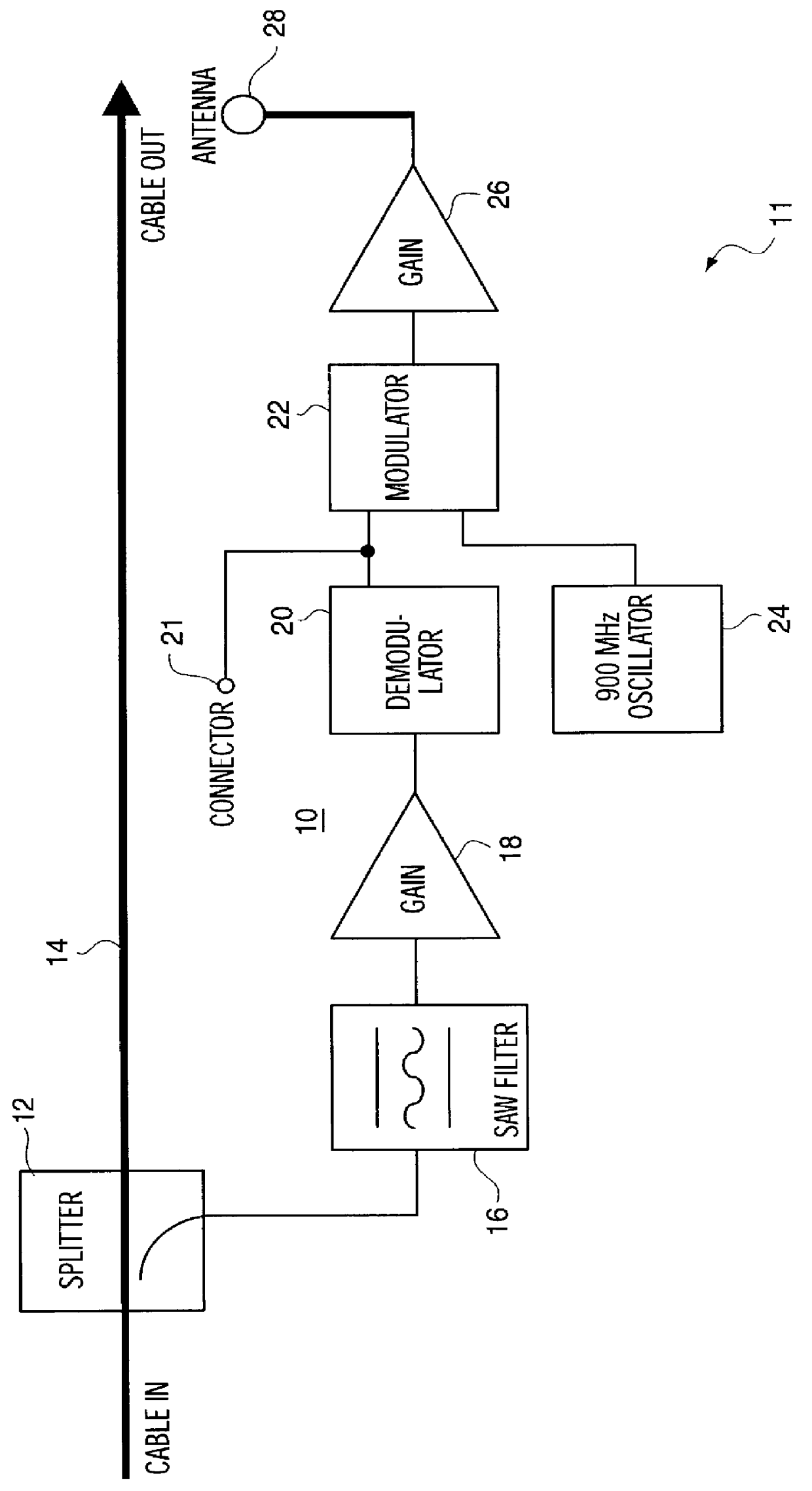

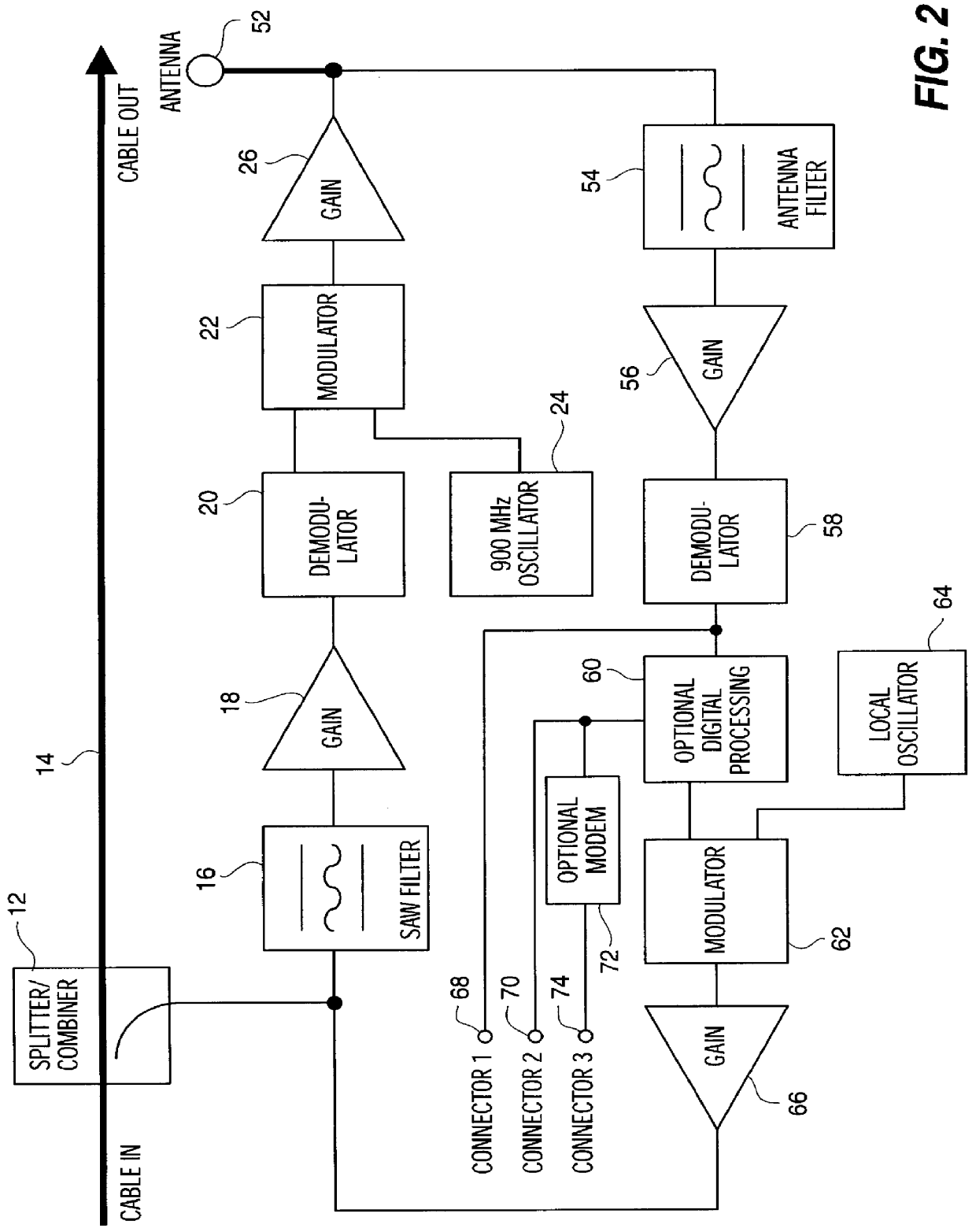

Tap antenna unit

The tap antenna unit includes signal splitting circuitry, coupled to a coaxial cable which is servicing a consumer electronic device, such as a television set, for splitting off a signal from the coaxial cable; a filter coupled to an output of the signal splitting circuitry for selecting a low-level sharp frequency band in the energy spectrum of the coaxial cable; circuitry for demodulating a signal carried by the low-level frequency band; circuitry for modulating the output signal onto a carrier in an unlicensed frequency band; and an output antenna which is coupled to the modulating circuitry and which is capable of transmitting the output modulated signal over a limited transmitting-receiving area.

Owner:LOGITECH EURO SA

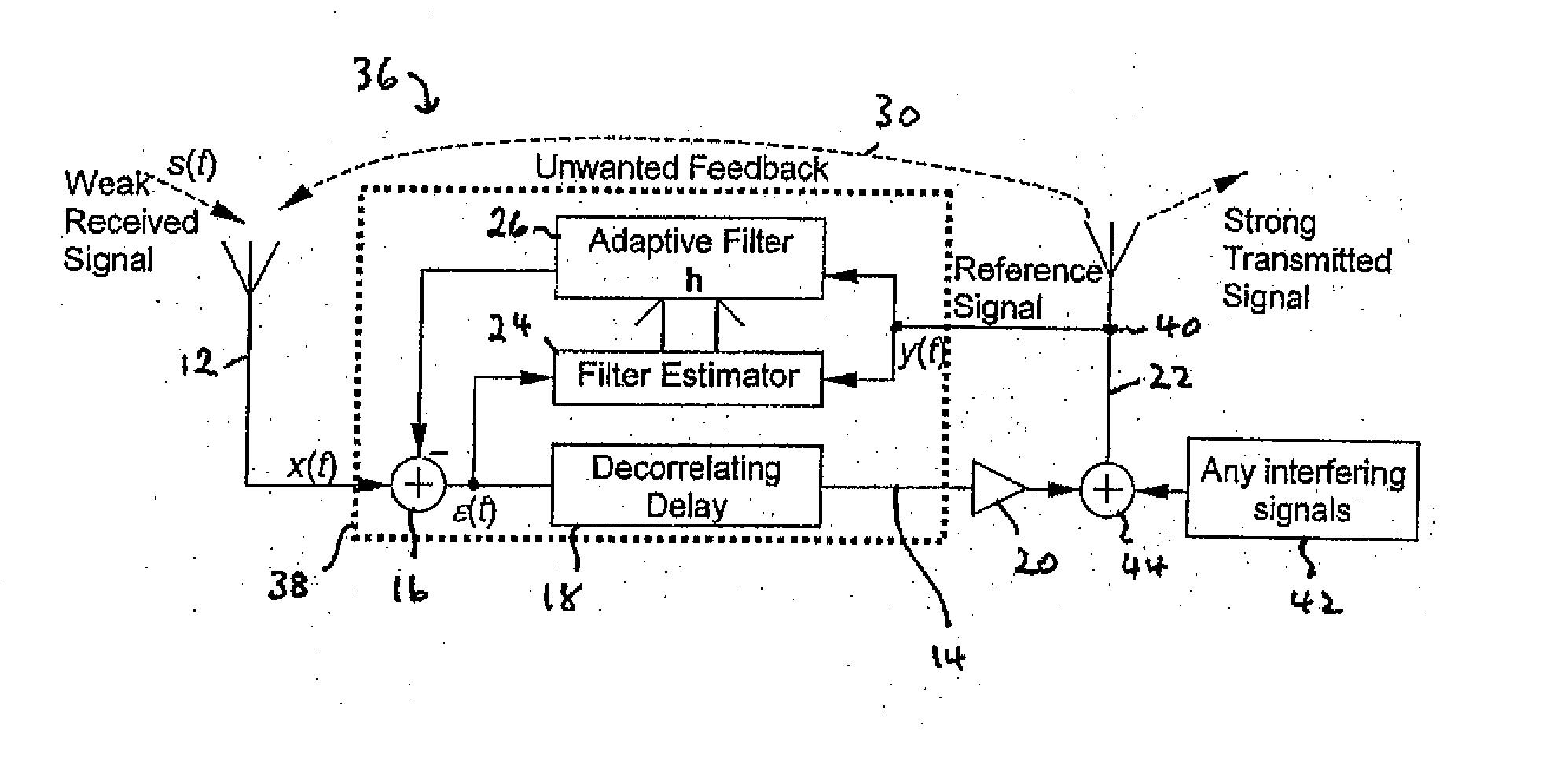

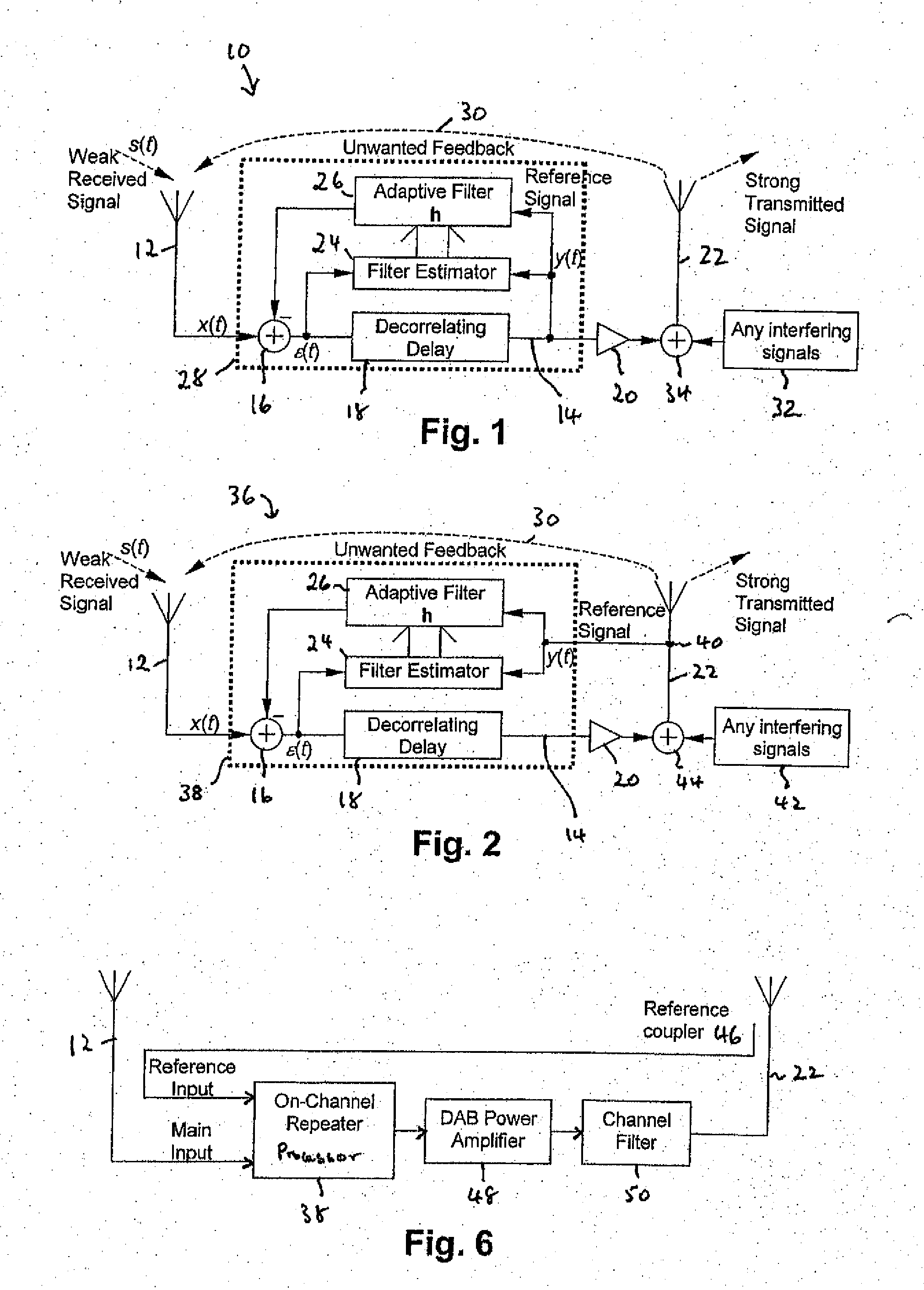

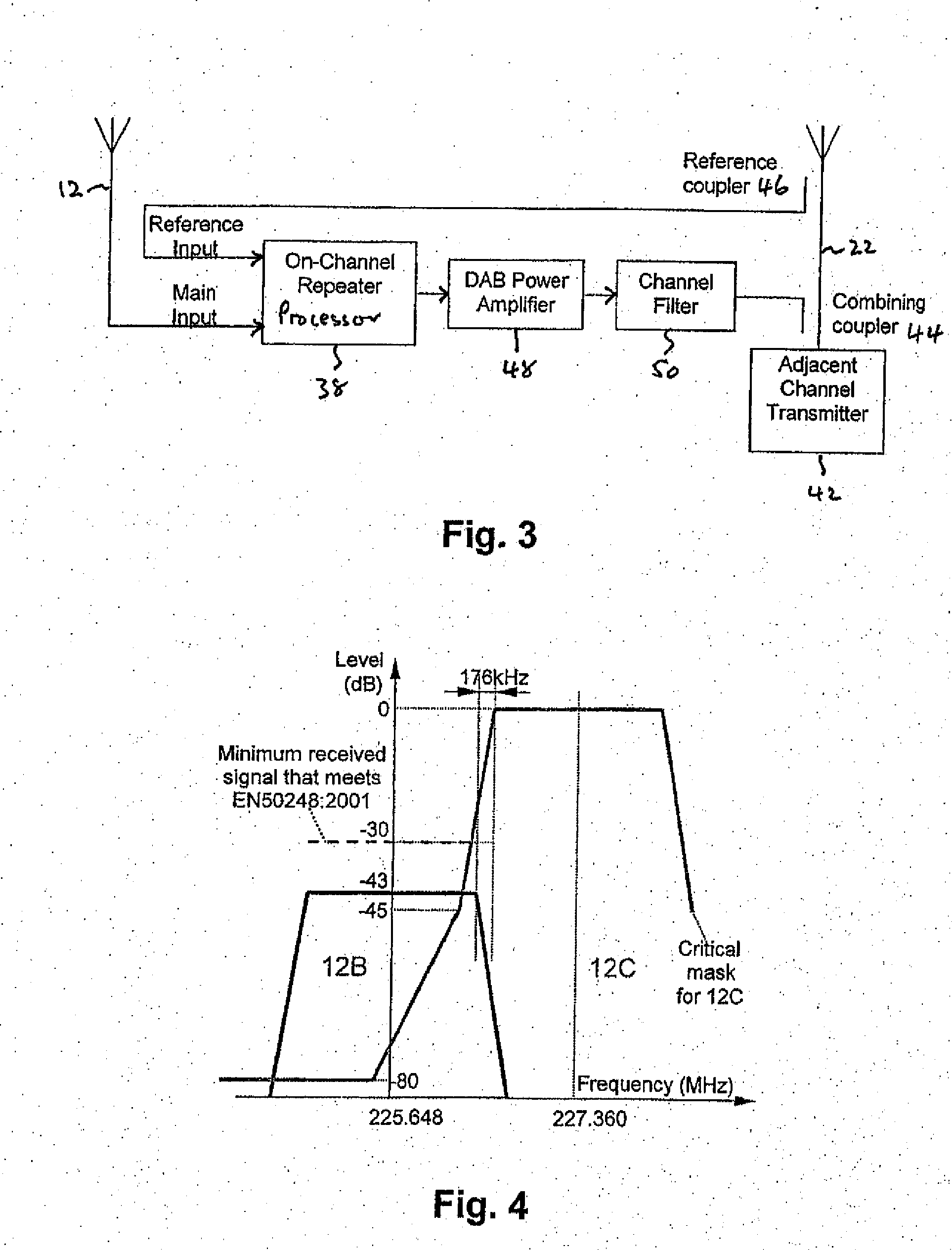

On-channel repeaters

ActiveUS20060264174A1Avoid instabilityPulse transformerRepeater/relay circuitsAudio power amplifierAdaptive filter

An on-channel repeater has a receiving antenna for receiving an RF signal and a transmitting antenna for transmitting on the same frequency as the input signal. An amplification path between the antennas provides substantially linear processing and includes a combiner, a decorrelating delay and a power amplifier. A filter estimator receives a reference signal and the combiner output and generates a plurality of control coefficients which are applied to an adaptive filter which filters the reference signal accordingly and applies its output to the combiner. The reference signal is derived not from the output of the decorrelating delay but rather from the output antenna after the power amplifier. Where there is an adjacent transmitter generating potentially interfering signals, the transmitter output is coupled to the same transmitter antenna.

Owner:BRITISH BROADCASTING CORP

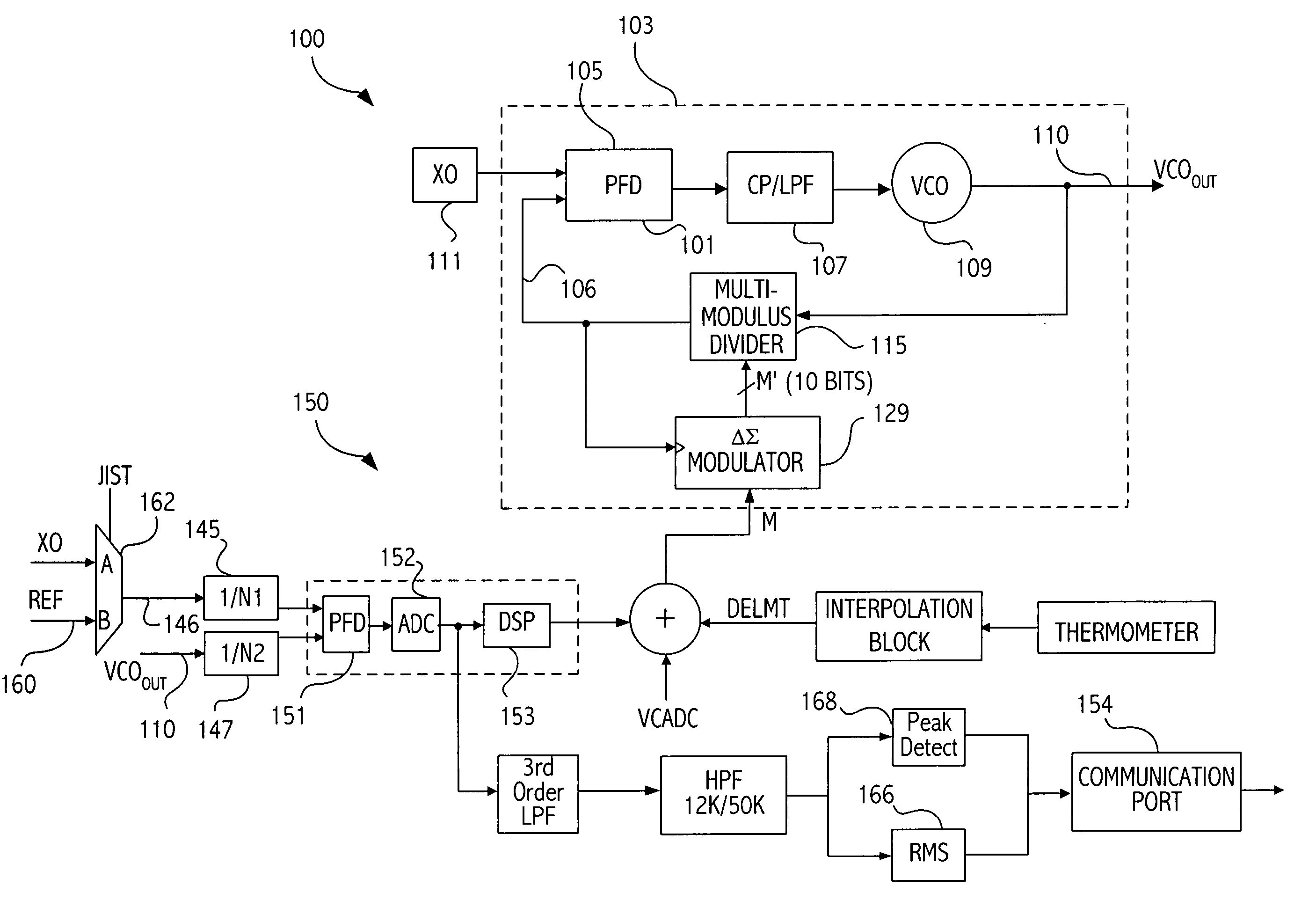

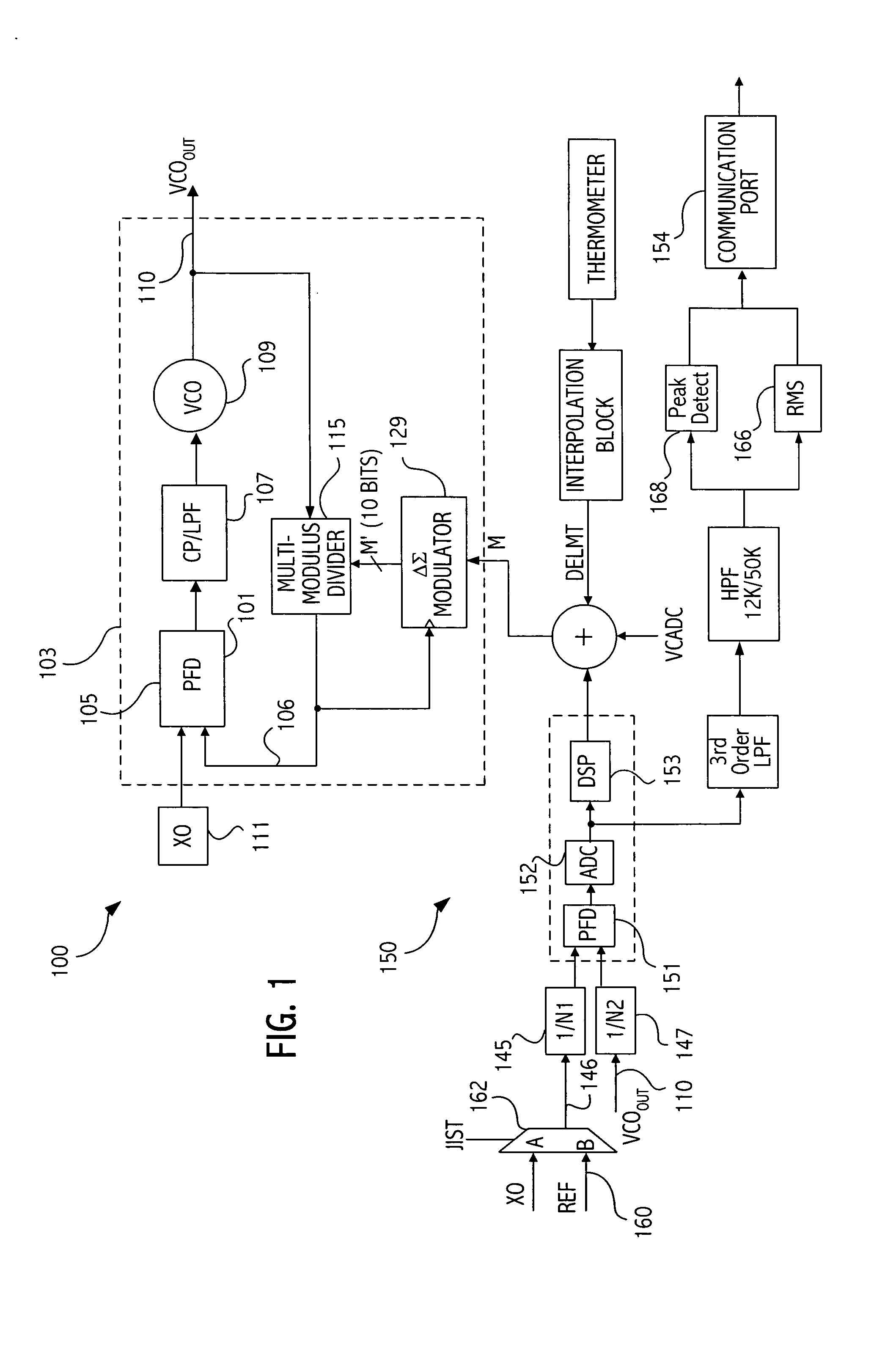

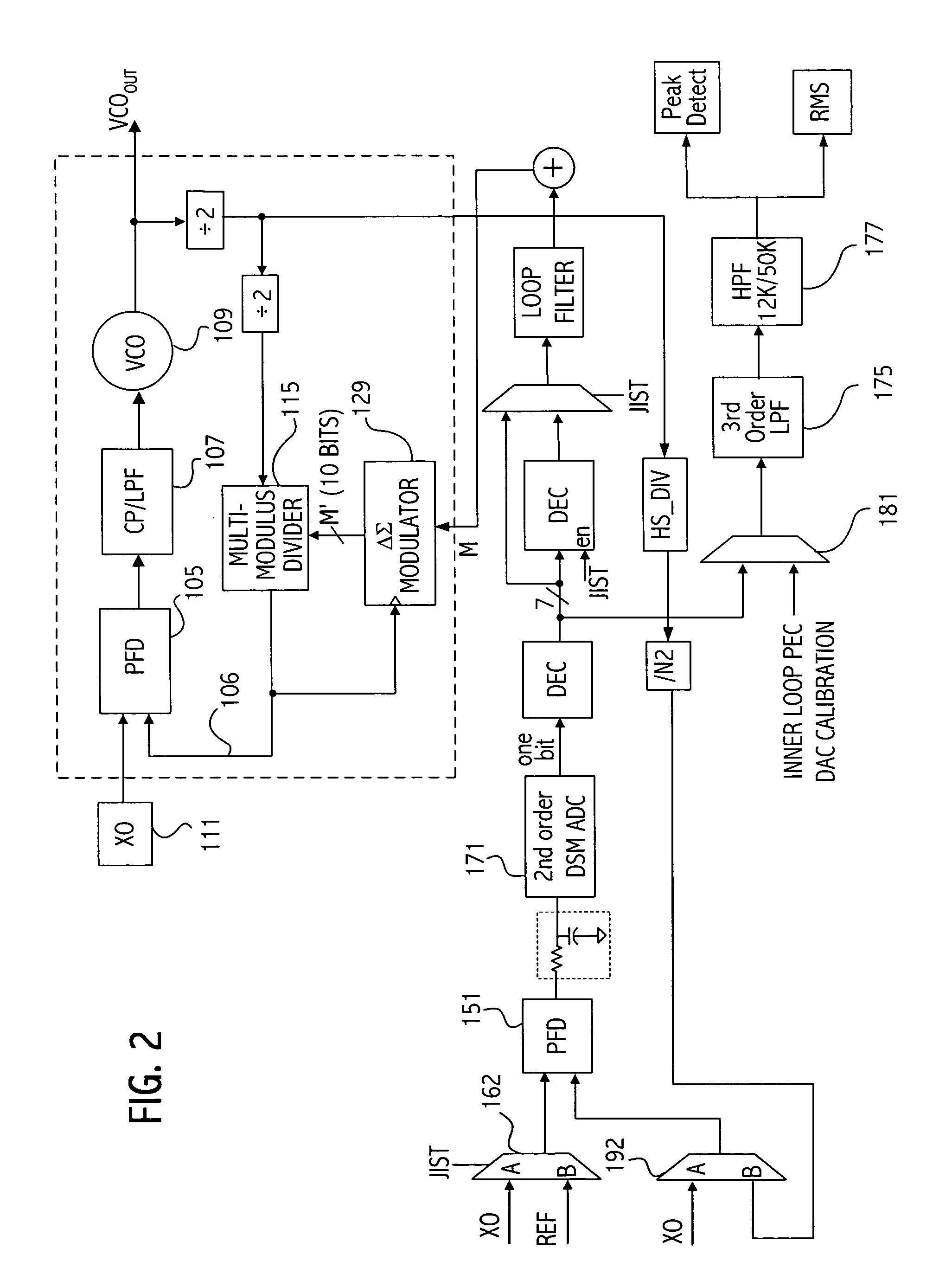

Jitter self test

Jitter is measured by receiving a first reference signal at a first phase-locked loop (PLL) circuit and generating at an output of the first phase-locked loop circuit an output signal based at least in part on the first reference signal, the output signal including a jitter component to be measured. A signal corresponding to the output signal and a signal corresponding to the first reference signal are compared in a phase detector of a second phase-locked loop circuit. A value corresponding to an output of the comparison is stored that includes information indicative of the measured jitter component.

Owner:SILICON LAB INC

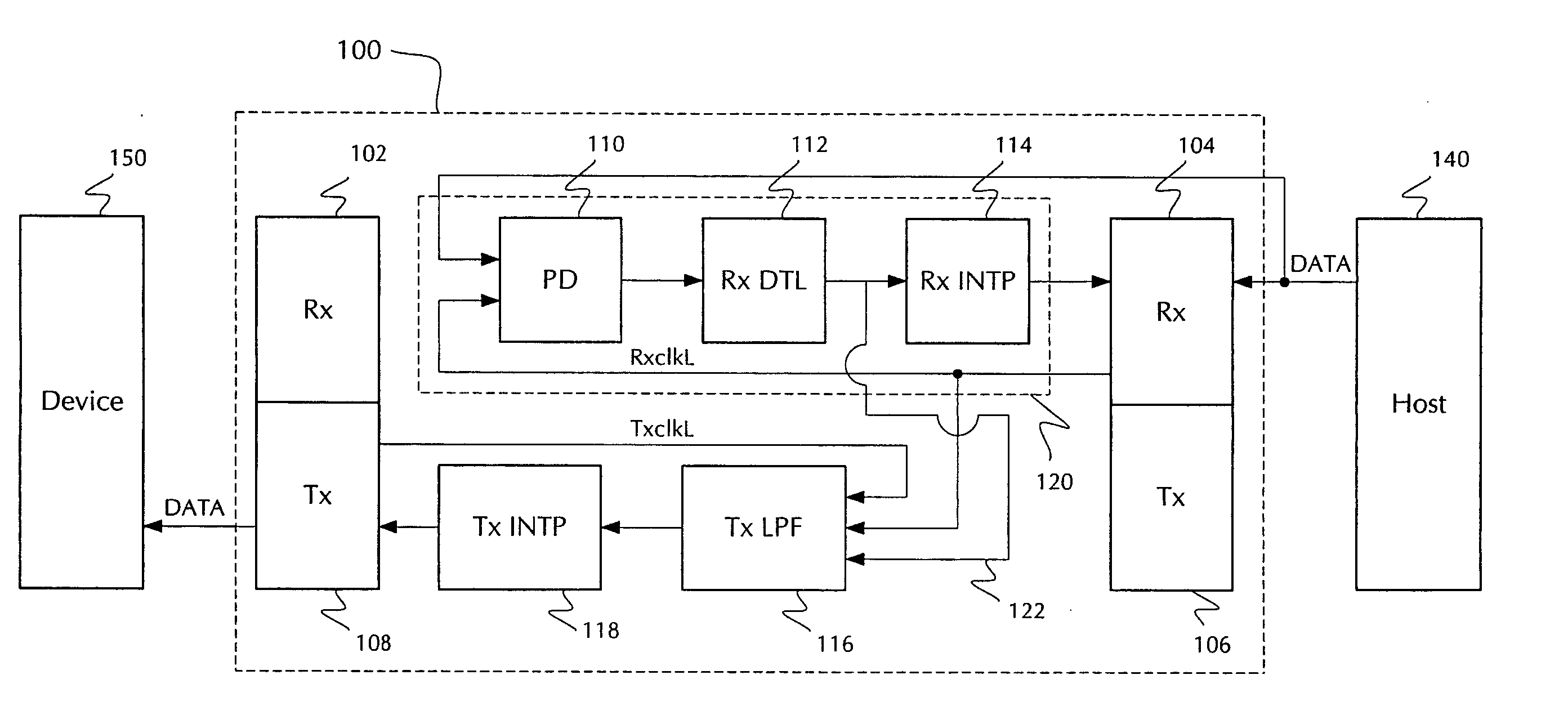

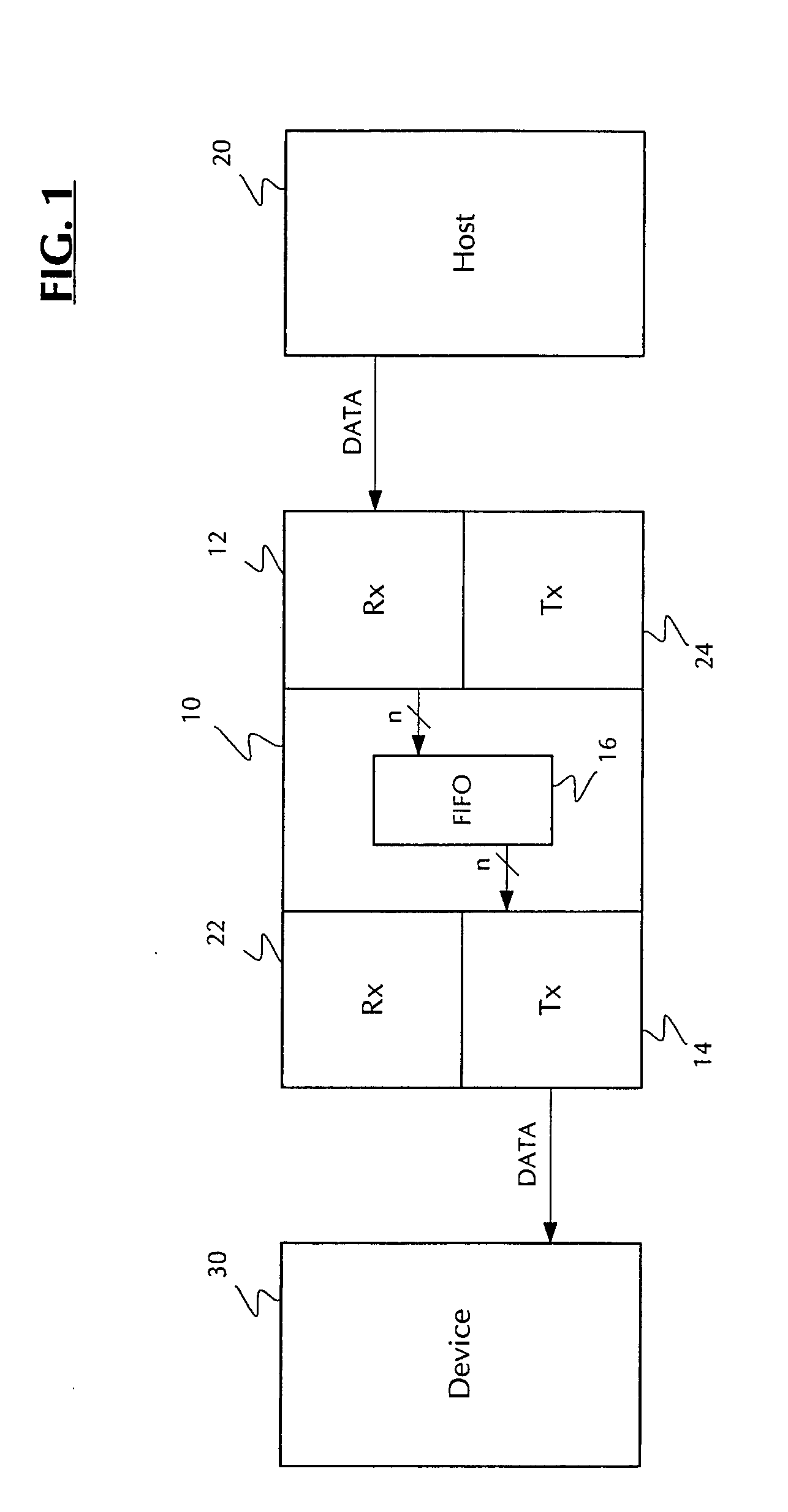

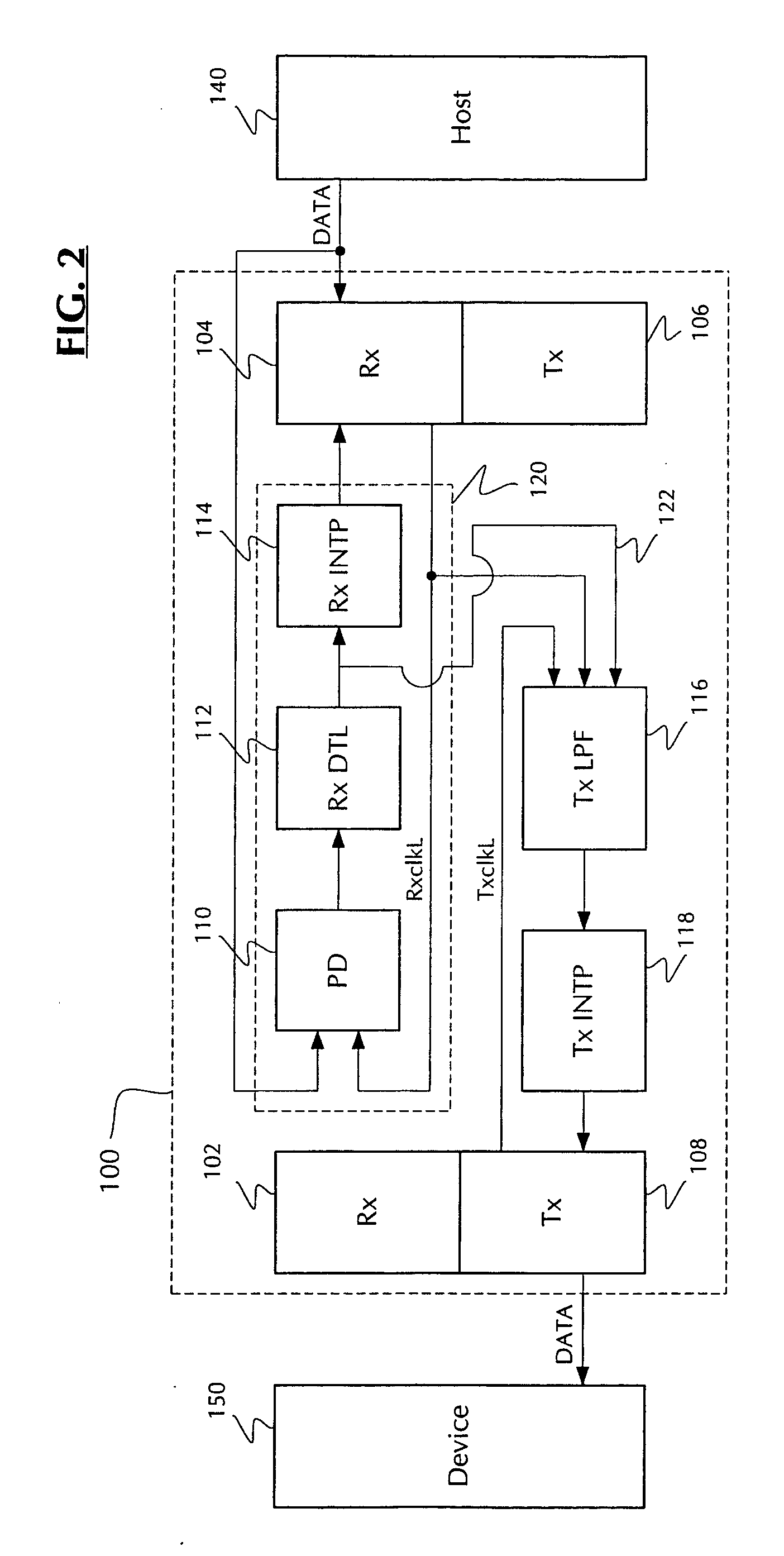

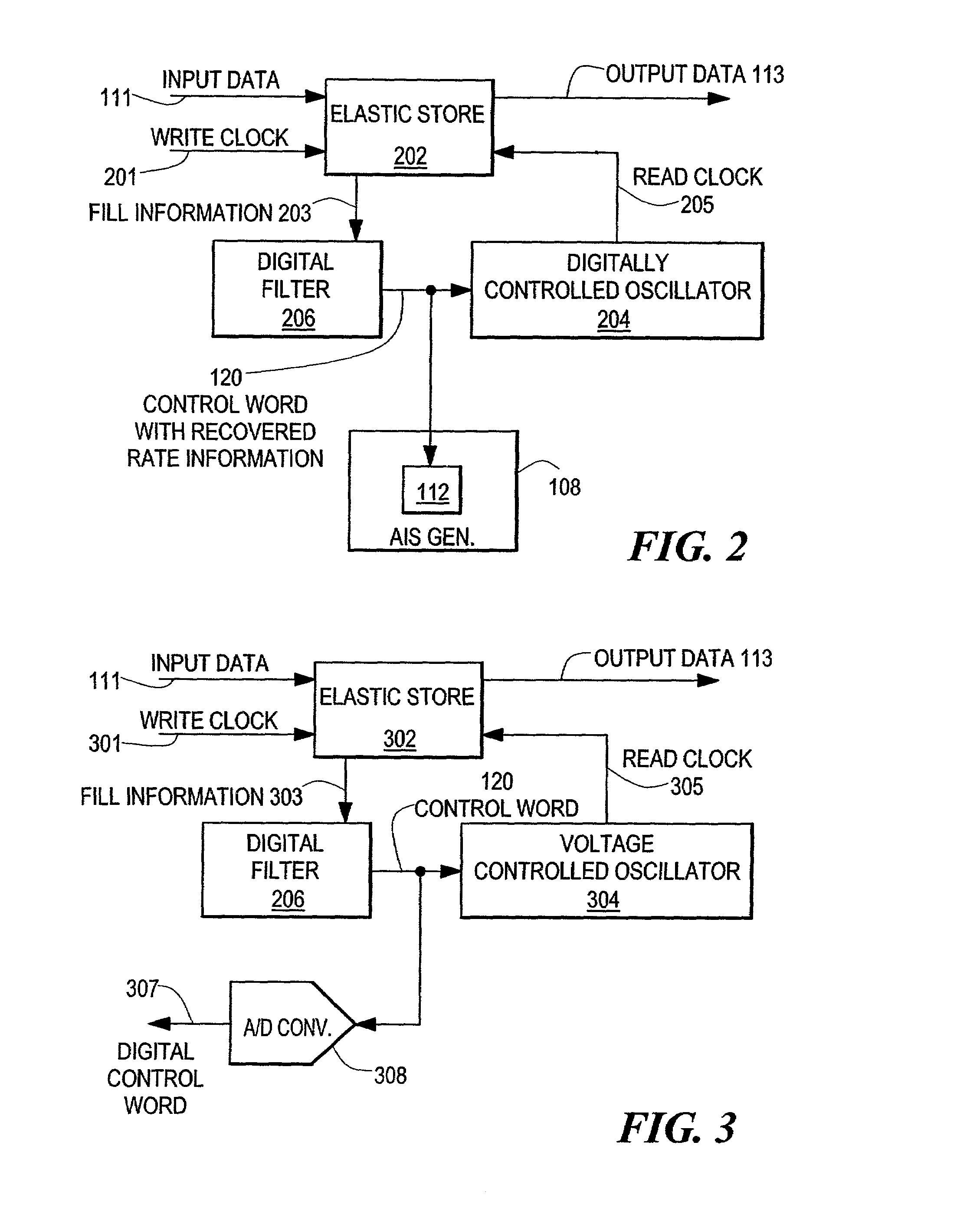

Architectures, circuits, systems and methods for reducing latency in data communications

ActiveUS20050034009A1Reduce in quantityReduce needPulse transformerError detection/correctionData streamTransceiver

Circuits, architectures, systems and methods for facilitating data communications and / or reducing latency in data communications. The architecture includes a clock recovery loop receiving data from a host device and providing a recovered clock signal, a filter circuit receiving recovered clock signal information and providing a control signal that adjusts the transmitter clock in response to recovered clock signal information and the two clock signals, and a transmitter receiving the control signal and transmitting data to a destination device in accordance with the transmitter clock. The circuitry generally includes a clock alignment block receiving first and second periodic signals and providing a control signal in response thereto, a filter for first periodic signal information, and a logic circuit configured to combine the control signal and the filtered information, thereby providing an adjustment signal for the second periodic signal. The systems generally relate to those that include the present architecture and / or circuit. The method generally includes determining a phase difference between first and second periodic signals, one of the periodic signals being recovered from a data stream; adjusting the other periodic signal in response to the phase difference and filtered information from the recovered periodic signal; and transmitting the data stream in accordance with said adjusted periodic signal. The present invention advantageously eliminates a FIFO memory in the data path, thereby reducing transceiver latency and improving system performance.

Owner:MARVELL ASIA PTE LTD

Transmission canceller for wireless local area network

ActiveUS20060240769A1Improve performanceIncrease the areaPulse transformerFrequency-division multiplex detailsTransceiverRepeater

A frequency translating repeater (200) for use in a wireless local area network includes a cancellation unit. Canceller (402) is controlled by control (401) to provide an injection signal for canceling leakage in a receive signal path. Reference coupler (403) provides a reference signal from the transmit signal, injection coupler (404) injects a correction signal, and sample coupler (405) provides a sample for feedback. A processor (510) receives the sample signal through a detector (415). Although the present invention is intended for a frequency translating repeater, it has broad applications in radio transceivers in general. One specific application is with frequency division duplex (FDD) handsets or base stations utilizing CDMA technologies such as W-CDMA and IS-2000 or 1XEV-DV / DO.

Owner:QUALCOMM INC

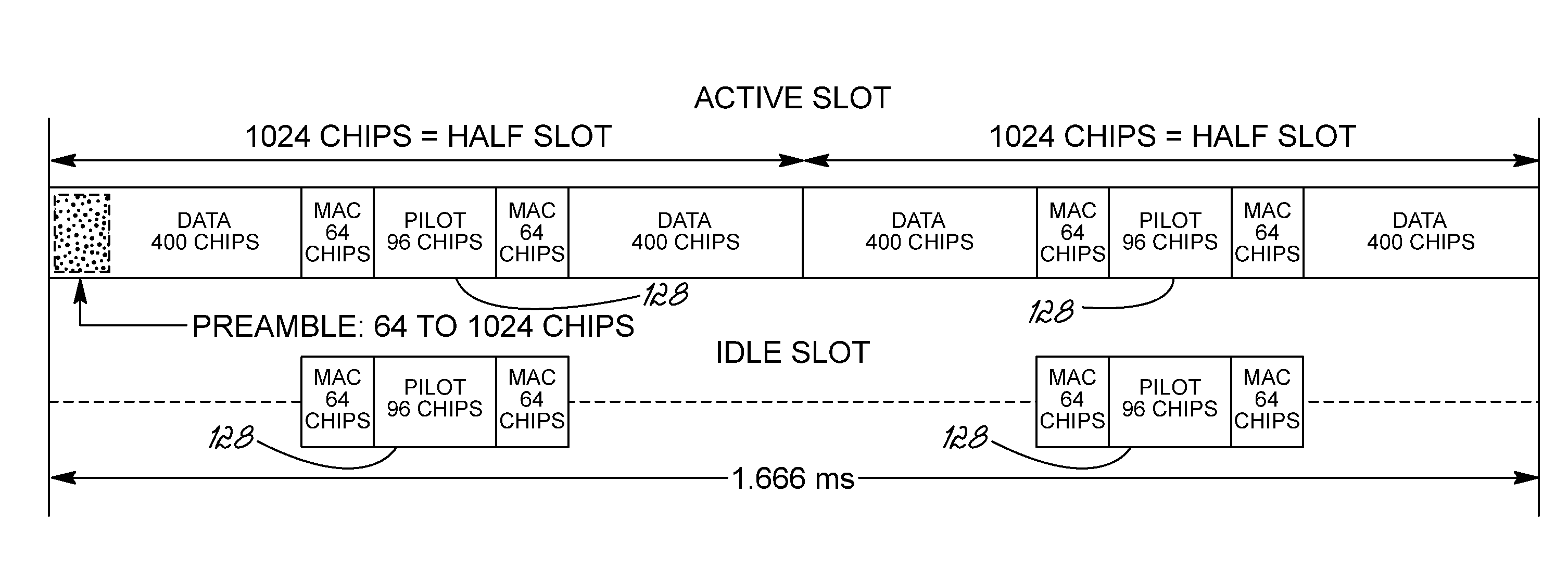

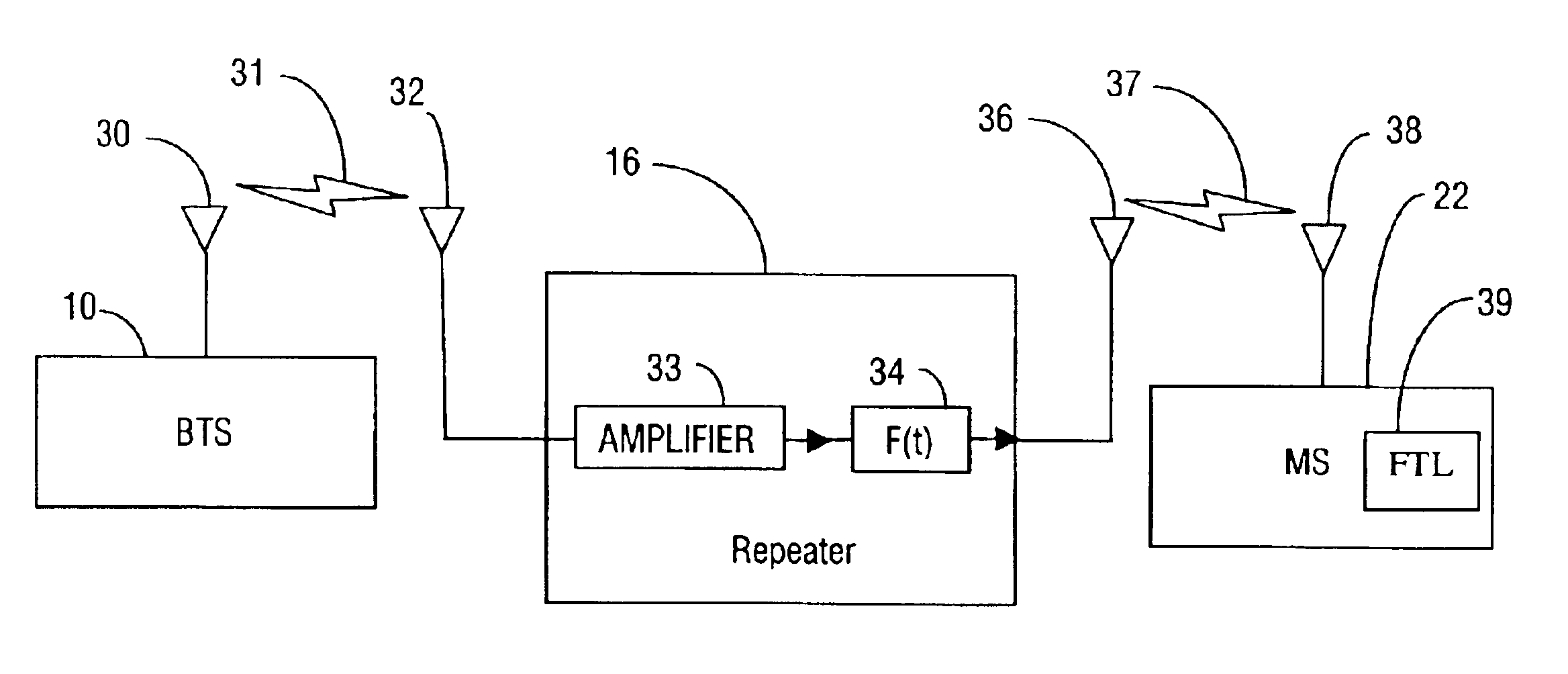

Forward link repeater frequency watermarking scheme

ActiveUS6961367B2Shorten repair timeMinimal impactRepeater/relay circuitsActive radio relay systemsMobile stationFrequency modulation

A forward link repeater frequency watermarking (FLRFWM) system and method that enable accurate position location of mobile stations in areas where repeaters are present by watermarking repeated signals with repeater information. A repeater watermarks a forward link signal with a (unique or non-unique) fast frequency modulation waveform watermark every time a signal passes through the repeater. A mobile station detects and / or identifies the fast frequency watermark on the forward link signal to determine repeater information that aids the network position determination entity or mobile station position location system in determining position location using AFLT and / or A-GPS systems. A forward link fast frequency watermarking system described herein achieves minimal impact on FL, AFLT, and GPS performance, good detection, identification and false alarm probabilities, short time-to-detect / identify, and good detection / identification sensitivity.

Owner:QUALCOMM INC

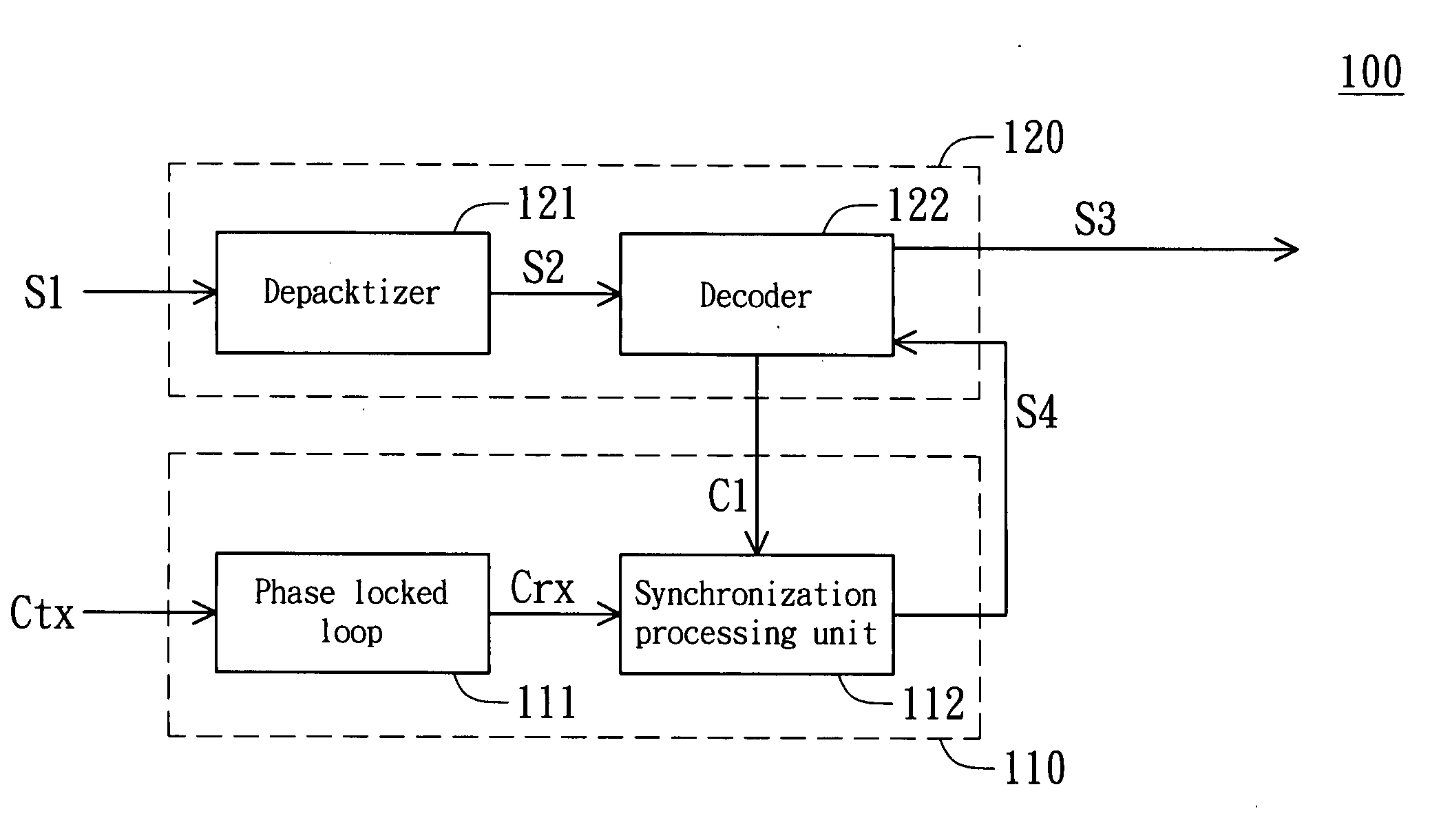

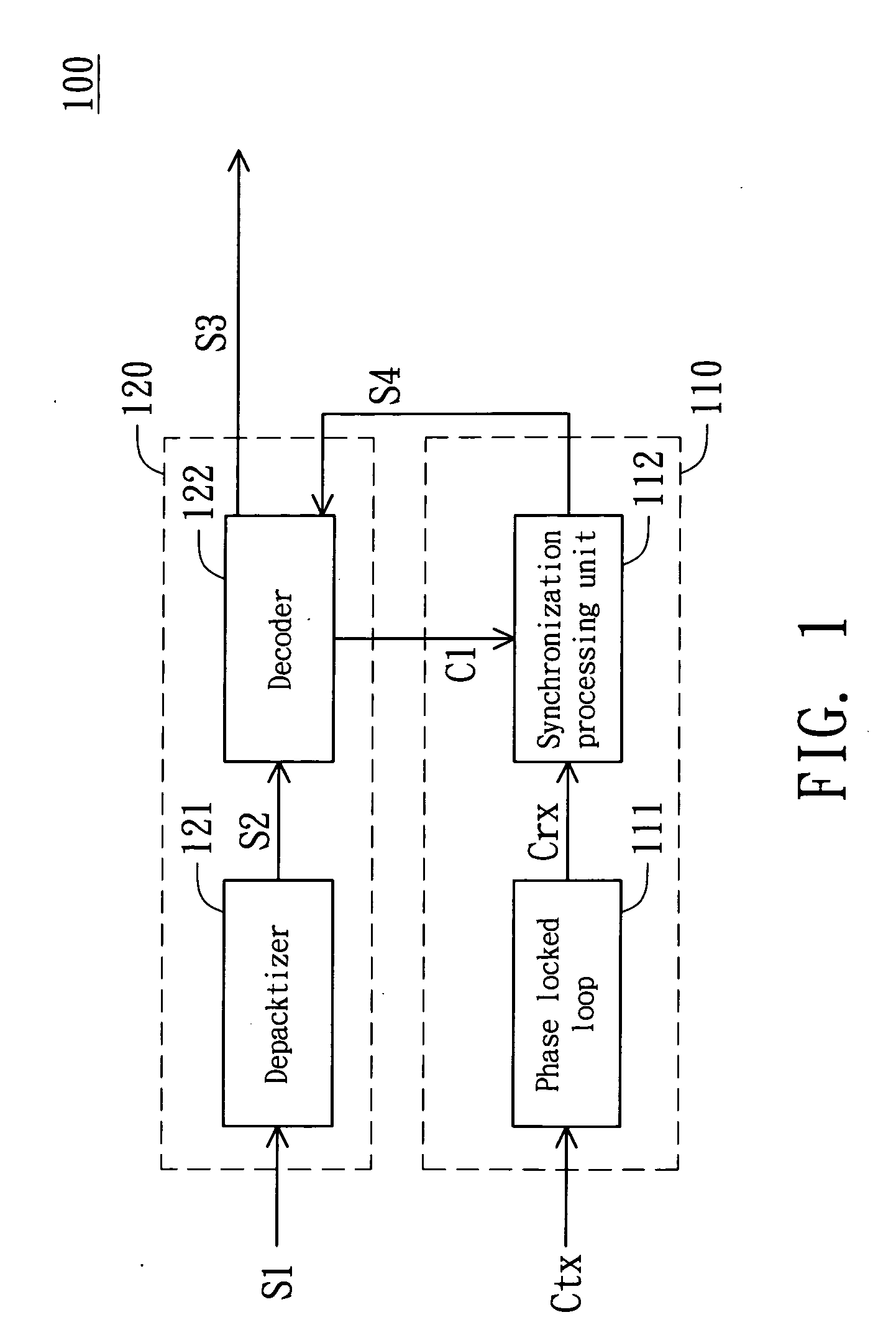

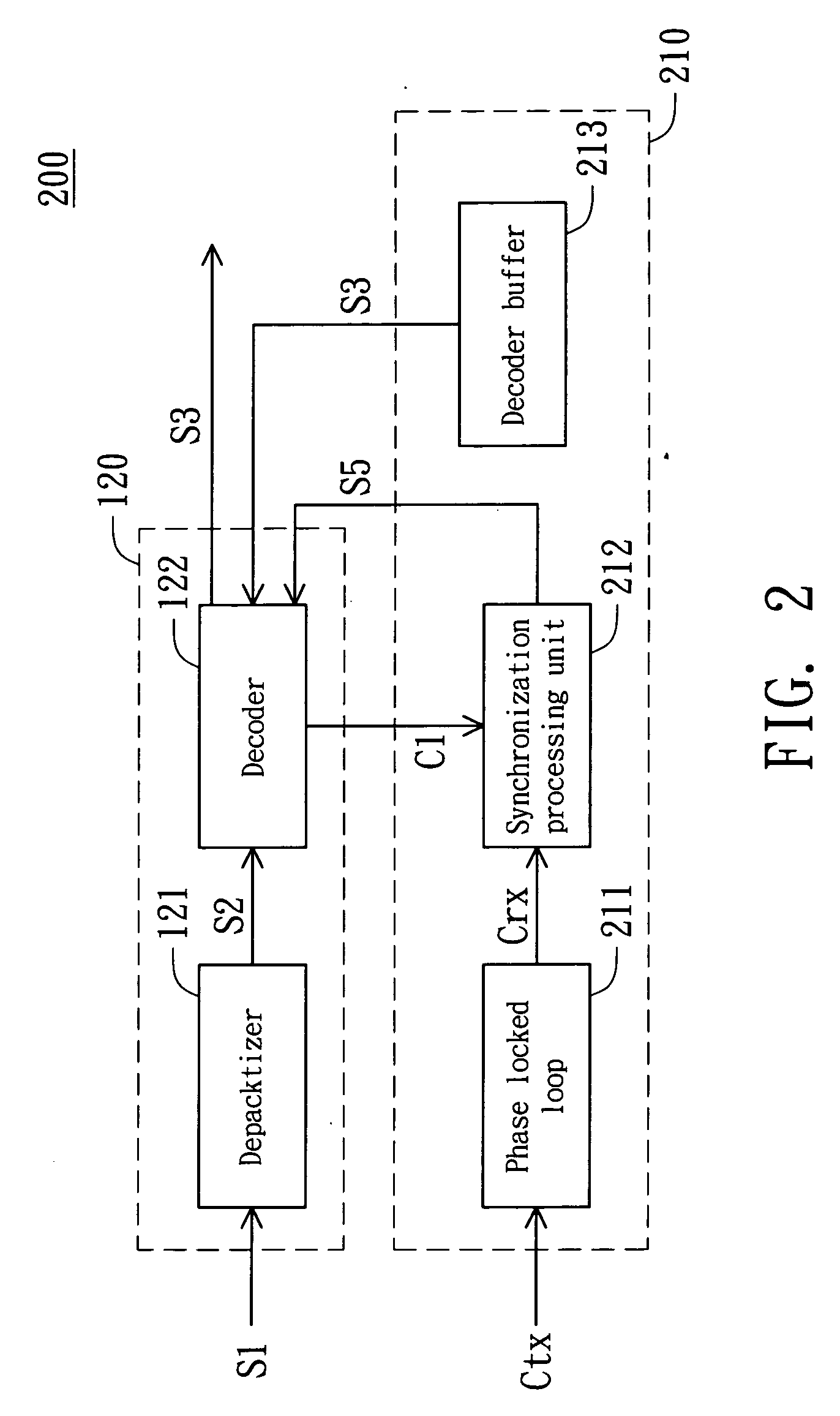

Timing synchronization module and method for synchronously playing a media signal

The timing synchronization module includes a phase locked loop (PLL) and a synchronization processing unit. The PLL receives an output-end clock signal. When the PLL receives the output-end clock signal for the first time, the PLL generates a reception-end clock signal according to the output-end clock signal. The synchronization processing unit receives a procedure clock signal and the reception-end clock signal. The output-end clock signal has M clocks after the reception-end clock signal is generated, while the reception-end clock signal has N clocks as generated. When the difference value of M and N is larger than a preset value, the synchronization processing unit removes the media signal corresponding to the procedure clock signal and generates the reception-end clock signal again. When the difference value is smaller than the preset value, the synchronization processing unit controls media signal playing according to the reception-end clock signal and the procedure clock signal.

Owner:QUISDA CORP

High speed interface apparatus

The present invention discloses a much higher speed interface apparatus which comprises a data driving means for decoding two-bit data signals using them as inputs to output four-level data signals; a reference voltage generating means for generating three-level reference voltages to discriminate the voltage levels of the four-level data signals; and a receiver means for comparing the four-level data signals and the three-level reference voltage signals using them as inputs and for encoding the resulting signals to output two data signals.

Owner:HYUNDAI ELECTRONICS IND CO LTD

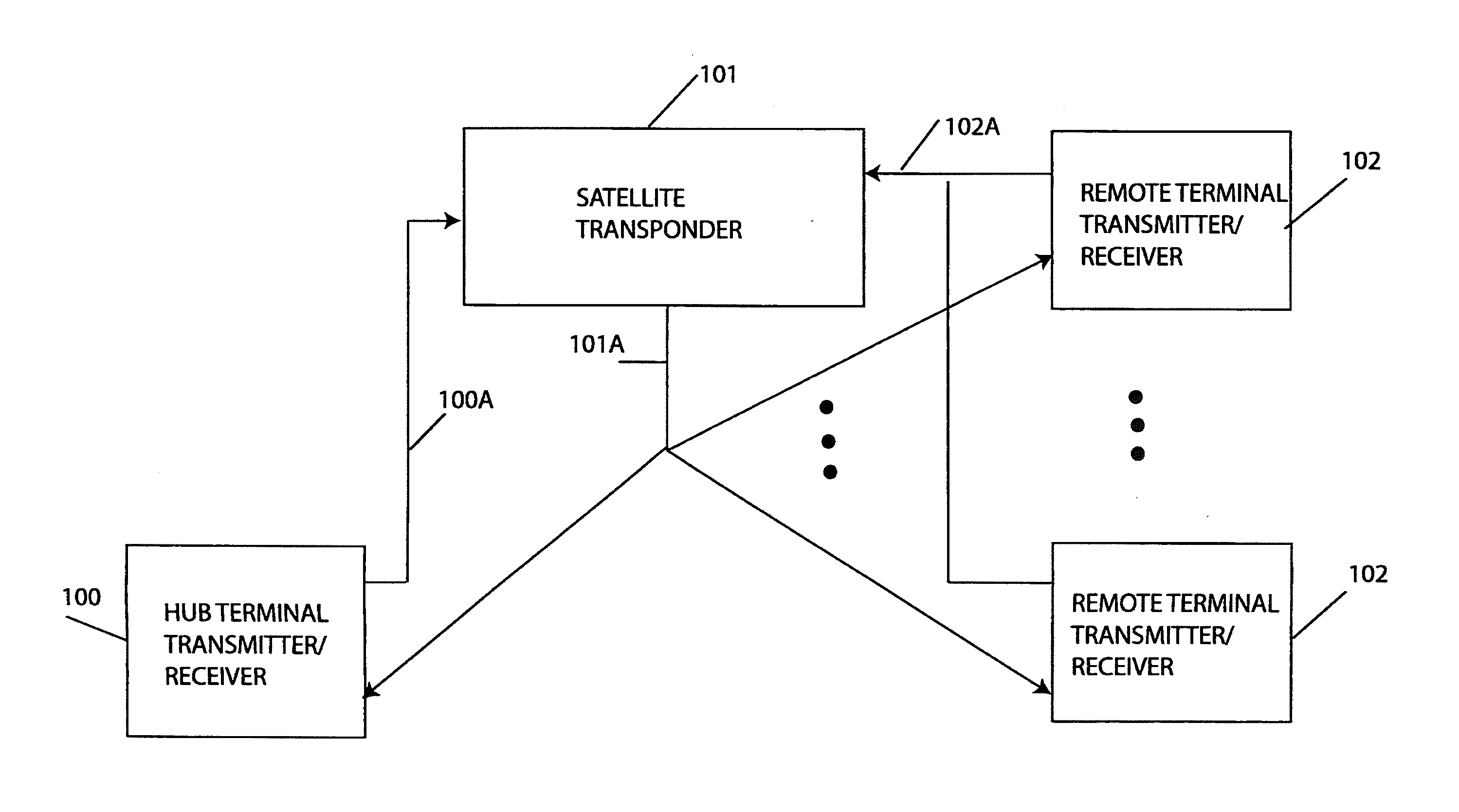

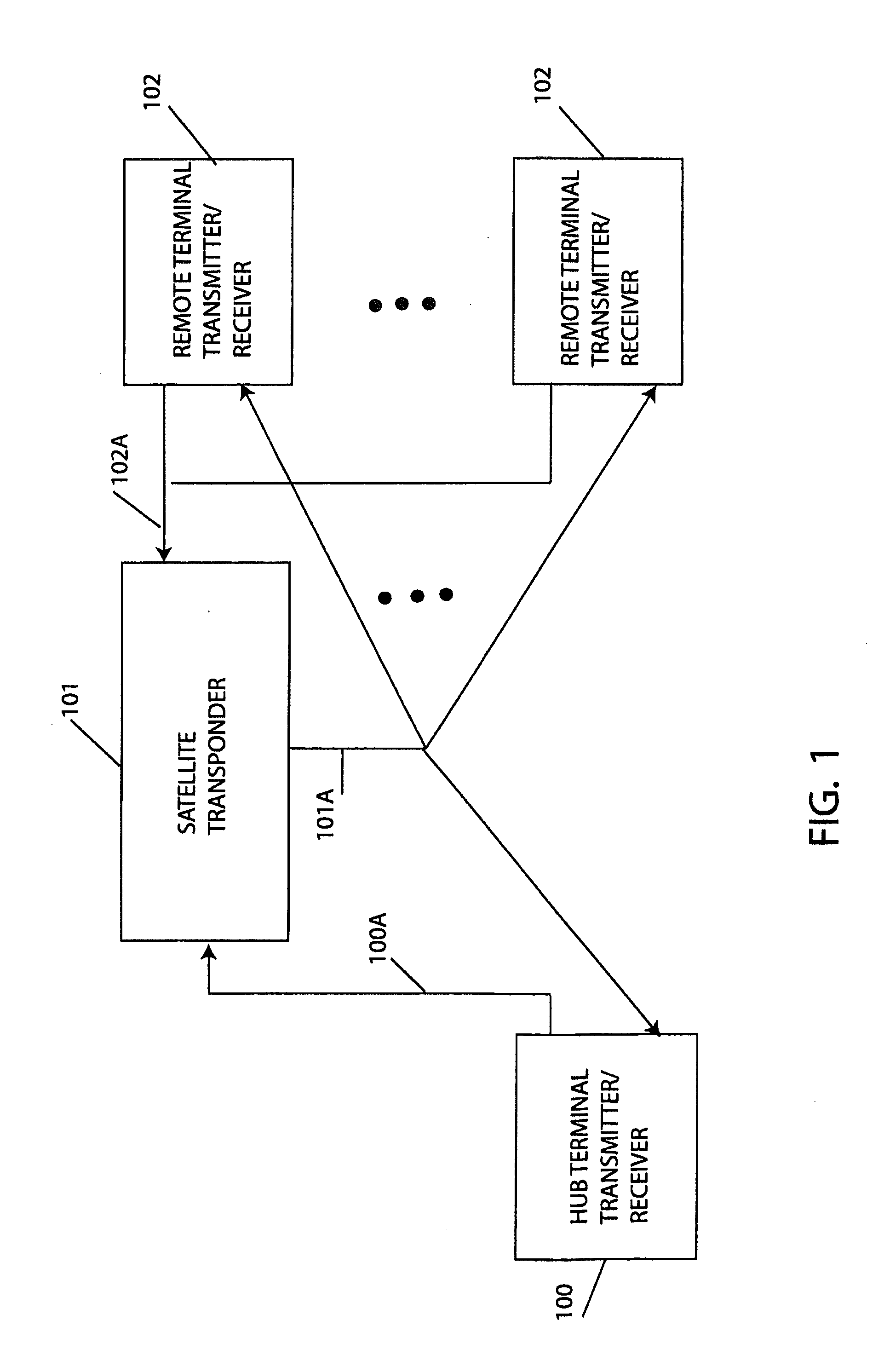

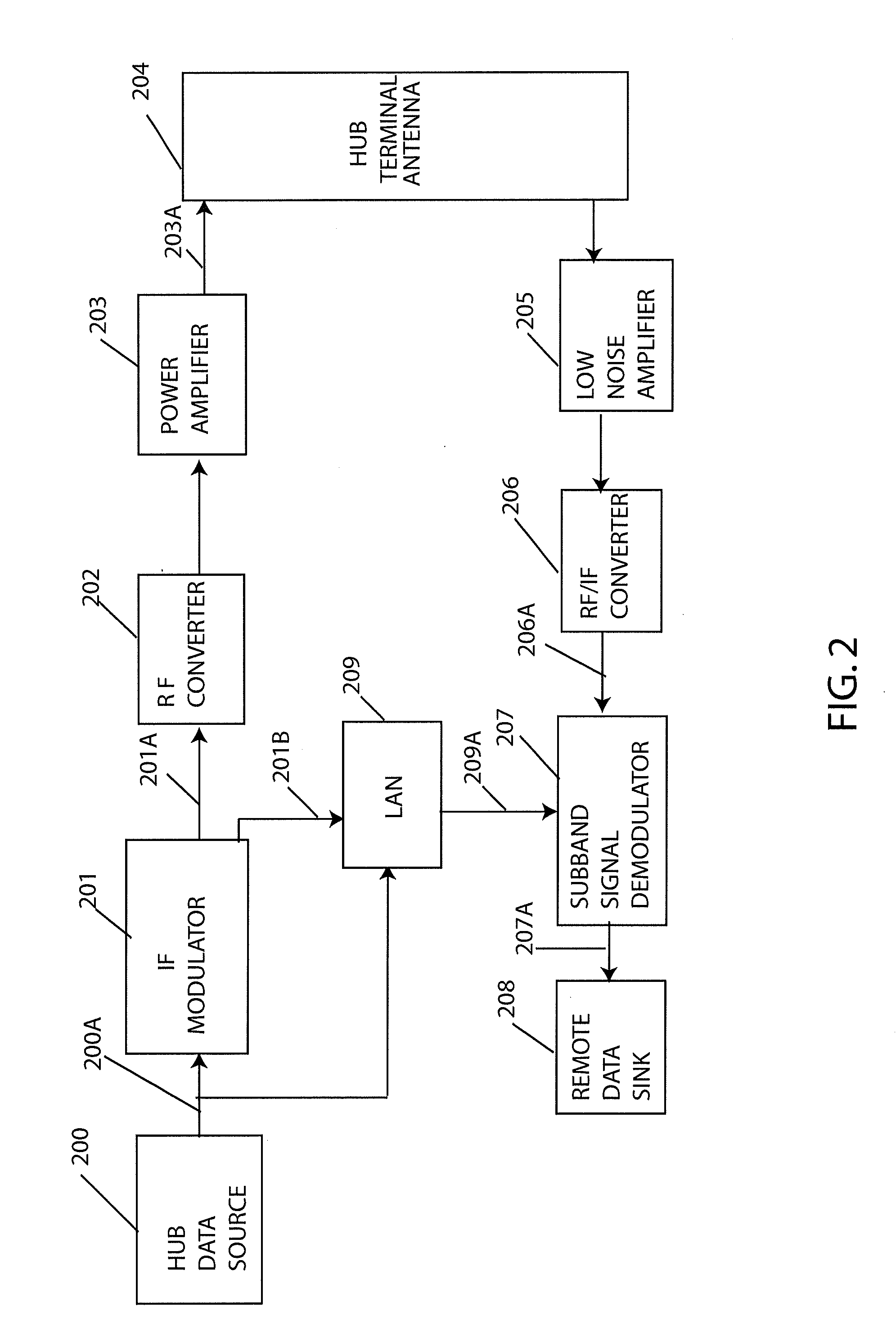

Method and apparatus for subband signal demodulation in a transponder satellite communication link containing a component of relayed interference

ActiveUS20110299572A1Large cancellation factorMaximal cancellationMultiple-port networksFrequency/rate-modulated pulse demodulationDigital dataPhase noise

A method and apparatus at a local terminal are described for demodulating a remote-terminal signal located at a subband offset frequency in a frequency subband of relayed interference from a transponder satellite link. The demodulation of the remote-terminal signal is accomplished by transferring the digital data that produced the local-terminal transmit signal to the local-terminal receiver. The digital data is time-delayed and converted to a narrowband offset-constellation signal that cancels the relayed interference in an adaptive equalizer. Providing cancellation in the subband of the relayed interference produces larger interference cancellation factors than those obtained in conventional broadband cancellation systems. A phase-noise error signal is also generated and used to increase cancellation levels limited by phase noise generated in the satellite link frequency converters. Additionally the receiver converter frequencies are chosen such that errors in estimating the subband offset frequency do not affect cancellation in the adaptive equalizer.

Owner:DATUM SYST

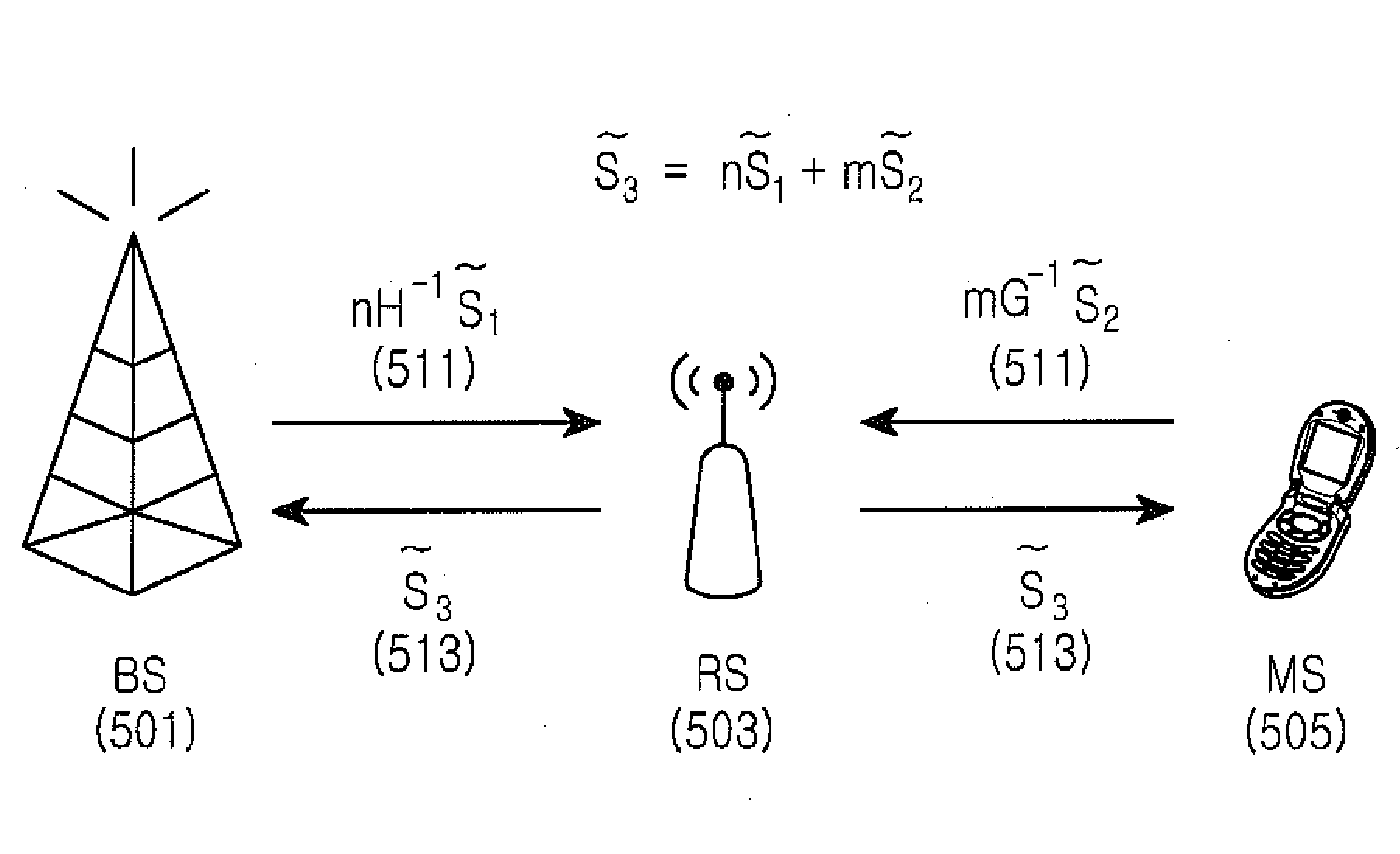

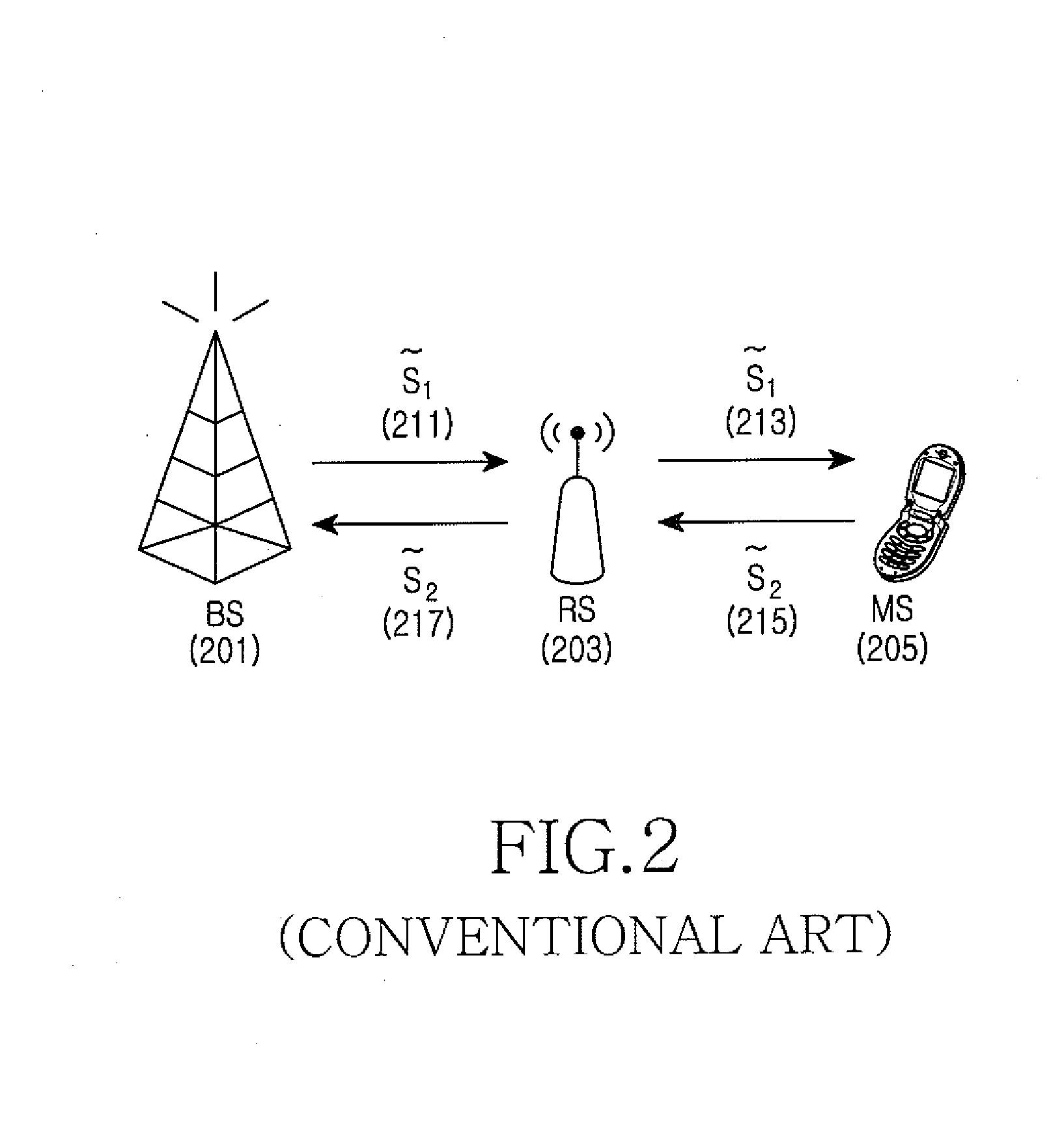

Apparatus and method for relaying in a wireless communication system

ActiveUS20080125032A1Increase system capacityFrequency-division multiplex detailsRepeater/relay circuitsPrecodingCommunications system

An apparatus and method for supporting relaying in a wireless communication system are provided. The apparatus and method include a transmitting apparatus which acquires channel information between the transmitting apparatus and an RS, pre-encodes a transmission signal to be transmitted to the RS with the channel information, transmits the pre-coded signal to the RS, and acquires, upon receipt of a signal from the RS, a signal transmitted by a receiving apparatus by eliminating the transmission signal transmitted to the RS from the received signal. Accordingly, the apparatus and method improve system capacity gain without adding time resources.

Owner:SAMSUNG ELECTRONICS CO LTD +1

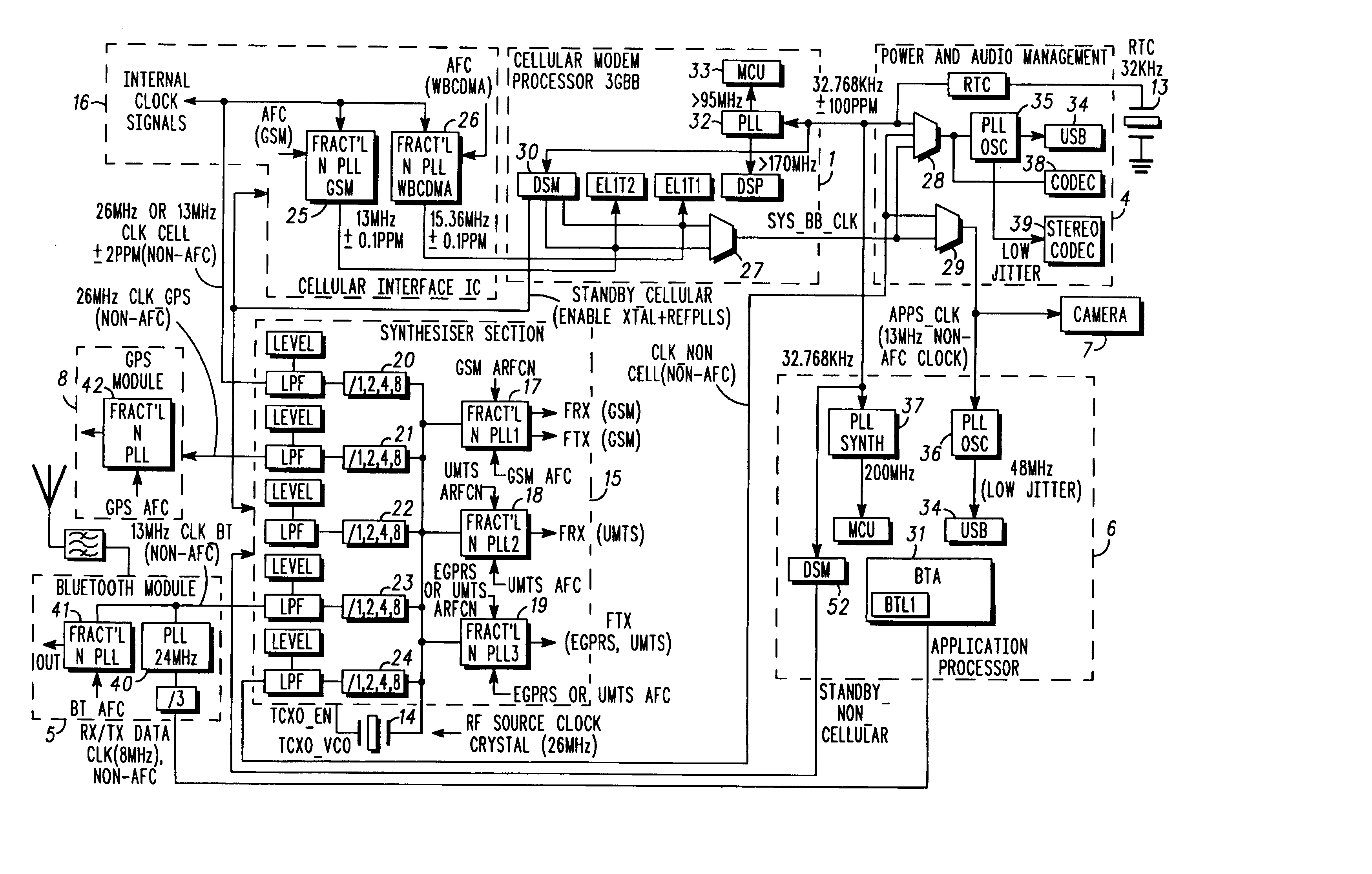

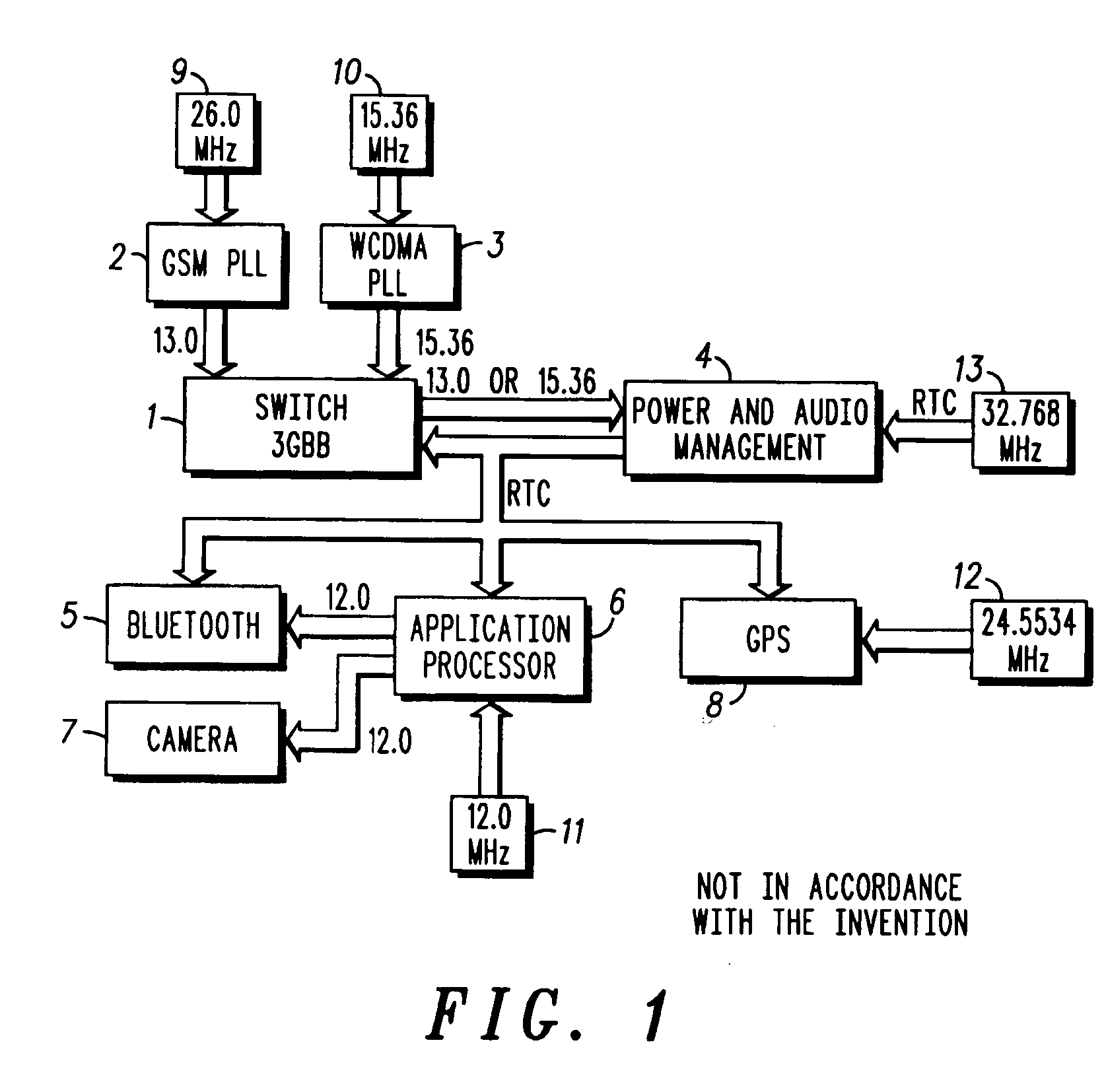

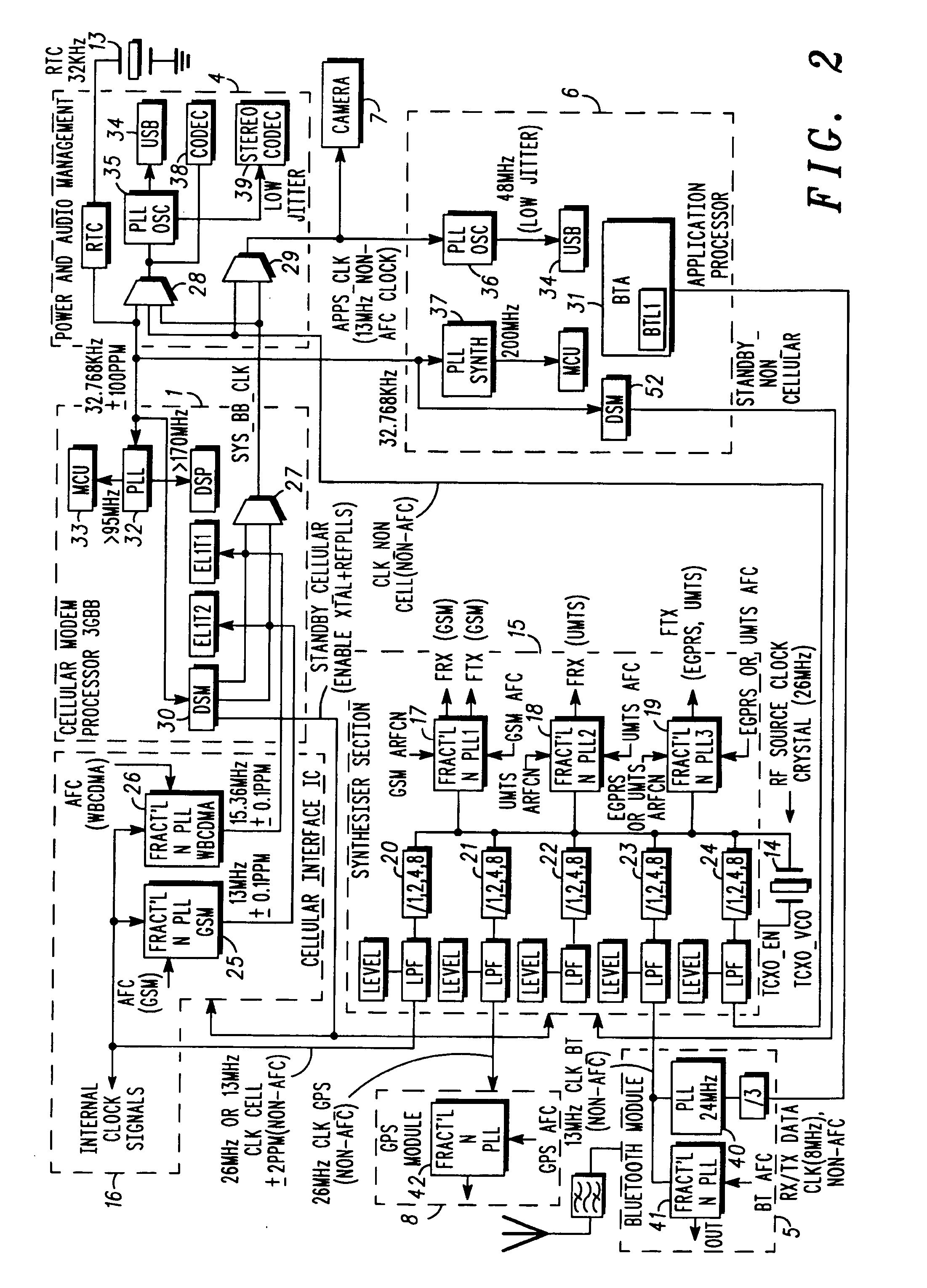

Apparatus for generating multiple clock signals of different frequency characteristics

InactiveUS20050042996A1Automatic scanning with simultaneous frequency displayPulse transformerClock rateComputer module

A terminal includes at least one wireless communication application module (1) and a plurality of further application modules (4, 5, 6, 8). Multiple radio frequency clock signals are generated for the different modules having respective clock frequency characteristics and including at least first and second clock frequencies that are not integral multiples nor sub-multiples of each other nor of a third frequency. The clock generation comprises reference frequency means (14), fractional-N phase-locked loop frequency synthesizer means (15) responsive to the reference frequency means, and different automatic frequency control means for adjusting clock frequencies relative to received signals. The reference frequency means (14) is arranged to supply a common reference frequency signal to a plurality of the fractional-N phase-locked loop frequency synthesizer means (17, 18, 19, 25, 26, 41,42) that supply the first and second clock frequencies respectively for the application modules. Selective activation means (30,52) selectively activates and de-activates the phase lock loop means as required by the corresponding application module or modules.

Owner:APPLE INC +1

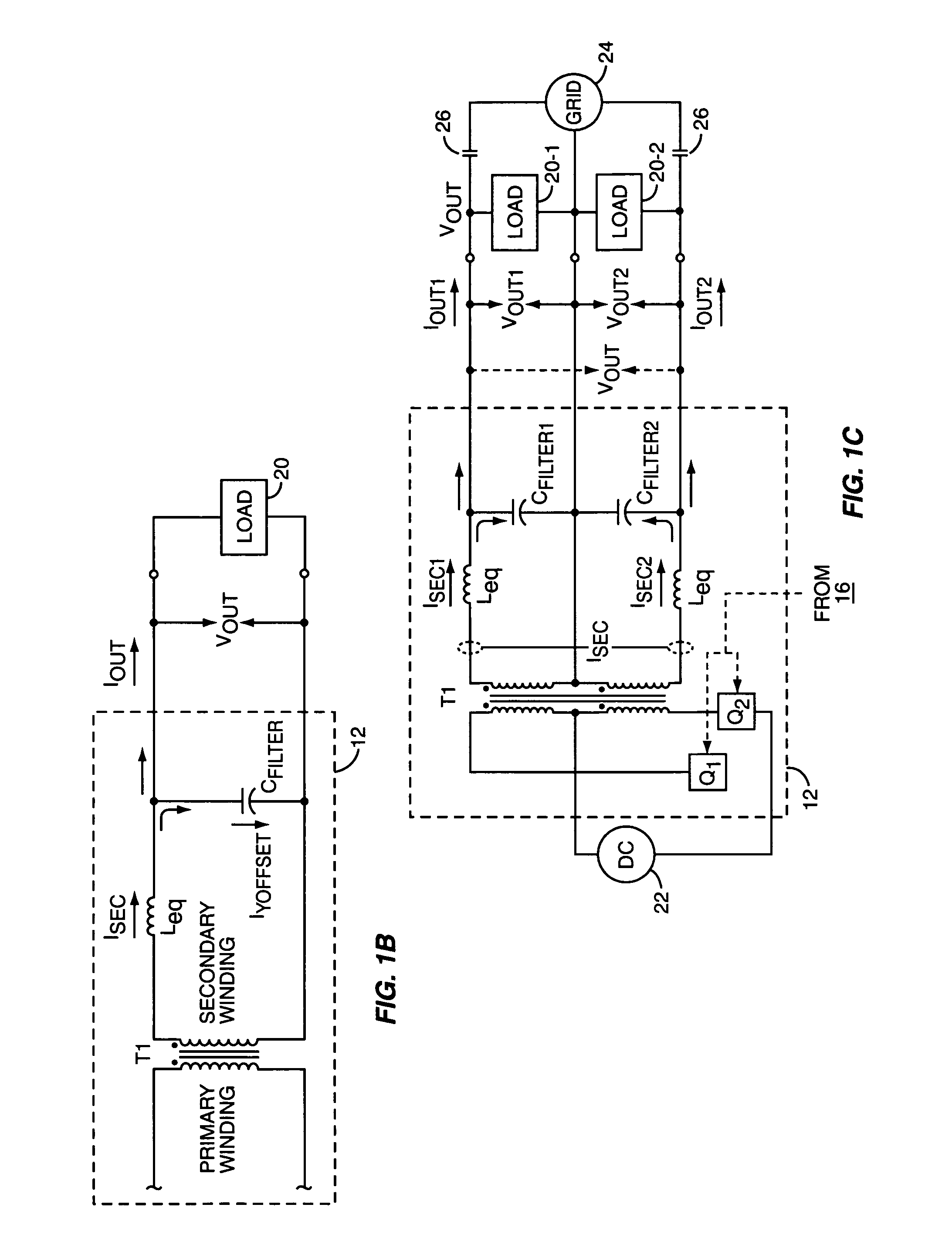

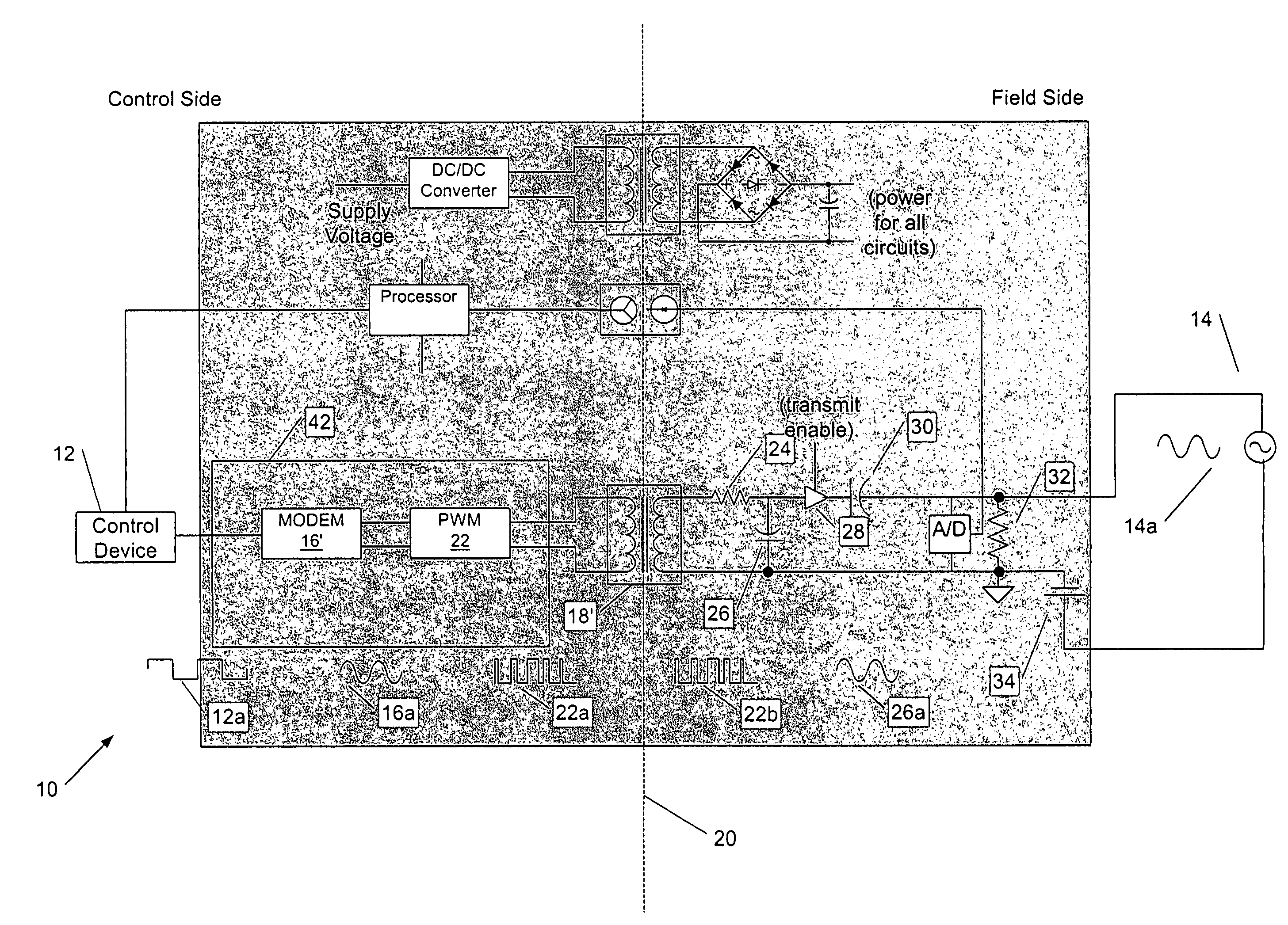

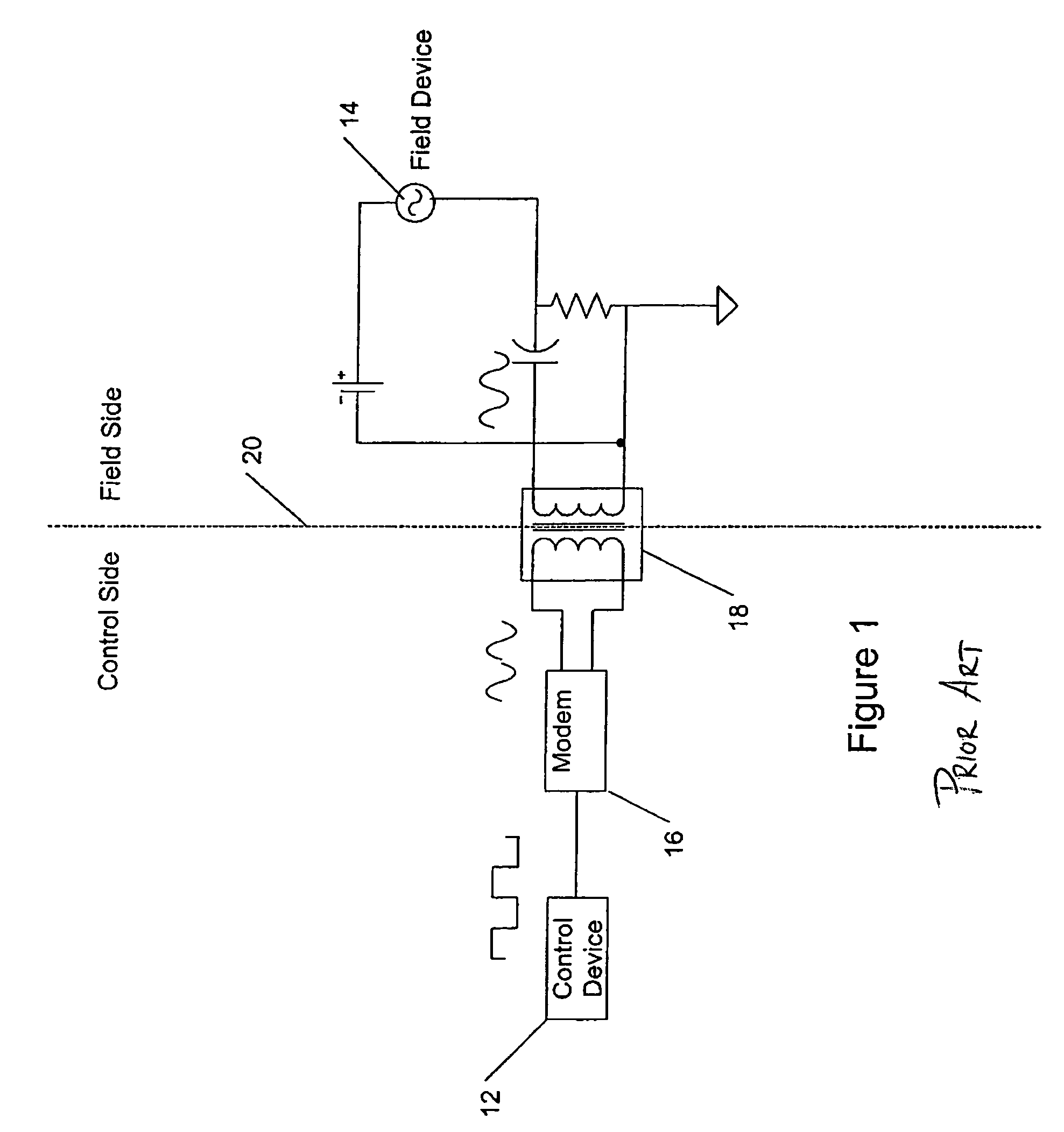

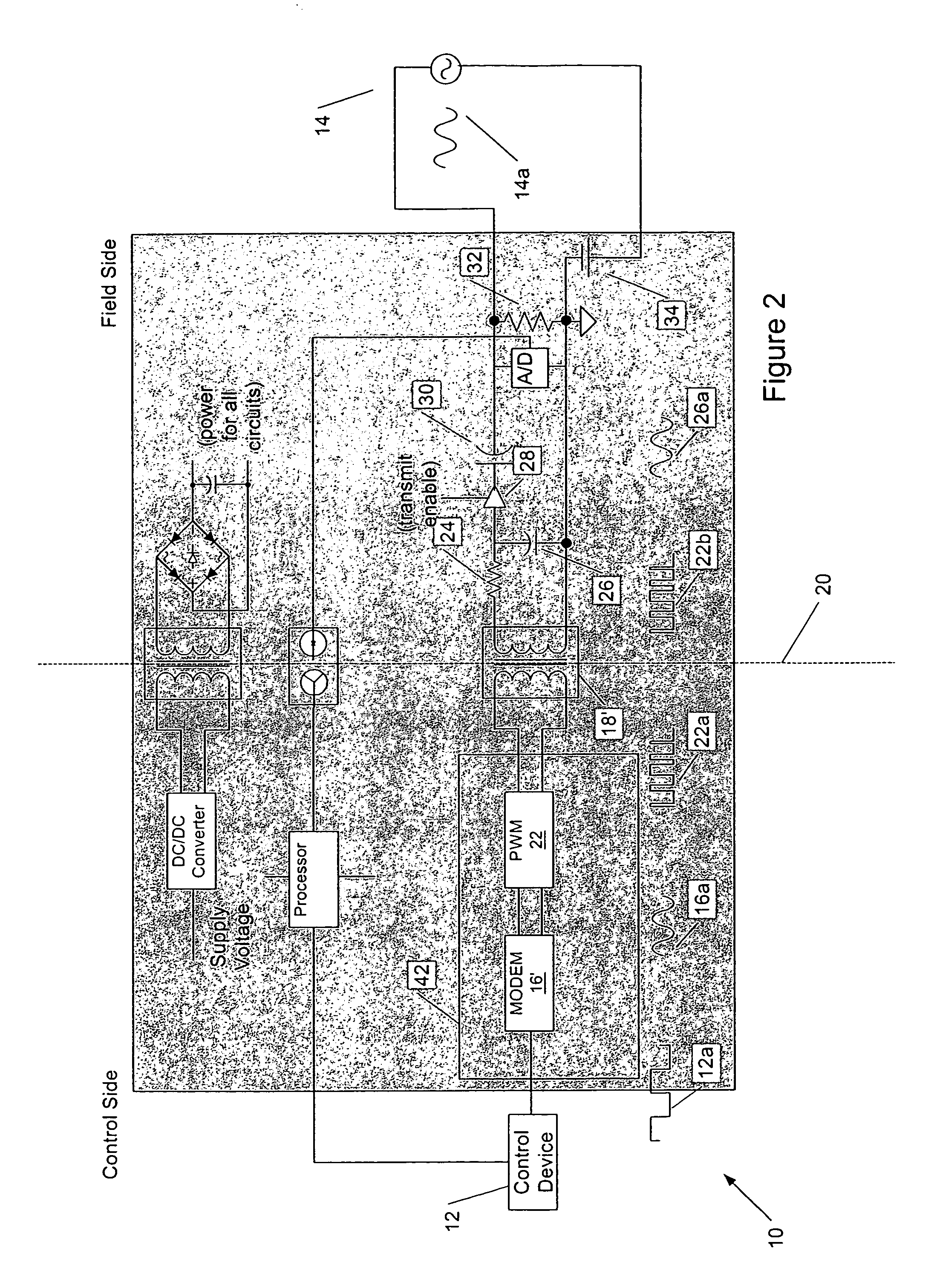

Control system methods and apparatus for inductive communication across an isolation barrier

Improved control apparatus and methods transfer information between devices, such as controllers and field devices, utilizing a modulator that generates a pulse width modulated (PWM) signal containing information to be transferred by a first of the devices, e.g., the controller, to the second device. A transformer or other inductive device transfers the PWM signal across the isolation barrier, where it is demodulated to analog form for application to the second device, e.g., the field device. Information transferred from the second device to the first device can be transferred in an amplitude modulated (AM) signal that utilizes, as its carrier, a fixed duty cycle output of the modulator that generates the PWM signal.

Owner:SCHNEIDER ELECTRIC SYST USA INC

Wireless relay system, wireless relay apparatus, and wireless relay method

A wireless relay system for relaying a radio signal transmitted from a first wireless station to a second wireless station via a wireless relay apparatus is disclosed. The wireless relay system includes a relay control part for receiving transmission symbols transmitted from the first wireless station and refraining from relaying a portion of the symbols, a pilot signal transmission part for transmitting a pilot signal that is inserted into a section of the portion of the transmission symbols, a coupling loop interference wave estimation part for receiving the pilot signal and estimating a coupling loop interference wave based on the pilot signal, and a coupling loop interference wave cancellation part for subtracting the estimated coupling loop interference wave from a reception signal.

Owner:NTT DOCOMO INC

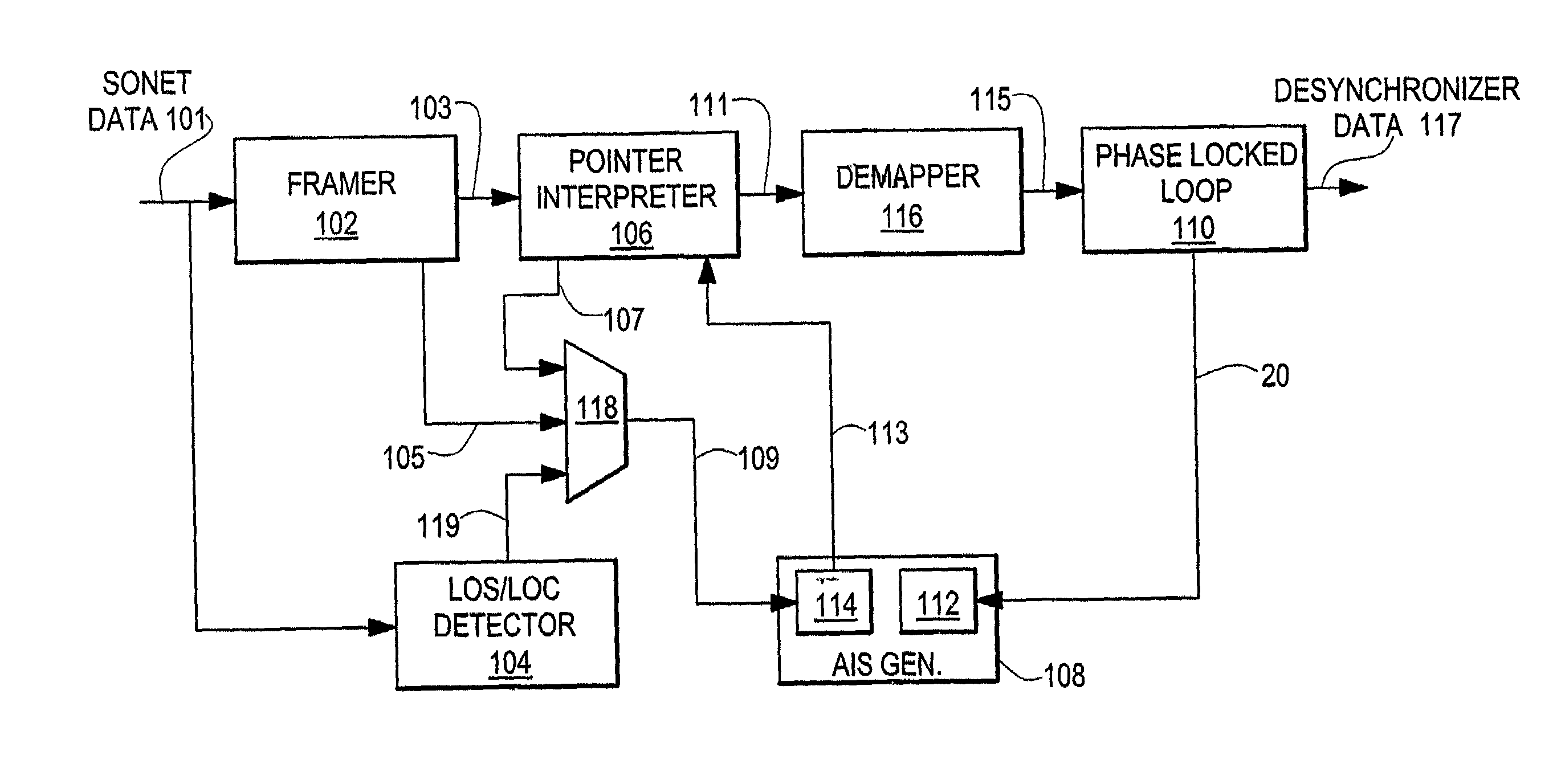

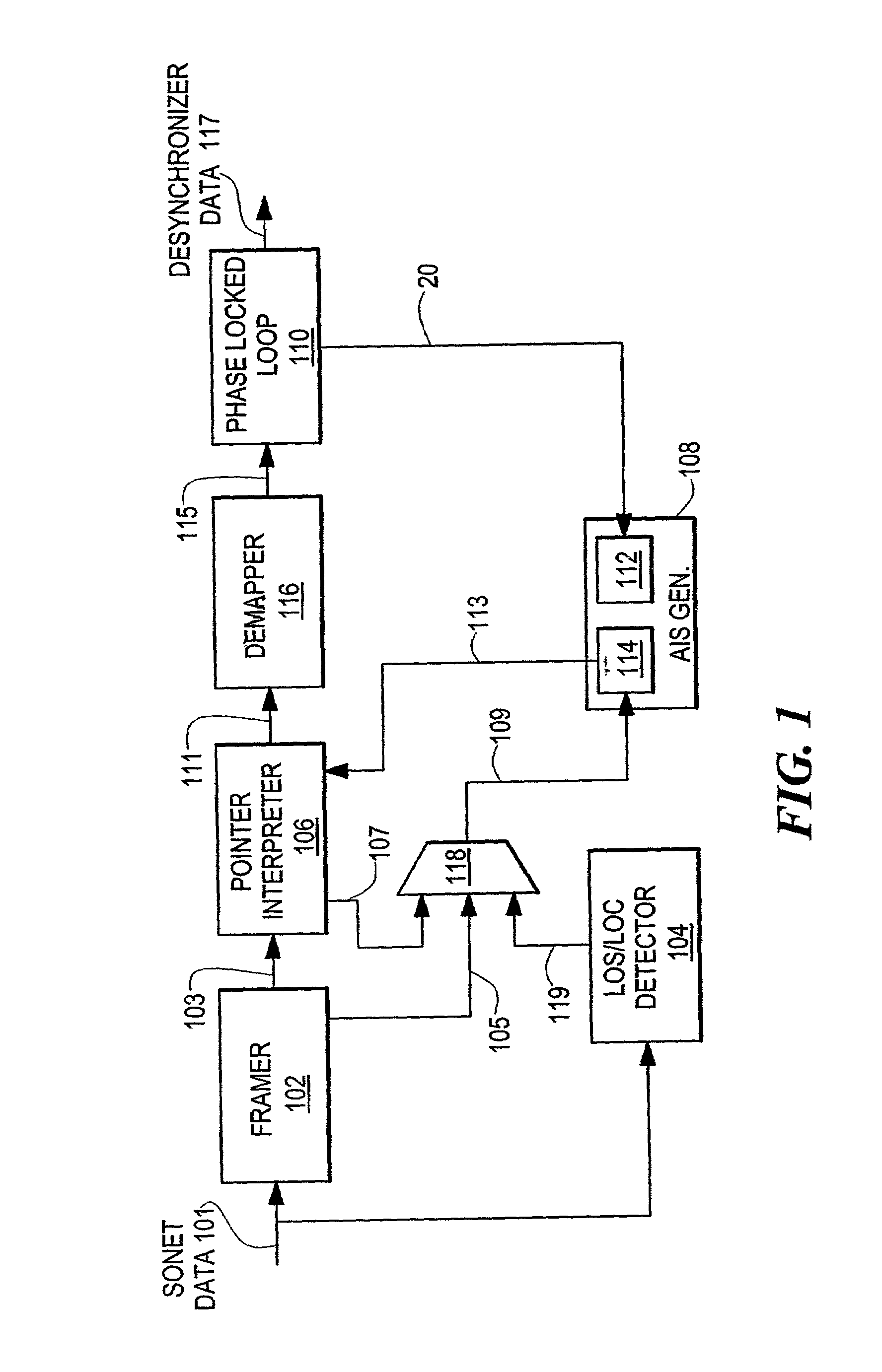

Method and apparatus for improving data integrity and desynchronizer recovery time after a loss of signal

ActiveUS6999480B2Avoid data lossMinimize data lossPulse transformerError preventionData streamData integrity

An apparatus and corresponding method for preventing data loss in network devices is disclosed. The present invention monitors an incoming data stream to a network device, or devices, and in the event that an error condition is detected, predetermined error data is inserted into the data stream, wherein the predetermined error data is provided at the same data rate as the recovered data rate internal to the network device. Thus, the network device will not have to adjust to a different data rate and potentially lose data during the adjustment period.

Owner:MACOM CONNECTIVITY SOLUTIONS LLC

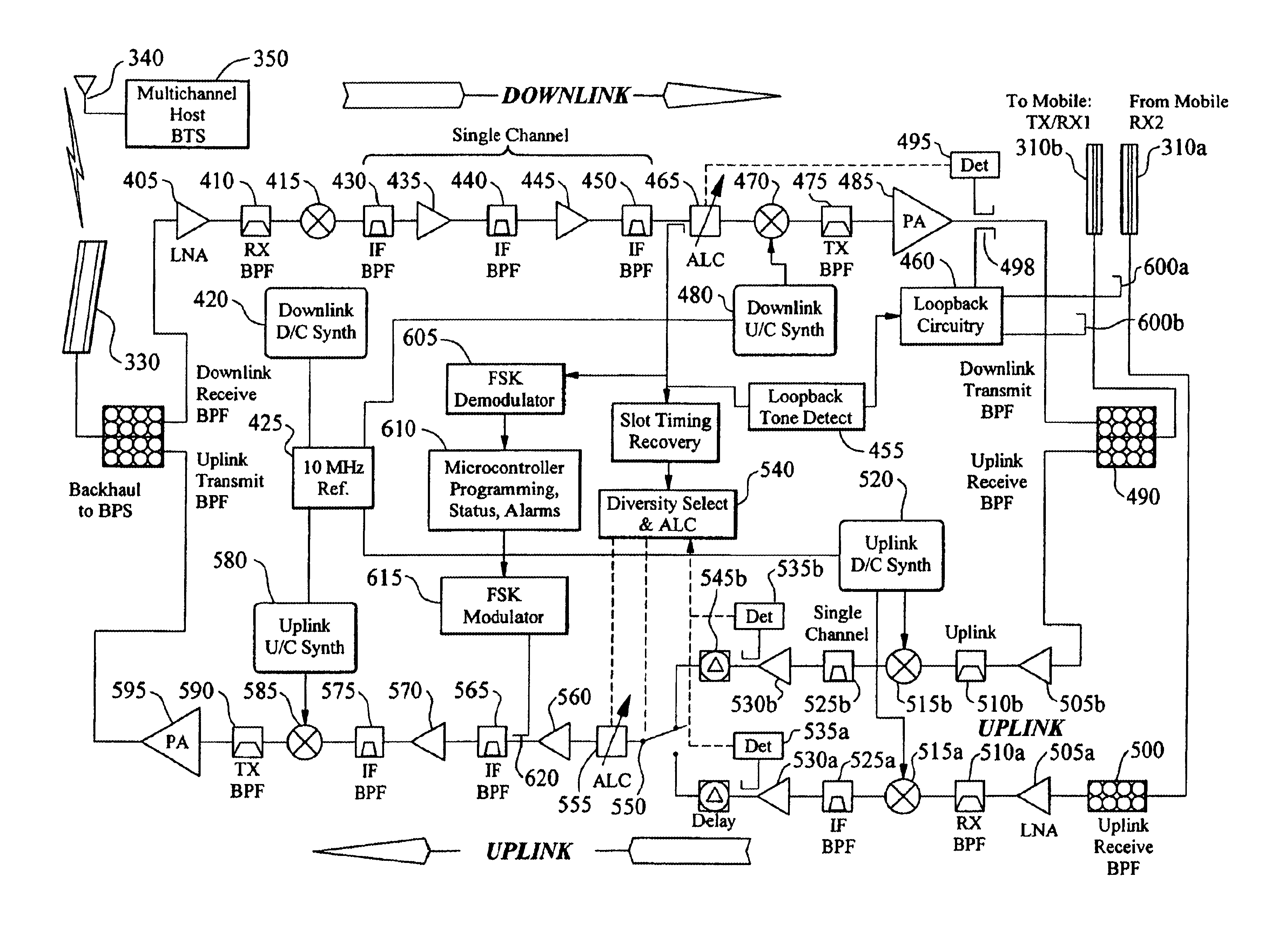

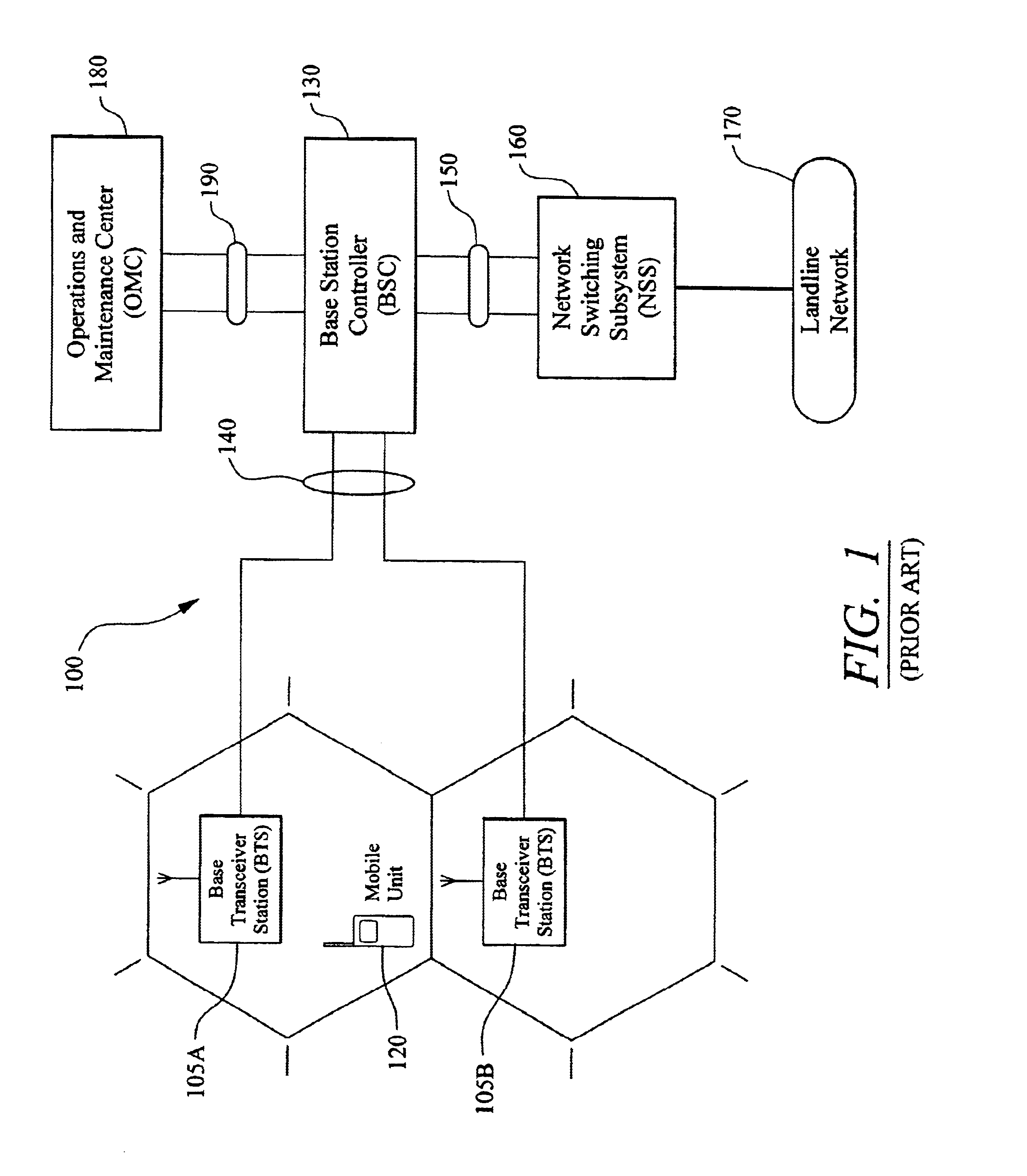

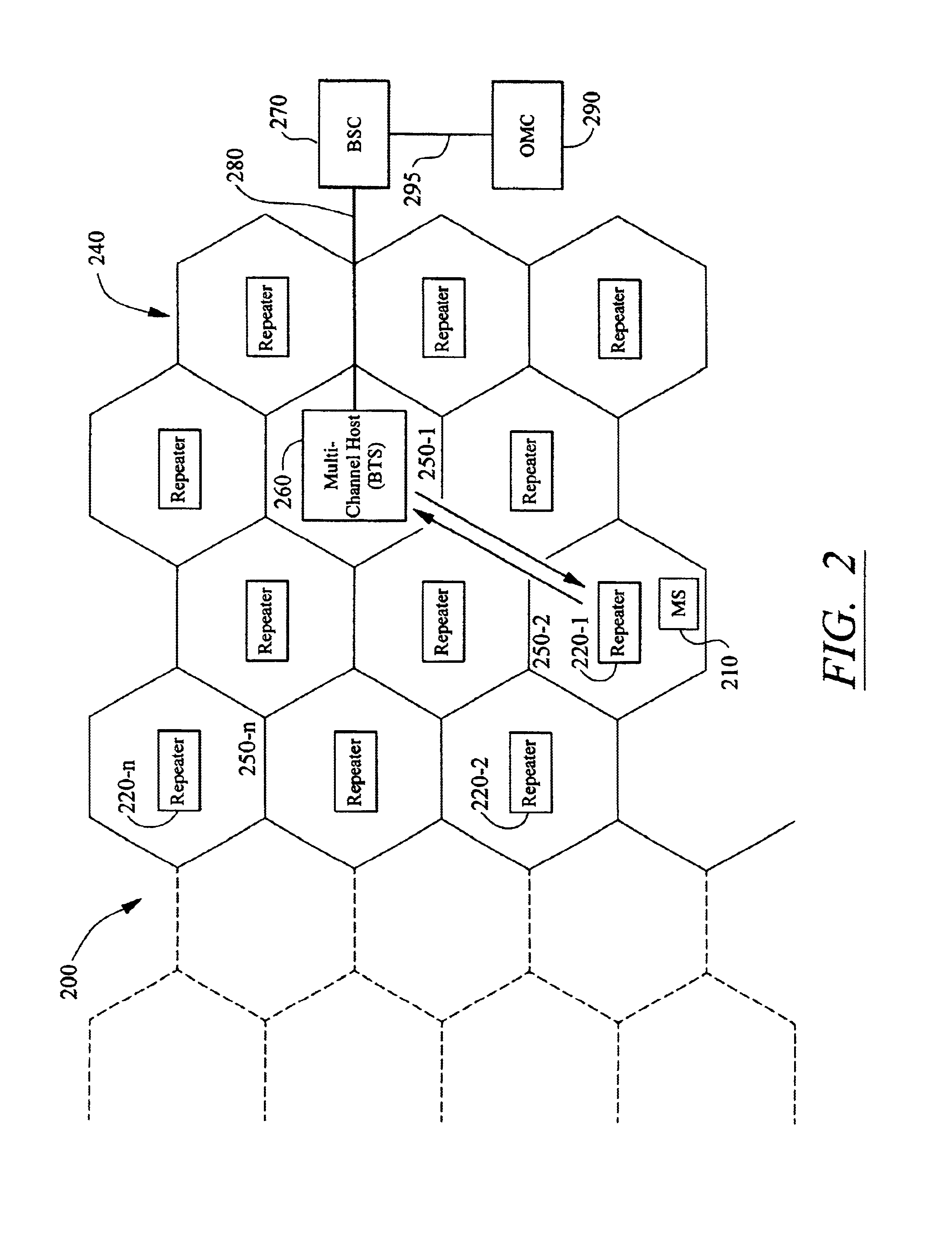

Method and apparatus employing wireless in-band signaling for downlink transmission of commands and uplink transmission of status for a wireless system repeater

InactiveUS6690662B1Accurate timingPulse transformerActive radio relay systemsIn-band signalingTransceiver

An approach to improving TDMA system operation is disclosed wherein in-band translator components are located in the center of remote cells which would normally contain a base transceiver system (BTS). The in-band. translators employ wireless in-band signaling for downlink transmission of commands from an operation and maintenance center (OMC) and uplink transmission of status-indicating and alarm signal data. The remotely located repeaters of the present invention have frequency shift key detection and demodulation capability incorporated in the downlink path, while also incorporating FSK modulation capability into the uplink path. This allows the repeater to extract commands from the serving BTS downlink signal and act on them. It also allows for the repeater to transmit status-indicating signals and alarms to the OMC via the uplink path to the serving BTS.

Owner:RATEZE REMOTE MGMT LLC

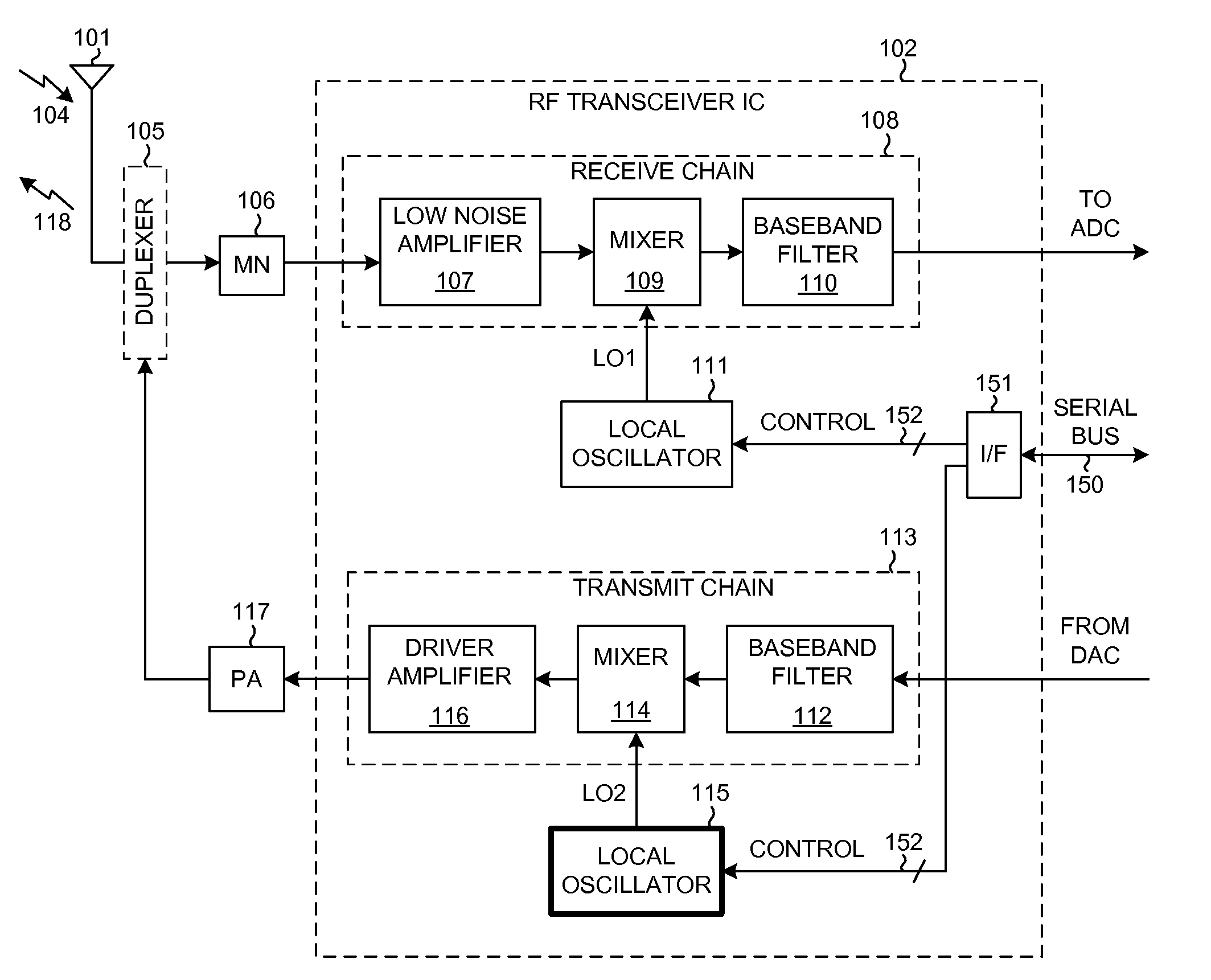

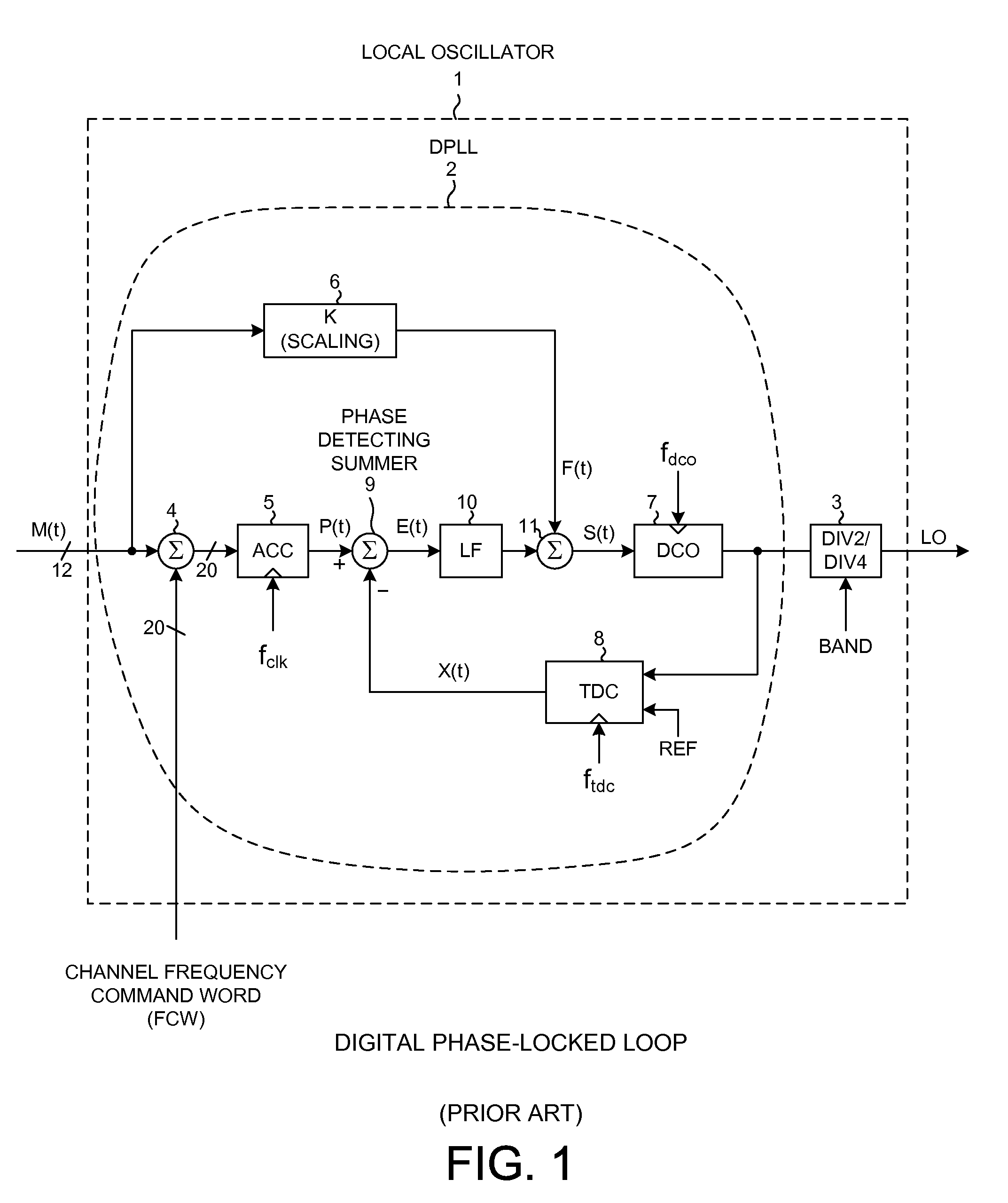

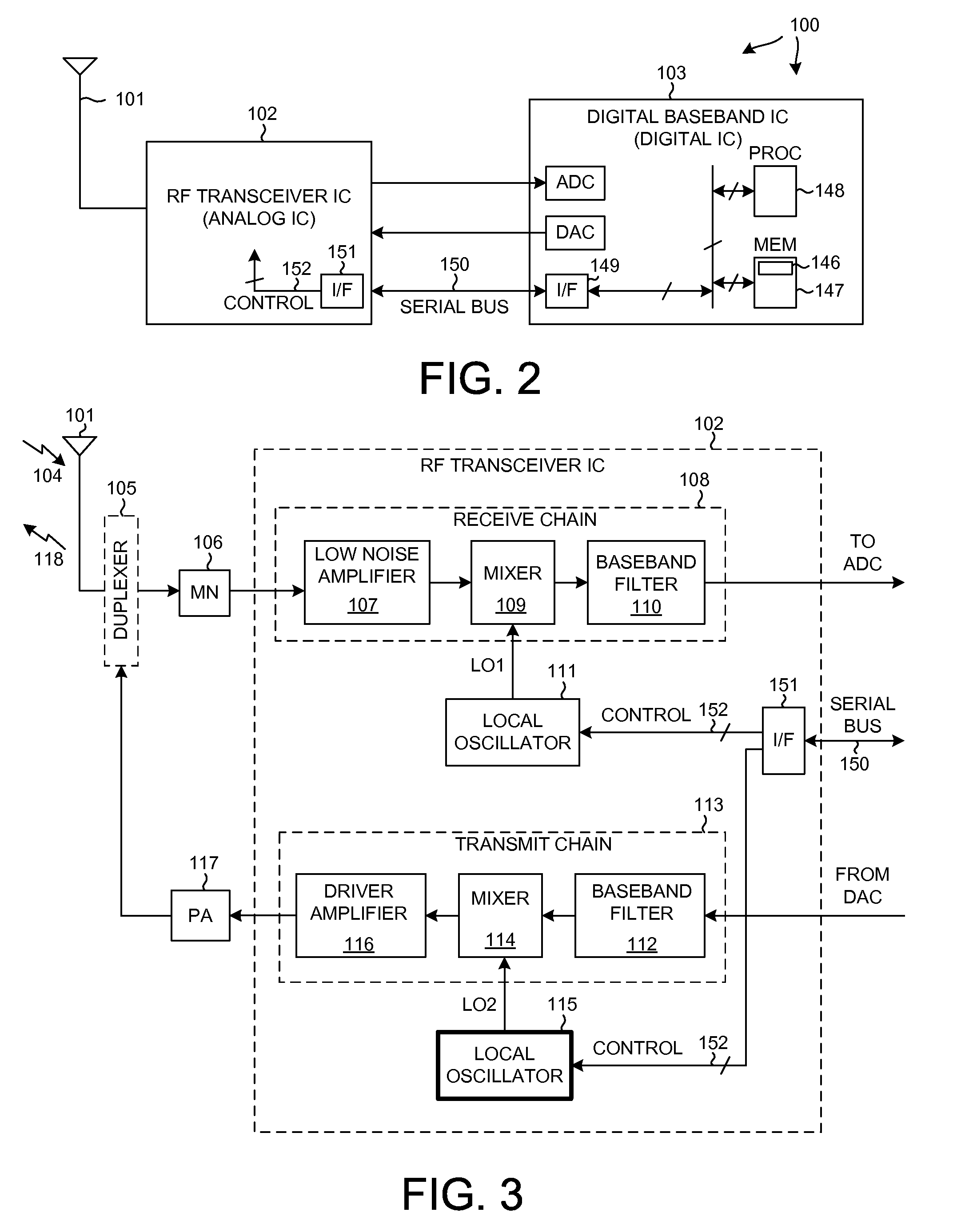

Multi-rate digital phase locked loop

InactiveUS20100310031A1Reduce power consumptionReduce digital imagePulse transformerPulse automatic controlDigital tuningHigh rate

A Digital Phase-Locked Loop (DPLL) involves a Time-to-Digital Converter (TDC) that receives a DCO output signal and a reference clock and outputs a first stream of digital values. Quantization noise is reduced by clocking the TDC at a high rate. Downsampling circuitry converts the first stream into a second stream. The second stream is supplied to a phase detecting summer of the DPLL such that a control portion of the DPLL can switch at a lower rate to reduce power consumption. The DPLL is therefore referred to as a multi-rate DPLL. A third stream of digital tuning words output by the control portion is upsampled before being supplied to the DCO so that the DCO can be clocked at the higher rate, thereby reducing digital images. In a receiver application, no upsampling is performed and the DCO is clocked at the lower rate, thereby further reducing power consumption.

Owner:QUALCOMM INC