Patents

Literature

4024 results about "Phase detector" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

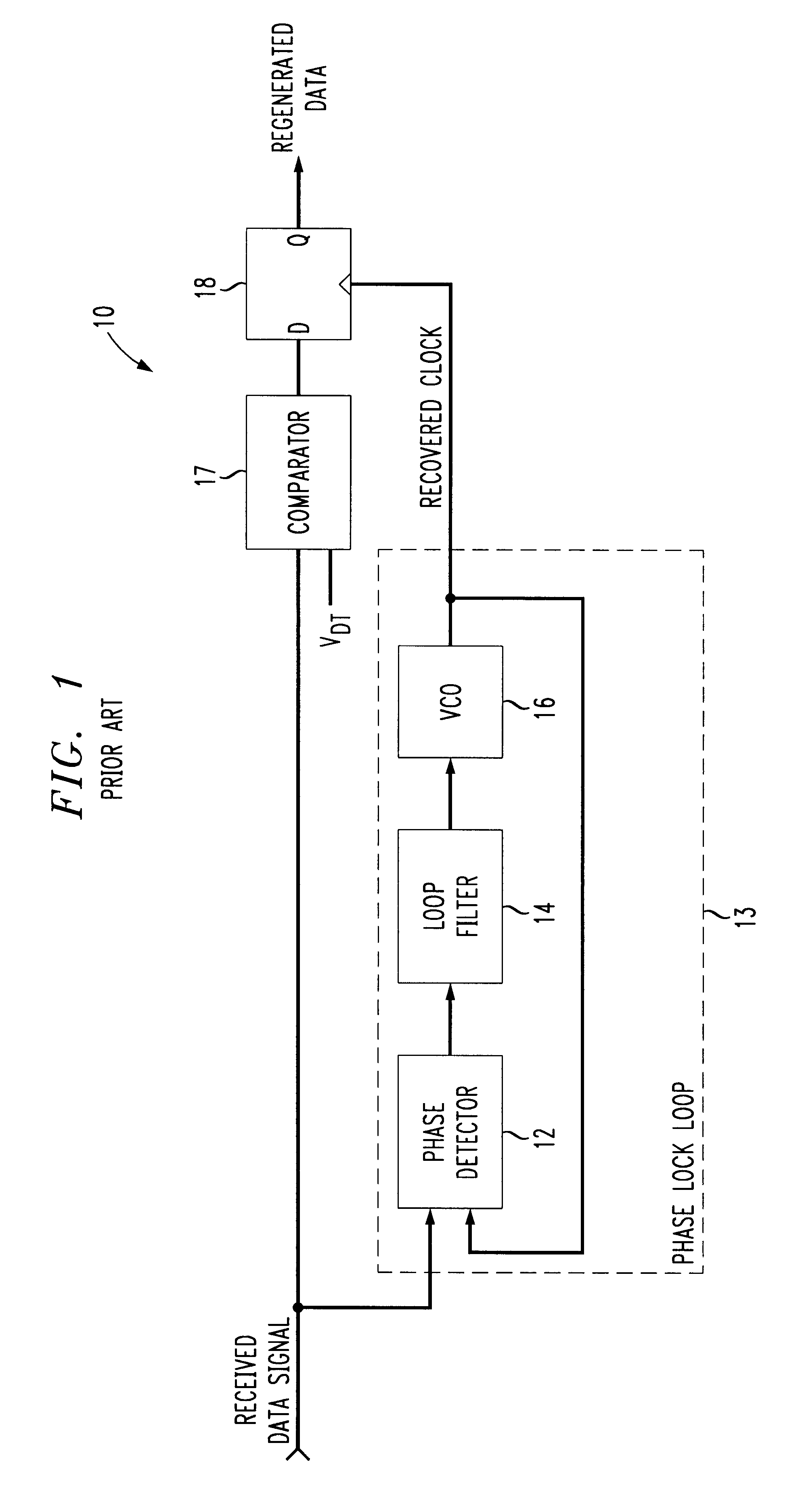

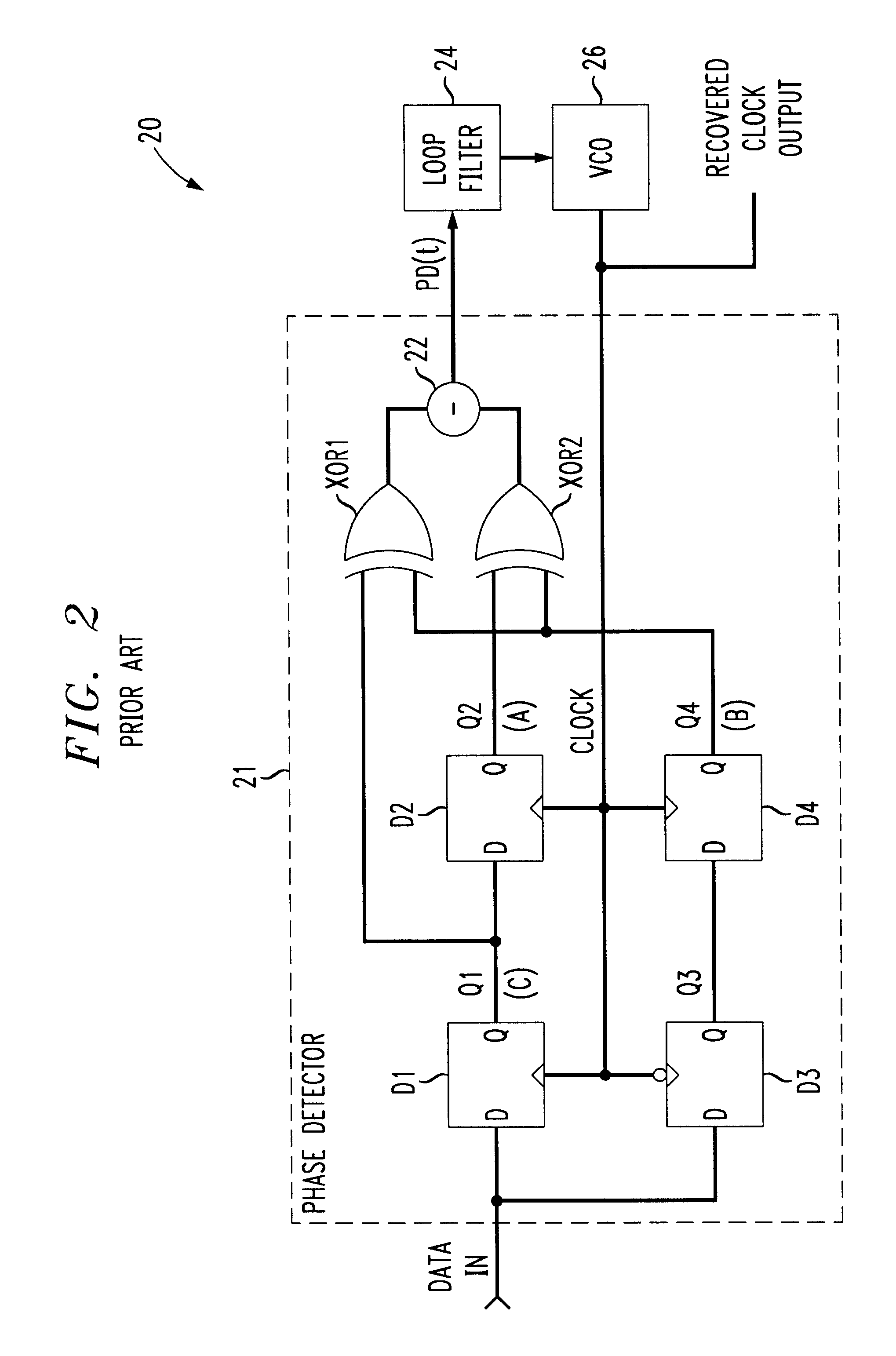

A phase detector or phase comparator is a frequency mixer, analog multiplier or logic circuit that generates a voltage signal which represents the difference in phase between two signal inputs. It is an essential element of the phase-locked loop (PLL).

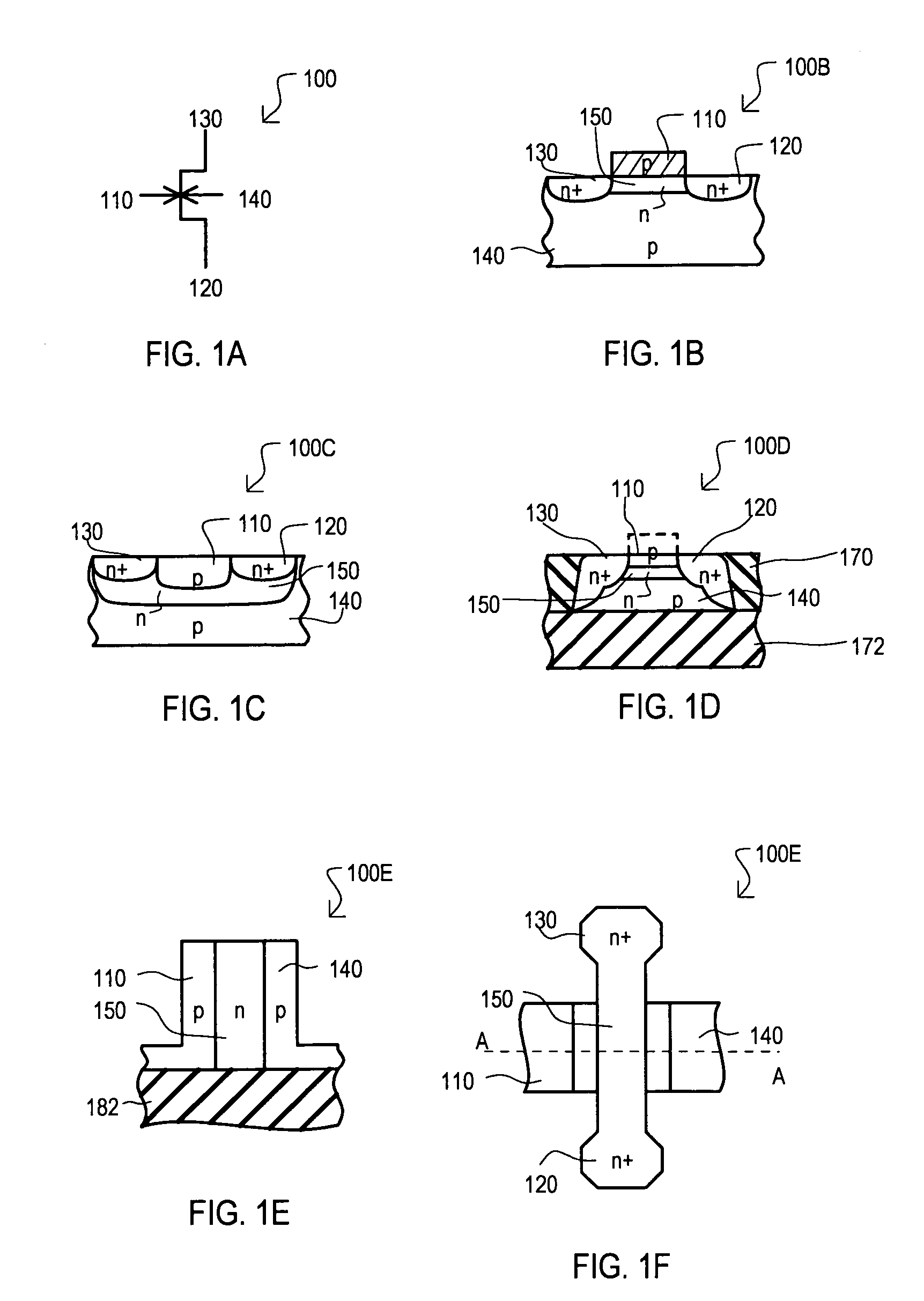

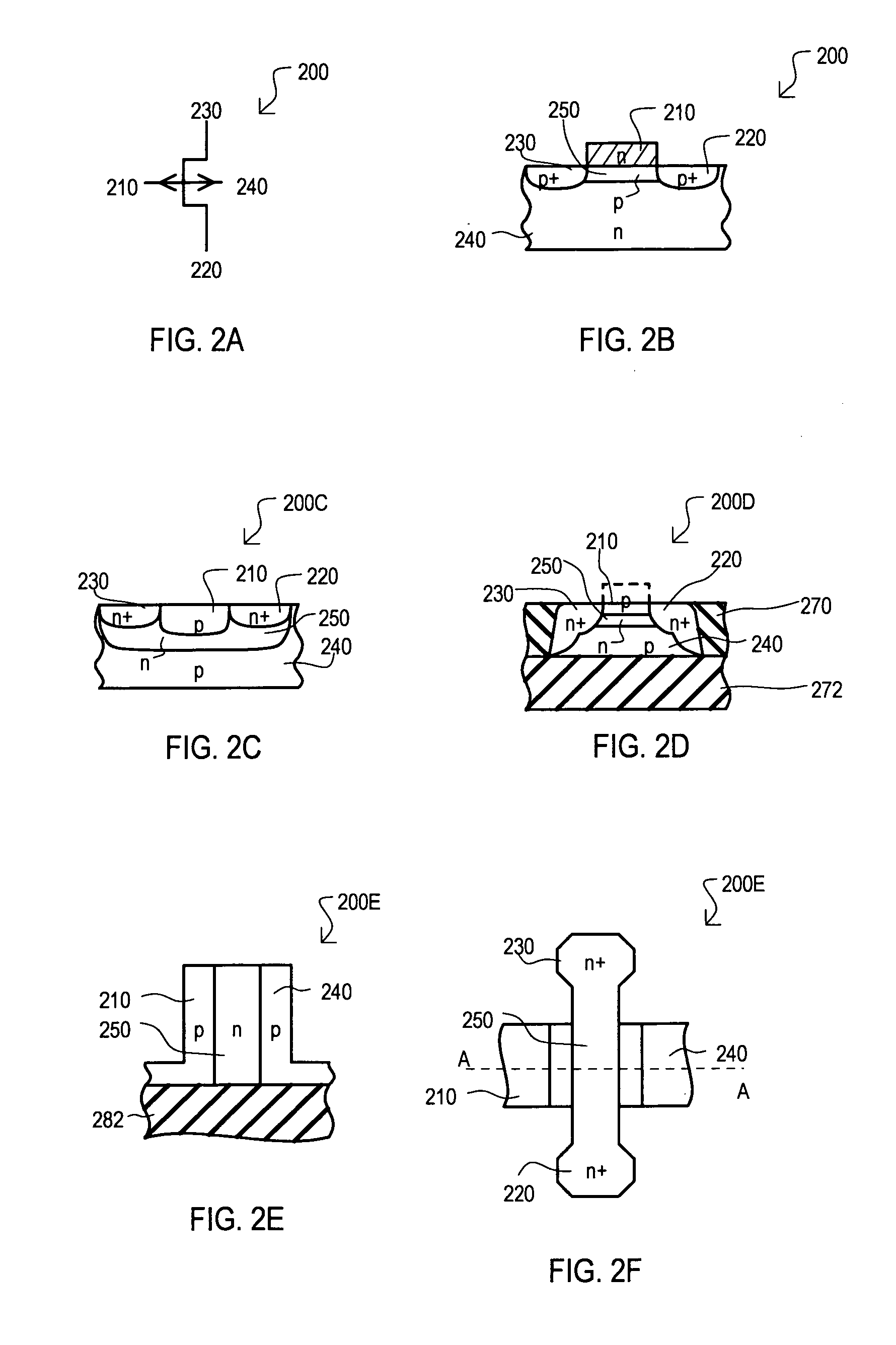

Method and circuit for multiplying signals with a transistor having more than one independent gate structure

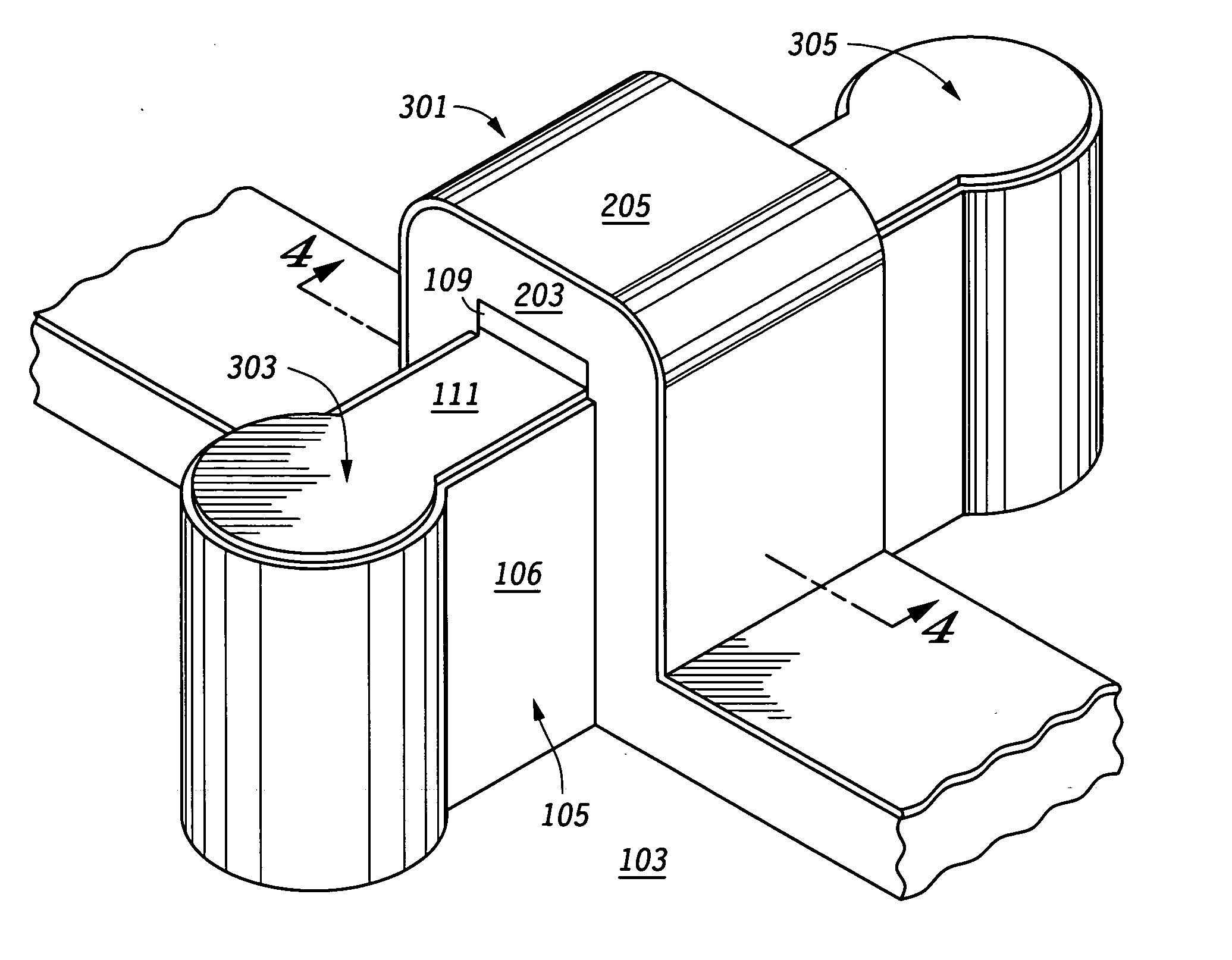

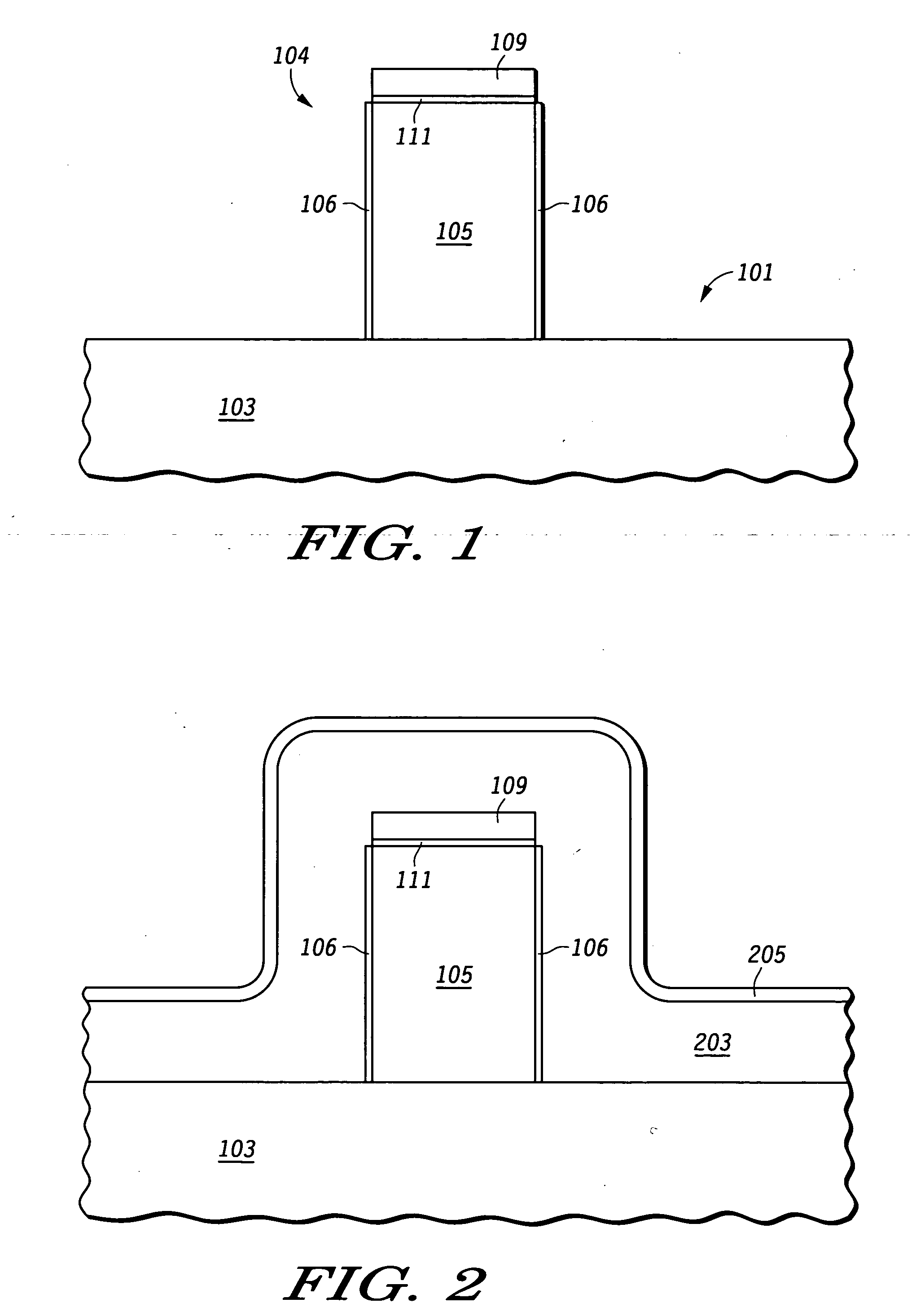

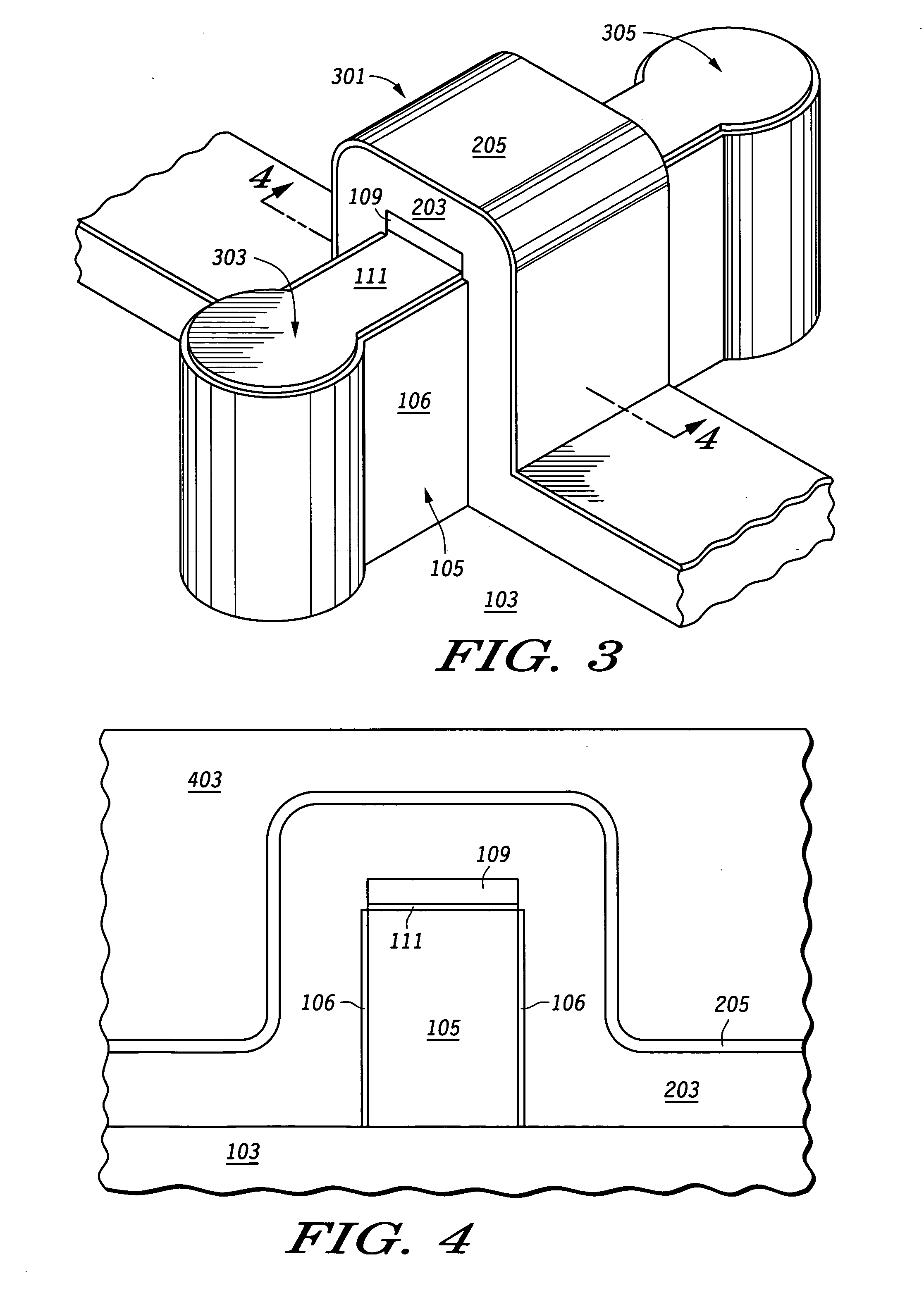

A double gate semiconductor device (2006) is used beneficially as a multiplier (2000). The double gate semiconductor device (2006) has a lateral fin (105) as the channel region with the gates formed opposite each other on both sides of the fin. The lateral positioning of the fin provides symmetry between the two gates. To increase drive current, multiple transistors are easily connected in parallel by having a continuous fin structure (2106) with alternating source / drain terminals (2120, 2122, 2124, 2126) in which the sources are connected together and the drains are connected together. Gates (2116, 2110) are positioned between each pair of adjacent source / drain terminals and electrically connected together. The multiplier (2000) may also be used as a mixer and further as a phase detector.

Owner:NORTH STAR INNOVATIONS

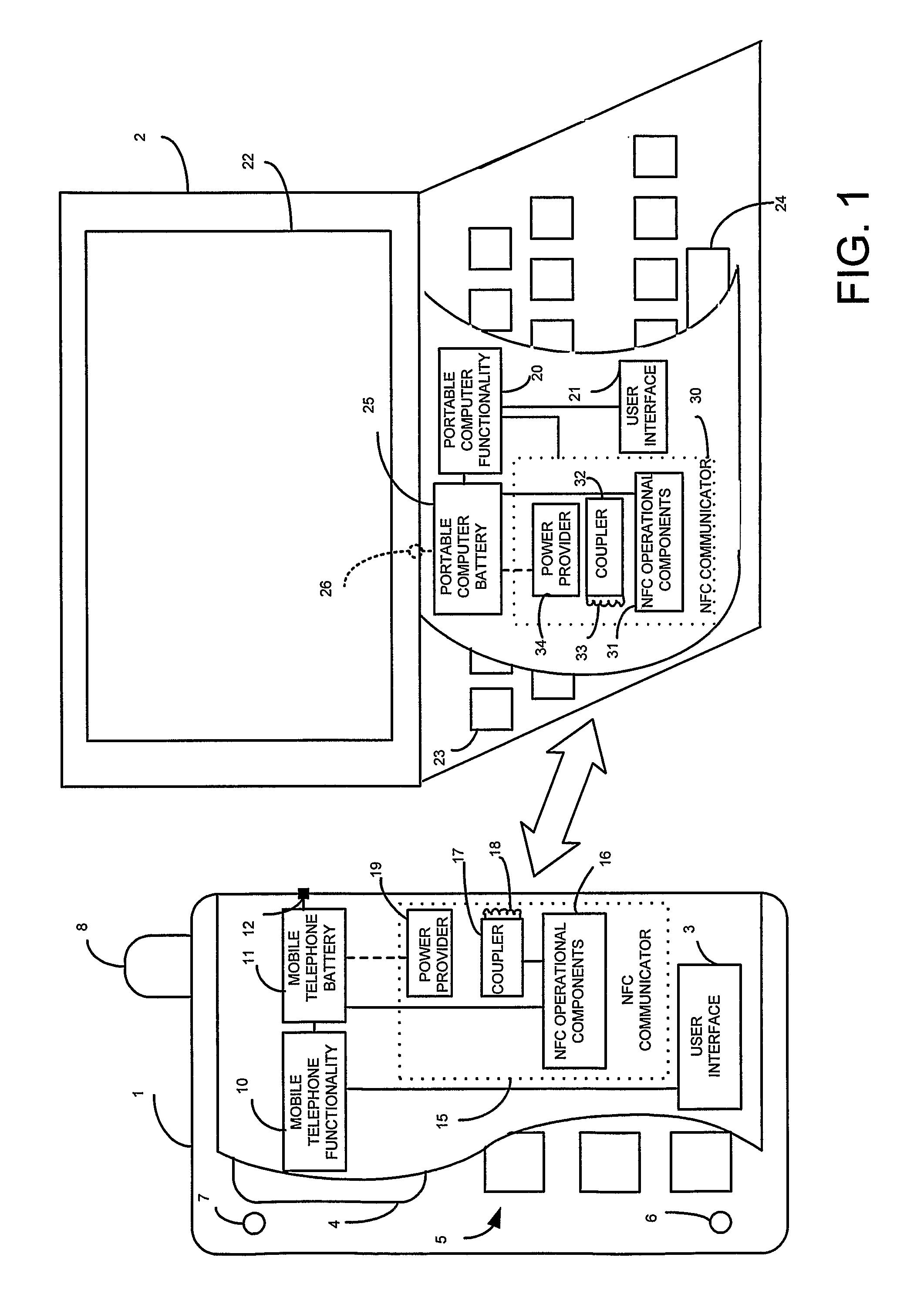

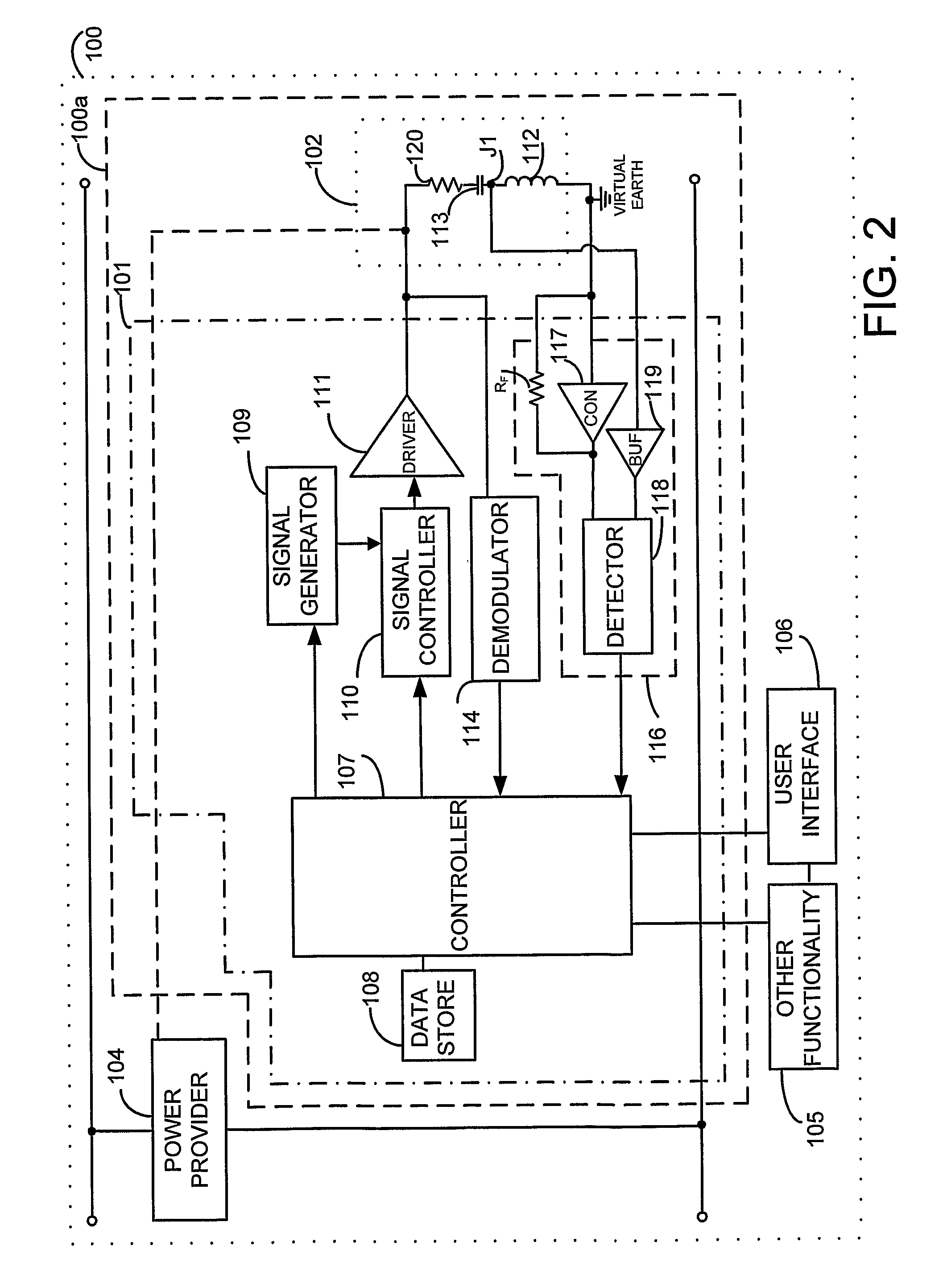

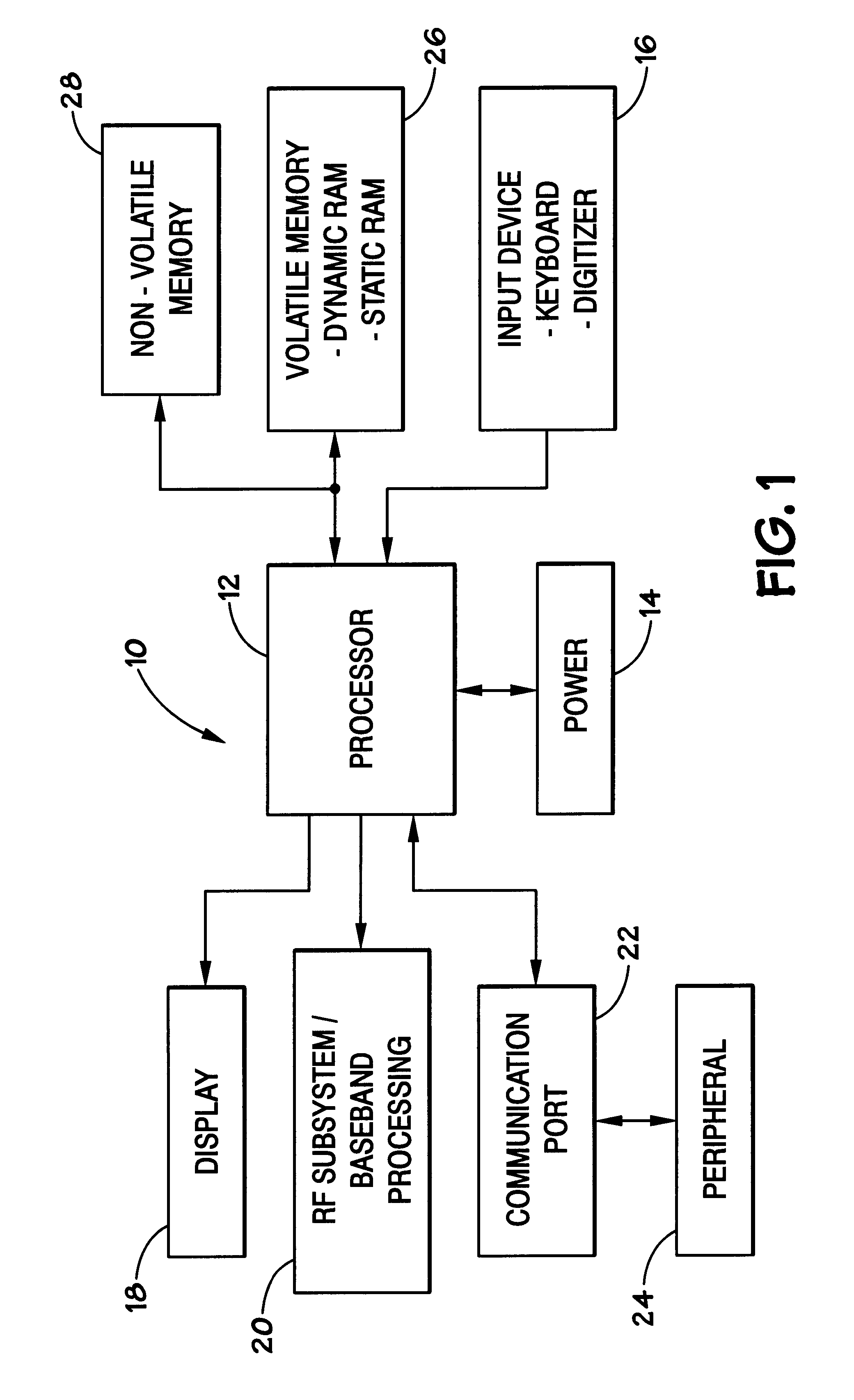

Near field RF communicators and near field RF communications enabled devices

ActiveUS8140010B2Avoid powerAvoid timeTransformersNear-field systems using receiversPhase detectorCurrent voltage

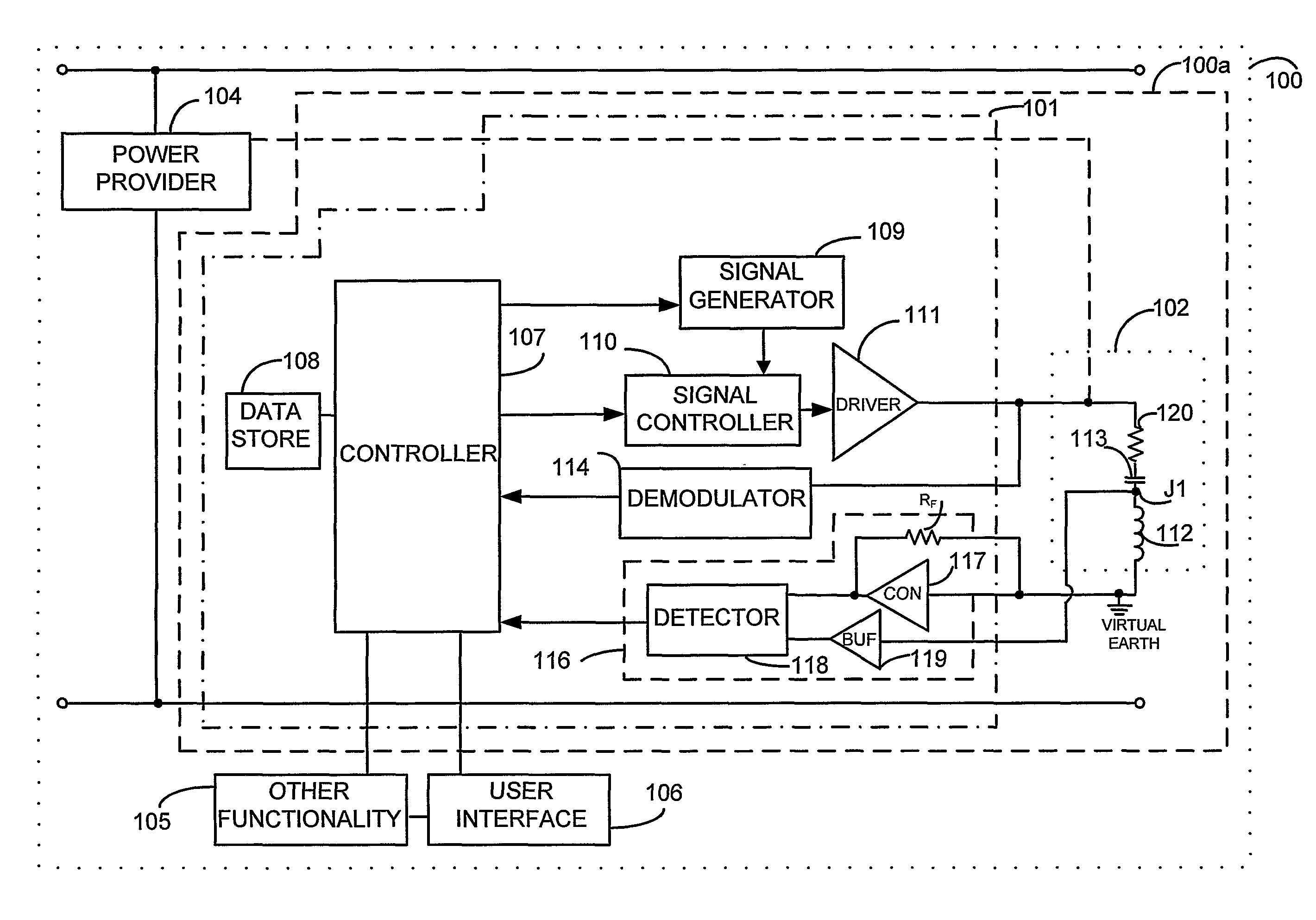

A near field RF communicator (100) has an inductive coupler (102) and a first signal provider (109, 110, 111) to cause the inductive coupler to provide a first signal that when inductively coupled to the inductive coupler of another near field RF communicator in near field range is insufficient to cause initiation of communication with that other near field RF communicator. A sensor (116) senses a change in an impedance of the inductive coupler (102) due to inductive coupling of the first signal between the inductive couplers of the said near field RF communicator and a said other near field RF communicator in near field range. A controller (107) determines whether or not another near field RF communicator is in near field range on the basis of any change in impedance sensed by the sensor and, if another near field RF communicator is determined to be in near field range, causes a second signal to be inductively coupled to the other near field RF communicator to initiate communication between the two near field RF communicators. The sensor may use a phase detector (118) to enable a change in impedance to be sensed by detecting a change in a current-voltage phase relationship resulting from a change in impedance.

Owner:NXP USA INC

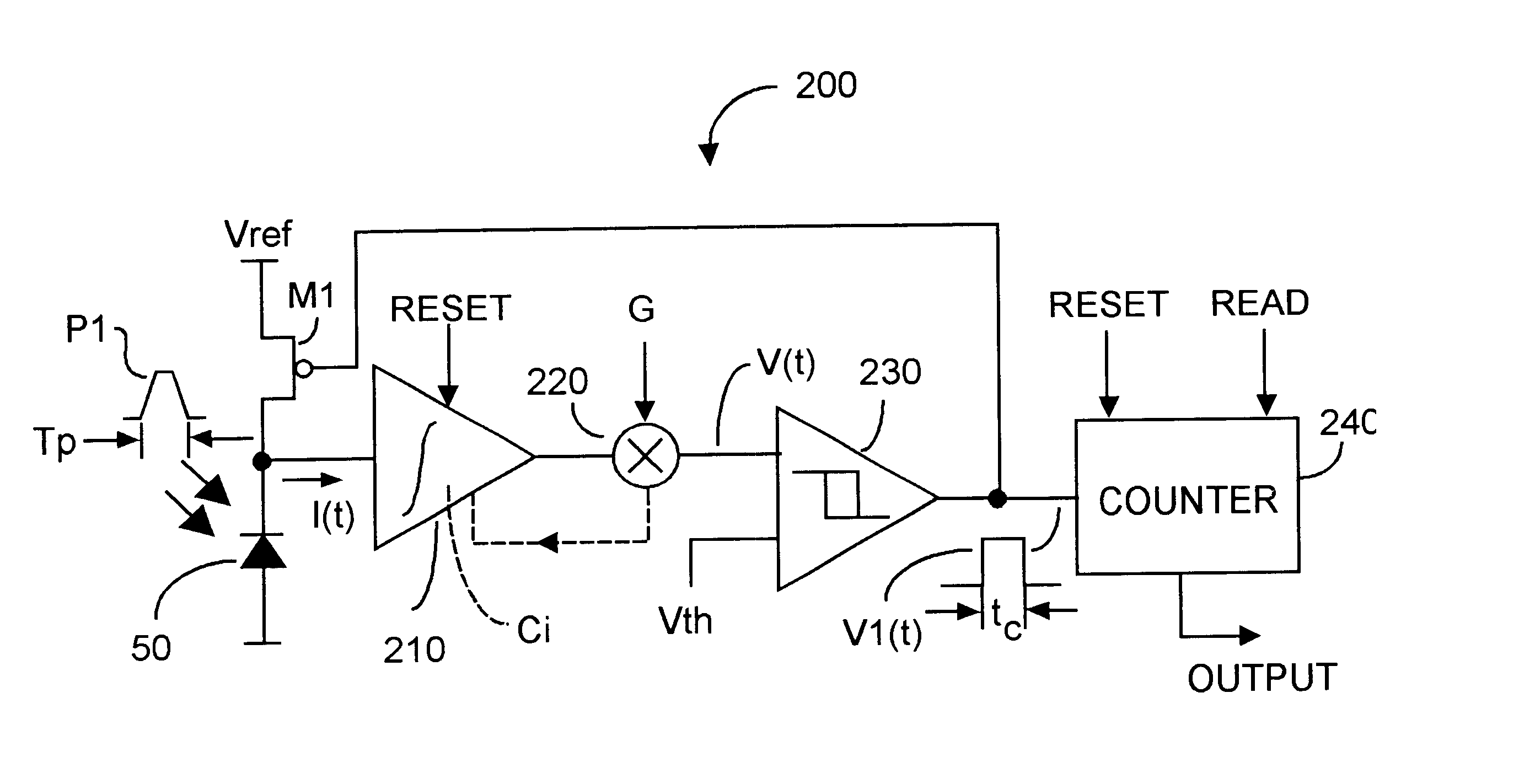

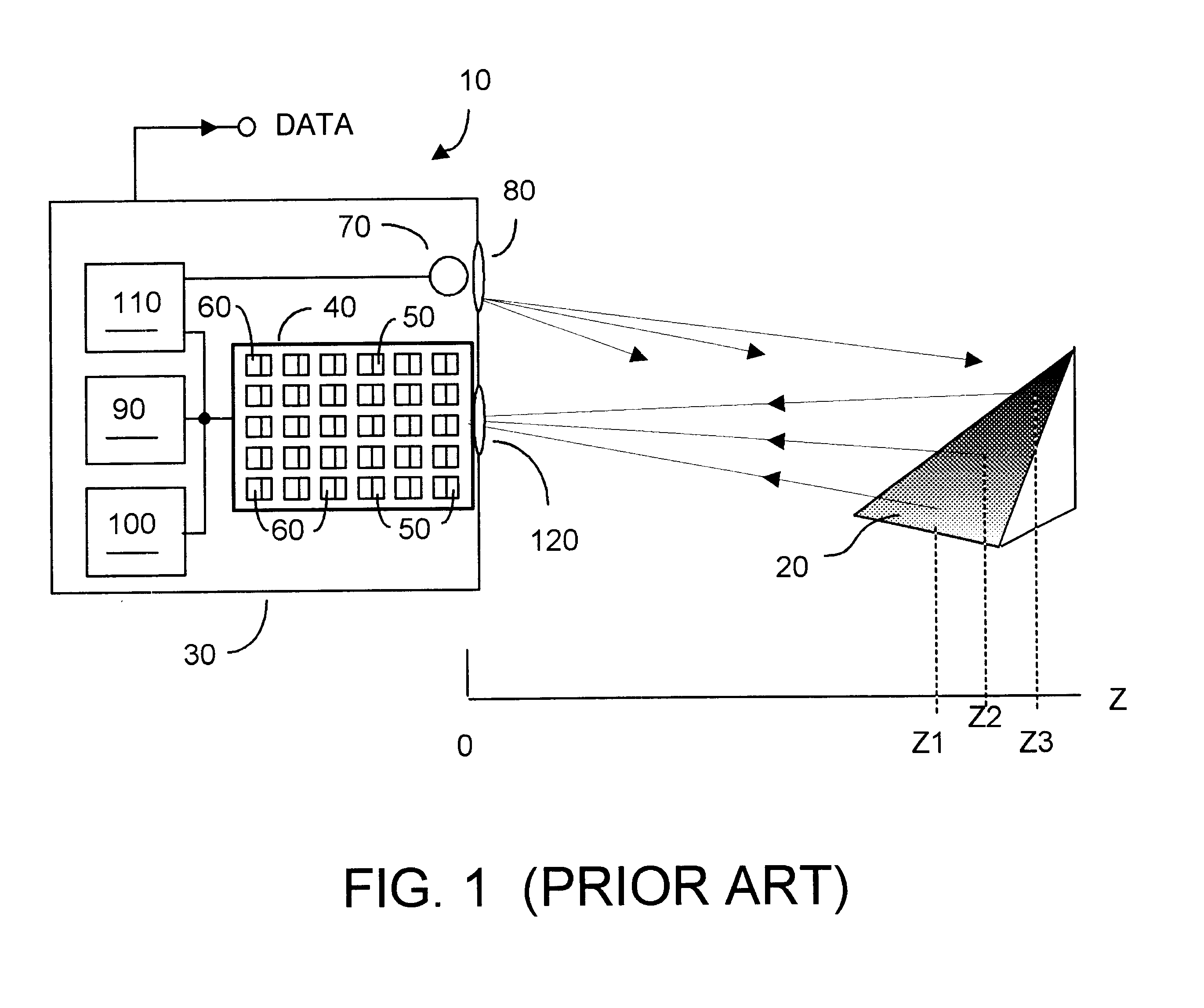

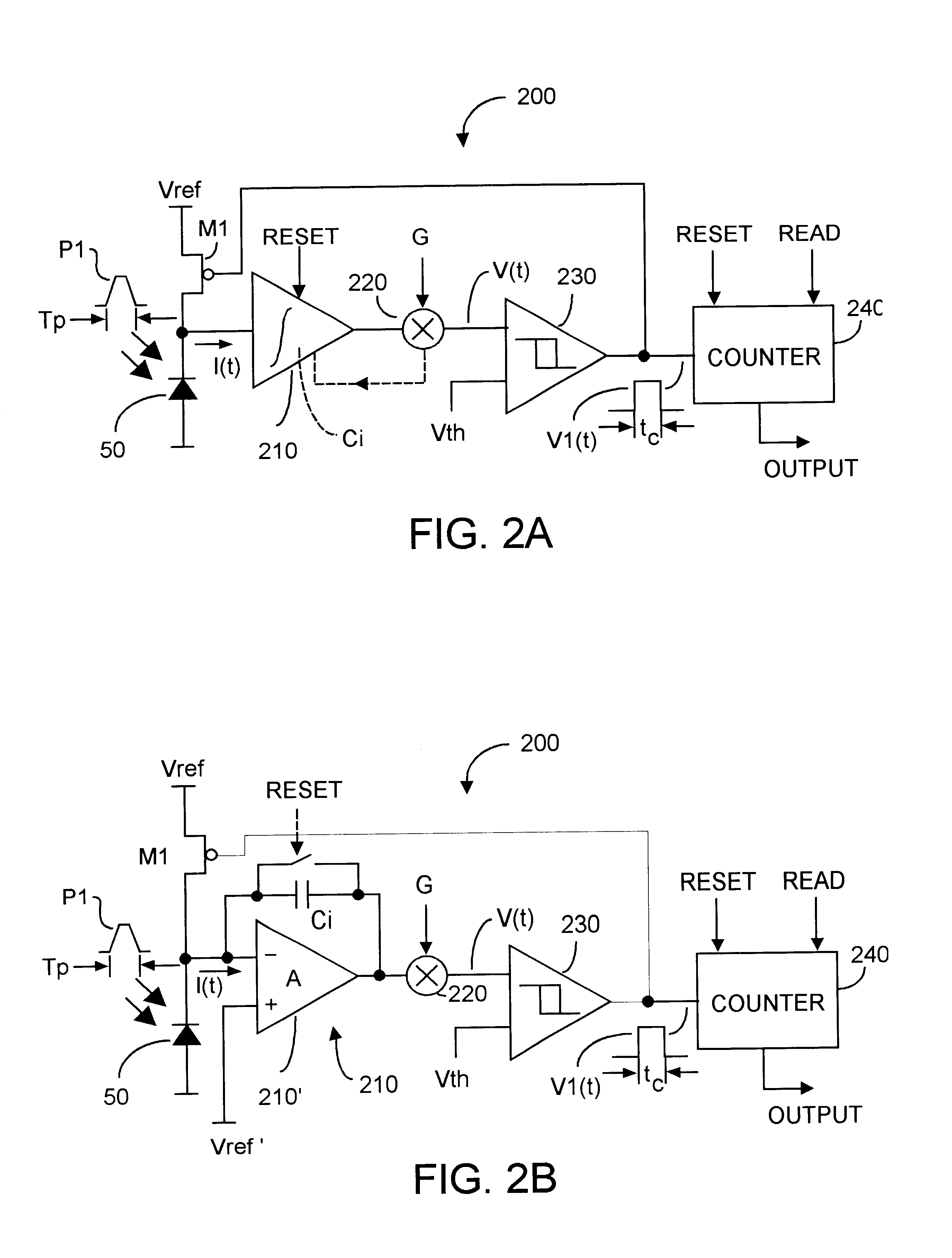

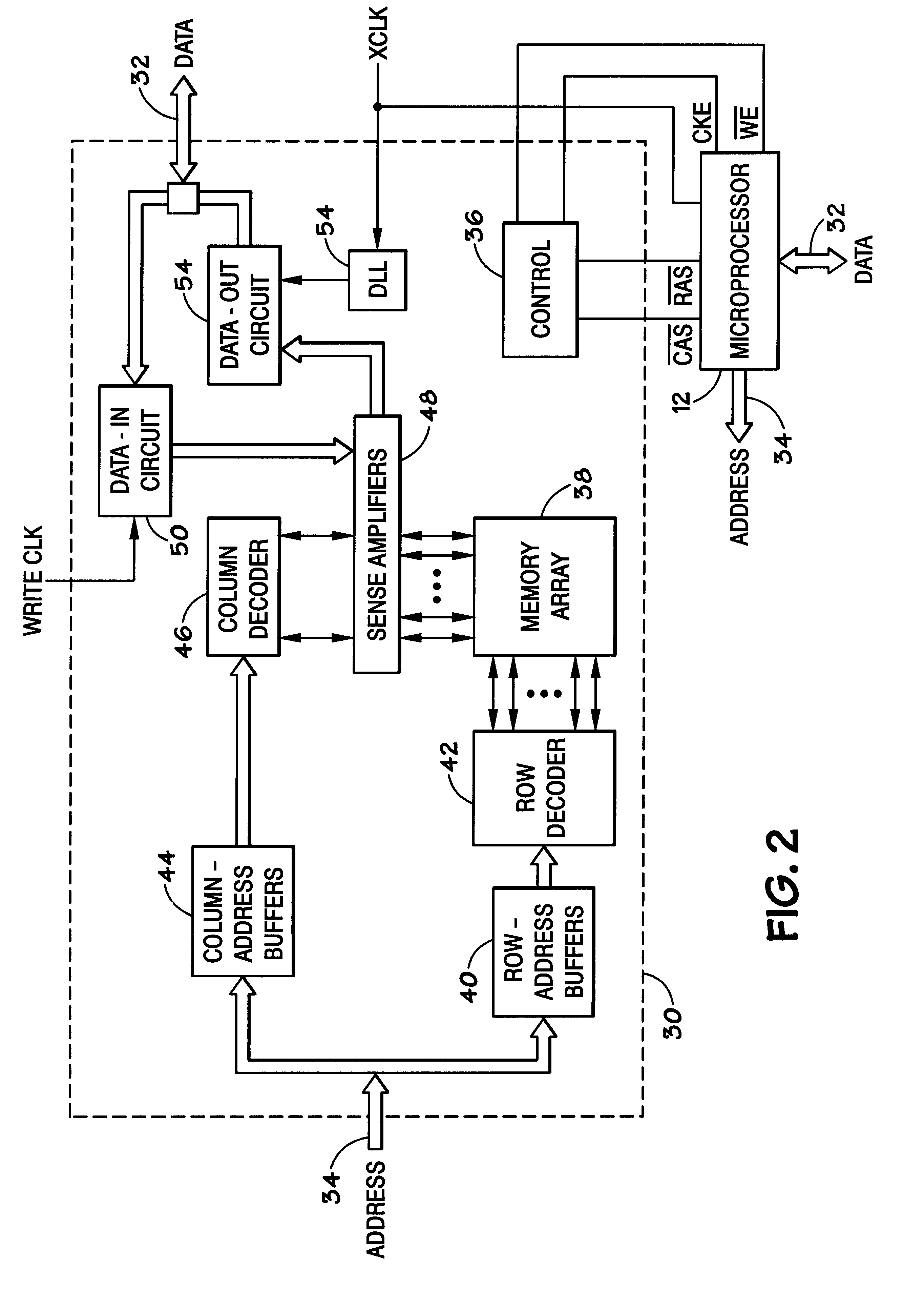

Method and system to enhance dynamic range conversion useable with CMOS three-dimensional imaging

InactiveUS6678039B2Low noiseLarge dynamic rangeTelevision system detailsOptical rangefindersCMOSContinuous measurement

High dynamic range brightness information is acquired by inputting detection current to a high (adjustable) gain resettable integrator whose output V(t) is compared to a Vth threshold by a comparator whose output is counted by a reset counter as V(t).gtoreq.Vth. When a desired count is attained, data acquisition ends, the counter is read, and the entire circuit is reset. A TOF data acquisition circuit includes first and second sequences of series-coupled delay units, and a like number of latch units coupled between respective delay units. A phase discriminator compares output from each chain and feedback a signal to one of the chains and to a comparator and can equalize delay through each chain. A control voltage is coupled to the remaining chain to affect through-propagation delay time. The latch units can capture the precise time when V(t).gtoreq.Vth. Successive measurement approximation can enhance TOF resolution.

Owner:MICROSOFT TECH LICENSING LLC

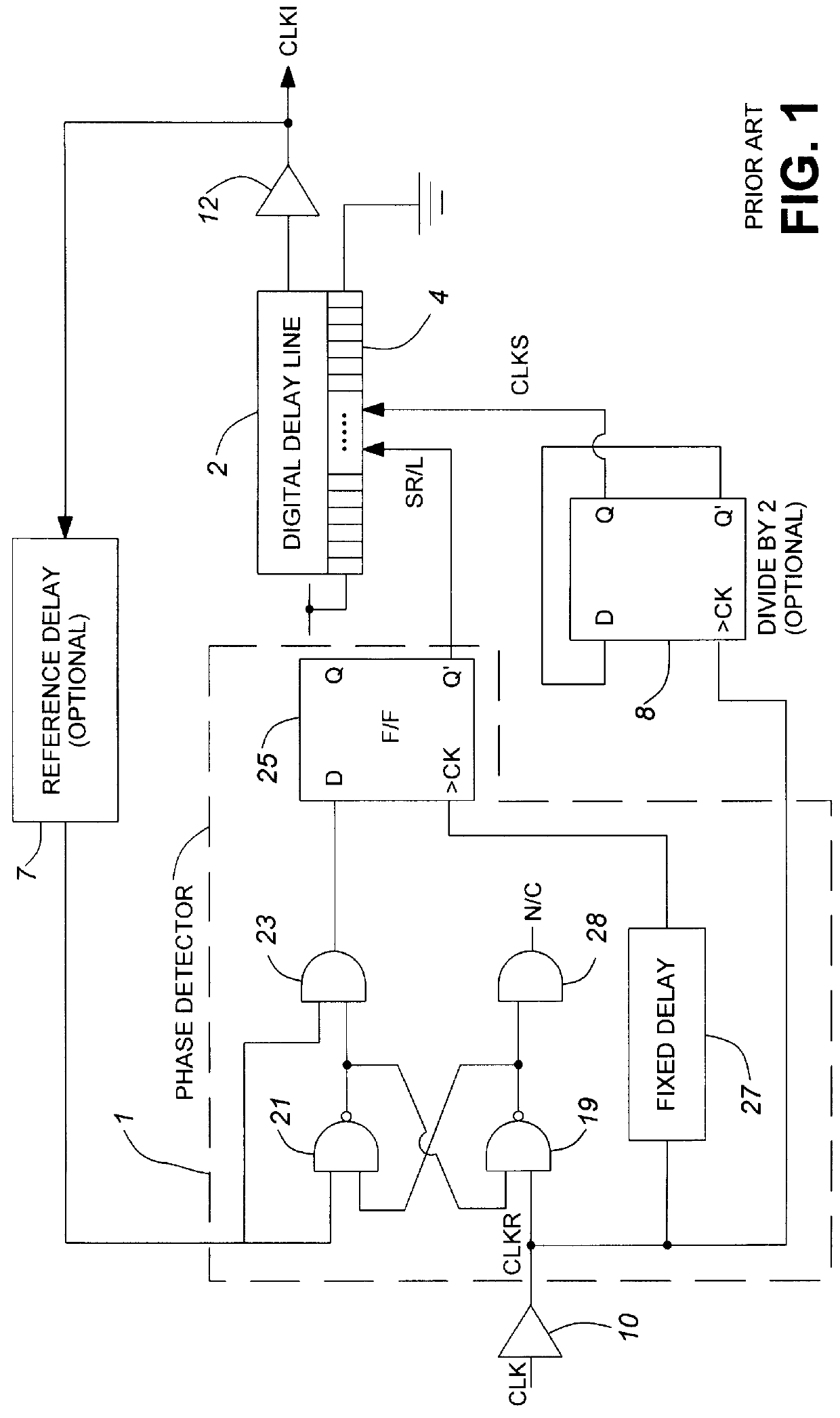

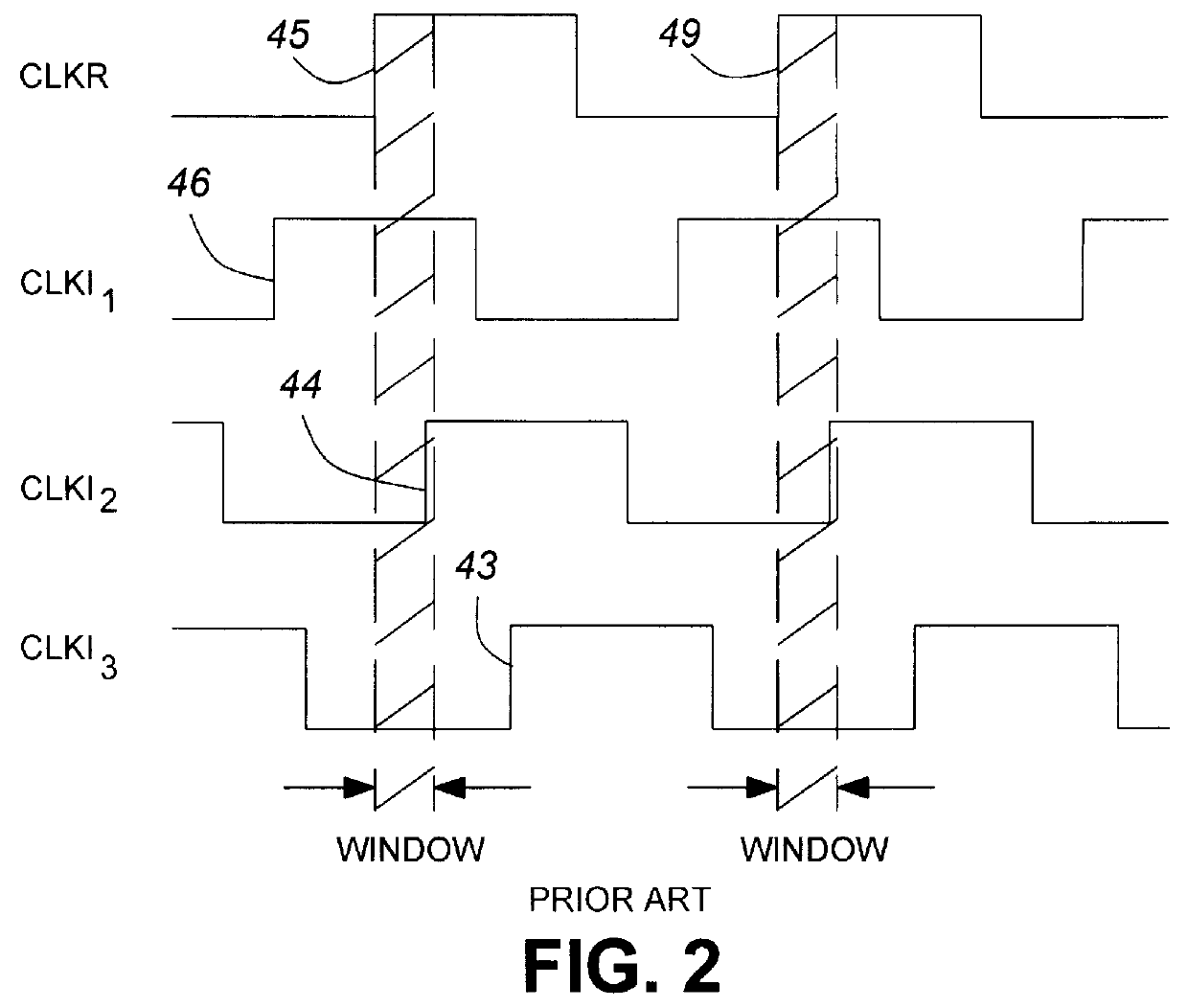

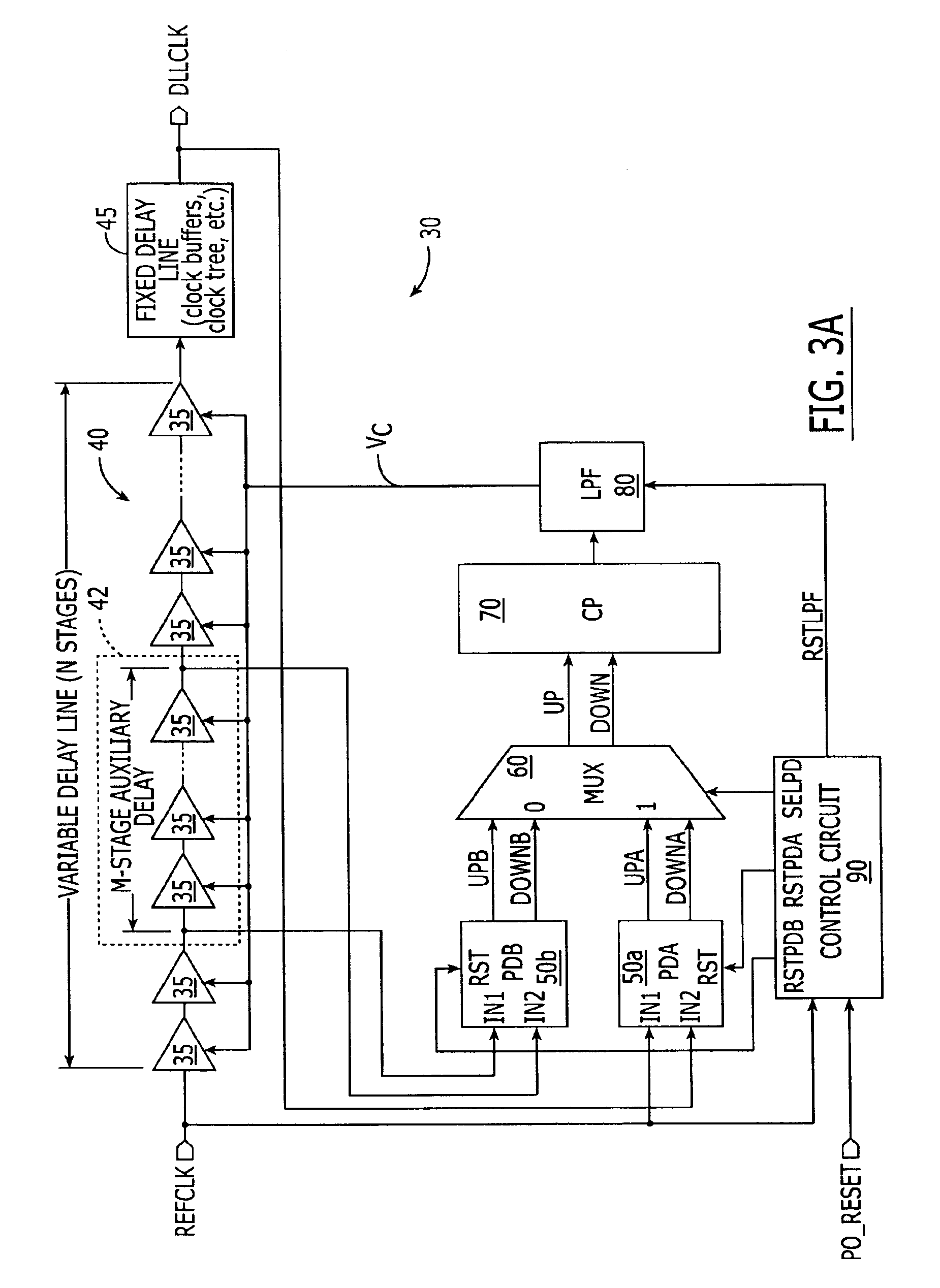

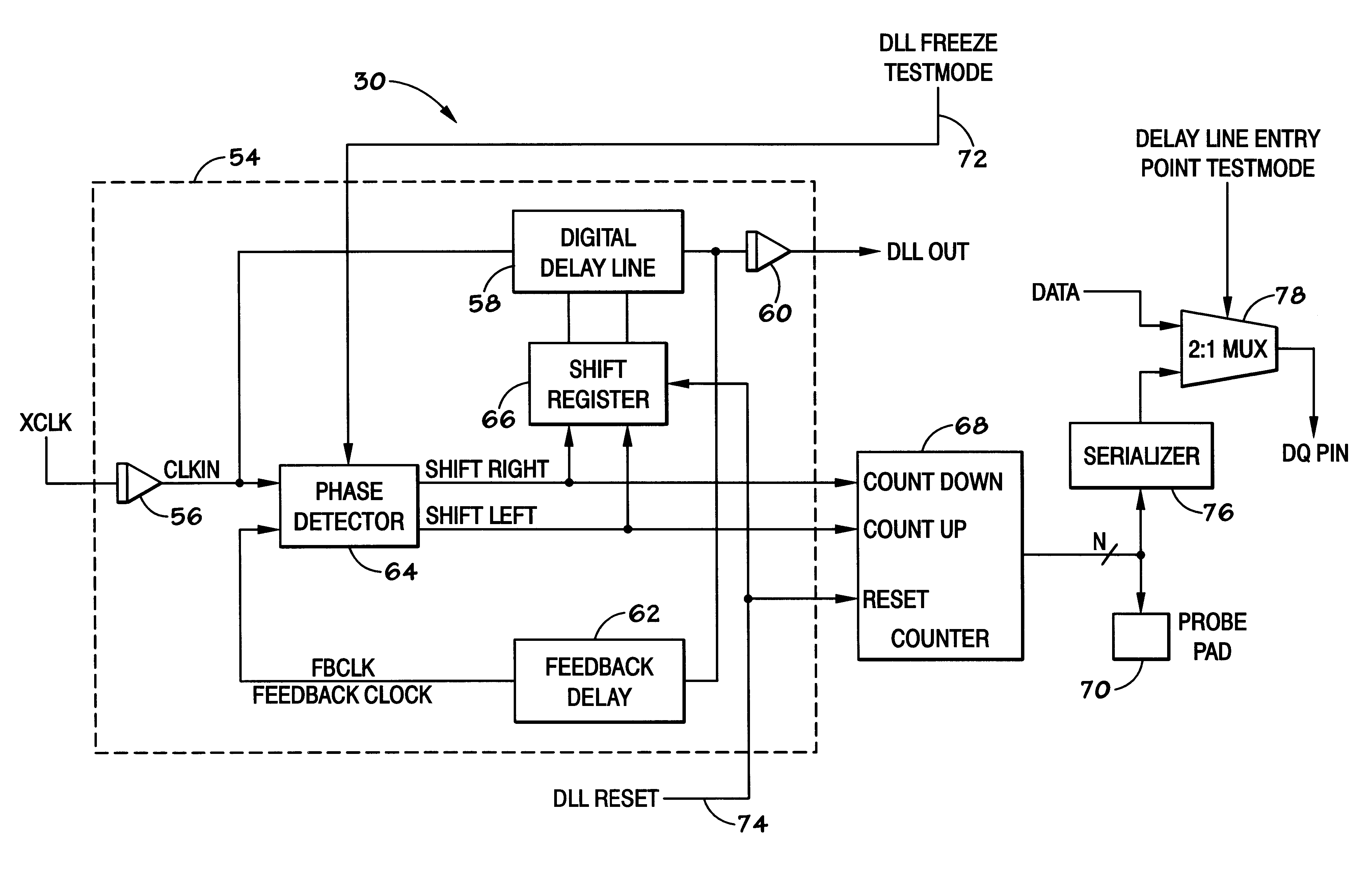

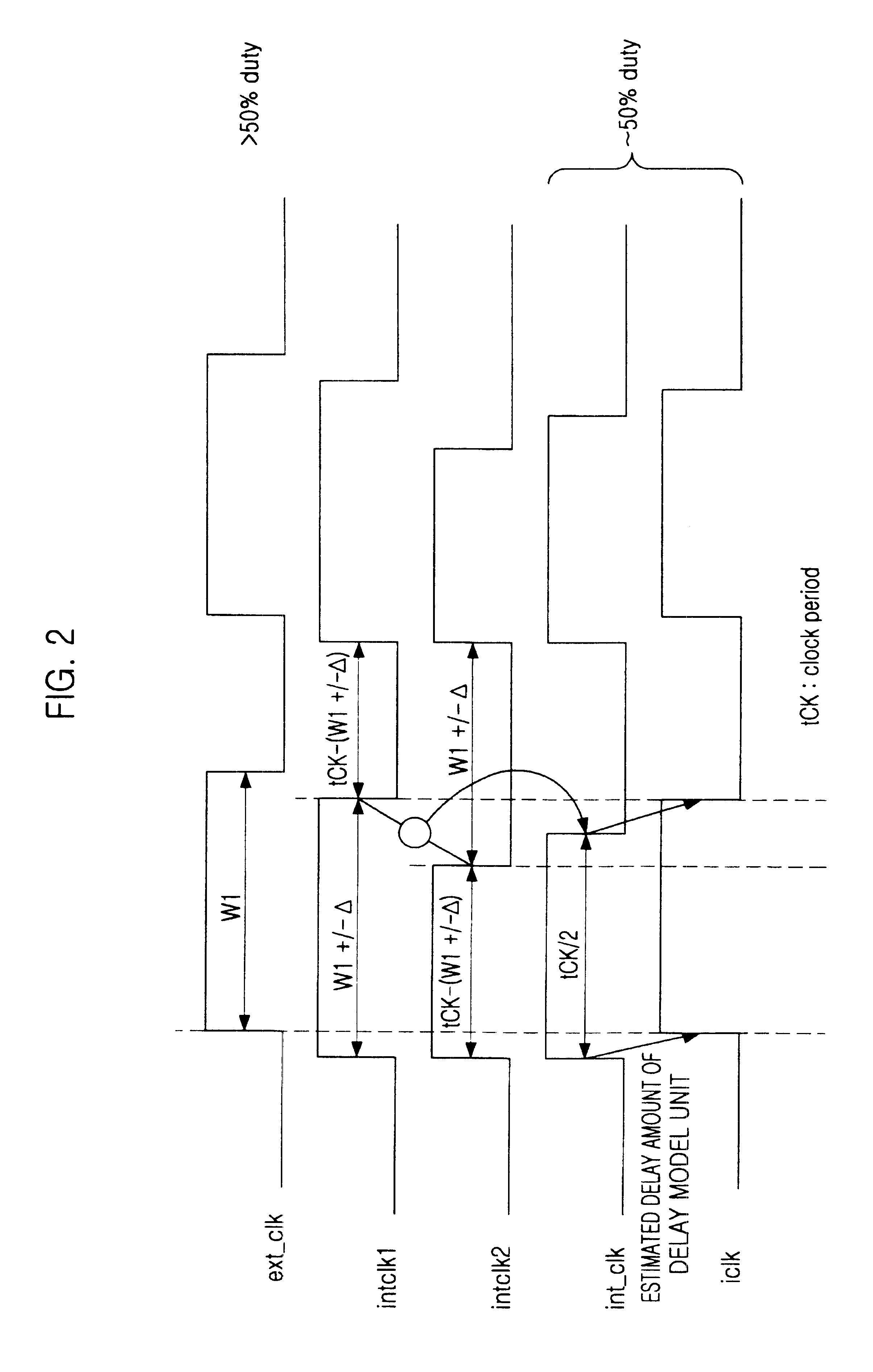

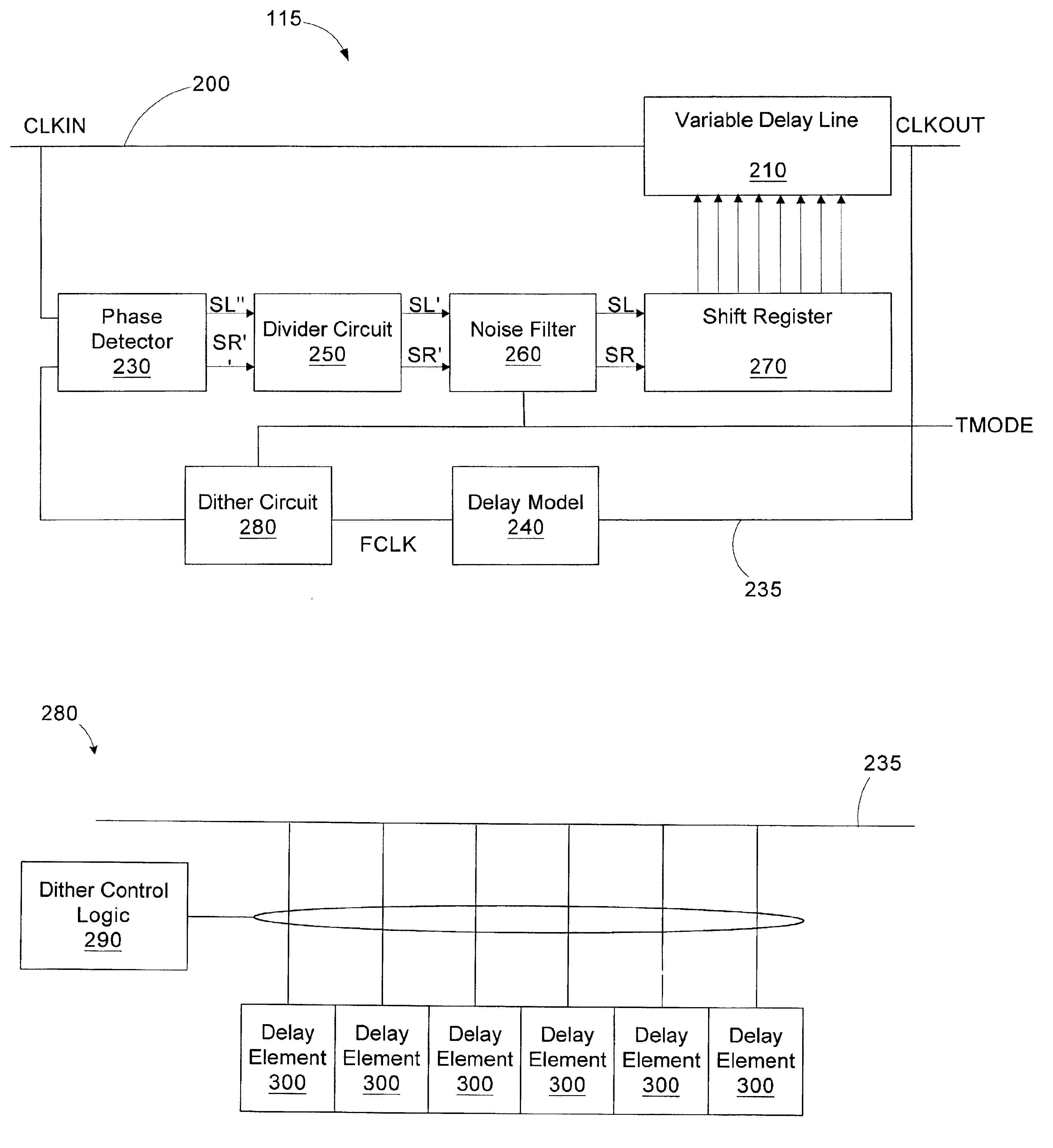

Digital delay locked loop

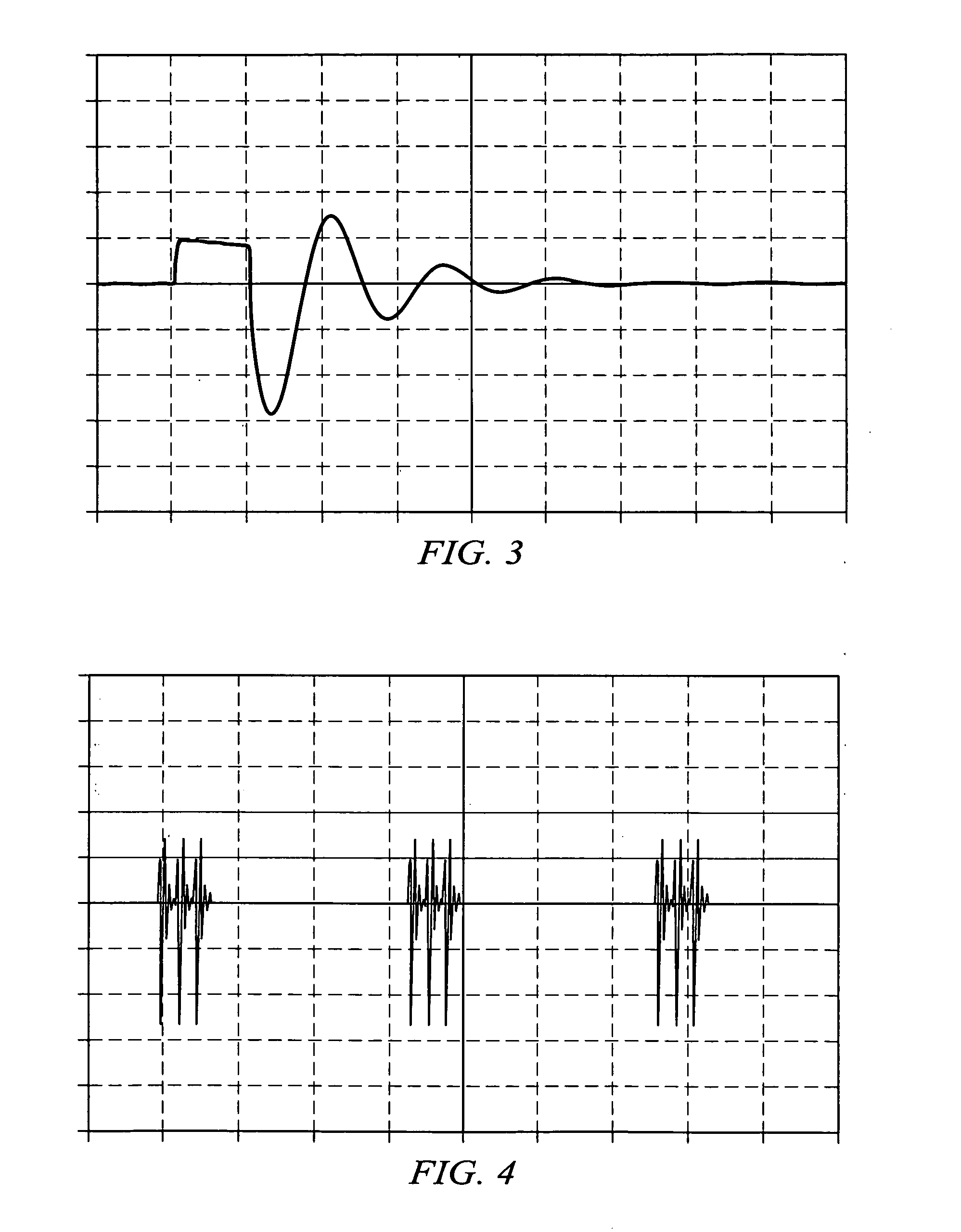

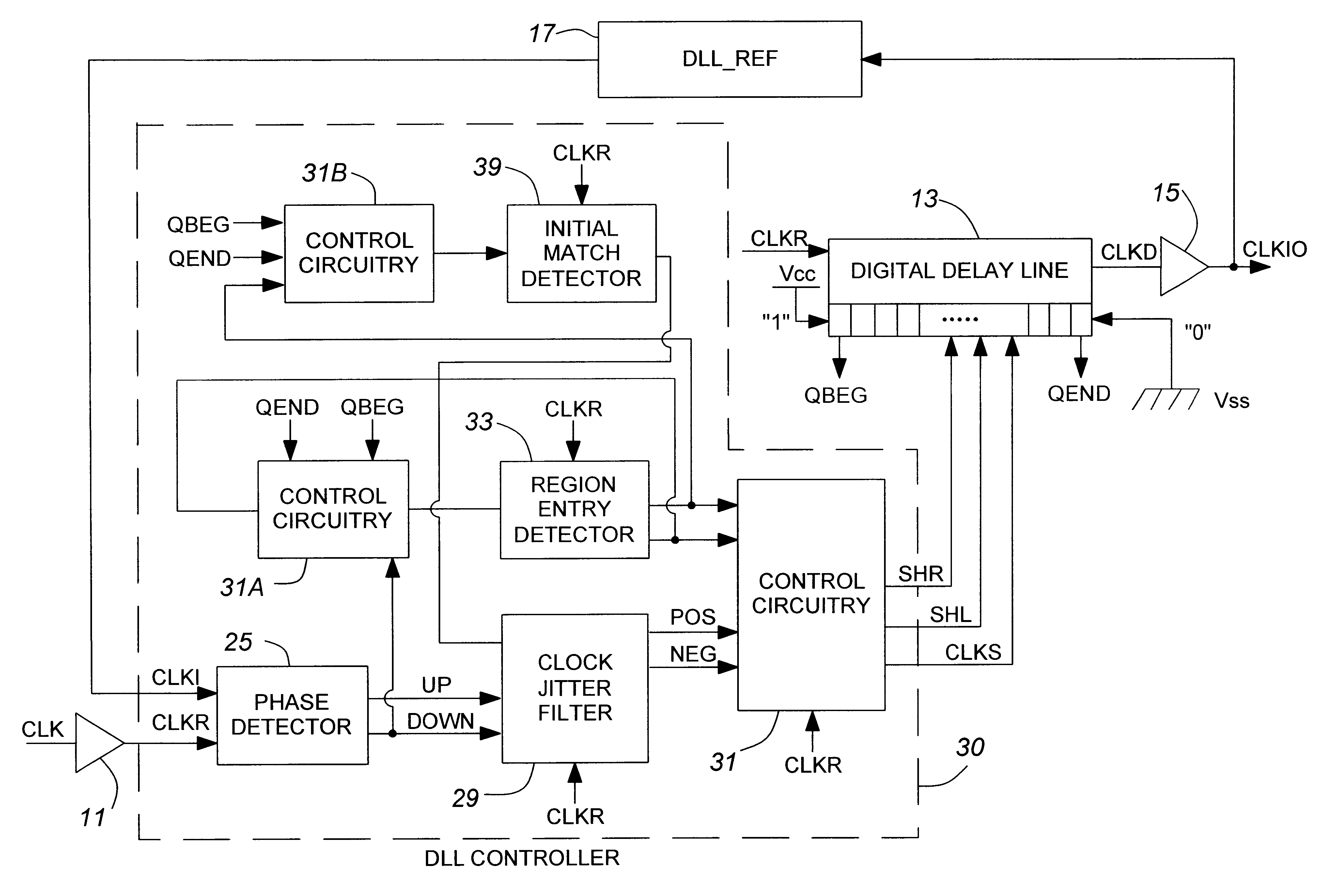

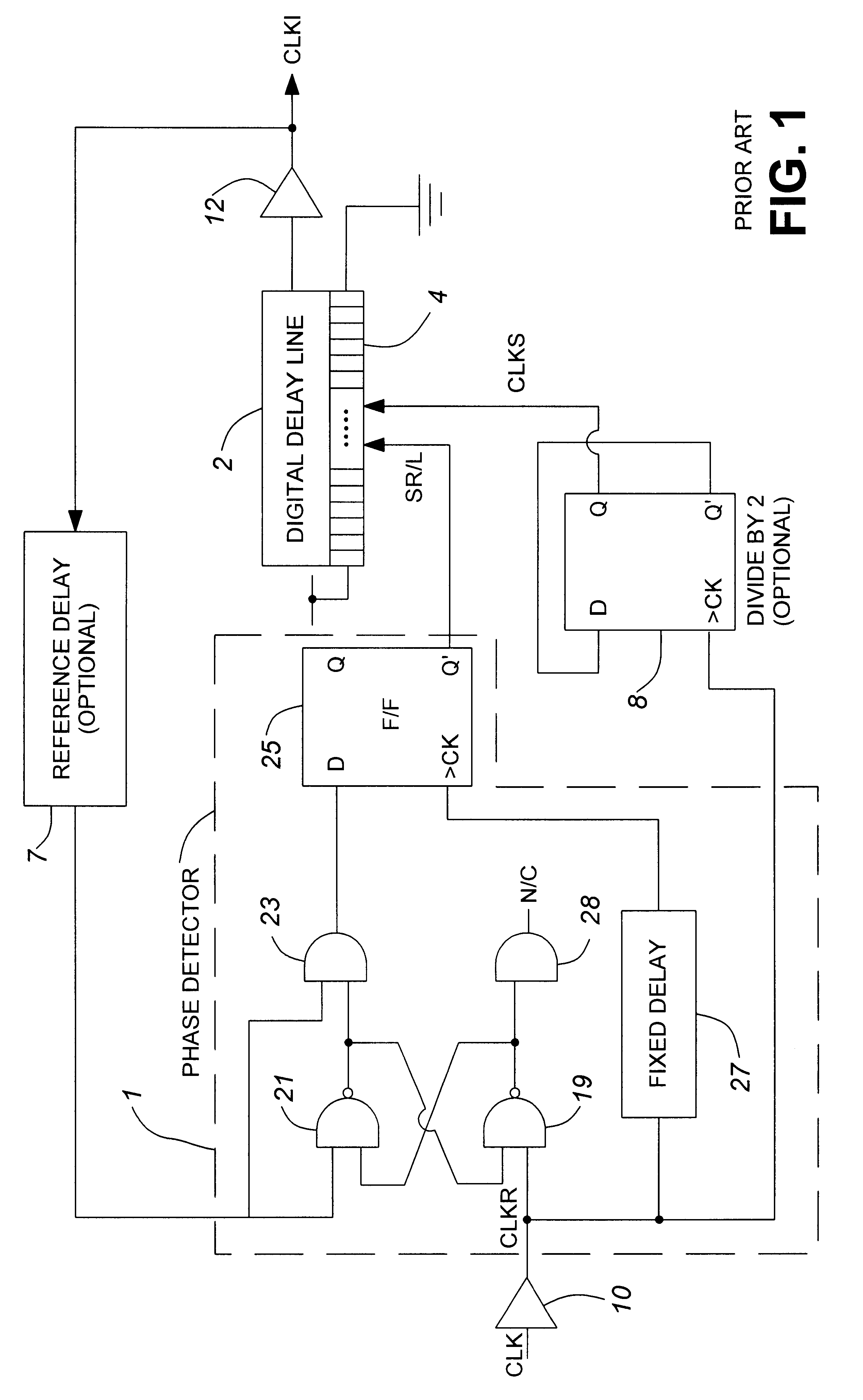

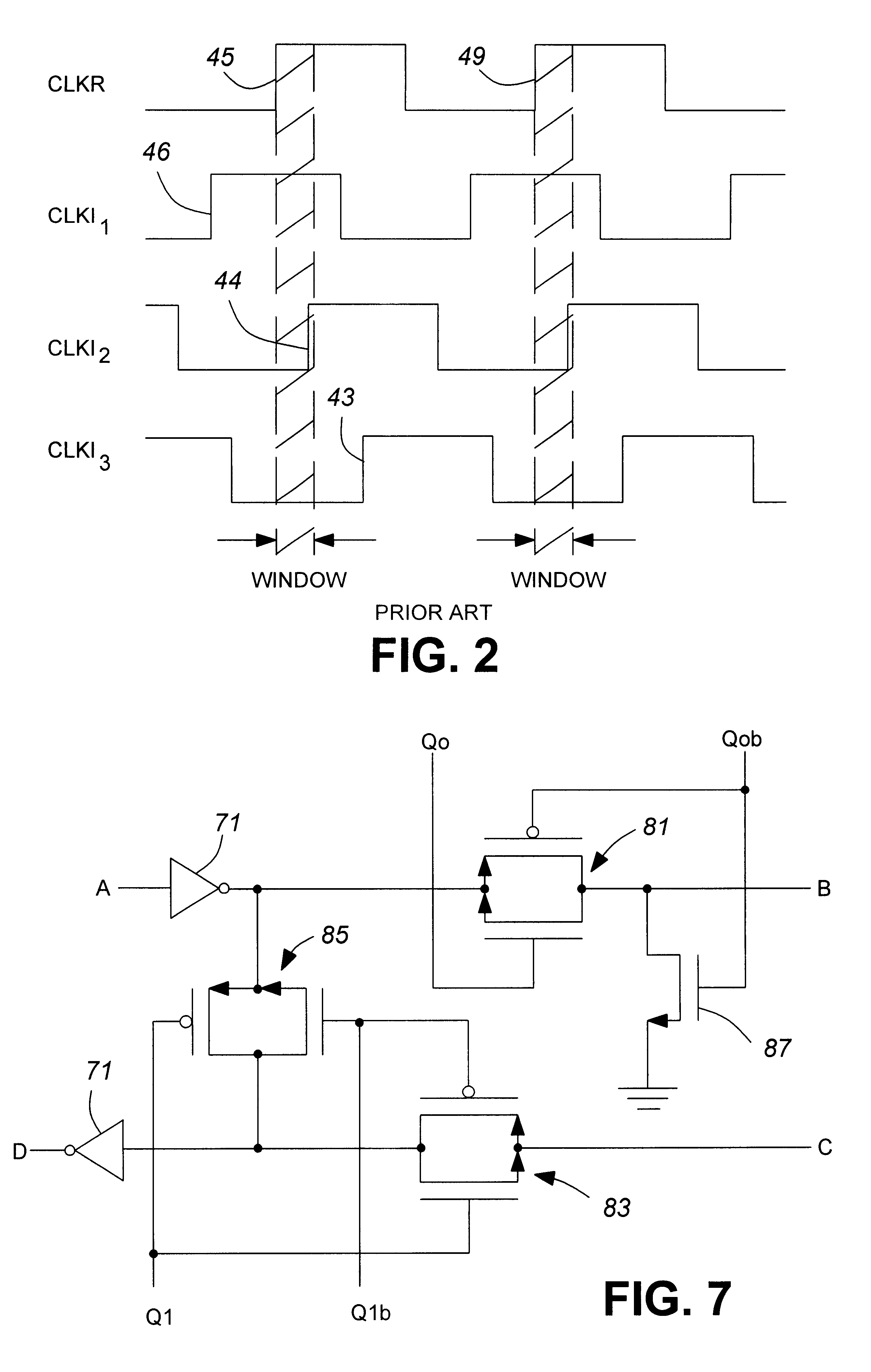

An improved edge-triggered fully digital delay locked loop (DLL), which maintains reliable synchronization from startup and in spite of system clock jitter is described. An internal clock signal is synchronized with a reference clock signal by propagating the reference clock signal through a variable digital delay path. A wide phase detection region surrounds a selected rising edge of the internal clock signal. The DLL loop is open as long as the internal clock signal and a target edge of the reference clock signal are not simultaneously within the phase detection region. To achieve a DLL locked condition, the variable delay is increased from a minimum setting until the edge of the phase detection region is shifted in time just past the target edge of the reference clock. Once the DLL loop has been closed, a clock jitter filter is enabled to reject reference clock jitter effects on the DLL locked condition. A digital phase detector controls the delay line propagation delay to establish synchronization between the internal clock and the reference clock. Unused delay elements within the variable delay path are deactivated to save power.

Owner:CONVERSANT INTPROP MANAGEMENT INC

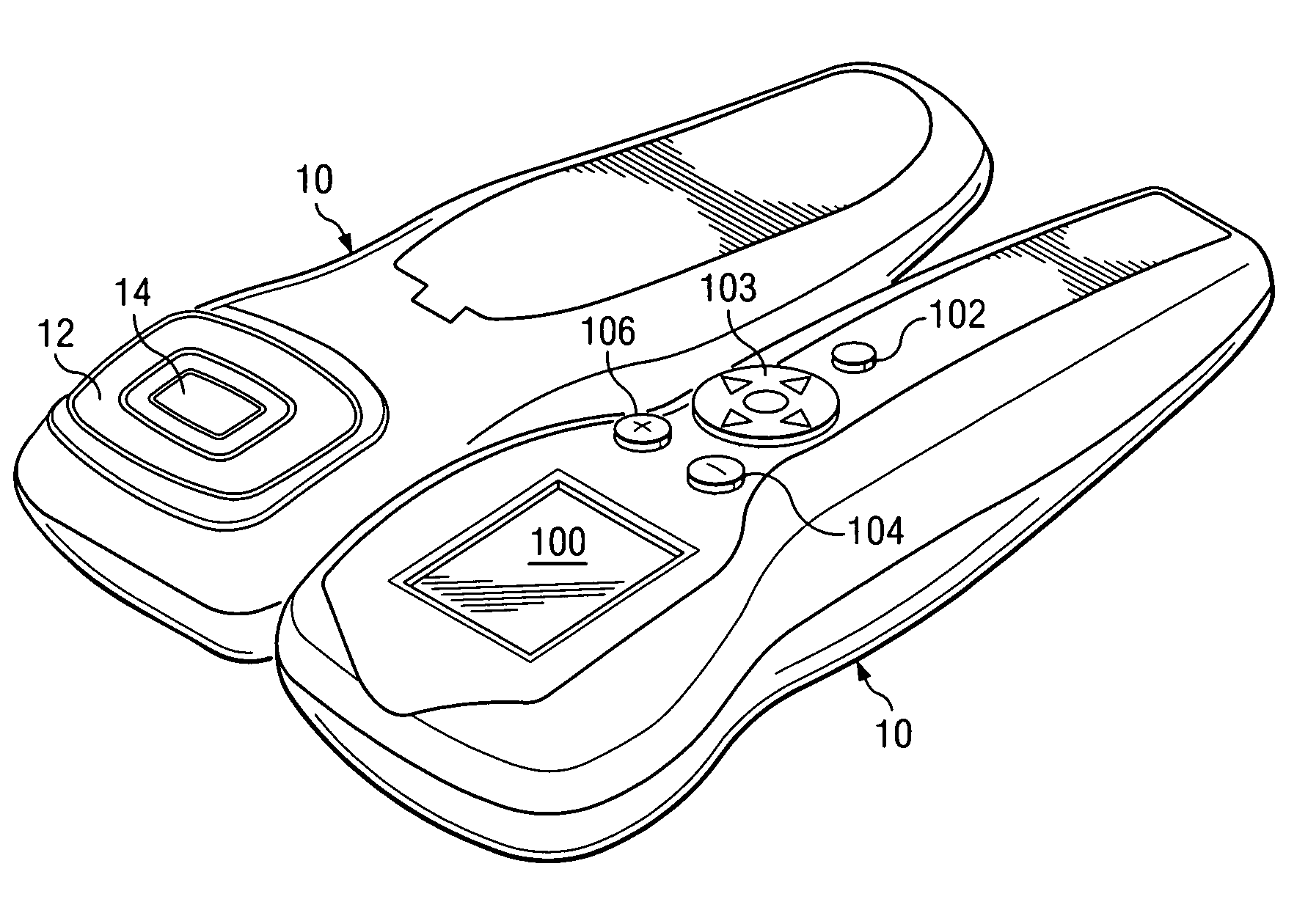

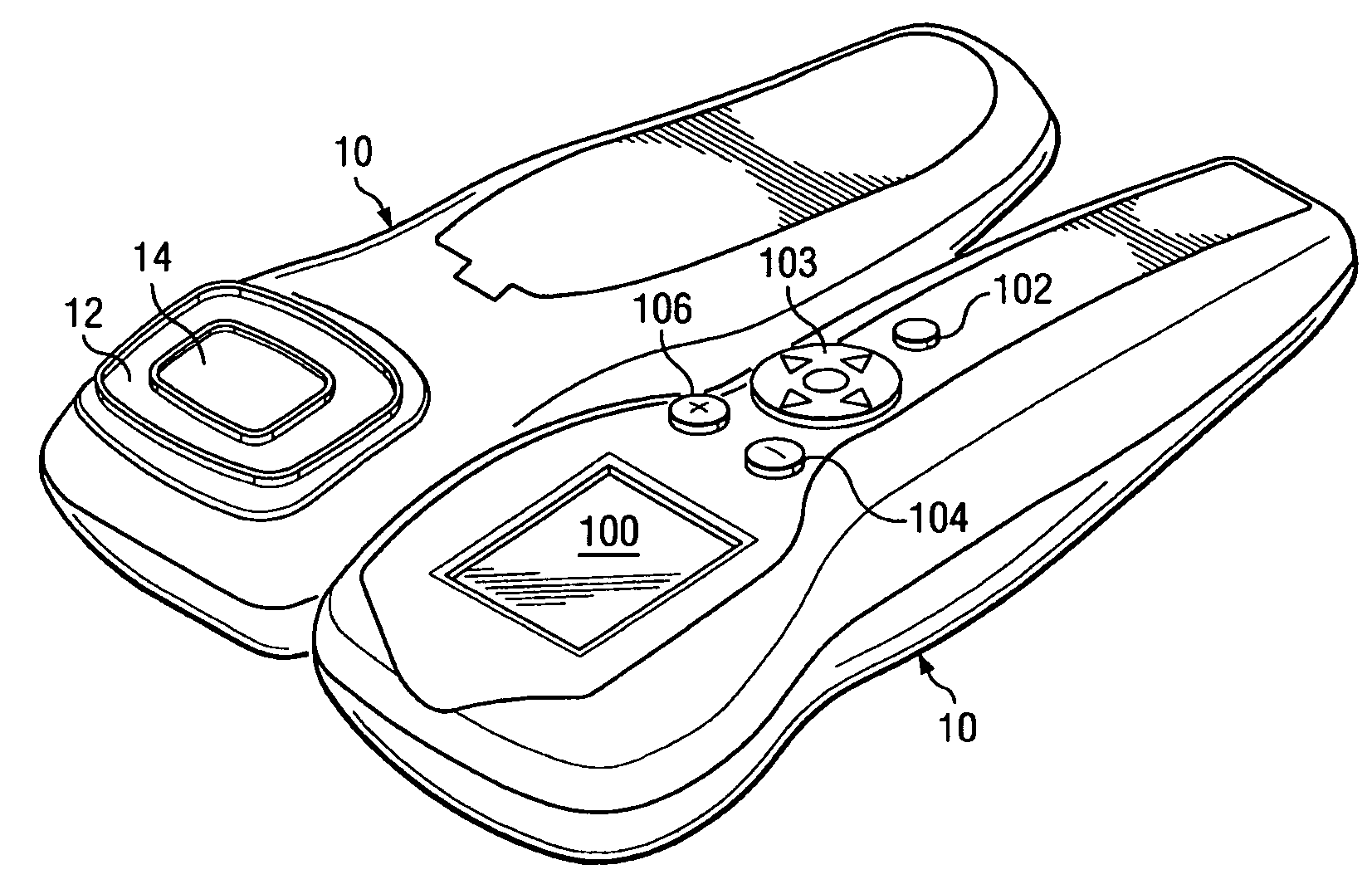

Non-invasive neuro stimulation system

A device (10, 50, 60, 70, 80, 90) is used to apply an electric pulse or spike to a patient to treat the patient. The device can have a series of preset treatments programmed therein. A user can select a treatment from menus displayed on a display (100). The impedance of the skin and underlying tissue to be treated can be measured prior to the treatment to locate active areas on the skin for treatment. The impedance measurement can be made at a sufficiently low level to avoid treatment of the patient that could cause a change in the impedance. A phase detector can be used to isolate the capacitance value in the impedance. The charge delivered to the patient can be measured and the device can adjust the charge as the skin impedance varies during treatment to deliver uniform charges to the skin. A variety of probes can be used with the device, with the device automatically detecting the type of probe attached. Multiple electrodes can be used on the probe, which allows the active areas in contact with the probe to be identified prior to treatment to allow the treatment to concentrate on the active areas.

Owner:HTK ENTERPRISES INC

Digital delay locked loop

Owner:CONVERSANT INTPROP MANAGEMENT INC

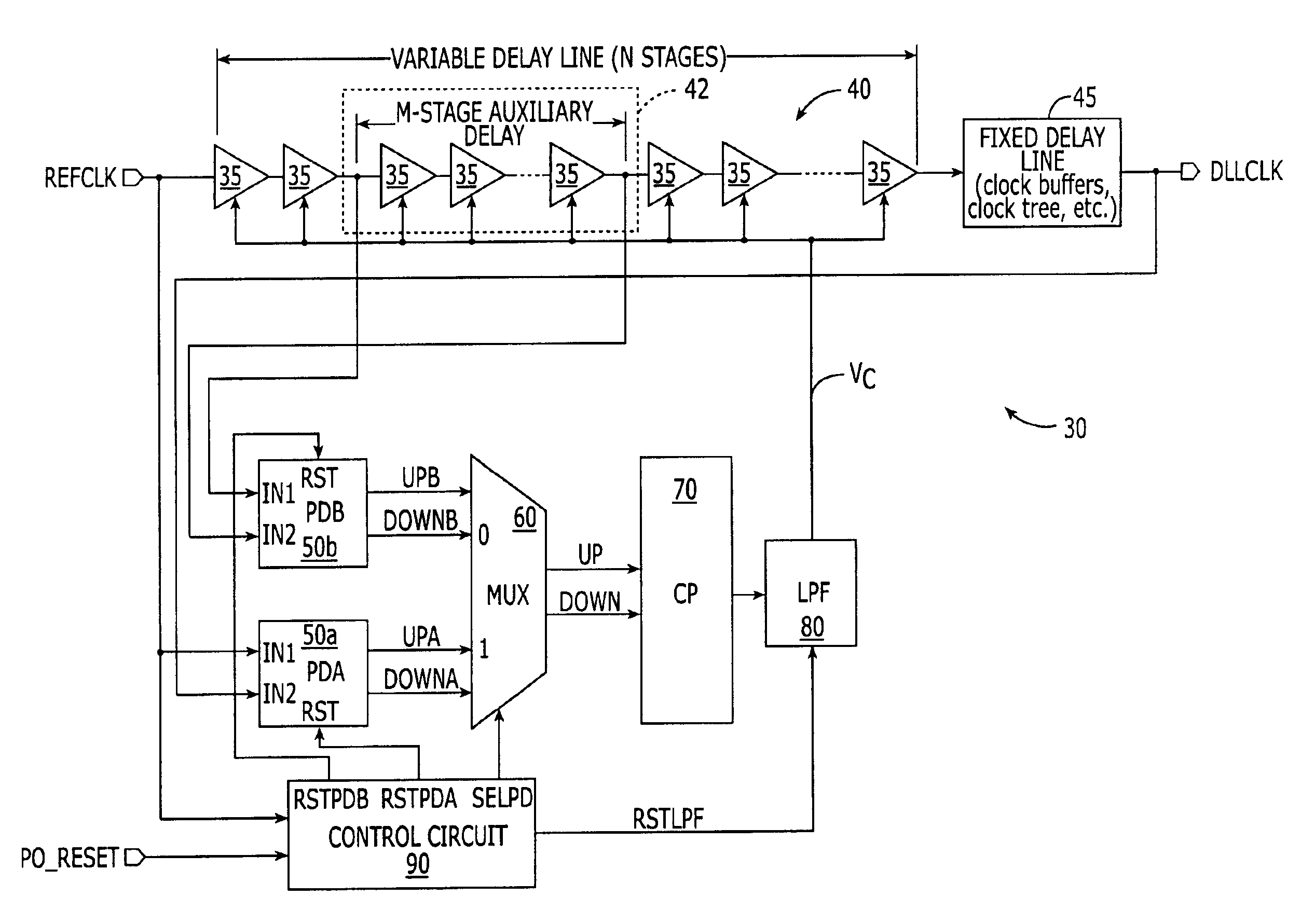

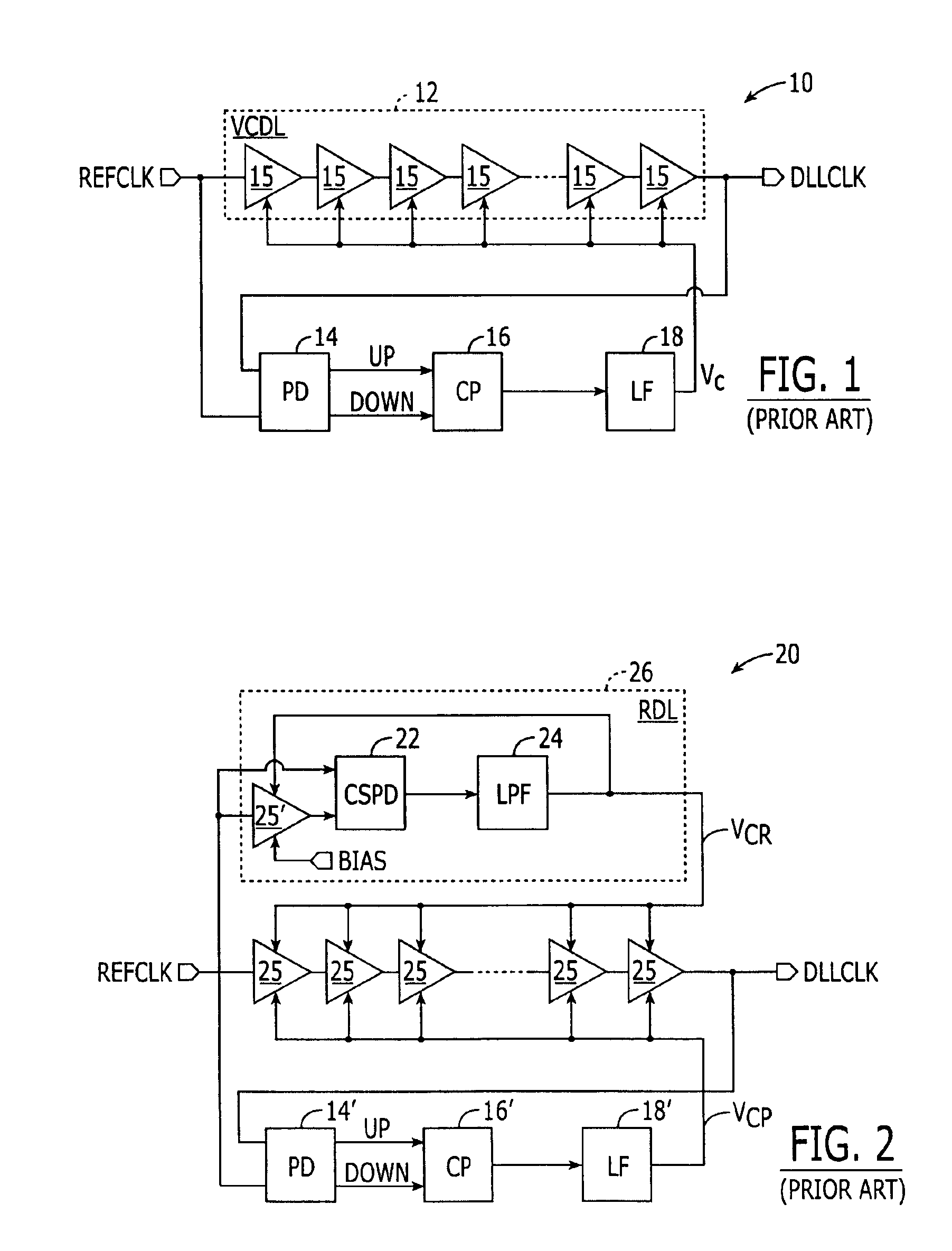

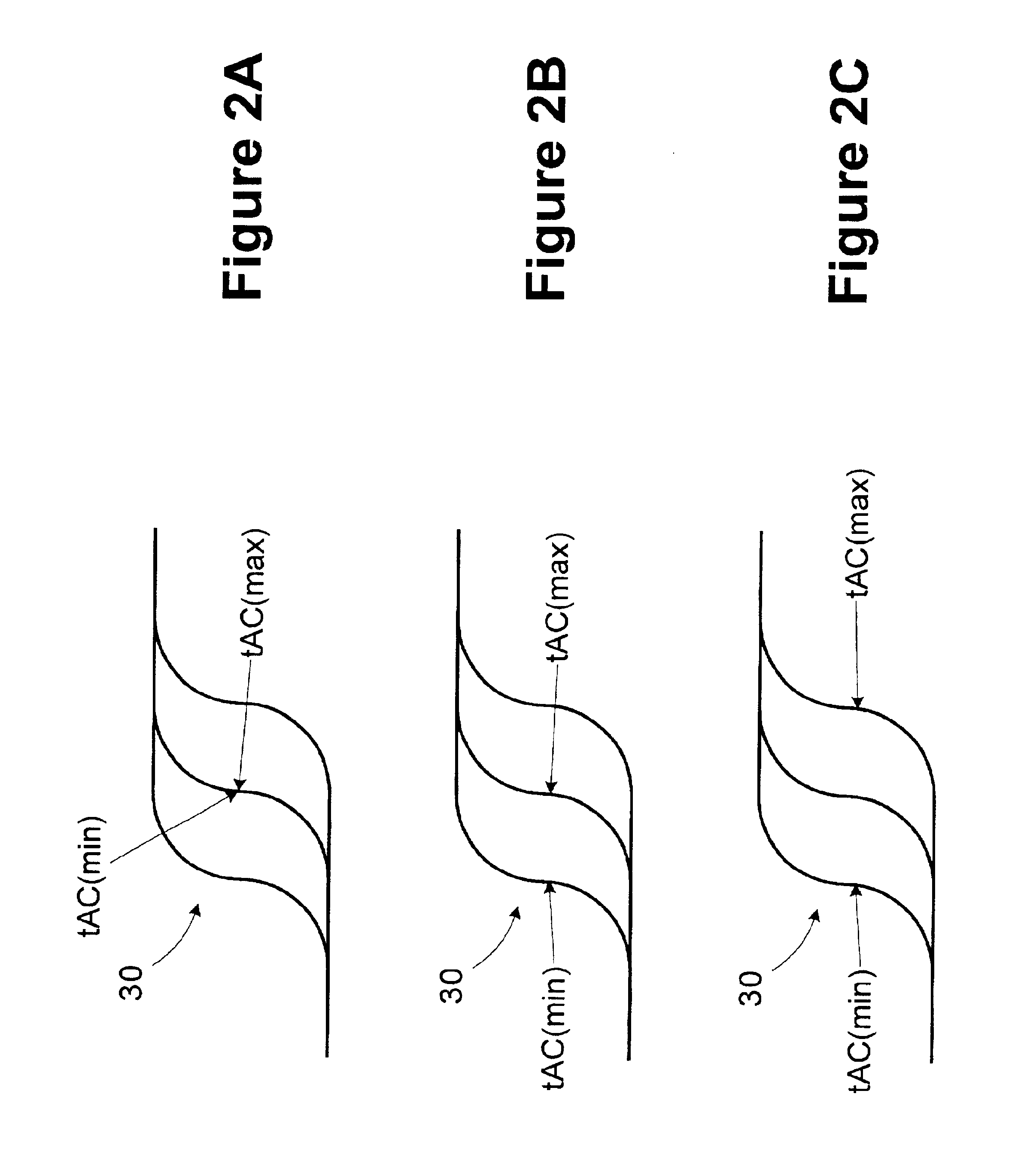

Delay-locked loop (DLL) integrated circuits having high bandwidth and reliable locking characteristics

Delay-locked loops have high bandwidth locking characteristics that are less susceptible process, voltage and temperature (PVT) variations. These DLLs are configured to support transition from a partial feedback loop lock condition to a full feedback loop lock condition during a start-up time interval, in order to insure that a multi-cycle lock condition is established at the time the DLL's clock signal output becomes available. The DLL may include a variable delay line that is responsive to a reference clock signal, an auxiliary phase detector that is electrically coupled to the variable delay line, and a main phase detector that is responsive to the reference clock signal and a feedback clock signal (DLLCLK). The auxiliary phase detector may be an edge-triggered SR-type phase detector and the main phase detector may be a three-state phase frequency detector.

Owner:INTEGRATED DEVICE TECH INC

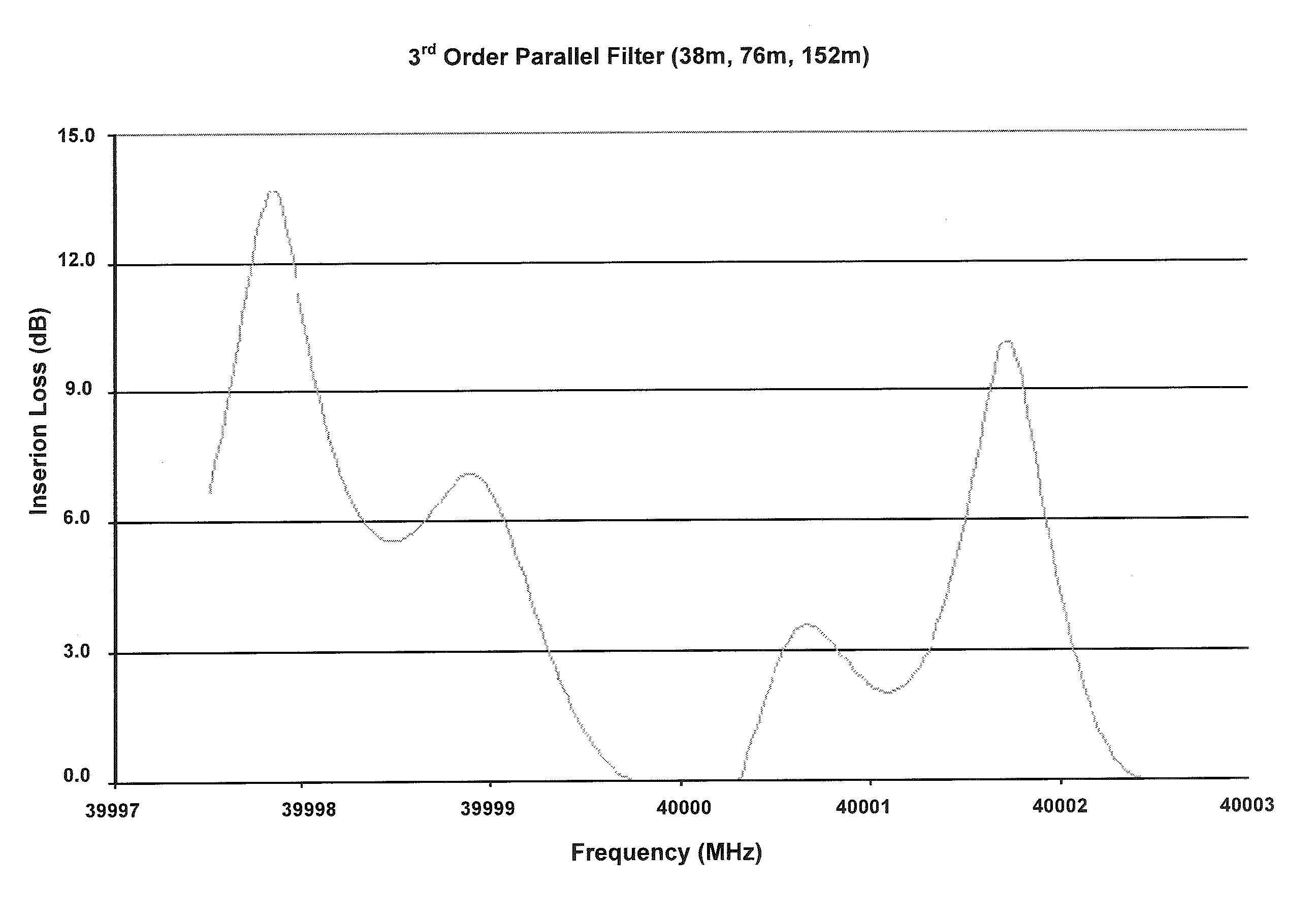

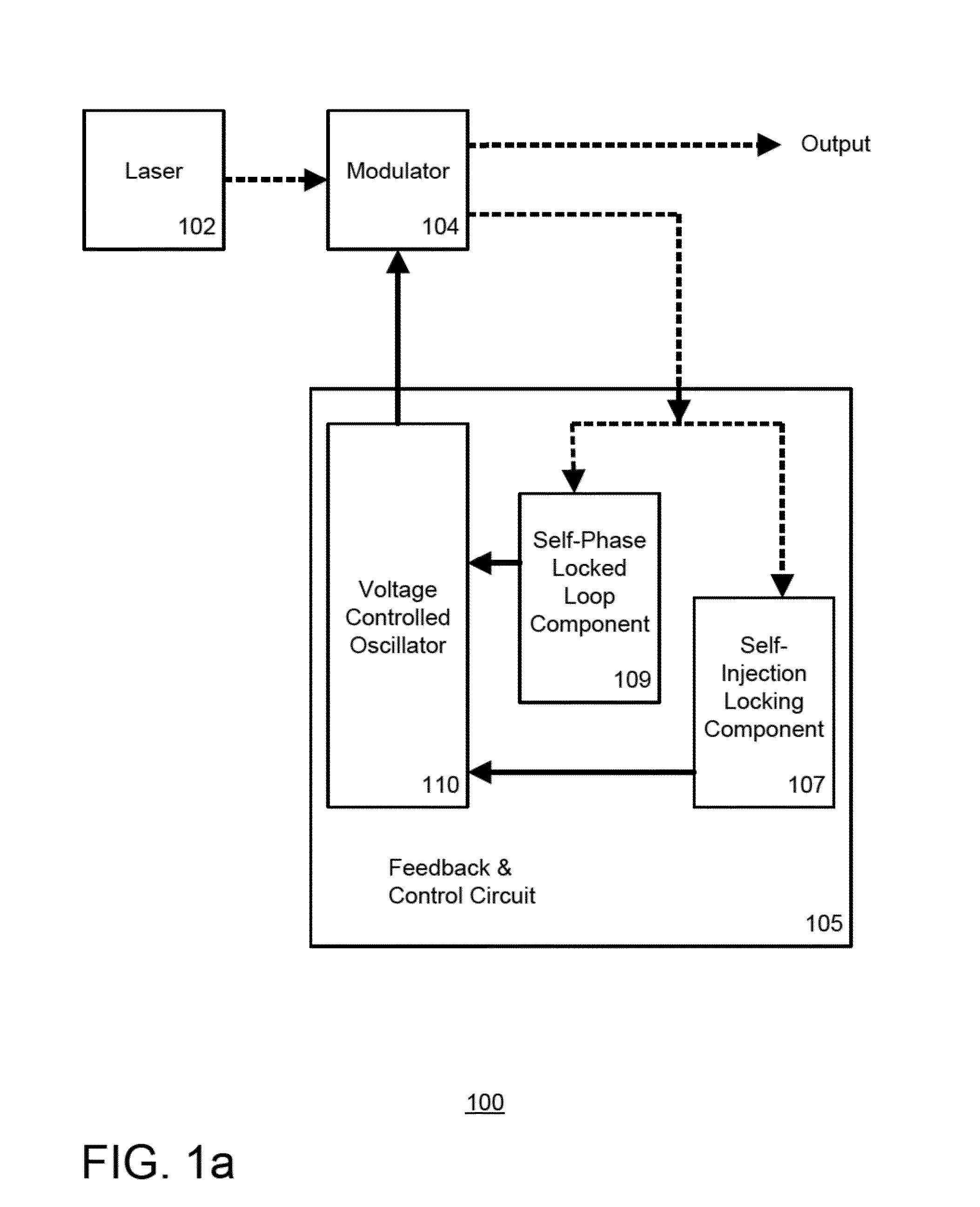

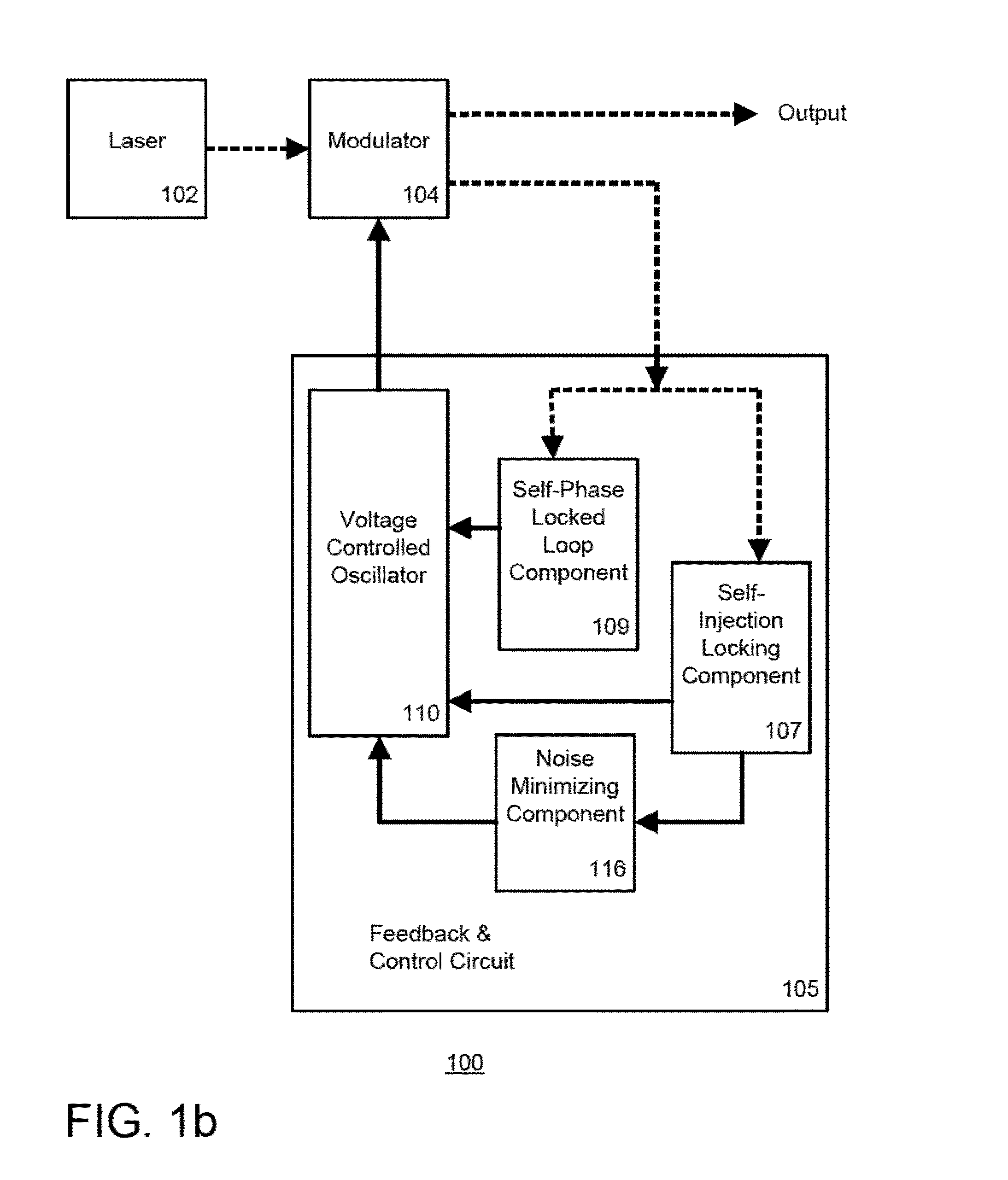

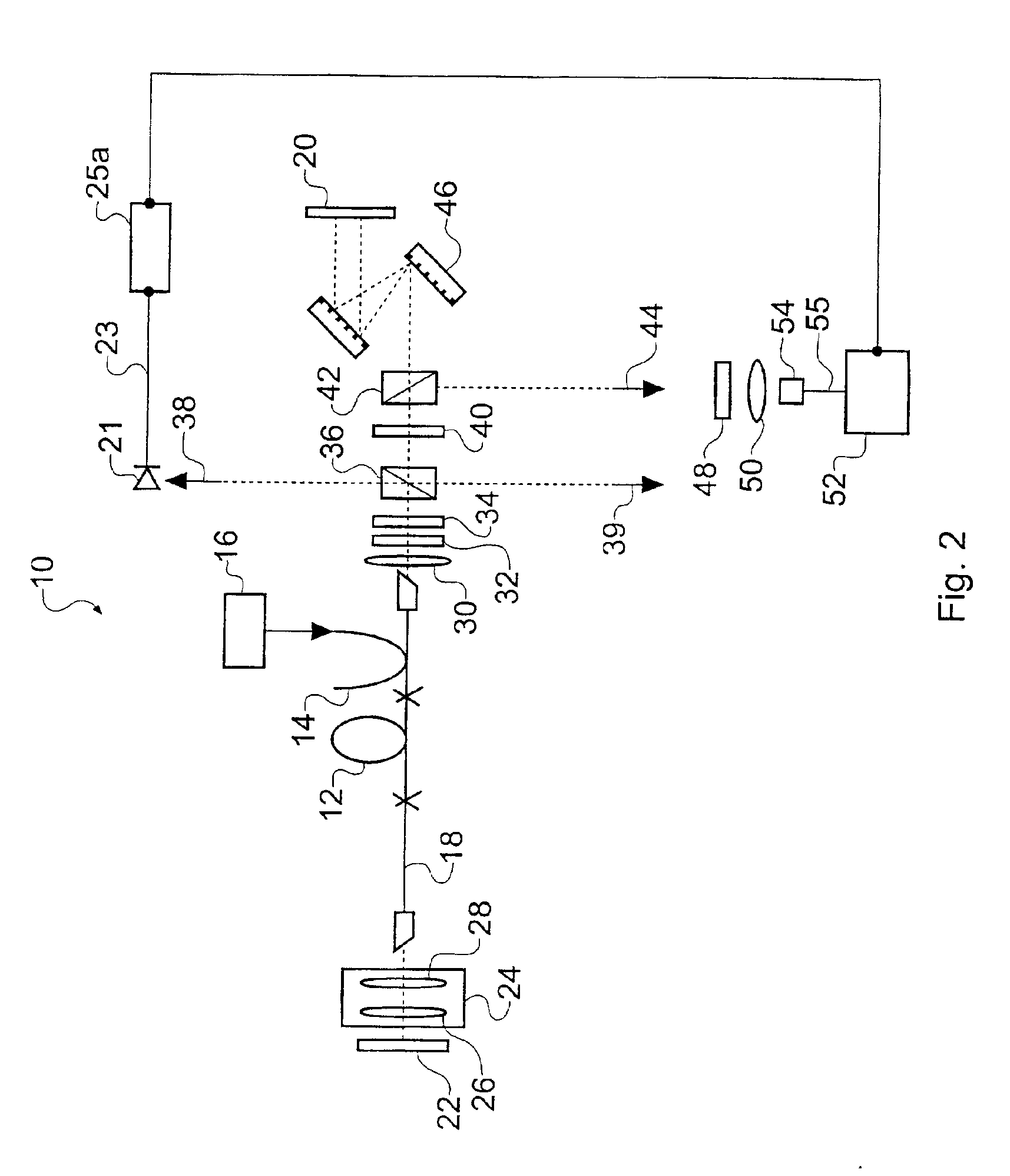

Self injection locked phase locked looped optoelectronic oscillator

Aspects of the disclosure relate generally to a circuit for sustaining an radio frequency (RF) modulated optical signal. The circuit may comprise a self injection locking component having a fiber optic delay line over which a portion of the optical signal propagates. The circuit may also comprise a self phase locked loop component having at least two fiber optic cables having different lengths and over which another portion of the optical signal propagates and a phase detector coupled to the at least two fiber optic cables and configured to determine a phase difference between the signals propagating over one of the respective fiber optic cables. The circuit may further comprise a voltage controlled oscillator configured to generate a stable oscillating signal in response to signals generated by each of the self injection locking and self phase locked loop components, the stable oscillating signal being configured to sustain the optical signal.

Owner:SYNERGY MICROWAVE CORP

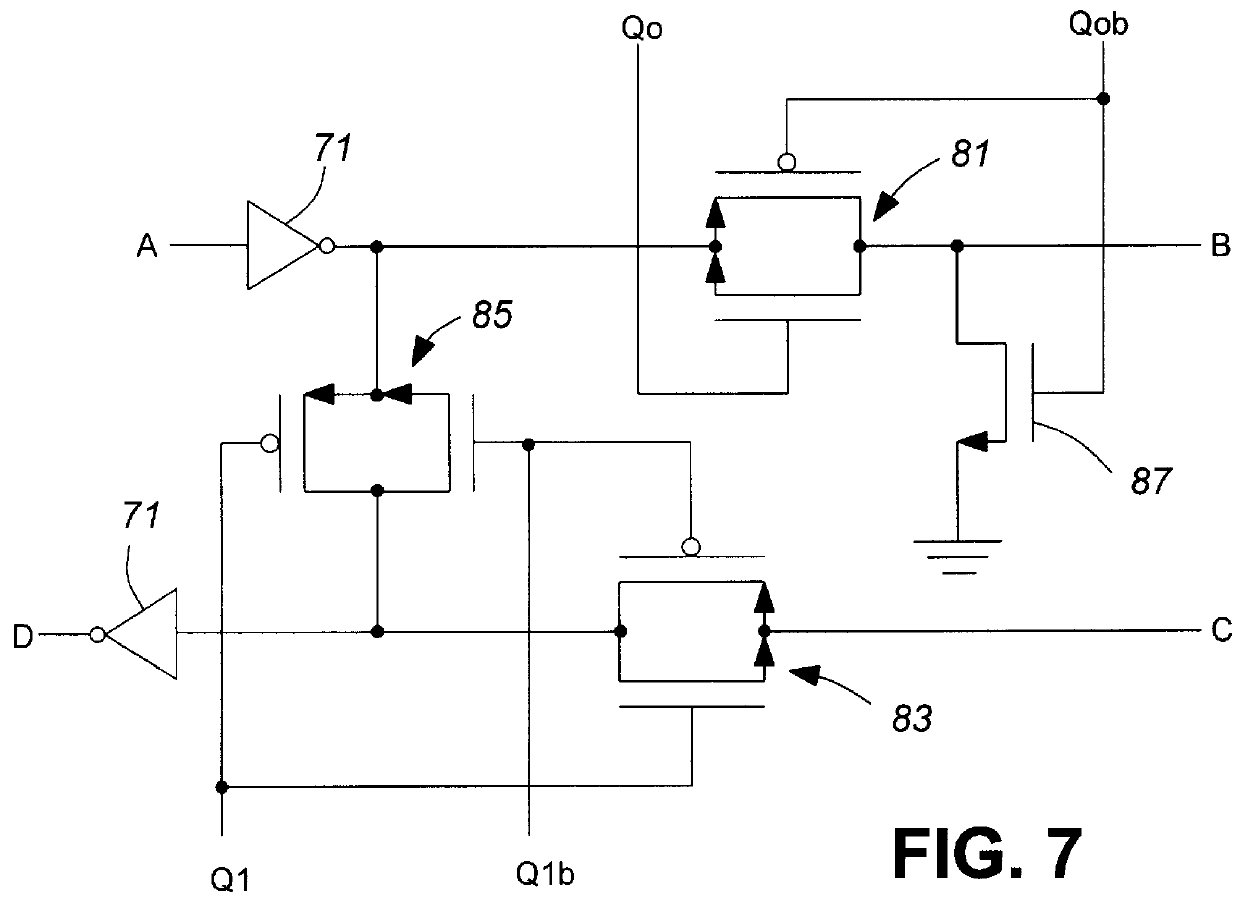

Linear phase interpolator and phase detector

ActiveUS20090103675A1Pulse automatic controlAngle demodulation by phase difference detectionPhase detectorOperating point

A novel interpolating phase detector for use in a multiphase PLL is described comprising an array of individual phase comparators, all operating at essentially the same operating point which permits the circuits to be designed simultaneously for high speed and for low power consumption. Two adjacent phase outputs of a multi-phase VCO may be selected and interpolated in between, by selectively attaching a variable number of phase comparators to each phase output and summing their phase error outputs. By varying the number of phase comparators attached to each phase output, interpolation can be achieved with high linearity.

Owner:RAMBUS INC

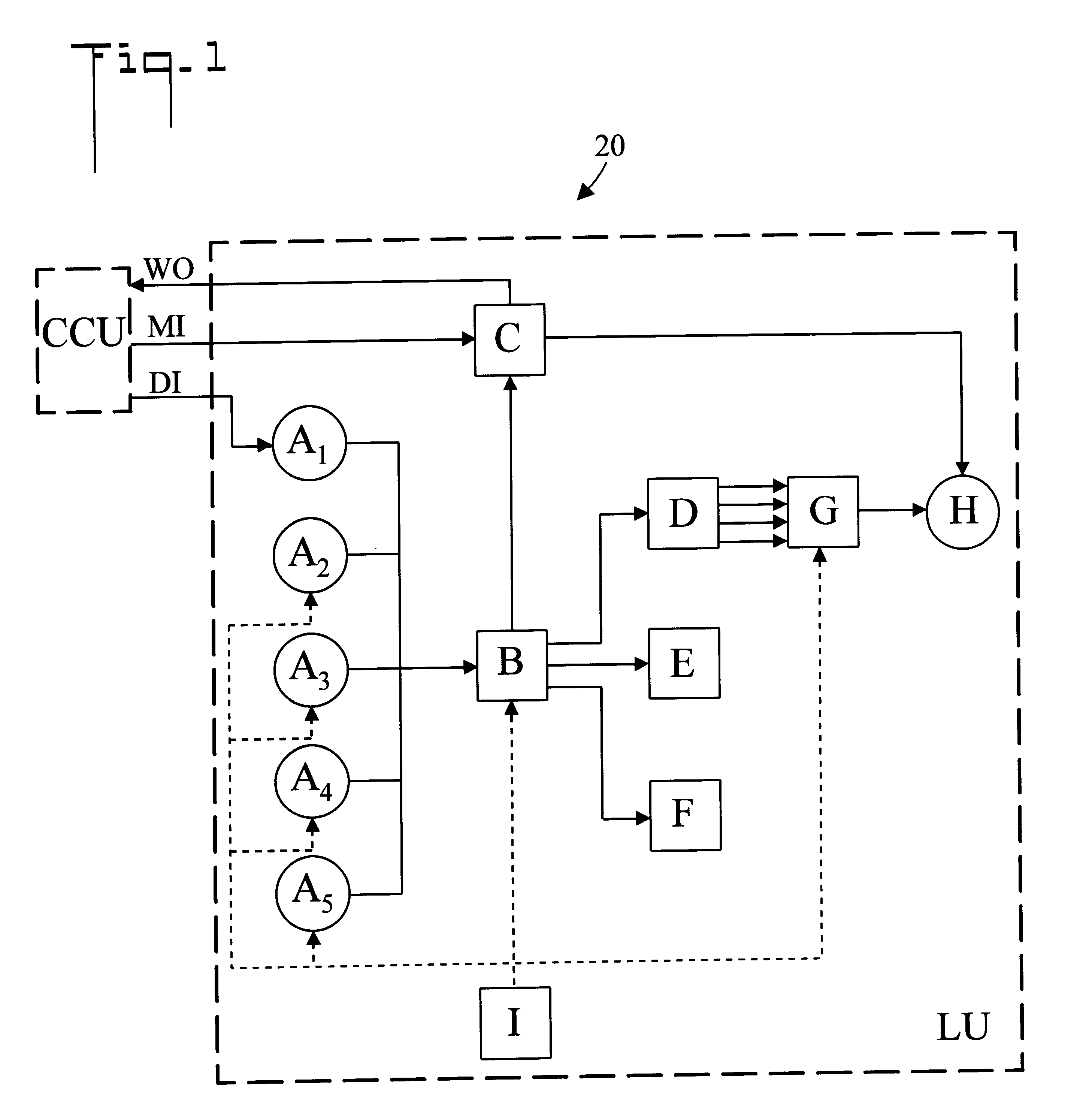

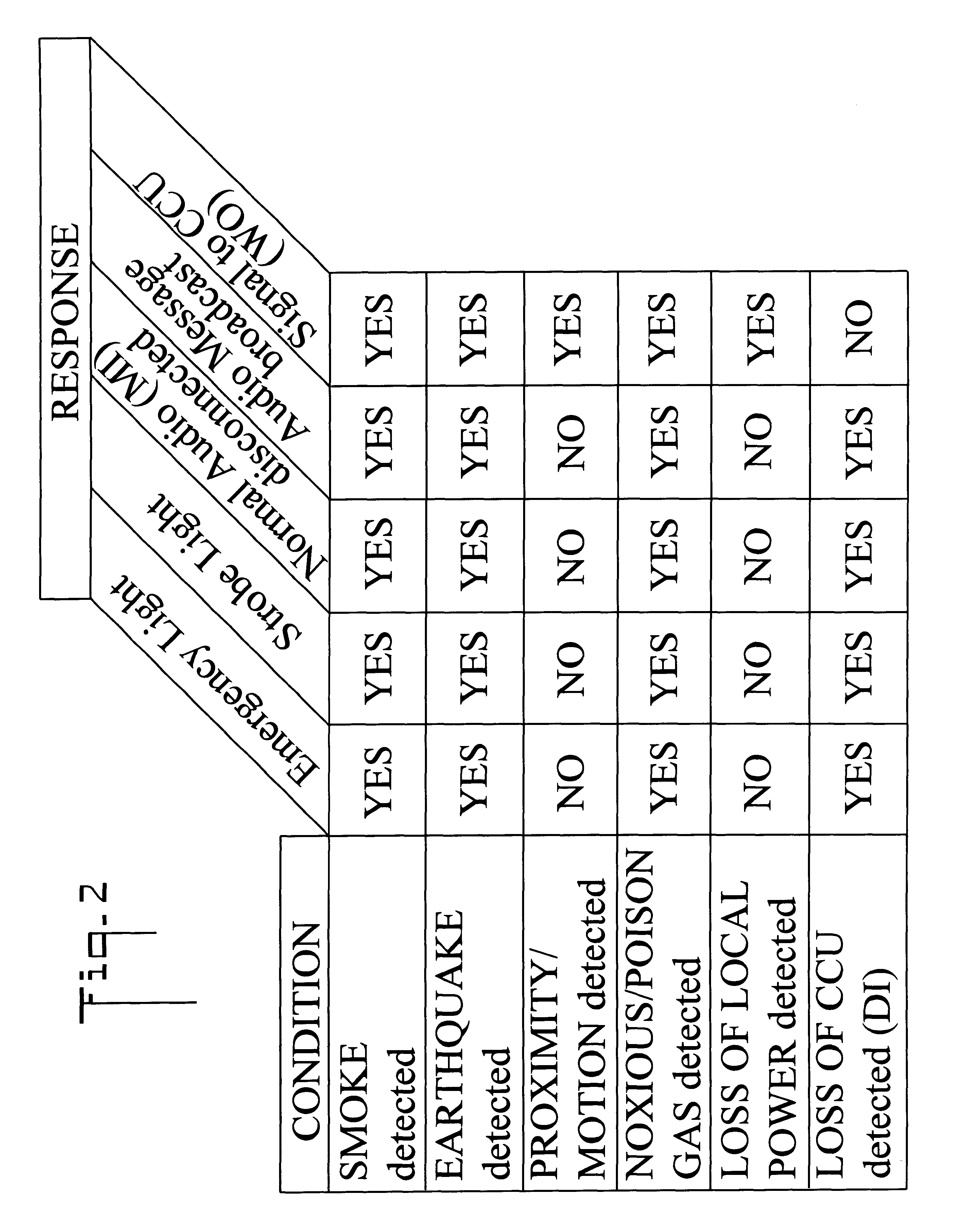

Warning system

InactiveUS6518878B1Frequency-division multiplex detailsTelephonic communicationSmoke detectorsPhase detector

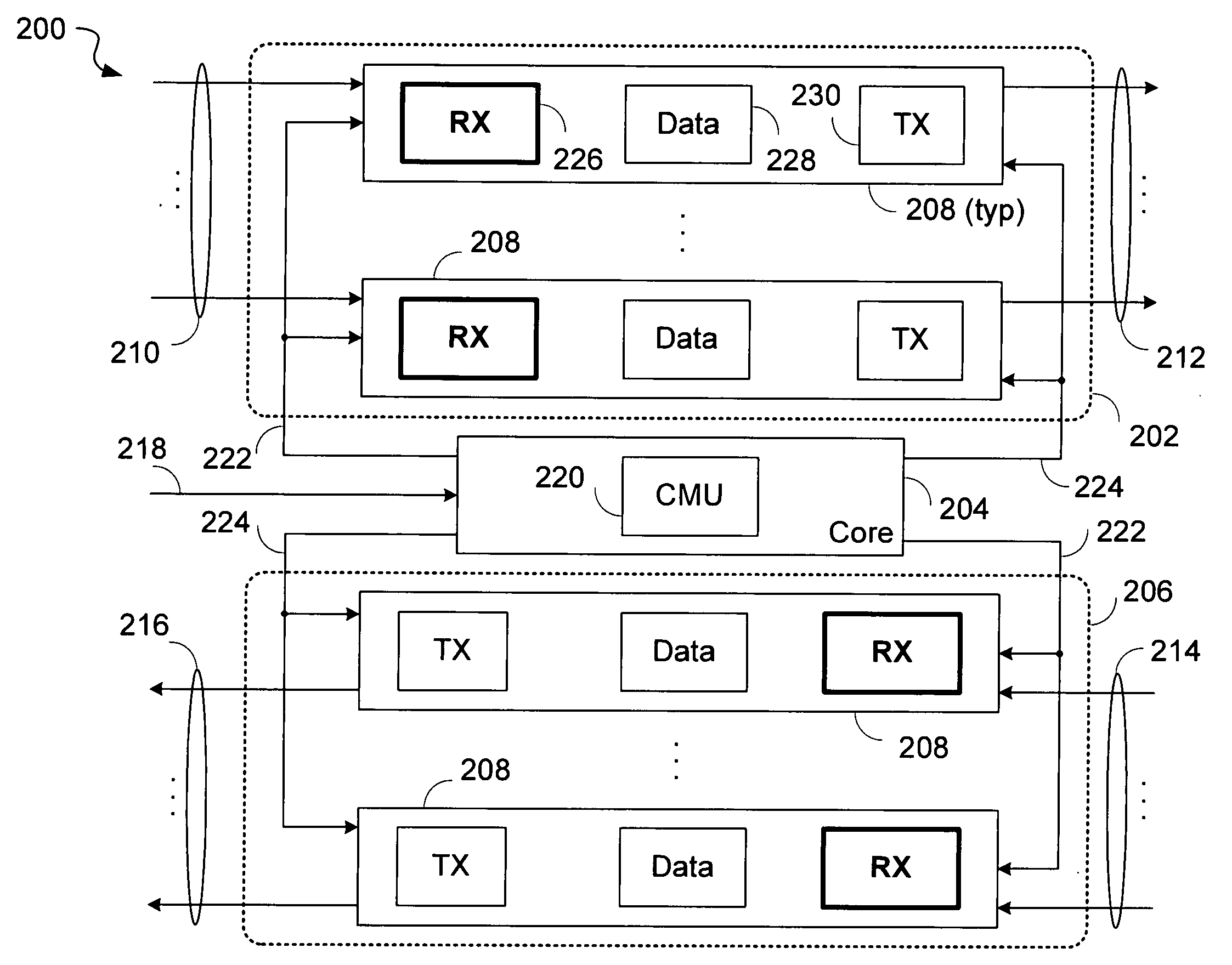

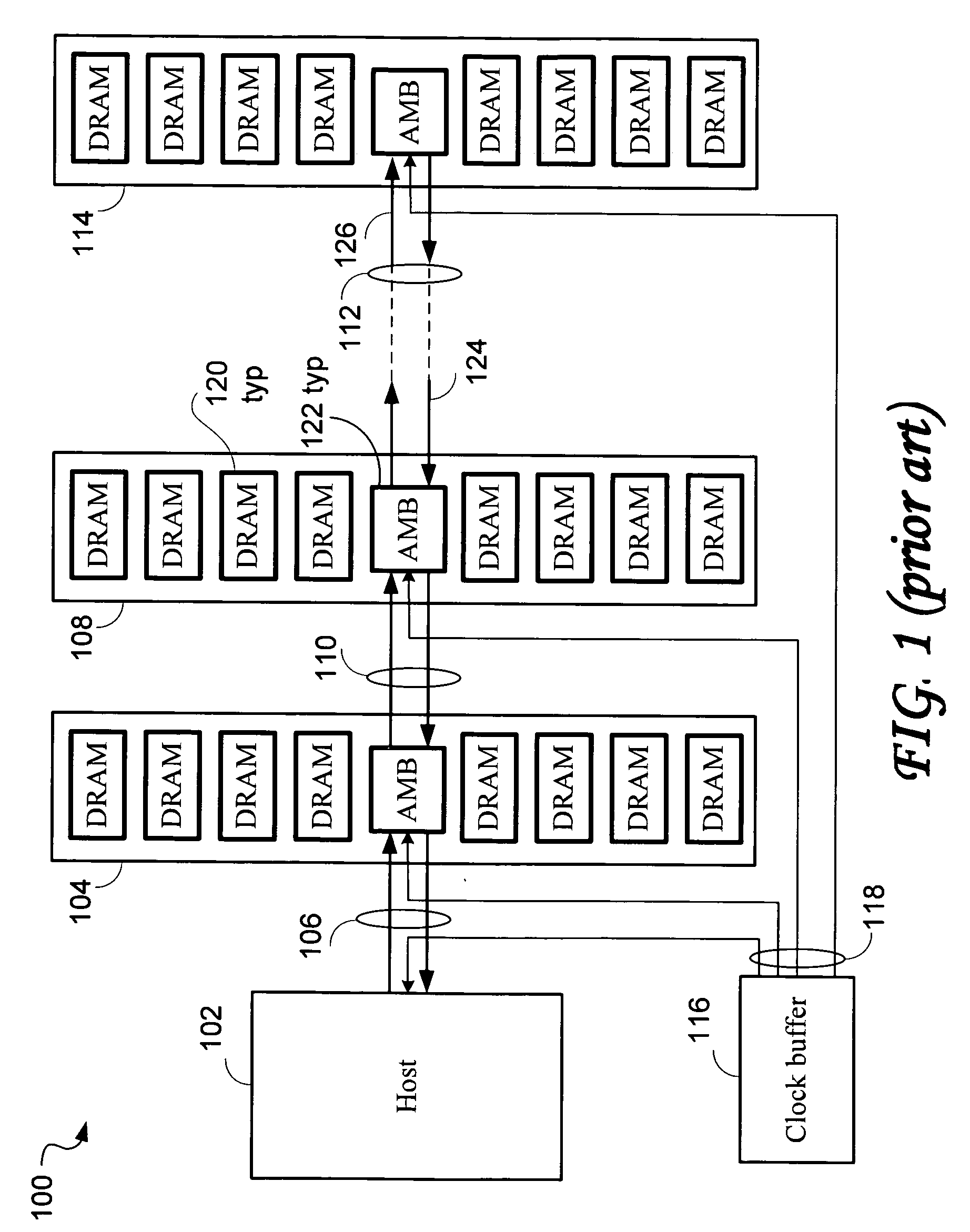

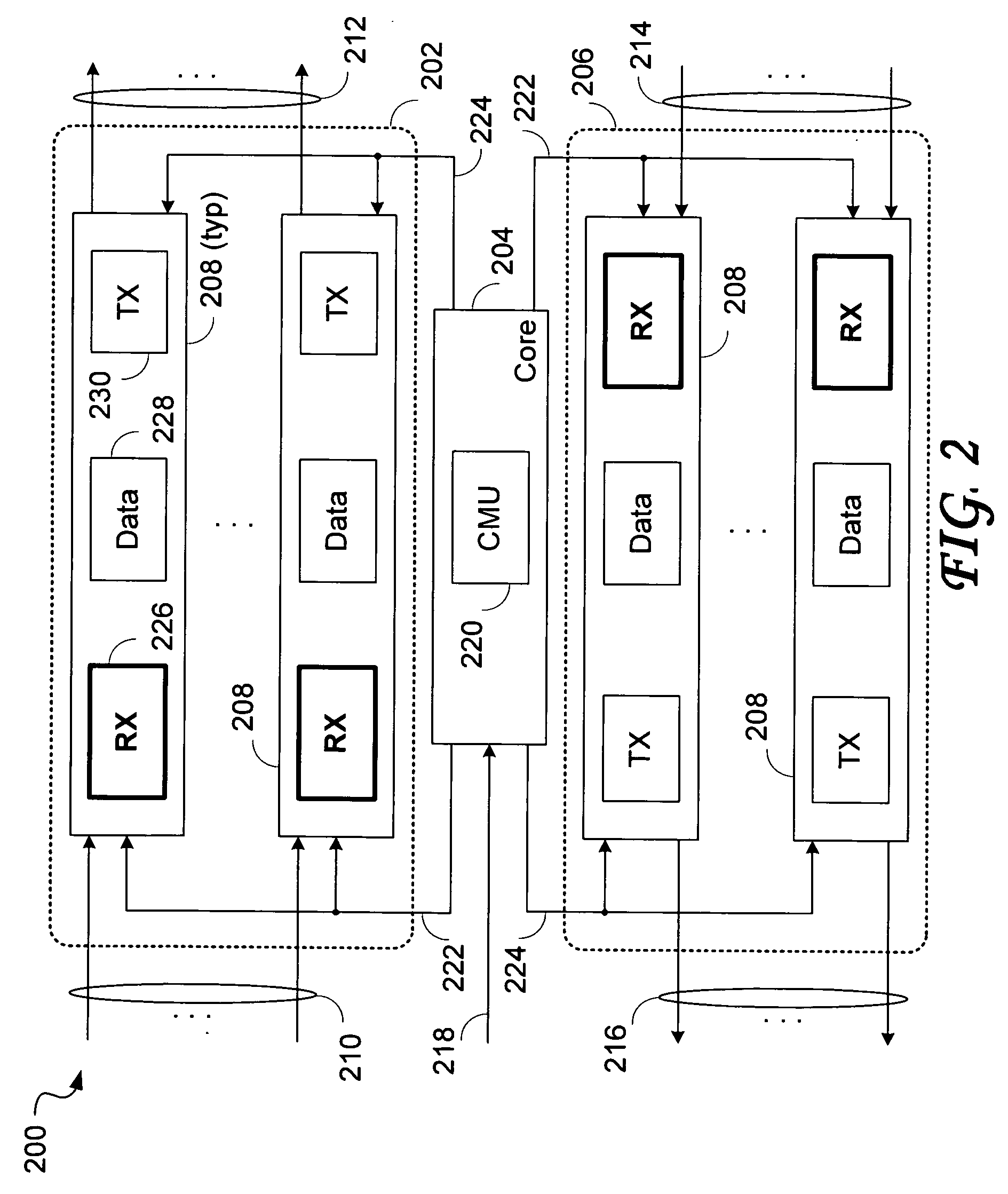

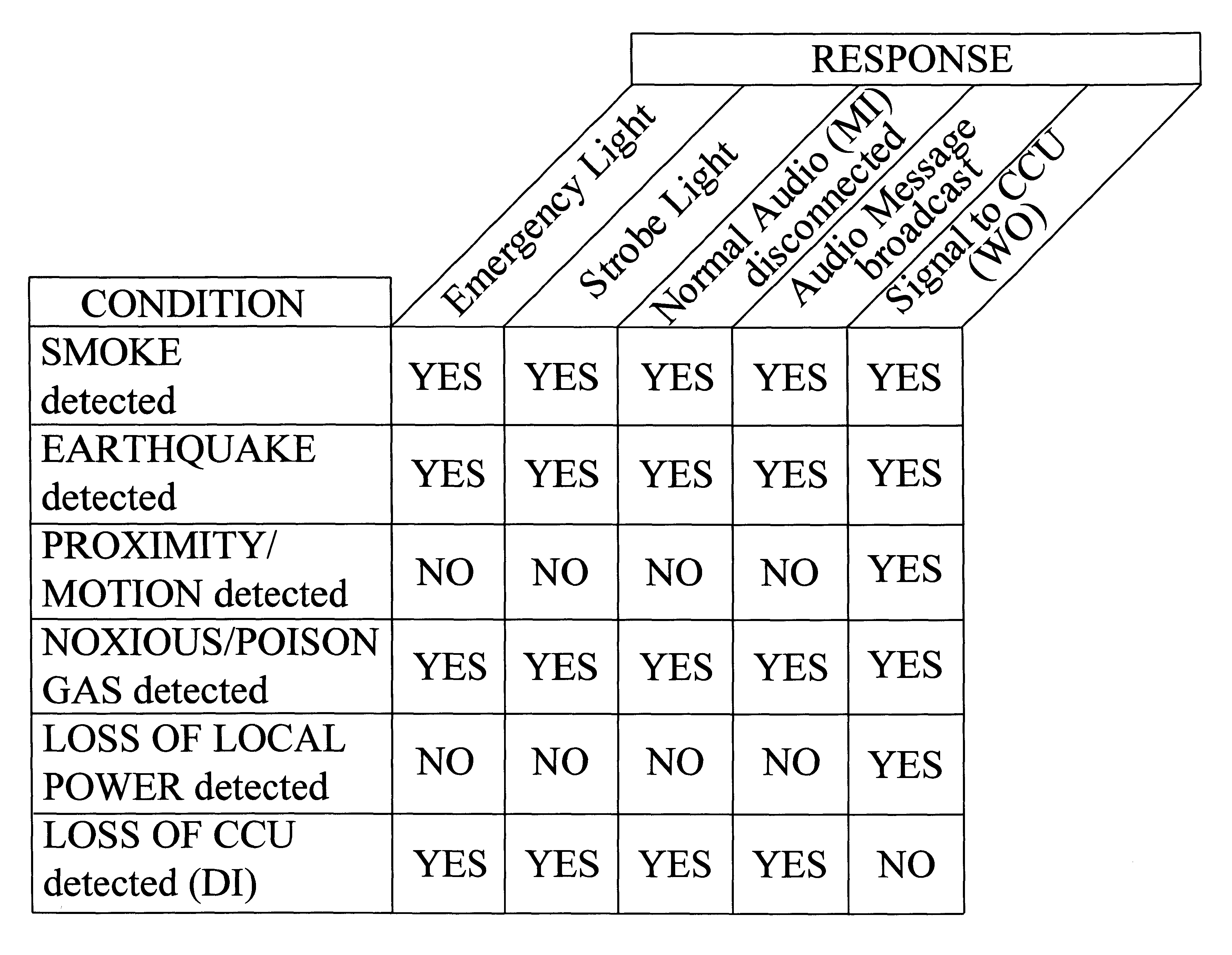

A warning system (20) includes a central control unit (CCU), and a plurality of local units (LU) connected to the central control unit (CCU). Each local unit (LU) includes a plurality of input trips (An), such as smoke detector, an earthquake detector, and gas detector, and a plurality of programmable responses, such as a bypass relay (C), a message delivered by a record / playback unit (D), an emergency light (E), and a strobe light (F). The input trips (An) also include a disconnect trip (A1), which is activated by a detector input signal (DI) sent from the central control unit (CCU), and indicates that the central control unit (CCU) has malfunctioned. The programmable responses include a warning output signal (WO) which is sent from the local unit (LU) to the central control unit (CCU) to indicate the presence of a local emergency at the local unit (LU).

Owner:WATCHGUARD ISLE

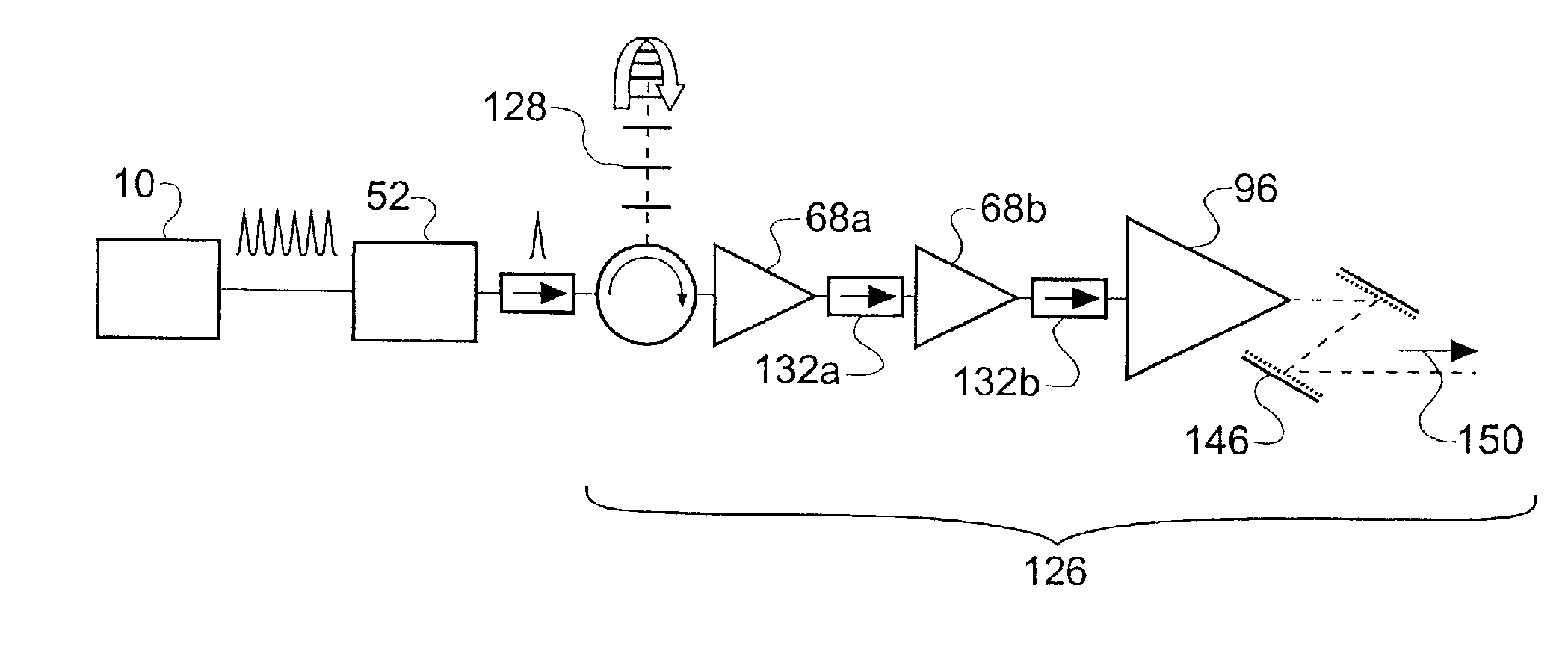

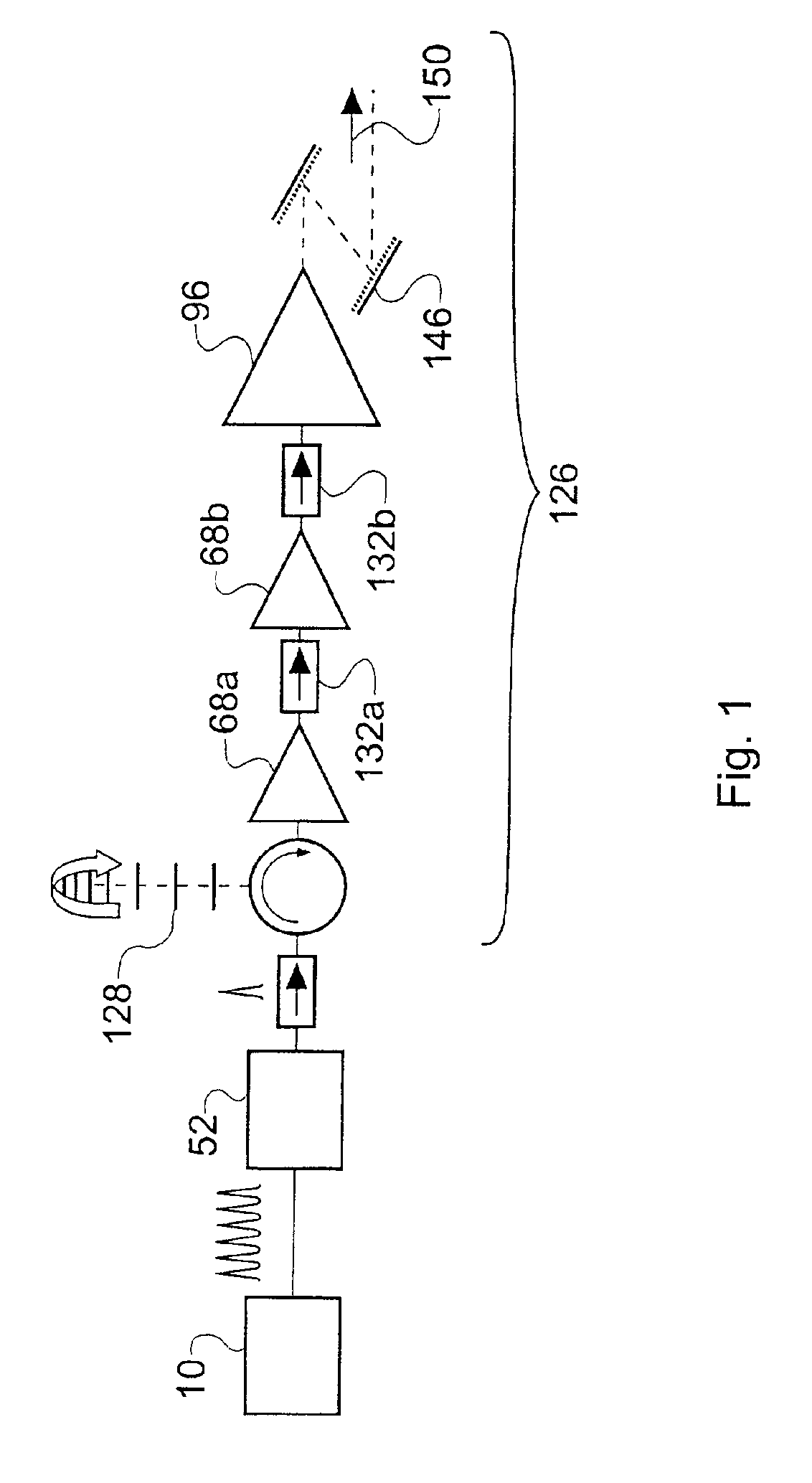

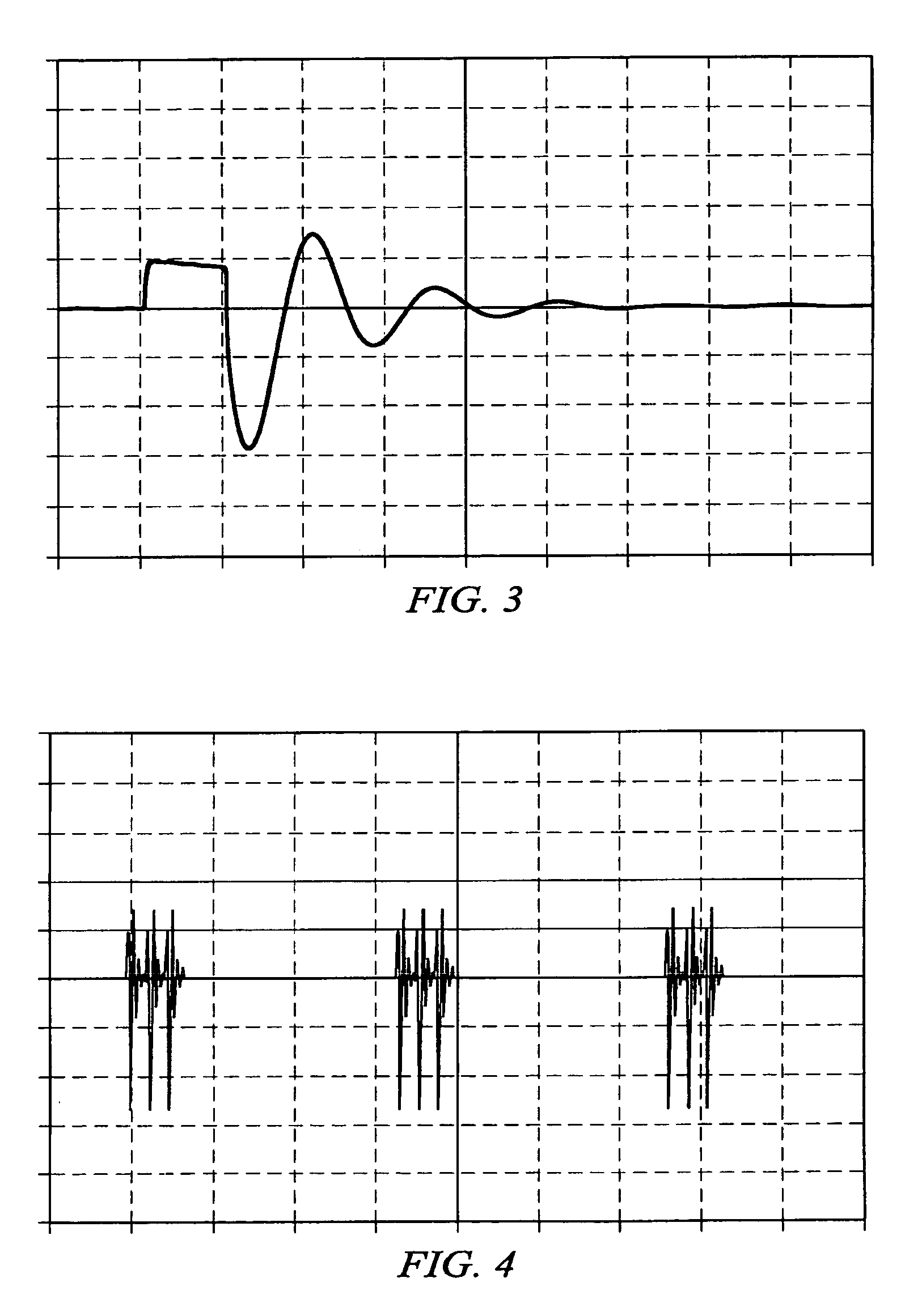

Pulsed light sources

InactiveUS6917631B2High saturationHigh energyLaser using scattering effectsActive medium shape and constructionPhase detectorLength wave

A source of pulses of coherent radiation at a wavelength of approximately 1 μm, comprises a pump source for producing pump light, a laser cavity comprising an Yb3+-doped gain medium arranged to receive the pump light, the laser cavity being modelocked to generate laser pulses at a defined repetition rate; a pulse detector arranged to generate a pulse selection signal indicative of the repetition rate; a pulse selector arranged to reduce the repetition rate of the laser pulses responsive to the pulse selection signal from the pulse detector by passing only selected ones of the laser pulses; and at least one optical amplifier for amplifying the laser pulses of reduced repetition rate. The at least one optical amplifier can be configured for chirped or parabolic pulse amplification.

Owner:UNIV OF SOUTHAMPTON

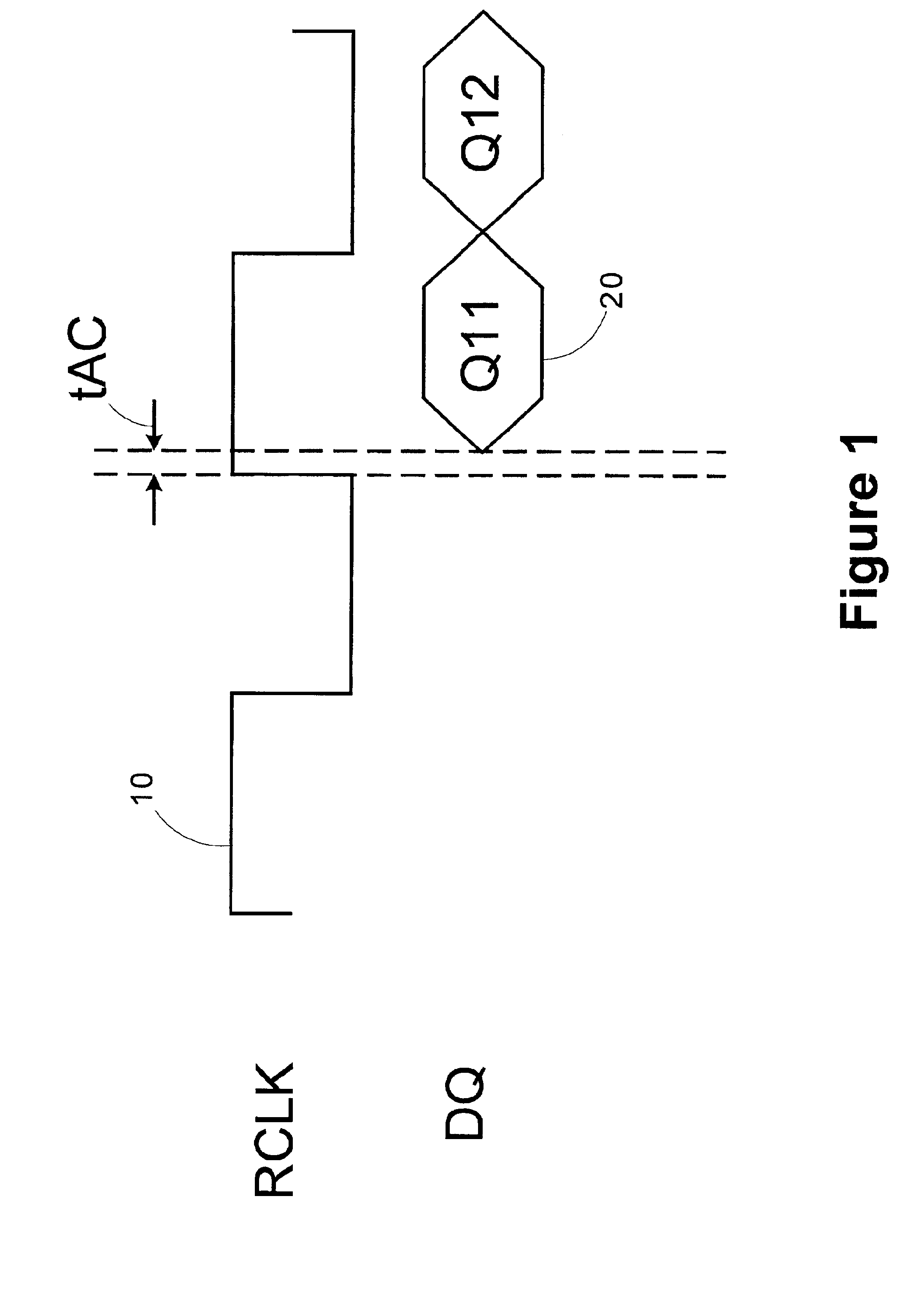

Method and apparatus for determining digital delay line entry point

A method and apparatus to characterize a synchronous device after it is packaged. For synchronous devices, such as SDRAMs implementing a Delay Locked Loop (DLL) to synchronize one signal, such as an external clock signal with a second signal, such as a data signal, a counter is coupled to the phase detector of the DLL to track the entry point of the delay line. The entry point information can be taken over a variety of voltages, temperatures, and frequencies to characterize the DLL. The counter may be located on the synchronous device or external to the device.

Owner:ROUND ROCK RES LLC

Dual mode QAM/VSB receiver

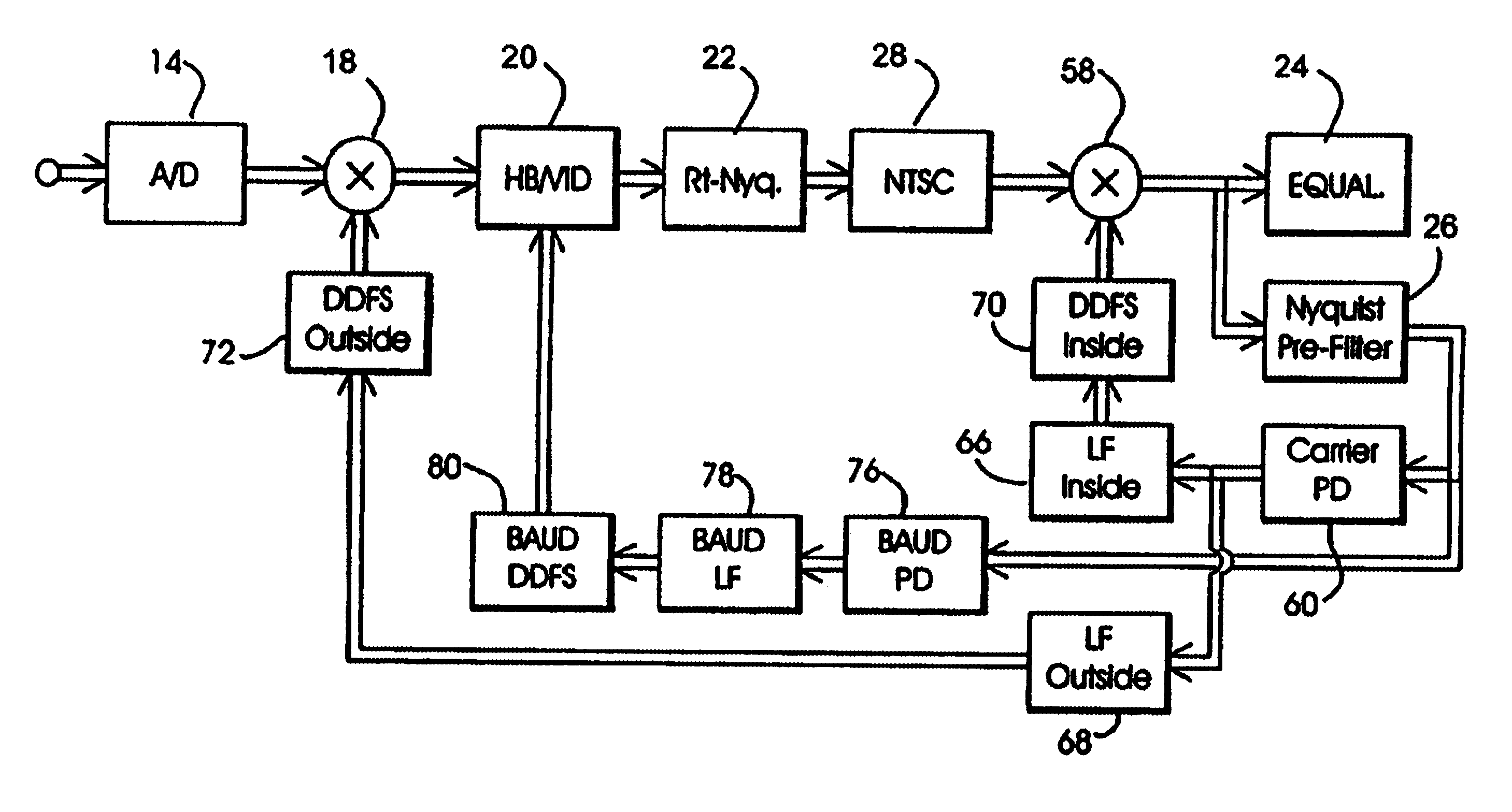

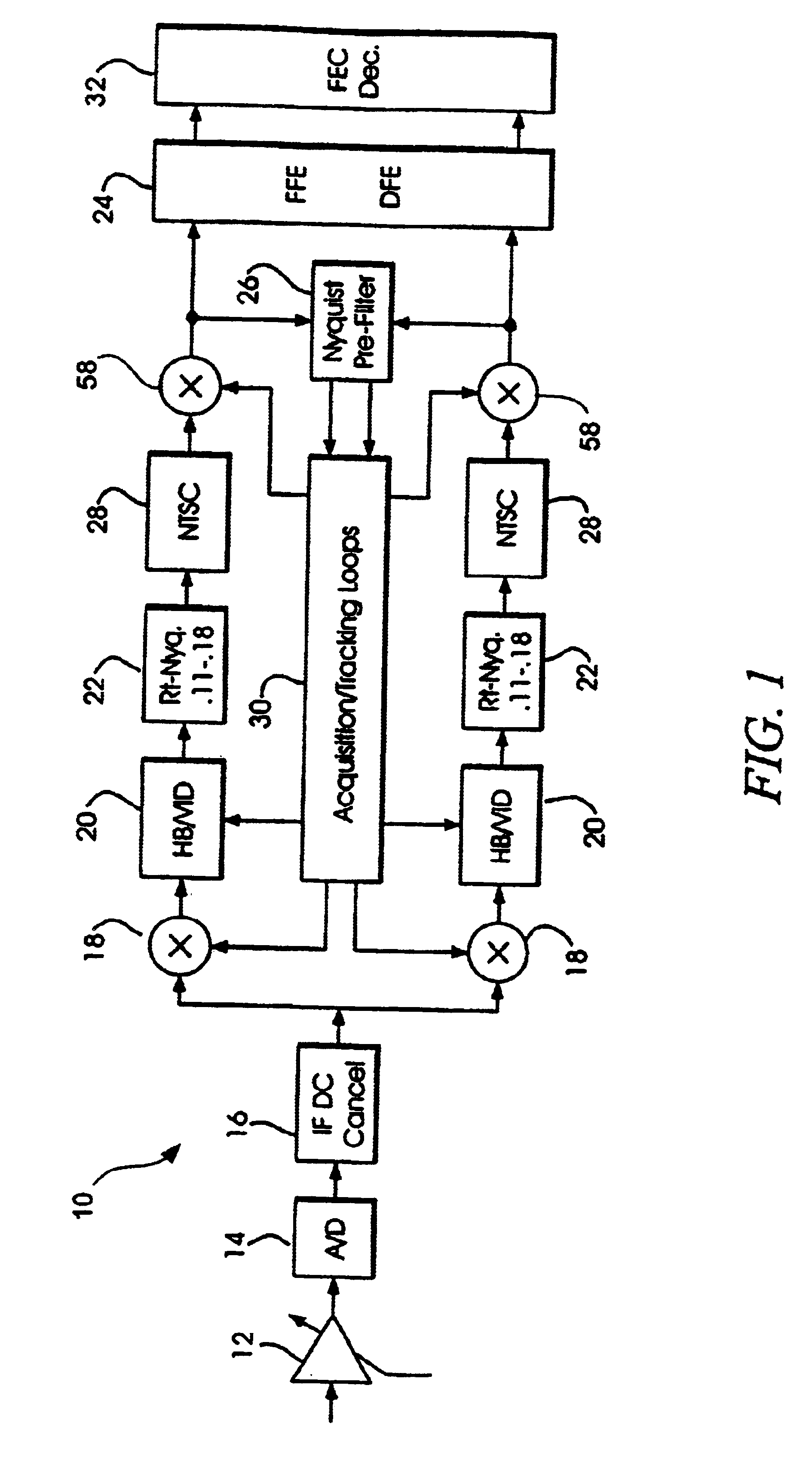

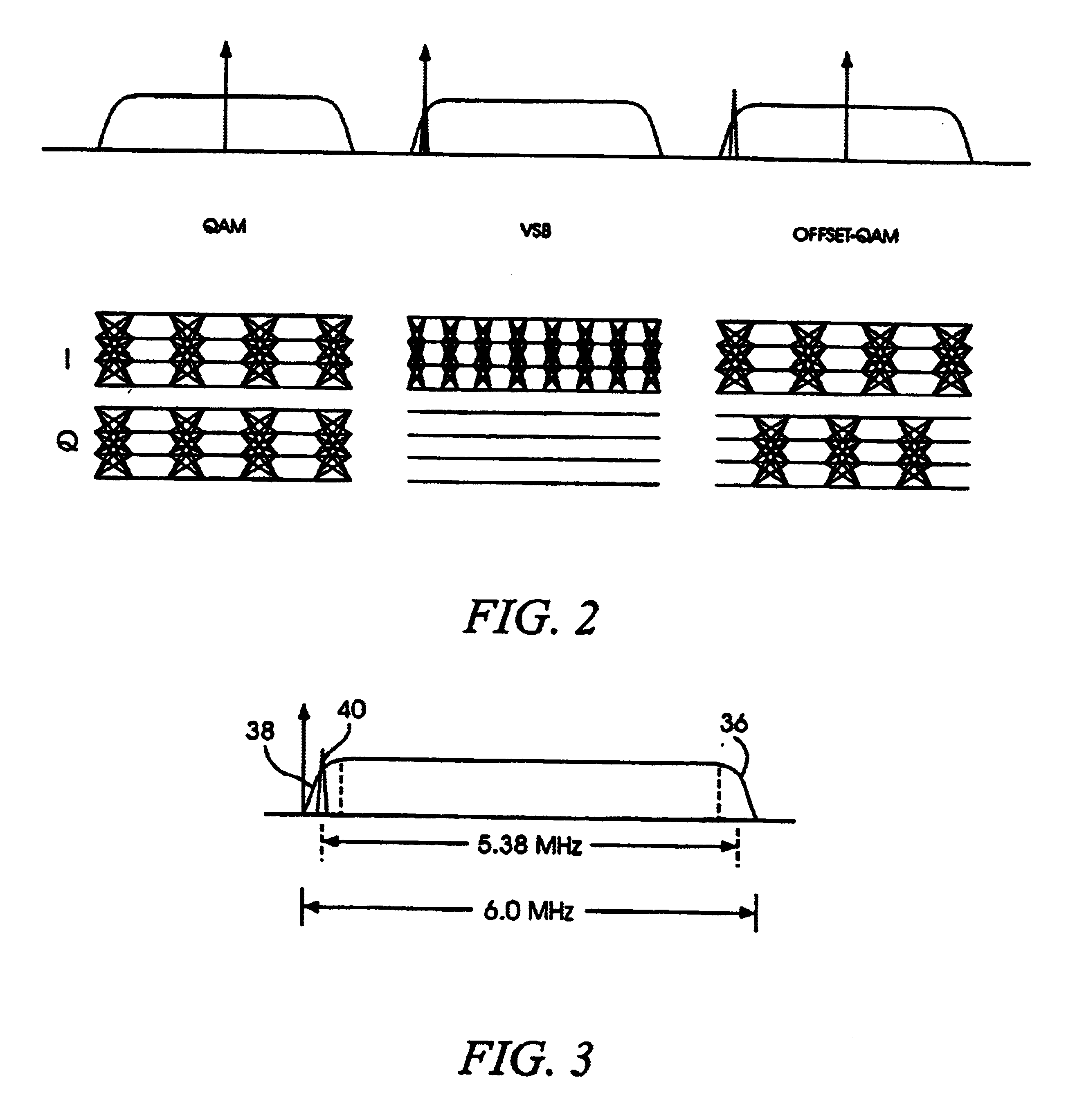

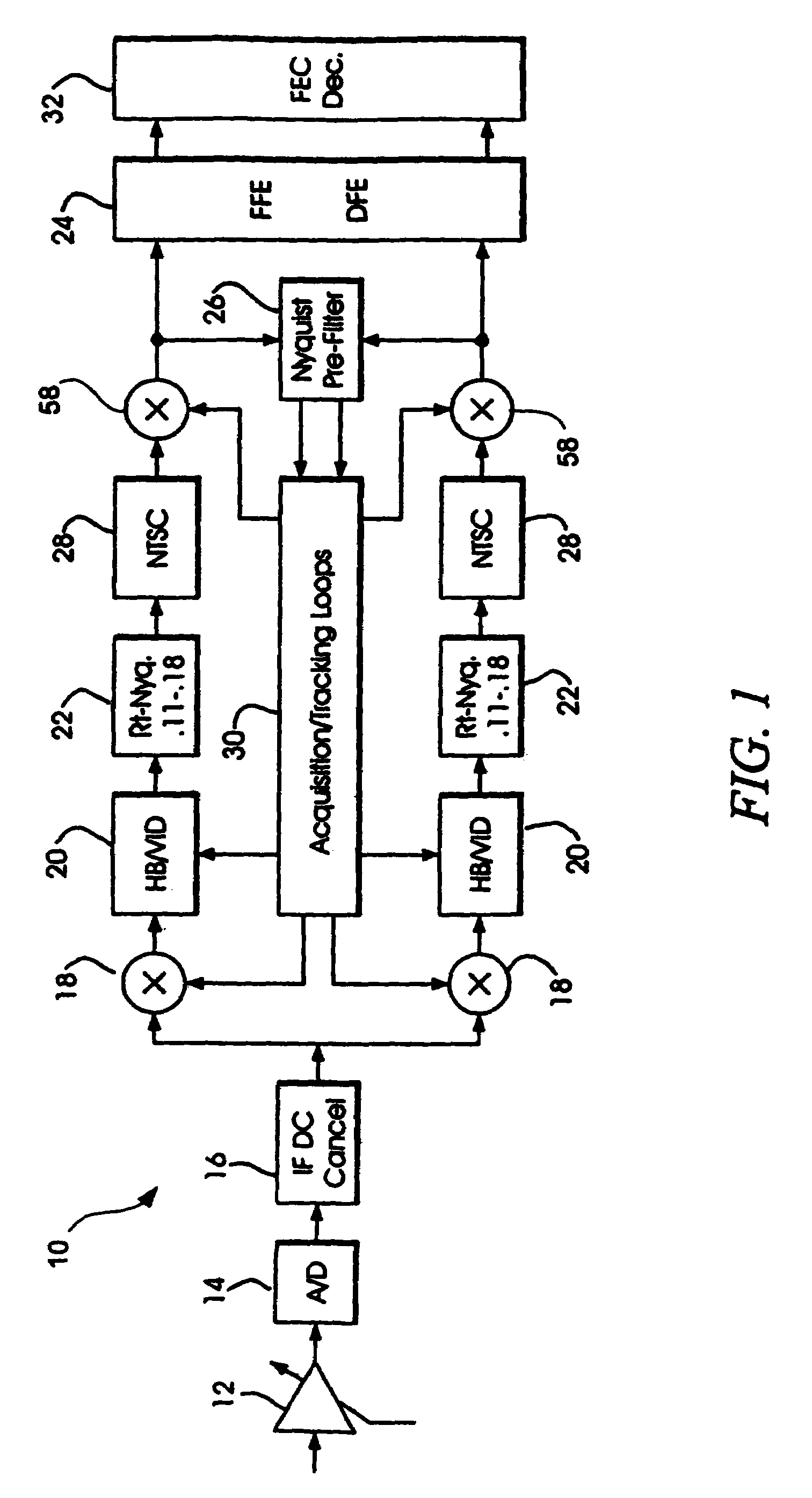

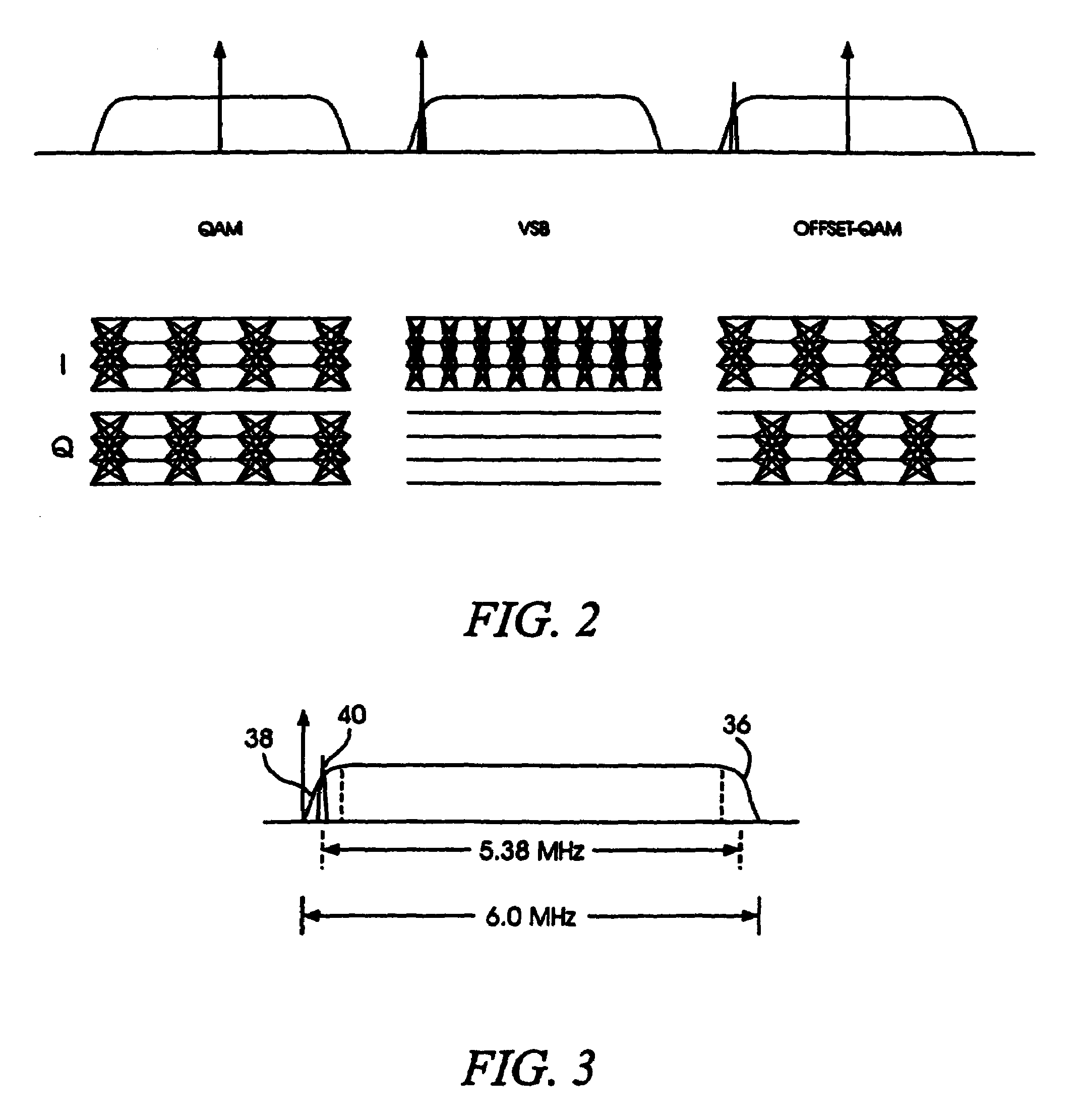

InactiveUS6842495B1Enhanced reliability symbolic decisionFacilitate decision-makingTelevision system detailsTelevision system scanning detailsPhase detectorTelevision receivers

A television receiver system capable of receiving and demodulating television signal information content that has been modulated and transmitted in accordance with a variety of modulation formats is disclosed. In particular, the system is able to accommodate receipt and demodulation of at least 8 and 16-VSB modulated signals in order to support US HDTV applications, as well as 64 and 256-QAM modulated signals, for European and potential US CATV implementations. The system includes carrier and timing recovery loops adapted to operate on an enhanced pilot signal as well as decision directed carrier phase recovery loops. Phase detectors operate on I and Q rail signals, or generate a Q rail from a Hilbert transform of the I rail. Decision directed loops incorporate a trellis decoder in order to operate on sequence estimated decisions for improved reliability in poor SNR environments.

Owner:AVAGO TECH INT SALES PTE LTD

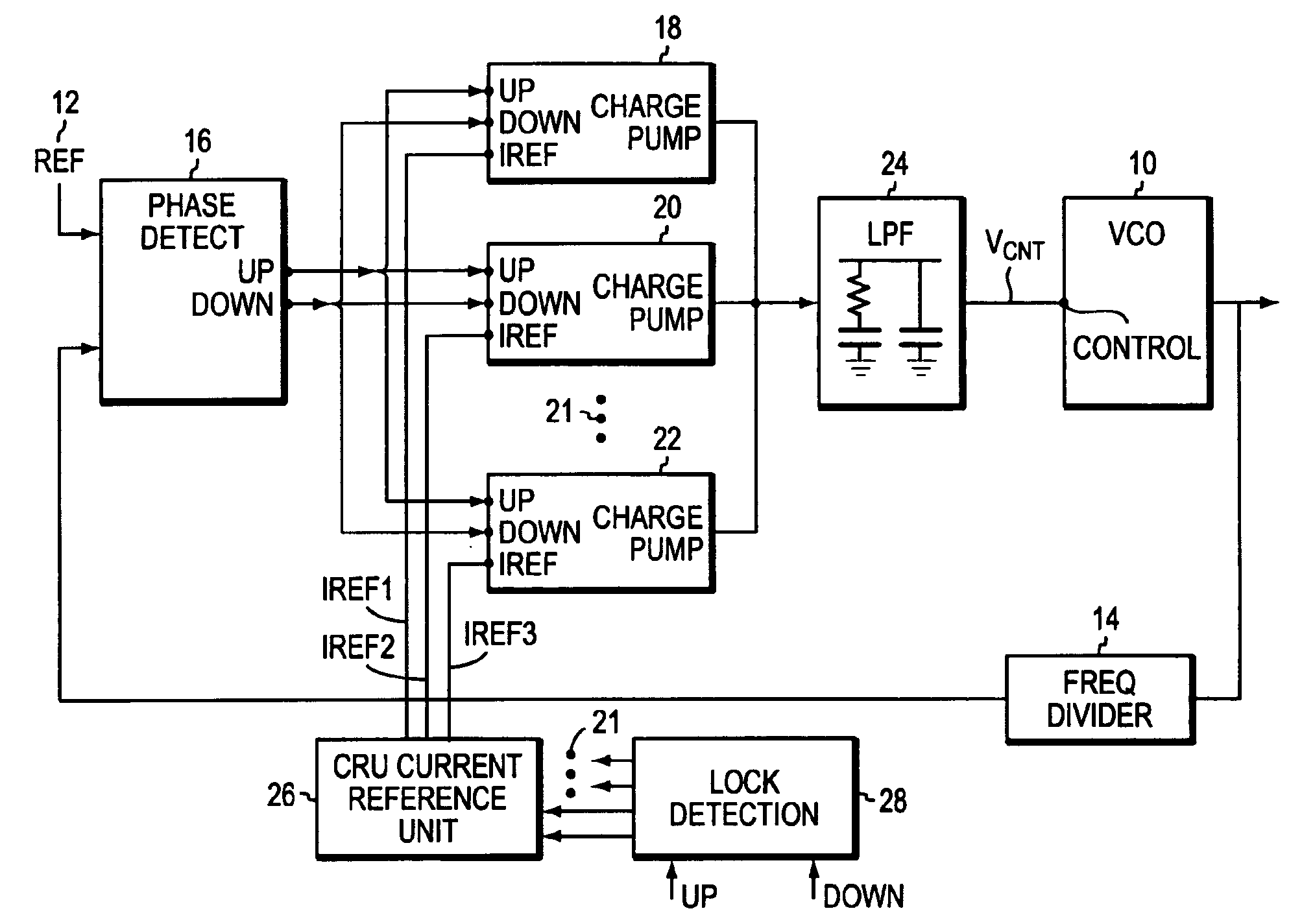

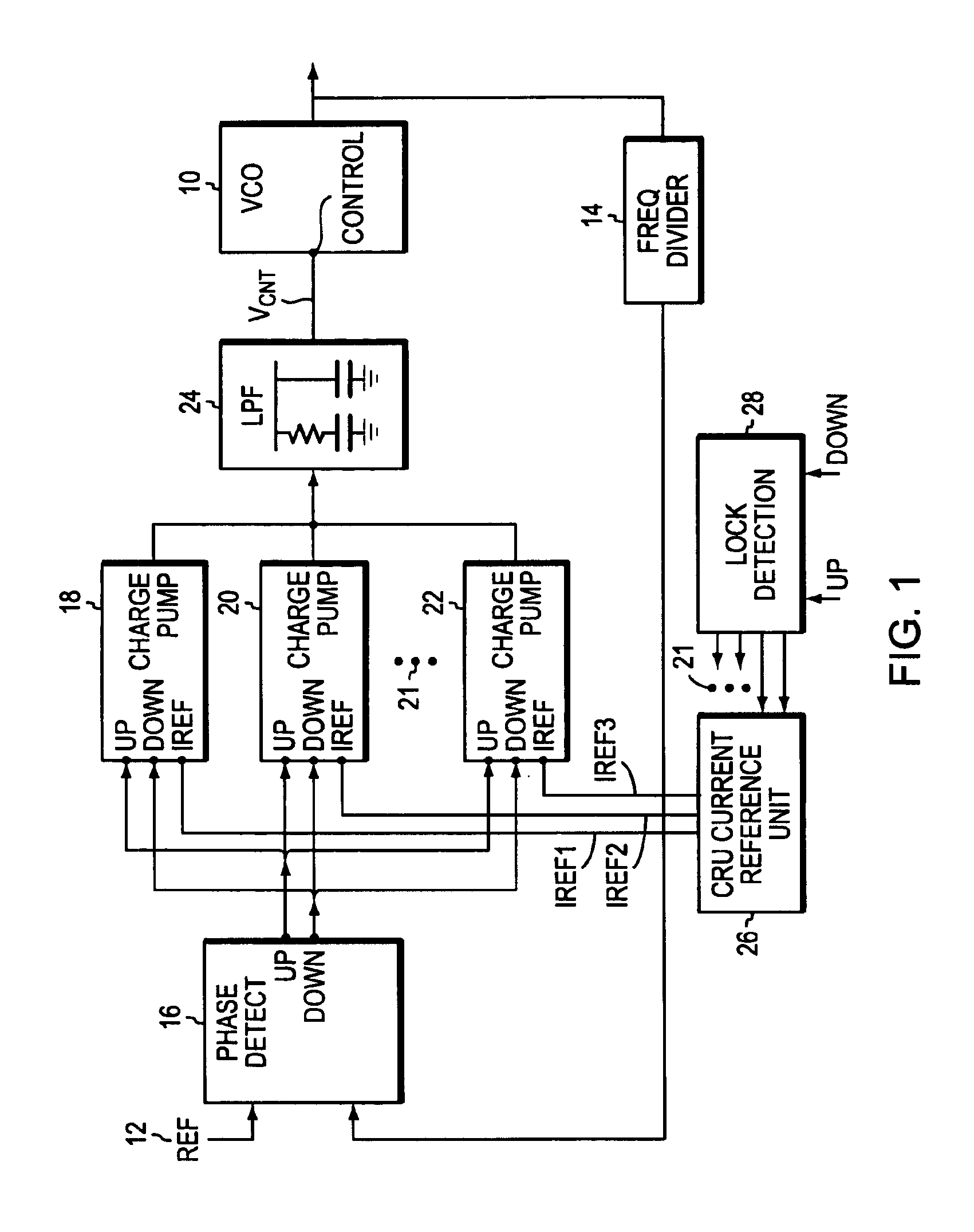

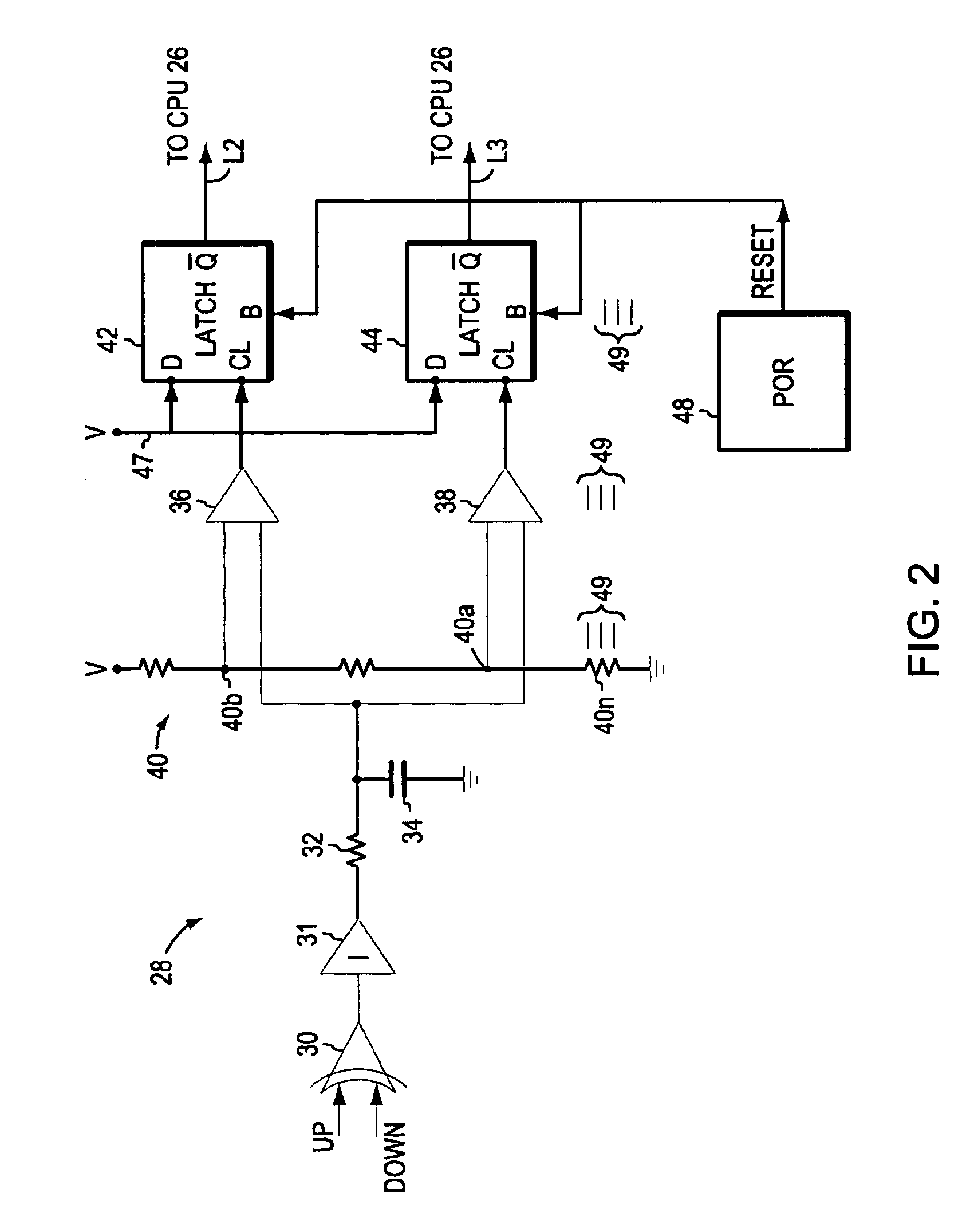

Circuitry to reduce PLL lock acquisition time

ActiveUS6940356B2Decrease frequency/phase errorFast frequencyPulse automatic controlOscillator tubesPhase detectorSwitched current

A phase locked loop, PLL, is described with multiple parallel charge pumps that are selectively disabled as phase lock is approached. A lock detection circuit is described that enabled reference currents to be fed to the parallel charge pumps. The error signal from a phase detector is arranged as UP and a DOWN signals that are averaged in the lock detector. When the average error is large, all the reference currents feed the charge pumps that provide a high loop gain to reduce the lock time. As the lock becomes closer selective reference currents are disabled to reduce loop gain so that a smooth transition to lock is made. Selectively switching currents into a low pass filter that usually follows a charge pump in a PLL circuit automatically reduces switching noise by the operation of the low pass filter.

Owner:SEMICON COMPONENTS IND LLC

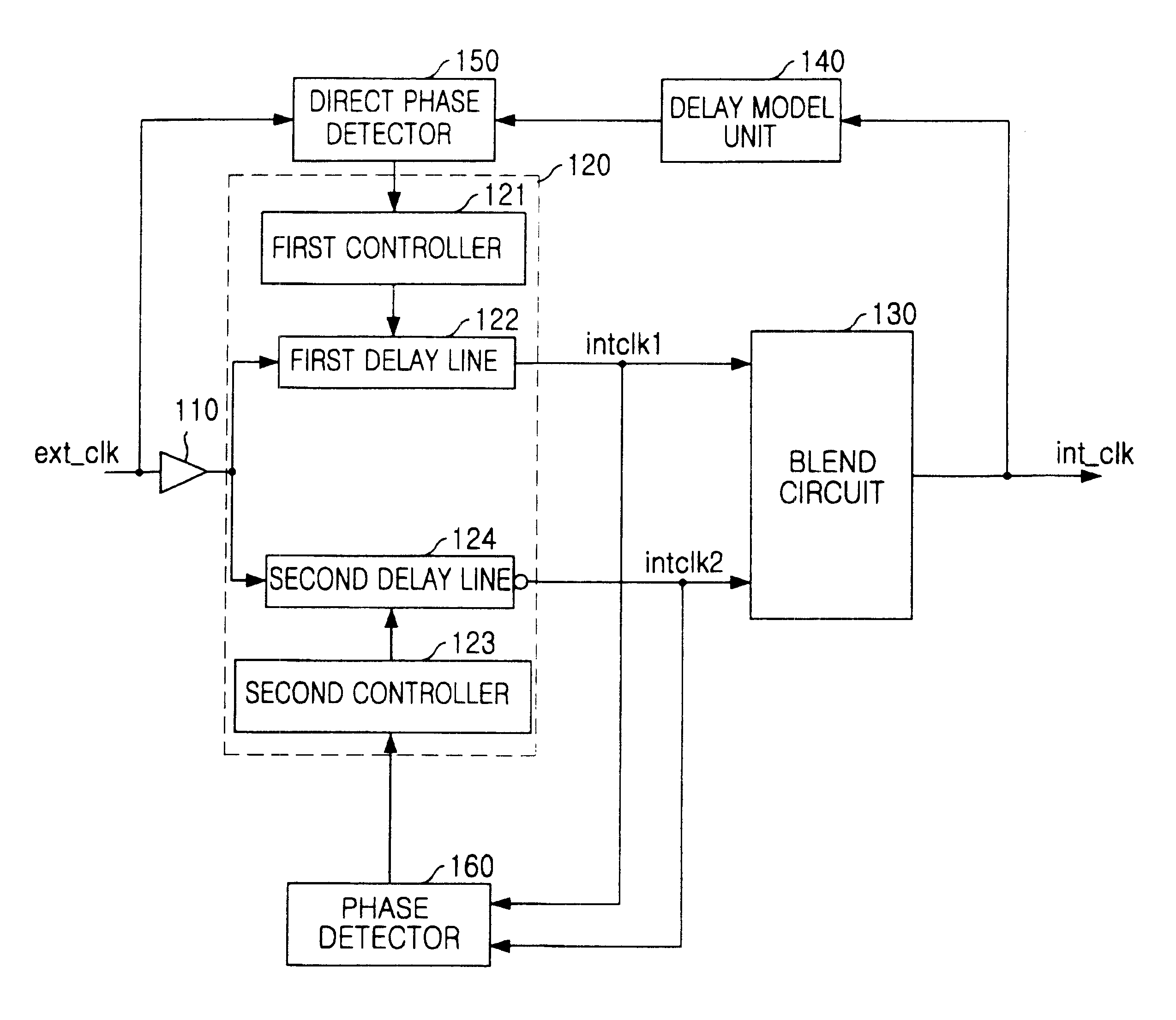

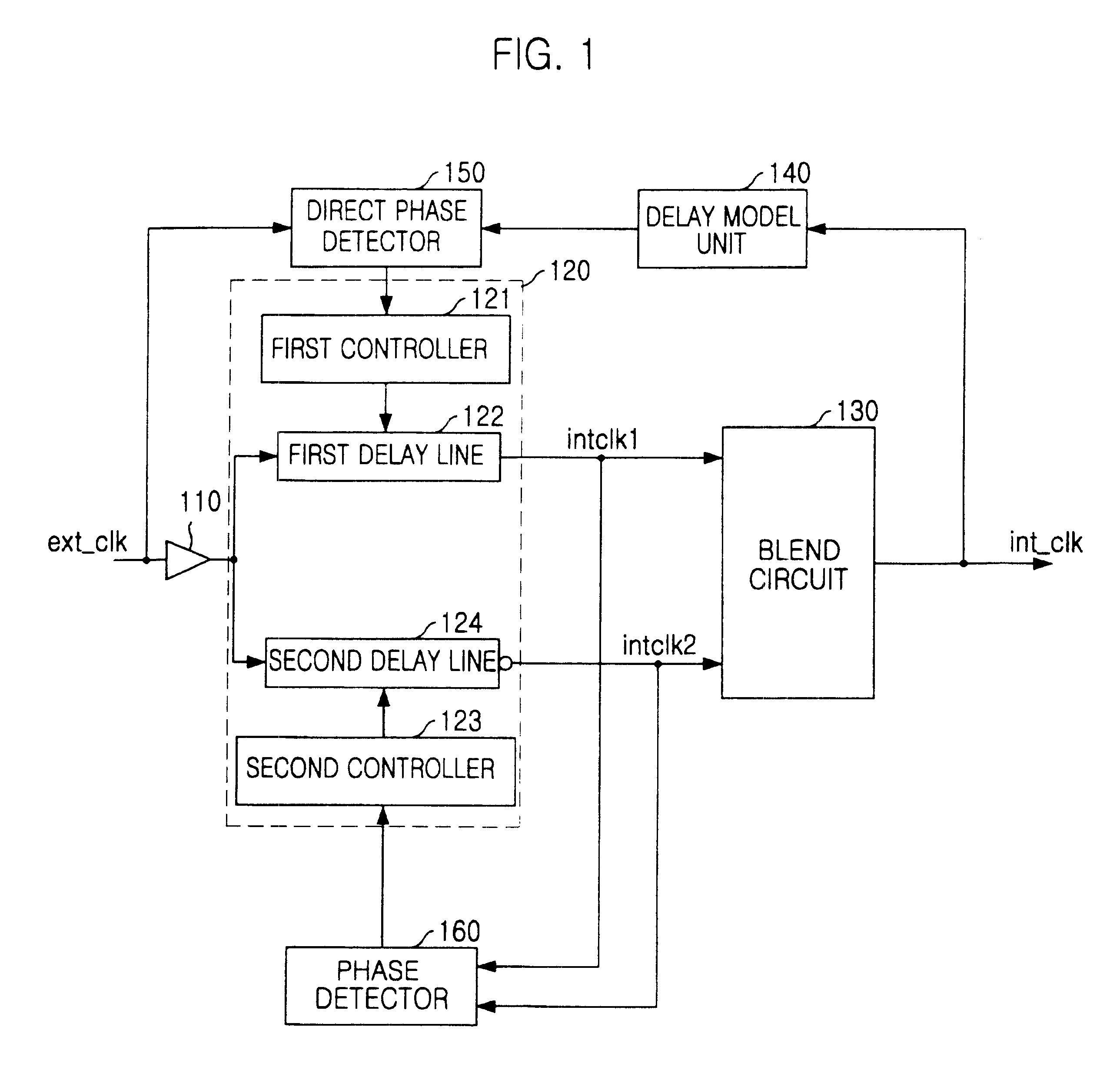

Digital DLL apparatus for correcting duty cycle and method thereof

InactiveUS6677792B2Pulse automatic controlContinuous to patterned pulse manipulationPhase detectorEngineering

A digital DLL apparatus and a method for correcting a duty cycle are disclosed. The digital DLL apparatus for correcting a duty cycle, includes: a buffer for producing a clock input signal; a delay line unit for receiving / delaying the clock input signal and outputting the clock input signal; a blend circuit for bypassing the first clock signal or producing a blended clock signal; a delay model unit for compensating a time difference of an external clock and an internal clock and generating a compensate clock signal; a direct phase detector for generating a first comparison signal; and a phase detector for generating a second comparison signal. The disclosed apparatus can correct the duty error by using the blend circuit and generate an internal clock signal having 50% of duty cycle.

Owner:SK HYNIX INC

Non-invasive neuro stimulation system

A device (10, 50, 60, 70, 80, 90) is used to apply an electric pulse or spike to a patient to treat the patient. The device can have a series of preset treatments programmed therein. A user can select a treatment from menus displayed on a display (100). The impedance of the skin and underlying tissue to be treated can be measured prior to the treatment to locate active areas on the skin for treatment. The impedance measurement can be made at a sufficiently low level to avoid treatment of the patient that could cause a change in the impedance. A phase detector can be used to isolate the capacitance value in the impedance. The charge delivered to the patient can be measured and the device can adjust the charge as the skin impedance varies during treatment to deliver uniform charges to the skin. A variety of probes can be used with the device, with the device automatically detecting the type of probe attached. Multiple electrodes can be used on the probe, which allows the active areas in contact with the probe to be identified prior to treatment to allow the treatment to concentrate on the active areas.

Owner:HTK ENTERPRISES INC

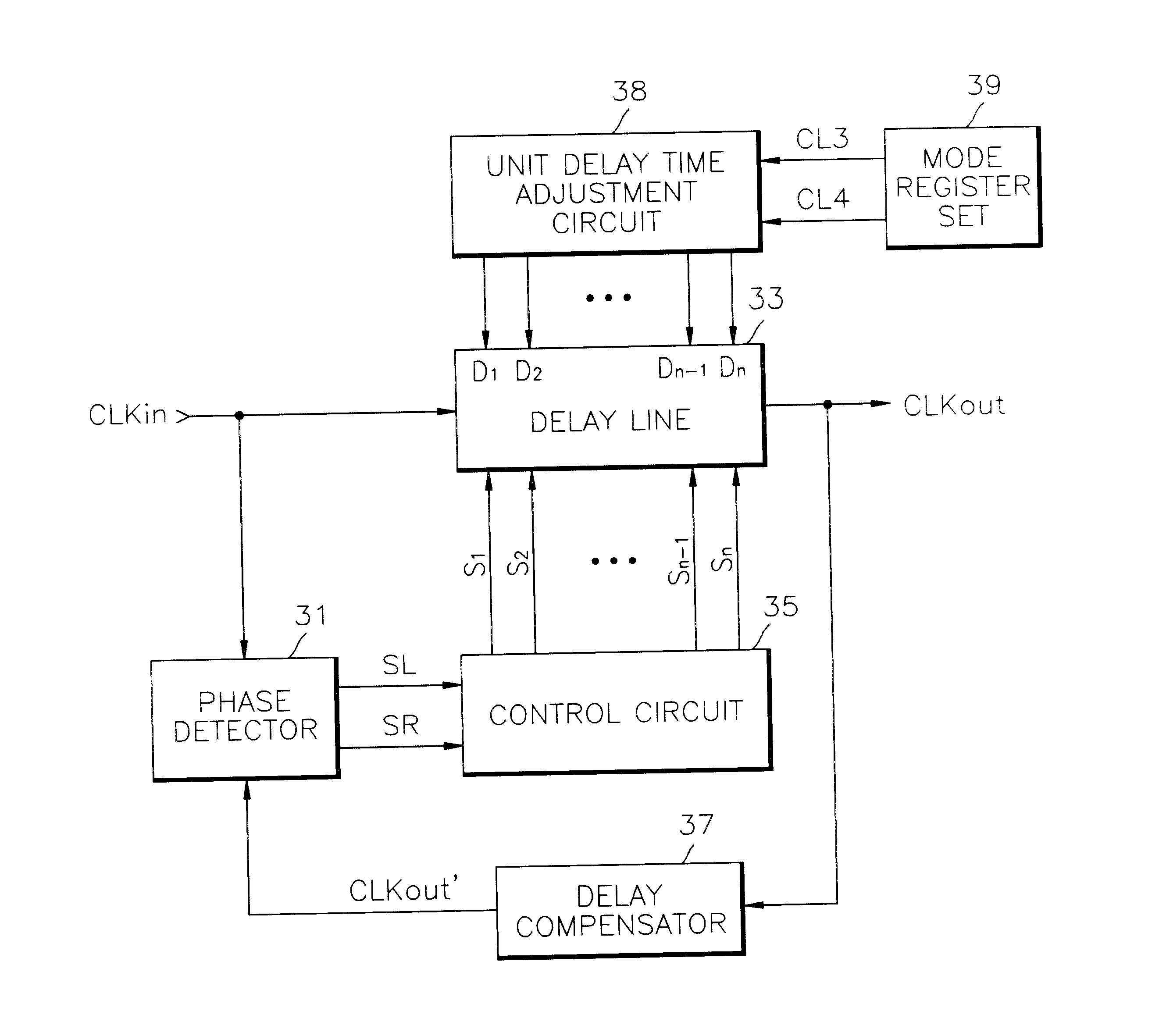

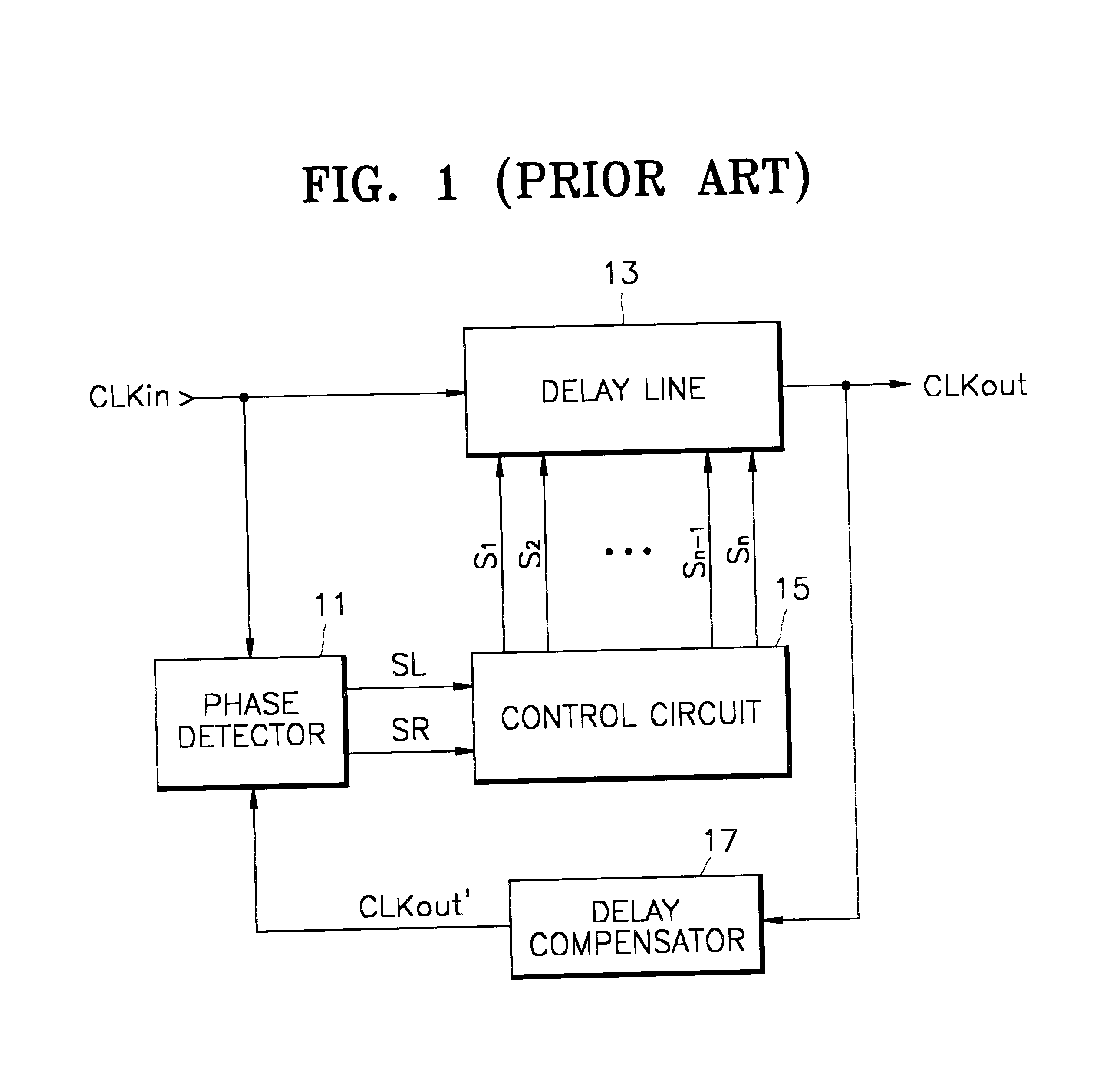

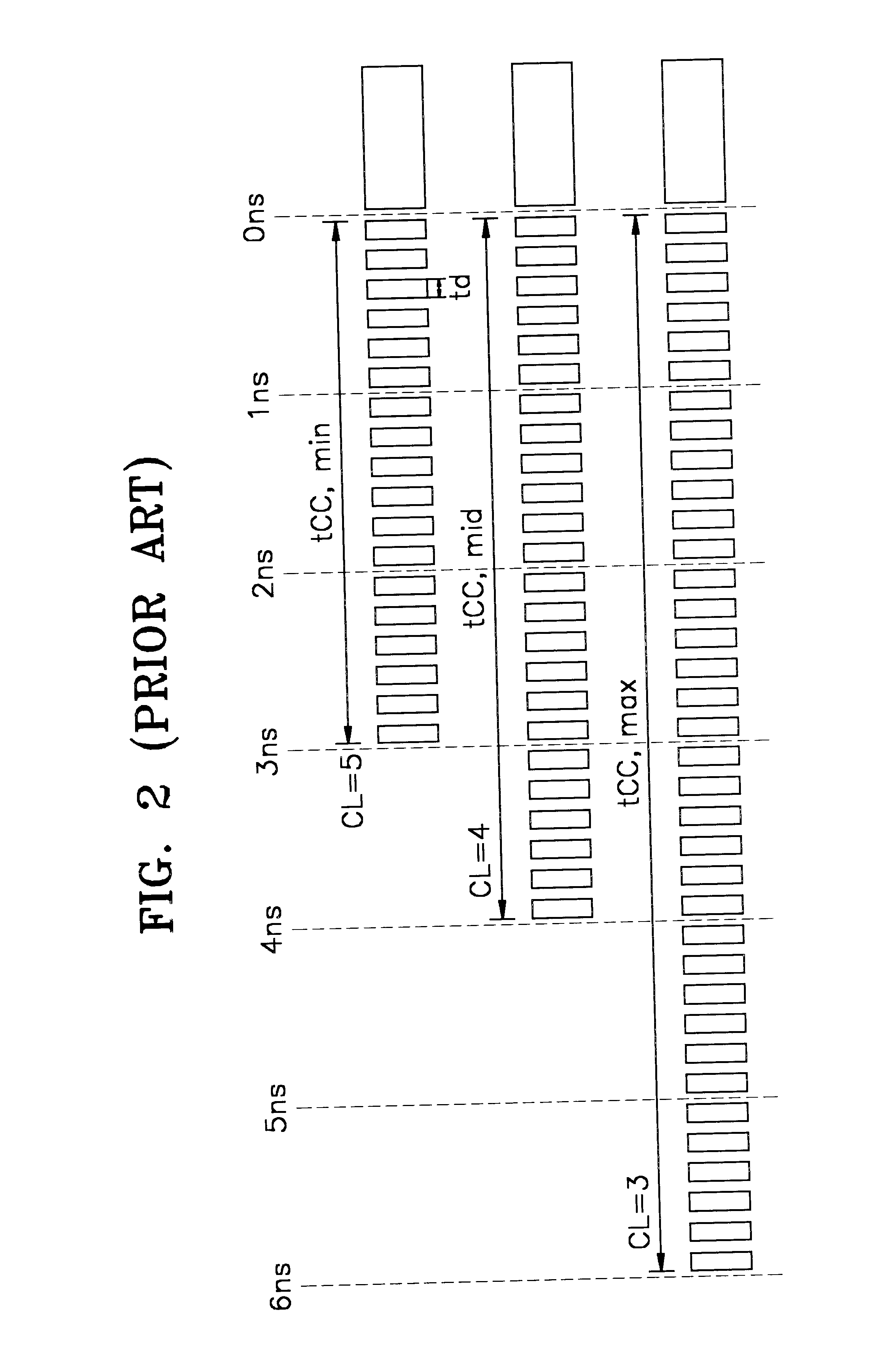

Delay locked loop circuit and method having adjustable locking resolution

A delay line receives an input clock signal and includes a cascaded plurality of unit delay circuits. A mode register set stores a value indicative of a column-address-strobe (CAS) latency of the memory device, and an adjustment circuit varies a delay time of the unit delay circuits according to the CAS latency stored in the mode register set. A phase detector detects a phase difference between the input clock signal and an output clock signal of the delay line, and a control circuit which controls an enabled state of the unit delay circuits according to an output of said phase detector.

Owner:SAMSUNG ELECTRONICS CO LTD

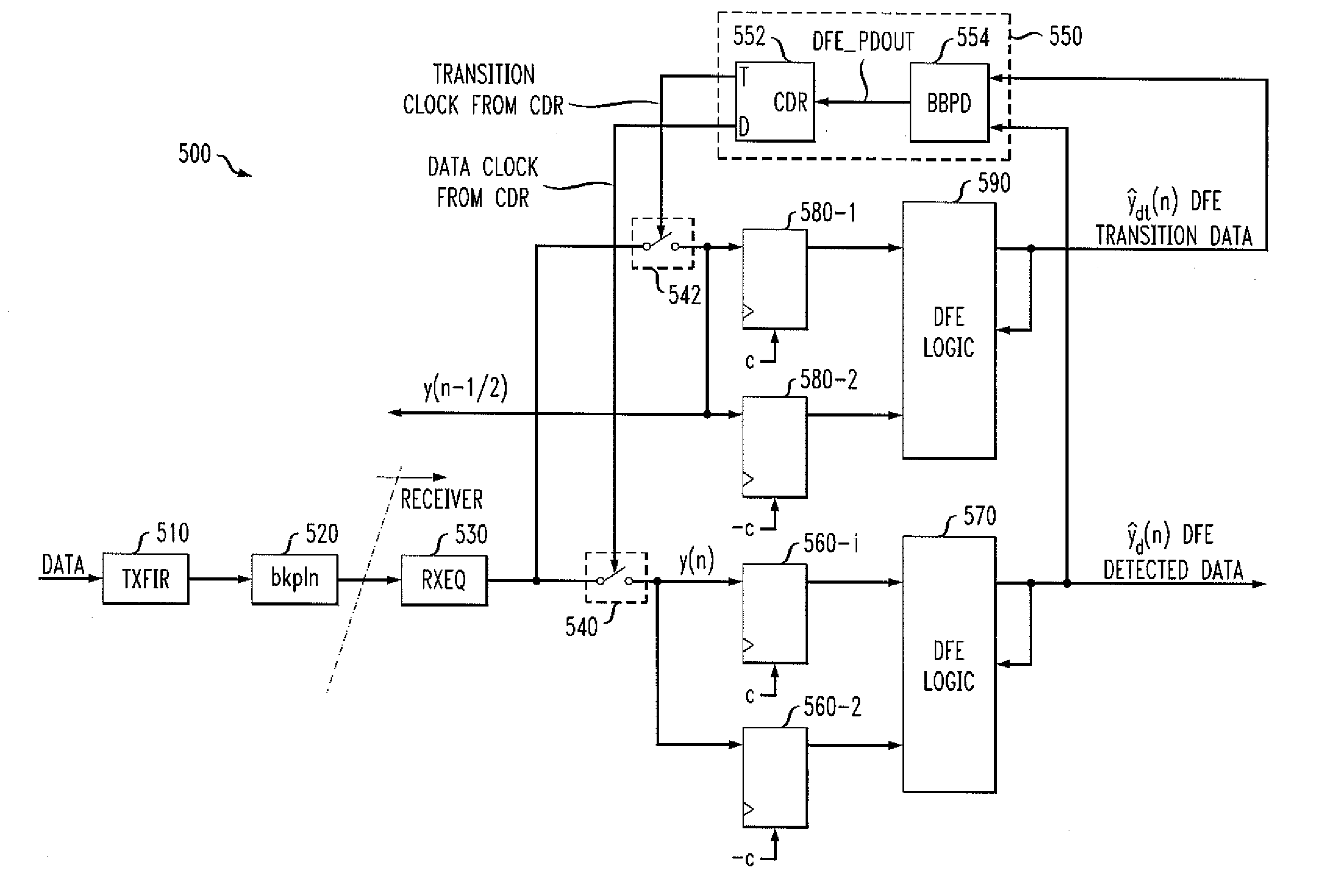

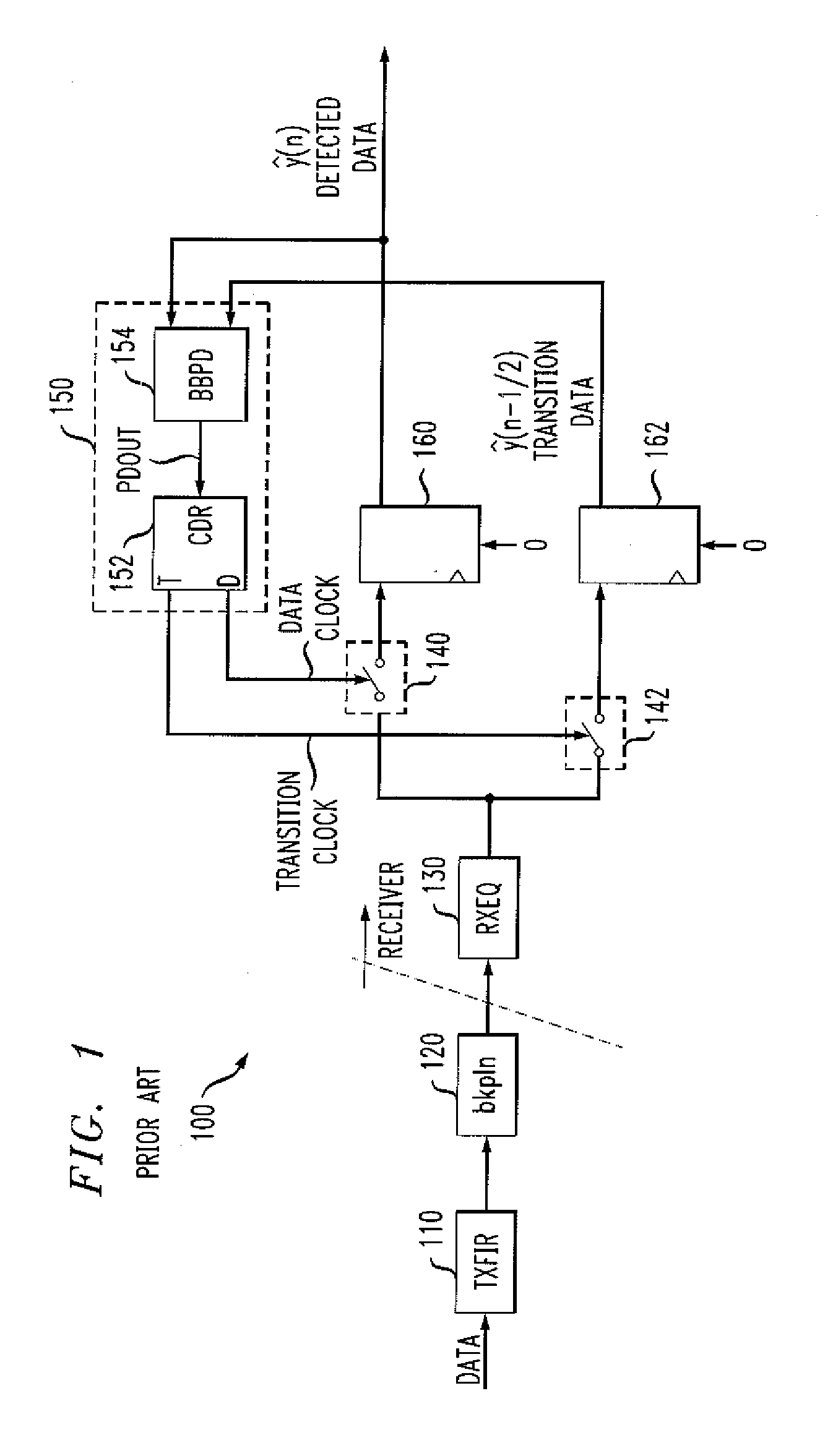

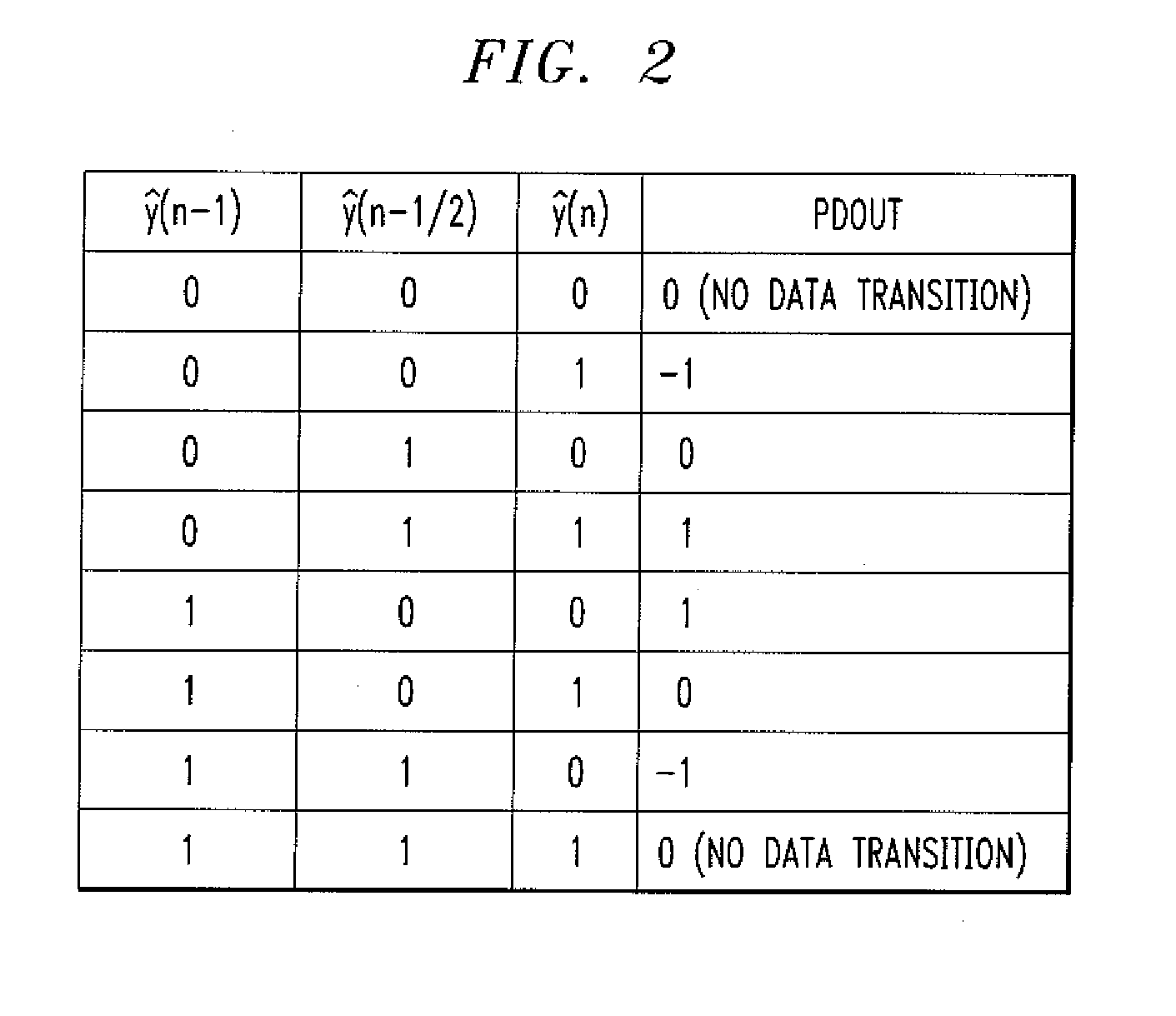

Method and apparatus for generating one or more clock signals for a decision-feedback equalizer using DFE detected data

Methods and apparatus are provided for generating one or more clock signals for a decision-feedback equalizer using DFE detected data. A received signal is sampled using a data clock and a transition clock to generate a data sample signal and a transition sample signal, respectively. A DFE correction is obtained for each of the data sample and transition sample signals to generate DFE detected data and a DFE transition data. The DFE detected data and DFE transition data are then applied to a phase detector that generates a signal to adjust a phase of one or more of the data clock and transition clock. In a multi-level implementation, the received signal is sampled using a clock associated with each of the levels and the samples are latched using a vertical slicing technique to generate DFE data associated with each of said levels.

Owner:AVAGO TECH INT SALES PTE LTD

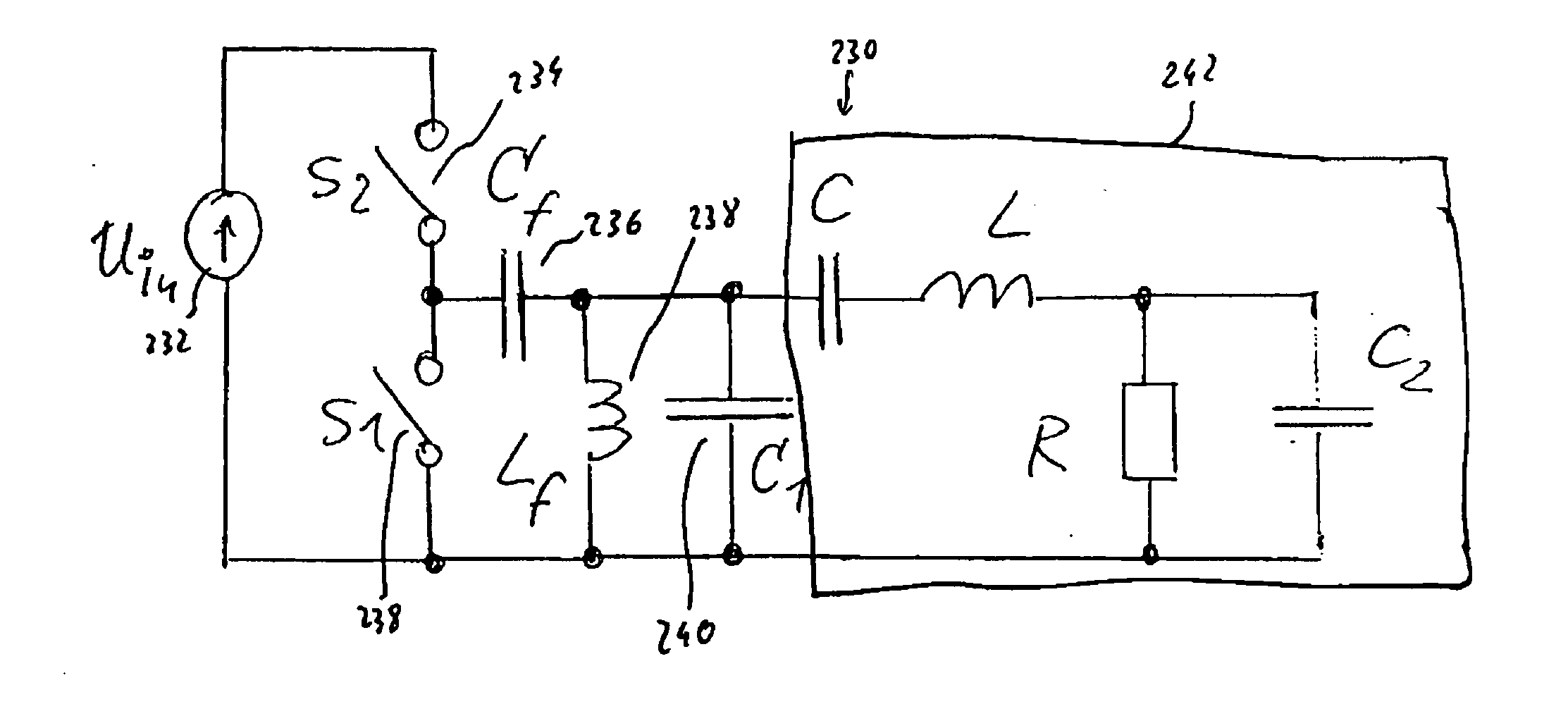

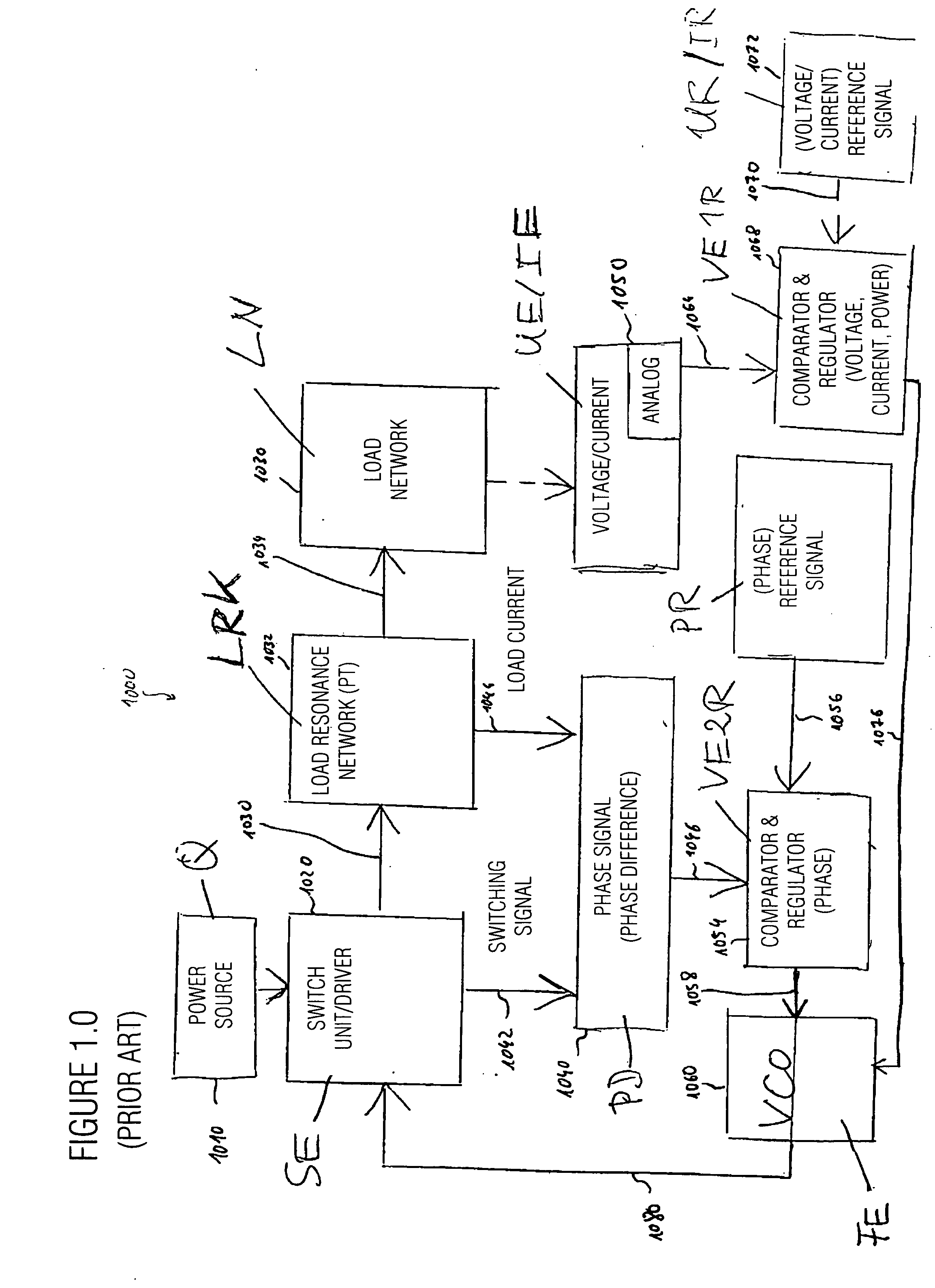

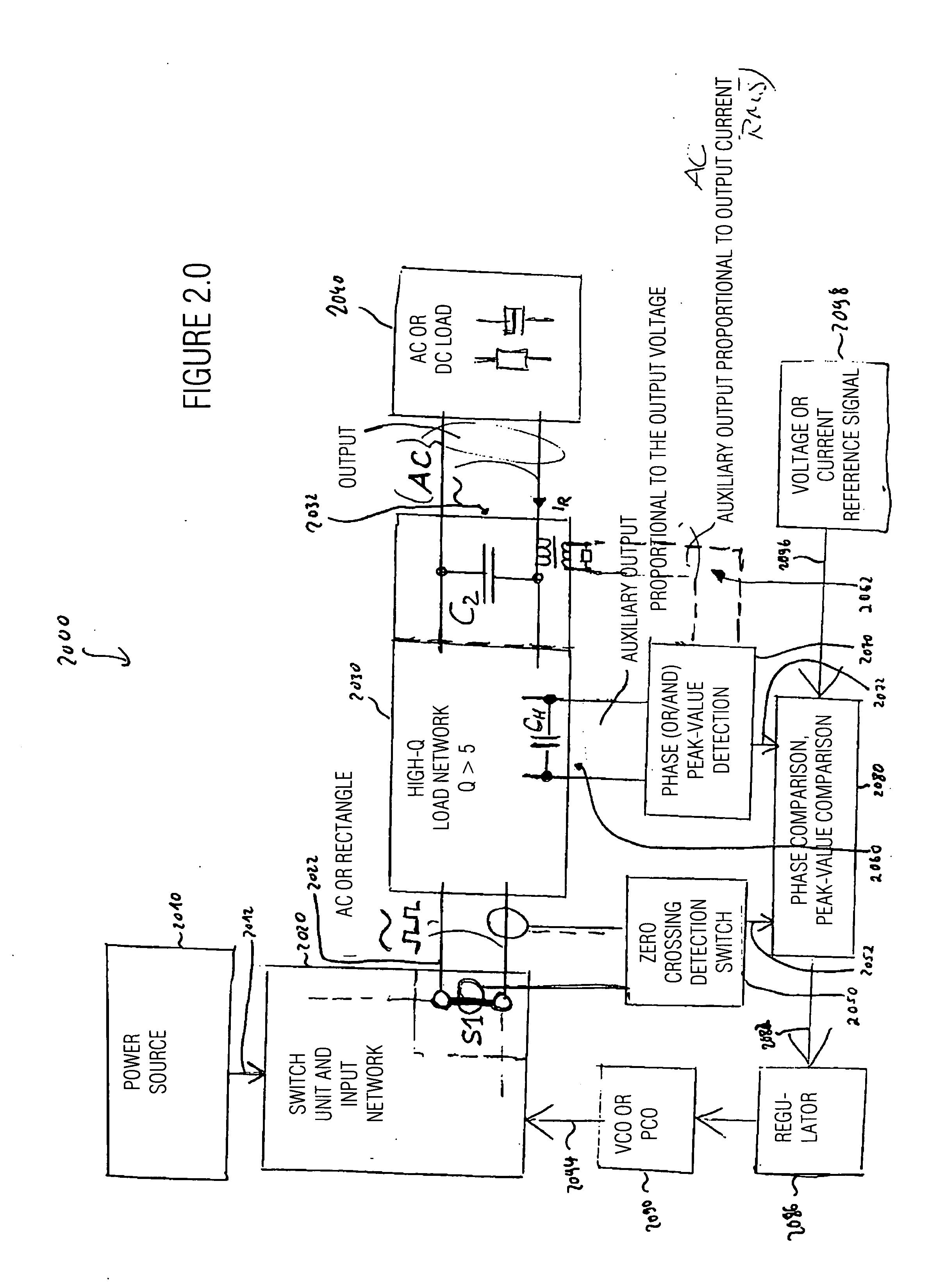

Control circuit for a switch unit of a clocked power supply circuit, and resonance converter

InactiveUS20060285366A1Low costLoss in of of efficiencyEfficient power electronics conversionAc-dc conversionDriver/operatorResonant converter

A control circuit for a switch unit of a clocked power supply circuit, the switch unit being designed to effect input-side excitation of a resonant transformer arrangement, comprises an input for receiving an auxiliary signal from the resonant transformer arrangement. The auxiliary signal exhibits an essentially fixed phase relation to a load alternating current flowing through a resonant circuit of the transformer arrangement. The control circuit further comprises a phase detector designed to detect reference crossing moments when the auxiliary signal crosses a predefined reference value, a driver controllable to switch the switch unit, and a synchronizer designed to synchronize a turn-on of the switch unit by the driver with regard to a phase position with the auxiliary signal so as to achieve a turn-on of the switch unit within a predetermined time interval around a zero crossing of a voltage present across the switch unit, or of a current flowing through the switch unit. The synchronizer is further designed to receive information about the reference crossing moments from the phase detector, and to provide a turn-on signal to the driver with a fixed phase delay at the reference crossing moments, so as to define turn-on moments at which the driver is to turn on the switch unit. The control circuit further comprises a detector designed to determine an amplitude information which depends on an amplitude or a mean value of the auxiliary signal, and a regulator designed to change an operating frequency in dependence on the amplitude information supplied by the detector, and to determine a period duration between turn-off moments at which the driver is to turn off the switch unit as a reciprocal of the operating frequency. An inventive resonance converter enables independent control of frequency and turn-on moments, or duty cycle, and thus enables a particularly efficient operation of the resonance converter, and a particularly precise regulation.

Owner:FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG EV +1

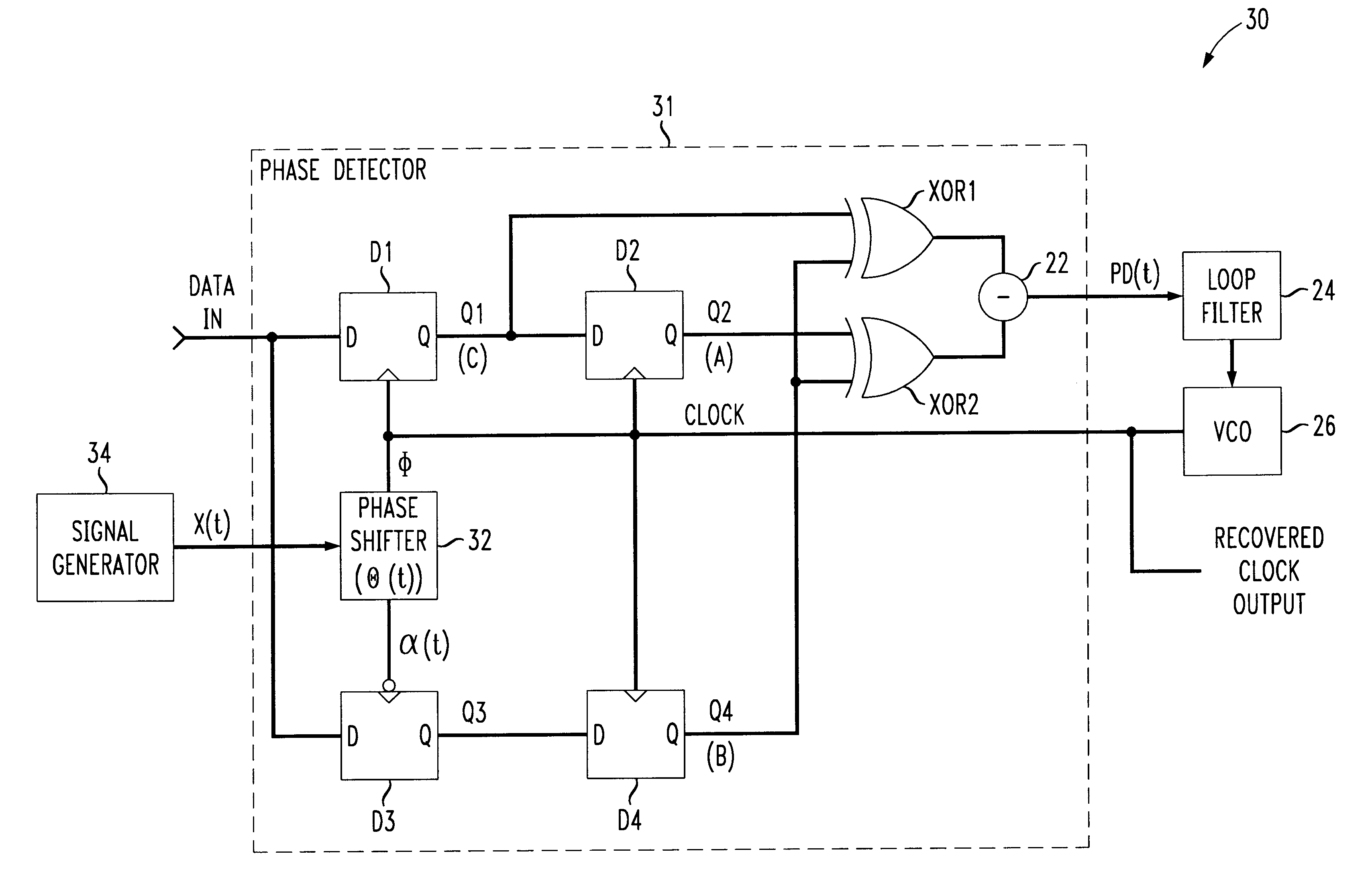

Self-aligned clock recovery circuit with proportional phase detector

InactiveUS6347128B1Pulse automatic controlGenerating/distributing signalsPhase differenceContinuous data

A self-aligned clock recovery circuit for synchronizing a local clock with an input data signal includes a sampling type phase detector for generating an output signal based on the phase difference between the local clock and the data signal timing. The phase detector obtains samples of consecutive data symbols at sampling times corresponding to transitions of the local clock, and obtains a data crossover sample at a sampling instant in between those of the consecutive data symbol samples. A phase shifter is employed to phase shift the local clock by an amount corresponding to a time varying modulation signal so as to obtain each data crossover sample at a variable sampling instant relative to the associated consecutive symbol samples. Logic circuitry determines whether the local clock appears to be early or late based on a comparison of the logic levels of the symbol samples and the associated data crossover sample, and provides a corresponding output signal through a filter to the local clock to adjust the clock accordingly. Since the relative sampling instants of successive data crossover samples are varied with time, the phase detector output signal amplitude is substantially proportional to the amount of phase error between the local clock and the symbol timing, thereby improving jitter properties of the clock recovery circuit.

Owner:AVAGO TECH INT SALES PTE LTD

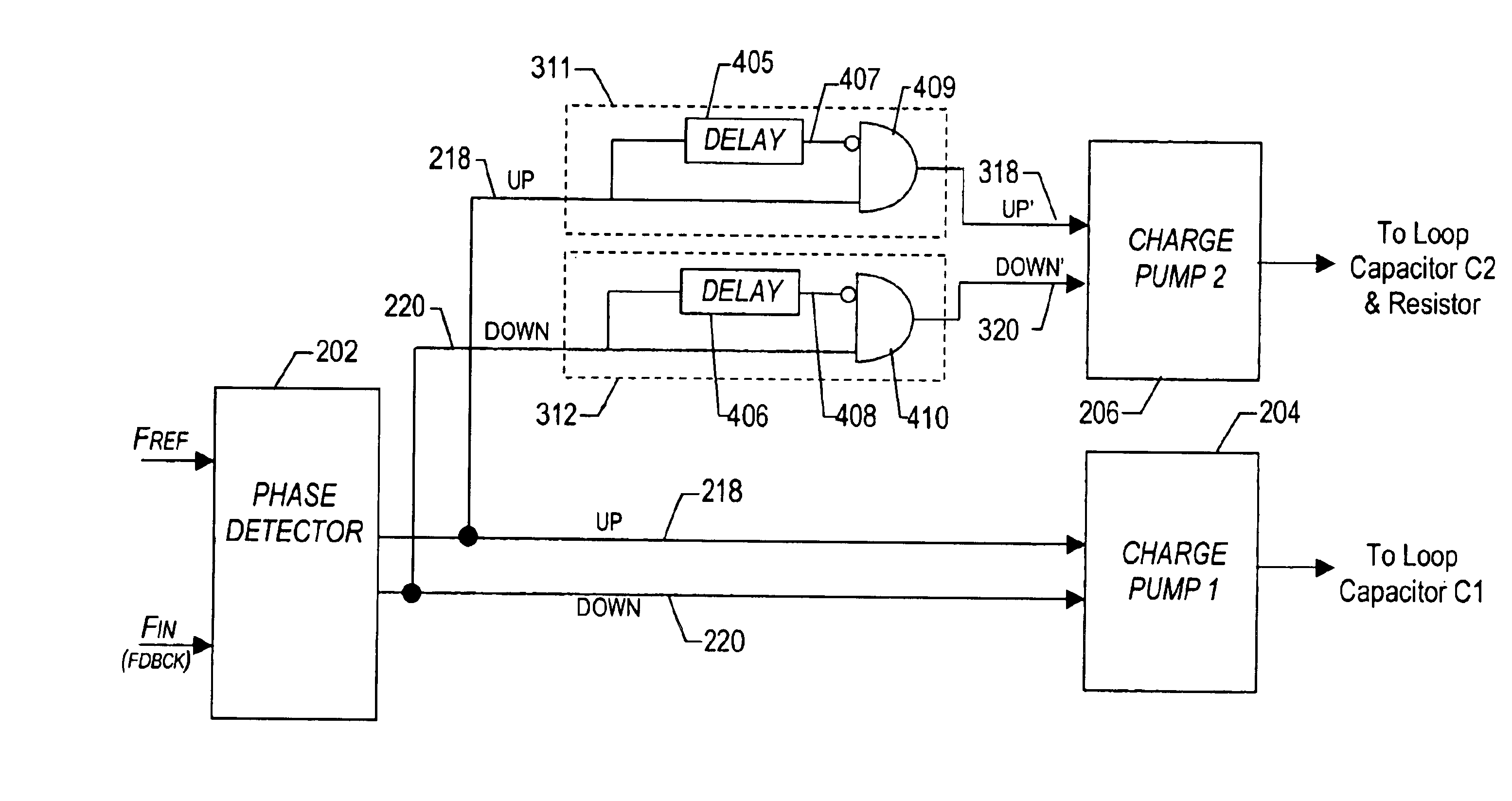

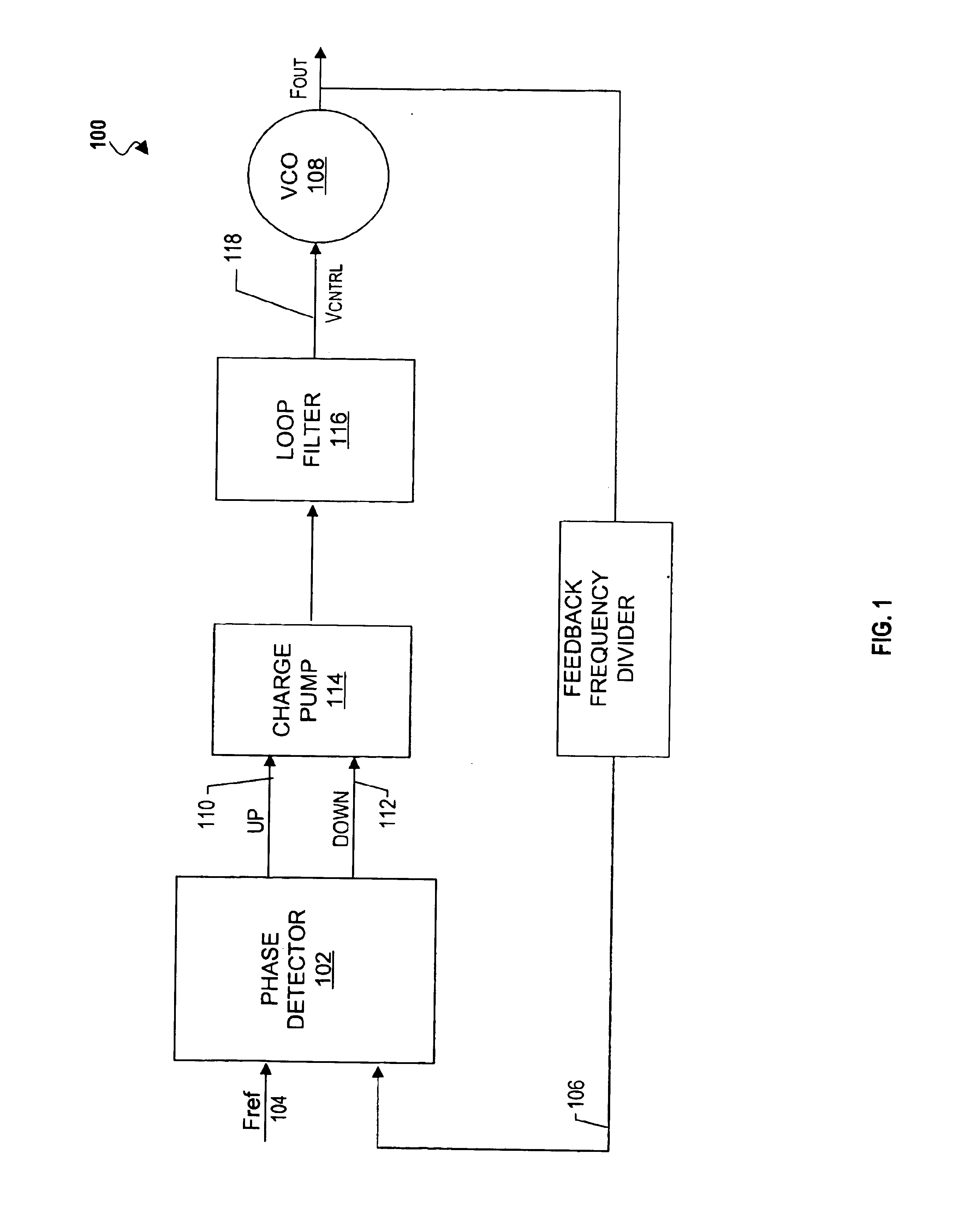

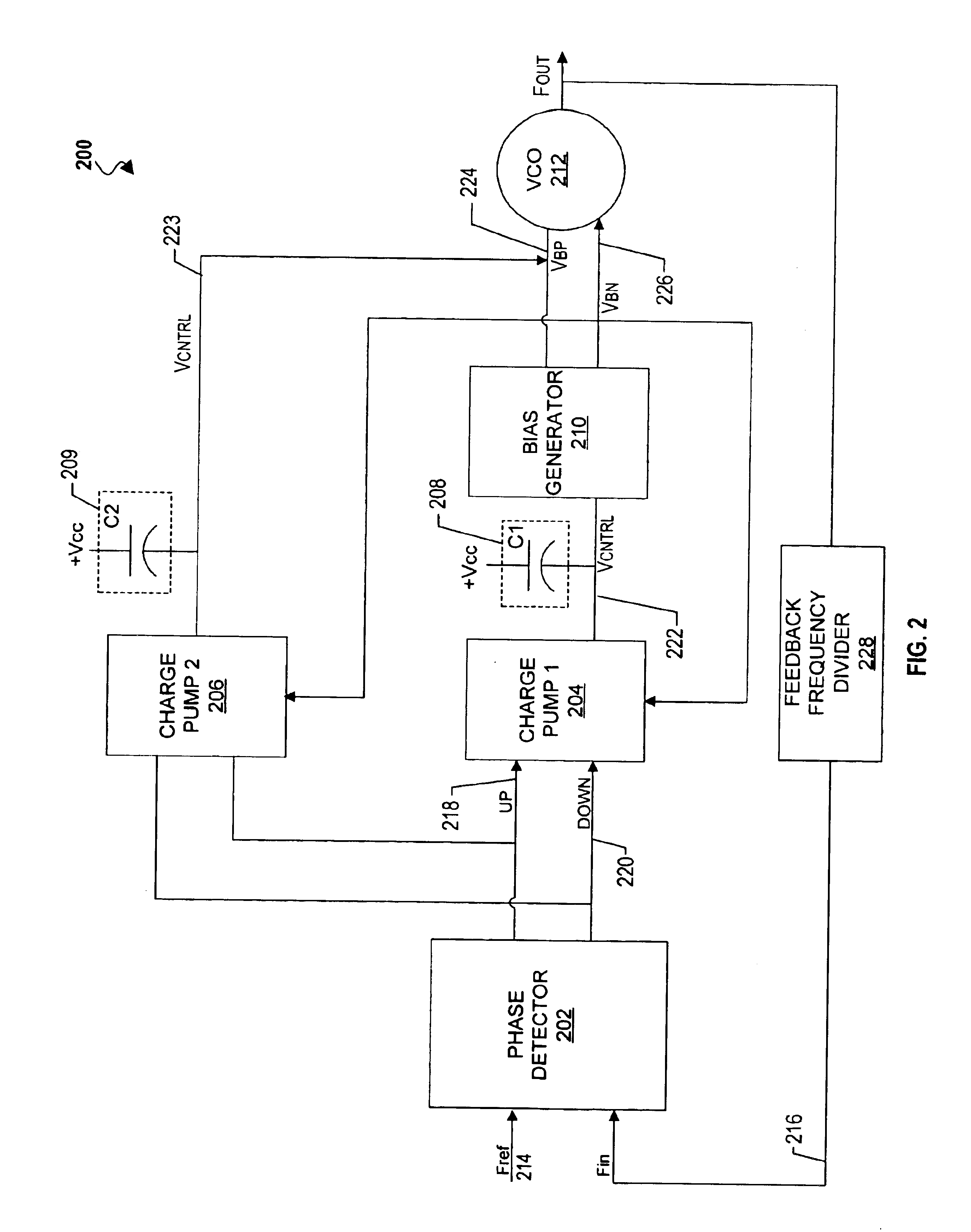

Method and apparatus for reducing lock time in dual charge-pump phase-locked loops

InactiveUS6937075B2Pulse automatic controlAngle demodulation by phase difference detectionPhase detectorControl signal

A phase-locked loop includes a phase detector to measure a phase offset between a reference clock signal and a feedback clock signal, and to generate first and second output control signals having a pulse width corresponding to the phase offset. The phase locked loop further includes a first pulse width control circuit coupled to the phase detector to reduce the pulse width of the first output control signal producing a first modified output control signal, a second pulse width control circuit coupled to the phase detector to reduce the pulse width of the second output control signal producing a second modified output control signal, a first charge pump coupled to the phase detector to provide a first charge signal responsive to the first and second output control signals, and a second charge pump coupled to the first and second pulse width control circuits to provide a second charge signal responsive to the first and second modified output control signals.

Owner:INTEL CORP

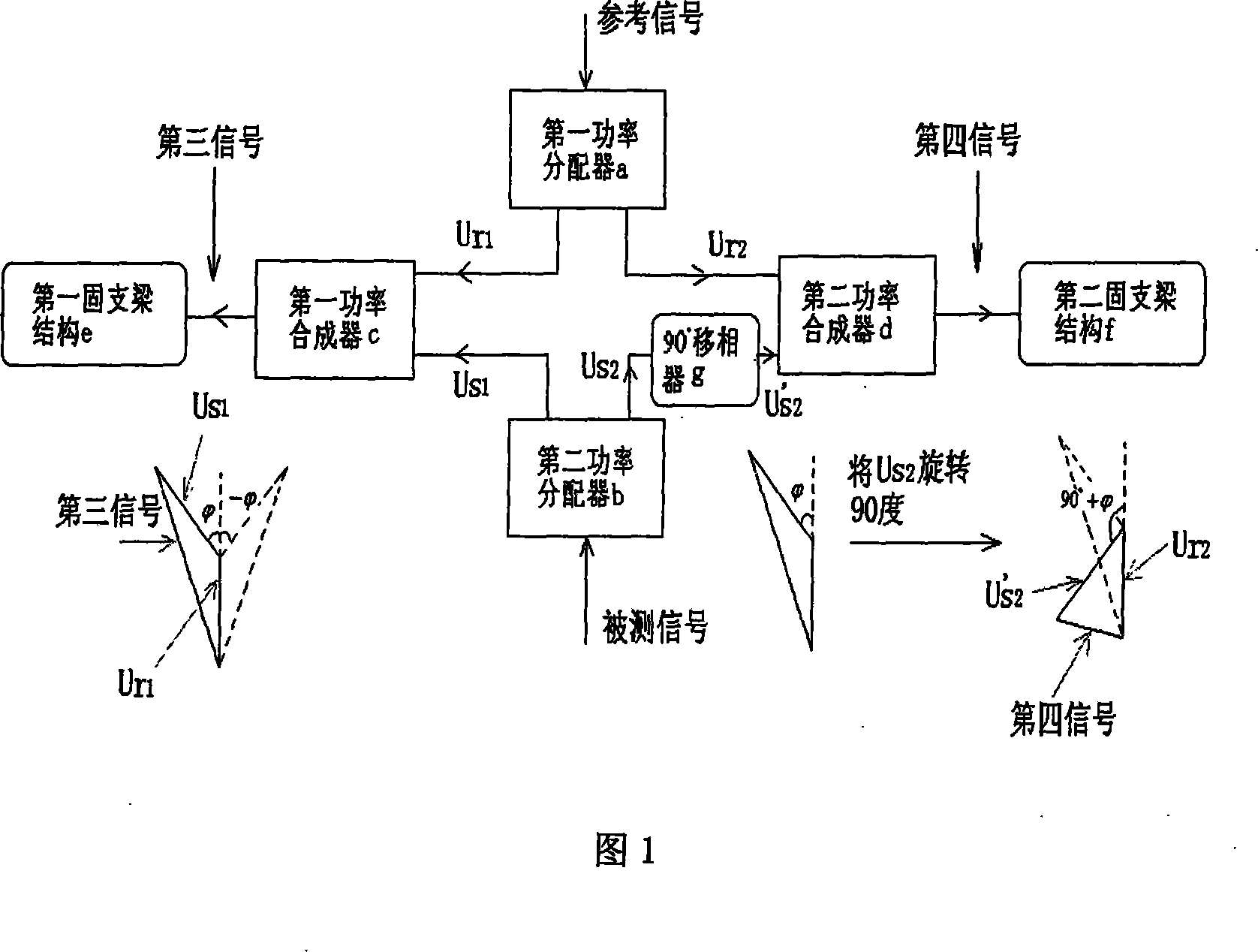

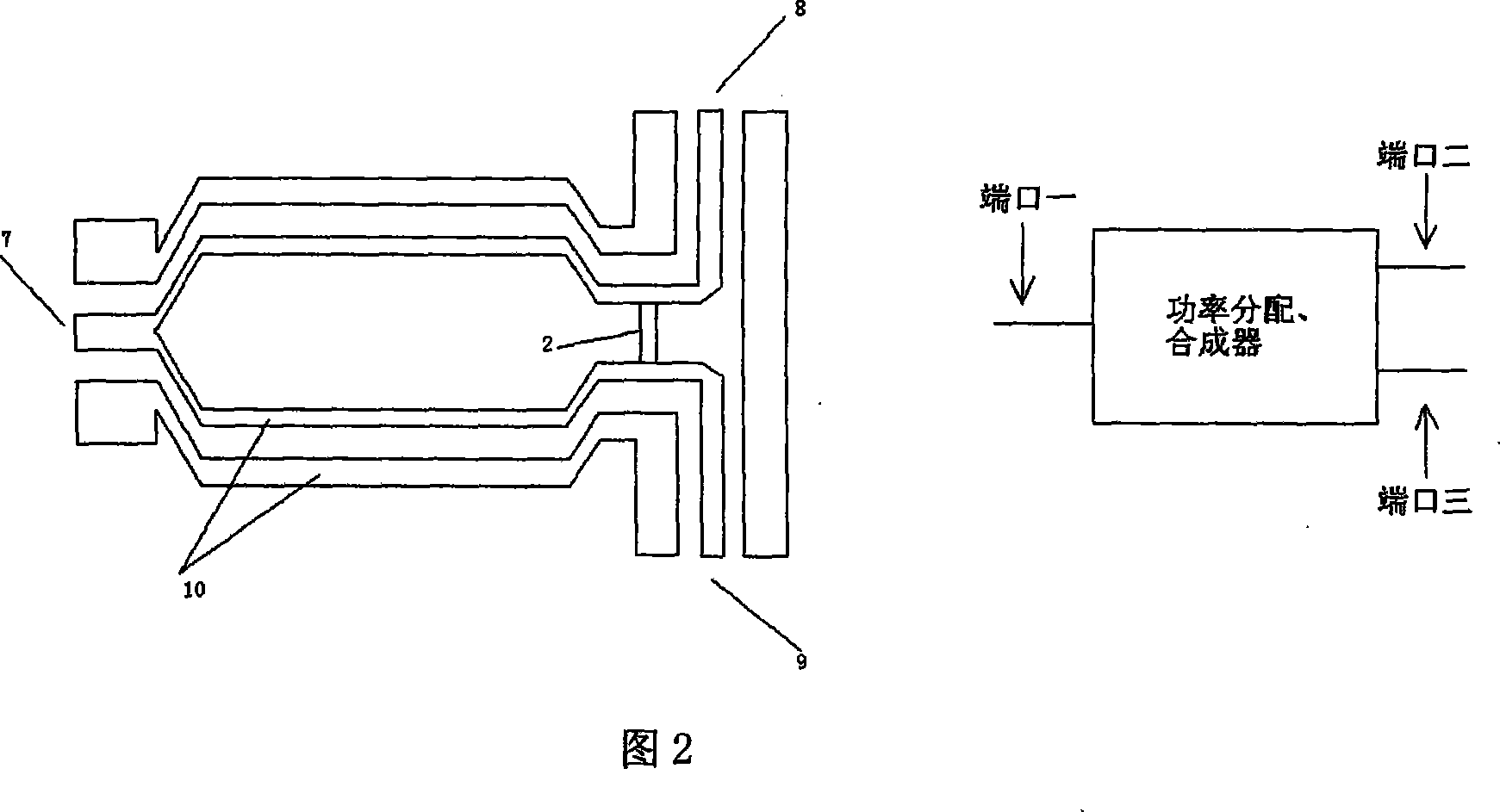

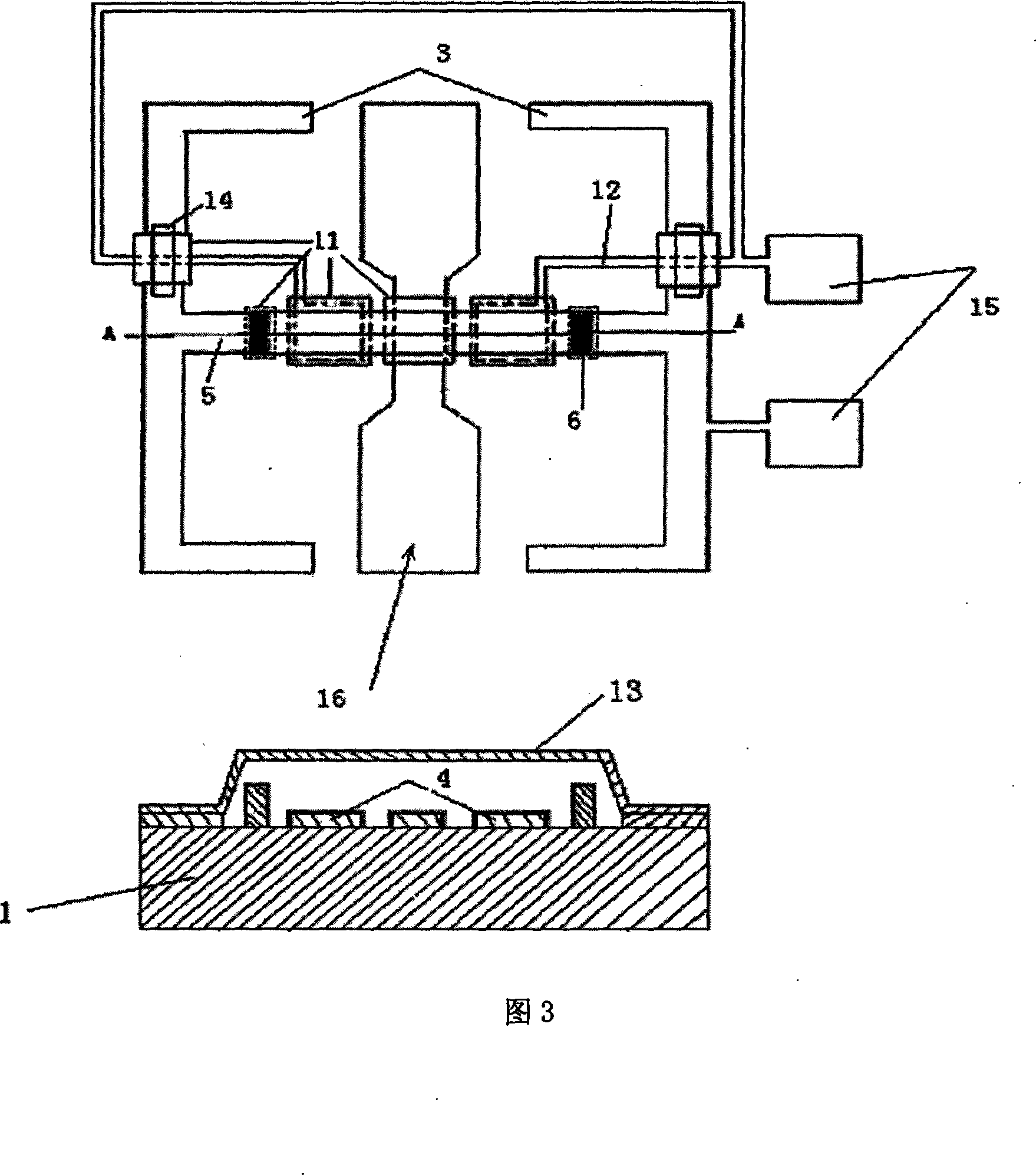

Microelectronic machinery orthogonal double channels microwave phase online detector and manufacturing method therefor

InactiveCN101034122AIncreaseIncreased bandwidthElectromagentic field characteristicsCapacitancePower combiner

this invention relates to power in direct-current circuits. The invention takes gallium arsenide as foundation (1). On the foundation has power divider, power synthesizer, 90deg phaser, solid beam structure. Power divider and power synthesizer composed by port one (7), port two(8), port three(8), dissymmetry coplane band line(10), nitride tantalum electric resistance. Solid beam structure includes signal input port(16), pier(5), solid beam(13), pedestal structure(6), sensing electrode(4), sensing electrode leader(12), capacitance detecting port(15), air bridge(14). There are nitriding silicon medium layer on the transmission line, pedestal structure and sensing electrode under solid beam, and sensing electrode leader under Air Bridge.

Owner:SOUTHEAST UNIV

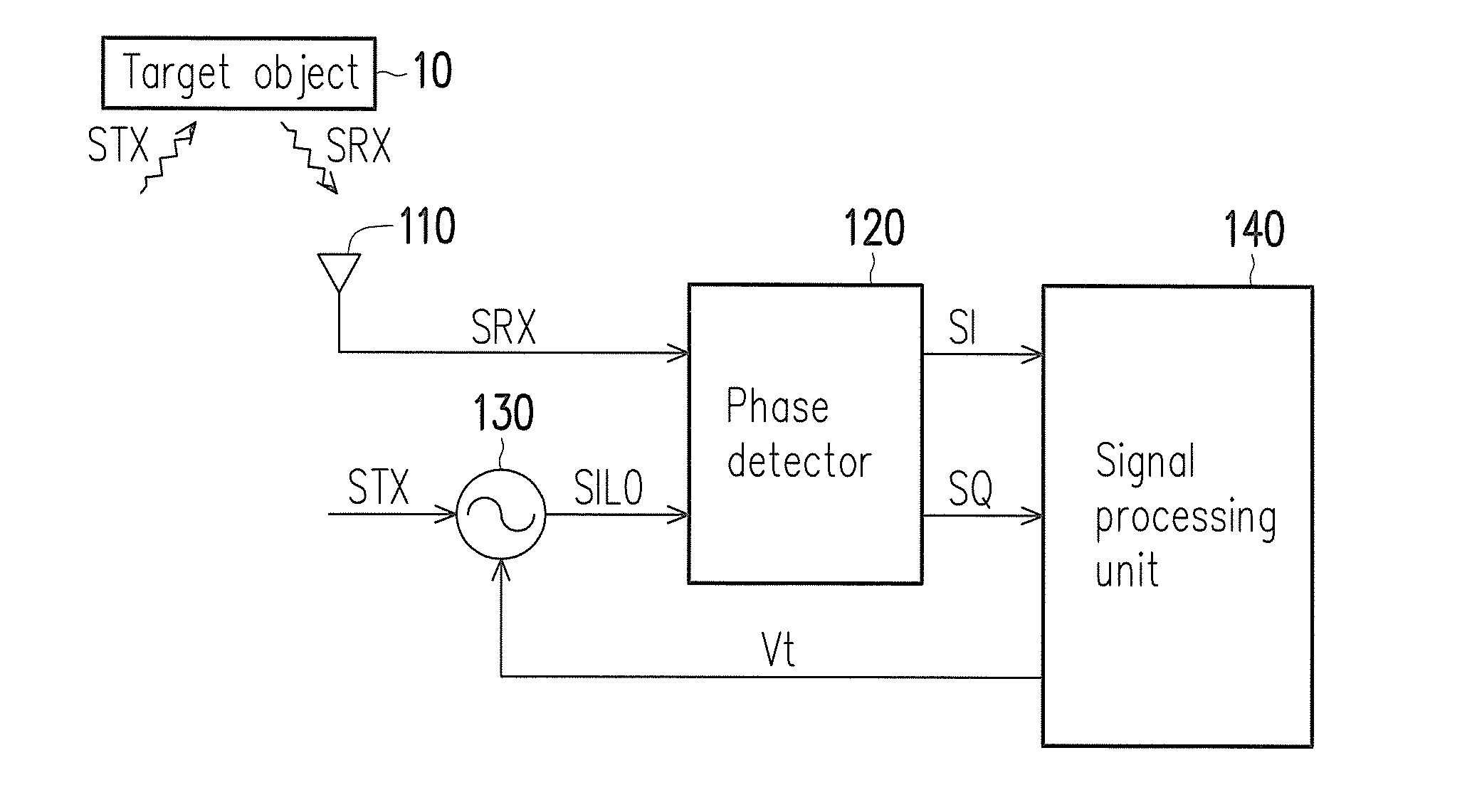

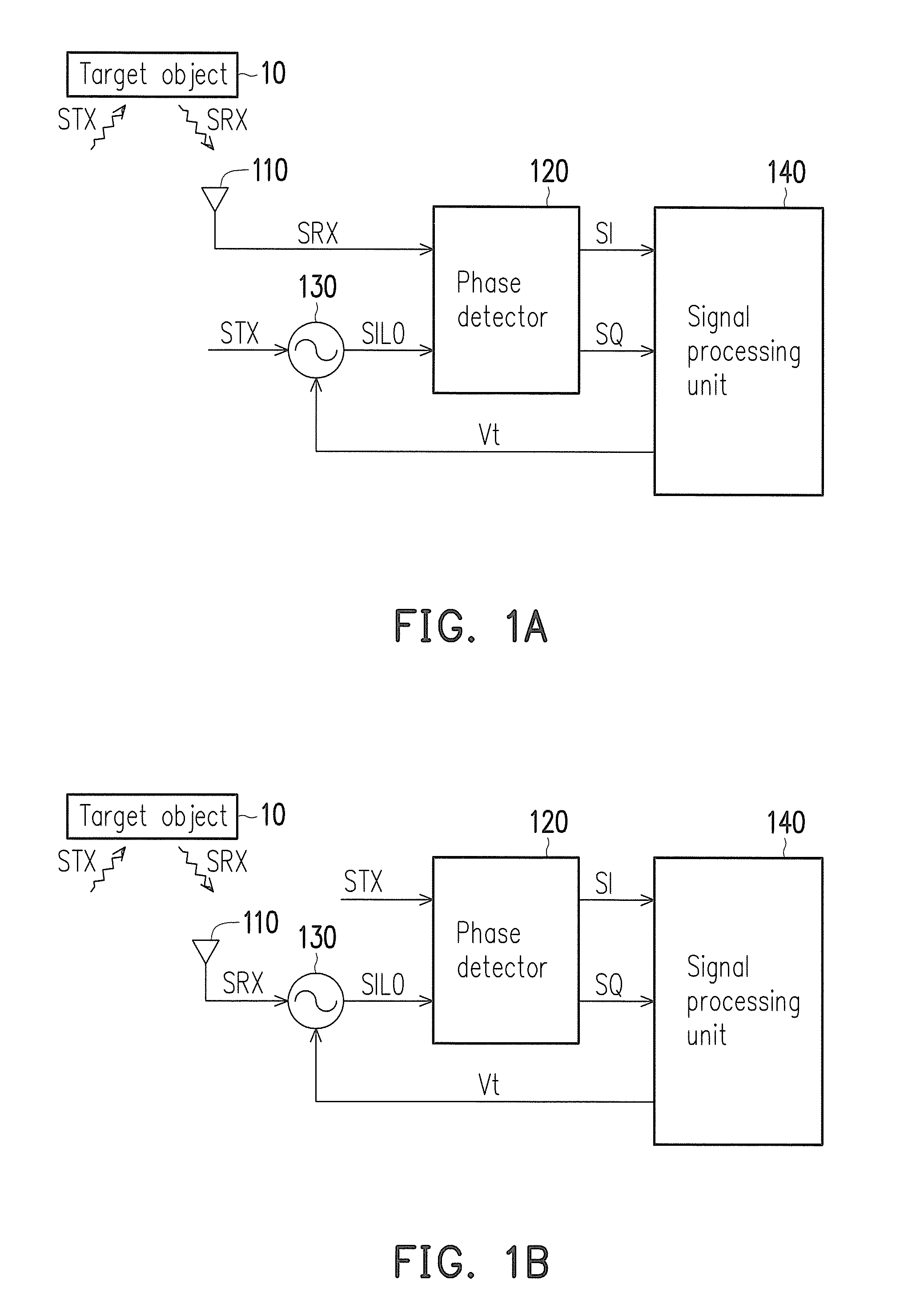

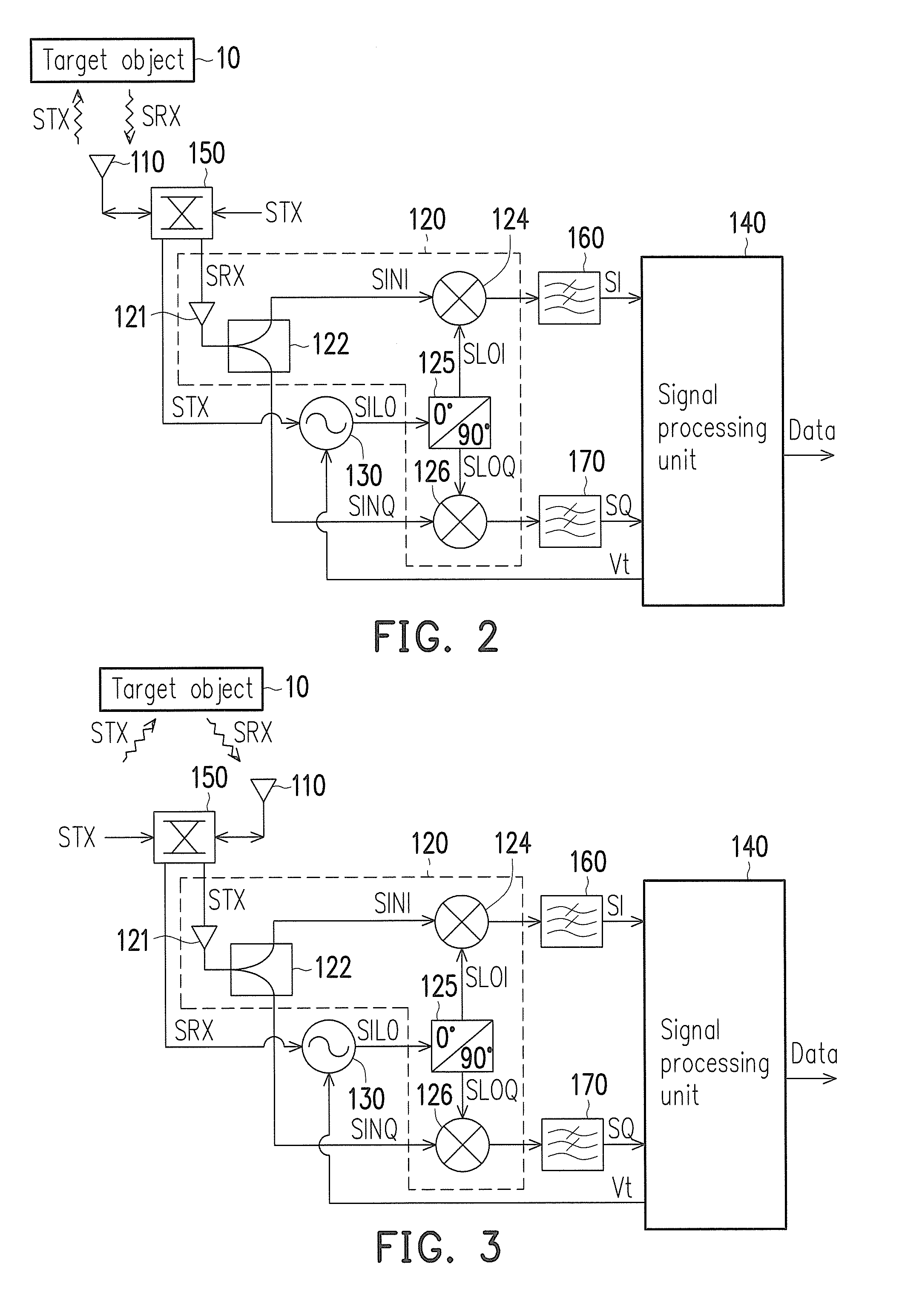

Motion detection device

ActiveUS20160187475A1Improve practicalityReduce power consumptionRadio wave reradiation/reflectionPhysicsPhase detector

A motion detection device is provided. The motion detection device includes a first antenna, a voltage-controlled oscillator, a phase detector and a signal processing unit. The first antenna receives a first signal generated by a second signal reflected by a target object, so as to output the first signal to the phase detector or the voltage-controlled oscillator. The voltage-controlled oscillator receives first signal or the second signal and receives a frequency adjustment signal, so as to generate an oscillating signal according to the frequency adjustment signal and the one of the first signal and the second signal. The phase detector receives the oscillating signal and another one of the first signal and the second signal, and generates a first phase output signal and a second phase output signal. The signal processing unit estimates motion parameters of the target object according to the first and the second phase output signal.

Owner:NAT SUN YAT SEN UNIV

Method and apparatus for characterizing a delay locked loop

A delay locked loop includes a forward path, a feedback path, a phase detector, logic, and a dither circuit. The forward path includes a delay line configured to receive an input clock signal and delay the input clock signal by a time interval to generate an output clock signal. The feedback path is configured to provide a feedback clock signal based on the output clock signal. The phase detector is configured to compare the input clock signal and the feedback clock signal and generate a shift signal if the output clock signal is not in phase with the input clock signal. The logic is coupled to the delay line and configured to receive the shift signal and control the time interval based on the shift signal. The dither circuit is coupled to the delay line and configured to introduce a delay responsive to an assertion of a test mode enable signal.

Owner:MICRON TECH INC

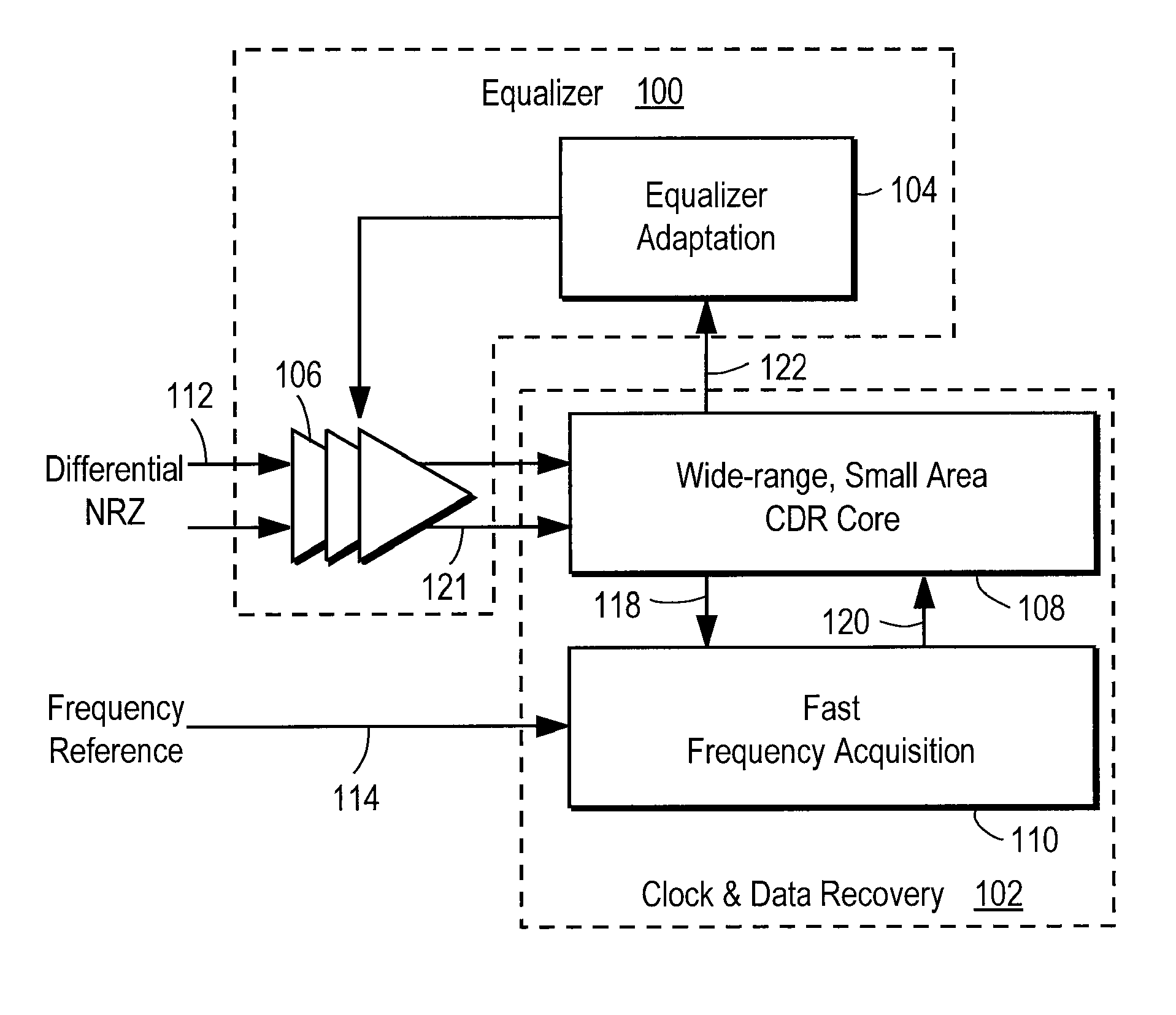

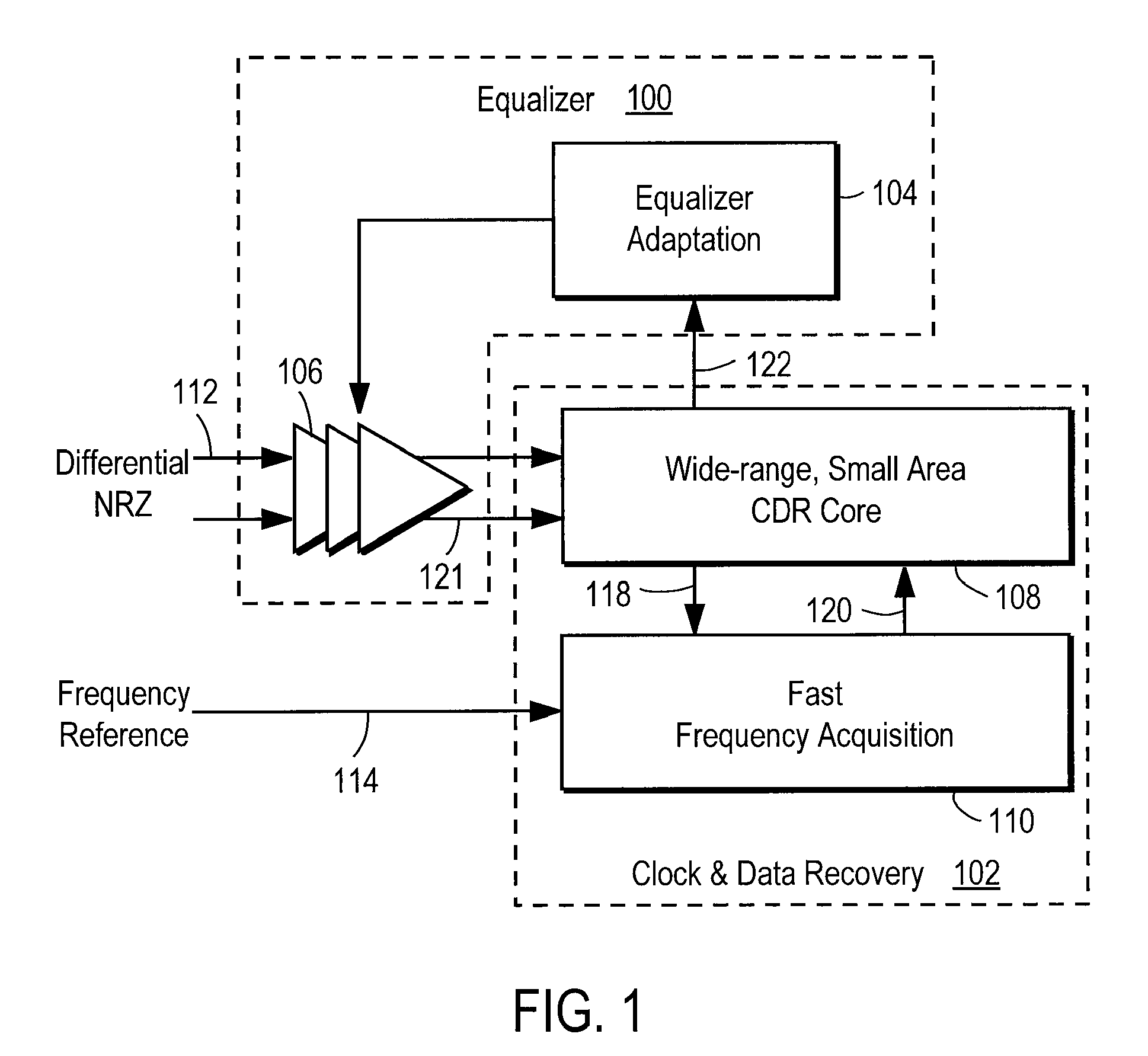

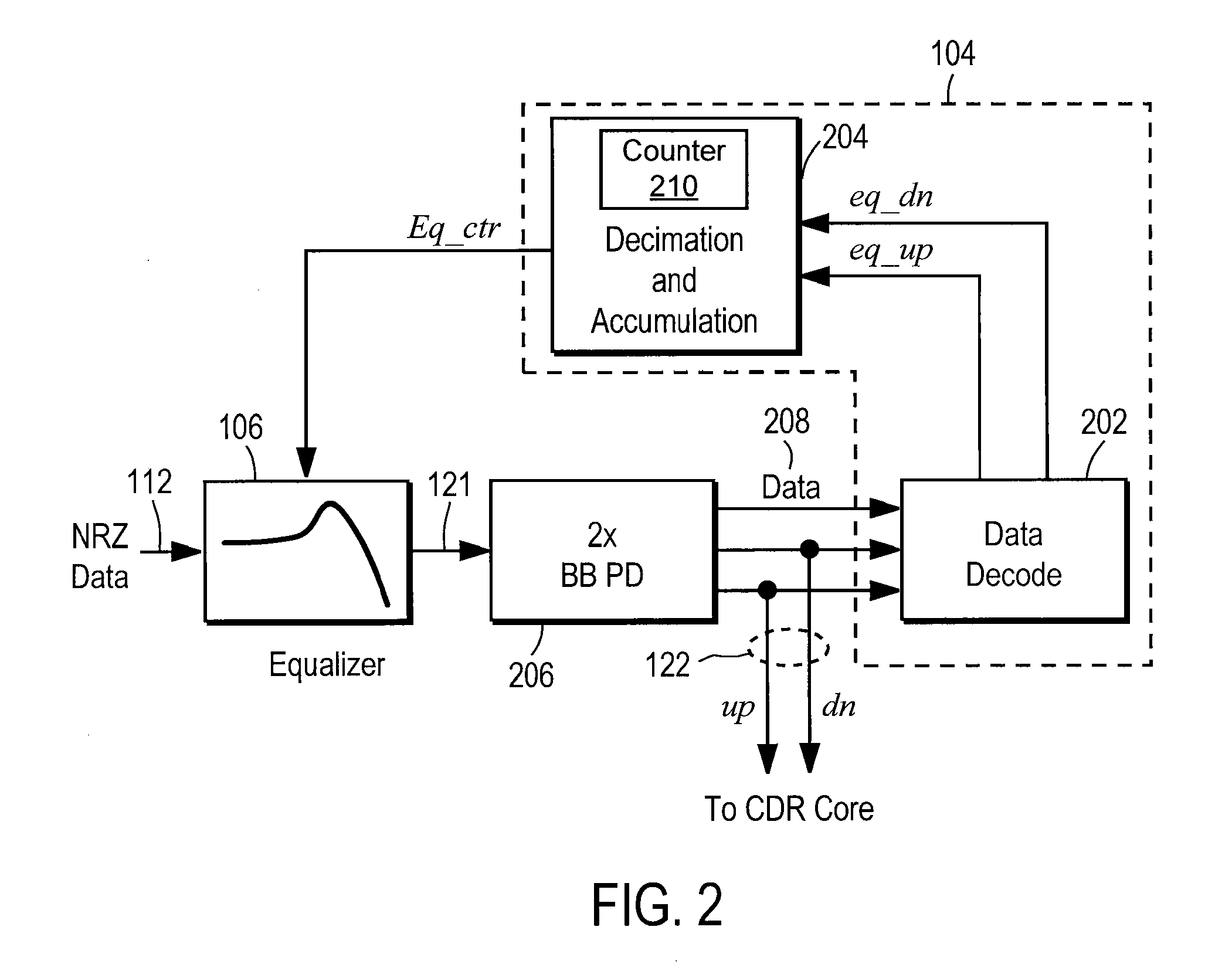

Adaptive equalizer for use with clock and data recovery circuit of serial communication link

ActiveUS20080247452A1Low costEffort-saving designMultiple-port networksReceiver initialisationPhase detectorTime information

An adaptive equalizer system for use in a serial communication link uses timing information generated by a phase detector of a clock and data recovery circuit of the serial communication link and a frequency pattern of the recovered data to determine whether the data received over the serial communication link is over-equalized or under-equalized. The equalizer strength of the adaptive equalizer system is adjusted based on such determination.

Owner:SILICON IMAGE INC

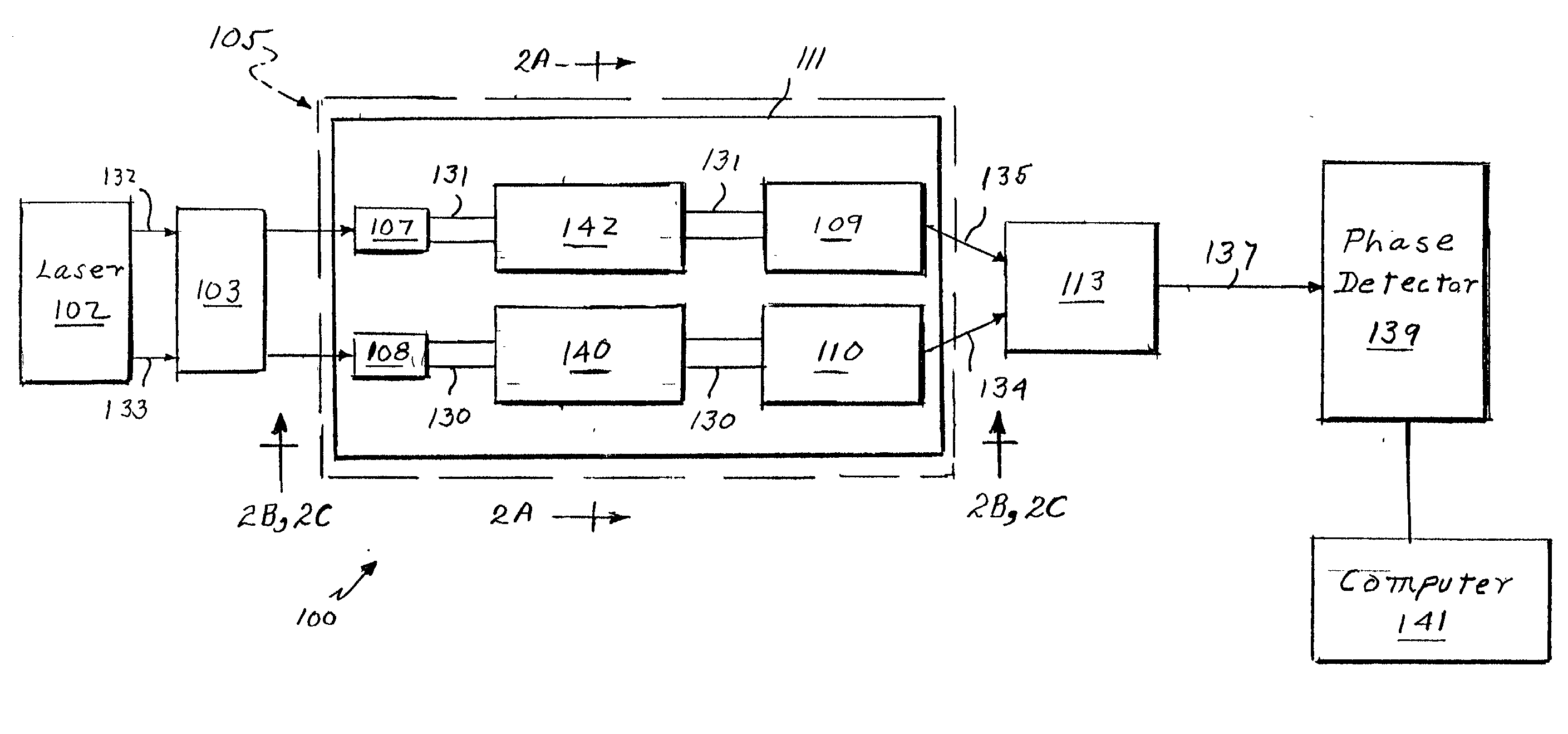

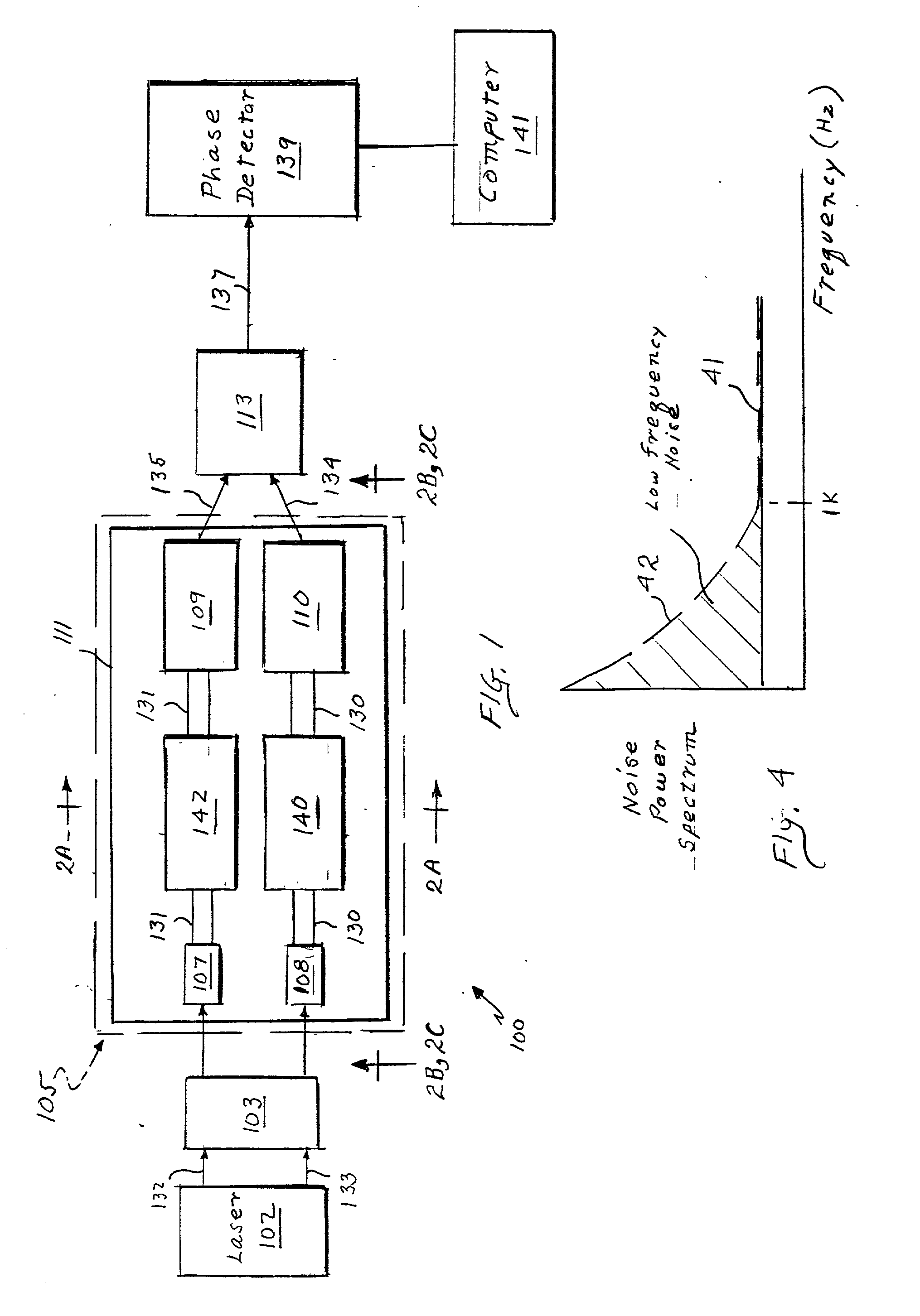

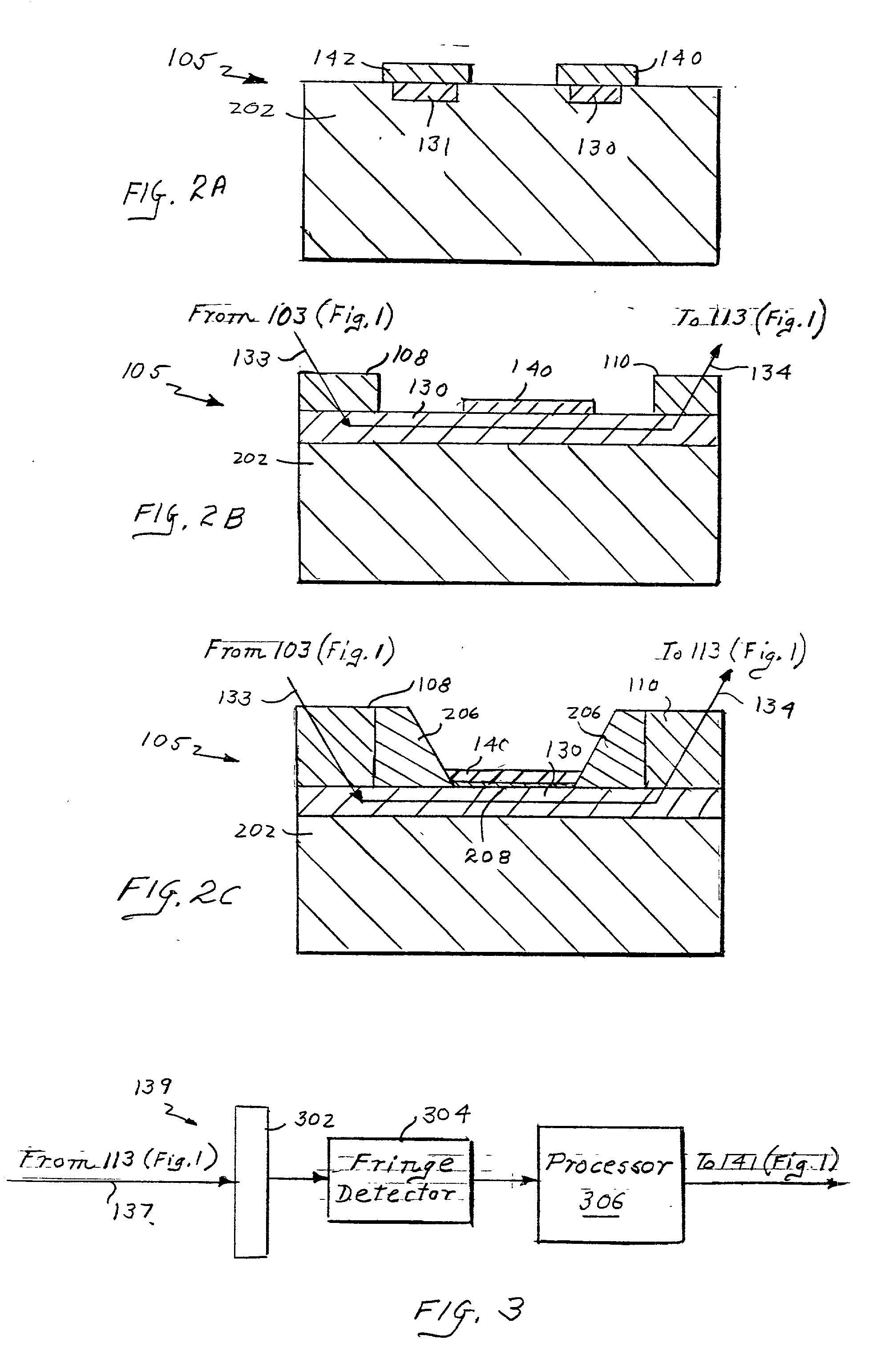

Doubly-differential interferometer and method for evanescent wave surface detection

InactiveUS20020003627A1Easy to disassembleMaterial analysis by observing effect on chemical indicatorPhase-affecting property measurementsReference sampleBio molecules

A high speed, highly sensitive optical sensing platform and a method for detecting and / or measuring characteristics of a substance in a measurement sample are disclosed. The platform includes at least one pair of optical paths formed in a waveguide, a light source for injecting optical beams along the optical paths, a light modulator for enabling the excitement of a transverse electric and a transverse magnetic guide modes, and a phase detector for detecting phase differences between the beams propagating along the optical paths. One of the optical paths has a target analyte of unknown concentration with a measurement sample bound to its upper surface, while the second optical path has a reference sample containing a known concentration of the target analyte bound to its upper surface. A guided mode modulator causes an optical beam to propagate through the waveguide sequentially as two polarized modes. The highly sensitive platform is especially useful for directly detecting and / or measuring very small numbers of small molecules, bio-molecules, microorganisms in a liquid or gaseous test sample.

Owner:PERFECT GALAXY INT

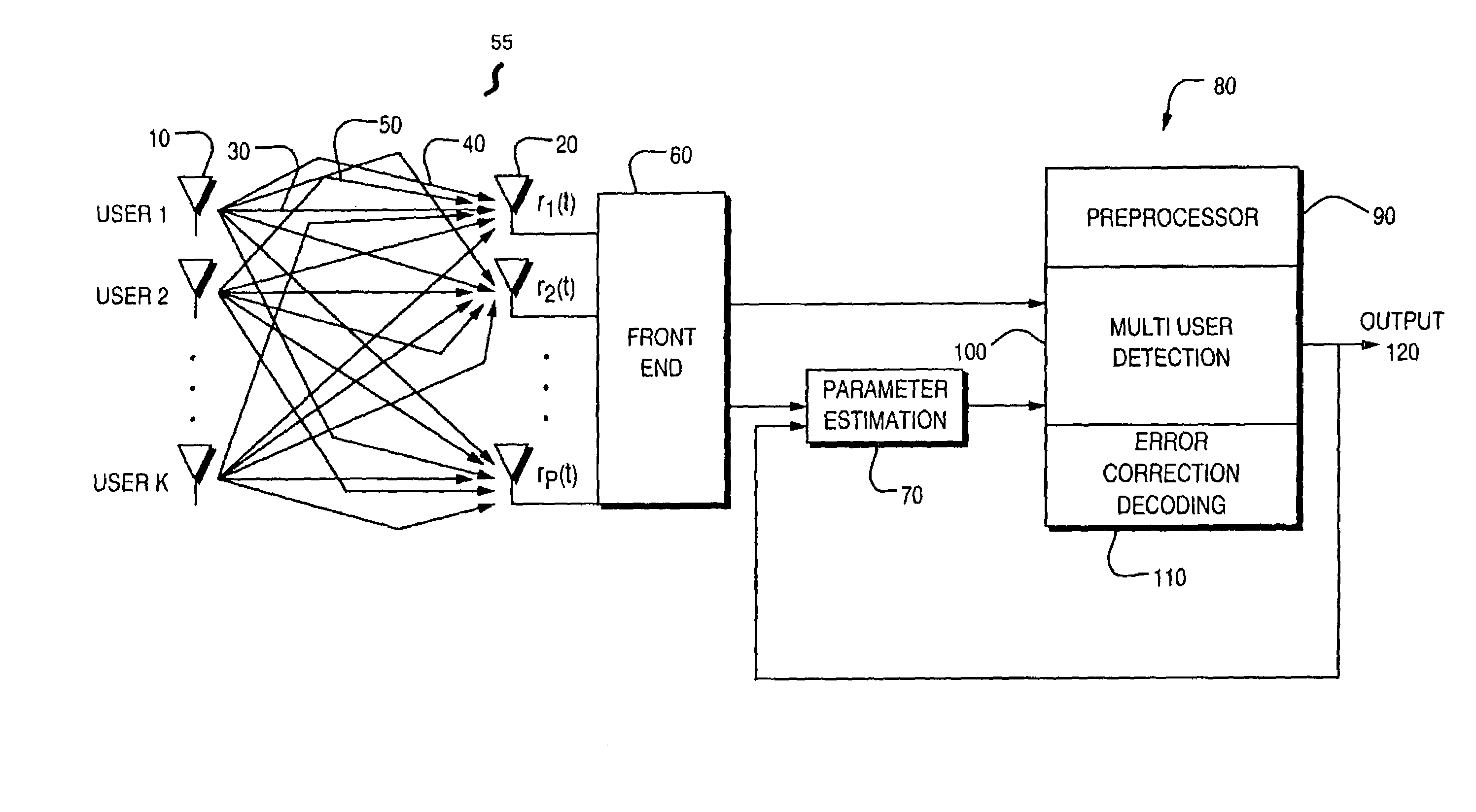

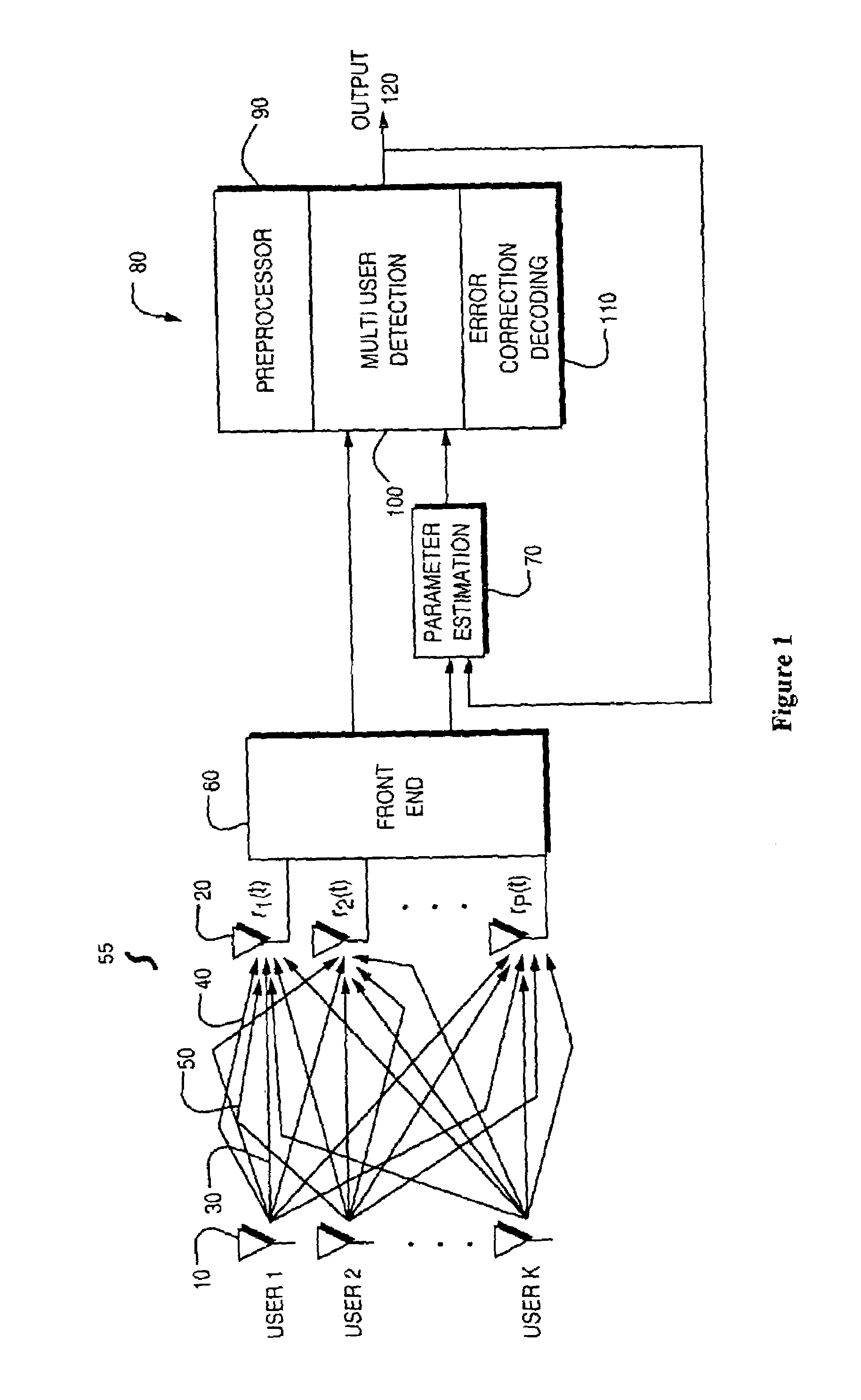

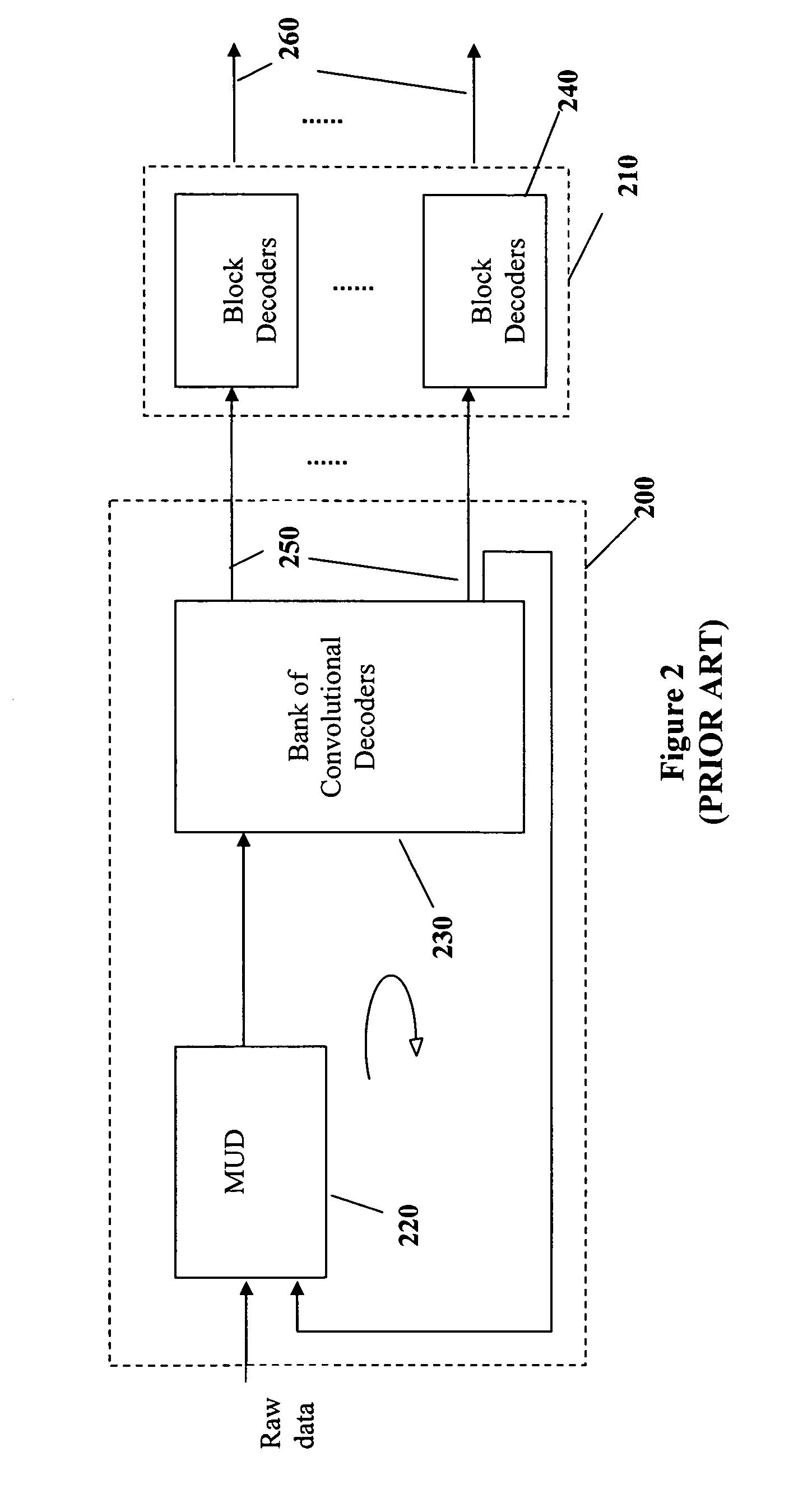

Reduced complexity multi-turbo multi-user detector

ActiveUS6967598B2Reduce the possibilityImprove performancePolarisation/directional diversityCode conversionPhase detectorRound complexity

A reduced complexity Turbo multi-user detector (MUD) processing system in multiple access communications channels that decreases the likelihood of improper decoding of the final values of interest and decreases the computation complexity for each iteration, thereby allowing for a reduction in the number of iterations performed and lowers the overall complexity without negatively impacting performance. In one form the present invention comprises a multi-user detector coupled to two or more decoder sections, two ore more recoders, and a compare and adjust section in such a manner that data flows iteratively to correct for errors in a computationally efficient manner.

Owner:COLLISION COMM INC

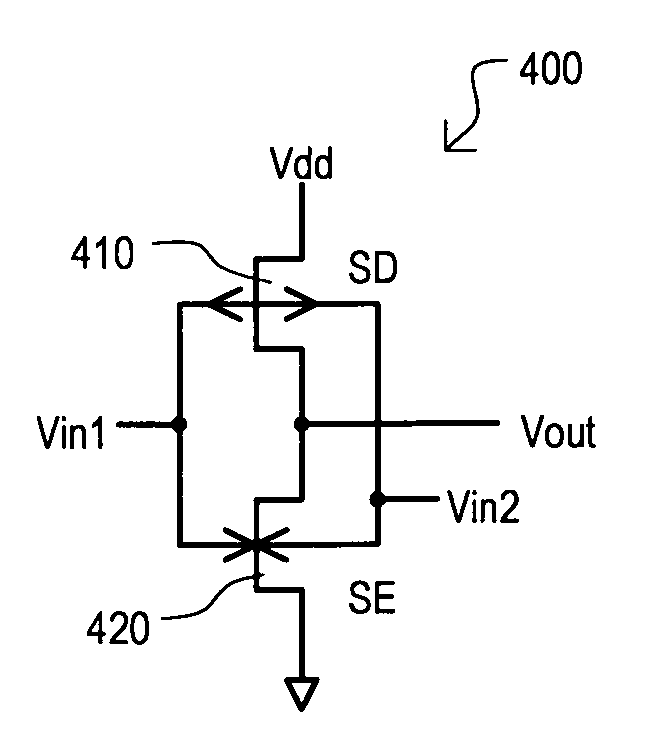

Circuit configurations having four terminal JFET devices

InactiveUS20070262793A1Logic circuits characterised by logic functionSolid-state devicesPhase detectorMultiplexer

Circuits using four terminal junction field effect transistors (JFETs) are disclosed. Such circuits can include various static and dynamic logic circuits, flip-flops, multiplexer, tri-state driver, phase detector, logic having variable speeds of operation, and / or analog circuit with such four terminal JFETs operating in a linear or nonlinear mode.

Owner:MIE FUJITSU SEMICON

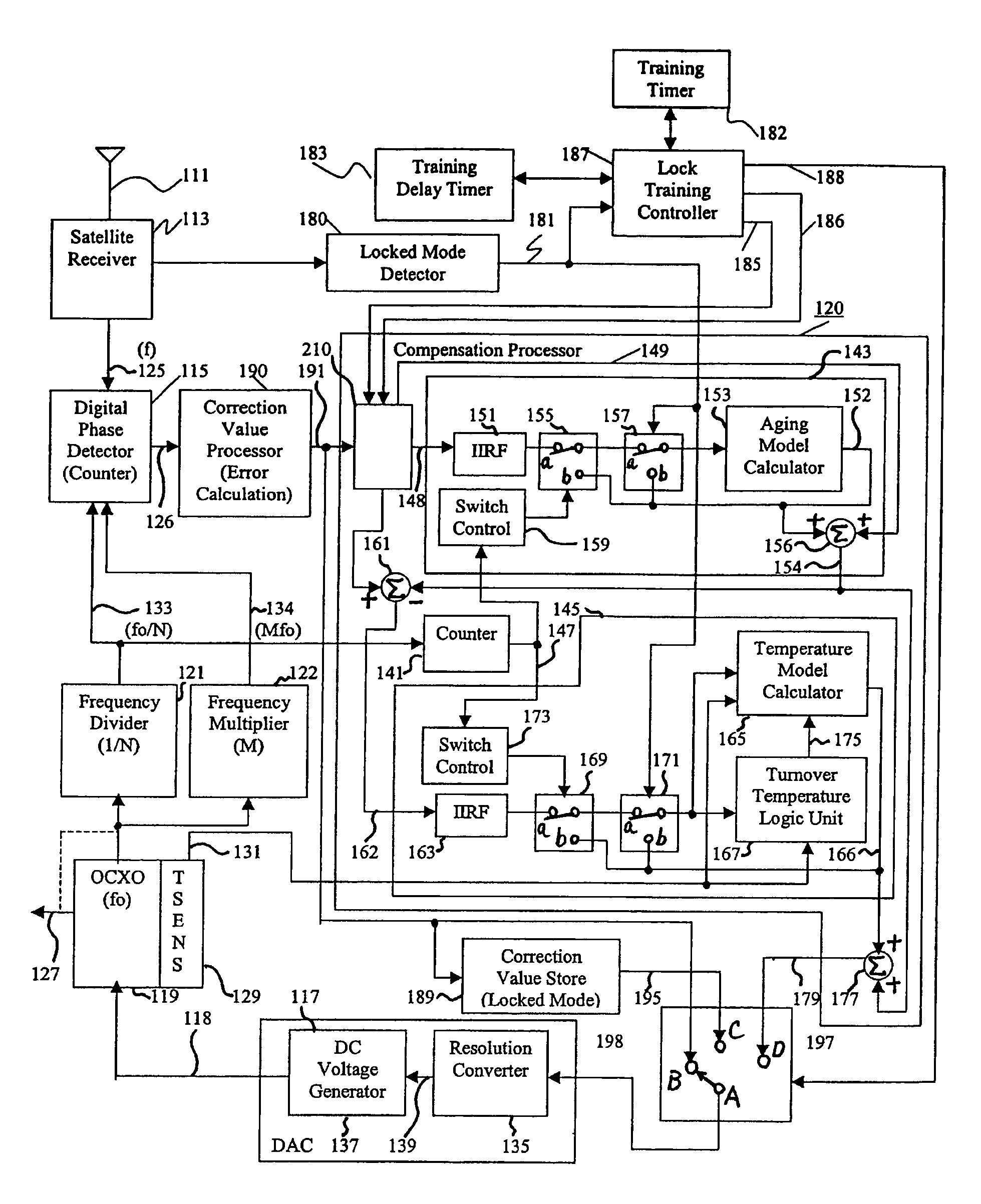

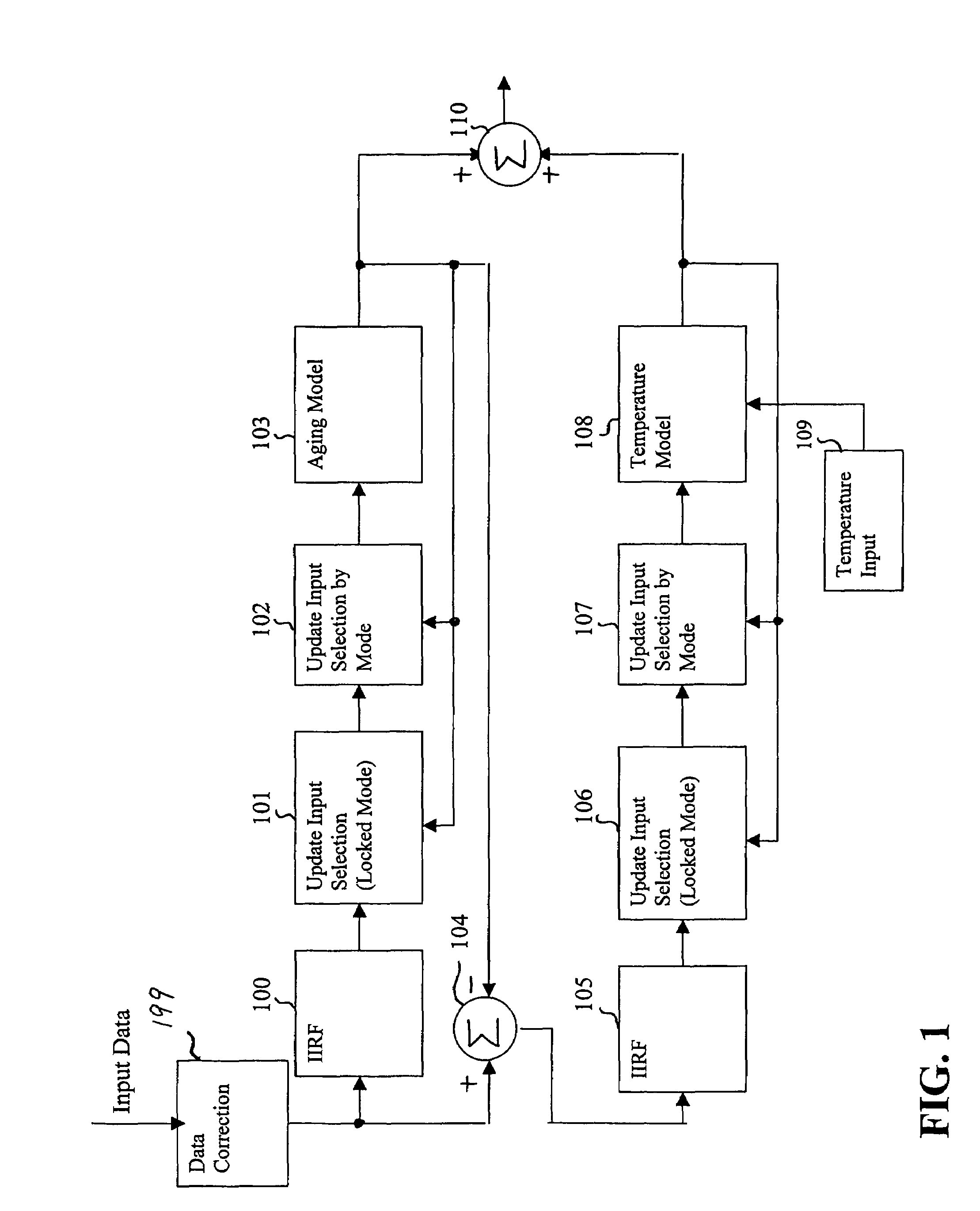

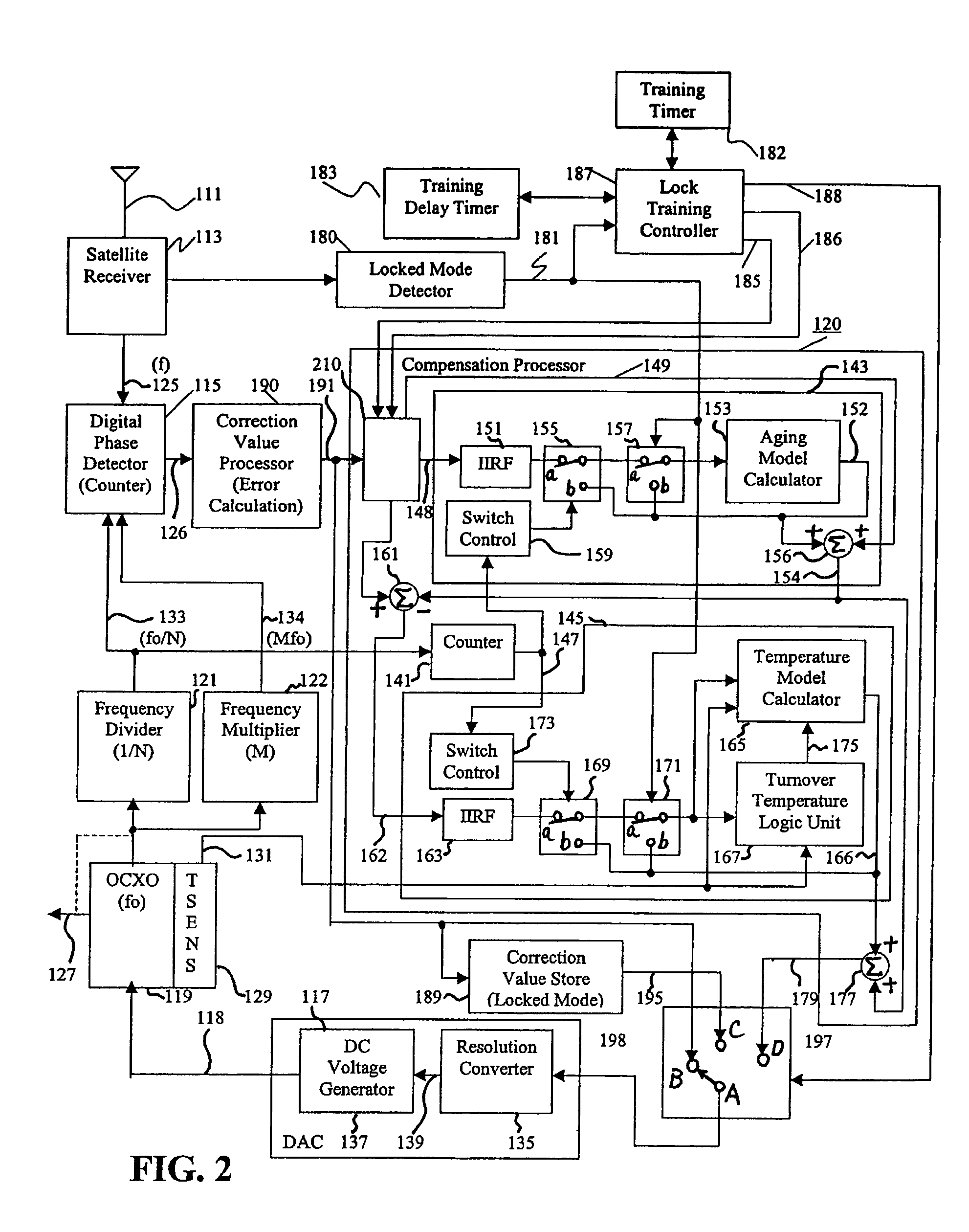

Reference timing signal apparatus and method

ActiveUS7015762B1Increase currentGood compensationRadiation pyrometryPulse automatic controlTraining periodAdaptive filter

A reference timing signal apparatus with a phase-locked loop (PLL) has a computer algorithm which adaptively models the multiple frequencies of an oscillator following a training period. The oscillator is part of a PLL and the oscillation frequency thereof is controlled in response to the phase detector output. The computer algorithm processes the control signal applied to the oscillator. The computer algorithm updates the characteristics of the model relating to the aging and temperature of the oscillator, using for example, a Kalman filter as an adaptive filter, in accordance with a cumulative phase error in the PLL calculated during a given time interval. By the algorithm, the subsequent model predicts the future frequency state of the oscillator on which it was trained. The predicted frequency of the model functions as a reference to correct the frequency of the oscillator in the event that no input reference timing signal is available. Also, the calculated phase error is stored and is used while no input reference timing signal or accurate predicted frequency value is available. With the model updating algorithm, oscillators of low stability performance may be used as cellular base station reference oscillator, which is based on satellite systems, for example, GPS, GLONASS or Galileo systems.

Owner:APPLE INC

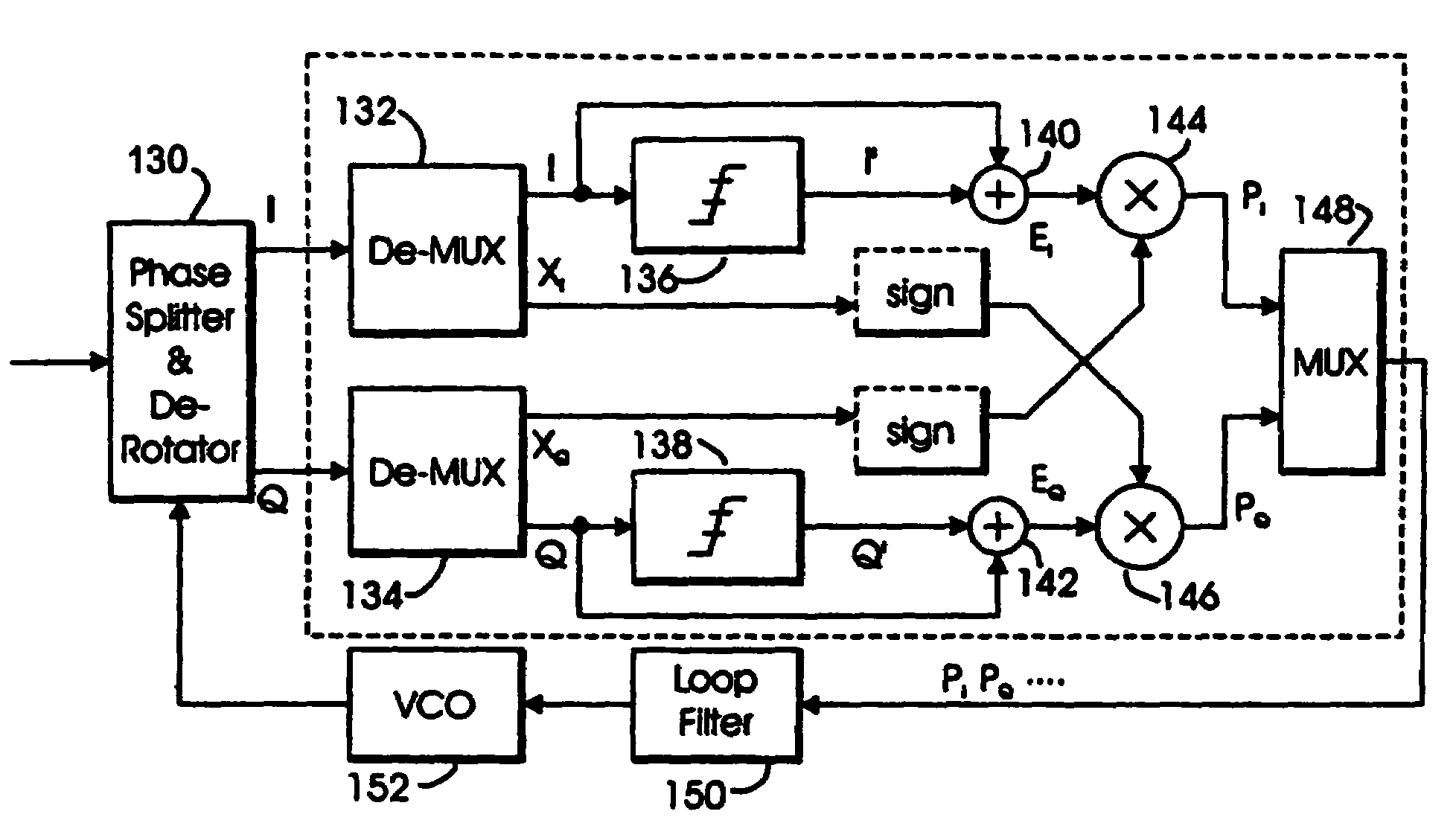

Dual mode QAM/VSB receiver

InactiveUS7403579B2Facilitate decision-makingTelevision system detailsTelevision system scanning detailsPhase detectorTelevision receivers

A television receiver system capable of receiving and demodulating television signal information content that has been modulated and transmitted in accordance with a variety of modulation formats is disclosed. In particular, the system is able to accommodate receipt and demodulation of at least 8 and 16-VSB modulated signals in order to support US HDTV applications, as well as 64 and 256-QAM modulated signals, for European and potential US CATV implementations. The system includes carrier and timing recovery loops adapted to operate on an enhanced pilot signal as well as decision directed carrier phase recovery loops. Phase detectors operate on I and Q rail signals, or generate a Q rail from a Hilbert transform of the I rail. Decision directed loops incorporate a trellis decoder in order to operate on sequence estimated decisions for improved reliability in poor SNR environments.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE