Patents

Literature

227 results about "Unit delay" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Unit delay. A network whose output is equal to the input delayed by one unit of time.

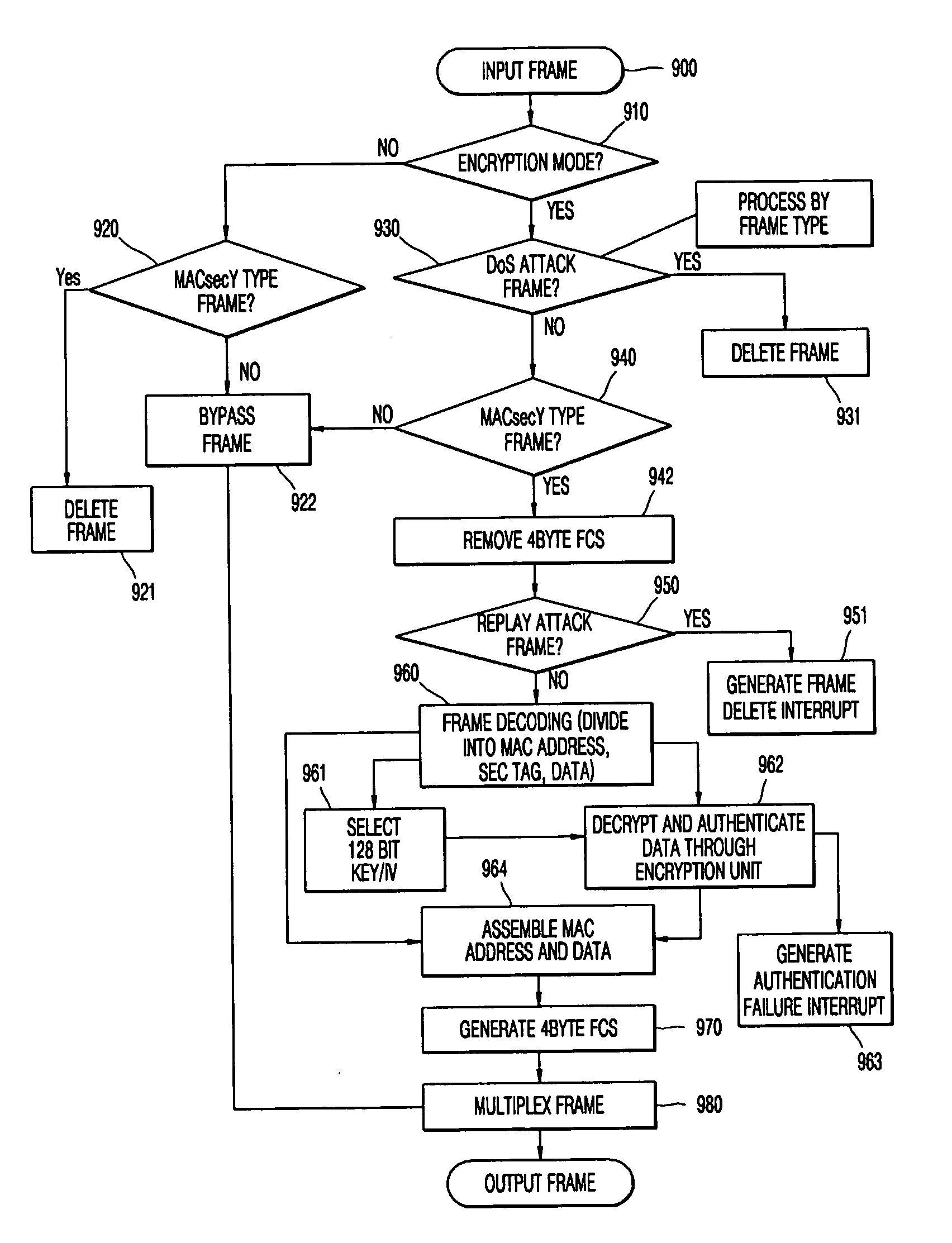

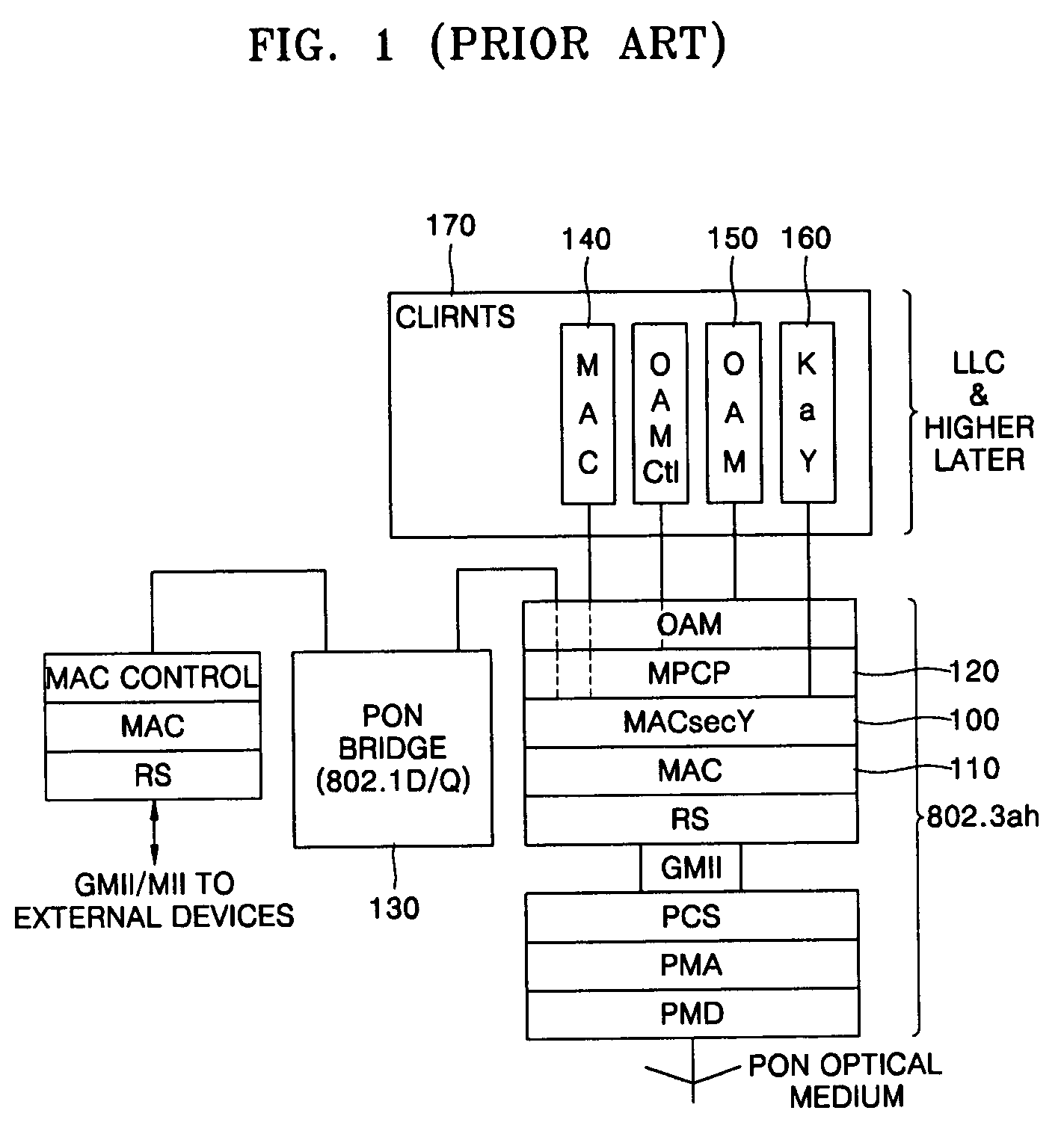

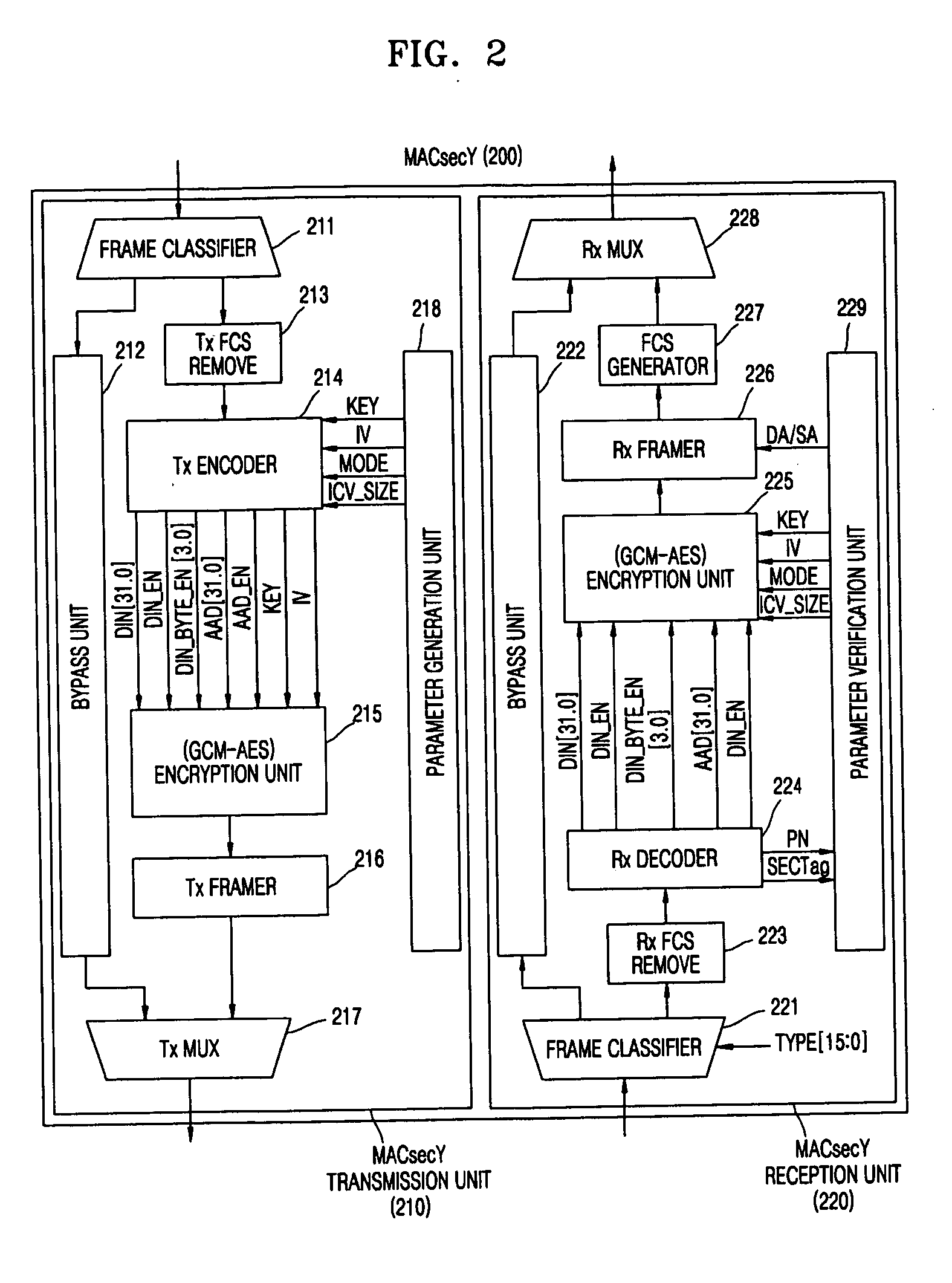

MAC security entity for link security entity and transmitting and receiving method therefor

InactiveUS20060136715A1Memory loss protectionUnauthorized memory use protectionMedia access controlOptical network unit

An apparatus and method for providing a security function of frames transmitted between optical network terminals (OLTs) and optical network units (ONUs) in an Ethernet passive optical network (EPON) providing media access control (MAC) services are provided. The apparatus includes: a frame classifier distinguishing the type of a frame, and based on the logical link identifier (LLID) of the distinguished frame, determining whether or not the frame is a security link to which a security function is to be applied; a bypass unit delaying a no-security-function frame so that a processing time for converting the security-function-applied frame classified in the frame classifier into an encrypted frame is the same as a time for processing the no-security-function frame; and a parameter generation unit transmitting in relation to each of the LLIDs, a parameter set value including a security-function-application setting signal used in the encryption, decryption and authentication of the frame, a frame decryption signal, an encryption mode selection signal, and an authentication intensity adjustment signal.

Owner:ELECTRONICS & TELECOMM RES INST

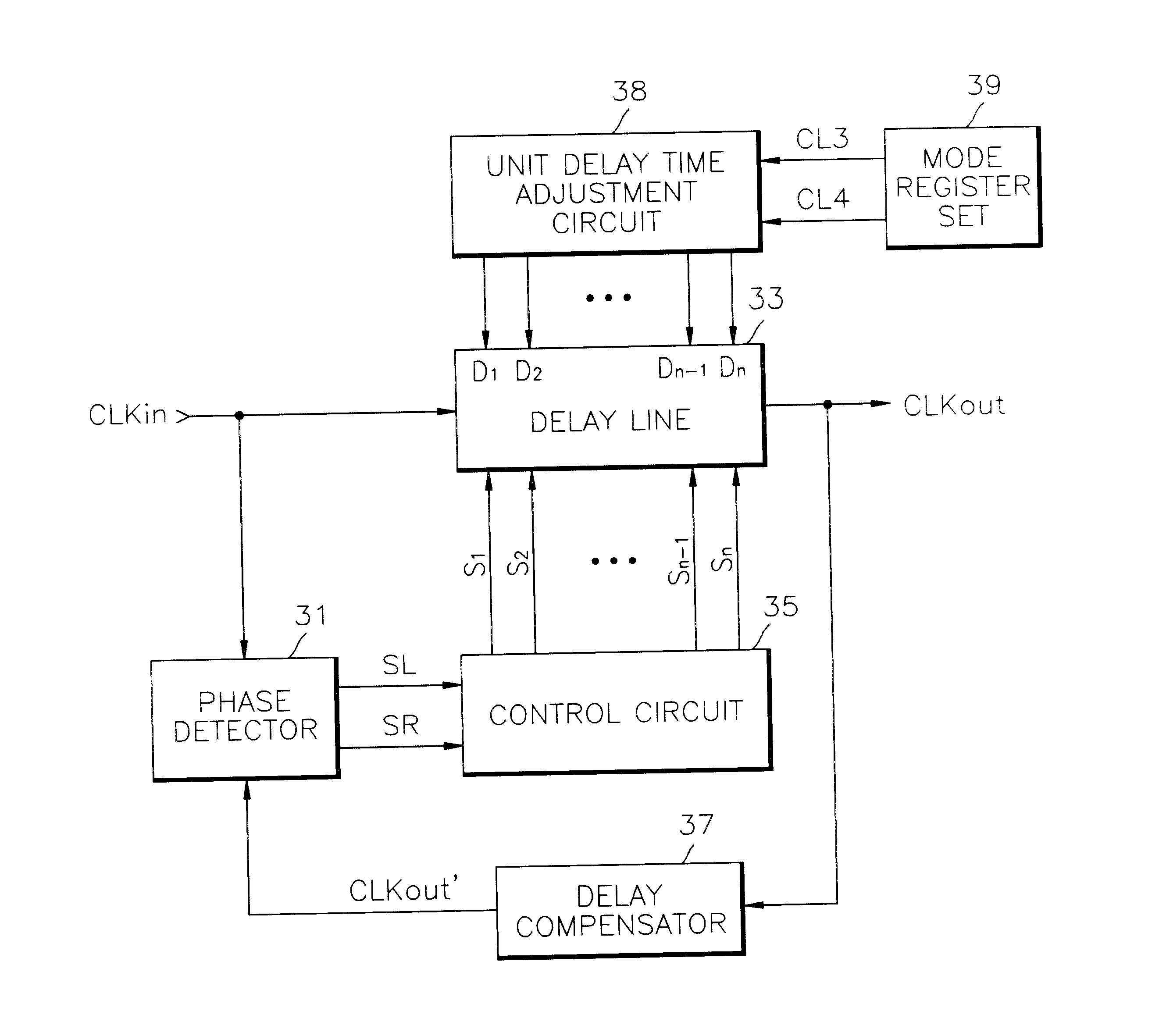

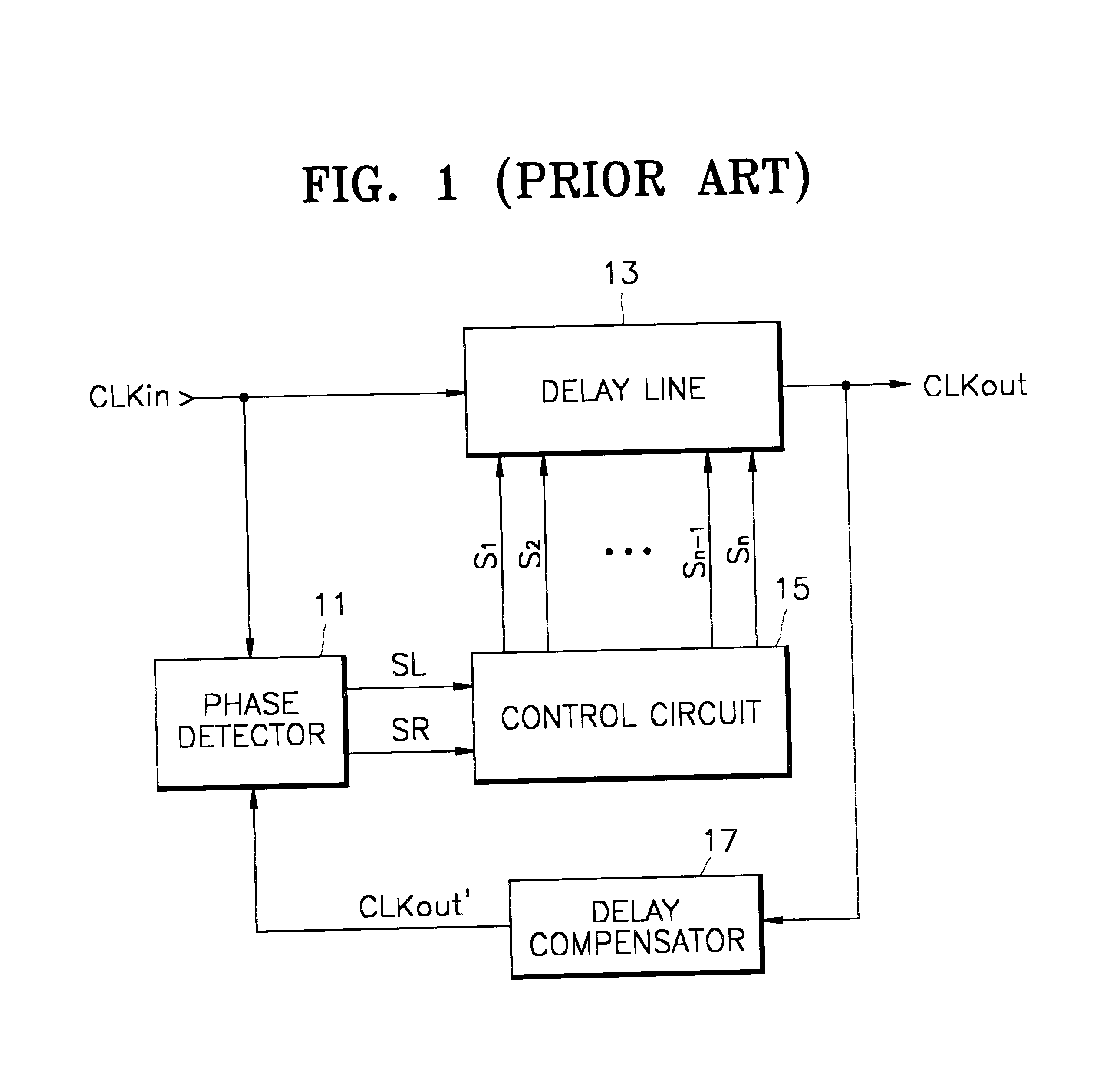

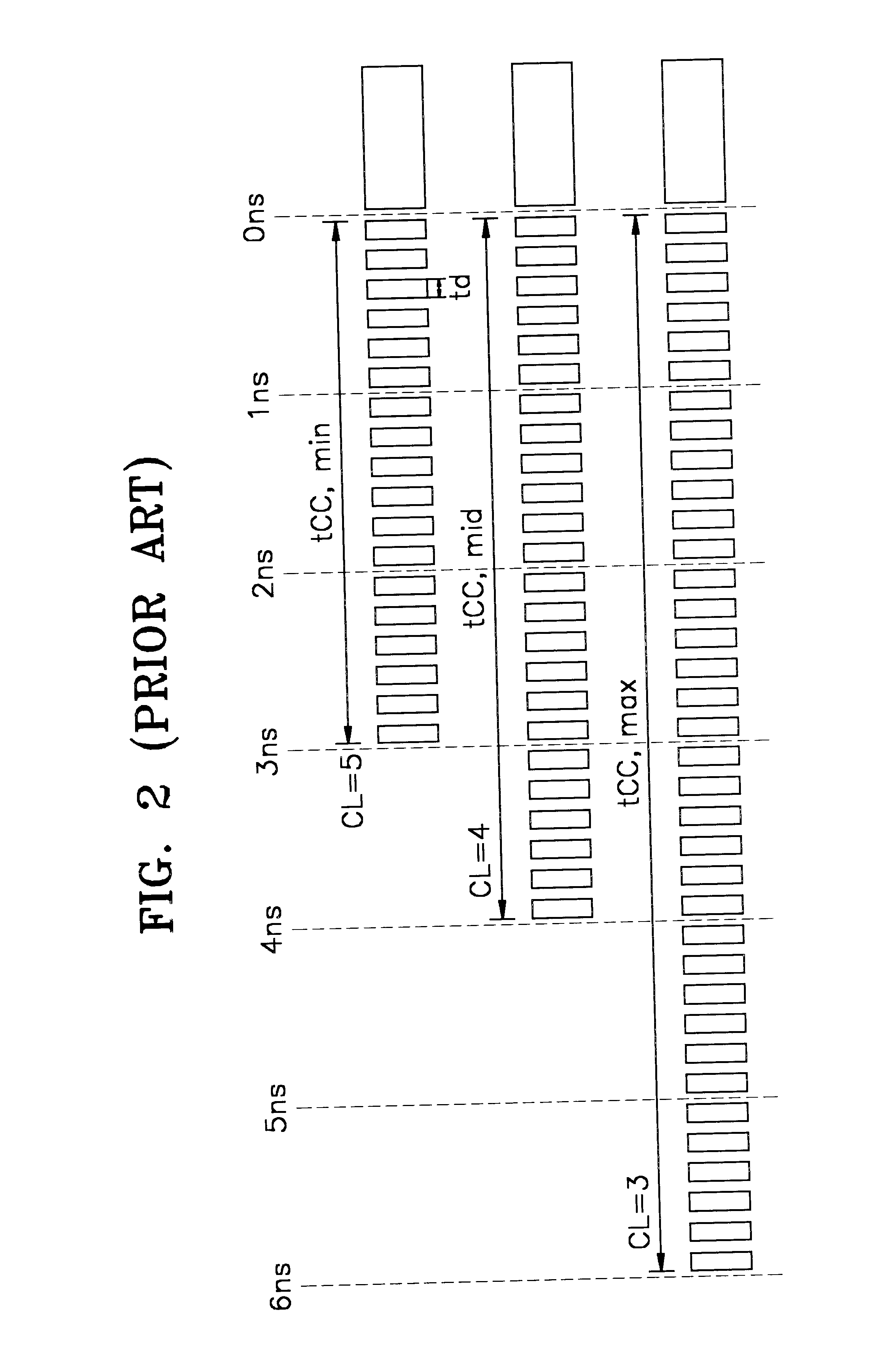

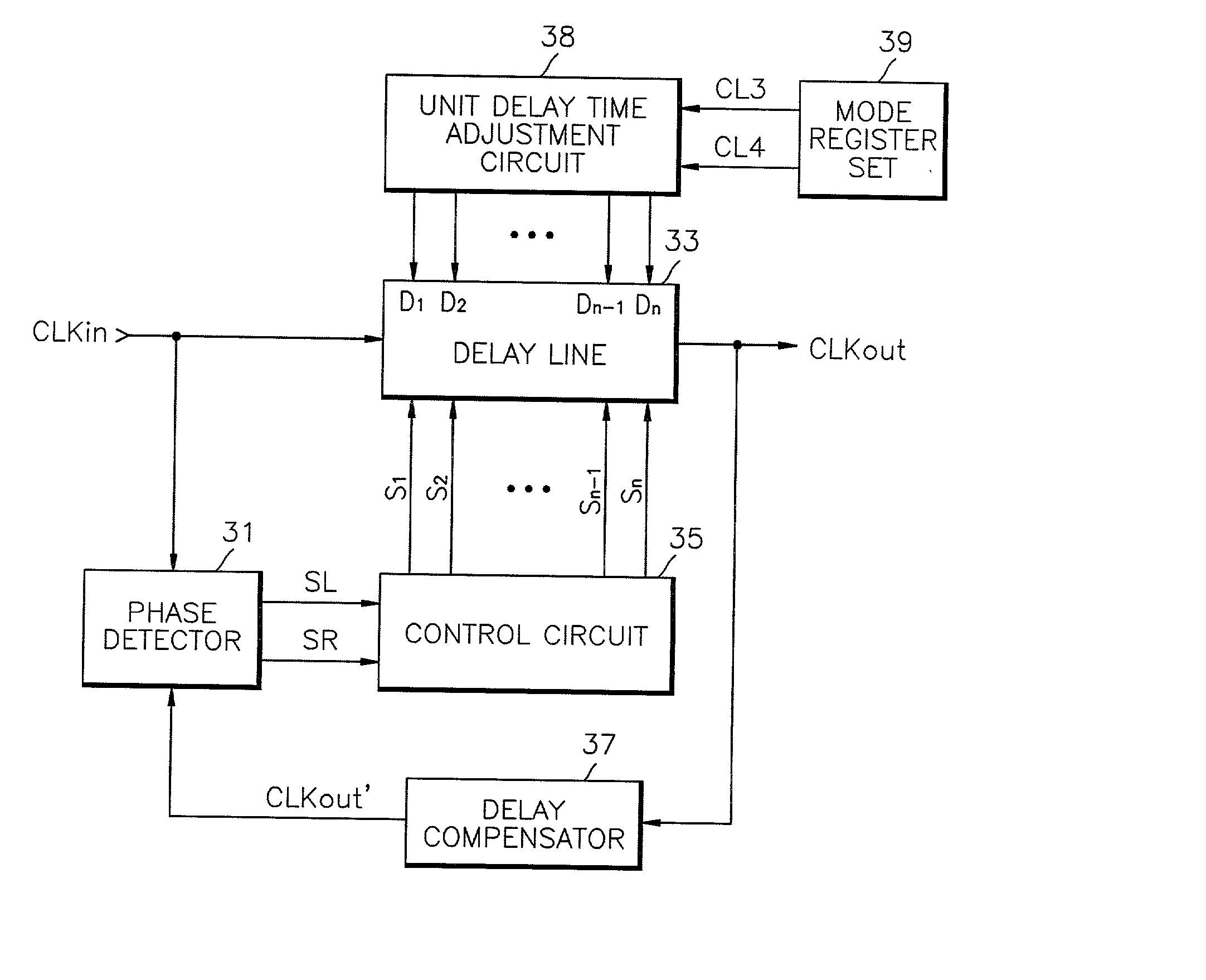

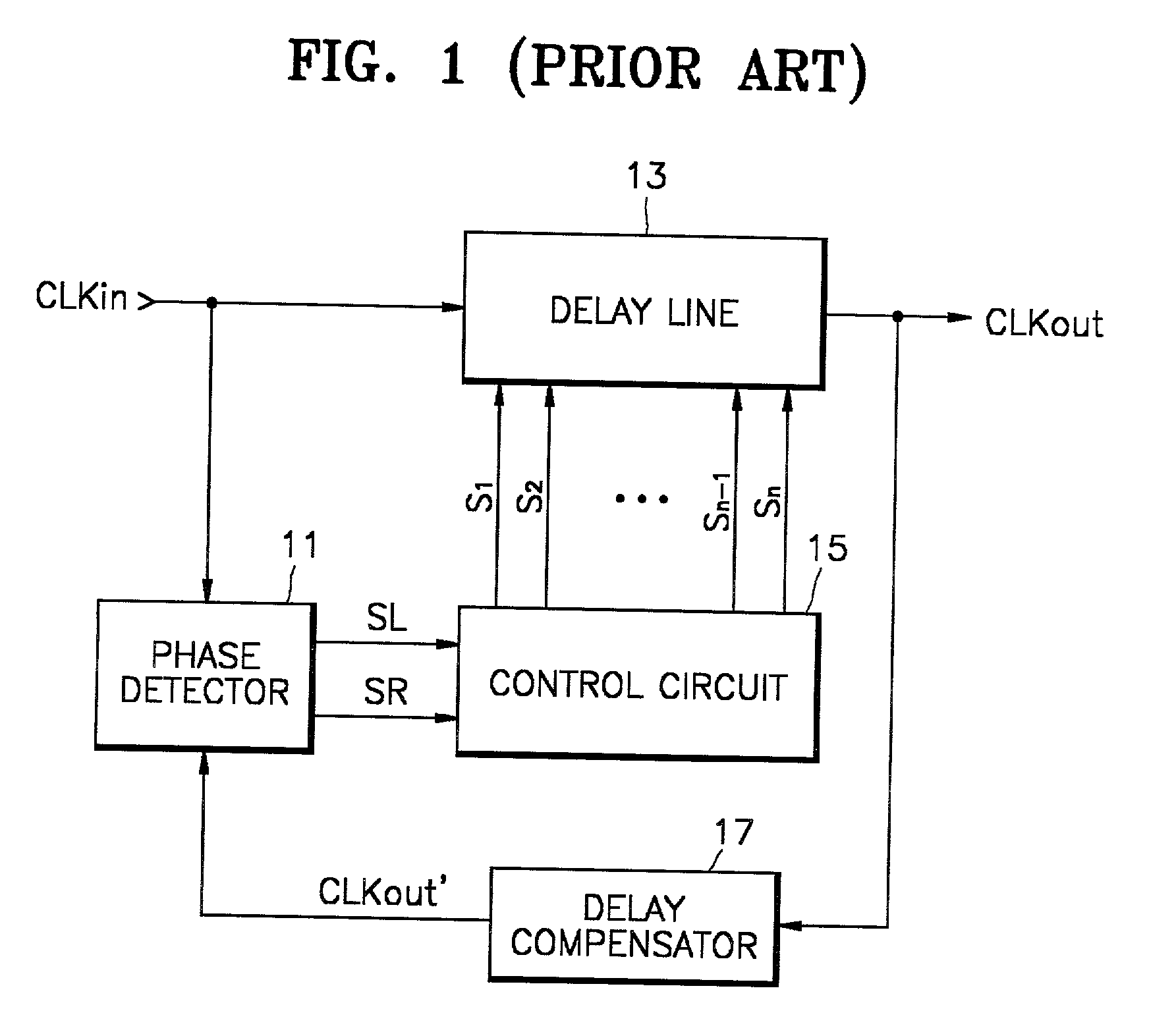

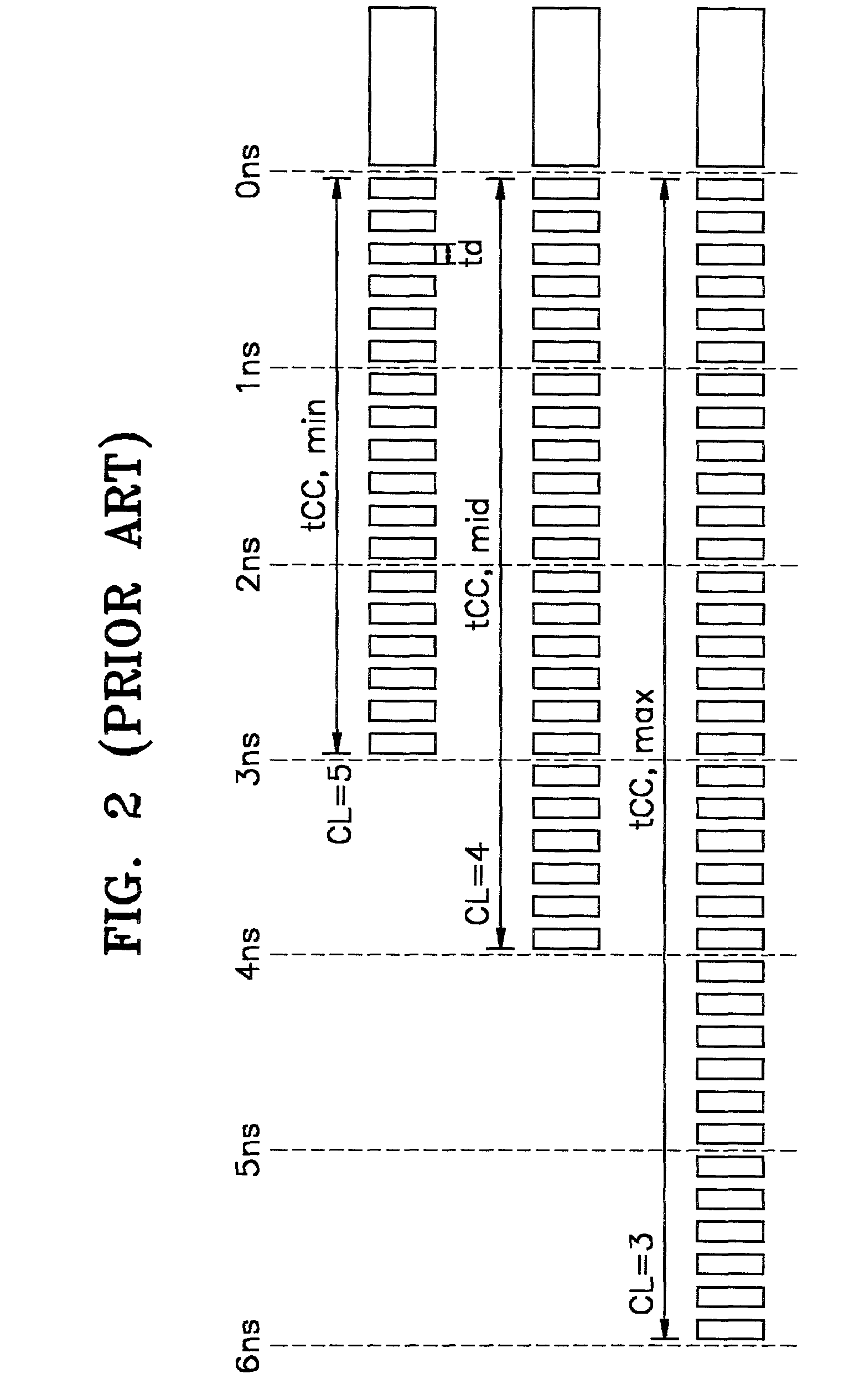

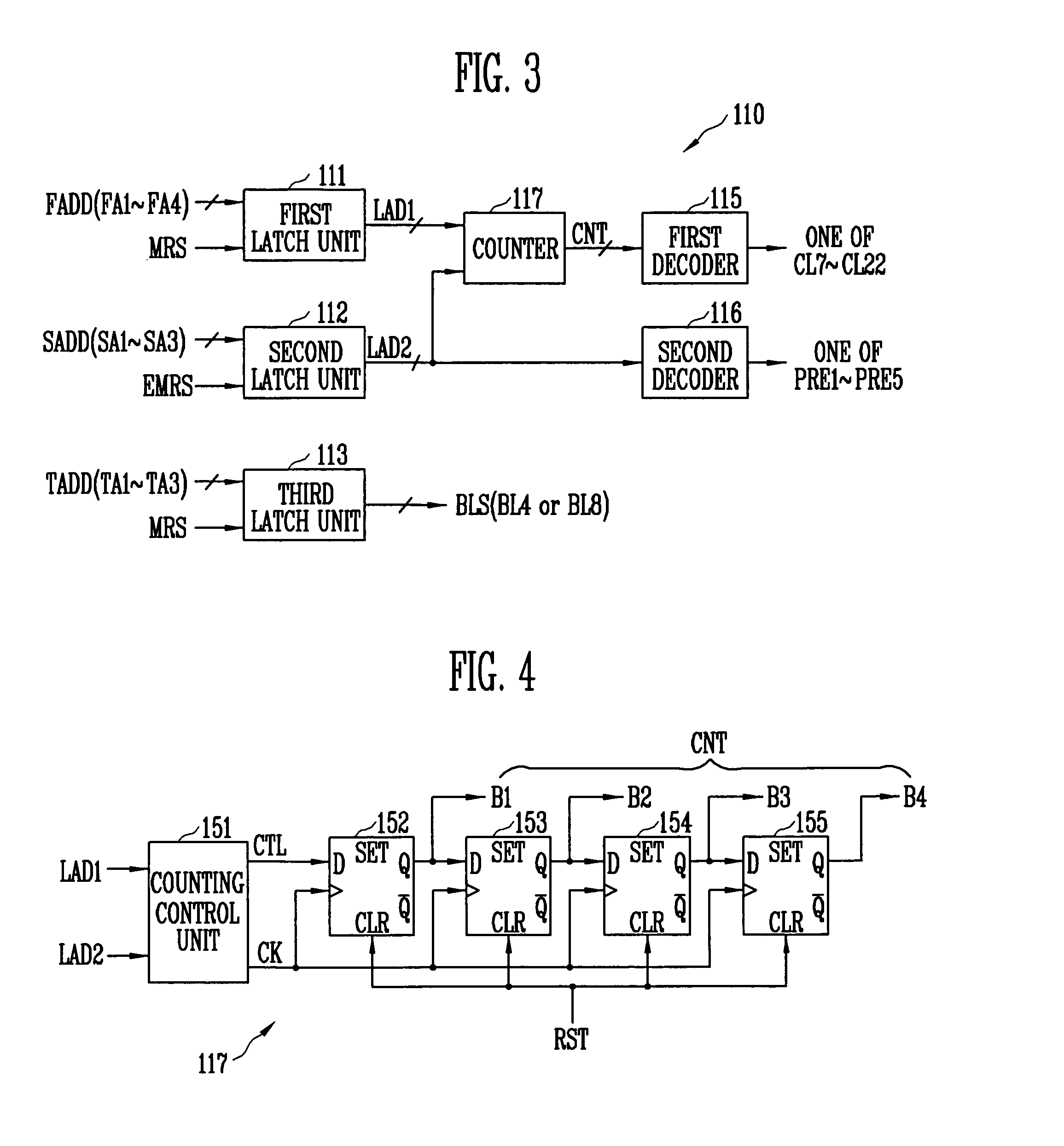

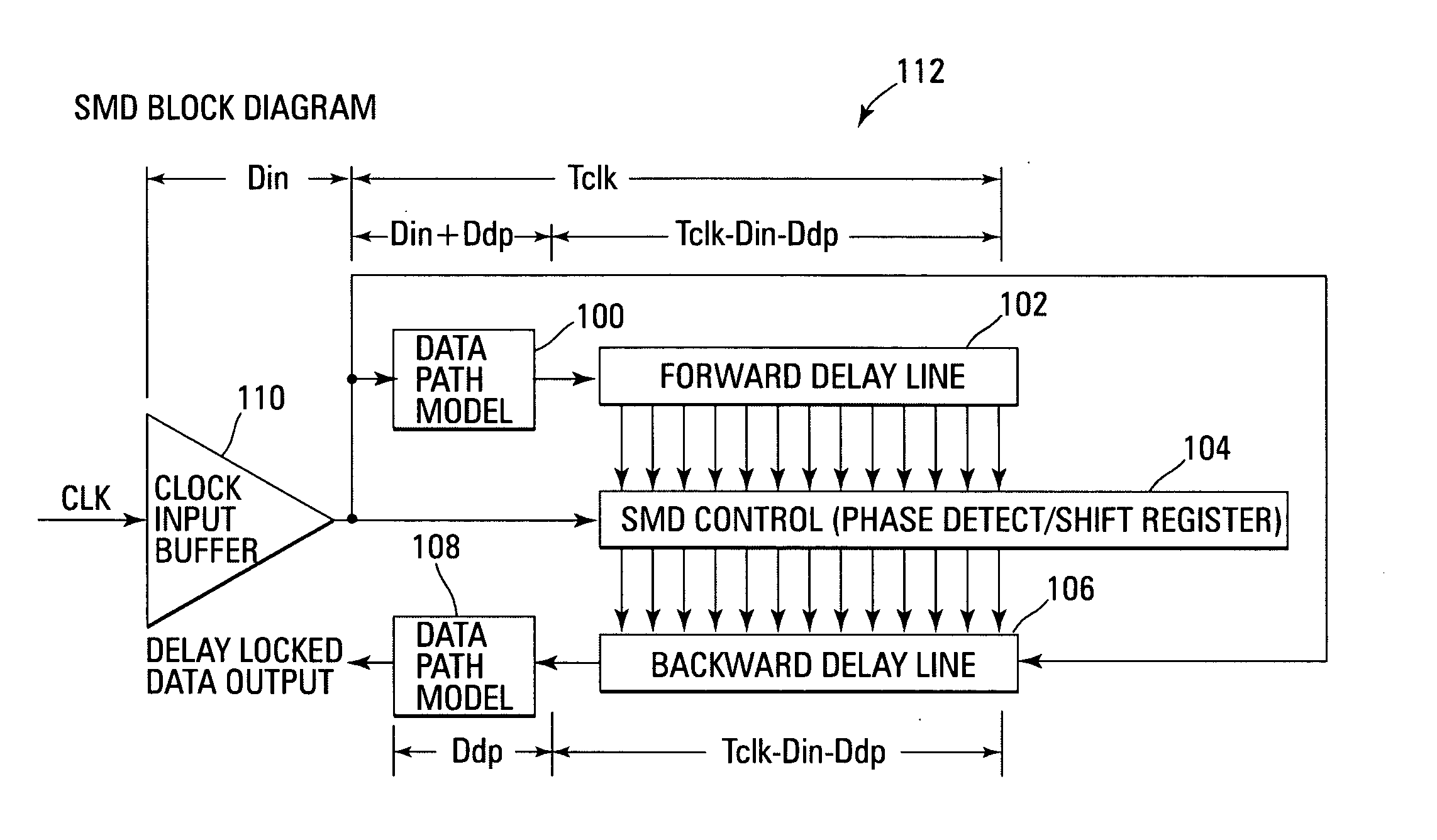

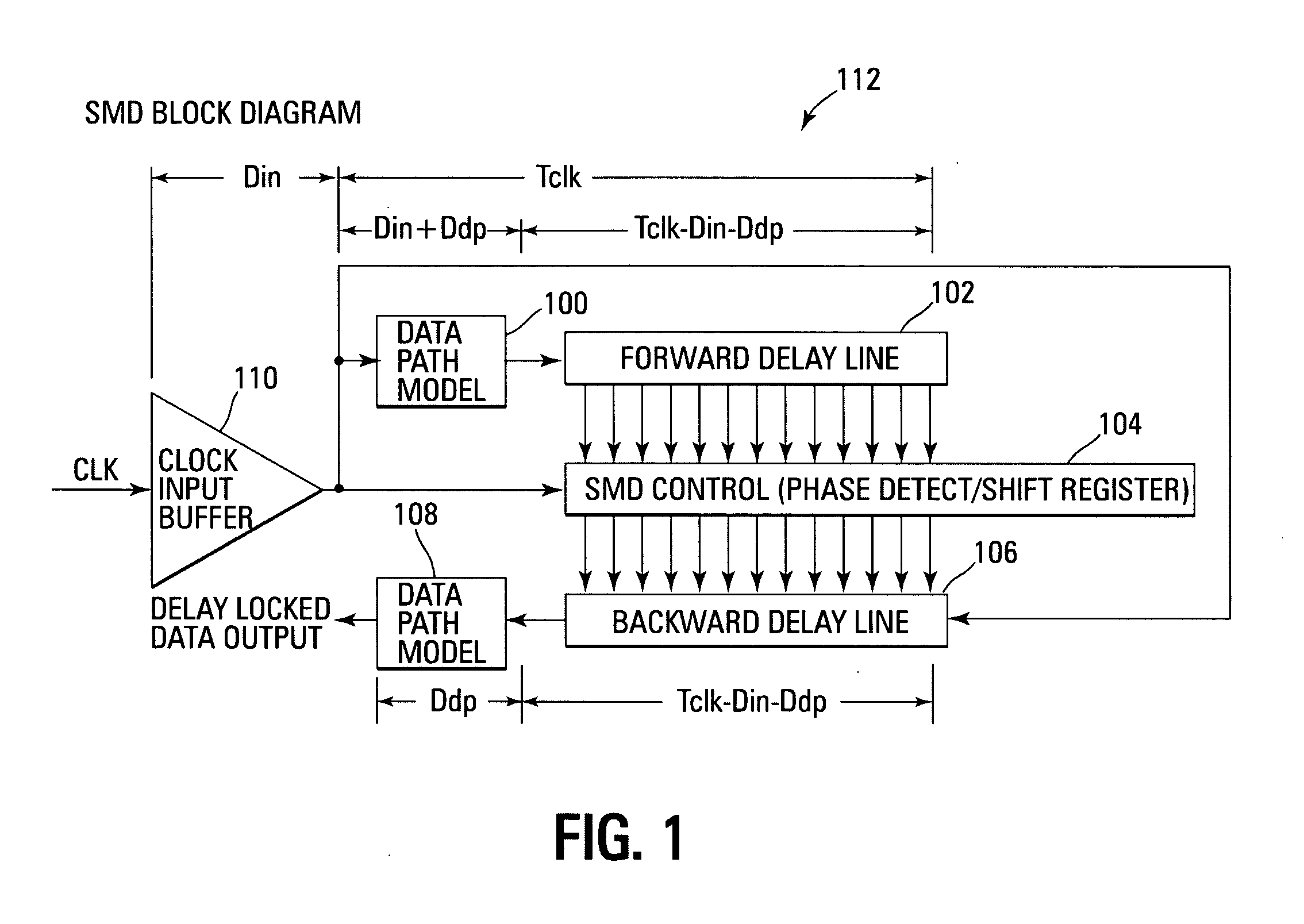

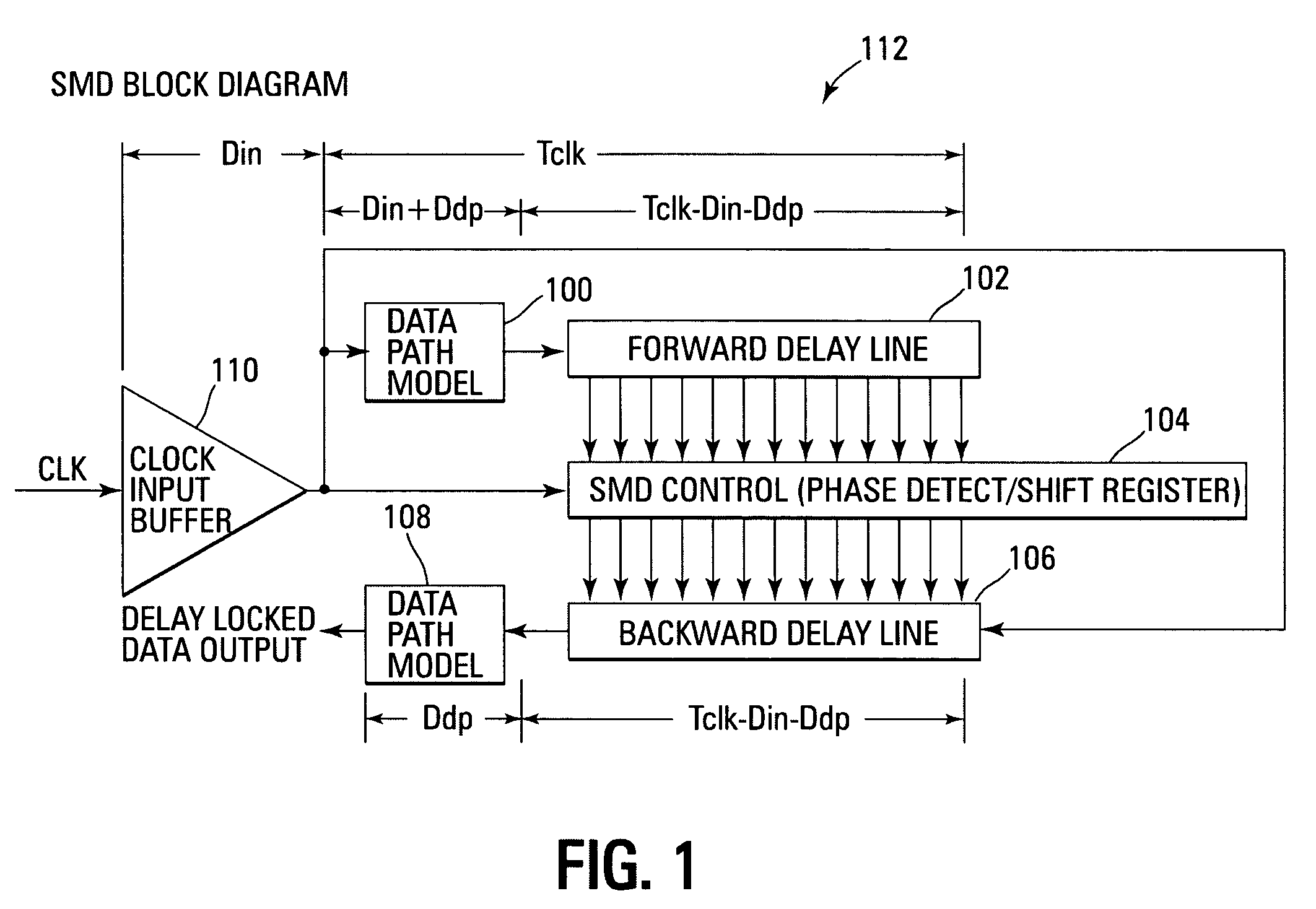

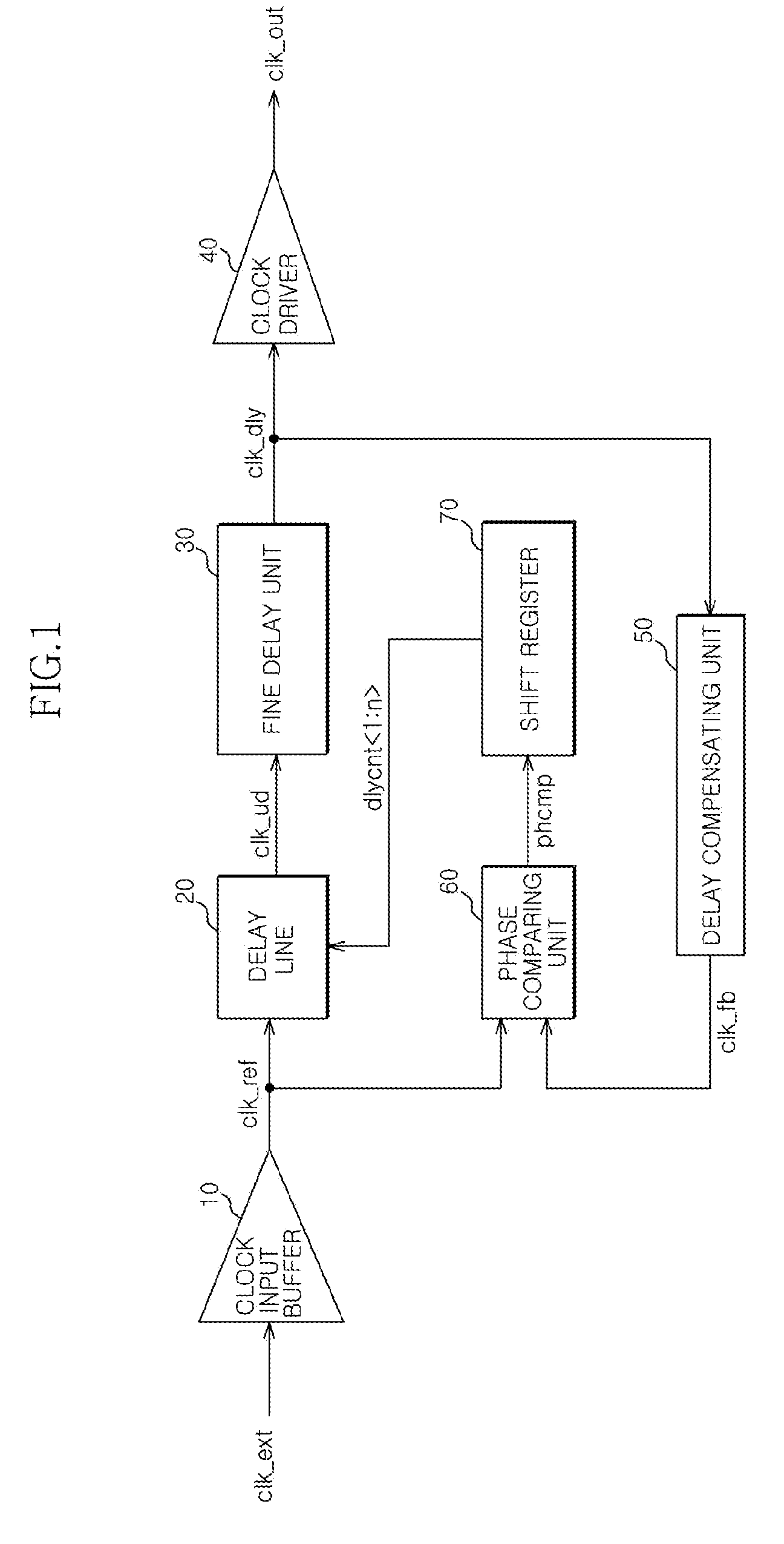

Delay locked loop circuit and method having adjustable locking resolution

A delay line receives an input clock signal and includes a cascaded plurality of unit delay circuits. A mode register set stores a value indicative of a column-address-strobe (CAS) latency of the memory device, and an adjustment circuit varies a delay time of the unit delay circuits according to the CAS latency stored in the mode register set. A phase detector detects a phase difference between the input clock signal and an output clock signal of the delay line, and a control circuit which controls an enabled state of the unit delay circuits according to an output of said phase detector.

Owner:SAMSUNG ELECTRONICS CO LTD

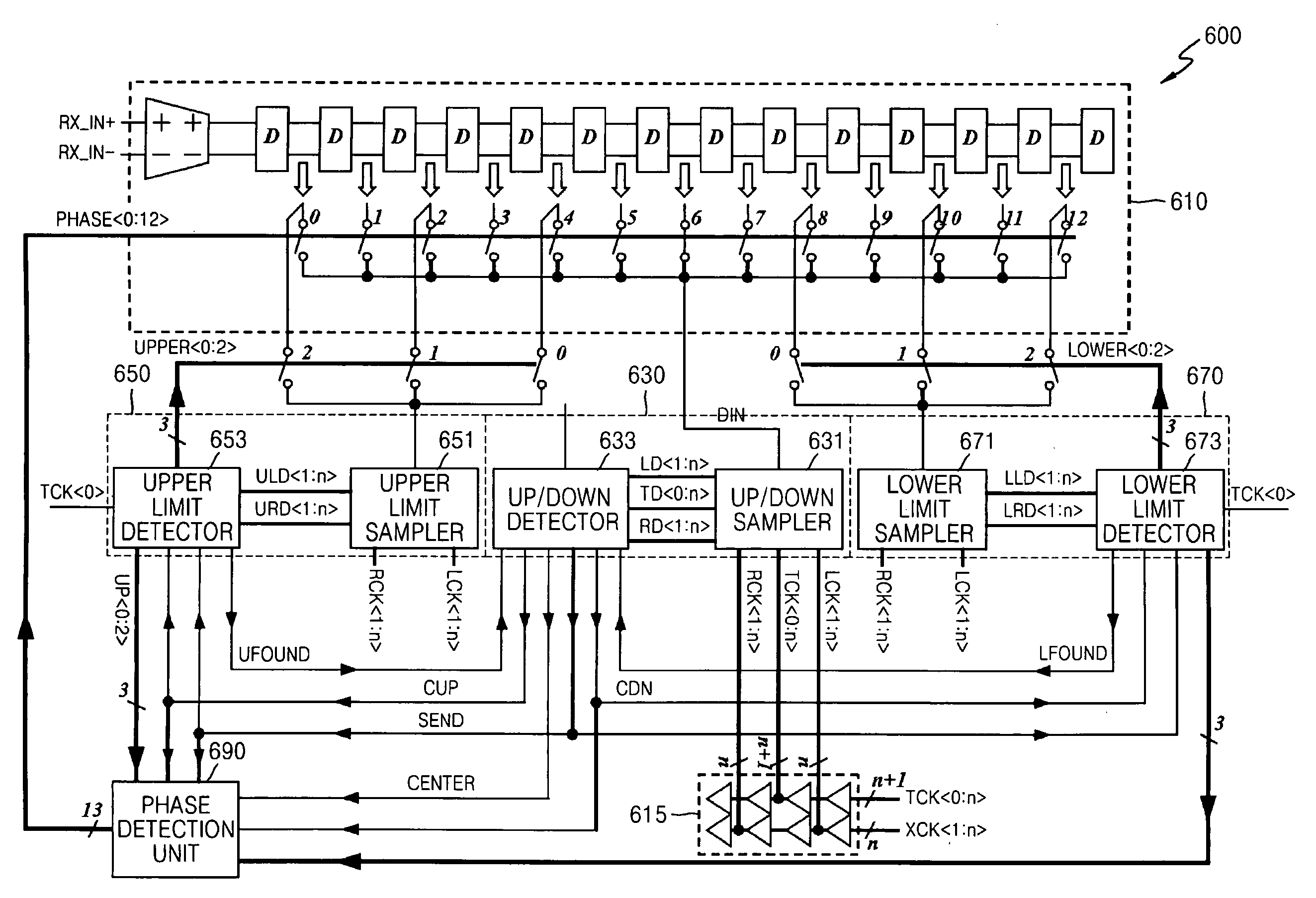

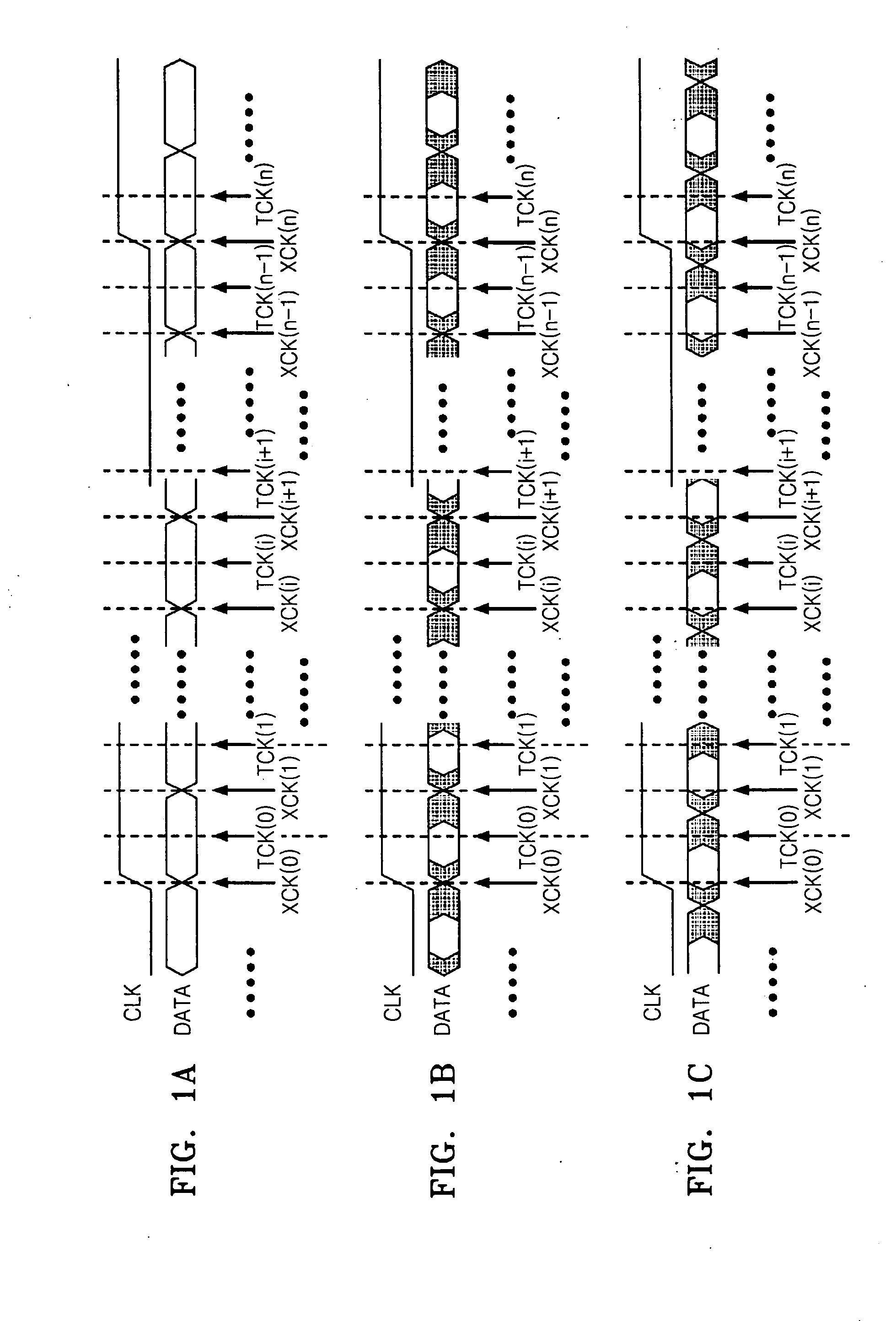

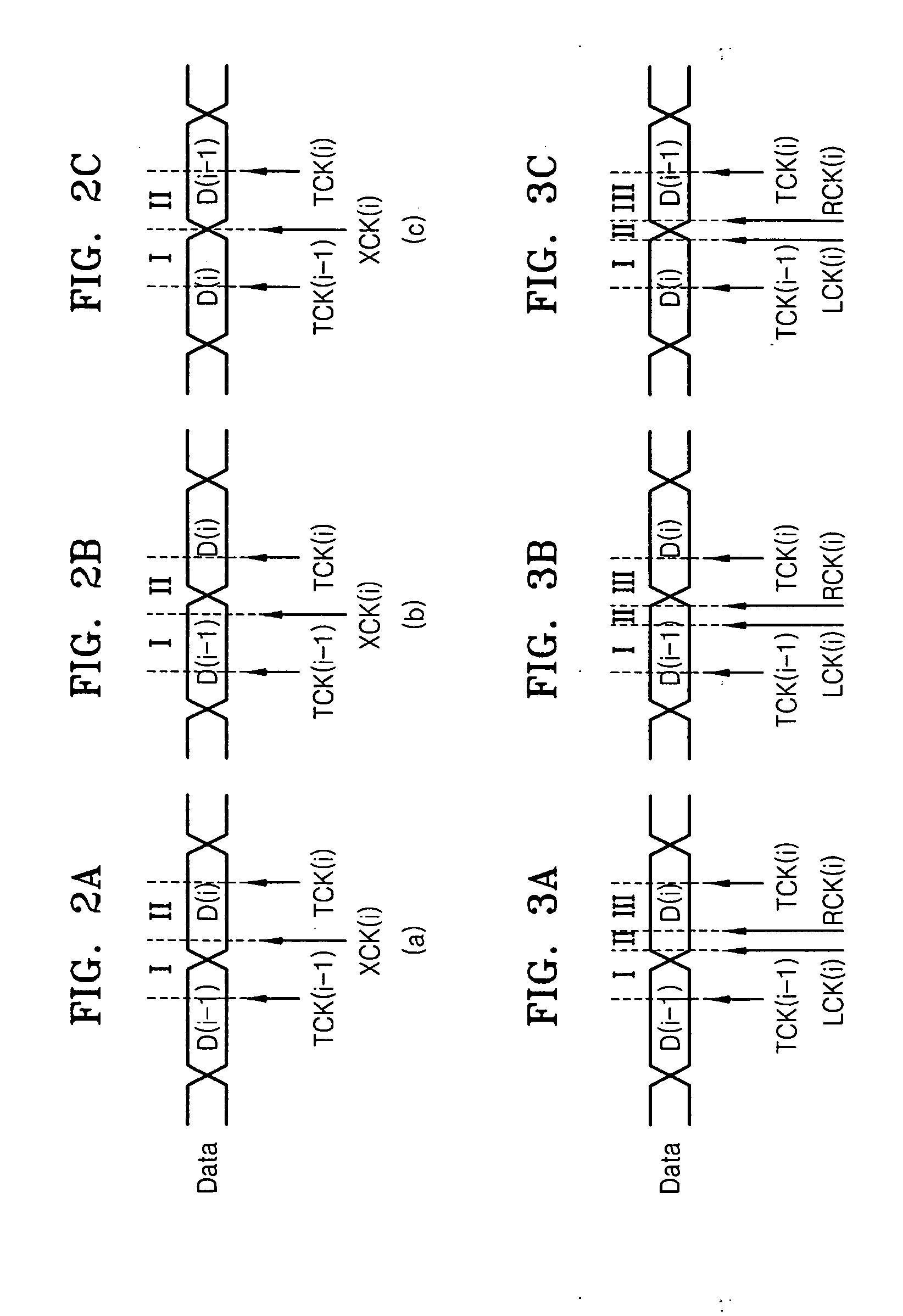

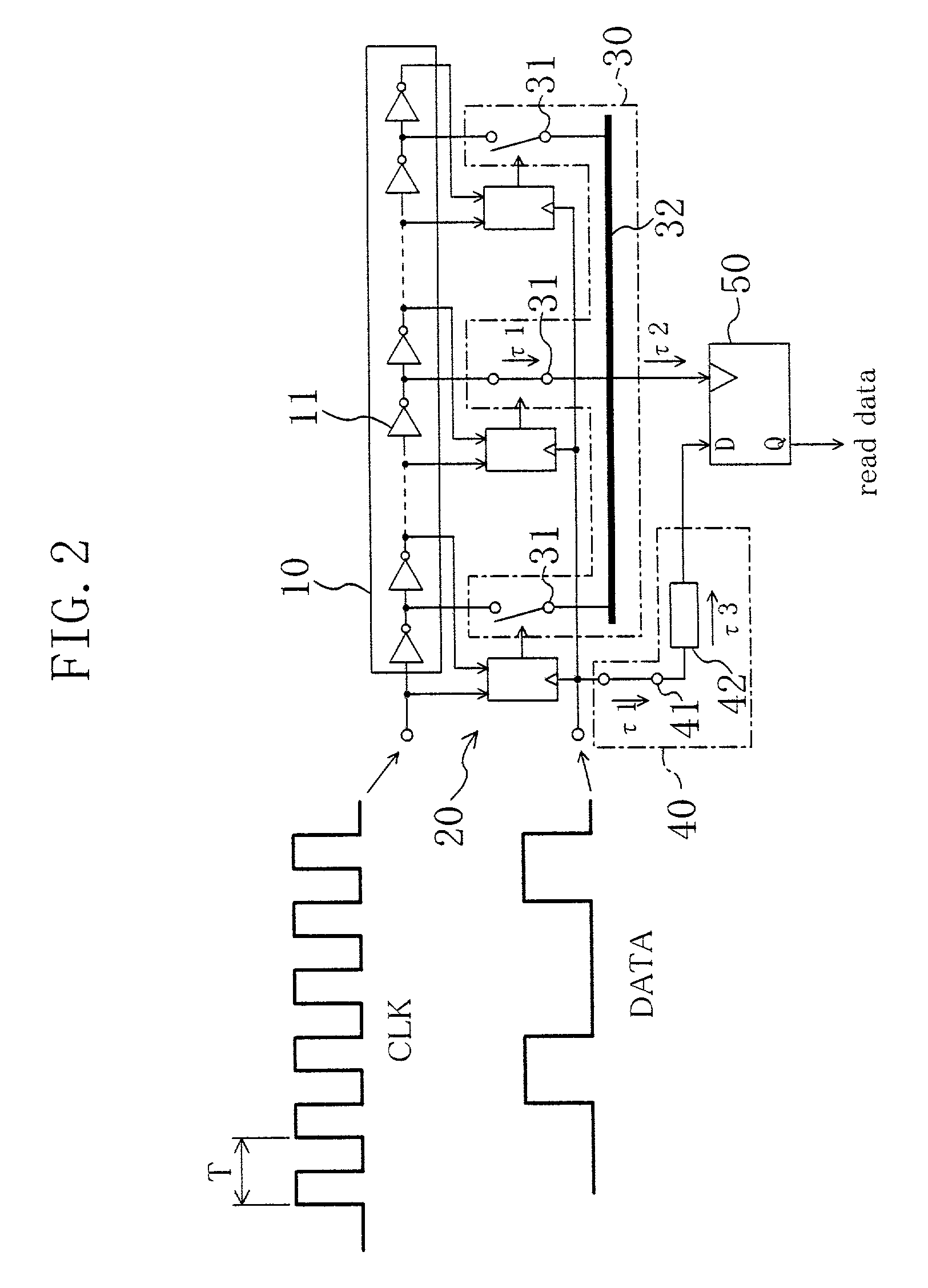

Deskewing method and apparatus, and data reception apparatus using the deskewing method and apparatus

InactiveUS20070297551A1Pulse automatic controlAngle demodulation by phase difference detectionLower limitData signal

Deskewing method and apparatus, and a data reception apparatus using the deskewing method and apparatus, in which the deskewing apparatus includes an up / down detection unit, a lower limit detection unit, an upper limit detection unit, a phase detection unit, and a buffer unit. The up / down detection unit samples a received data signal in response to a data sampling clock signal, a first edge sampling clock signal, and a second edge sampling clock signal and determines in which of first through third areas of the data signal the logic level of the data signal transitions by using the result of the sampling, wherein the data sampling clock signal, the first edge sampling clock signal, and the second edge sampling clock signal are sequentially activated. The lower limit detection unit detects a lower limit of the first area if the logic level of the data signal transitions in the first area. The upper limit detection unit detects an upper limit of the third area if the logic level of the data signal transitions in the third area. The phase detection unit determines a delay amount indicating the amount by which the data signal is to be delayed according to the upper limit detected by the upper limit detection unit and the lower limit detected by the lower limit detection unit. The buffer unit delays the data signal by the delay amount determined by the phase detection unit. The deskewing apparatus can optimize data sampling by efficiently reducing data skew. In addition, the deskewing apparatus can minimize data restoration errors by reducing an accumulation of jitter.

Owner:SAMSUNG ELECTRONICS CO LTD

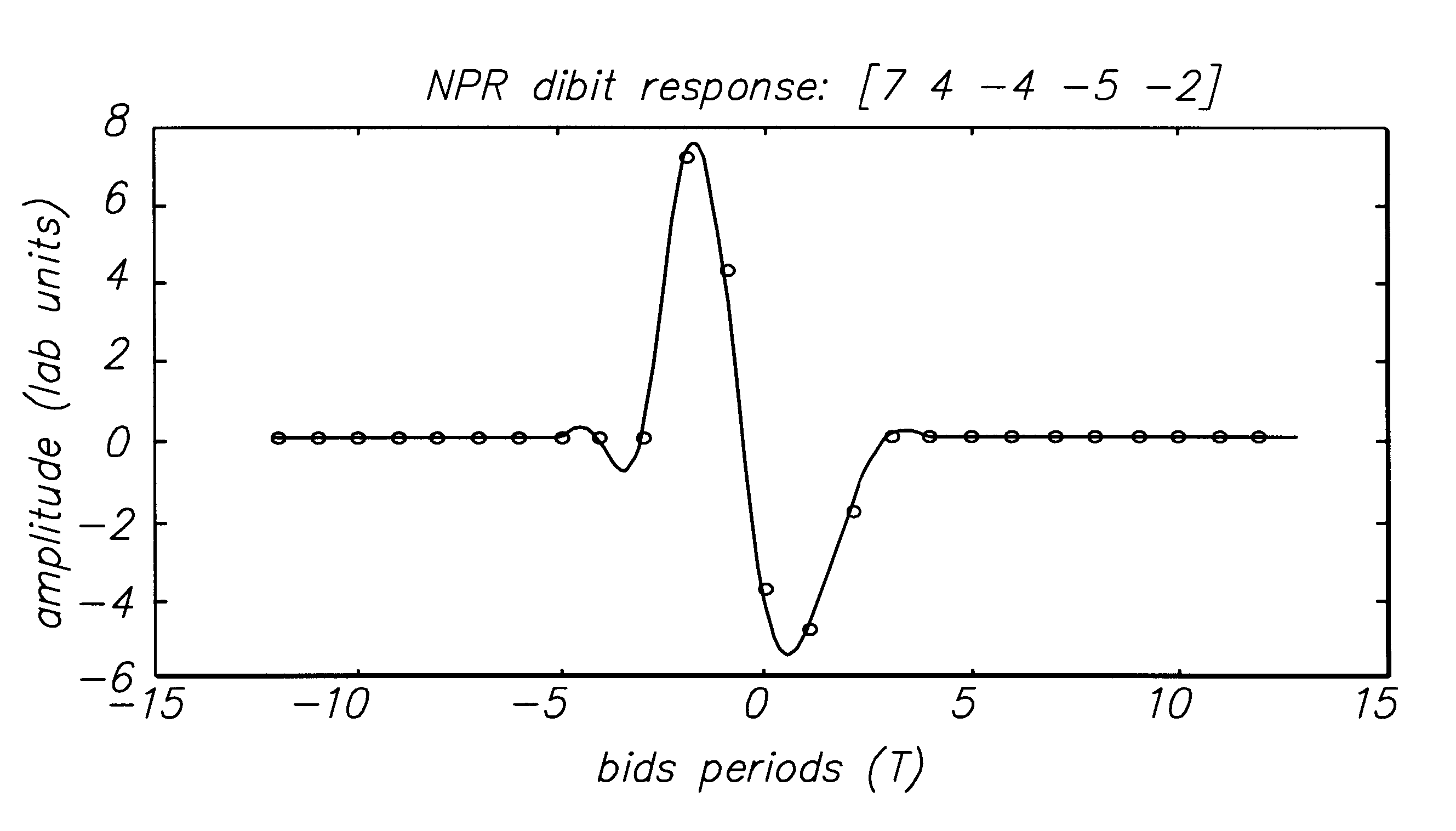

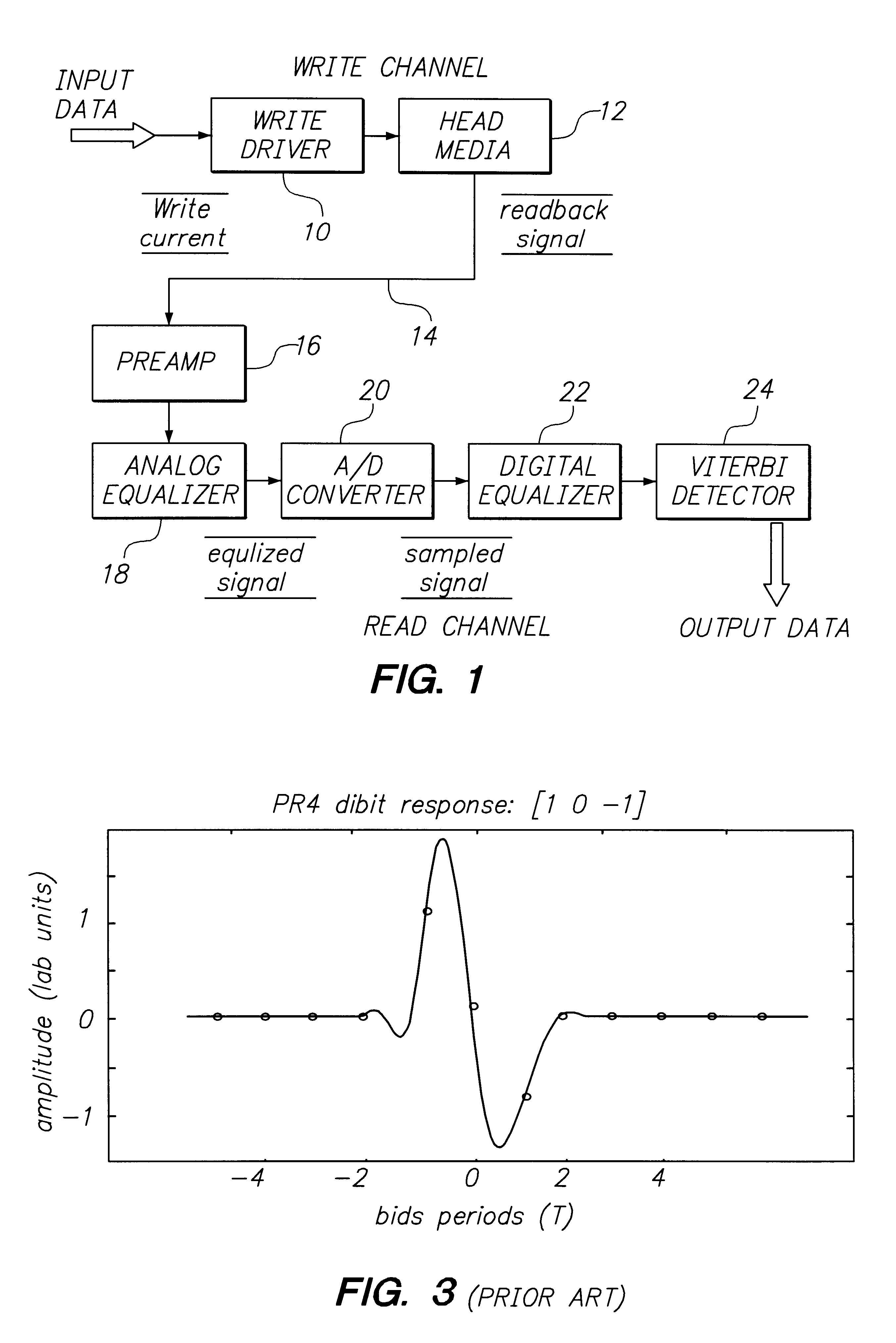

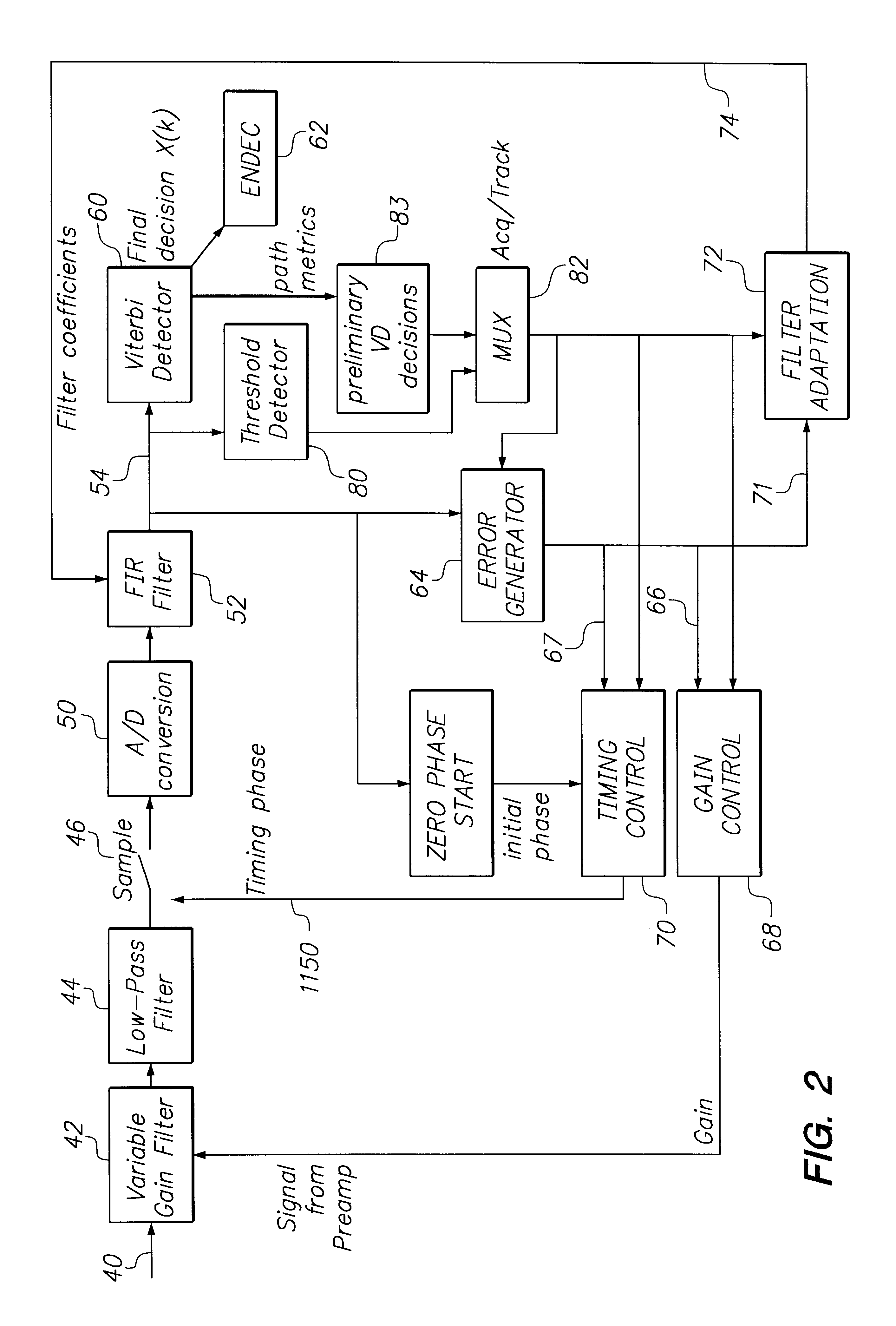

Class of fixed partial response targets in a PRML sampled data detection channel

InactiveUS6249398B1Modification of read/write signalsRecord information storageFrequency spectrumMagnetic media

A new class of fixed partial response targets are disclosed for use in a PRML magnetic medium read channel. The preferred embodiment exhibits an equalization response characterized by the polynomial 7+4*D-4*D2-5*D3-2*D4, where D represents the unit delay operator. This read channel target provides improved matching to the inherent magnetic channel over the known canonical class of targets (1-D)(1+D){circumflex over ( )}N, and thereby reduces equalization losses. The improved spectral matching reduces amplification of noise in the channel, thereby reducing bit-error-rates. The new class of targets also exhibits a spectral null at DC, reducing problems for offset cancellation circuitry and making the disk drive less sensitive to thermal asperities. It also exhibits a spectral depression rather than a spectral null at the Nyquist frequency, making quasi-catastrophic error sequences virtually impossible. The new class of target simplifies coding and allows RLL code ratios that approach unity, improving effective recording densities, while significantly reducing BER.

Owner:LUCENT TECH INC +1

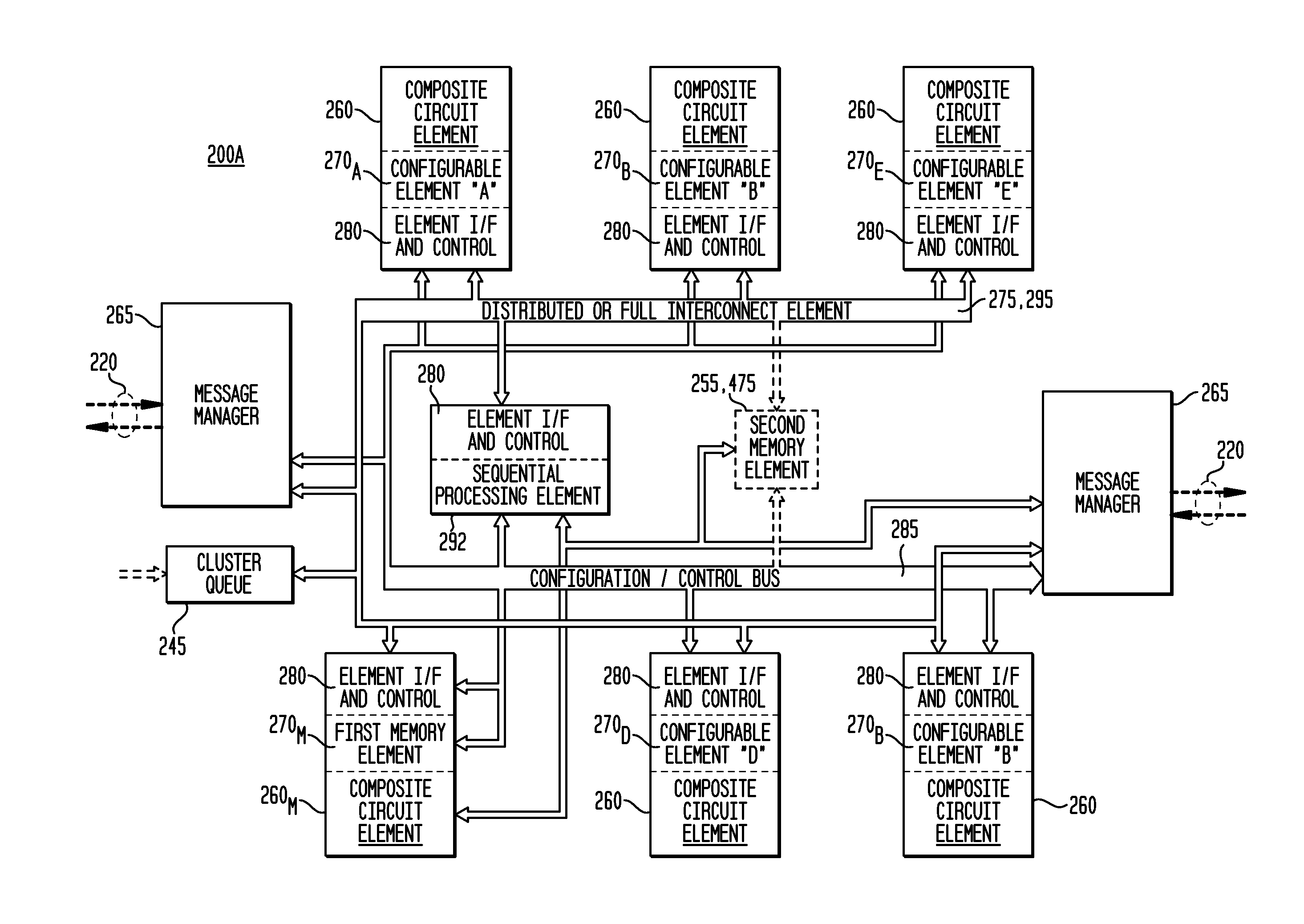

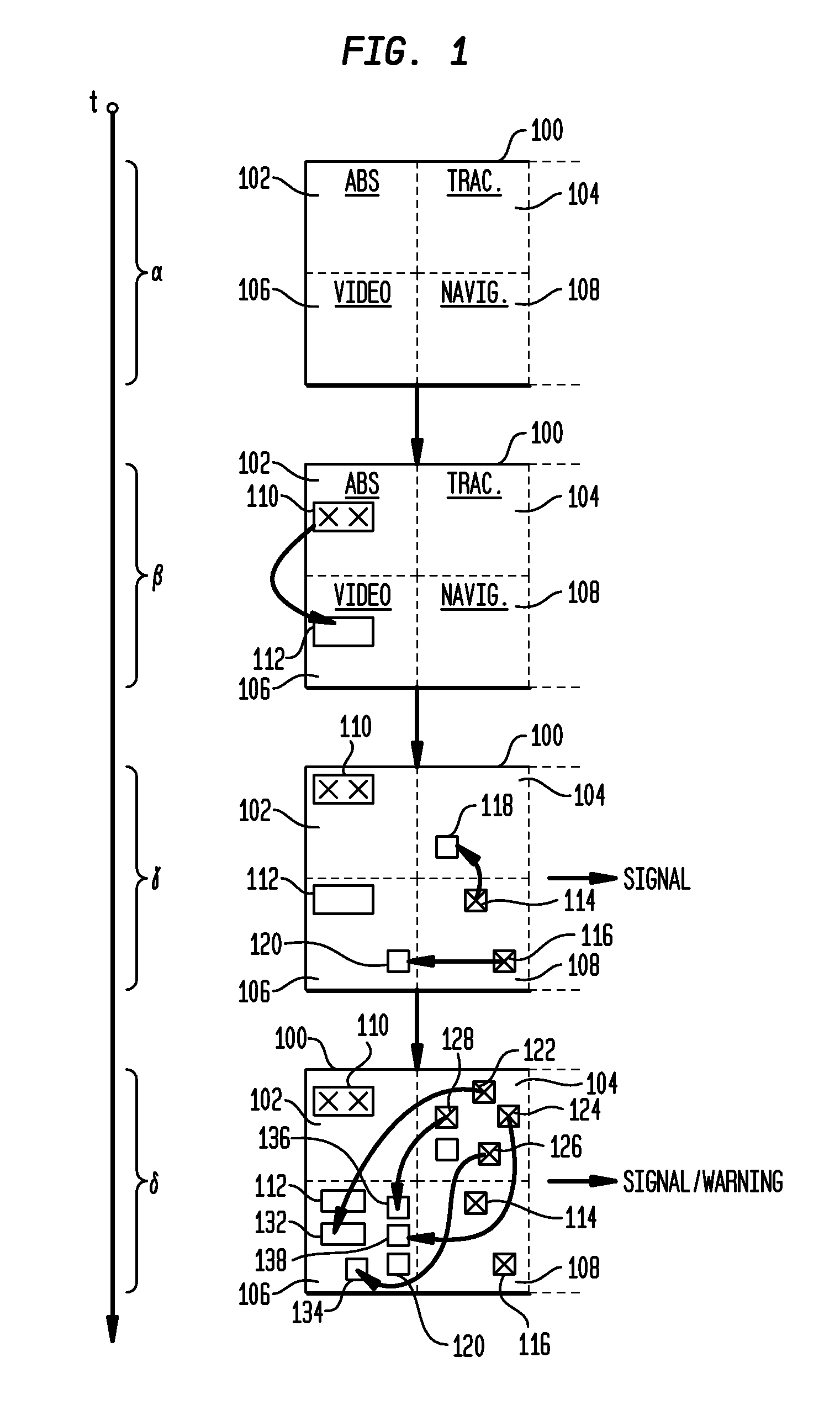

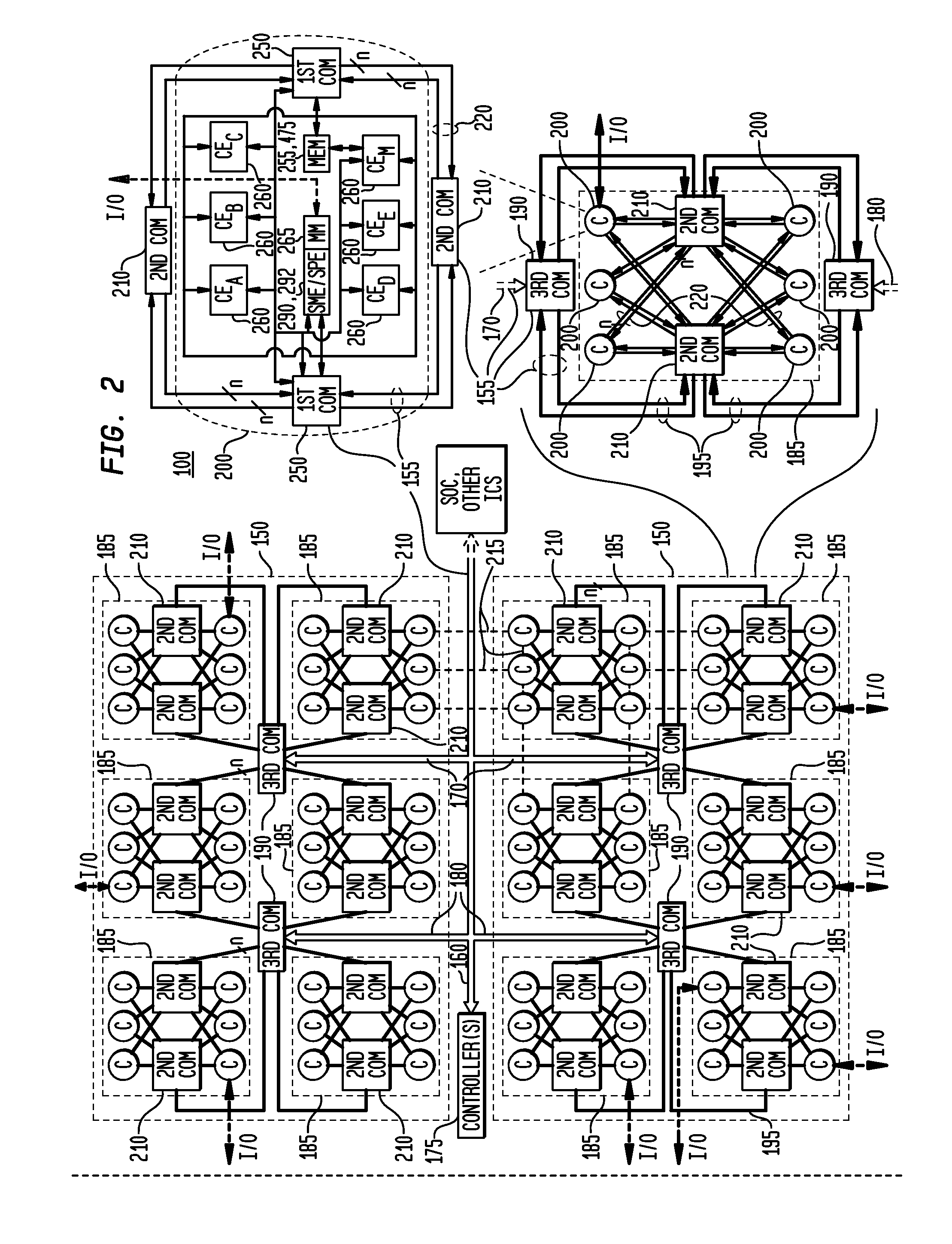

Hierarchically-Scalable Reconfigurable Integrated Circuit Architecture With Unit Delay Modules

InactiveUS20120126850A1Significant resiliencyError detection/correctionFail-safe circuitsData operationsTime delays

The exemplary embodiments provide a reconfigurable integrated circuit architecture having a predetermined, unit timing increment (or delay) for both data operations and data word transfers within every zone and between zones, which are independent of application placement and routing. An exemplary IC comprises a plurality of circuit zones, with each zone comprising: a plurality of composite circuit elements, a plurality of cluster queues, and a full interconnect bus. Each composite circuit element comprises: a configurable circuit element circuit and an element interface and control circuit, with the element interface and control circuit comprising an input queue and an output queue. Each cluster queue comprises an element interface and control having an input queue and an output queue. The full interconnect bus couples every output queue within the zone to every input queue within the zone. Any data operation performed by a composite circuit element, any data word transfer through a cluster queue, and any data word transfer over the first full interconnect bus, is completed within a predetermined unit time delay which is independent of application placement and application data routing on the reconfigurable IC.

Owner:ELEMENT CXI

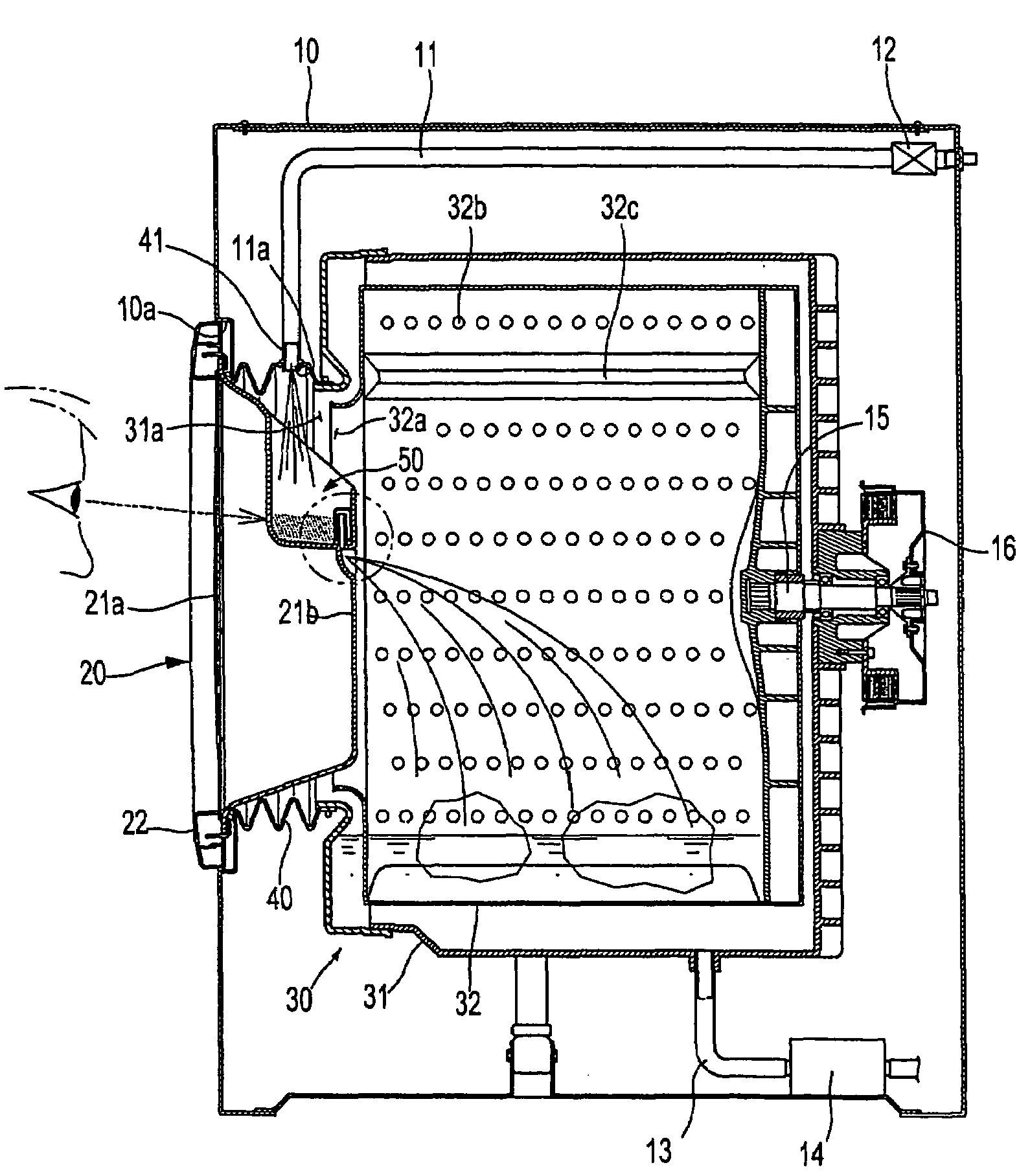

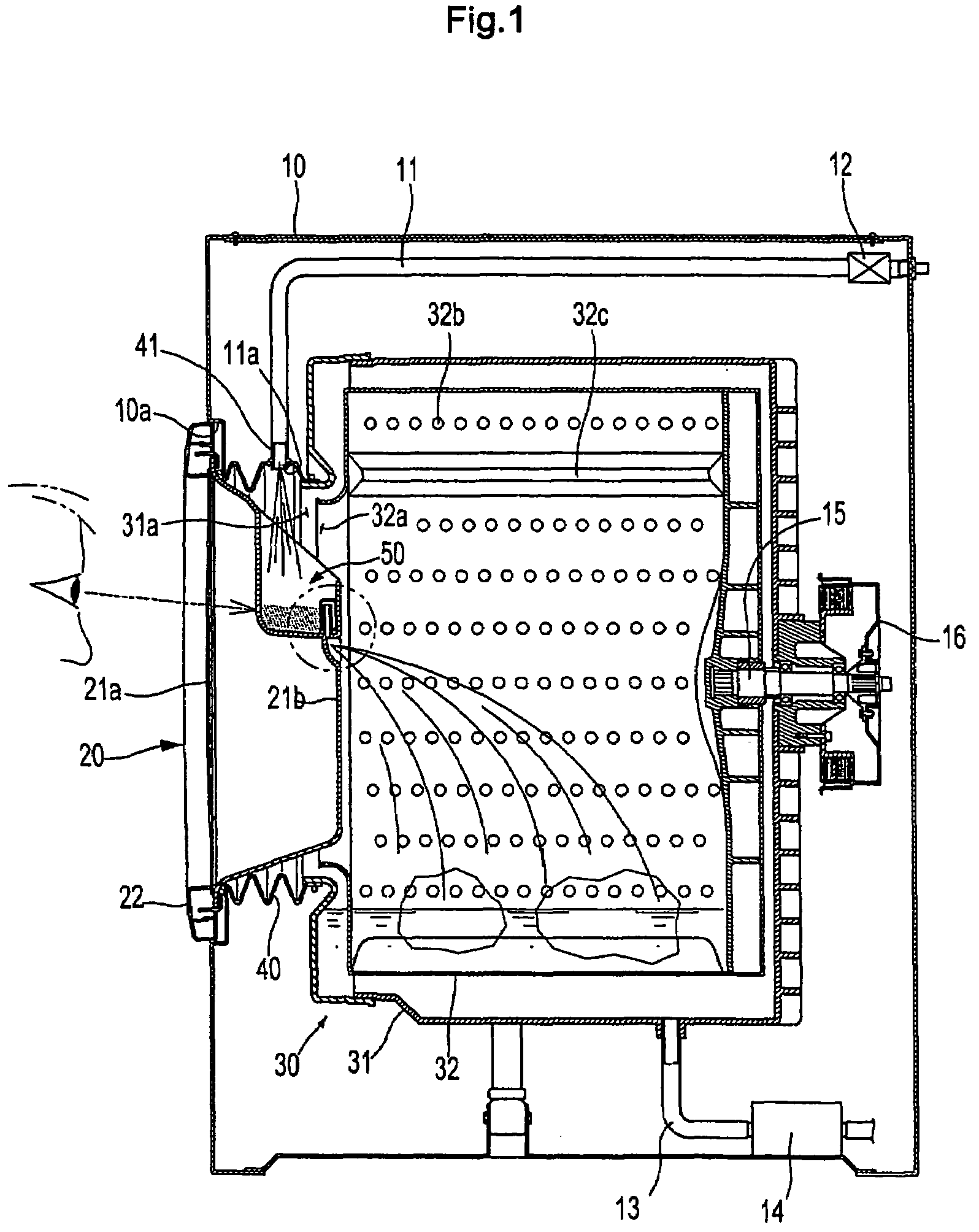

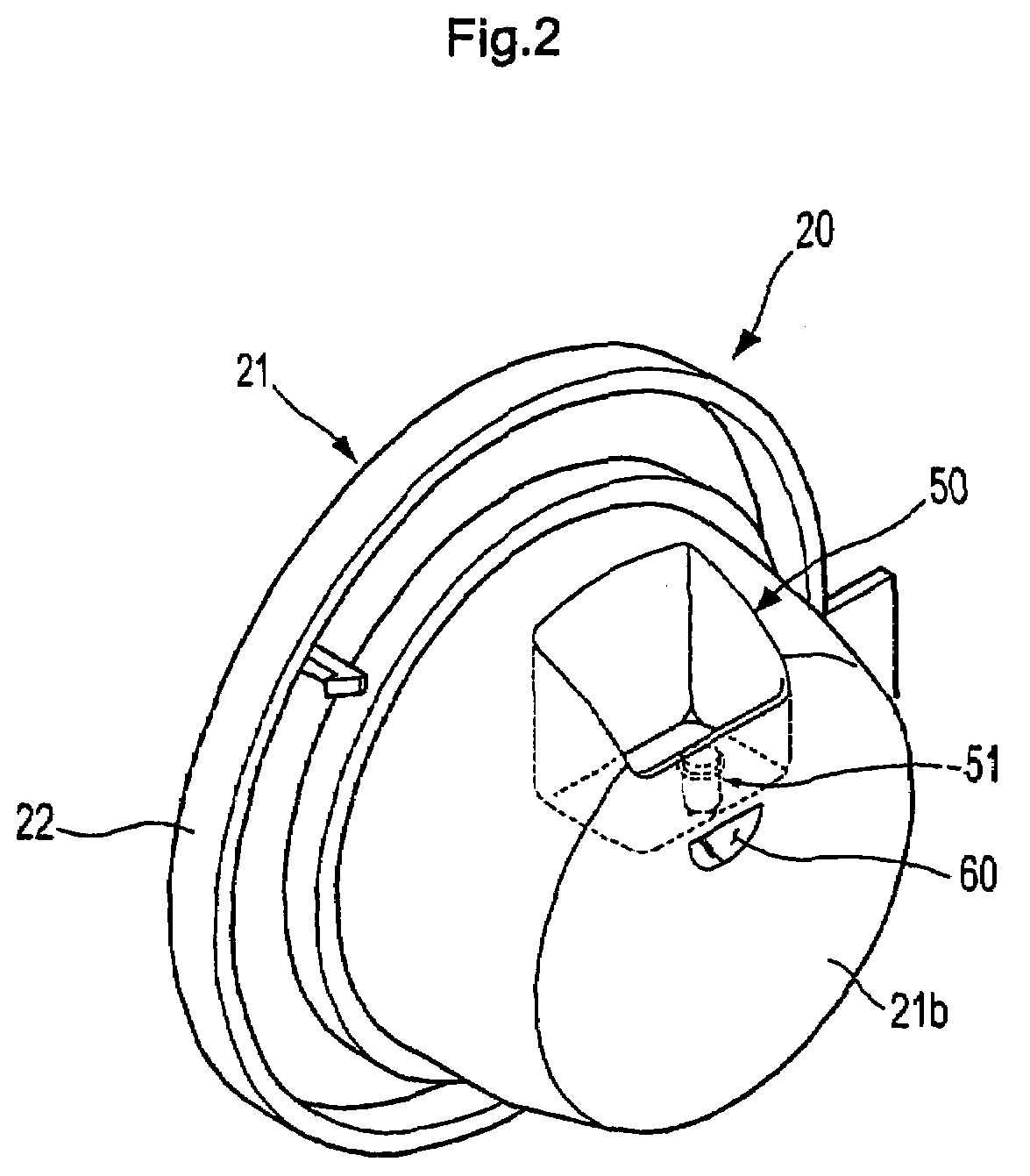

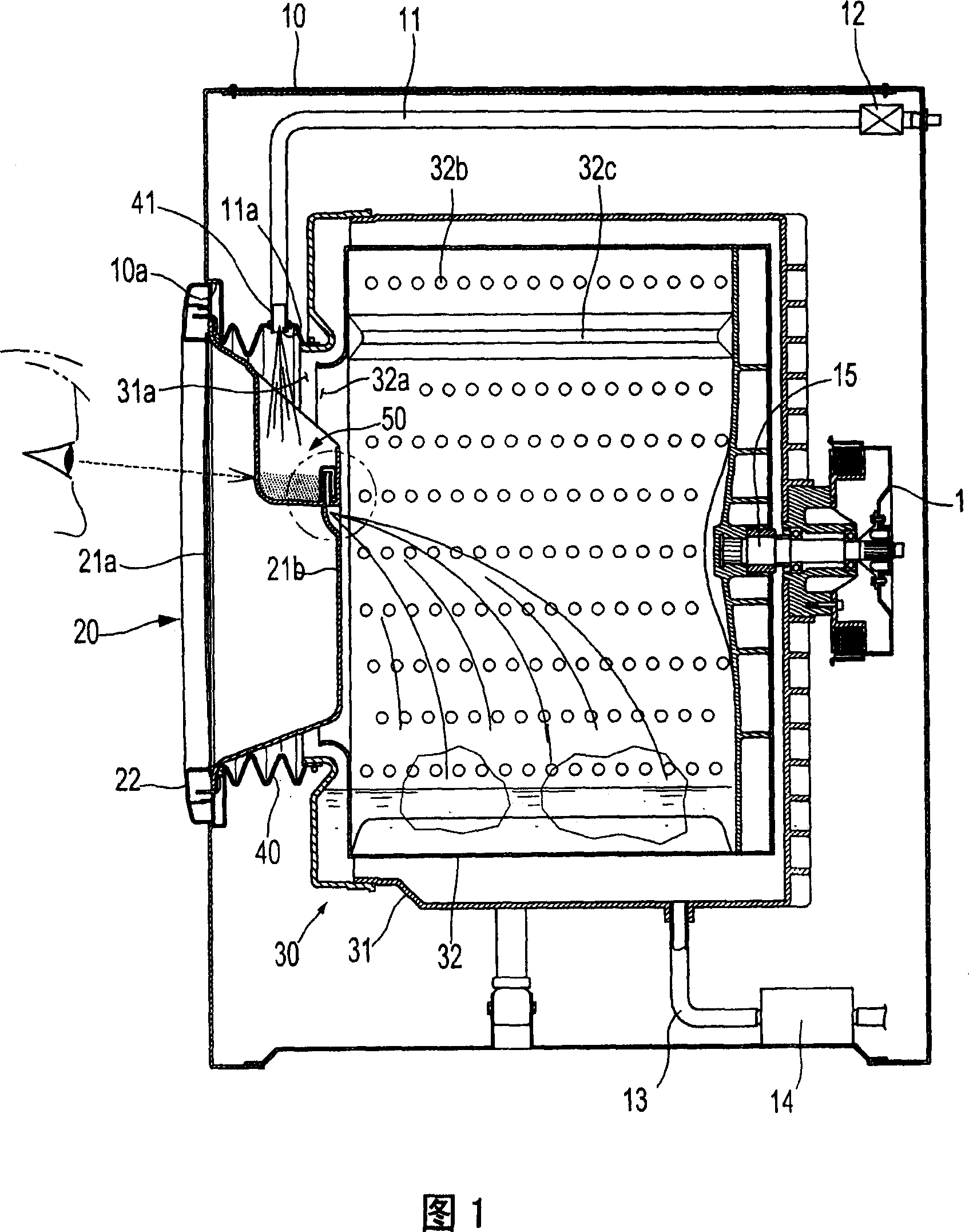

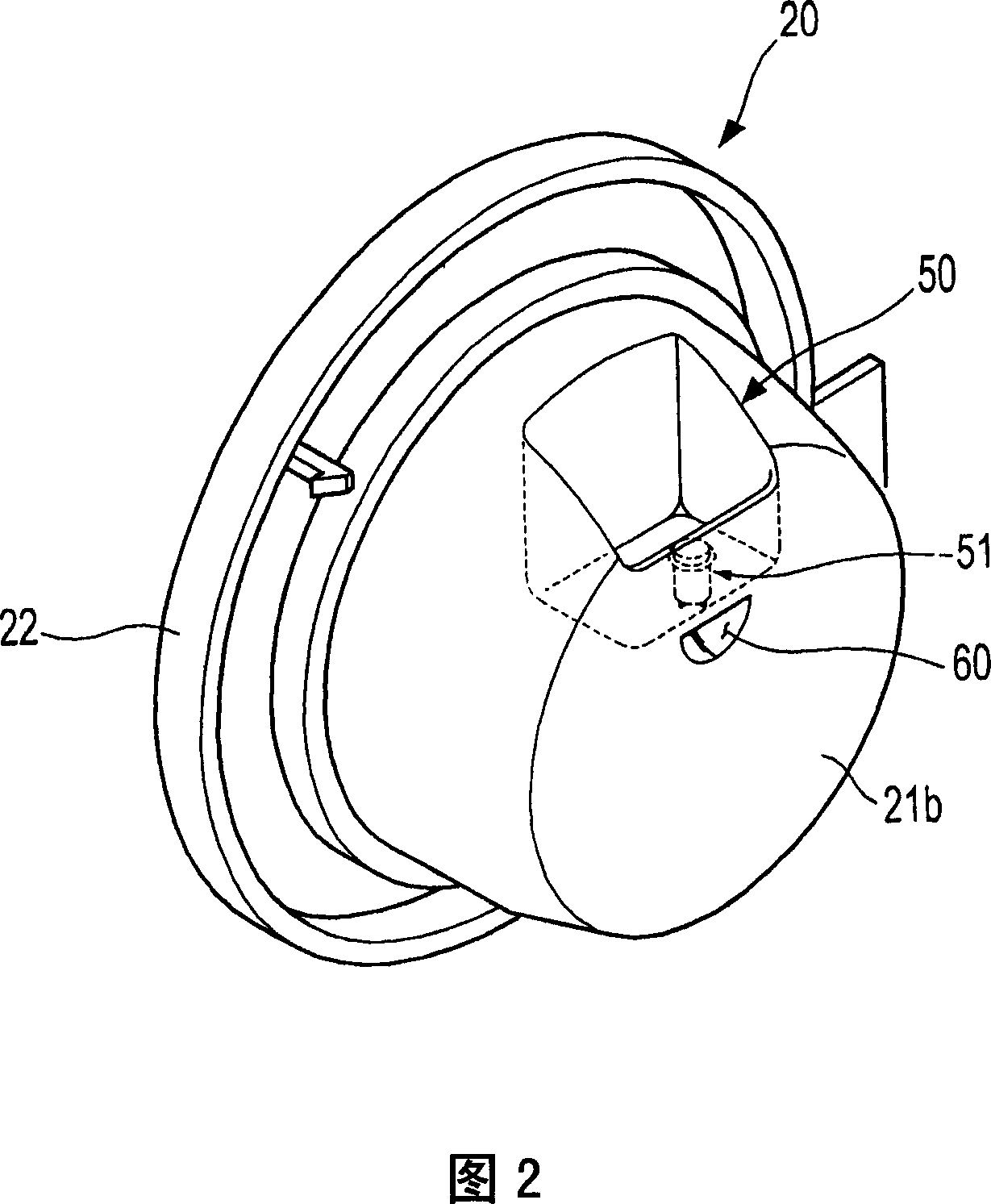

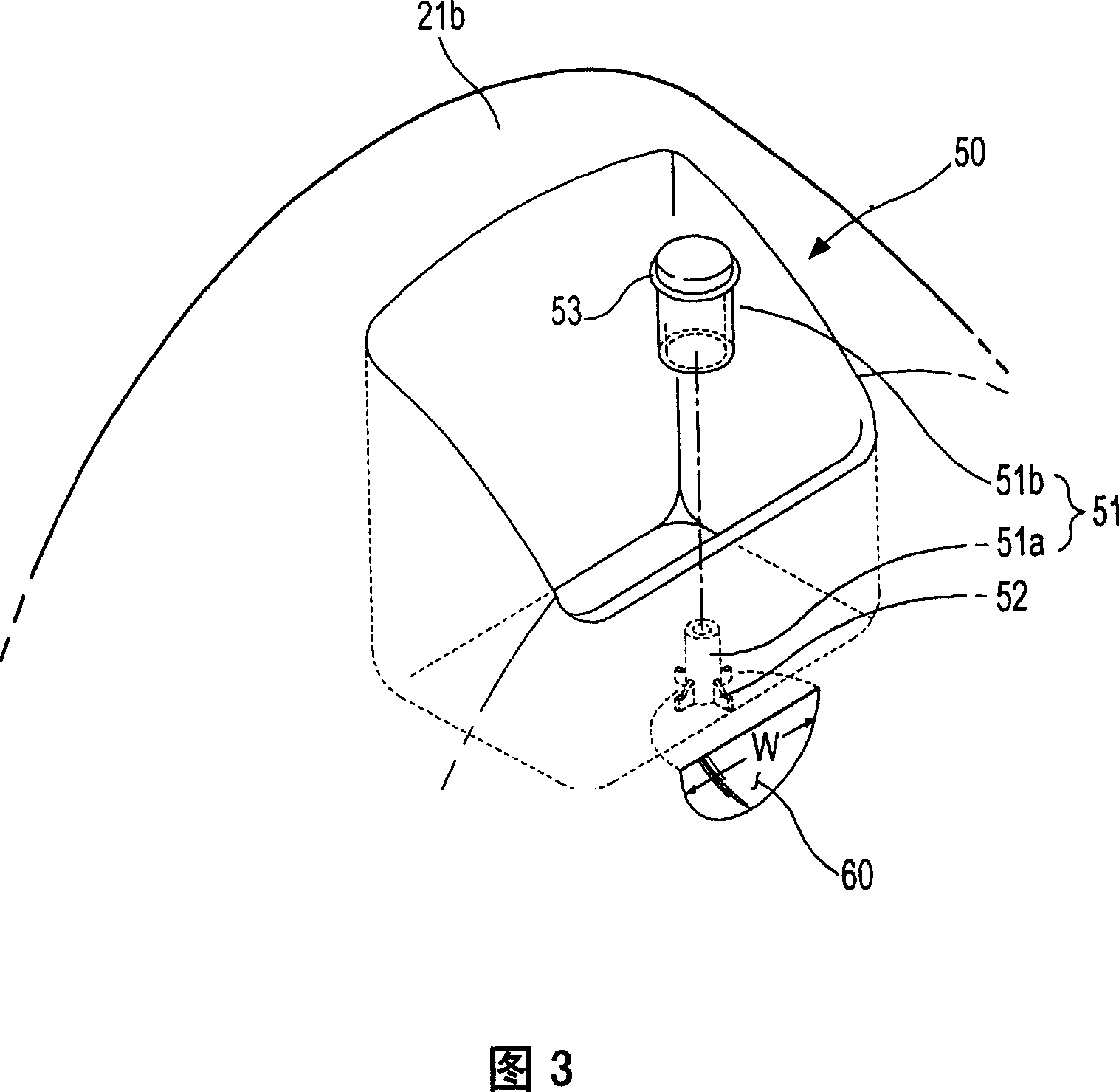

Drum washing machine with detergent supply device

InactiveUS20070240456A1Easy to manufactureLow production costOther washing machinesTextiles and paperSiphonWater level

A drum washing machine having a detergent supply device supplying water containing detergent to a washing tub. The detergent supply device is integrally formed with a door of the washing machine. The detergent supply device is provided with a discharge unit discharging detergent dissolved in the water to the washing tub when the level of the water supplied to the detergent supply device reaches a designated value. The discharge unit delays the discharge of the washing water supplied to the detergent supply device by a siphon, thus improving the solubility of the detergent.

Owner:SAMSUNG ELECTRONICS CO LTD

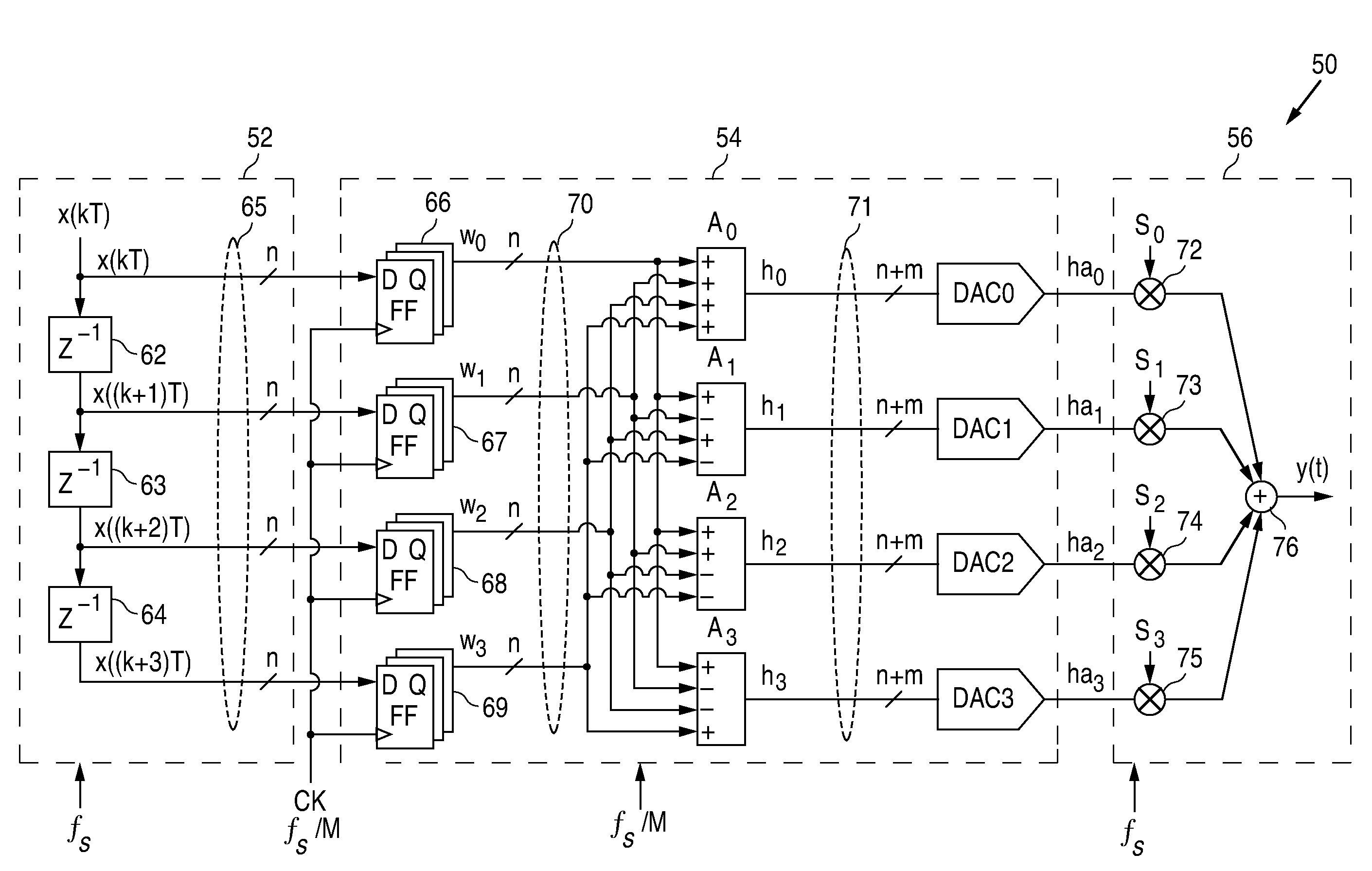

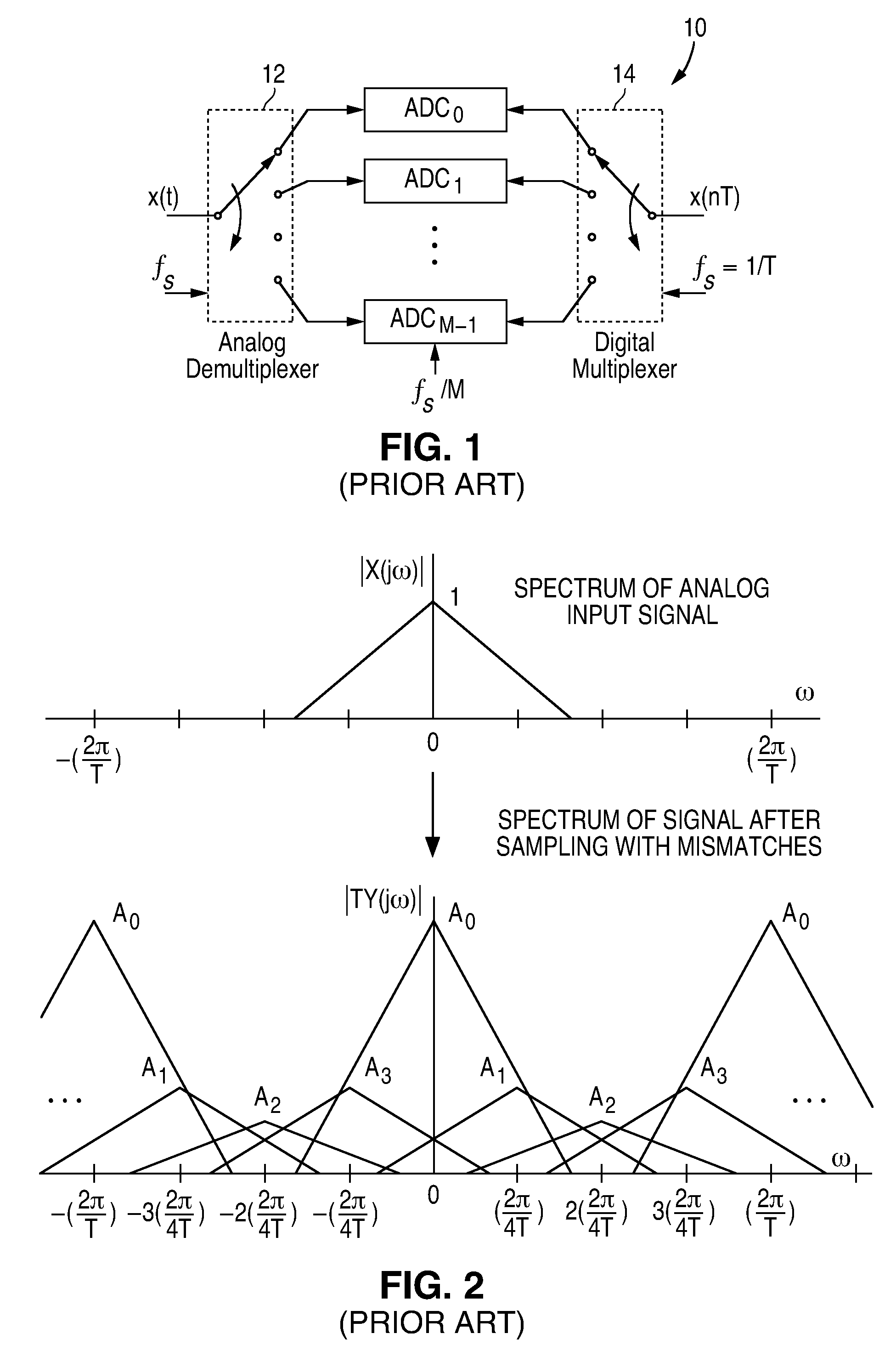

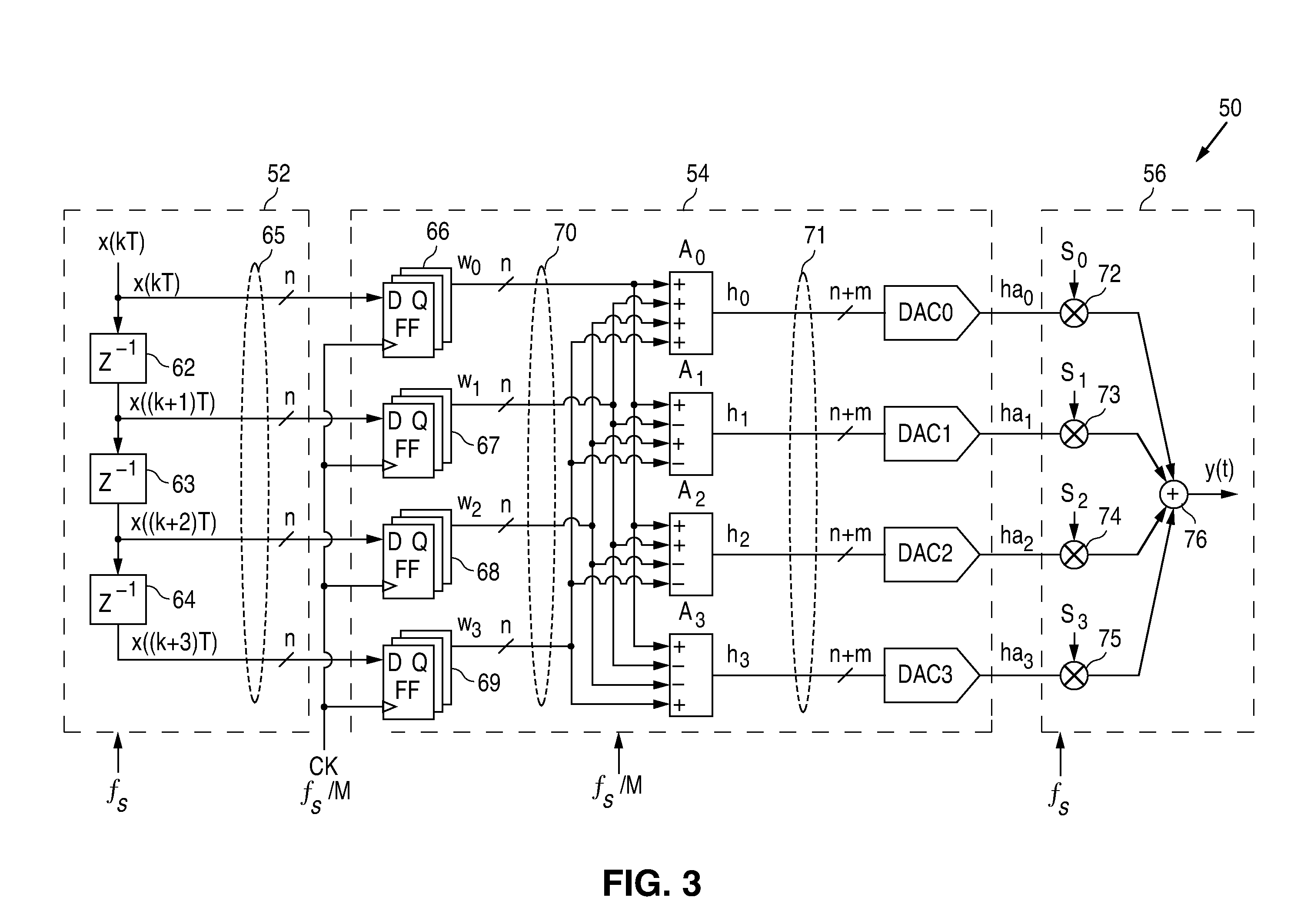

Parallel digital-to-analog-converter

ActiveUS7372386B1Electric signal transmission systemsDigital-analogue convertorsDigital dataData transformation

A method for performing parallel digital-to-analog conversion of an n-bit digital input data signal at a frequency of fs including receiving the n-bit digital input data signal; generating M−1 delayed input data signals, M being the number of parallel conversions channels, the M−1 delayed input data signals having respective increasing amount of unit delay, the digital input data signal and the M−1 delayed input data signals forming M digital signals; holding the M digital signals for a first time period; performing a data transformation of the M digital signals using an M×M Hadamard matrix; generating M (n+m)-bit transformed digital data signals; converting each of the M transformed digital data signals to M analog signals; and performing a reverse data transformation of the M analog signals based on the M×M Hadamard matrix to generate an output analog signal indicative of the n-bit digital input data signal.

Owner:NAT SEMICON CORP

Delay locked loop circuit and method having adjustable locking resolution

A delay line receives an input clock signal and includes a cascaded plurality of unit delay circuits. A mode register set stores a value indicative of a column-address-strobe (CAS) latency of the memory device, and an adjustment circuit varies a delay time of the unit delay circuits according to the CAS latency stored in the mode register set. A phase detector detects a phase difference between the input clock signal and an output clock signal of the delay line, and a control circuit which controls an enabled state of the unit delay circuits according to an output of said phase detector.

Owner:SAMSUNG ELECTRONICS CO LTD

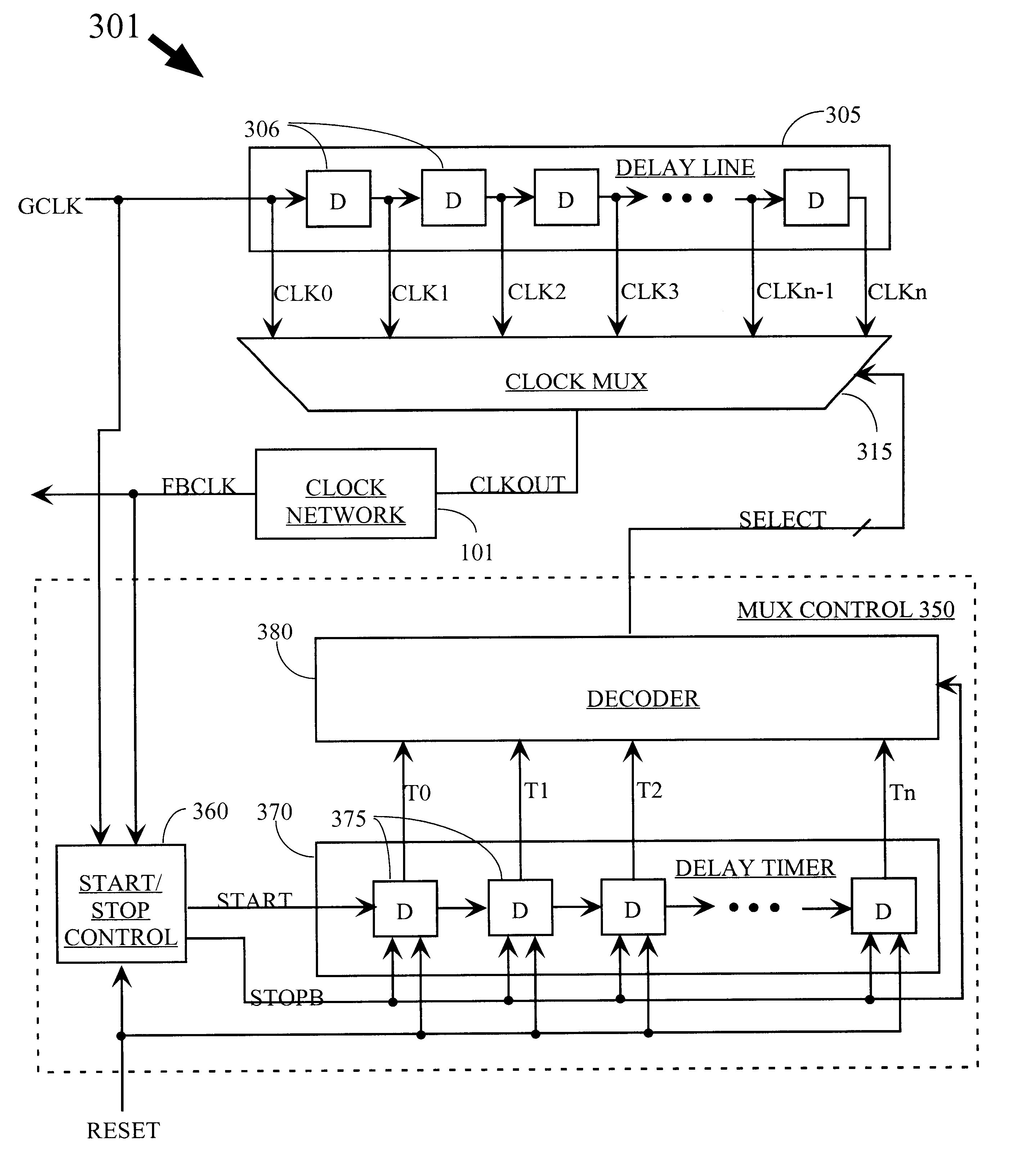

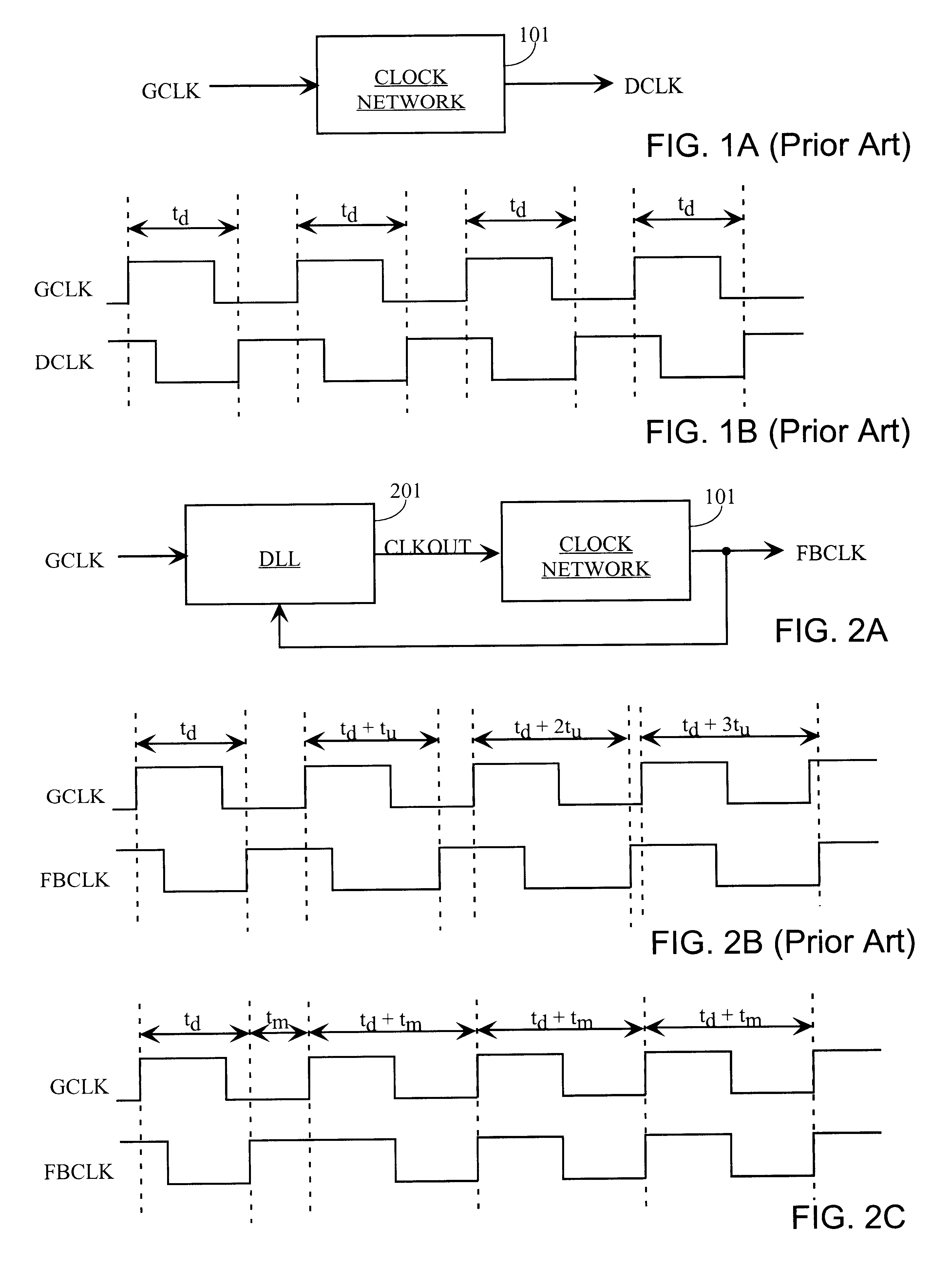

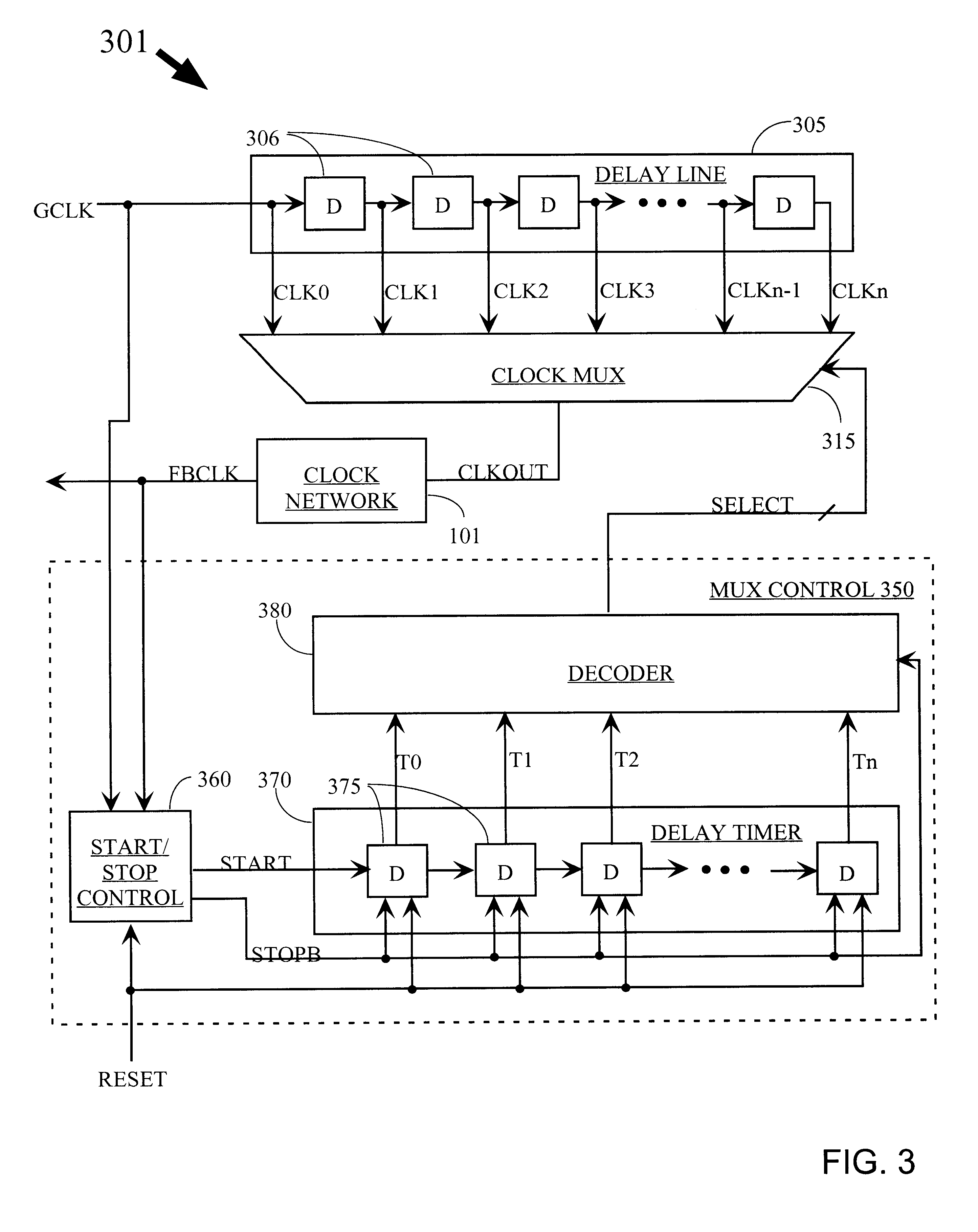

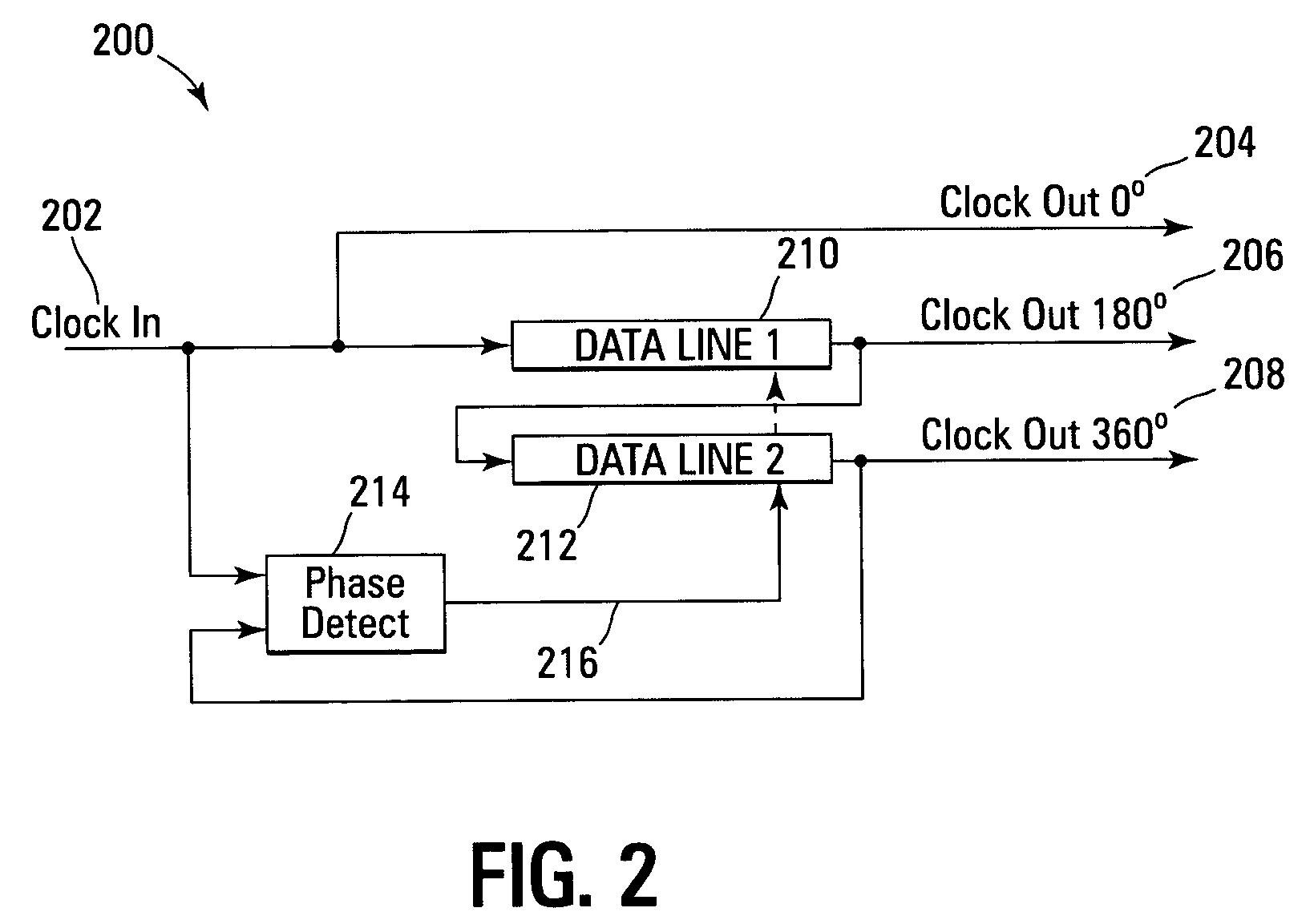

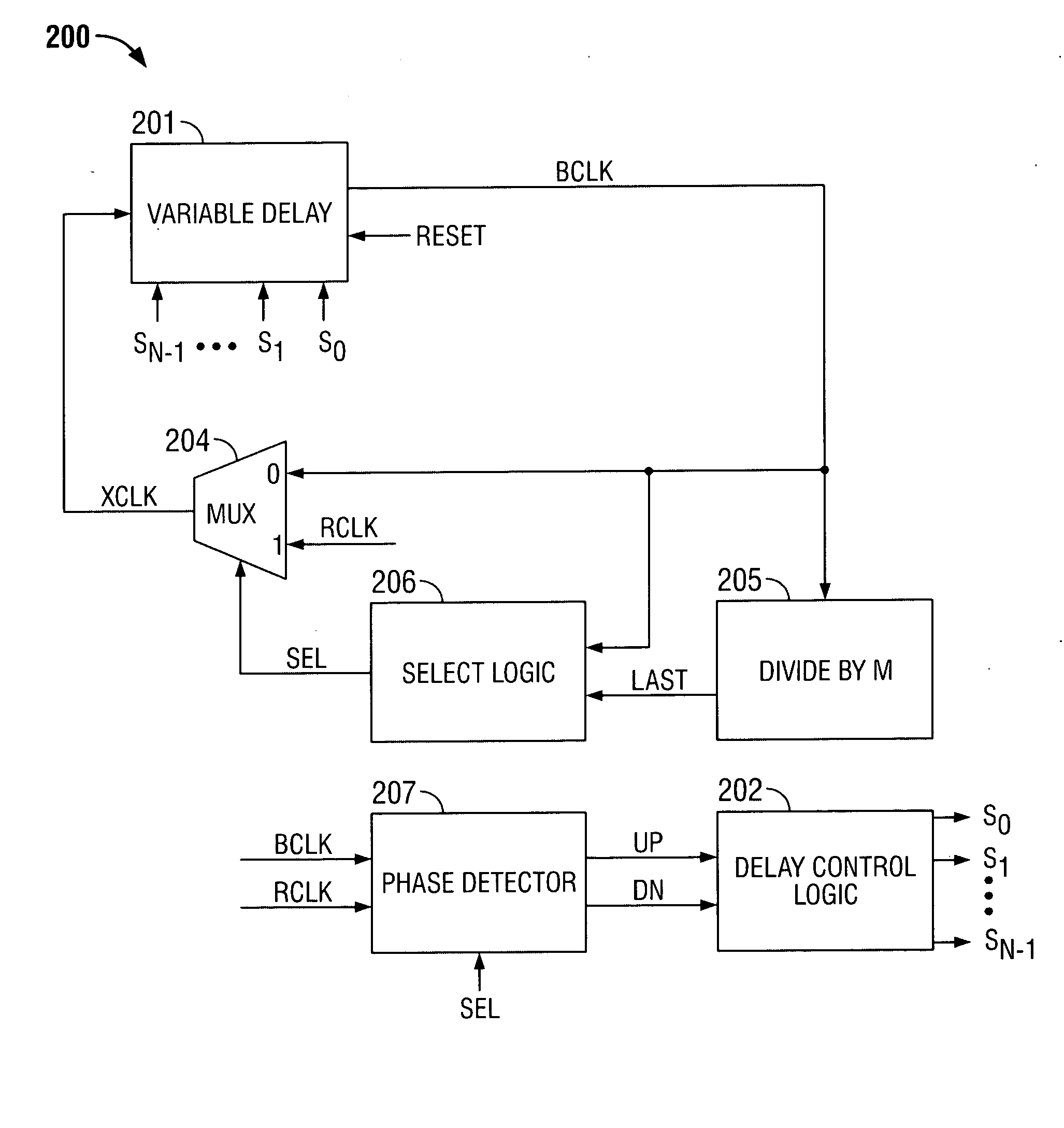

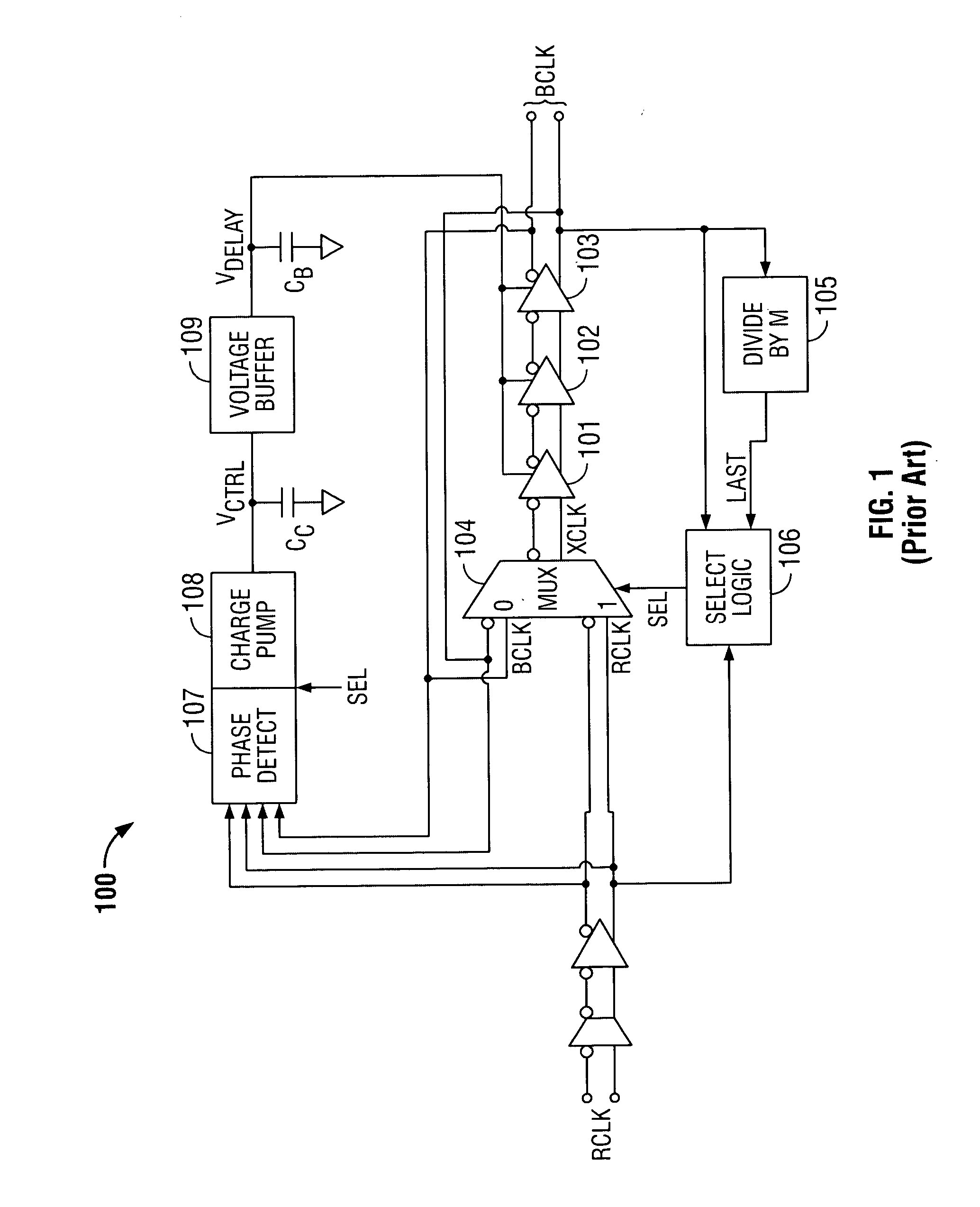

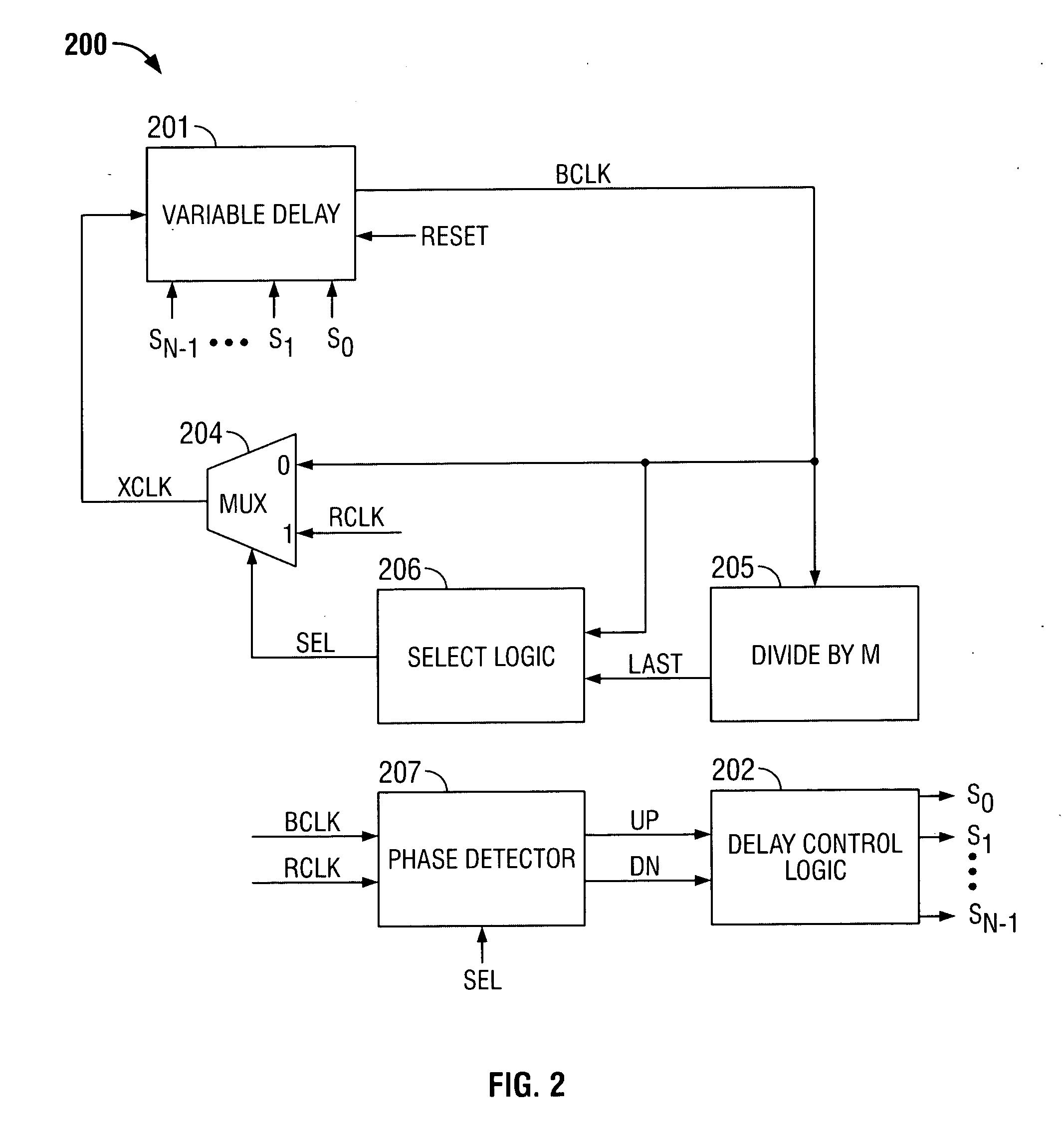

One-shot DLL circuit and method

InactiveUS6255880B1Reduce noiseHigh simulationPulse automatic controlTime-division multiplexMultiplexerDelay-locked loop

A delay-lock loop (DLL) circuit and method that accept an input clock signal and a feedback clock signal, and provide the necessary additional delay to synchronize the feedback clock signal to the input clock signal. Unlike previous circuits and methods, a single synchronization step is sufficient, provided that the frequency of the input clock signal is stable. A circuit according to the invention includes an input clock terminal supplying an input clock signal, and a delay line driven by the input clock signal and supplying a plurality of intermediate clock signals delayed from the input clock signal by incremental unit delays. A clock multiplexer selects from among these intermediate clock signals, under control of a multiplexer control circuit, the clock signal that provides the necessary additional delay to synchronize the feedback clock signal to the input clock signal. The output clock signal from the clock multiplexer is distributed through the clock network to provide the distributed clock signal as well as the feedback clock signal.

Owner:XILINX INC

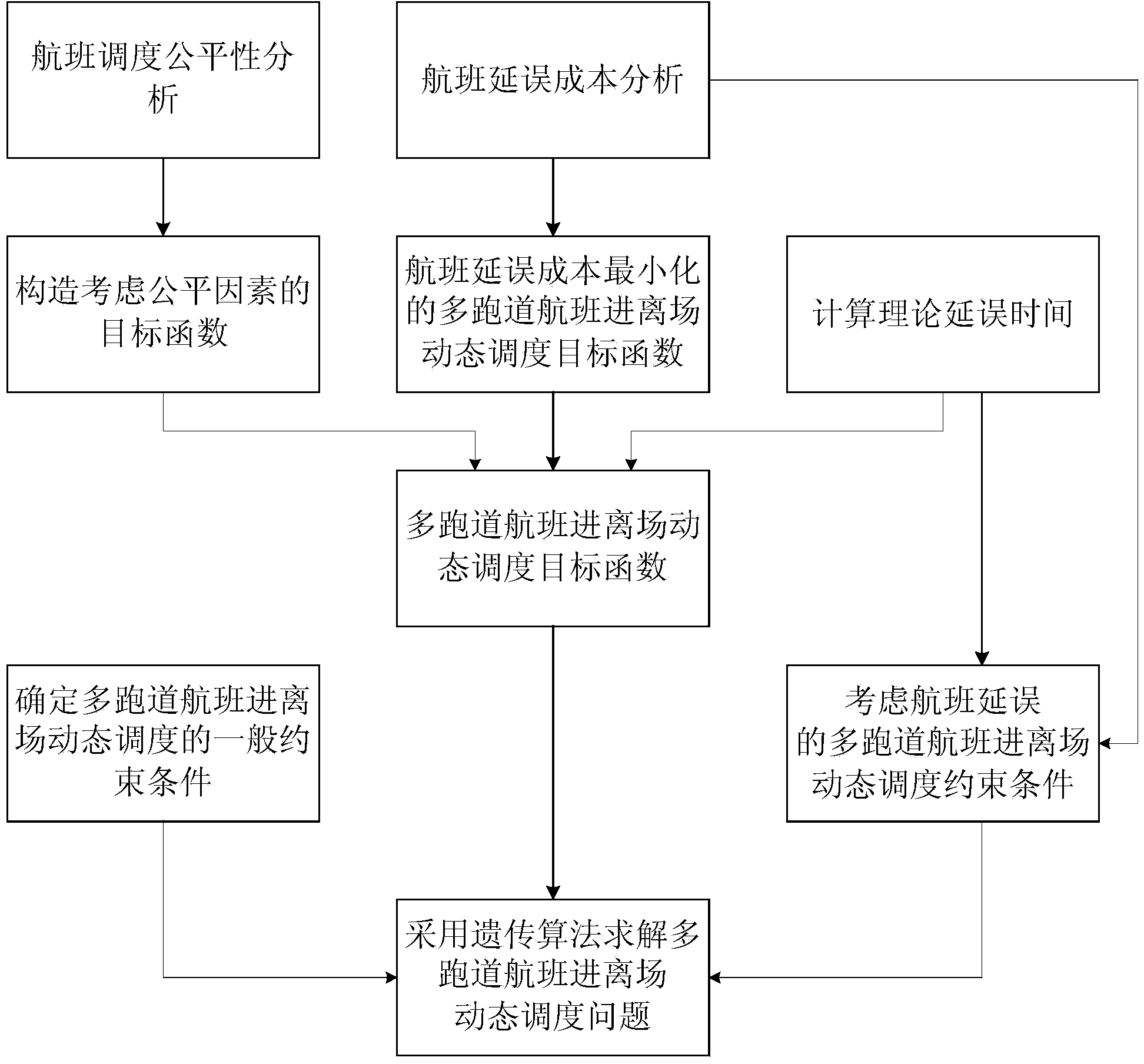

Dynamic scheduling method for multi-runway flight getting in and out

ActiveCN103778481ARapid evolutionImprove utilization efficiencyGenetic modelsForecastingGenetic algorithmDelayed time

The invention discloses a dynamic scheduling method for multi-runway flight getting in and out. The method comprises the following steps that flight delay cost is analyzed, and a flight delay cost minimization objective function for multi-runway flight getting in and out scheduling is provided; theoretic delay time is calculated, and flight delay time of different aircraft types is converted into delay time of unit delay cost; fairness of multi-runway scheduling is analyzed, and the objective function considering the fair factor is built; ordinary constrain conditions of multi-runway flight dynamic scheduling are provided; the multi-runway flight scheduling constrain conditions considering flight delay are designed; the dynamic scheduling problem of multi-runway flight getting in and out is solved by adopting the genetic algorithm, dynamic scheduling of multi-runway flight getting in and out is achieved, and the purposes of improving the runway using rate and reducing the flight delay cost are achieved. According to the method, influence on multi-runway scheduling caused by flight delay is sufficiently considered, and the purposes of improving the runway using rate and reducing the flight delay cost are achieved.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

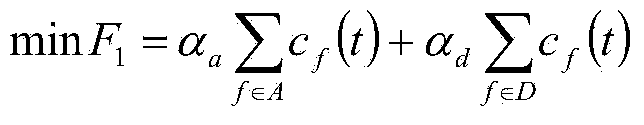

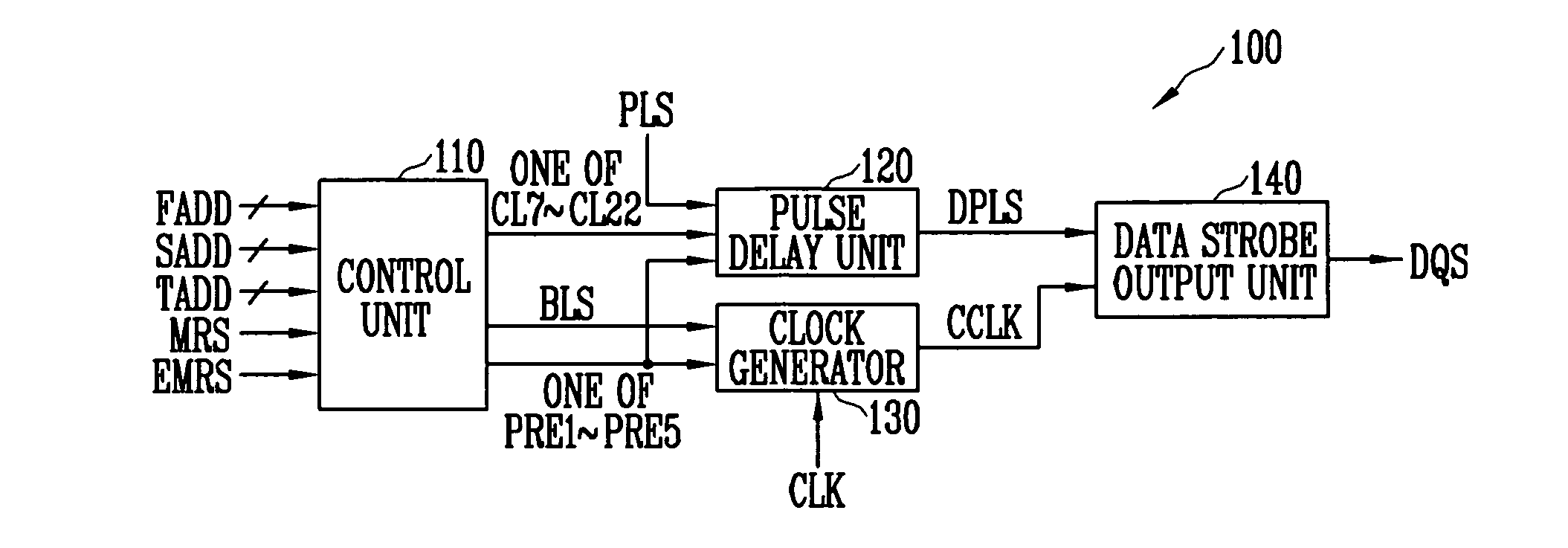

Data strobe signal generator for generating data strobe signal based on adjustable preamble value and semiconductor memory device with the same

InactiveUS20070291558A1Stabilized data output operationIncrease speedDigital storageHigh speed memoryControl signal

A data strobe signal generator according to the present invention includes a control unit, a pulse delay unit, a clock generator, and a data strobe output unit. The control unit generates a CAS latency signal and a preamble signal. The pulse delay unit delays a pulse signal for predetermined time and outputs a delayed pulse signal. The clock generator outputs a control clock signal. The data strobe output unit outputs a data strobe signal. The data strobe signal generator and the semiconductor memory device having the same according to the present invention generate a data strobe signal based on an adjustable preamble value, thereby ensuring the stabilized data output operation of a high-speed memory device.

Owner:SK HYNIX INC

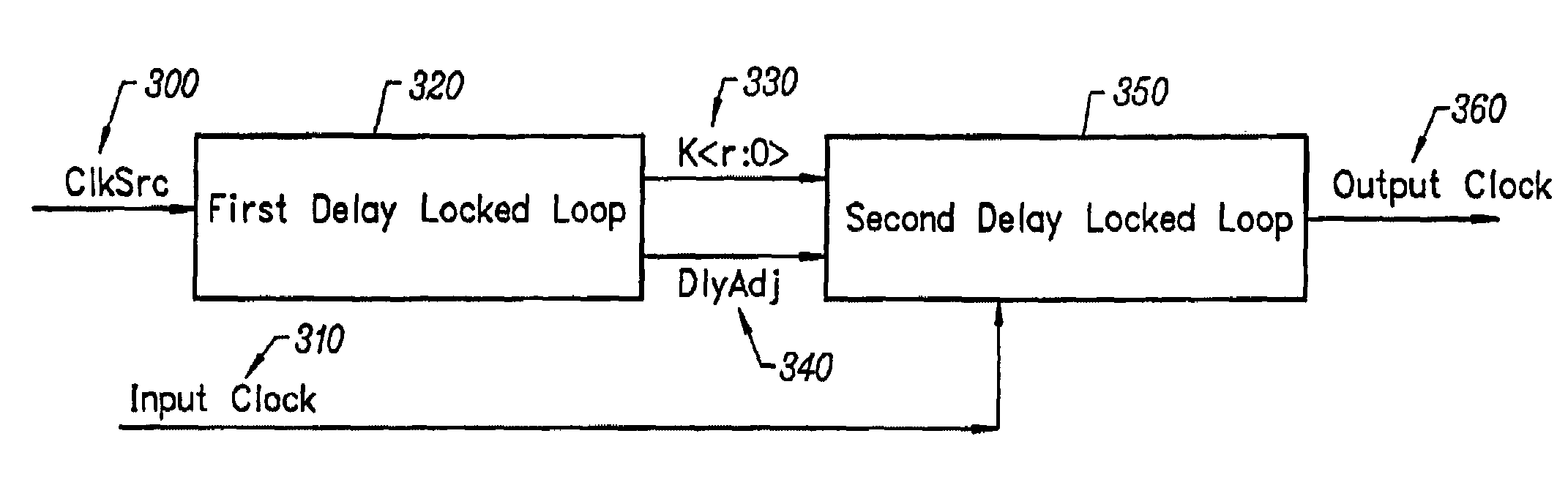

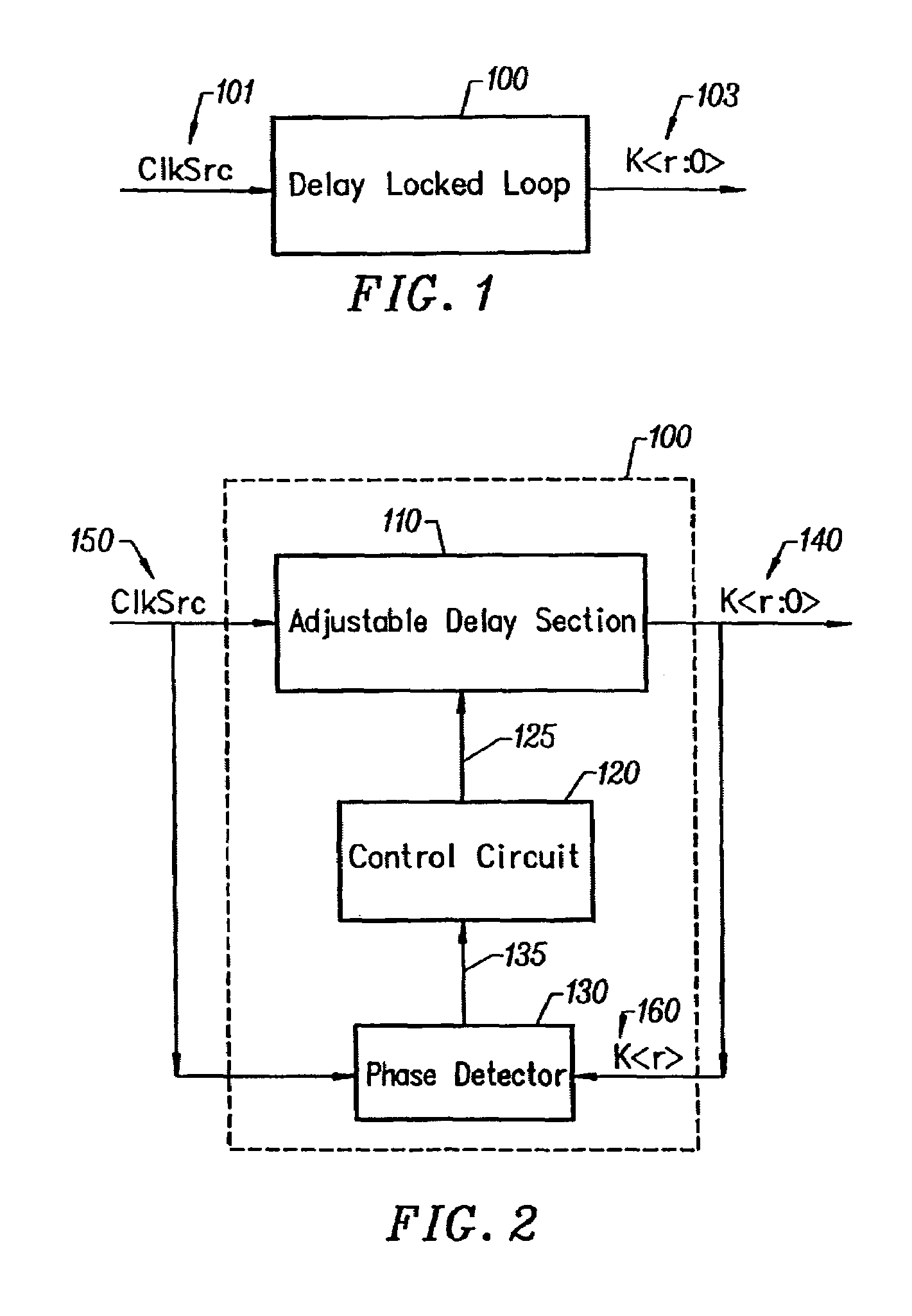

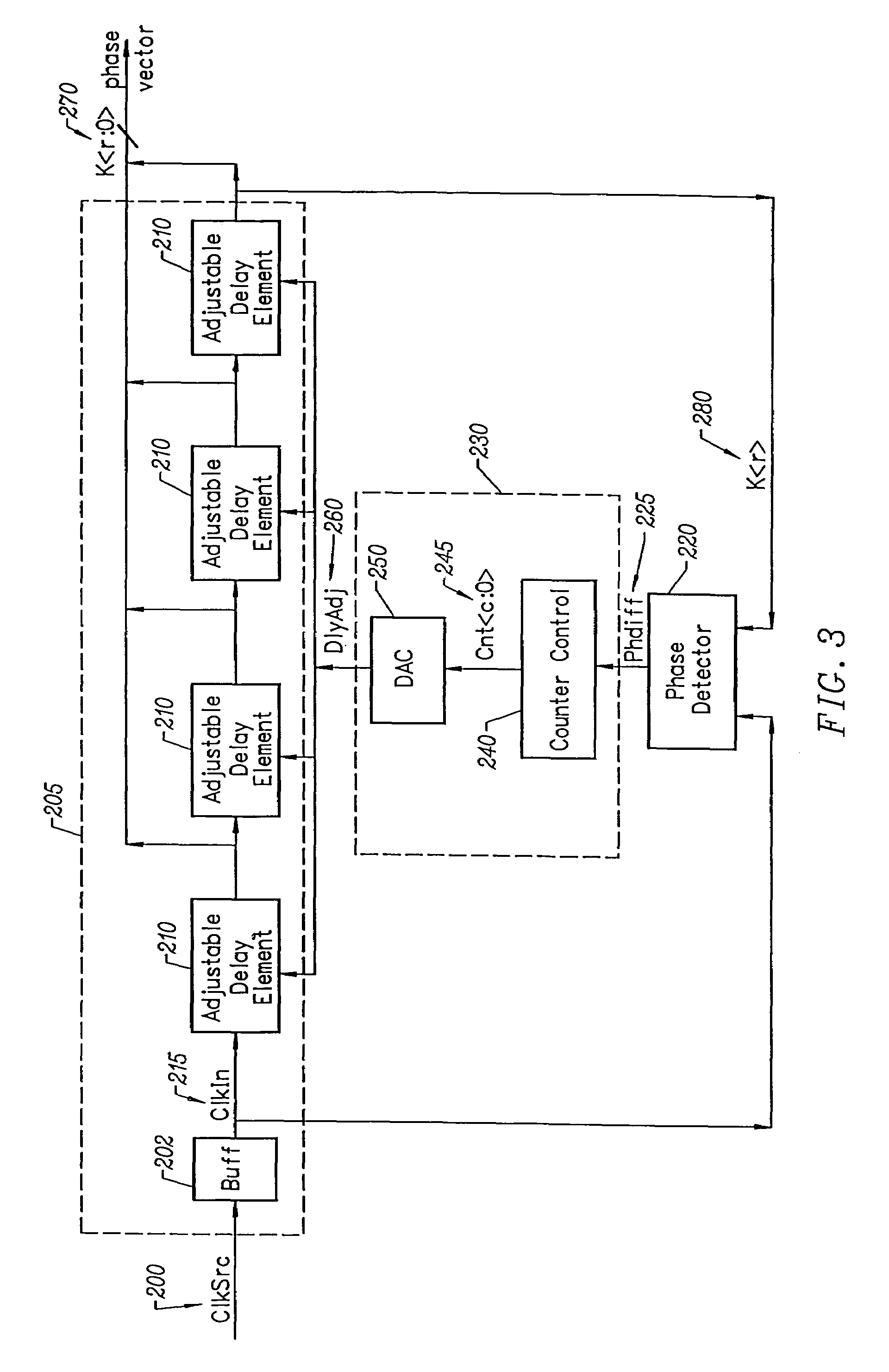

Delay locked loop circuitry for clock delay adjustment

InactiveUS7039147B2Reduce loop jitterMultiple input and output pulse circuitsSynchronisation information channelsPhase detectorPhase shifted

Delay locked loop circuitry for generating a predetermined phase relationship between a pair of clocks. A first delay-locked loop includes a delay elements arranged in a chain, the chain receiving an input clock and generating, from each delay element, a set of phase vectors, each shifted a unit delay from the adjacent vector. The first delay-locked loop adjusts the unit delays in the delay chain using a delay adjustment signal so that the phase vectors span a predetermined phase shift of the input clock. A second delay-locked loop selects, from the first delay-locked loop, a pair of phase vectors which brackets the phase of an input clock. A phase interpolator receives the selected pair of vectors and generates an output clock and a delayed output clock, the amount of the delay being controlled by the delay adjustment signal of the first delay-locked loop circuitry. A phase detector compares the delayed output clock with the input clock and adjusts the phase interpolator, based on the phase comparison, so that the phase of the delayed output clock is in phase with the input clock. As a result, there is a predetermined phase relationship between the output clock and the input clock, the phase relationship being the amount of delay between the output clock and the delayed output clock. Different phase relationships between the input and output clock are possible depending on the number of unit delays used in the path of the, delayed output clock or the output clock.

Owner:RAMBUS INC

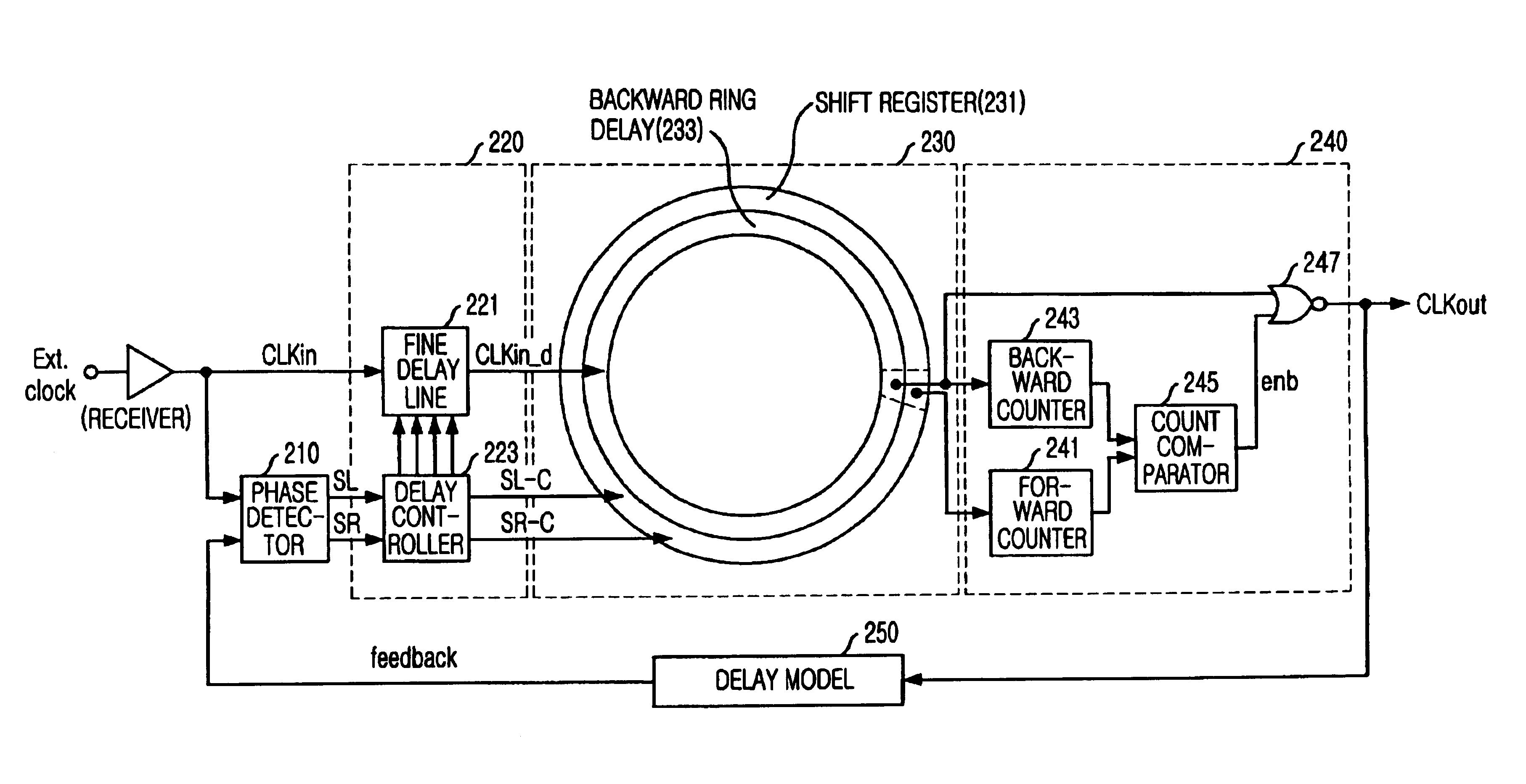

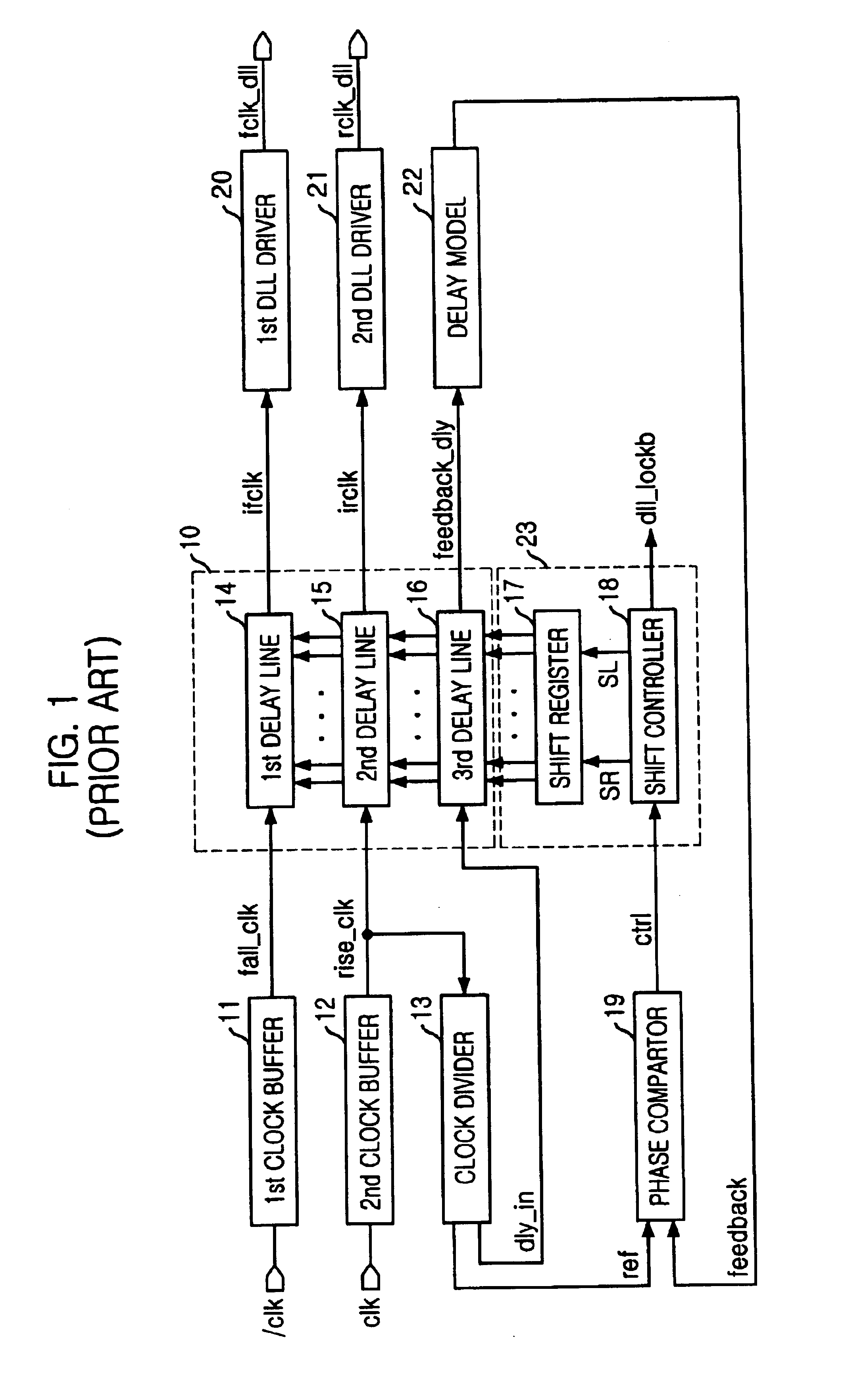

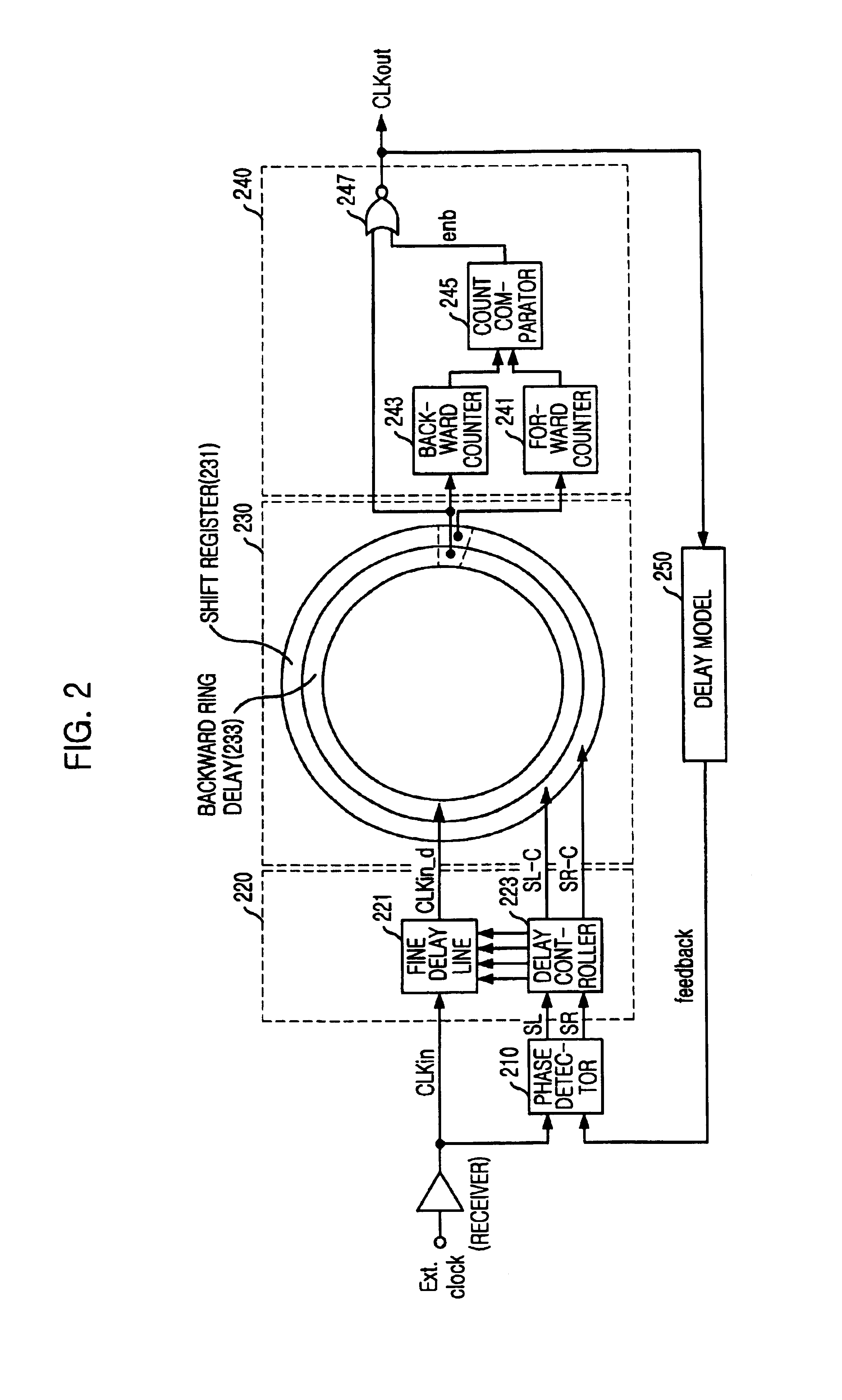

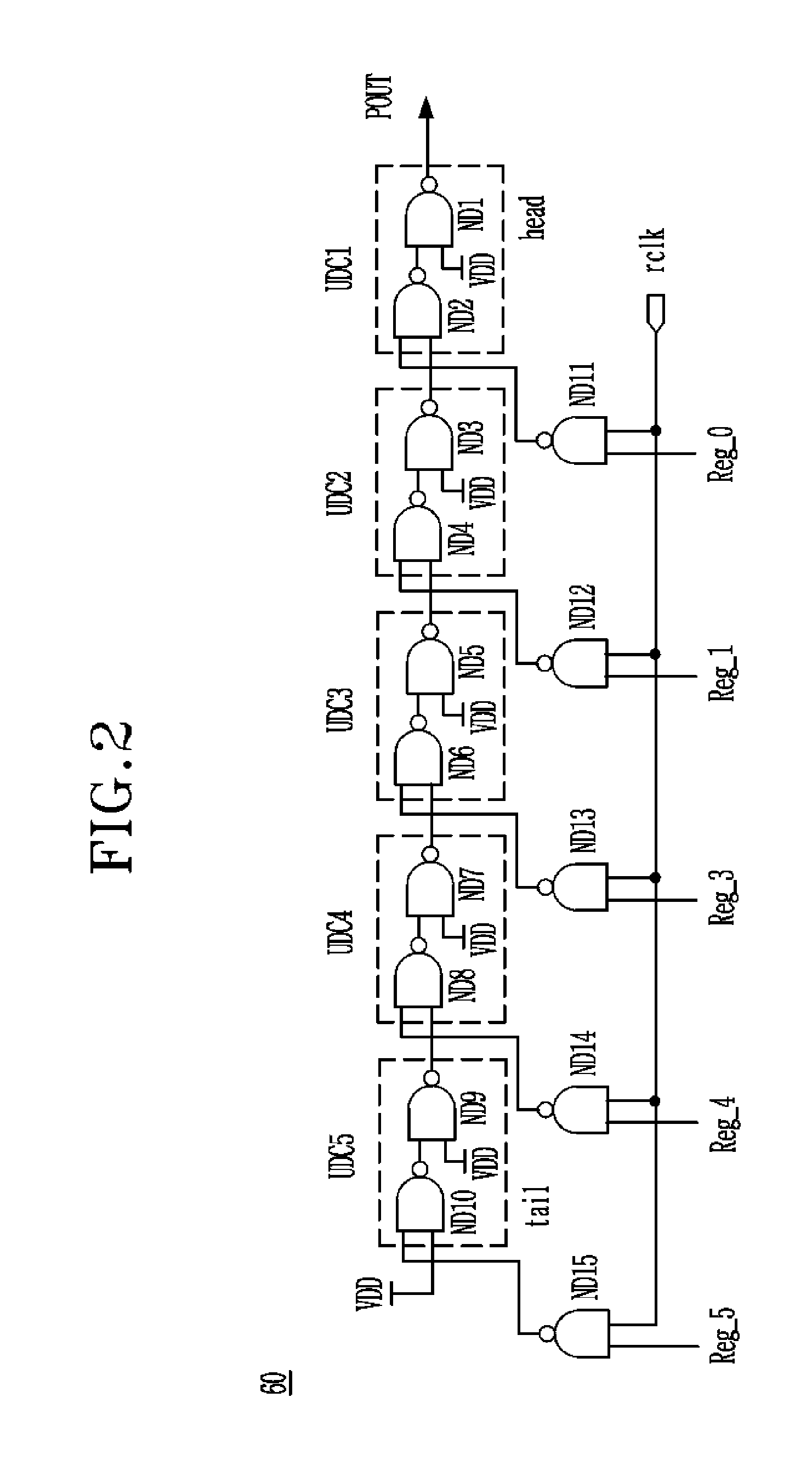

Ring-resister controlled DLL with fine delay line and direct skew sensing detector

InactiveUS6919745B2Effectively minimizing jitterPulse automatic controlSingle output arrangementsDelay-locked loopControl delay

The present invention related to a ring-resister controlled DLL with fine delay line and a direct skew sensing detector, which is applicable to circuitry for compensating skew between external and internal clocks. The ring-register controlled delay locked loop according to the present invention comprises: a first delay group including a plurality of unit delay elements which are lineally coupled to each other for delaying an input clock signal; a second delay group including a plurality of unit delay elements which are circularly coupled to each other for delaying an output signal from the first delay group; a first control means for determining an amount of lineal delay in the first delay group; and a second control means for determining an amount of circular delay in the first delay group.

Owner:SK HYNIX INC

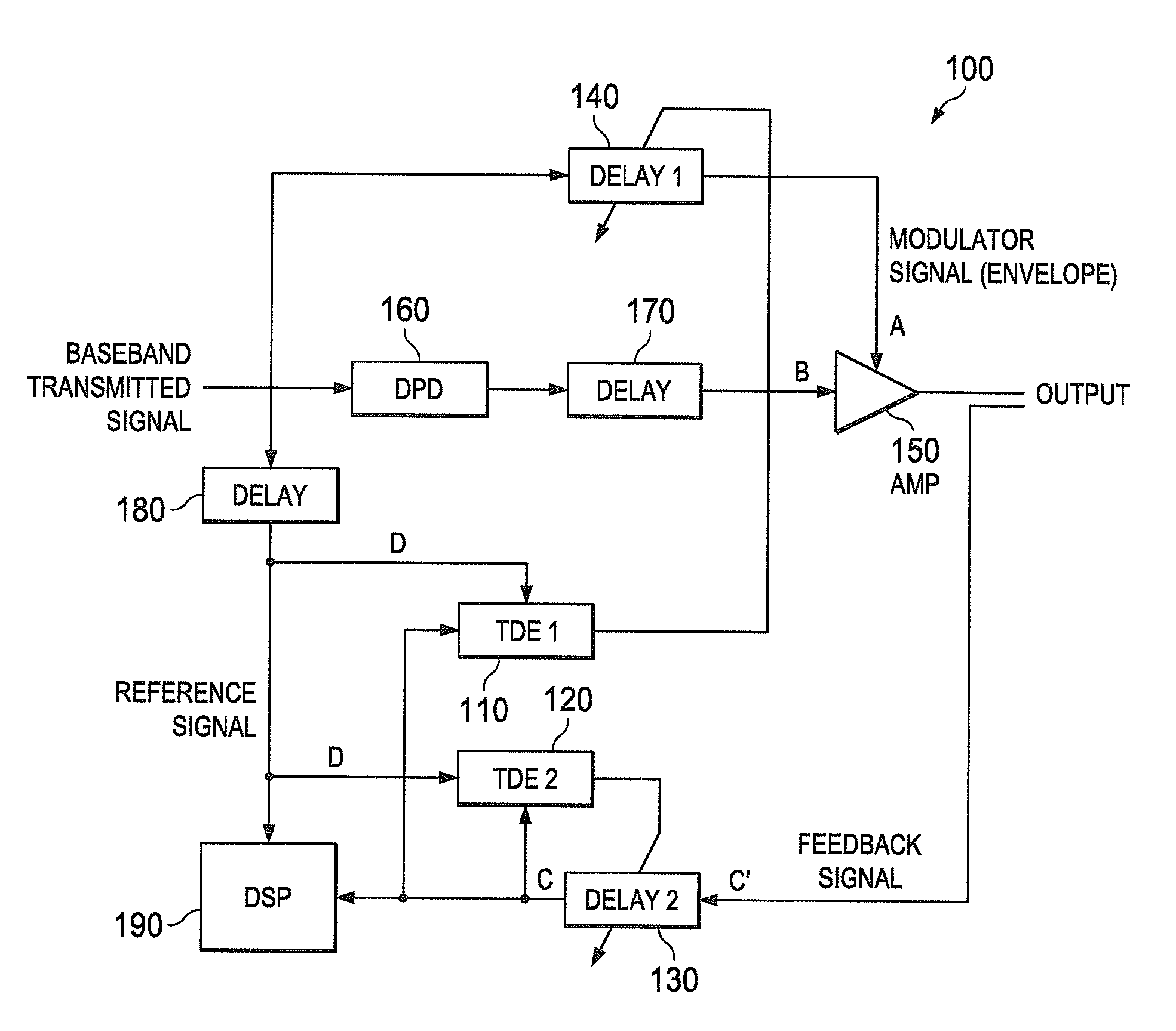

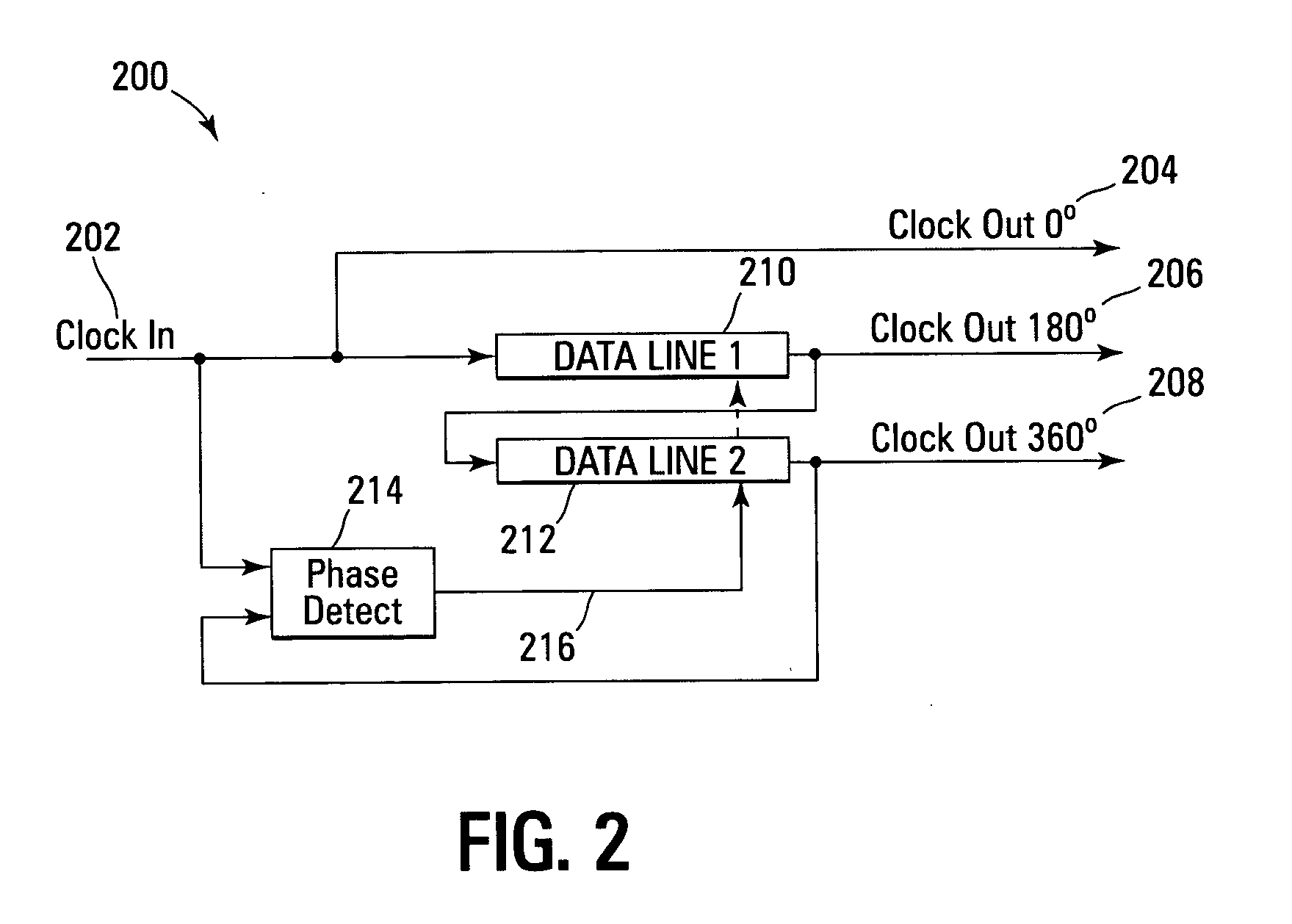

Dual time alignment architecture for transmitters using EER/et amplifiers and others

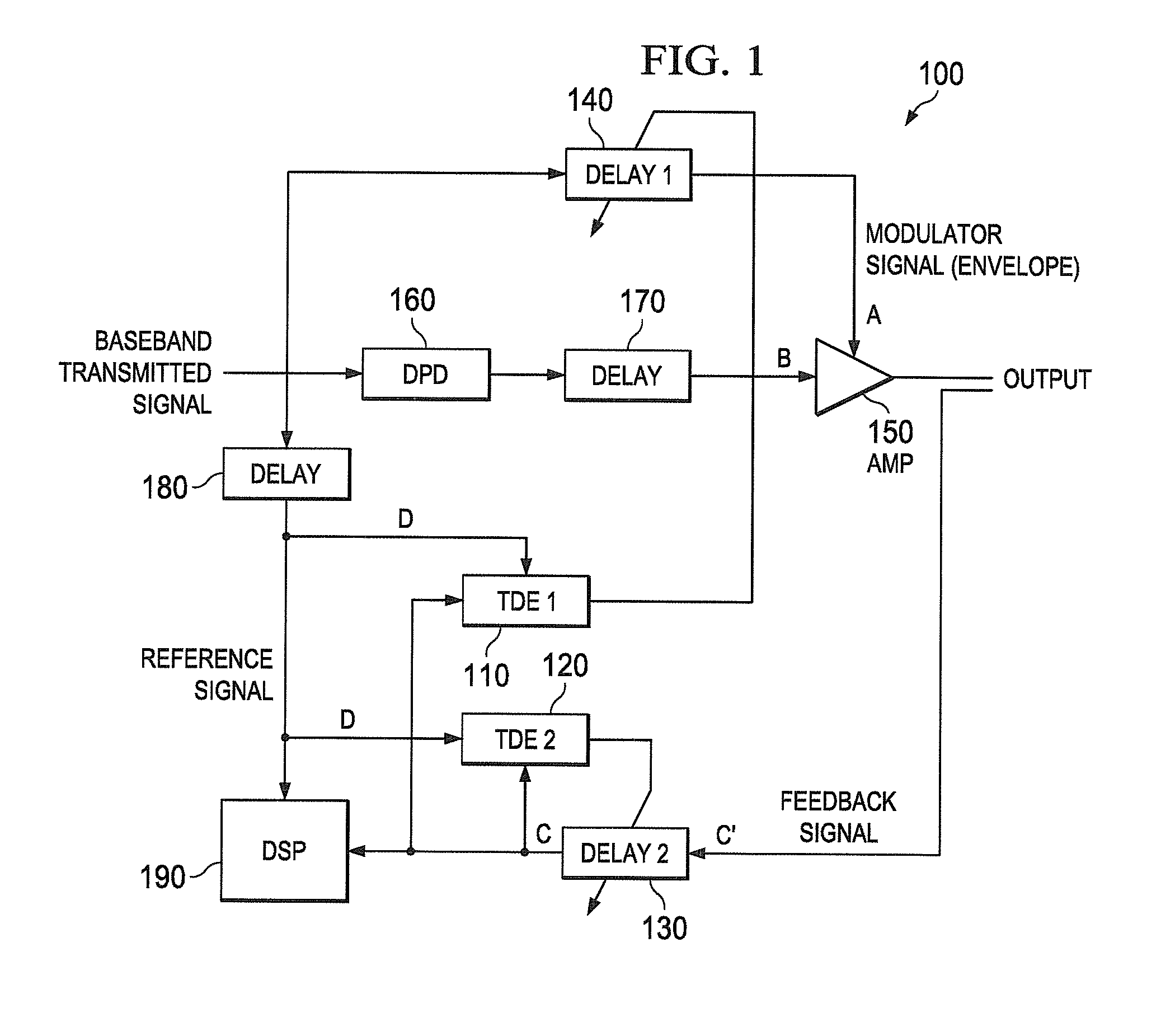

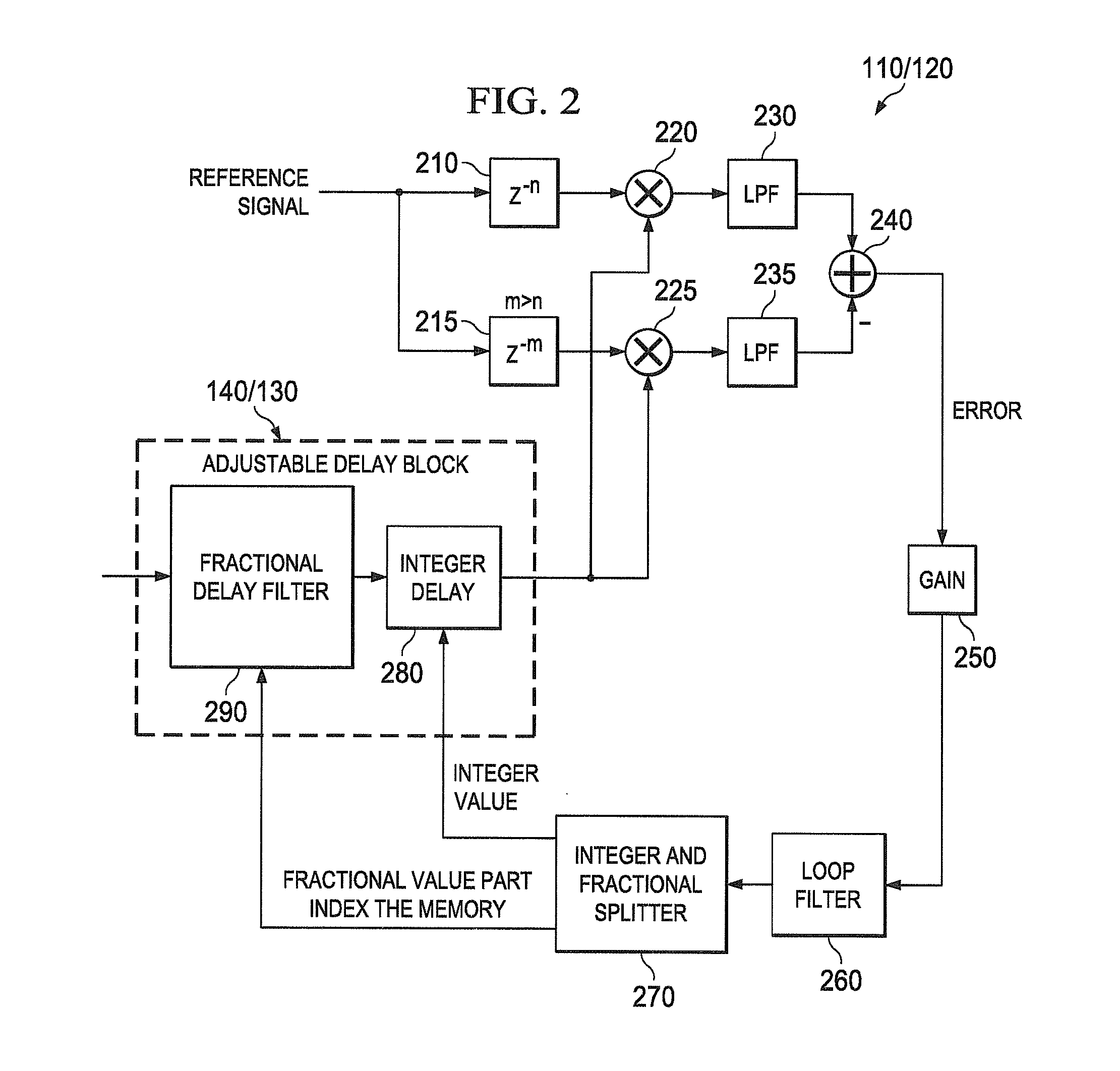

InactiveUS20110260790A1Amplifier modifications to reduce non-linear distortionNegative-feedback-circuit arrangementsAudio power amplifierEngineering

An apparatus and method linearize a power amplifier in a transmitter by using a dual time alignment scheme. A first adjustable time delay unit delays a modulator signal input of a power amplifier. A first time delay estimator estimates a time delay between the delayed feedback signal and the reference signal, and adjusts the first adjustable time delay unit based on the estimated time delay between the delayed feedback signal and the reference signal. A second adjustable time delay unit delays the feedback signal. And a second time delay estimator estimates the time delay between the delayed feedback signal and the reference signal, and adjusts the second adjustable time delay unit based on the estimated time delay between the delayed feedback signal and the reference signal.

Owner:SAMSUNG ELECTRONICS CO LTD

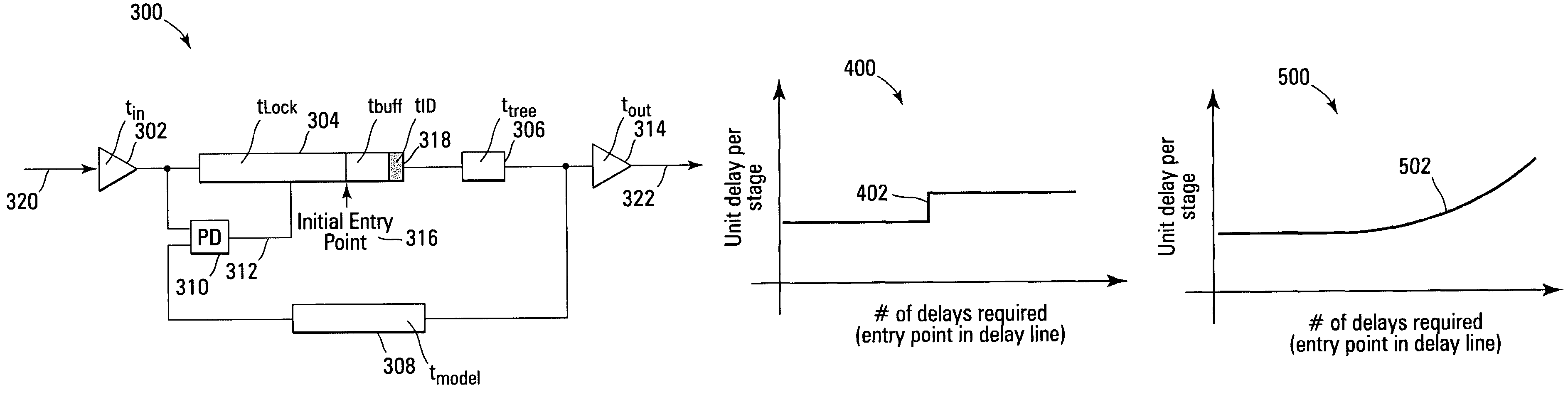

Graduated delay line for increased clock skew correction circuit operating range

ActiveUS20060261869A1Reduce circuit sizeHigh resolutionPulse automatic controlDigital storageTime delaysGranularity

Clock synchronization and skew adjustment circuits are described that utilize varying unit delay elements in their delay lines in either a graduated or a stepped unit time delay arrangement, allowing a reduced circuit implementation and improved lock characteristics. These graduated or a stepped unit time delays allow reduction in the number of the fine unit delay elements of the delay lines by placing a fine delay element granularity at the most critical timings to sense and adjust for the portion of the clock signal time period that are high speed or critical. This allows clock synchronization and skew adjustment circuits to be implemented in an optimized manner that exhibits a reduced overall circuit size and power consumption, while having improved lock characteristics over a wide range of frequencies.

Owner:MICRON TECH INC

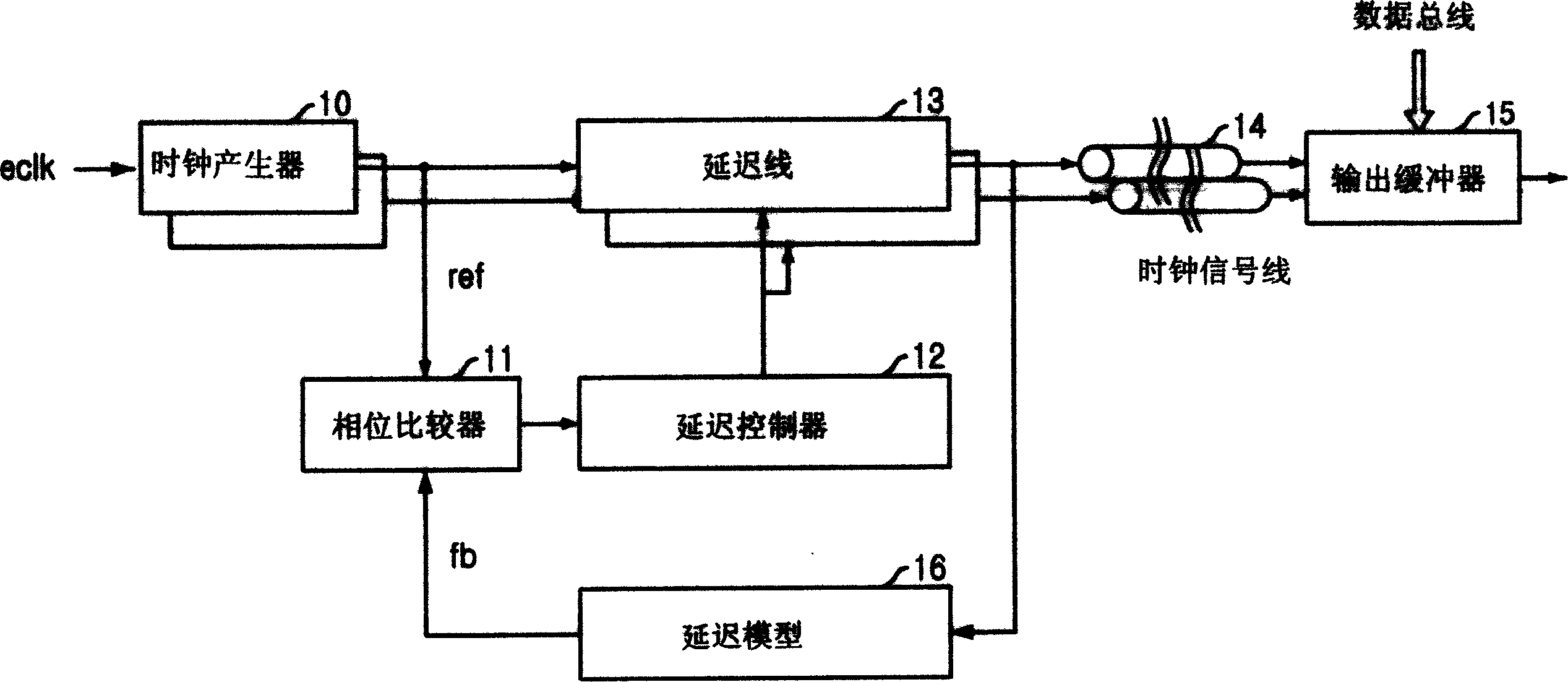

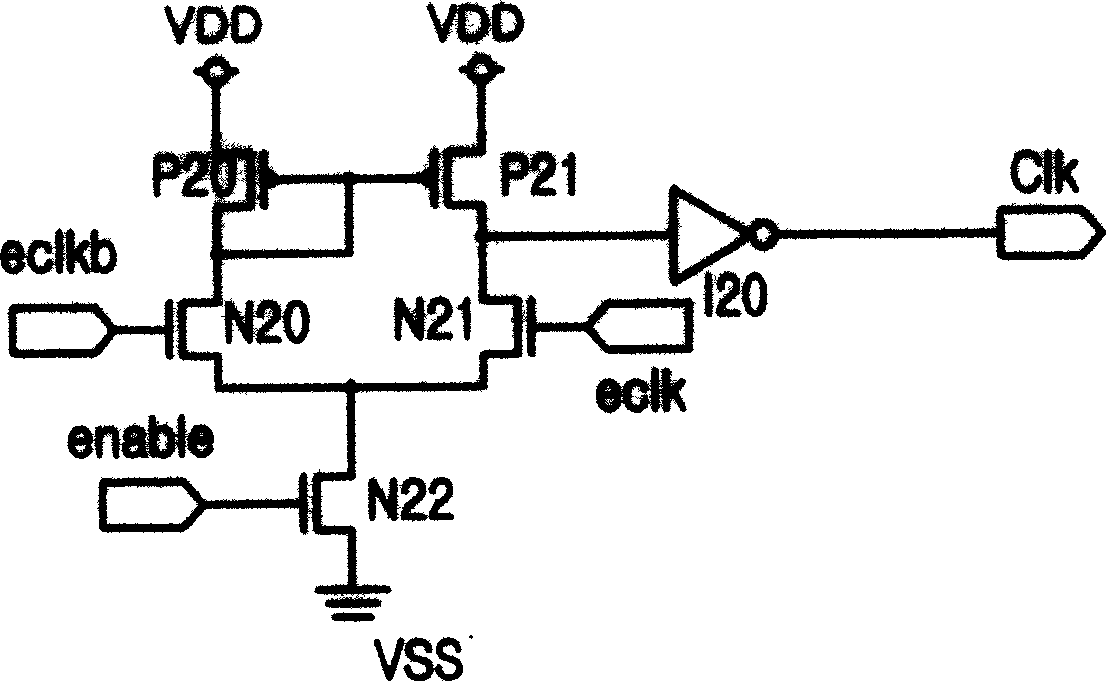

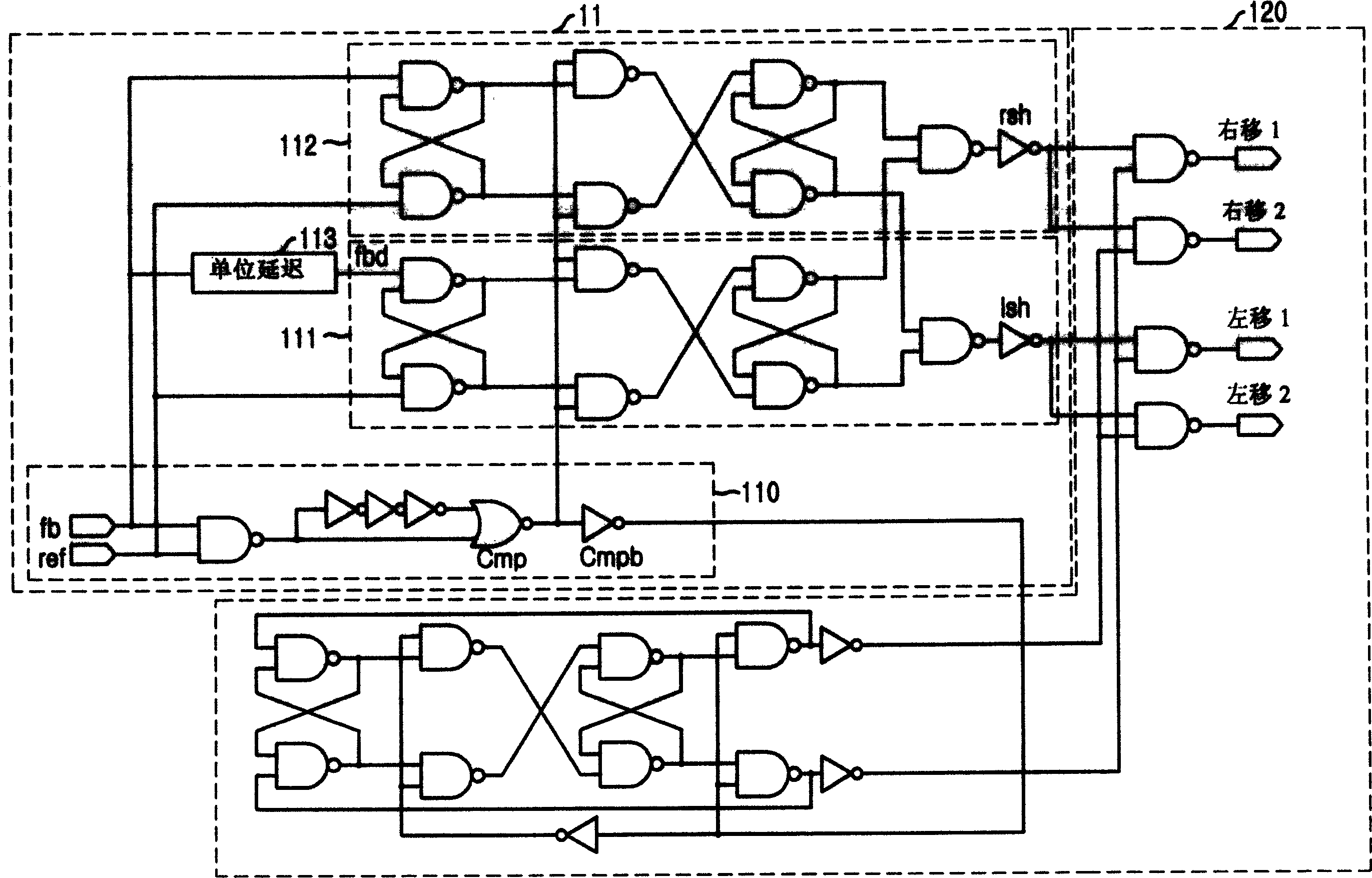

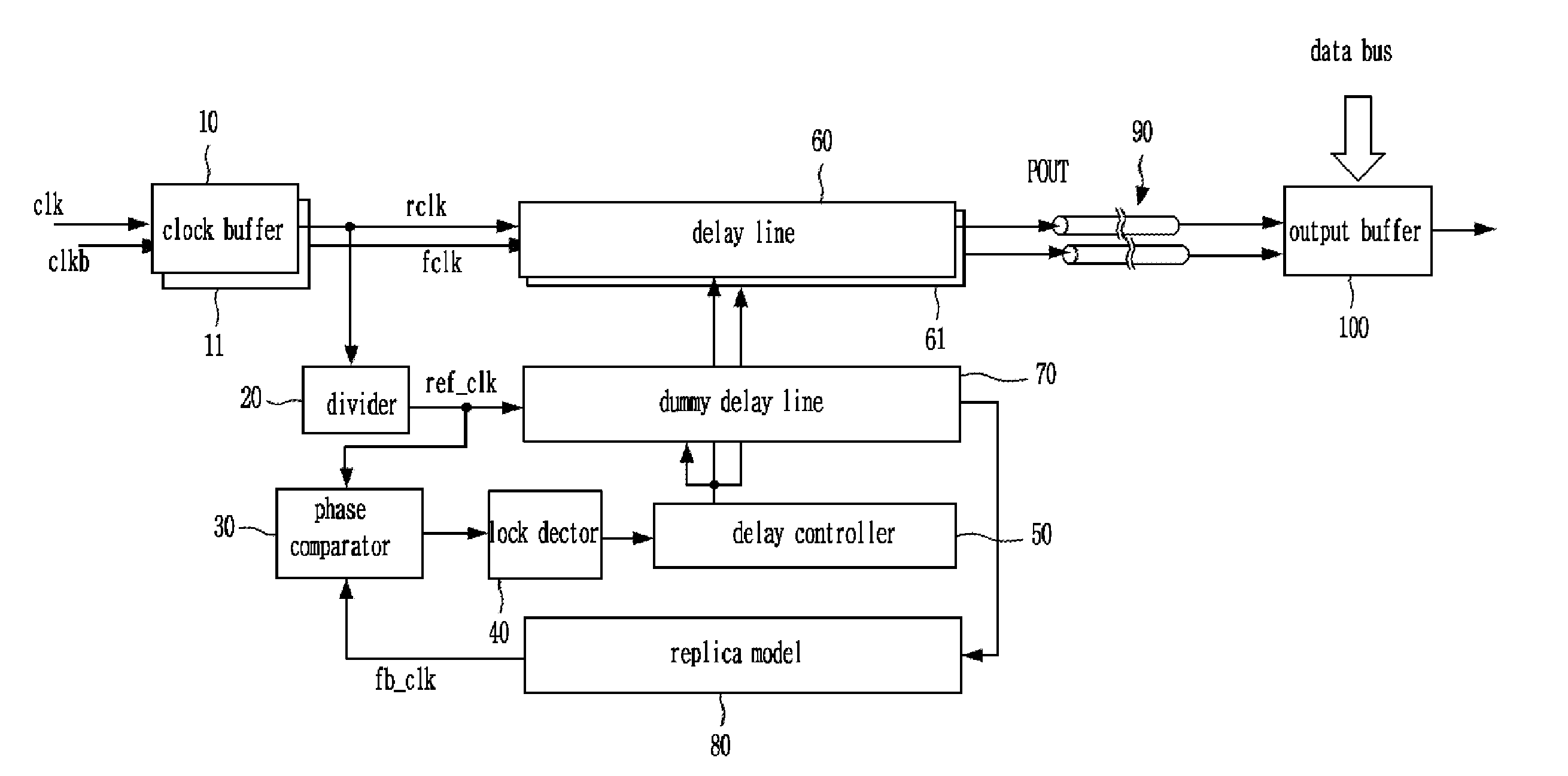

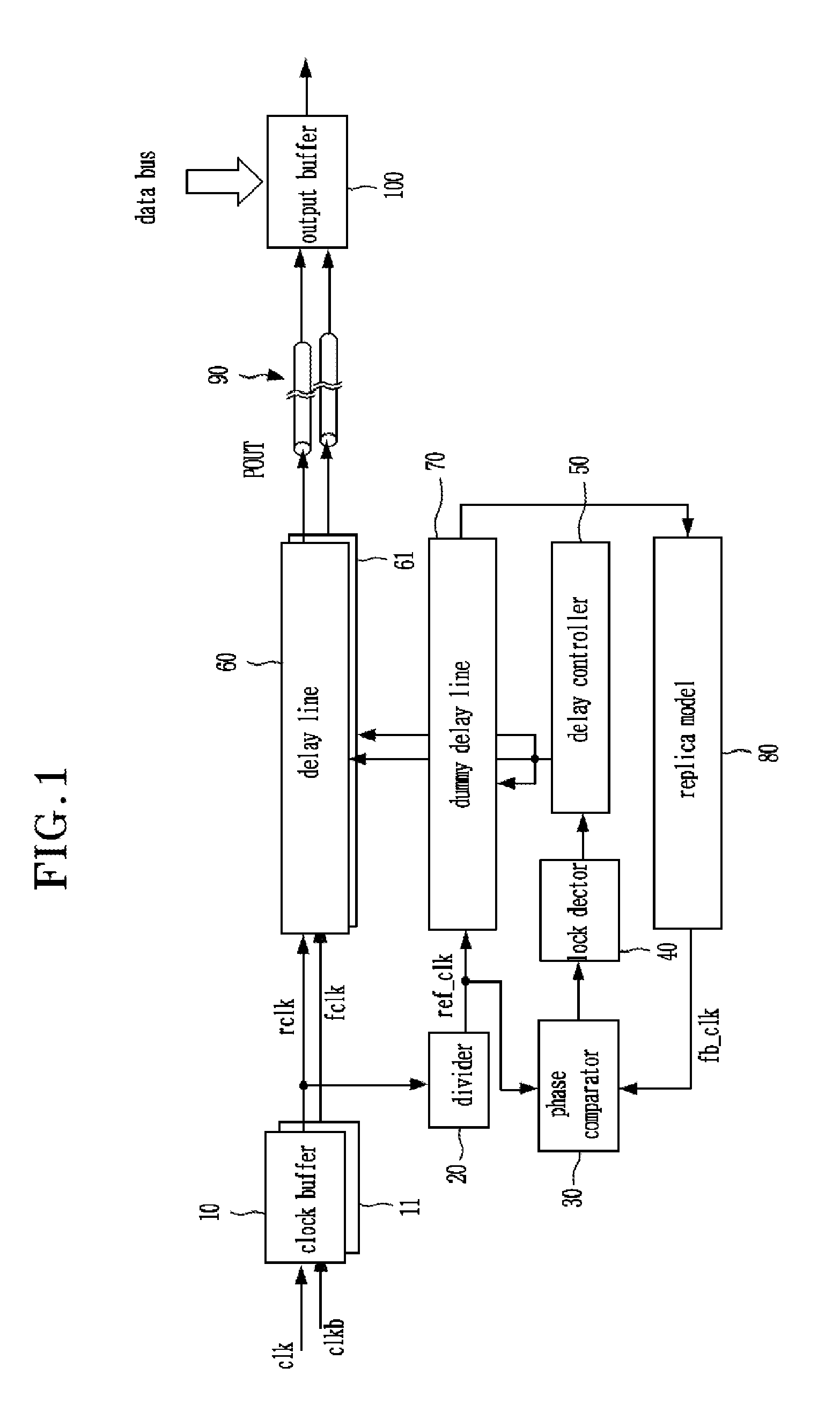

Digital delay locked loop and control method thereof

A digital delay locked loop(DLL) and a method for controlling the same are provided to improve the reliability of the DLL circuit by minimizing jitter. A digital delay locked loop(DLL) includes a clock generation unit, a delay line, a delay model, a phase comparison unit, a jitter detection unit and a delay control unit. The clock generation unit generates a source clock and a reference clock. The delay line is provided with a plurality of unit delays to delay the source clock by a predetermined time. The delay model reflects the delay time of the practical inner circuit on the output of the delay line. The phase comparison unit compares the reference clock with the phase of the feedback clock outputted from the delay model. The jitter detection unit detects the maximum jitter time in response to the phase comparison signal outputted from the phase comparison unit to output the multi-delay enable signal. And, the delay control unit controls the delay amount of the delay line to the unit delay or the multi-delay unit in response to the phase comparison signal and the multi-delay enable signal.

Owner:SK HYNIX INC

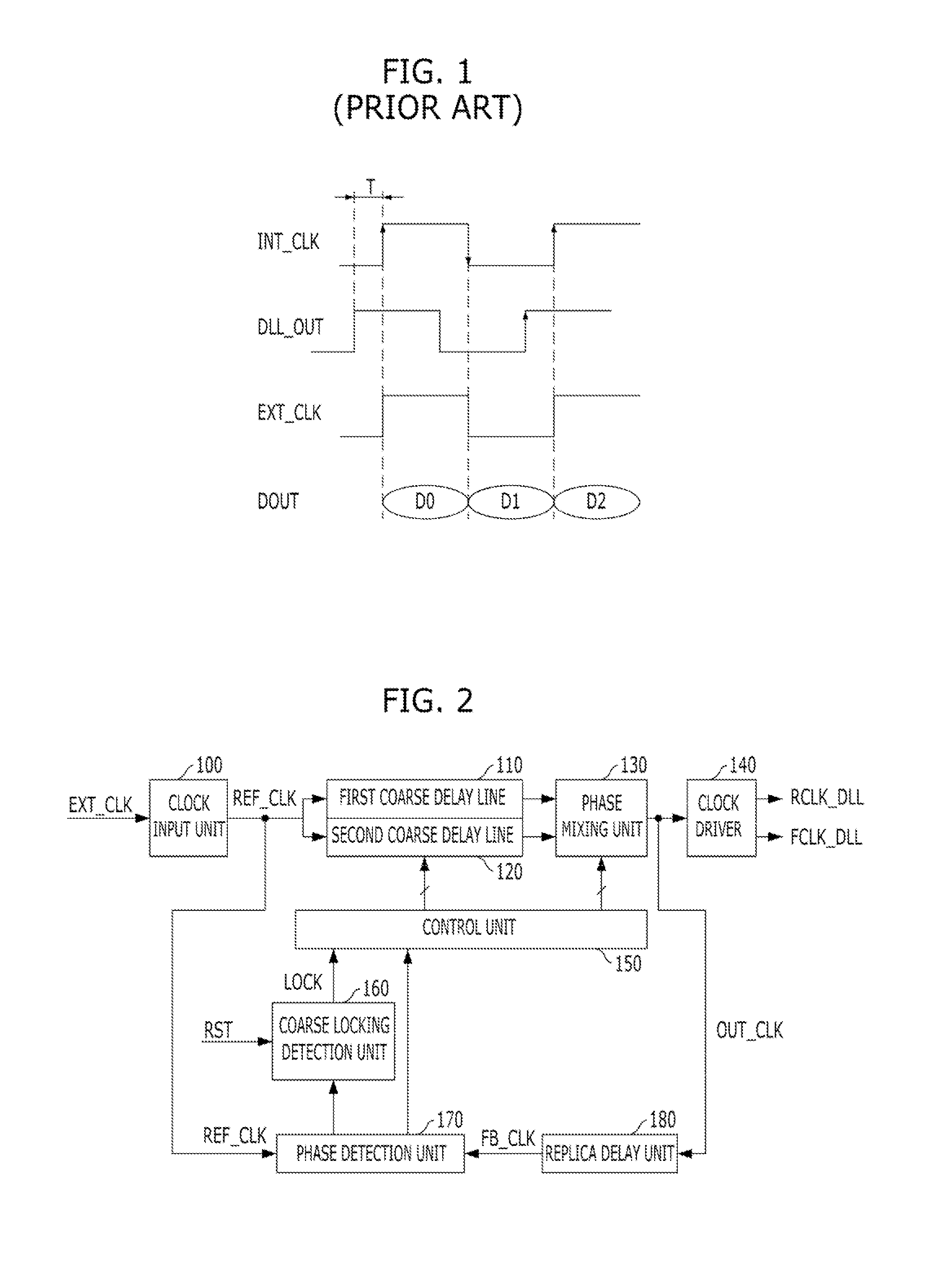

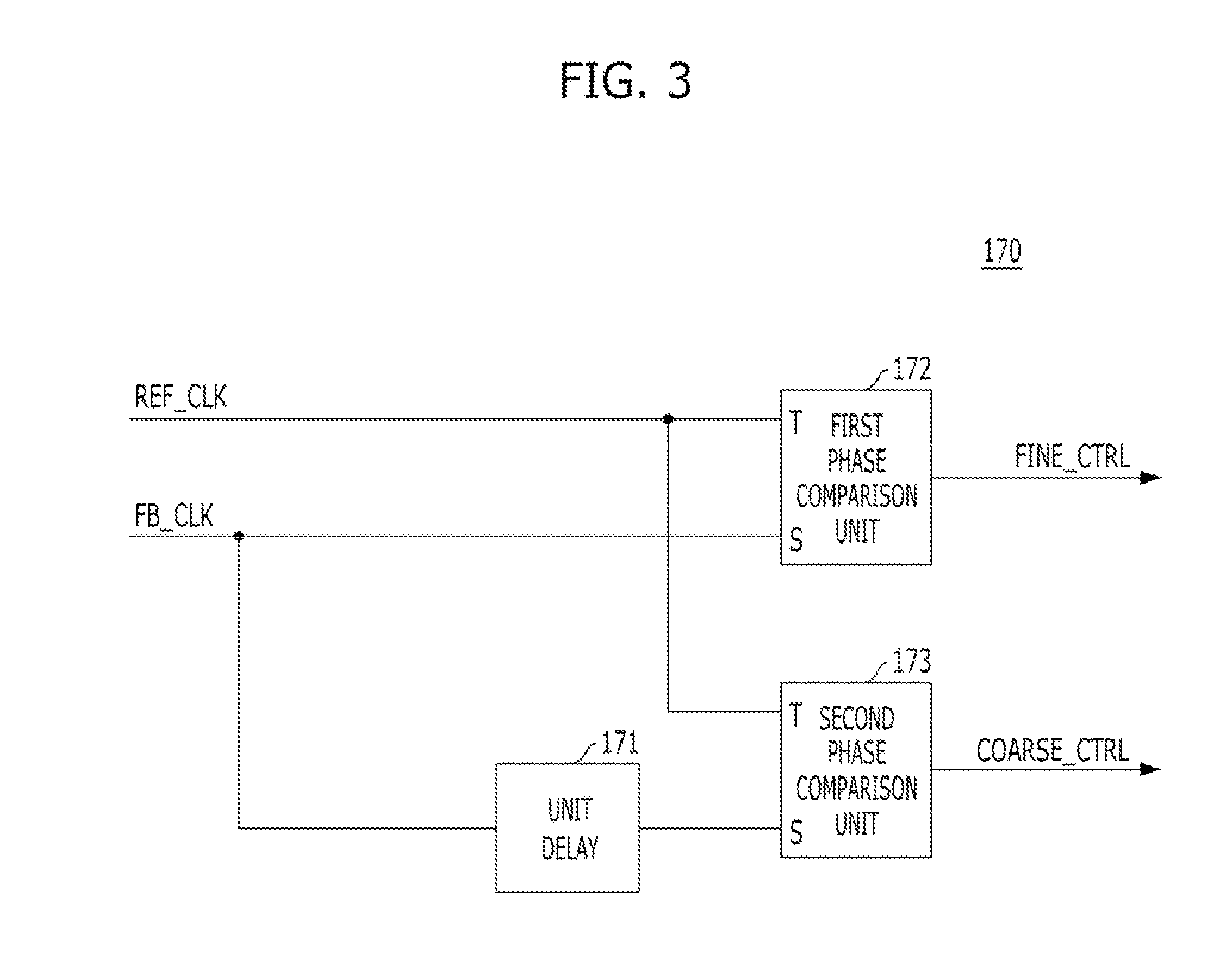

Delay locked loop circuit and method of driving the same

The DLL comprises a coarse delay line configured to have a plurality of unit delays and delay an reference dock to output a delayed clock, a fine delay line configured to delay the delayed clock to output a delayed output clock, a replica delay unit configured to delay the delayed output clock by an expected modeling value to output a feedback clock, a phase detection unit configured to compare a phase of the feedback clock with a phase of the reference clock to generate first to third phase detection signals based on a result of the comparison, a locking detection unit configured to output a locking signal by selecting a first locking detection signal or a second locking detection signal, and a control unit configured to control the coarse and fine delay lines in response to the locking signal and the first phase detection signal.

Owner:SK HYNIX INC

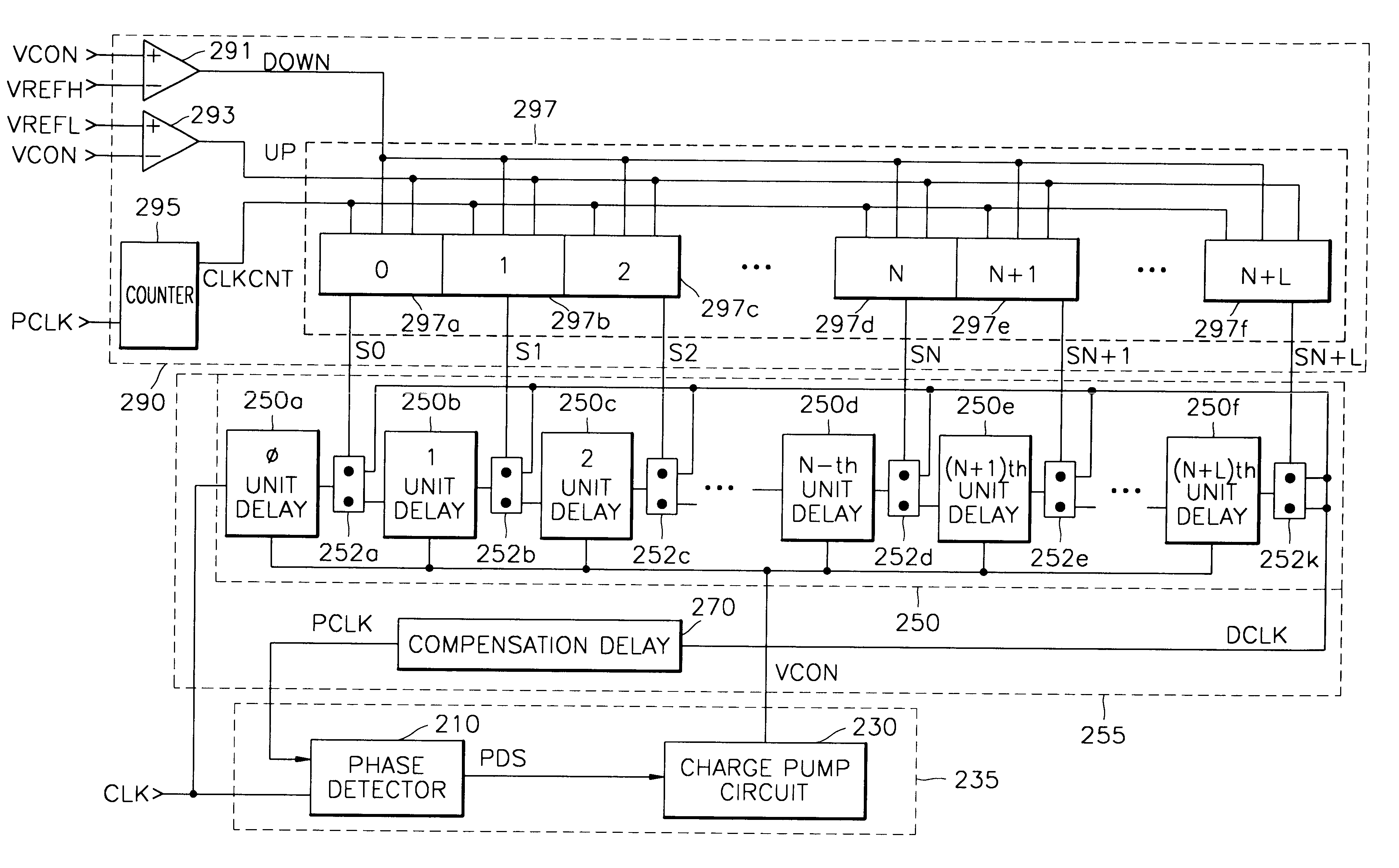

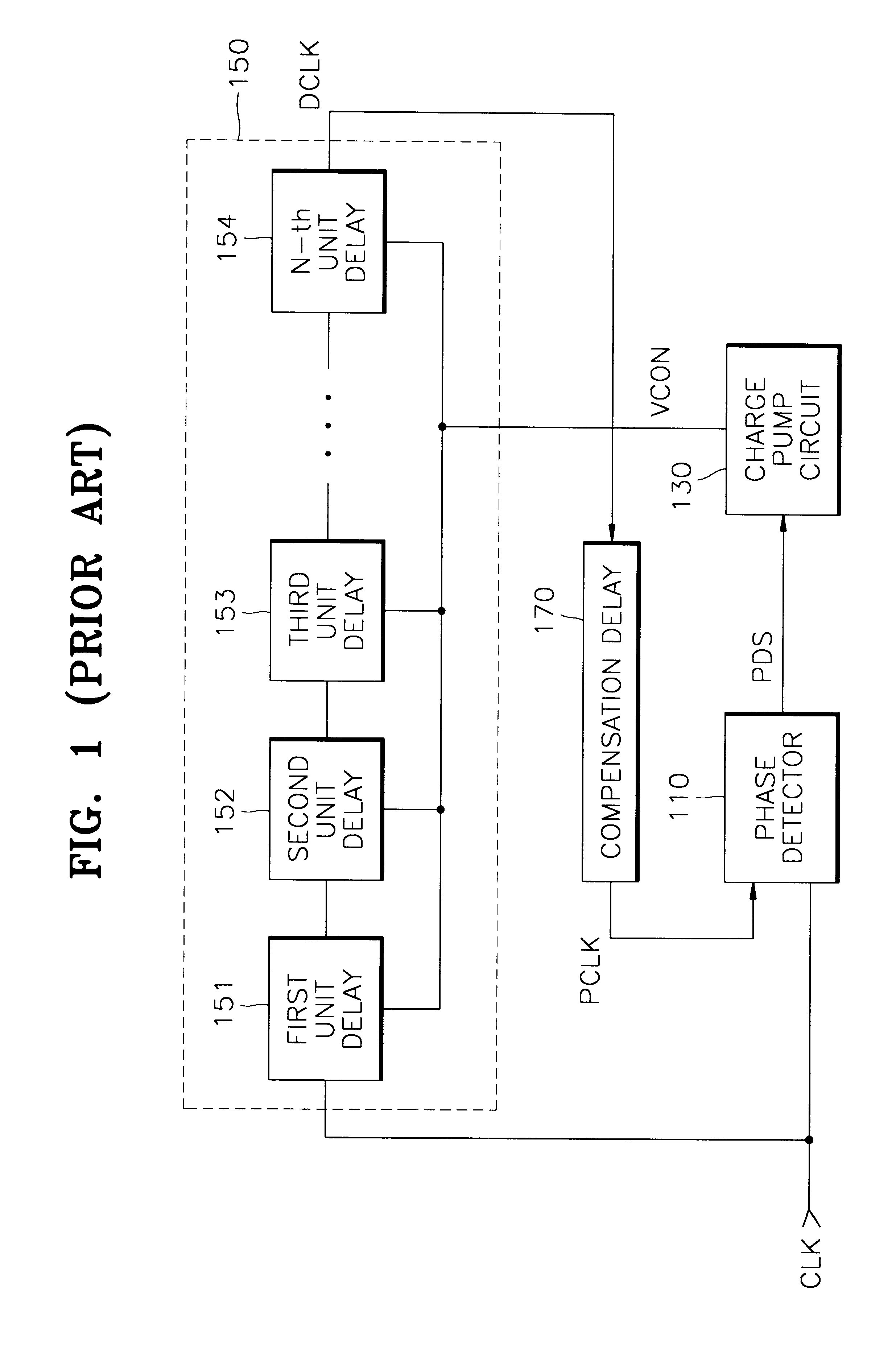

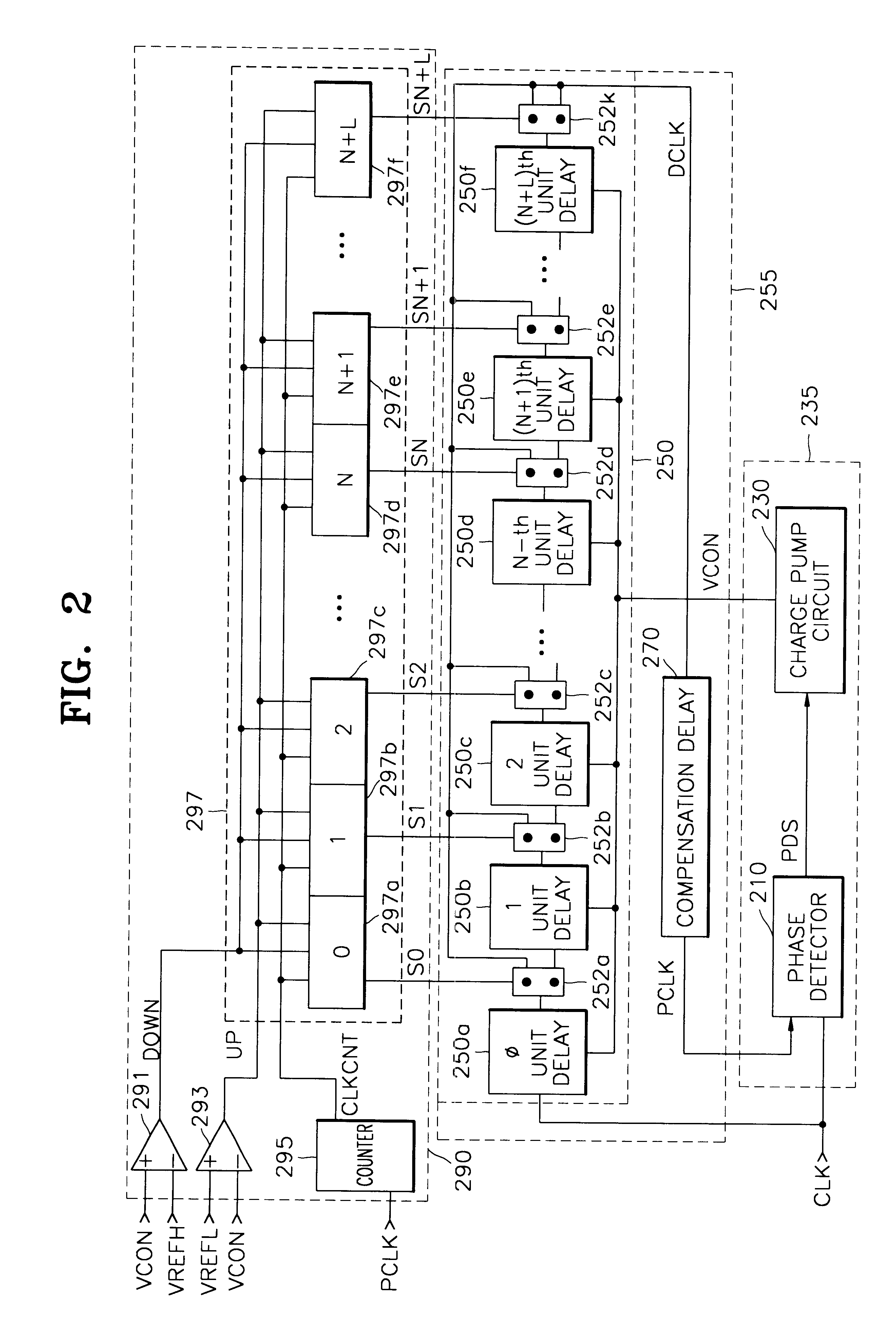

Phase locked loop integrated circuits having dynamic phase locking characteristics and methods of operating same

InactiveUS6329854B1Reduce sensitivityPulse automatic controlSingle output arrangementsShift registerControl signal

Phase locked loop integrated circuits include a phase detection circuit, a variable delay device and a delay control circuit. The variable delay device and delay control circuit provide improved characteristics by increasing the signal frequency bandwidth of the delay locked loop integrated circuit in a preferred manner. The phase detection circuit is configured to perform the functions of comparing first and second periodic signals and generating a phase control signal (e.g., VCON) having a first property (e.g., magnitude) that is proportional to a difference in phase between the first and second periodic signals. The delay control circuit is responsive to the phase control signal VCON and generates a delay control signal that is provided to the variable delay device. The delay control circuit may comprise a counter, a first comparator, a second comparator and a shift register. The variable delay device includes a variable delay line and a compensation delay device. The variable delay line may contain a string of unit delay devices and a string of switches that each have an input electrically coupled to an output of a corresponding unit delay device. Each of the unit delay devices in the string may provide a fixed delay or a variable delay that is influenced (e.g., increased) by changes (e.g., increases) in the magnitude of the phase control signal VCON.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor device

A semiconductor device may include a delay line including a first group of unit delay cells and a second group of unit delay cells. The first group of unit delay cells and the second group of unit delay cells may be configured for delaying a phase of a clock by a unit cycle of a reference frequency. The reference frequency may serve as a reference for distinguishing between a first frequency and a second frequency. The semiconductor device may include a reservoir capacitor located adjacent to one or more of the unit delay cells of the first group. Only the first group of the unit delay cells may be used to delay the phase of the clock.

Owner:SK HYNIX INC

Graduated delay line for increased clock skew correction circuit operating range

ActiveUS7471130B2Reduce circuit sizeHigh resolutionPulse automatic controlDigital storageTime delaysTime segment

Clock synchronization and skew adjustment circuits are described that utilize varying unit delay elements in their delay lines in either a graduated or a stepped unit time delay arrangement, allowing a reduced circuit implementation and improved lock characteristics. These graduated or a stepped unit time delays allow reduction in the number of the fine unit delay elements of the delay lines by placing a fine delay element granularity at the most critical timings to sense and adjust for the portion of the clock signal time period that are high speed or critical. This allows clock synchronization and skew adjustment circuits to be implemented in an optimized manner that exhibits a reduced overall circuit size and power consumption, while having improved lock characteristics over a wide range of frequencies.

Owner:MICRON TECH INC

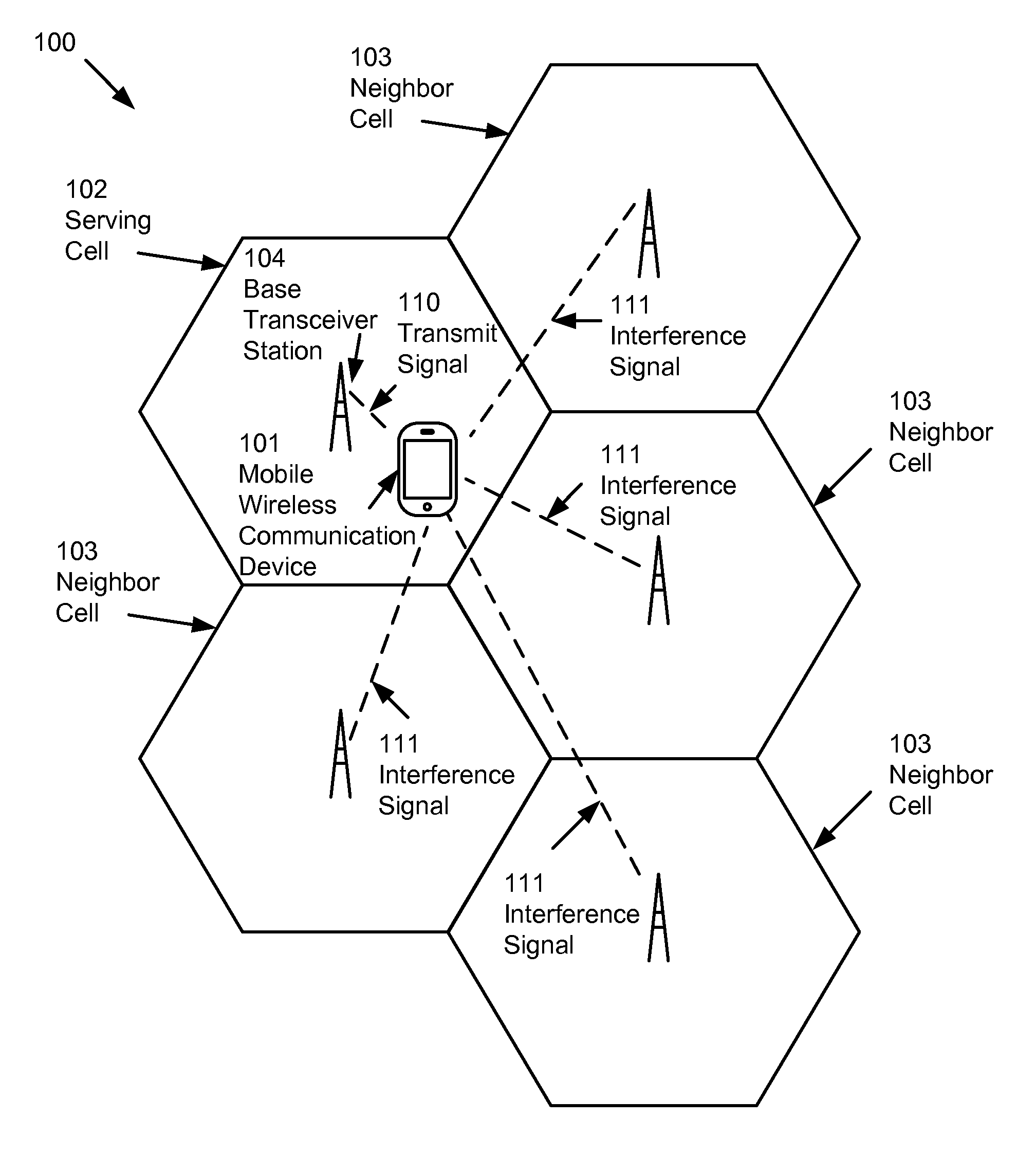

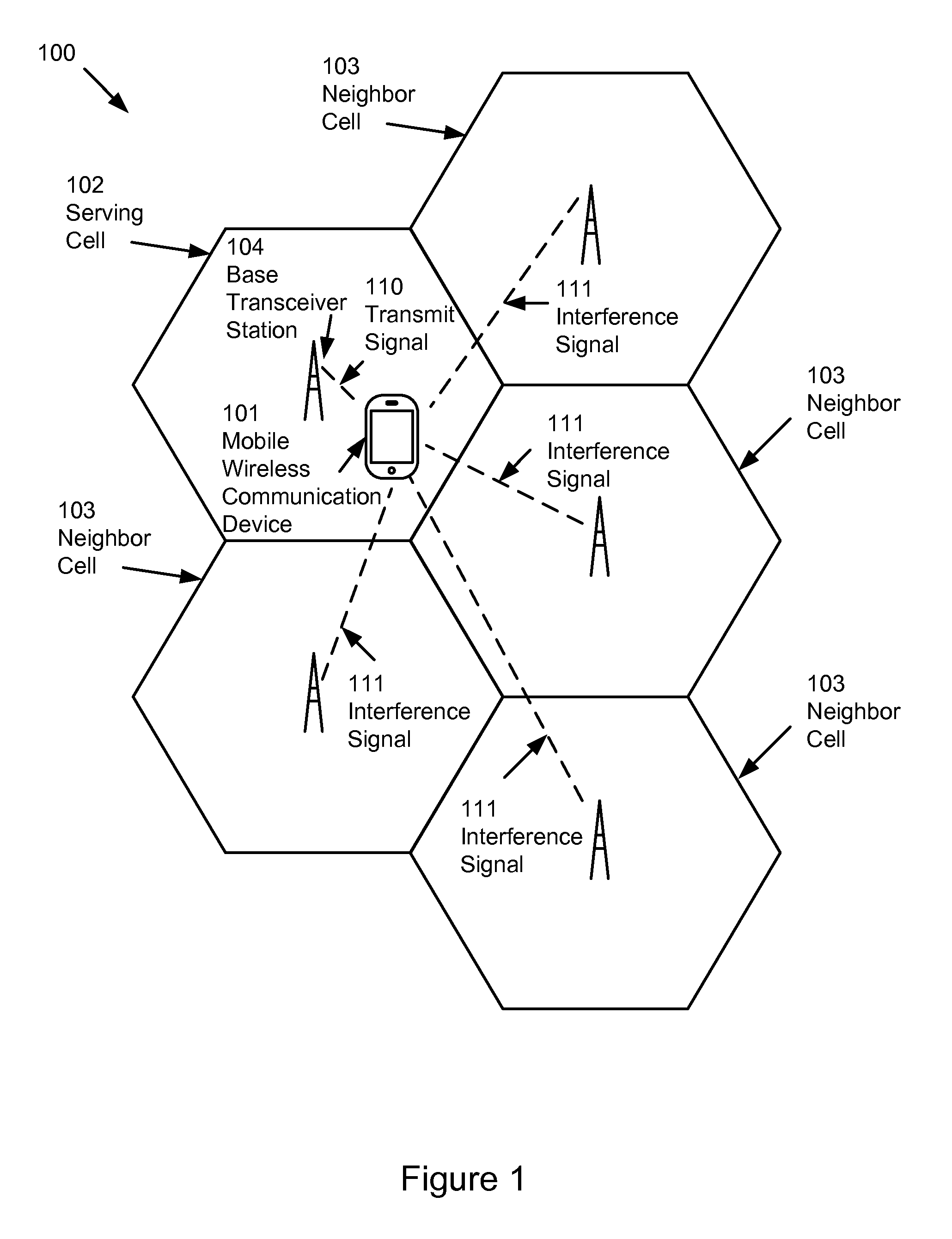

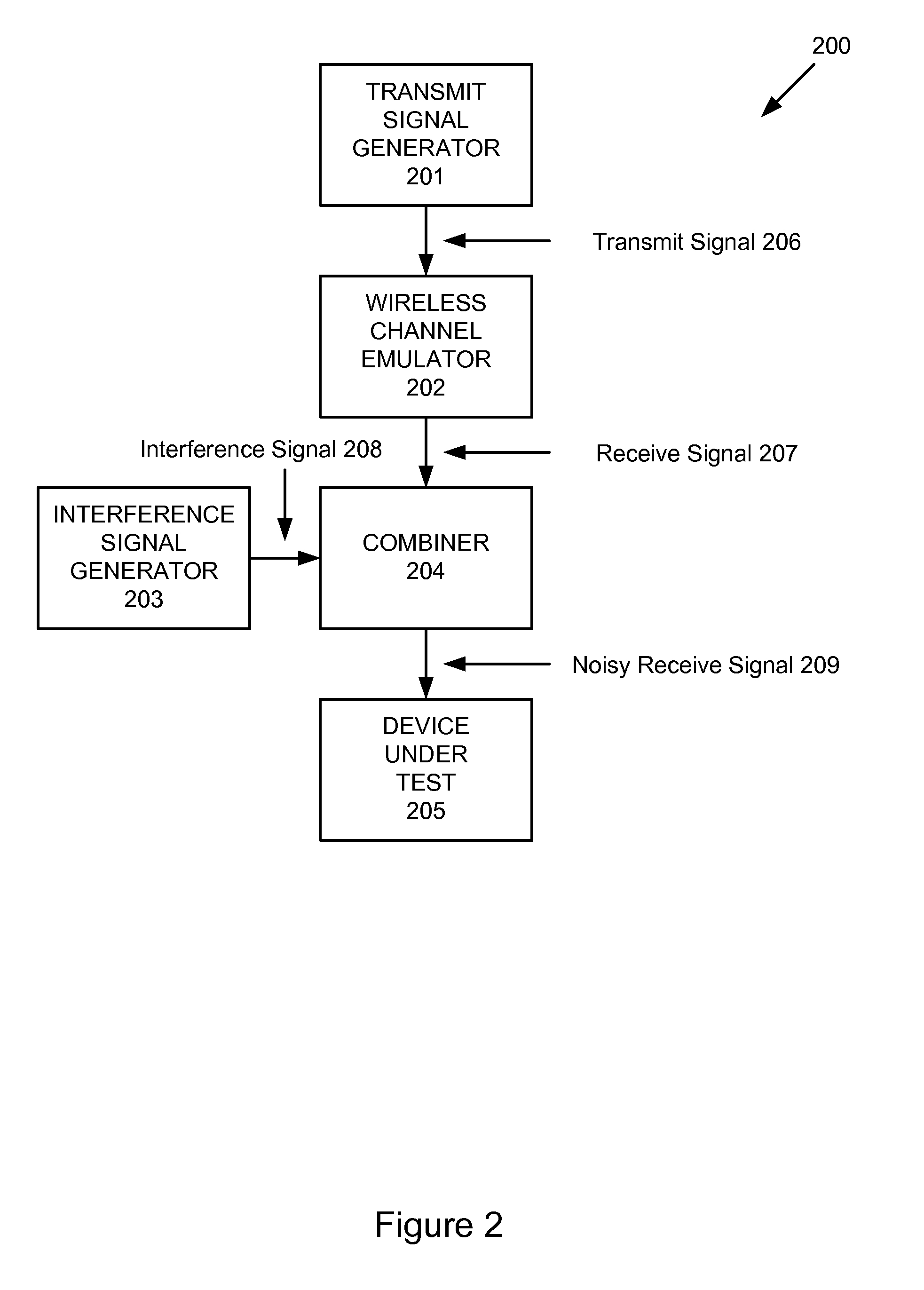

Method and apparatus to generate wireless test signals

A method of generating a noisy receive signal for testing the performance of a mobile wireless communication device is described. A signal generator unit generates a transmit signal that frequency hops among a set of carrier frequency channels in a cyclic pattern having a time duration T. A wireless channel emulator unit generates a receive signal by modifying the transmit signal and also generates an interference signal by modifying the receive signal. The wireless channel emulator unit delays the interference signal relative to the receive signal by an integer multiple of the time duration T. The receive signal and the interference signal are combined by a combiner unit to generate the noisy receive signal.

Owner:APPLE INC

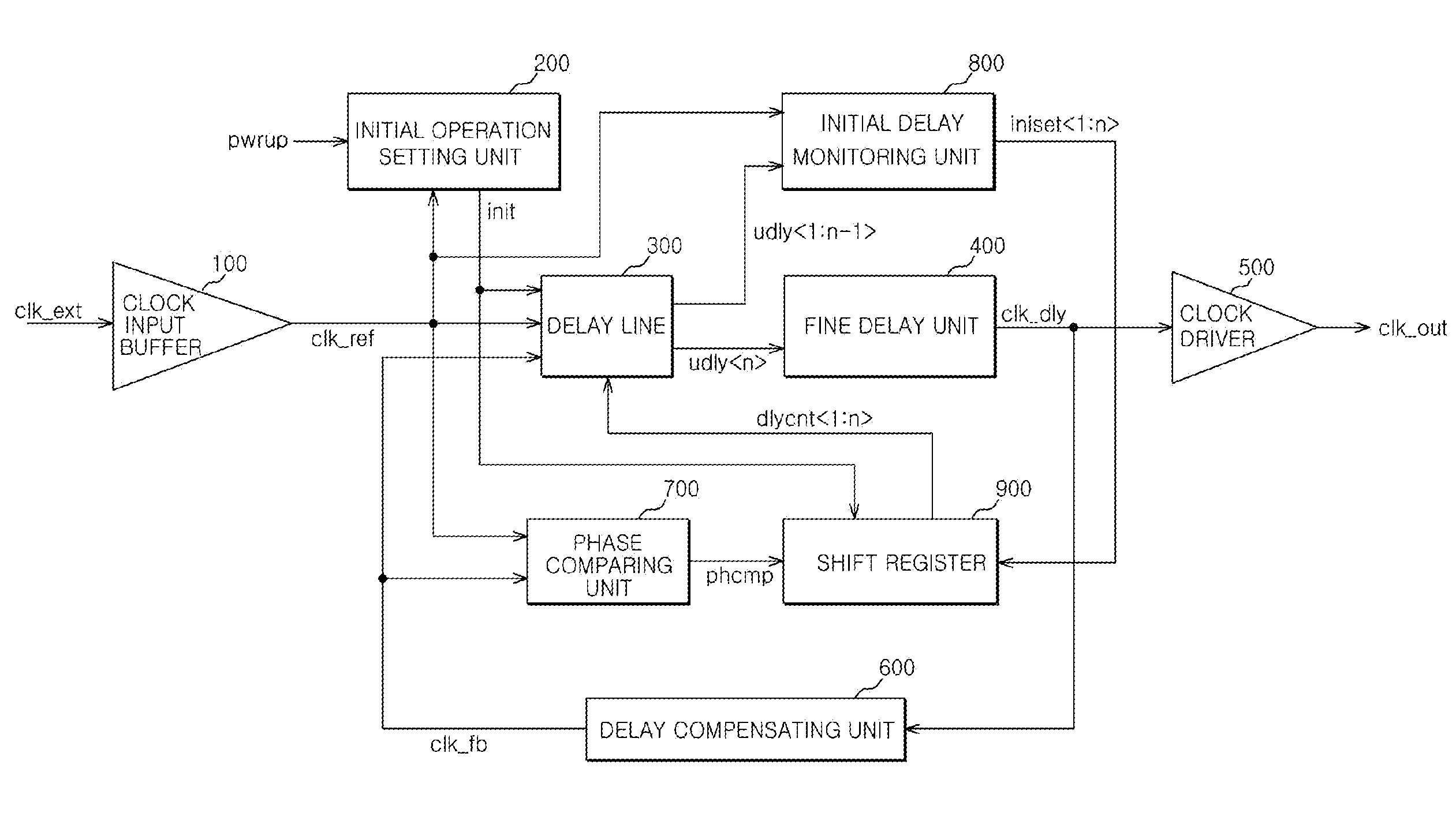

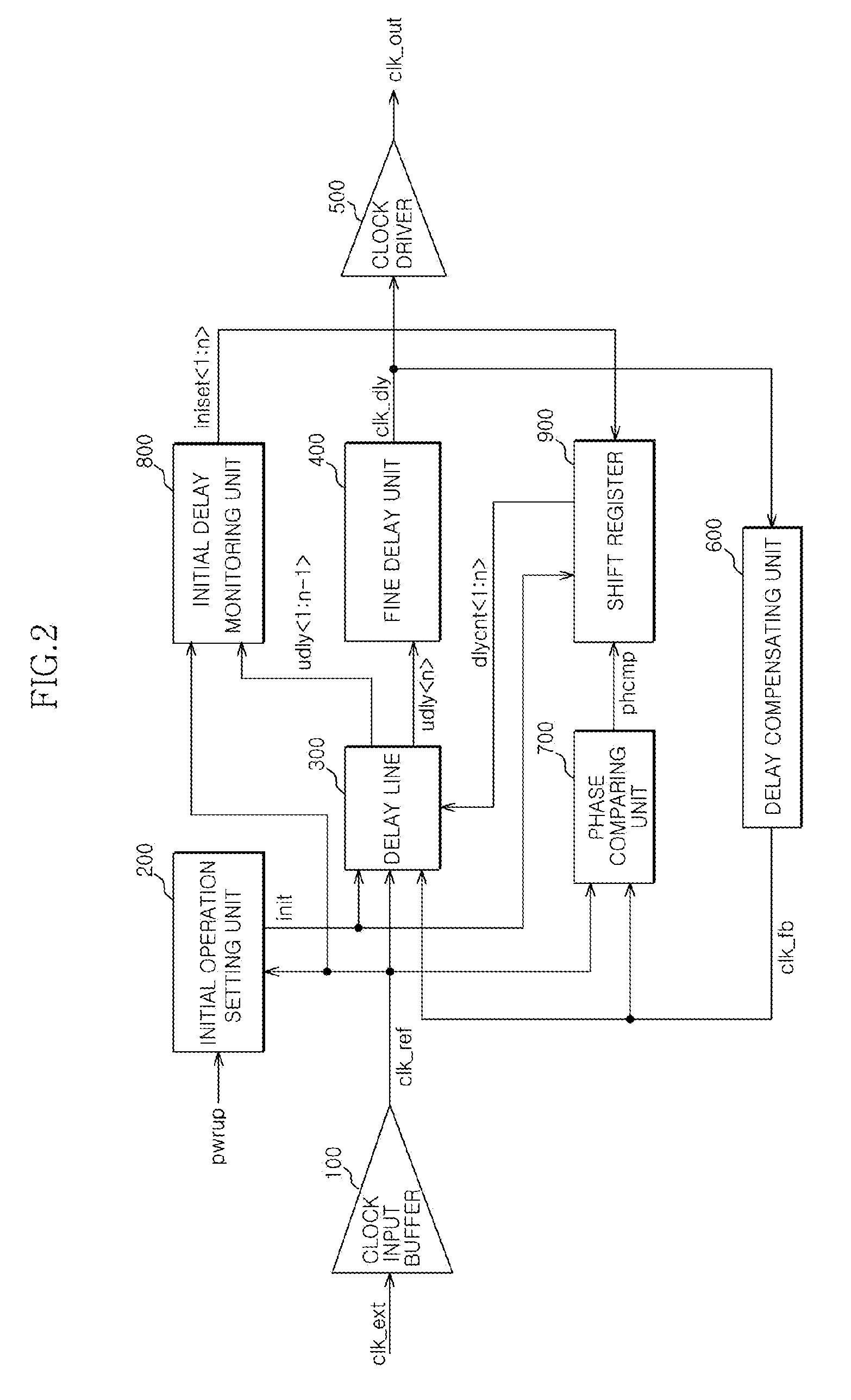

Dll circuit and method of controlling the same

A delay locked loop (DLL) circuit includes an initial operation setting unit configured to generate an initial operation signal in response to a reference clock signal and an operation start signal; a shift register configured to generate a delay control code in response to the initial operation signal, a phase comparison signal, and an initial setting code; a delay line configured to delay the reference clock signal or a feedback clock signal in response to the initial operation signal and the delay control code, thereby generating a plurality of unit delay clock signals; and an initial delay monitoring unit configured to generate the initial setting code in response to the reference clock signal and the plurality of unit delay clock signals.

Owner:SK HYNIX INC

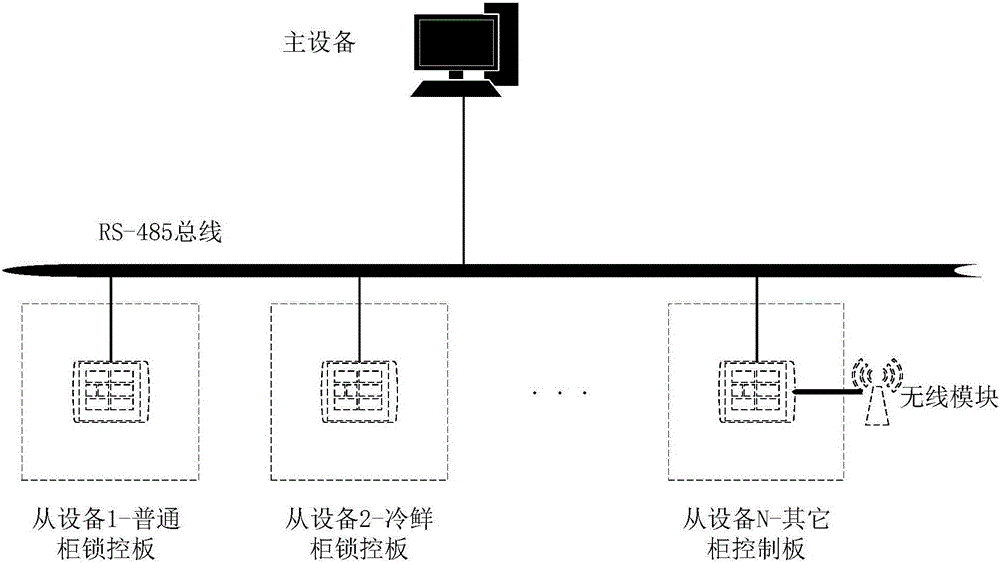

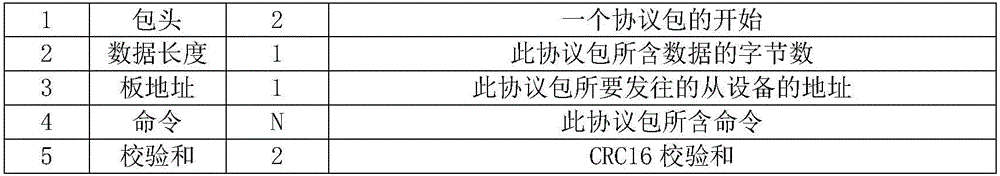

RS485-bus-based intelligent cabinet communication method and system

InactiveCN107181659ASolve conflictsAvoid changing the host computer programData switching networksTimestampProtocol for Carrying Authentication for Network Access

The invention relates to an RS485-bus-based intelligent cabinet communication method and system communication between master and slave devices. The master device is connected to at least one slave device by the RS485 bus and slave devices have different address numbers. The method comprises: S1, self definition of a communication protocol format and a command format in a communication protocol is carried out, wherein a preset field expresses a timestamp / user data; and S2, the master device obtains identity information of all the slave devices by following steps: the master device sends broadcast commands to all the slave devices, wherein the timestamps / user data in the broadcast commands at this time are used for identifying unit delay time; the slave devices determine the delay time of the slave devices based on the address numbers and the unit delay time and send return commands including the identity information of the slave devices after waiting with the local delay time after receiving the broadcast commands. Therefore, a conflict problem can be solved; and the master device can obtain addresses of all slave devices automatically without designation.

Owner:SHENZHEN PRAFLY TECH

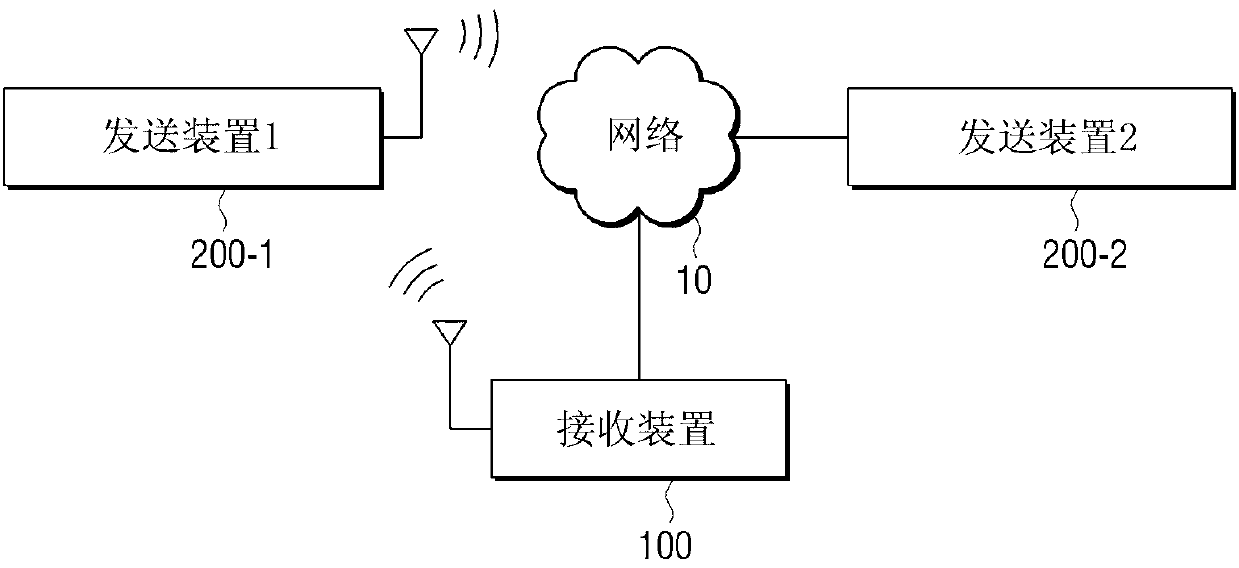

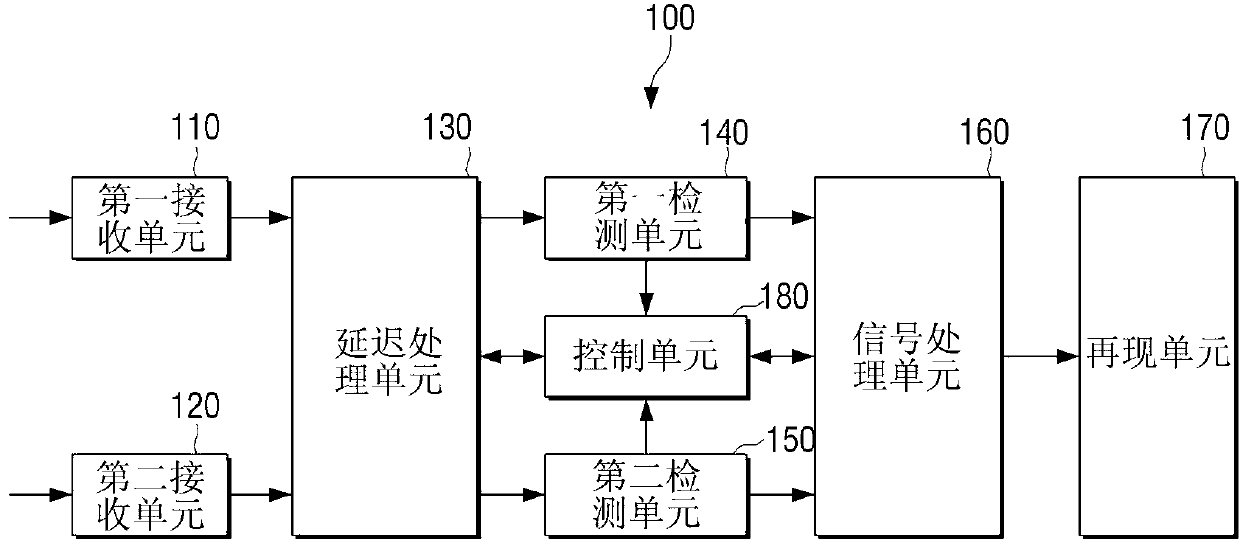

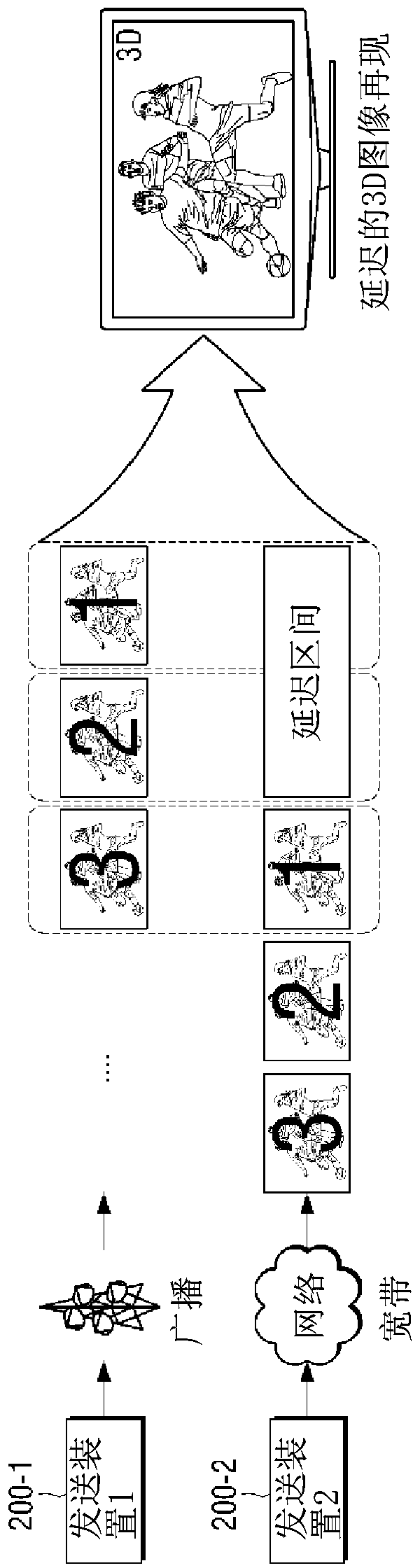

Reception device for receiving a plurality of real-time transfer streams, transmission device for transmitting same, and method for playing multimedia content

InactiveCN103329551AImprove qualityPulse modulation television signal transmissionSelective content distributionComputer networkTime transfer

Disclosed is a reception device. The reception device includes: a first reception unit receiving a first real-time transfer stream via a broadcast network; a second reception unit receiving a second real-time transfer stream via a communication network; a delay-processing unit delaying at least one of the first and second real-time transfer streams for synchronization; a first detection unit detecting first data from the first real-time transfer stream; a second detection unit detecting second data from a second real-time transfer stream; a signal-processing unit combining the first data and the second data so as to constitute multimedia content; and a playing unit playing the multimedia content. Accordingly,the multimedia content may be stably played.

Owner:SAMSUNG ELECTRONICS CO LTD

Drum washing machine

A drum washing machine having a detergent supply device supplying water containing detergent to a washing tub is disclosed. The detergent supply device has simple structure, so it is easy to manufacture the drum washing machine and the cost is reduced. The detergent supply device is integrally formed with a door without being installed in front surface of upper part of the main part, so it has simple structure. The detergent supply device is provided with a discharge unit discharging detergent dissolved in the water to the washing tub when the level of the water supplied to the detergent supply device reaches a designated value. The discharge unit delays the discharge of the washing water supplied to the detergent supply device by a siphon, thus improving the solubility of the detergent.

Owner:SAMSUNG ELECTRONICS CO LTD

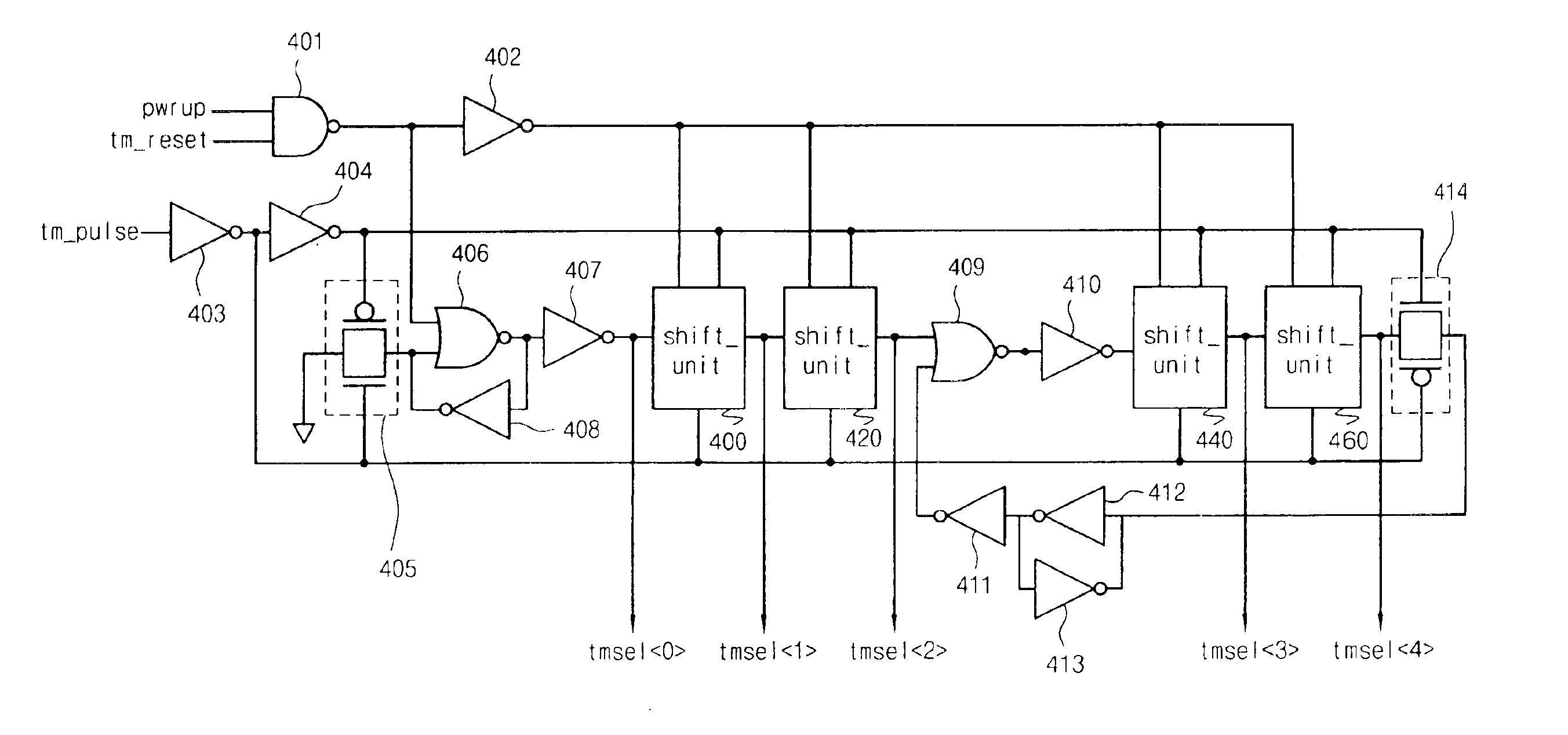

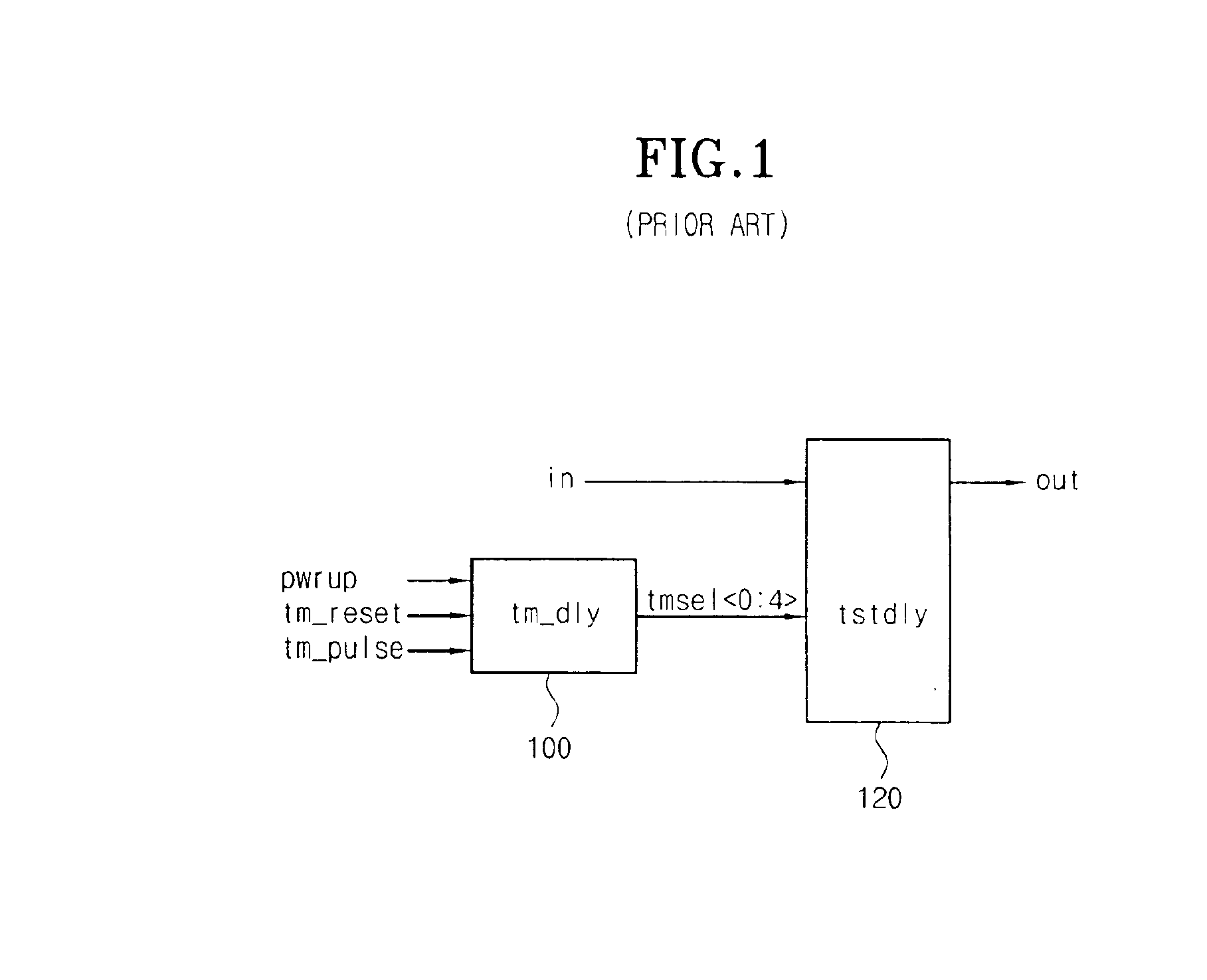

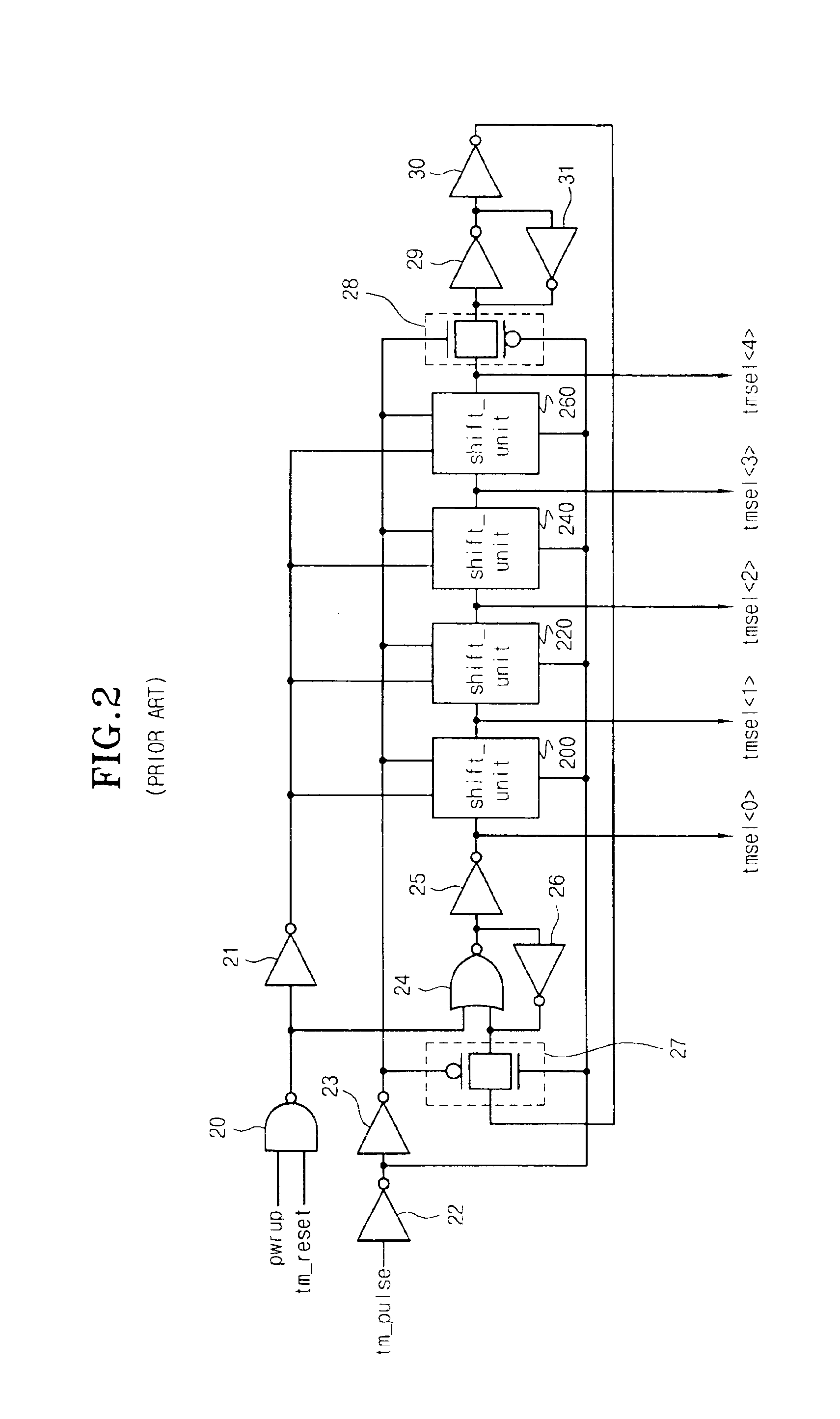

Method for controlling delay time of signal in semiconductor device

A method for controlling a delay time of a signal in a semiconductor device is disclosed, which comprises the steps of: a) applying a test mode pulse signal; b) generating N number of test mode selection signals which are synchronized with the falling edges of the test mode pulse signal to respond sequentially; c) sequentially regenerating the (N−1)th test mode selection signal after the Nth test mode selection signal is generated; and d) repeating step c, wherein an input signal inputted to the semiconductor device is delayed by a predetermined time to be outputted as an output signal only when first to the (N−1)th test mode selection signals are enabled, and the delayed times are different from each other according to the first to the (N−1)th test mode selection signals. In the method, delay degree of a predetermined signal can be freely adjusted in a test mode. Further, a desired delay degree can be set by means of an external signal, regardless of the number of unit delay devices constituting a delay circuit.

Owner:SK HYNIX INC

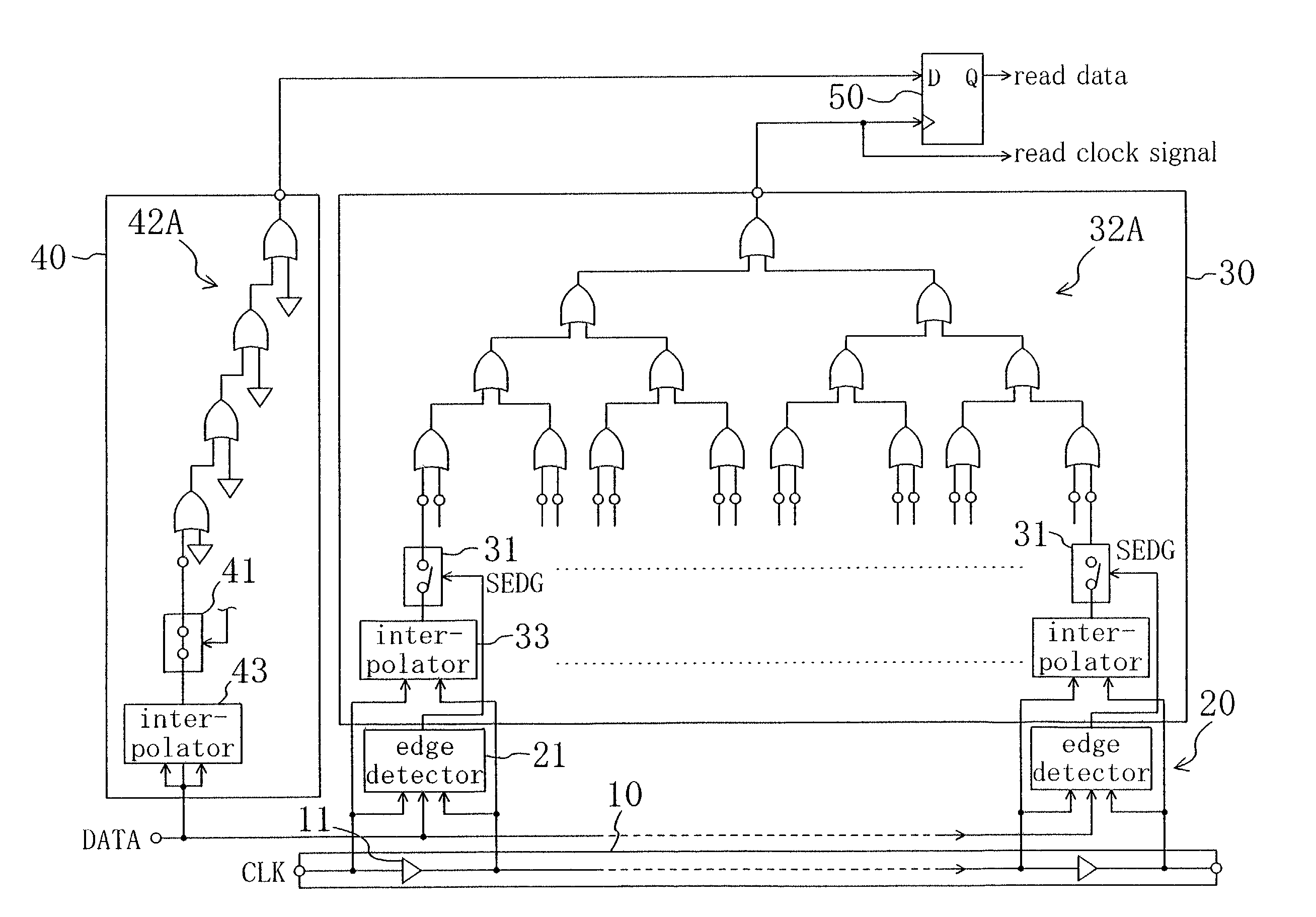

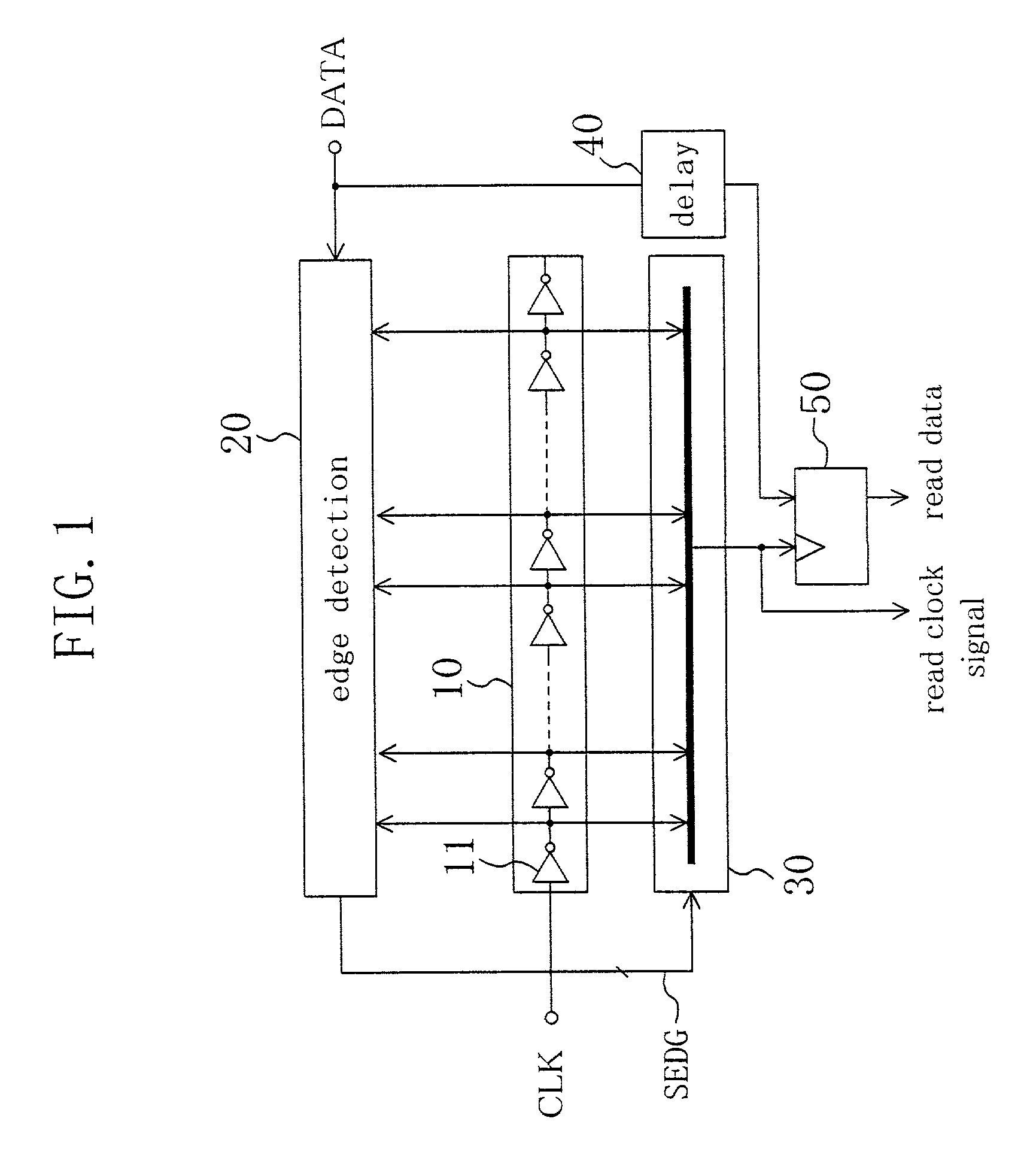

Circuit and system for extracting data

InactiveUS6970521B2Quick responseMore dataPulse automatic controlSingle output arrangementsData signalComputer science

A data extracting circuit extracts data much more accurately at a much higher response speed. A clock transfer section propagates an input clock signal through unit delay devices thereof. An edge detecting section locates an edge of the clock signal, which edge is being propagated through the clock transfer section, for a time represented by a given edge of an input data signal. In response to an edge detection signal indicating the clock signal edge located, a clock selecting section selects one of outputs of the delay devices, and presents the output as a clock input to a latch.

Owner:PANASONIC CORP

Digital frequency-multiplying DLLs

InactiveUS20050127964A1Reduce resolutionVary numberPulse automatic controlCounting chain pulse countersPhase mixingDelayed time

Digital delay-locked loops (DLLs) and methods are provided for signal frequency multiplication. Analog delay elements of typical frequency-multiplying DLLs are replaced with digital and digitally-controlled elements including a variable delay line. The number of unit delay elements in the delay line can be selected to produce a desired output signal delay. Phase-mixing of multiple variable delay line outputs achieves finer delay-time adjustments.

Owner:MICRON TECH INC

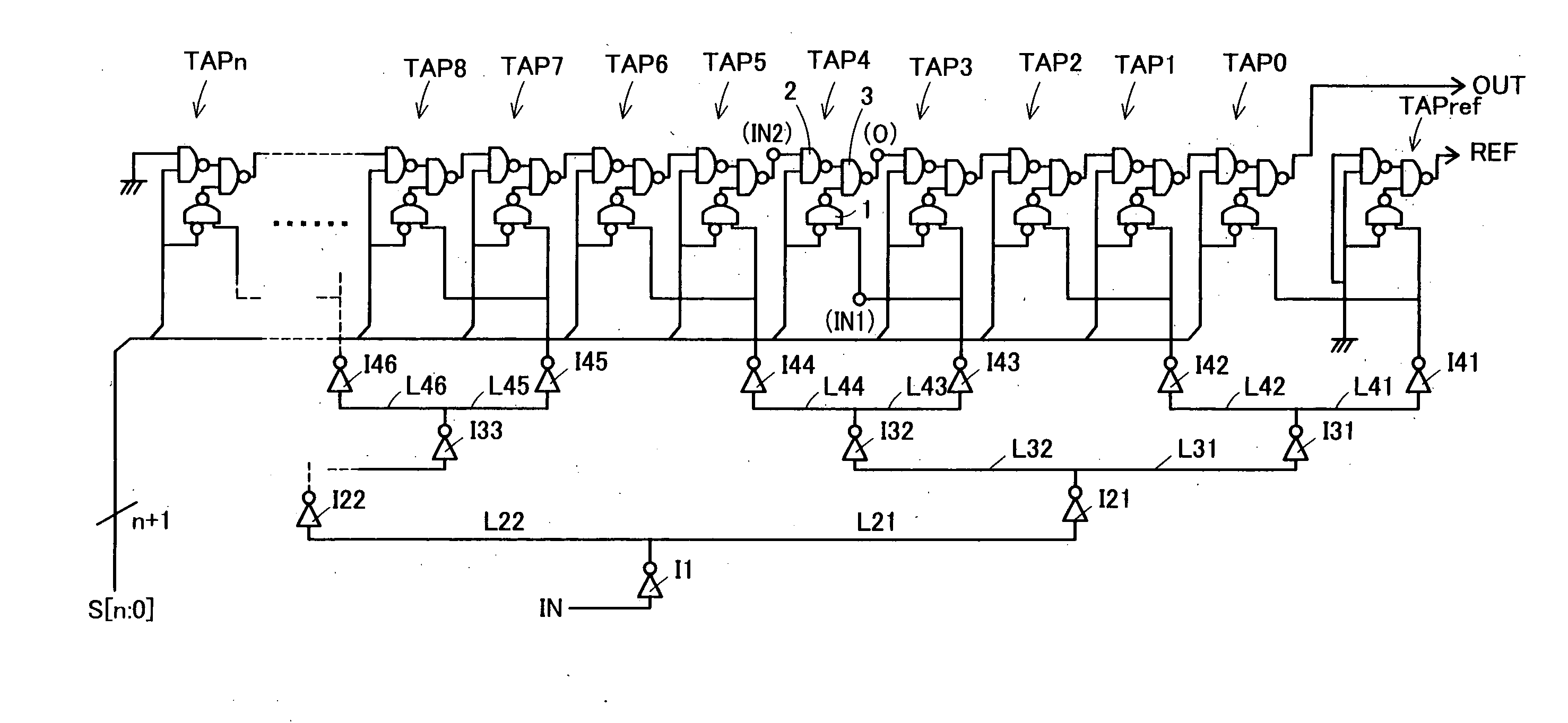

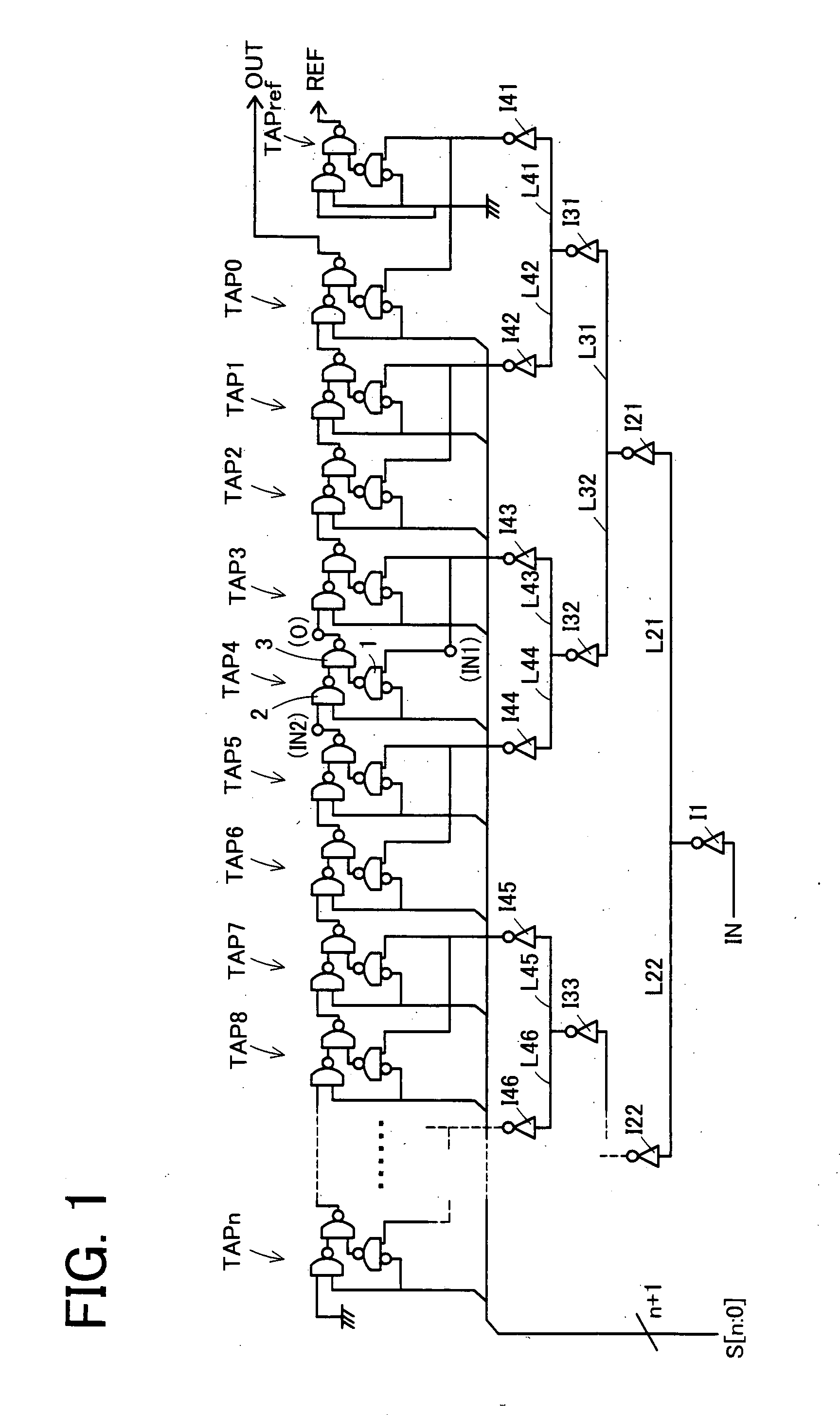

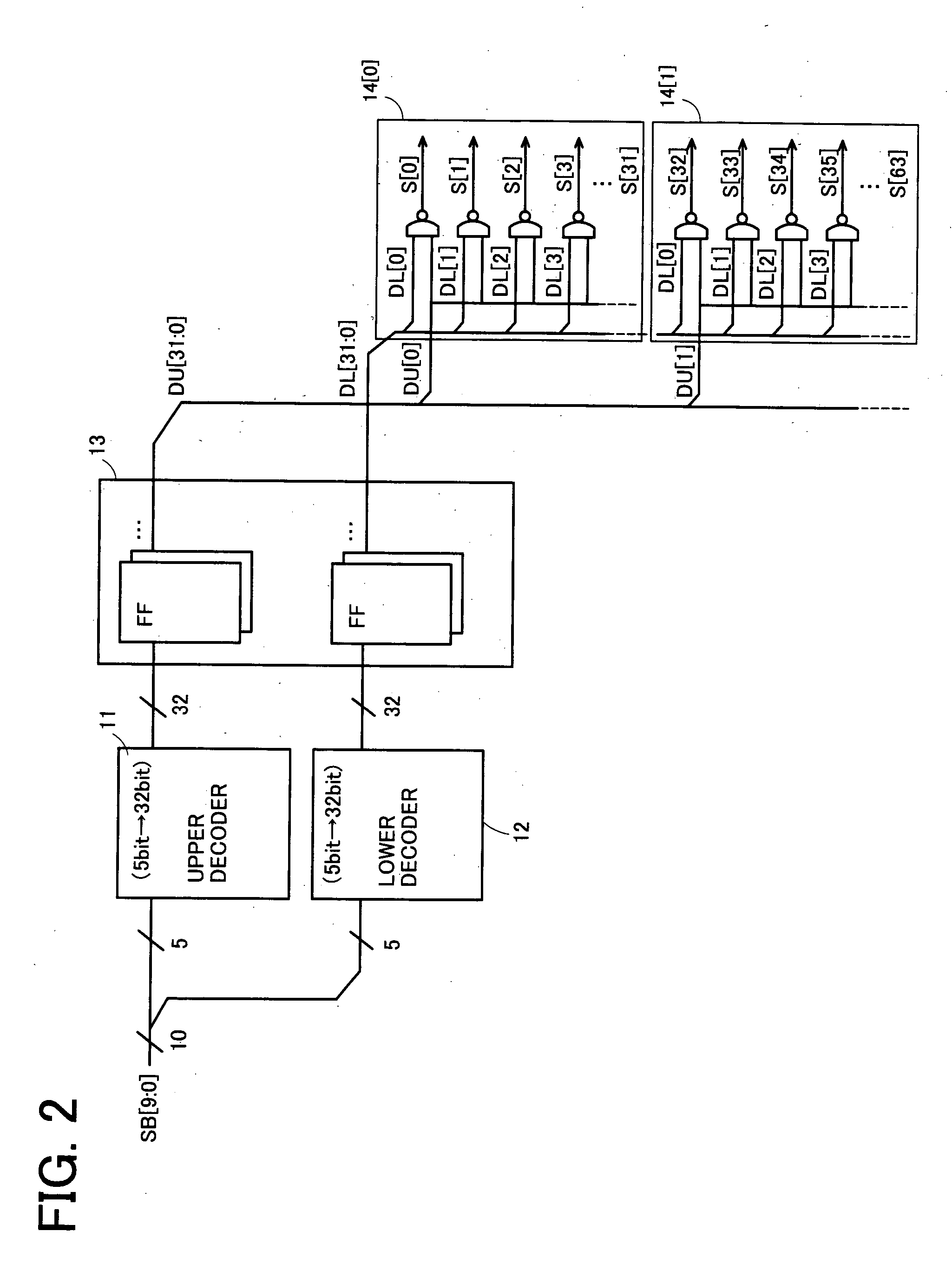

Delay circuit and control method of the delay circuit

InactiveUS20050168259A1Enhanced output signalPrevent wrong additionSingle output arrangementsTime-delay networksNAND gateEngineering

A delay circuit is constructed by connecting taps TAP0-n for providing with a unit delay time (τ) in series on multiple stages. Each tap has the same configuration and an objective signal is inputted to a signal input terminal IN1. The output terminal of a preceding stage tap is connected to a between-stages connecting terminal IN2. An output terminal O is connected to the between-stages connecting terminal of a next stage tap. The signal input terminal and the between-stages connecting terminal are connected to one input terminal of NAND gates 1, 2 and a tap selection signal is inputted to the other input terminal. The output terminal is connected to a NAND gate 3. One of the NAND gates 1, 2 functions as a logical inversion gate corresponding to a tap selection signal so as to enable propagation of the signal. At this time, in the other NAND gate, the output signal is fixed to high level and the NAND gate 3 also functions as a logical inversion gate. The objective signal is propagated by the NAND gates 1, 3 and the preceding stage signal is propagated by the NAND gates 2, 3. By constructing the NAND gates 1, 2 with the same structure, the unit delay time (τ) can be matched accurately.

Owner:SOCIONEXT INC

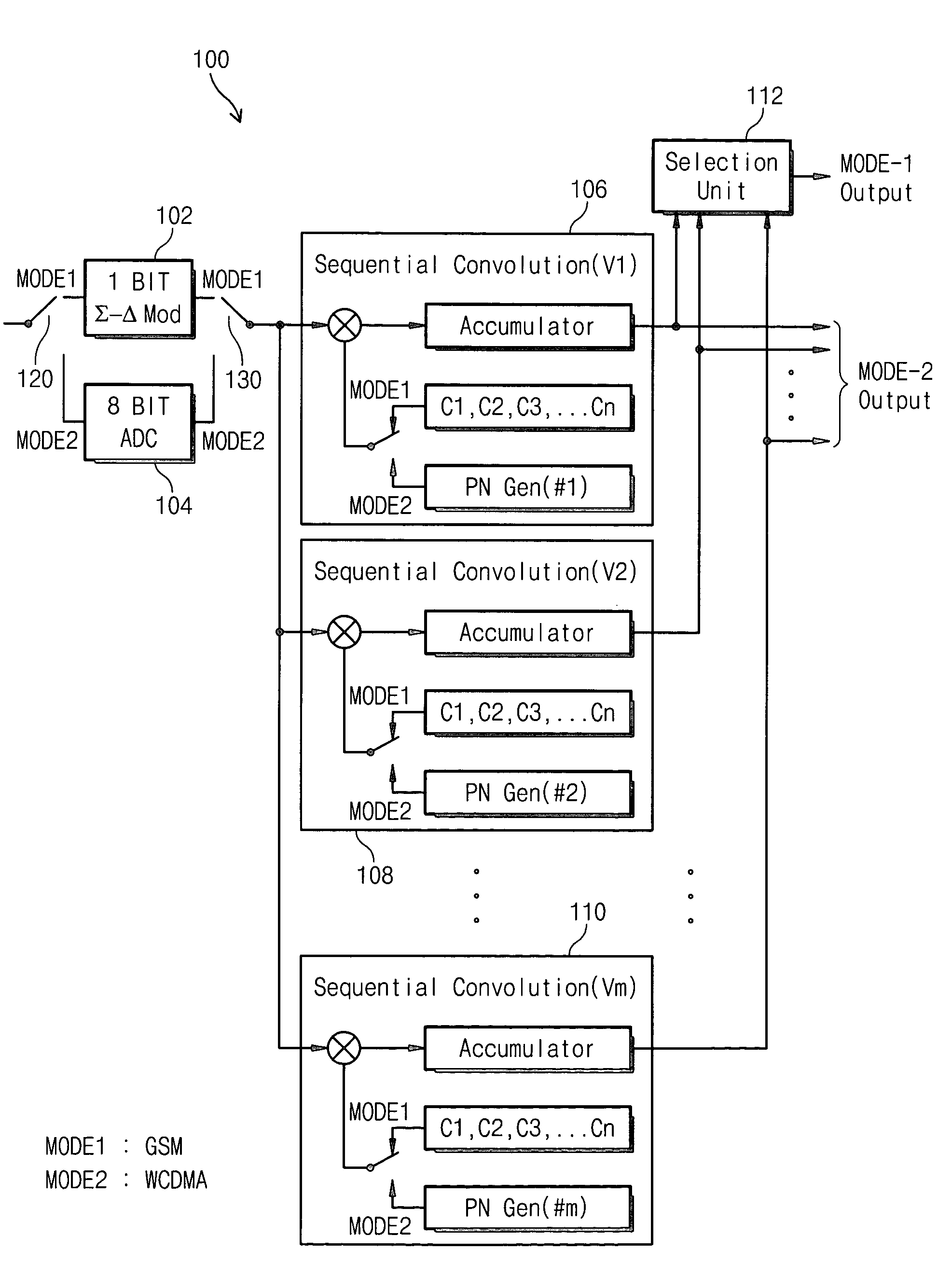

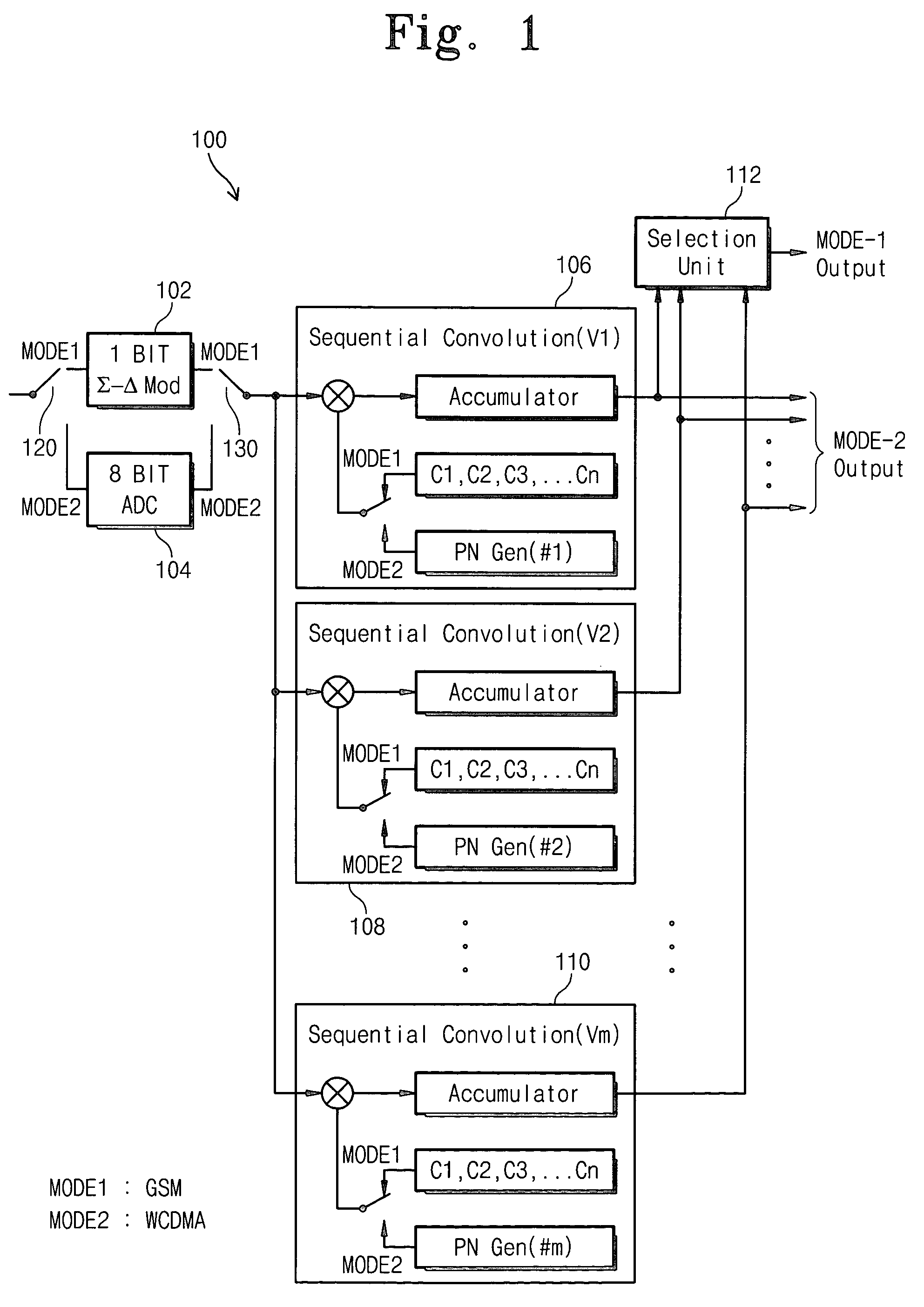

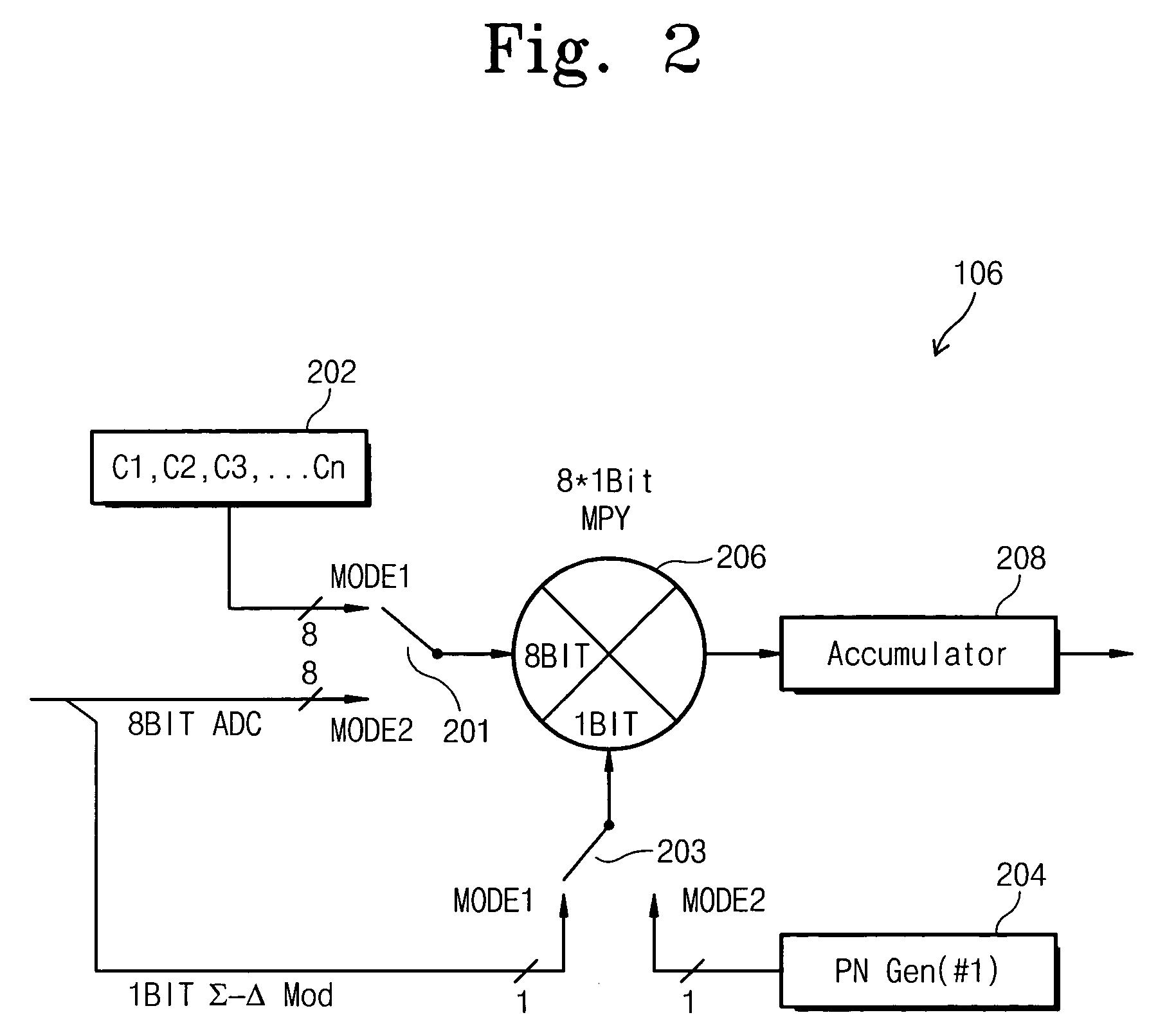

Multi-mode communication device operable in GSM/WCDMA

There is provided a multi-mode communication system which is operable according to different operating modes, such as GSM and WCDMA. The multi-mode communication system includes first and second switching units, a delta-sigma modulator, an analog-to-digital converter, sequential convolution units and a selection unit. The delta-sigma modulator samples an analog signal, which is inputted through the first switching unit in one mode, into 1-bit digital signal. In another mode, the analog-to-digital converter samples an analog signal, which is inputted through the first switching unit into an n-bit digital signal. The sequential convolution units multiply filter factors with the output of the delta-sigma modulator, which is inputted through the second switching unit at the first mode, and multiply PN codes by the output of the analog-to-digital converter, which is inputted through the second switching unit at the second mode, to generate WCDMA output waveforms. The selection unit delays the outputs of the sequential convolution units by a predetermined time at the GSM mode to restore GSM output waveforms. Accordingly, the multi-mode communication system is operable according to multimodes, such as GSM mode and WCDMA mode.

Owner:SAMSUNG ELECTRONICS CO LTD