Patents

Literature

1045 results about "NAND gate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In digital electronics, a NAND gate (NOT-AND) is a logic gate which produces an output which is false only if all its inputs are true; thus its output is complement to that of an AND gate. A LOW (0) output results only if all the inputs to the gate are HIGH (1); if any input is LOW (0), a HIGH (1) output results. A NAND gate is made using transistors and junction diodes. By De Morgan's theorem, a two-input NAND gate's logic may be expressed as AB=A+B, making a NAND gate equivalent to inverters followed by an OR gate.

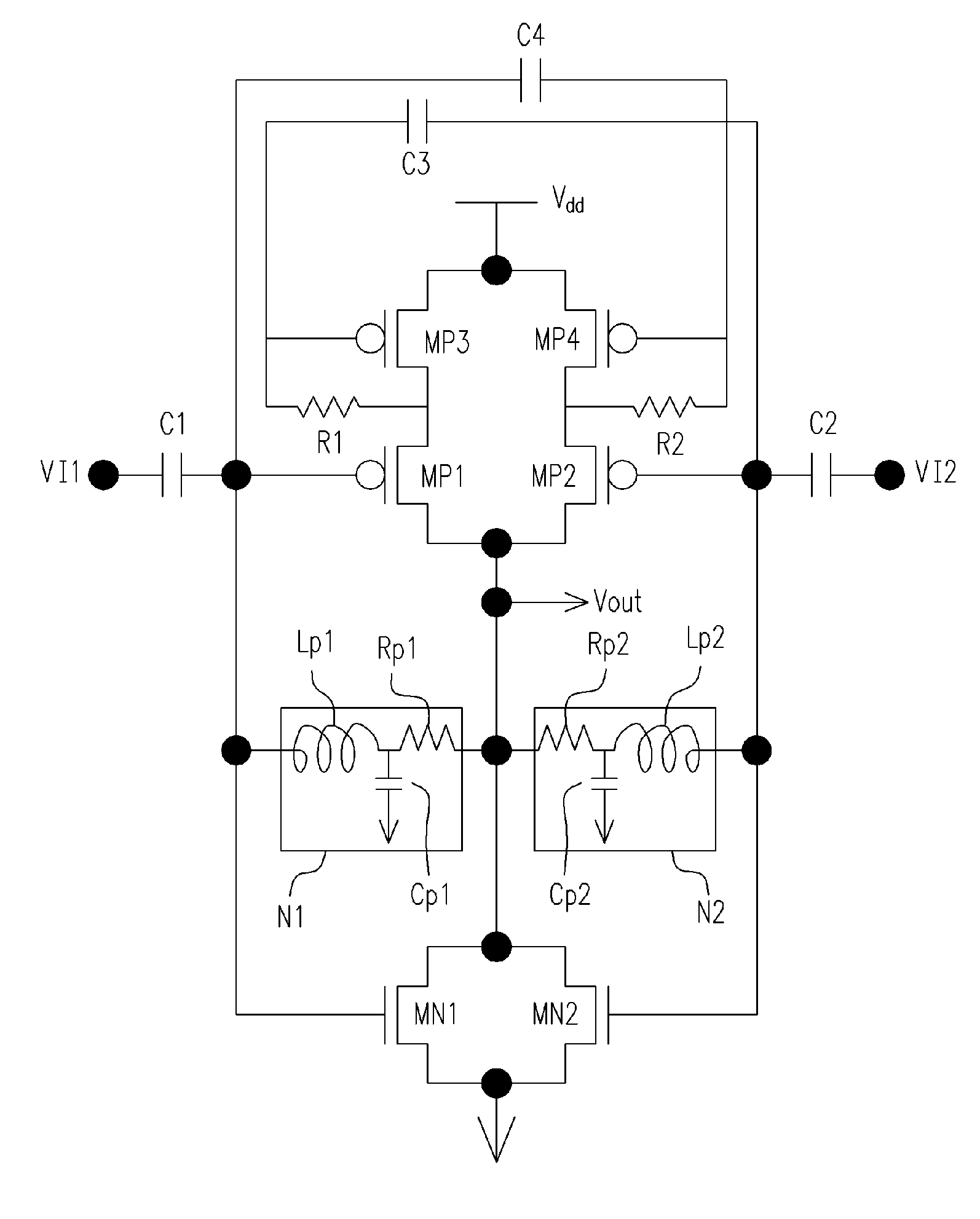

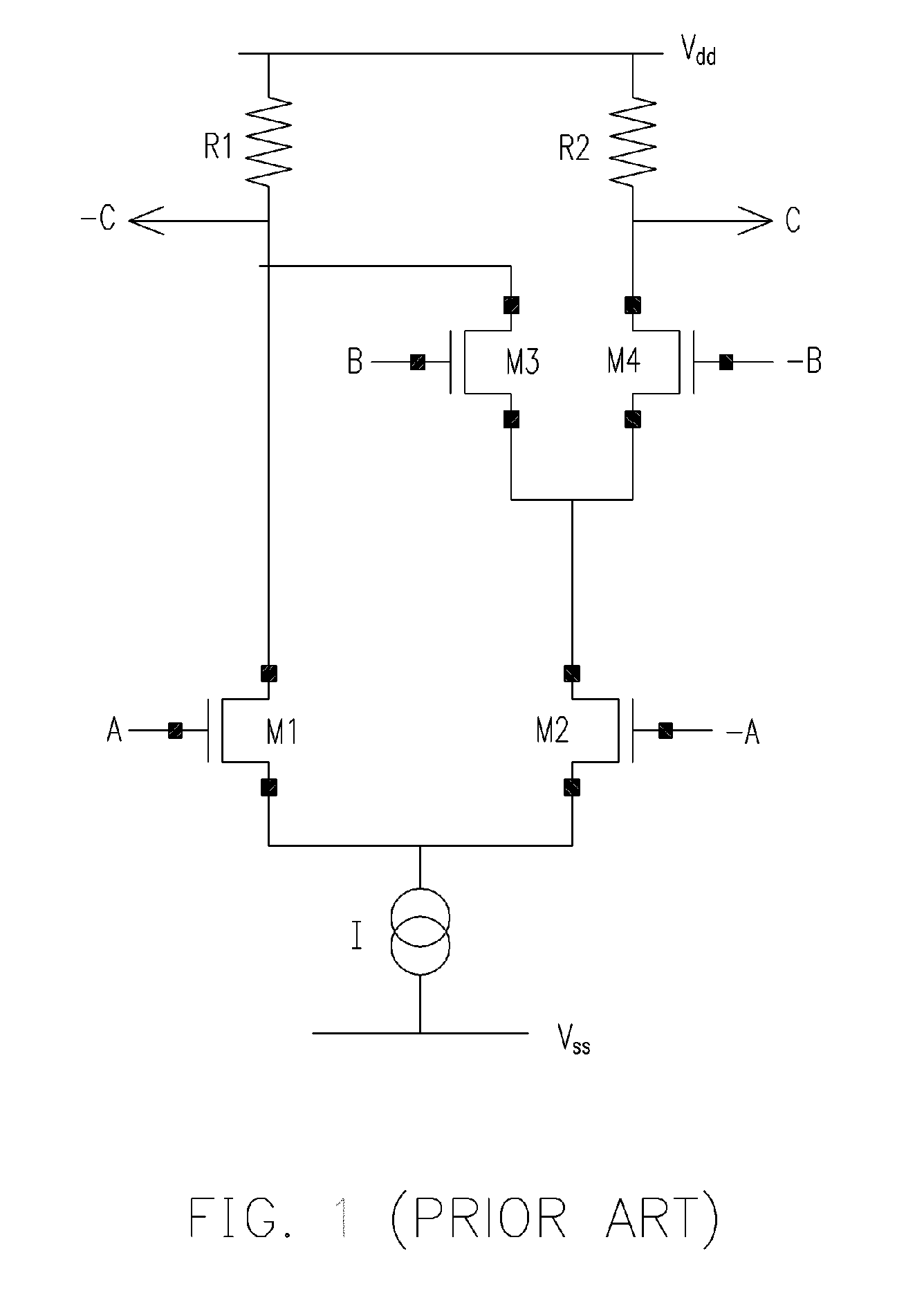

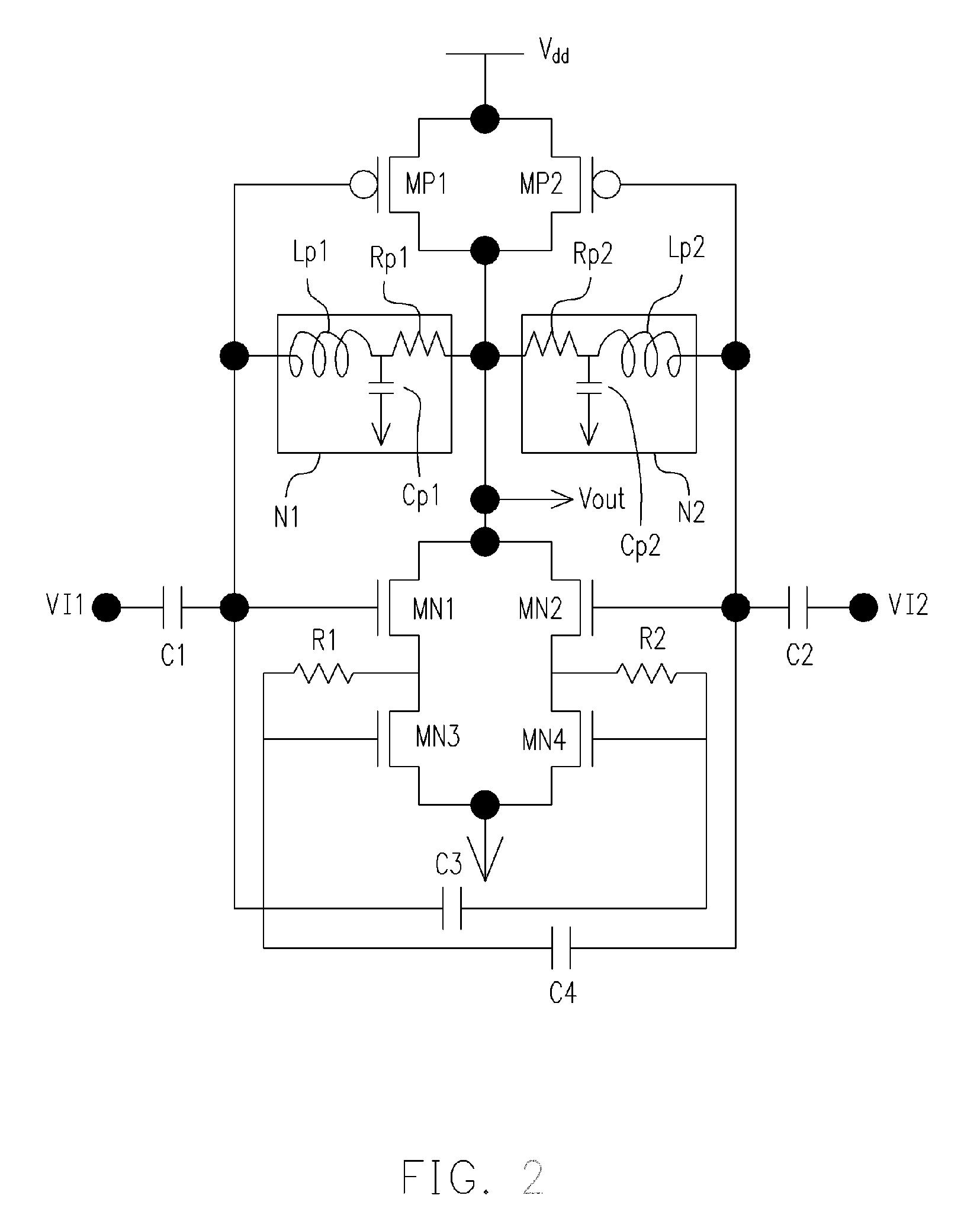

Self dc-bias high frequency logic gate, high frequency NAND gate and high frequency nor gate

InactiveUS20060197557A1Electric power will not be wastedNot to wasteReliability increasing modificationsMultiple input and output pulse circuitsNOR gateNAND gate

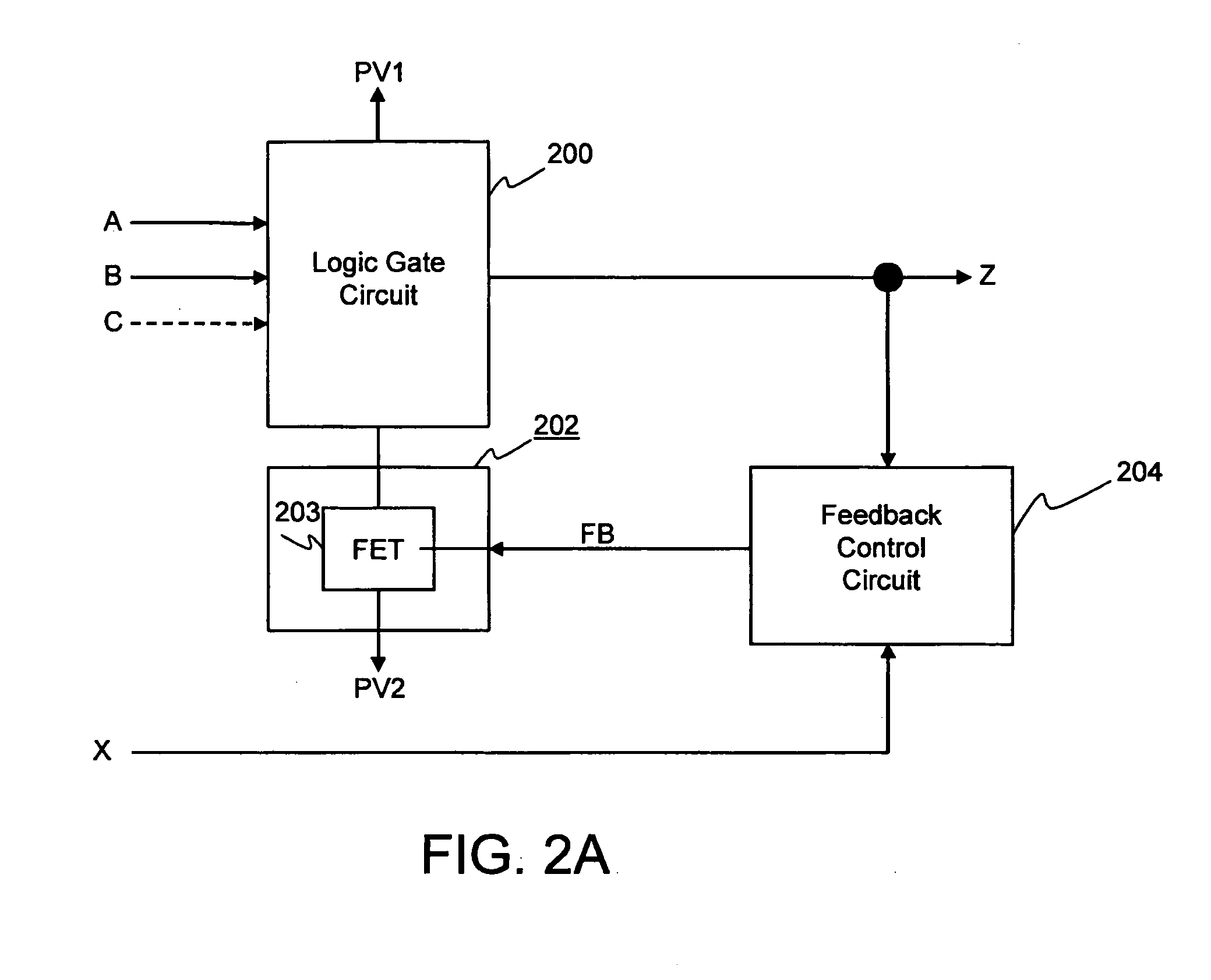

A self DC-bias high frequency logic gate is disclosed. The logic gate comprises at least one input terminal and one output terminal for performing Boolean operation on the high frequency input signals. The logic gate is characterized in that each transistor is coupled to an impedance matching network. The impedance matching network comprises a first terminal and a second terminal. Wherein, the first terminal is coupled to a gate of the transistor, and the second terminal is coupled to a drain of the transistor for providing an operation voltage to the transistor. When a gate of an N-type transistor and a gate of a P-type transistor are coupled with each other, and a drain of the N-type transistor and a drain of the P-type transistor are also coupled with each other, a common impedance matching network is shared with both the N-type transistor and the P-type transistor.

Owner:SUNPLUS TECH CO LTD

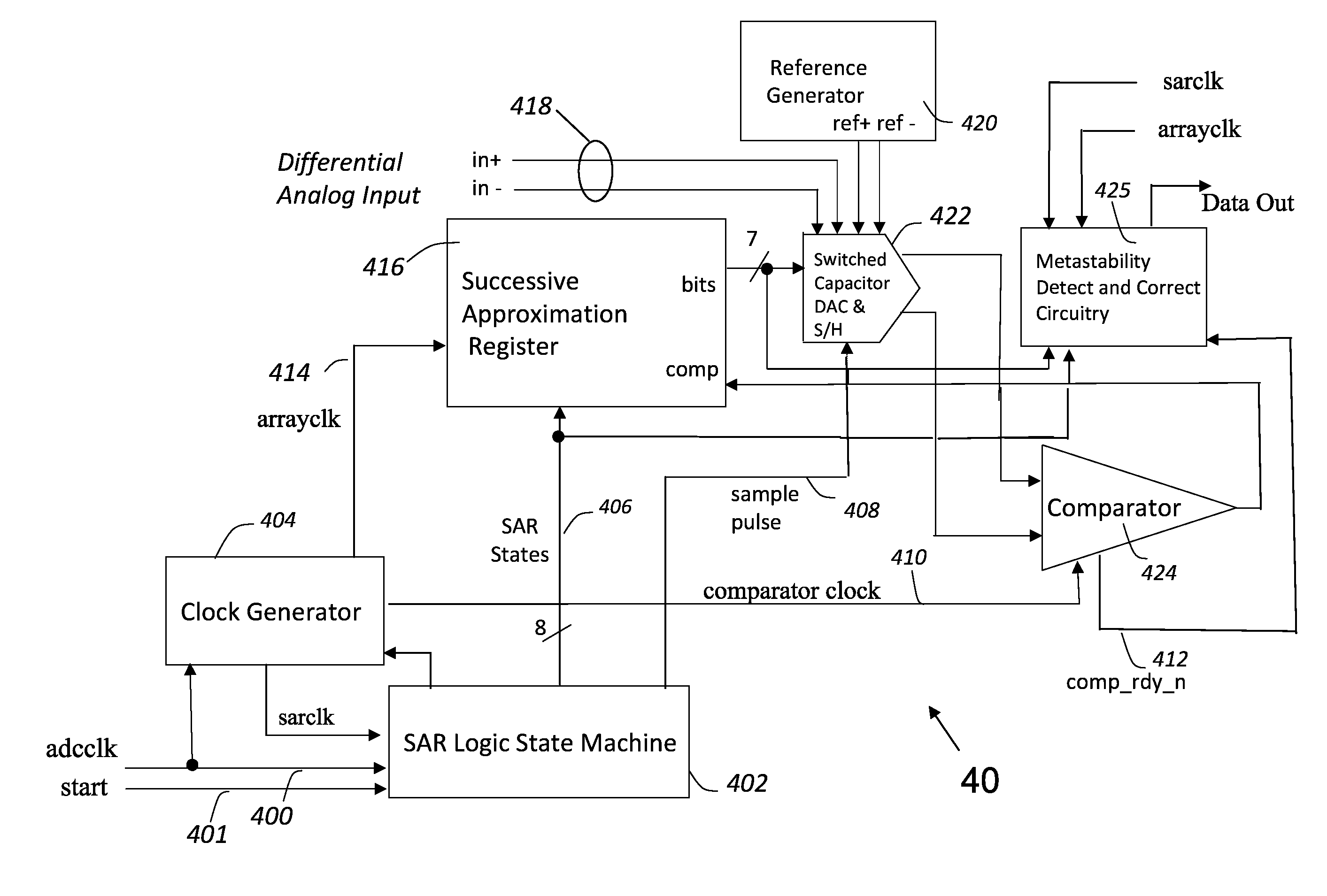

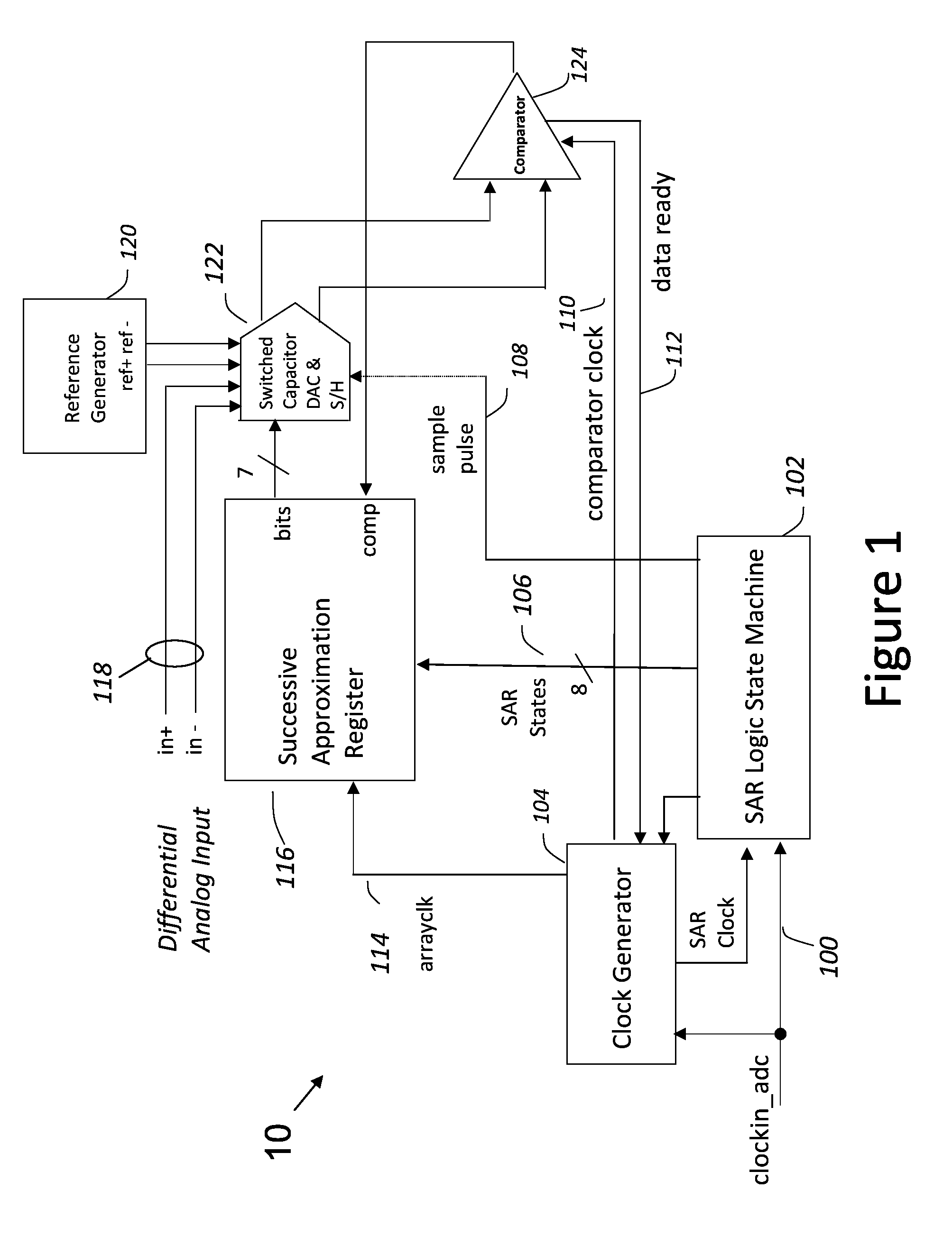

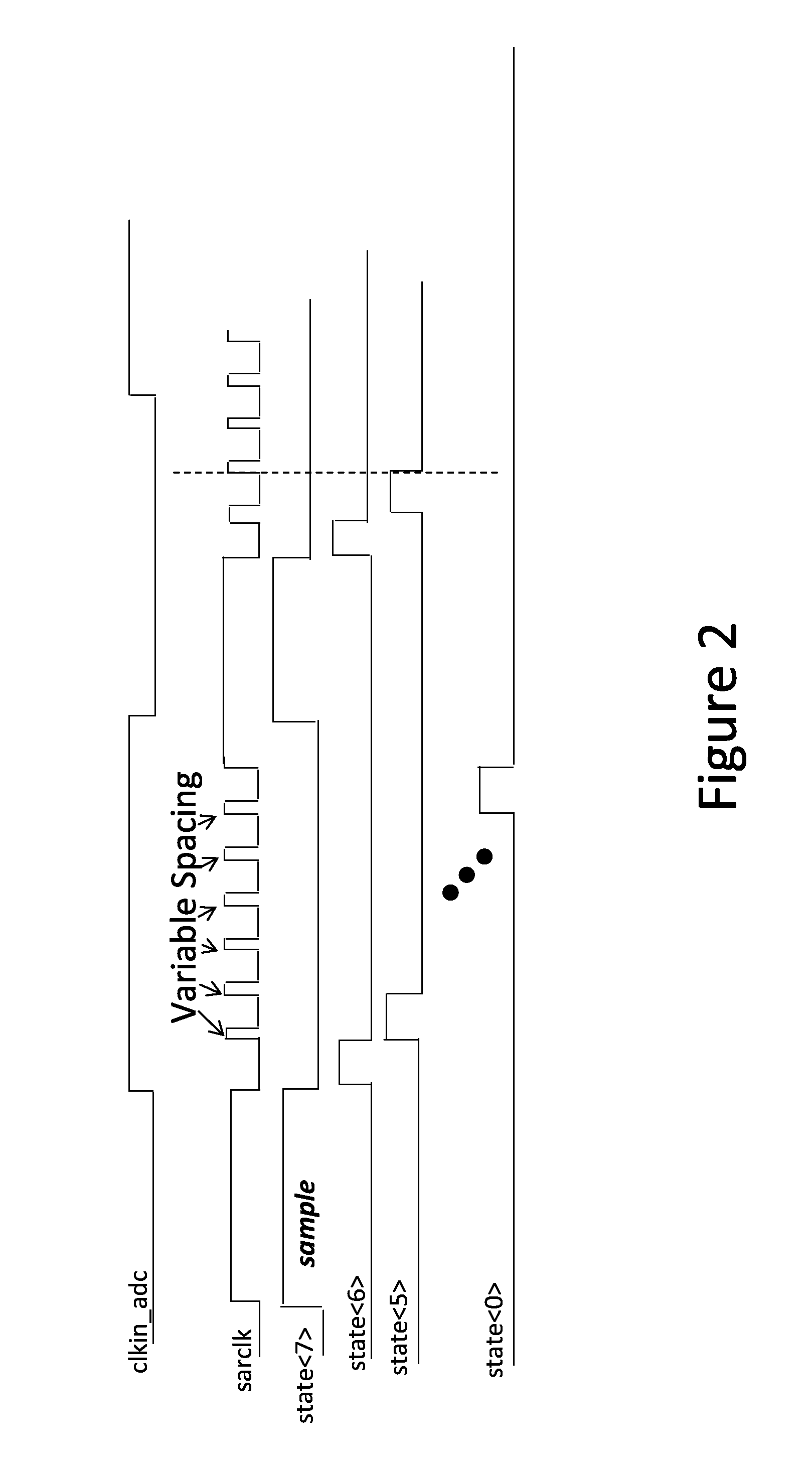

Metastability error detection and correction system and method for successive approximation analog-to-digital converters

ActiveUS8957802B1Electric signal transmission systemsAnalogue-digital convertersDigital down converterNAND gate

A system and method are provided for the detection and correction of metastability errors in a successive approximation analog to digital converter (ADC). The successive approximation ADC (40) includes a comparator unit (424) that includes a NAND gate circuit (550) that outputs a comp_rdy_n signal when the comparator (500) has latched a result. ADC (40) includes a metastability detection and correction circuit (425) that includes a first logic circuit (700) that monitors the comp_rdy_n signal and detects a metastable event if that signal is not received within a portion of a conversion time period of the ADC. Responsive to detection of a metastable event, a second logic circuit (750) generates a correct conversion code at the output of the ADC. If no metastable event is detected during a conversion cycle of the ADC, the second logic circuit (750) outputs the conversion codes determined by the comparator (500).

Owner:CADENCE DESIGN SYST INC

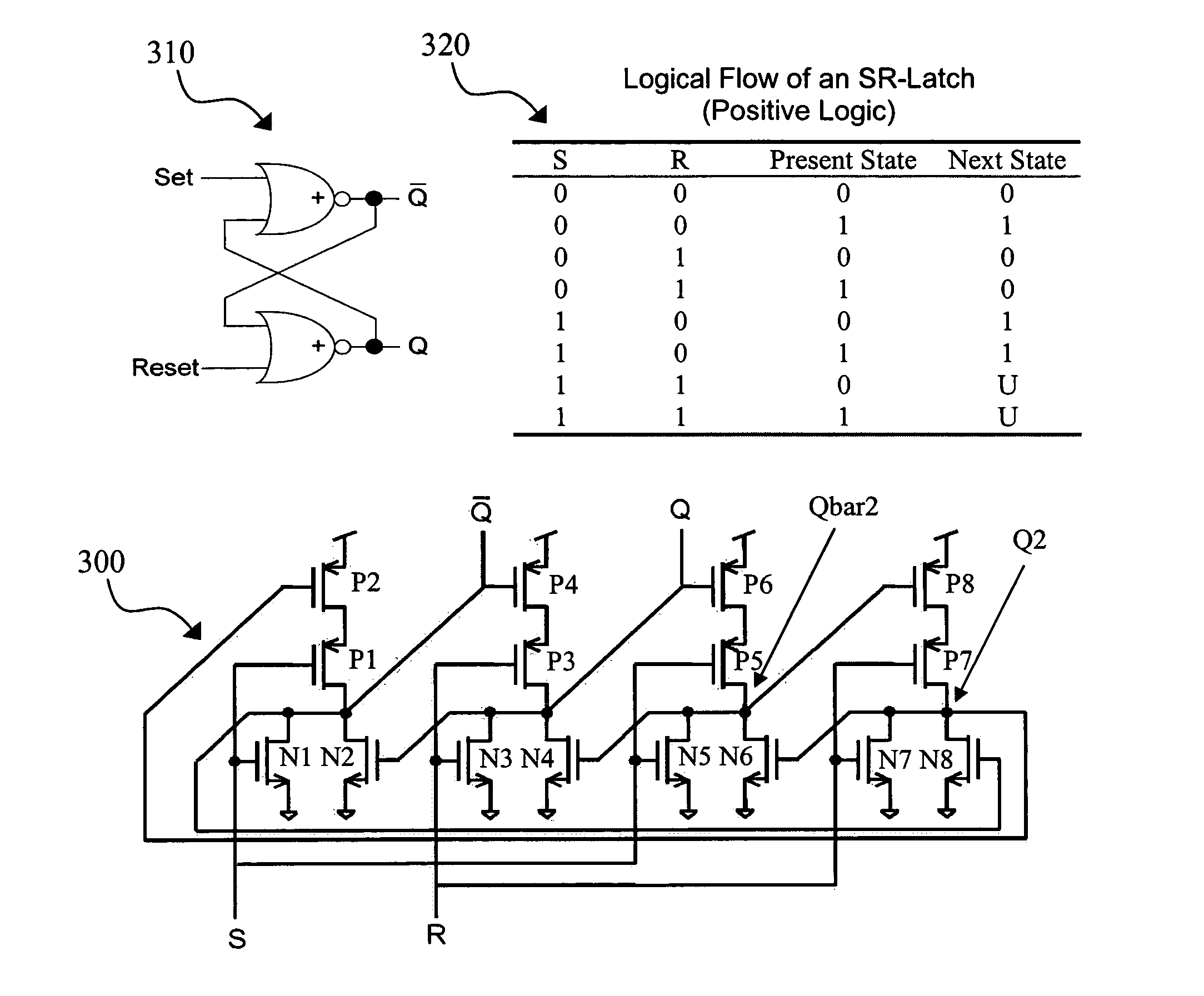

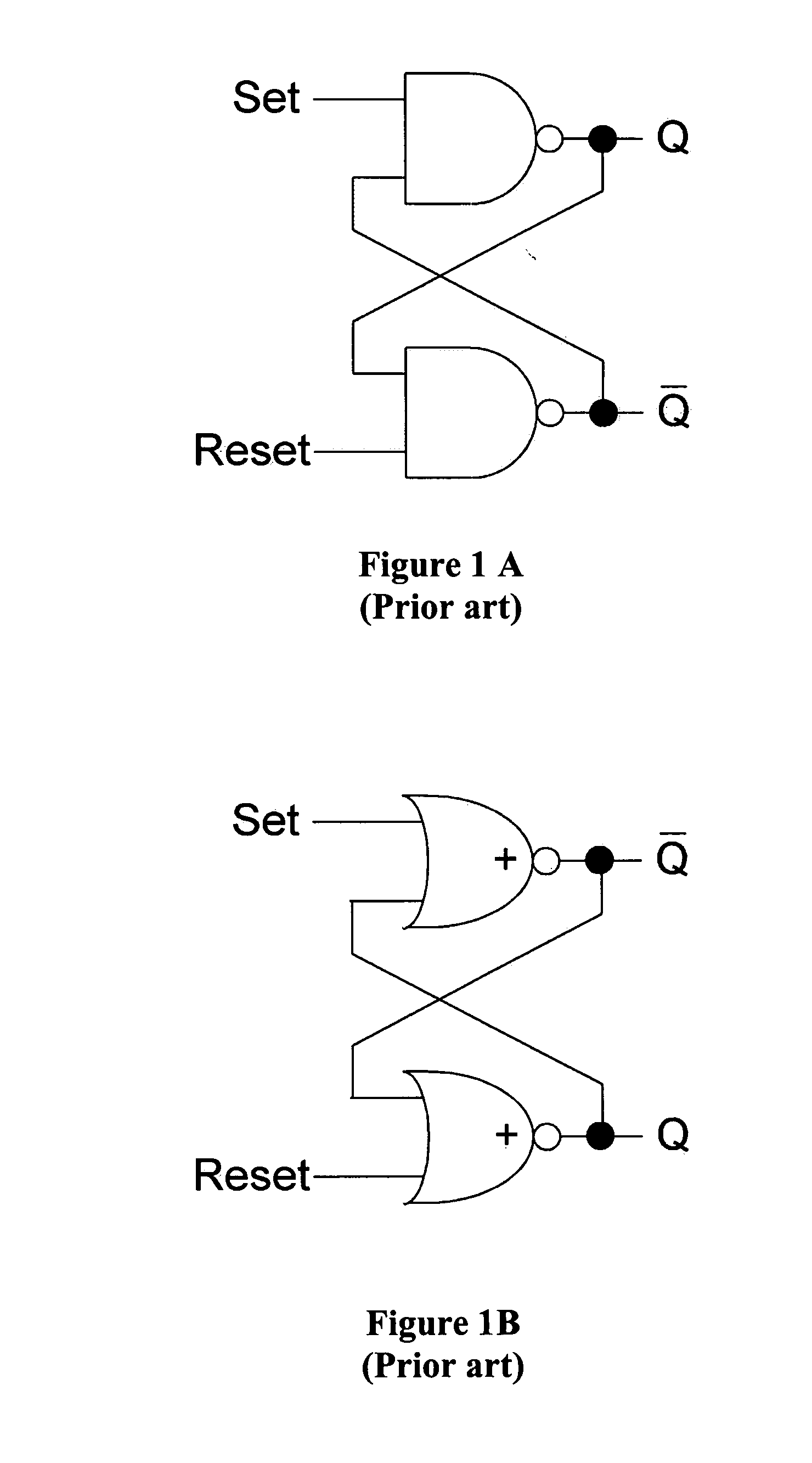

Redundant single event upset supression system

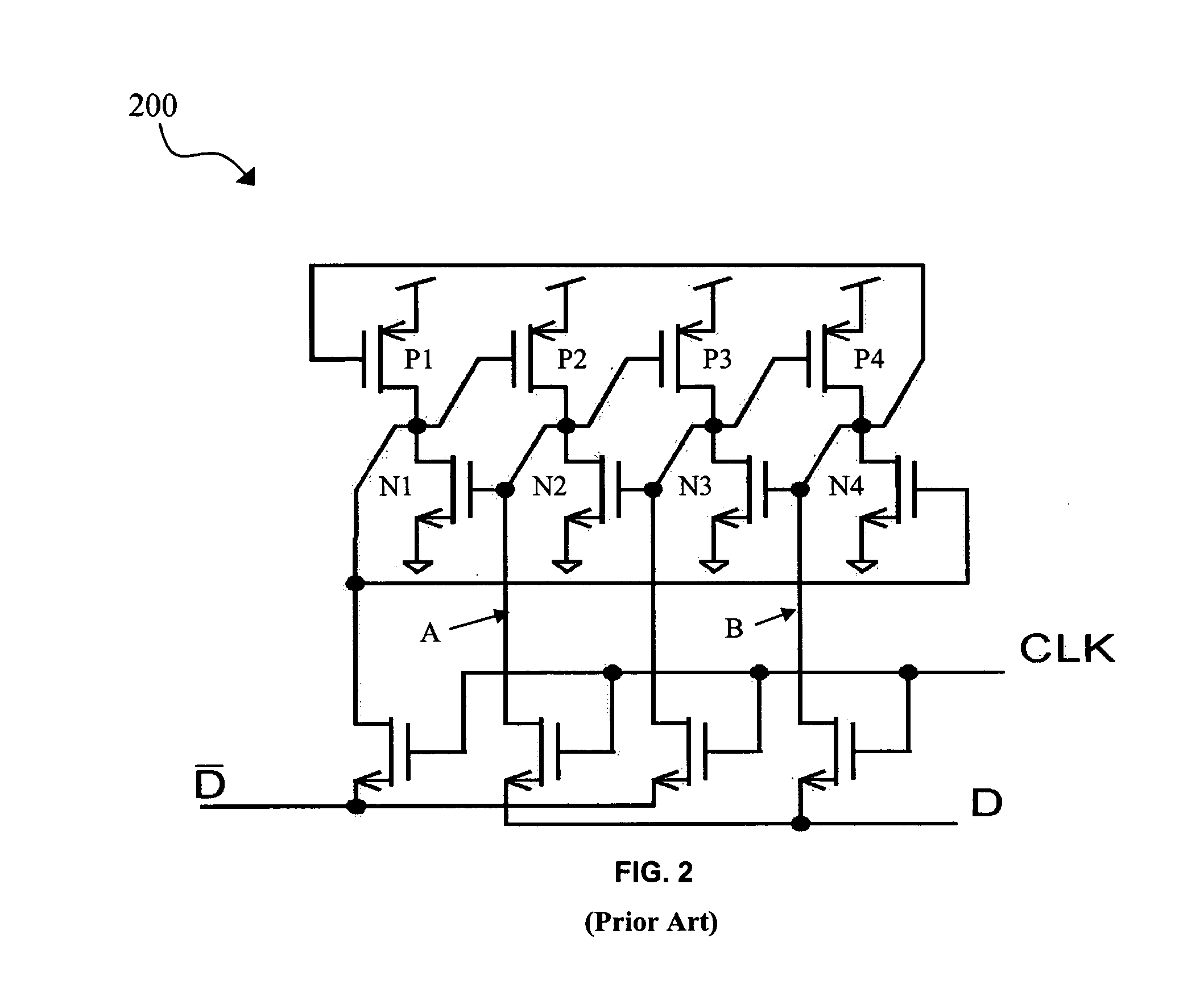

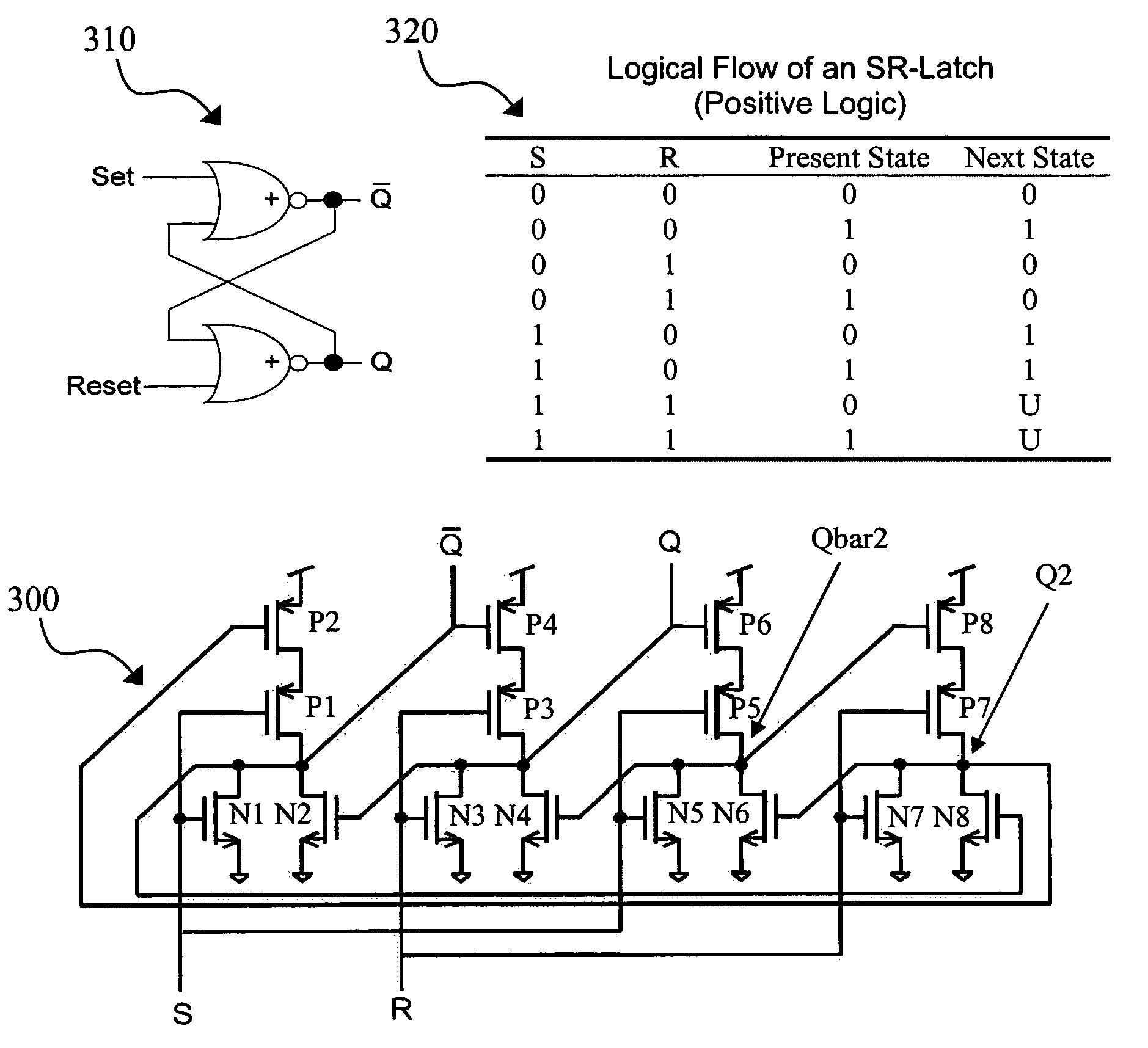

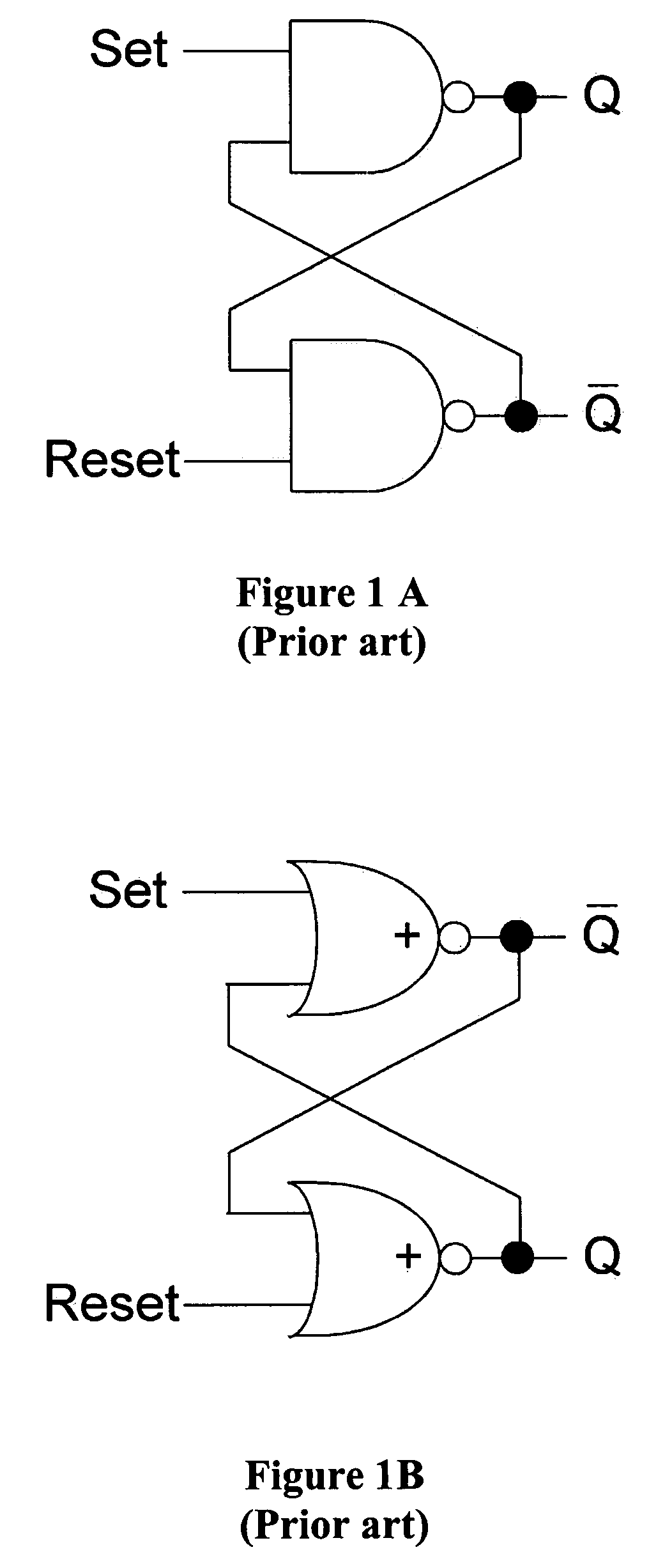

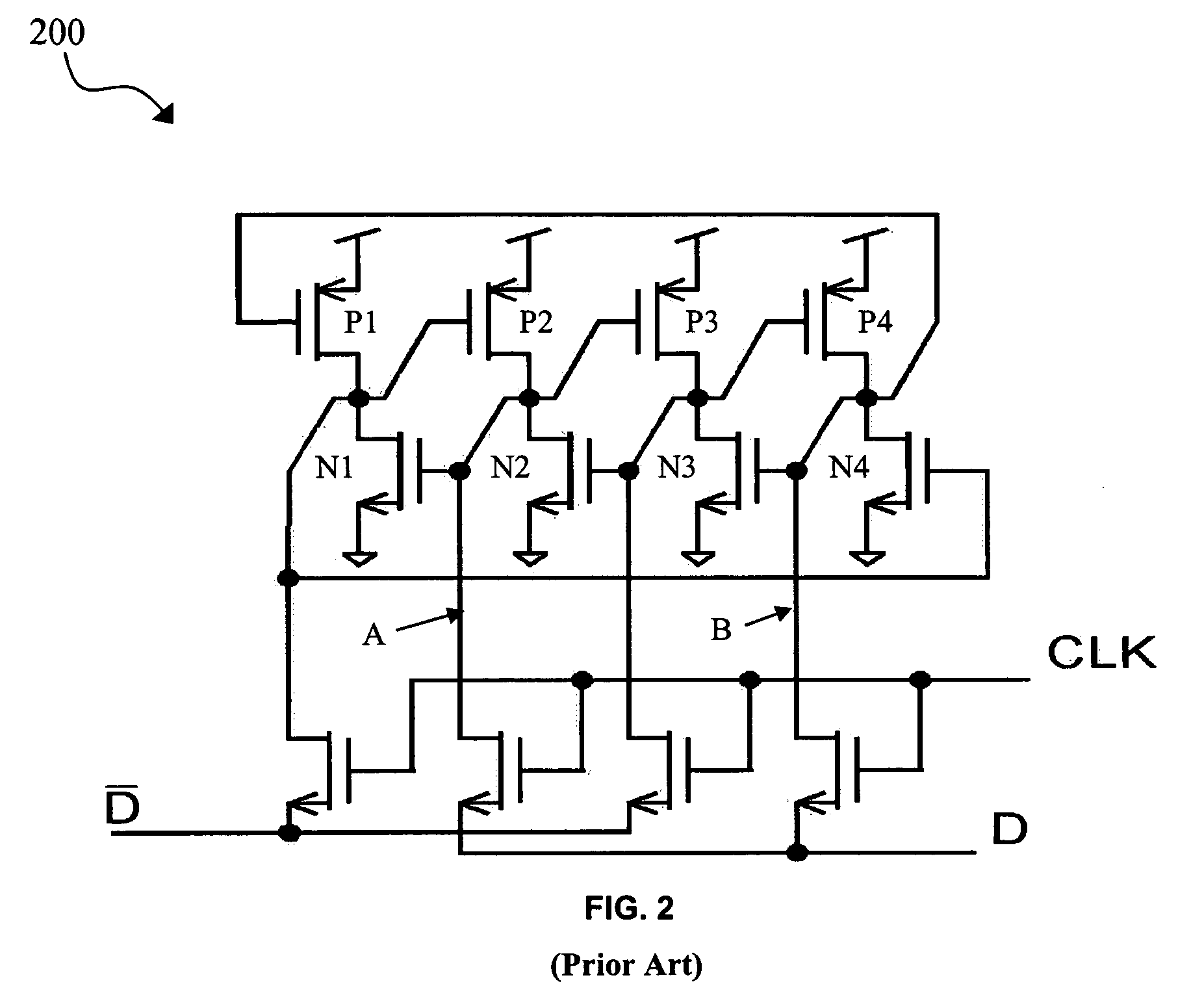

CMOS transistors are configured to operate as either a redundant, SEU-tolerant, positive-logic, cross-coupled Nor Gate SR-flip flop or a redundant, SEU-tolerant, negative-logic, cross-coupled Nand Gate SR-flip flop. The register can operate as a memory, and further as a memory that can overcome the effects of radiation. As an SR-flip flop, the invention can be altered into any known type of latch or flip-flop by the application of external logic, thereby extending radiation tolerance to devices previously incapable of radiation tolerance. Numerous registers can be logically connected and replicated thereby being electronically configured to operate as a redundant circuit.

Owner:FERMI RESEARCH ALLIANCE LLC

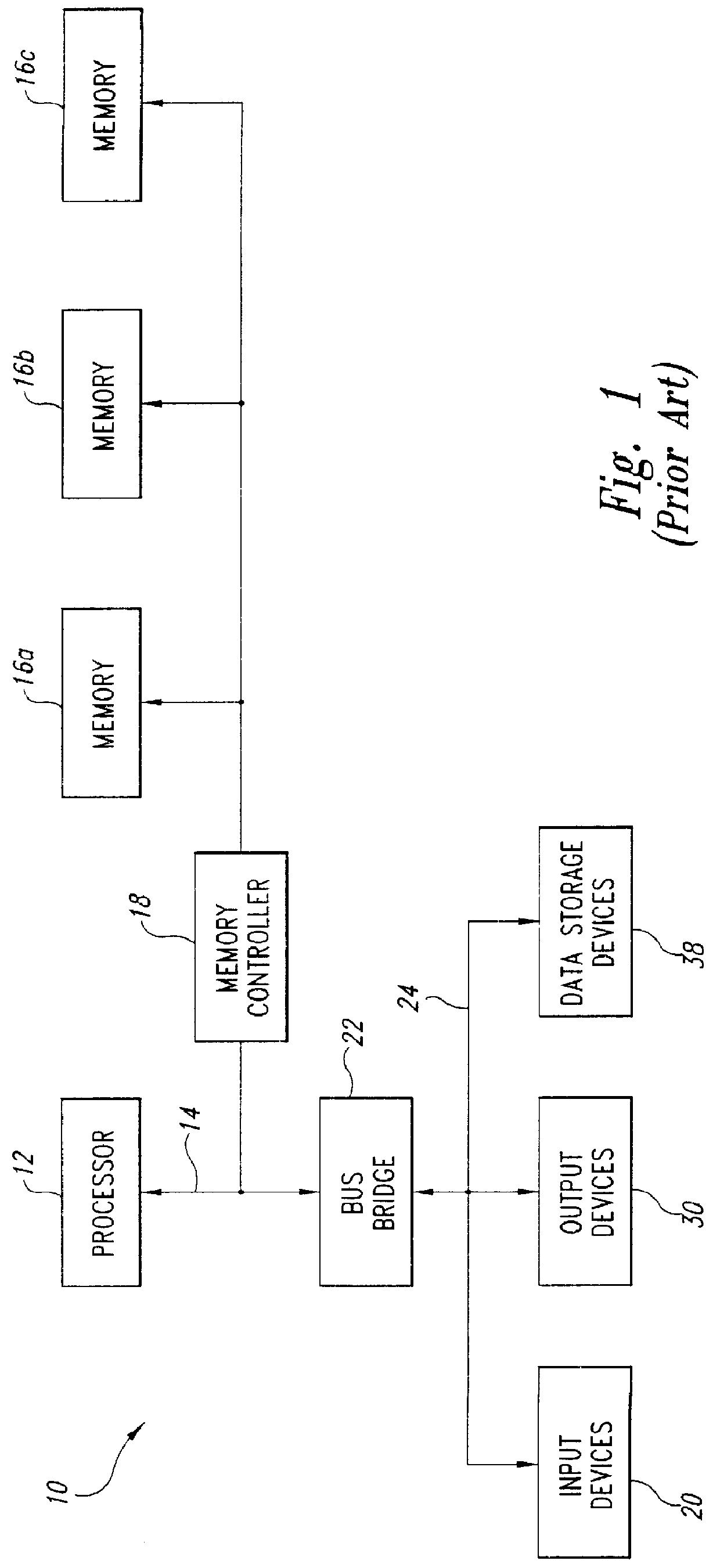

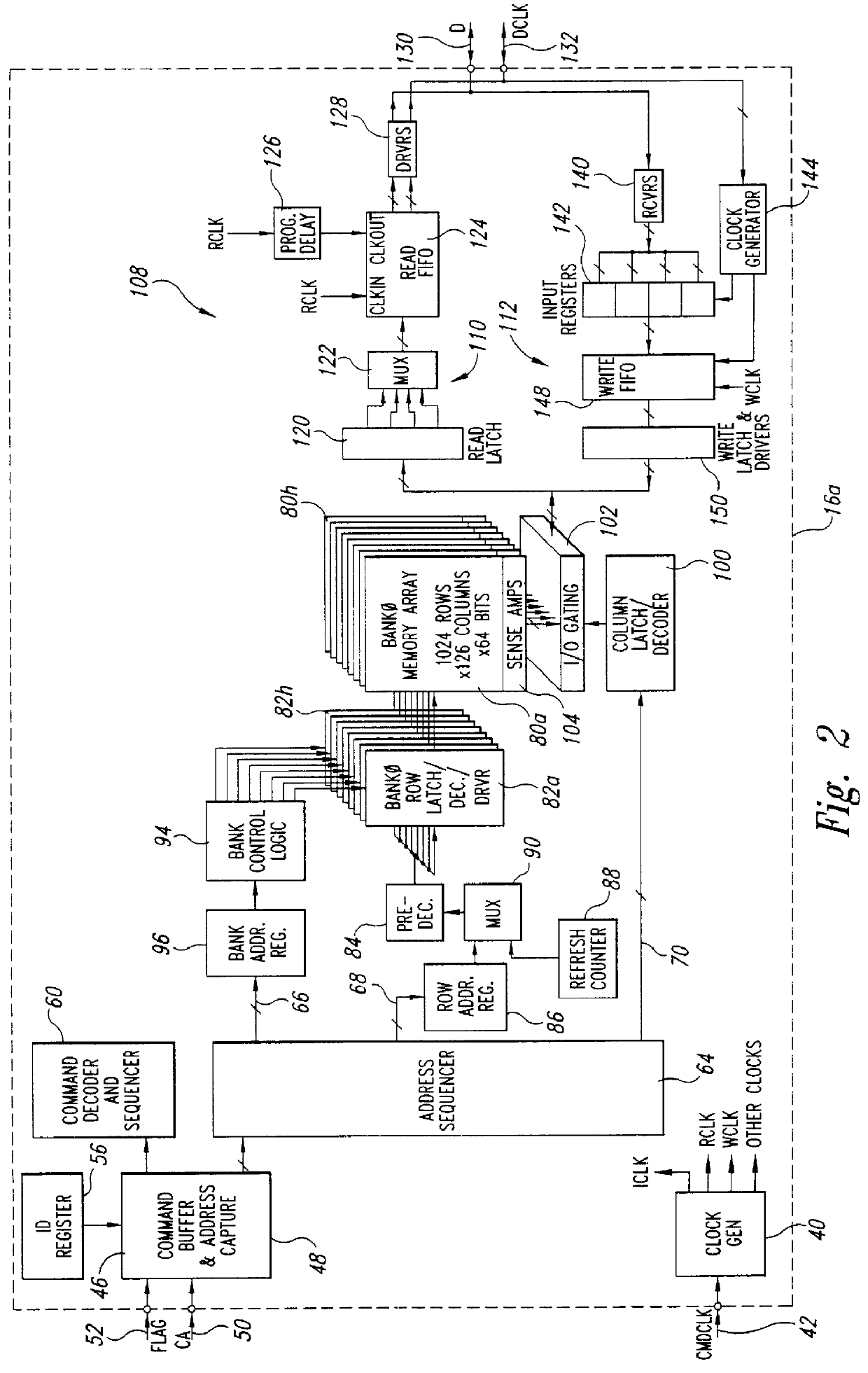

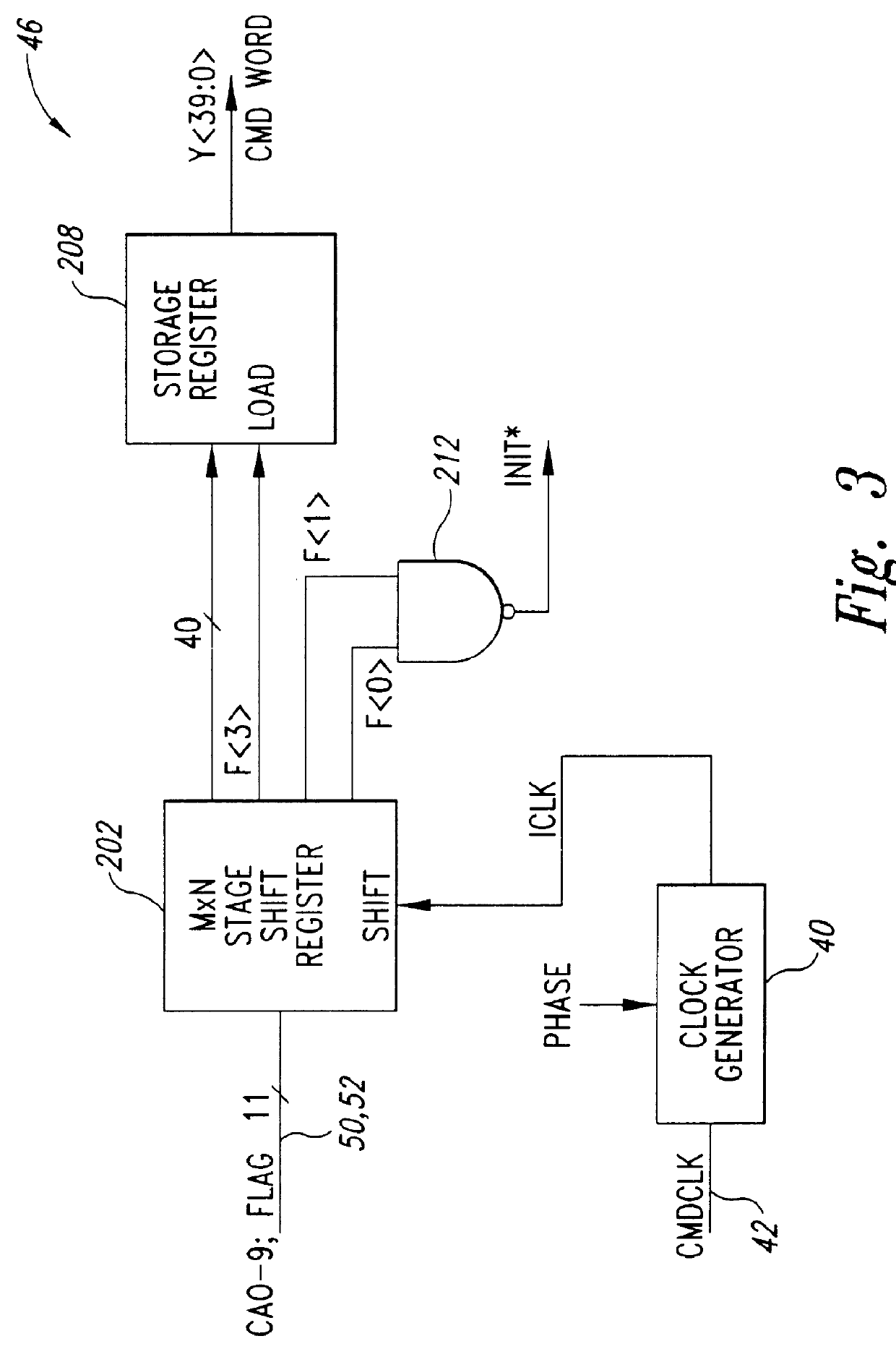

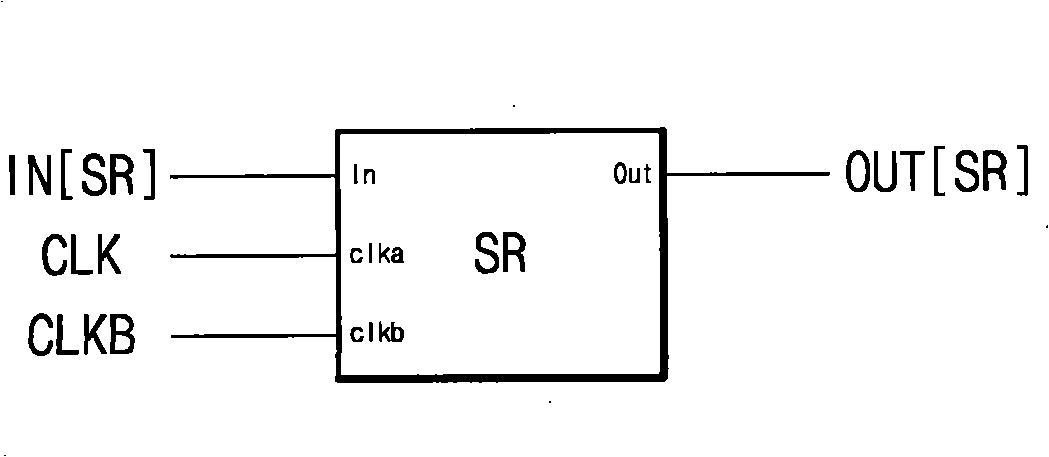

Method and apparatus for detecting an initialization signal and a command packet error in packetized dynamic random access memories

InactiveUS6167495AIncrease chanceMemory loss protectionError detection/correctionShift registerNAND gate

A system for detecting an initialization flag signal and distinguishing it from a normal flag signal having half the duration of the initialization flag signal. The initialization flag detection system may be included in the command buffer of a packetized DRAM that is used in a computer system. In one embodiment, the initialization flag detection system includes a pair of shift registers receiving the flag signal at their respective data inputs. One of the shift registers is clocked by a signal corresponding to an externally applied to command clock signal, while the other shift register is clocked by a quadrature clock signal. Together, the shift registers store a number of samples taken over a duration that is longer than the duration of the normal flag signal. The outputs of the shift registers are applied to a logic circuit, such as a NAND gate, that generates an initialization signal when all of the samples stored in the shift registers correspond to the logic levels of the flag signal. In another embodiment, the initialization flag detection system includes a plurality of latches receiving the flag signals at their data inputs. The latches are clocked by respective strobe signals corresponding to the command clock signal, but having phases that differ from each other. The outputs of the latches are applied to a logic circuit, such as a NAND) gate. Finally, in another embodiment of the invention, the bits of the command packet are sampled along with the flag signal and compared to the samples of the flag signal to detect when a command packet having a predetermined pattern does not correspond to a flag signal having a predetermined pattern.

Owner:MICRON TECH INC

Redundant single event upset supression system

CMOS transistors are configured to operate as either a redundant, SEU-tolerant, positive-logic, cross-coupled Nor Gate SR-flip flop or a redundant, SEU-tolerant, negative-logic, cross-coupled Nand Gate SR-flip flop. The register can operate as a memory, and further as a memory that can overcome the effects of radiation. As an SR-flip flop, the invention can be altered into any known type of latch or flip-flop by the application of external logic, thereby extending radiation tolerance to devices previously incapable of radiation tolerance. Numerous registers can be logically connected and replicated thereby being electronically configured to operate as a redundant circuit.

Owner:FERMI RESEARCH ALLIANCE LLC

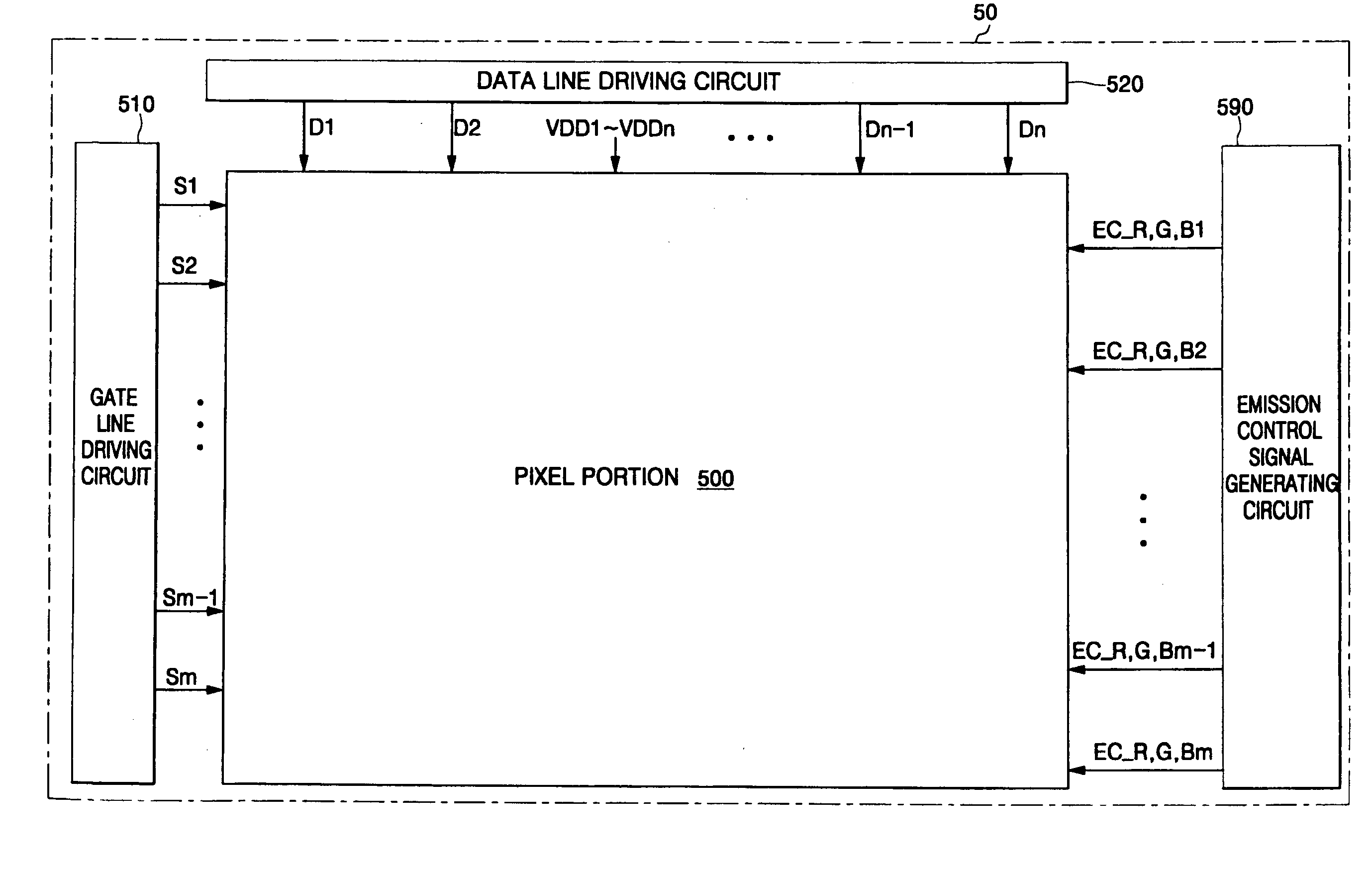

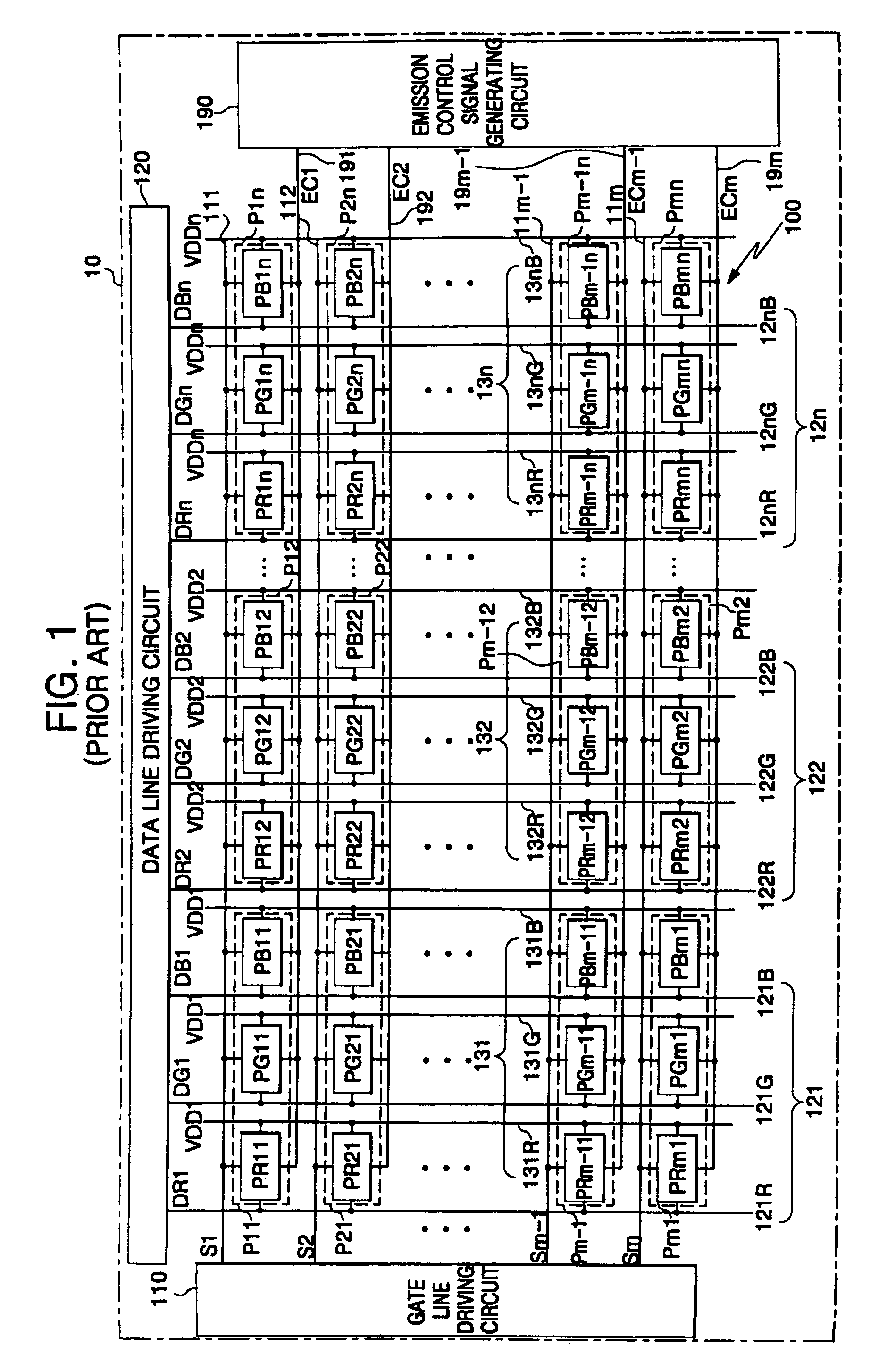

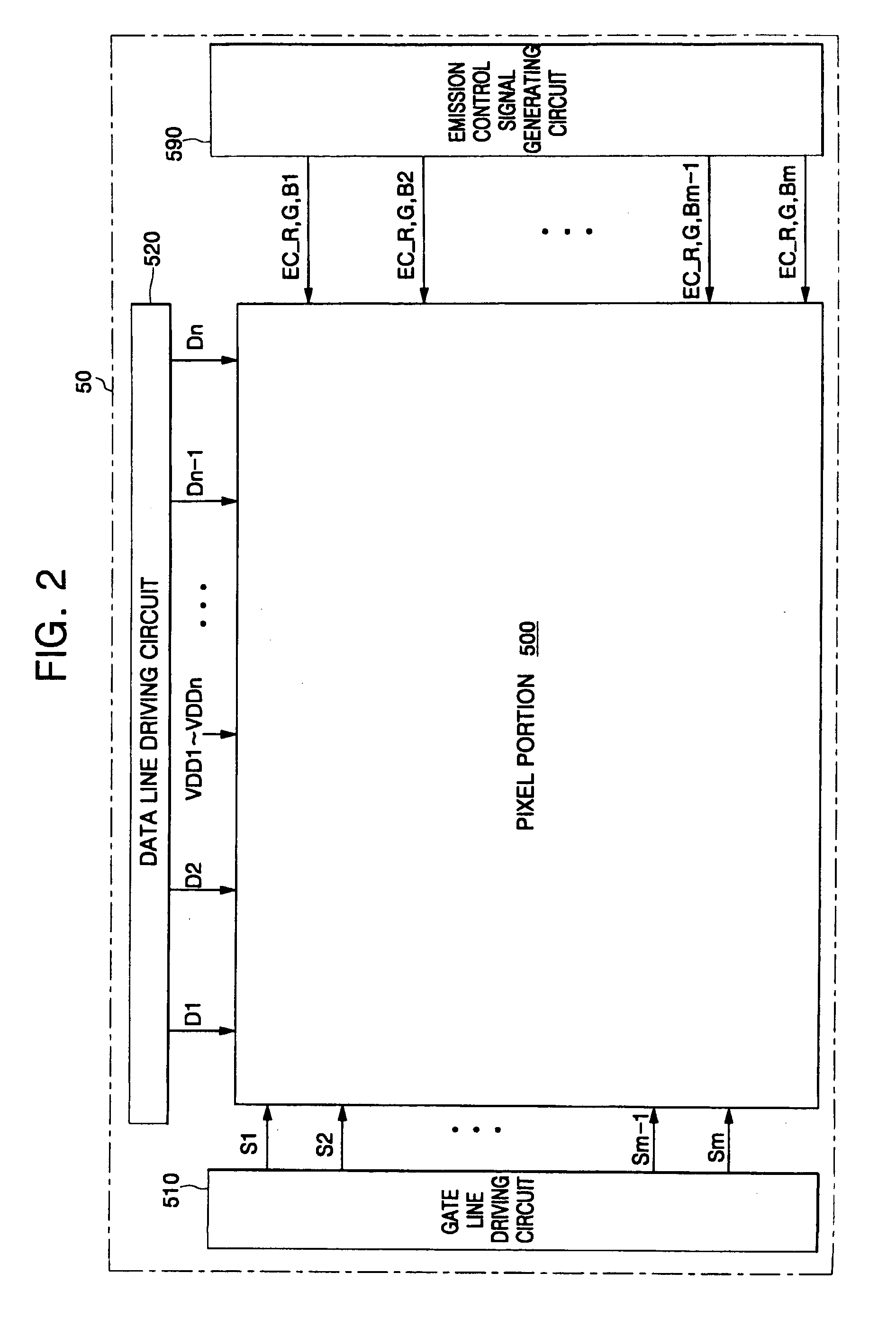

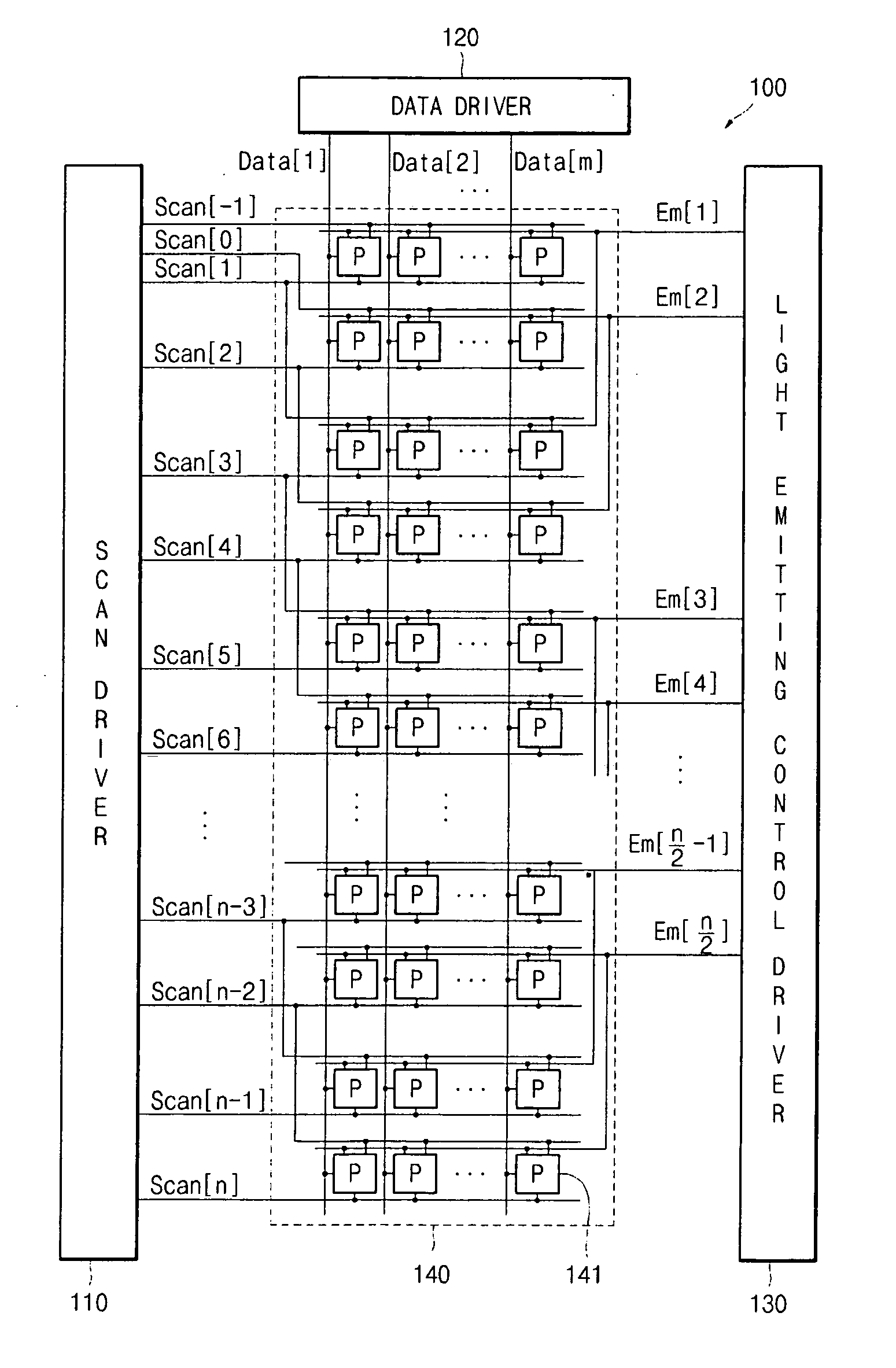

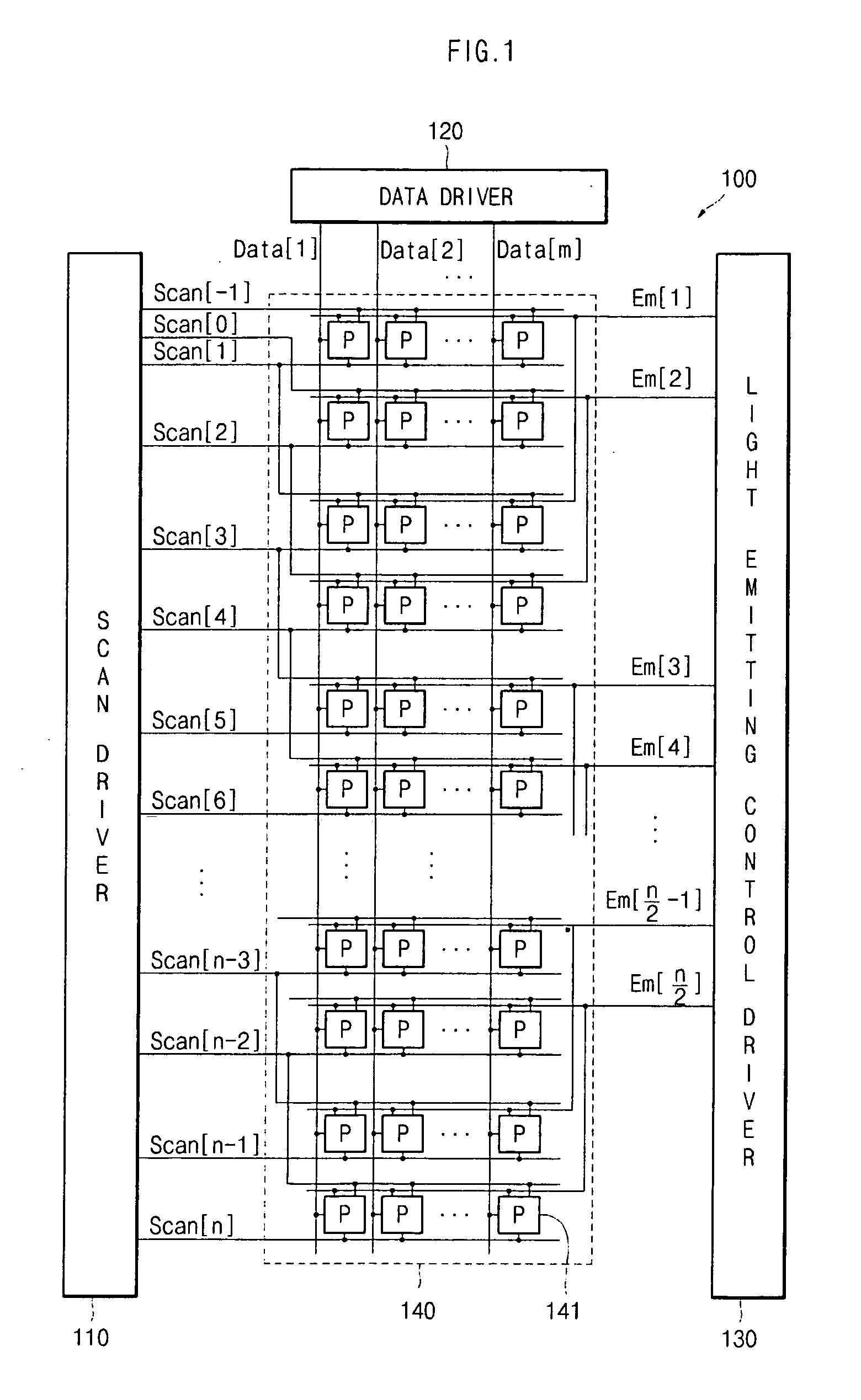

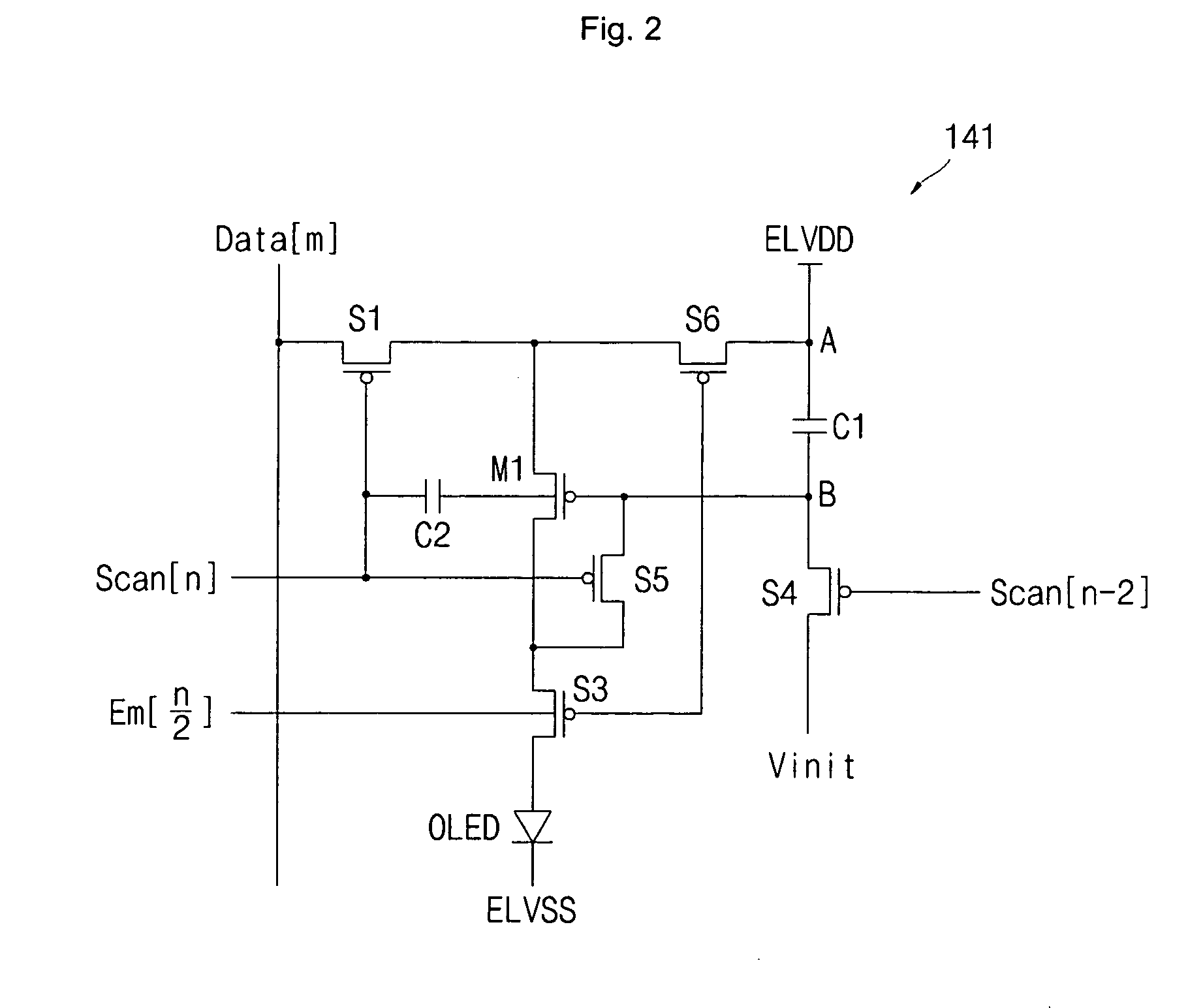

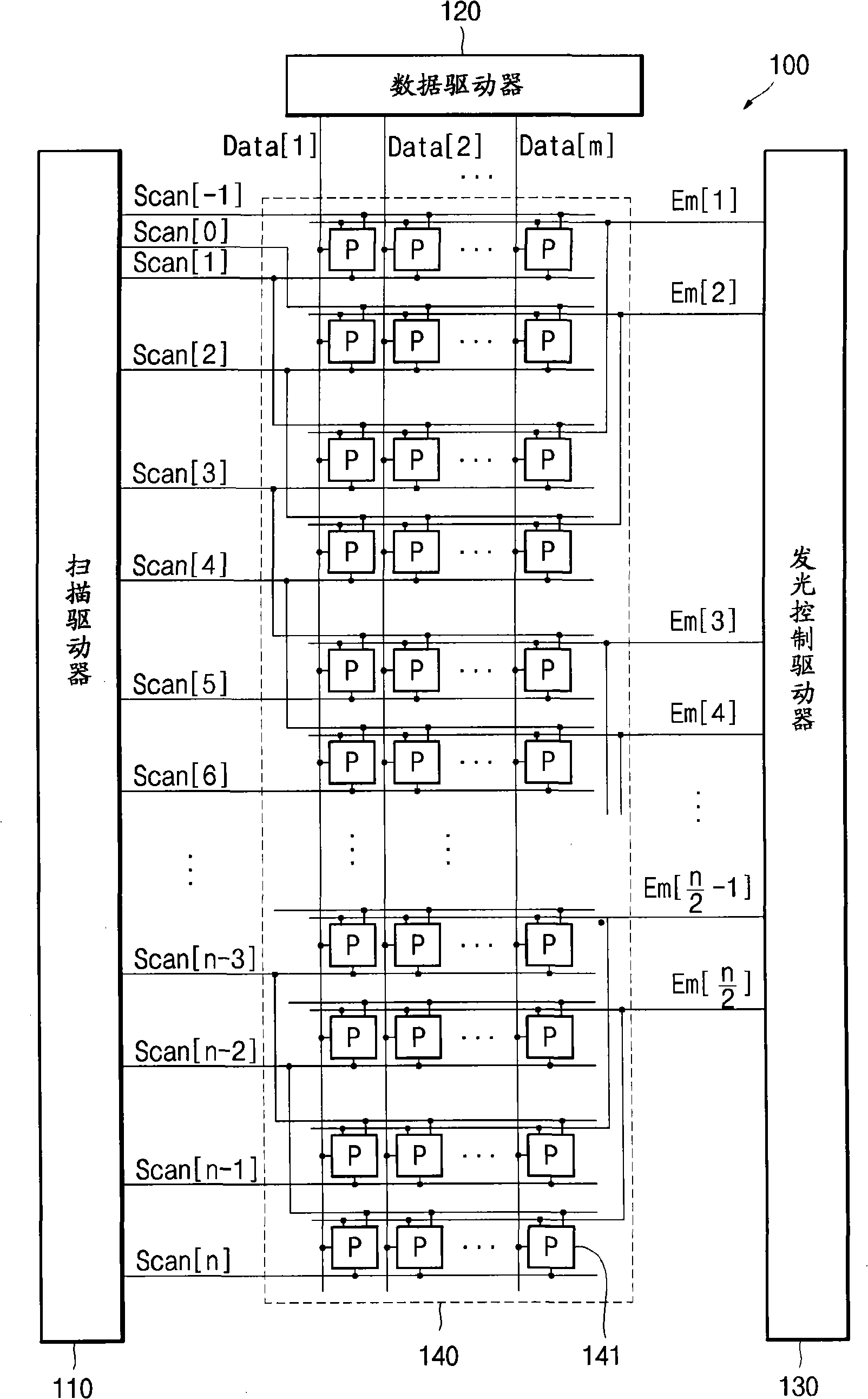

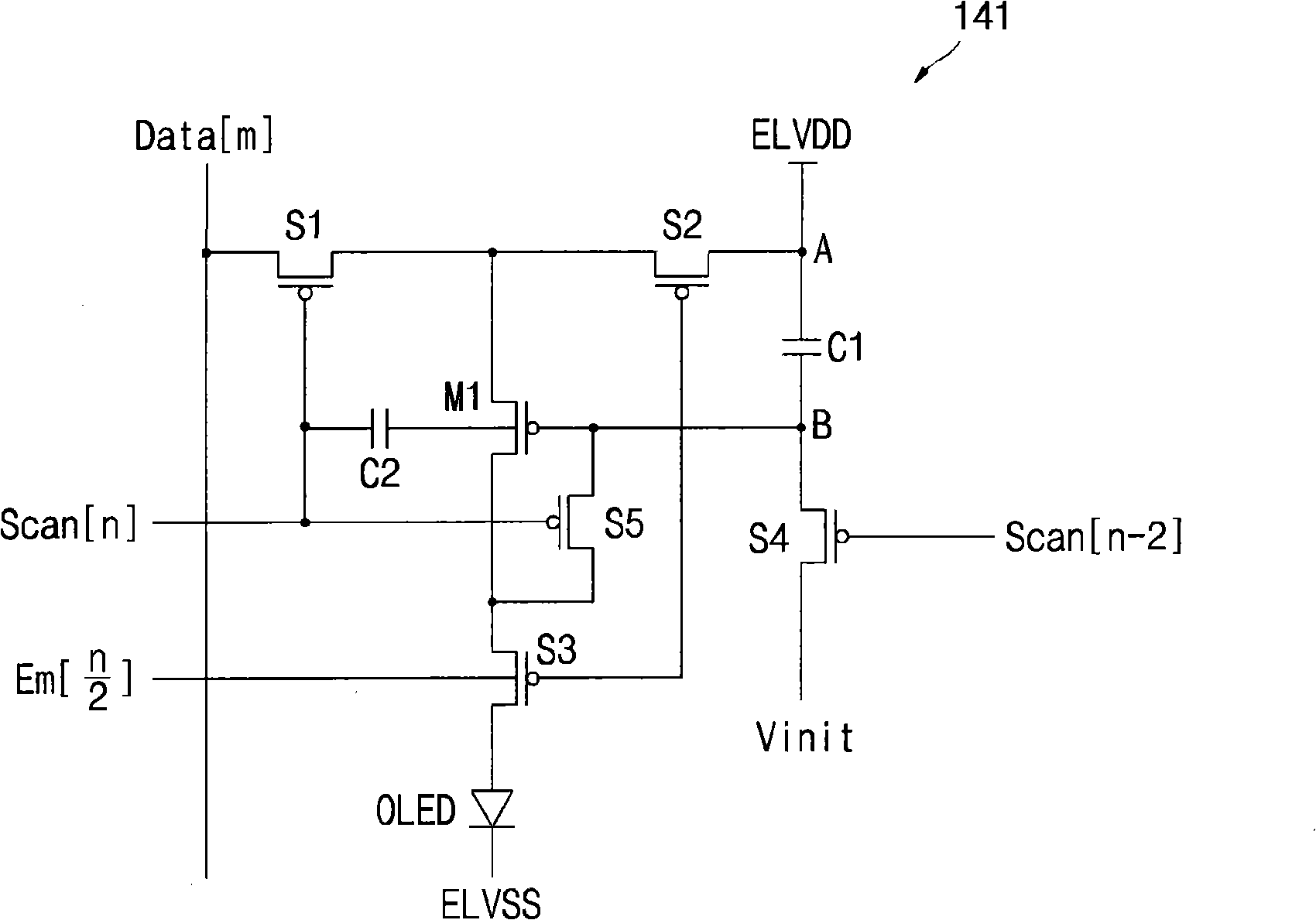

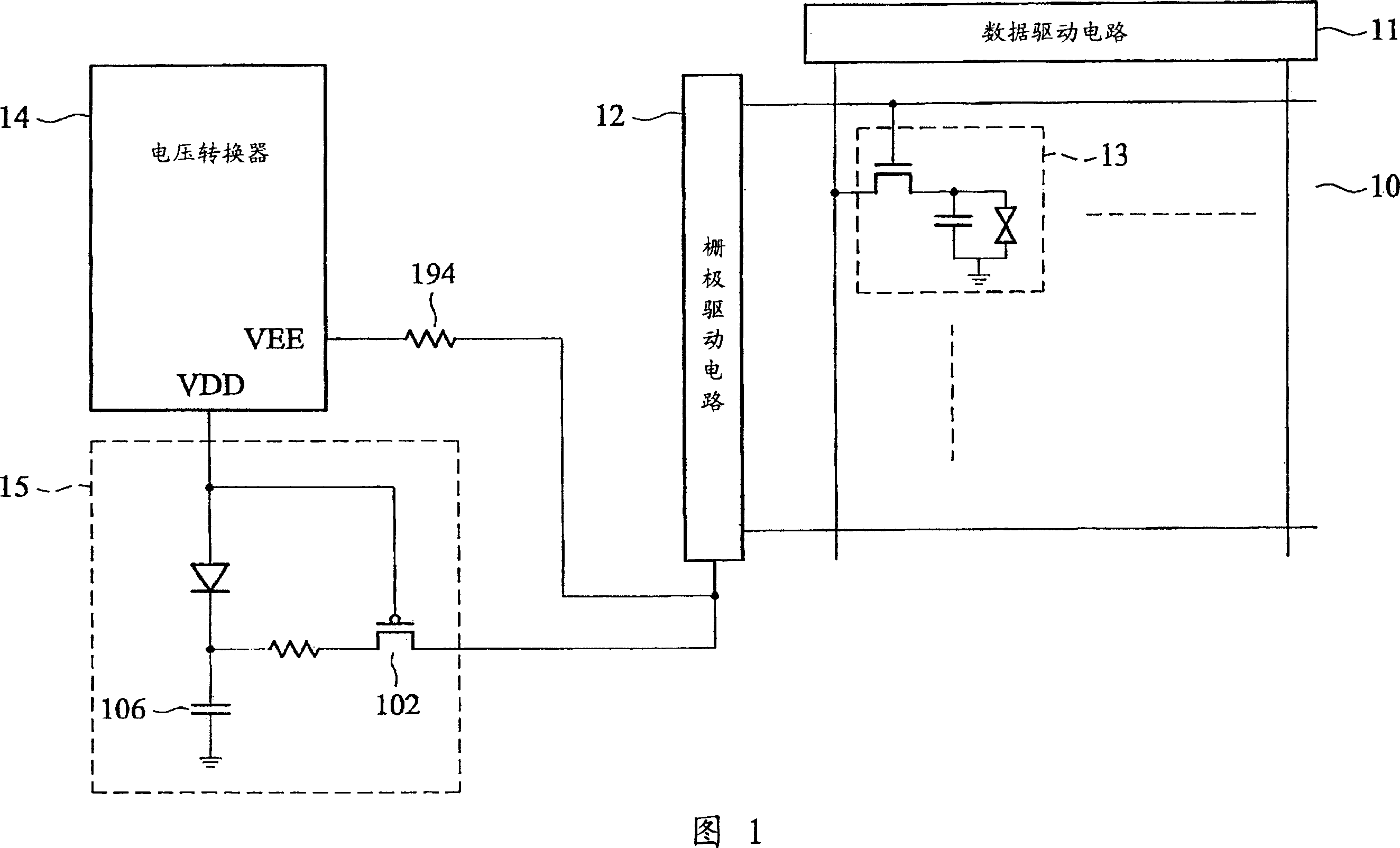

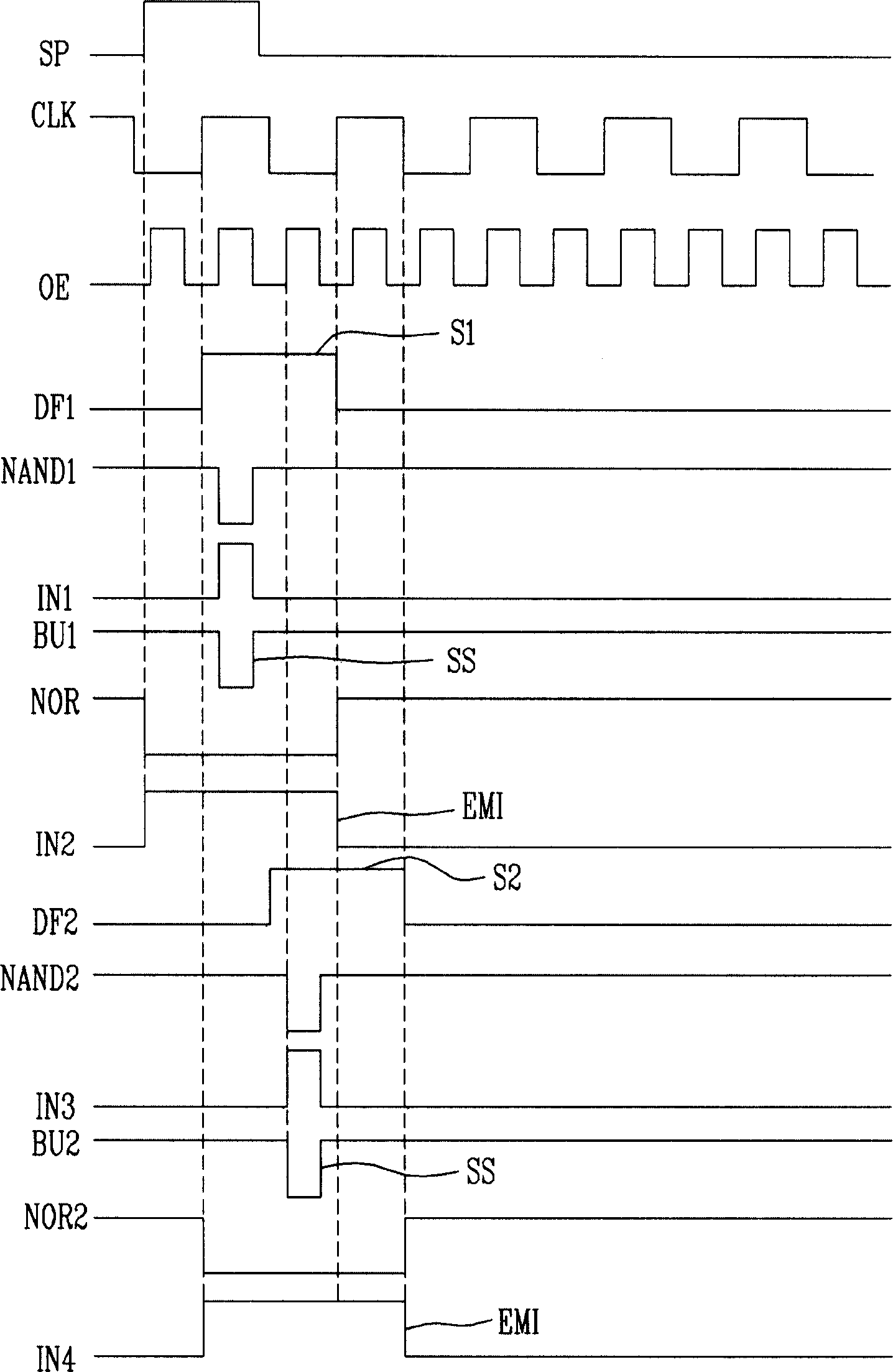

Amoled display and driving method thereof

InactiveUS20050116656A1Extended service lifeStatic indicating devicesElectroluminescent light sourcesShift registerControl signal

An emission control circuit for controlling emission of R, G, B EL elements and method for driving an organic light emitting diode display using the same. An emission control signal generating circuit of a flat panel display includes a plurality of pixels. Each pixel includes a plurality of EL elements, and emission of the elements is controlled by emission control signals. The circuit includes a first signal generating device for generating one of the emission control signals, and a plurality of second signal generating devices for generating other ones of the emission control signals using an output signal of the first signal generating device and an external control signal. The first signal generating device may include a shift register. Each of the plurality of second signal generating devices may include a NAND gate using the external signal and the external control signal, or an inverted signal thereof, as two inputs.

Owner:SAMSUNG DISPLAY CO LTD

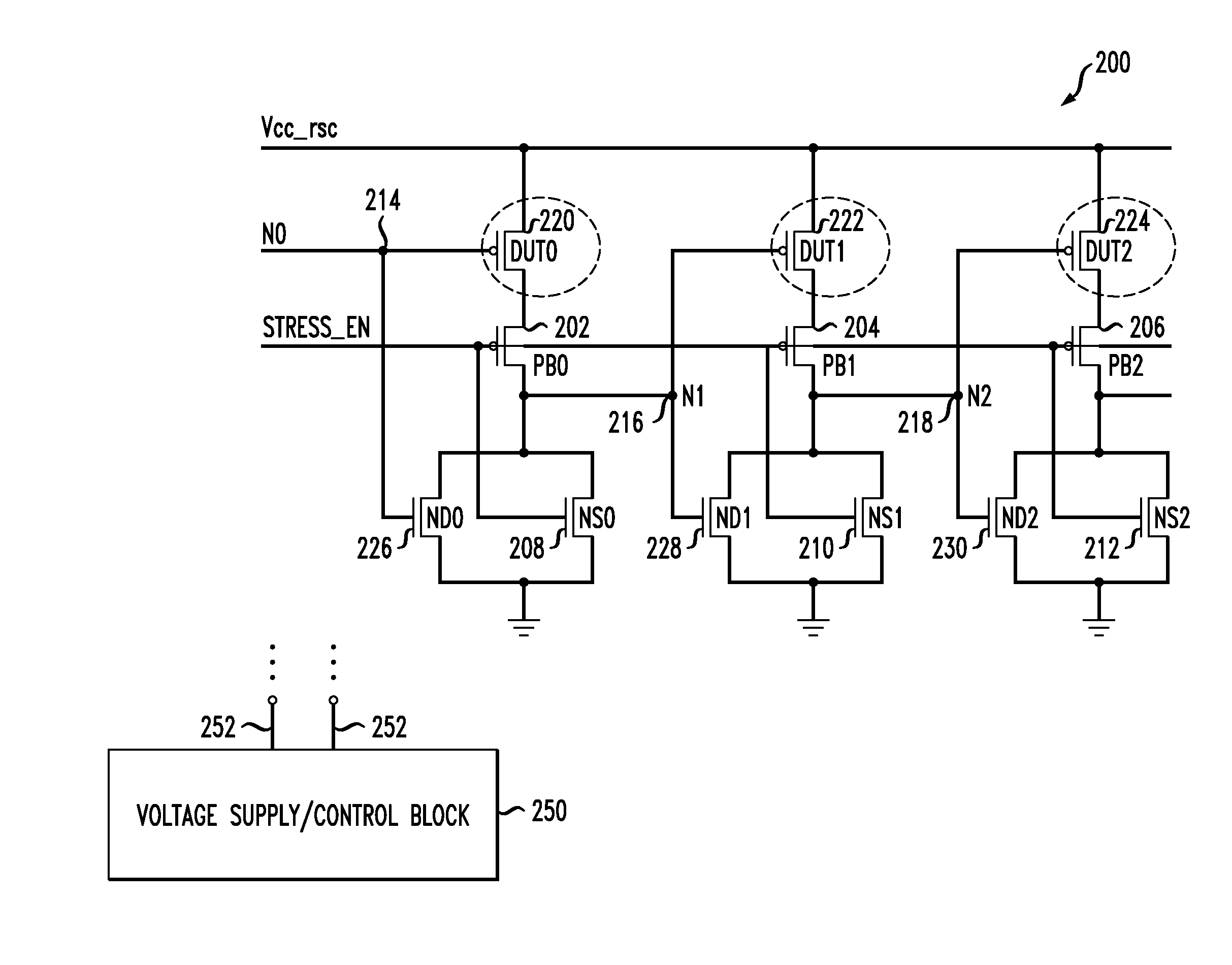

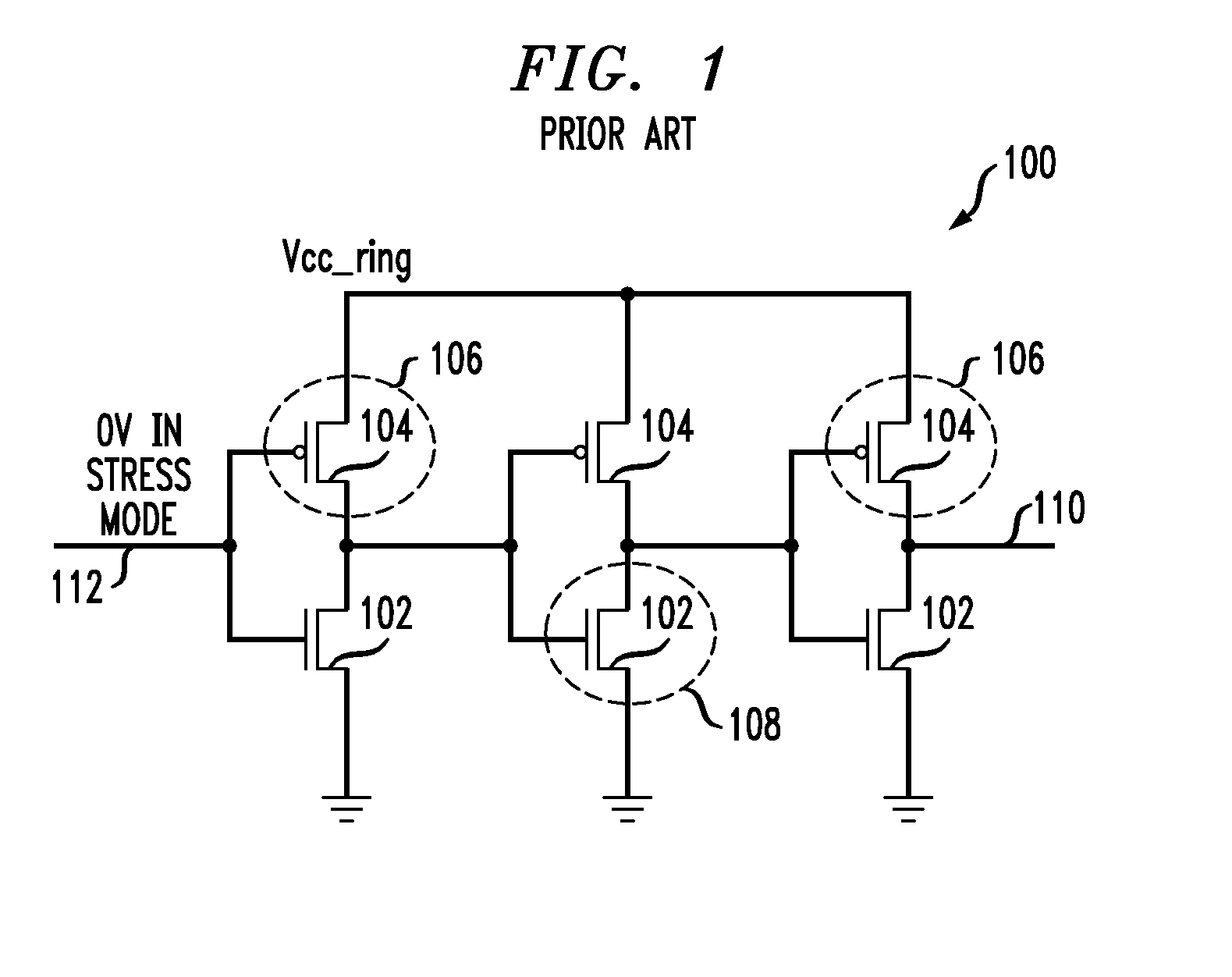

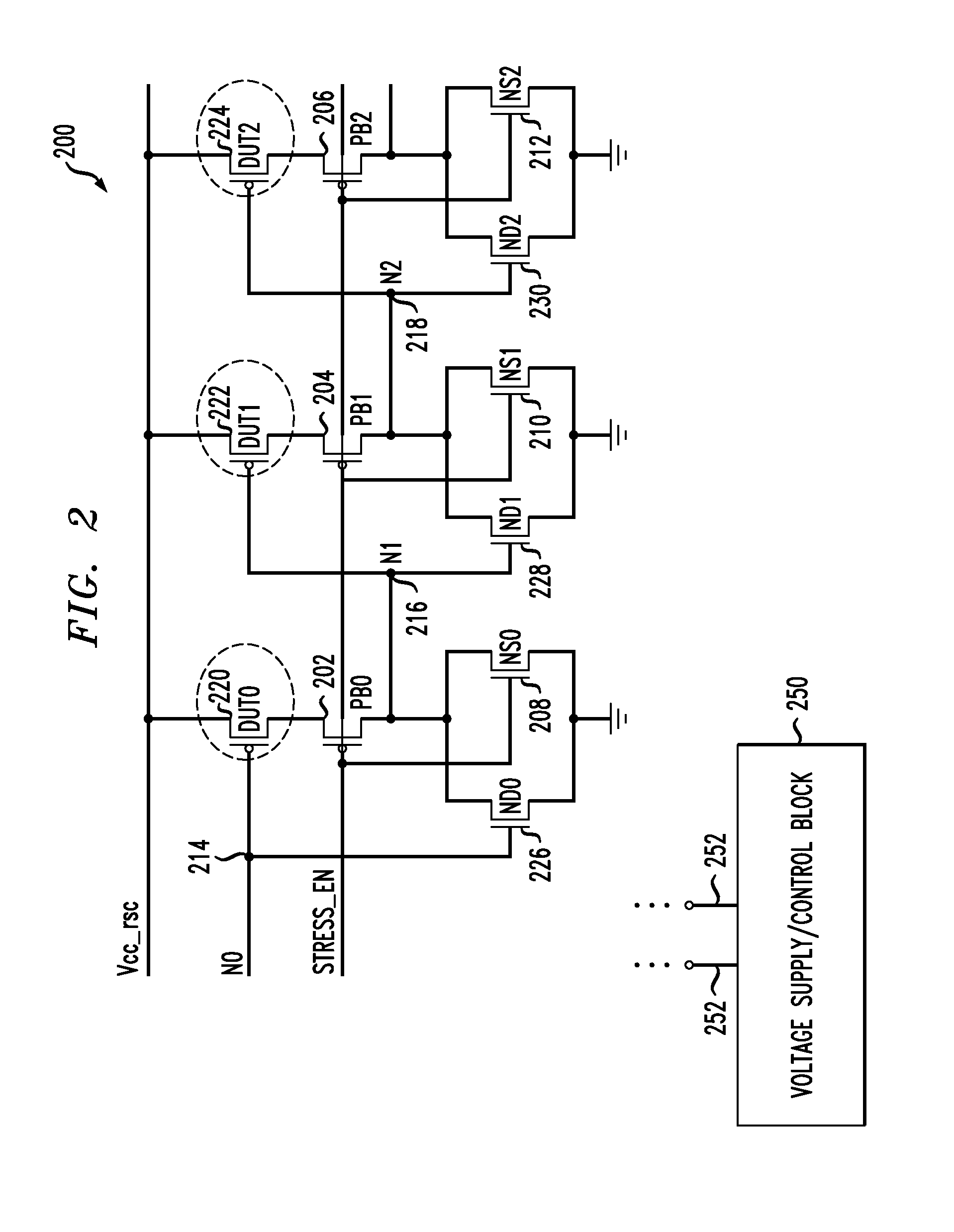

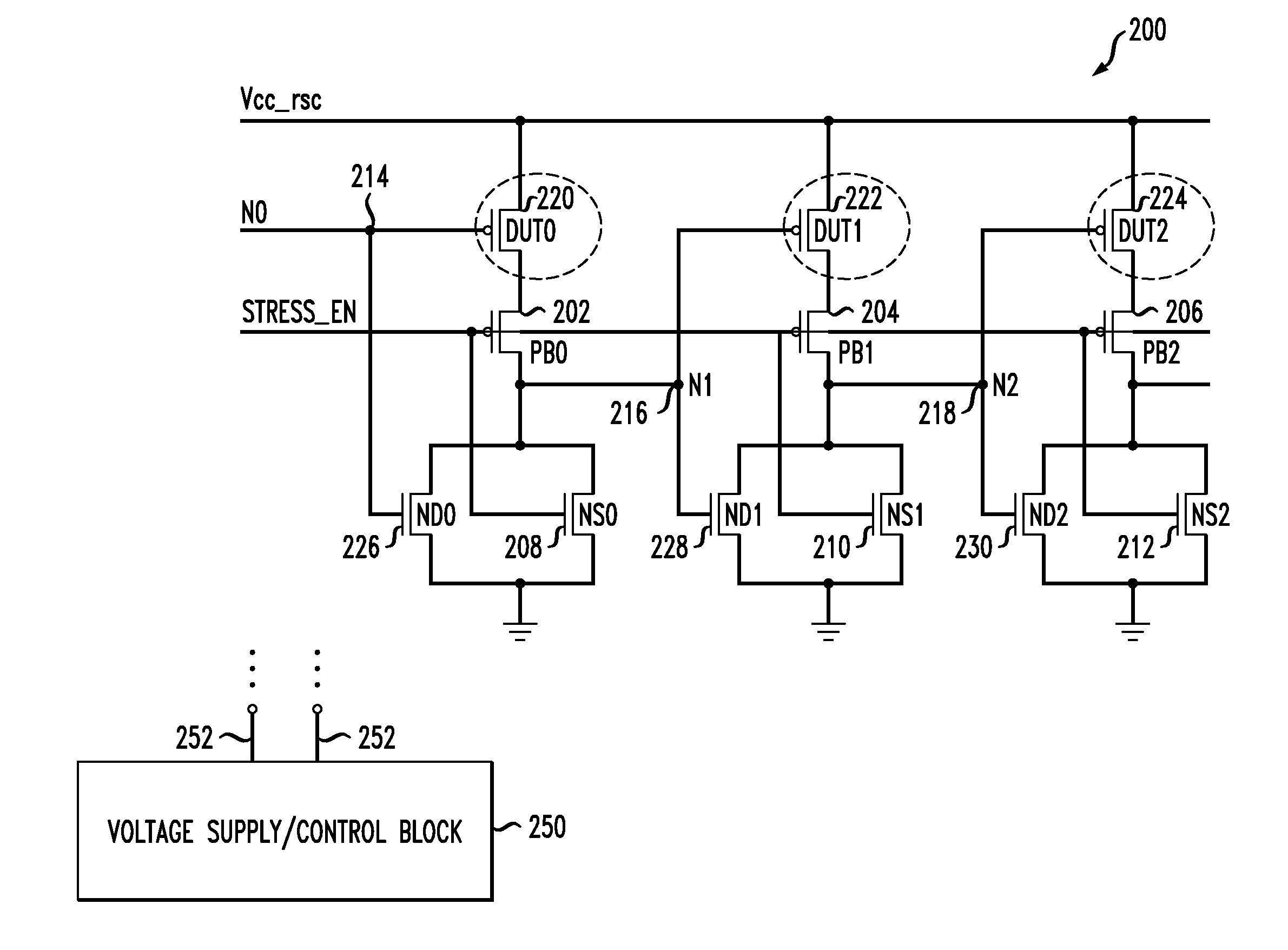

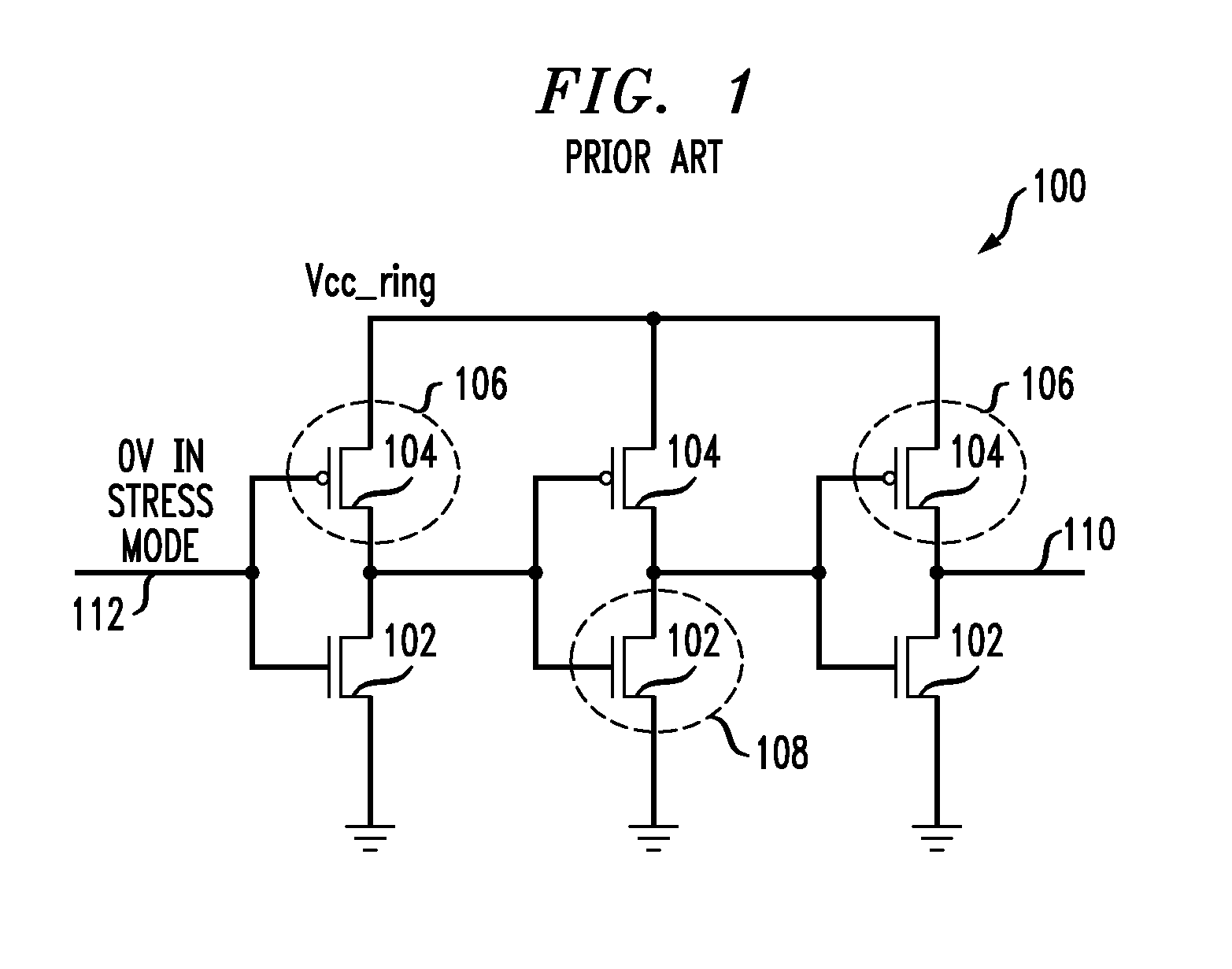

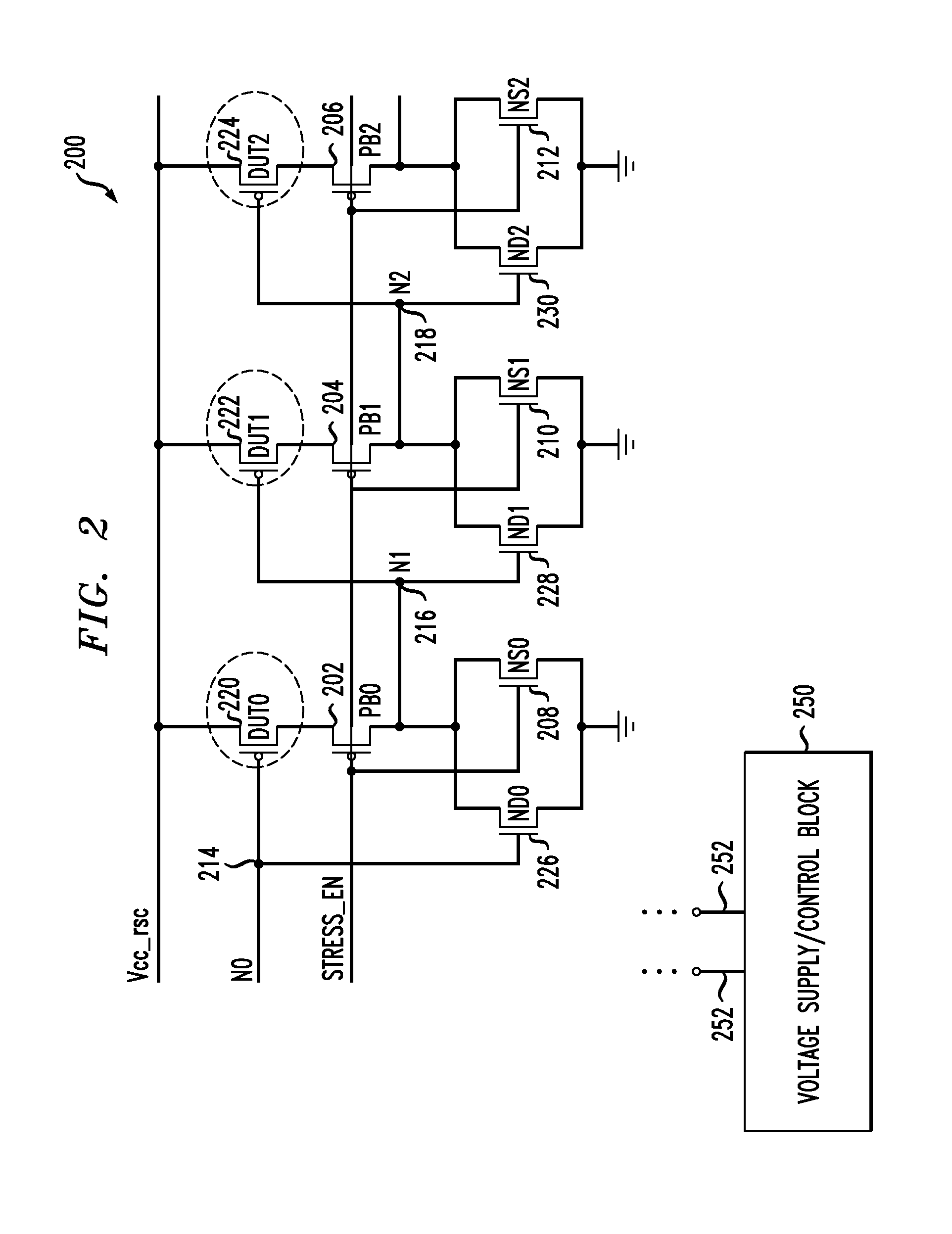

Circuits and design structures for monitoring nbti (negative bias temperature instability) effect and/or pbti (positive bias temperature instability) effect

ActiveUS20090189703A1High power supply voltageResistance/reactance/impedencePulse generation by logic circuitsNOR gateNAND gate

A ring oscillator has an odd number of NOR-gates greater than or equal to three, each with first and second input terminals, a voltage supply terminal, and an output terminal. The first input terminals of all the NOR-gates are interconnected, and each of the NOR-gates has its output terminal connected to the second input terminal of an immediately adjacent one of the NOR-gates. During a stress mode, a voltage supply and control block applies a stress enable signal to the interconnected first input terminals, and an increased supply voltage to the voltage supply terminals. During a measurement mode, this block grounds the interconnected first input terminals, and applies a normal supply voltage to the voltage supply terminals. Also included are an analogous NAND-gate based circuit, a circuit combining the NAND- and NOR-aspects, a circuit with a ring oscillator where the inverters may be coupled directly or through inverting paths, and circuits for measuring the bias temperature instability effect in pass gates.

Owner:GLOBALFOUNDRIES US INC

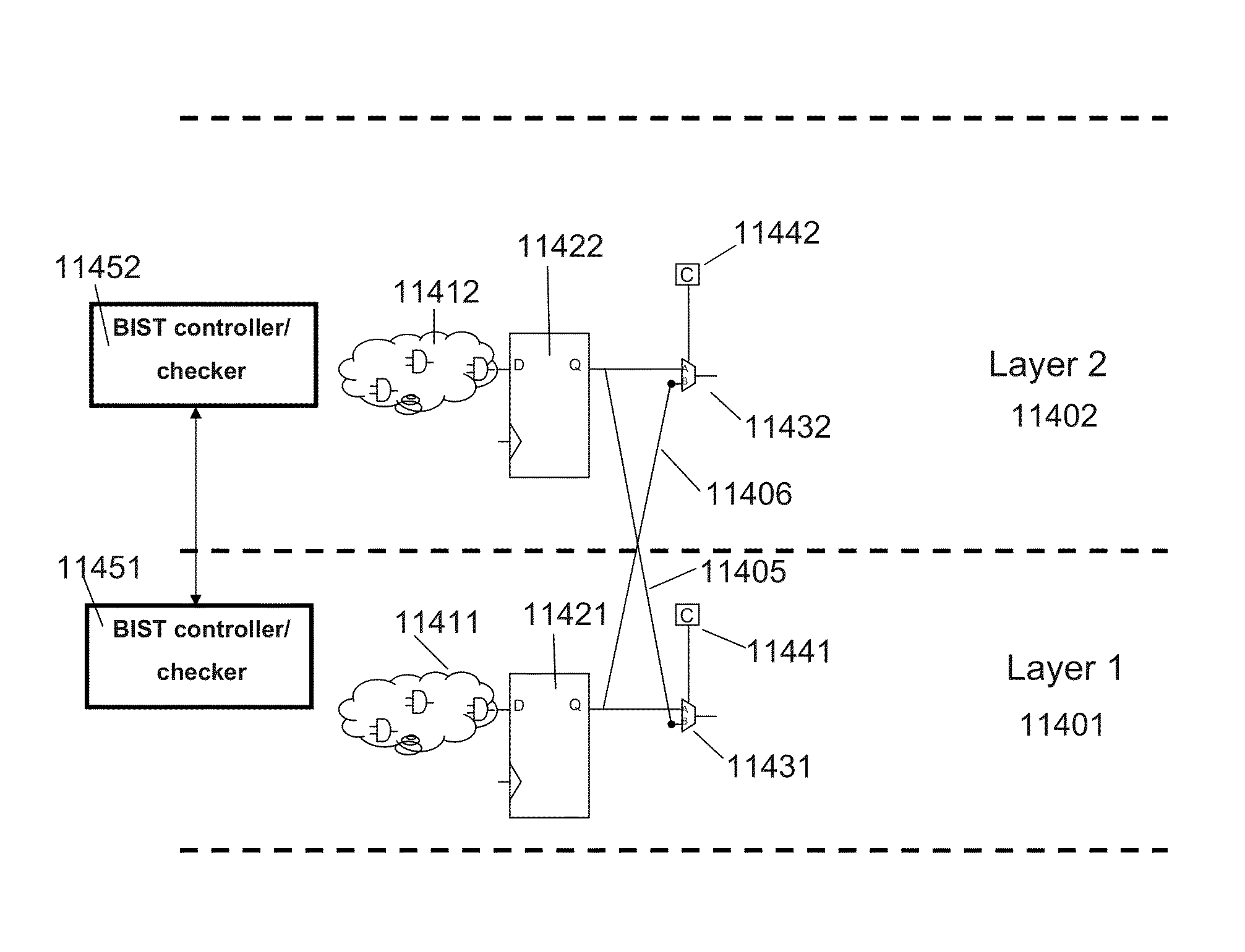

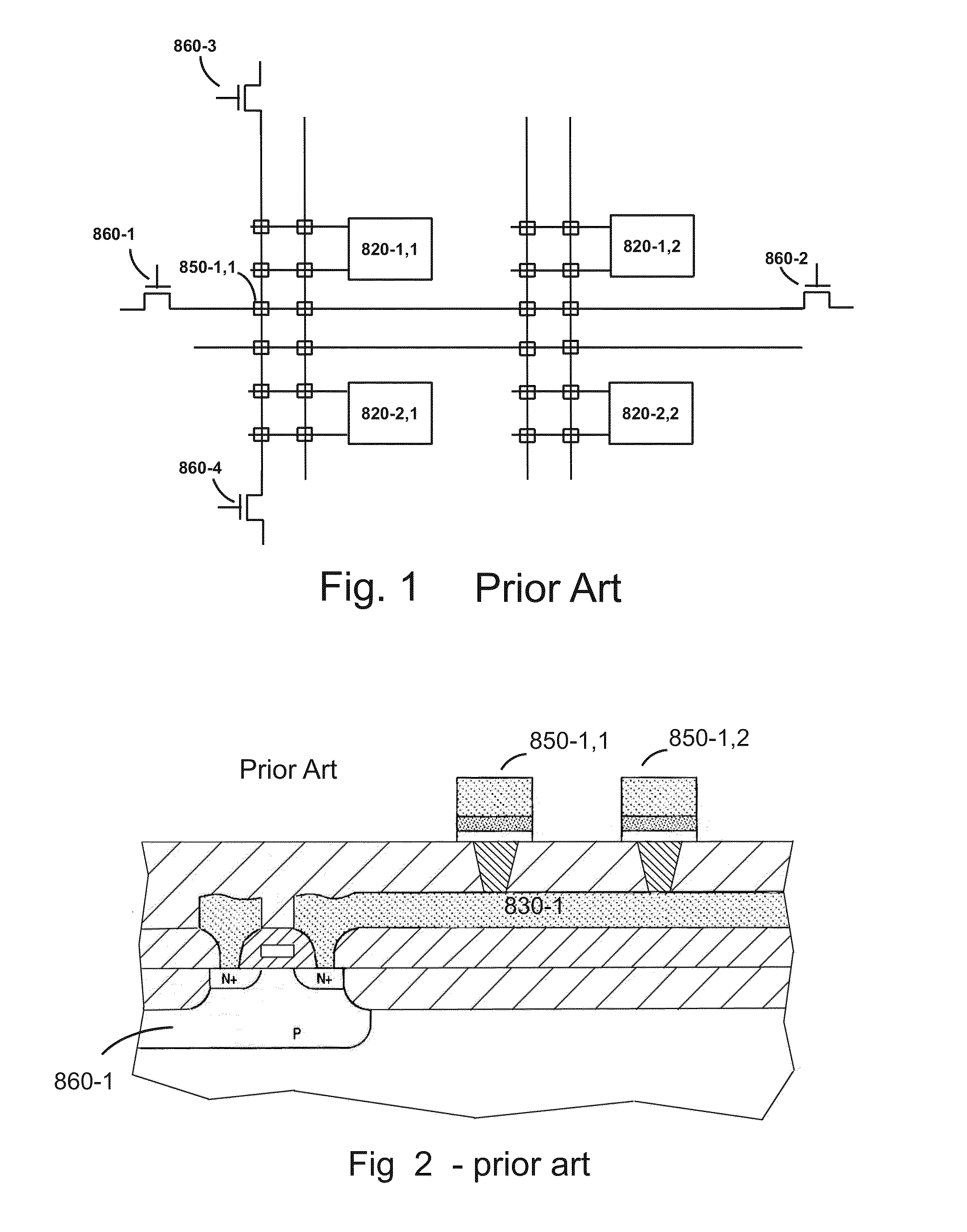

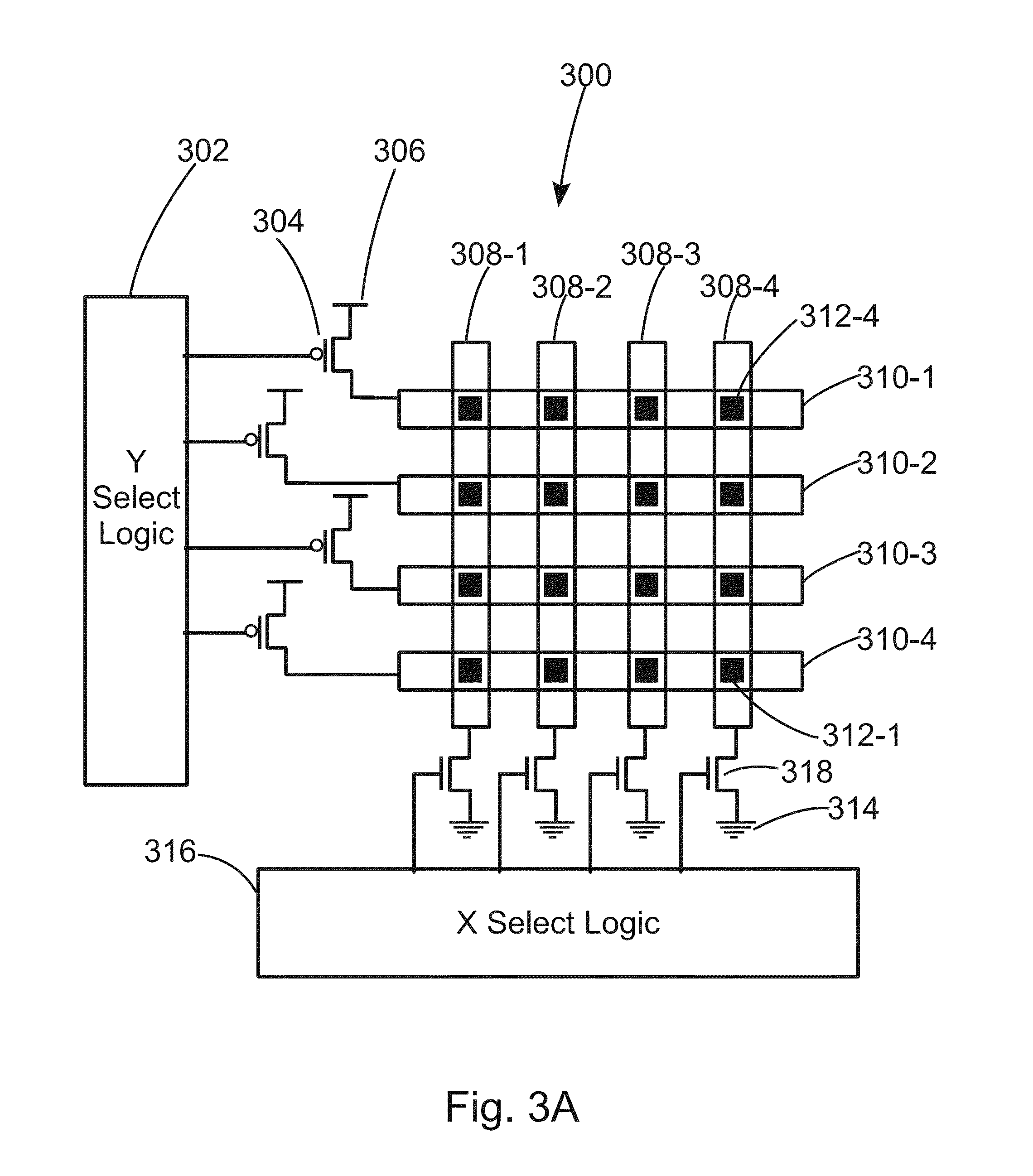

Semiconductor device and structure

ActiveUS8362482B2Reduce high cost of manufacturingReduced flexibilityTransistorSemiconductor/solid-state device testing/measurementDevice materialNOR gate

A semiconductor device including a first layer including first transistors, wherein first logic circuits are constructed by the first transistors, and wherein the first logic circuits include at least one of Inverter, NAND gate, or NOR gate; and a second layer overlaying said first layer, the second layer including second transistors, wherein second logic circuits are constructed by the second transistors; wherein each logic circuit in the first logic circuits has inputs and at least one first output, the inputs are connected to the second logic circuits; wherein each logic circuit in the second logic circuits has a second output, and wherein the first transistors include first selectors adapted to selectively replace at least one of the at least one first outputs with at least one of the second outputs.

Owner:SAMSUNG ELECTRONICS CO LTD

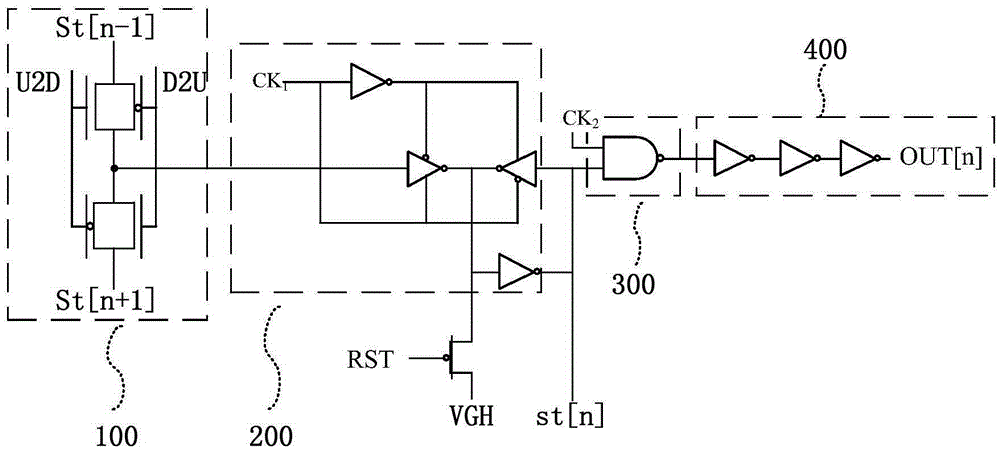

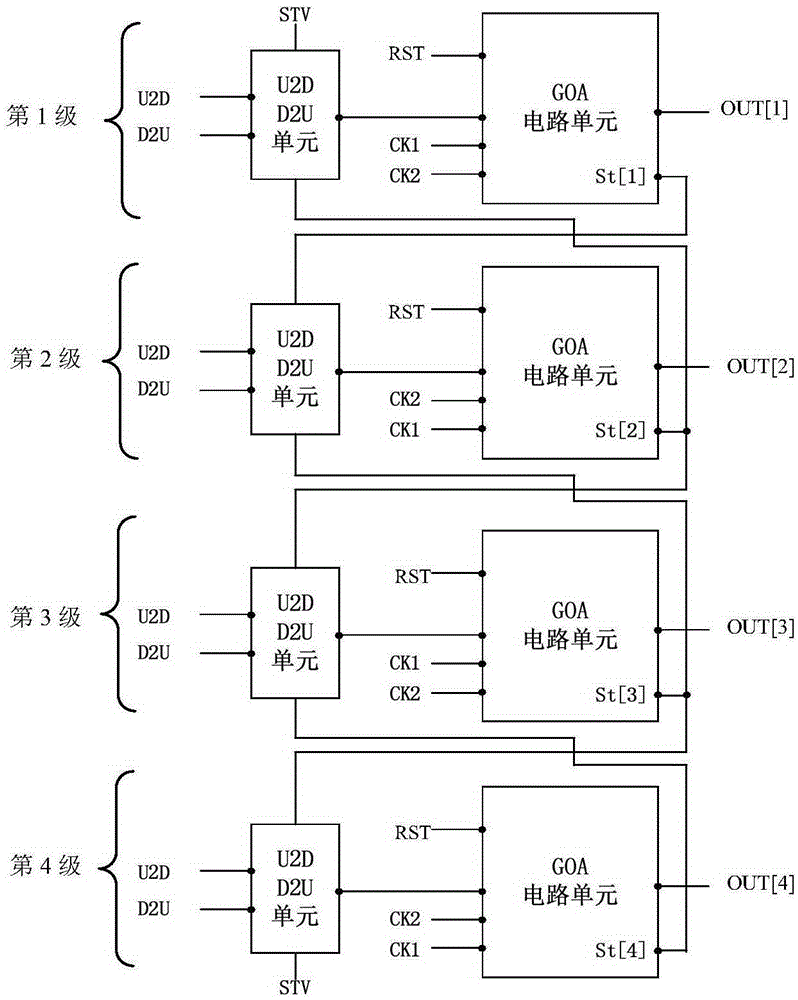

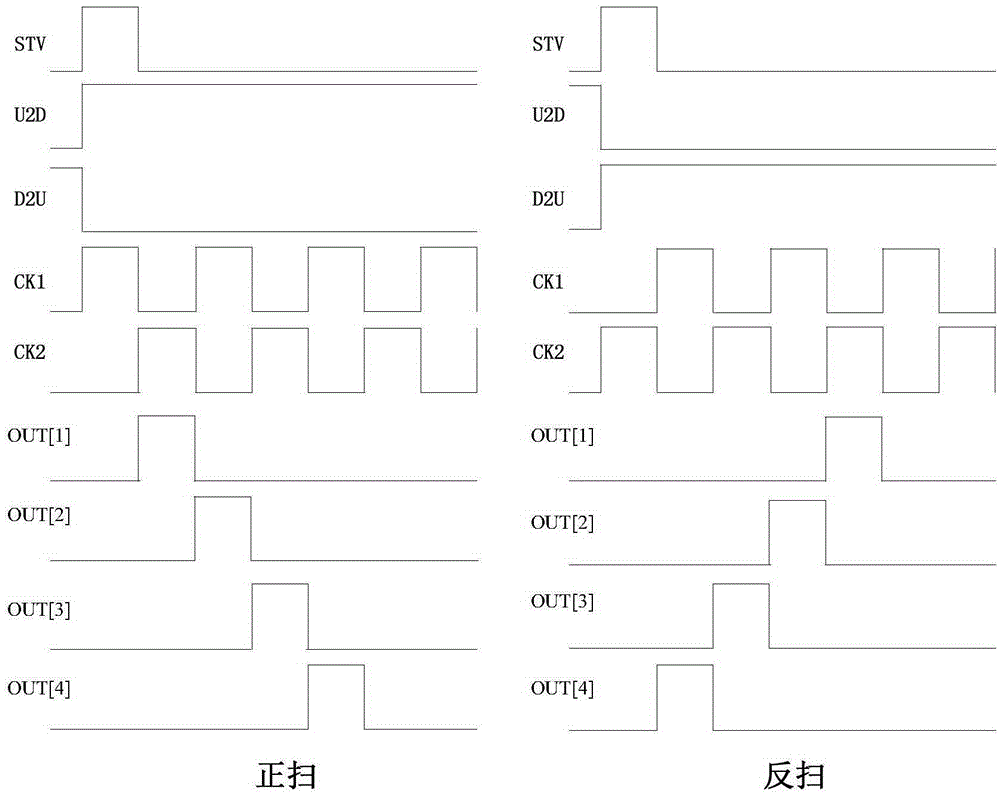

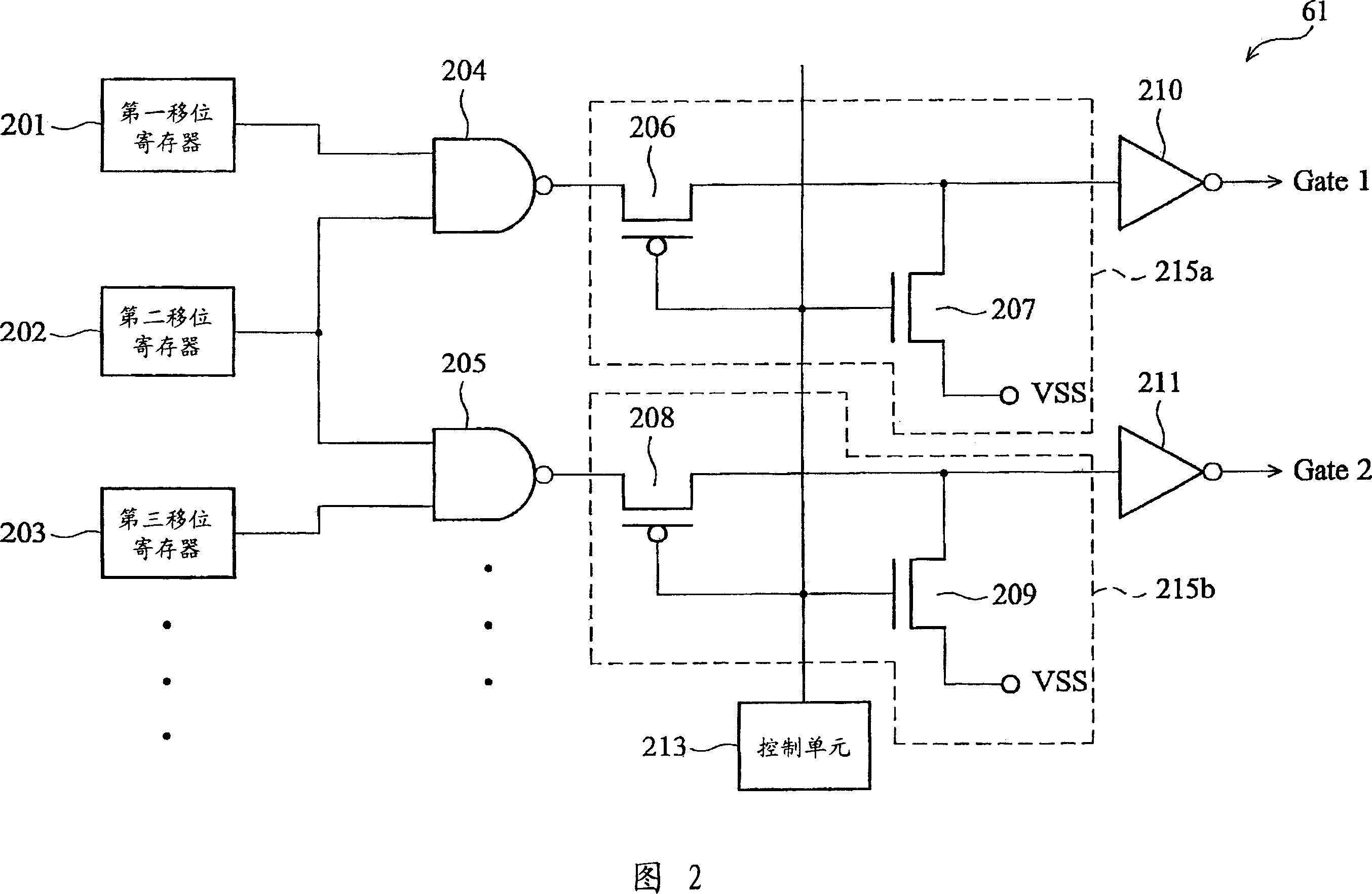

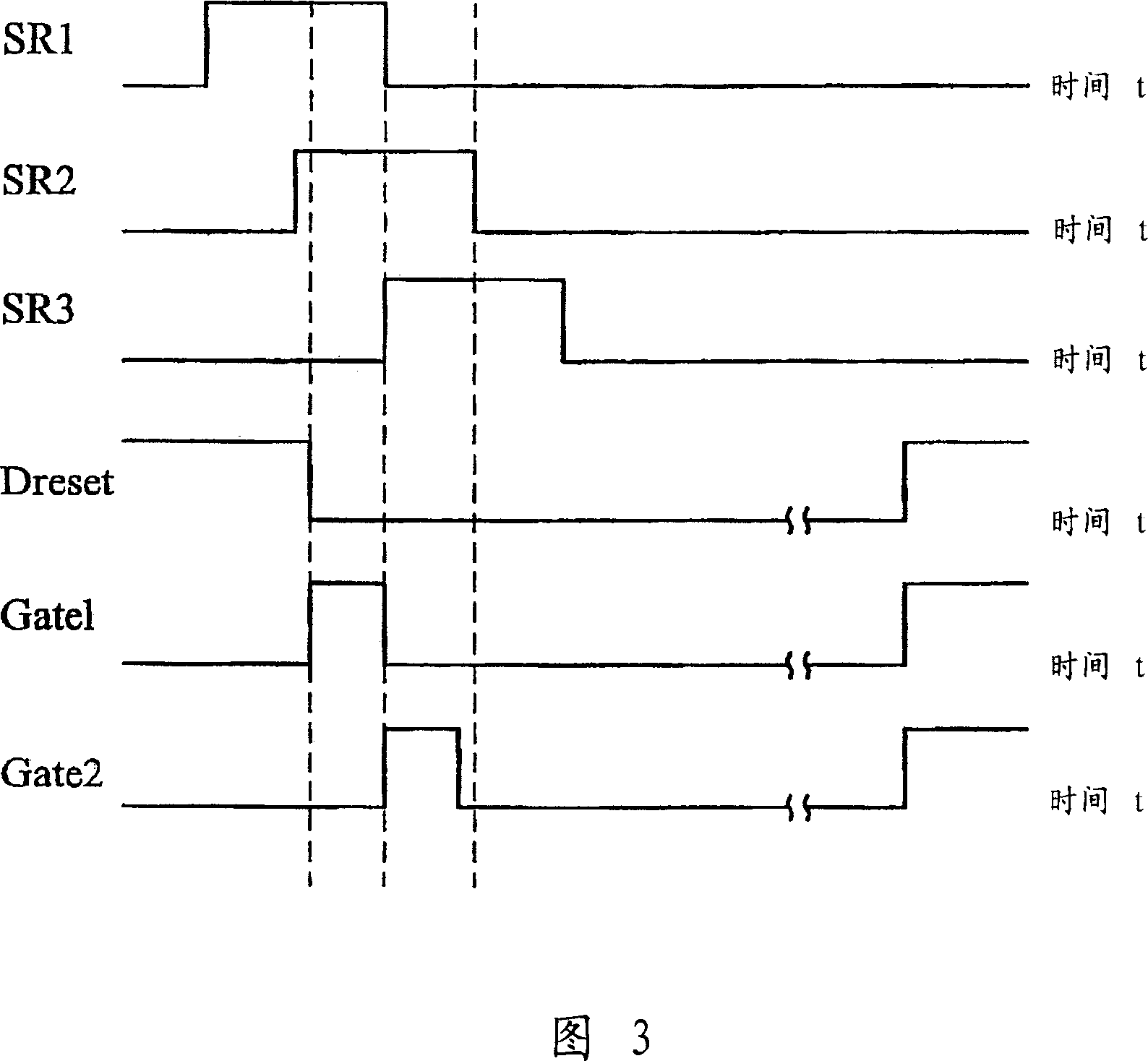

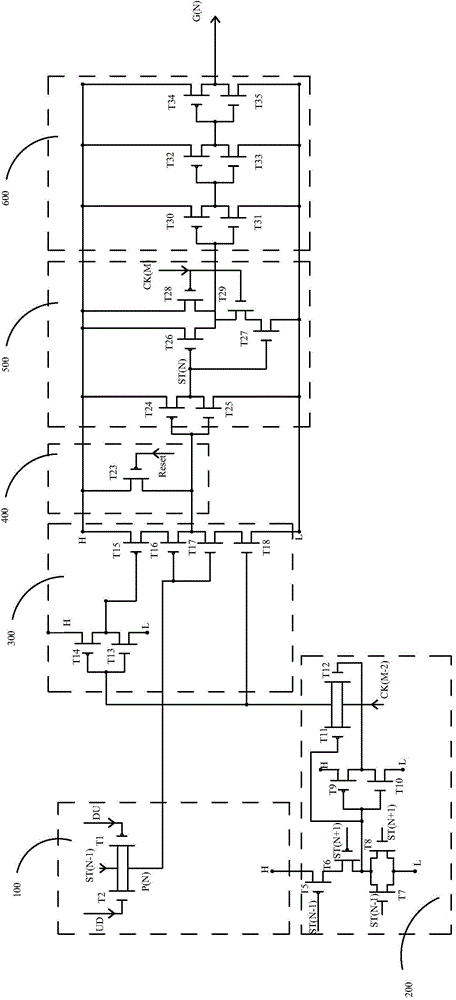

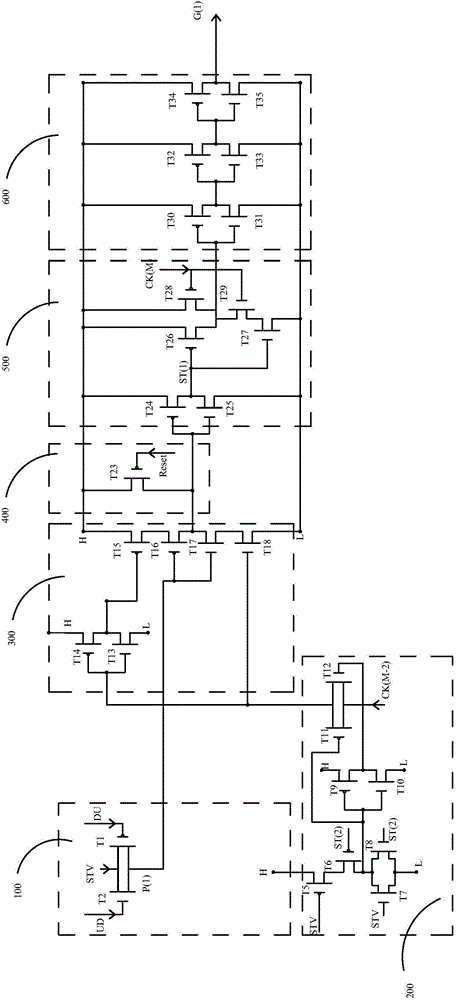

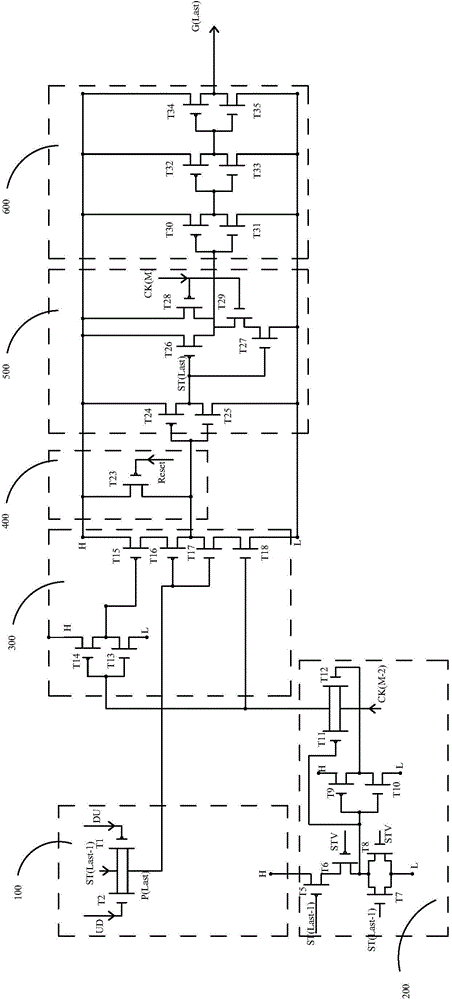

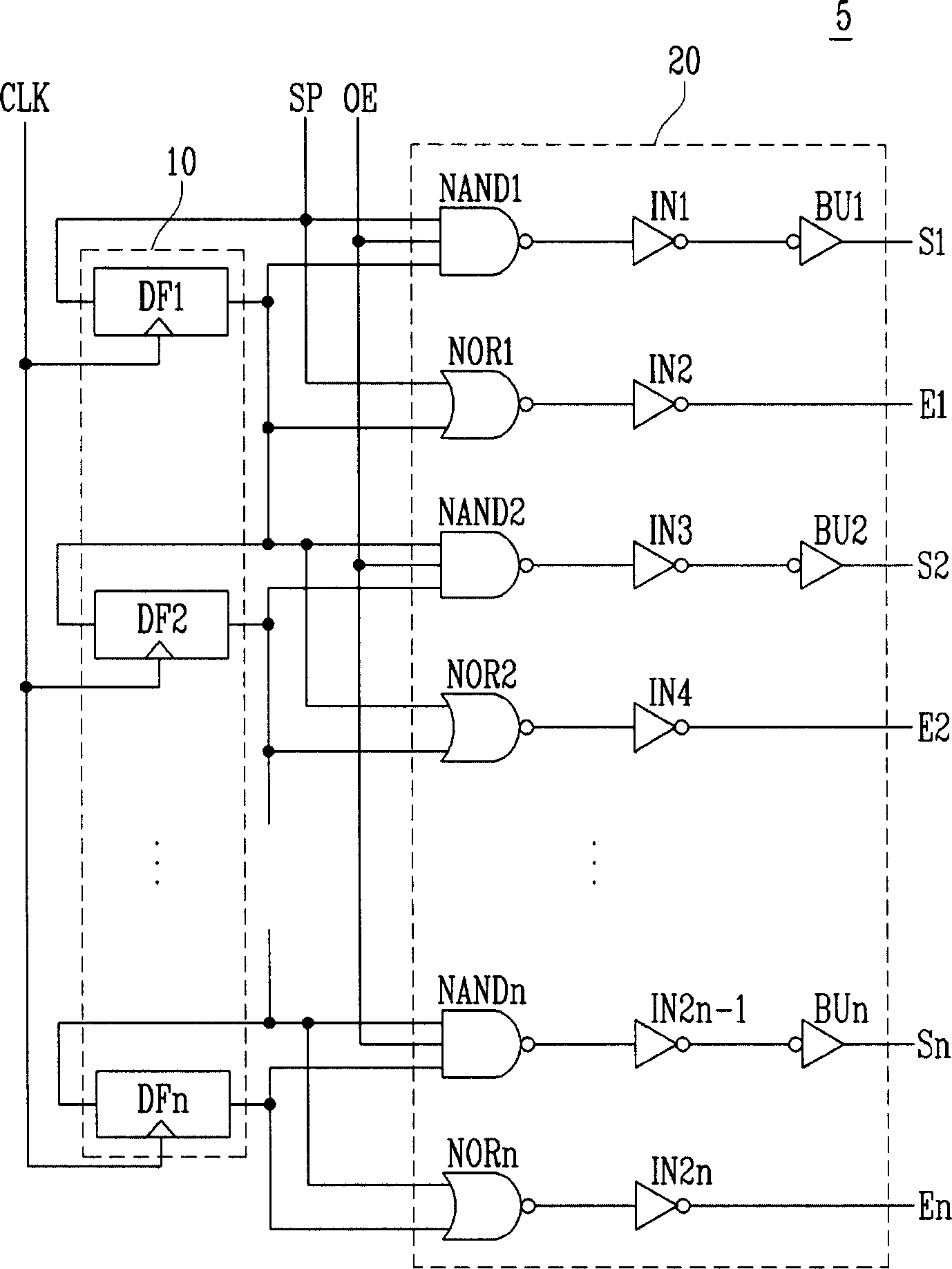

Scan driving circuit and display device thereof

ActiveCN105355179AReduce power consumptionReduce signal linesStatic indicating devicesControl signalNAND gate

The invention discloses a scan driving circuit and a display device thereof. The scan driving circuit of the invention comprises an input unit, a latch unit, an NAND gate signal processing unit and an output buffering unit; and the input unit is configured to control the output of the input unit according to the different input combinations of last-level level transmission control signals, current-level level transmission control signals and next-level level transmission control signals of a current time sequence so as to output the current-level level transmission control signals of a next time sequence. Compared with the prior art, the scan driving circuit and the display device thereof of the invention can realize front and back scanning functions without relying on front and back scanning signals; the signal line and devices of the circuit are greatly reduced, and therefore, the design of a narrow frame can be benefitted, and the power dissipation of the circuit can be decreased; and the structure of existing substrate integrated circuit unit is not required to be modified, and the implementation difficulty of the scan driving circuit is low, the scan driving circuit has a high promotion value.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

Circuits and design structures for monitoring NBTI (negative bias temperature instability) effect and/or PBTI (positive bias temperature instability) effect

A ring oscillator has an odd number of NOR-gates greater than or equal to three, each with first and second input terminals, a voltage supply terminal, and an output terminal. The first input terminals of all the NOR-gates are interconnected, and each of the NOR-gates has its output terminal connected to the second input terminal of an immediately adjacent one of the NOR-gates. During a stress mode, a voltage supply and control block applies a stress enable signal to the interconnected first input terminals, and an increased supply voltage to the voltage supply terminals. During a measurement mode, this block grounds the interconnected first input terminals, and applies a normal supply voltage to the voltage supply terminals. Also included are an analogous NAND-gate based circuit, a circuit combining the NAND- and NOR-aspects, a circuit with a ring oscillator where the inverters may be coupled directly or through inverting paths, and circuits for measuring the bias temperature instability effect in pass gates.

Owner:GLOBALFOUNDRIES US INC

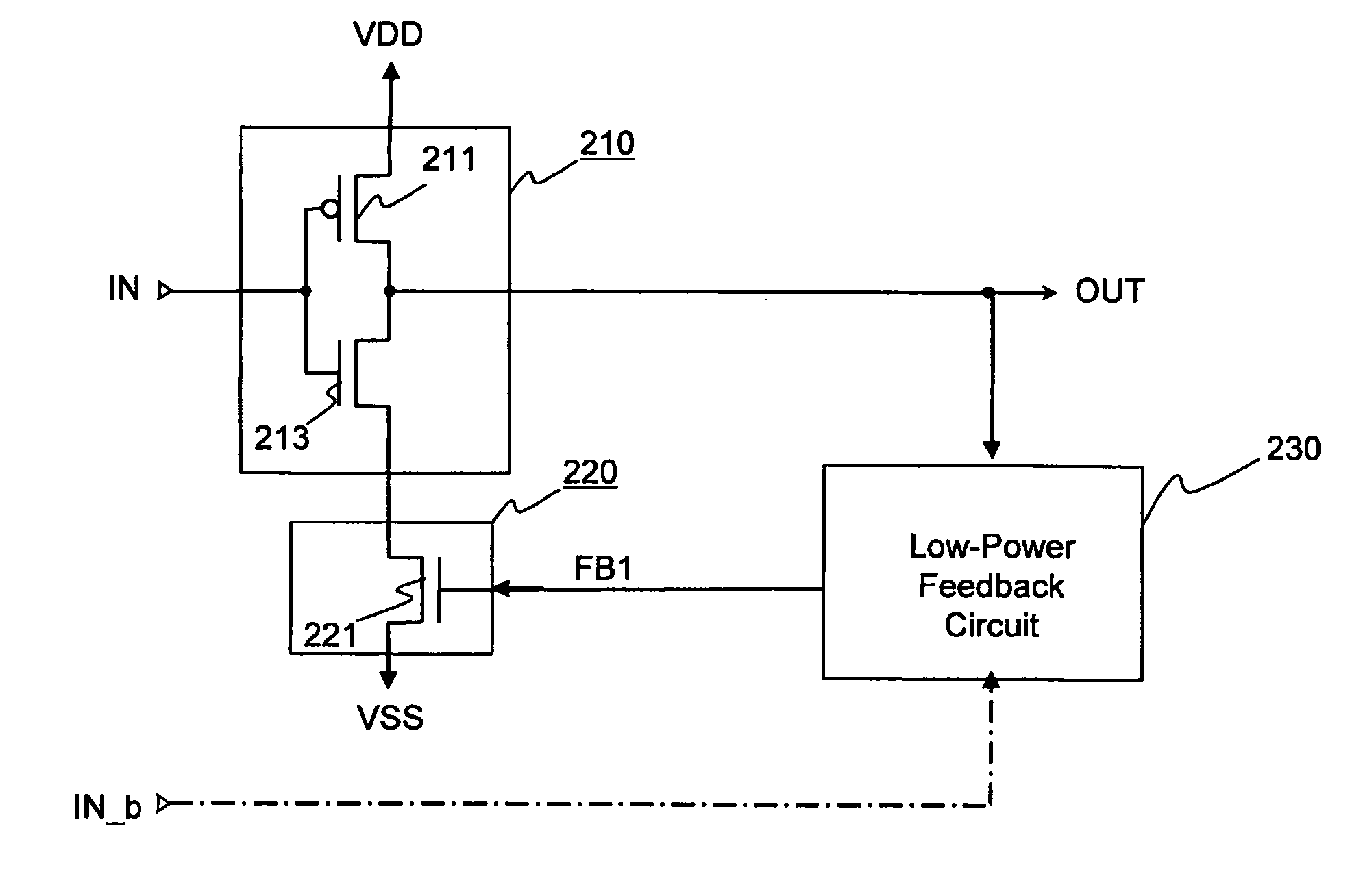

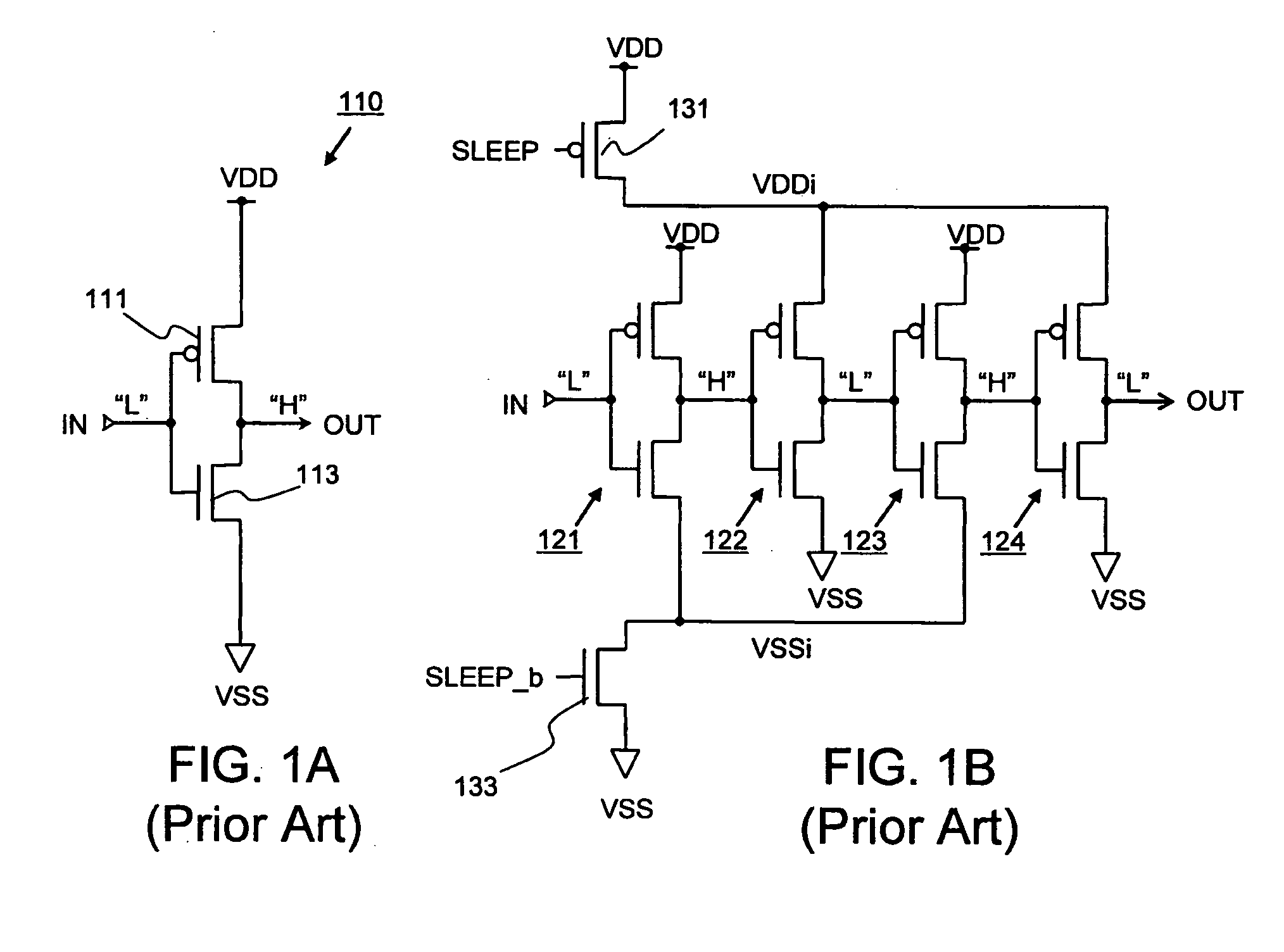

Semiconductor integrated circuit having current leakage reduction scheme

InactiveUS20070075743A1Reduce power consumptionIncrease speedTransistorReliability increasing modificationsCMOSNOR gate

A semiconductor integrated circuit includes a CMOS controlled inverter consisting of series-connected PMOS and NMOS transistors. The source of the NMOS transistor is coupled to a ground line through an additional NMOS transistor for power gating of voltage VSS. The source of the PMOS transistor can be coupled to a power supply line through an additional PMOS transistor for power gating of voltage VDD. The inverter receives an input signal IN and its complementary version that has transitioned earlier than the input signal. In response to the input signal, the inverter produces an output signal. A NAND gate that receives the output signal and the complementary input signal controls the power gating NMOS transistor. A NOR gate that receives the output signal and the complementary input signal controls the power gating PMOS transistor. The power gating to the CMOS inverter is performed by feedback of the output signal and the complementary input signal, with the result that current leakage reduction through the CMOS controlled inverter is achieved. A self leakage reduction with power gating transistors is applicable to another type of logic gates such as NAND, NOR and Exclusive-OR, AND, OR.

Owner:CONVERSANT INTPROP MANAGEMENT INC

Organic light emitting display

InactiveUS20080246697A1Reduce module process costImprove reliabilityElectrical apparatusStatic indicating devicesShift registerElectricity

An organic light emitting display includes: a first shift register which is electrically coupled with a clock line, a negative clock line, and an initial drive line; a first NAND gate which is electrically coupled with the initial drive line, a first light emitting control line which is an output line of the first shift register, and a first clock line; a second NAND gate which is electrically coupled with the initial drive line, the first light emitting control line, and a second clock line; a first pixel part which is electrically coupled with a first scan line which is an output line of the first NAND gate; a second pixel part which is electrically coupled with a second scan line which is an output line of the second NAND gate; a third pixel part which is electrically coupled with the first scan line; and a fourth pixel part which is electrically coupled with the second scan line.

Owner:SAMSUNG DISPLAY CO LTD

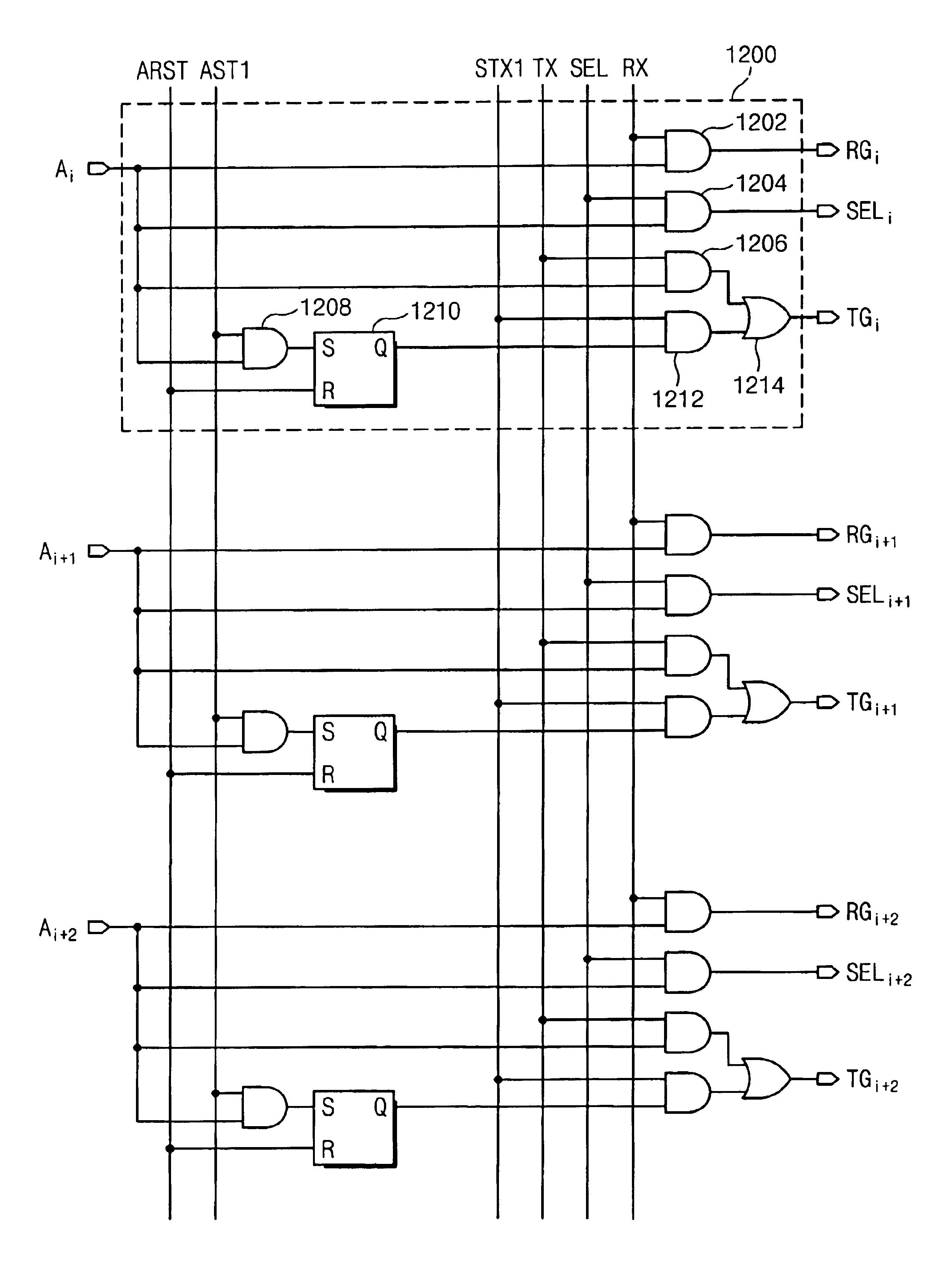

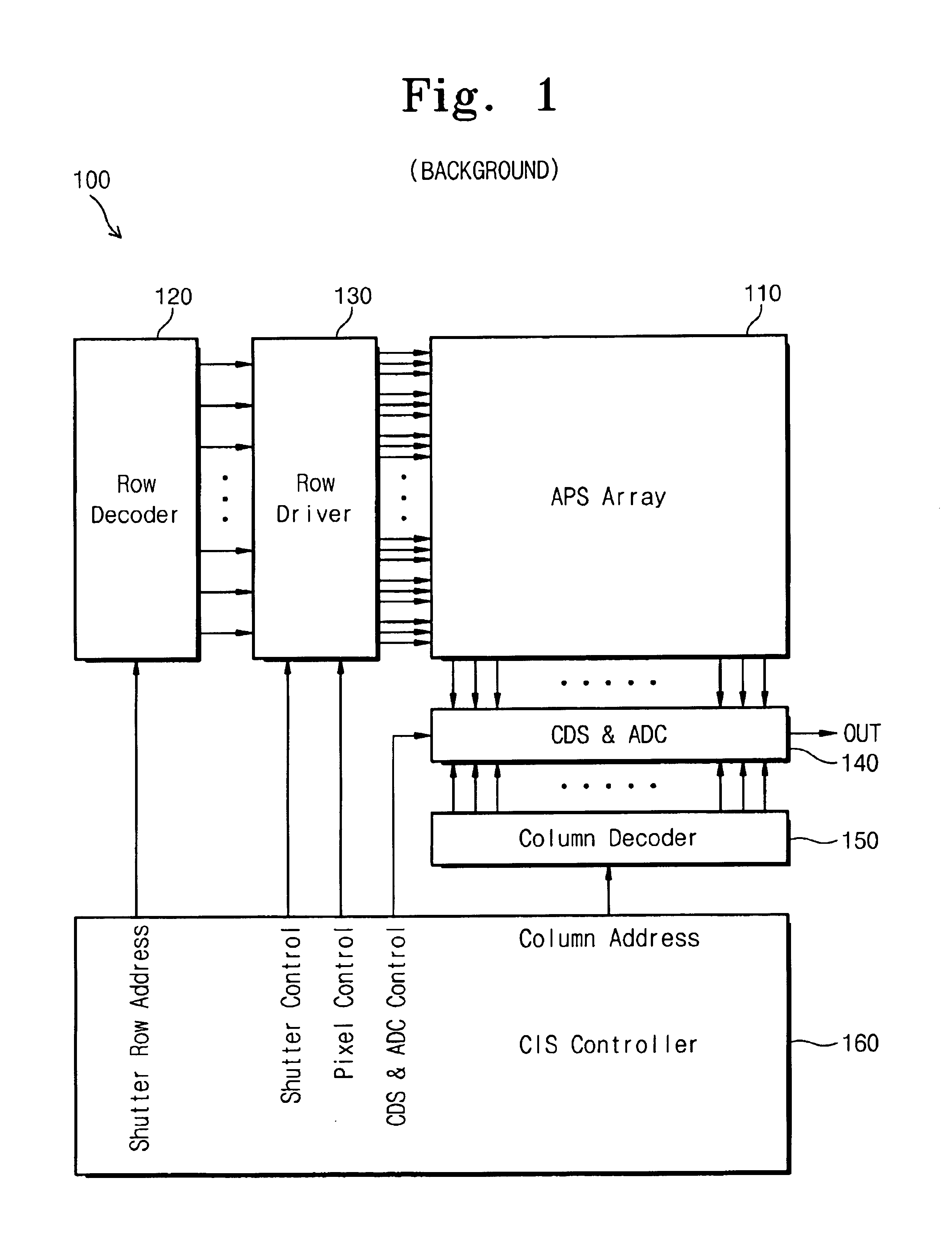

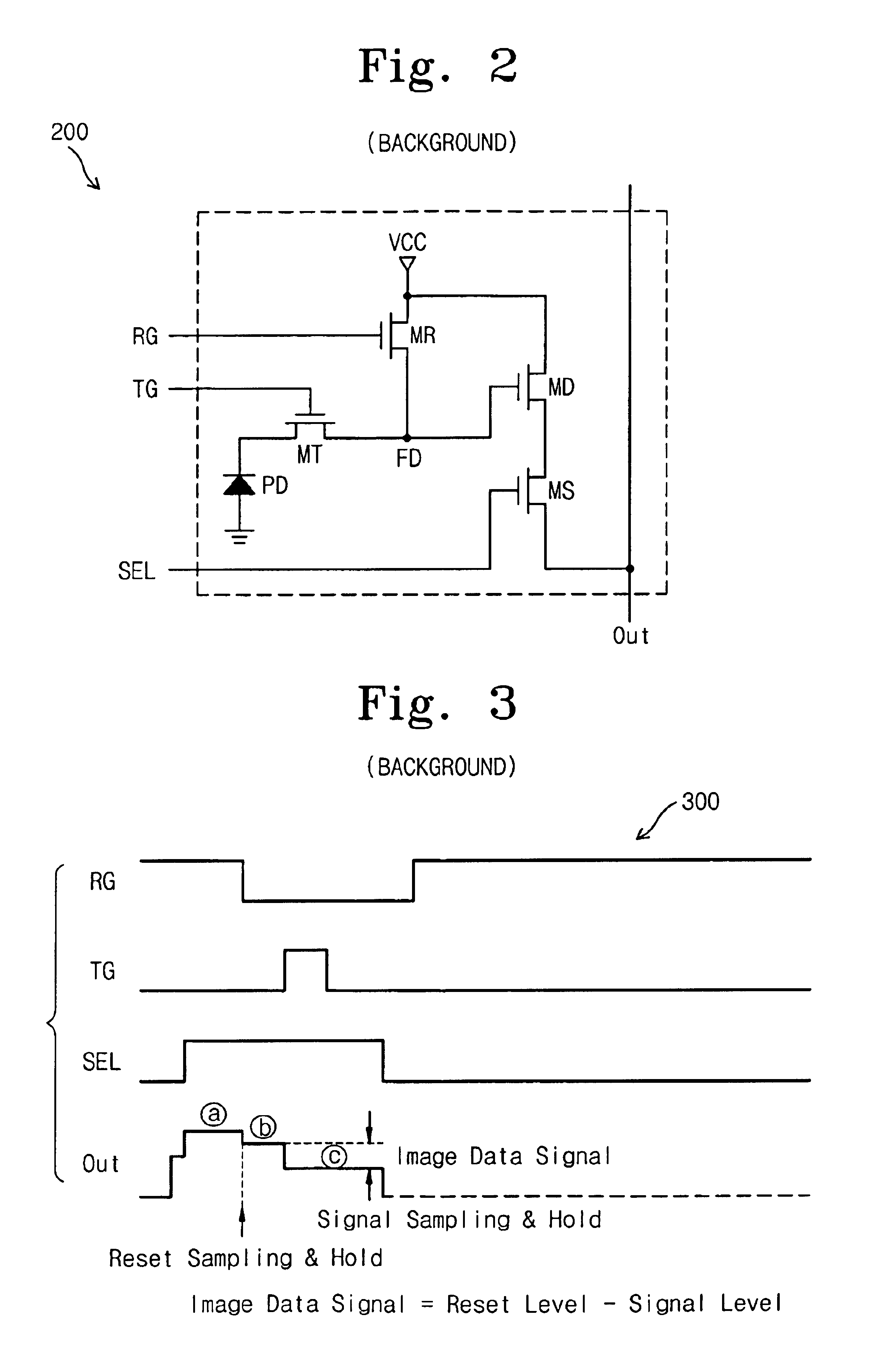

CMOS image sensor having row decoder capable of shutter timing control

Owner:SAMSUNG ELECTRONICS CO LTD

Organic light emitting display

InactiveCN101281719AReduce processing costsImprove reliabilityElectrical apparatusStatic indicating devicesShift registerScan line

An organic light emitting display includes: a first shift register which is electrically coupled with a first clock line, a second inverted clock line, and an initial drive line; a first NAND gate which is electrically coupled with the initial drive line, a first light emitting control line which is an output line of the first shift register, and a third clock line; a second NAND gate which is electrically coupled with the initial drive line, the first light emitting control line, and a fourth clock line; a first pixel part which is electrically coupled with a first scan line which is an output line of the first NAND gate; a second pixel part which is electrically coupled with a second scan line which is an output line of the second NAND gate; a third pixel part which is electrically coupled with the first scan line; and a fourth pixel part which is electrically coupled with the second scan line.

Owner:SAMSUNG DISPLAY CO LTD

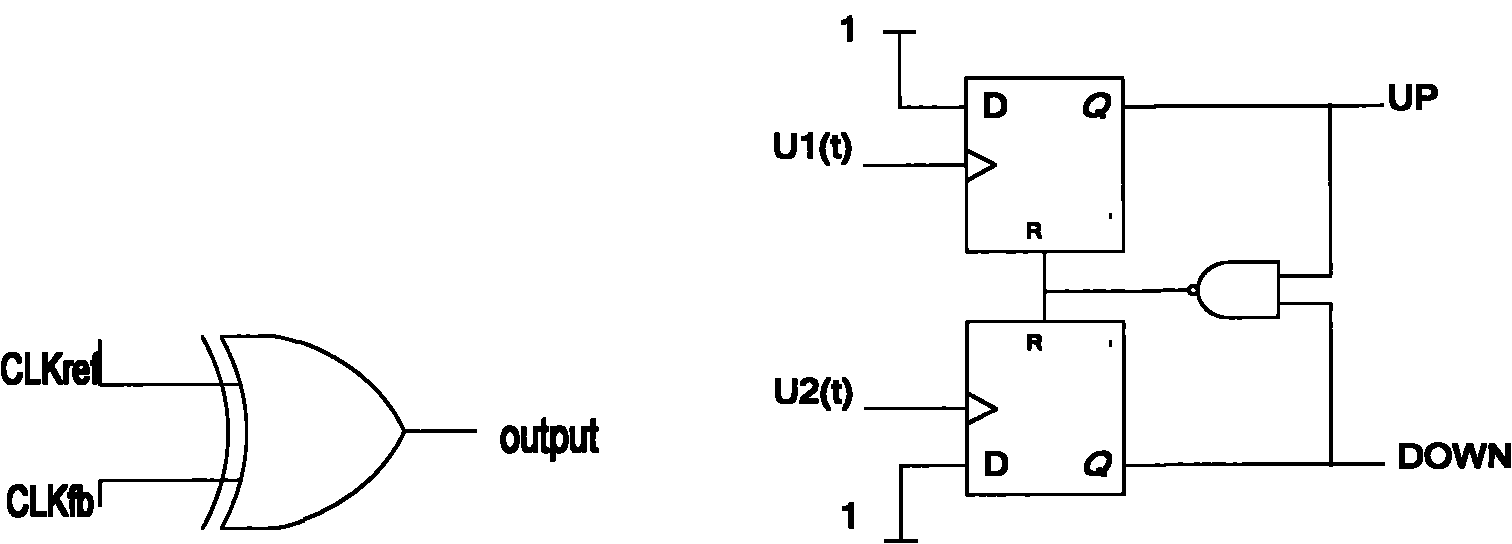

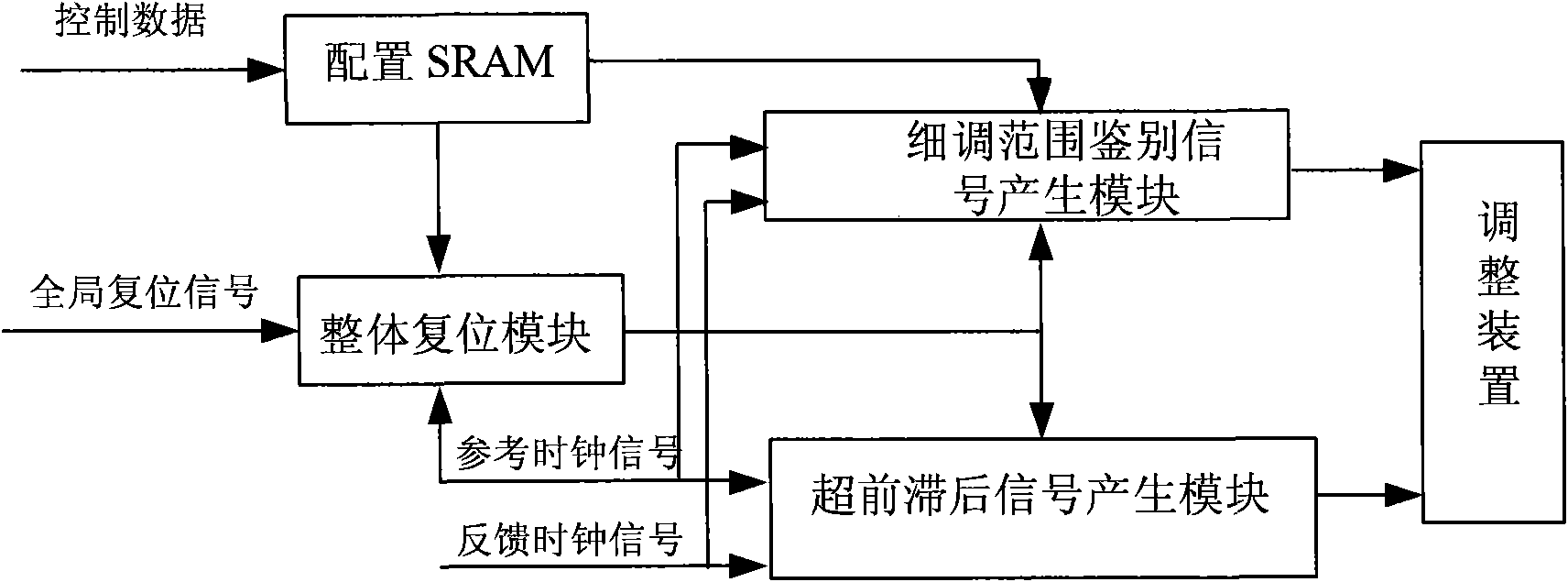

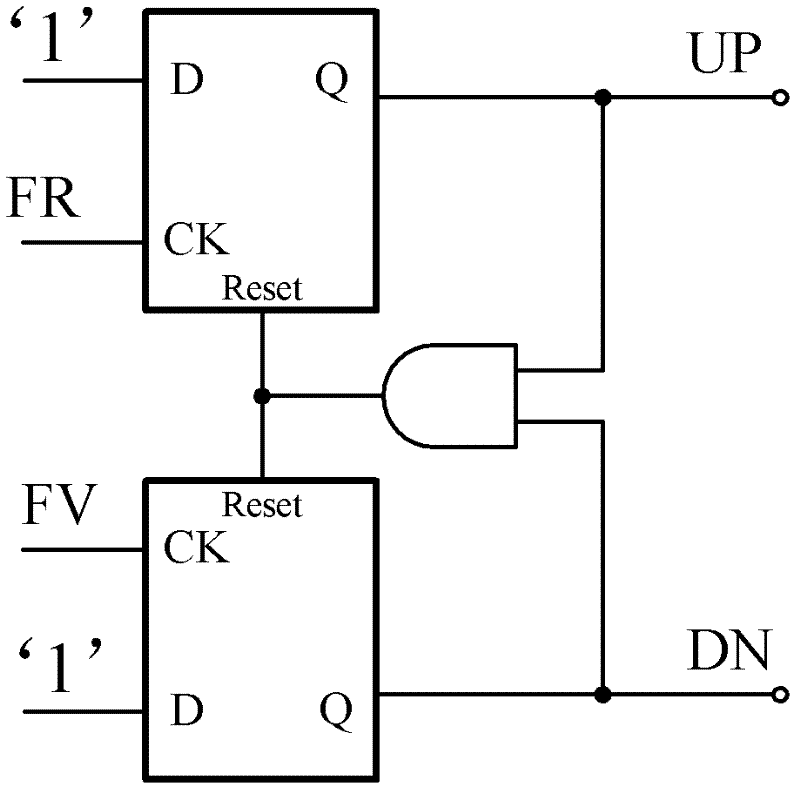

Configurable phase discriminator for time-delay locking ring

ActiveCN101789784AAdjust lock timeImprove controllabilityPulse automatic controlDiscriminatorPhase detector

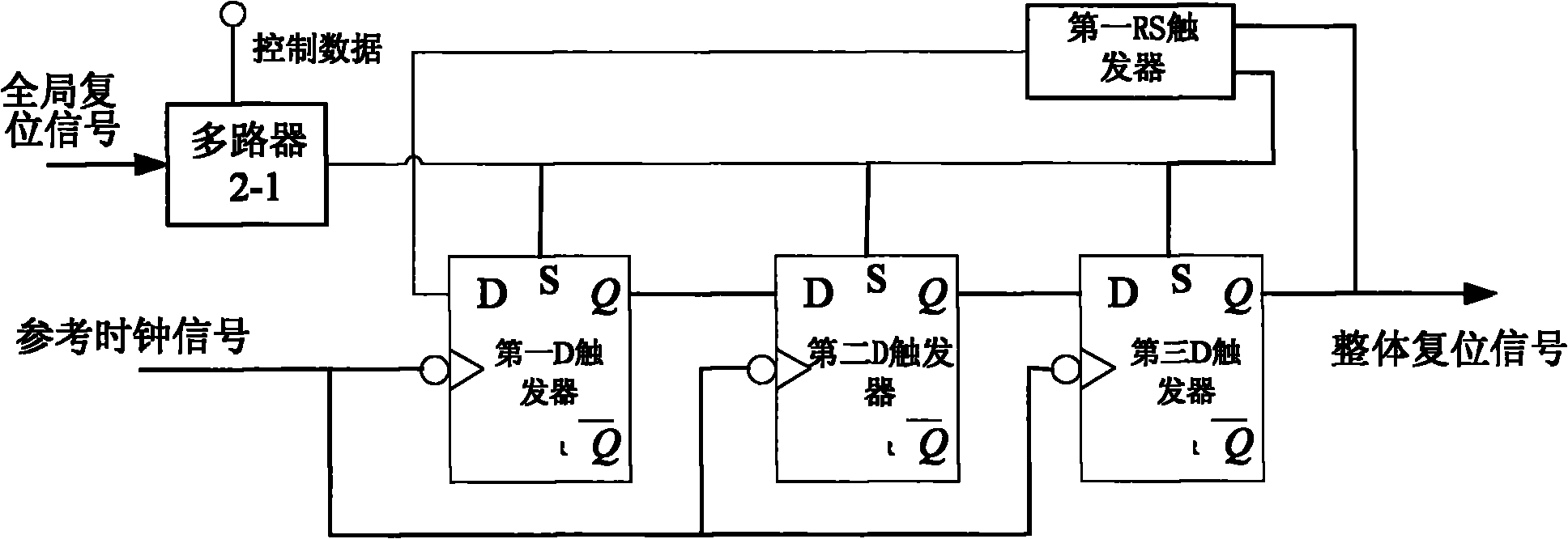

The invention relates to a configurable phase discriminator for a time-delay locking ring, which comprises a configurable SRAM, an integral resetting module, an advanced-lagged signal generating module and a fine adjusting range identification signal generating module. Data in the embedded configurable SRAM is changed and different phase discriminating precisions are set according to different application requirements, so as to realize the controllability of fine and rough adjusting; meanwhile, as the embedded configurable SRAM controls different starting moments of fine adjusting, the structure of hardware does not need to be changed in the using process and the locking time of a loop circuit can be adjusted only by changing a code stream in the SRAM according to the requirements. In addition, the advanced-lagged signal generating module which is composed of two D triggers and three RS triggers is used for sampling and outputting two input clock signals and judging whether the two input clock signals are advanced or lagged; the fine adjusting range identification signal generating module which is composed of a nand gate and two pulse generating circuits is used not only for judging whether the phase difference of the two clocks reaches the set fine adjusting range, but also for controlling the starting time of fine adjusting by controlling the pulse generating width.

Owner:BEIJING MXTRONICS CORP +1

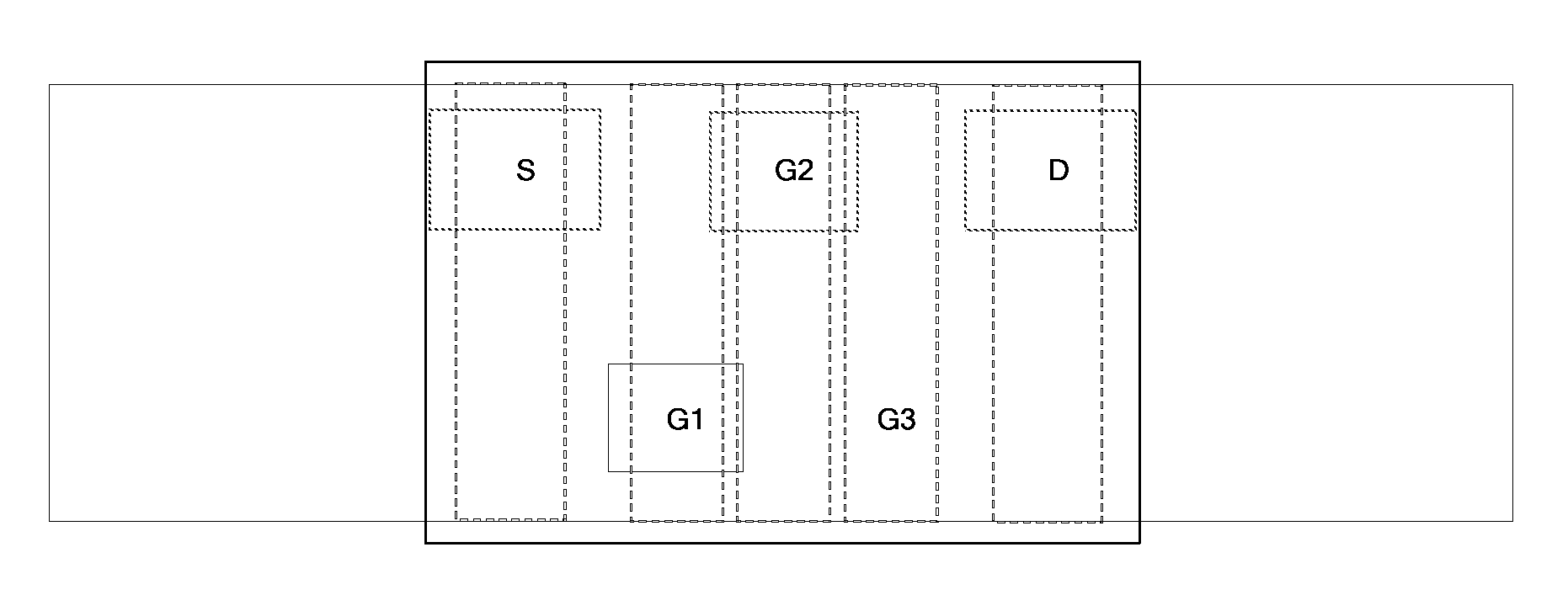

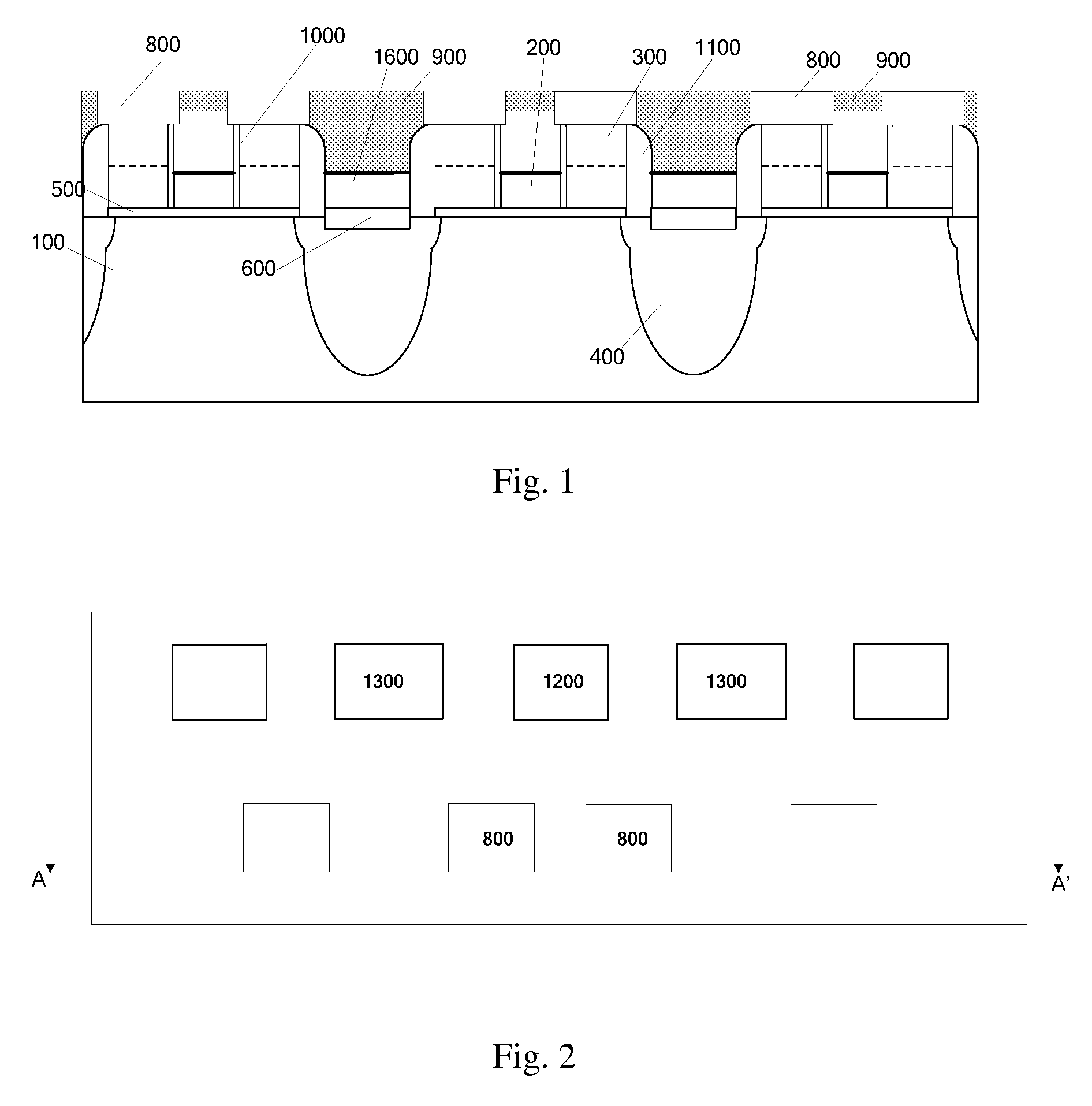

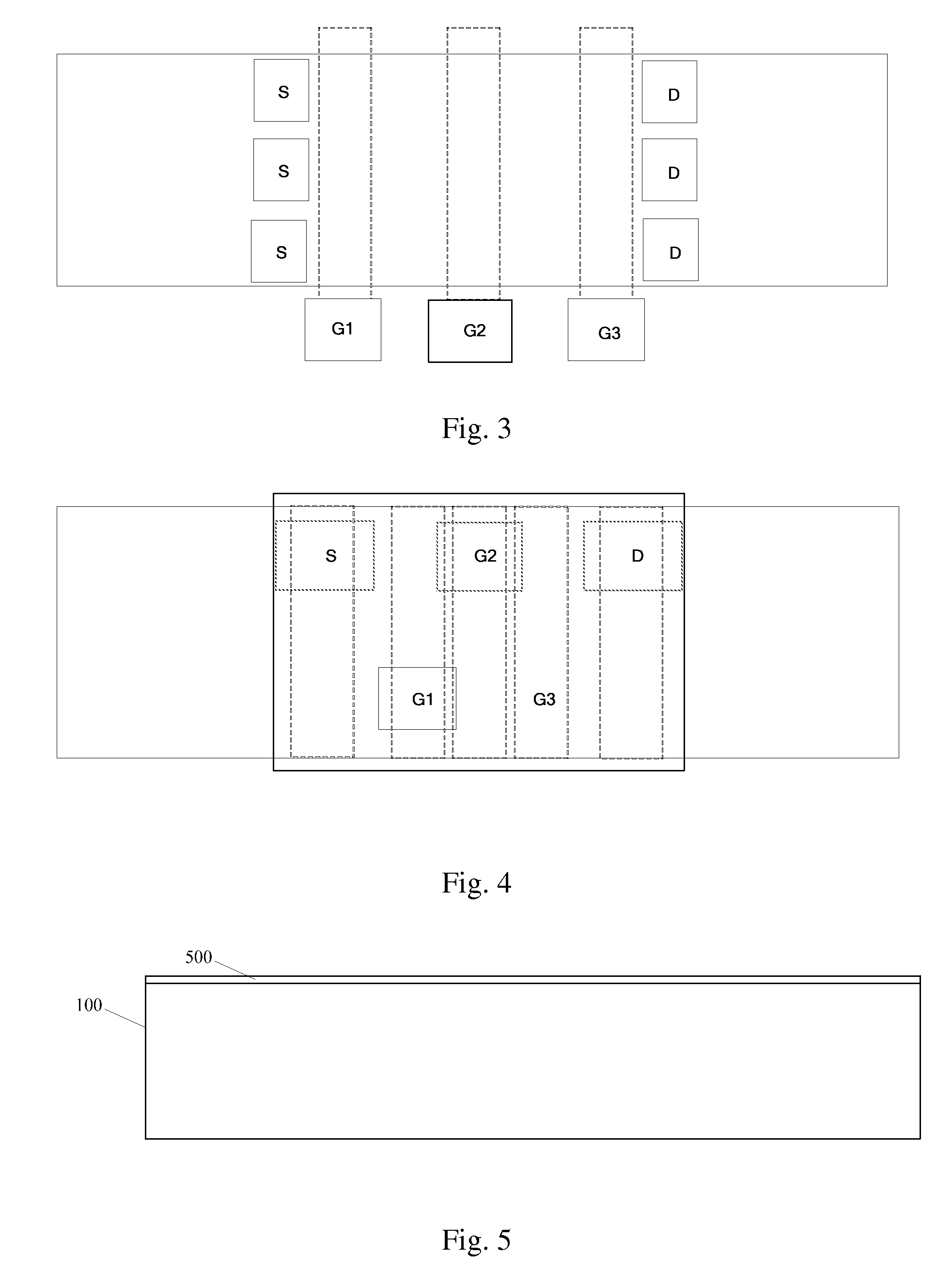

NAND structure and method of manufacturing the same

InactiveUS20120319185A1Small sizeIncrease storage capacitySolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerGate insulator

The present invention provides a NAND gate structure, comprising: a substrate; a gate insulation layer formed on the substrate; a source / drain region formed in the substrate; a middle gate formed on the gate insulator layer, a first gate and a second gate on each side of the middle gate, first sidewall spacers between the first gate and the middle gate and between the second gate and the middle gate, and second sidewall spacers outside the first gate and the second gate, wherein, a first contact hole region is provided on the middle gate, second contact hole regions are provided respectively on the first gate and the second gate, and the first contact hole region and the second contact hole regions are in staggered arrangement. The present invention proposes a new NAND structure and a method of manufacturing the same. With the NAND structure, about 30-50% area of the chip may be effectively reduced.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

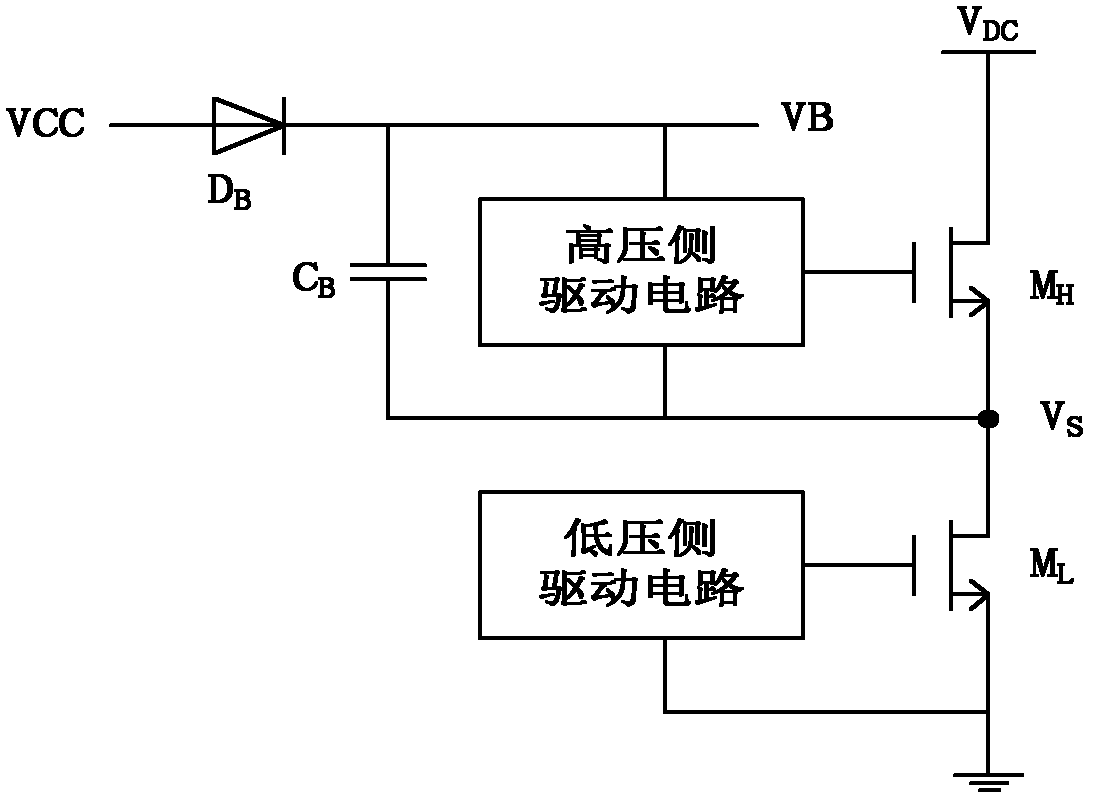

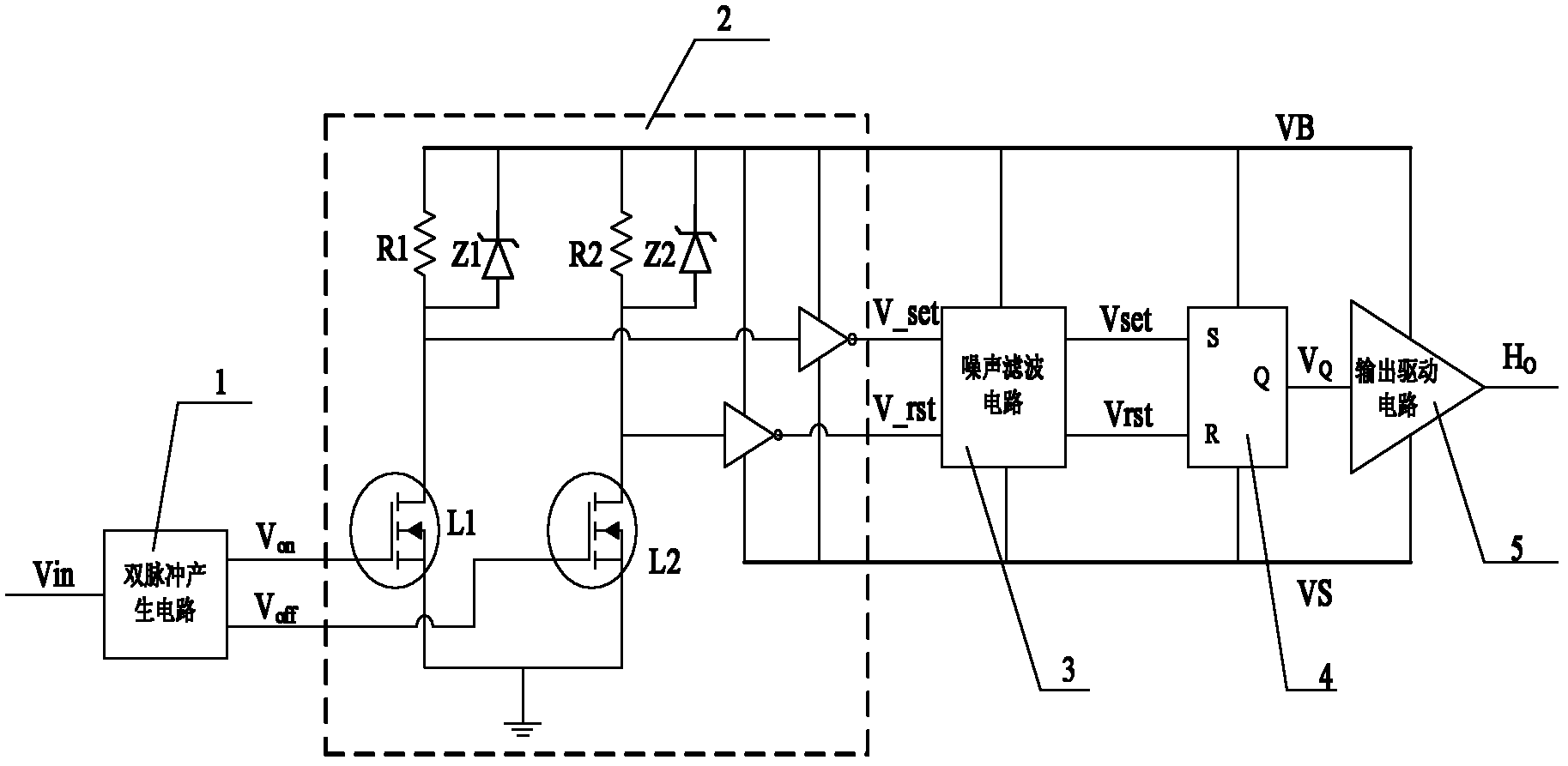

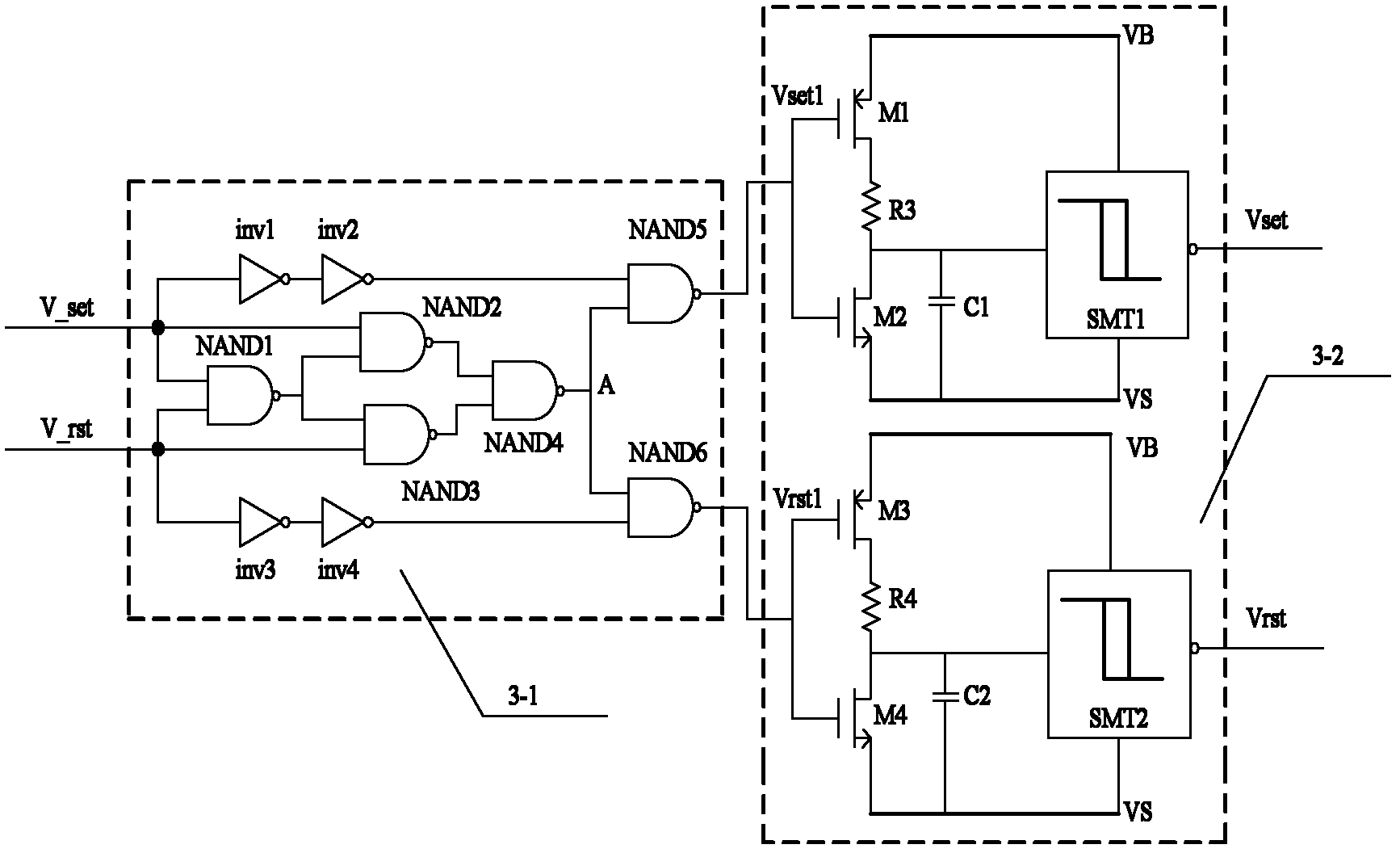

High-voltage side grid drive circuit resistant to power supply noise interference

ActiveCN102611425AReduce the impact of working statusGuarantee signalReliability increasing modificationsNAND gateHemt circuits

A high-voltage side grid drive circuit resistant to power supply noise interference comprises a floating power supply VB-VS, a dual pulse generating circuit, a high-voltage level shift circuit, a noise filtering circuit including a random detuning noise filtering circuit, an RS (reset-set) trigger and an output drive circuit. A common-mode noise filtering circuit is connected onto the random detuning noise filtering circuit, a first output end and a second output end of the common-mode noise filtering circuit are connected with a first input end and a second input end of the random detuning noise filtering circuit, and the common-mode noise filtering circuit comprises six NAND gates and four inverters and is capable of effectively filtering power supply common-mode noises generated during floating of the high-voltage side power supply VB, so that false triggering of the high-voltage side circuit caused by common-mode noise interference is avoided. The common-mode noise filtering circuit adopting a pure digital circuit and without a passive device is simple in structure, and suitable for application of chips of the high-voltage side grid drive circuit, a half-bridge drive circuit and an intelligent power module and the like.

Owner:SOUTHEAST UNIV

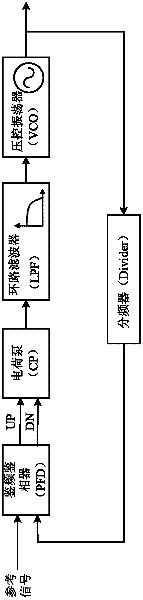

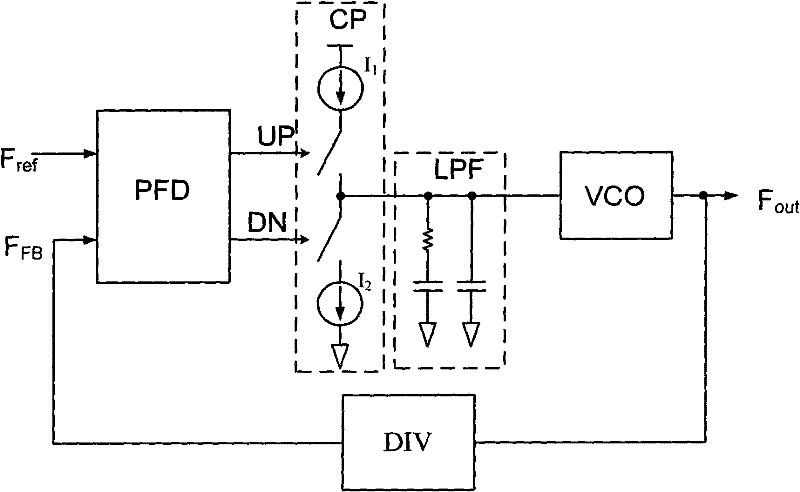

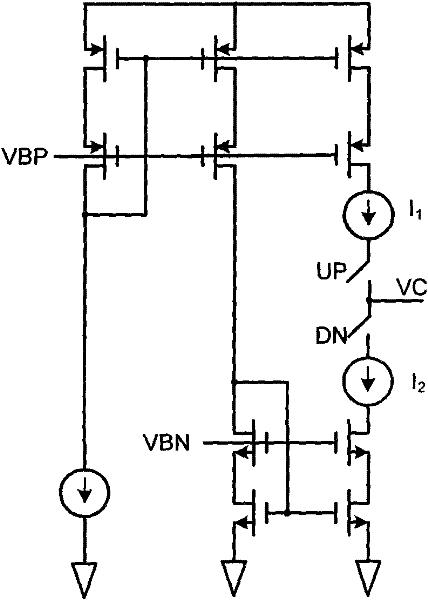

Fully differential frequency and phase detector with adjustable reset delay

InactiveCN102291127AReduce phase detection errorHigh sensitivityPulse automatic controlDiscriminatorControl signal

The invention discloses a fully differential reset delay adjustable frequency and phase discriminator, which comprises four RS triggers, nand gates G0, a delay control circuit DL and two output buffer circuits, wherein all the four RS triggers have the structures that two nand gates are crossed and coupled; all nand gates are fully differential static CMOS (Complementary Metal Oxide Semiconductor) logics with positive feedback; the DL delay circuit is formed by cascading three delay fixed units and three delay controllable units; and each buffer circuit is formed by cascading fully differential phase inverters with transistors of multiplied sizes and positive feedback. Reset signals generated by the nand gates G0 are delayed by the DL circuit to perform reset control on the four RS triggers; and four paths of pulse control signals are output by the second RS trigger and the fourth RS trigger through the buffer circuits which are connected with the second RS trigger and the fourth RS trigger respectively. The discriminator has the advantages of small phase discrimination error, controllable reset delay, high driving capacity and high matching degree output of the four paths of pulse control signals and can be used for a high-performance phase locked frequency synthesizer.

Owner:XIDIAN UNIV

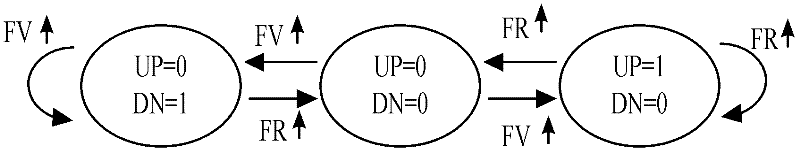

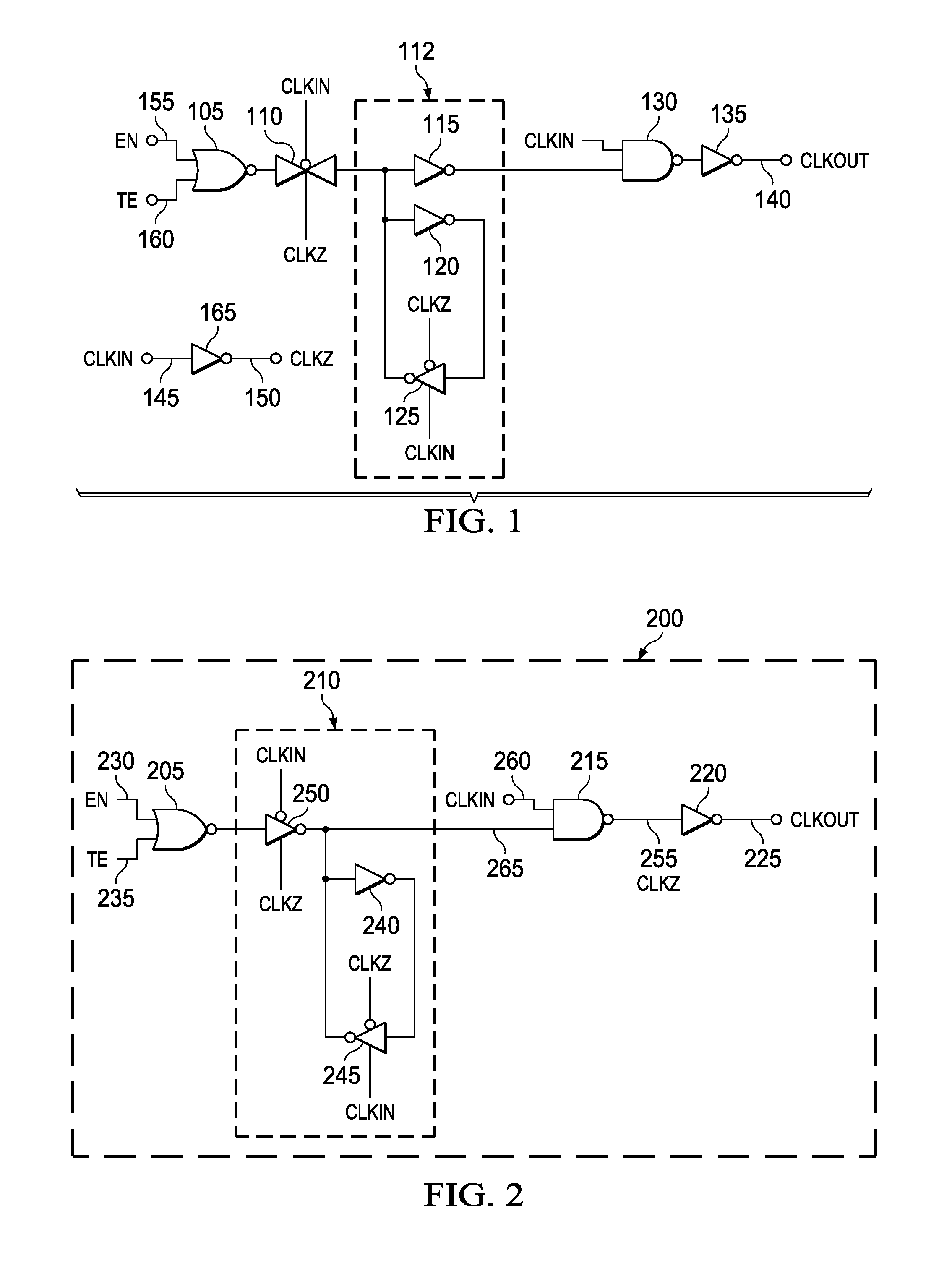

Low clock-power integrated clock gating cell

In an integrated clock gating (ICG) cell a latch is coupled to a NOR gate. The NOR gate receives an enable signal. The latch is configured to generate a latch output in response to the state of the enable signal. The latch includes a tri-state inverter. A NAND gate is coupled to the latch and the NAND gate is configured to generate an inverted clock signal in response to the latch output and a clock input.

Owner:TEXAS INSTR INC

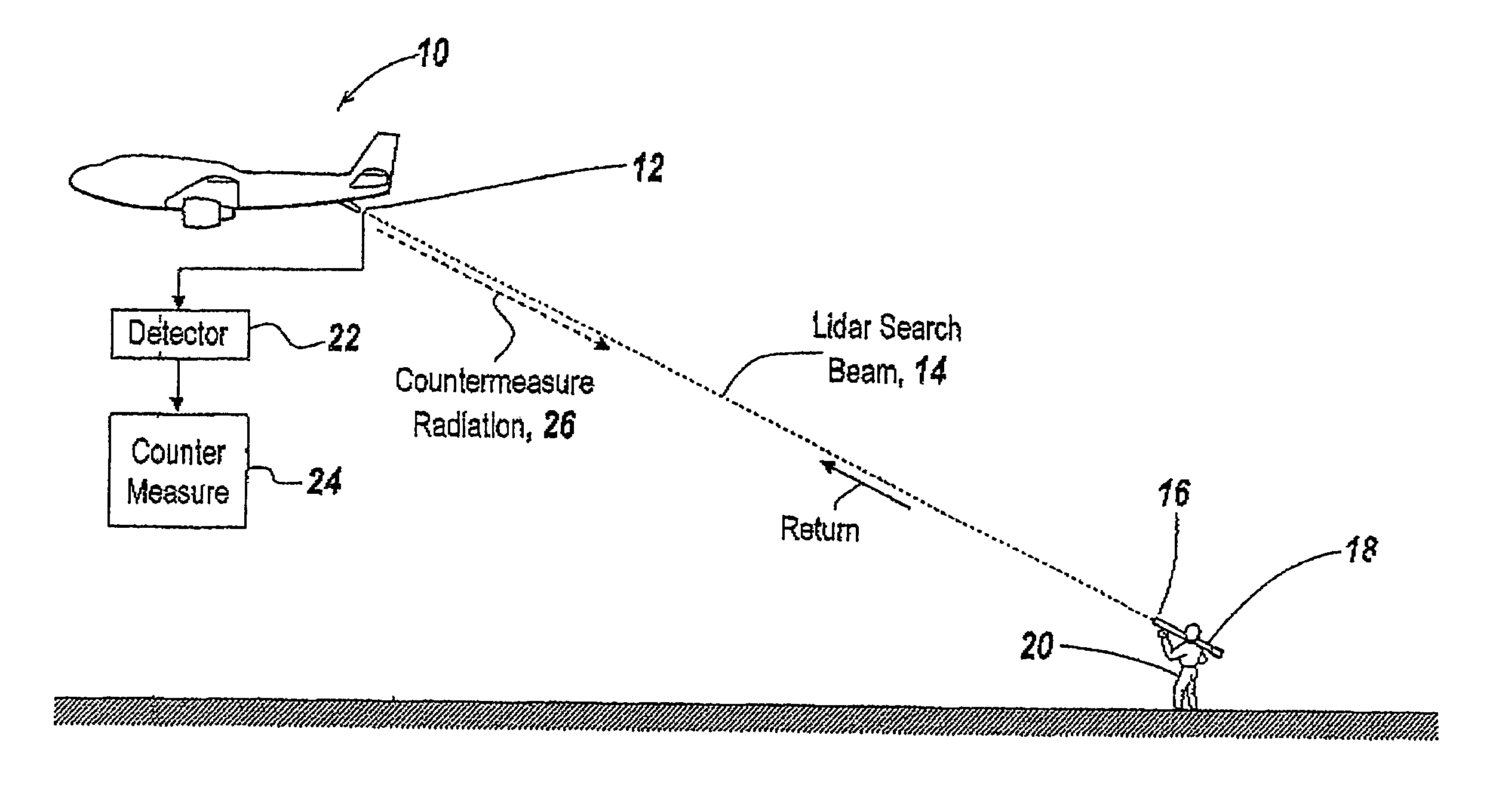

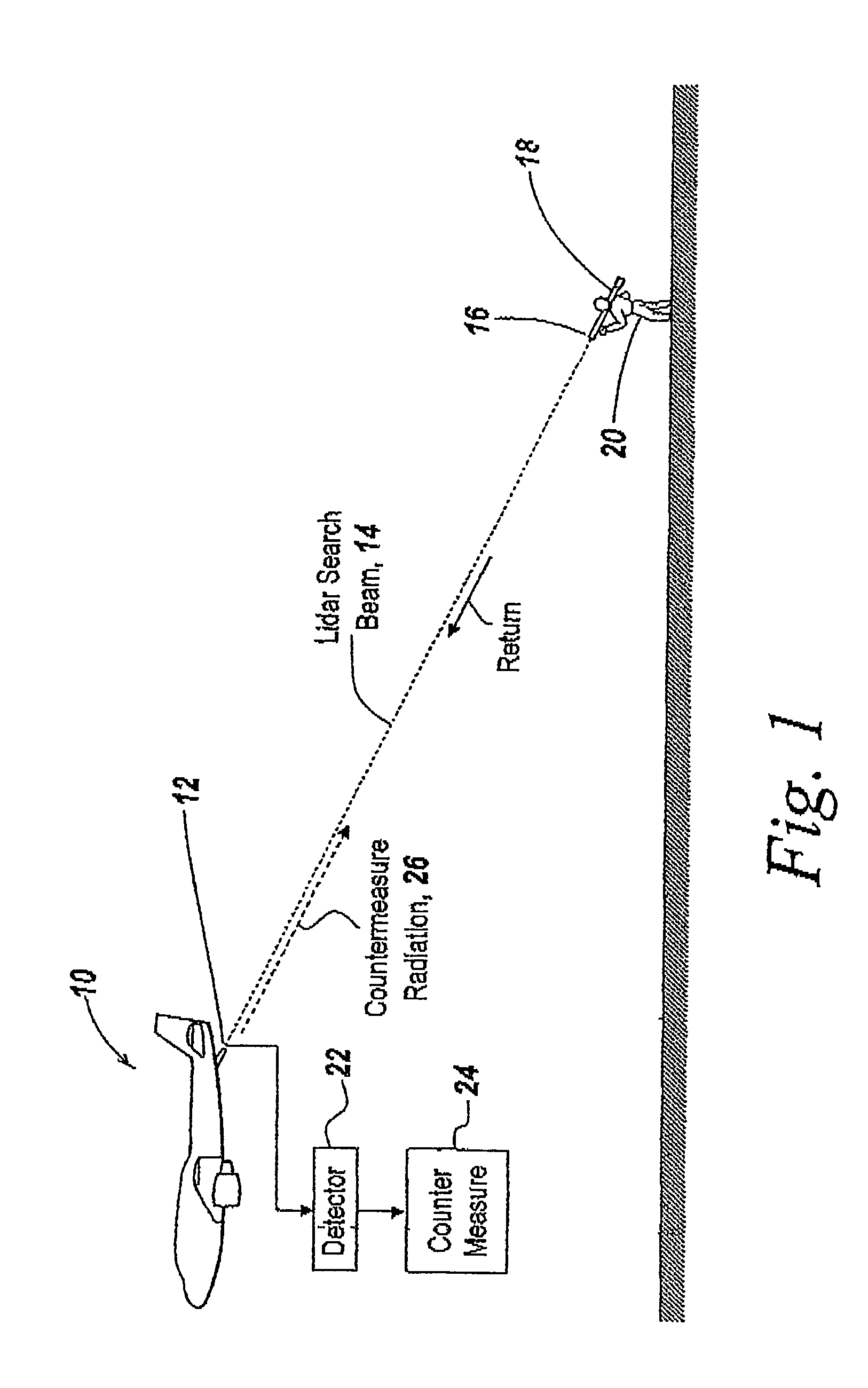

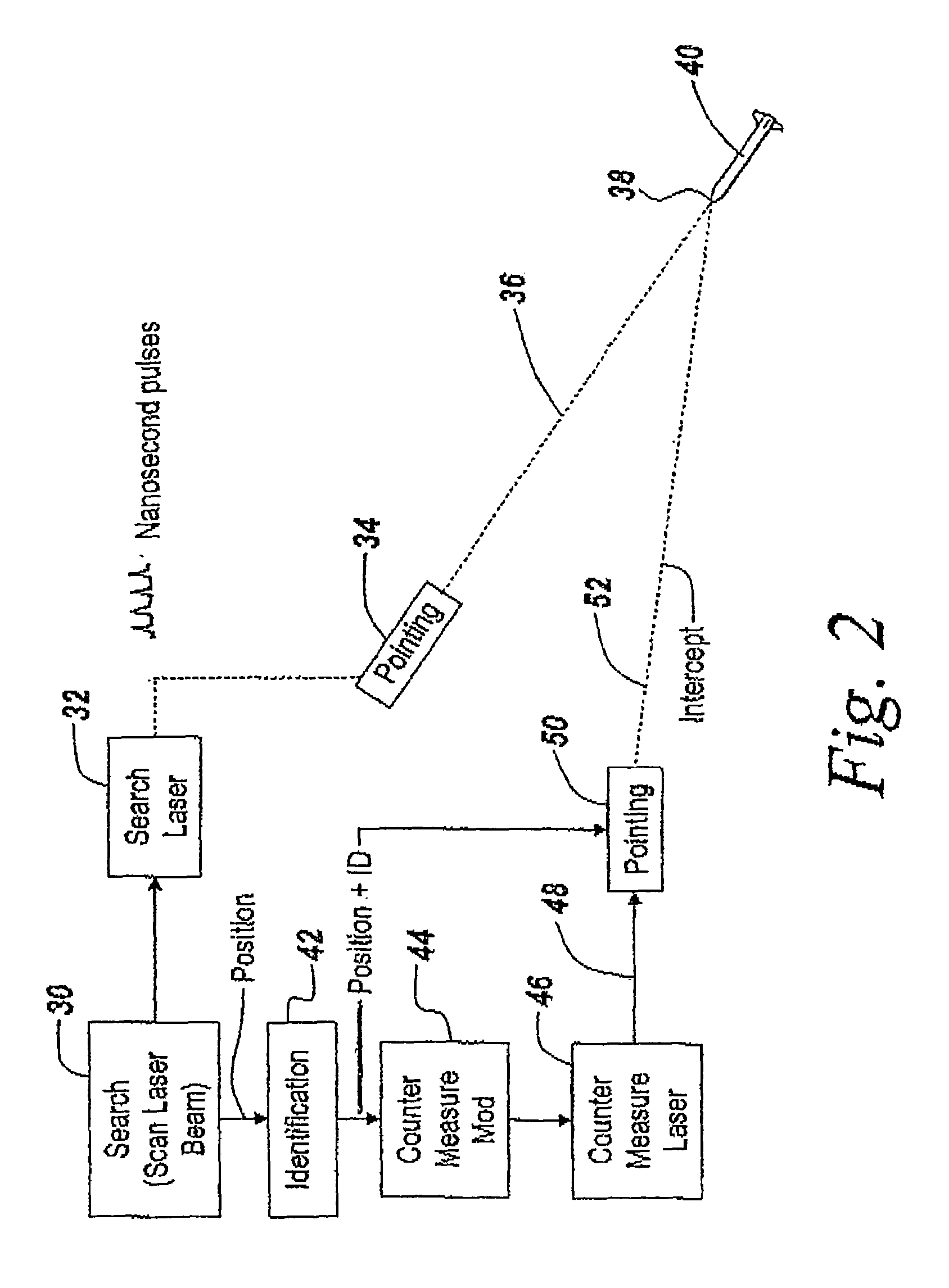

Active sensor receiver detector array for countermeasuring shoulder-fired missiles

InactiveUS7193691B2Improve signal-to-noise ratioTotal current dropDefence devicesOptical rangefindersNAND gateDetector array

A focal plane architecture is provided which includes direct reading of an array of infrared detectors, each coupled to its own threshold circuit, the output of which is coupled to one input of a NAND gate, with the other input to the NAND gate being provided with a delayed threshold circuit output, thus to permit discrimination against ground clutter. This architecture results in an ultra fast frame read out, inherent discrimination of compact targets, photon counting at infrared wavelengths, and programmable range gating by exterior selection of array events within an expected return time for a transmitted pulse.

Owner:BAE SYST INFORMATION & ELECTRONICS SYST INTERGRATION INC

Grid drive circuit, liquid crystal display device and electronic device

InactiveCN101046940ASolve the problem of afterimage after shutdownStatic indicating devicesShift registerLiquid-crystal display

The present invention relates to a grid drive circuit. It includes first shift register for outputting first signal, second shift register for outputting second signal, NAND gate, first switch device, second switch device, control unit and inverter. The NAND gate has two input ends which are respectively coupled with first signal and second signal. The input end of the first switch device is coupled with output end of NAND gate, the output end of second switch device is coupled with output end of first switch device, its input end is coupled with high voltage level. The control unit can output control signal, and is coupled with first switch device and second switch device. The input end of said inverter is coupled with output end of second switch device, and the output end of said inverter can output grid drive signal.

Owner:TPO DISPLAY

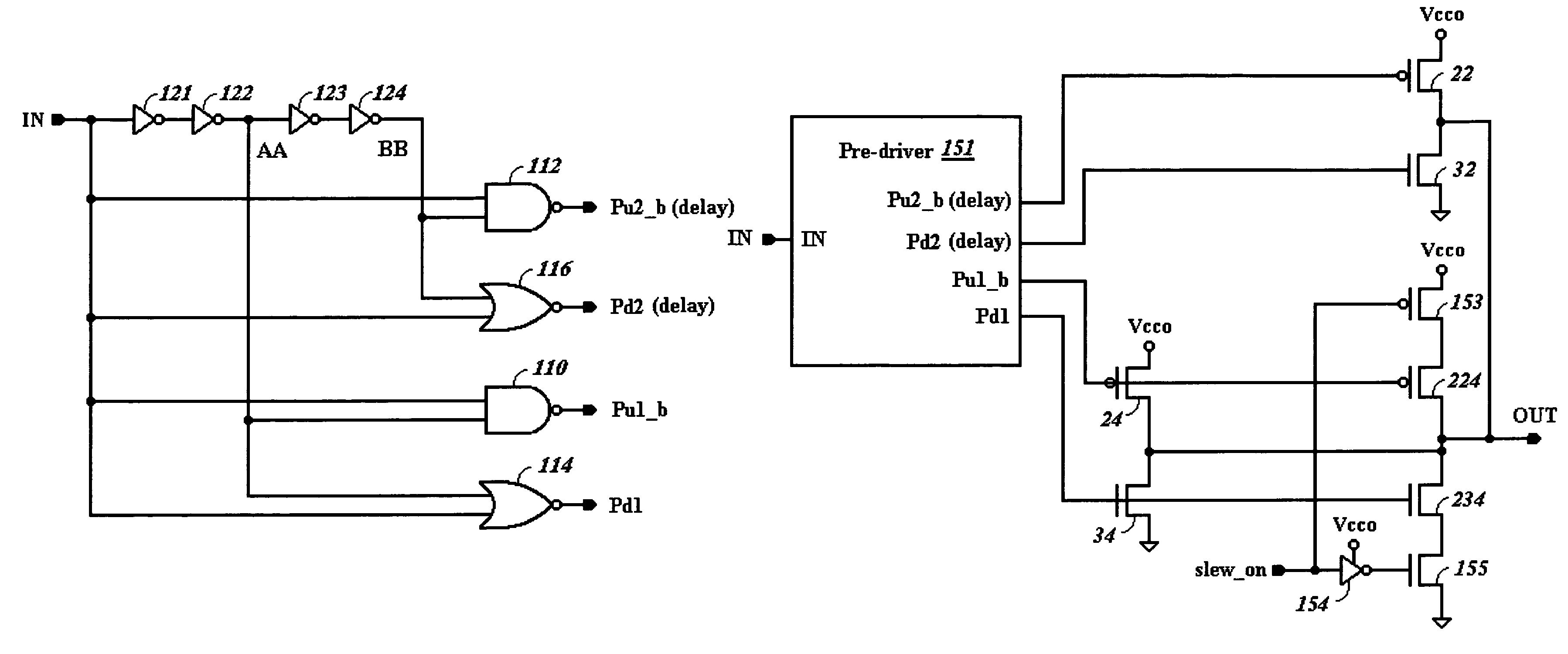

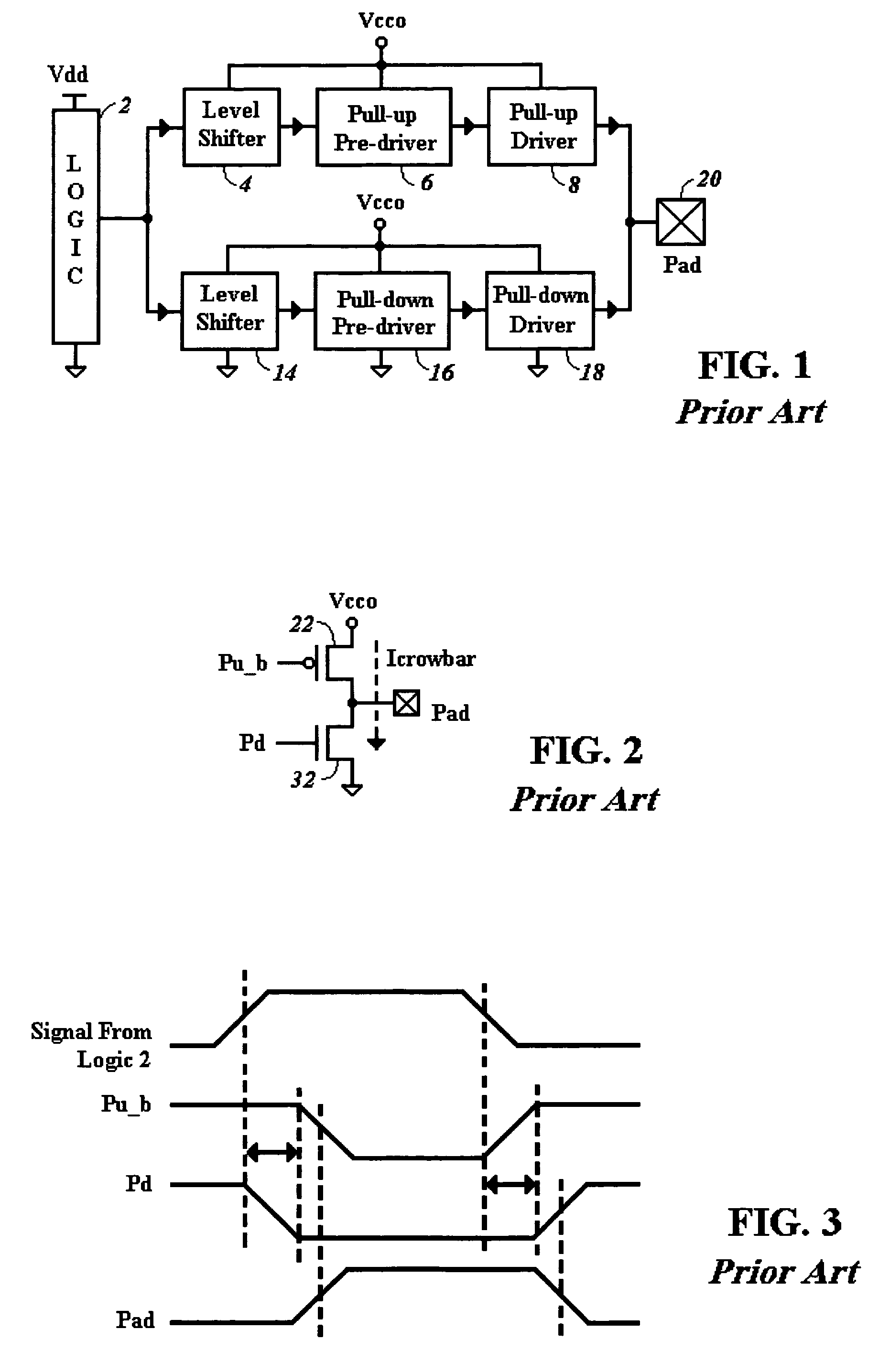

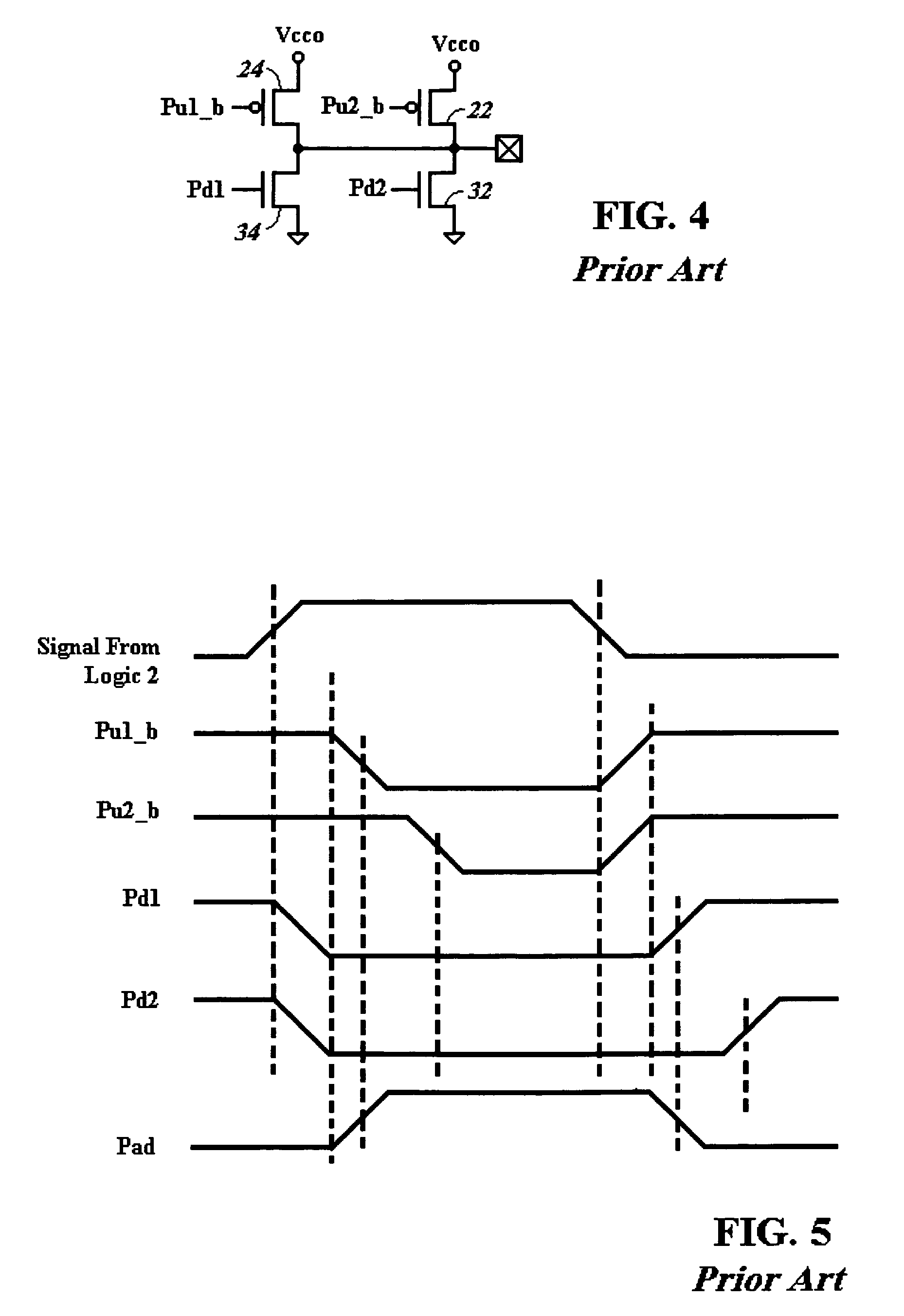

Large loading split I/O driver with negligible crowbar

ActiveUS7317333B1Easy to controlPower reduction in field effect transistorsPulse automatic controlDriver circuitNOR gate

A pre-driver for large I / O pull-up and pull-down transistors is provided so that the I / O pull-up and pull-down transistors do not experience crowbar current, and the pre-driver circuit likewise does not experience crowbar current or require large driver transistors. One pre-driver circuit includes two NAND gates and two NOR gates with delay circuitry provided by two series inverters from a data input to a first node, and two additional series inverters from the first node to a second node. A further pre-driver circuit includes feedback from the pre-driver outputs to ensure its NMOS and PMOS transistors do not turn on together to create crowbar, while allowing faster switching. With the pre-driver circuit embodiments, a conventional level shifter can be used. Further with the pre-driver circuitry, slew rate control can be provided in the pull-up and pull-down driver circuitry, rather than in the pre-driver circuitry.

Owner:XILINX INC

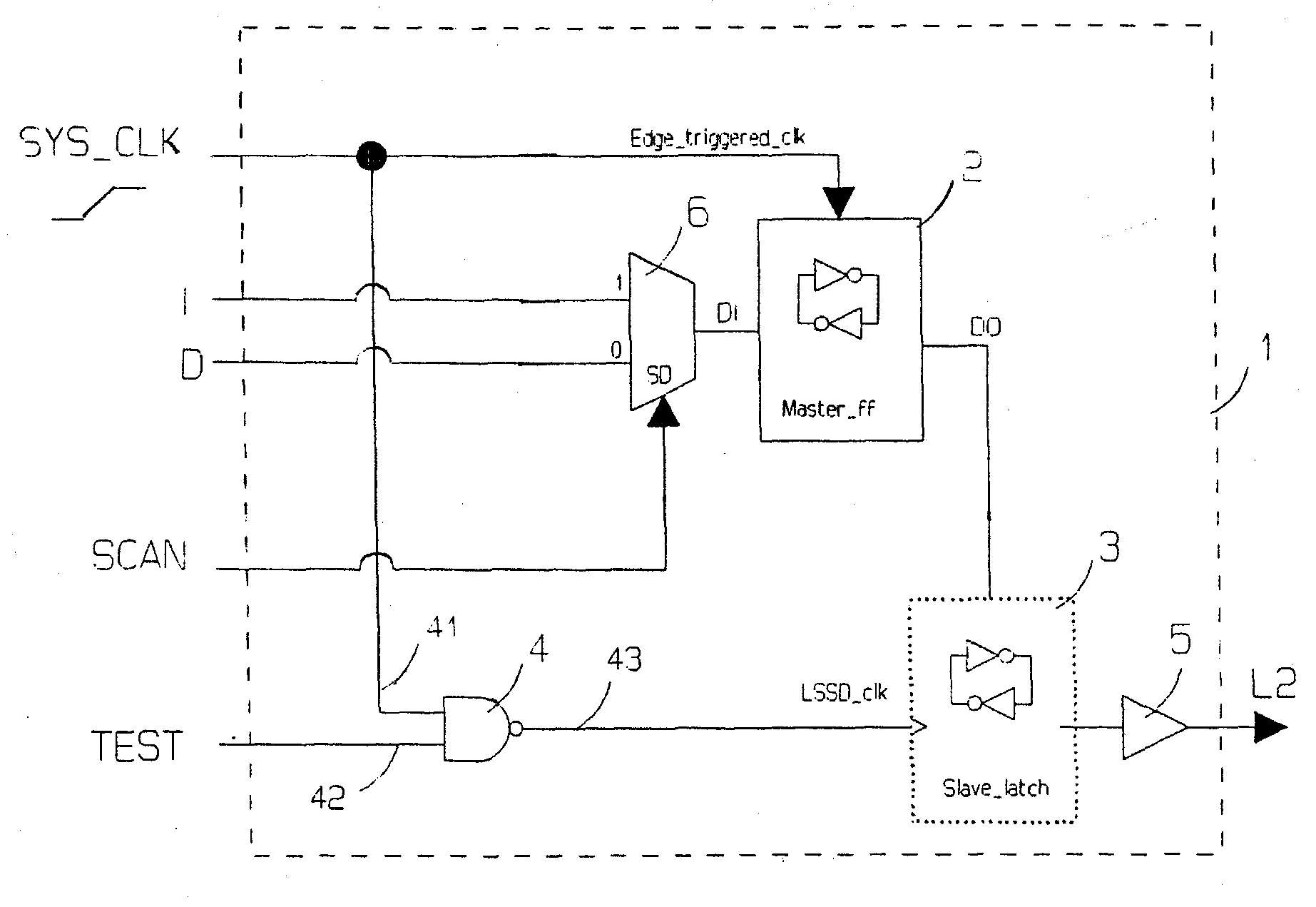

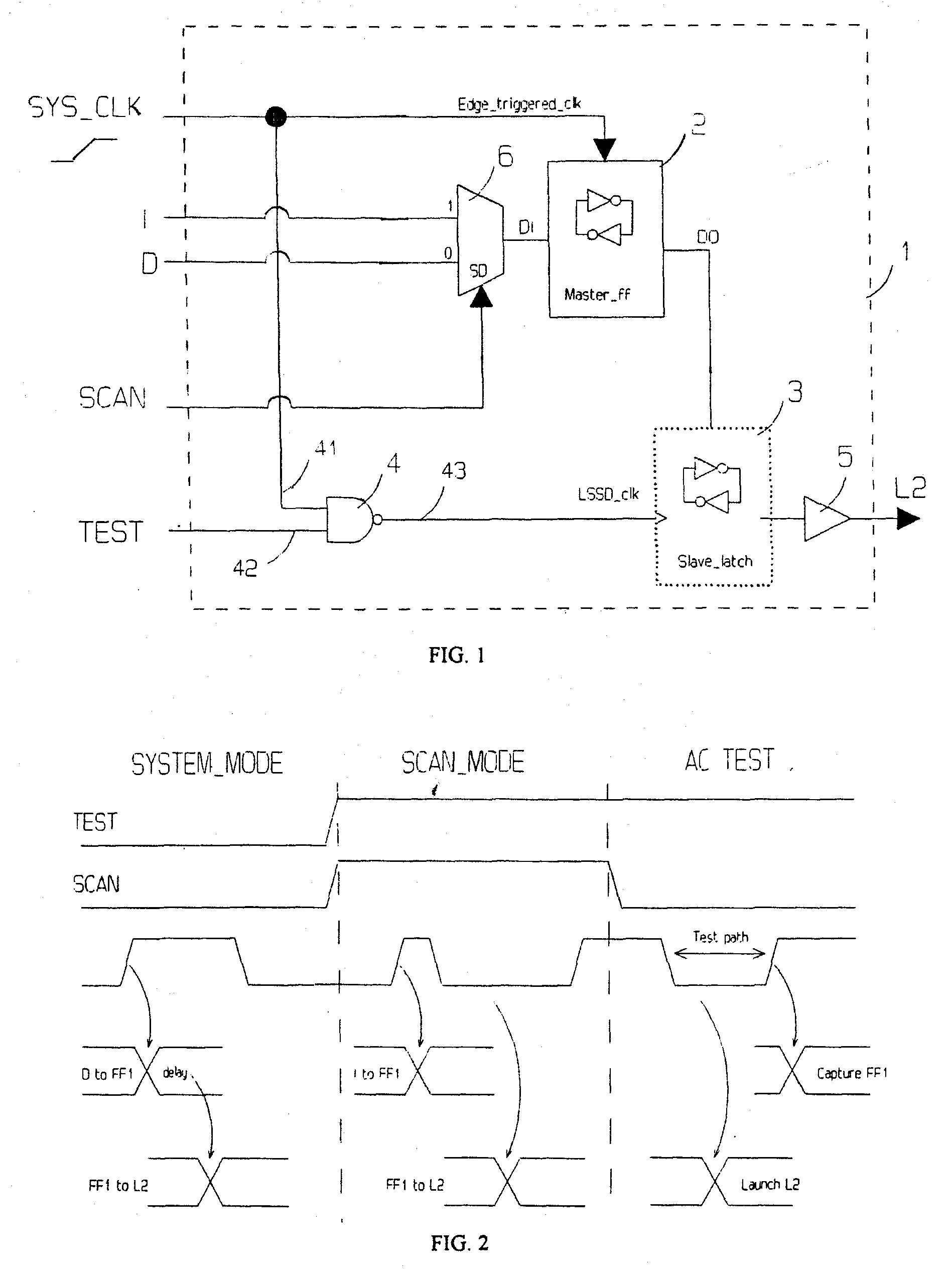

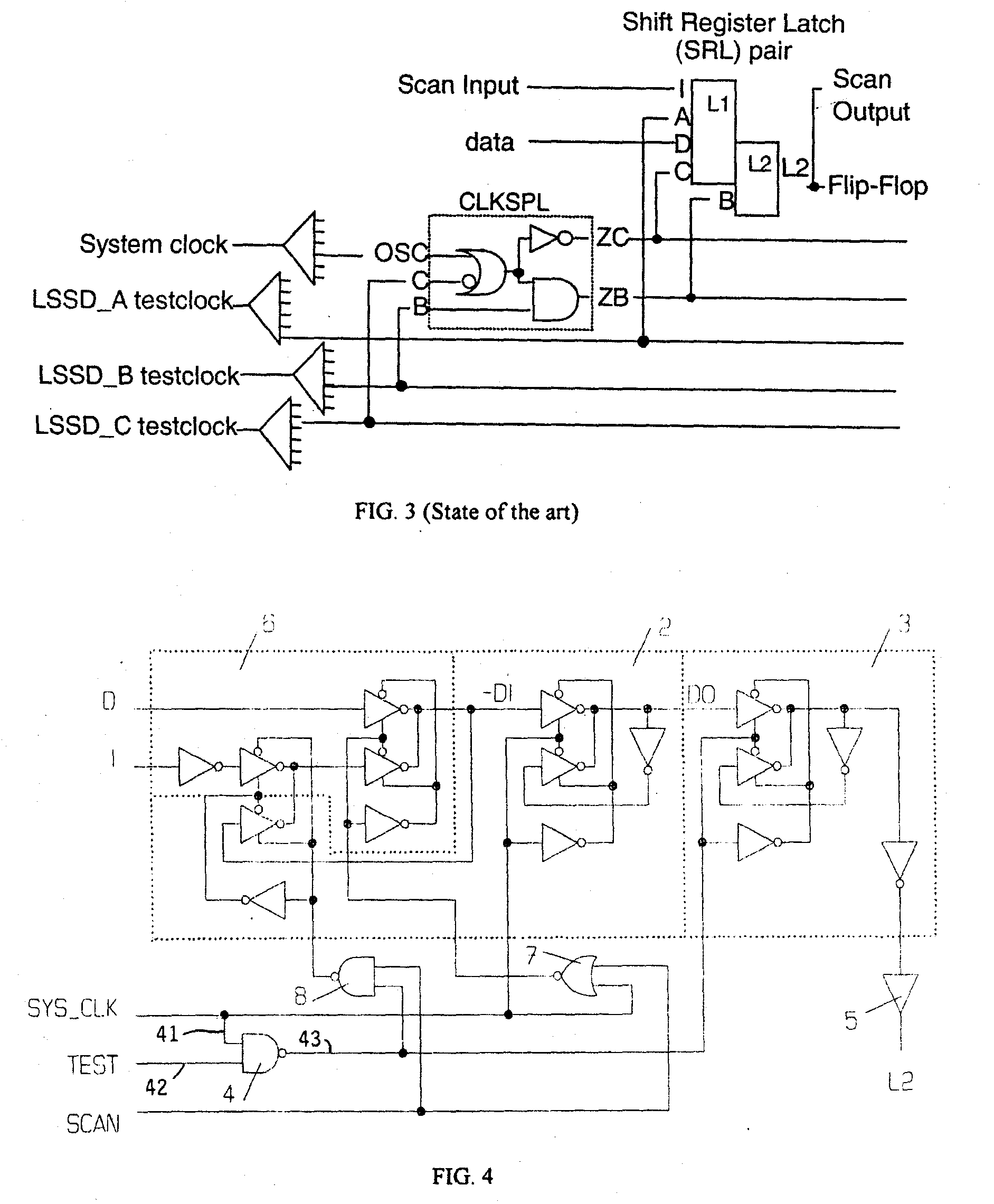

Edge-triggered master + LSSD slave binary latch

InactiveUS20050216806A1Easy to useImprove driving abilityElectronic circuit testingElectric pulse generatorNAND gateEngineering

Disclosed is a binary latch that operates as an edge-triggered flip-flop and which is LSSD-testable. The binary latch comprises an edge triggered master flip-flop (2), with a clock input connected to the system clock (SYS_CLK), with a data input (DI) and with an output (DO), a level sensitive scan design (LSSD) slave latch (3), connected to the output (DO) of the master flip-flop (2), a NAND gate (4) with a first input (41) connected to the system clock (SYS_CLK), a second input (42) connected to a test input (TEST) and with an output (43) connected to the LSSD slave latch clock input (LSSD_clk).

Owner:IBM CORP

GOA circuit of low-temperature polycrystalline silicon thin film transistor

ActiveCN104464659AImprove performanceReduce the numberStatic indicating devicesElectricityTransmission gate

The invention provides a GOA circuit of a low-temperature polycrystalline silicon thin film transistor. The GOA circuit is used for forward scan transmission and comprises a plurality of cascaded GOA units, N is set to be a positive integer, a plurality of N-type transistors and a plurality of P-type transistors are adopted in the N class GOA unit, and the N class GOA unit comprises a transmission part (100), a transmission control part (200), a data storage part (300), a data clearing part (400), an output control part (500) and an output buffering part (600). Signals are transmitted between the upper and lower levels through a transmission gate, converted through an NOR gate logical unit and an NAND gate logical unit and stored and transmitted through a timing sequence phase inverter and a phase inverter, the problems that an LTPS single type TFT device is poor in circuit stability and large in power consumption, and the single type GOA circuit TFT leaks electricity are solved, the performance of the circuit is optimized, and the ultra-narrow frame or frameless design can be achieved.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

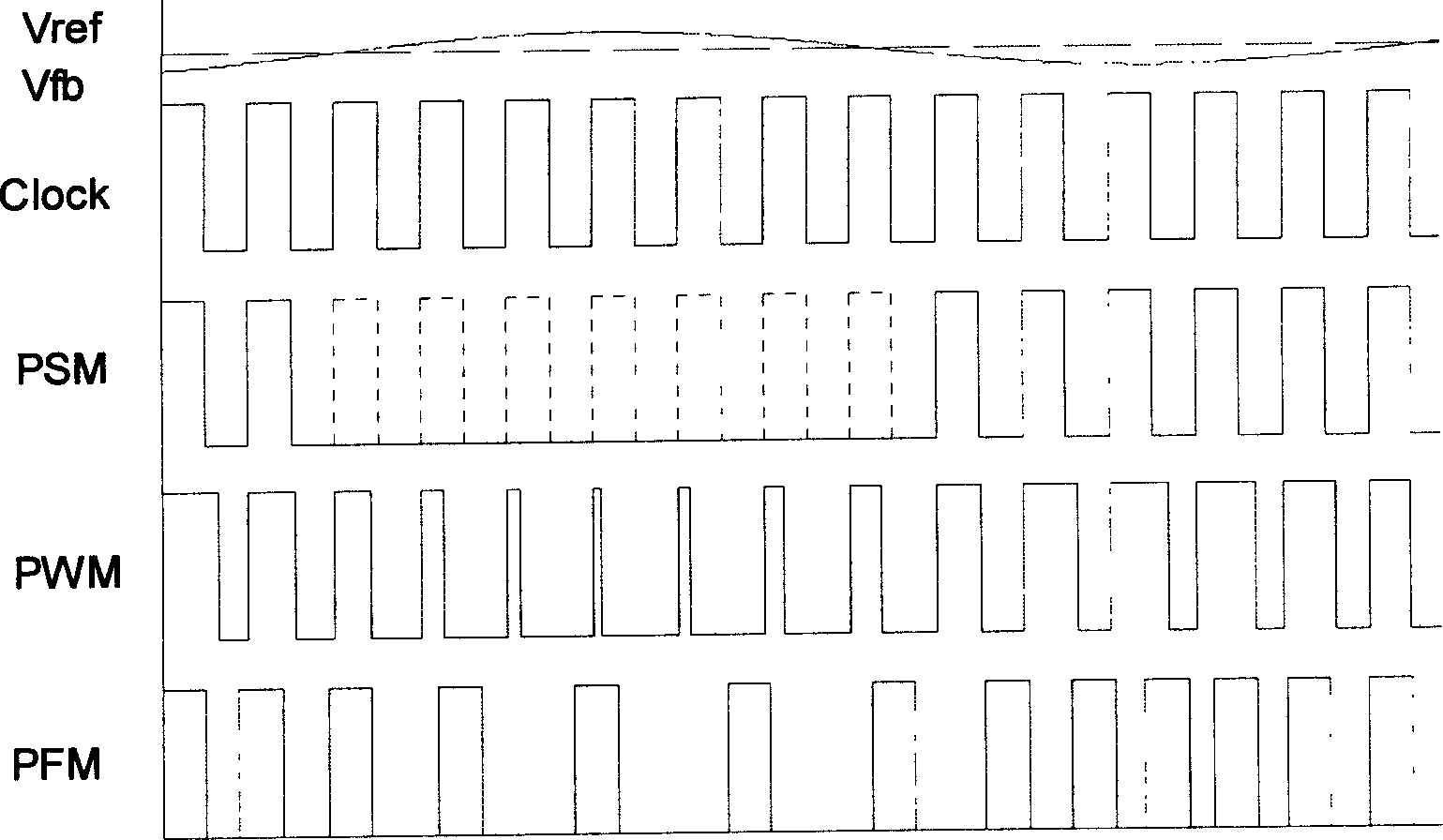

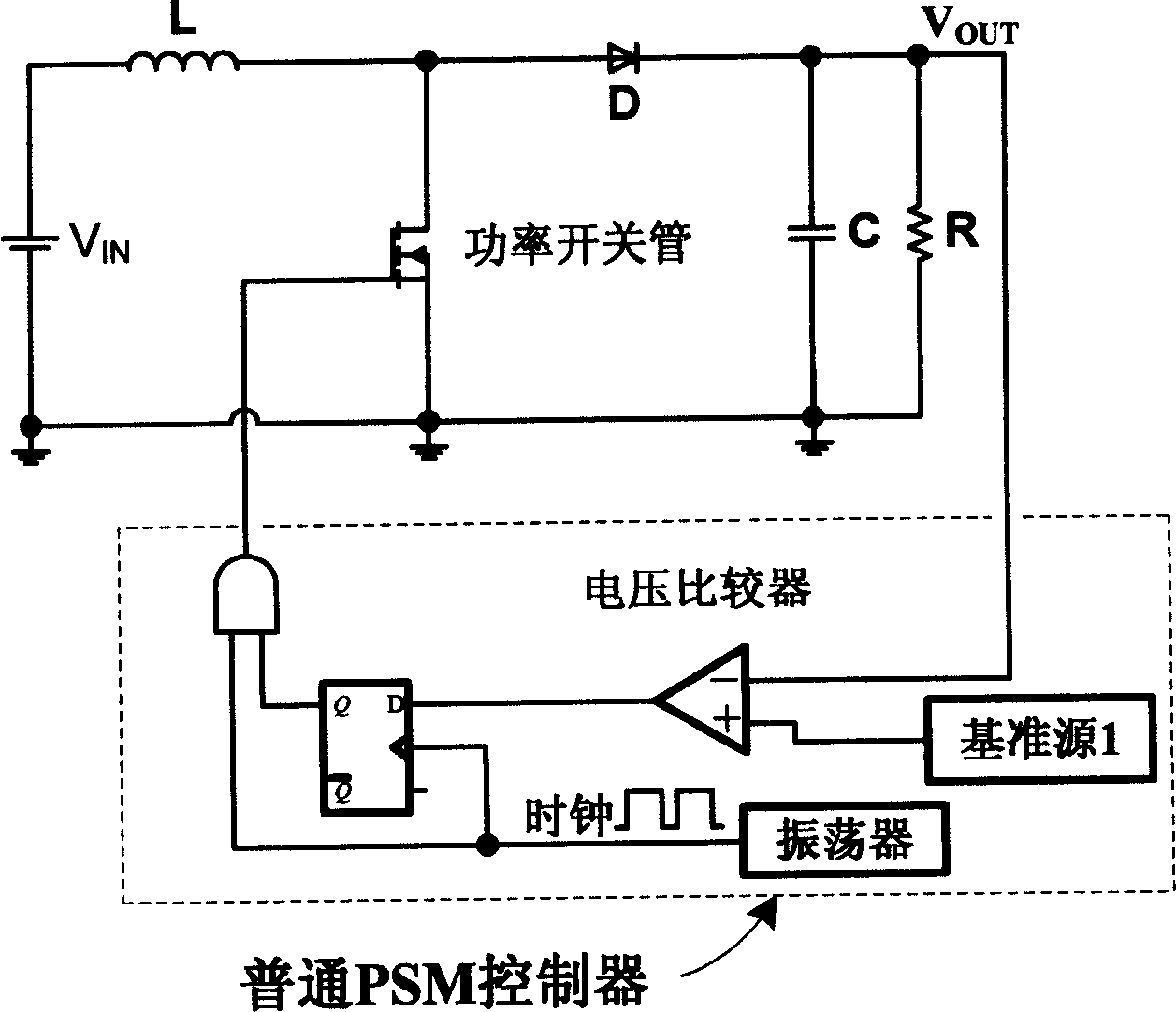

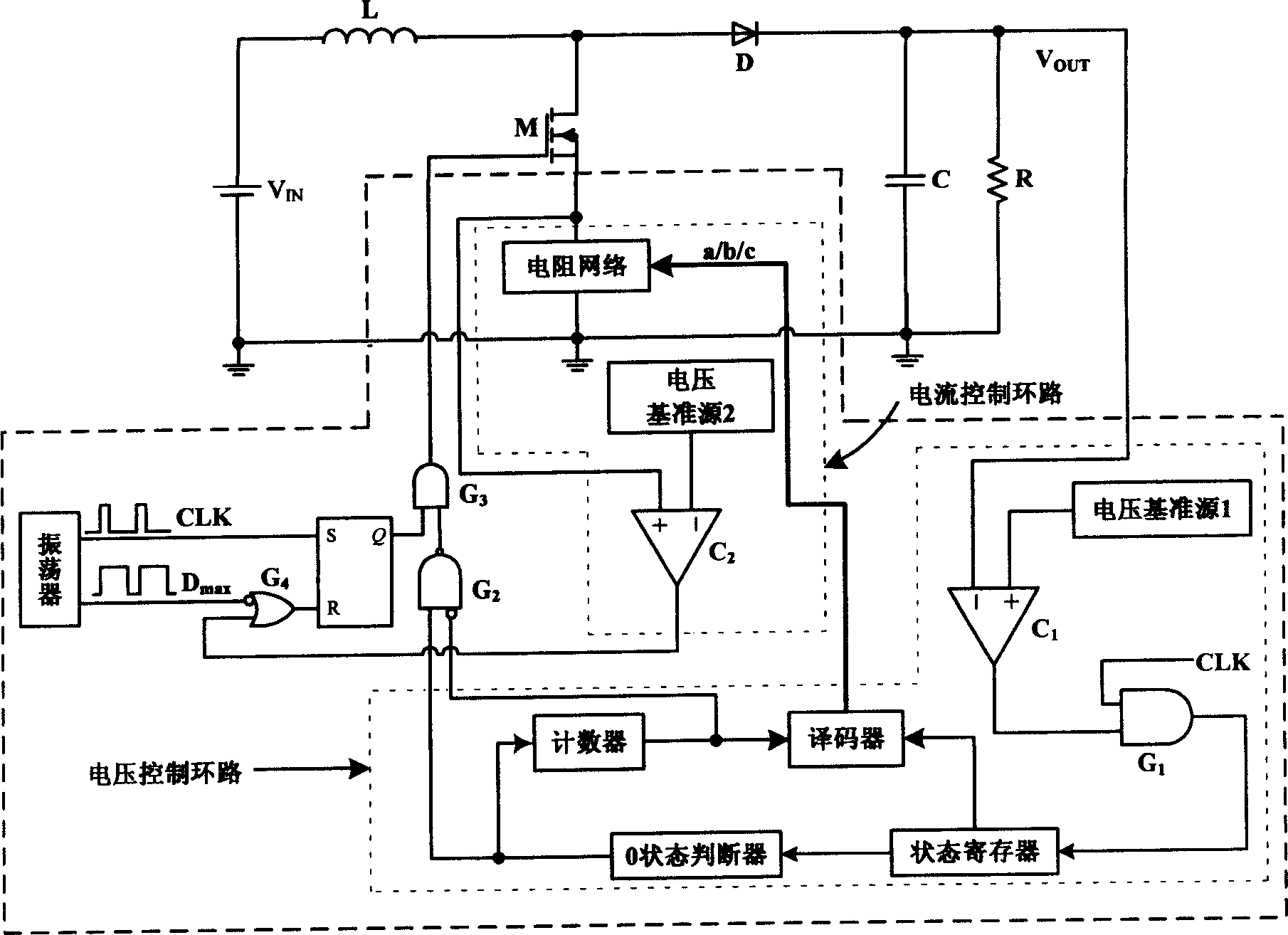

Optimized pulse over-cycle modulation switch stabilized voltage power supply controller

InactiveCN1852013AImprove efficiencyReduce switching timesDc-dc conversionElectric variable regulationControl signalNAND gate

This invention relates to an optimized pulse crossover modulation switch regulated supply controller composed of a voltage control loop, a current control loop and a primary control gate, in which, the voltage control loop is composed of a voltage comparator, a voltage primary source, an AND gate, a state register, a zero state judgment device, a counter and a decoder to realize the ordinary PSM modulation, the current control loop is composed of a resistor network, the voltage comparator and the voltage primary source to generate different current limit values by controlling the resistor network based on the voltage comparator signals of the local and the last clock periods to realize the conversion of three kinds of duty ratios, said primary control gate is composed of a vibrator, OR gate, a RS trigger, a NAND gate and an AND gate to generate the control signals for conducting or stopping power switch tubes.

Owner:COMTECH TECH SHENZHEN

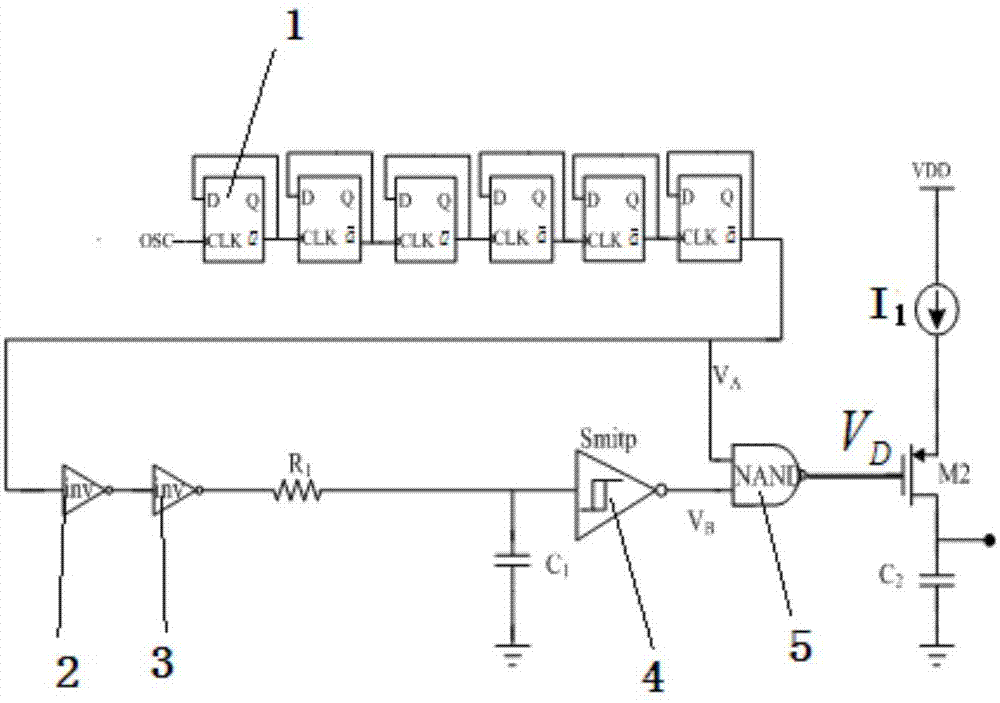

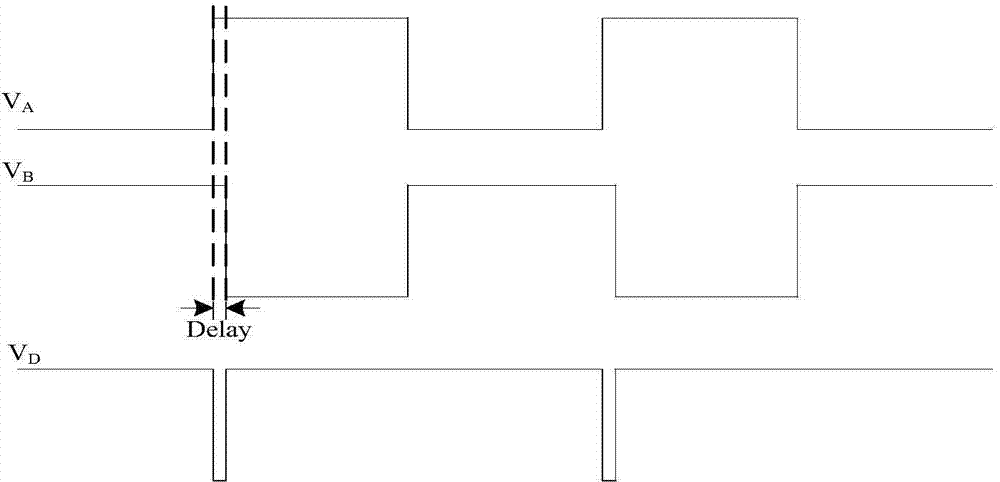

Digital soft start circuit in switching power source

InactiveCN103904875AReduce complexityReduce the valueEfficient power electronics conversionPower conversion systemsSchmitt triggerNAND gate

The invention discloses a digital soft start circuit in a switching power source. The digital soft start circuit comprises a frequency divider composed of six D triggers. The of each D trigger is connected with the clock signal input end of the next D trigger, the of the sixth D trigger serves as the output end and generates a clock signal VA and the clock signal input end of the first D trigger is connected with a clock signal of a whole loop; the clock signal VA serves as an input signal, a rising delayed clock signal VC is generated through two phase inverters and an RC series loop, the clock signal VC is then shaped and filtered through a Schmitt trigger, and therefore a clock signal VB is obtained; a control clock signal VD is obtained by the clock signal VA and the clock signal VB through a NAND gate, the clock signal VD is connected with a grid electrode of an MOS tube M2 after clock absorption and controls the MOS tube M2 to be connected and disconnected, a source electrode and a drain electrode of the MOS tube M2 are connected with a constant current source I1 and a capacitor C2 respectively, the capacitor C2 is intermittently charged by the constant current source I1, and therefore a soft start voltage is obtained. The complexity of the circuit is reduced and the circuit is conveniently integrated in a chip.

Owner:HEFEI UNIV OF TECH

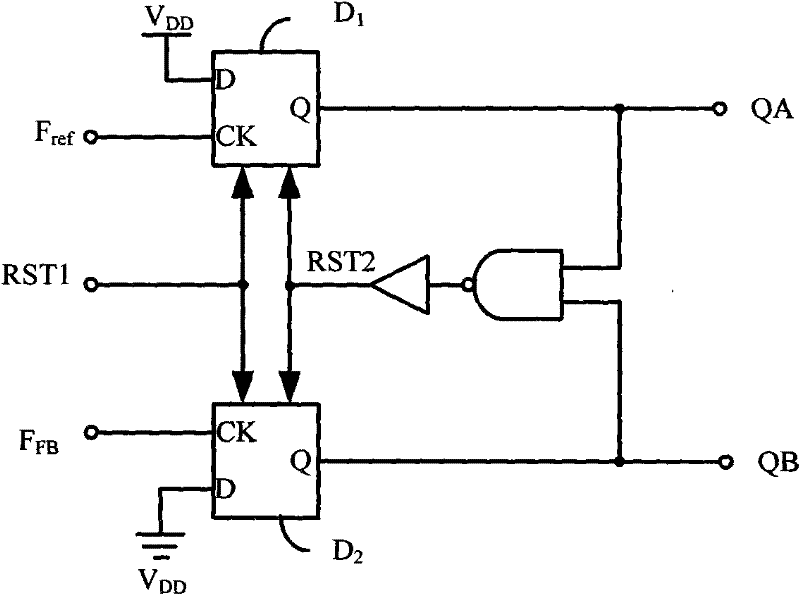

Frequency discrimination phase discriminator and method applying to phase-locked loop

The embodiment of the invention discloses a frequency discrimination phase discriminator. The phase discriminator comprises two D triggers D1 and D2, as well as a nand gate NA1 and a buffer 1, the output ends of the two D triggers D1 and D2 are utilized as an input end of the nand gate; an output end of the nand gate NA1 passes through the buffer 1 to utilize as a second reset terminal RST 2 of the two D triggers, and the output ends of the D trigger D1 and the D trigger D2 can respectively obtain signal Q1 and Q2; and the phase discriminator also comprises a timing control unit, the signals Q1 and Q2 are input signals of the timing control unit, and the timing control unit is used for controlling phase and pulse width of an output signal of the frequency discrimination phase discriminator. The invention also discloses a charge pump phase locked loop applying to the frequency discrimination phase discriminator and a method of a phase locked loop applying to the frequency discrimination phase discriminator. The technical scheme of the phase discriminator and the phase locked loop and the method can effectively avoid an error caused by mismatch charge pump current through a simple circuit structure.

Owner:ARKMICRO TECH

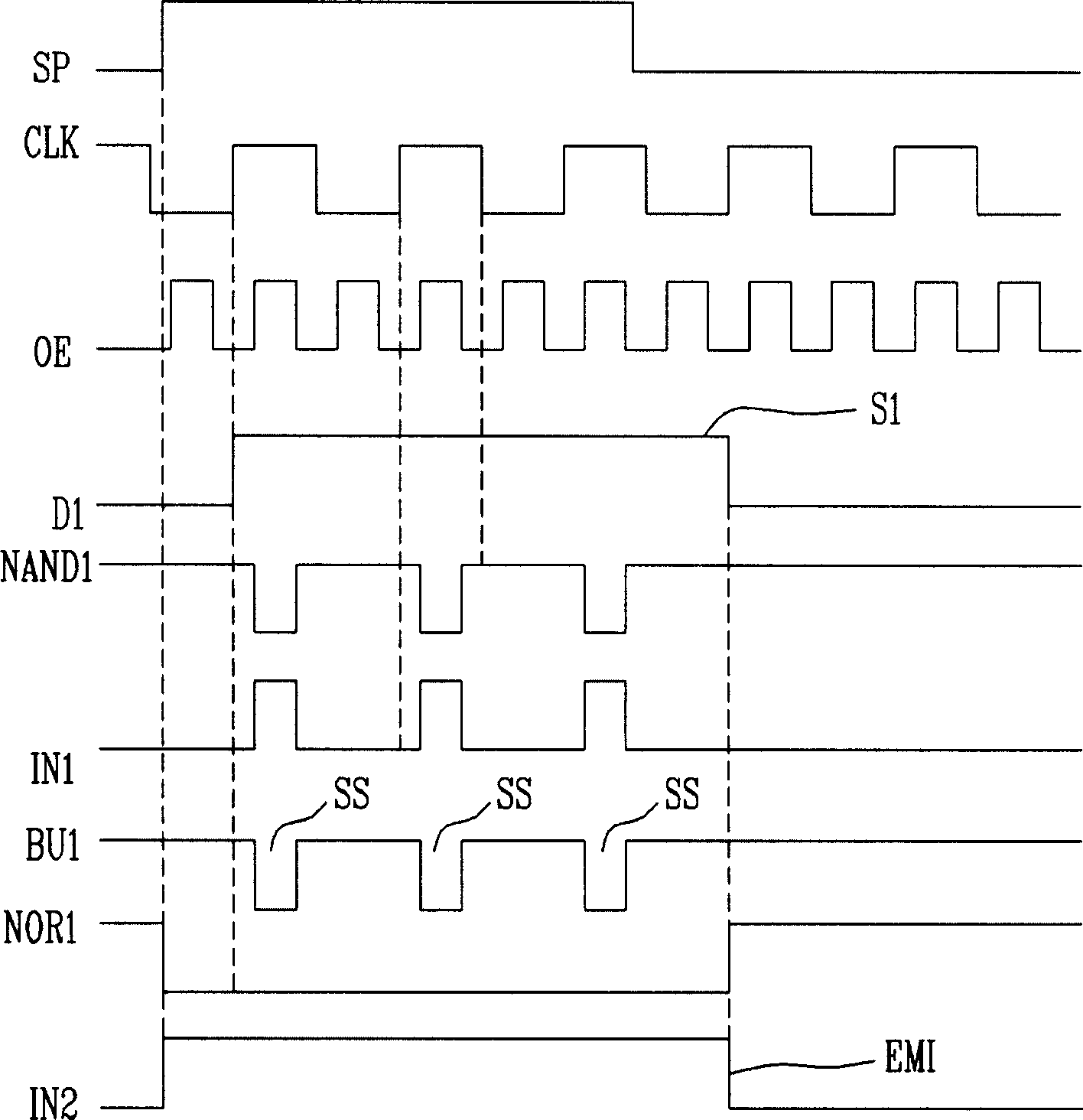

Scan driver, organic light emitting display using the same, and method of driving the organic light emitting display

The invention discloses an embodiment of a scan driver, which can freely adjust the width of an emission control signal. An embodiment of the scan driver includes: a shift register configured to sequentially shift the start pulse in response to a clock signal to generate a sampling pulse; a NOR gate connected to each emission control line and configured to The emission control signal is generated in response to at least two sampling pulses; and the NAND gate is connected to each scanning line to generate scanning signals in response to the at least two sampling pulses. At least one of the two sampling pulses input to the NAND gate is input through an inverter. Therefore, the width of the start pulse is controllable to freely adjust the width of the emission control signal. Therefore, the brightness of an organic light emitting display employing the scan driver can be freely adjusted.

Owner:SAMSUNG DISPLAY CO LTD

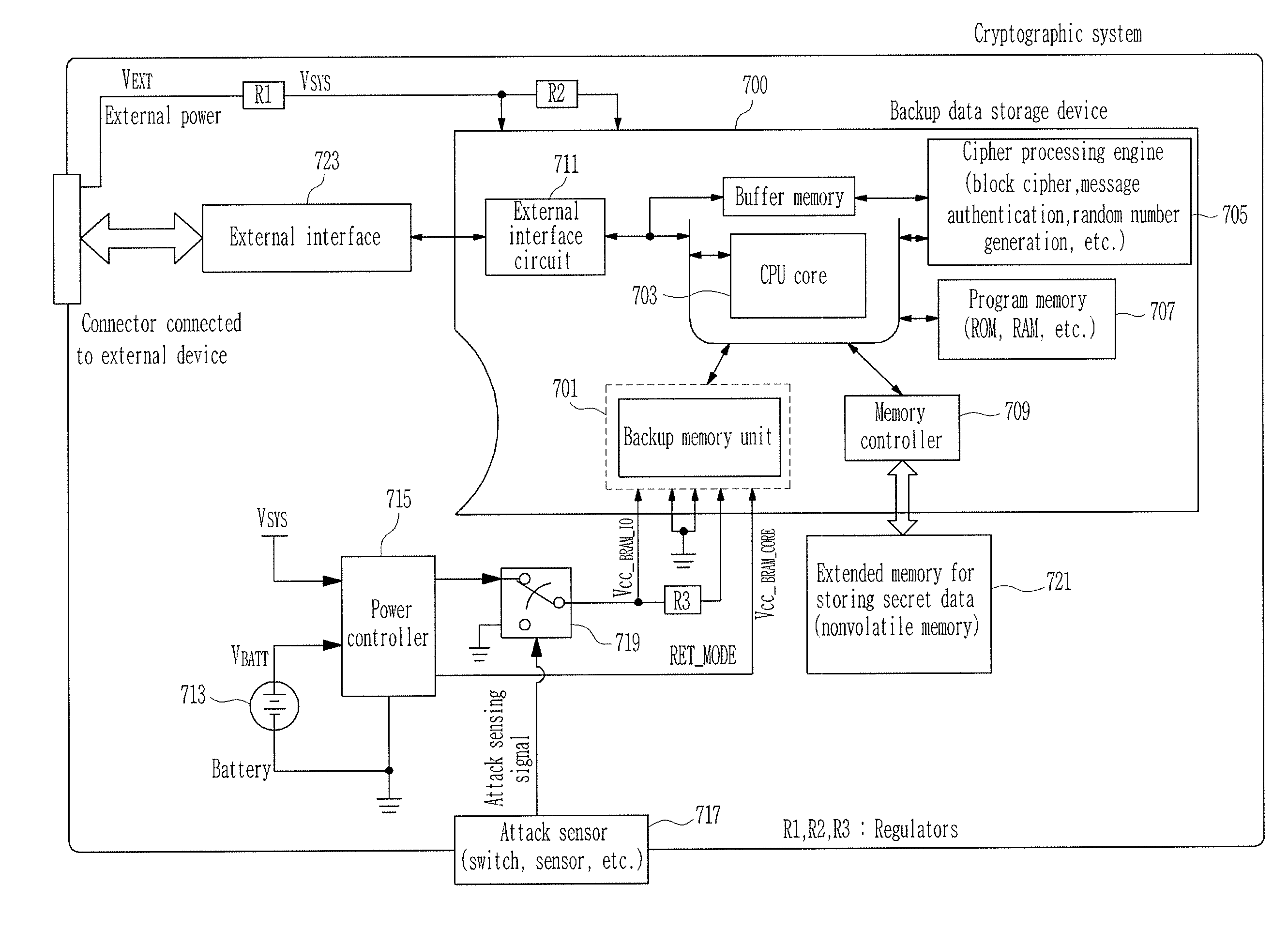

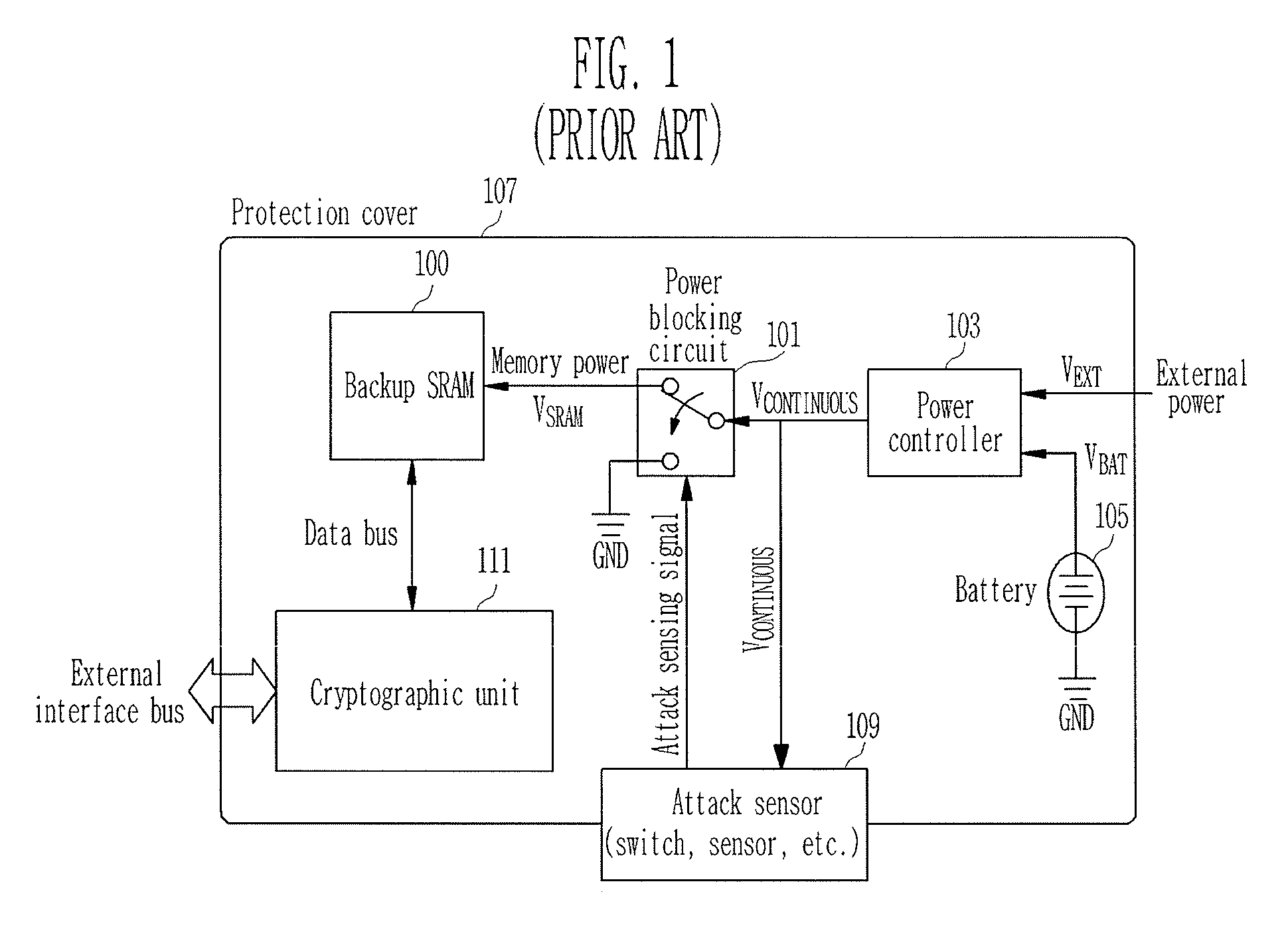

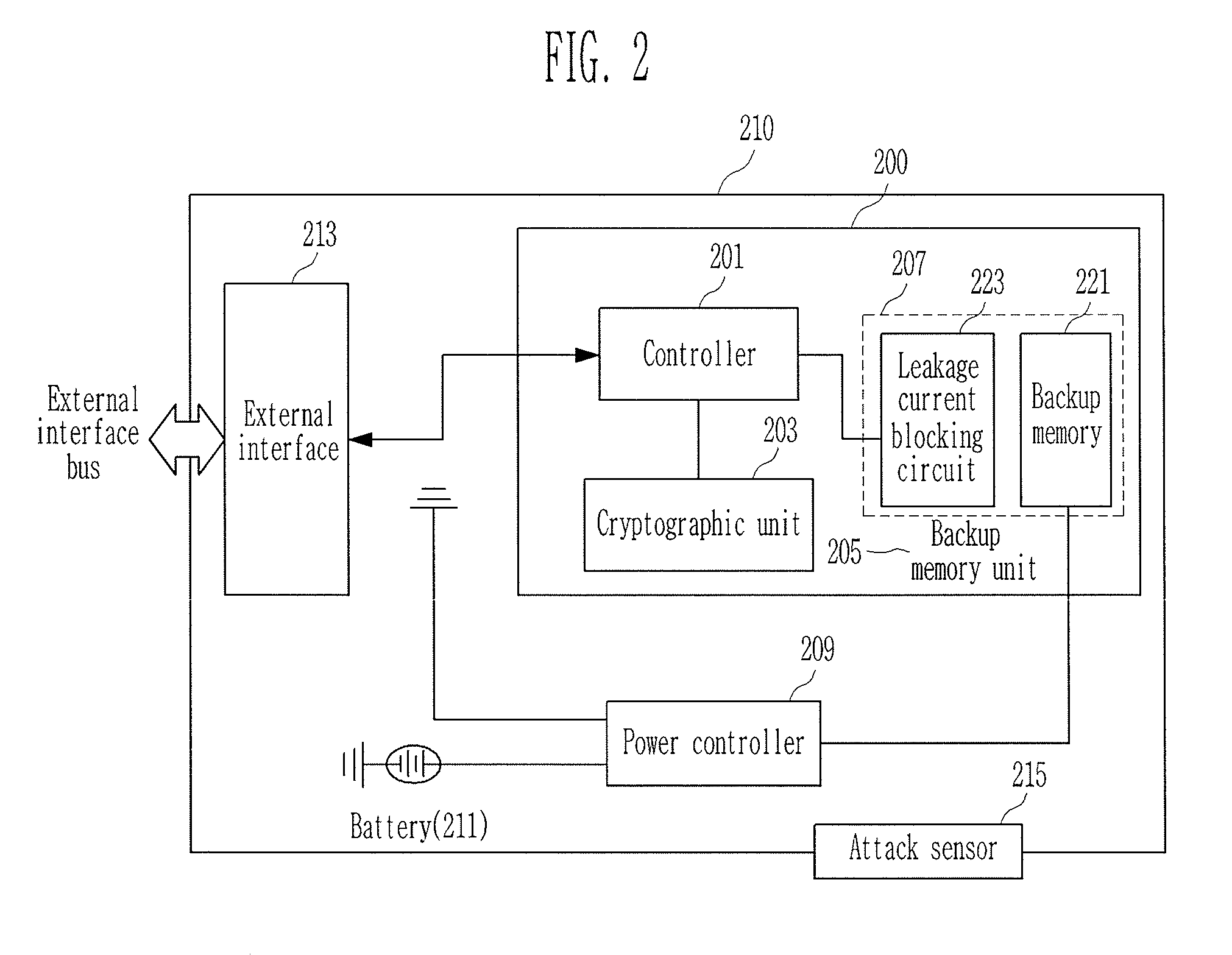

Encrypted backup data storage device and storage system using the same

An encrypted backup data storage device and a storage system using the same are provided. A backup memory stores at least one of plain-text data and a secret key. A leakage current blocking circuit includes at least one inverter and a complementary metal oxide semiconductor (CMOS) NAND gate circuit and cuts off leakage current paths formed by the lines connected to the battery backup memory.

Owner:ELECTRONICS & TELECOMM RES INST

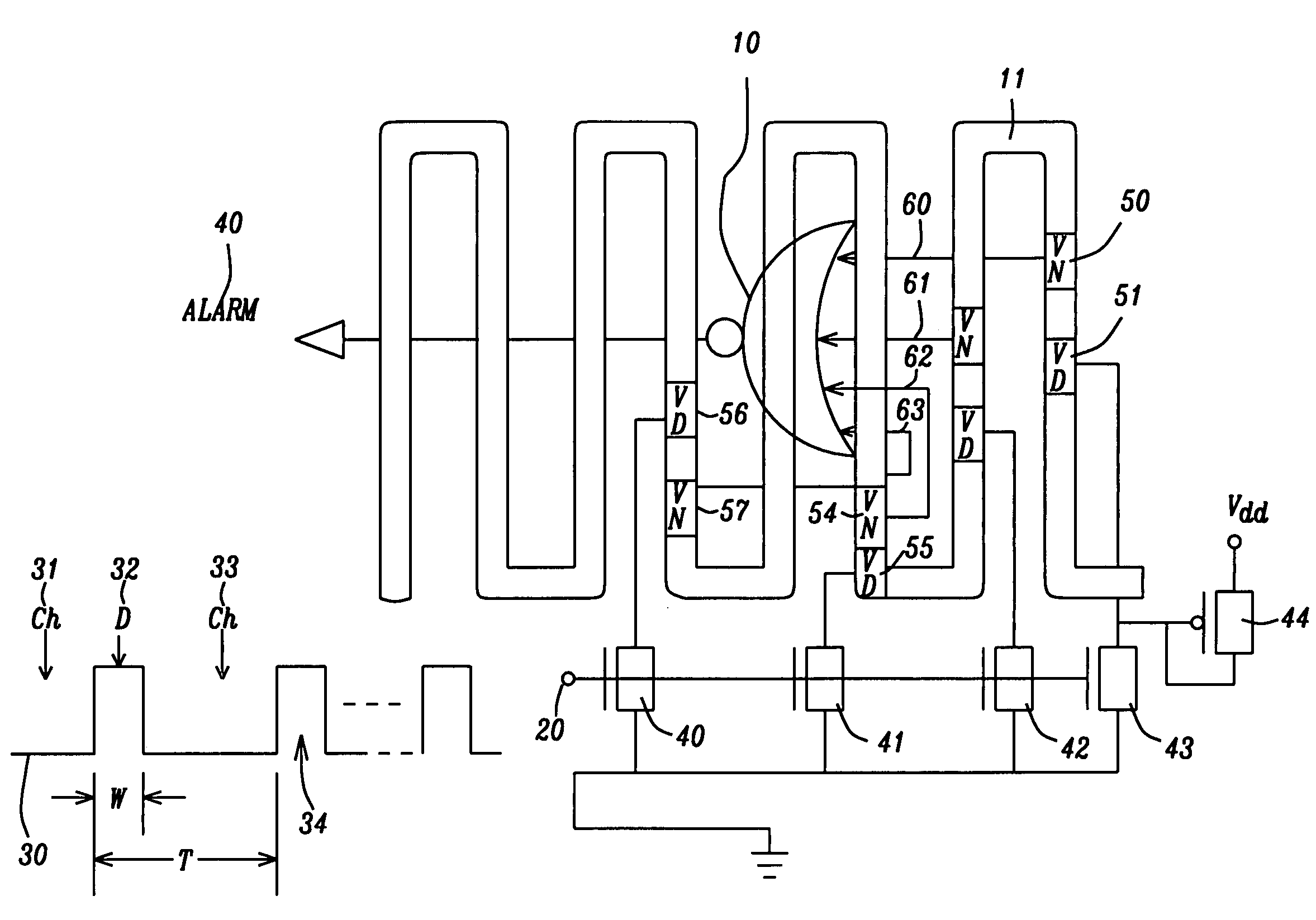

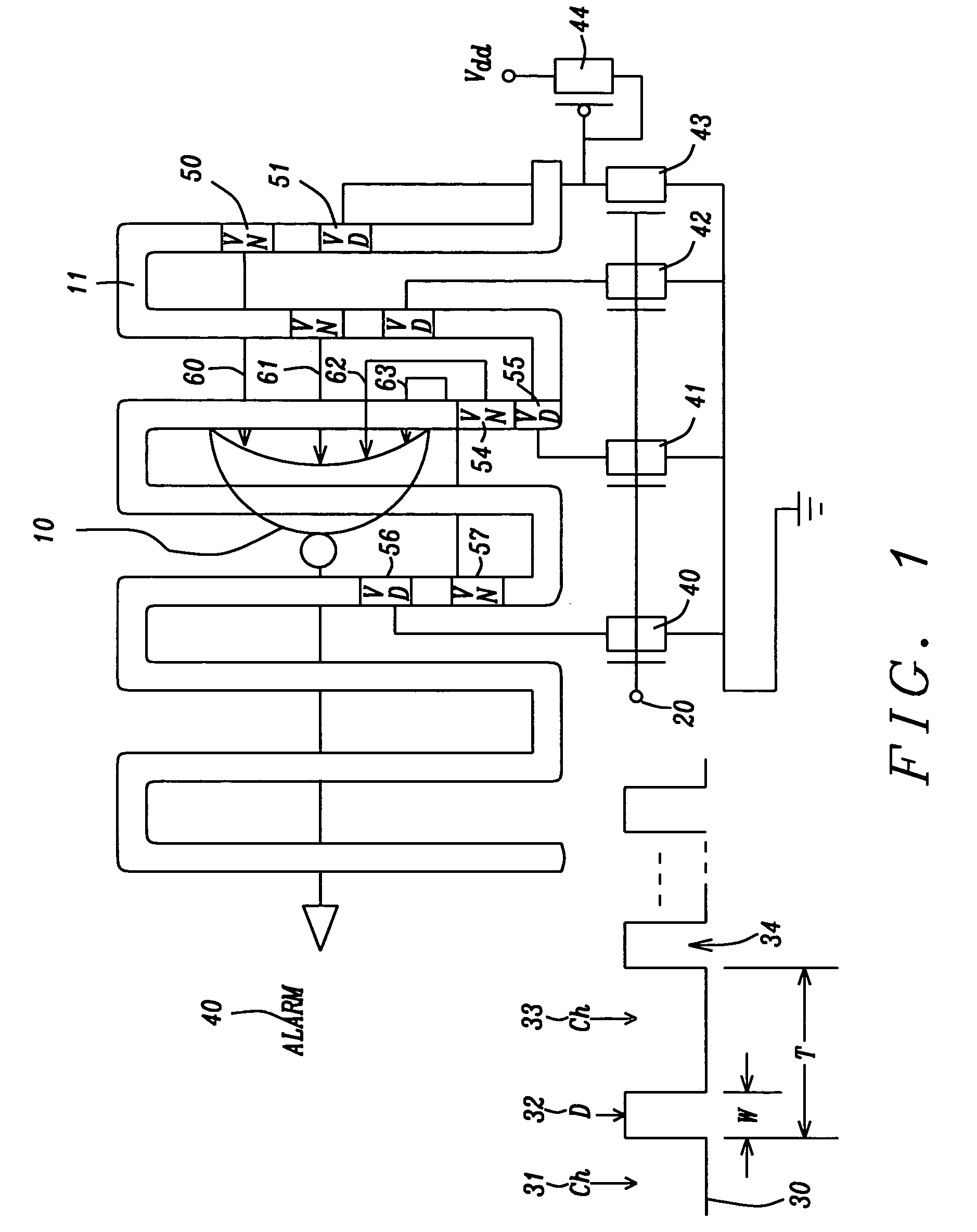

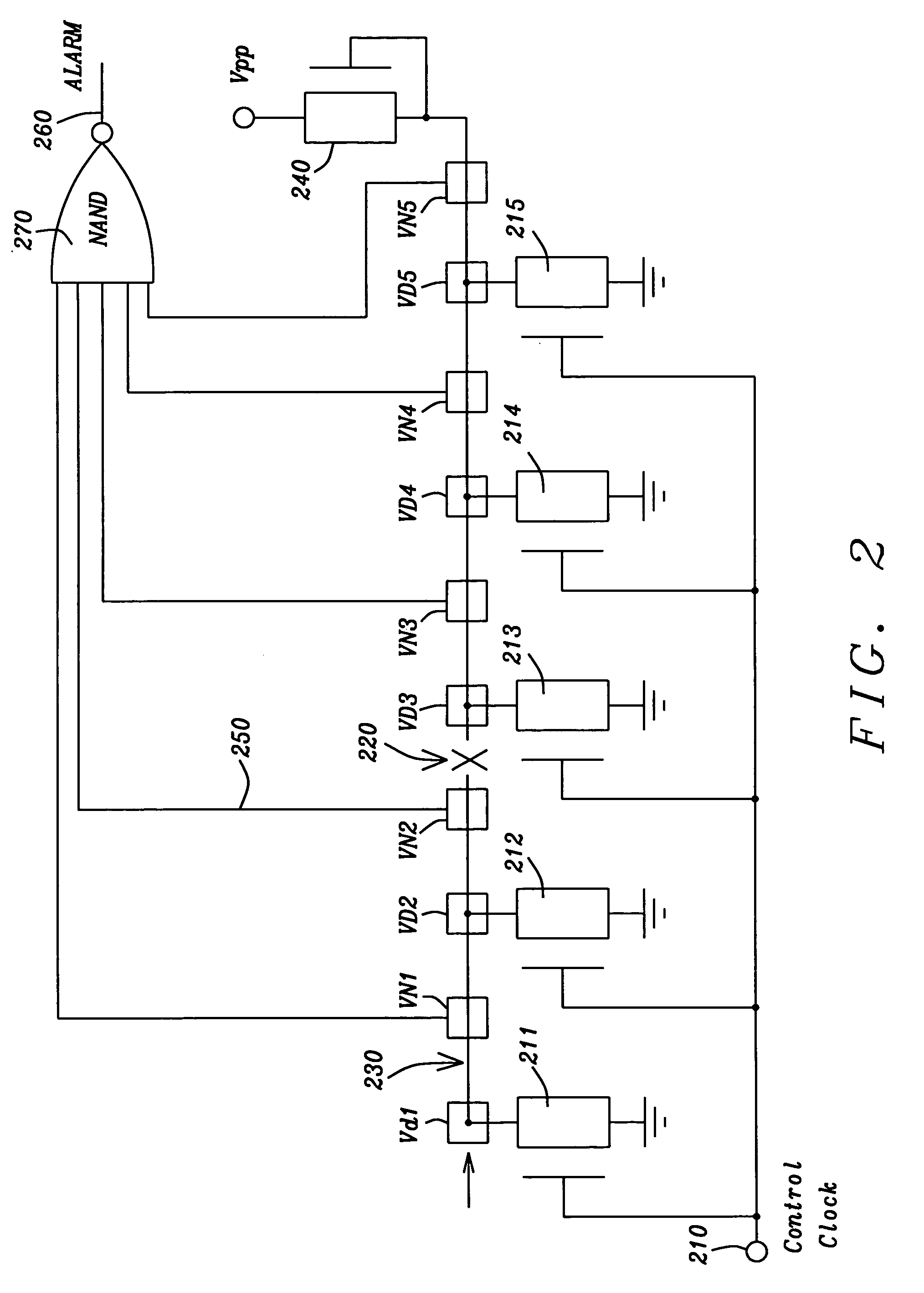

Die anti-tampering sensor

InactiveUS20060044138A1Low powerSimple circuit implementationSemiconductor/solid-state device detailsSolid-state devicesProgrammable read-only memoryNAND gate

This sensor circuit and method for defending against tampering with an integrated circuit die uses metal wire loops to protect the circuitry. In addition, these metal wire loops have several via pairs along its length. One of the vias of the via pair goes to a NAND gate which detects a break in a section of a metal wire loop. A second via of the via pair is used to periodically discharge a metal wire loop to remove residual charge, in preparation for charging the metal wire loop and detecting any uncharged section. A given integrated circuit can have one or more metal wire loops on top of the circuitry to be protected. Each metal wire loop has one or more NAND gates. These outputs of the NAND gates can be fed into OR gates to produce an overall signal which activates an alarm or other security action such as erasure of electrically erasable programmable read only memory (EEPROM).

Owner:KARMIC DESIGN USA