Configurable phase discriminator for time-delay locking ring

A delay-locked loop and phase detector technology, applied in the automatic control of power, electrical components, etc., can solve problems such as clock cycle and cycle jitter, limit the performance of the phase detector, and incorrect phase difference information, etc., to achieve the realization principle Simplicity, improved jitter performance, effects for reusability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] Below in conjunction with accompanying drawing and specific embodiment the present invention is described in further detail:

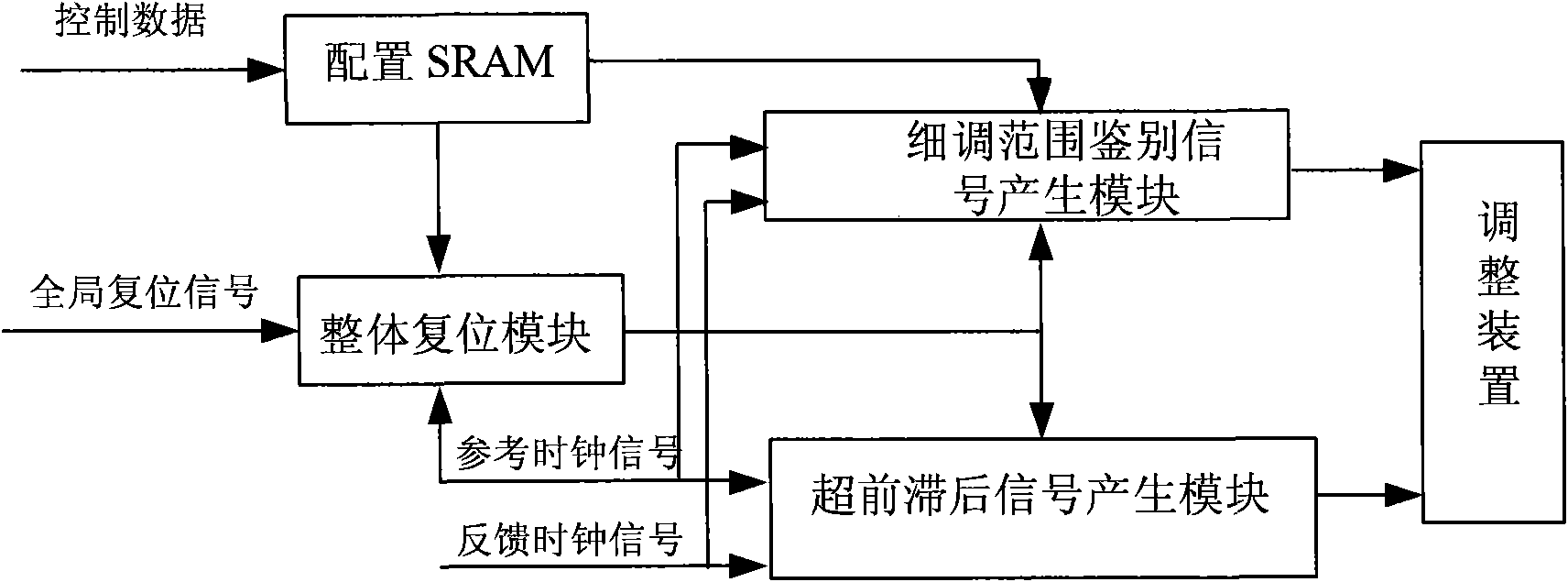

[0029] Such as figure 2 Shown is a schematic structural diagram of the configurable phase detector of the present invention, which includes a configuration SRAM, an overall reset module, a lead-lag signal generation module and a fine-tuning range discrimination signal generation module.

[0030] Configure the SRAM to store and control the data flow of the configurable performance index of the configurable phase detector. The configurable characteristics of the configurable phase detector of the present invention include whether the global reset signal input to the overall reset module is effective at high level or low level, And the pulse width of the pulse generating circuit in the fine-tuning range discrimination signal generating module, the pulse width directly represents the phase difference between the reference clock signal and the feedb...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More