Patents

Literature

245 results about "Clock network" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

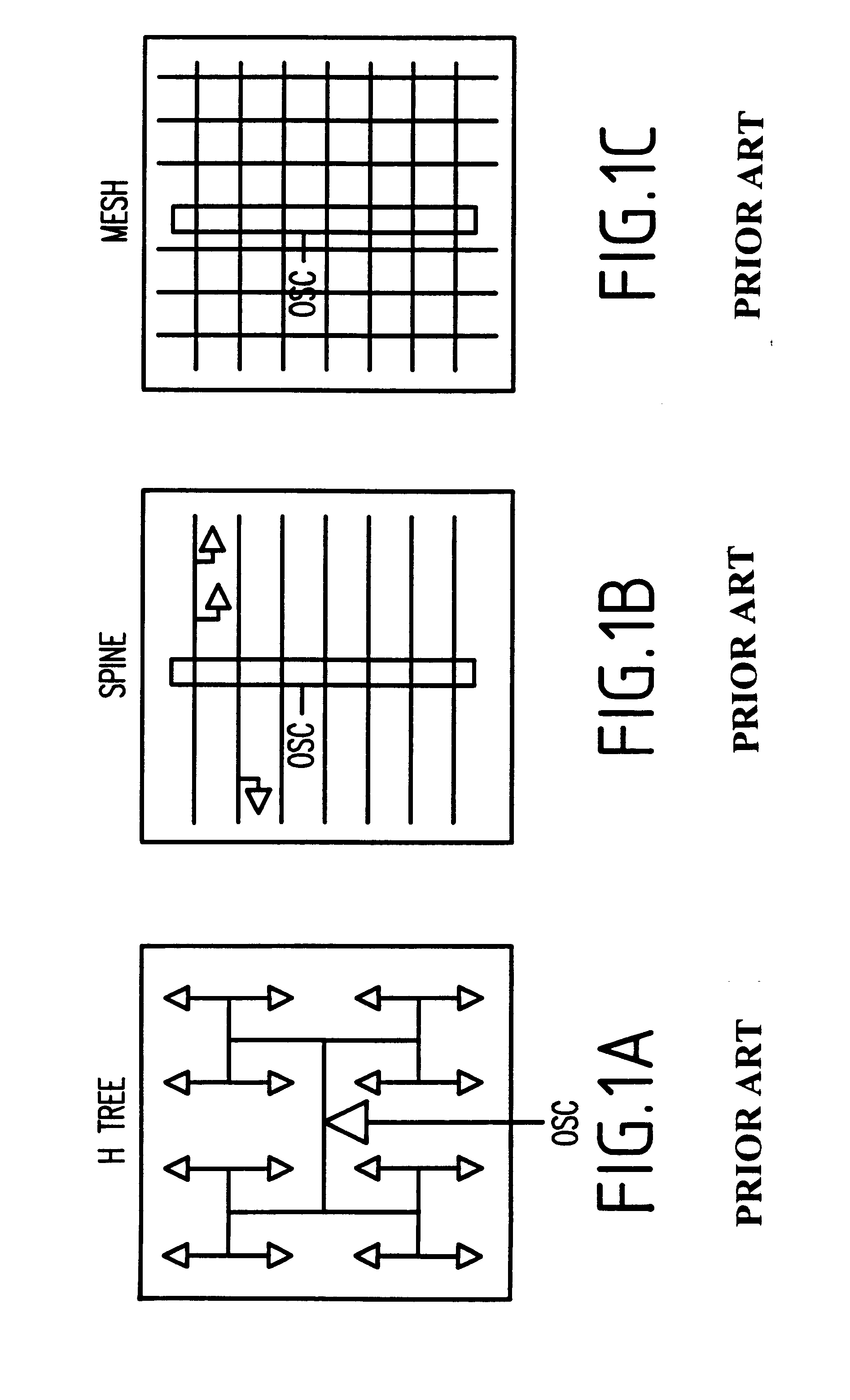

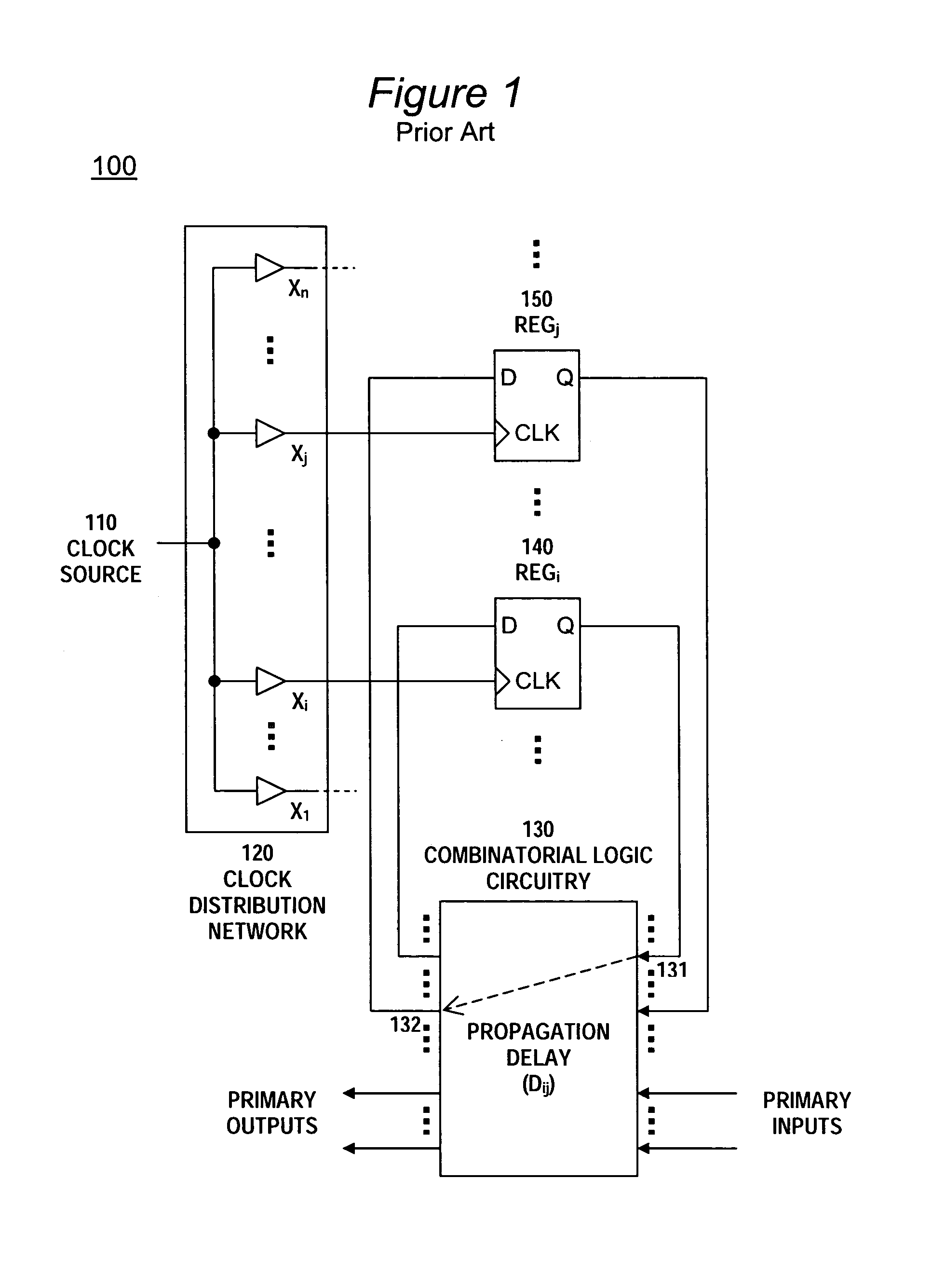

A clock network or clock system is a set of synchronized clocks designed to always show exactly the same time by communicating with each other. Clock networks usually consist of a central master clock kept in sync with an official time source, and one or more slave clocks which receive and display the time from the master.

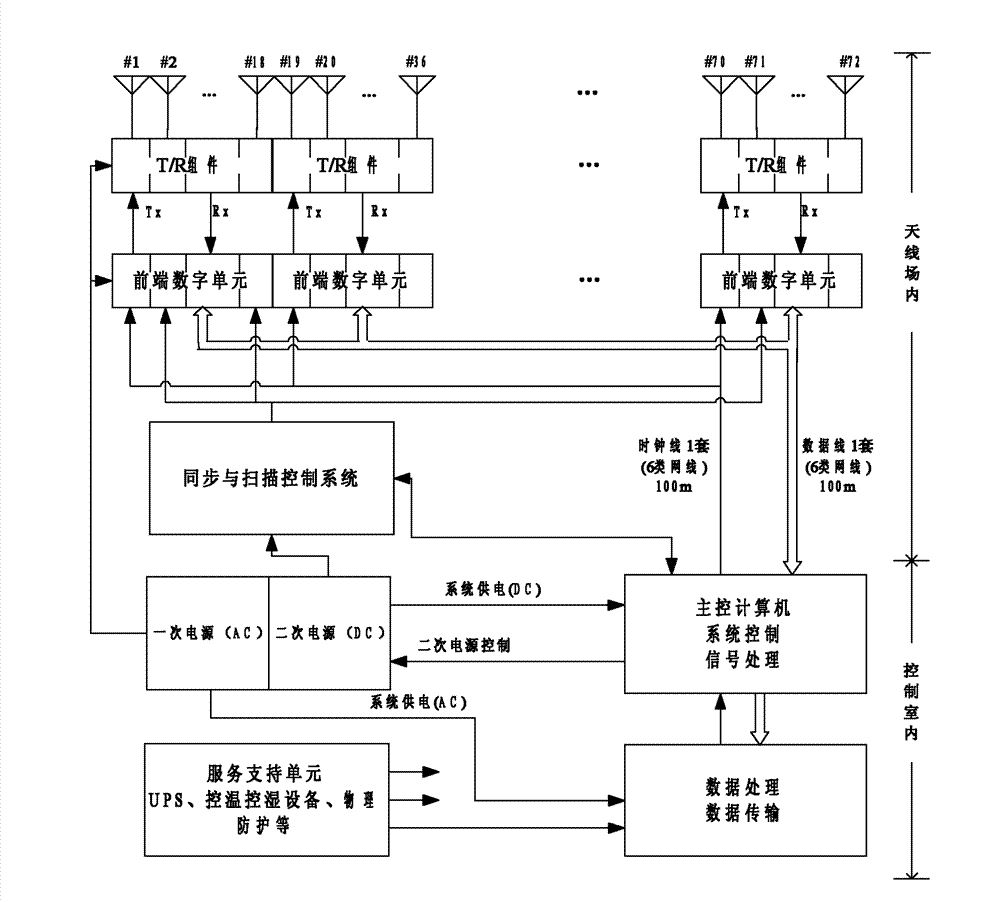

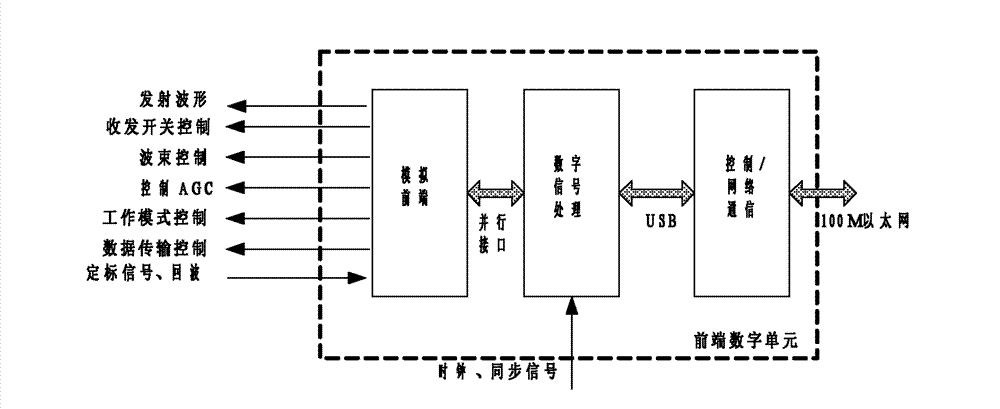

Distributed active phased array radar and beam forming method thereof

ActiveCN102955155AImprove radar performanceRealize real-time compensationRadio wave reradiation/reflectionLow noiseClock network

The invention relates to distributed active phased array radar and a beam forming method thereof. A transceiving component array consists of digital transceiving components which comprise analog front ends, power amplifiers, low-noise amplifiers and front-end digital units. The distributed active phased array radar further comprises a central processor, the central processor is connected with the multiple front-end digital units through a local area network by means of the hierarchical distributed processing technology, and used for setting operating modes of all of the front-end digital units and waveform data and receiving baseband data to guarantee reliability of target echo data subjected to digital synthesis and sending public clock signals to the front-end digital units through a clock network to guarantee synchronization of clock signals of each port. The multiple front-end digital units are correspondingly distributed in an antenna array, and each front-end digital unit is matched with one transceiving component. The distributed active phased array radar and the beam forming method thereof have the advantages of high flexibility, flexibility in data processing mode and improvement of phased array radar performances.

Owner:NAT SPACE SCI CENT CAS

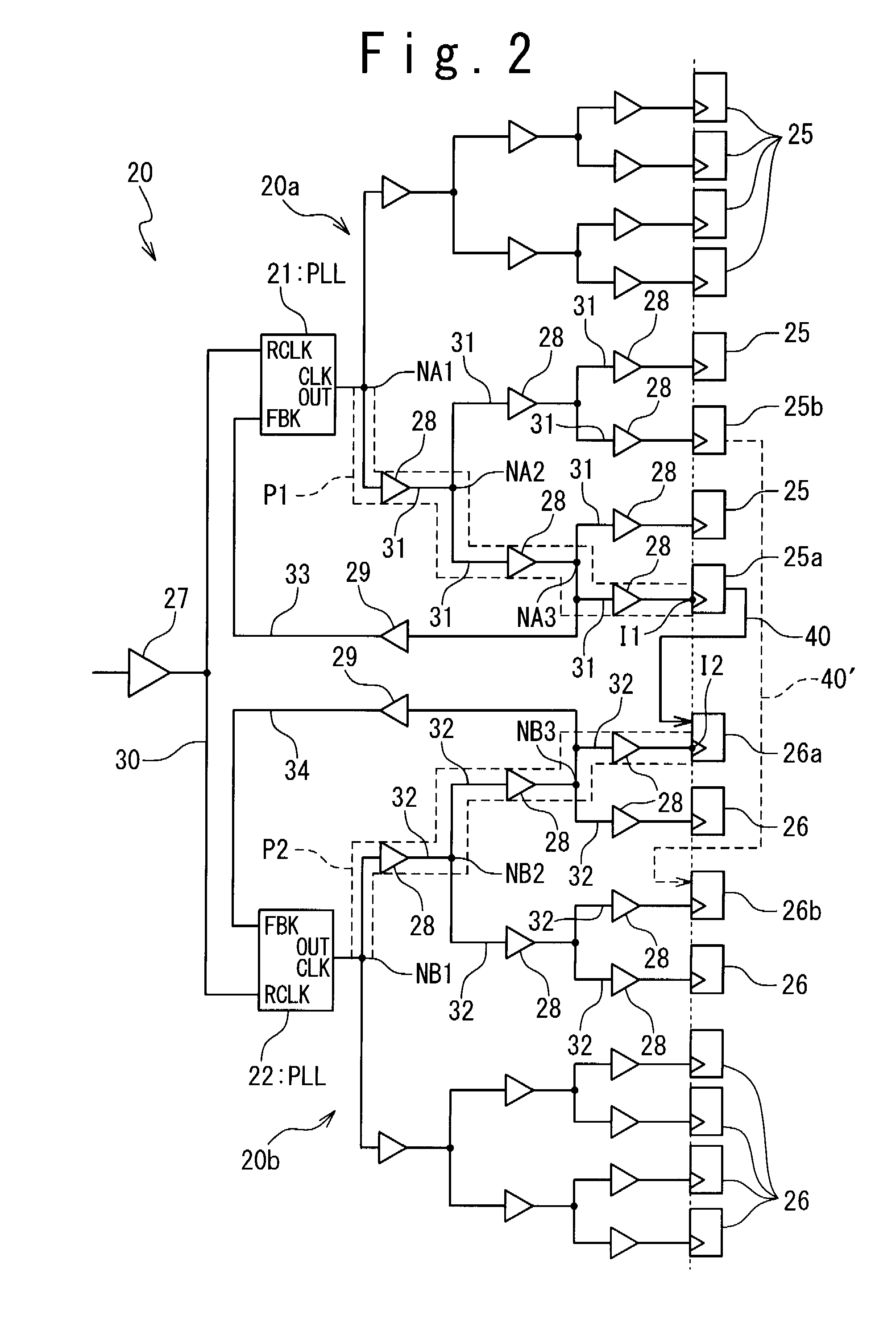

Method and apparatus for routing low-skew clock networks

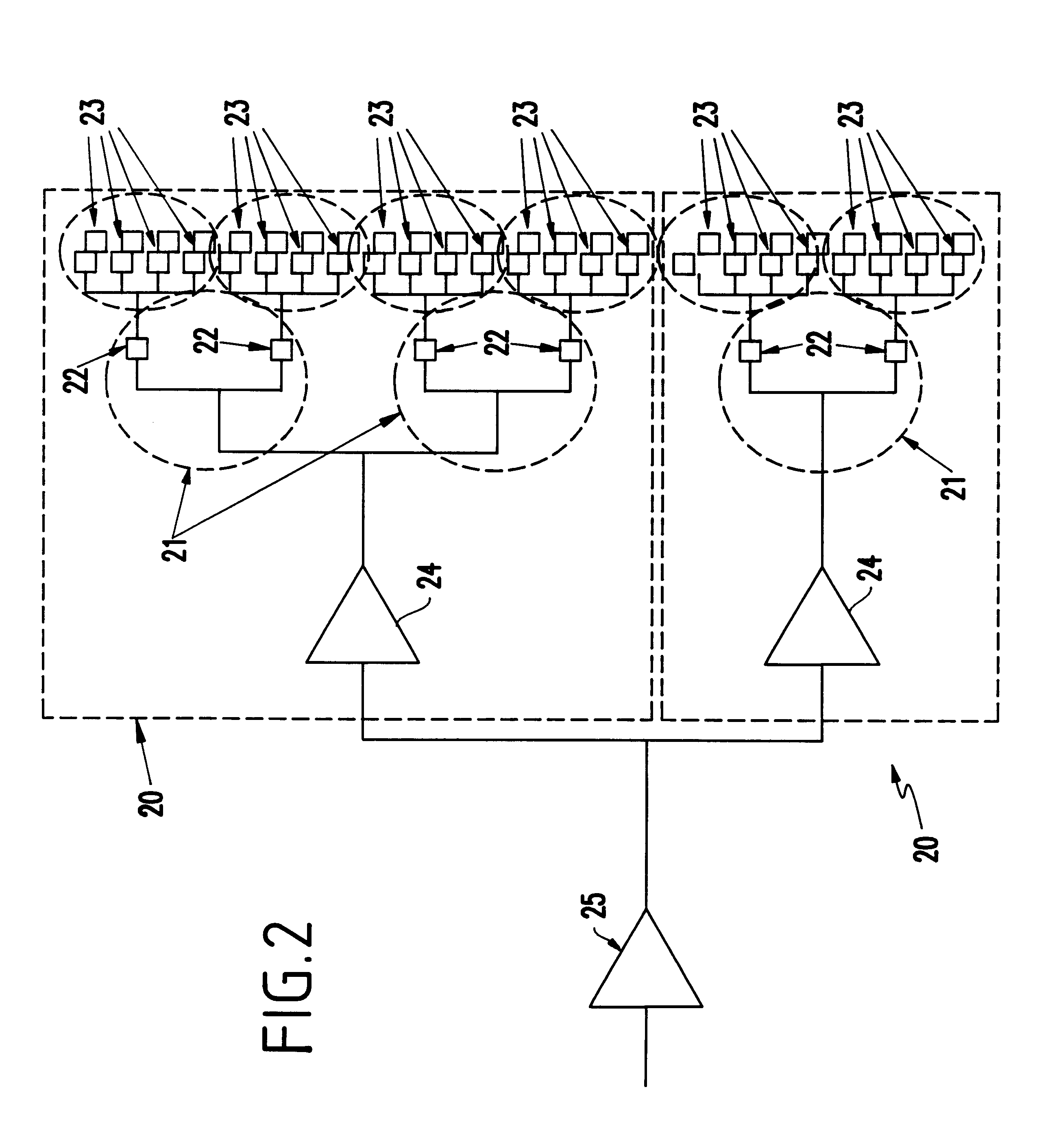

An integrated circuit chip comprises a plurality of clock distribution sub-networks each including a clock input for receiving a clock signal, each of the clock distribution sub-networks having a capacitance, as seen from the clock input, substantially equivalent to others of the clock distribution sub-networks; and a structured clock buffer having a size based on a load of the clock distribution sub-networks, and providing the clock signal to the clock distribution sub-networks.

Owner:IBM CORP

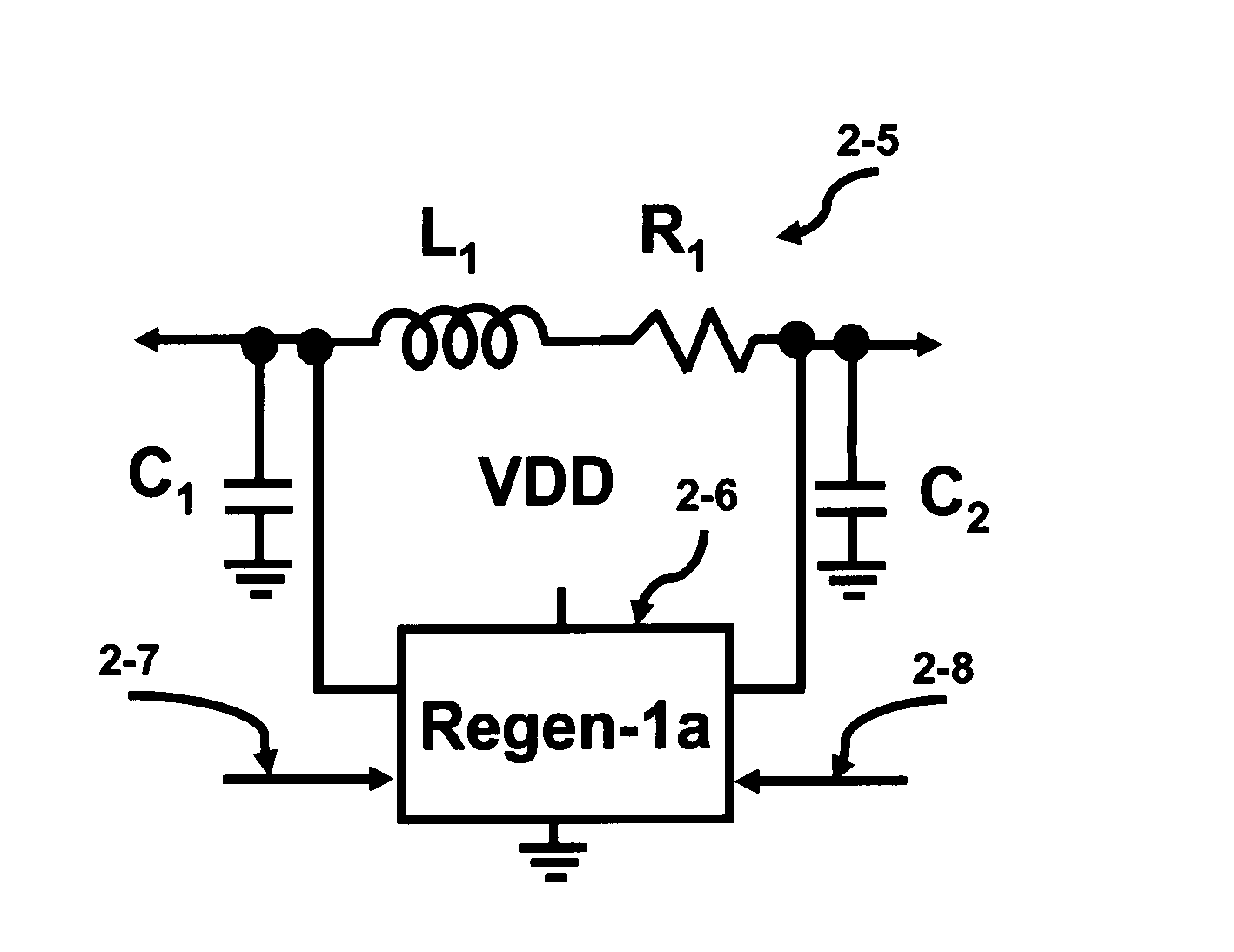

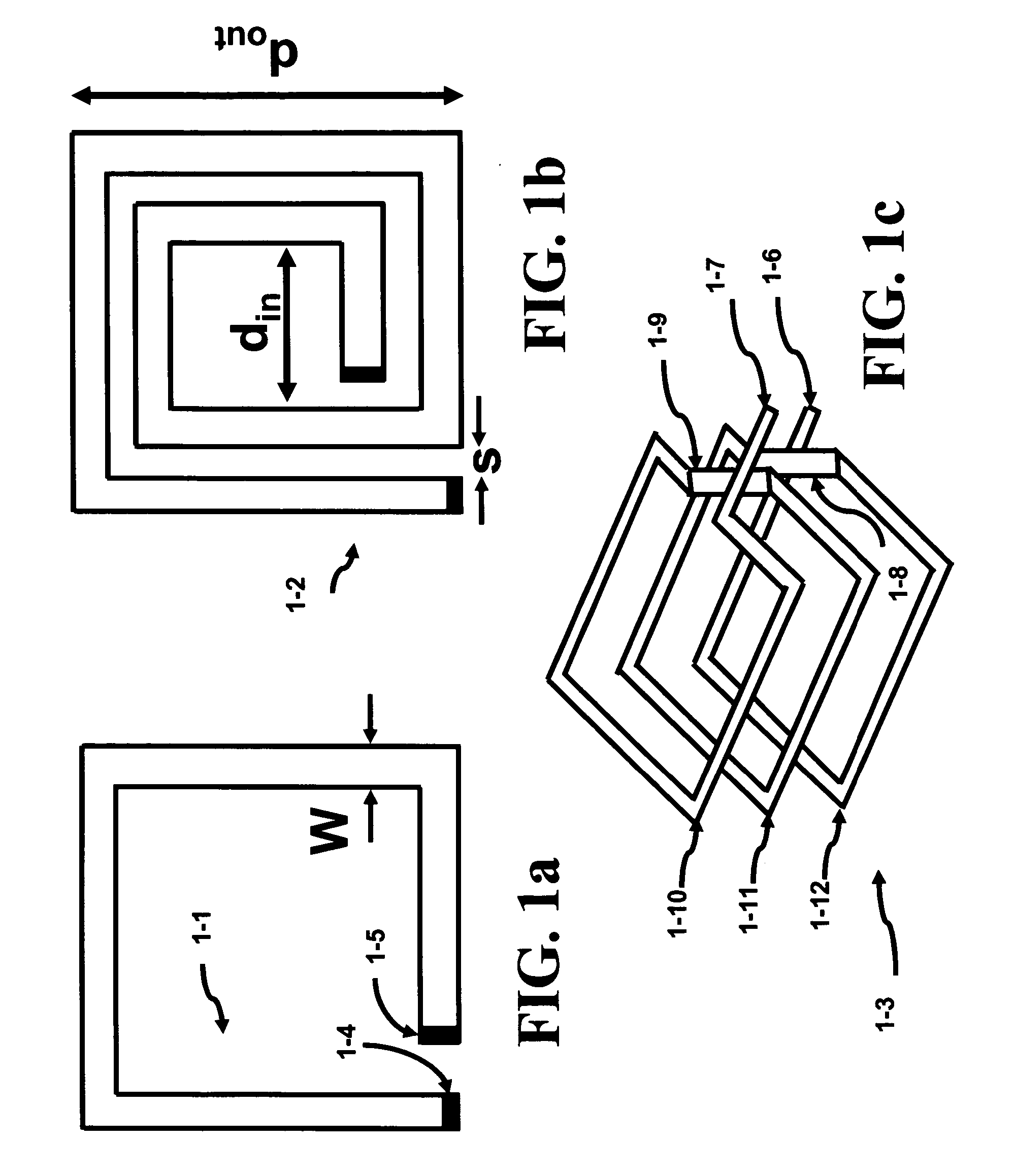

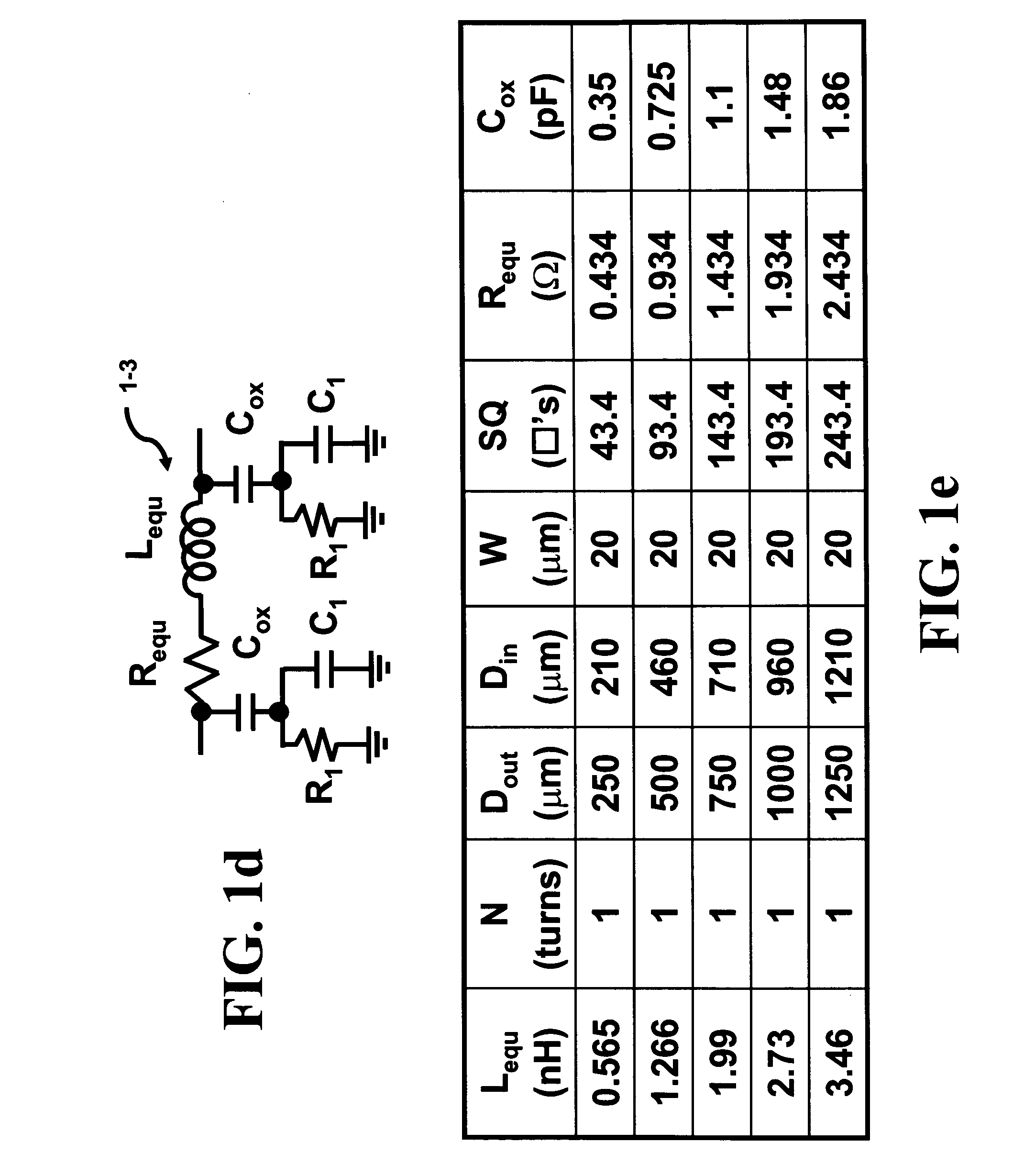

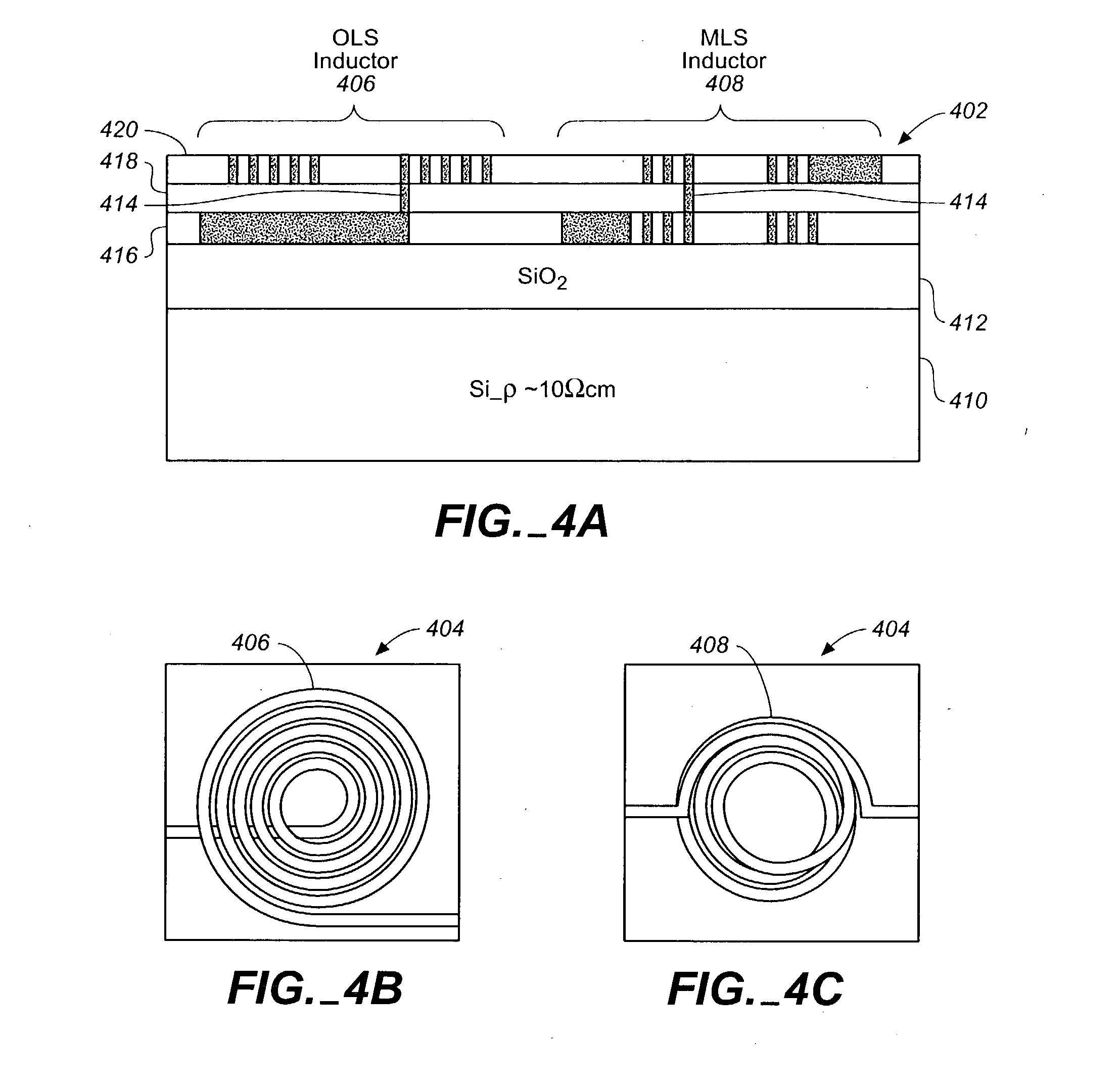

Frequency adjustment techniques in coupled LC tank circuits

CMOS LC tank circuits and flux linkage between inductors can be used to distribute and propagate clock signals over the surface of a VLSI chip or μprocessor. The tank circuit offers an adiabatic behavior that recycles the energy between the reactive elements and minimizes losses in a conventional sense. Flux linkage can be used to orchestrate a number of seemingly individual and distributed CMOS LC tank circuits to behave as one unit. Several frequency-adjusting techniques are presented which can be used in an distributed clock network environment which includes an array of oscillators. A passive flux linkage, mechanical, and finite state machine technique of frequency adjustment of oscillators are described.

Owner:INTELLECTUAL VENTURES HOLDING 81 LLC

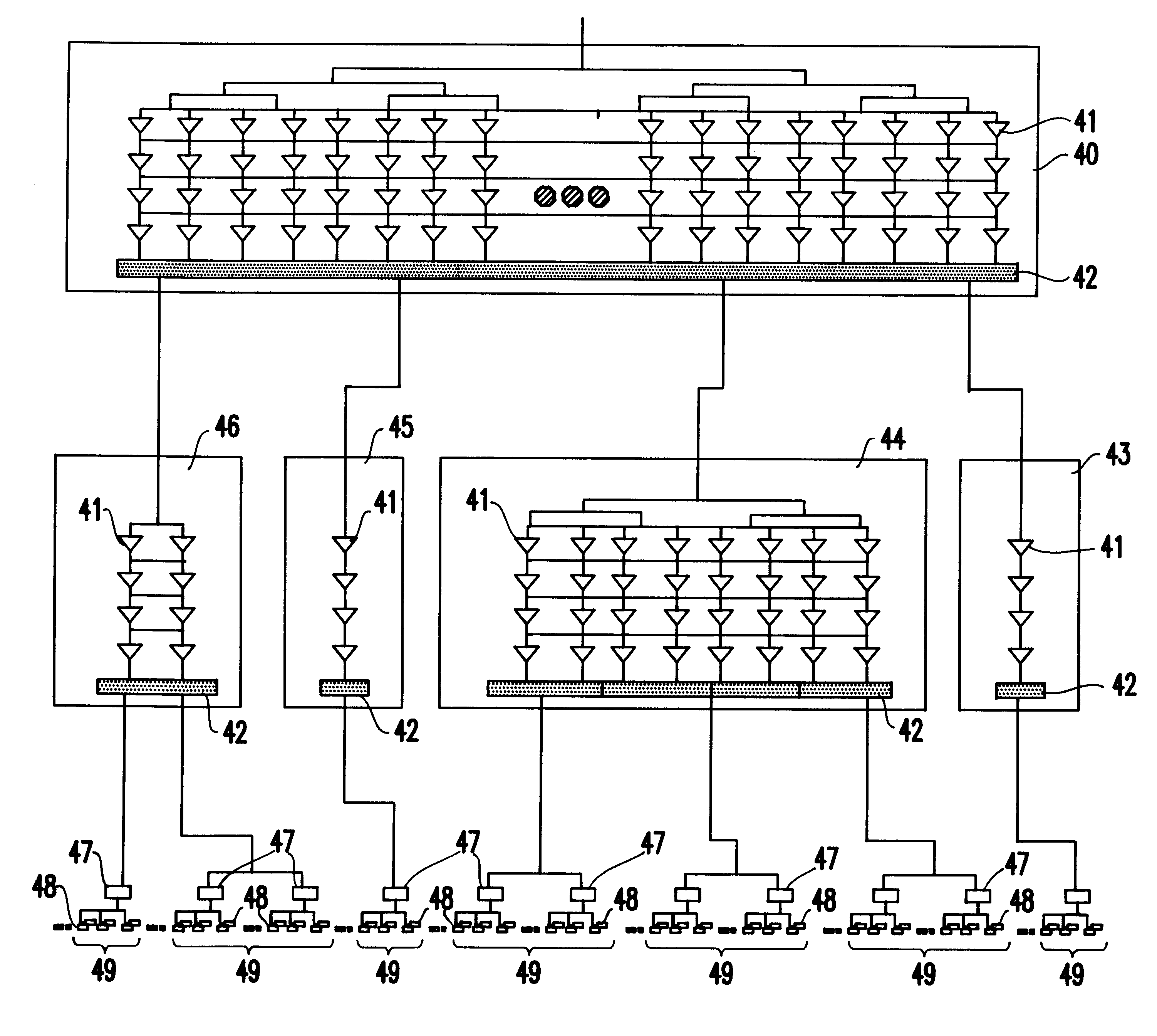

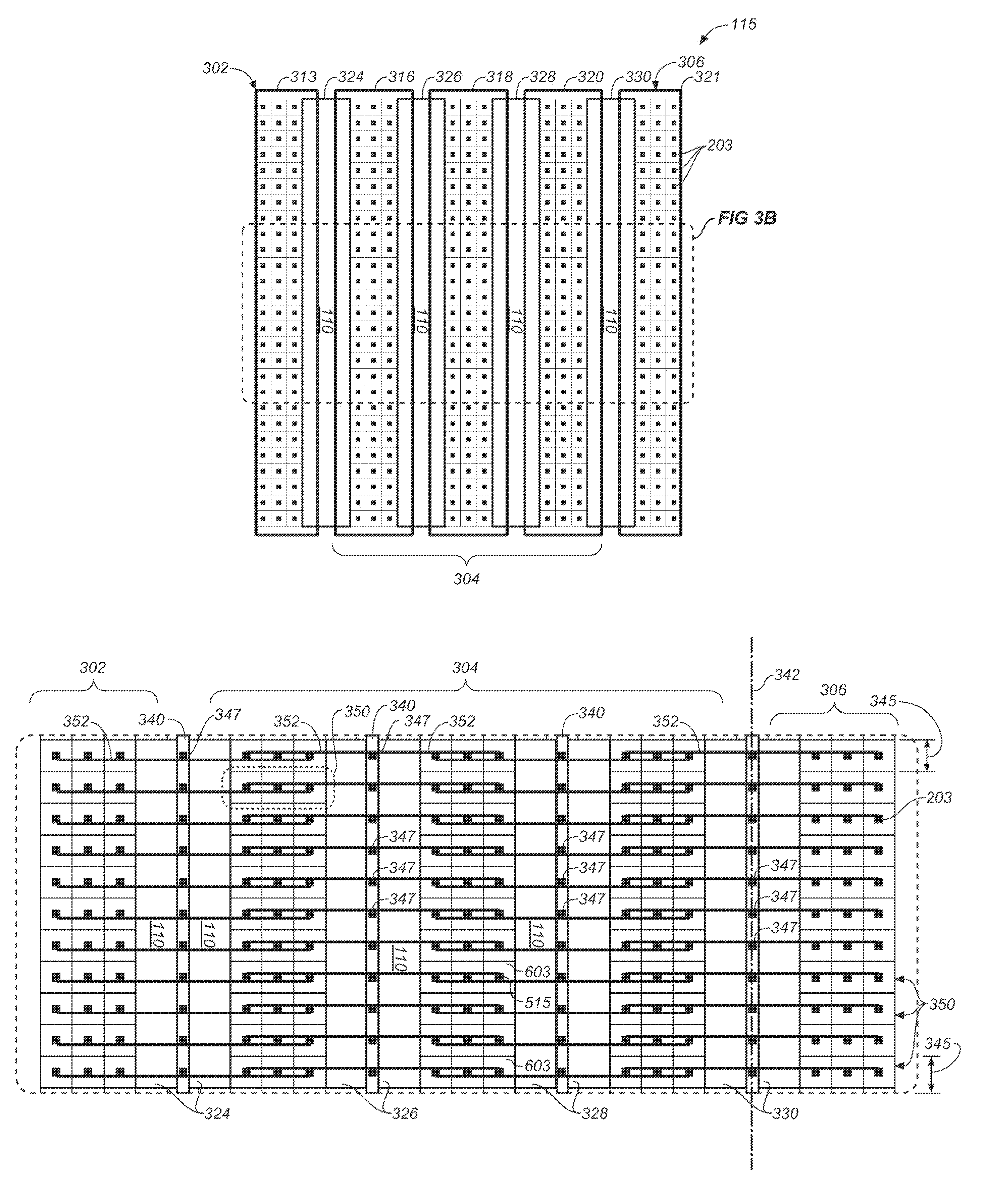

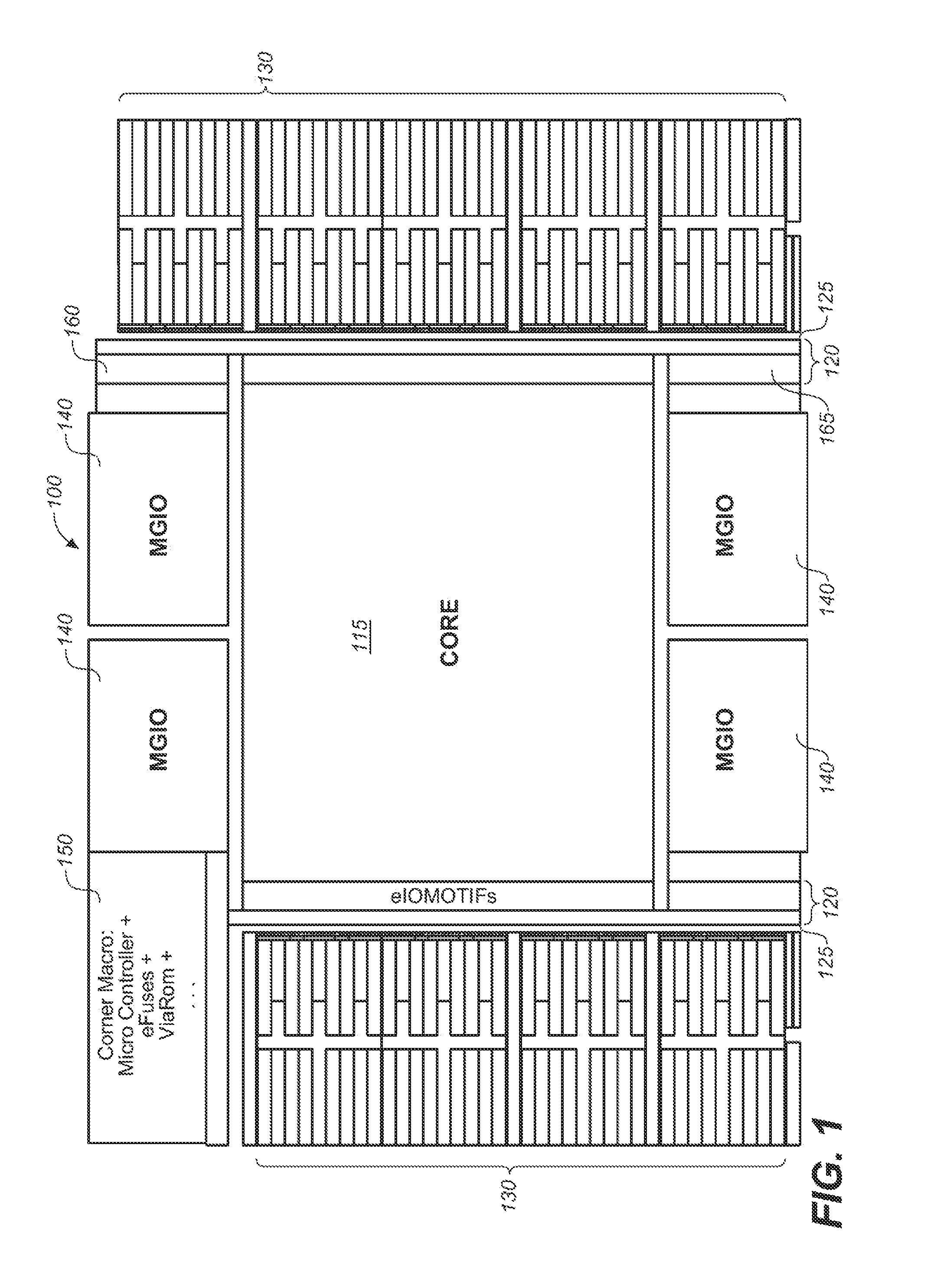

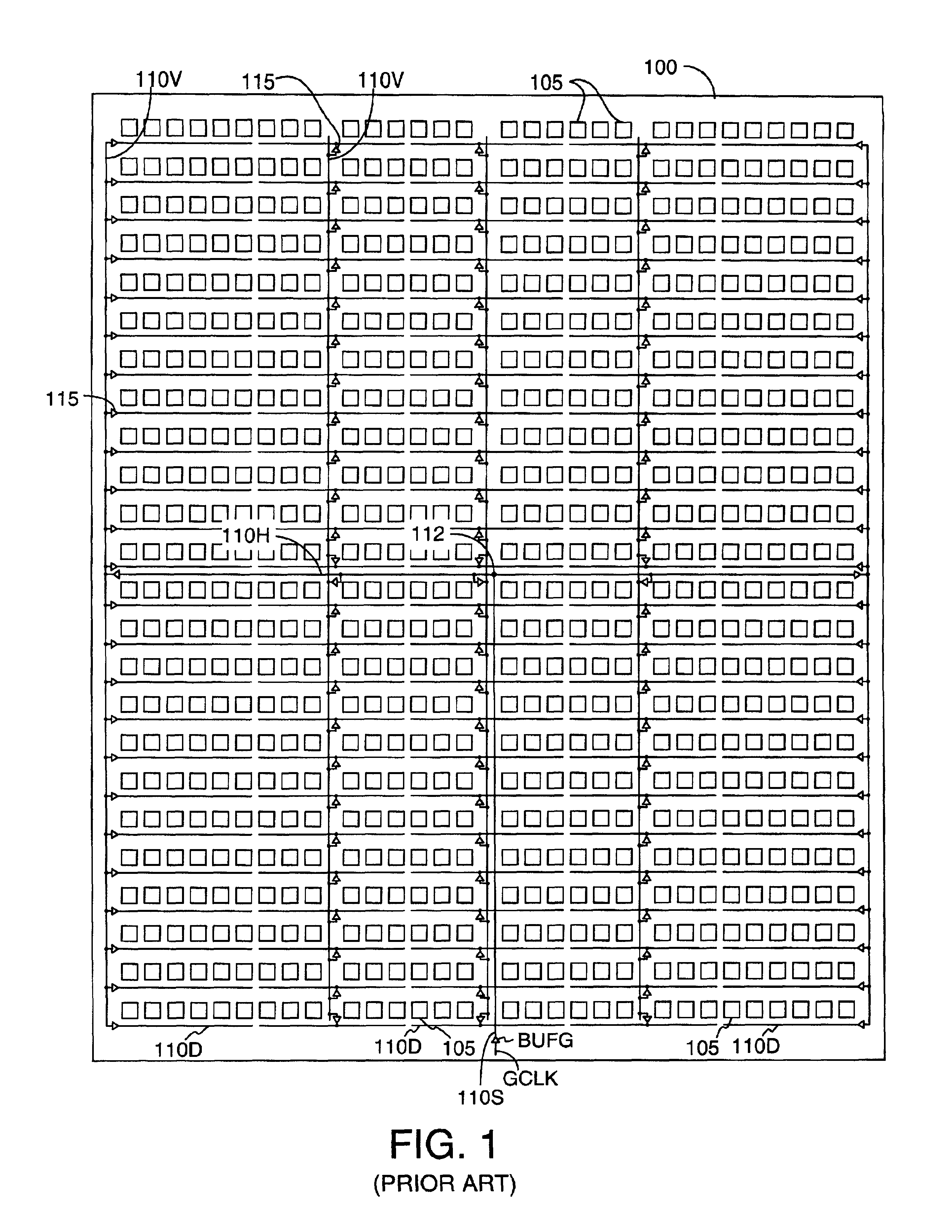

Clock network fishbone architecture for a structured ASIC manufactured on a 28 NM CMOS process lithographic node

InactiveUS8629548B1Low levelEasy constructionPower reduction in field effect transistorsPower reduction by control/clock signalLogic cellAnd logic unit

A clock architecture for a Structured ASIC chip, manufactured using a CMOS process is shown. A via-configurable logic block (VCLB) architecture in the Structured ASIC has a core region containing memory and logic cells arranged in columns that are supplied by a clock network having a global clock network tree and a low-level clock mesh to distribute the global clock signal in a repeating pattern. The clock mesh has a fishbone configuration in outline and allows for scalable expansion of the clock network. In one embodiment 36 global clocks may be provided to the Structured ASIC, with four clocks per logic cell. The VCLB Structured ASIC chip is manufactured on a 28 nm CMOS process lithographic node, having several metal layers but preferably is programmable on a single via layer.

Owner:INTEL CORP

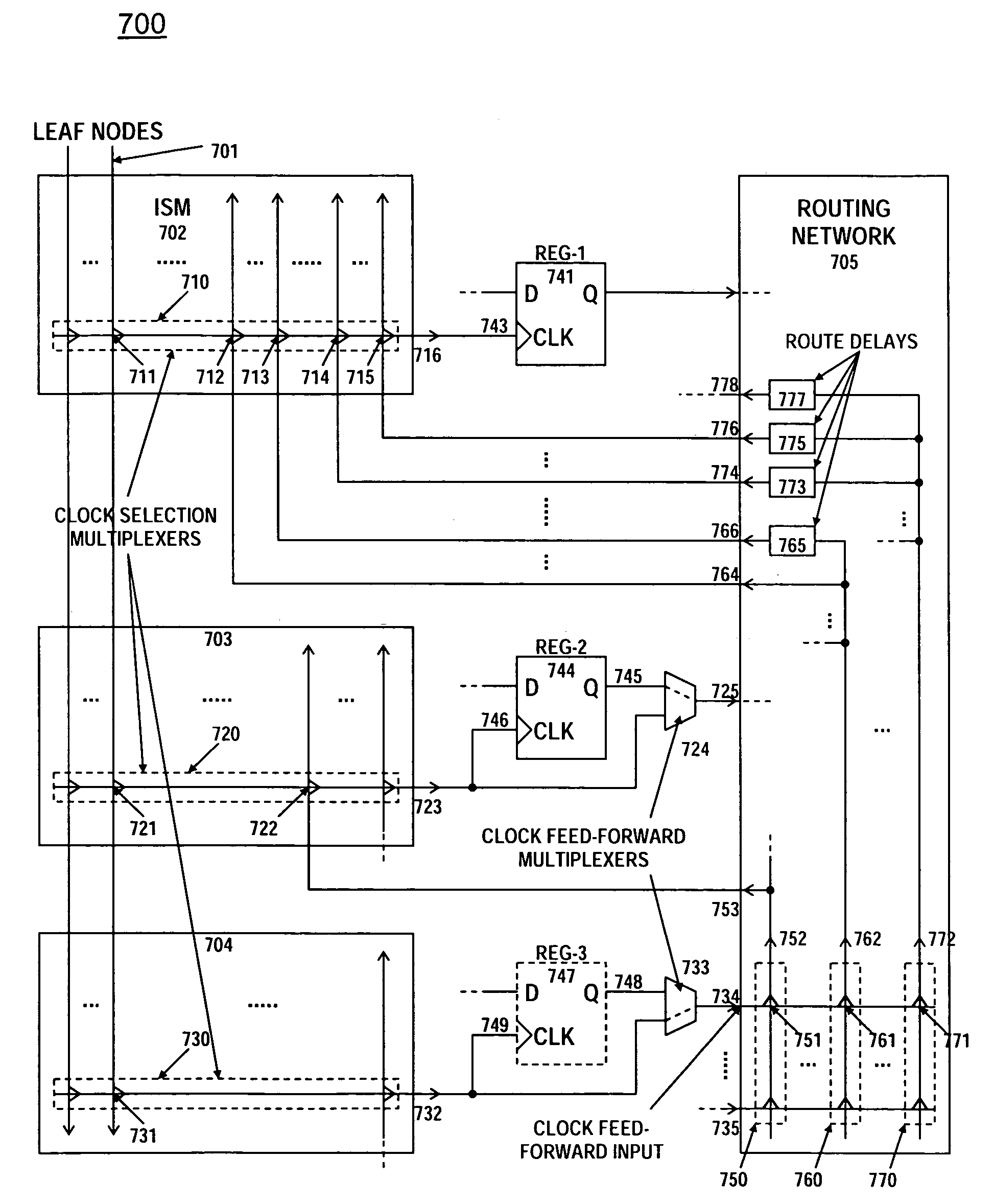

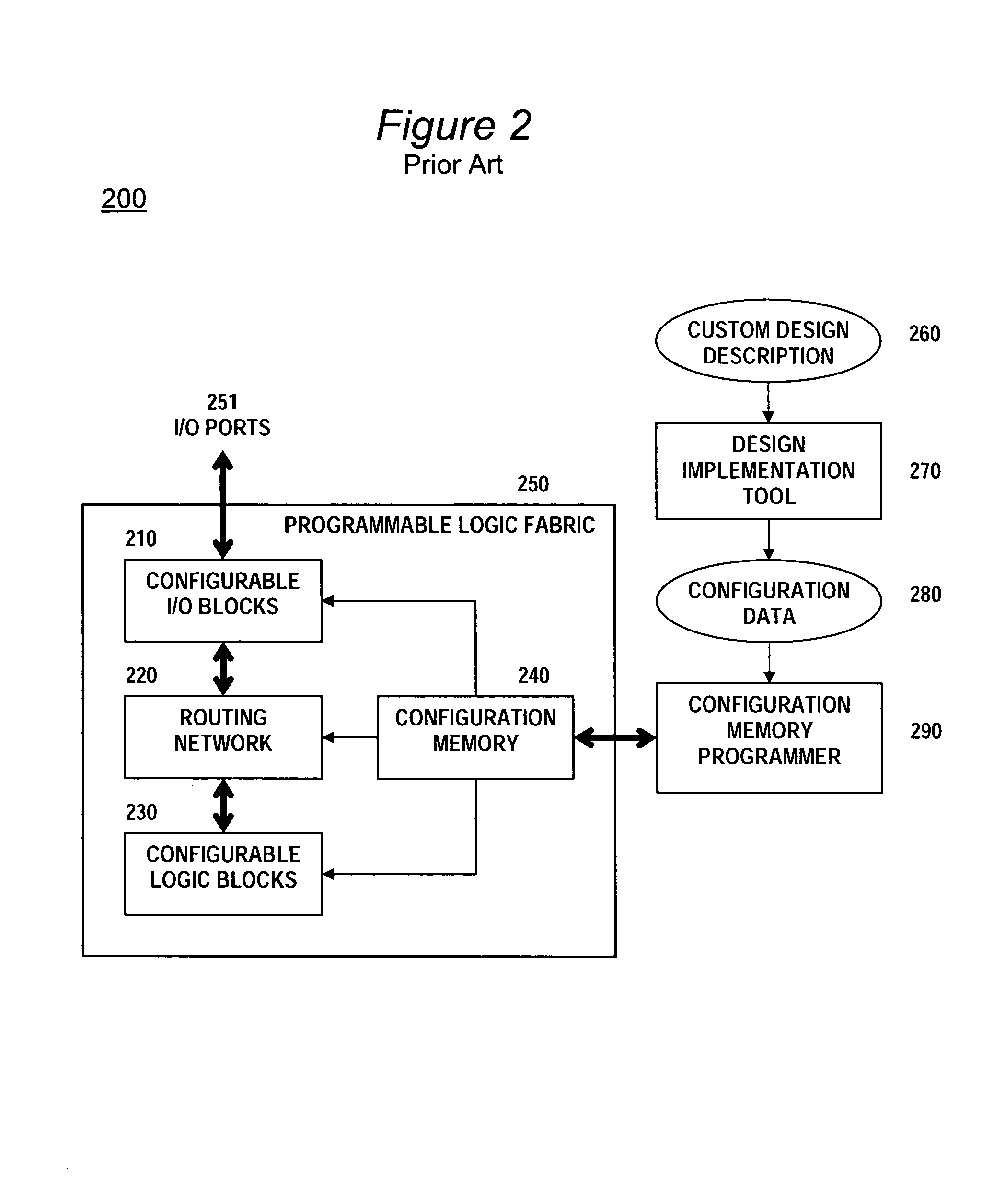

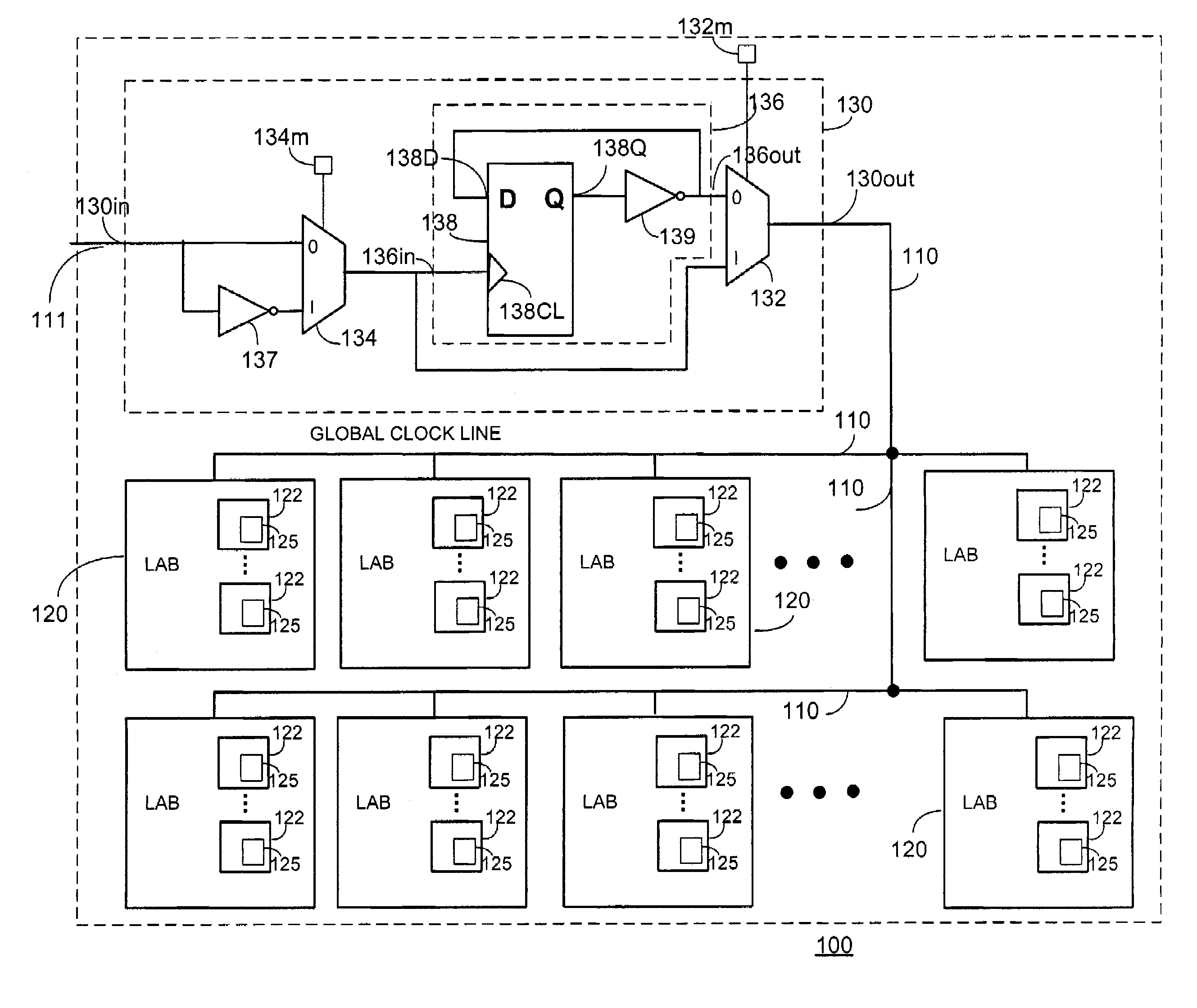

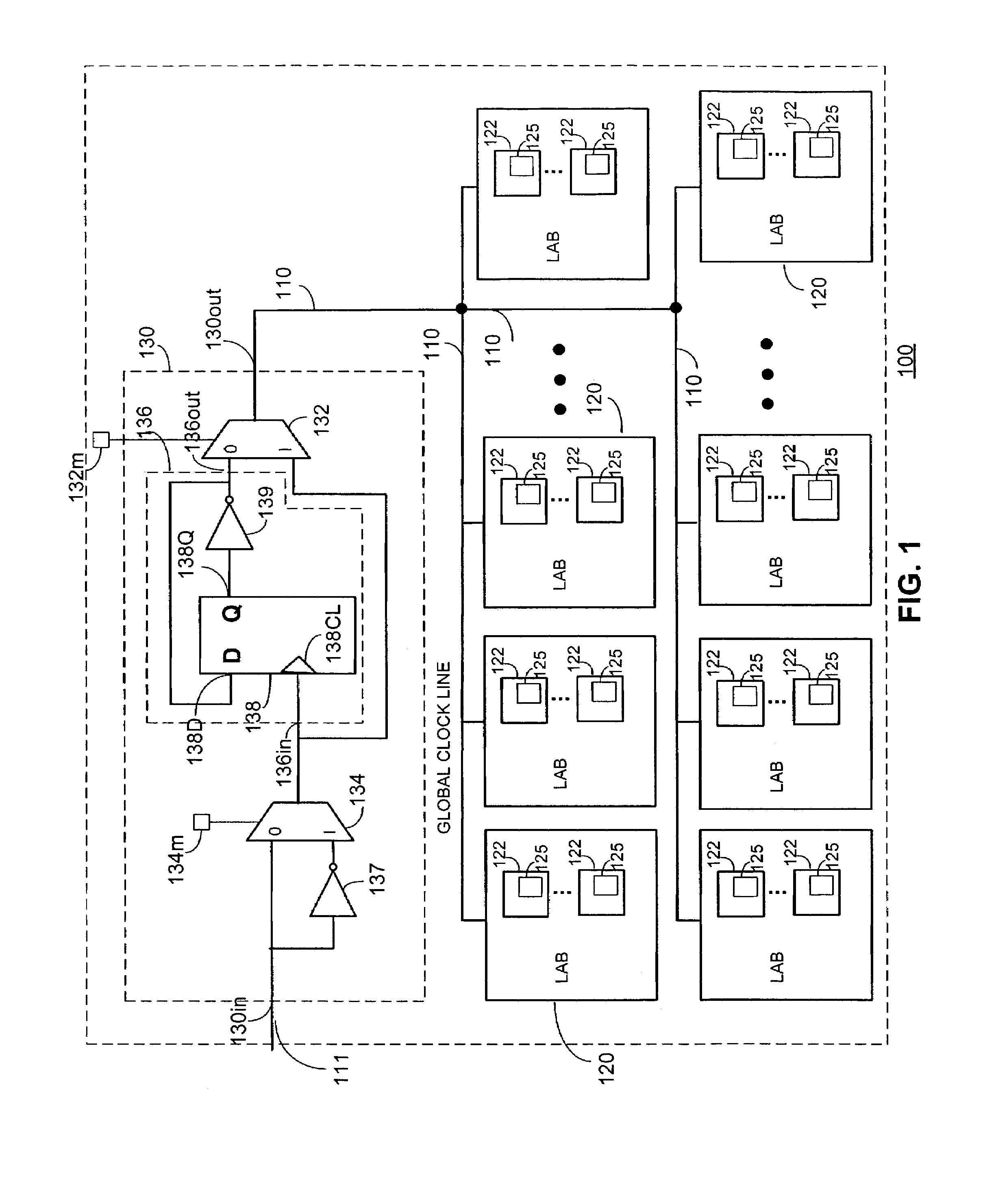

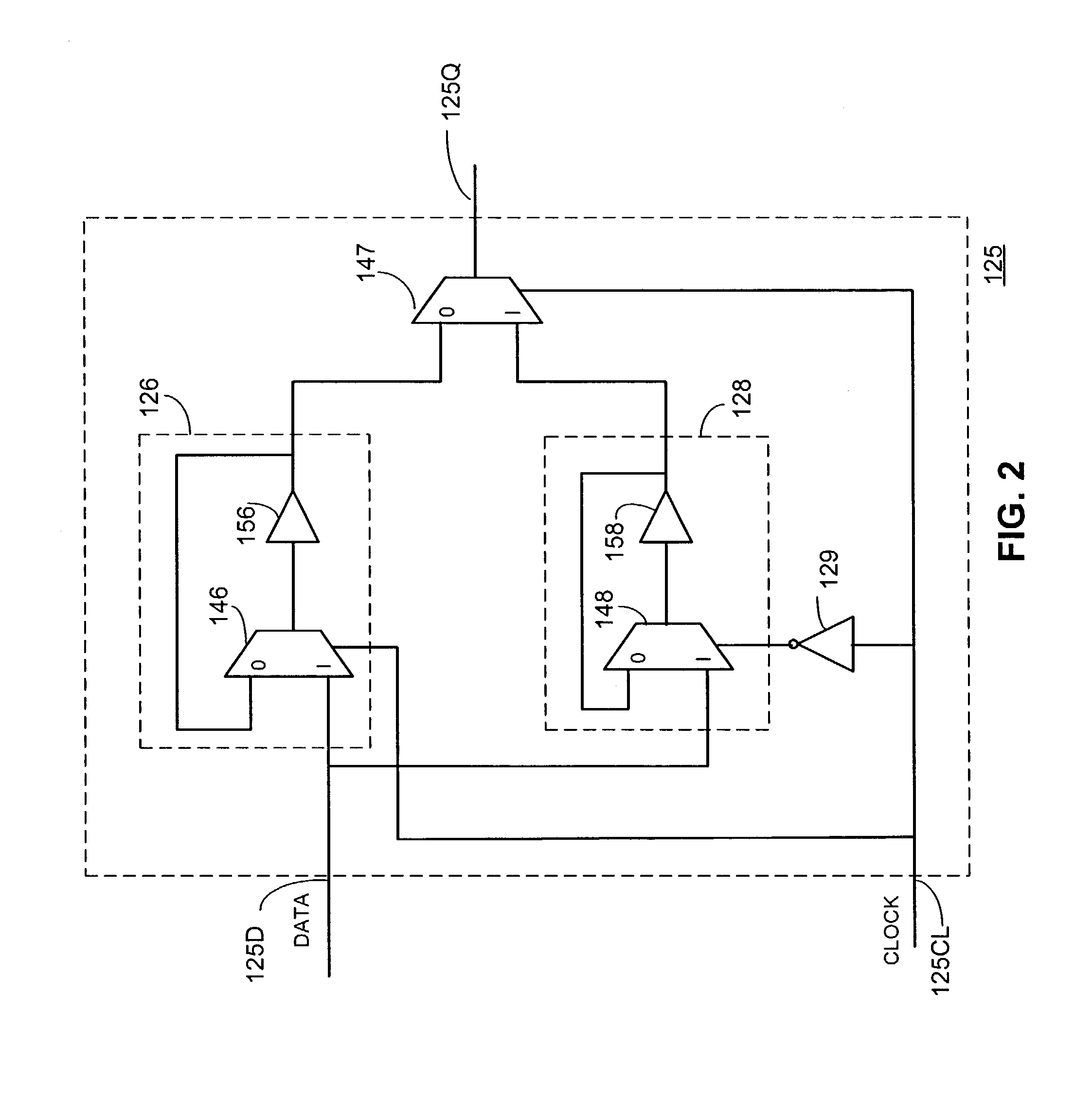

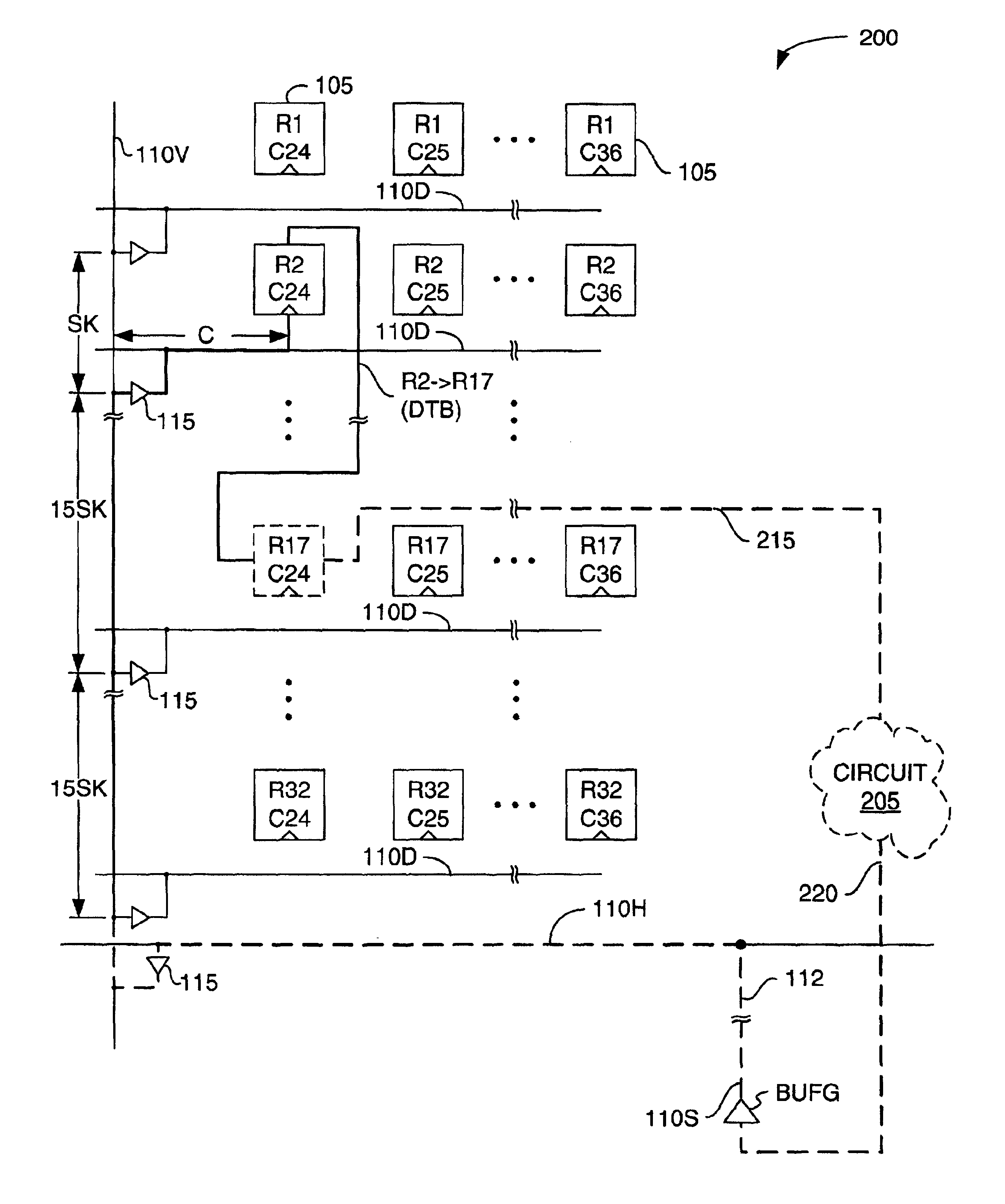

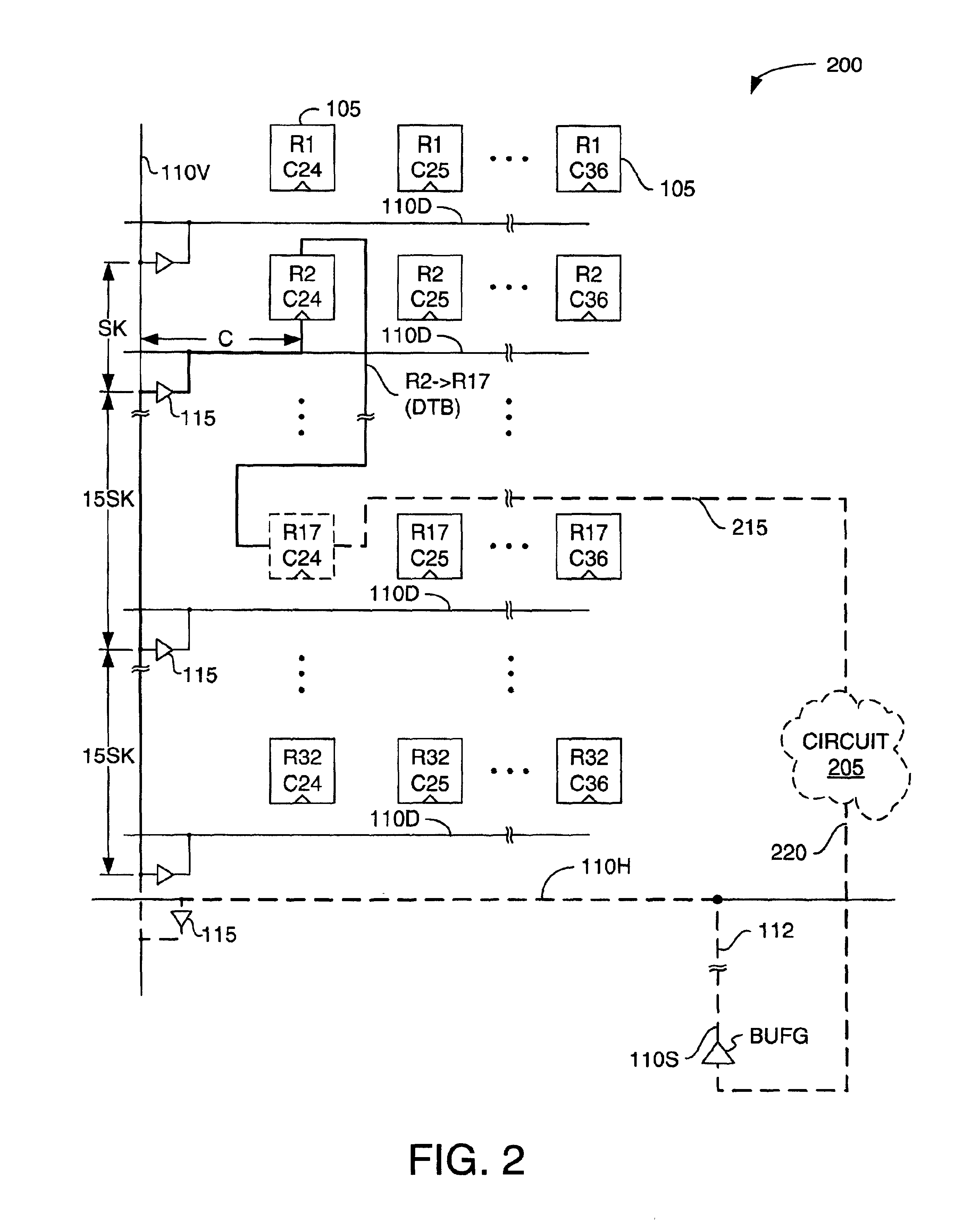

Apparatus and method for clock skew adjustment in a programmable logic fabric

InactiveUS7362135B1Minimize operating periodMinimize clock periodSolid-state devicesCAD circuit designProcessor registerProgrammable logic device

A programmable logic fabric includes configurable logic block (CLB) containing registers and combinatorial logic elements. An input switch matrix distributes incoming signals to CLB inputs or inputs of embedded logic elements including a register clock. A routing network allows a variety of routing paths with distinct delays to be selected to route the CLB outputs to the input switch matrices. Presented clock delay insertion architectures allow a leaf node of dedicated clock network and a register clock input can be alternatively routed through the routing network, thereby allowing for the generation of a variable amount of clock delay. Required clock delay for each register minimizing the clock period is computed by clock skew optimization program. A set of alternative clock routes is generated for each register clock where each route delay is close to the corresponding required delay while satisfying the monotone increasing conditions. Optimal clock route for each register clock can be efficiently selected from the alternative clock routes by an integer monotonic program to reduce the clock period of a custom design implemented in the fabric.

Owner:CHANG HYUN TAEK

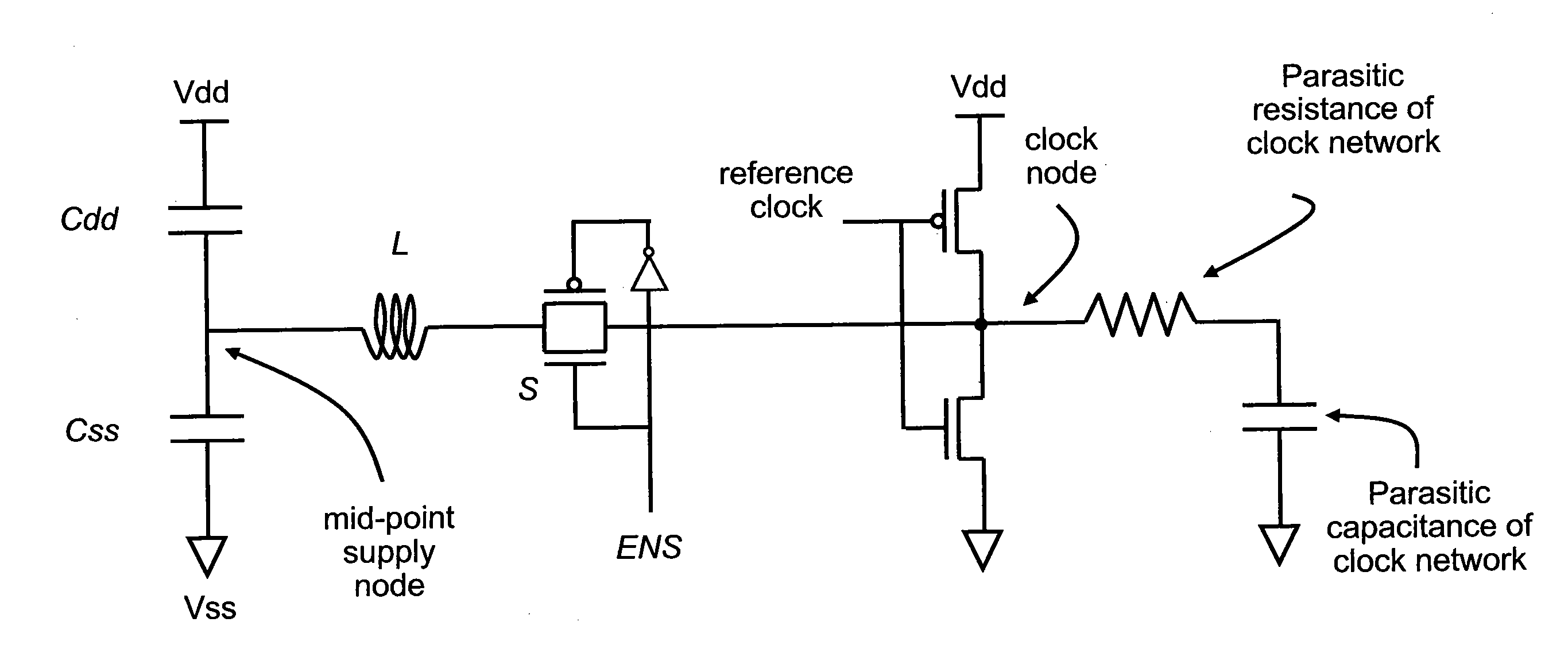

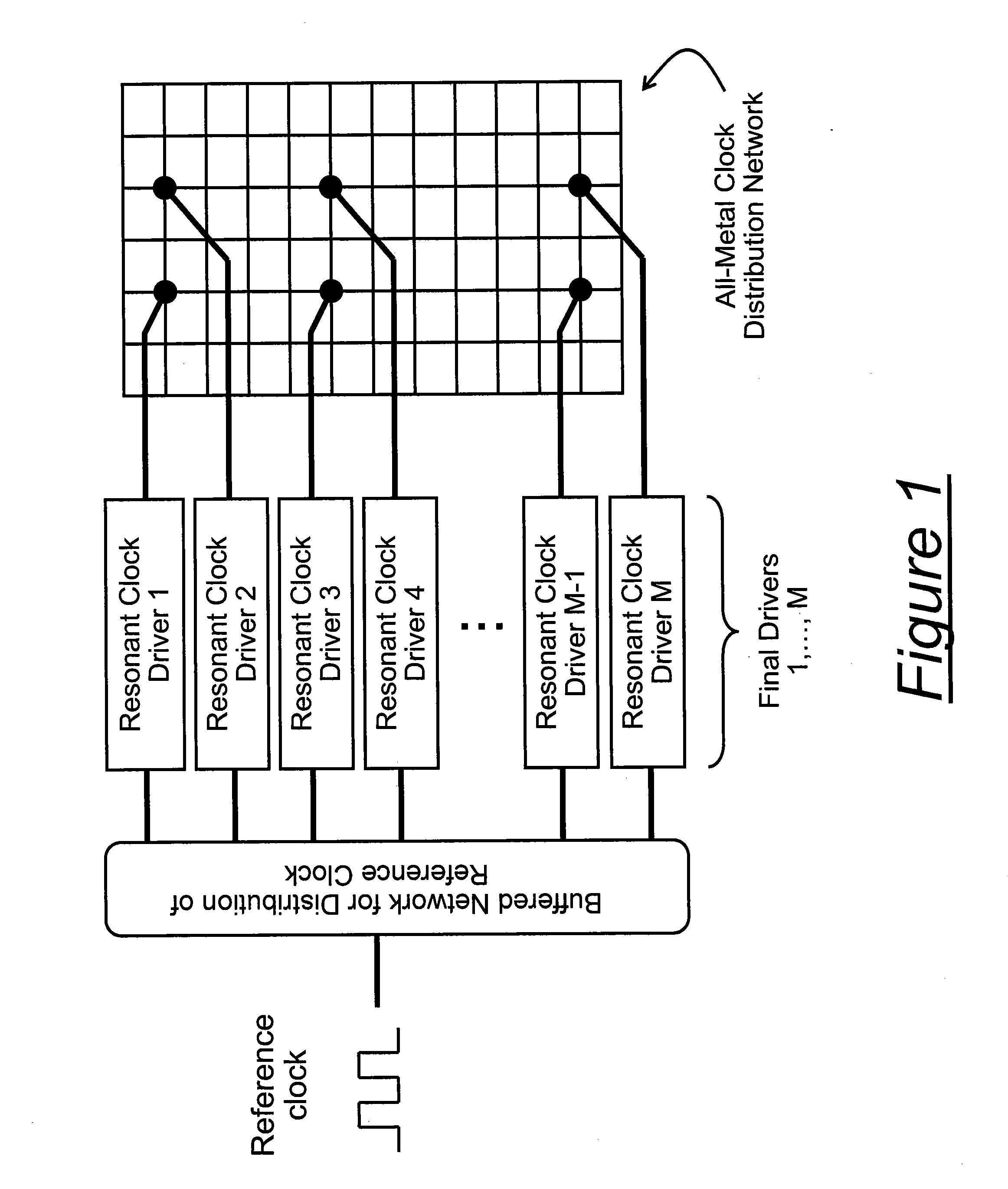

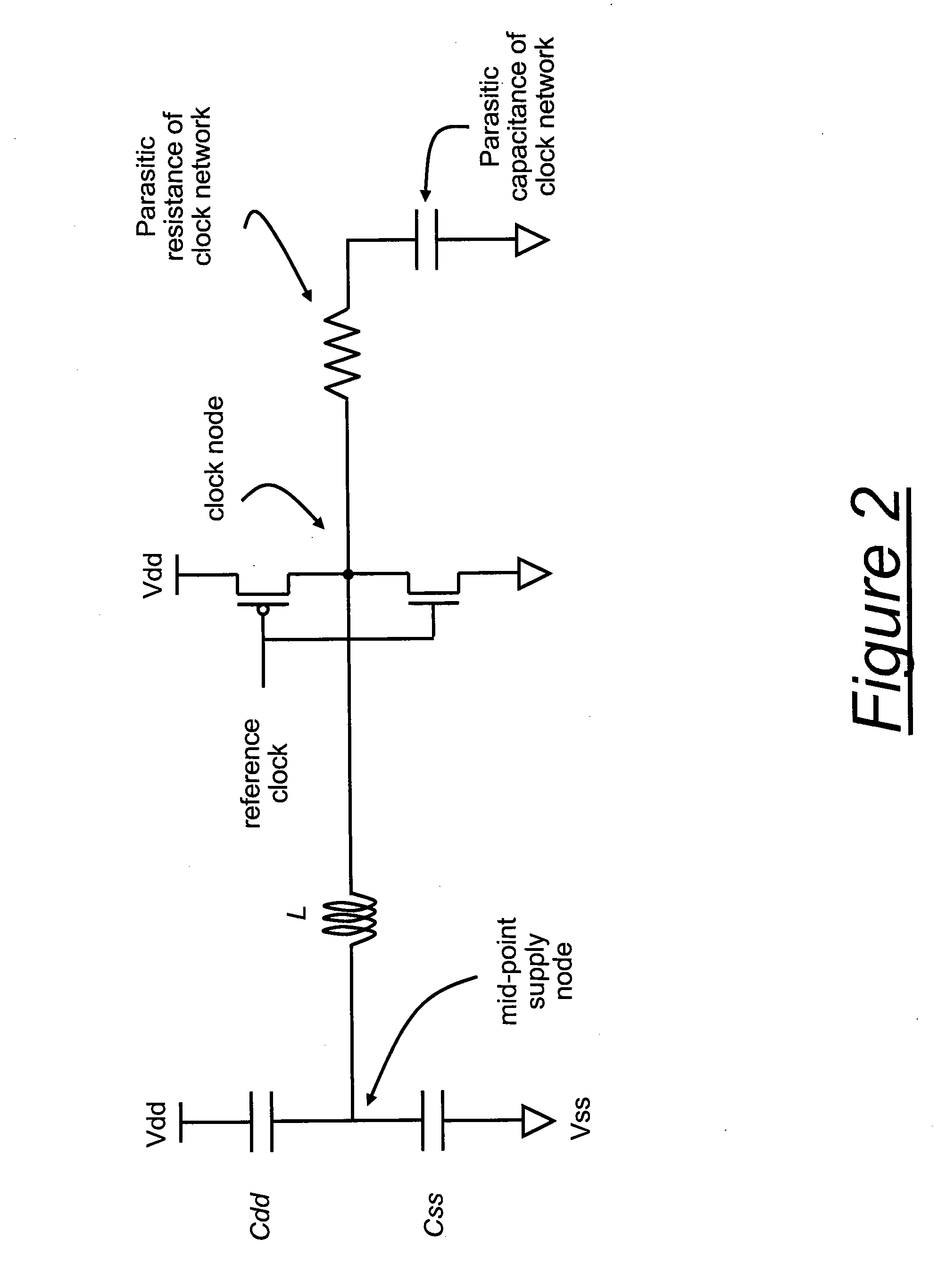

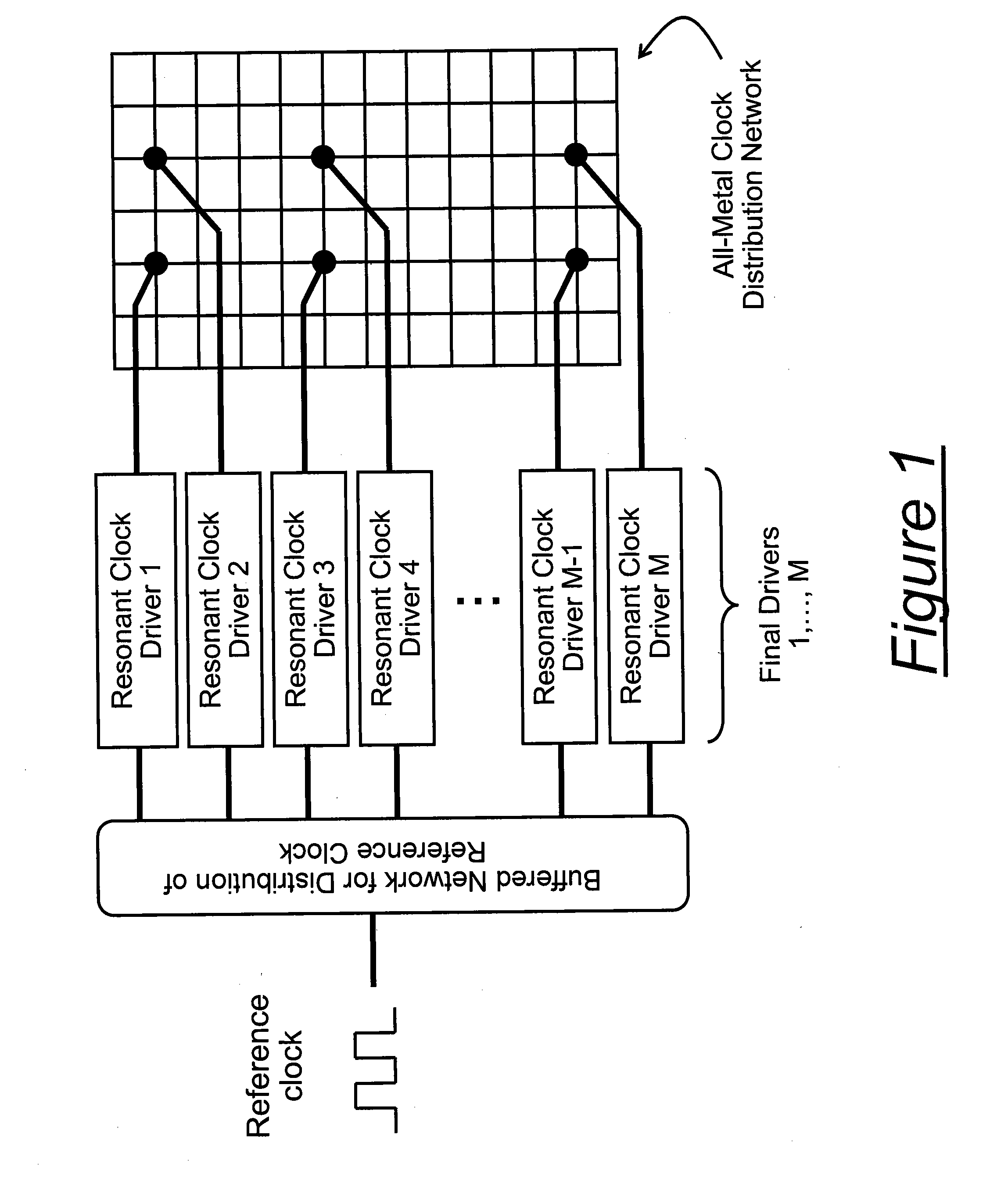

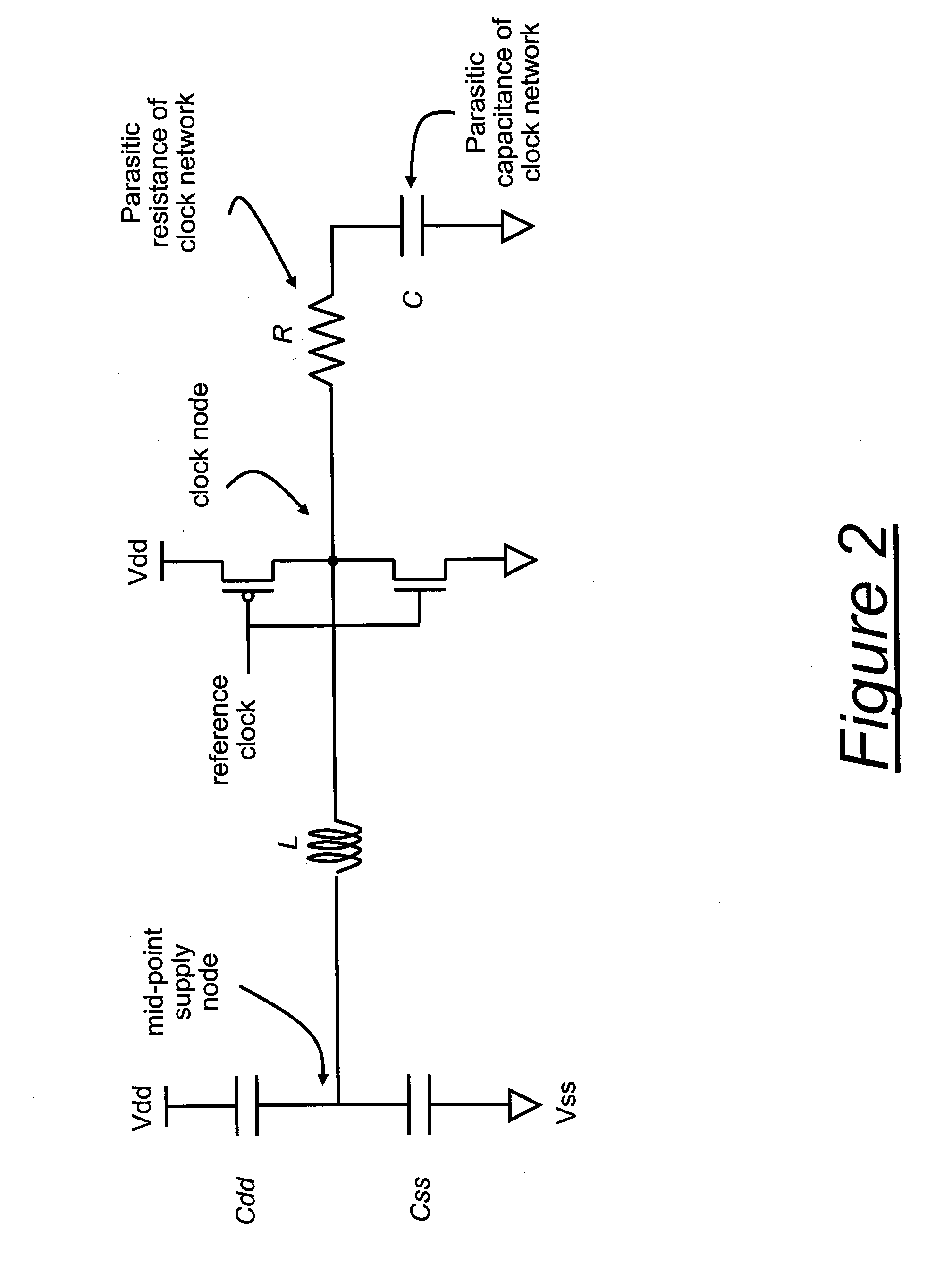

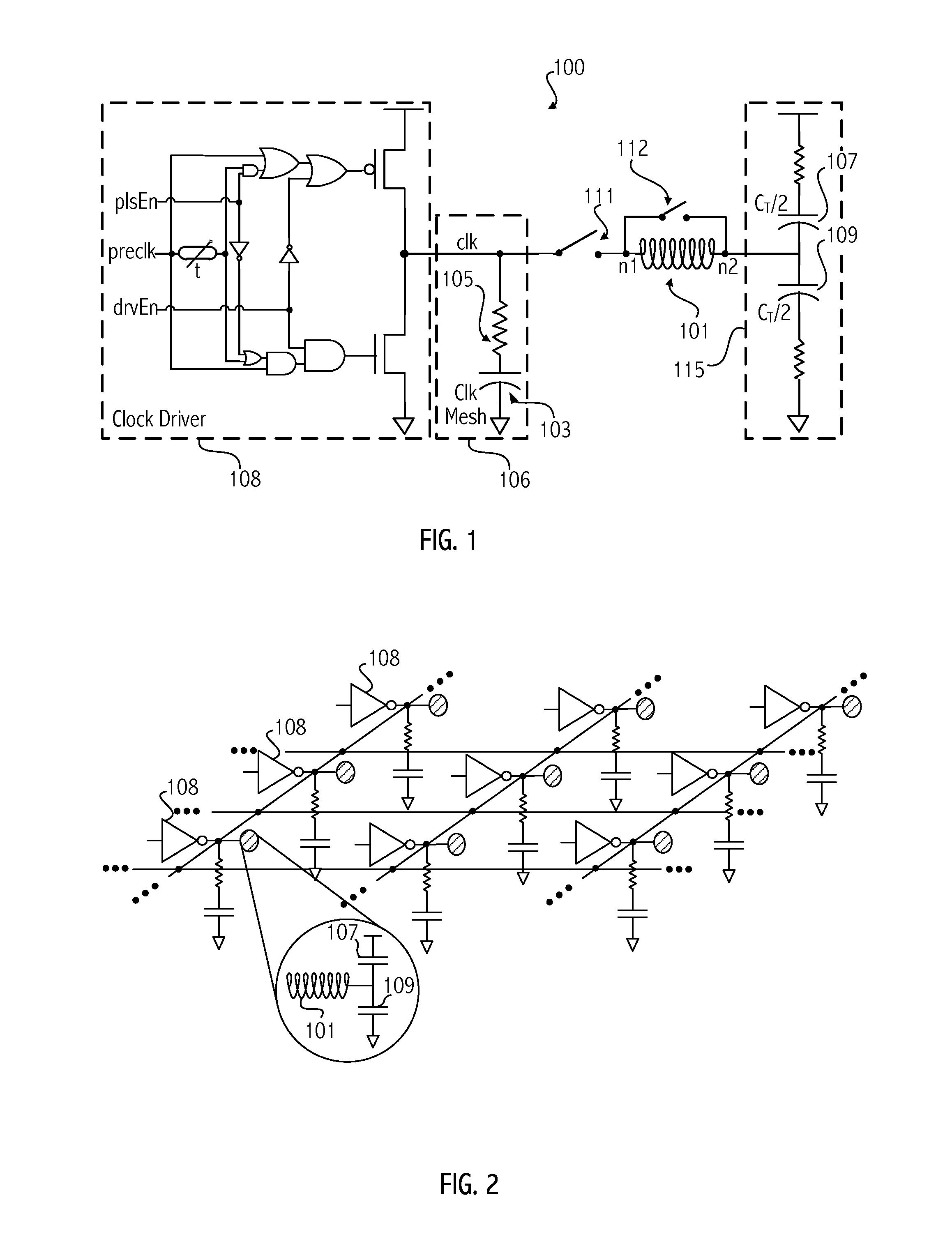

Architecture for operating resonant clock network in conventional mode

An architecture for resonant clock distribution networks is proposed. The proposed architecture allows for the energy-efficient operation of the resonant clock distribution network in conventional mode, so that it meets target specifications for the clock waveform. Such an architecture is generally applicable to semiconductor devices with multiple clock frequencies, and high-performance and low-power clocking requirements such as microprocessors, ASICs, and SOCs. Moreover, it is applicable to at-speed testing and to binning of semiconductor devices according to achievable performance levels.

Owner:CYCLOS SEMICON

Architecture for frequency-scaled operation in resonant clock distribution networks

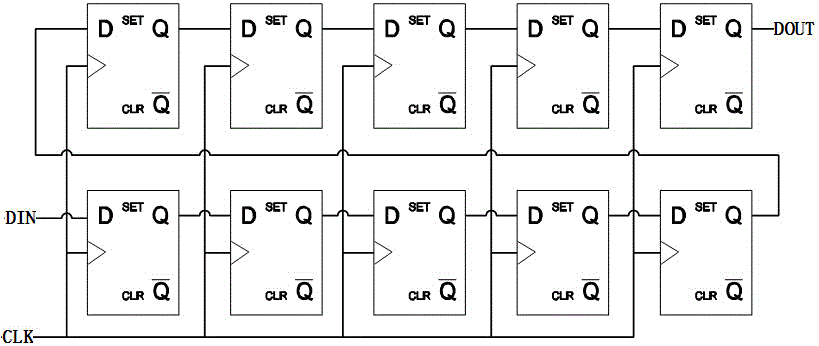

An architecture for resonant clock distribution networks is proposed. This architecture allows for the energy-efficient operation of a resonant clock distribution network at multiple clock frequencies through the deployment of flip-flops that can be selectively enabled. The proposed architecture is primarily targeted at the design of resonant clock networks with integrated inductors and exhibits no inductor overheads. Such an architecture is generally applicable to semiconductor devices with multiple clock frequencies, and high-performance and low-power clocking requirements such as microprocessors, ASICs, and SOCs. Moreover, it is applicable to the binning of semiconductor devices according to achievable performance levels.

Owner:CYCLOS SEMICON

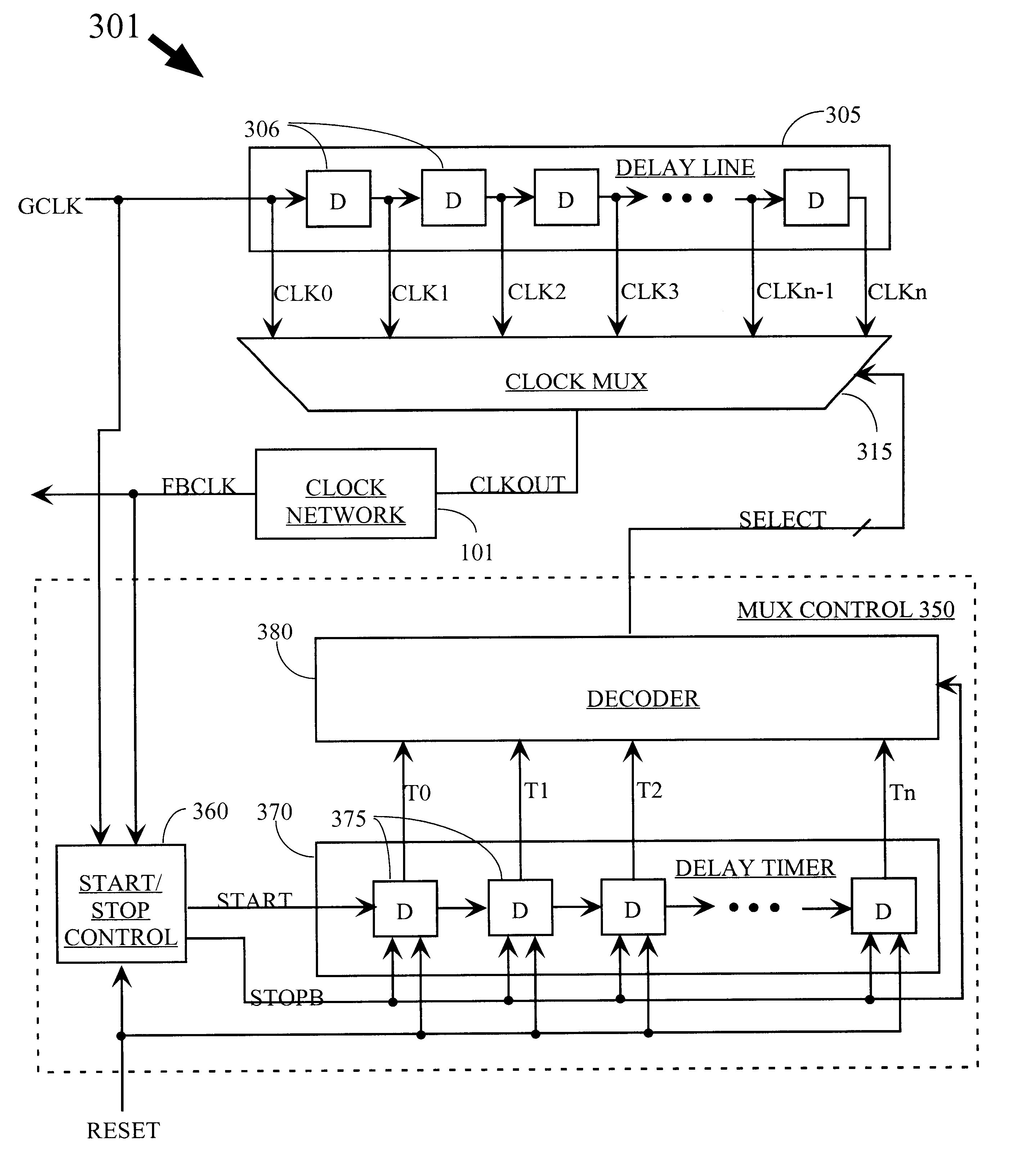

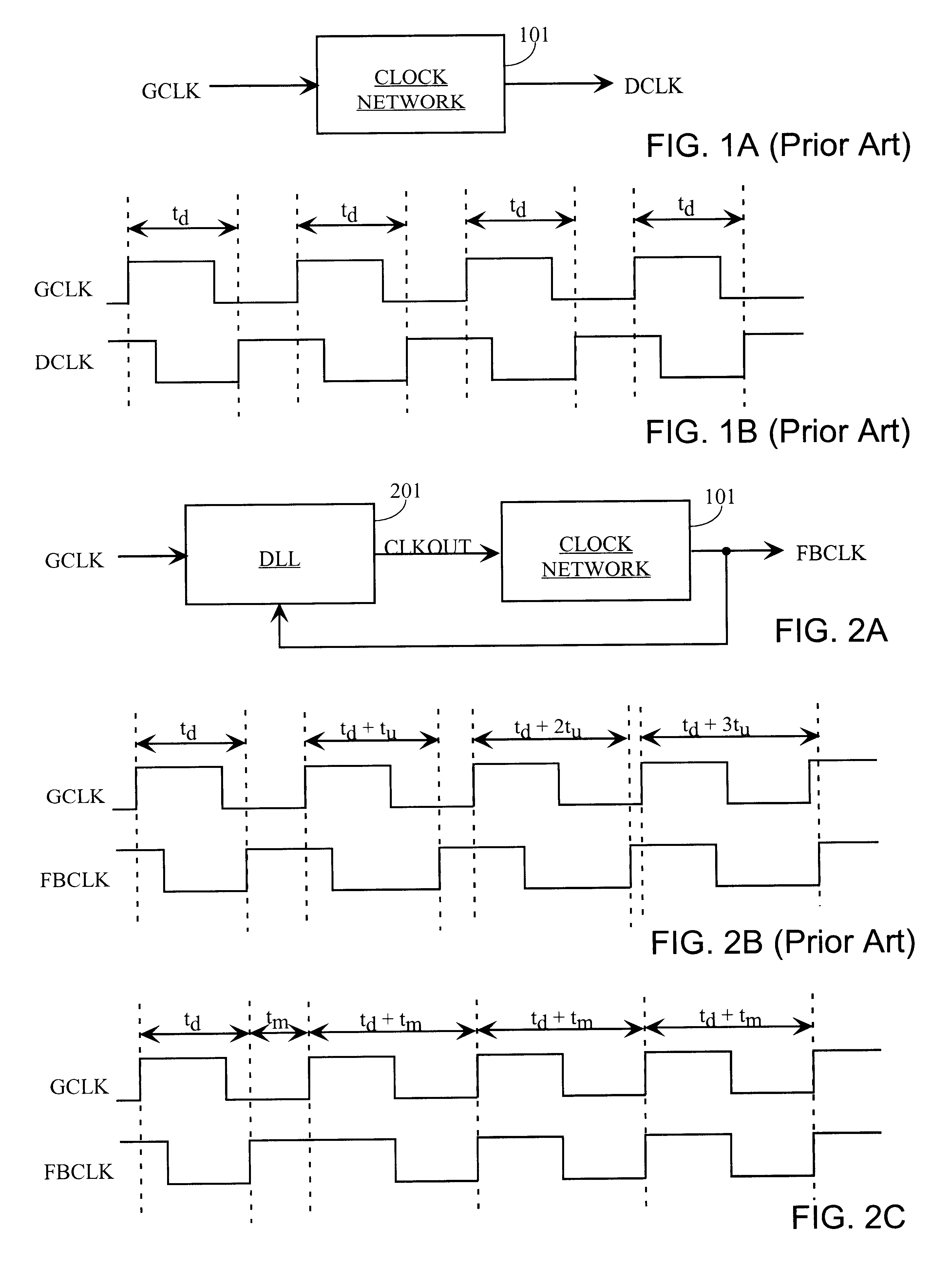

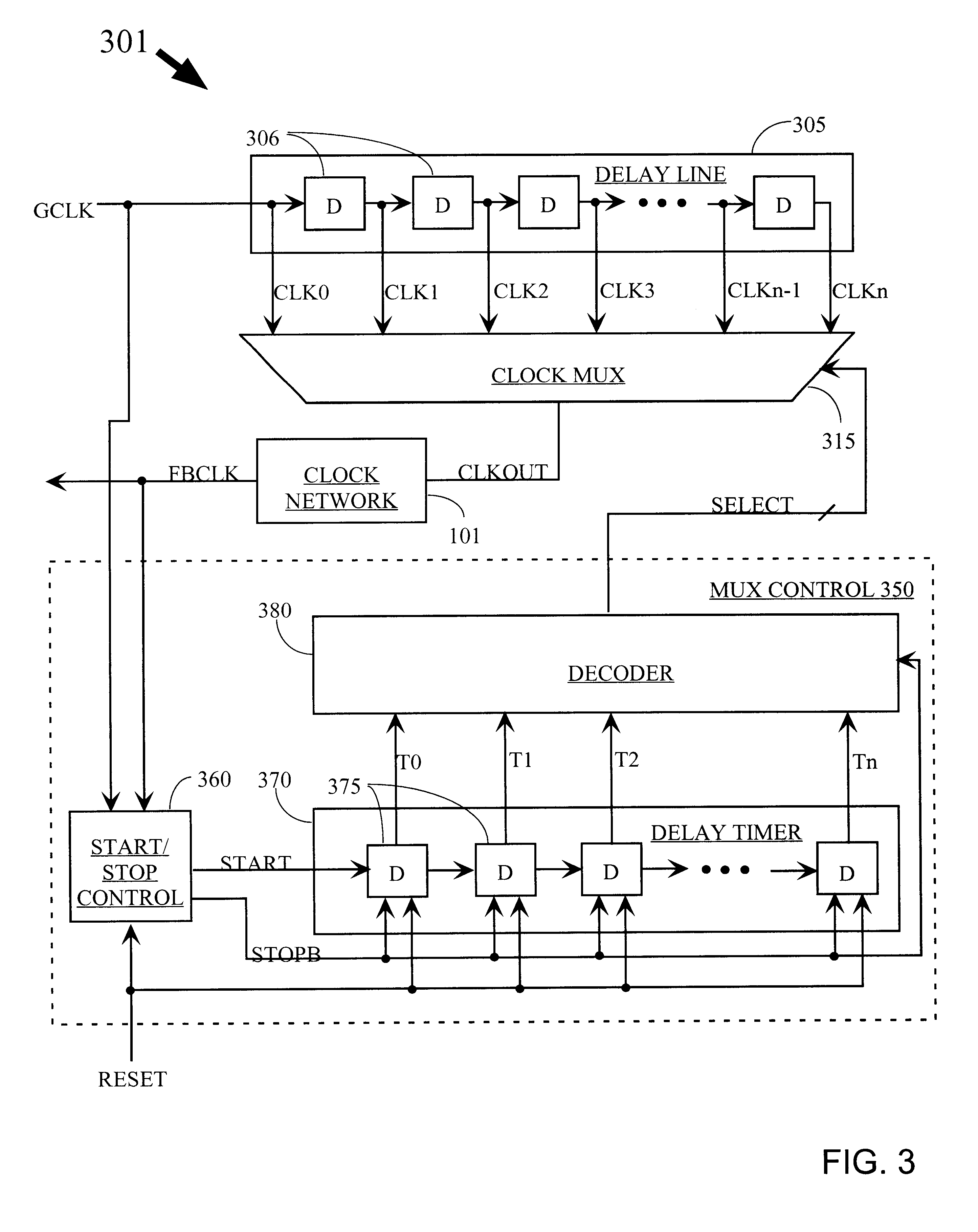

One-shot DLL circuit and method

InactiveUS6255880B1Reduce noiseHigh simulationPulse automatic controlTime-division multiplexMultiplexerDelay-locked loop

A delay-lock loop (DLL) circuit and method that accept an input clock signal and a feedback clock signal, and provide the necessary additional delay to synchronize the feedback clock signal to the input clock signal. Unlike previous circuits and methods, a single synchronization step is sufficient, provided that the frequency of the input clock signal is stable. A circuit according to the invention includes an input clock terminal supplying an input clock signal, and a delay line driven by the input clock signal and supplying a plurality of intermediate clock signals delayed from the input clock signal by incremental unit delays. A clock multiplexer selects from among these intermediate clock signals, under control of a multiplexer control circuit, the clock signal that provides the necessary additional delay to synchronize the feedback clock signal to the input clock signal. The output clock signal from the clock multiplexer is distributed through the clock network to provide the distributed clock signal as well as the feedback clock signal.

Owner:XILINX INC

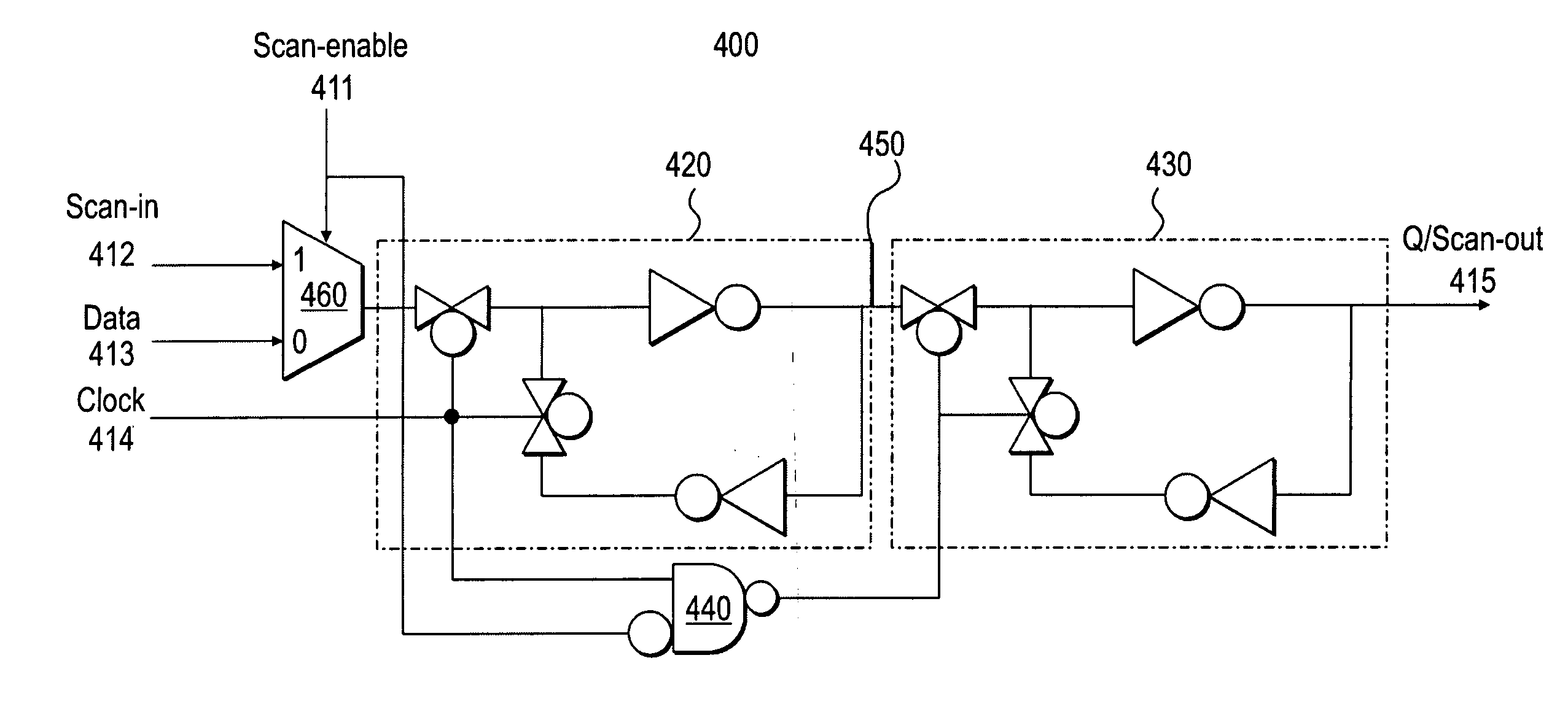

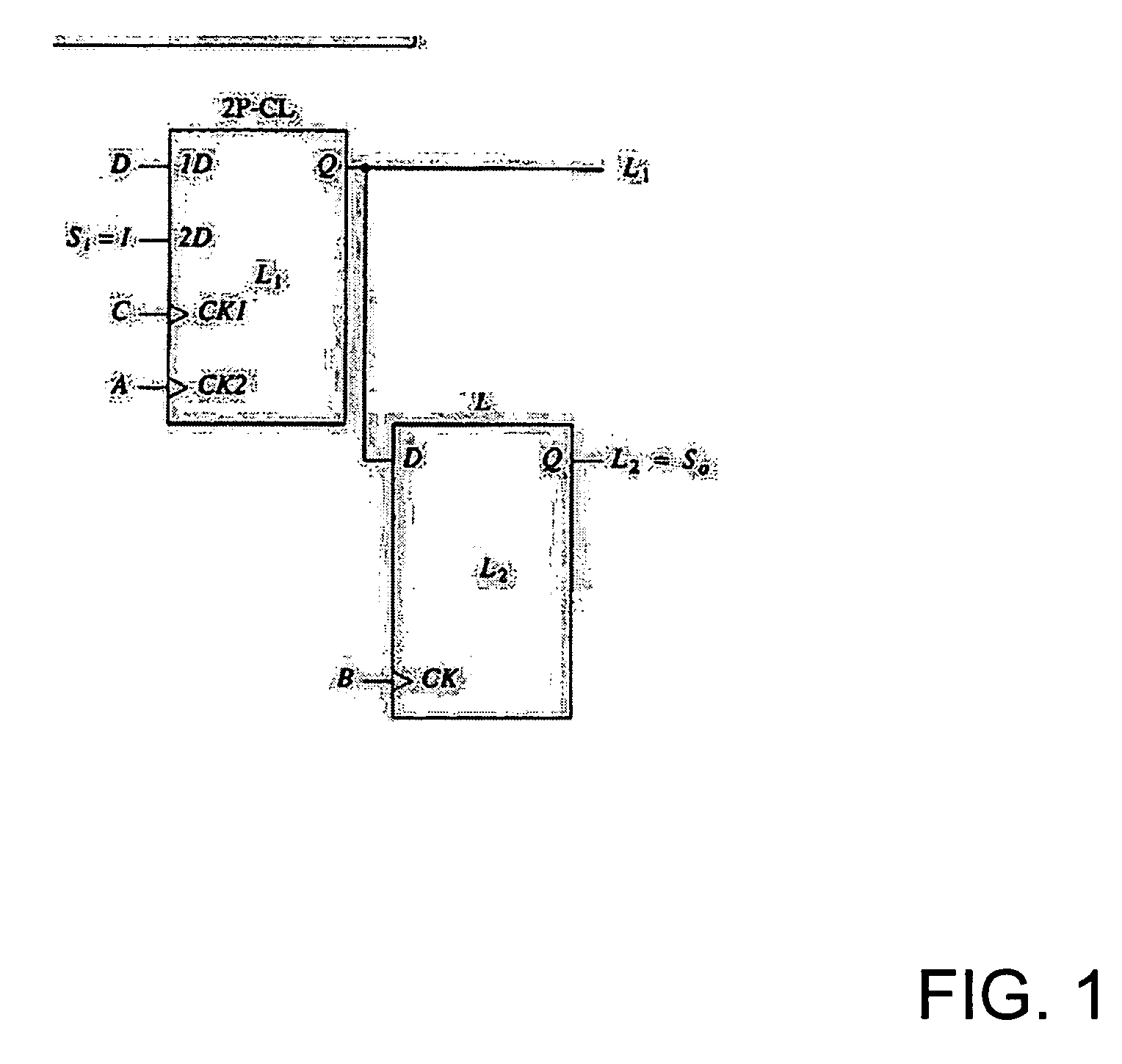

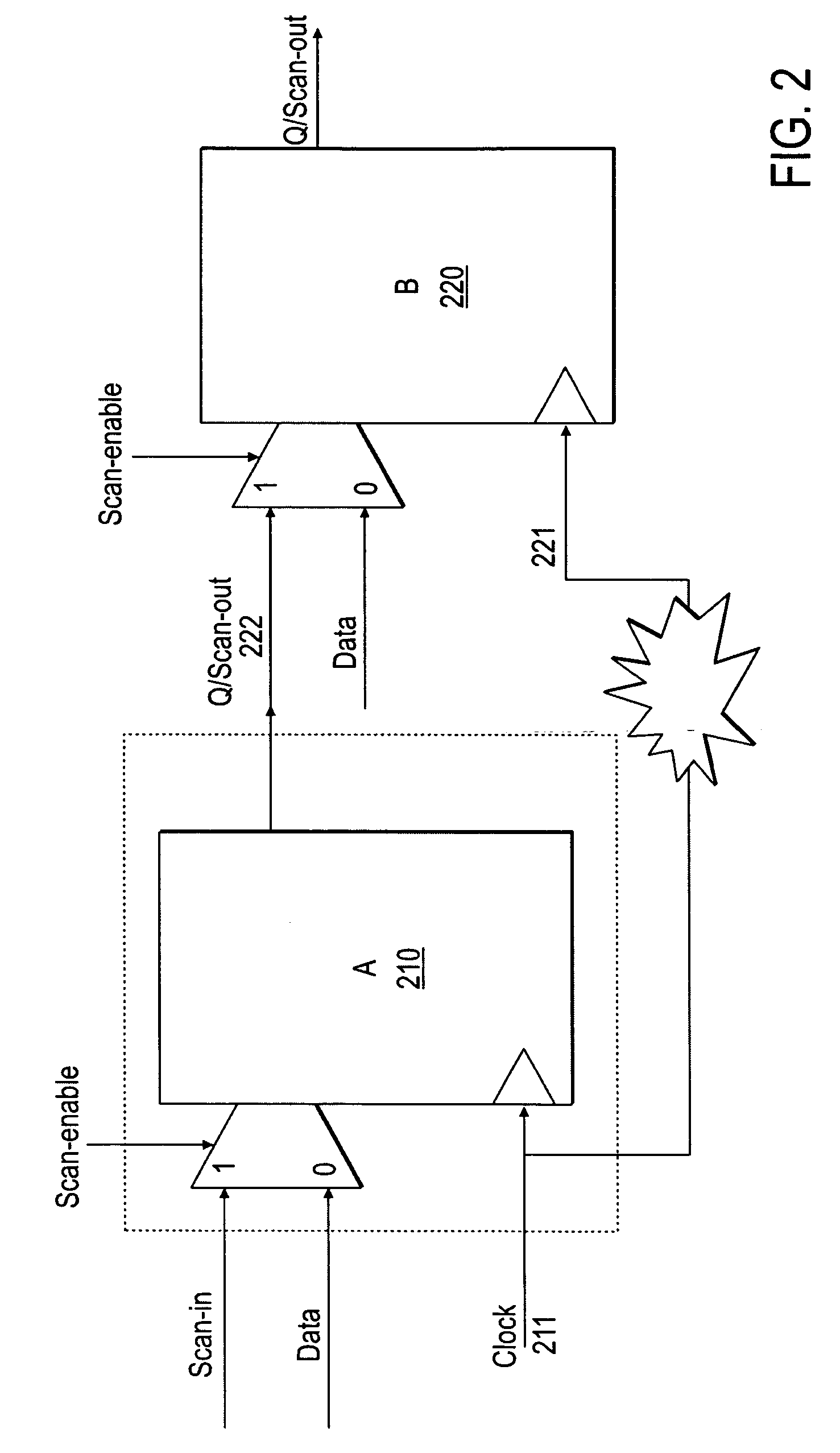

Method and system for clock skew independent scan register chains

InactiveUS20060095819A1Electronic circuit testingElectric pulse generatorClock networkComputer science

A method and system for system for clock skew independent scan chains are disclosed. In one embodiment, a method comprises connecting a plurality of mux-D scan registers in a chain configuration, wherein a first mux-D scan register of the plurality is associated with a first clock network, and a second mux-D scan register of the plurality is associated with a second clock network. The plurality of mux-D scan registers have a scan mode. The first mux-D scan register and the second mux-D scan register become clock skew independent by controlling a scan-enable signal and a clock signal.

Owner:CADENCE DESIGN SYST INC

Constraining clock skew in a resonant clocked system

ActiveUS20140062562A1Electric pulse generatorGenerating/distributing signalsCapacitanceClock network

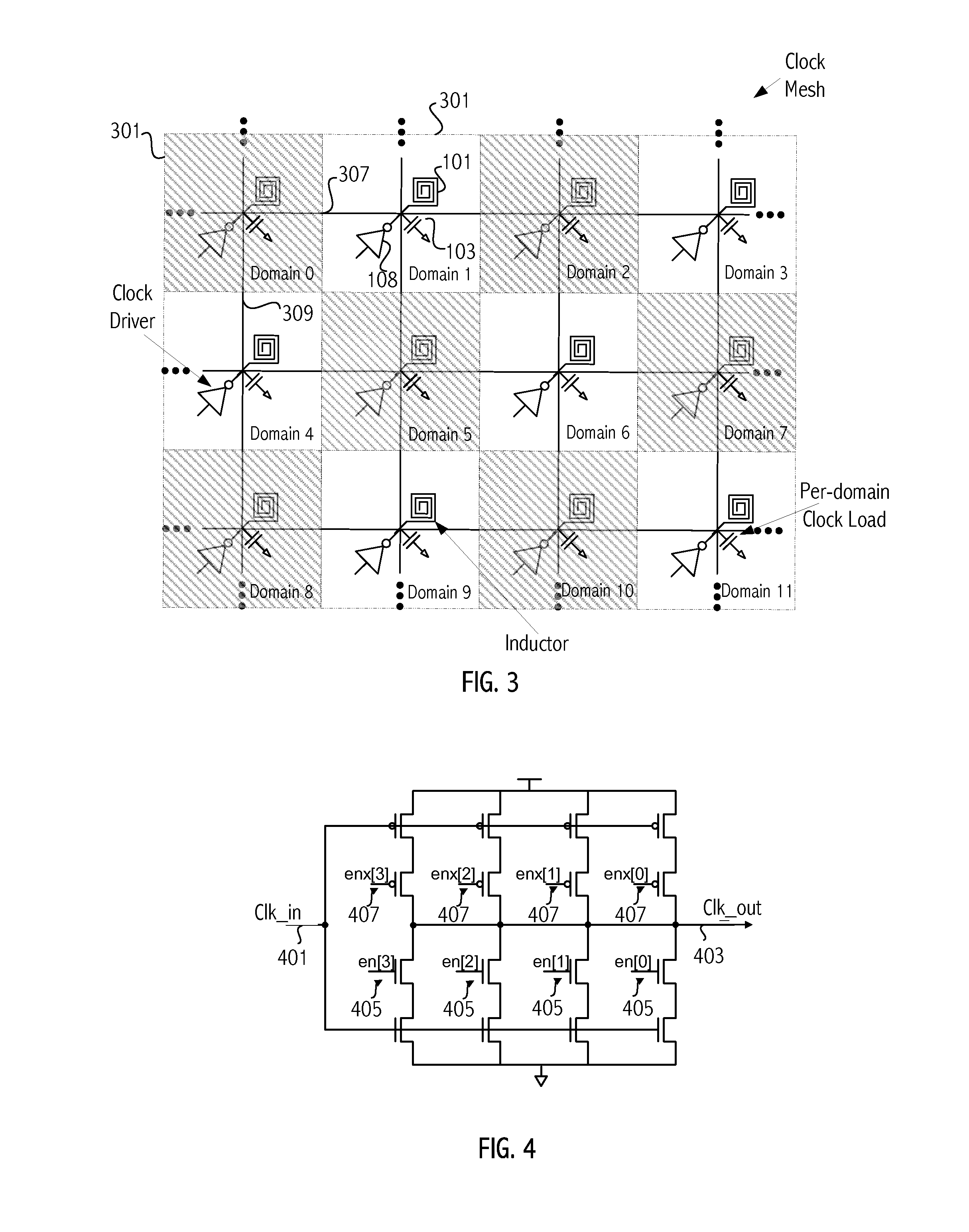

An integrated circuit includes a plurality of resonant clock domains of a resonant clock network. Each resonant clock domain has at least one clock driver that supplies a portion of clock signal to an associated resonant clock domain. The resonant clock network operates in a resonant mode with inductors connected to pairs of resonant clock domains at boundaries between the resonant clock domains. Each inductor forms an LC circuit with clock load capacitance in the pair of resonant clock domains to which the inductor is connected.

Owner:ADVANCED MICRO DEVICES INC

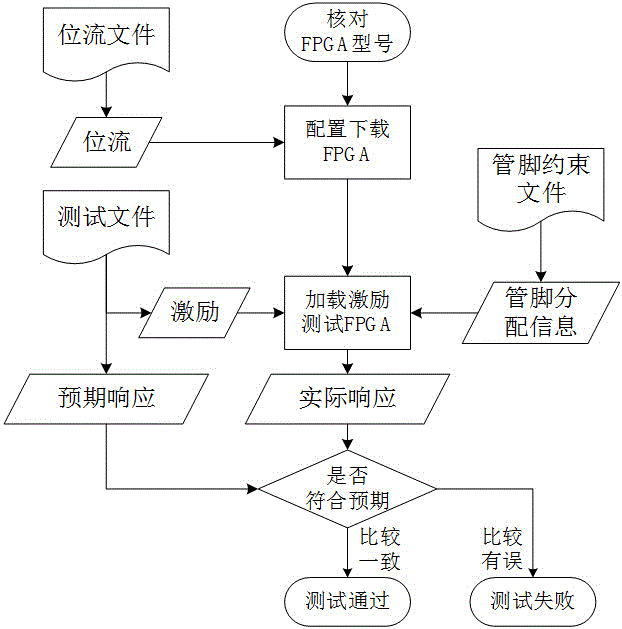

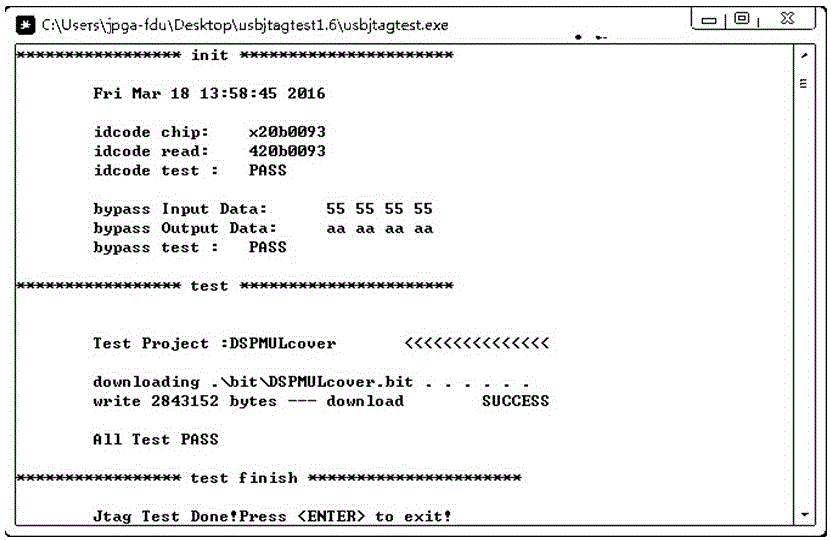

Function traversal testing method for high performance SoC FPGA

ActiveCN105866665AImprove test coverageImprove test efficiencyElectrical testingTest efficiencyComputer hardware

The invention belongs to the technical field of integrated circuits, and relates to a function traversal testing method for high performance SoC FPGA. A set of complete function traversal testing method is established for CLB, BRAM, DSP, CM, IOB, clock network, interconnection and other resources in the high performance SoC FPGA, and corresponding bit stream is generated to apply excitation on an FPGA port and read back the response of the FPGA port. The response is compared with an expected result to realize the traversal covering test on the Soc FPGA resources. The test method is applicable to various high performance Soc FPGA with complex function and abundant resources and if of high application value in the FPGA test field. The test coverage rate and the test efficiency are high, the test cost is low, and the transferability and the universality are good.

Owner:FUDAN UNIV

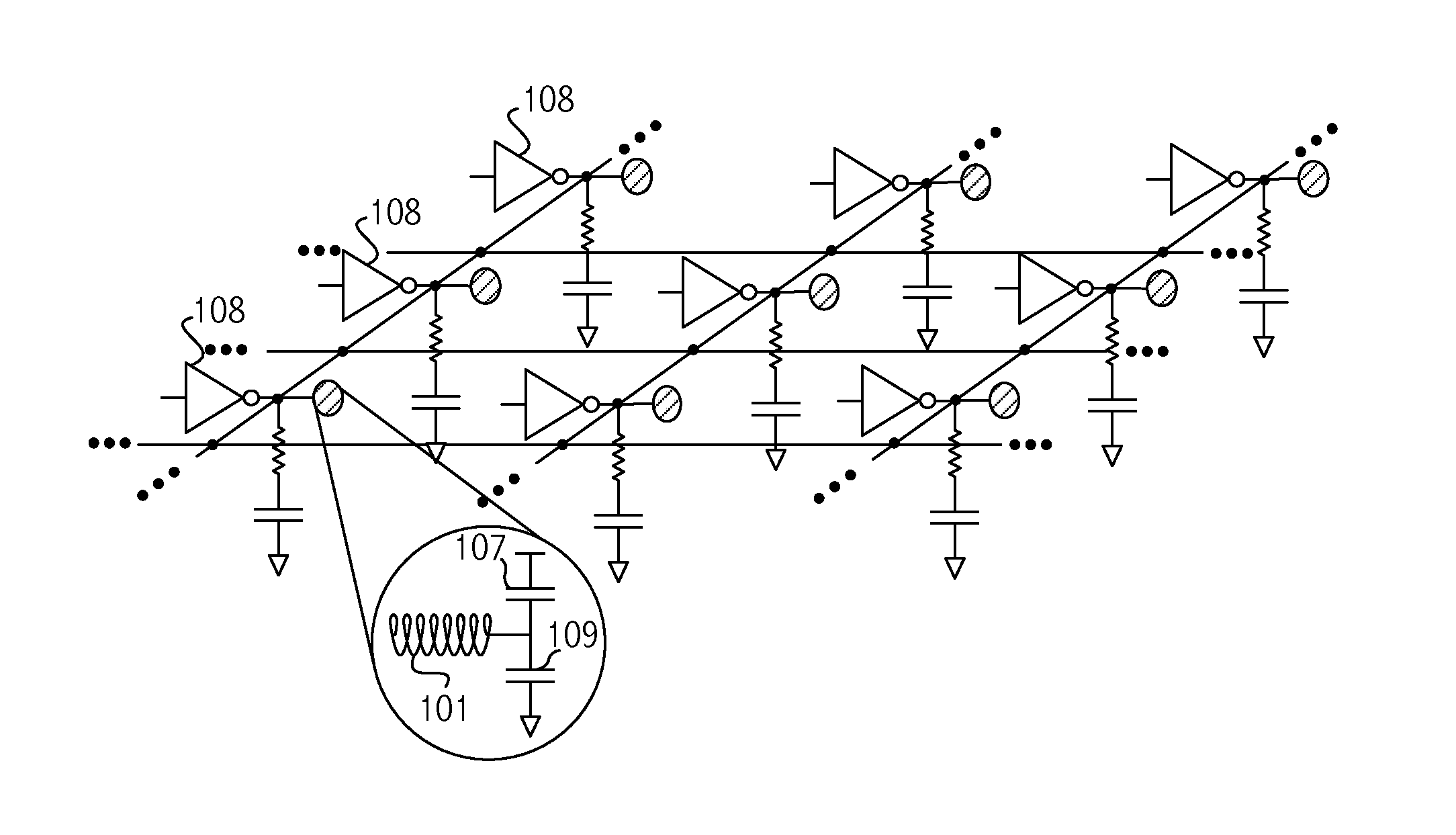

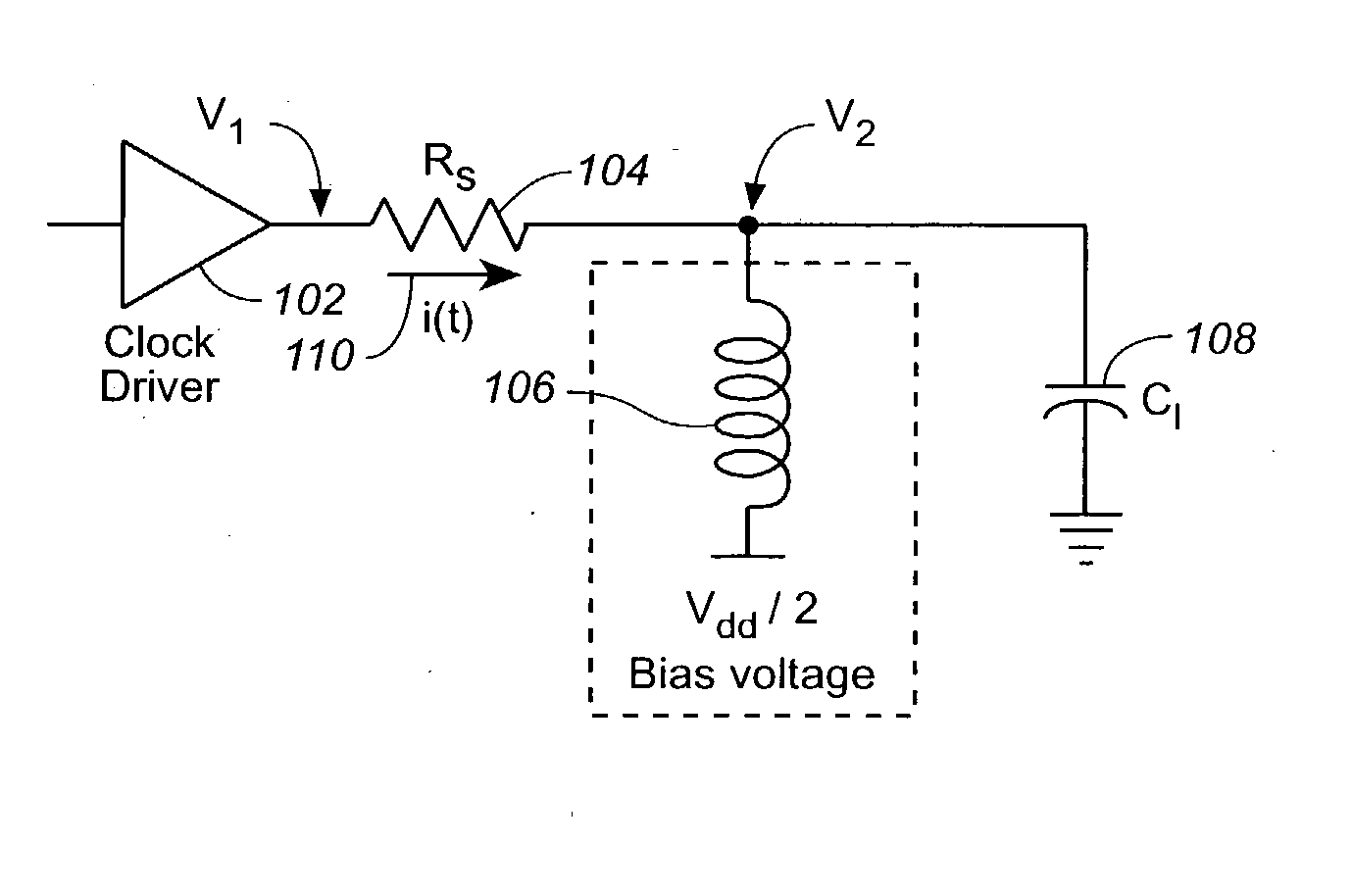

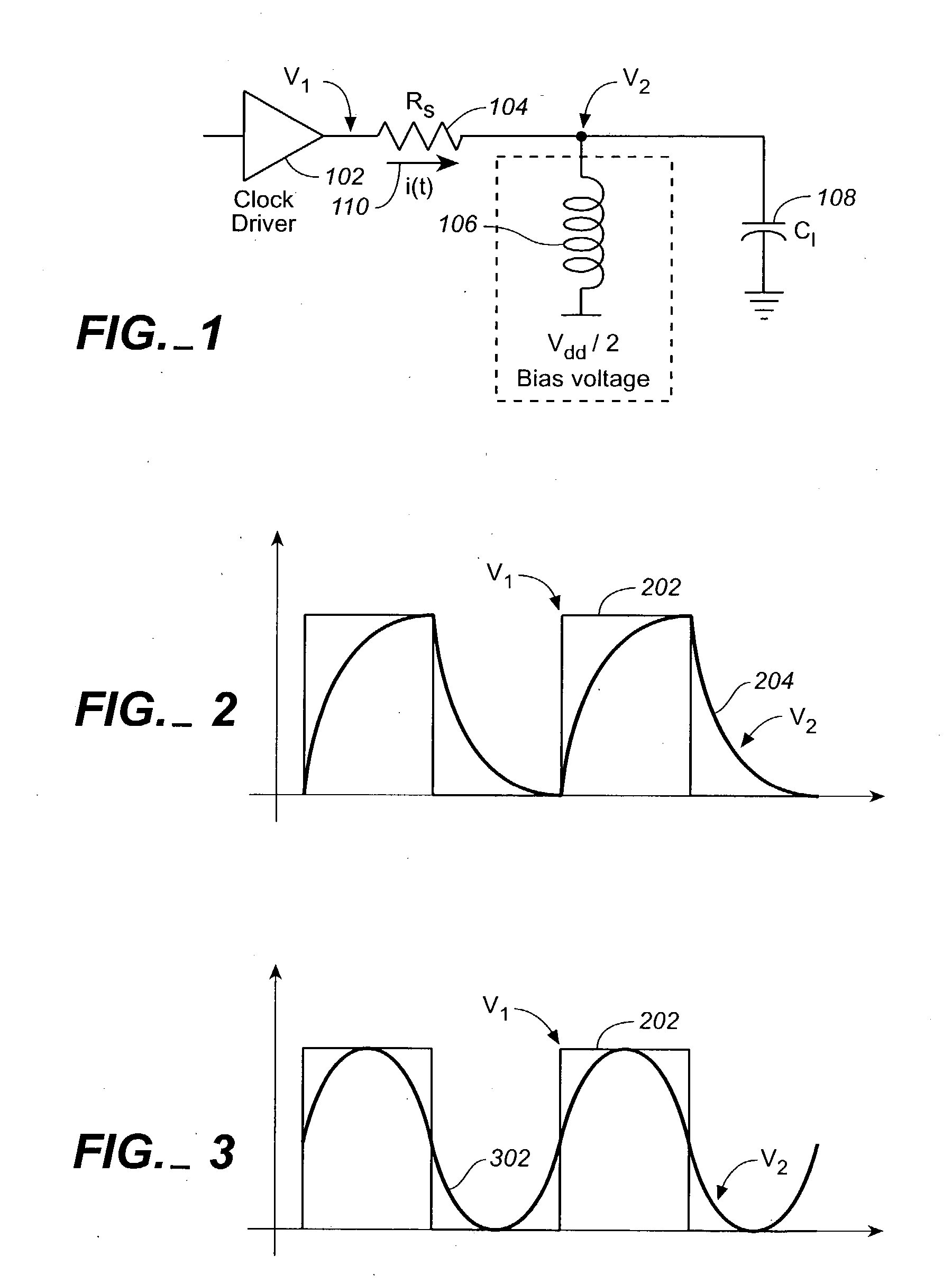

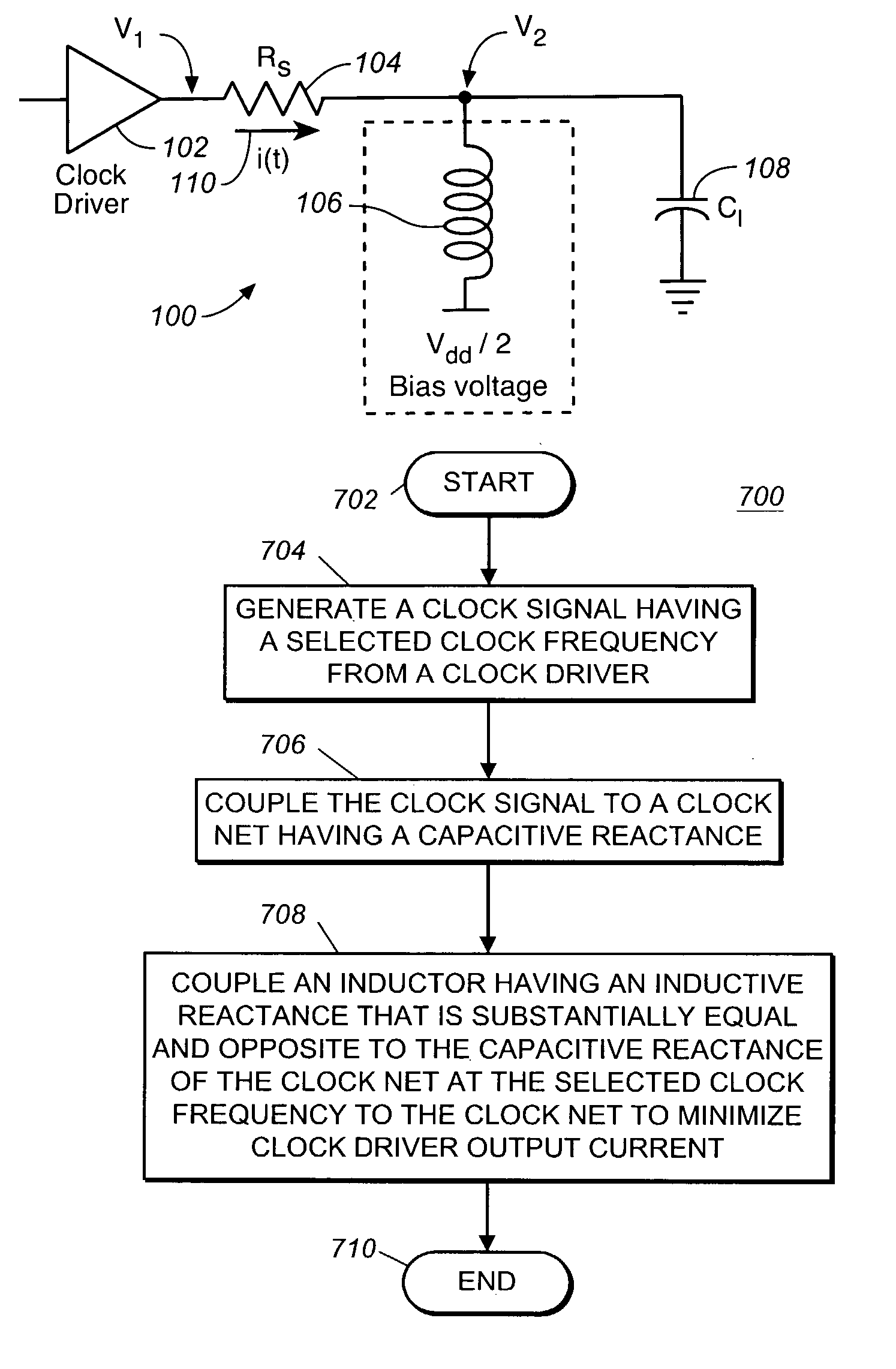

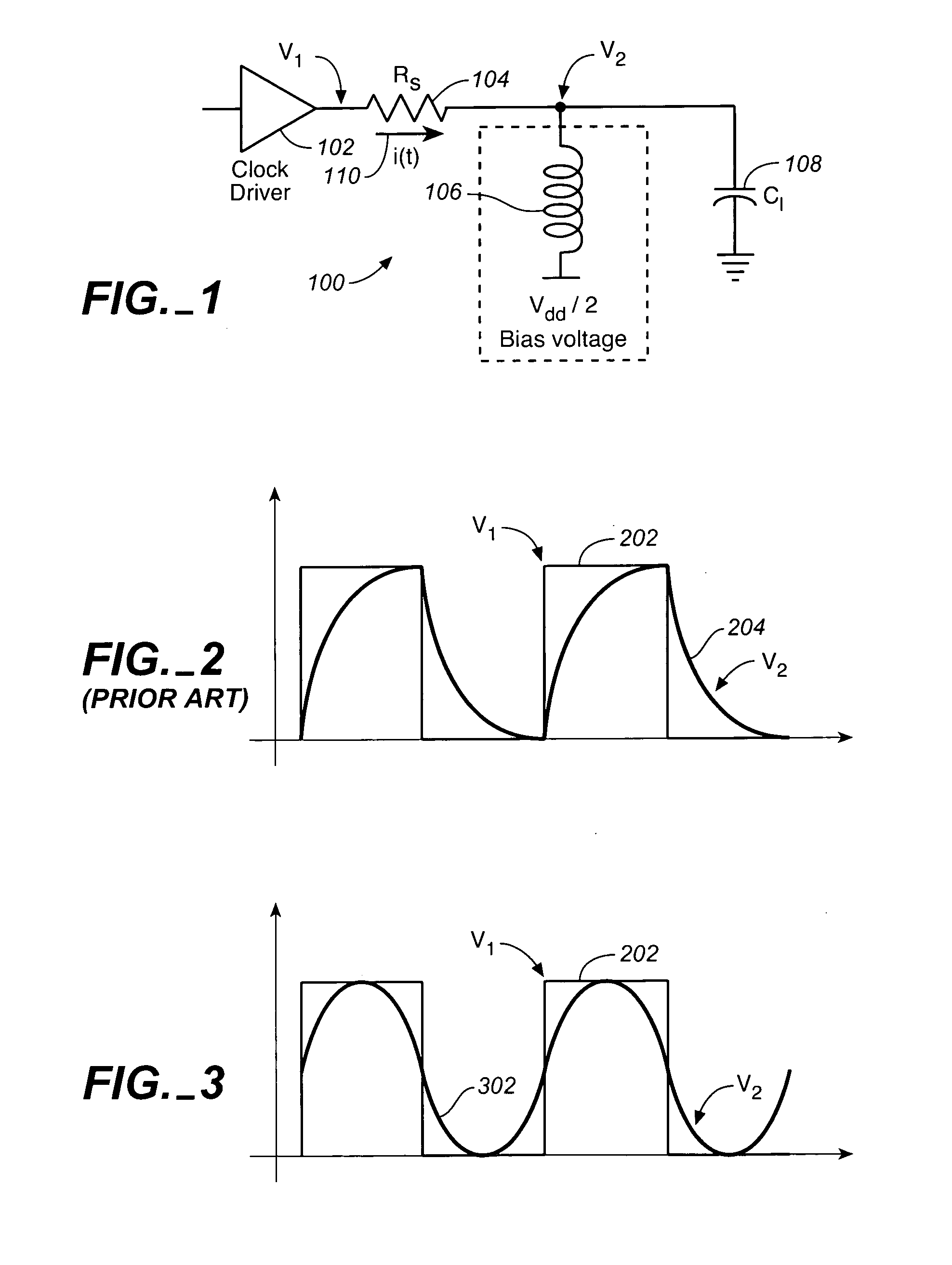

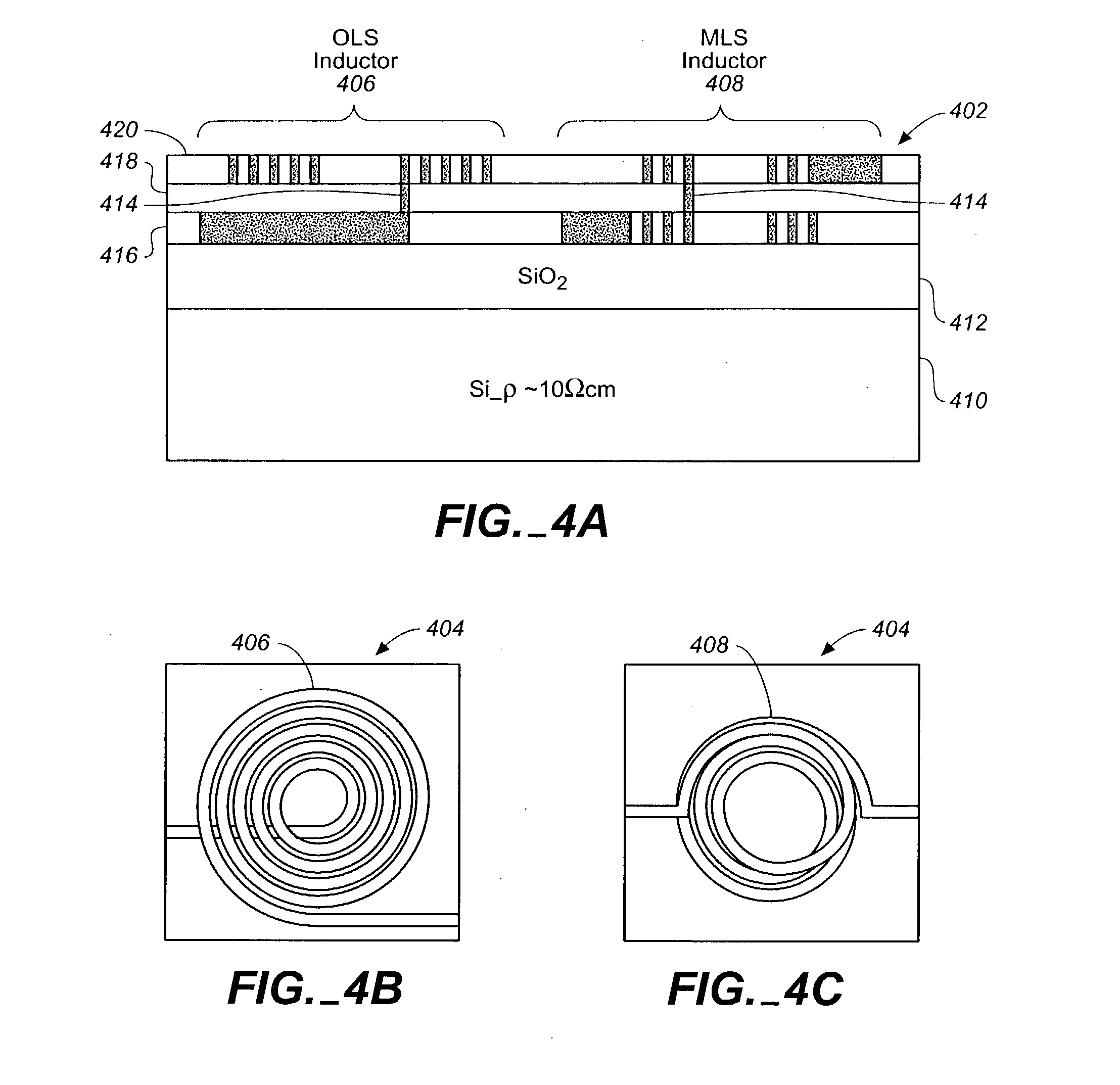

Energy recycling in clock distribution networks using on-chip inductors

InactiveUS20040158758A1Generating/distributing signalsSpecial data processing applicationsPower flowClock rate

A clock distribution network for an integrated circuit includes a clock driver for generating a clock signal having a selected clock frequency, a clock net coupled to the clock driver wherein the clock net has a capacitive reactance, and an inductor coupled to the clock net wherein the inductor has an inductive reactance that is substantially equal to the capacitive reactance of the clock net at the selected clock frequency to minimize clock driver output current.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

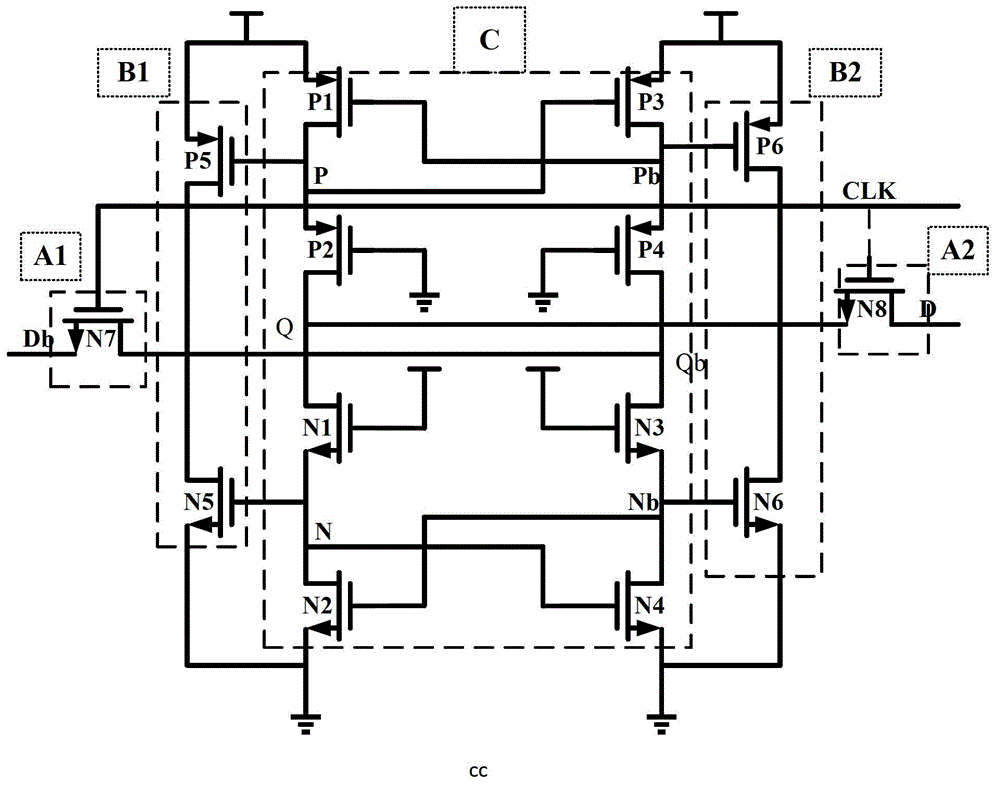

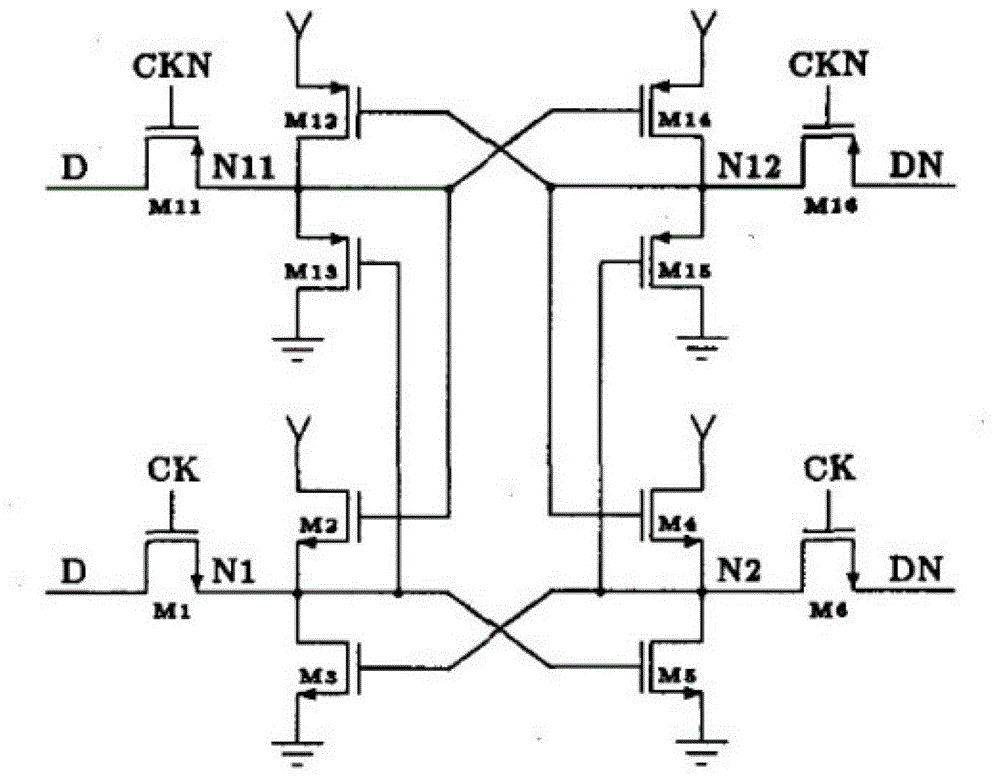

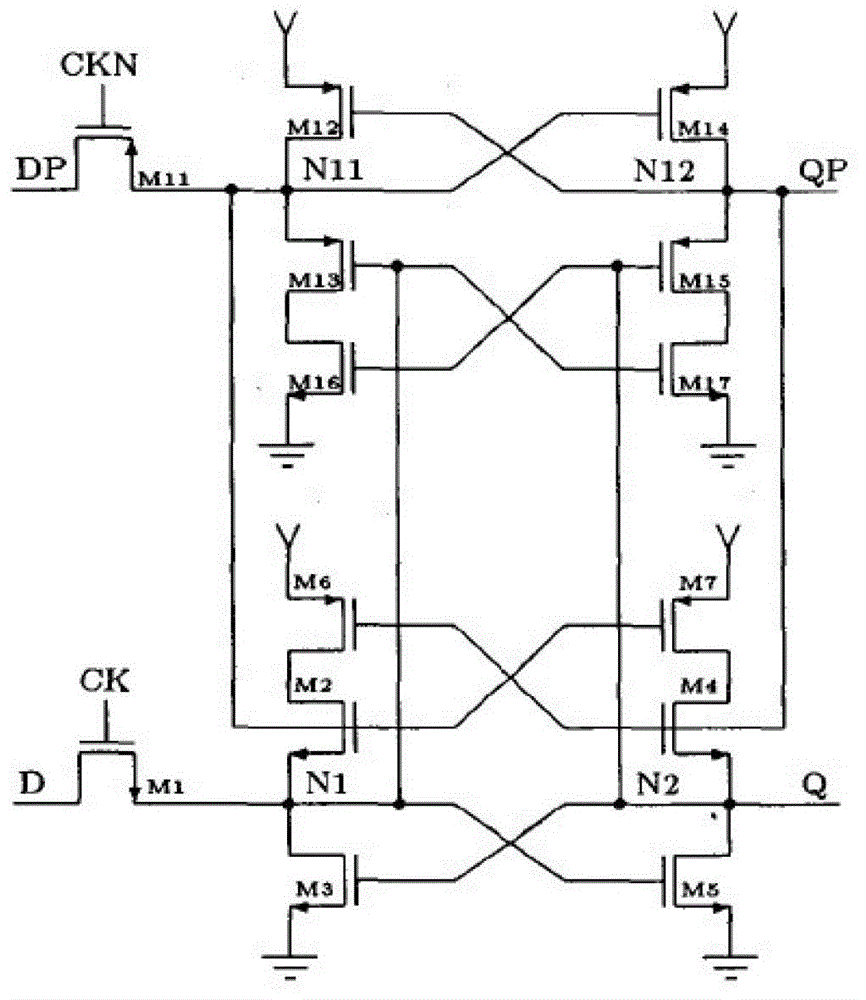

Novel static random access memory (SRAM) storage unit preventing single particle from turning

ActiveCN102723109ARealize the ability of flip reinforcementReduce rollover recovery timeDigital storageStatic random-access memoryClock network

The invention discloses a novel static random access memory (SRAM) storage unit preventing a single particle from turning. The storage unit comprises a first input / output port, a first potential turning recovery driving circuit, a voltage retaining circuit, a second potential turning recovery driving circuit and a second input / output port which are connected in series with one another sequentially. An automatic recovery function for voltage turning when a sensitive node is impacted by a high-energy particle can be realized; according to a simulation result of a TSMC 0.18 mu_m process, a turning threshold value LETth is more than 500 MeV / (mg.cm<2>); compared with the conventional storage unit preventing the single particle from turning, the SRAM storage unit has the characteristic of high writing speed; the recovery time can be effectively shortened; by adopting a unidirectional clock and a small-clock amplitude, a clock network is relatively simple and relatively high in reliability; the clock is only connected with the gate of a read-write transistor, and the clock load is relatively small; and the sensitive node can be used for reinforcing multi-node turning of the single particle, which is caused by drains positioned on a P-type tube and an N-type tube..

Owner:XI AN JIAOTONG UNIV

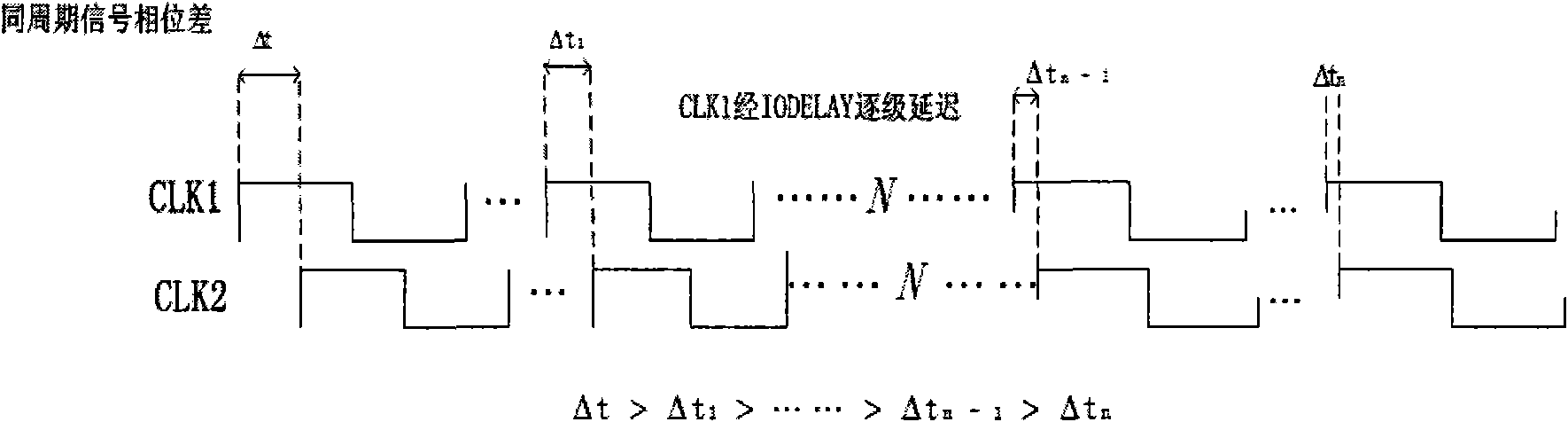

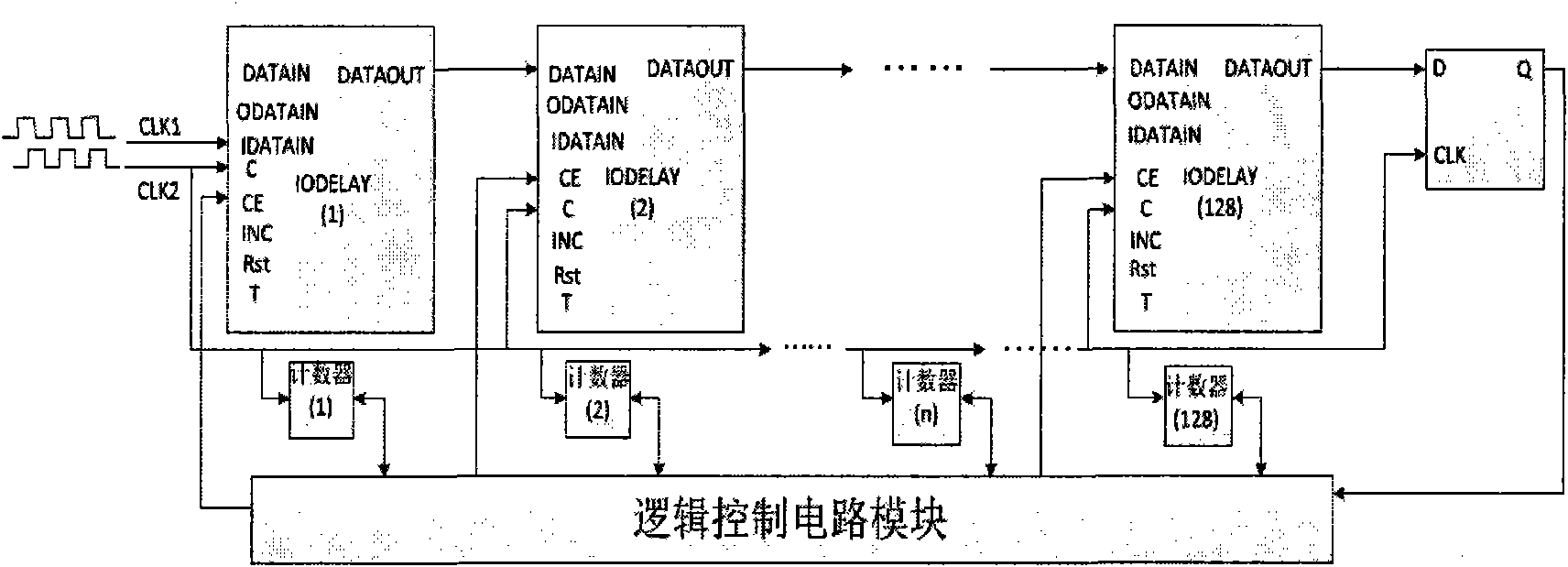

Method for measuring phase difference of common-period signals based on delay unit dedicated for FPGA

InactiveCN101915875AHigh precisionHigh resolutionVoltage-current phase anglePhase differenceClock network

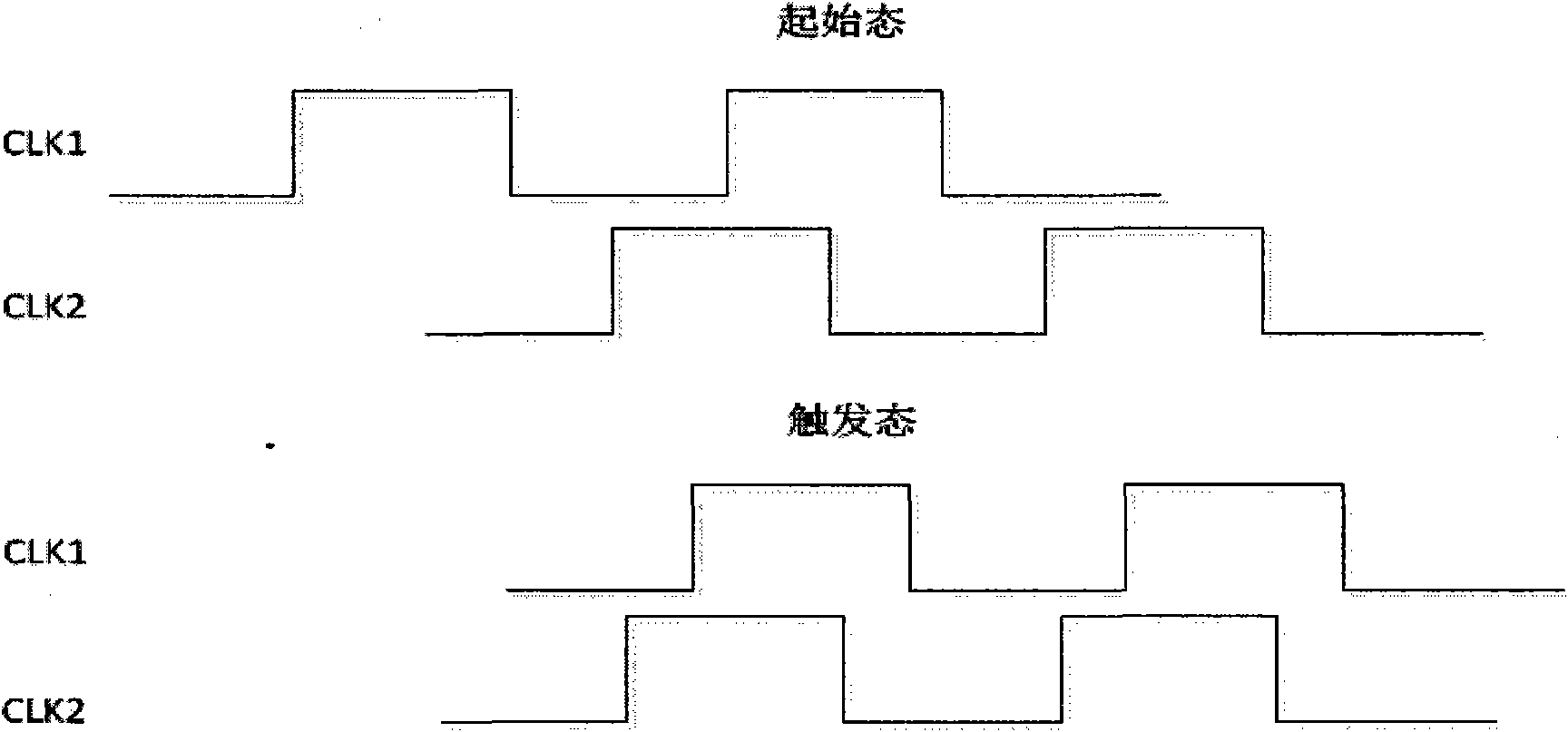

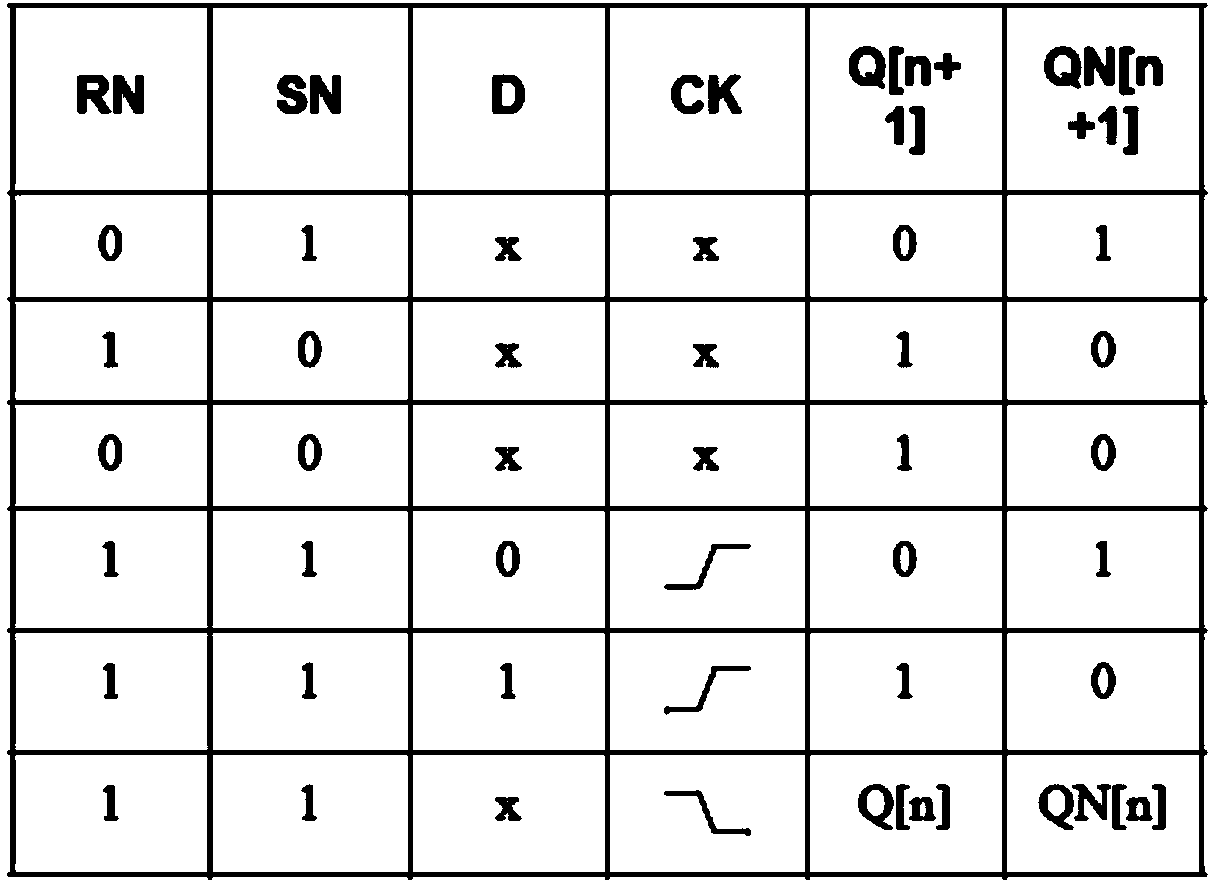

The invention discloses a circuit for measuring phase difference of common-period signals, which comprises 128 IODELAYs (programmable input and output delay units dedicated for Xilinx FPGA), a D trigger, 128 6-digital counters, a logic control circuit and two paths of common-period signals to be measured: the first path of period signals CLK1 and the second path of period signals CLK2. The method provides a method for measuring the phase difference of the common-period signals in high accuracy, which comprises the following steps: the CLK1 is sent to input ends of the IODELAYs and input to a D end of the D trigger after step-by-step delay by the IODELAYs; the CLK2 is input to a CLK end of the D trigger and CLK ends of the counters through a global clock network; and variation of a Q value at an output end of the D trigger is detected, thus obtaining edge coincidence information of the CLK1 and the CLK2 after the delay and achieving the aim of measuring the phase difference of the common-period signals according to the delay amount of the IODELAYs.

Owner:XIDIAN UNIV

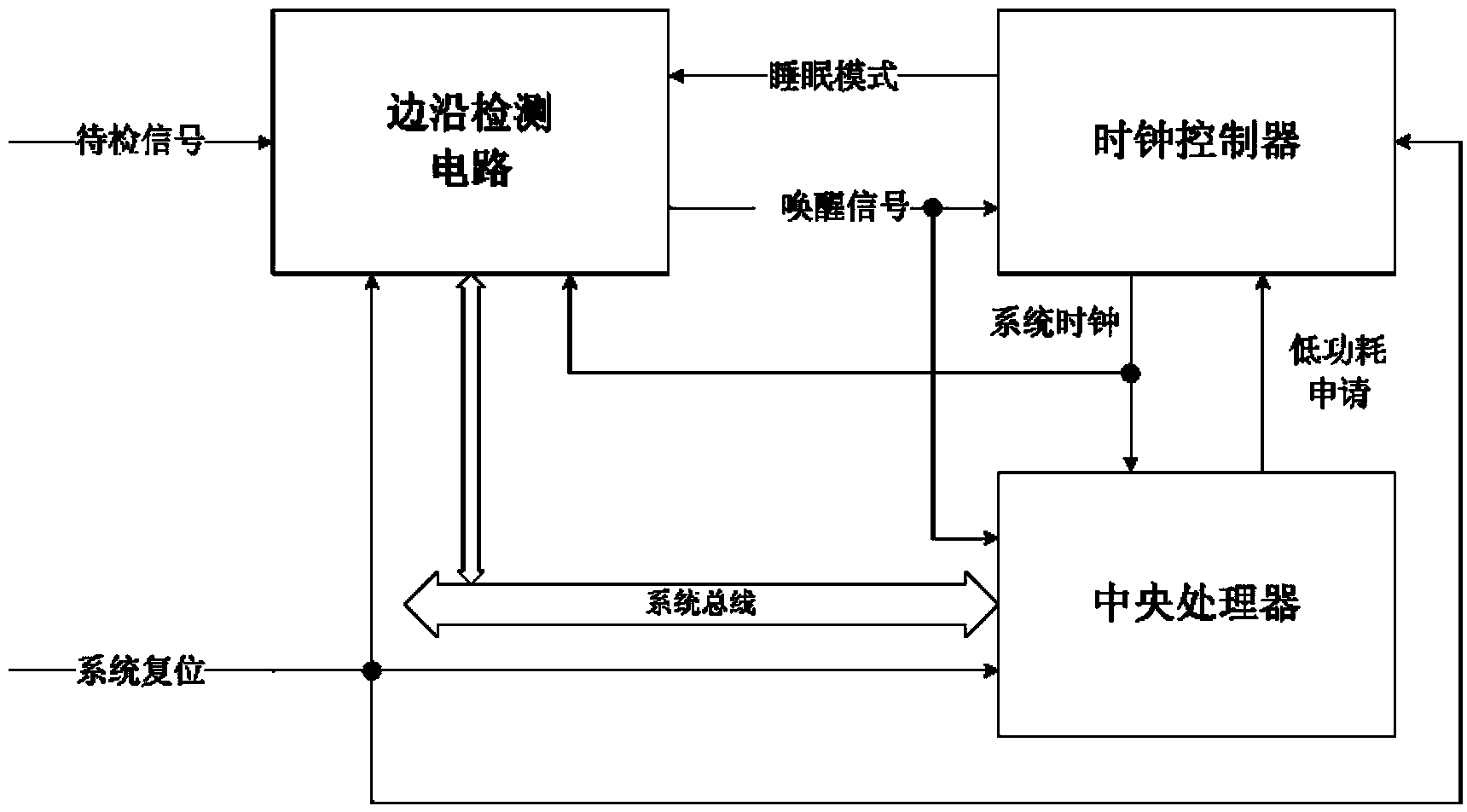

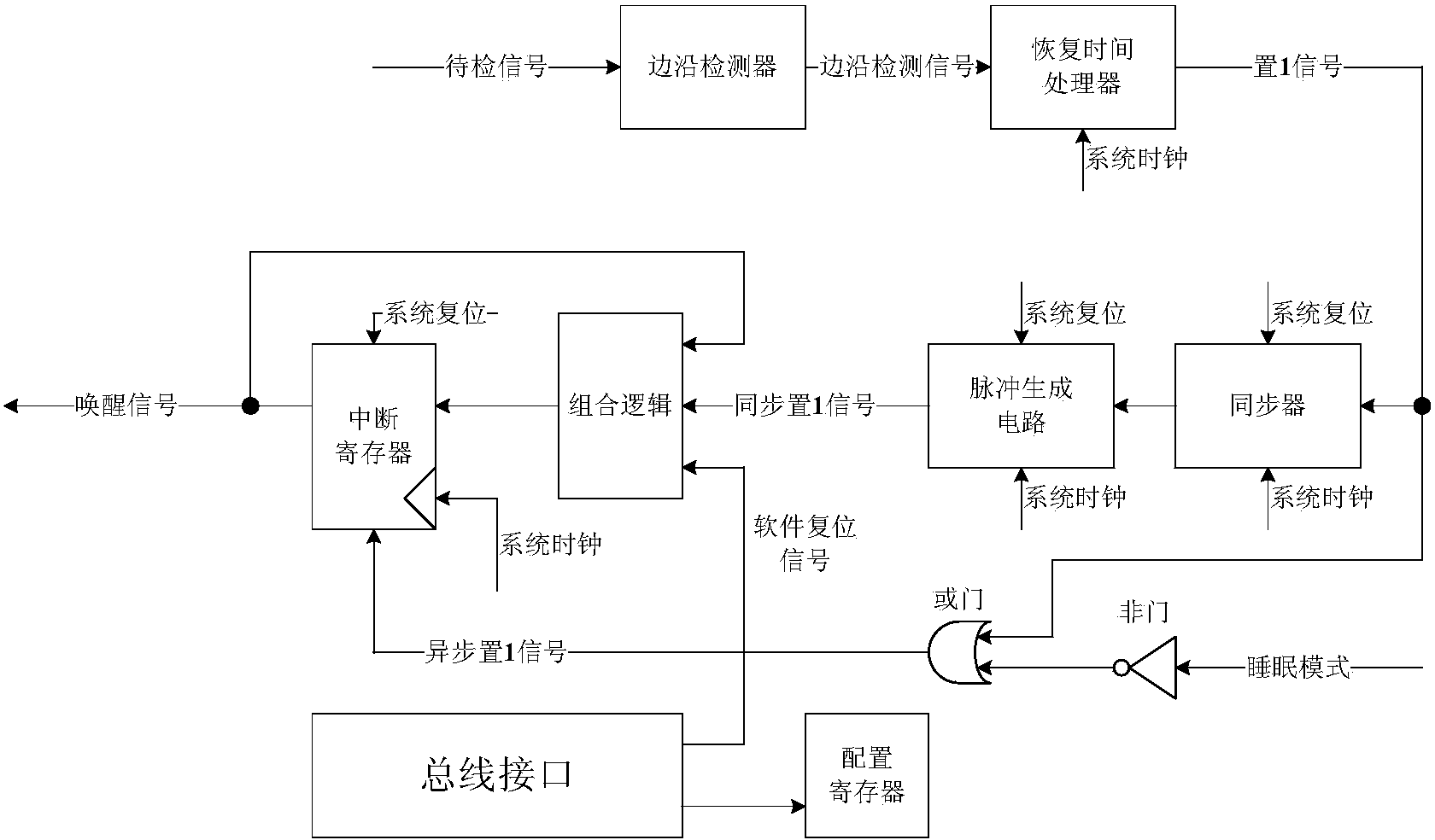

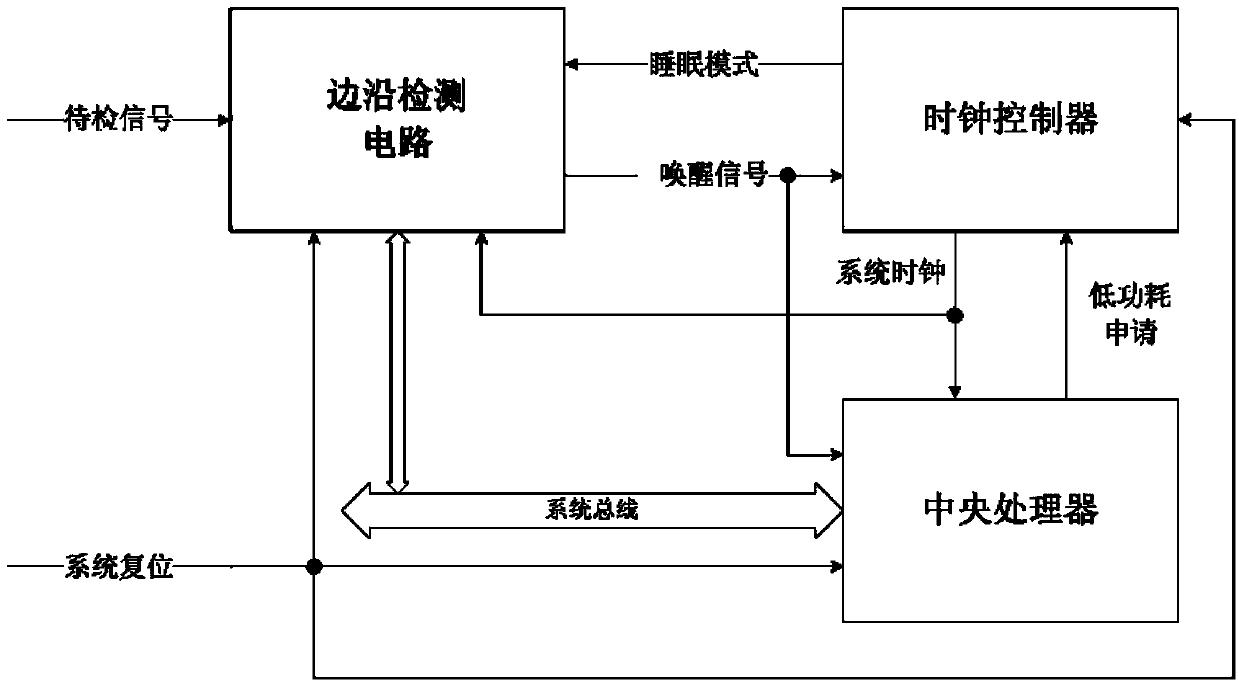

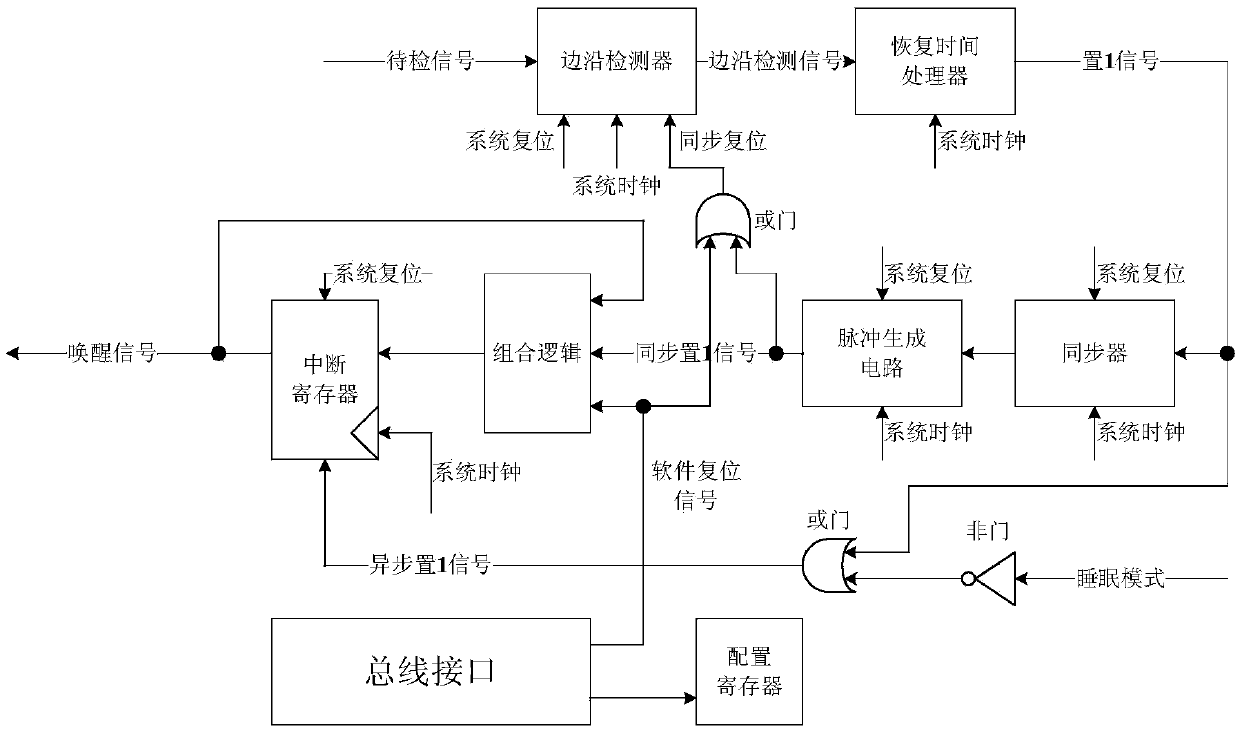

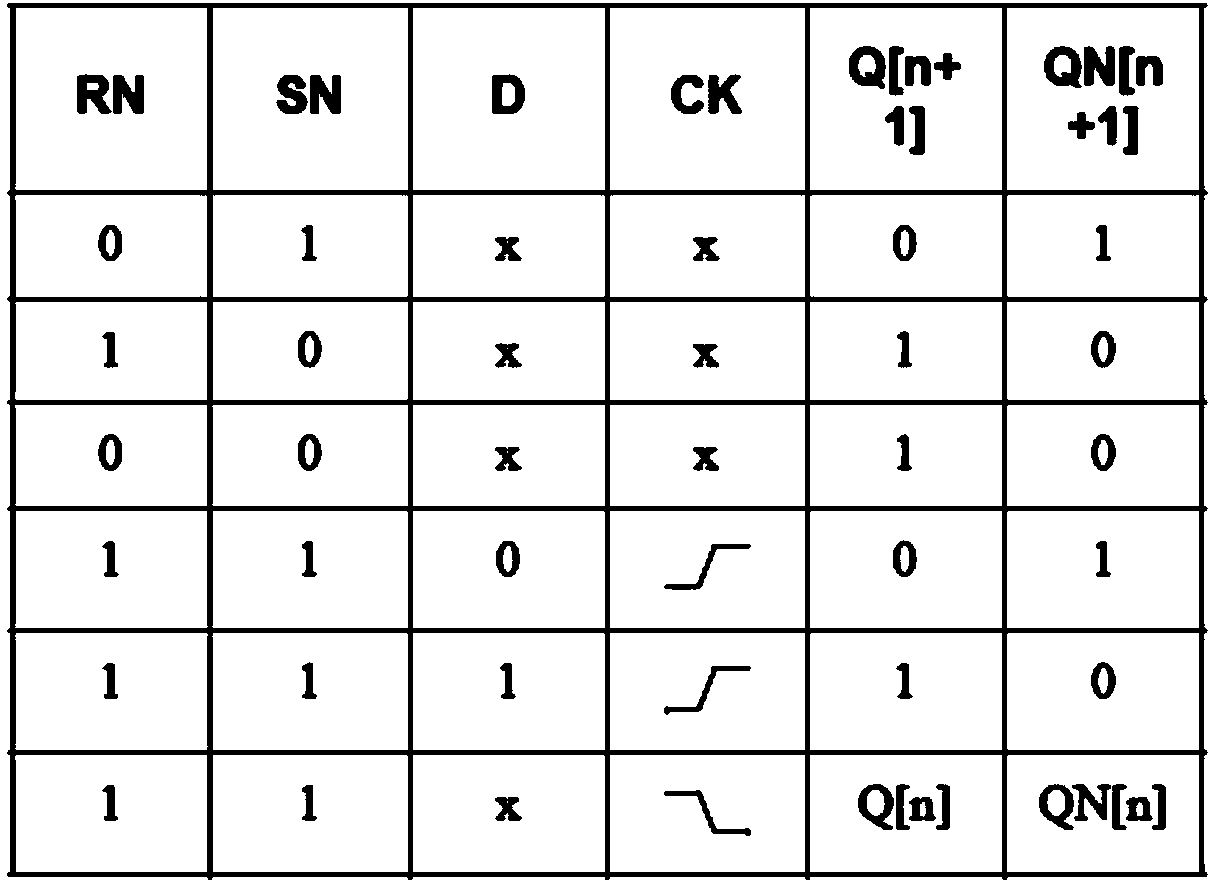

Chip and method for achieving sleep mode wake-up through edge detection circuit

ActiveCN103645794AImplement wake-up from sleep modeEfficient consumptionPower supply for data processingGenerating/distributing signalsClock networkEngineering

The invention provides a chip and method for achieving sleep mode wake-up through an edge detection circuit. A central processing unit is used for sending a low-power-consumption application to a clock controller; the clock controller is used for closing a clock circuit according to the lower-power-consumption application, temporarily stopping providing a system clock for the edge detection circuit and the central processing unit and triggering entering a sleep mode; in the sleep mode, the edge detection circuit is used for detecting a signal to be detected and generating a wake-up signal according to the signal to be detected; the clock controller is used for switching on the clock circuit according to the wake-up signal, renewedly providing the system clock for the edge detection circuit and the central processing unit and sending a sleep mode signal to the edge detection circuit to trigger entering a common mode. The chip can shut down all clock networks and all clock generation circuits and wake up the sleep mode without affecting functions. In this way, the power consumption of the chip is lowered to the lowest degree.

Owner:GIGADEVICE SEMICON (BEIJING) INC

Reduced power consumption clock network

InactiveUS6975154B1Volume/mass flow measurementPower supply for data processingPower consumptionClock network

An exemplary reduced-power-consumption network includes a frequency divider coupled through global clock lines to a plurality of double-edge triggered registers. Another exemplary network includes a plurality of individually programmable frequency dividers coupled through local clock lines to a plurality of double-edge triggered registers.

Owner:ALTERA CORP

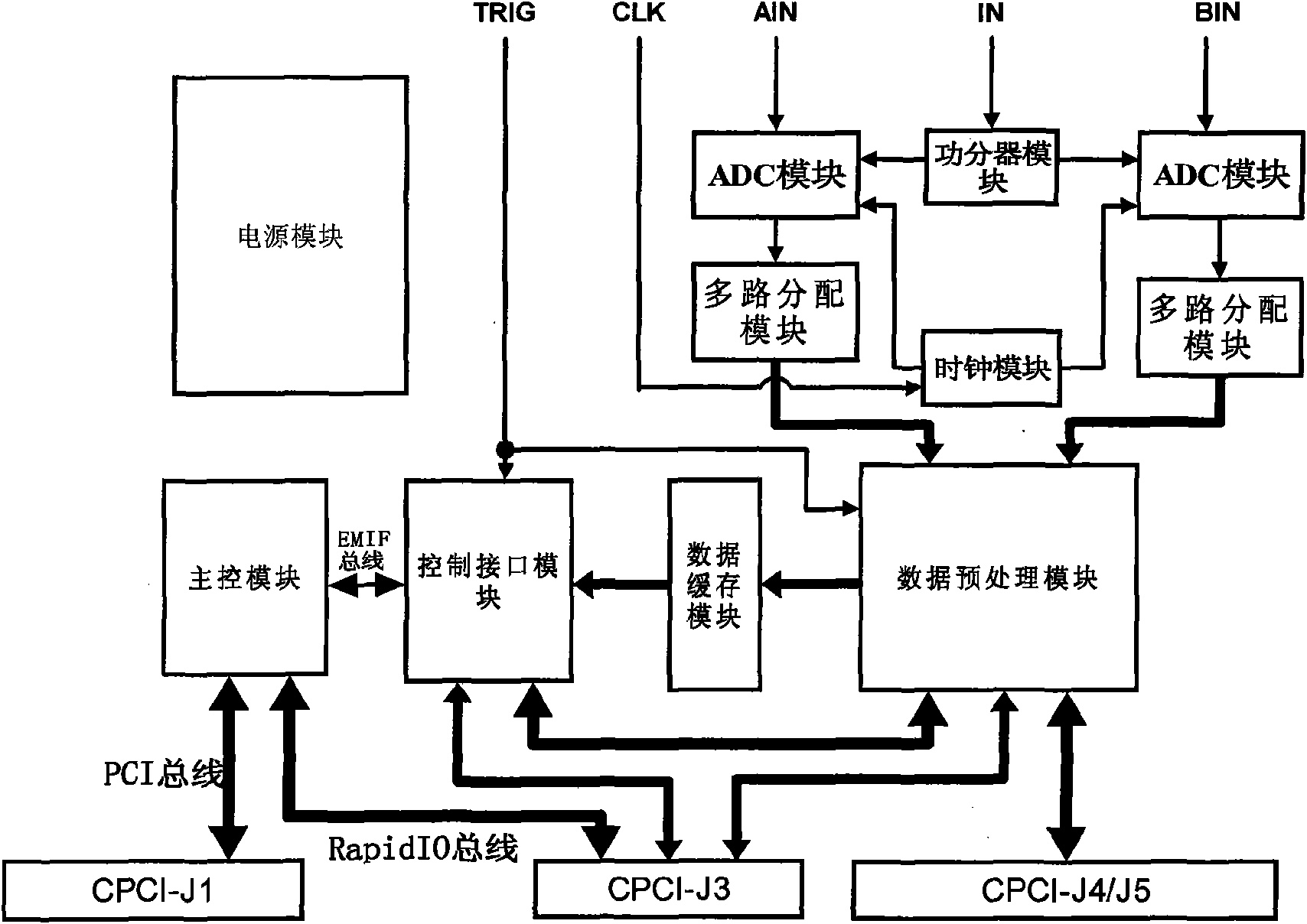

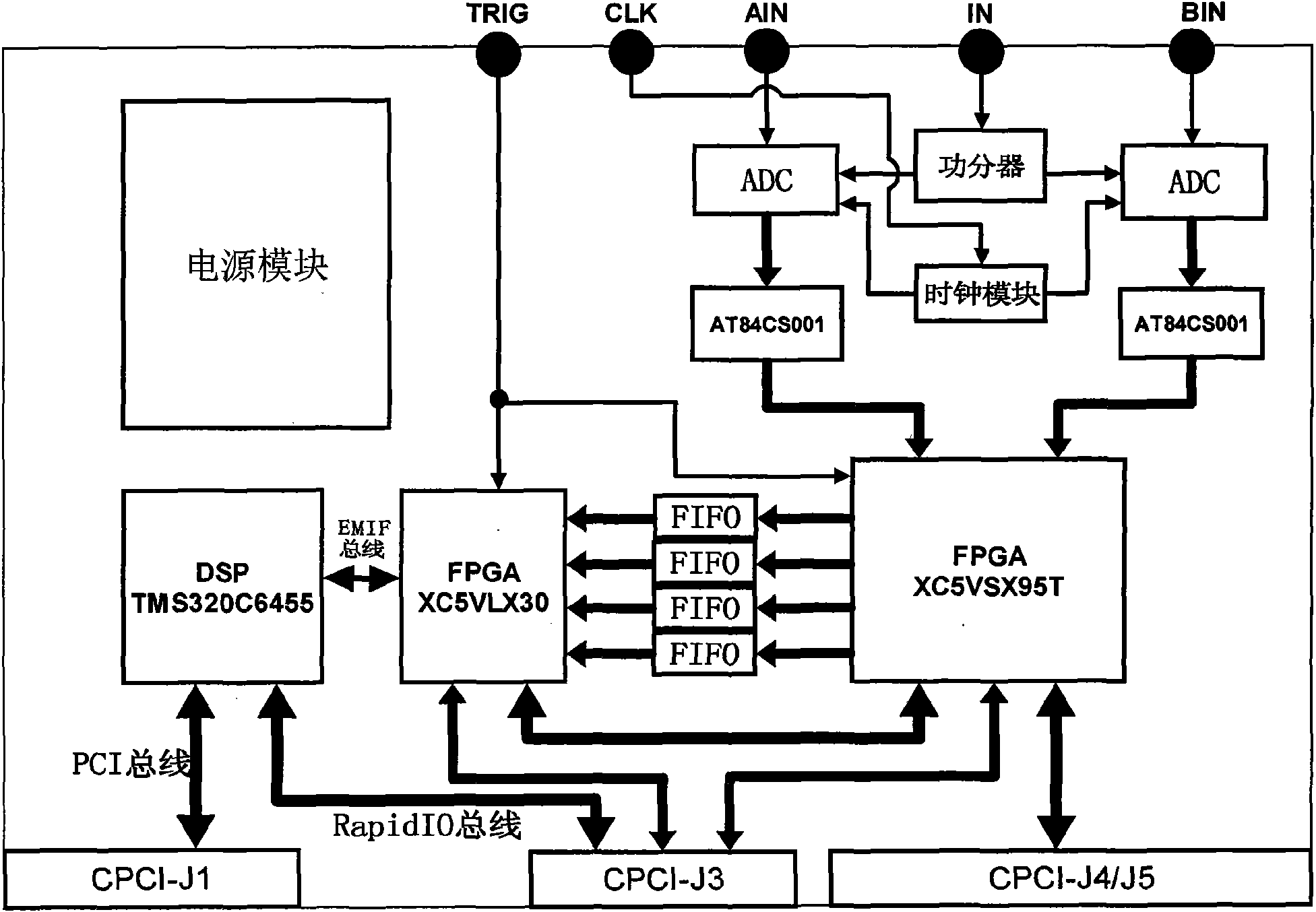

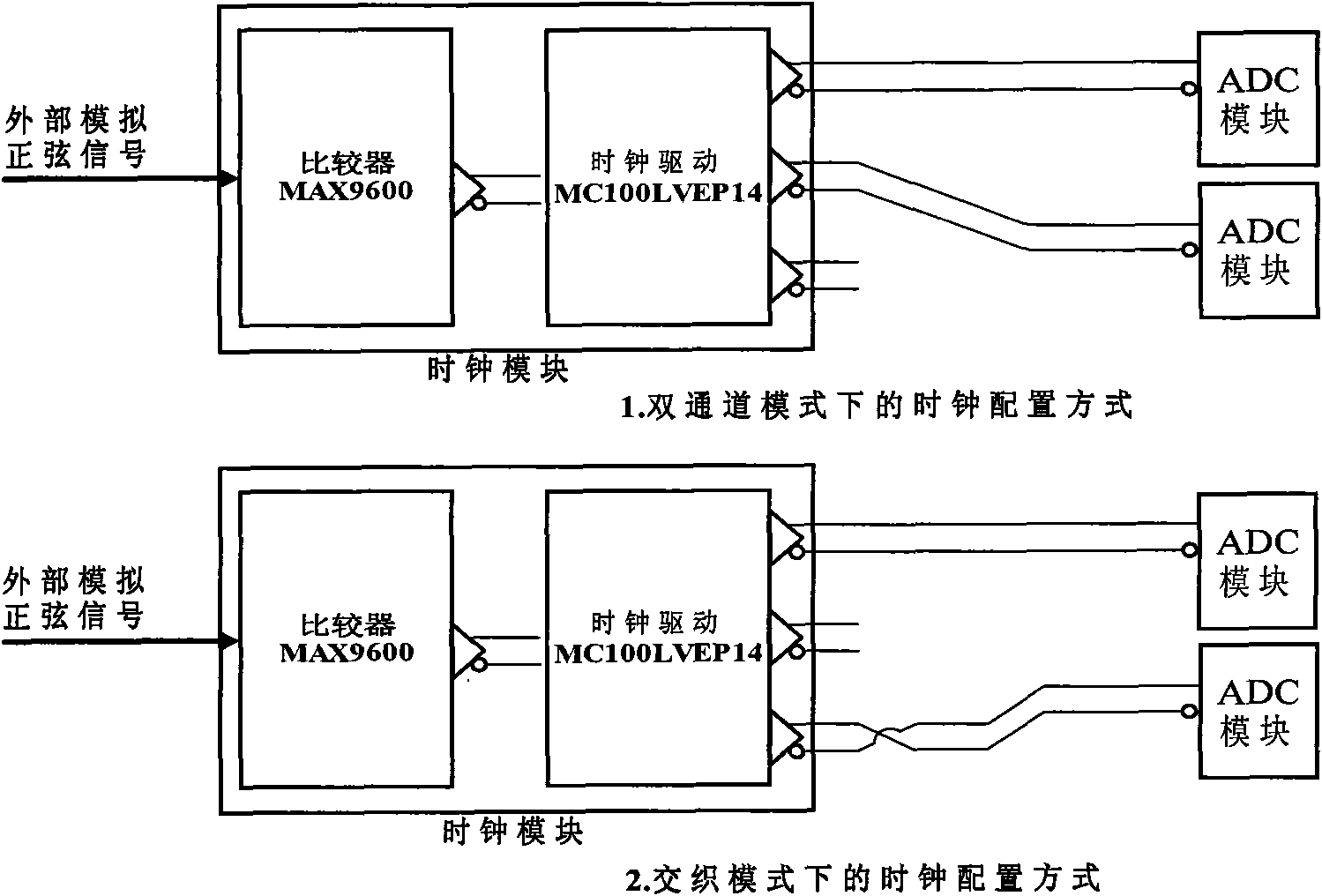

Dual-mode signal acquiring board

InactiveCN101587498AStrong signal processing abilityImprove signal sampling qualityData acquisition and loggingMode controlData acquisition

The invention relates to a dual-mode signal acquiring board, belonging to the technical field of data acquisition. The acquiring board comprises a power supply module, a clock module, a power divider module, an ADC module, a multiplex allocation module, a data preprocessing module, a data caching module, a control interface module and a main control module, and can implement the functions of dual-mode data acquisition, multiple-triggering mode control, data caching, data preprocessing and data transmission, the invention solves the problems that the interchannel synchronization under GSPS data acquisition velocity, multiple-triggering mode control, data preprocessing and transmitting, data caching clock network distribution are not easy to implement, the invention also solves the technical problem for implementing the interweave sampling of ADC chip of two GSPS sampling rates, the invention is suitable for the data acquisition conditions with high sampling velocity and input bandwidth requirement being applied to SAR radar echo signal acquisition, radar signal spying receiving, frequency storing interference and software radio and so on.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

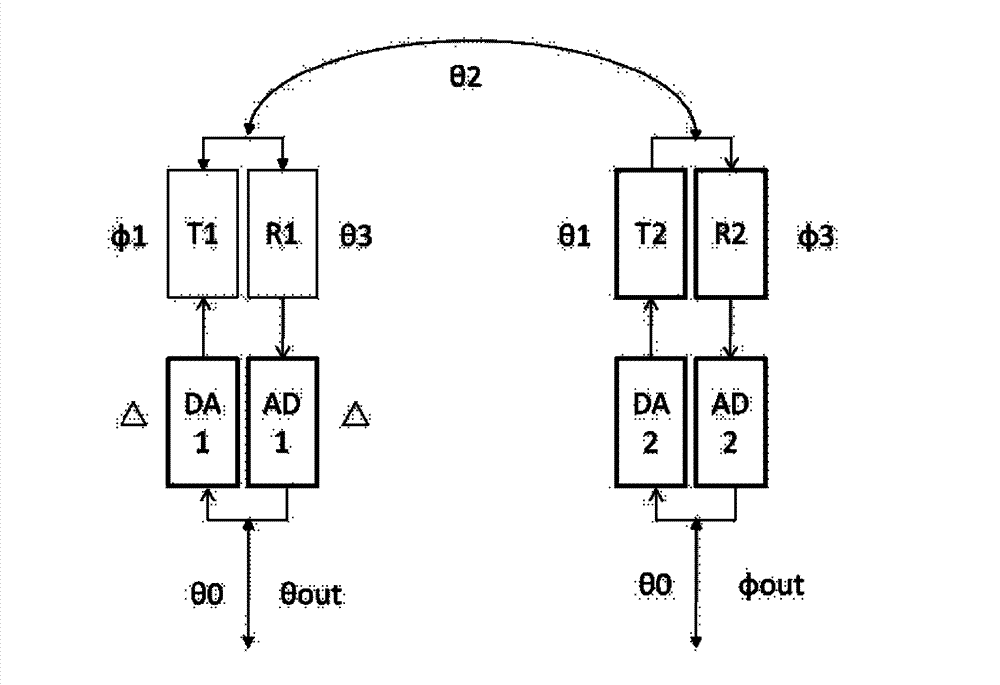

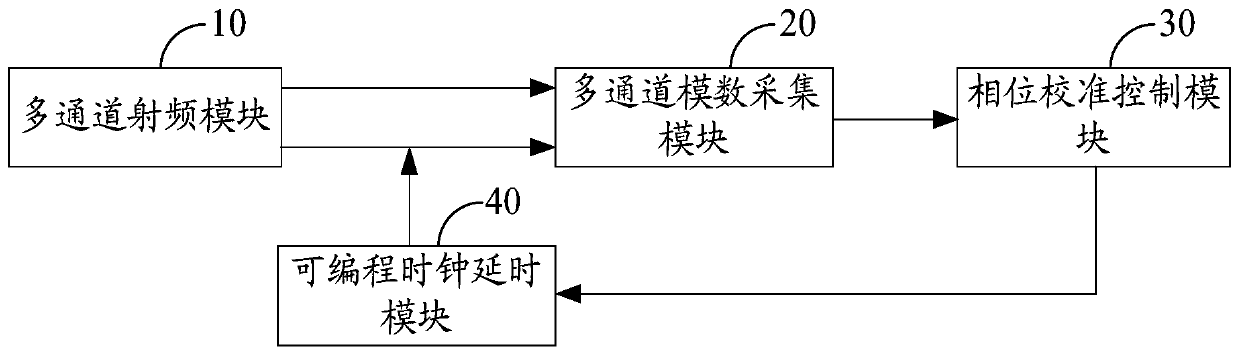

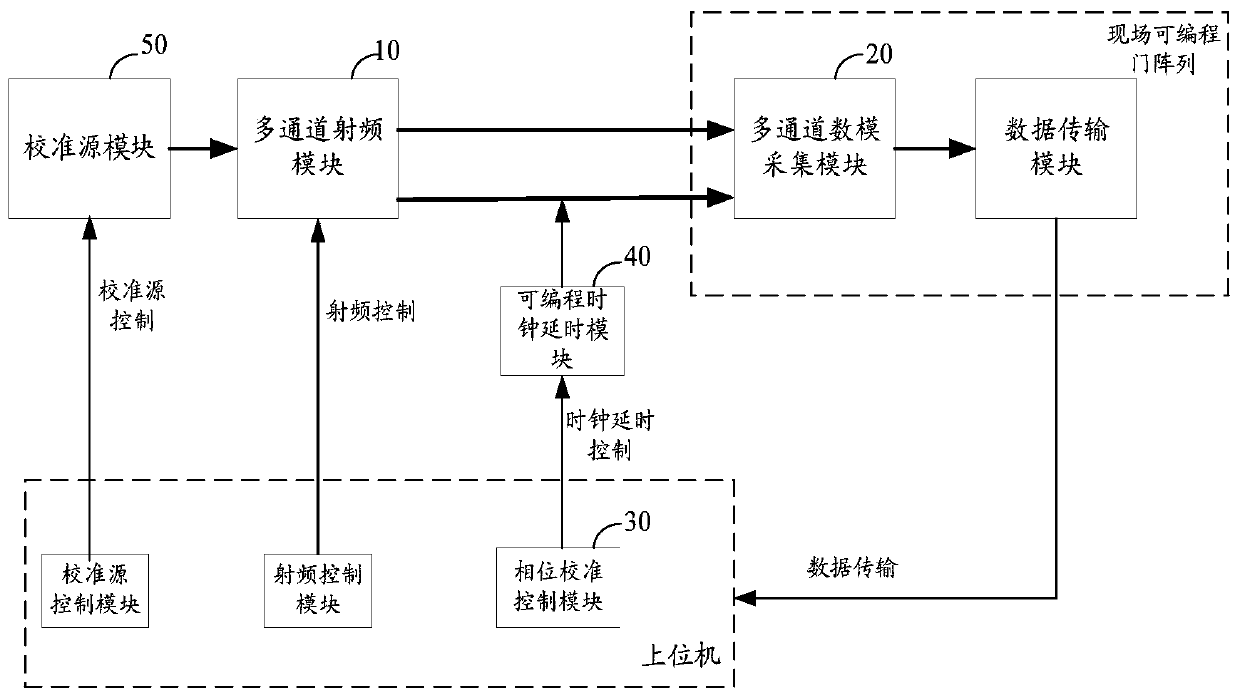

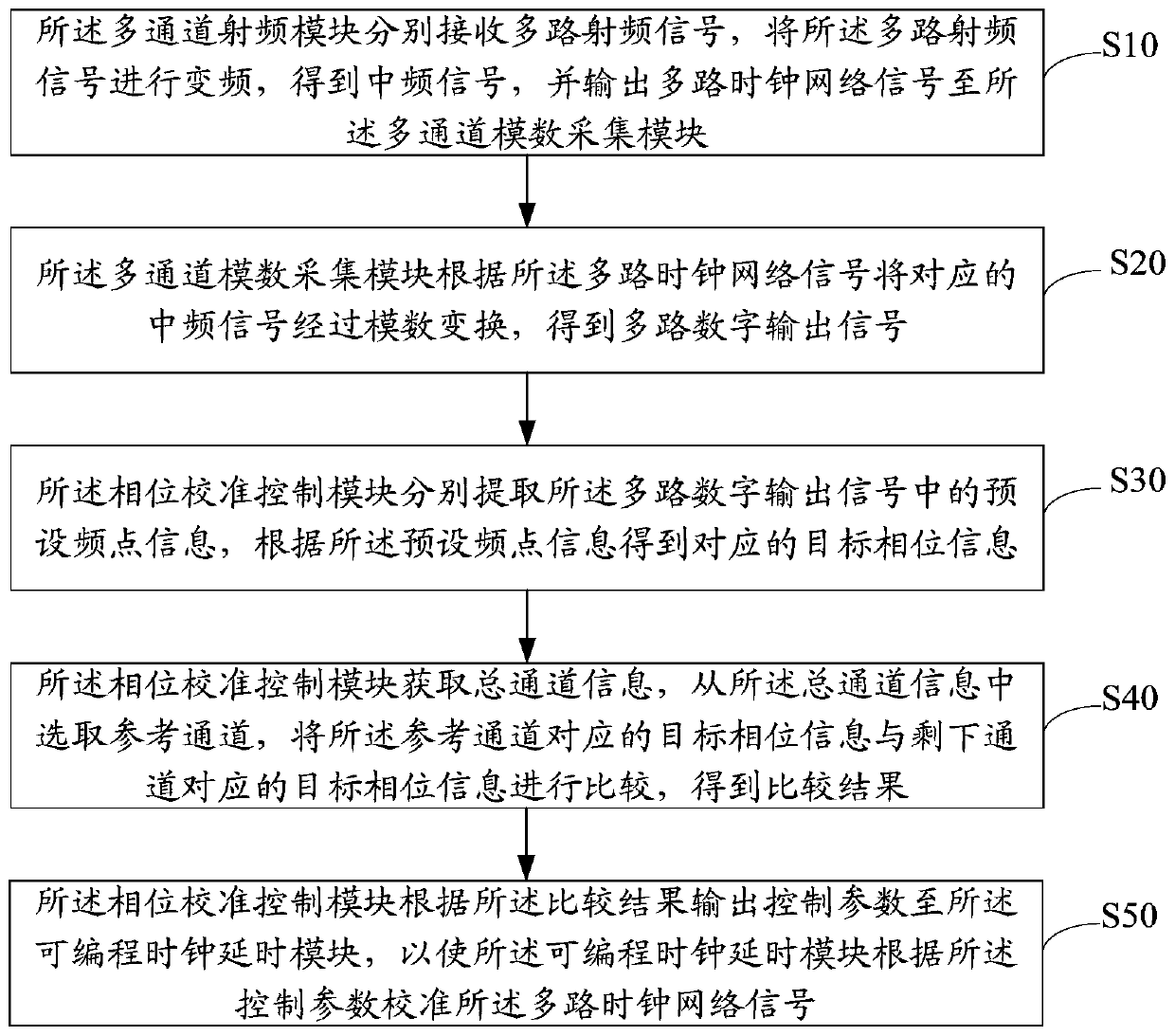

Multi-channel synchronous acquisition phase calibration system and method

The invention discloses a multi-channel synchronous acquisition phase calibration system and method, and the system comprises a multi-channel radio frequency module which is used for receiving a plurality of paths of radio frequency signals, obtaining intermediate frequency signals according to the plurality of paths of radio frequency signals, and outputting a plurality of paths of clock network signals; a multi-channel analog-to-digital acquisition module which is used for converting the corresponding intermediate frequency signals into multi-channel digital output signals according to the multi-channel clock network signals; a phase calibration control module which is used for obtaining corresponding target phase information according to preset frequency point information in the multiple paths of digital output signals; a phase calibration control module which is used for selecting reference channels, comparing the target phase information corresponding to the reference channel with the target phase information corresponding to the rest channels, and outputting a control parameter to a programmable clock delay module according to a comparison result, so that the programmable clock delay module calibrates the multi-path clock network signal according to the control parameter, thereby realizing calibration of the multi-path clock network signal.

Owner:武汉能钠智能装备技术股份有限公司

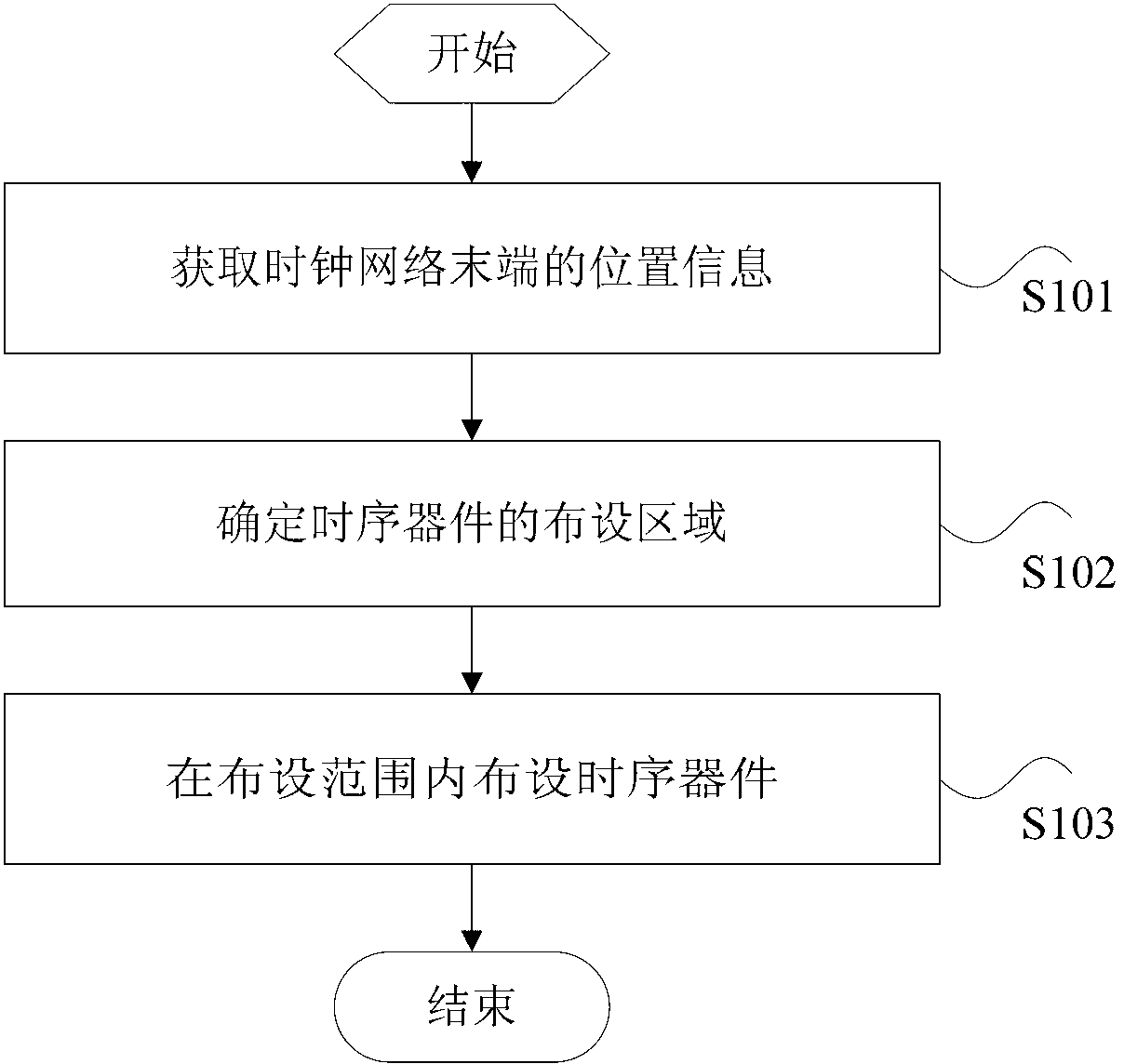

Method and device for constructing clock network

ActiveCN103259526ASolve resource problemsReduce resource costsLogic circuitsClock networkComputer science

The invention discloses a method and device for constructing a clock network. The method for constructing the clock network comprises the steps of obtaining position information of the tail end of the clock network and setting time sequence devices in a setting area. The tail end of the clock network is a wire or a point for setting the time sequence devices in the clock network. When the tail end of the clock network is the wire used for setting the time sequence devices, the tail end of the clock network is used as a symmetry axis to determine the setting area of the time sequence devices, and when the tail end of the clock network is the point used for setting the time sequence devices, the tail end of the clock network is used as a center to determine the setting area of the time sequence devices. By means of the method and device for constructing the clock network, the problem hat in the prior art, resource cost is high or design period is long when the clock network is constructed is solved, and therefore the effects of lowering resource cost for constructing the clock network and shortening constructing period are achieved.

Owner:LOONGSON TECH CORP

Energy recycling in clock distribution networks using on-chip inductors

InactiveUS7082580B2Minimise currentGenerating/distributing signalsSpecial data processing applicationsPower flowClock rate

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

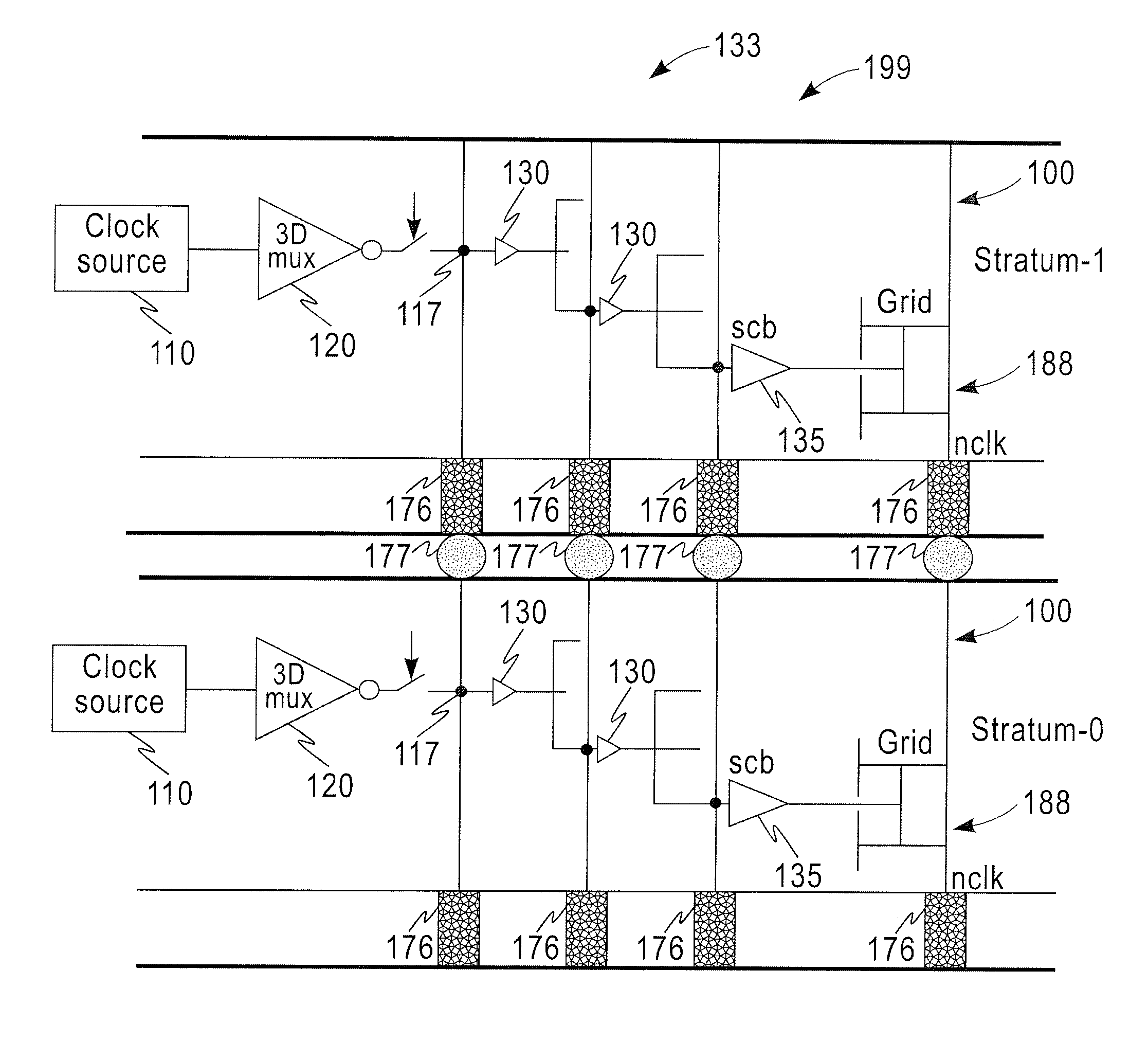

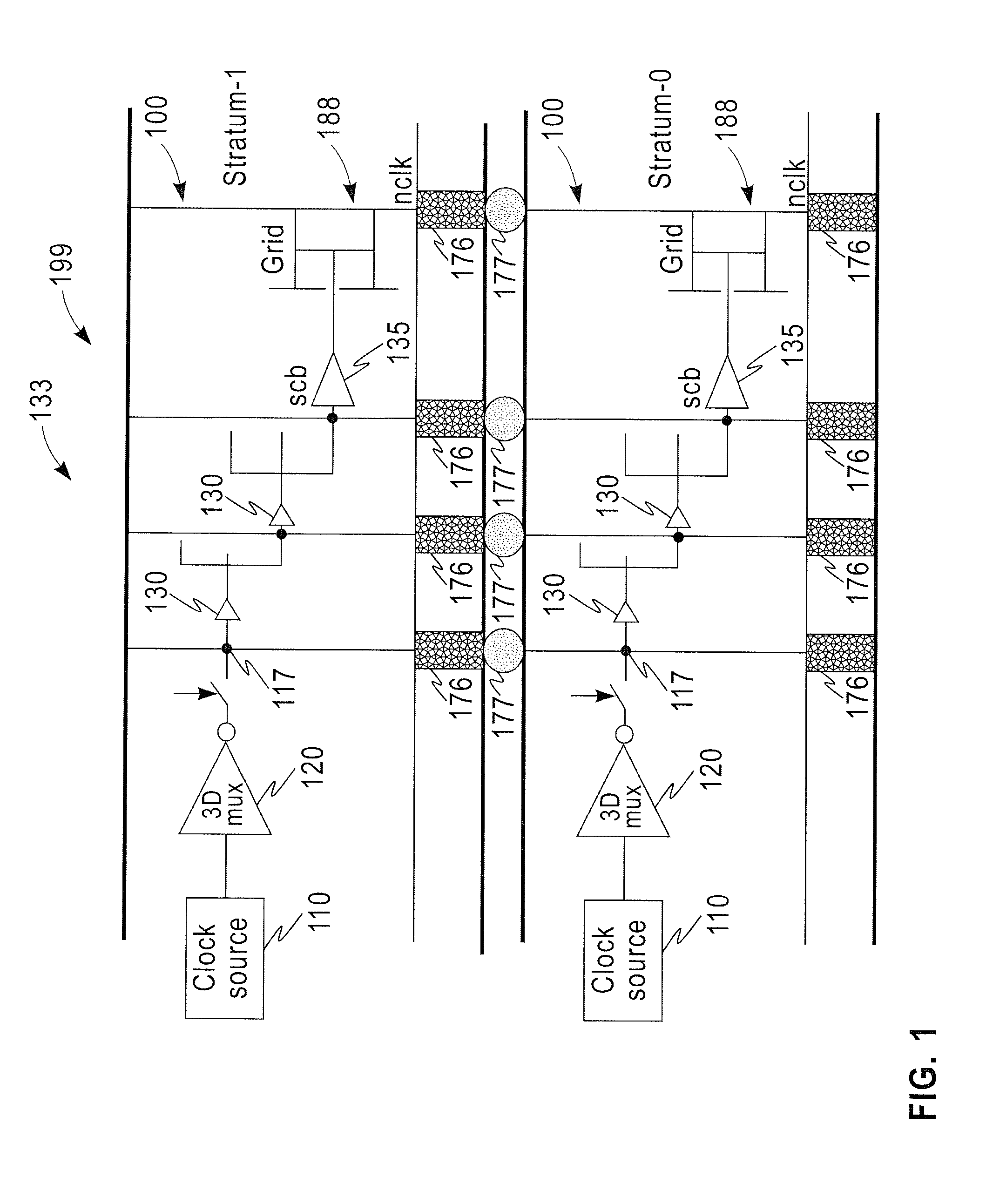

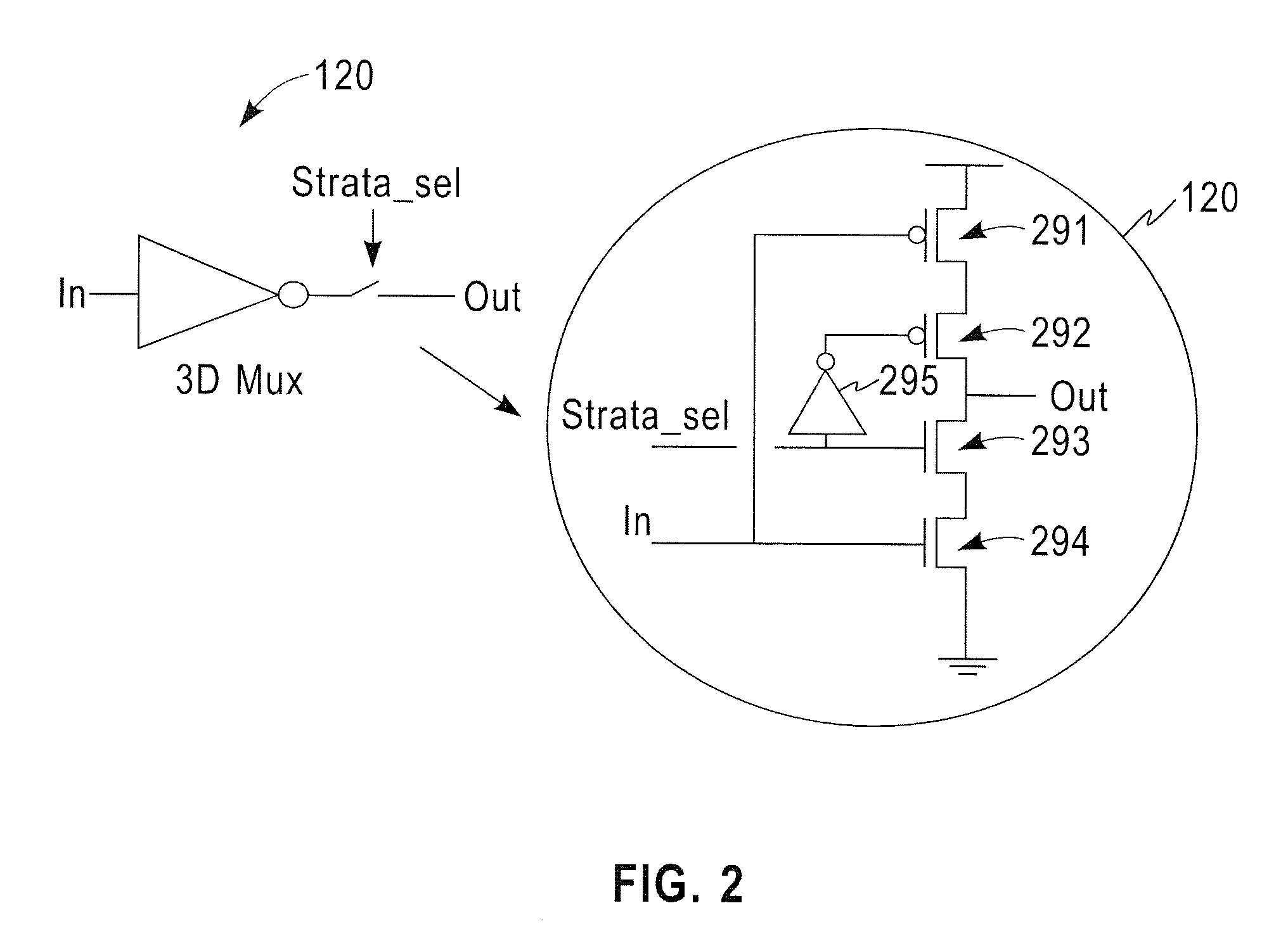

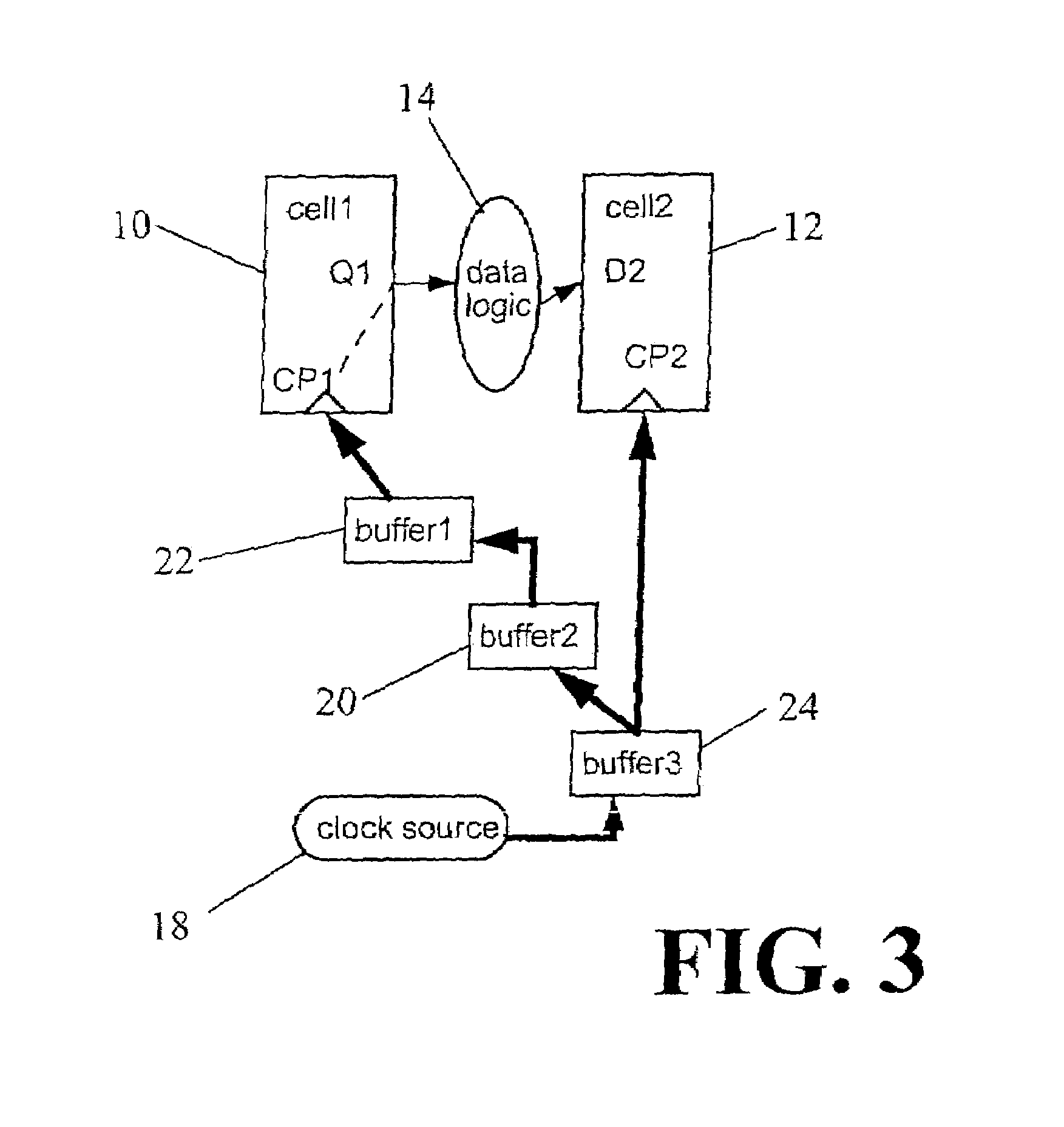

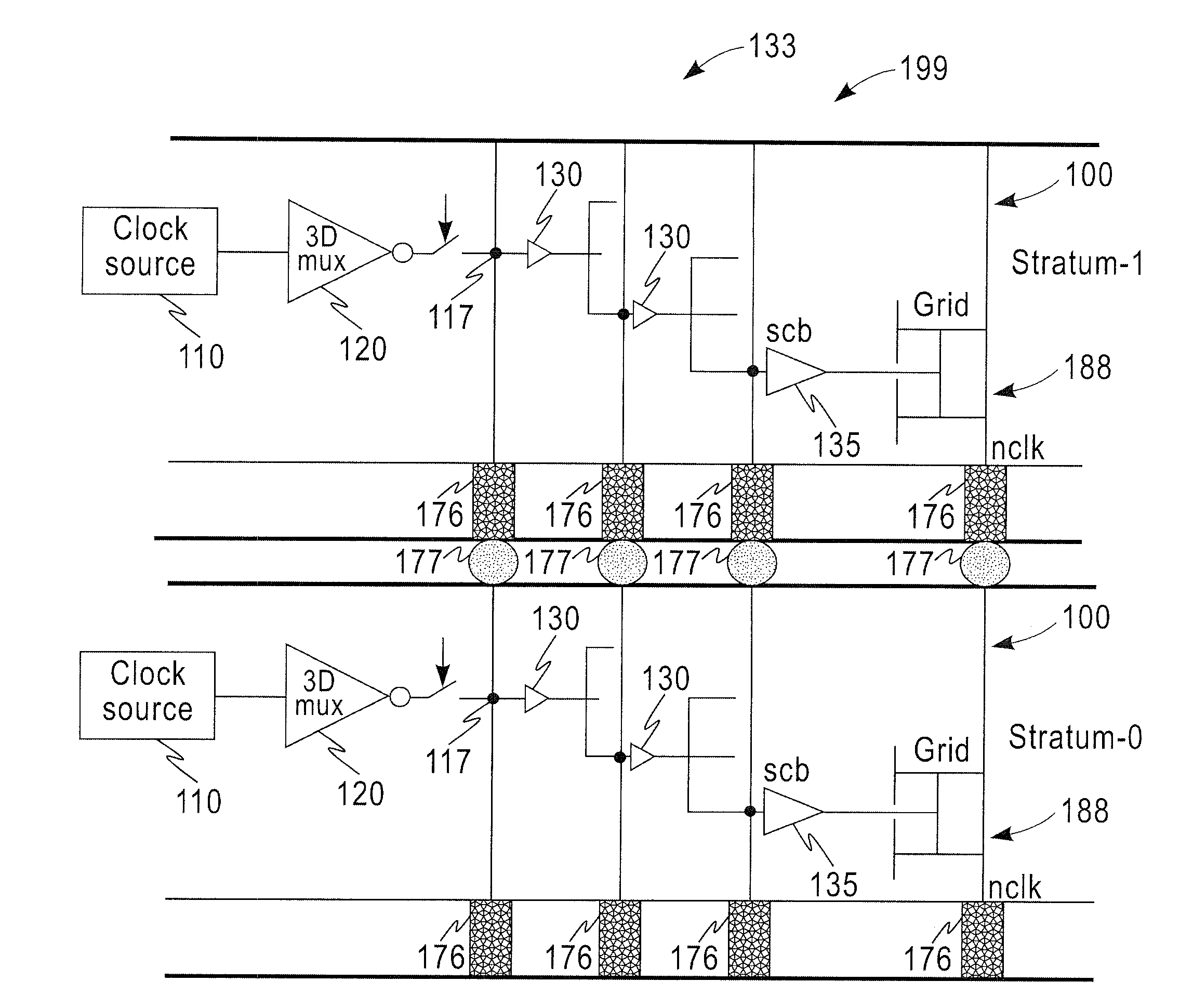

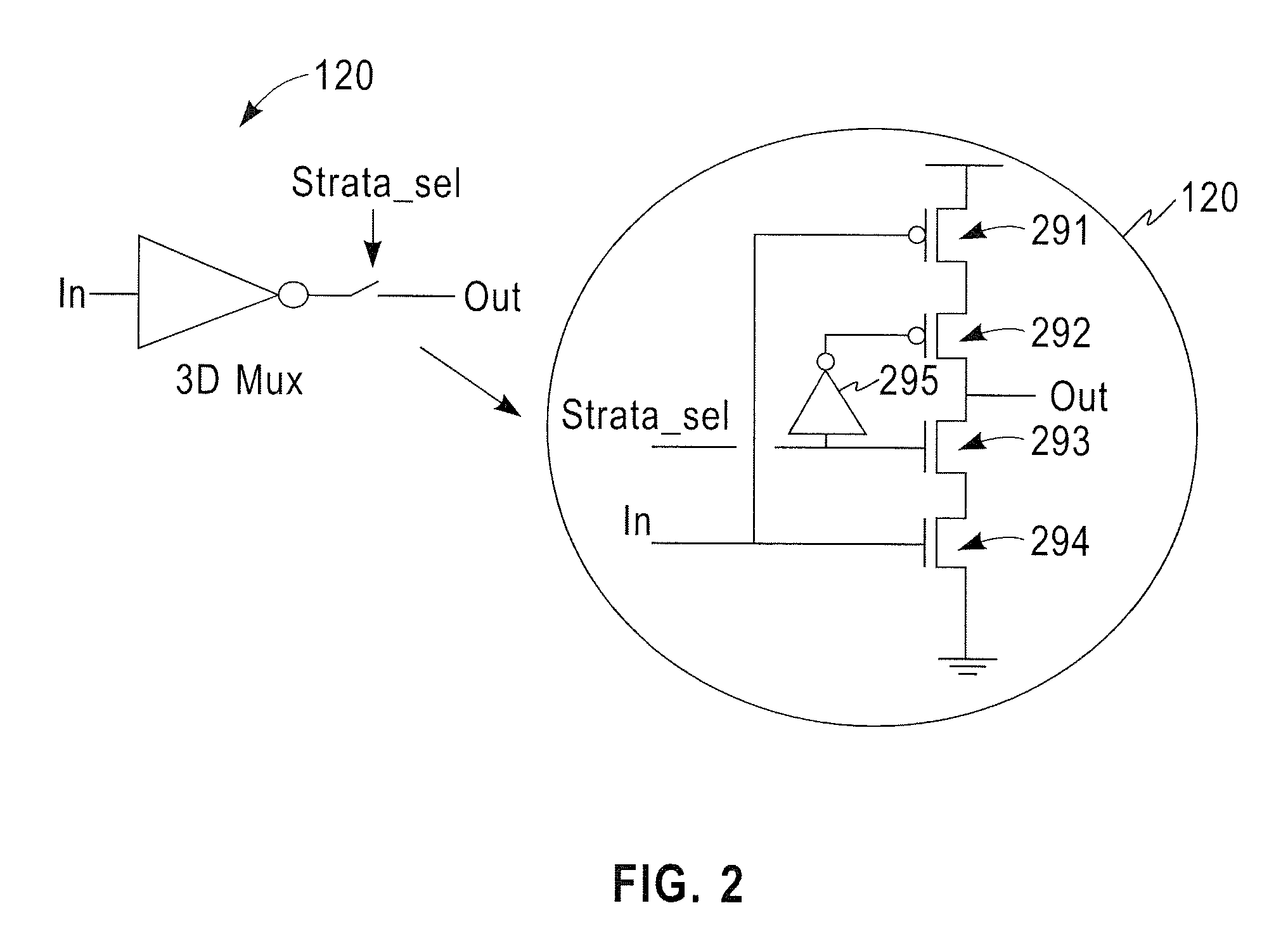

Synchronizing global clocks in 3D stacks of integrated circuits by shorting the clock network

ActiveUS20130049827A1Reduce skewPulse automatic controlSemiconductor/solid-state device detailsMultiplexerClock tree

There is provided a clock distribution network for synchronizing global clock signals within a 3D chip stack having two or more strata. On each of the two or more strata, the clock distribution network includes a clock grid having a plurality of sectors for providing the global clock signals to various chip locations, a multiple-level buffered clock tree for driving the clock grid and including at least a root and a plurality of clock buffers, and one or more multiplexers for providing the global clock signals to at least a portion of the buffered clock tree. Inputs of at least some of the plurality of clock buffers on each of the two or more strata are shorted together using chip-to-chip interconnects to reduce skewing of the global clock signals with respect to the various chip locations.

Owner:GLOBALFOUNDRIES US INC

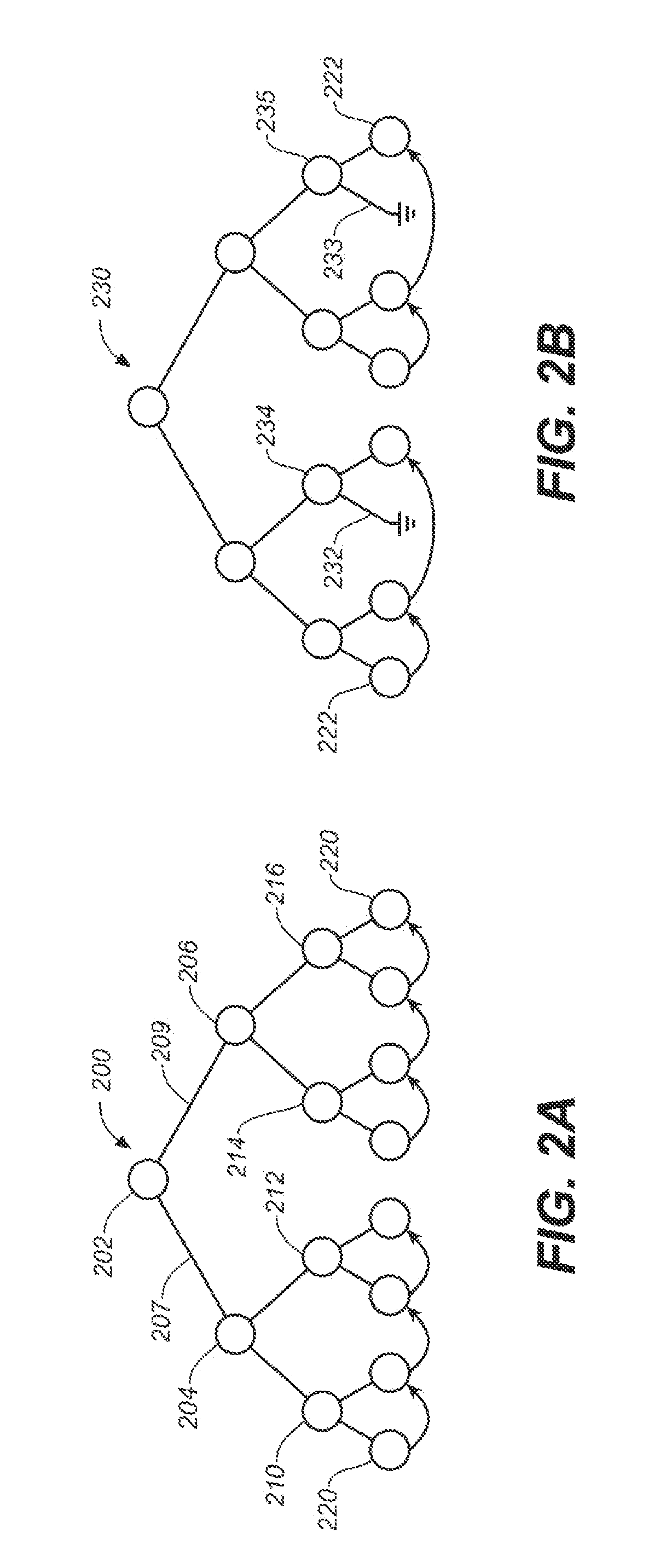

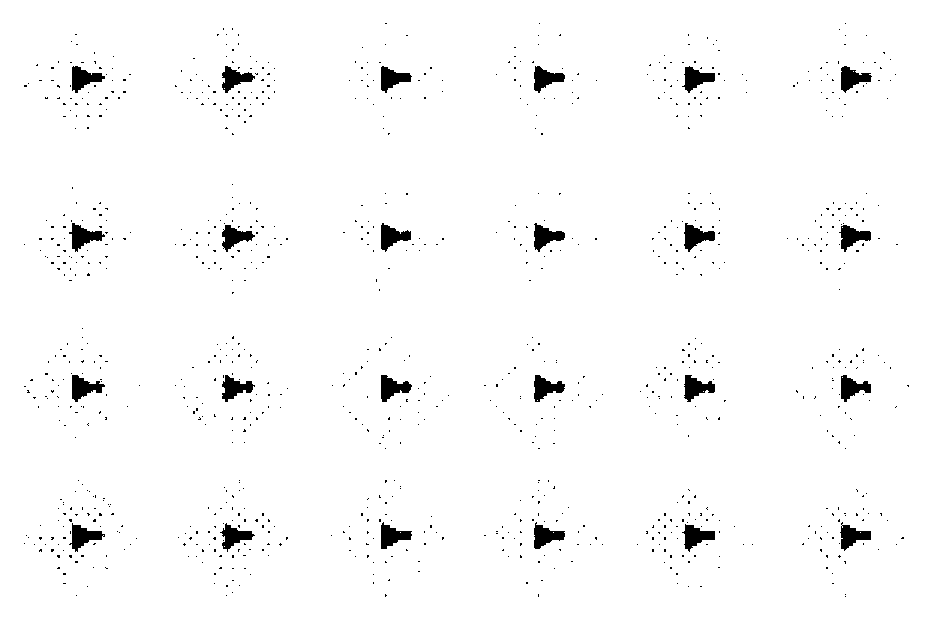

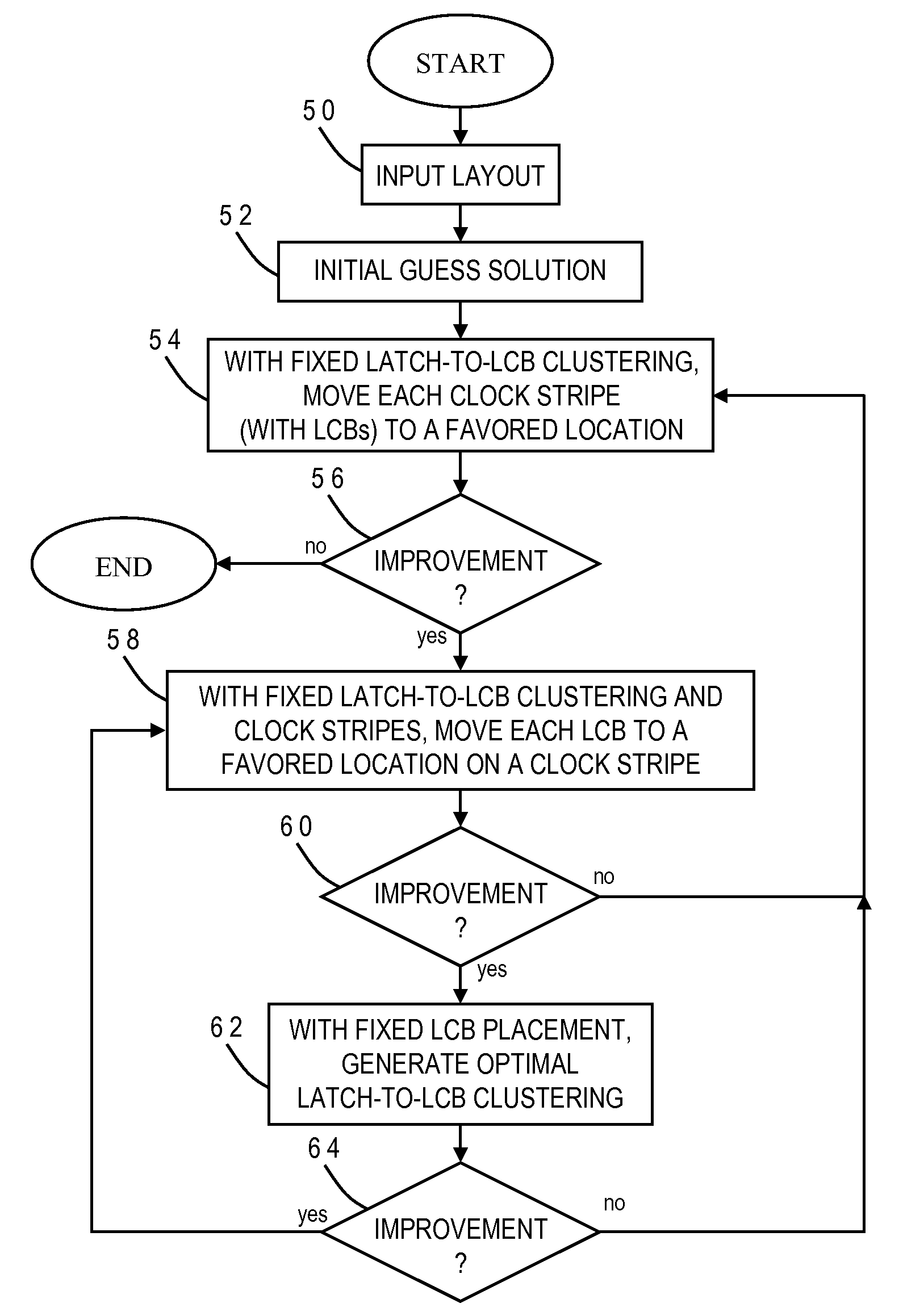

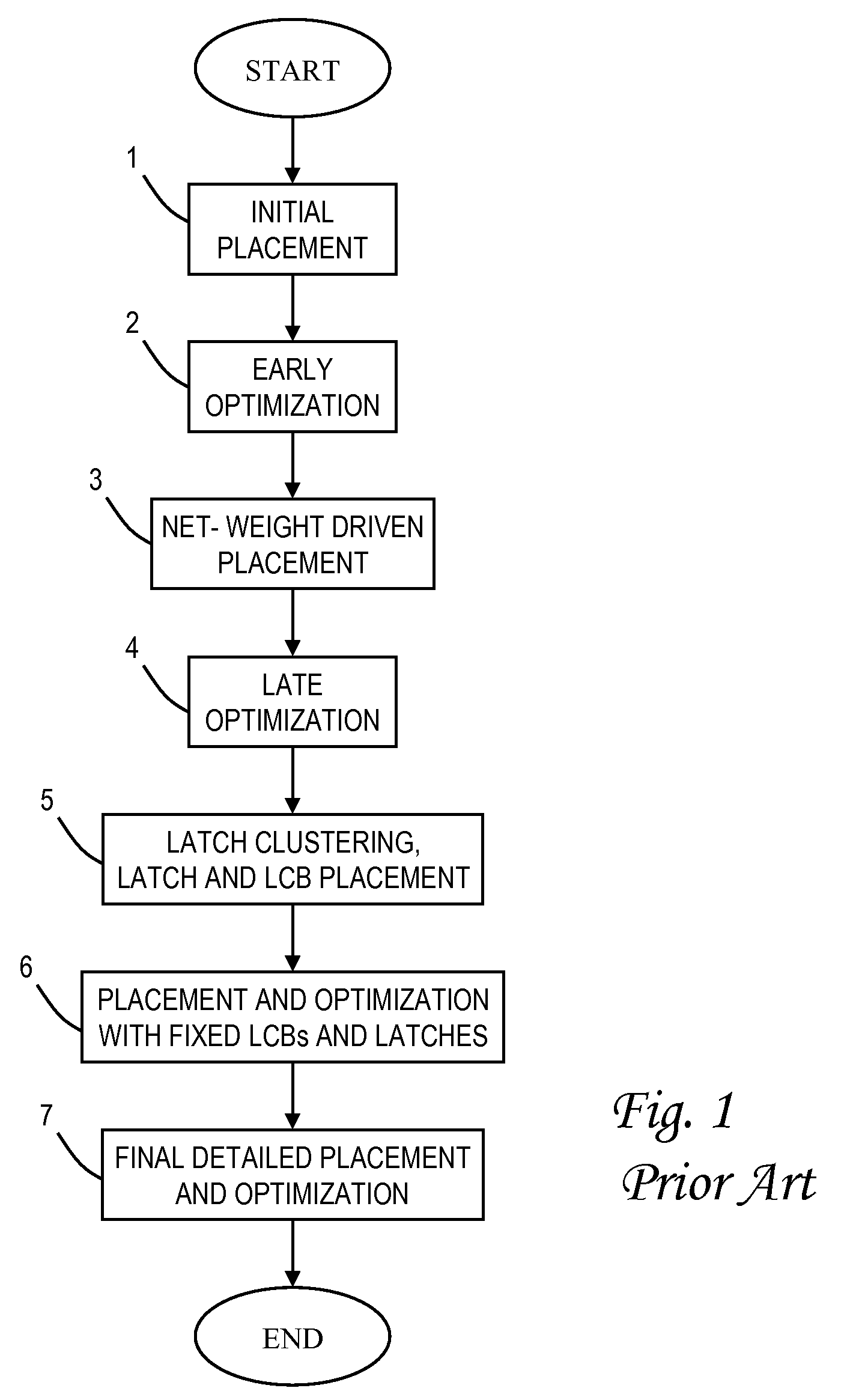

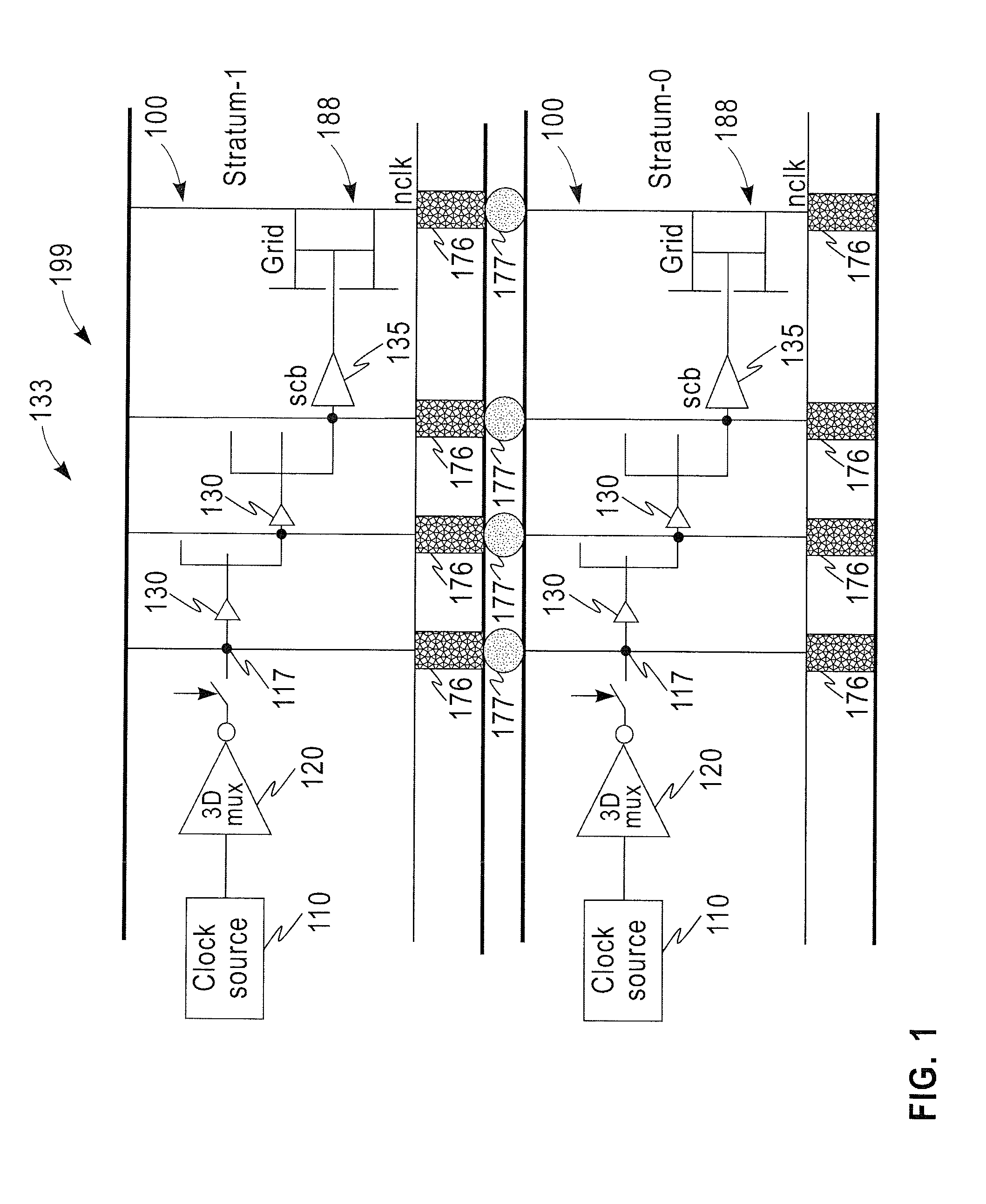

Regular local clock buffer placement and latch clustering by iterative optimization

InactiveUS20090193377A1Simple methodMore flexibility in the location of clock componentsComputer aided designSpecial data processing applicationsCapacitanceClock network

Power, routability and electromigration have become crucial issues in modem microprocessor designs. In high performance designs, clocks are the highest consumer of power. Arranging clocking components with regularity so as to minimize the capacitance of the clock nets can help reduce clock power, however, it may hurt performance due to some loss of flexibility in physically placing those components. The present invention provides techniques to optimally design a clock network by logically assigning clusters of the latches to respective clock distribution structures, placing clock pins at favored pin locations, and placing clock distribution structures directly underneath the clock pins. The clock distribution structures may be moved to favored distribution locations along the clock stripes, and new optimal clustering generated between the latches and the clock distribution structures. These three optimizations are preferably repeated iteratively to derive a local optimal solution for the clock network.

Owner:GLOBALFOUNDRIES INC

Methods and circuits for measuring clock skew on programmable logic devices

InactiveUS6862548B1Accurately measuring skewDigital circuit testingPulse automatic controlProgrammable logic deviceClock network

Owner:XILINX INC

Chip allowing sleep mode and method

ActiveCN103631360AImplement wake-up from sleep modeEfficient consumptionPower supply for data processingGenerating/distributing signalsClock networkEngineering

The invention provides a chip allowing a sleep mode and a method. A clock controller is used for applying to switch off a clock circuit according to low power consumption, a system clock is suspended to be provided for an edge detecting circuit and a central processing unit, and the sleep mode is executed in a triggering mode. Under the sleep mode, the edge detecting circuit is used for detecting signals to be detected and generating rousing signals according to the signals to be detected; the clock controller is used for switching on the clock circuit according to the rousing signals and providing the system clock again for the edge detecting circuit and the central processing unit, sleep mode signals are sent to the edge detecting circuit, and a common mode is executed in a triggering mode. The chip allowing the sleep mode and the method are used for switching off all clock networks and all clock generating circuits and rousing the sleep mode on the premise that functions are not influenced, and therefore the power consumption of the chip is reduced, and the power consumption of the chip is made to be minimized.

Owner:GIGADEVICE SEMICON (BEIJING) INC

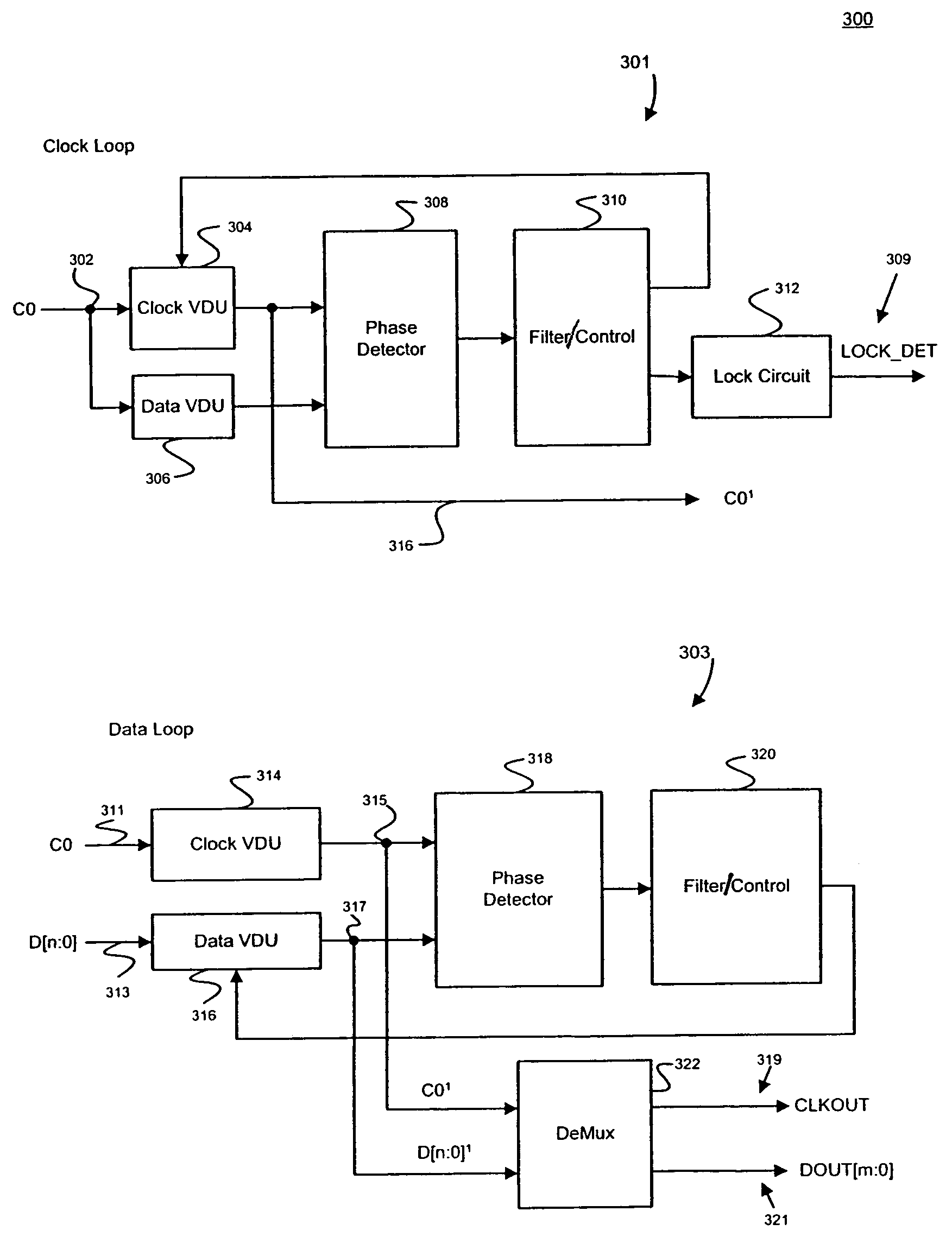

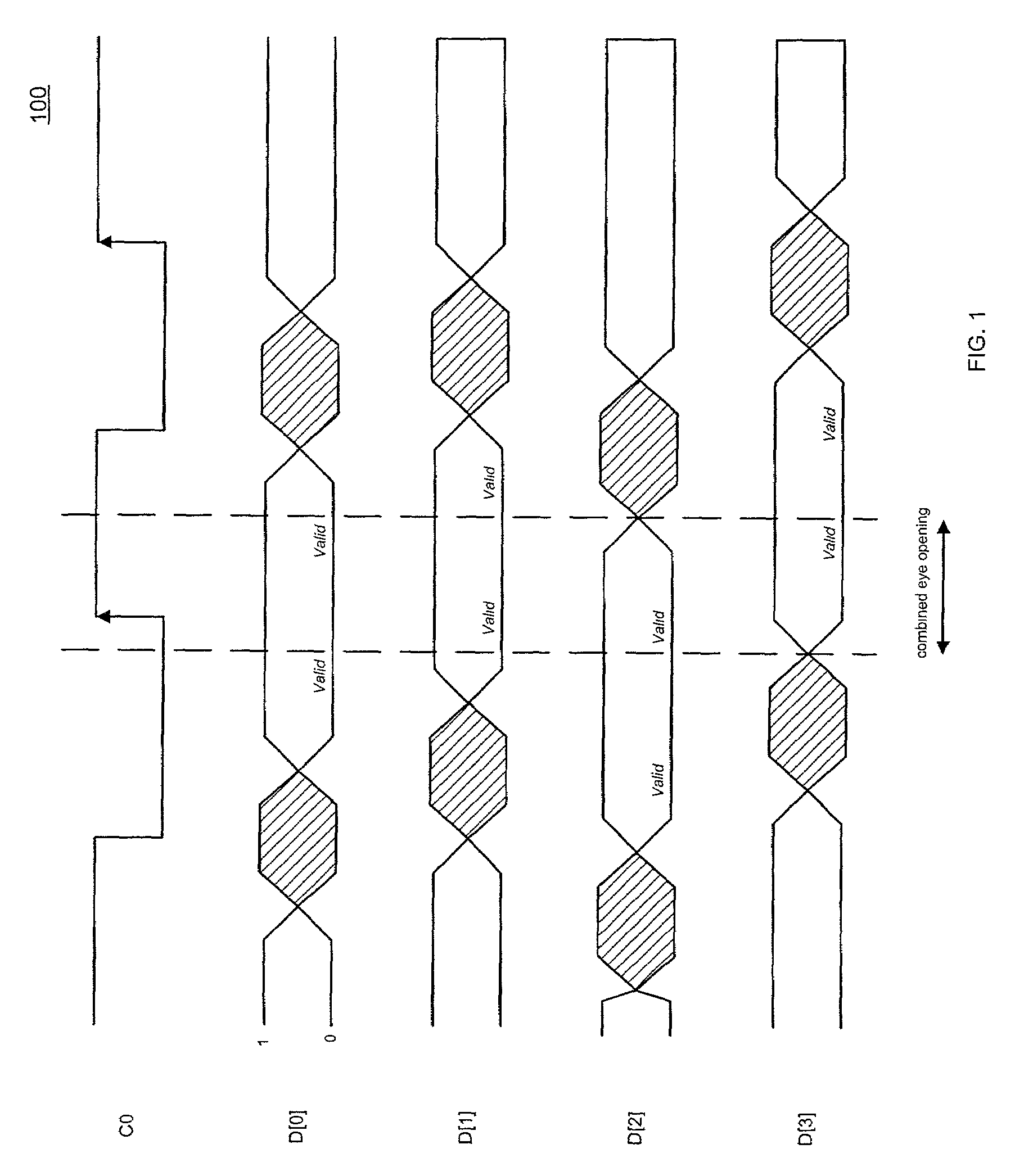

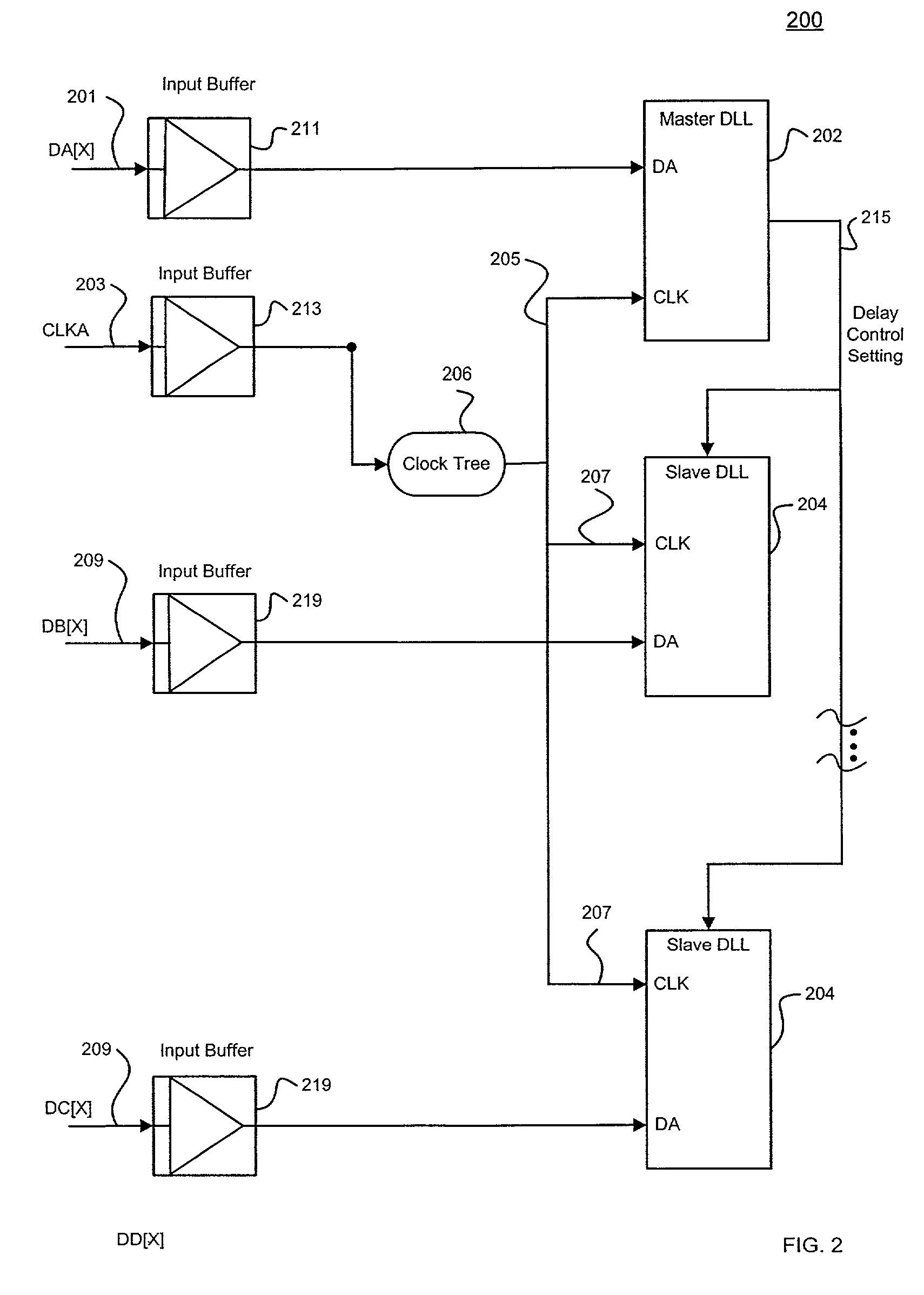

Distributed clock network using all-digital master-slave delay lock loops

ActiveUS7139348B1Synchronisation information channelsPulse automatic controlControl signalDigital master

A distributed clock circuit for clocking high speed data at various different physical locations on a chip while improving setup and hold times. The clock circuit includes a master delay lock loop (DLL) circuit configured to lock a global clock signal with a first data signal, and output a clock delay control signal when the global clock signal is locked. The clock circuit further includes one or more slave DLL circuits, coupled to receive the clock delay control signal to lock a local clock signal with a local data signal, wherein the local clock signal is based on the global clock signal.

Owner:MACOM CONNECTIVITY SOLUTIONS LLC

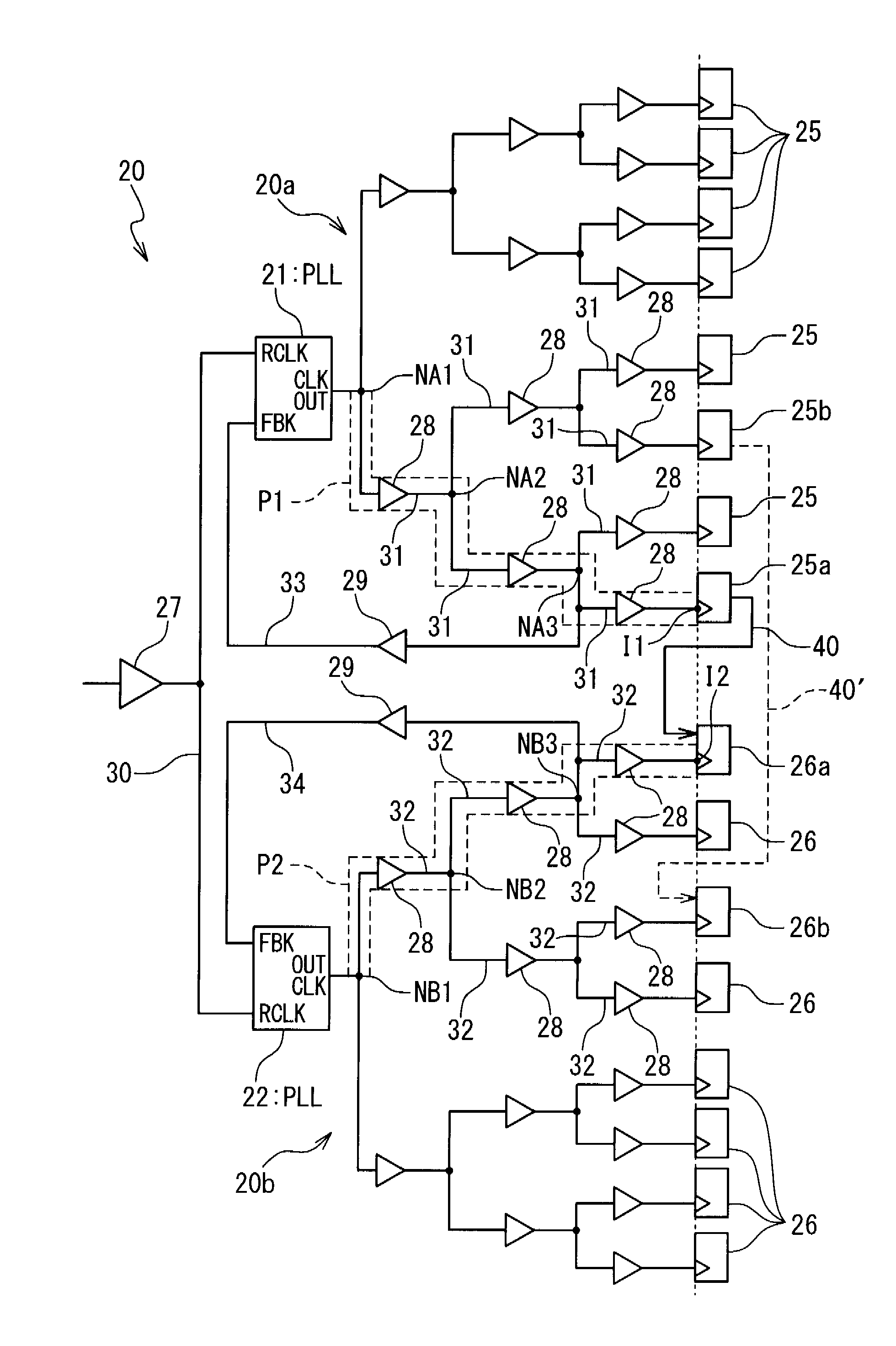

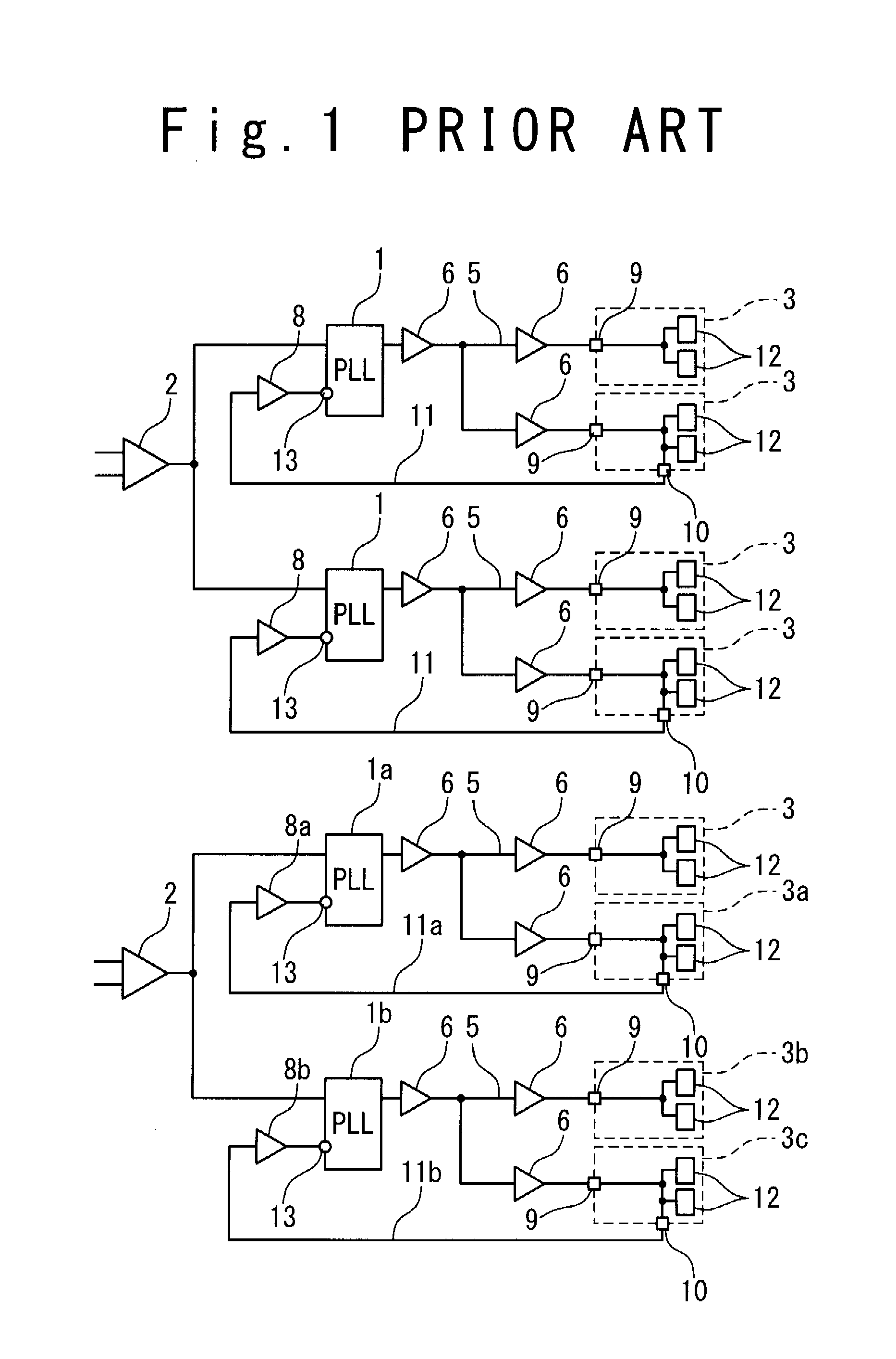

Clock distribution circuit, semiconductor integrated circuit and method of designing clock distribution circuit

InactiveUS20070286323A1Avoid differencesEnsure correct executionPulse automatic controlError detection/correctionClock networkData transmission

A clock distribution circuit, which is provided in IC that has a first sequential circuit receiving first clock through a first branch node on a first clock network, a second sequential circuit receiving second clock through a second branch node on a second clock network, and a data transfer path between the first and second sequential circuits, includes: a first PLL receiving a first feedback clock that is the first clock branched at the first branch node and outputting the first clock to the first clock network based on the first feedback clock; and a second PLL receiving a second feedback clock that is the second clock branched at the second branch node and outputting the second clock to the second clock network based on the second feedback clock. A branch node is provided at least one of between the first PLL and the first branch node and between the second PLL and the second branch node.

Owner:RENESAS ELECTRONICS CORP

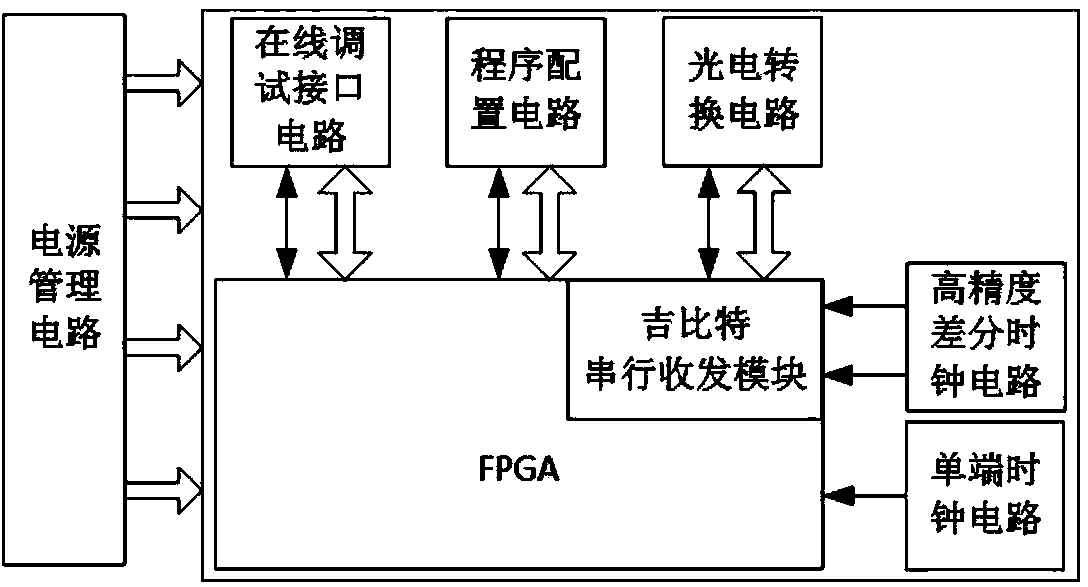

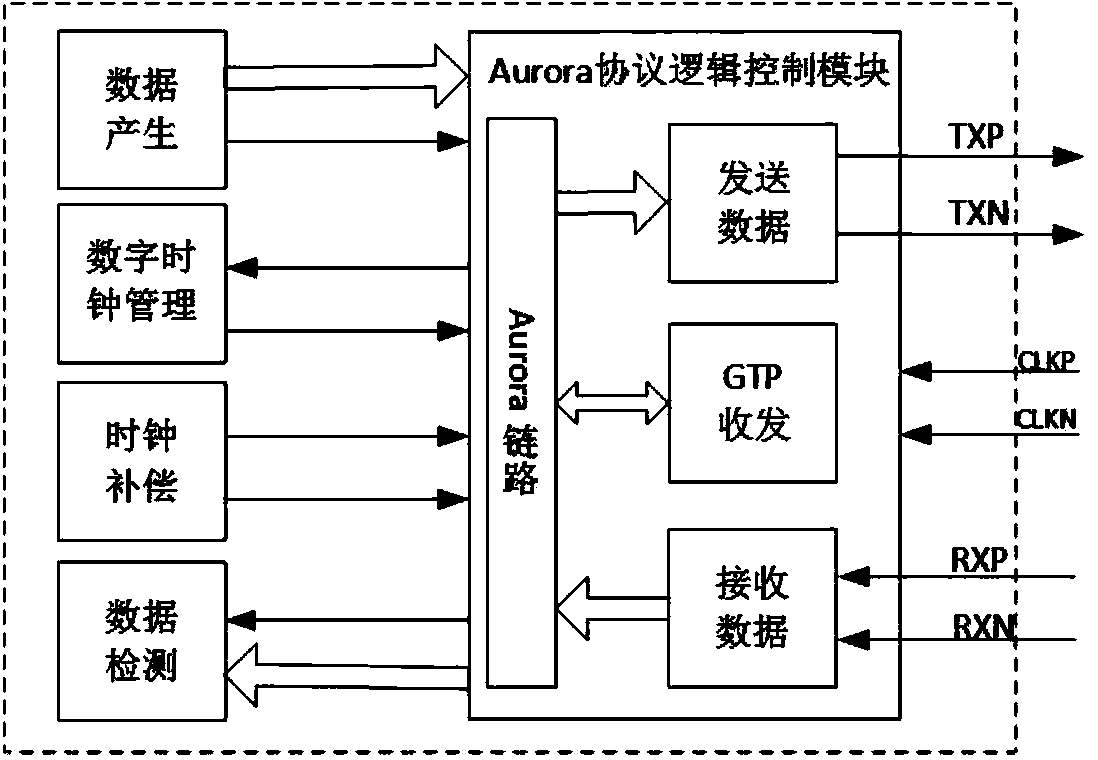

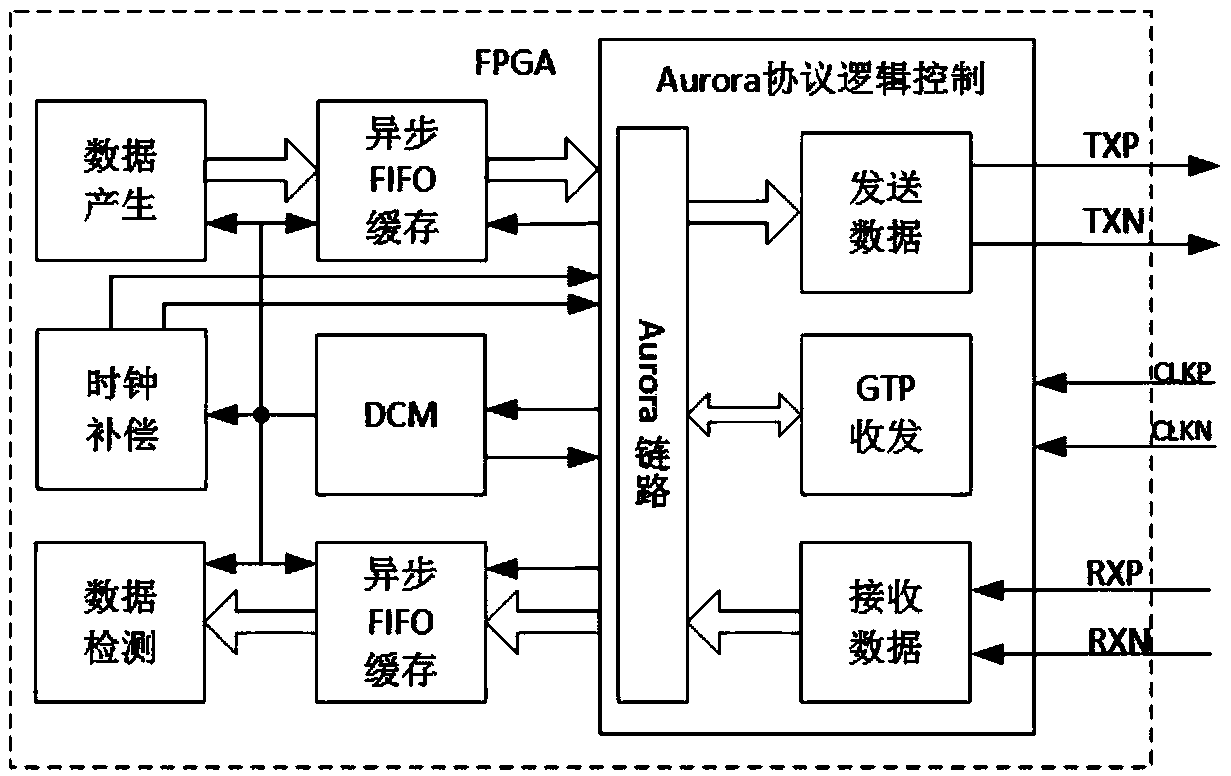

Fiber data transmission method based on asynchronous communication mode

ActiveCN104022828AReduce error rateReduce bit errorsError preventionFibre transmissionFiberAsynchronous serial communication

The invention relates to a fiber data transmission method based on an asynchronous communication mode. According to the method, an employed high speed data transmission circuit is realized by employing an internal function design mode of an FPGA chip, the realized logic functions comprise data generation, digital clock management, clock compensation, data detection, asynchronous FIFO caching based on Gray code counting and Aurora protocol logic control, and the functions of data generation, digital clock management, clock compensation, data detection and Aurora protocol logic control are realized by employing an FPGA standard setting mode. The method is characterized by realizing asynchronous FIFO caching based on Gray code counting, clock network generation and a transmission circuit function. The method employs a fiber data transmission method combining the asynchronous FIFO caching based on the Gray code counting mode with an Aurora protocol, and thereby data transmission accuracy is improved.

Owner:TIANJIN UNIV

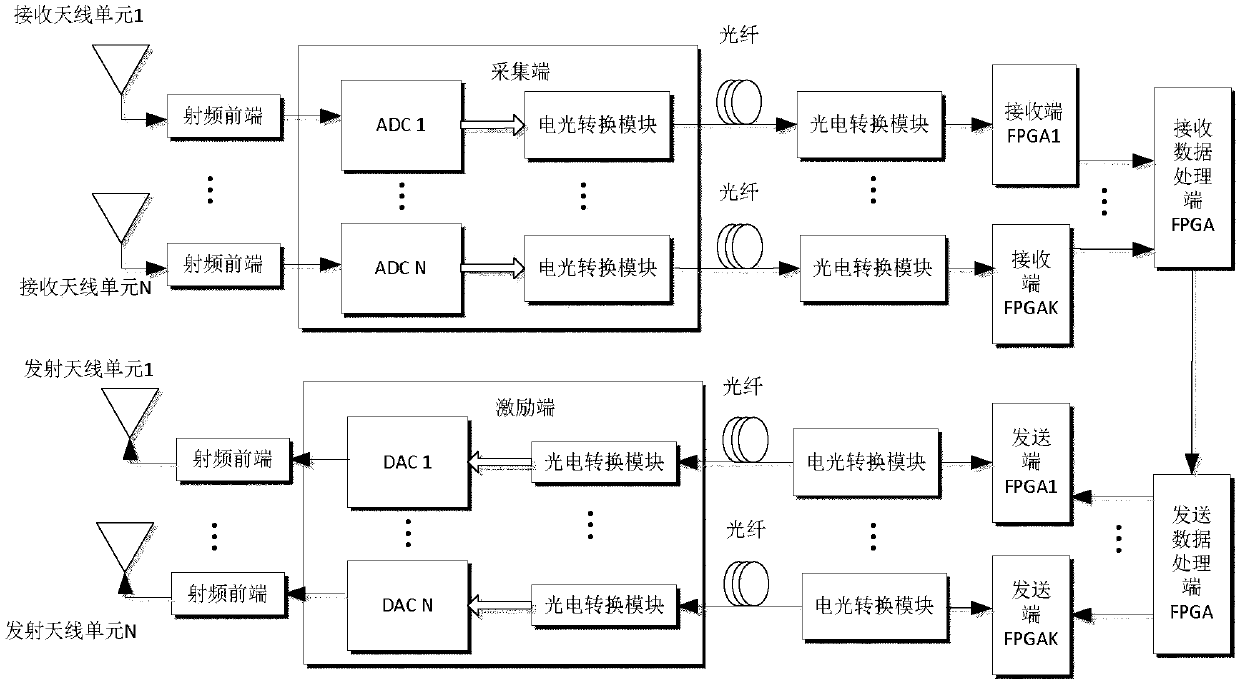

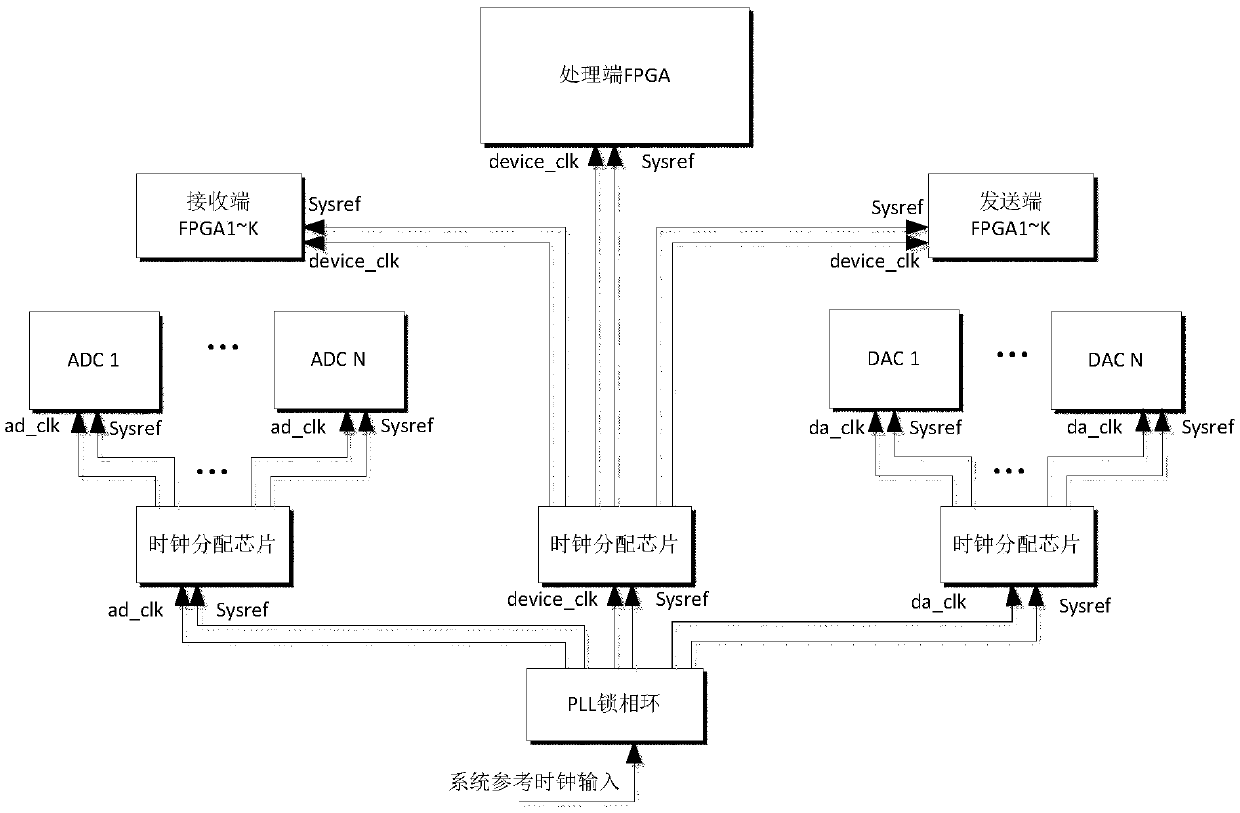

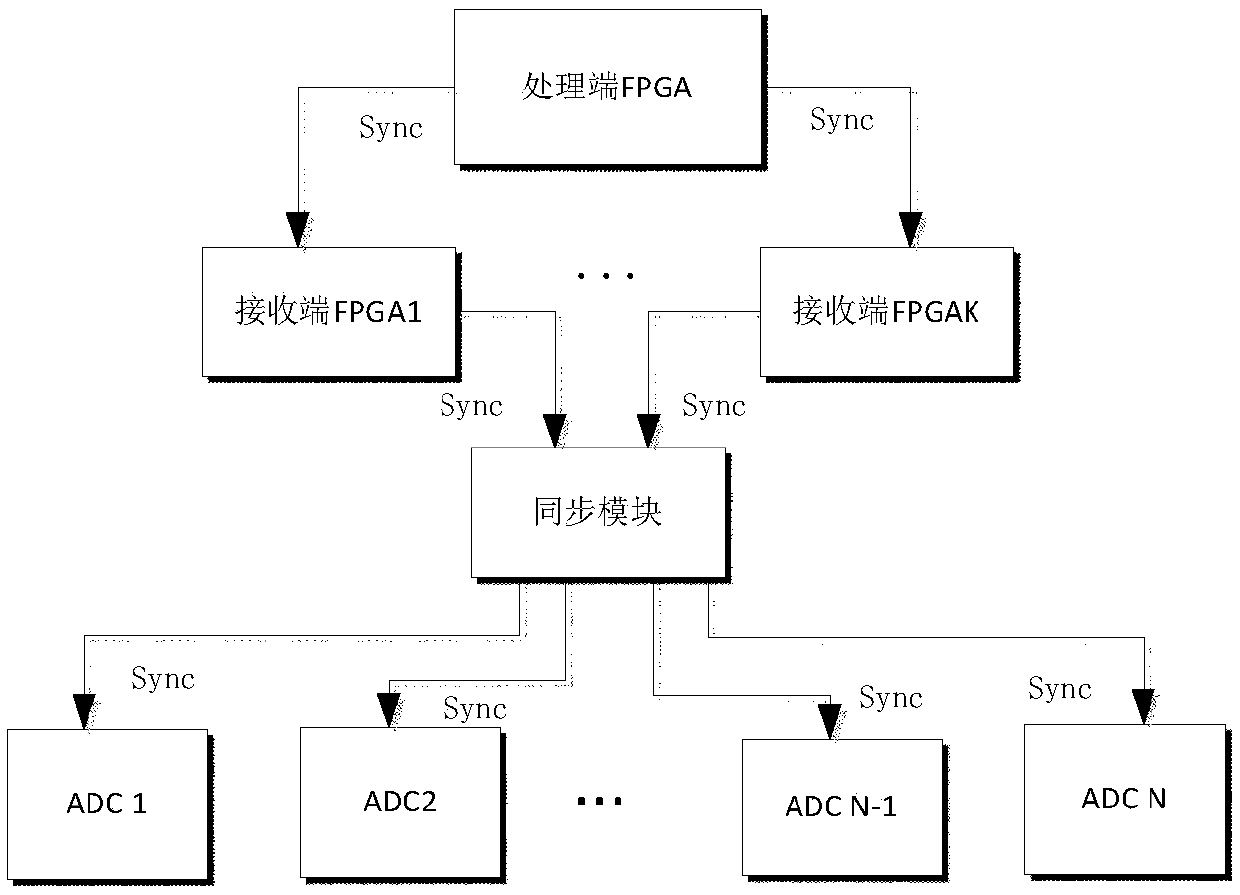

Method for synchronous transmission of digital array antenna baseband excitation data

InactiveCN109639403AReduce phase errorEliminates fixed phase deviationSynchronisation by photonic/optical meansData synchronizationIntermediate frequency

The invention discloses a method for synchronous transmission of digital array antenna baseband excitation data. The method is featured by small channel phase error, simple processing of digital processing part and low power consumption baseband excitation data. In the method, optical fiber is adopted as a long-distance transmission media between a collecting end and a receiving end, 1-N ADC1-ADCNof the collecting end perform data sampling on RF signals, and convert the signal into an intermediate frequency signal, packages data according to a JESD204B protocol and converts the data into a high-speed serial data flow, and sends the data flow to an electro-optical conversion module to be converted into optical signal, then an optical fiber photoelectric conversion module recovers the optical signal into an electric signal and sends the electric signal to the receiving end FPGA1-FPGAK to complete data recovery, then data is aligned through channel calibration, sample signals with data aligned are simultaneously transmitted to a received data processing end FPGA, and a full link data synchronous transmission homologous synchronous clock network synchronizes data.

Owner:10TH RES INST OF CETC

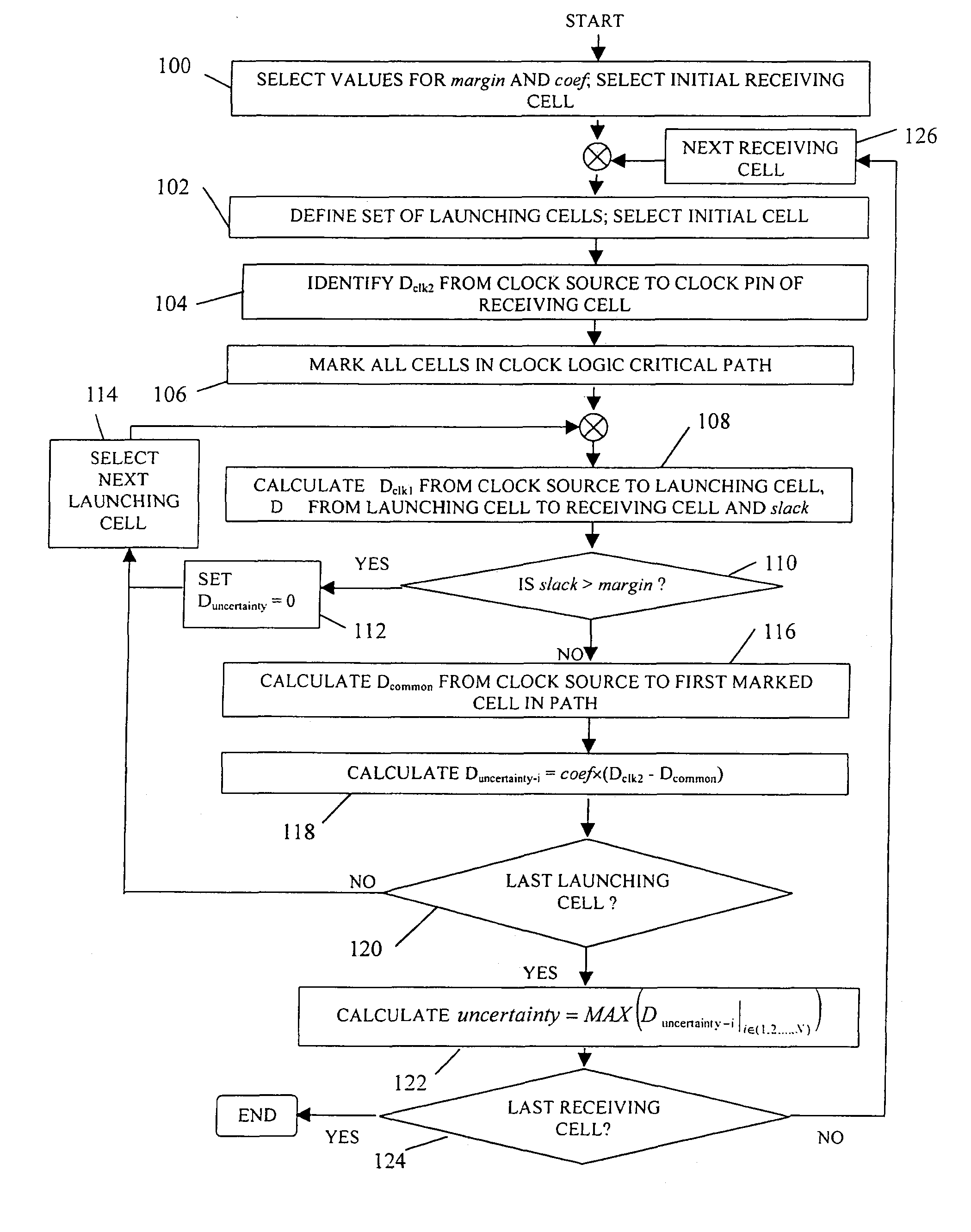

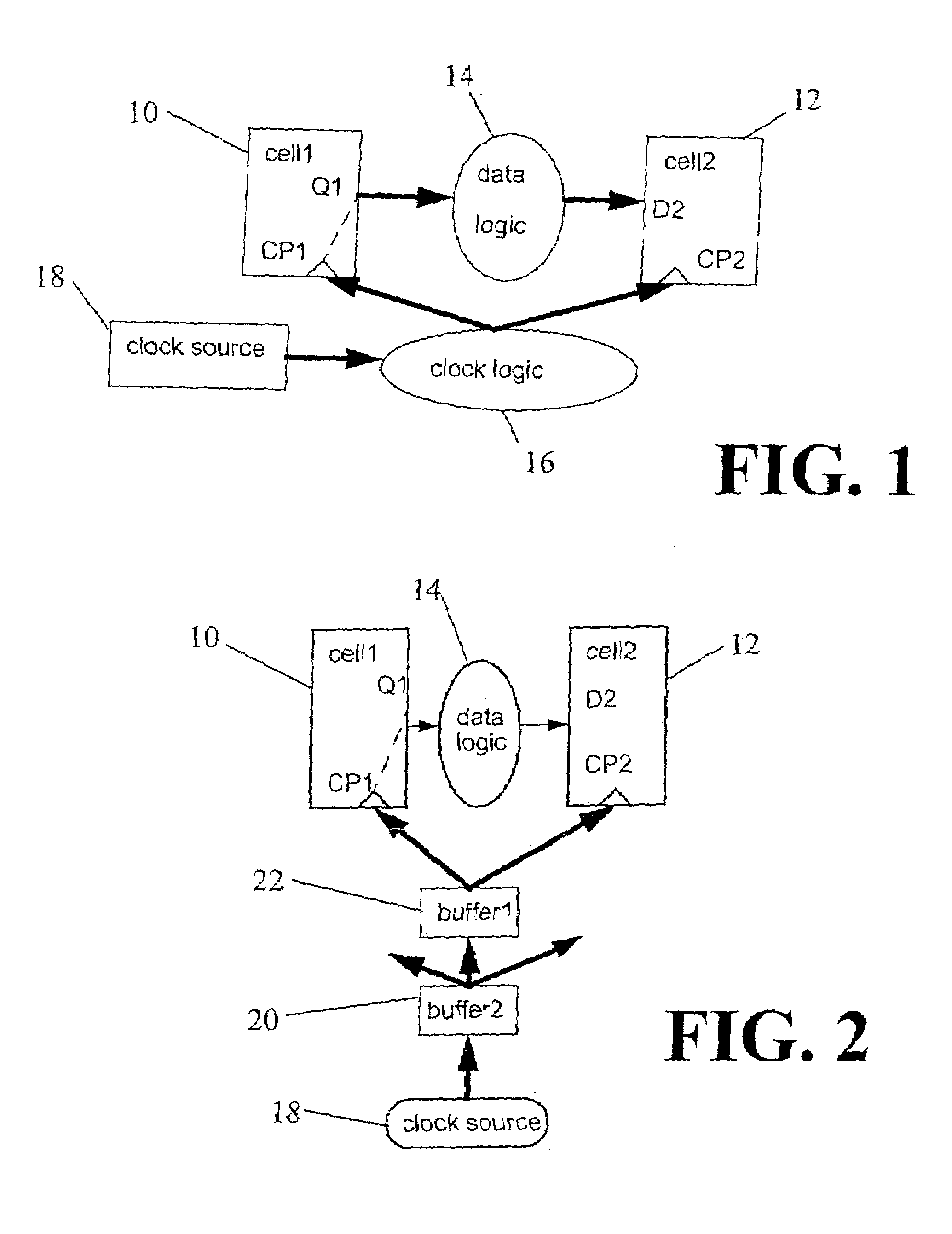

Optimizing IC clock structures by minimizing clock uncertainty

ActiveUS7096442B2Efficient in computation and memory usageInaccurate estimationDetecting faulty computer hardwareElectrical testingCommon pathGravitation

Clock uncertainty between a receiving cell and a launching cell of a net is estimated by back-tracing a first path from the receiving cell toward the clock source and marking each cell having a predetermined characteristic along the first path. A second path from the launching cell toward the clock source is back-traced to a common one of the marked cells having the predetermined characteristic. Clock uncertainty is calculated based on the portion of the first path from the common marked cell having the predetermined characteristic to the receiving cell. Clock uncertainty is calculated if a slack does not exceed a margin value. In one embodiment, a clock net in the form of a tree is optimized by forcing a first buffer to the center of gravity of a plurality of buffers having nets without timing violations to maximize a common path from the root to the forced buffer and minimize the non-common paths from the forced buffer to the leaves, thereby minimizing clock uncertainty.

Owner:BELL SEMICON LLC

Synchronizing global clocks in 3D stacks of integrated circuits by shorting the clock network

ActiveUS8525569B2Reduce skewPulse automatic controlSemiconductor/solid-state device detailsMultiplexerClock tree

There is provided a clock distribution network for synchronizing global clock signals within a 3D chip stack having two or more strata. On each of the two or more strata, the clock distribution network includes a clock grid having a plurality of sectors for providing the global clock signals to various chip locations, a multiple-level buffered clock tree for driving the clock grid and including at least a root and a plurality of clock buffers, and one or more multiplexers for providing the global clock signals to at least a portion of the buffered clock tree. Inputs of at least some of the plurality of clock buffers on each of the two or more strata are shorted together using chip-to-chip interconnects to reduce skewing of the global clock signals with respect to the various chip locations.

Owner:GLOBALFOUNDRIES US INC