Function traversal testing method for high performance SoC FPGA

A traversal test, high-performance technology, applied in the direction of measuring electricity, measuring devices, measuring electrical variables, etc., to achieve the effects of high test efficiency, strong portability, and strong versatility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

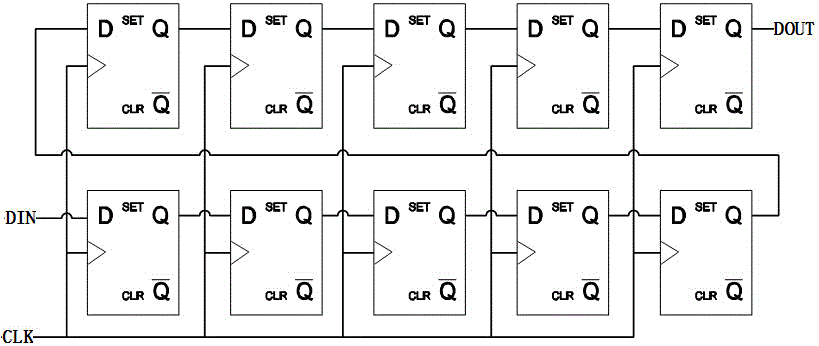

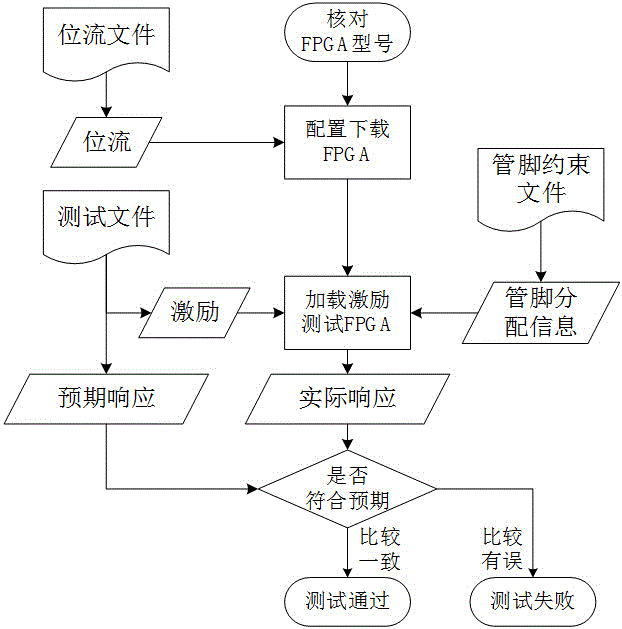

[0029] The implementation block diagram of the internal resource module function traversal test method of SoC FPGA is shown in Figure 1. The specific process is as follows:

[0030] First, design and generate bitstream files and pin constraint files for testing specified resources, and write test files (including test incentives and expected responses) according to the test methods of each resource module;

[0031] After checking the FPGA model, download the bit stream to the FPGA chip to complete the configuration of the FPGA;

[0032] Then, apply excitation signals to each port of FPGA according to the test file and pin constraint file, and read back the response signal of each output port of FPGA at the same time;

[0033] Finally, compare the actual response signal of the FPGA with the expected response signal in the test file. If they are consistent, the test is passed; otherwise, the test fails.

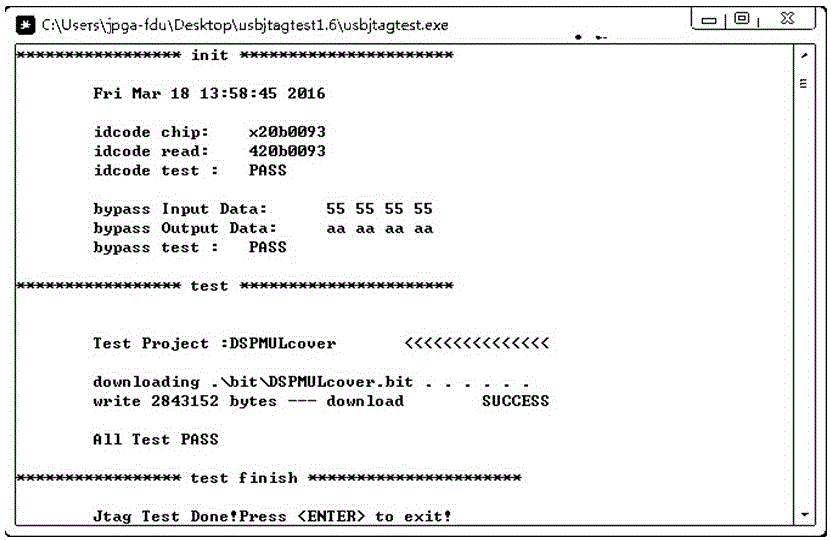

[0034] The result of software operation can be a graphical interface or ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com