Patents

Literature

1424 results about "Asic technology" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

An ASIC (application-specific integrated circuit) is a microchip designed for a special application, such as a particular kind of transmission protocol or a hand-held computer. You might contrast it with general integrated circuits, such as the microprocessor and the random access memory chips in your PC.

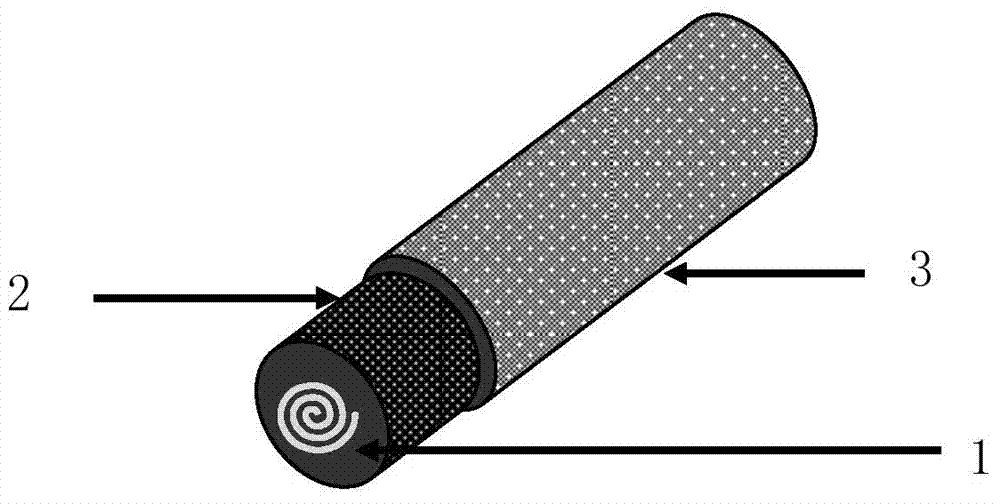

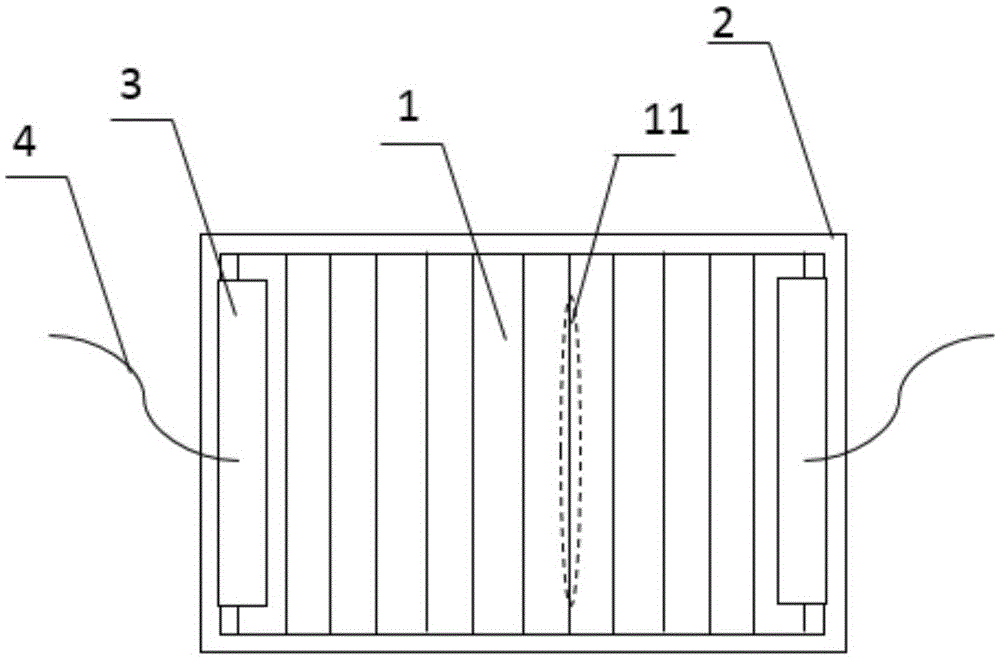

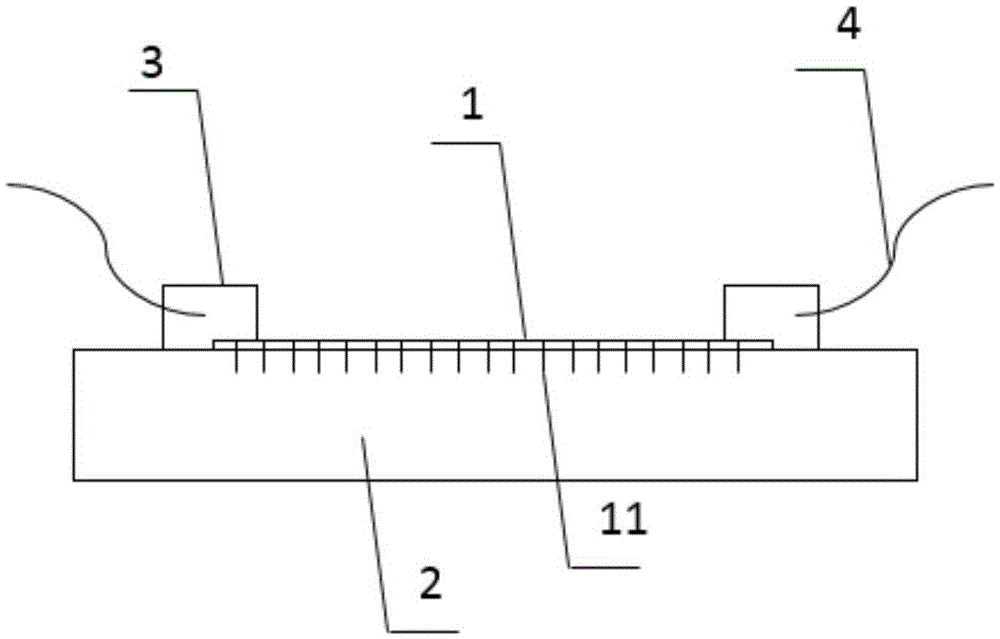

Full-carbon coaxial line and manufacturing method thereof

InactiveCN103943925AStable structureFast heat conductionCarbon-silicon compound conductorsWaveguidesElectrical conductorCoaxial line

The invention discloses a full-carbon coaxial line and a manufacturing method of the full-carbon coaxial line, and belongs to the technical field of integrated circuits. Graphene serves as a monatomic layer thickness, is coiled into a cylinder and form an inner conductor of the coaxial line with a small radius (can be as small as the nm level), and the inner conductor of the coaxial line transfers currents. Meanwhile, a signal layer or multiple layers of graphene serve(s) as an outer conductor of the coaxial line to form a boundary of electromagnetic waves in a space, and graphite oxide serves as medium materials between the inner conductor and the outer conductor to limit and guide oriented transmission of electromagnetic wave energy. The coaxial line is quite small in size and applicable to radio-frequency and microwave integrated circuits.

Owner:PEKING UNIV

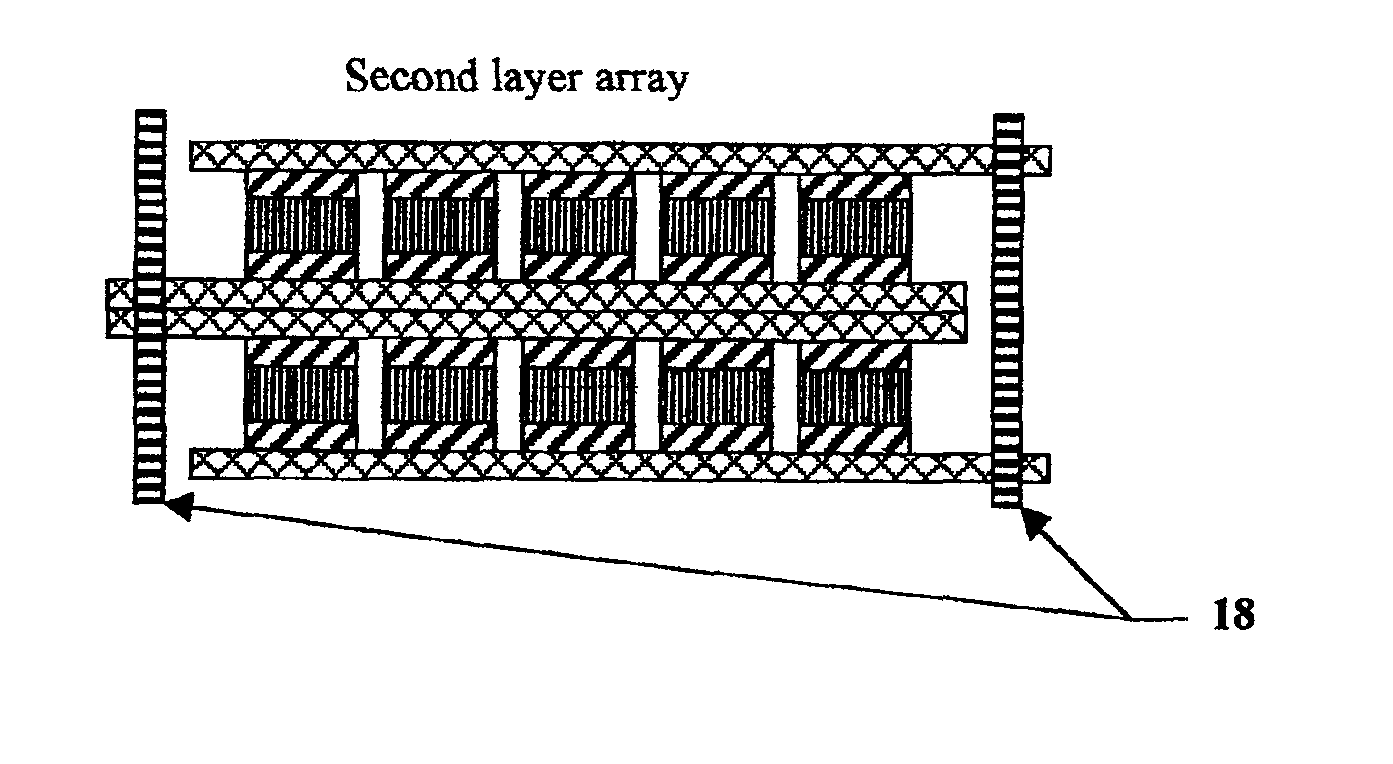

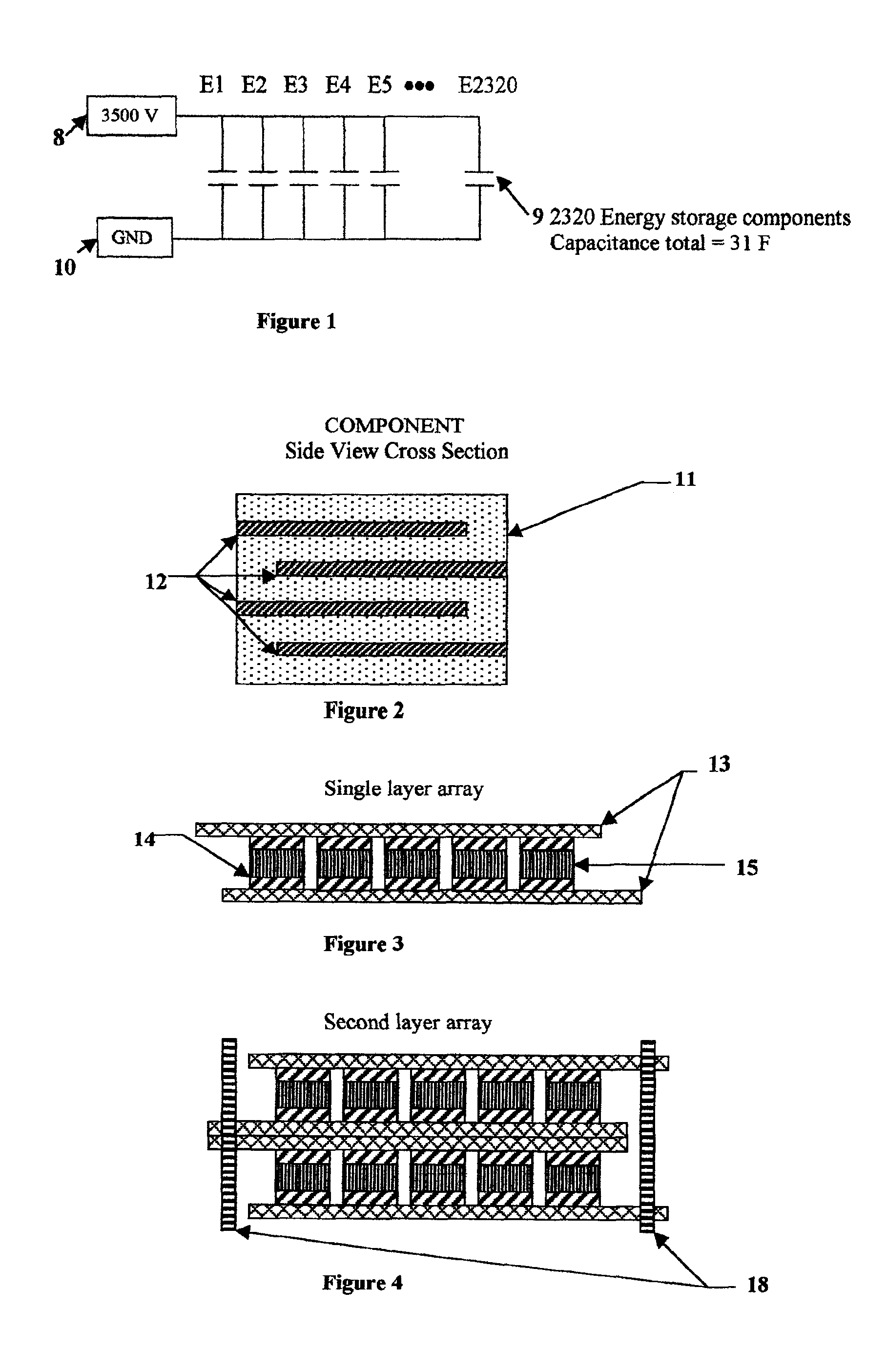

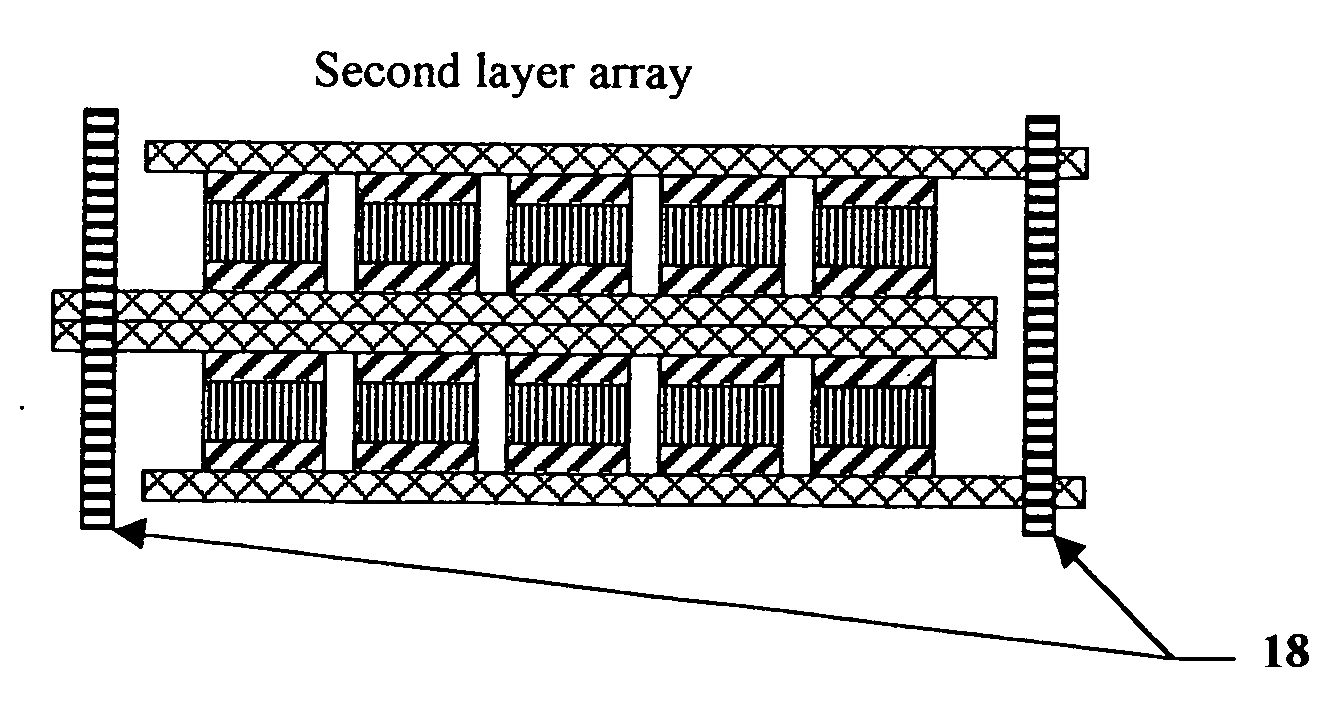

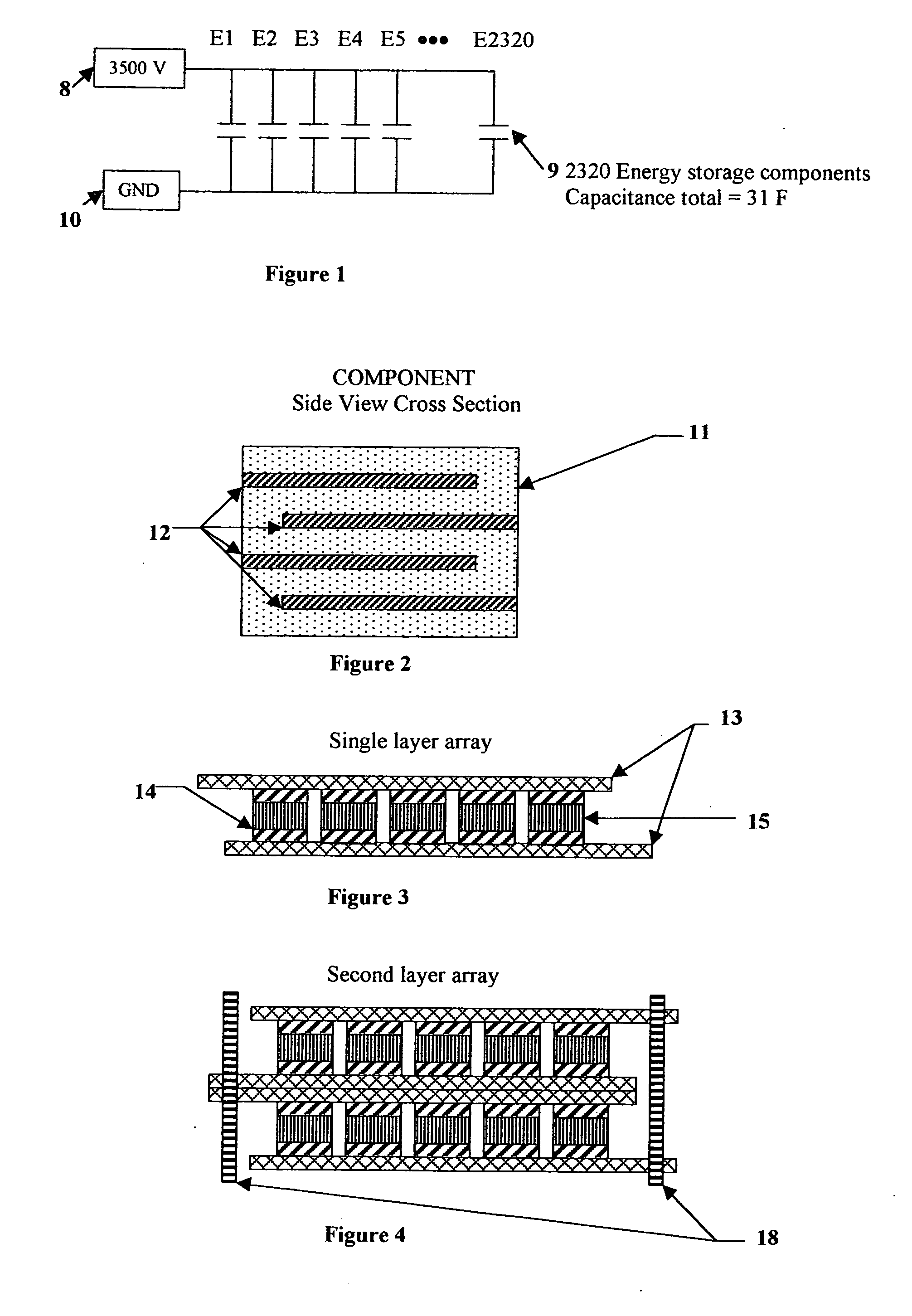

Electrical-energy-storage unit (EESU) utilizing ceramic and integrated-circuit technologies for replacement of electrochemical batteries

InactiveUS7033406B2Reduce sinteringLowering hot-isostatic-pressing temperatureElectrical storage systemFixed capacitor electrodesBarium titanatePermittivity

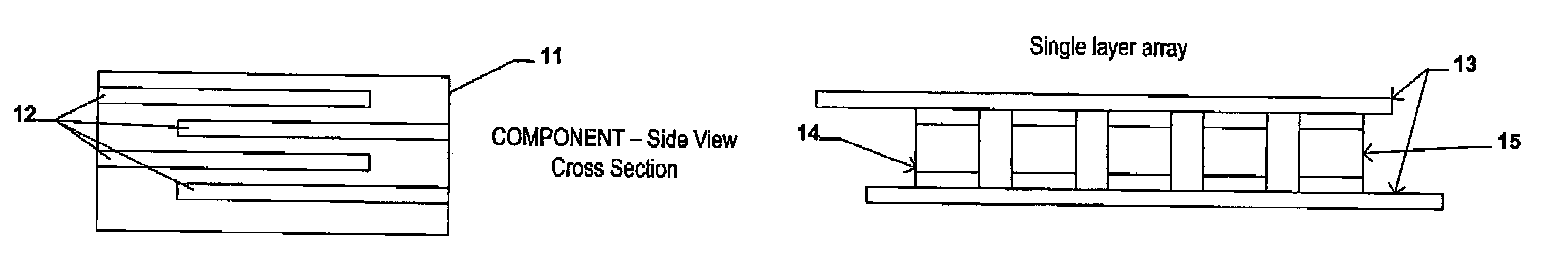

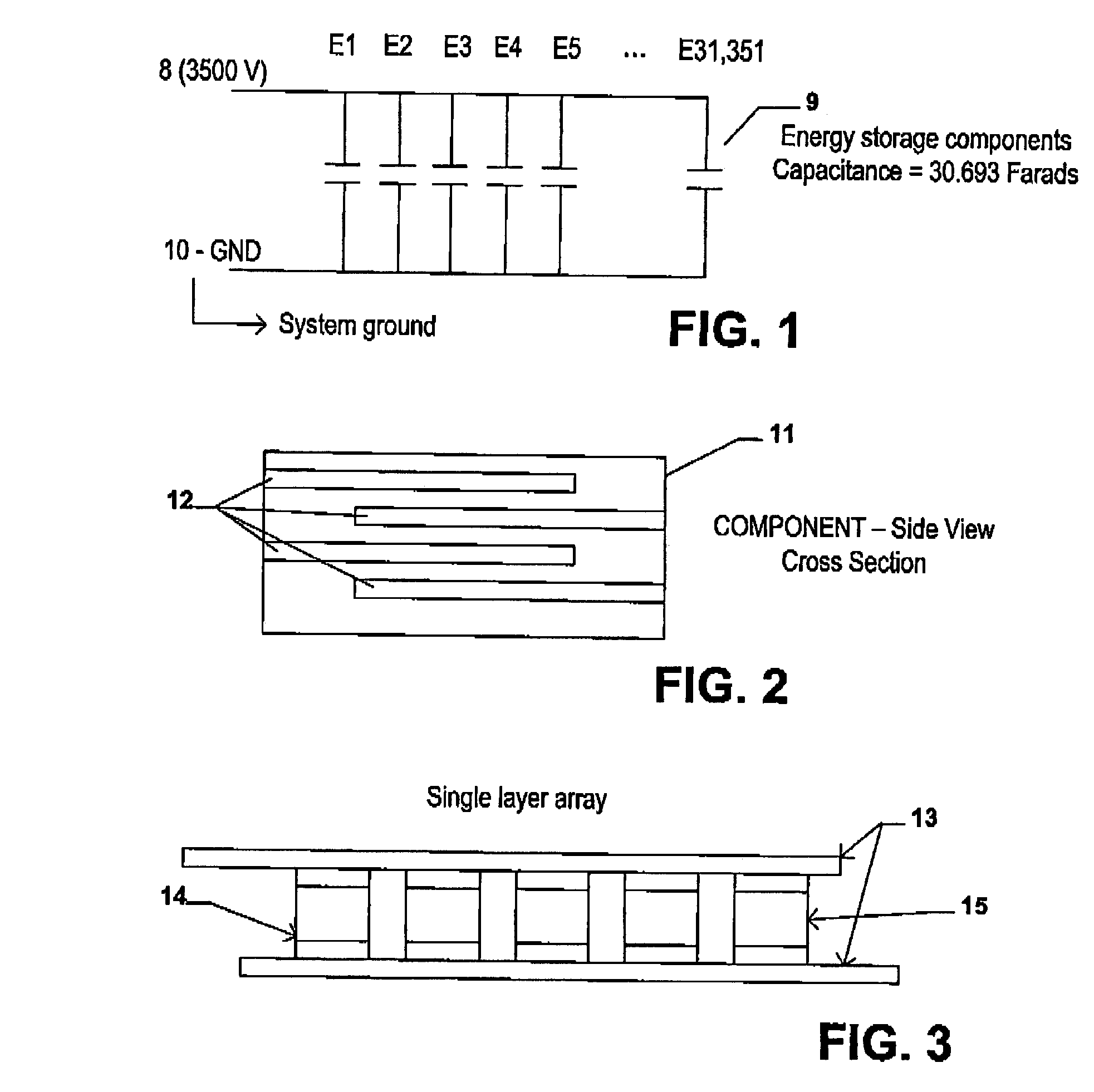

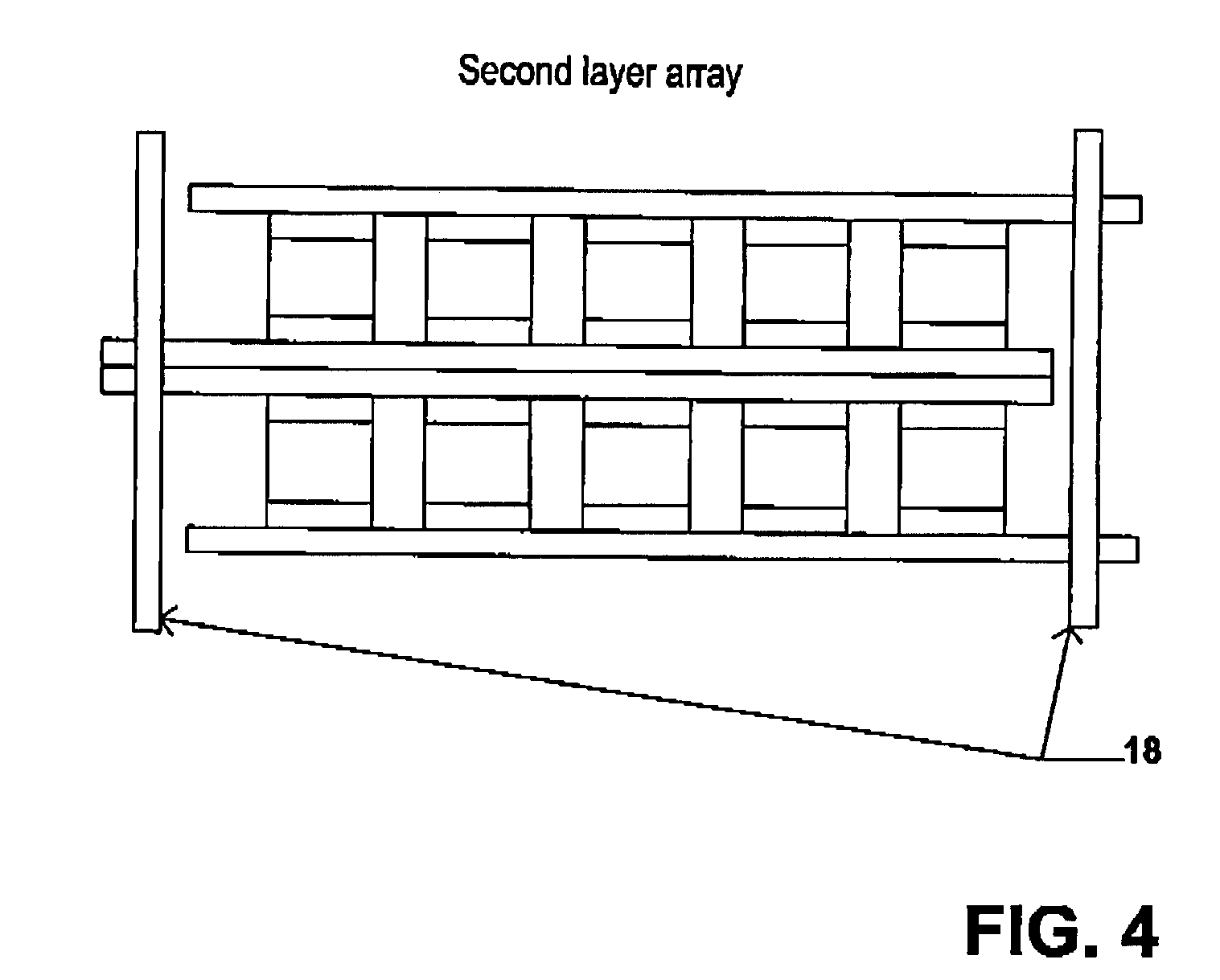

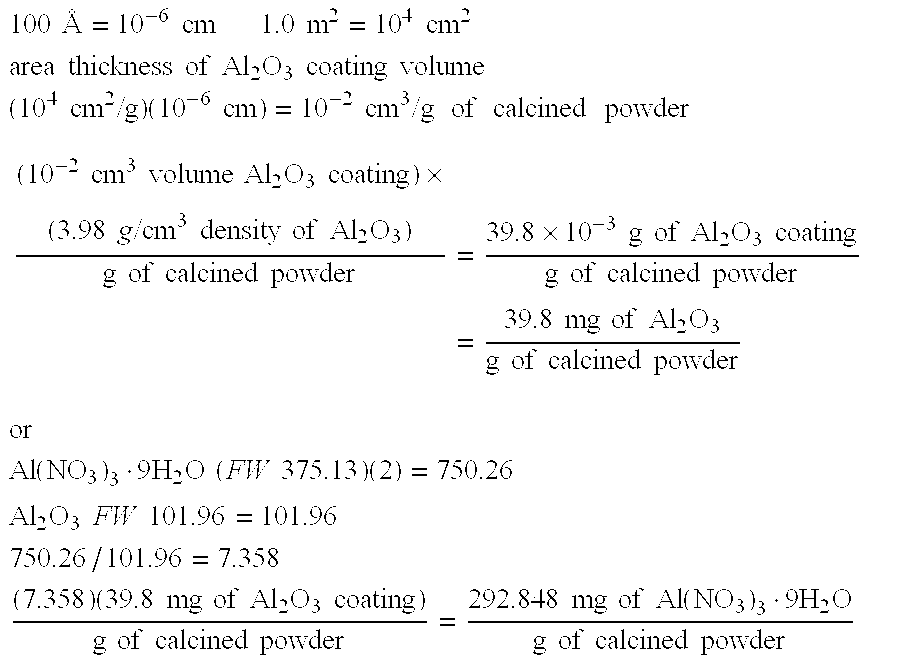

An electrical-energy-storage unit (EESU) has as a basis material a high-permittivity composition-modified barium titanate ceramic powder. This powder is double coated with the first coating being aluminum oxide and the second coating calcium magnesium aluminosilicate glass. The components of the EESU are manufactured with the use of classical ceramic fabrication techniques which include screen printing alternating multilayers of nickel electrodes and high-permittivitiy composition-modified barium titanate powder, sintering to a closed-pore porous body, followed by hot-isostatic pressing to a void-free body. The components are configured into a multilayer array with the use of a solder-bump technique as the enabling technology so as to provide a parallel configuration of components that has the capability to store electrical energy in the range of 52 kW·h. The total weight of an EESU with this range of electrical energy storage is about 336 pounds.

Owner:EESTOR

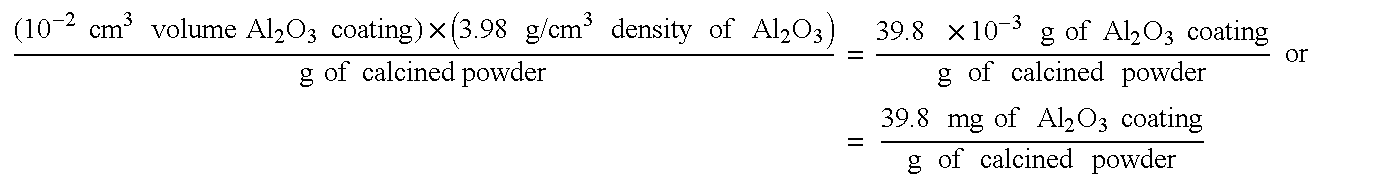

Utilization of poly(ethylene terephthalate) plastic and composition-modified barium titanate powders in a matrix that allows polarization and the use of integrated-circuit technologies for the production of lightweight ultrahigh electrical energy storage units (EESU)

InactiveUS7466536B1Low costLower sintering temperatureCell electrodesFixed capacitor dielectricManufacturing technologyBarium titanate

An electrical-energy-storage unit (EESU) has as a basis material a high-permittivity composition-modified barium titanate ceramic powder. This powder is single coated with aluminum oxide and then immersed in a matrix of poly(ethylene terephthalate) (PET) plastic for use in screen-printing systems. The ink that is used to process the powders via screen-printing is based on a nitrocellulose resin that provide a binder burnout, sintering, and hot isostatic pressing temperatures that are allowed by the PET plastic. These lower temperatures that are in the range of 40° C. to 150° C. also allows aluminum powder to be used for the electrode material. The components of the EESU are manufactured with the use of conventional ceramic and plastic fabrication techniques which include screen printing alternating multilayers of aluminum electrodes and high-permittivity composition-modified barium titanate powder, sintering to a closed-pore porous body, followed by hot-isostatic pressing to a void-free body. The 31,351 components are configured into a multilayer array with the use of a solder-bump technique as the enabling technology so as to provide a parallel configuration of components that has the capability to store at least 52.22 kW·h of electrical energy. The total weight of an EESU with this amount of electrical energy storage is 281.56 pounds including the box, connectors, and associated hardware.

Owner:EESTOR

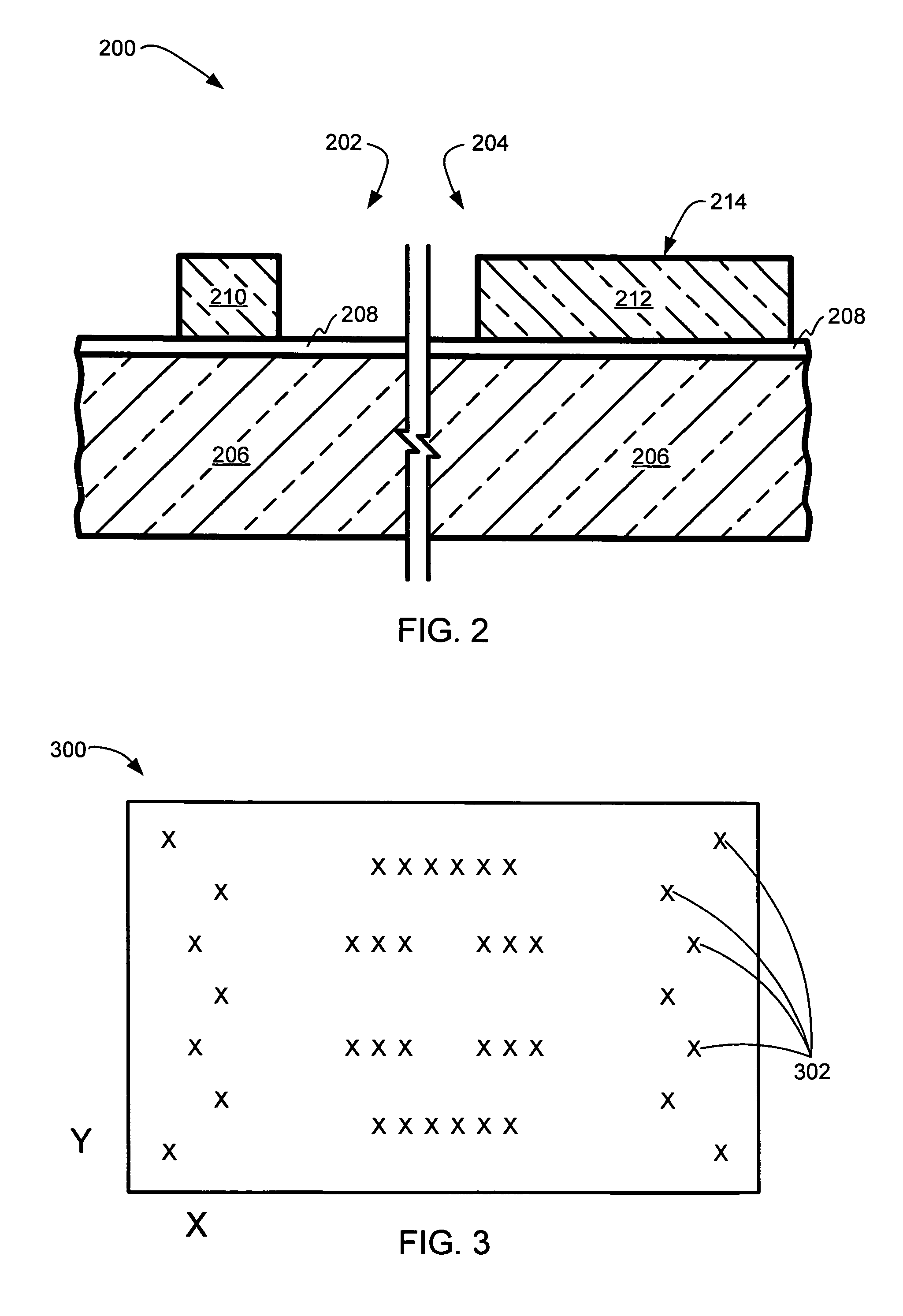

In-line voltage contrast determination of tunnel oxide weakness in integrated circuit technology development

InactiveUS7101722B1Semiconductor/solid-state device testing/measurementRead-only memoriesTechnology developmentCell region

A method for determination of tunnel oxide weakness is provided. A tunnel oxide layer is formed on a semiconductor wafer. At least one poly gate is formed on the tunnel oxide layer in a flash memory region of the semiconductor wafer. At least one poly island, which is substantially larger than the poly gate, is formed on the tunnel oxide layer in a voltage contrast cell region of the semiconductor wafer. The poly island and the tunnel oxide layer therebeneath form a voltage contrast tunnel oxide cell. A voltage contrast measurement is performed on the voltage contrast tunnel oxide cell. The voltage contrast measurement is then compared with prior such voltage contrast measurements on other such voltage contrast tunnel oxide cells. The tunnel oxide weakness of the tunnel oxide layer is then determined from the voltage contrast measurement comparisons.

Owner:ADVANCED MICRO DEVICES INC

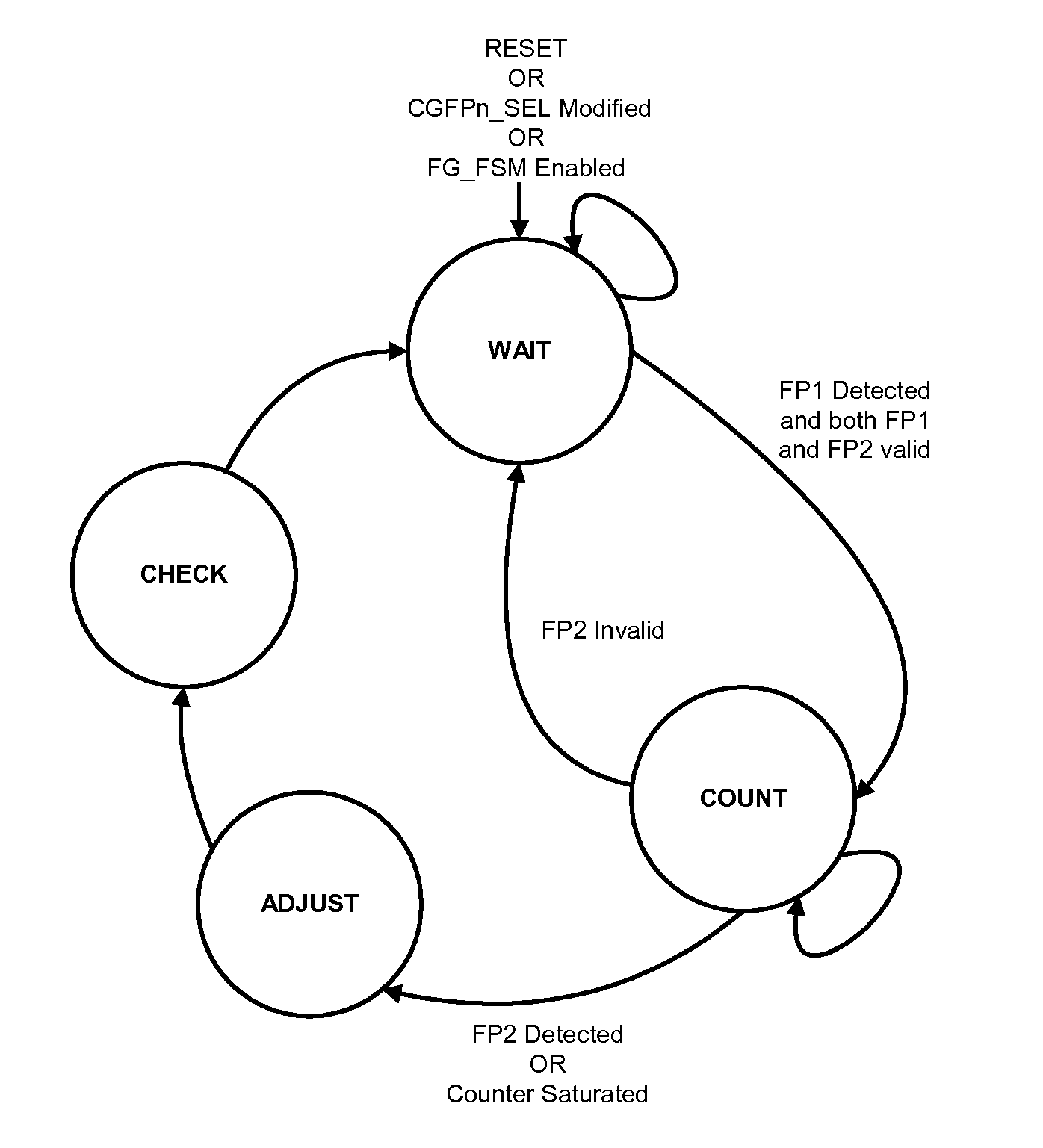

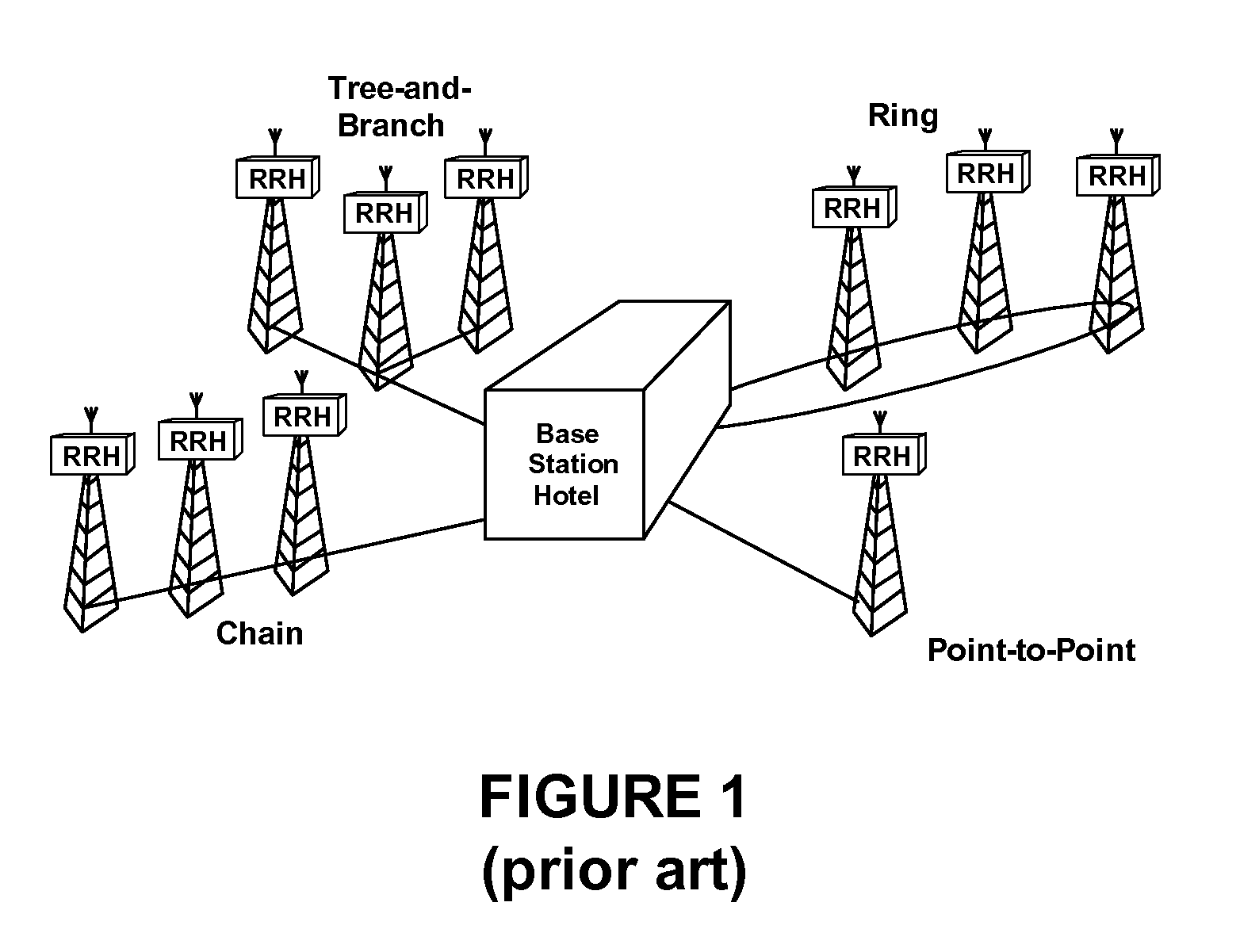

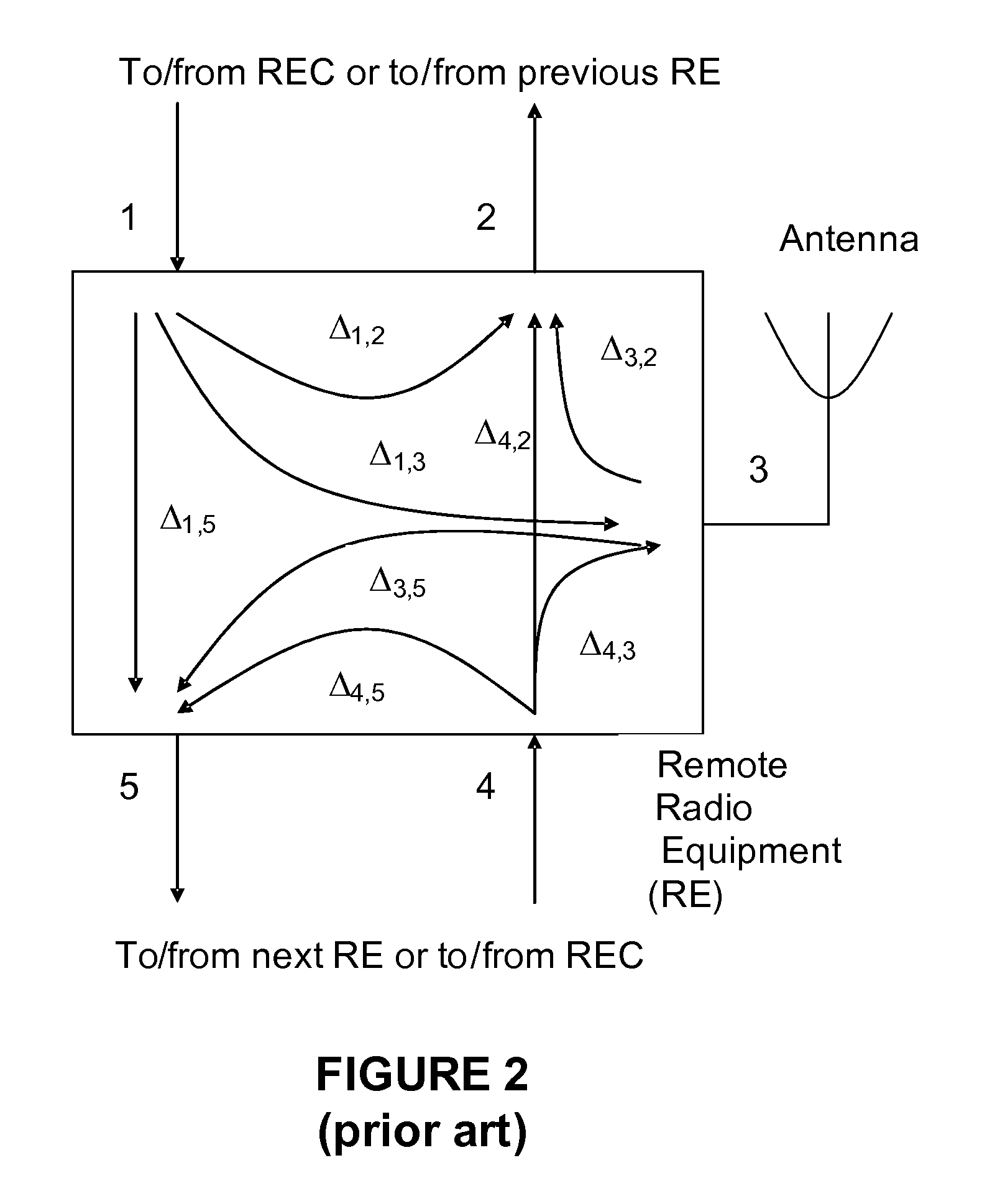

Delay measurements and calibration methods and apparatus for distributed wireless systems

InactiveUS7940667B1High delay measurement accuracyReduce significant maintenance costSynchronisation arrangementError preventionDiversity schemeComputer science

Delay measurement and delay calibration methods and apparatus are described for use within distributed wireless base stations employing a remote radio head topology. The methods and apparatus are usable in any system that requires accurate delay measurement and / or constant delay through an electronic device. The methods and apparatus for measuring delay embody a highly accurate distributed delay measurement architecture that handles multiple delay paths within distributed wireless base stations employing a remote radio head topology. The method and apparatus are amenable to implementation with current integrated circuit technology. The methods and apparatus for calibrating electronic delay within distributed base stations employing a remote radio head topology are useful for implementing distributed wireless base stations where transmit diversity is desired. Using the methods disclosed herein, delay within a distributed wireless base station can be measured and calibrated to achieve very deterministic delay characteristics at the system level.

Owner:MICROSEMI SOLUTIONS (US) INC

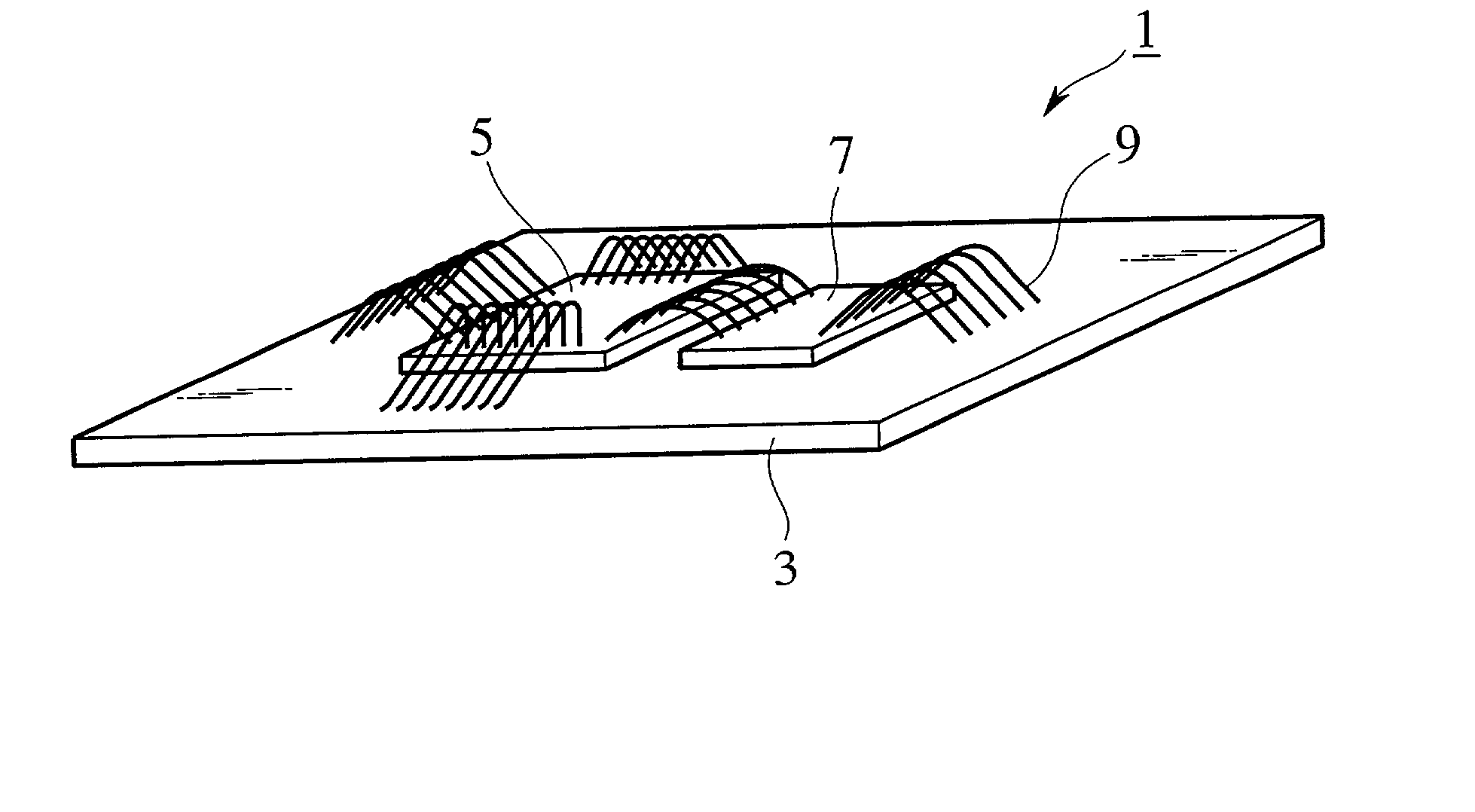

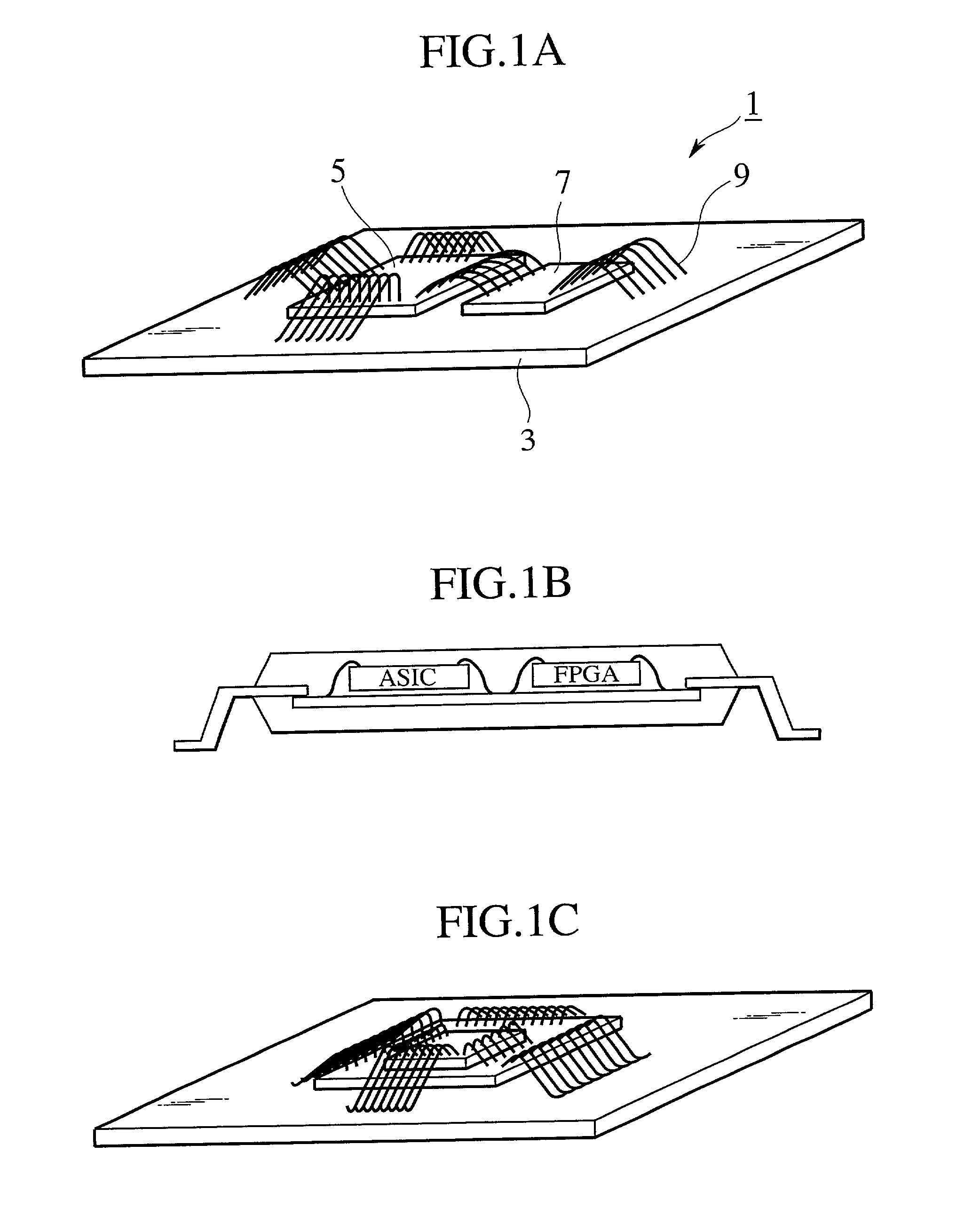

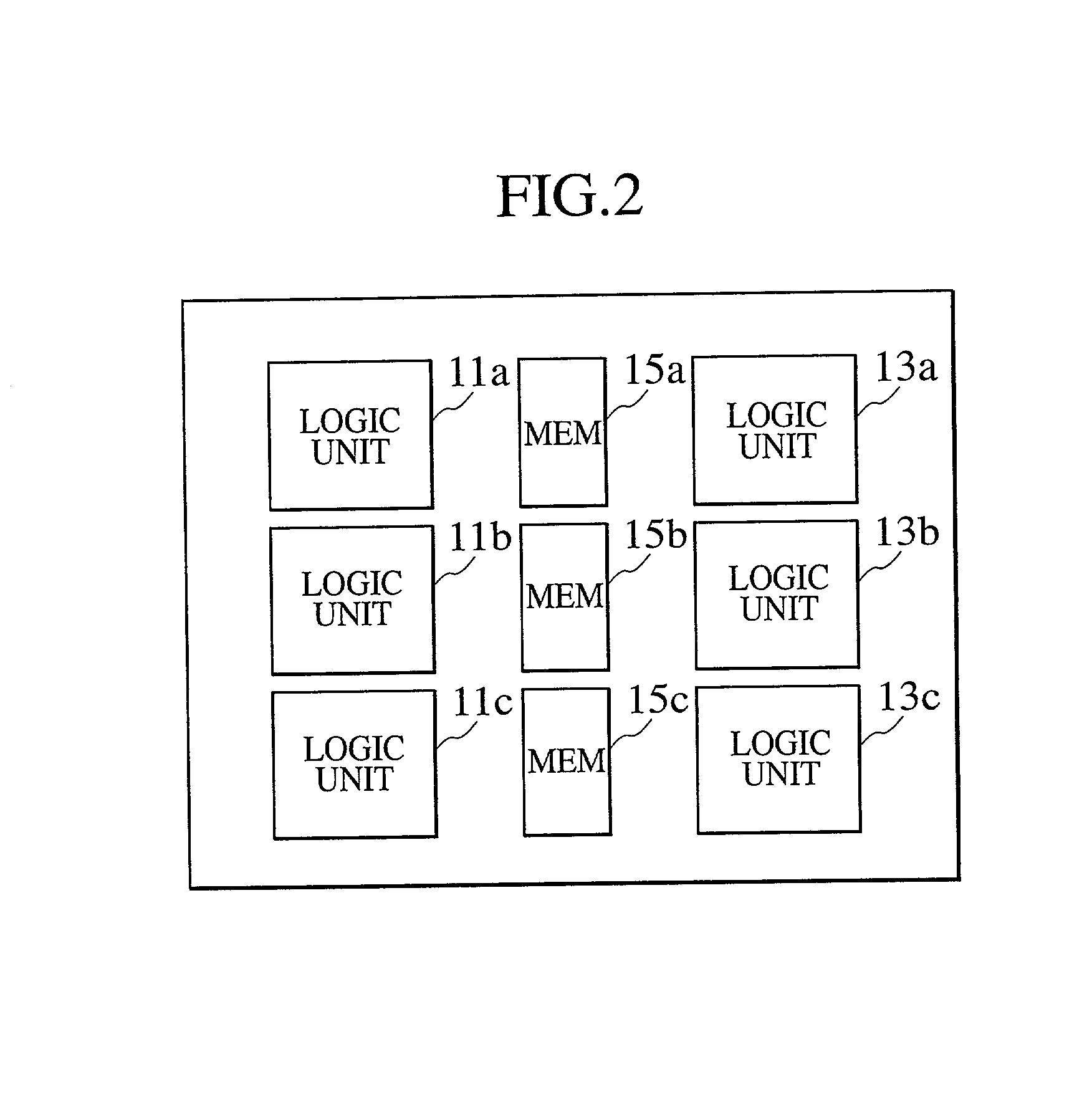

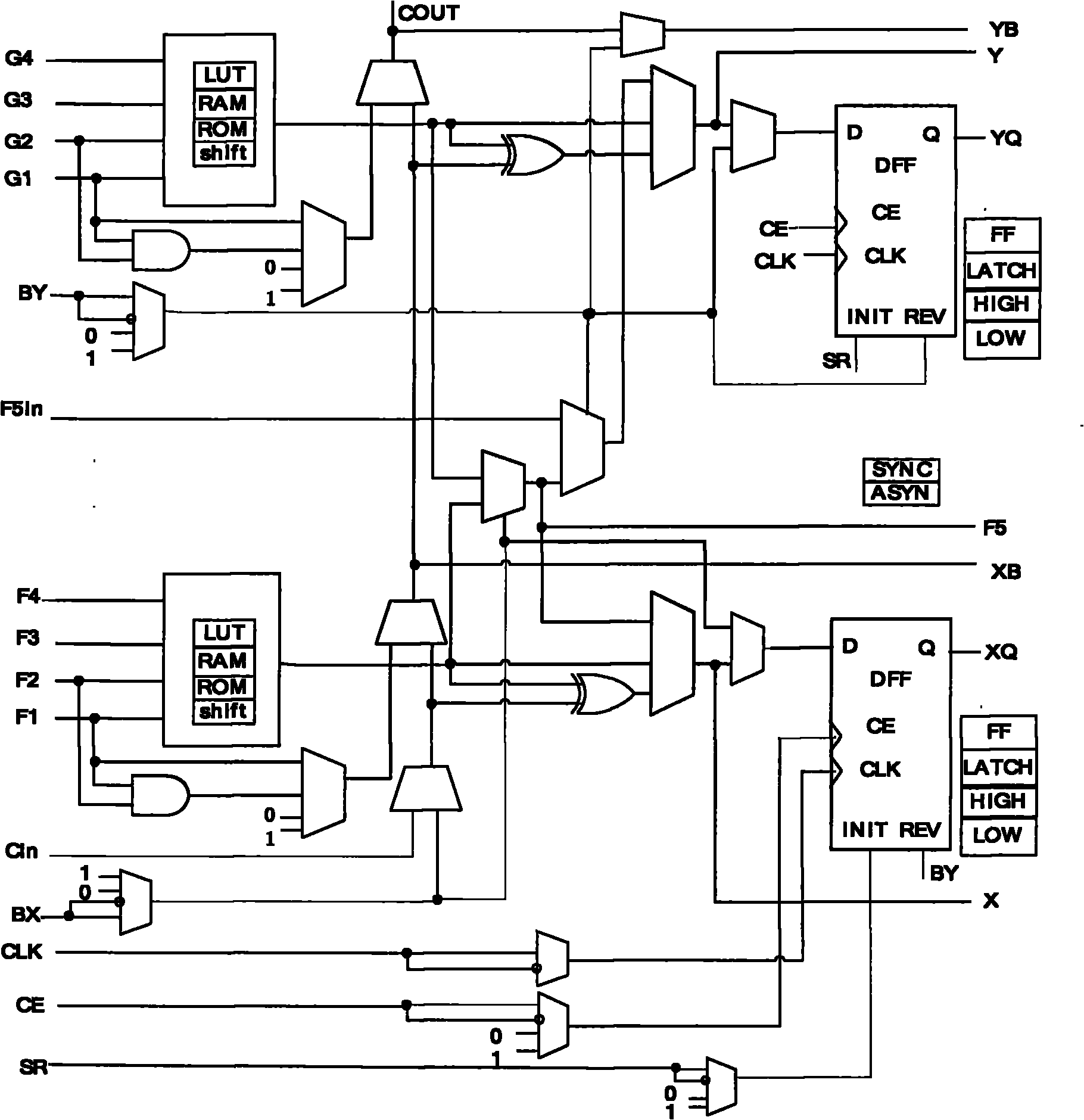

Electronic circuit device and hybrid integrated circuit with an asic and an FPGA

InactiveUS20020066956A1Semiconductor/solid-state device detailsSolid-state devicesControl signalSemiconductor chip

An improved hybrid integrated circuit is provided in order that the specification can quickly be modified and adjusted when required without need for preparing a new mask and without need for compromising the performance of the hybrid integrated circuit. The hybrid integrated circuit comprises: a common substrate on which an electrode pattern is formed; a first monolithic semiconductor chip designed by the use of an ASIC technology and mounted on the common substrate; a second monolithic semiconductor chip designed by the use of an FPGA technology and mounted on the common substrate; and external terminals provided for the common substrate; and an insulating material encapsulating the first monolithic semiconductor chip and the second monolithic semiconductor chip, wherein the second monolithic semiconductor chip is provided with a storage element which is rewritable by means of a control signal given through the external terminal in order to store circuit configuration data with which internal connections of the second monolithic semiconductor chip are modified to form a hardware configuration within the second monolithic semiconductor chip corresponding to a predetermined operational specification, and wherein the first monolithic semiconductor chip and the second monolithic semiconductor chip cooperate with each other by exchanging signals through the electrode pattern of the common substrate in order to implement the predetermined operational specification.

Owner:KK TOSHIBA

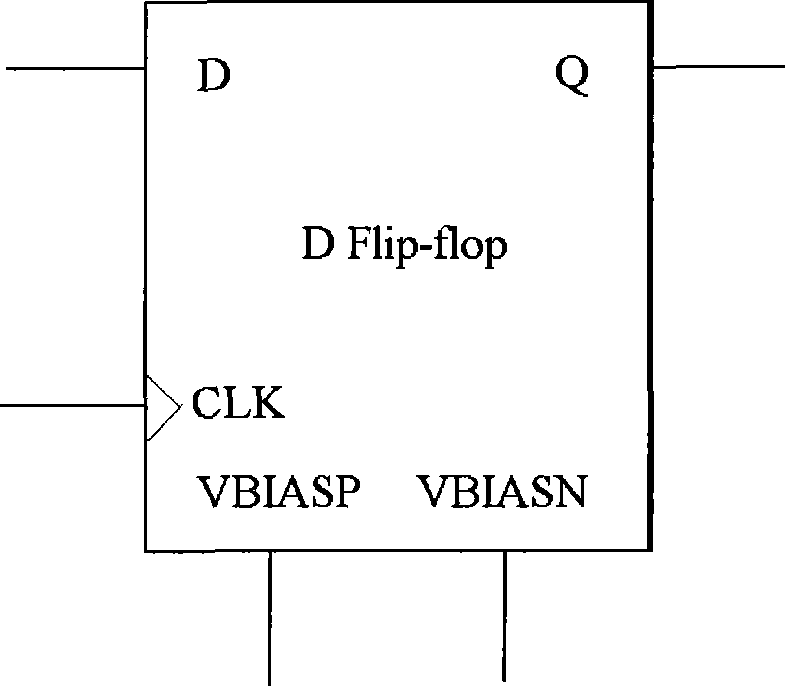

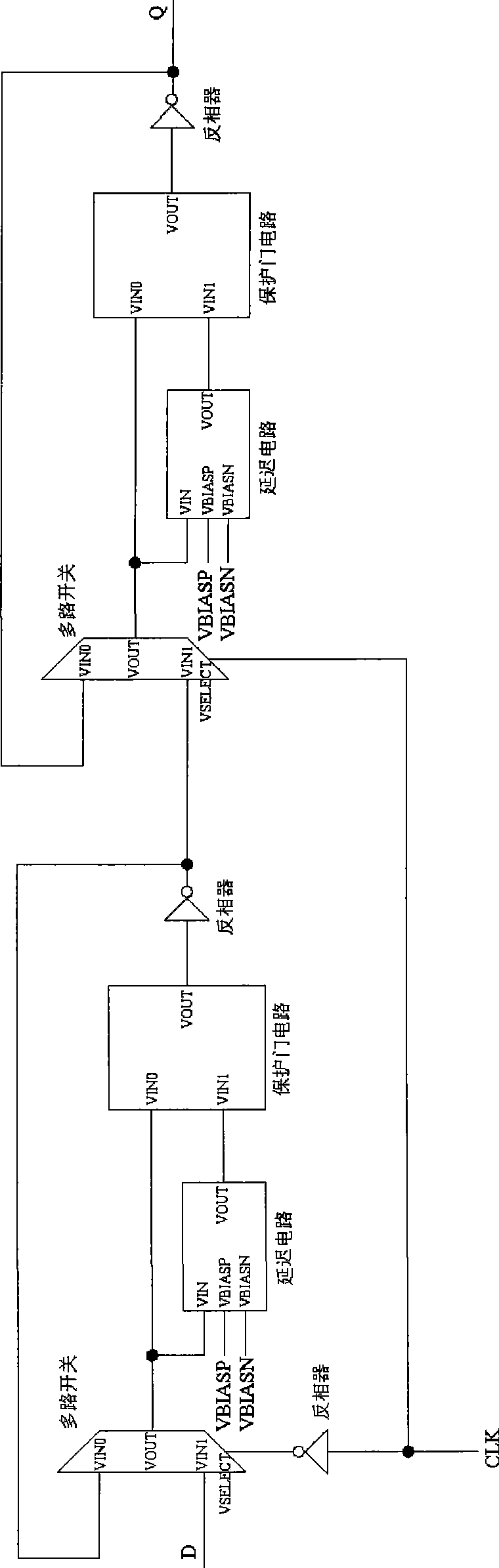

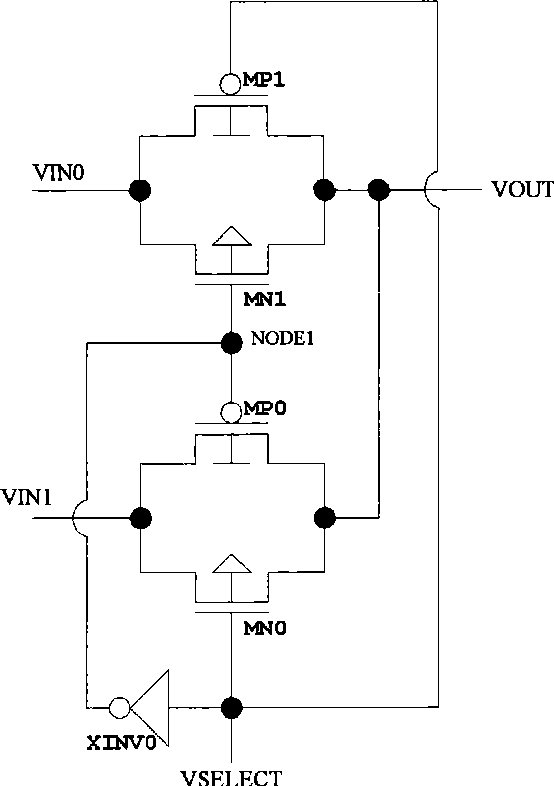

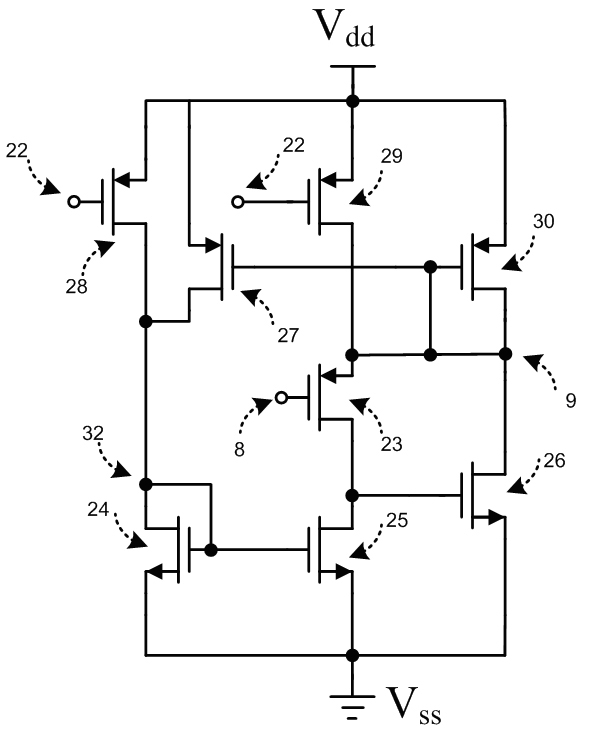

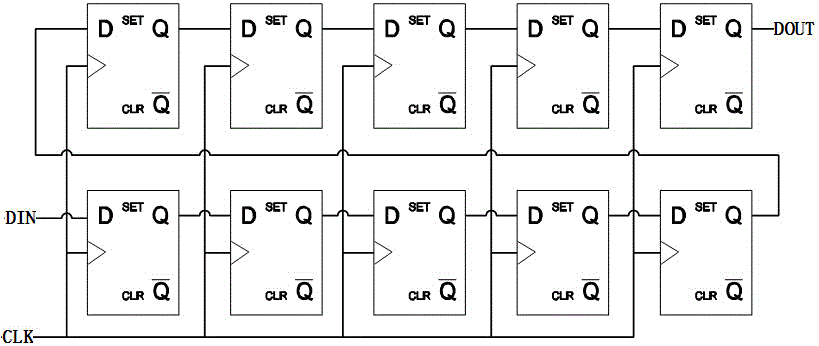

Single particle upset and single particle transient pulse resisiting D trigger

InactiveCN101499788ASingle event upsetCapable of single-event transient pulse performanceSingle output arrangementsElectronic switchingMultiway switchingRadiation resistance

The invention relates to a D trigger used for single particle upsetting resistance and single particle transient pulse in the technical filed of an integrated circuit, comprising two multichannel switches, two delay circuits, two protecting gate circuits and three inverters; wherein, the multichannel switches are used for forming a feedback loop for latching data; the delay circuits are used for generating signals in delay modes; the protecting gate circuits are used for filtering voltage transient fluctuation of the input signals; in the feedback loop of the D trigger, data input signal D and the delayed mode thereof enter the protecting gate circuit; and the output signals of the protecting gate circuit filter the delayed voltage transient fluctuation of the data input signal D and the width of the voltage transient fluctuation is not wider than the delay of the delay circuit. The invention can be applied to application occasions needing higher radiation resistance, leads the single particle upsetting resistance and single particle transient pulse performance of D trigger to reach the same level as a time sampling D trigger; and simultaneously, the increasing of the unit area is less than that of the time sampling D trigger and the working speed is superior to that of the time sampling D trigger.

Owner:SHANGHAI JIAO TONG UNIV

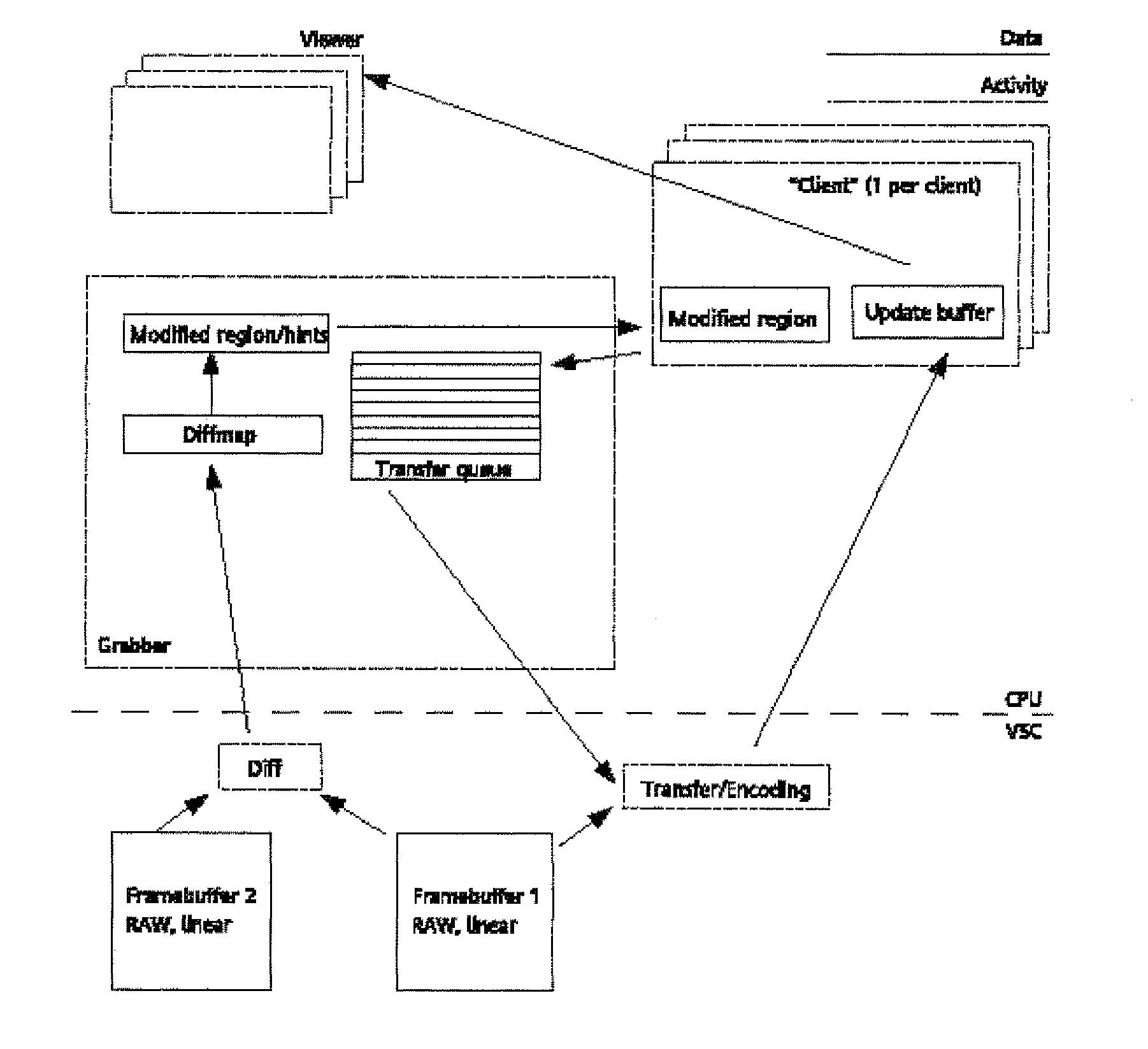

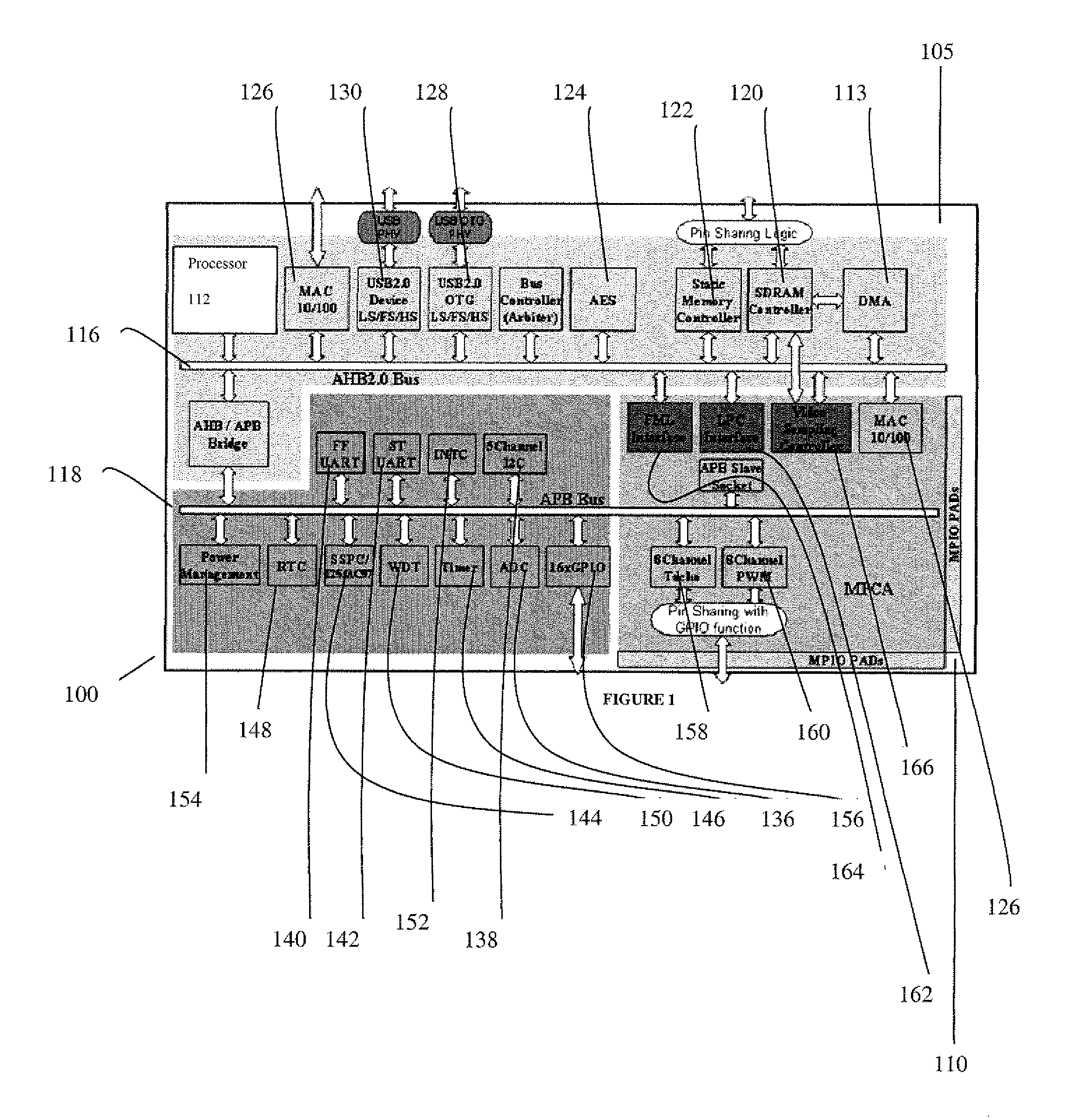

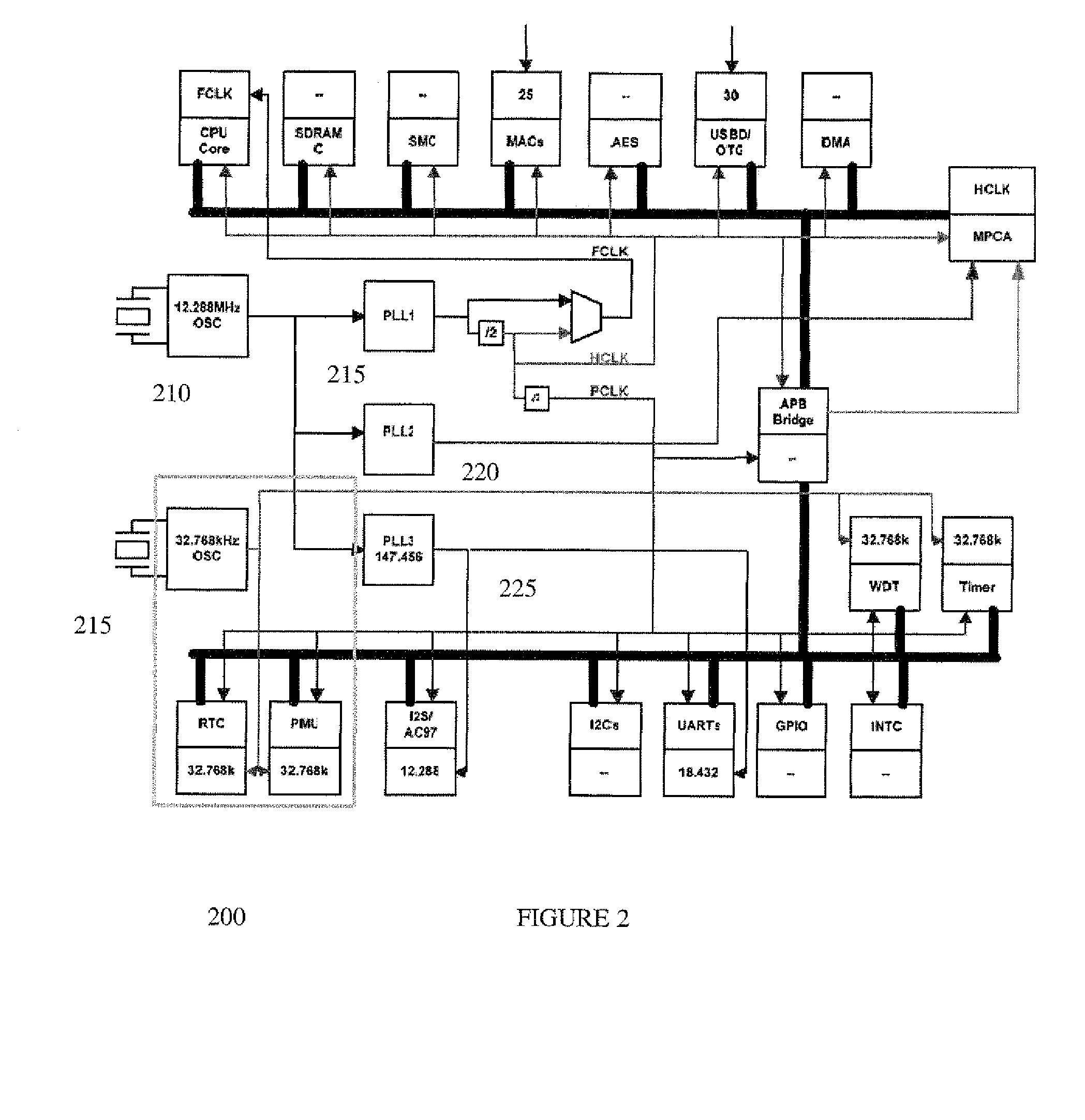

Architecture And Method For Remote Platform Control Management

ActiveUS20090013056A1Easy to customizeMinimizes server downtimeCharacter and pattern recognitionCathode-ray tube indicatorsMass storageUSB

An integrated circuit is a baseboard management controller that is a fully integrated system-on-a-chip microprocessor incorporating function blocks and interfaces that provide remote management solution. The integrated circuit uses a microprocessor, a media co-processor to accelerate video processing, and a set of system and peripheral functions that are useful in a variety of remote management applications. It further includes an integrated USB high-speed device and an OTG interface to support keyboard, mouse and mass storage emulation without additional external components, and two integrated MII LAN interfaces and one FSB interface, a memory controller to support a variety of static and dynamic memory components, an encryption controller to ensure secure remote management sessions and IPMI2.0-compliant BMC interfaces. The integrated circuit is based on structured ASIC technology, which enables easy customization of function blocks according to customer demands or new industry standards.

Owner:RARITAN AMERICA

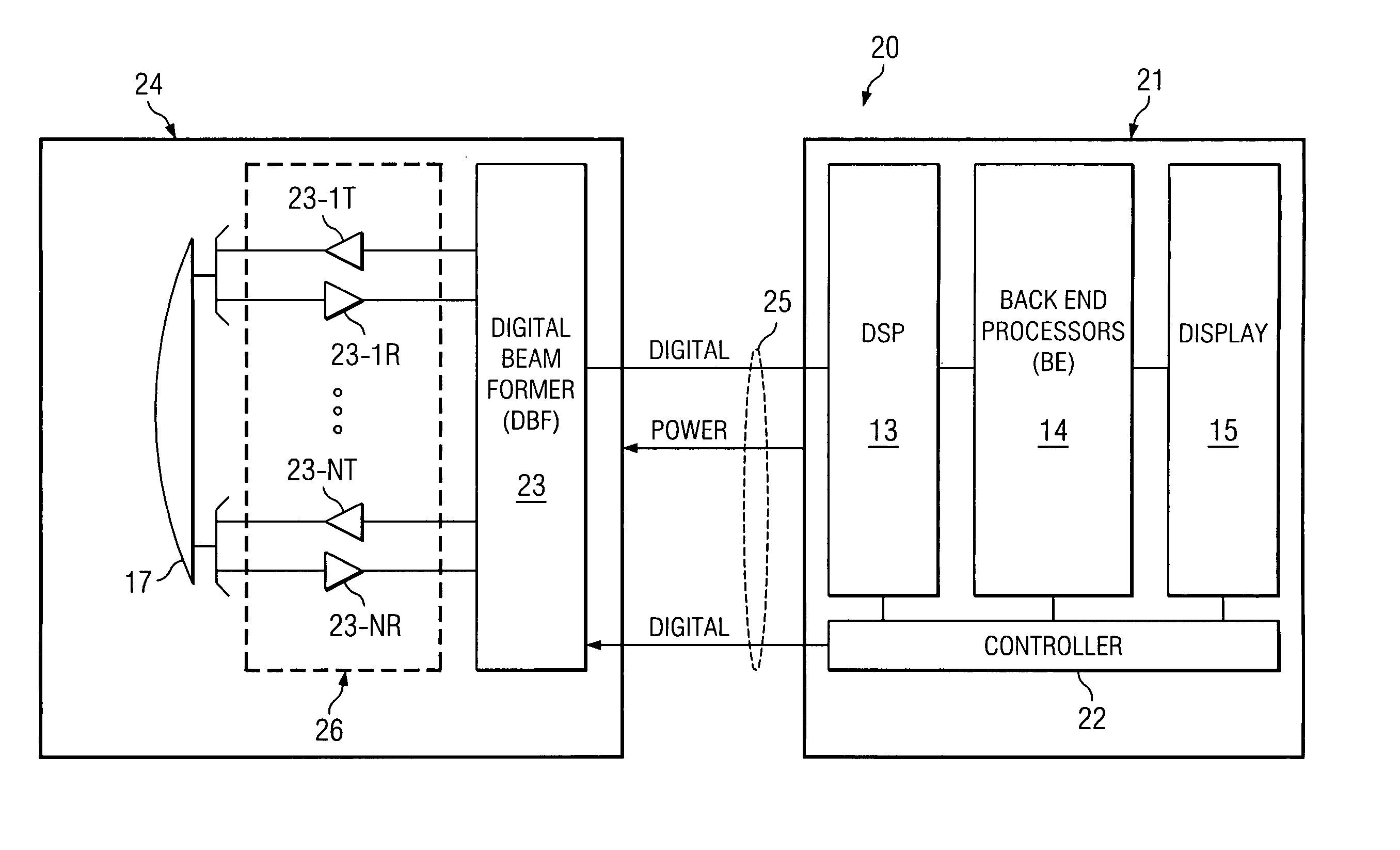

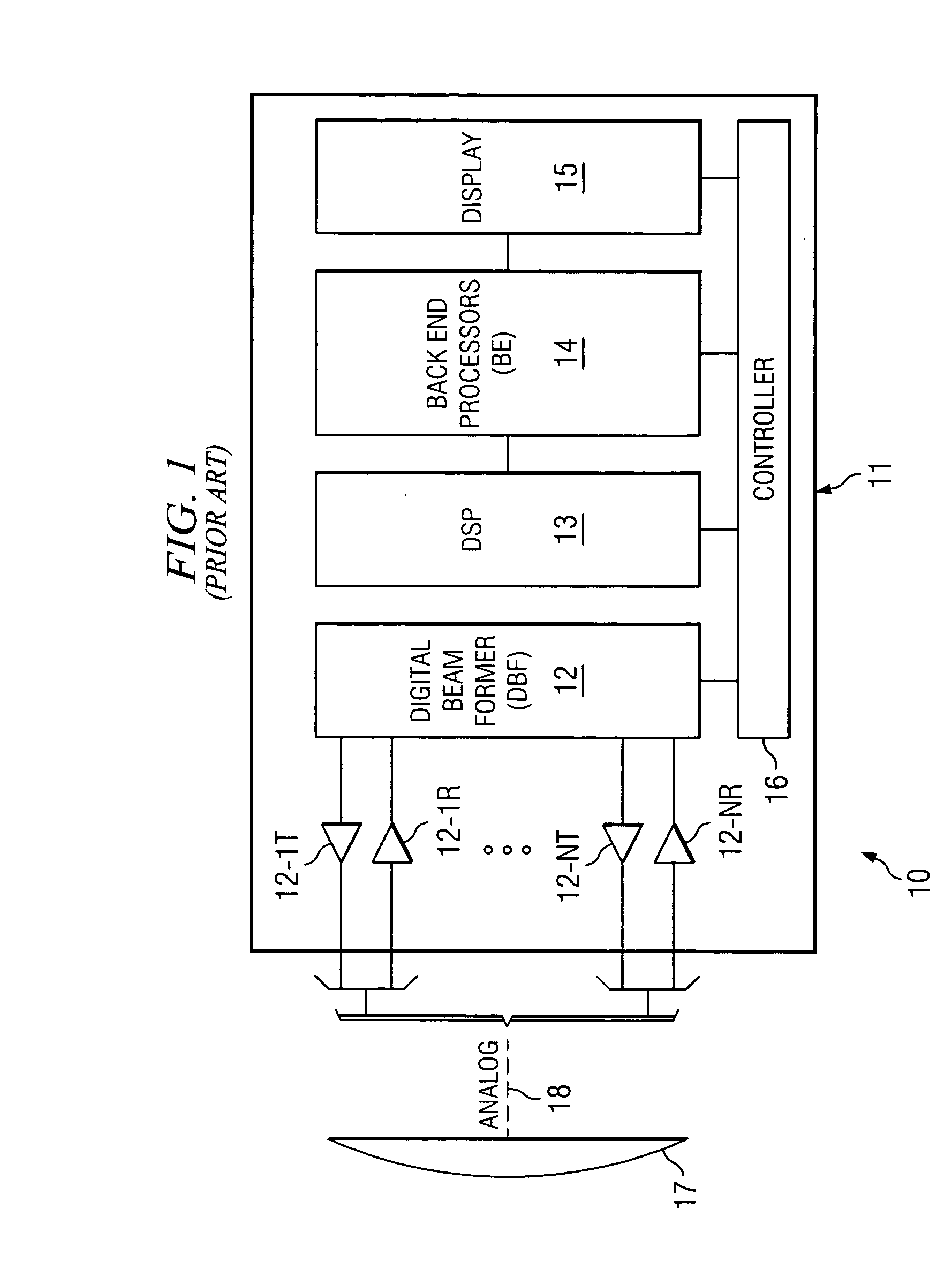

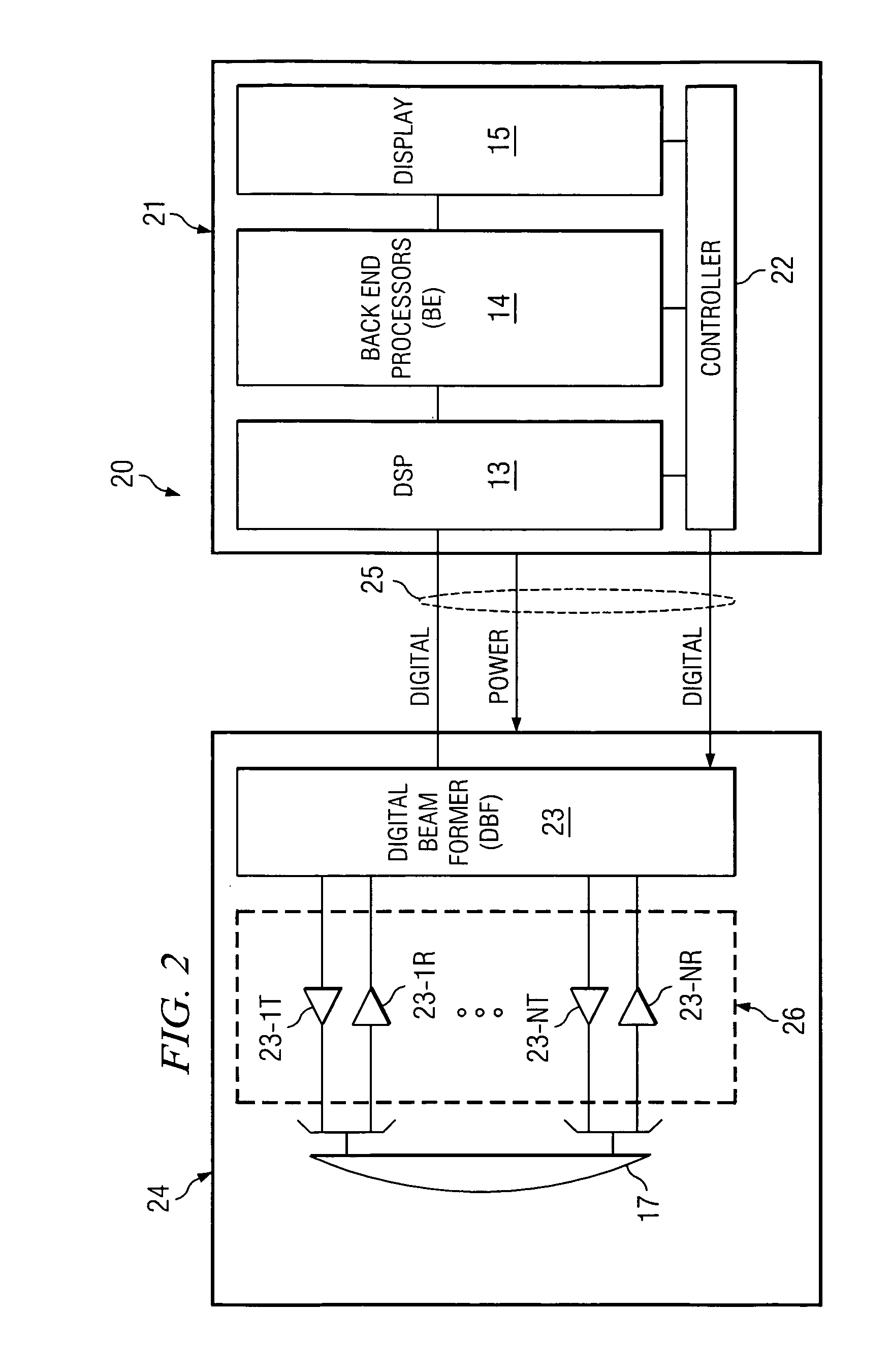

Ultrasonic transducer having a thin wire interface

InactiveUS20060058655A1Highly integratedReduce needInfrasonic diagnosticsSonic diagnosticsUltrasonic sensorSonification

The present invention is directed to an ultrasound system and method which, in one embodiment, partitions the main body processing such that a portion of the processing is contained within the transducer thereby reducing the need for a multiplicity of high performance cables running between the transducer and the main body. This is possible through the use of a unique architecture to allow for proper power management given the small transducer size and an architecture that exploits the high levels of integration possible on integrated circuit technologies allowing for its implementation in a few highly integrated circuits with virtually no external components outside of the ICs.

Owner:SONOSITE

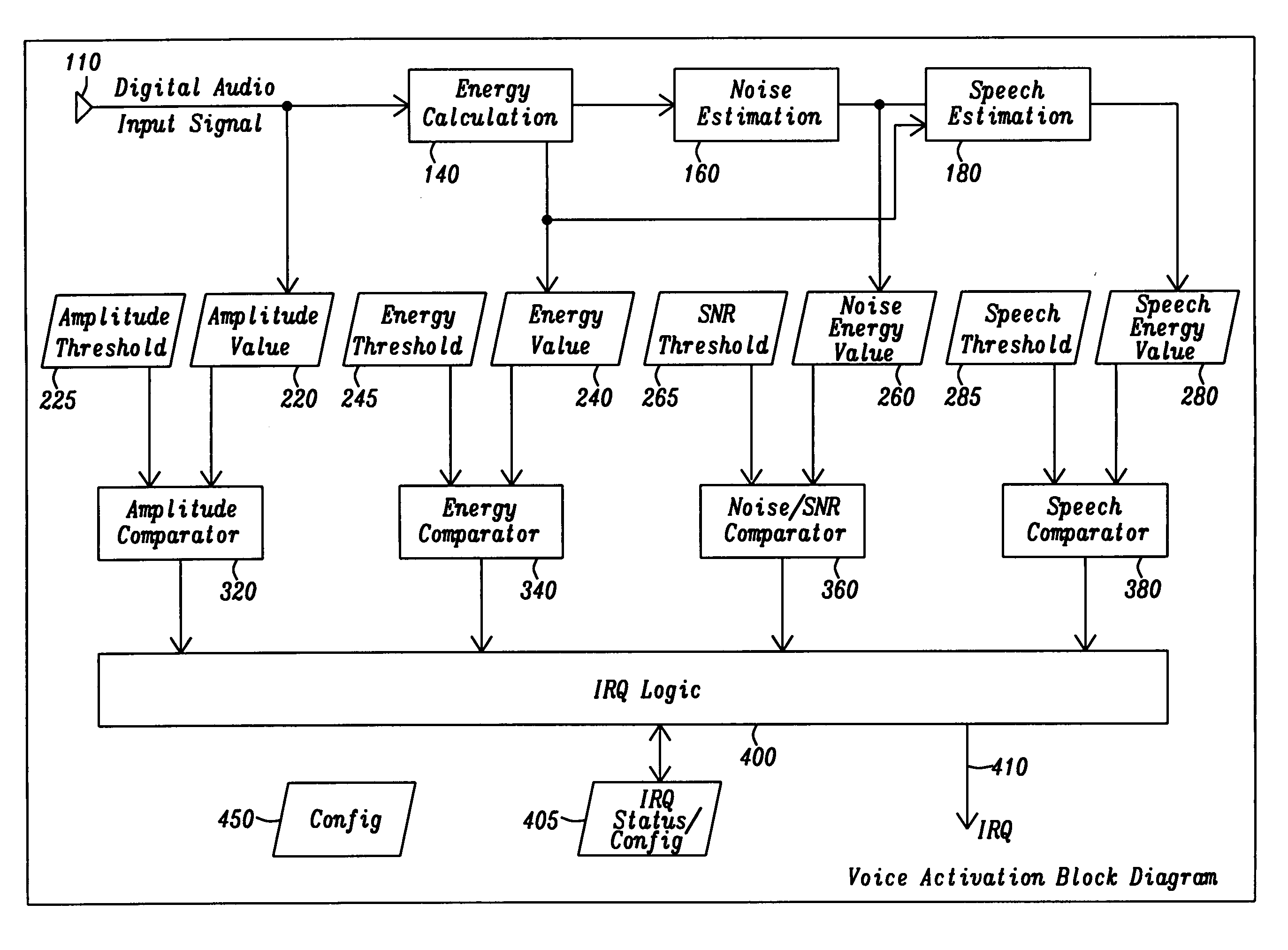

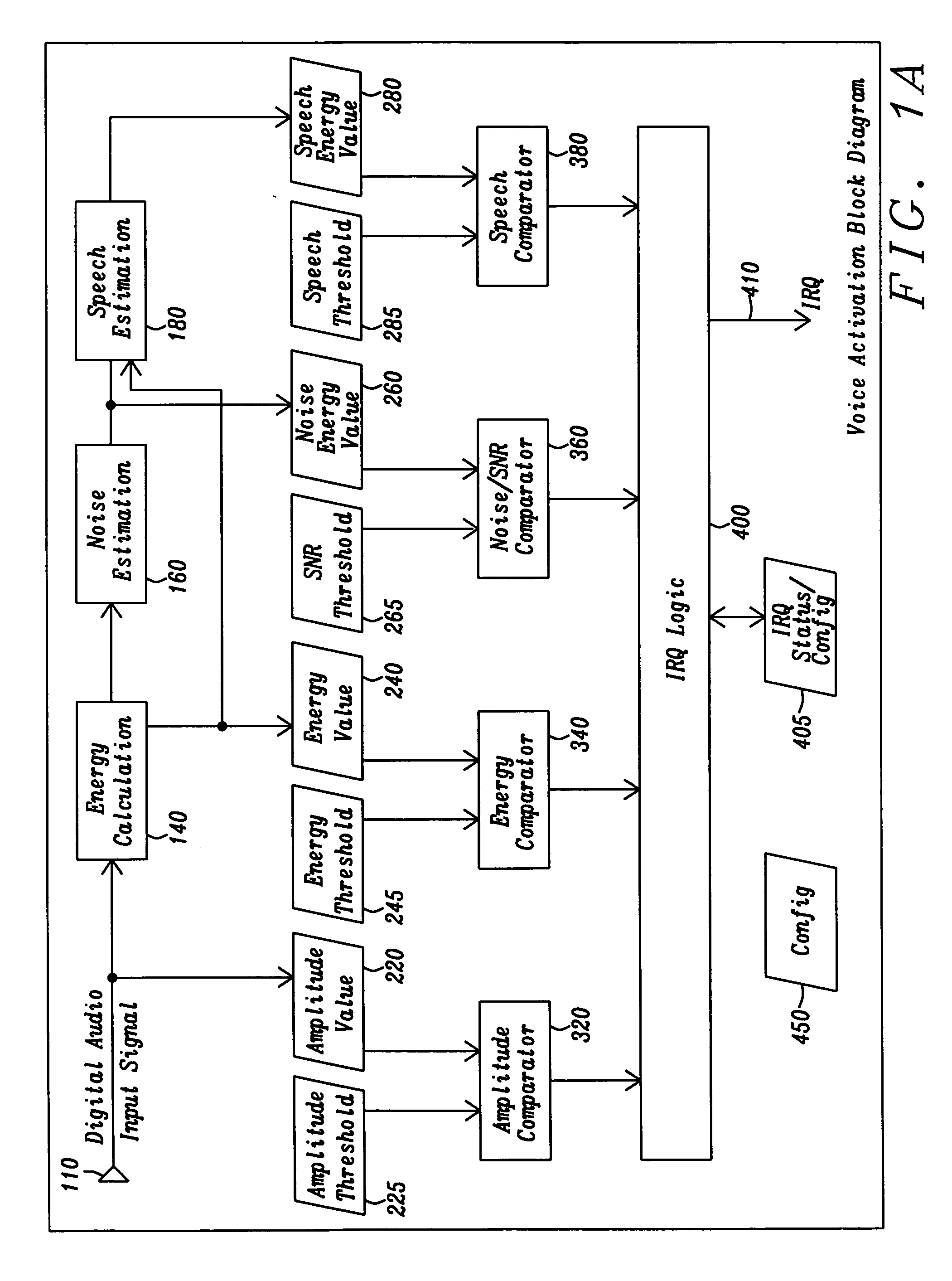

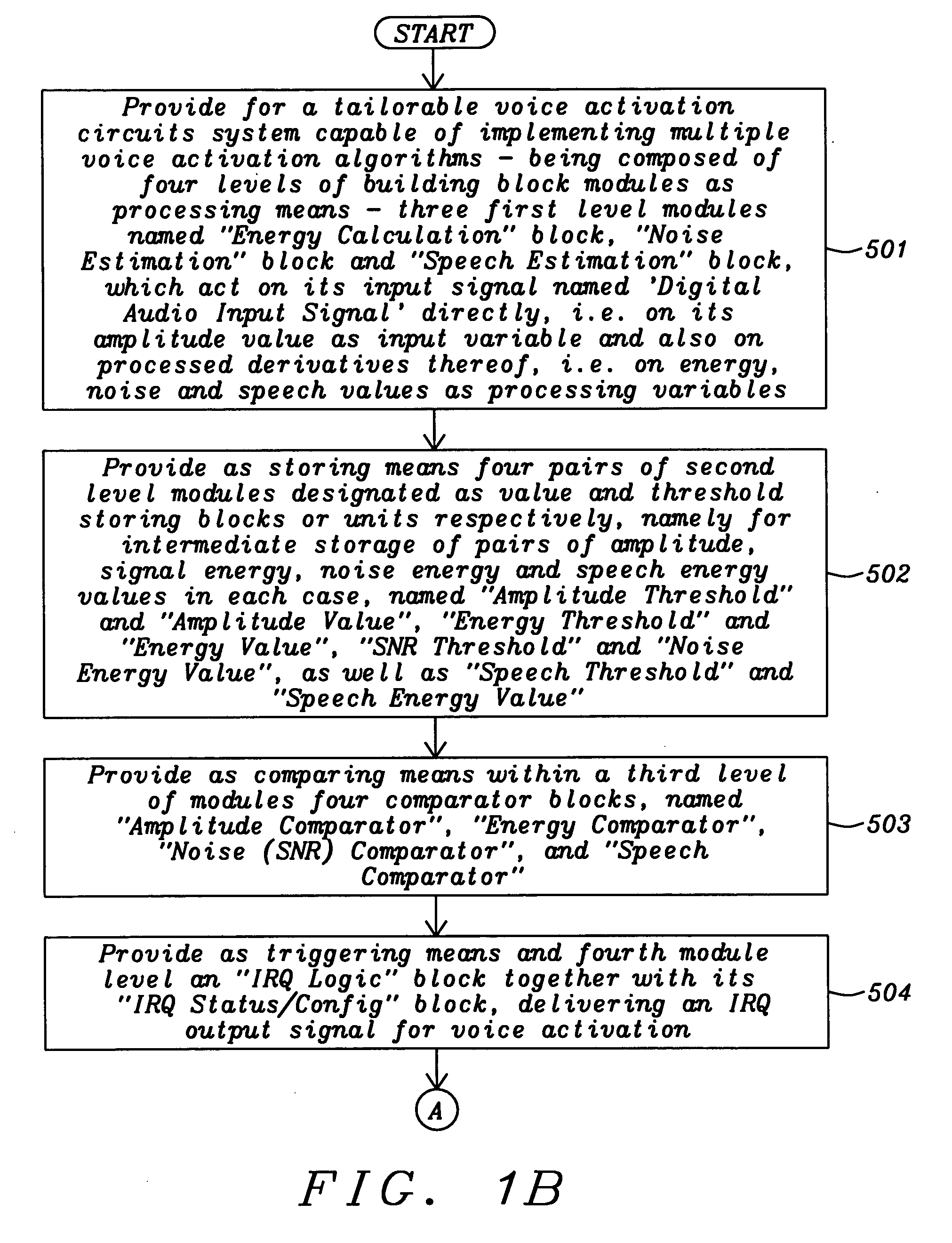

Voice activation

A circuit and a method are given, to realize a very flexible voice activation system using a modular building block approach, that is adaptively tailored to handle certain relevant and case specific operational characteristics describing most of the possible acoustical differing environmental cases to be found in the field of speech recognition. Included are determinations of “Noise estimation and “Speech estimation” values, done effectively without use of Fast Fourier Transform (FFT) methods or zero crossing algorithms only by analyzing the modulation properties of human voice. Said circuit and method are designed in order to be implemented with a very economic number of components, capable to be realized with modern integrated circuit technologies.

Owner:DIALOG SEMICONDUCTOR GMBH

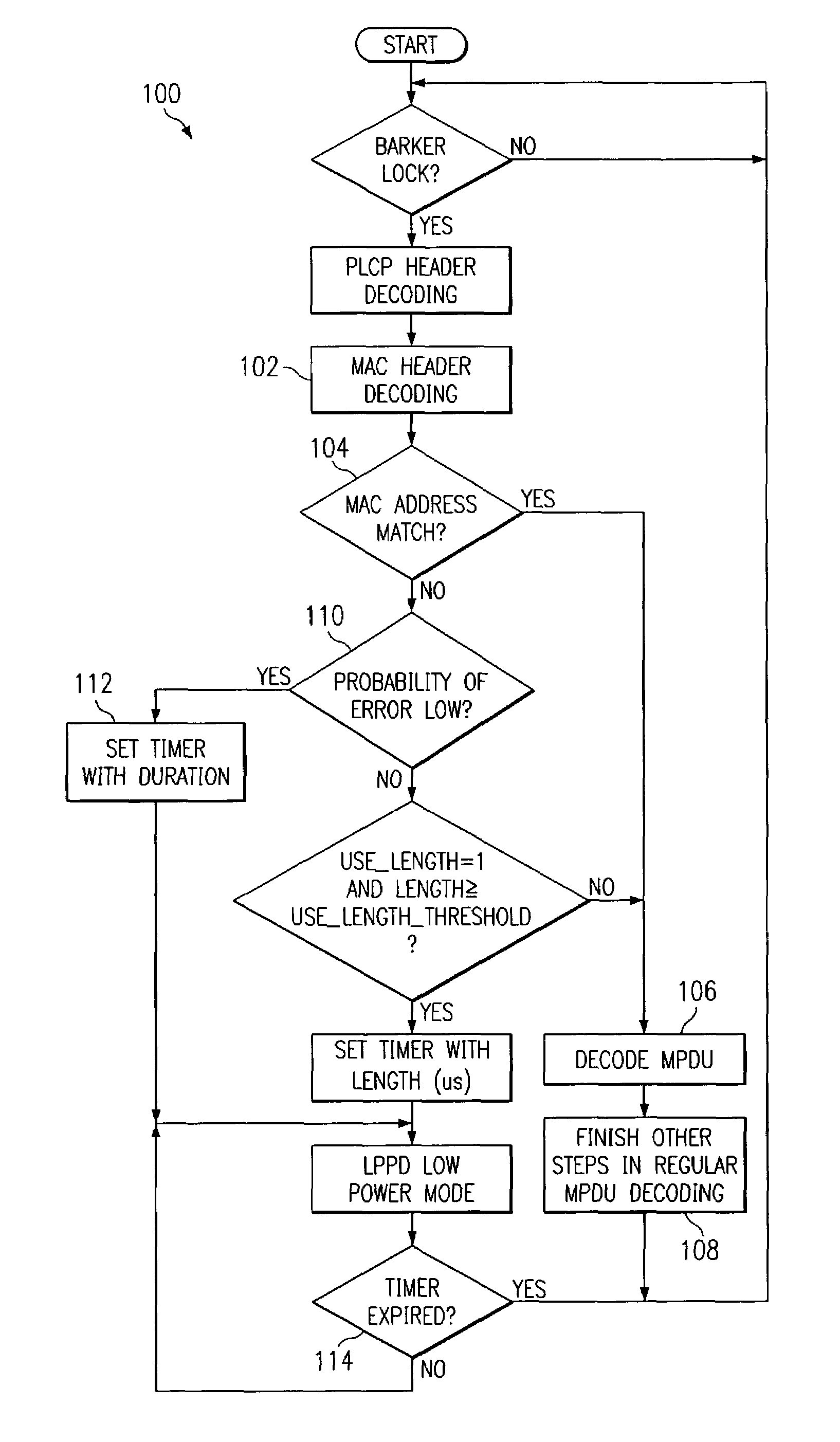

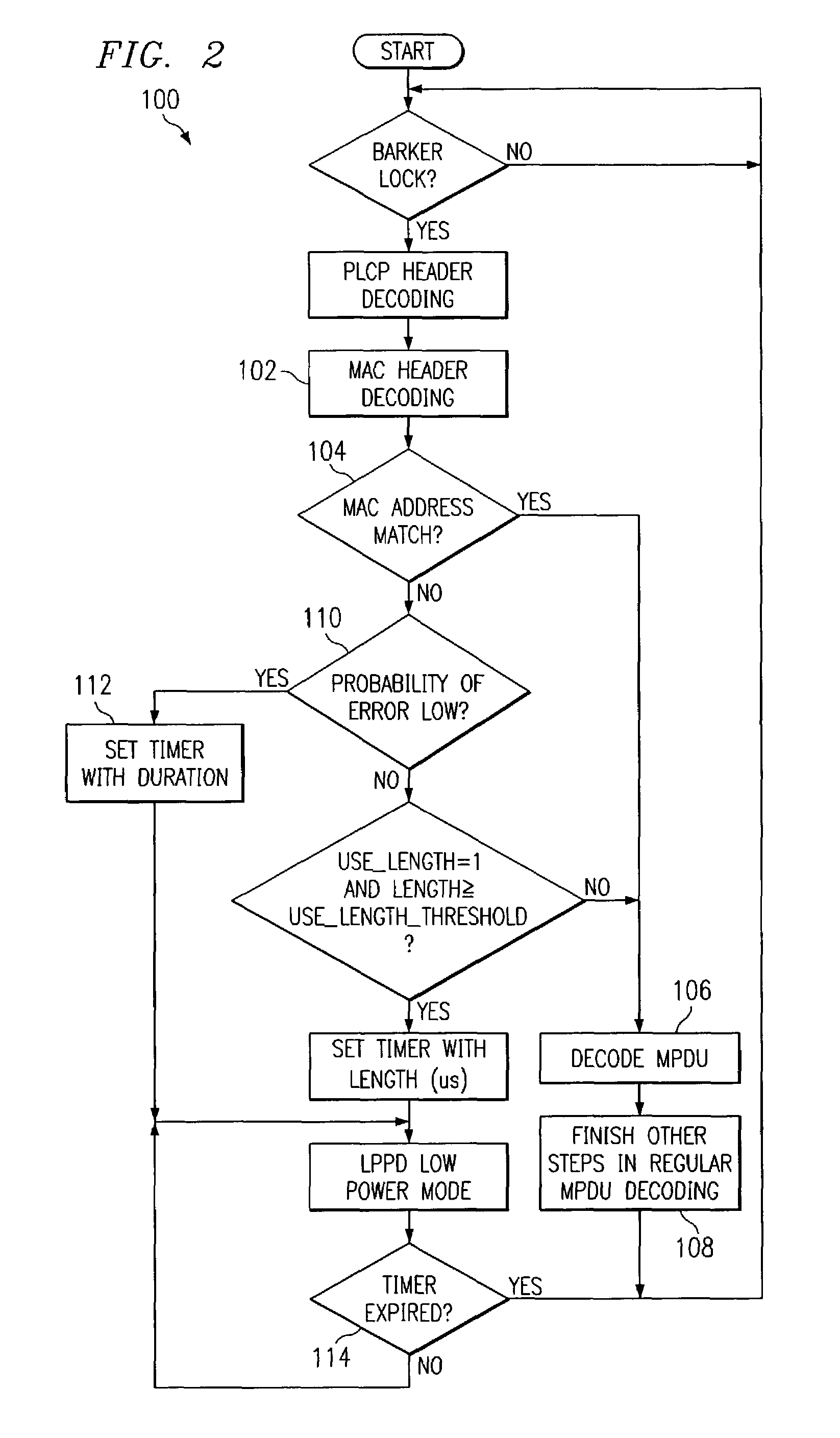

Low power packet detector for low power WLAN devices

ActiveUS7403511B2Reduce power consumptionEnergy efficient ICTPower managementComputer scienceAsic technology

A low power packet detector (LPPD) can significantly reduce the average power consumption of WLAN devices. The LPPD takes advantages of 802.11 protocols to turn on and off selected modules of an 802.11 receiver based on the packets on the medium and the decoding stages. The LPPD can be implemented mostly in firmware with minor hardware modifications to existing chips or be implemented in ASIC technology that takes full advantages of the power saving made possible by it.

Owner:TEXAS INSTR INC

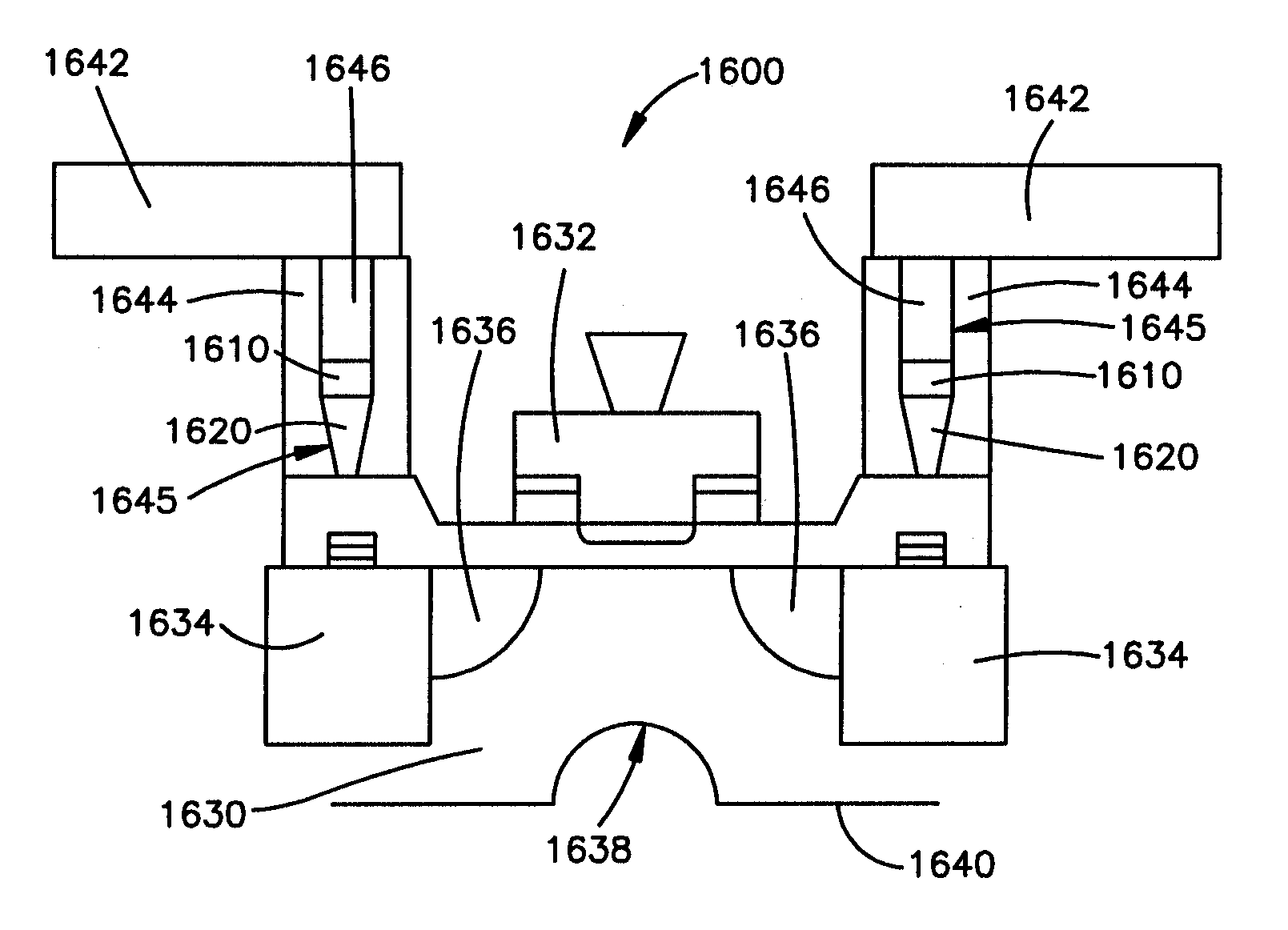

Electrical-energy-storage unit (EESU) utilizing ceramic and integrated-circuit technologies for replacement of electrochemical batteries

InactiveUS20060210779A1Fast chargingSolution to short lifeStacked capacitorsPrimary cellsBarium titanateElectrical battery

An electrical-energy-storage unit (EESU) has as a basis material a high-permittivity composition-modified barium titanate ceramic powder. This powder is double coated with the first coating being aluminum oxide and the second coating calcium magnesium aluminosilicate glass. The components of the EESU are manufactured with the use of classical ceramic fabrication techniques which include screen printing alternating multilayers of nickel electrodes and high-permittivitiy composition-modified barium titanate powder, sintering to a closed-pore porous body, followed by hot-isostatic pressing to a void-free body. The components are configured into a multilayer array with the use of a solder-bump technique as the enabling technology so as to provide a parallel configuration of components that has the capability to store electrical energy in the range of 52 kW·h. The total weight of an EESU with this range of electrical energy storage is about 336 pounds.

Owner:EESTOR

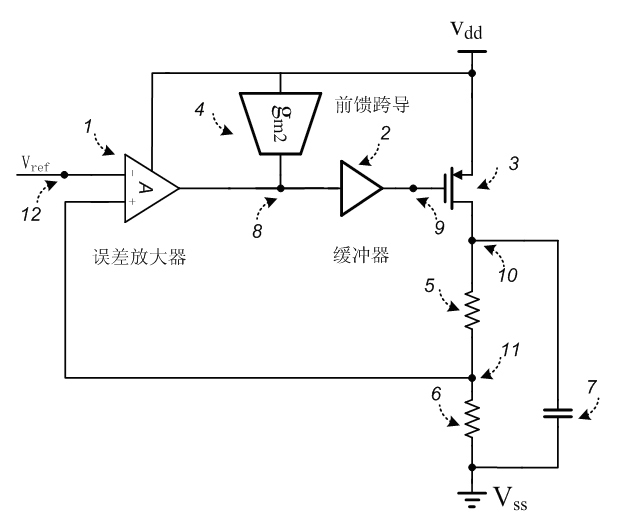

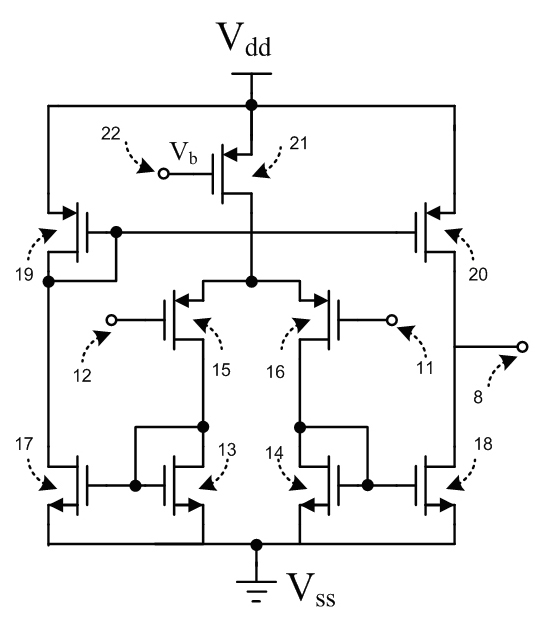

High mains rejection ratio low dropout voltage linear voltage regulator with feedforward transconductance

InactiveCN101853040AHigh rejection ratioSuppression Ratio OptimizationElectric variable regulationCapacitanceDropout voltage

The invention belongs to the technical field of integrated circuits and specifically relates to a high mains rejection ratio low dropout voltage linear voltage regulator with a feedforward transconductance, which consists of an error amplifier, a buffer, a PMOS pass transistor, a feedforward transconductance, two feedback resistors and a filter capacitor, wherein the error amplifier is a current mirror amplifier consisting of a tail current source, a PMOS input differential pair and three groups of current mirrors. The mains voltage fluctuation influences the output mainly via two paths of the PMOS pass transistor and the parasitic resistor of and PMOS pass transistor. The feedforward transconductance transforms the perturbation of the mains voltage into the perturbation of the current, and then the perturbation of the current is transformed into the in-phase voltage perturbation of the grid of the pass transistor via the parasitic resistor of the error amplifier. The influence of the mains voltage perturbation on the output can be eliminated by the control of the gain of the feedforward transconductance so as to realize high mains rejection ratio. The invention can optimize the mains rejection ratio within a wider range of load current and does not reduce the efficiency of the low dropout voltage linear voltage regulator.

Owner:FUDAN UNIV

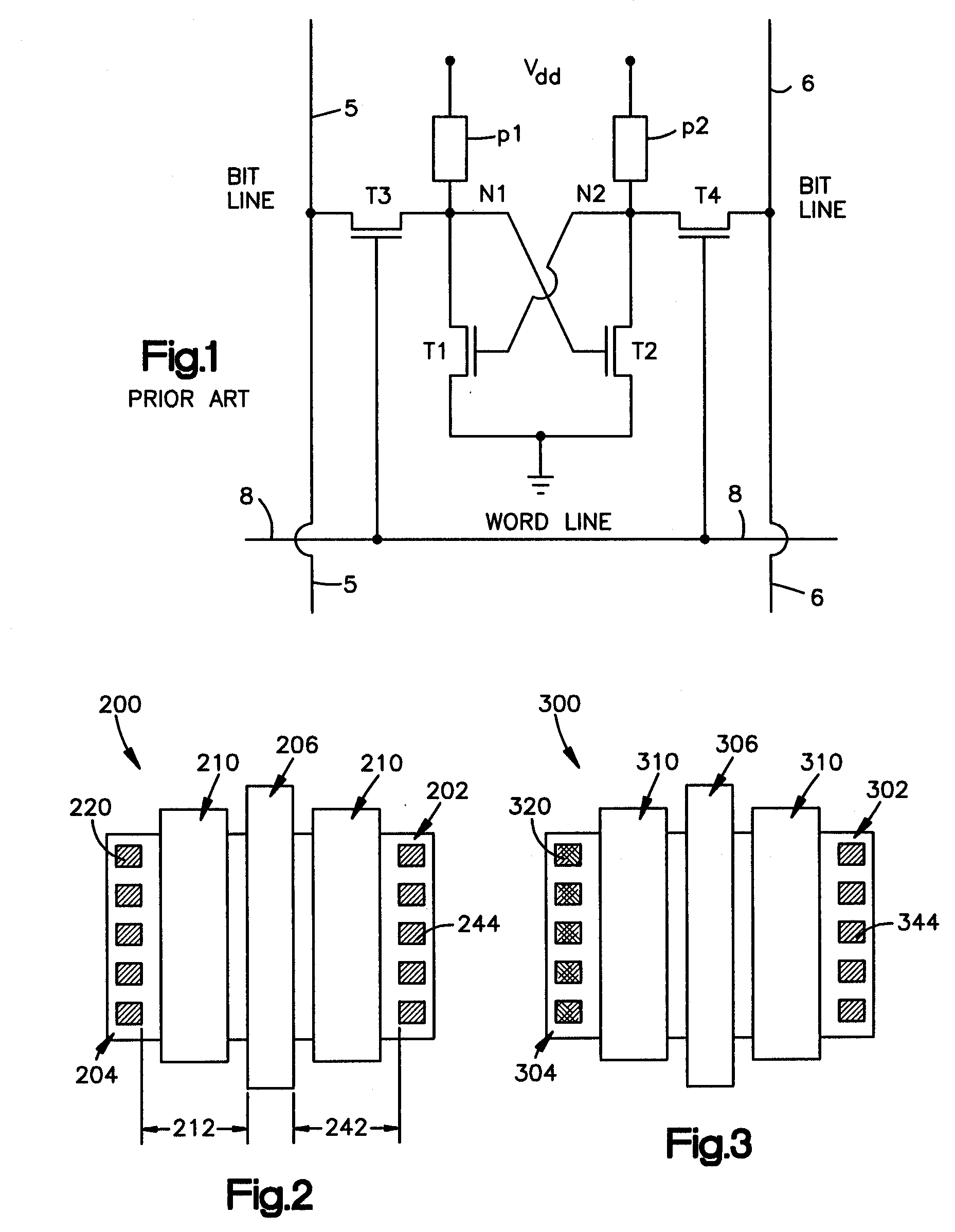

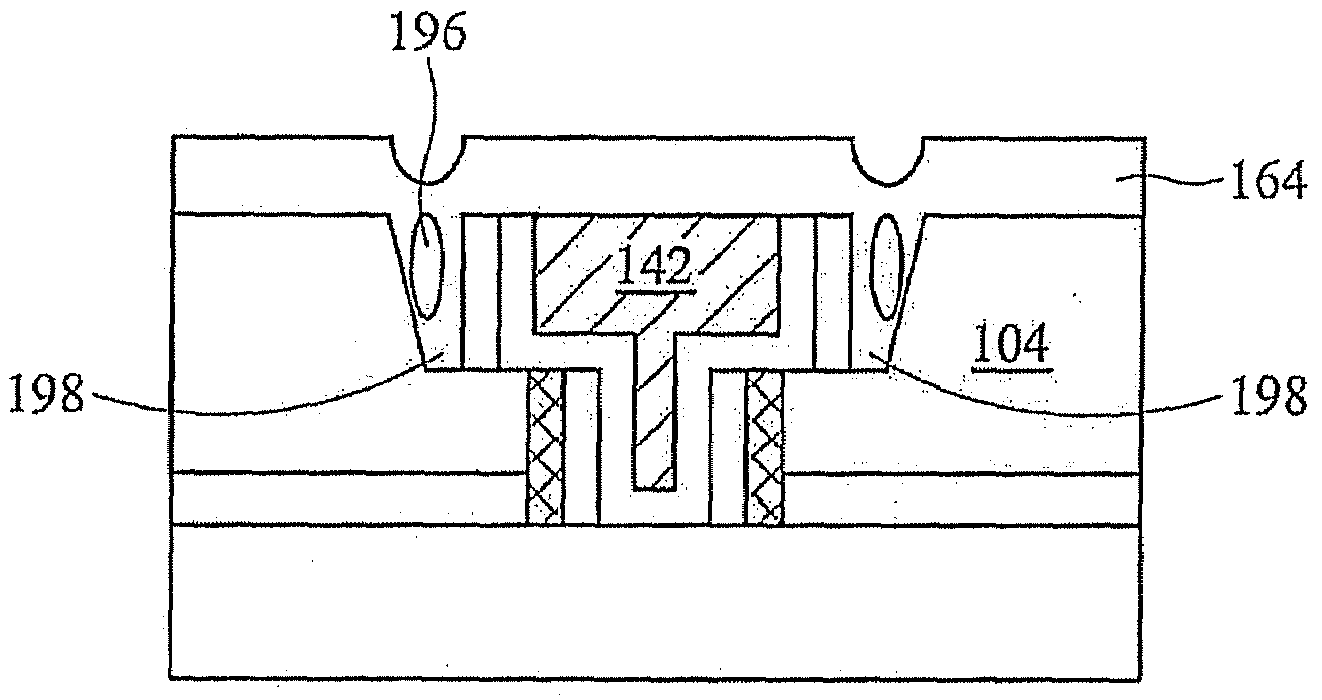

Structure and method for local resistor element in integrated circuit technology

ActiveUS20050167786A1Reduce capacityEliminate inductive effectsTransistorSemiconductor/solid-state device detailsMOSFETDevice material

A method and system for forming a semiconductor device having superior ESD protection characteristics. A resistive material layer is disposed within a contact hole on at least one of the contact stud upper and lower surface. In preferred embodiments, the integral resistor has a resistance value of between about one Ohm and about ten Ohms, or between 10 and 100 Ohms. Embodiments of the resistive layer include sputtered silicon material, a tunnel oxide, a tunnel nitride, a silicon-implanted oxide, a silicon-implanted nitride, or an amorphous polysilicon. Embodiments of the invention include SRAMs, bipolar transistors, SOI lateral diodes, MOSFETs and SiGe Transistors.

Owner:GLOBALFOUNDRIES US INC

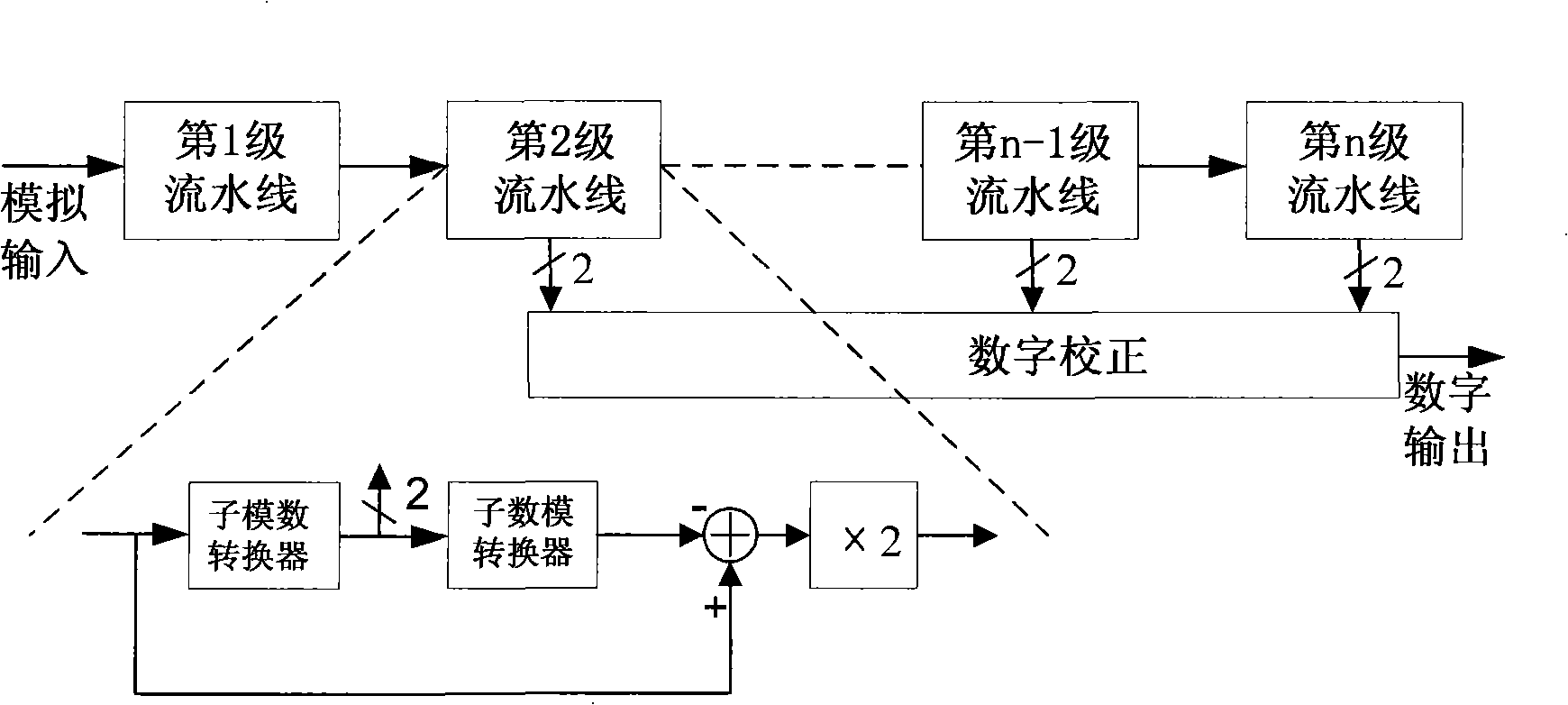

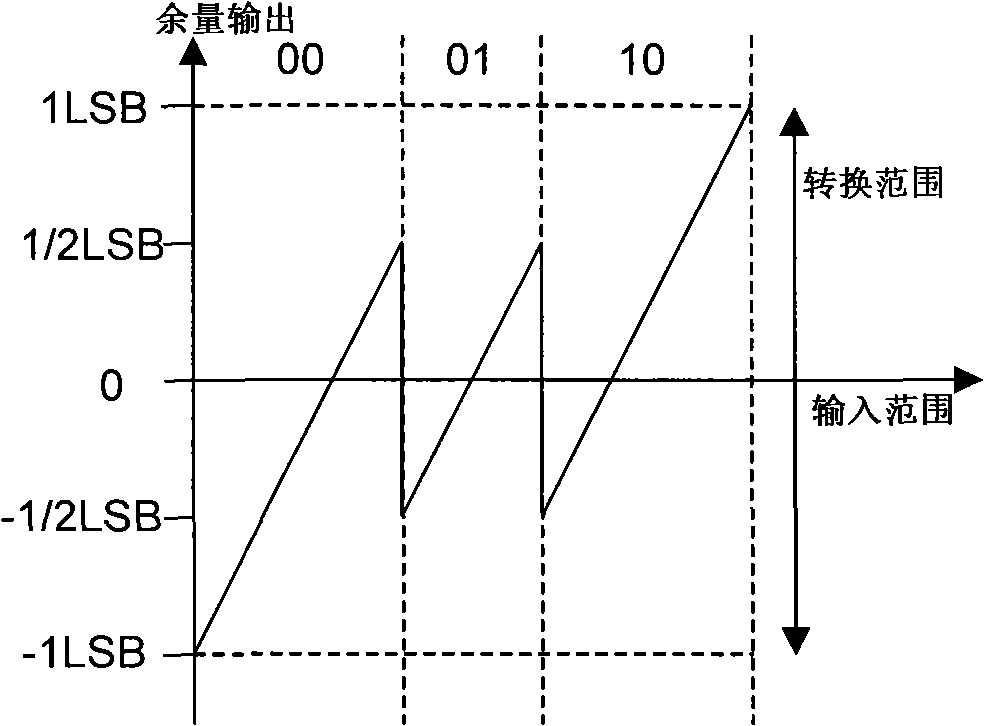

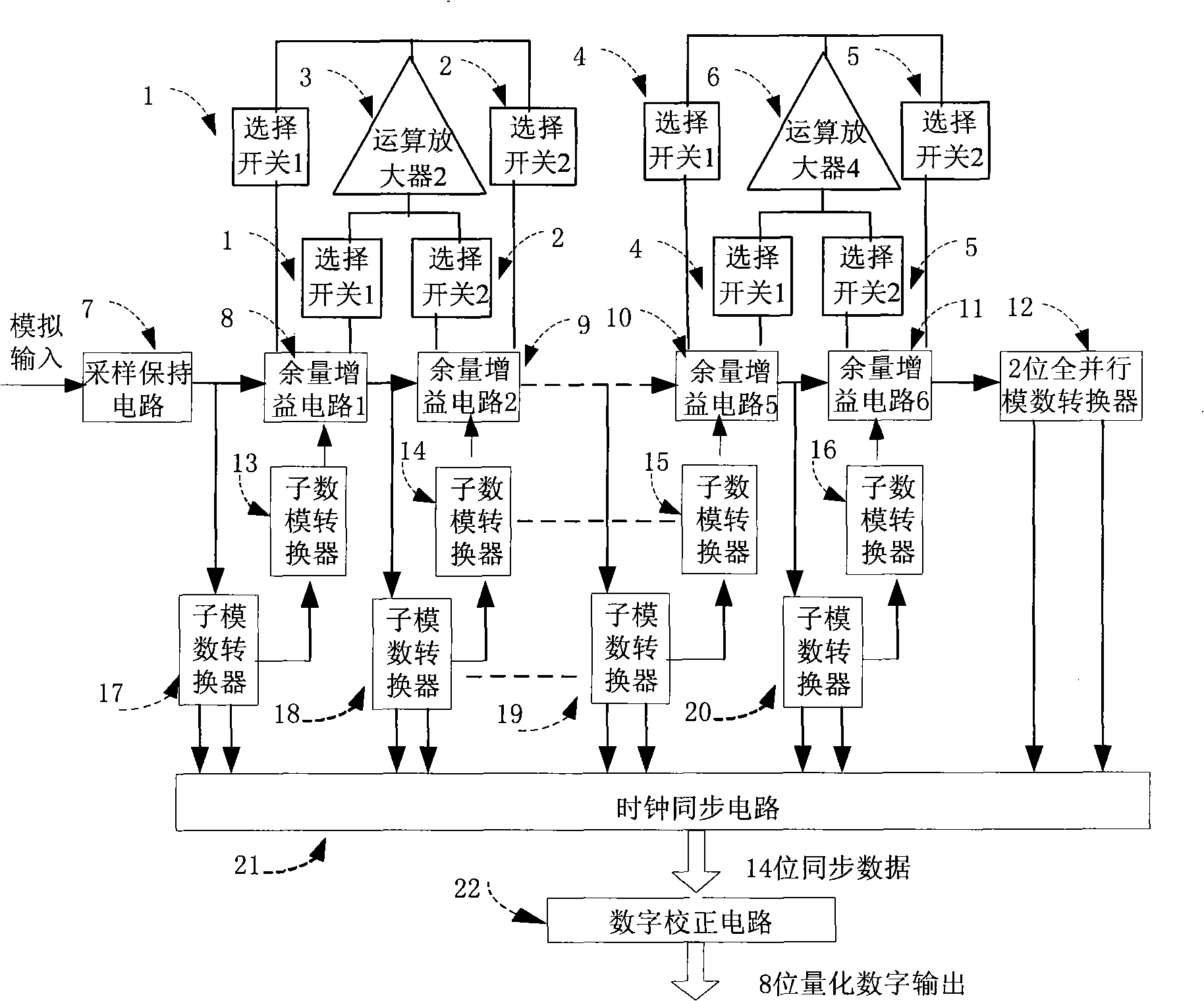

Low-power consumption assembly line a/d converter by sharing operation amplifier

InactiveCN101277112AHigh gainHigh bandwidthElectric analogue storesElectronic switchingAssembly lineEngineering

The present invention belongs to a technical field of an integrated circuit, and particularly to a low power consumption production line analog-digital converter which adopts an operational amplifier sharing. The analog-digital converter is composed of an input sampling holding circuit, a six-stage allowance gain circuit, an one-stage double-digit all-parallel analog-digital converter, a converting switch which is used for operational amplifier sharing, six sub-analog-digital converters, six sub-digital-analog converters, a production line output clock synchronous circuit and a digital correcting circuit. The sampling holding circuit and the six-stage allowance gain circuit are connected in sequence. The last stage is a double-digit all-parallel analog-digital converter. The input end of each stage of allowance gain circuit is connected with each stage of sub-analog-digital converter. Two continuous stages shares one operational amplifier. After the output clock synchronous circuit, the data with 14 digits is obtained, and after the digital correction of the digital correcting circuit, the final eight digit quantized output is obtained. The analog-digital converter realizes high speed and low power consumption.

Owner:FUDAN UNIV

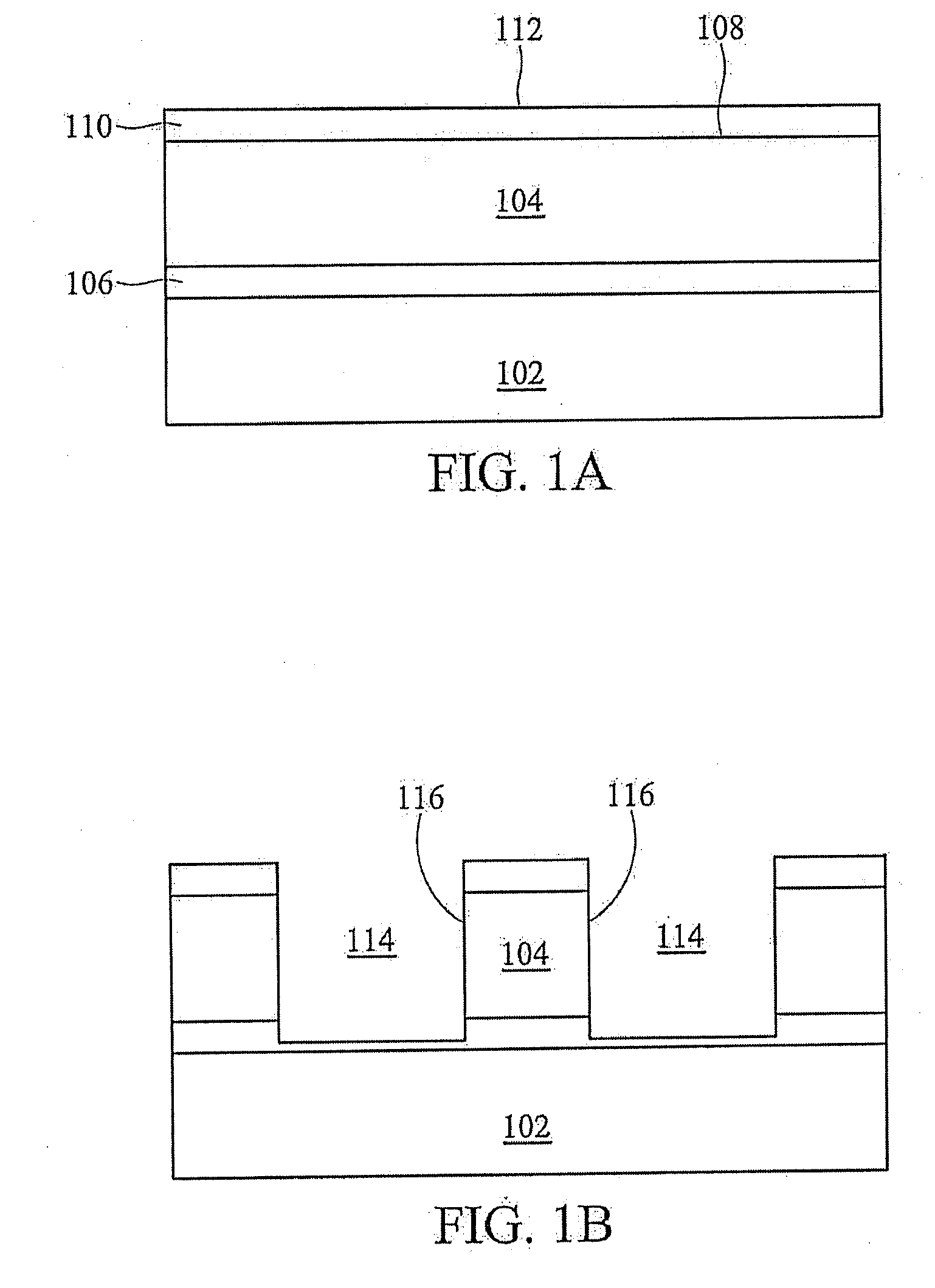

Air gap structure design for advanced integrated circuit technology

InactiveUS20090081862A1Solid-state devicesSemiconductor/solid-state device manufacturingProtection layerSemiconductor

A method for forming air gaps between interconnect structures in semiconductor devices provides a sacrificial layer formed over a dielectric and within openings formed therein. The sacrificial layer is a blanket layer that is converted to a material that is consumable in an etchant composition that the dielectric material and a subsequently formed interconnect material are resistant to. After the interconnect material is deposited a planarized surface including portions of the dielectric material, vertical sections of the converted material and portions of the interconnect material is produced. The etchant composition then removes the converted material thereby forming voids. A capping layer is formed over the structure resulting in air gaps. A sidewall protection layer may be optionally formed between the interconnect structure and the sacrificial material. In some embodiments an ARC layer may be formed over the dielectric and form part of the planar surface.

Owner:TAIWAN SEMICON MFG CO LTD

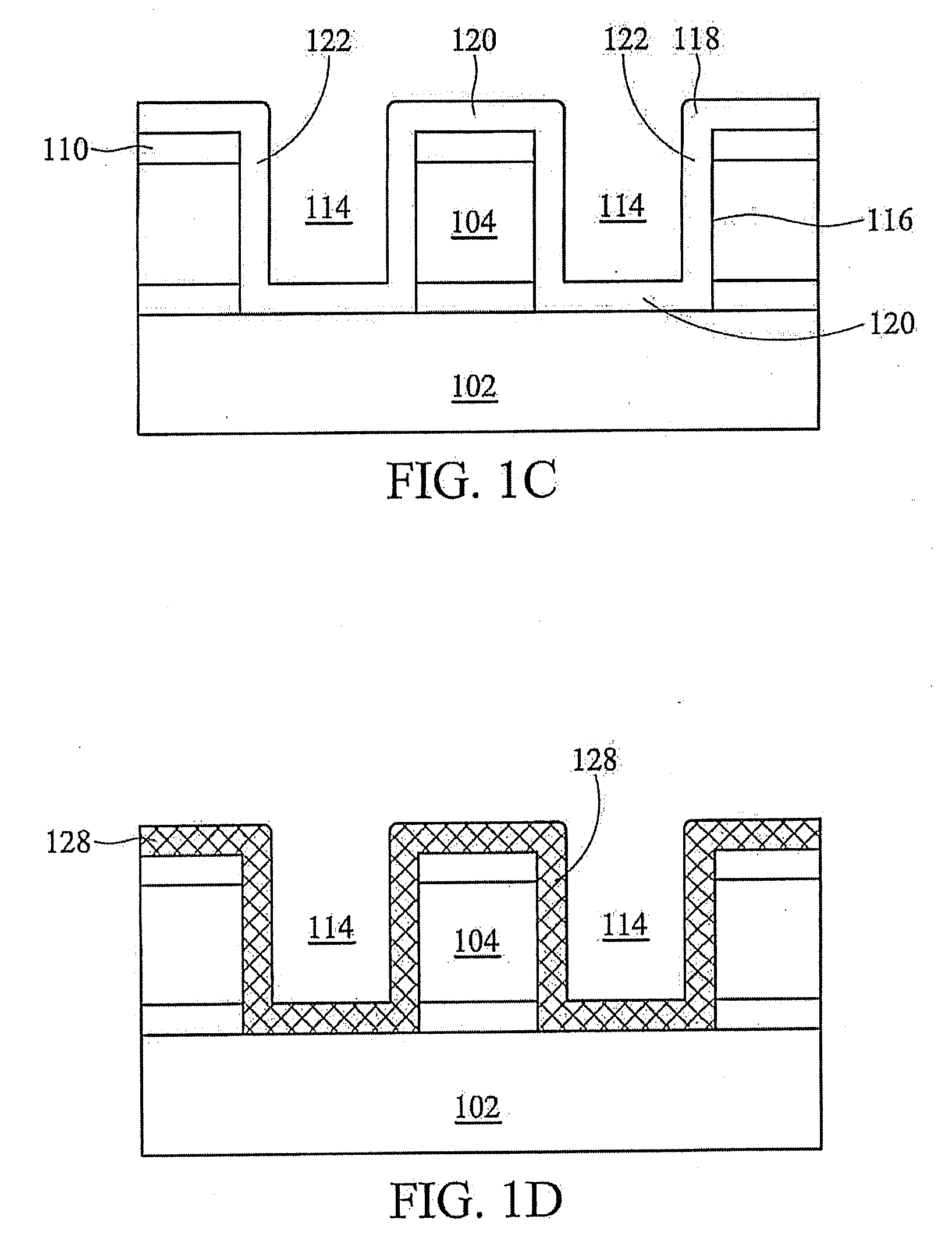

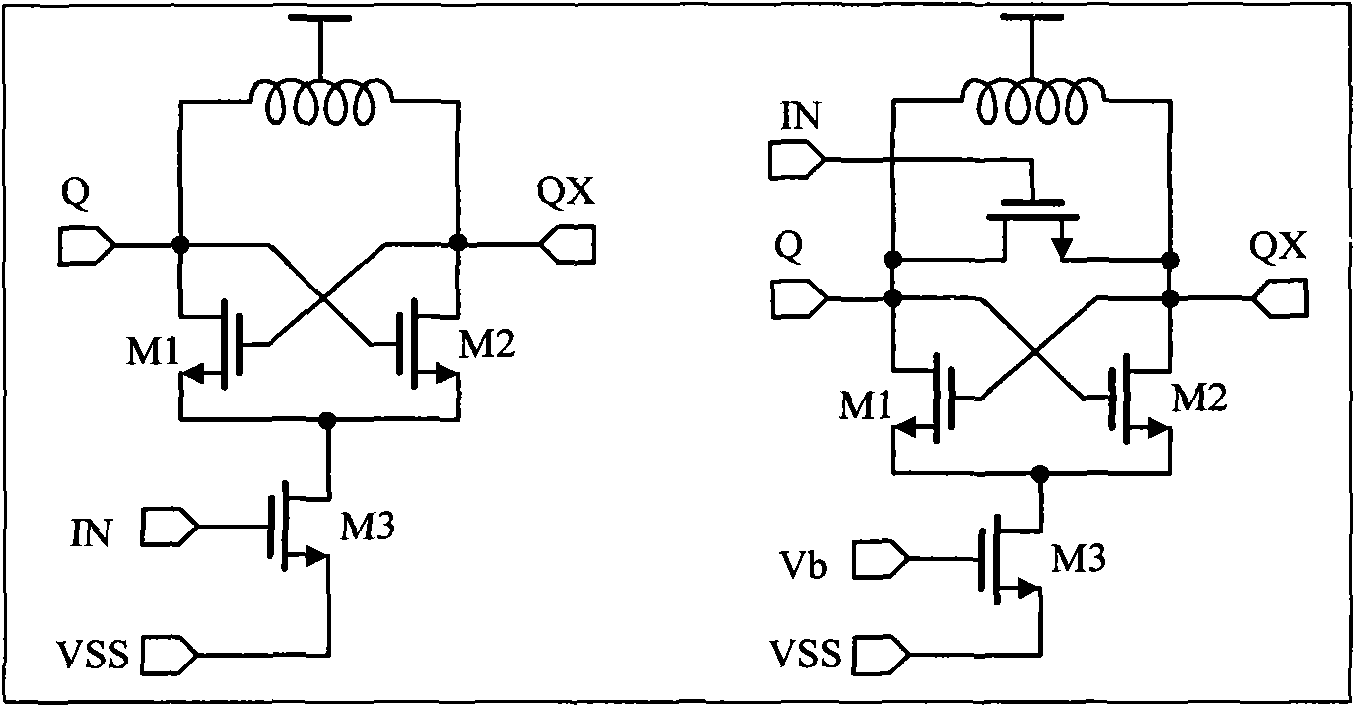

Injection locking frequency divider

InactiveCN101777871AThe injection method increasesIncreased injected energyOscillations generatorsInjection lockedCapacitance

The invention relates to an injection locking frequency divider used in the integrated circuit of a radio receiver, belonging to the technical field of integrated circuits of radio frequency radio receivers. The injection locking frequency divider is formed by an inductance-capacitance oscillator, a tuning circuit, a signal injection circuit and a current source biasing circuit, wherein the tuning circuit comprises a numerical control capacitor array tuner and a varactor tuner. Under the condition of no external input excitation, the inductance-capacitance oscillator self-oscillates by certain frequency. The tuning circuit tunes the self-oscillating frequency through varying the load of the resonant cavity of the oscillator. The signal injection circuit injects input signals into the resonant cavity of the oscillator to realize the traction and the locking of the self-oscillating frequency of the oscillator and to further the frequency halving of the input signals. Compared with the prior art, the invention has the advantages that the circuit can realize high working frequency under low power consumption and the working frequency range is wide.

Owner:FUDAN UNIV

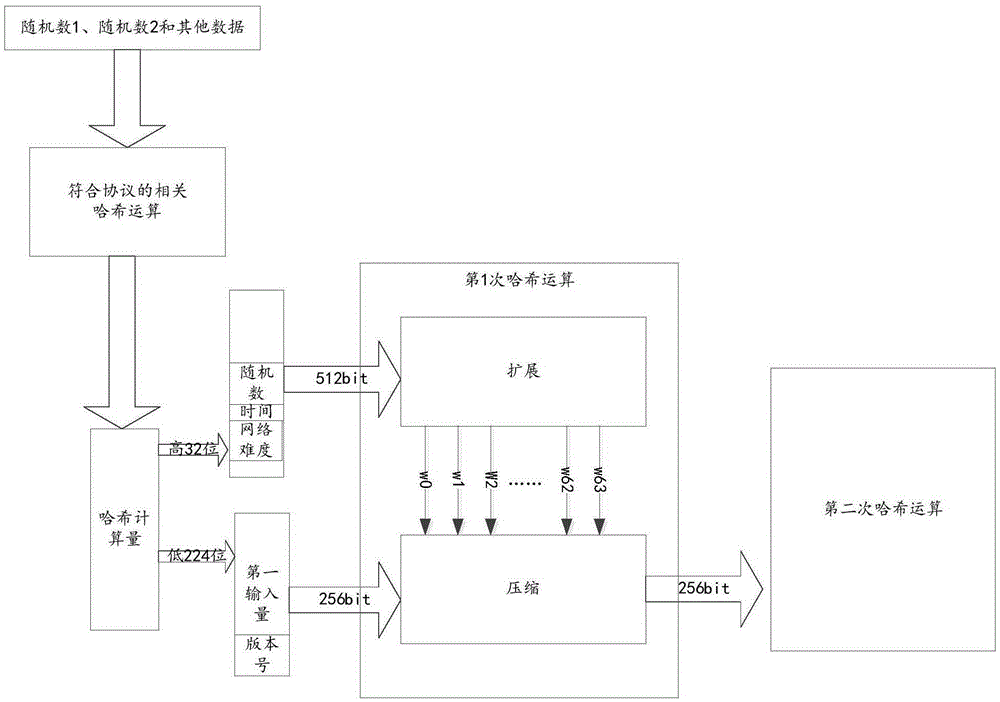

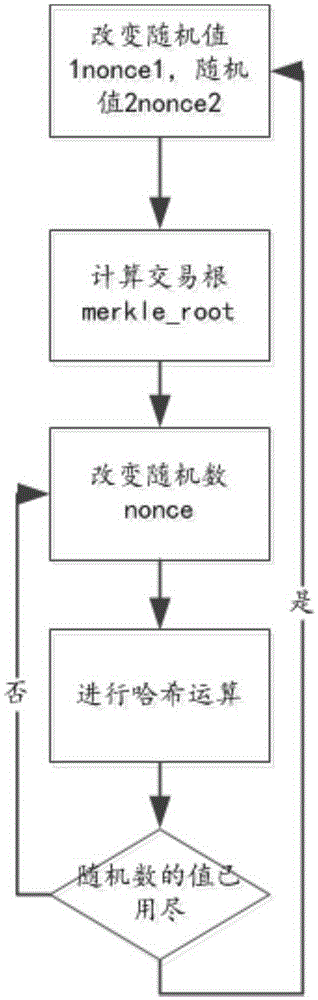

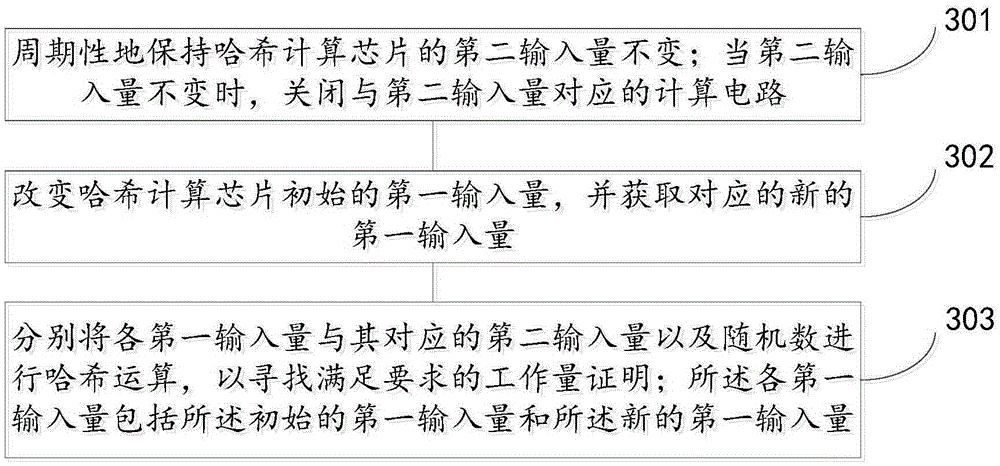

Optimizing method, device and circuit for Hash computing chip of bitcoin proof of work

InactiveCN105245327AReduce computationReduce power consumptionEncryption apparatus with shift registers/memoriesIntegrated circuitAsic technology

The invention discloses an optimizing method, device and circuit for Hash computing chip of bitcoin proof of work, and relates to the technical field of cipher computing, computer network and integrated circuits. The optimizing method comprises that a second input of the Hash computing chip is kept constant periodically, and when the second input is constant, a computing circuit corresponding to the second input is switched off; an initial first input of the Hash computing chip is changed, and a corresponding new first input is obtained; and Hash computing is carried out on each first input, the corresponding second input and a random number to search proof of work that satisfies the requirement, and each first input comprise the initial first input and the new first input. The method, device and circuit provided by the invention greatly reduce the power consumption of the circuit.

Owner:BEIJING BITMAIN TECH LTD

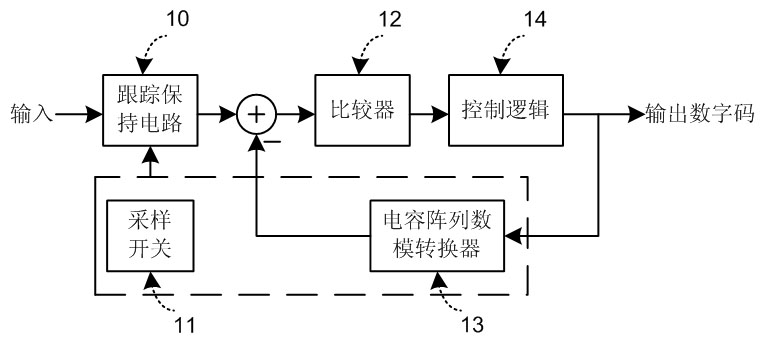

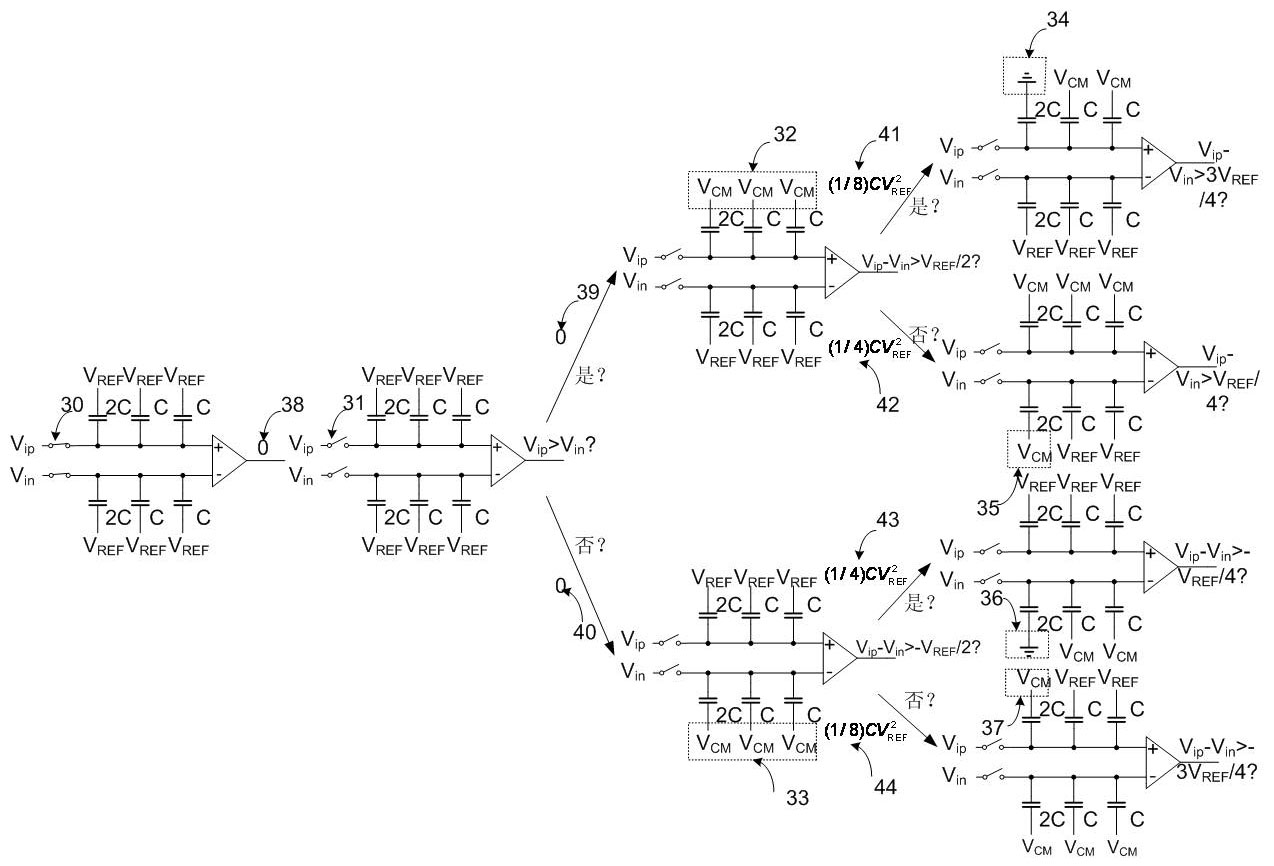

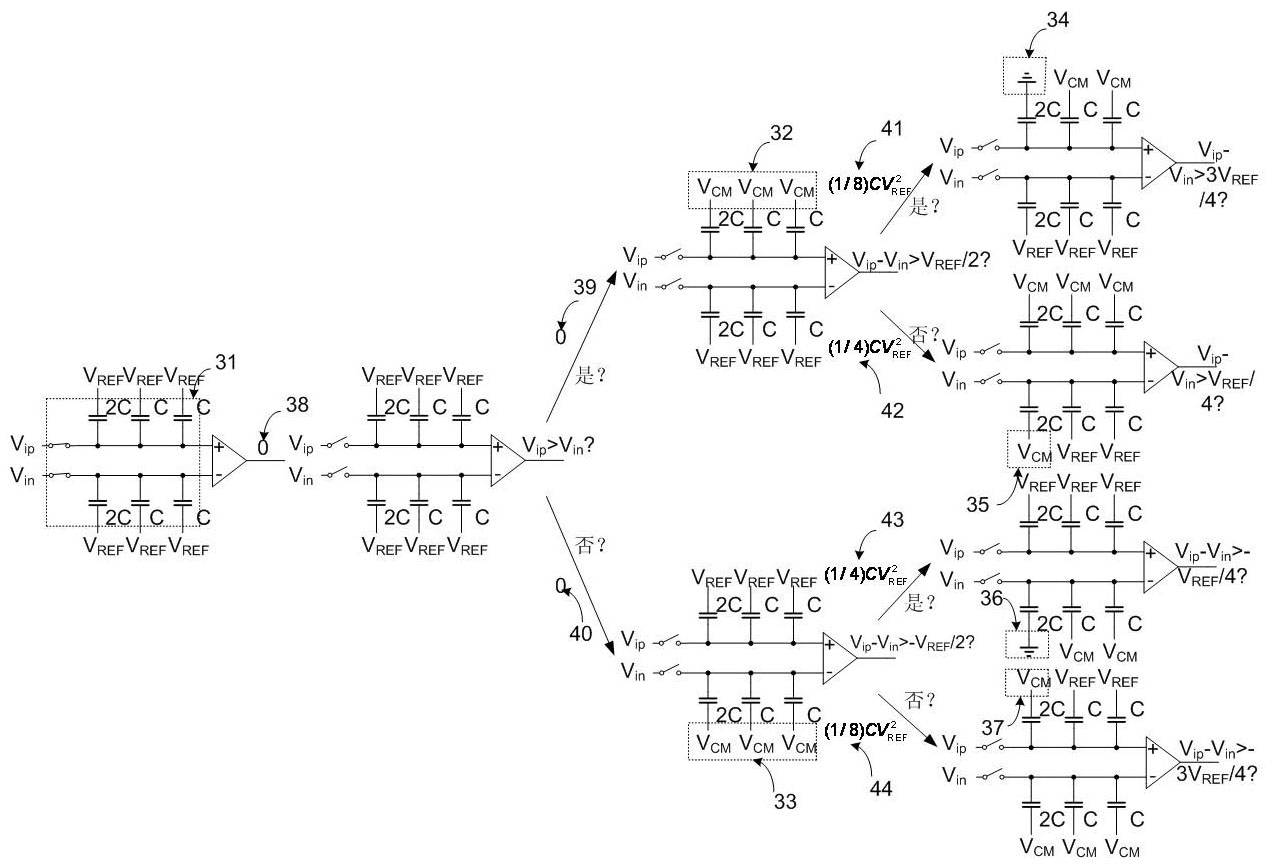

Successive approximation type analog-to-digital converter of energy-saving capacitor array

ActiveCN102006075AAnalogue/digital conversionElectric signal transmission systemsCapacitanceDigital analog converter

The invention belongs to the technical field of integrated circuits, in particular to a successive approximation type analog-to-digital converter of an energy-saving capacitor array. The analog-to-digital converter comprises a sampling switch, a track and hold circuit, a comparator, control logic and a capacitor array digital-to-analog converter, wherein the capacitor array digital-to-analog converter adopts a switch mode of the novel capacitor array digital-to-analog converter provided by the invention. By using the mode, the average switch consumption of the capacitor can be reduced.

Owner:FUDAN UNIV

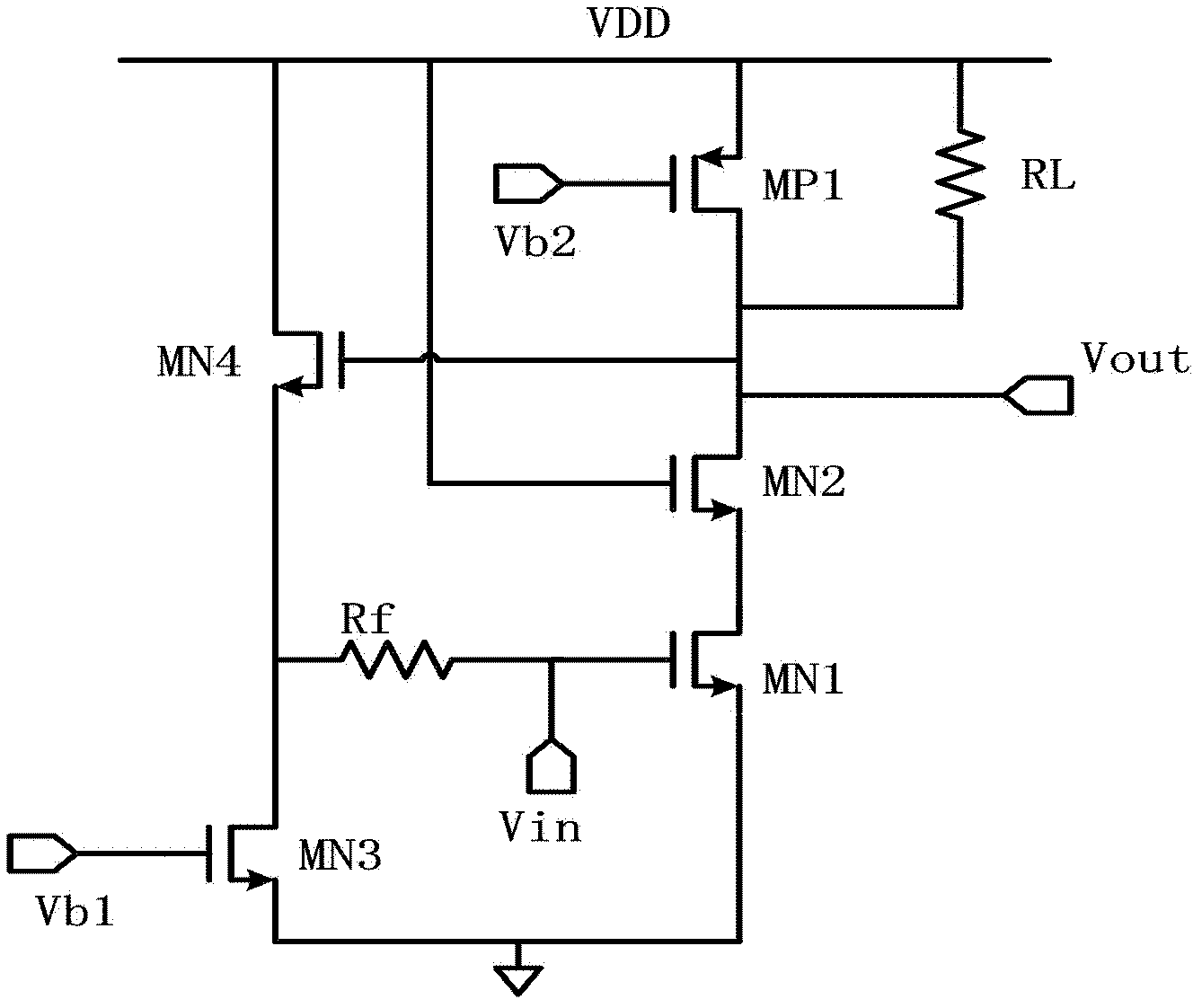

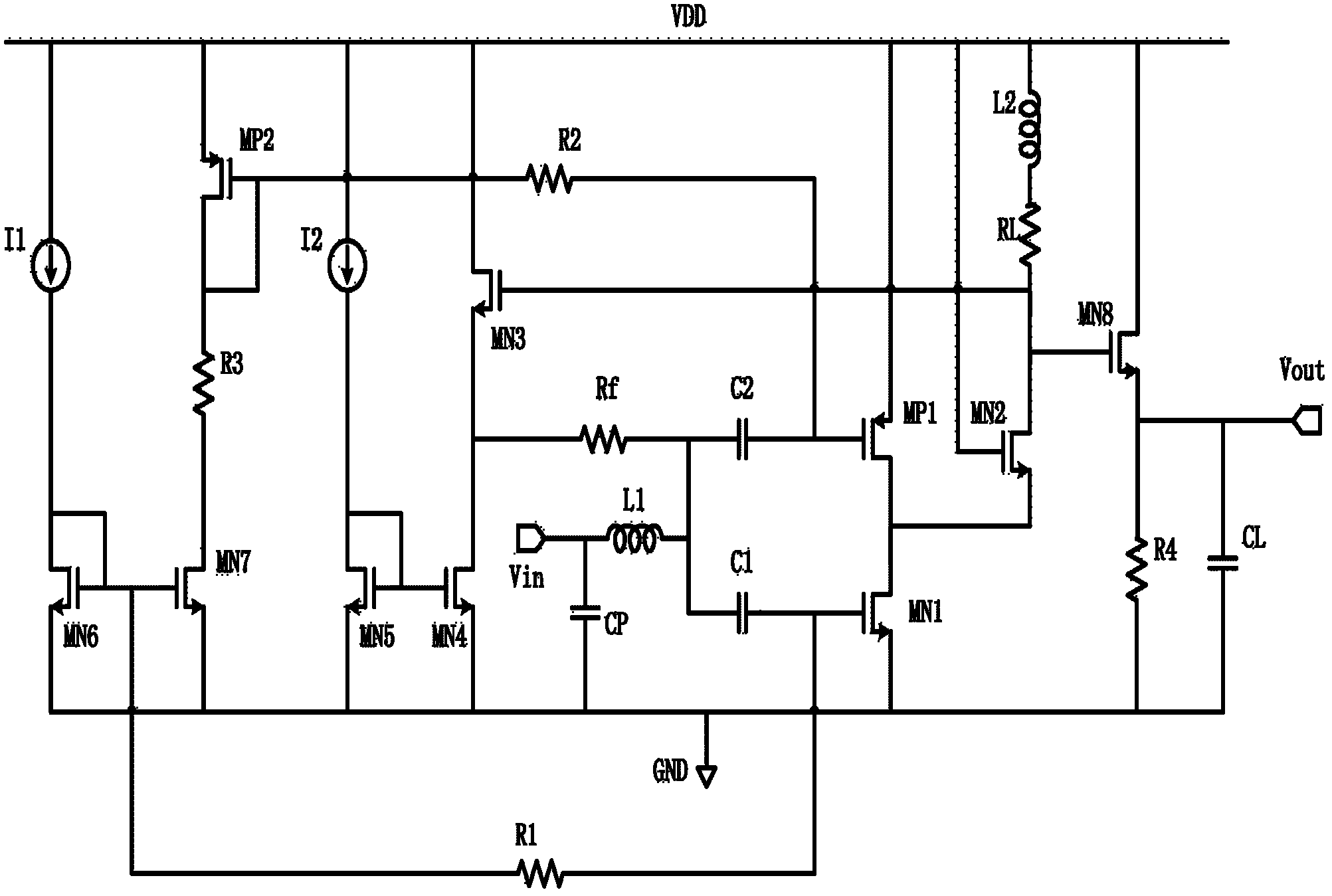

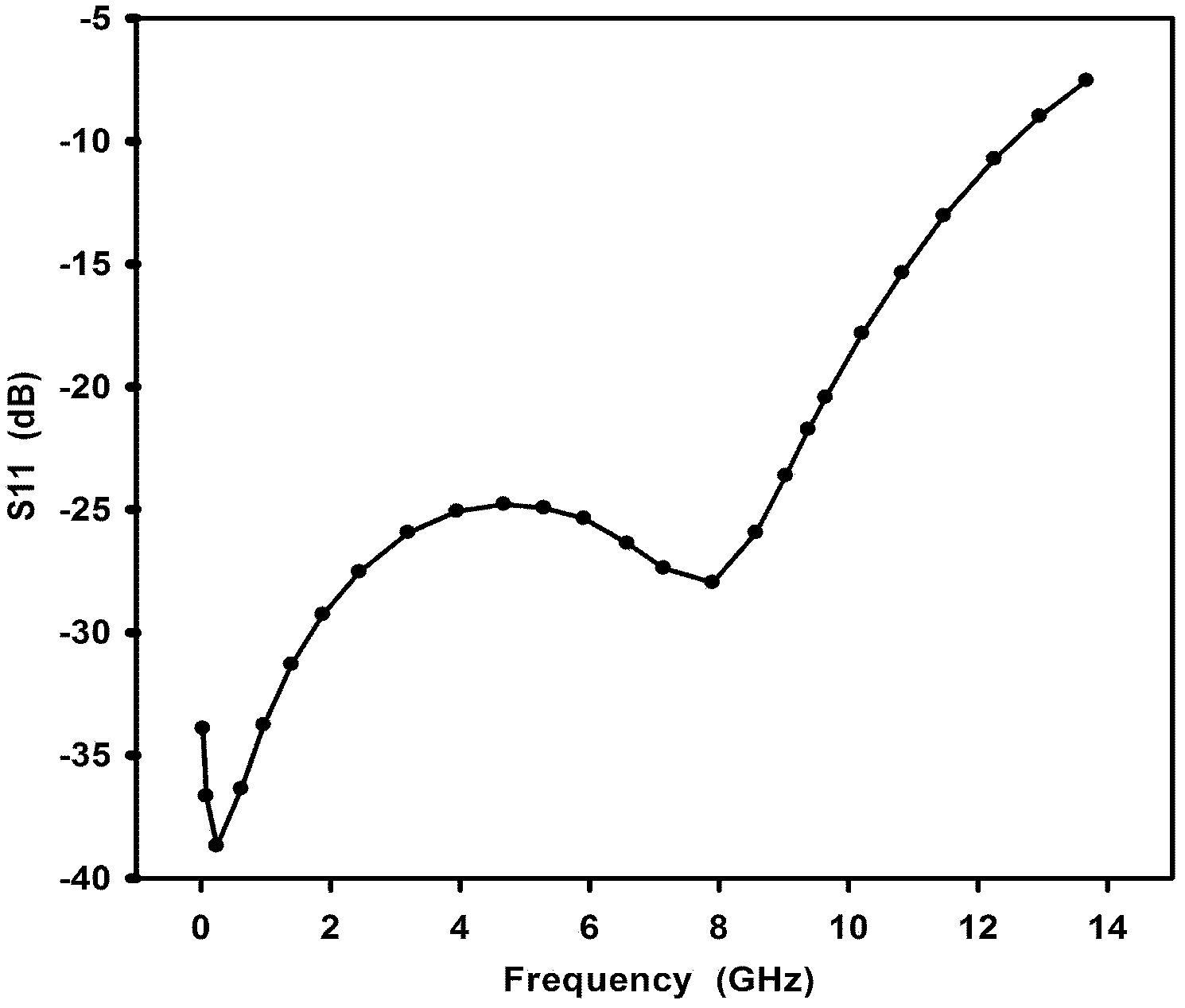

Radio-frequency ultra-wideband low-noise amplifier based on inductance compensation

InactiveCN102497167AImprove transconductanceHigh gainAmplifier modifications to reduce noise influenceHigh frequency amplifiersUltra-widebandTuned amplifier

The invention discloses a radio-frequency ultra-wideband low-noise amplifier based on inductance compensation, relating to a radio-frequency integrated circuit technology. The radio-frequency ultra-wideband low-noise amplifier mainly consists of an input amplification-stage circuit, a feedback-stage circuit, a matching-stage circuit, a load-stage circuit, a bias-stage circuit and an output buffering-stage circuit jointly. According to the radio-frequency ultra-wideband low-noise amplifier, both the input matching stage and the load stage are subjected to inductance compensation, and the sensitivity of the low-noise amplifier on the technology is reduced by adopting a current multiplexing technology with independent bias, so that the performance is more stable, the ultra-wideband is also realized, and the working frequency range is 0.1-12GHz; meanwhile, the radio-frequency ultra-wideband low-noise amplifier gets favorable indexes, such as noise, linearity, gain, power consumption and the like and is suitable for an ultra-wideband multi-standard wireless communication receiving system.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

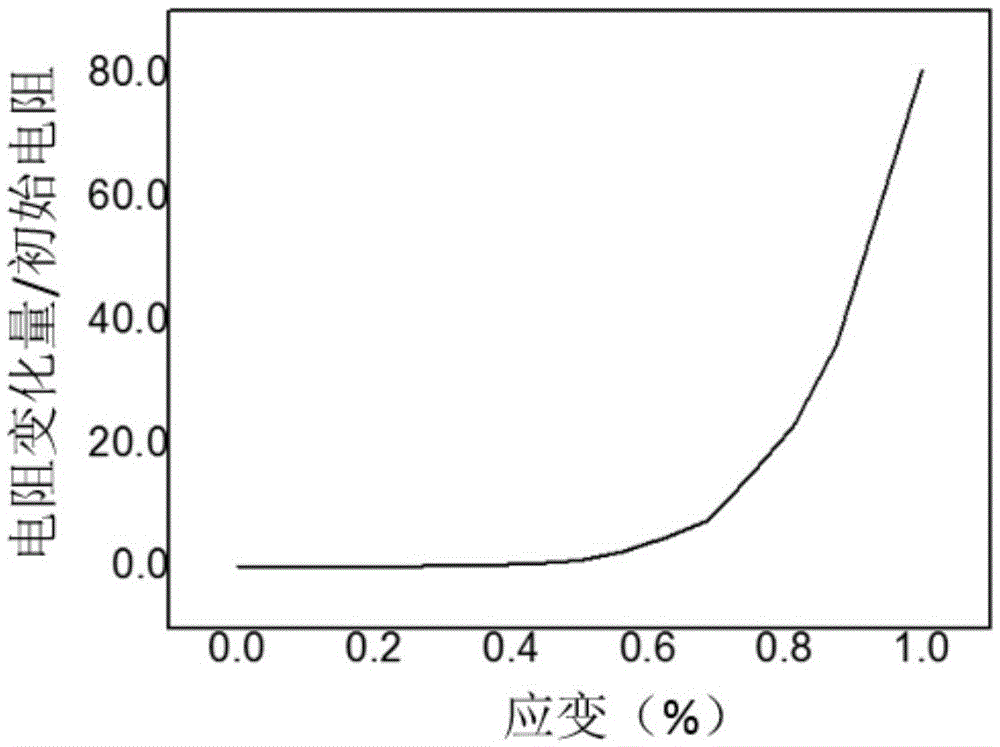

Metallic film flexible strain sensor and preparation method therefor

ActiveCN105627905ASimple structureHigh sensitivitySubsonic/sonic/ultrasonic wave measurementUsing electrical meansNanoscopic scaleStrain sensor

The invention discloses a metallic film flexible strain sensor and a preparation method therefor. The sensor comprises a metallic film, a flexible base material, and at least two contacts. The metallic film is attached to the flexible base material in a weak attaching manner. The metallic film is provided with at least one through directional long crack, wherein the width of the directional long crack is at a nanometer scale. The directional long crack passes through the metallic film to the interior of the flexible base material in a thickness direction, and the direction of the directional long crack is perpendicular to a stretching direction. When the metallic film generates stretching deformation along with the flexible base material, the crack of the metallic film is extended and even broken. When the stretching deformation of the flexible base material is released, the crack of the metallic film narrows and finally returns to an initial state. The sensor is simple in structure, is higher in sensitivity, is simple in preparation technology, is abundant in raw material, is compatible with a conventional integrated circuit, and is convenient for large-scale production.

Owner:TSINGHUA UNIV

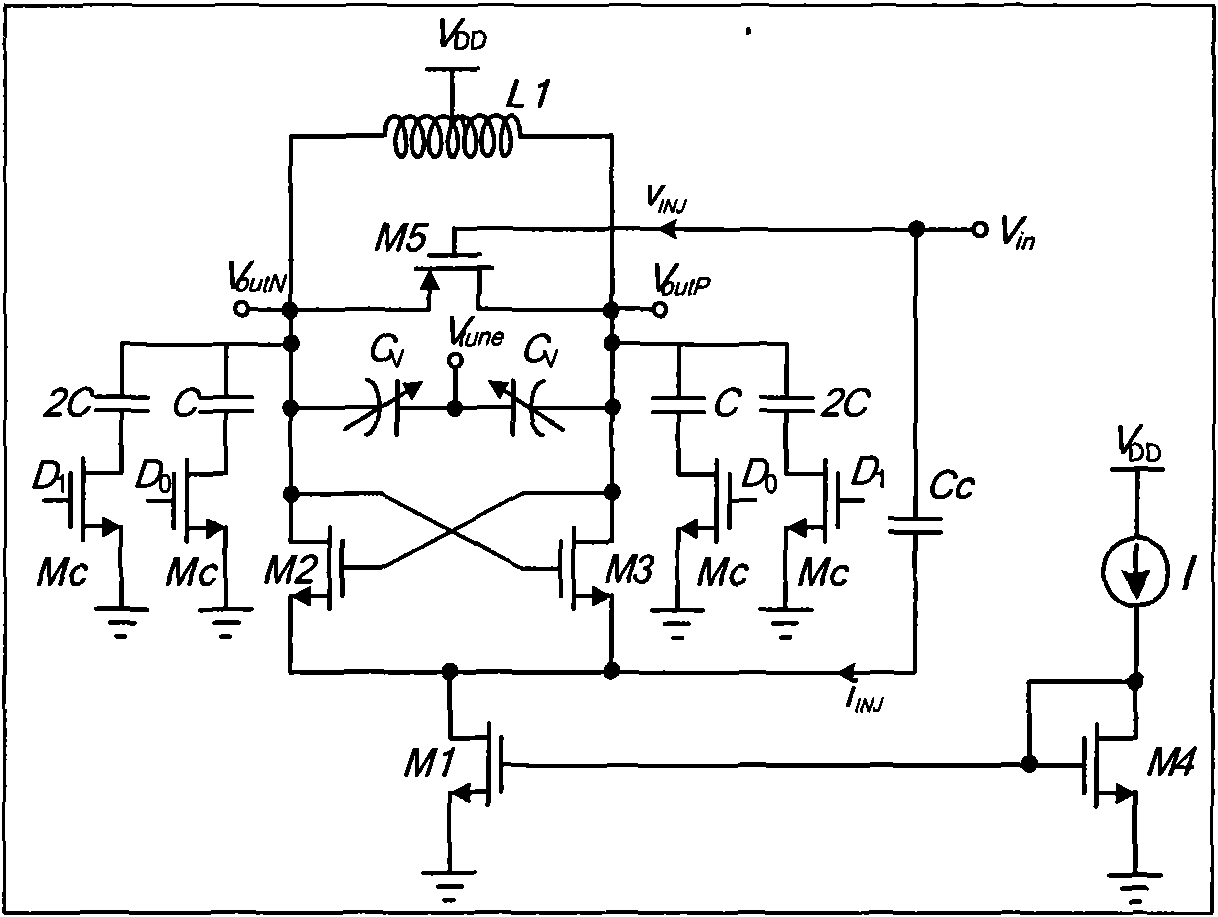

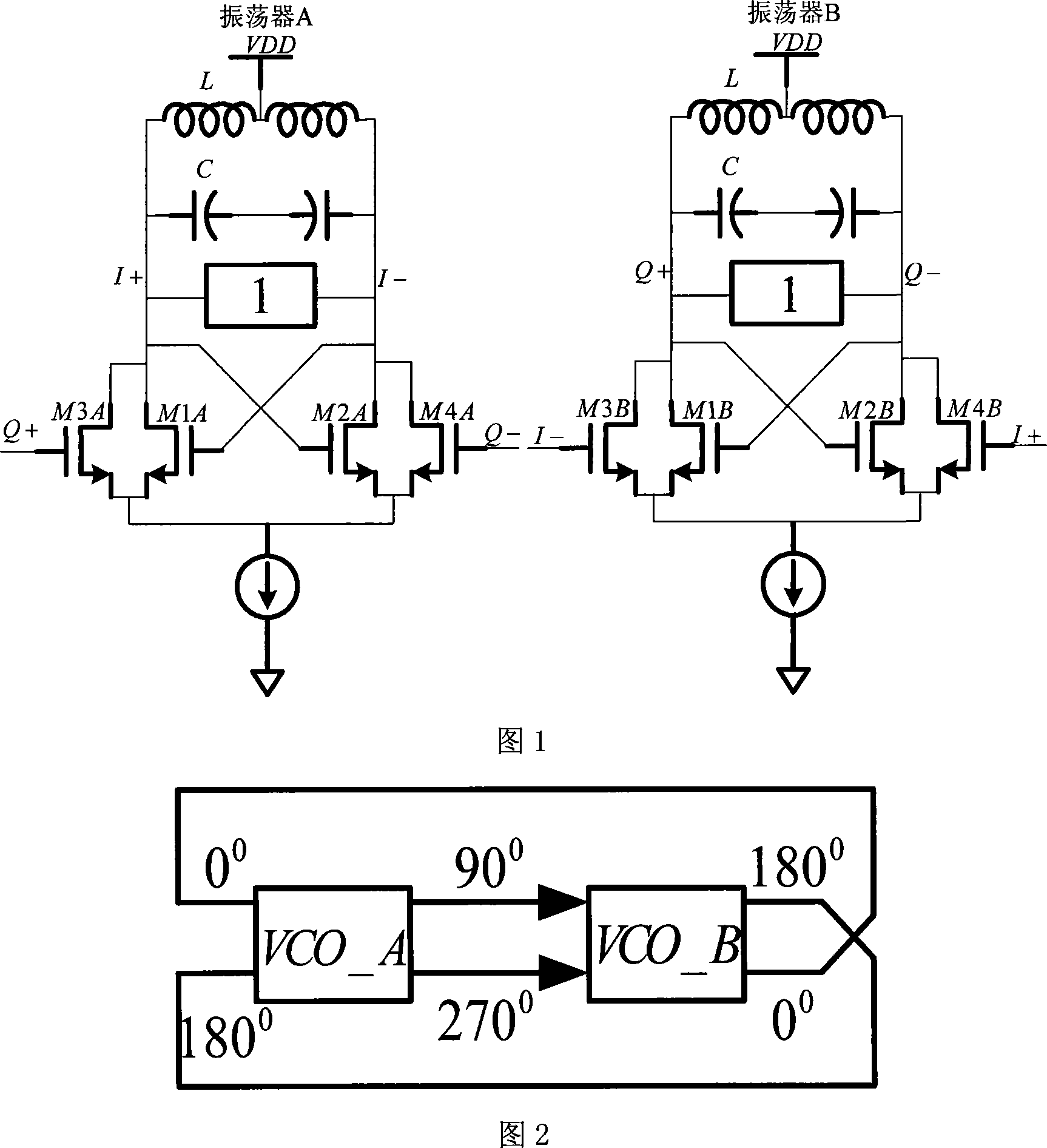

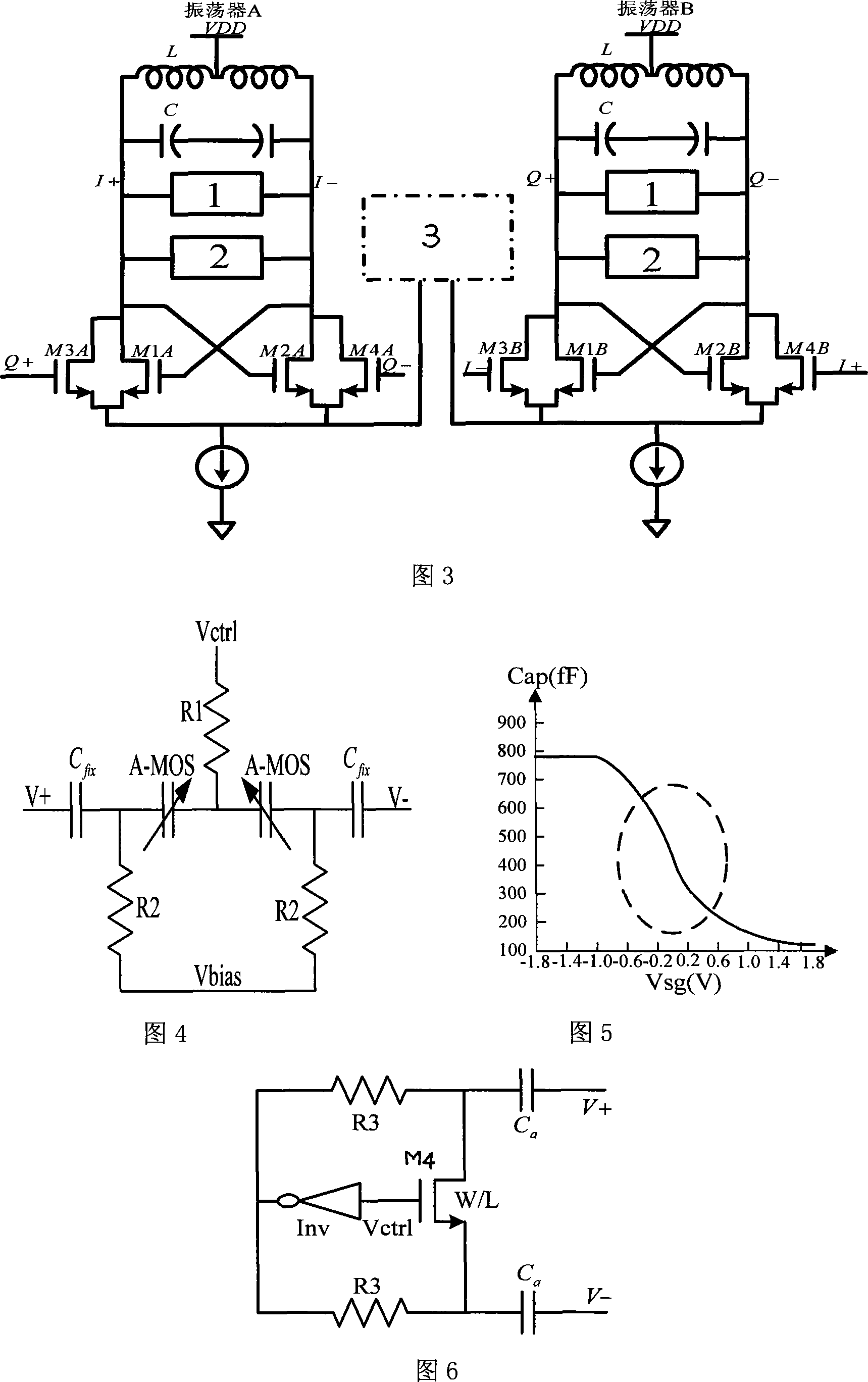

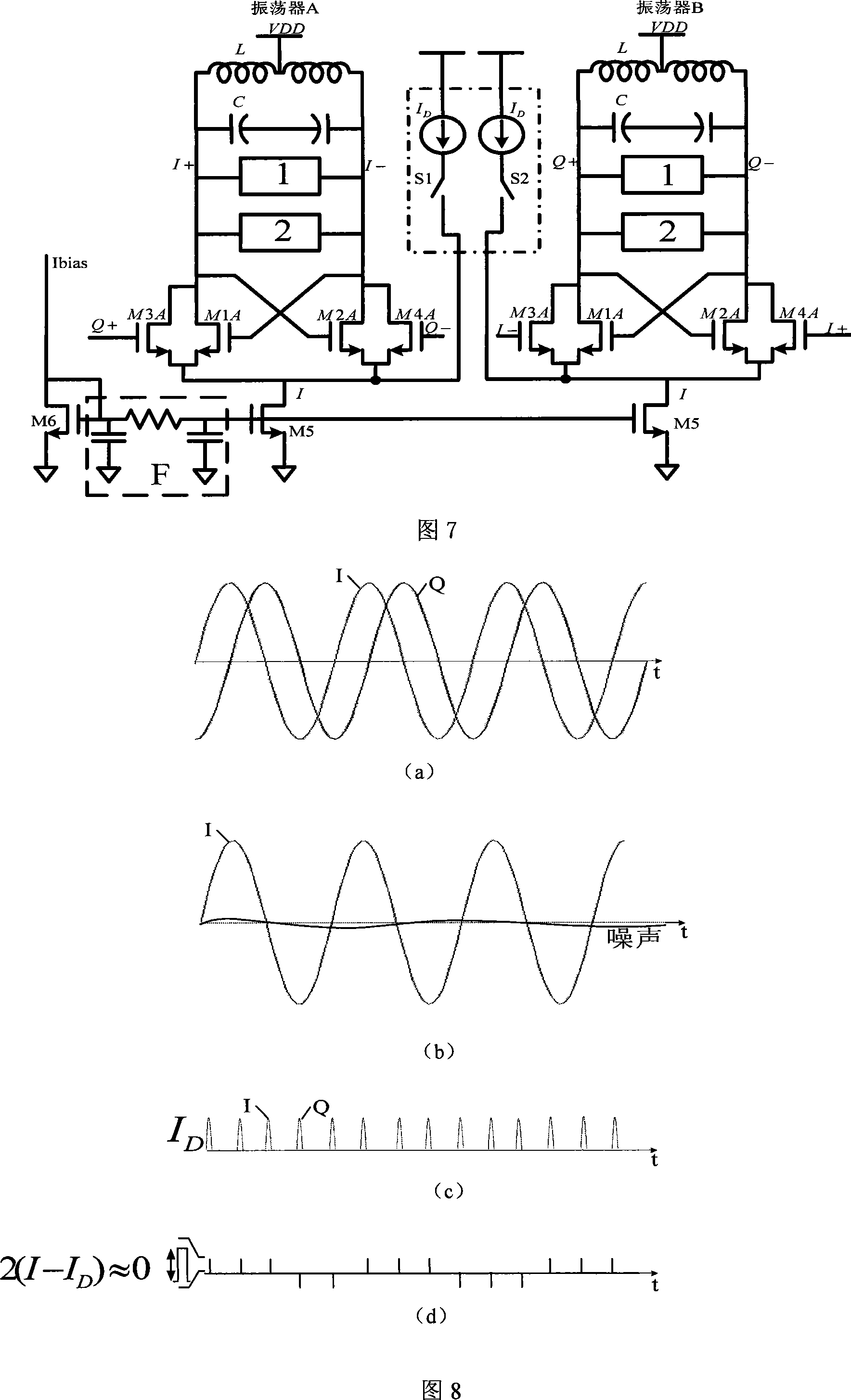

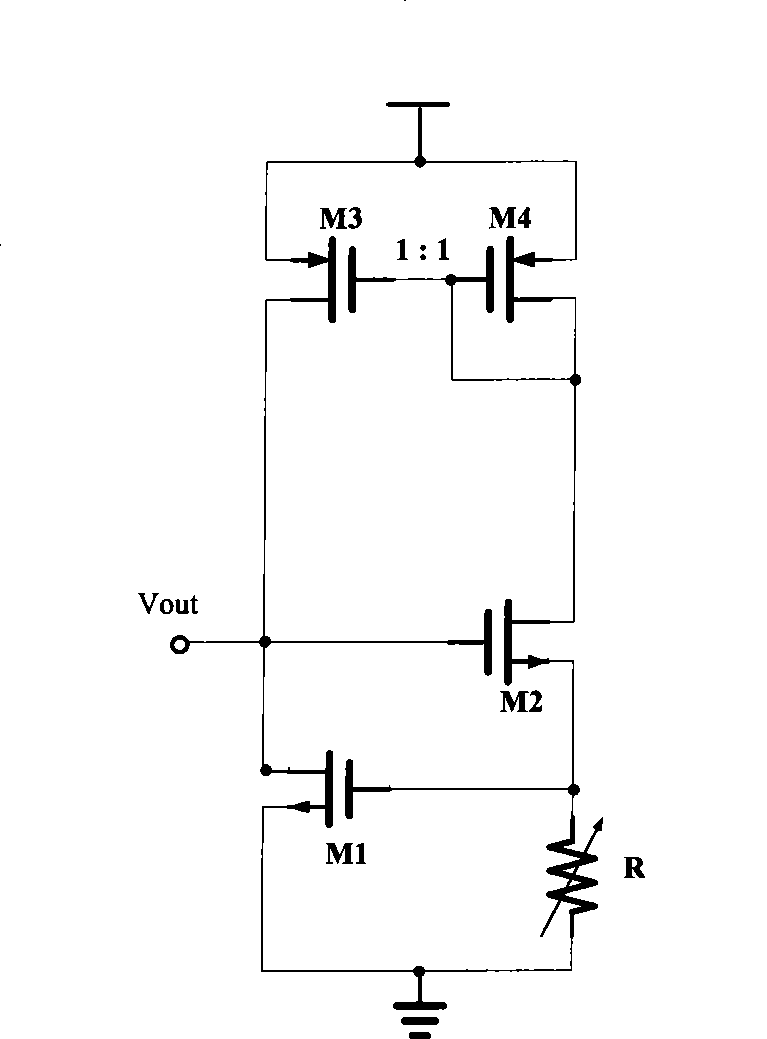

LC orthogonal voltage controlled oscillator capable of reducing flicker noise

InactiveCN101183851AReduce 1/f noiseOscillations generatorsFrequency-changer modificationsPhase noiseQuadrature oscillator

The invention relates to an LC quadrature VCO (voltage controlled oscillator) which can reduce the intermittent noise, belonging to the technical field of integrated circuit, . The invention is characterized in that two negative resistance oscillators are connected together with a quadrature coupler to output quadrature signals; the reduced phase noise is implemented by using a more linear narrow-band turning variable capacitor structure, multiband switching digital array with a lower parasitic capacitance and an intermittent noise eliminating circuit reducing the intermittent noise getting into the LC oscillator when inputting voltage crossing the zero point.

Owner:FUDAN UNIV

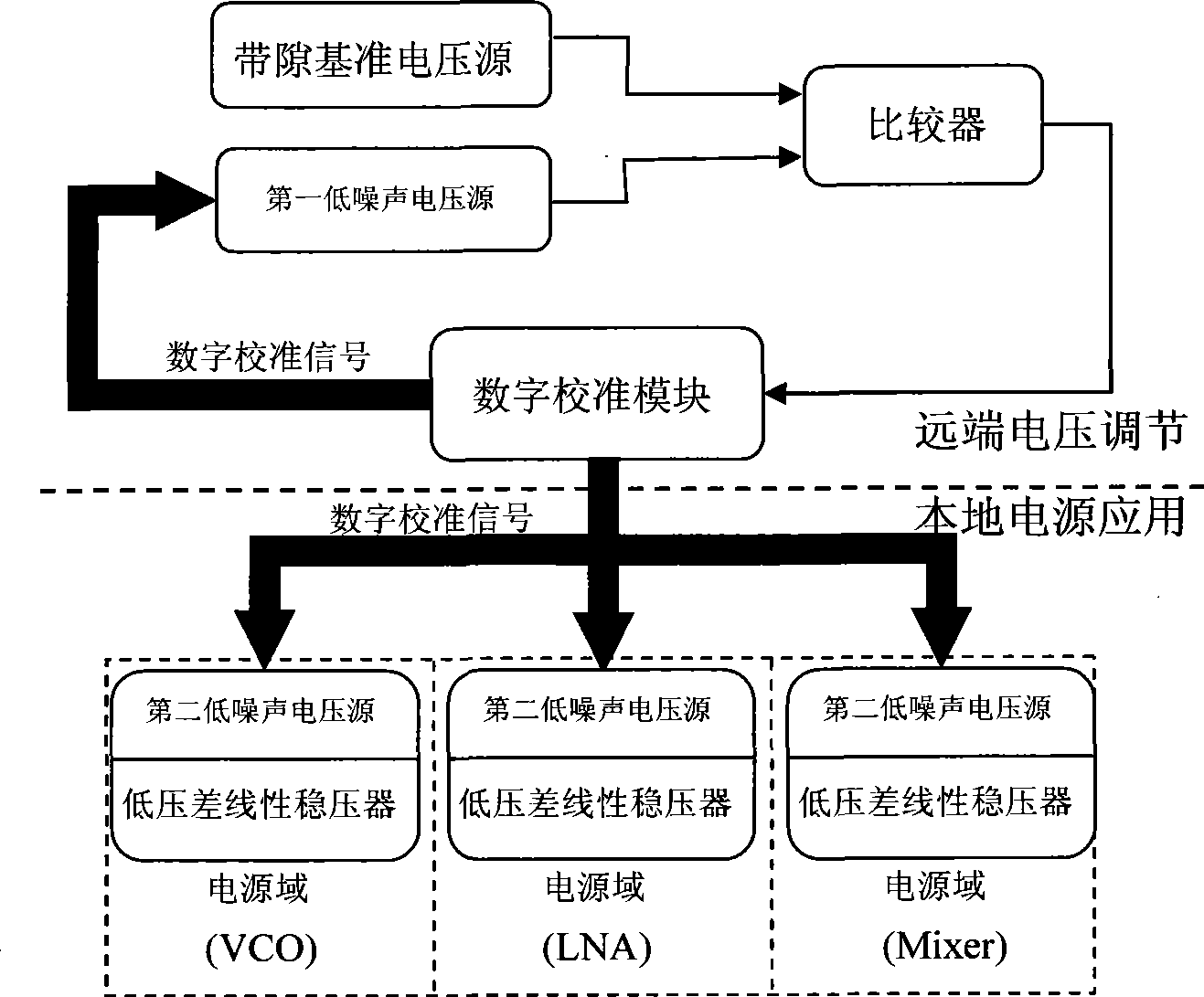

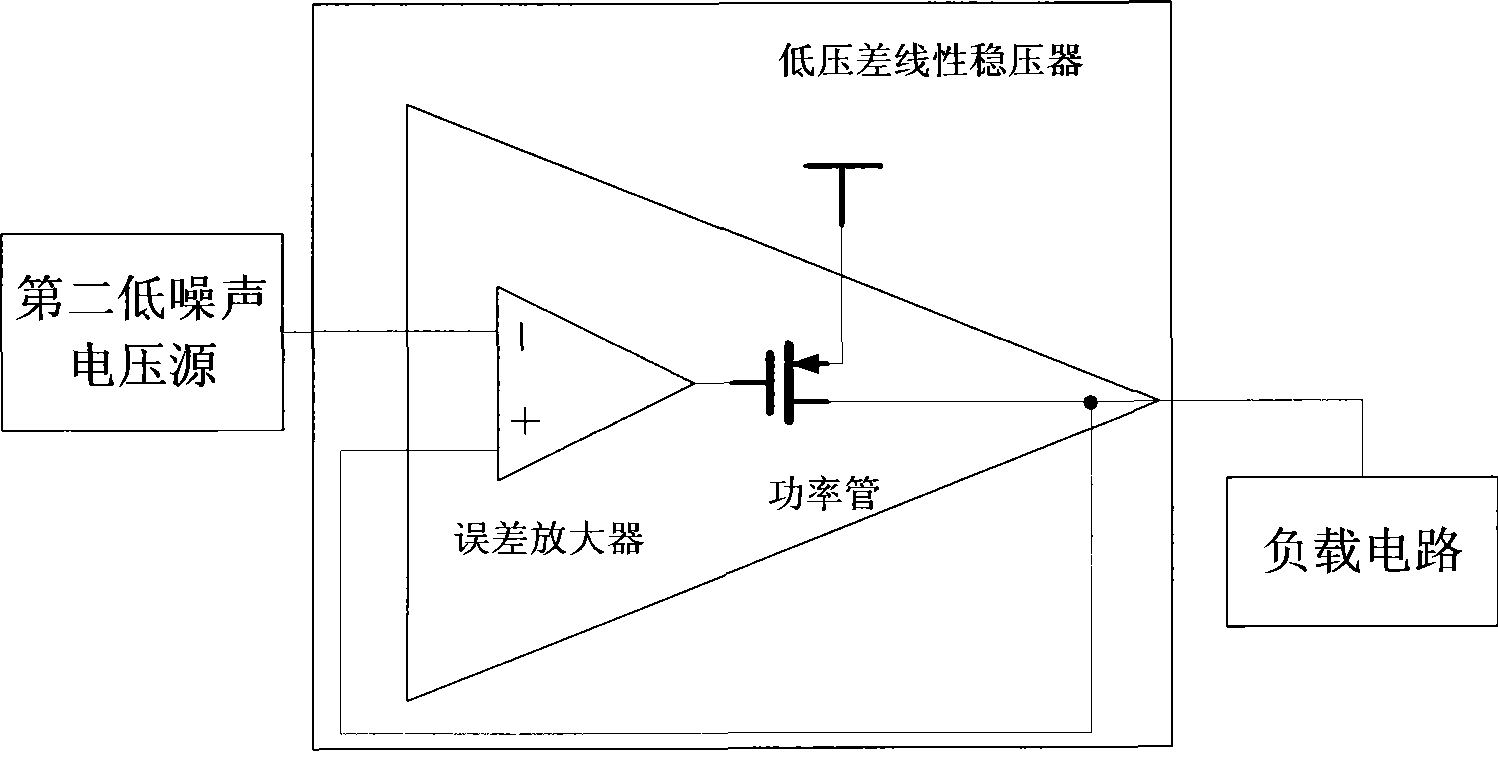

Totally- integrated low noise power supply system in chip of radio frequency receiver

InactiveCN101393466AImproved output noise performanceReduce output noiseTransmissionElectric variable regulationLinear regulatorTuned radio frequency receiver

The invention relates to a fully integrated low-noise power supply system for a radio-frequency receiver chip, which relates to the technical field of an integrated circuit of a radio-frequency wireless receiver. The fully integrated low-noise power supply system for the radio-frequency receiver chip comprises a remote voltage regulation end and a local power application end, wherein both outputs of a first low-noise voltage source and a band gap reference voltage source are connected to input ends of a comparator; an output end of the comparator is connected with an input end of a digital calibration module the output of which is fed back to an input of the first low-noise voltage source; the local power application end consists of a plurality of power domains, wherein a low dropout linear regulator consists of a power tube and an error amplifier; the output end of the power tube is connected with a load circuit, and a grid electrode of the power tube is connected with the output end of the error amplifier; and an anode or a cathode of the error amplifier is respectively and correspondingly connected with output ends of a second low-noise power source and the power tube, so as to form a negative feedback system. The fully integrated low-noise power supply system for the radio-frequency receiver chip improves the noiseproof performance, does not require an on chip or off chip capacitor, and obviously improves the system integration.

Owner:SHANGHAI JIAO TONG UNIV

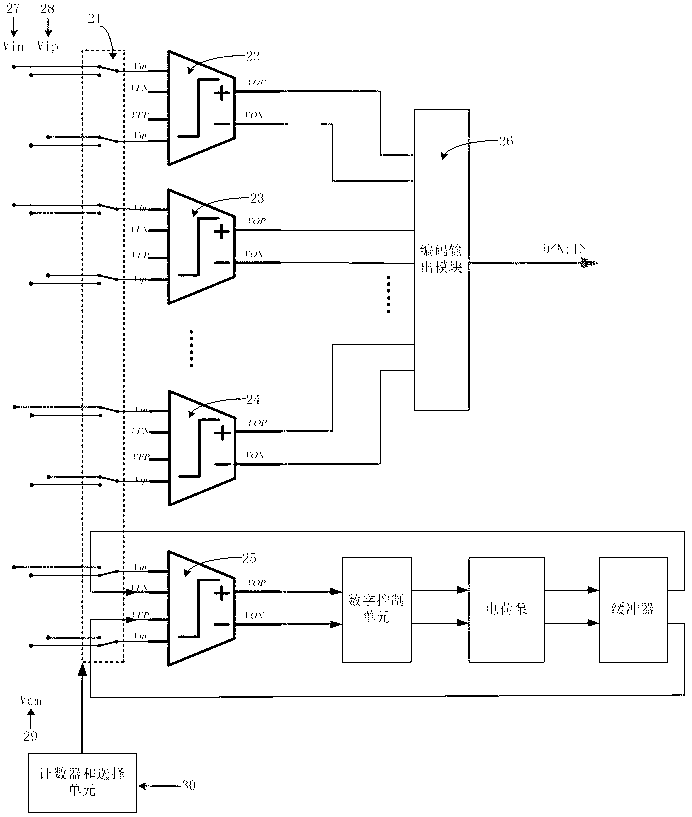

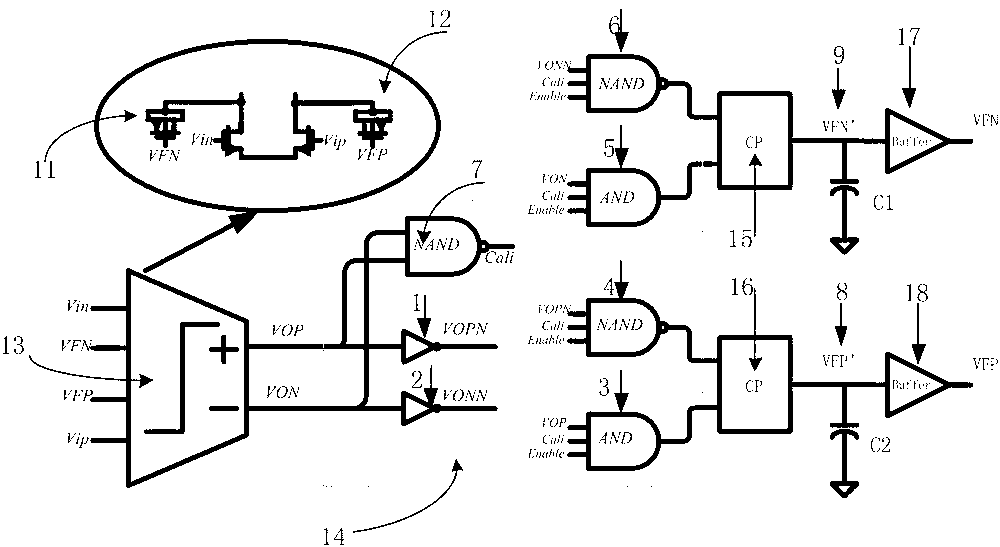

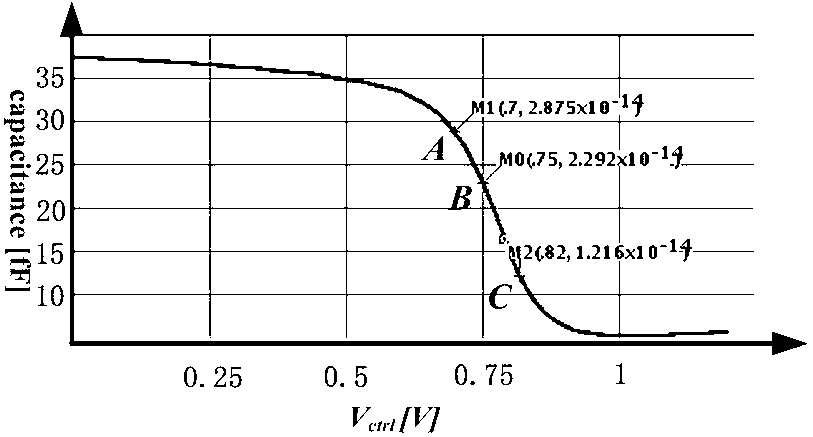

Method for correcting offset of high-speed high-precision large-range low-power-consumption dynamic comparator

ActiveCN102843136AHigh precisionReduce power consumptionAnalogue/digital conversion calibration/testingCapacitanceEngineering

The invention belongs to the technical field of integrate circuits and in particular relates to a method for correcting offset of a high-speed high-precision large-range low-power-consumption dynamic comparator. The comparator is a core part of an analog-to-digital converter. The invention provides a new real-time correction method. By utilization of the characteristic that the capacitance value of variable capacitance of a metal oxide semiconductor (MOS) tube working in an inversion layer is linearly continuously variable along with the regulating voltage, load capacitance at the output end of the comparator is subjected to fine adjustment precisely until the differential input of the comparator is zero. The offset voltage generated by mismatch of devices of the comparator and the influence generated by fine adjustment on the output load capacitance of the comparator are counteracted mutually, so that the offset voltage of the comparator is corrected. By the method, the 1sigma offset voltage of the comparator can be effectively reduced by three hundred times and can be reduced to 66 MuV from the typical value of 29.4 mV.

Owner:FUDAN UNIV

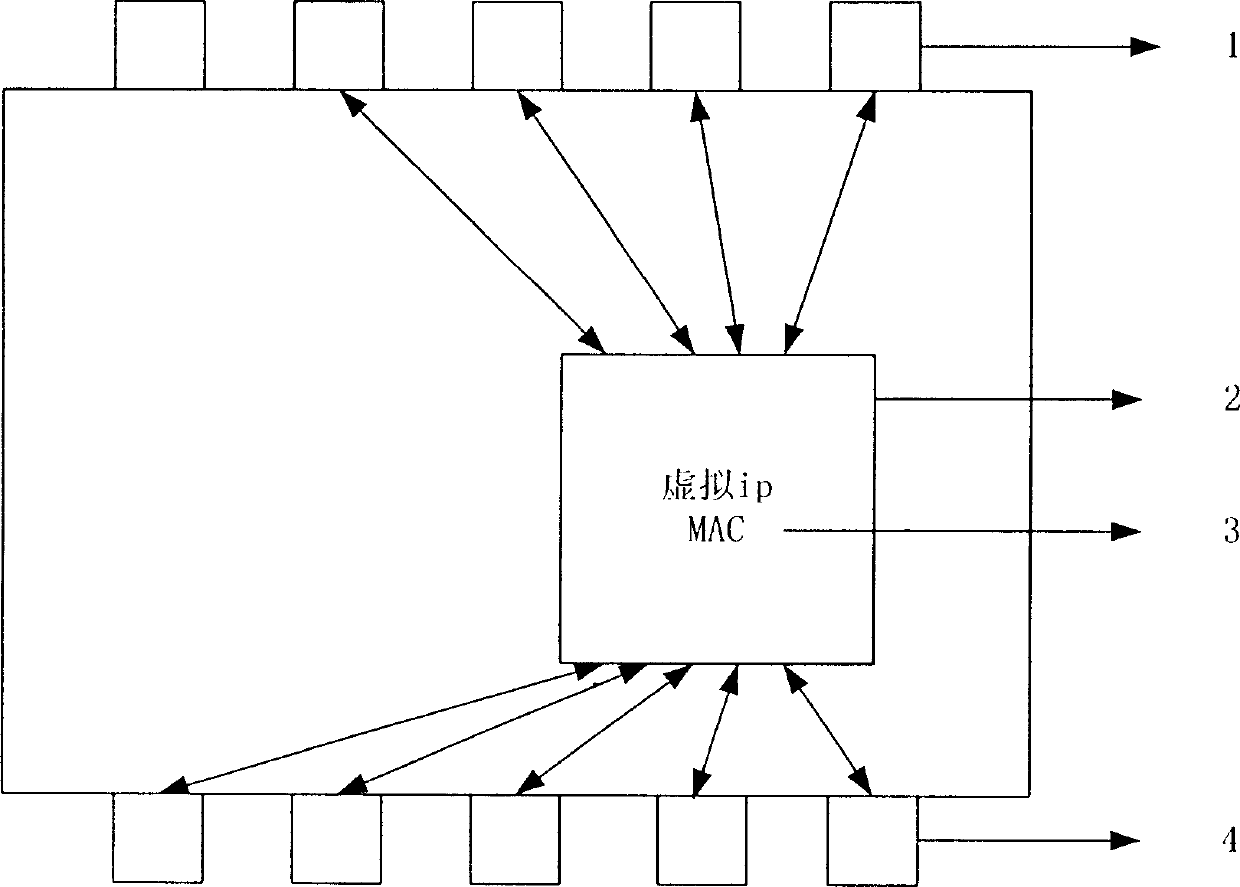

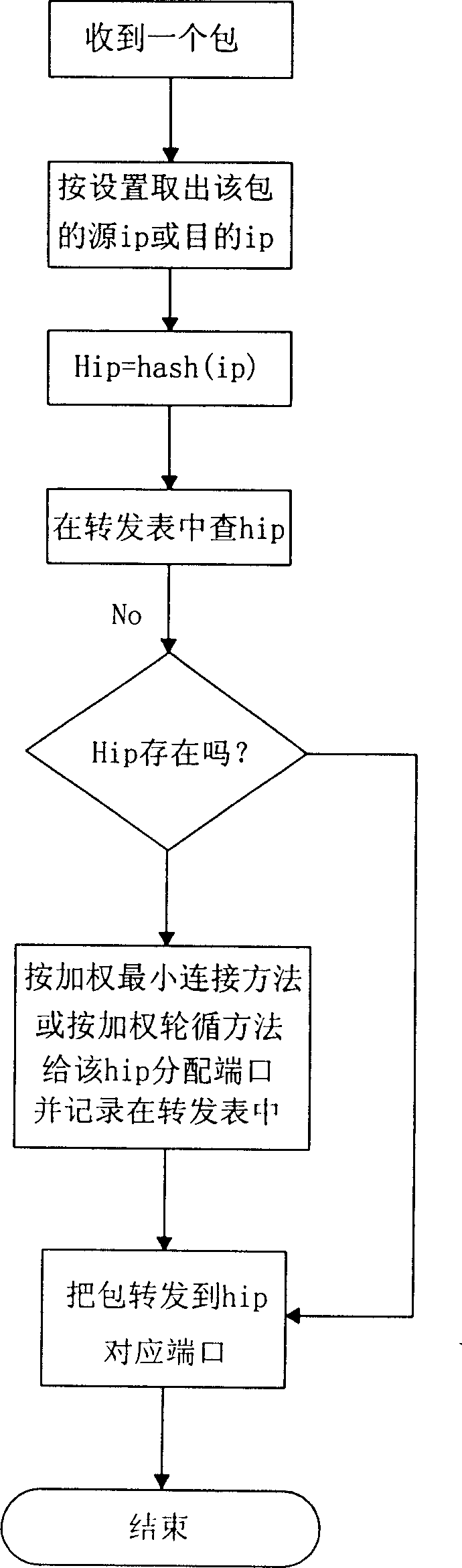

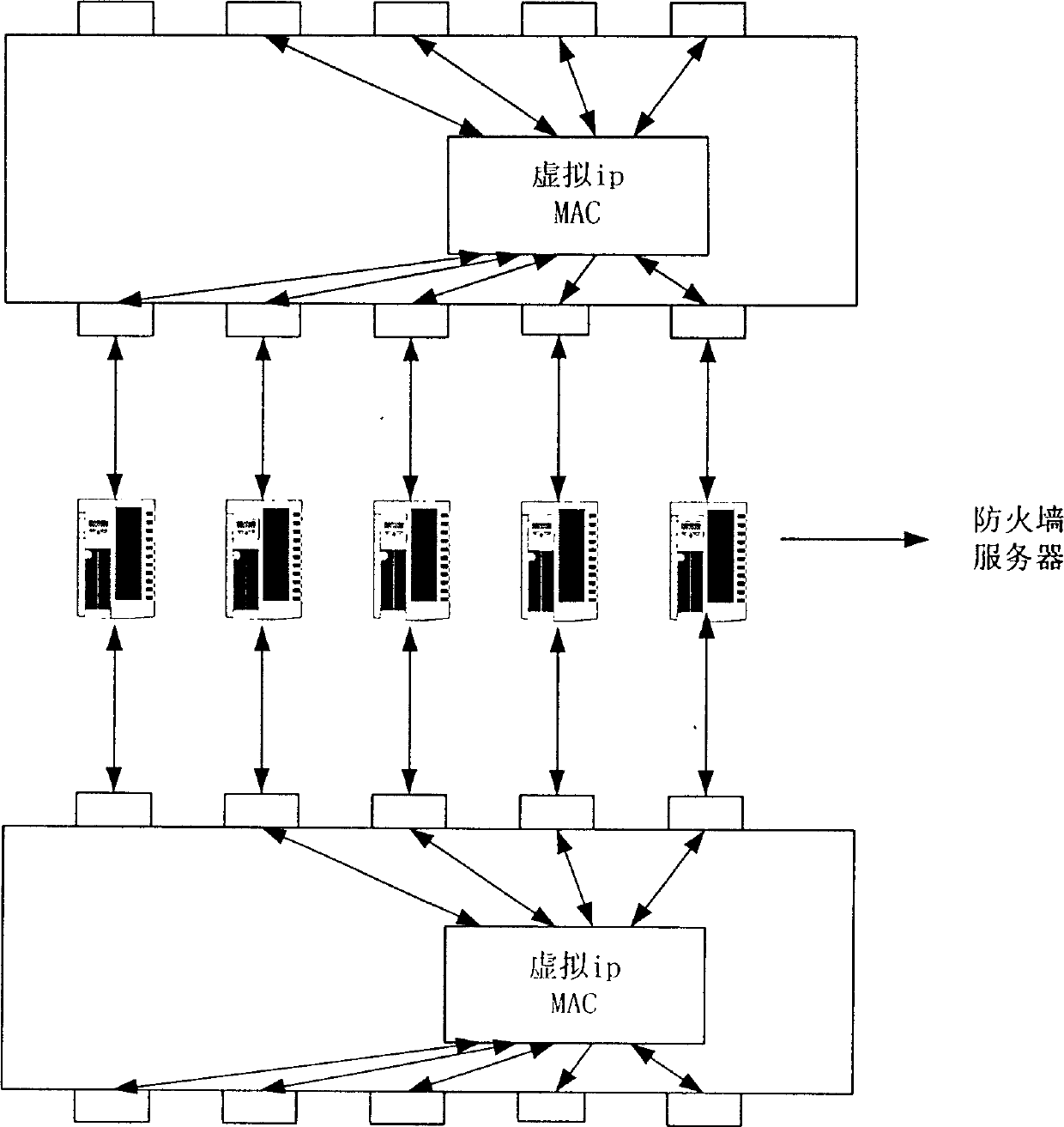

Single address traffic distributor of cluster network

InactiveCN1595906AImprove extended processing capabilitiesData switching networksTraffic capacityIp address

The invention provides a single address flow sorter of group network. The sorter binds several physical terminals into a virtual physical terminal to extend the upstream flow, and allocates network flow to different processing joints according to the IP address of client terminal and upgrade the process ability. The data pack applying the IP is allocated with a different physical terminal, the process is realized with ASIC technology, the flow classification accordance is to work out Hash value to the client terminal IP address, because the data of the same user is allocated to the same physical terminal, thus it can provides continuous service to the joint connected to the physical joint.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

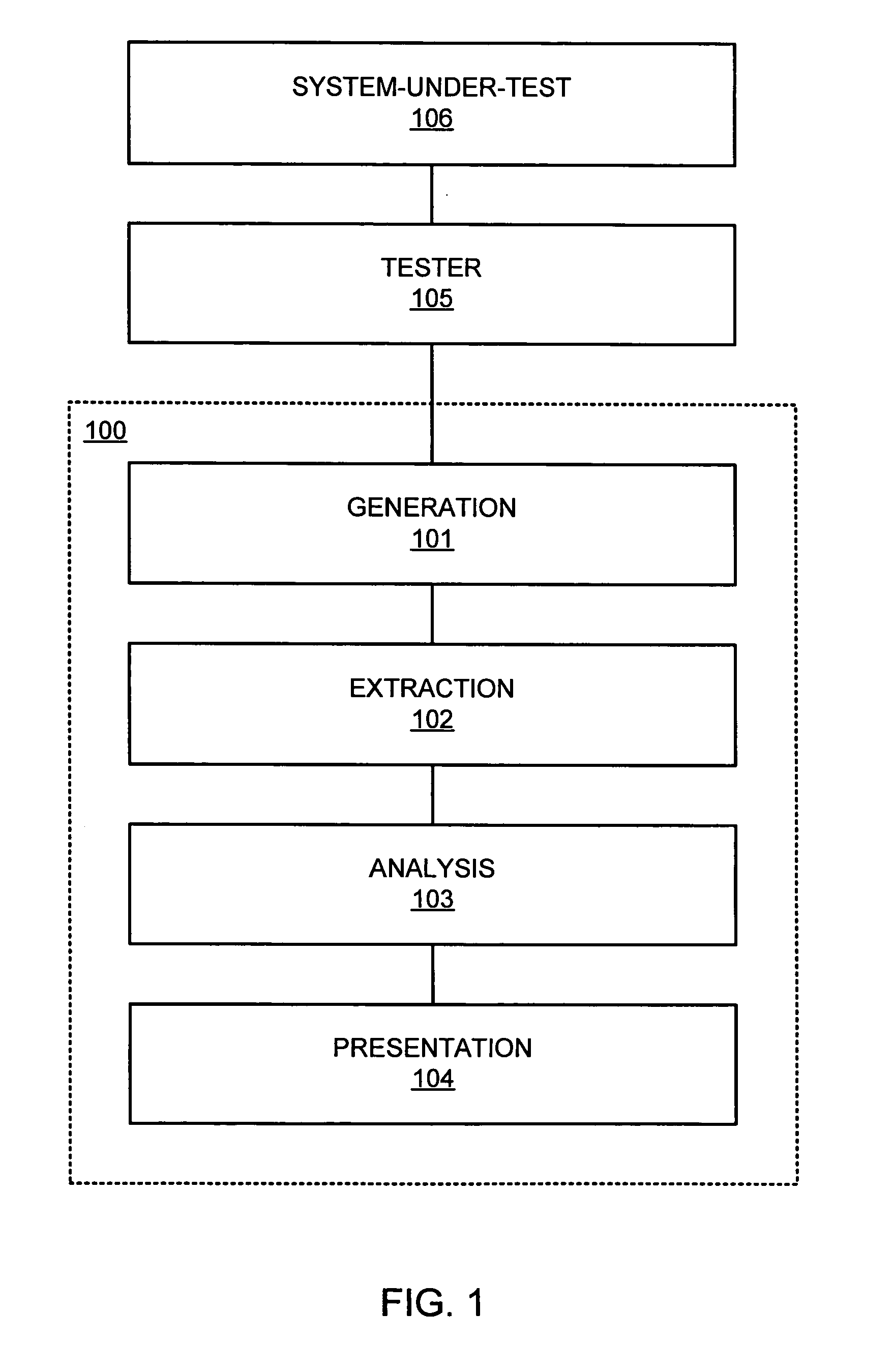

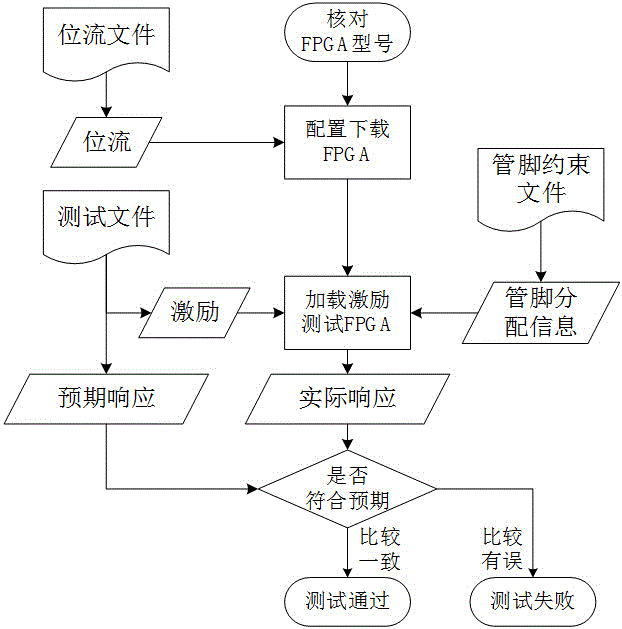

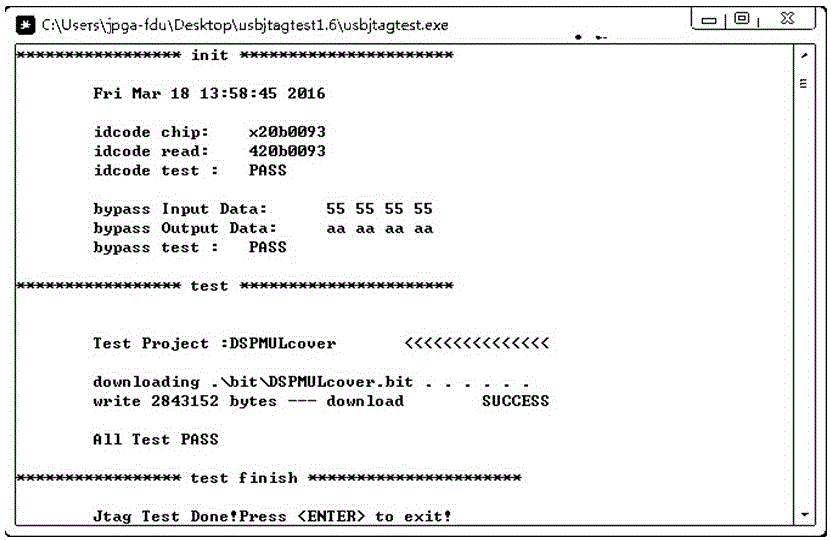

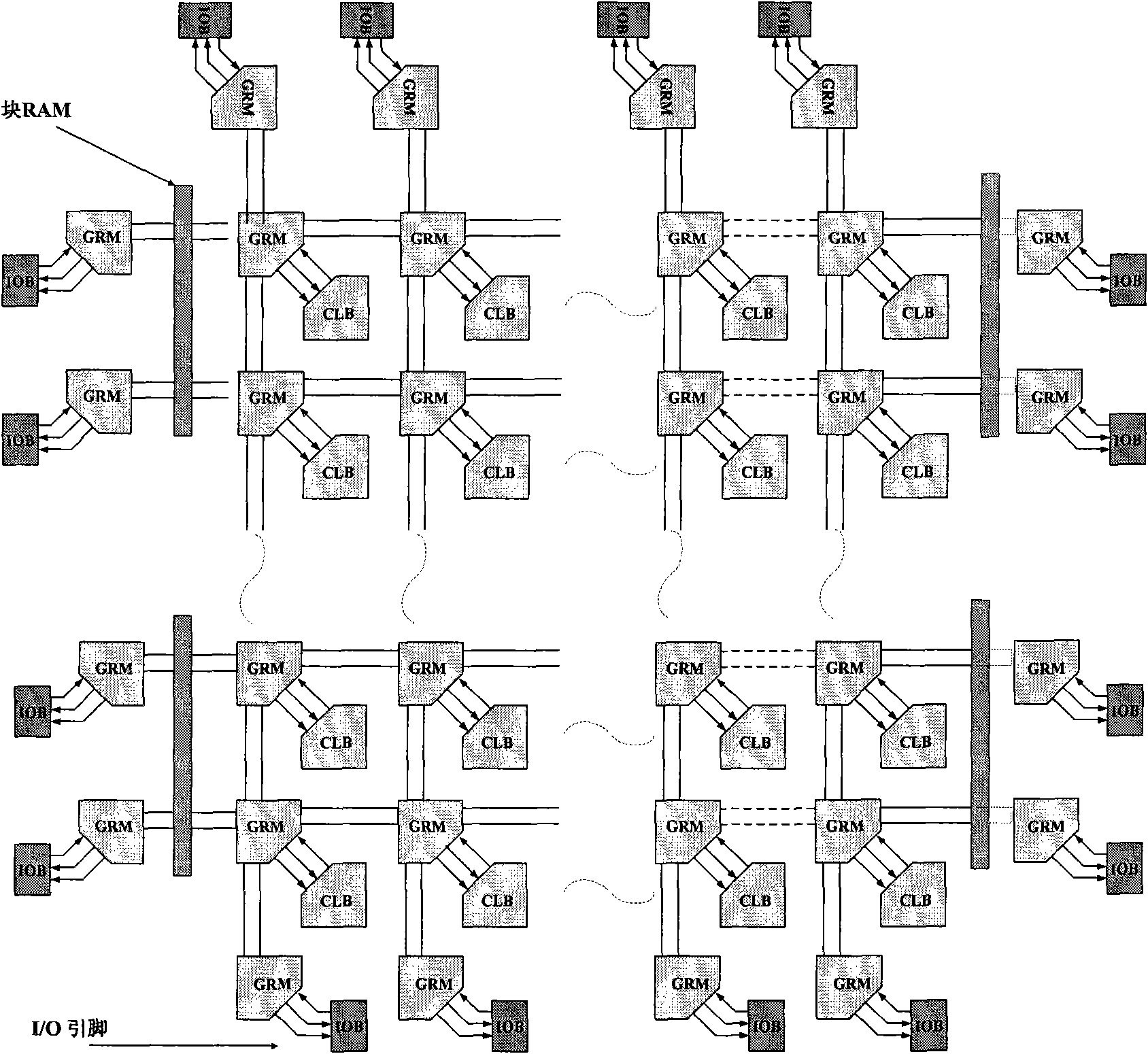

Function traversal testing method for high performance SoC FPGA

ActiveCN105866665AImprove test coverageImprove test efficiencyElectrical testingTest efficiencyComputer hardware

The invention belongs to the technical field of integrated circuits, and relates to a function traversal testing method for high performance SoC FPGA. A set of complete function traversal testing method is established for CLB, BRAM, DSP, CM, IOB, clock network, interconnection and other resources in the high performance SoC FPGA, and corresponding bit stream is generated to apply excitation on an FPGA port and read back the response of the FPGA port. The response is compared with an expected result to realize the traversal covering test on the Soc FPGA resources. The test method is applicable to various high performance Soc FPGA with complex function and abundant resources and if of high application value in the FPGA test field. The test coverage rate and the test efficiency are high, the test cost is low, and the transferability and the universality are good.

Owner:FUDAN UNIV

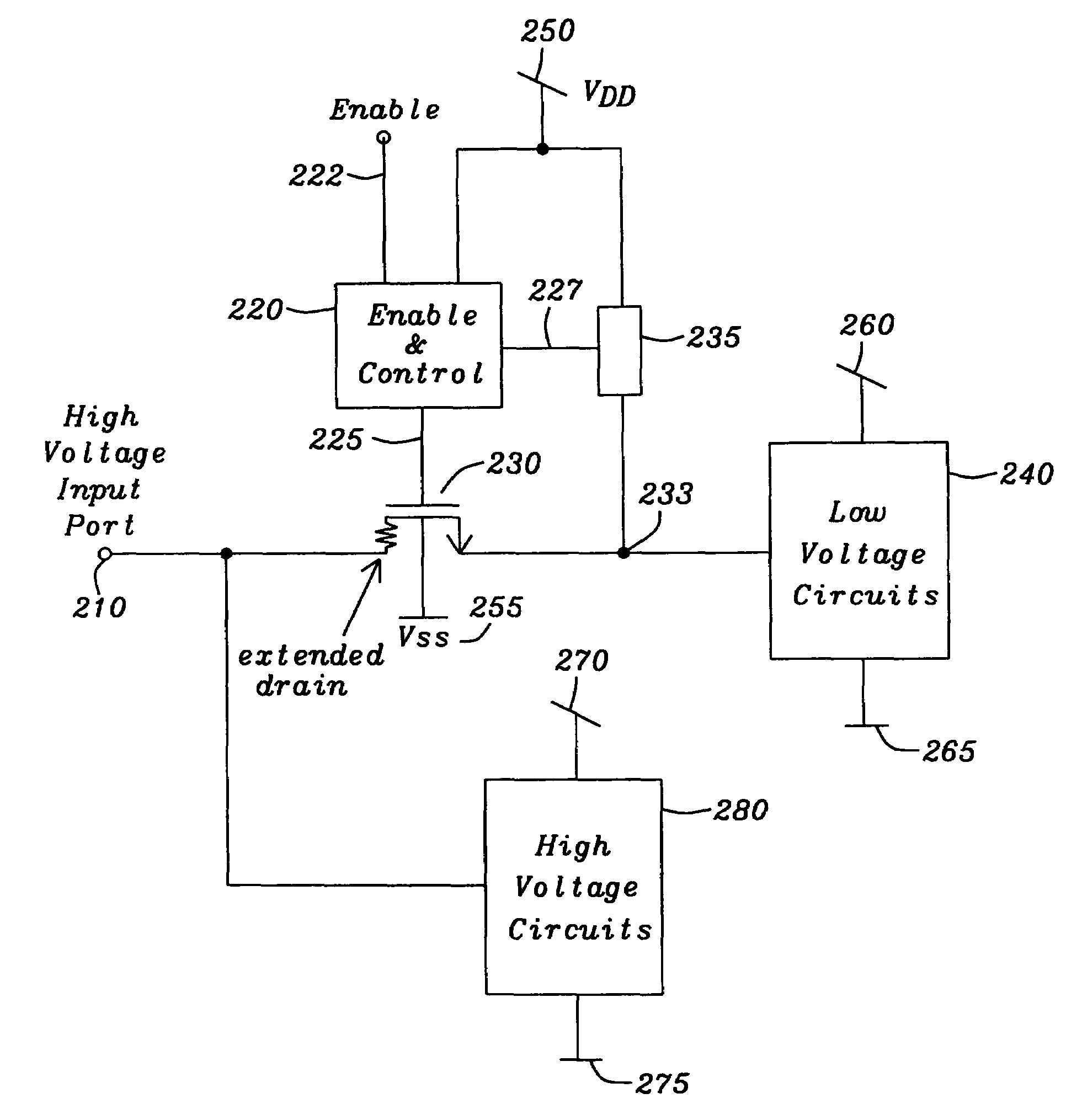

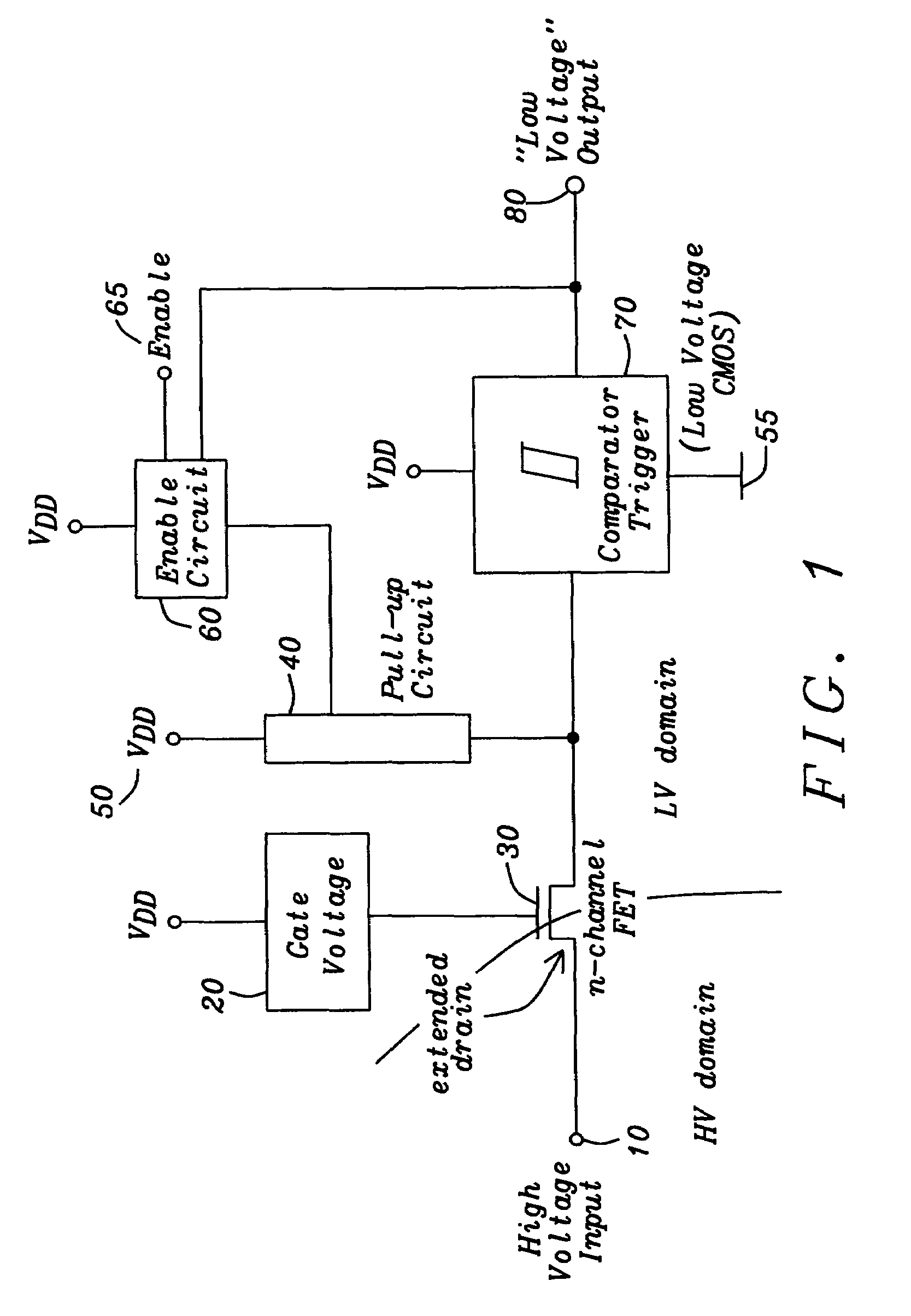

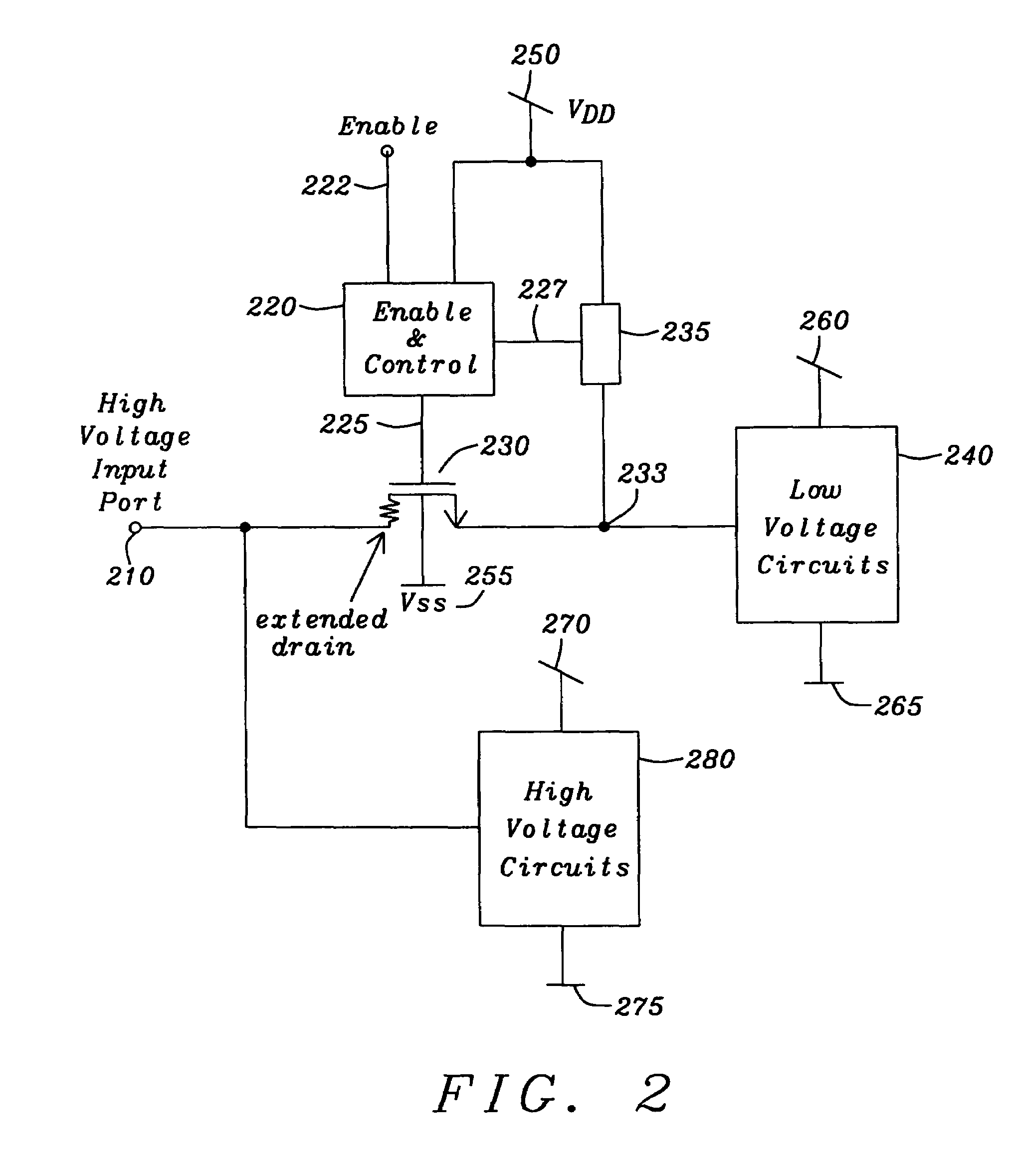

Digital CMOS-input with N-channel extended drain transistor for high-voltage protection

ActiveUS7236002B2Low costFail-safe circuitsReliability increase in field effect transistorsCMOSElectronic systems

A circuit and a method are given, to realize an electronic system for combined usage at differing voltage ranges as defined by a low-voltage range for operating standard CMOS devices and a high-voltage range exceeding said standard CMOS low-voltage operating range significantly by multiples and thus necessarily utilizing input ports with an intrinsic high-voltage protection feature. Said circuit and method are designed in order to be implemented with a very economic number of components, capable to be realized with standard modern integrated circuit technologies in CMOS technology.

Owner:DIALOG SEMICONDUCTOR GMBH

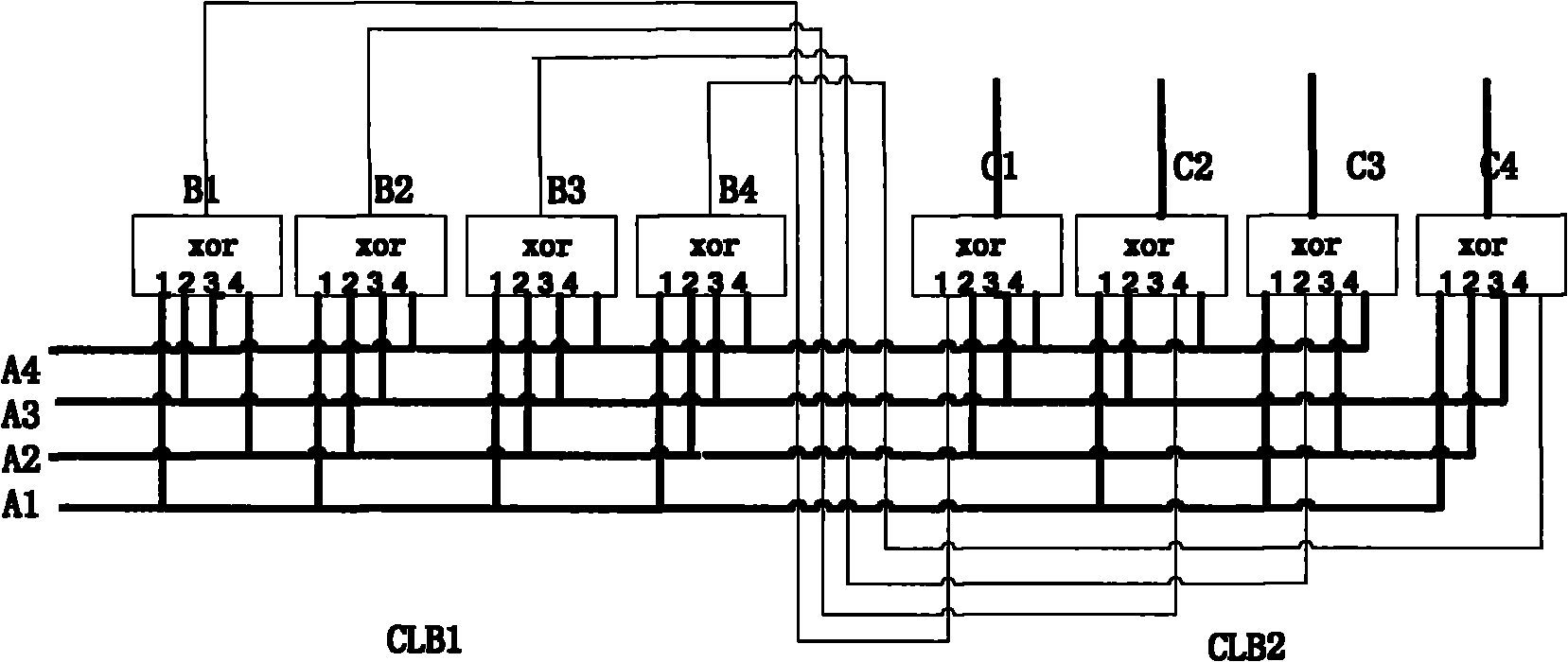

Traversal test method of configurable logic block (CLB) of field programmable gate array (FPGA) based on look-up table structure

ActiveCN101865977AReduce occupancyRelieve pressureElectrical testingCode pointField-programmable object array

The invention belongs to the technical field of an integrated circuit, in particular to a traversal test method of a configurable logic block (CLB) of a field programmable gate array (FPGA) based on a look-up table (LUT) structure. The method comprises: carrying out traversal tests on the single-point fault of an LUT, testing the multiple-point fault of the LUT, carrying out traversal tests on a distributive RAM, assigning the initial value of the trigger to be 0 or 1, carrying out level fixing on a setting terminal and a resetting terminal, leading the enabling to be invalid, and carrying out traversal tests on setting, resetting and enabling and the like. The invention can complete all the tests on the confronting manufacturing of all the CLBs in FPGA chips, and can cover all the basic logic devices, programmable code points and internal interconnection resources inside the CLBs. The configuration times, configuration difficulty and test time required by the test can all be greatly optimized.

Owner:FUDAN UNIV

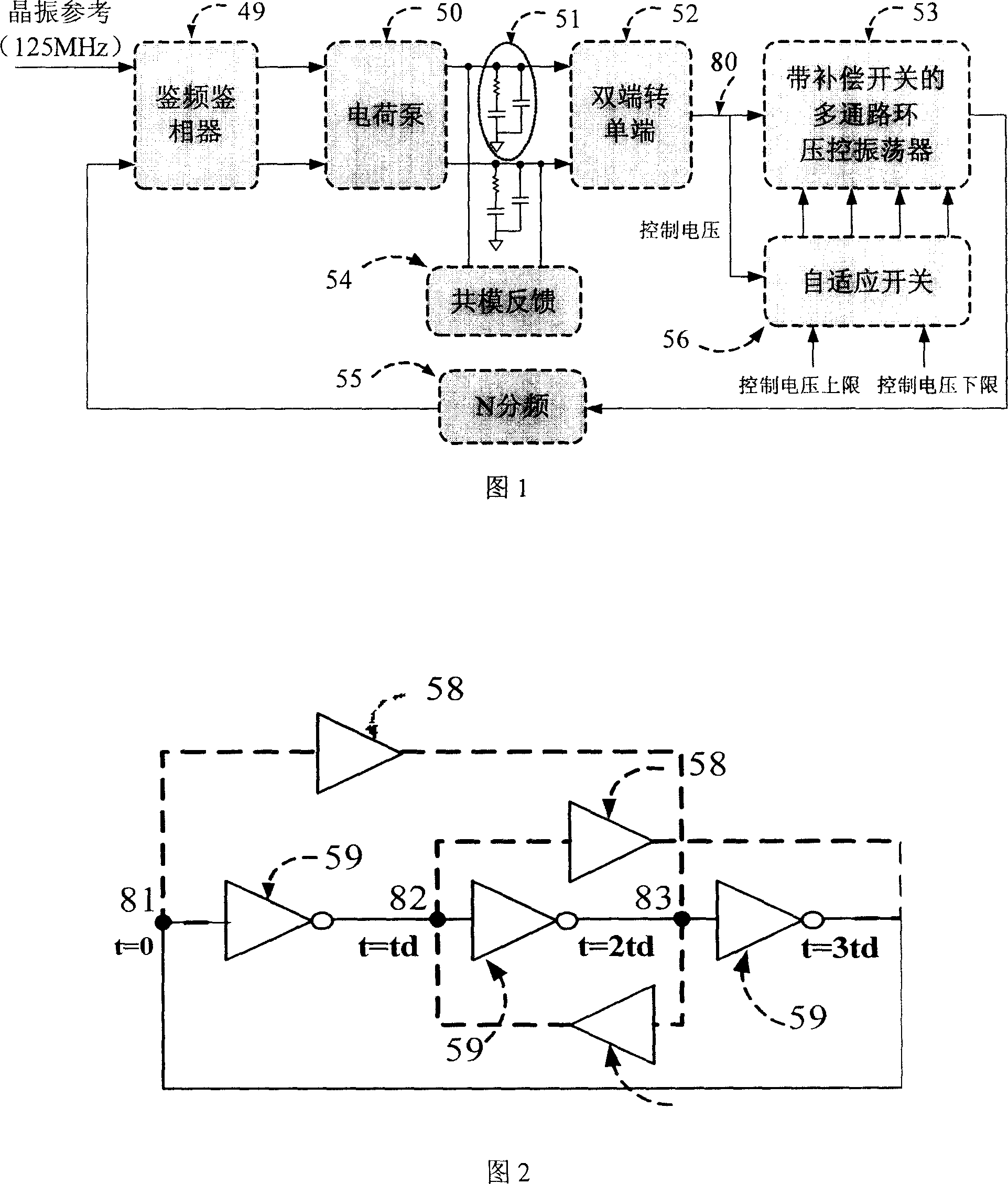

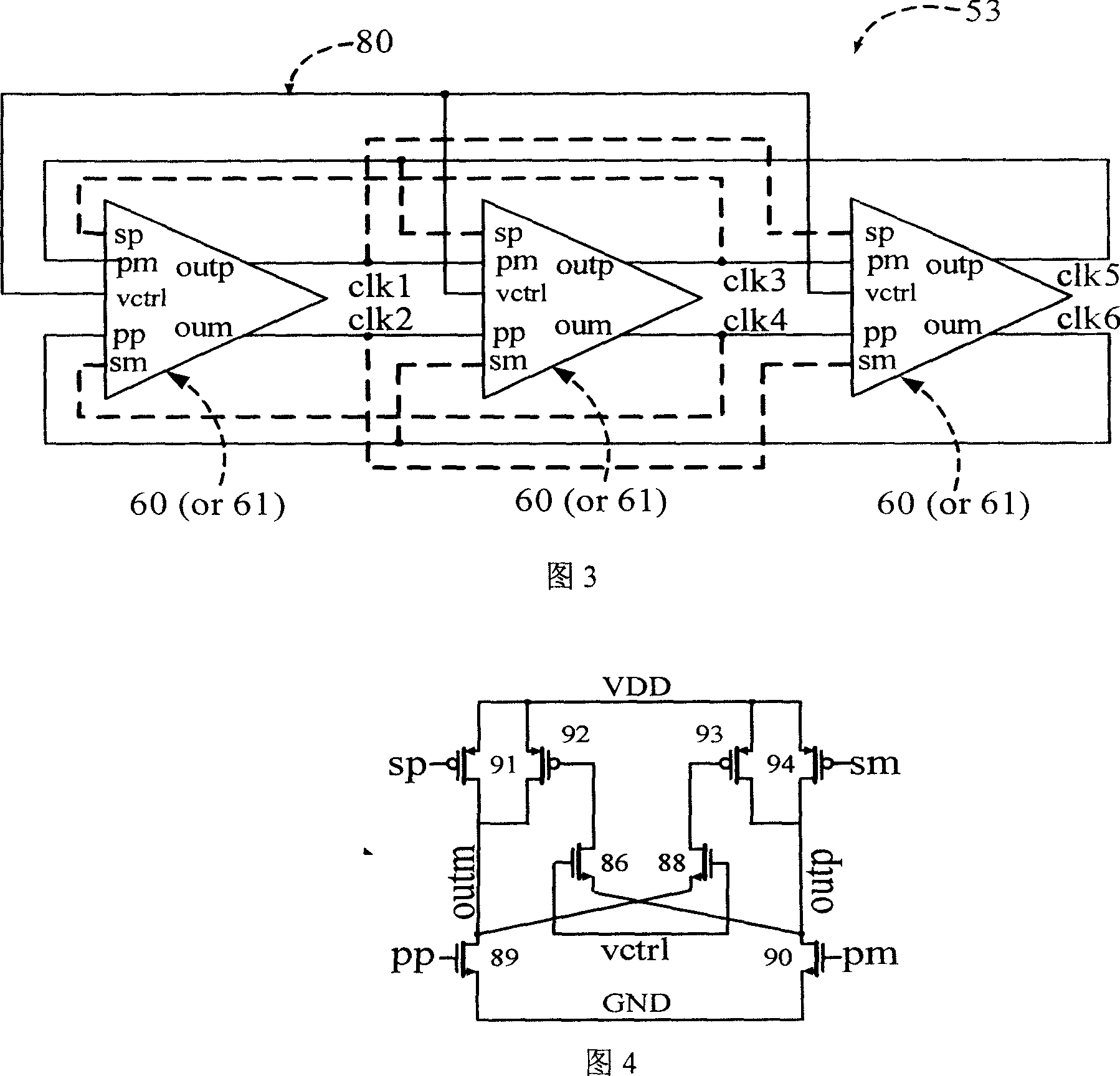

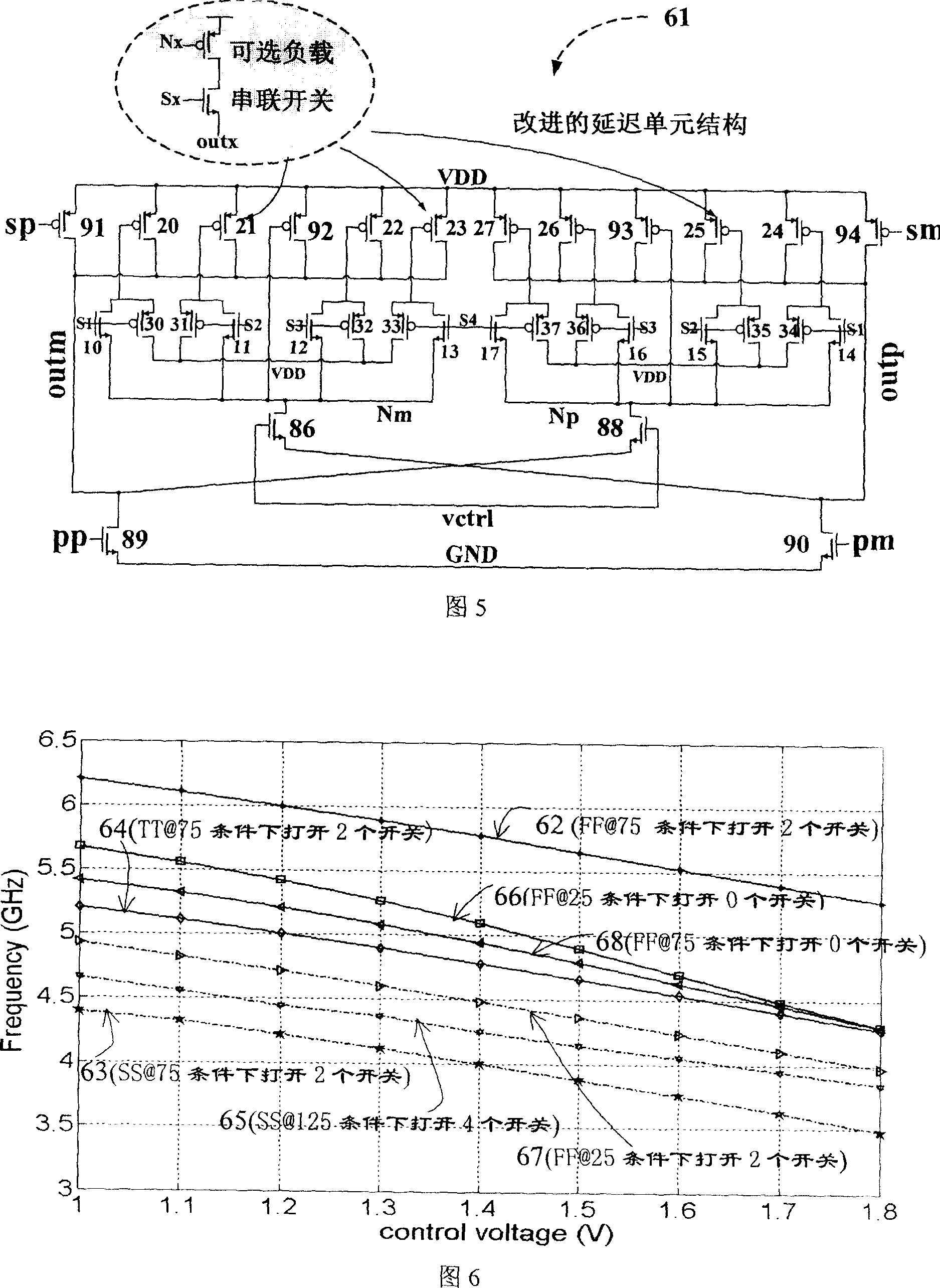

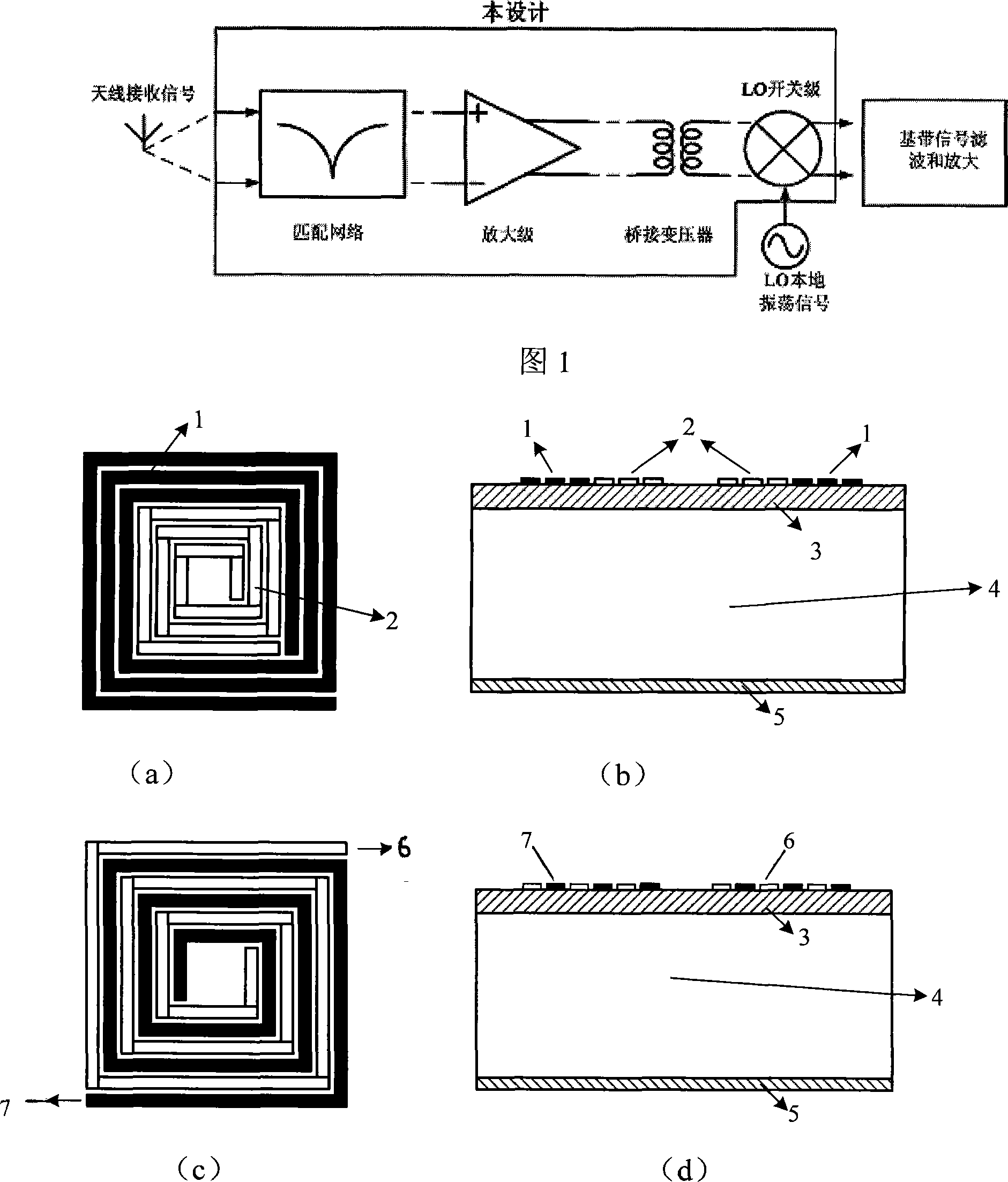

Adaptive process and temperature compensated high frequency ring-oscillating phase-locking ring circuit

InactiveCN1937410ASolve process problemsSolve temperature problemsPulse automatic controlRing circuitPhase locked loop circuit

It is a high frequency loop oscillation type phase locked loop circuit with self-accommodation frequency compensation. It consists of a multichannel loop type voltage-control oscillator with self-accommodate central frequency correction function,a difference electric charge pump, a linear double / single conversion circuit, a frequency divider, etc. The voltage-control oscillator possesses two gain channels, fast and slow. Its load transistor connects in serial into the voltage control channel to form a positive feedback. A selectable load array and a switch designed for technology and temperature compensation work in parallel with the original PMOS load. According to the conditions of technology and temperature, an auto-switch control module monitors the loop's lockup status and decides the number of parallel loads. Via self-accommodation feedback monitoring and compensation, it greatly reduces the dependency of the phase lock loop against the technology and temperature.

Owner:FUDAN UNIV

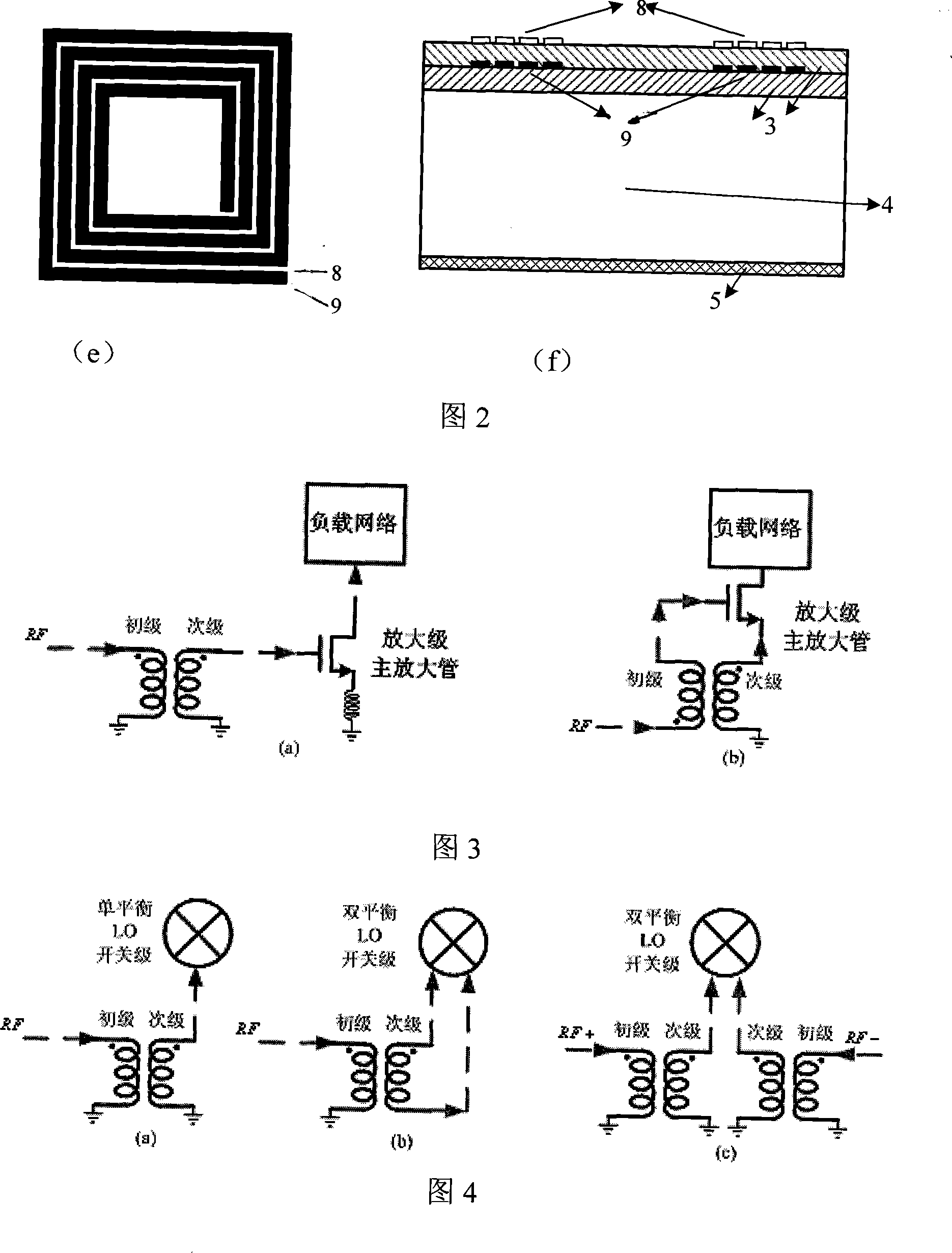

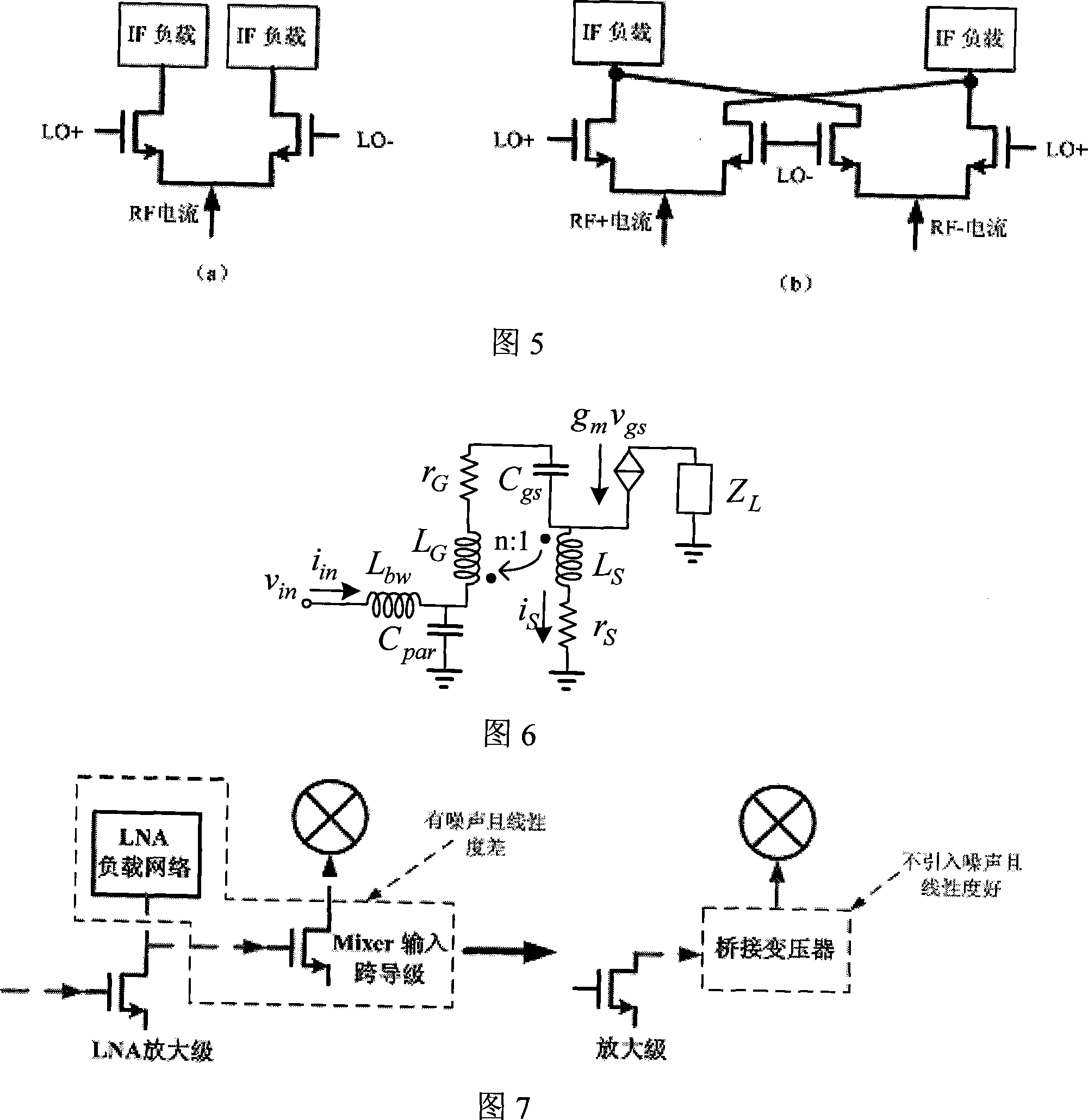

Low-power consumption wireless receiver radio frequency front end circuit

The invention relates to a low power consumption RF front-end circuit of the wireless receiver, belonging to the technical field of the integrated circuit of the RF wireless receiver, , comprising an RF input matching network, an amplifier stage, a bridge transformer, an LO switch stage, an IF load and a current source bias circuit; wherein, the RF input matching network implements the impedance matching between an antenna and the amplifier stage; the amplifier stage is used for amplifying the signal, the bridge transformer transfers the signal amplified to the LO switch stage and implements DC isolation between the front stage and back stage; the LO switch stage is used for implementing frequency mixing of the RF current signal and the LO signal and outputting alternatively the IF signalon an outputting differential load. Compared with the traditional RF front-end circuit, the circuit structure can use an on-chip integrated transformer or an on-chip inductor to implement inputting matching, and use the on-chip integrated transformer to implement the amplifying and downward frequency mixing of the RF signals perfectly, which simplifies the circuit structure. The circuit can be used in a low power supply voltage environment, and has the advantages of low DC power consumption, and less circuit noise and signal distortion.

Owner:FUDAN UNIV