Patents

Literature

269 results about "Ring circuit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In electricity supply design, a ring final circuit or ring circuit (often incorrectly called a ring main or informally a ring) is an electrical wiring technique developed and primarily used in the United Kingdom. This design enables the use of smaller-diameter wire than would be used in a radial circuit of equivalent total current. The reduced diameter conductors in the flexible cords connecting an appliance to the plug intended for use with sockets on a ring circuit are individually protected by a fuse in the plug. Its advantages over radial circuits are therefore reduced quantity of copper used, and greater flexibility of appliances and equipment that can be connected.

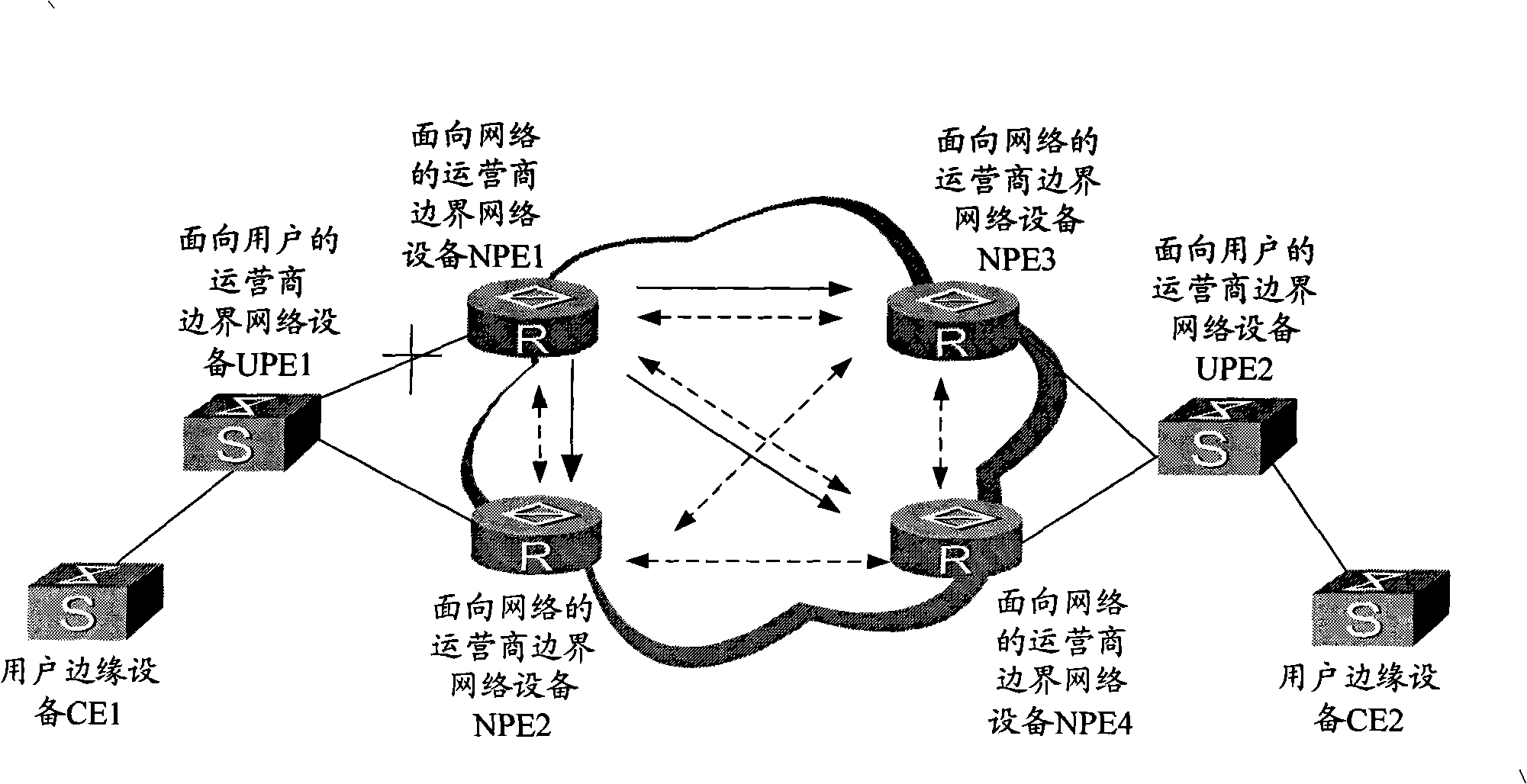

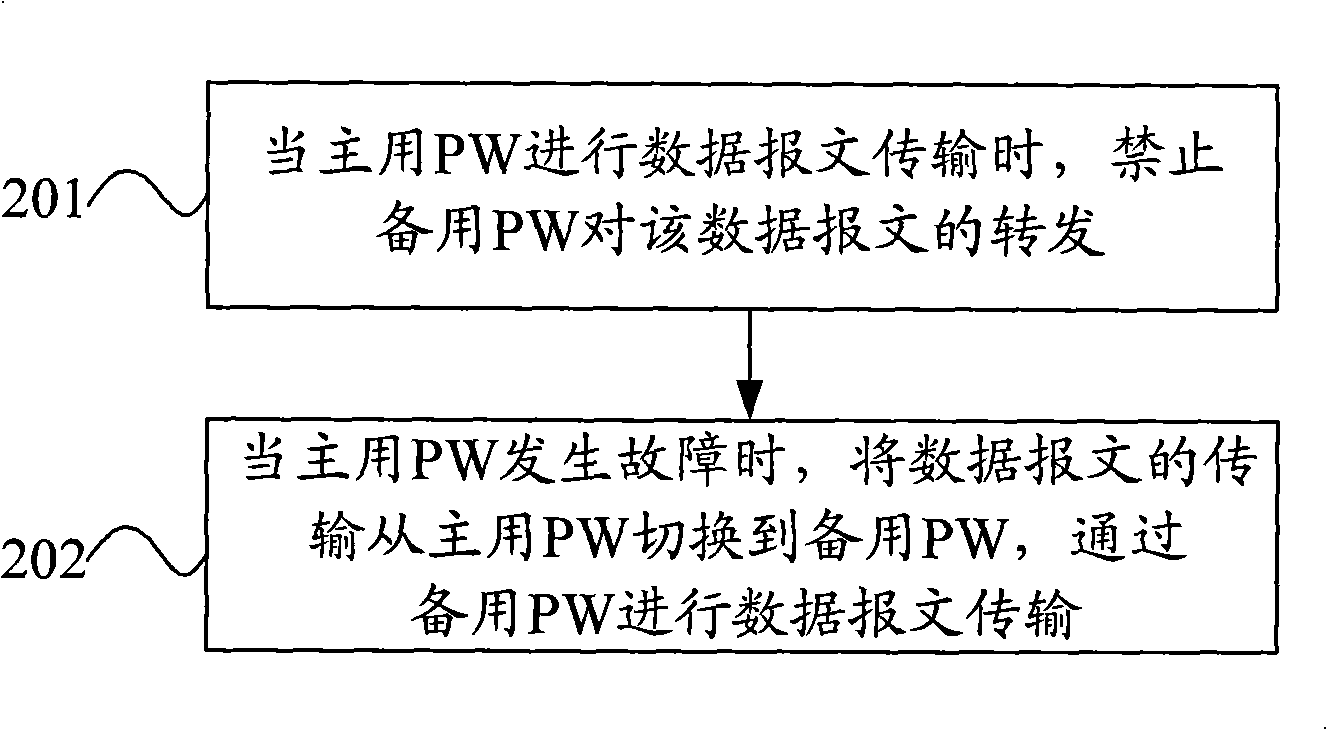

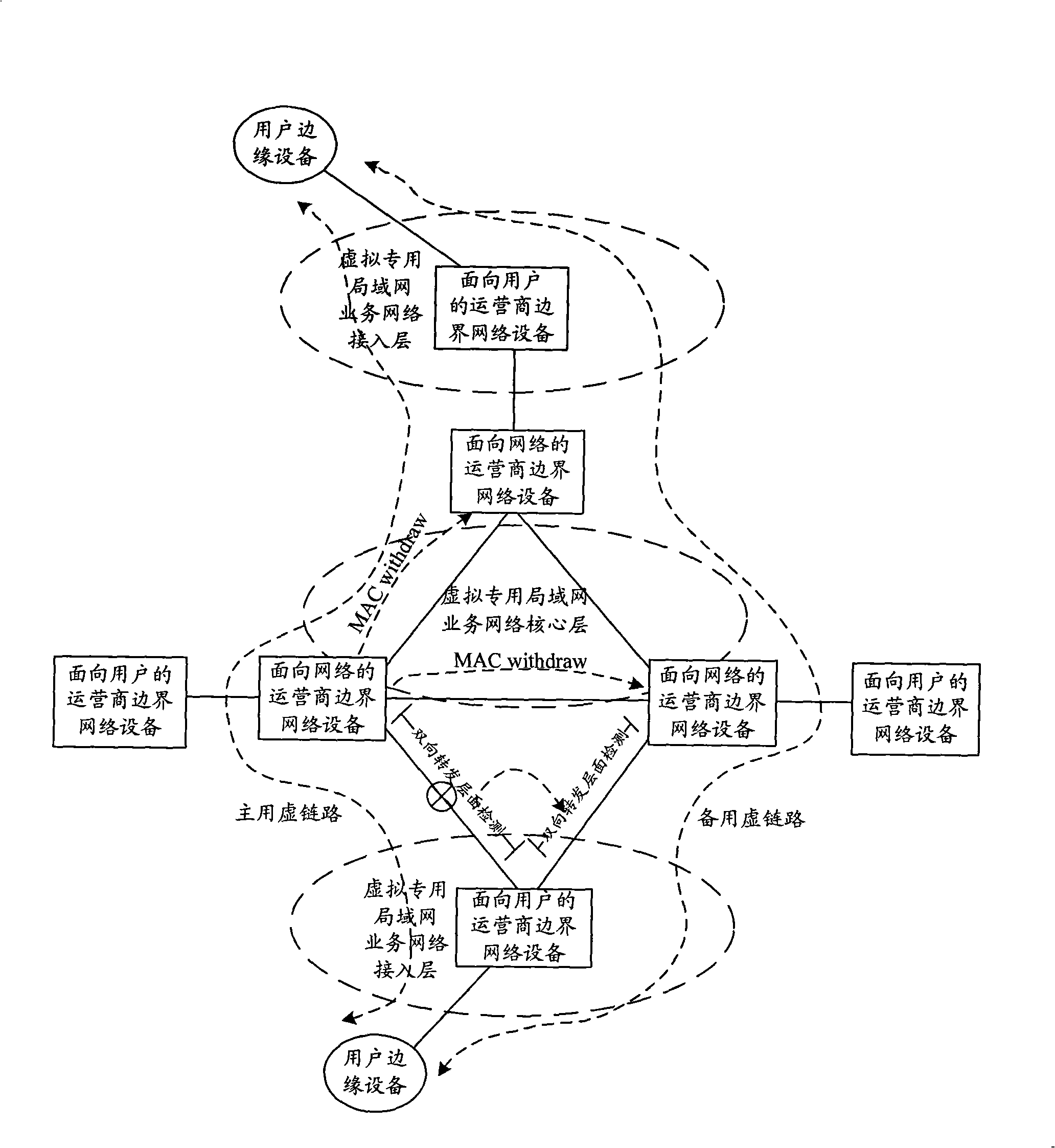

Data transmission method, apparatus and system in VPLS network

InactiveCN101340351AReduce the burden onImprove QoSError preventionNetworks interconnectionRing circuitData transmission

The embodiment of the invention discloses a method for transmitting data in a virtual special LAN service (VPLS) network, a device and a system thereof. A main virtual link circuit PW and a ready-for-use virtual link circuit PW are arranged in the VPLS network. The method for transmitting data comprises that: when the main virtual link circuit PW transmits the data message, the forwarding of the data message by the ready-for-use virtual link circuit PW is prohibited; when the main PW goes wrong, the transmission of the data message is switched to the ready-for-use PW from the main PW, and the data message is transmitted by the ready-for-use PW. Due to the embodiment of the invention, the forming of a ring circuit between UPE and NPE which are accessed in a way of double-returning is avoided; when the main PW goes wrong, the link circuits can be switched quickly, and the convergence of the link circuits is accelerated, therefore, QoS of the VPLS network is improved.

Owner:HUAWEI TECH CO LTD

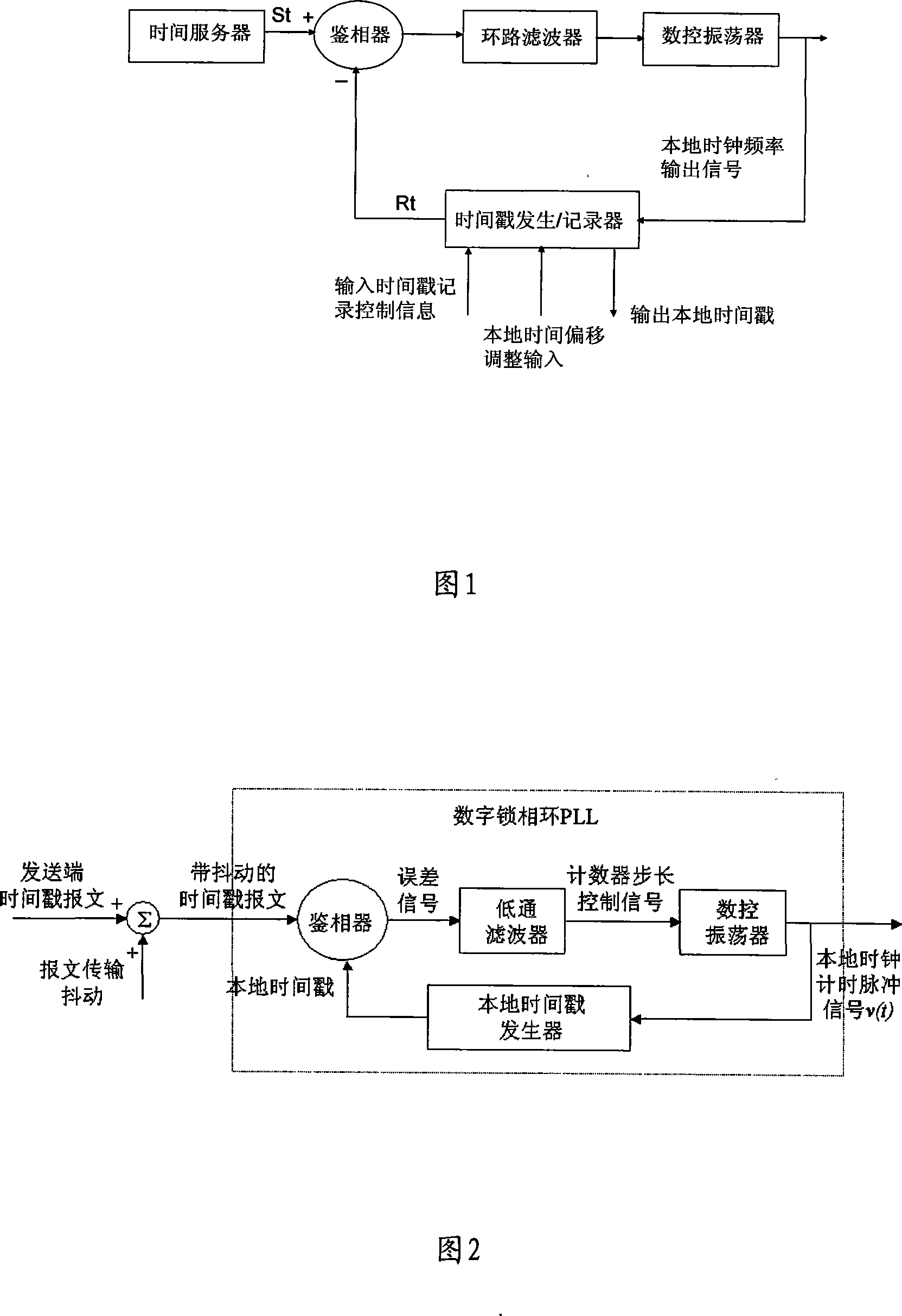

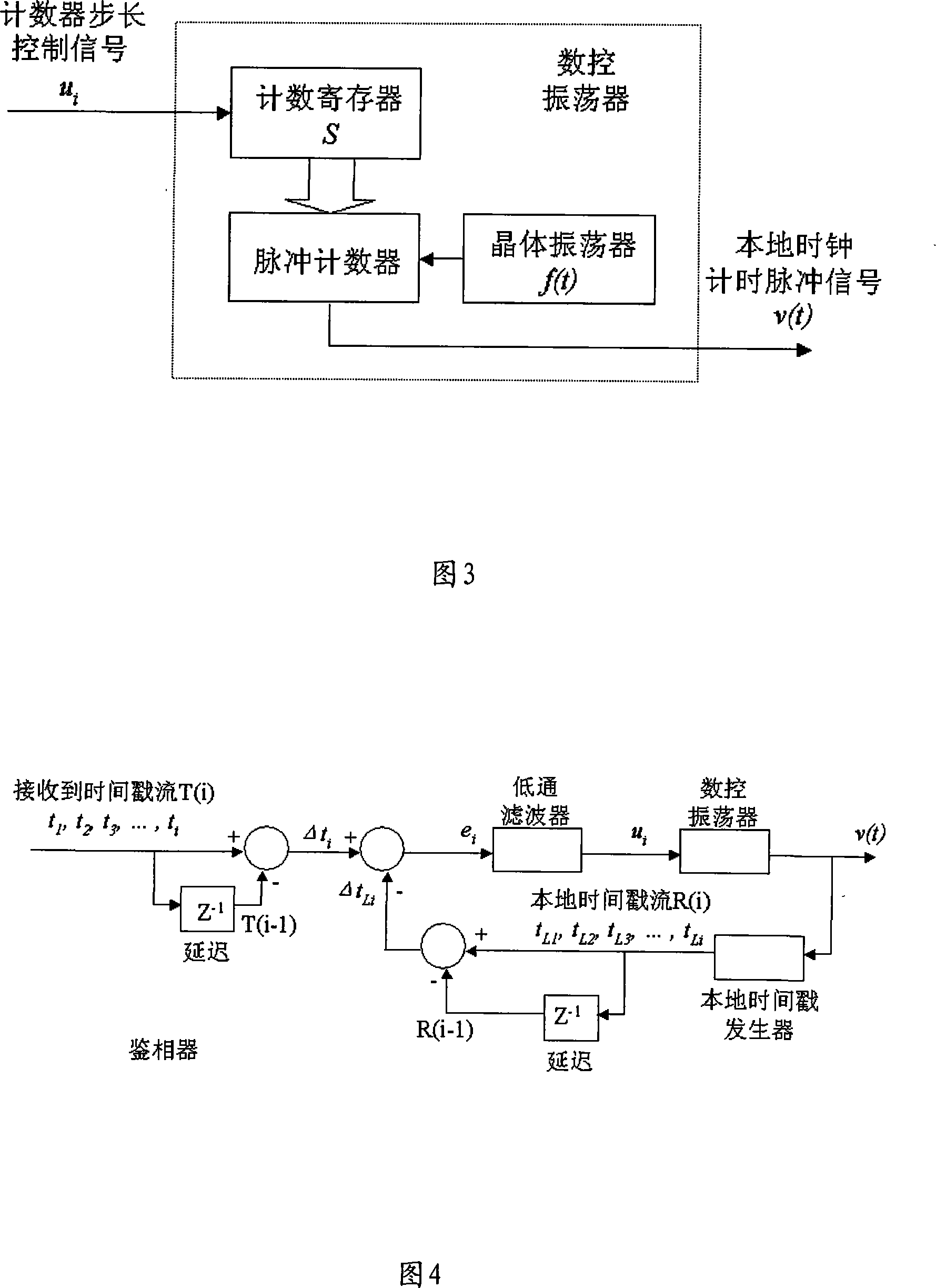

Method for realizing integrated time stamp clock synchronous phase-locked loop

InactiveCN101083523AGuaranteed validityPulse automatic controlSynchronising arrangementLoop filterRing circuit

The invention involves a method of digital phase-locked loop for timestamp clock synchronization and equipment. Firstly, the server sends a value, which includes the message S (t) to timestamp, as the input synchronized signal. Take the time on which timestamp the server sent arriving at phase-locked loop as the recording time R (t) of local time. Then take the local timestamp according to the local clock frequency as reference input signal. The numerically controlled adjusts the output frequency according to ring circuit signal by filter. Lastly, the timestamp creater / recorder output the signal as the local clock frequency according to the output signal created by DOC. Under the condition that the invention use larger drift mobility and the lower stability oscillator, the system can provide high accuracy time synchronism.

Owner:SOUTH CHINA UNIV OF TECH

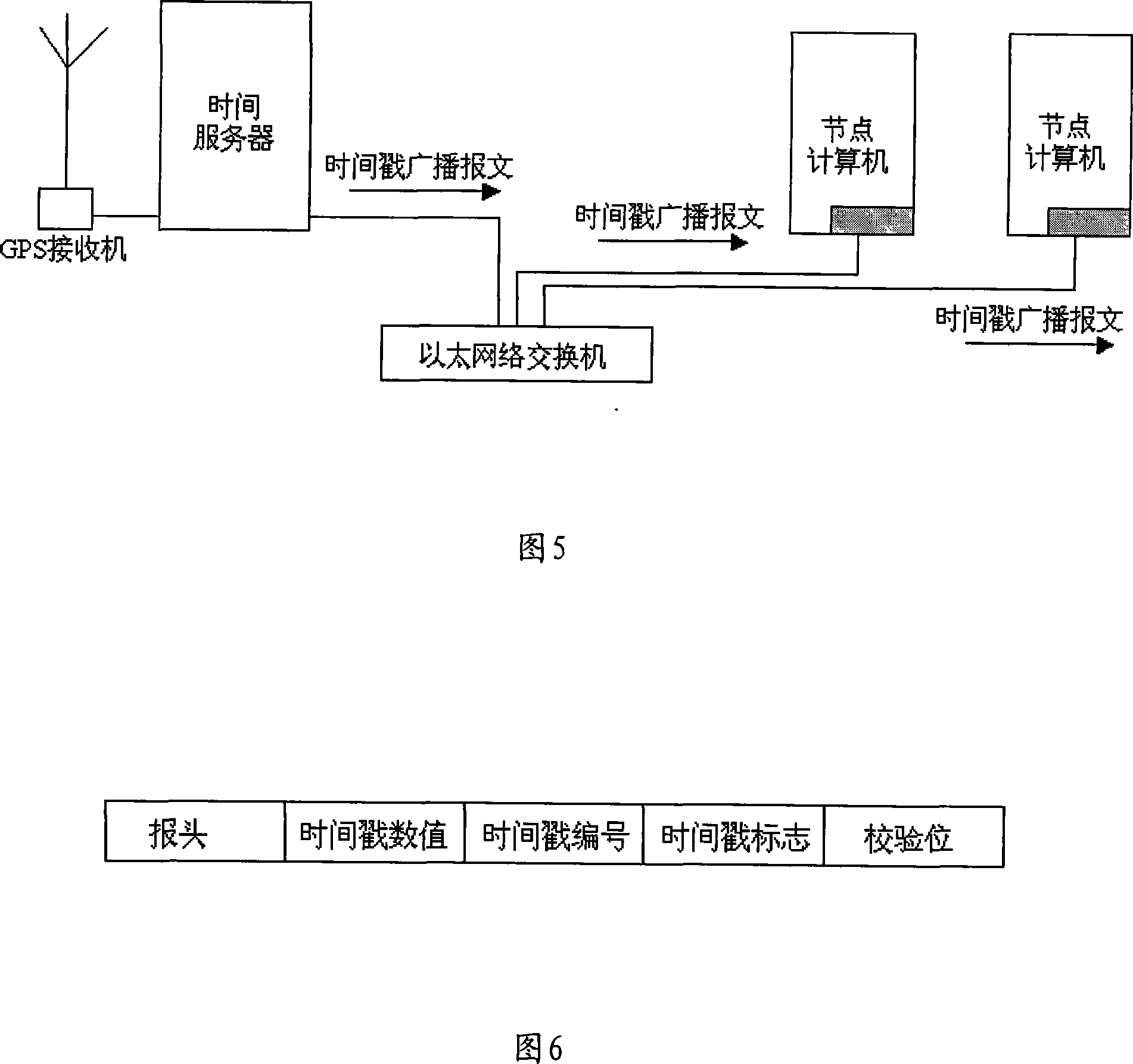

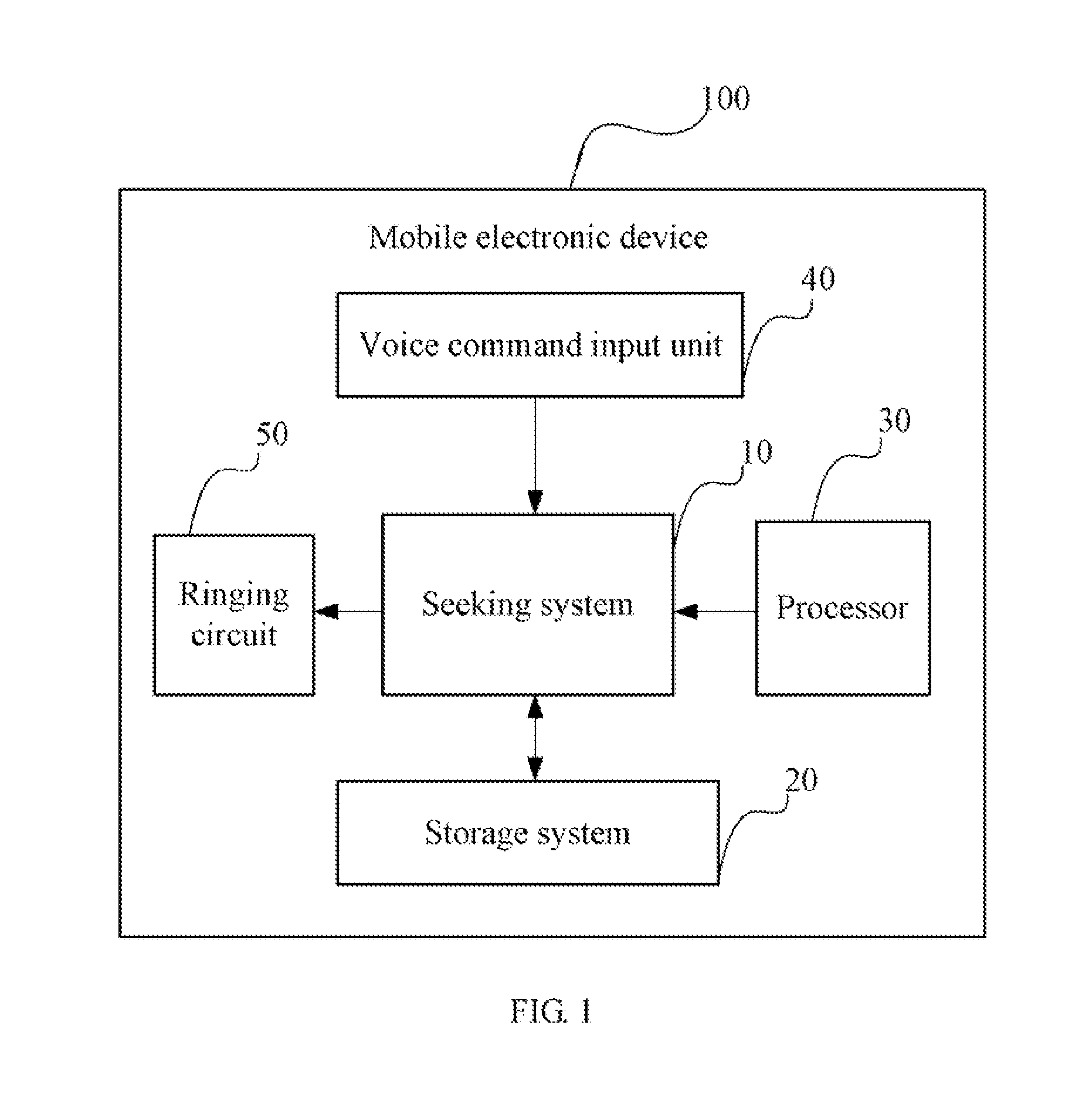

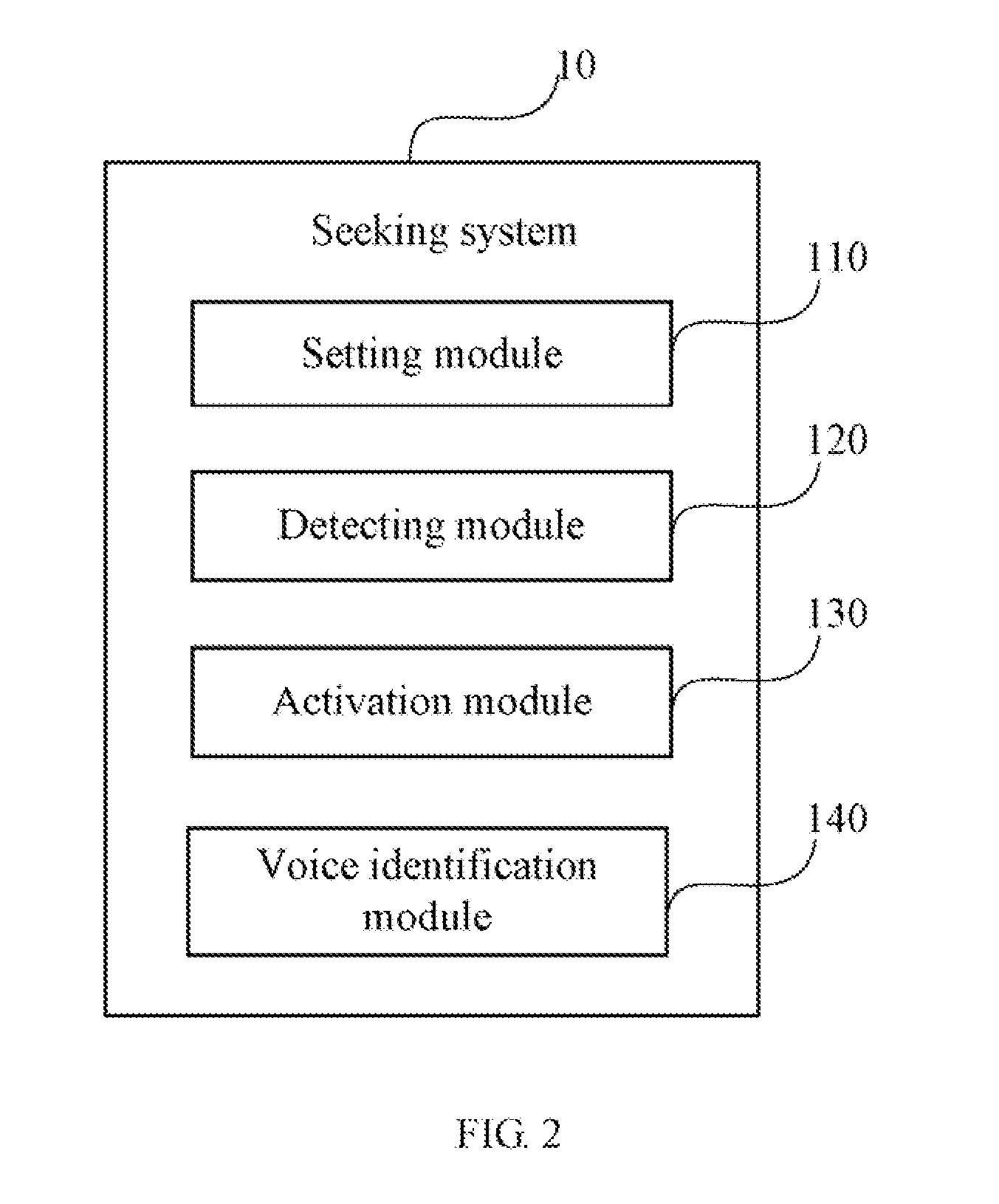

Mobile electronic device and method for locating the mobile electronic device

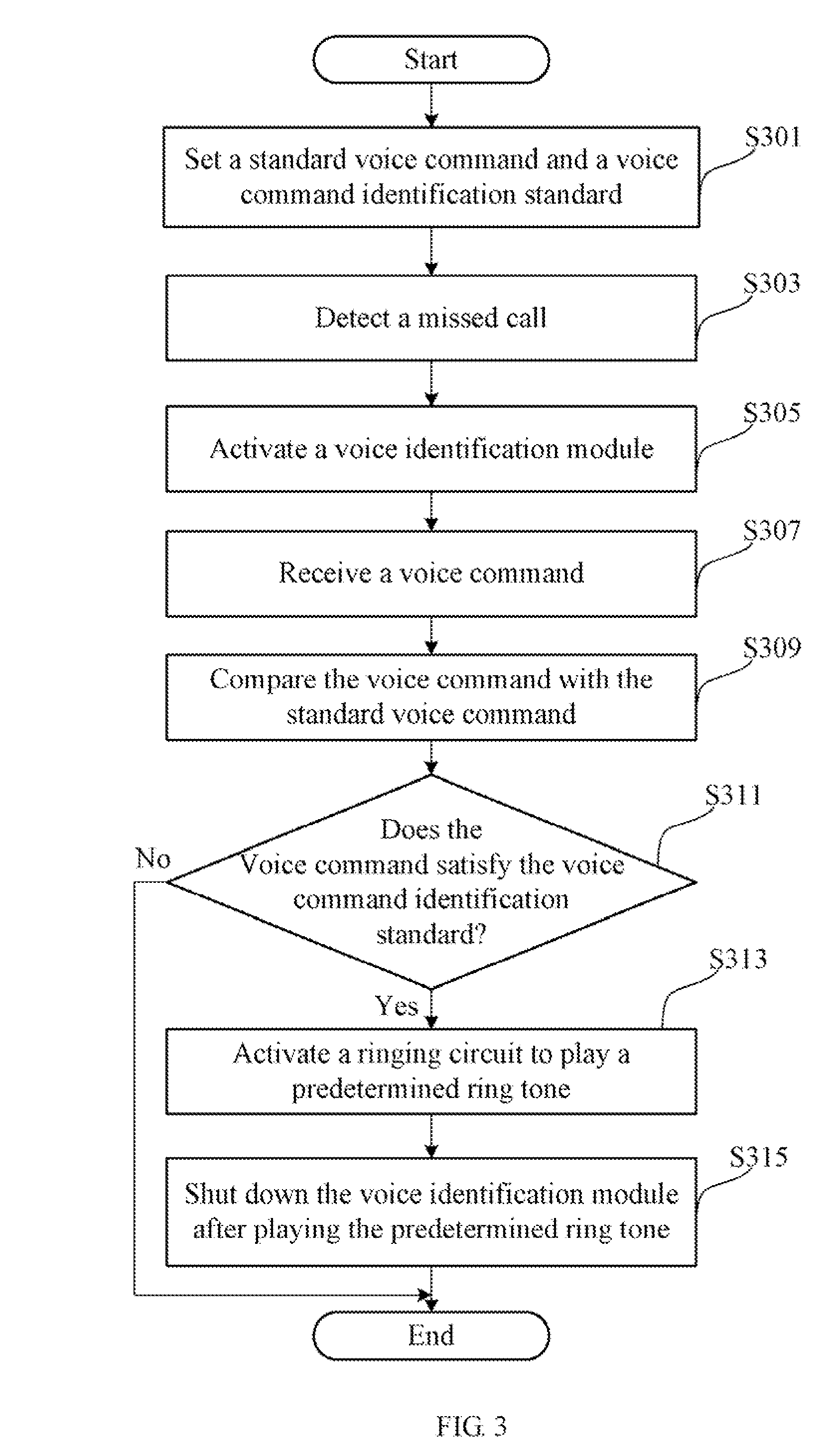

ActiveUS20100216446A1Easy to findDevices with voice recognitionSpeech analysisComputer hardwareRing circuit

A mobile electronic device stores a standard voice command and a voice command identification standard. When an incoming call is regarded as a missed call and a voice command is detected, the mobile electronic device compares characteristics of the voice command with characteristics of the standard voice command, so as to determine if the voice command satisfies the voice command identification standard. The mobile electronic device further activates a ringing circuit to play a predetermined ring tone in response that the voice command satisfies the voice command identification standard, so as to help a user locate the mobile electronic device even if the mobile electronic device is in a silent mode.

Owner:CHI MEI COMM SYST INC

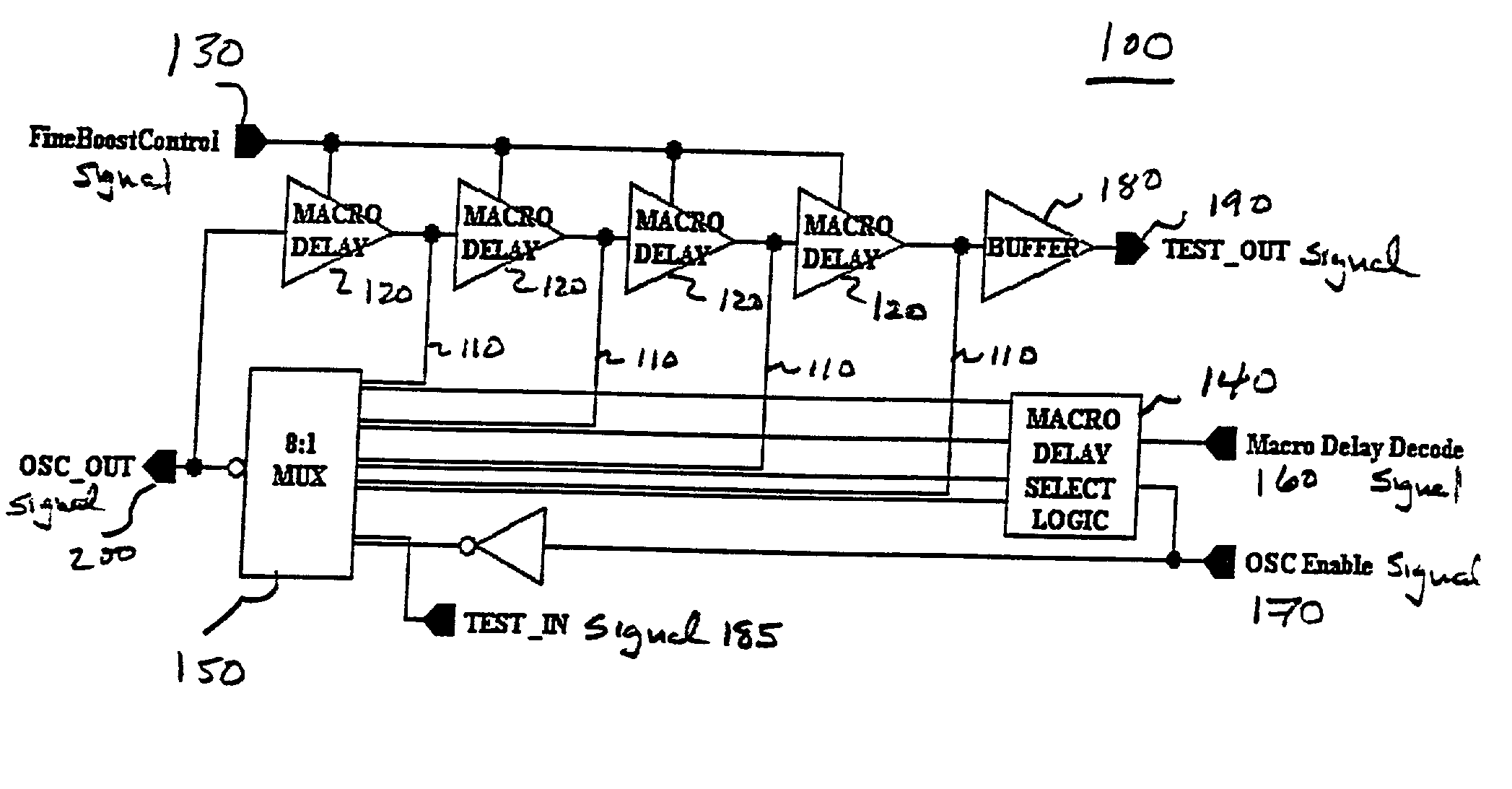

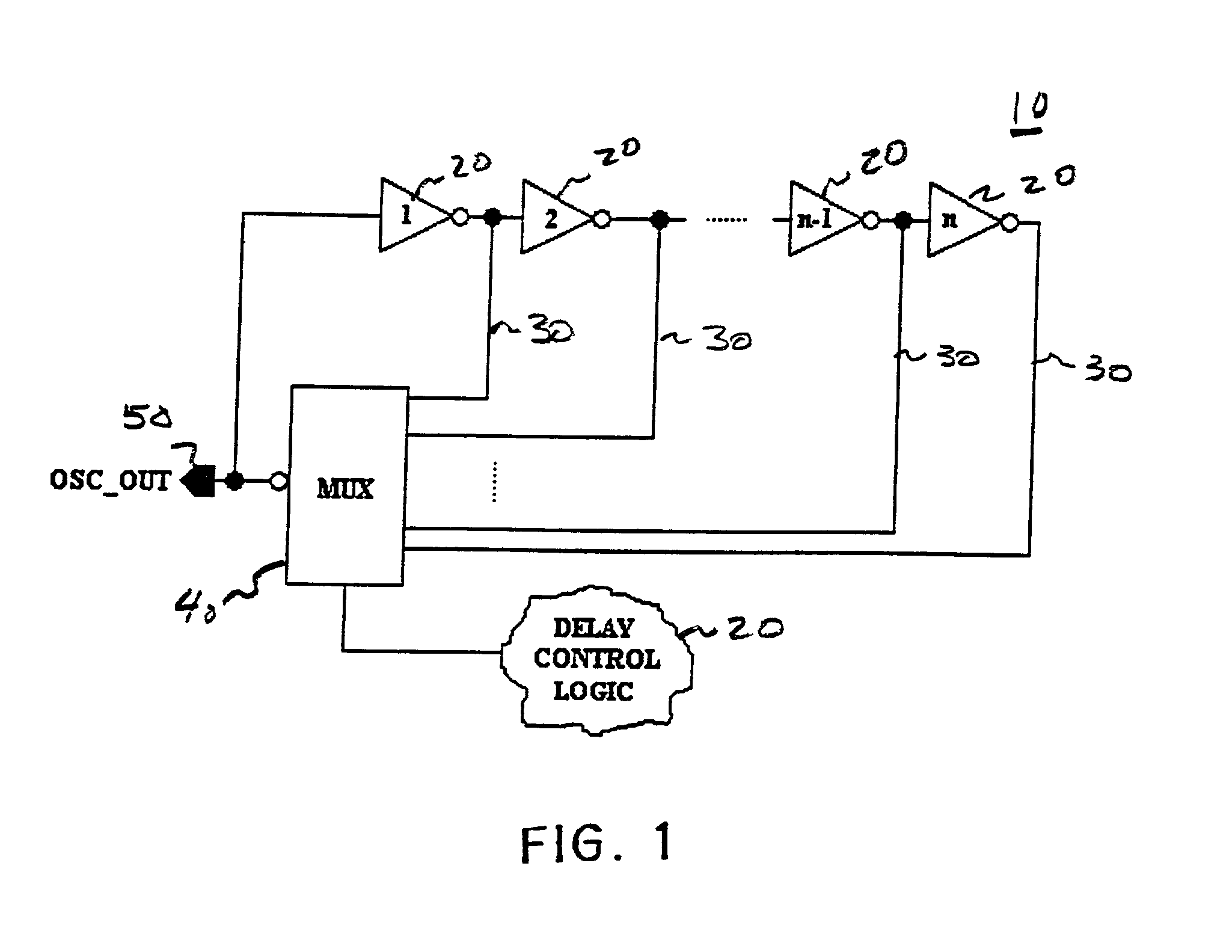

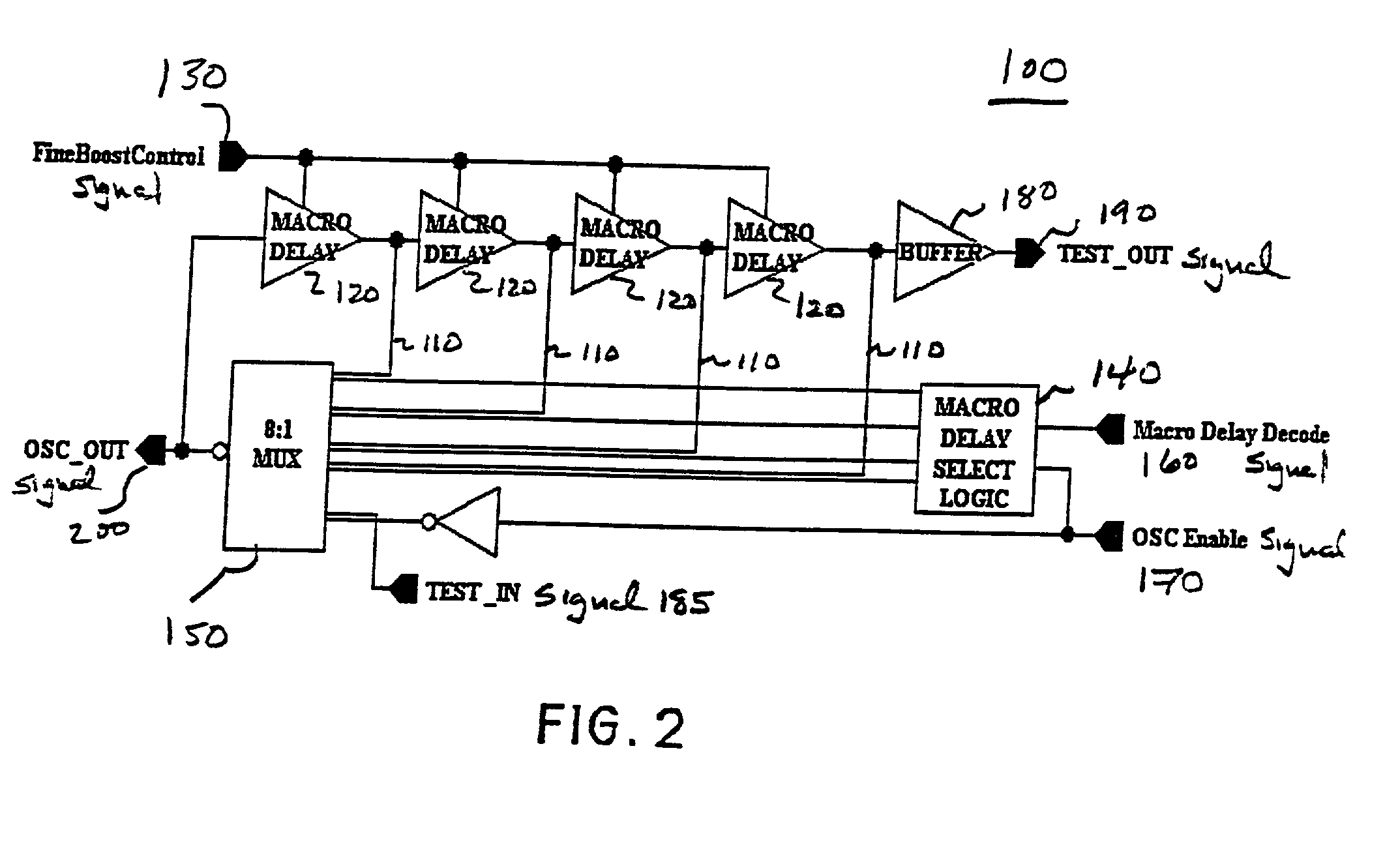

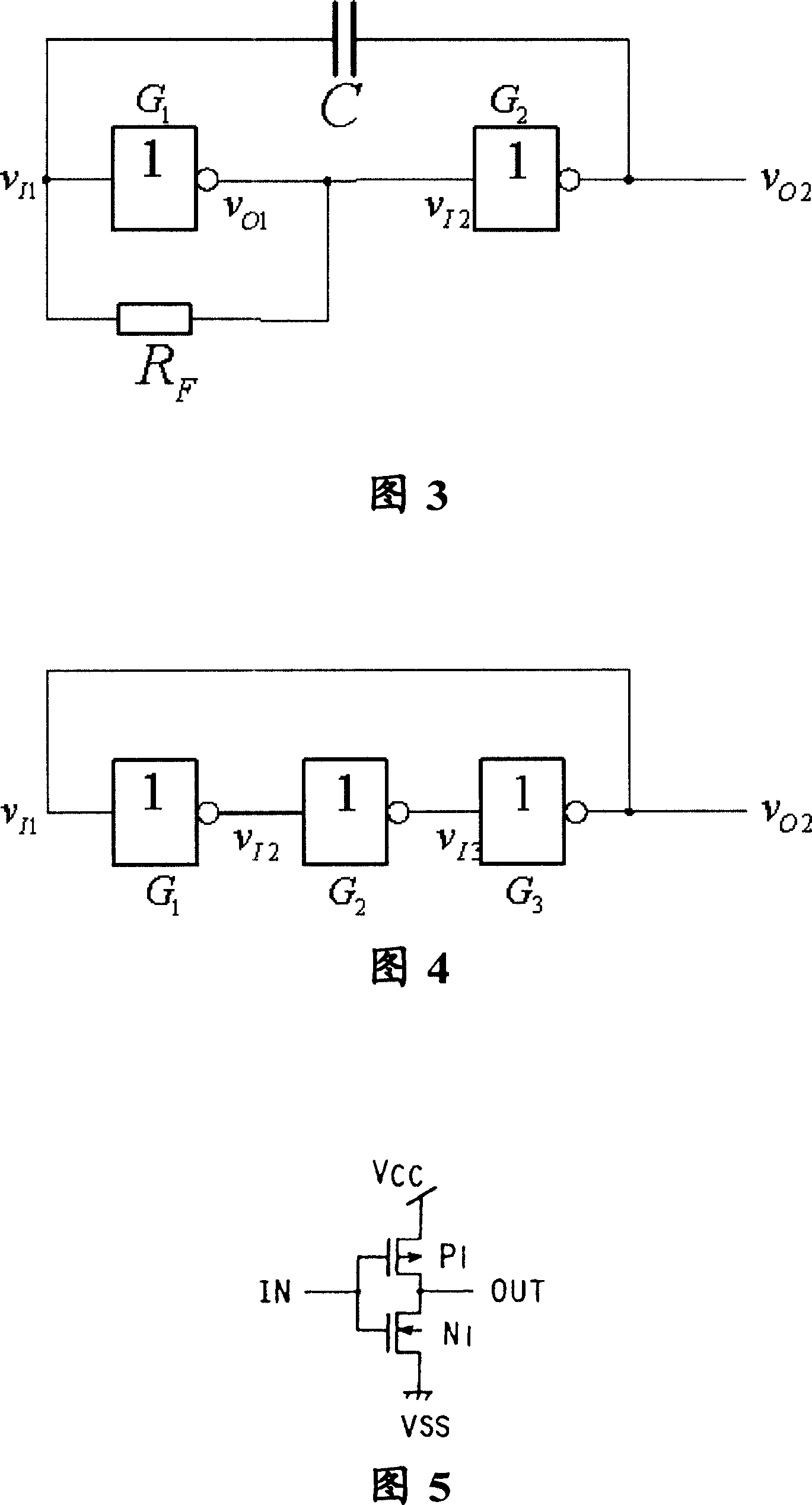

Ring oscillator with adjustable delay

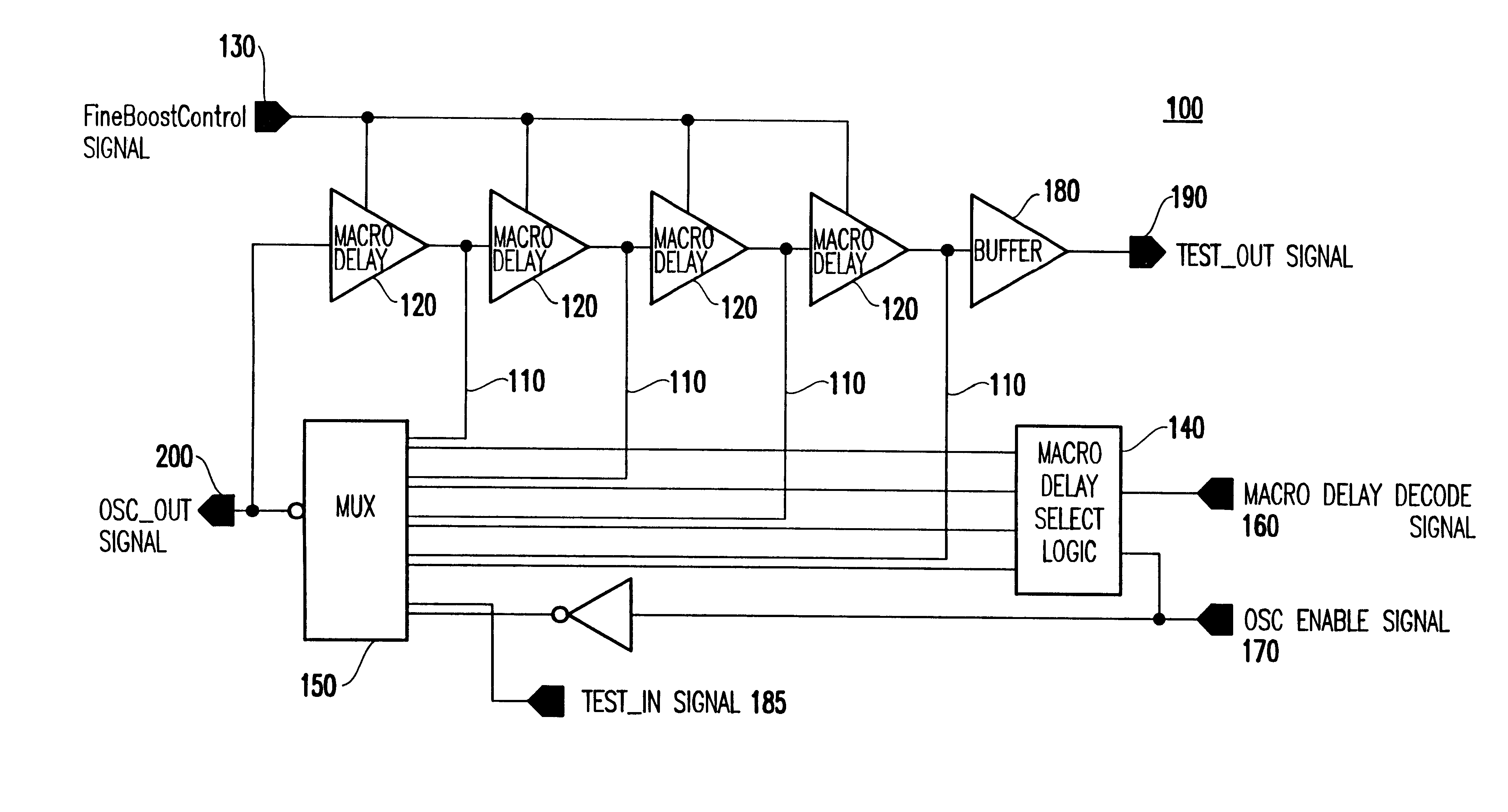

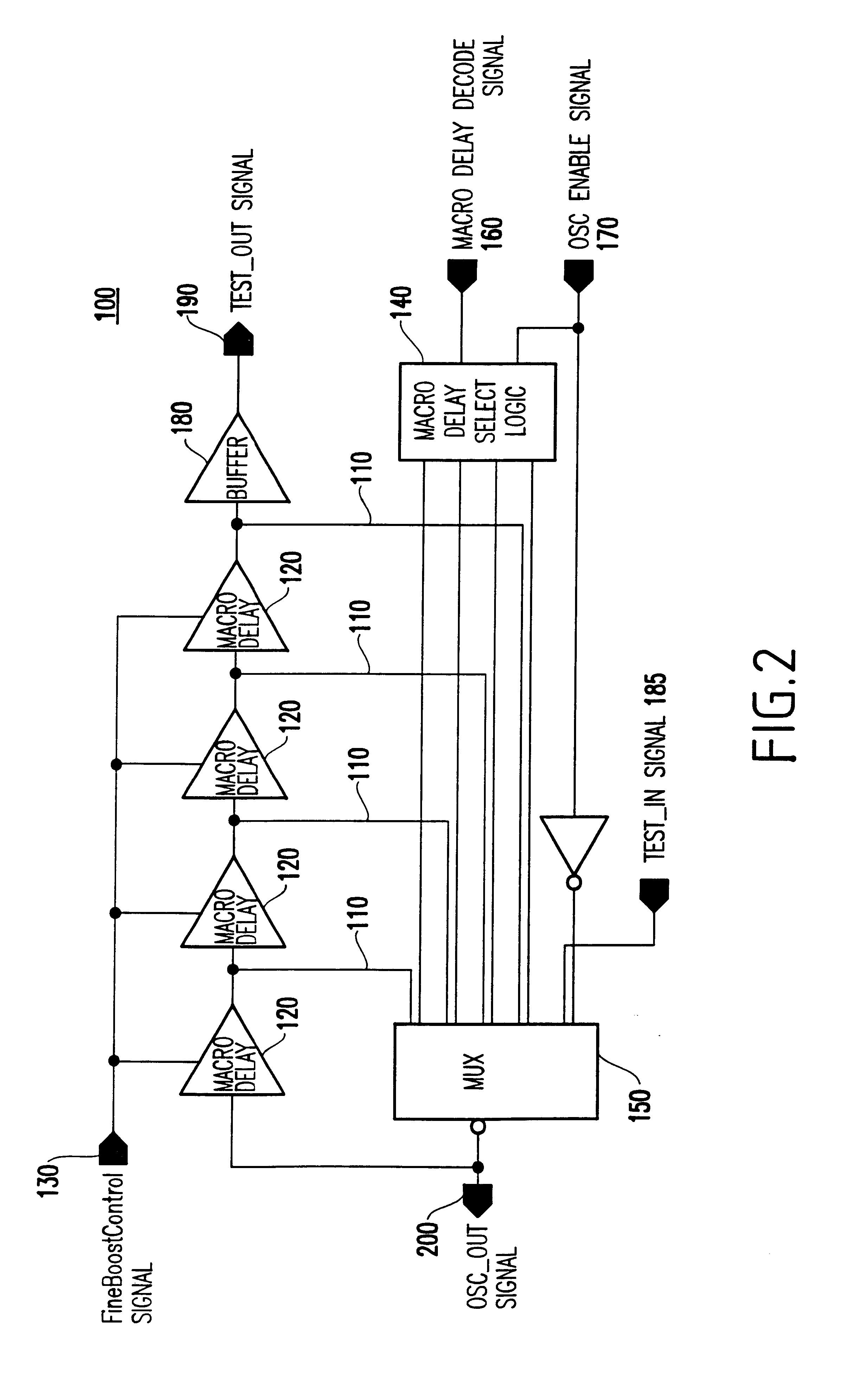

A variable-frequency digital ring oscillator provides small and consistent frequency adjustments throughout a locked range. The ring oscillator of the invention is standard cell placeable and operates at the technology limits to provide small and precise delay changes that is inexpensive to implement. The digital variable-frequency ring oscillator includes multiple macro delay elements forming an inverter ring circuit, each element having an individual macro delay unit that in turn is comprised of multiple adjustable delay units. All of these adjustable delay units are controlled by a single delay control signal.

Owner:GOOGLE LLC

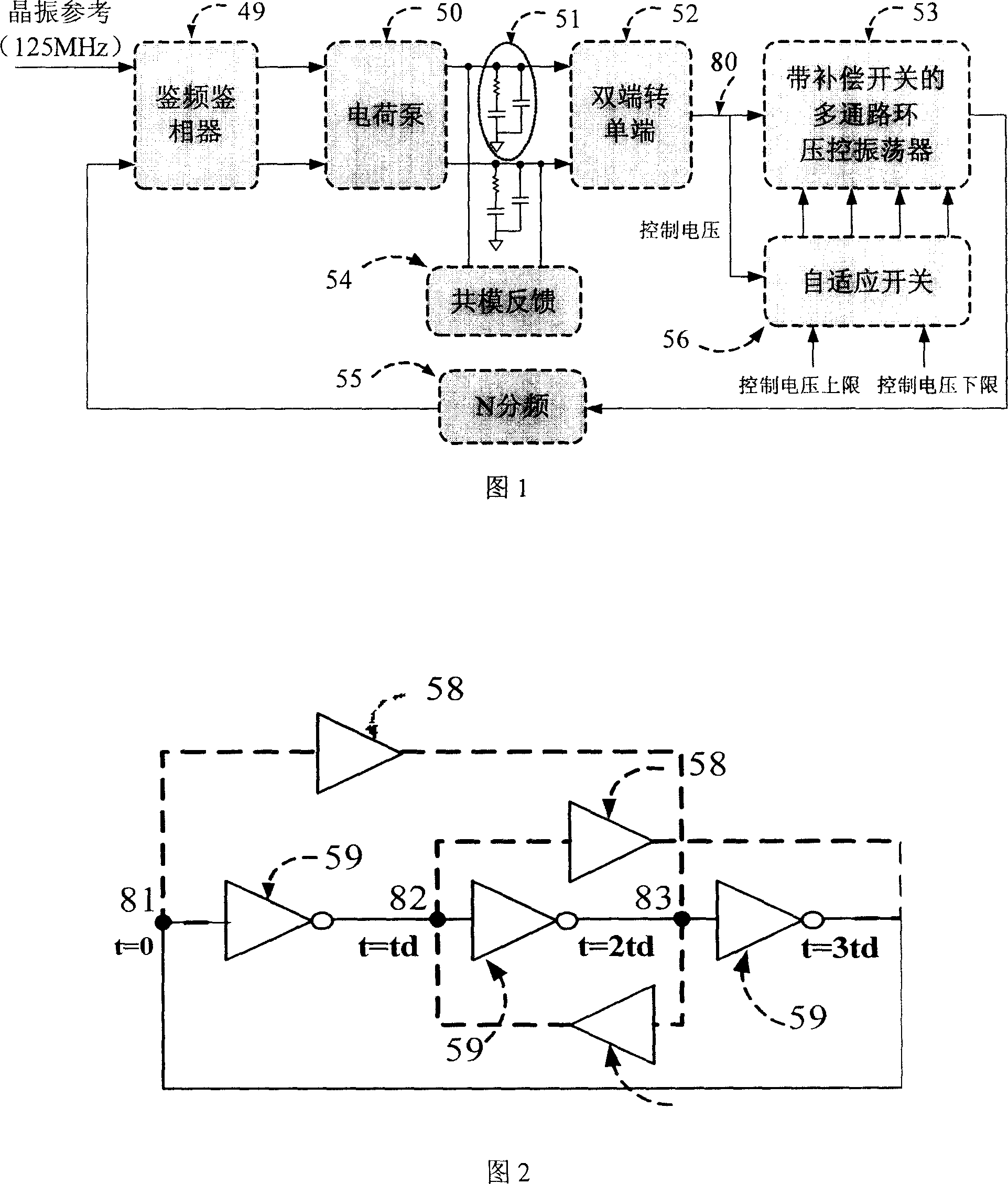

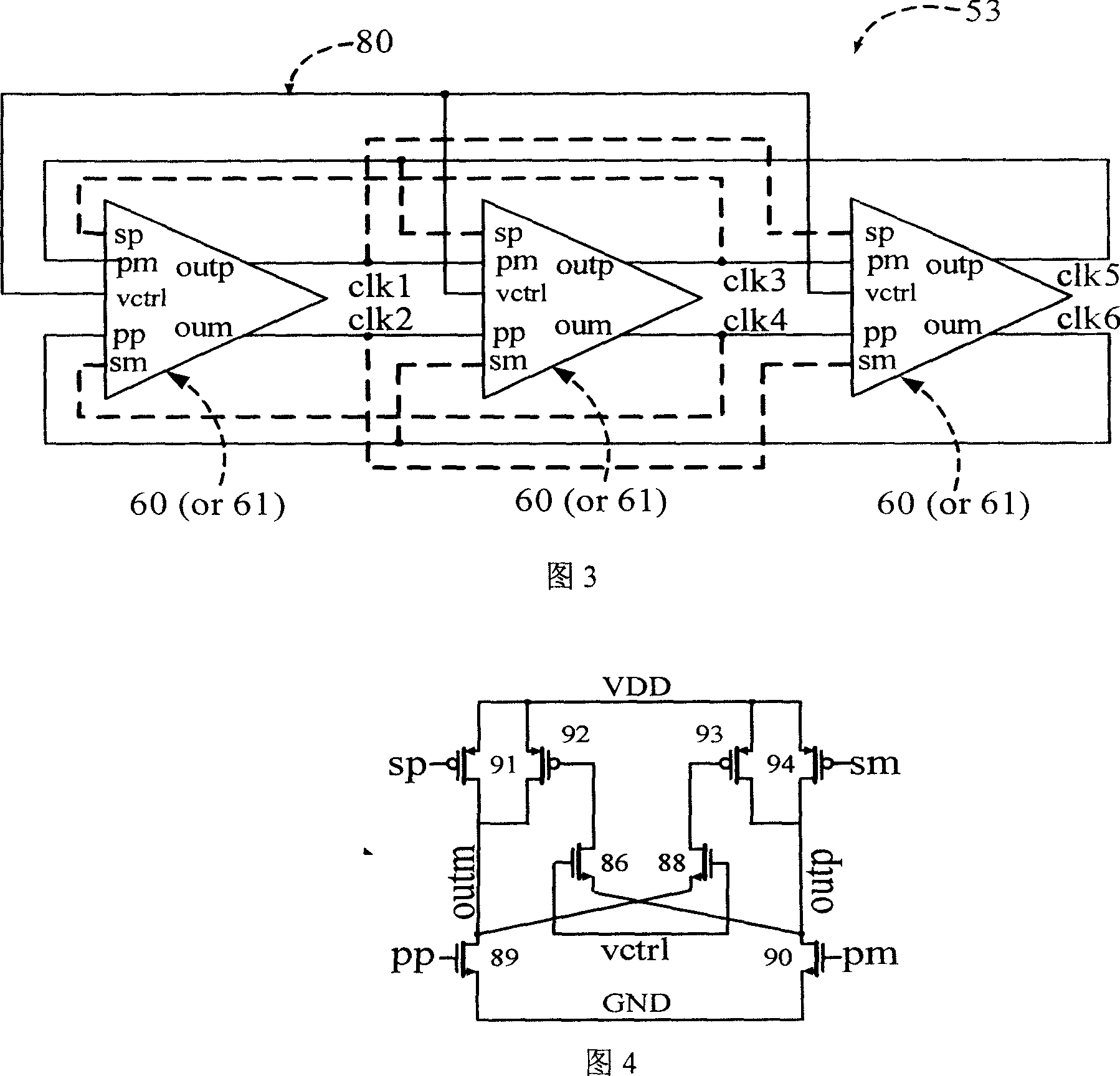

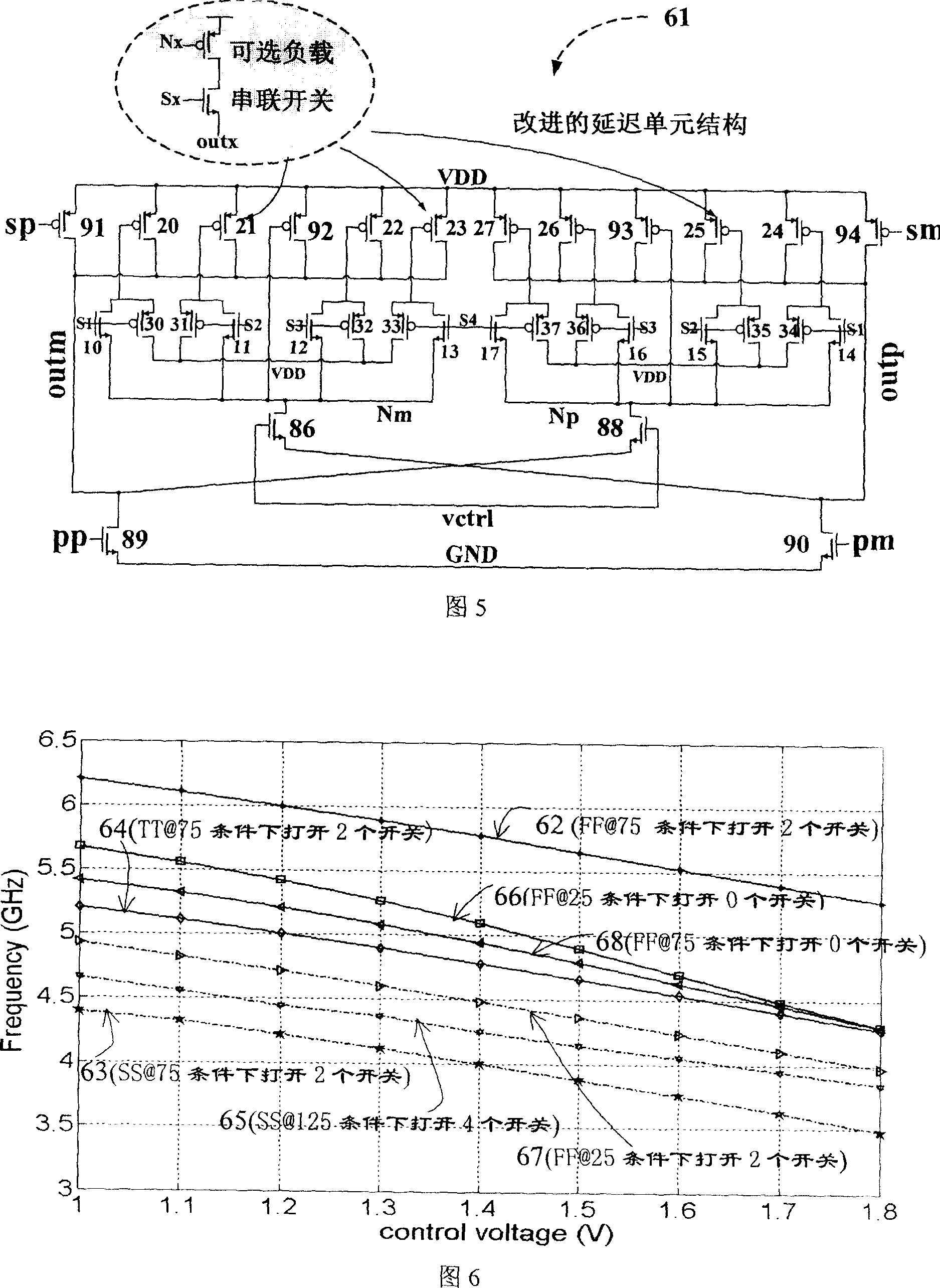

Adaptive process and temperature compensated high frequency ring-oscillating phase-locking ring circuit

InactiveCN1937410ASolve process problemsSolve temperature problemsPulse automatic controlRing circuitPhase locked loop circuit

It is a high frequency loop oscillation type phase locked loop circuit with self-accommodation frequency compensation. It consists of a multichannel loop type voltage-control oscillator with self-accommodate central frequency correction function,a difference electric charge pump, a linear double / single conversion circuit, a frequency divider, etc. The voltage-control oscillator possesses two gain channels, fast and slow. Its load transistor connects in serial into the voltage control channel to form a positive feedback. A selectable load array and a switch designed for technology and temperature compensation work in parallel with the original PMOS load. According to the conditions of technology and temperature, an auto-switch control module monitors the loop's lockup status and decides the number of parallel loads. Via self-accommodation feedback monitoring and compensation, it greatly reduces the dependency of the phase lock loop against the technology and temperature.

Owner:FUDAN UNIV

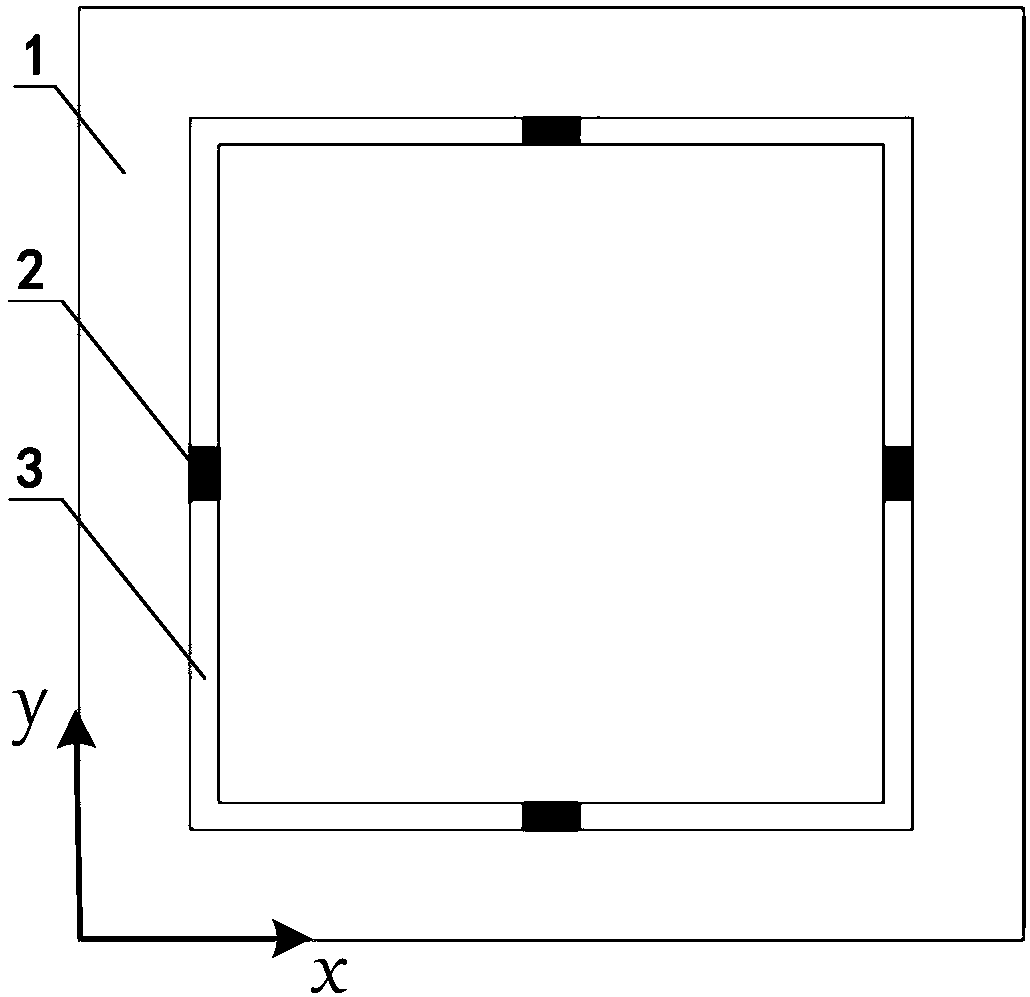

Double-layer cascaded dual-polarized broadband absorbing type frequency selective surface

ActiveCN108682952APromote absorptionDoes not reduce gainRadiating element housingsRing circuitBand width

The invention relates to a double-layer cascaded dual-polarized broadband absorbing type frequency selective surface. A conventional wave absorbing frequency selective structure is designed to be a bandpass type frequency selective structure which has limited pass band width and has difficulty in covering low frequency. According to the invention, a double-ring reflective plane is adopted, a waveabsorbing ring is designed on the other surface of the reflective plane, and the double-layer cascaded dual-polarized broadband absorbing type frequency selective surface is constructed by the combination of a single-ring circuit analog absorber. Therefore, insertion loss in a low frequency passband is low, and an extremely wide absorbing band can be generated near a high frequency place.

Owner:HANGZHOU DIANZI UNIV

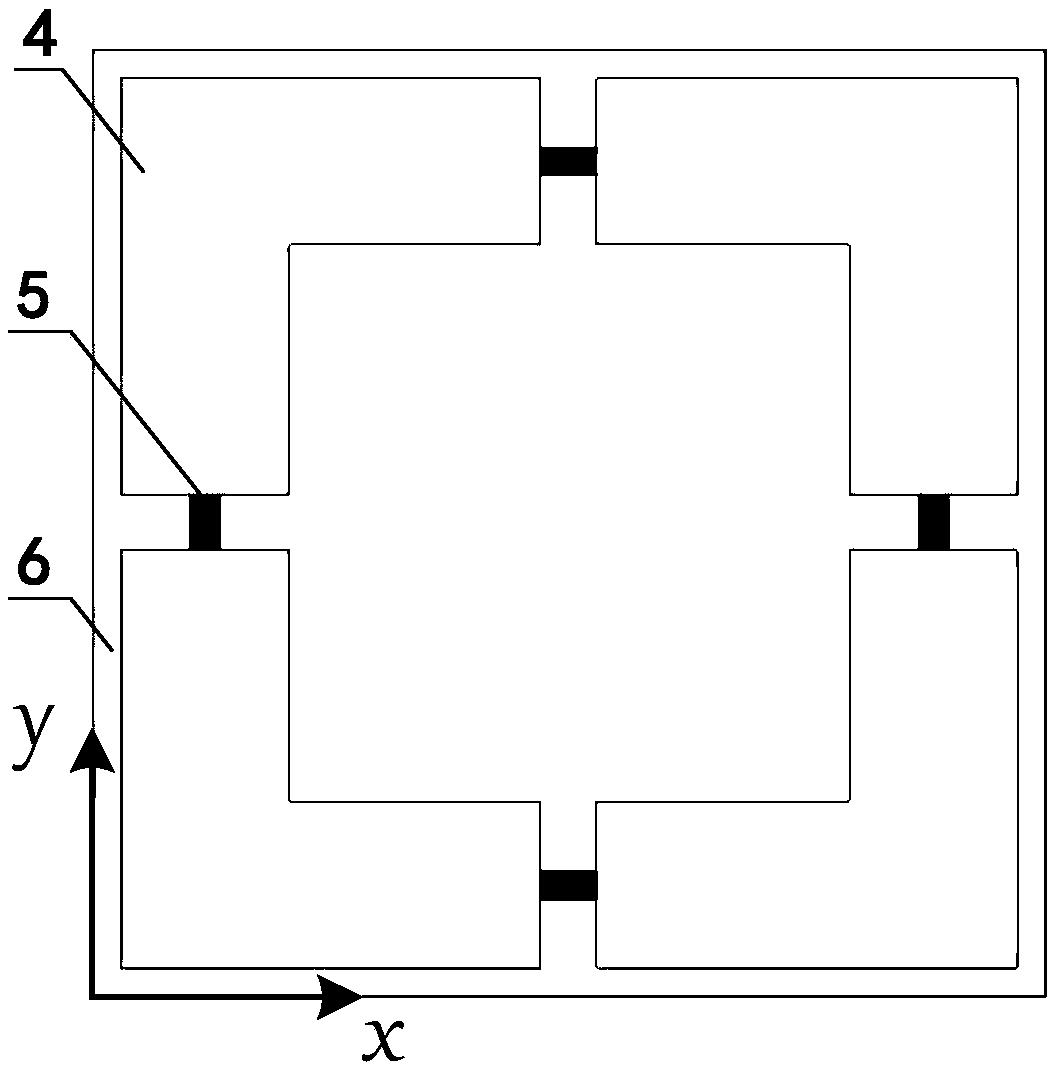

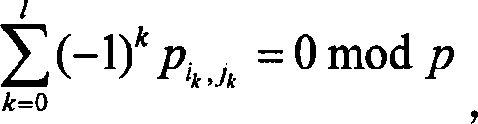

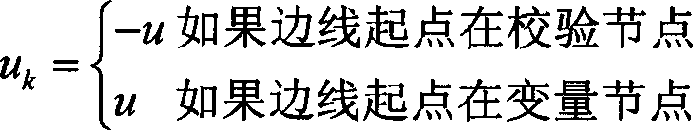

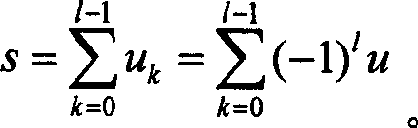

Construction method of non-regular permutation matrix LDPC code and its device

InactiveCN1794621ASimple designSimplify implementation complexityError preventionError correction/detection using multiple parity bitsRing circuitH matrix

This invention relates to a method for constructing new non-standard replacement matrix LDPC codes characterizing that under the principle of optimizing the smallest ring circuit, it takes each sub-block as the smallest unit and utilizes a binary chart with weight to determine the position of the sub-block and the deviation of circulation shift: simplifying the binary chart with bit as the unit of the LDPC code to that with a sub-block as the unit based on the property of the matrix of a replacement unit, then applying the traditional PEG algorithm with the bit as the unit to the new chart with the sub-block as the unit to determine the position of every replacement unit matrix of the H matrix and finally utilizing the ring circuit property of the LDPC code to decide the deviation of circular shift of each replacement unit matrix.

Owner:PEKING UNIV

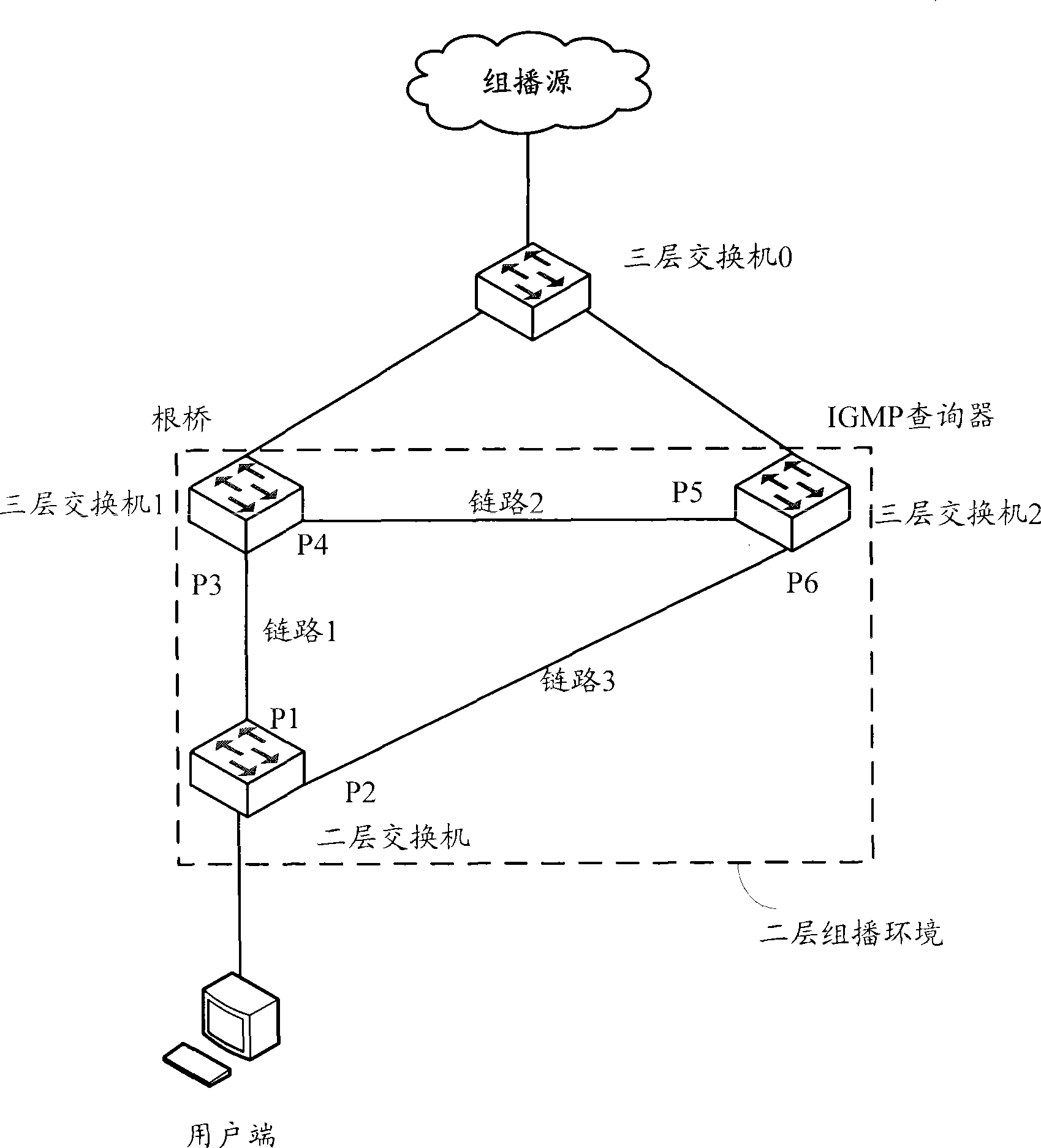

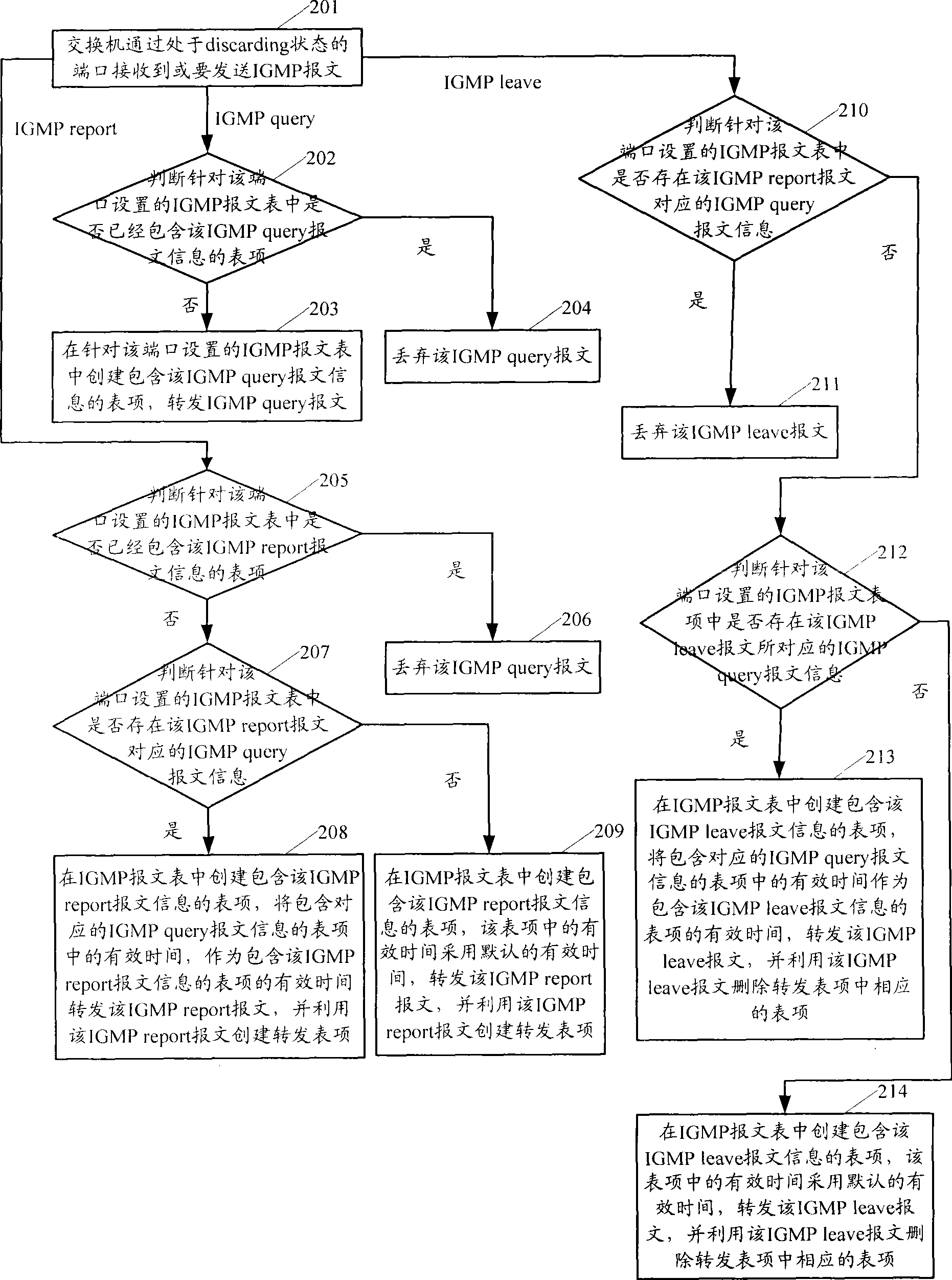

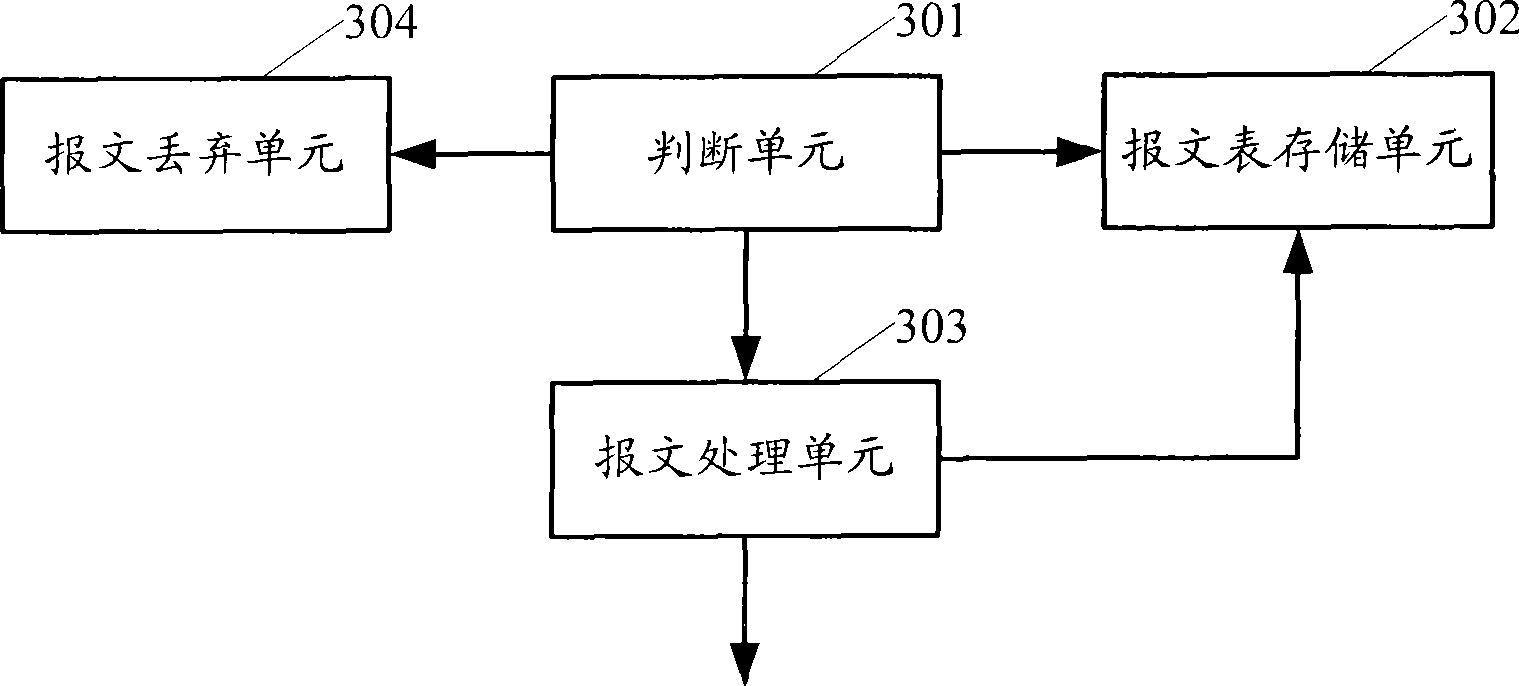

Method and device for processing IGMP message

InactiveCN101448003AShorten the timeAvoid broadcastingData switching networksRing circuitComputer network

Owner:NEW H3C TECH CO LTD

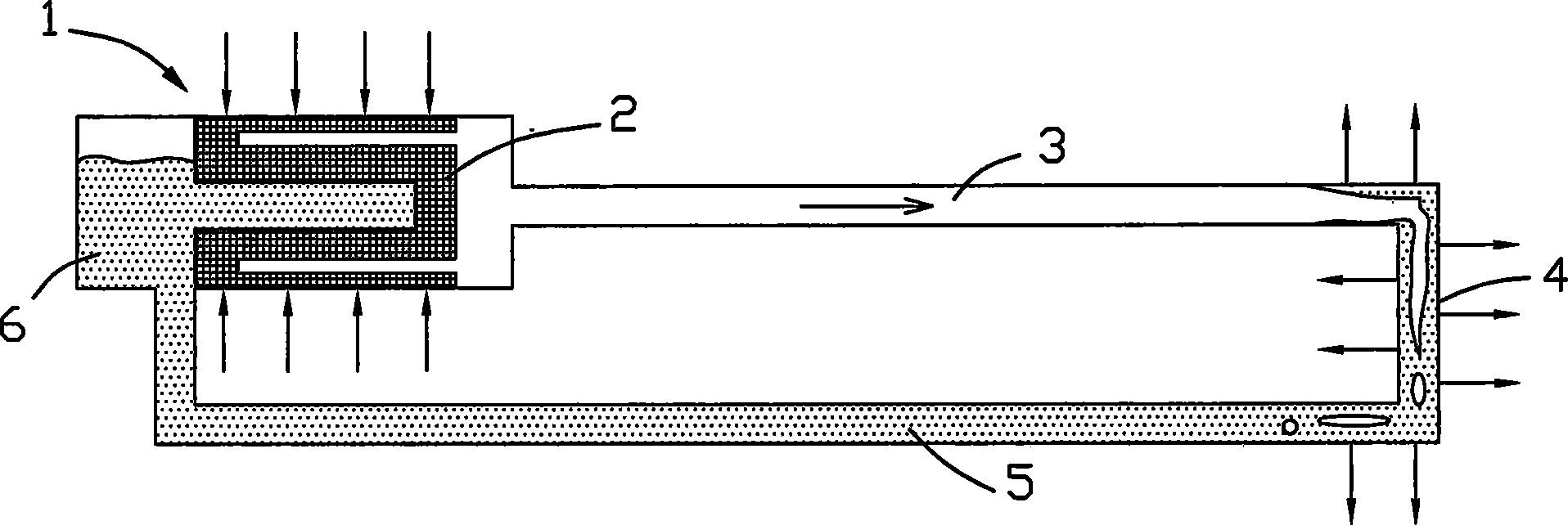

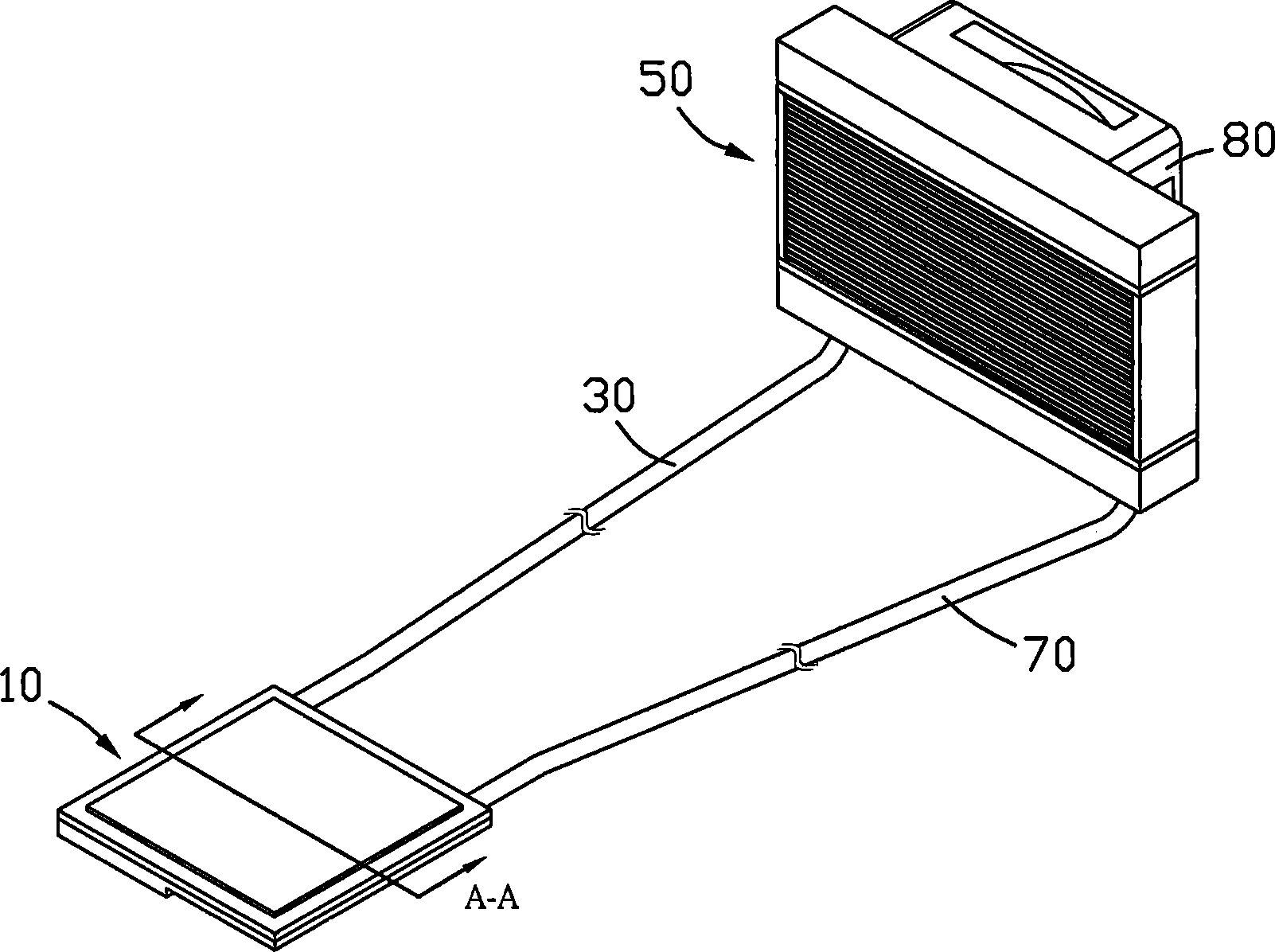

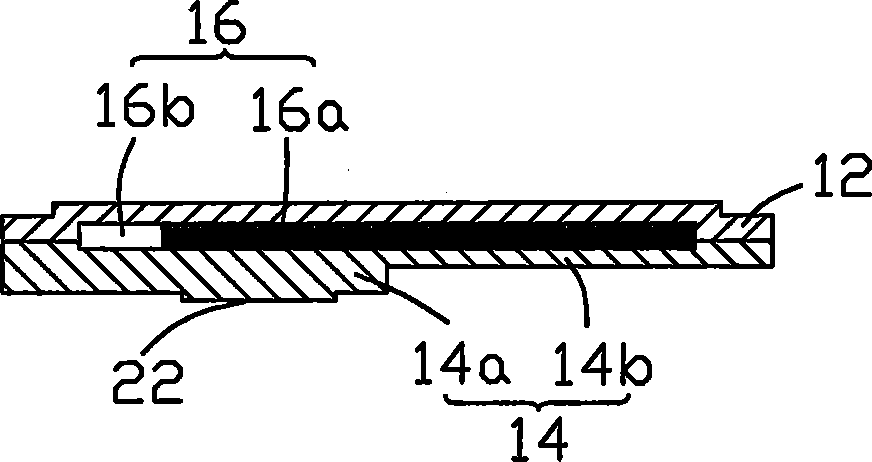

Ring type heat exchanging system

InactiveCN1873360AOvercome the disadvantages of desiccationOvercome unreasonable design flawsDigital data processing detailsIndirect heat exchangersRefluxRing circuit

The present invention provides a ring circuit heat exchange equipment. It includes an evaporation portion, a steam conduit, a condensation portion and a reflux conduit. Said evaporation portion is a closed cavity body its interior is equipped with a multiple microflow channel capillary structure, said capillary structure can separate the cavity body space into liquid phase microflow channel zone and steam channel zone, said two channel zones are series-connected with said condensation portion respectively by means of external steam conduit and reflux conduit so as to form a complete ring circuit type heat exchange radiation system. Said condensation portion is formed from fins and condensation tube. Said invention not only has high heat transfer efficiency, but also can obtain good heat exchange effect.

Owner:FU ZHUN PRECISION IND SHENZHEN +1

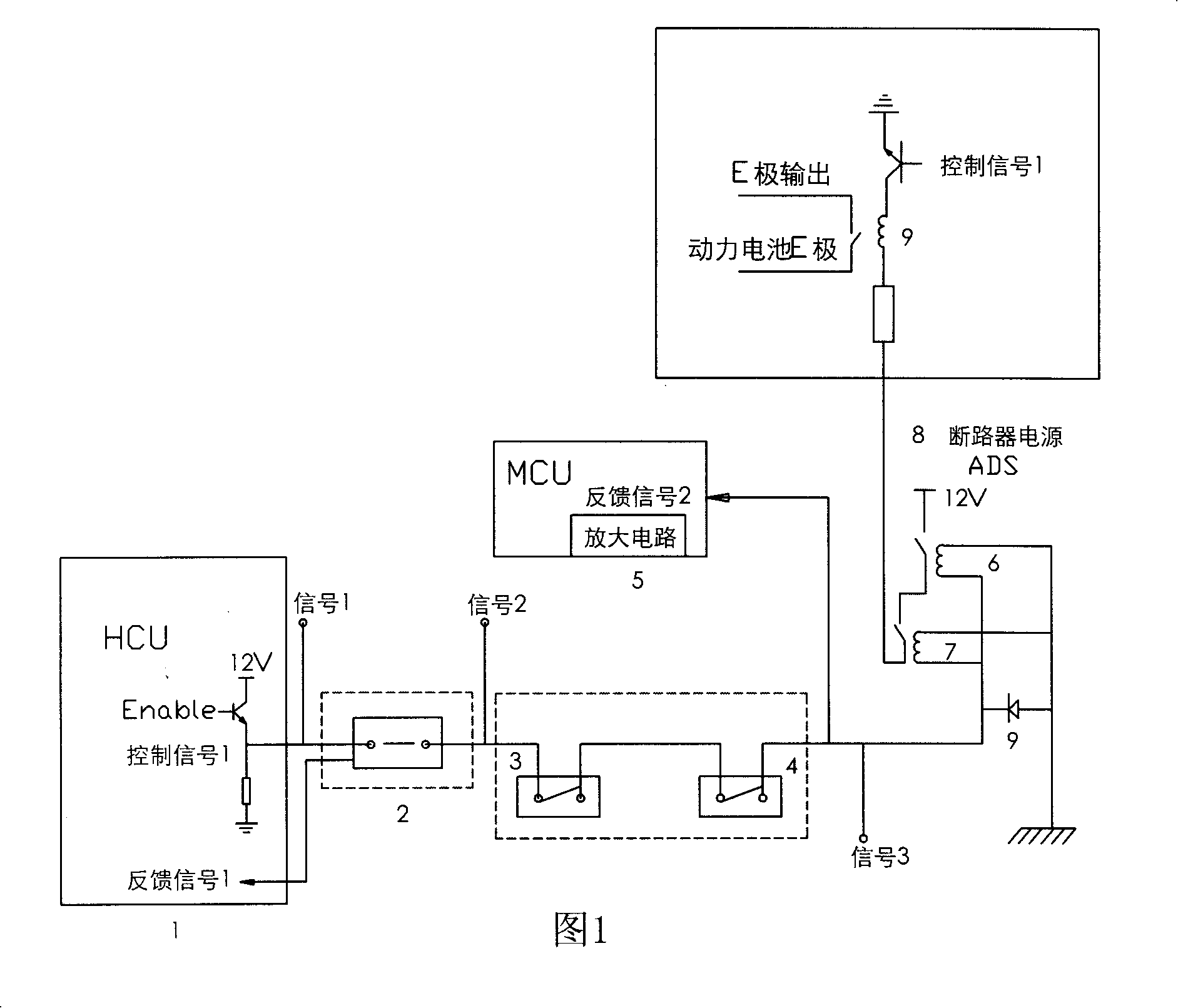

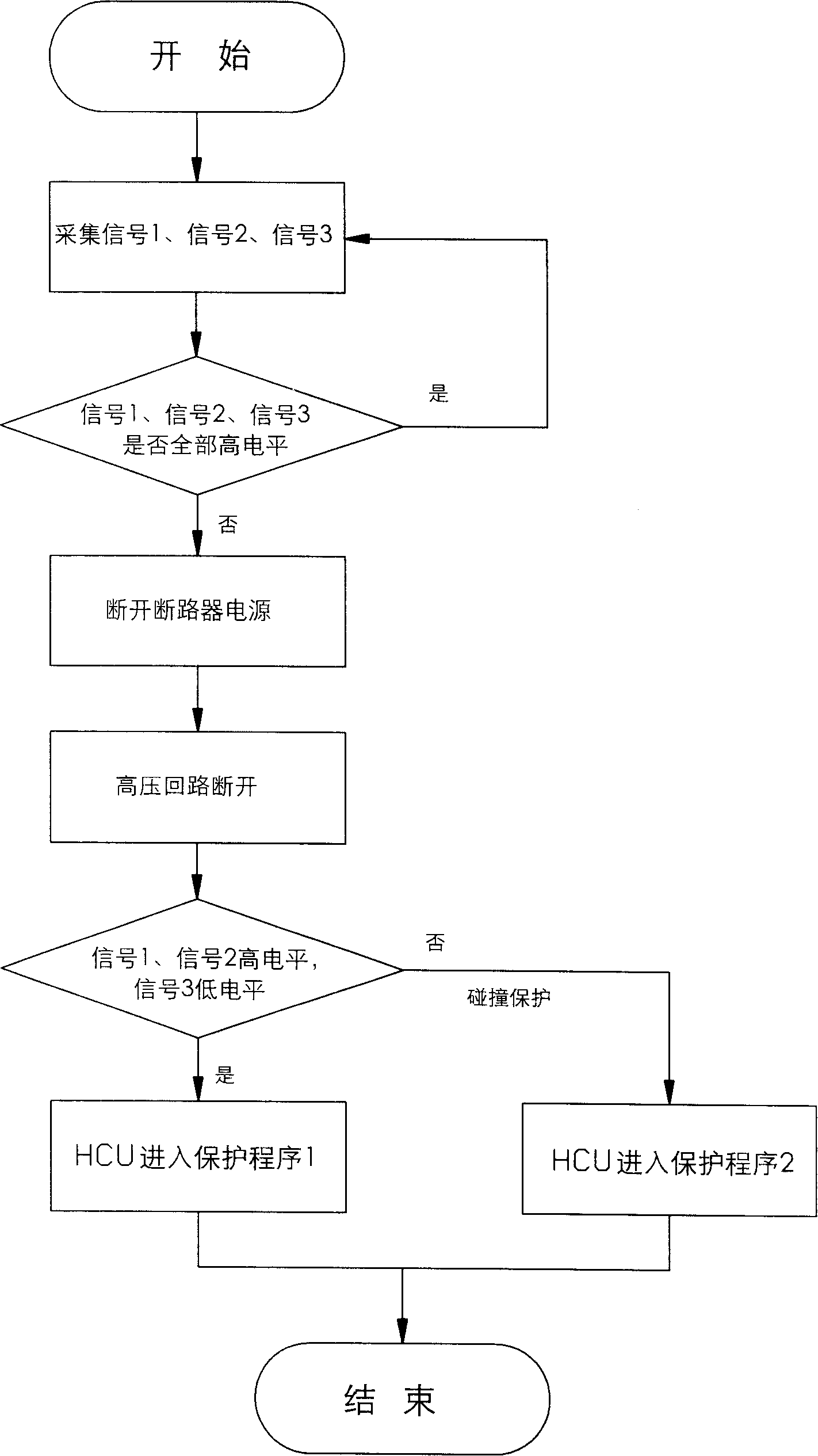

Safety system of mix dynamical automobile

ActiveCN101157337AAvoid harmElectric devicesPedestrian/occupant safety arrangementRing circuitElectrical battery

A safety protection system for hybrid vehicles is characterized in that the invention consists of a signal control loop formed by connecting a collision sensor 2, open circuit protection sensors 3, 4 and control relays 7,6 in series, and a high-voltage ring circuit interlocked loop formed by connecting contact points of the control relays 7,6 and an open circuit relay 9 of a power battery in series; an entire controller HCU provides 12v power for the loop and connects with a control switch at an input end and provides a control signal Enable; the open circuit relay 9 also connects with a control switch and shares the control signal Enable; when in danger, the high-voltage loop can cut off automatically and can release the residual charge on the driving side of a motor; when vehicles are collided, the ring circuit interlocking can cut off the high-voltage loop automatically to prevent the battery from shot cutting, and to prevent people from being attacked by the electricity of the high-voltage loop.

Owner:CHERY AUTOMOBILE CO LTD

Detection circuit for washing machine door cover

ActiveCN102024306ASmooth transmissionAvoid the problem of not receiving the door opening and closing informationOther washing machinesAlarmsDIACRing circuit

The invention relates to the field of home appliances and discloses a detection circuit for a washing machine door cover, which comprises a microswitch and a washing machine main control unit, wherein the microswitch is switched on and off by using the door cover, the washing machine main control unit is used for detecting the on and off states of the microswitch and respectively connected with two ends of the microswitch through ports A and B, the washing machine main control unit sends a pulse signal through the port A and receives the pulse signal through the port B to form an annular circuit. The scheme discards the mode that the washing machine main control unit in the prior art passively receives an opening / closing signal of the door cover, an active detection mode is adopted, and a bidirectional triode thyristor acts to control the operating state of the motor, which realizes that the opening / closing information of the door cover is detected in real time and avoids the problem that the opening / closing information of the door cover can not be rightly received by the washing machine main control unit due to the failure of a peripheral circuit in the prior art.

Owner:FOSHAN SHUNDE HAIER ELECTRIC APPLIANCES CO LTD

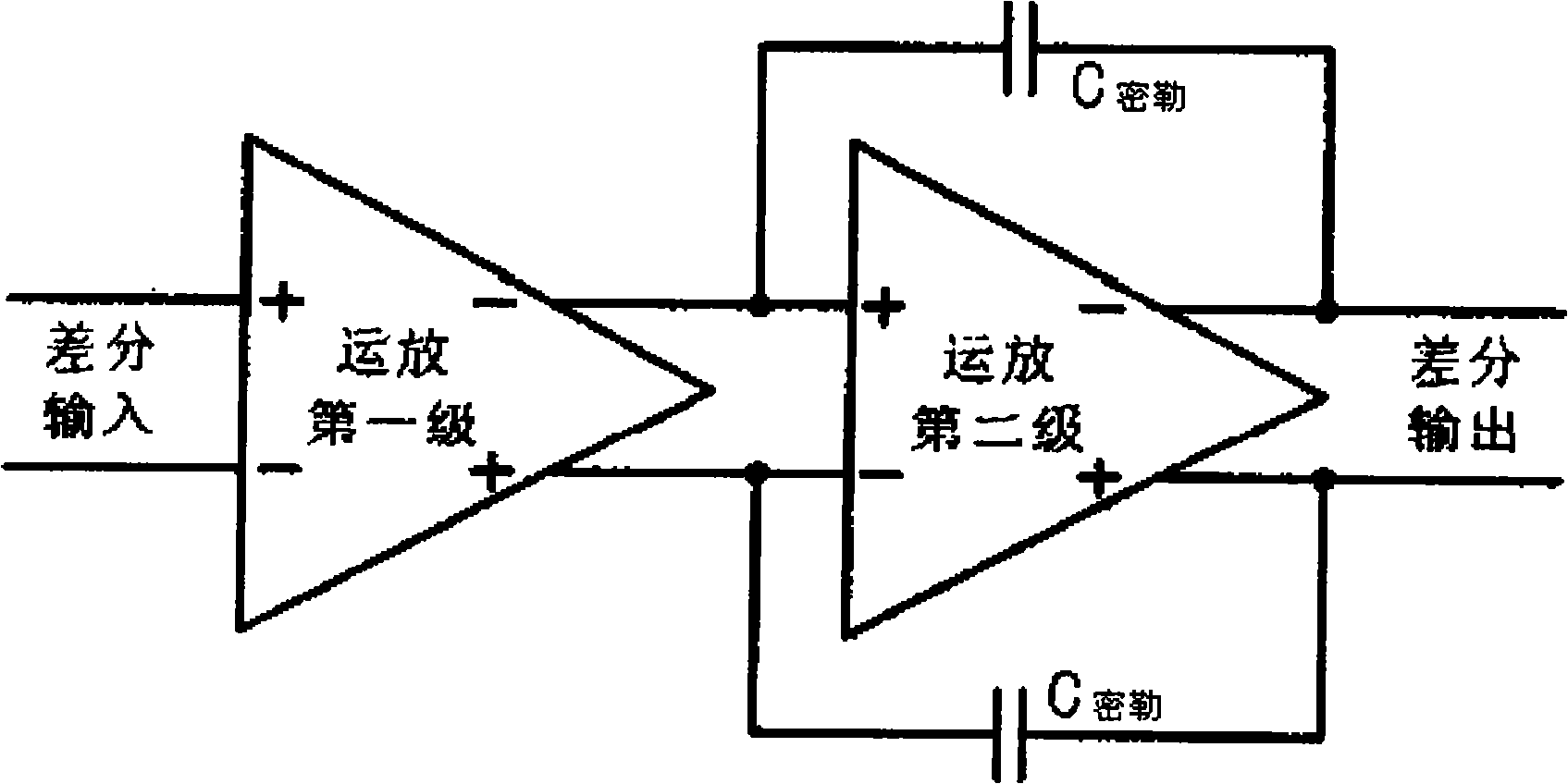

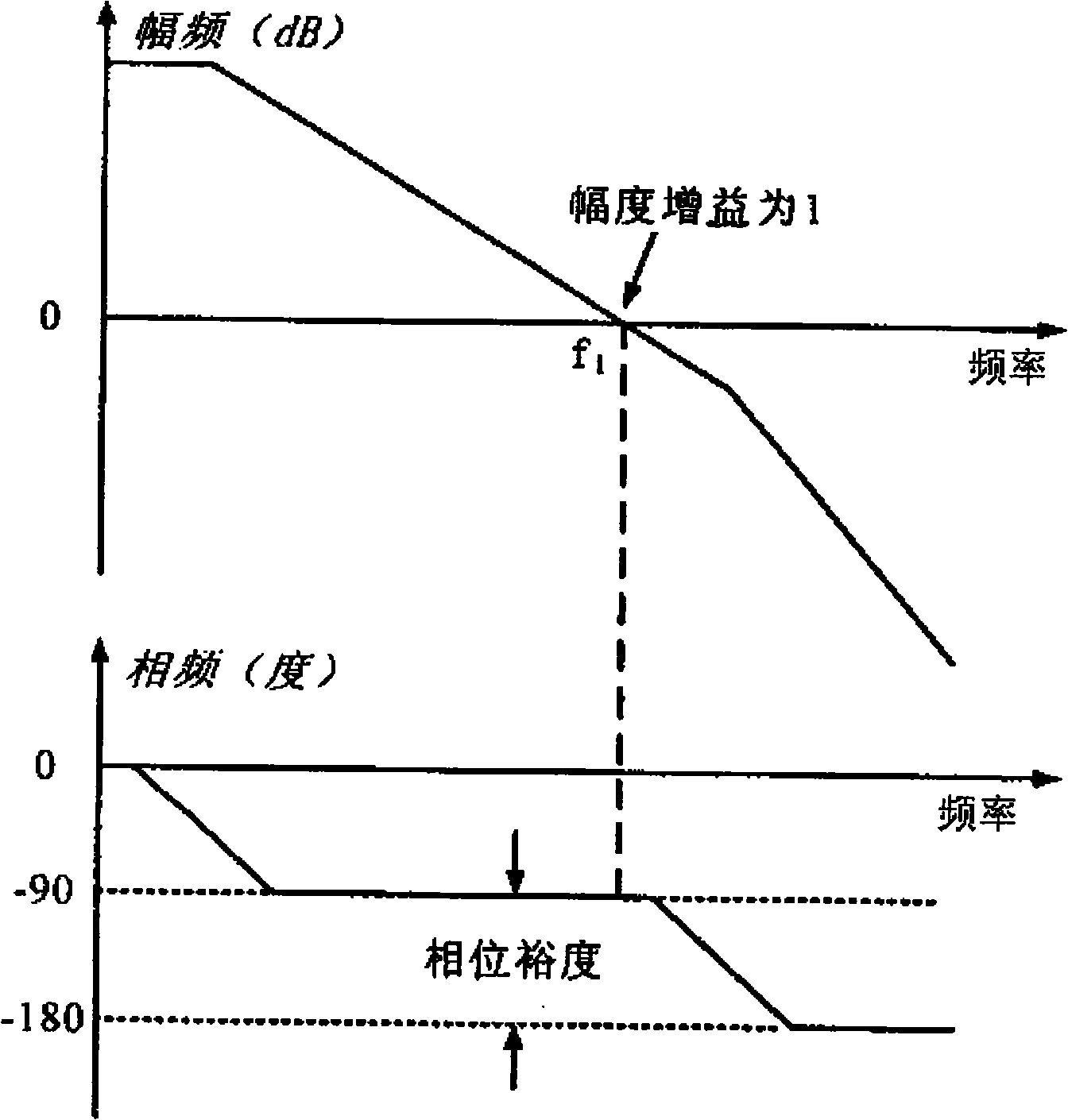

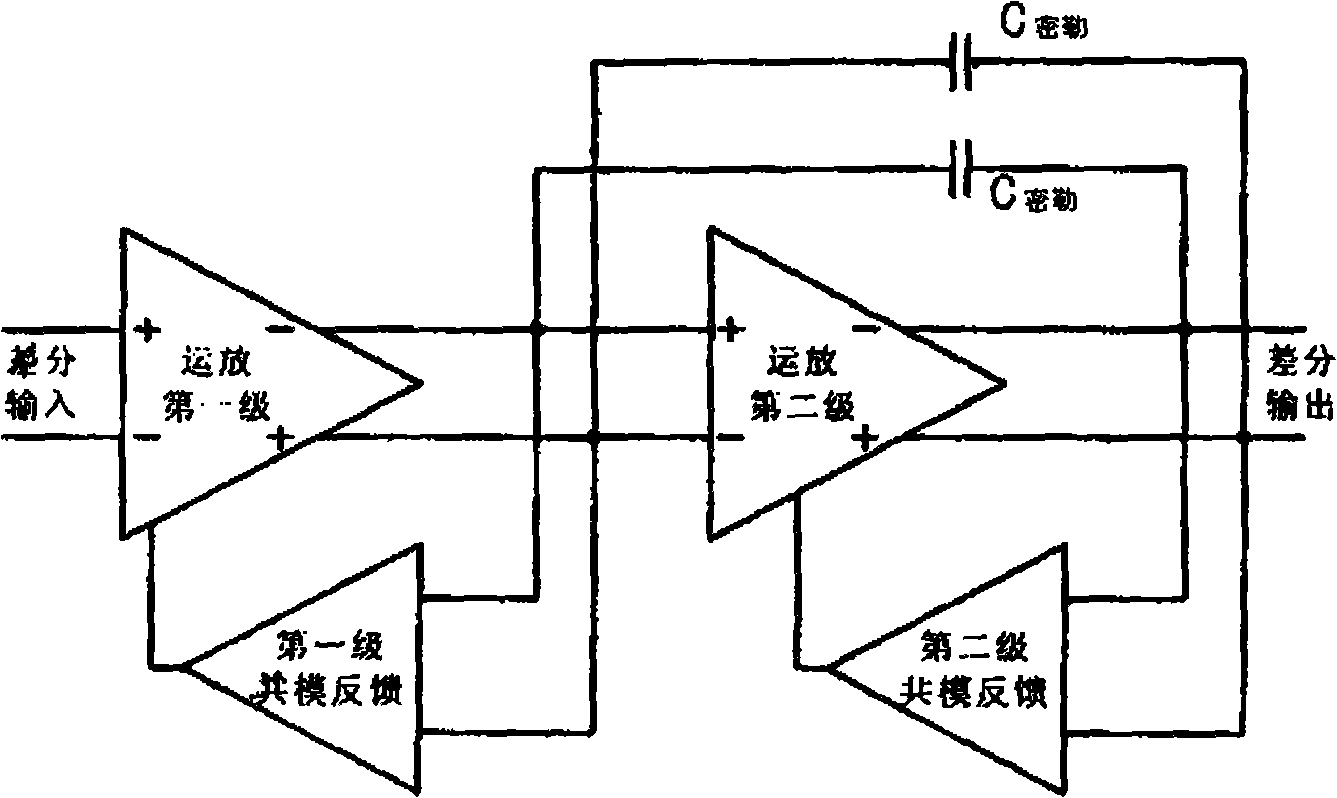

Method for compensating frequency of wideband common mode feedback loop of two-stage operational amplifier

InactiveCN101355346ASimple designReduce power consumptionDifferential amplifiersDc-amplifiers with dc-coupled stagesRing circuitControl signal

The invention discloses a method for compensating the frequency of a broadband common mode feedback ring circuit for a two-stage operational amplifier, belonging to the field of analog integrated circuit design. A broadband feedback amplifier in the two-stage operational amplifier with the Miller compensation is used as the common mode feedback ring circuit so as to reduce the area and the power consumption of the common mode feedback circuit; the two-stage operational amplifier has only one main pole in the range of the unit gain bandwidth, a fully differential input and output structure is adopted, the sampling of the common mode output level is performed by the differential output end; and a control signal fed back by the common mode simultaneously controls the output level of a first-stage common mode and the output level of a second-stage common mode of the operational amplifier through a controllable bias circuit. The frequency of the main pole of the broadband feedback amplifier is far higher than the unit gain bandwidth of the operational amplifier, therefore the margin of phase position of the common mode ring circuit is basically equal to that of the operational amplifier, thereby forming the stable feedback ring circuit. The method has the advantages of few elements for a common mode feedback circuit, lower power consumption of the common mode feedback circuit and simpler and more convenient circuit design.

Owner:RESEARCH INSTITUTE OF TSINGHUA UNIVERSITY IN SHENZHEN

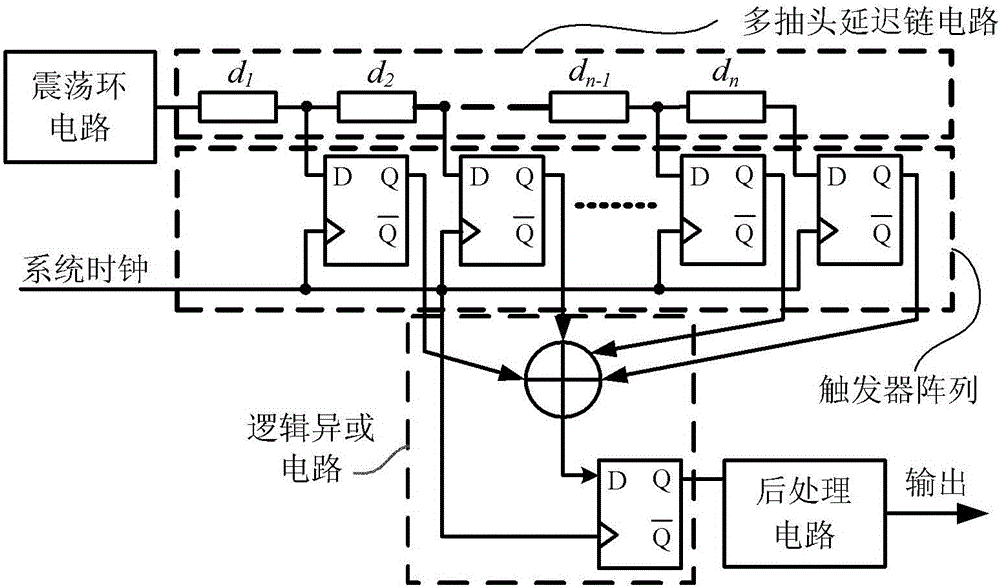

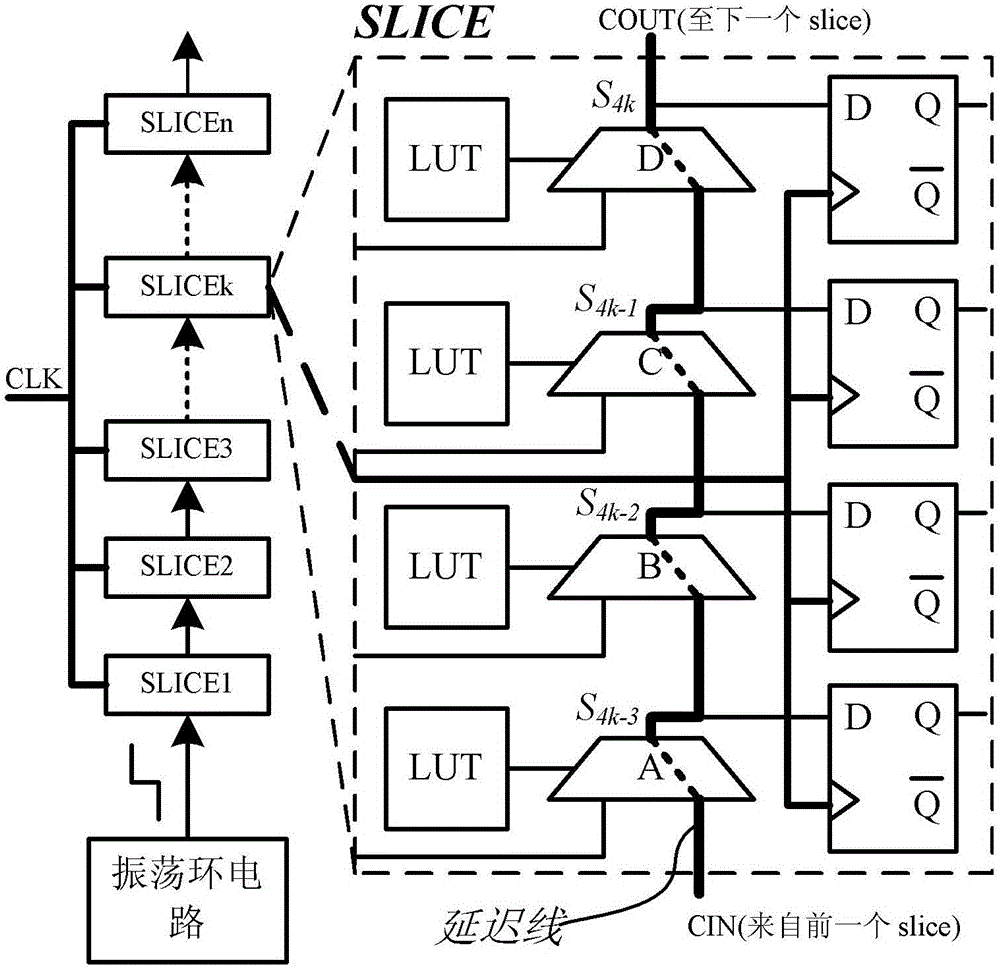

FPGA-based true random number generator

The invention discloses an FPGA-based true random number generator. The FPGA-based true random number generator comprises an oscillating ring circuit, a multi-tap signal delay chain, a trigger array, a logic XOR circuit and a postprocessing circuit. A clock signal generated by the oscillating ring circuit is fed into the signal delay chain, the trigger array samples the level states of all taps of the delay chain under the control of a system clock, acquisition results of all triggers are subjected to logic XOR processing and sent into the postprocessing circuit, and output of the postprocessing circuit is a generated binary true random number sequence. The FPGA-based true random number generator not only can generate random numbers at a rate as high as possible, but also can guarantee the quality of the random numbers.

Owner:UNIV OF SCI & TECH OF CHINA

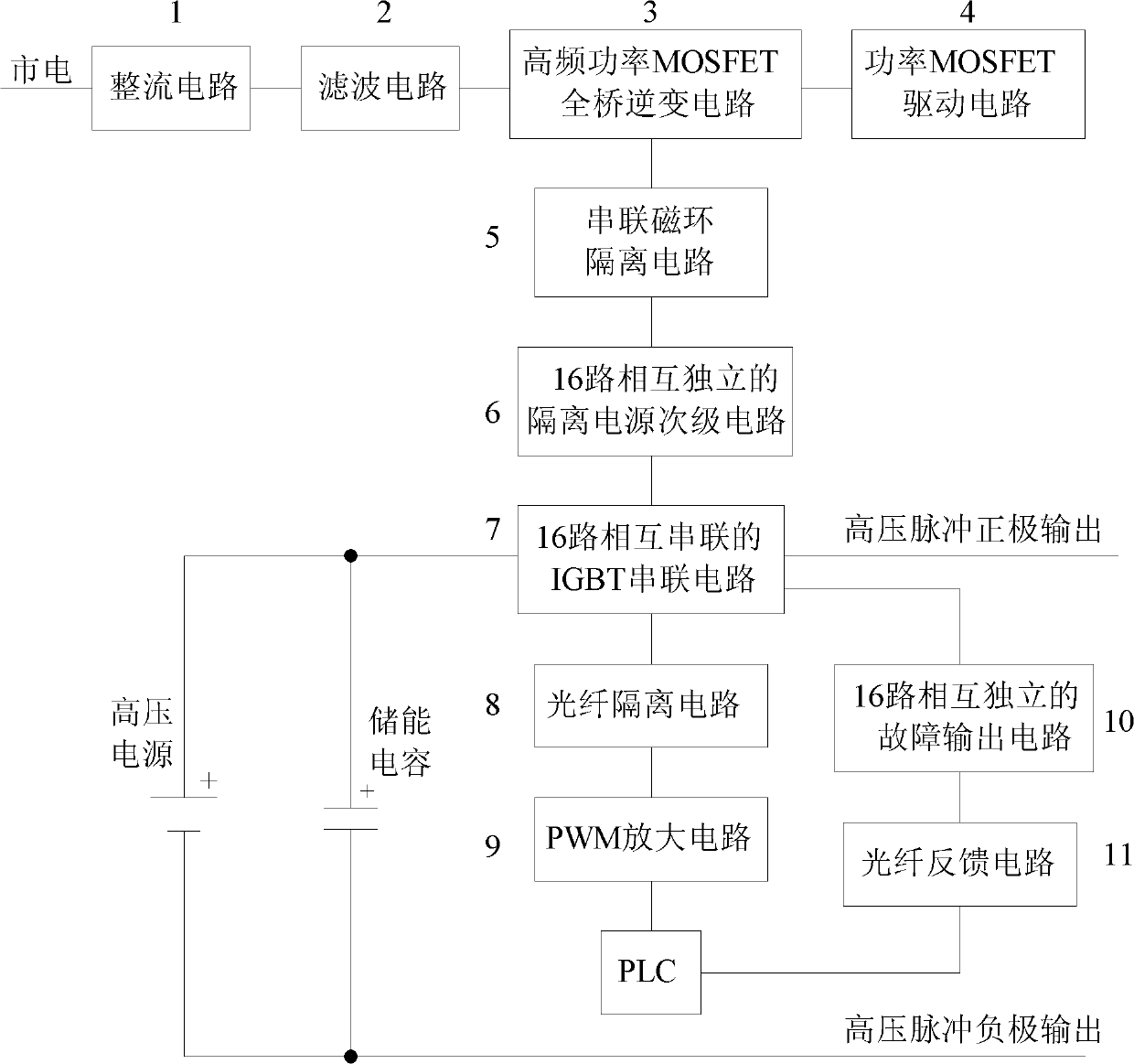

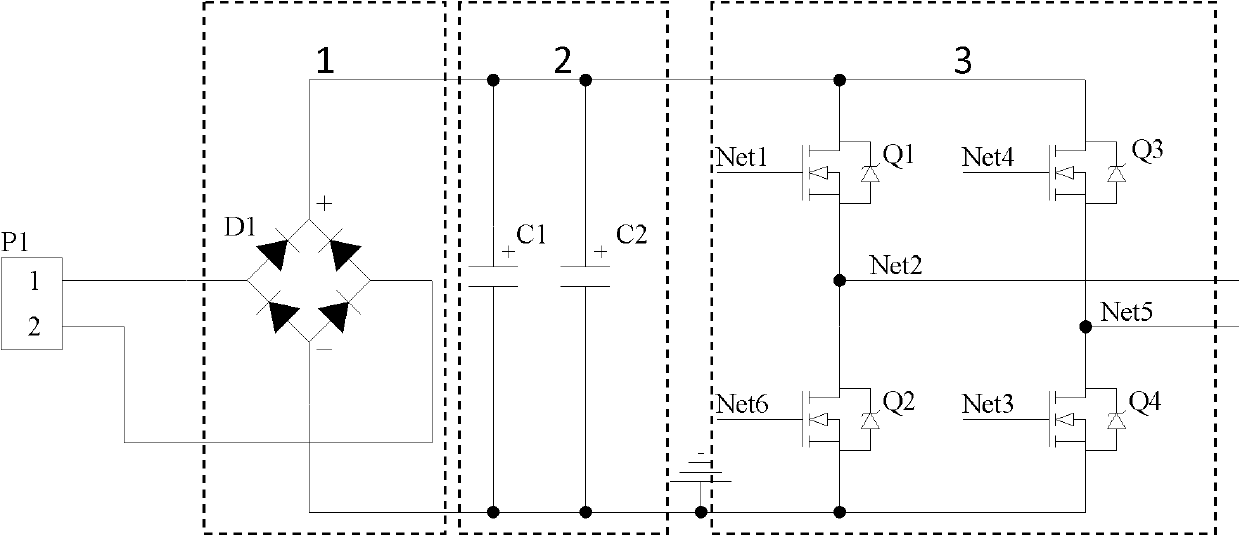

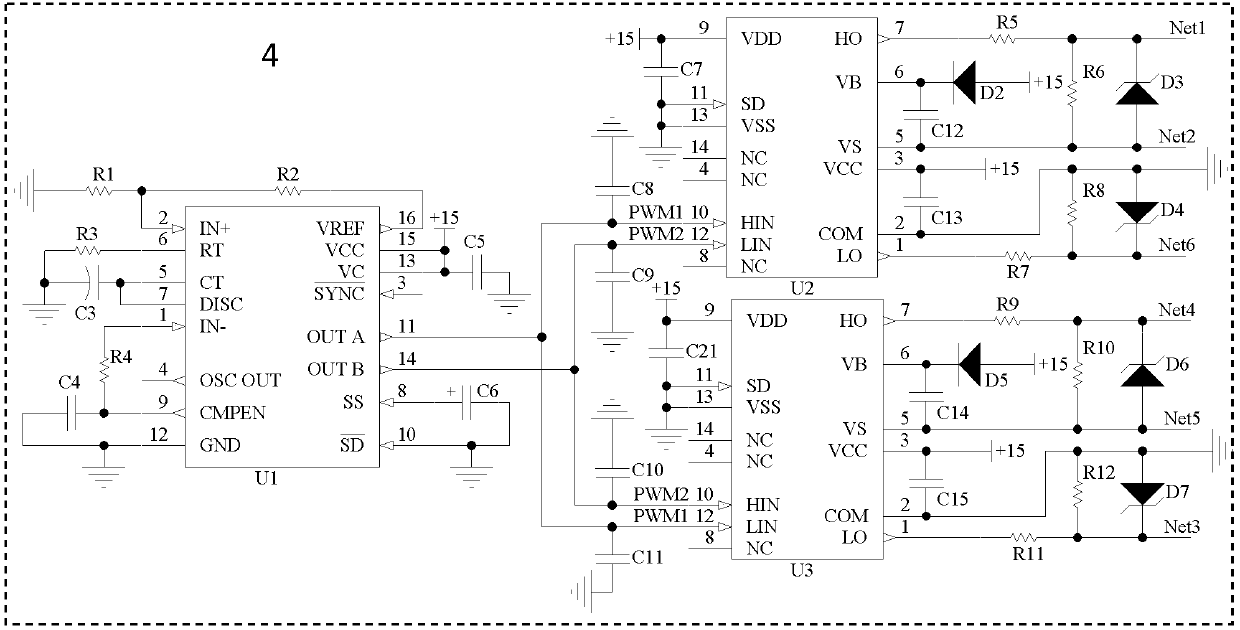

Insulated gate bipolar translator (IGBT) series connection type high-voltage pulse generator

InactiveCN102611413AReduce distractionsGuaranteed normal transmissionElectric pulse generator circuitsCapacitanceHigh frequency power

Owner:ZHEJIANG UNIV

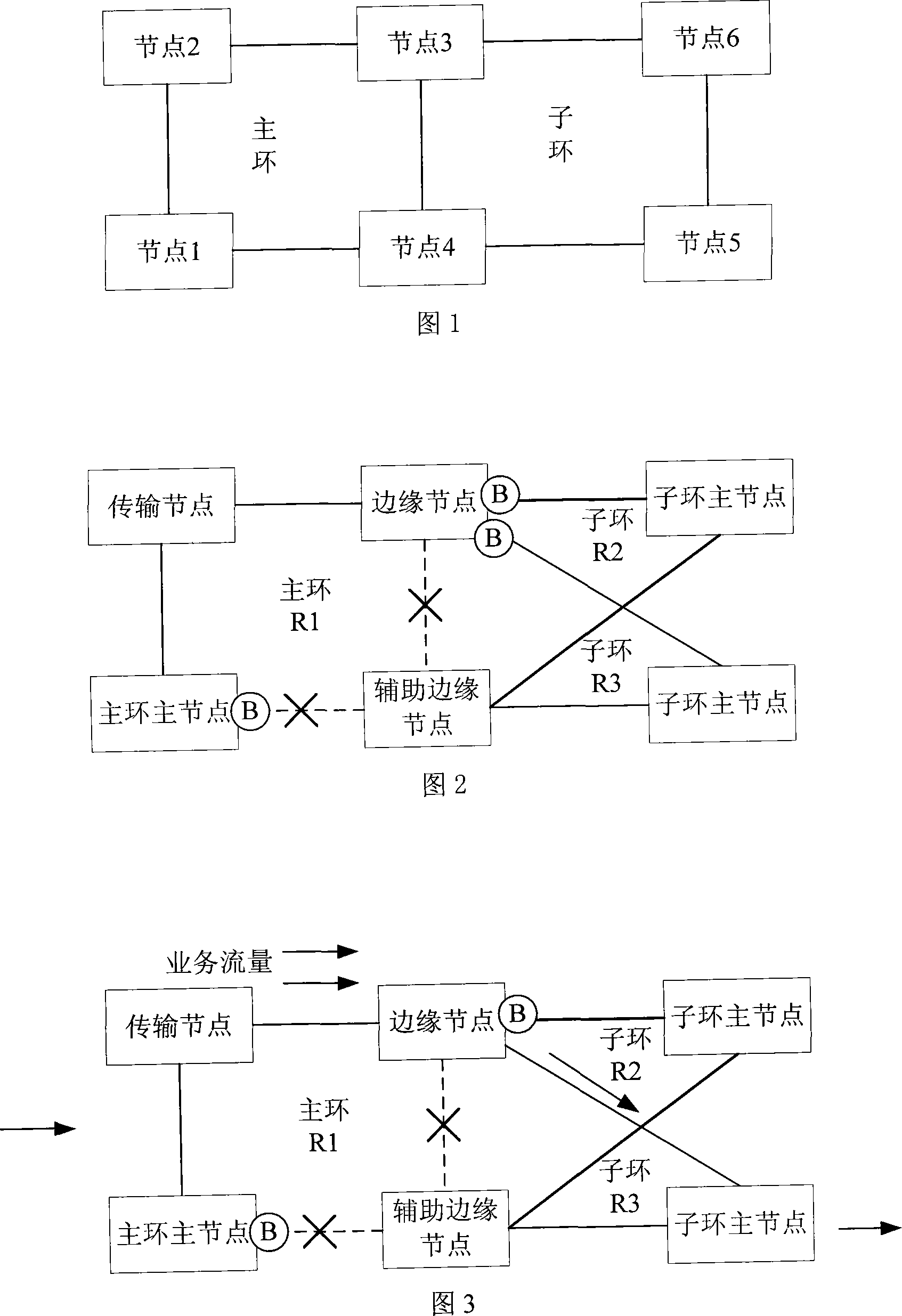

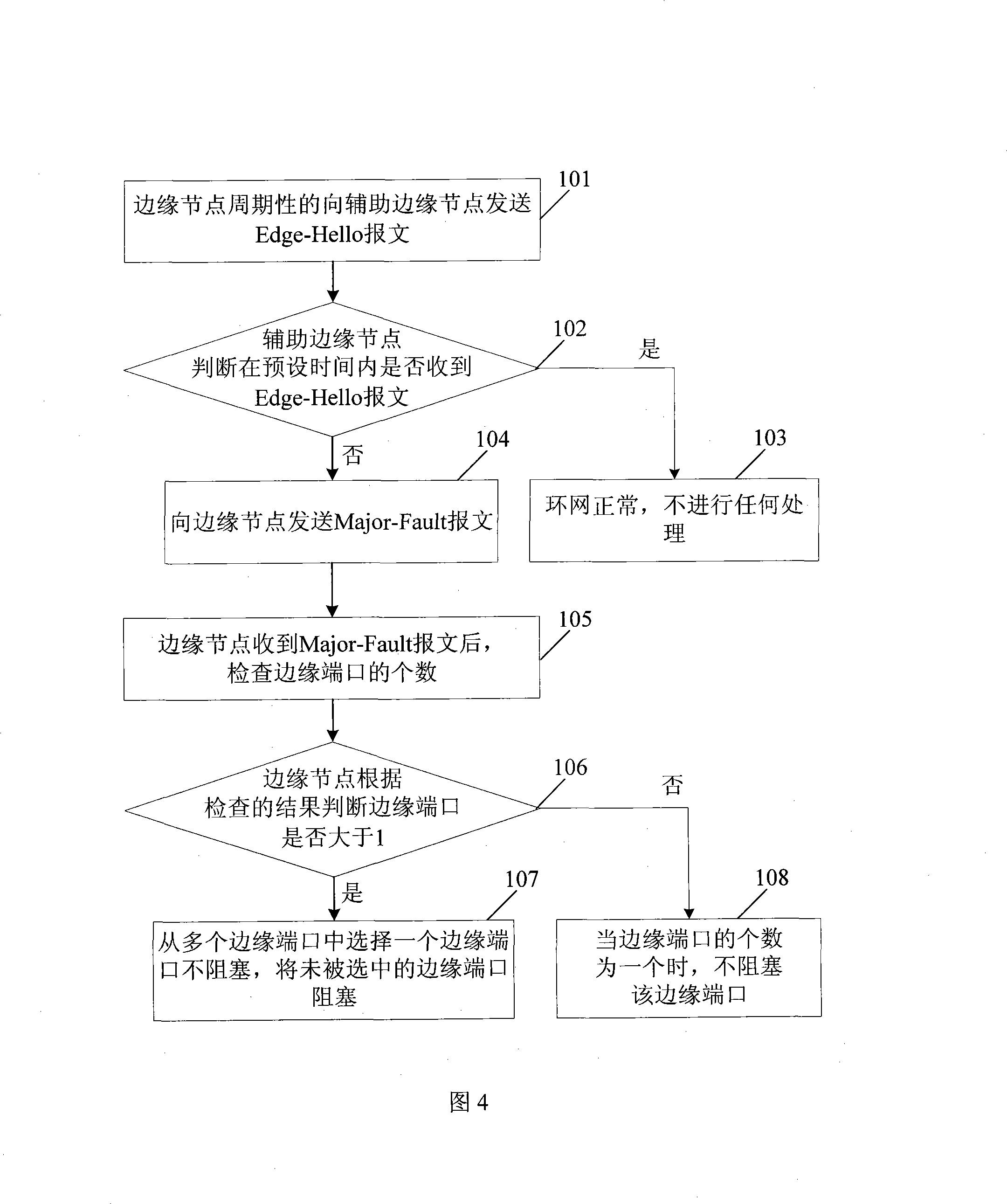

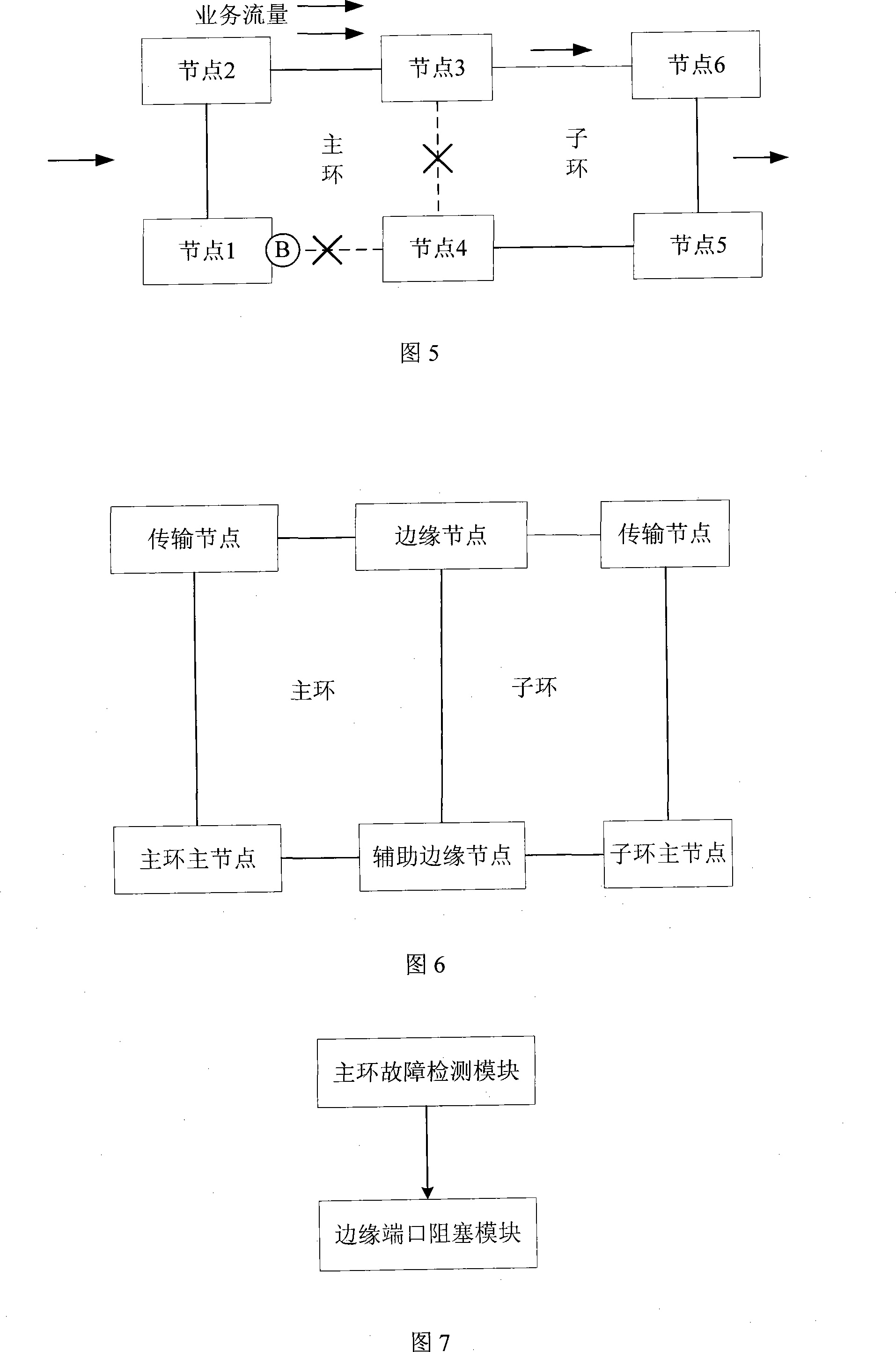

Method for edge port block in ethernet ring, ethernet ring system and device

InactiveCN101247306AImprove troubleshooting capabilitiesImprove practicalityData switching networksMultiple edgesRing circuit

The invention discloses a method for blocking edge port in Ethernet ring network, Ethernet ring network system and equipment, belonging to the communication field. The method comprises: after receiving the main ring fault notice message transmitted by an auxiliary edge node, an edge node checks the number of the edge port; unblocking the edge port when the edge port has a number of one; selecting one edge port from multiple edge ports unblocked and blocking unselected edge port when the edge port has more than one; the edge node and auxiliary edge node of the system. The equipment comprises a main ring fault detection module and an edge port block module. When the main ring has multi-point fault, one edge port is unblocked and other edge ports are blocked, thereby ensuring the normal transmission of business flow and preventing broadcasting ring circuit.

Owner:HUAWEI TECH CO LTD

Ring oscillator with adjustable delay

A variable-frequency digital ring oscillator provides small and consistent frequency adjustments throughout a locked range. The ring oscillator of the invention is standard cell placeable and operates at the technology limits to provide small and precise delay changes that is inexpensive to implement. The digital variable-frequency ring oscillator includes multiple macro delay elements forming an inverter ring circuit, each element having an individual macro delay unit that in turn is comprised of multiple adjustable delay units. All of these adjustable delay units are controlled by a single delay control signal.

Owner:GOOGLE LLC

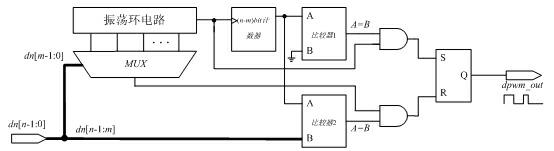

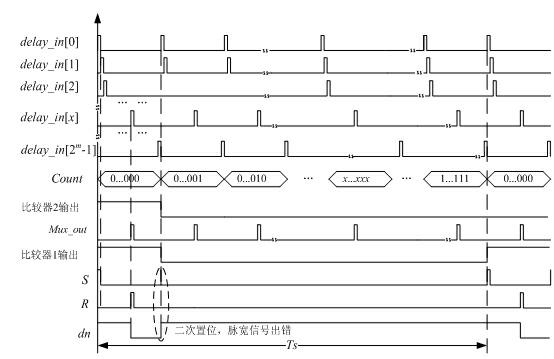

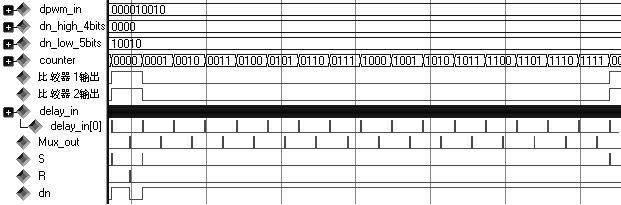

Whole-course adjustable digital pulse width modulator based on oscillation ring circuit

ActiveCN102158208AGuaranteed Effective ResolutionEasy to adjust speedPulse duration/width modulationRing circuitControl signal

Owner:SOUTHEAST UNIV

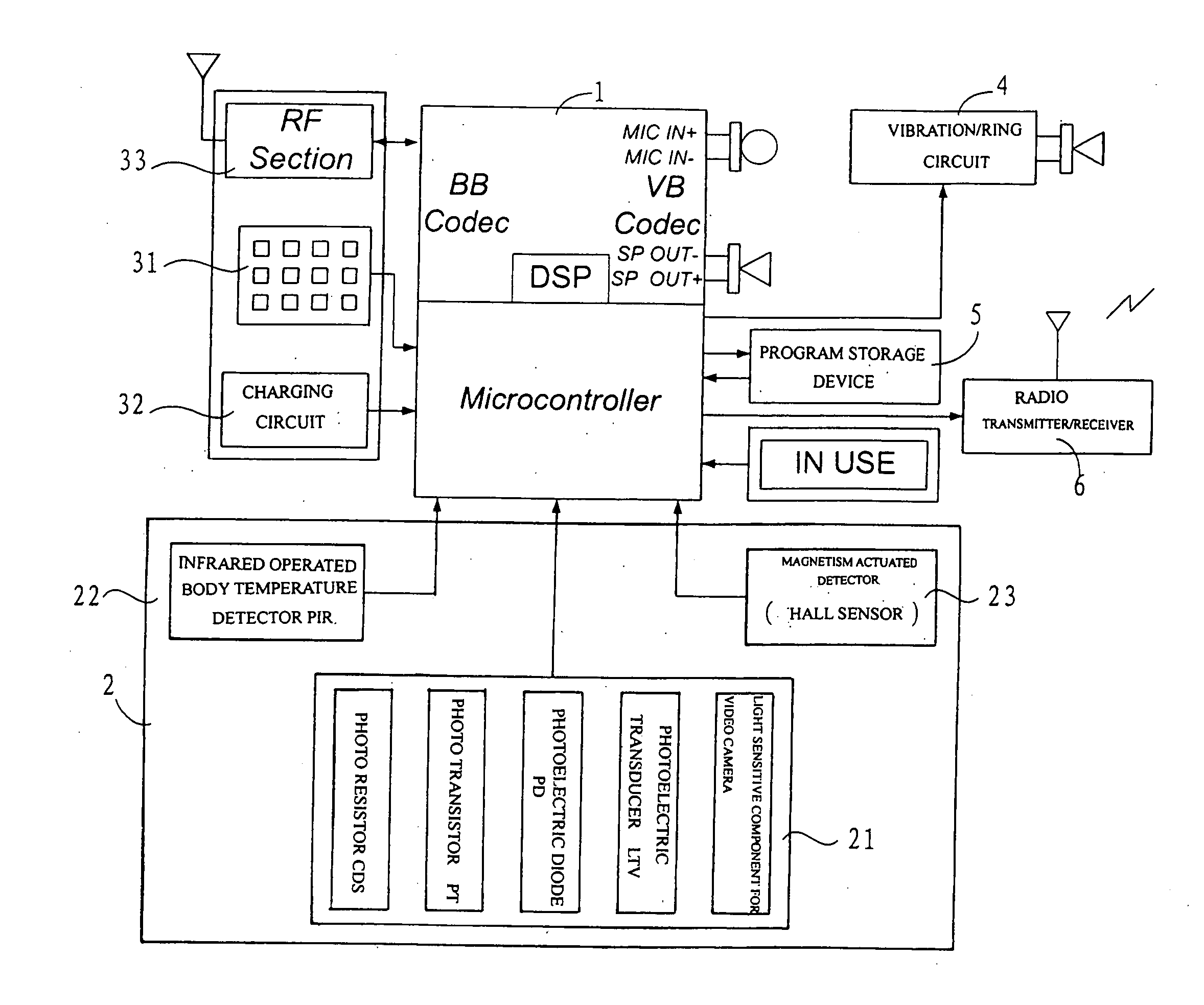

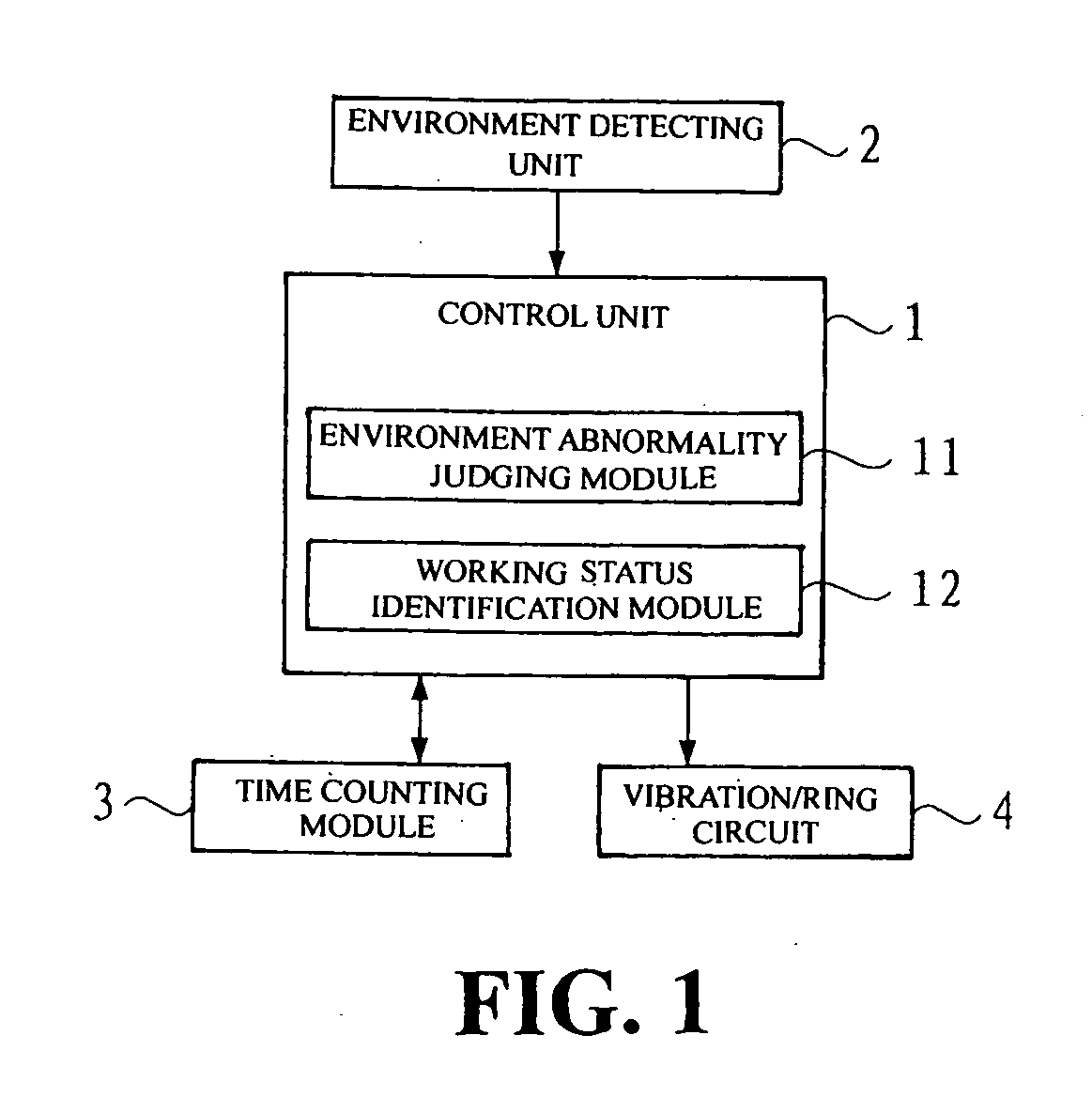

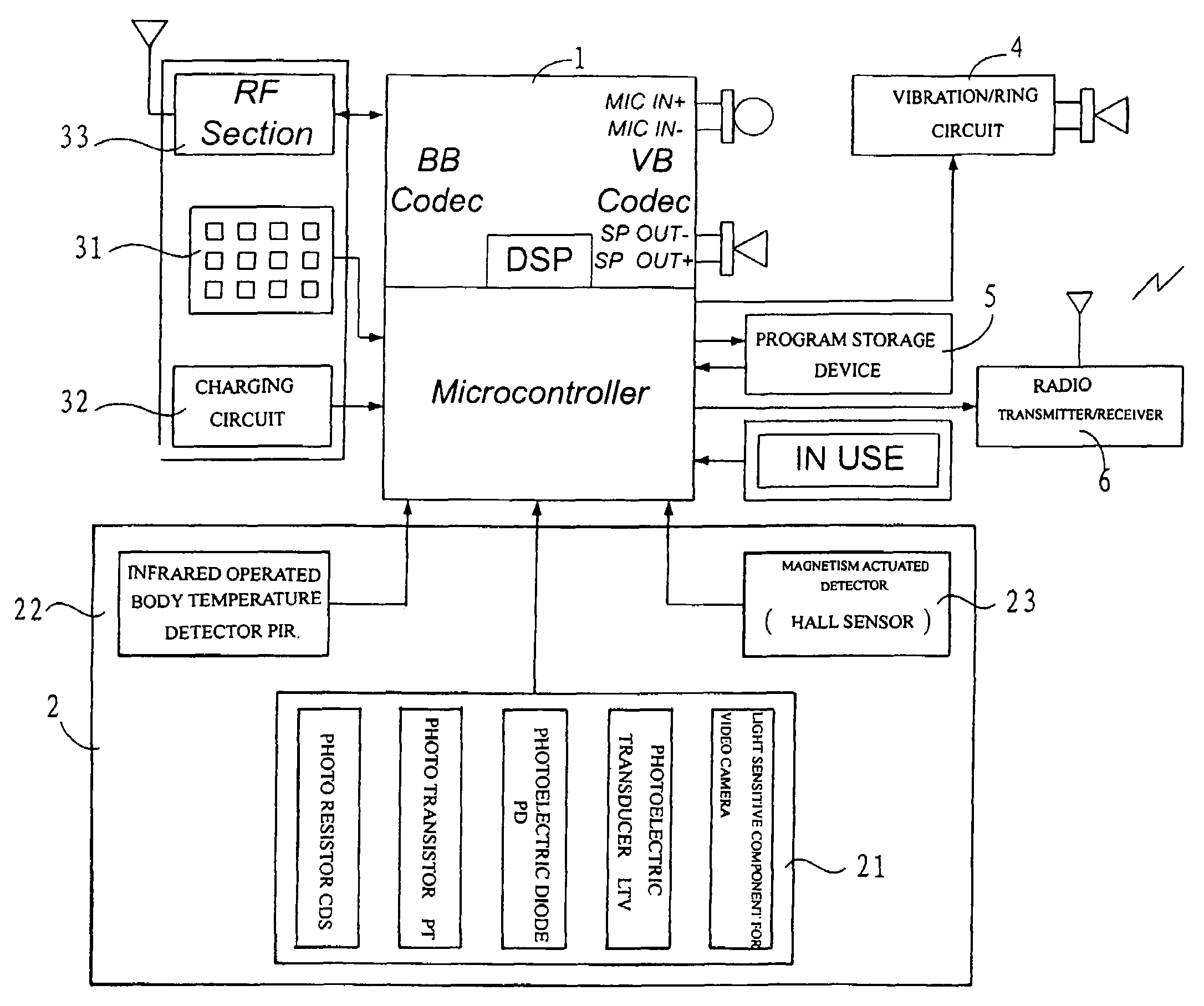

Re-positioning reminder for personal portable electronic equipment

InactiveUS20060258407A1Supplement and expand functionSpecial service for subscribersActive radio relay systemsRing circuitEngineering

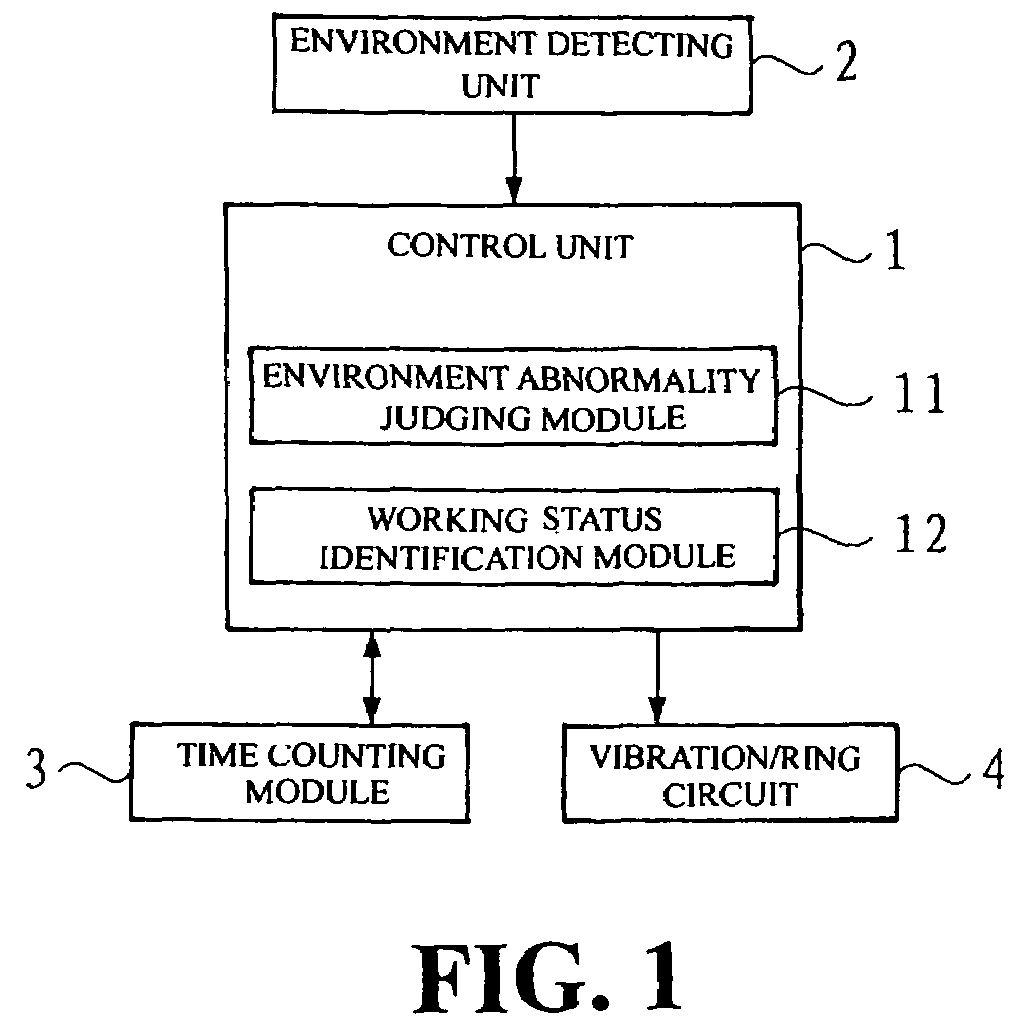

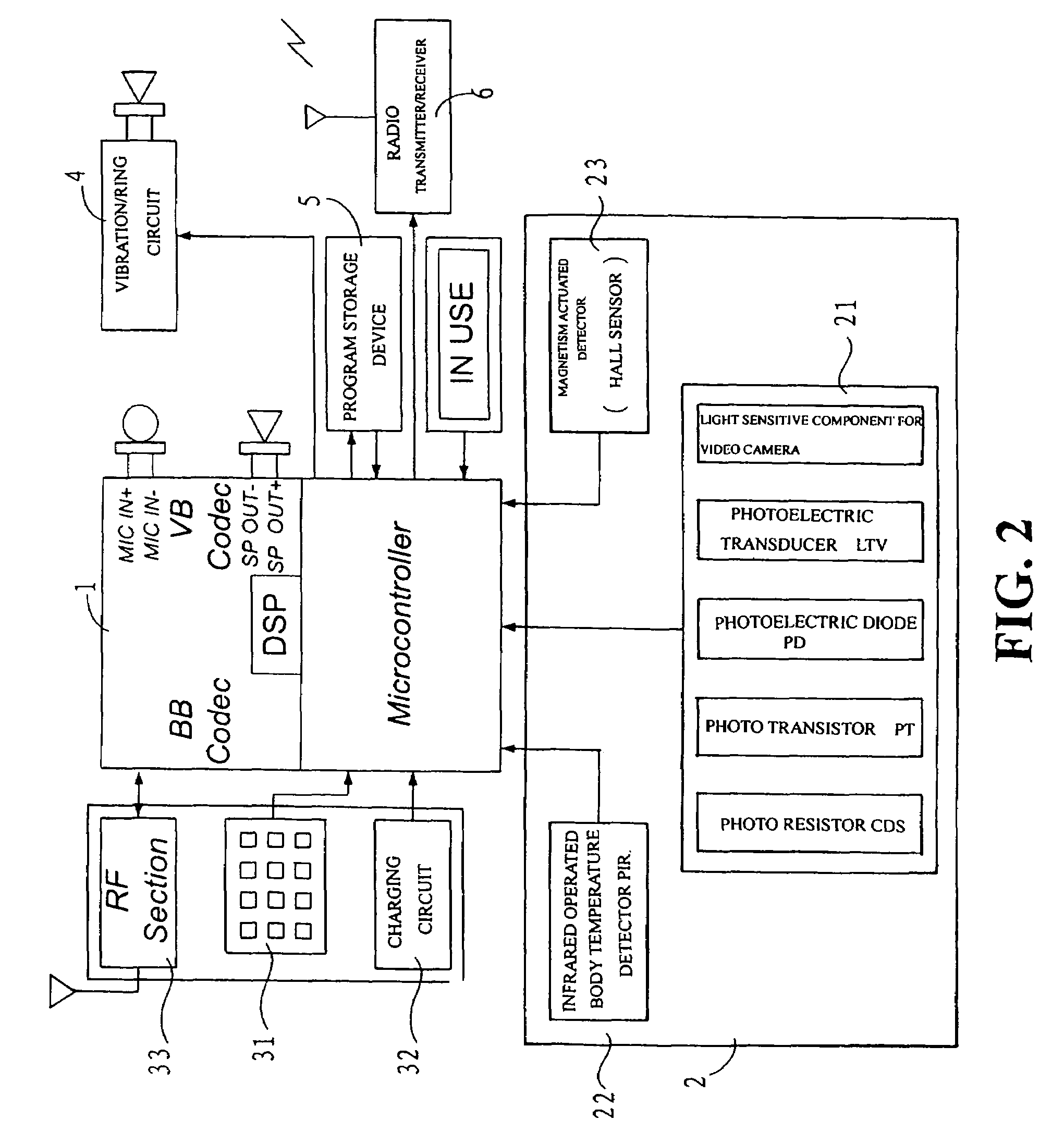

The present invention relates to a re-positioning reminder for personal portable electronic equipment. Such a reminder is housed in the electronic equipment and is at least equipped with an environment detecting unit, a control unit, a time counting module and at least one vibration / ringing circuit; wherein the environment detecting unit is used to monitor the outer surroundings and generates a monitoring value; the control unit is coupled to the environment detecting unit for the reception of the monitoring value which is compared with a preset value in the control unit to check if the environment is in a normal state or not and keeps the time counting module under its control; the time counting module is connected to the control unit and can start a time countdown according to the preset time; the vibration / ringing circuit is connected to the control unit and is controlled by the control unit to send off an alarm at the termination of the time countdown procedure to remind a user to put a personal portable electronic equipment back to a preset place so as to prevent the same from being lost as a result of ignorance.

Owner:ALCON TELECOMM

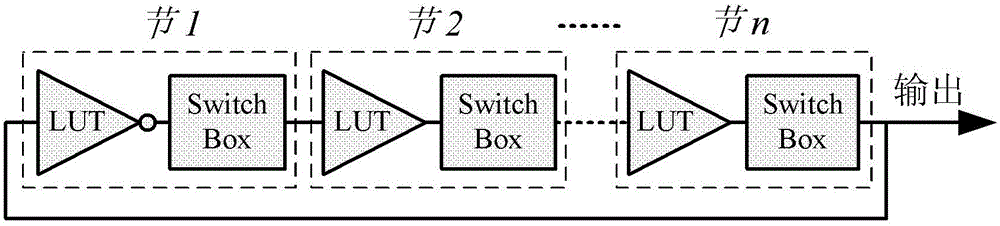

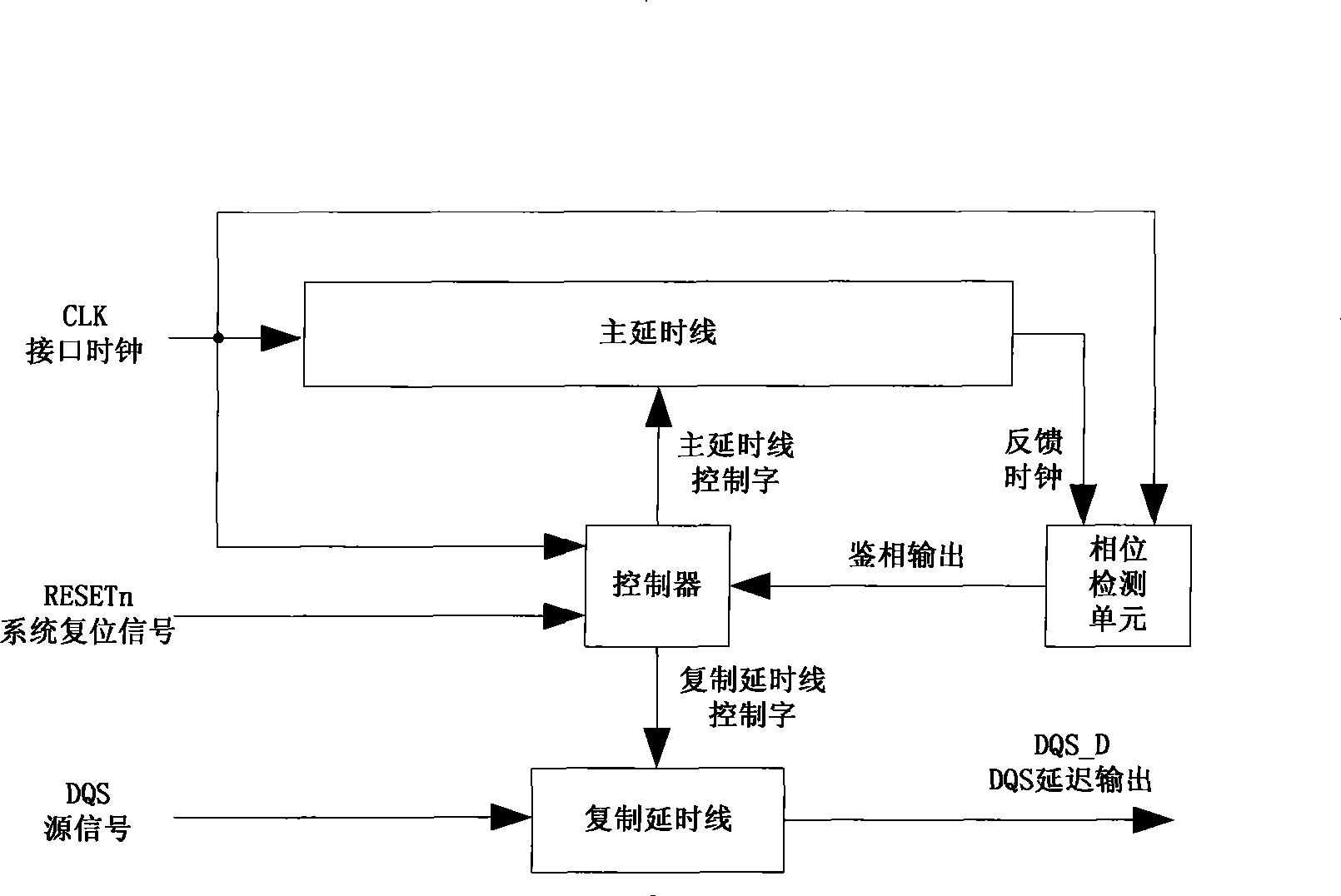

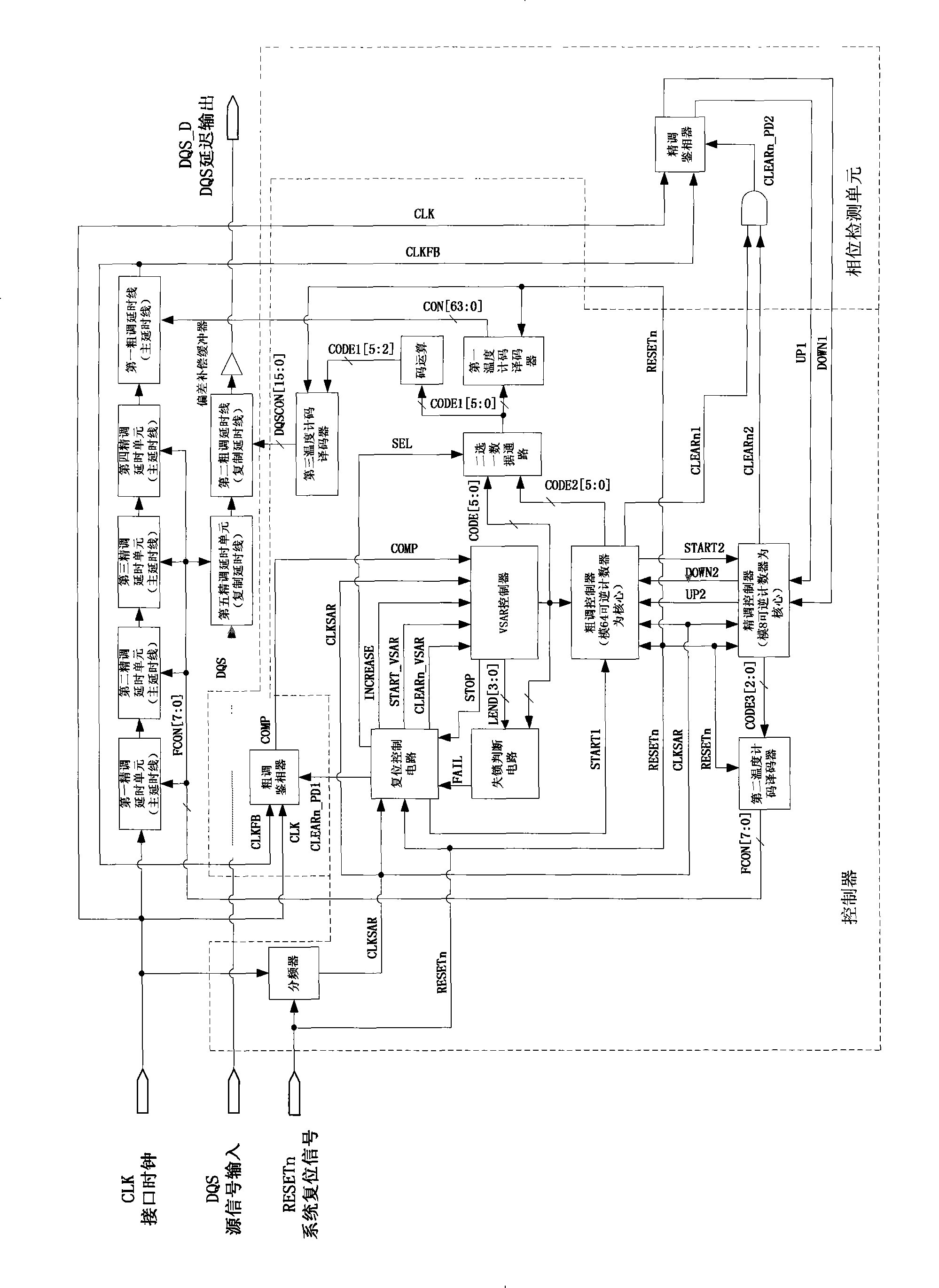

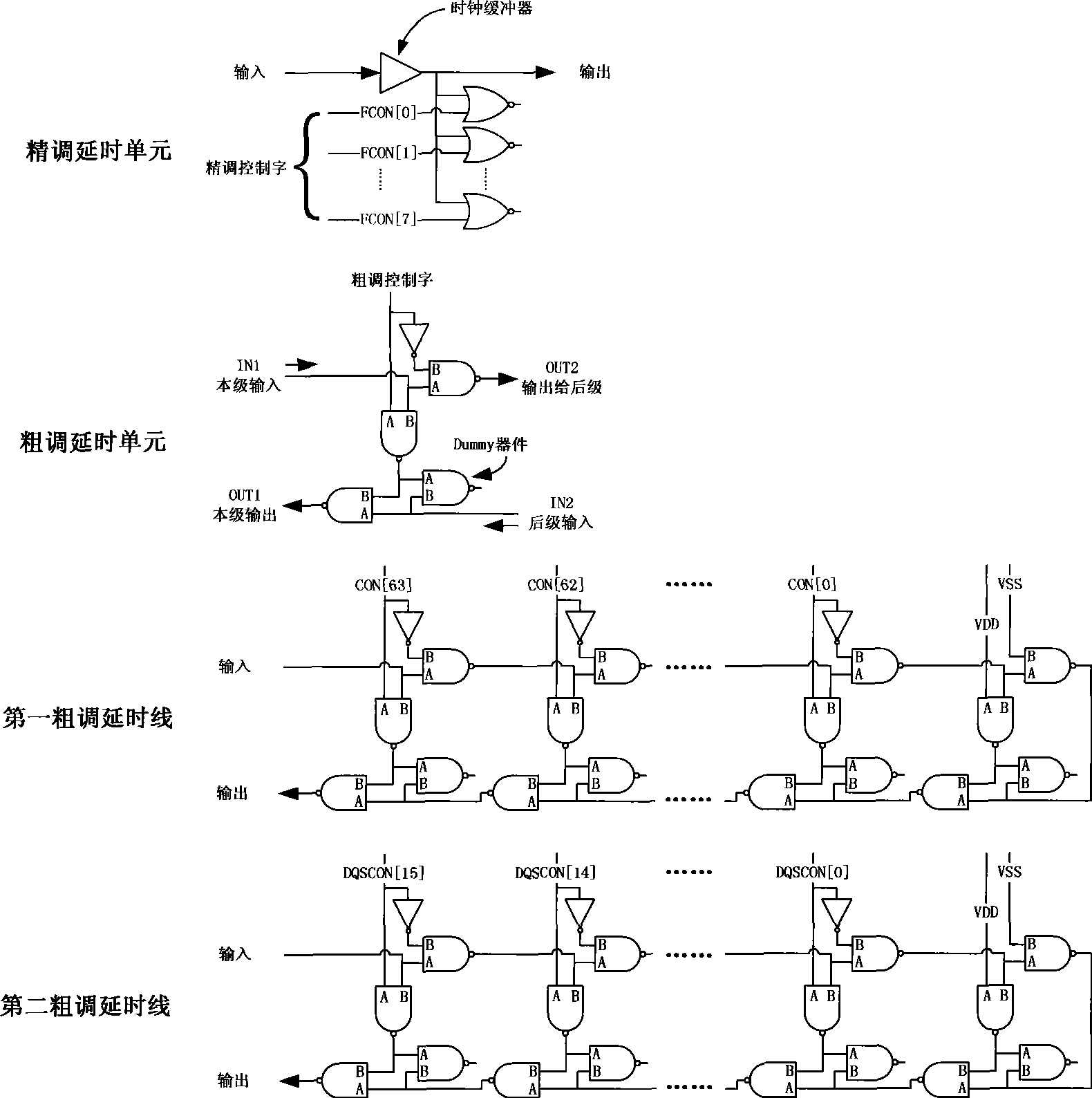

Full digital time-delay locking loop circuit

InactiveCN101504861AImprove compatibilityPulse automatic controlDigital storageRing circuitTime delays

The invention discloses a full digital time delay locking ring circuit, which comprises a main time delay wire, a controller, a phase detection unit and a duplicate time delay wire, wherein a clock interface of the main time delay wire is connected with a clock interface of the controller and a clock interface of the phase detection unit respectively; a feedback clock interface of the main time delay wire is connected with another clock interface of the phase detection unit; an output end of the phase detection unit is connected with an input end of the controller; and an output end of the controller is connected with an input end of the main time delay wire and an input end of the duplicate time delay wire respectively. The full digital time delay locking ring circuit widens the operating frequency range and improves the compatibility with a DDR controller.

Owner:SOUTHEAST UNIV

Re-positioning reminder for personal portable electronic equipment

InactiveUS7248840B2Supplement and expand functionActive radio relay systemsSpecial service for subscribersRing circuitEngineering

The present invention relates to a re-positioning reminder for personal portable electronic equipment. Such a reminder is housed in the electronic equipment and is at least equipped with an environment detecting unit, a control unit, a time counting module and at least one vibration / ringing circuit; wherein the environment detecting unit is used to monitor the outer surroundings and generates a monitoring value; the control unit is coupled to the environment detecting unit for the reception of the monitoring value which is compared with a preset value in the control unit to check if the environment is in a normal state or not and keeps the time counting module under its control; the time counting module is connected to the control unit and can start a time countdown according to the preset time; the vibration / ringing circuit is connected to the control unit and is controlled by the control unit to send off an alarm at the termination of the time countdown procedure to remind a user to put a personal portable electronic equipment back to a preset place so as to prevent the same from being lost as a result of ignorance.

Owner:ALCON TELECOMM

Ring-shaped light-emitting heat-dissipating fan

ActiveUS20180163960A1Enhancing user visual experienceLarge luminous areaPlanar light sourcesPump componentsRing circuitLight guide

A ring-shaped light-emitting heat-dissipating fan comprises a base having a ring-shaped frame and a pivot portion; a fan pivotally disposed at the pivot portion; a ring-shaped light guide having an upper top surface, a lower top surface, an inner lateral surface, and an outer lateral surface; a lid disposed on the ring-shaped frame, with the ring-shaped light guide disposed between the base and the lid, and a receiving space formed between the lid and the ring-shaped light guide; and a ring-shaped circuit board disposed on an upper top surface of the ring-shaped light guide in the receiving space and having thereon a plurality of light-emitting elements arranged annularly. Therefore, the ring-shaped flat region dispenses with any receiving recesses for receiving the light-emitting elements. The ring-shaped circuit board controls color of light emitted from the light-emitting elements and their light emission cycles.

Owner:THERMALTAKE

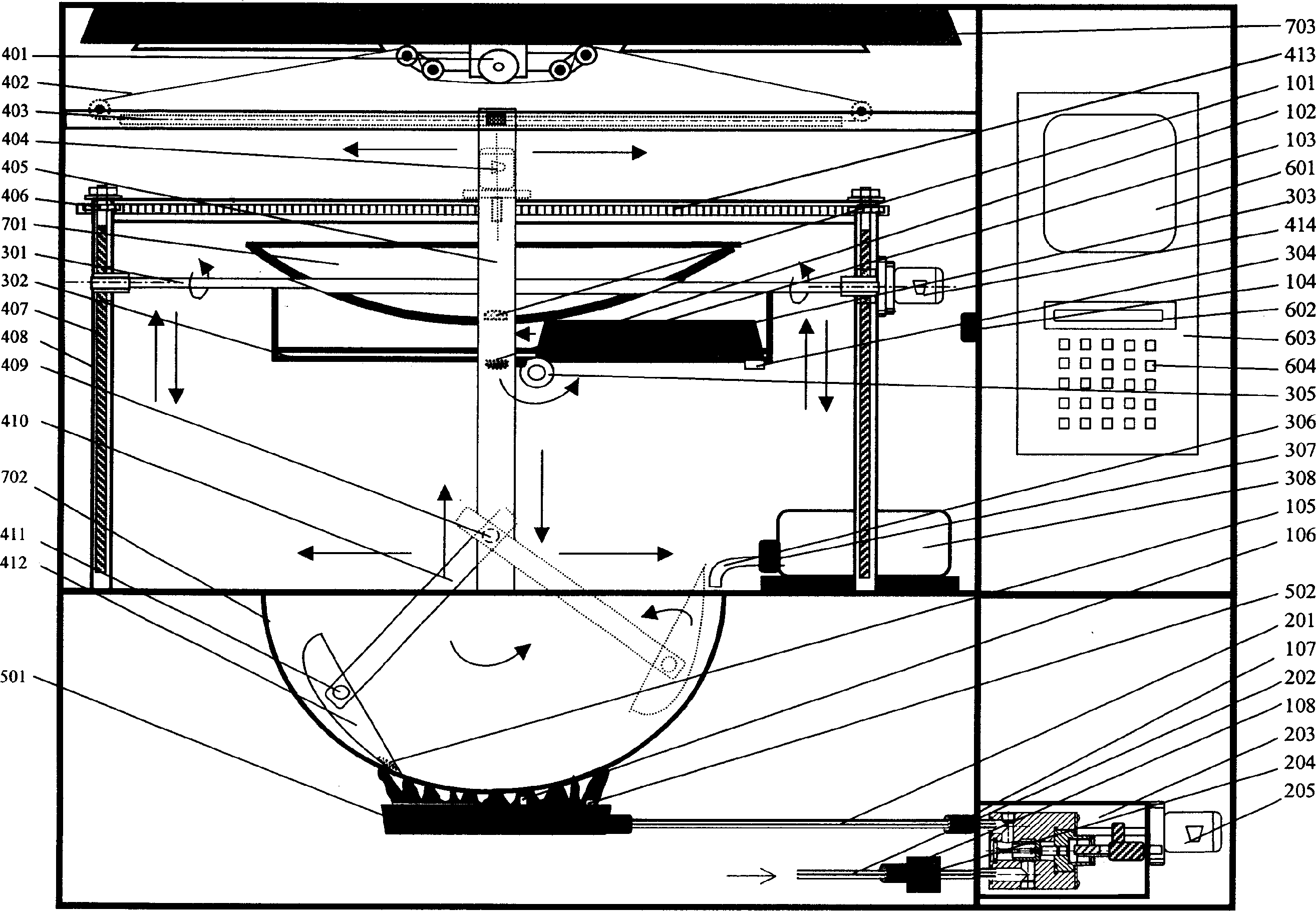

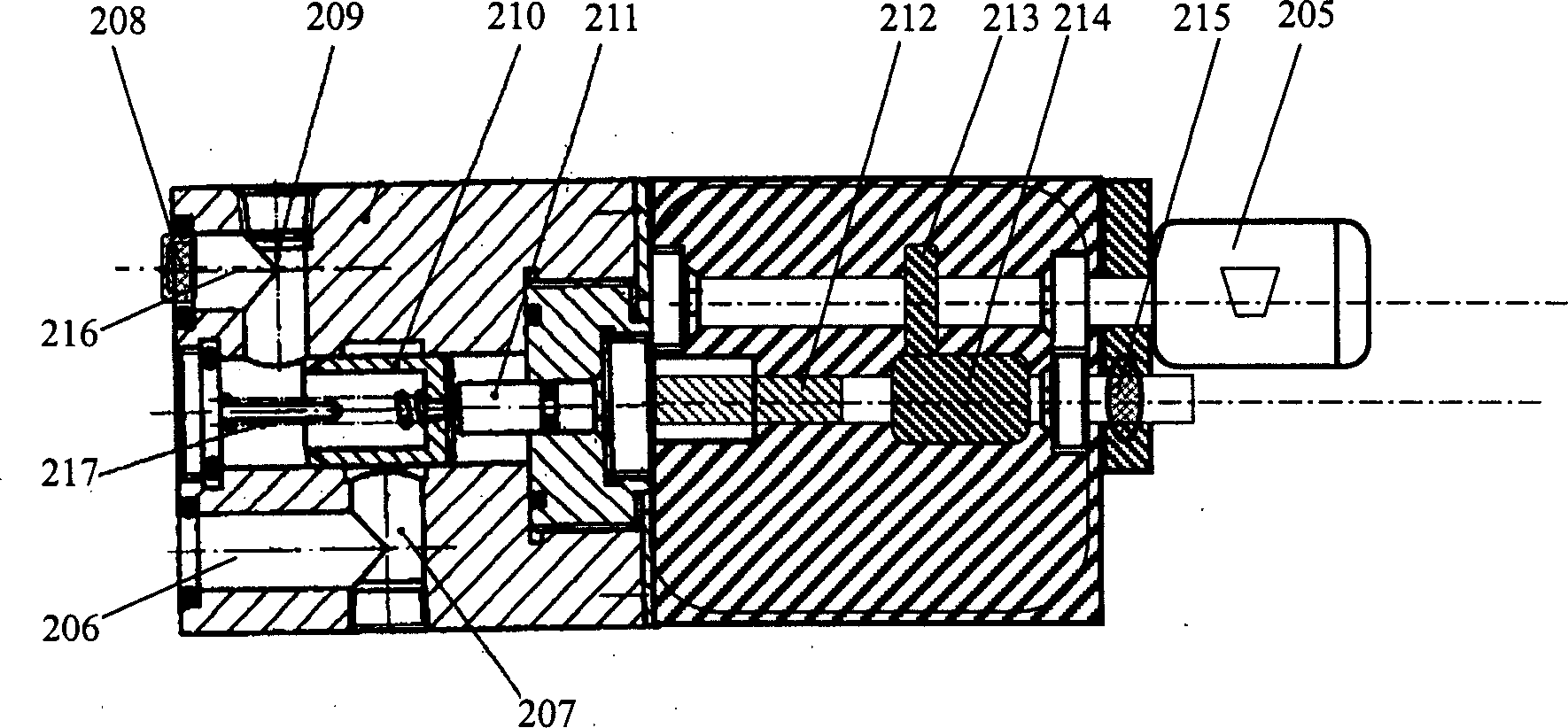

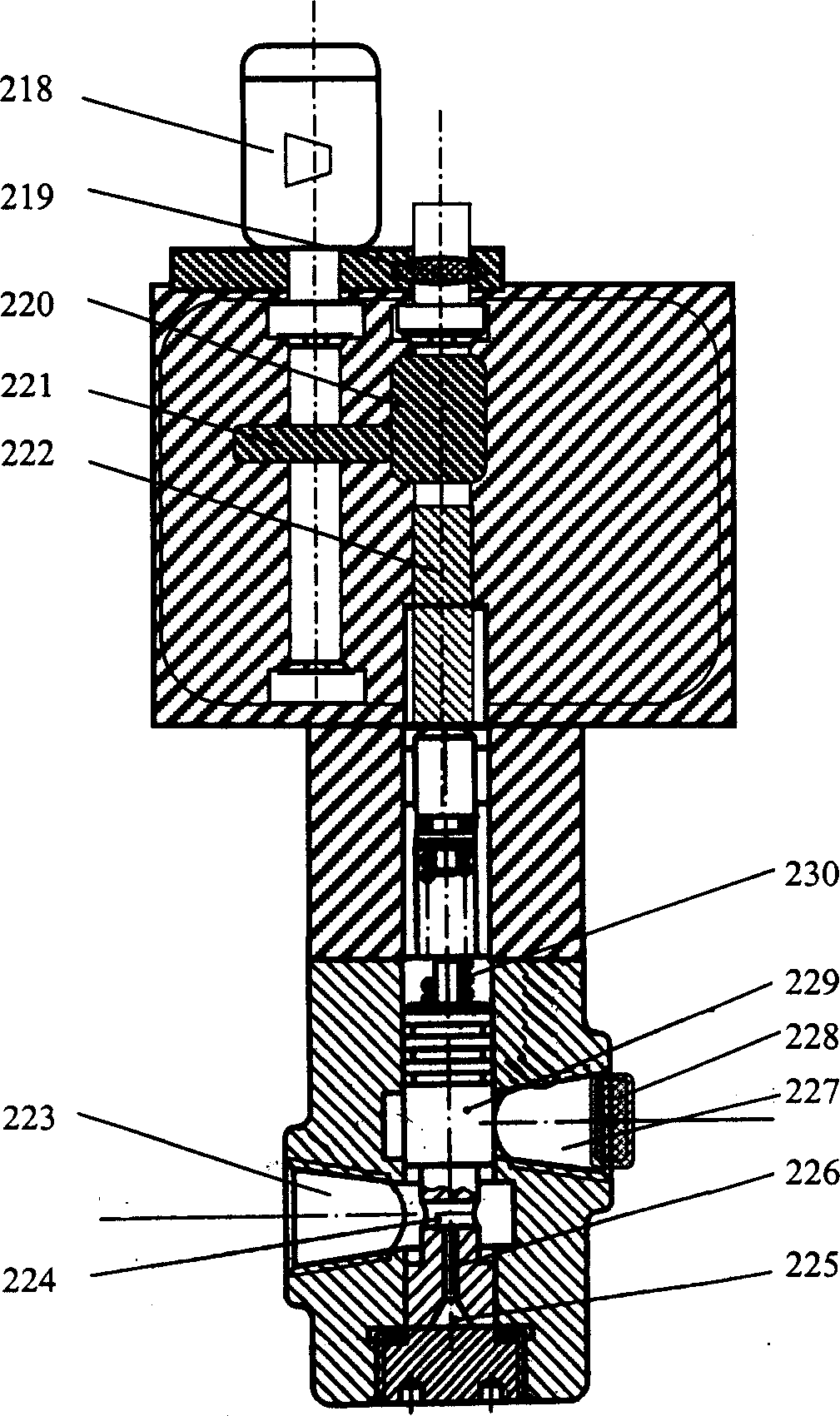

Automatic cooking machine and cooking gas regulating system

InactiveCN1494852AAutomatic and accurate dynamic determinationControl the fire stateTime-controlled ignitorsRing circuitState parameter

The present invention relates to a cooking gas flame regulating system. The system includes sensor, processing circuit and gas regulator. The described sensor portion includes the flame state sensor for detecting heat transfer medium and cooked material, etc. related to flame and flame mainly-regulating ring circuit of cooking machine which is formed from flame state sensor, processing circuit and gas regulator, and the described sensor portion also includes operation state sensor for detecting regulation displacement, valve opening, gas component and state parameter of gas regulator and its flame fine-regulating ring circuit formed from the operation state sensor, etc.

Owner:AIC ROBOTICS TECH

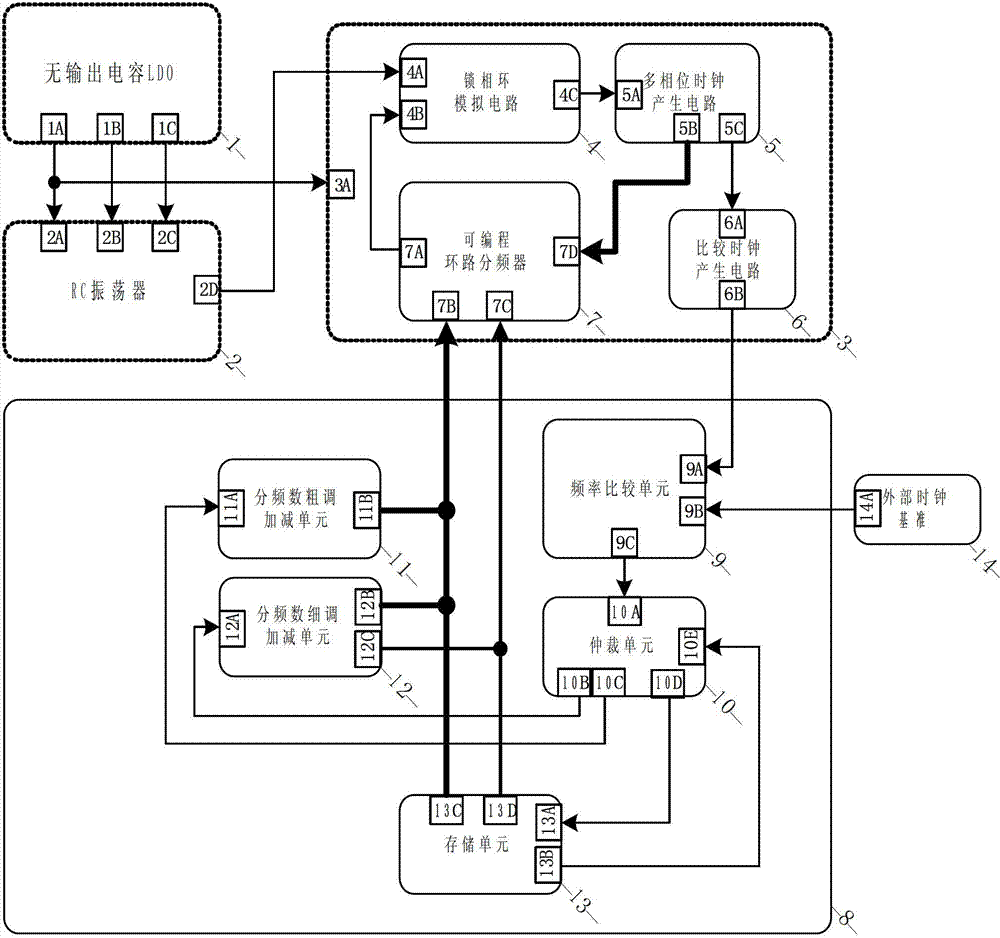

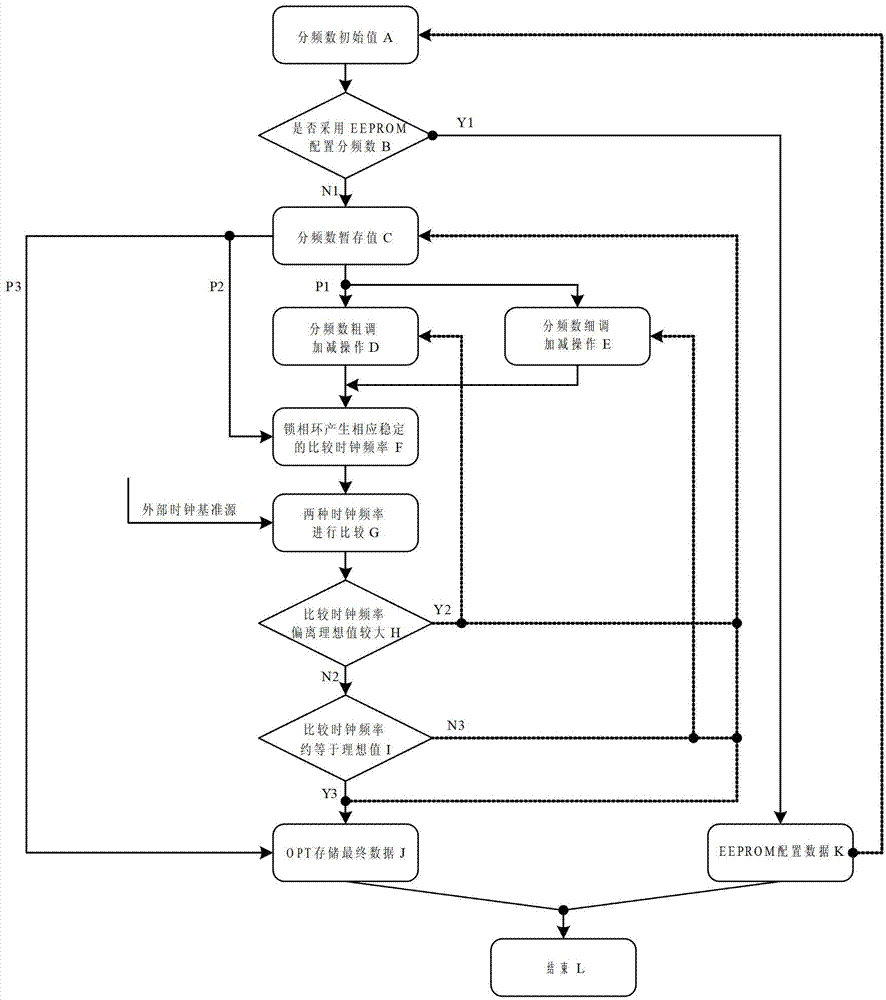

Crystal oscillator-free realization circuit and method for USB host interface

ActiveCN102790617AReduce use costImplement crystal-free technologyPulse automatic controlCapacitanceRing circuit

A crystal oscillator-free realization circuit for a USB (Universal Serial Bus) host interface comprises an output capacitorless LDO (Low Drop Out Regular), an RC (Resistor-Capacitor) oscillator connected with the output capacitorless LDO, a phase-locked ring connected with the RC oscillator, a clock self-calibrating module connected with the phase-locked ring circuit and an external clock reference, wherein the phase-locked ring circuit comprises a phase-locked ring simulation circuit, a multi-phase clock generation circuit connected with the phase-locked ring simulation circuit, a programmable loop frequency divider connected with the multi-phase clock circuit and a comparison generation circuit connected with the phases-locked ring simulation circuit; the clock self-calibration module comprises a frequency comparison unit, an arbitration circuit connected with the frequency comparison unit, a frequency division coarse tuning adding and subtracting unit connected with the arbitration unit, a frequency division fine tuning adding and subtracting unit connected with the arbitration unit and a memory unit. The invention further provides a crystal oscillator-free realization method for the USB host interface. According to the crystal oscillator-free realization method and system disclosed by the invention, the use cost of the external oscillator crystal is saved.

Owner:CHENGDU ANALOG CIRCUIT TECH INC

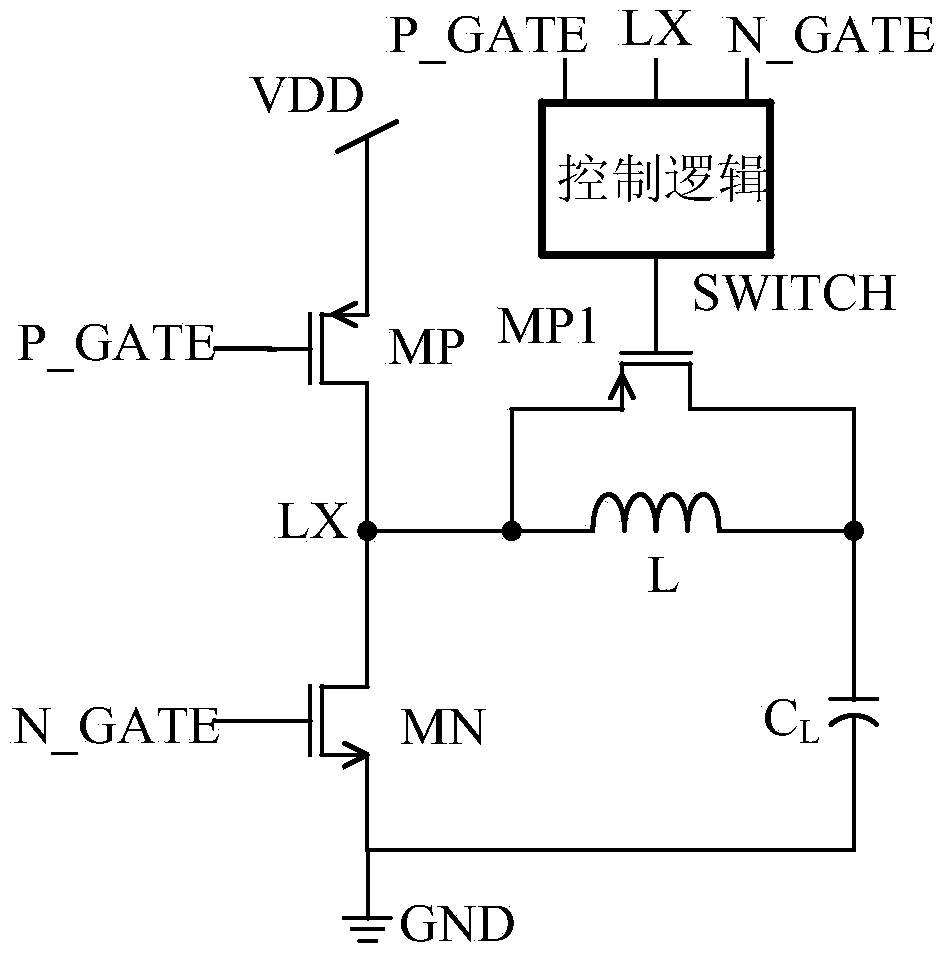

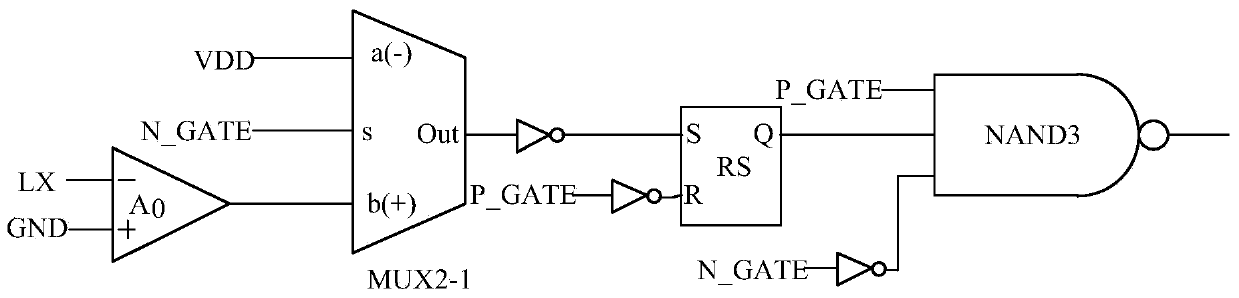

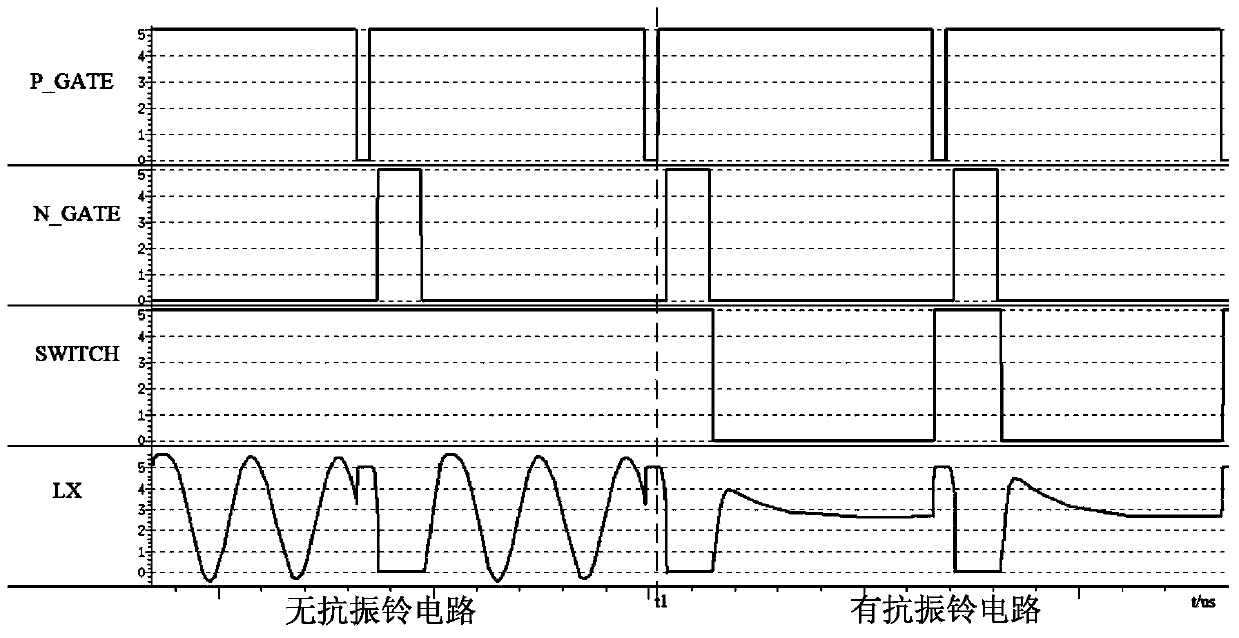

Anti-ringing circuit for integrated voltage-reducing direct current/direct current (DC/DC) switch converter

InactiveCN103427624AAchieving the goal of anti-ringingPower conversion systemsRing circuitControl signal

The invention relates to an electronic circuit technology, in particular to an anti-ringing circuit in an integrated voltage-reducing direct current / direct current (DC / DC) switch converter. The anti-ringing circuit for the integrated voltage-reducing DC / DC switch converter is characterized by further comprising a P-type field effect transistor and a control logic circuit. A source electrode of the P-type field effect transistor is connected with one end of an inductor L, a drain electrode of the P-type field effect transistor is connected with the other end of the inductor L, a grid electrode of the P-type field effect transistor is connected with the input end of the control logic circuit, and three input ends of the control logic circuit are connected with a P-channel metal oxide semiconductor (PMOS) tube control signal, an N-channel metal oxide semiconductor (NMOS) tube control signal and a ringing signal respectively. The anti-ringing circuit for the integrated voltage-reducing DC / DC switch converter has the advantages that one P-type field effect transistor connected to two ends of the inductor is added based on a traditional voltage-reducing DC / DC switch converter, and the anti-ringing purpose of the integrated voltage-reducing DC / DC switch converter is achieved. The anti-ringing circuit is especially suitable for the DC / DC switch converter.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

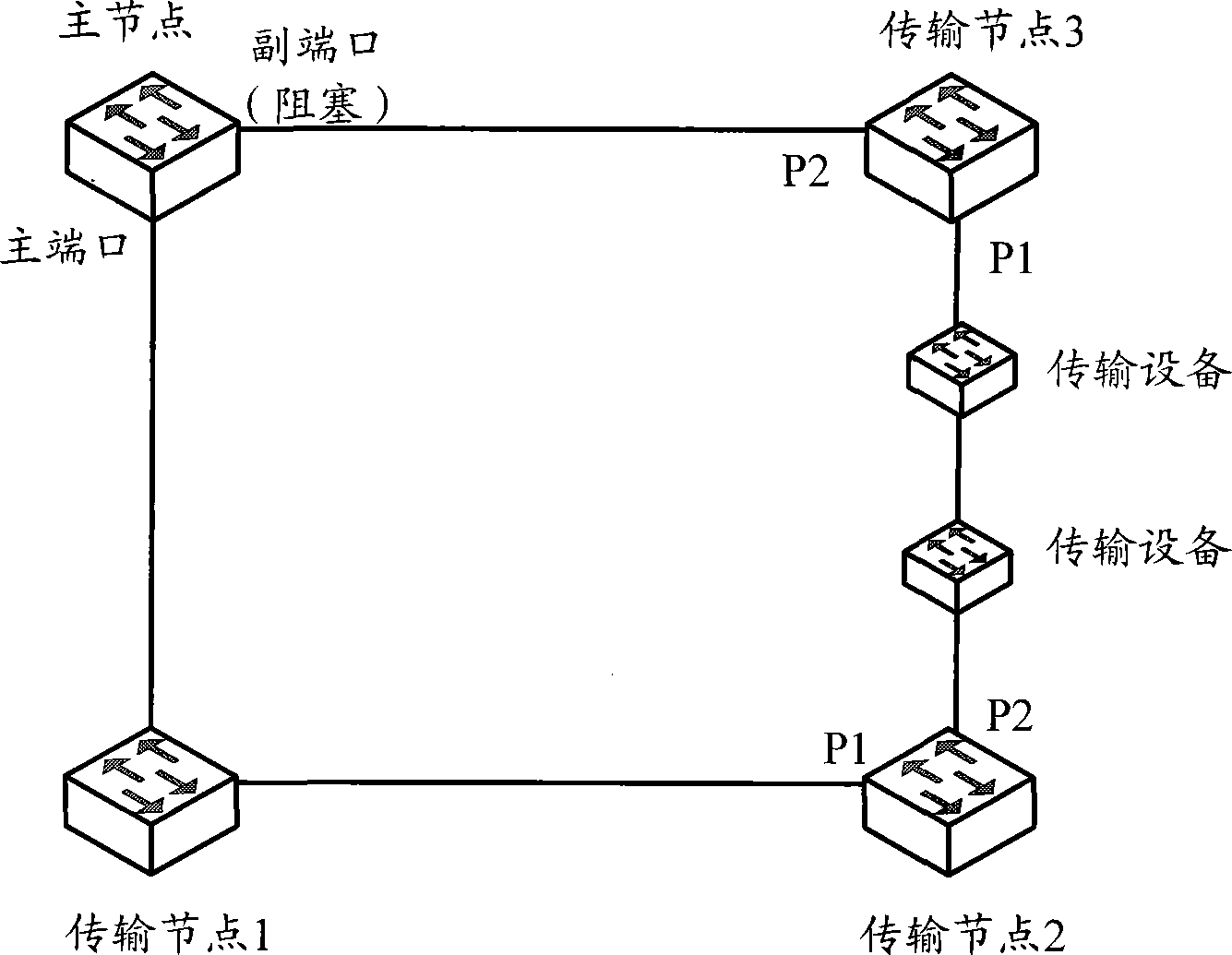

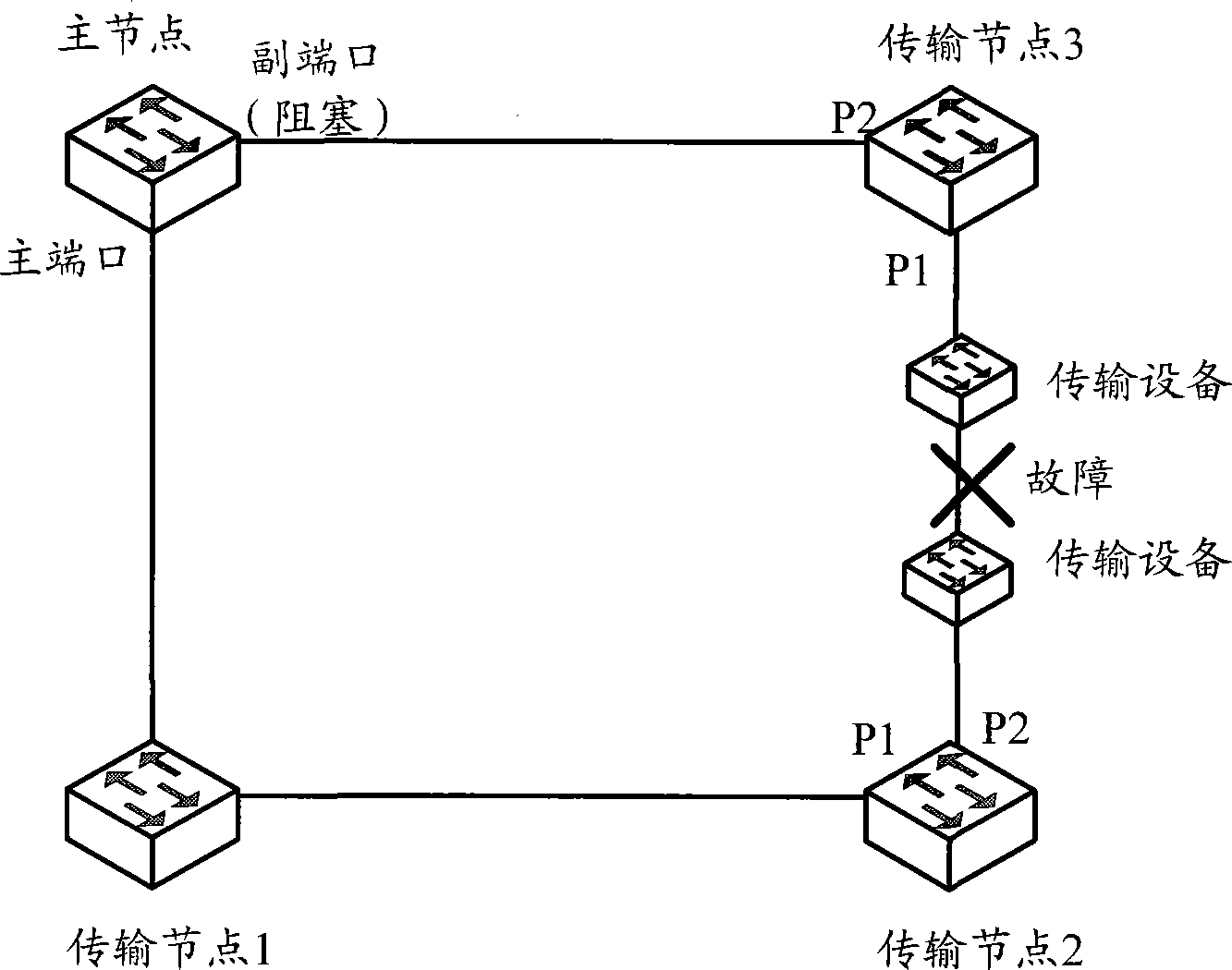

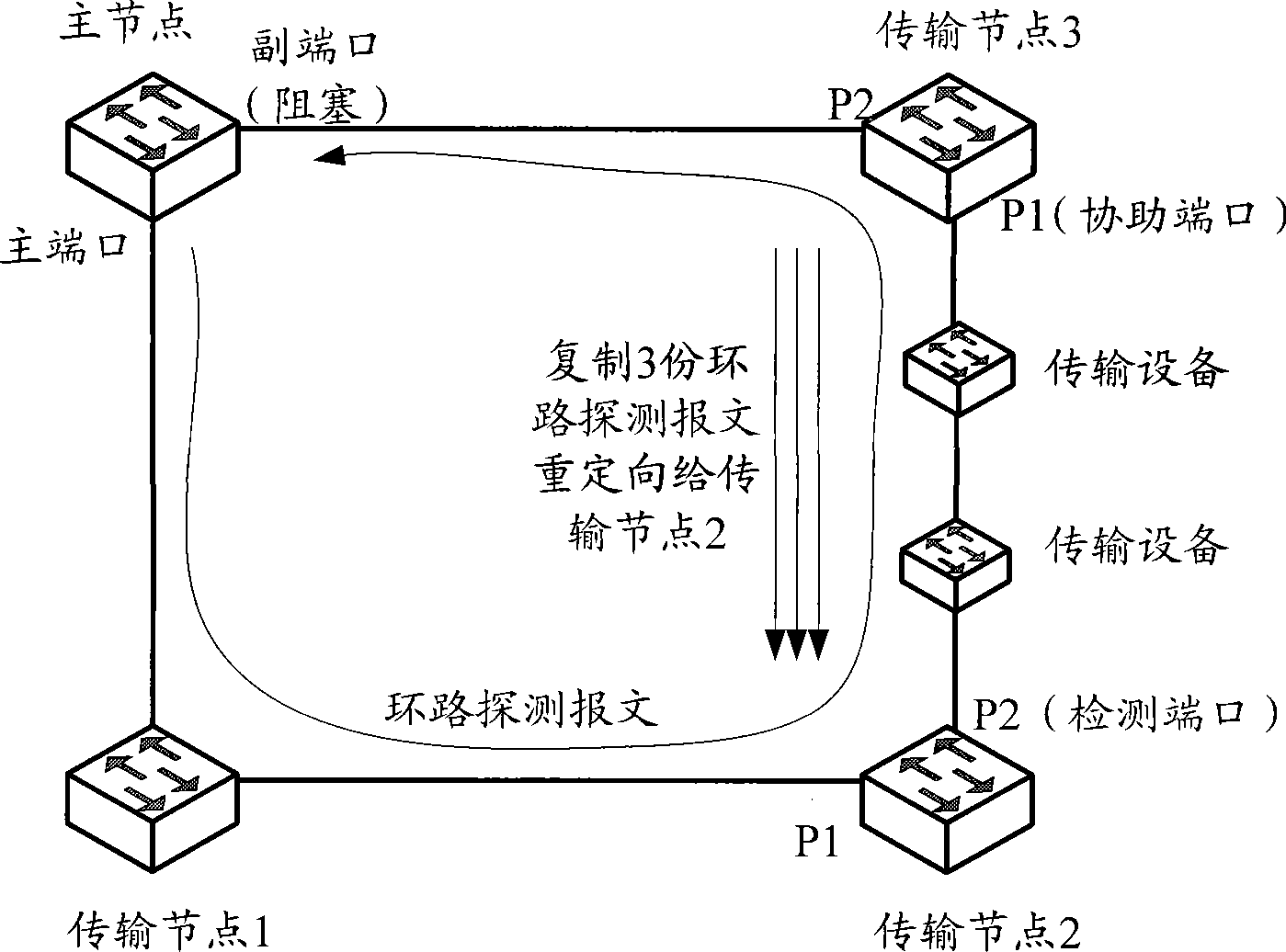

Method and system for RRPP loop link switching

The invention provides a rapid ring protection protocol (RRPP) ring link switching method and a system thereof. Transmission node ports which directly link a RRPP ring and a transmission equipment link are enabled with a fault detection feature, one port of the ports enabled with the fault detection feature, which firstly receives a ring circuit detection message sent from a master node, is used as a detection port, and the other port is used as an assistant port. The method comprises that the transmission node where the assistant port locates forwards a ring circuit detection message after receiving the ring circuit detection message via the assistant port, and copies N ring circuit detection messages and redirects to the detection port via the assistant port, wherein, N is an integer larger than 1; and the transmission node where detection port locates notifies the link fault to the master node if not receiving the ring circuit detection message via the detection port within a set time period after sending the ring circuit detection message via the detection port. The method and the system can reduce traffic interrupting time in the RRPP ring when a fault occurs in the transmission equipment link.

Owner:NEW H3C TECH CO LTD

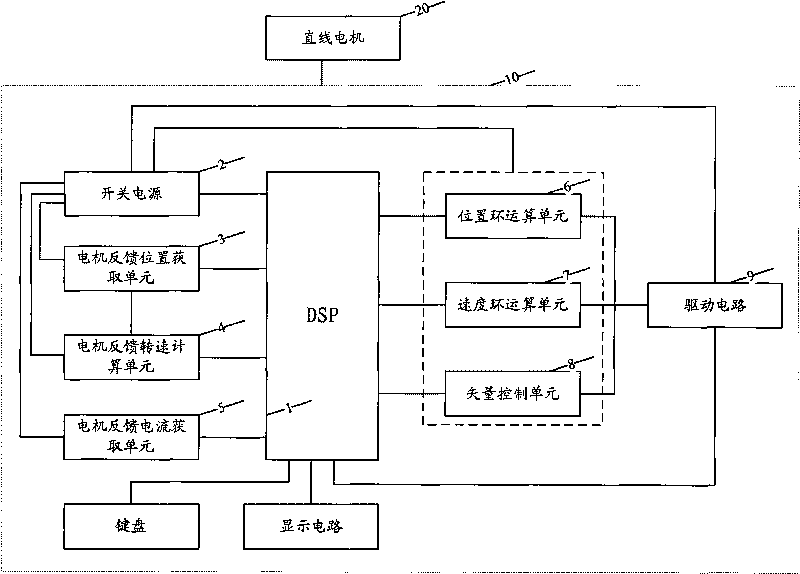

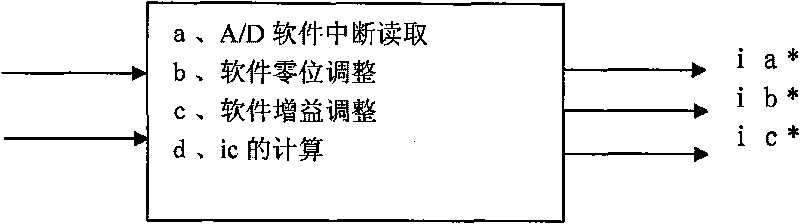

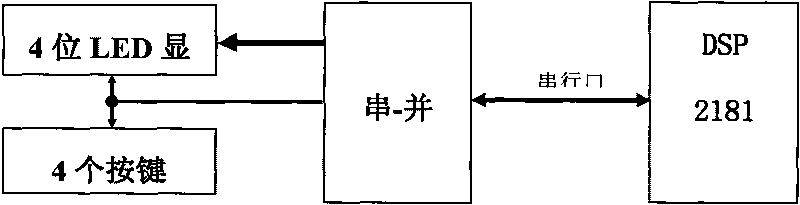

Servo system for linear motor

InactiveCN101697466AAvoid interferenceAC motor controlVector control systemsControl vectorRing circuit

The invention discloses a servo system for a linear motor. The servo system comprises a linear motor and a linear motor driver, wherein the linear motor driver comprises a DSP, a switch power supply, a drive circuit, a motor feedback position acquisition unit, a motor feedback rotary speed computing unit, a motor feedback current acquisition unit, a position ring computing unit, a speed ring computing unit, and a vector control unit, wherein the DSP controls a position ring circuit, a speed ring circuit and a current ring circuit of a linear motor; the motor feedback position acquisition unit obtains the actual position of a motor rotor; the motor feedback rotary speed computing unit works out the actual rotary speed of the motor according to the actual position of the motor rotor and the measuring time; and the motor feedback current acquisition unit samples by a resistor, sends the sample to an AD converter through linear opto coupling insulation, and sends the sampling signal to the DSP through a serial port after converting to the analogue signal to the digital signal. The servo system adopts a structure integrating power supply, drive and control, and mixes strong current signals and weak current signals, so that the servo system can avoid the interference among various signals of strong current, weak current, switch power supply and the like.

Owner:SHANGHAI DIANJI UNIV +1

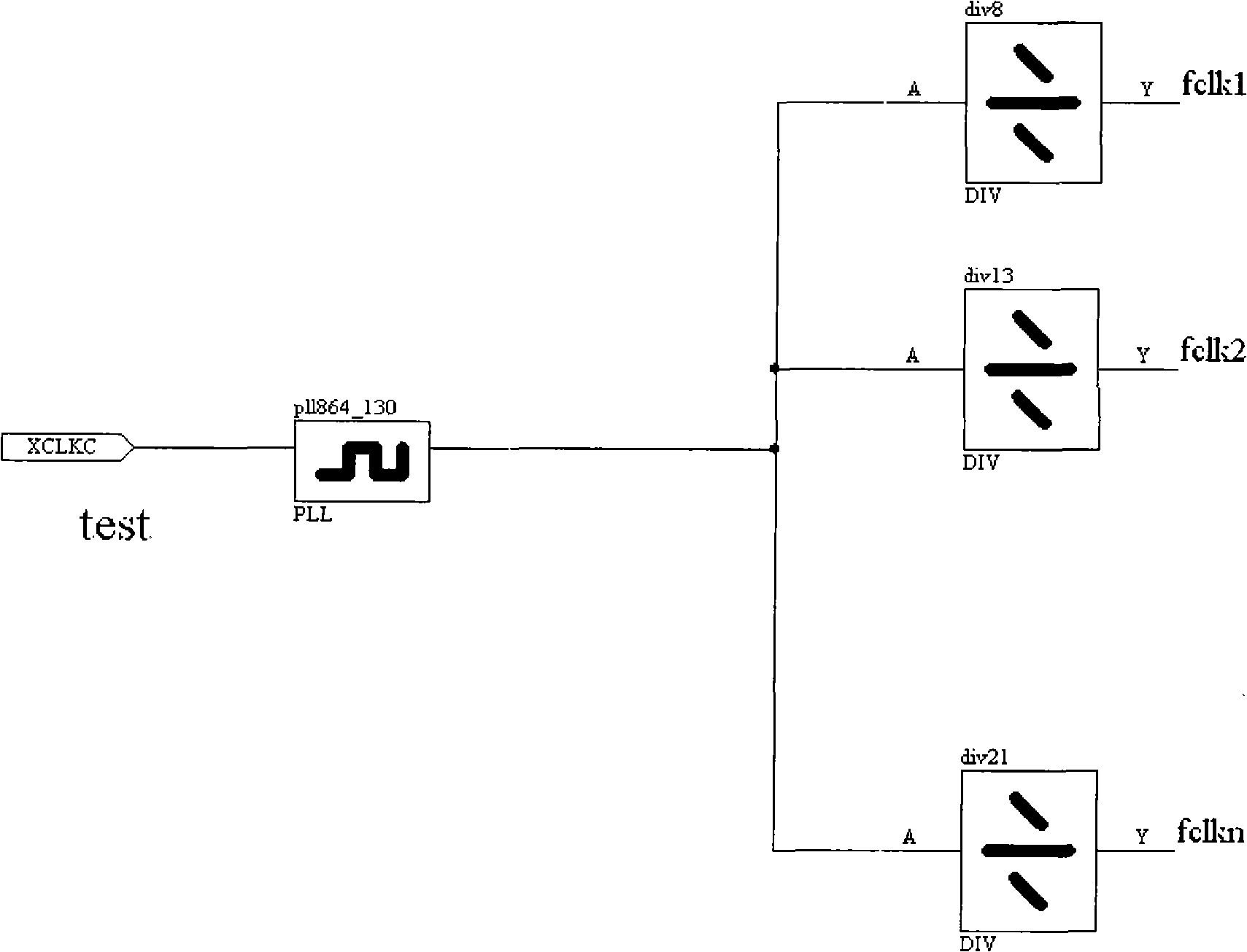

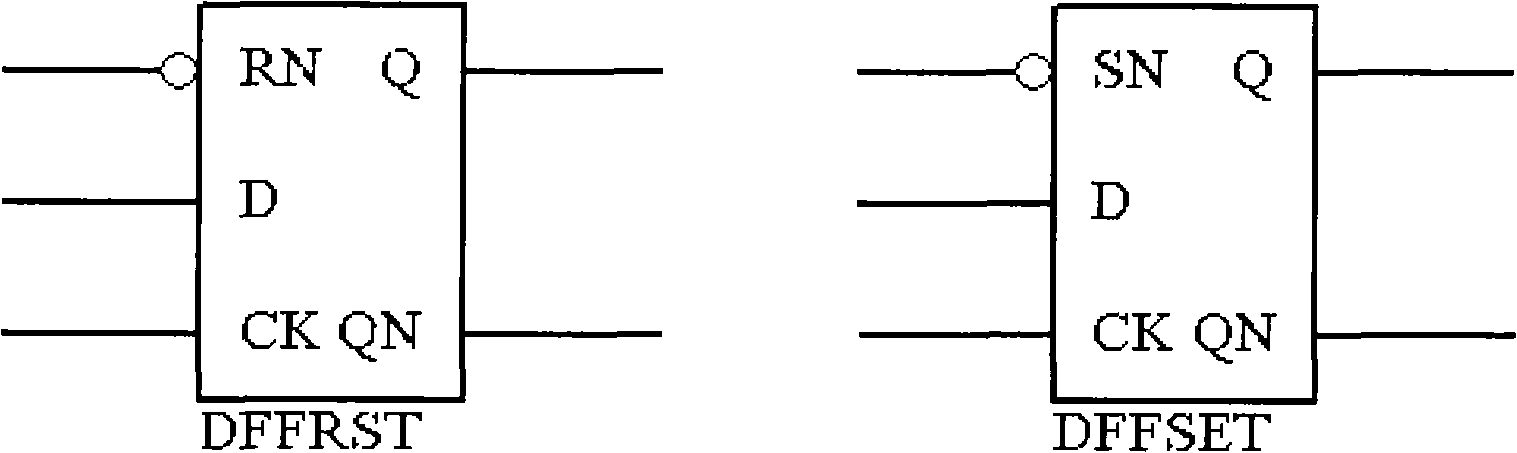

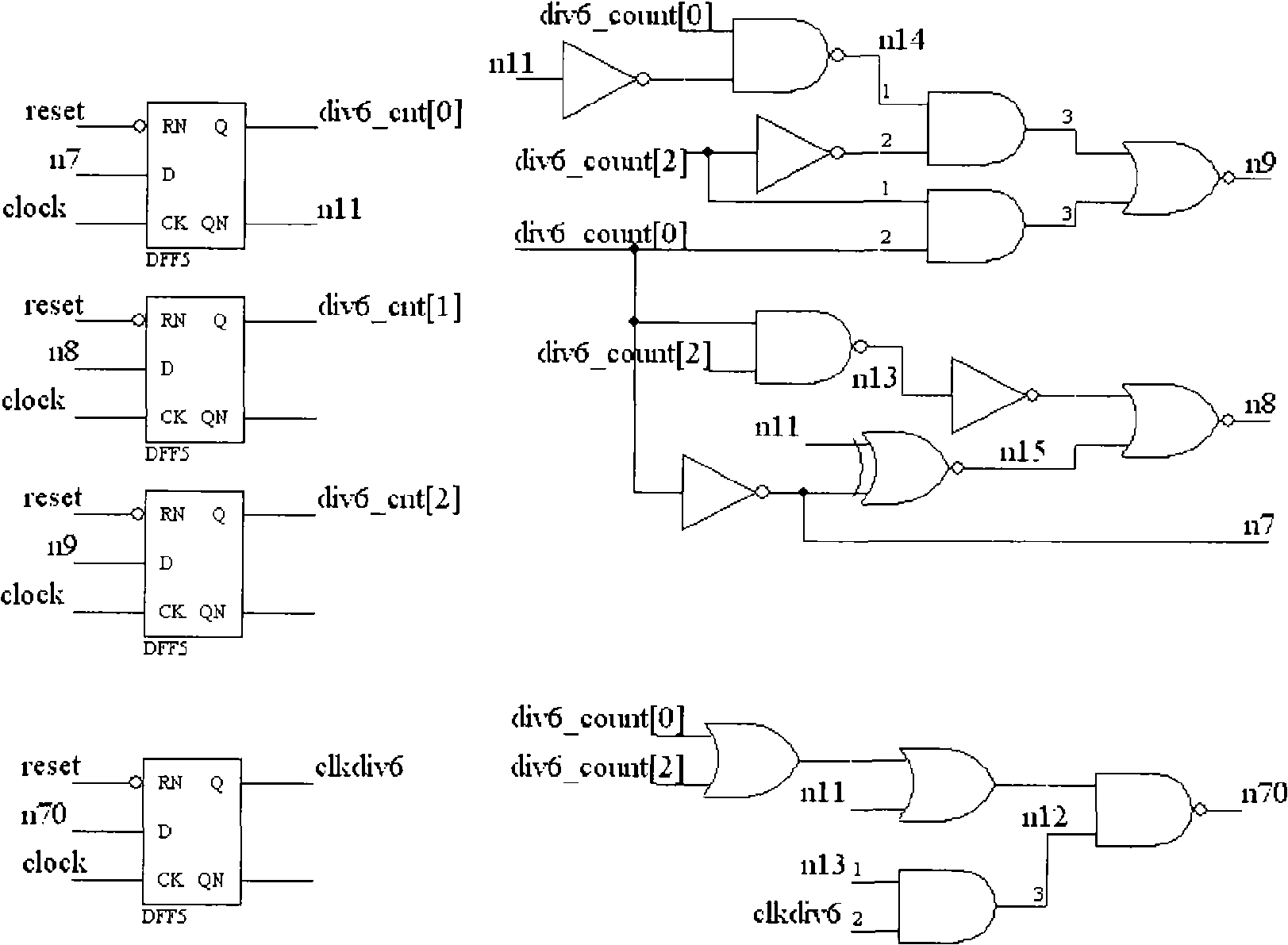

Clock frequency dividing method based on trigger ring and clock frequency dividing circuit thereof

InactiveCN101291149ASmall scaleLower latencyContinuously circulated pulse countersCounting chain synchronous pulse countersRing circuitClock rate

The present invention relates to a clock frequency division technology for an integrated circuit, in particular to a clock frequency division method based on a trigger ring and a clock frequency division circuit thereof. The method is to orderly connect data input ends and data output ends of a plurality of triggers to form a trigger ring circuit. The number of the triggers with set ends and reset ends in the trigger ring is selected according to the requirement of the frequency division circuit for a duty ratio. The positions of the triggers with set ends and reset ends are determined according to the requirement of a clock waveform. The trigger ring circuit accesses a system frequency division circuit, and a spare data output end of the last trigger is used as an output end of the trigger ring circuit so as to realize clock frequency division. The number of the frequency division of the method and the circuit structure thereof do not influence the highest frequency of the working circuit. The normal work of the frequency division circuit can be at a comparatively high clock frequency, and the clock frequency division can be realized in the manner of cascade connection of the frequency division circuit so that the scale of the circuit realization can be properly reduced.

Owner:VIMICRO CORP

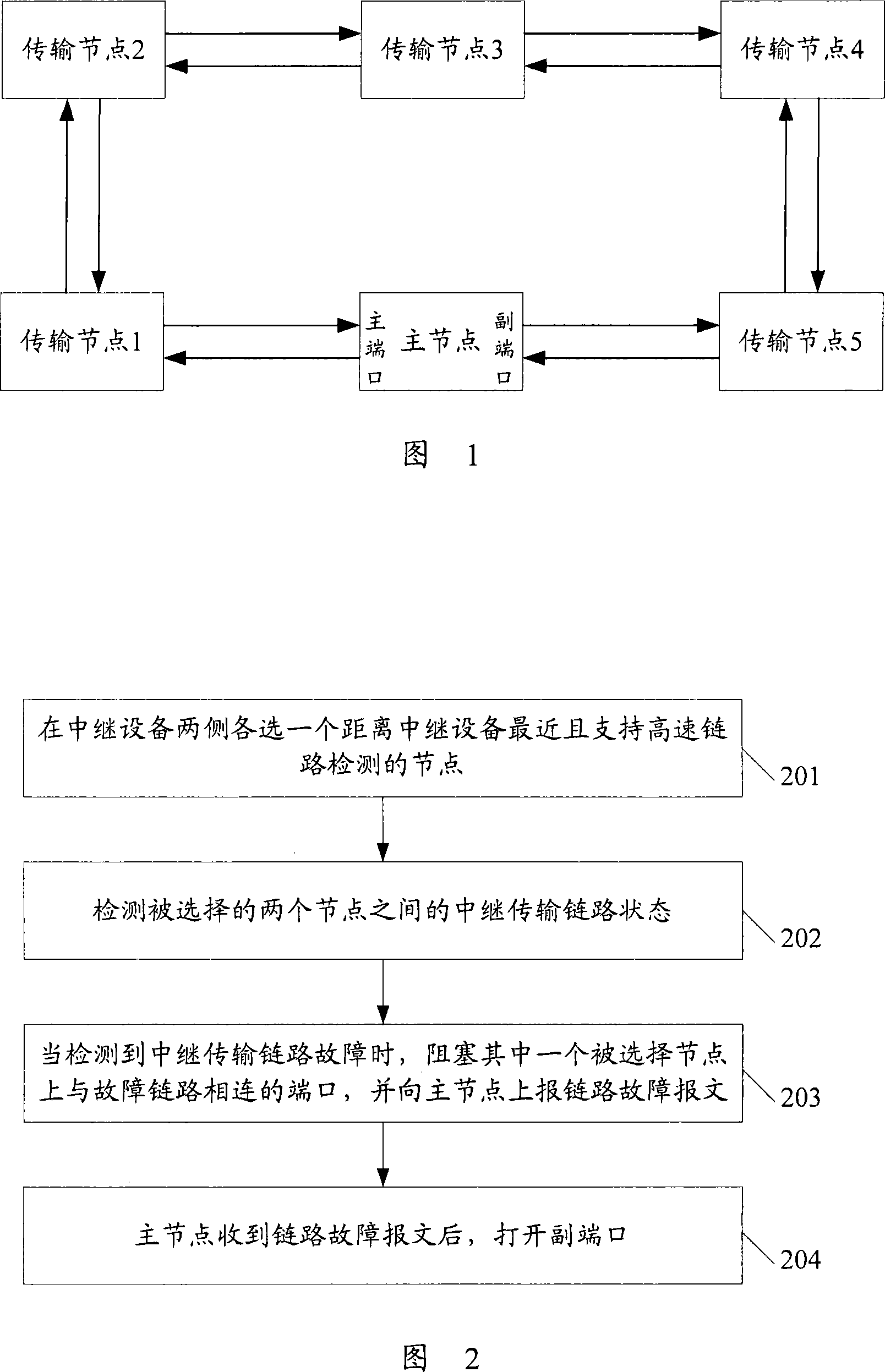

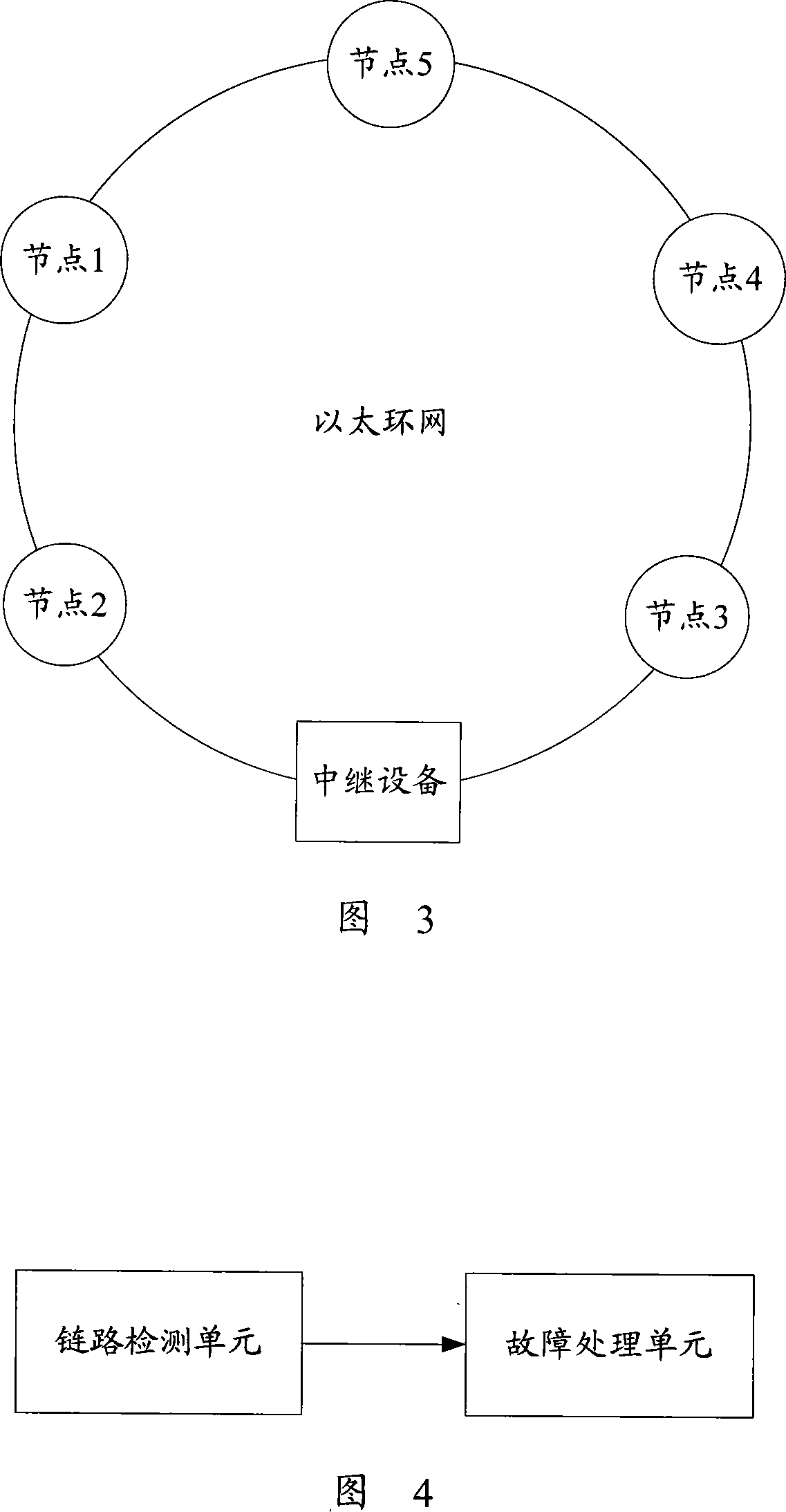

Ethernet ring protection method, system and device

ActiveCN101222402AAvoid it happening againFast protection switchingLoop networksRing circuitHigh-speed link

The invention provides a method for protecting an Ethernet. The method is used for the Ethernet comprising trunk equipment and comprises the following steps: nodes which are close to the trunk equipment and support the high speed link detection are chosen on two sides of the trunk equipment; the relay transmission link state between the two chosen nodes are detected; when the failure of the relay transmission link is detected, one interface which is positioned on one chosen node and connected with the failure link is blocked and a link failure message is reported to a main node; after the main node receives the link failure message, an auxiliary interface is opened. In addition, the invention also provides an Ethernet protection system and a node. The technical proposal provided by the invention can realize quick protection switching and avoid the generation of a ring circuit in the Ethernet comprising the trunk equipment.

Owner:NEW H3C TECH CO LTD

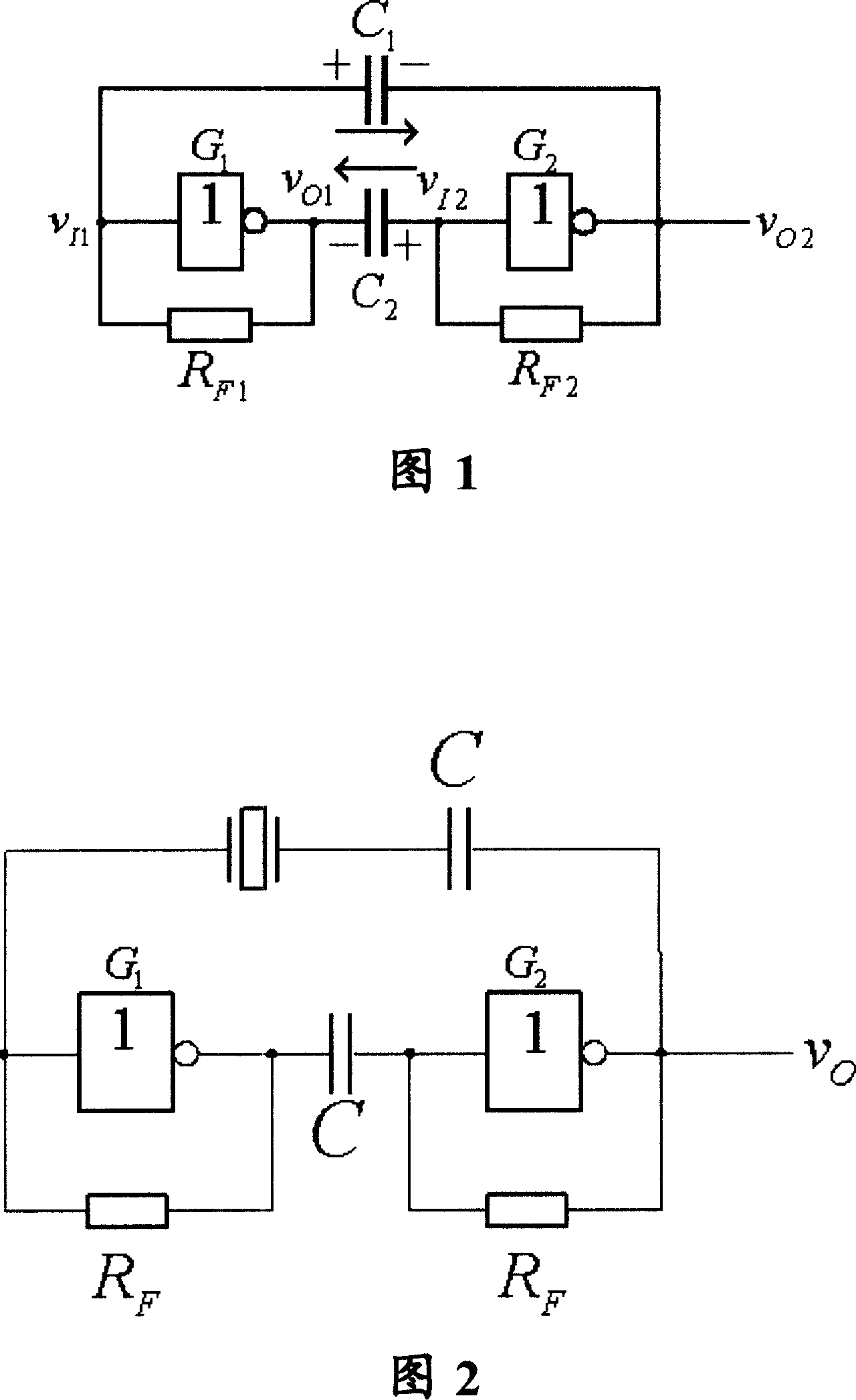

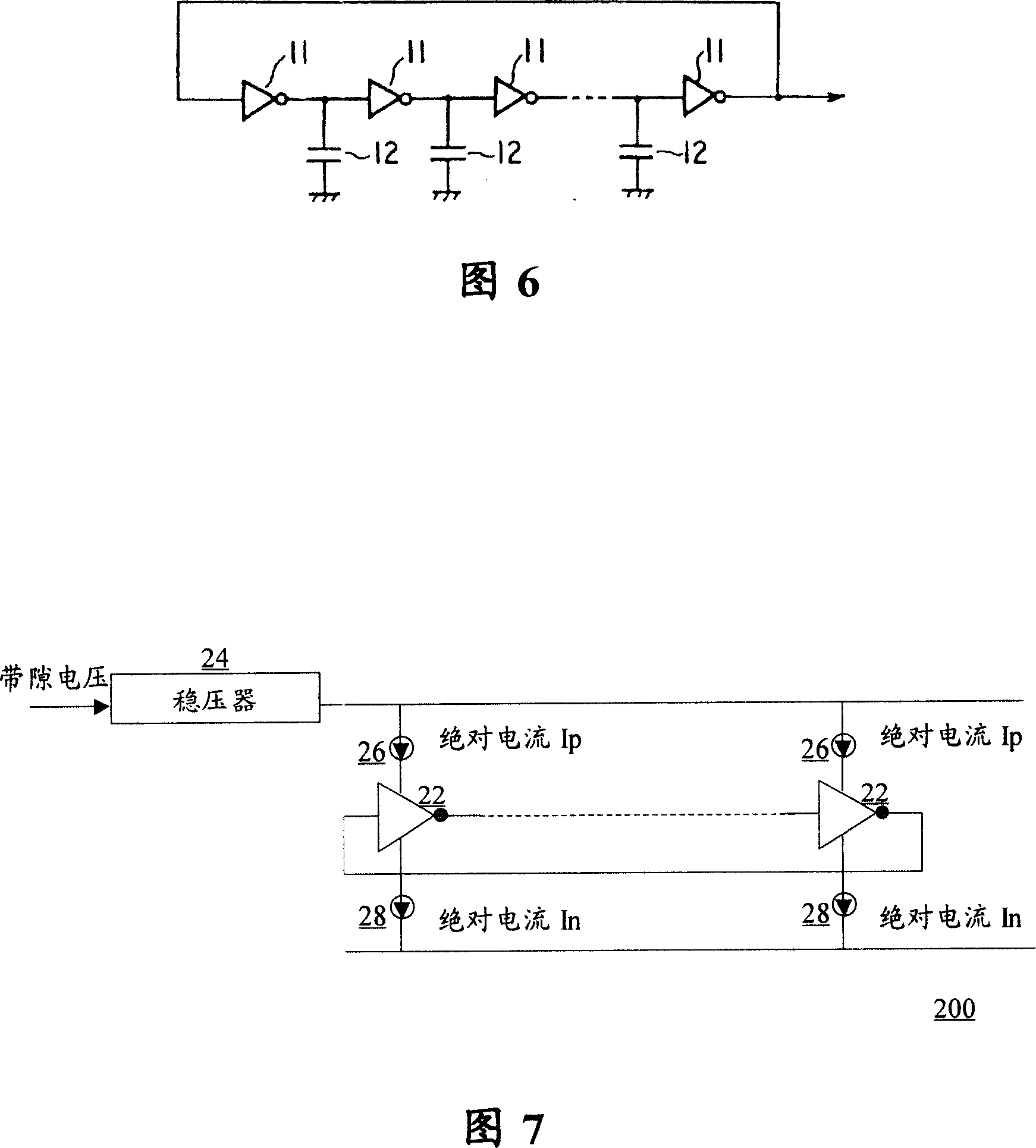

Oscillation frequency fluctuation reduced ring oscillation circuit and IC chip equipped with the circuit

The invention discloses a ring shape oscillating circuit that consists of a regulator that is connected between the band gap voltage and the power source access end of the inverter and is used for providing stable band gap voltage for the inverter; a power source absolute current circuit that is connected to the power source access end of the inverter and is used for converting the accessed band gap voltage so as to provide power source absolute current for the inverter; an earth absolute current circuit that is connected with the earth end of the inverter and is used for converting the accessed band gap voltage so as to provide earth absolute current for the inverter. The invention also provides an integrated circuit chip that has ring shape circuit.

Owner:ANALOGIX CHINA SEMICON

Method and device for detecting and processing link failure in RRPP (Rapid Ring Protect Protocol) ring network

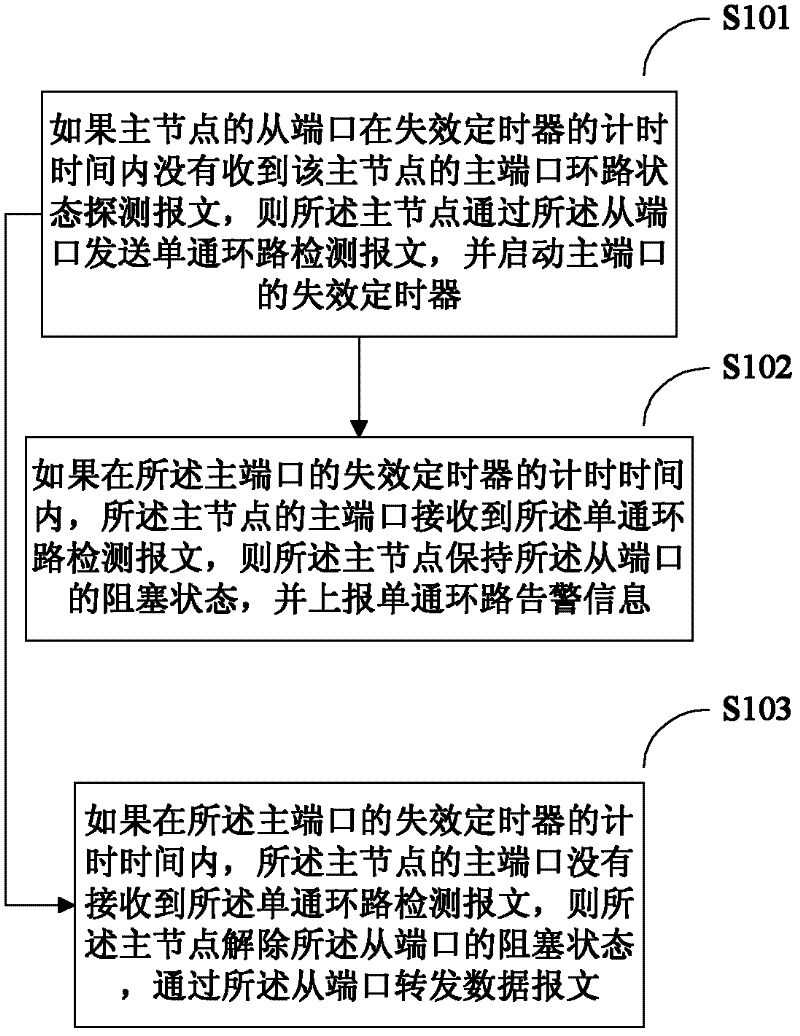

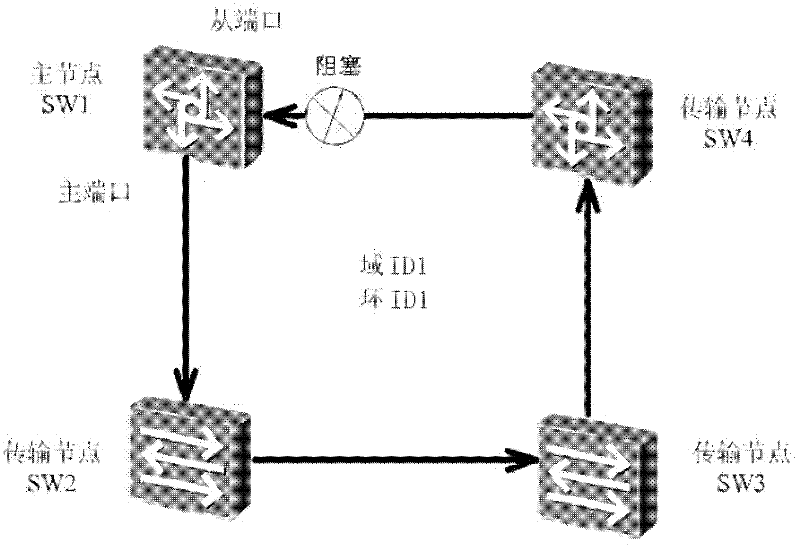

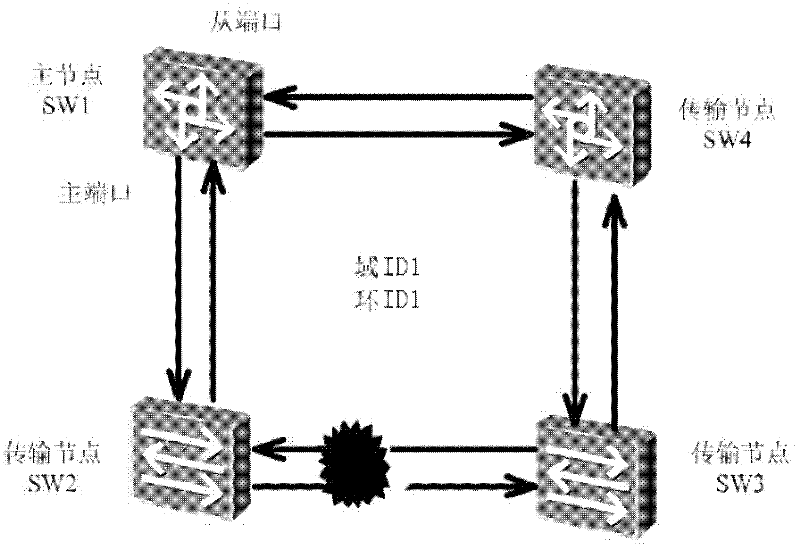

The invention provides a method for detecting and processing a link failure in a RRPP (Rapid Ring Protect Protocol) ring network. The method comprises the following steps: if a slave port of a main node does not receive a ring-circuit state detection message within timing time of an invalidation timer, the main node transmits a single-pass ring circuit detection message through the slave port and starts the invalidation timer of a main port; if the main port of the main node receives the single-pass ring circuit detection message within the timing time of the invalidation timer of the main port, the main node maintains the block state of the slave port and reports single-pass ring circuit warning information; and if the main port of the main node does not receive the single-pass ring circuit detection message, the main node removes the block state of the slave port and transmits a data message through the slave port. The embodiment of the invention also provides the main node in the RRPP ring network. According to the method provided by the invention, the slave port is continuously blocked when the link failure is discovered to be a unidirectional failure, so that the storm of the data message, generated in a reverse ring circuit, is avoided, the warning information is timely reported and the stability of a ring circuit service is increased.

Owner:HUAWEI TECH CO LTD