FPGA-based true random number generator

A true random number and generator technology, applied in the field of FPGA-based digital circuit design, can solve the problem that the random number generator cannot generate random numbers at the highest rate, and achieve the effect of ensuring quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

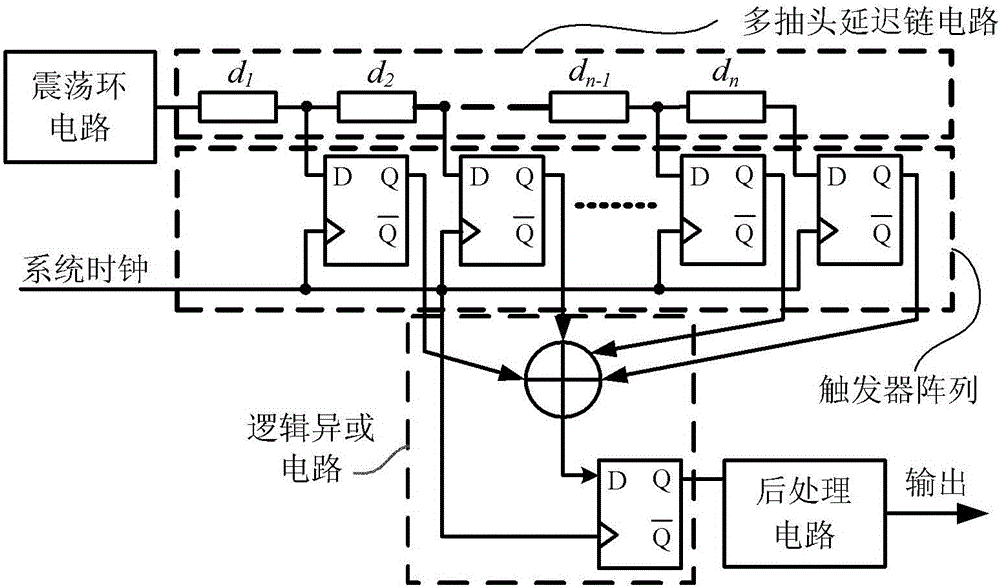

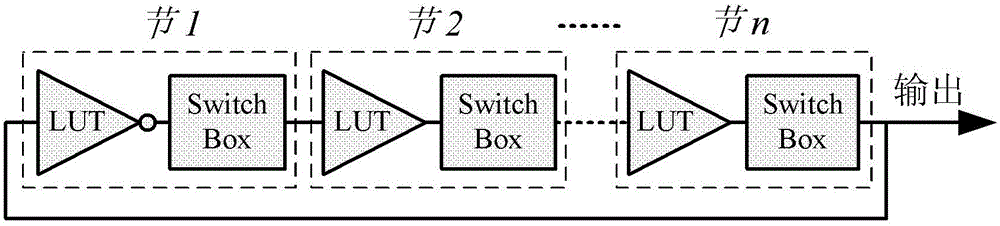

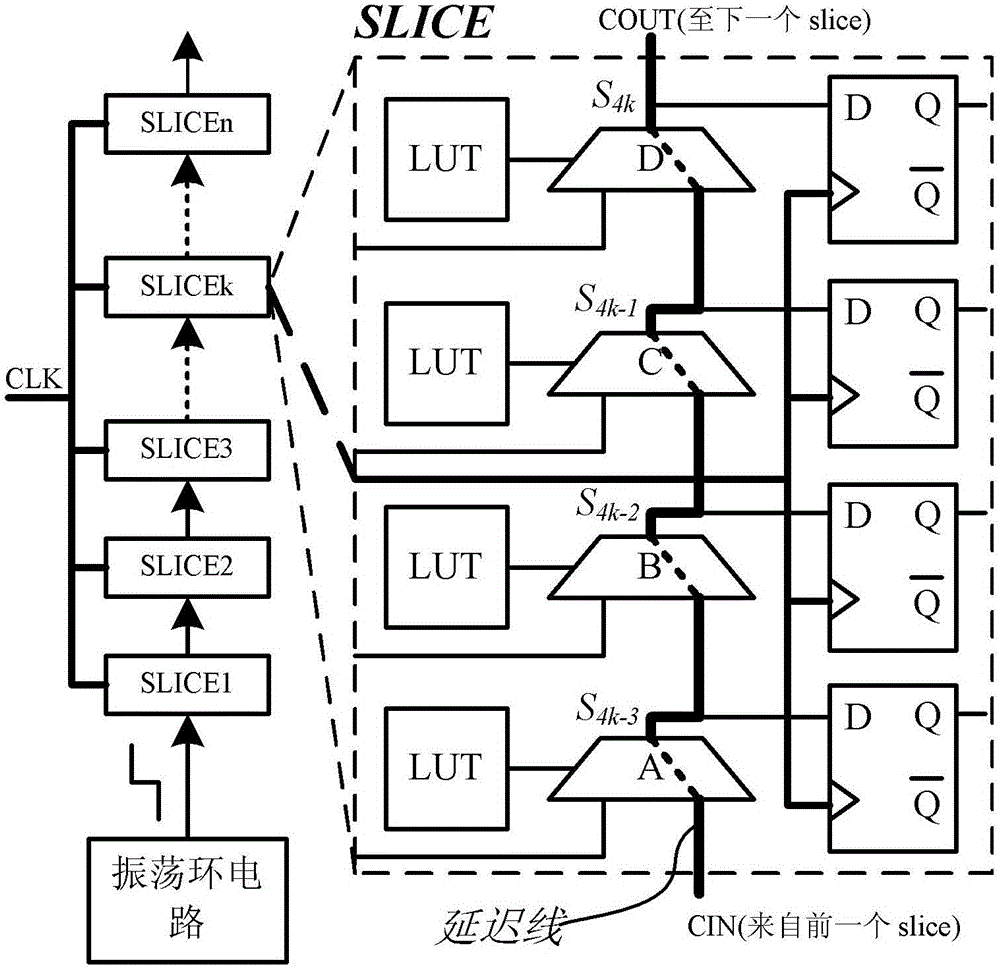

[0019] As we all know, the oscillation ring circuit will oscillate spontaneously, and the signal output by any node on the oscillation ring circuit is a clock signal. The oscillation ring circuit is generally composed of a number of delay units in series with a NOT gate, and the delay amount of each delay unit and the number of delay units determine the frequency of the output clock signal. Since the digital signal passes through the logic device, redundant jitter will be generated at the moment of level inversion, that is, there is an uncertain amount of jitter between the moment of the actual inversion of the signal level and the moment of ideal inversion, and the number of delay units of the oscillation ring affects the Total jitter of the output clock signal. Generally, the more delay units there are, the greater the amount of jitter, but the lower the frequency of the clock signal.

[0020] The present invention exploits the jitter of such a clock signal as a source of e...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More