Patents

Literature

137 results about "Digital circuit design" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method and system for counting events within a simulation model

InactiveUS6470478B1Monitor performanceDigital circuit testingDetecting faulty computer hardwareTheoretical computer scienceLinear feedback shift register

A method and system that utilize the expressiveness of hardware description languages for efficiently and comprehensively monitoring performance characteristics of a digital circuit design during simulation. According to the present invention, a design entity that is part of a digital circuit design is first described utilizing a hardware description language. Next, a counting instrument is described utilizing the same hardware description language. The counting instrument is designed to detect occurrences of a count event within the design entity during simulation of the digital circuit design. The counting instrument is associated with the design entity utilizing a non-conventional call, such that the counting instrument may be utilized to monitor each instantiation of the design entity within the simulation model without the instrumentation entity becoming incorporated into the digital circuit design. In association with the counting instrument, a linear feedback shift register is automatically generated for recording the number of occurrences of the count event within the design entity.

Owner:GLOBALFOUNDRIES INC

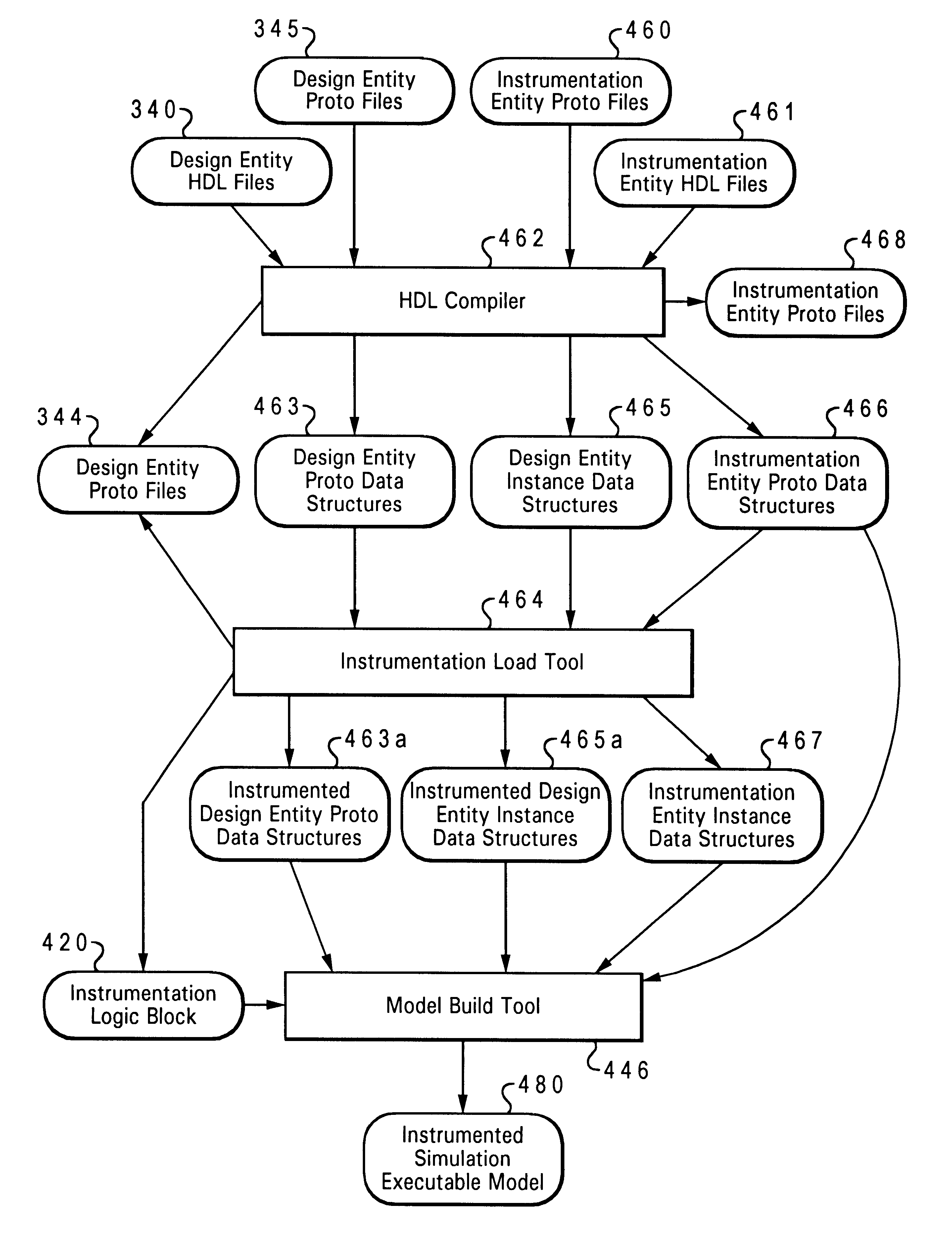

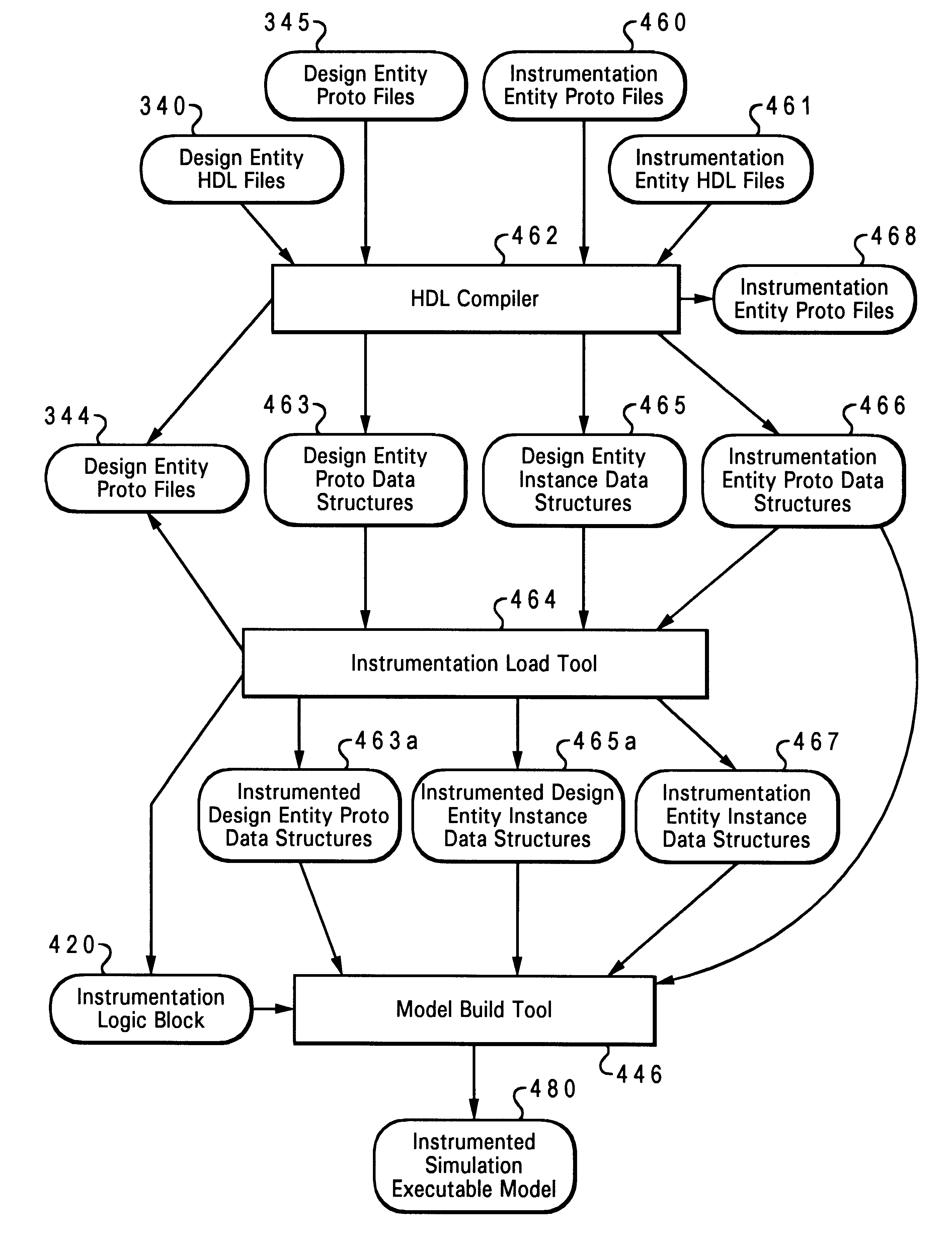

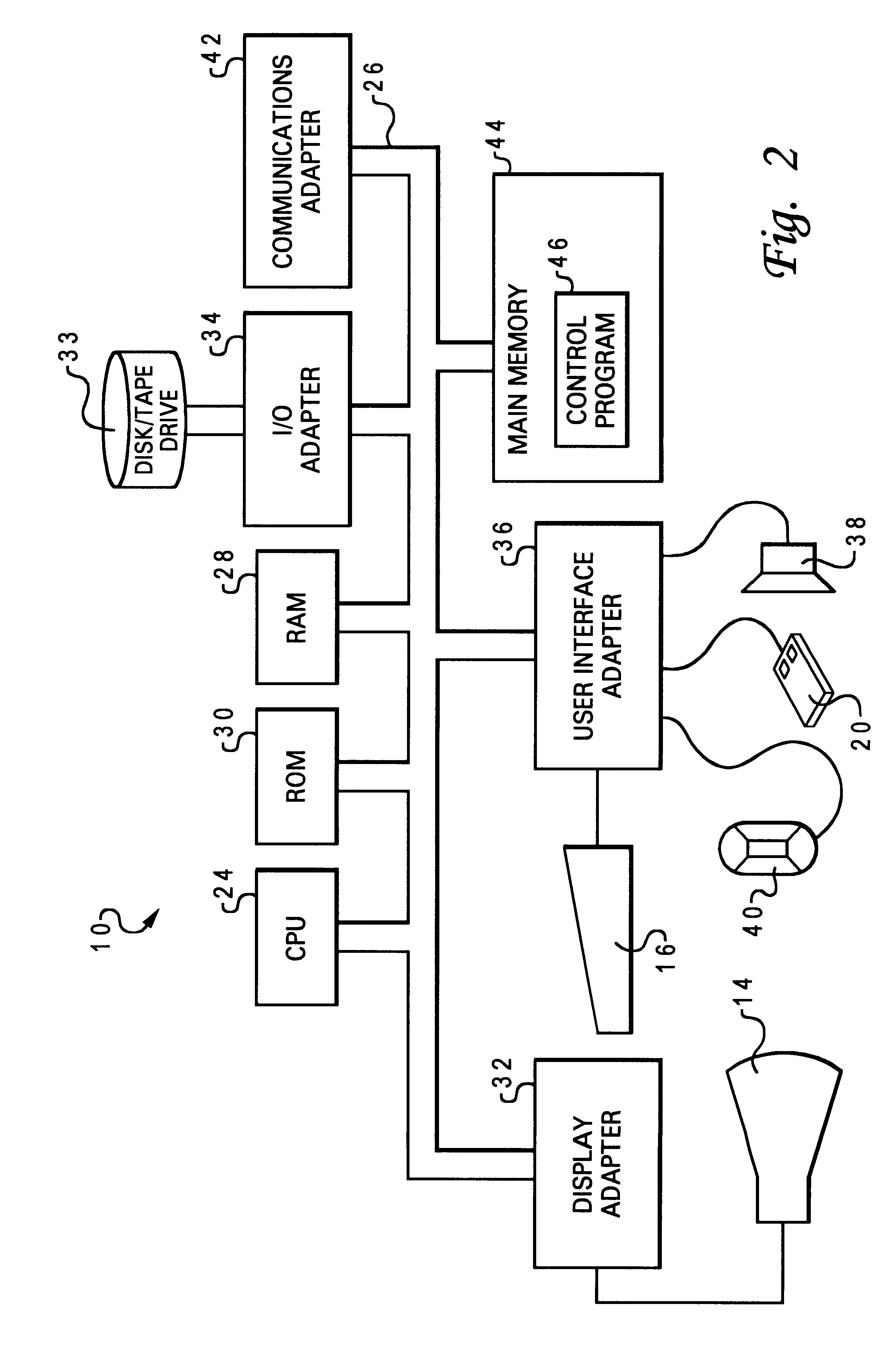

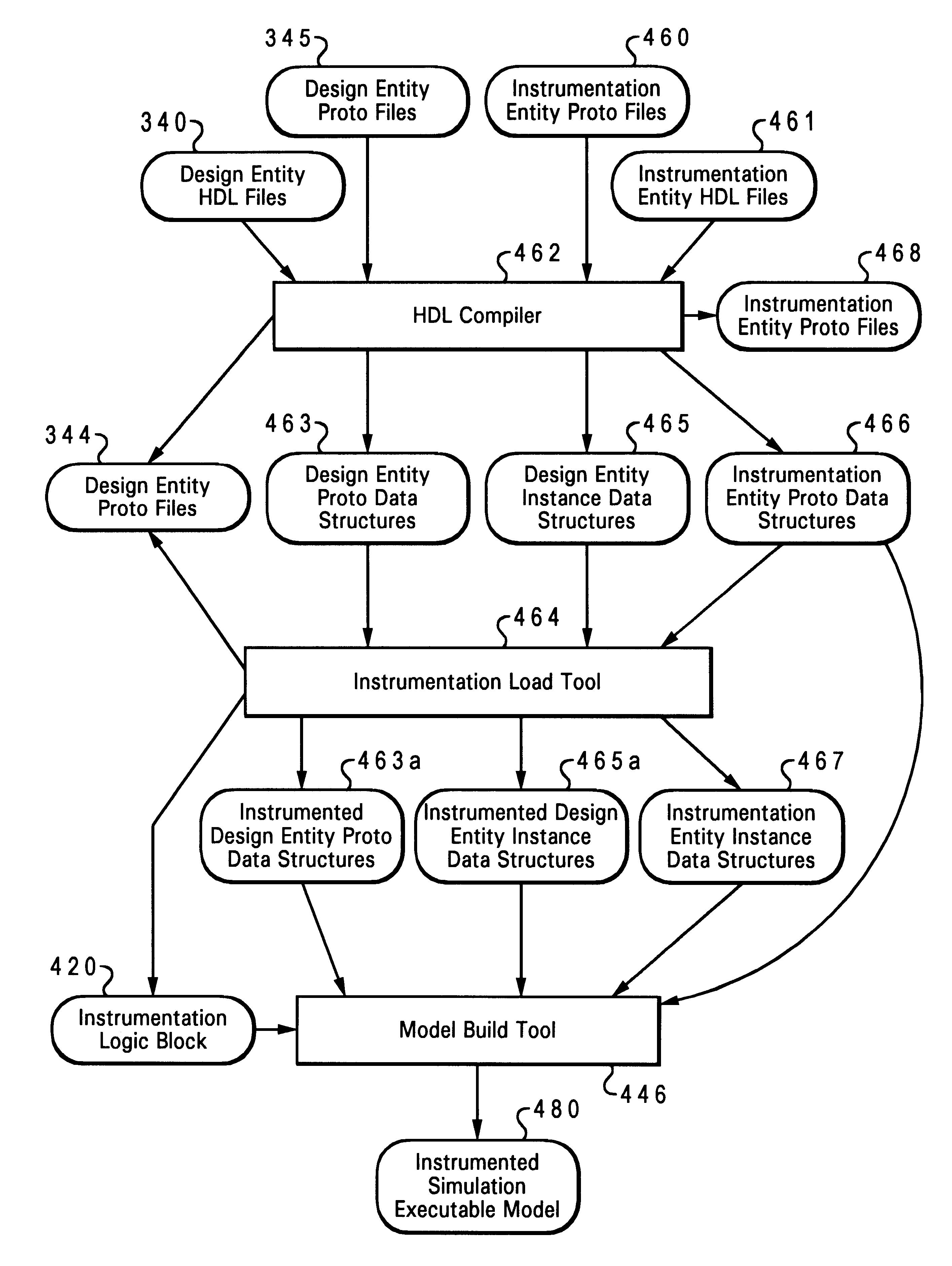

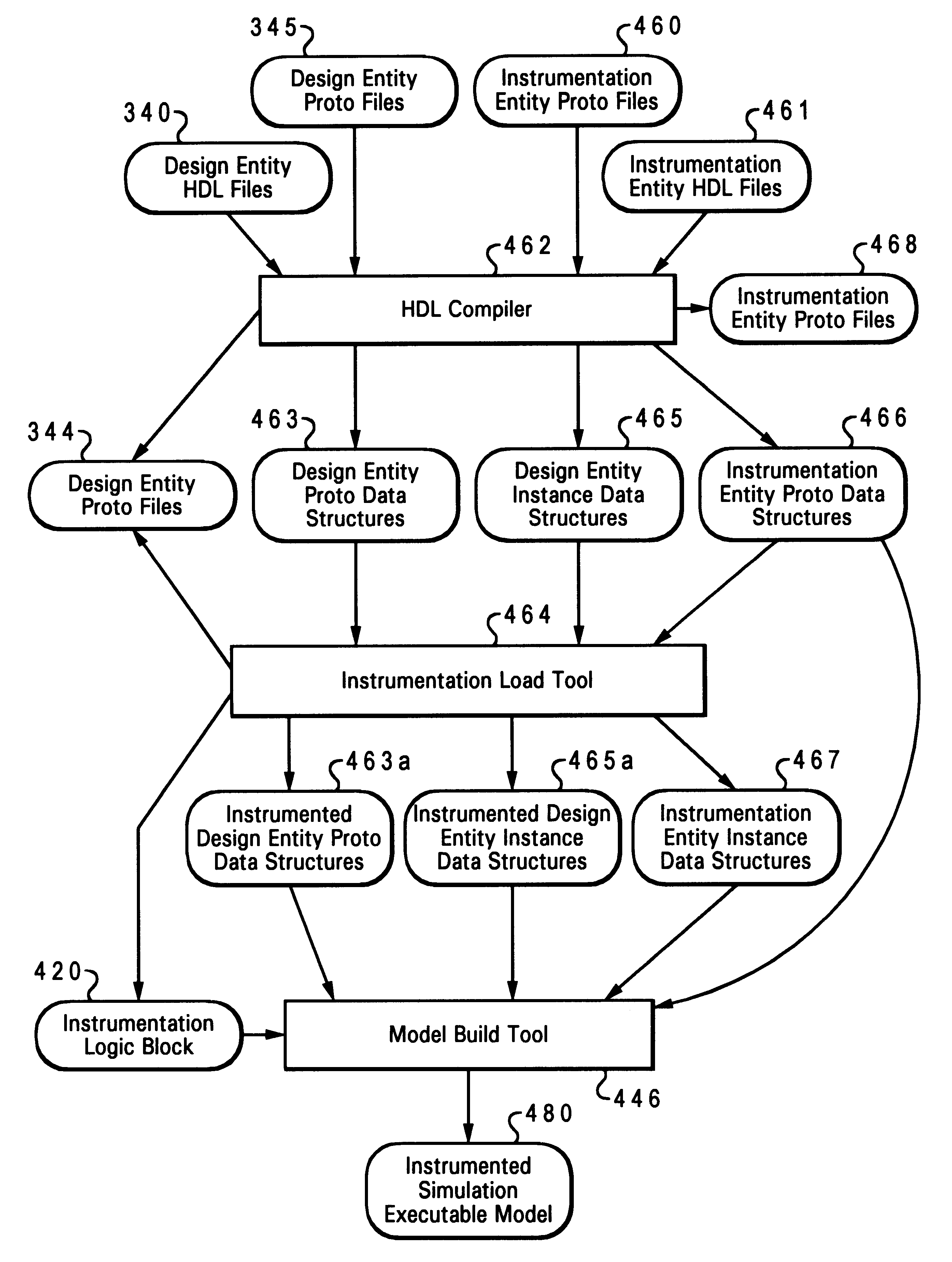

Method and system for instrumenting simulation models

InactiveUS6195627B1Complex designEasy to instrumentAnalogue computers for electric apparatusCAD circuit designTheoretical computer scienceCircuit design

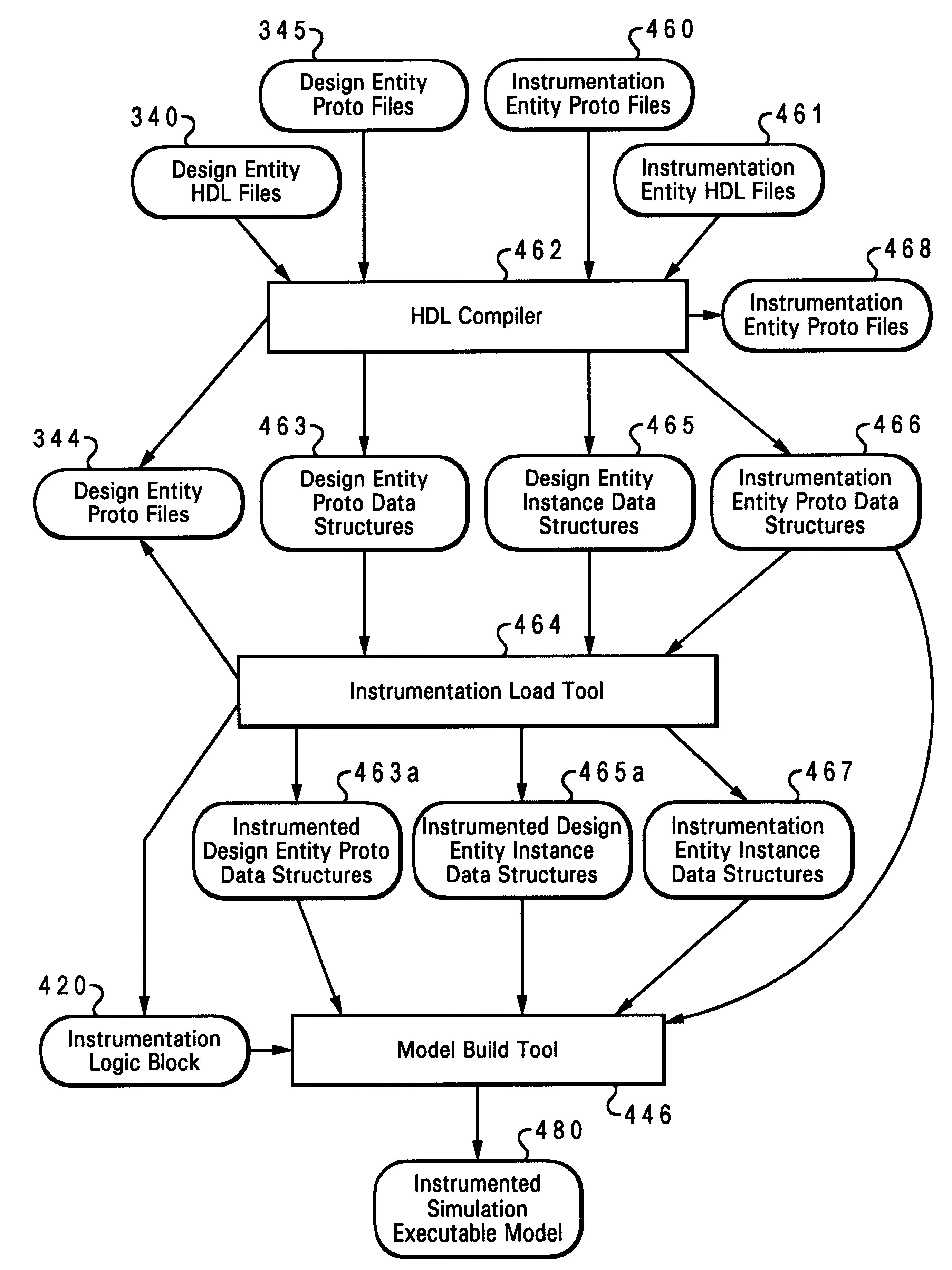

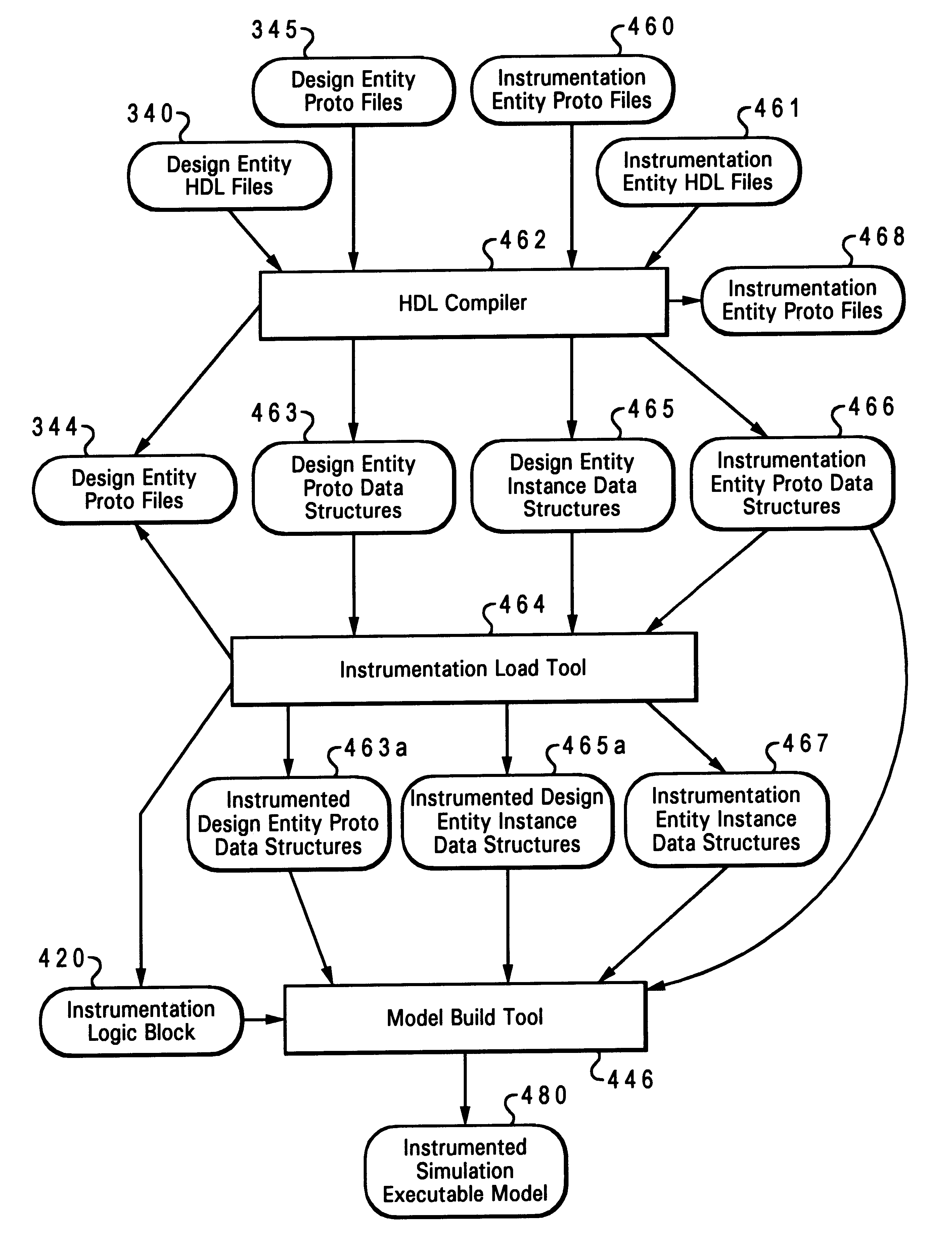

A method and system are disclosed that utilize the expressiveness of hardware description languages for efficiently and comprehensively monitoring performance characteristics of a digital circuit design during simulation. According to the present invention, a design entity that is part of a digital circuit design is first described utilizing a hardware description language. Next, an instrumentation entity is described utilizing the same hardware description language. Thereafter, the design entity is instantiated in at least one instance within a simulation model of a digital circuit design. Finally, the instrumentation entity is associated with the design entity utilizing a non-conventional call, such that the instrumentation entity may be utilized to monitor each instantiation of the design entity within the simulation model without the instrumentation entity becoming incorporated into the digital circuit design.

Owner:GLOBALFOUNDRIES INC

Method and system for selectively disabling simulation model instrumentation

InactiveUS6195629B1Complex designEasy to instrumentAnalogue computers for electric apparatusCAD circuit designComputer architectureSimulation testing

A method and system are disclosed that utilize the expressiveness of hardware description languages for selectively disabling instrumentation during simulation of a digital circuit design. According to the present invention, an instrumentation entity, described utilizing a hardware description language to include an output signal to indicate an occurrence of an event during simulation, is implemented into a simulation model of a digital circuit design. Next, the output signal is associated with a unique output storage element. Finally, a disable mechanism uniquely associated with said output signal is provided, such that the output signal may be selectively masked by disabling the storage element during simulation testing of the digital circuit design.

Owner:GLOBALFOUNDRIES INC

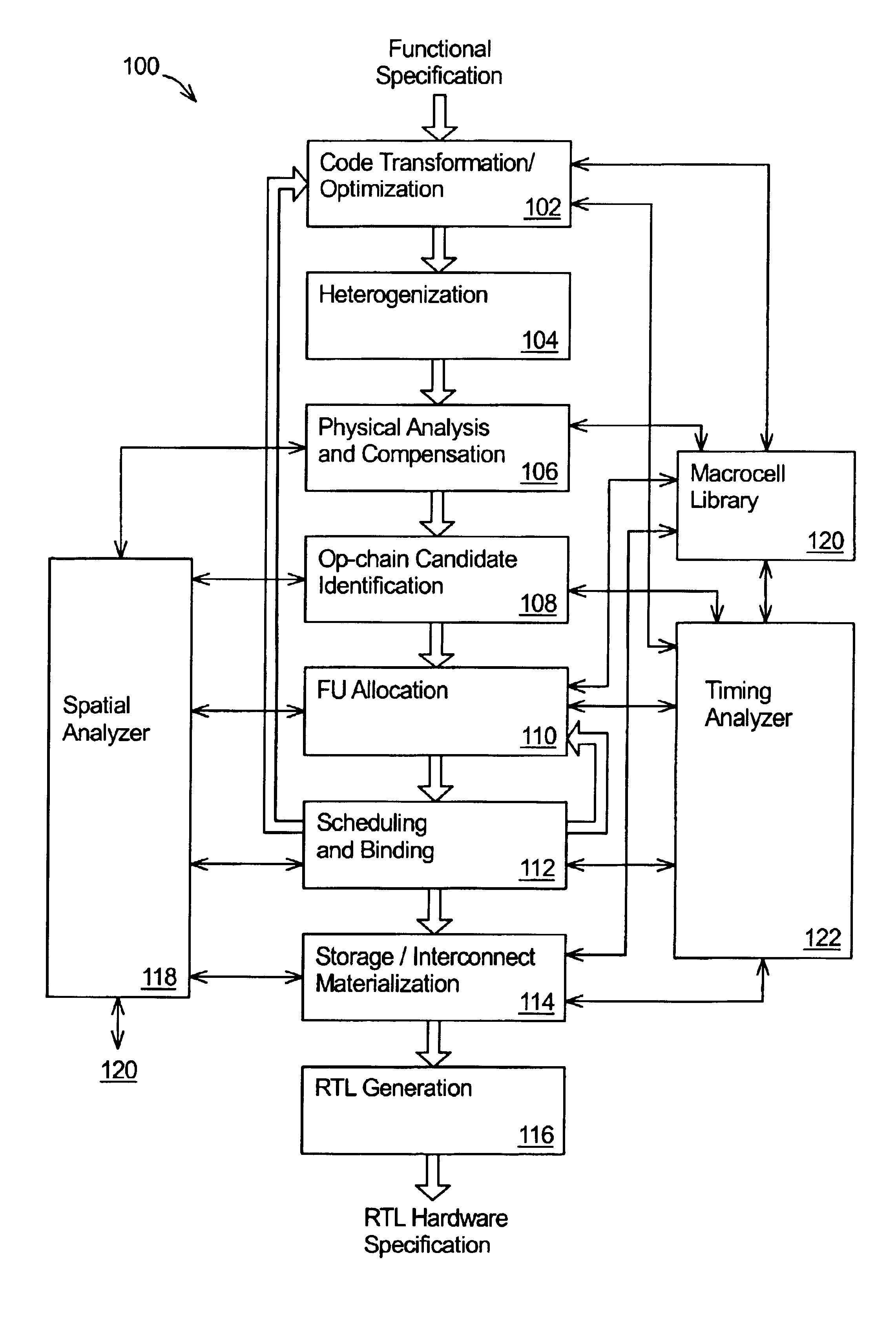

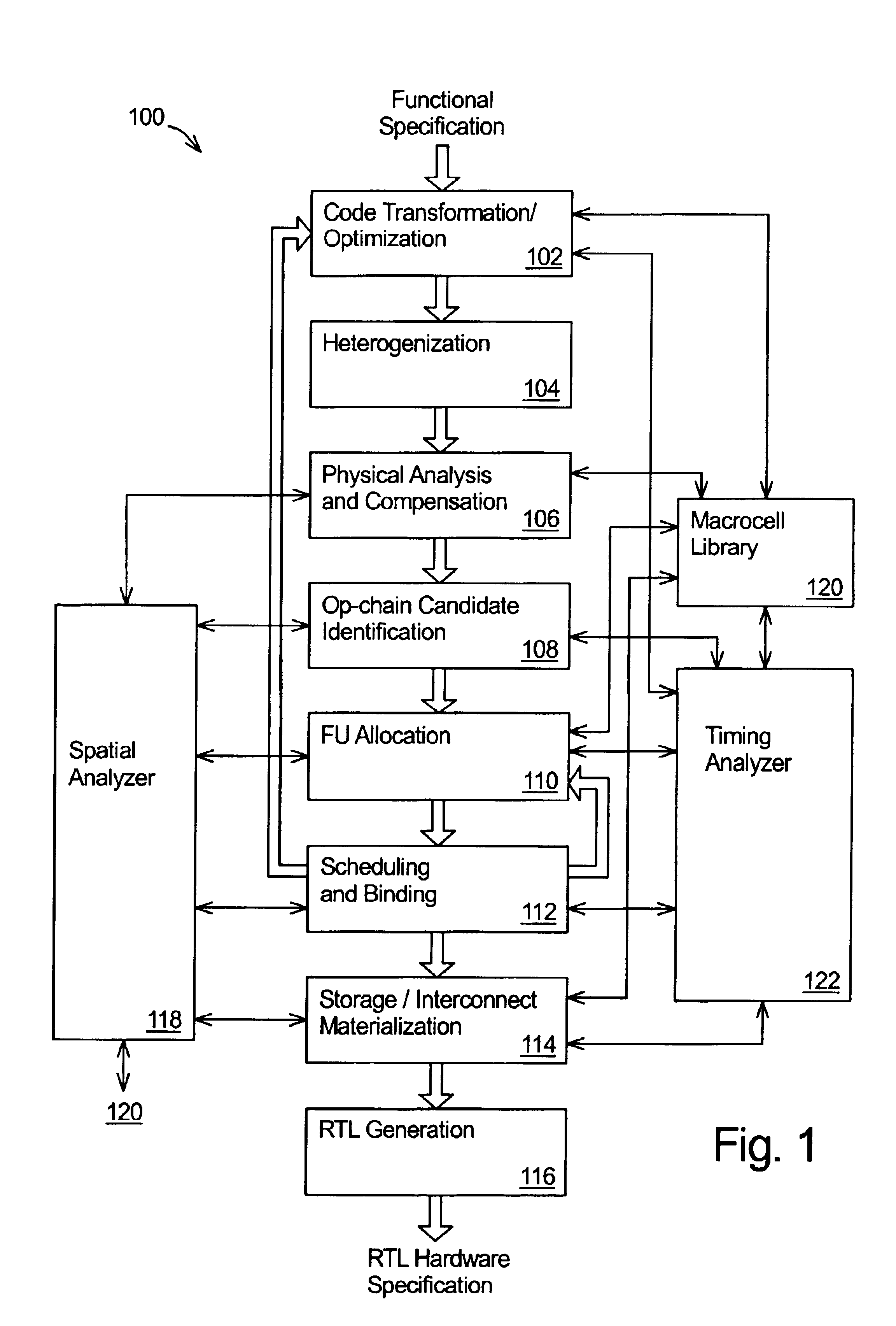

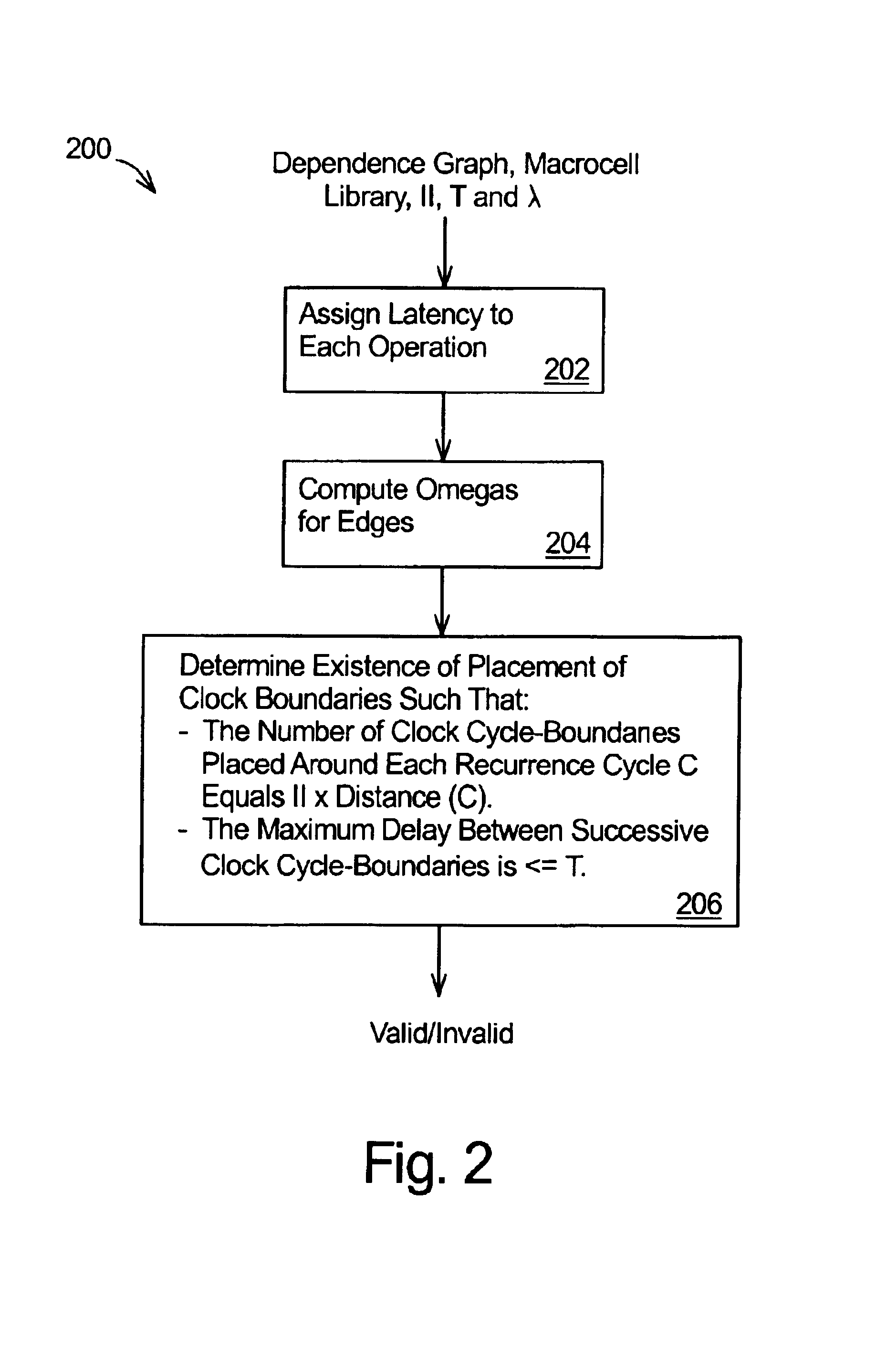

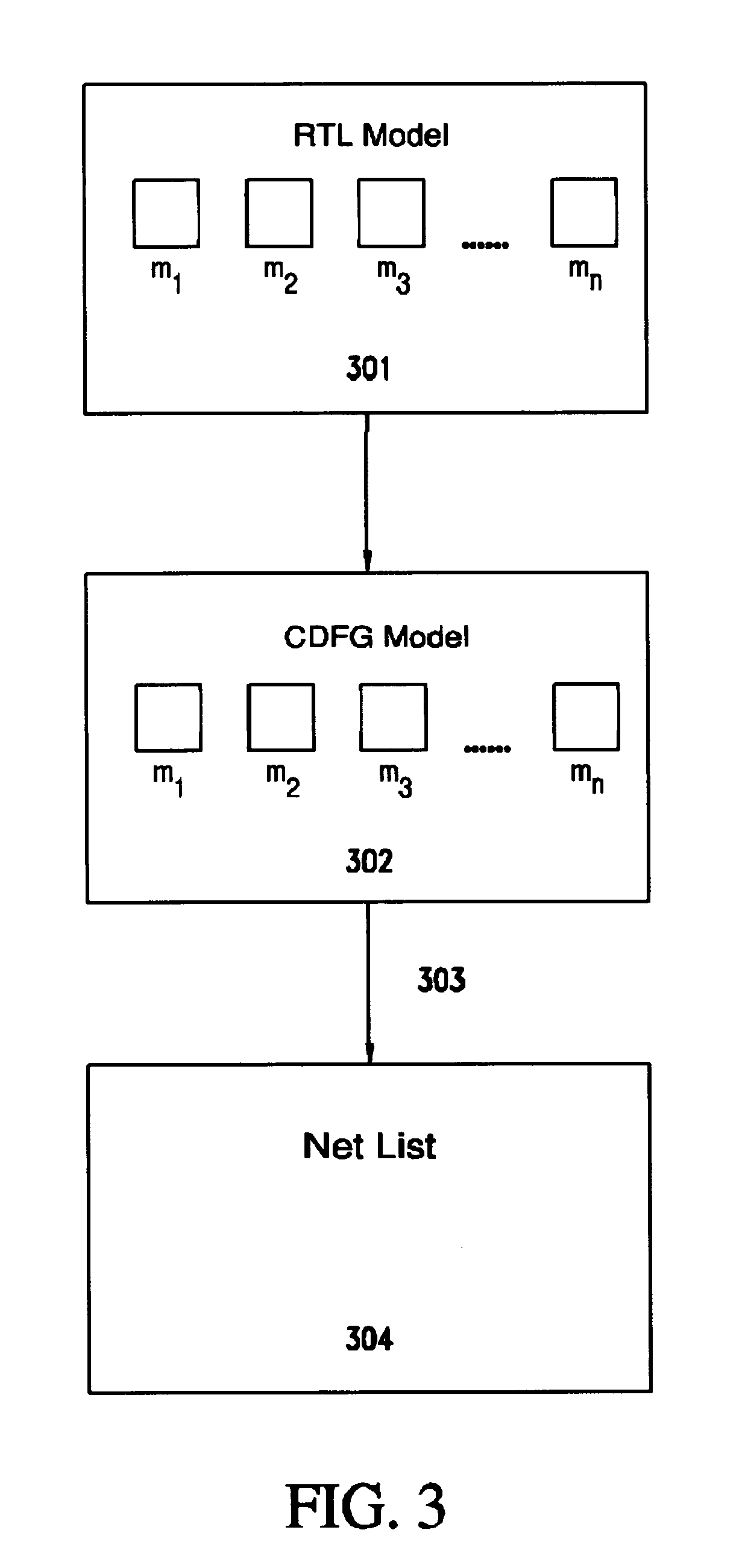

Methods and apparatus for digital circuit design generation

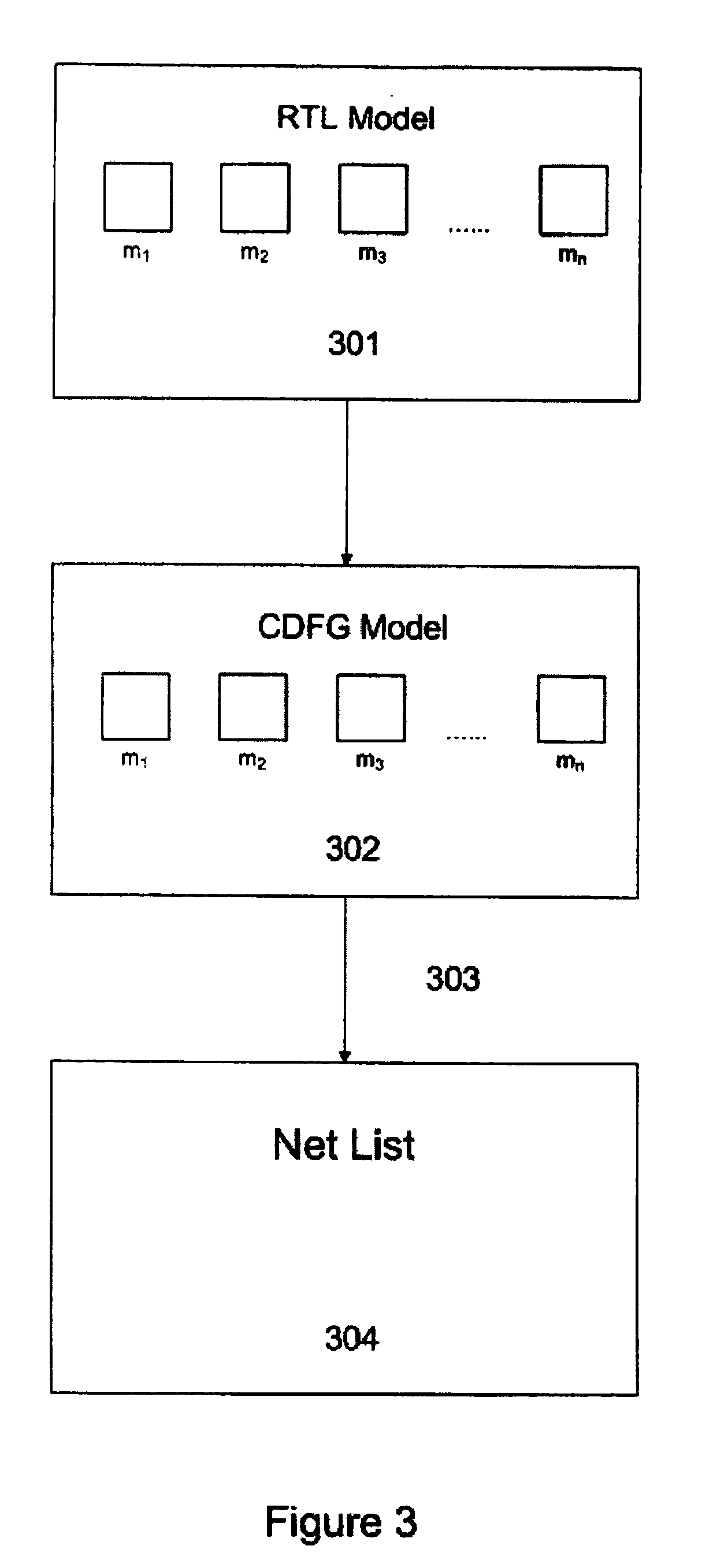

InactiveUS6952816B2Extended maintenance periodImprove routabilityCAD circuit designSoftware simulation/interpretation/emulationTheoretical computer scienceFunctional specification

A technique for synthesizing digital circuit designs by incorporating timing convergence and routability considerations. In one aspect, the invention provides a system and programmatic method for generating a circuit design from a functional specification according to at least one design objective. An intermediate representation of the functional specification is formed. The intermediate representation is analyzed for identifying a physical instantiation that will possibly result in unacceptable interconnect delay or congestion. Functional units are allocated from among a plurality of candidate functional units for performing operations of the intermediate representation. Operations are scheduled to occur at specified times on said selected functional units. An architectural representation of the circuit design is formed according to results of scheduling.

Owner:SAMSUNG ELECTRONICS CO LTD

Method of circuit verification in digital design

InactiveUS6728939B2Reduce designEasy to understandComputer aided designSoftware simulation/interpretation/emulationComputer architectureValidation methods

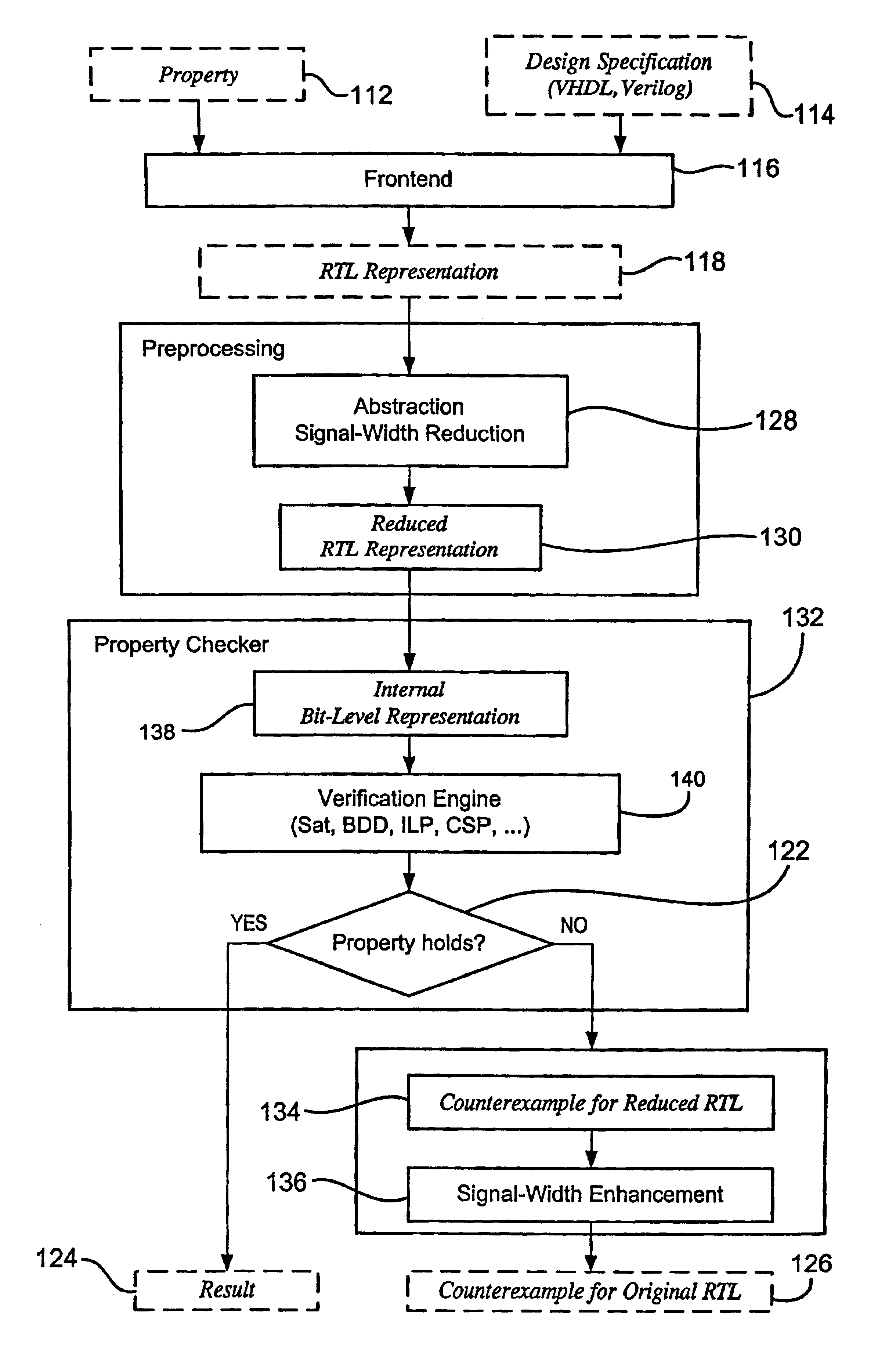

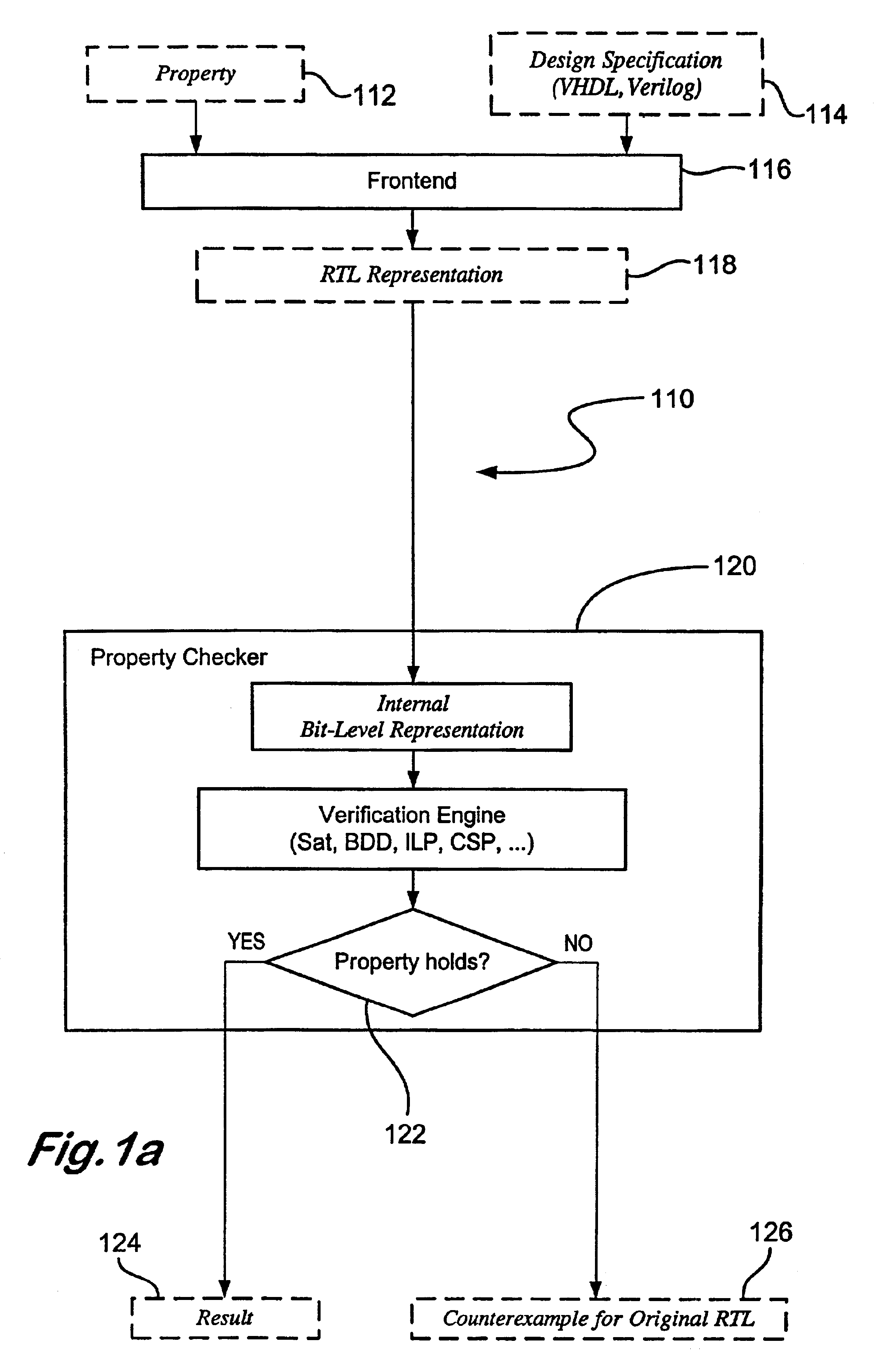

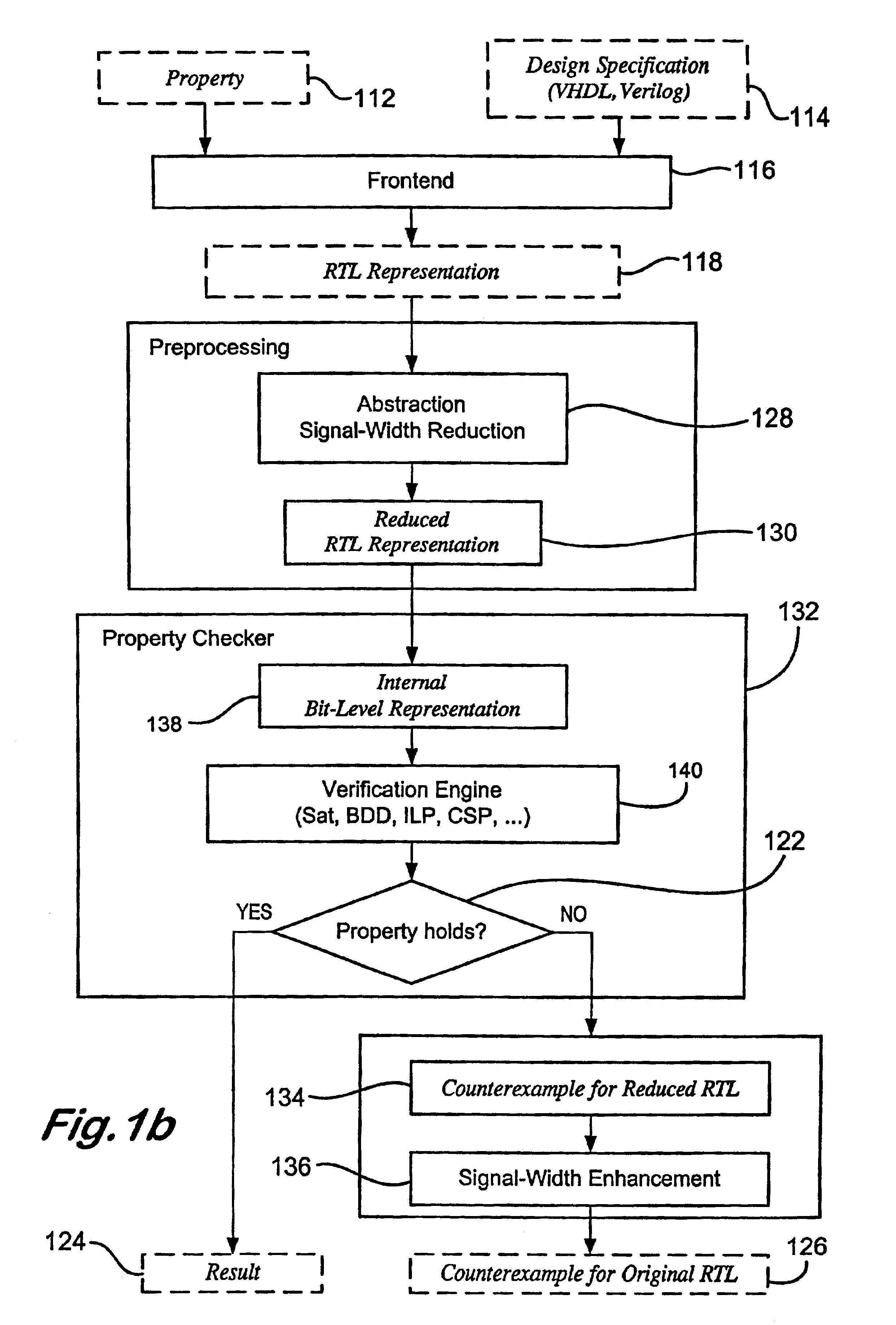

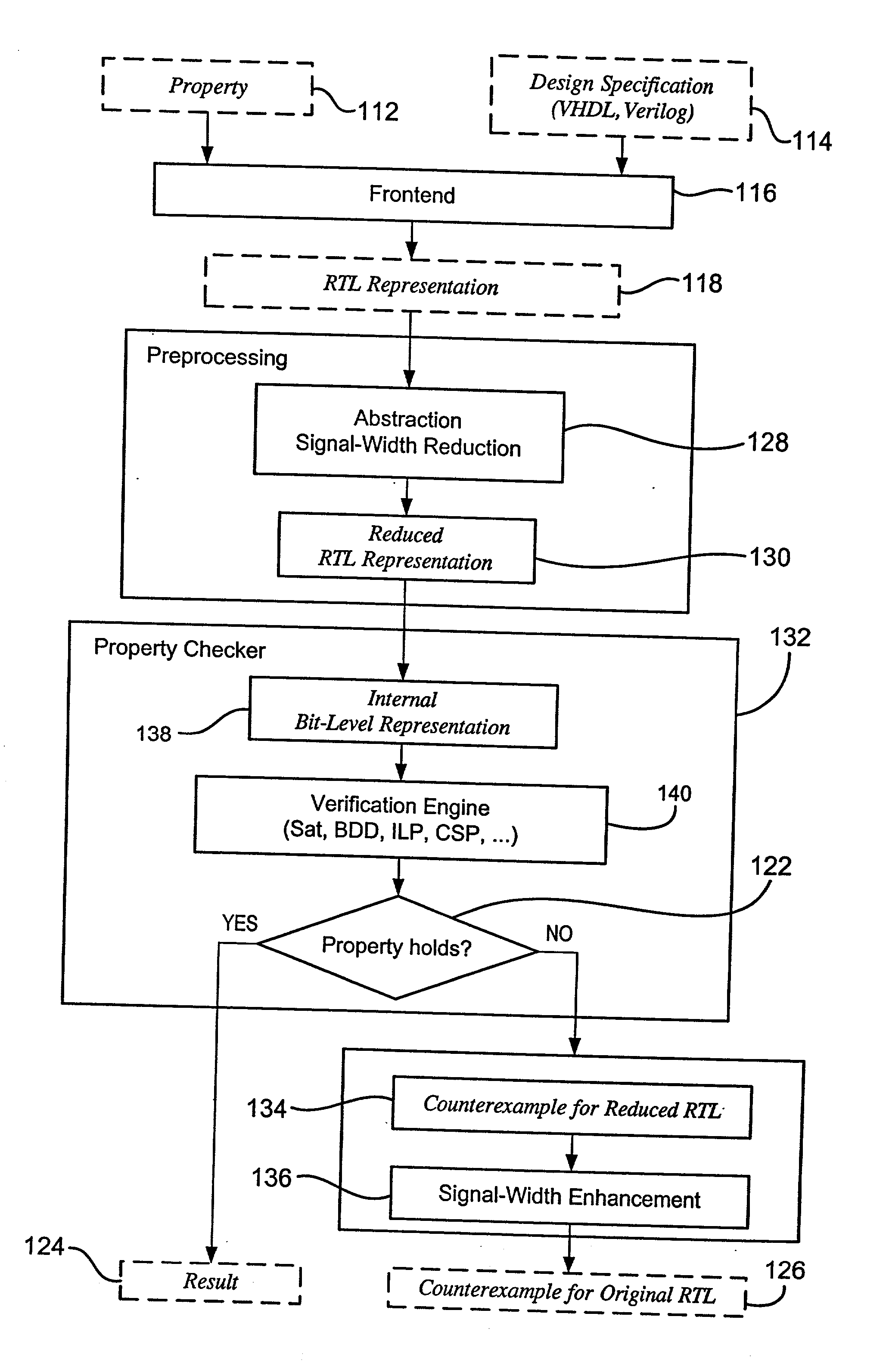

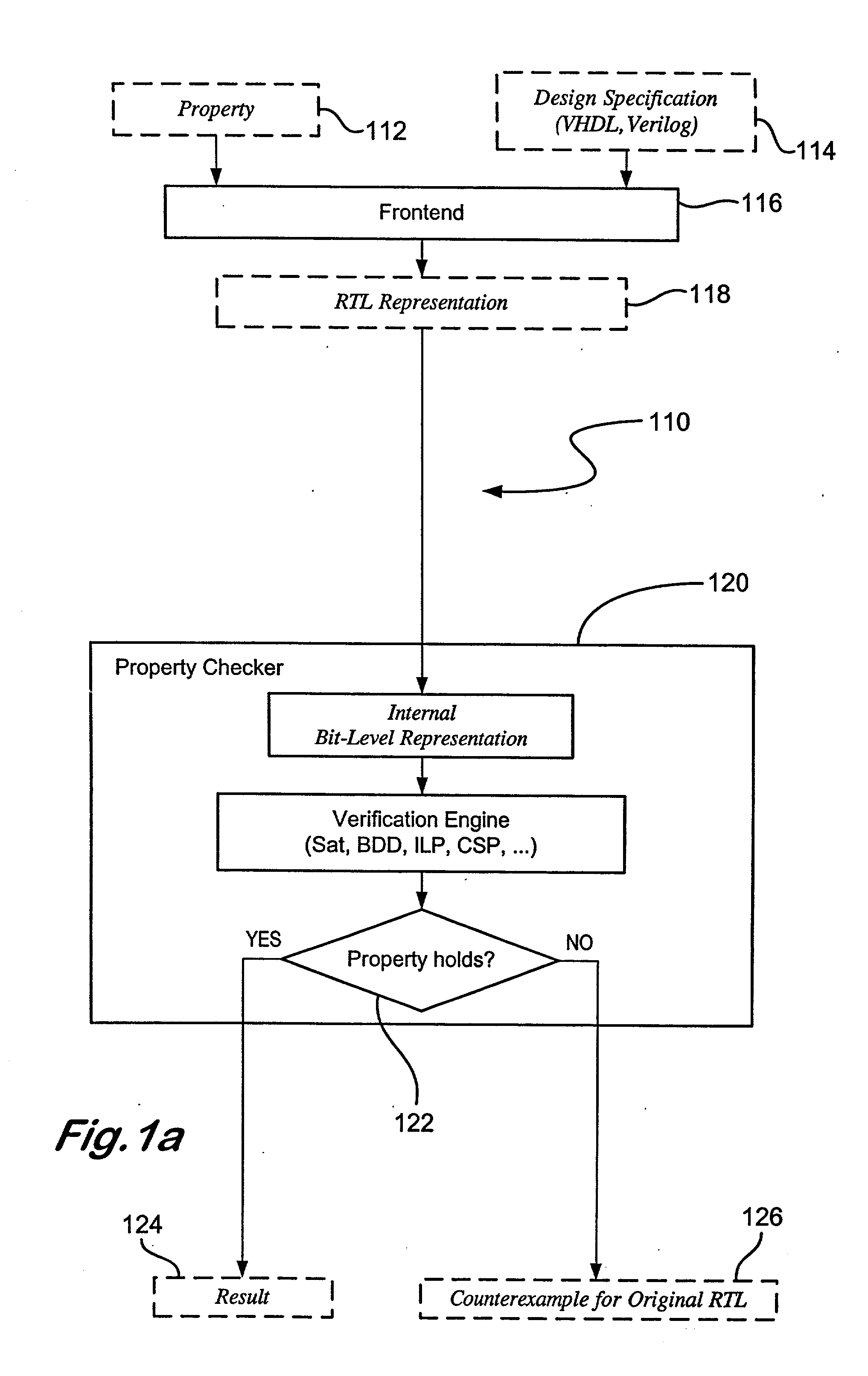

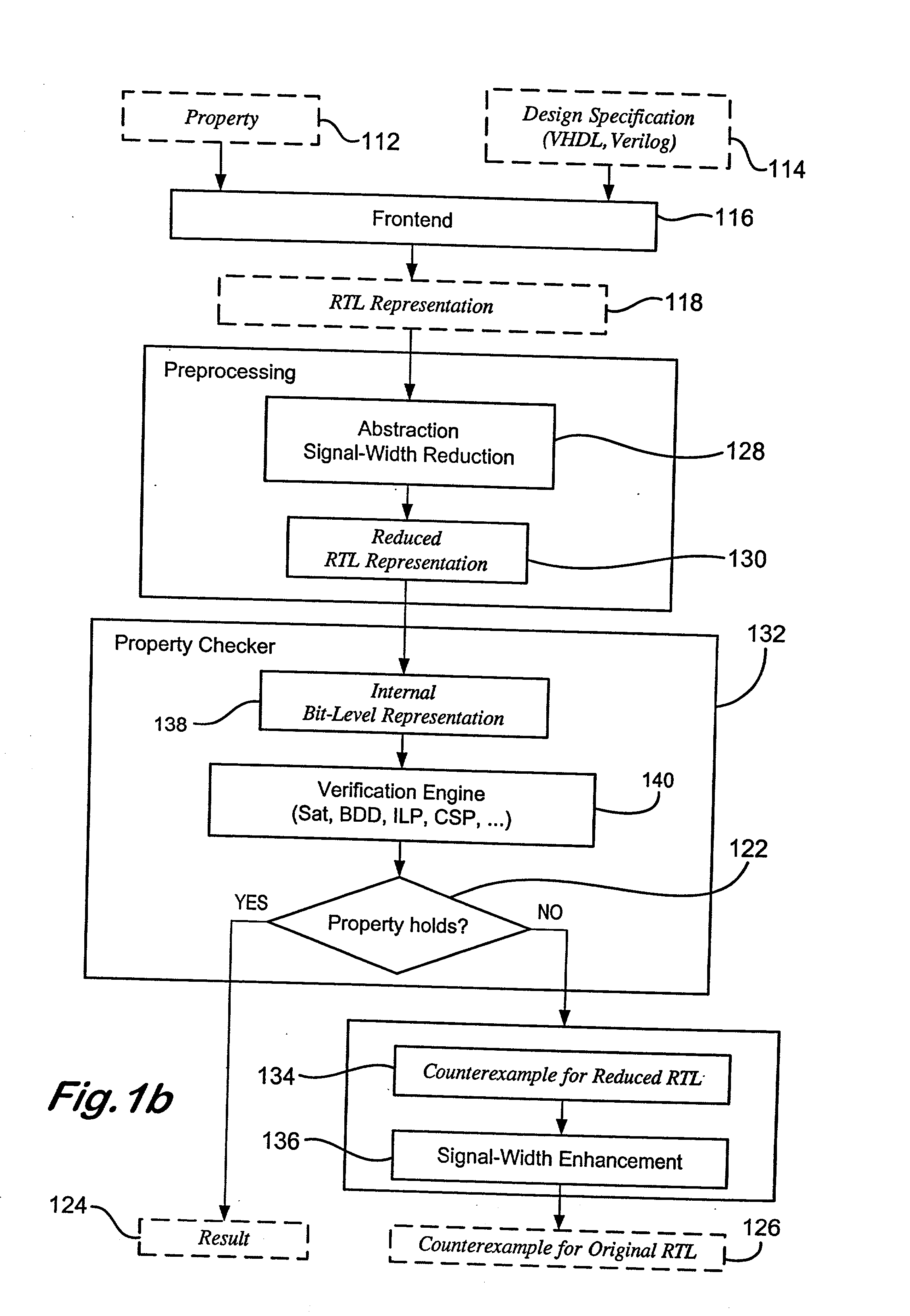

The present invention relates to a method of circuit verification in digital design and in particular, relates to a method of register transfer level property checking to enable the same. Today's electrical circuit designs frequently contain up to several million transistors, and circuit designs need to be checked to ensure that circuits operate correctly. Formal methods for verification are becoming increasingly attractive since they confirm design behavior without exhausting simulating a design. A digital circuit design verification method, prior to a property checking process for each property of a non-reduced RTL model, determines a reduced RTL model which retains specific signal properties of a non-reduced RTL model which are to be checked. A linear signal width reduction causes an exponential reduction of the induced state space. Reducing state space sizes in general goes hand in hand with reduced verification runtimes, thus speeding up verification tasks.

Owner:ONESPIN SOLUTIONS

Method and system for incrementally compiling instrumentation into a simulation model

InactiveUS6223142B1Complex designEasy to instrumentAnalogue computers for electric apparatusCAD circuit designParallel computingInstrumentation

A method and system are disclosed that utilize the expressiveness of hardware description languages for incrementally compiling instrumentation logic into a simulation model of a digital circuit design. According to the present invention, a simulation model that includes a design entity file of a digital circuit design is generated. Next, an instrumentation entity file is associated with the design entity file, thereby producing an instrumented design entity file. Finally, and during the process of compiling the simulation model, for the instrumented design entity file: searching for a consistent and previously compiled version of said instrumented design entity file. In response to finding a consistent and previously compiled version, loading the consistent and previously compiled version into the simulation model. In response to finding no consistent and previously compiled version, loading and compiling the instrumented design entity file.

Owner:IBM CORP

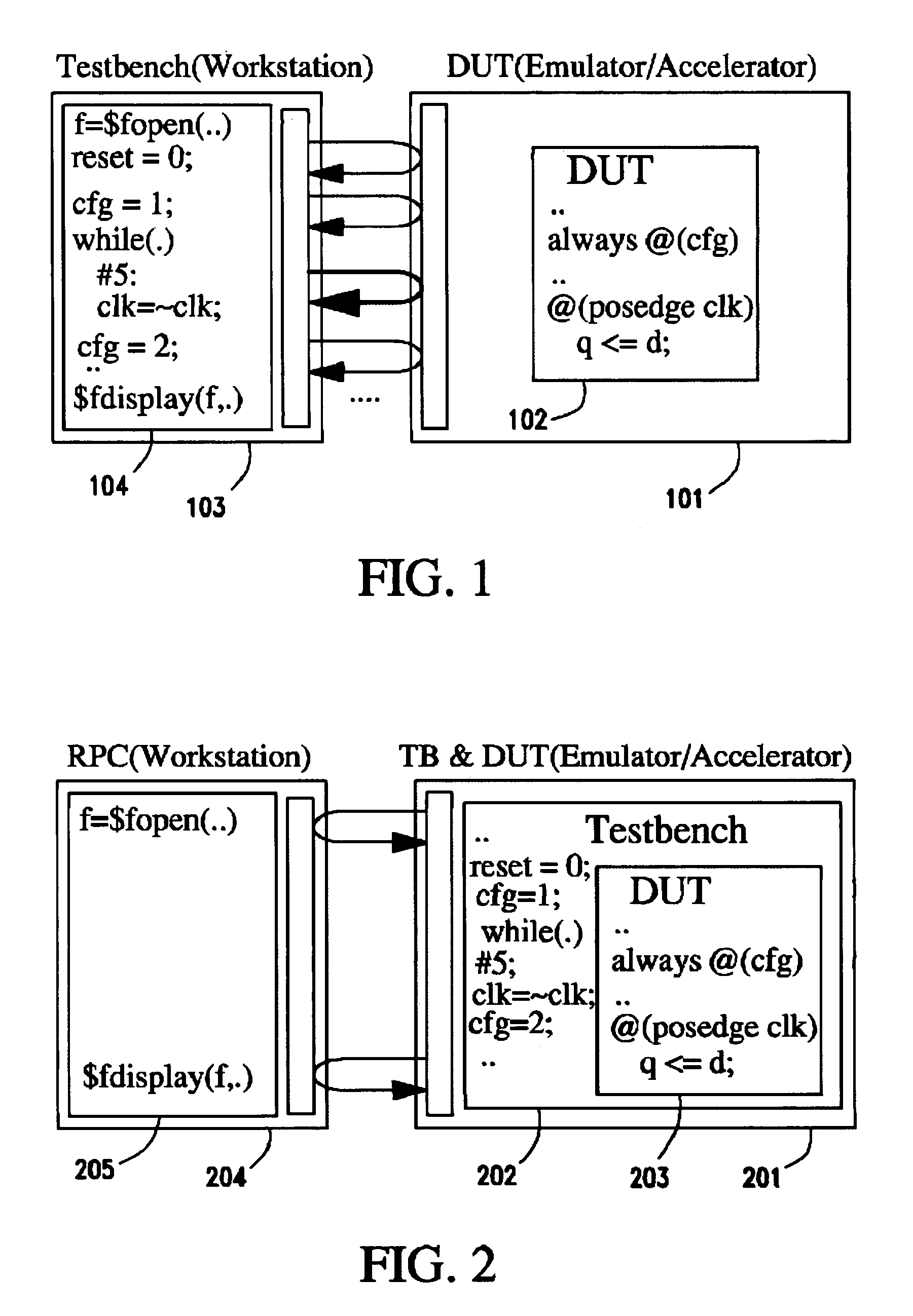

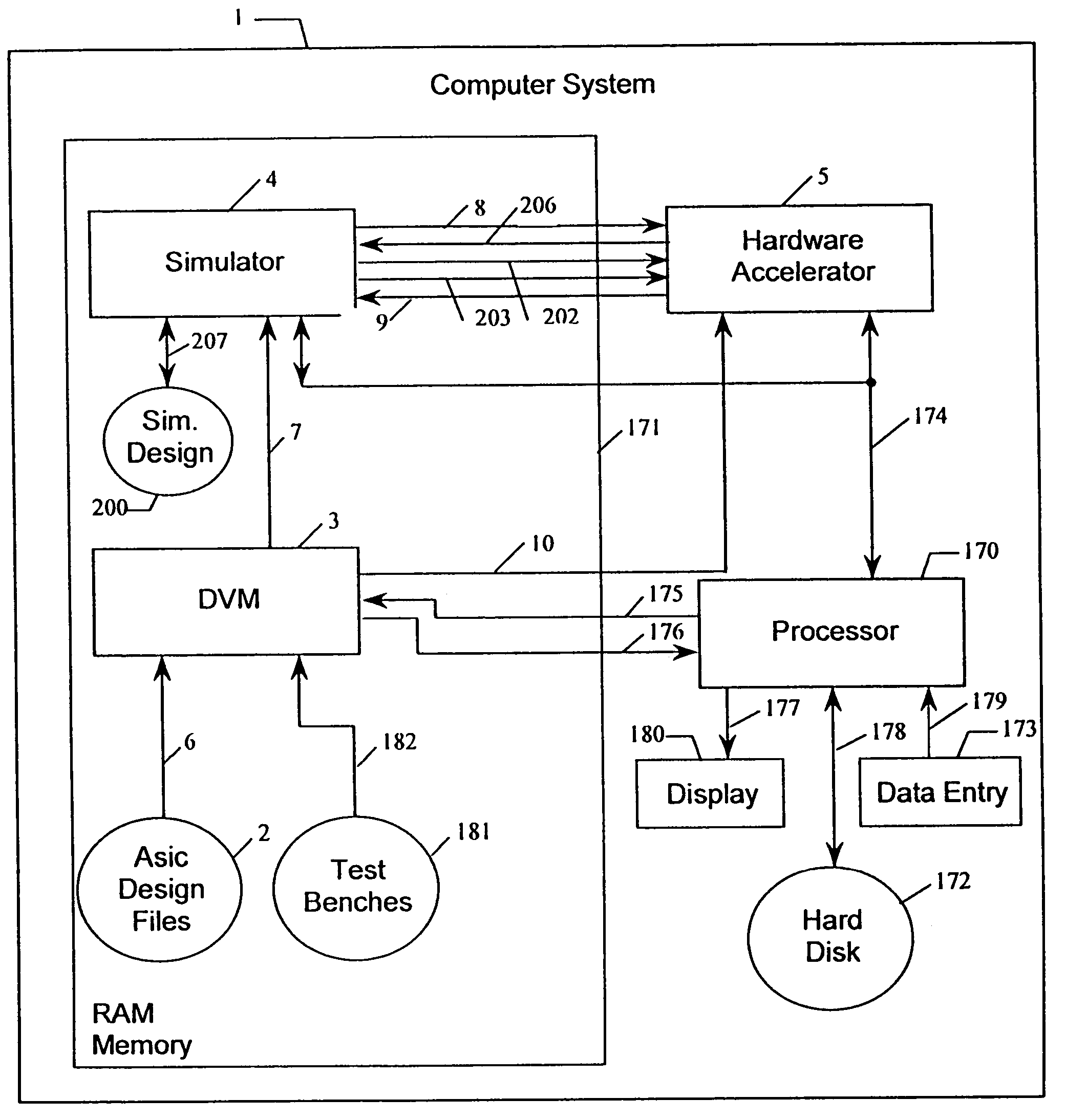

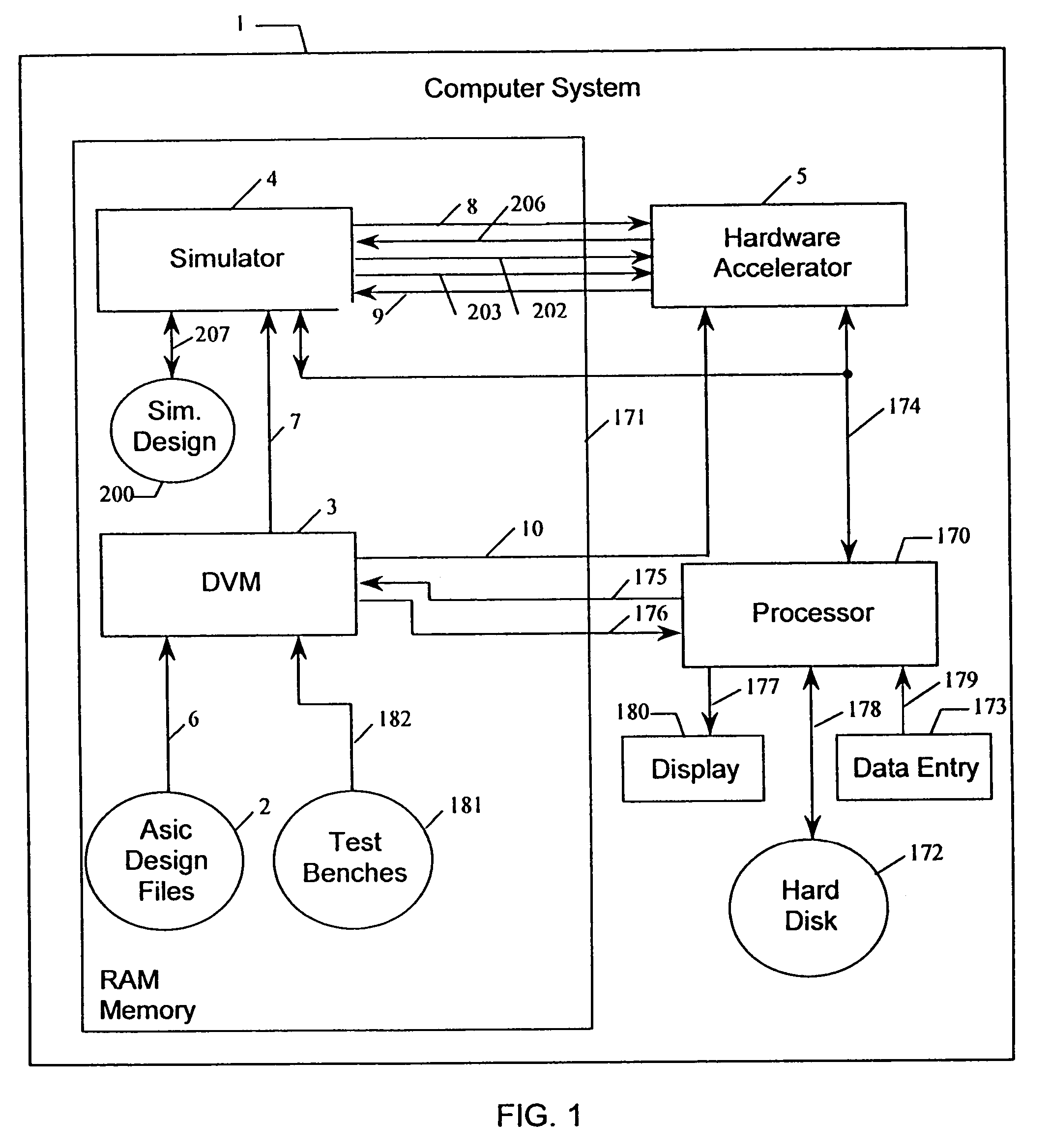

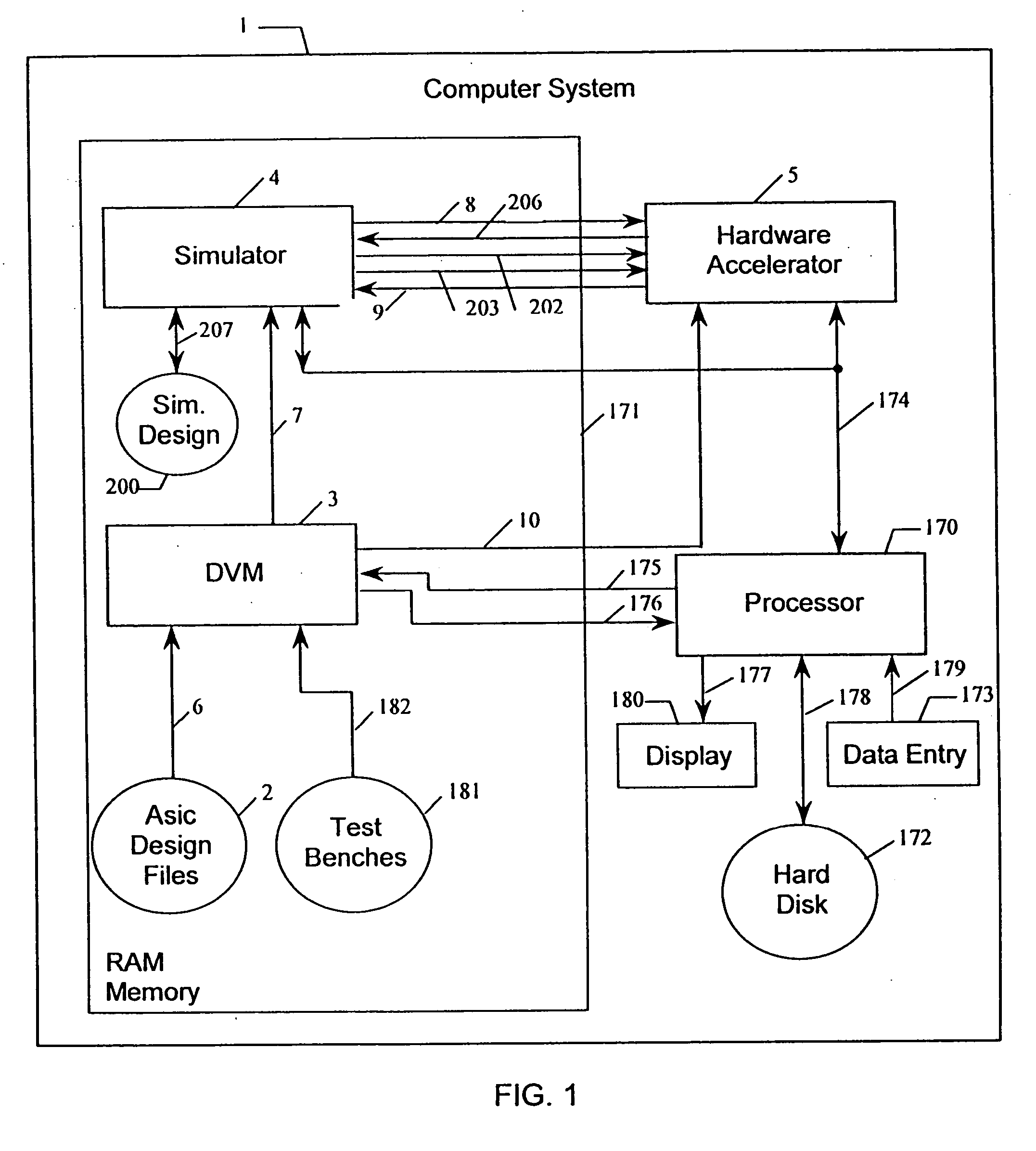

Method and system for hardware accelerated verification of digital circuit design and its testbench

ActiveUS20050144585A1Quick verificationOvercomes drawbackElectrical testingComputer aided designConcurrent computingValidation methods

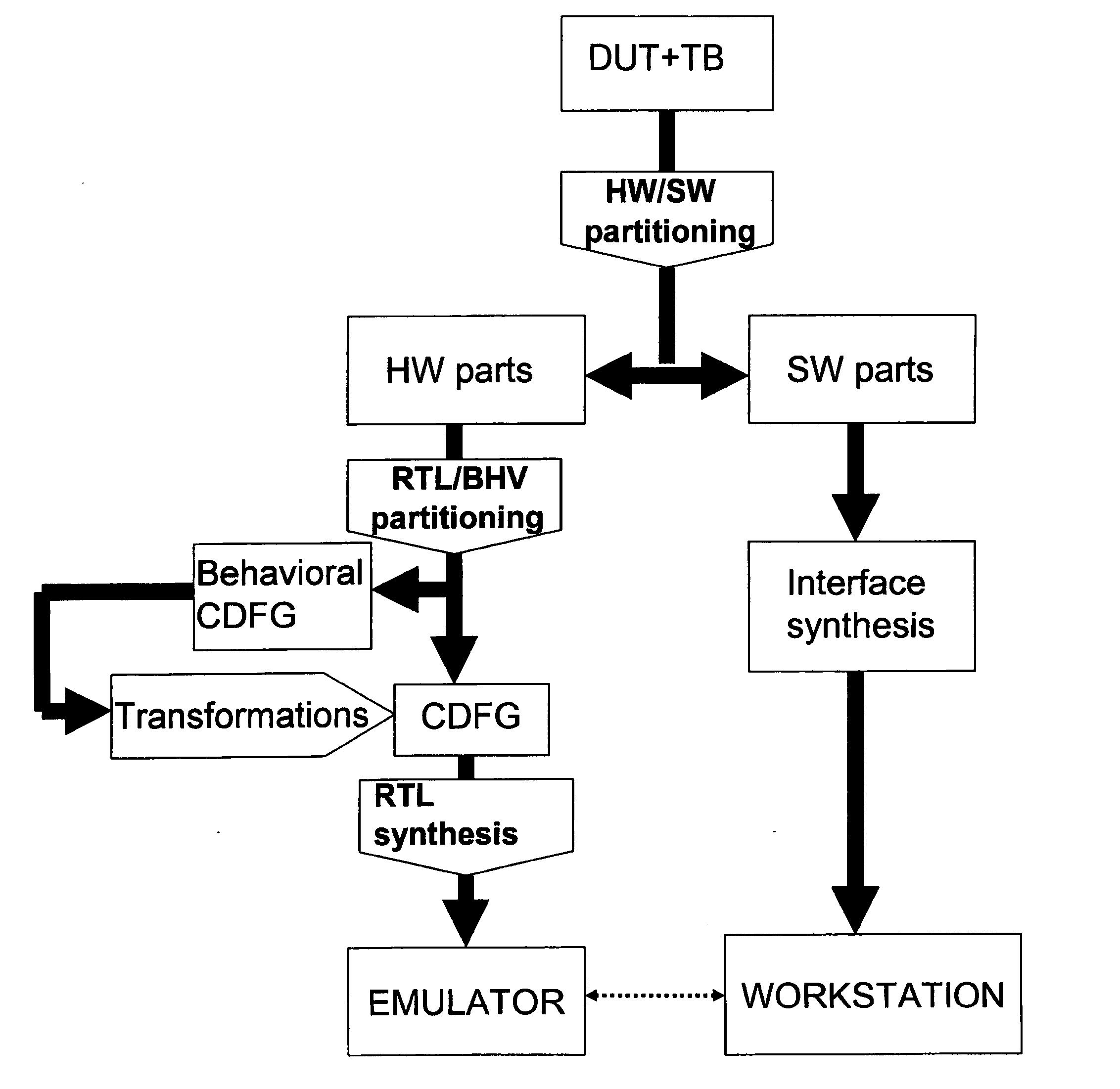

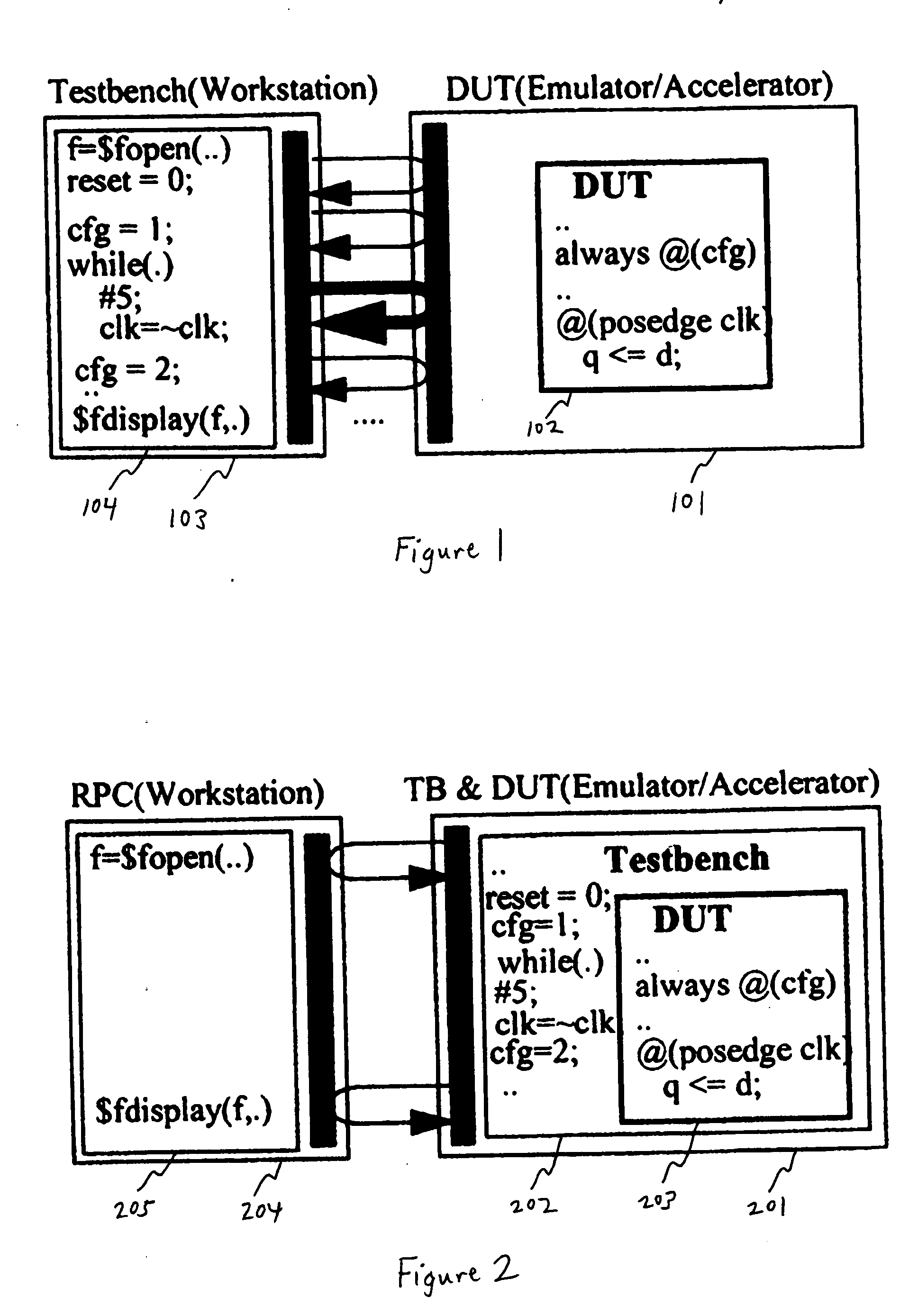

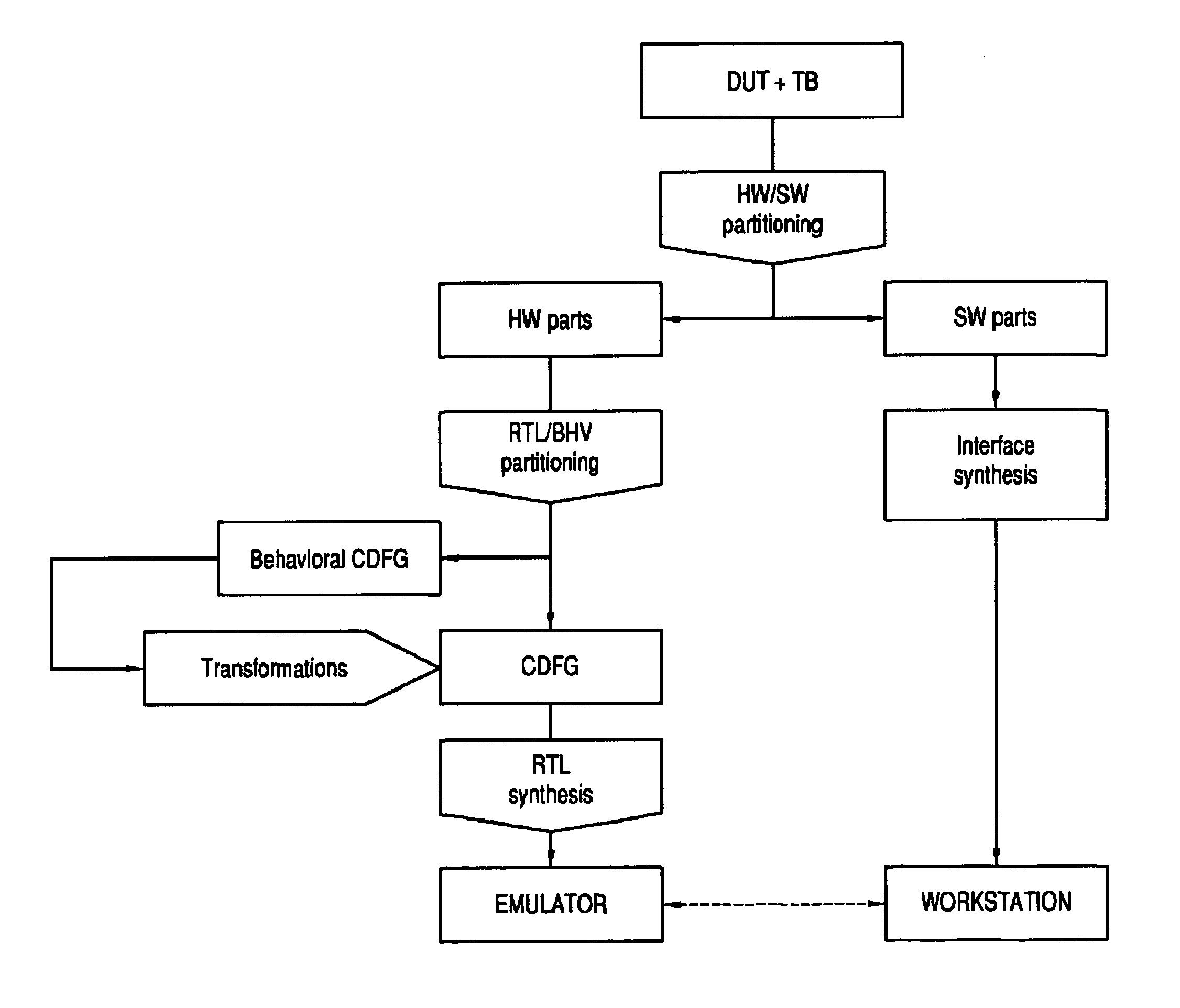

A system and method is presented for synthesizing both a design under test (DUT) and its test environment (i.e., the testbench for the DUT), into an equivalent structural model suitable for execution on a reconfigurable hardware platform. This may be achieved without any change in the existing verification methodology. Behavioral HDL may be translated into a form that can be executed on a reconfigurable hardware platform. A set of compilation transforms are provided that convert behavioral constructs into RTL constructs that can be directly mapped onto an emulator. Such transforms are provided by introducing the concepts of a behavioral clock and a time advance finite state machine (FSM) that determines simulation time and sequences concurrent computing blocks in the DUT and the testbench.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

Hardware simulator instrumentation

InactiveUS6202042B1Complex designEasy to instrumentCAD circuit designSoftware simulation/interpretation/emulationComputer hardwareHardware simulator

A method and system are disclosed that utilize the expressiveness of hardware description languages for providing comprehensive runtime monitoring during hardware accelerated simulation of a digital circuit design. According to the present invention a design entity forming part of a digital circuit design that will be translated and assembled into a simulation executable model, is described utilizing a hardware description language. Next, an instrumentation entity designed to send a failure signal in response to detecting an occurrence of a failure event within the simulation executable model is described utilizing the same hardware description language. Thereafter, a simulation test is initiated on the simulation executable model utilizing a hardware simulator. Finally, during the simulation test, and in response to receiving a failure signal from the instrumentation entity, the simulation test is terminated such that the failure event may be efficiently identified and diagnosed.

Owner:IBM CORP

Method of circuit verification in digital design

InactiveUS20020138812A1Reduce designEasy to understandComputer aided designSoftware simulation/interpretation/emulationComputer architectureCircuit design

The present invention relates to a method of circuit verification in digital design and in particular relates to a method of register transfer level property checking to enable the same. Today's electrical circuit designs frequently contain up to several million transistors and circuit designs need to be checked to ensure that circuits operate correctly. Formal methods for verification are becoming increasingly attractive since they confirm design behavior without exhaustively simulating a design. The present invention provides a digital circuit design verification method wherein, prior to a property checking process for each property of a non-reduced RTL model, a reduced RTL model is determined, which reduced RTL model retains specific signal properties of a non-reduced RTL model which are to be checked. A linear signal width reduction causes an exponential reduction of the induced state space. Reducing state space sizes in general goes hand in hand with reduced verification runtimes, and thus speeding up verification tasks.

Owner:ONESPIN SOLUTIONS

Method and system for hardware accelerated verification of digital circuit design and its testbench

ActiveUS7257802B2Quick verificationOvercomes drawbackElectrical testingComputer aided designConcurrent computingValidation methods

A system and method is presented for synthesizing both a design under test (DUT) and its test environment (i.e., the testbench for the DUT), into an equivalent structural model suitable for execution on a reconfigurable hardware platform. This may be achieved without any change in the existing verification methodology. Behavioral HDL may be translated into a form that can be executed on a reconfigurable hardware platform. A set of compilation transforms are provided that convert behavioral constructs into RTL constructs that can be directly mapped onto an emulator. Such transforms are provided by introducing the concepts of a behavioral clock and a time advance finite state machine (FSM) that determines simulation time and sequences concurrent computing blocks in the DUT and the testbench.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

Automatic adjustment for counting instrumentation

InactiveUS6212491B1Complex designEasy to instrumentCAD circuit designSoftware simulation/interpretation/emulationDesign cycleComputer science

A method and system are disclosed that utilize the expressiveness of hardware description languages for automatically adjusting counting rates of instrumentation within a simulation model of a digital circuit design, during simulation of said digital circuit design. According to the present invention a design entity that will be incorporated into a simulation model of a digital circuit design is described utilizing a hardware description language. The design entity operates, during simulation, in conformity with a design cycle that consists of a multiple of a simulator cycle. Next, an instrumentation entity is described utilizing the same hardware description language. The description of the instrumentation entity contains logic to detect occurrences of a count event that occurs in conformity with the design cycle during simulation. Thereafter, an instrumentation logic block associated with the instrumentation entity is automatically generated and utilized for counting occurrences of the count event detected by the instrumentation entity. Finally, the design cycle is encoded within the instrumentation entity, such that the output logic block is automatically adjusted to count in conformity with the design cycle.

Owner:IBM CORP

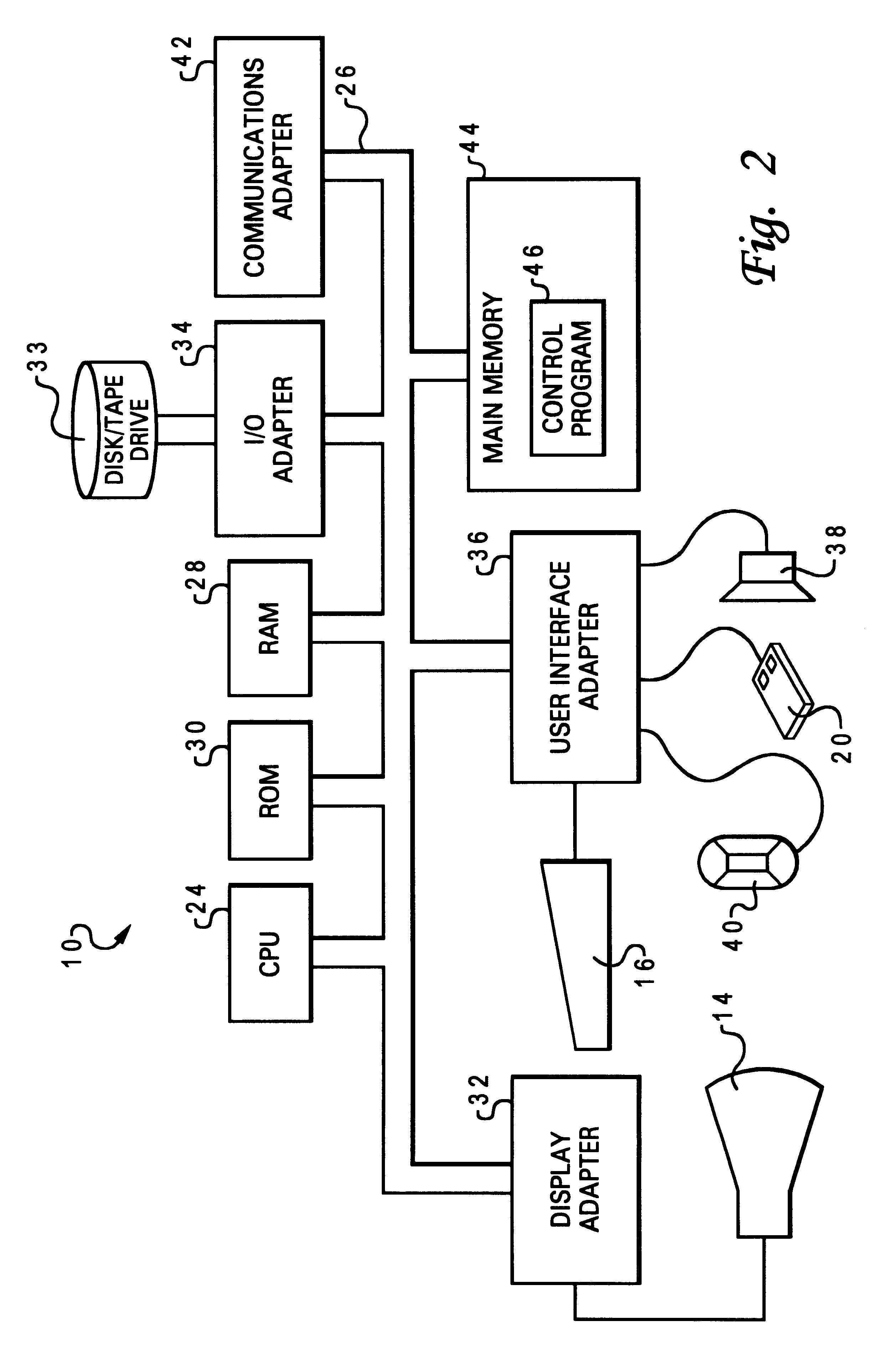

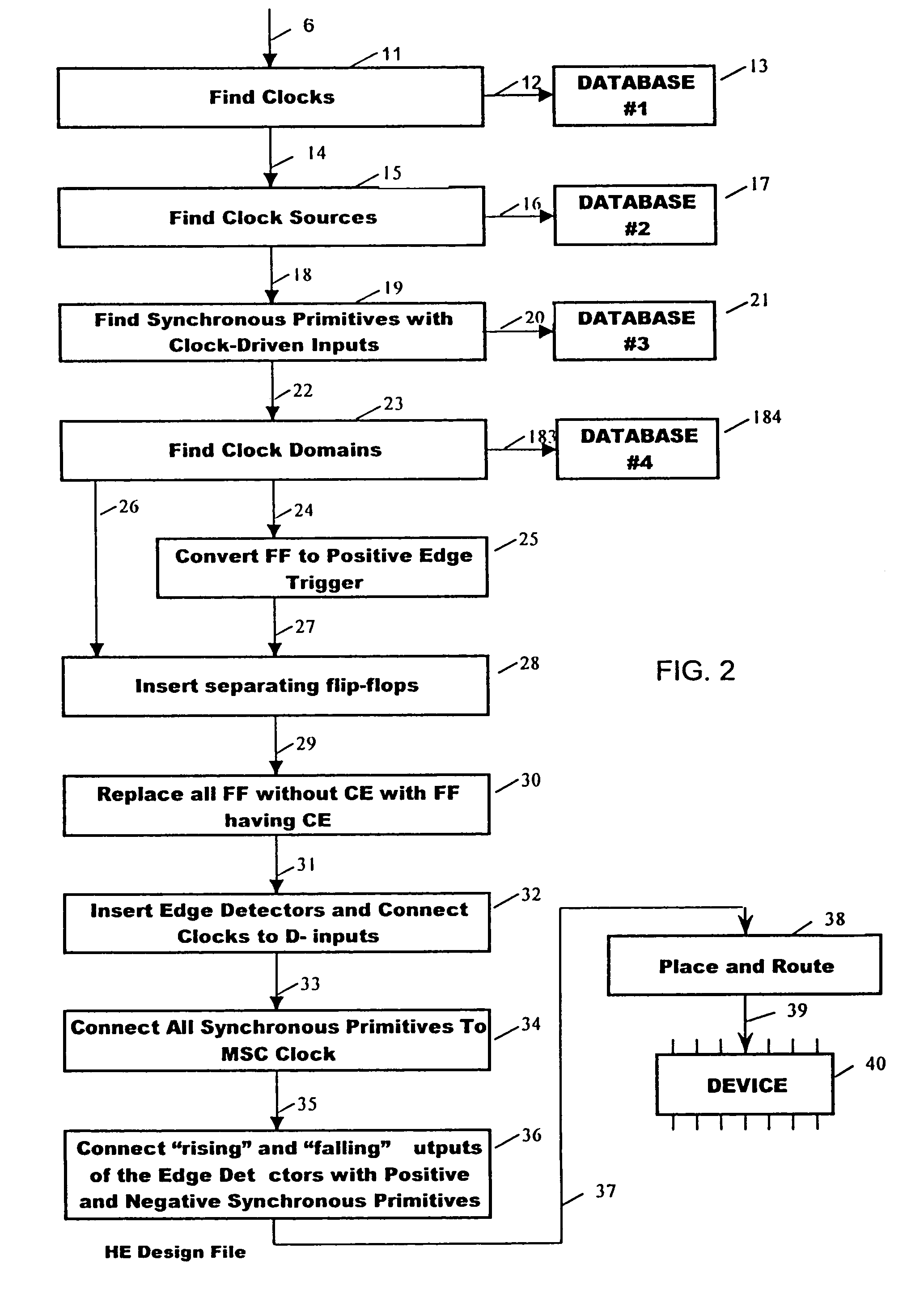

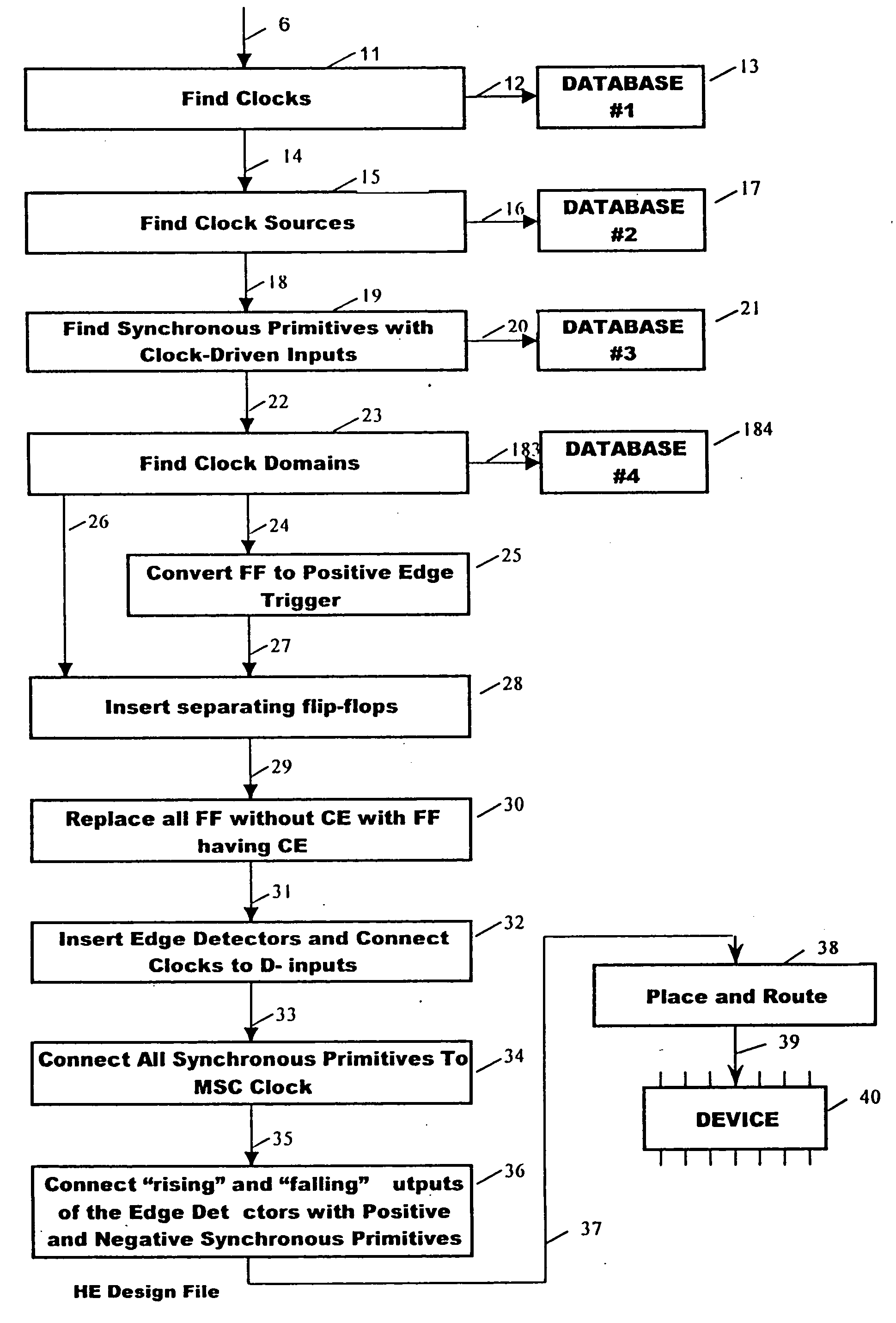

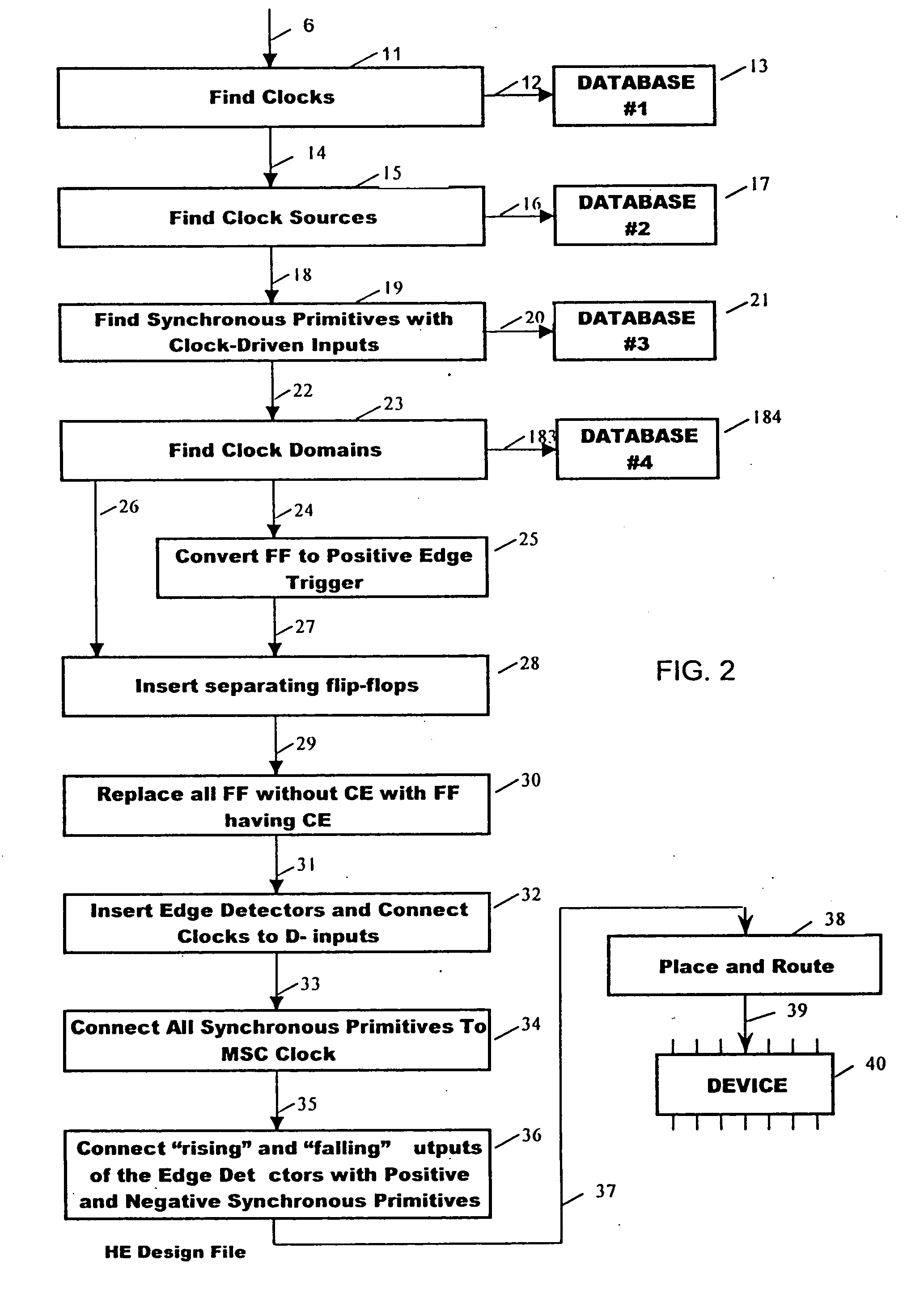

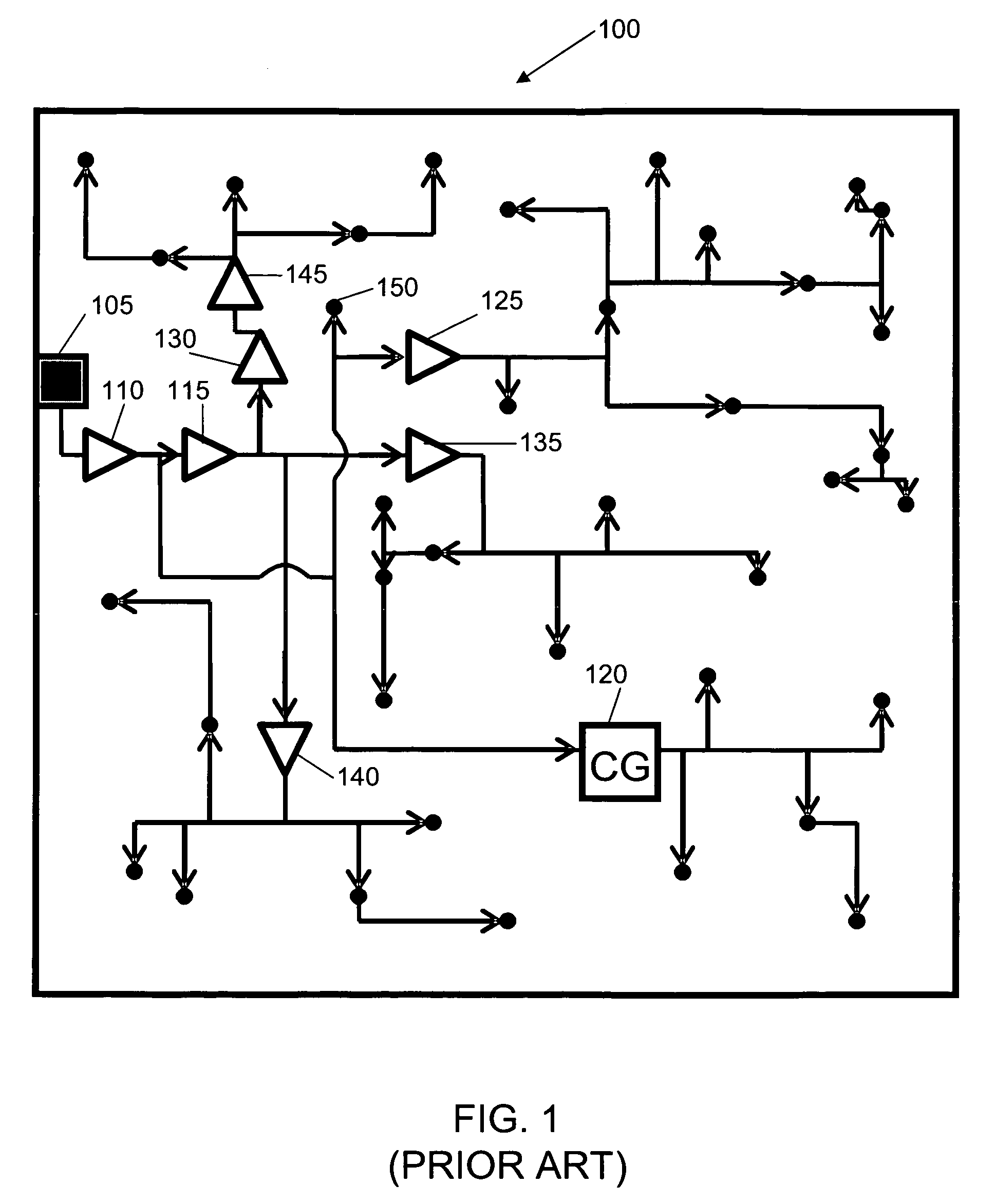

Method and apparatus for accelerating the verification of application specific integrated circuit designs

ActiveUS7003746B2Digital data processing detailsAnalogue computers for electric apparatusDetector circuitsField-programmable gate array

A method and system for accelerating software simulator operation with the aid of reprogrammable hardware such as Field Programmable Gate Array devices (FPGA). The method and system aid in emulation and prototyping of Application Specific Integrated Circuits (ASIC) digital circuit designs by means of reprogrammable devices. The system includes a design verification manager and software program that includes subroutines of finding clock sources, finding synchronous primitives that are receiving clock signals from the clock sources, and a subroutine for inserting edge detector circuits between such clock sources and synchronous primitives. This new method allows eliminating of clock timing issues by applying basic design clocks to the clock enable instead of clock trigger inputs and generating and applying to clock trigger inputs a new clock that is automatically delayed in respect to all other clocks in the design. This system solves the major obstacle for automatic retargeting of ASIC designs into reprogrammable devices that have different timings of the clocking chains in ASICs and FPGAs that result in triggering of associated flip-flops and latches at different times.

Owner:HYDUKE STANLEY M +1

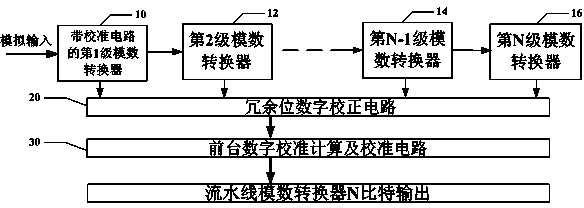

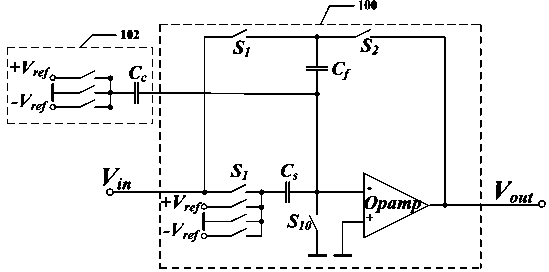

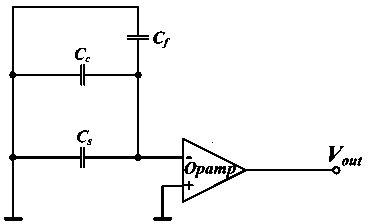

Pipeline ADC (analog to digital converter) and error calibration method thereof

ActiveCN104363020ASimple designCalibration Static Degradation IssuesAnalogue-digital convertersAnalogue/digital conversion calibration/testingCapacitanceDigital down converter

The invention discloses a foreground digital calibration method applicable to a pipeline ADC (analog to digital converter). On the basis of the structure of the traditional pipeline ADC, a level-calibrated adding circuit is added on a level with the error required to be calibrated. During calibration period, four special inputs are supported for the level-calibrated adding circuit with an error level required to be calibrated and a sampling capacitor, and by the aid of the foreground digital calibration computing and calibrating circuit, a calibration level capacitor mismatch error, a operational amplifier mismatch error and a sub-DAC (digital to analog converter) reference voltage error are extracted. During the normal working period, the foreground digital calibration computing and calibrating circuit works. The foreground digital calibration method is simple in structure, few additional elements are added, sequential control is easy, few registers are required, and digital circuit design is low in difficulty and short in period. By the use of the foreground digital calibration method, static characteristics of the pipeline ADC is calibrated excellently, and a certain calibration effect of dynamic characteristics of the pipeline ADC is achieved.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

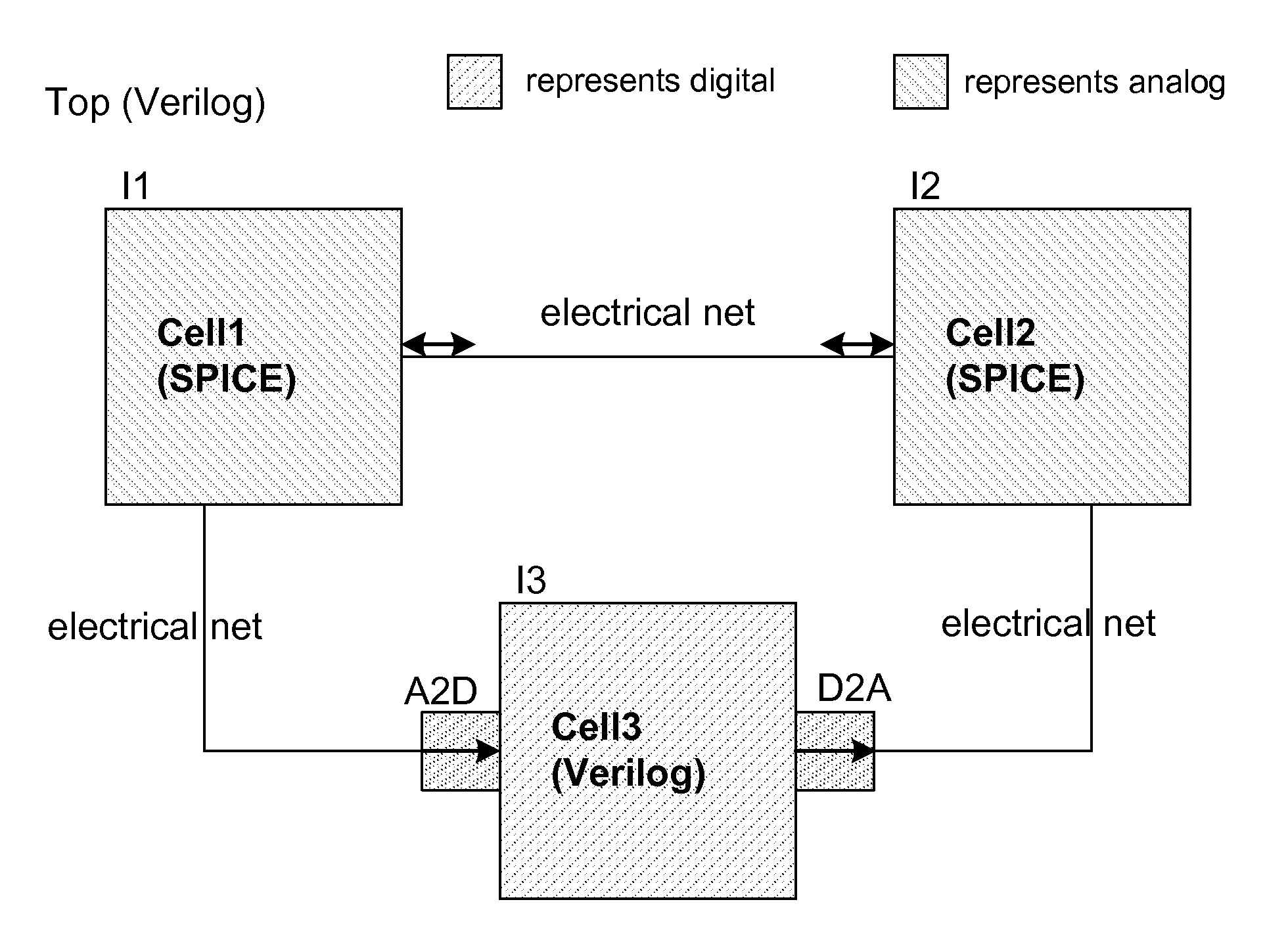

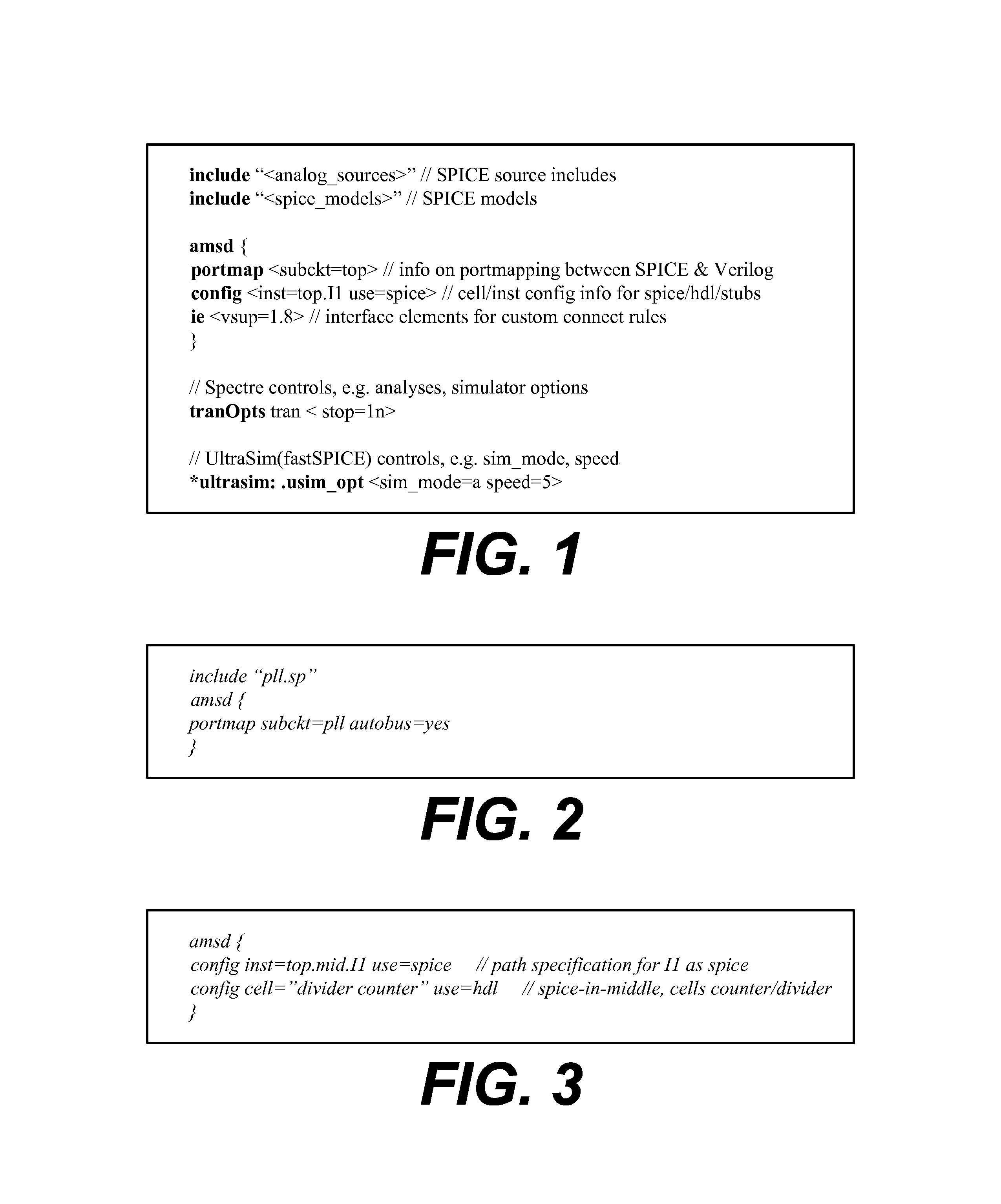

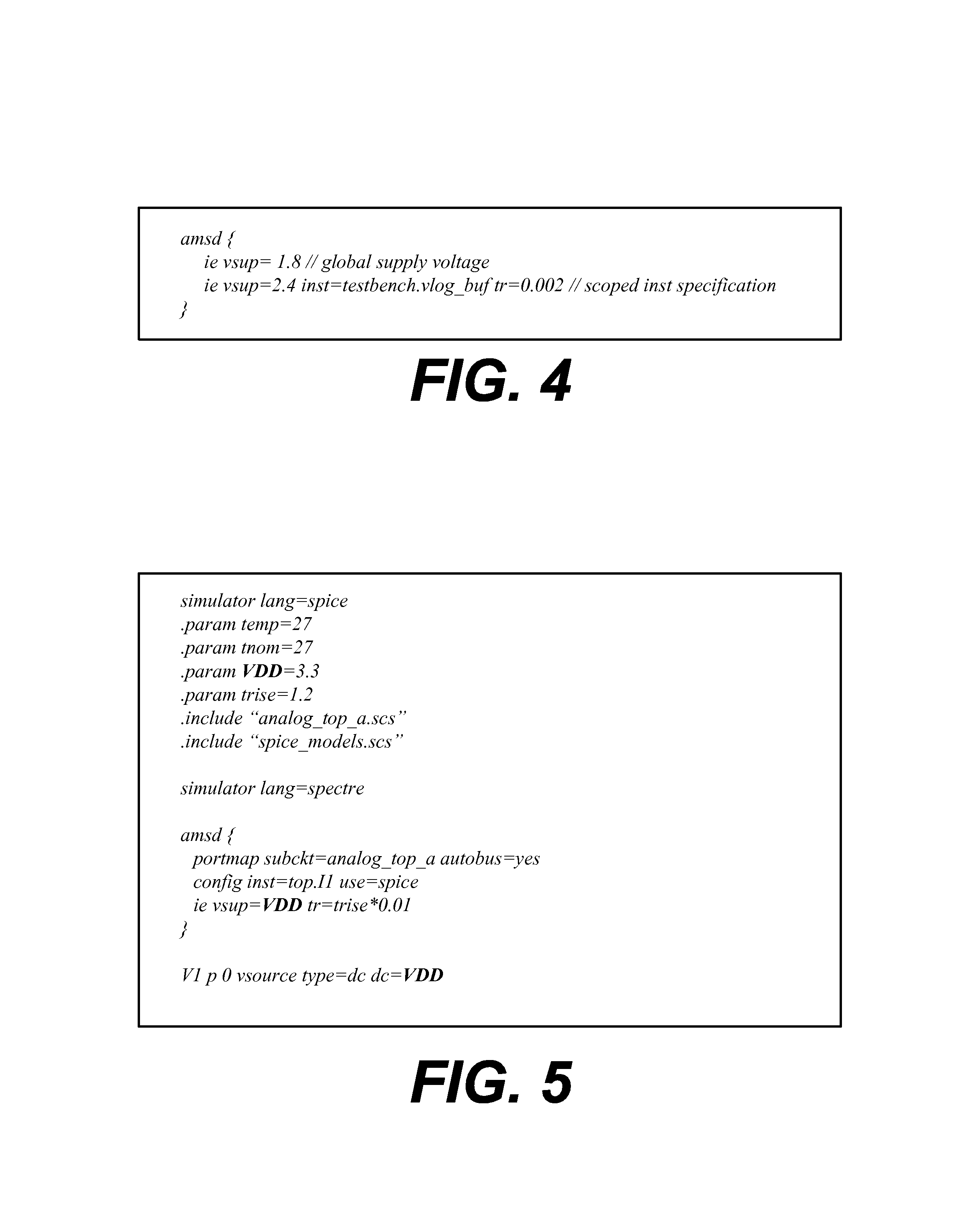

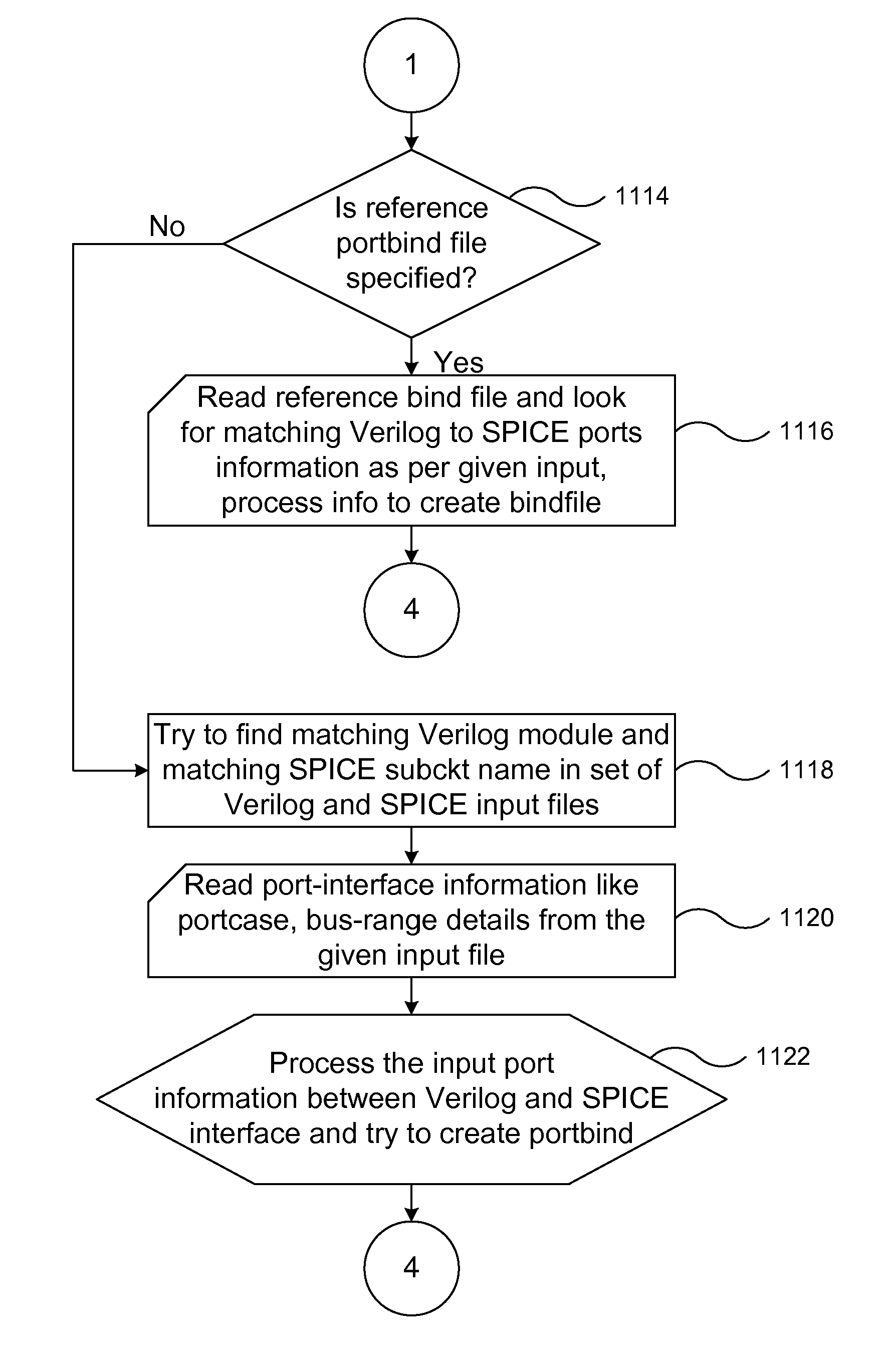

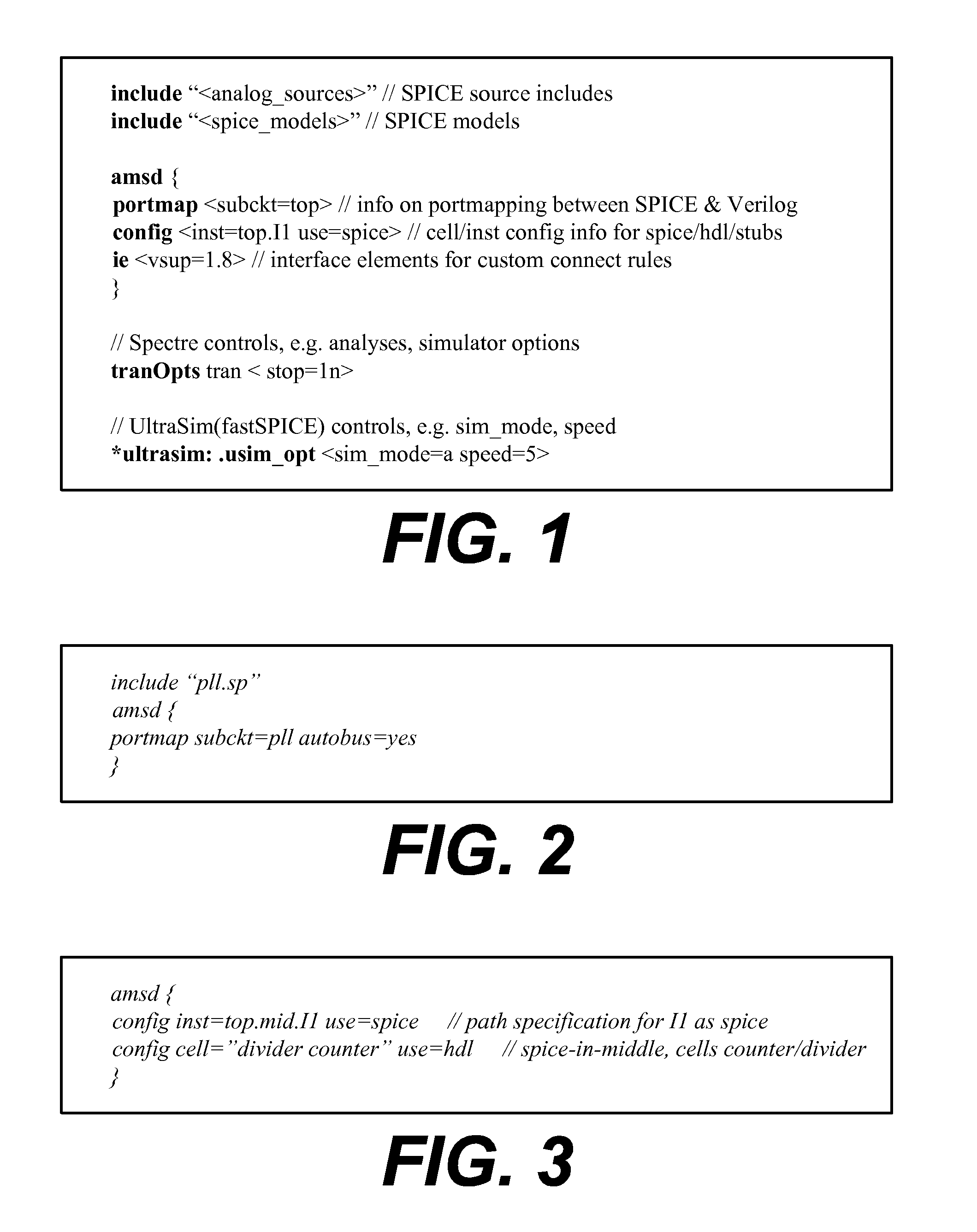

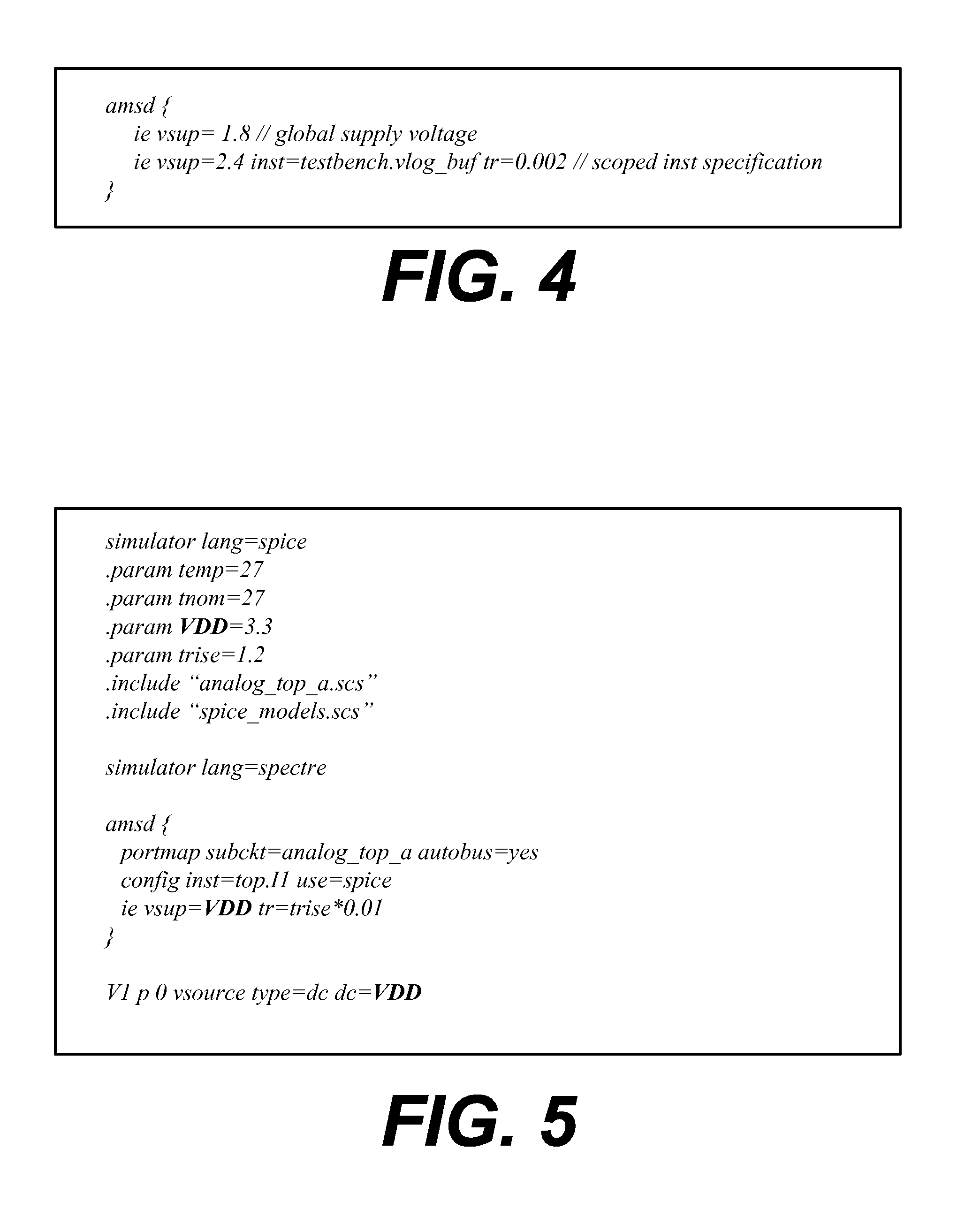

Method and apparatus for AMS simulation of integrated circuit design

ActiveUS8201137B1Ease and abilityEasy to createDetecting faulty computer hardwareAnalogue computers for electric apparatusAnalog circuit designUser input

A method to create an integrated circuit that includes digital and analog components comprising: displaying on a computer system display, user input to the computer system that specifies parameter information to determine a binding between an analog circuit design component and a digital circuit design component; saving the user specified parameter information within a file that also specifies at least a portion of the analog circuit design; associating the analog circuit design component a first design block of an integrated circuit that also includes a second digital design block coupled to the first design block; using parameter information to determine a binding between the first analog circuit design component and the first digital circuit design component; saving the determined binding in computer readable storage media.

Owner:CADENCE DESIGN SYST INC

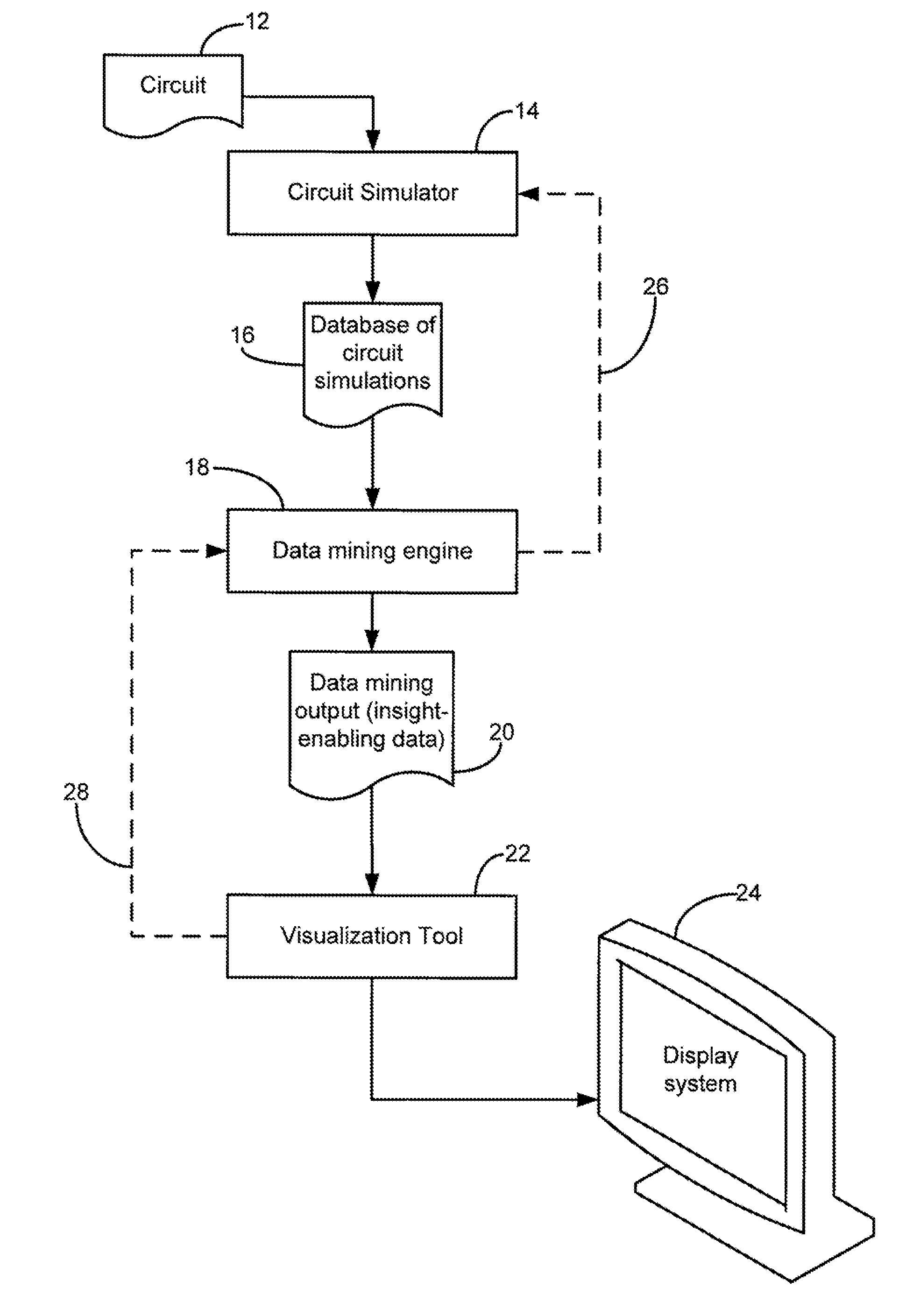

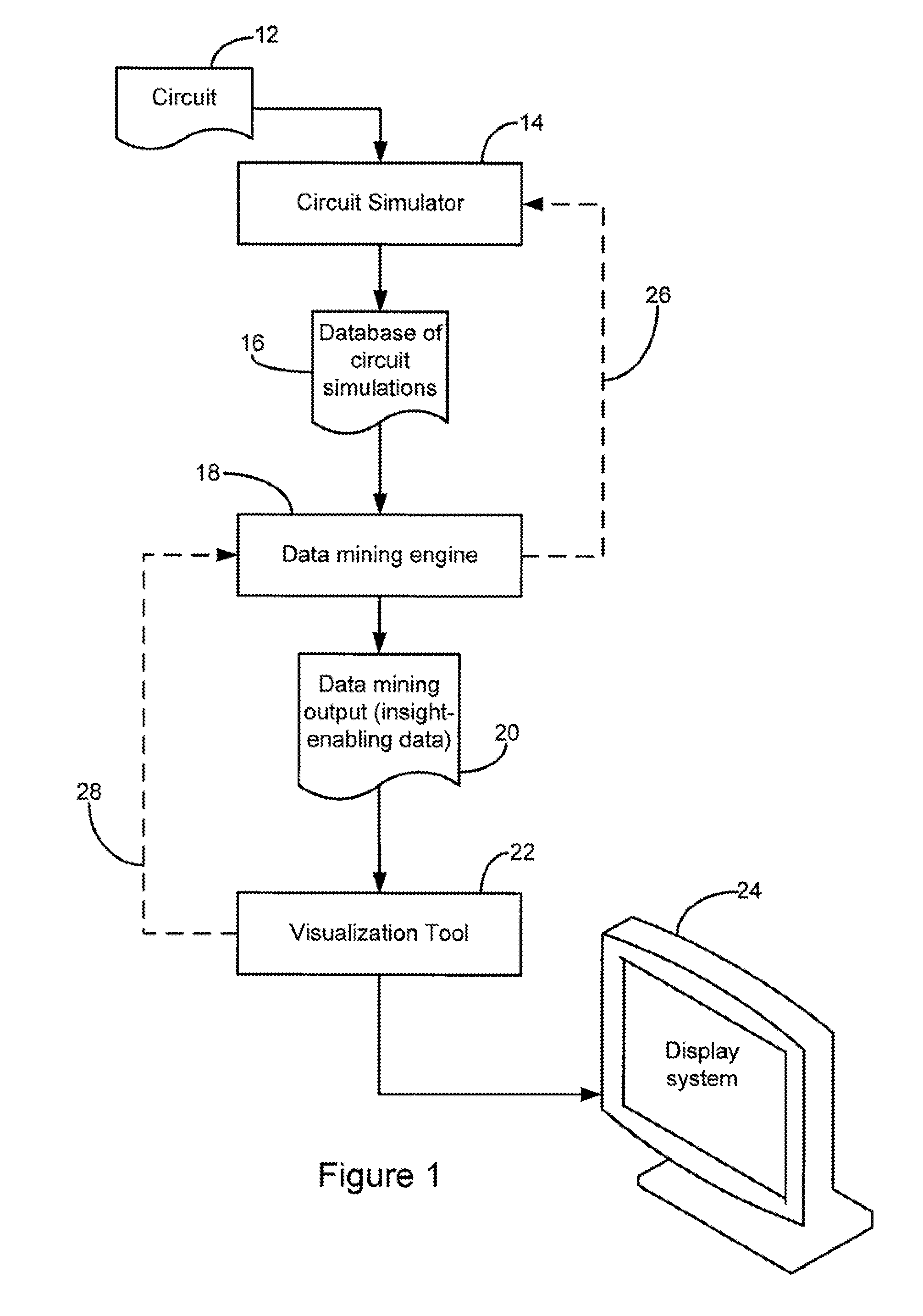

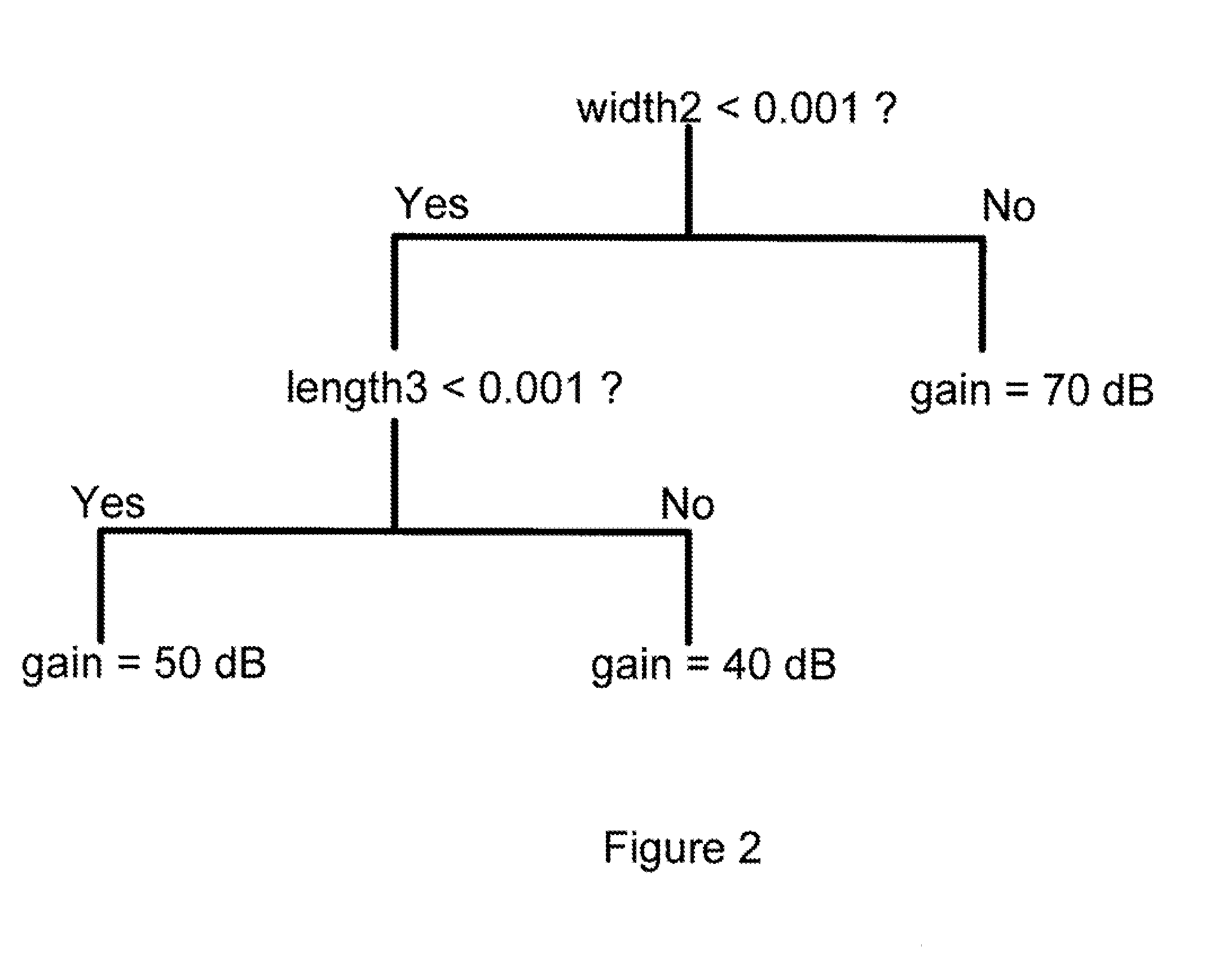

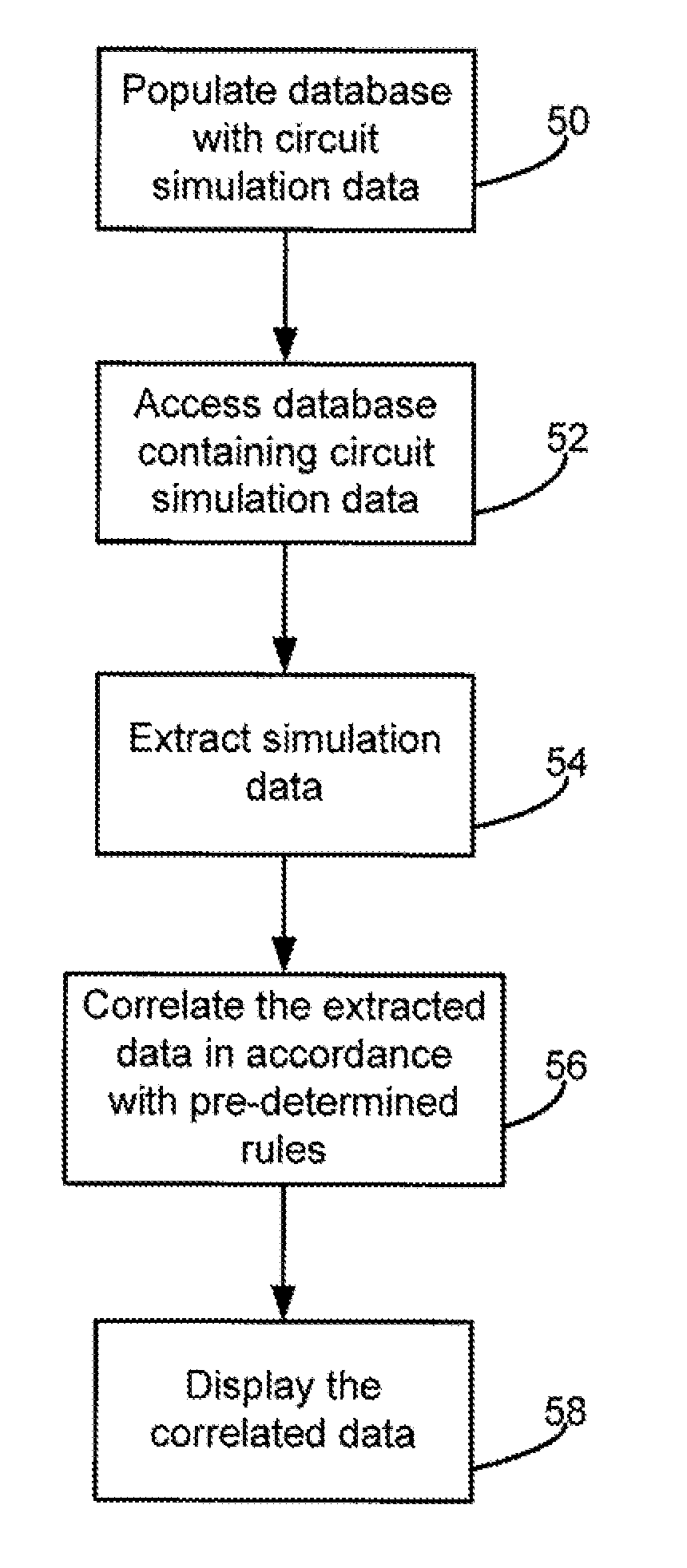

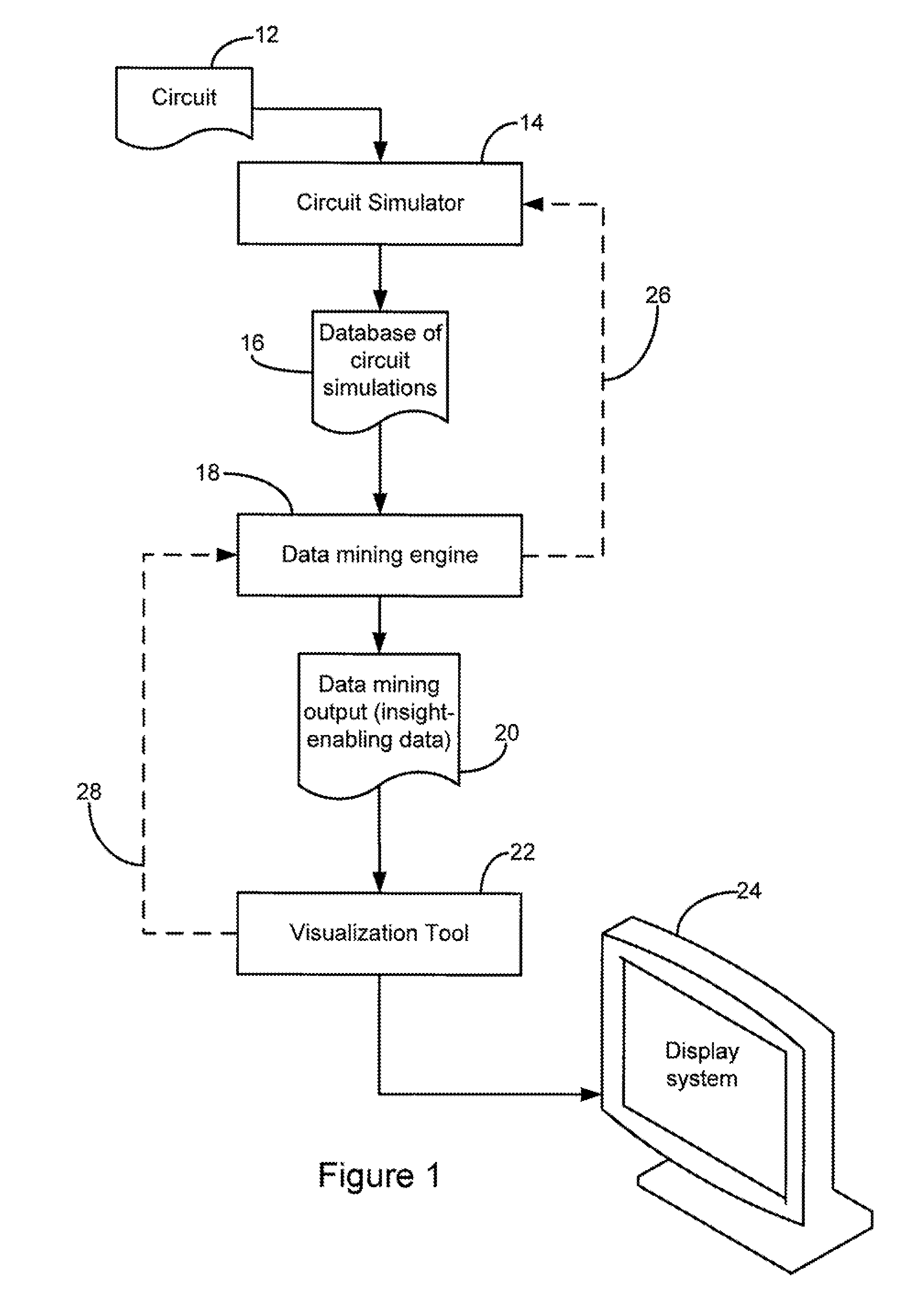

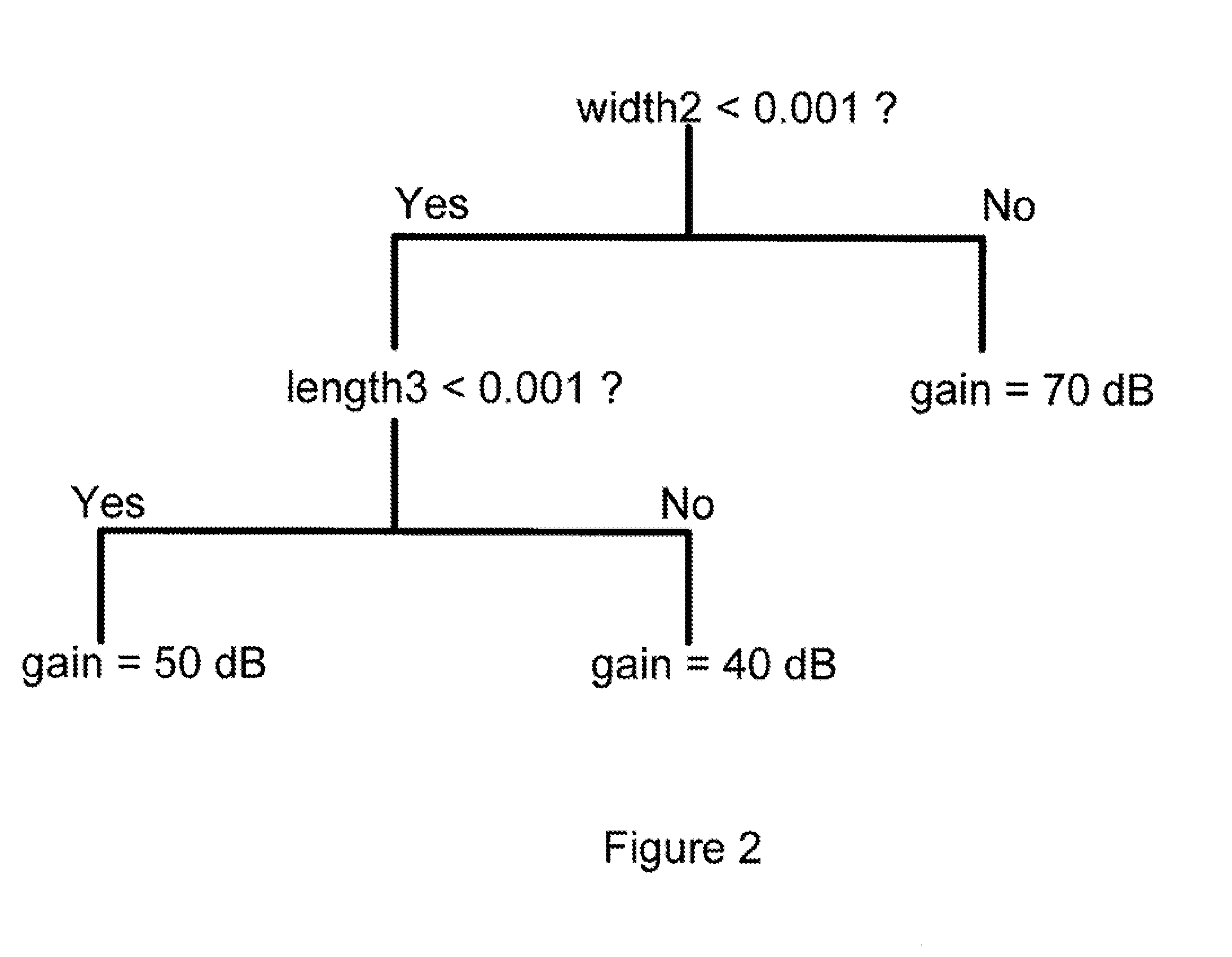

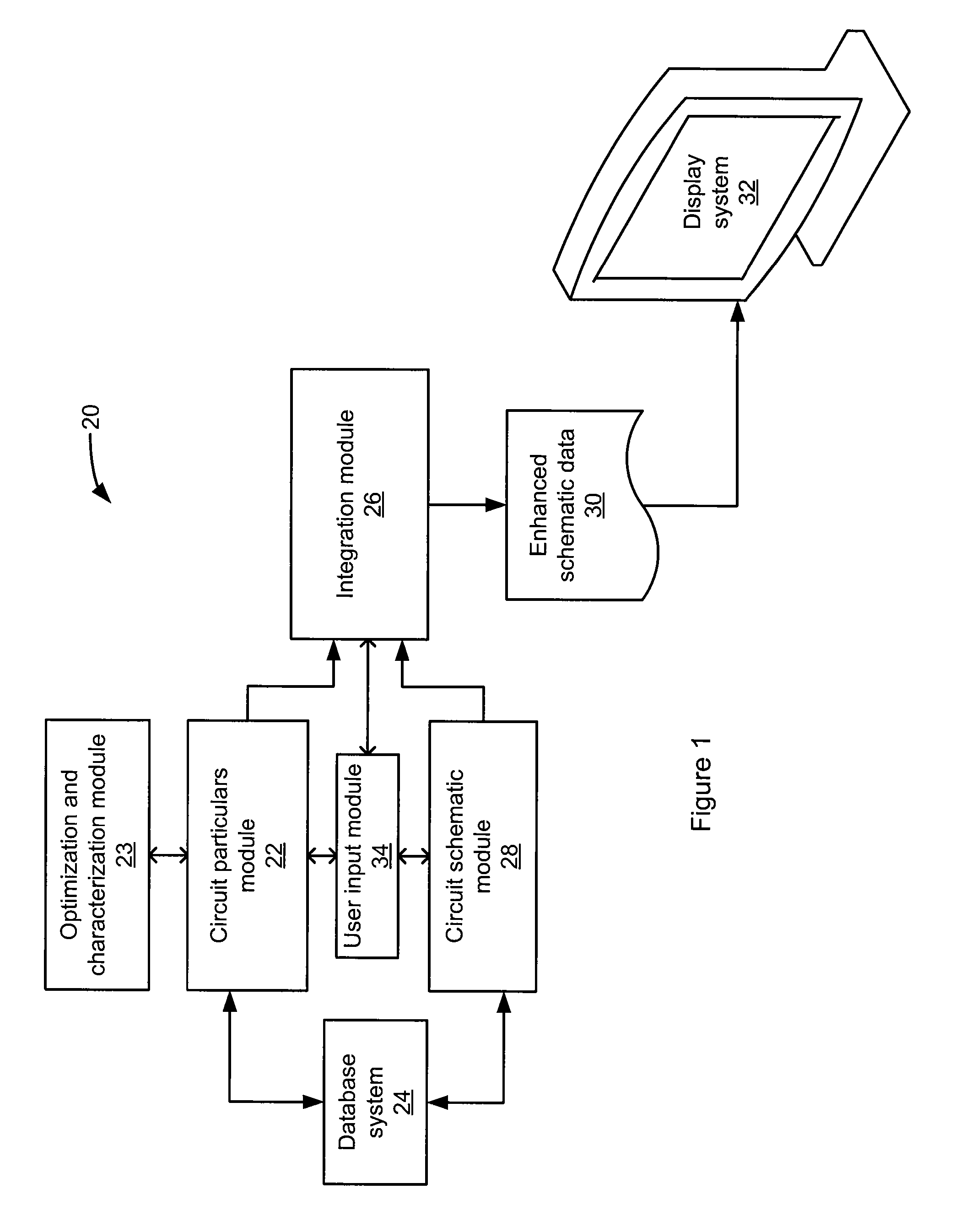

Data-mining-based knowledge extraction and visualization of analog/ mixed-signal/ custom digital circuit design flow

ActiveUS20080022232A1Detecting faulty computer hardwareComputation using non-denominational number representationGraphicsKnowledge extraction

A system and method of generating a set of circuit simulation data, applying data mining to for knowledge extraction from the data, and graphically presenting the extracted knowledge in a format that is easy to digest to a designer.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

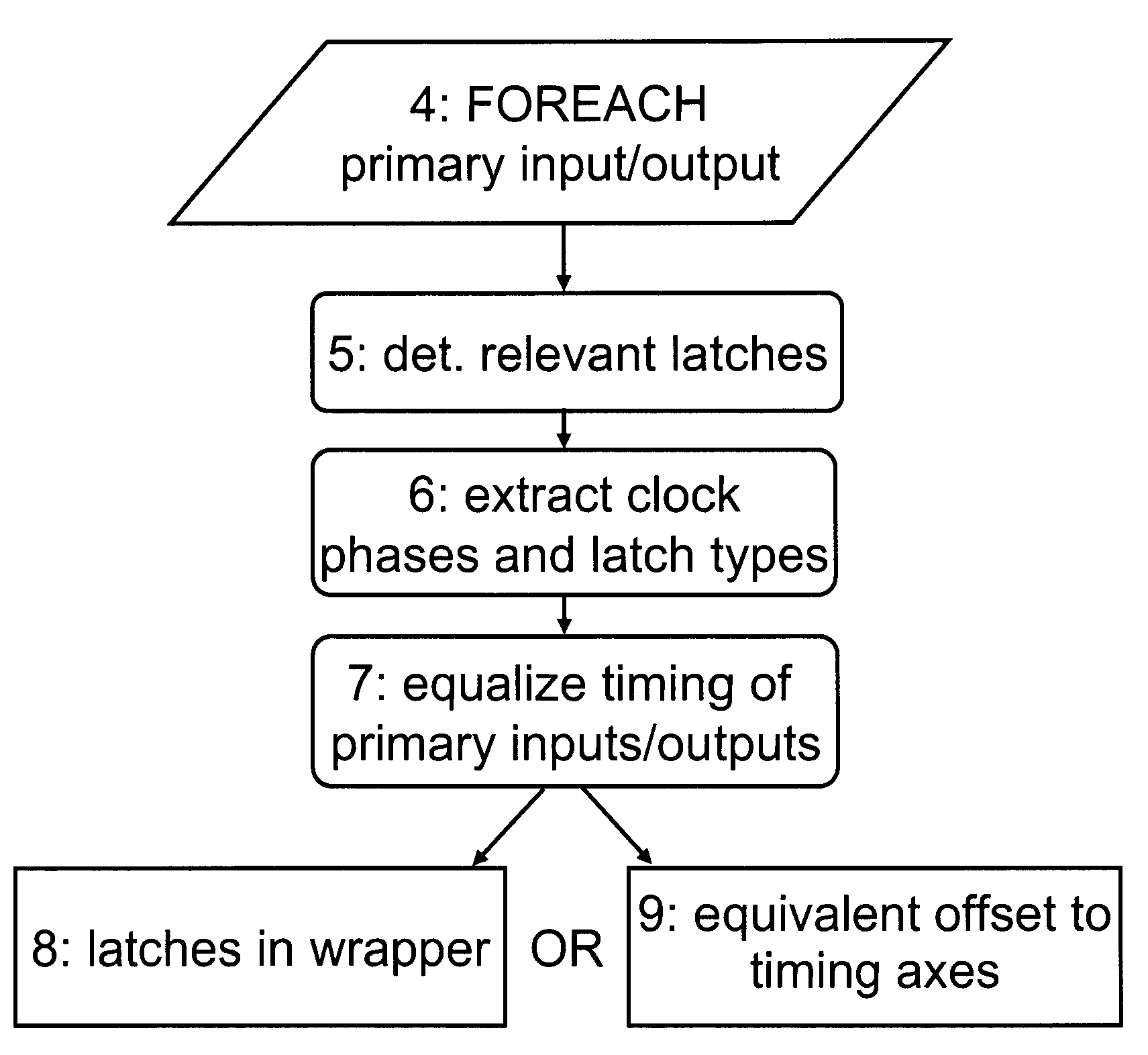

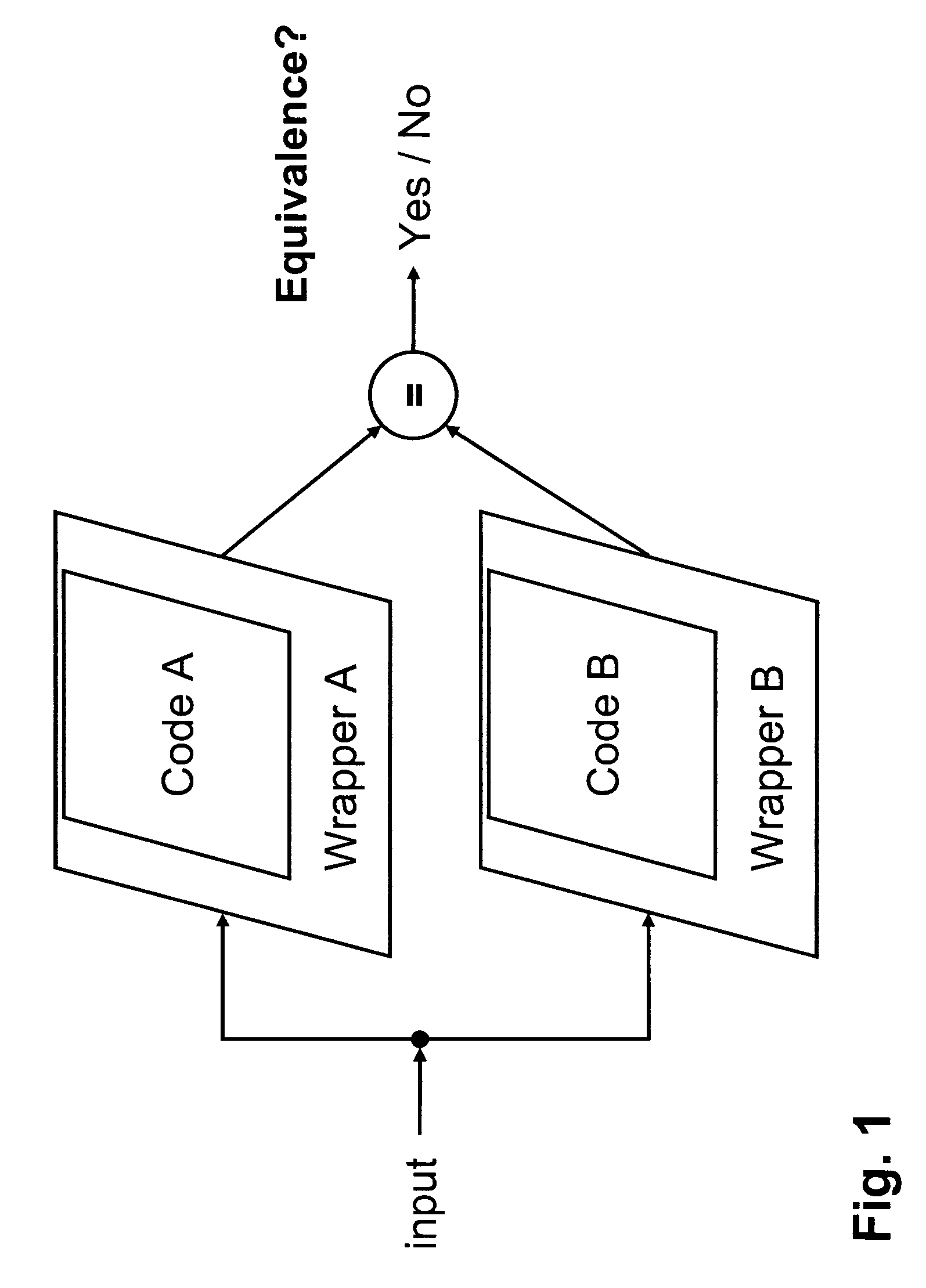

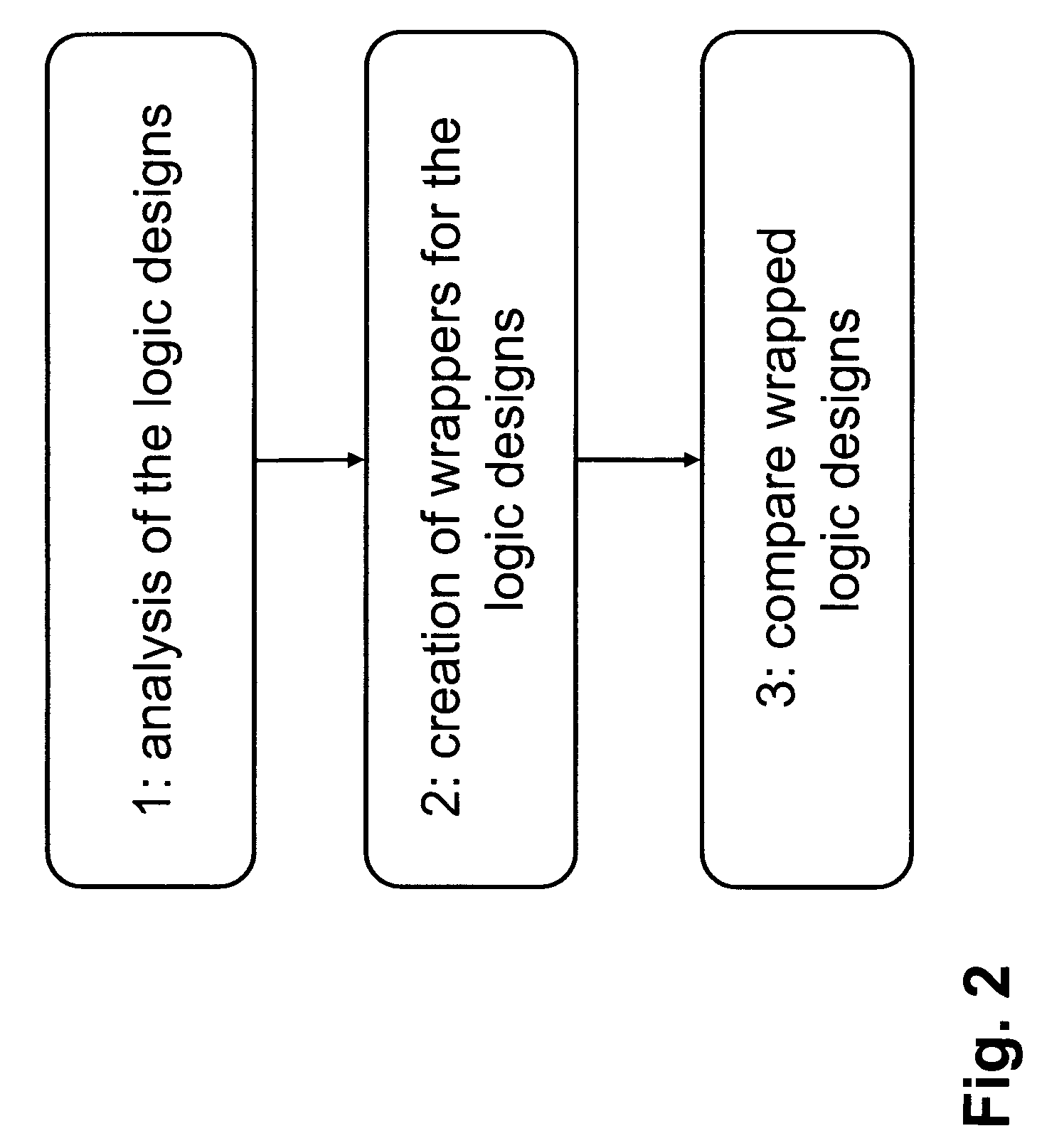

Method and system for verifying the equivalence of digital circuits

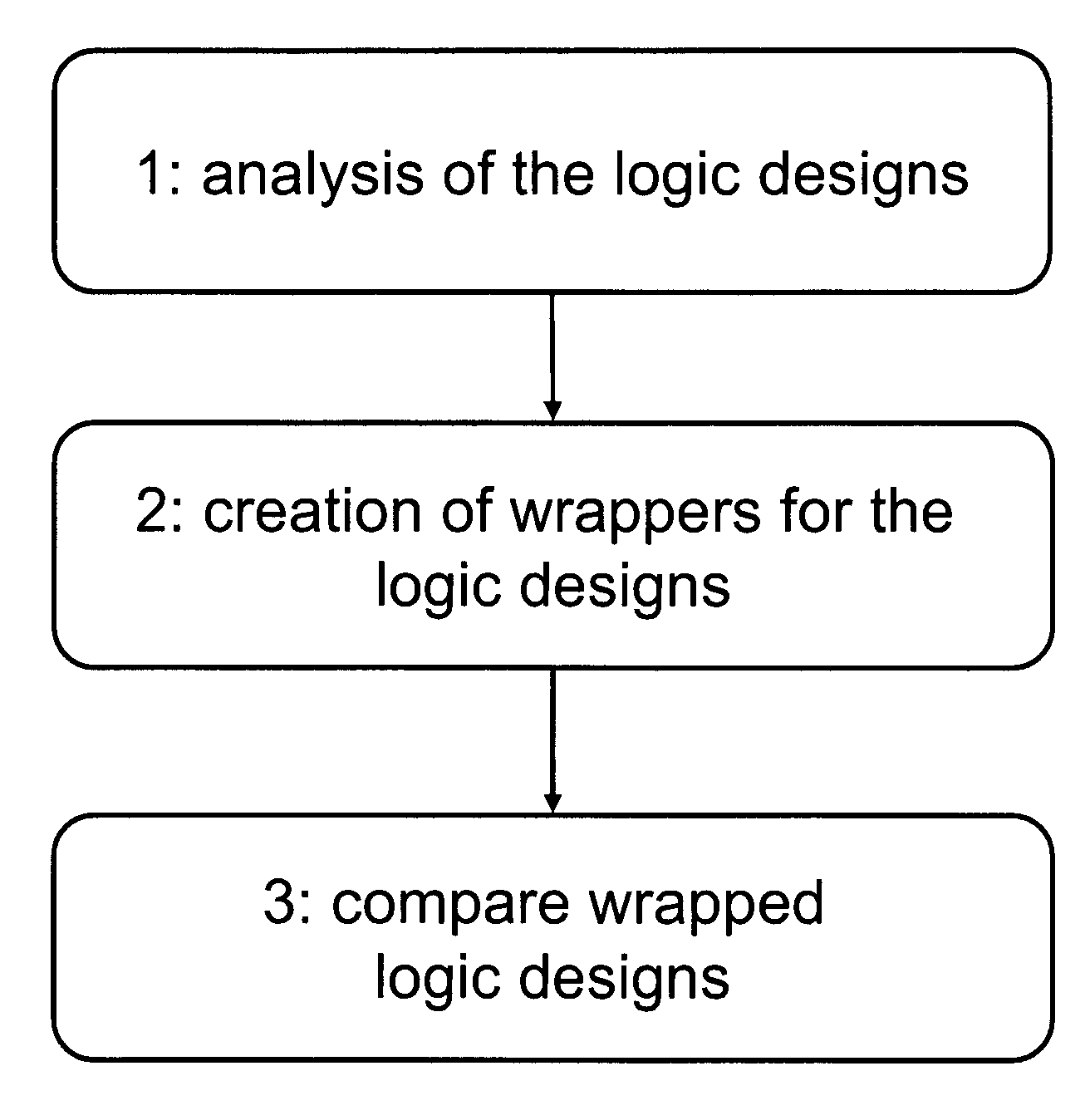

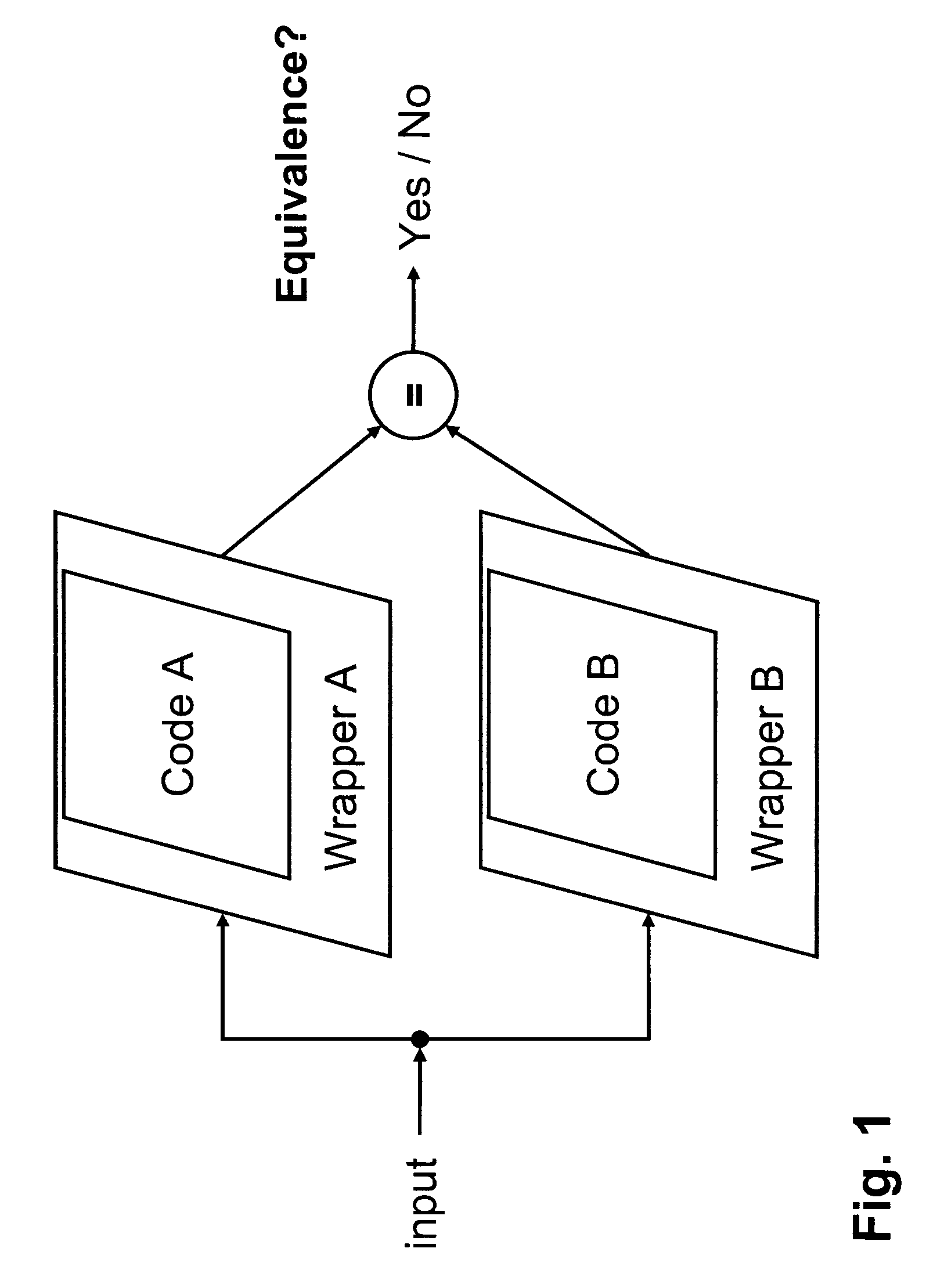

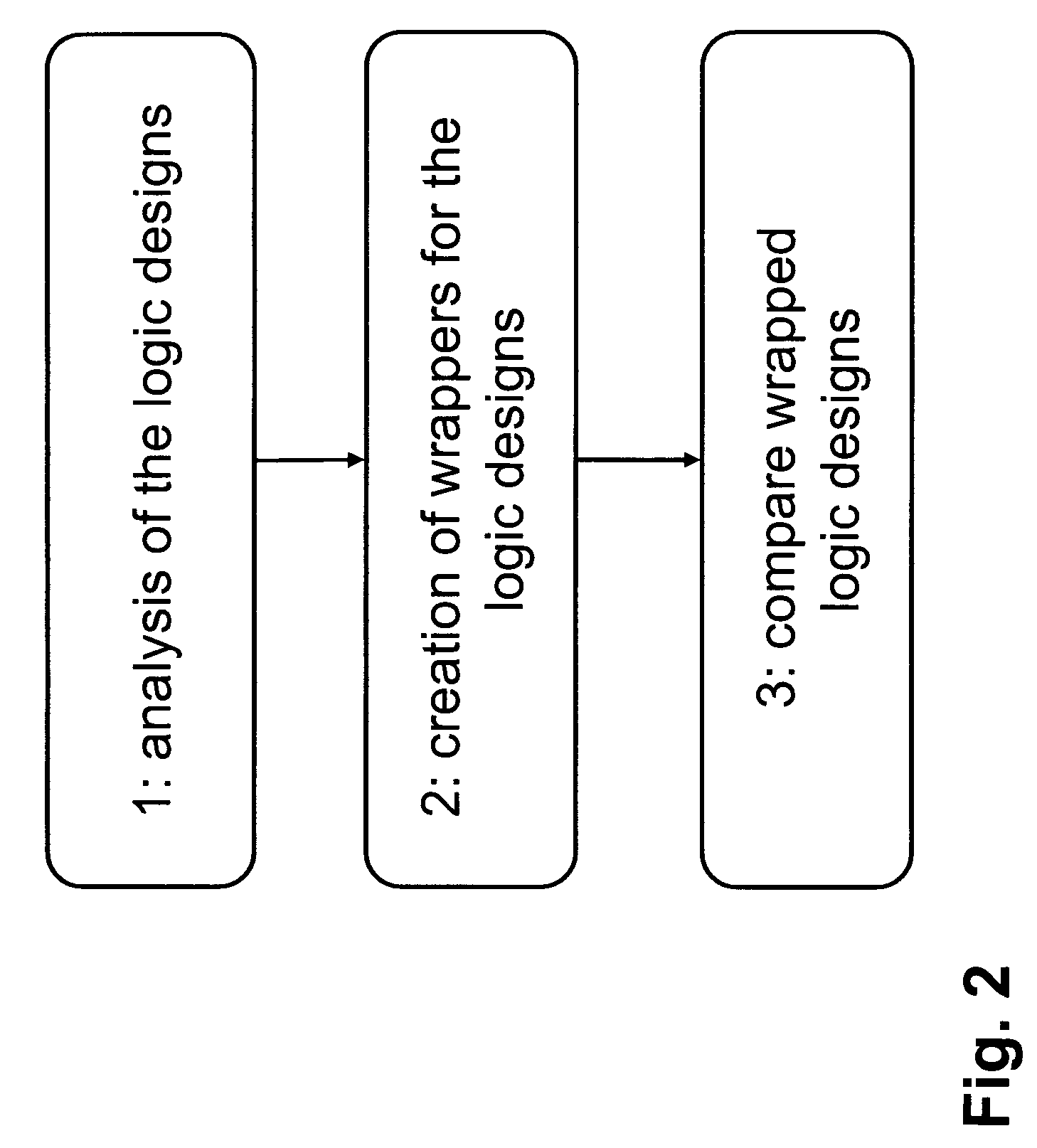

InactiveUS20070226664A1Automatic detectionComputer aided designSoftware simulation/interpretation/emulationControl signalDesign methods

The automatic verification of designs of digital circuits for their equivalence, wherein logic designs implemented in different hardware description languages (HDLs) and different design methodologies are compared. The designs (Code A, Code B) are modified by adding special wrappers (Wrapper A, Wrapper B), and used to equalize the timing of pairs of selected input signals and selected output signals of the logic designs. The wrappers drive certain signals of the designs that are not relevant for actual comparison, such signals including clock signals, clock control signals, scan-path signals, scan-path control signals, and reset signals. In a preferred embodiment, HDL descriptions of logic designs are analyzed. Based on this analysis, the wrappers are implemented as changes to the HDL descriptions. In another embodiment, RTL and / or gate-level netlists are analyzed and modified.

Owner:GLOBALFOUNDRIES INC

Method and apparatus for accelerating the verification of application specific integrated circuit designs

ActiveUS20050081170A1Analogue computers for electric apparatusComputer aided designDetector circuitsField-programmable gate array

A method and system for accelerating software simulator operation with the aid of reprogrammable hardware such as Field Programmable Gate Array devices (FPGA). The method and system aid in emulation and prototyping of Application Specific Integrated Circuits (ASIC) digital circuit designs by means of reprogrammable devices. The system includes a design verification manager and software program that includes subroutines of finding clock sources, finding synchronous primitives that are receiving clock signals from the clock sources, and a subroutine for inserting edge detector circuits between such clock sources and synchronous primitives. This new method allows eliminating of clock timing issues by applying basic design clocks to the clock enable instead of clock trigger inputs and generating and applying to clock trigger inputs a new clock that is automatically delayed in respect to all other clocks in the design. This system solves the major obstacle for automatic retargeting of ASIC designs into reprogrammable devices that have different timings of the clocking chains in ASICs and FPGAs that result in triggering of associated flip-flops and latches at different times.

Owner:HYDUKE STANLEY M +1

Data-mining-based knowledge extraction and visualization of analog/mixed-signal/custom digital circuit design flow

ActiveUS7707533B2Detecting faulty computer hardwareComputation using non-denominational number representationGraphicsKnowledge extraction

A system and method of generating a set of circuit simulation data, applying data mining to for knowledge extraction from the data, and graphically presenting the extracted knowledge in a format that is easy to digest to a designer.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

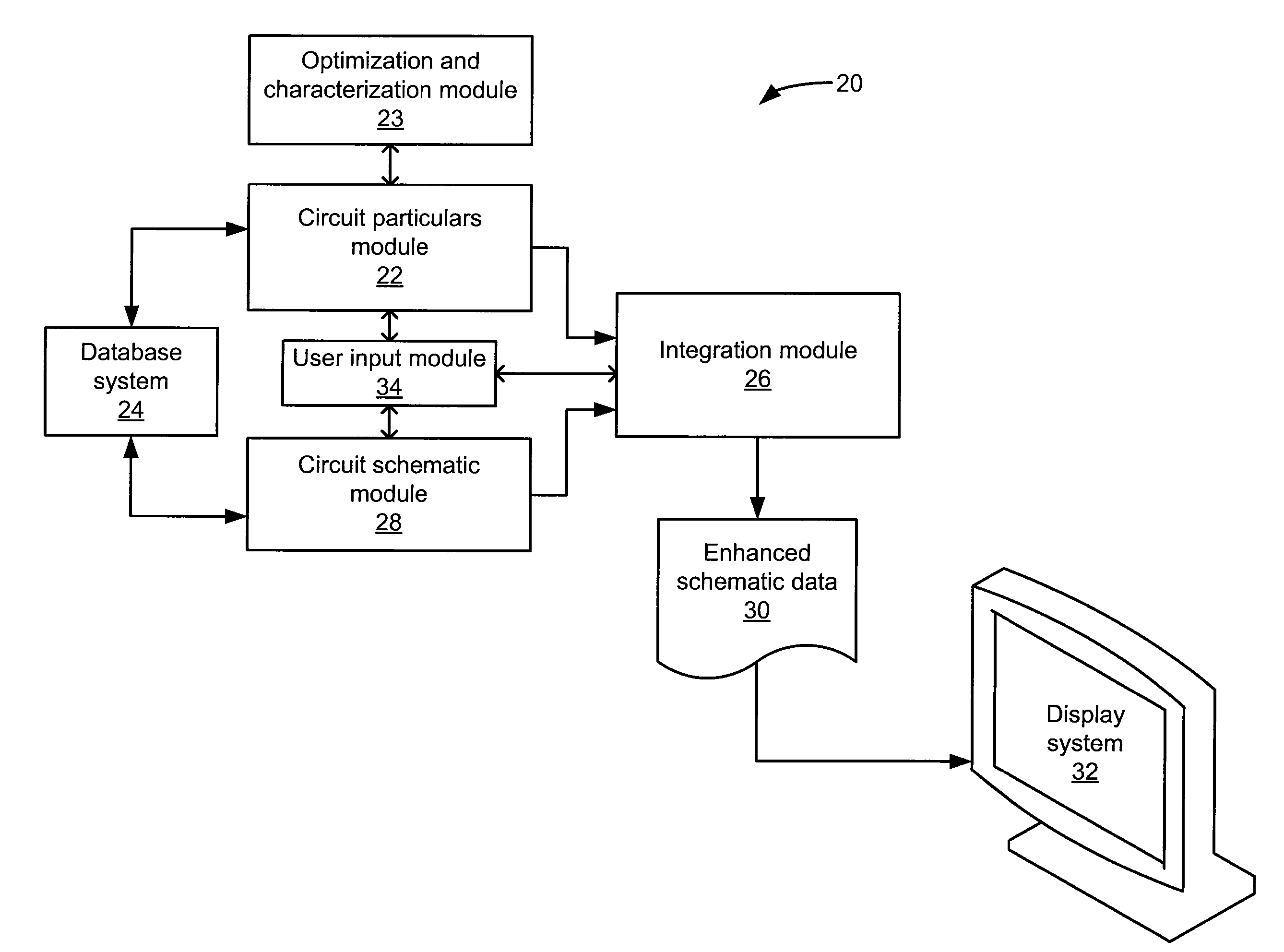

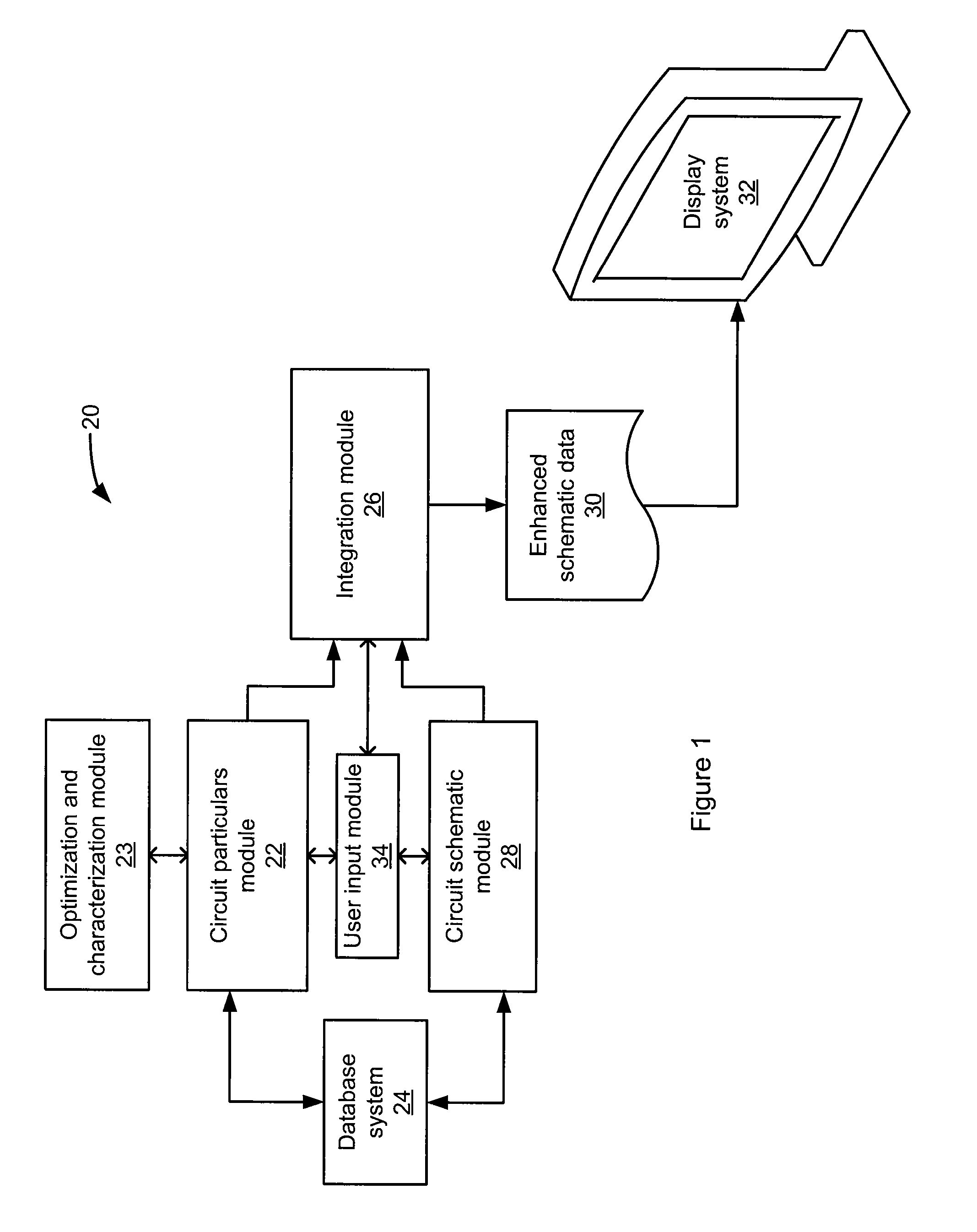

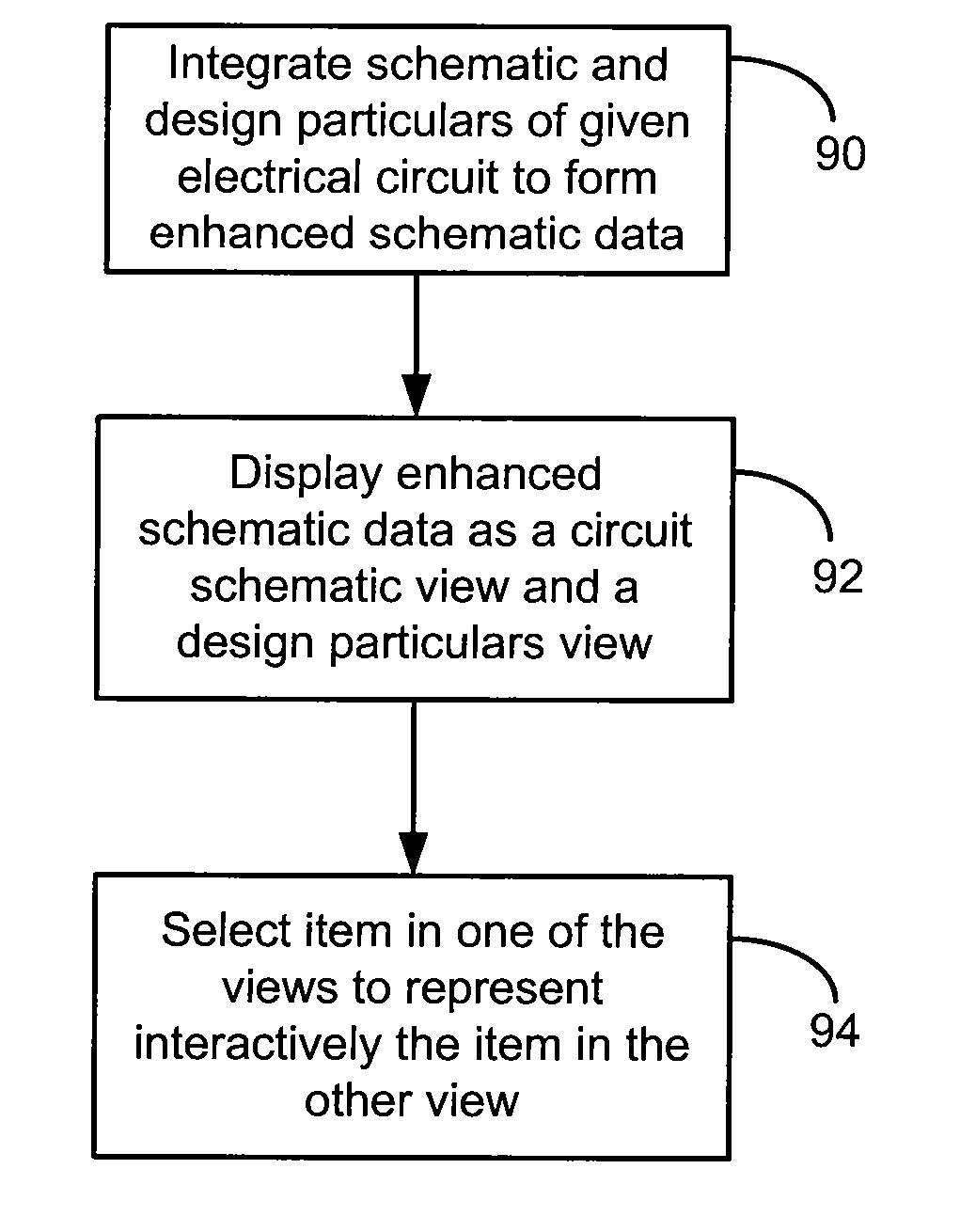

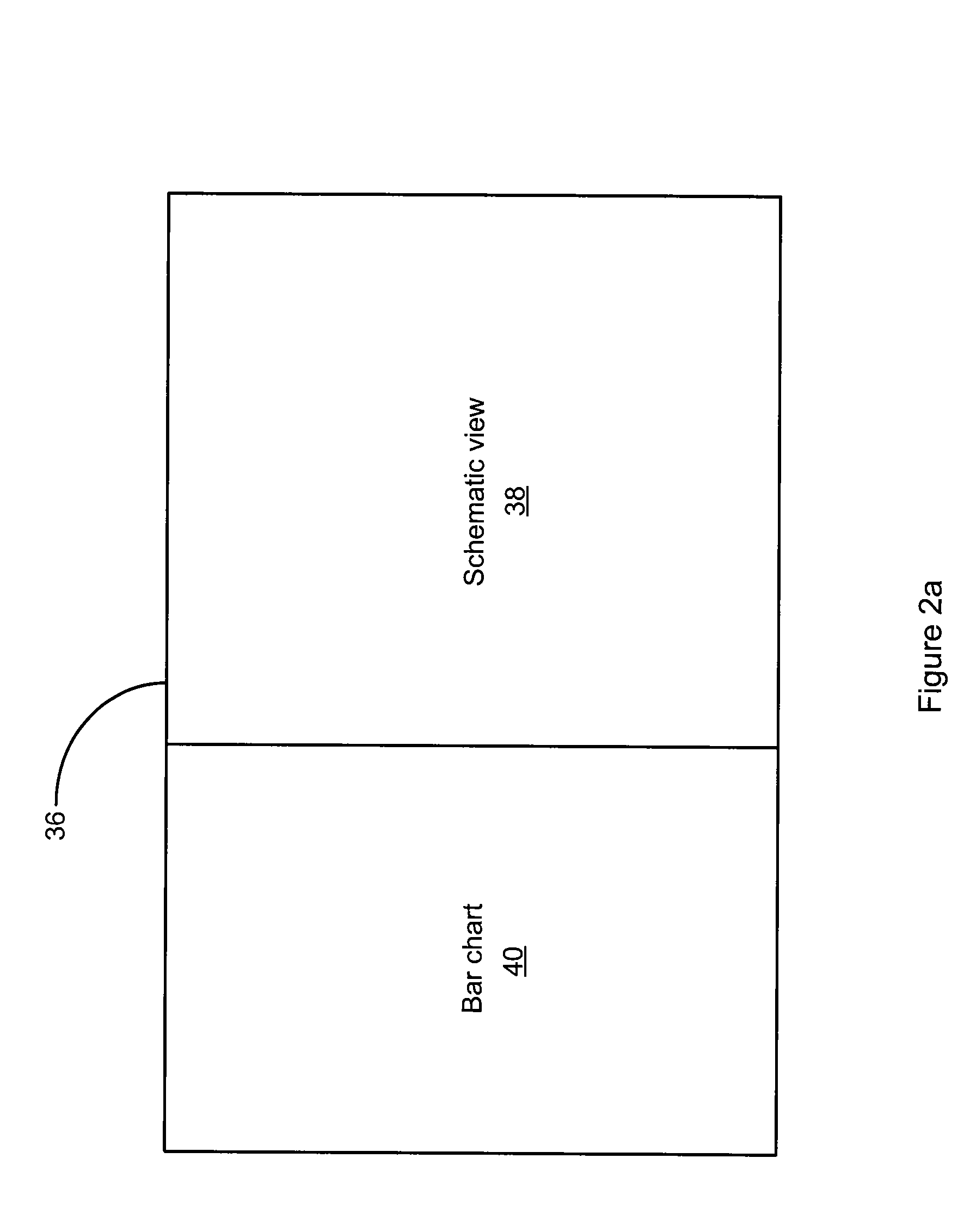

Interactive schematic for use in analog, mixed-signal, and custom digital circuit design

ActiveUS20080022251A1Detecting faulty computer hardwareComputer programmed simultaneously with data introductionComputer scienceOptimization problem

For application to analog, mixed-signal, and custom digital circuits, a system and method to improve the flow of setting up a set of simulations, a characterization, or optimization problem via an interactive circuit schematic. A system and method to visualize circuit simulation data in which at least one of the views is an enhanced, interactive schematic view.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

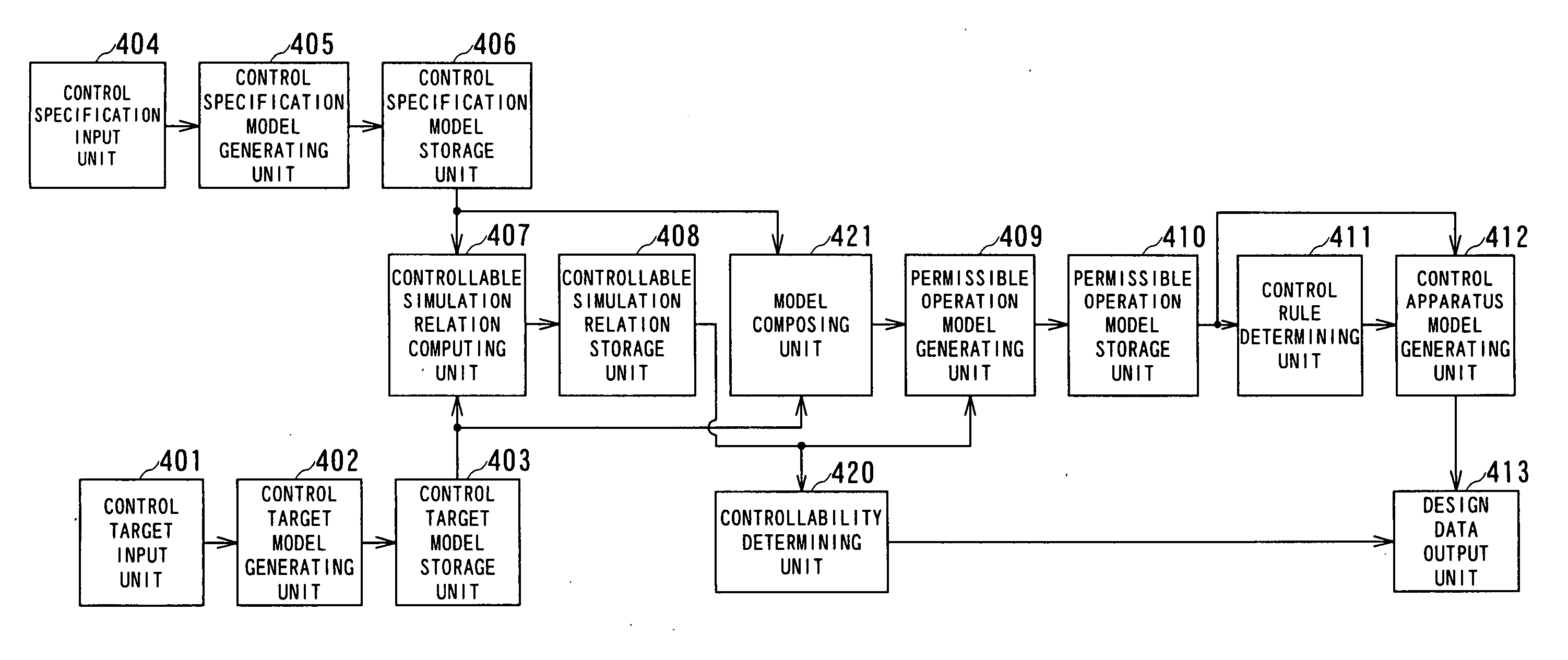

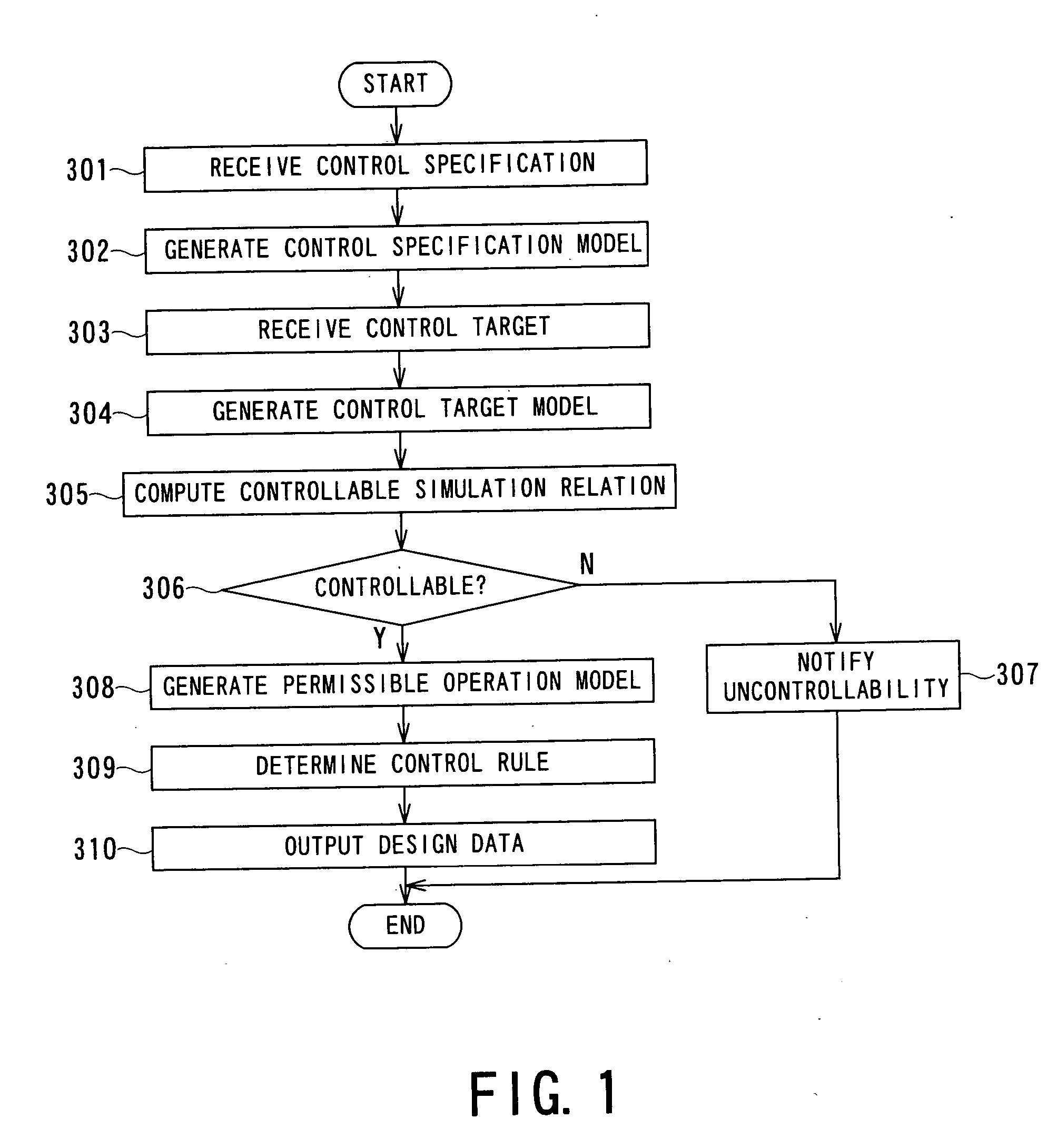

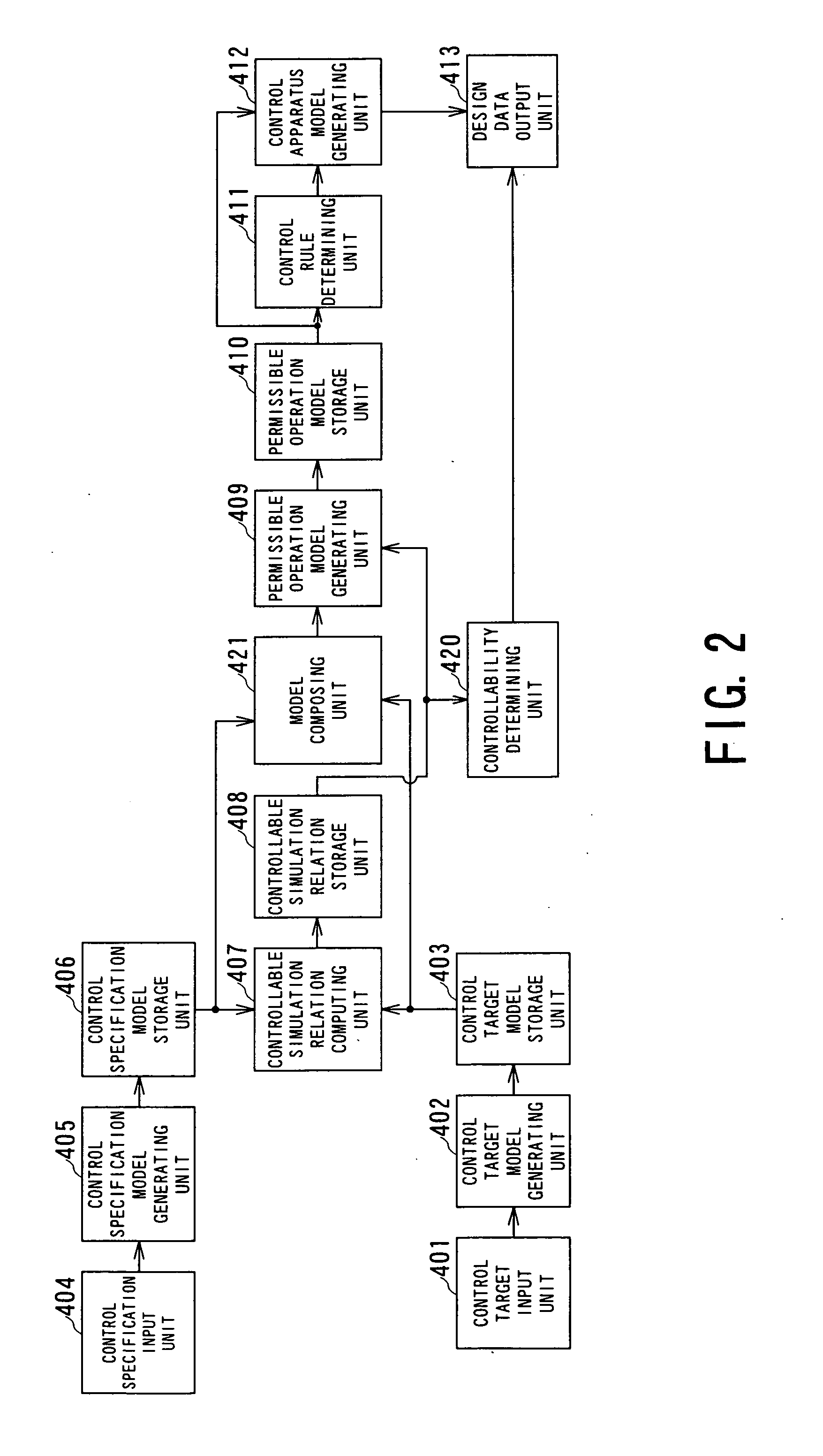

Automatic design apparatus, automatic design method, and automatic design program of digital circuit

InactiveUS20070179639A1Reduce problem sizeLink editingSimulator controlCanonical modelTheoretical computer science

An automatic digital-circuit design apparatus receives a control target model written in a design description language, generates a control target model represented by a finite state machine model, stores the generated control target model, receives a control specification model written in a design description language, generates a control specification model represented by a finite state machine model, stores the generated control specification model, generates a control apparatus synthesis model by composing the generated control target model and the generated control specification model, computes controllable simulation relation, stores the computed controllable simulation relation, determines whether the control apparatus synthesis model is a model capable of providing the control, generates a permissible operation model, stores the generated permissible operation model, determines a control rule, generates a control apparatus model represented by a finite state machine, and converts the control apparatus model to a control apparatus model written in a design description language.

Owner:KK TOSHIBA

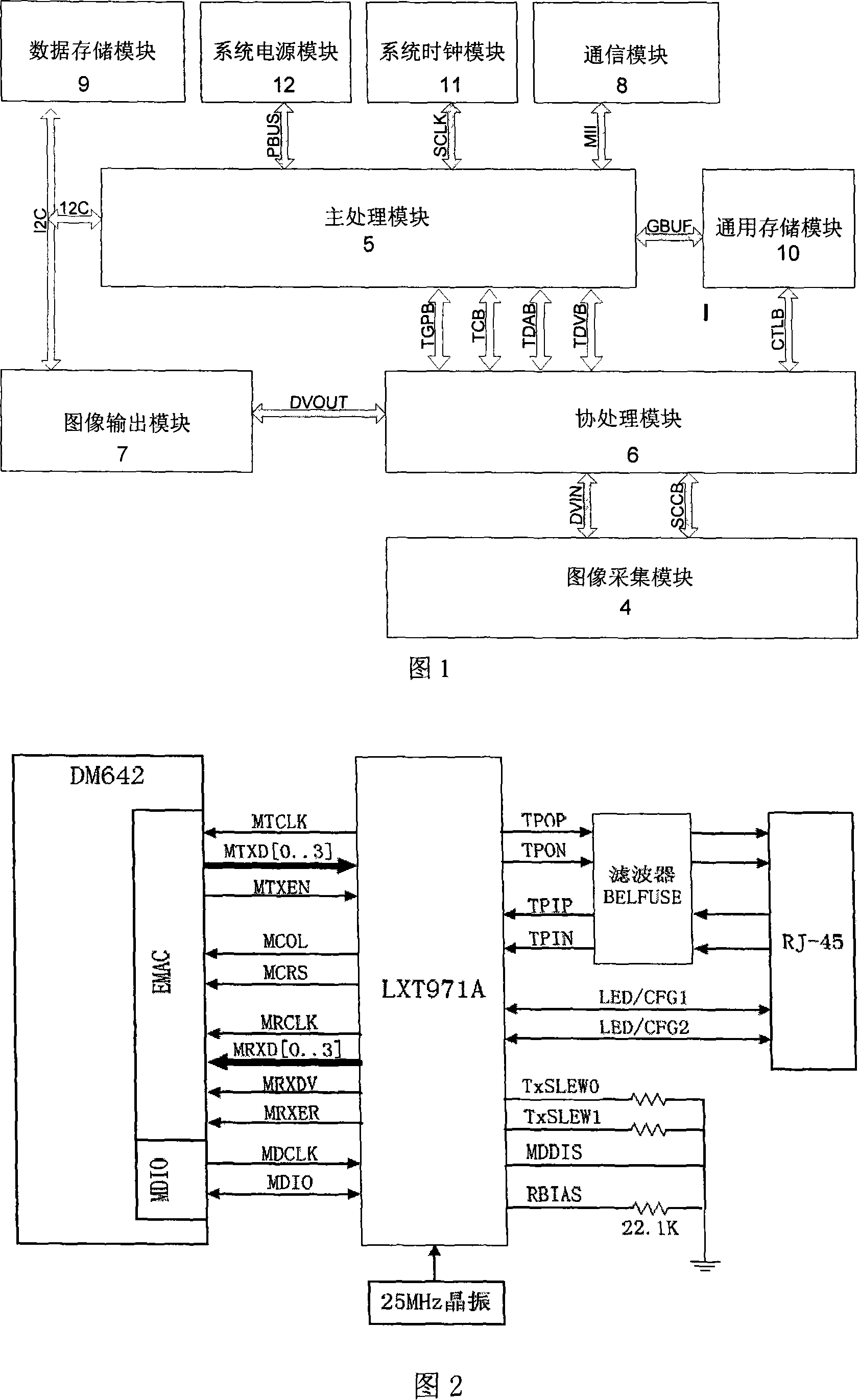

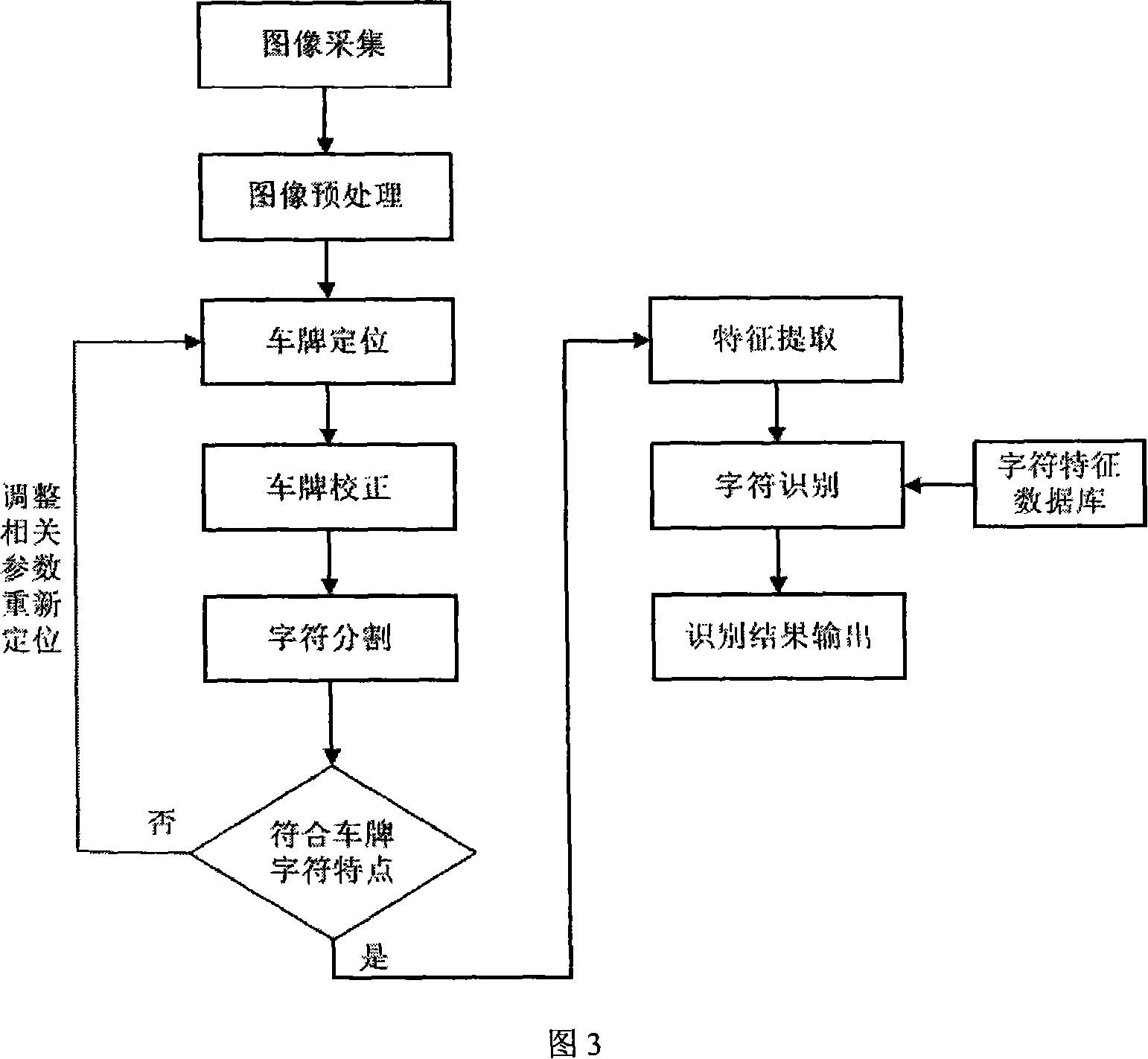

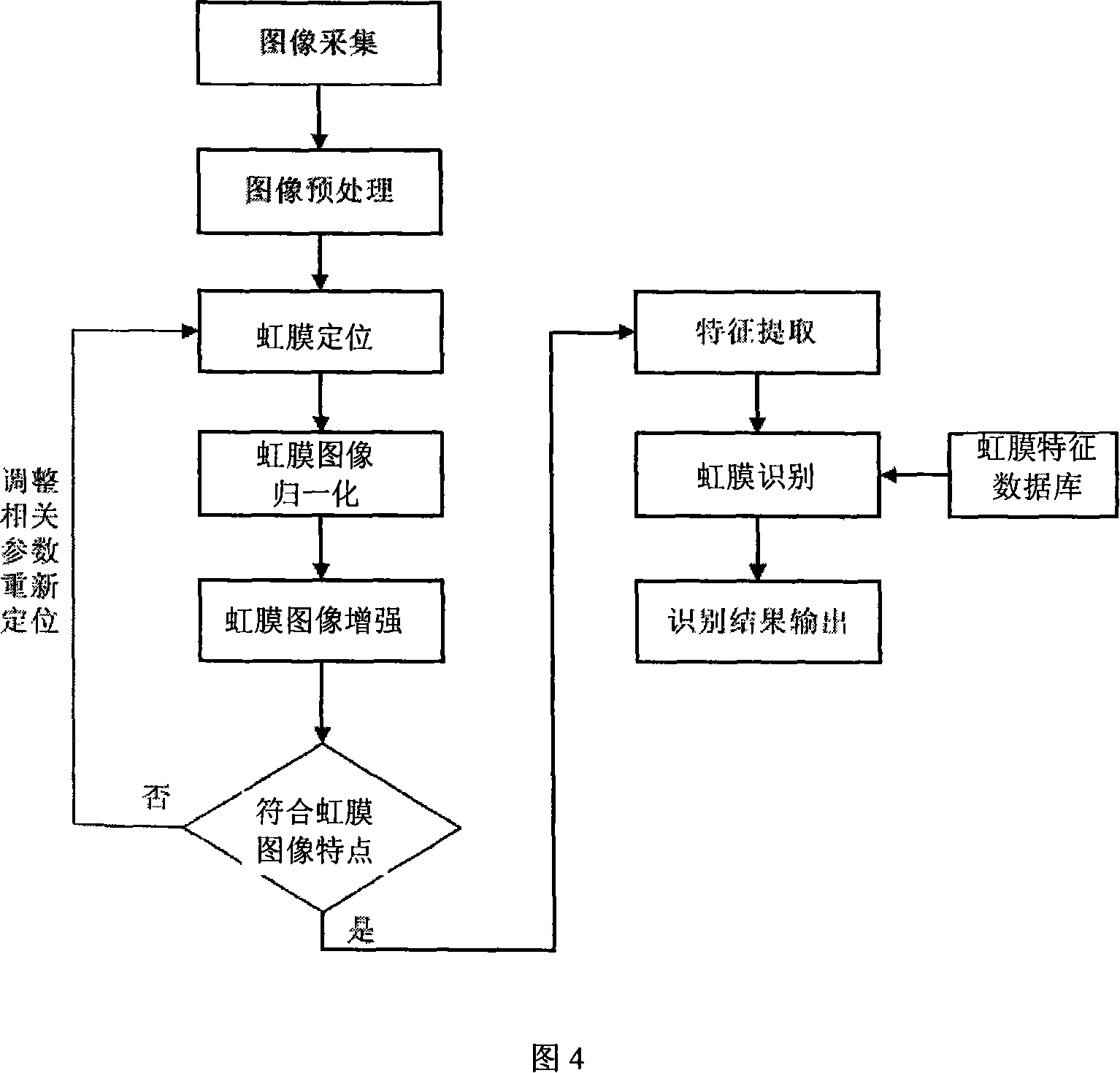

Built-in intelligent network video camera with recognition function

InactiveCN101127830ARealize full digital image acquisitionRealize the network transmission functionTelevision system detailsCharacter and pattern recognitionSoftware designNetwork management

The utility model relates to an embedded type intelligent network video camera with recognition functions, which adopts the most advanced design pattern of embedded digital circuits and integrates image acquisition, compression, storage, specific content identification, transmission, and the control technique (if necessary) into a whole. Hardware design and software design are combined to achieve flexible application, presettable functions, network management, network configuration, and other purposes. The utility model adopts CMOS image acquisition units to conduct the original image acquisition with a large DSP as the master core, the programmability of which improves the system tailoring property and reduces the system development costs. At the same time, the utility model can materialize feature extraction, target identification with the powerful DSP computing capacity to realize the intelligentization of video cameras. The video cameras are also provided with complete video output interfaces to directly furnish the image outputs of field installation and surveillance interfaces; the network interface supports the TCP / IP protocol and provides the signal transmission channel, and can conduct data upload through the remote computer control interface. The utility model also has the order instruction and set-up functions to achieve the purpose of remote control, thus laying a sound foundation for future establishment of regional security monitoring systems.

Owner:SHANGHAI UNIV +1

Interactive schematic for use in analog, mixed-signal, and custom digital circuit design

ActiveUS7761834B2Detecting faulty computer hardwareComputer programmed simultaneously with data introductionSoftware engineeringSchematic maps

For application to analog, mixed-signal, and custom digital circuits, a system and method to improve the flow of setting up a set of simulations, a characterization, or optimization problem via an interactive circuit schematic. A system and method to visualize circuit simulation data in which at least one of the views is an enhanced, interactive schematic view.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

Method and apparatus for ams simulation of integrated circuit design

ActiveUS20120198405A1Ease and abilityEasy to readComputer aided designSoftware simulation/interpretation/emulationAnalog circuit designUser input

Owner:CADENCE DESIGN SYST INC

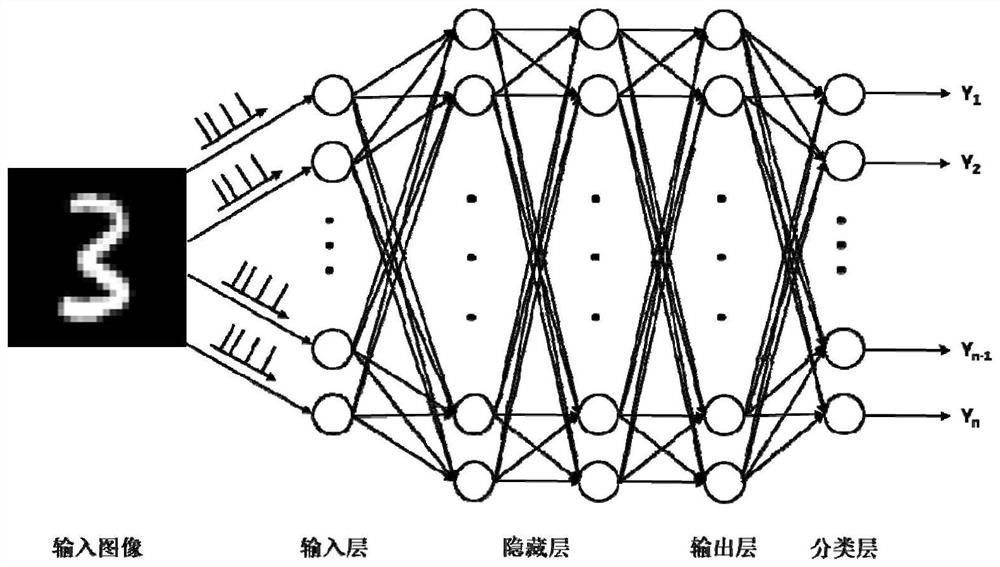

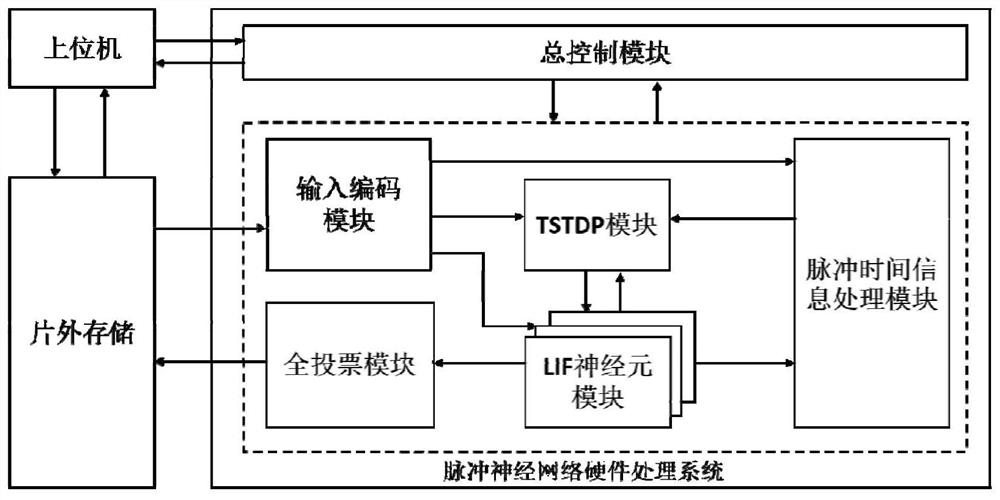

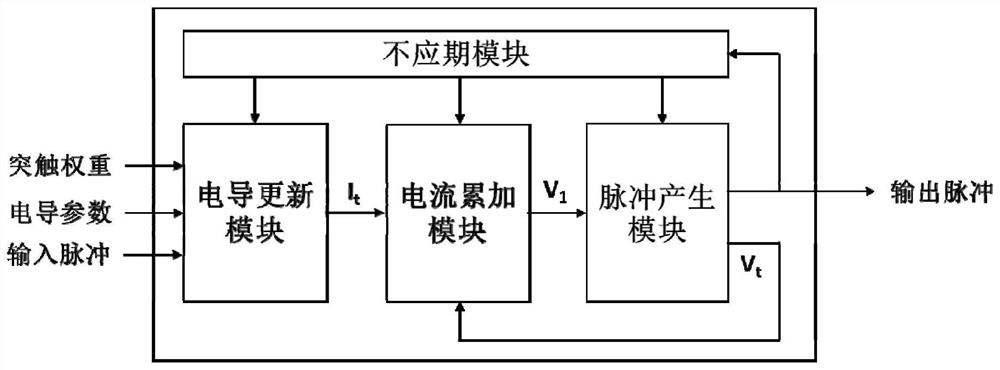

Image recognition system and method based on spiking neural network

PendingCN112784976AAccelerate the lossCharacter and pattern recognitionPhysical realisationTime informationInformation processing

The invention discloses an image recognition system and method based on a pulse neural network. The system comprises an upper computer, an off-chip memory, a master control module, an input coding module, an LIF neuron module, a pulse time information processing module, a TSTDP module and a full voting module. The method comprises the following steps: a training stage: training synaptic weights between an input layer and a hidden layer, between the hidden layers and between the hidden layer and an output layer of the spiking neural network; a benchmarking stage: training a synaptic weight between an output layer of the spiking neural network and a full voting classification layer; in the recognition stage, the output layer votes for the full-voting classification layer by adopting a full-voting mechanism, and image recognition is carried out. The invention provides a full voting output decoding mechanism capable of reducing information loss, and the problem of output decoding information loss of a pulse neural network caused by a traditional voting mechanism is effectively improved. The method can be widely applied to the technical field of artificial neural network and digital circuit design.

Owner:SUN YAT SEN UNIV

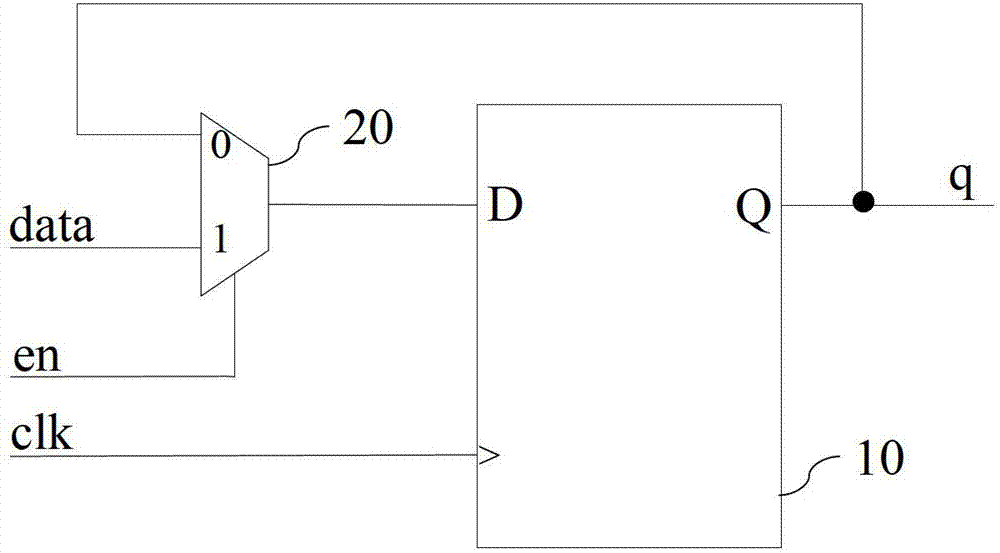

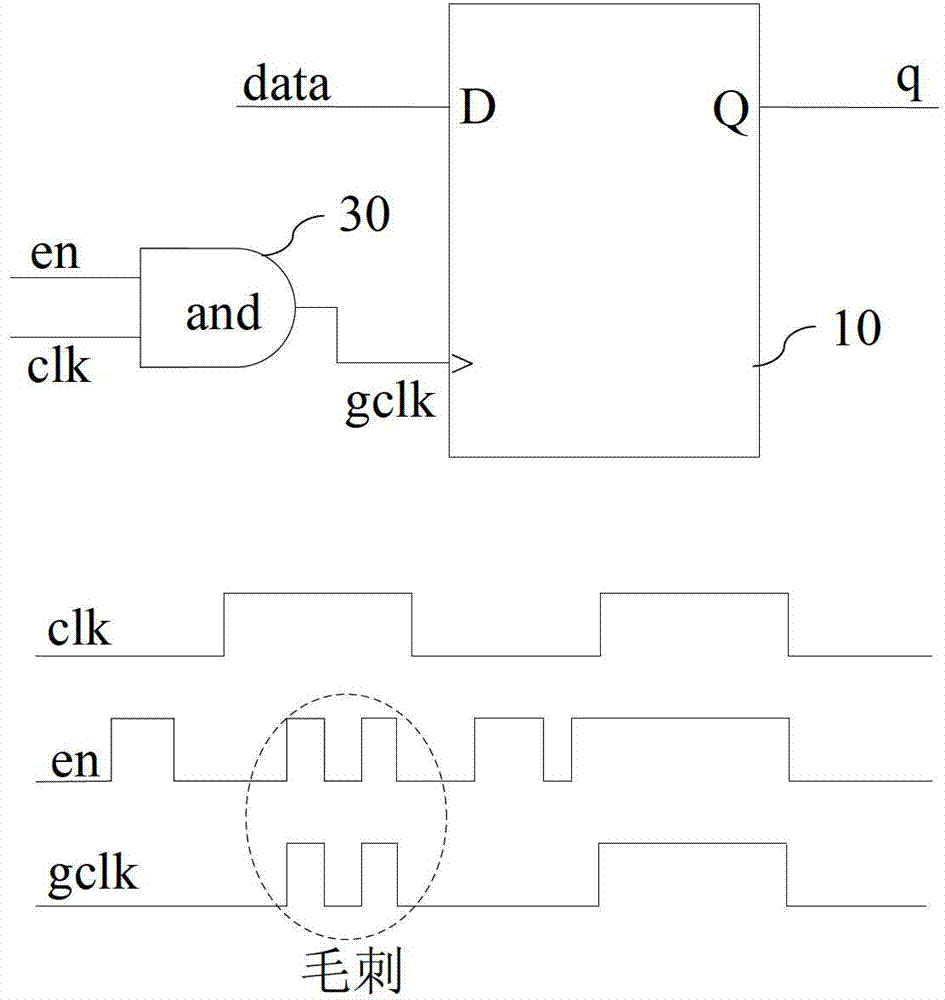

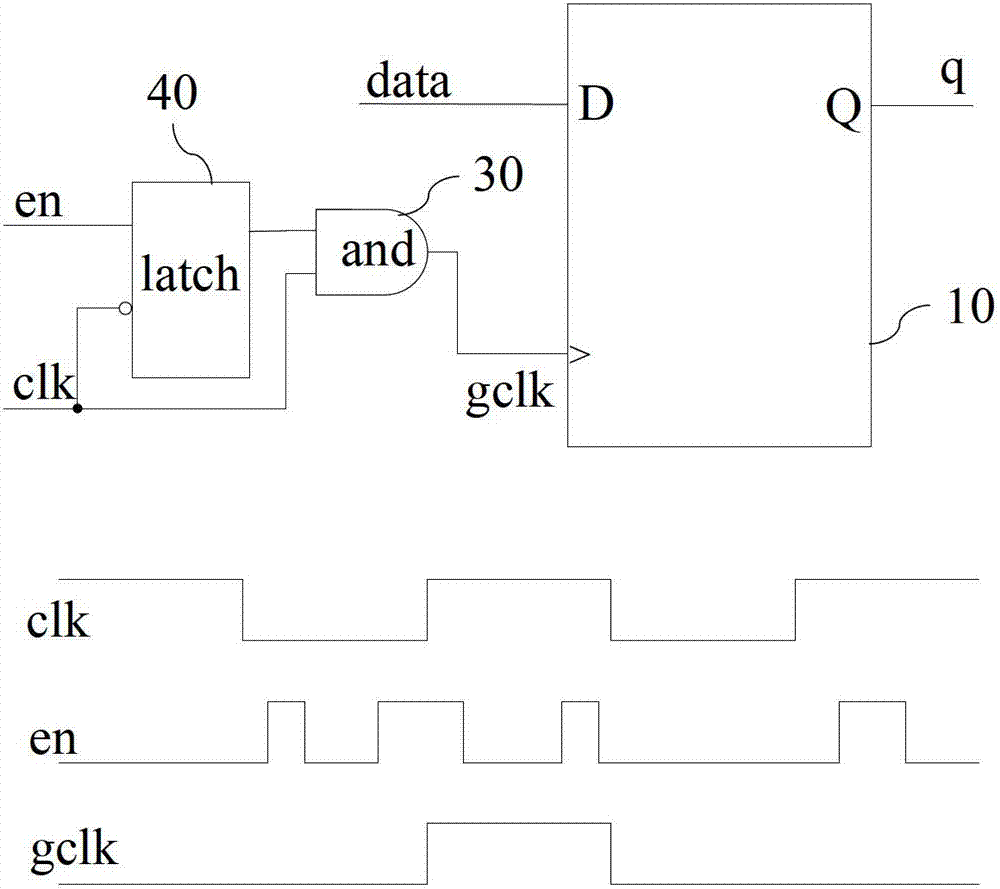

Clock gating circuit used for double-edge trigger

ActiveCN102857198ATroubleshoot functional errorsGuaranteed functionElectric pulse generatorLogic cellEngineering

The invention discloses a clock gating circuit used for a double-edge trigger. The clock gating circuit is a logic unit, wherein the logic unit has four input ends and two output ends including a first input end, a second input end, a third input end, a fourth input end, a first output end and a second output end, wherein the first input end is connected with the first output end, the second input end is connected with the second output end, the third input end is used for receiving an enable signal, the fourth input end is used for receiving a clock signal, the first output end is used for outputting and receiving a clock control signal of the double-edge trigger of a clock gating; and the second output end is used for outputting a inversion signal from the first output end. On a rising edge and a descending edge of the clock signal, when the enable signal is in low level, the first output end is used for copying the first input end; and on the rising edge and the descending edge of the clock signal, when the enable signal is in high level, the first output end is used for copying the second output end. The clock gating circuit can be directly applied in the design of a digital circuit containing the double-edge trigger and is normal in function, thereby effectively solving the problems of burrs and circuit function errors of the traditional clock gating unit.

Owner:RDA TECH

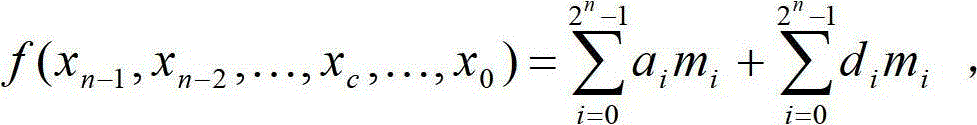

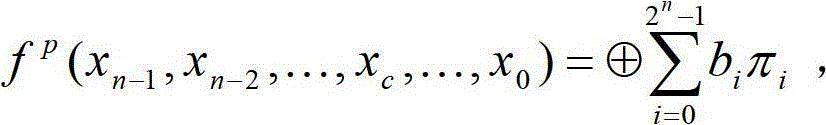

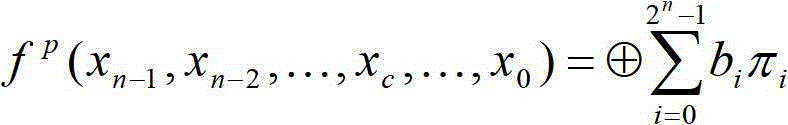

Fixed polarity conversion method for design of digital circuit

ActiveCN102982205AThe quick list technique establishes the minimum area respectivelyReduce areaSpecial data processing applicationsElectrical polarityFunctional expression

The invention discloses a fixed polarity conversion method for design of a digital circuit. The method comprises the following steps of: firstly reading in an SOP (Sum-of-Products) expansion of a Boolean logic function containing irrelative items; respectively establishing a minterm index table and an irrelative item index table by utilizing a quick list technology; and finally, searching the optimal irrelative item for choice, selecting an appropriate irrelative item to be read in an FPRM (Fixed Polarity Reed Muller) functional expression to obtain an FPRM expansion with lest and items. The method has the advantages that the conversion of fixed polarity from the SOP expansion of the Boolean logic function containing the irrelative items to an RM expansion in the design process of the digital circuit is realized; through the test of ten 10 MCNC (microelectronics center of north carolina) Benchmark circuits, the result shows that: compared with the fixed polarity conversion method which does not consider the irrelative items, the method has the advantages that the FPRM expansion can be effectively simplified, and the RM logic circuit with smaller area, lower power consumption and faster speed is obtained.

Owner:NINGBO UNIV

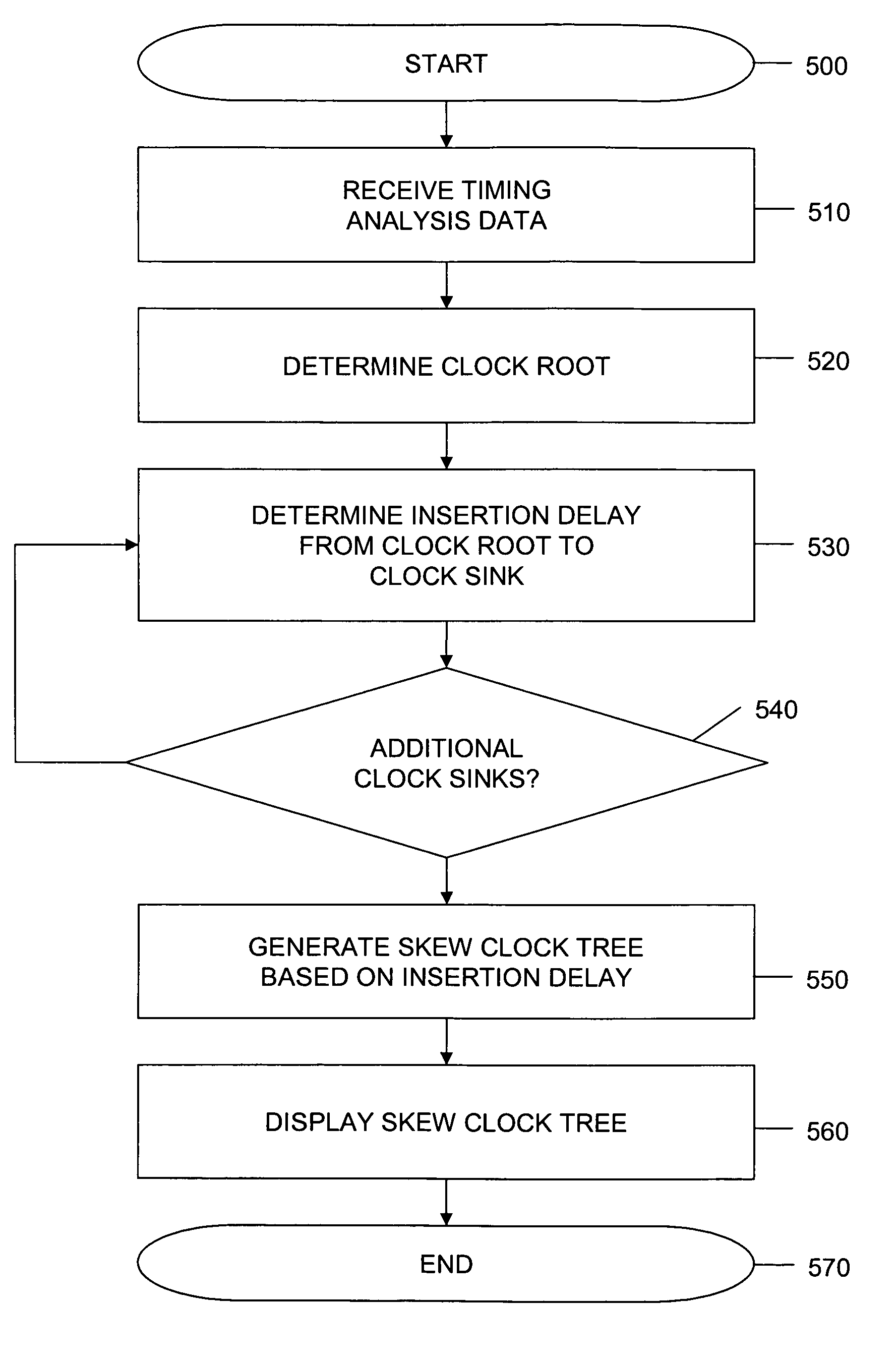

Skew clock tree

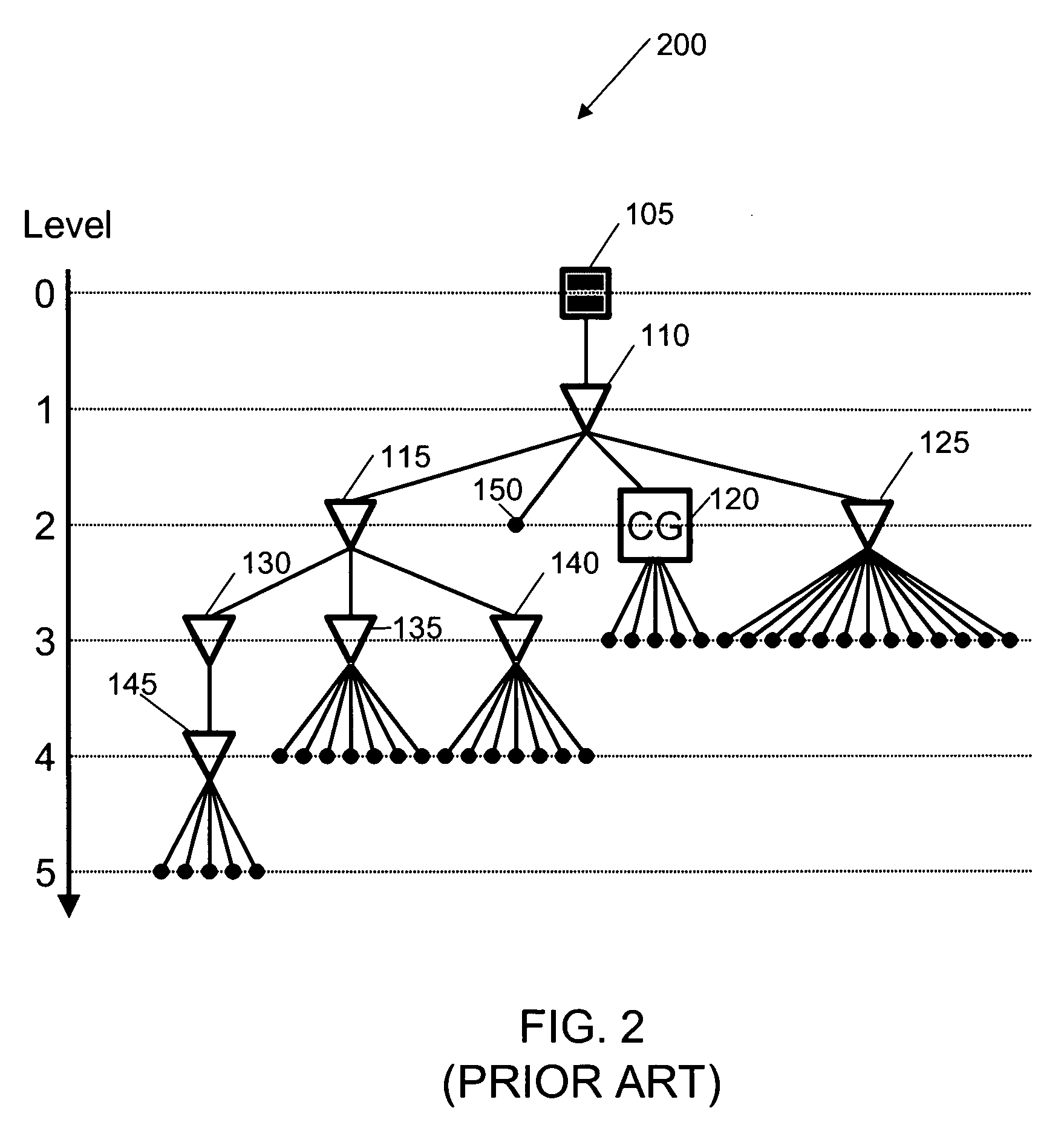

InactiveUS20070288875A1Computer programmed simultaneously with data introductionComputer aided designGraphicsAnalysis data

A method, graphical user interface, and computer program product on a computer readable medium are disclosed for presenting a user with a display of a skew clock tree for a digital circuit design. In the preferred embodiment, a computer system receives timing analysis data for a digital circuit. The computer system determines a propagation time delay between a first clock root and each of a plurality of clock sinks of the digital circuit associated with the first clock root based on the timing analysis data. The computer system then displays the first clock root and each clock sink associated with the first clock root of the skew clock tree along an axis representing time delay. In the displayed skew clock tree, each clock sink is positioned along the axis relative to the first clock root based on each clock sink's determined propagation time delay.

Owner:AZURO UK

Digital signal impedance match circuit designing method

InactiveCN105653752AReduce debugging linksHigh precisionSpecial data processing applicationsCapacitanceImpedance matching

The invention discloses a digital signal impedance match circuit designing method. A PCB plate layer required is designed according to circuit complicate conditions; each layer is defined with different features; an impedance match circuit is employed; a schematic diagram is designed in a simulation system; input or output features of each device is activated; and different matching effects can be simulated via inputting different impedance, capacitance value, inductance value and walking line length values. By the use of the technical scheme, a digital circuit designer can design the impedance match circuit for a to-be-designed circuit in the simulation system, so well-designed and fixed circuit can be directly applied to a practical circuit and a debugging link for the practical circuit can be reduced; a large amount of time can be reduced and circuit designing accuracy can be improved; in particular, for high-frequency and radio-frequency circuit designs, debugging and rectifying links can be greatly reduced; and the circuit can be designed once for all and high output digital signal precision can be achieved.

Owner:王丽香

Method and system for verifying the equivalence of digital circuits

InactiveUS7890901B2Computer aided designSoftware simulation/interpretation/emulationControl signalComputer science

The automatic verification of designs of digital circuits for their equivalence, wherein logic designs implemented in different hardware description languages (HDLs) and different design methodologies are compared. The designs (Code A, Code B) are modified by adding special wrappers (Wrapper A, Wrapper B), and used to equalize the timing of pairs of selected input signals and selected output signals of the logic designs. The wrappers drive certain signals of the designs that are not relevant for actual comparison, such signals including clock signals, clock control signals, scan-path signals, scan-path control signals, and reset signals. In a preferred embodiment, HDL descriptions of logic designs are analyzed. Based on this analysis, the wrappers are implemented as changes to the HDL descriptions. In another embodiment, RTL and / or gate-level netlists are analyzed and modified.

Owner:GLOBALFOUNDRIES INC

Implementing asynchronous first-in first-out data transmission by double-port direct access storage device

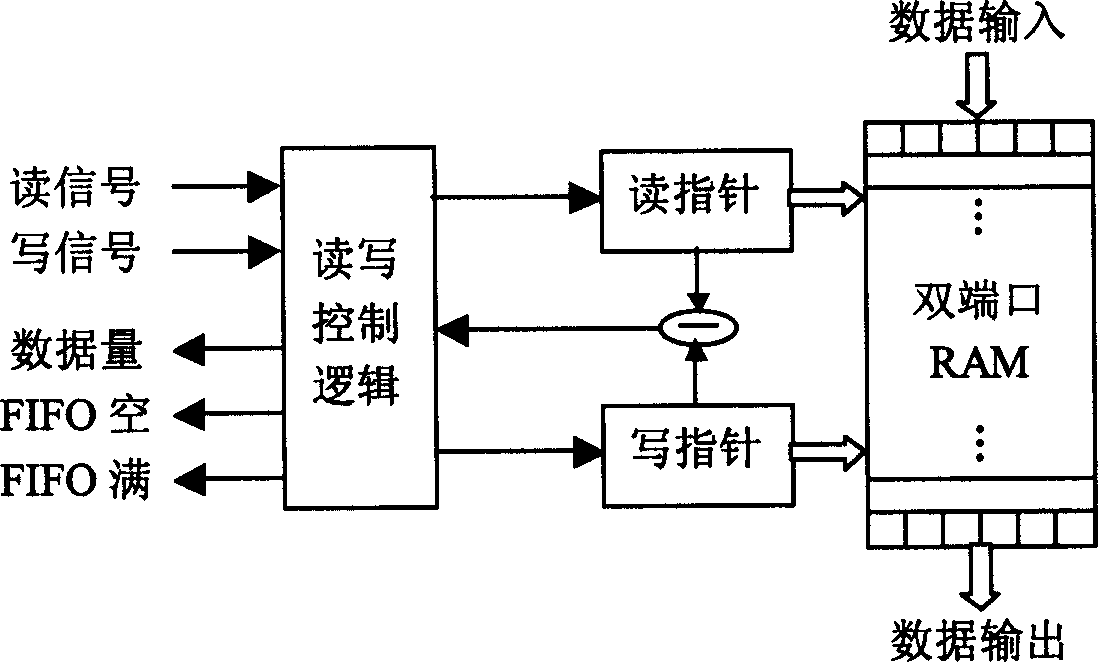

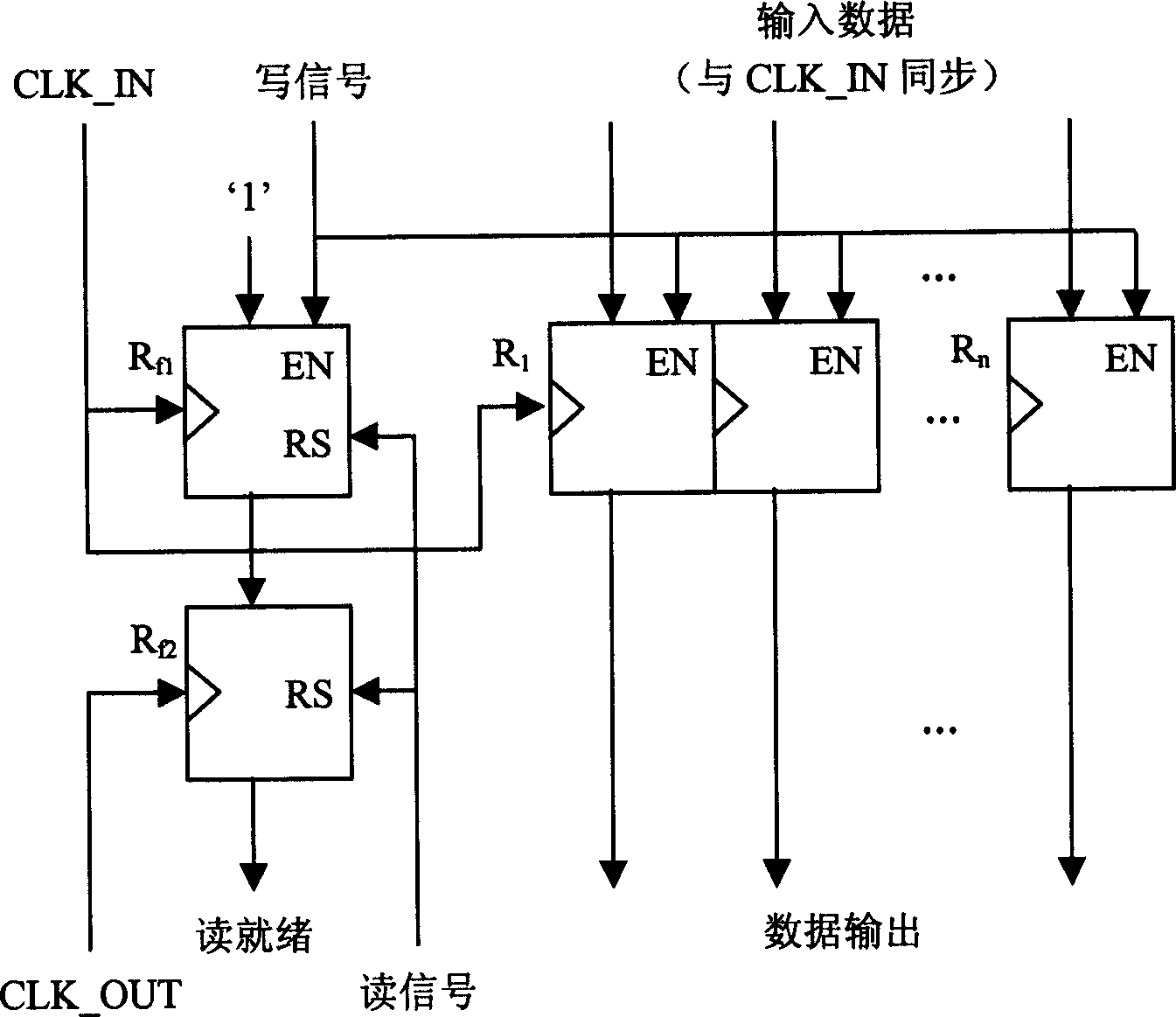

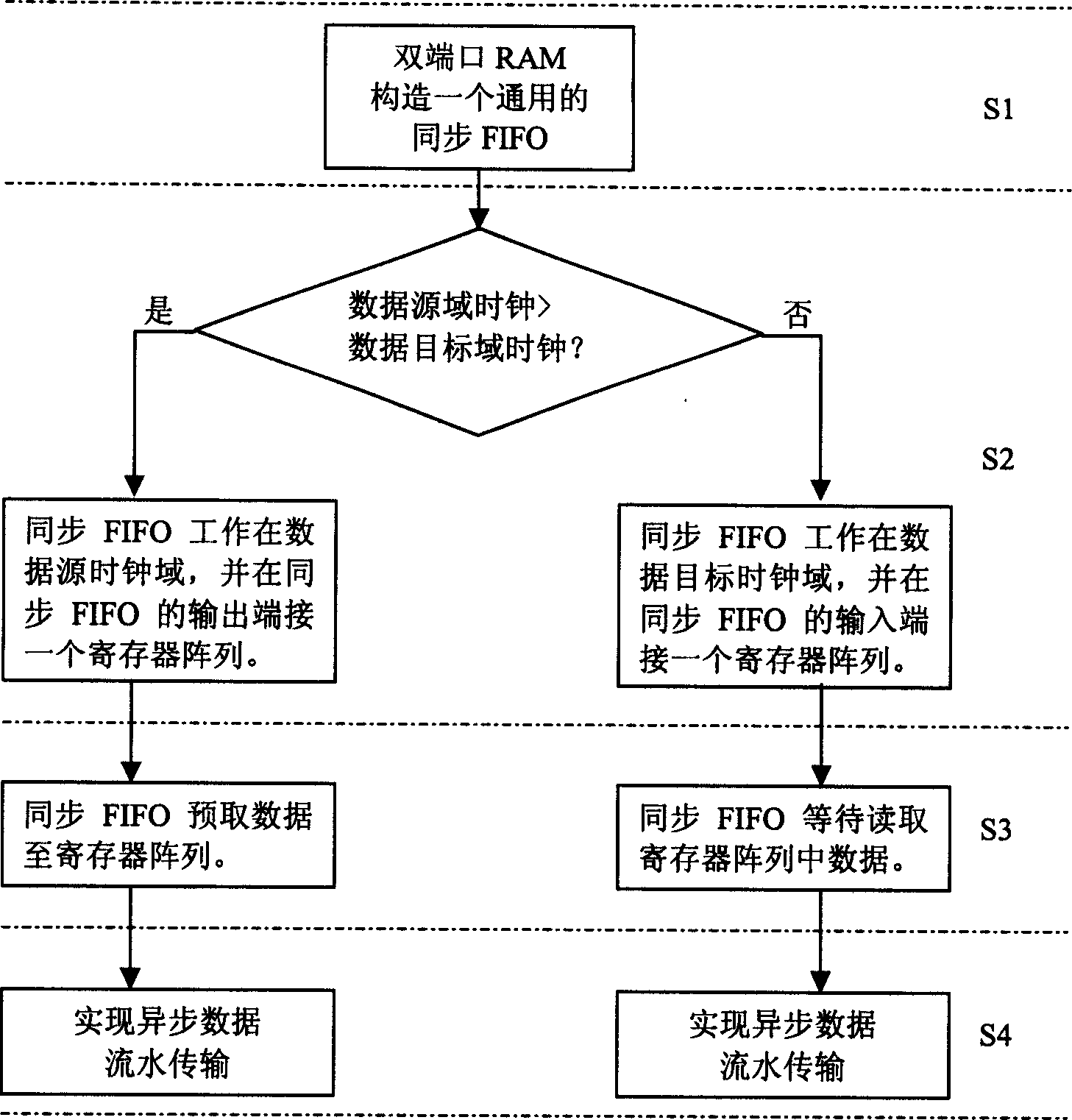

InactiveCN1560868AImplement bidirectional burst transferAccurate timingDigital storageElectric digital data processingProcessor registerSynchronous control

The invention relates to a method for realizing asynchronous FIFO data transmission with dual port random access memory. The invention designs a bridge FIFO for asynchronous data transmission, the new FIFO is based on dual port RAM, the dual port RAM is packaged into a universal synchronous FIFO through synchronous control logic, and then uses a small register array to form an asynchronous interface. The steps are: S1: uses dual port RAM to form a universal asynchronous FIFO, S2: determines the data clock region, S3: reads the data, S4: realizes asynchronous data transmission. The FIFO designed with the invention, it can provide the quantity of data in FIFO accurately, thus the two sides of the data transmission can start data reading and writing operations and it upgrades the data transmission efficiency effectively.

Owner:北京中科算源资产管理有限公司