Clock gating circuit used for double-edge trigger

A technology of double-edge triggering and clock gating, applied in the direction of electrical components, electric pulse generation, pulse generation, etc., can solve the problems that the clock gating circuit cannot realize the original design intention, the double-edge D flip-flop 50 circuit function error, etc., to achieve Solve the problem of circuit function error, the effect of normal function

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

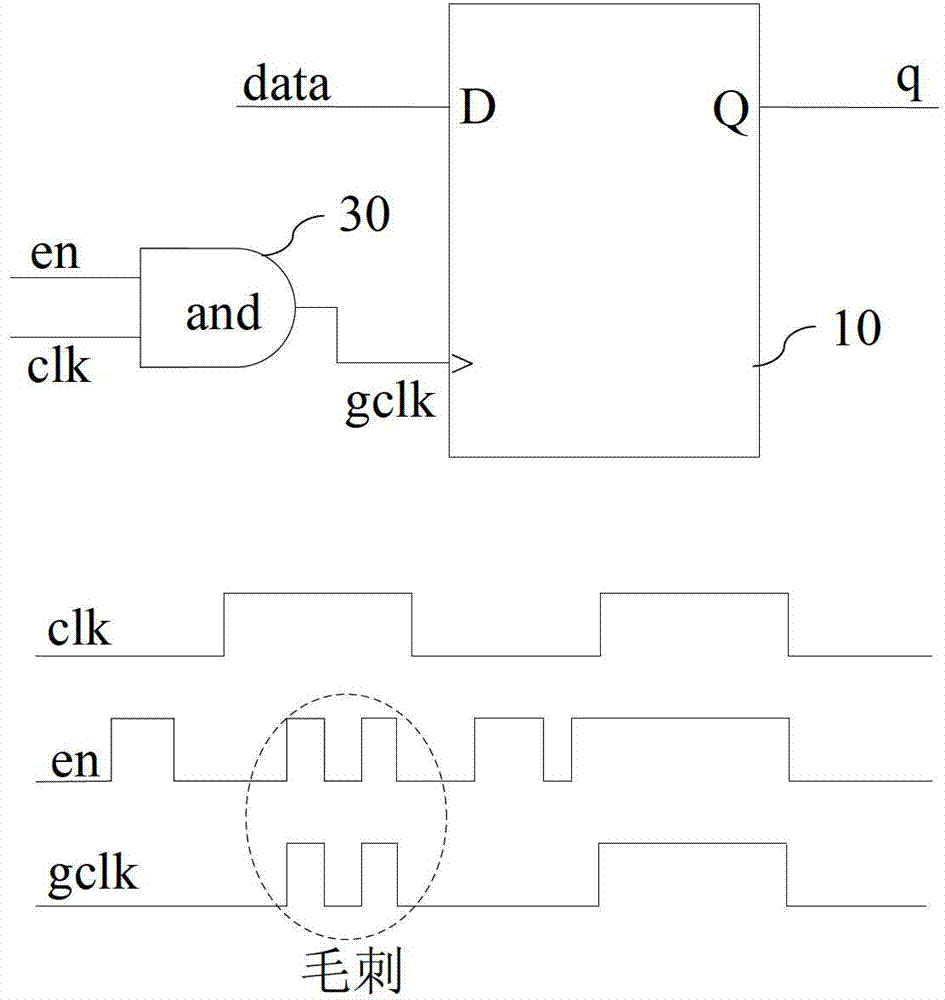

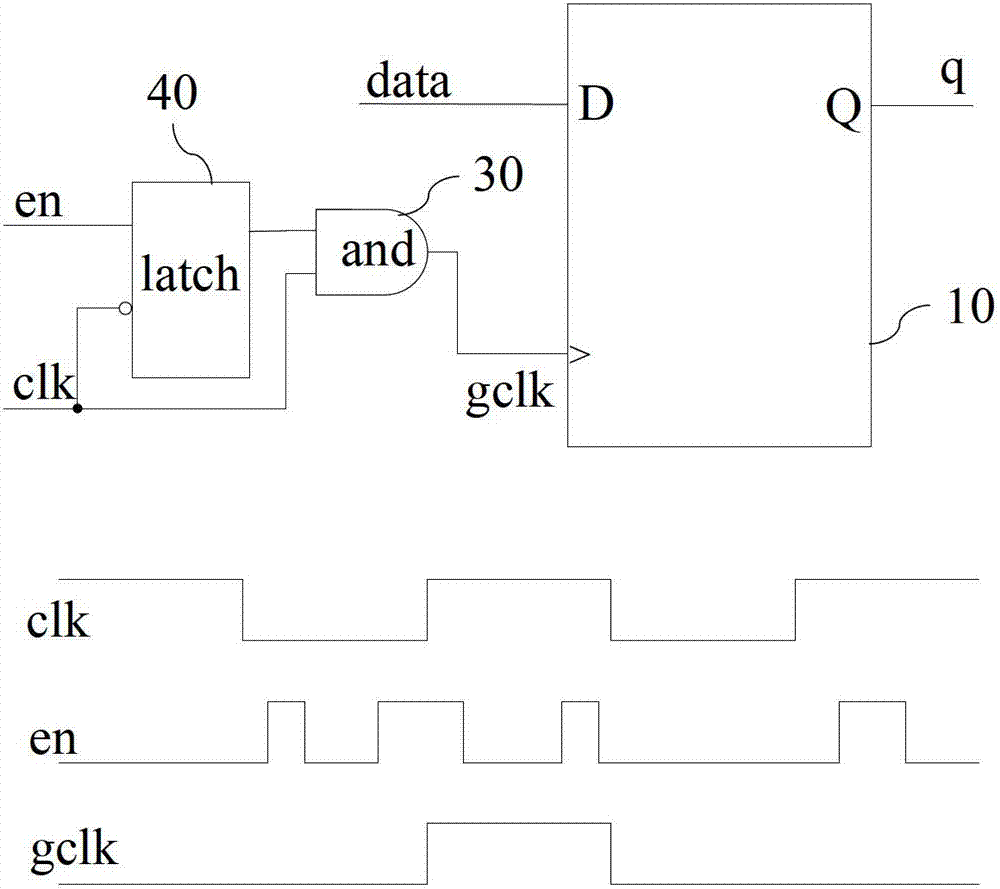

[0039] The applicant believes that a clock gating circuit that meets the application requirements of a double-edge trigger should meet the following requirements:

[0040] 1. When the enable signal en is unstable in the high-level state or low-level state of the clock signal clk, the clock control signal gclk serving as the clock input of the double-edge trigger should not have glitches.

[0041] 2. When the enable signal en is at low level, the clock control signal gclk remains in its original state, and there is no change of rising edge or falling edge. At this time, the double-edge trigger stops working; when the enable signal en is at high level, the clock control signal The signal gclk flips along with the high and low level flips of the clock signal clk, and the double-edge trigger works normally at this time.

[0042] 3. Ensure that the duty cycle of the clock control signal gclk is consistent with that of the clock signal clk when the clock control signal gclk is worki...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More