Patents

Literature

564 results about "High- and low-level" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

High-level and low-level, as technical terms, are used to classify, describe and point to specific goals of a systematic operation; and are applied in a wide range of contexts, such as, for instance, in domains as widely varied as computer science and business administration.

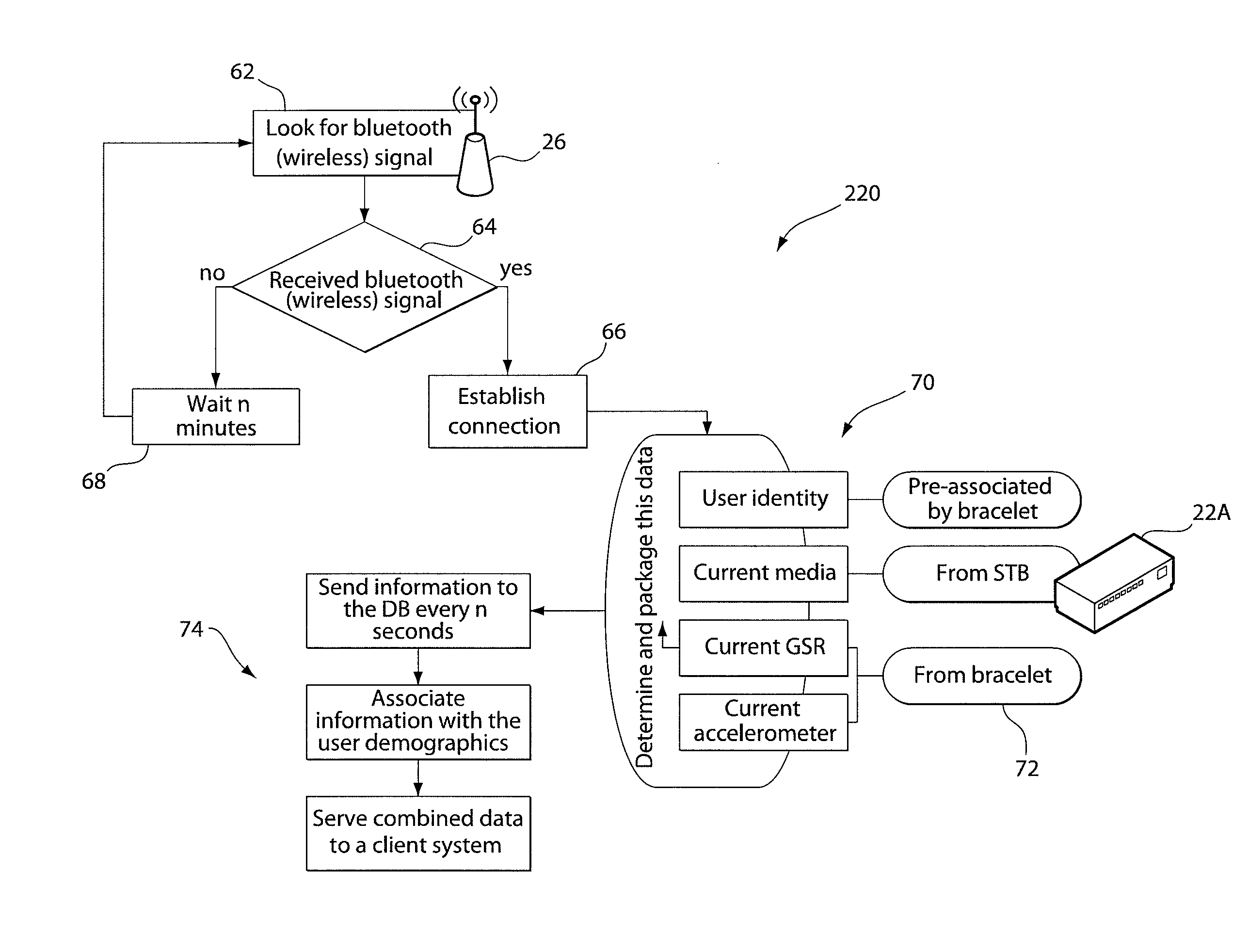

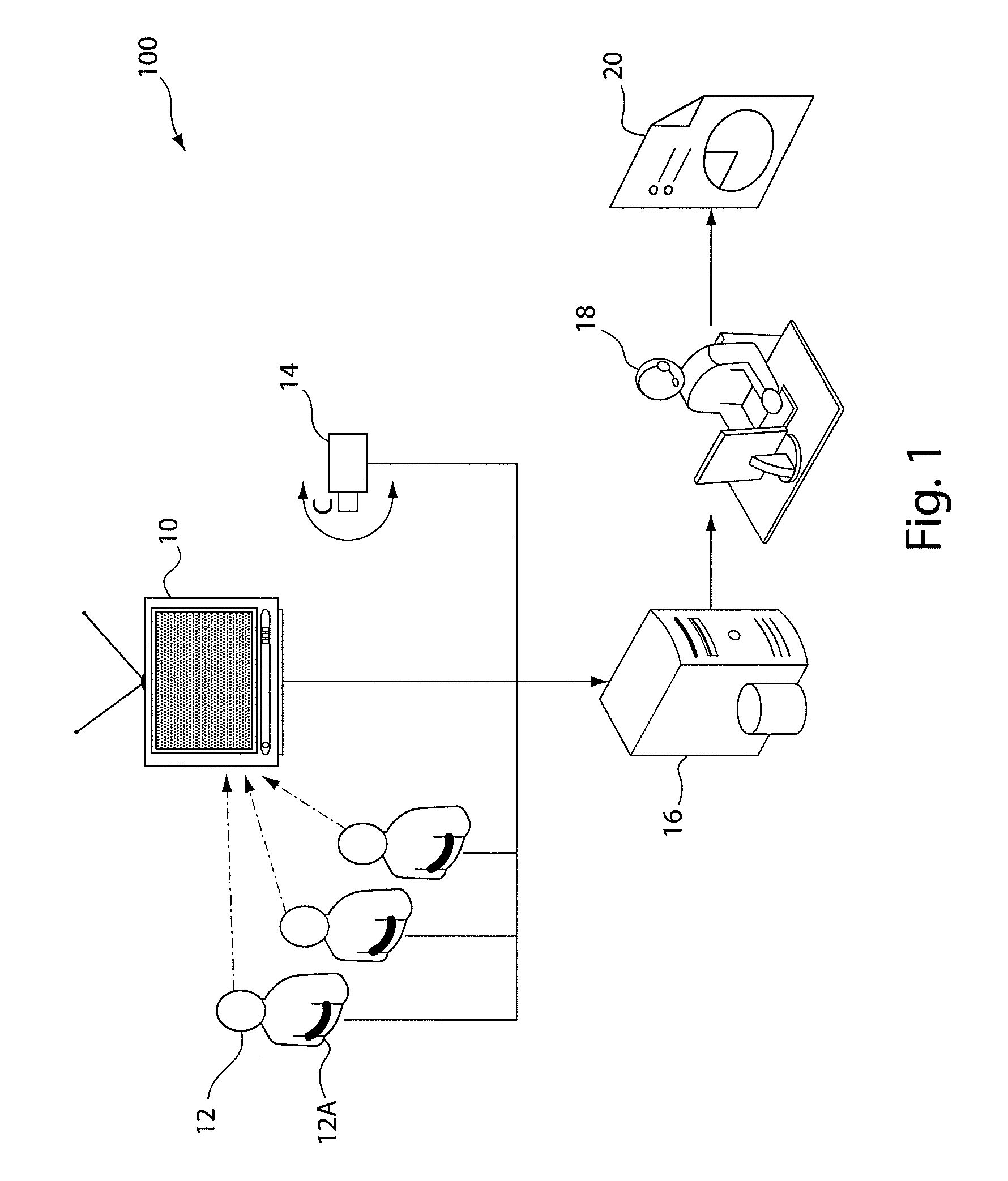

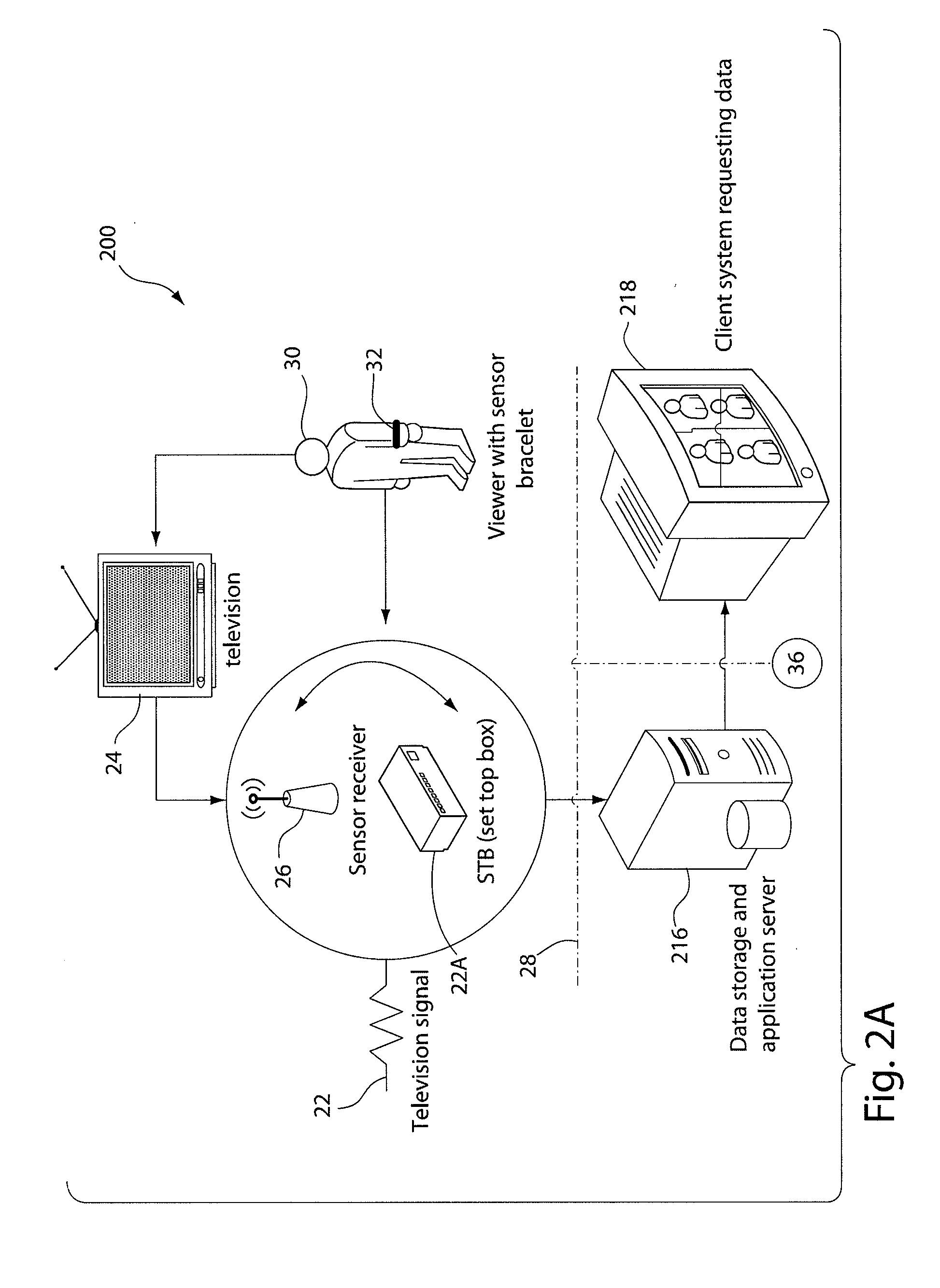

Method and System For Measuring User Experience For Interactive Activities

The present invention is directed to a method and system for measuring the biometric (physically, behaviorally, biologically and self-report based) responses of an audience to a presentation or interactive experience that provides a sensory stimulating experience and determining a measure of the level and pattern of engagement of that audience and impact of the presentation or interactive experience. In particular, the invention is directed to a method and system for measuring one or more biometrically based responses of one or more persons being exposed to the presentation in order to determine the moment-to-moment pattern or event based pattern and overall level of engagement. The method and system can include eye tracking to determine areas of the presentation that correspond to high and low levels of biometric responses suggesting high and low levels of visual impact. Further, the invention can be used to determine whether the presentation or the content in the presentation is more effective in a population relative to other presentations (or content) and other populations and to help identify elements of the presentation that contribute to the high level of engagement or impact and the effectiveness and success (or failure) of the presentation for that population.

Owner:THE NIELSEN CO (US) LLC

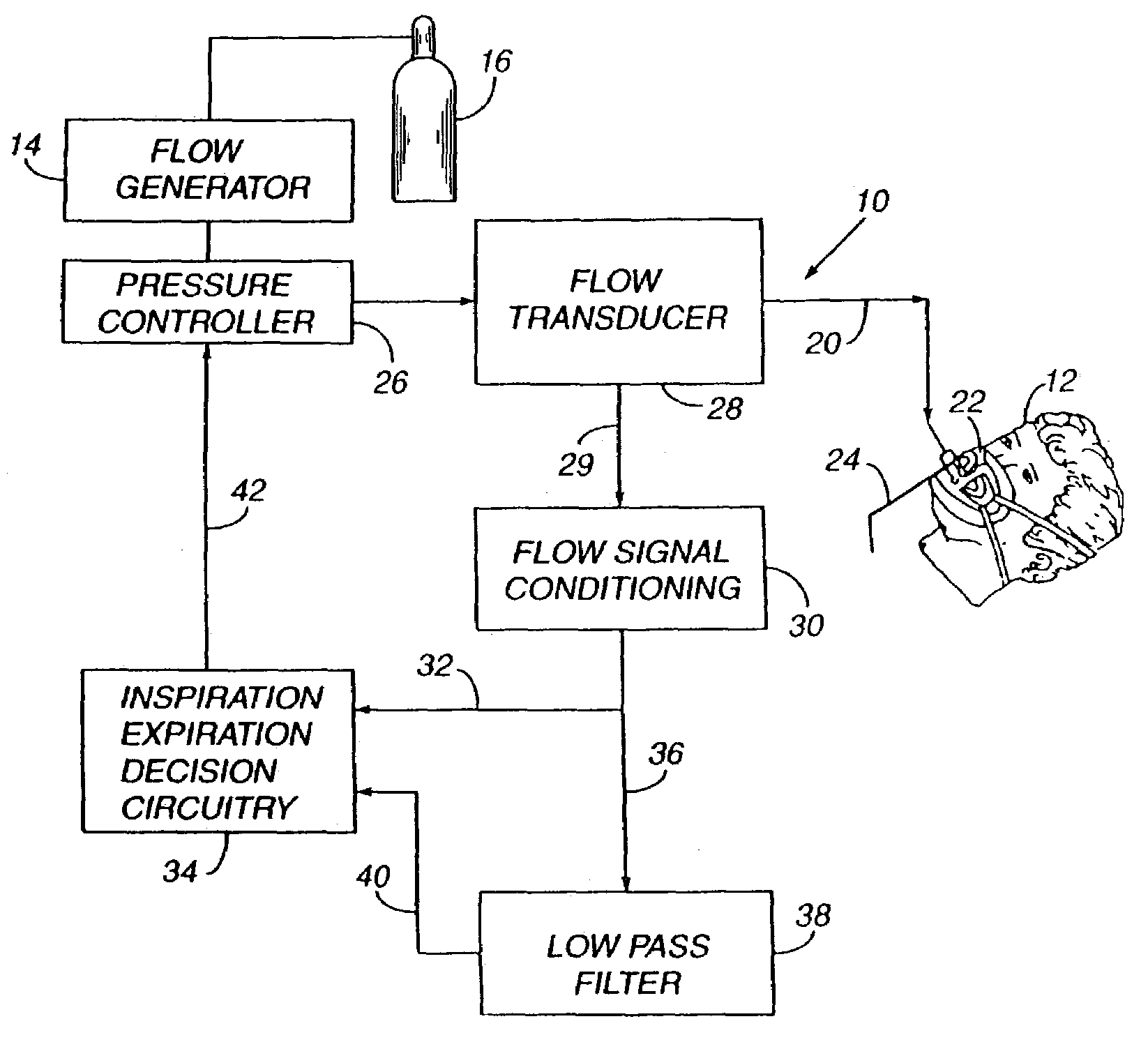

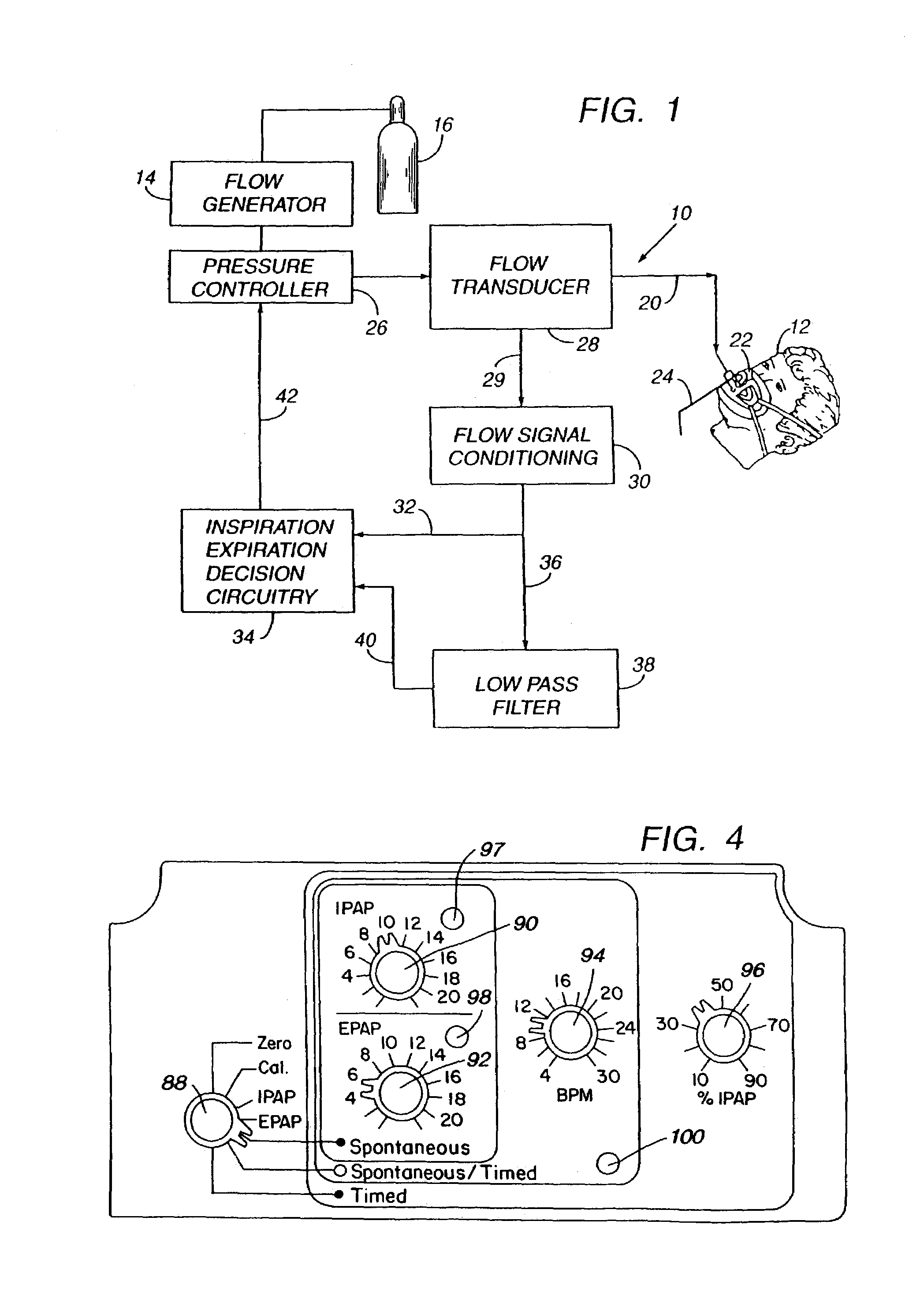

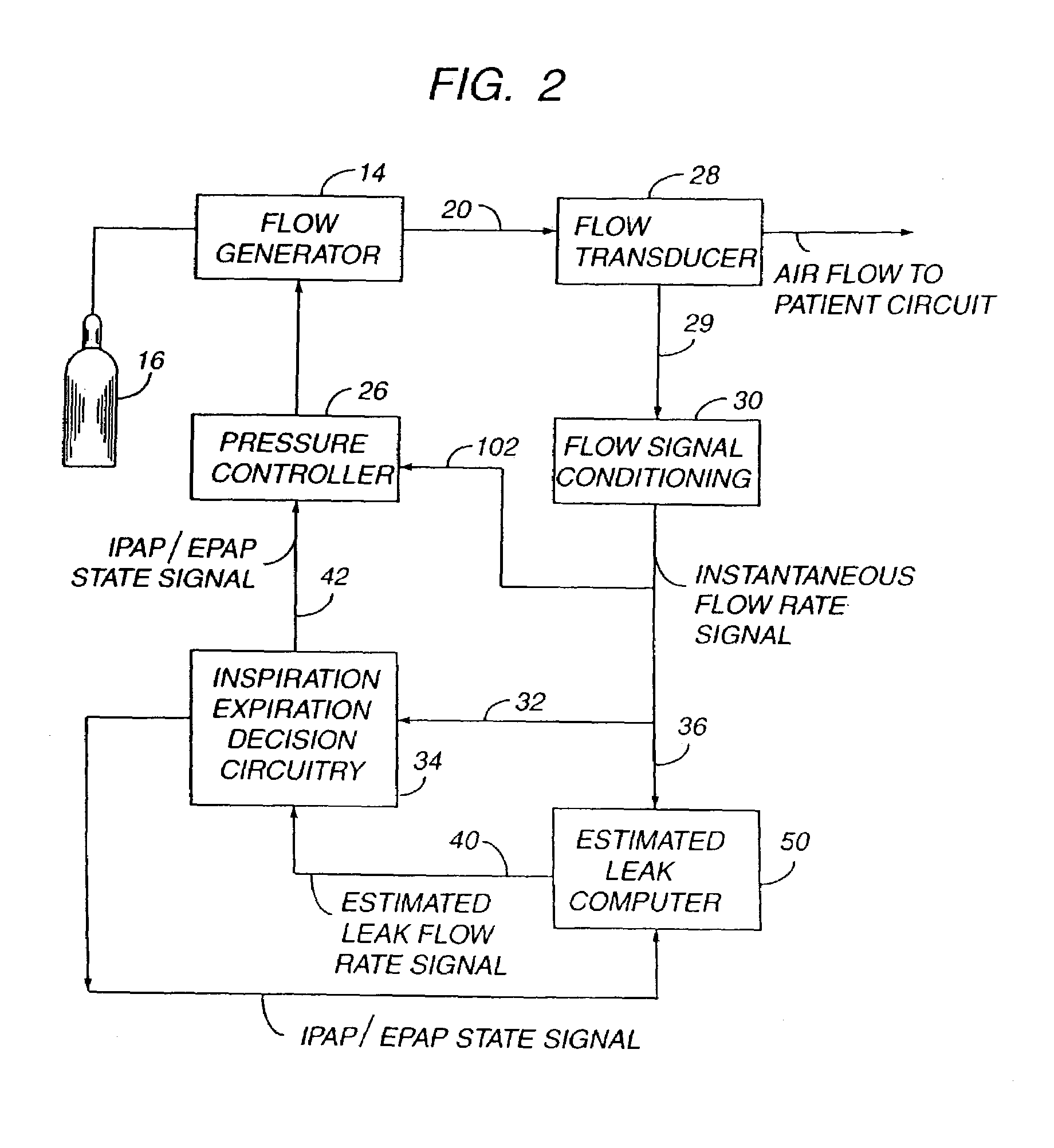

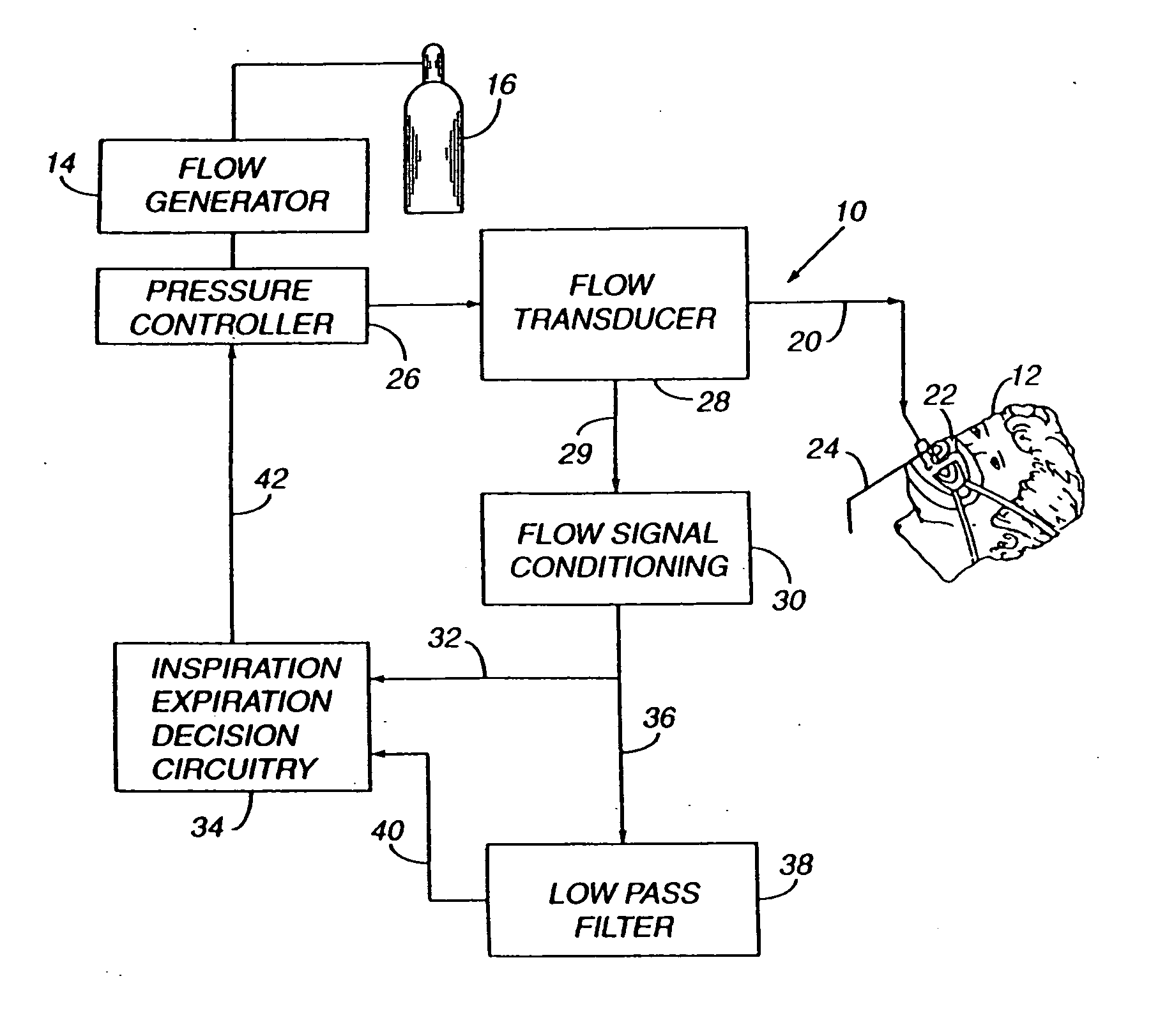

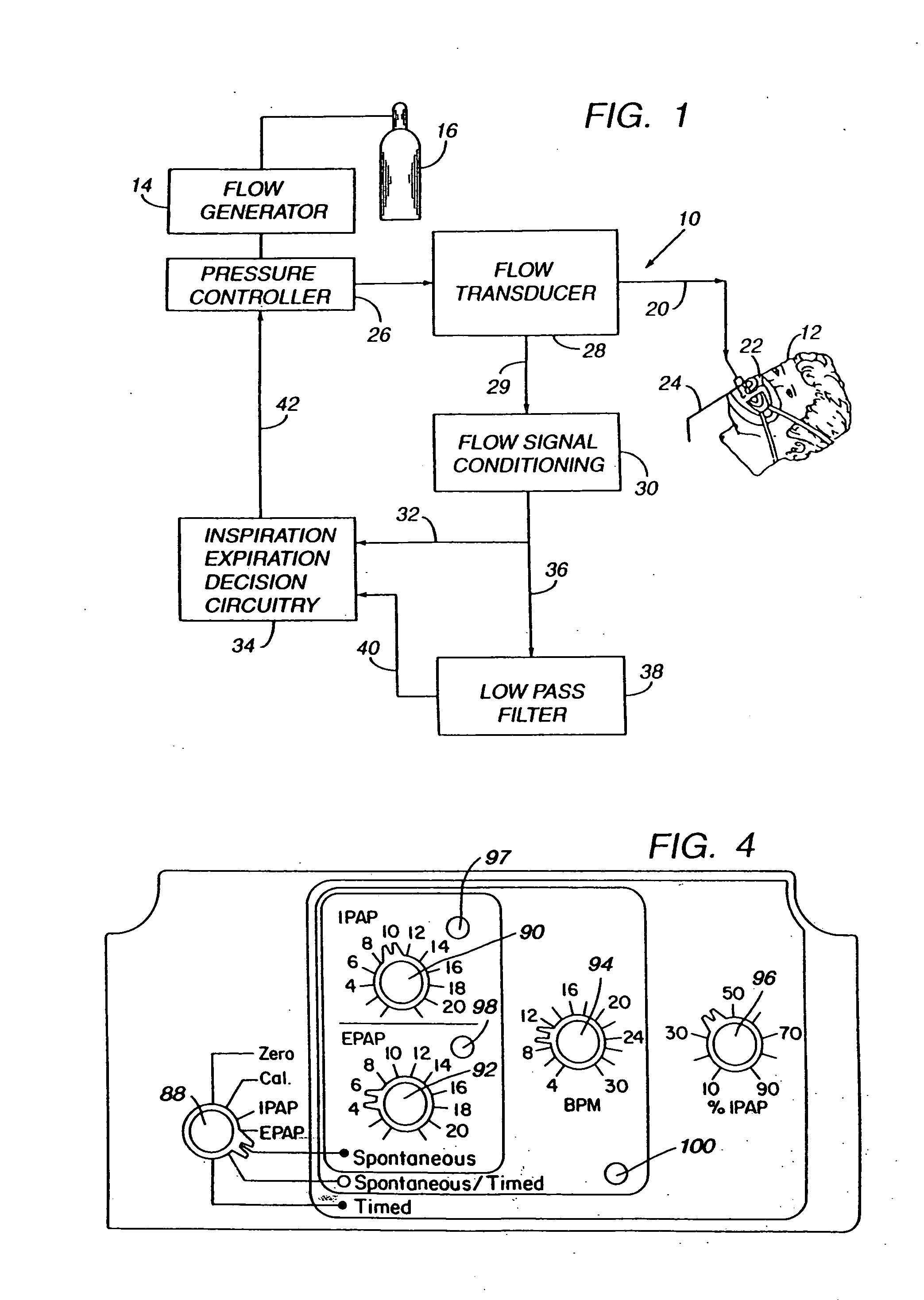

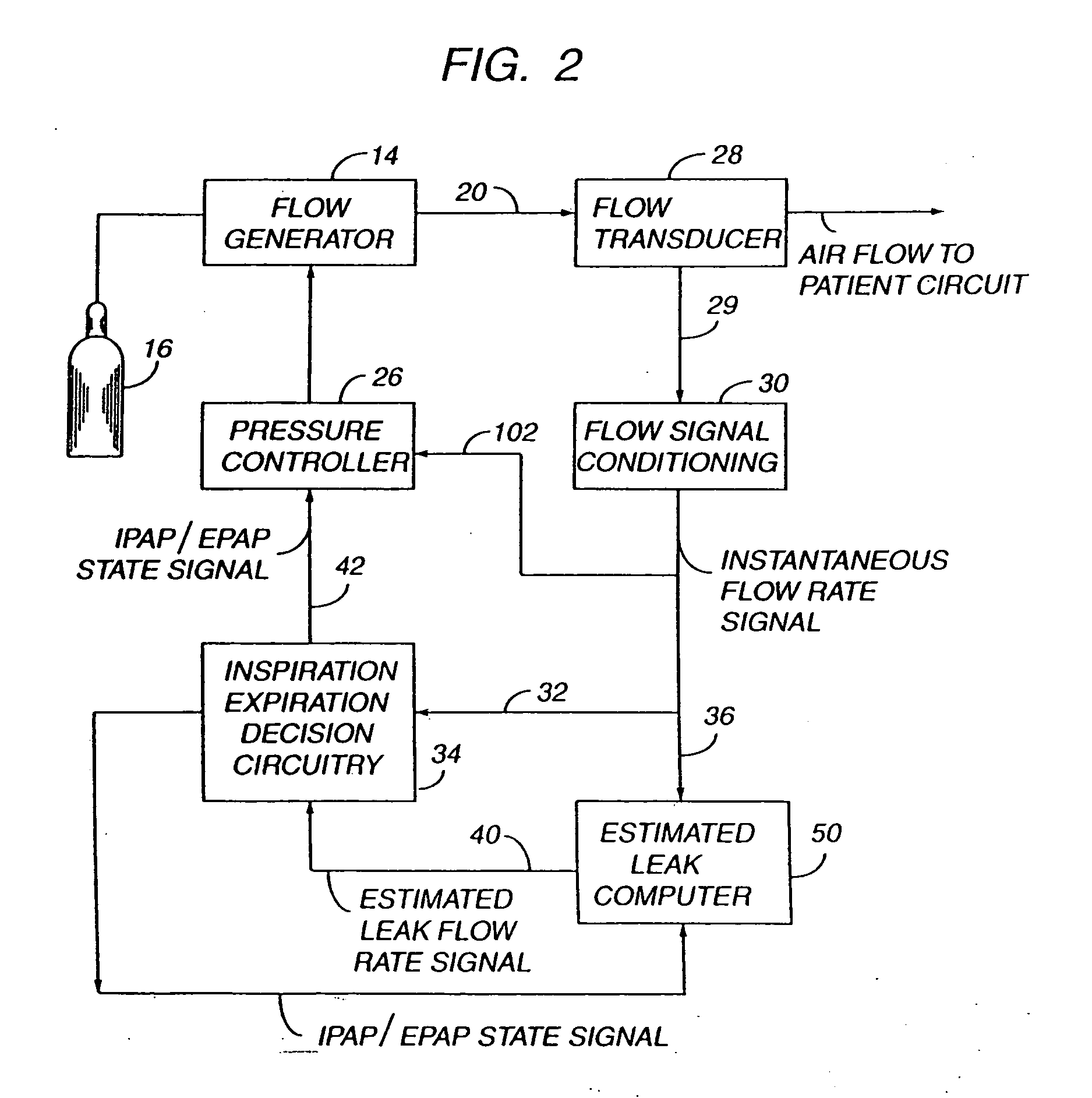

Sleep apnea treatment apparatus

InactiveUS7013892B2Reduce pressureEasy to operateRespiratorsOperating means/releasing devices for valvesSleep researchClinical study

Improved methodology and apparatus for the clinical study and treatment of sleep apnea which incorporates one or more of the following features: (1) application of mono-level, alternating high and low level, or variable positive airway pressure generally within the airway of the patient with the mono-level, high and low level, or variable airway pressure generally being coordinated with and / or responsive to the spontaneous respiration of the patient, (2) usage of adjustably programmable pressure ramp circuitry capable of producing multiple pressure ramp cycles of predetermined duration and pattern whereby the ramp cycles may be customized to accommodate the specific needs of an individual sleep apnea patient so as to ease the patient's transition from wakefulness to sleep, (3) remote control or patient-sensed operation of the apparatus, (4) employment of safety circuitry, reset circuitry and minimum system leak assurance circuitry, controls and methods, and (5) utilization of clinical control circuitry whereby sleep disorder data may be compiled and appropriate therapy implemented during a one-night sleep study.

Owner:RIC INVESTMENTS LLC

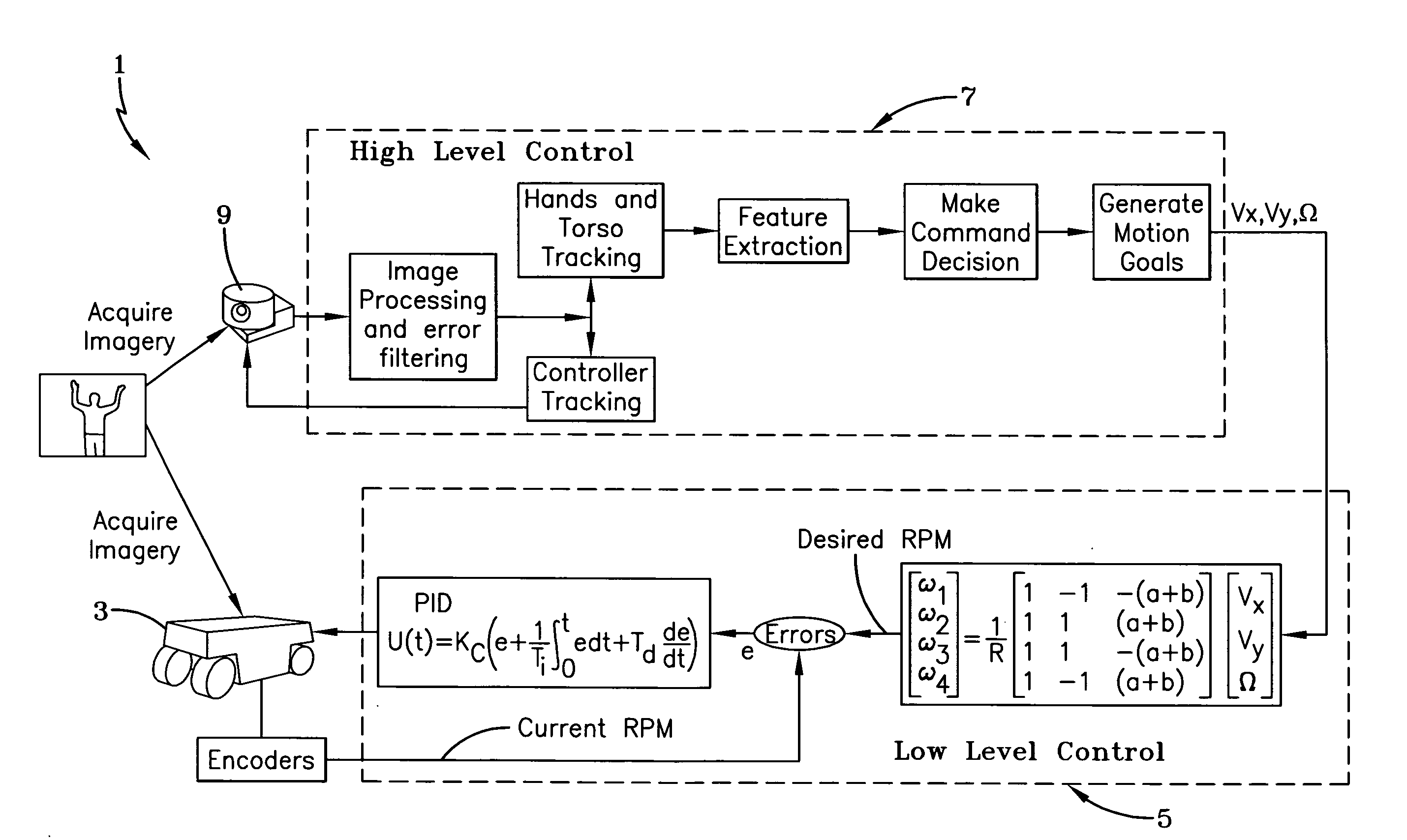

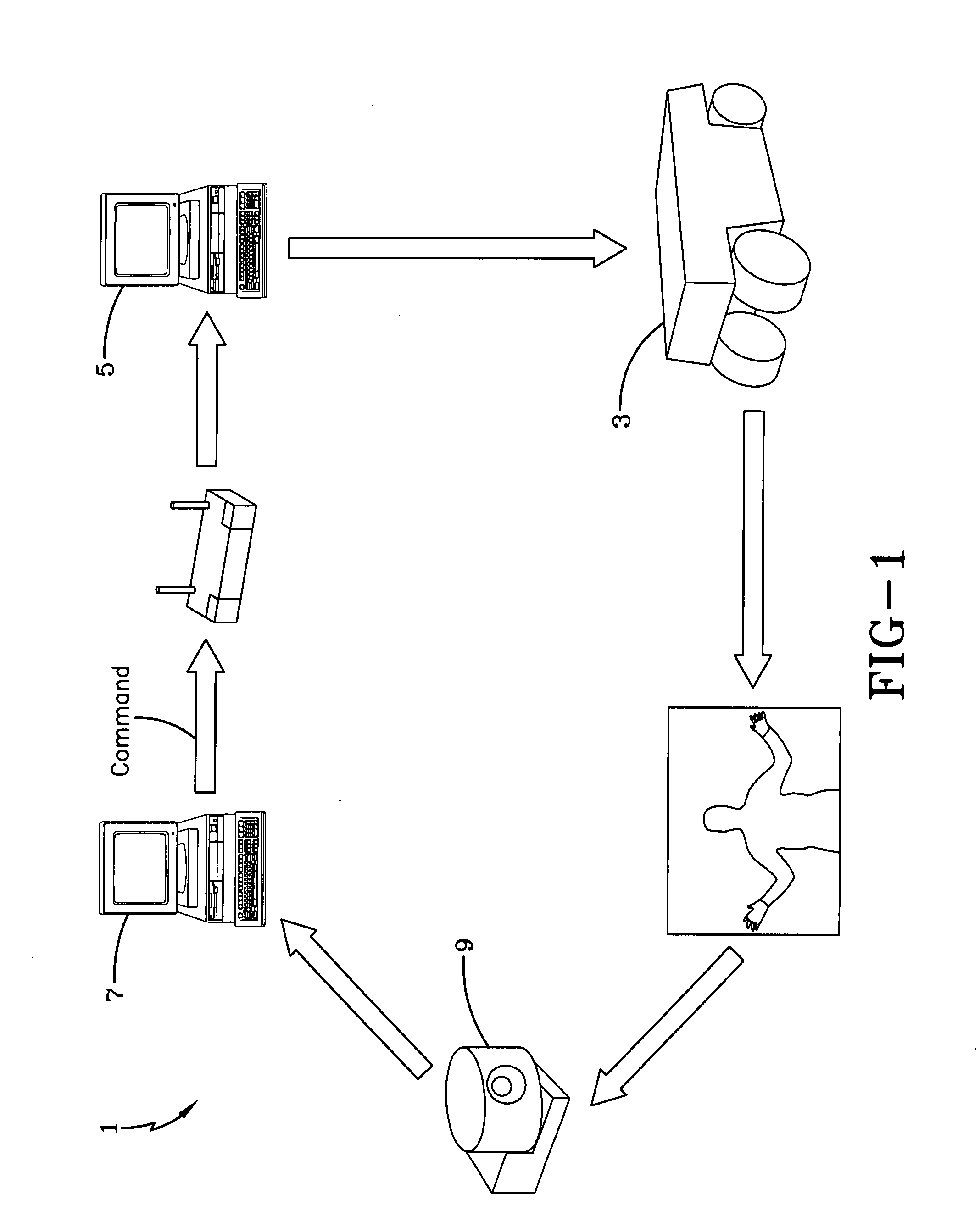

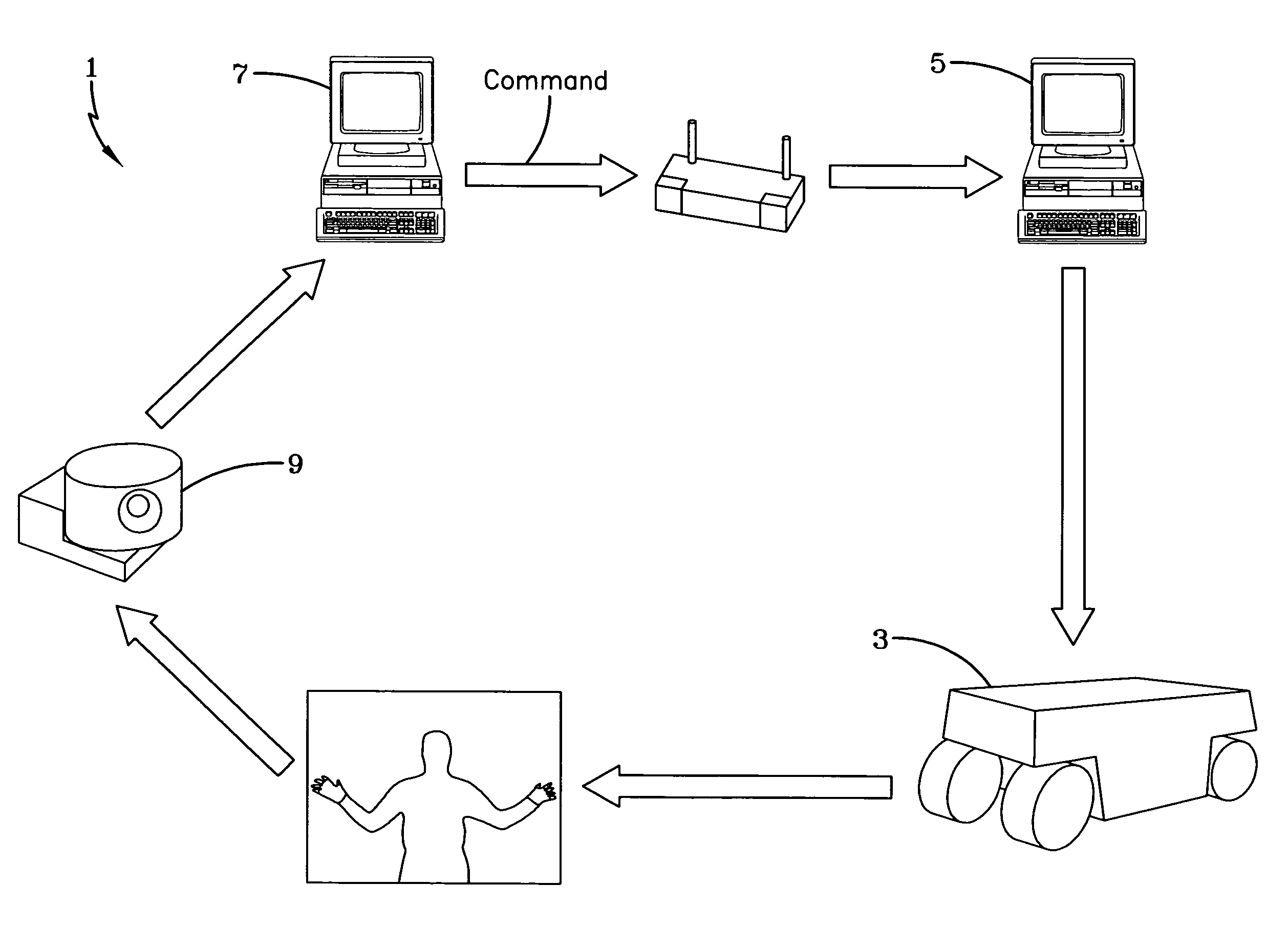

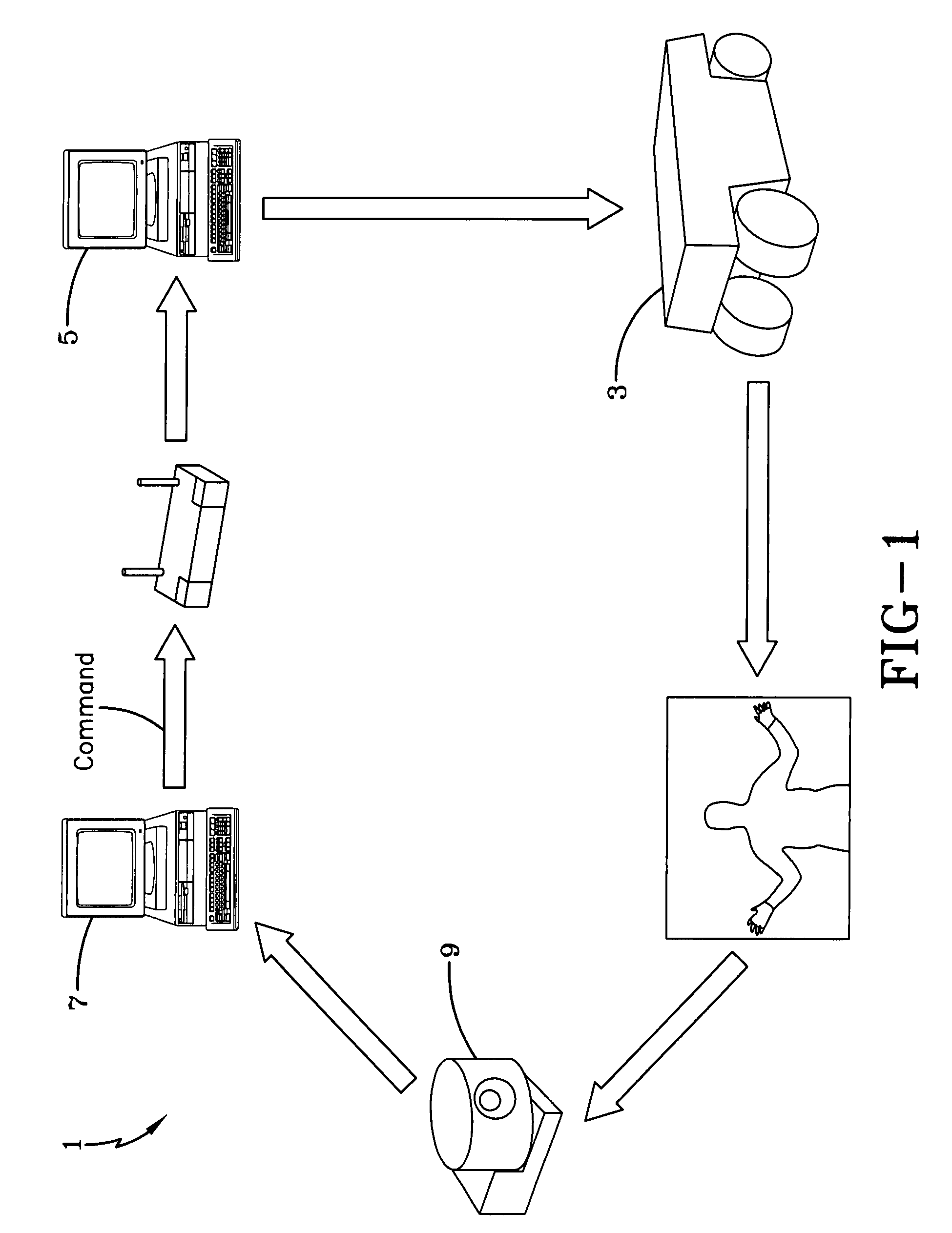

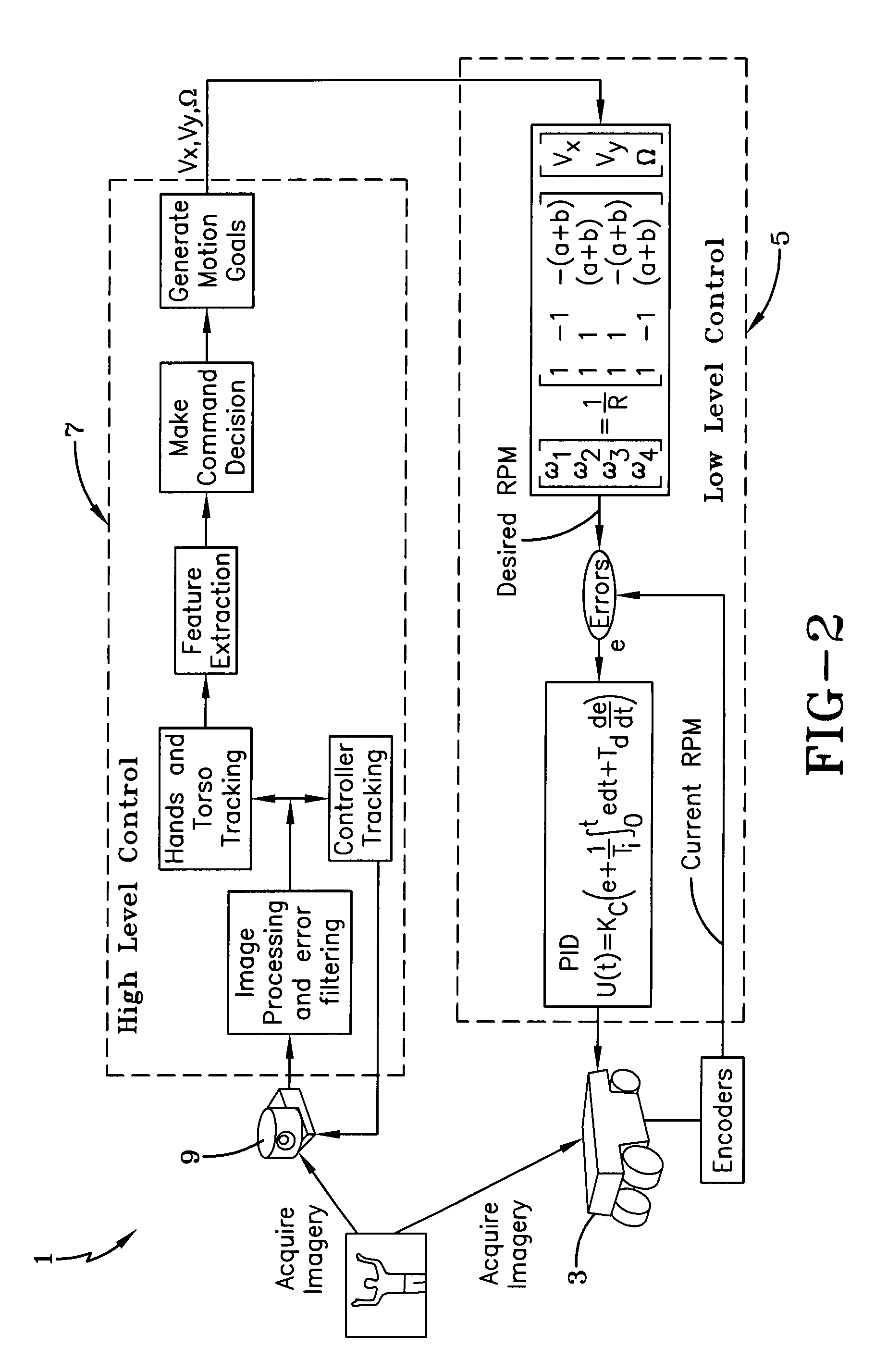

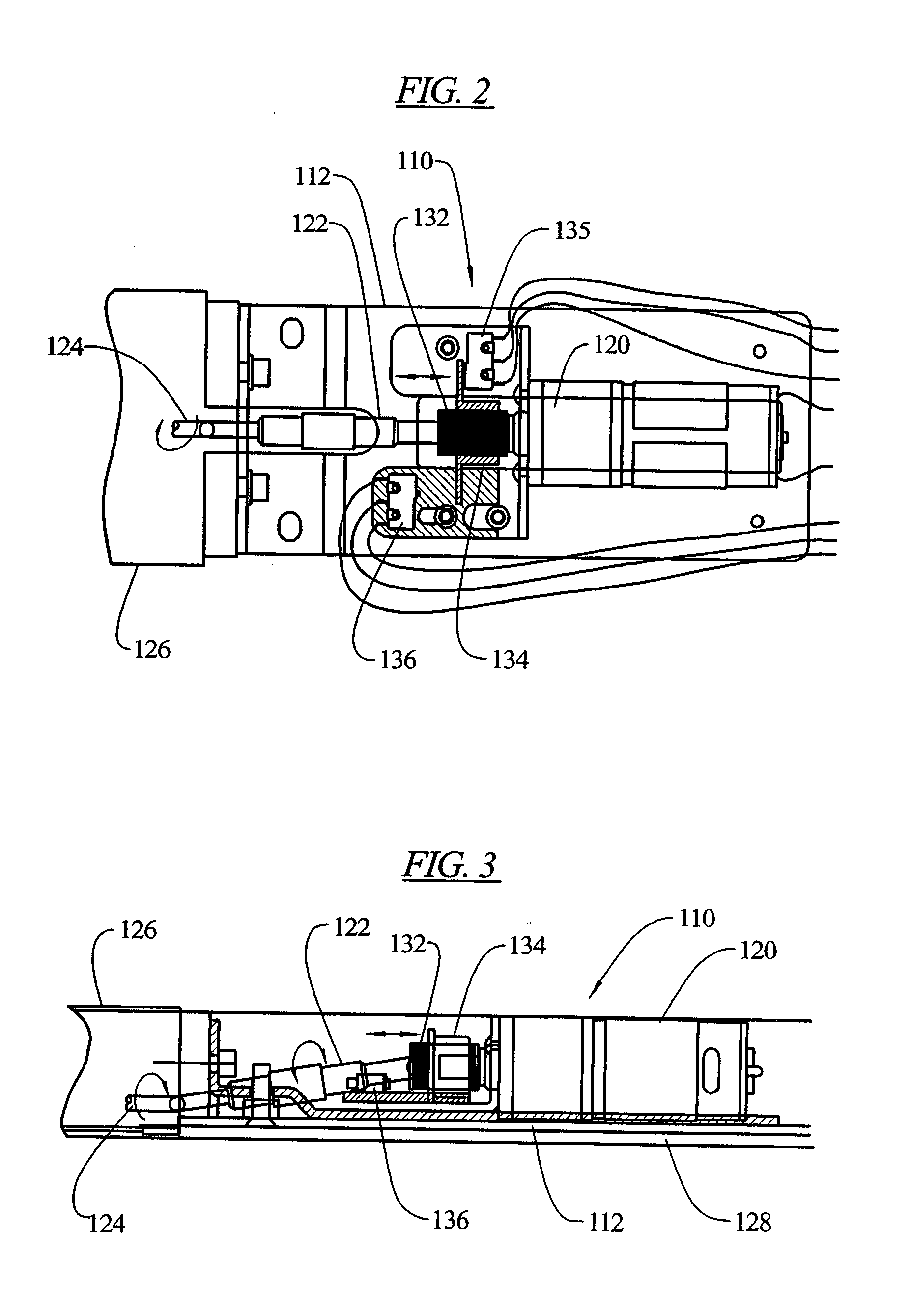

Robotic gesture recognition system

InactiveUS20080085048A1Lower levelDigital computer detailsAcceleration measurementLower body partApplication software

A gesture recognition system enabling control of a robotic device through gesture command by a user is provided, comprising a robotic unit, a video or infrared camera affixed to the robotic unit, computing means, and high and low level of control gesture recognition application code capable of enabling the system to locate points of left hand, right hand, upper torso and lower torso of the user in the video imagery and convert it to waveform data, correlate the waveform data to user command data, and form corresponding control voltage command(s) for production of electric current voltage(s) to drive one or more of the electric motors or actuators of the robotic device to thereby control same. In addition, a computer software program is provided for use in the gesture recognition system described above.

Owner:DEPT OF THE NAVY NAVAIR

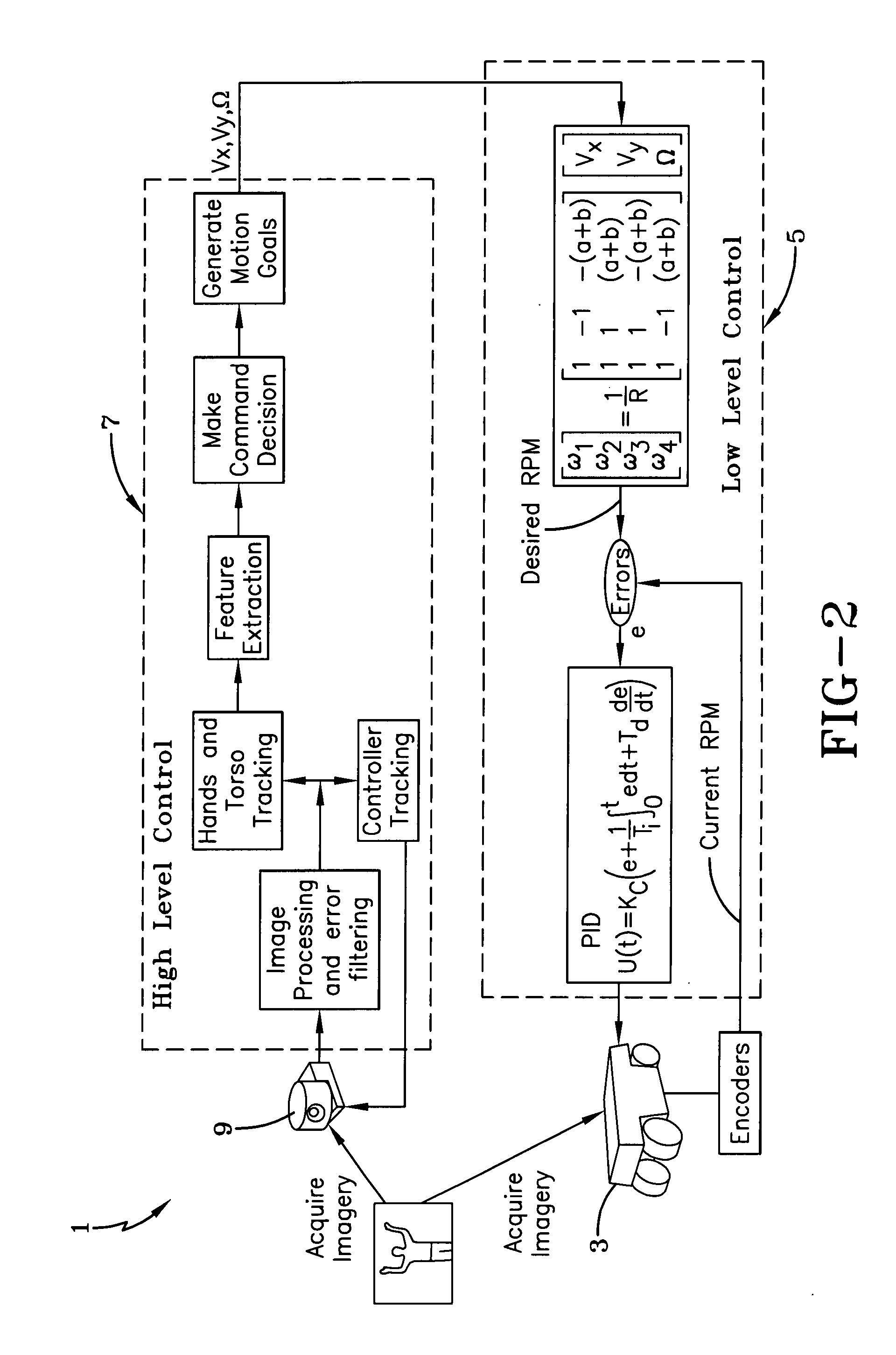

Robotic gesture recognition system

InactiveUS7606411B2Lower levelDigital computer detailsAcceleration measurementLower body partApplication software

A gesture recognition system enabling control of a robotic device through gesture command by a user is provided, comprising a robotic unit, a video or infrared camera affixed to the robotic unit, computing means, and high and low level of control gesture recognition application code capable of enabling the system to locate points of left hand, right hand, upper torso and lower torso of the user in the video imagery and convert it to waveform data, correlate the waveform data to user command data, and form corresponding control voltage command(s) for production of electric current voltage(s) to drive one or more of the electric motors or actuators of the robotic device to thereby control same. In addition, a computer software program is provided for use in the gesture recognition system described above.

Owner:DEPT OF THE NAVY NAVAIR

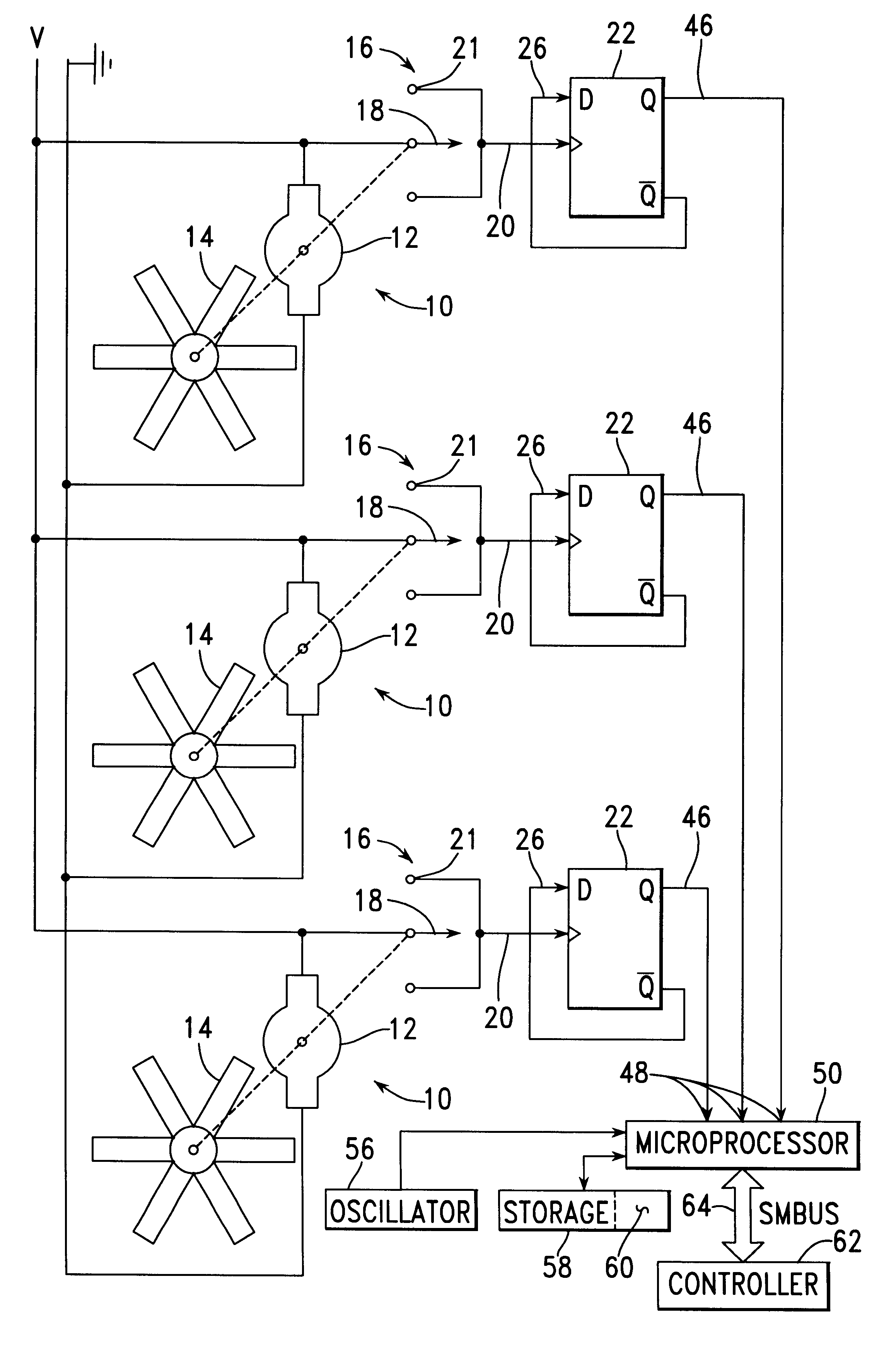

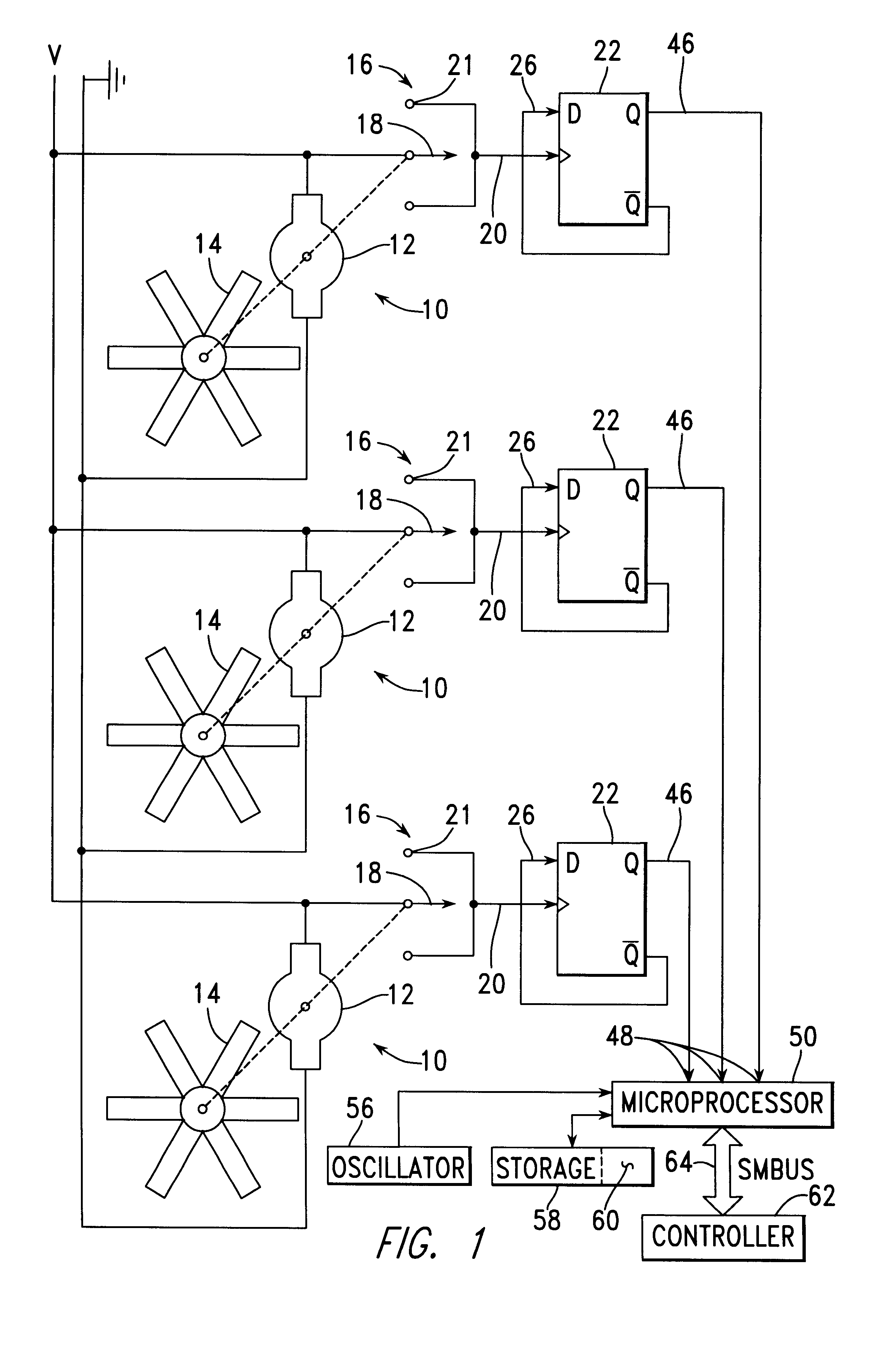

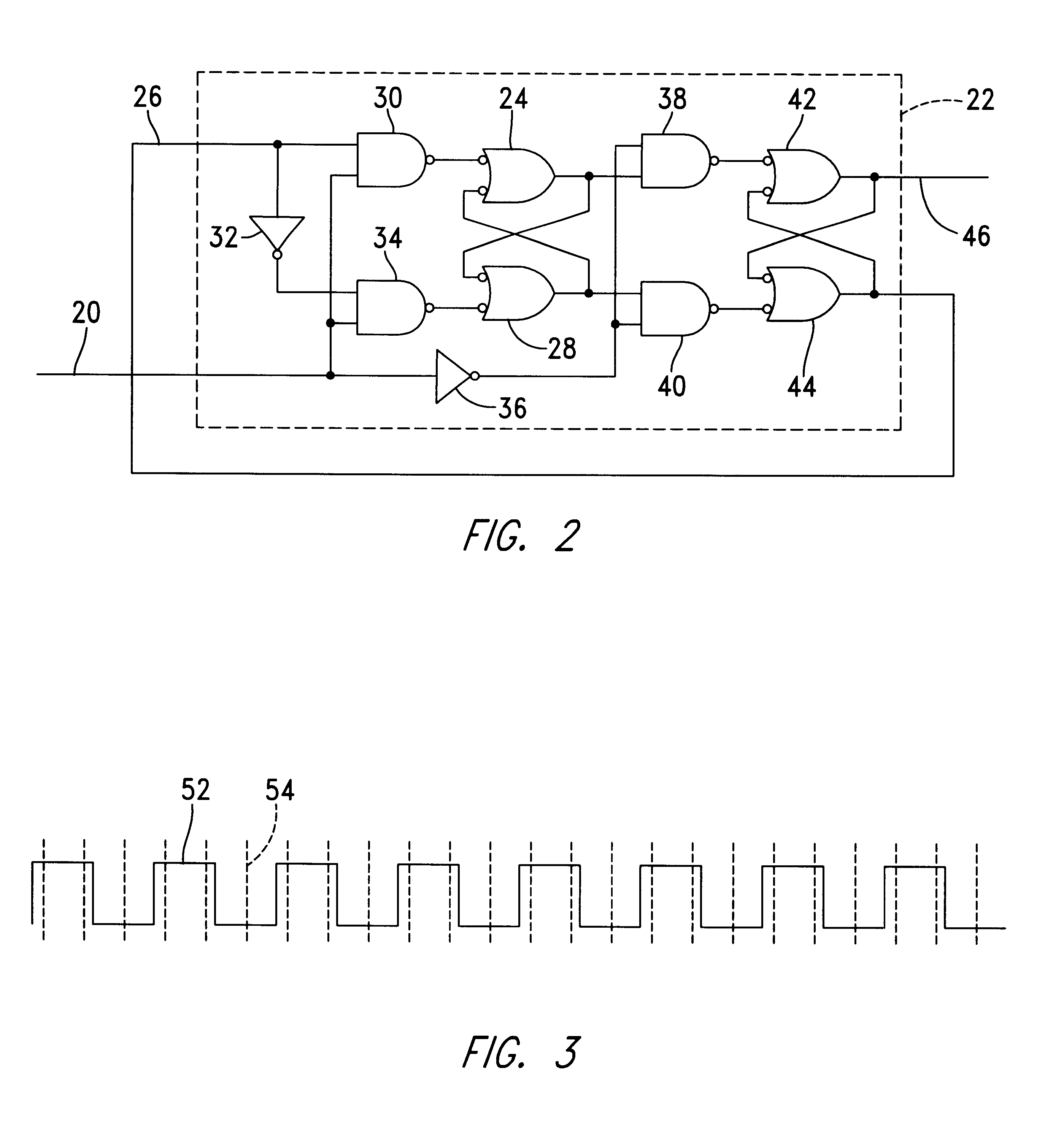

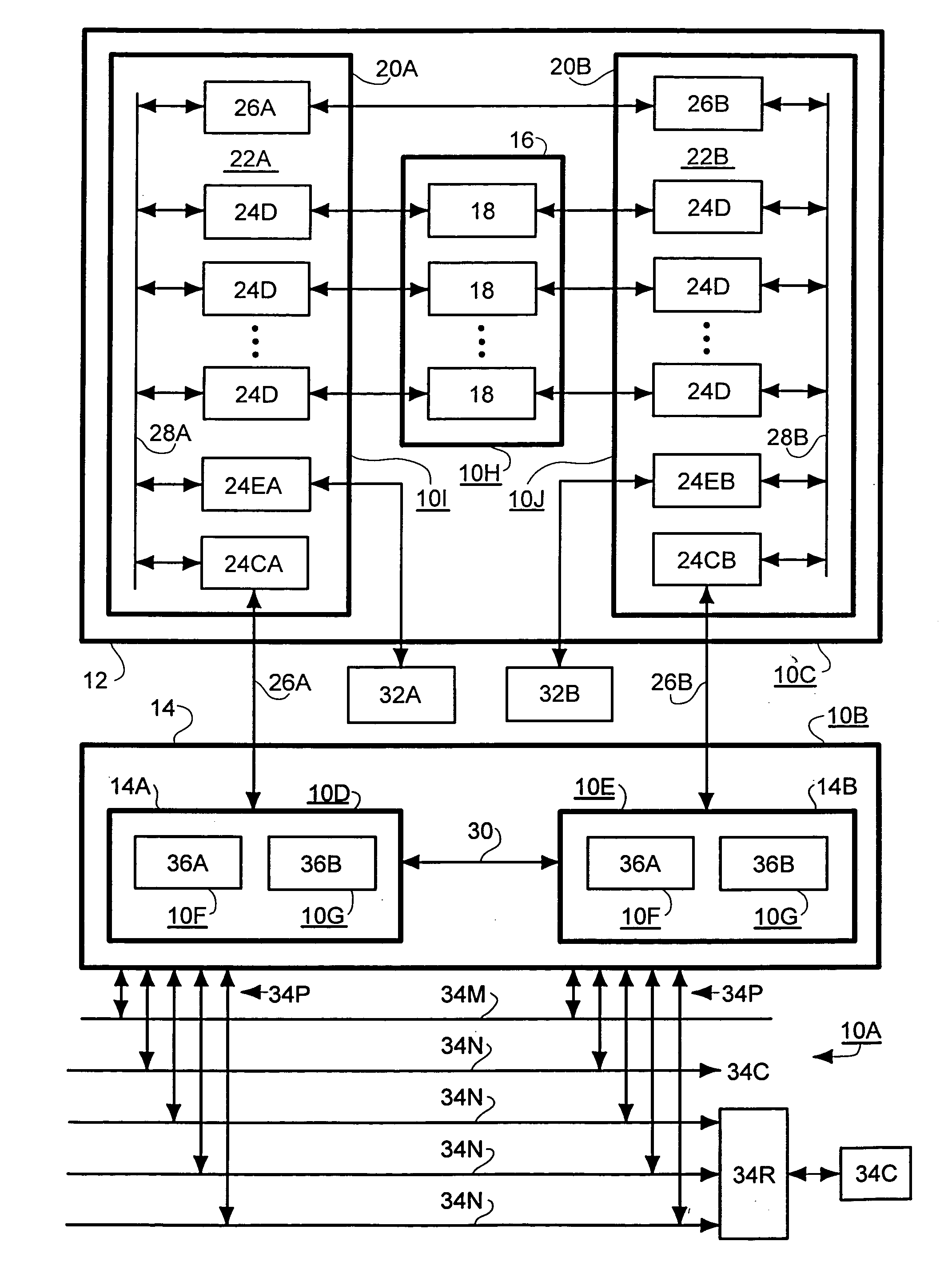

Apparatus and method for monitoring fan speeds within a computing system

InactiveUS6400113B1DC motor speed/torque controlElectric motor controlSignal generatorComputing systems

Apparatus for monitoring fan speeds within a computing system includes a tachometer turning with the fan, providing a tachometer signal including a number of pulses during each revolution of the fan. This tachometer signal is provided as an input to a signal generator in the form of a flip-flop, which generates a square-wave signal having transitions between high and low levels corresponding to tachometer signal pulses. The square-wave signals are provided as inputs to separate input ports of a microprocessor. These input ports are sequentially sampled at a rate providing at least two samples per period of the fastest square-wave signal, so that transitions of each square wave signal during a predetermined time interval can be detected and counted. For each input port, the number of counted transitions is compared to a stored acceptable value to establish whether the fan is operating in an acceptable speed range.

Owner:IBM CORP

Multiple hierarichal/peer domain file server with domain based, cross domain cooperative fault handling mechanisms

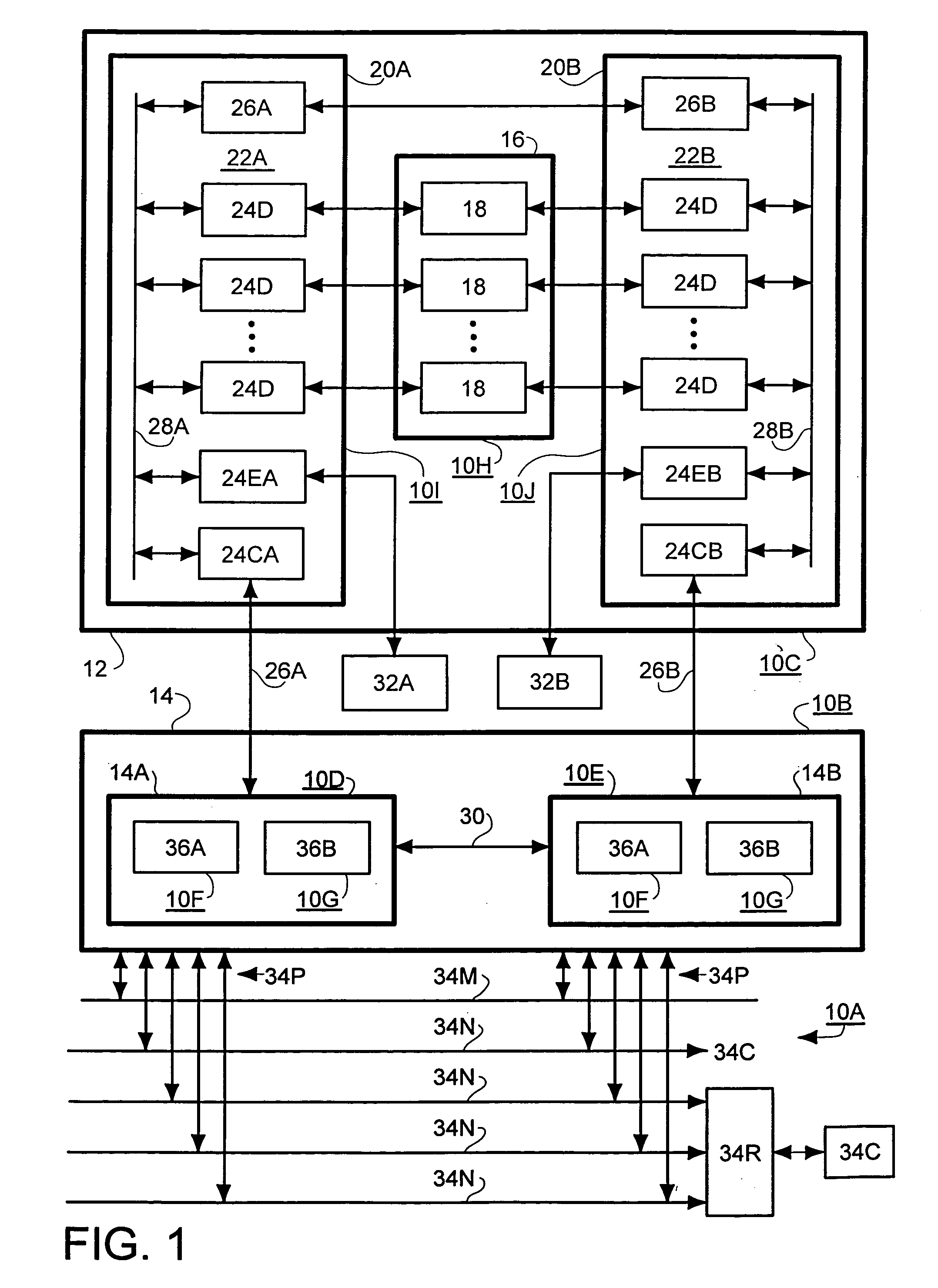

InactiveUS20040153710A1Error preventionEmergency protective arrangements for automatic disconnectionA domainFile server

A shared system resoure such as a file server includes an integrated, cooperative cluster of domains that include hierarchically related domains and peer related domains, each performing functions supporting the services provided by the system resource. Hierarchically related domains include a higher level domain and a lower level domain respectively performing higher and lower level operations of functions supporting the system resource services and peer related domains include parallel domains performing operations in mutual support of functions supporting the system resource services. A domain may include fault handling mechanisms operating independently of and cooperatively with fault handling mechanisms of other domains, and domain may be comprised of domains. In hierarchically related domains, the lower level domain includes peer related domains performing operations in mutual support of functions of the upper level domain and peer domain includes a monitoring mechanism monitoring operations of the other peer domain that are related to the operations performed in support of the upper level domain. Each monitoring mechanism is responsive to detection of a failure in the other peer domain for directing the peer domain in which the monitoring mechanism resides in assuming the operations performed by the peer domain in support of related functions of the upper level domain independently of operations of the peer domain and independently of a source of the failure in the other peer domain.

Owner:EMC IP HLDG CO LLC

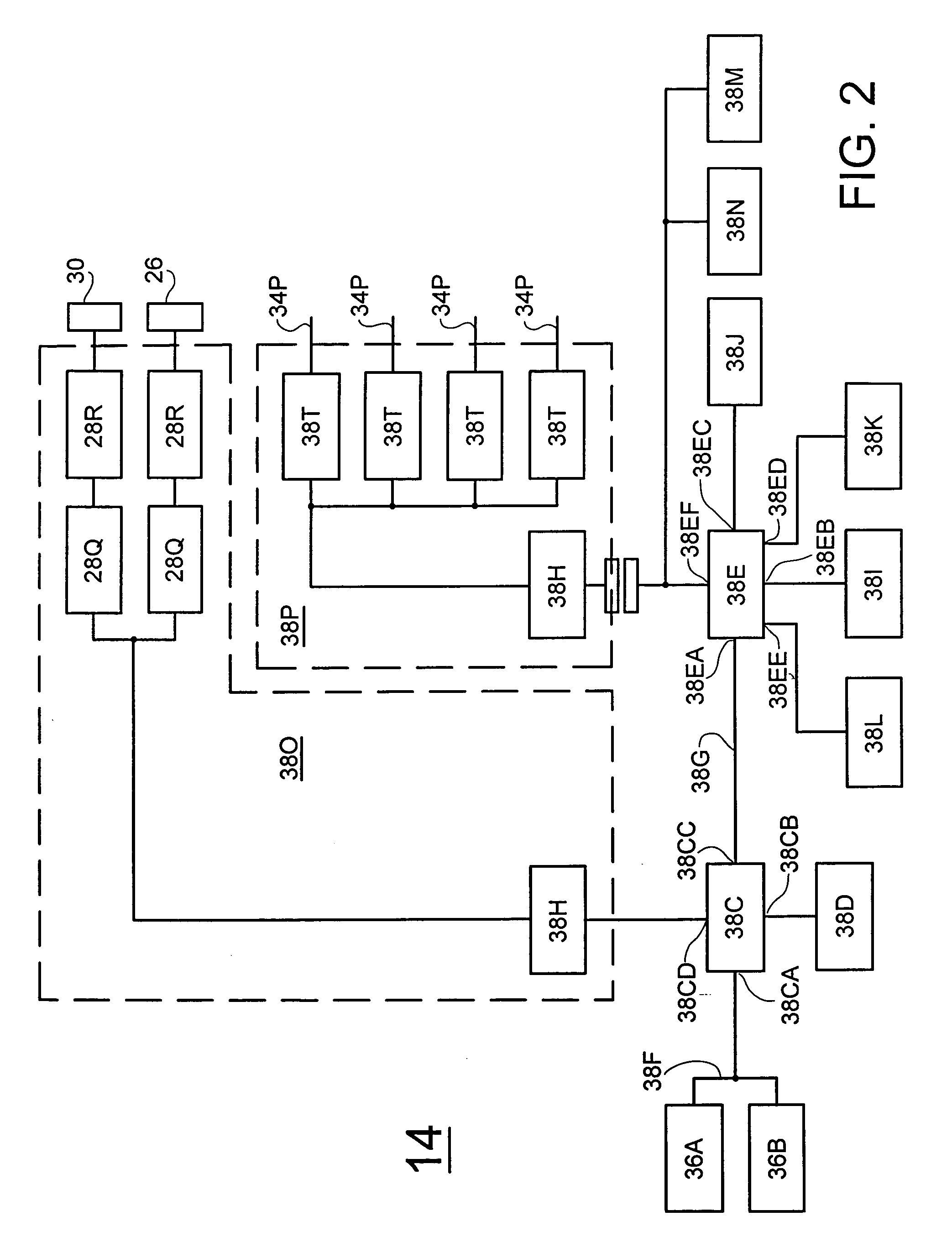

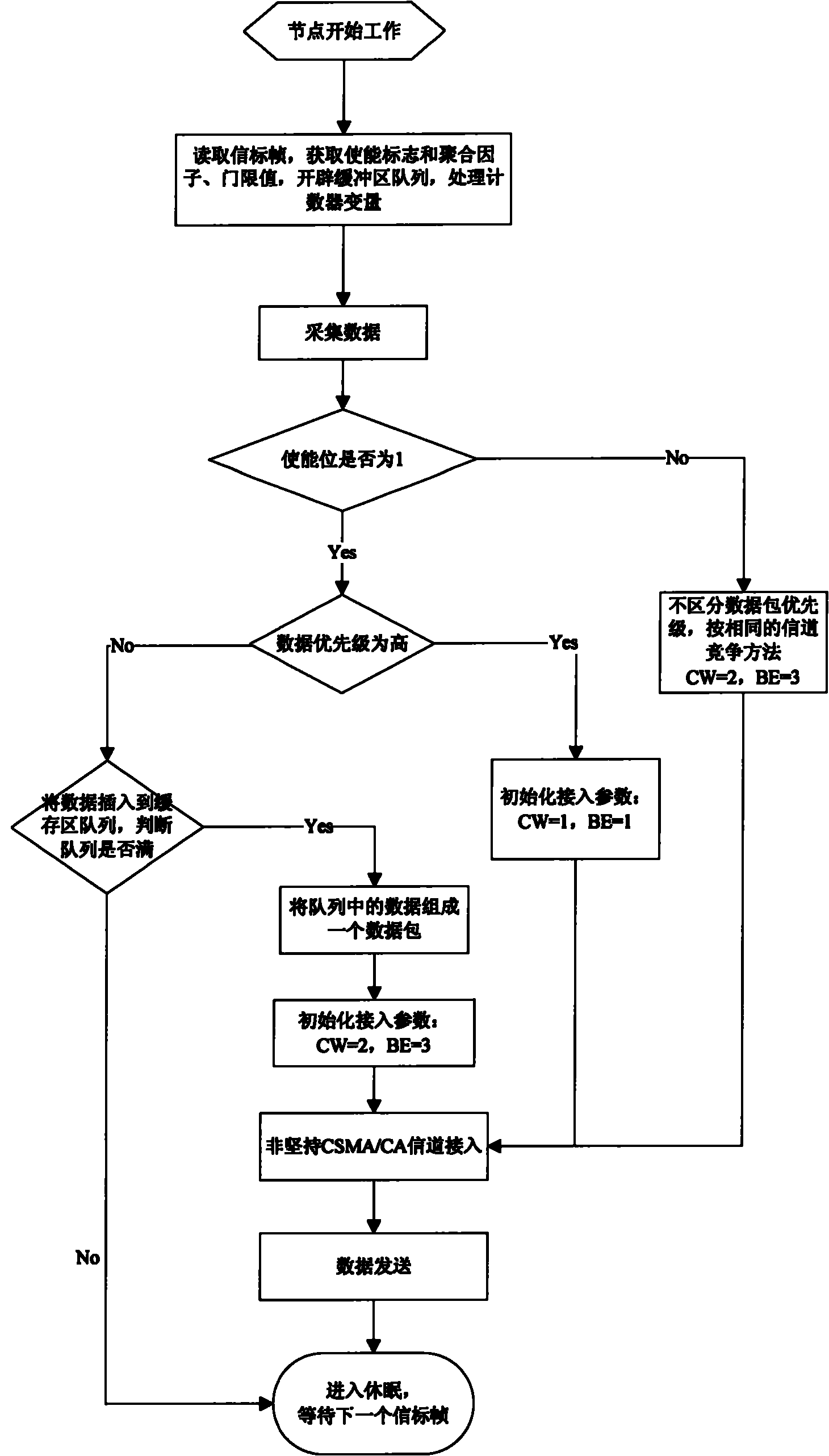

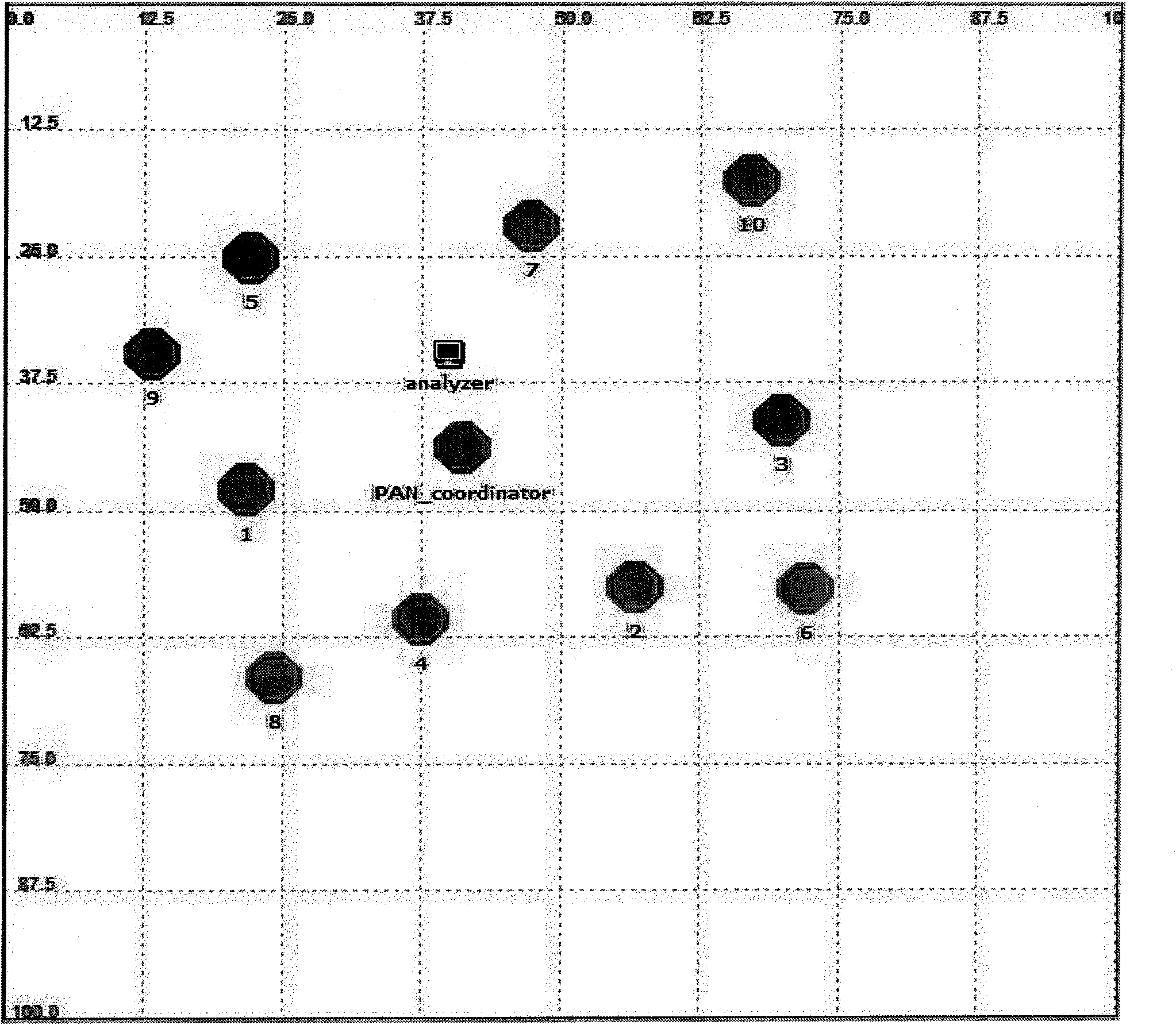

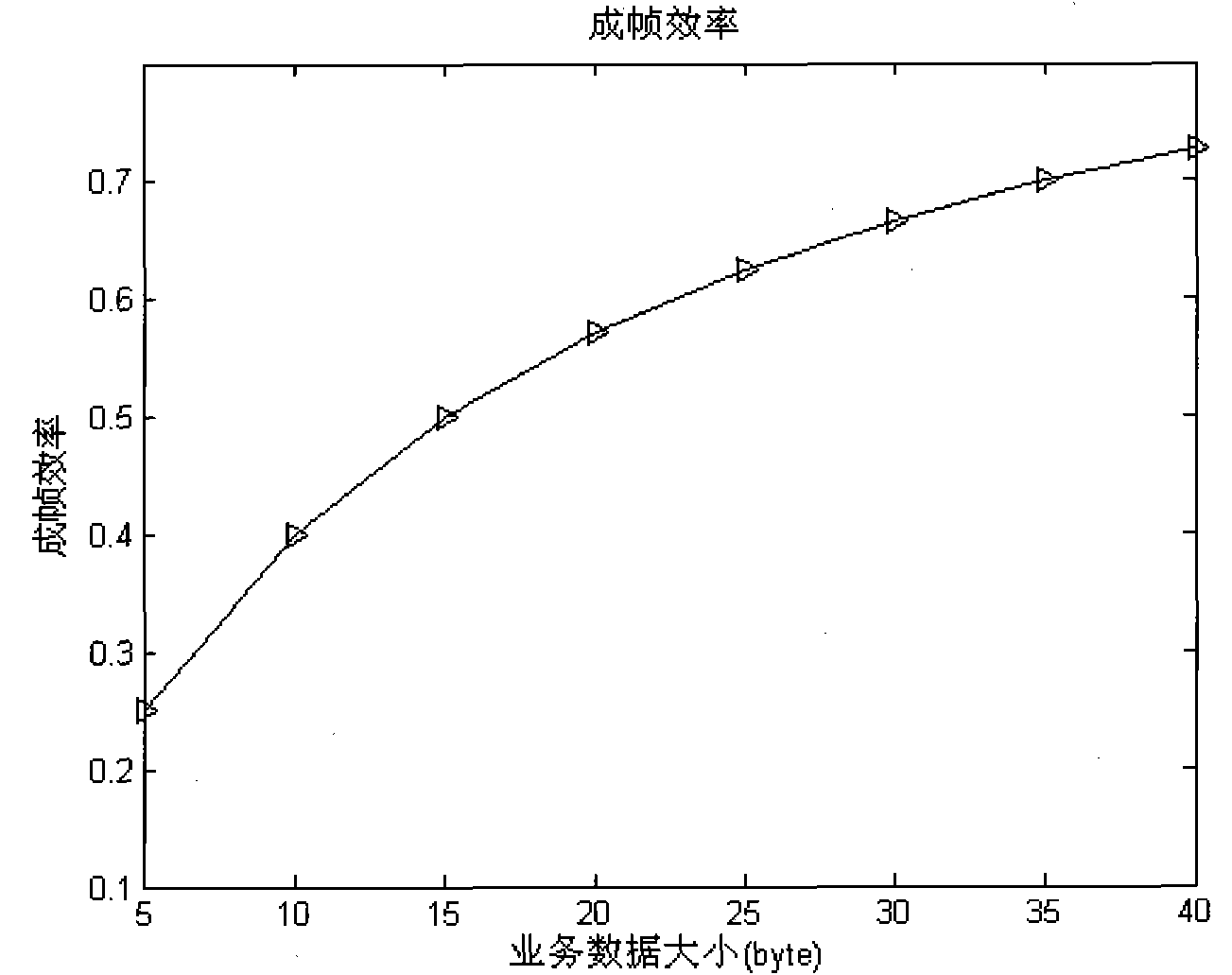

Data priority-based channel contention access method for wireless sensor network

InactiveCN101795498AImprove timelinessIncrease configuration flexibilityEnergy efficient ICTNetwork topologiesAccess methodNetwork packet

The invention discloses a data priority-based channel contention access method for a wireless sensor network. The method of the invention ensures different performance index requirements by adopting different channel access mechanisms according to the priority levels (high and low levels) of data packets. In addition, aggregation factors are introduced into the transmission of the data packets, and the data packets are aggregated by using the local calculation and storage capacity of a node on the premise of meeting the specific network performance requirement, so the framing efficiency is improved and the energy consumption efficiency is further improved. Through the parameter aggregation factors, the network can be flexibly selected between the energy consumption efficiency and the data average packet delay.

Owner:SOUTHEAST UNIV

Sleep apnea treatment apparatus

InactiveUS20060118112A1Easy to operateReduce pressureRespiratorsOperating means/releasing devices for valvesPositive airway pressureRemote control

Improved methodology and apparatus for the clinical study and treatment of sleep apnea which incorporates one or more of the following features: (1) application of mono-level, alternating high and low level, or variable positive airway pressure generally within the airway of the patient with the mono-level, high and low level, or variable airway pressure generally being coordinated with and / or responsive to the spontaneous respiration of the patient, (2) usage of adjustably programmable pressure ramp circuitry capable of producing multiple pressure ramp cycles of predetermined duration and pattern whereby the ramp cycles may be customized to accommodate the specific needs of an individual sleep apnea patient so as to ease the patient's transition from wakefulness to sleep, (3) remote control or patient-sensed operation of the apparatus, (4) employment of safety circuitry, reset circuitry and minimum system leak assurance circuitry, controls and methods, and (5) utilization of clinical control circuitry whereby sleep disorder data may be compiled and appropriate therapy implemented during a one-night sleep study.

Owner:RIC INVESTMENTS LLC

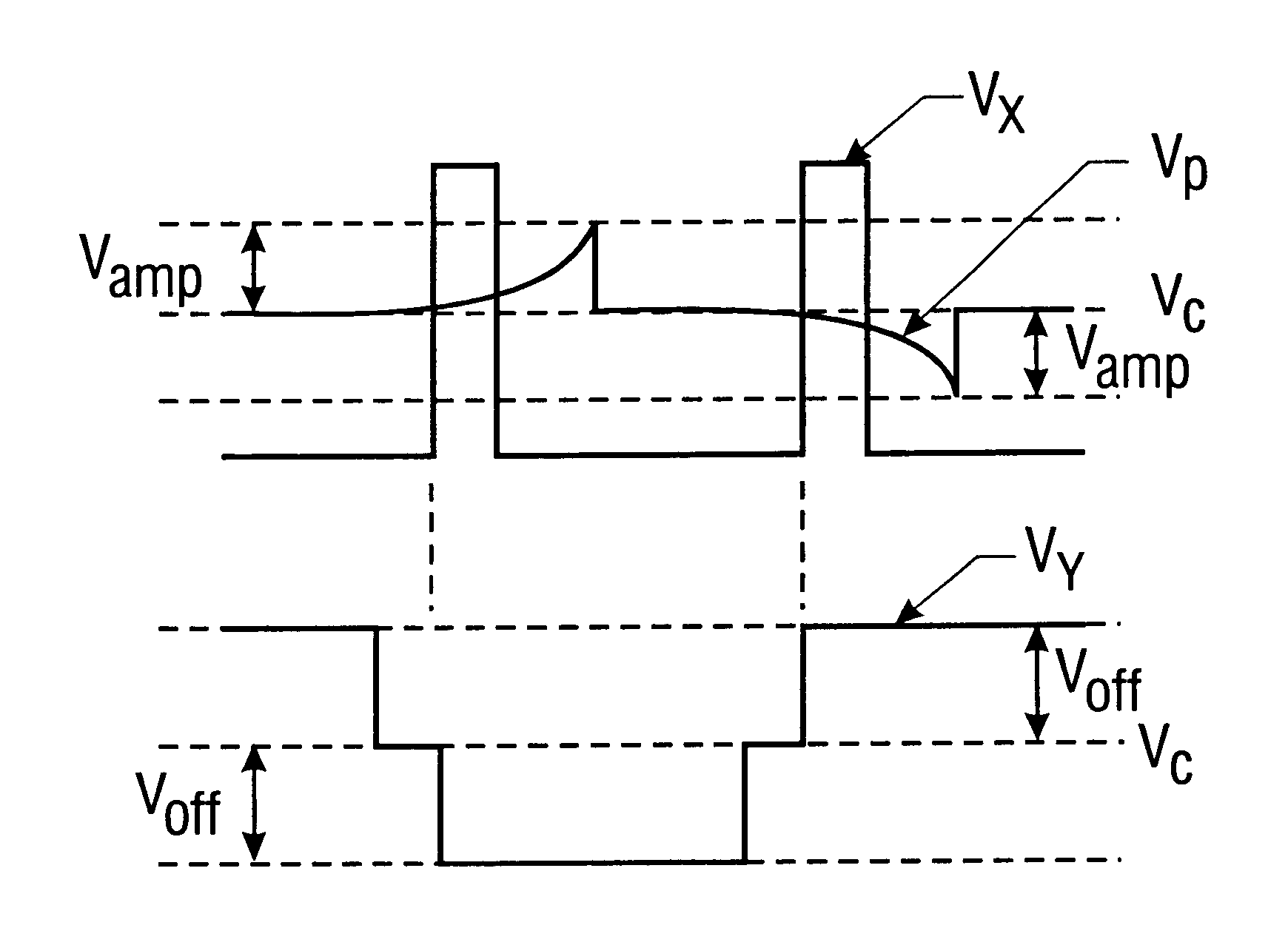

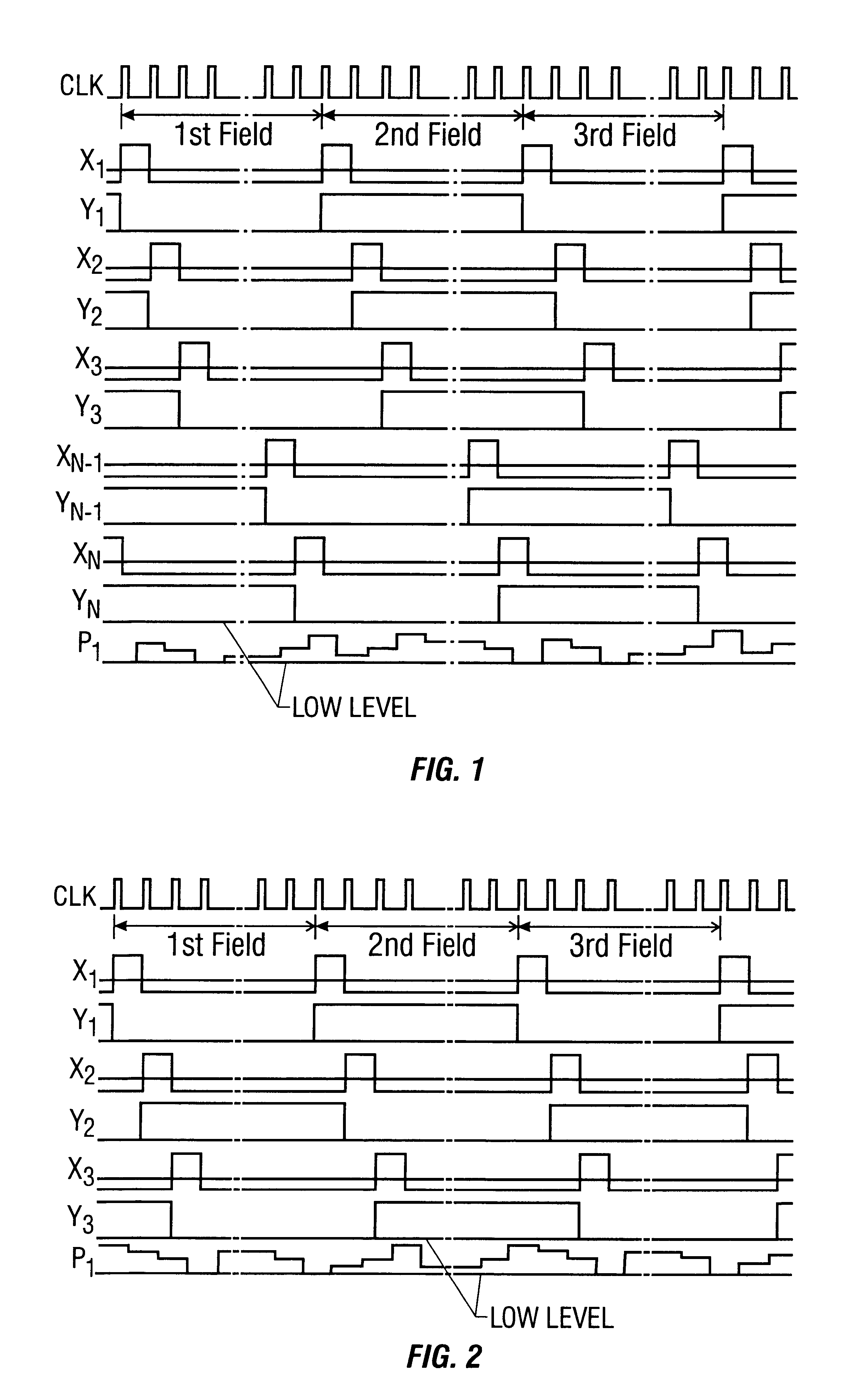

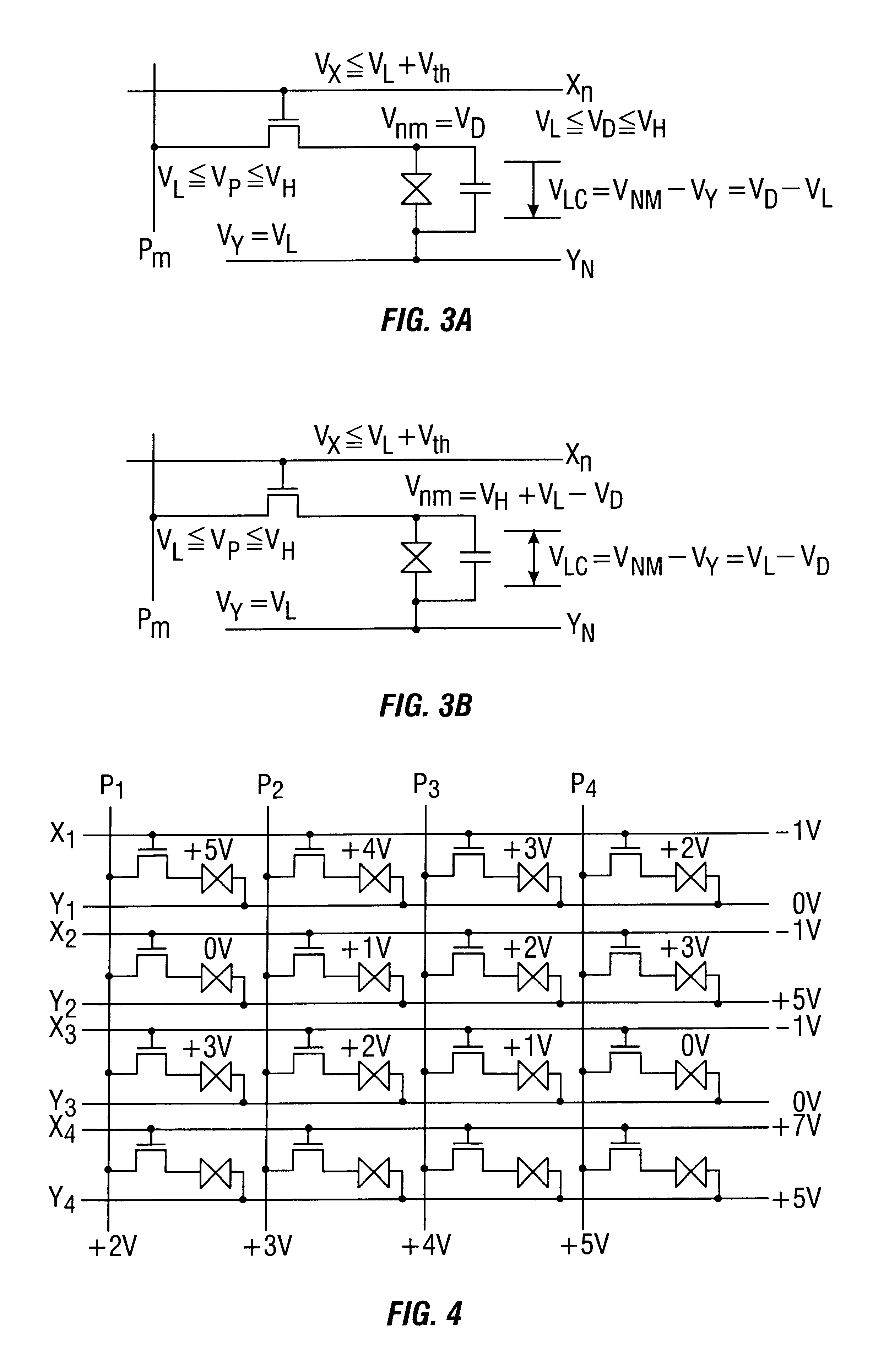

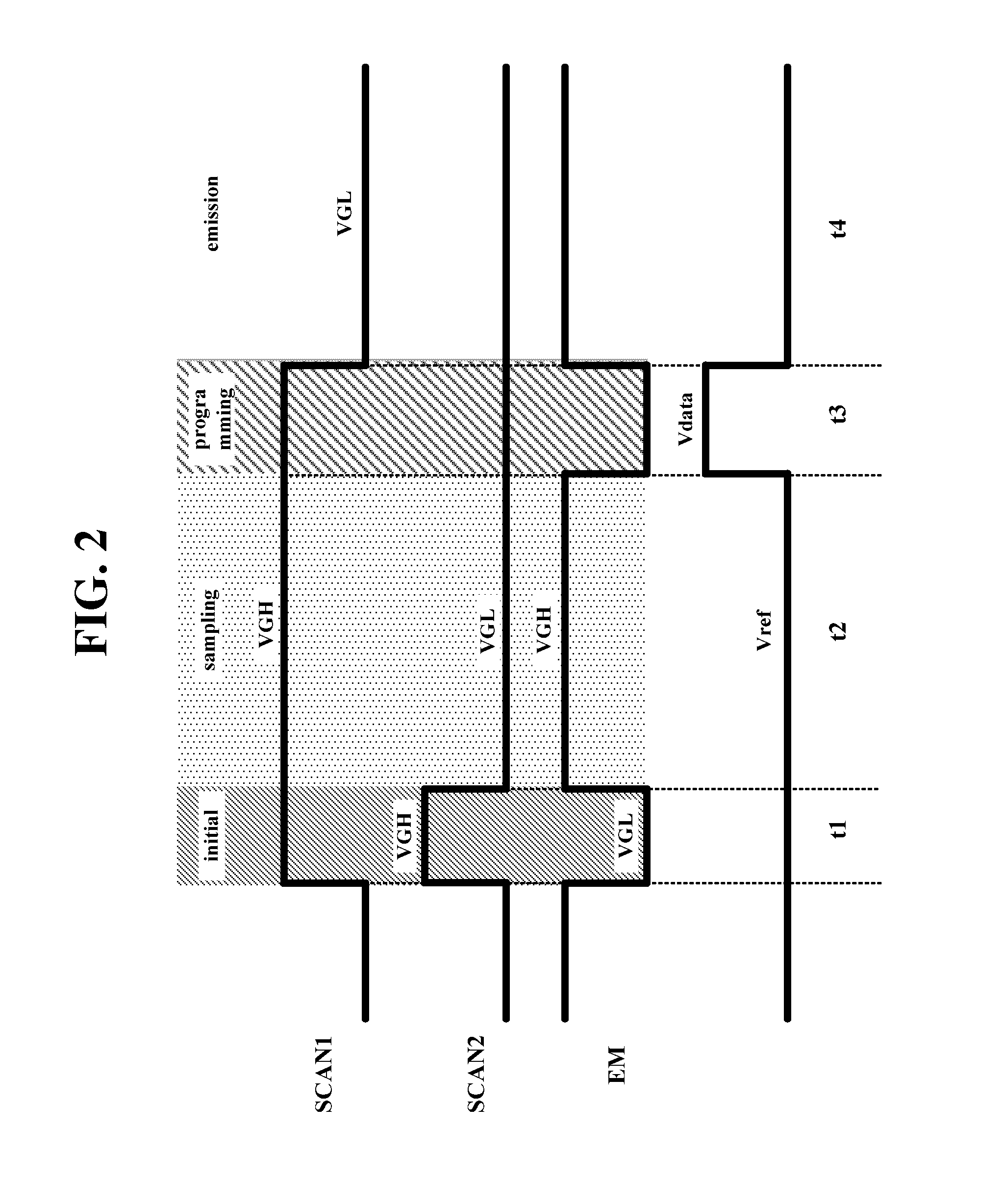

Driving method of active matrix display device

InactiveUS6911962B1Disorder in alignmentReduce potential variation rangeCathode-ray tube indicatorsInput/output processes for data processingIn planeLiquid-crystal display

In a liquid crystal display device of the in-plane switching mode (IPS mode), the potential of data that is output from a data driver is set at values between potentials that are given to common lines. Two levels, i.e., high and low levels, are prepared for the potential to be given to the common lines and the potential is inverted between those levels in every field, whereby the polarity of a voltage between both electrodes of a pixel is inverted. As a result, the potential variation ranges of signals that are output from the data driver and a scan driver can be greatly reduced from those of the conventional case, which contributes to reduction in the power consumption of the drivers. Since the voltage applied to a switching element for controlling each pixel can be reduced, the load of the switching element can also be reduced.

Owner:SEMICON ENERGY LAB CO LTD

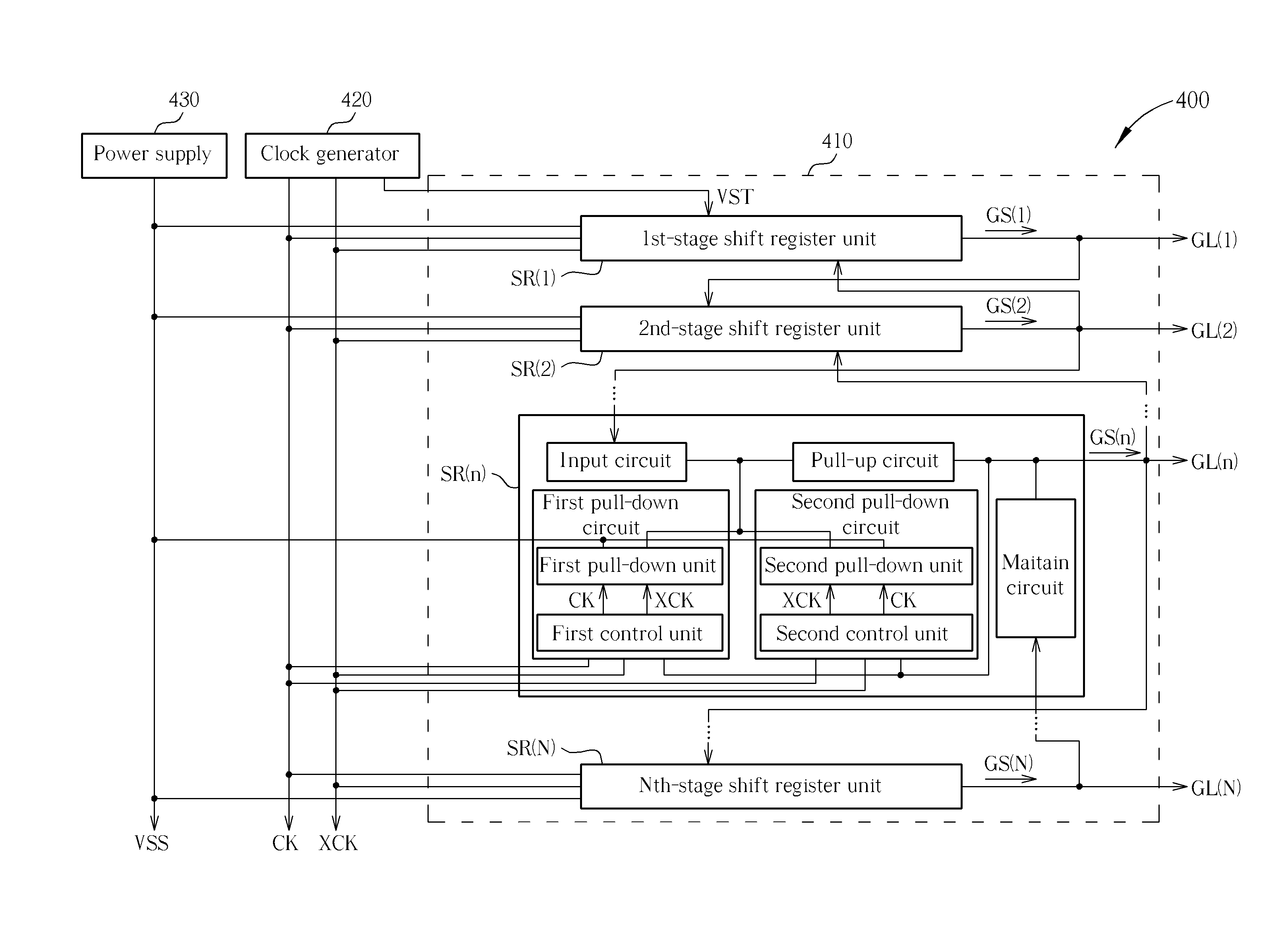

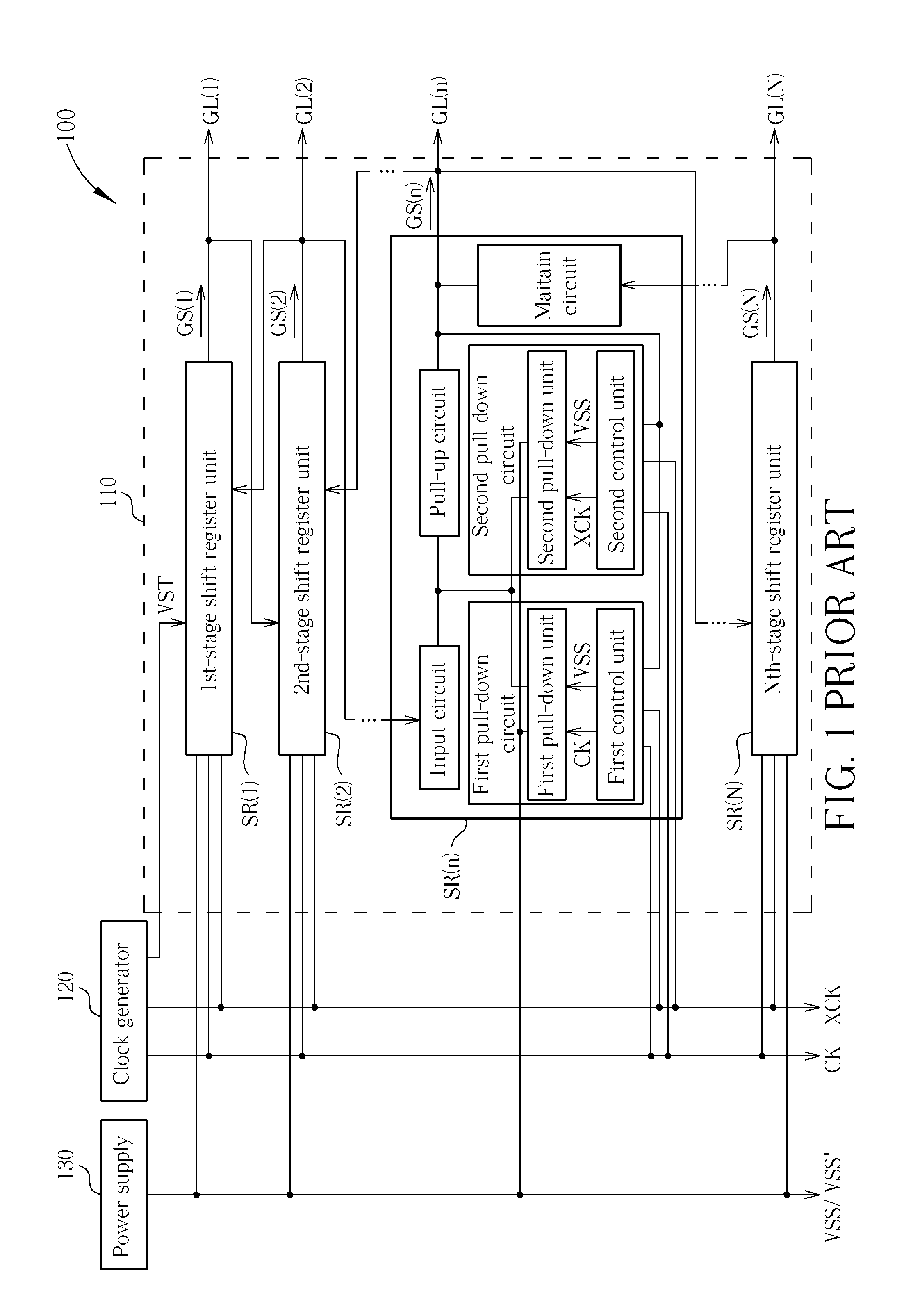

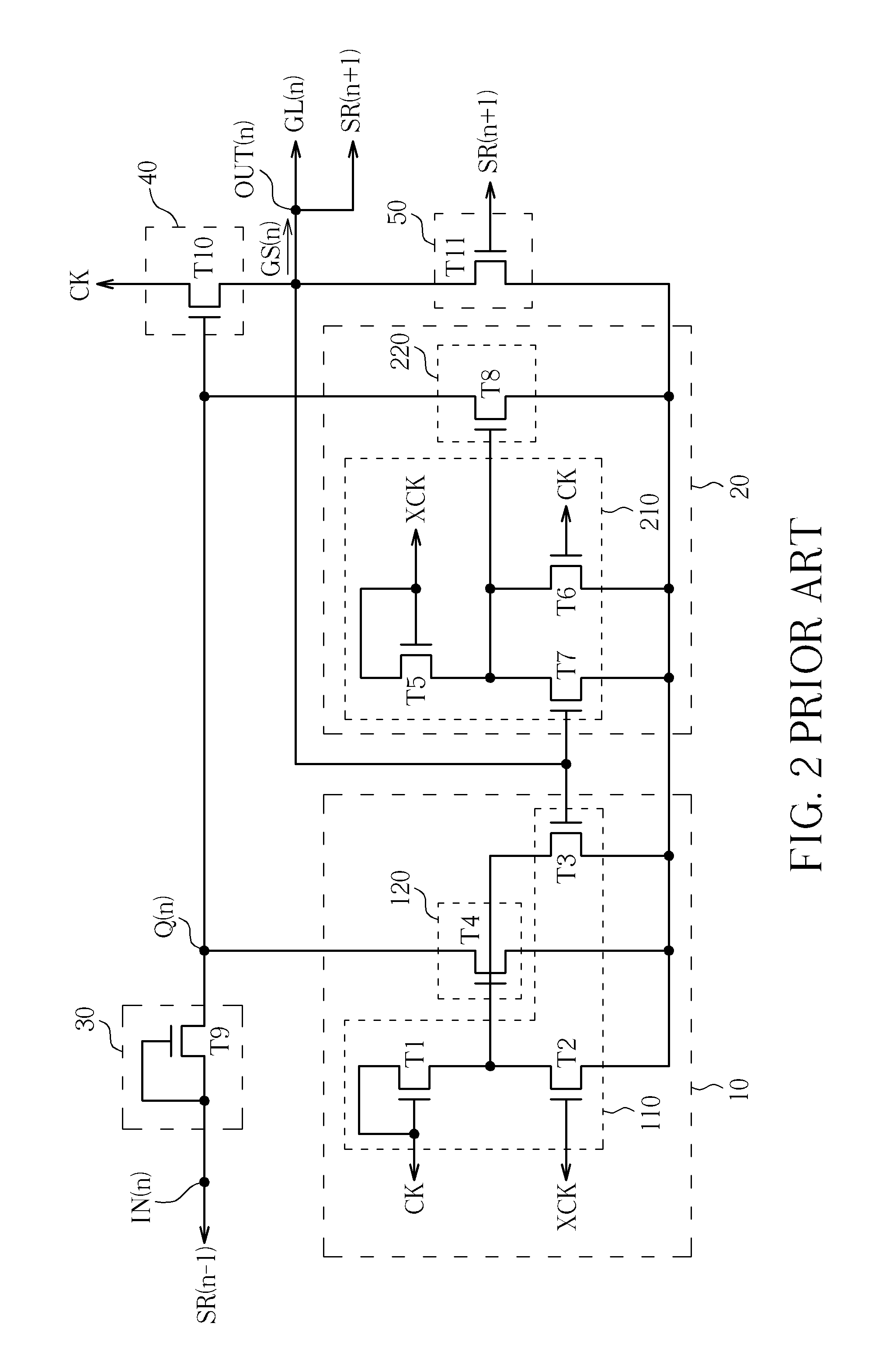

Shift register and a liquid crystal display device having the same

A shift register of an LCD device operates based on two clock signals and maintains the gate voltage of an output transistor switch using two pull-down transistor switches. The gate voltages of the pull-down transistor switches are switched periodically between the high and low level of the clock signals. During the output period, the transistor switches have negative gate-source voltages so as to reduce leakage.

Owner:AU OPTRONICS CORP

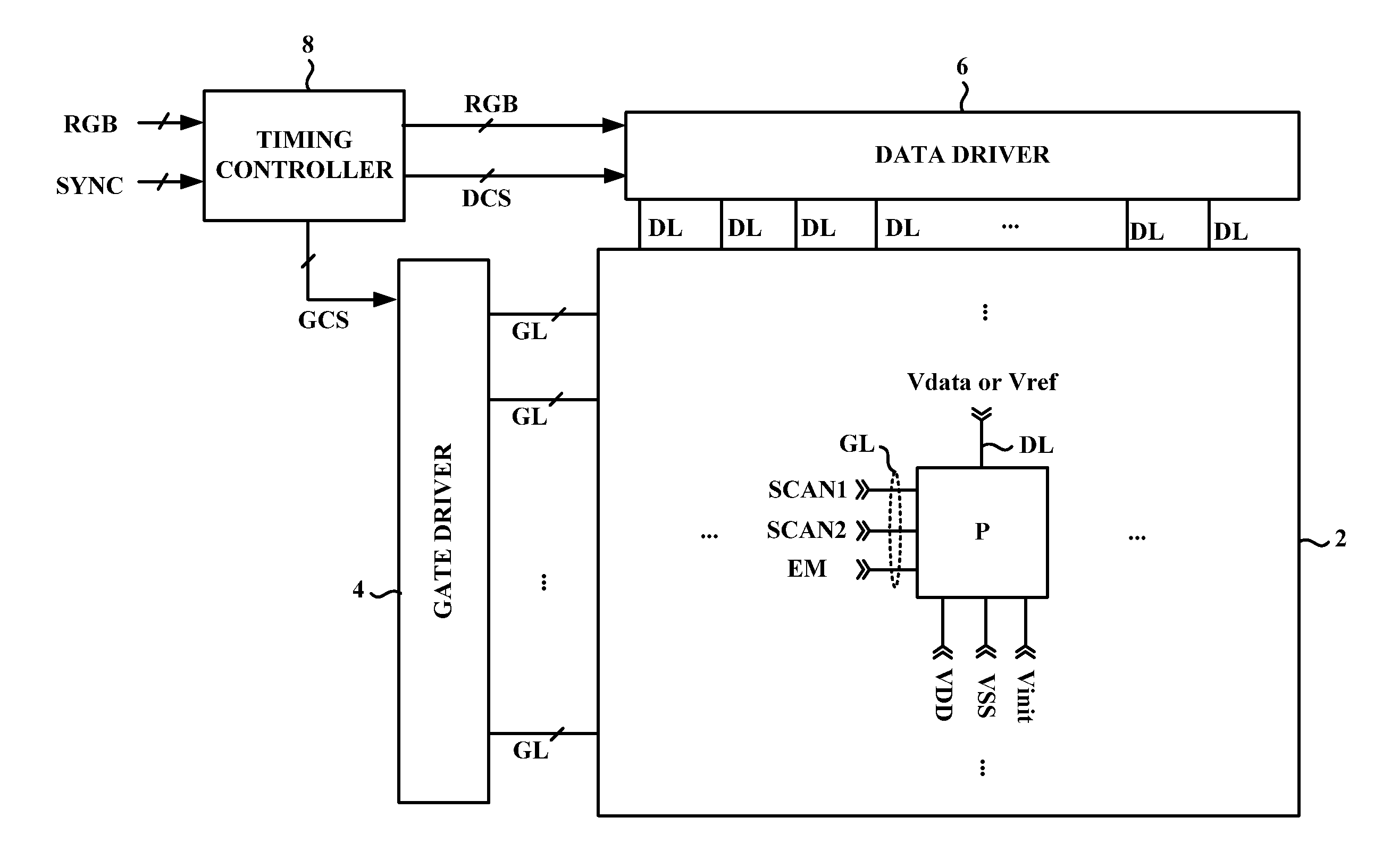

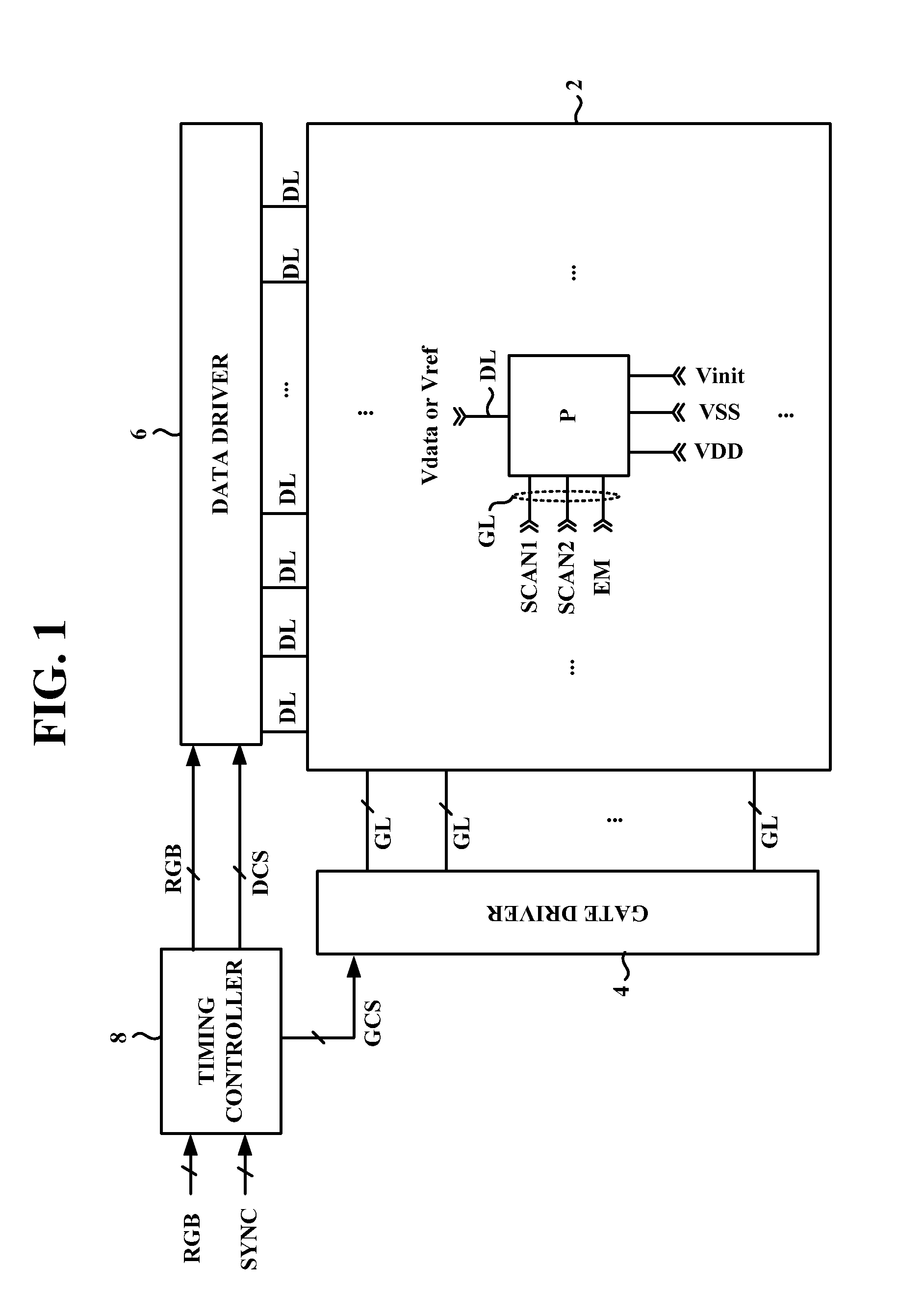

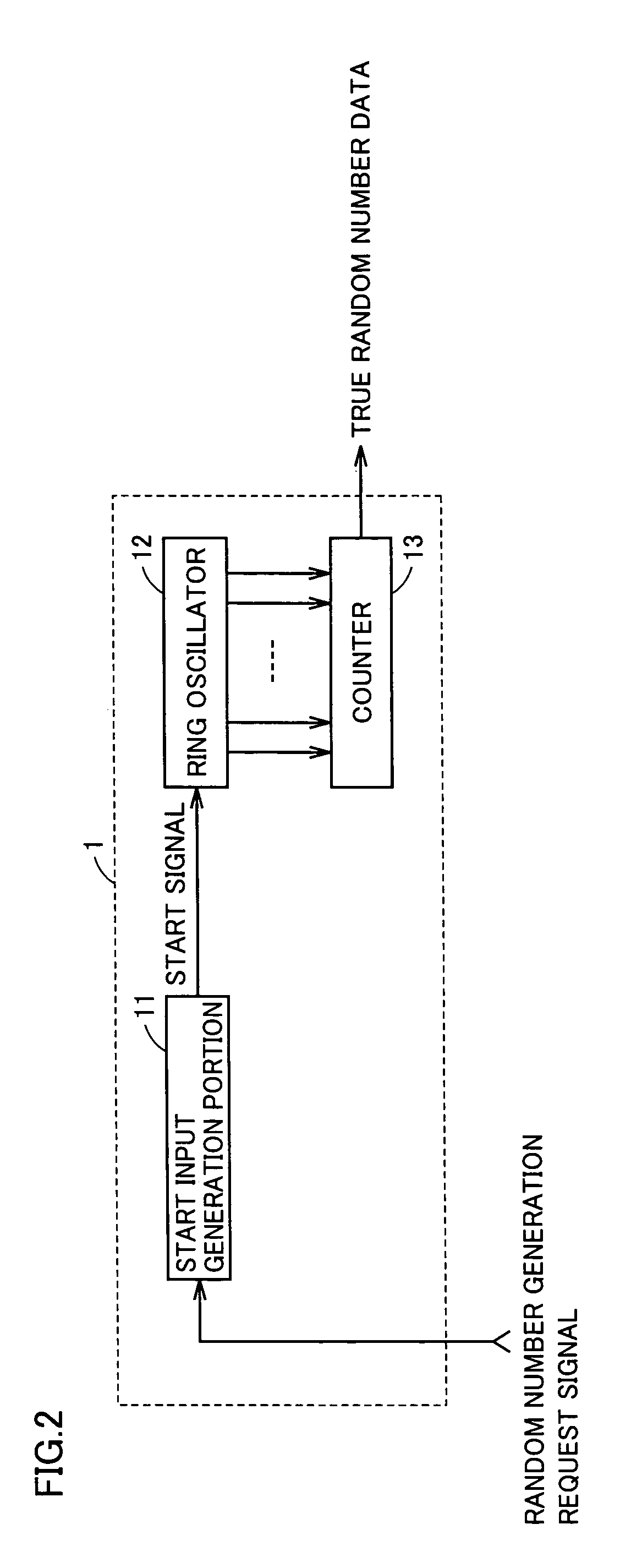

Organic light emitting diode display device and method for driving the same

ActiveUS20140184665A1Reduce brightness deviationImprove picture qualityCathode-ray tube indicatorsInput/output processes for data processingDisplay deviceEngineering

Discussed are an organic light emitting diode (OLED) display device and a method for driving the same. The OLED display device includes pixels each including a light emitting element, and a pixel driving circuit. The pixel driving circuit includes a driving switching element connected in series between high and low-level voltage supply lines, together with the light emitting element, a first switching element for connecting a data line and a first node connected to a gate of the driving switching element in response to a first scan signal, a second switching element for connecting an initialization voltage supply line and a second node connected to a source of the driving switching element in response to a second scan signal, and a third switching element for connecting the high-level voltage supply line and a drain of the driving switching element in response to an emission signal.

Owner:LG DISPLAY CO LTD

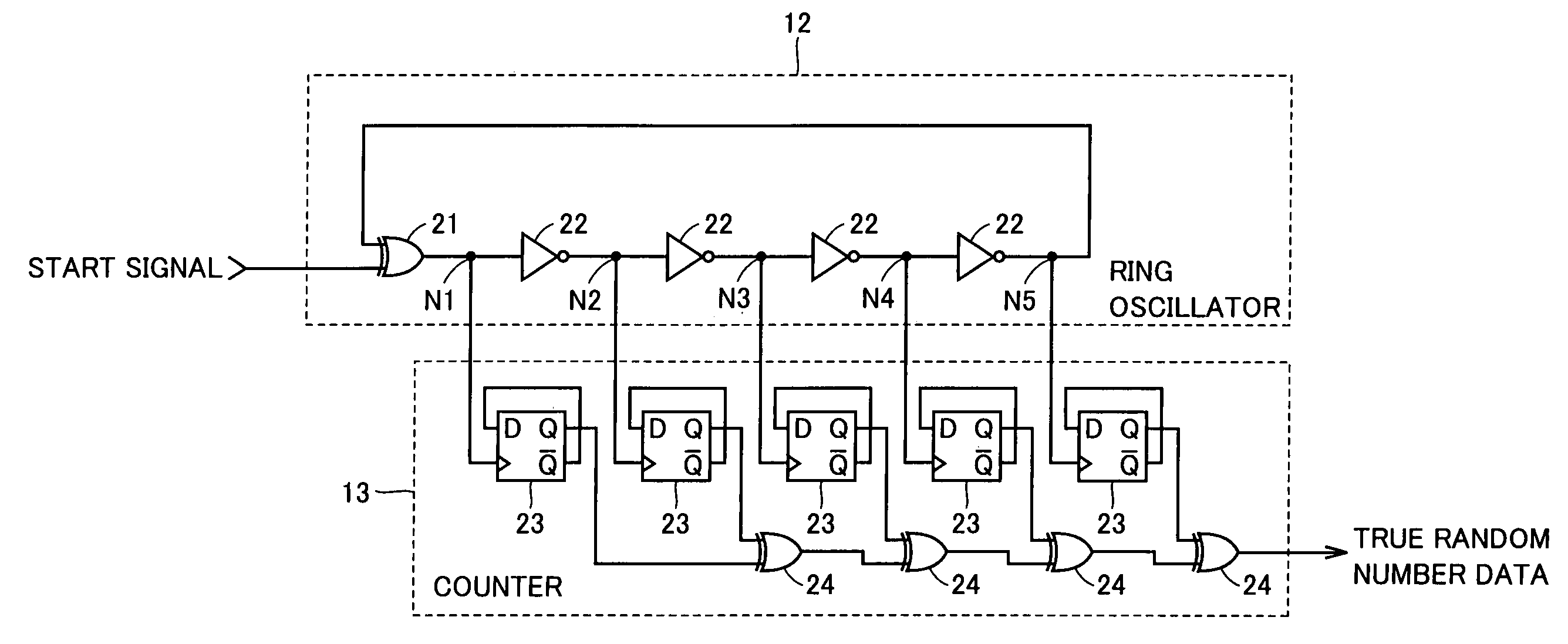

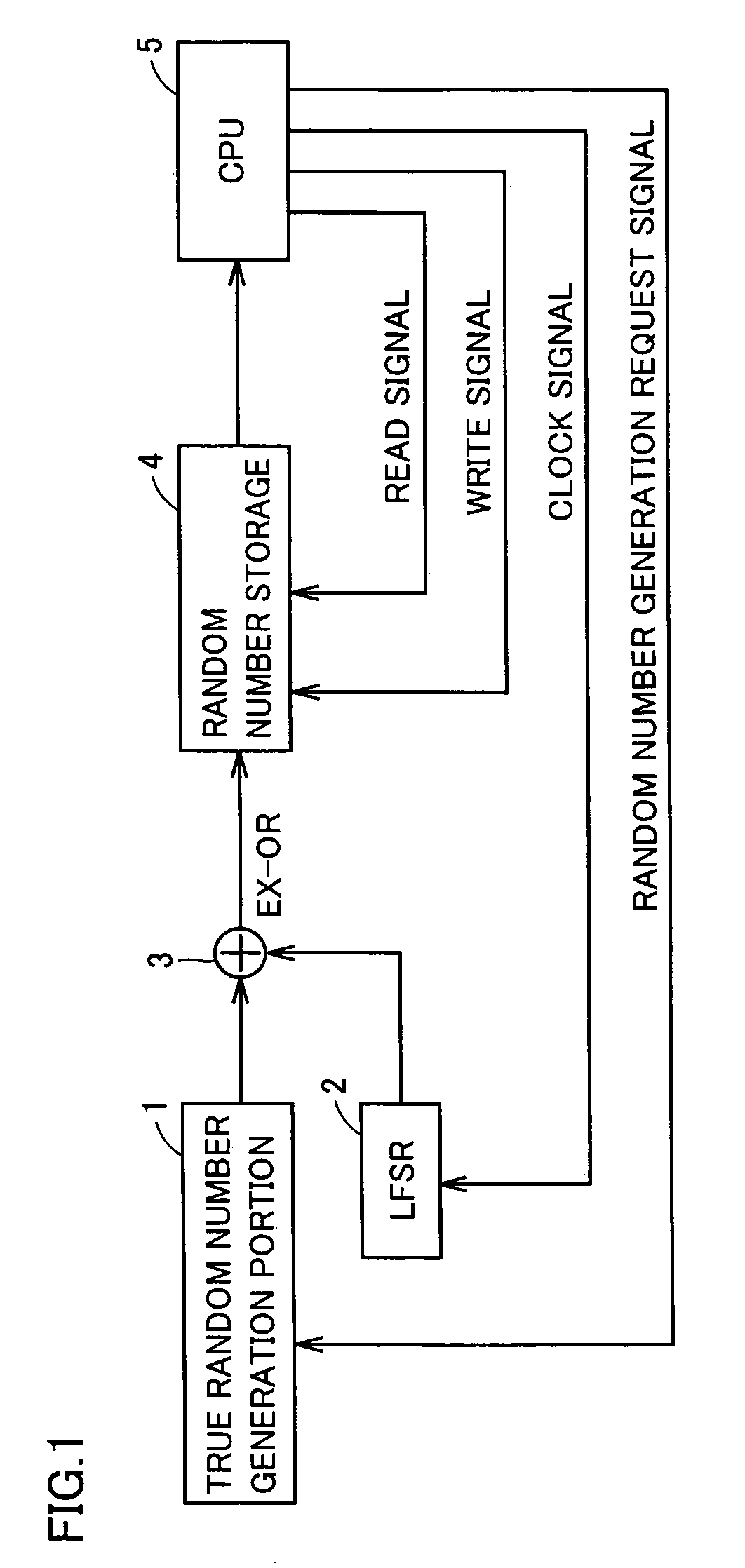

Random number generator with ring oscillation circuit

ActiveUS7424500B2Reduce power consumptionImprove performanceRandom number generatorsElectrical apparatusStable stateDelayed time

A random number generator includes a ring oscillator having an EX-OR gate and four inverters together forming a loop. This loop enters stable state for a start signal having the low level and oscillates for the start signal having the high level. When the start signal has a pulse of a width shorter than the loop's delay time, output nodes responsively, sequentially enter metastable state hovering between the high and low levels. The metastable waveform becomes smaller with time and finally disappears. As metastable state cannot be controlled in longevity, it disappears at any random number node. A counter thus outputs a signal serving as true random number data depending on the longevity of the metastable state. A random number generator miniaturized and having reduced power consumption, and of high performance can thus be implemented.

Owner:RENESAS LSI DESIGN CORP +1

SIM (subscriber identity module) card clamping seat, mobile terminal and method for identifying hot plugging of SIM card

ActiveCN102709725ATroubleshoot hotplug issuesEasy identification of hot plugPower supply linesCoupling contact membersEngineeringComputer terminal

The embodiment provided by the invention provides a SIM (subscriber identity module) card clamping seat, a mobile terminal and a method for identifying the hot plugging of a SIM card. In the prior art, a base of the SIM card clamping seat is provided with a metal contact and a first fixed metal pin connected with the metal contact. According to the invention, on the basis of the prior art, an additional metal spring plate is arranged on the base of the SIM card clamping seat for being in an unpressed state and in contact with a high level when the SIM card is not inserted, being in a pressed state and in contact with a low level when the SIM card is inserted and identifying the insertion and the plug-out of the SIM card by transmitting the high and low levels to a main chip of the mobile terminal. The invention relates to the field of mobile communication; the insertion and the plug-out of the SIM card can be identified without increasing devices, so that the space of a main board is further saved; and the production process is also not influenced and the production cost is reduced.

Owner:ZTE CORP

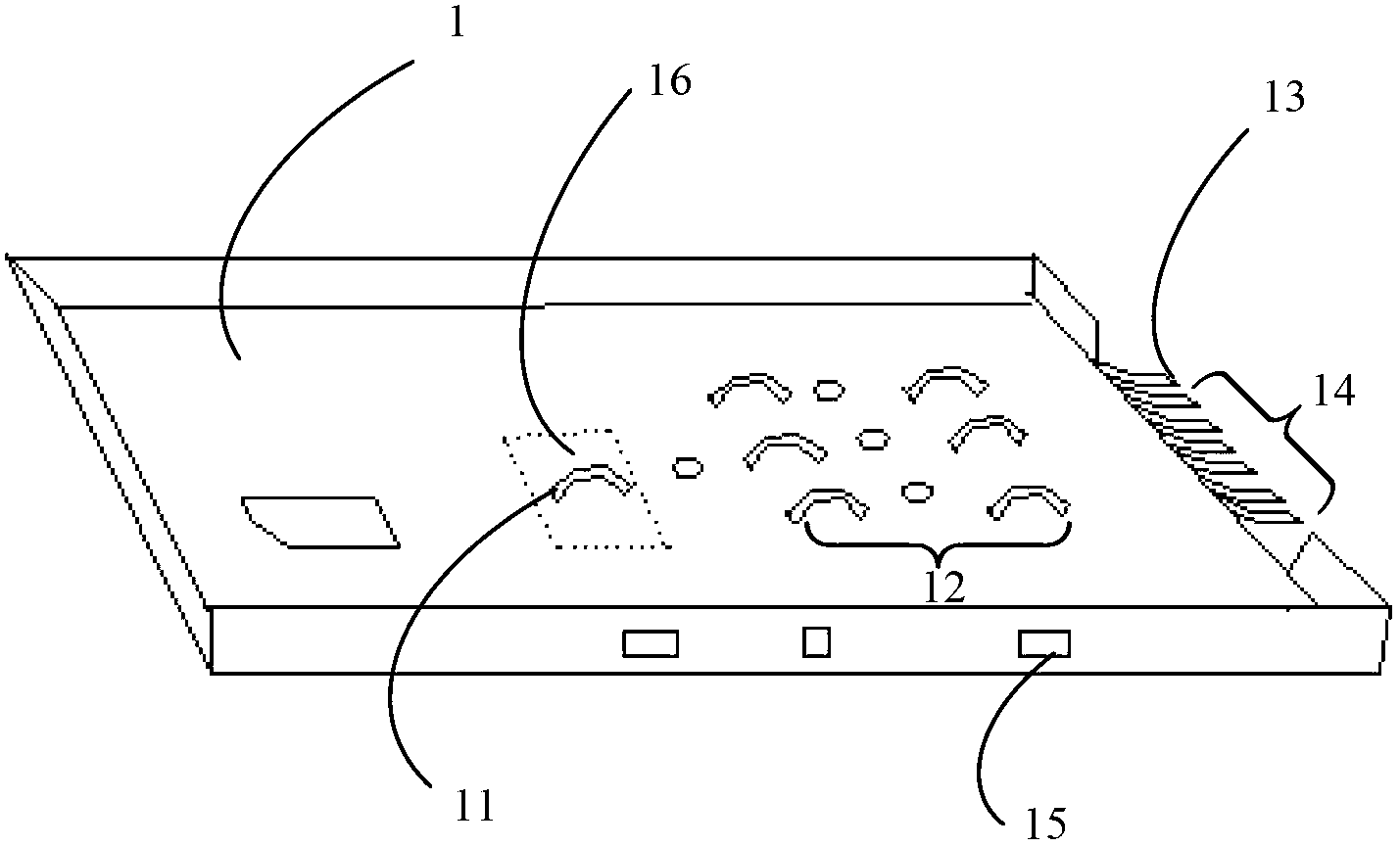

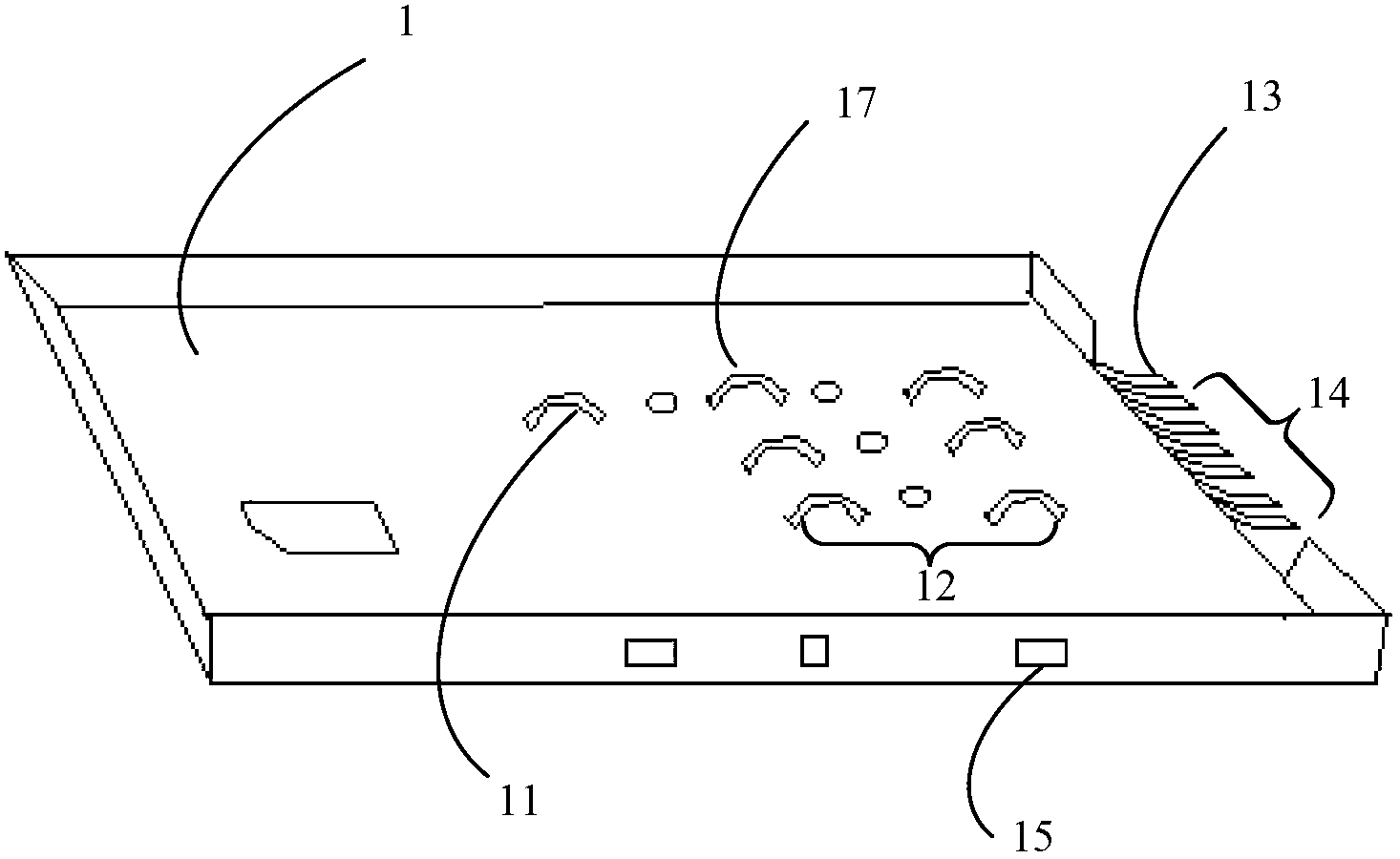

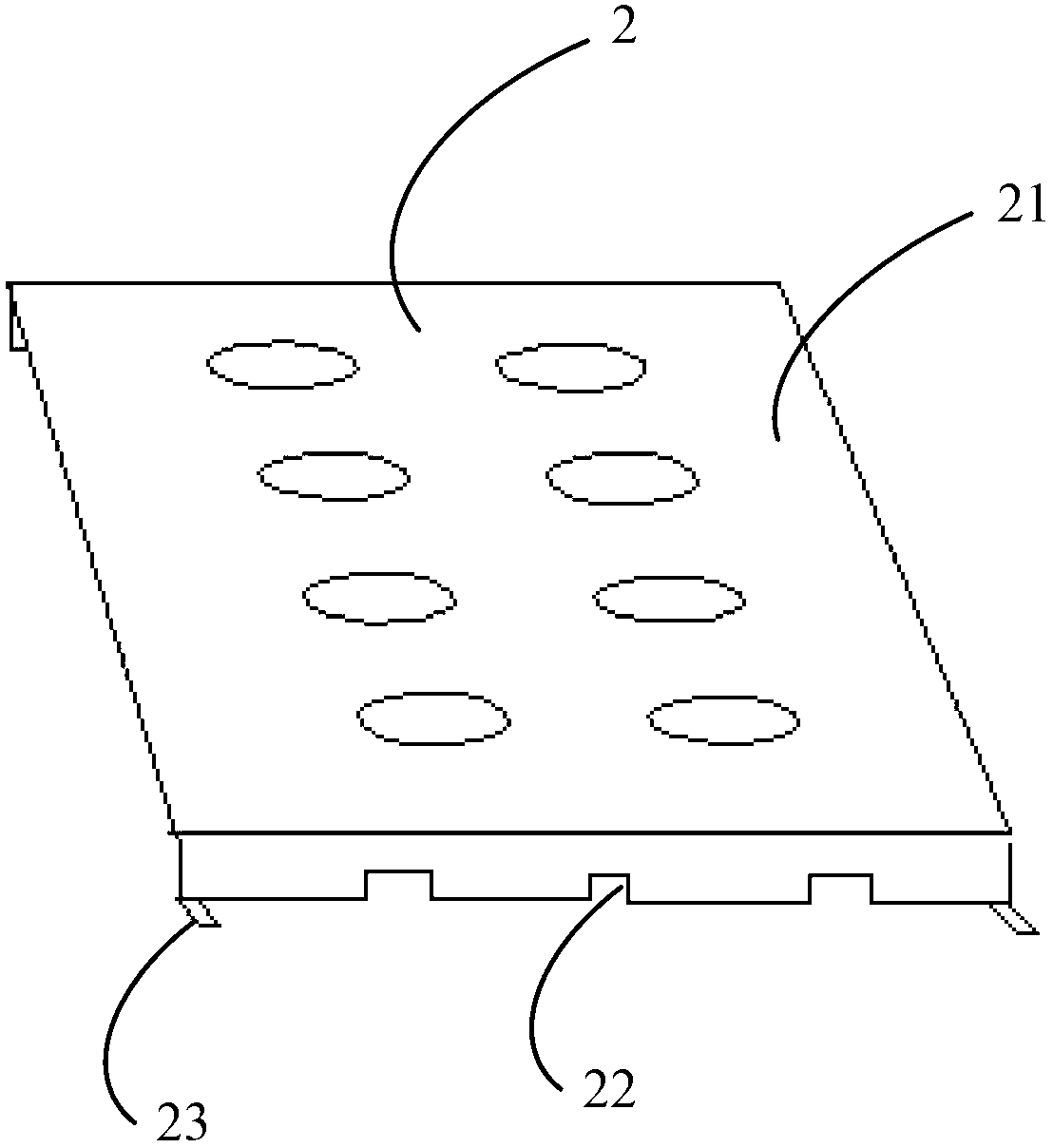

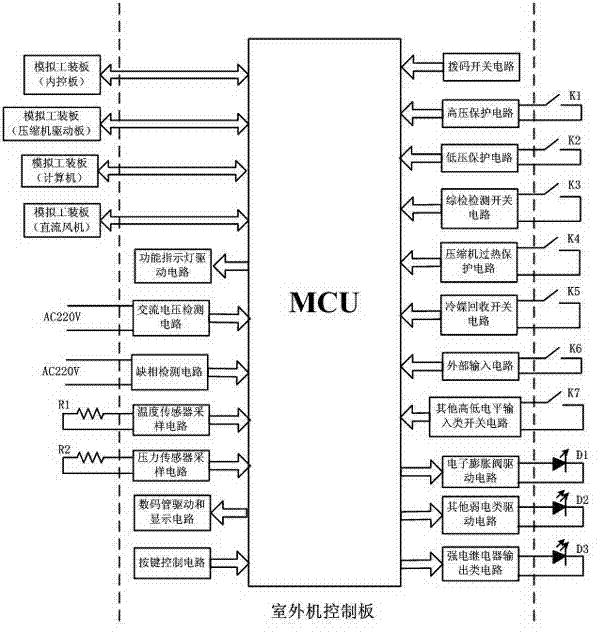

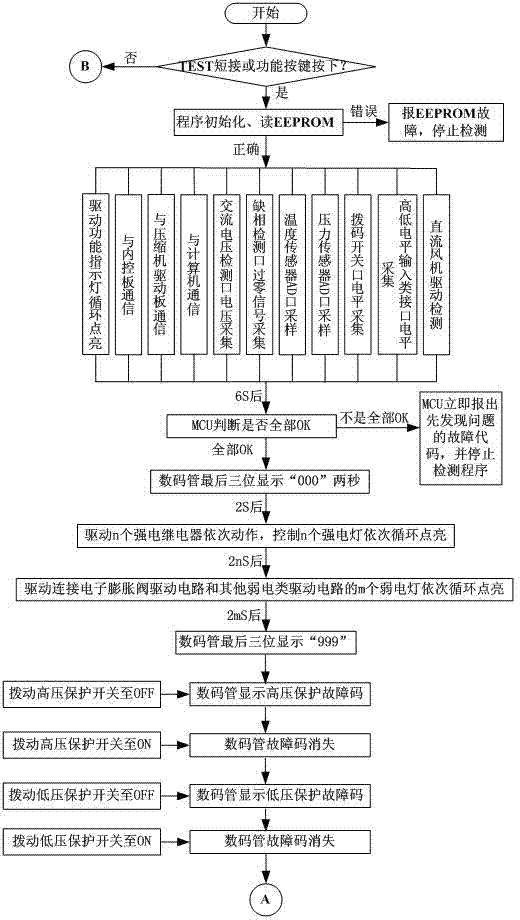

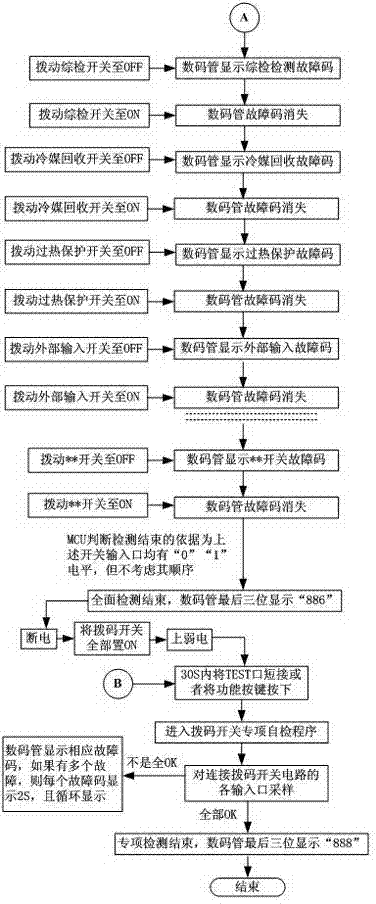

Method for automatically detecting air conditioner outdoor unit control panel

InactiveCN102789230AAvoid damageImprove accuracyElectronic circuit testingElectric testing/monitoringEngineeringWeak current

The invention discloses a method for automatically detecting an air conditioner outdoor unit control panel, which adopts different detection modes according to different functional circuits on the outdoor unit control panel, and mainly comprises communication circuit detection, direct current fan drive circuit detection, sensor sampling circuit detection, high and low level input circuit detection, weak current drive circuit or relay circuit detection and the like. The special method for automatically detecting the air conditioner outdoor unit control panel provided by the invention not only can prevent the control panel to be detected from being damaged during the detection process, can qualitatively determining and quantitatively detecting all the functional circuits of the control panel to be detected through adopting a mode which combines manual judgment and automatic judgment, but also can detect both two states of 'on' and 'off' of a switching input, so the accuracy of the detection result is improved, and the detection efficiency is also taken into consideration.

Owner:HISENSE (SHANDONG) AIR CONDITIONING CO LTD

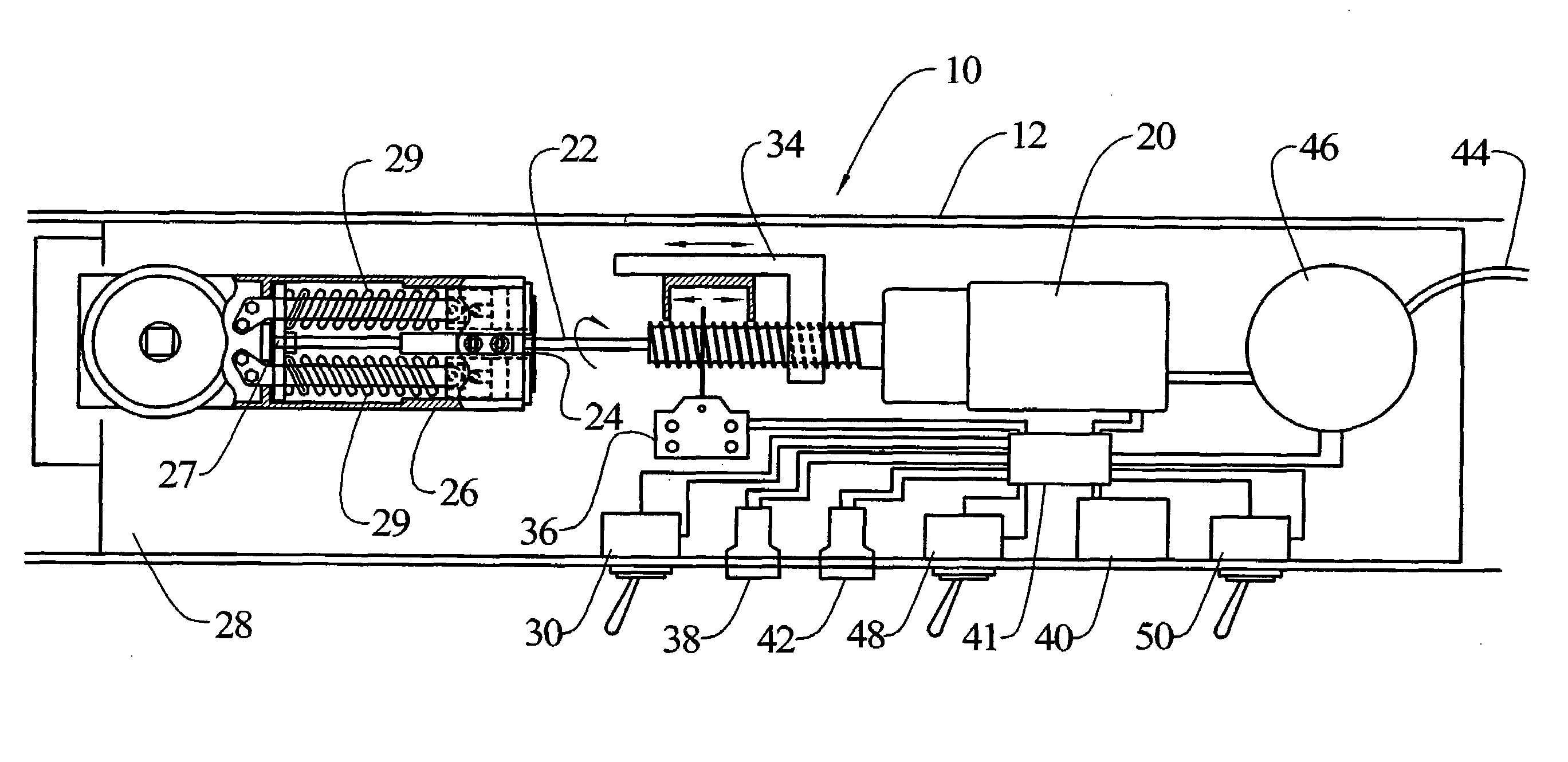

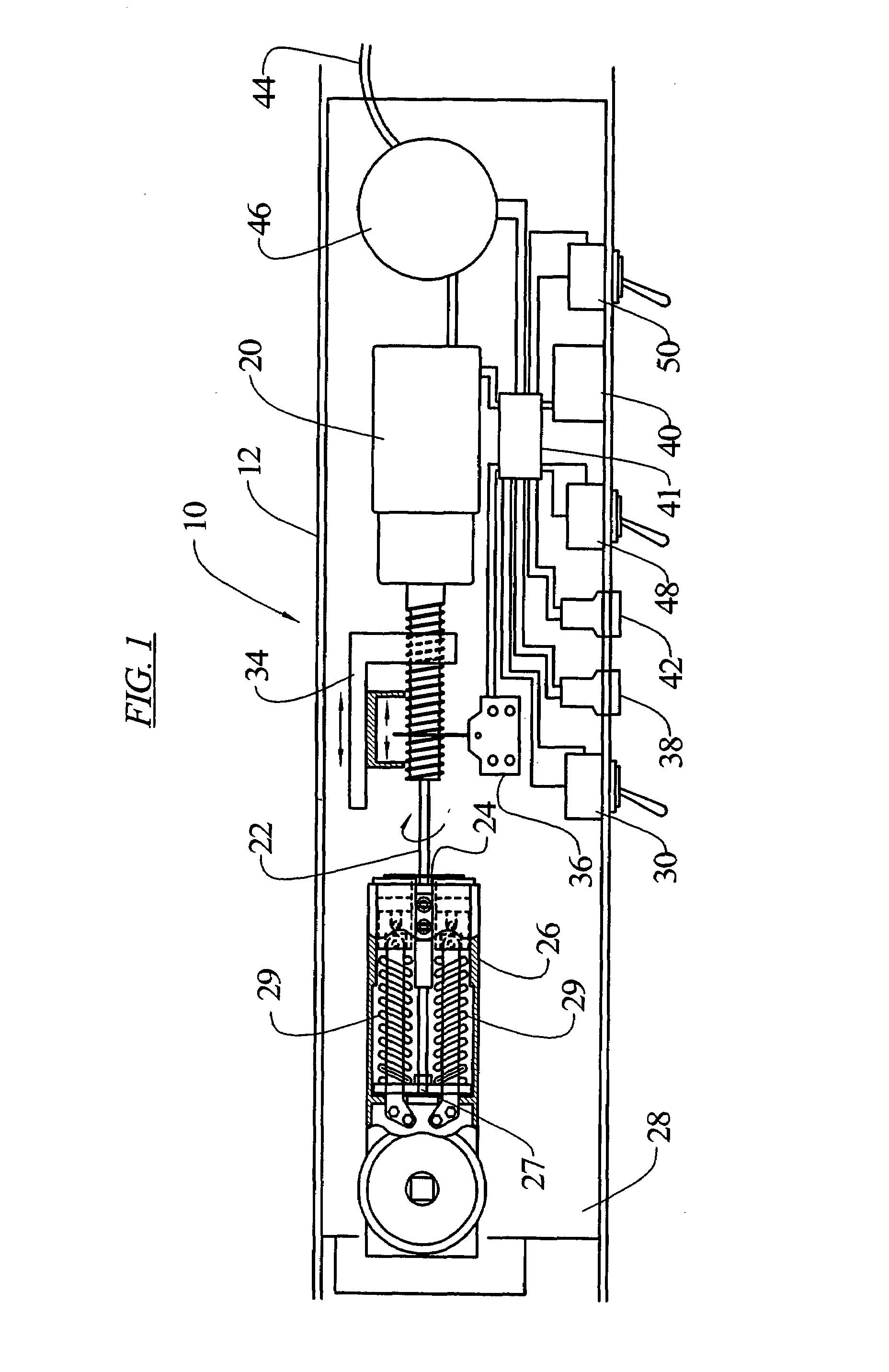

Door closer power adjusting device

ActiveUS7234201B2Easy to openProvide securityBuilding braking devicesMan-operated mechanismEngineeringHigh pressure

A door closer power adjusting device for a door closer having a spindle driven by a compressed spring with a movable plate for adjusting spring compression, or with a screw for adjusting spring compression, between a high and low level of compression. A powered unit moves the plate in a first direction to achieve the low level of compression and in a second direction to achieve the high level of compression. A switch activates the powered unit in the first direction and a first switch is engaged when the spring is compressed to the low level of compression to deactivate the powered unit. A timing circuit activates the powered unit in a second direction after passage of a predetermined time. A second switch is engaged when the spring is compressed to the high level of compression to deactivate the powered unit.

Owner:C R LAURENCE

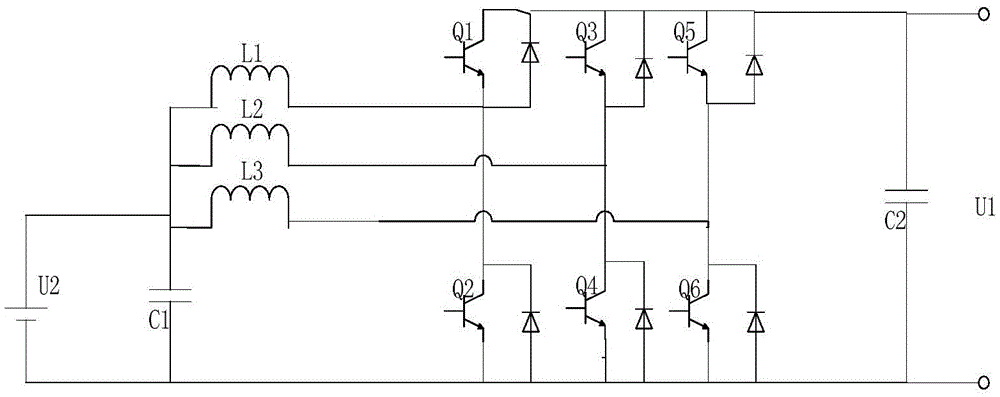

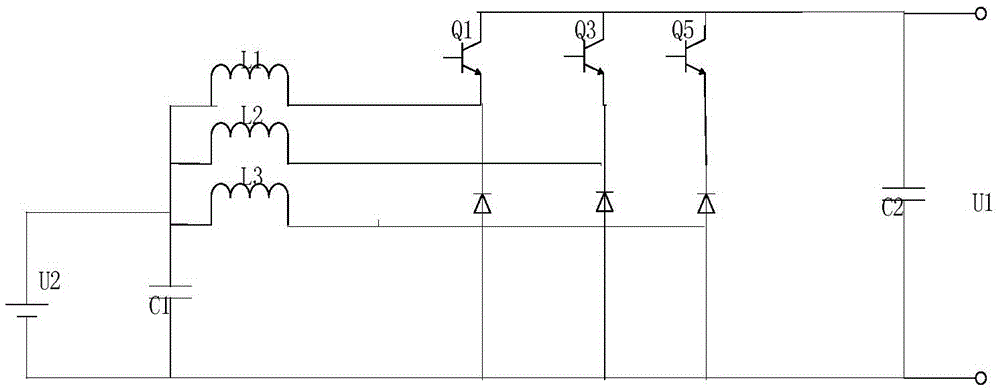

Braking energy recovery system for electric vehicle

ActiveCN105480098AReduce stressSmall rippleElectric devicesElectrodynamic brake systemsCapacitanceEnergy recovery

The invention relates to a braking energy recovery system for an electric vehicle, comprising a three-phase staggered two-way half-bridge circuit, a gear selection circuit, a sampling hold circuit, a digital chip, a voltage sampling circuit, a current sampling circuit and a driving circuit which are sequentially connected. Two-way half-bridge DC / DC converters are connected in parallel, the three-phase staggered two-way half-bridge circuit serves as a main circuit topology of the system, high and low levels are output through an I / O port to control the switching-on / off of relays so as to select different power requirement gears, and finally, the purpose of recovering the braking energy of motors with different output power is realized. According to the invention, the reliability of the device is improved, current ripples are reduced, and the volume of inductors and the capacity of capacitors are reduced, so that the device is easier to realize; the system can be used for multiple DC motors with different output power requirements; the system can effectively prevent current from being out of control under fault conditions so as to quickly finish overcurrent protection; and in addition, a three-phase staggered DC / DC converter system and an active inverter system are consistent in structure, thereby being favorable for realizing a modular structure of an electric vehicle system.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

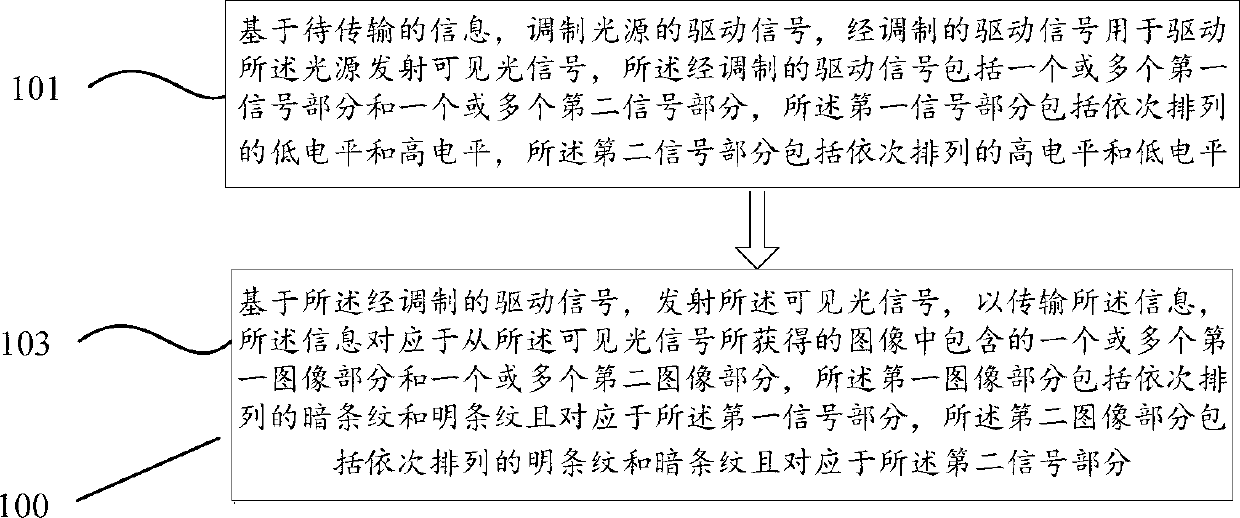

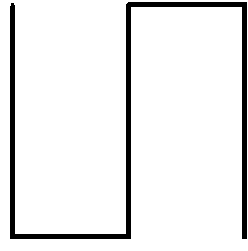

Methods and apparatuses for information transmission/obtaining by using visible optical signal

InactiveCN104168060ATransmission is fast and more accurateAvoid flickeringClose-range type systemsInformation transmissionComputer science

Owner:ZHUHAI HENGQIN GREAT AIM VISIBLE LIGHT COMM TECH

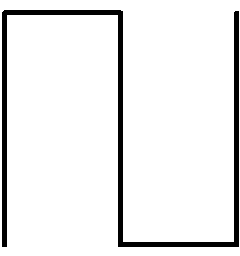

Method and facilities for large scale preparing fresh water by seawater icing

InactiveCN1923714ASave energySolve technical problemsSeawater treatmentWater/sewage treatment by freezingEcological environmentSea ice

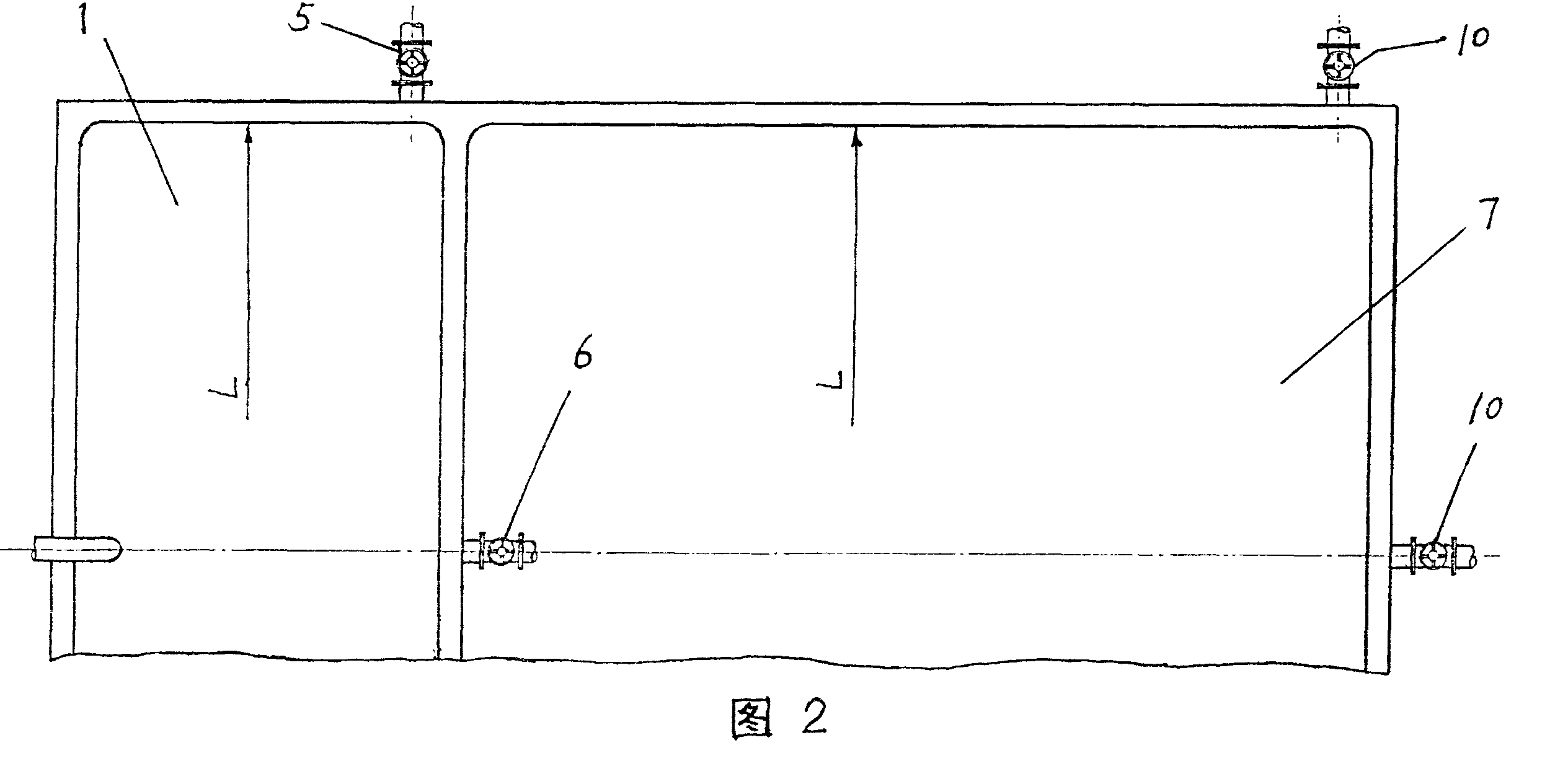

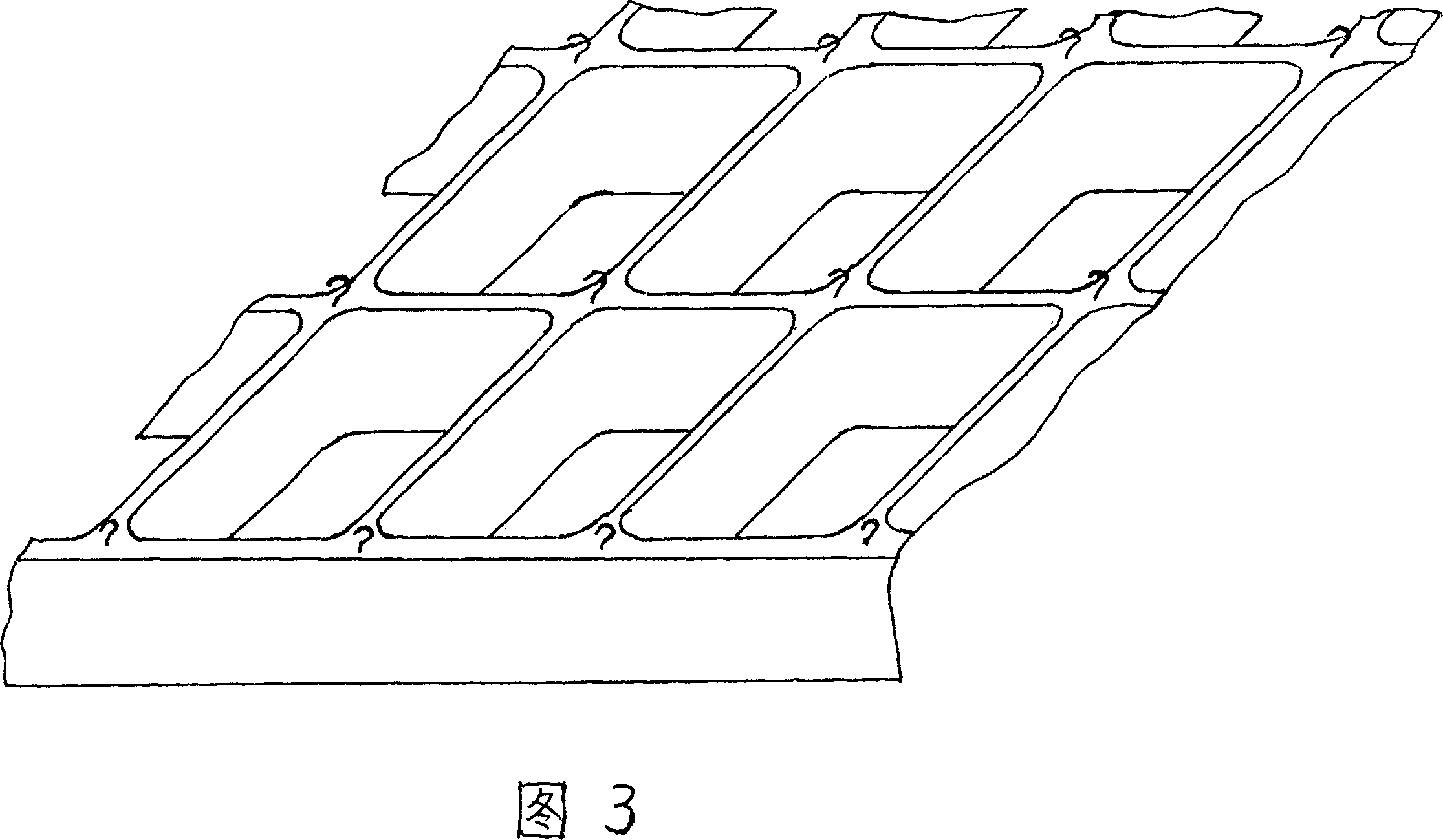

The invention discloses a preparing method and equipment of fresh water through large-scale icy sea water, which is characterized by the following: collecting sea ice directly in winter; preparing mutual cascading structure of high and low level pools; making the depth of high-level pool more than the depth of low level pool to enlarge the area of low level pool by 2 times.

Owner:薛廷芳 +1

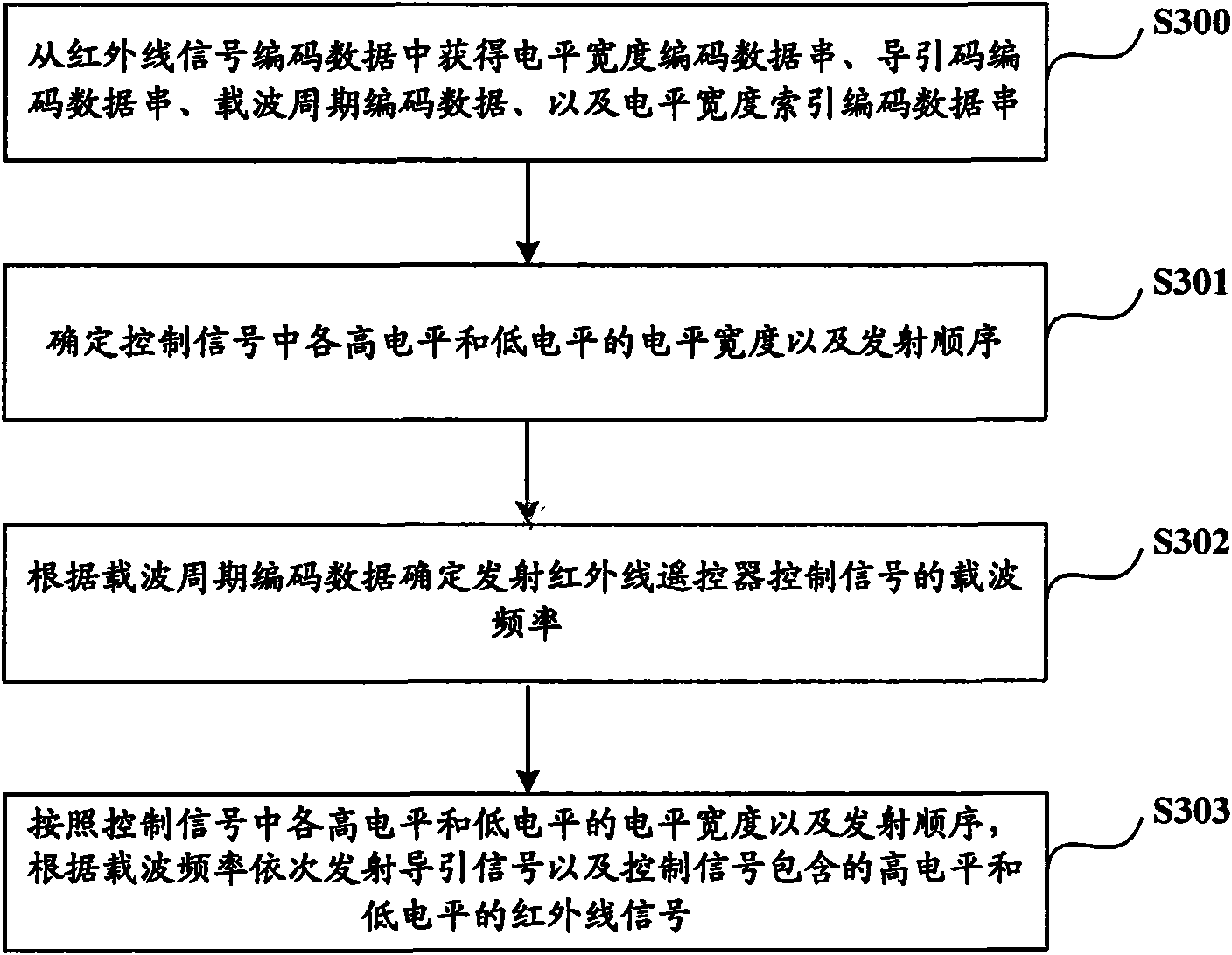

Learning method and transmitting method of infrared cod signal and remote controller

InactiveCN101989379ASave storage spaceSave the amount of encoded dataNon-electrical signal transmission systemsRemote controlLearning methods

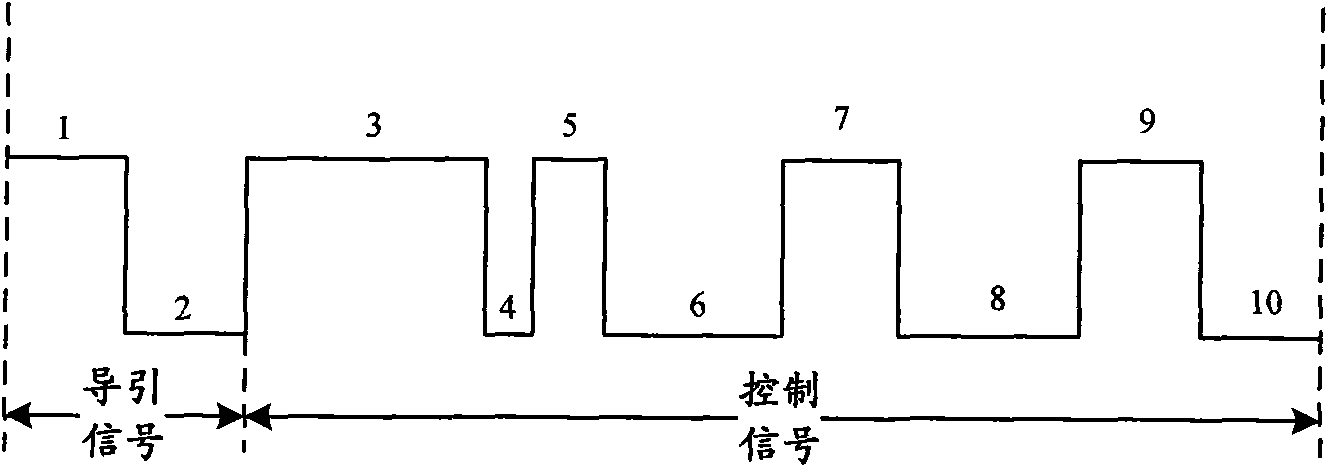

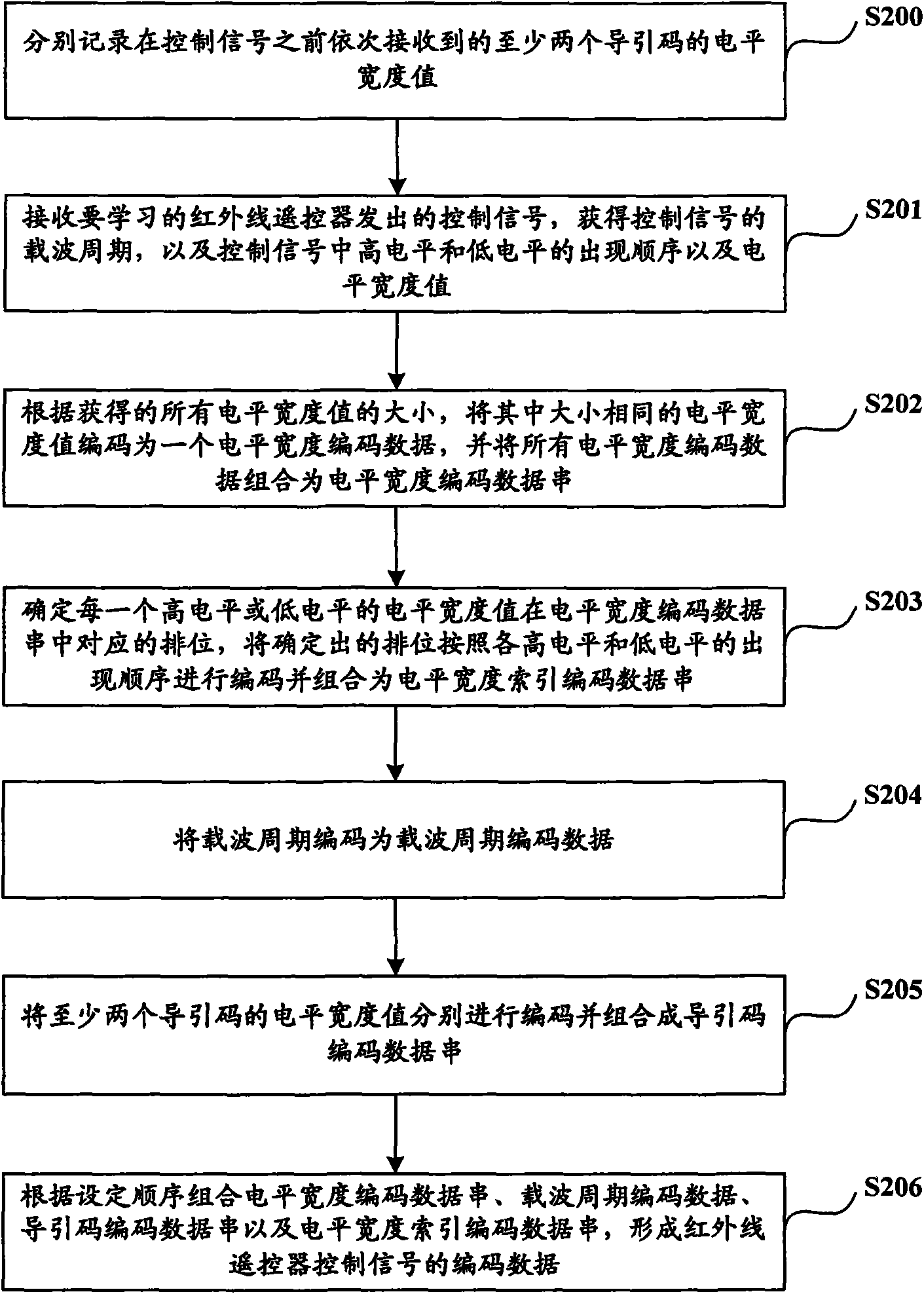

The invention relates to a remote control technology, in particular to an infrared code signal learning technology in the remote control technology, and the invention discloses a learning method and a transmitting method of the infrared cod signal of a remote controller and the remote controller, which are used for realizing the learning and the reduction of the infrared code signal of the remote controller and reducing the code data volume as much as possible so as to save the storage space. According to the learning technology of the infrared code signal, which is provided by the embodiment of the invention, indexes can be established for different level widths and can be coded and stored according to the sort orders of high and low levels; the width and the order of the levels can be sequentially determined according to the coding and the sort order of the indexes, thereby the code data volume can be greatly saved and the storage space of the remote controller can be saved when the infrared code signal appears repeatedly at the same level width.

Owner:NINGBO JIATIANXIA INTELLIGENT SYST

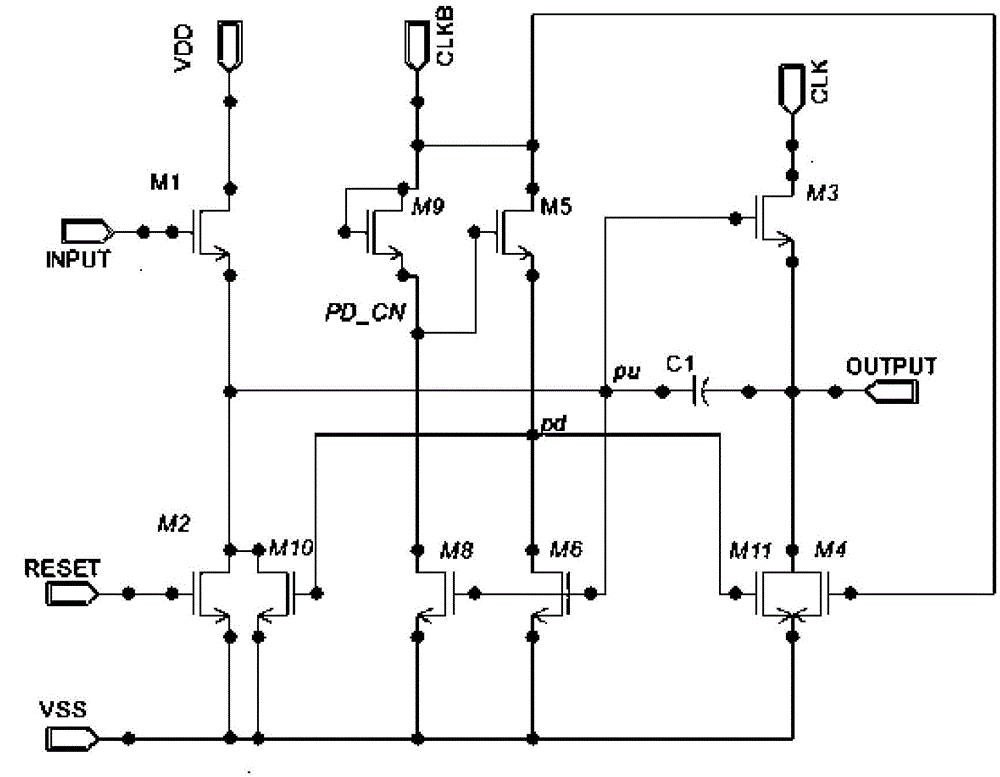

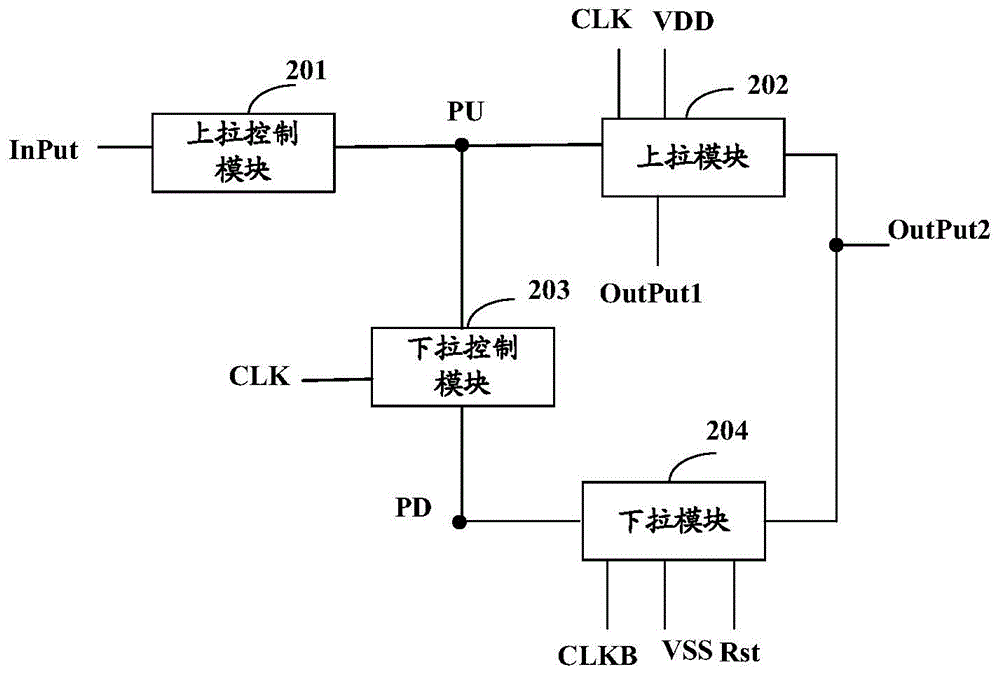

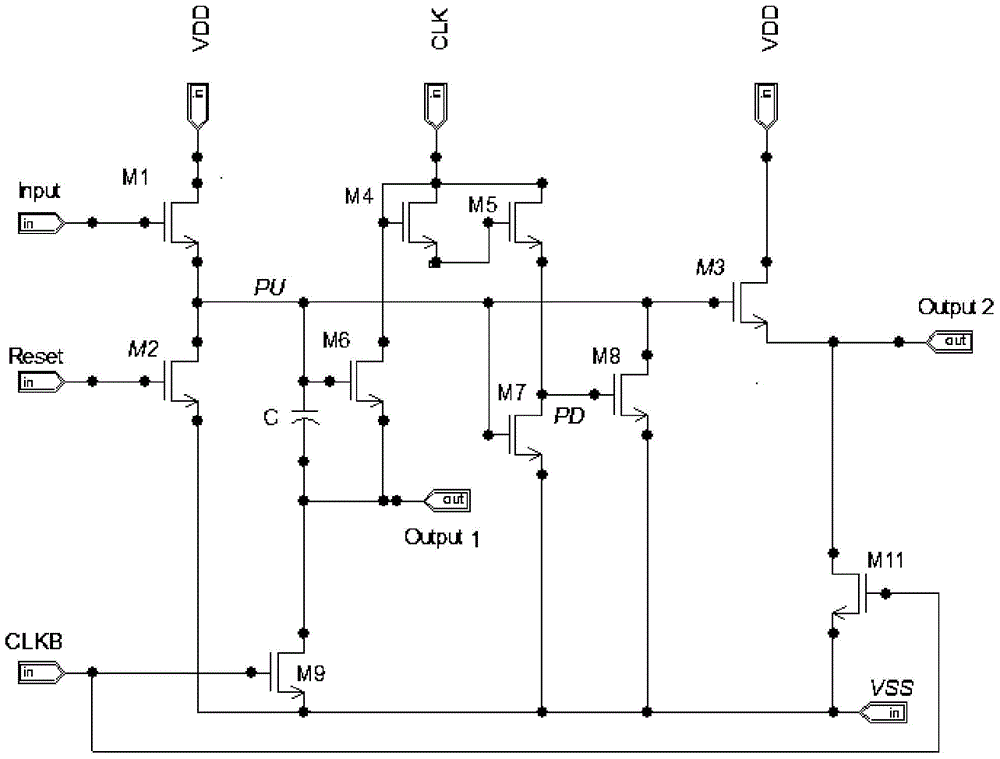

Shift register unit, grid driving circuit and display device

ActiveCN103985341AReduce power consumptionStatic indicating devicesDigital storageShift registerControl signal

The invention discloses a shift register unit, a grid driving circuit and a display device. Specifically, the shift register unit comprises a pull-up control module, a pull-up module, a pull-down control module and a pull-down module; the pull-up module provides a first clock signal to a transmission signal output terminal according to a pull-up control signal and provides first direct-current supply voltage to a grid driving signal output terminal according to the pull-up control signal and the first clock signal, wherein the first clock signal is input by a first clock signal input terminal. Due to the fact that the first direct-current supply voltage is used as input of a transistor, used for outputting grid driving signals, in the pull-up module, the transistor has no capacity coupling effects, namely, due to the fact that high and low level conversion does not exist in the first direct-current supply voltage, stray capacitance generated by the transistor cannot be charged or discharged frequently, power losses are reduced and the problem that power consumption of a common shift register unit is high is solved.

Owner:BOE TECH GRP CO LTD +1

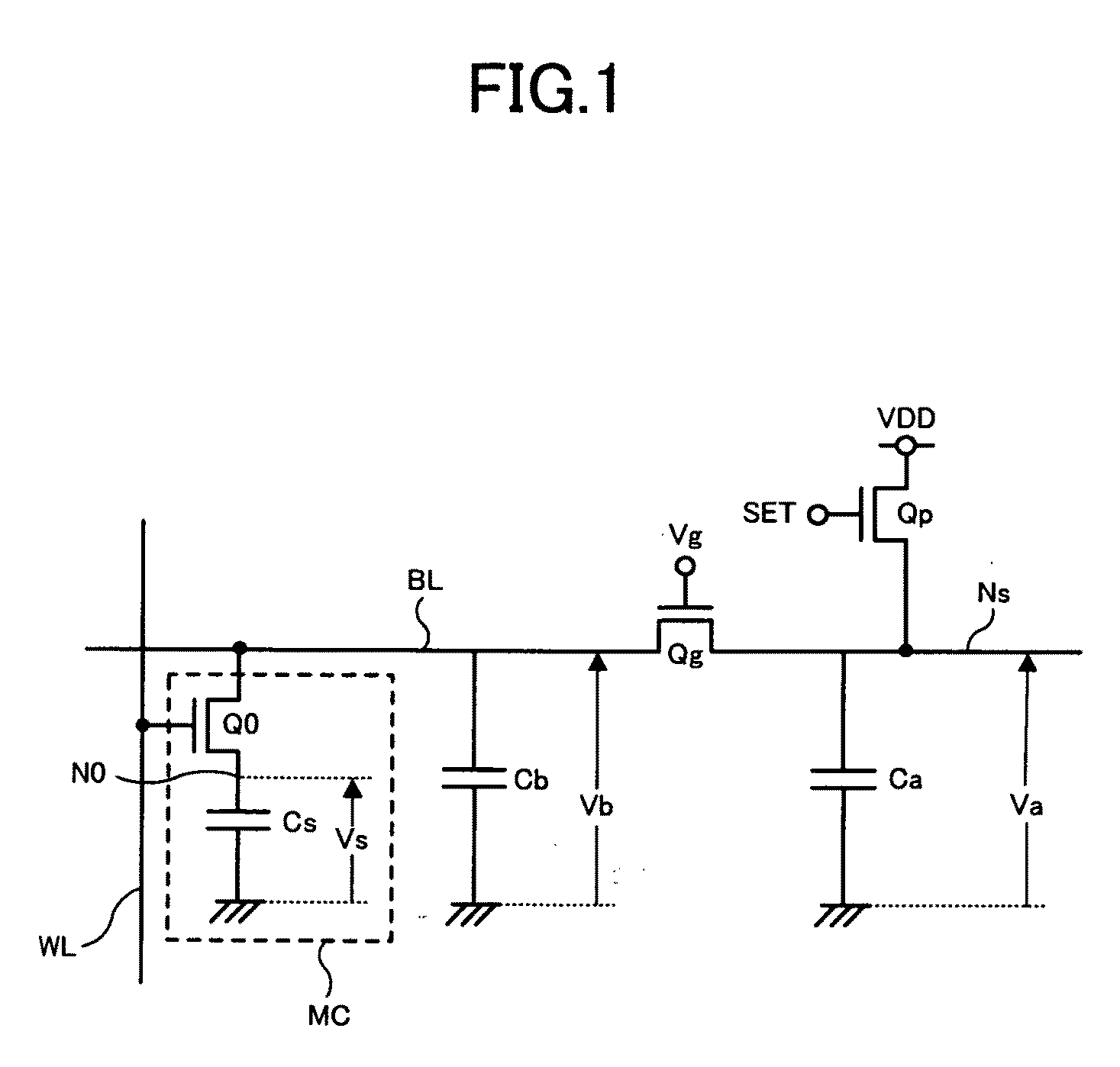

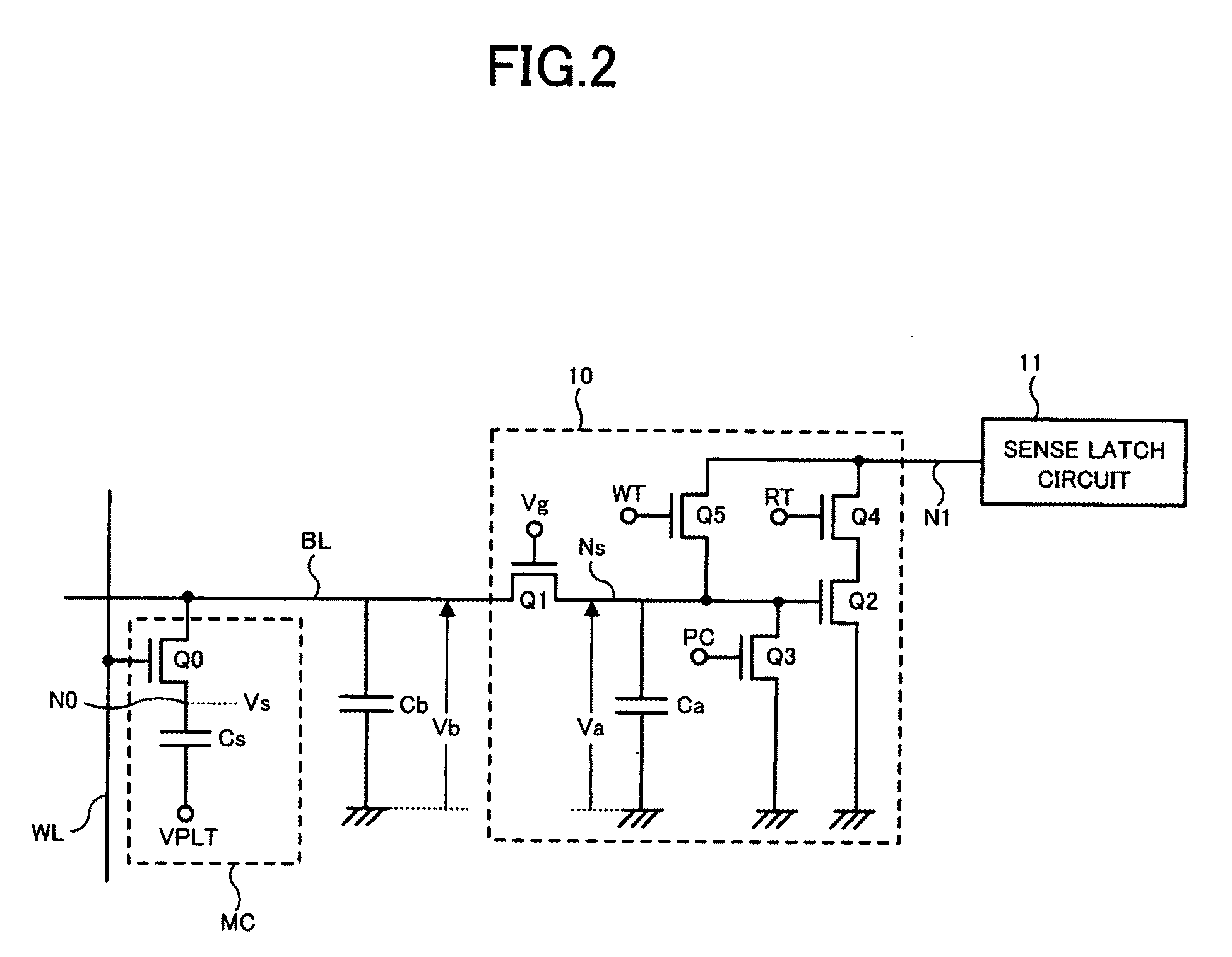

Sense amplifier circuit and semiconductor memory device

ActiveUS20100054065A1Excellent operating marginImprove reliabilityRead-only memoriesDigital storageBit lineAudio power amplifier

A single-ended sense amplifier circuit amplifies a signal of a memory cell and transmitted through a bit line, and comprises first and second MOS transistors. The first MOS transistor supplies a predetermined voltage to the bit line and controls connection between the bit line and a sense node in response to a control voltage, and the second MOS transistor has a gate connected to the sense node and amplifies a signal transmitted from the bit line via the first MOS transistor. The predetermined voltage is supplied to the bit line before read operation and is set to a value such that a required voltage difference at the sense node between high and low level data of the memory cell can be obtained near a changing point between a charge transfer mode and a charge distributing mode within a range of a read voltage of the memory cell.

Owner:LONGITUDE LICENSING LTD

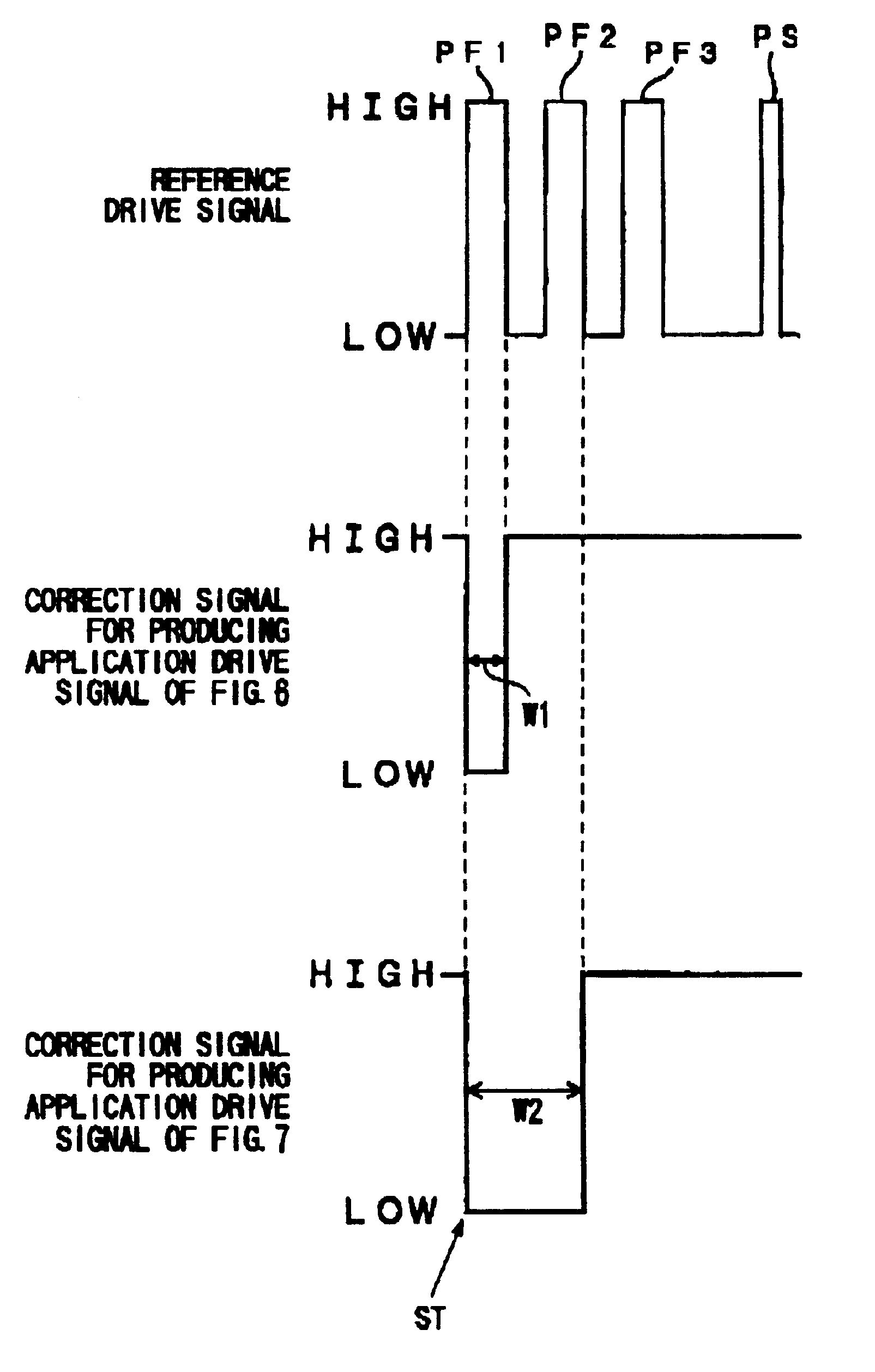

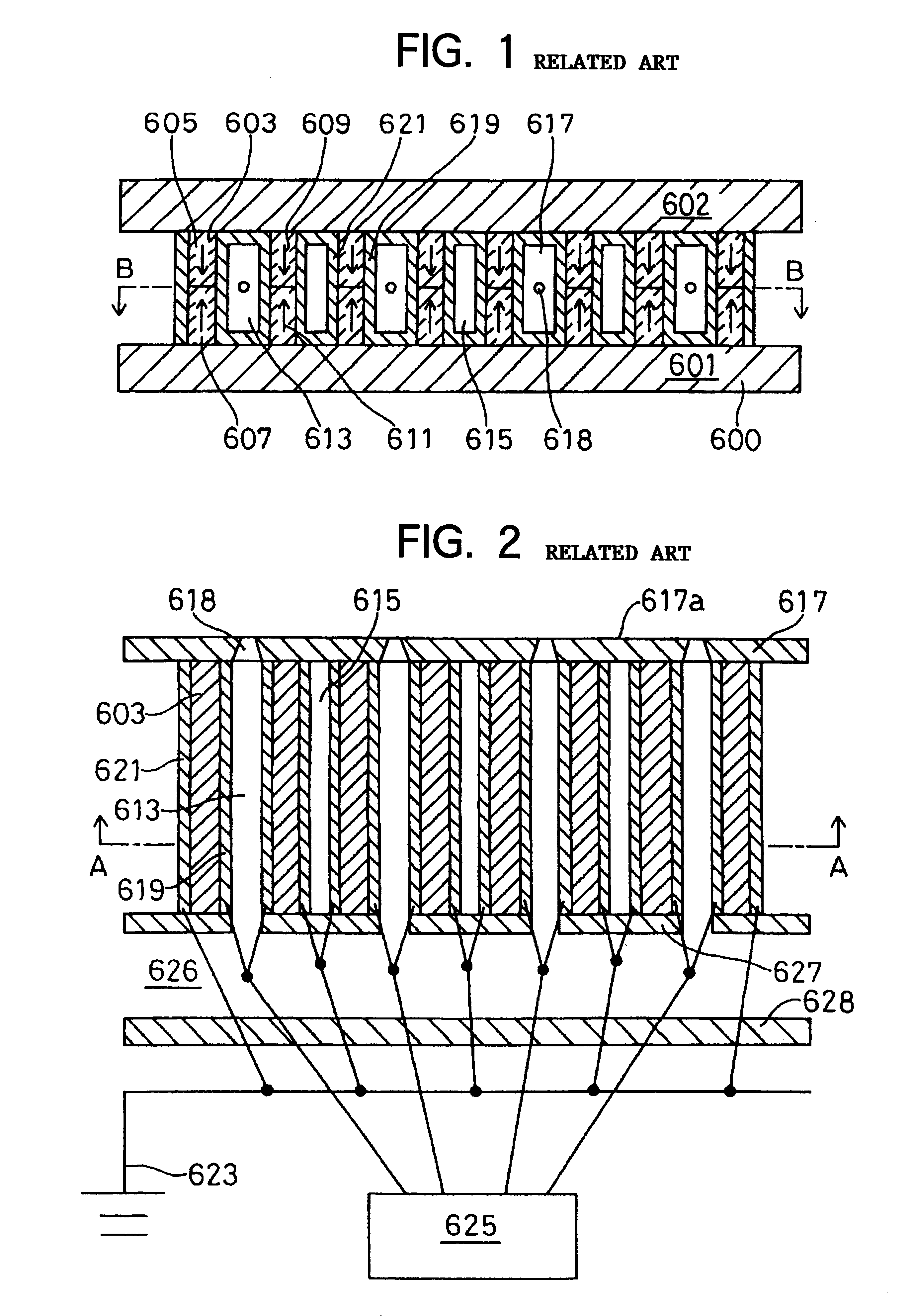

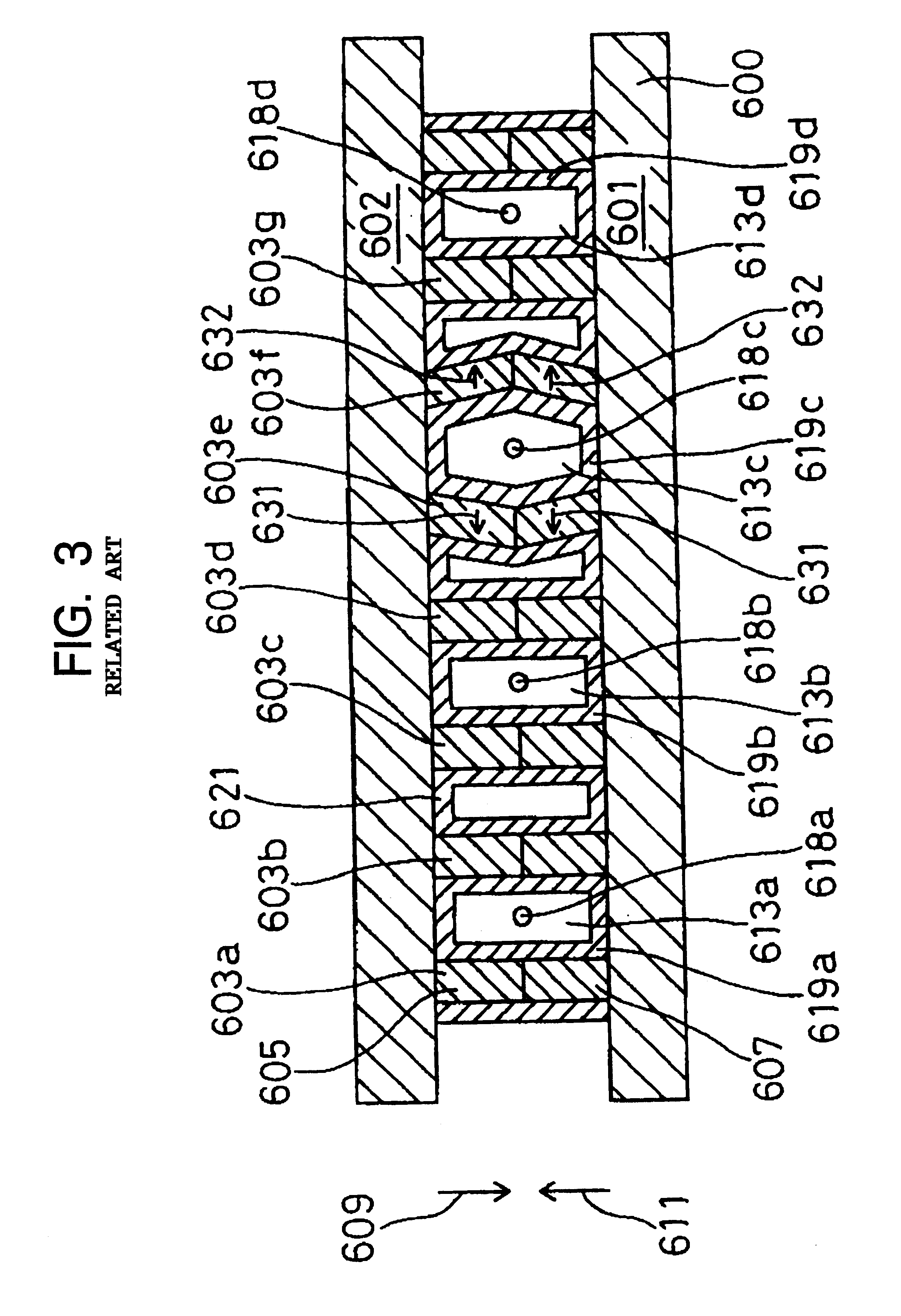

Ink ejecting device

When a print data reception circuit 2 receives a print command, the print data reception circuit 2 transmits data indicating this to a drive signal generating circuit 6, and also transmits data indicating a desired member of ejections per dot to a drive signal correction circuit 8. Based on memory content of a reference data storage circuit 4, the drive signal generating circuit 6 produces a reference drive signal, which includes a predetermined maximum number of ejection pulses for printing each single dot, and transmits it to the drive signal correction circuit 8. The drive signal correction circuit 8 produces a print drive signal by removing unnecessary ejection pulses from the reference drive signal, in accordance with the desired number of ejection pulses indicated in the print command, and than transmits the print drive signal to a charge / discharge circuit 10. The charge / discharge circuit 10 controls electric potential difference between electrodes 619, 921 in accordance with high and low levels of the application drive signal. The piezoelectric material between the electrodes 619 and 621 deforms according to the electric potential difference, so that a desired number of ink droplets are ejected.

Owner:BROTHER KOGYO KK

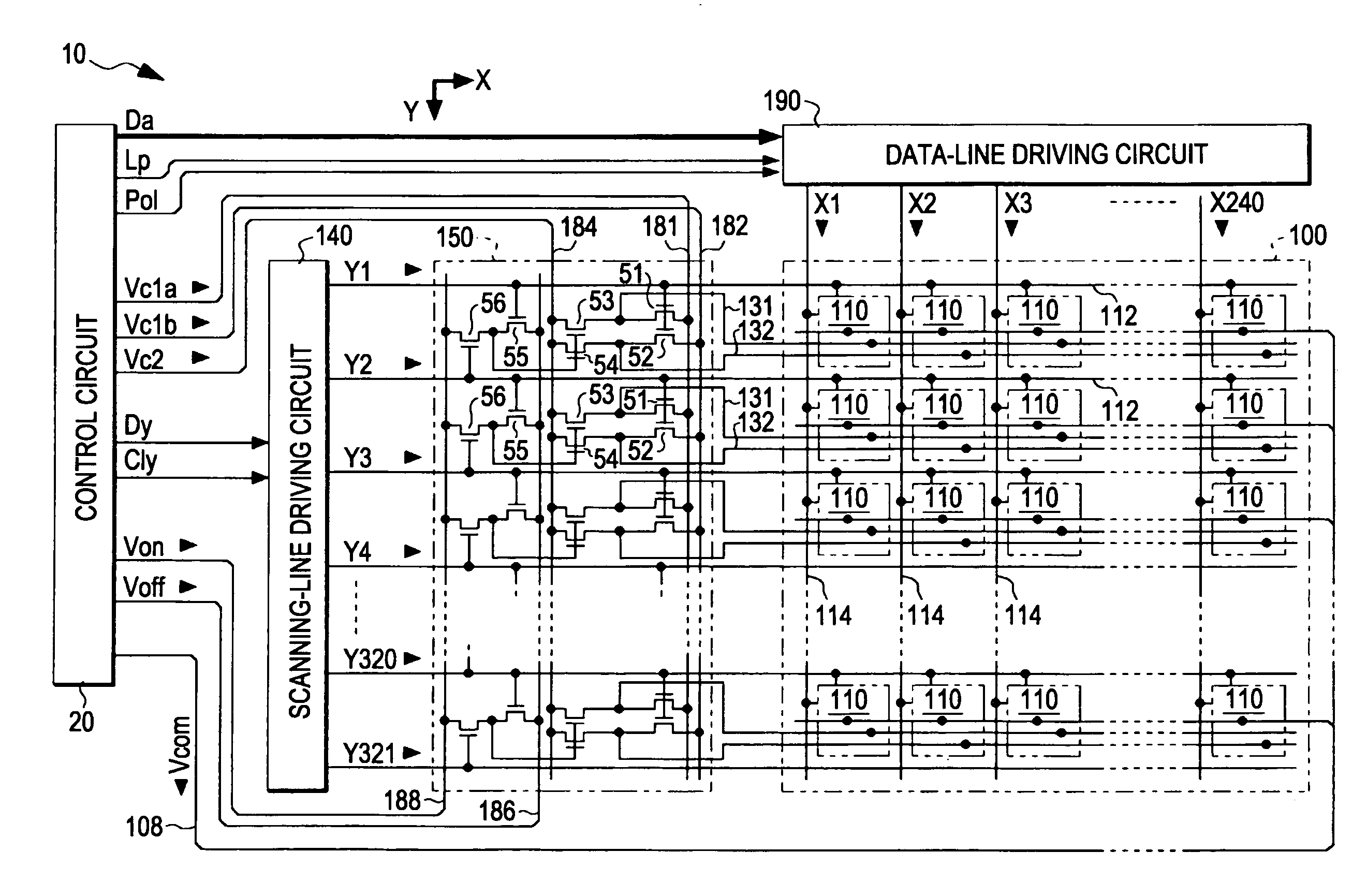

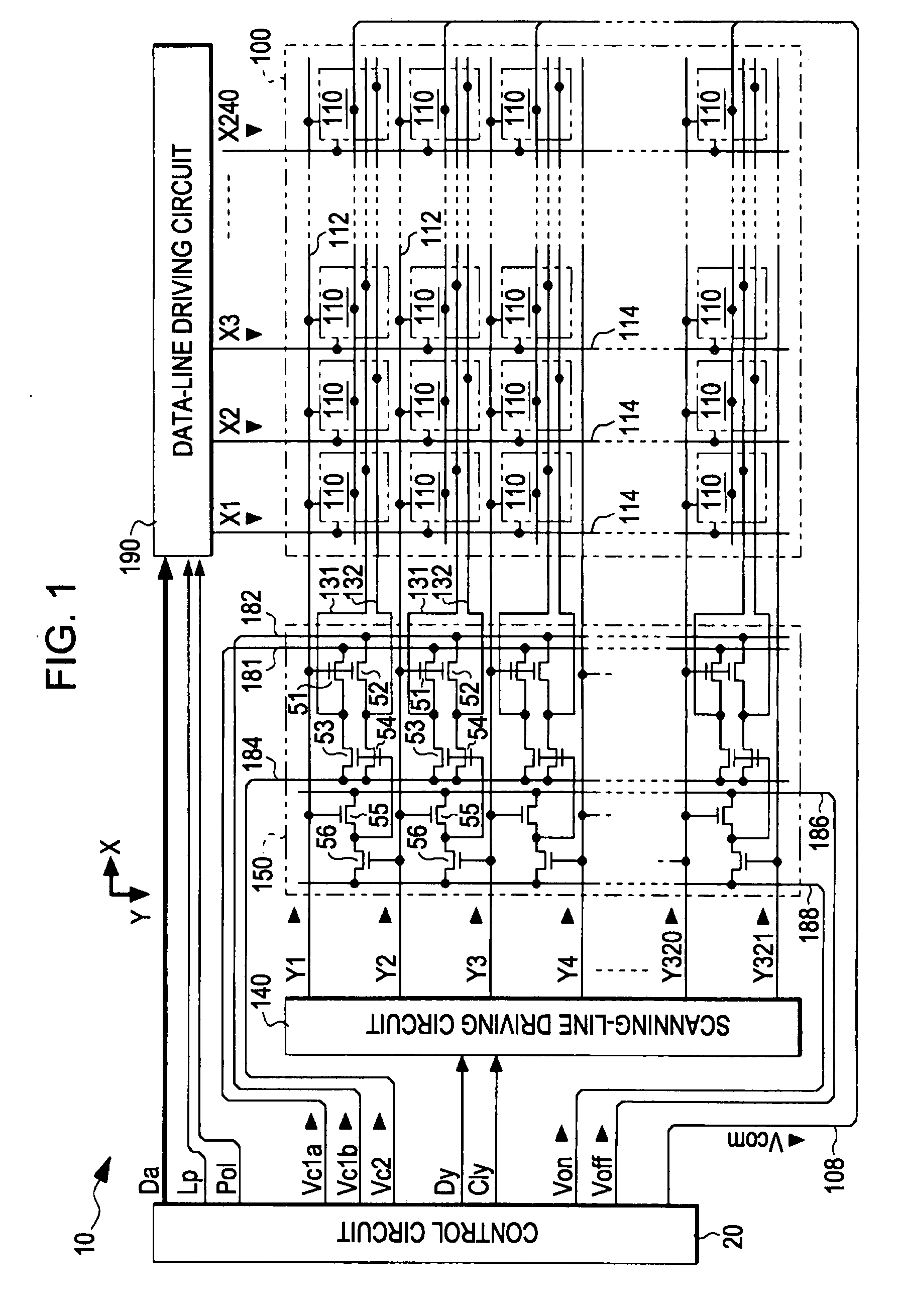

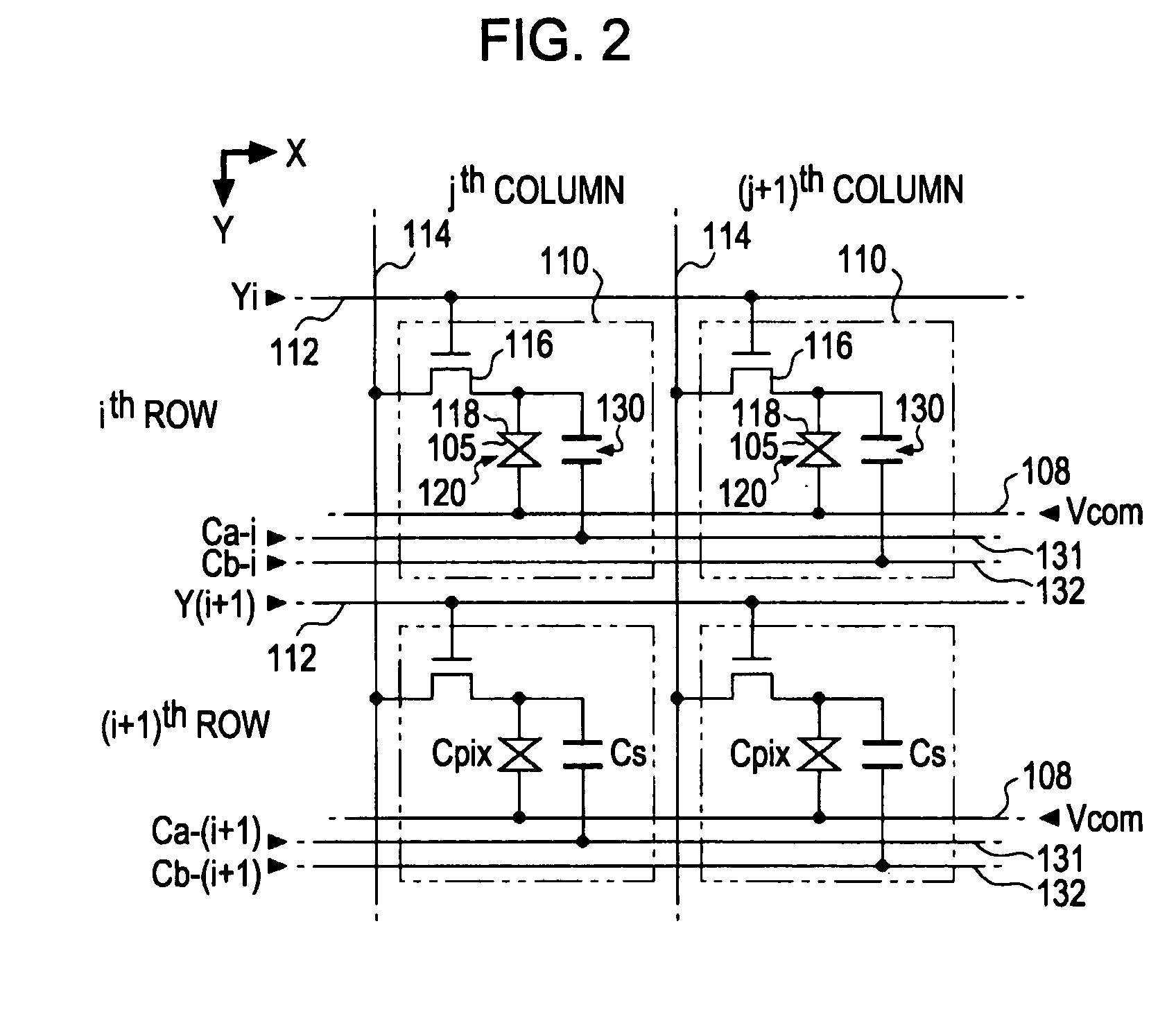

Electrooptic device, driving circuit, and electronic device

ActiveUS20080055300A1Reduce the voltage amplitudeSimple circuit configurationCathode-ray tube indicatorsNon-linear opticsHigh- and low-levelCapacitance

A driving circuit of an electrooptic device includes: a plurality of scanning lines; a plurality of data lines; first and second capacitor lines; a common electrode; pixels; a scanning-line driving circuit; a capacitor-line driving circuit; and a data-line driving circuit. The pixels each include: a pixel switching element; a pixel capacitor disposed between the pixel switching element and the common electrode; and a storage capacitor. When the one scanning line is selected, the capacitor-line driving circuit shifts the voltage of a first (or second) capacitor line corresponding to one scanning line to one of higher and lower levels from a predetermined voltage by a predetermined value, and holds the predetermined voltage after a scanning line apart from the one scanning line by a predetermined number of lines is selected until the one scanning line is selected again.

Owner:JAPAN DISPLAY WEST

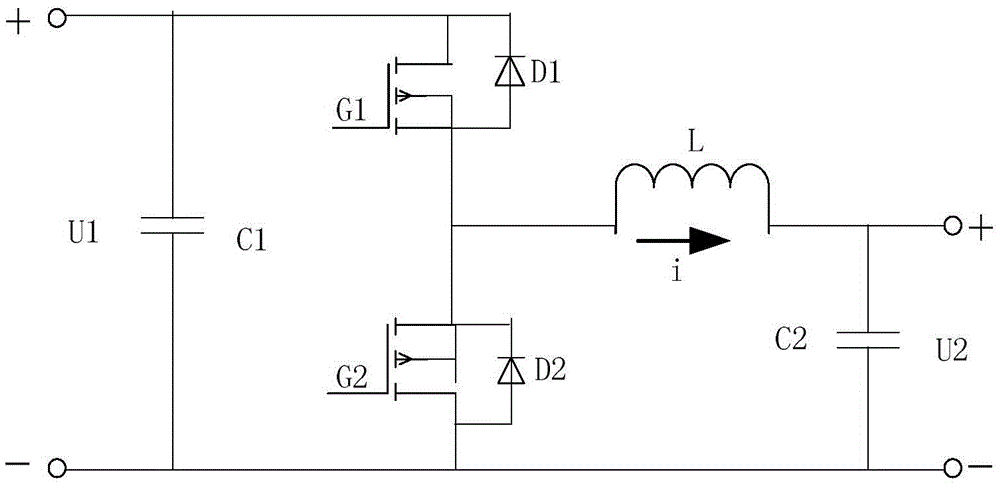

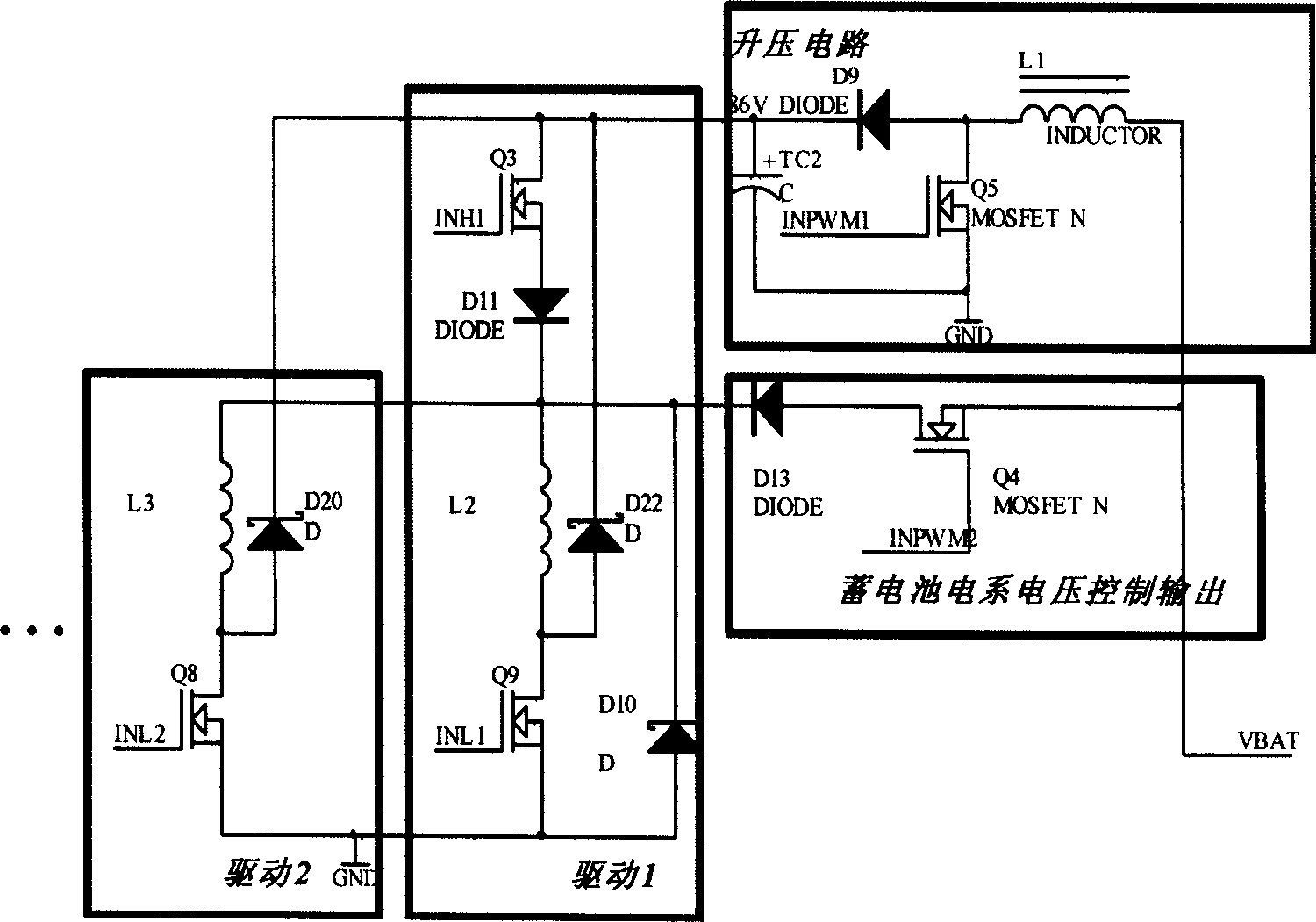

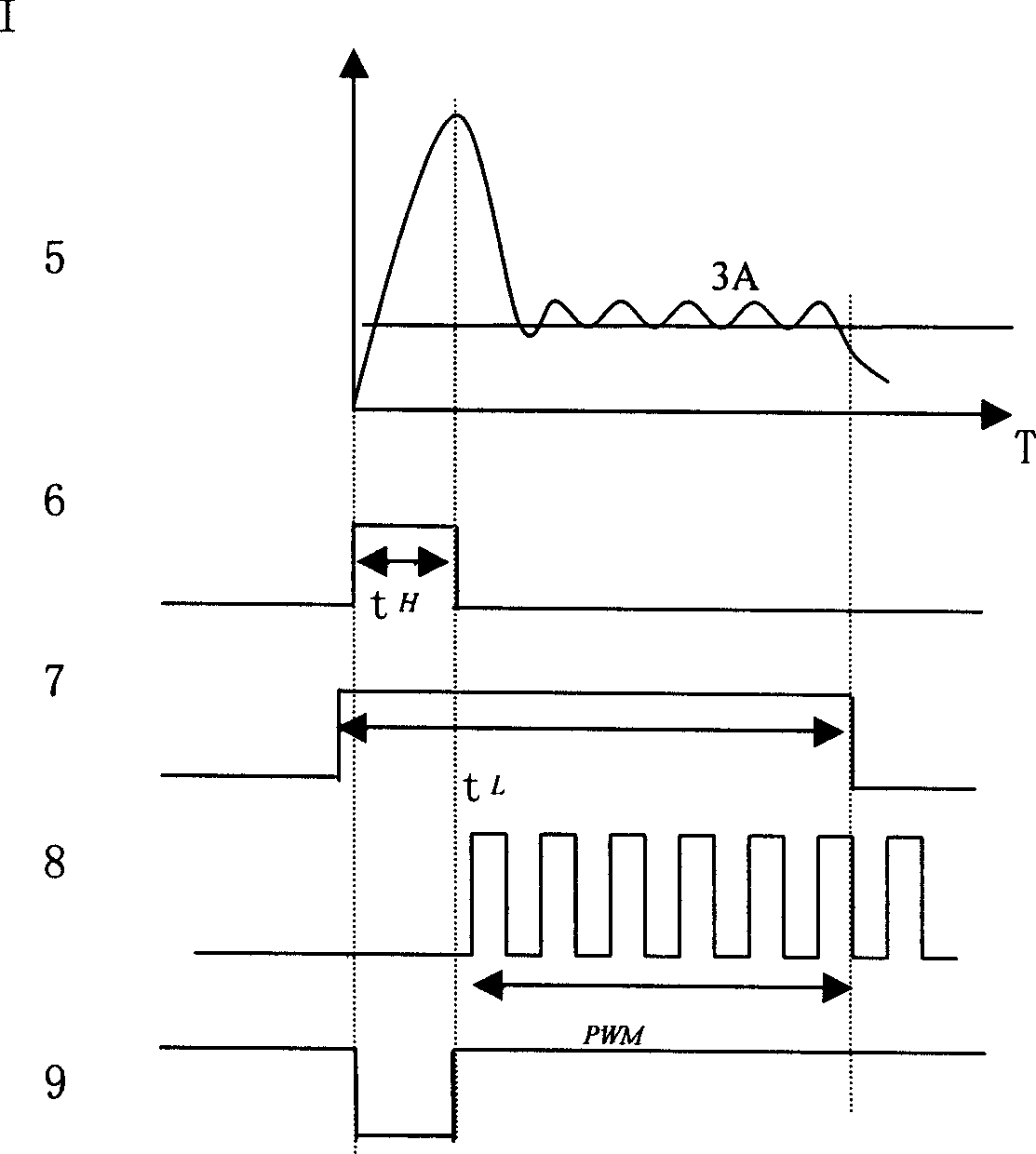

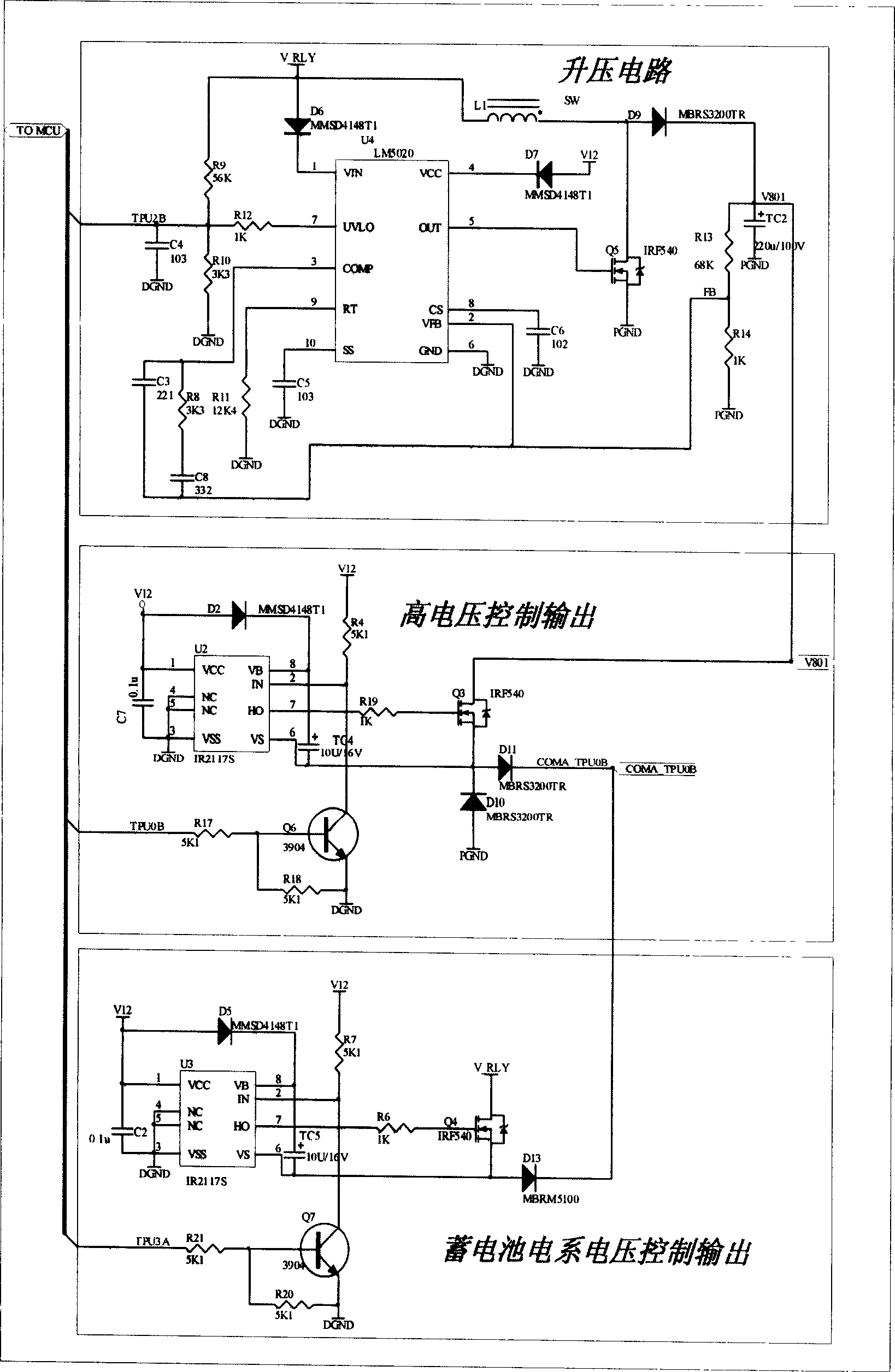

Drive circuit of high and low level switch combination with voltage boost circuit

InactiveCN1728497AImprove fuel injection qualityReduce power consumptionBatteries circuit arrangementsOperating means/releasing devices for valvesSolenoid valveLow voltage

The invention is related to electric control technical area for diesel engine or other area needed for driving electromagnet (valve) in high speed. Drive circuit with power supply in two stages is adopted for controlling fuel injector. Pulse from high voltage power supply supplies instantaneous large current to make electromagnetic valve drive needle valve of fuel injector to be turned to open quickly. Power supply from low voltage maintains needle valve of fuel injector in open state. High voltage is generated from boost up circuit; and amplitude of current for turning needle valve to open quickly is adjusted through pulse width for controlling conduction of high voltage in order to obtain optimal response speed. Low voltage is from accumulator; and amplitude of current is adjusted through PWM mode. Advantages are: favorable quality of fuel jet, and reduced power loss, and raised use ratio of device since switches are multiplexing used for high and low positions.

Owner:镇江江奎科技有限公司

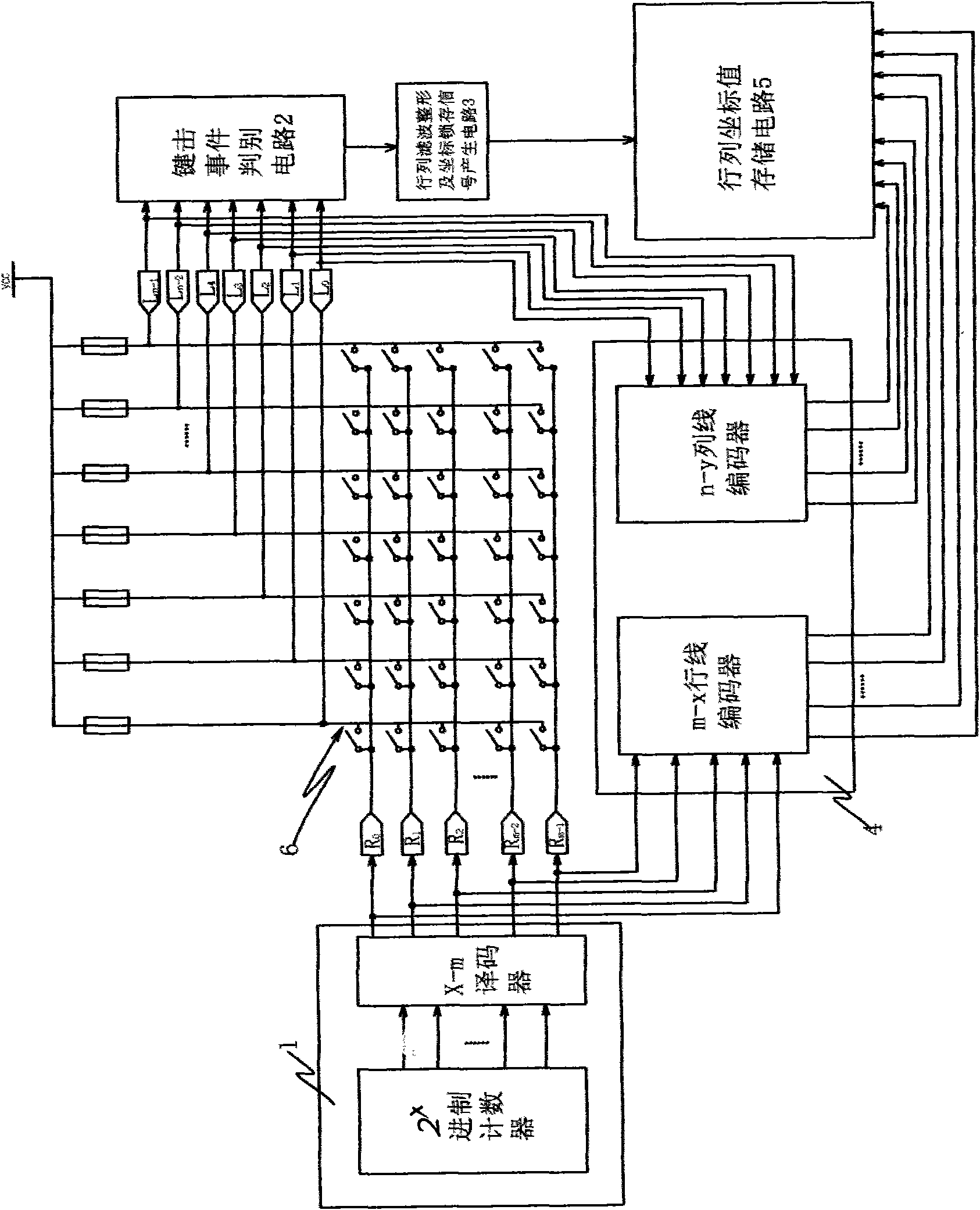

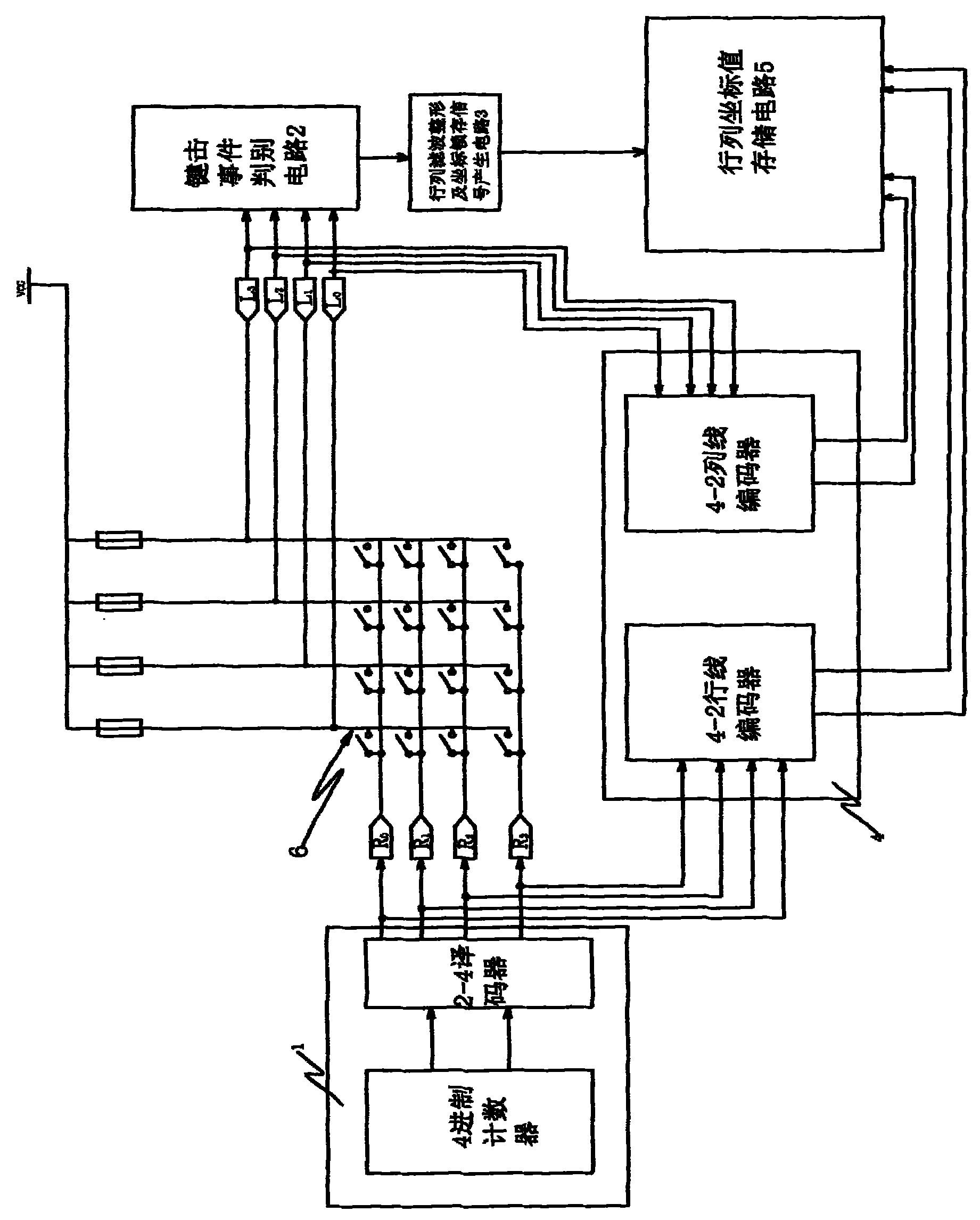

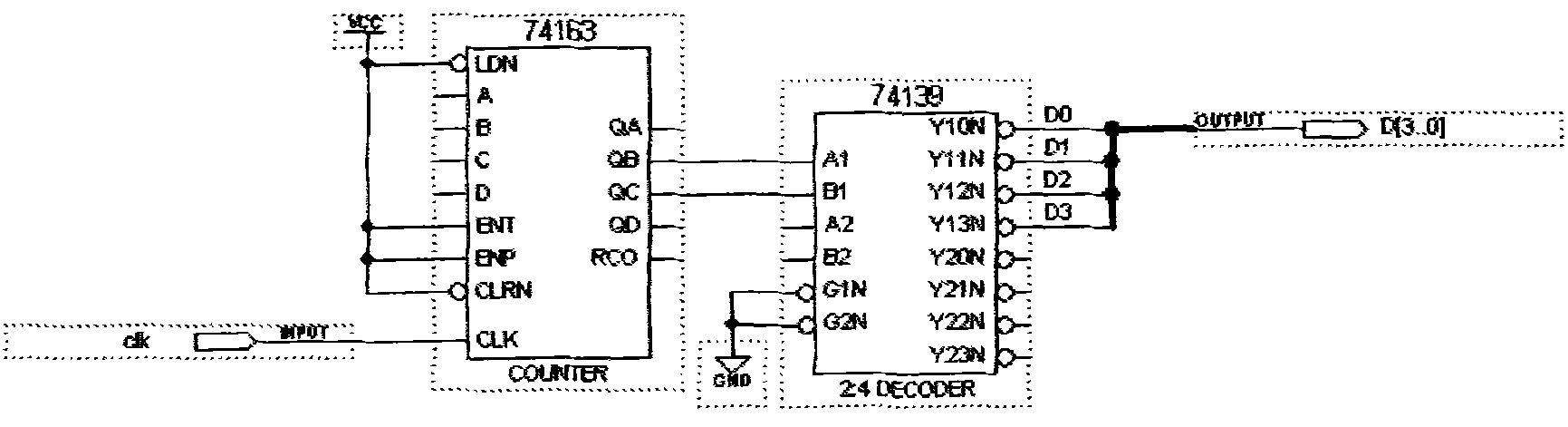

Determinant linear array coordinate scanning circuit

InactiveCN101789793ASimple designEasy to implementInput/output for user-computer interactionDynamic codingHigh- and low-levelVIT signals

The invention discloses a determinant linear array coordinate scanning circuit, comprising an m-channel pulse distribution circuit, a key press event judging circuit, a determinant signal filter shaping and coordinate latch signal generating circuit, a determinant coordinate coding circuit and a determinant coordinate value storage circuit. The m-channel pulse distribution circuit sequentially outputs low level at a line port of an m*n matrix key press circuit, a key press event indicating circuit judges the occurrence of the key press event according to the high and low level at a row port, the determinant coordinate coding circuit 4 codes the line port and the row port to the determinant coordinate according to the current state value, after the key press event indicating signal is generated, the output result of the current determinant coordinate coding circuit is latched in the coordinate value storage circuit by using the latch signal generated by the determinant signal filter shaping and coordinate latch signal generating circuit, and the determinant coordinate value of the coordinate value storage circuit is the coordinate of the key currently pressed. The determinant linear array coordinate scanning circuit has the advantages of concise design, convenient implementation, low hardware cost and no loss of generality.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA ZHONGSHAN INST

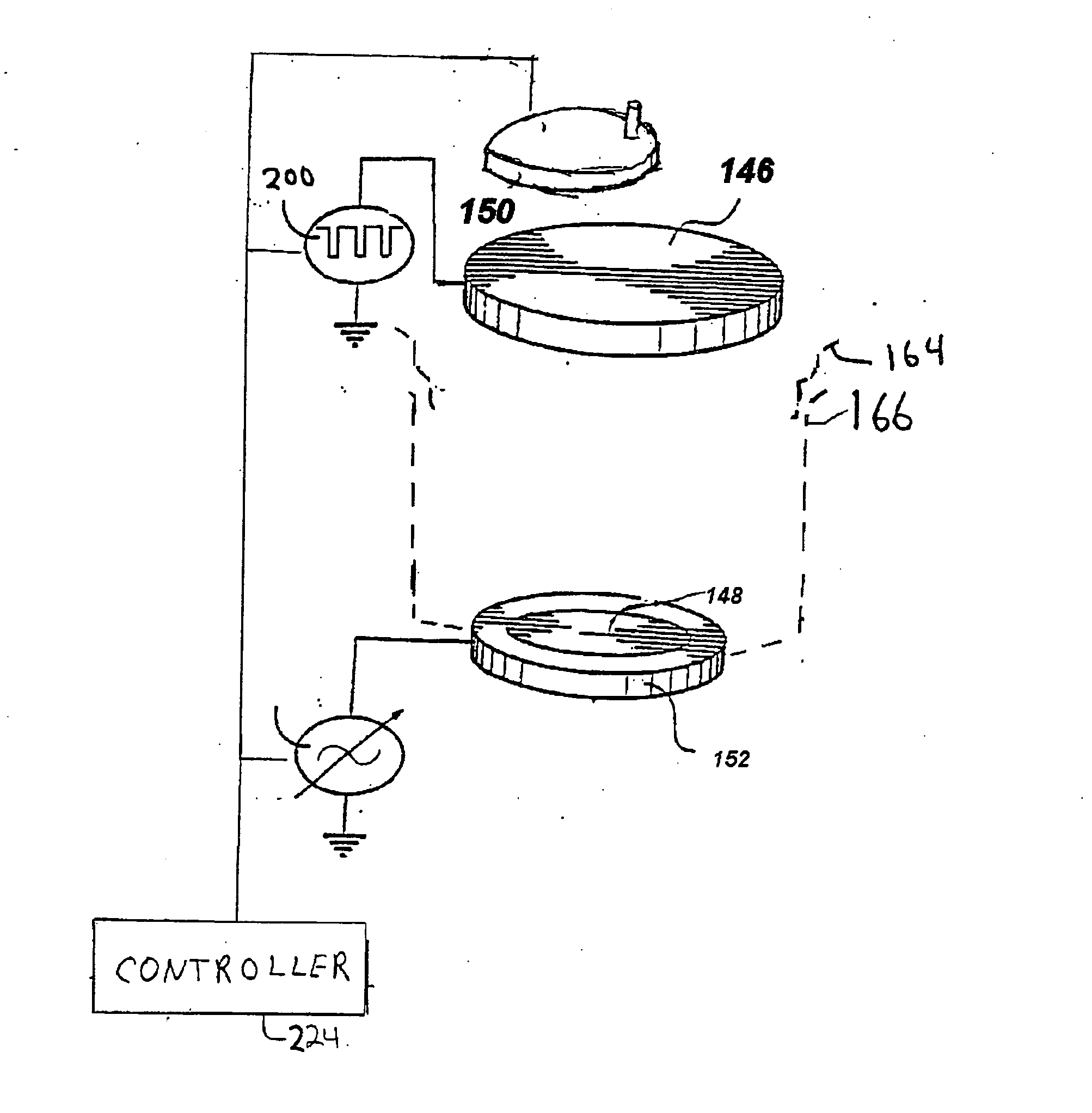

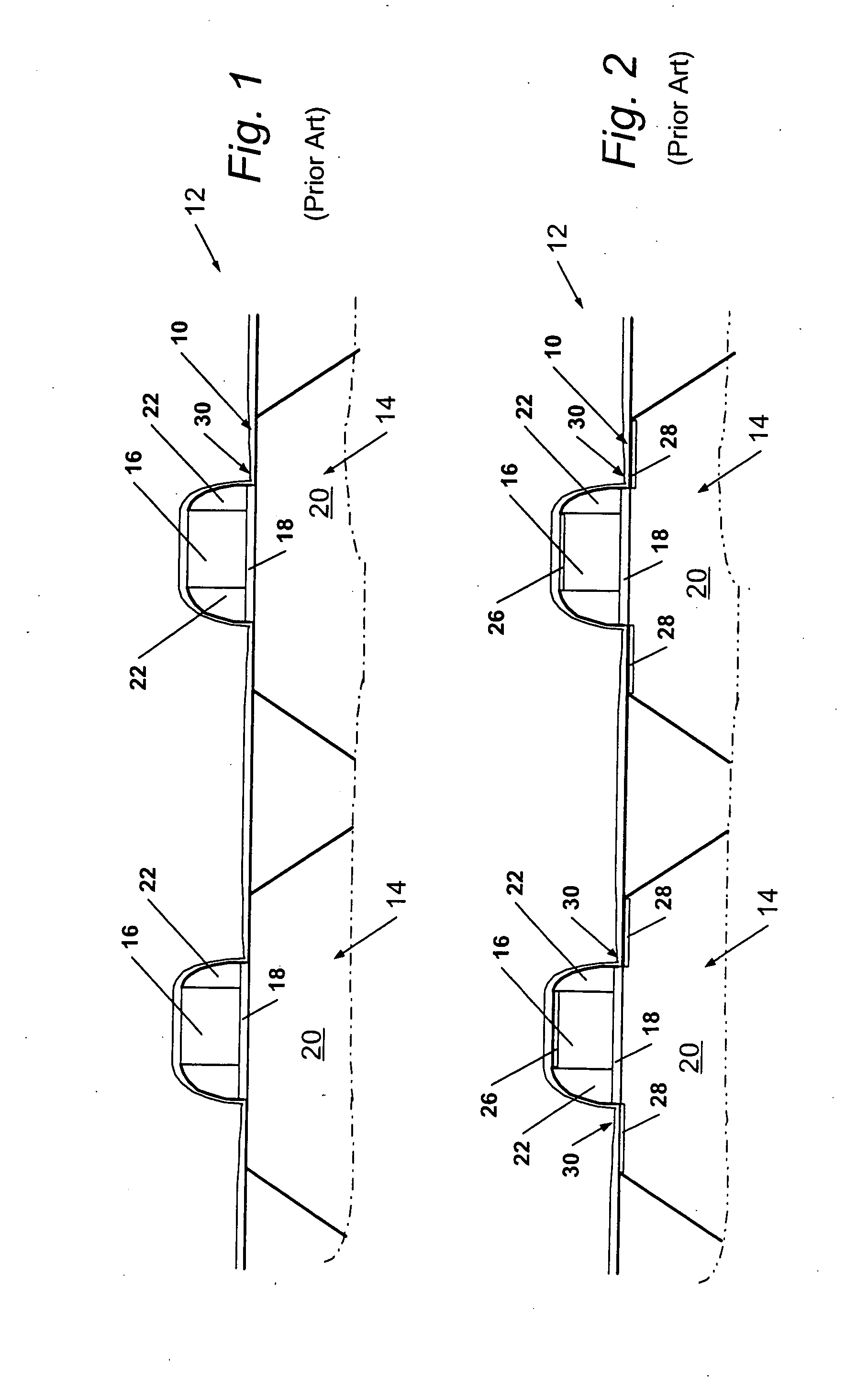

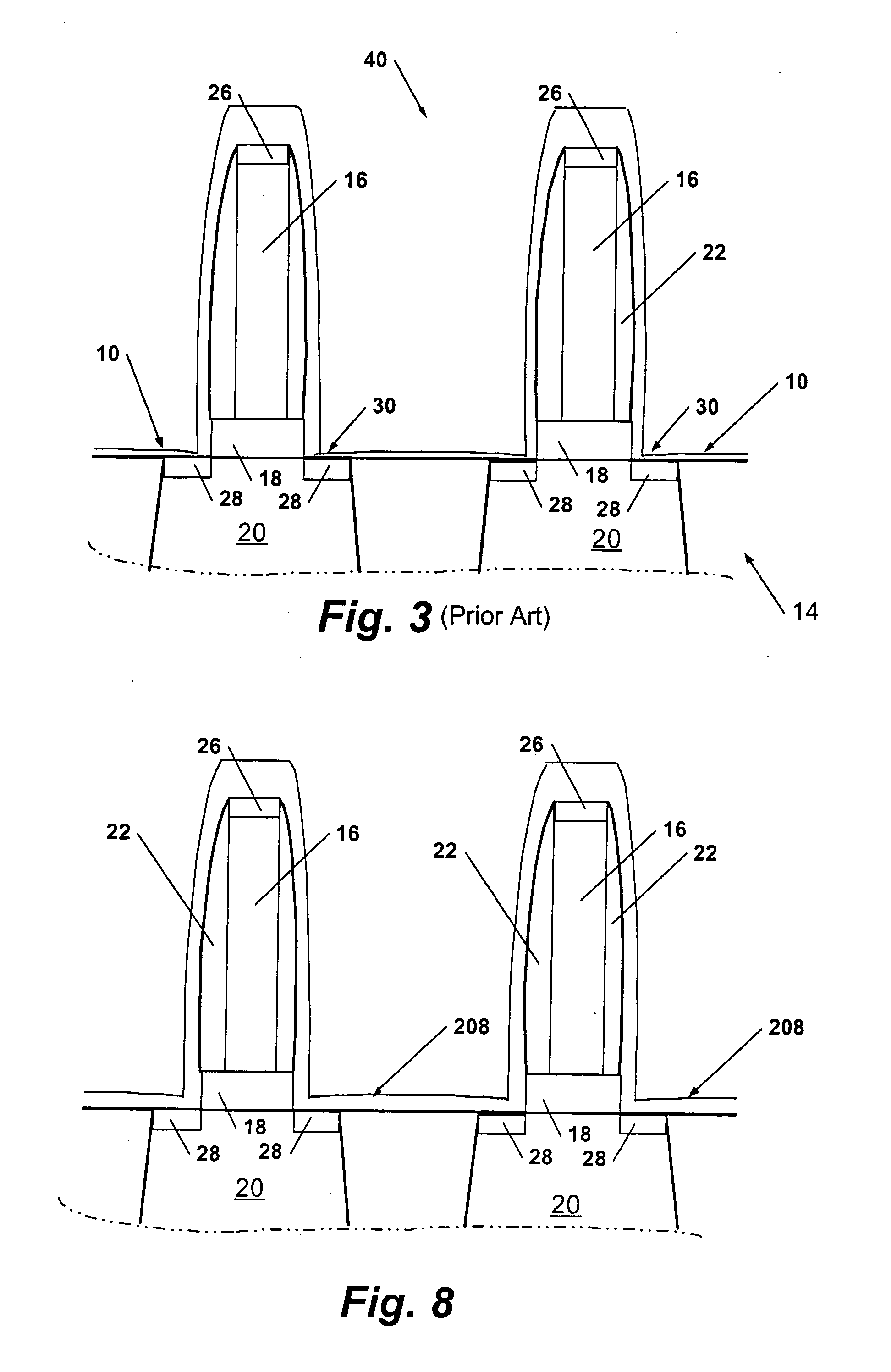

Pulsed magnetron for sputter deposition

InactiveUS20050247554A1Reduce rateReduce the chance of sputteringCellsElectric discharge tubesThin layerSputter deposition

A magnetron sputter reactor for sputtering deposition materials such as nickel and cobalt, for example, and its method of use, in which self-ionized plasma (SIP) sputtering is promoted. SIP is promoted by a small magnetron having poles of unequal magnetic strength and a high power applied to the target during sputtering. One embodiment of the present inventions is directed to sputter depositing a metal layer by biasing a sputter target with pulsed power in which the power applied to the target alternates between low and high levels. The high levels are, in one embodiment, sufficiently high to maintain a plasma for ionizing deposition material. The low levels are, in one embodiment, sufficiently low such that the power applied to the target during the high and low levels is, on average, low enough to facilitate deposition of thin layers if desired.

Owner:APPLIED MATERIALS INC

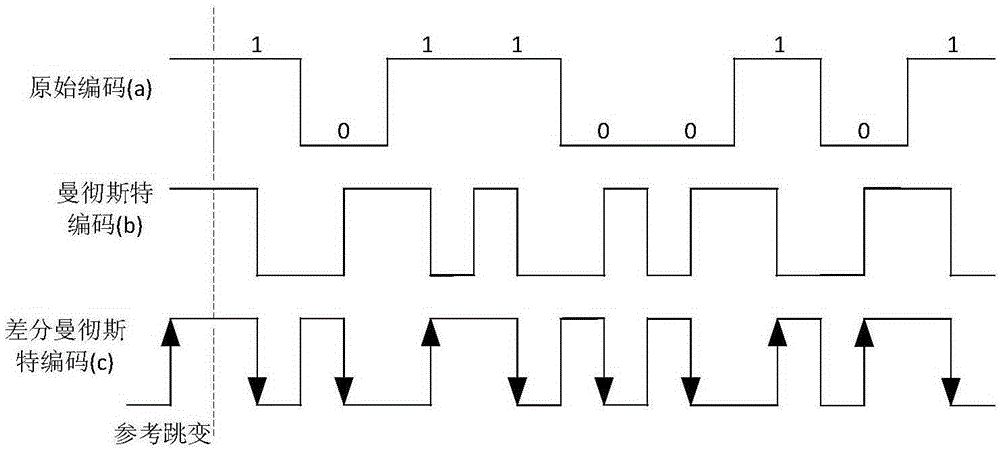

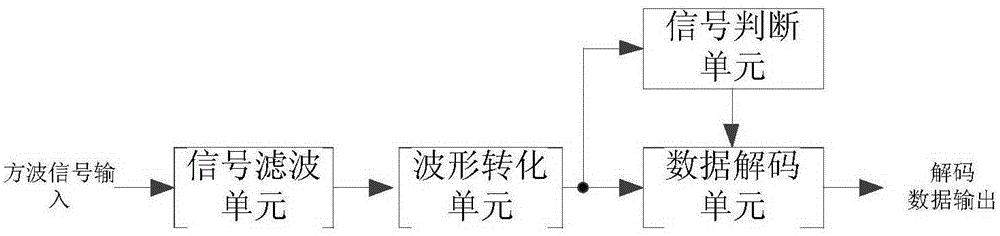

Differential Manchester decoding circuit and method

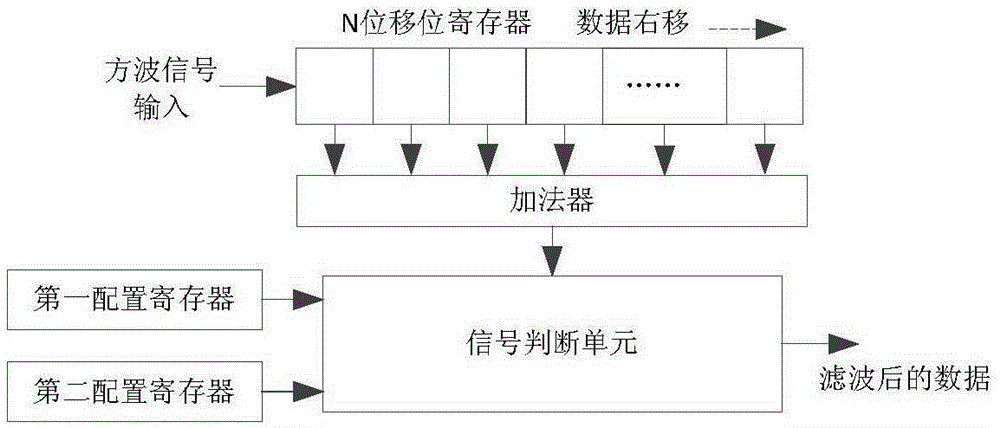

The invention belongs to the technical field of wireless communications and provides a differential Manchester decoding circuit and method. The circuit comprises: a waveform conversion unit for sampling a received square wave signal to obtain a high level or a low level and performing computing operations of different types on a sampling counter to convert the square wave signal into a triangular wave signal; a signal judgment unit for judging the high and low levels of the triangular wave signal by use of a preset high level threshold and a preset low level threshold, respectively, and recovering decoding clock and intermediate data by judging the wave crests and the wave troughs of the triangular wave signal; and a data decoding unit for performing twice sampling on the intermediate data with the decoding click and performing EXCLUSIVE OR processing on the sampled data to obtain decoded data. The differential Manchester decoding circuit is capable of eliminating the influence of clock skew by virtue of self-addition and self-subtraction of the sampling counter, and is simple in circuit structure and low in error code occurrence rate.

Owner:WUHAN RUINAJIE ELECTRONICS TECH

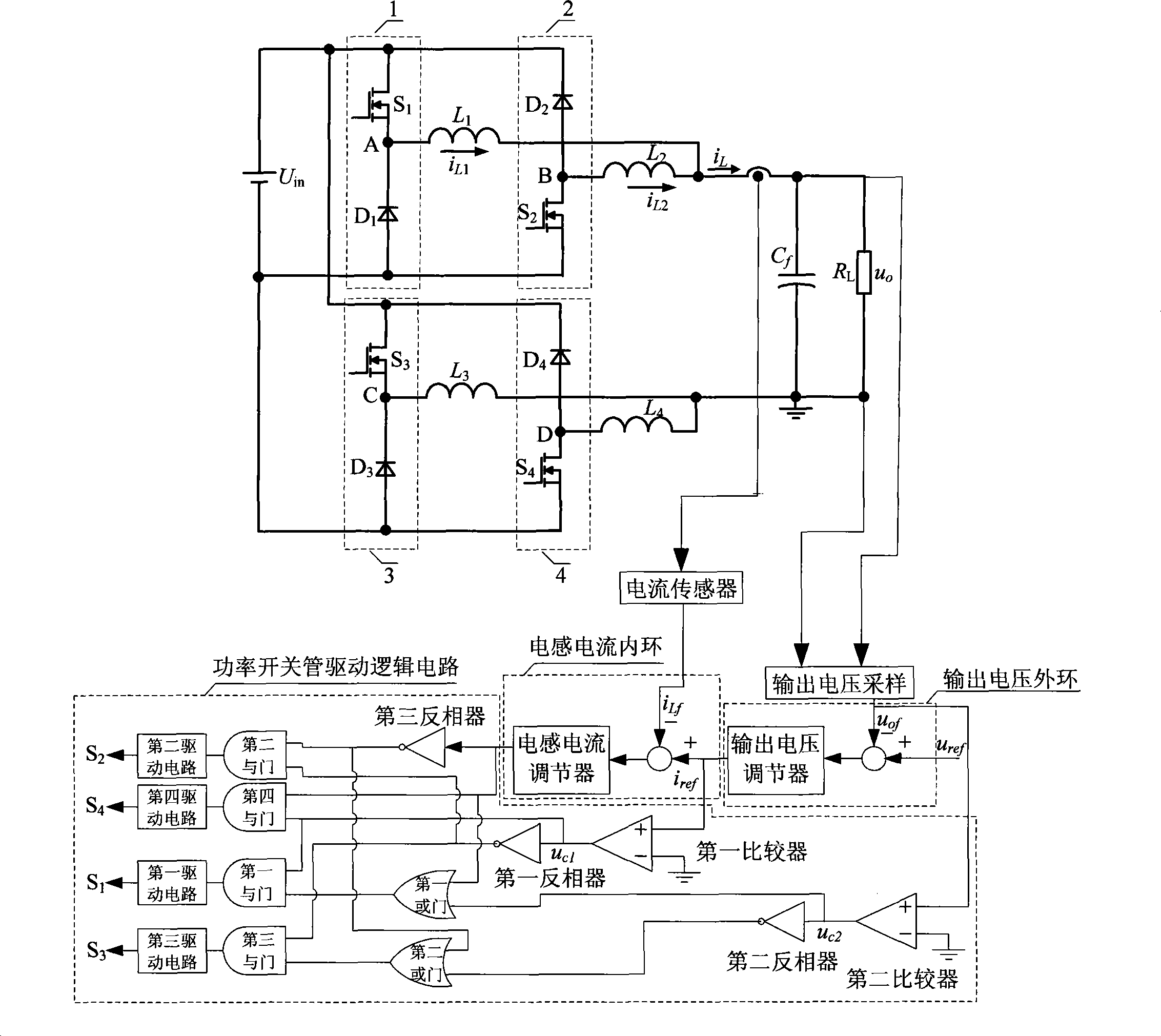

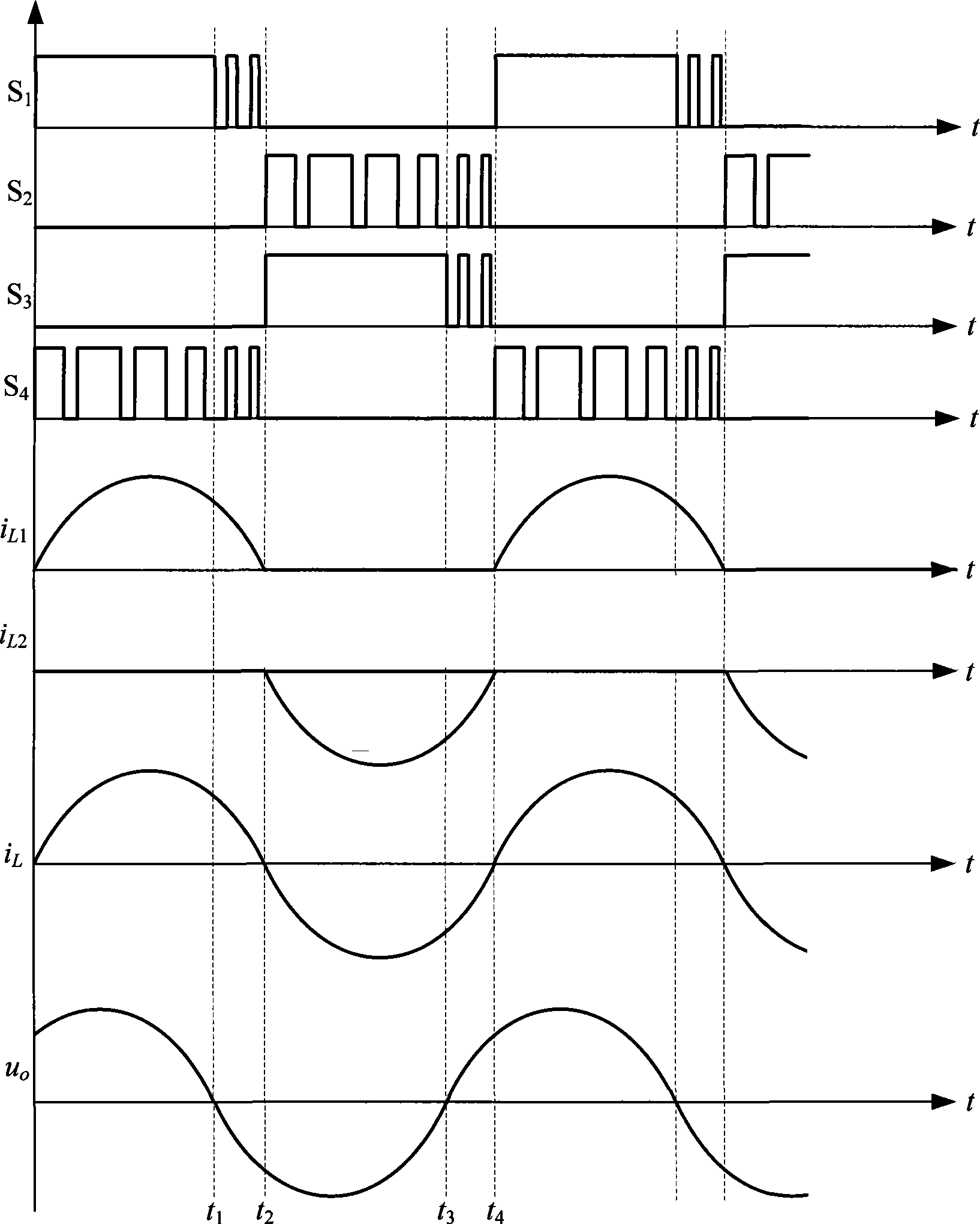

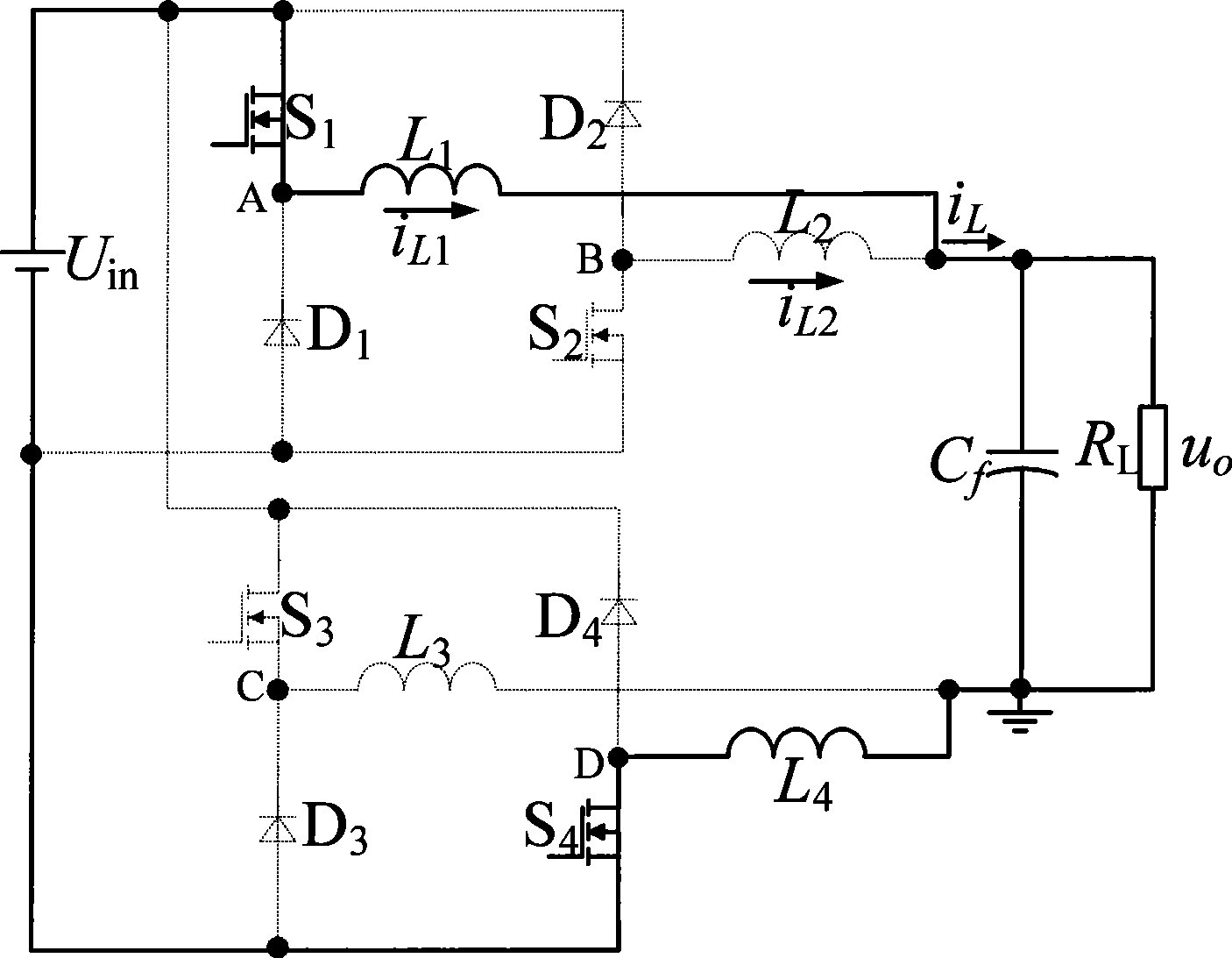

Double step-down bridge type inverter controlling method for single current sensor

The invention discloses a method for controlling a single current sensor double-decompression bridge-type inverter, which belongs to methods for controlling inverters. The invention adopts a single current sensor to collect inverter inductor current, and an output voltage outer ring receives an inverter output voltage feedback signal and an output voltage set signal, and outputs a set inductor current. An inductor current inner ring receives the set inductor current and the inductor current feedback signal, and outputs a logic control signal. The power switch tube drives a logic circuit to receive the logic control signal, the inductor current feedback signal and the output voltage feedback signal, and to output high and low level actuating signals of each power switch tube. The method only needs a current sensor, the cost is reduced, simultaneously, the volume and weight of a filter can be reduced through adopting the control method, and the efficiency of the inverter is improved.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

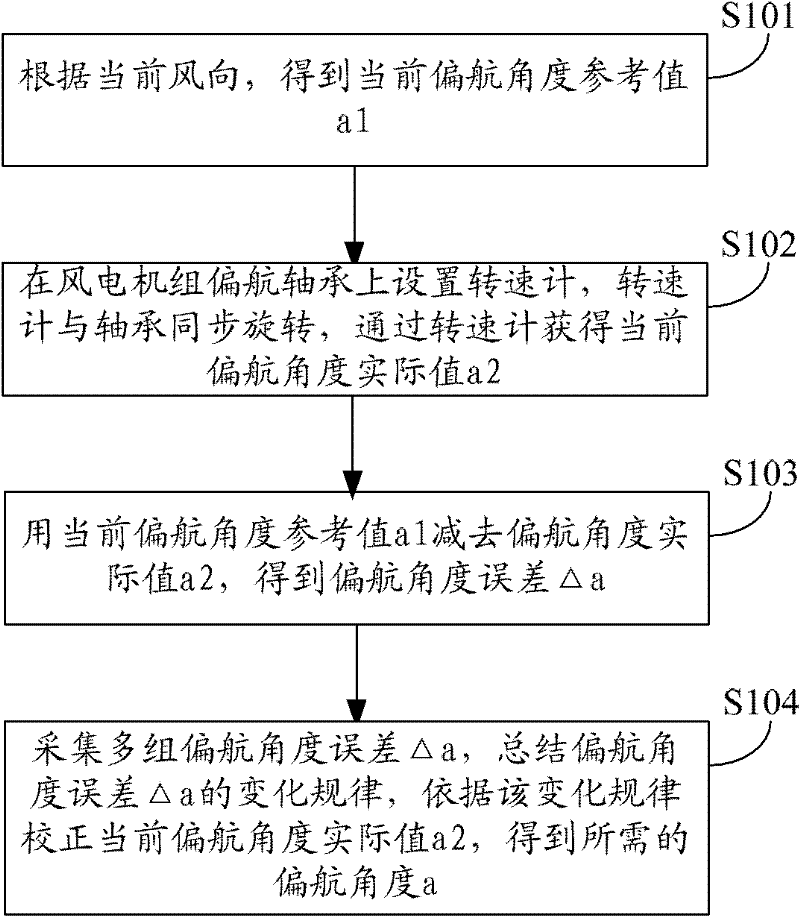

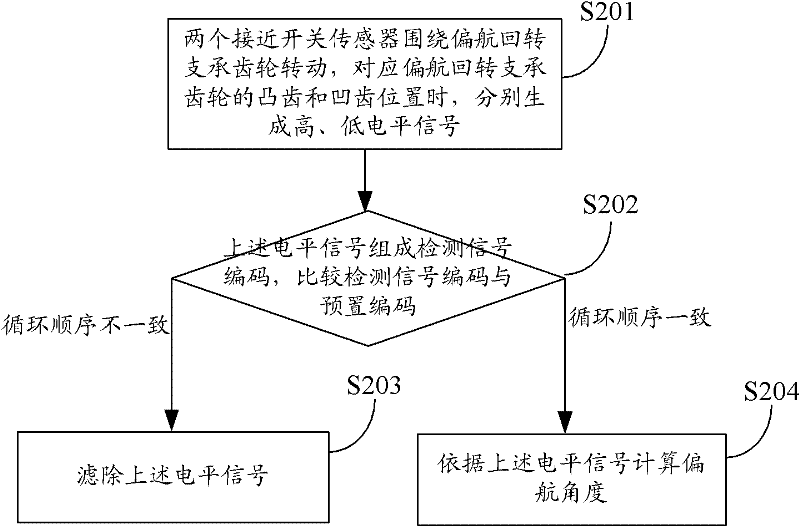

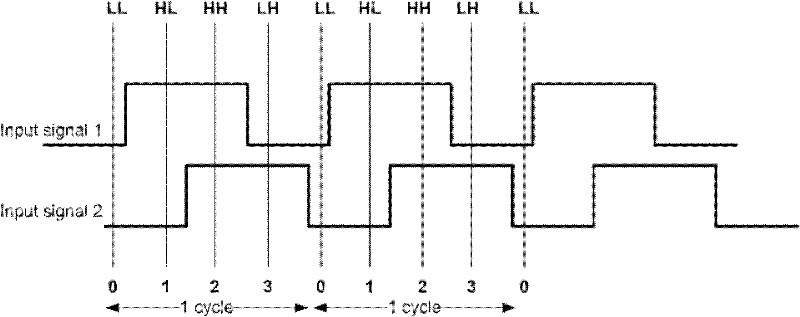

Method and system for computing yaw angle of fan

The invention relates to a method for computing a yaw angle of a fan. In a cabin of the fan, at least two approach switch sensors are arranged at a position adjacent to a yaw rotary supporting gear. The method comprises the following steps of: when the fan yaws and the approach switch sensors rotate around the yaw rotary supporting gear and correspond to convex teeth and concave teeth positions of the yaw rotary supporting gear, generating different level signals; combining the level signals into a detection signal code, comparing the detection signal code with a preset code, and if cyclic sequences are not accordant, filtering out the level signals; and if the cyclic sequences are accordant, computing the yaw angle according to the level signals. The invention also discloses a system forcomputing the yaw angle of the fan. By the invention, high and low level signals for computation of the yaw angle are normal signals; inaccurate computation of the yaw angle, caused by a fault signal, is effectively avoided; and the computation accuracy of the yaw angle is guaranteed.

Owner:SANY ELECTRIC CO LTD

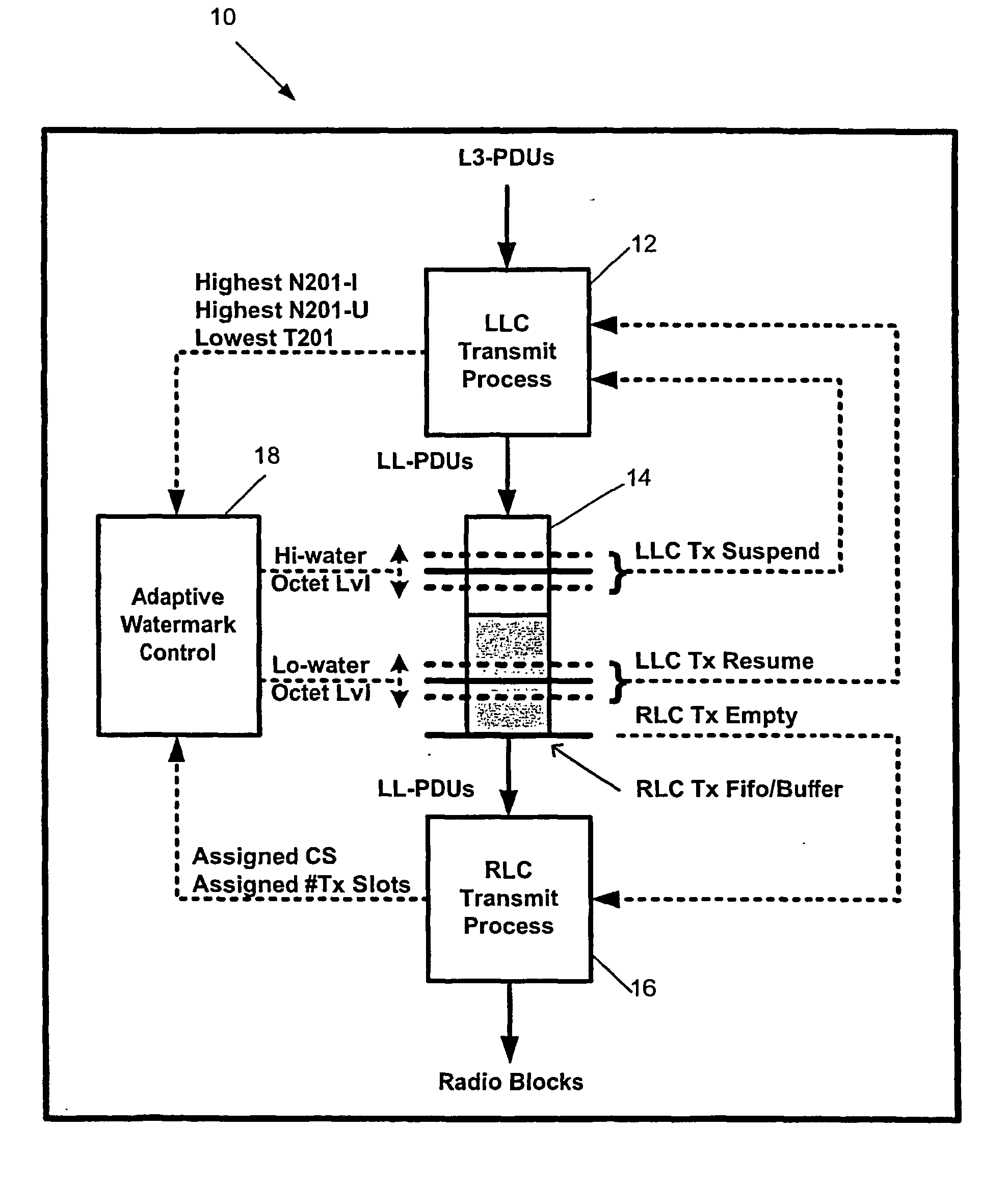

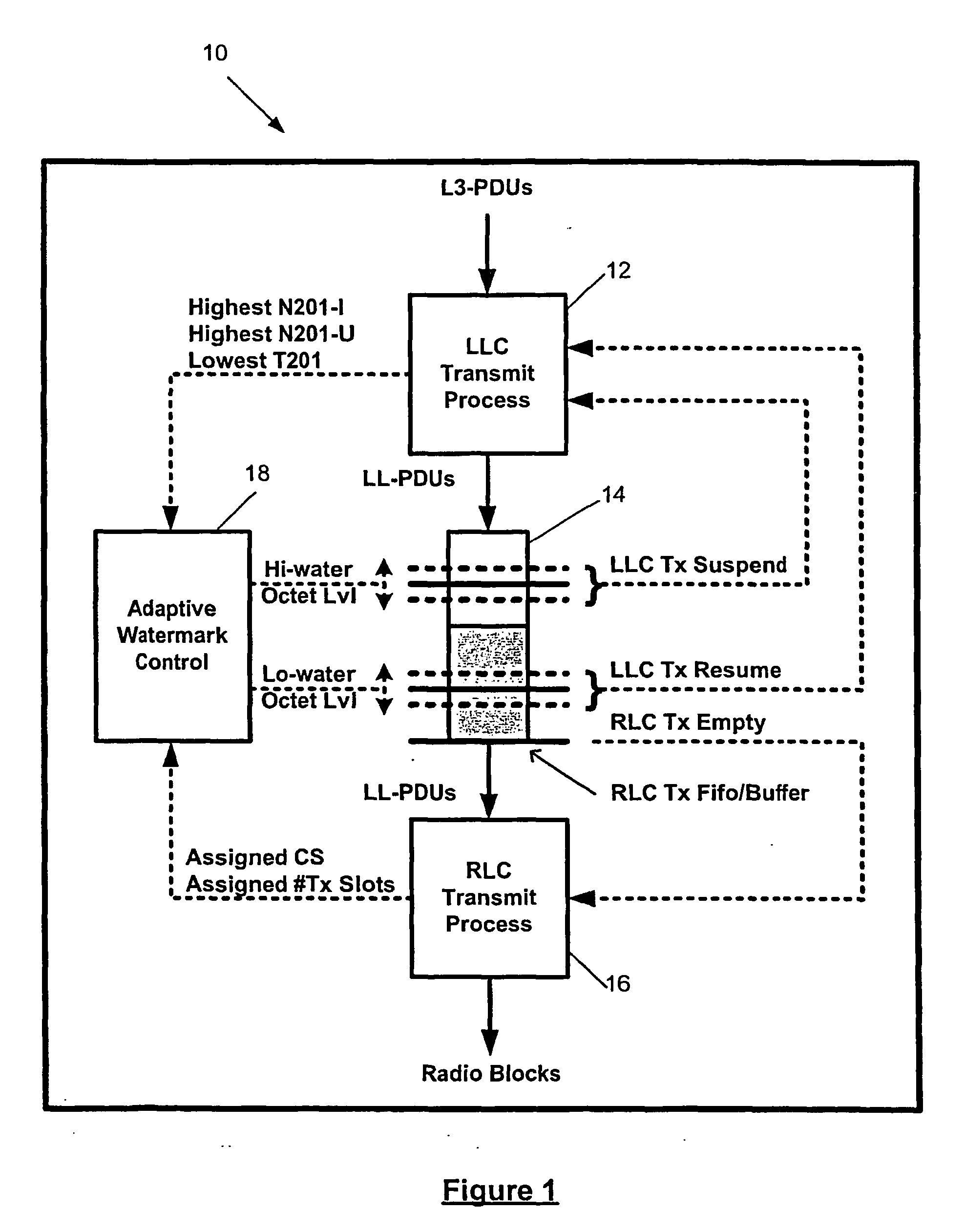

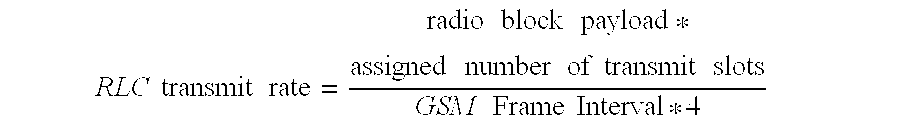

Method of and apparatus for adaptive control of data buffering in a data transmitter

InactiveUS20060168313A1Improve the level ofError preventionNetwork traffic/resource managementControl dataSelf adaptive

A data transmitter (10) divides incoming data for transmission into data blocks and passes them in frame transmission order to a radio link stage (16) via a serial frame buffer (14). The buffer (14) holds the data frames until the radio link stage (16) is able to transmit them. The incoming data has associated with it various parameters. The radio link stage (16) has allocated to it radio link resources. The parameters and resources, which change independently of each other from time to time, are supplied to a controller (18) which calculates high and low buffer levels therefrom. The controller (18) controls the passing of the data frames through the frame buffer (14) to maintain the number of frames in the buffer at any instant of time at a level between the calculated high and low levels.

Owner:QUALCOMM INC