Differential Manchester decoding circuit and method

A decoding circuit and decoding method technology, applied in the field of differential Manchester decoding circuit, can solve the problems of high bit error rate and difficult to achieve accurate sampling clock

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

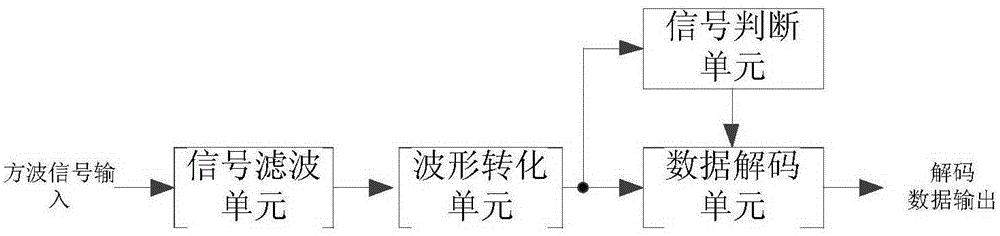

[0047] figure 2A specific structural block diagram of the differential Manchester decoding circuit provided by Embodiment 1 of the present invention is shown, and for convenience of description, only parts related to the embodiment of the present invention are shown. In this embodiment, the circuit includes: a waveform conversion unit, a signal judgment unit, a data decoding unit and a signal filtering unit.

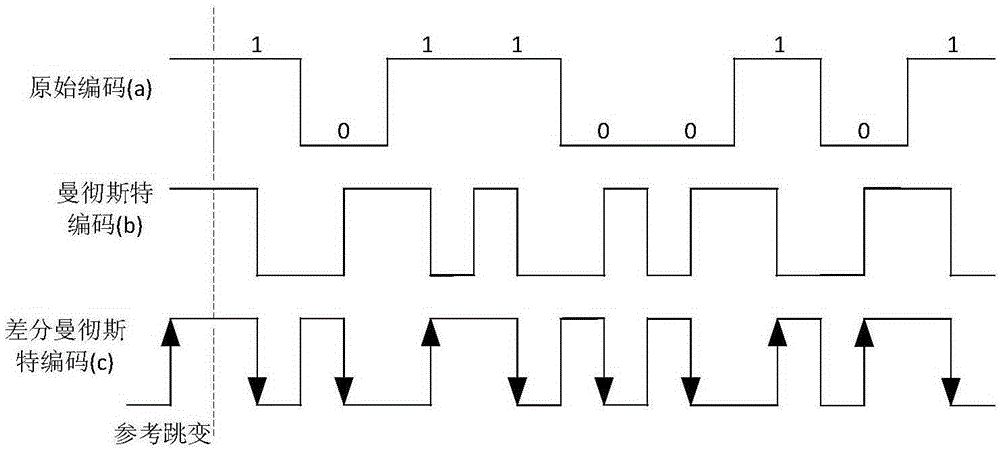

[0048] It should be noted that in wireless communication, differential Manchester coding is widely used due to its advantages of high efficiency and coupling clock coding information. Differential Manchester encoding is sent out after encoding. When the wireless receiving end receives the sent waveform, it is amplified by the amplifier and then quantized by the fixed level comparator to obtain the digital signal.

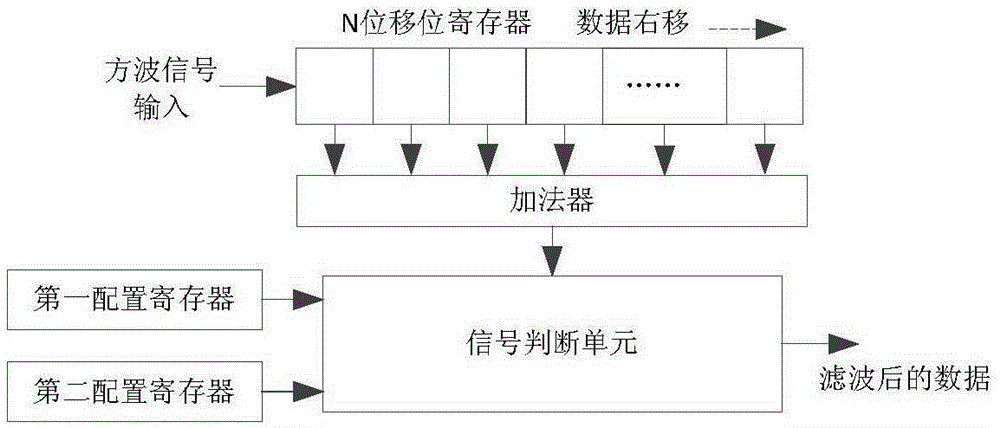

[0049] Wherein, the signal filtering unit is configured to perform average window filtering on the received digital signal to obtain the square wave signal...

Embodiment 2

[0067] Image 6 It shows the implementation flow of the differential Manchester decoding method provided by Embodiment 2 of the present invention, and the details are as follows:

[0068] Before step S601, the method also includes:

[0069] performing averaging window filtering on the received digital signal to obtain the square wave signal.

[0070] Specifically, input the received digital signal to an N-bit shift register, where N is a positive integer greater than or equal to 8;

[0071] summing each bit in the shift register through an adder;

[0072] Comparing the summation result with the first configuration register and the second configuration register, wherein, if the summation result is greater than or equal to the value of the first configuration register, the filtered data is 1, and if the summation If the result is less than or equal to the value of the second configuration register, the filtered data will be 0. In other cases, the filtered data will remain unc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More