Patents

Literature

239 results about "Sort order" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Natural sort order. Natural sort order is an ordering of strings in alphabetical order, except that multi-digit numbers are ordered as a single character. Natural sort order has been promoted as being more human-friendly ("natural") than the machine-oriented pure alphabetical order.

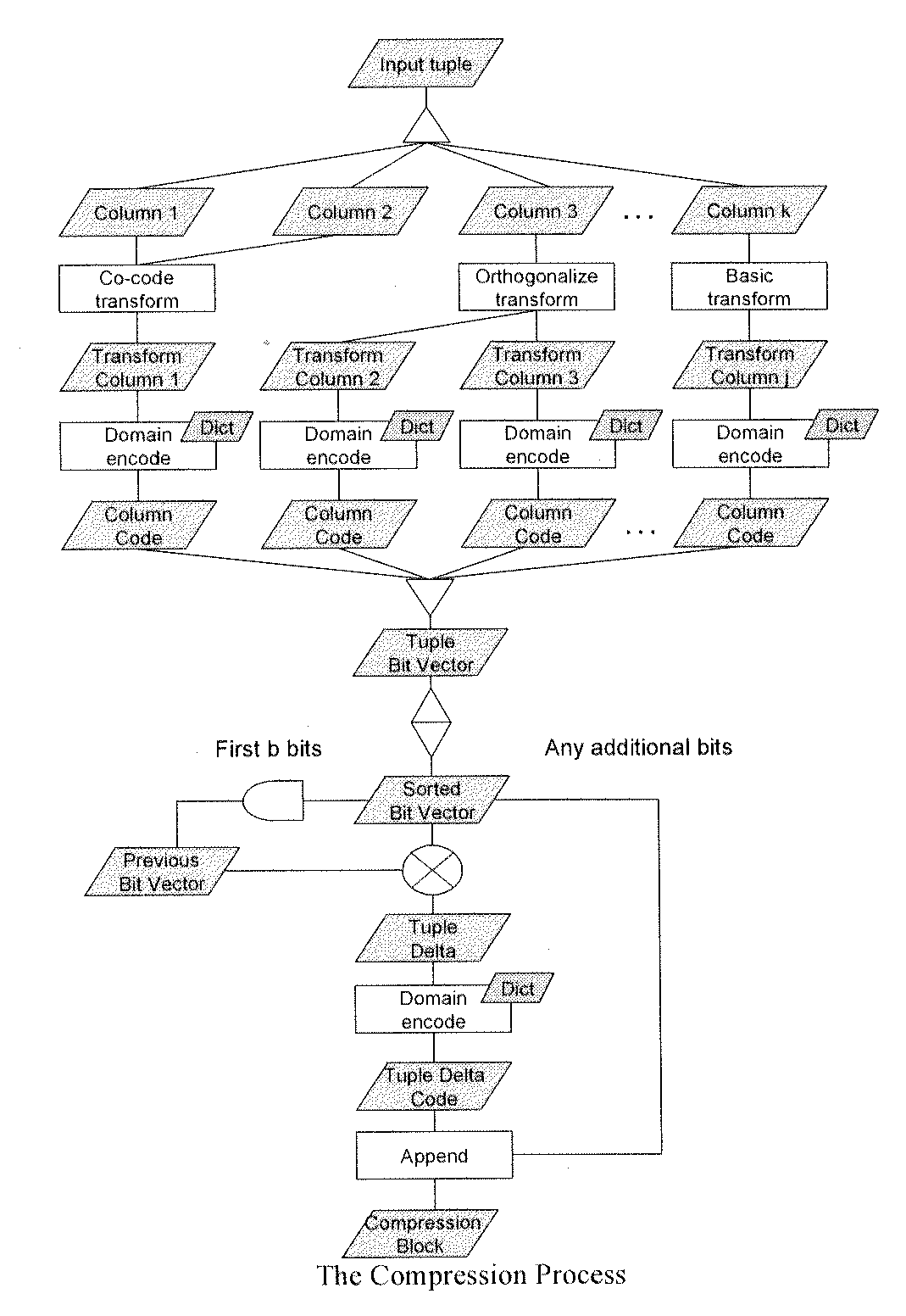

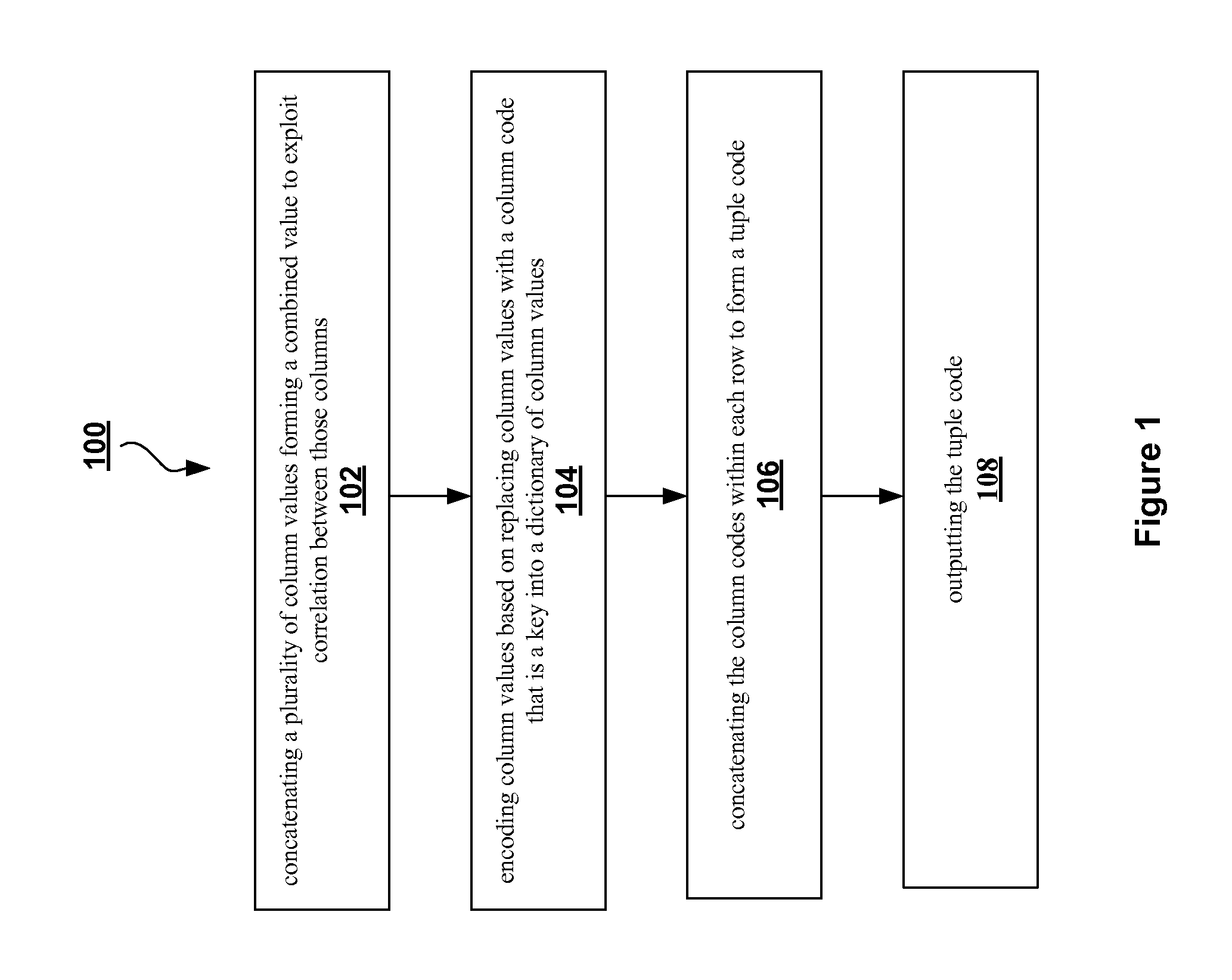

Compression method for relational tables based on combined column and row coding

InactiveUS20090006399A1Digital data information retrievalDigital data processing detailsVariable-length codeTheoretical computer science

A robust method to compress relations close to their entropy while still allowing efficient queries. Column values are encoded into variable length codes to exploit skew in their frequencies. The codes in each tuple are concatenated and the resulting tuplecodes are sorted and delta-coded to exploit the lack of ordering in a relation. Correlation is exploited either by co-coding correlated columns, or by using a sort order that can leverage the correlation. Also presented is a novel Huffman coding scheme, called segregated coding, that preserves maximum compression while allowing range and equality predicates on the compressed data, without even accessing the full dictionary. Delta coding is exploited to speed up queries, by reusing computations performed on nearly identical records.

Owner:IBM CORP

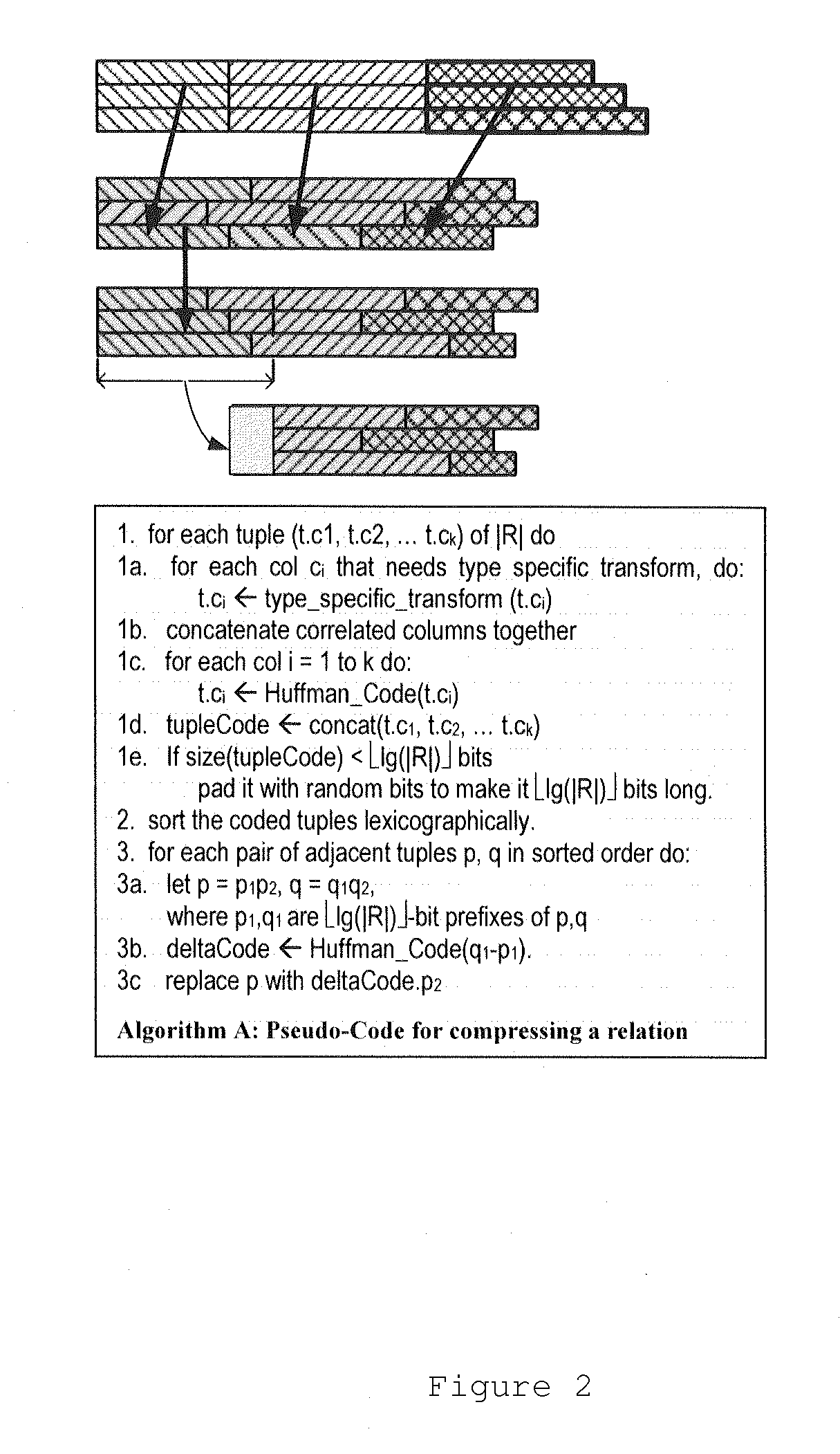

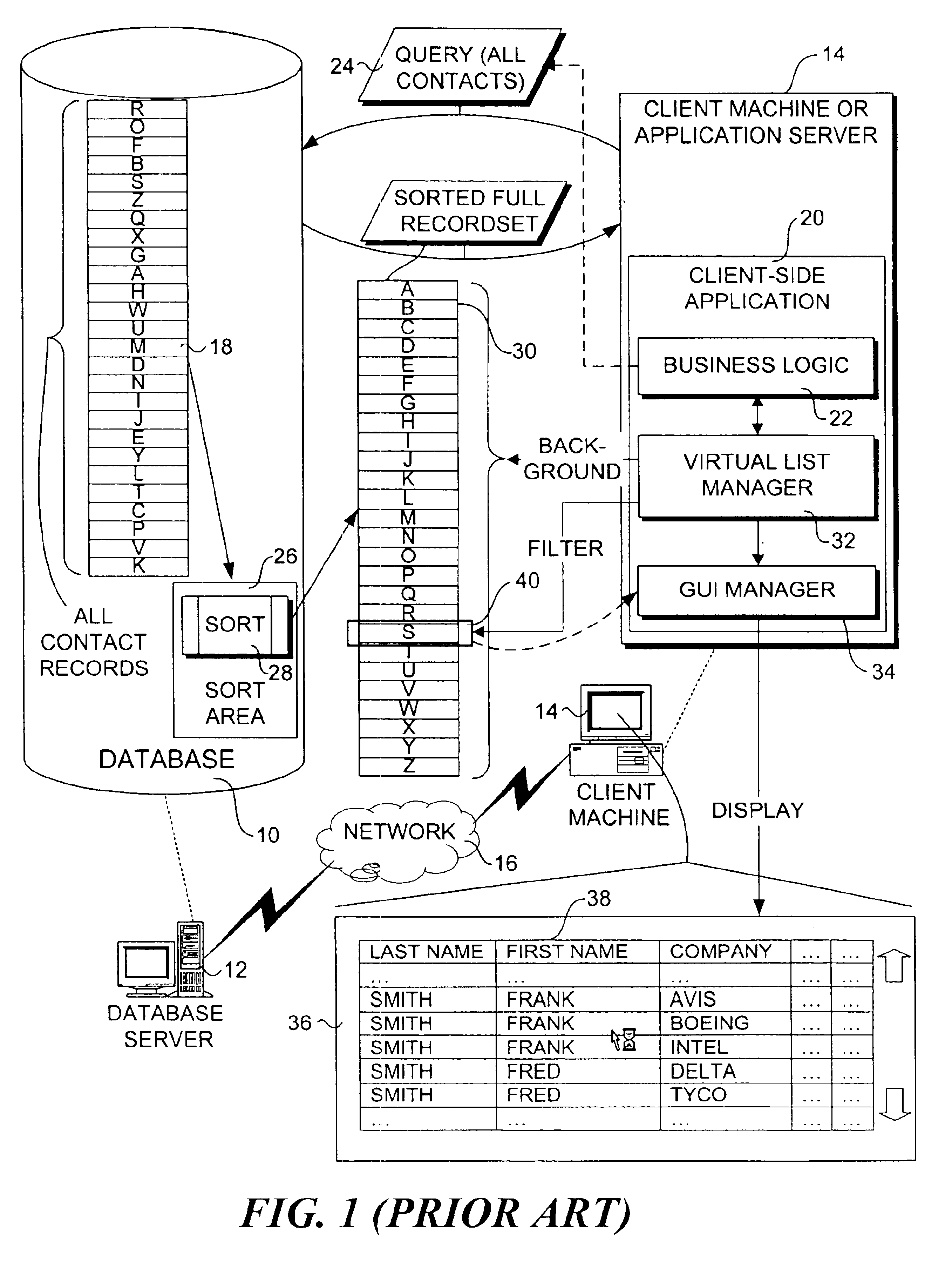

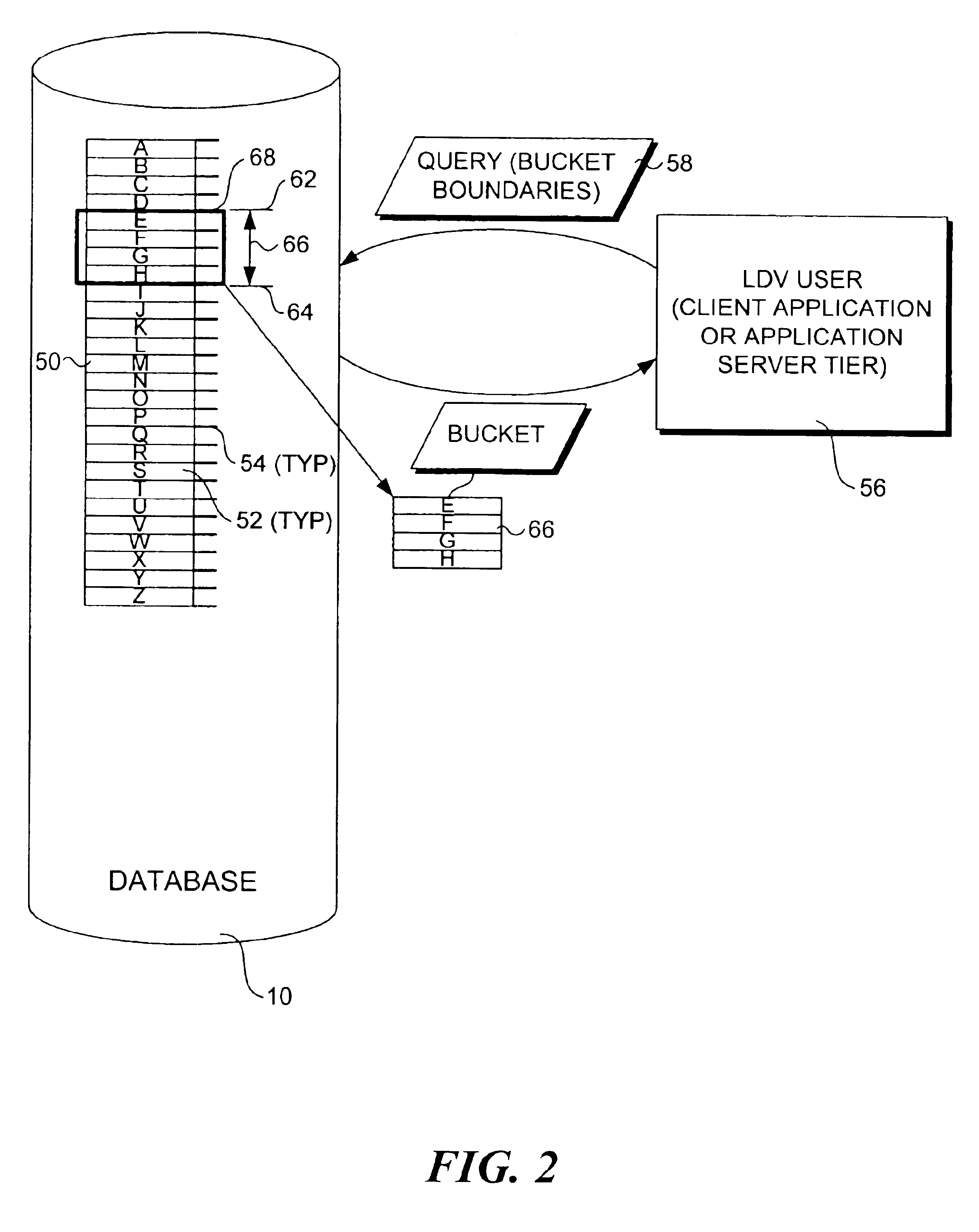

Method and system for access and display of data from large data sets

InactiveUS6907422B1Lower latencyReduce decreaseData processing applicationsRelational databasesData setData mining

A method and system for accessing and display of data records from large data sets. The method includes defining a plurality of boundaries to logically partition the large data set into a plurality of buckets in accordance with a predefined sort order. The sort order is based on data stored in at least two columns of a database table in which at least a base portion of each data record is stored. In response to a request to retrieve a data record or group of related records, such as all contacts having a given first and last name, a determination is made to which bucket the data record or at least a portion of group of related records are stored in. A query is then formulated to retrieve a subset of the large set of records from the database corresponding to data records contained in the bucket.

Owner:ORACLE INT CORP

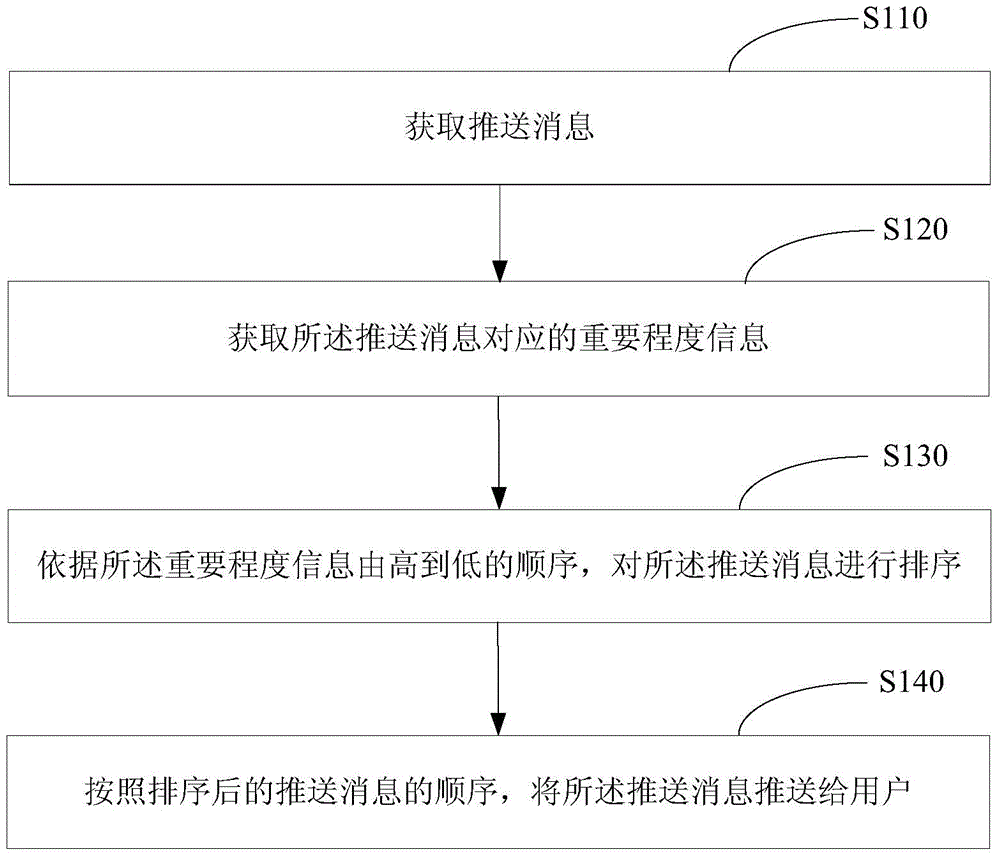

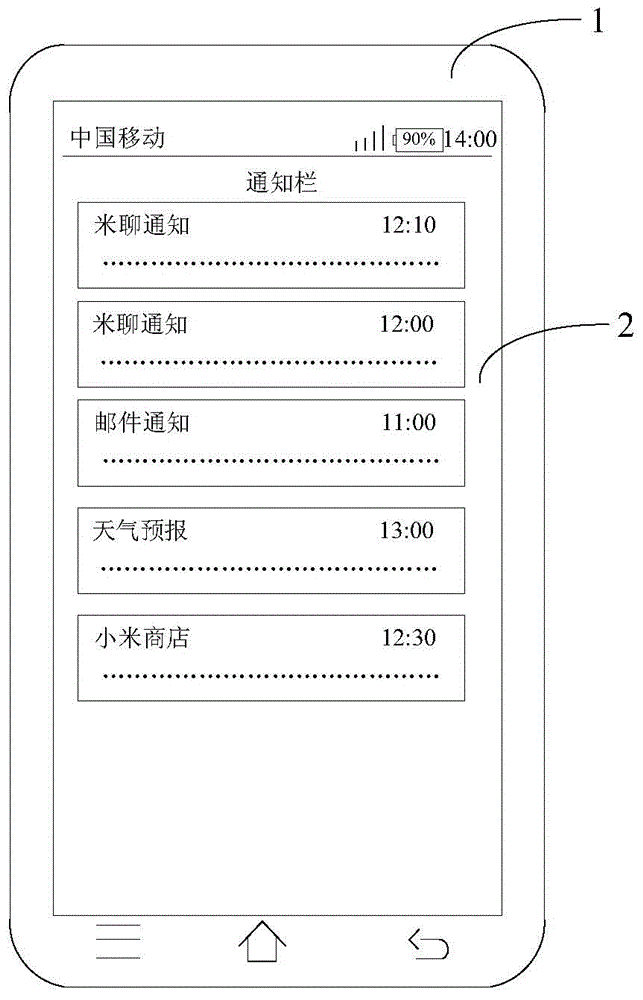

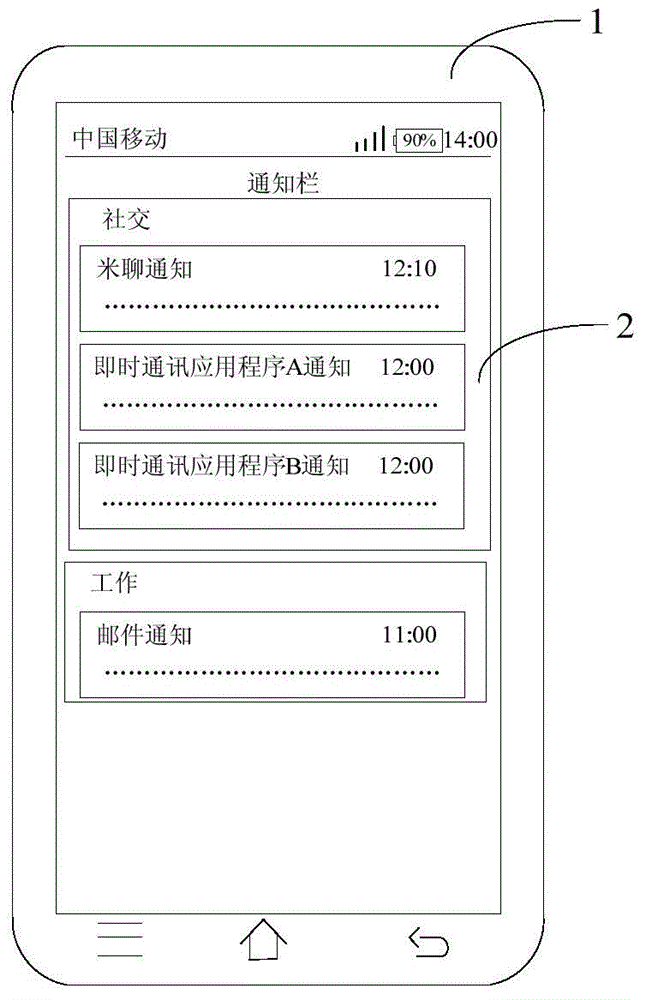

Push message display method and push message display device

InactiveCN104572942AAvoid browsingSemantic analysisSpecial data processing applicationsDisplay deviceComputer engineering

An embodiment of the invention discloses a push message display method and a push message display device. The push message display method includes acquiring types of push messages and importance degree information corresponding to the types of the push messages; sorting the push messages in a descending order according to the importance degree information corresponding to different types; pushing the push messages to users according to the sort order of the push messages. By the method, the push messages important to the users can be recognized automatically and pushed to the users; the push messages are sorted in the descending order according to the importance degrees of the push messages and are pushed to the users according to the sort order thereof, so that the users are prevented from browsing a large number of uninterested push messages.

Owner:XIAOMI INC

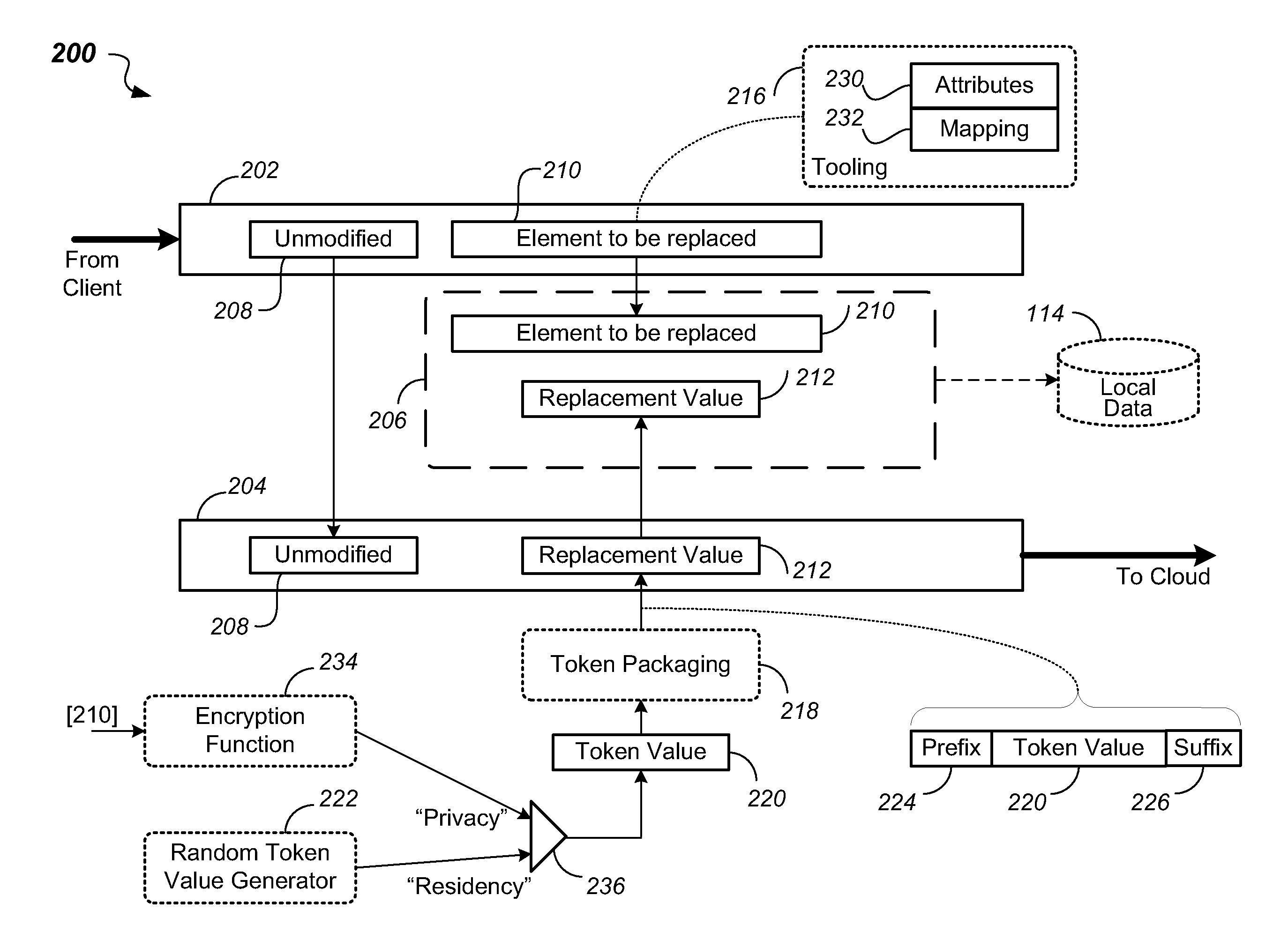

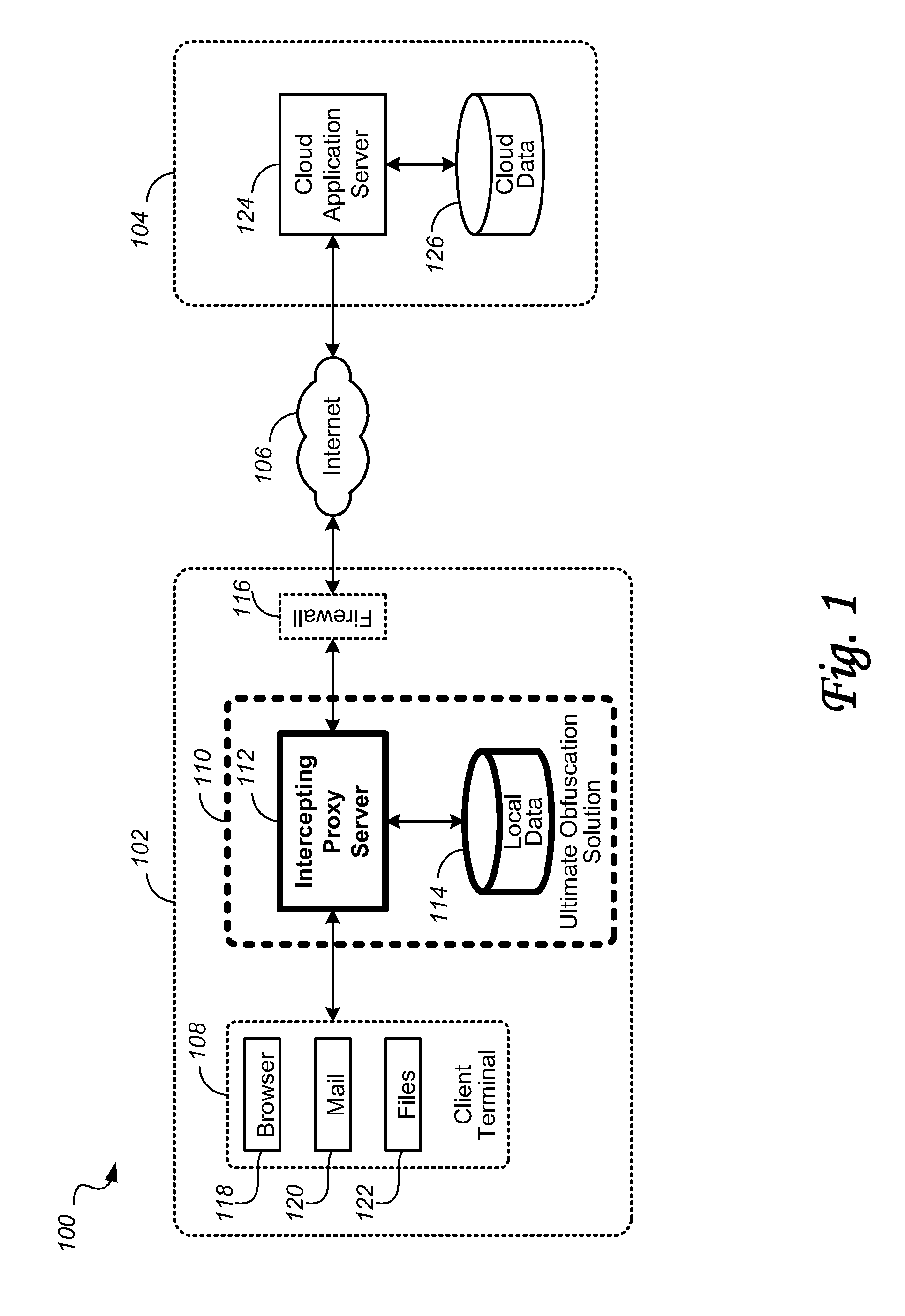

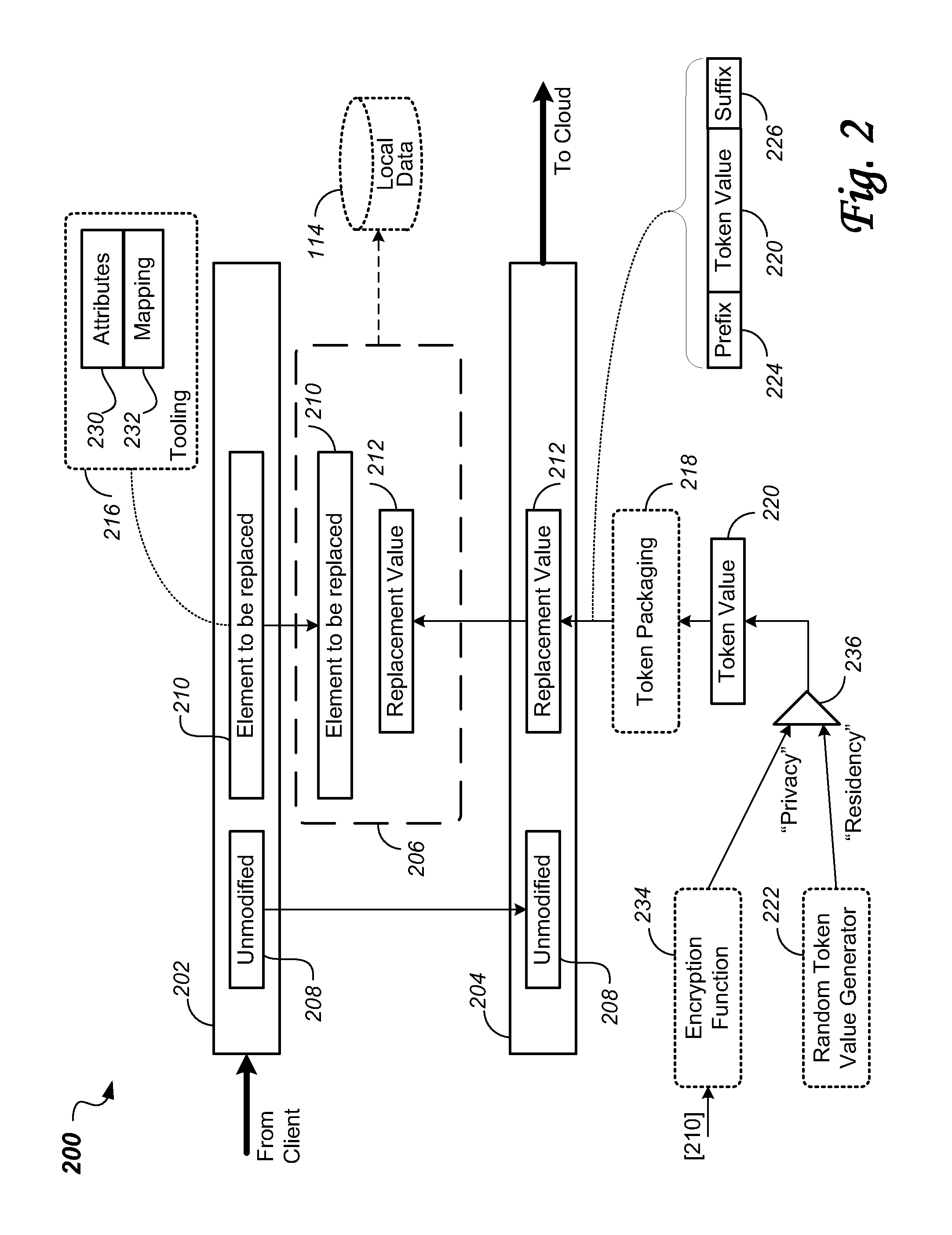

System and method of sort-order preserving tokenization

ActiveUS20120278897A1Digital data processing detailsAnalogue secracy/subscription systemsData compressionProxy server

An intercepting proxy server processes traffic between an enterprise user and a cloud application. The intercepting proxy server provides interception of real data elements in communications from the enterprise to the cloud and replacing them with obfuscating tokens. Tokens included in results returned from the cloud, are intercepted by the intercepting proxy server, and replaced with the corresponding real data elements. In order for the sort order of the tokens to correspond to the sort order of the corresponding real data elements, a sort order preserving data compression is performed on parts of the real data elements, and the compressed values concatenated with the obfuscated tokens, thus producing sortable tokens which, even though they are obfuscated, appear in the correct sort order in the cloud application.

Owner:CA TECH INC

System for identifying and sorting orders

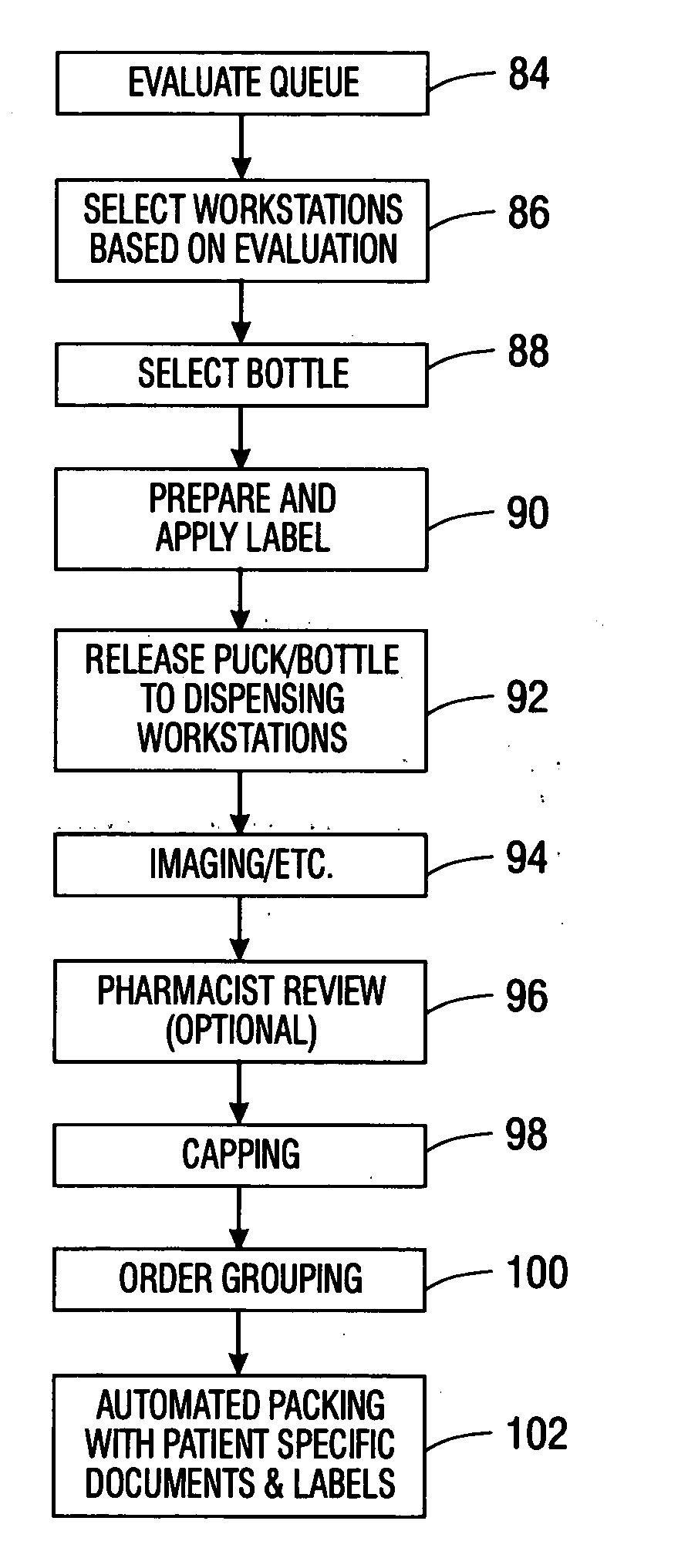

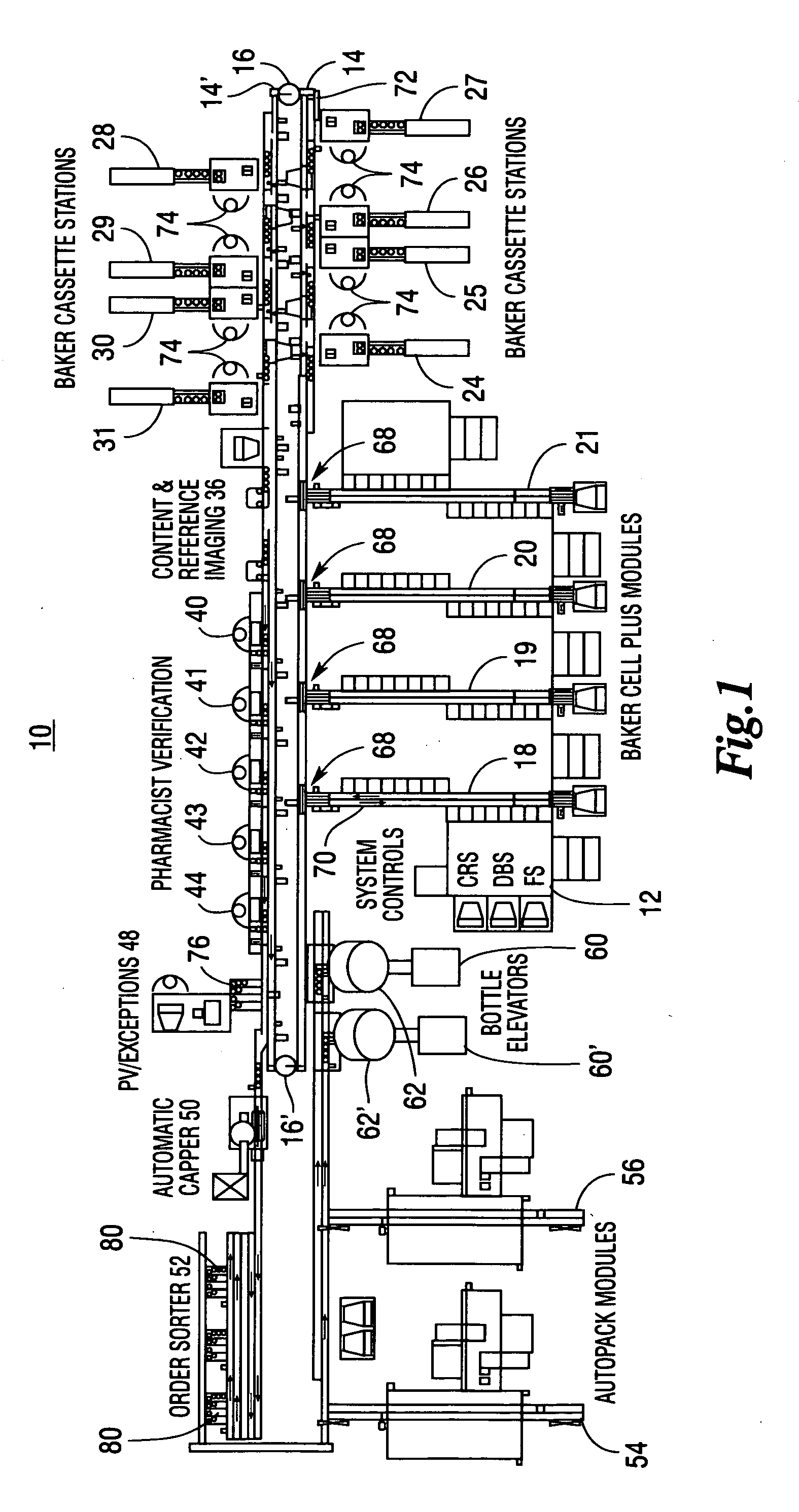

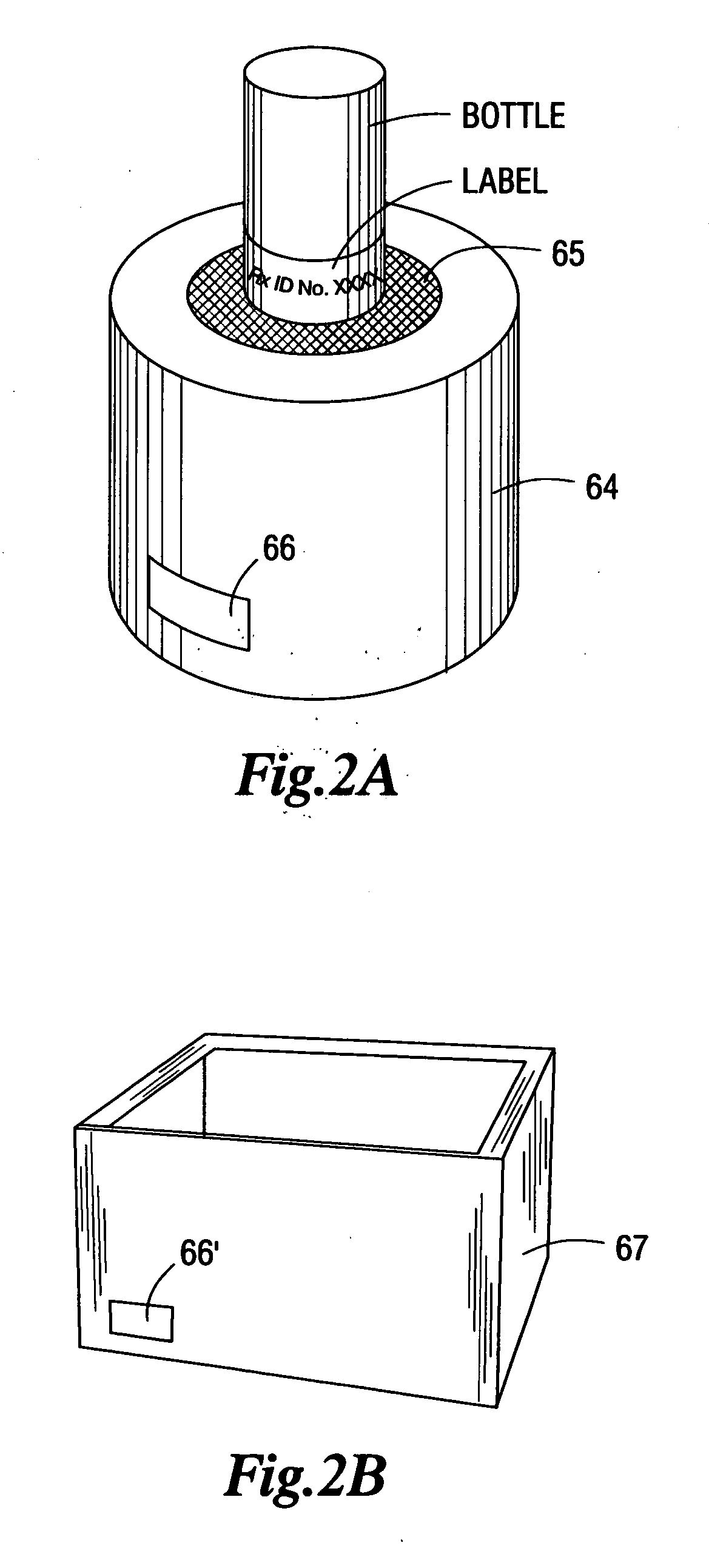

InactiveUS20050171813A1Data processing applicationsDrug and medicationsOrder formMedical prescription

A method of discriminating between orders is comprised of evaluating a queue of orders based on whether each prescription within each order can be filled in an automated or non-automated manner. A set of workstations for each prescription is then determined based on the evaluating. For those orders that can be filled entirely in an automated manner, the set of workstations for each prescription excludes a pharmacist review workstation. Another aspect of the present disclosure is directed to a method of operating a prescription filling facility of the type having automated equipment and non-automated equipment for filling orders, the improvement comprising identifying an order that can be filled with automated equipment and routing at least one container to be filled for the order in a manner that eliminates a review of the order by a pharmacist. Because of the rules governing abstracts, this abstract should not be relied upon in construing the claims

Owner:MCKESSON AUTOMATION SYST

Order sorting method and system

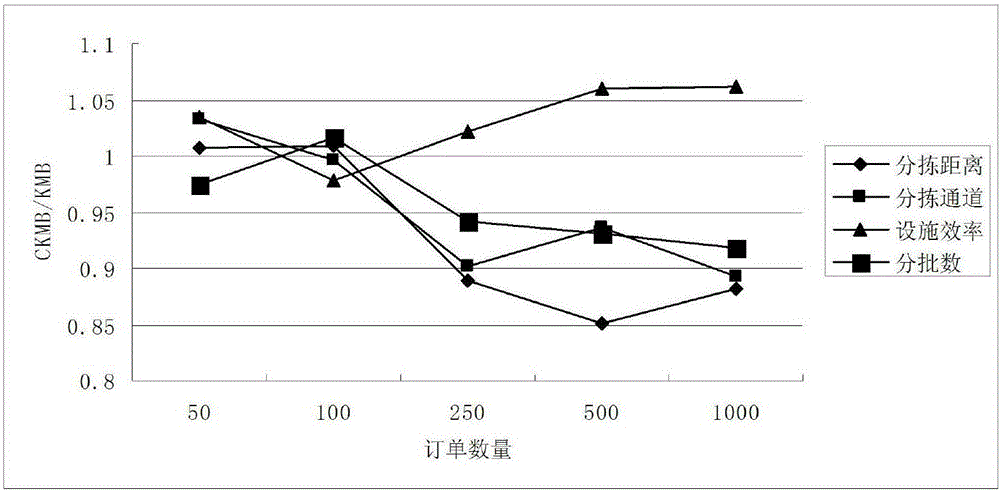

InactiveCN101968860AComputationally efficientReduce operating costsResourcesSorting problemComputer science

The embodiment of the invention provides order sorting method and system. The method comprises the steps of: generating a storehouse plane layout according to the putting condition of storehouse shelves; then computing the shortest path between nodes in a storehouse; finding out the positions, sizes and the weight of goods required for an order from pre-stored data; computing the shortest path and distance between any two pieces of required goods by using the shortest path between the nodes; and computing the optimal sorting path according to the capacity of sorting equipment and the required quantity of the required goods in the order so as to sort orders by the sorting equipment according to the optimal sorting path. The embodiment of the invention can effectively compute the sorting path, reduce the working cost, enhance the working efficiency, and solve the problems of inconsistent shelf arrangement, relatively small shelf height, and small expense difference caused by storing and taking the goods on different layers of shelves of the same goods position; and sorting workers mainly need to optimize order sorting problem in the horizontal movement distance for sorting work.

Owner:BEIJING WUZI UNIVERSITY

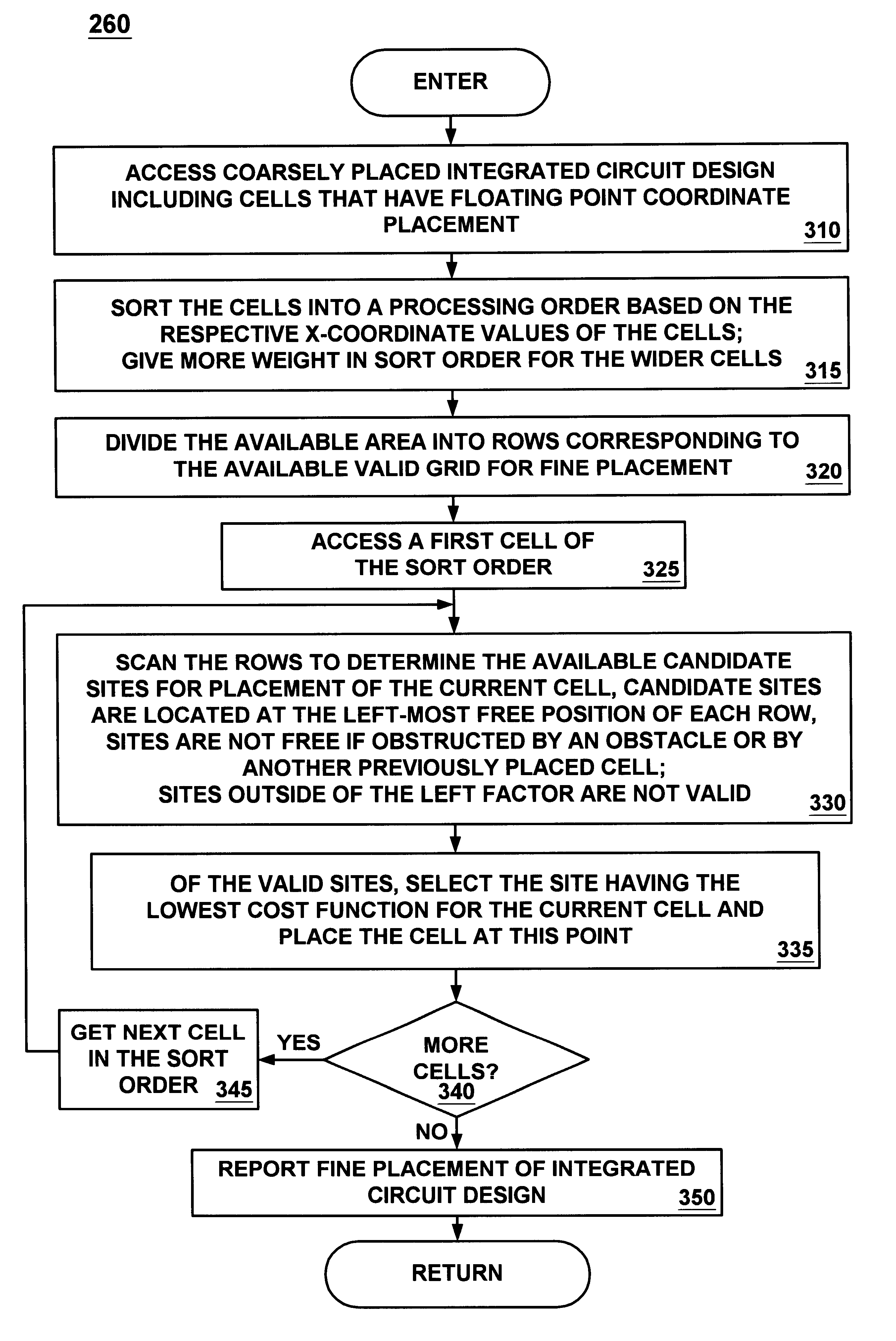

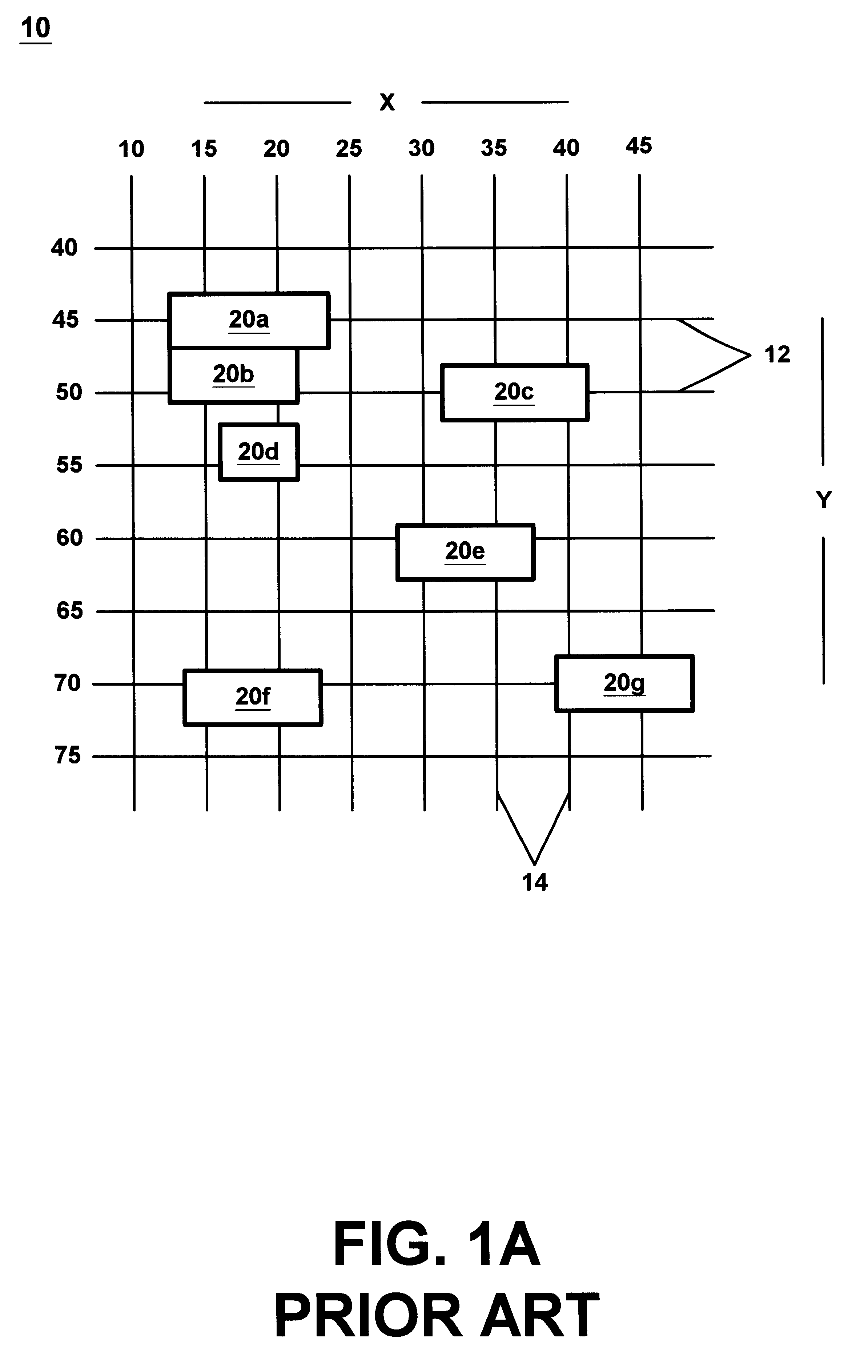

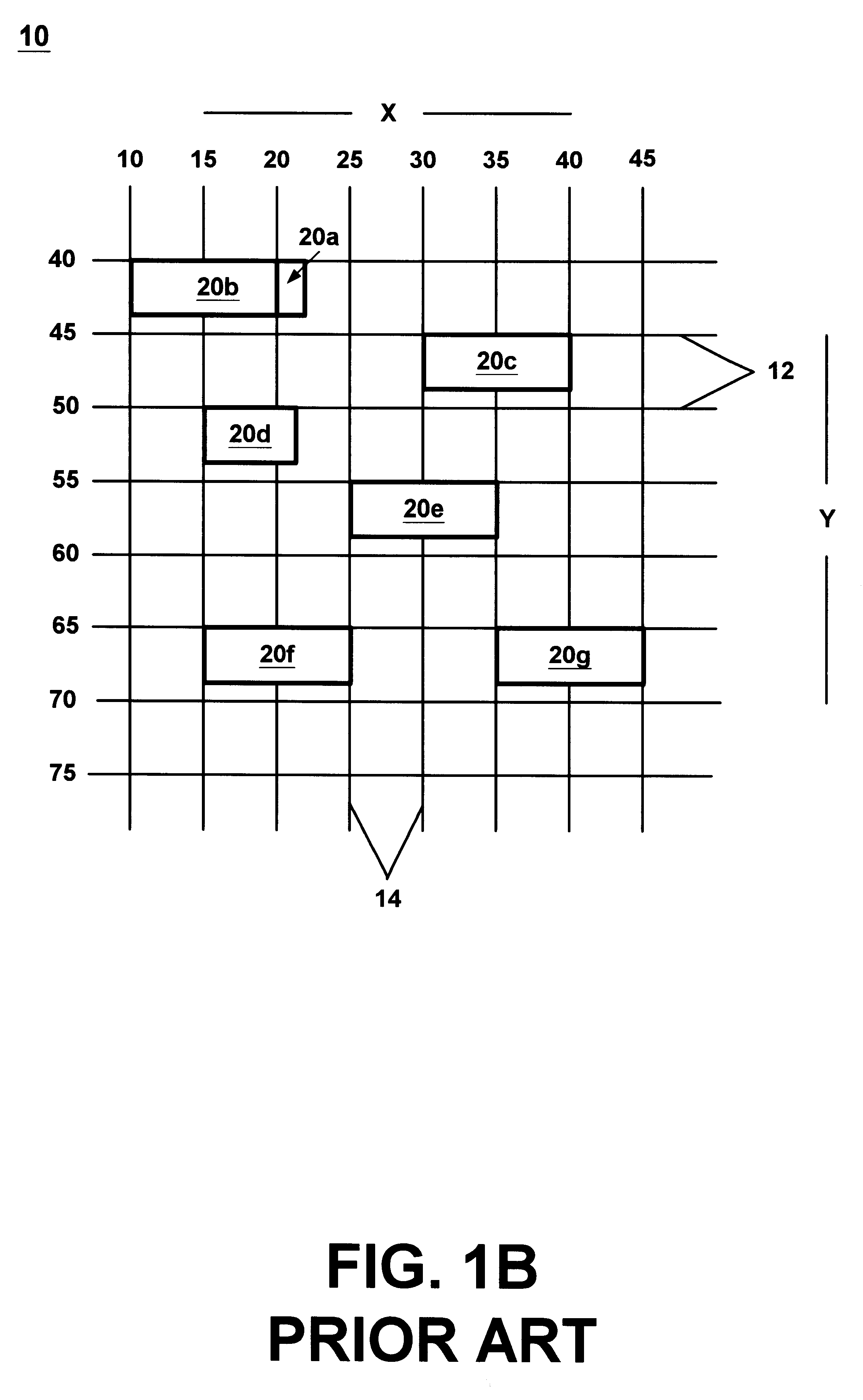

Method and system for high speed detailed placement of cells within an integrated circuit design

InactiveUS6370673B1Computer aided designSpecial data processing applicationsEngineeringFloating point

A method and system for high speed detailed placement of cells within an integrated circuit design. The novel detailed placement system receives a set of cells of an integrated circuit design where the cells have undergone coarse placement. Cells have variable width but the same height (or vice-versa). The cells are each assigned an initial coordinate position, e.g., using floating point precision values. During detailed placement, the cell coordinates are assigned to x-axis and y-axis grid lines. The detailed placement process sorts the cells based on their coordinates along a first axis, e.g., their x-axis coordinates; sort order dictates cell placement order. In one embodiment, sort order preference is given to the wider cells. For a given cell, placement is performed by scanning through the rows of the substrate and selecting the left-most positioned vacant site of each row as a candidate site for placement. A site is vacant if it does not contain a previously placed cell. Of the candidate sites, a valid site having the lowest cost (e.g., the nearest site) is selected for the cell. Some candidate sites are invalid due to the presence of obstructions or incompatible metal layers. A candidate site can also be invalid if it lies too far to the left of the cell, based on a left factor. Placement from left to right along the rows continues in this manner until all cells are placed. Alternatively, the process could run right to left, down to up or up to down.

Owner:SYNOPSYS INC

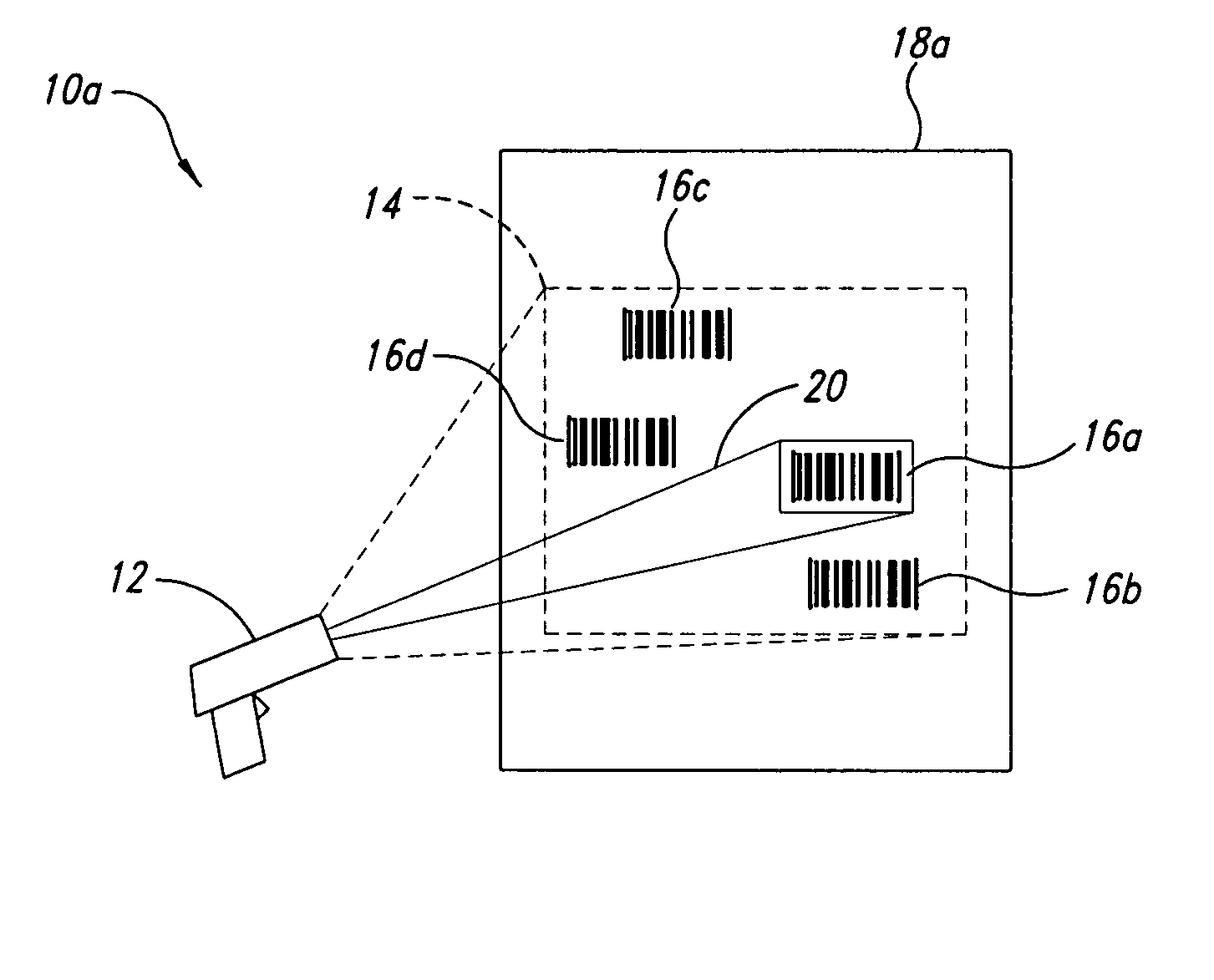

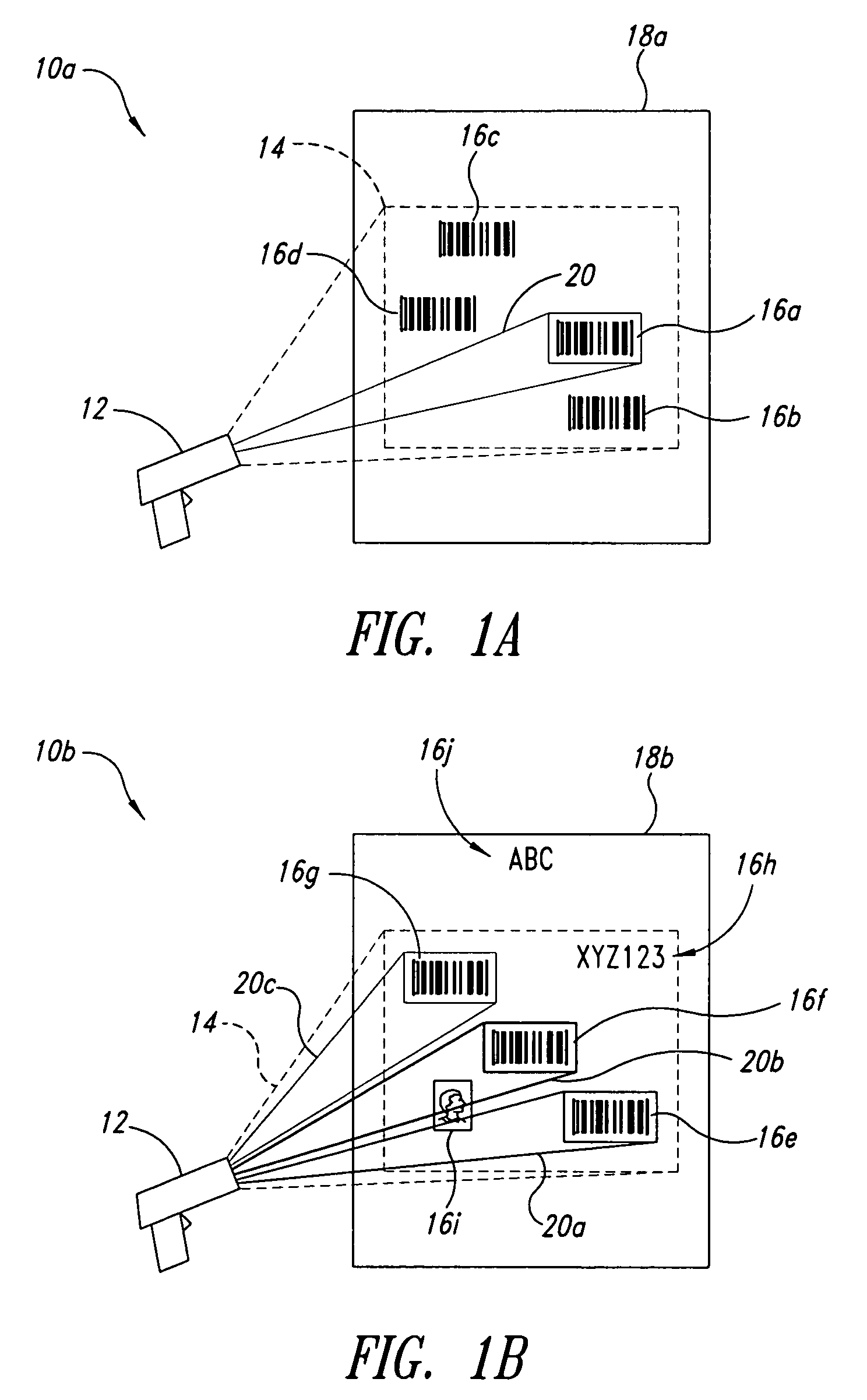

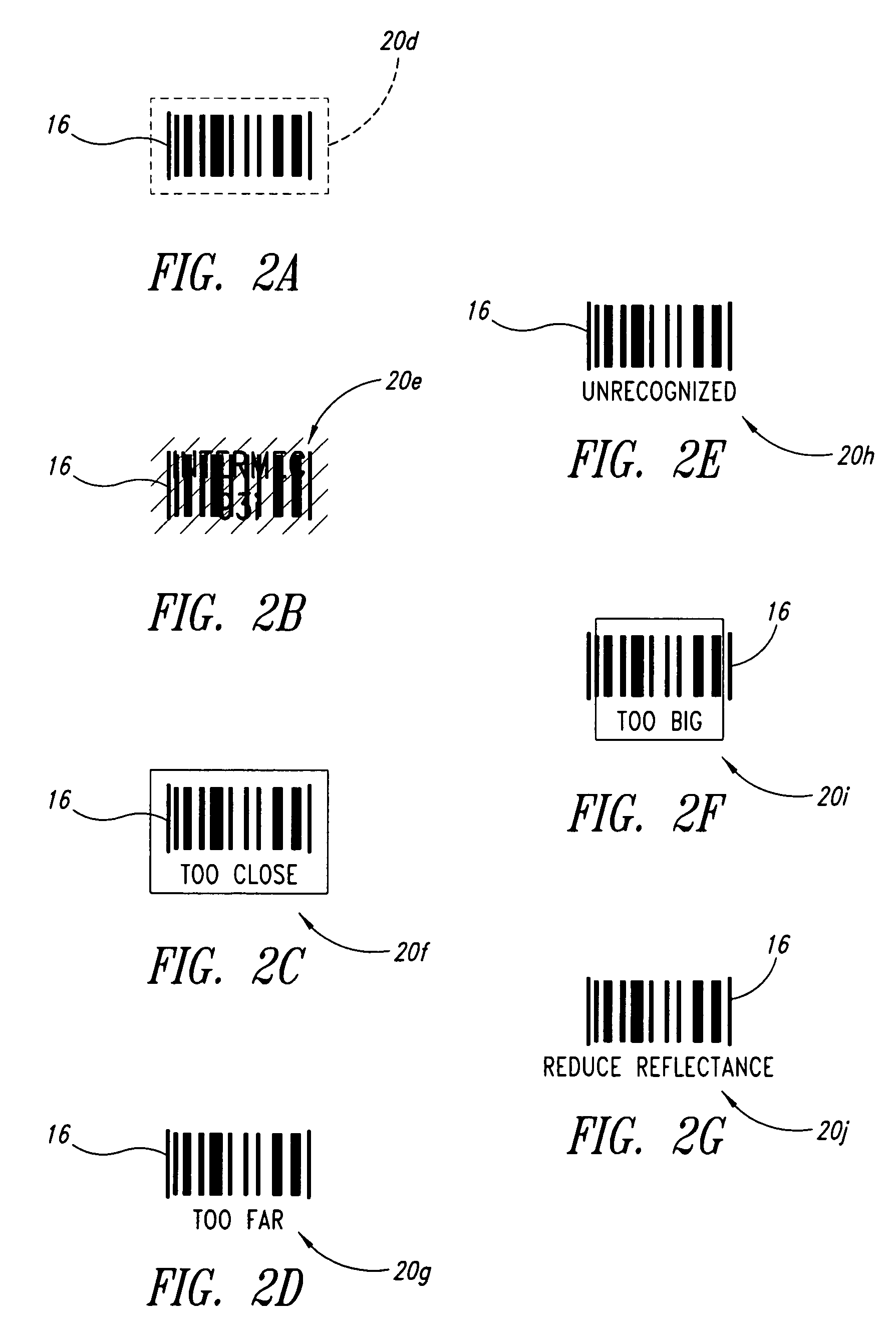

Methods, apparatuses and articles for automatic data collection devices, for example barcode readers, in cluttered environments

ActiveUS7392951B2Enhance the imageCharacter and pattern recognitionRecord carriers used with machinesSymbolic SystemsBarcode reader

Owner:INTERMEC IP CORP

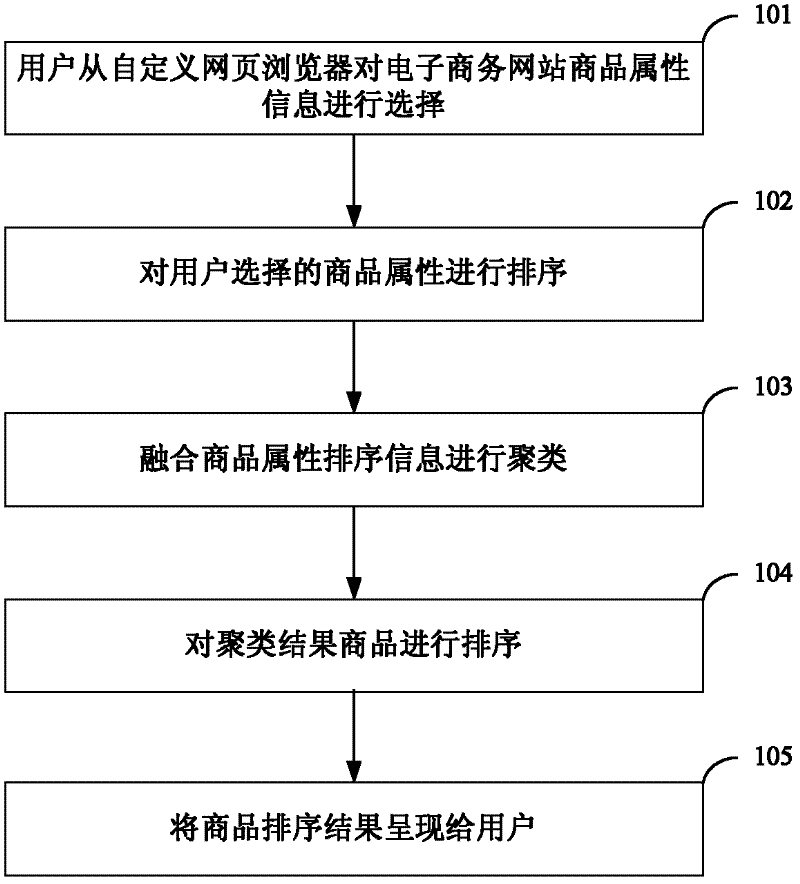

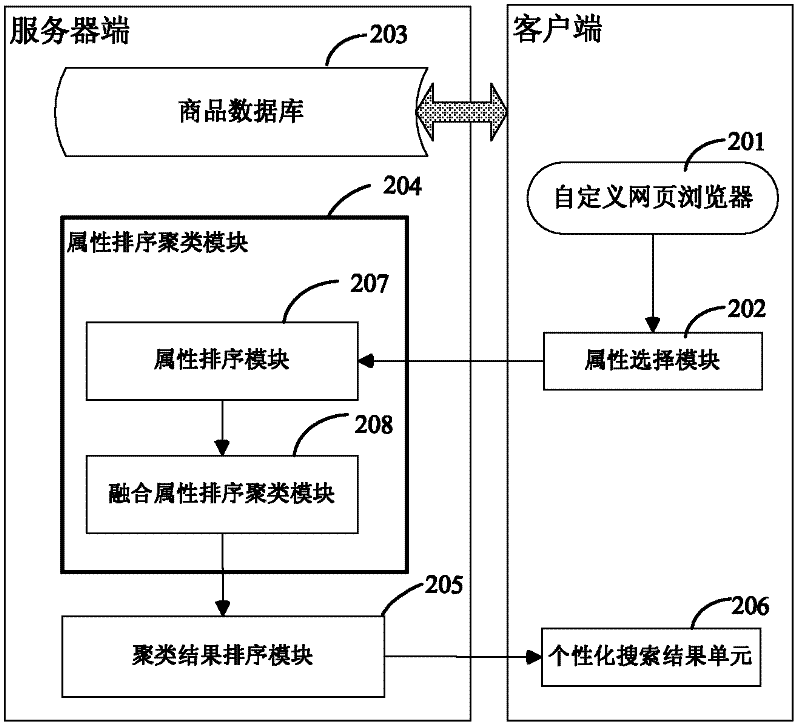

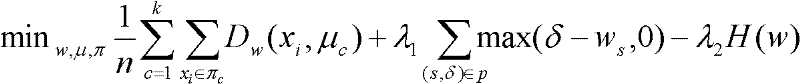

Method and device for personalized searching of commodities sequenced based on attributes

InactiveCN102419779AAccurate collectionSimple processSpecial data processing applicationsMarketingPersonalizationThe Internet

The invention belongs to the technical field of electronic commerce, and relates to a method and a device for personalized searching of commodities in an electronic commerce activity, in particular to a method and a device for personalized searching of commodities which are sequenced based on attributes. The method and the device are used by a user to search and find needed commodities by using a computer during online shopping. The method comprises the following steps of: collecting and analyzing interests of the user in commodity attribute information by analyzing electronic commerce data from the internet; converting the commodity attributes concerned by the user into attribute sequencing knowledge in data mining; merging the attribute sequencing knowledge as future knowledge; clustering the future knowledge by using a semi-supervised clustering method; and finally, sequencing the commodities in a clustering result, and presenting commodity searching results to the user so as to guide the user to select the commodities. The method is simple in technical process, convenient for operation, accurate in information acquisition, scientific in sort order and high in searching speed, and the device is simple in structure and flexible in operation, so the method and the device can be used for replacing a commodity searching technology and commodity searching equipment in the conventional electronic commerce.

Owner:QINGDAO TECHNOLOGICAL UNIVERSITY

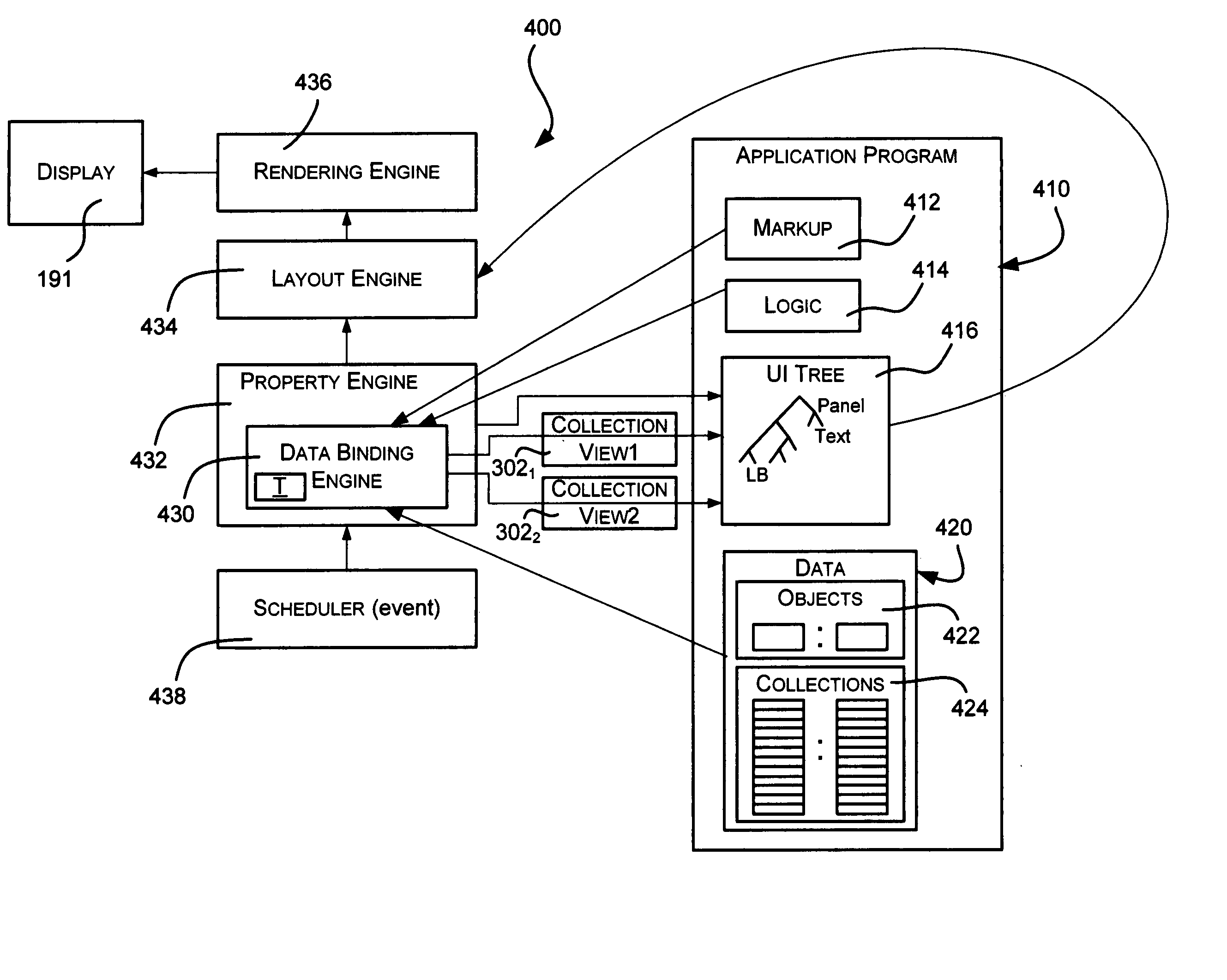

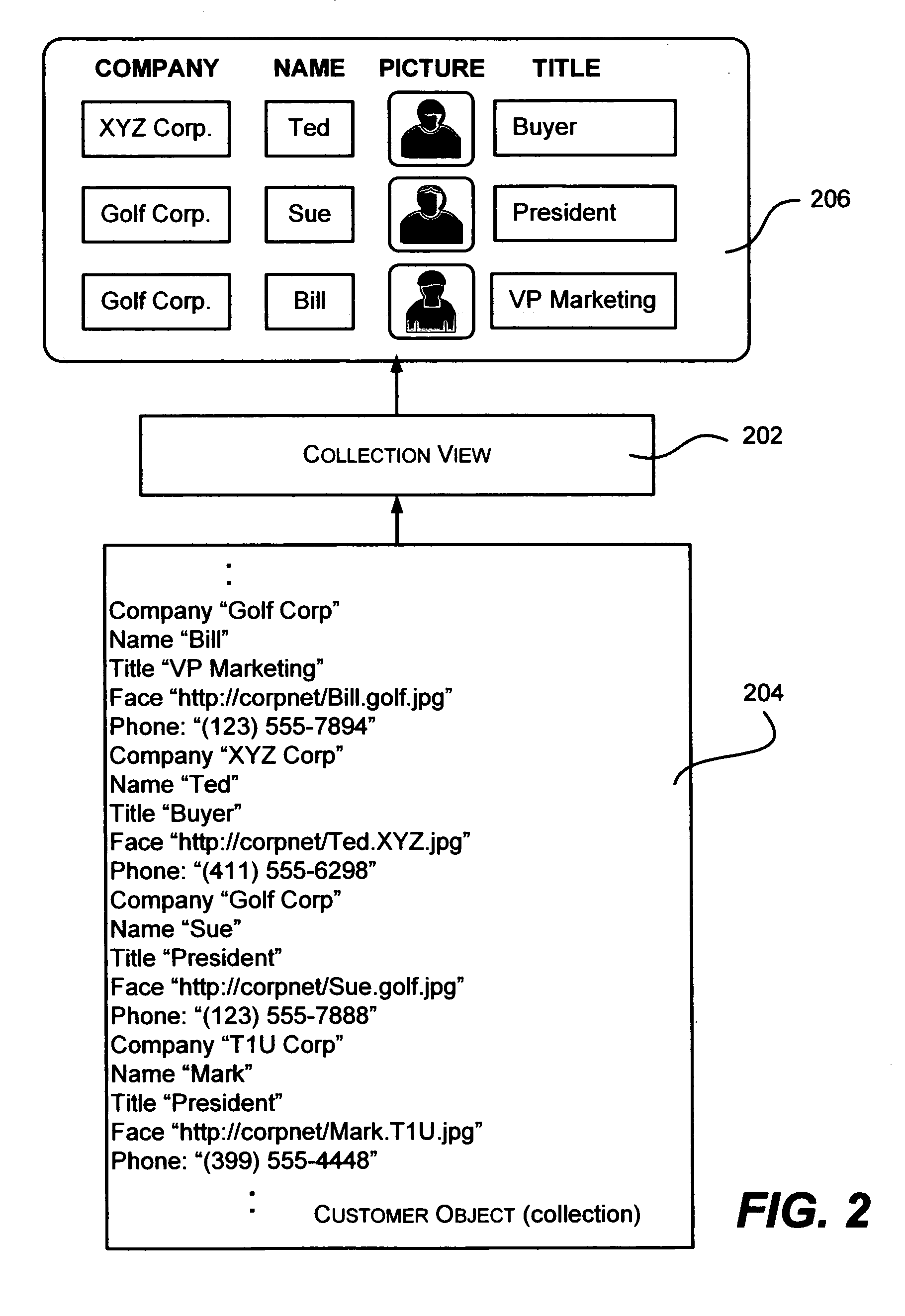

Collection view objects for displaying data collection items in user interface elements

InactiveUS20060090139A1Good choiceEasy to watchDigital data processing detailsNatural language data processingEeg dataSemantics

Described are collection view objects, which provide a user interface view over a data collection, where each view may have its own sort order, filter and / or grouping criteria, as well as current item semantics. A user interface element is bound to a data collection, such as via markup language (e.g., XAML). At runtime, a collection view object is instantiated as an indirection between the data collection and the user interface element, whereby a collection of data items is viewed according to how each collection view object is currently configured with respect to sorting, filtering and / or grouping. Multiple collection views may be specified on the same data collection, whereby distinct simultaneous views of the data items may be presented in different user interface elements. The collection view object dynamically updates the displayed data as changes are made in the data collection. A current item may be selected within the collection view.

Owner:MICROSOFT TECH LICENSING LLC

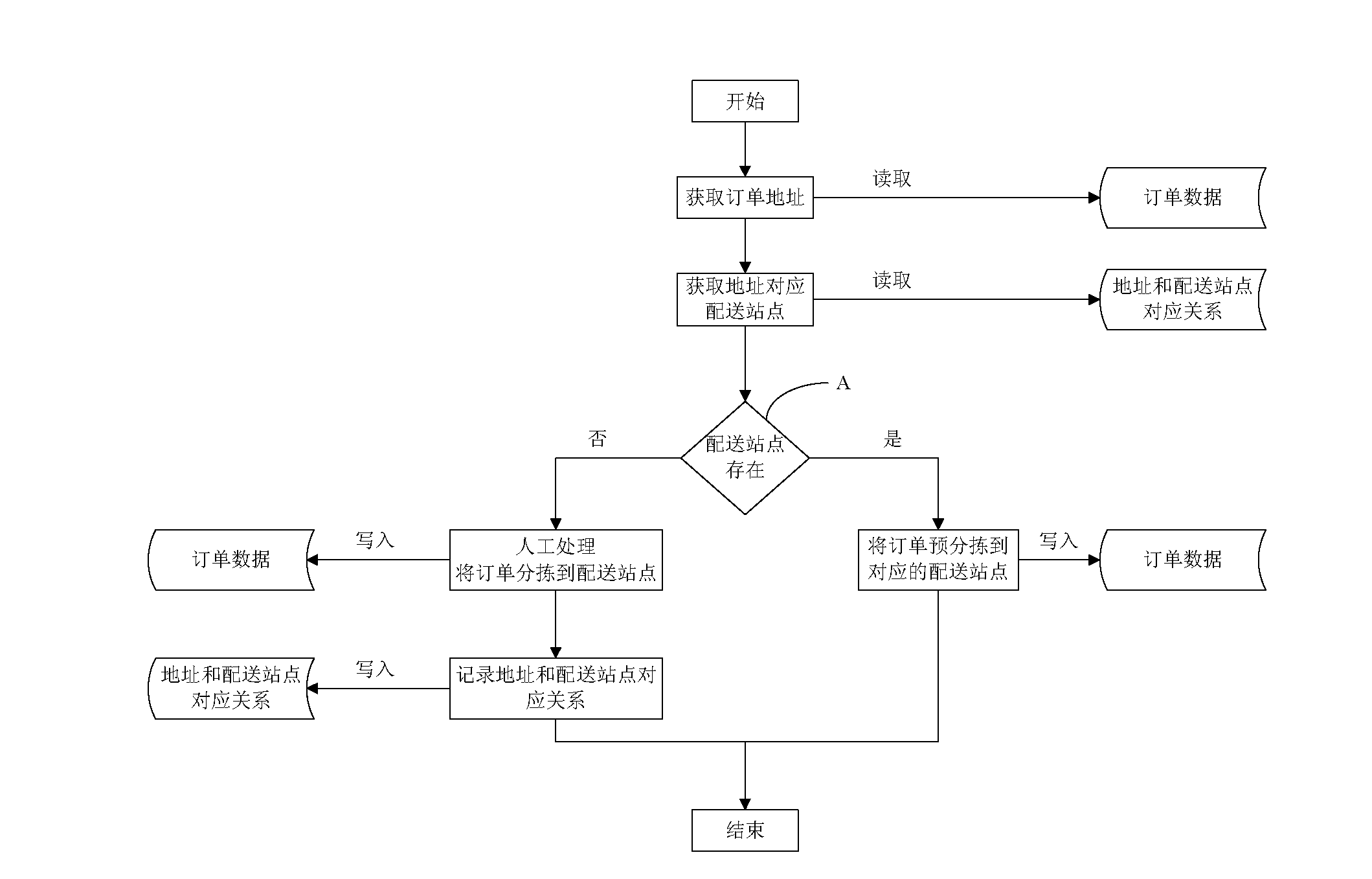

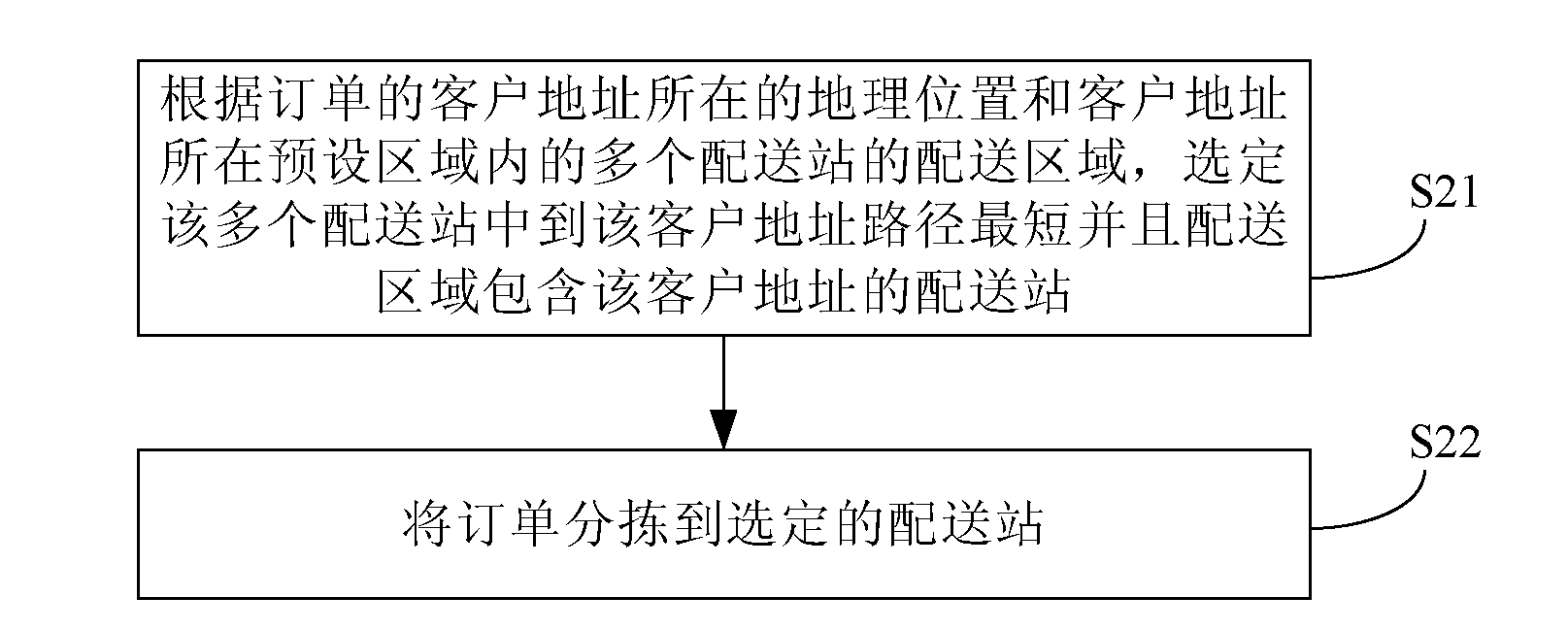

Method and device for pre-sorting order

ActiveCN103020790AHigh manual maintenance efficiencyImprove matching efficiencyLogisticsShortest distanceGeolocation

The invention provides a method and a device for pre-sorting an order. By adopting the method and the device, the efficiency and the success rate in address matching during order pre-sorting can be improved, the manual maintaining efficiency is improved, and the error rate in pre-sorting is reduced. The method comprises the following steps in sequence: selecting a delivery station from a plurality of delivery stations according to the geographical position of the address of the customer providing the order and the delivery areas of the plurality of delivery stations within the preset area of the customer address, wherein the selected delivery station has the shortest distance from the customer address, and the customer address is within the delivery areas; and then sorting the order to the selected delivery station.

Owner:BEIJING JINGDONG ZHENSHI INFORMATION TECH CO LTD

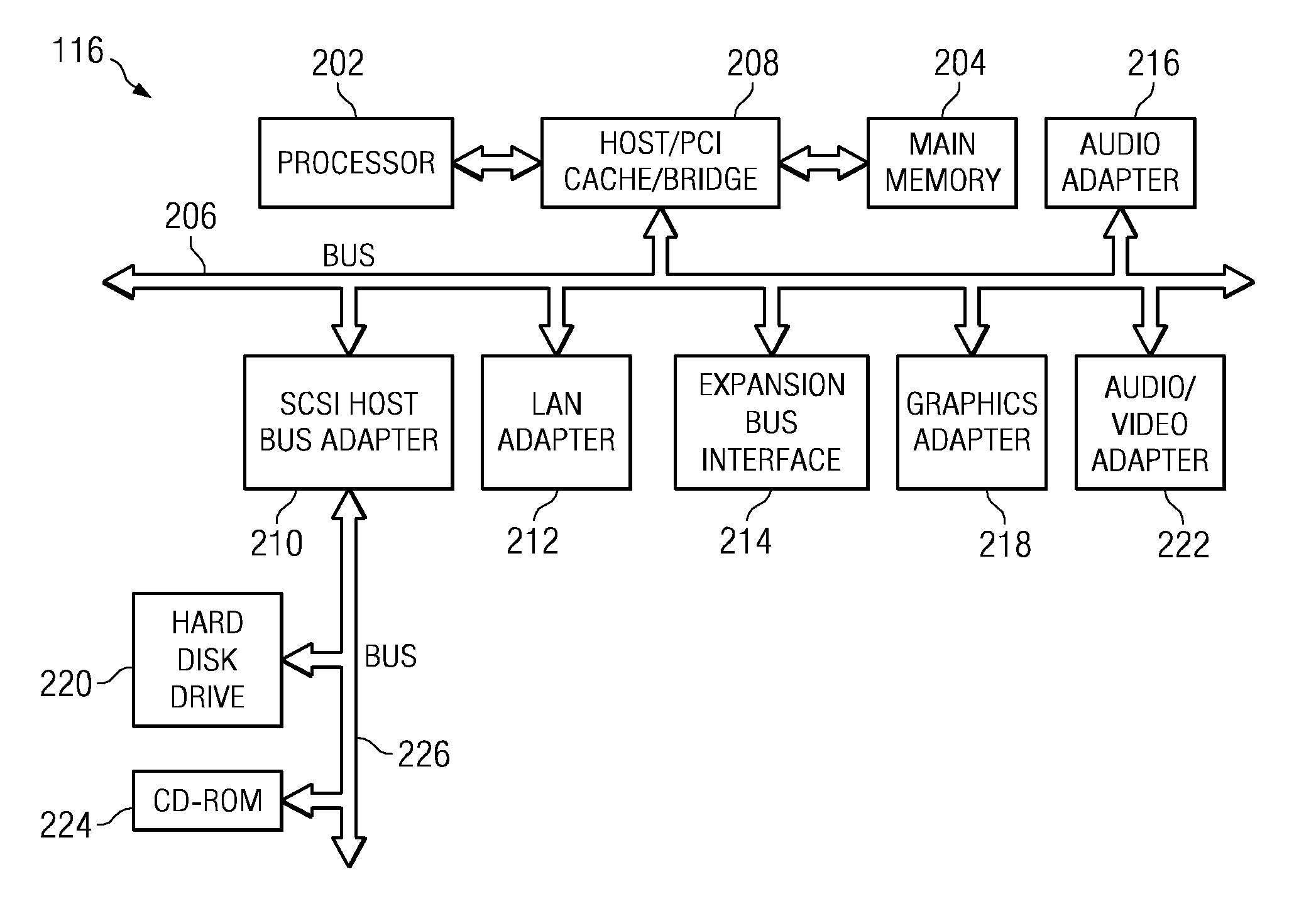

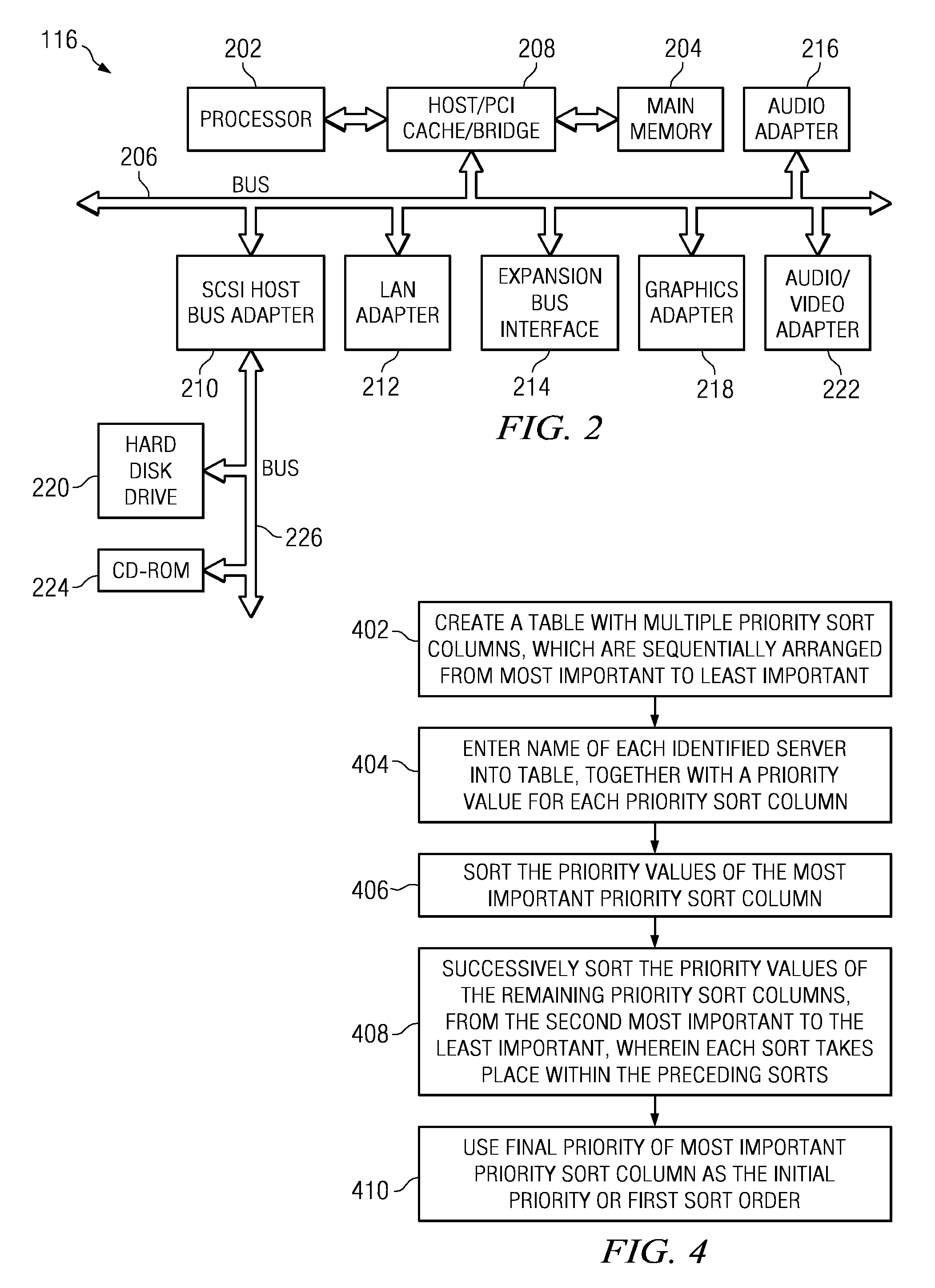

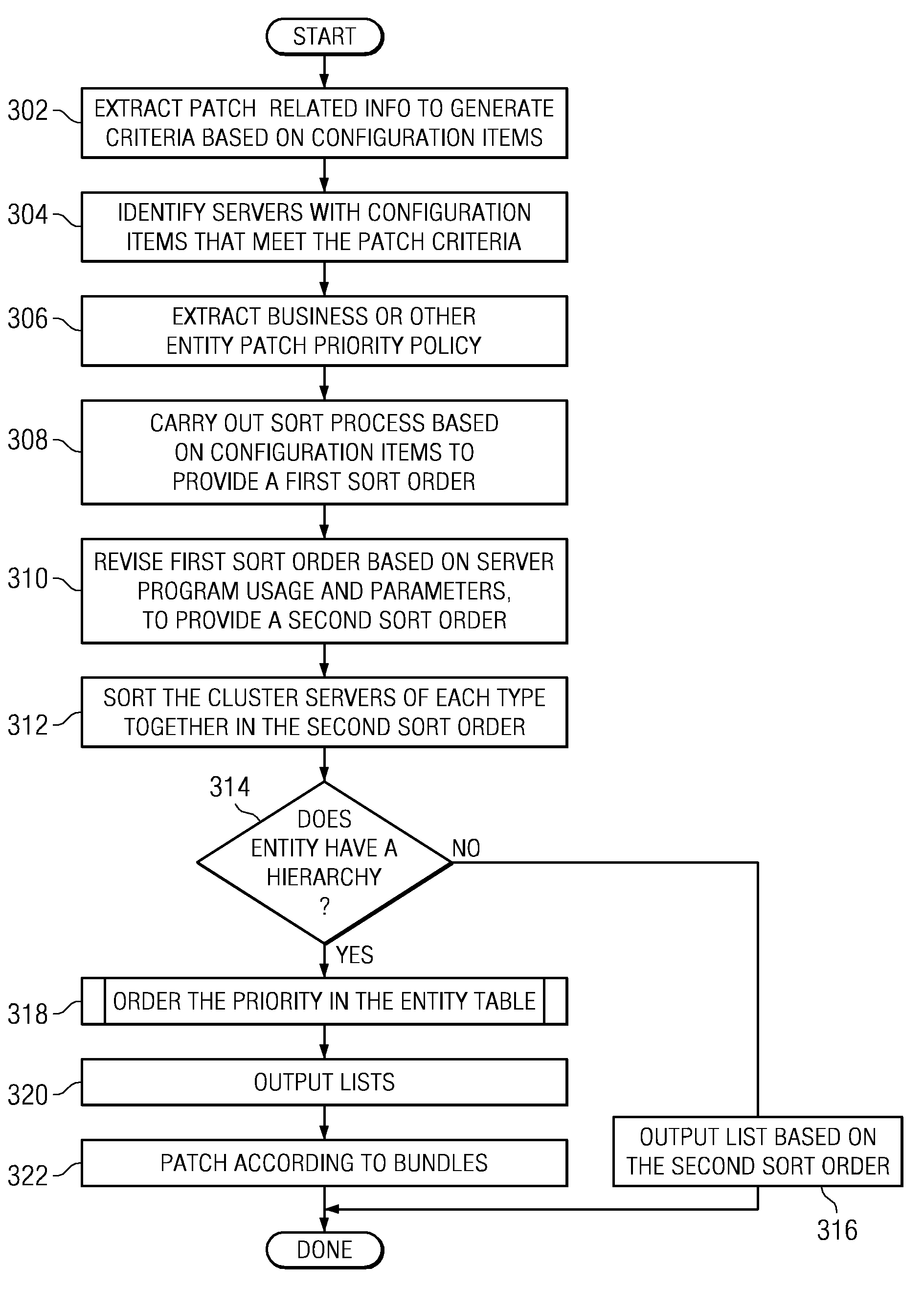

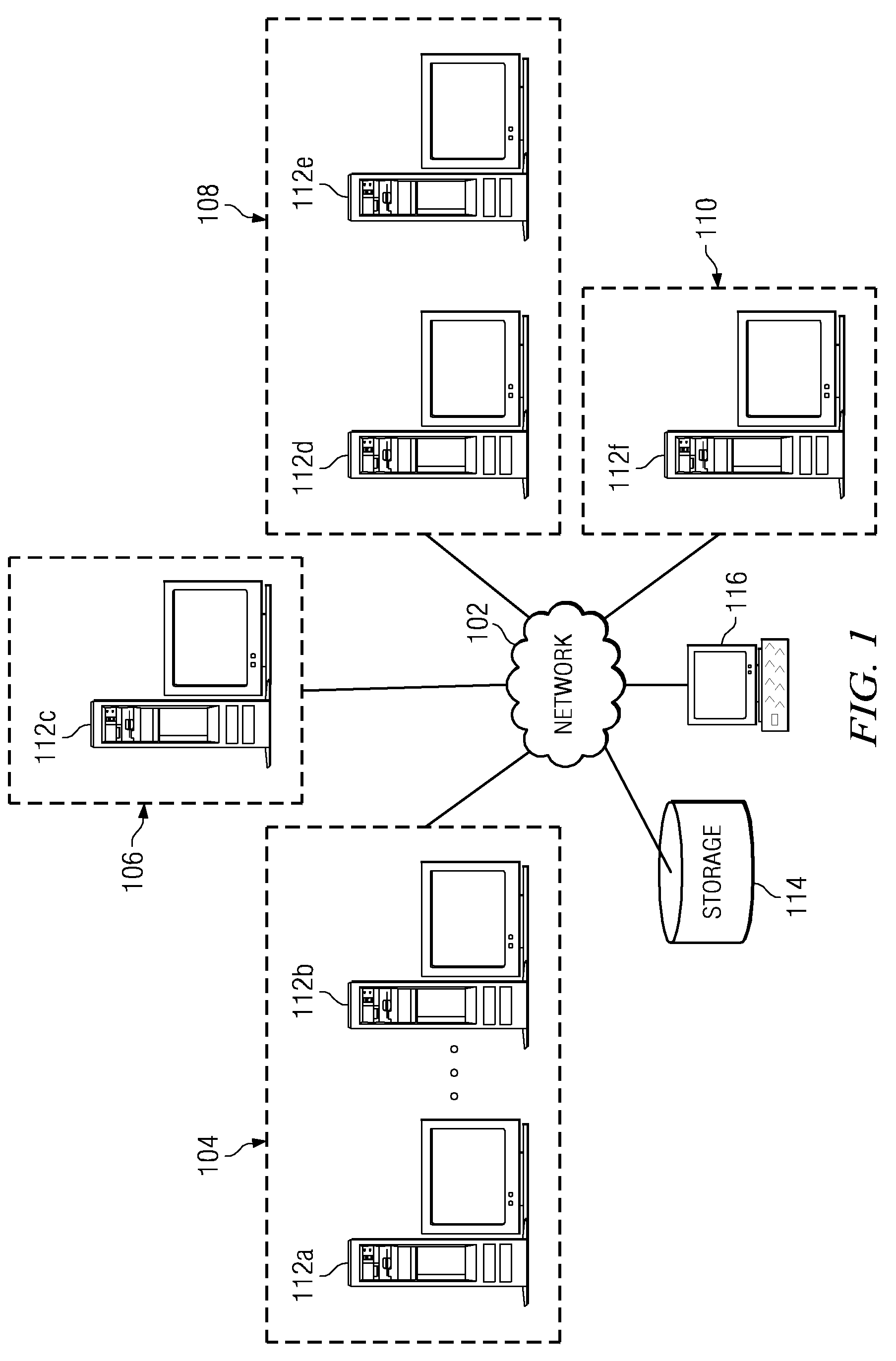

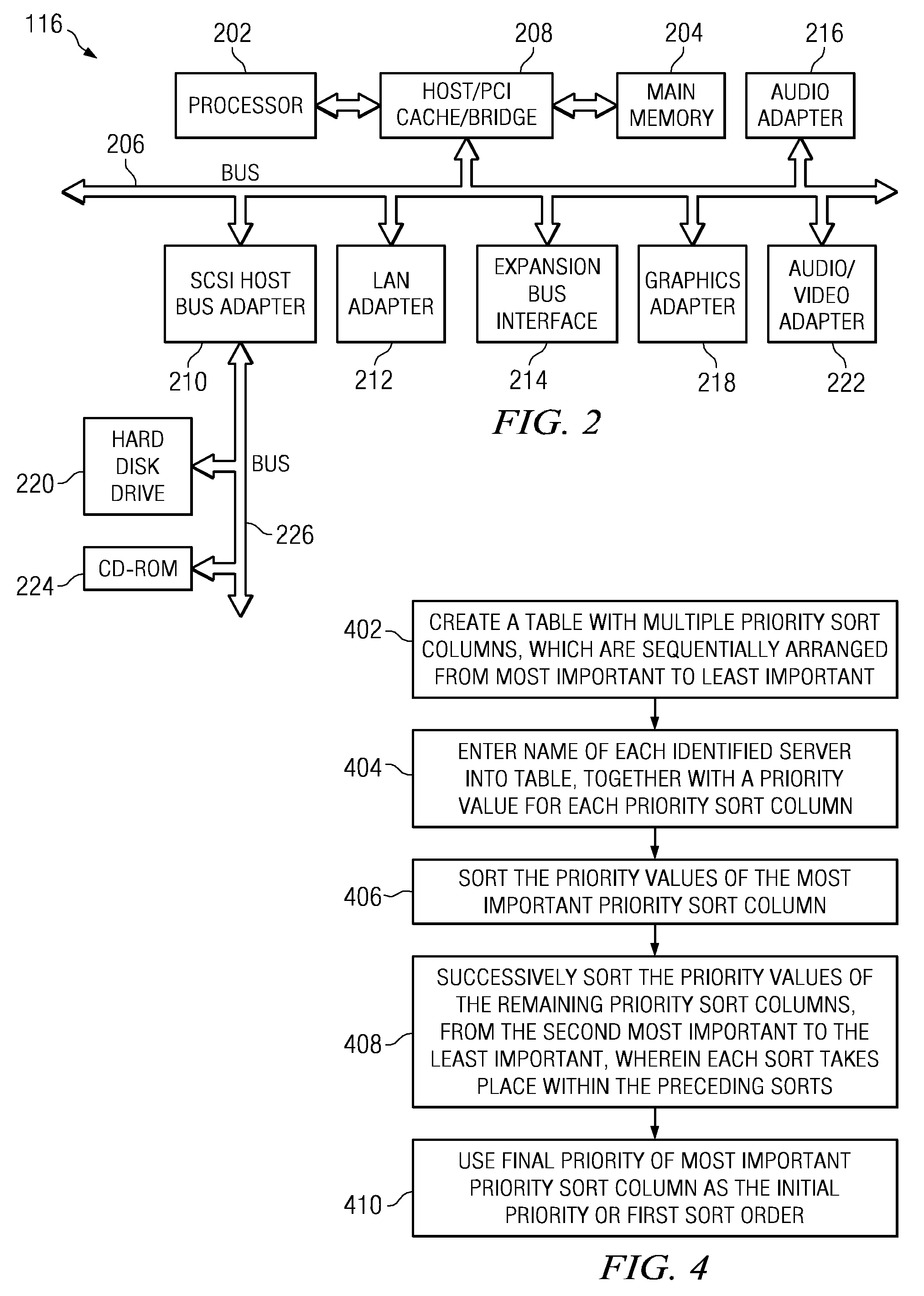

Method for determining priority for installing a patch into multiple patch recipients of a network

InactiveUS20090100419A1Multiple digital computer combinationsProgram loading/initiatingServer allocationDistributed computing

Embodiments of the invention provide a computer implemented method and system for installing a patch on at least some of the servers of a network having multiple servers. The method comprises the steps of identifying a plurality of servers of the network that each requires installation of the patch, and assigning two or more priority values to each of the identified servers. The priority values for a given identified server are each associated with a different criterion in a set of criteria. The method further comprises selectively processing the assigned priority values for respective identified servers, in order to determine an initial priority, comprising a first sort order, for installing the patch on each identified server. The first sort order is revised in accordance with information pertaining to prior use of respective identified servers, to provide a second sort order. The patch is installed on each of the identified servers, in an order determined at least in part by the second sort order. As an option, one or more additional sort orders can be provided for use in determining the order for installing the patch.

Owner:IBM CORP

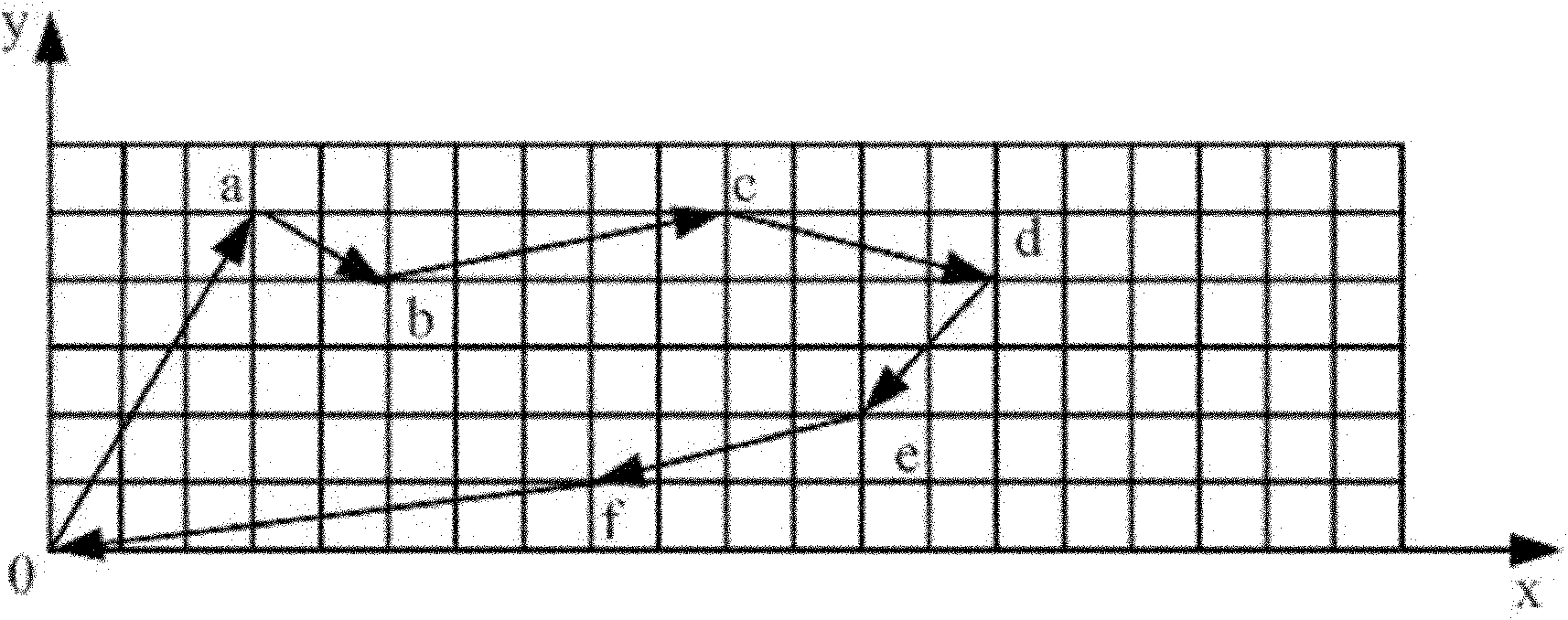

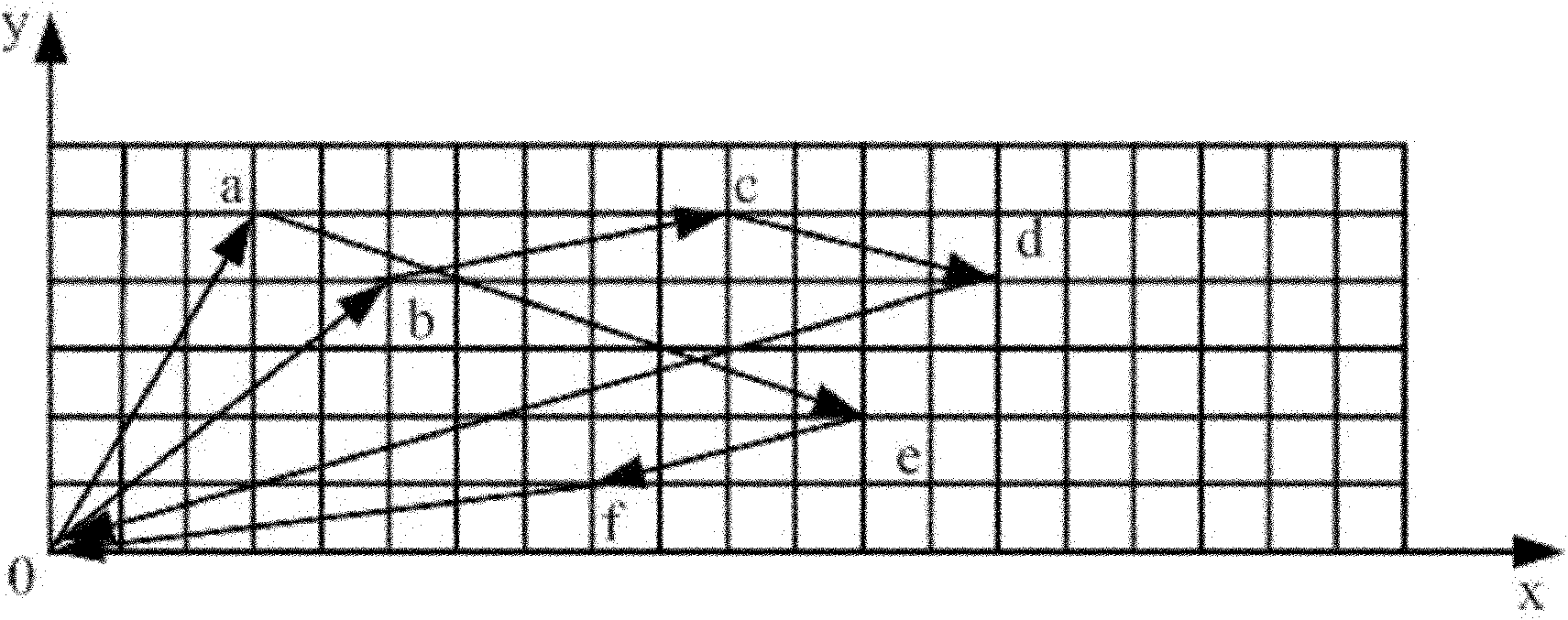

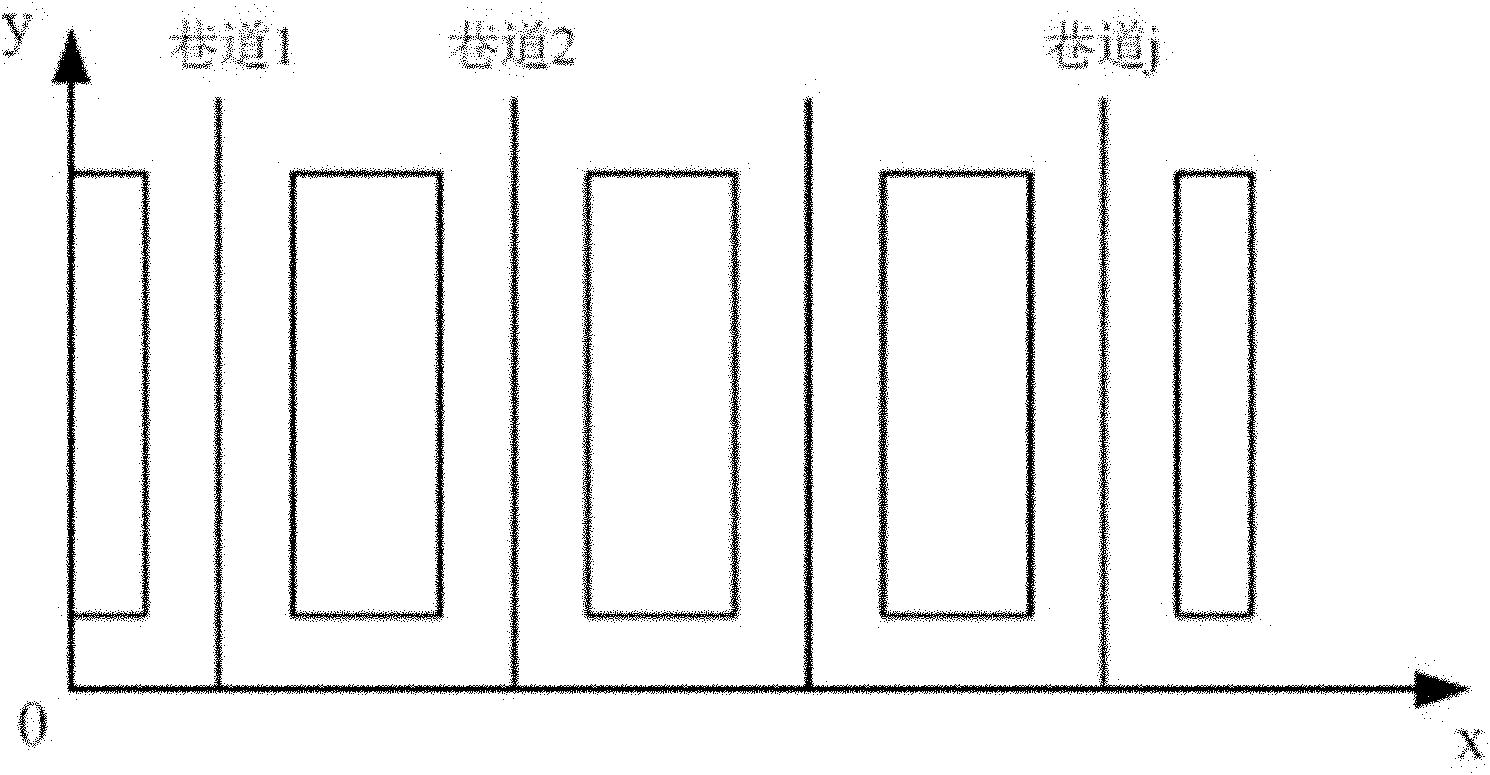

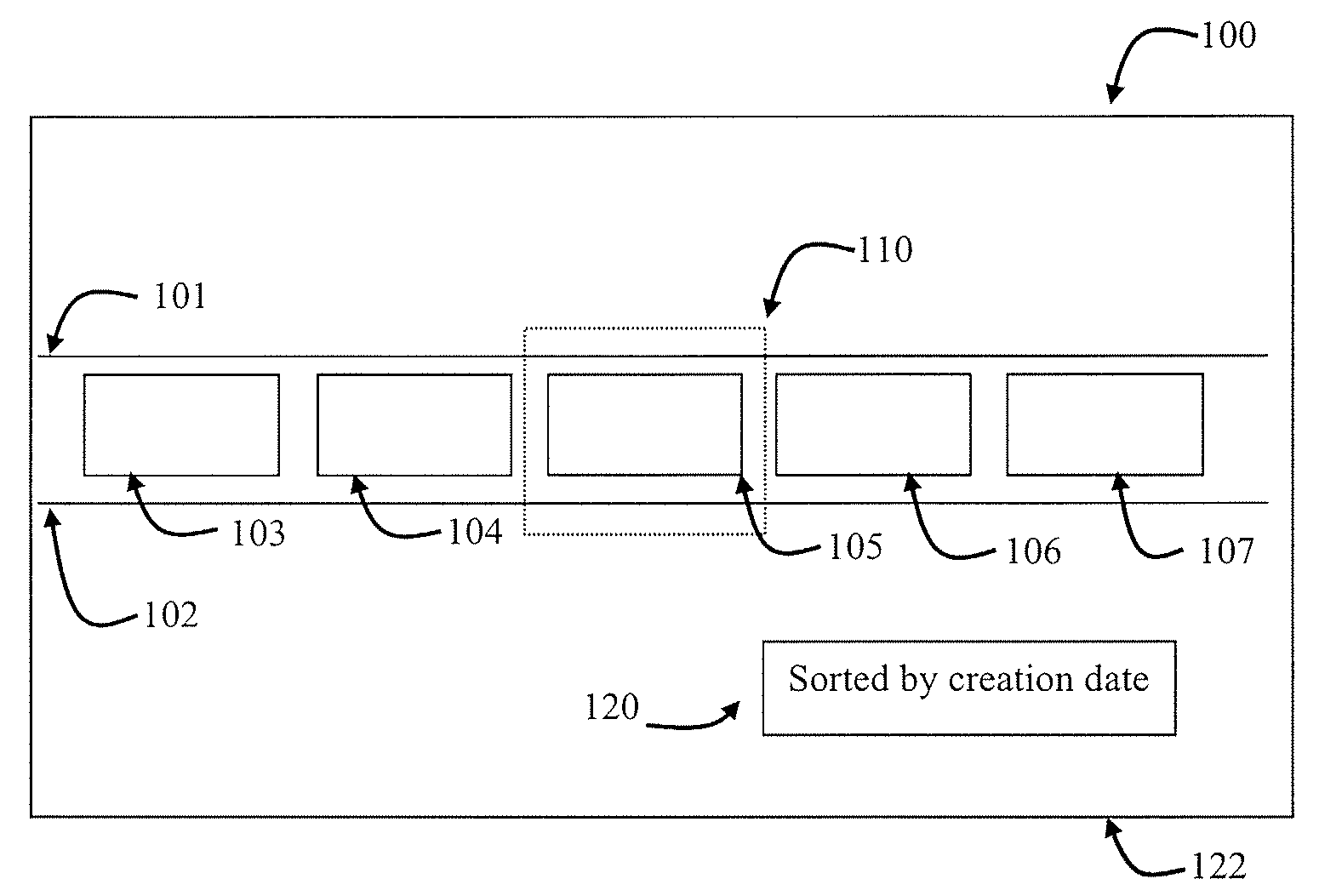

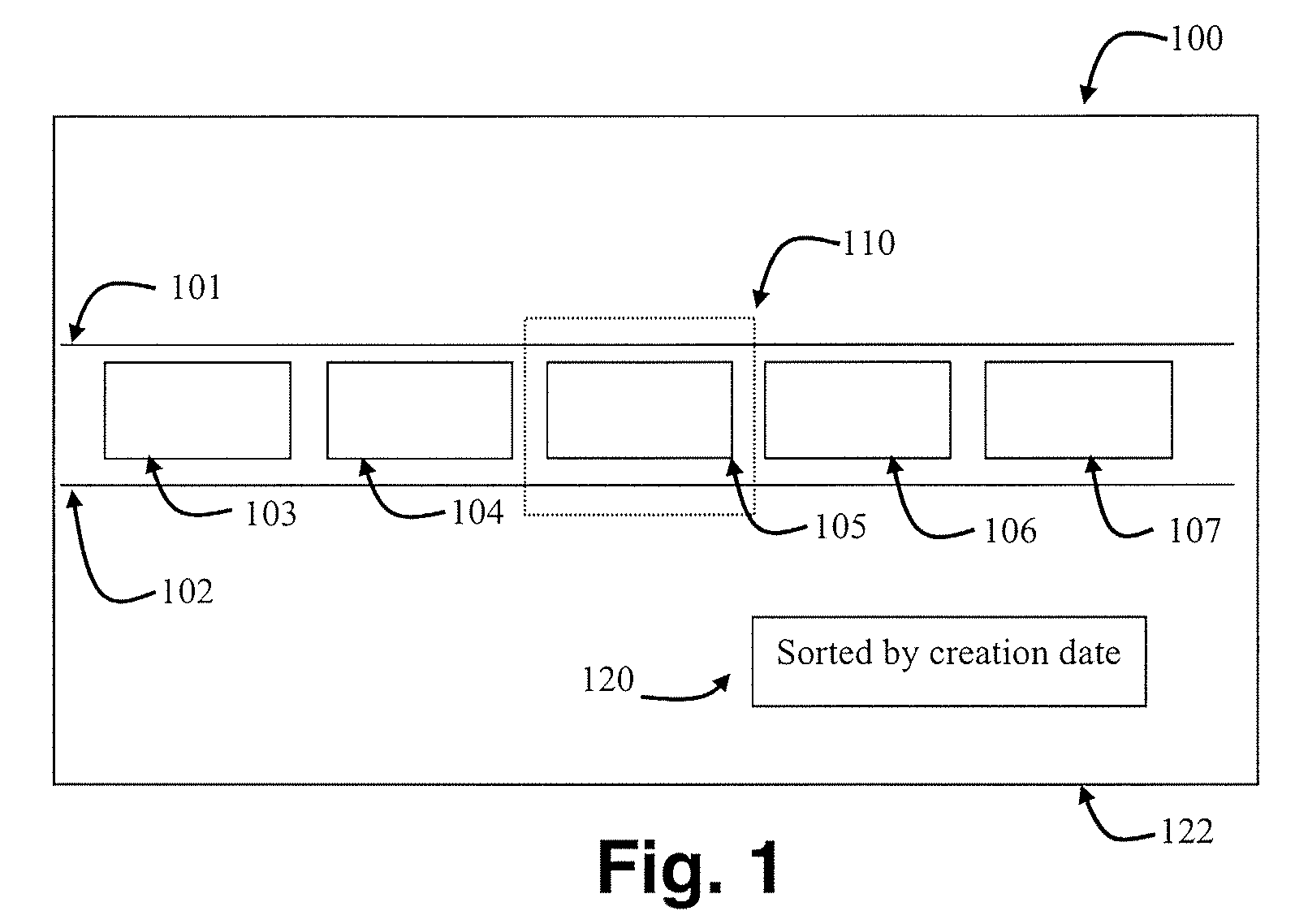

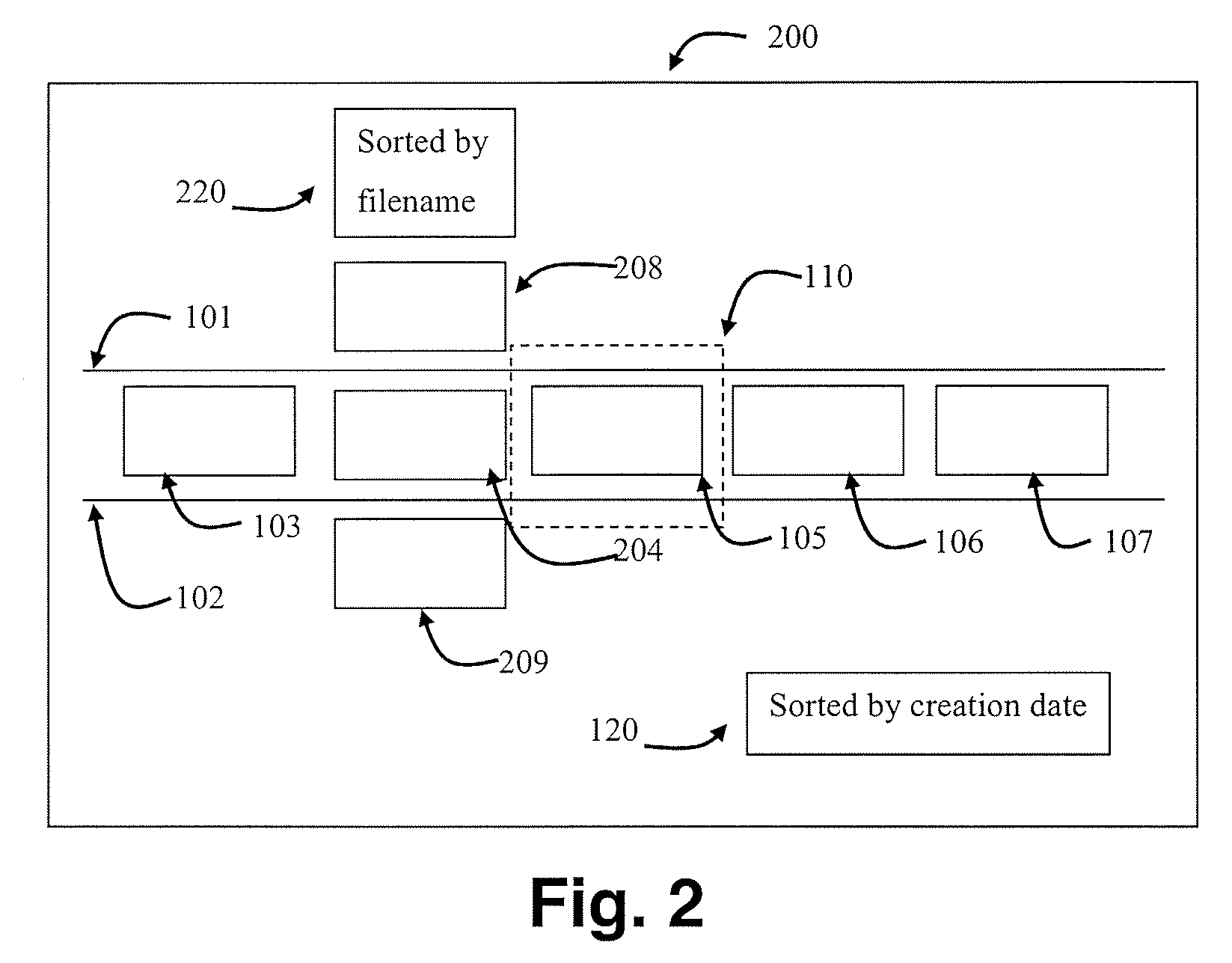

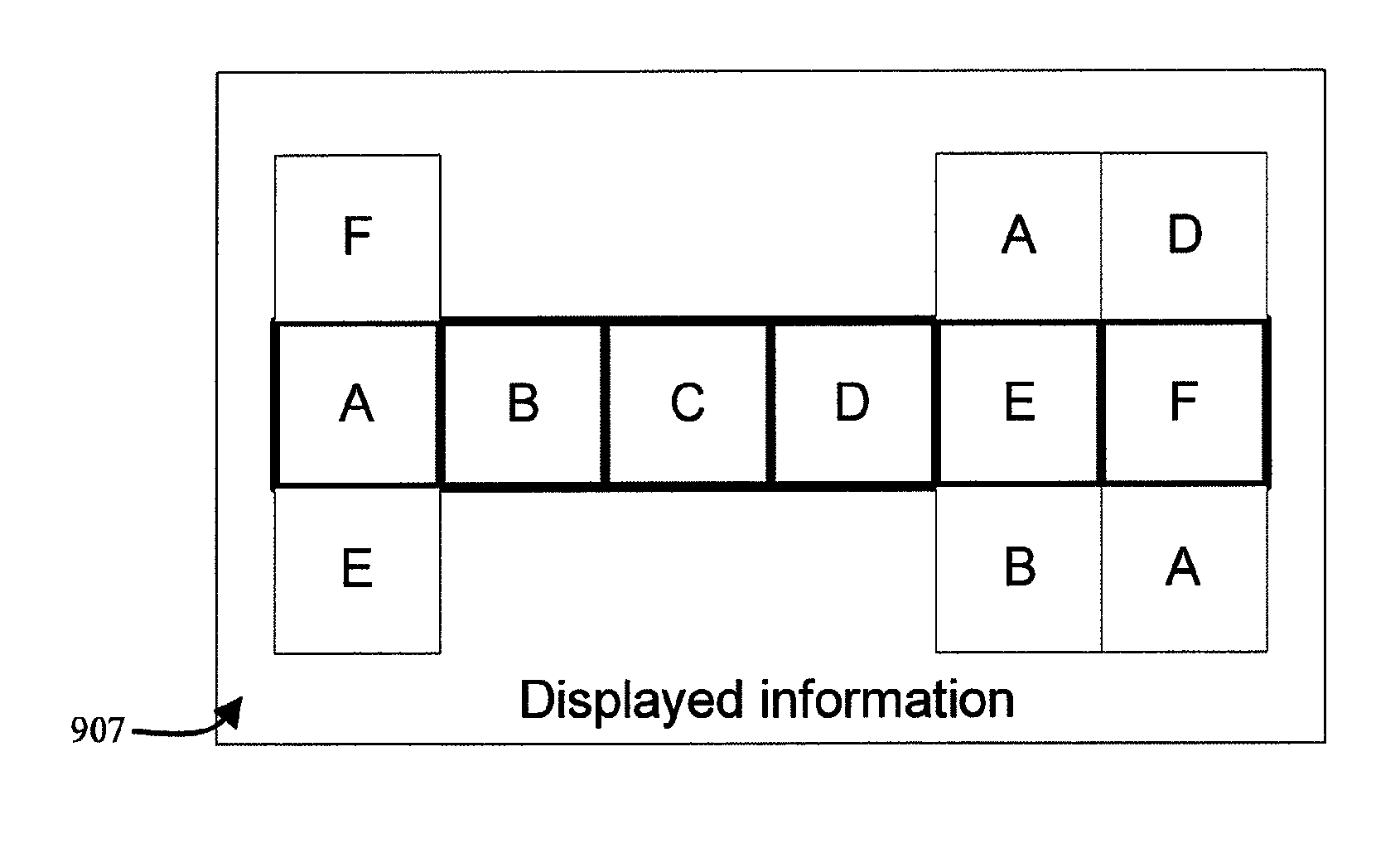

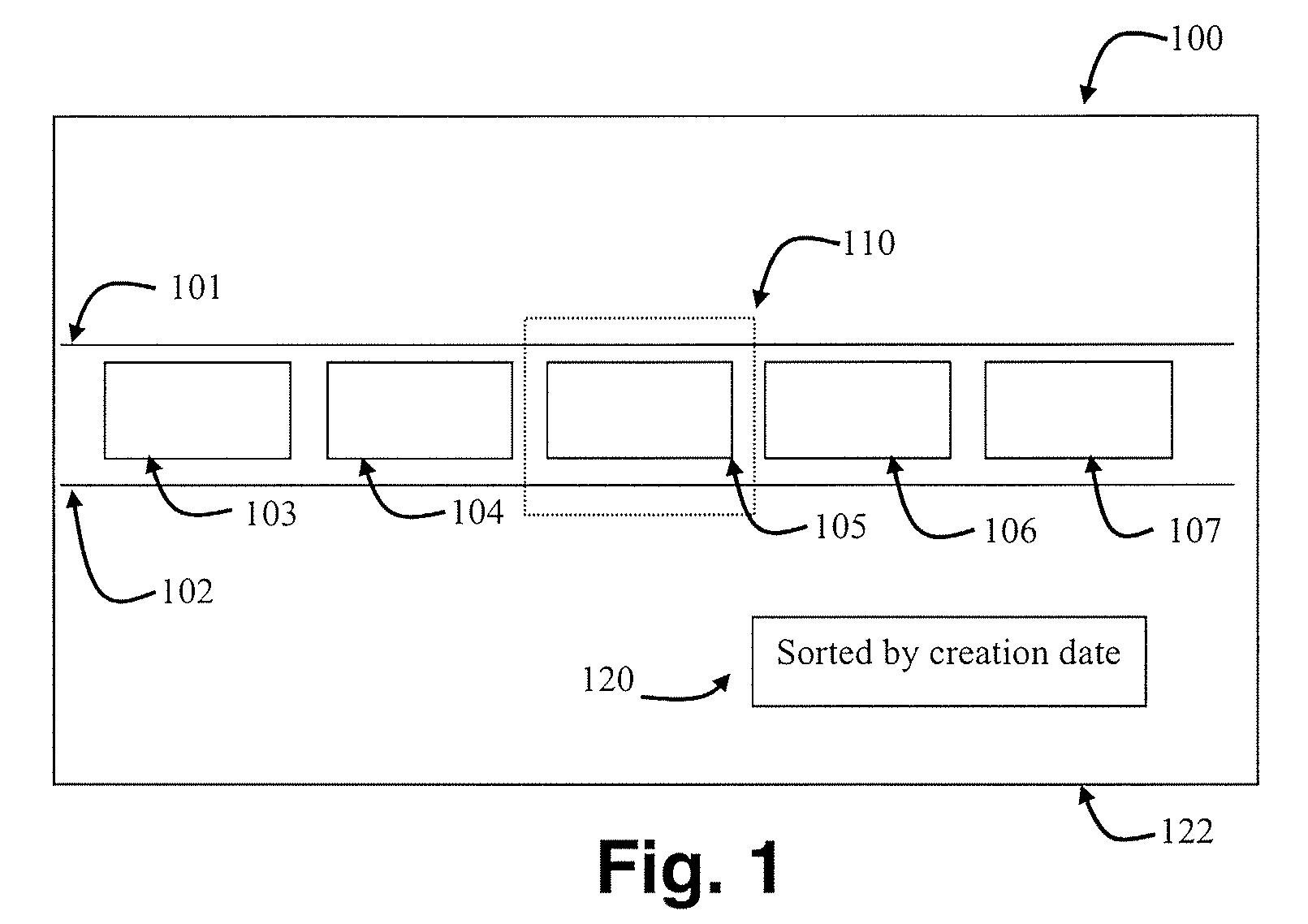

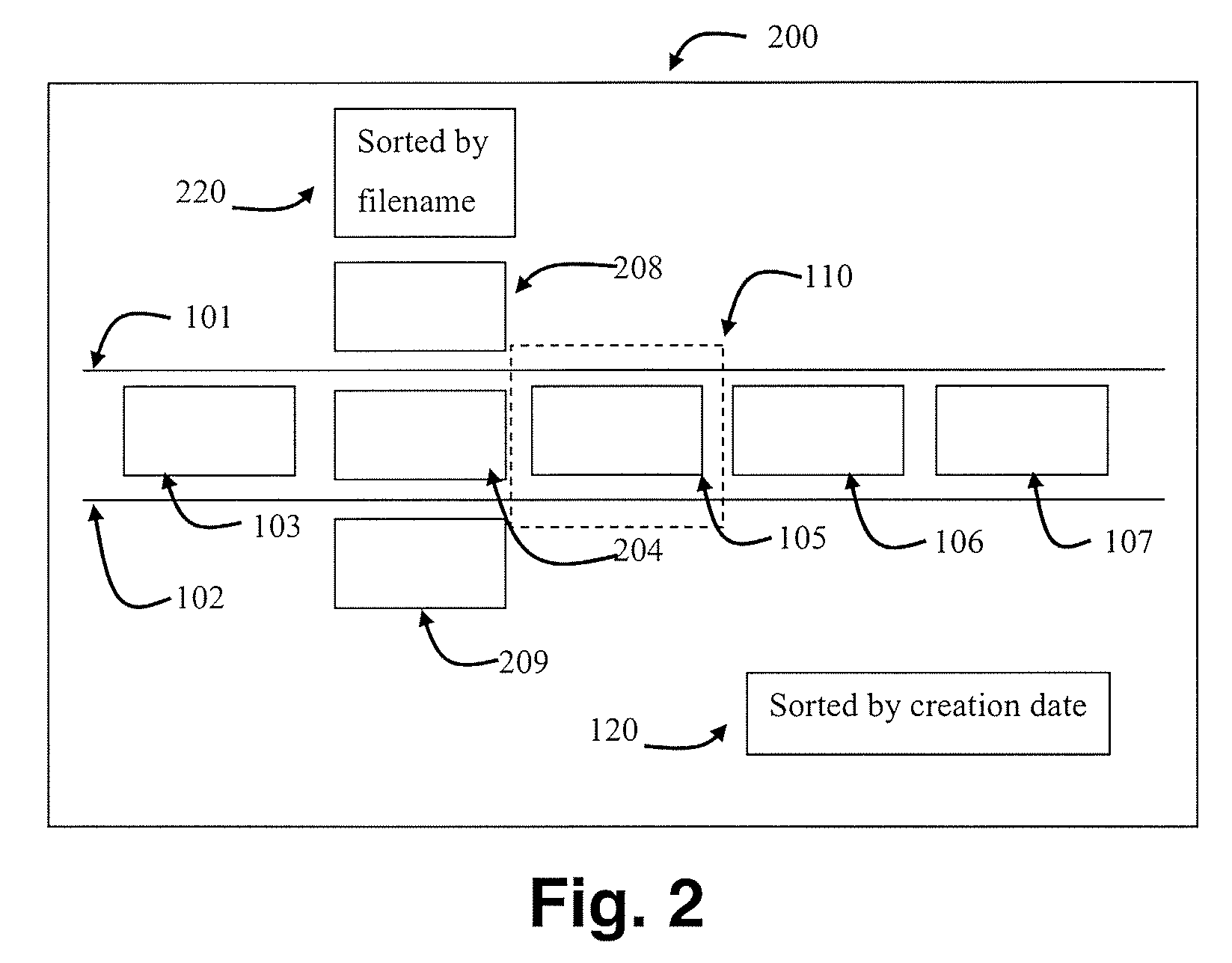

Method for navigating large image sets using sort orders

A method of displaying (100, 200) items from a collection (1200) of items including a first item (204) is provided. The method determines (400) a first sort order (901) of the collection, and at least one alternate sort order (902) of the collection. At least items adjacent to the first item in the first sort order, and in the alternate sort order, are then compared (505). The method then displays a portion (103-107,208,209) of the items associated with the first item in each of the first sort order (103-107) and in the alternate sort order (208,209) based on the comparison.

Owner:CANON KK

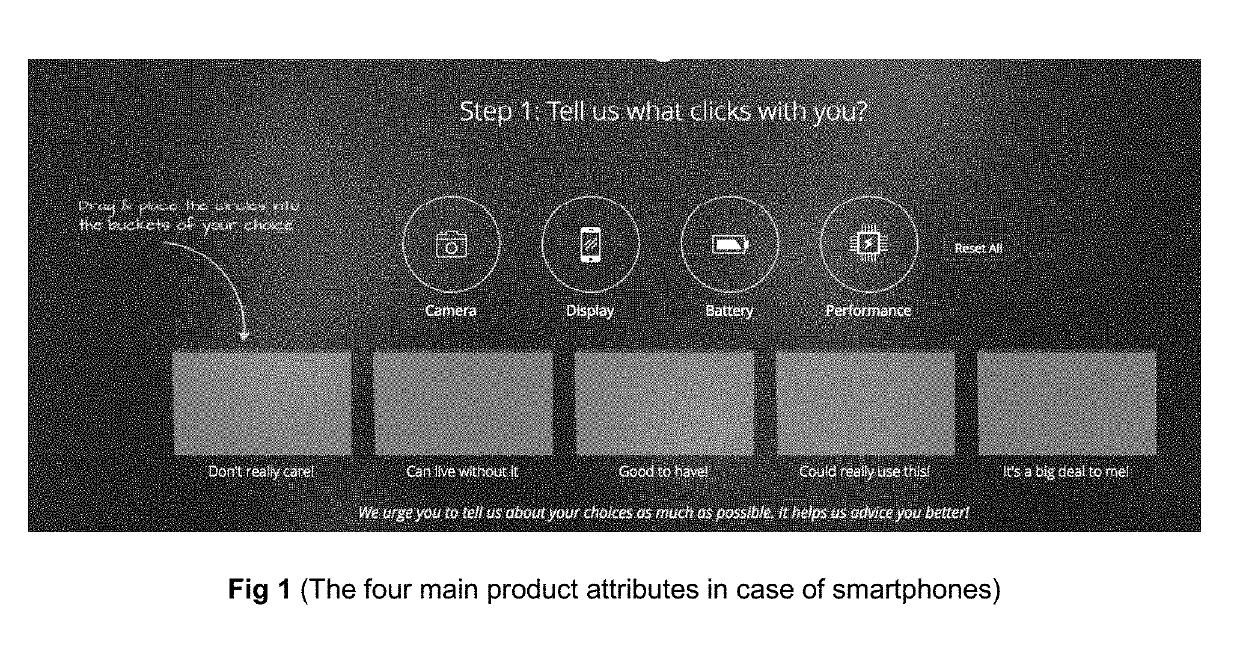

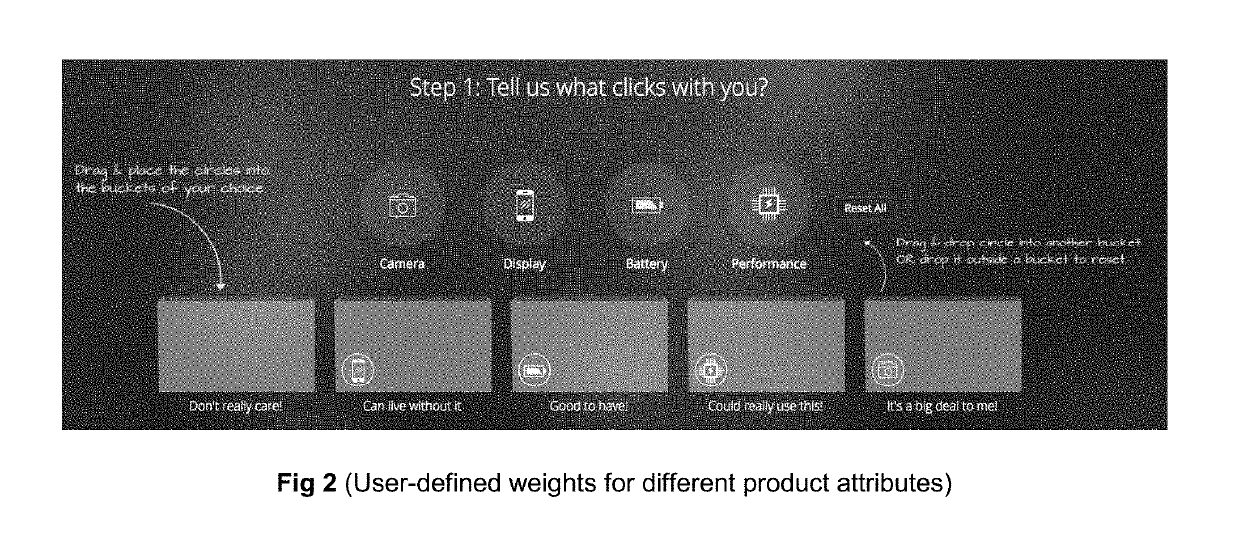

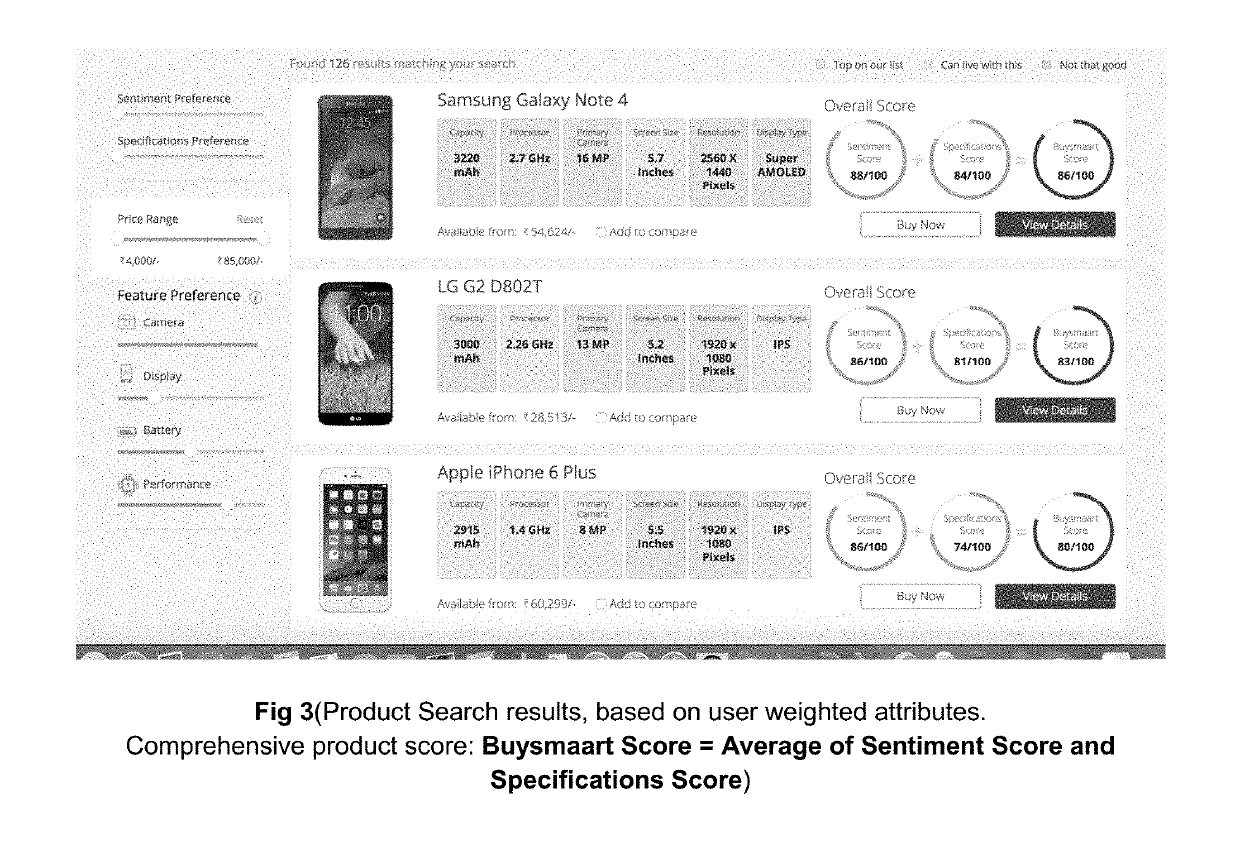

Method for product search using the user-weighted, attribute-based, sort-ordering and system thereof

InactiveUS20190318407A1Digital data information retrievalBuying/selling/leasing transactionsSentiment scoreData mining

A computer-implemented method for product search using the User-Weighted, Attribute-Based, Sort-Ordering comprising the steps of: computing of specification score for product attribute; computing of sentiment score for product attribute; characterized by steps of: —extracting reviews for each product from multiple sources; detecting the attributes described in each product review; detecting the polarity (positive / negative) of the user review with respect to each attribute converting the said attributes into a numerical score for each attribute which captures all the information about that attribute from user-ratings; computing an overall product score using the specifications score and sentiment score for individual product attributes; and displaying the search results sorted according to the overall product score.

Owner:GIRIDHARI DEVANATHAN

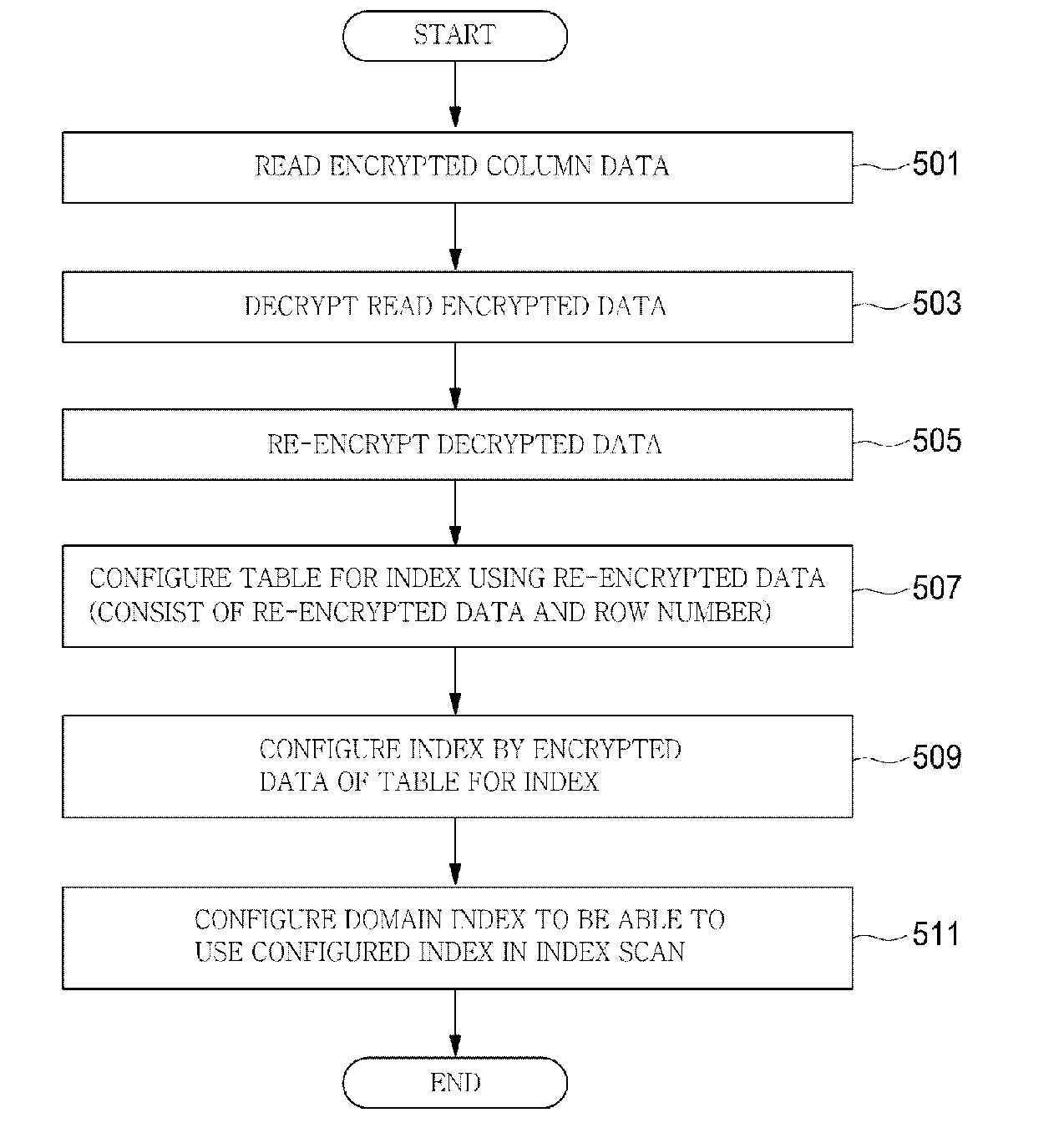

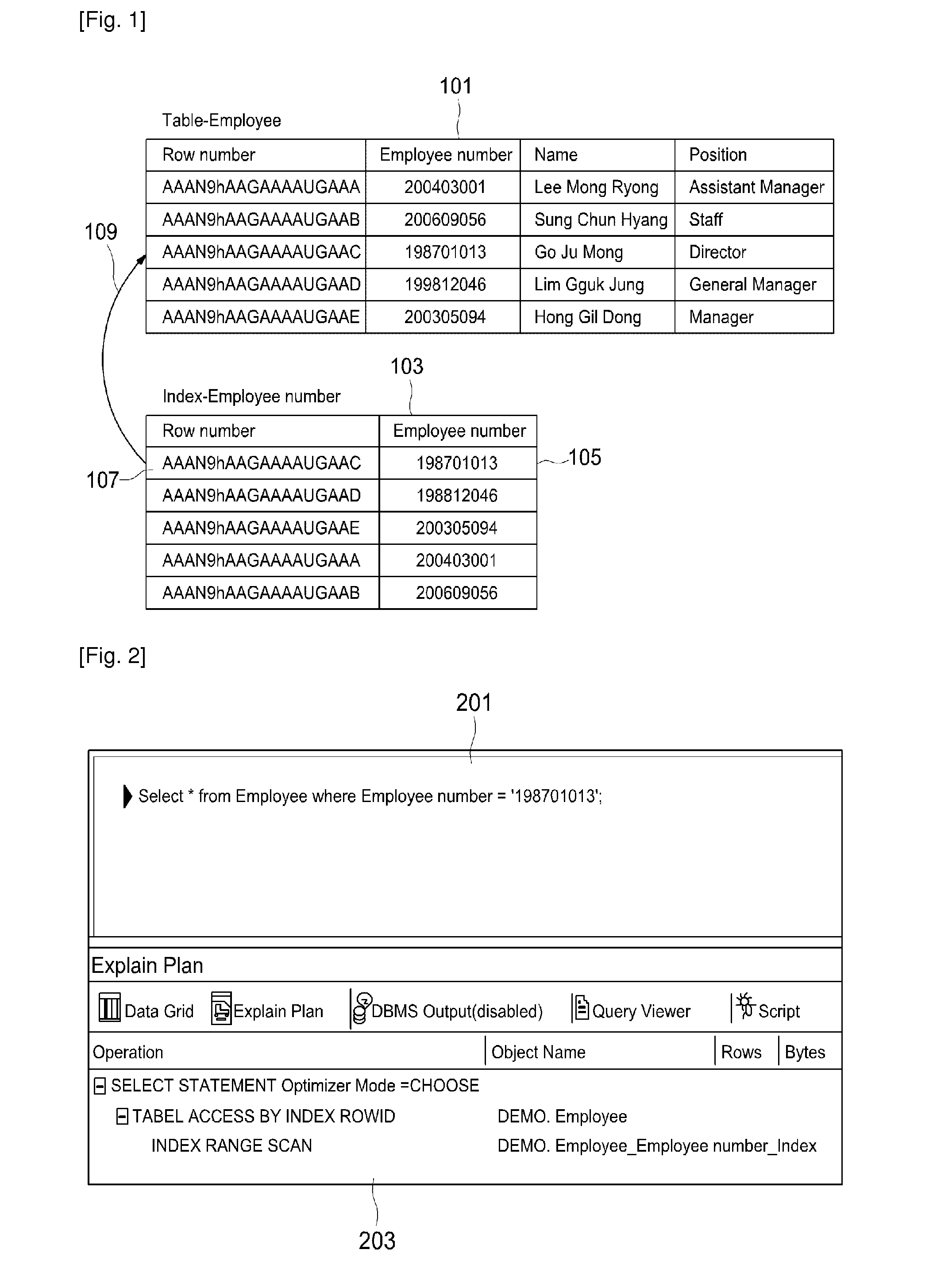

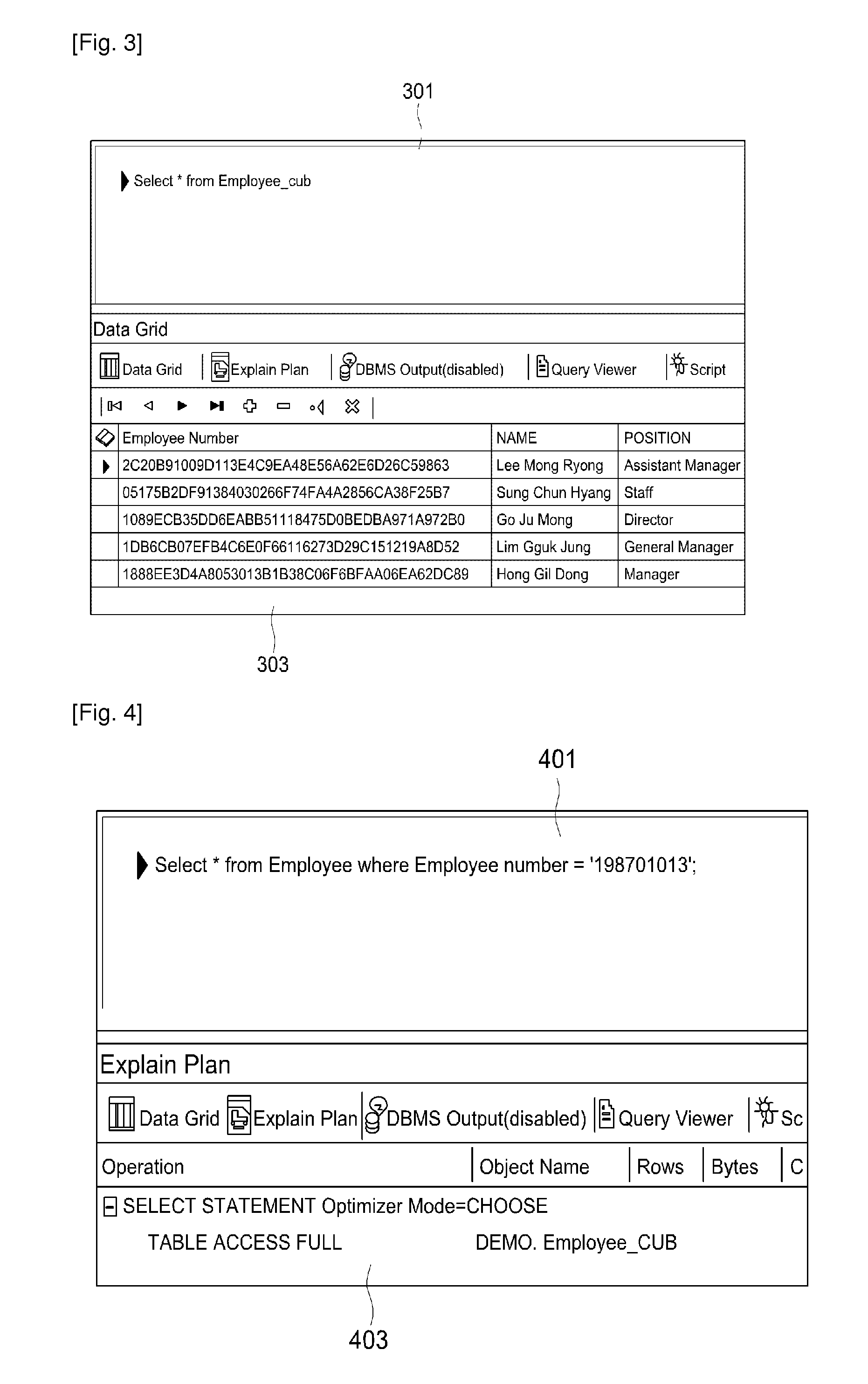

Method for indexing encrypted column

ActiveUS20100169665A1Improve search capabilitiesMaintain independenceDigital data processing detailsUnauthorized memory use protectionPlaintextDatabase

The present invention relates to a method of creating indexes so that an index scan can be worked for columns in a database encrypted by means of secrete key cipher algorithm. The method of creating indexes according to the present invention comprises the steps of: re-encrypting to be able to maintain the sort ordering based on a plain text; creating new indexes based on the re-encrypted data; and configuring domain index architecture of encrypted columns so that the created index is used for the index scan in a query

Owner:EGLOBAL SYST

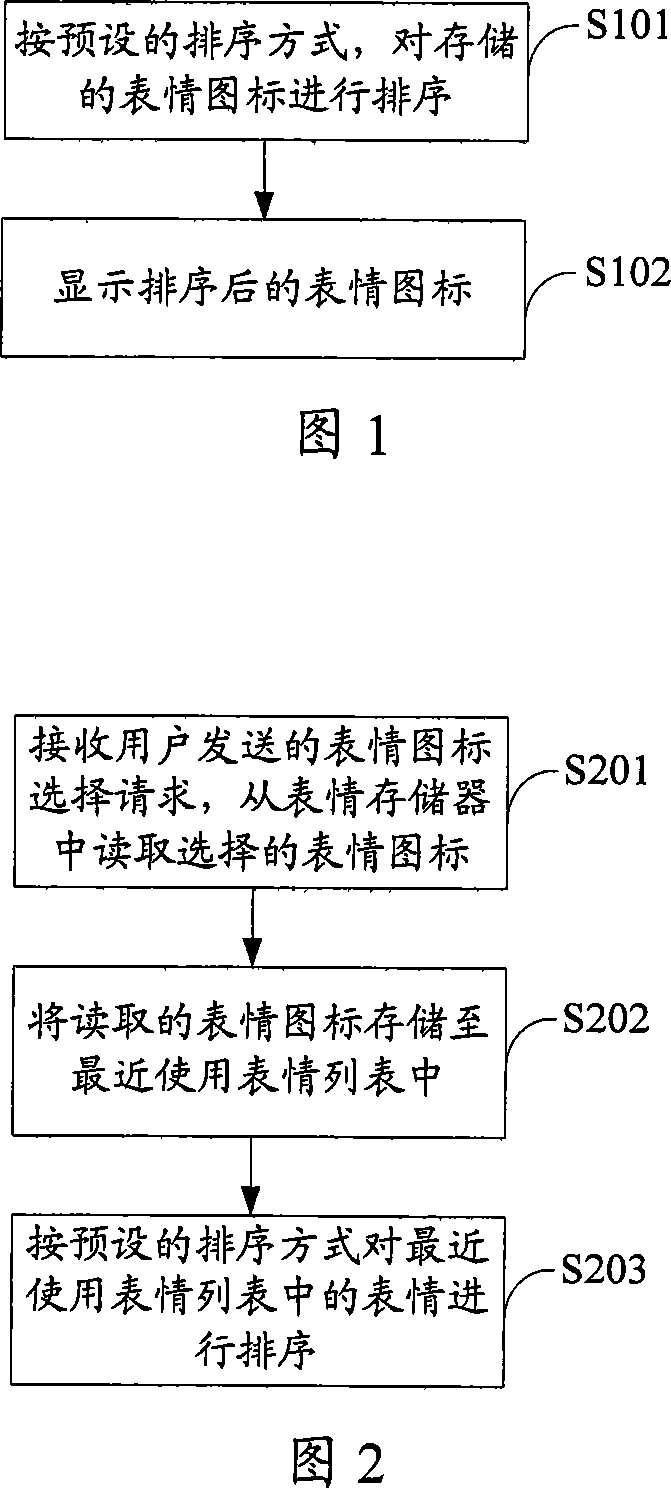

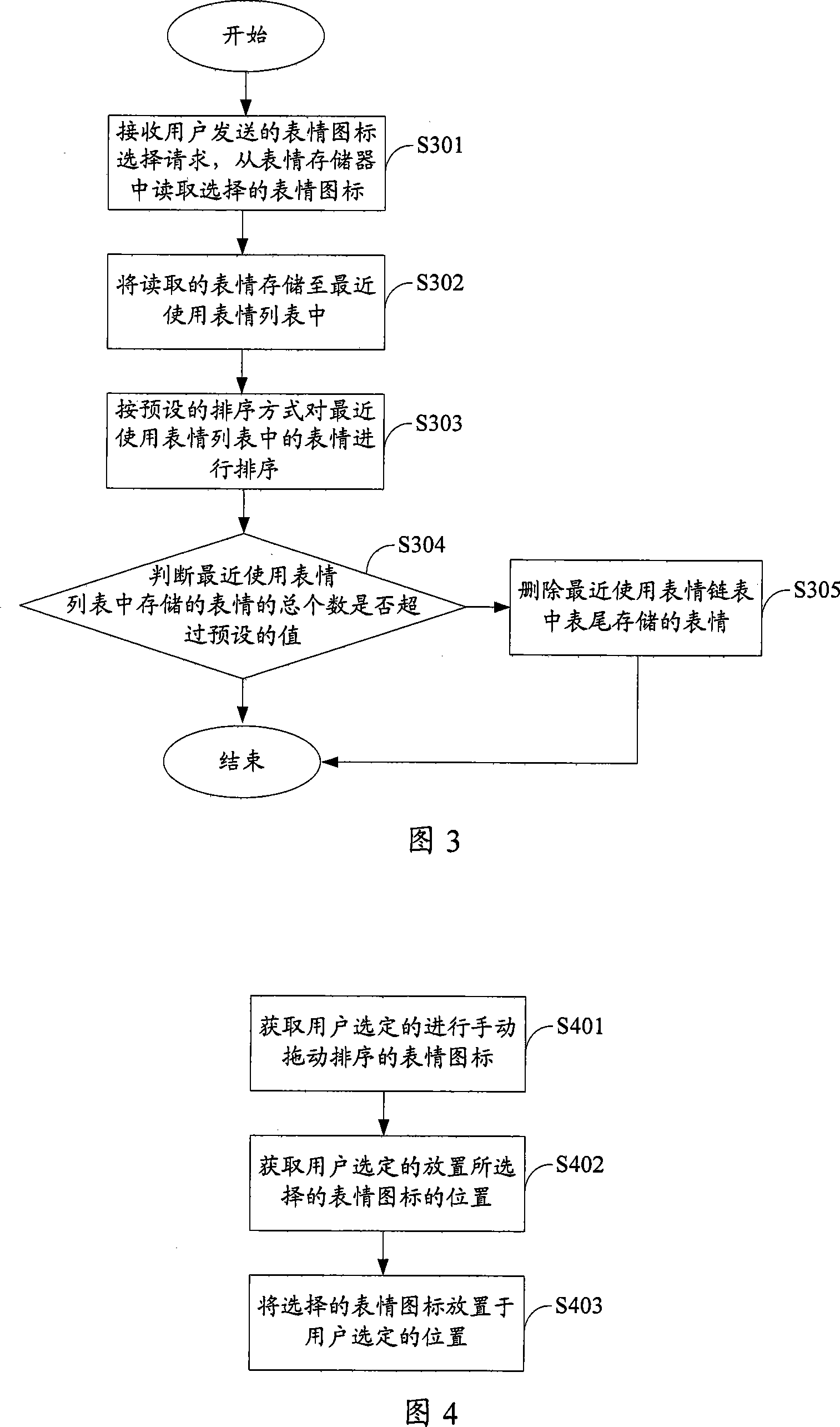

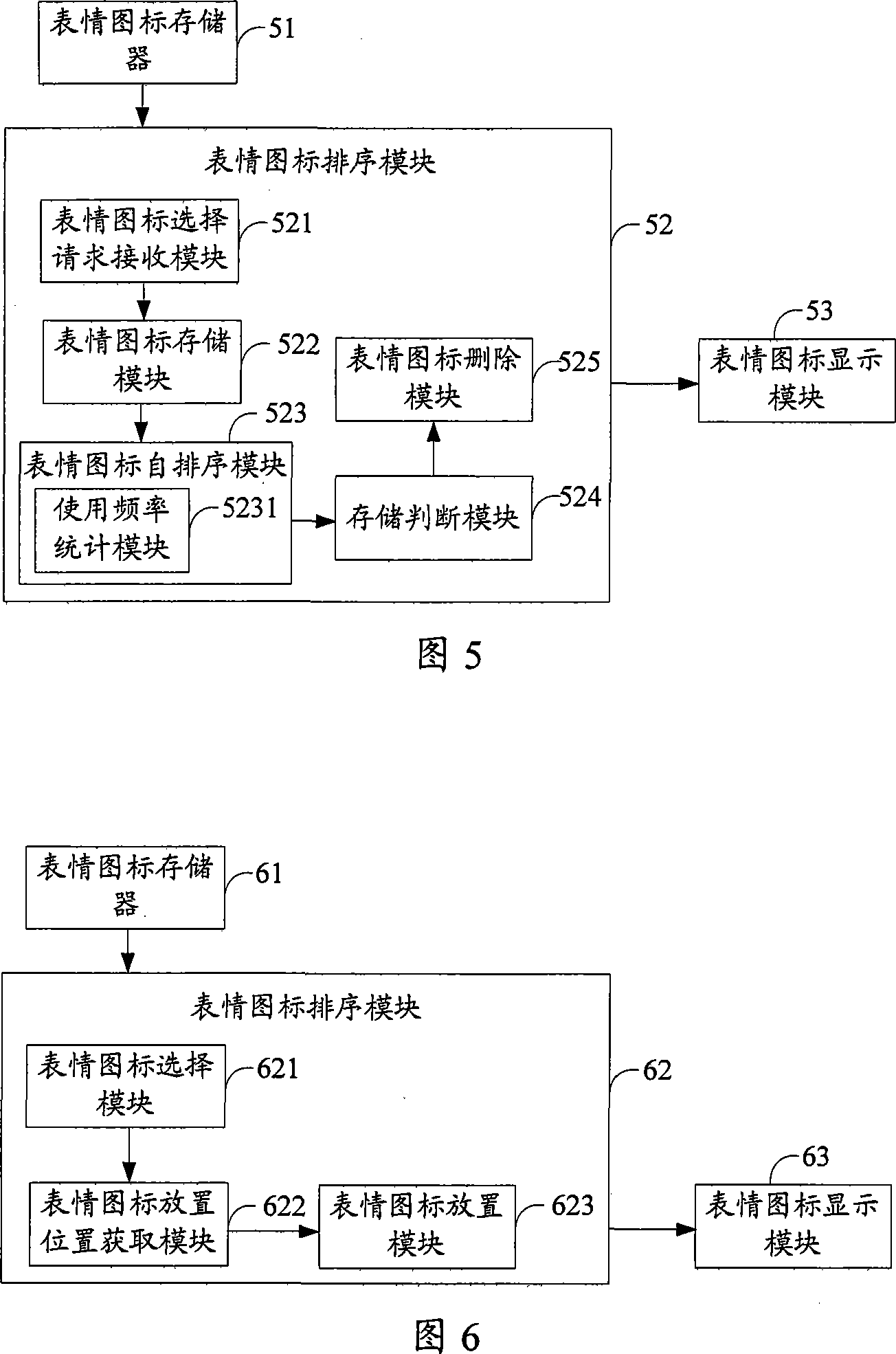

A display method and system for emotion icons

InactiveCN101146056AEasy to operateFacilitate communicationData switching networksSpecial data processing applicationsPersonalizationComputer science

The invention is applicable to the instant communication field and provides a displaying method and a system of expression icons. The method includes the following steps: sort the expression icons in an expression icon memory by preset a sorting order, and display the expression icons after sorting. In the inventive embodiment, sort the expression icons by the order after sorting and display the expression icons after sorting to users, in order to simplify users searching and selection operation of the common expression icons, quicken the communication among users and meet individual requirement of the users.

Owner:TENCENT TECH (SHENZHEN) CO LTD

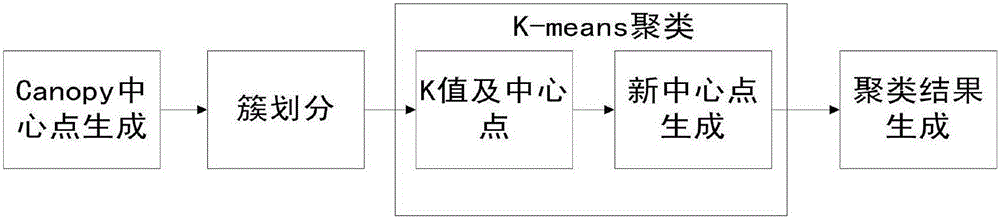

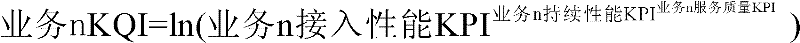

Order batching method based on improved K-Means algorithm

ActiveCN105678607AAvoid blindnessReduce distanceCharacter and pattern recognitionBuying/selling/leasing transactionsData setLogistics management

The invention discloses an order batching method based on an improved K-Means algorithm, and the method is based on data mining. The method comprises the following steps: 1, conducting vectorization of a data set and obtaining an order set X; 2, obtaining a distance threshold T1 and a distance threshold T2 through a cross-validation method; 3, using a Canopy algorithm to obtain a cluster number K and a center point; 4, using the K and the center point obtained in the previous step and the improved K-Means algorithm to conduct clustering; and 5, after obtaining a final clustering result, sorting orders according to the average arrival time of the orders of each cluster, and obtaining a result of order batching. The method can accurately batch a large number of logistics orders, so that the efficiency of sorting operation is improved and the time taken for the sorting step is reduced.

Owner:HEFEI UNIV OF TECH

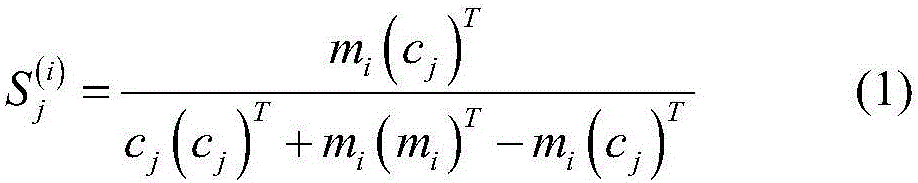

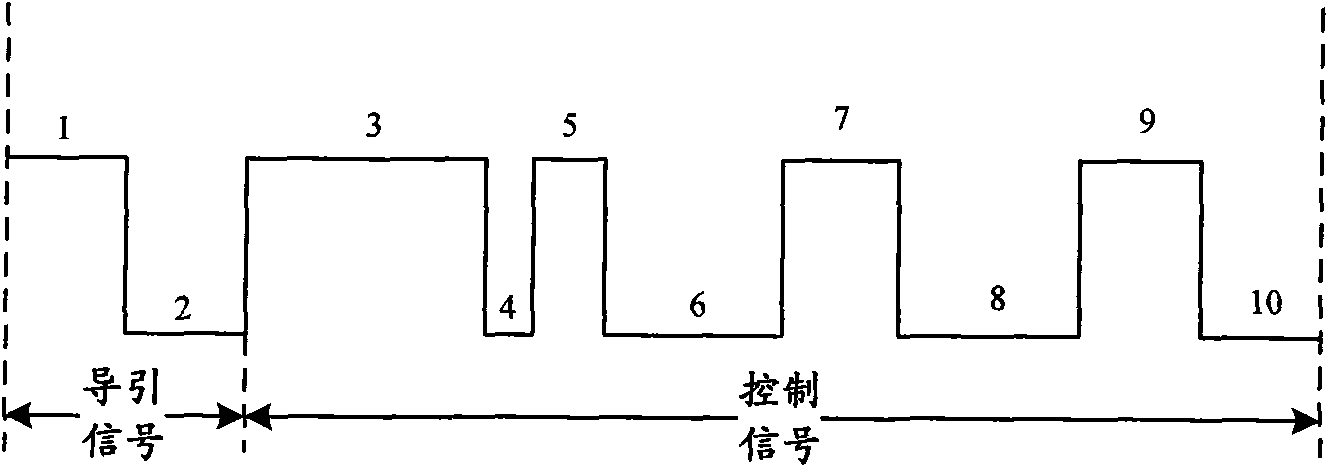

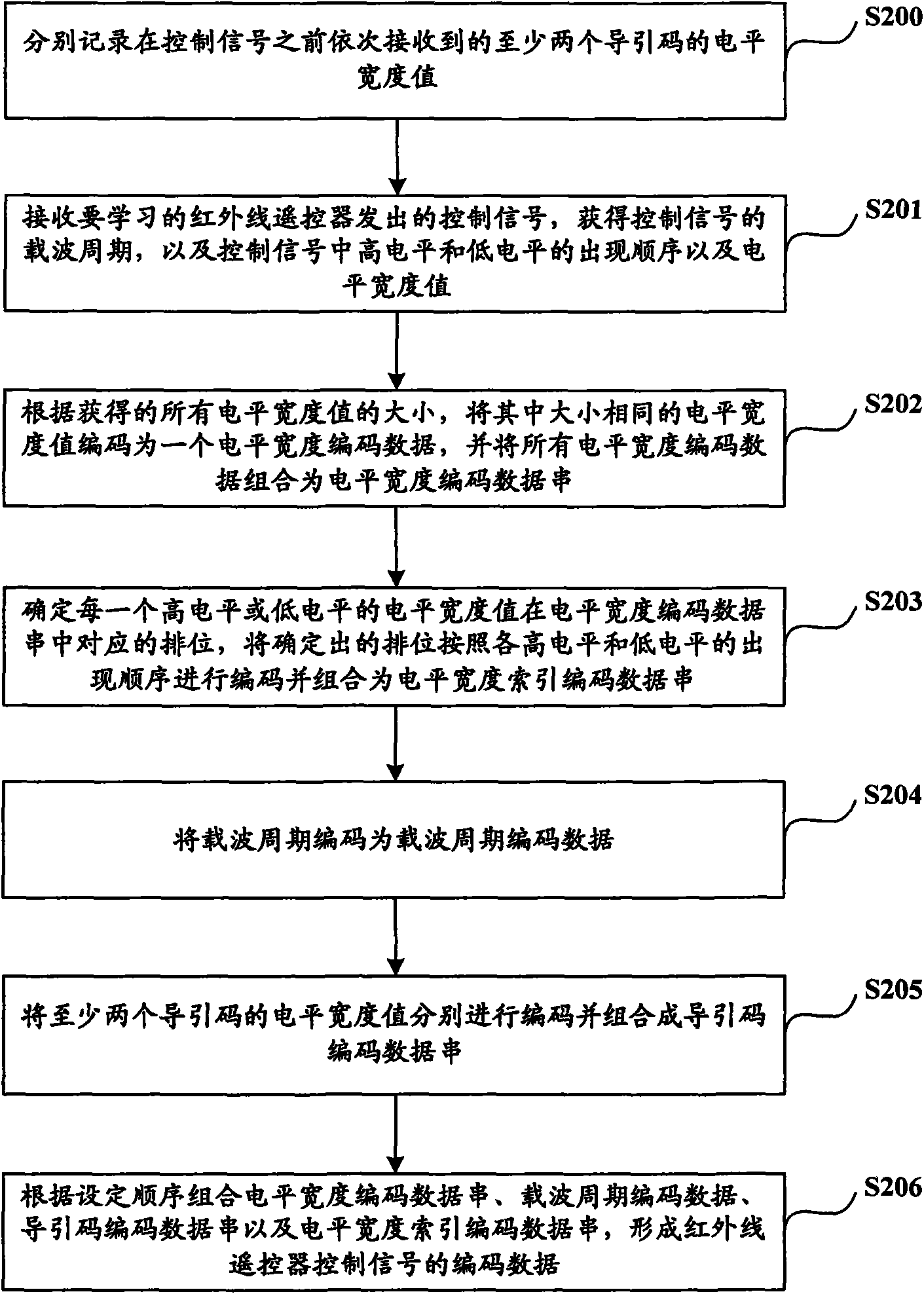

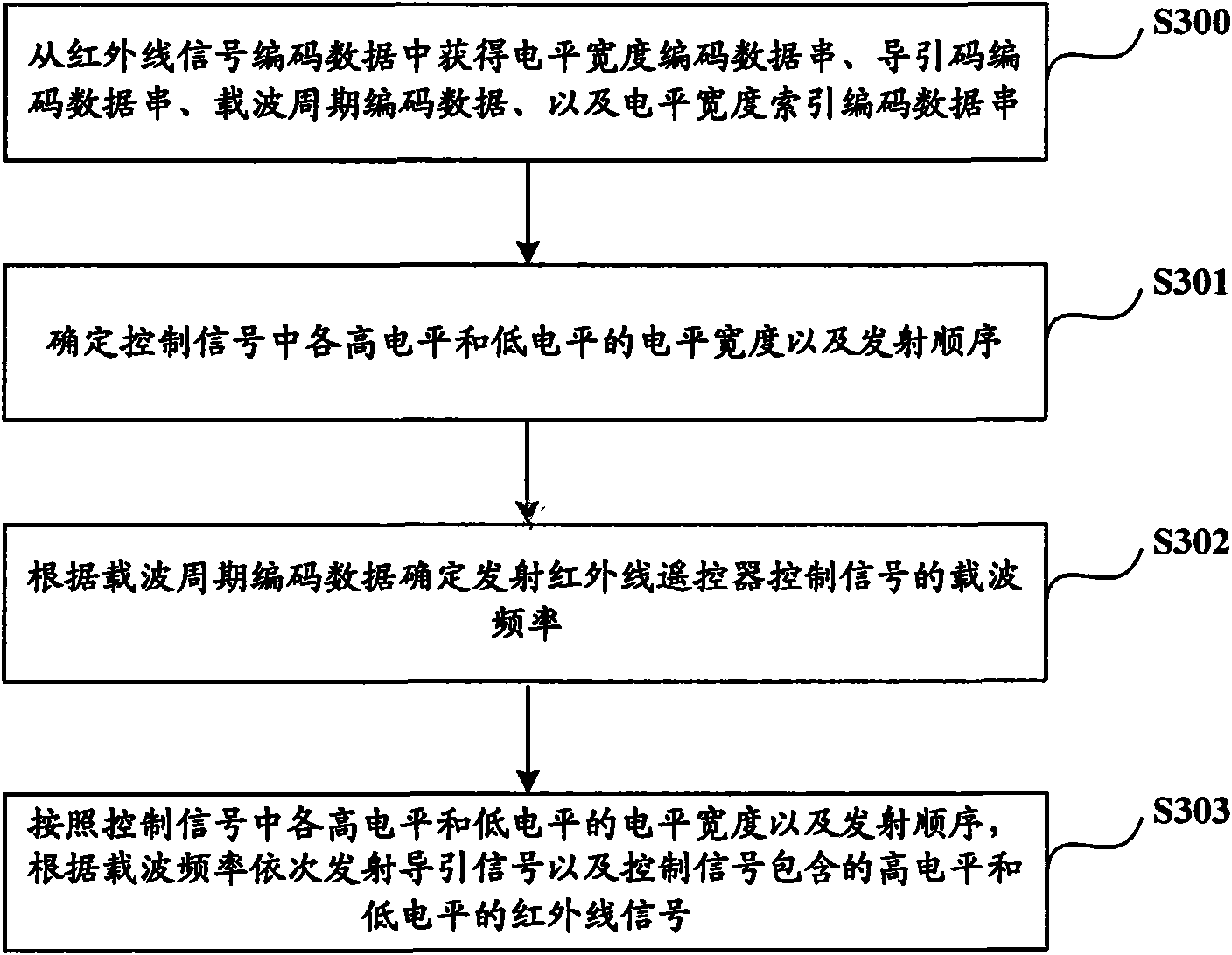

Learning method and transmitting method of infrared cod signal and remote controller

InactiveCN101989379ASave storage spaceSave the amount of encoded dataNon-electrical signal transmission systemsRemote controlLearning methods

The invention relates to a remote control technology, in particular to an infrared code signal learning technology in the remote control technology, and the invention discloses a learning method and a transmitting method of the infrared cod signal of a remote controller and the remote controller, which are used for realizing the learning and the reduction of the infrared code signal of the remote controller and reducing the code data volume as much as possible so as to save the storage space. According to the learning technology of the infrared code signal, which is provided by the embodiment of the invention, indexes can be established for different level widths and can be coded and stored according to the sort orders of high and low levels; the width and the order of the levels can be sequentially determined according to the coding and the sort order of the indexes, thereby the code data volume can be greatly saved and the storage space of the remote controller can be saved when the infrared code signal appears repeatedly at the same level width.

Owner:NINGBO JIATIANXIA INTELLIGENT SYST

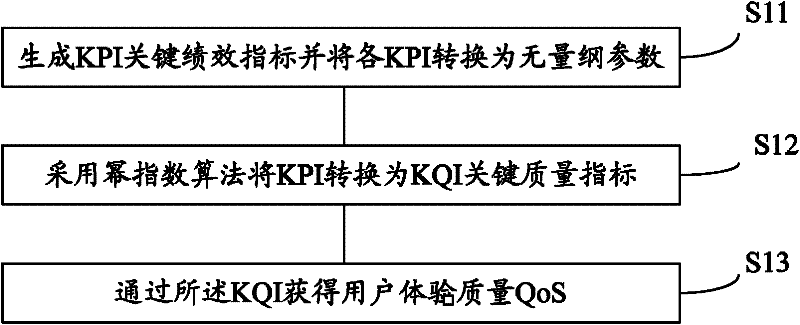

User experience quality sensing method of mobile data network

InactiveCN102355691AAccurate quality of experienceAccurately reflectWireless communicationQuality of serviceService experience

The invention discloses a user experience quality sensing method of a mobile data network, comprising the following steps of: based on the difference of services, taking a network, a network element and a link as analysis objects, and respectively generating KPIs (Key Performance Indicators) according to the equipment log, the network management report and the signalling data; converting each KPI into a dimensionless parameter; converting each KPI into a KQI (Key Quality Indicator) through a power exponent algorithm, wherein the power exponent method is to generate an experience factor sequence for service characteristics of each service according to the sort order of the service characteristics, take the experience factor having high affection degree to the user experience as the root and take the experience factor having lower affection degree to the user experience as the power exponent to establish the algorithm for converting the KPI into the KQI. Thus, the KQI can reflect the user experience to the specific services more accurately, and the QoS (Quality of Service) obtained through the KQI is more accurate.

Owner:BEIJING ZHONGCHUANG TELECOM TEST

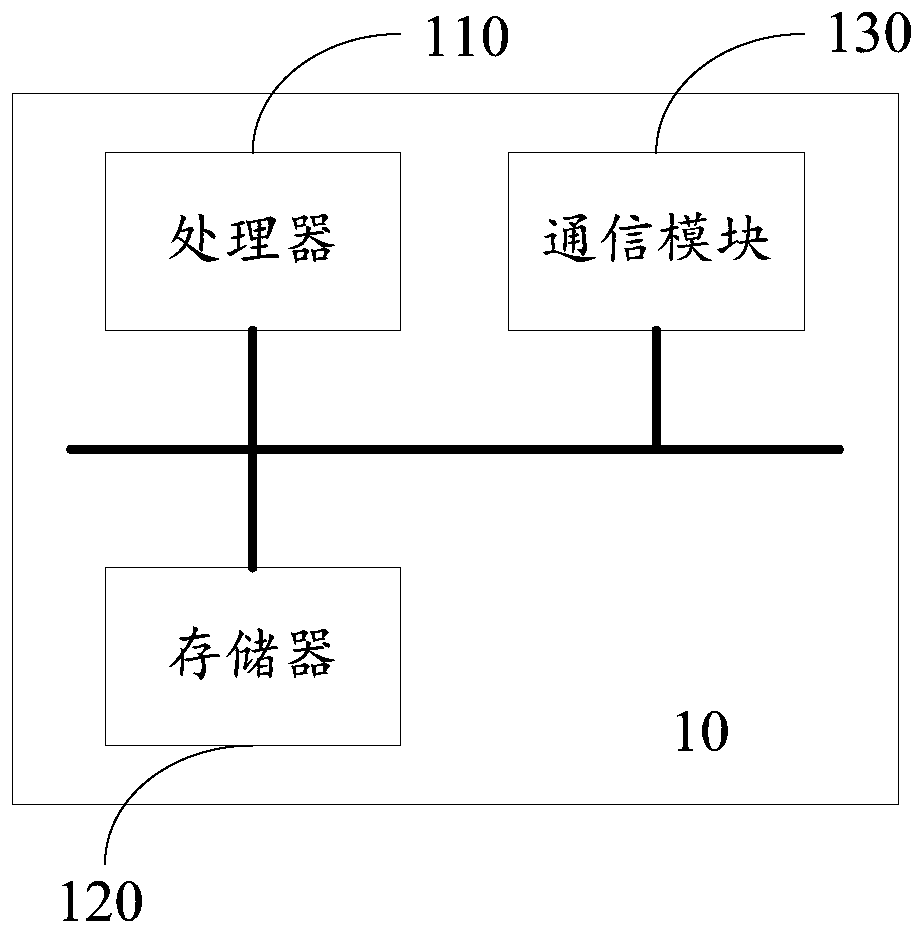

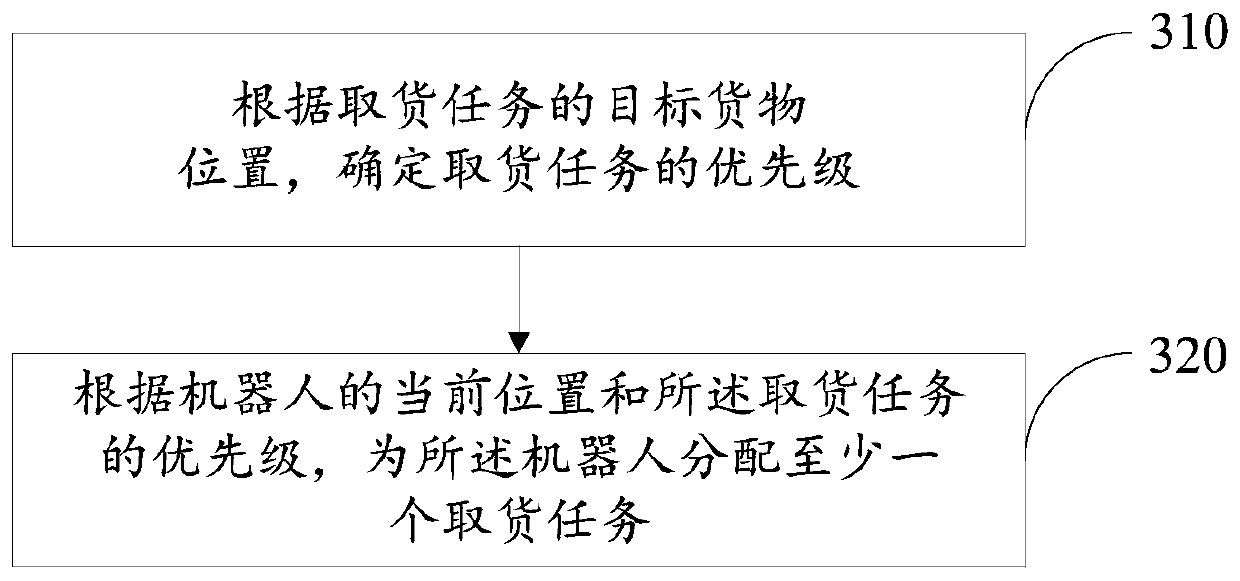

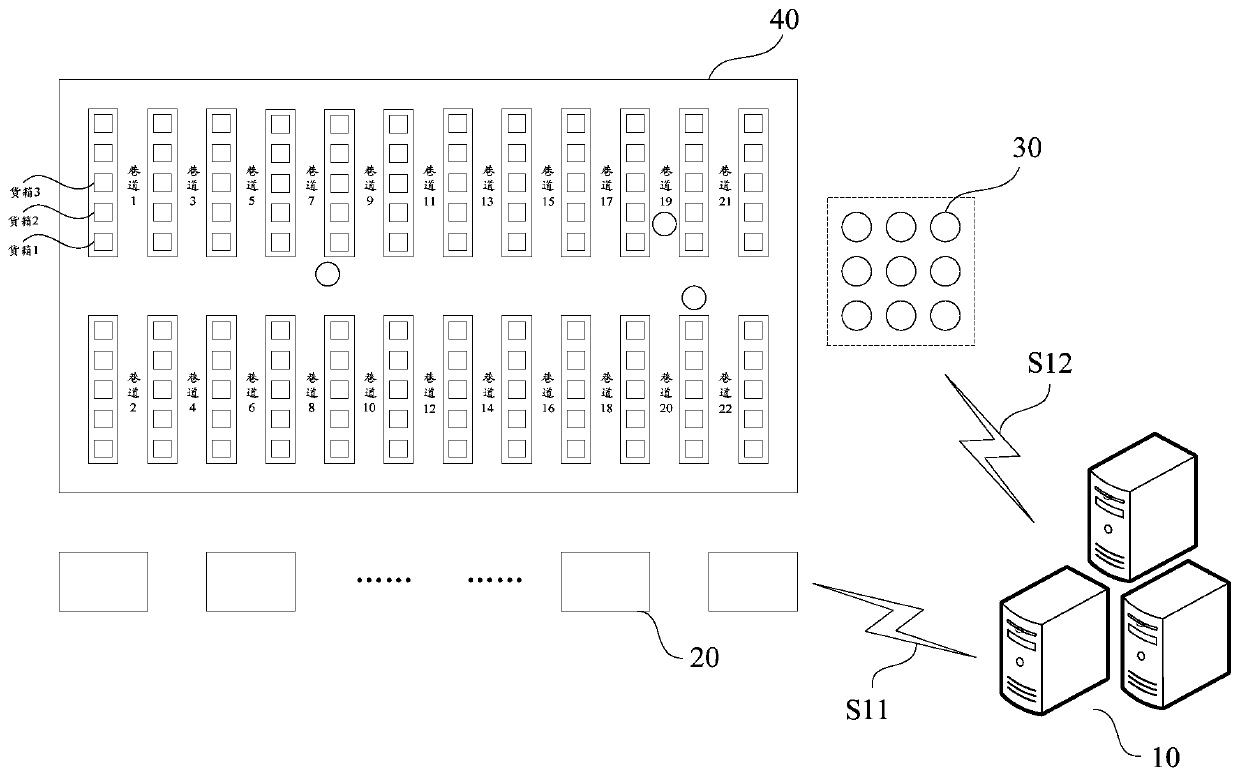

Goods taking task allocation method and goods sorting system thereof

ActiveCN110239868AImprove convenienceBreak through the one-to-one binding relationshipResourcesLogisticsComputer scienceSort order

The embodiment of the invention relates to a goods taking task allocation method and a goods sorting system thereof. The goods taking task allocation method comprises the following steps that according to the target goods position of a goods taking task, and the priority of the goods taking task is determined; and at least one goods taking task is distributed for a robot according to the current position of the robot and the priority of the goods taking task. According to the method, planning and optimization planning can be carried out on a plurality of robots and a plurality of pickup tasks, a binding relation between a single robot and a specific pickup task is broken through, so that the optimization degree of the goods taking tasks is improved, and the goods sorting efficiency corresponding to the sorting orders is improved.

Owner:HAI ROBOTICS CO LTD

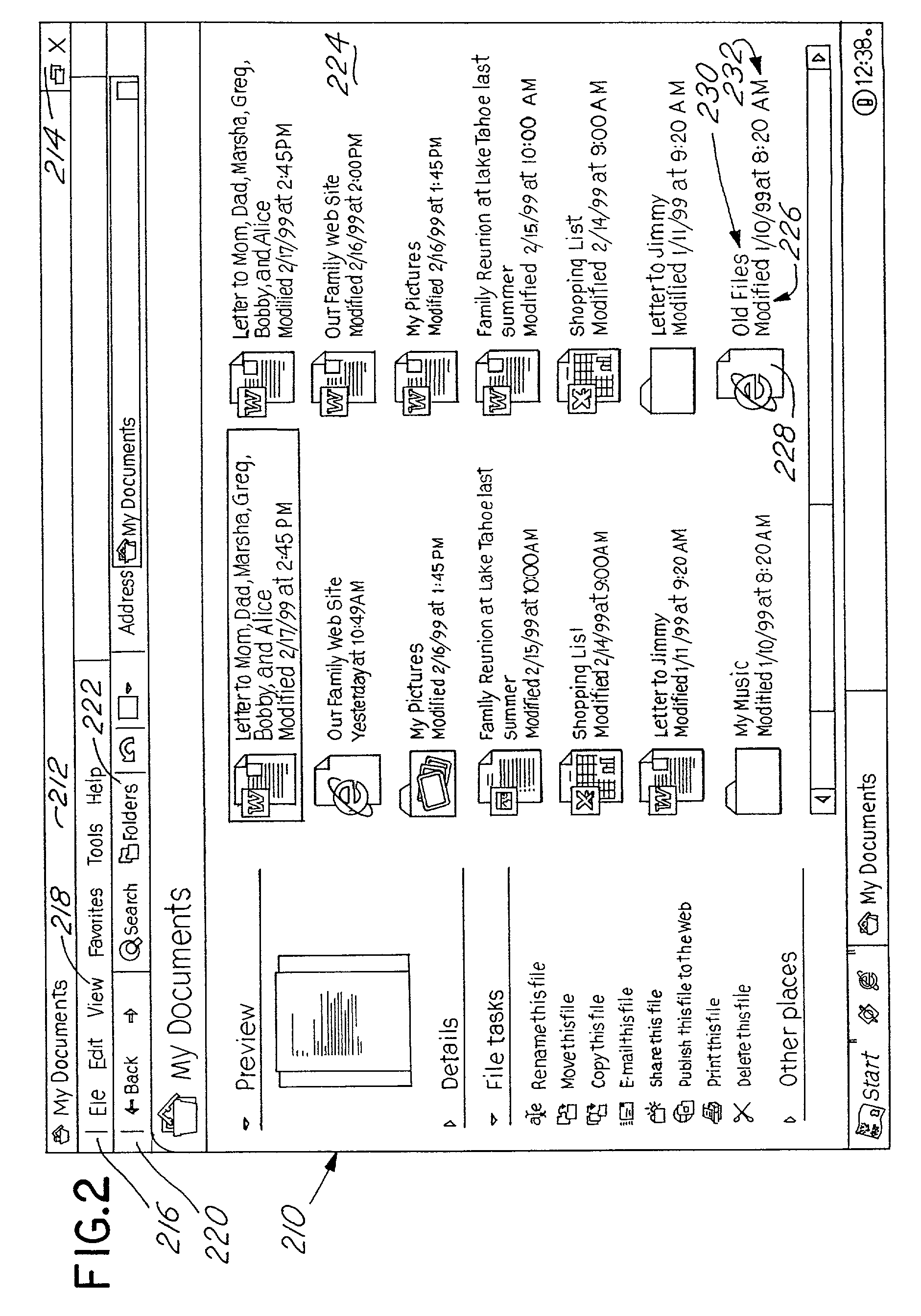

Displaying graphical information and user selected properties on a computer interface

InactiveUS7188319B2Easy to identifyOvercomes drawbackProgram initiation/switchingInput/output processes for data processingGraphicsRelevant information

A new way of providing pertinent information about an item (e.g., a text file, a picture file, a music file, video file, or any other similar file) is provided. The invention provides graphical information about the item along with user-selectable properties that are specific to that item. The invention further provides a way of sorting the items by the user-selectable properties and communicating the sort order to the user. The invention thereby provides the user with a way of quickly finding pertinent information about the item.

Owner:MICROSOFT TECH LICENSING LLC

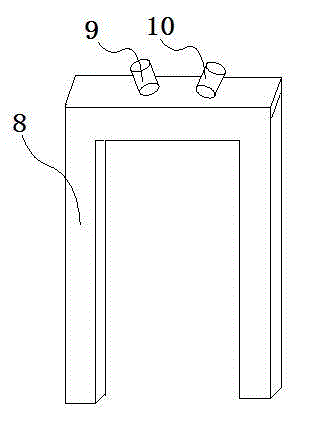

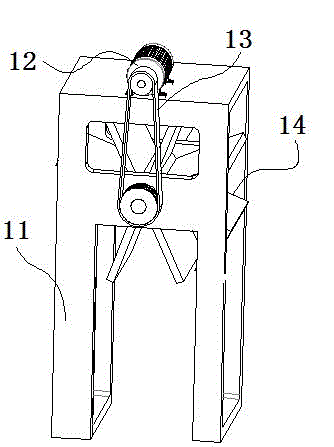

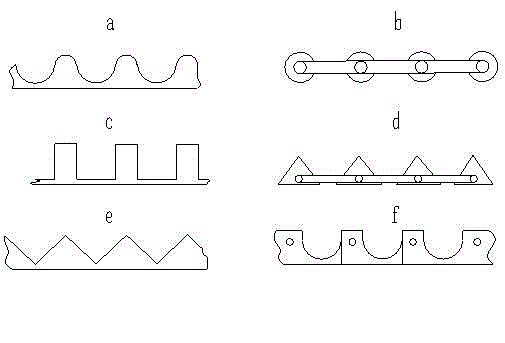

Orienting sorting ordering feeding system for fresh corncobs and orienting sorting ordering method thereof

InactiveCN103934206AOrderly arrangement of materialsAchieve one-way orientationSortingFresh foodEngineering

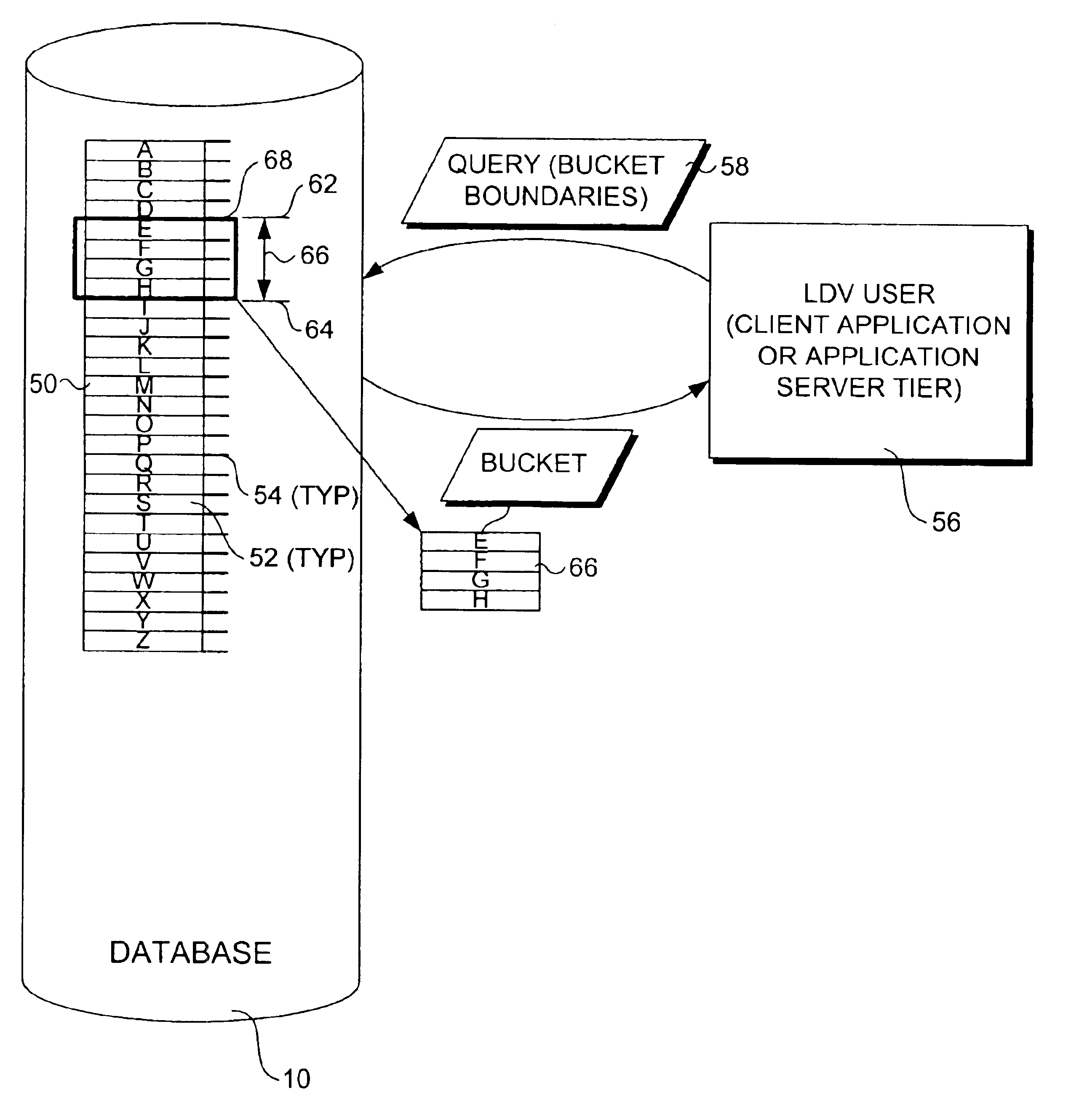

The invention relates to an orienting sorting ordering feeding system for fresh food corncobs and an orienting sorting ordering method thereof. The feeding system comprises an ordering feeding device I, a signal-row transmission device II, an on-line size and direction detection device III, an orientating sorting device IV, a corncob recovery device V, a forward-direction single-row transmission device VI, a reverse-direction single-row transmission device VII and a computer VIII. The ordering method includes: (1) a step of tiling, ordering, grouping and feeding stacked fresh corncobs through the automatic feeding device I; (2) transmitting the corncobs dropped from the automatic feeding device I through the signal-row transmission device II in a single row manner; (3) subjecting the corncobs transmitted on the signal-row transmission device II to on-line size detection, shape detection and direction detection through the sorting device IV; and (4) sorting and ordering the fresh corncobs by the orientating sorting device IV under the control of the computer according to the detection results of the sorting device IV, transmitting corncobs with unqualified sizes to the corncob recovery device V through rotation of a poking wheel on the orientating sorting device IV; transmitting corncobs with qualified sizes and a direction reverse to the set direction into the reverse-direction single-row transmission device VII, and transmitting corncobs with qualified sizes and the same direction as the set direction into the forward-direction single-row transmission device VI, thus achieving sorting ordering feeding of the fresh corncobs.

Owner:JILIN NORMAL UNIV

Determining priority for installing a patch into multiple patch recipients of a network

InactiveUS8181173B2Multiple digital computer combinationsProgram loading/initiatingServer allocationDistributed computing

A method, computer program product, and system are disclosed for installing a patch on at least some of the servers of a network having multiple servers. A plurality of servers of the network are identified that requires installation of the patch. Two or more priority values are assigned to each of the identified servers. The priority values for a given identified server are each associated with a different criterion in a set of criteria. The assigned priority values are selectively processed for respective identified servers, in order to determine an initial priority, comprising a first sort order, for installing the patch on each identified server. The first sort order is revised in accordance with information pertaining to prior use of respective identified servers, to provide a second sort order. The patch is installed on each of the identified servers, in an order determined by the second sort order.

Owner:IBM CORP

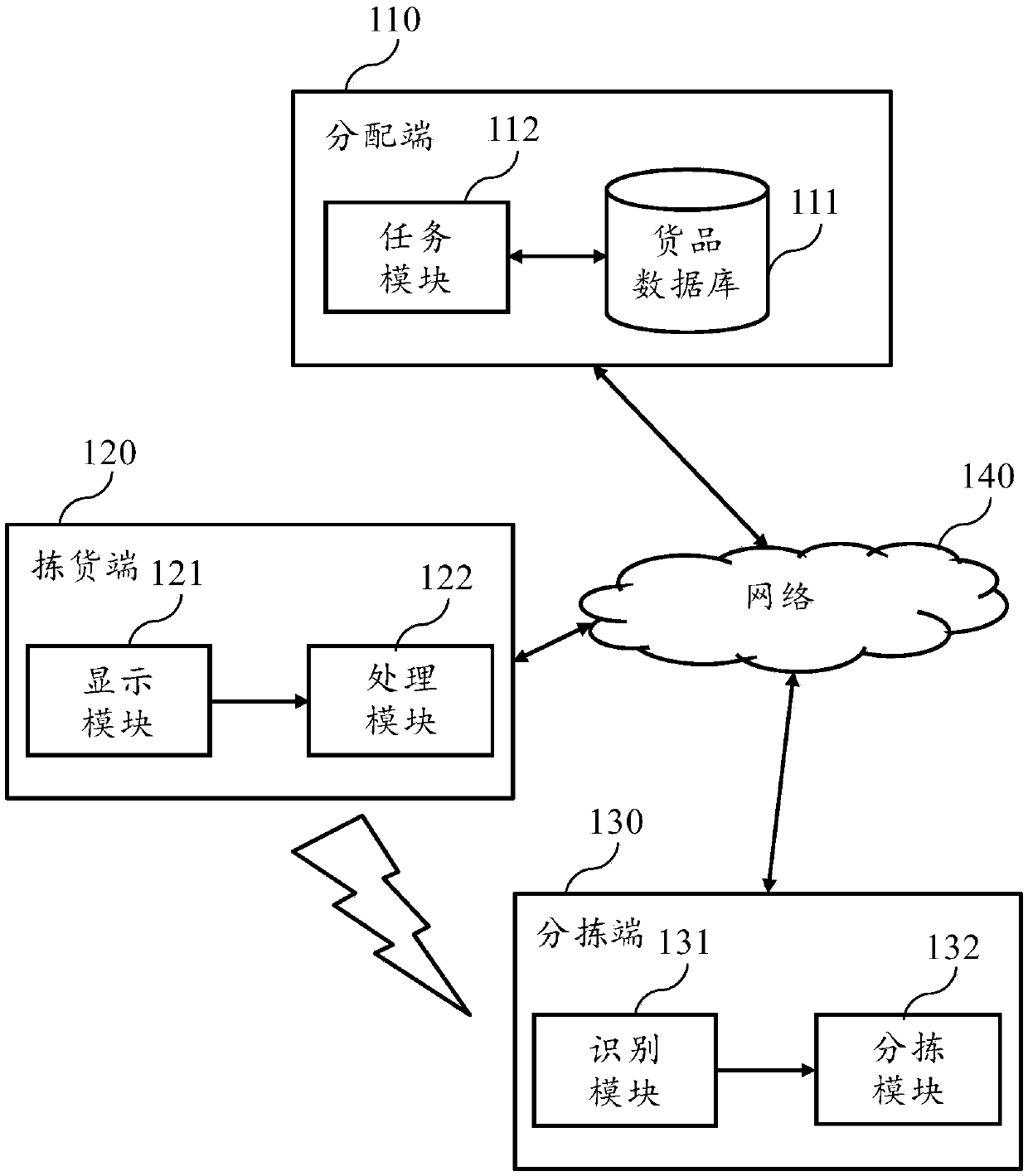

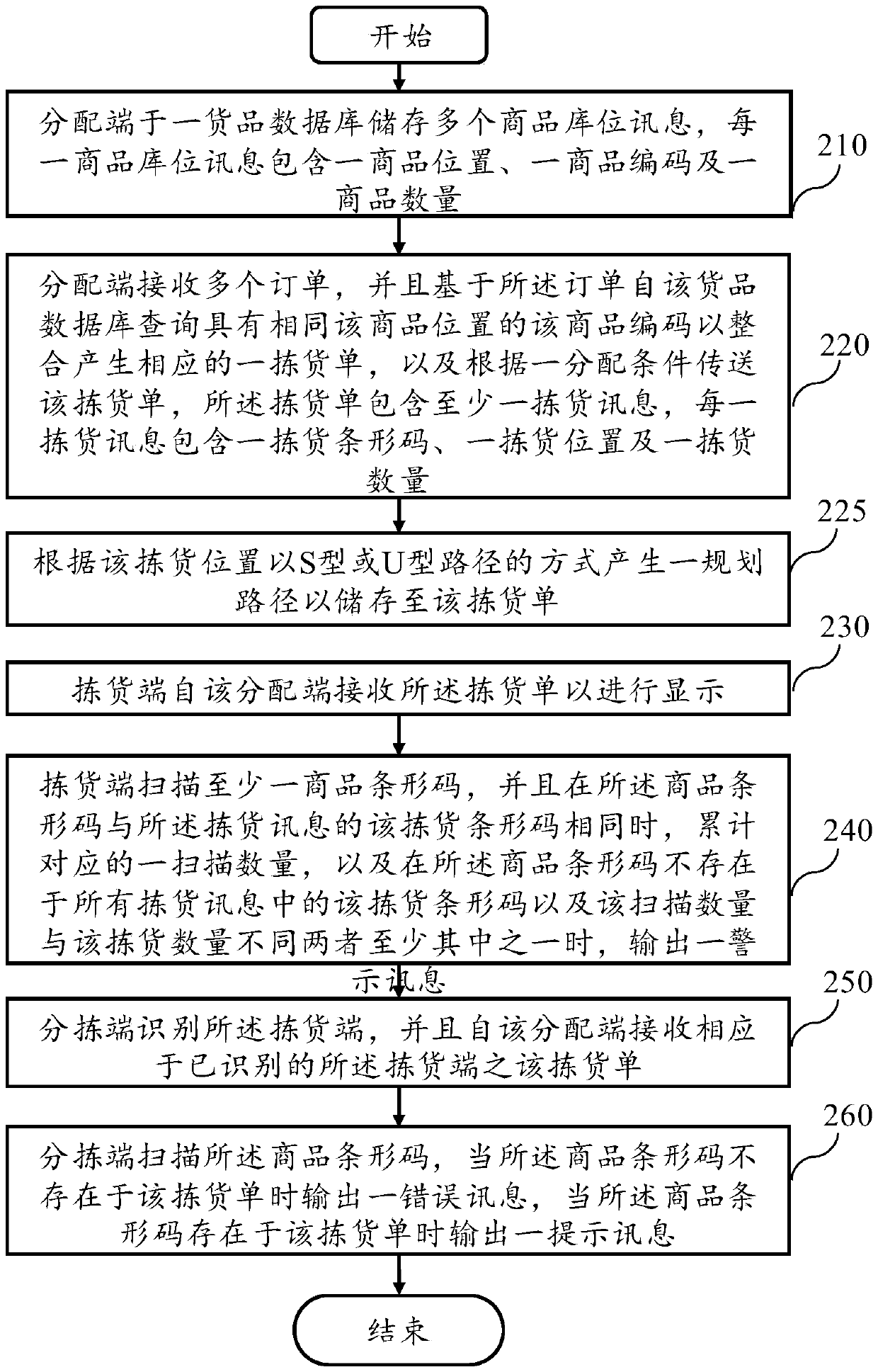

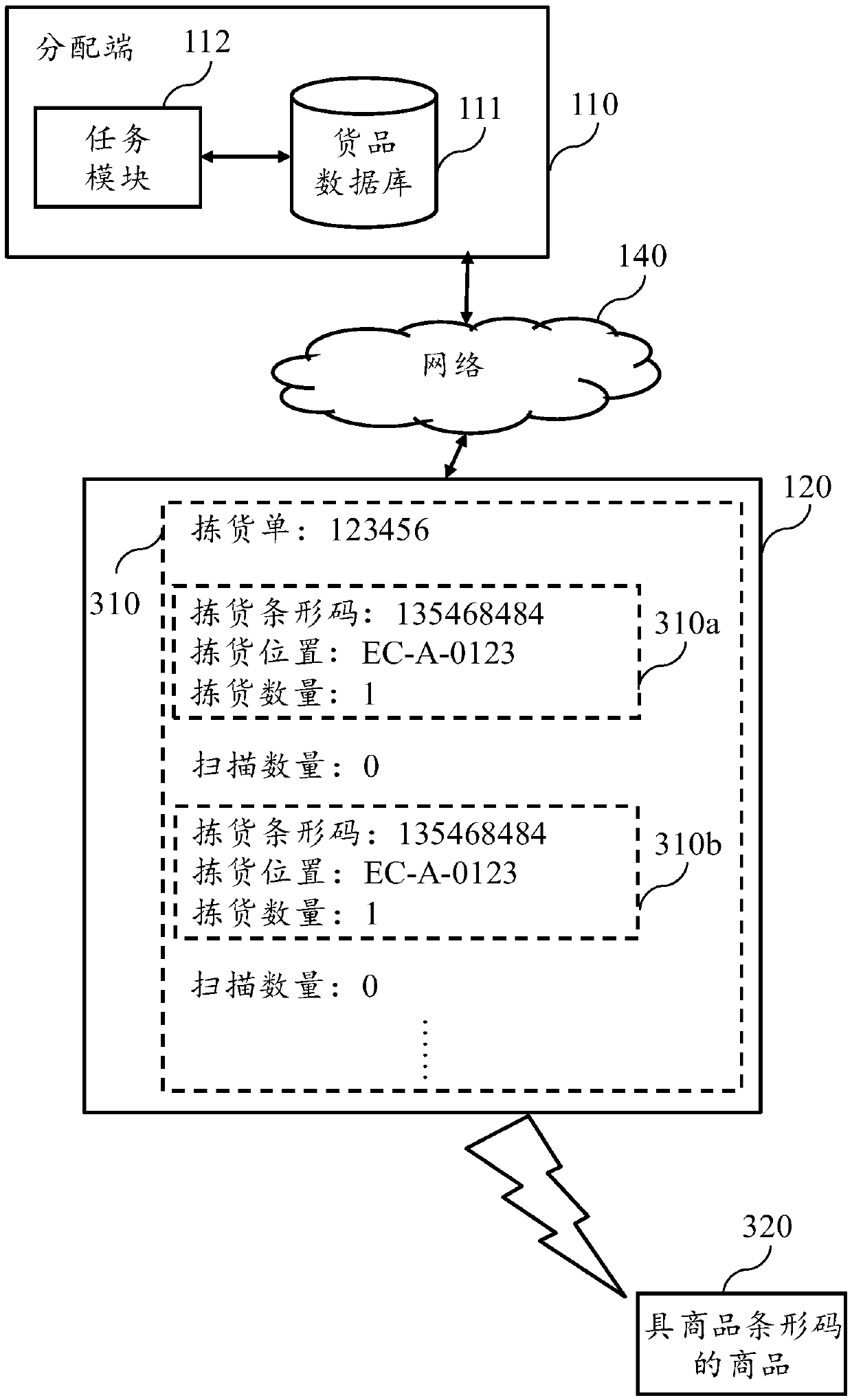

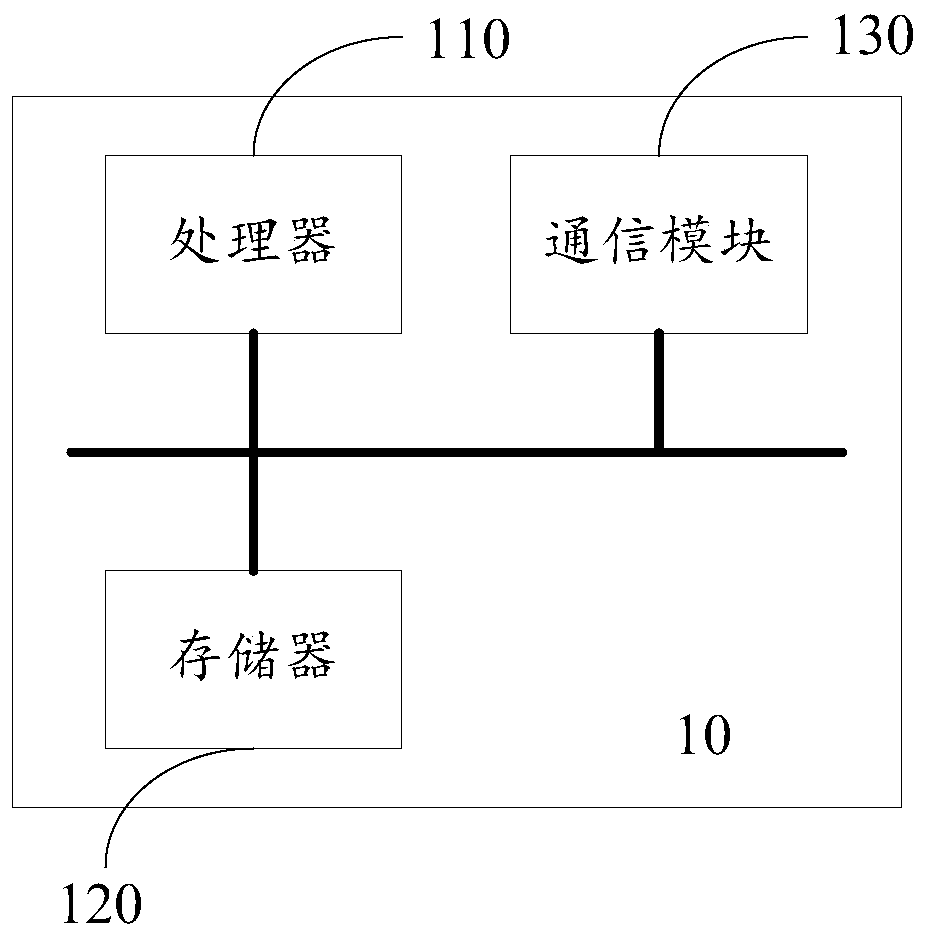

Sorting and distributing system based on barcode scanning and method thereof

InactiveCN105512847AImprove the efficiency of sorting and distributionLogisticsBarcodeComputer engineering

The invention provides a sorting and distributing system based on barcode scanning and a method thereof. Commodity codes with the same commodity position are queried at a distributing end based on an order to generate a picking order, and the sorting order is transmitted to a picking end for display according to distribution conditions. Then, the picking end scans a commodity barcode, 1 is added to the number of picked commodities if the commodity barcode is the same as a picking barcode, and warning information is output when the commodity barcode does not exist and / or when the number of scanned commodities and the number of picked commodities are not the same. A sorting end is used for identifying the picking end, receiving the corresponding picking order and scanning a commodity barcode. The sorting end outputs error information if the commodity barcode does not exist in the picking order, and the sorting end outputs prompt information if the commodity barcode exists in the picking order. Therefore, the efficiency of sorting and distributing is improved.

Owner:INVENTEC PUDONG TECH CORPOARTION +1

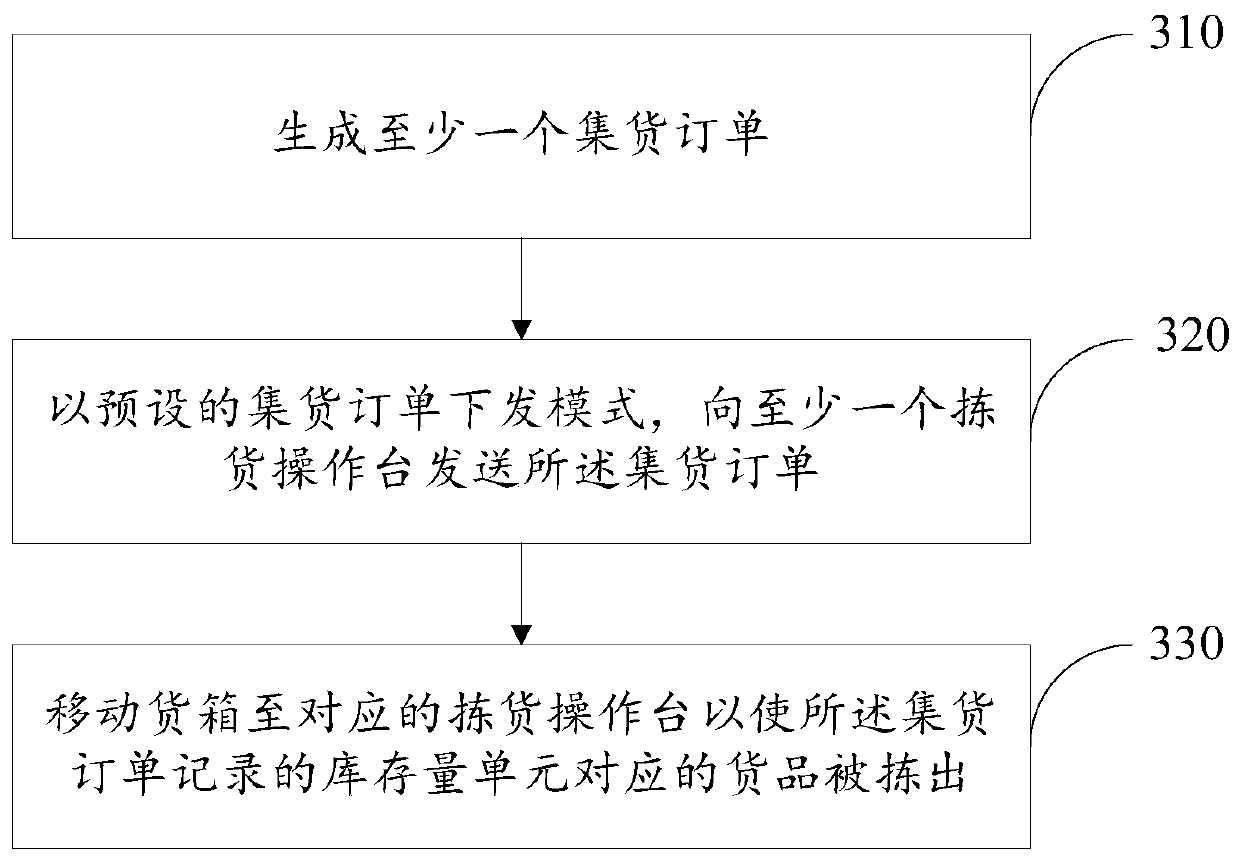

Goods sorting method and goods sorting system

ActiveCN110245890AImprove picking efficiencySimple processProgramme controlResourcesOrder formTransport engineering

The embodiment of the invention relates to a goods sorting method and a goods sorting system thereof. The goods sorting method comprises the steps of generating at least one goods collection order, wherein each goods collection order is composed of a preset number of sorting orders, and a plurality of stock units are recorded; sending the goods collection order to at least one goods picking operation table in a preset goods collection order issuing mode; and moving the cargo boxes to the corresponding picking operation tables so as to pick out the cargoes corresponding to the stock units recorded by the collection orders. According to the method, a large number of sorting orders can be processed at the same time in the mode of generating and issuing the goods collection orders, and the efficiency of goods sorting operation is well improved.

Owner:HAI ROBOTICS CO LTD

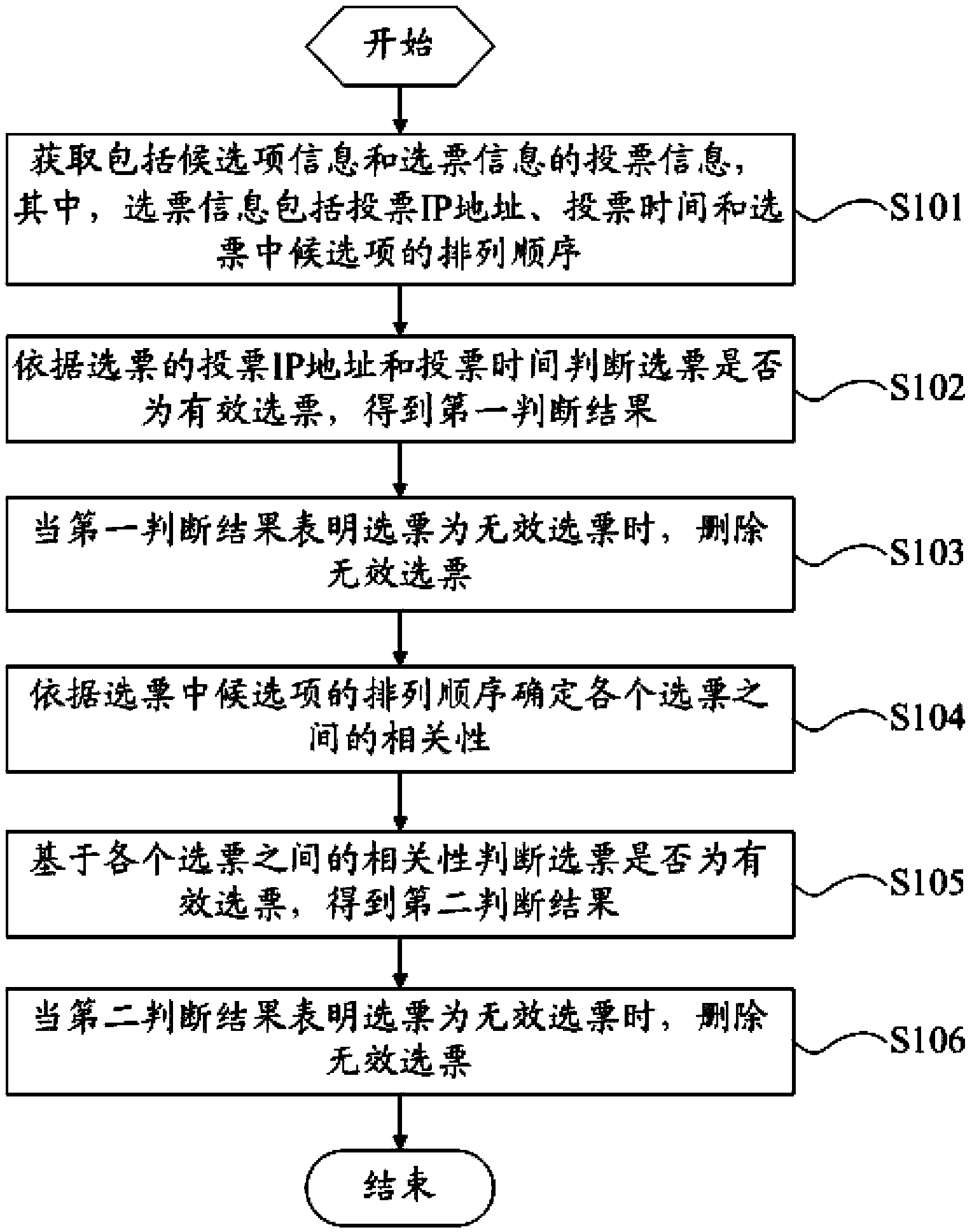

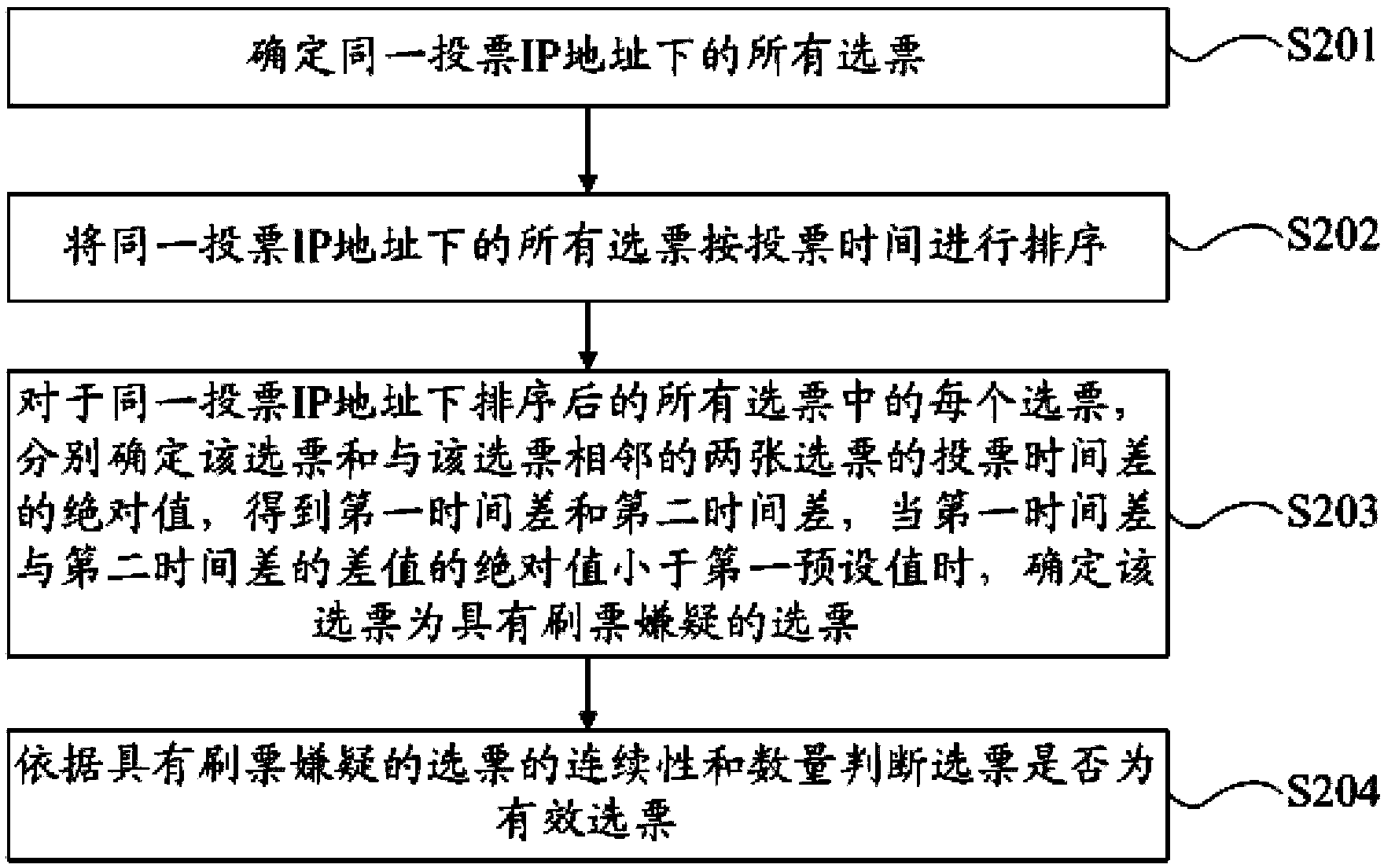

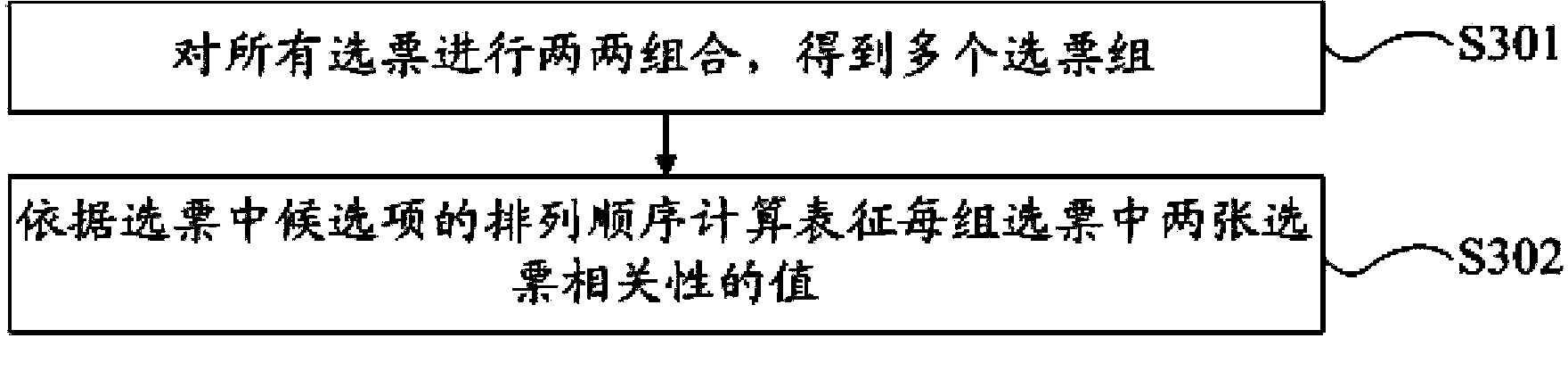

Method, device and system for processing voting information

InactiveCN103886667AImprove fairnessReduce the impactVoting apparatusTransmissionIp addressComputer science

The invention provides a method, device and system for processing voting information. The method for processing voting information comprises the following steps: obtaining candidate item information and vote information, wherein the vote information comprises a voting internet-protocol (IP) address, voting time, and sort order of the candidate items in the vote; judging whether the vote is a valid vote according to the voting IP address and the voting time of the vote, so as to obtain a first judgment result; deleting an invalid vote when the first judgment result shows that the vote is the invalid vote; determining the pertinence of each vote according to the sort order of the candidate items in the vote; judging whether the vote is the valid vote based on the pertinence of each vote, so as to obtain a second judgment result; and deleting the invalid vote when the second judgment result proves that the vote is the invalid vote. By adopting the method, device and system for processing voting information, which is provided by the invention, the problem of repeated voting in network voting of the prior art is solved, and the vote with the repeated voting phenomenon is deleted, so that the network voting result is more fair.

Owner:杭州数能科技有限公司

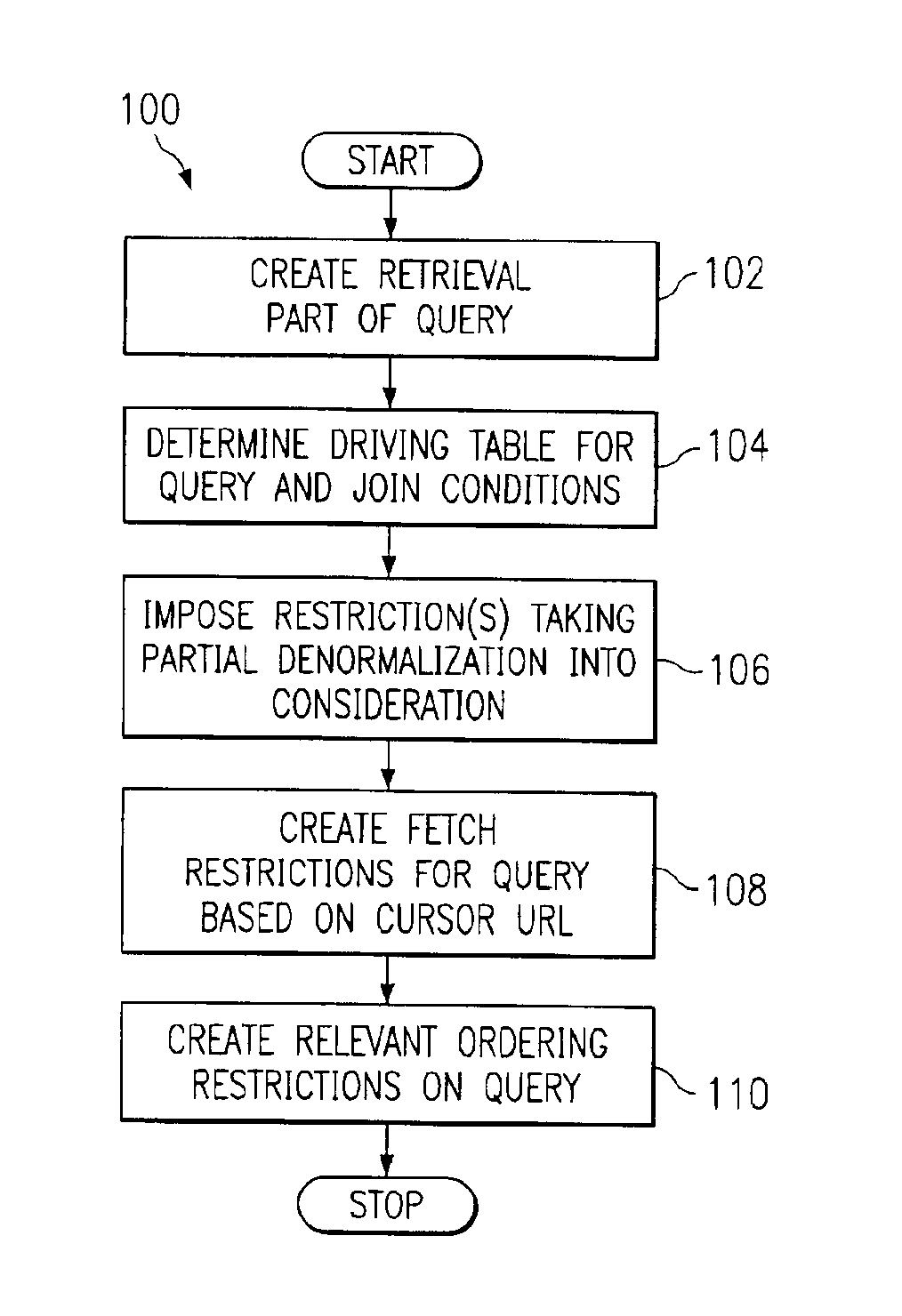

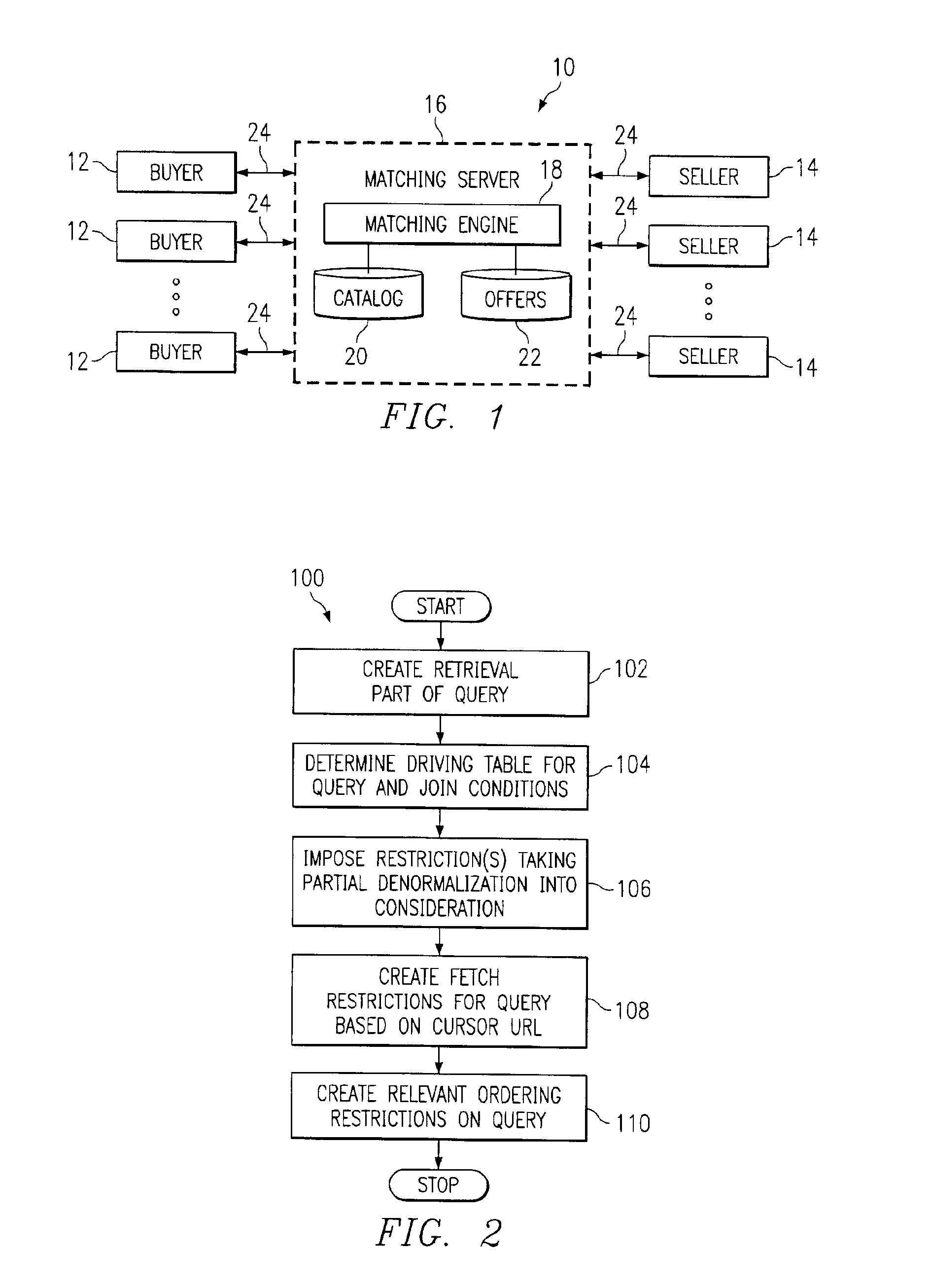

Sorted-paged retrieval of hierarchical data from relational databases

InactiveUS6898593B1Improve retrieval efficiencyImprove efficiencyData processing applicationsObject oriented databasesPagingRelational table

A method for sorted-paged retrieval of hierarchical data from a relational database is disclosed, which includes the use of one or more relational table equi-join terms in a query to increase the retrieval efficiency, suitable restrictions imposed on the join terms to further increase the retrieval efficiency, partial de-normalization or replication of information to improve the efficiency of the join operation(s) and thus further increase the retrieval efficiency, and proper cursor management to keep track of the current location of the cursor(s) involved. As a result, specific pages of objects can be efficiently retrieved from a database, while the specified sort orders and restrictions imposed by the original retrieval requests can be maintained.

Owner:BLUE YONDER GRP INC

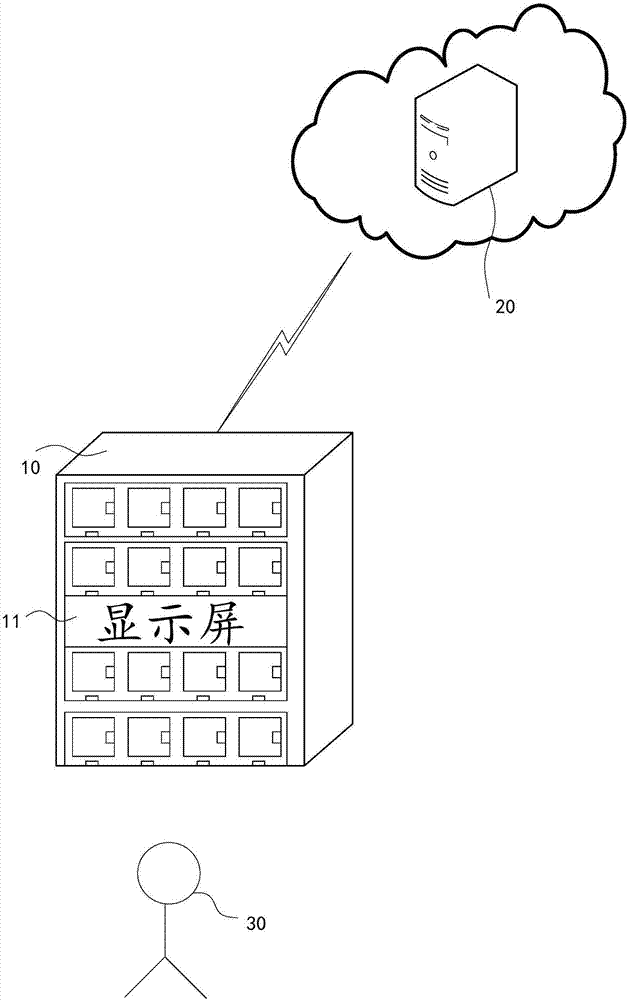

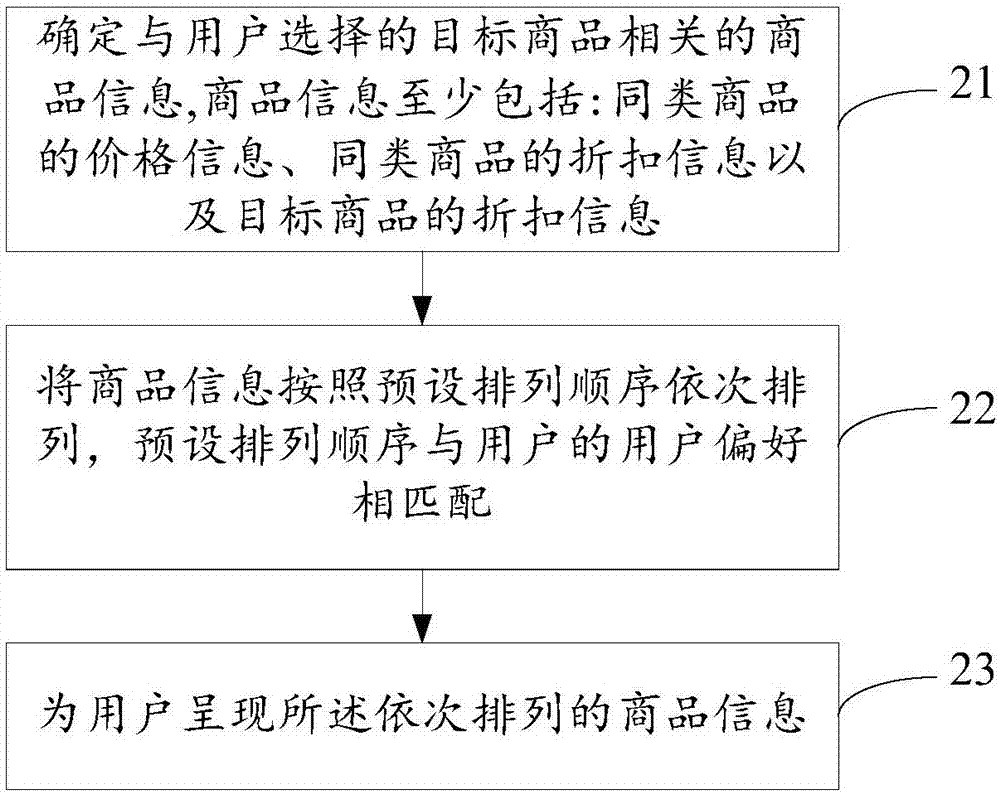

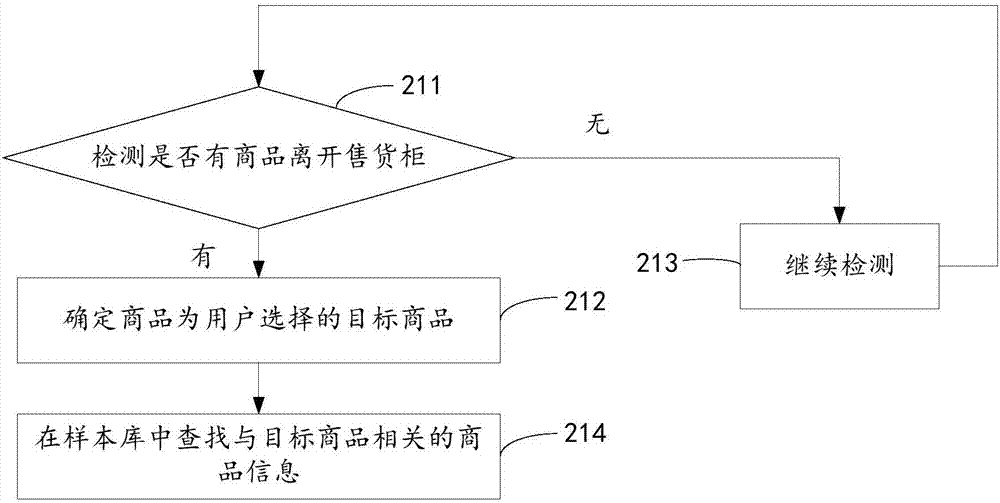

Commodity presentation method and device and automatic vending machine

ActiveCN107154109AReduce inconvenienceSave shopping timeCoin-freed apparatus detailsBuying/selling/leasing transactionsComputer sciencePurchasing process

The invention relates to the technical field of commodity recommendation, in particular to a commodity presentation method and device and an automatic vending machine. The method comprises the following steps: determining commodity information related to a target commodity selected by a user, wherein the commodity information at least comprises specification and price information of commodities of the same classification, discount information of the commodities of the same classification and discount information of the target commodity; sequentially arranging the commodity information according to a preset sort order, wherein the preset sort order is matched with user preference of the user; presenting the sequentially ordered commodity information for the user. According to the method, the commodity information related to the target commodity selected by the user is determined, and the related commodity information is presented for the user according to the user preference, so that the user can rapidly choose the favored commodities, and inconvenience brought by excessively high time consumption due to commodity selection in the purchasing process of the user is reduced. The purchasing time of the user is saved, and the purchasing experience of the user is increased.

Owner:SHENZHEN GENUINE INNOVATIVE TECH CO LTD

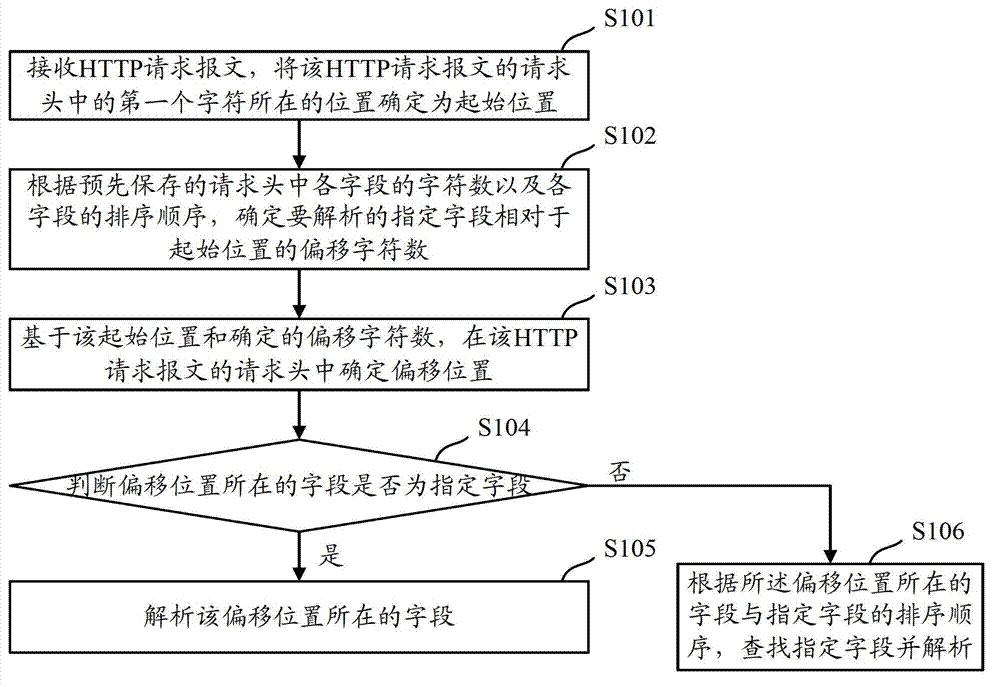

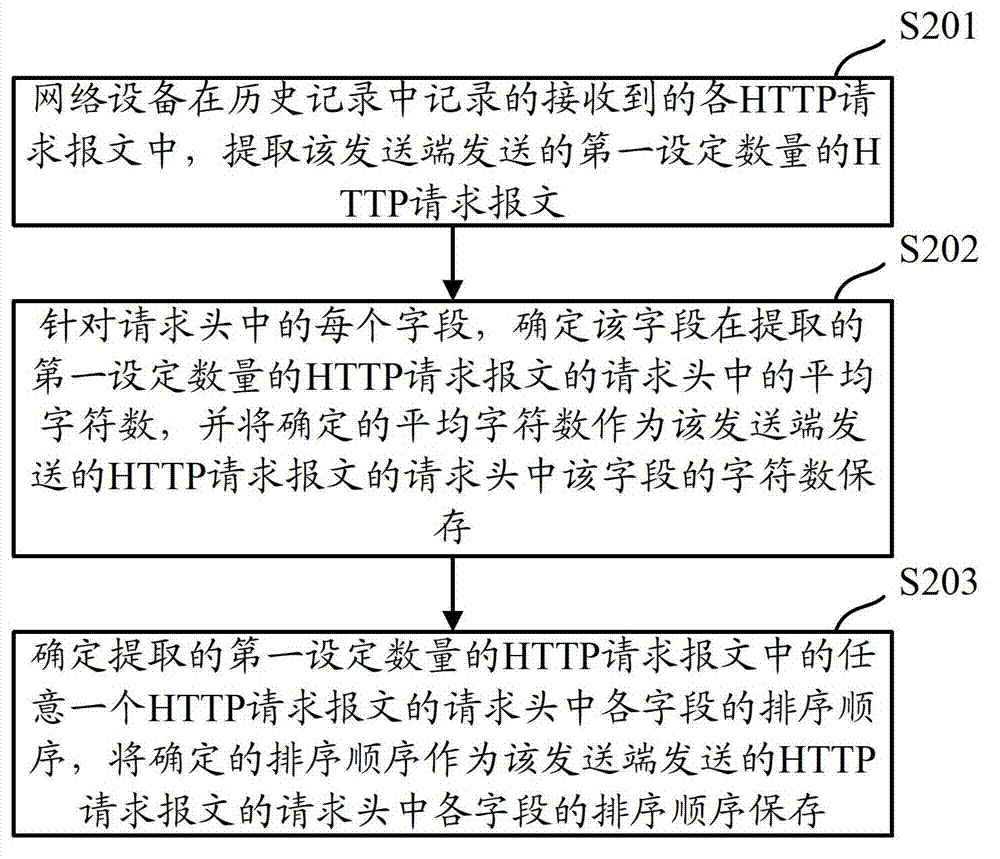

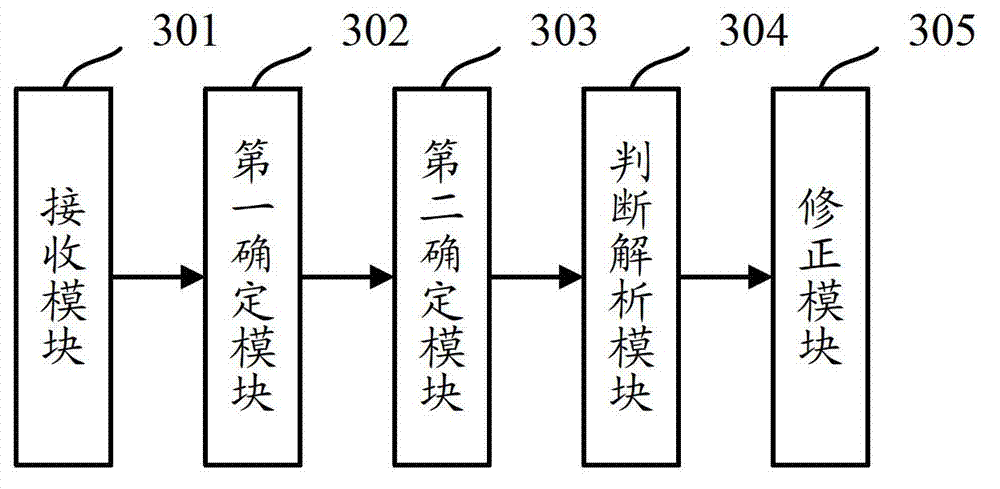

Method and device for processing message

ActiveCN102780619AImprove efficiencyData switching networksHyper text transport protocolMatch algorithm

The invention discloses a method and a device for processing a message, to solve the problem of lower efficiency in processing the HTTP (hyper text transport protocol) request message in the prior art. The method comprises the steps as follows: when analyzing the appointed field in the HTTP request message, confirming the number of offset characters of the appointed field relative to the starting position of a request header according to the character number and the sort order of fields in the pre-stored request header, and confirming the offset position in the request header based on the number of the offset characters; and when the field of the offset position is the appointed field, analyzing the field, and otherwise, continuing to search and analyze the appointed field according to the sort order of the appointed field and the field of the offset position. According to the method, network equipment can directly skip a plurality of fields not required to be analyzed and search the appointed field, it is not necessary to analyze every character in the request header or search all ending characters in the request header through a matching algorithm, so that the efficiency in processing the HTTP message is improved.

Owner:BEIJING XINWANG RUIJIE NETWORK TECH CO LTD

Method for navigating large image sets using sort orders

A method of displaying items from a collection of items including a first item is provided. The method determines a first sort order of the collection, and at least one alternate sort order of the collection. At least items adjacent to the first item in the first sort order, and in the alternate sort order, are then compared. The method then displays a portion of the items associated with the first item in each of the first sort order and in the alternate sort order based on the comparison.

Owner:CANON KK